Patents

Literature

768 results about "Isotropic etching" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Isotropic etching is a method commonly used in semiconductors to remove material from a substrate via a chemical process using an etchant substance. The etchant may be in liquid-, gas- or plasma-phase, although liquid etchants such as buffered hydrofluoric acid (BHF) for silicon dioxide etching are more often used. Unlike anisotropic etching, isotropic etching does not etch in a single direction, but rather etches in multiple directions within the substrate. Any horizontal component of the etch direction may therefore result in undercutting of patterned areas, and significant changes to device characteristics. Isotropic etching may occur unavoidably, or it may be desirable for process reasons.

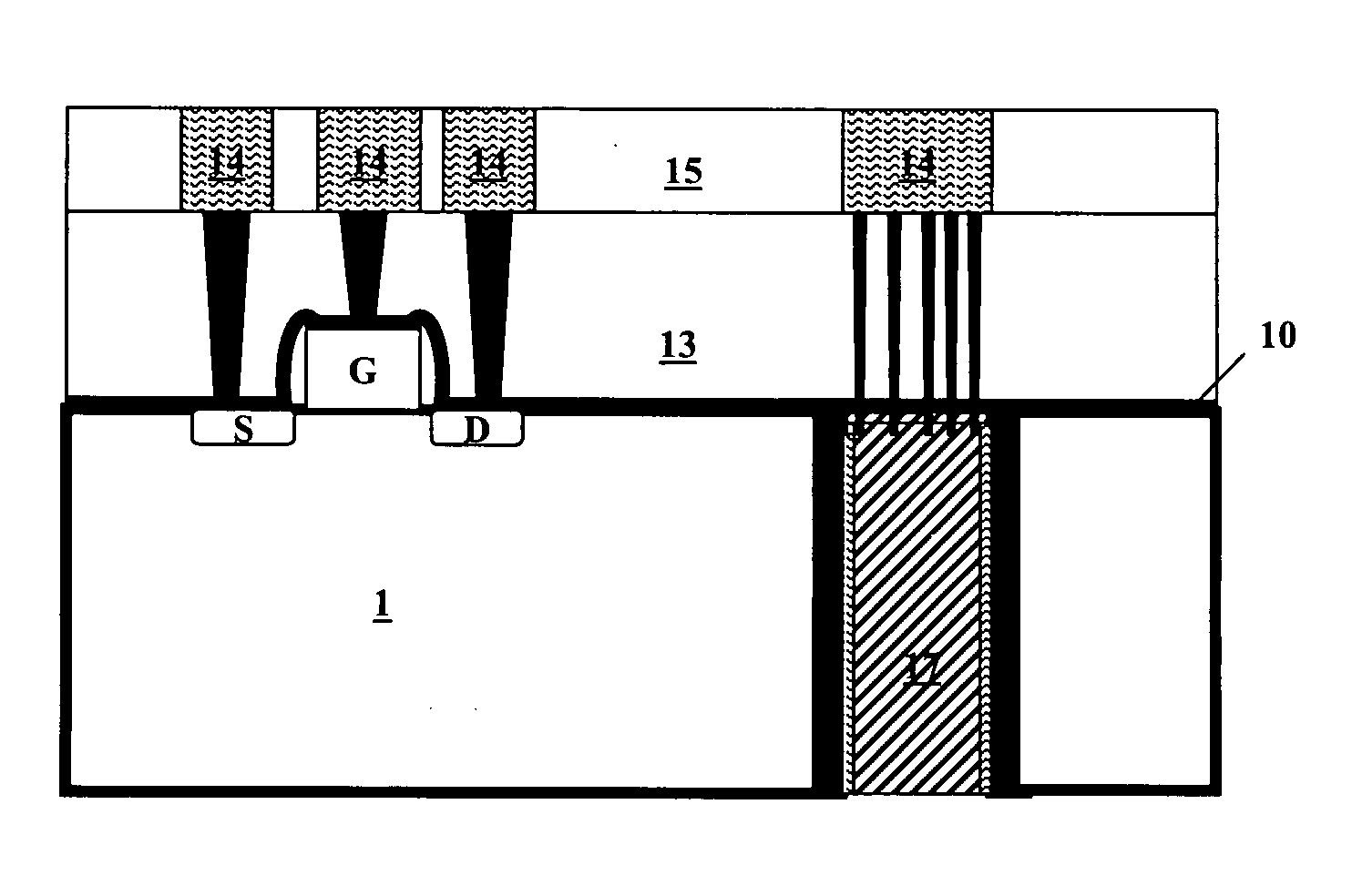

Formation of deep via airgaps for three dimensional wafer to wafer interconnect

InactiveUS20060223301A1Semiconductor/solid-state device detailsSolid-state devicesConductive materialsSemiconductor

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

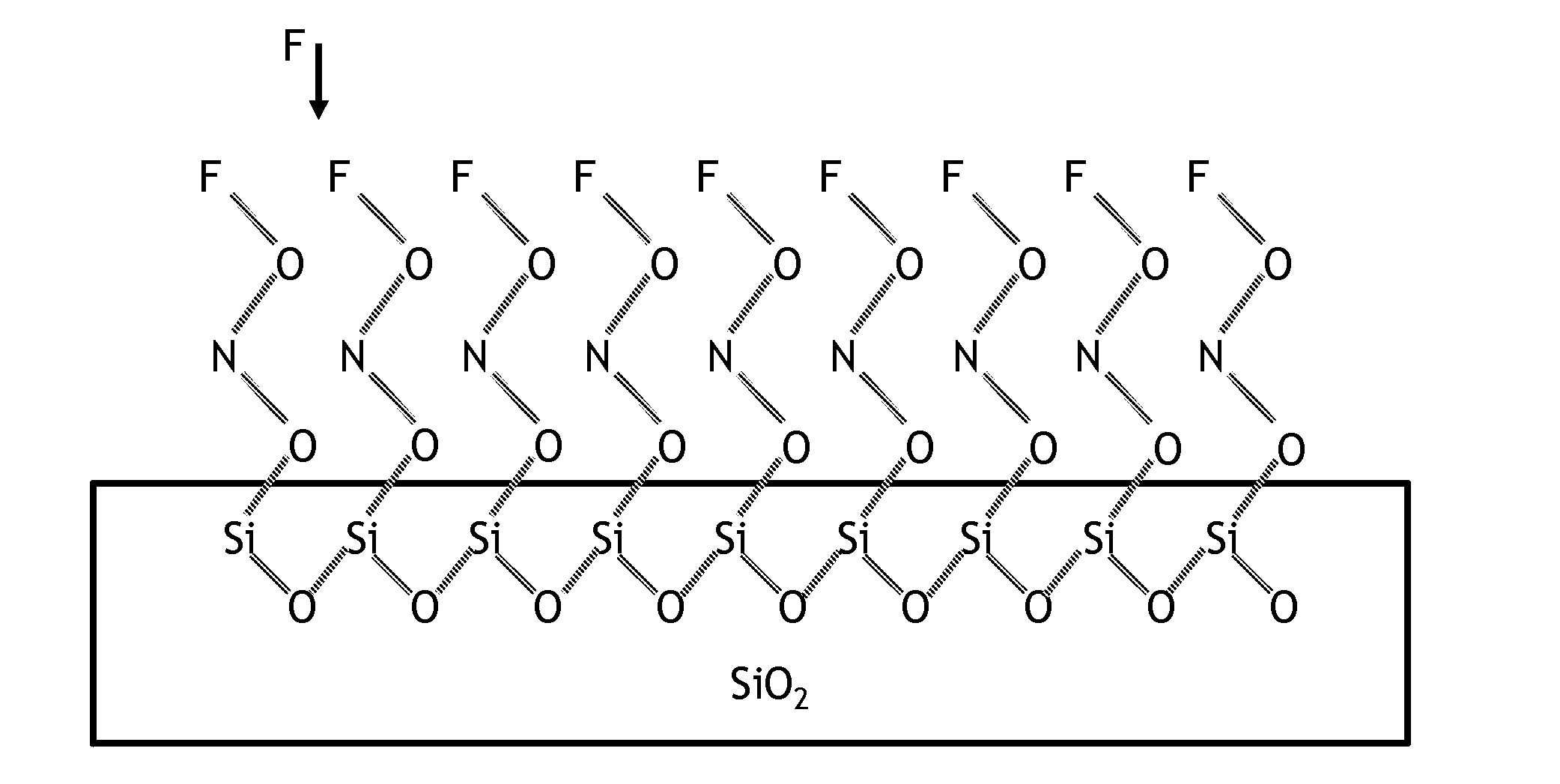

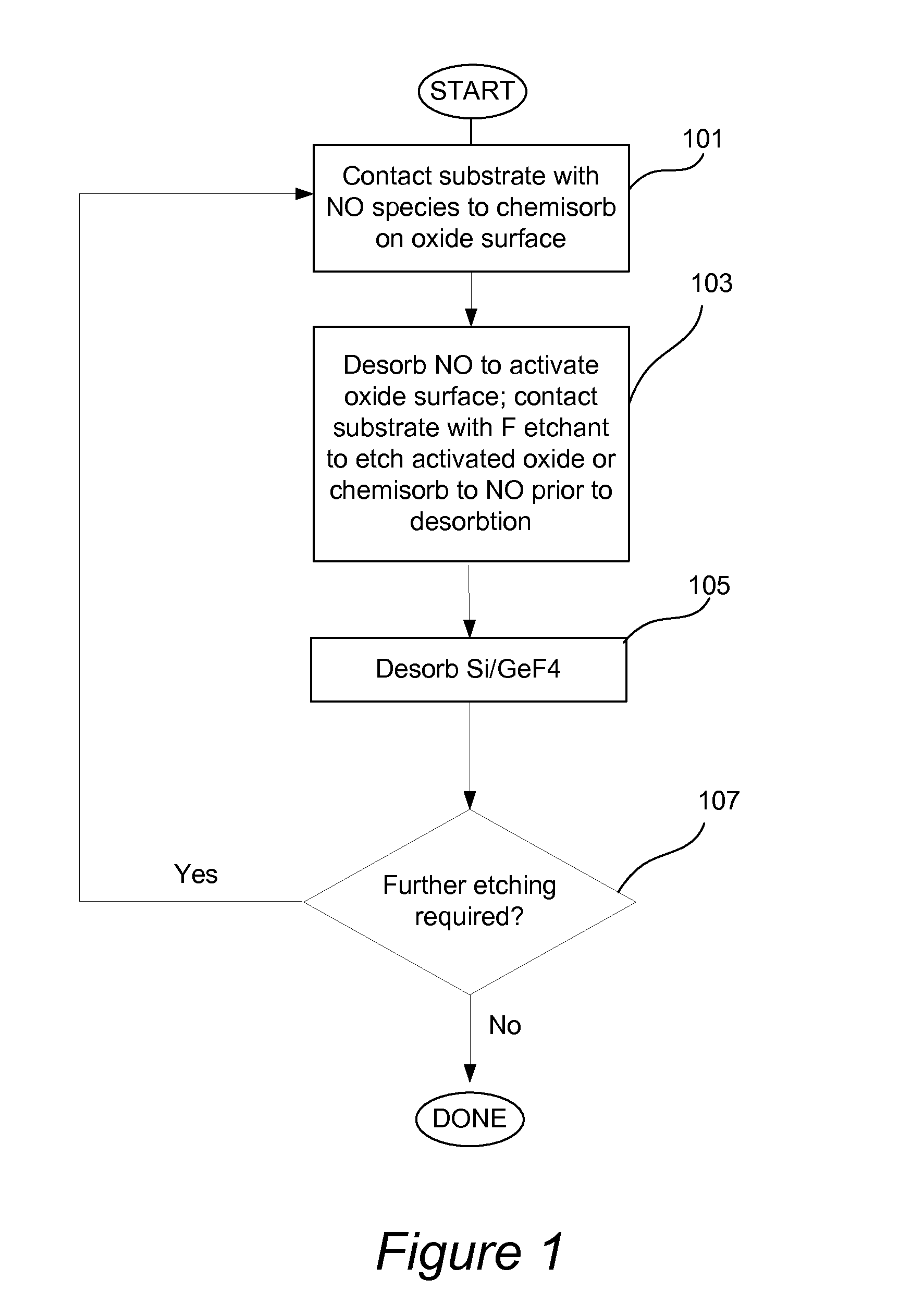

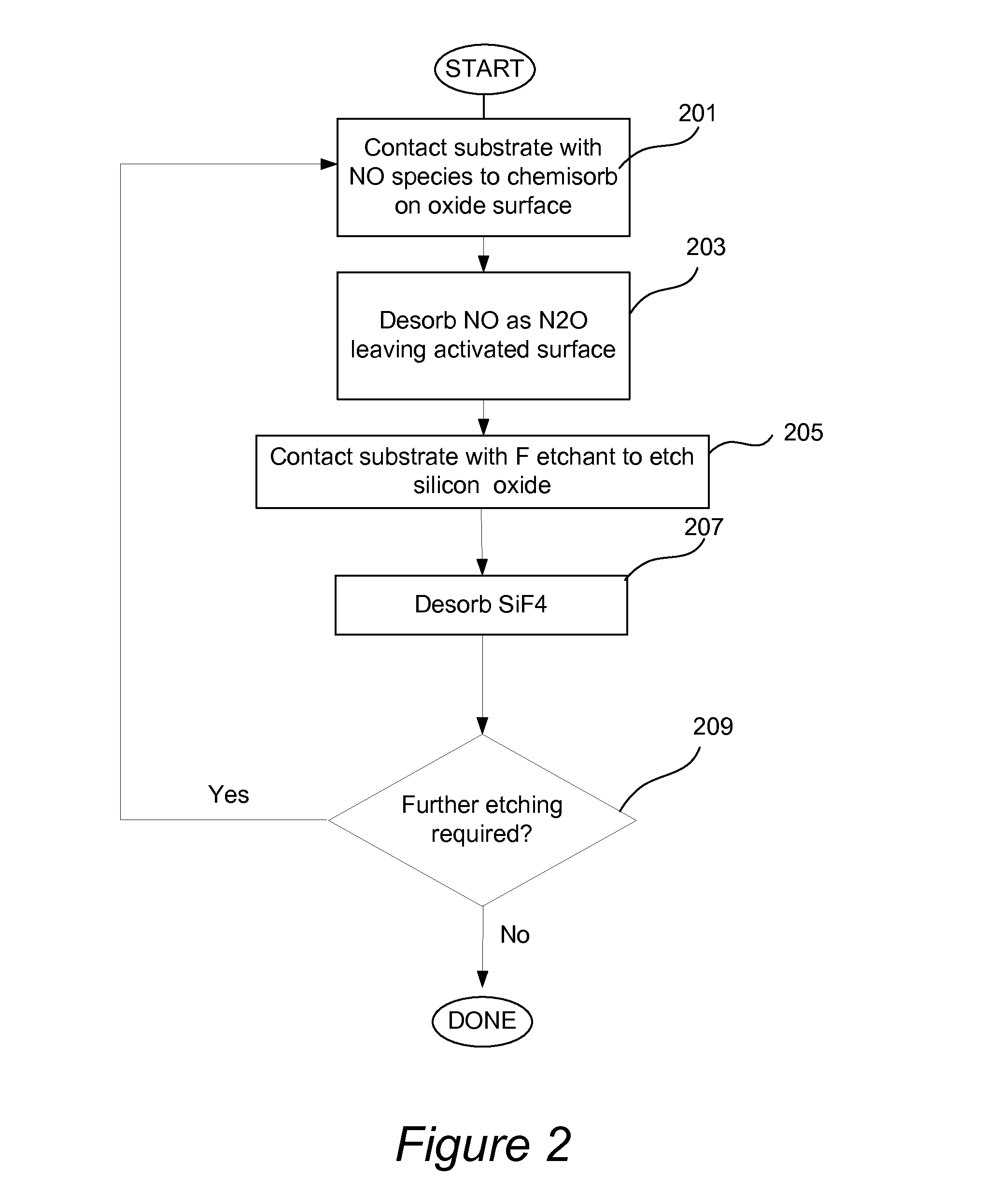

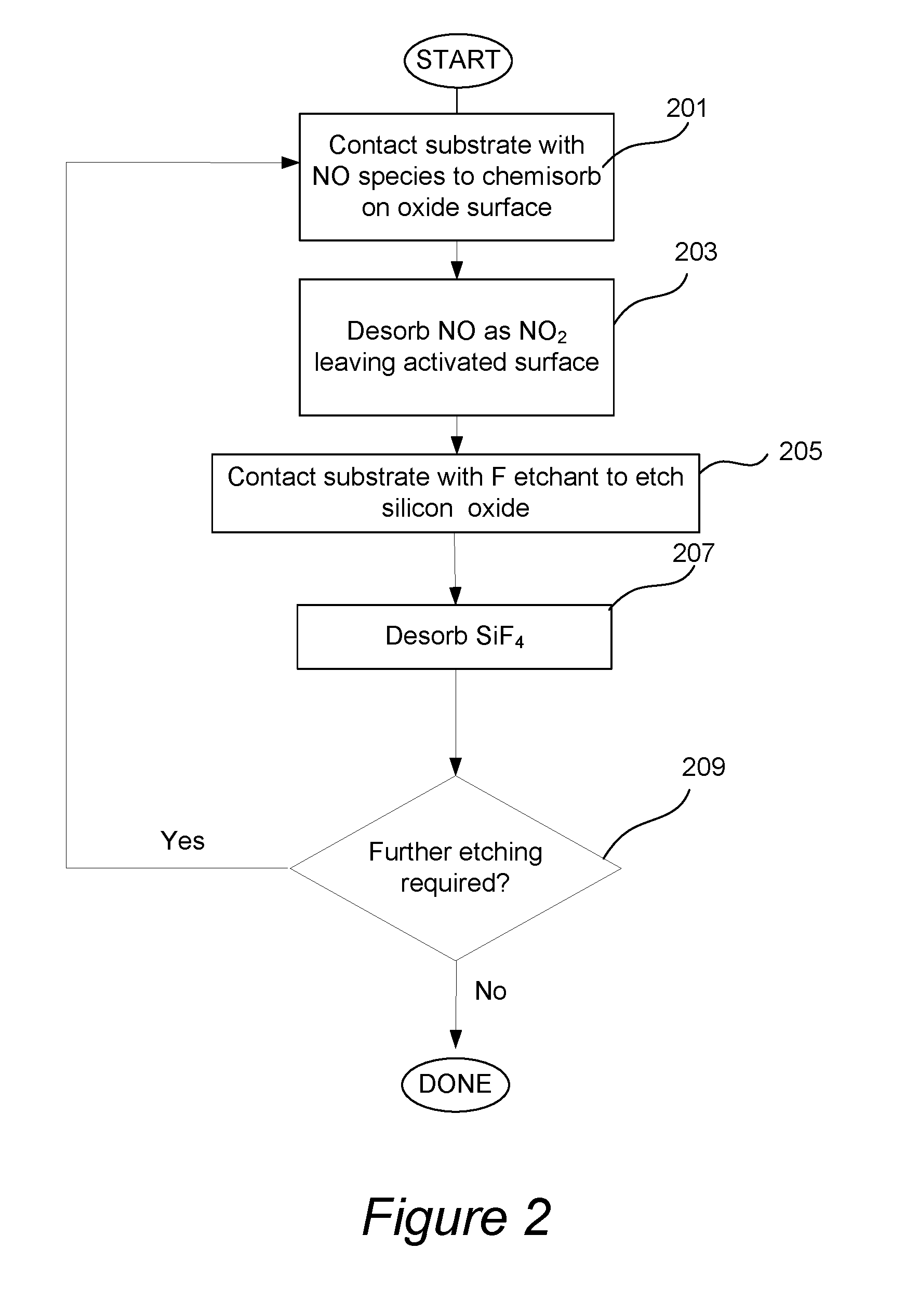

Isotropic atomic layer etch for silicon oxides using no activation

ActiveUS20160196969A1Electric discharge tubesSemiconductor/solid-state device manufacturingGate dielectricSilicon oxide

Methods for controlled isotropic etching of layers of silicon oxide and germanium oxide with atomic scale fidelity are provided. The methods make use of NO activation of an oxide surface. Once activated, a fluorine-containing gas or vapor etches the activated surface. Etching is self-limiting as once the activated surface is removed, etching stops since the fluorine species does not spontaneously react with the un-activated oxide surface. These methods may be used in interconnect pre-clean applications, gate dielectric processing, manufacturing of memory devices, or any other applications where accurate removal of one or multiple atomic layers of material is desired.

Owner:LAM RES CORP

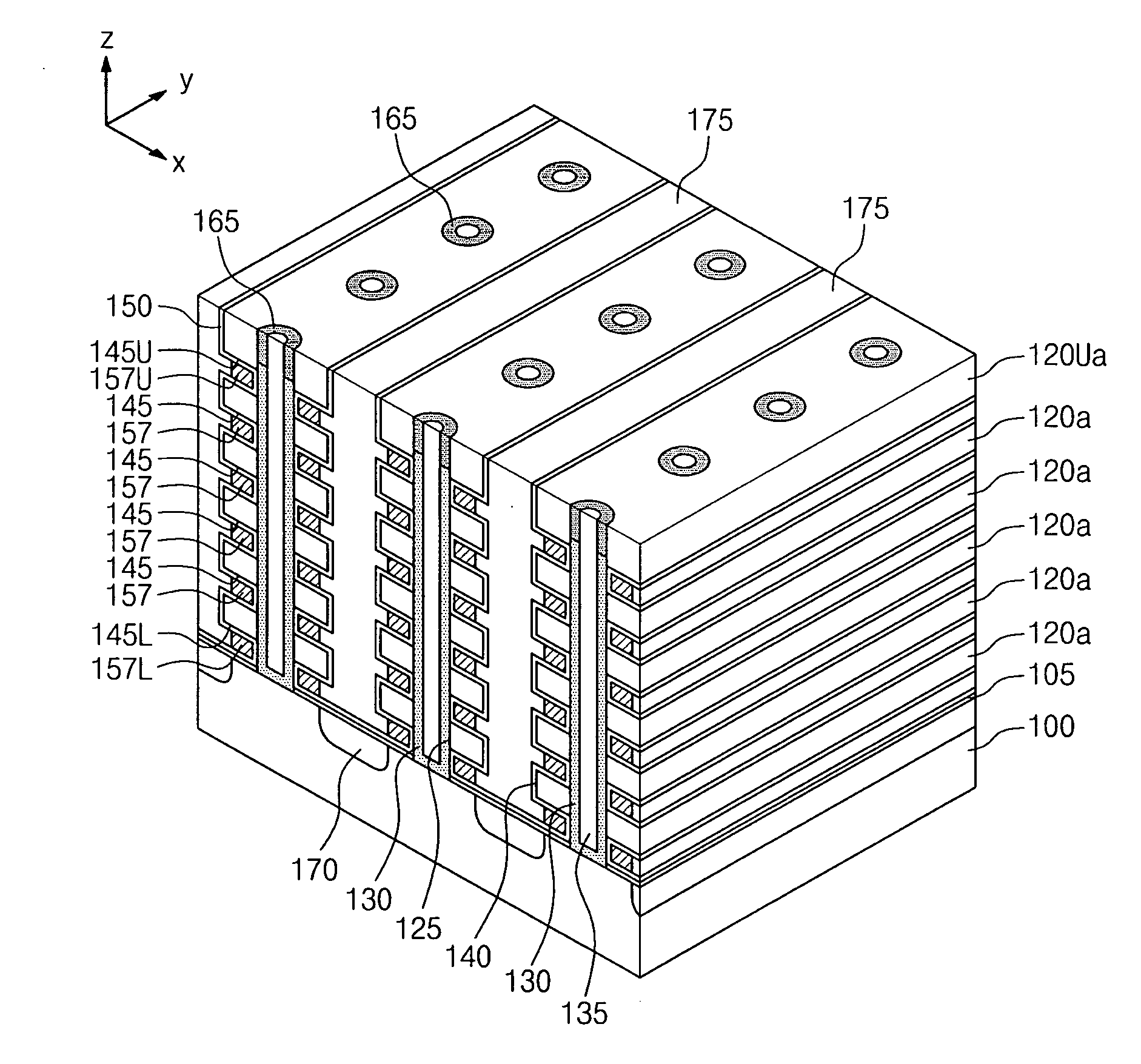

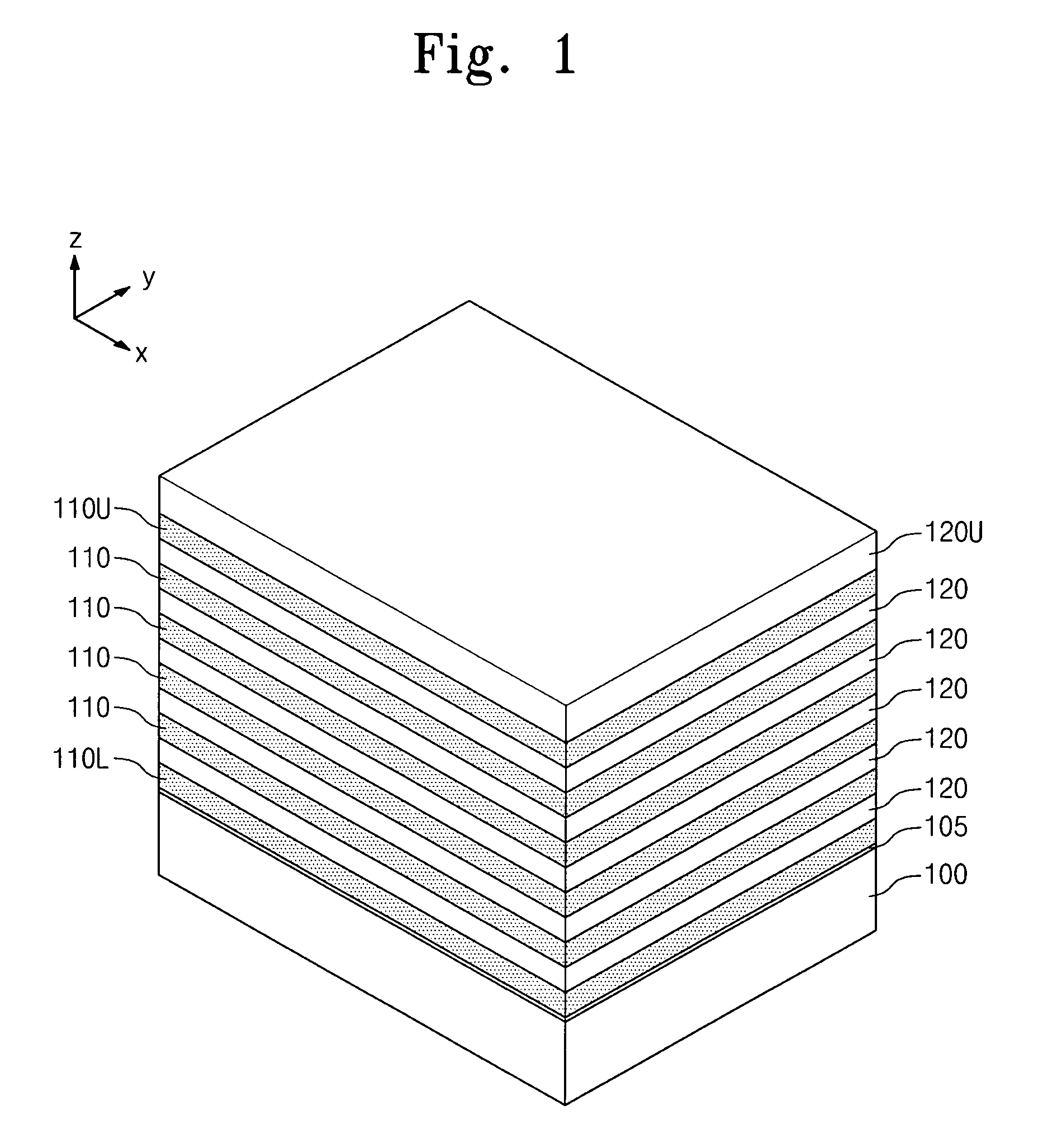

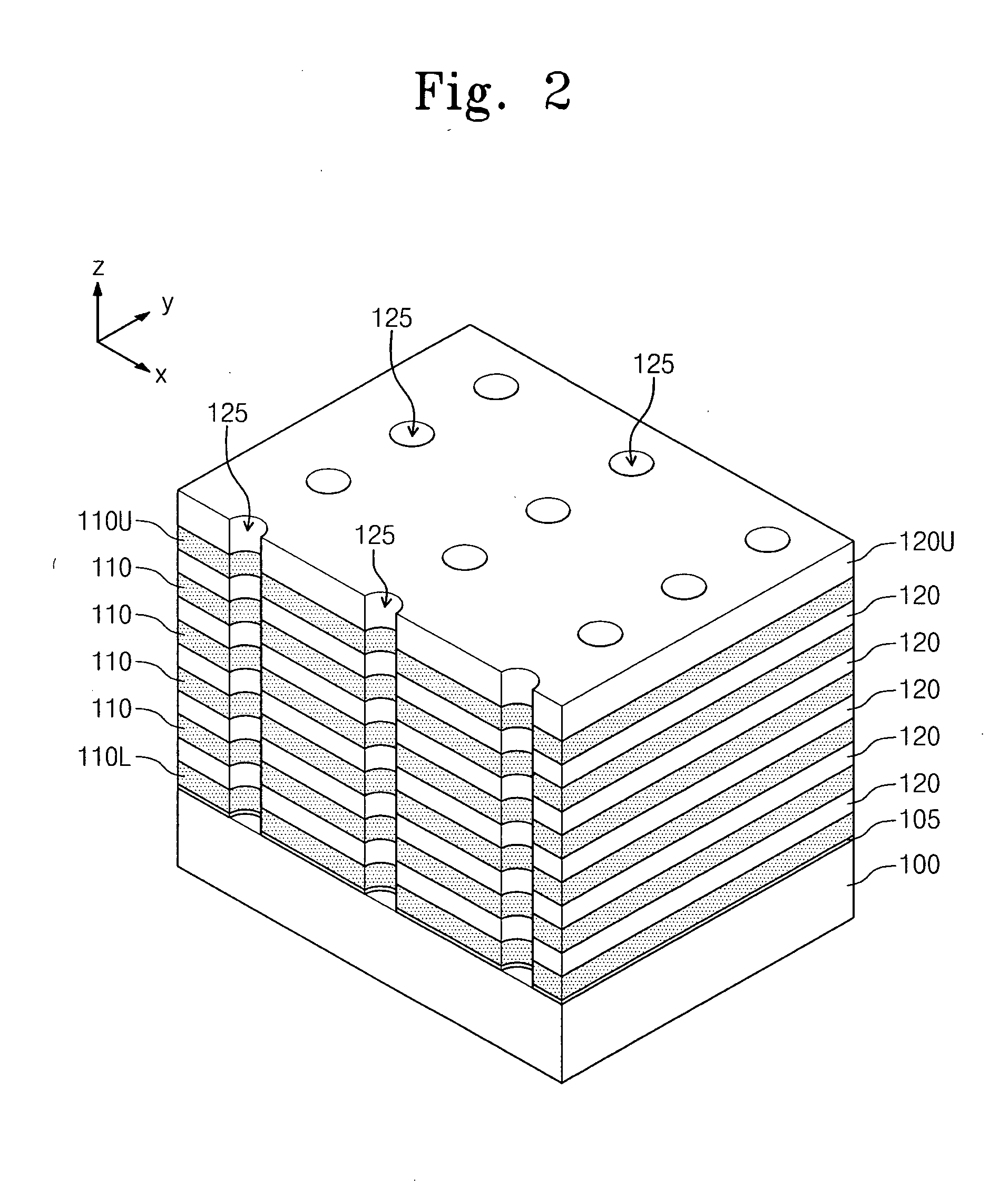

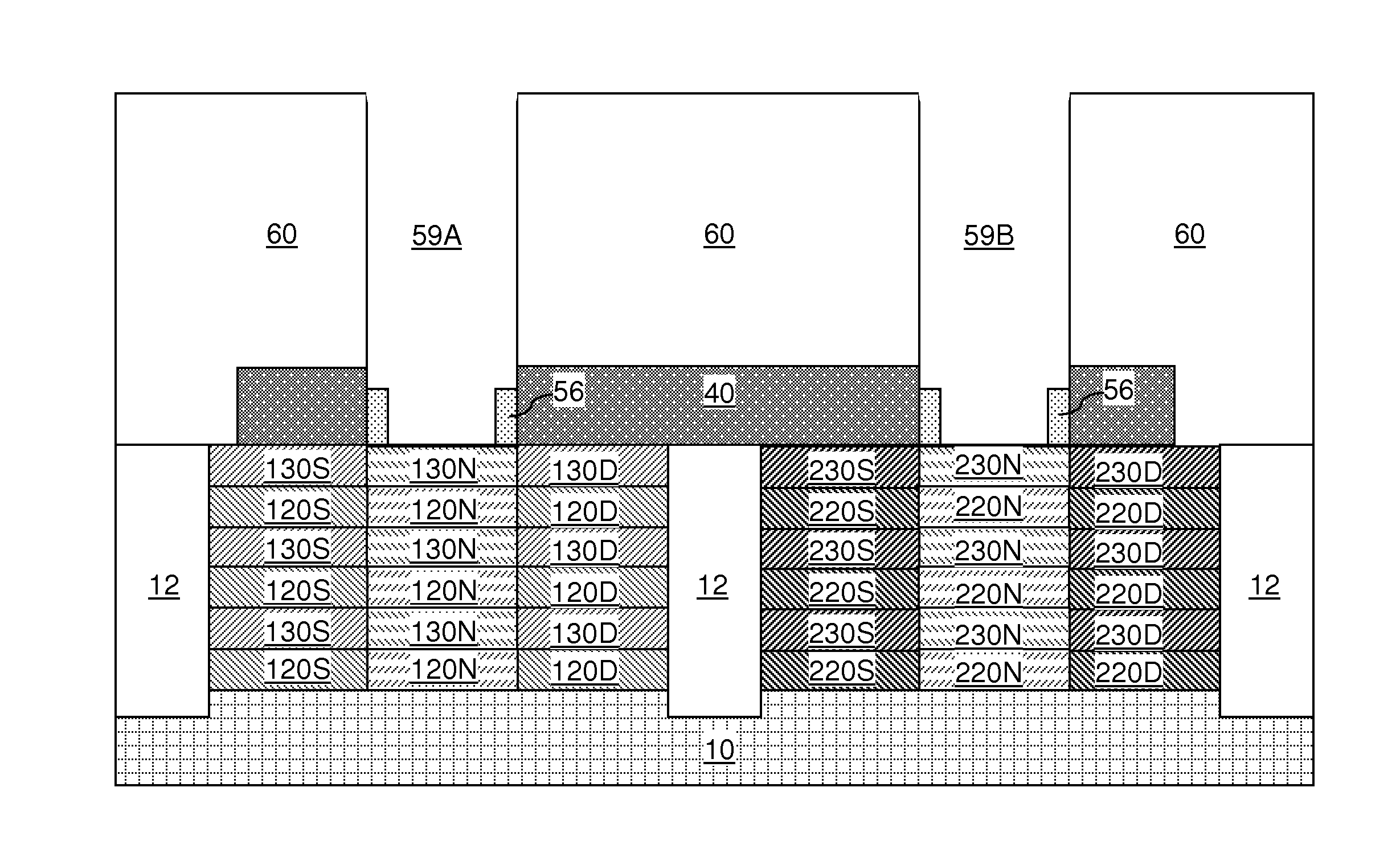

Three-dimensional semiconductor memory device and method of fabricating the same

ActiveUS20110076819A1Improve reliabilityIncrease process marginSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

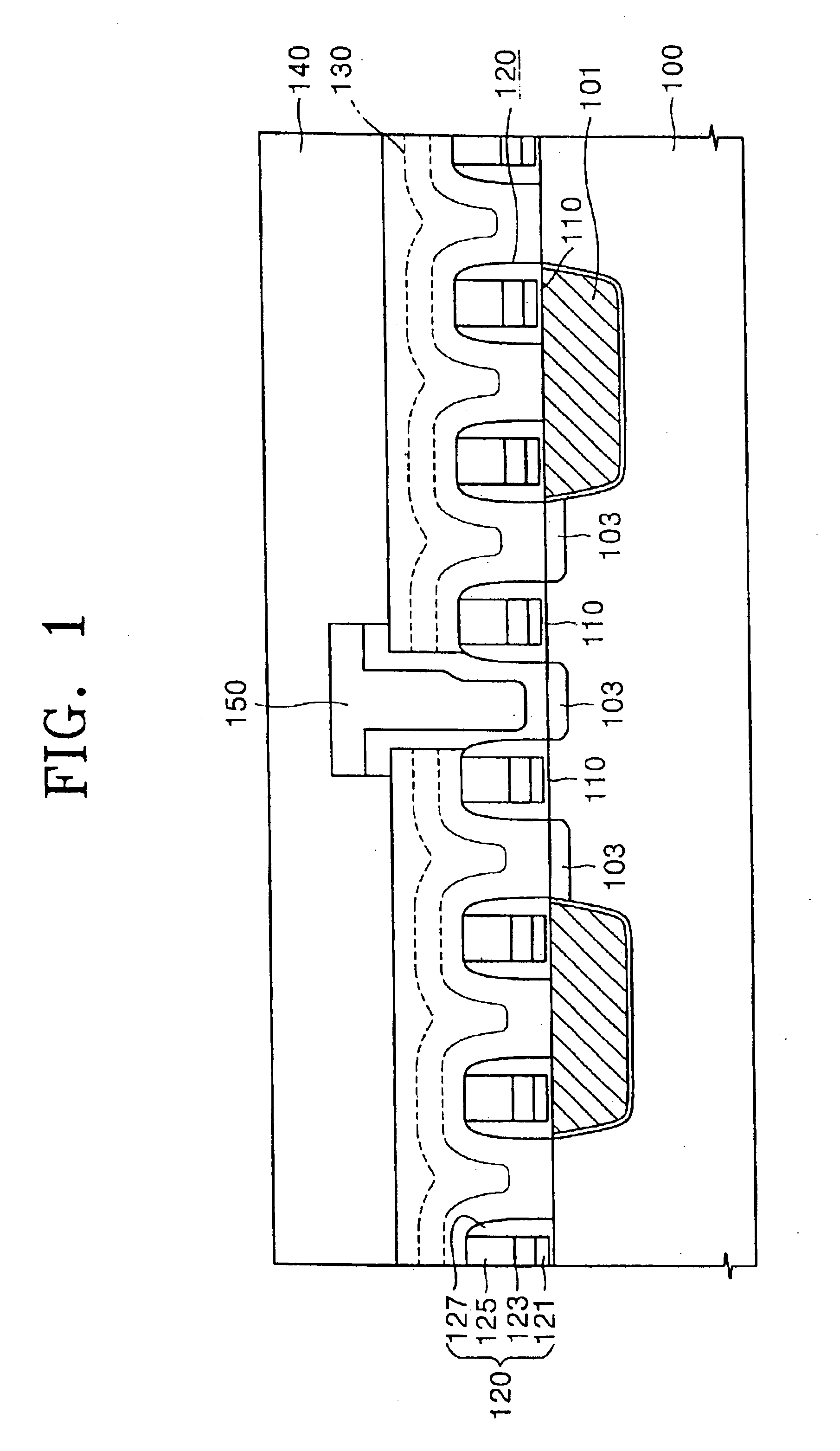

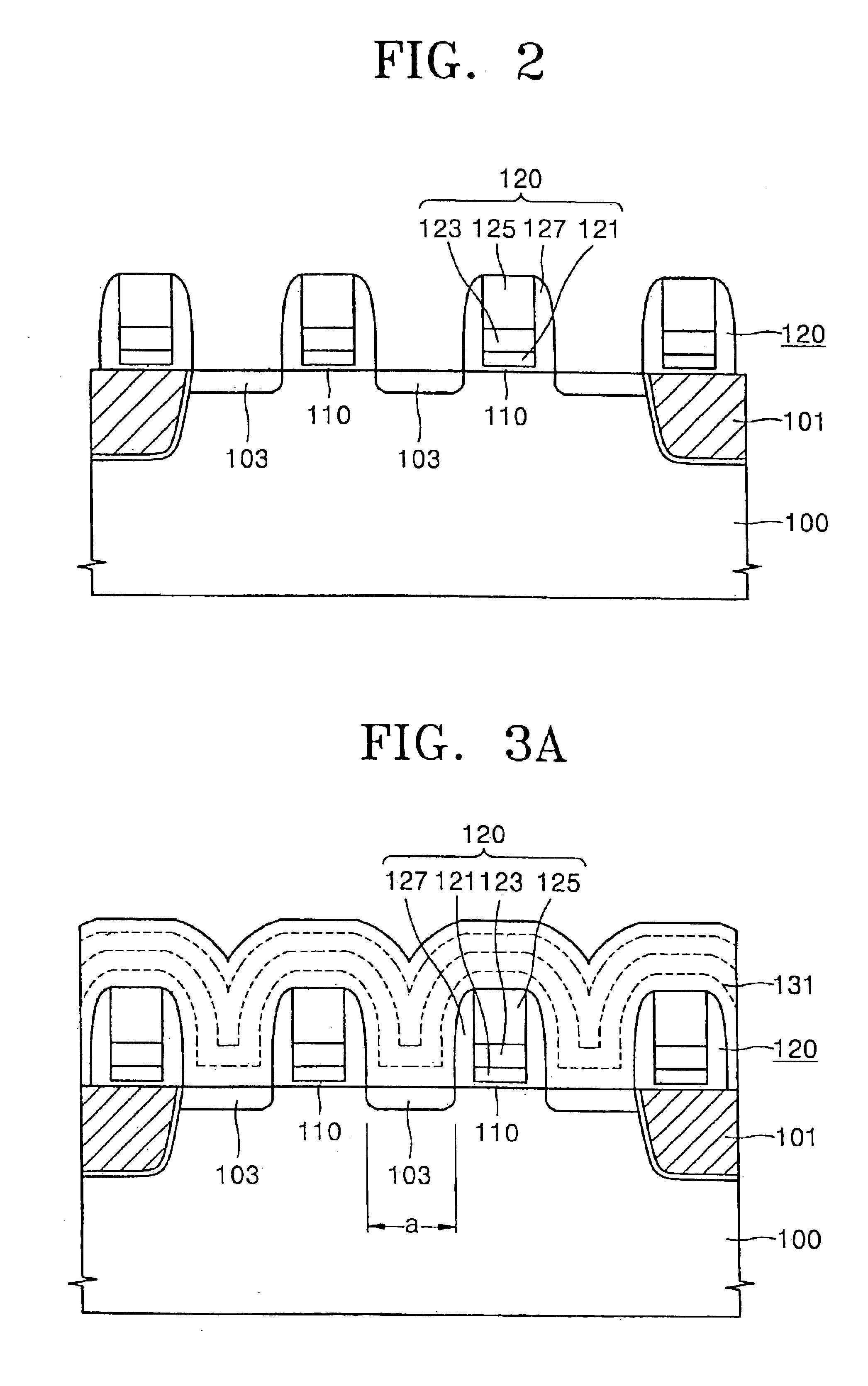

A method of fabricating a semiconductor memory device includes alternately and repeatedly stacking sacrificial layers and insulating layers on a substrate, forming an active pattern penetrating the sacrificial layers and the insulating layers, continuously patterning the insulating layers and the sacrificial layers to form a trench, removing the sacrificial layers exposed in the trench to form recess regions exposing a sidewall of the active pattern, forming an information storage layer on the substrate, forming a gate conductive layer on the information storage layer, such that the gate conductive layer fills the recess regions and defines an empty region in the trench, the empty region being surrounded by the gate conductive layer, and performing an isotropic etch process with respect to the gate conductive layer to form gate electrodes in the recess regions, such that the gate electrodes are separated from each other.

Owner:SAMSUNG ELECTRONICS CO LTD

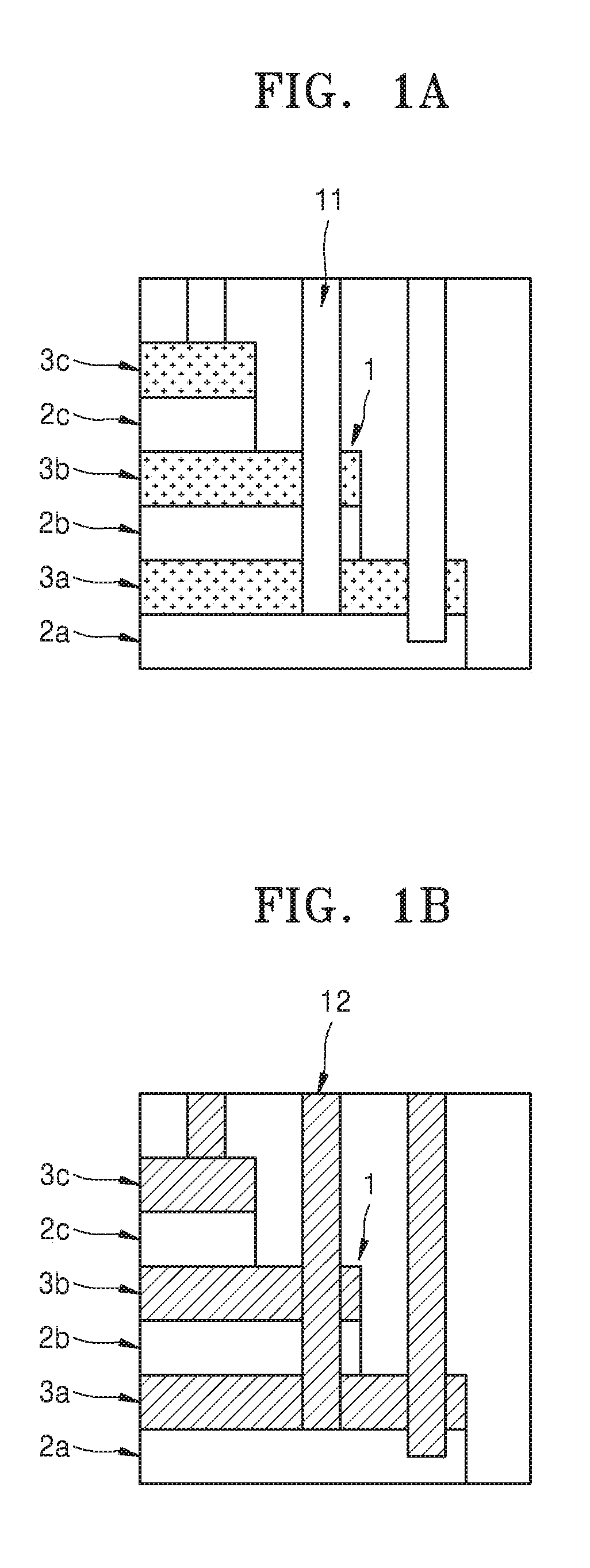

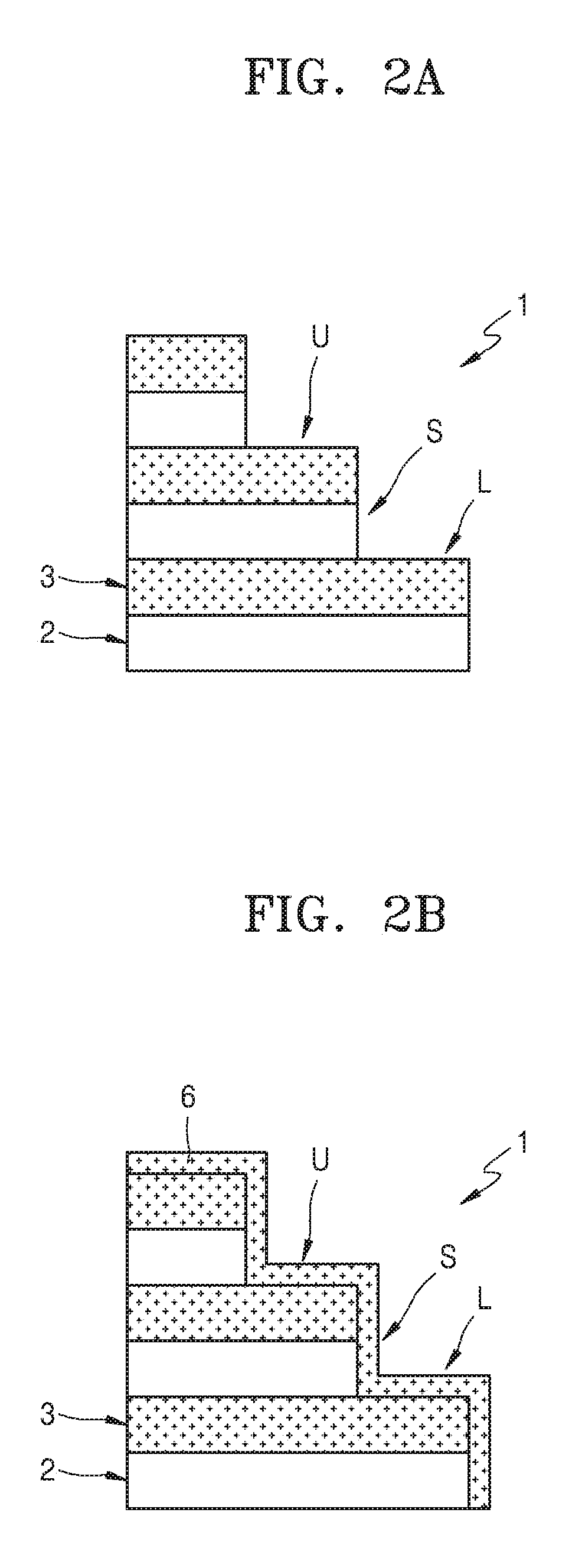

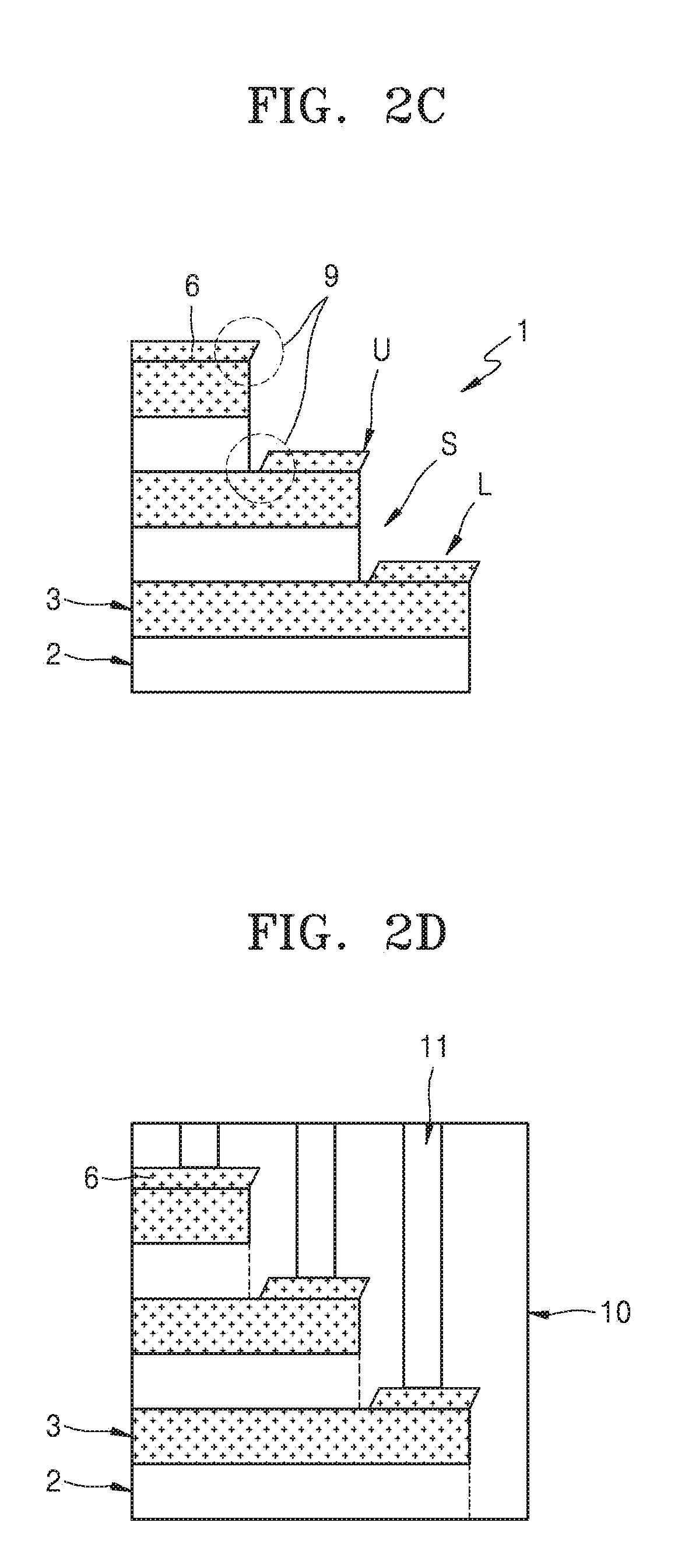

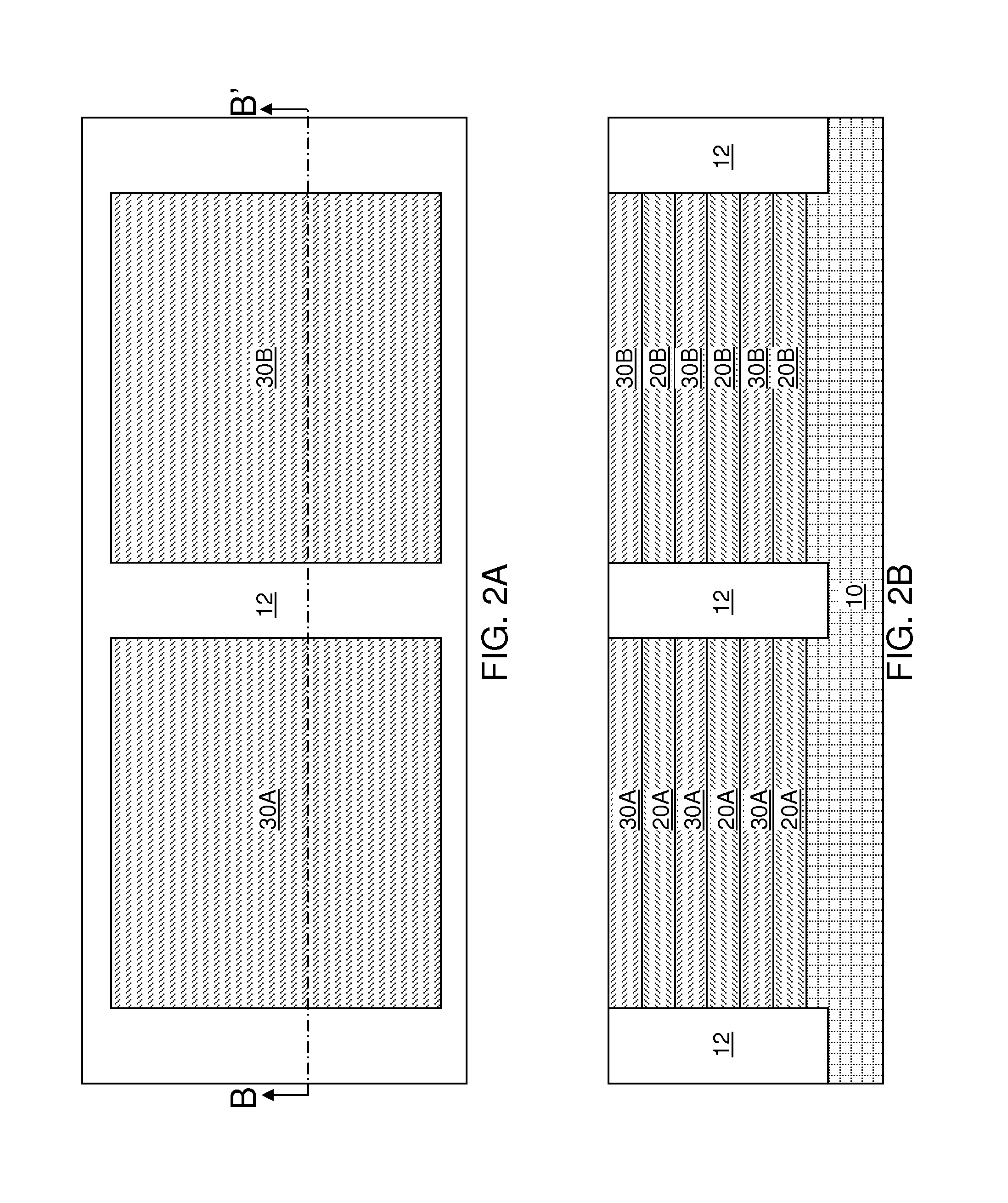

Method of processing a substrate and a device manufactured by the same

ActiveUS20190148398A1Prevent excessive etchingImprove the immunitySolid-state devicesSemiconductor/solid-state device manufacturingEngineeringLine structure

Provided is a substrate processing method capable of preventing over-etching of a part of a stair-case structure due to an etching solution, when a barrier layer is selectively formed on a VNAND device having the stair-case structure. The substrate processing method includes: alternately stacking a first insulating layer and a second insulating layer; forming a stepped structure having an upper surface, a lower surface, and a side surface connecting the upper surface to the lower surface by etching the first insulating layer and the second insulating layer that are stacked; densifying the stepped structure; forming a barrier layer on the densified second insulating layer; and performing isotropic etching on at least a part of a sacrificial word line structure including the second insulating layer and the barrier layer. During etching the barrier layer at the isotropic etching step, the second insulating layer is not etched or etched a little to an ignorable degree.

Owner:ASM IP HLDG BV

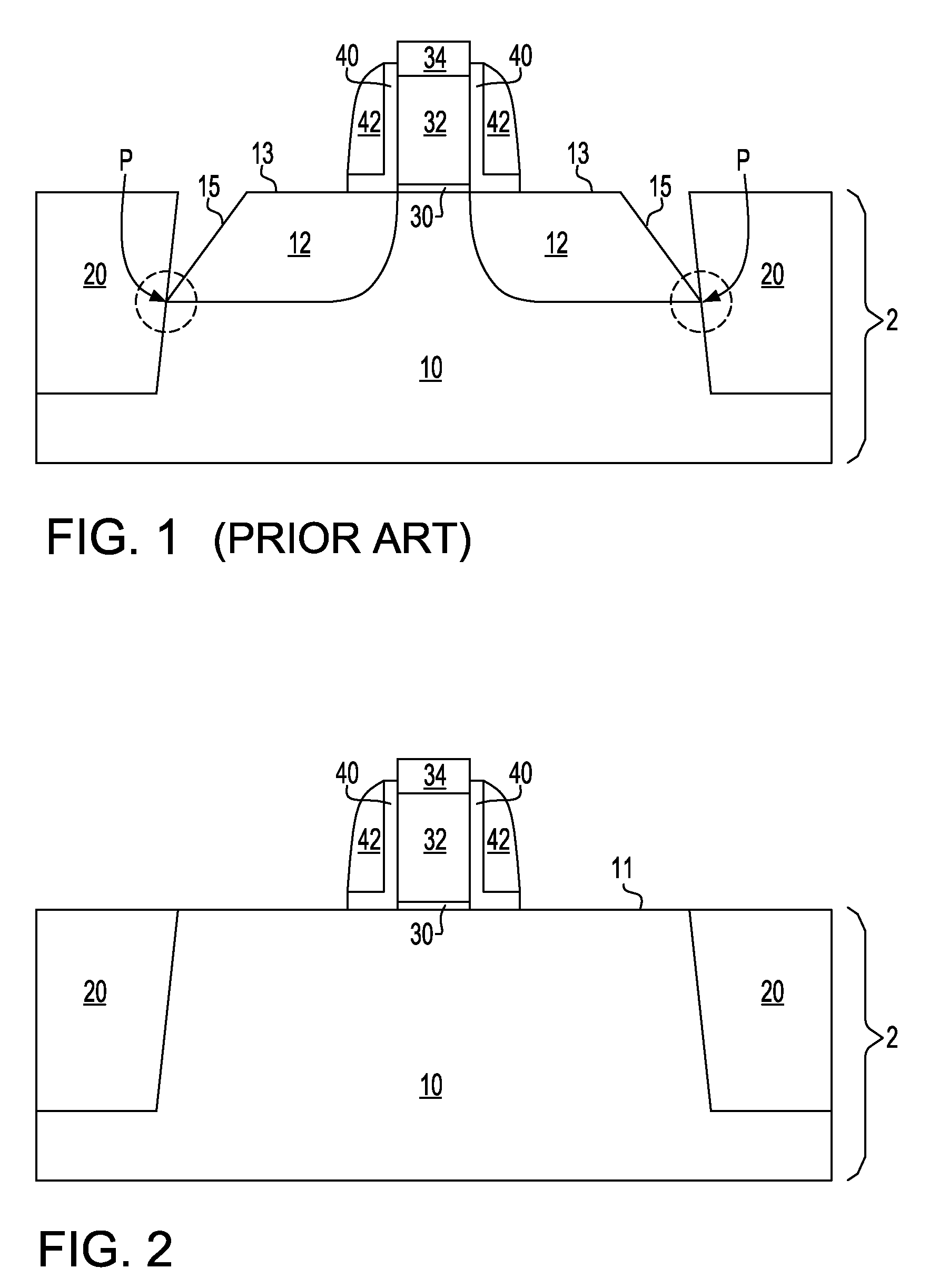

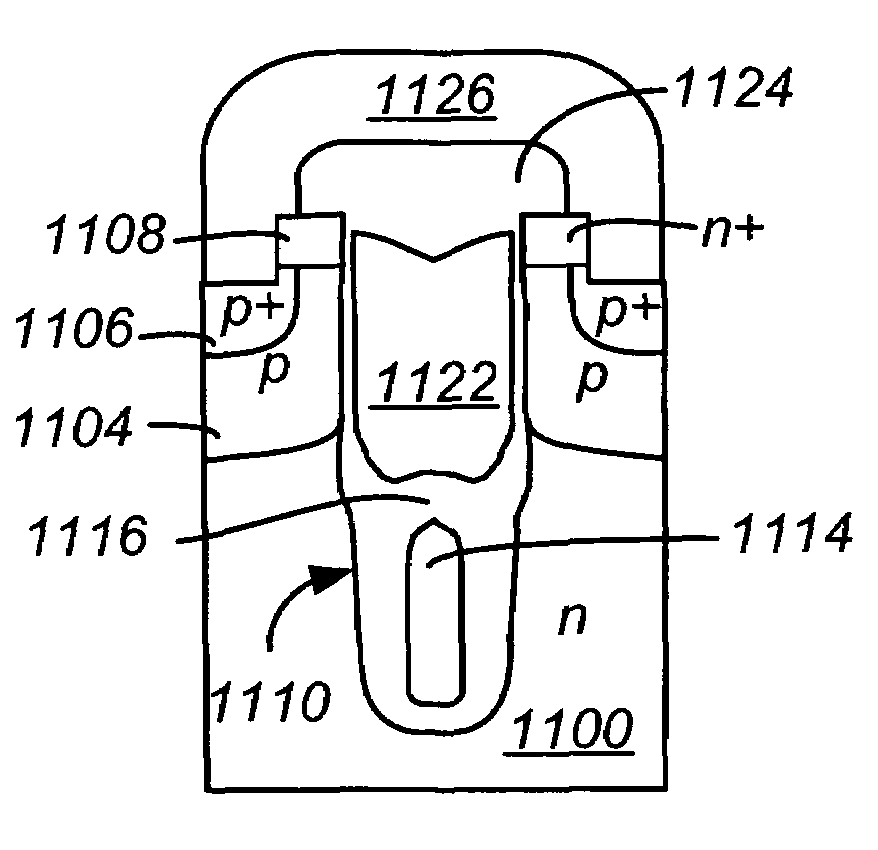

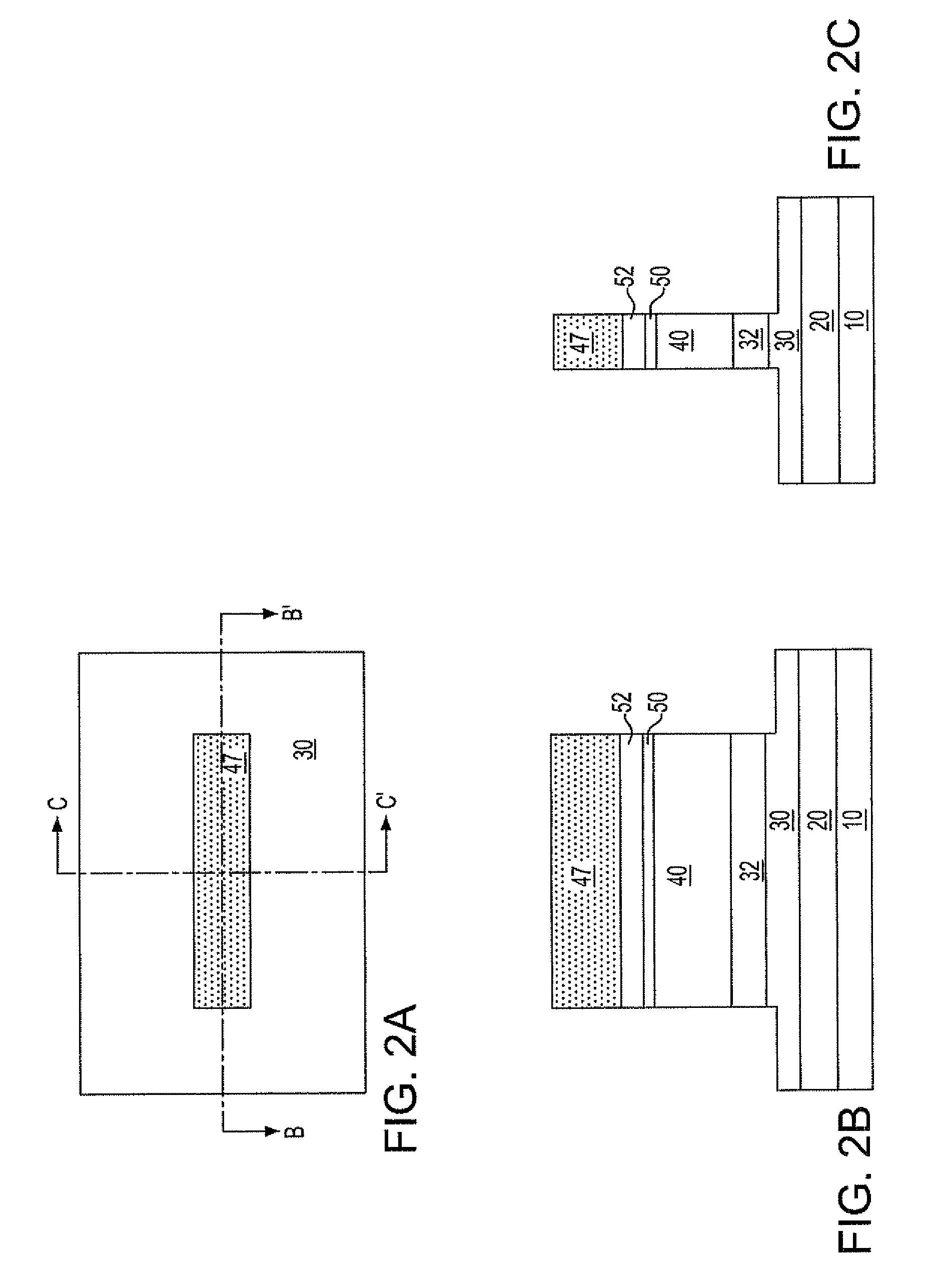

Body-contacted finfet

ActiveUS20090008705A1Semiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricSemiconductor materials

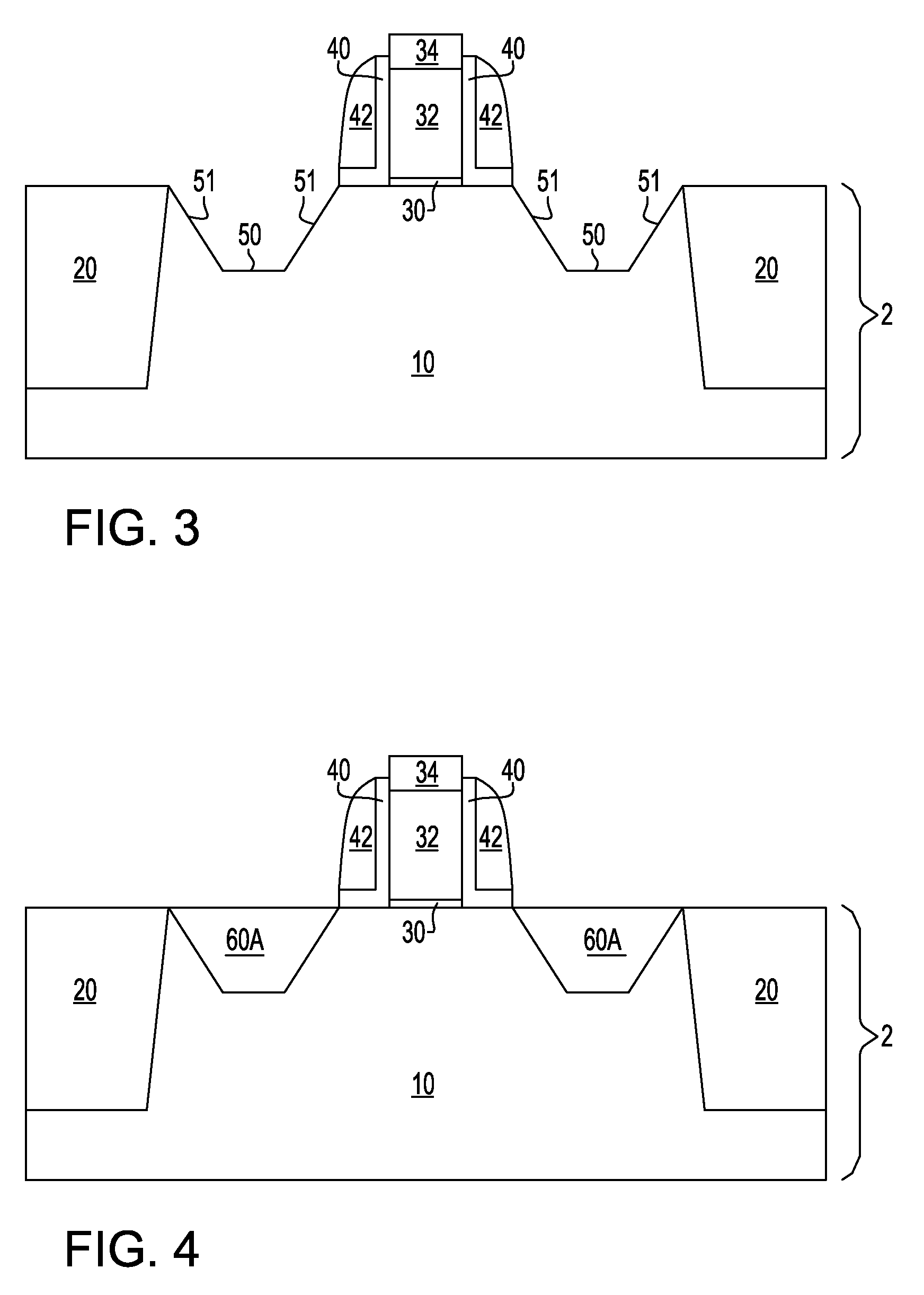

A silicon containing fin is formed on a semiconductor substrate. A silicon oxide layer is formed around the bottom of the silicon containing fin. A gate dielectric is formed on the silicon containing fin followed by formation of a gate electrode. While protecting the portion of the semiconductor fin around the channel, a bottom portion of the silicon containing semiconductor fin is etched by a isotropic etch leaving a body strap between the channel of a finFET on the silicon containing fin and an underlying semiconductor layer underneath the silicon oxide layer. The fin may comprise a stack of inhomogeneous layers in which a bottom layer is etched selectively to a top semiconductor layer. Alternatively, the fin may comprise a homogeneous semiconductor material and the silicon containing fin may be protected by dielectric films on the sidewalls and top surfaces of the silicon containing fin.

Owner:GLOBALFOUNDRIES US INC

Amorphous etch stop for the anisotropic etching of substrates

ActiveUS7045407B2Semiconductor/solid-state device manufacturingSemiconductor devicesAnisotropic etchingCantilever

Methods of forming an amorphous etch stop layer by implanting a substrate with an element that is electrically neutral within the substrate are described. The use of elements that are electrically neutral within the substrate prevents electrical interference by the elements if they diffuse to other areas within the substrate. The amorphous etch stop layer may be used as a hard mask in the fabrication of transistors or other devices such as a cantilever.

Owner:INTEL CORP

Isotropic atomic layer etch for silicon oxides using no activation

ActiveUS9425041B2High selectivityReduce defective rateElectric discharge tubesSemiconductor/solid-state device manufacturingGate dielectricSilicon oxide

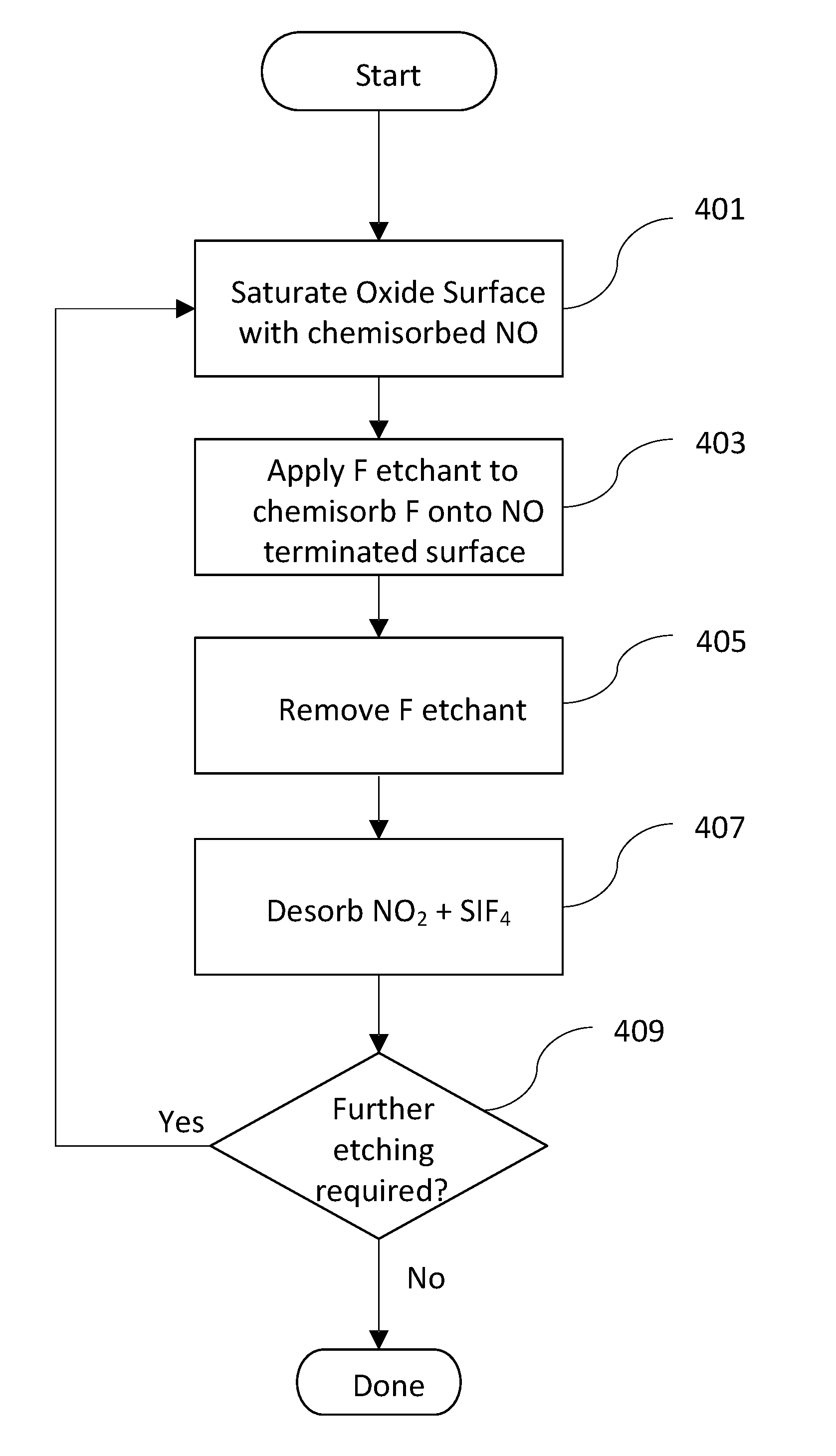

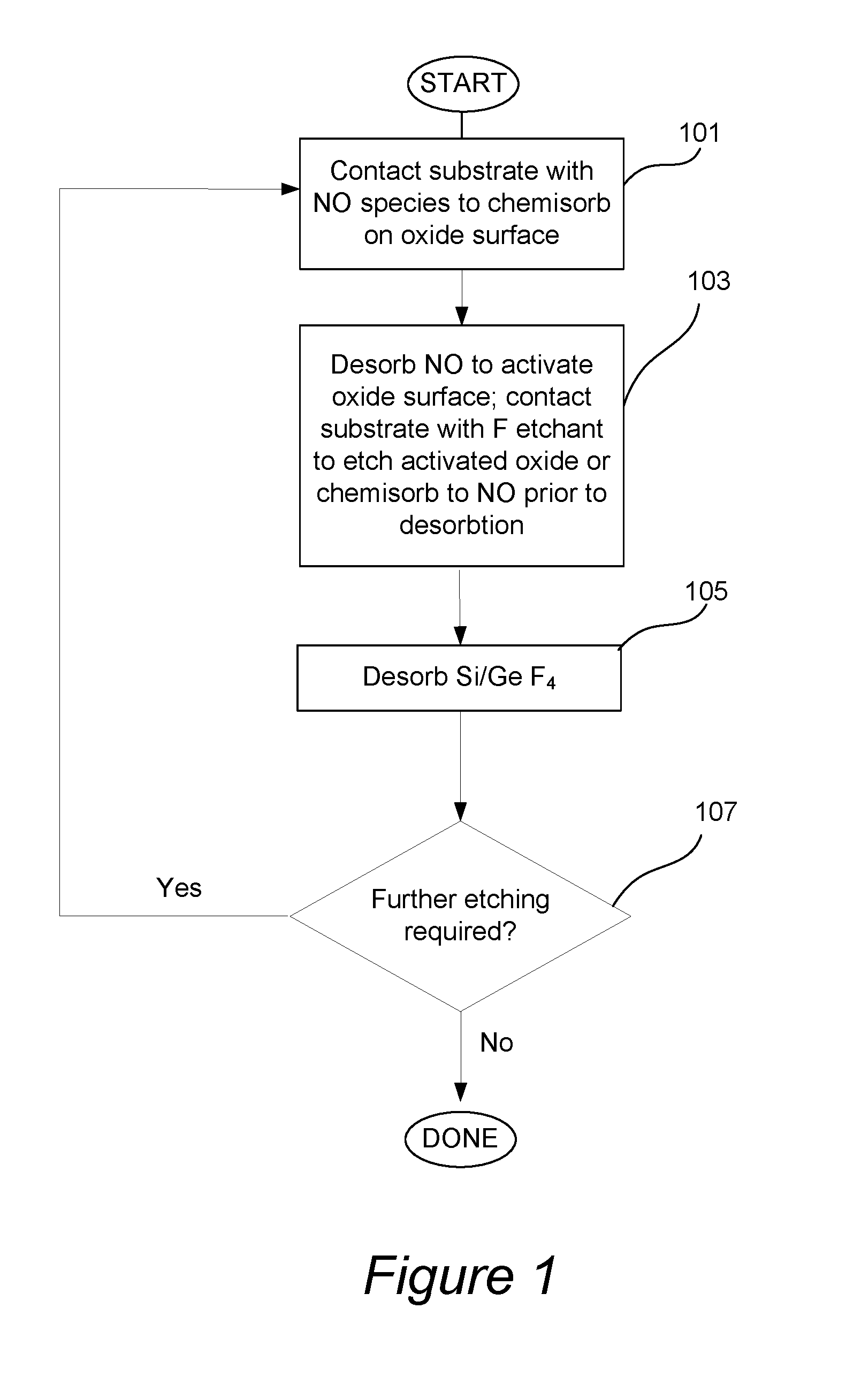

Methods for controlled isotropic etching of layers of silicon oxide and germanium oxide with atomic scale fidelity are provided. The methods make use of NO activation of an oxide surface. Once activated, a fluorine-containing gas or vapor etches the activated surface. Etching is self-limiting as once the activated surface is removed, etching stops since the fluorine species does not spontaneously react with the un-activated oxide surface. These methods may be used in interconnect pre-clean applications, gate dielectric processing, manufacturing of memory devices, or any other applications where accurate removal of one or multiple atomic layers of material is desired.

Owner:LAM RES CORP

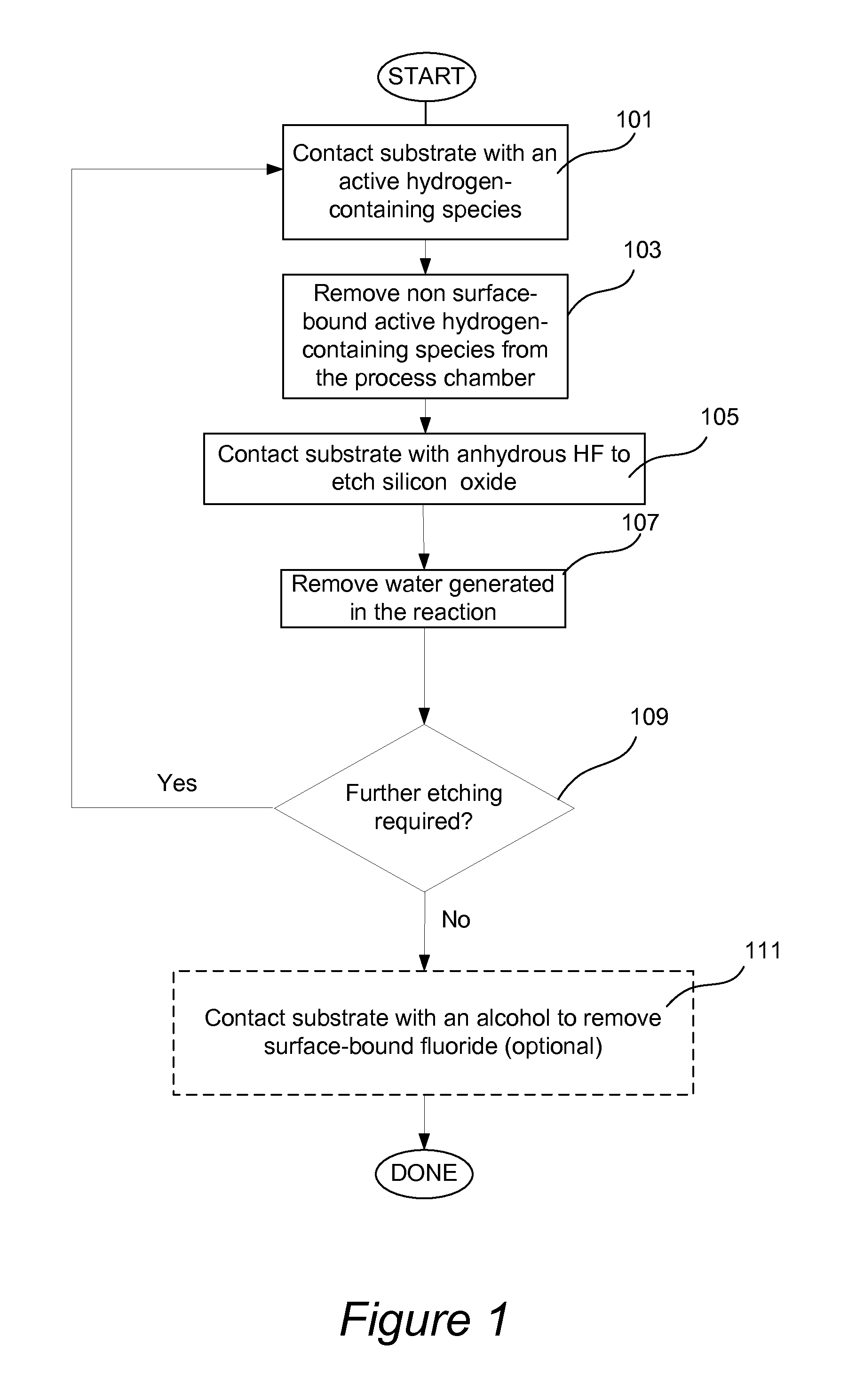

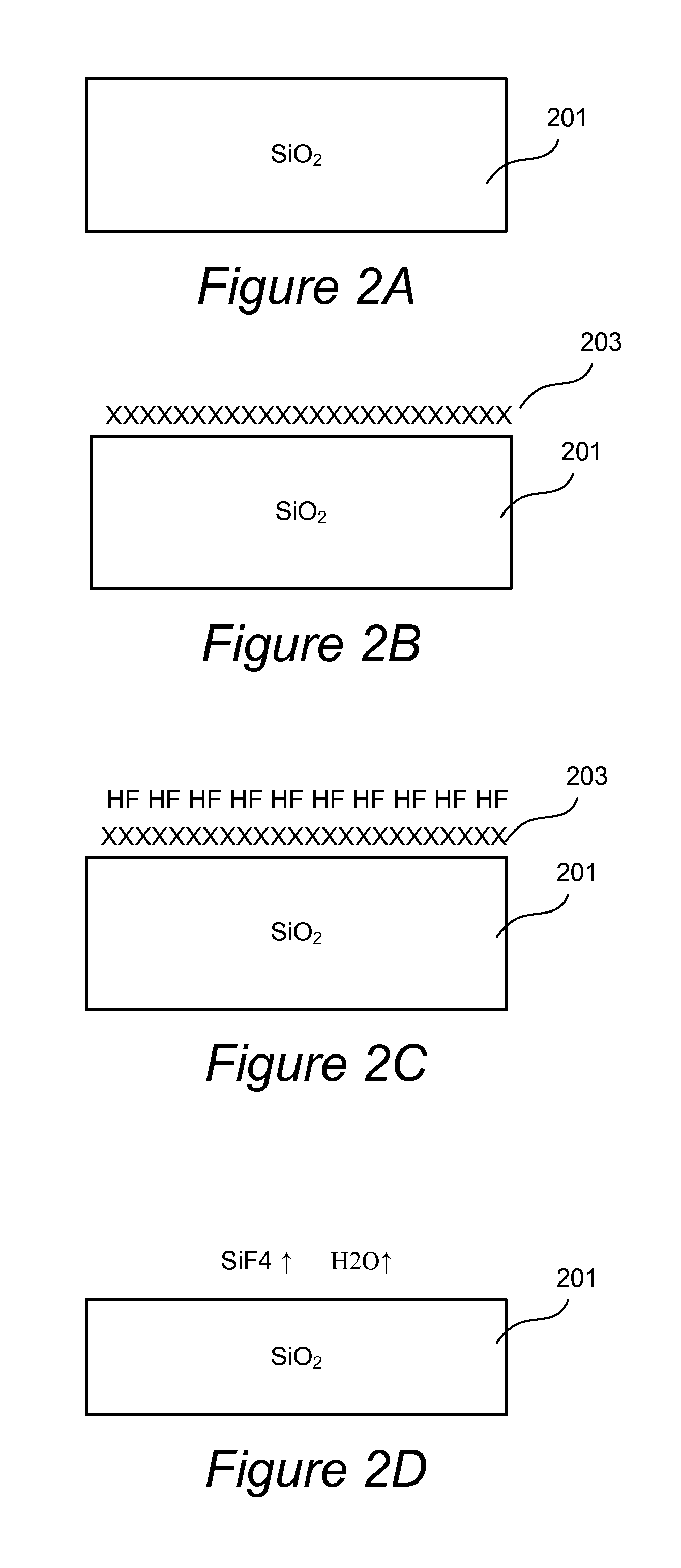

Isotropic atomic layer etch for silicon and germanium oxides

ActiveUS9431268B2Rapid and controlled changeElectric discharge tubesSemiconductor/solid-state device manufacturingAlcoholHydrogen

Methods for controlled isotropic etching of layers of silicon oxide and germanium oxide with atomic scale fidelity are provided. The methods make use of a reaction of anhydrous HF with an activated surface of an oxide, with an emphasis on removal of water generated in the reaction. In certain embodiments the oxide surface is first modified by adsorbing an OH-containing species (e.g., an alcohol) or by forming OH bonds using a hydrogen-containing plasma. The activated oxide is then etched by a separately introduced anhydrous HF, while the water generated in the reaction is removed from the surface of the substrate as the reaction proceeds, or at any time during or after the reaction. These methods may be used in interconnect pre-clean applications, gate dielectric processing, manufacturing of memory devices, or any other applications where accurate removal of one or multiple atomic layers of material is desired.

Owner:LAM RES CORP

Self-aligned non-volatile random access memory cell and process to make the same

A self aligned method of forming a semiconductor memory array of floating gate memory cells in a semiconductor substrate has a plurality of spaced apart isolation regions on the substrate substantially parallel to one another. An active region is between each pair of adjacent isolation regions. The active and isolation regions are formed in parallel and in the column direction. In the row direction, strips of spaced apart silicon nitride are formed. A source line plug is formed between adjacent pairs of silicon nitride and is in contact with a first region in the active regions, and the isolation regions. The strips of silicon nitride are removed and isotropically etched. In addition, the materials beneath the silicon nitride are also isotropically etched. Polysilicon spacers are then formed in the row direction parallel to the source line plug and adjacent to the floating gates to form connected control gates. A second region is formed between adjacent, spaced apart, control gates. A bit line is formed in the bit line direction contacting the second region in the space between the control gates.

Owner:SILICON STORAGE TECHNOLOGY +1

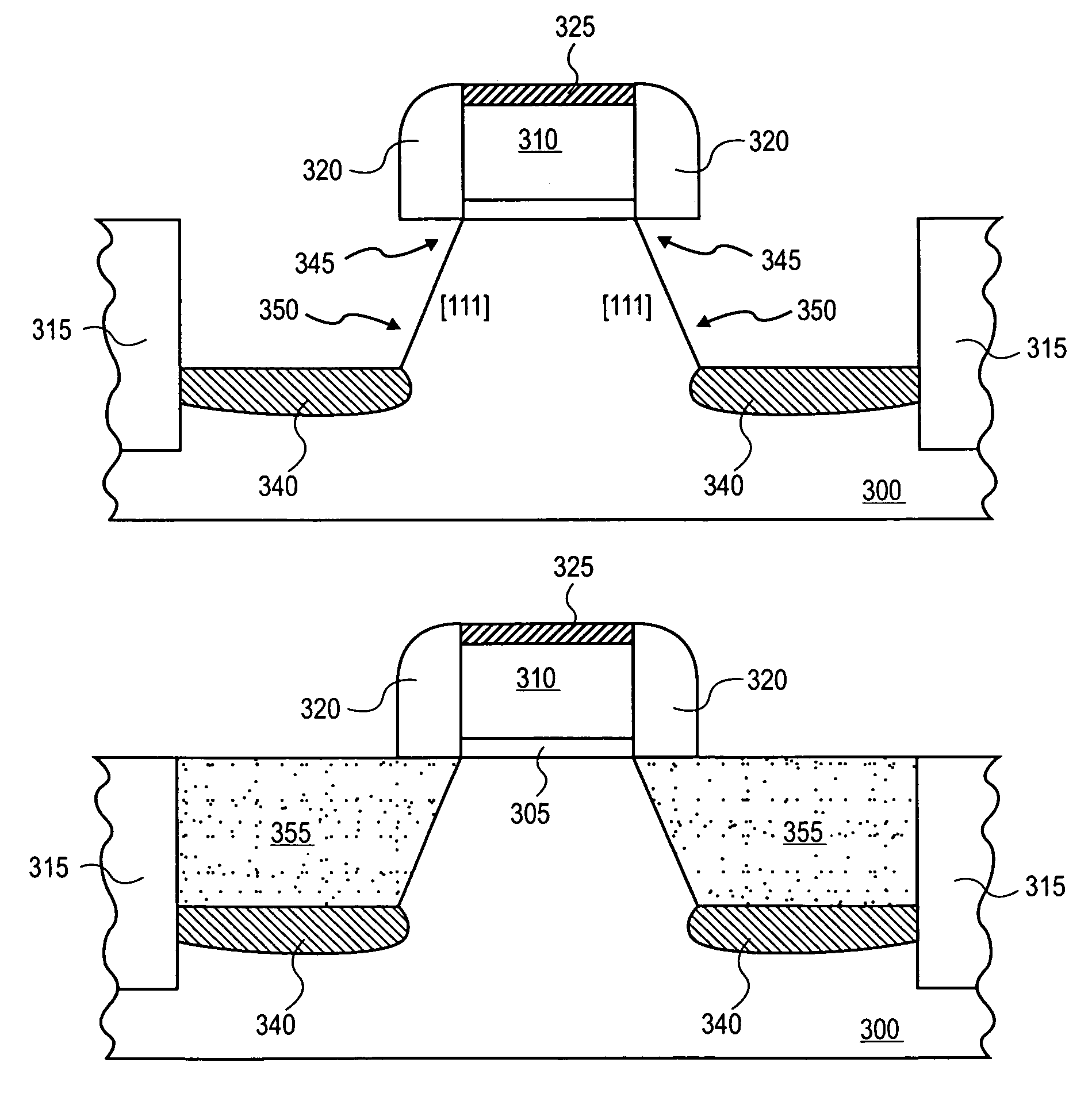

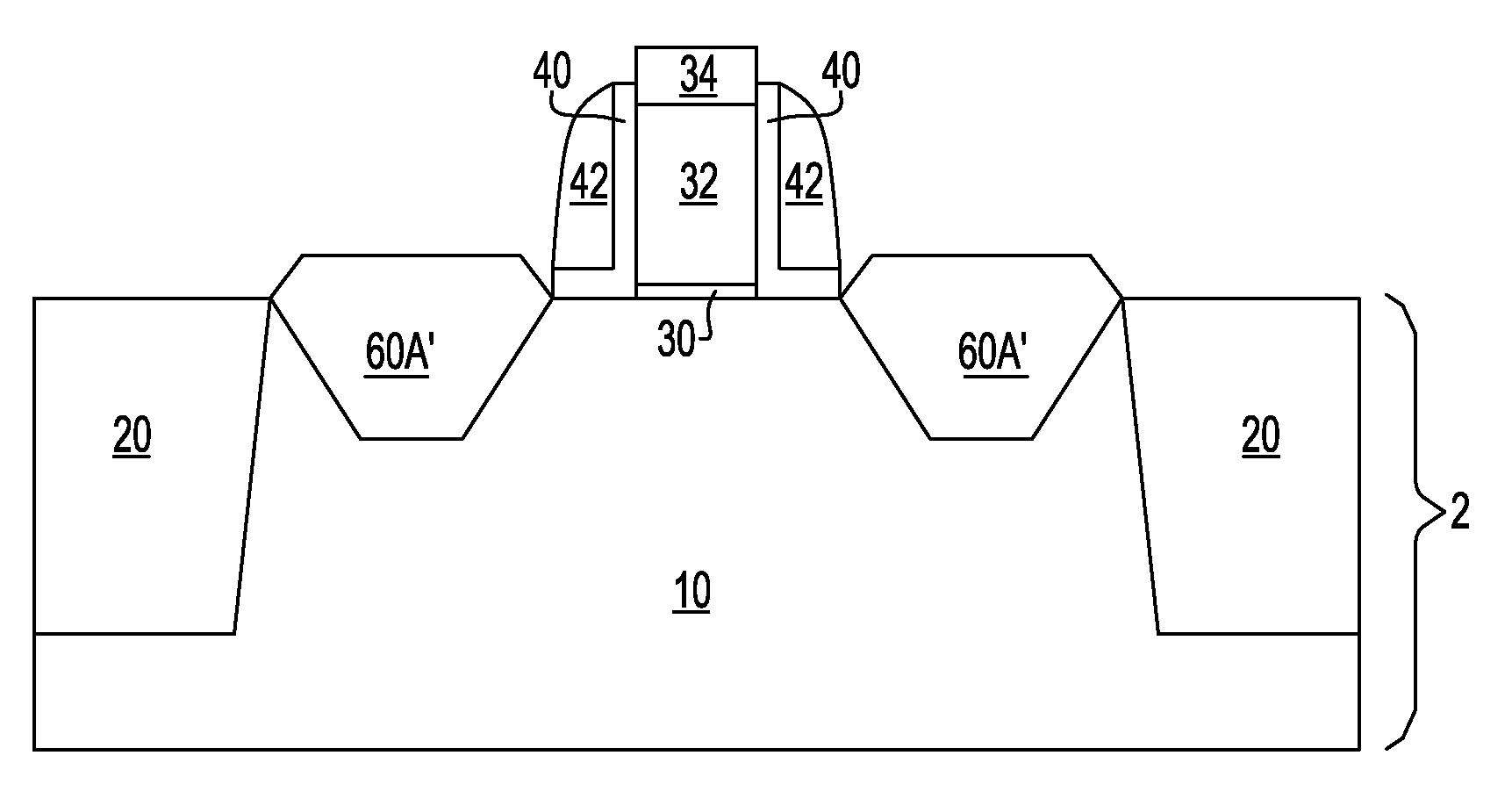

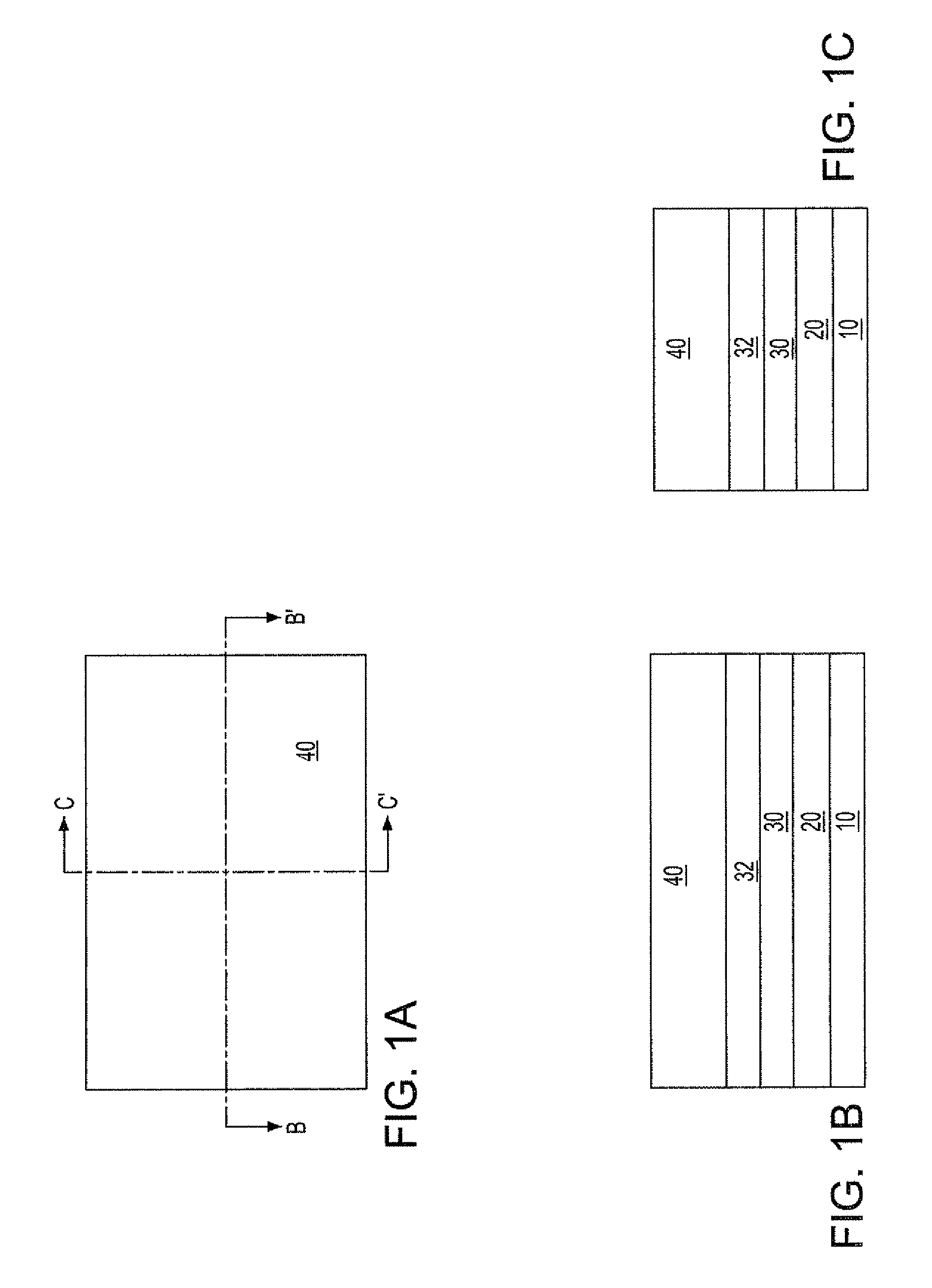

Crystallographic recess etch for embedded semiconductor region

InactiveUS20080237634A1Enhanced inhibitory effectRelieve pressureSemiconductor/solid-state device manufacturingSemiconductor devicesLattice mismatchSemiconductor

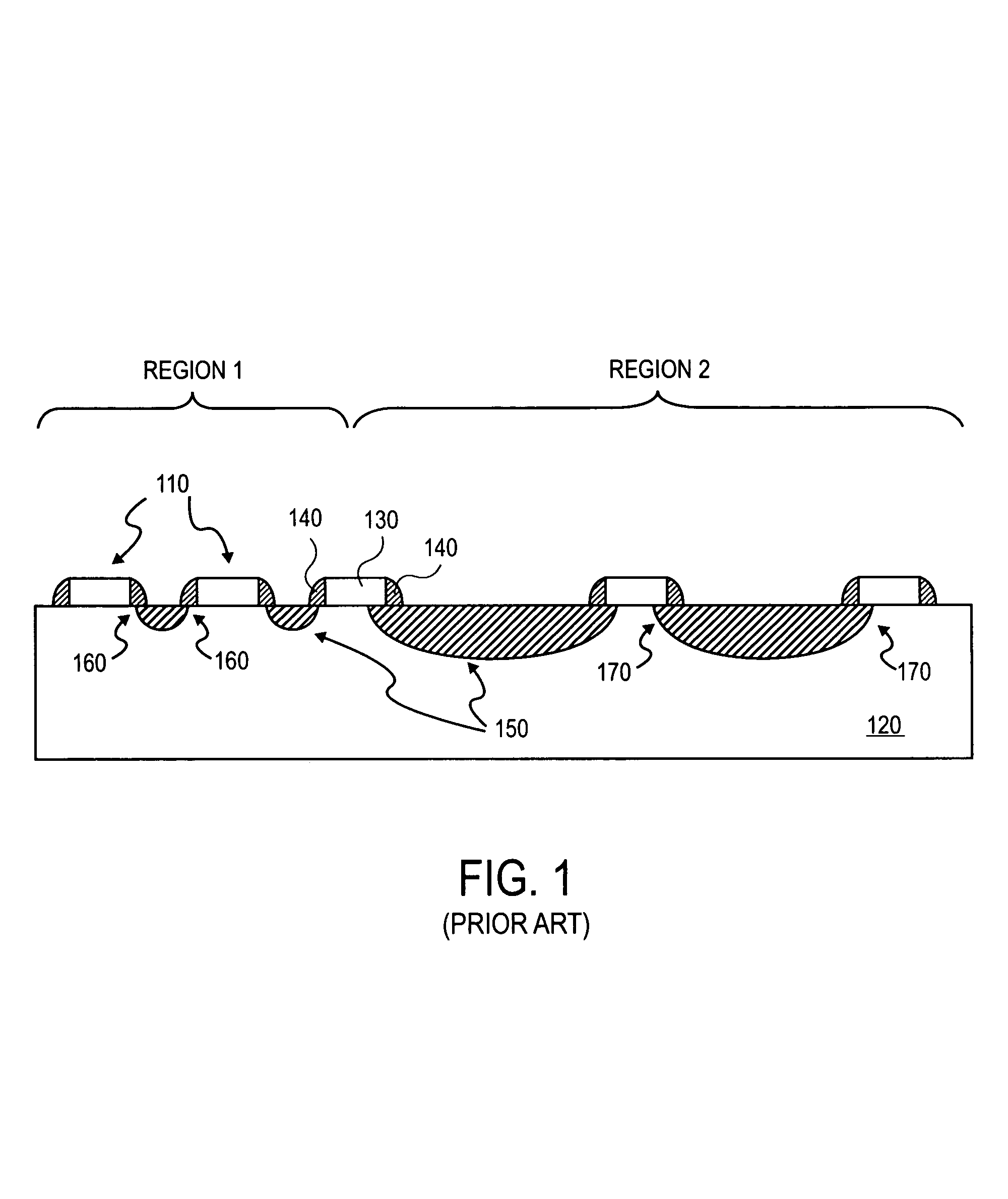

Source and drain regions of an FET are etched by a crystallographic anisotropic etch to form a cavity surrounded by crystallographic facets. The exposure of the sidewalls of shallow trench isolation (STI) is avoided or reduced compared to the prior art. The crystallographic anisotropic etch may be combined with an isotropic etch or a recess etch to create undercuts beneath gate spacers and / or a pegging line beneath a top surface of the STI. The at least one cavity is then filled with a lattice-mismatched embedded material so that stress is applied to the channel of the FET. The resulting structure has increased containment of the embedded semiconductor region by shallow trench isolation. A reduction in stress due to the unconstrained sidewall area and an increase in the junction current due to the recessing of the pegging line are eliminated or alleviated.

Owner:IBM CORP

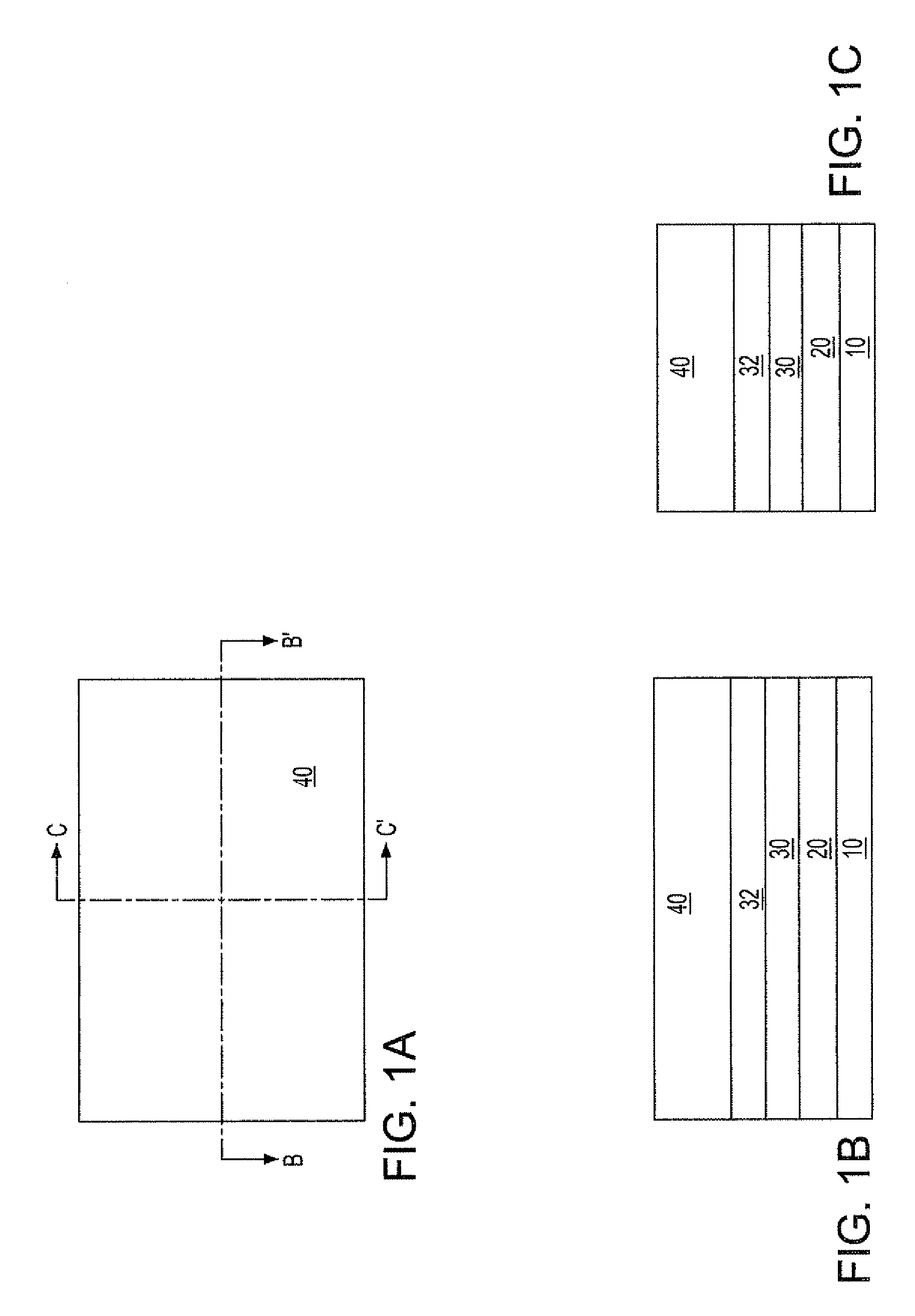

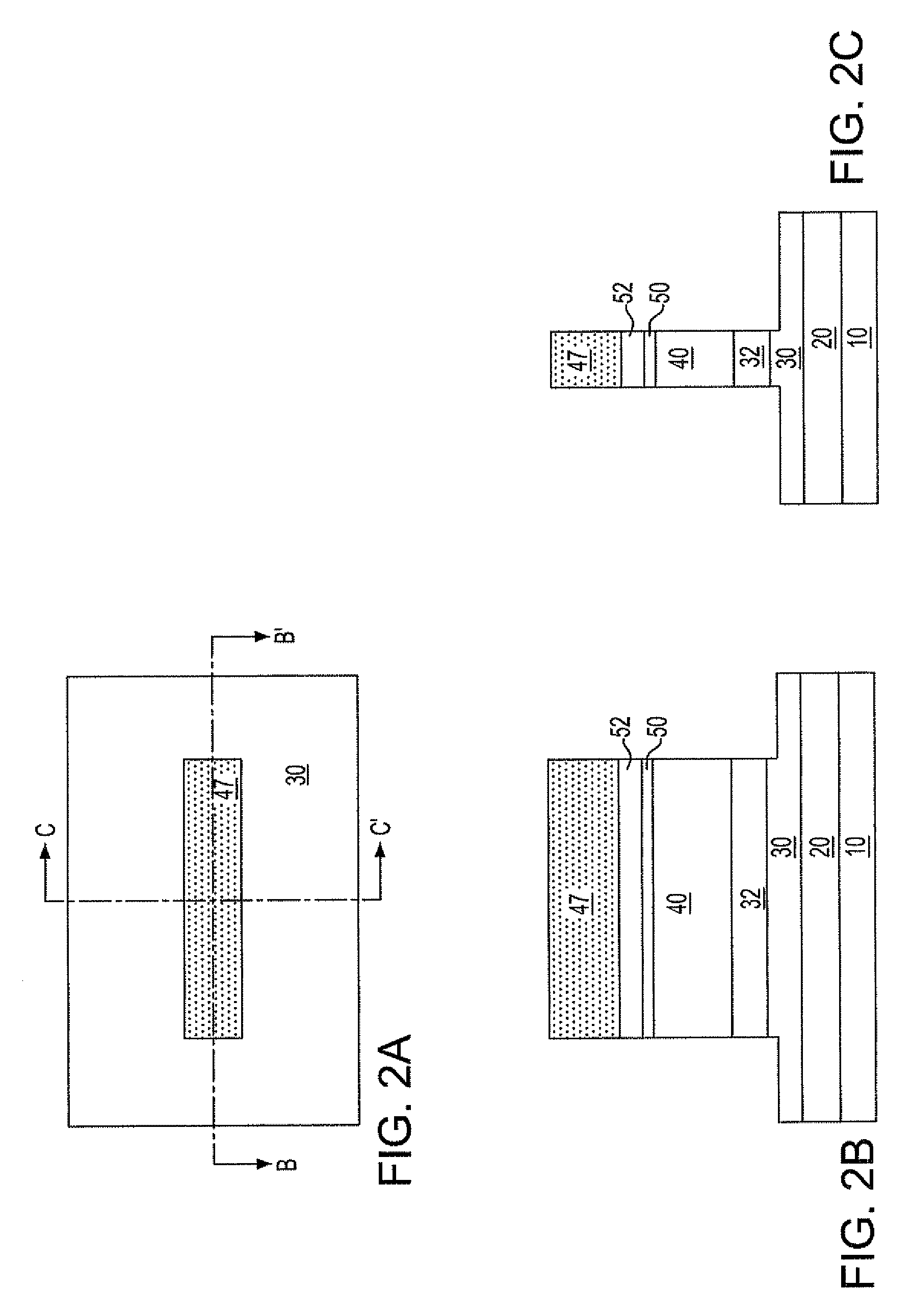

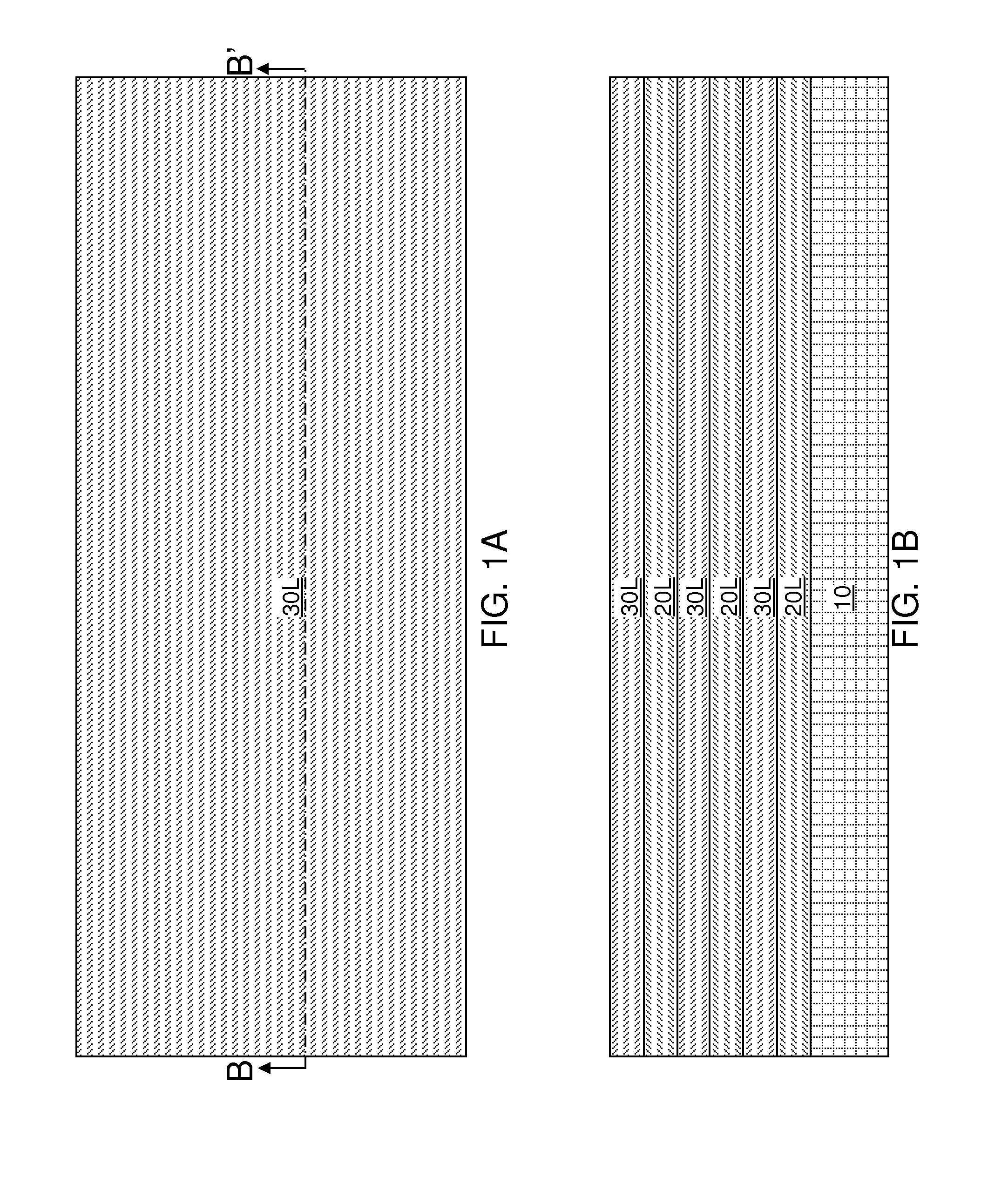

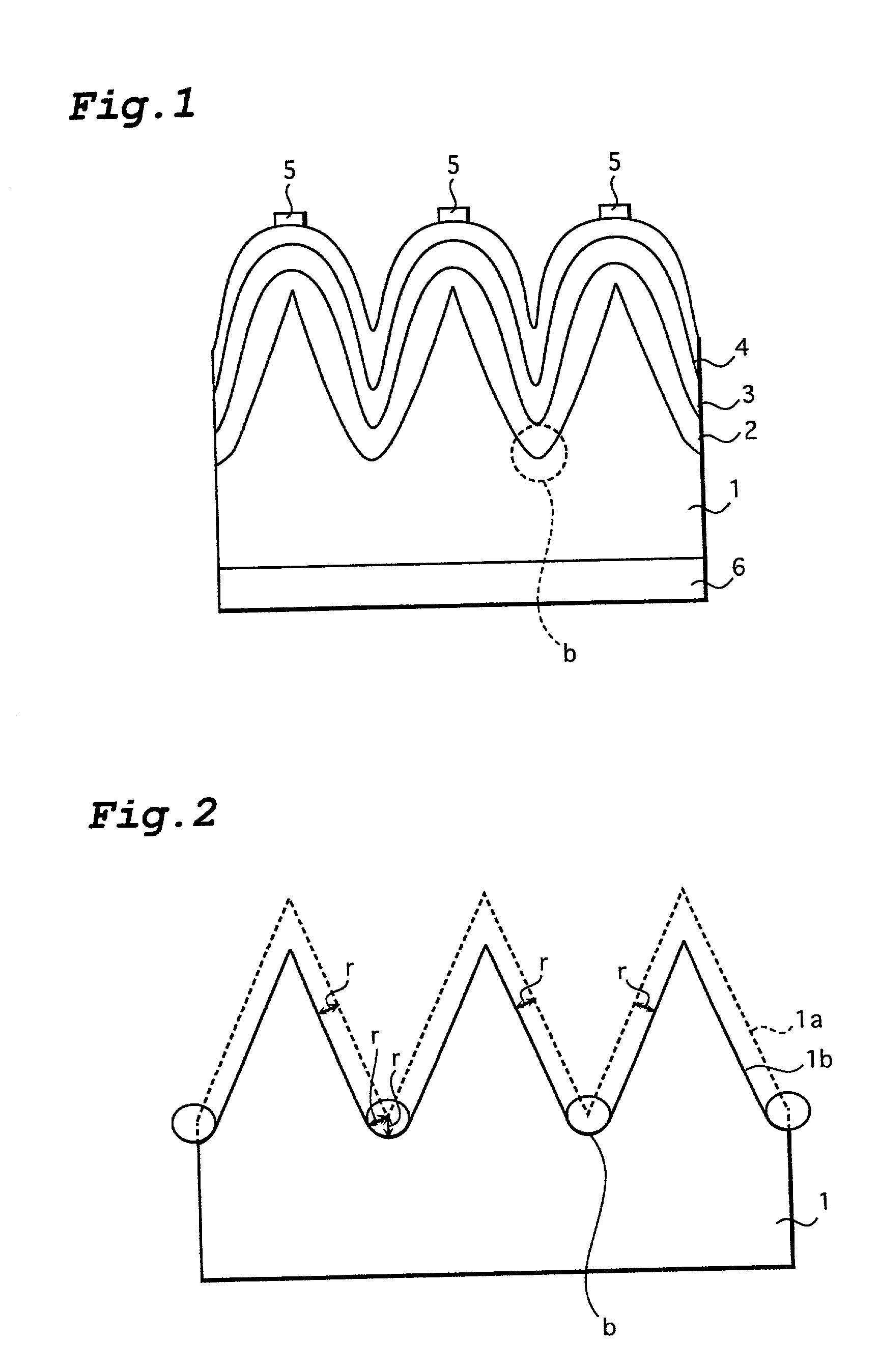

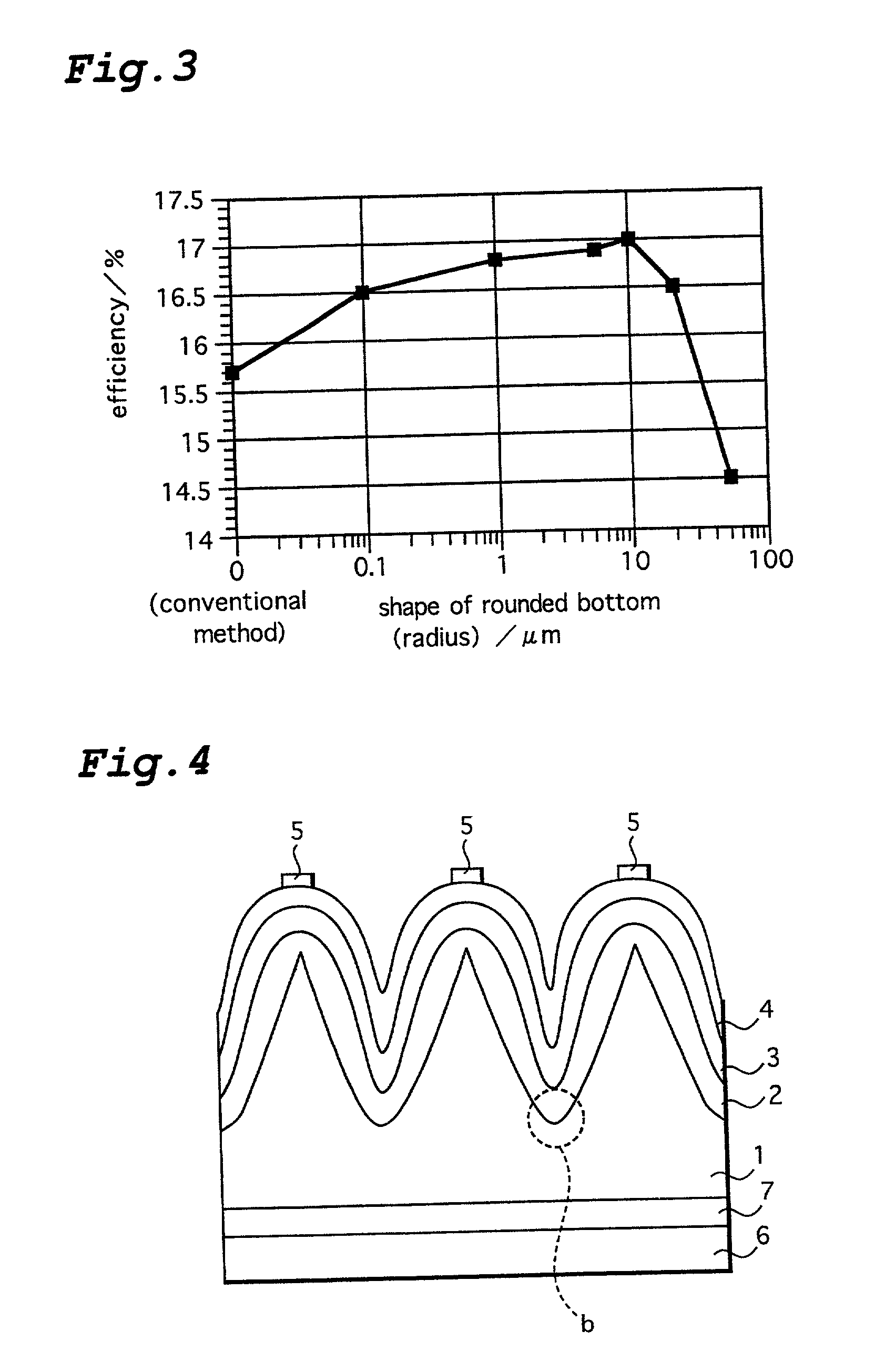

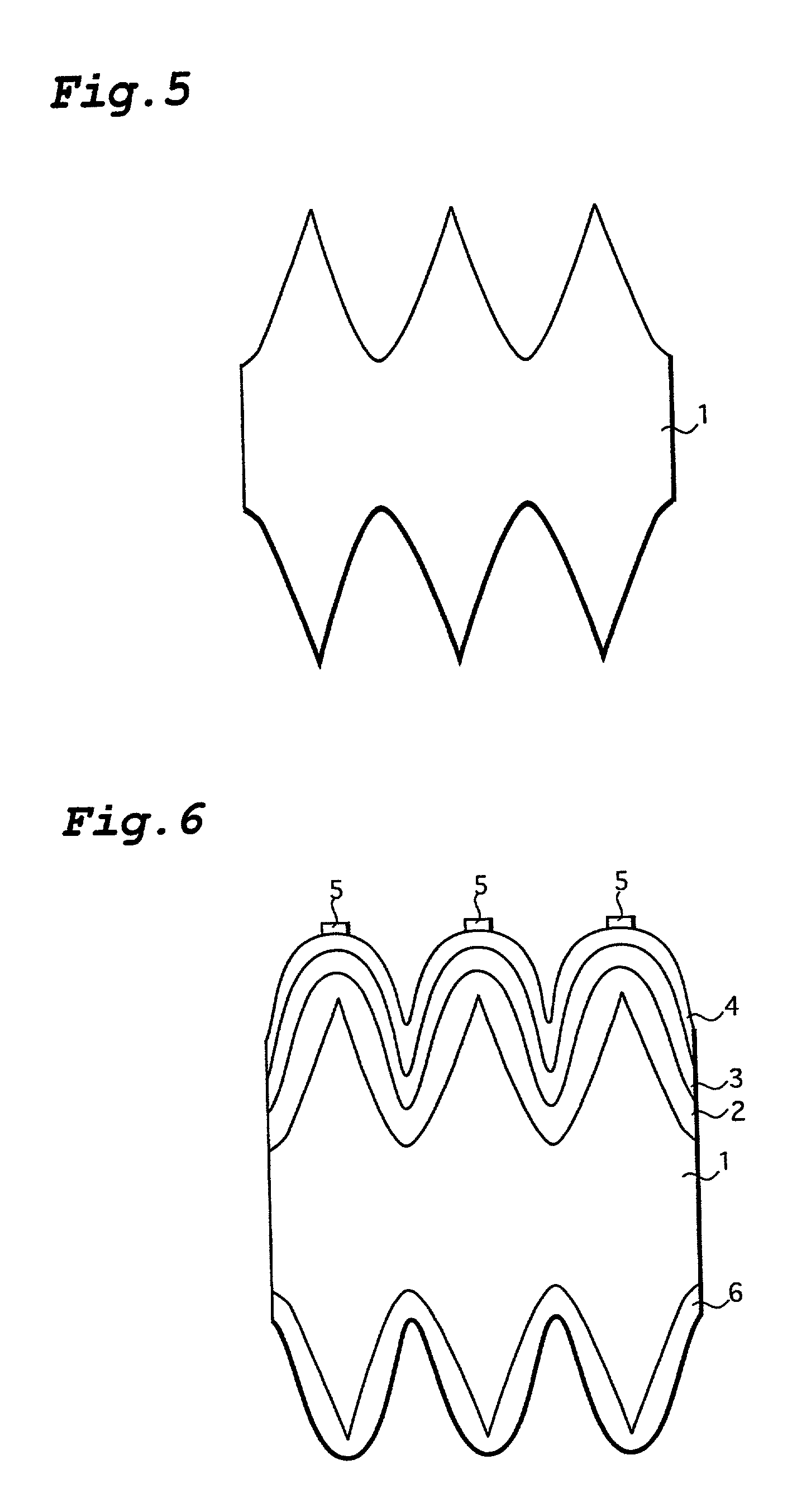

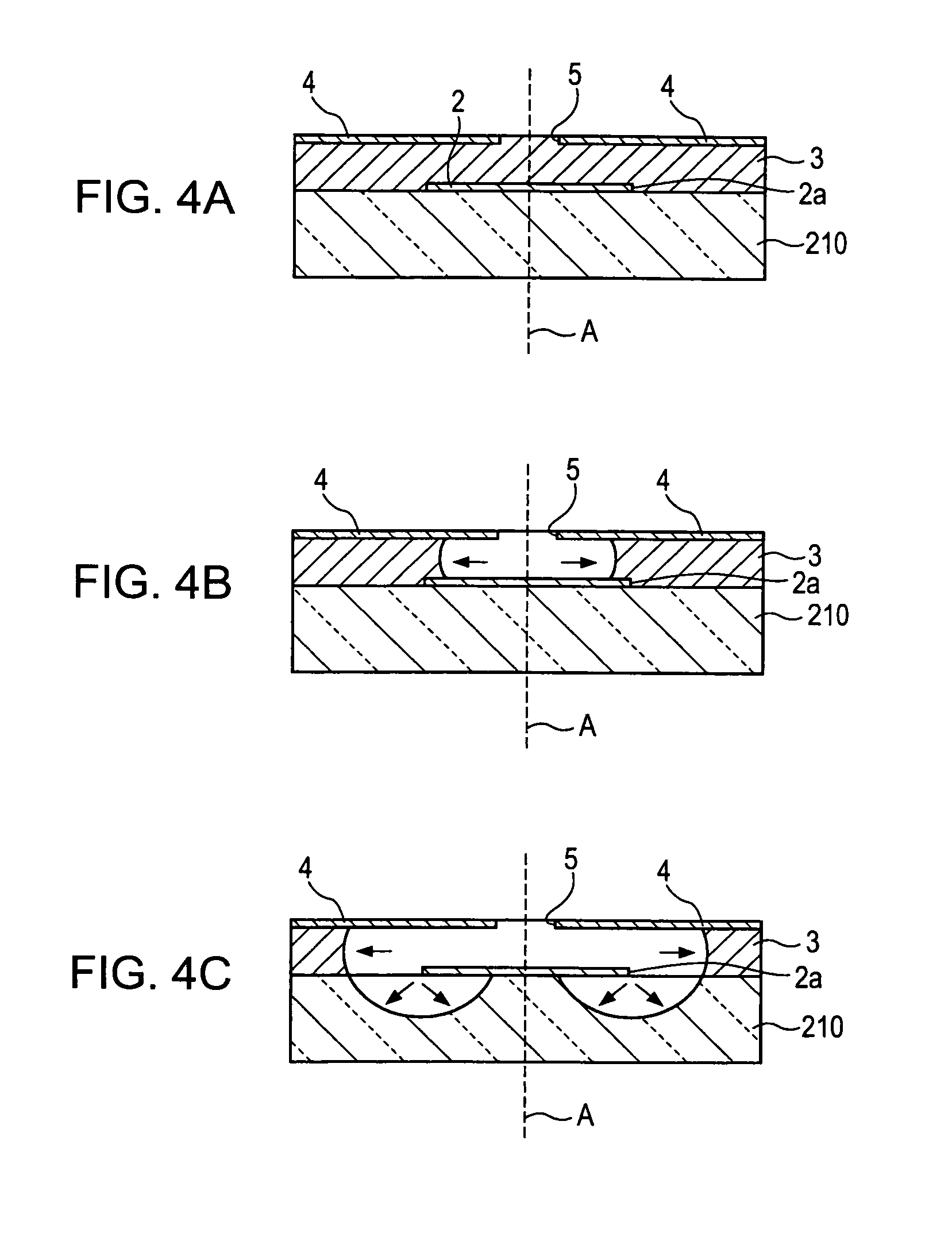

Photovoltaic element and method for manufacture thereof

InactiveUS6207890B1Lowered open circuit voltage circuitLowered circuit short circuitPV power plantsSolid-state devicesSolar lightAmorphous silicon

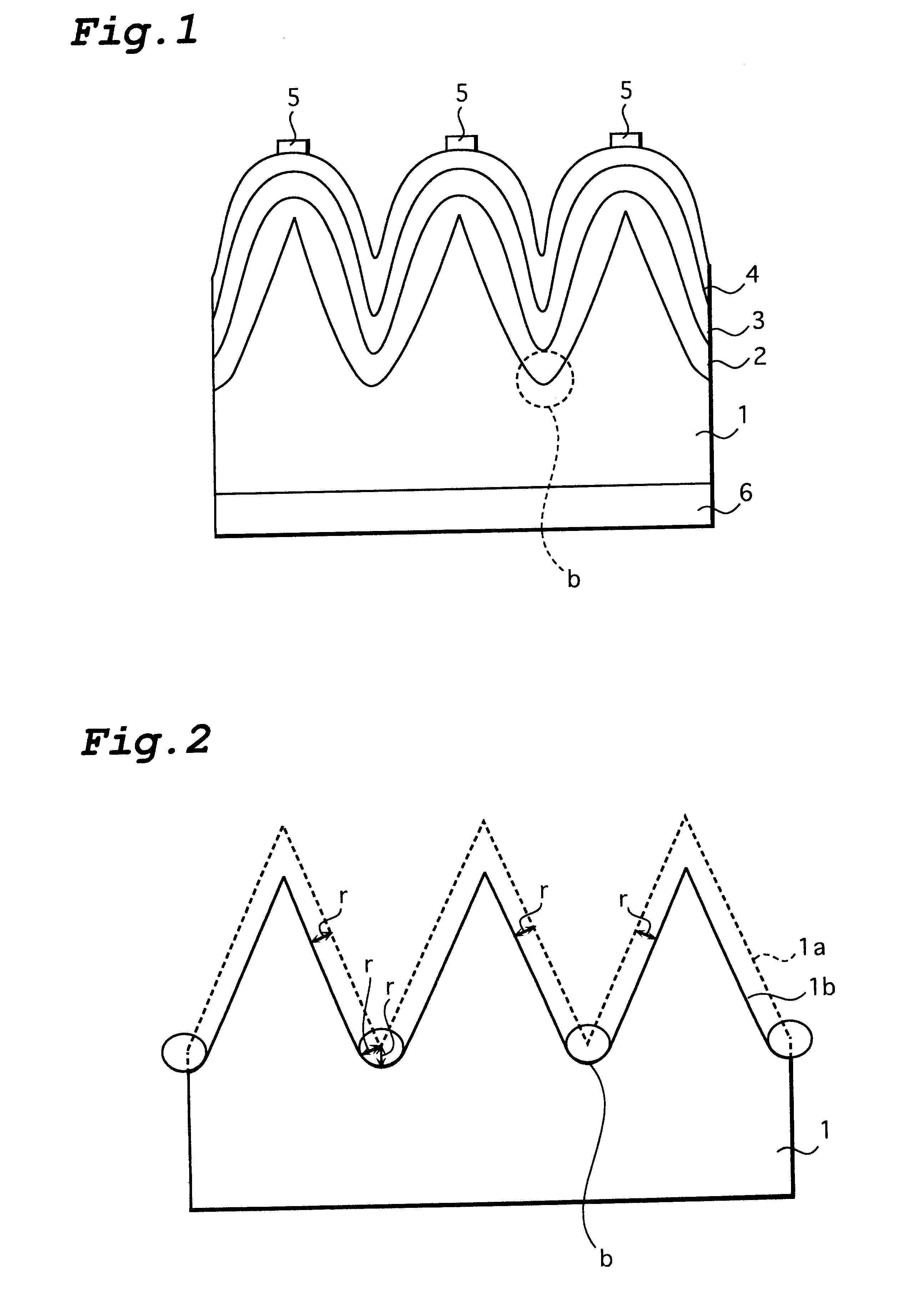

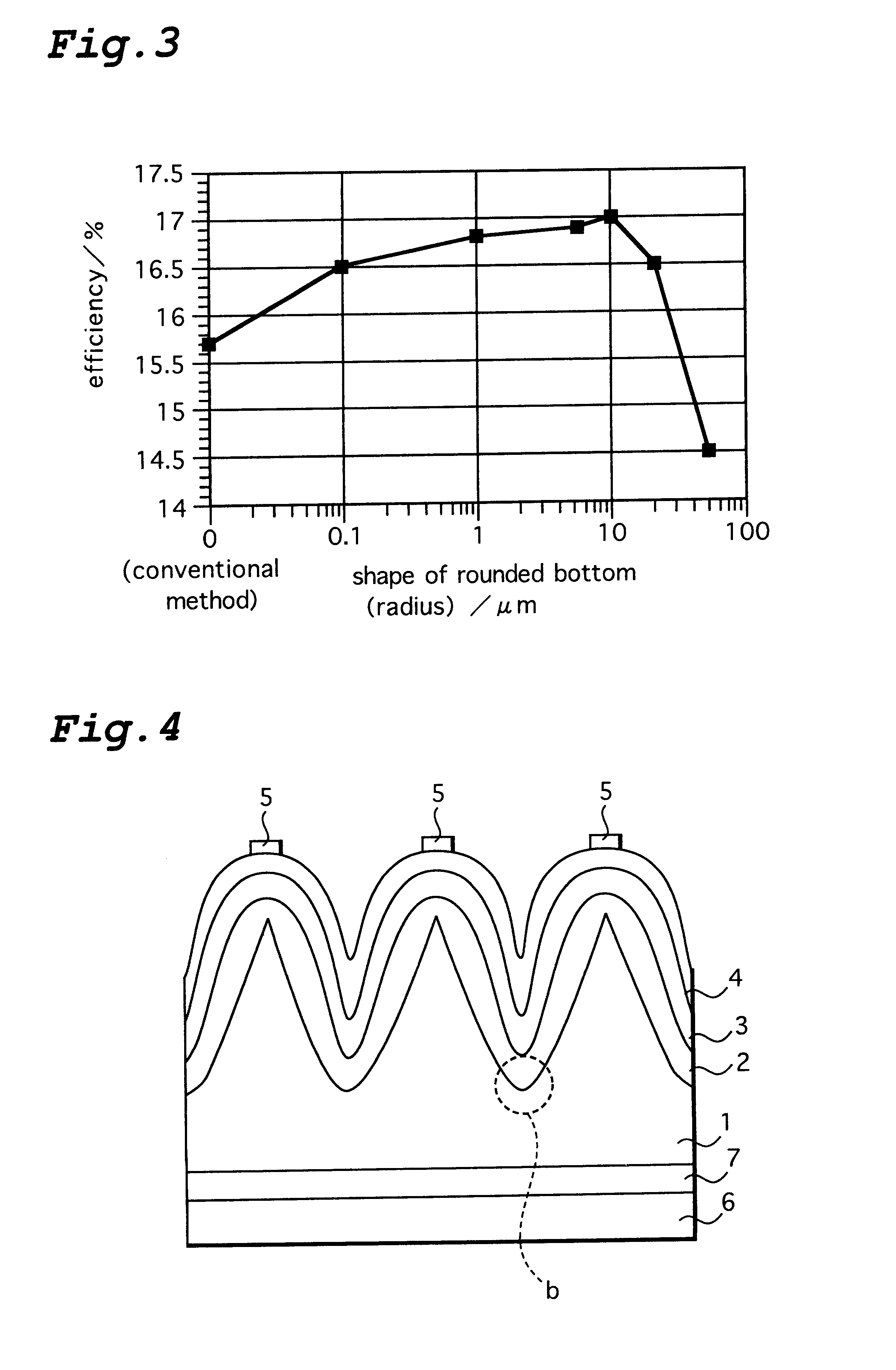

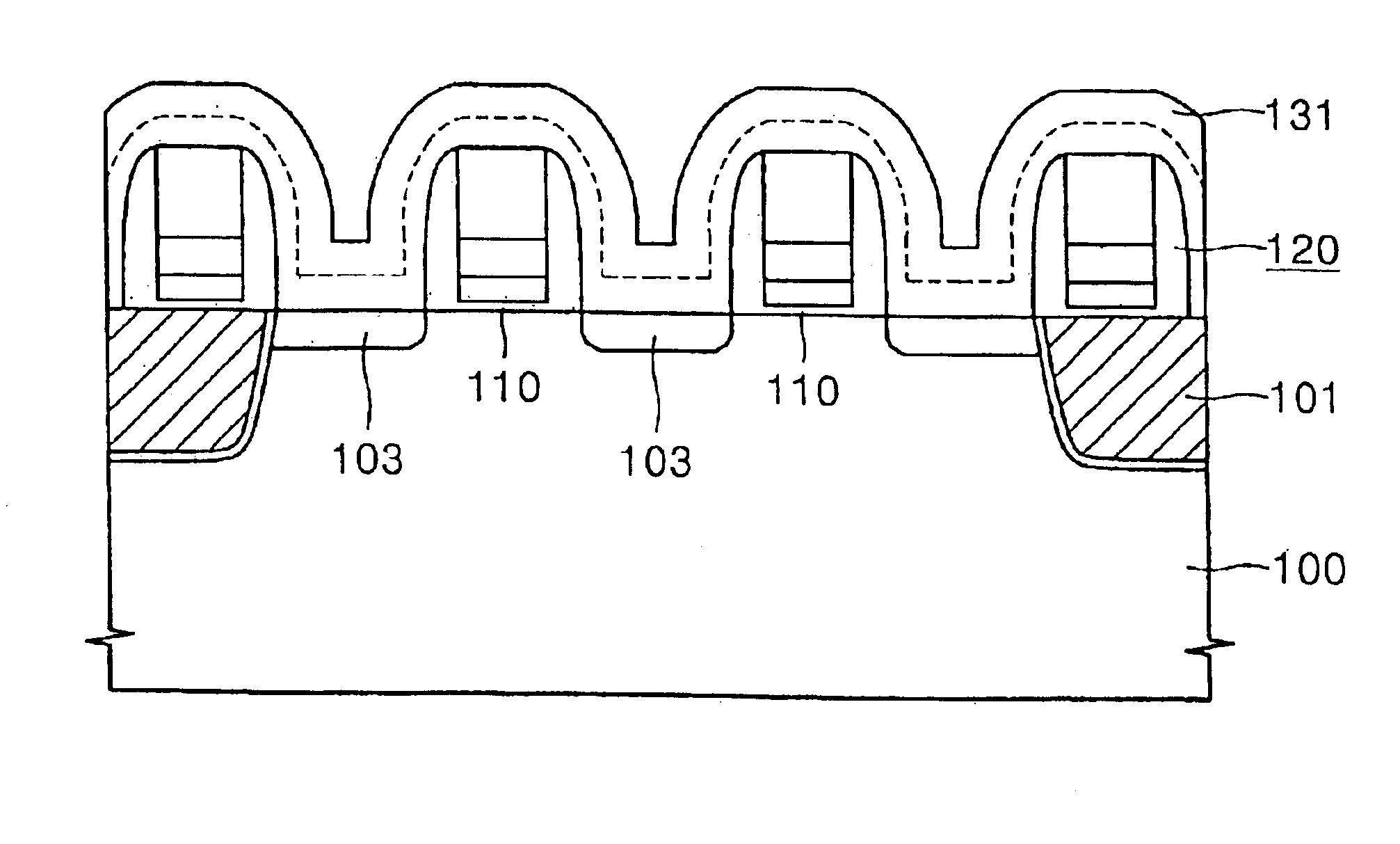

A photovoltaic element which directly converts an optical energy such as solar light into an electric energy. After many uneven sections are formed on the surface of an n-type crystalline silicon substrate (1), the surface of the substrate (1) is isotropically etched. Then the bottoms (b) of the recessed sections are rounded and a p-type amorphous silicon layer (3) is formed on the surface of the substrate (1) through an intrinsic amorphous silicon layer (2). The shape of the surface of the substrate (1) after isotropic etching is such that the bottoms of the recessed sections are slightly rounded and therefore the amorphous silicon layer can be deposited in a uniform thickness.

Owner:SANYO ELECTRIC CO LTD

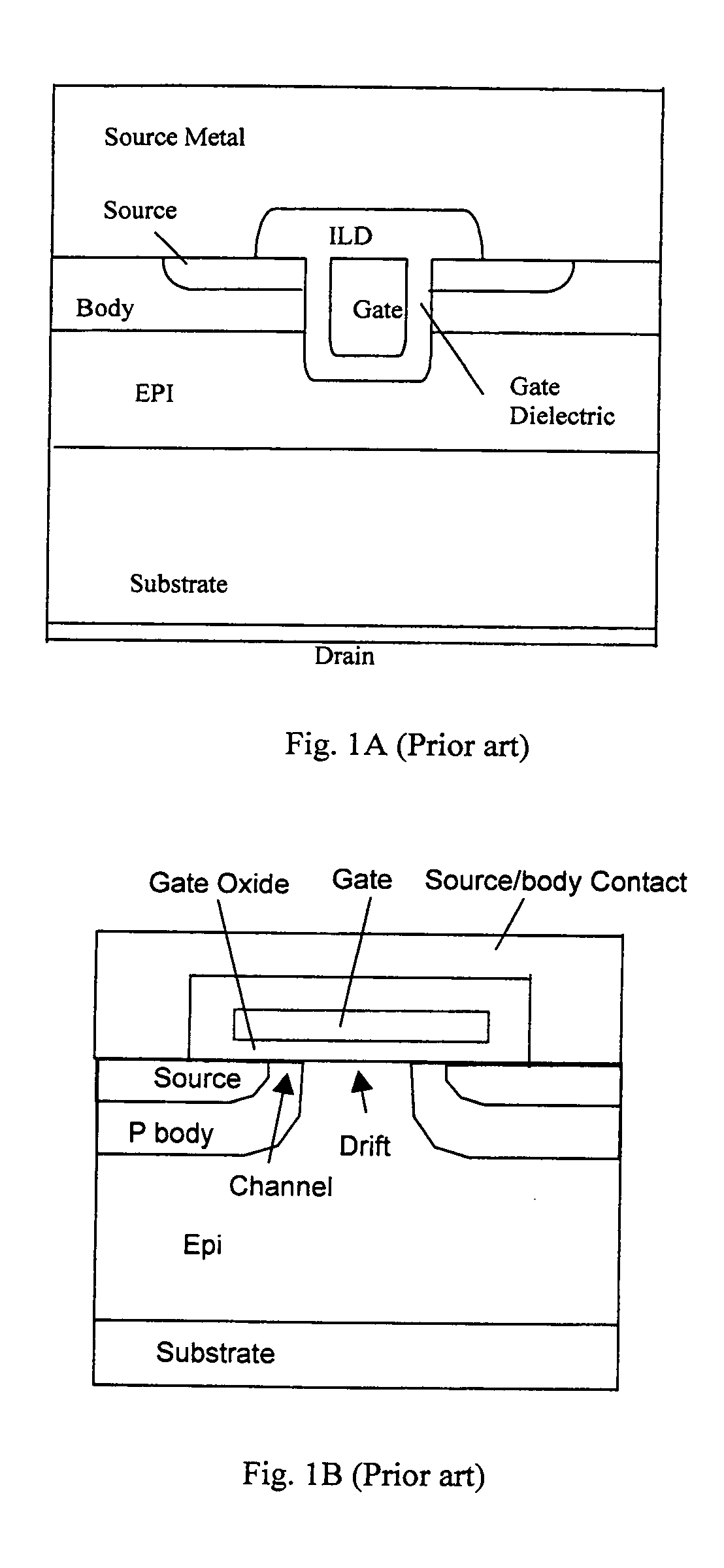

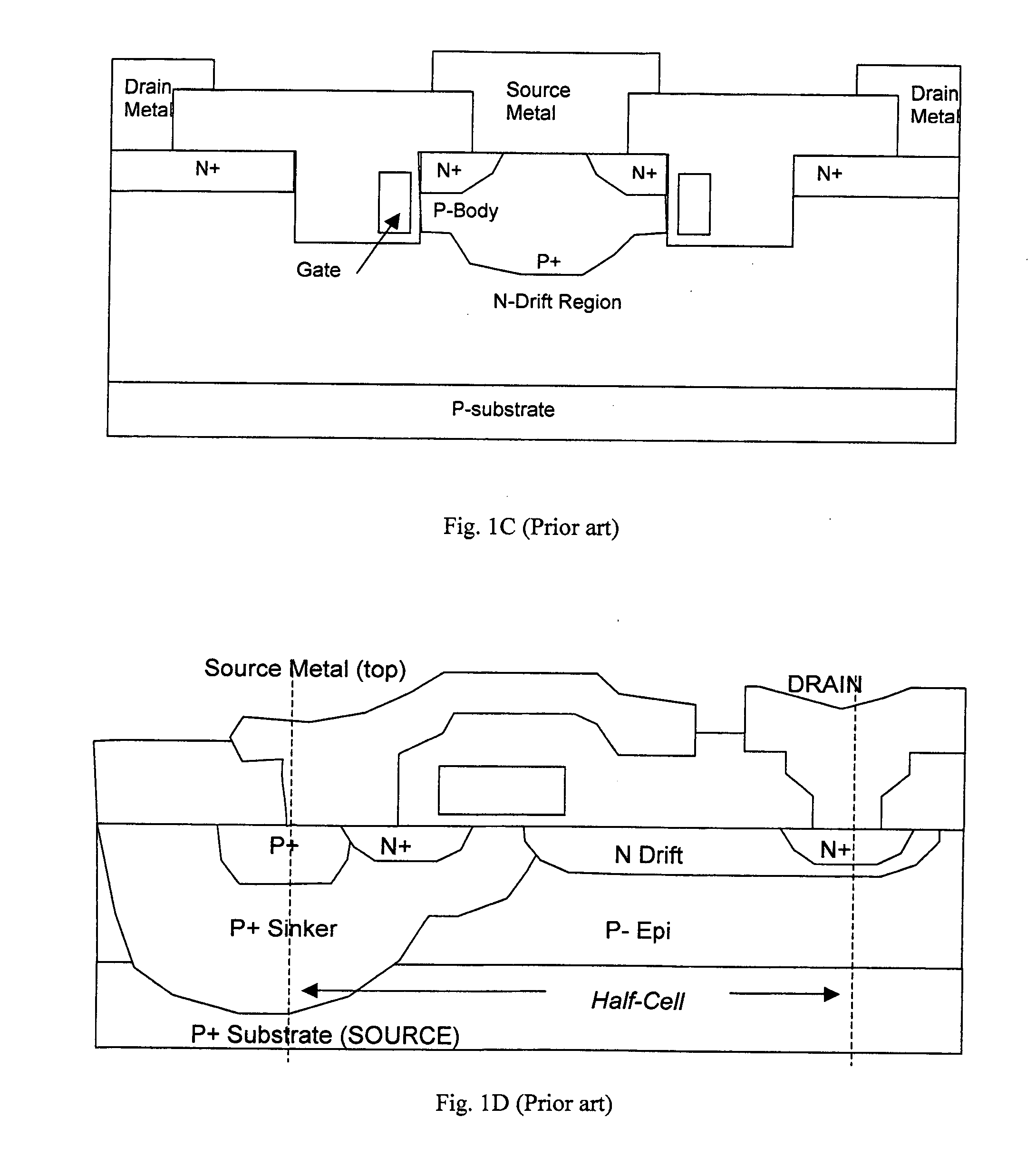

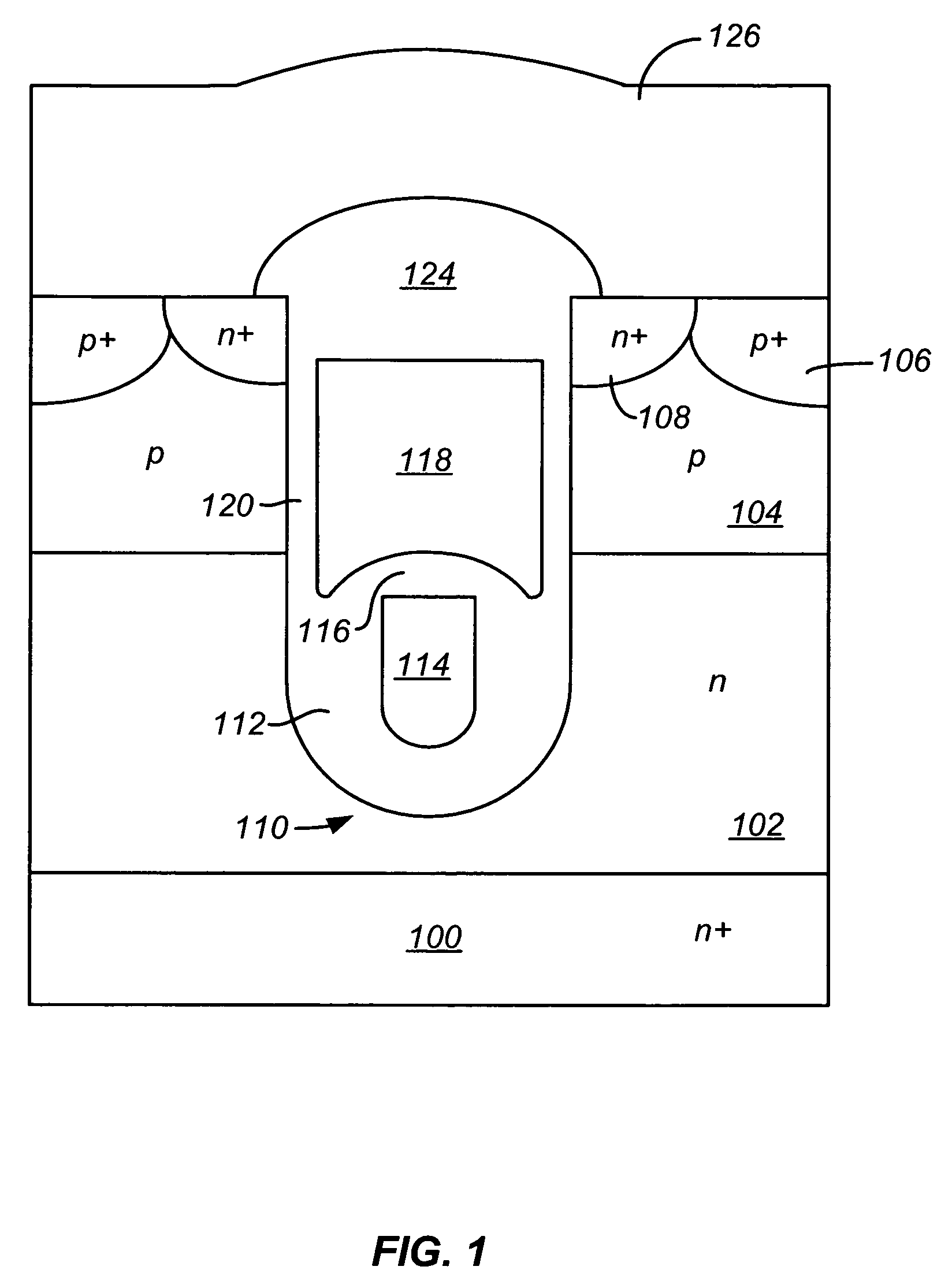

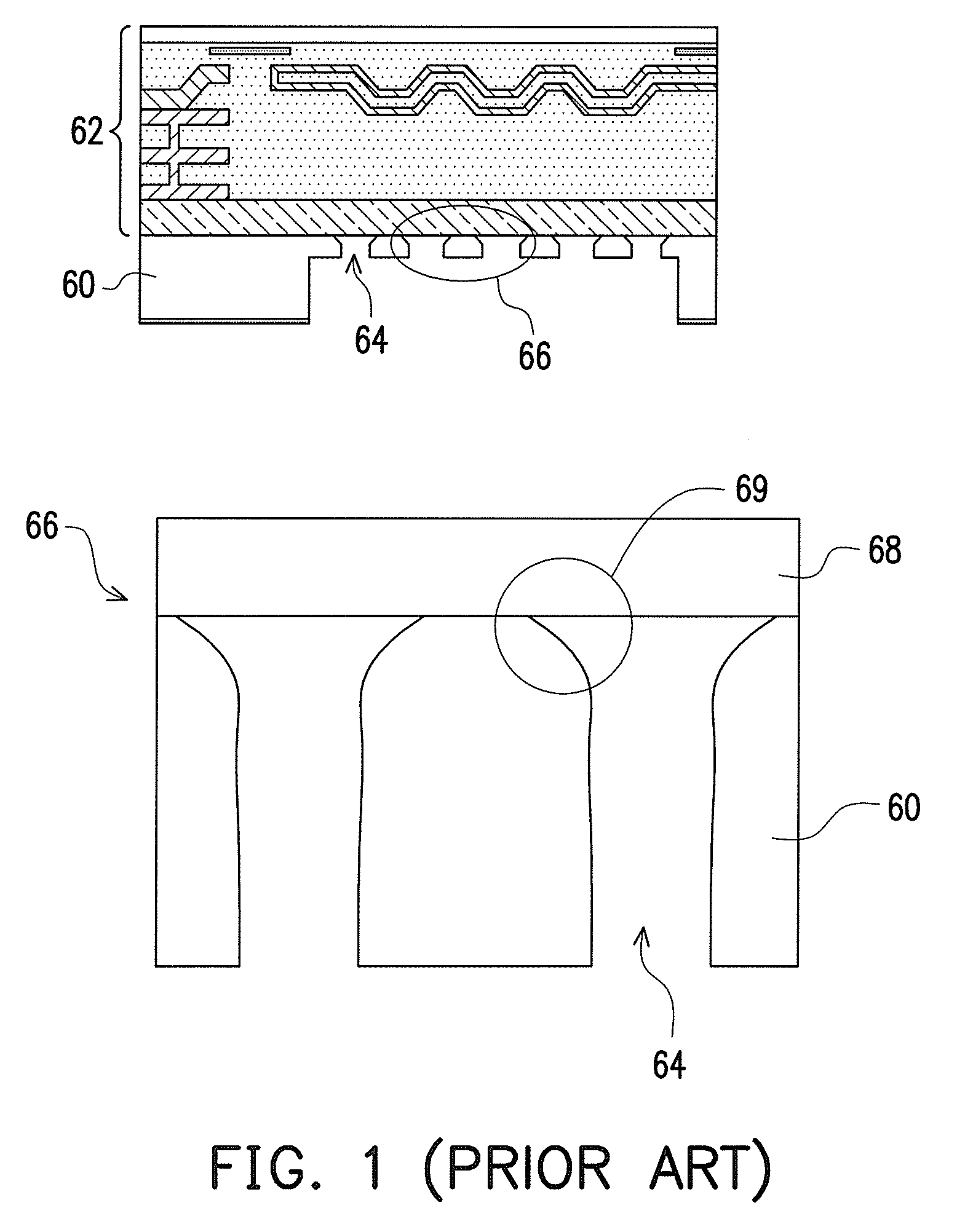

Inverted-trench grounded-source fet structure using conductive substrates, with highly doped substrates

ActiveUS20080035987A1Reduced cell pitchReduce manufacturing costTransistorSemiconductor/solid-state device manufacturingMOSFETCapacitance

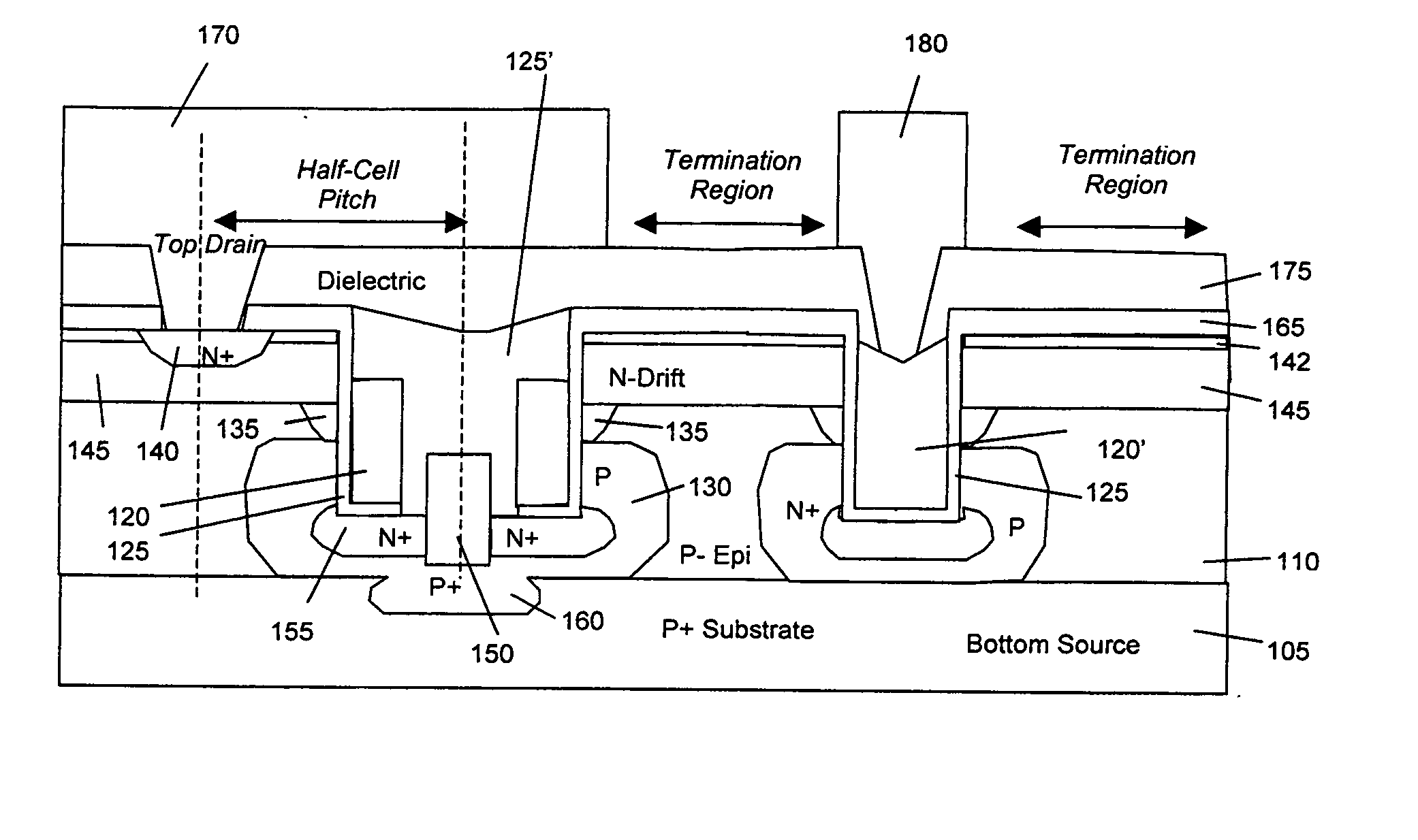

This invention discloses an improved trenched metal oxide semiconductor field effect transistor (MOSFET) device that includes a trenched gate surrounded by a source region encompassed in a body region above a drain region disposed on a bottom surface of a substrate. The MOSFET cell further includes a shielded gate trench (SGT) structure below and insulated from the trenched gate. The SGT structure is formed substantially as a round hole having a lateral expansion extended beyond the trench gate and covered by a dielectric linen layer filled with a trenched gate material. The round hole is formed by an isotropic etch at the bottom of the trenched gate and is insulated from the trenched gate by an oxide insulation layer. The round hole has a lateral expansion beyond the trench walls and the lateral expansion serves as a vertical alignment landmark for controlling the depth of the trenched gate. The MOSFET device has a reduced gate to drain capacitance Cgd depending on the controllable depth of the trenched gate disposed above the SGT structure formed as a round hole below the trenched gate.

Owner:ALPHA & OMEGA SEMICON LTD

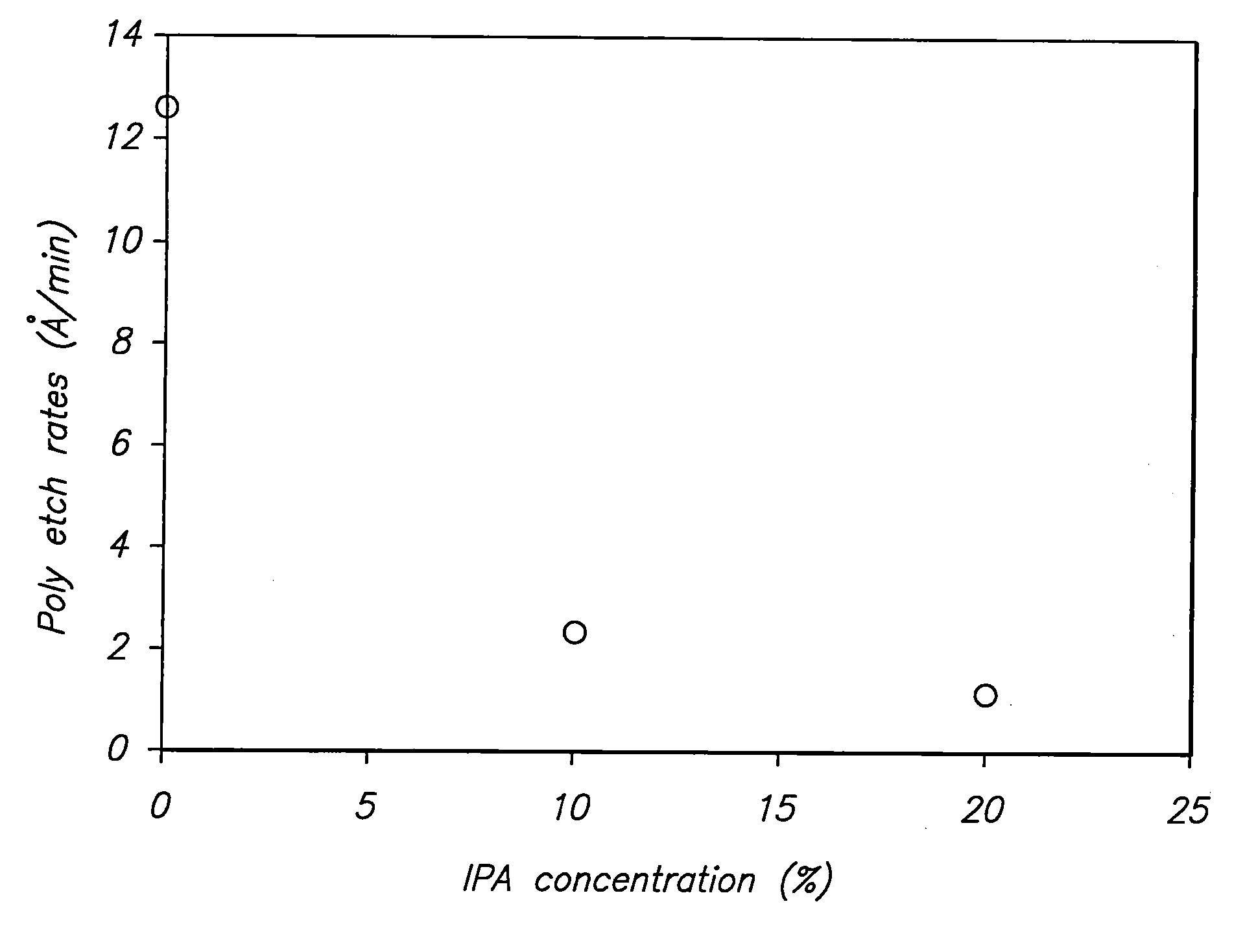

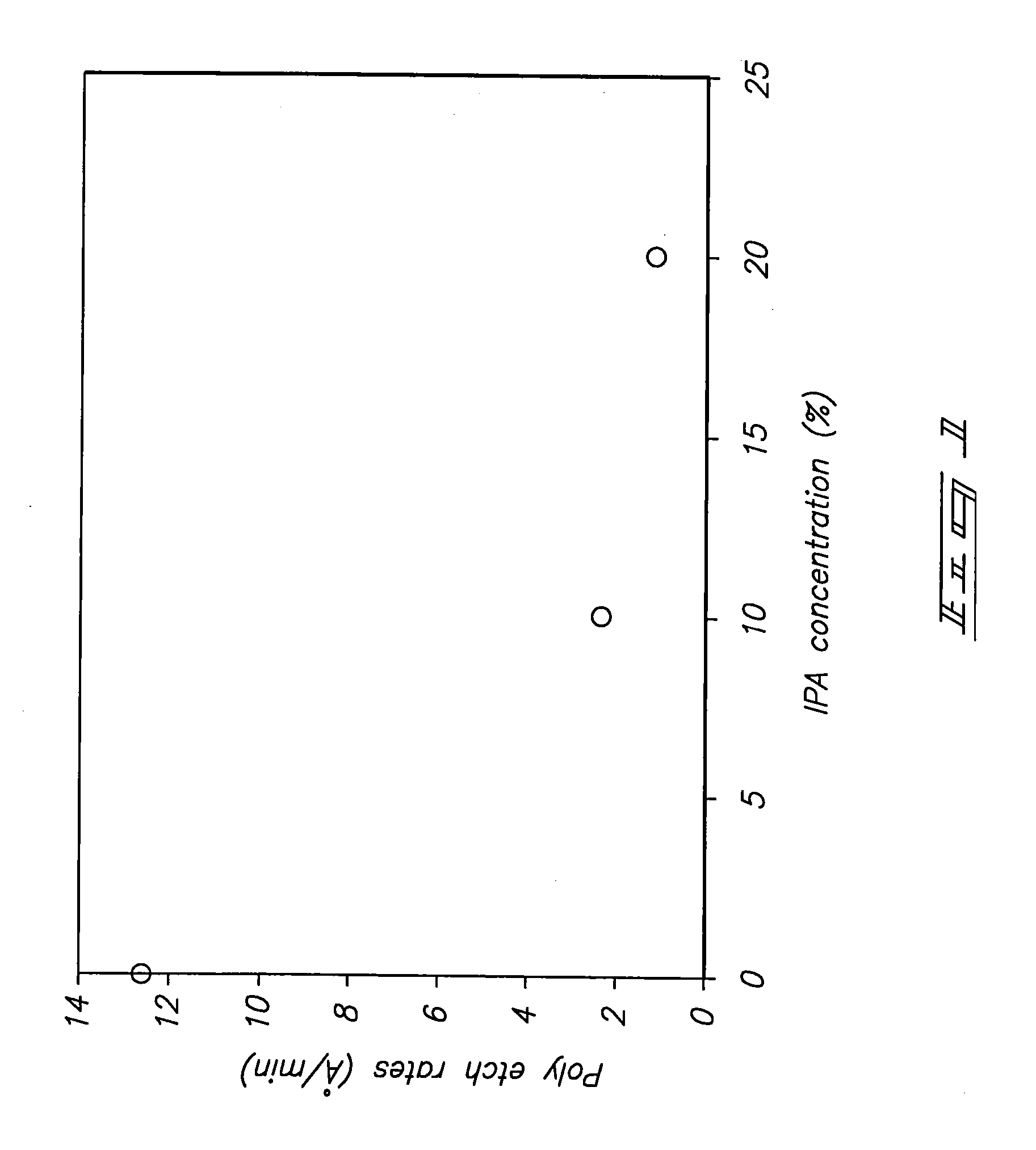

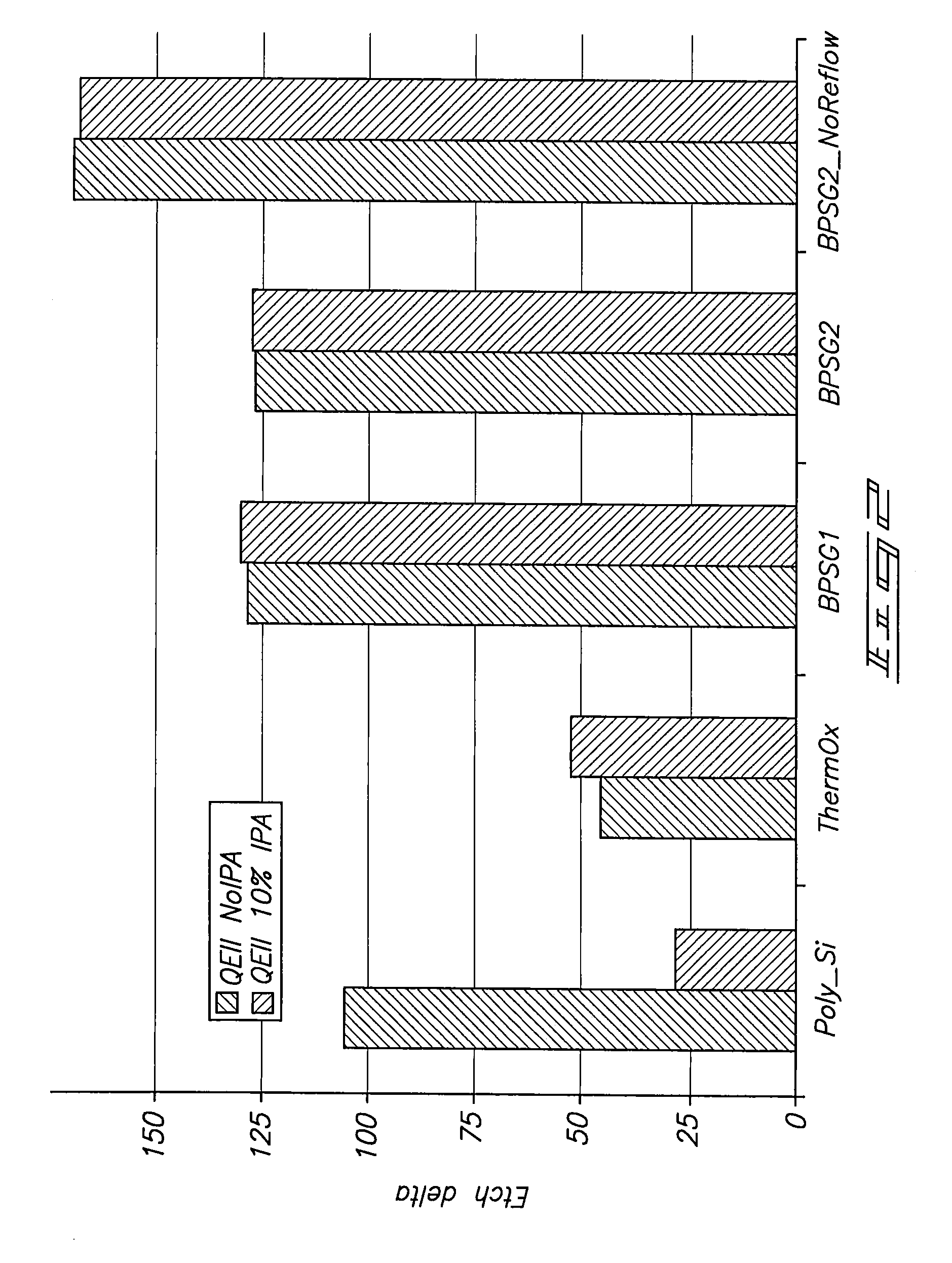

Etch Compositions and Methods of Processing a Substrate

InactiveUS20070145009A1Decorative surface effectsSemiconductor/solid-state device manufacturingChemistryIsotropic etching

The invention includes an etchant composition containing isopropyl alcohol and one or more of HF, NH4F and tetramethyl ammonium fluoride (TMAF). The invention encompasses a method of processing a substrate. A substrate is provided which has a first material containing at least one of polysilicon, monocrystalline silicon and amorphous silicon, and a second material. The substrate is exposed to an etch composition which comprises isopropyl alcohol and at least one of HF, NH4F and TMAF. The invention includes a method of processing a semiconductor construction including providing a construction which has a capacitor electrode material and an oxide material along at least a portion of the capacitor electrode material. At least some of the oxide material is removed by isotropic etching utilizing an etchant composition comprising isopropyl alcohol.

Owner:MICRON TECH INC

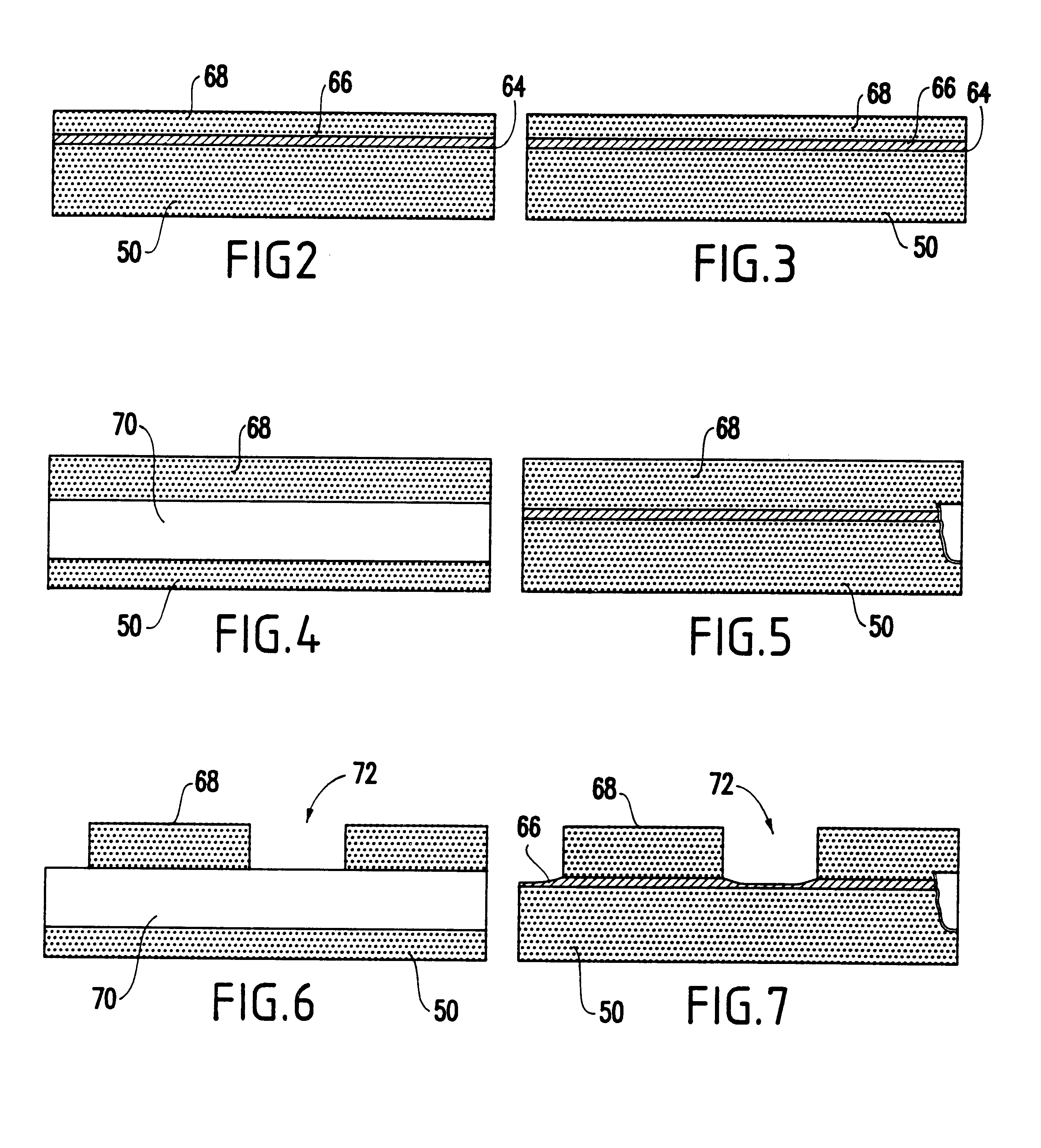

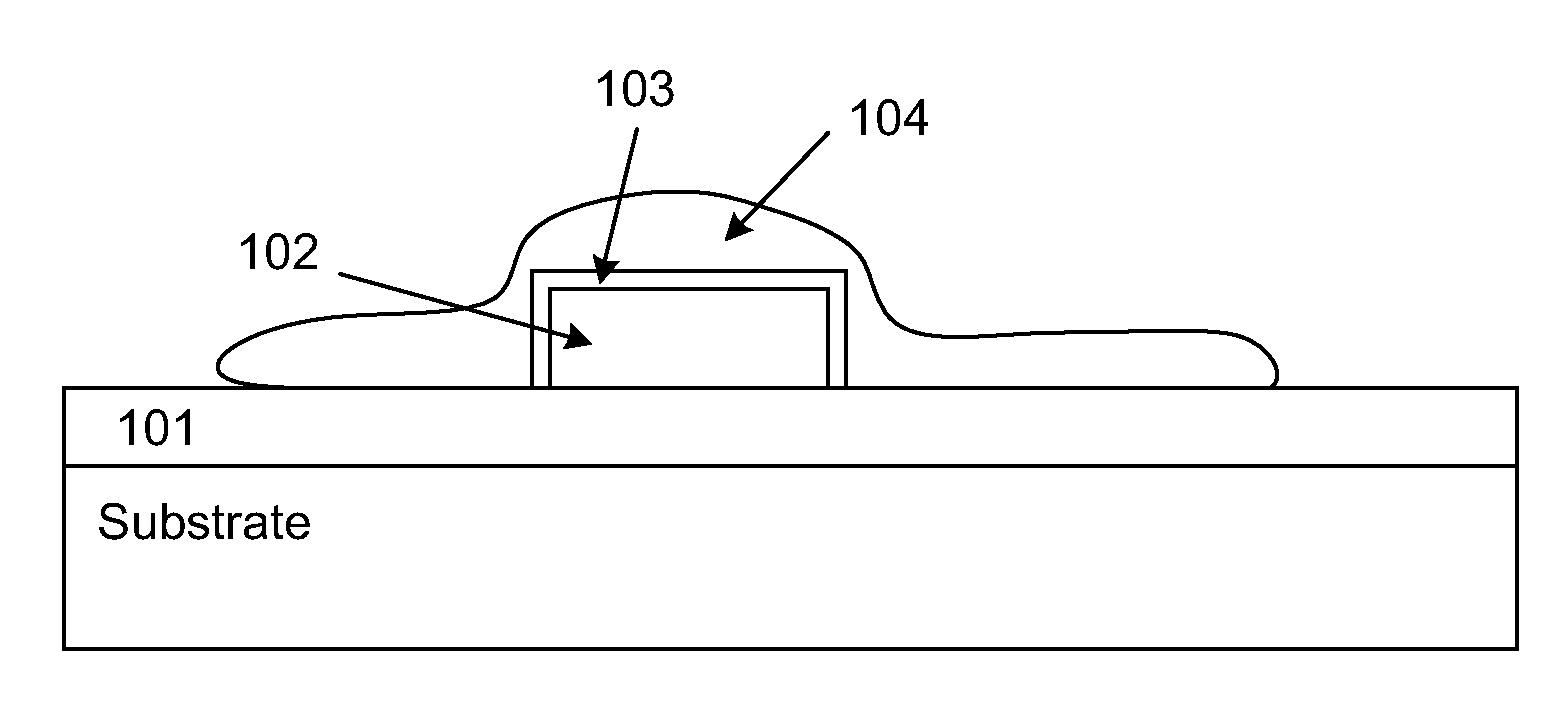

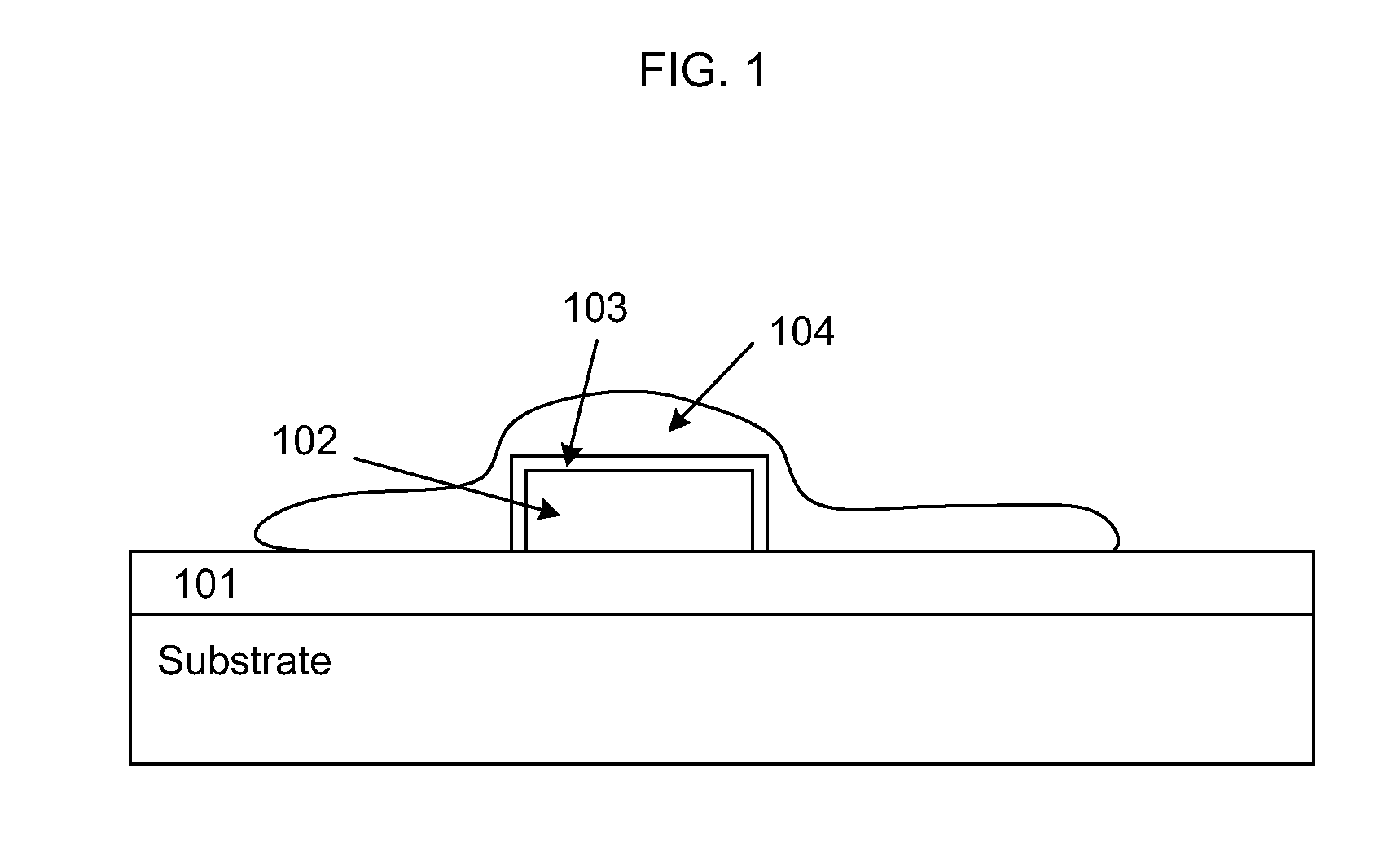

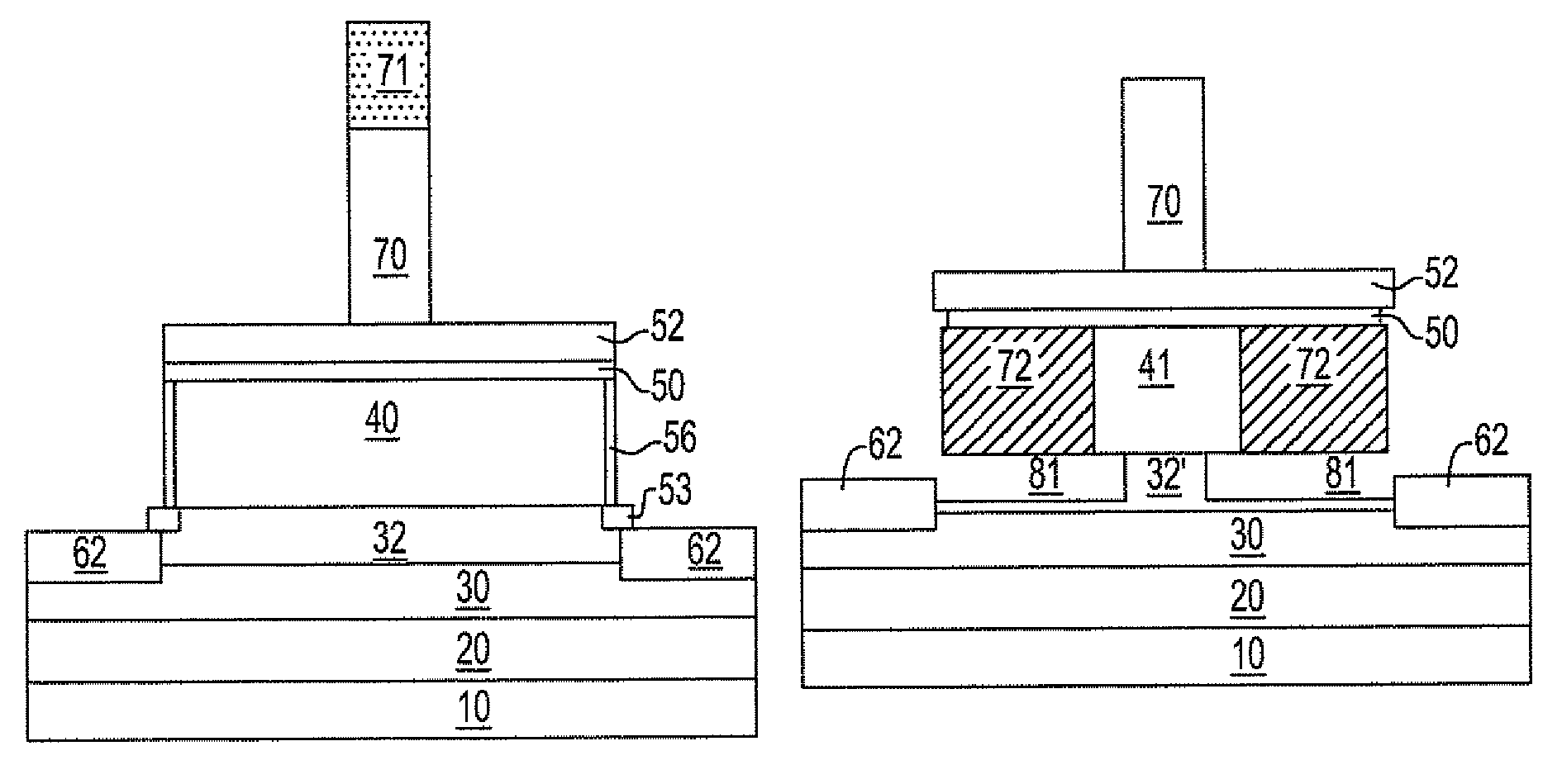

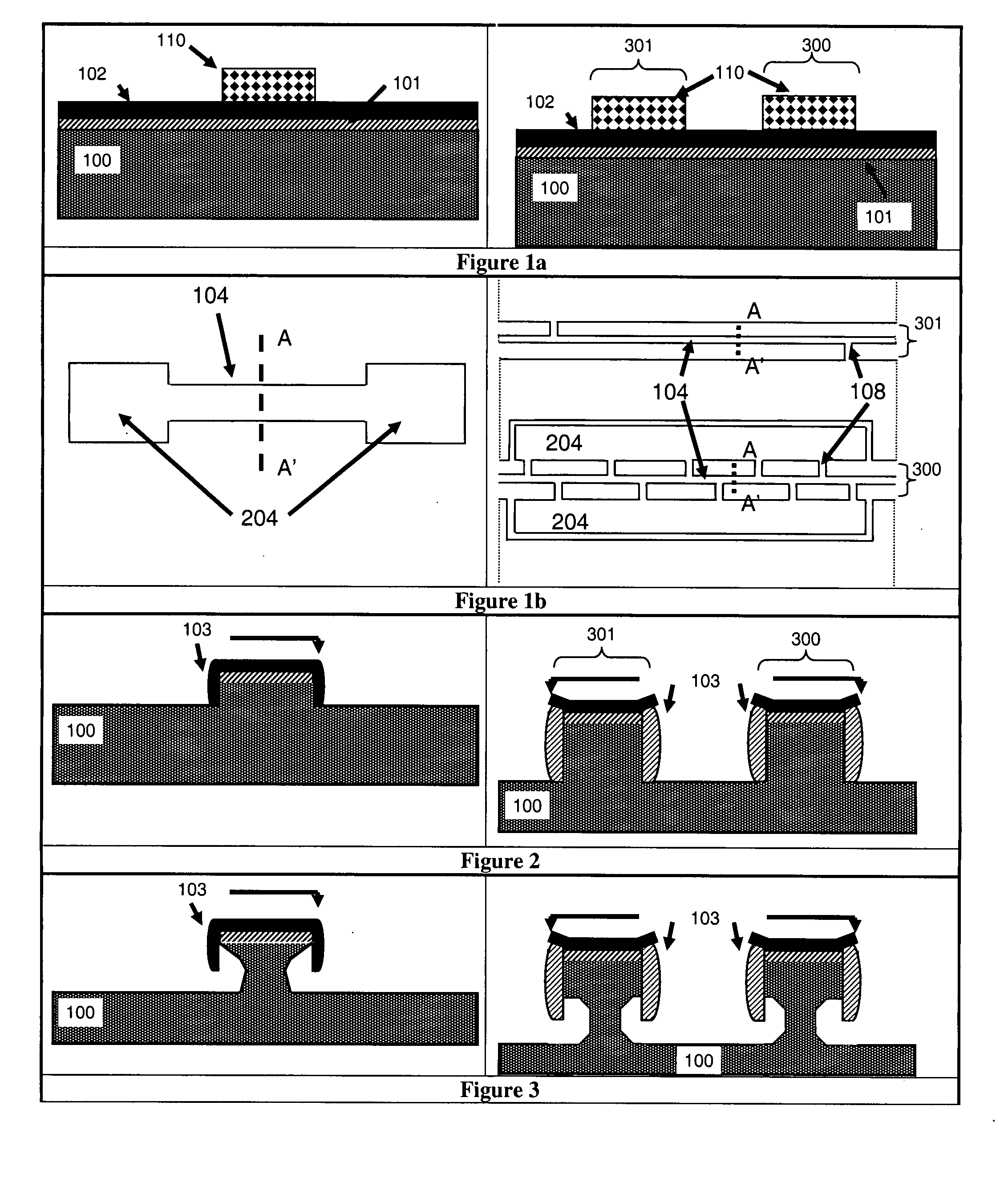

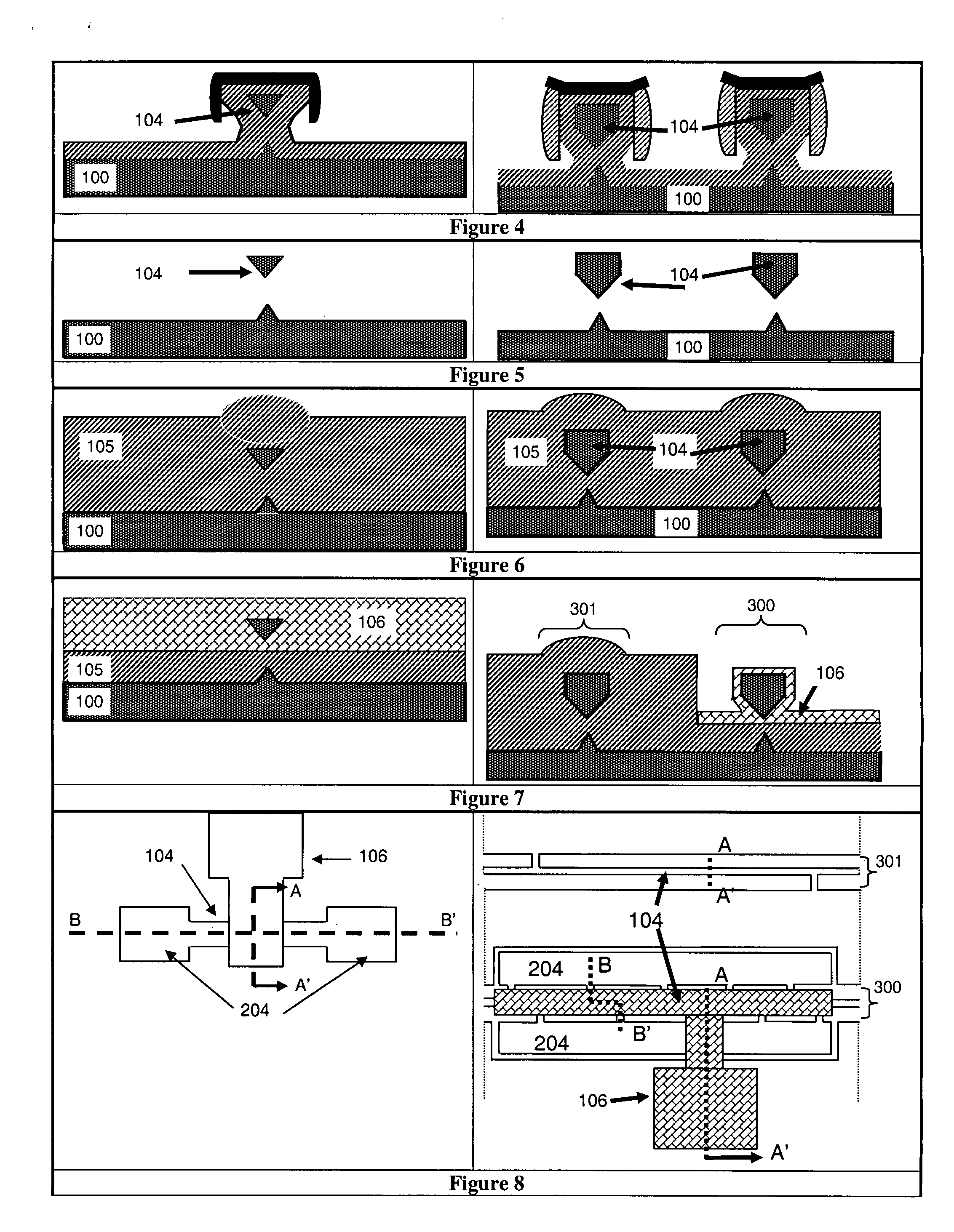

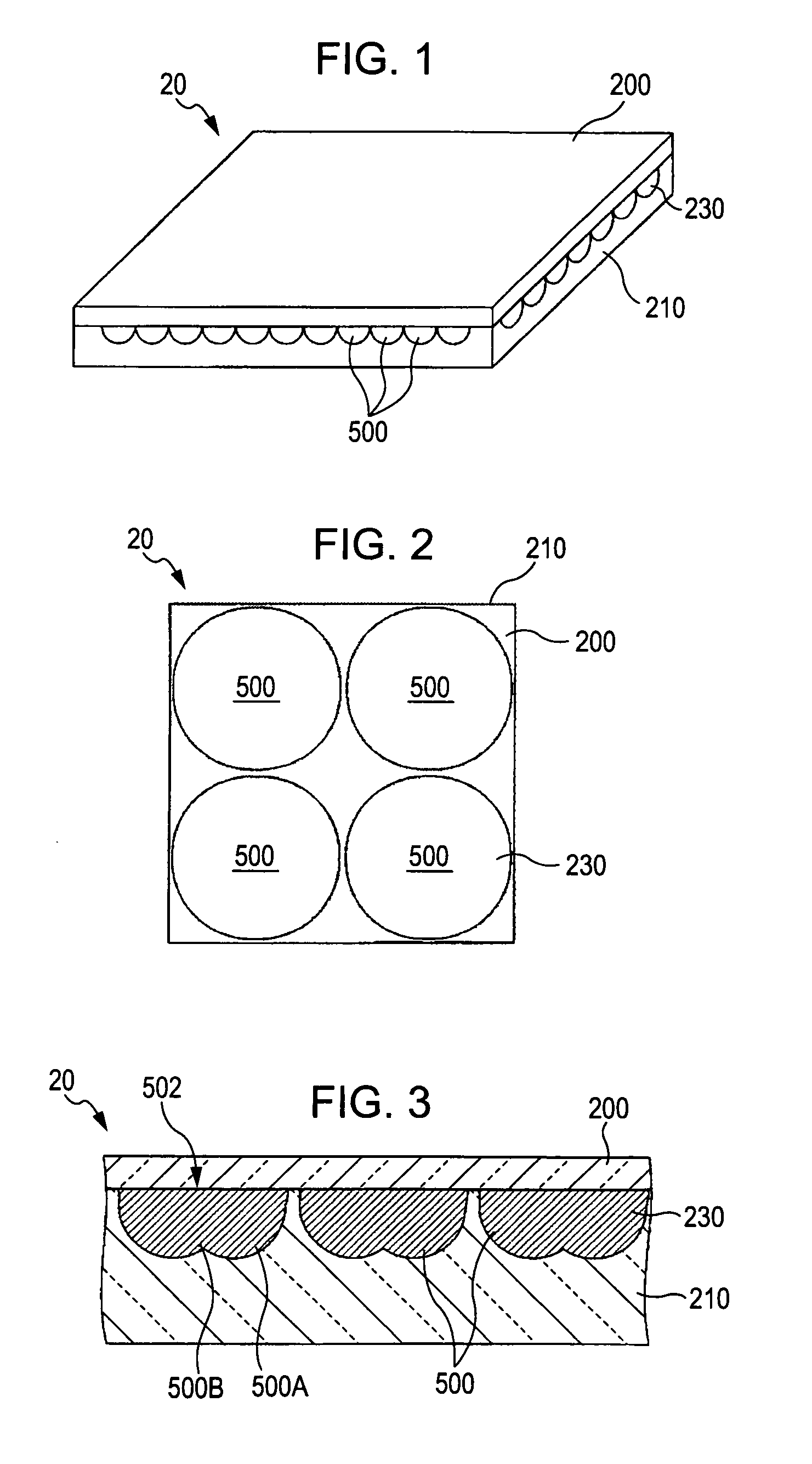

Profile Engineered Thin Film Devices and Structures

ActiveUS20090085095A1Improve performanceEasy to controlTransistorPrinted circuit aspectsDielectricElectrical conductor

The present invention relates to electrically active devices (e.g., capacitors, transistors, diodes, floating gate memory cells, etc.) having dielectric, conductor, and / or semiconductor layers with smooth and / or dome-shaped profiles and methods of forming such devices by depositing or printing (e.g., inkjet printing) an ink composition that includes a semiconductor, metal, or dielectric precursor. The smooth and / or dome-shaped cross-sectional profile allows for smooth topological transitions without sharp steps, preventing feature discontinuities during deposition and allowing for more complete step coverage of subsequently deposited structures. The inventive profile allows for both the uniform growth of oxide layers by thermal oxidation, and substantially uniform etching rates of the structures. Such oxide layers may have a uniform thickness and provide substantially complete coverage of the underlying electrically active feature. Uniform etching allows for an efficient method of reducing a critical dimension of an electrically active structure by simple isotropic etch.

Owner:ENSURGE MICROPOWER ASA

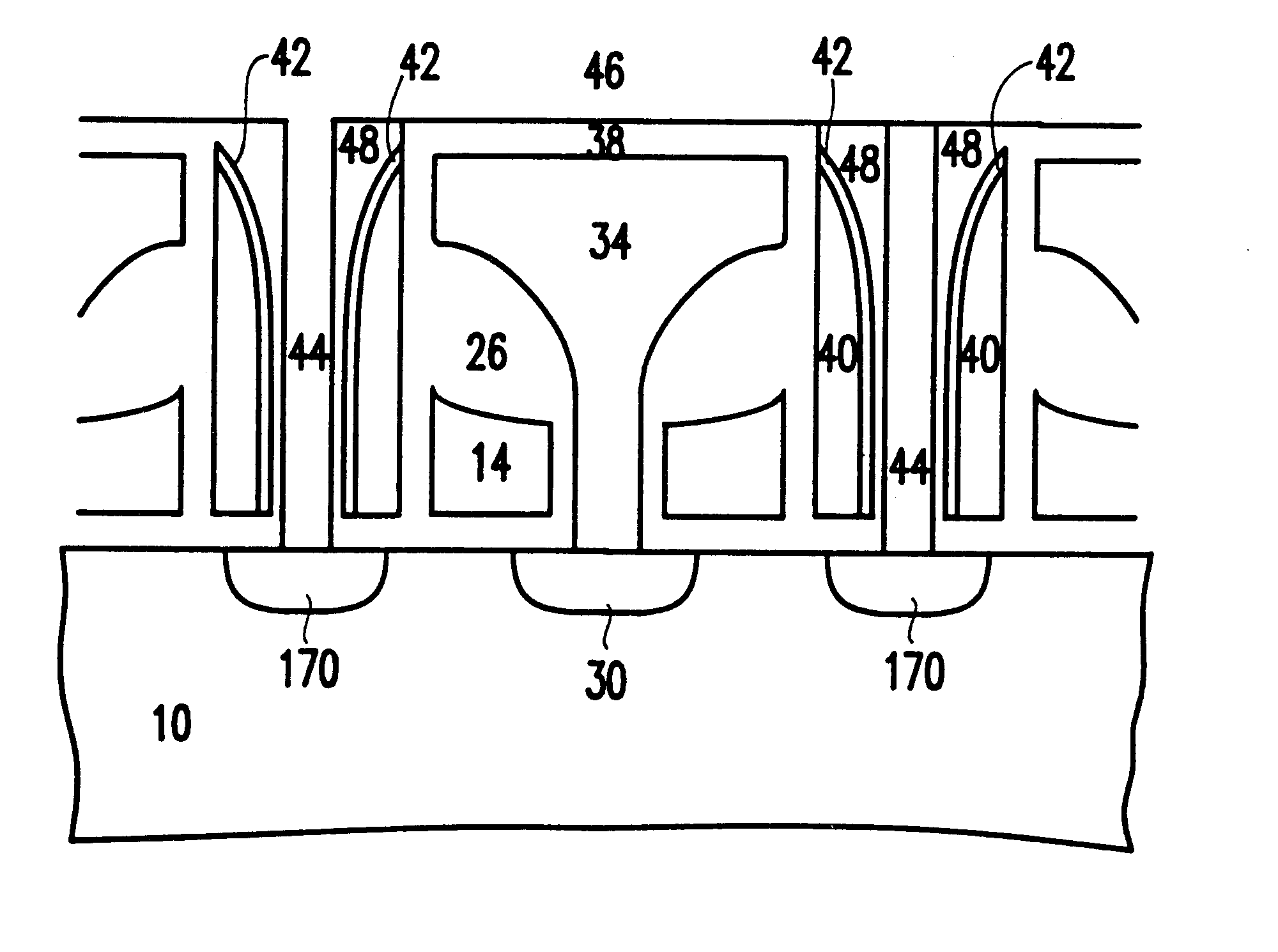

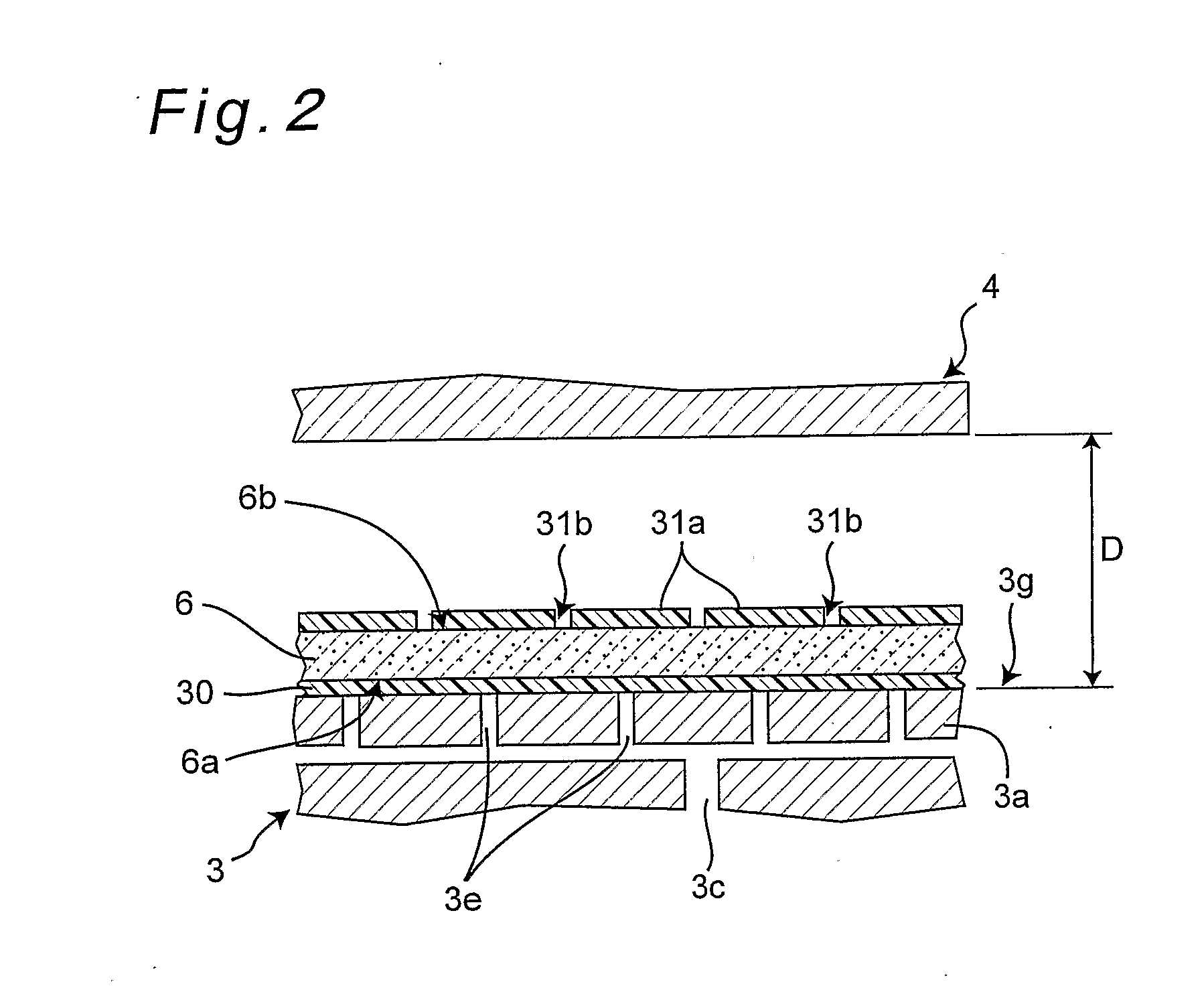

Method for fabricating semiconductor device and forming interlayer dielectric film using high-density plasma

InactiveUS6867141B2Simple processGood step coverageTransistorSemiconductor/solid-state device detailsDielectricHigh density

A method for fabricating a semiconductor device and forming an insulating film used therein, includes forming an isolation insulating film on a semiconductor wafer and forming gates, separated by gaps having a predetermined distance, on an active region. Next, a first interlayer dielectric film is deposited to a predetermined thickness on the semiconductor wafer having the gates, so that the gaps between the gates are not completely filled. Then, a sputtering etch is performed entirely on a surface of the first interlayer dielectric film. Thereafter, the first interlayer dielectric film is partially removed through isotropic etching. Next, a second interlayer dielectric film is deposited on the first interlayer dielectric film so that the gaps between the gates are completely filled. According to the above method, a gap between gate patterns can be completely filled without a void by performing sputtering etch on interlayer dielectric films formed on gate patterns, thereby enhancing the reliability of a semiconductor device.

Owner:SAMSUNG ELECTRONICS CO LTD

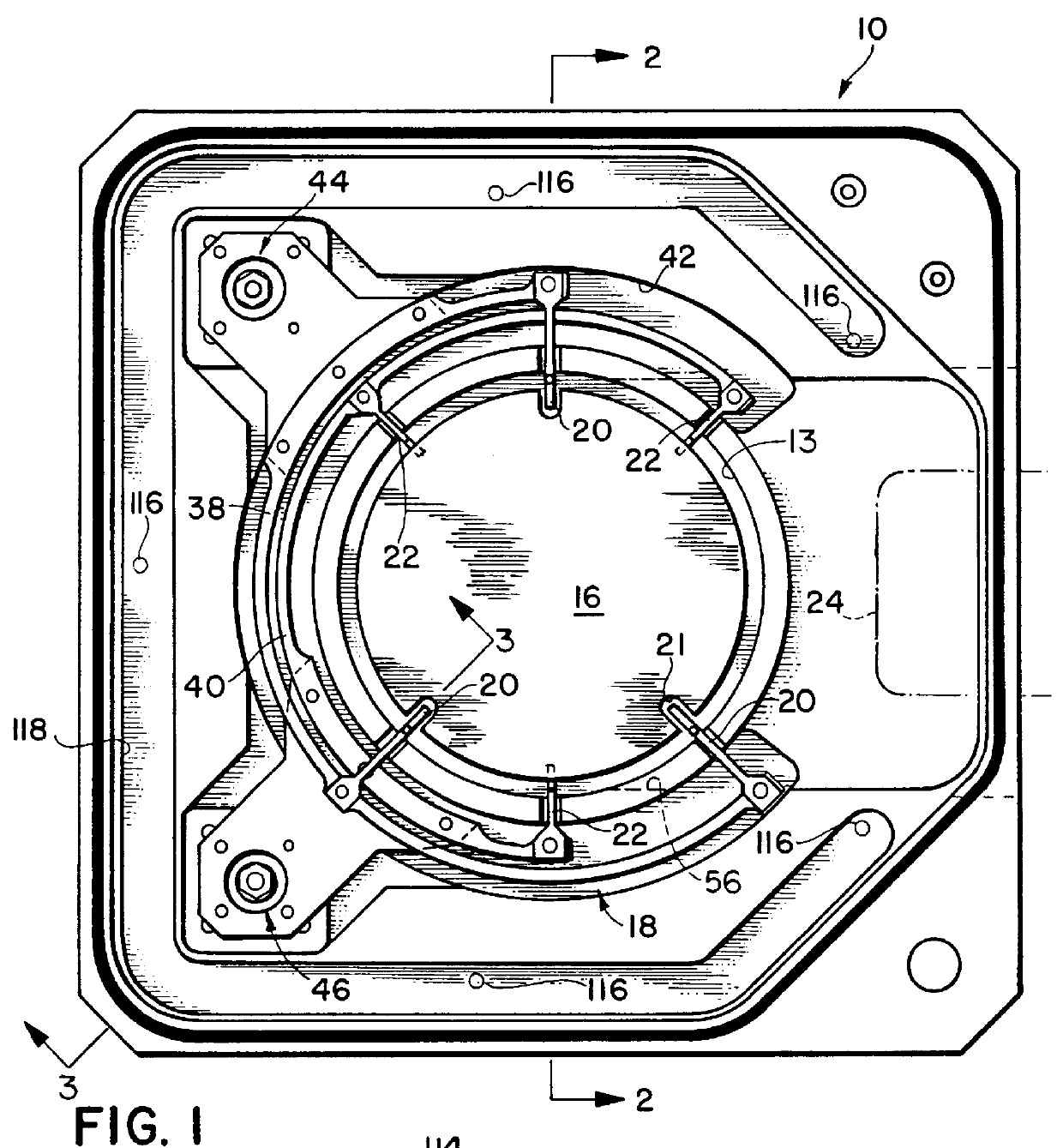

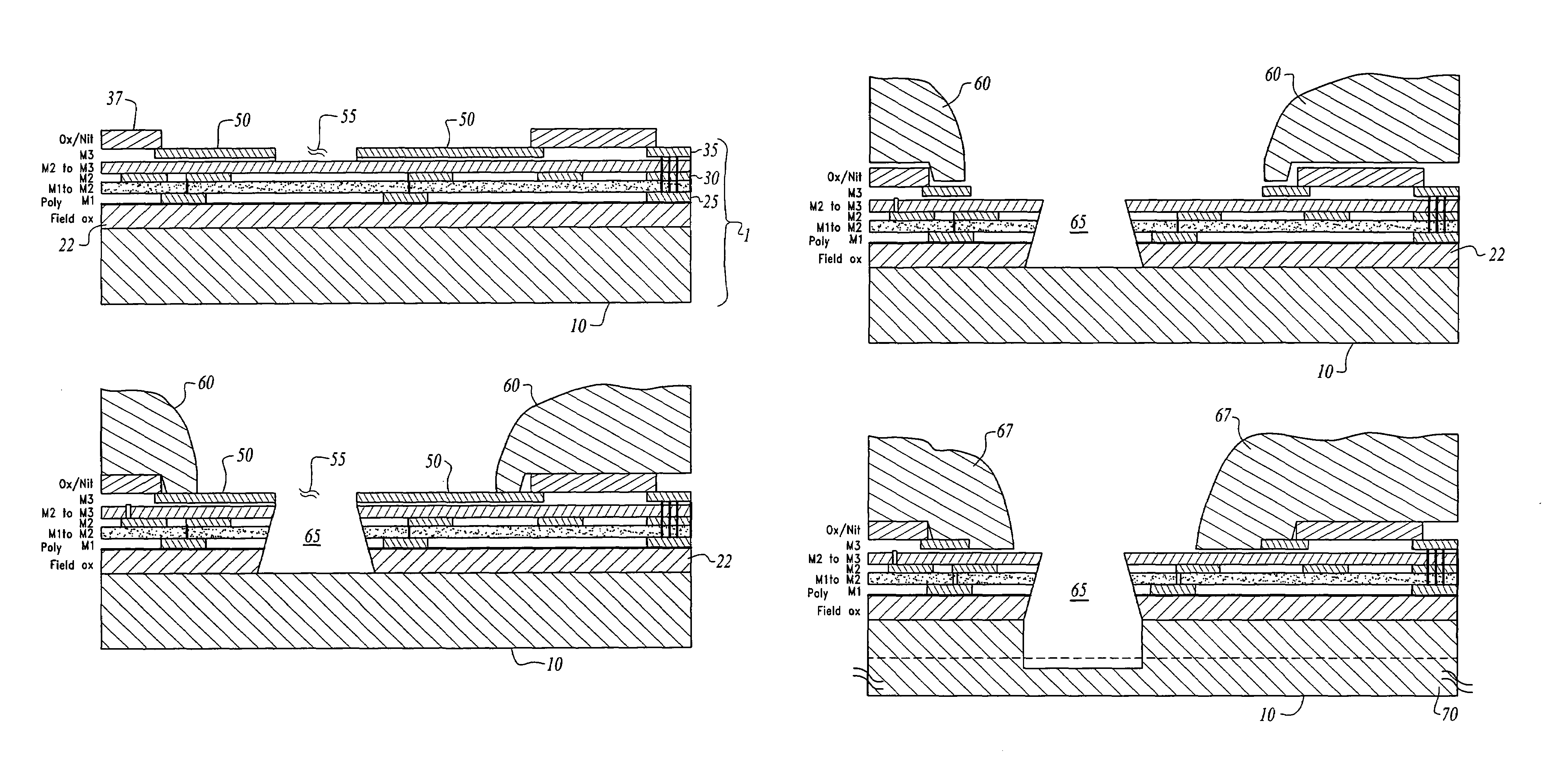

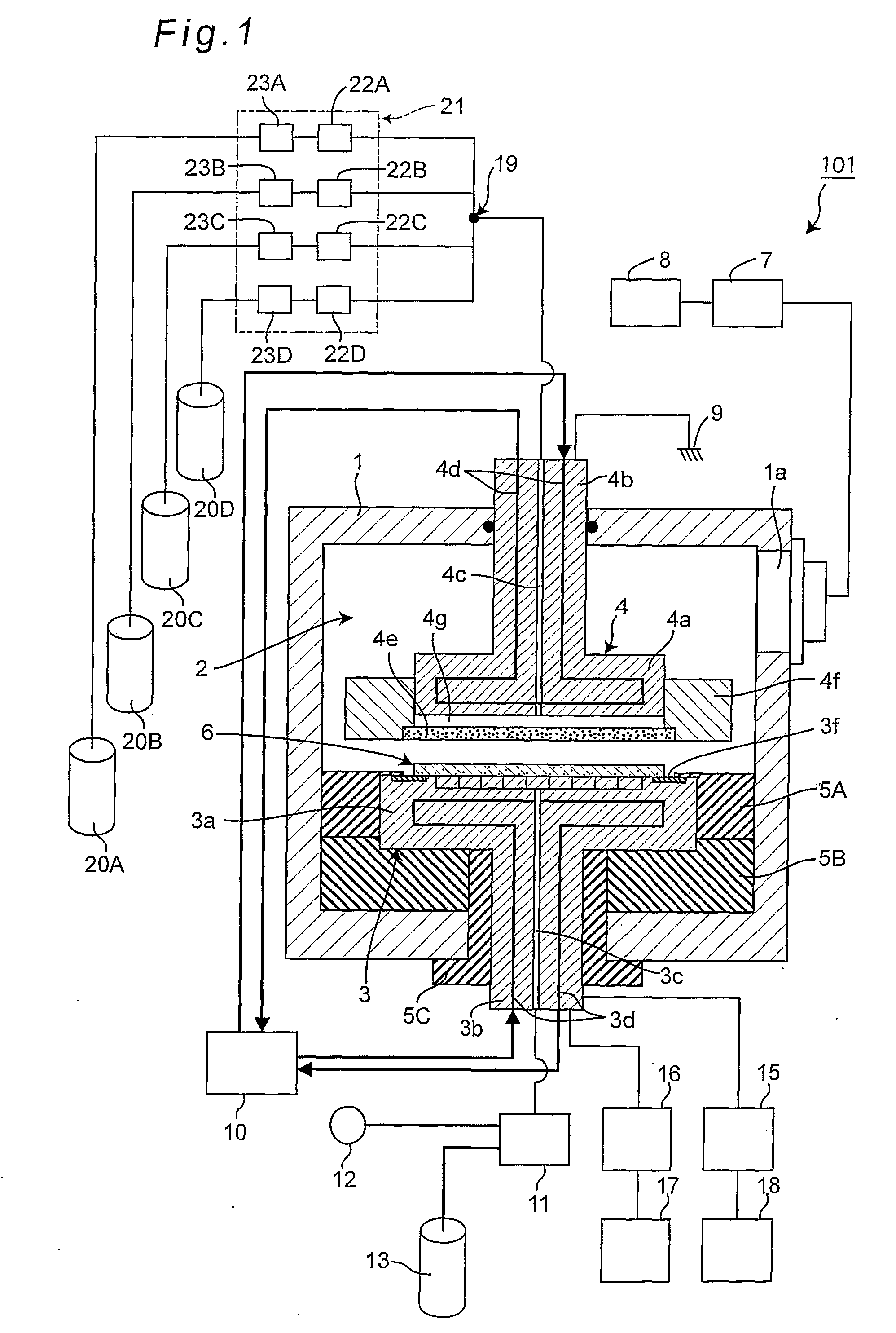

Process for PECVD of silicon oxide using TEOS decomposition

InactiveUSRE36623E1Eliminate depositsAvoid failureElectric discharge tubesPretreated surfacesHigh rateSilicon oxide

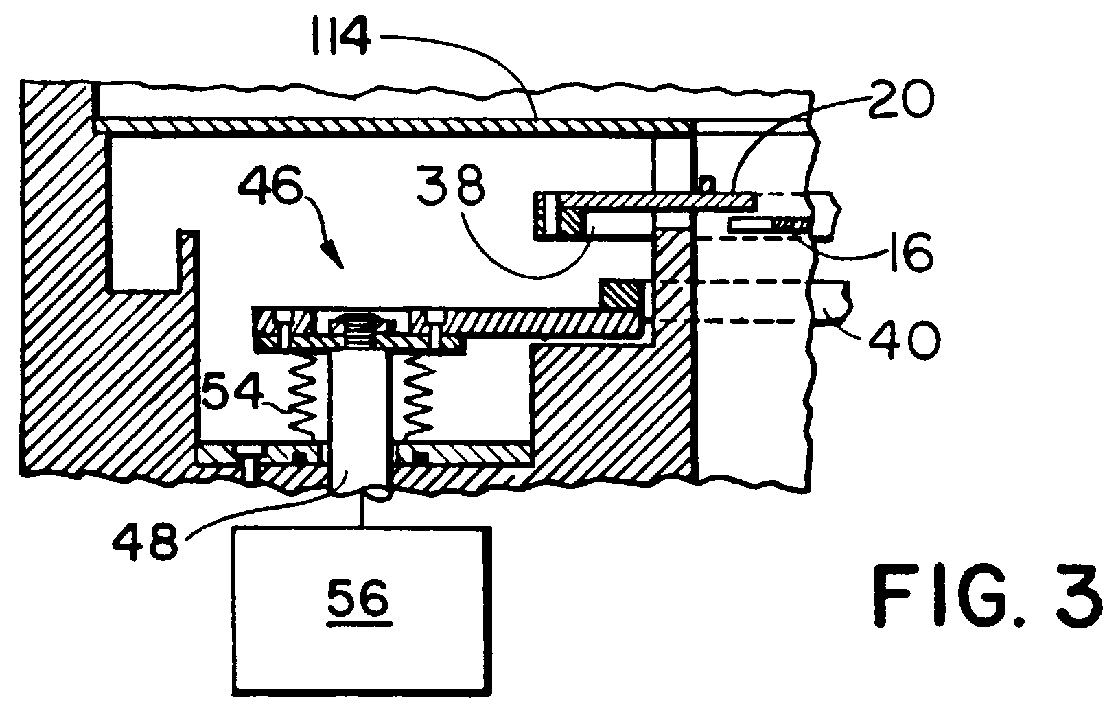

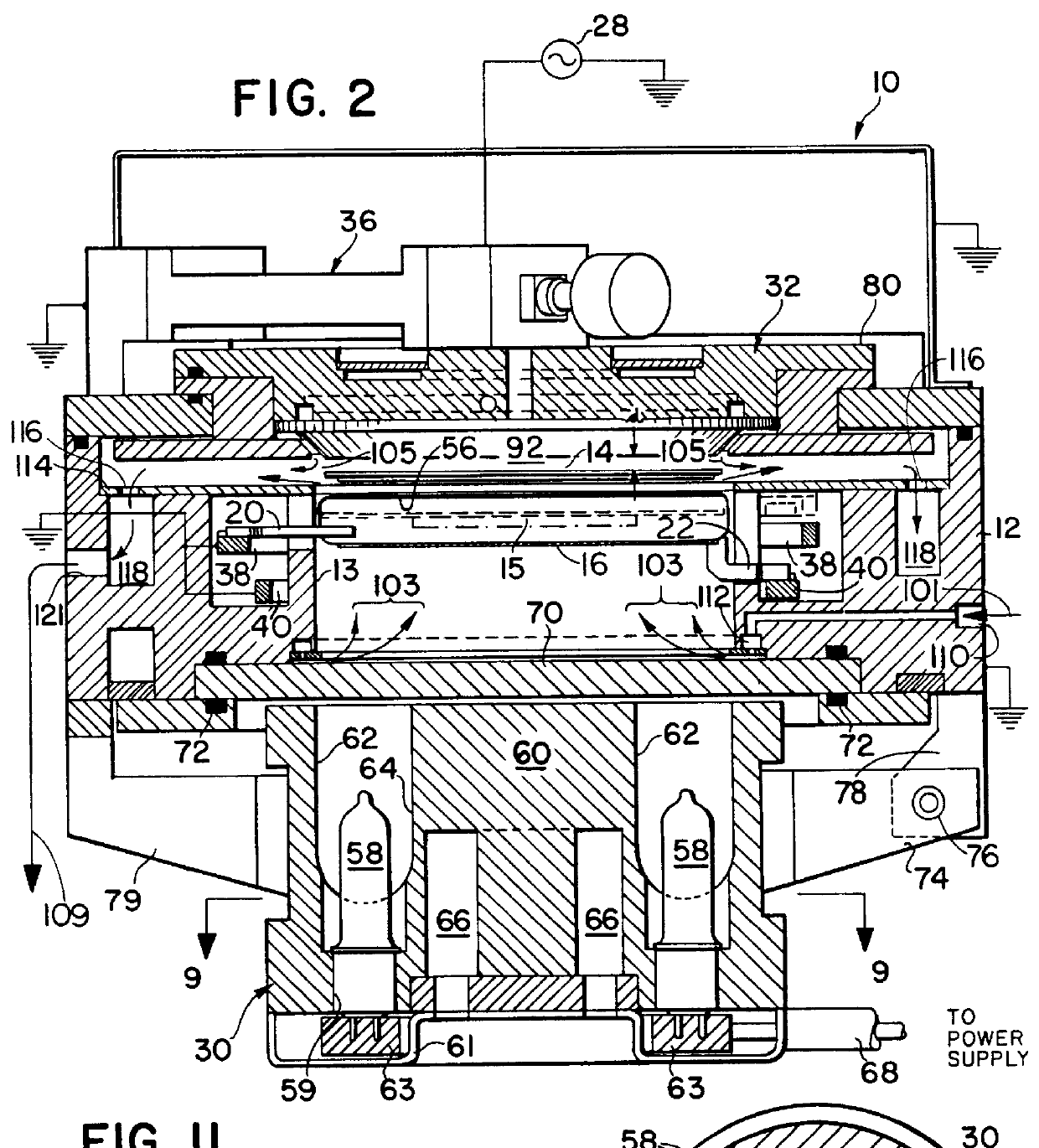

A high pressure, high throughput, single wafer, semiconductor processing reactor is disclosed which is capable of thermal CVD, plasma-enhanced CVD, plasma-assisted etchback, plasma self-cleaning, and deposition topography modification by sputtering, either separately or as part of in-situ multiple step processing. The reactor includes cooperating arrays of interdigitated susceptor and wafer support fingers which collectively remove the wafer from a robot transfer blade and position the wafer with variable, controlled, close parallel spacing between the wafer and the chamber gas inlet manifold, then return the wafer to the blade. A combined RF / gas feed-through device protects against process gas leaks and applies RF energy to the gas inlet manifold without internal breakdown or deposition of the gas. The gas inlet manifold is adapted for providing uniform gas flow over the wafer. Temperature-controlled internal and external manifold surfaces suppress condensation, premature reactions and decomposition and deposition on the external surface. The reactor also incorporates a uniform radial pumping gas system which enables uniform reactant gas flow across the wafer and directs purge gas flow downwardly and upwardly toward the periphery of the wafer for sweeping exhaust gases radially away from the wafer to prevent deposition outside the wafer and keep the chamber clean. The reactor provides uniform processing over a wide range of pressures including very high pressures. A low temperature CVD process for forming a highly conformal layer of silicon dioxide is also disclosed. The process uses very high chamber pressure and low temperature, and TEOS and ozone reactants. The low temperature CVD silicon dioxide deposition step is particularly useful for planarizing underlying stepped dielectric layers, either alone or in conjunction with a subsequent isotropic etch. A preferred in-situ multiple-step process for forming a planarized silicon dioxide layer uses (1) high rate silicon dioxide deposition at a low temperature and high pressure followed by (2) the deposition of the conformal silicon dioxide layer also at high pressure and low temperature, followed by (3) a high rate isotropic etch, preferably at low temperature and high pressure in the sane reactor used for the two oxide deposition steps. Various combinations of the steps are disclosed for different applications, as is a preferred reactor self-cleaning step.

Owner:APPLIED MATERIALS INC

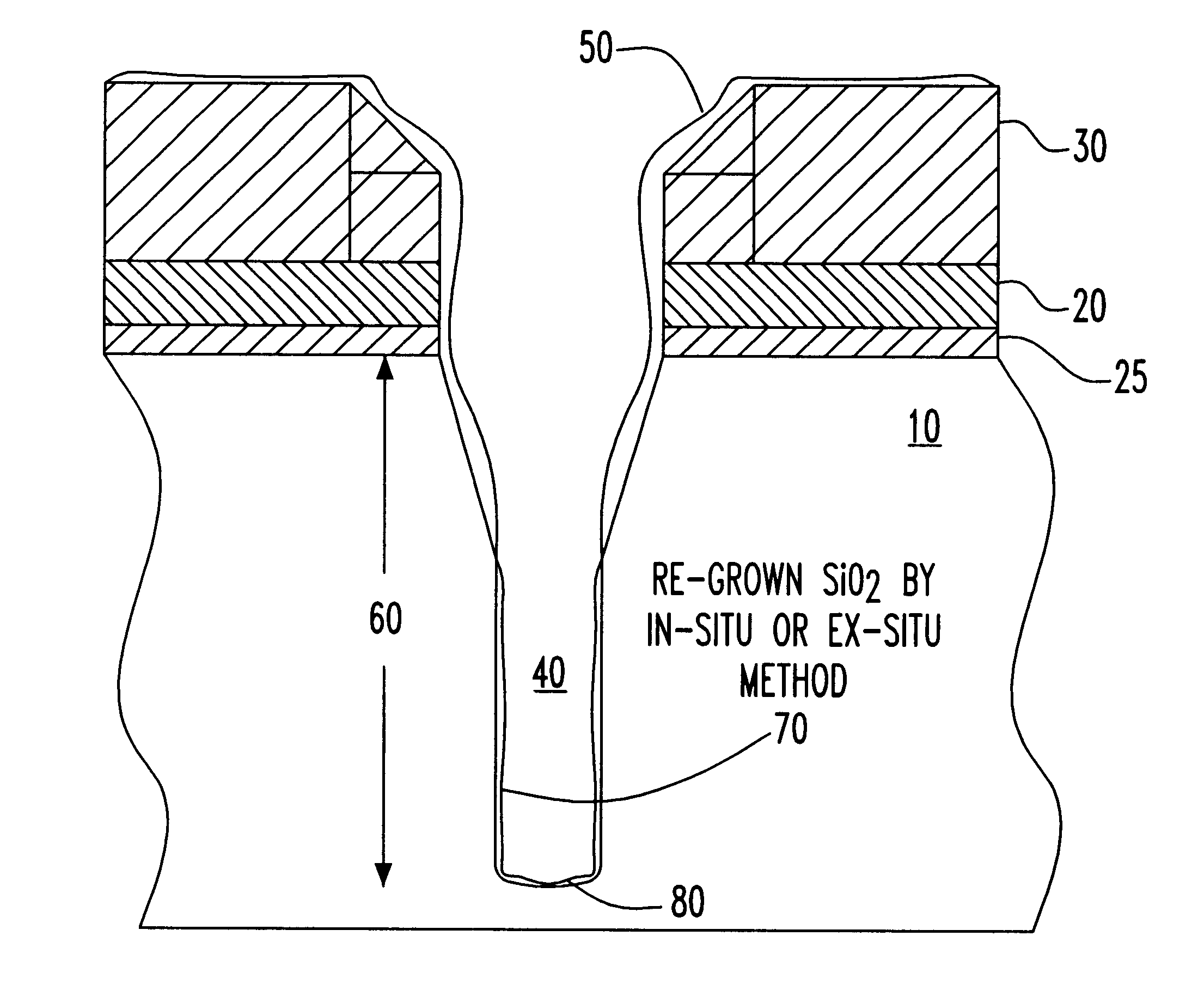

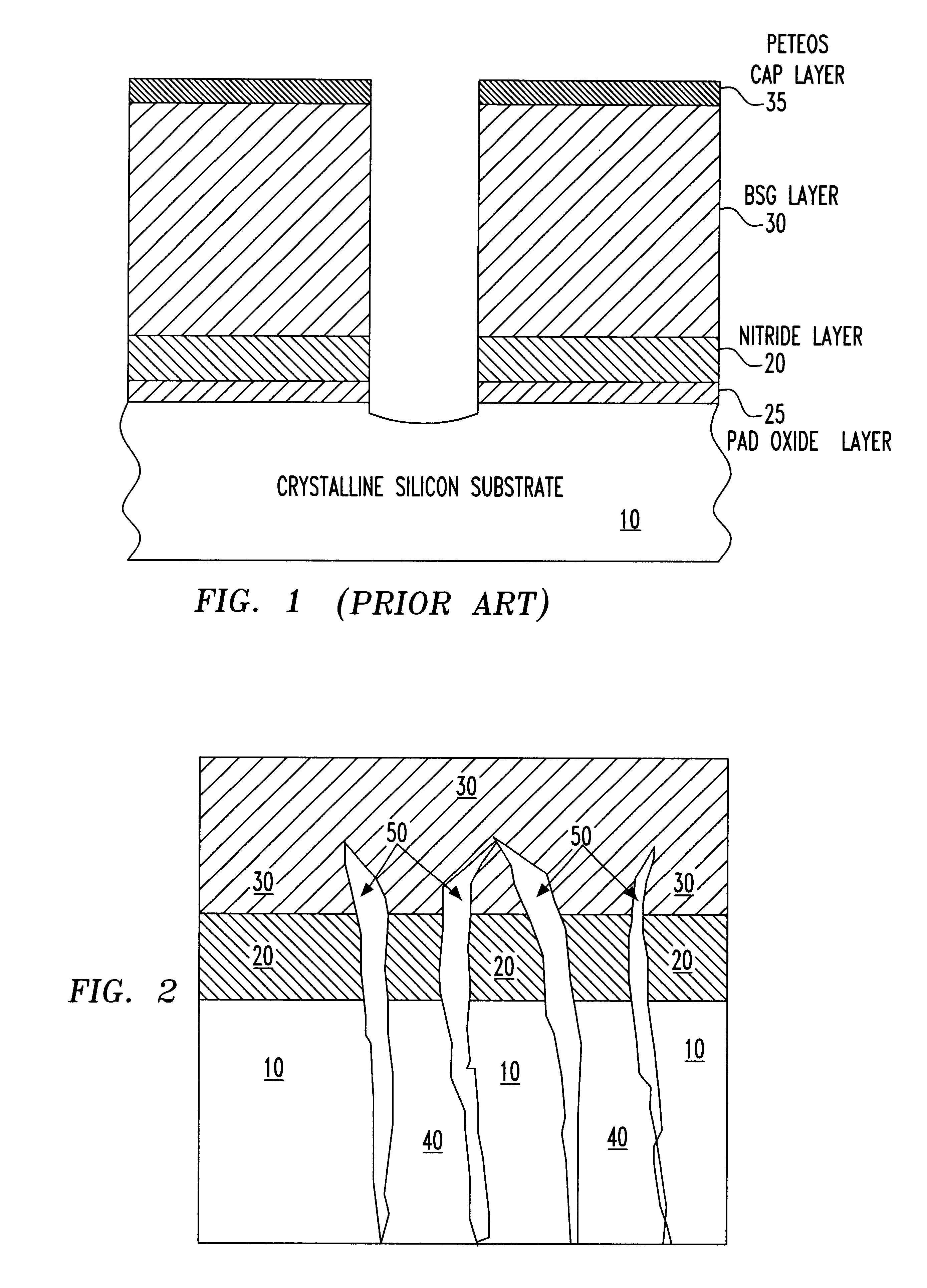

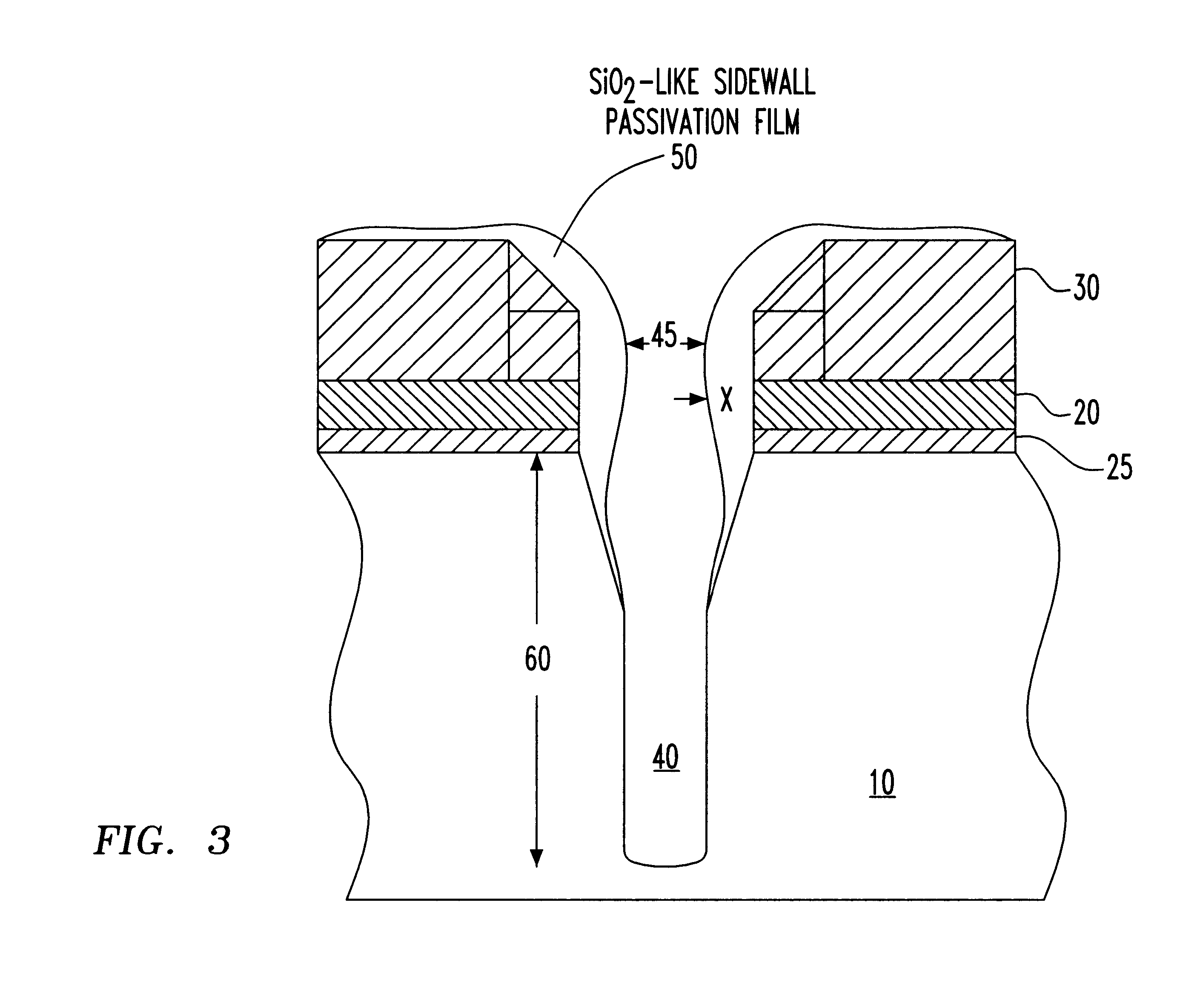

Method of reducing RIE lag for deep trench silicon etching

InactiveUS6284666B1Eliminating and at least minimizing RIE lagEliminating or at least minimizing RIE lagTransistorSemiconductor/solid-state device manufacturingHydrofluoric acidGas phase

A method of minimizing RIE lag (i.e., the neutral and ion fluxes at the bottom of a deep trench (DT) created during the construction of the trench opening using a side wall film deposition)) in DRAMs having a large aspect ratio (i.e., <30:1) is described. The method forms a passivation film to the extent necessary for preventing isotropic etching of the substrate, hence maintaining the required profile and the shape of the DT within the substrate. The RIE process described provides a partial DT etched into a substrate to achieve the predetermined depth. The passivation film is allowed to grow to a certain thickness still below the extent that it would close the opening of the deep trench. Alternatively, the passivation film is removed by a non-RIE etching process. The non-RIE process that removes the film can be wet etched with chemicals, such as hydrofluoric acid (buffered or non buffered) or, alternatively, using vapor phase and / or non-ionized chemicals, such as anhydrous hydrofluoric acid. The controlled thickness of the film allows achieving a predetermined DT depth for high aspect ratio structures.

Owner:INFINEON TECH AG +1

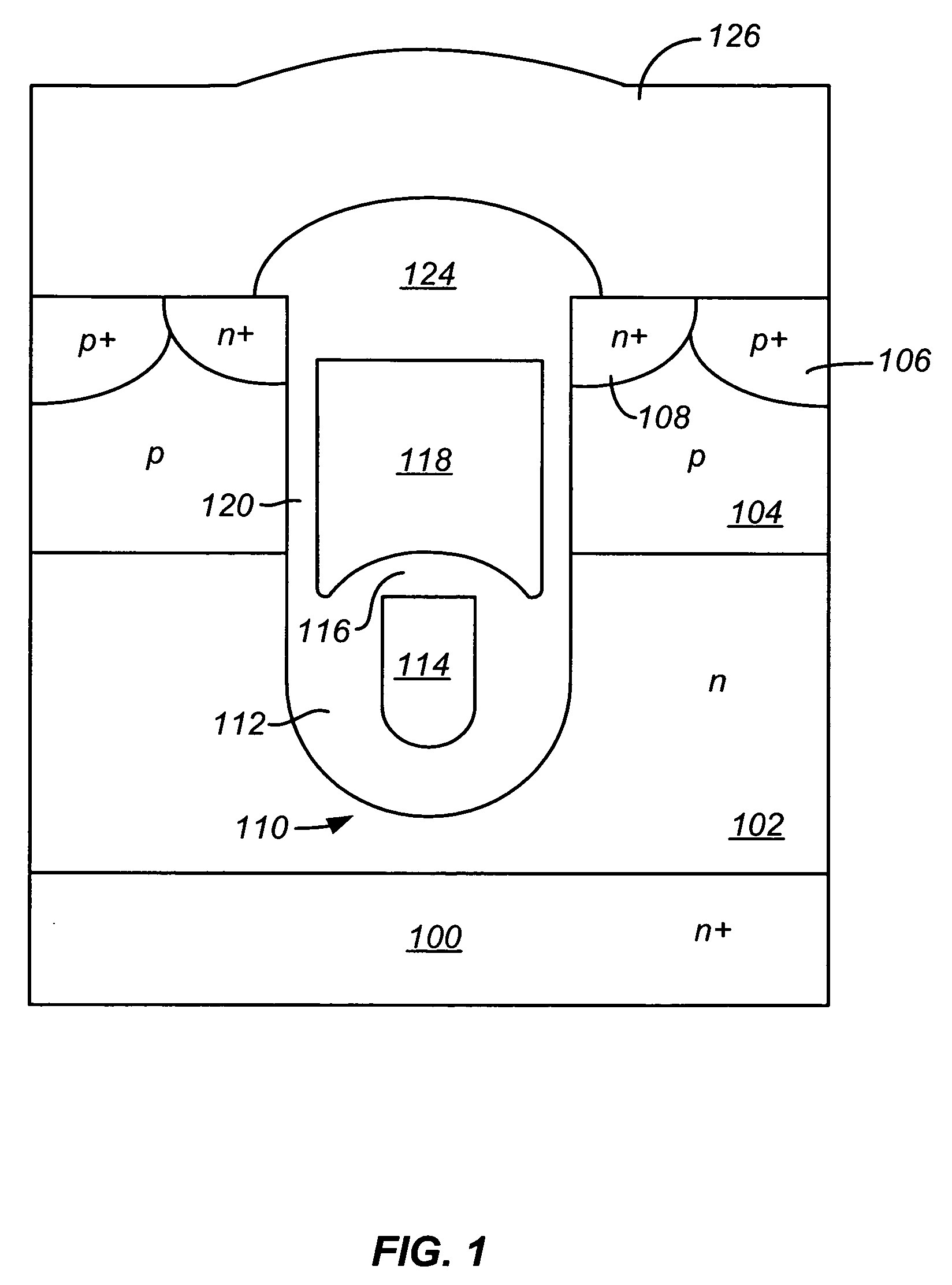

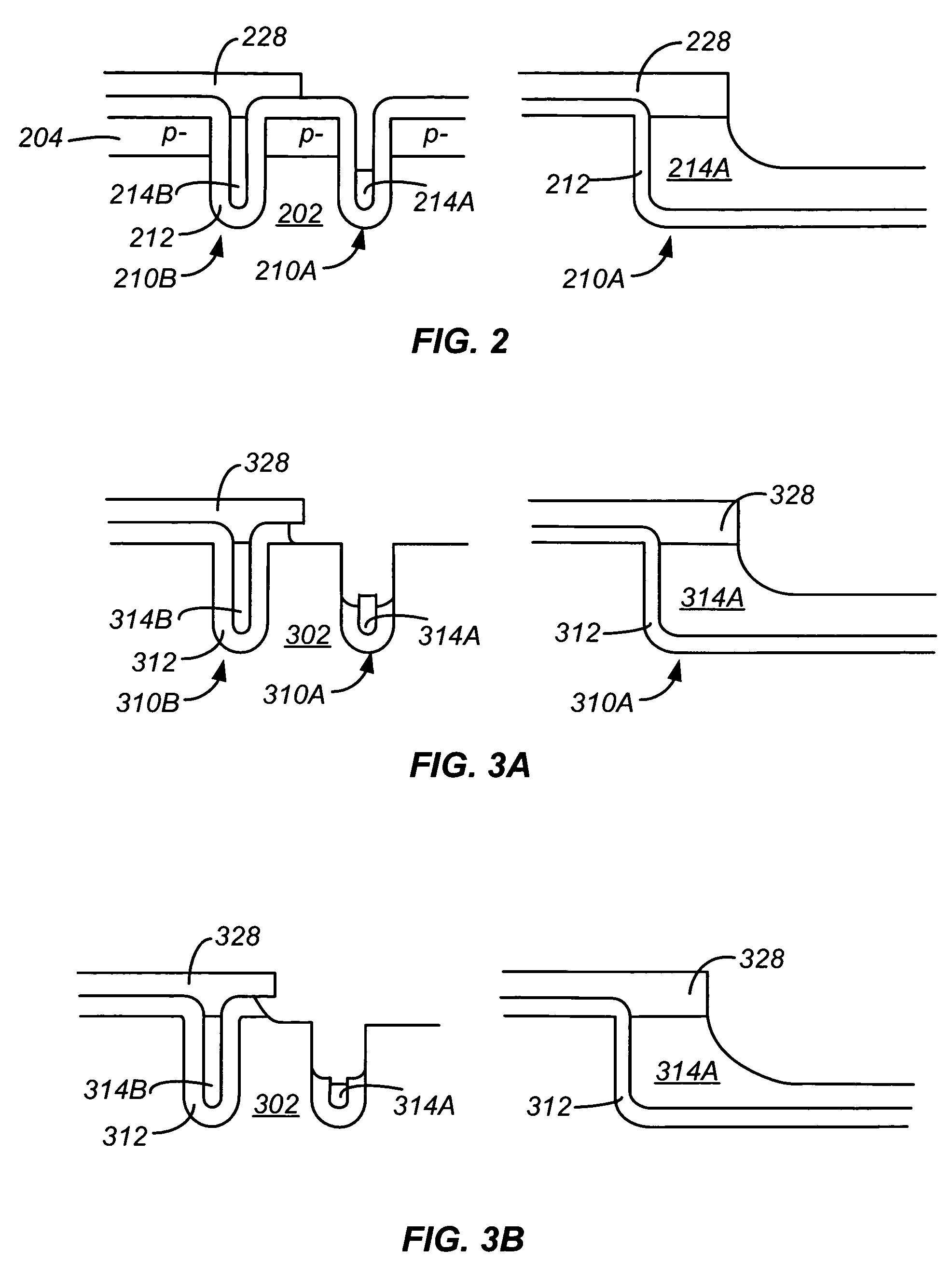

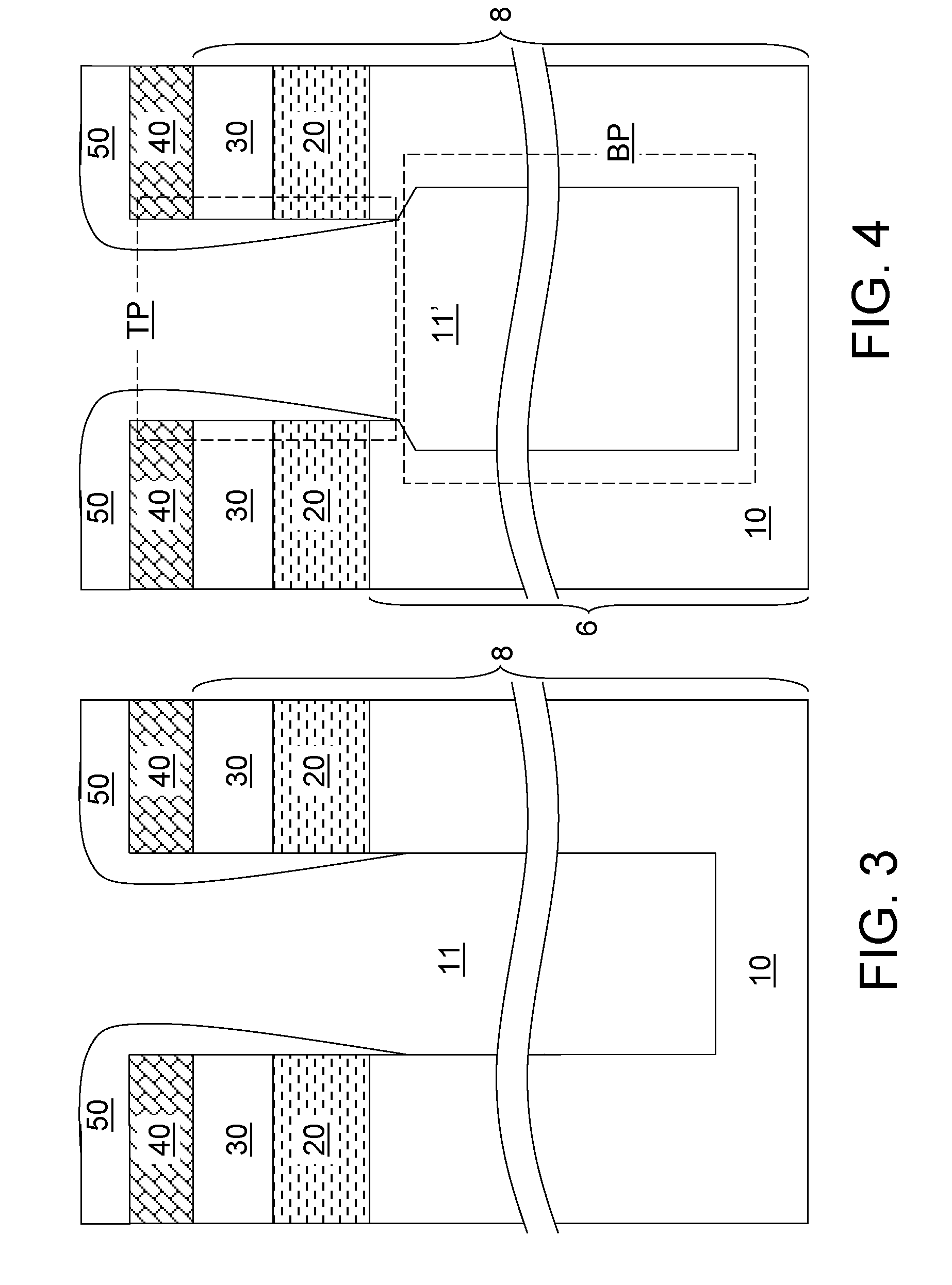

Structures and methods for forming shielded gate field effect transistors

ActiveUS20070032020A1Semiconductor/solid-state device manufacturingSemiconductor devicesConductive materialsEngineering

A field effect transistor is formed as follows. A trench is formed in a semiconductor region. A dielectric layer lining the trench sidewalls and bottom is formed. The trench is filled with a conductive material. The conductive material is recessed into the trench to thereby form a shield electrode in a bottom portion of the trench. The recessing of the conductive material includes isotropic etching of the conductive material. An inter-electrode dielectric (IED) is formed over the recessed shield electrode.

Owner:SEMICON COMPONENTS IND LLC

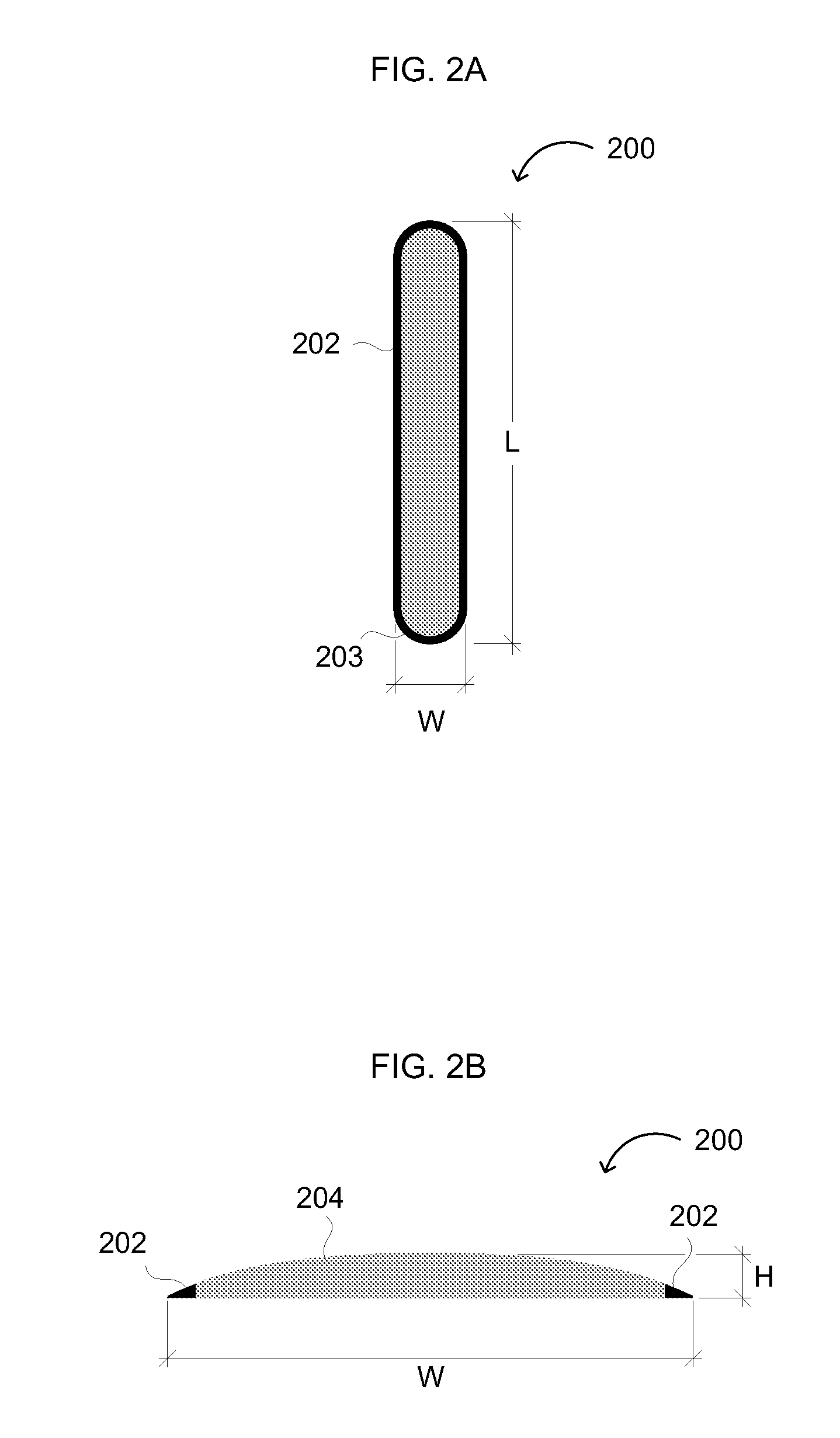

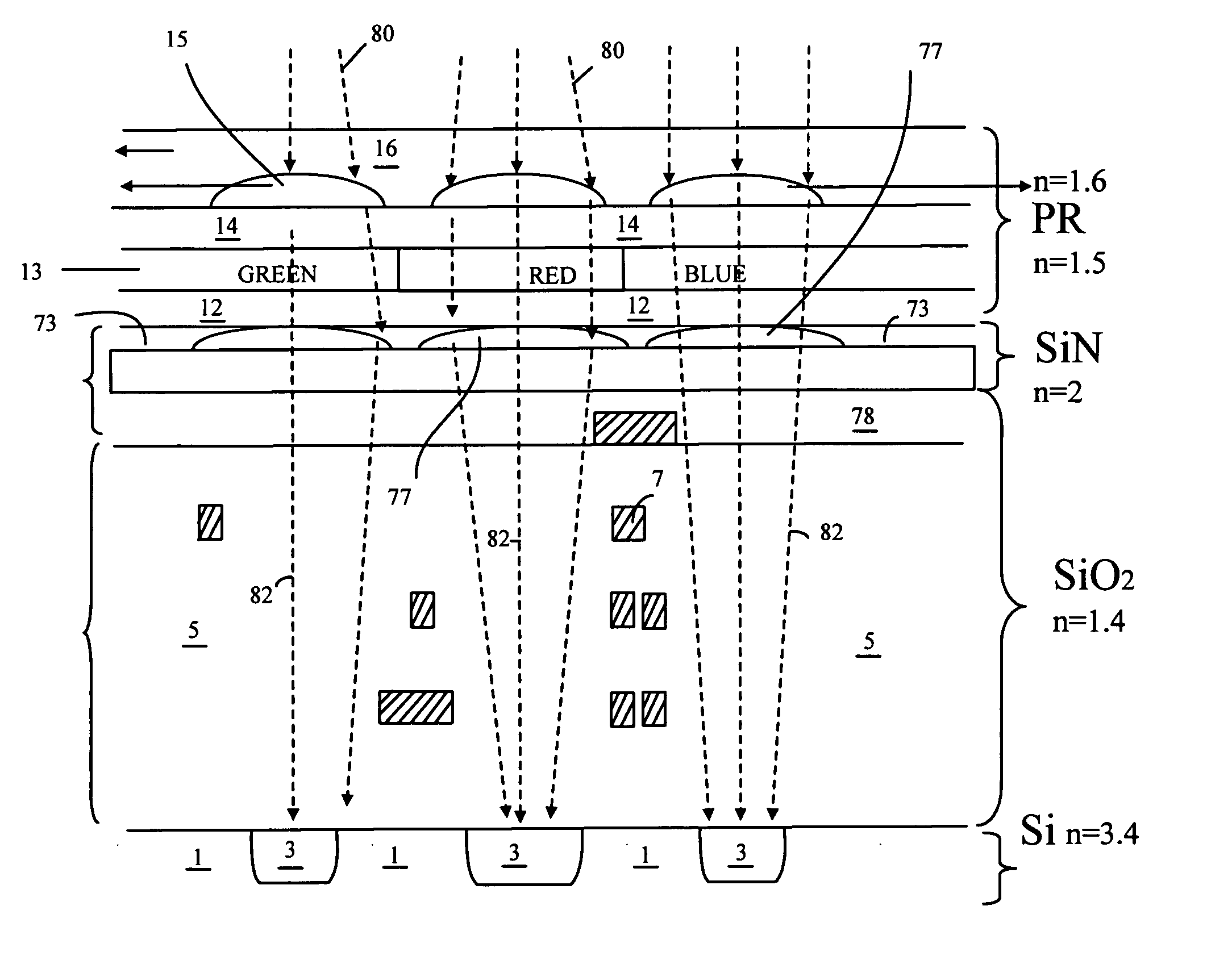

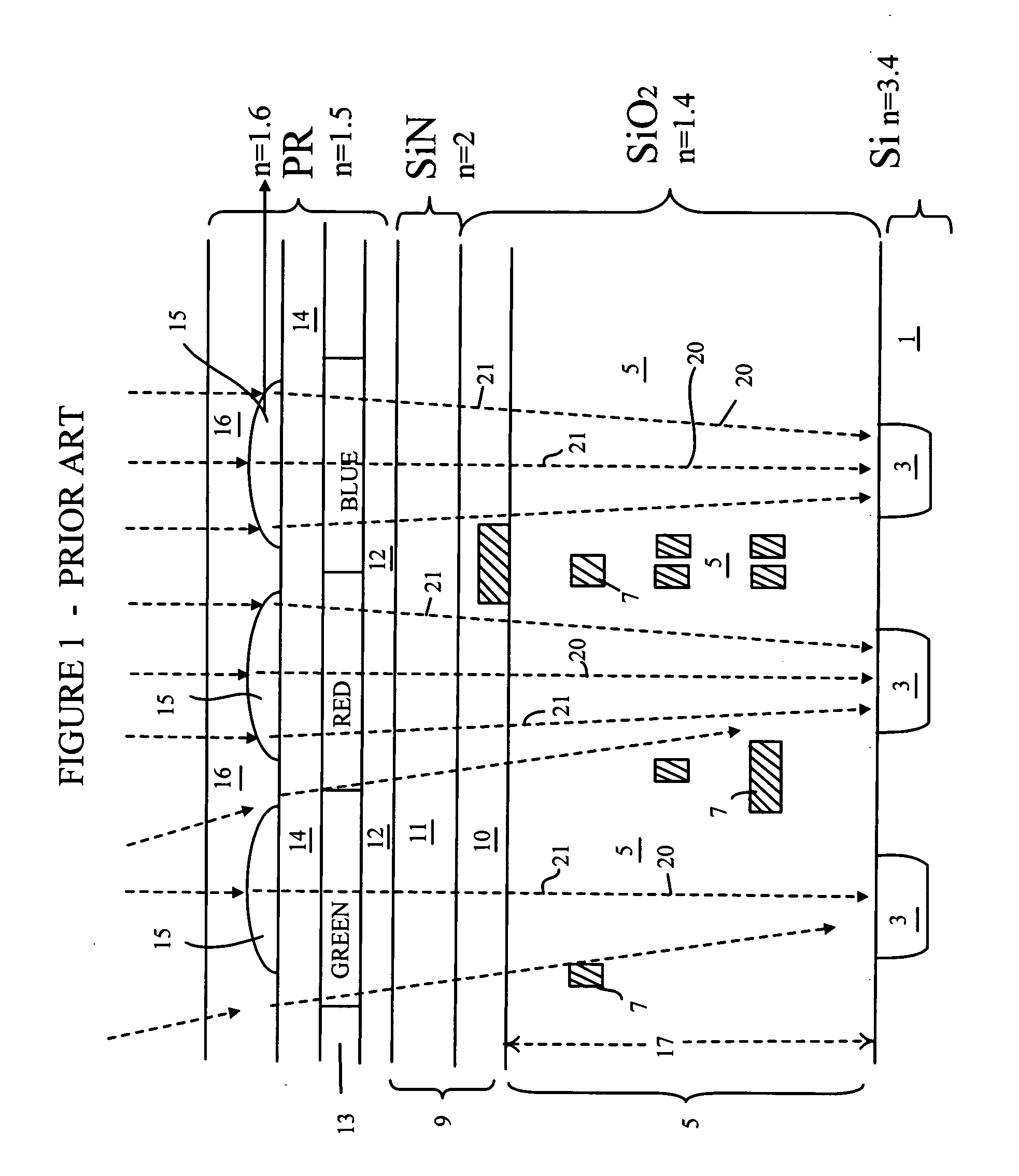

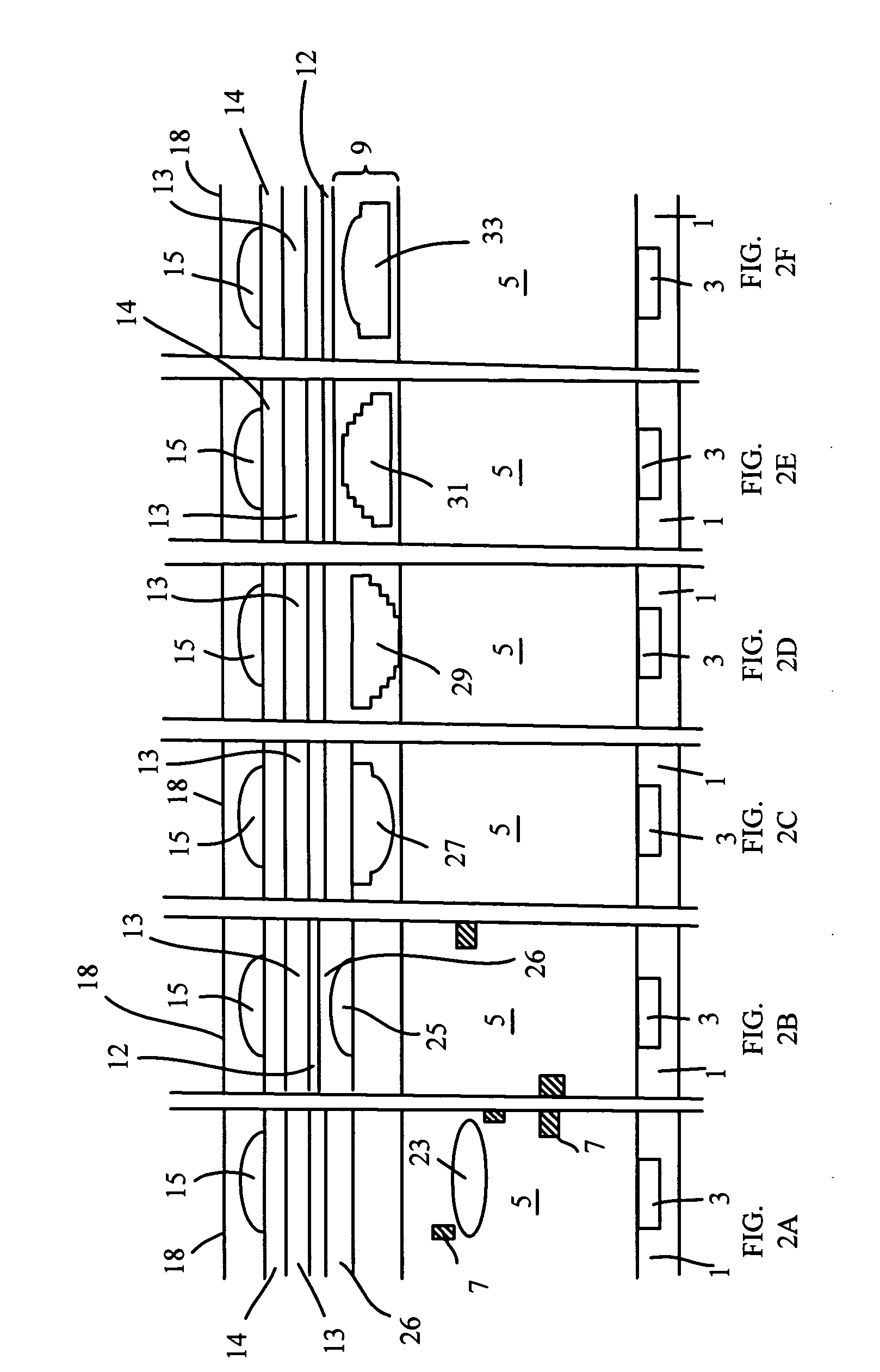

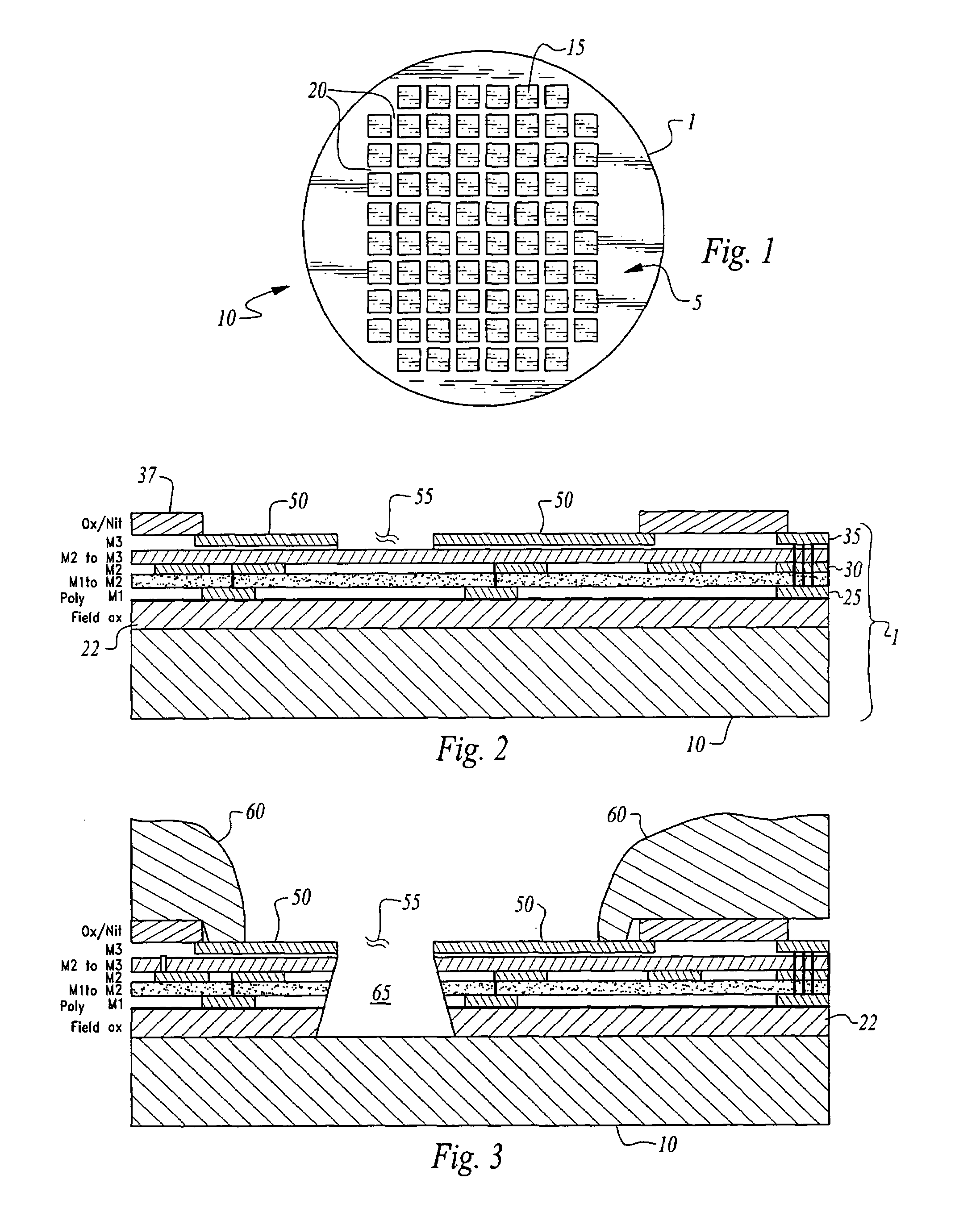

Lens structures suitable for use in image sensors and method for making the same

InactiveUS20050274968A1Solid-state devicesSemiconductor/solid-state device manufacturingResistPhotosensitive polymer

An image sensor includes a double-microlens structure with an outer microlens aligned over an inner microlens, both microlenses aligned over a corresponding photosensor. The inner or outer microlens may be formed by a silylation process in which a reactive portion of a photoresist material reacts with a silicon-containing agent. The inner or outer microlens may be formed by step etching of a dielectric material, the step etching process including a series of alternating etch steps including an anisotropic etching step and an etching step that causes patterned photoresist to laterally recede. Subsequent isotropic etching processes may be used to smooth the etched step structure and form a smooth lens. A thermally stable and photosensitive polymeric / organic material may also be used to form permanent inner or outer lenses. The photosensitive material is coated then patterned using photolithography, reflowed, then cured to form a permanent lens structure.

Owner:TAIWAN SEMICON MFG CO LTD

Methods for forming shielded gate field effect transistors

ActiveUS7476589B2Semiconductor/solid-state device manufacturingSemiconductor devicesEngineeringConductive materials

A field effect transistor is formed as follows. A trench is formed in a semiconductor region. A dielectric layer lining the trench sidewalls and bottom is formed. The trench is filled with a conductive material. The conductive material is recessed into the trench to thereby form a shield electrode in a bottom portion of the trench. The recessing of the conductive material includes isotropic etching of the conductive material. An inter-electrode dielectric (IED) is formed over the recessed shield electrode.

Owner:SEMICON COMPONENTS IND LLC

Hybrid nanomesh structures

An alternating stack of first and second semiconductor layers is formed. Fin-defining mask structures are formed over the alternating stack. A planarization dielectric layer and first and second gate cavities therein are subsequently formed. The first and second gate cavities are extended downward by etching the alternating stack employing a combination of the planarization layer and the fin-defining mask structures as an etch mask. The second semiconductor material is isotropically etched to laterally expand the first gate cavity and to form a first array of semiconductor nanowires including the first semiconductor material, and the first semiconductor material is isotropically etched to laterally expand the second gate cavity and to form a second array of semiconductor nanowires including the second semiconductor material. The first and second gate cavities are filled with replacement gate structures. Each replacement gate structure laterally can surround a two-dimensional array of semiconductor nanowires.

Owner:GLOBALFOUNDRIES INC

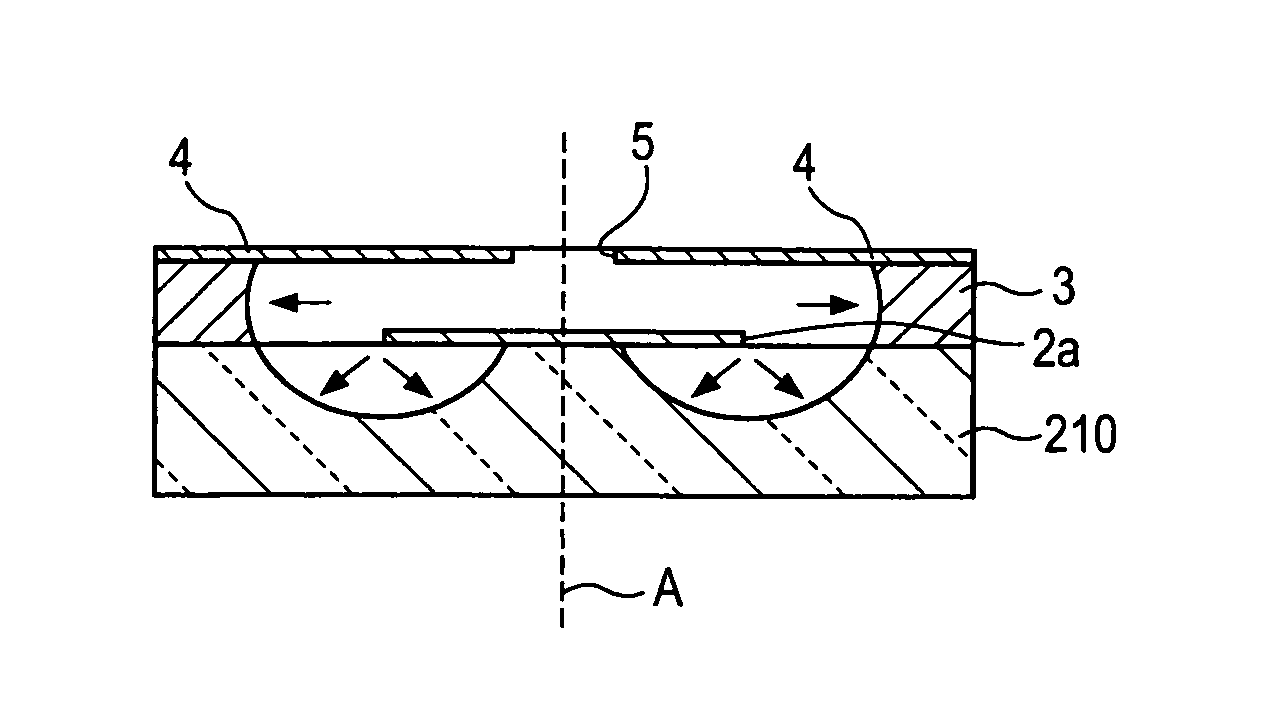

Photovoltaic element and method for manufacture thereof

InactiveUS20010029978A1Improve featuresReduce defectsPV power plantsSolid-state devicesSolar lightAmorphous silicon

A photovoltaic element which directly converts an optical energy such as solar light into an electric energy. After many uneven sections are formed on the surface of an n-type crystalline silicon substrate (1), the surface of the substrate (1) is isotropically etched. Then the bottoms (b) of the recessed sections are rounded and a p-type amorphous silicon layer (3) is formed on the surface of the substrate (1) through an intrinsic amorphous silicon layer (2). The shape of the surface of the substrate (1) after isotropic etching is such that the bottoms of the recessed sections are slightly rounded and therefore the amorphous silicon layer can be deposited in a uniform thickness.

Owner:SANYO ELECTRIC CO LTD

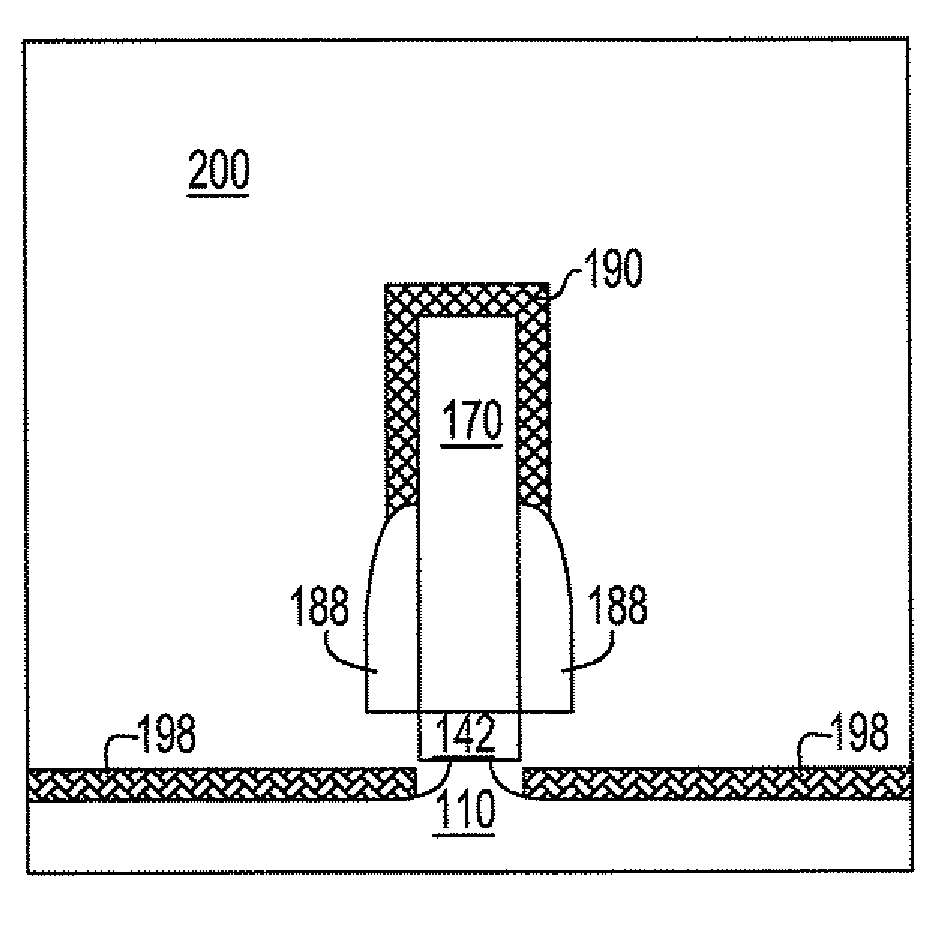

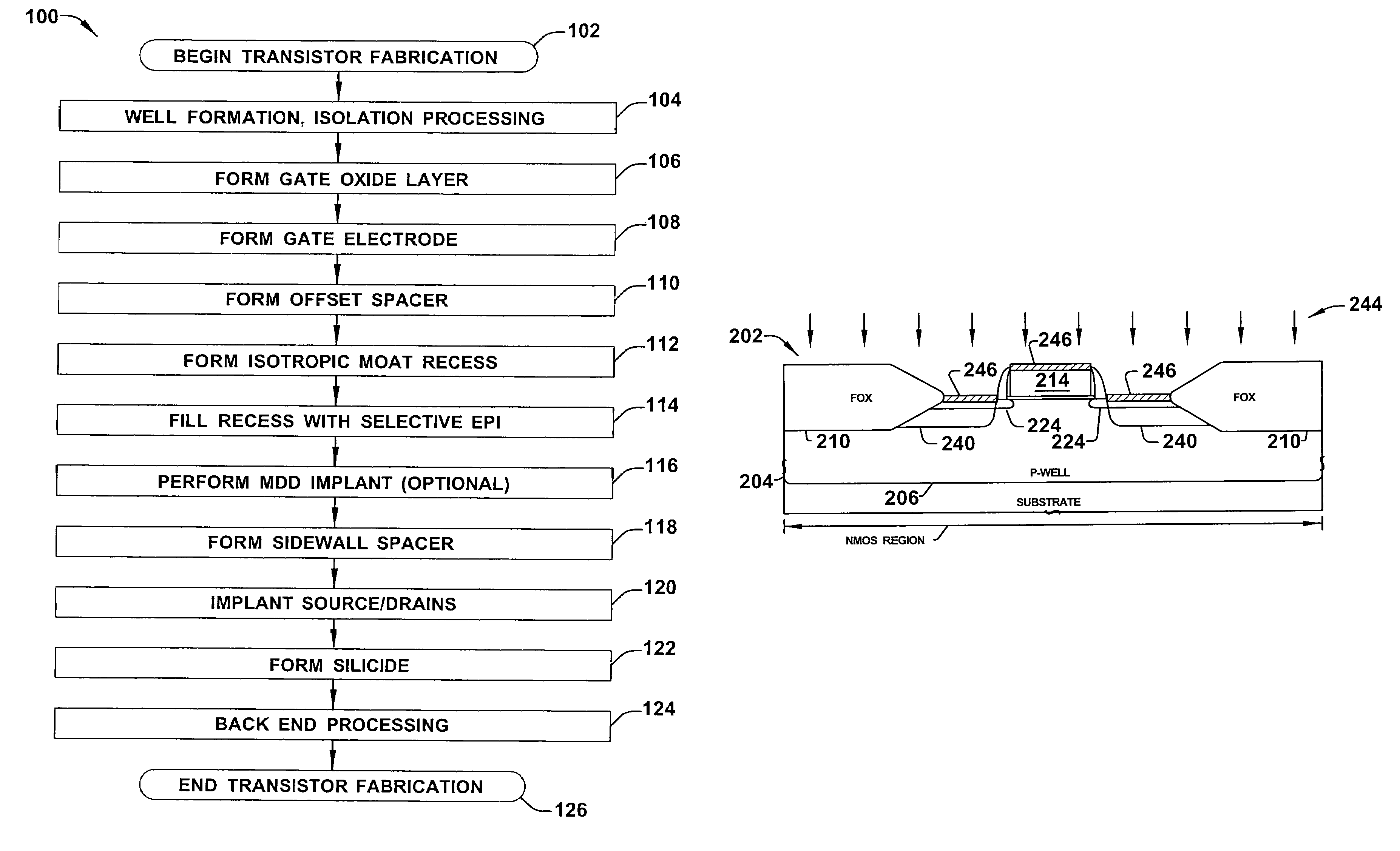

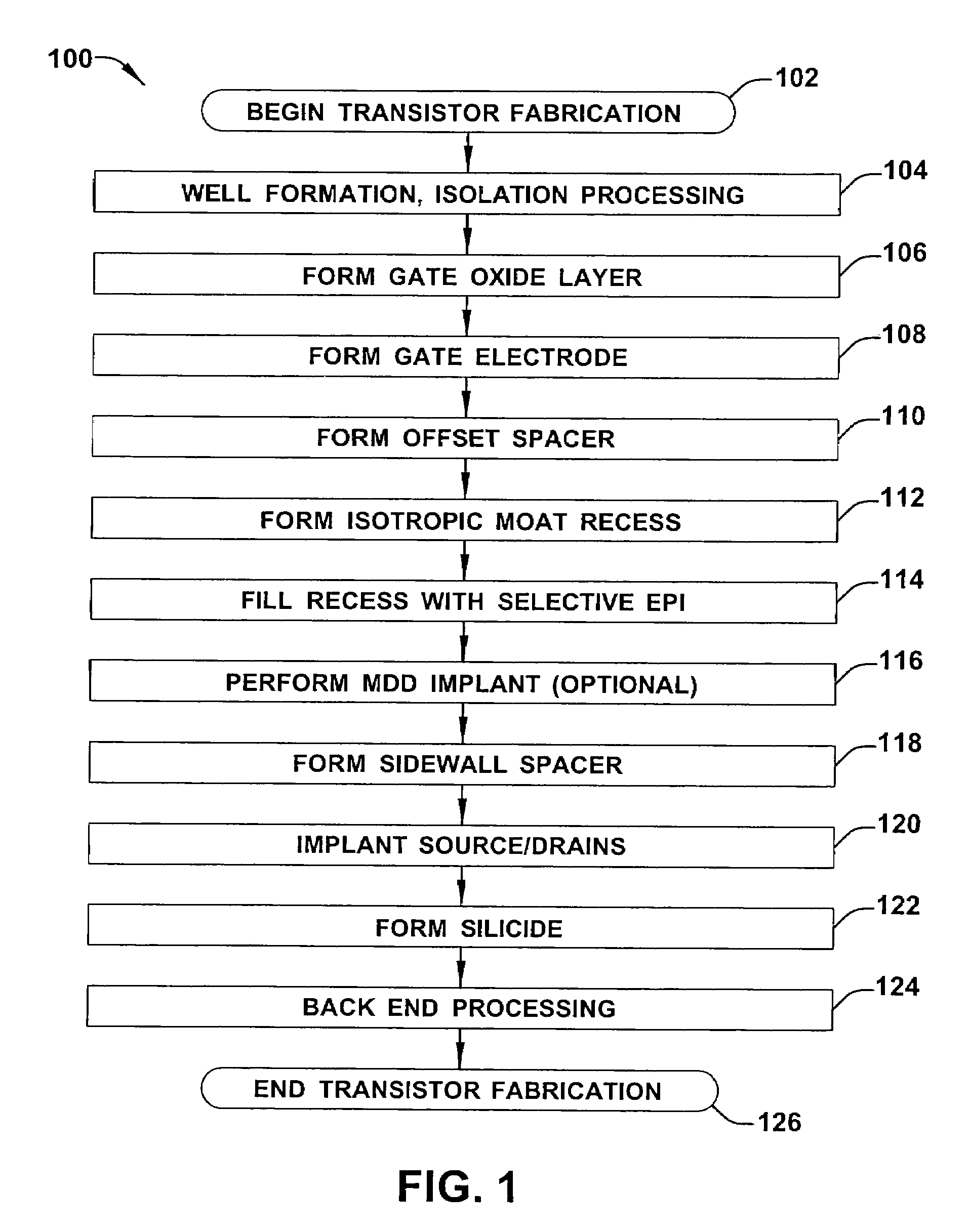

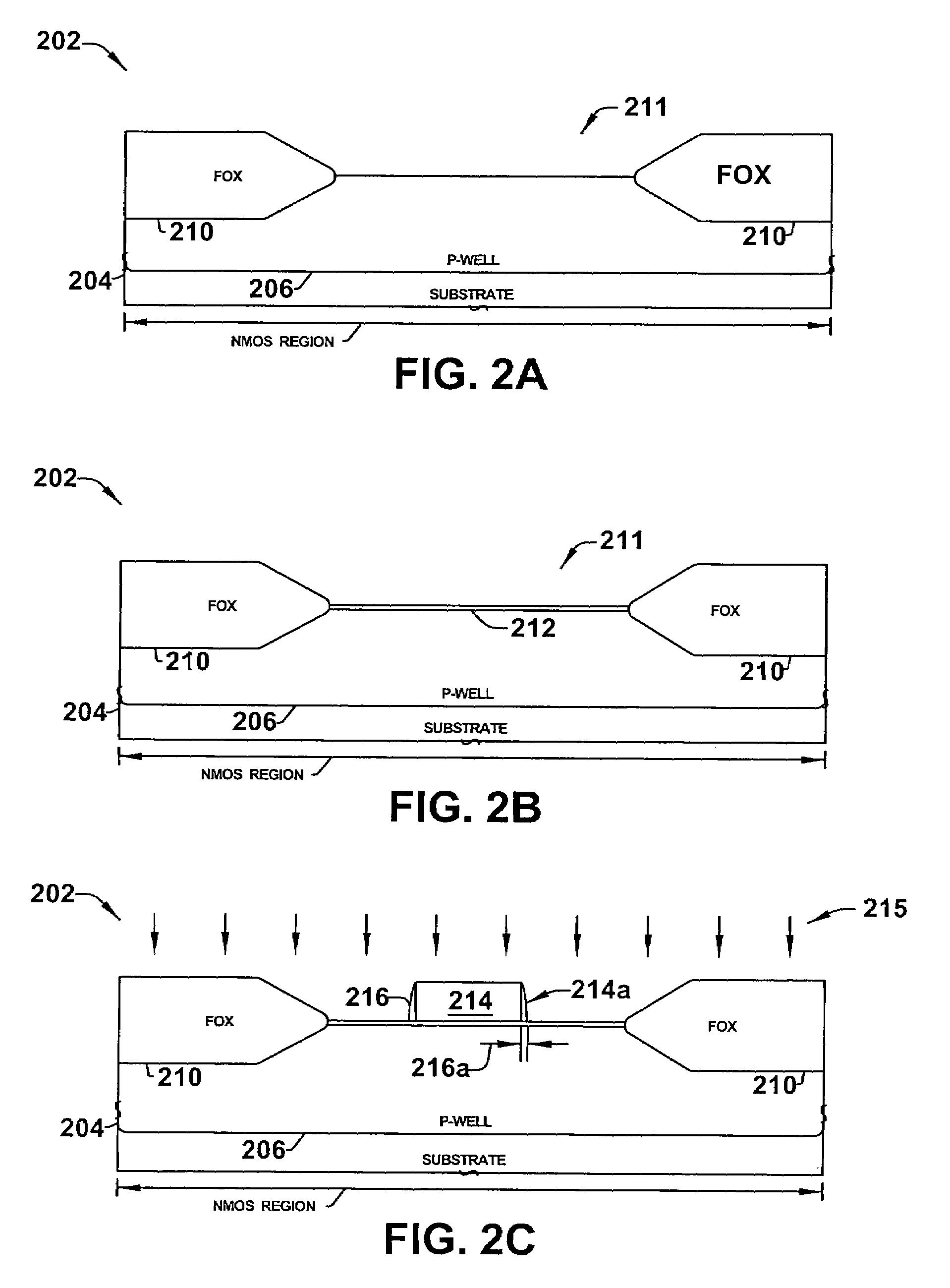

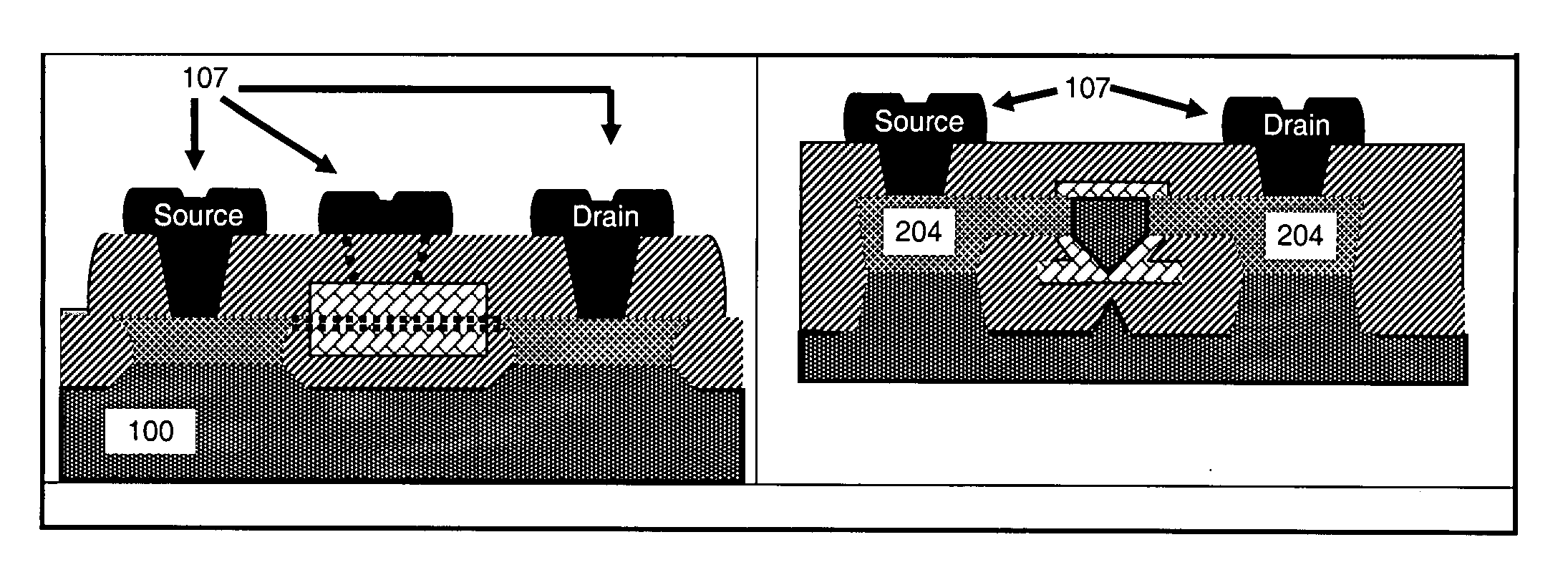

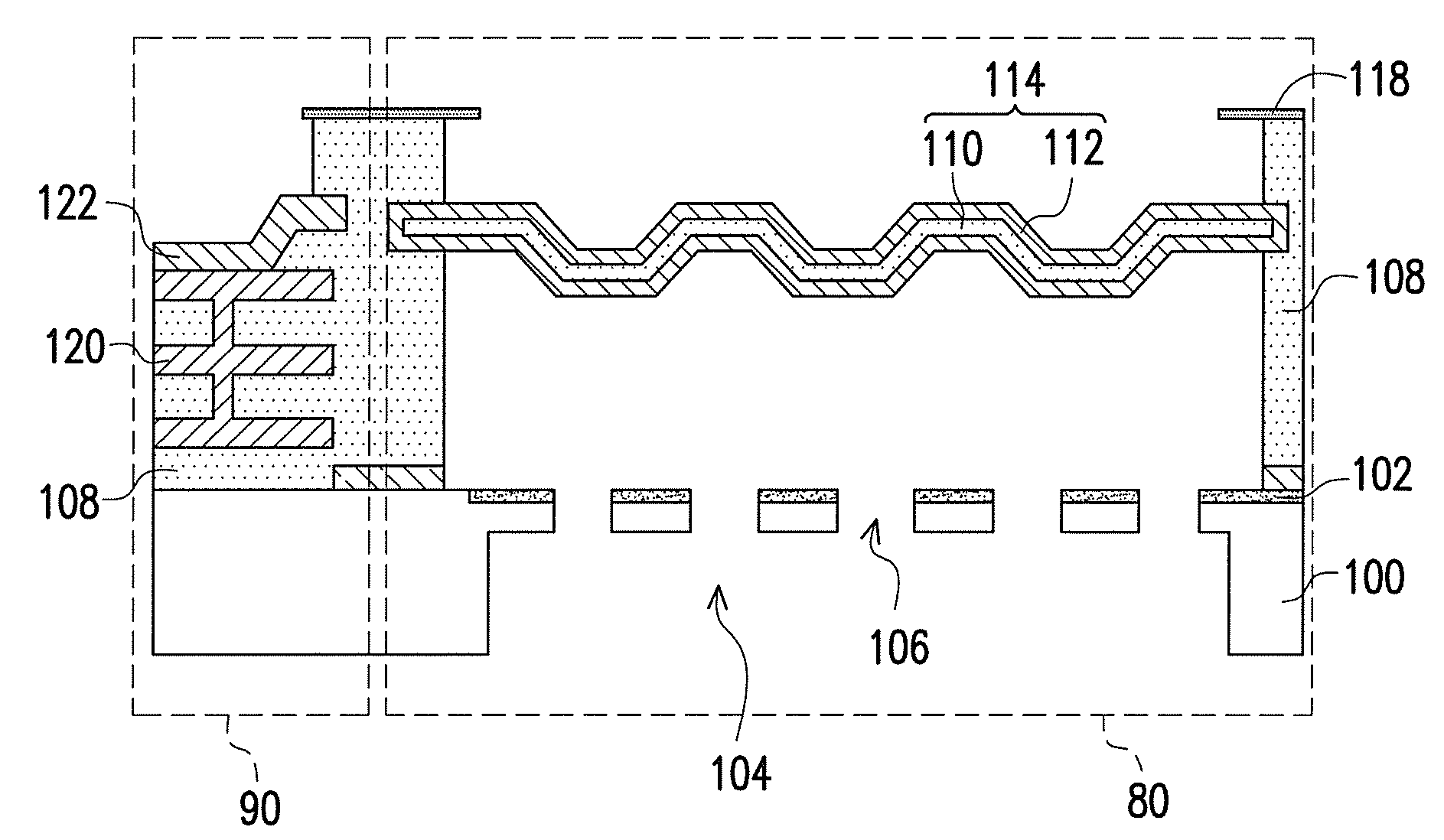

Increased drive current by isotropic recess etch

ActiveUS7060579B2Improve mobilityHigh carrier mobilityTransistorSemiconductor/solid-state device manufacturingStress inducedDriving current

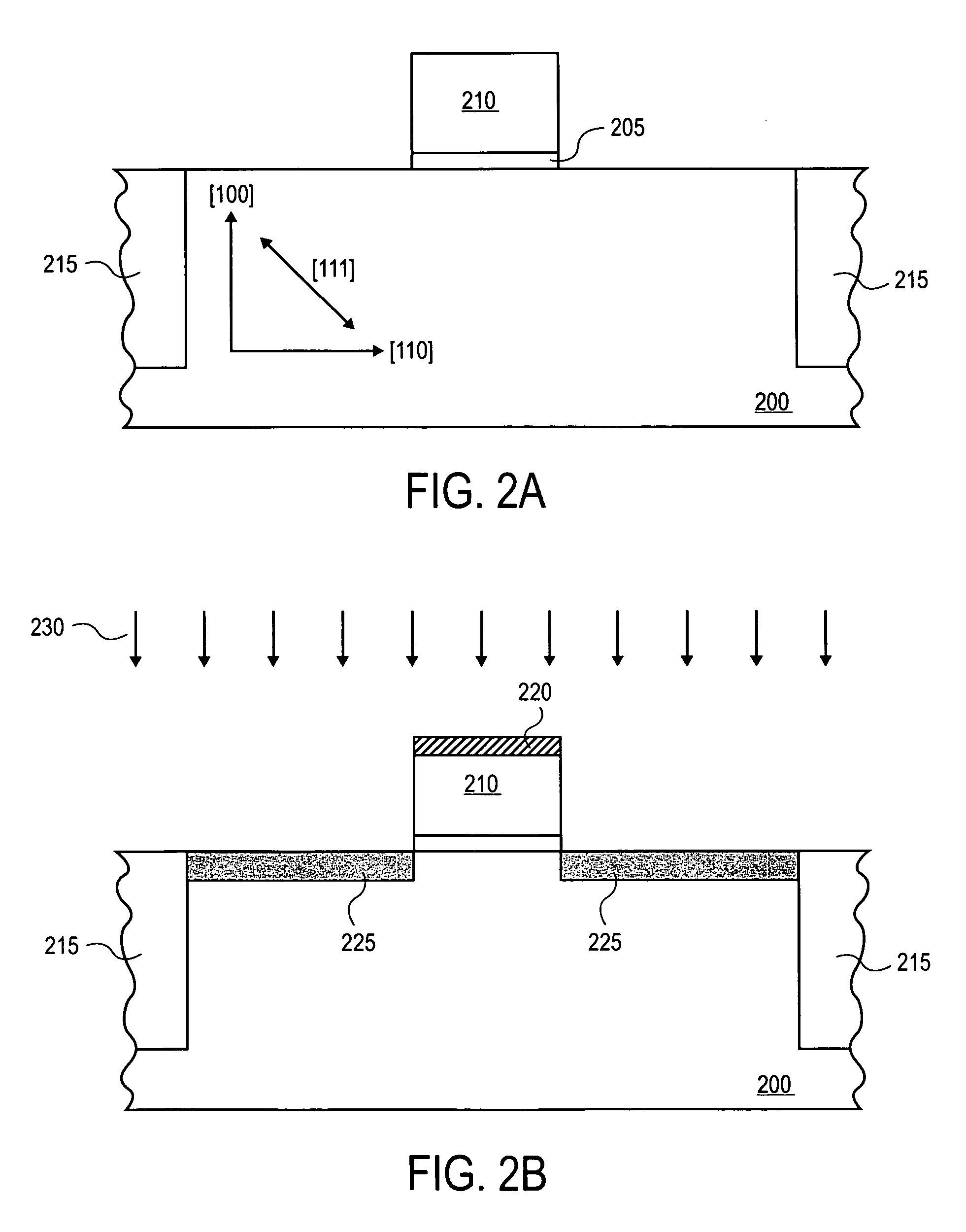

A method (100) of forming a transistor includes forming a gate structure (108) over a semiconductor body and forming recesses (112) using an isotropic etch using the gate structure as an etch mask. The isotropic etch forms a recess in the semiconductor body that extends laterally in the semiconductor body toward a channel portion of the semiconductor body underlying the gate structure. The method further includes epitaxially growing silicon (114) comprising stress-inducing species in the recesses. The source and drain regions are then implanted (120) in the semiconductor body on opposing sides of the gate structure.

Owner:TEXAS INSTR INC

Method for precision integrated circuit die singulation using differential etch rates

A preprocessed semiconductor substrate such as a wafer is provided with a metal etch mask which defines singulation channels on the substrate surface. An isotropic etch process is used to define a singulation channel with a first depth extending into the semiconductor substrate material. A second anisotropic etch process is used to increase the depth of the singulation channel while providing substantially vertical singulation channel sidewalls. The singulation channel can be extended through the depth of the substrate or, in an alternative embodiment, a predetermined portion of the inactive surface of the substrate removed to expose the singulation channels. In this manner, semiconductor die can be precisely singulated from a wafer while maintaining vertical die sidewalls.

Owner:NYTELL SOFTWARE LLC

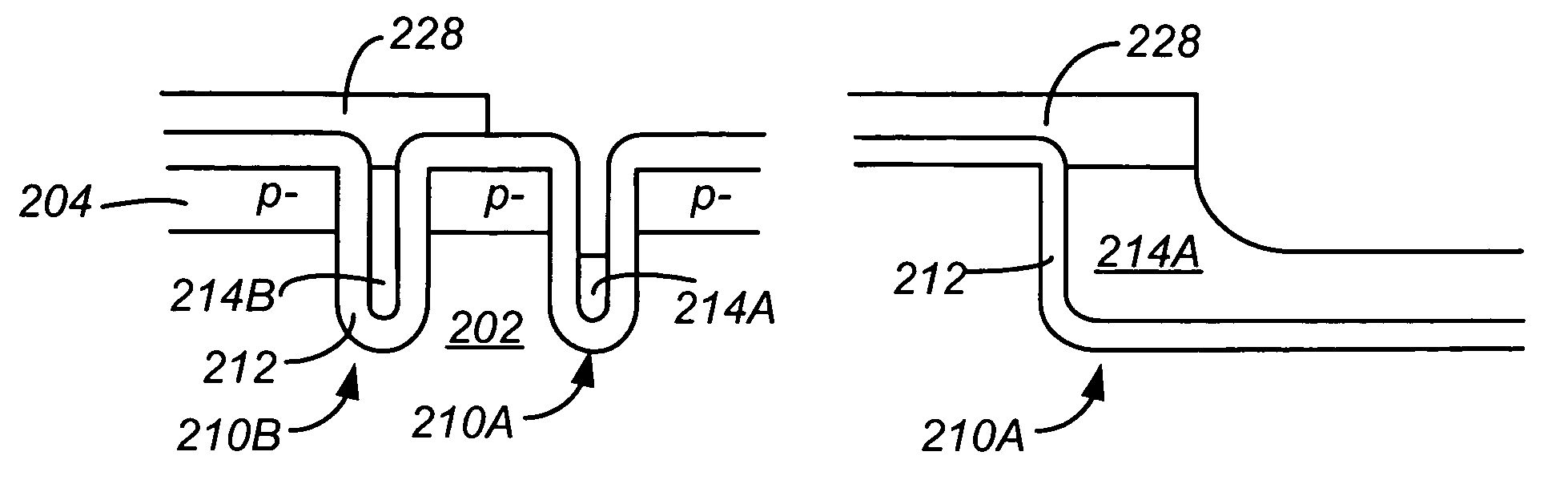

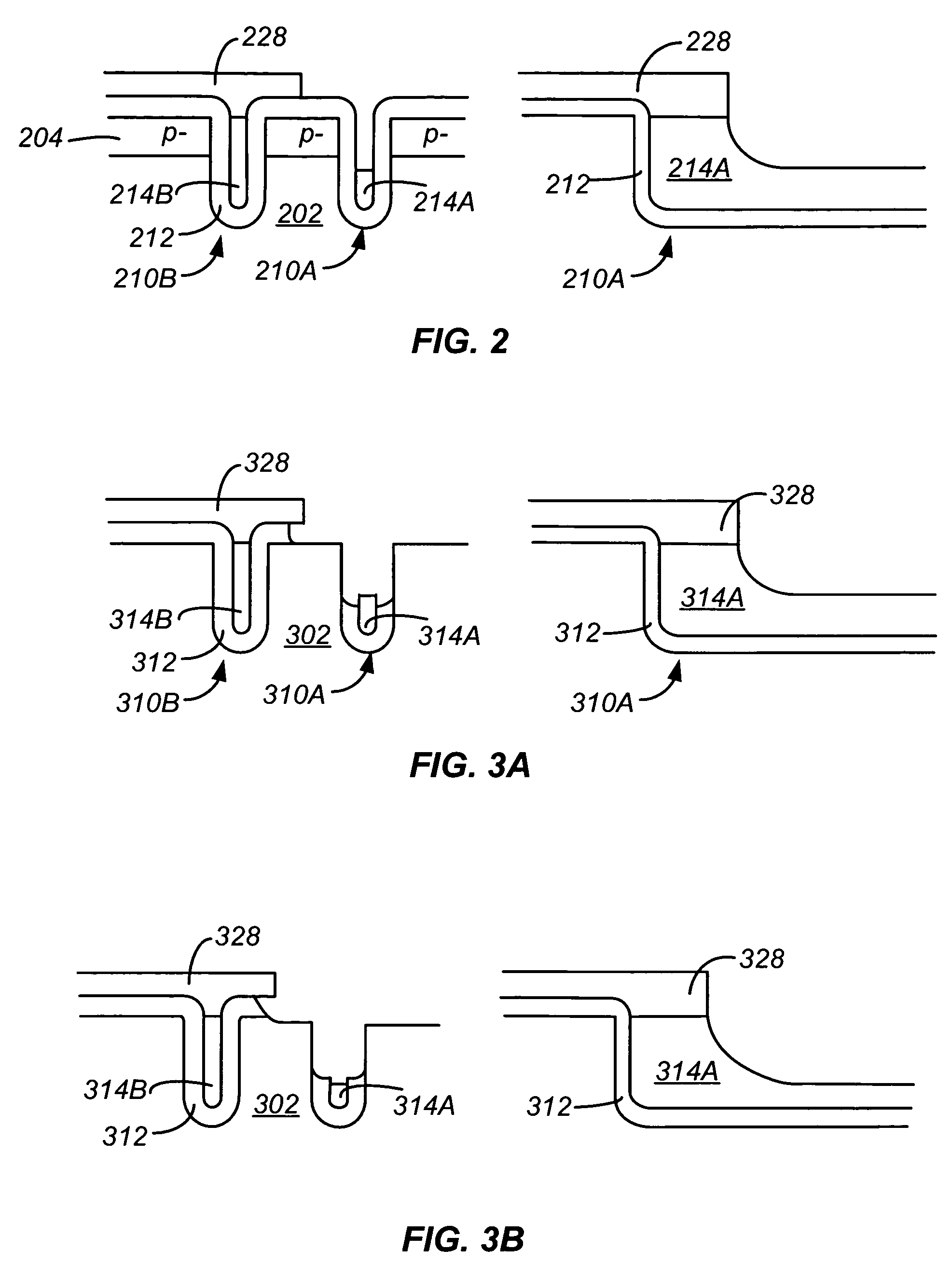

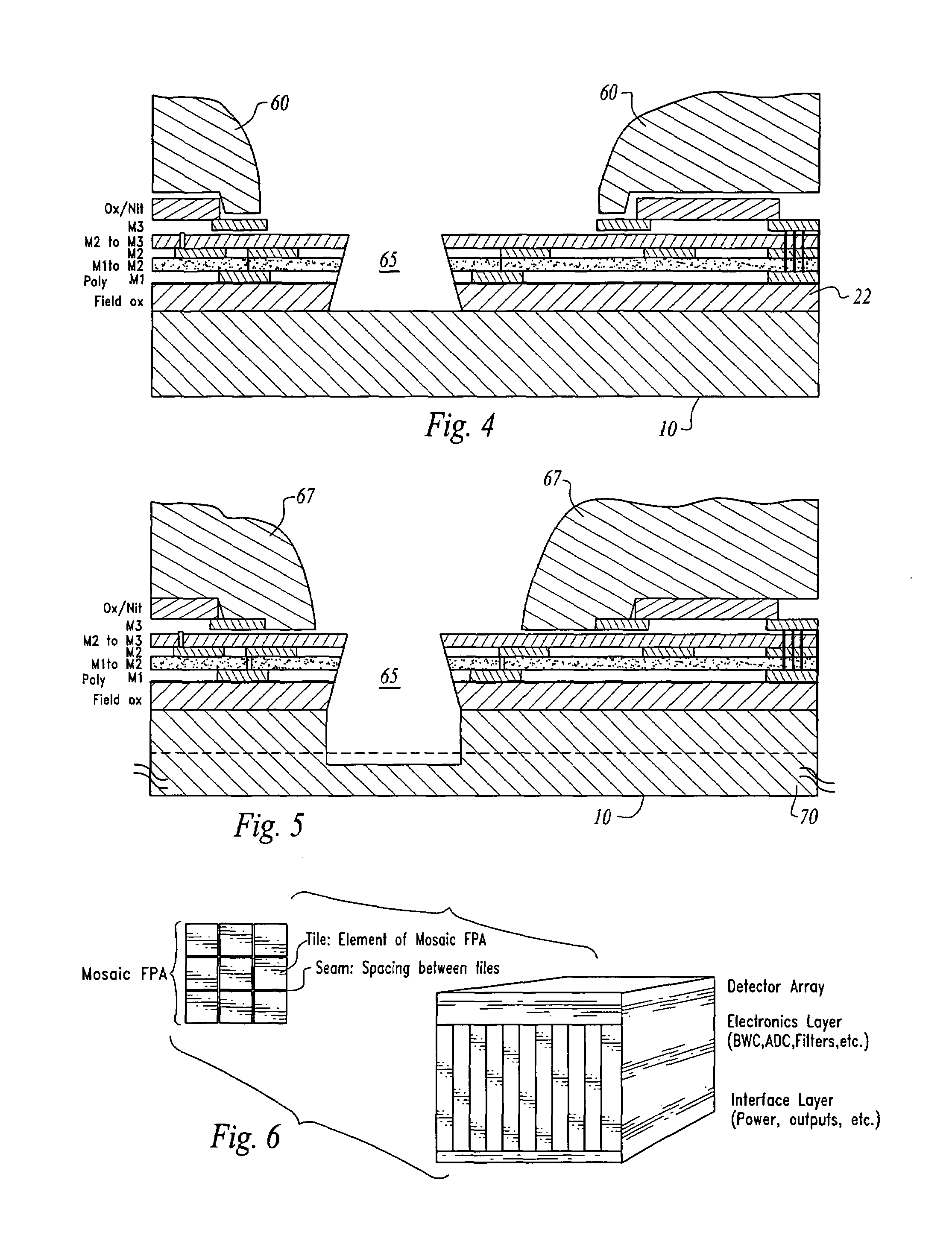

Soi deep trench capacitor employing a non-conformal inner spacer

InactiveUS20090289291A1Simplified and cost-effective manufacturing sequenceTransistorSolid-state devicesDielectricDiffusion barrier

A bottle shaped trench for an SOI capacitor is formed by a simple processing sequence. A non-conformal dielectric layer with an optional conformal dielectric diffusion barrier layer underneath is formed on sidewalls of a deep trench. Employing an isotropic etch, the non-conformal dielectric layer is removed from a bottom portion of the deep trench, leaving a dielectric spacer covering sidewalls of the buried insulator layer and the top semiconductor layer. The bottom portion of the deep trench is expanded to form a bottle shaped trench, and a buried plated is formed underneath the buried insulator layer. The dielectric spacer may be recessed during formation of a buried strap to form a graded thickness dielectric collar around the upper portion of an inner electrode. Alternately, the dielectric spacer may be removed prior to formation of a buried strap.

Owner:GLOBALFOUNDRIES INC

Method of manufacturing a body-contacted finfet

ActiveUS7485520B2Semiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricSemiconductor materials

Owner:GLOBALFOUNDRIES US INC

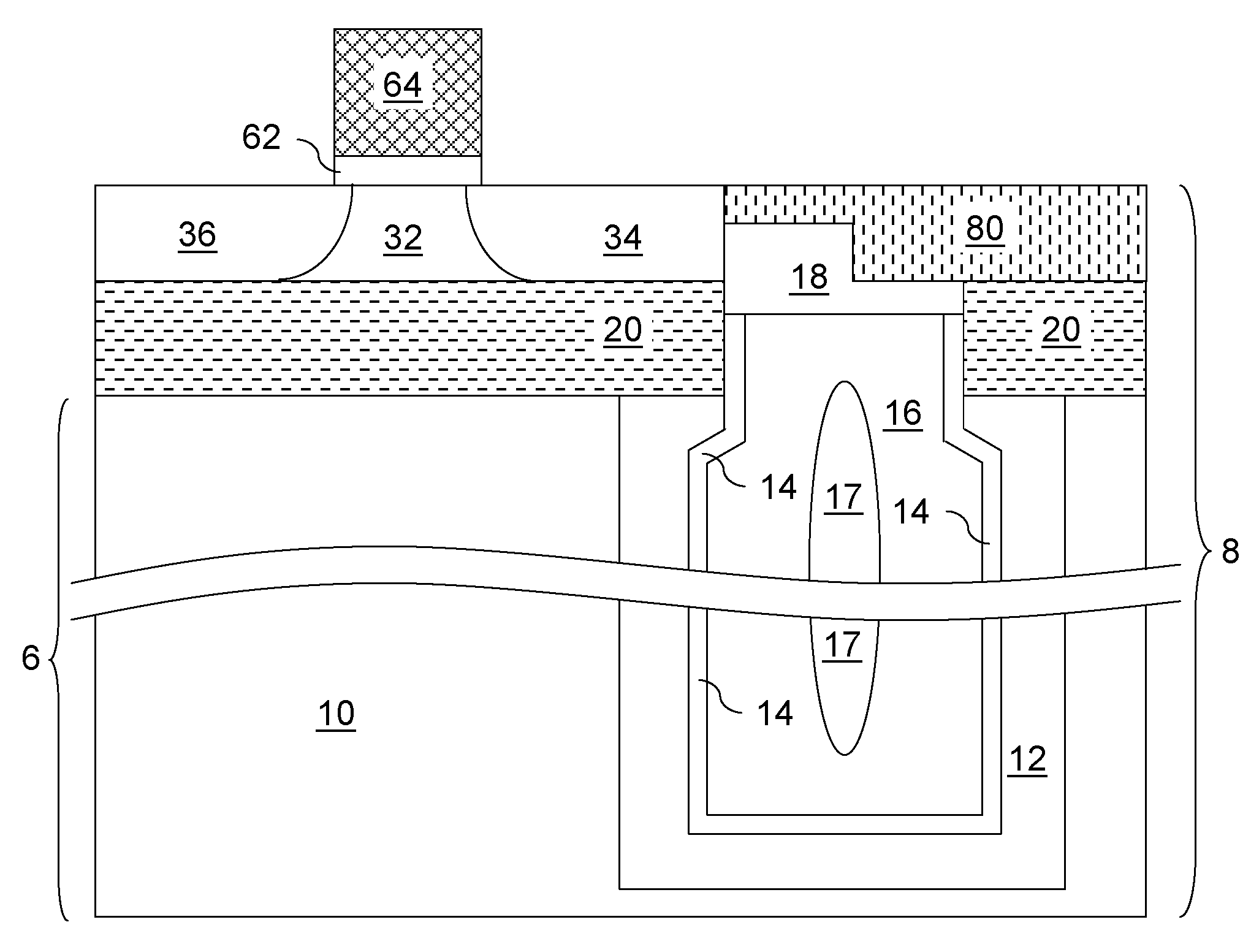

Fabrication of silicon nano wires and gate-all-around MOS devices

InactiveUS20070298551A1Quality improvementEnhance the quantum effectNanoinformaticsSemiconductor/solid-state device manufacturingMOSFETCapacitance

The invention relates to methods for manufacturing semiconductor devices. Processes are disclosed for implementing suspended single crystal silicon nano wires (NWs) using a combination of anisotropic and isotropic etches and spacer creation for sidewall protection. The core dimensions of the NWs are adjustable with the integration sequences: they can be triangular, rectangular, quasi-circular, or an alternative polygonal shape. Depending on the length of the NWs, going from the sub-micron to millimeter range, the NWs may utilize support from anchors to the side, during certain processing steps. By changing the lithographic dimensions of the anchors compared to the NWs, the anchors may be reduced or eliminated during processing. The method covers, among other things, the integration of Gate-All-Around NW (GAA-NW) MOSFETs on a bulk semiconductor. The GAA structure may consist of a silicon core fabricated as specified in the invention, surrounded by any usable gate dielectric, and finally by a gate material, such as polysilicon or metal. The source and drain of the GAA-NW may be connected to the bulk semiconductor to avoid self heating of the device over a wide range of operating conditions. The GAA-NW MOS capacitor can also be used for the integration of a Gate-All-Around optical phase modulator (GAA modulator). The working principle for the optical modulator is modulation of the refractive index by free carrier accumulation or inversion in a MOS capacitive structure, which changes the phase of the propagating light.

Owner:ECOLE POLYTECHNIQUE FEDERALE DE LAUSANNE (EPFL)

Method of manufacturing microlens, microlens, microlens array, electro-optical device, and electronic apparatus

InactiveUS7372631B2Inhibition of shortened lifespanSacrificing display performanceSemiconductor/solid-state device manufacturingOptical articlesMicro lens arrayMask layer

A method of manufacturing a microlens includes: forming on a transparent substrate an etching stop layer in a lens formation region where a curved lens surface of the microlens is to be formed, the etching stop layer having an island shape as a planar shape thereof; forming an intermediate layer on the etching stop layer; forming an etching mask layer on the intermediate layer, the etching mask layer having an opening at a position facing the etching stop layer; and etching, by means of isotropic etching, the intermediate layer from the opening, and etching the transparent substrate and the intermediate layer from a side of the etching stop layer.

Owner:SEIKO EPSON CORP

CMOS microelectromechanical system (MEMS) device and fabrication method thereof

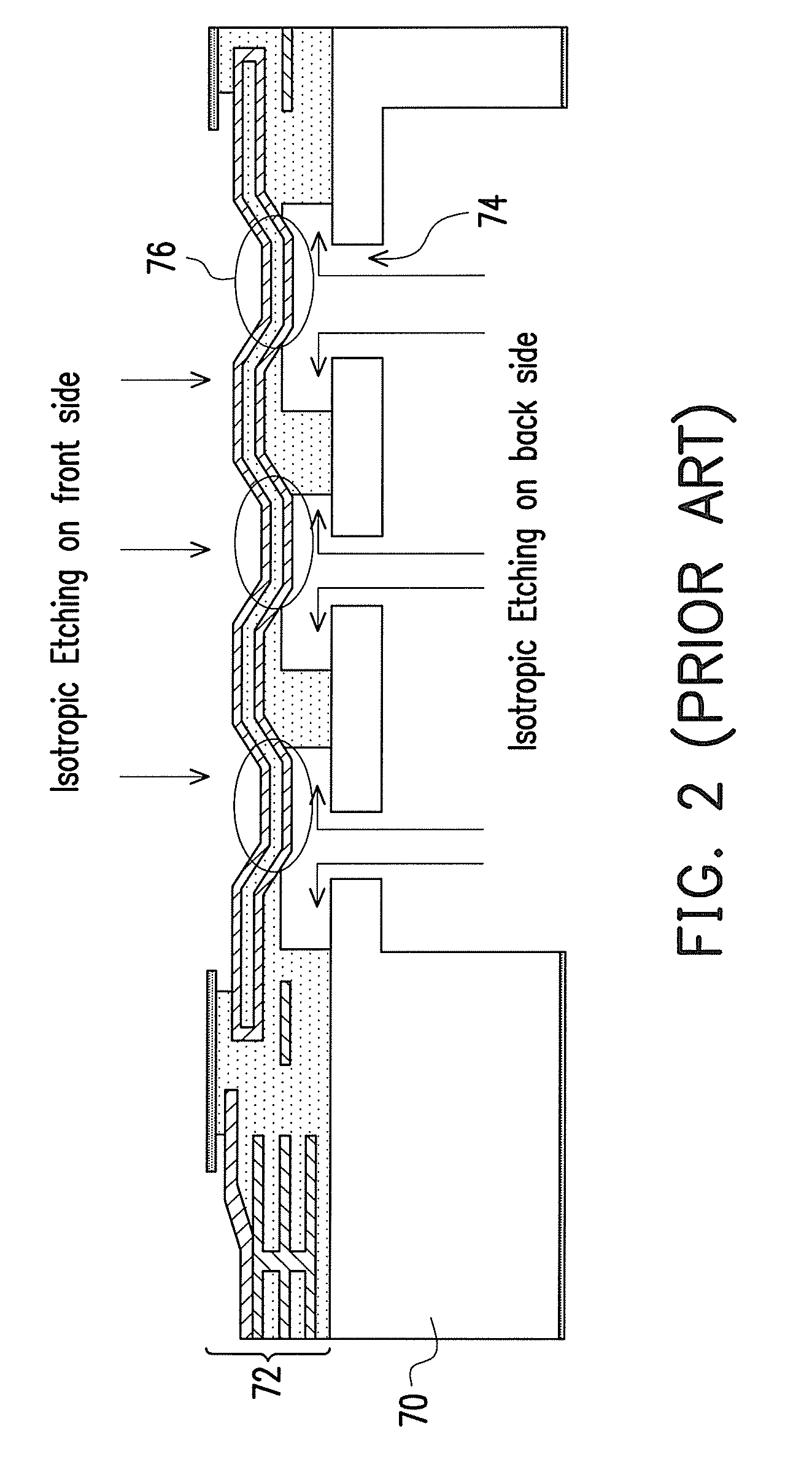

ActiveUS20100330722A1Reduce undercuttingReduce harmFluid pressure measurement by electric/magnetic elementsSemiconductor/solid-state device manufacturingCMOSMicroelectromechanical systems

A method for fabricating the MEMS device includes providing a substrate. Then, a structural dielectric layer is formed over the substrate at a first side, wherein a diaphragm is embedded in the structural dielectric layer. The substrate is patterned from a second side to form a cavity in corresponding to the diaphragm and a plurality of venting holes in the substrate. An isotropic etching process is performed from the first side and the second side of the substrate via vent holes to remove a dielectric portion of the structural dielectric layer for exposing a central portion of the diaphragm while an end portion is held by a residue portion of the structural dielectric layer.

Owner:SOLID STATE SYST

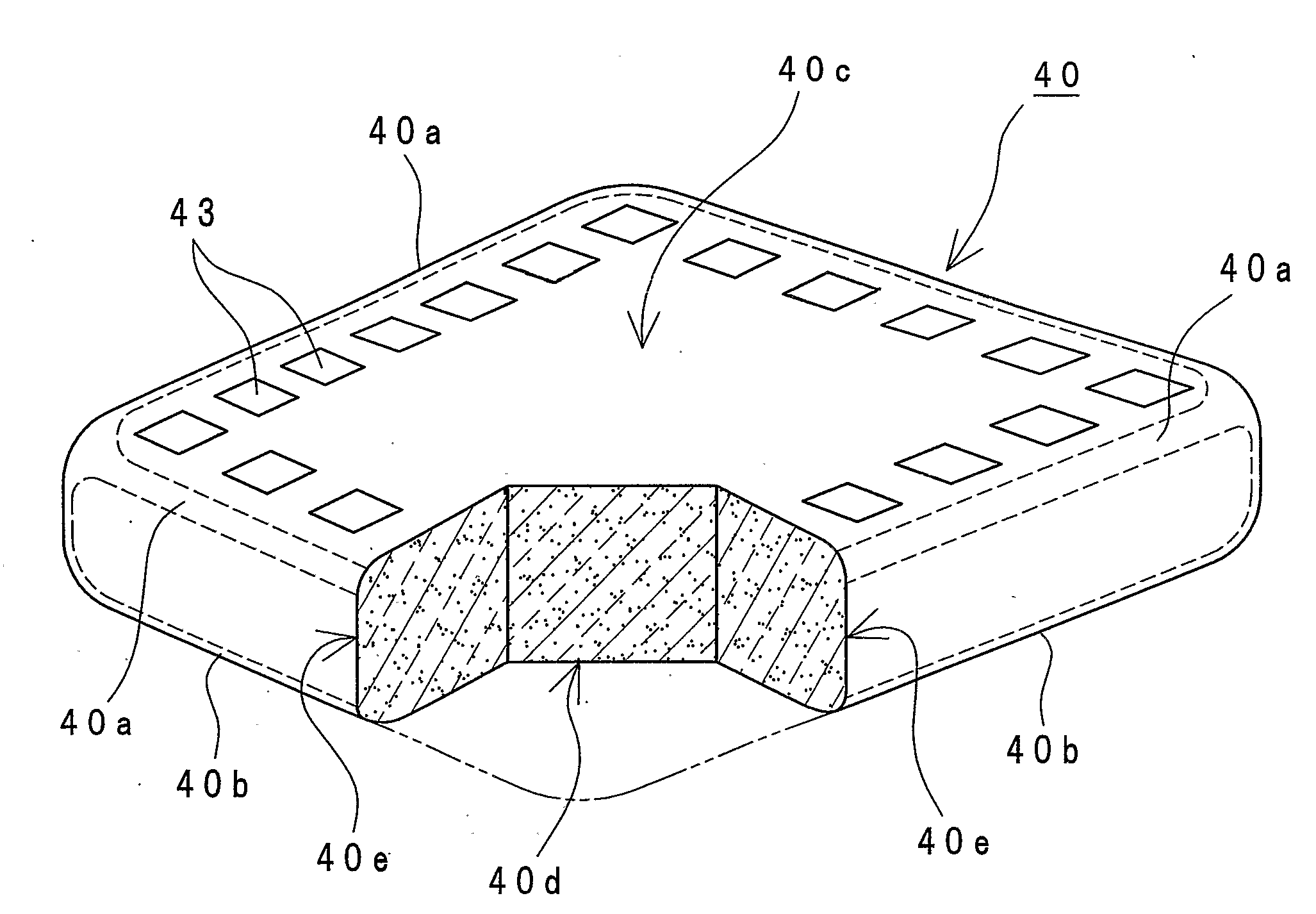

Manufacturing Method for Semiconductor Chips, and Semiconductor Chip

ActiveUS20090057838A1Easily brokenReduced strengthElectric discharge tubesSemiconductor/solid-state device detailsSemiconductor chipPlasma etching

In a manufacturing method for performing plasma etching on a second surface of a semiconductor wafer that has a first surface where an insulating film is placed in dividing regions and the second surface which is opposite from the first surface and on which a mask for defining the dividing regions is placed thereby exposing the insulating film from etching bottom portions by removing portions that correspond to the dividing regions and subsequently continuously performing the plasma etching in the state in which the exposed surfaces of the insulating film are charged with electric charge due to ions in the plasma thereby removing corner portions put in contact with the insulating film in the device-formation-regions, isotropic etching is performed on the semiconductor wafer at any timing.

Owner:PANASONIC CORP