Patents

Literature

297results about How to "Increase process margin" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

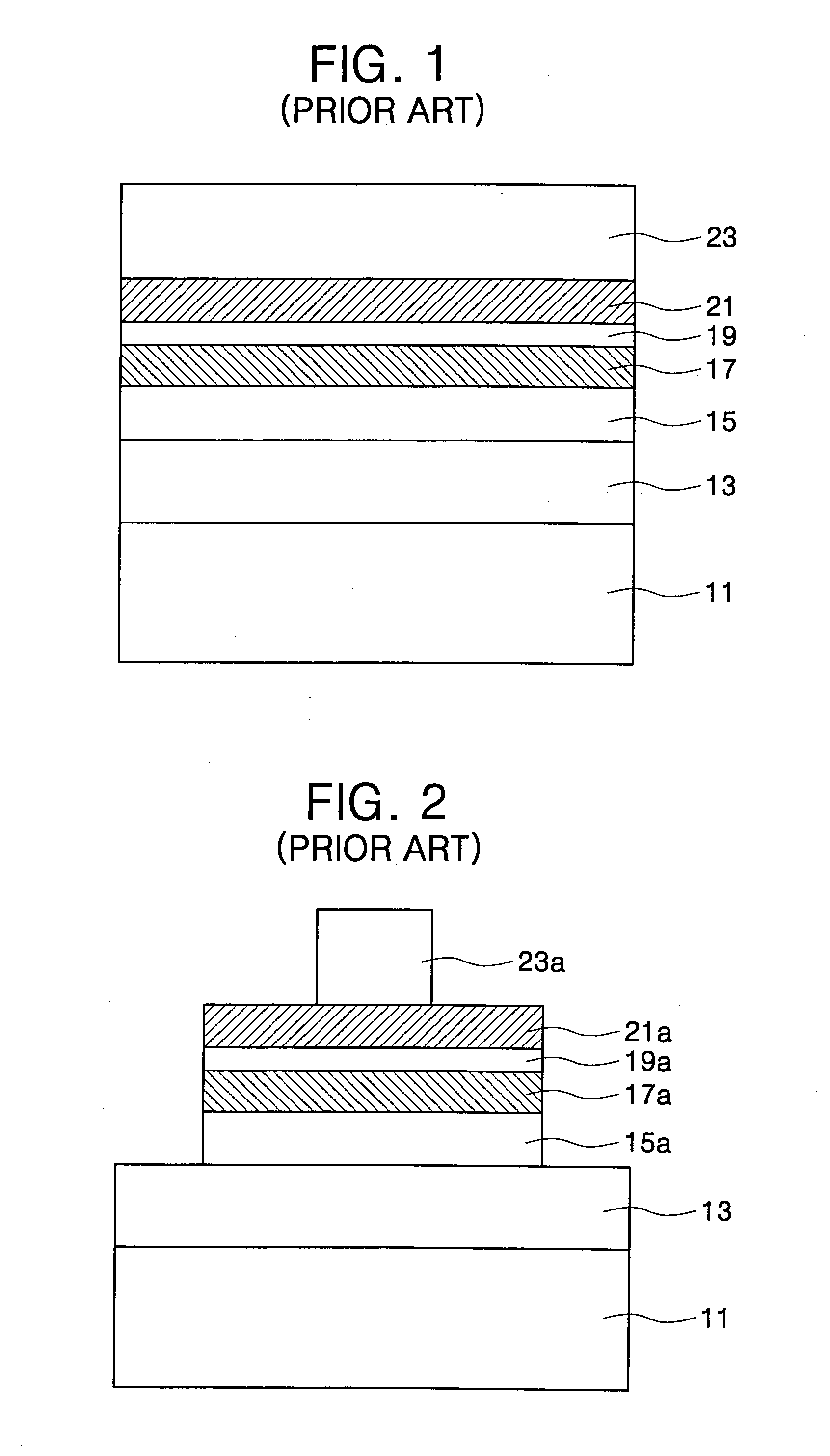

Method for fabricating semiconductor device capable of scribing chips with high yield

ActiveUS20050269702A1Improve production yieldSpeed up preparationSemiconductor/solid-state device detailsSolid-state devicesDevice materialInterconnection

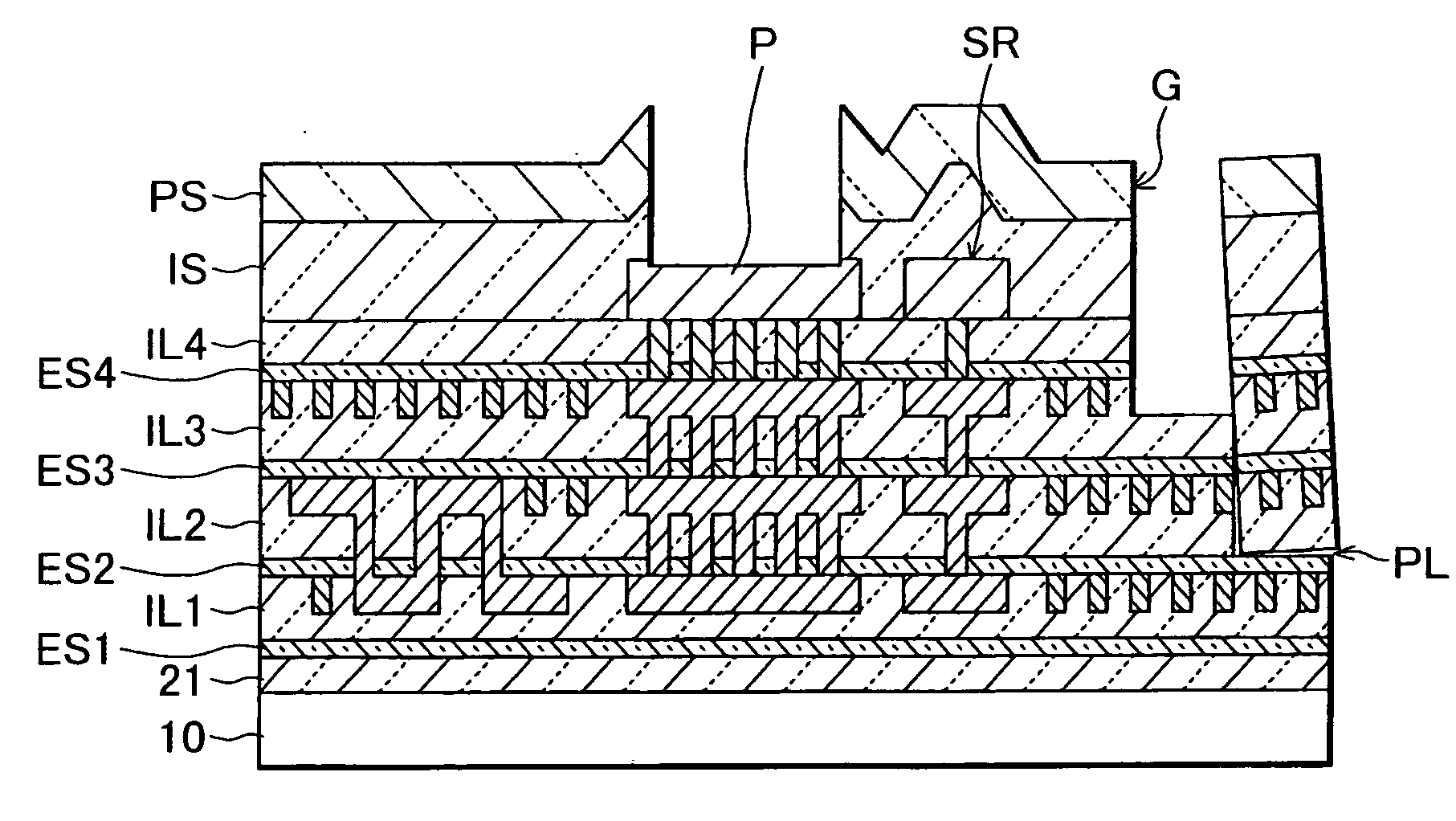

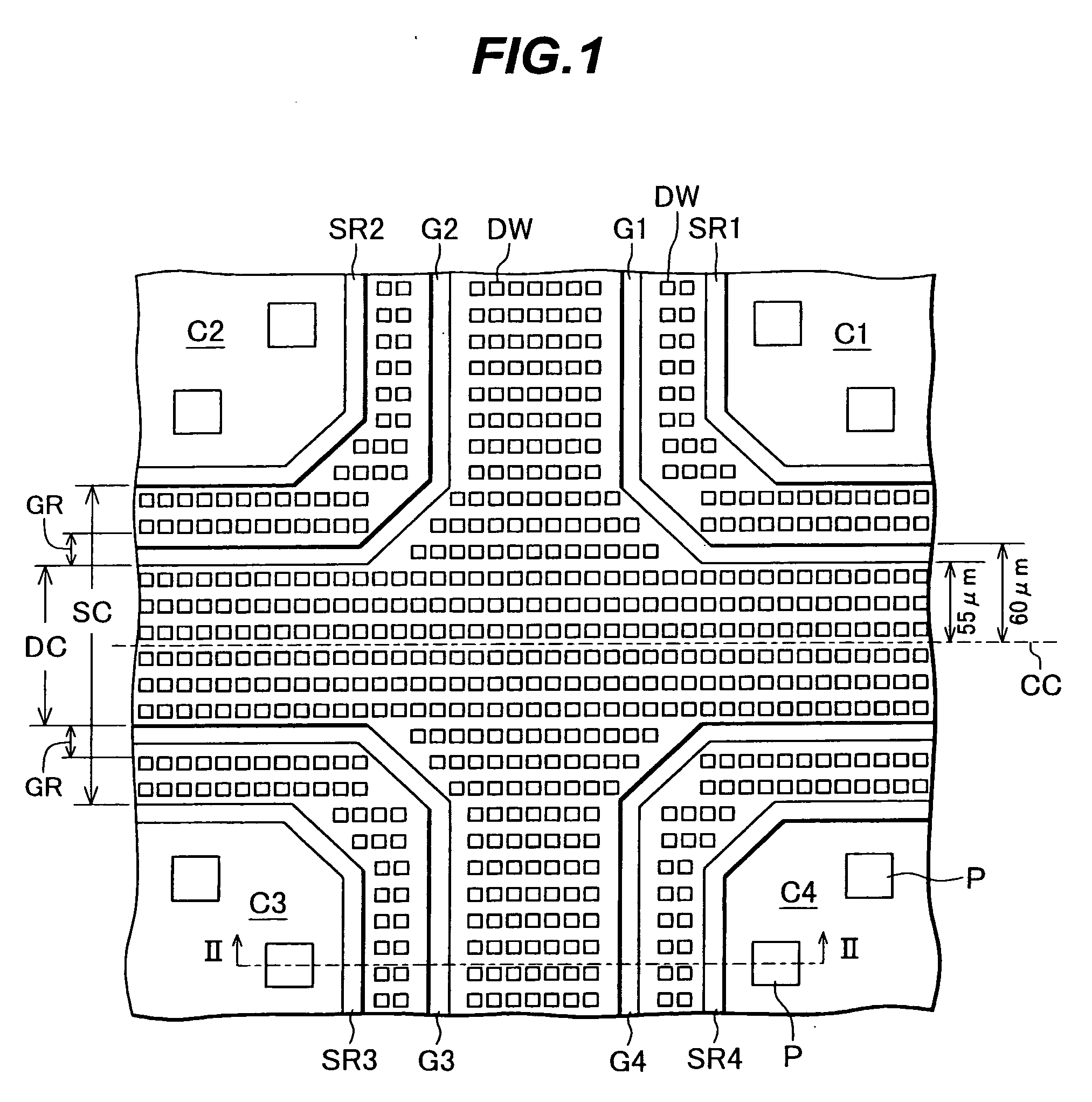

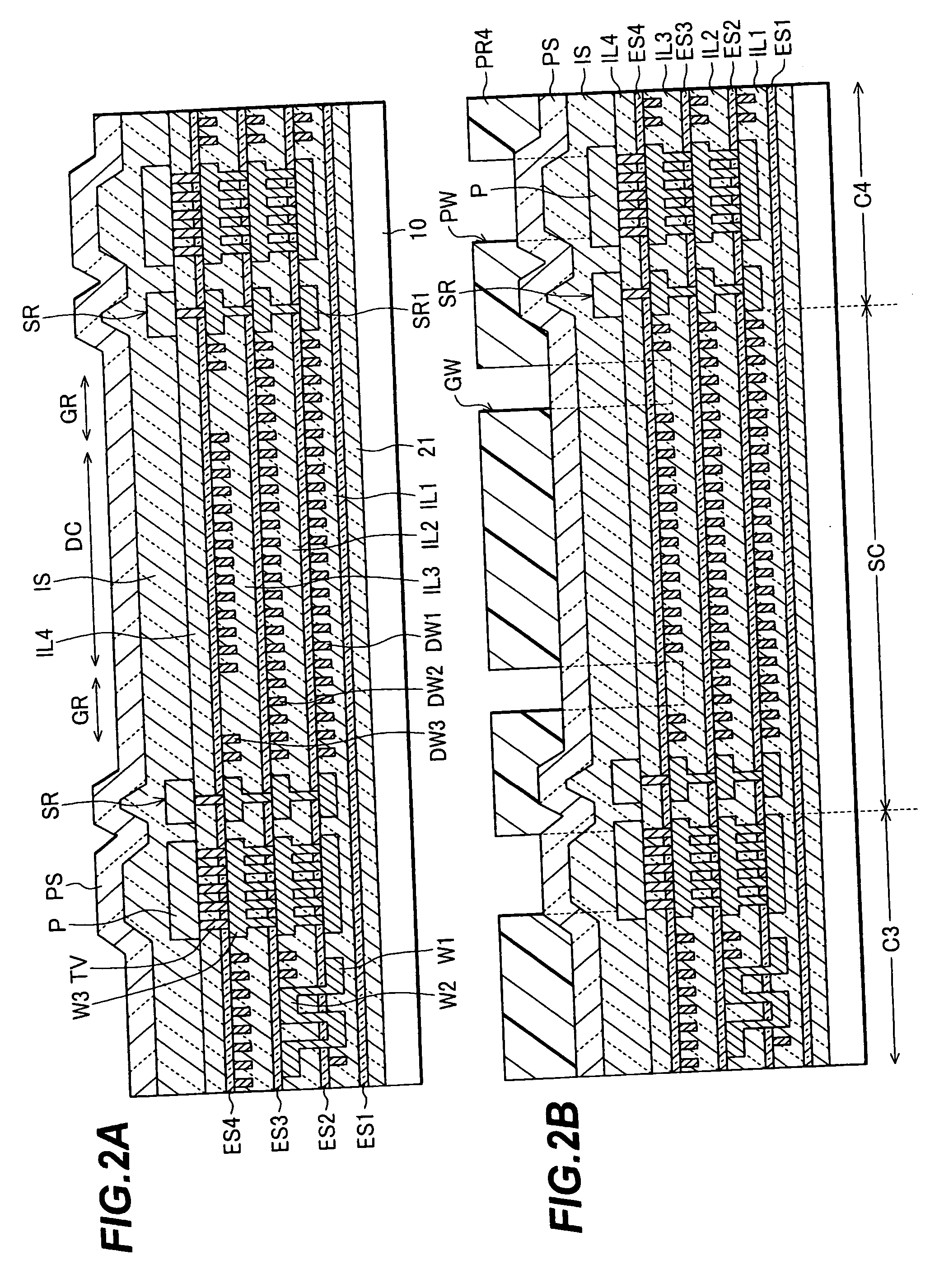

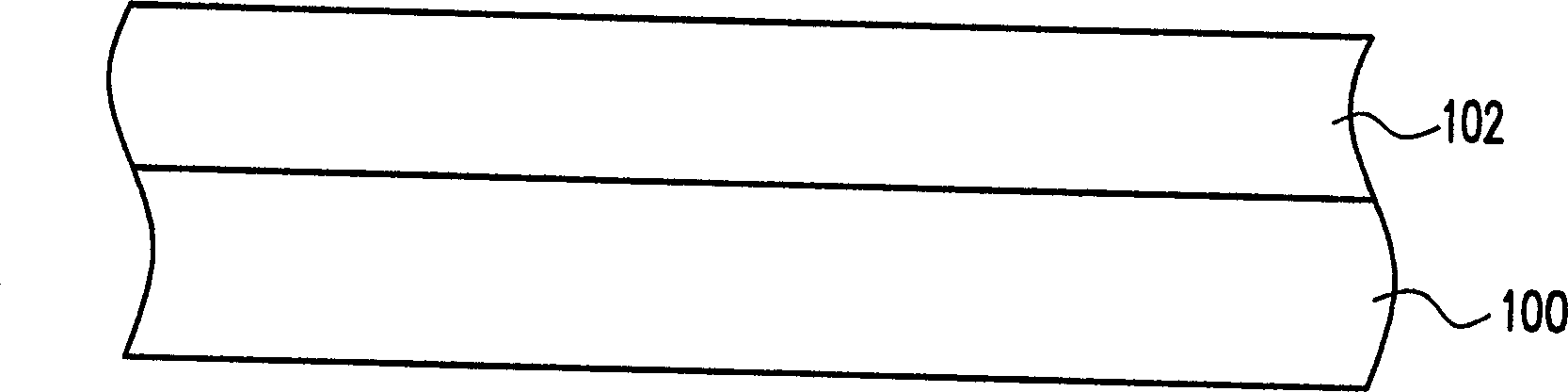

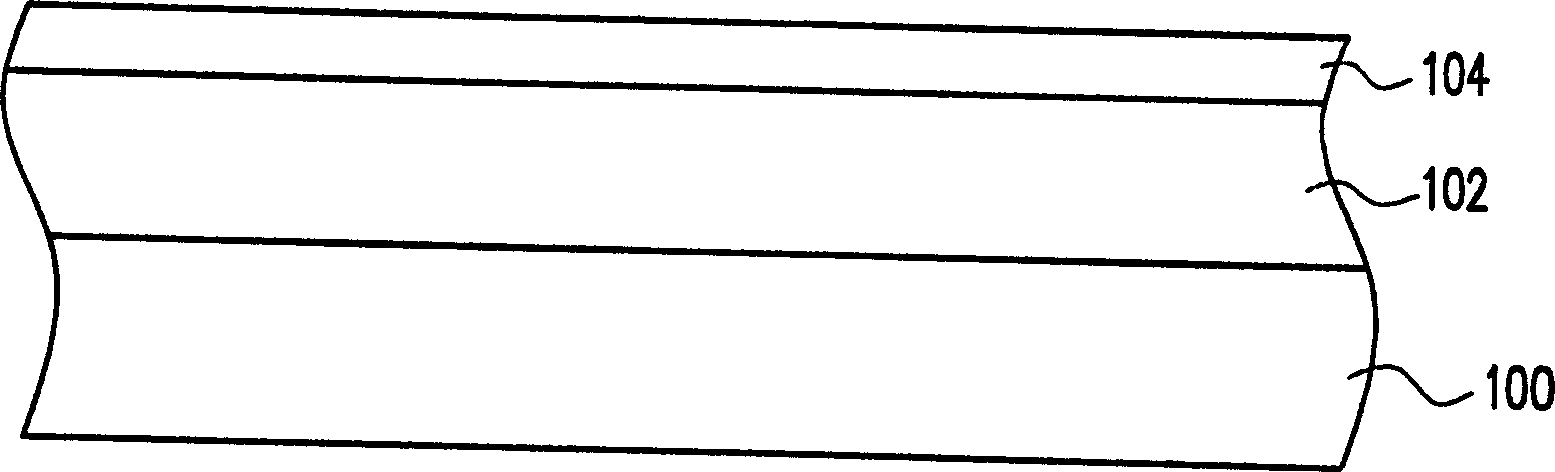

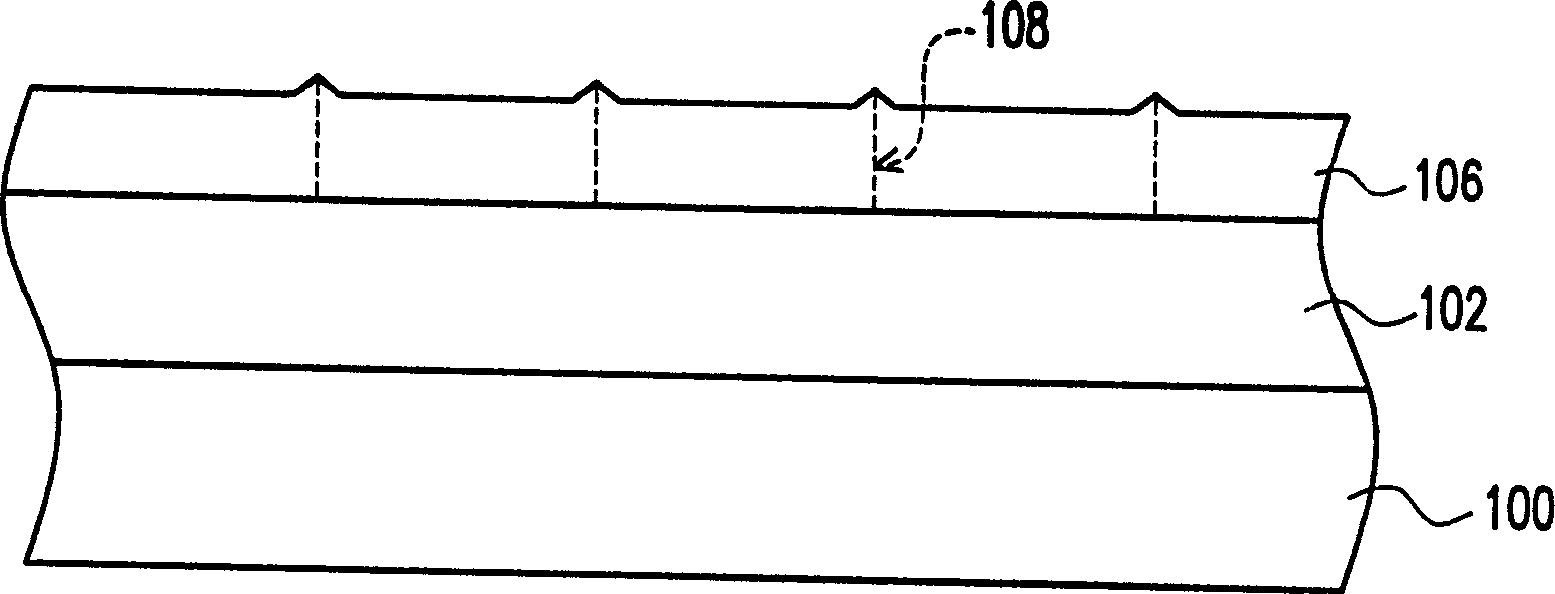

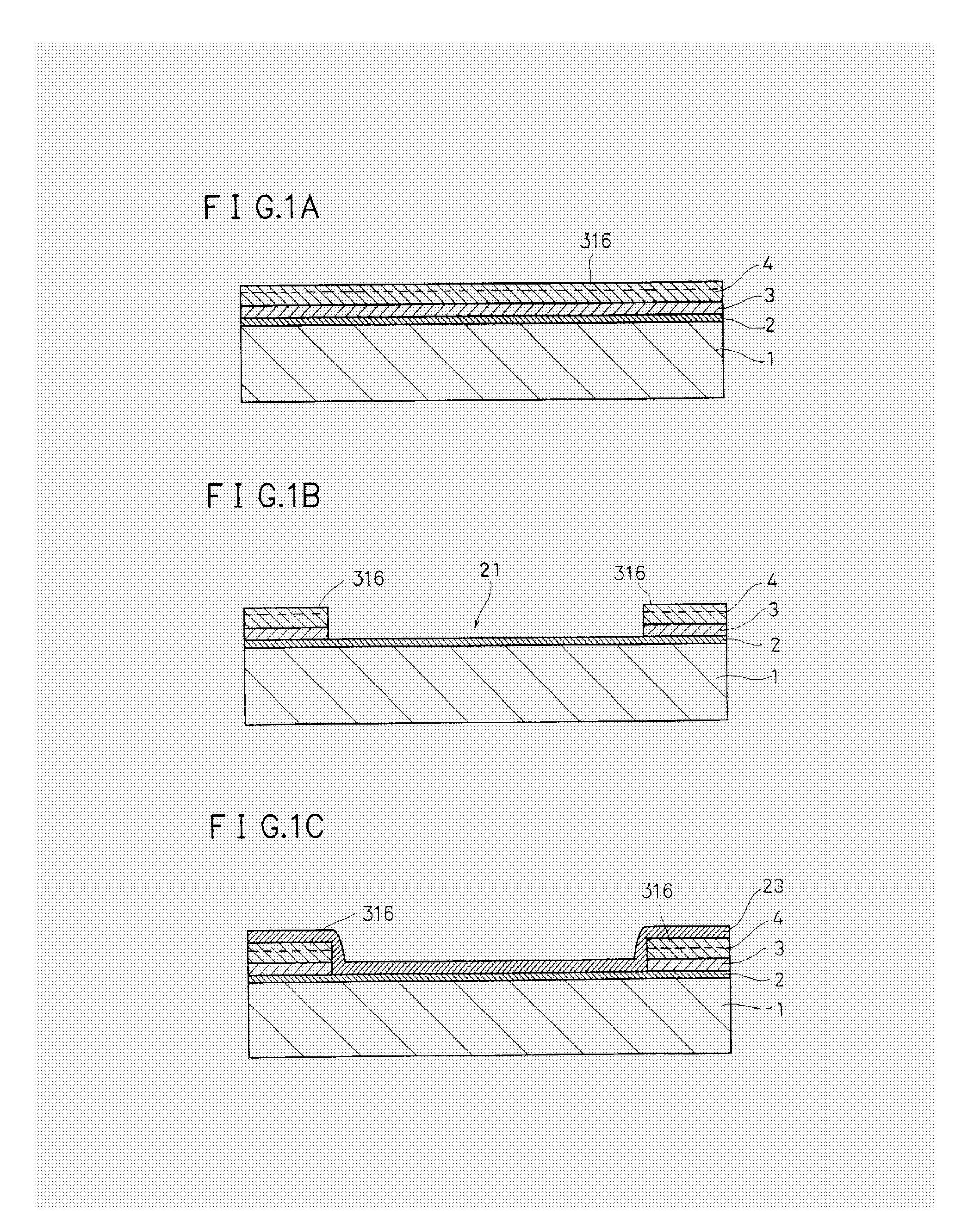

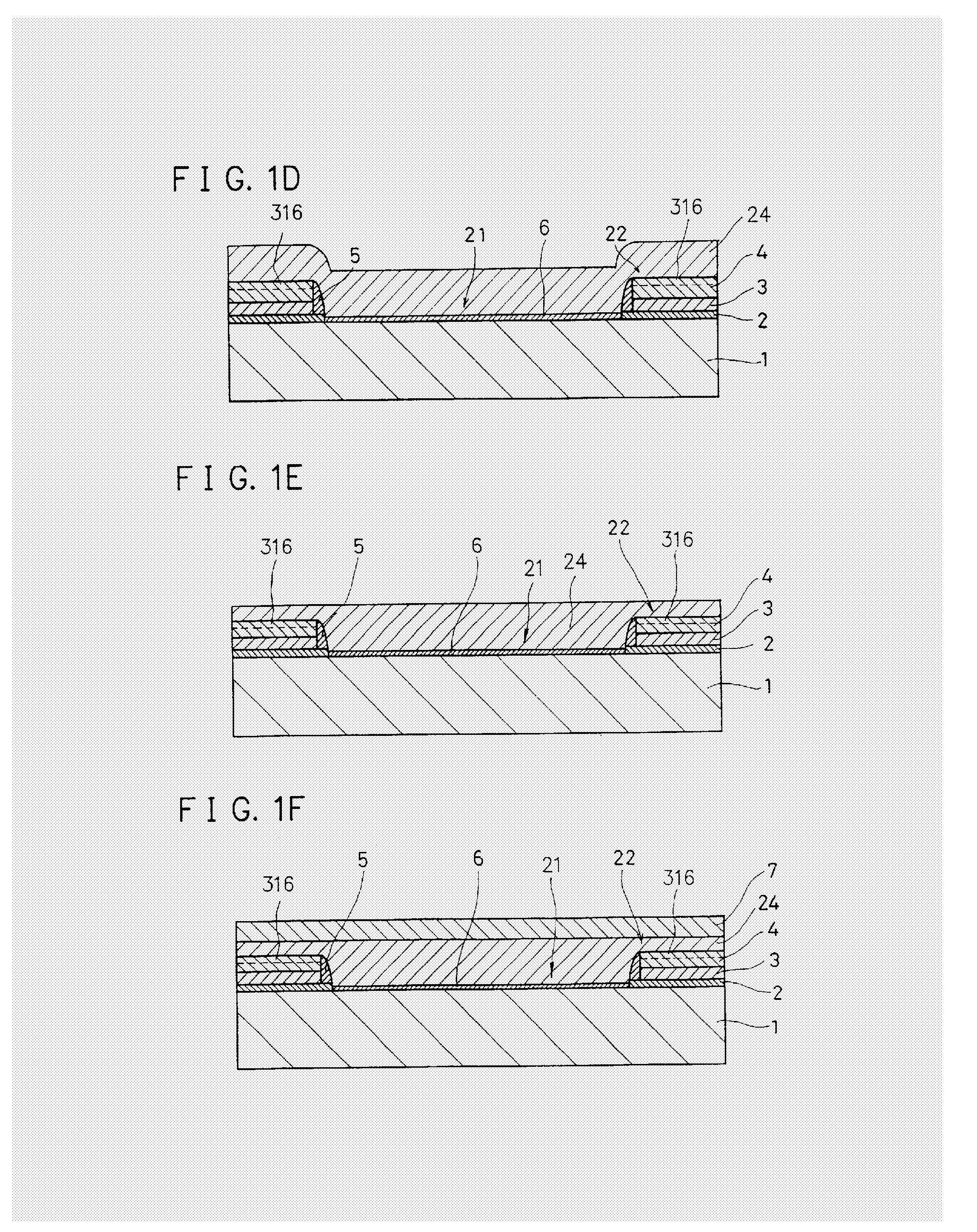

A method for fabricating a semiconductor device in which a scribe area can be diced with high yield. The method for fabricating a semiconductor device comprises (a) a step for providing a semiconductor wafer having a plurality of chip areas in which semiconductor elements are formed, and a scribe area for separating the plurality of chip areas and including dicing areas with groove forming areas being defined to surround each chip area on the outer side of the dicing area in the scribe area, (b) a step for arranging a multilayer interconnection structure where interlayer insulation films and interconnection layers are formed alternately above the semiconductor wafer along with dummy lines, (c) a step for forming a cover layer covering the multilayer interconnection structure and including a passivation layer, and (d) a step for forming a groove surrounding each of the plurality of chip areas and penetrating at least the passivation layer from above in the groove forming area.

Owner:FUJITSU LTD

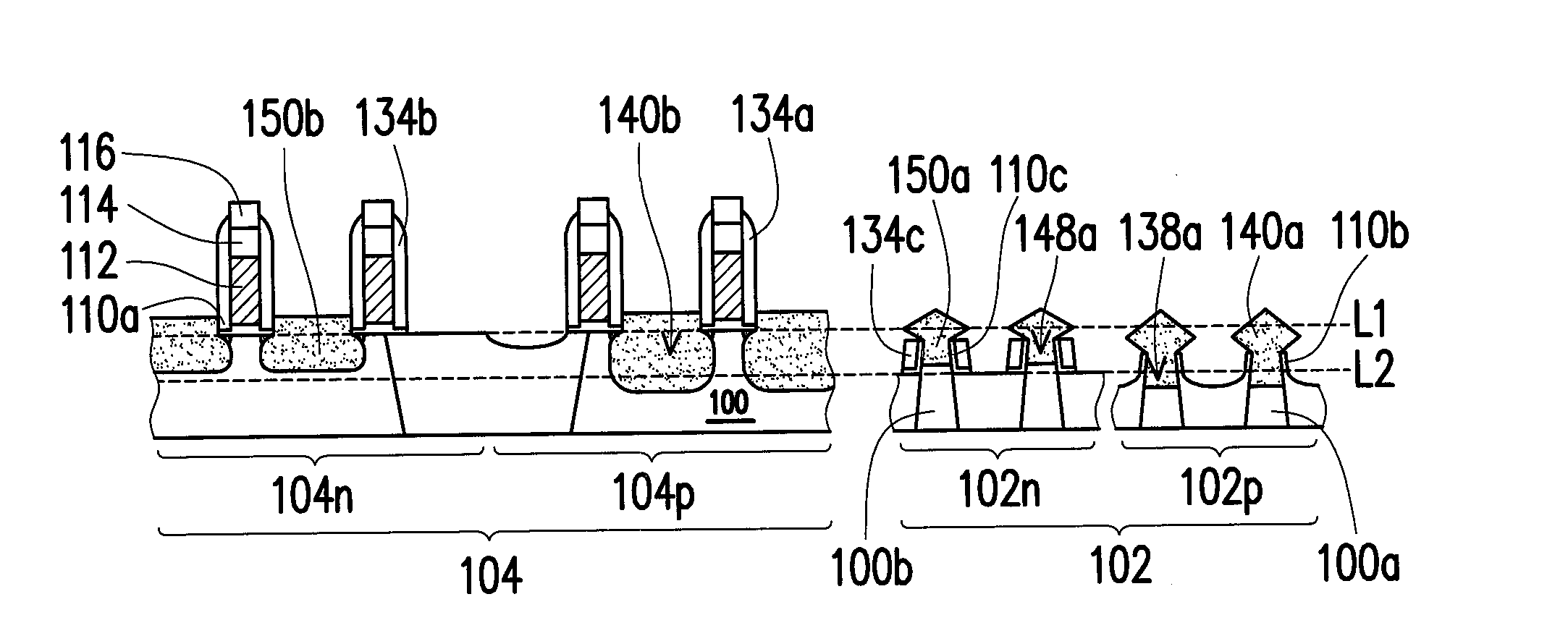

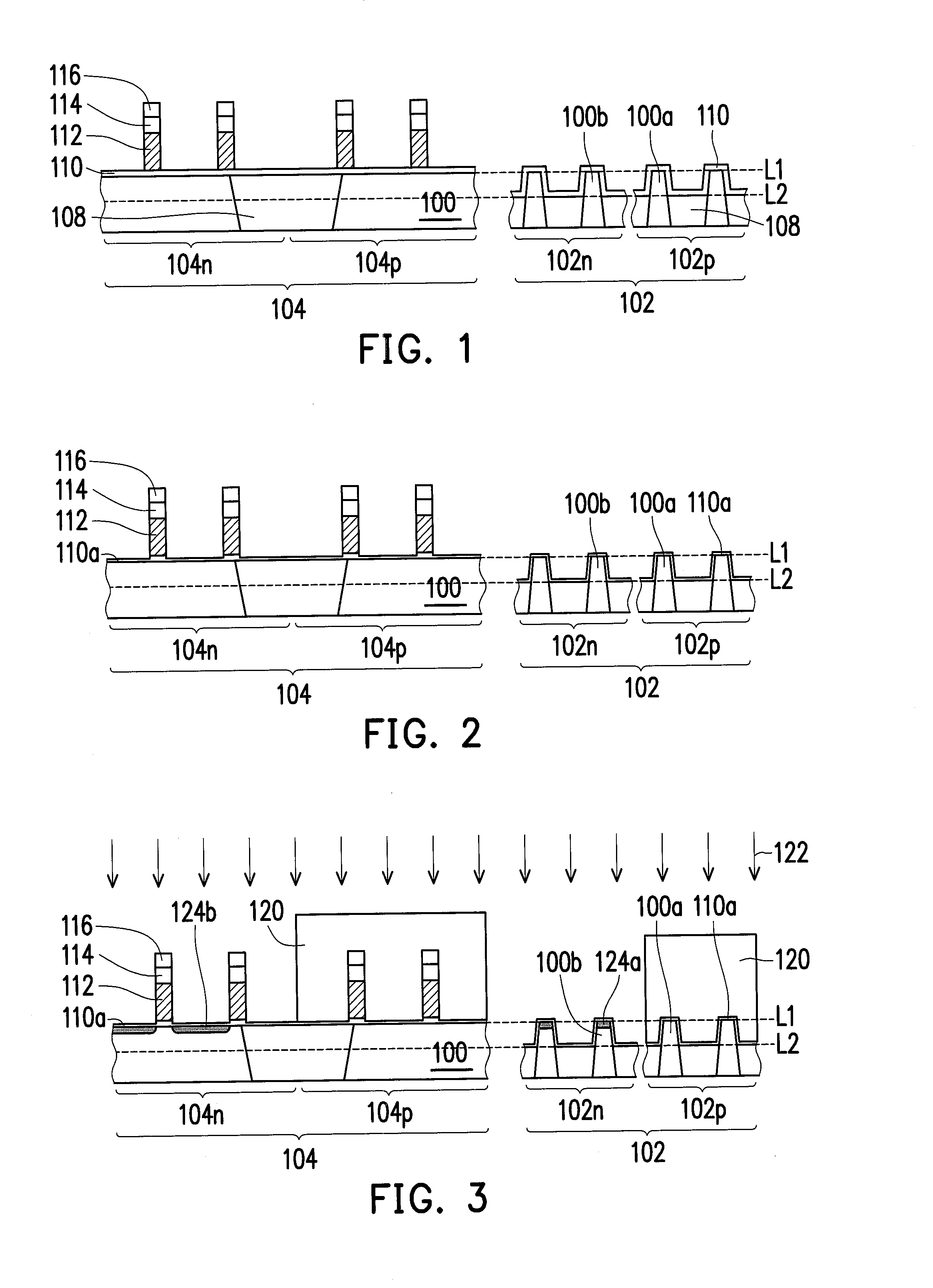

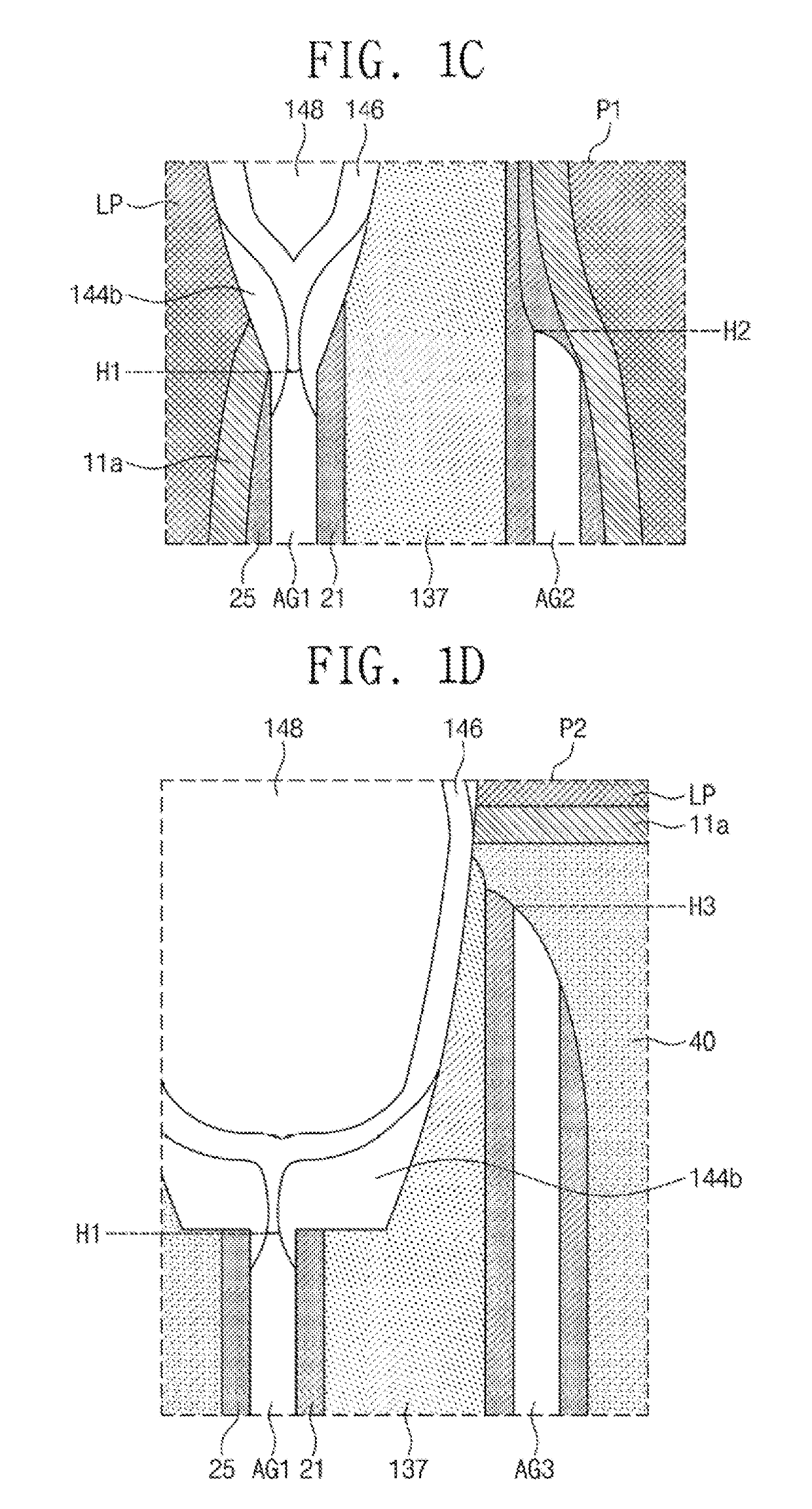

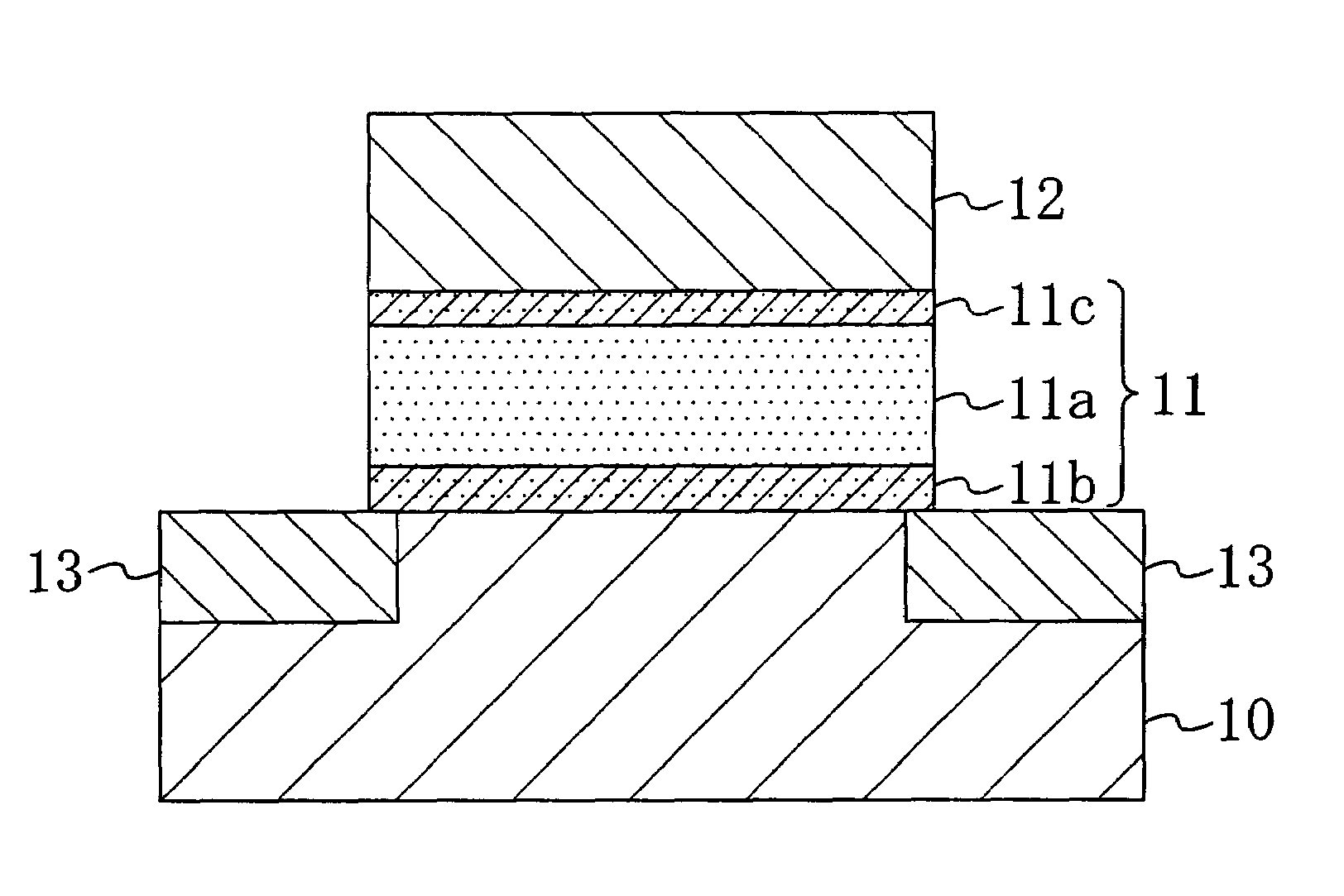

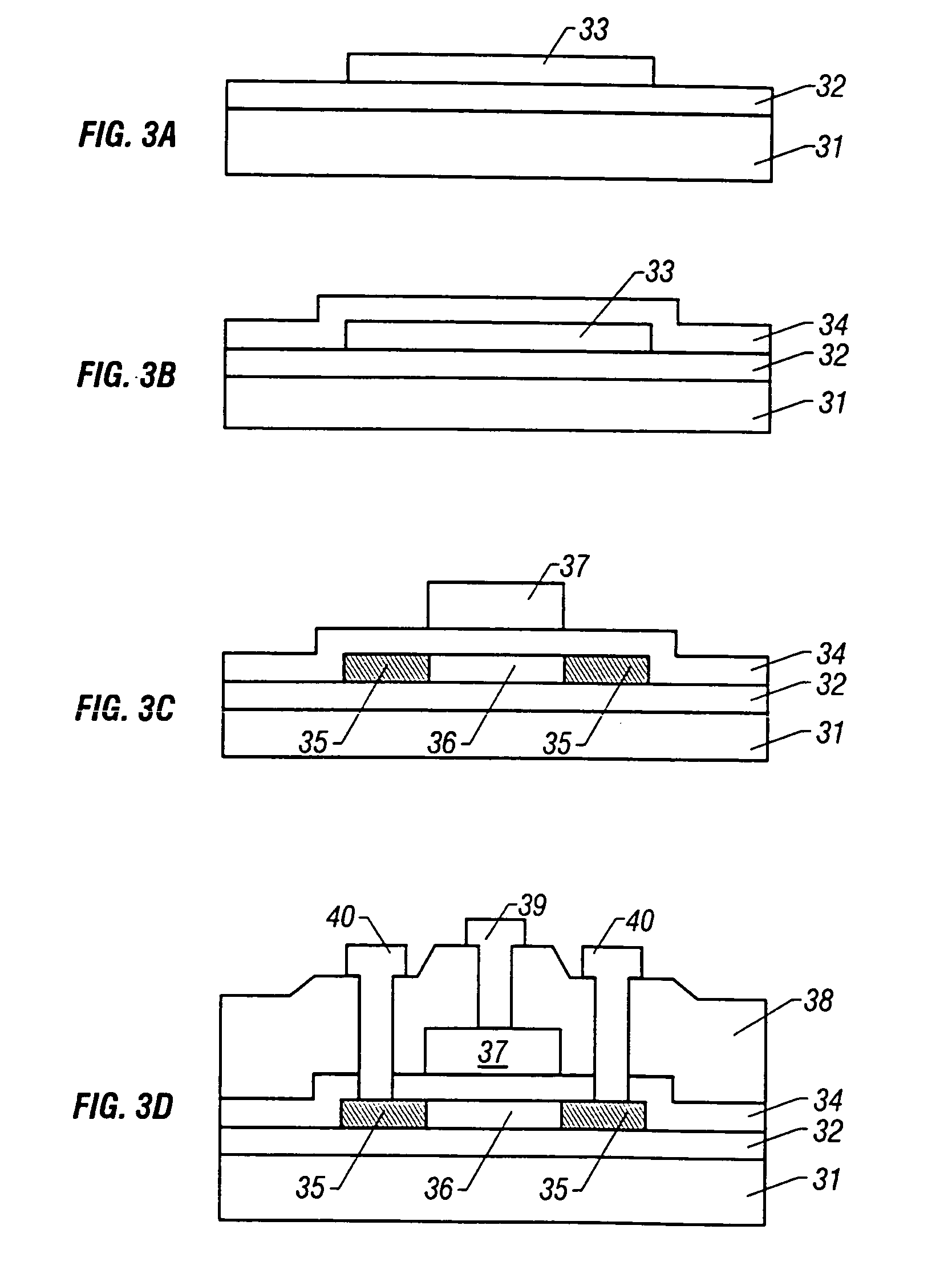

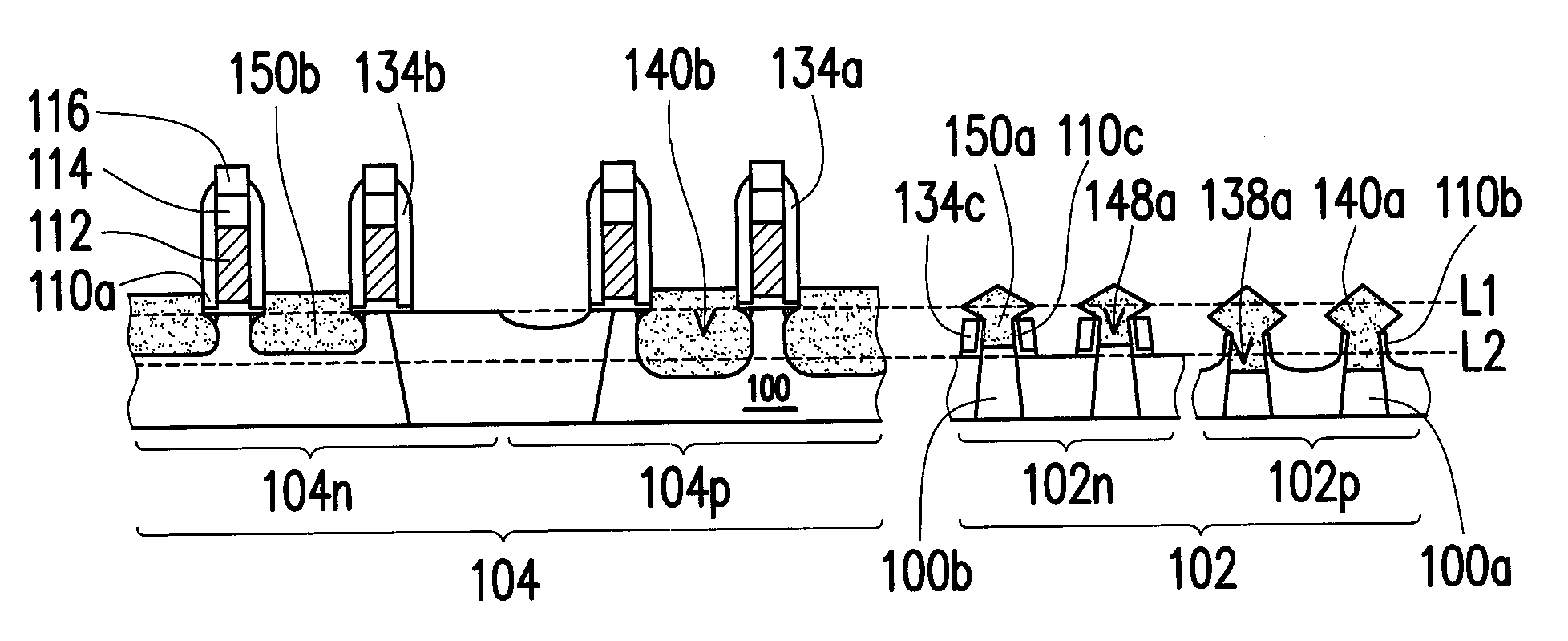

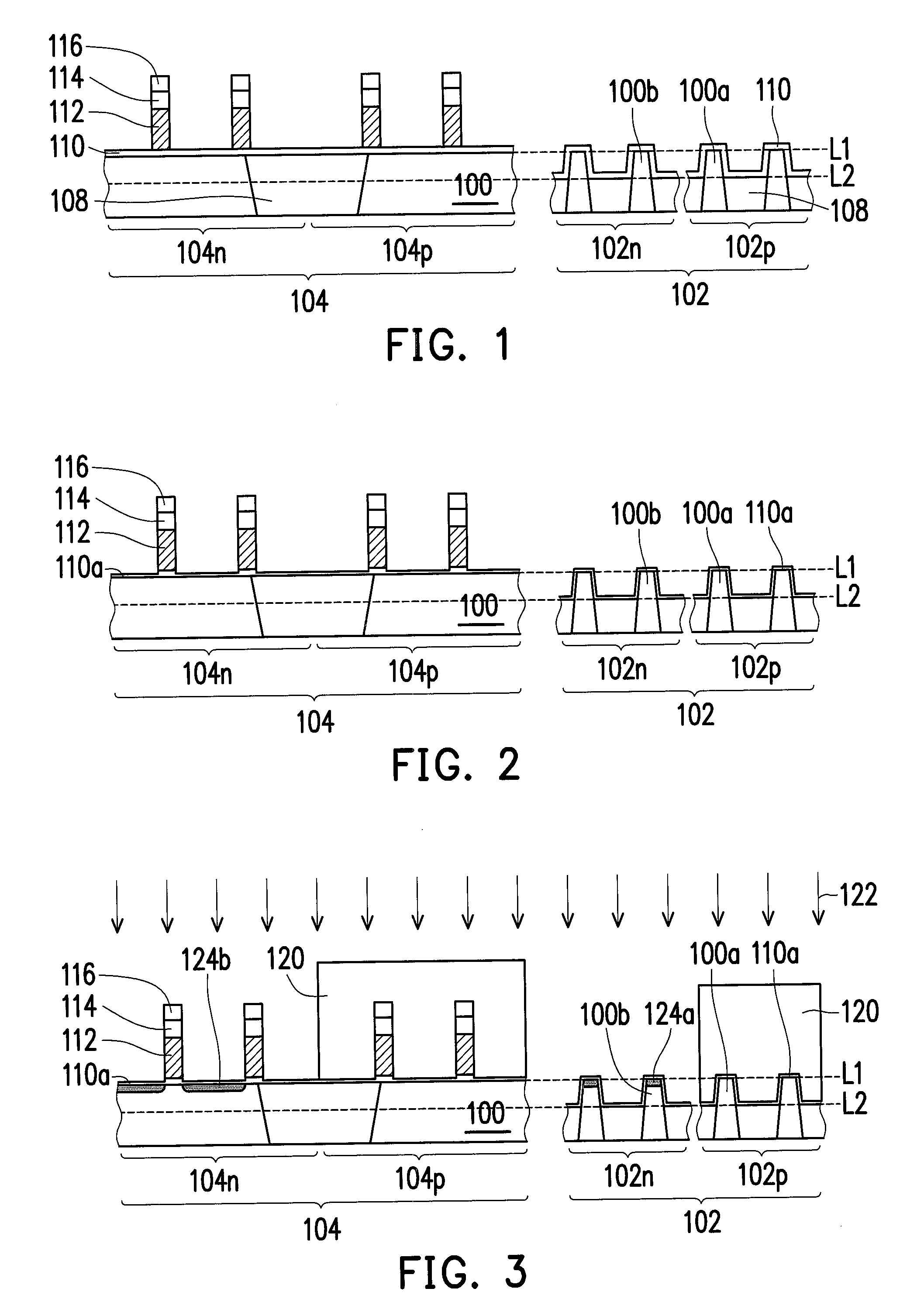

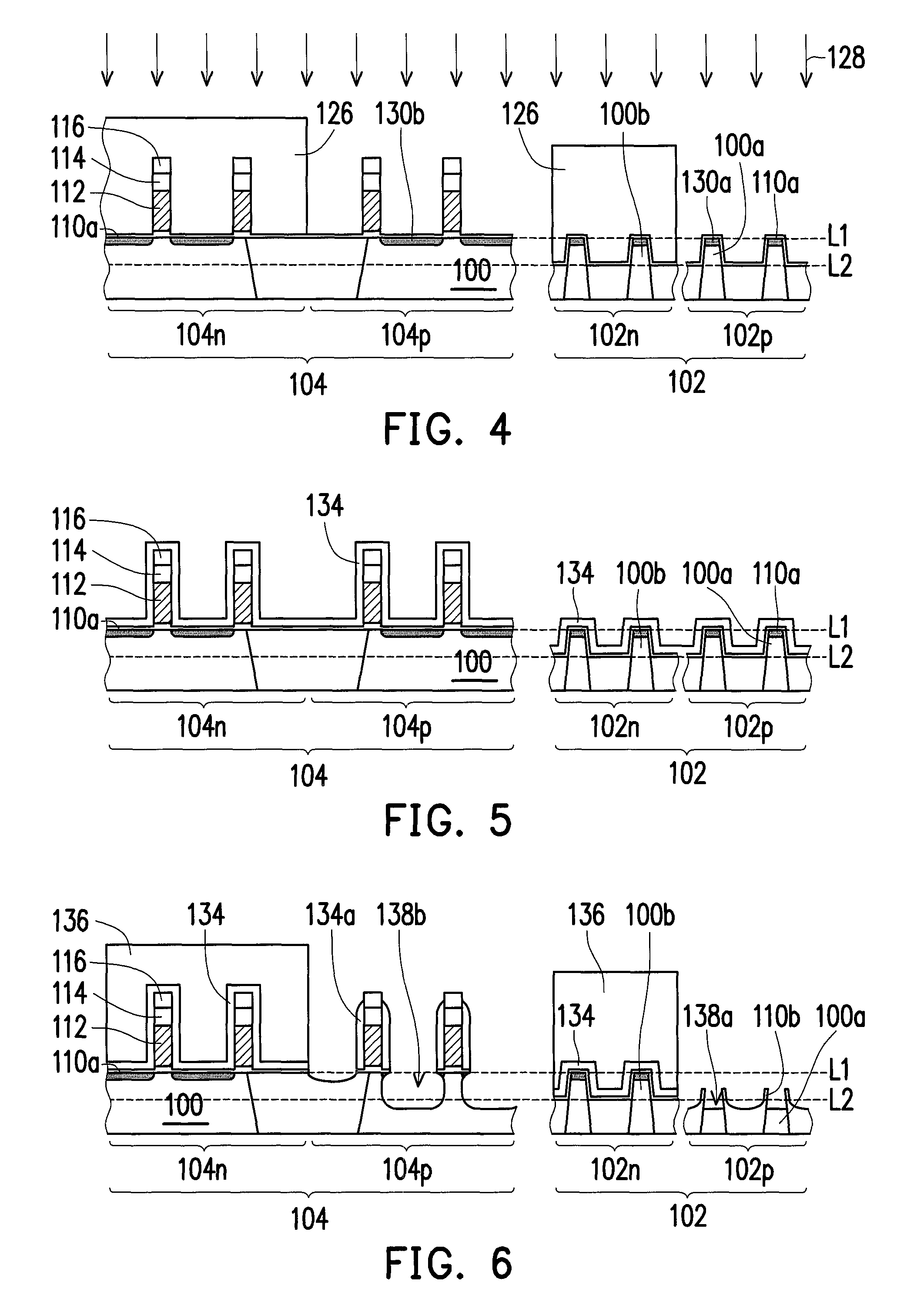

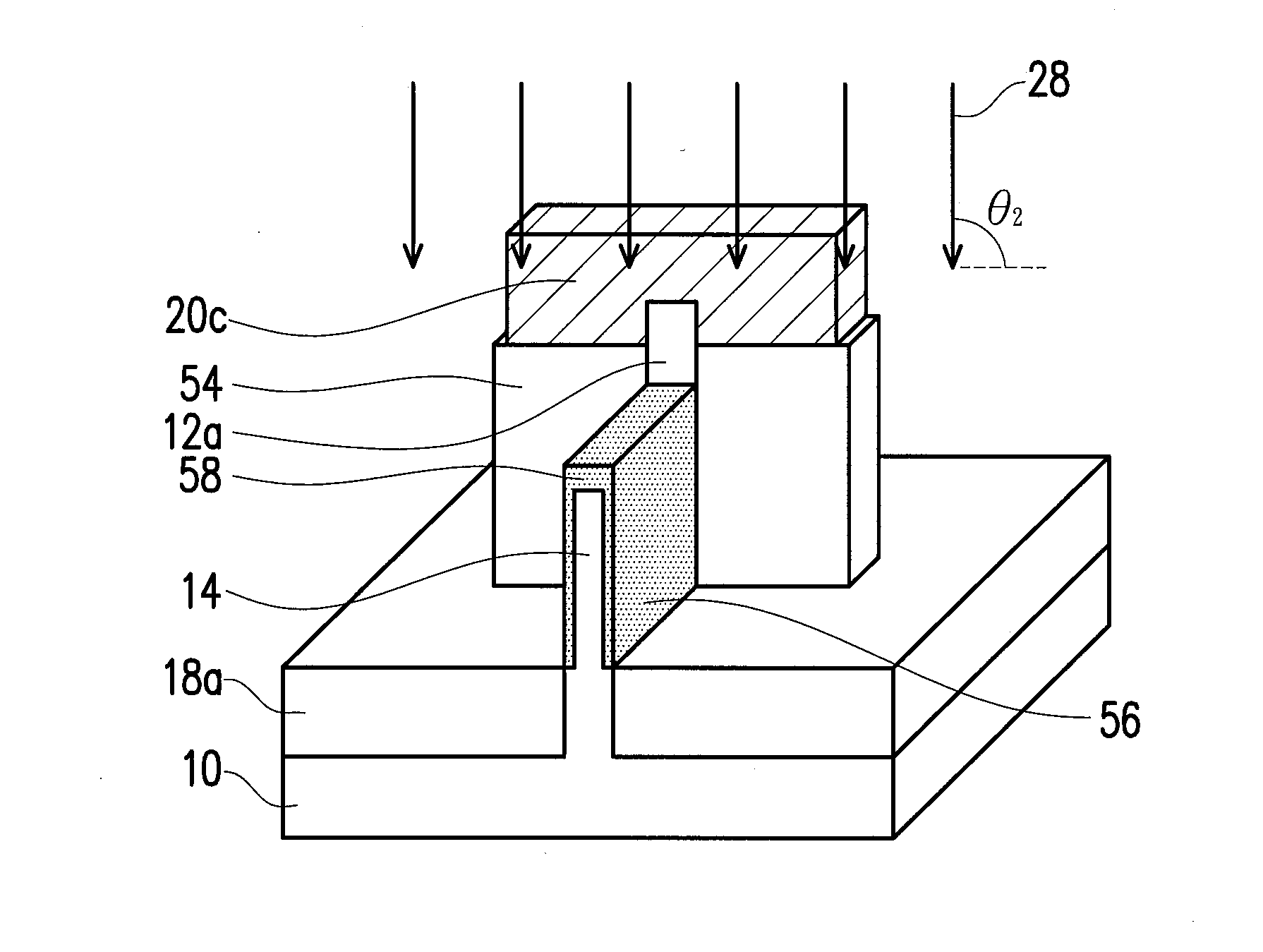

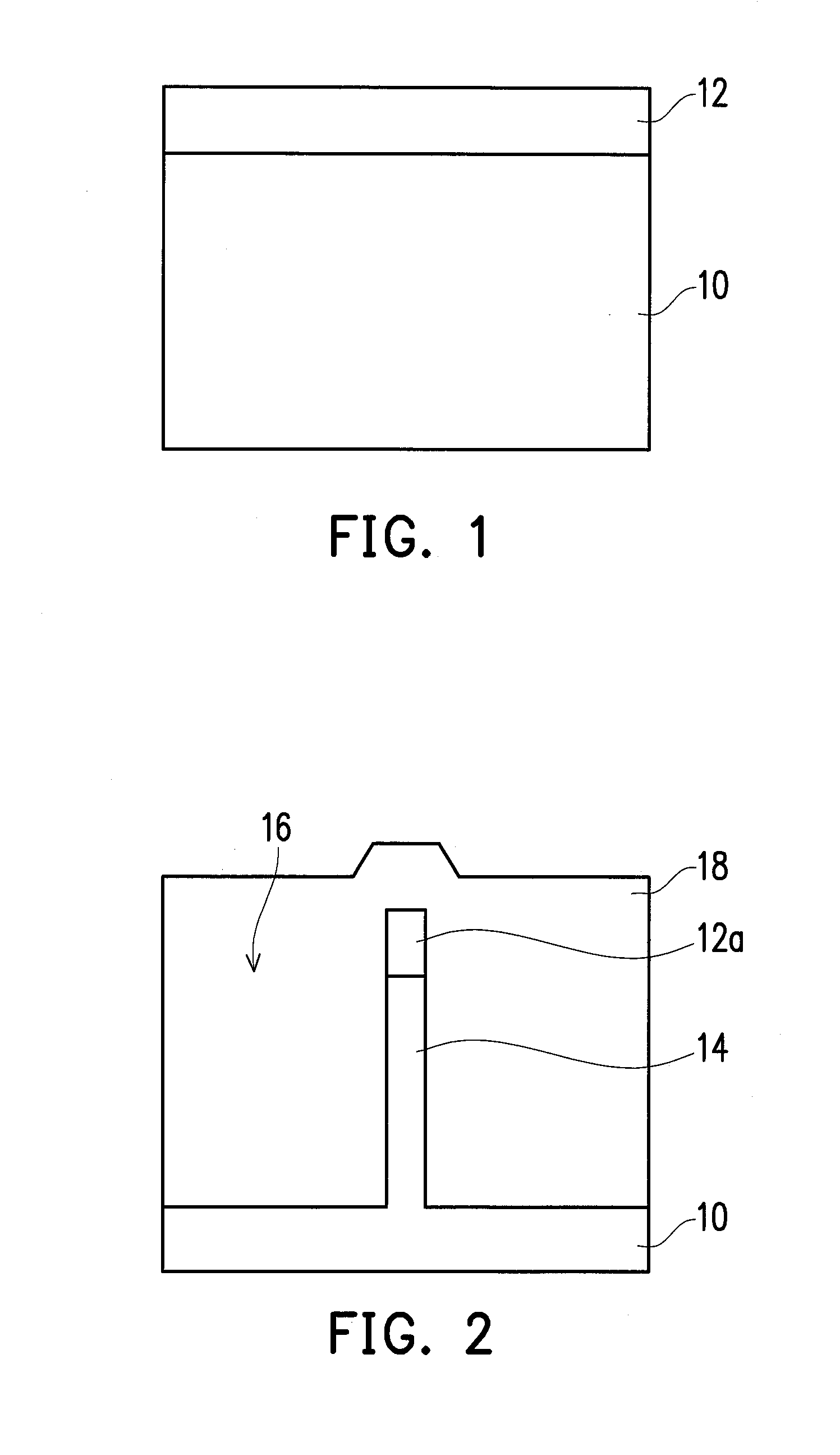

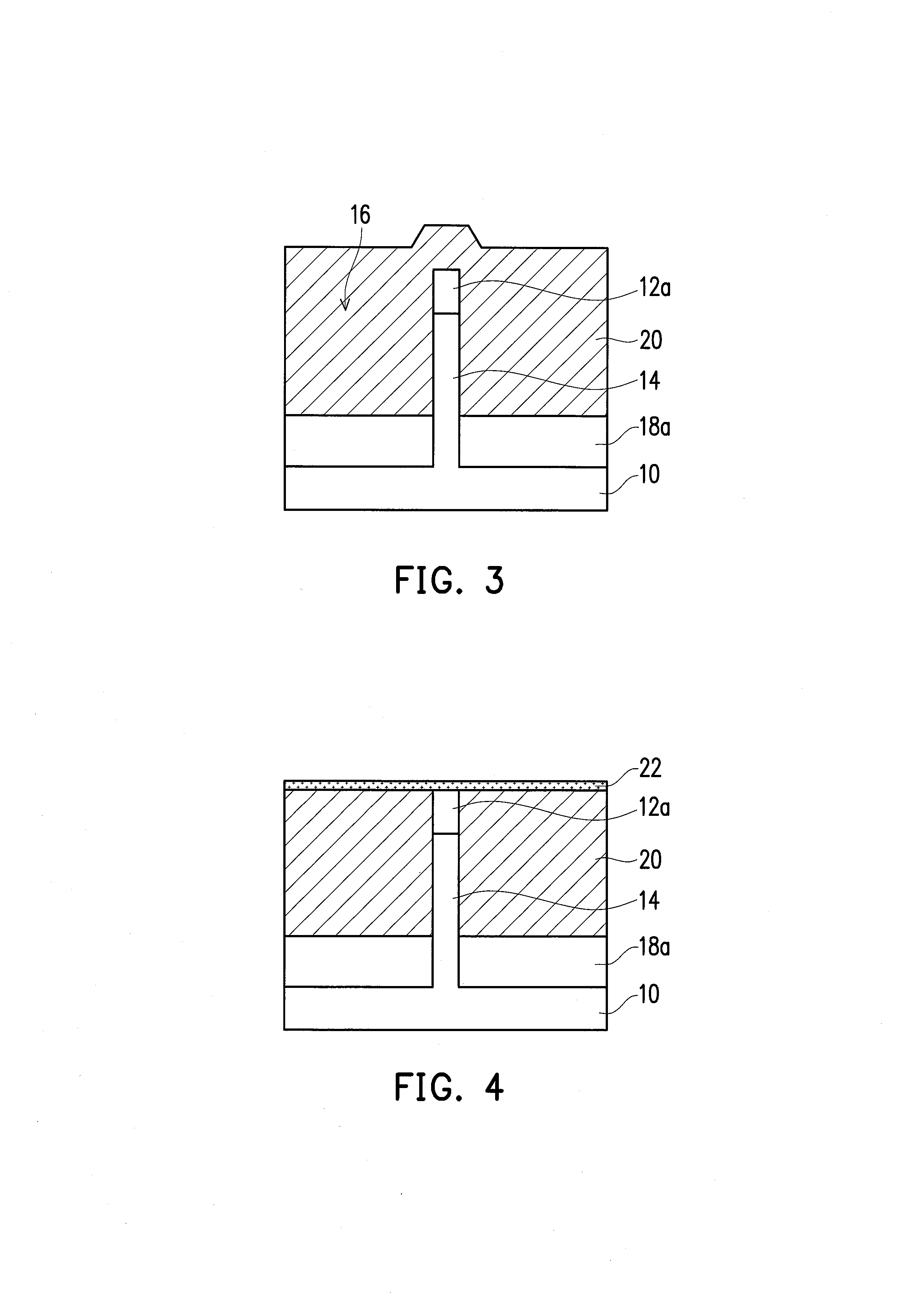

PROCESS FOR FABRICATING FIN-TYPE FIELD EFFECT TRANSISTOR (FinFET) STRUCTURE AND PRODUCT THEREOF

ActiveUS20150091059A1Reduce thicknessEasy to disassembleSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringField-effect transistor

A process for fabricating a fin-type field effect transistor (FinFET) structure is described. A semiconductor substrate is patterned to form a fin. A spacer is formed on the sidewall of the fin. A portion of the fin is removed, such that the spacer and the surface of the remaining fm together define a cavity. A piece of a semiconductor compound is formed from the cavity, wherein the upper portion of the piece of the semiconductor compound laterally extends over the spacer.

Owner:UNITED MICROELECTRONICS CORP

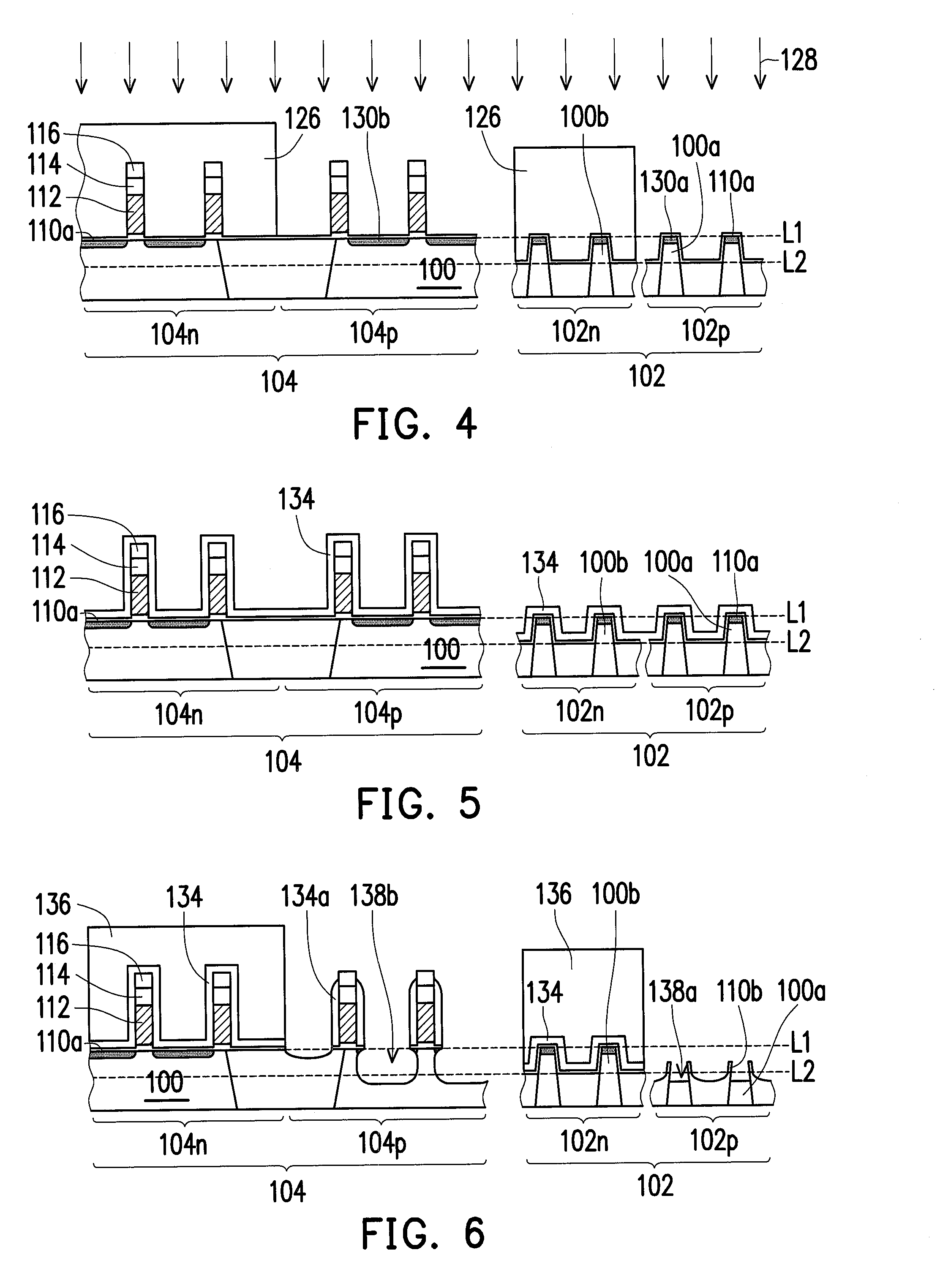

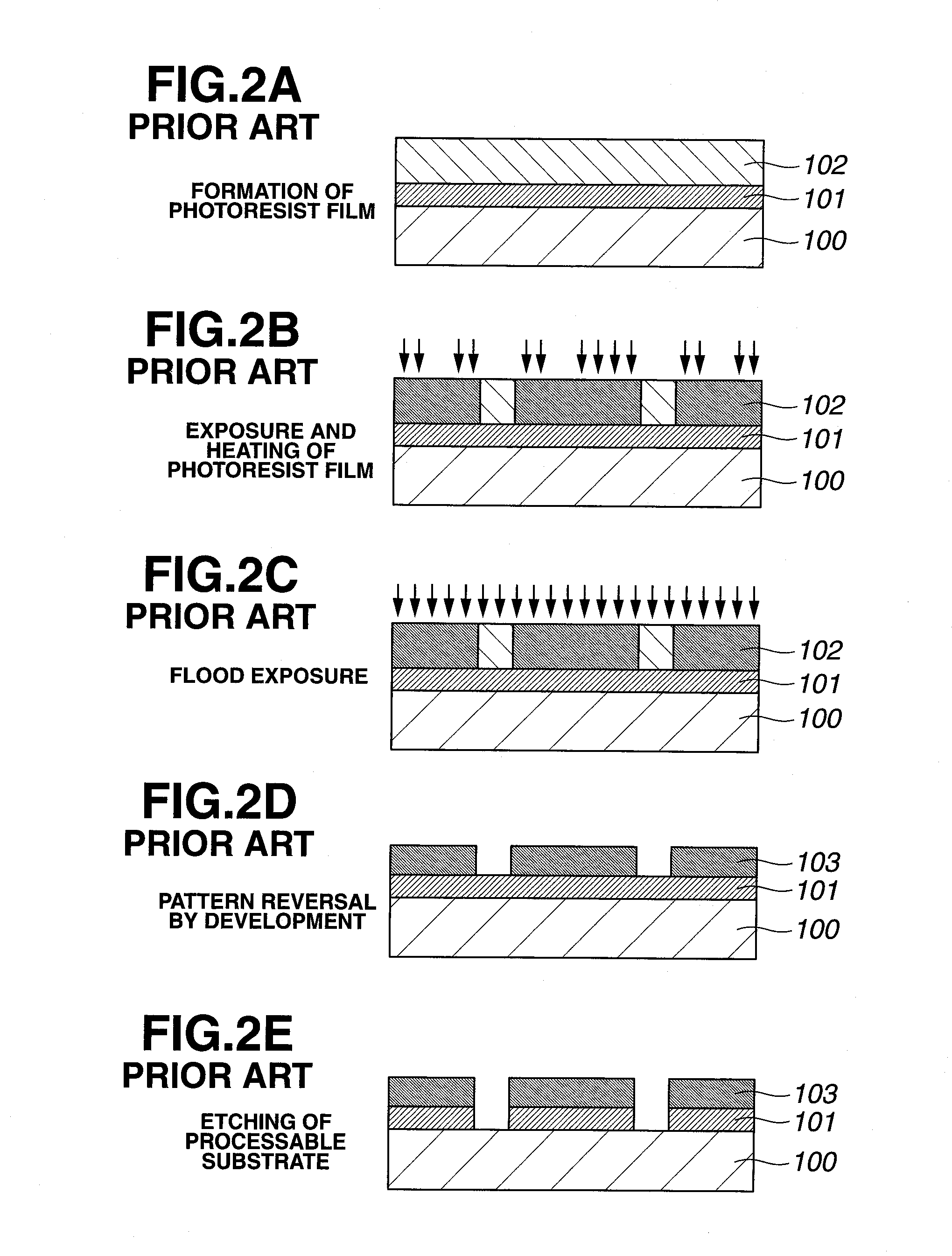

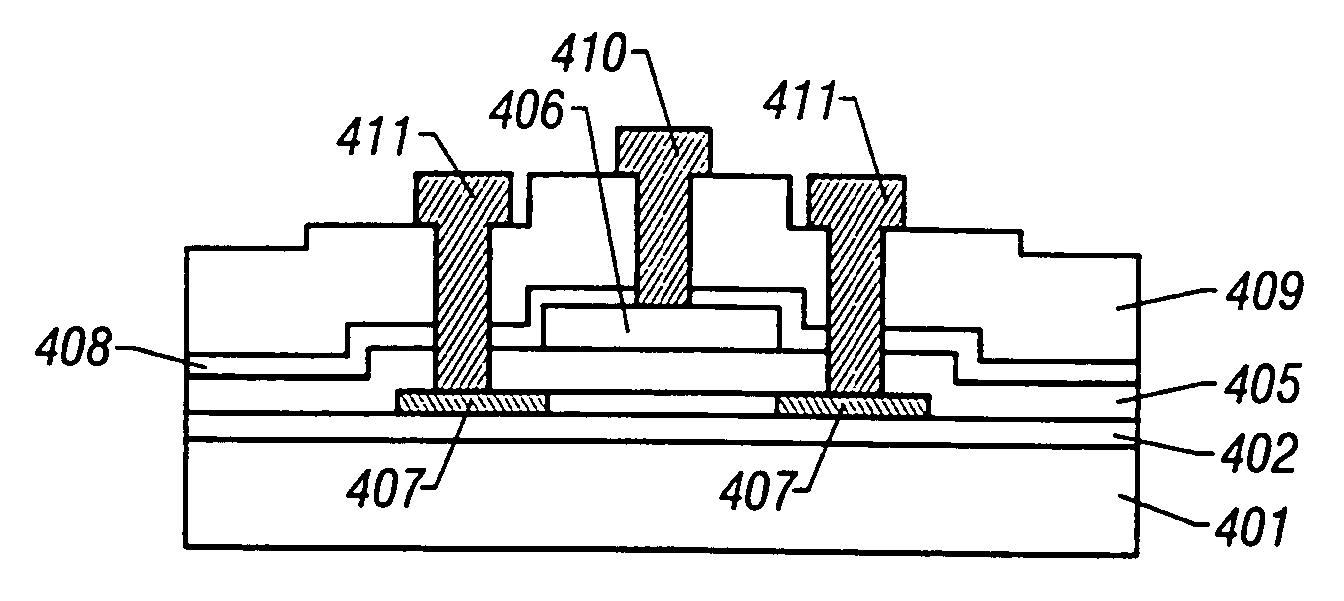

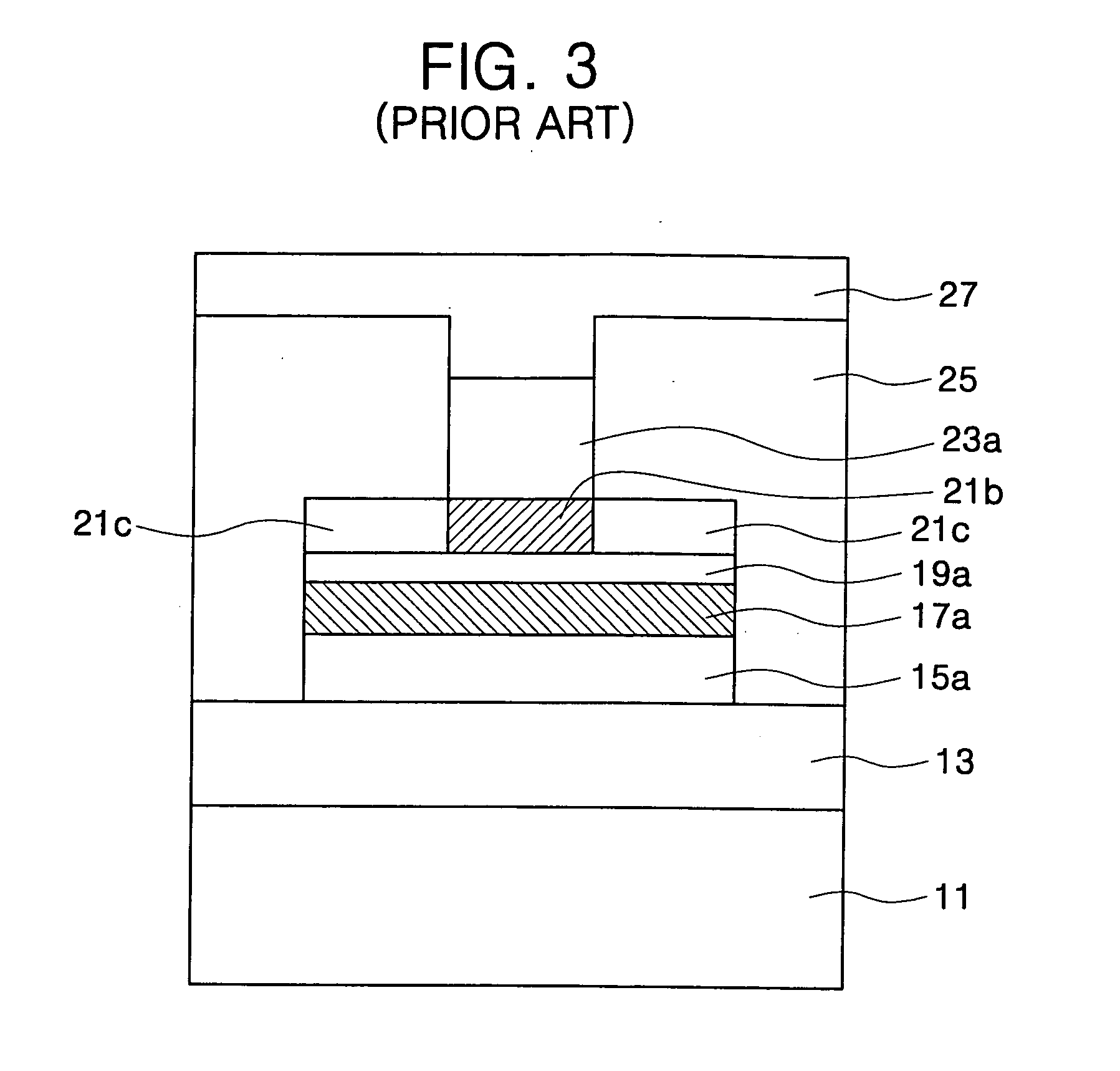

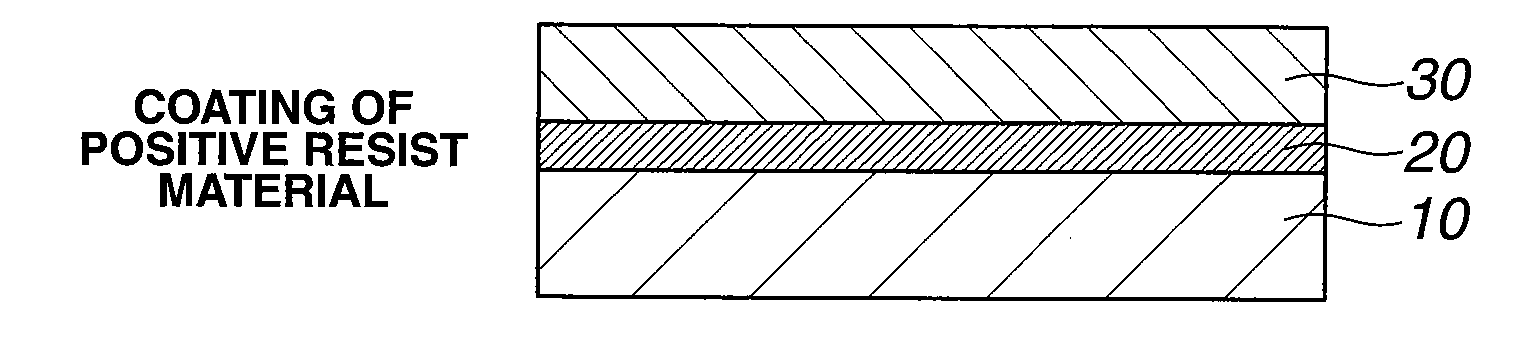

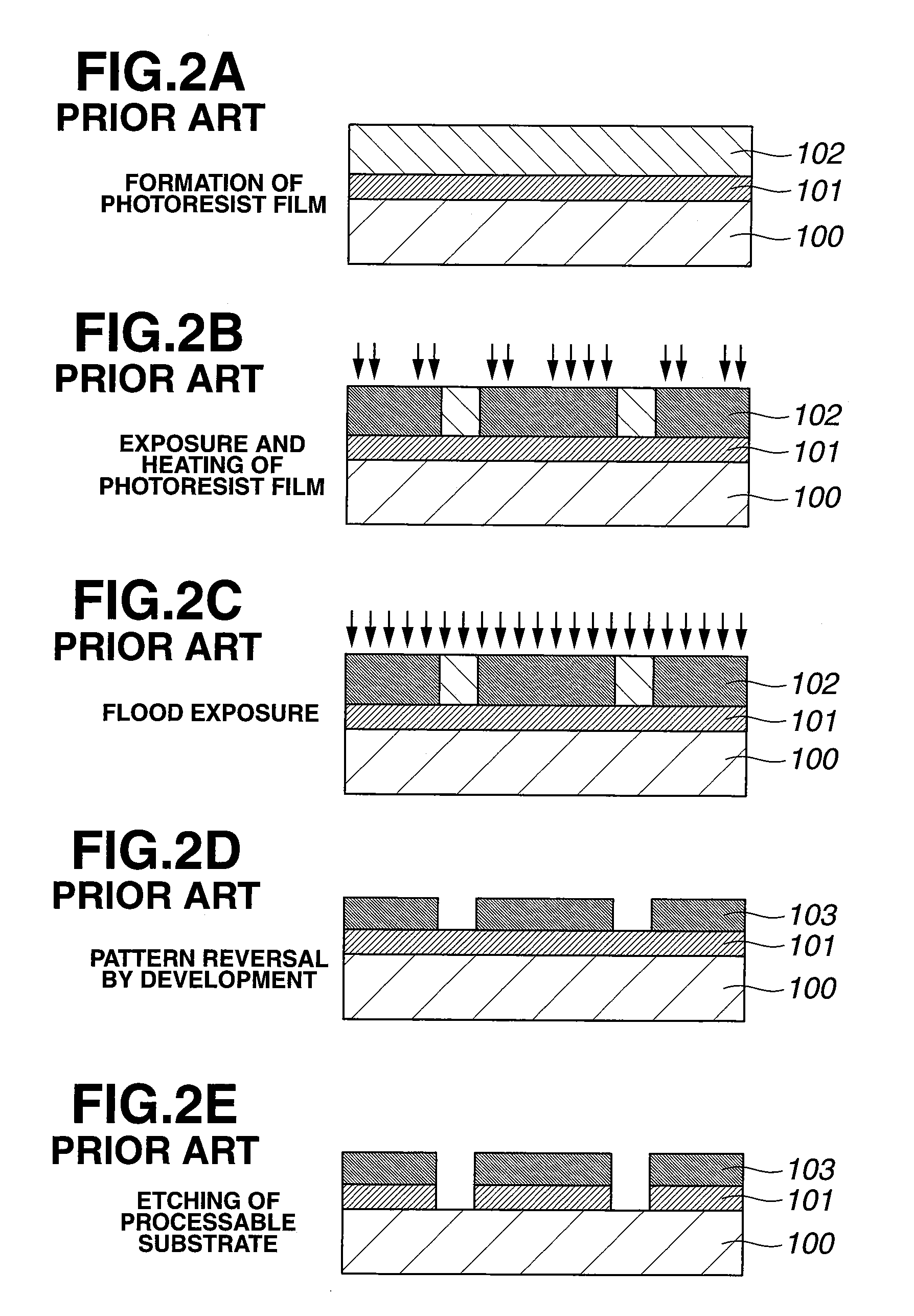

Patterning process

ActiveUS20100203457A1High resolution performanceIncrease process marginSemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusSolubilityResist

A pattern is formed by coating a chemically amplified positive resist composition comprising a resin comprising acid labile group-containing recurring units and a photoacid generator onto a substrate, drying to form a resist film, exposing the resist film to high-energy radiation through a phase shift mask including a lattice-like first shifter and a second shifter arrayed on the first shifter and consisting of lines which are thicker than the line width of the first shifter, PEB, developing to form a positive pattern, illuminating or heating the positive pattern to eliminate acid labile groups for increasing alkaline solubility and to induce crosslinking for imparting solvent resistance, coating a reversal film, and dissolving away the positive pattern in an alkaline wet etchant to form a pattern by way of positive / negative reversal.

Owner:SHIN ETSU CHEM IND CO LTD

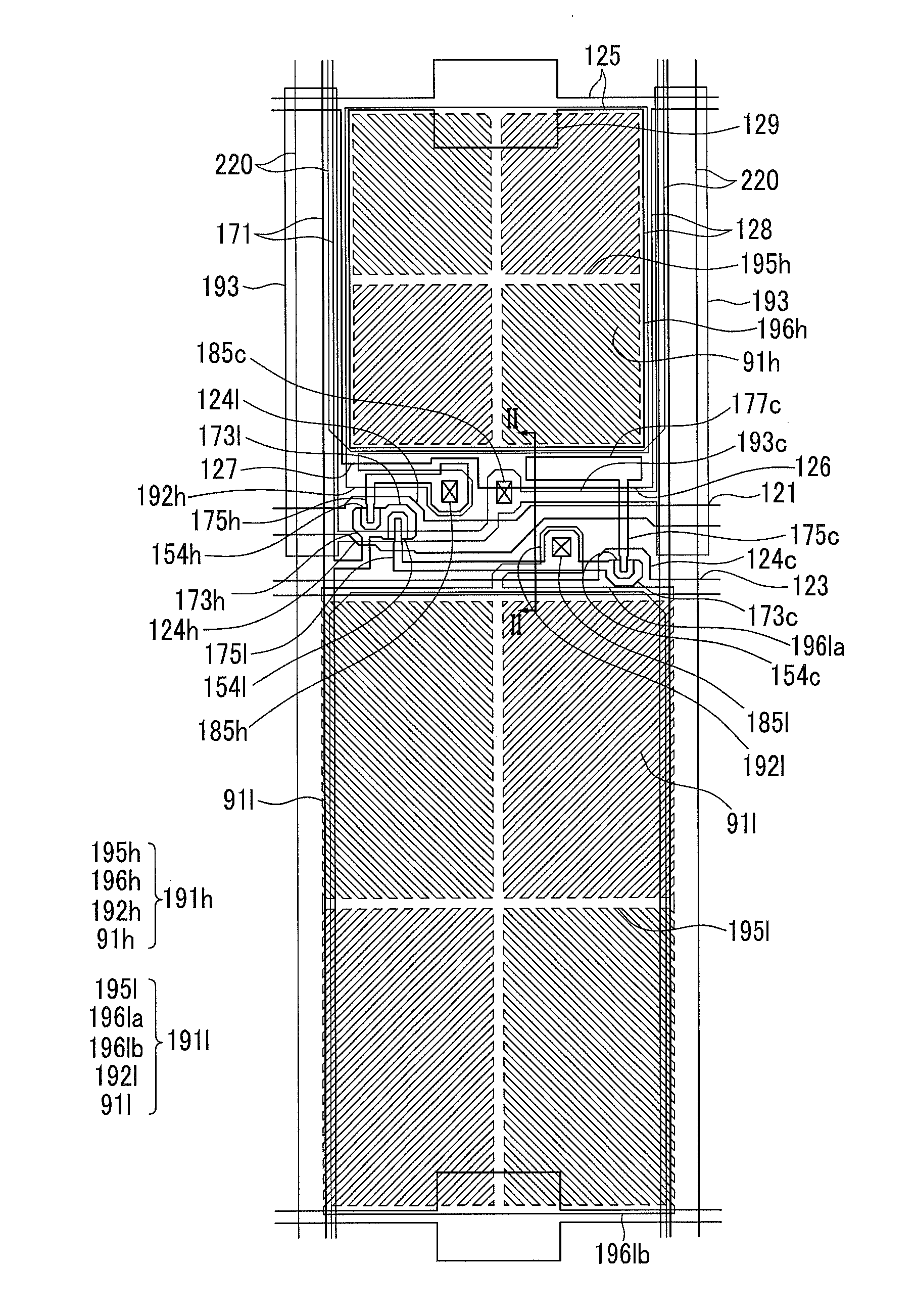

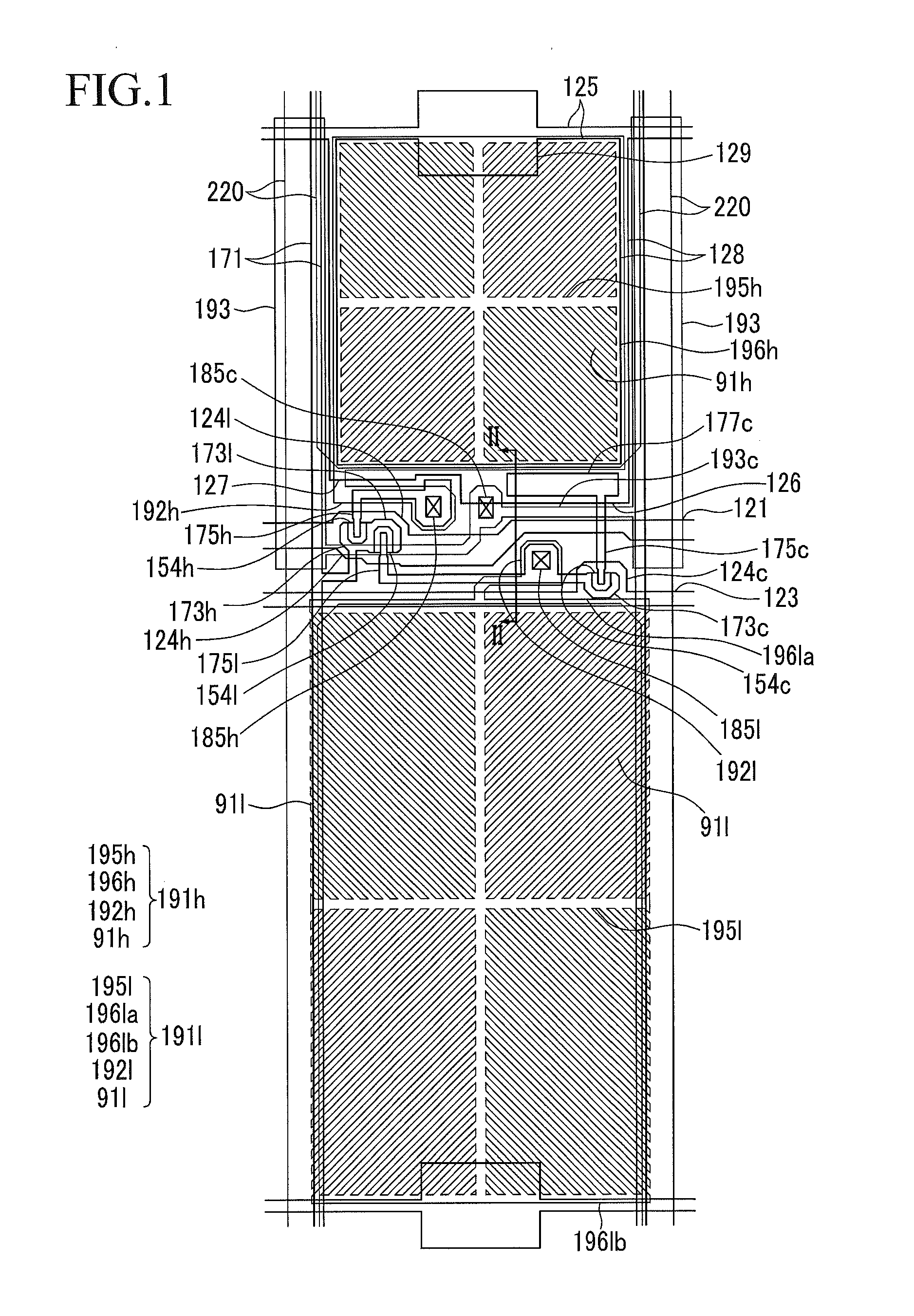

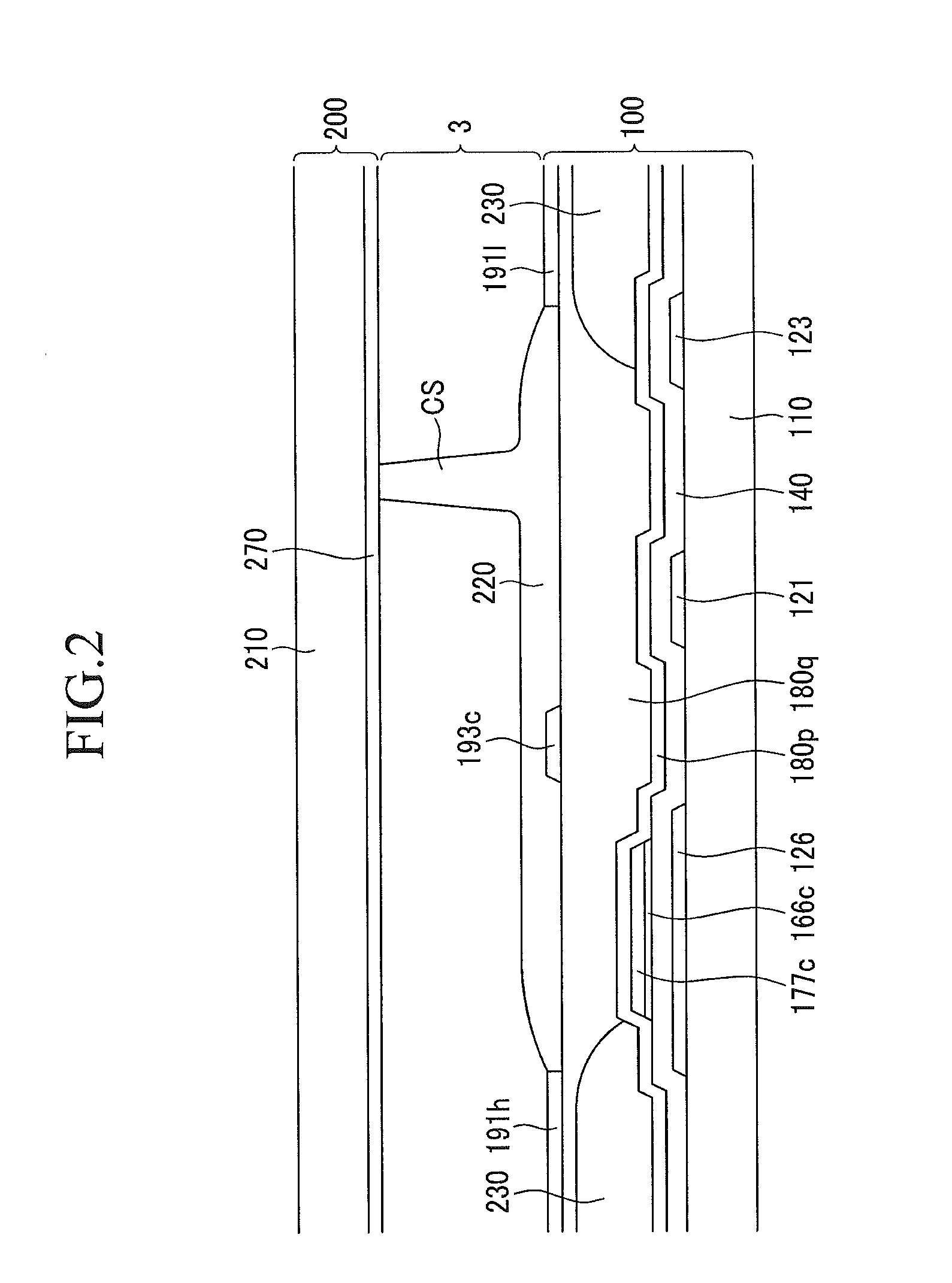

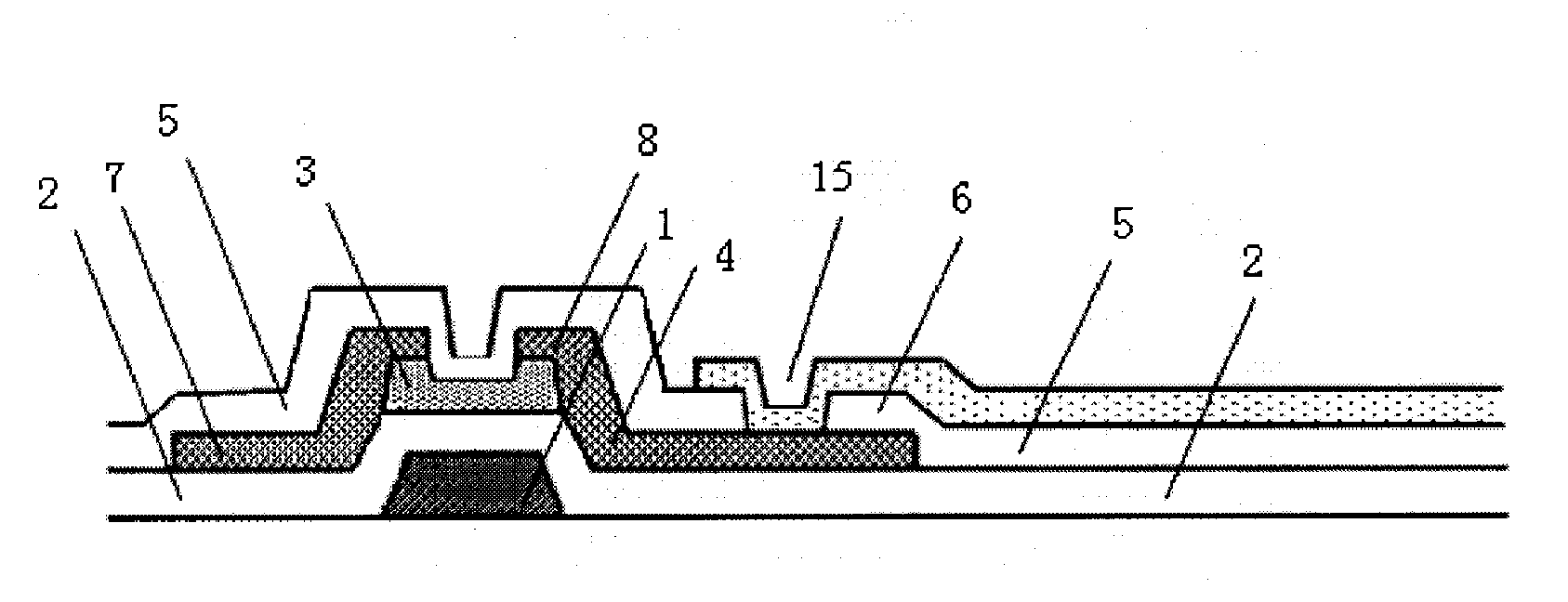

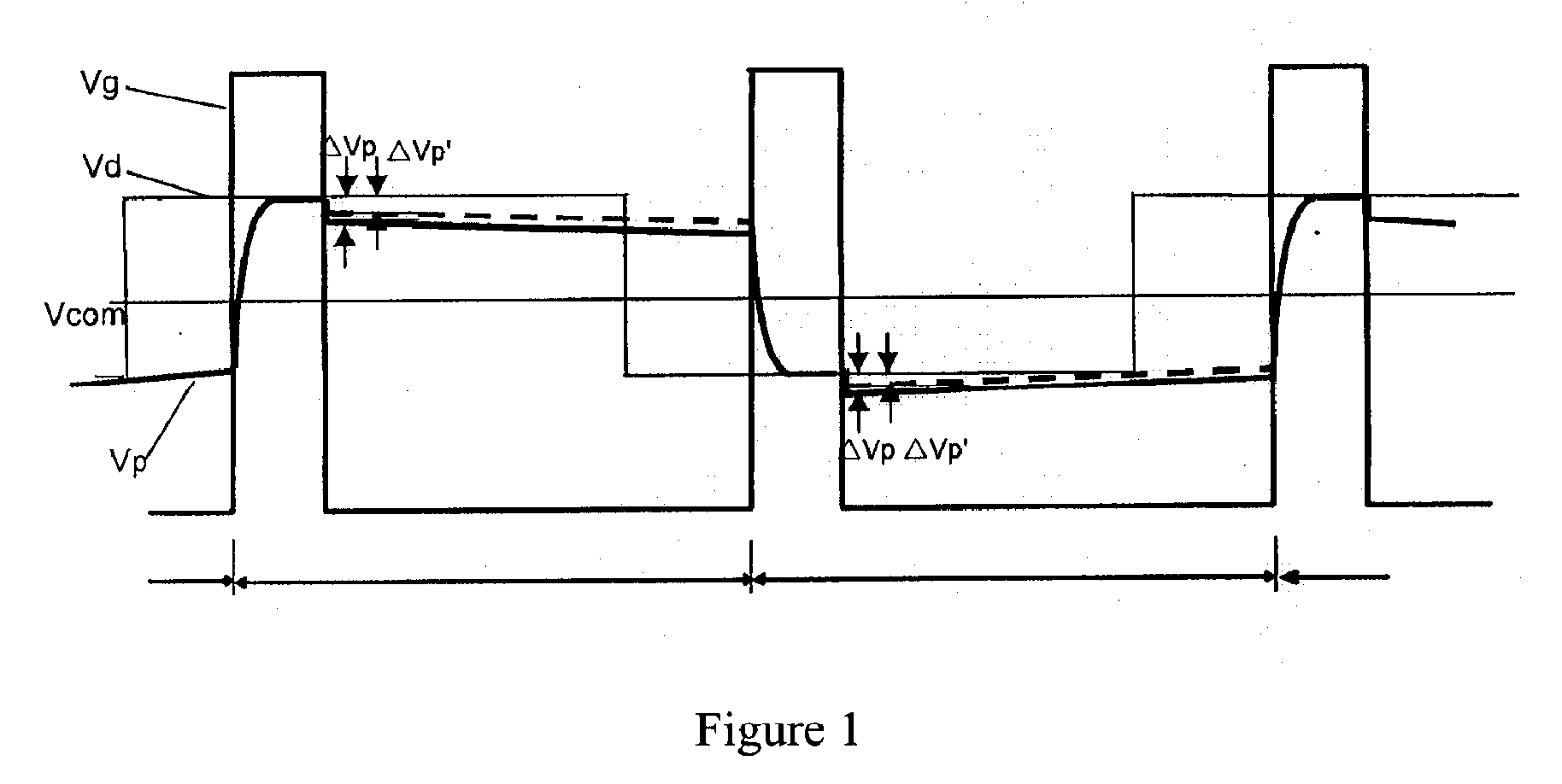

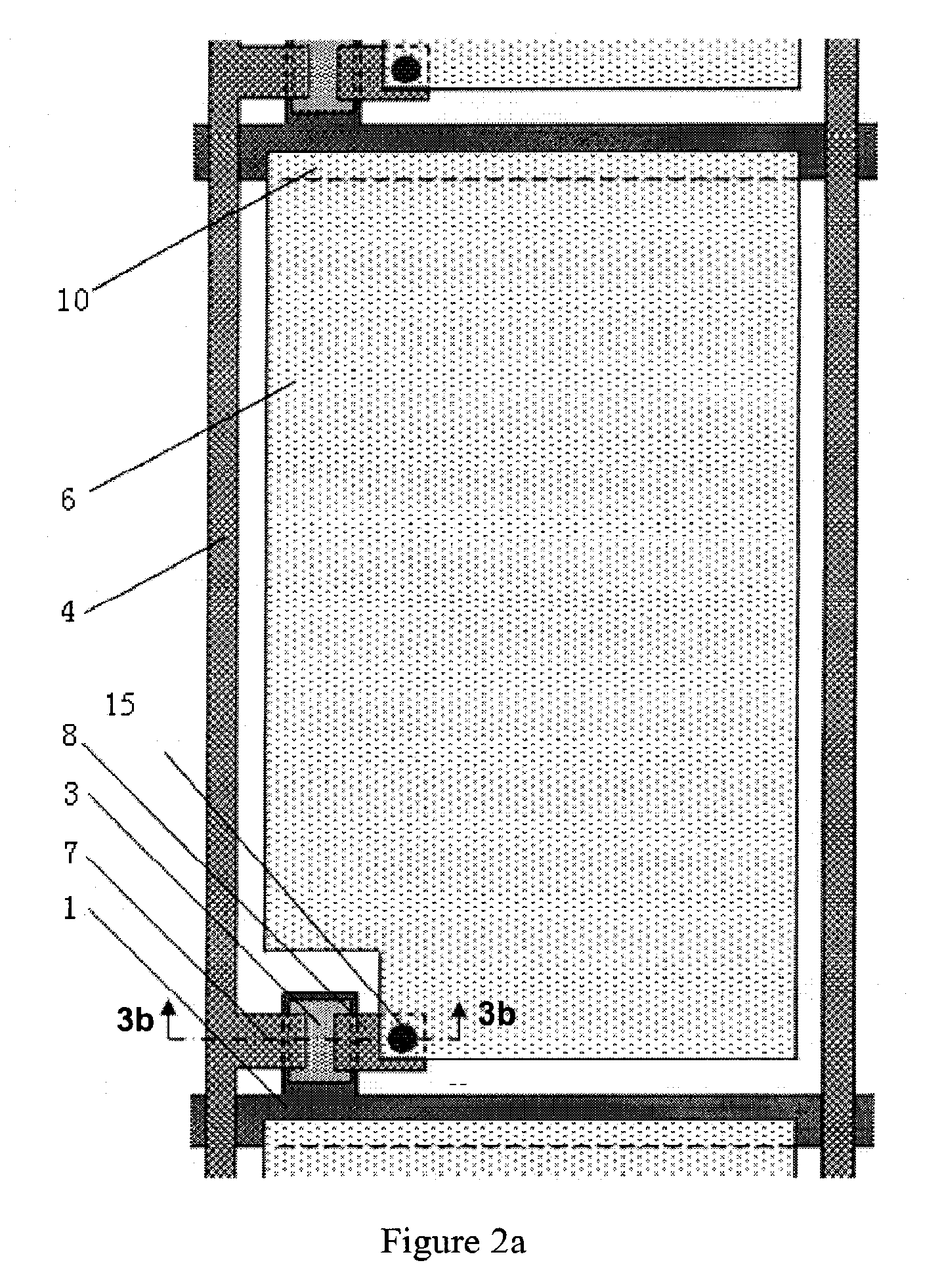

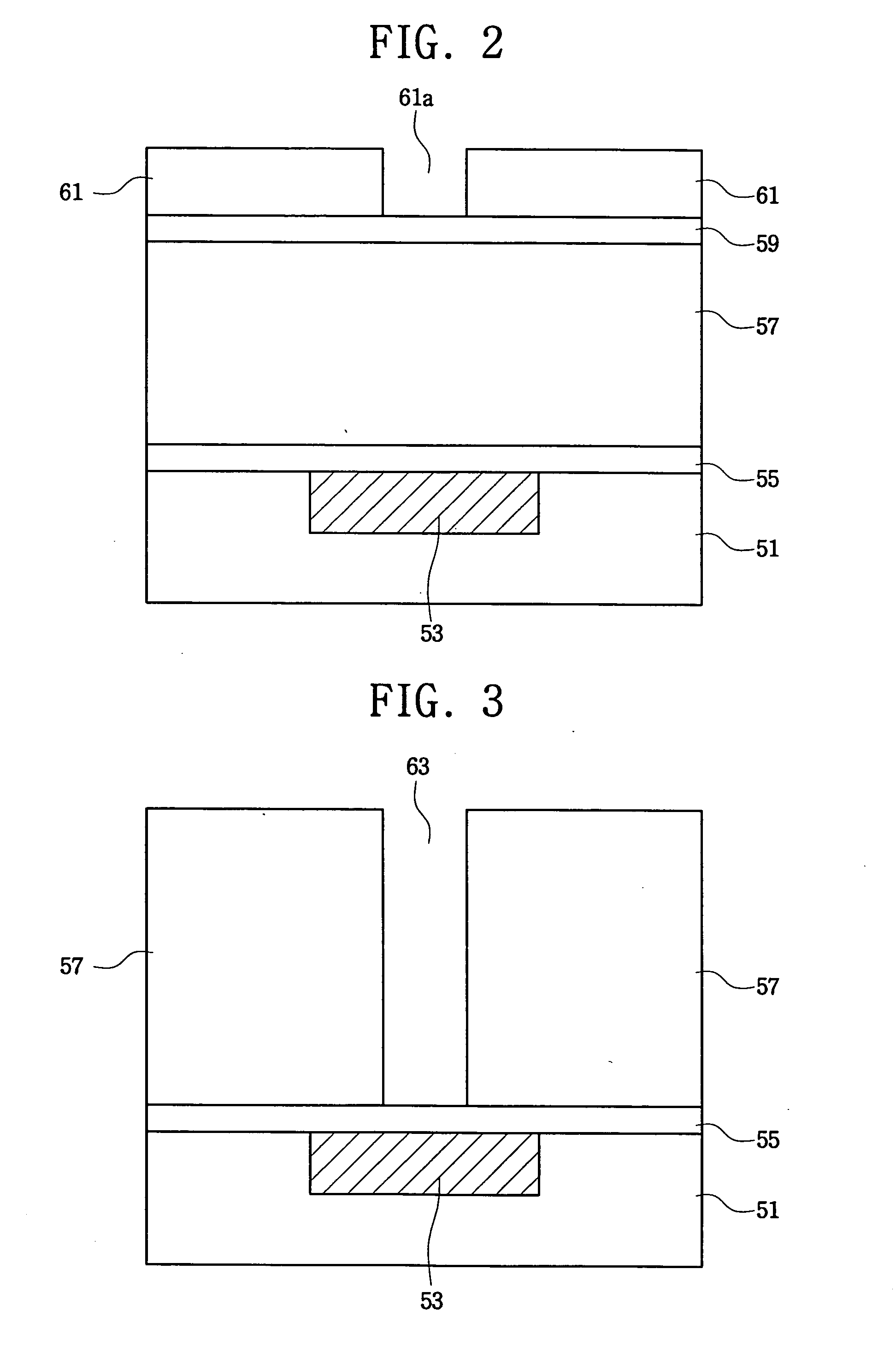

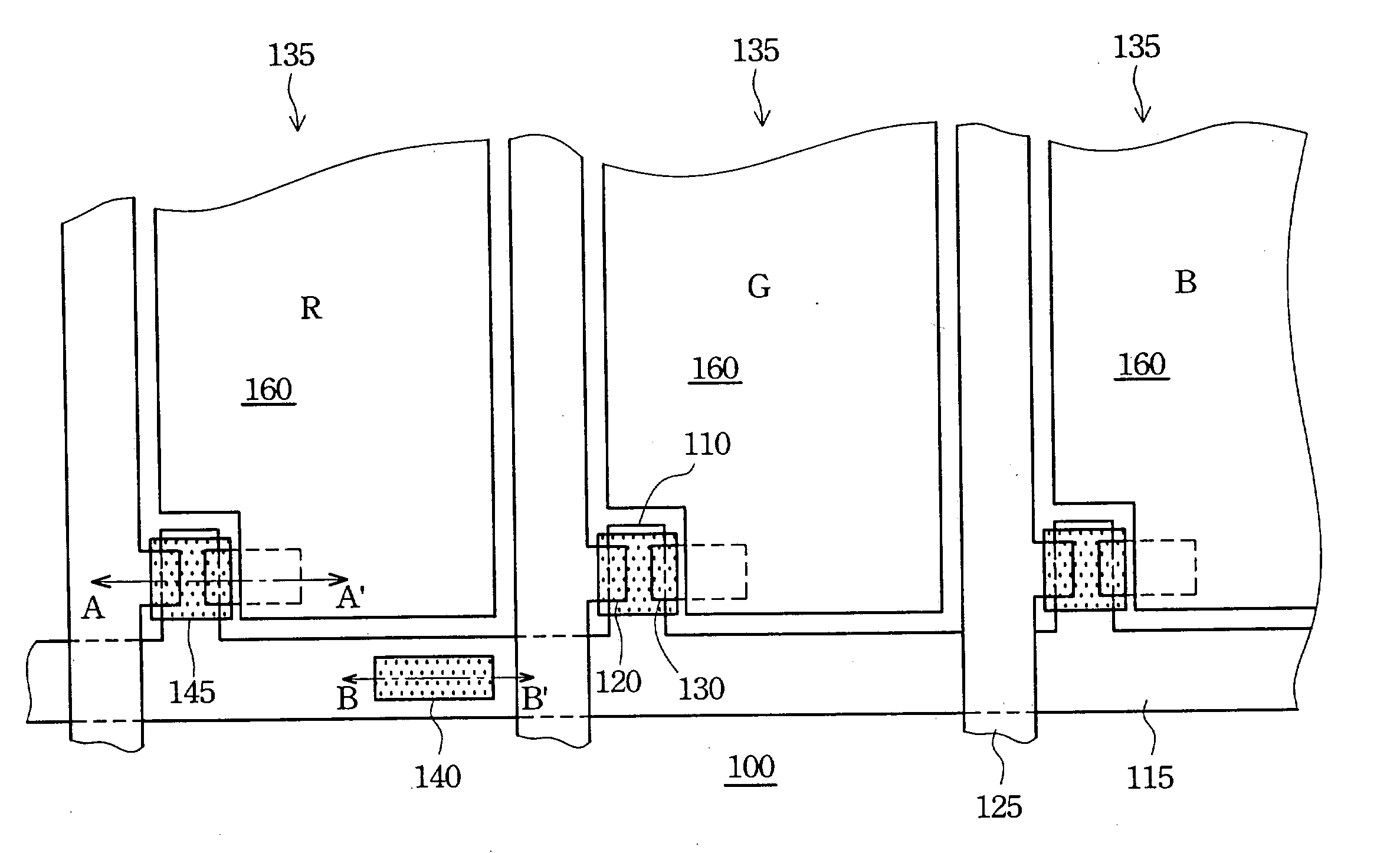

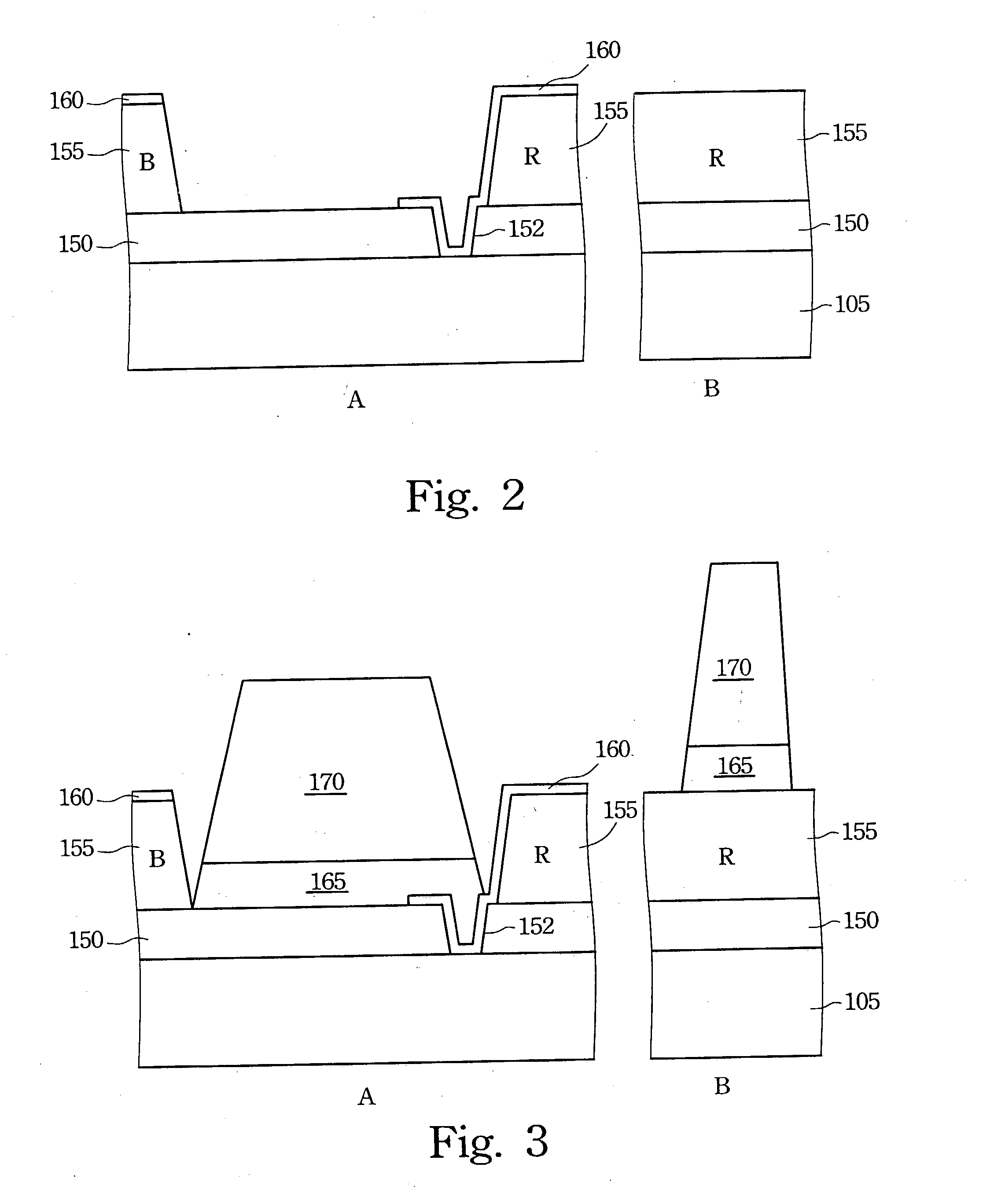

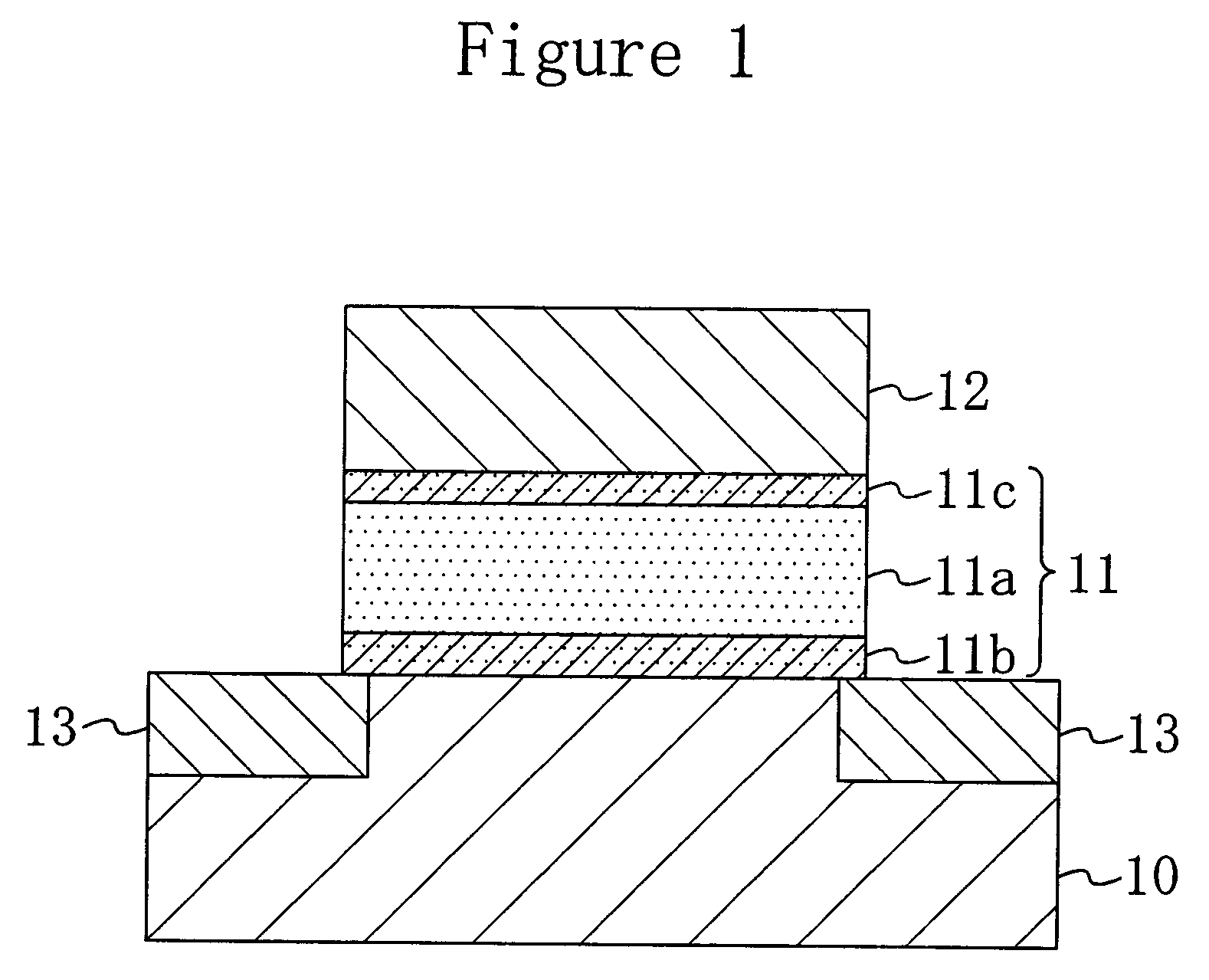

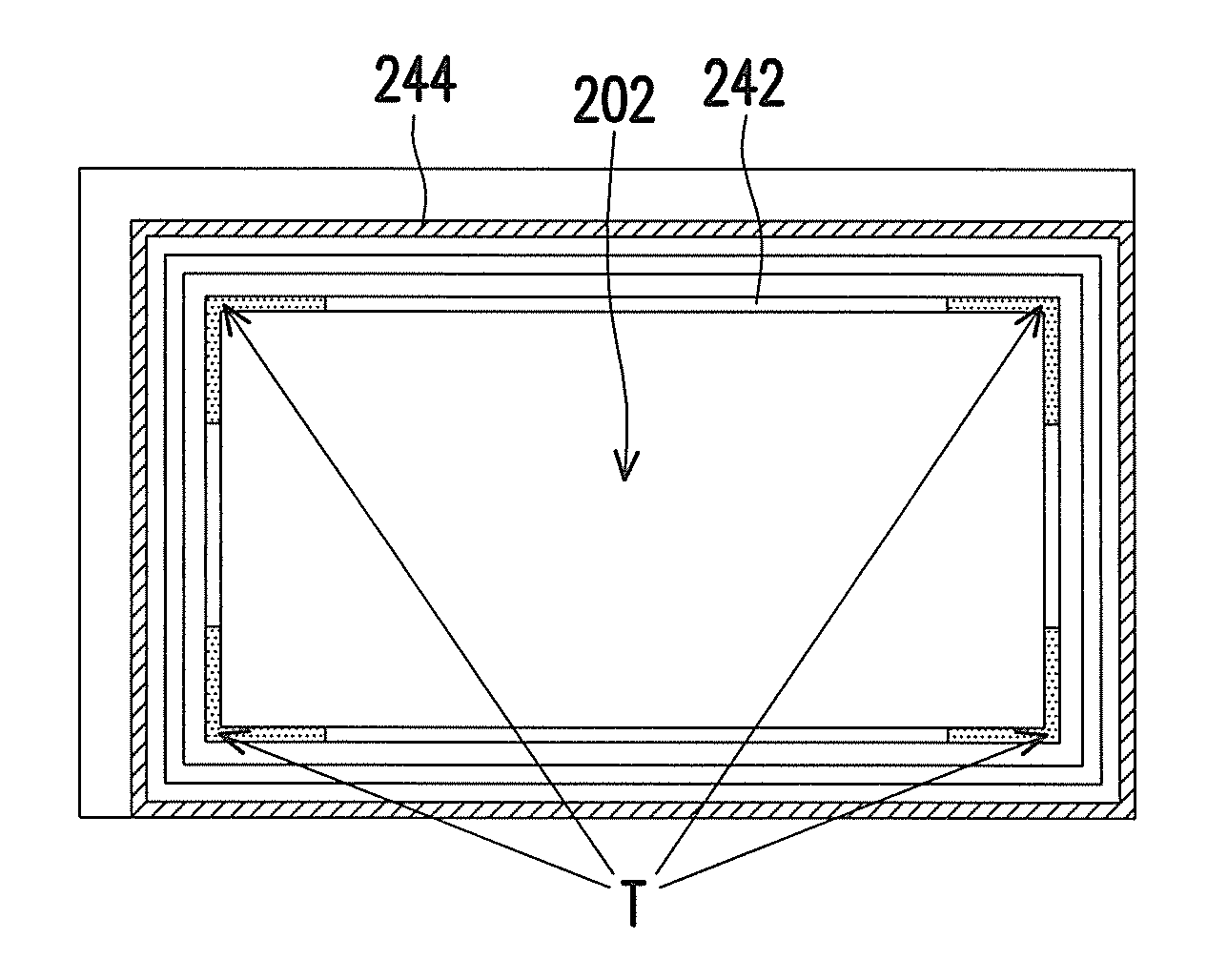

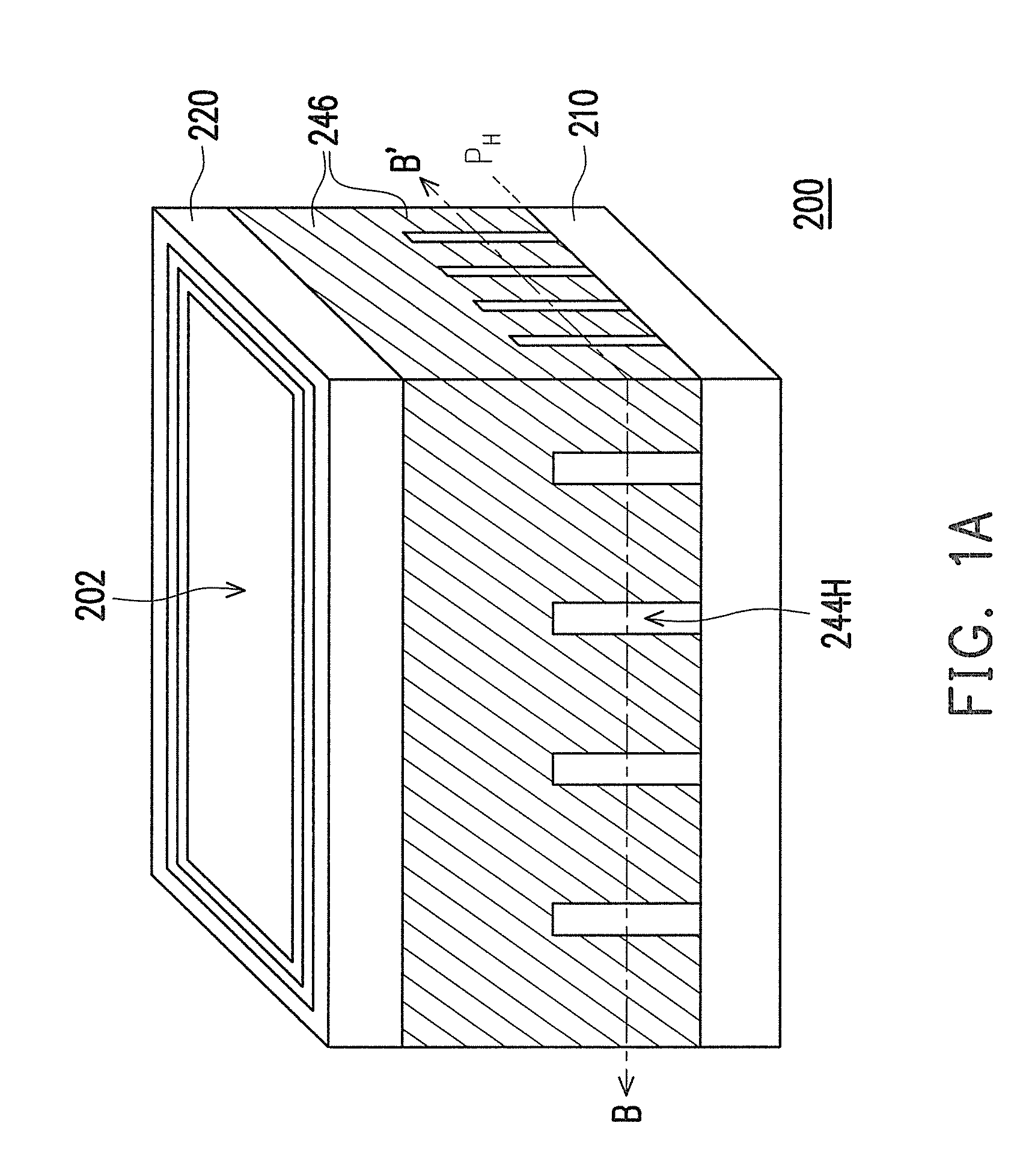

Liquid crystal display and manufacturing method thereof

ActiveUS20130077031A1Simple manufacturing processIncrease process marginSemiconductor/solid-state device manufacturingNon-linear opticsLiquid-crystal displayTransistor

A manufacturing method of a liquid crystal display includes: forming a thin film transistor on a first substrate; forming a color filter on the thin film transistor; forming a pixel electrode on the color filter; and forming a light blocking member including a column spacer protruded from the light blocking member on the color filter. The forming the light blocking member uses a mask including a first region, a second region, and a third region. The first region passes light generated from a light exposer, the second region includes a blocking filter layer which selectively passes the light generated from the light exposer, and the third region blocks the light generated from the light exposer.

Owner:SAMSUNG DISPLAY CO LTD

Method for making polysilicon layer

InactiveCN1501449ALarge crystal sizeImprove uniformityPolycrystalline material growthSemiconductor/solid-state device manufacturingLiquid-crystal displayCrystalline silicon

The present invention discloses a method for making polycrystalline silicon layer which comprises, providing a substrate, forming a breaker having a plurality of ditches on the substrate, forming a non-crystalline silicon layer on the breaker, proceeding a laser annealing process to form a polycrystalline silicon. The invention can be applied into the production of low-temperature polycrystalline silicon thin film transistor LCDs.

Owner:AU OPTRONICS CORP

Thin film transistor, manufacturing method thereof, and TFT LCD using the same

ActiveUS20080105874A1Cgs can be reducedImprove display qualitySolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerEngineering

A thin film transistor (TFT) that comprises a gate electrode on a substrate, a gate insulation layer on the gate electrode, an active layer having a source region, a drain region, and a channel region on the gate insulation layer, and a source electrode and a drain electrode formed over the source region and drain region of the active layer respectively and facing each other with respect to the channel region. The profile of channel region between the source electrode and drain electrode is changed in a bend line. A method for forming the TFT is also provided.

Owner:BEIJING BOE OPTOELECTRONCIS TECH CO LTD +1

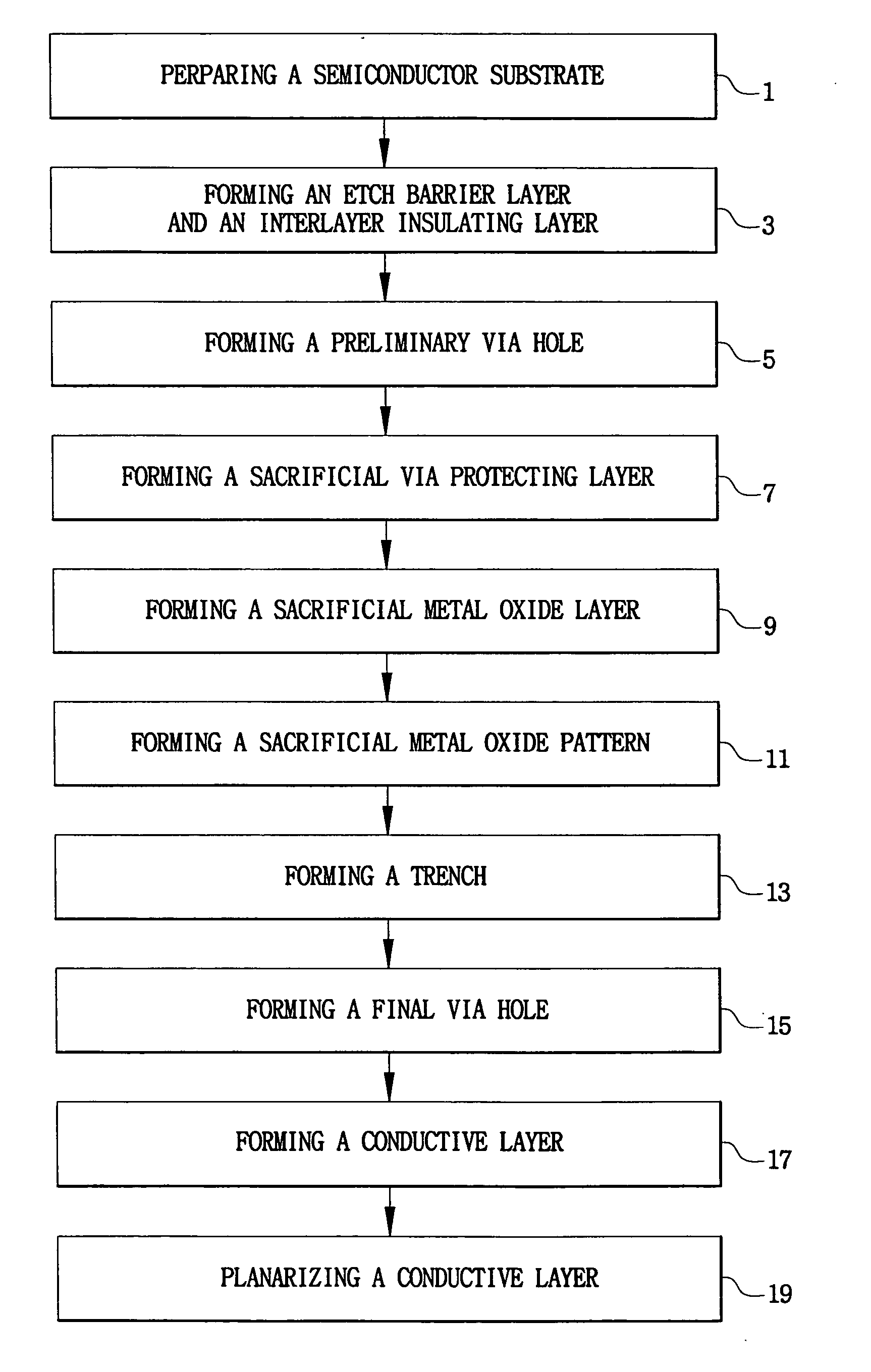

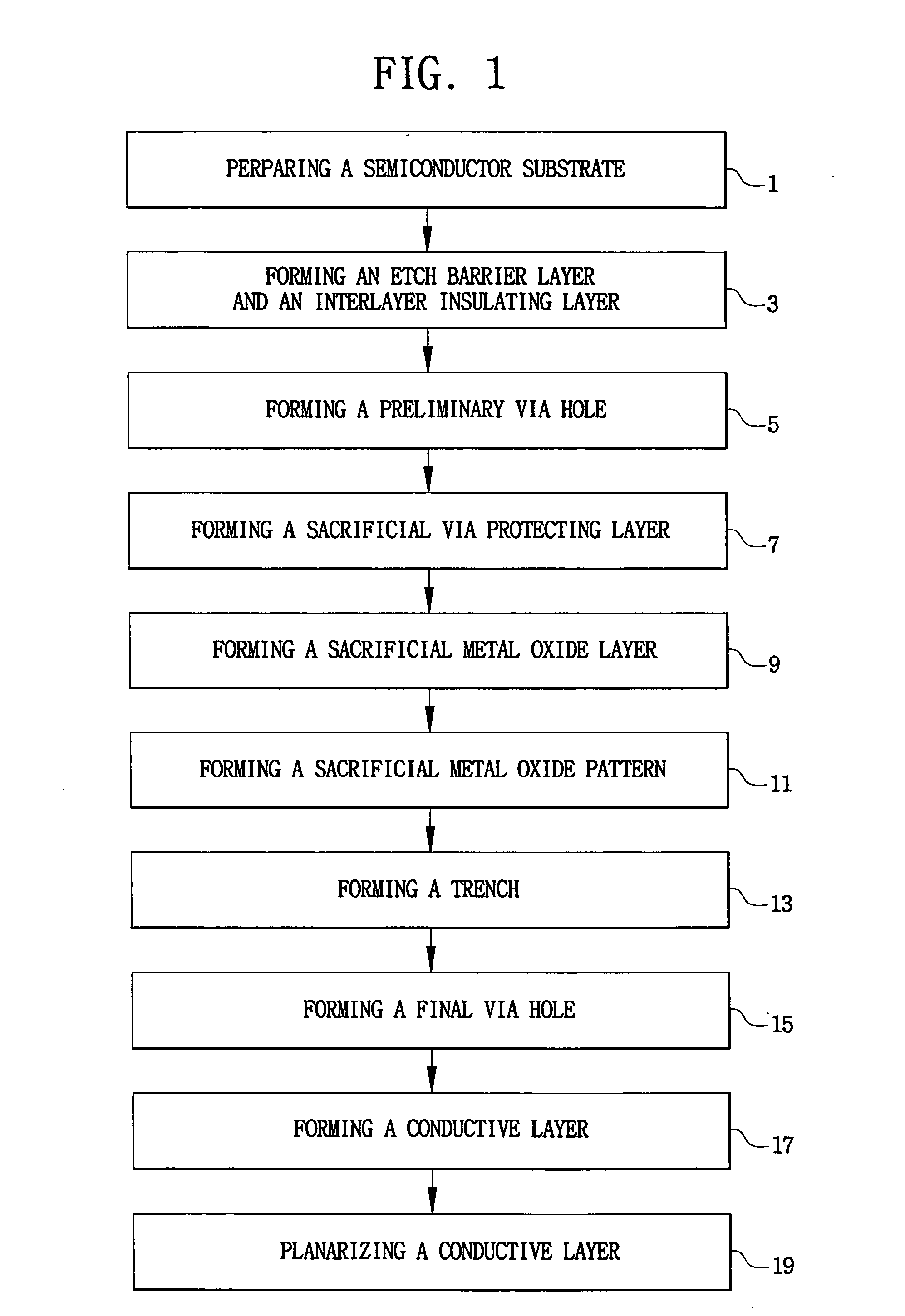

Method of forming dual damascene metal interconnection employing sacrificial metal oxide layer

ActiveUS20050124149A1Increase process marginReduce reflectivitySemiconductor/solid-state device manufacturingSemiconductor devicesInterconnectionSacrificial metal

There is provided a method of forming a dual damascene metal interconnection by employing a sacrificial metal oxide layer. The method includes preparing a semiconductor substrate. An interlayer insulating layer is formed on the semiconductor substrate, and a preliminary via hole is formed by patterning the interlayer insulating layer. A sacrificial via protecting layer is formed on the semiconductor substrate having the preliminary via hole to fill the preliminary via hole, and cover an upper surface of the interlayer insulating layer. A sacrificial metal oxide layer is formed on the sacrificial via protecting layer, the sacrificial metal oxide layer is patterned to form a sacrificial metal oxide pattern having an opening crossing over the preliminary via hole, and exposing the sacrificial via protecting layer. The sacrificial via protecting layer and the interlayer insulating layer are etched using the sacrificial metal oxide pattern as an etch mask to form a trench located inside the interlayer insulating layer.

Owner:SAMSUNG ELECTRONICS CO LTD

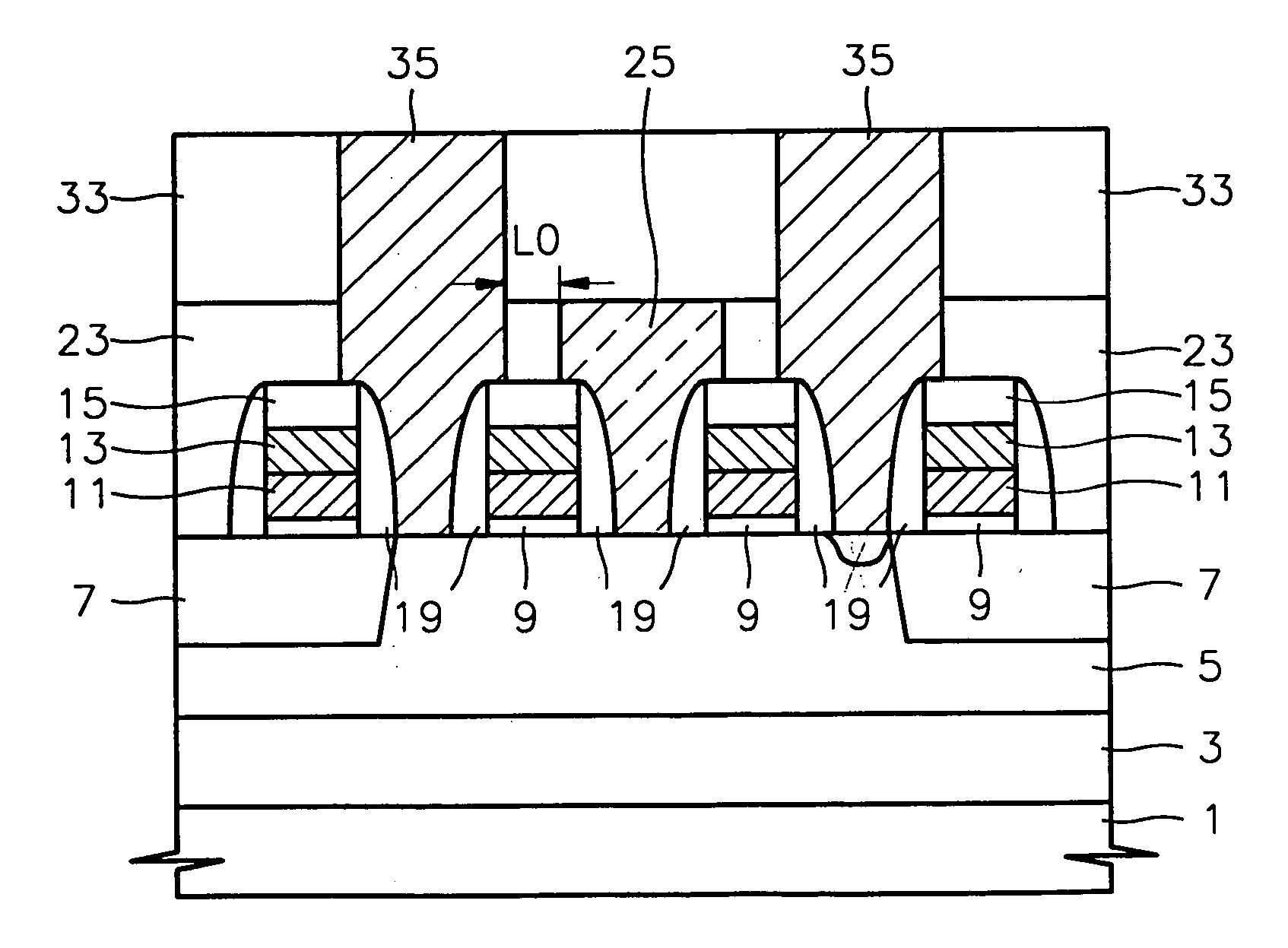

Semiconductor memory device having self-aligned contacts and method of fabricating the same

InactiveUS20050167758A1Prevent short-circuitingIncrease process marginTransistorSolid-state devicesBit lineEngineering

Owner:SAMSUNG ELECTRONICS CO LTD

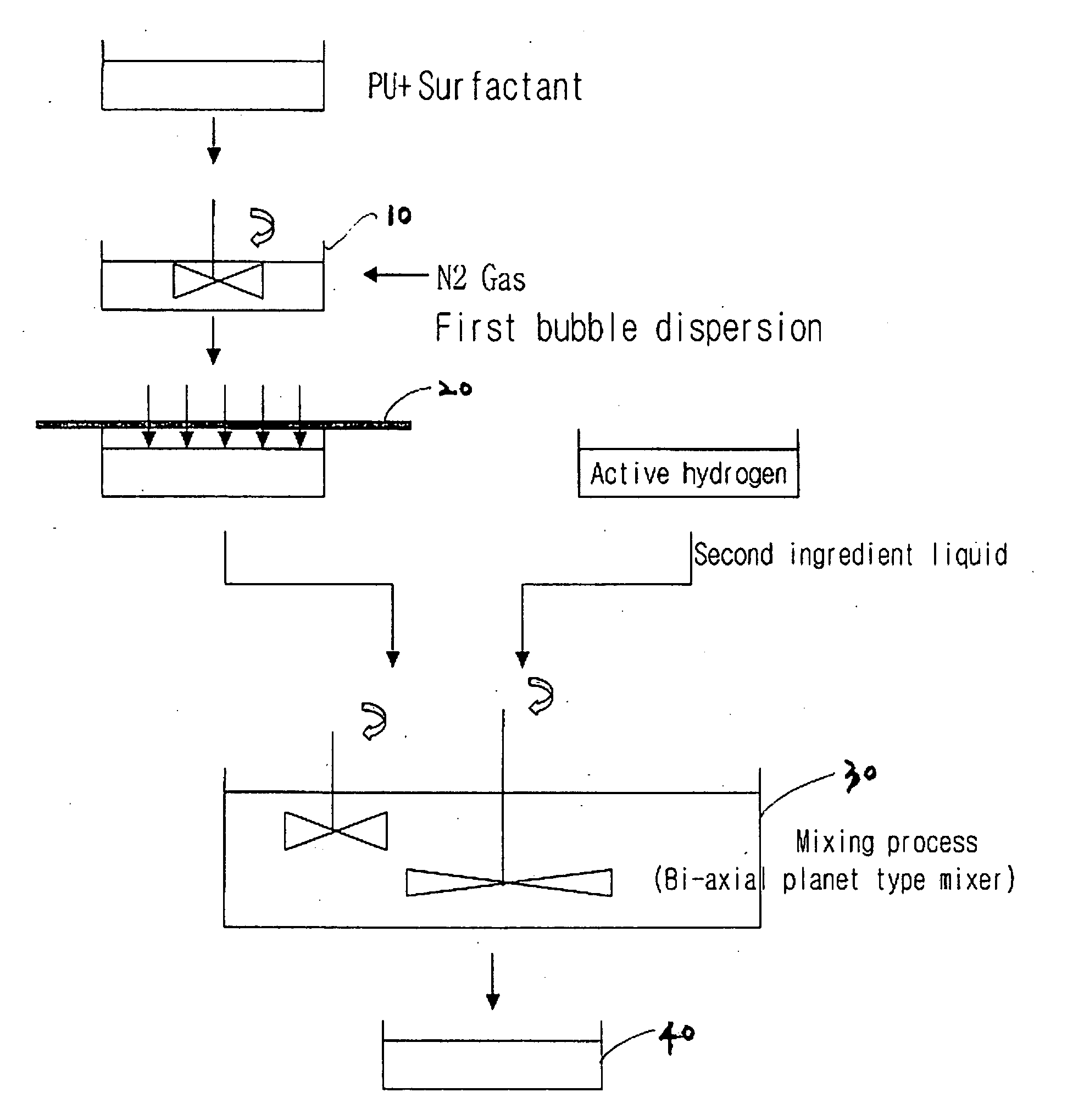

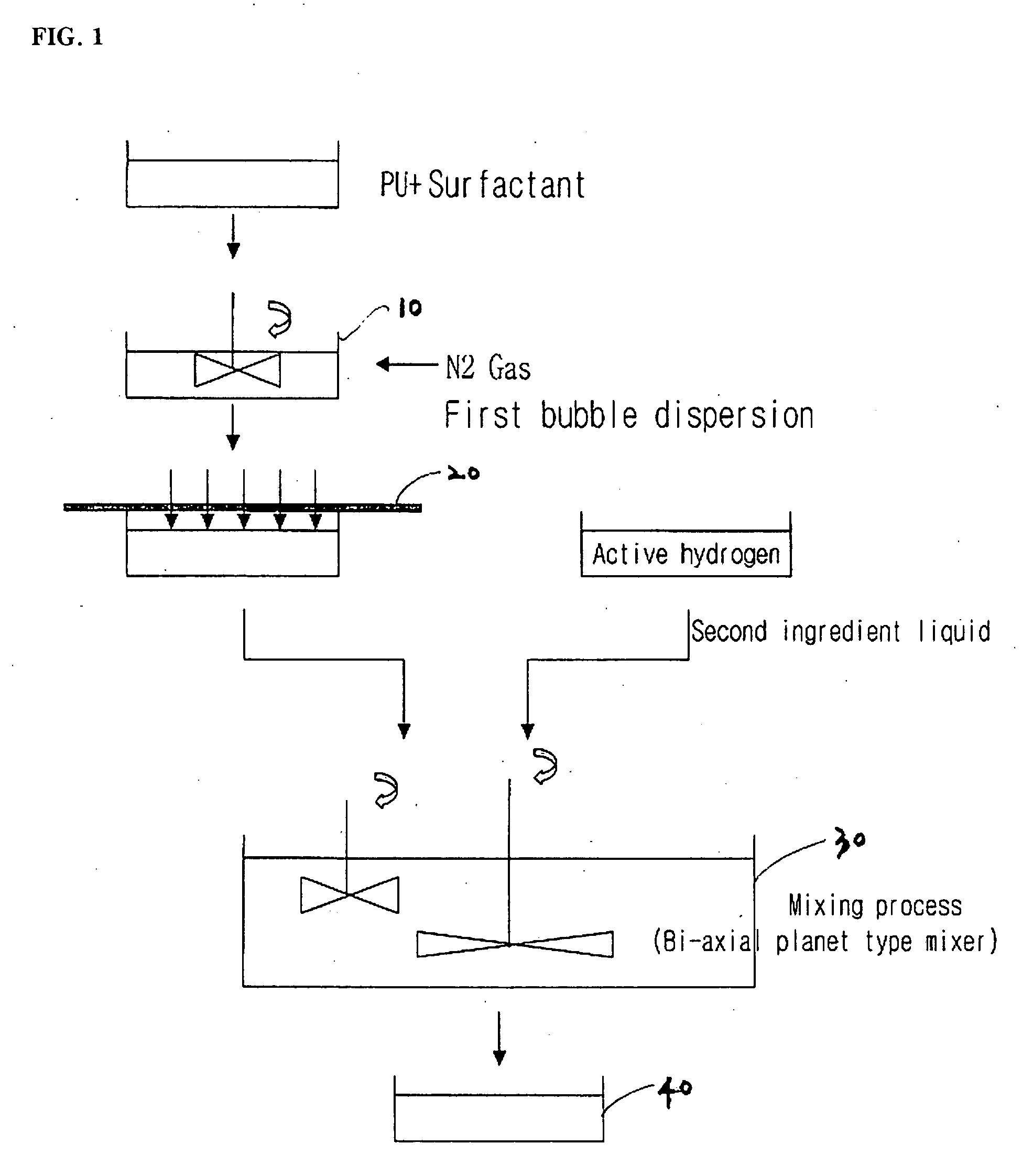

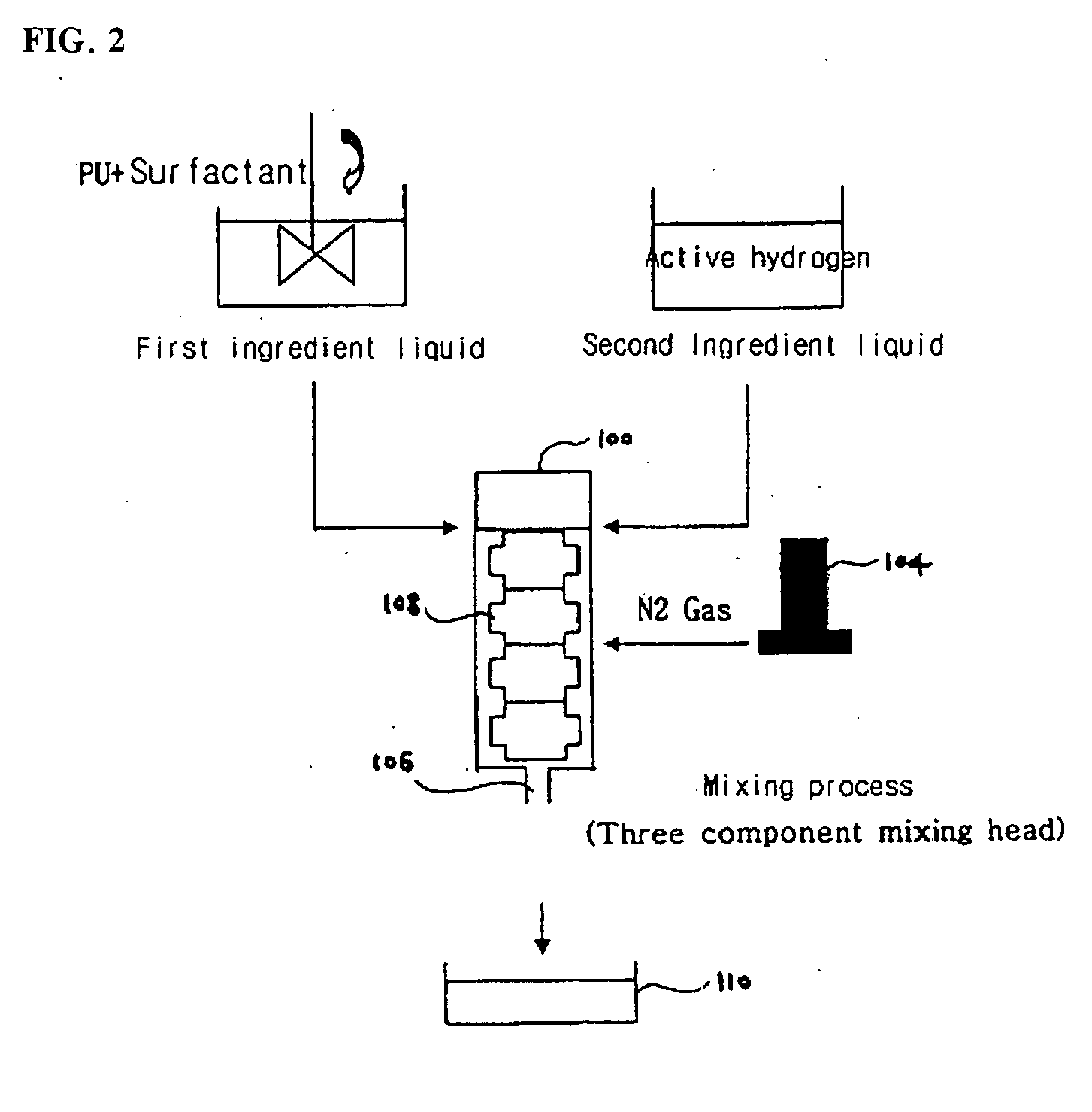

Method of fabricating polyurethane foam with micro pores and polishing pad therefrom

InactiveUS20060022368A1Good flexibilitySimplify the manufacturing processSemiconductor/solid-state device manufacturingFlexible-parts wheelsHydrogenAdditive ingredient

To provide a method of fabricating a polyurethane foam with micro pores, and a polishing pad therefrom, the method including steps of (a) adding a nonionic surfactant into at least one of a first ingredient including an isocyanate group-containing compound and a second ingredient including an active hydrogen group-containing compound, (b) agitating and mixing the mixture of the first ingredient and the second ingredient while adding a non-reactive gas thereto, (c) discharging the mixture out of a container at a predetermined rate, and (d) injecting the discharged mixture into a mold so as to form a mold body into a predetermined shape.

Owner:DONG SUNG A & T

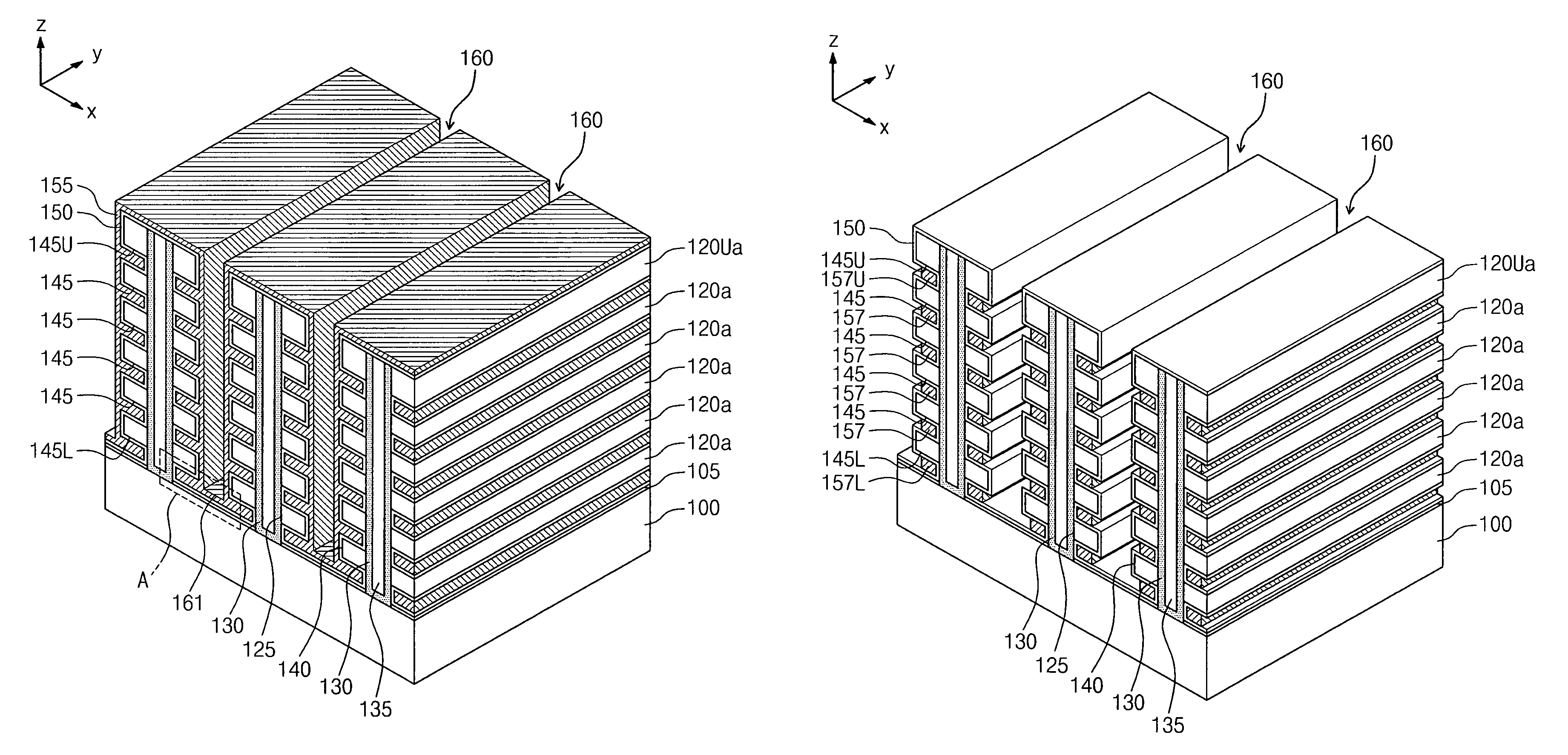

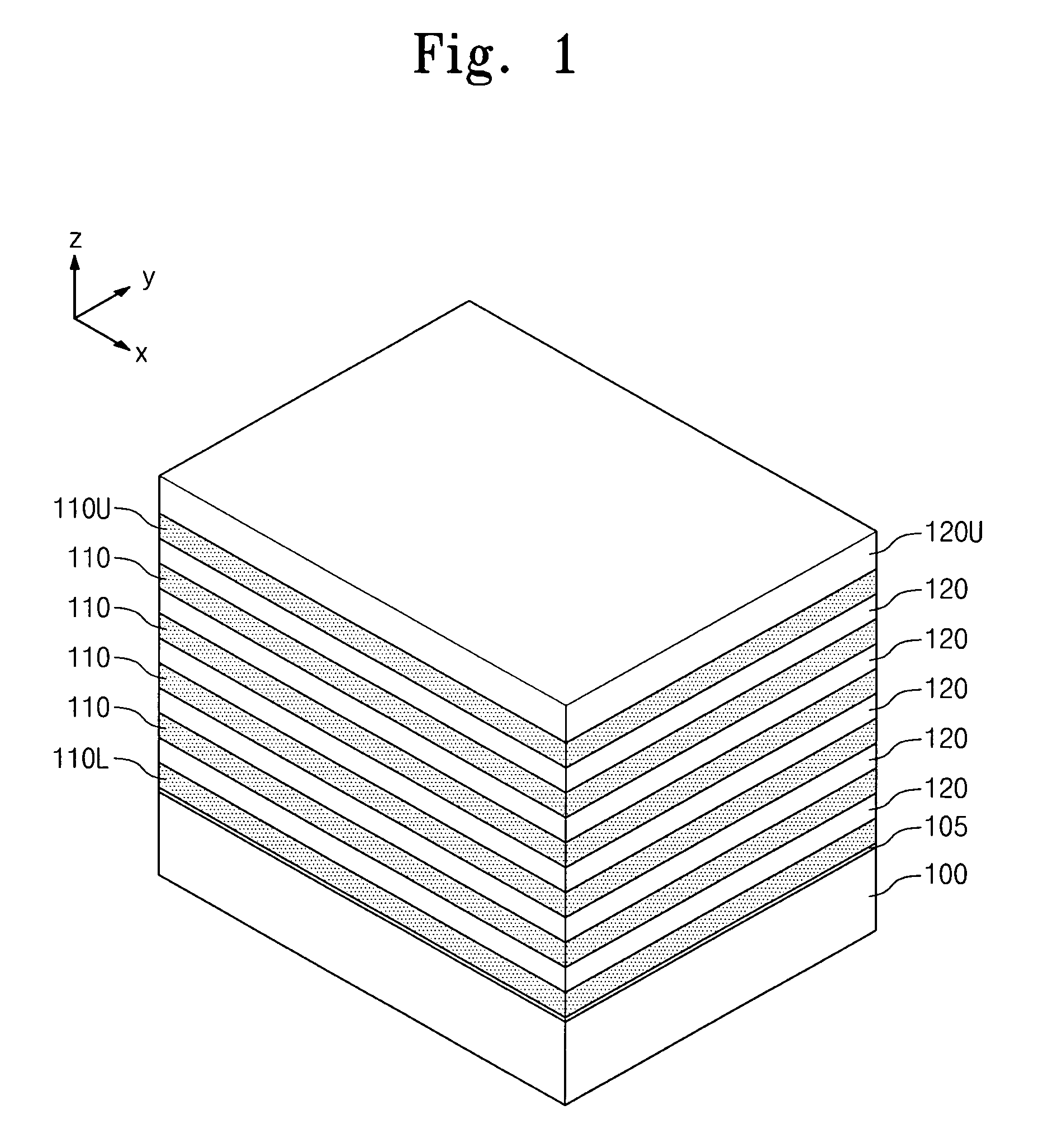

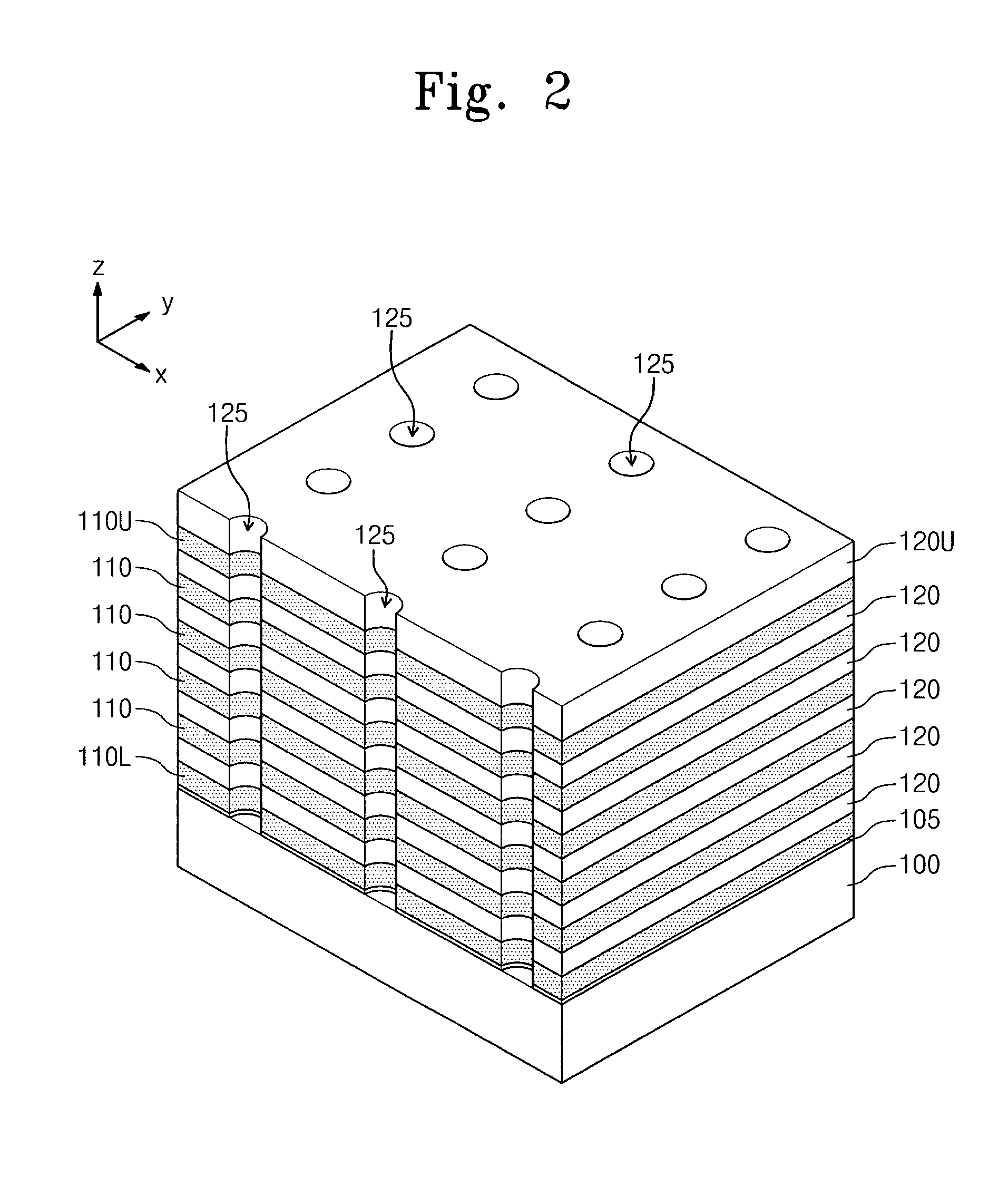

Three-dimensional semiconductor memory device and method of fabricating the same

ActiveUS8383482B2Improve reliabilityIncrease process marginSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

A method of fabricating a semiconductor memory device includes alternately and repeatedly stacking sacrificial layers and insulating layers on a substrate, forming an active pattern penetrating the sacrificial layers and the insulating layers, continuously patterning the insulating layers and the sacrificial layers to form a trench, removing the sacrificial layers exposed in the trench to form recess regions exposing a sidewall of the active pattern, forming an information storage layer on the substrate, forming a gate conductive layer on the information storage layer, such that the gate conductive layer fills the recess regions and defines an empty region in the trench, the empty region being surrounded by the gate conductive layer, and performing an isotropic etch process with respect to the gate conductive layer to form gate electrodes in the recess regions, such that the gate electrodes are separated from each other.

Owner:SAMSUNG ELECTRONICS CO LTD

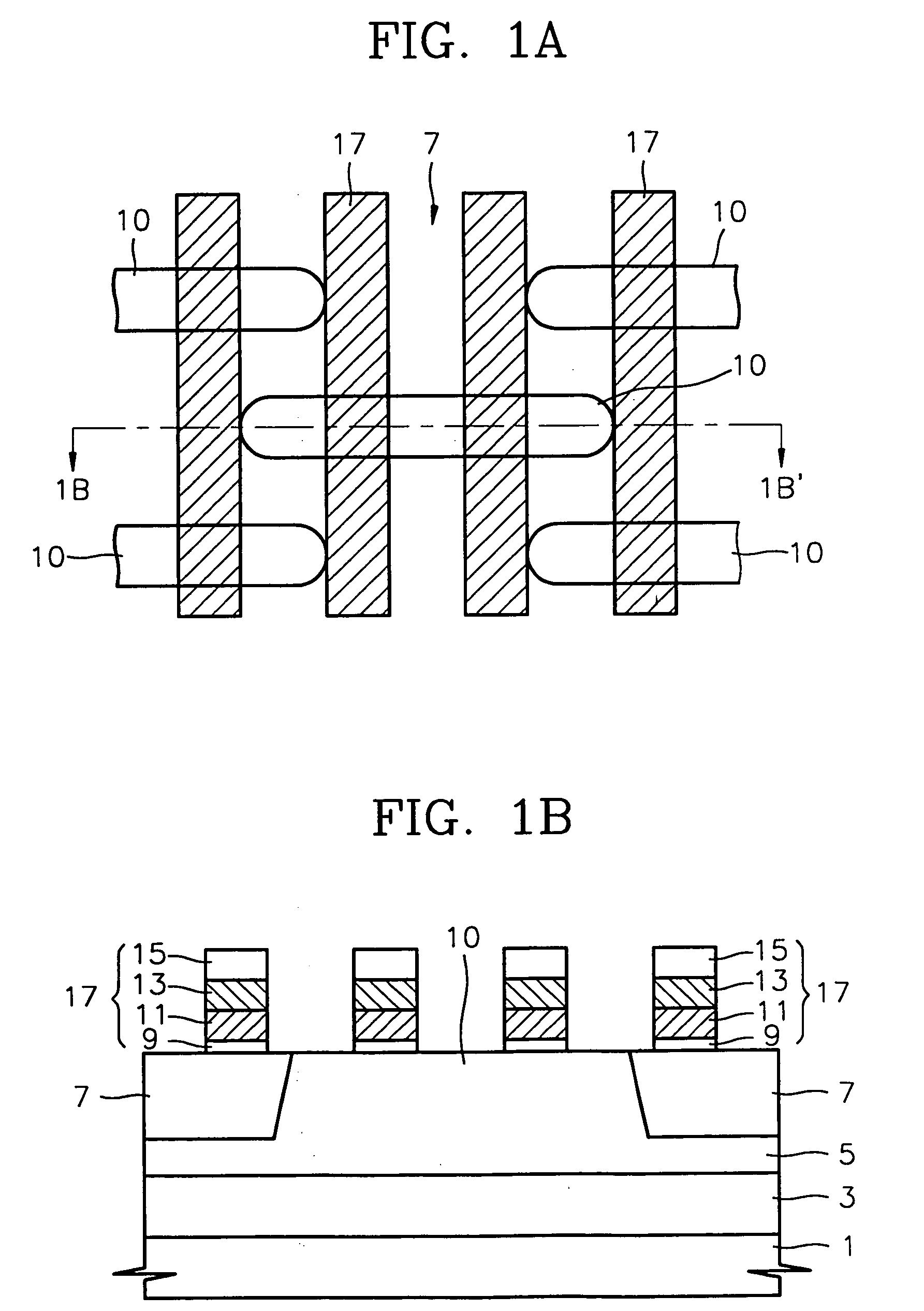

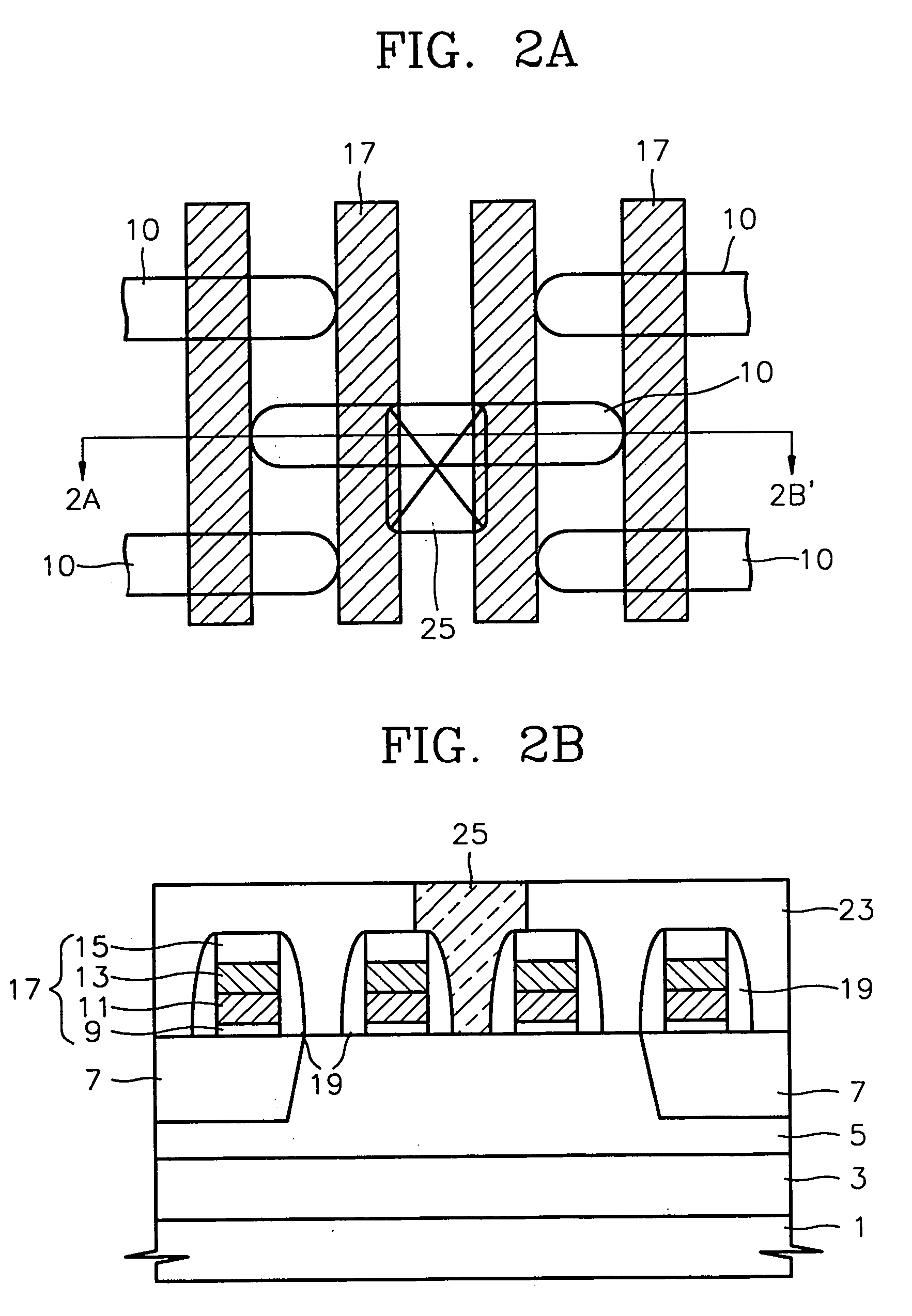

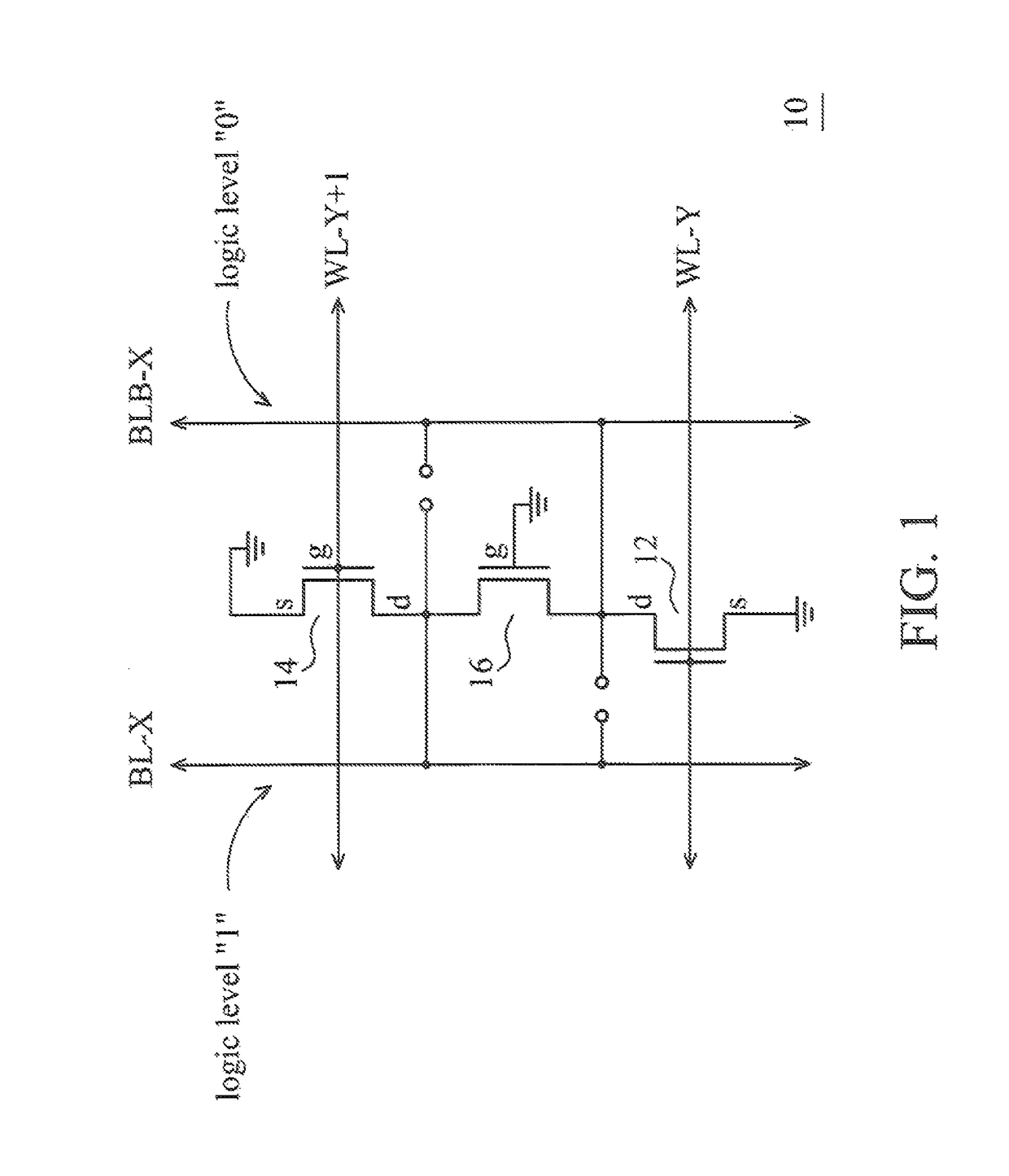

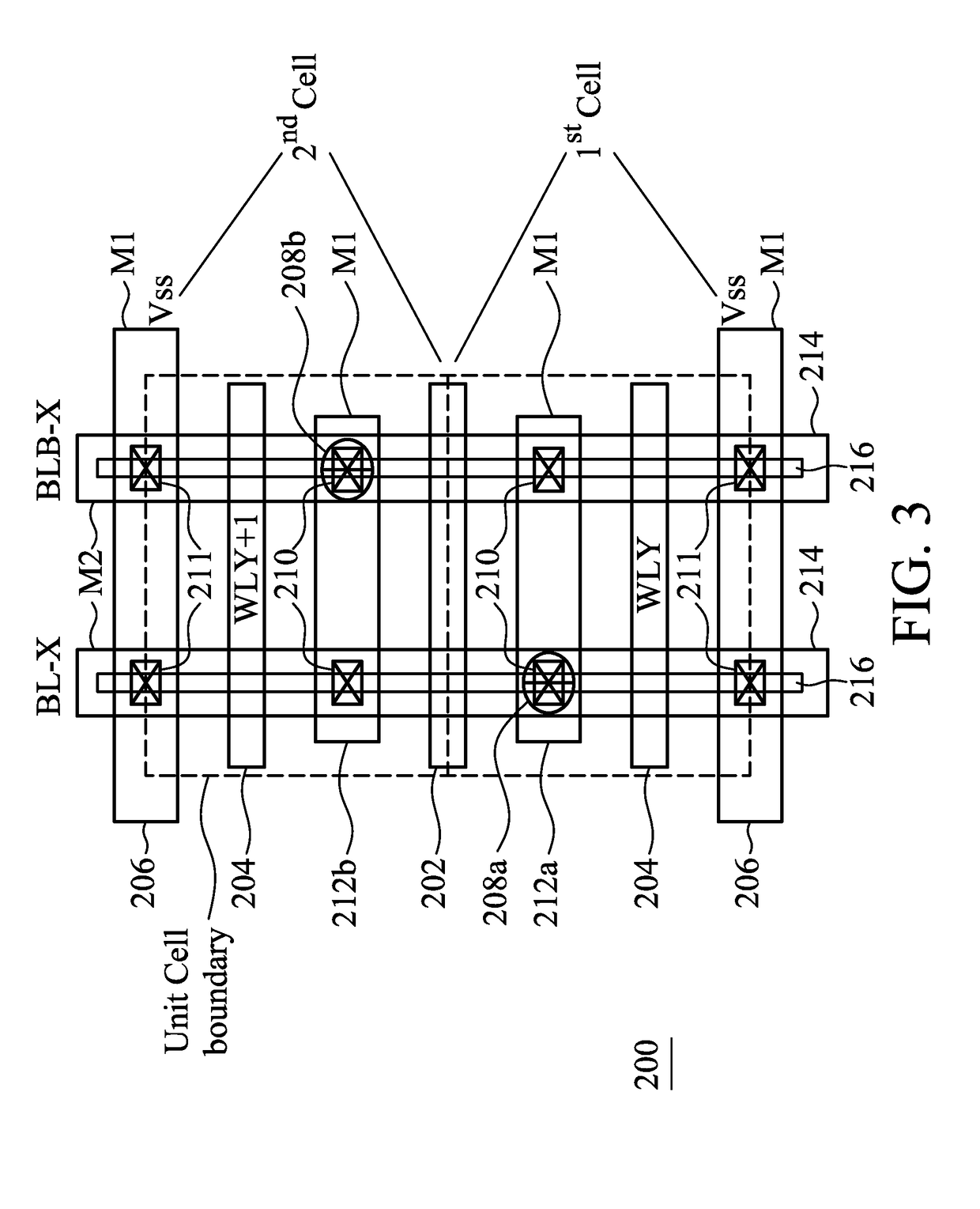

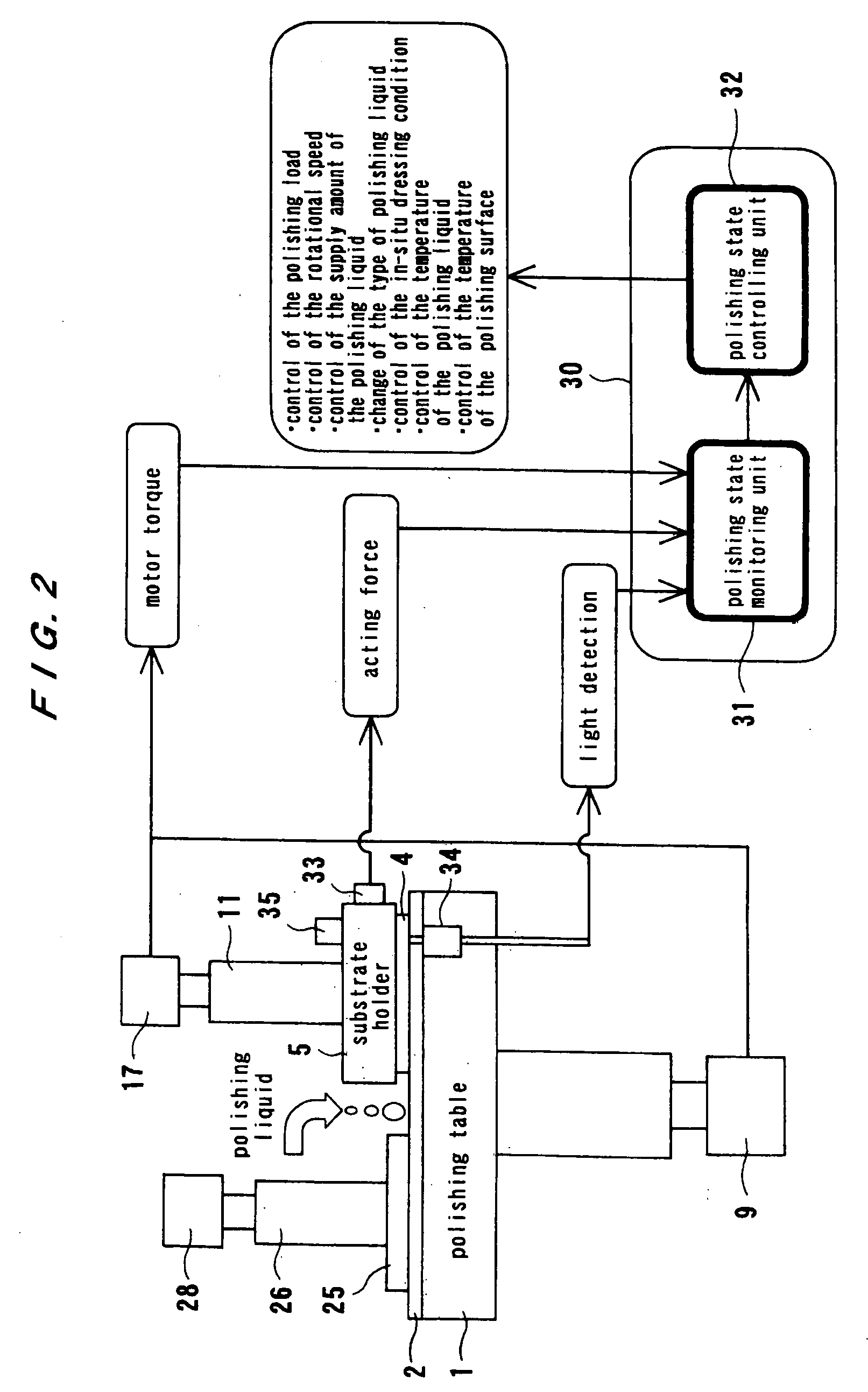

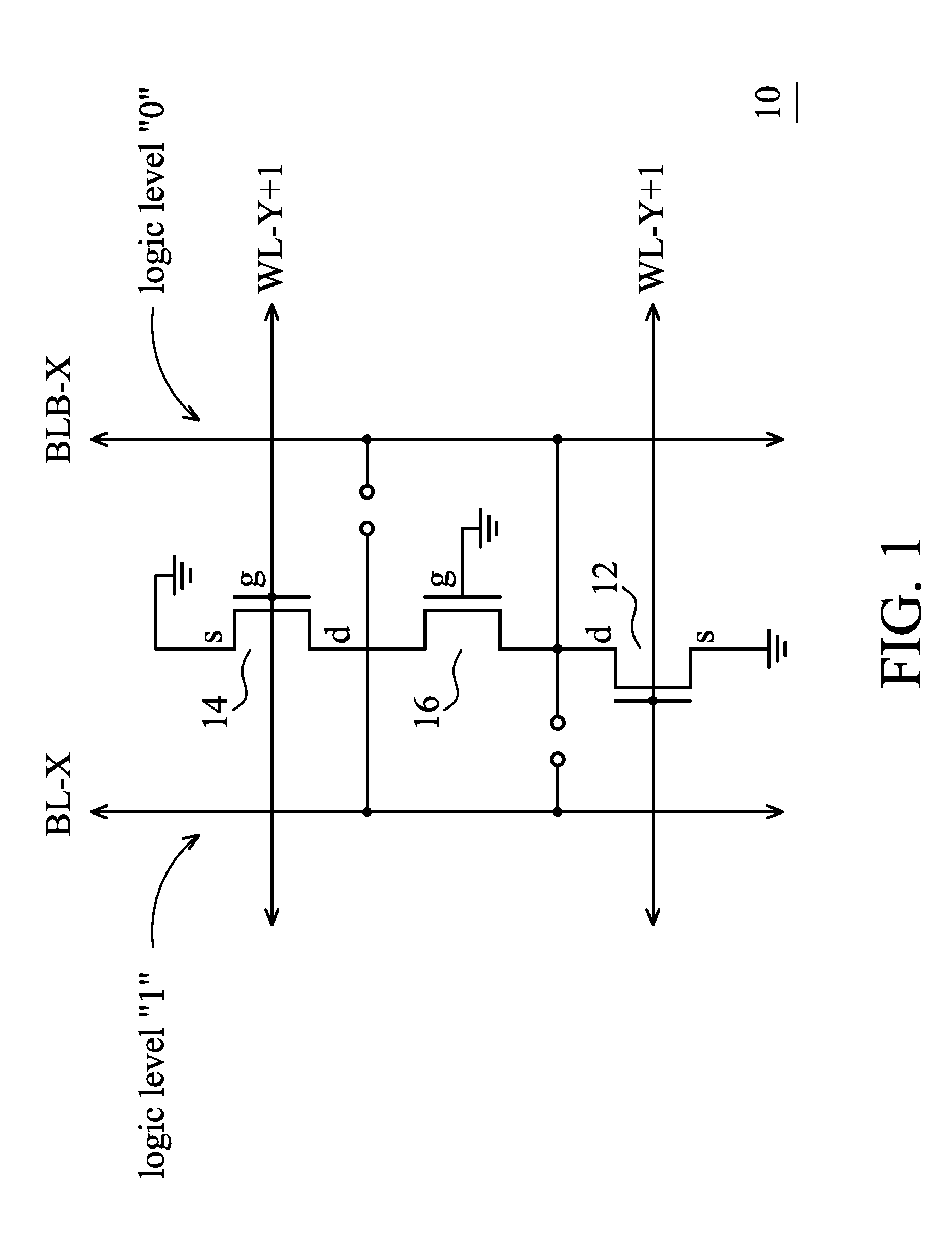

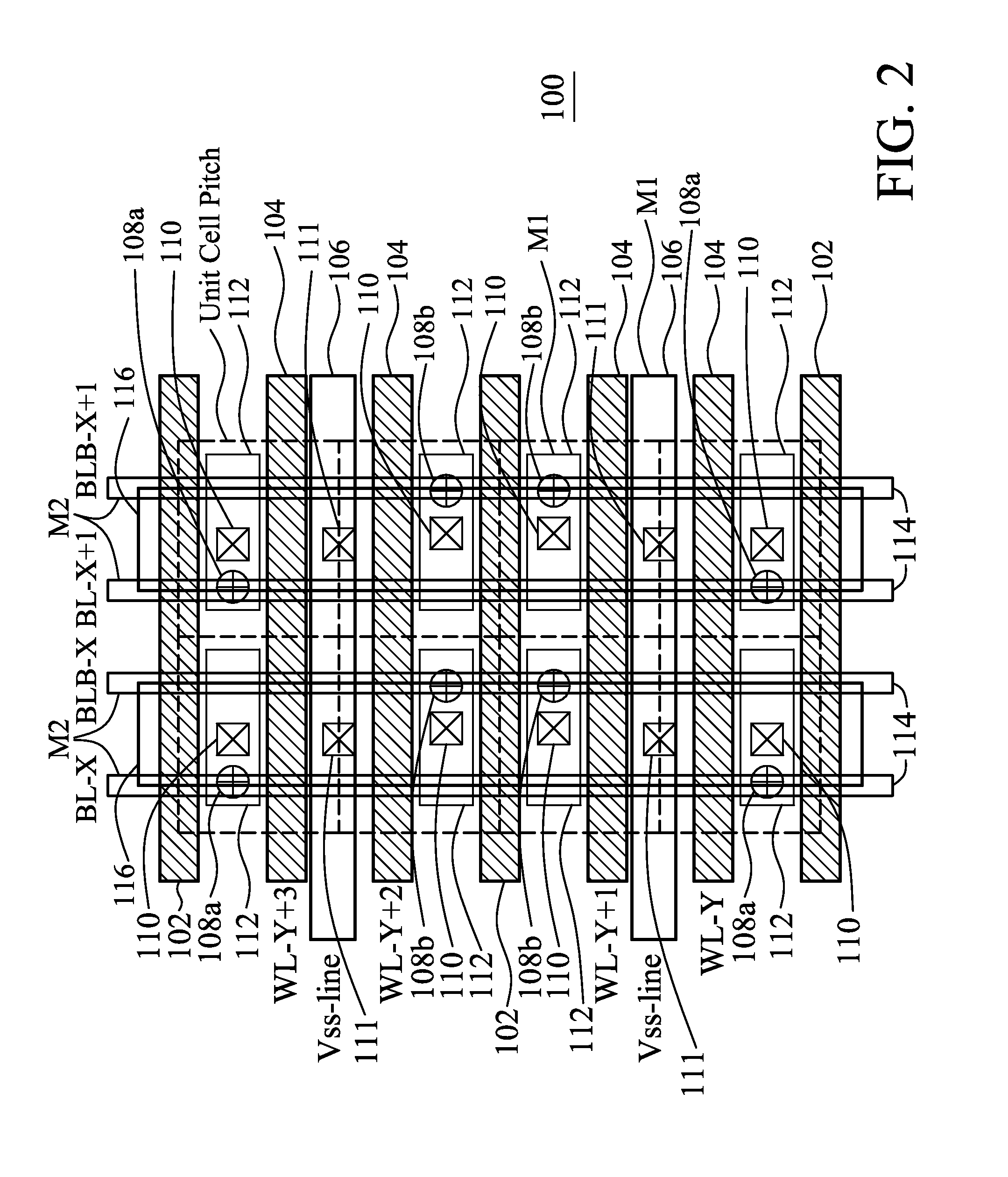

ROM cell having an isolation transistor formed between first and second pass transistors and connected between a differential bitline pair

ActiveUS8120939B2Balance performanceIncrease process marginSolid-state devicesRead-only memoriesBit lineEngineering

A semiconductor memory cell array includes an elongated continuous active region. First and second pass transistors are formed in the elongated continuous active region and form part of first and second adjacent memory cells, respectively, of a column of memory cells in the array. An isolation transistor is formed in the elongated continuous active region between the first and second pass transistors and biased in an off state. First and second word lines are coupled to the gates of the pass transistors for applying a reading voltage. The array includes a differential bit line pair including first and second bit lines, a first logic value being encoded into the memory cells by connecting the pass transistors to the first bit line and a second logic value being encoded into the memory cells by connecting the pass transistors to the second bit line.

Owner:TAIWAN SEMICON MFG CO LTD

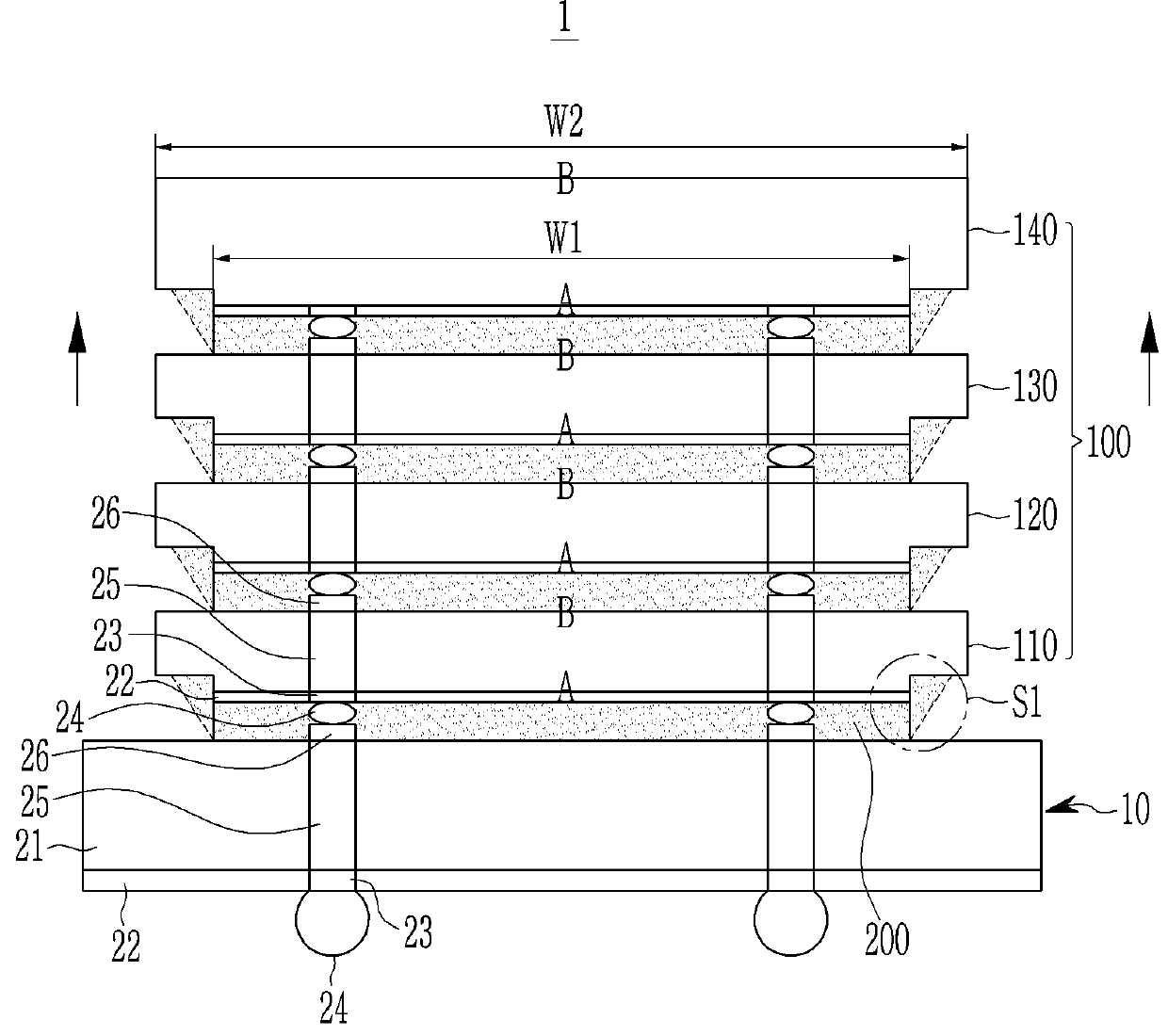

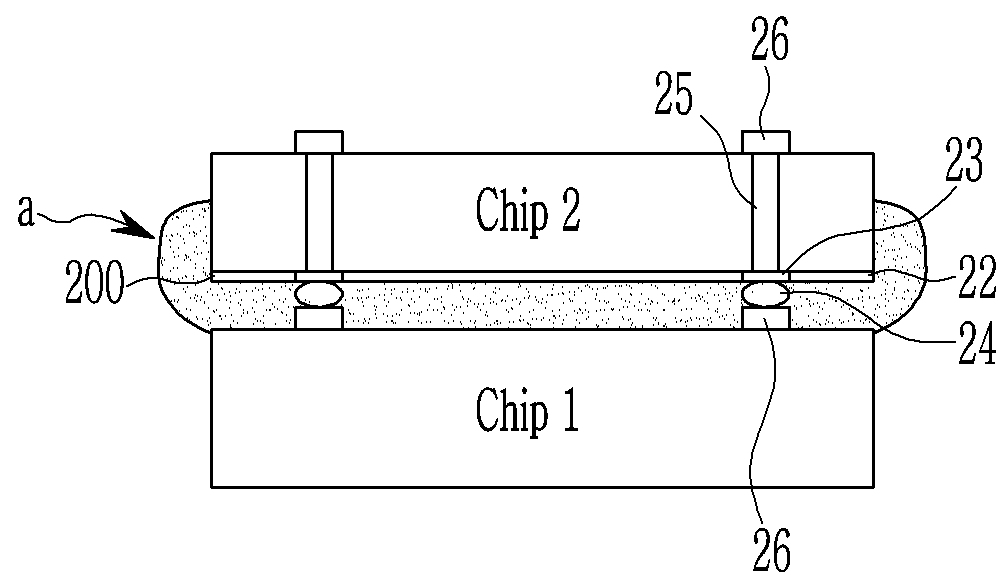

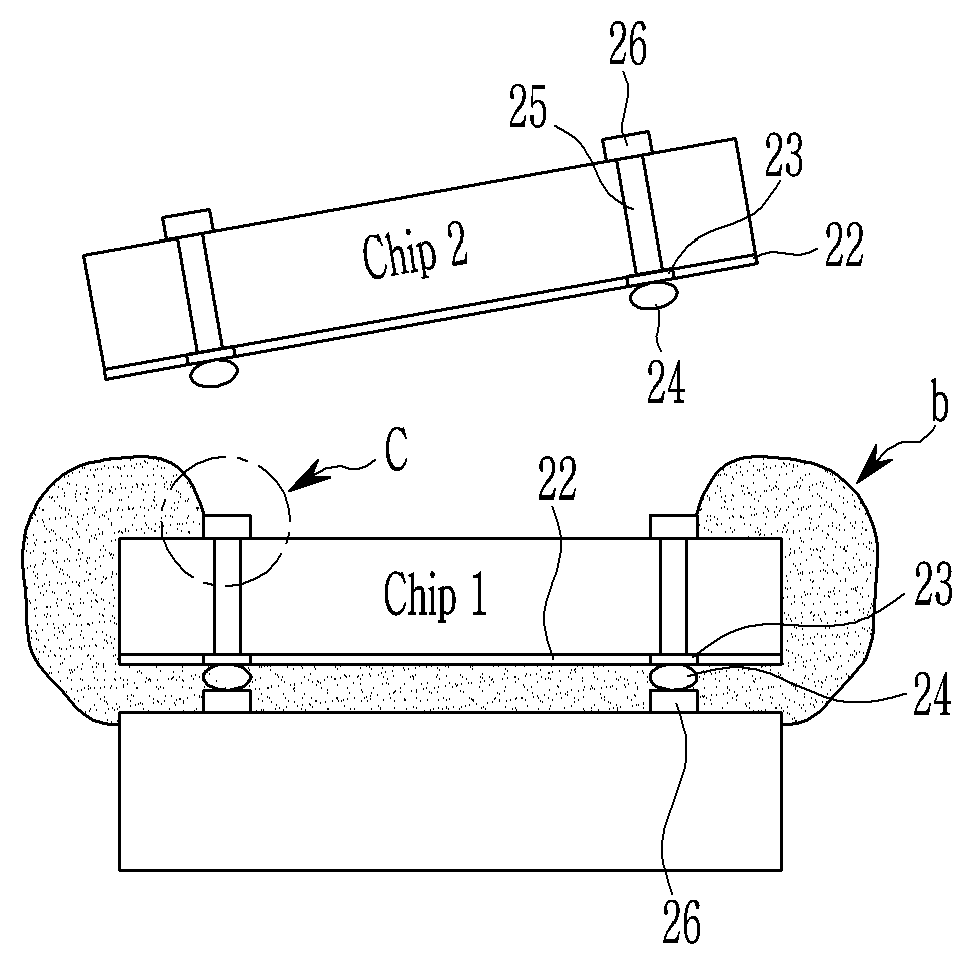

Semiconductor package and fabrication method thereof

ActiveUS20180166420A1Increase process marginImprove warpageSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSemiconductor package

A semiconductor package includes a semiconductor chip in which a side step or a side slope formed toward an inactive surface from an active surface is included and a width of the active surface is smaller than a width of the inactive surface, and an underfill which is disposed on the active surface and positioned at an inner side of the edge of the semiconductor chip.

Owner:SAMSUNG ELECTRONICS CO LTD

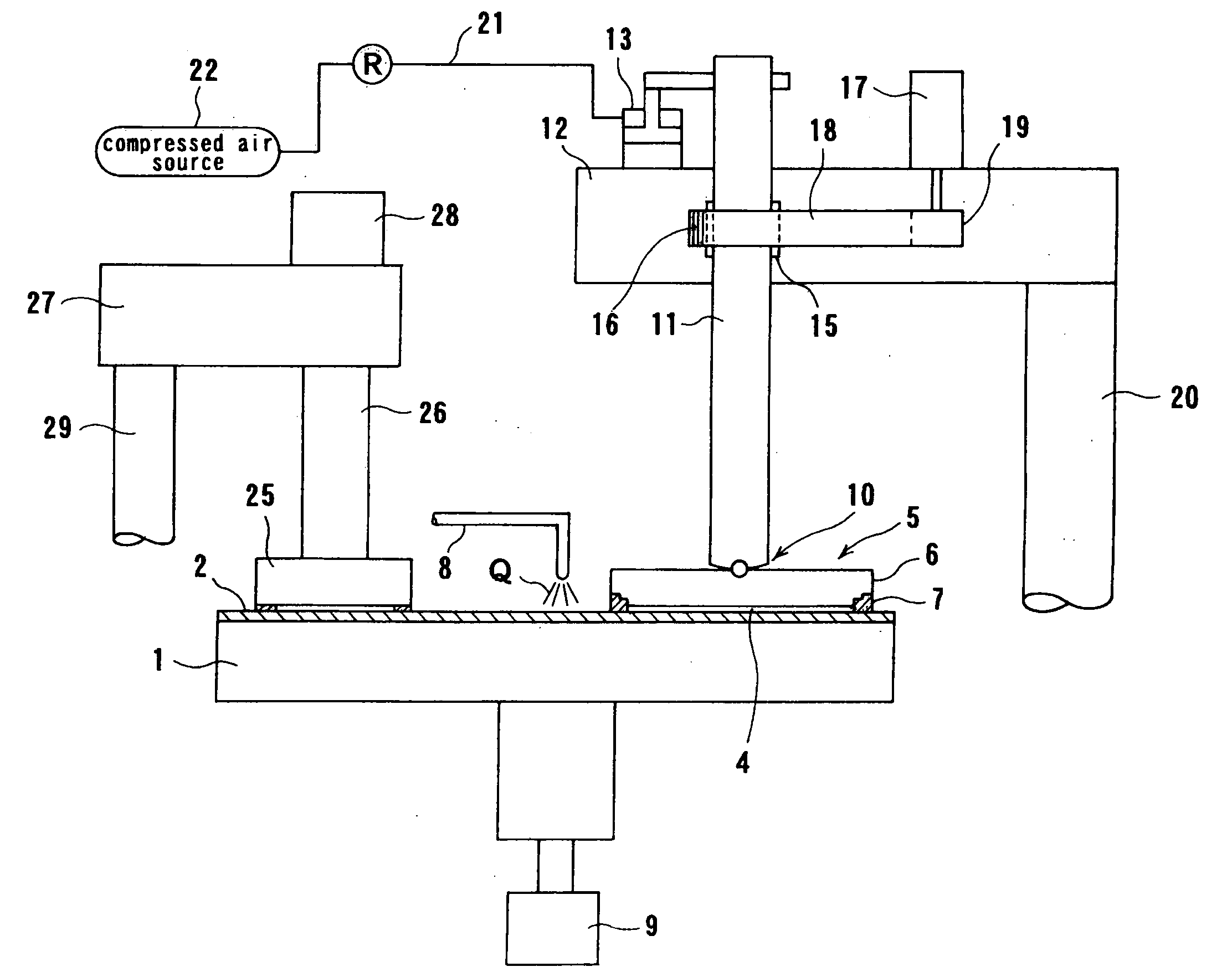

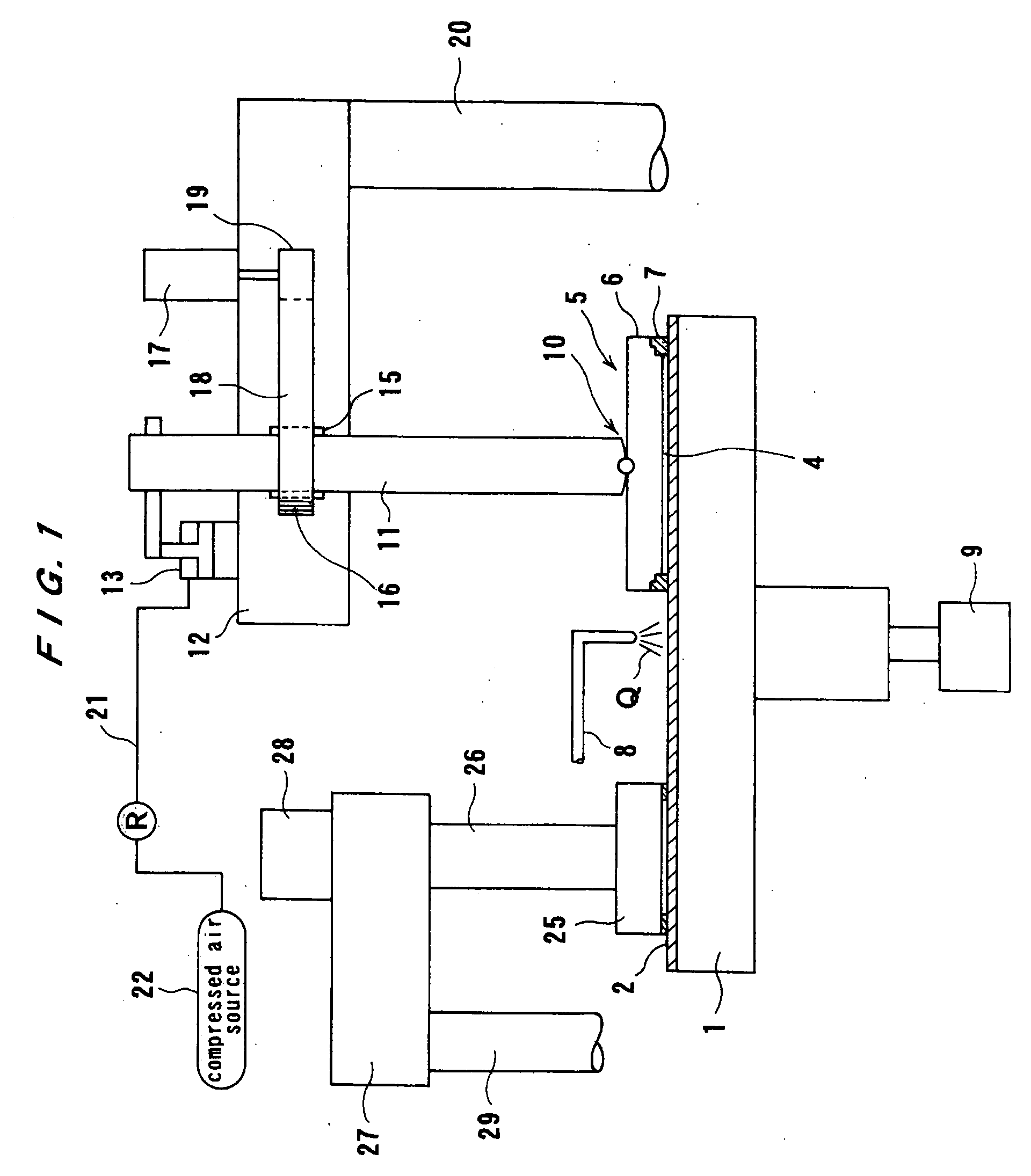

Polishing apparatus

InactiveUS20050112998A1Increase process marginPrevent peelingSemiconductor/solid-state device manufacturingLapping machinesEngineeringSemiconductor

A polishing apparatus is used for polishing a substrate such as a semiconductor wafer to a flat finish. The polishing apparatus includes a polishing tool having a polishing surface, a substrate holder configured to hold a substrate, a monitoring device configured to monitor a polishing state of the surface of the substrate being polished, and a controlling device configured to change a polishing condition on the basis of the polishing state of the surface of the substrate being polished detected by the monitoring device.

Owner:EBARA CORP +1

ROM cell and array structure

ActiveUS20110069527A1Balance performanceIncrease process marginSolid-state devicesRead-only memoriesBit lineArray data structure

A semiconductor memory cell array includes an elongated continuous active region. First and second pass transistors are formed in the elongated continuous active region and form part of first and second adjacent memory cells, respectively, of a column of memory cells in the array. An isolation transistor is formed in the elongated continuous active region between the first and second pass transistors and biased in an off state. First and second word lines are coupled to the gates of the pass transistors for applying a reading voltage. The array includes a differential bit line pair including first and second bit lines, a first logic value being encoded into the memory cells by connecting the pass transistors to the first bit line and a second logic value being encoded into the memory cells by connecting the pass transistors to the second bit line.

Owner:TAIWAN SEMICON MFG CO LTD

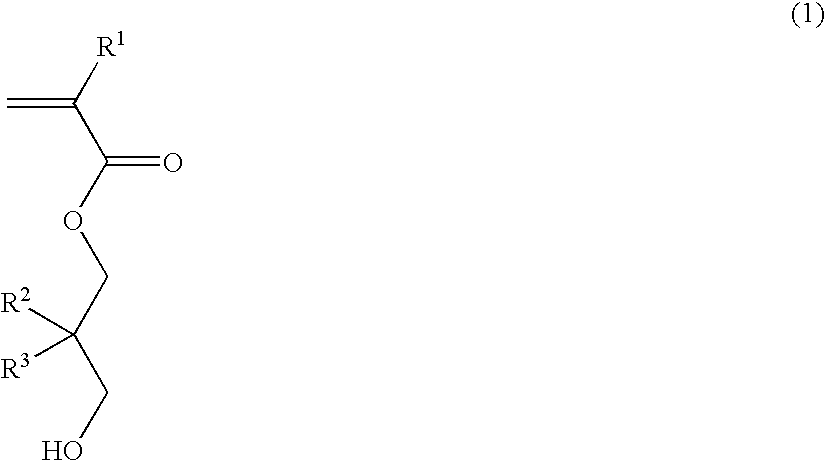

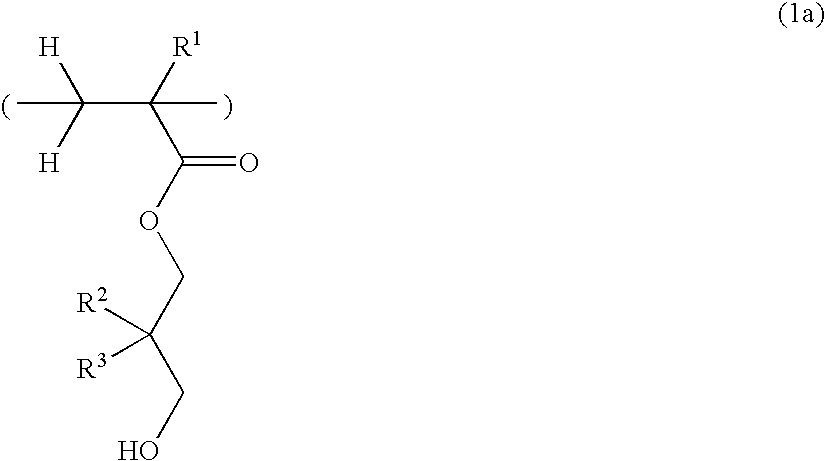

Hydroxyl-containing monomer, polymer, resist composition, and patterning process

ActiveUS20090239179A1High transparencyHigh resolutionOrganic chemistryOrganic compound preparationResistRadiation sensitivity

A hydroxyl-containing monomer of formula (1) is provided wherein R1 is H, F, methyl or trifluoromethyl, R2 and R3 are monovalent C1-C15 hydrocarbon groups, or R2 and R3 may form an aliphatic ring. The monomers are useful for the synthesis of polymers which have high transparency to radiation of up to 500 nm and the effect of controlling acid diffusion so that the polymers may be used as a base resin to formulate radiation-sensitive resist compositions having a high resolution.

Owner:SHIN ETSU CHEM IND CO LTD

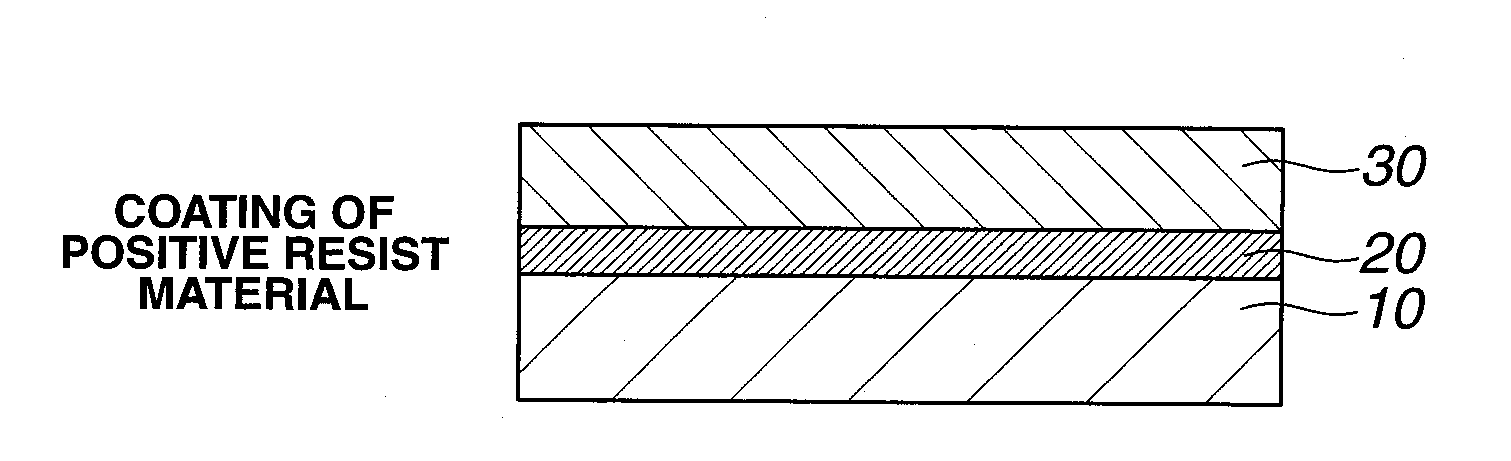

Method of utilizing dual-layer photoresist to form black matrixes and spacers on a control circuit substrate

ActiveUS20040100596A1Improve throughputIncrease process marginNon-linear opticsOptoelectronicsOptical density

A method of utilizing dual-layer photoresist to form black matrixes and spacers on a control circuit substrate is provided. The dual-layer photoresist is composed of a layer of black resin and a layer of transparent photoresist. The black resin, of which optical density is greater than three, is mainly used to achieve the effect of black matrix. The transparent photoresist is mainly used to satisfy the needed cell gap between two transparent substrates.

Owner:HANNSTAR DISPLAY CORPORATION

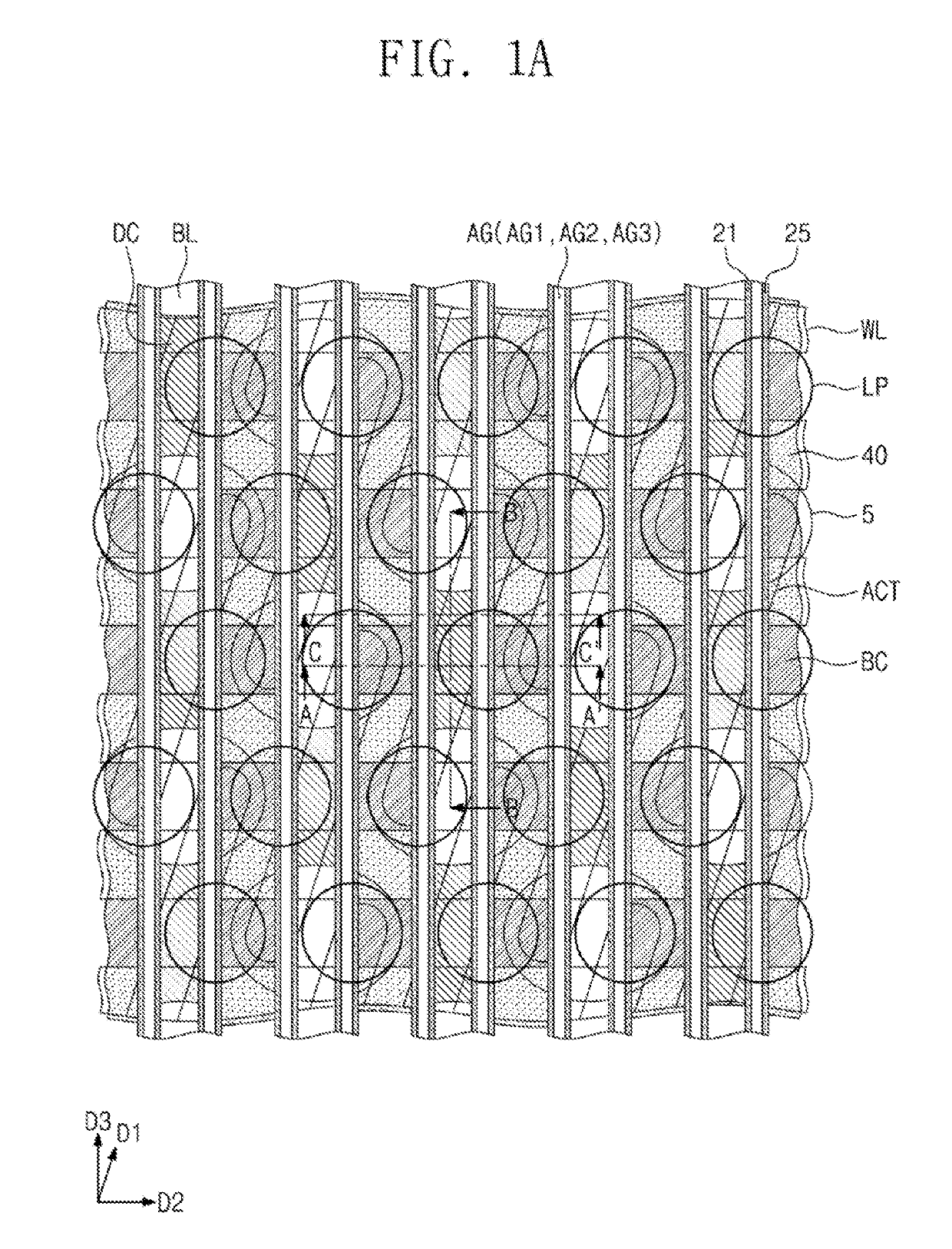

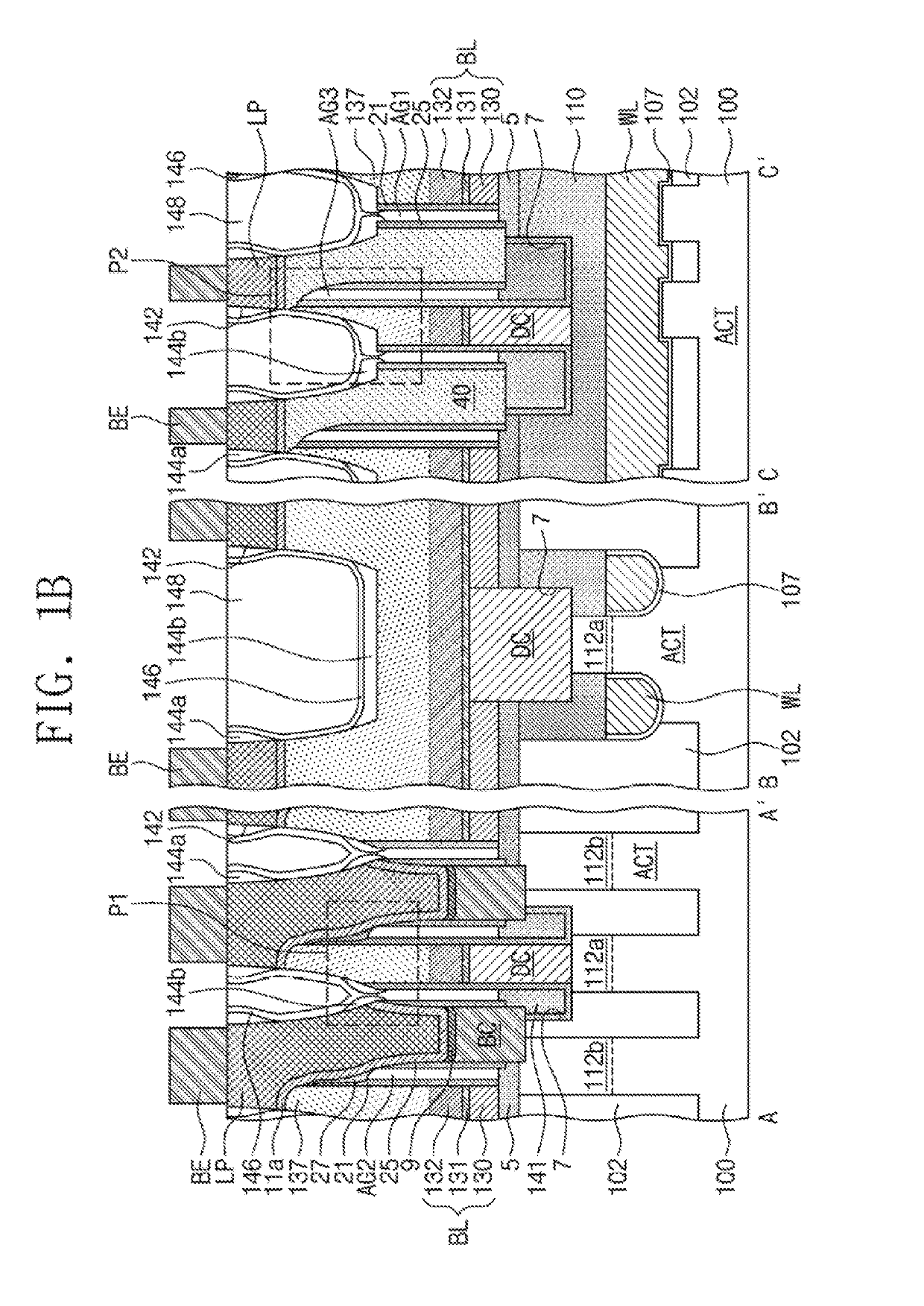

Semiconductor memory device and method of fabricating the same

ActiveUS20190164975A1Improve reliabilityIncrease process marginTransistorSemiconductor/solid-state device detailsBit lineSemiconductor

Provided are a semiconductor memory device and a method of fabricating the same. The semiconductor memory device may include: a first impurity doped region and a second impurity doped region spaced apart from each other in a semiconductor substrate, a bit line electrically connected to the first impurity doped region and crossing over the semiconductor substrate, a storage node contact electrically connected to the second impurity doped region, a first spacer and a second spacer disposed between the bit line and the storage node contact, and an air gap region disposed between the first spacer and the second spacer. The first spacer may cover a sidewall of the bit line, and the second spacer may be adjacent to the storage node contact. A top end of the first spacer may have a height higher than a height of a top end of the second spacer.

Owner:SAMSUNG ELECTRONICS CO LTD

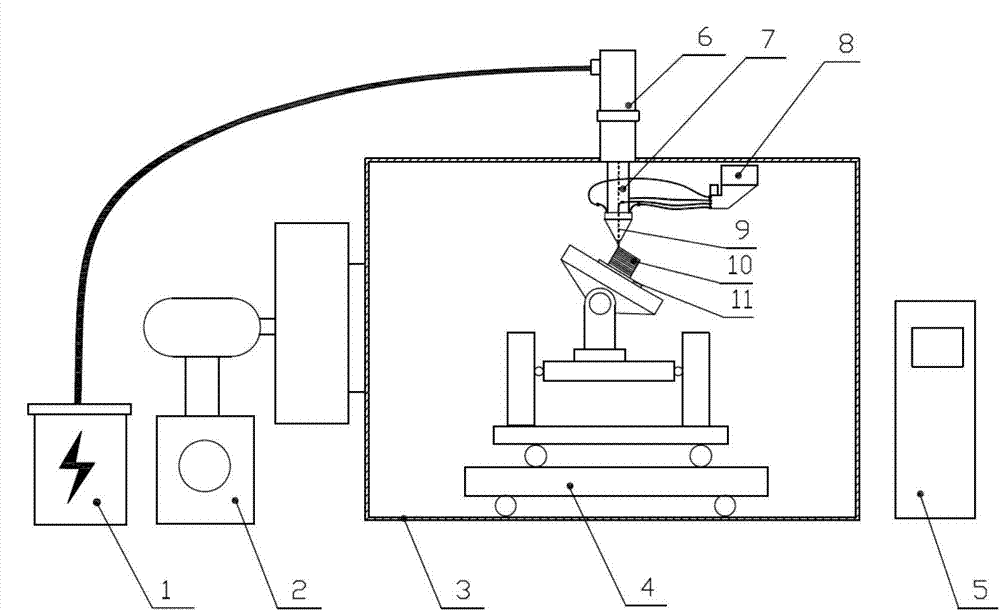

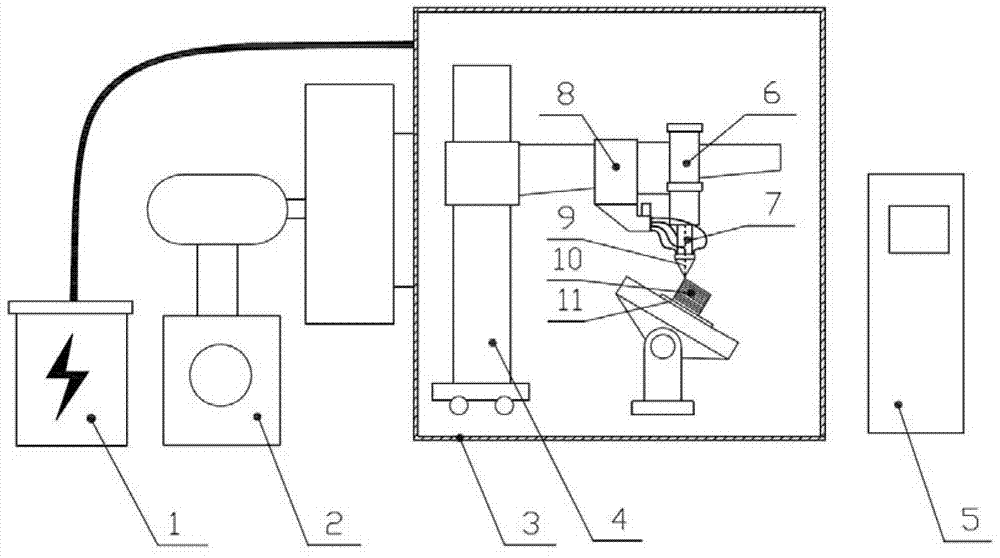

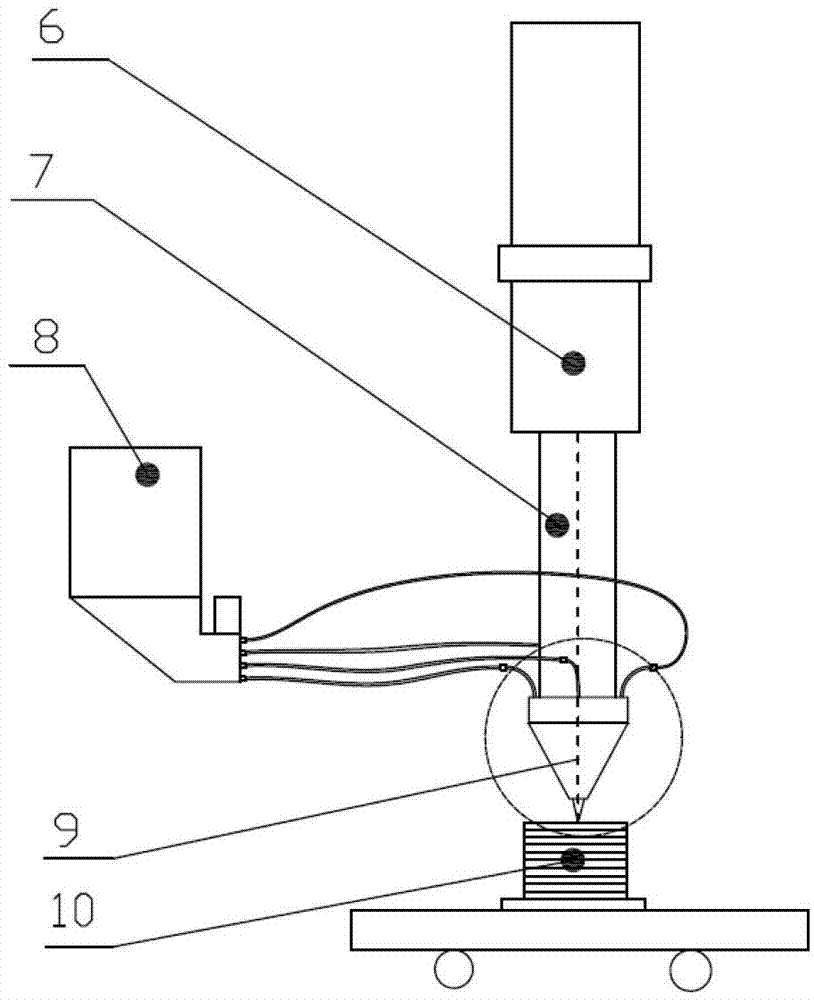

Electron beam synchronous powder feeding and quick forming method

InactiveCN102764889AImprove protectionAvoid mixingAdditive manufacturing apparatusMolten spray coatingMelting tankChemical composition

The invention discloses an electron beam synchronous powder feeding and quick forming method. The method includes that metal powder is fed to a portion, which is intersected with beam current, of a to-be-processed surface, in a coaxial or paraxial manner, and the portion can be positioned in a molten pool or at the front of the molten pool. The electron beam synchronous powder feeding and quick forming method is characterized in that an electron beam bombards a workpiece to form the molten pool, the molten pool moves relative to the surface of the workpiece, the metal powder is simultaneously fed to a thermal action zone to participate in melting, and processing is implemented. As the powder is fed, the synchronous powder feeding and quick forming method has the advantages that speed is fast, quality is good, chemical composition and structure property of a part can be conveniently regulated and controlled, and the method is particularly applicable to preparing high-gradient and multi-step materials and structures and also can be used for processing parts with fine appearances and dimensions. Compared with wire feeding technology, the electron beam synchronous powder feeding and quick forming method has the powder does not interfere with the part, technological difficulty is low, and the method is easy to control.

Owner:BEIJING AERONAUTICAL MFG TECH RES INST

Semiconductor device and method for producing the same

InactiveUS7157780B2Reduce defectsImprove heat resistanceTransistorSolid-state devicesHydrogenNitrogen

A gate electrode is formed on a substrate via a gate insulating film. The gate insulating film includes a high dielectric constant film containing a metal, oxygen and hydrogen, and a lower barrier film formed below the high dielectric constant film and containing a metal, oxygen, silicon and nitrogen.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

Method of manufacturing a semiconductor device

InactiveUS7393723B2Improving decarbonizationImproving step coverage propertyTransistorSolid-state devicesHydrogenEngineering

A method of manufacturing a semiconductor device that forms laminate layers includes the steps of reducing contamination containing the single bond of carbon on at least one part of a surface on which the laminate films are formed by activated hydrogen before the laminate films are formed, and forming the laminate films on the surface on which the laminate films are formed.

Owner:SEMICON ENERGY LAB CO LTD

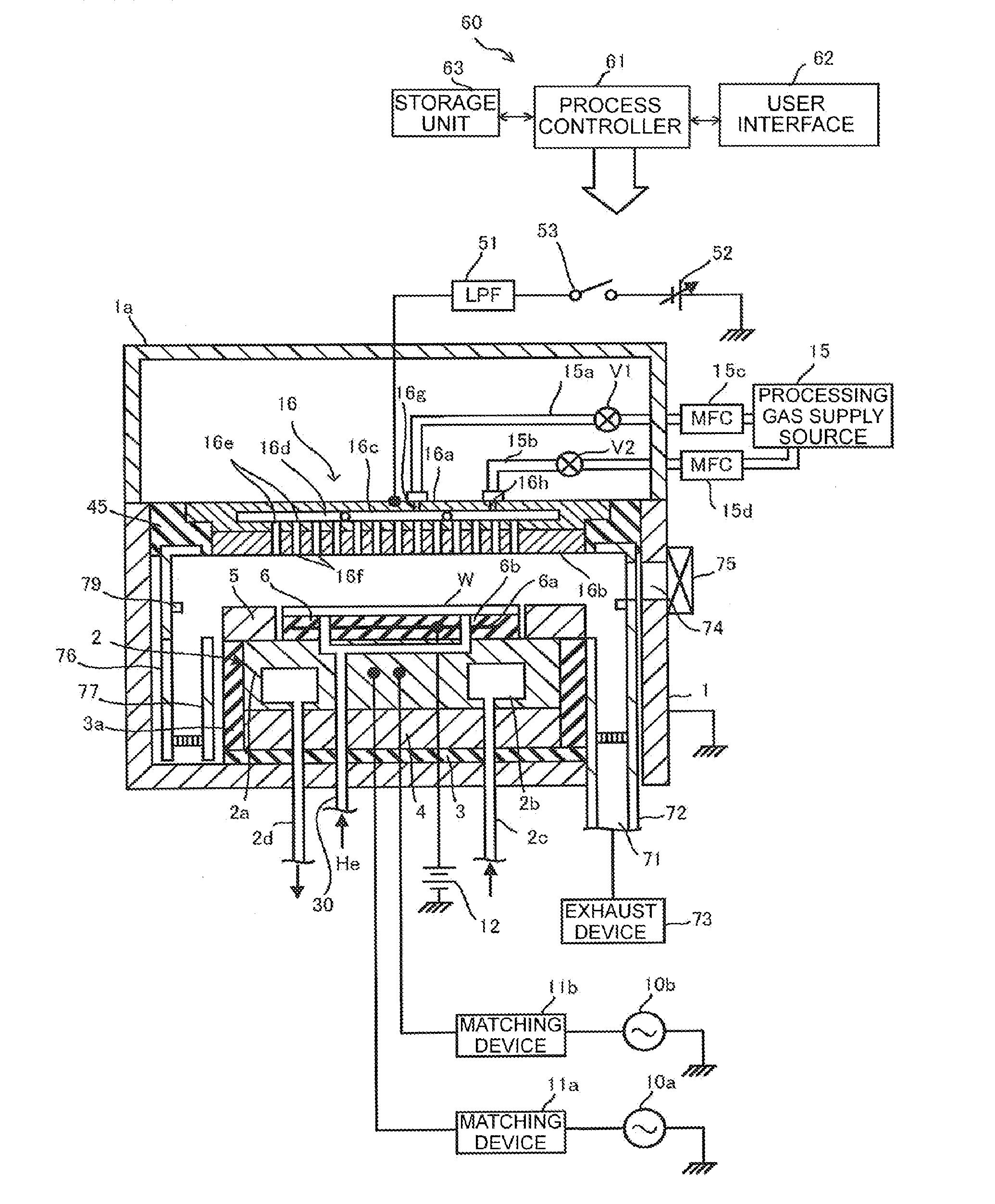

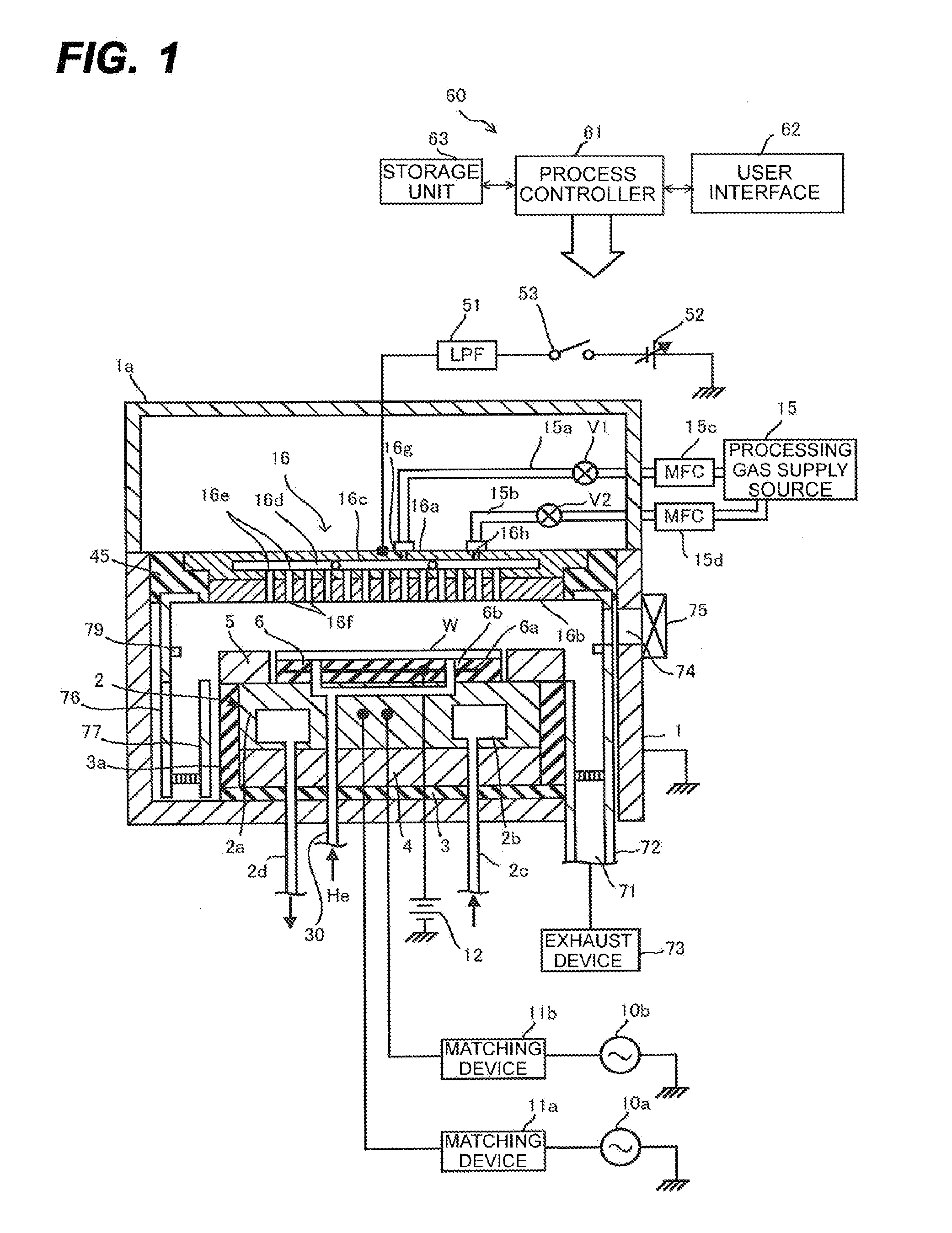

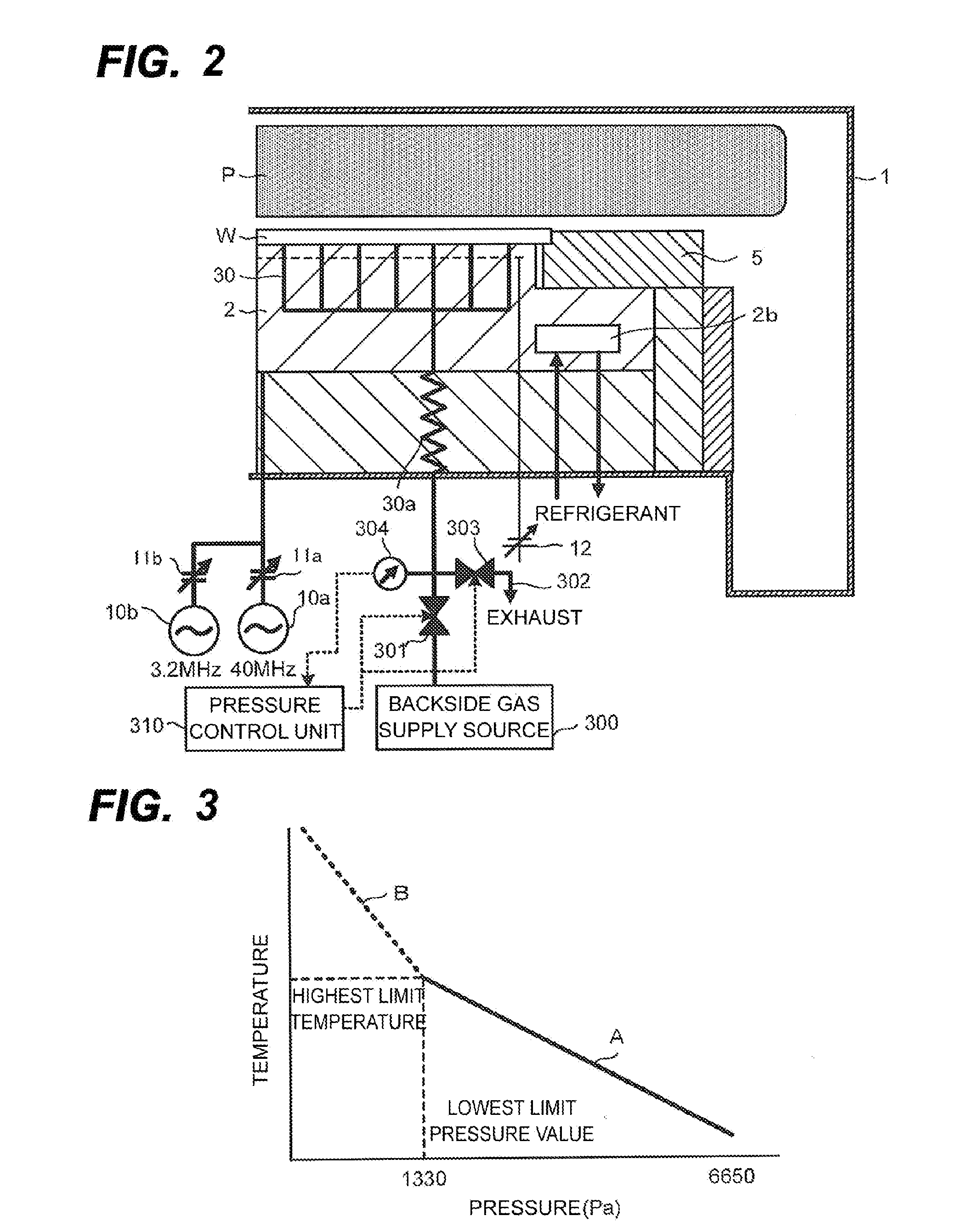

Substrate temperature control method and plasma processing apparatus

ActiveUS20120227955A1Increased process marginExpand control rangeTemperatue controlSemiconductor/solid-state device manufacturingPlasma processingLower limit

Provided are a substrate temperature control method and a plasma processing apparatus using the method. The method includes: disposing a substrate on a placing table provided in a vacuum processing chamber; supplying a heat conduction gas between a rear surface of the substrate and the placing table; detecting a pressure of the heat conduction gas; comparing the detected pressure value with a set pressure value; controlling the supply of the heat conduction gas so that the detected pressure value becomes the set pressure value; and alternately repeating a first period where the set pressure value is set to be a first set pressure value that is higher than a low pressure value and equal to or higher than the lowest limit pressure value and a second period where the set pressure value is set to be a second set pressure value that is lower than the low pressure value.

Owner:TOKYO ELECTRON LTD

FinFET structure with cavities and semiconductor compound portions extending laterally over sidewall spacers

ActiveUS9166024B2Reduce thicknessEasy to disassembleSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringField-effect transistor

A process for fabricating a fin-type field effect transistor (FinFET) structure is described. A semiconductor substrate is patterned to form a fin. A spacer is formed on the sidewall of the fin. A portion of the fin is removed, such that the spacer and the surface of the remaining fm together define a cavity. A piece of a semiconductor compound is formed from the cavity, wherein the upper portion of the piece of the semiconductor compound laterally extends over the spacer.

Owner:UNITED MICROELECTRONICS CORP

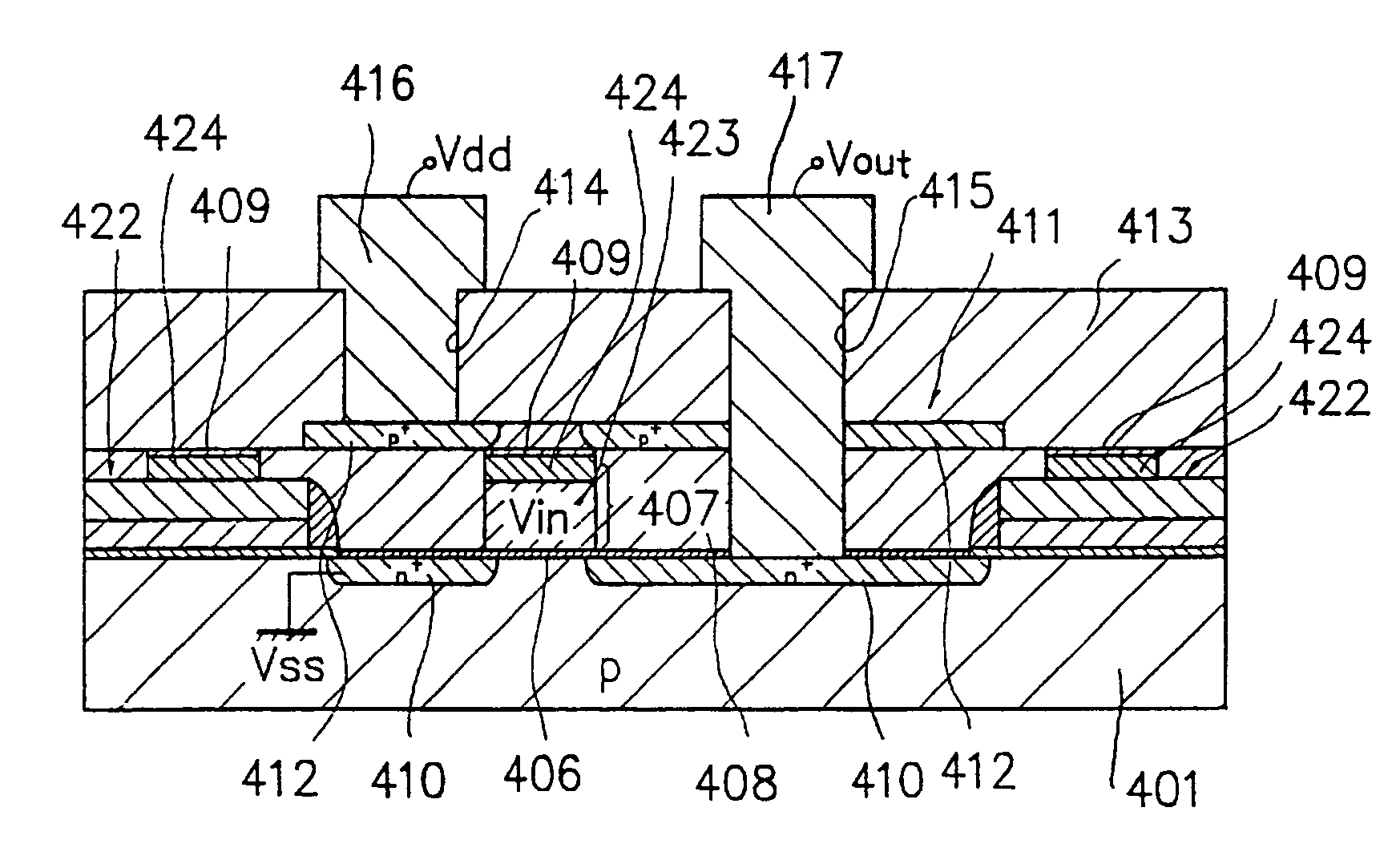

Semiconductor device, a method of manufacturing the semiconductor device and a method of deleting information from the semiconductor device

InactiveUS20050242377A1Increase process marginEasy and proper formationSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialLOCOS

A semiconductor device and a method for manufacturing the same and method for deleting information in use of the semiconductor device, in which field shield isolation or a trench type isolation between elements is used with suppression of penetration of field oxide into element active region of the device, that is, a defect involved in conventional LOGOS type process, are disclosed. A non-LOCOS insulating device isolation block is formed in a semiconductor substrate. The non-LOCOS insulating device isolation block uses a field shield element isolation structure or trench type element isolation structure. After gate electrode wiring layers are formed in a field region and an active region to the same level, a pad polysilicon film formed on the entire surface to cover the patterns of these gate electrode wiring layers is polished by chemical mechanical polishing (CMP) using the cap insulating films of the gate electrode wiring layers as stoppers, thereby forming the gate electrode wiring layers into separated patterns. With this arrangement, even when the width of the gate electrode wiring layer is reduced to the exposure limit in photolithography, the pad polysilicon film can be separated and patterned.

Owner:UNITED MICROELECTRONICS CORP

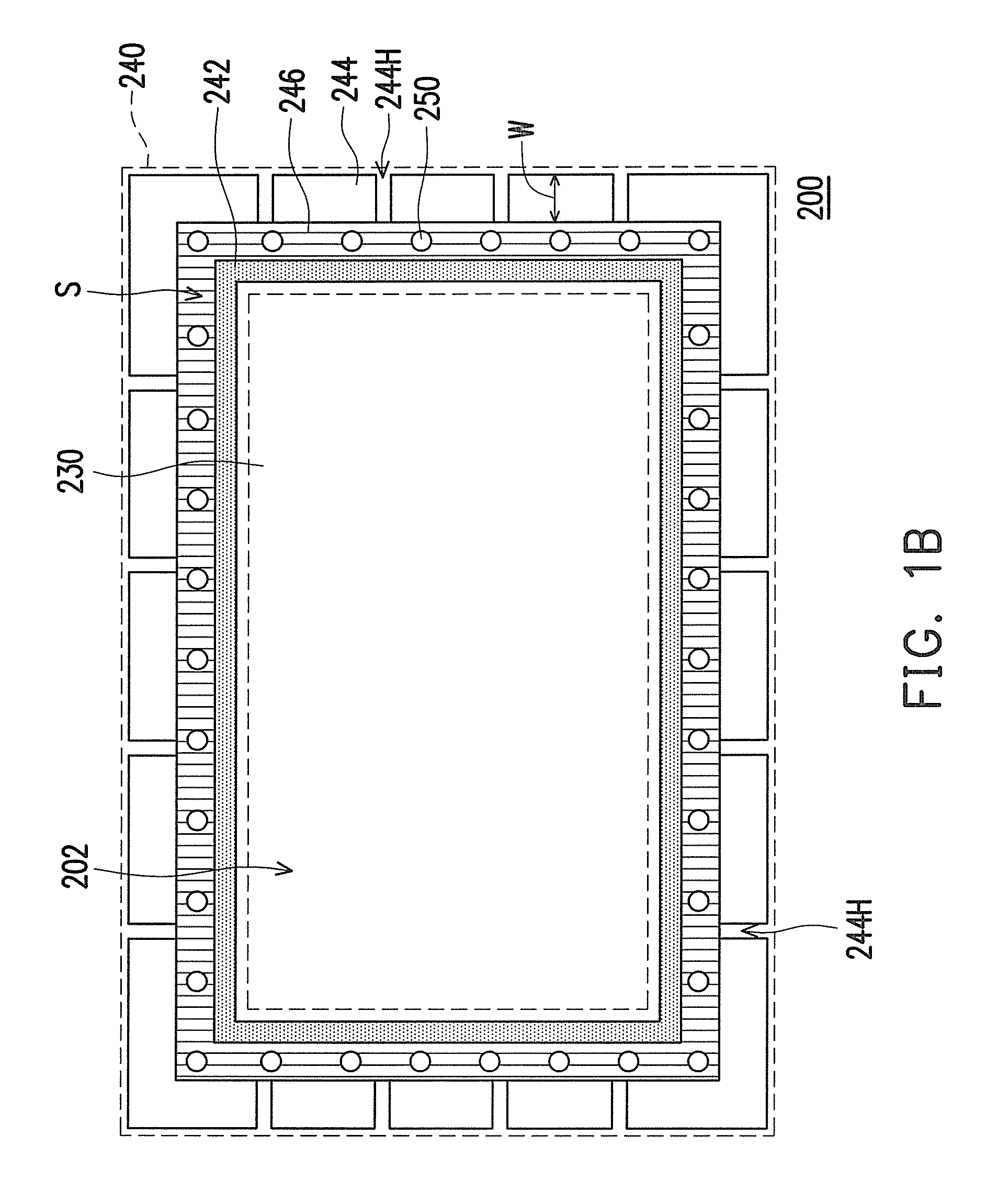

Display panel and sealing structure

An LCD panel includes a first substrate, a second substrate, a displaying medium and a sealing structure, wherein the second substrate is located at the side opposite to the first substrate and the displaying medium is located between the first substrate and the second substrate for displaying an image. The sealing structure is located between the first substrate and the second substrate to seal the displaying medium, wherein the sealing structure includes an inner wall, an outer wall and a sealant. The inner wall disposed surrounding the displaying medium and the outer wall disposed surrounding the inner wall together form a sealant-disposing space therebetween. The outer wall has a plurality of side wall holes and the sealant is disposed in the sealant-disposing space. In this way, the sealing structure is able to enhance the structure strength in a limited layout space and promote the process margin.

Owner:AU OPTRONICS CORP

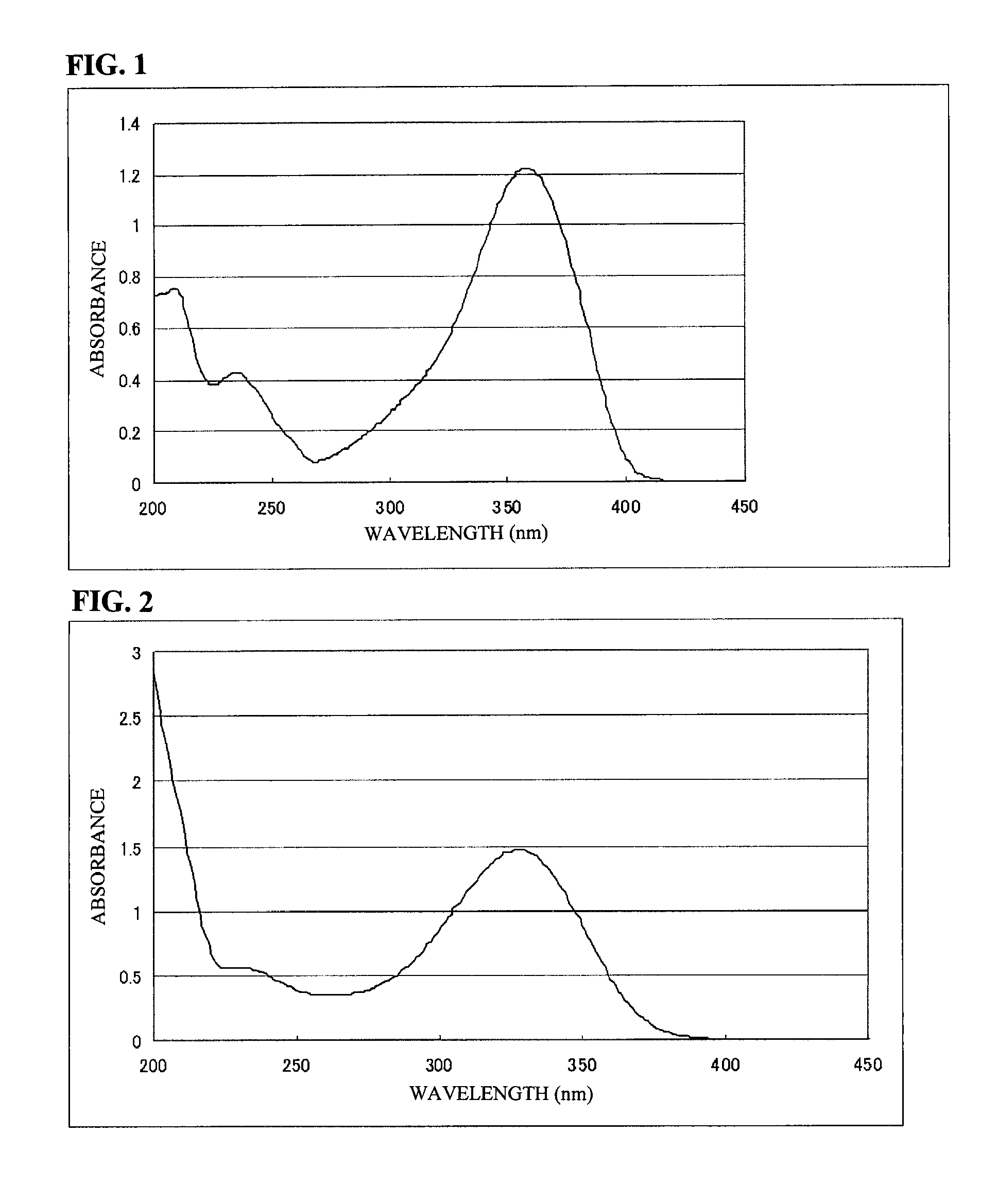

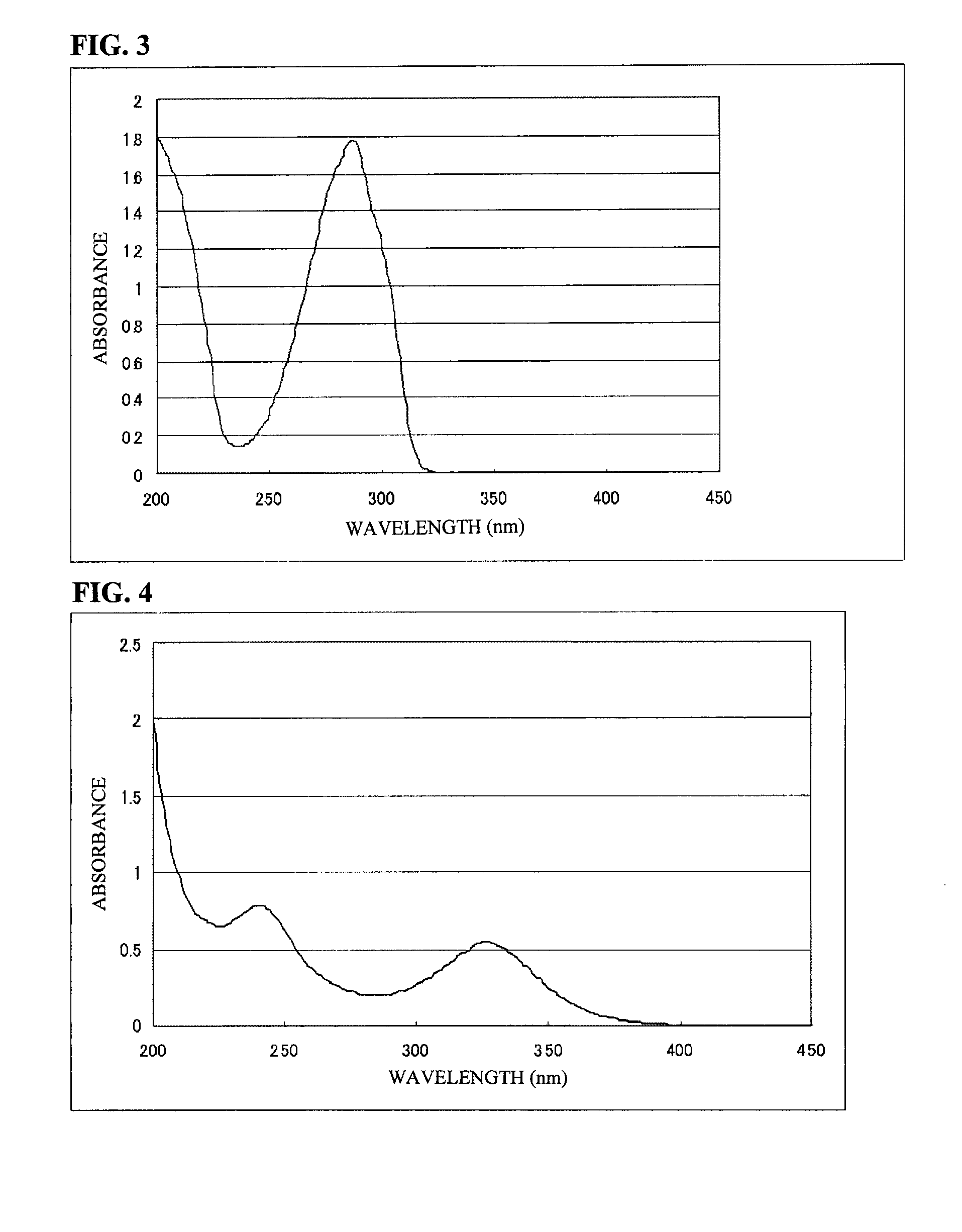

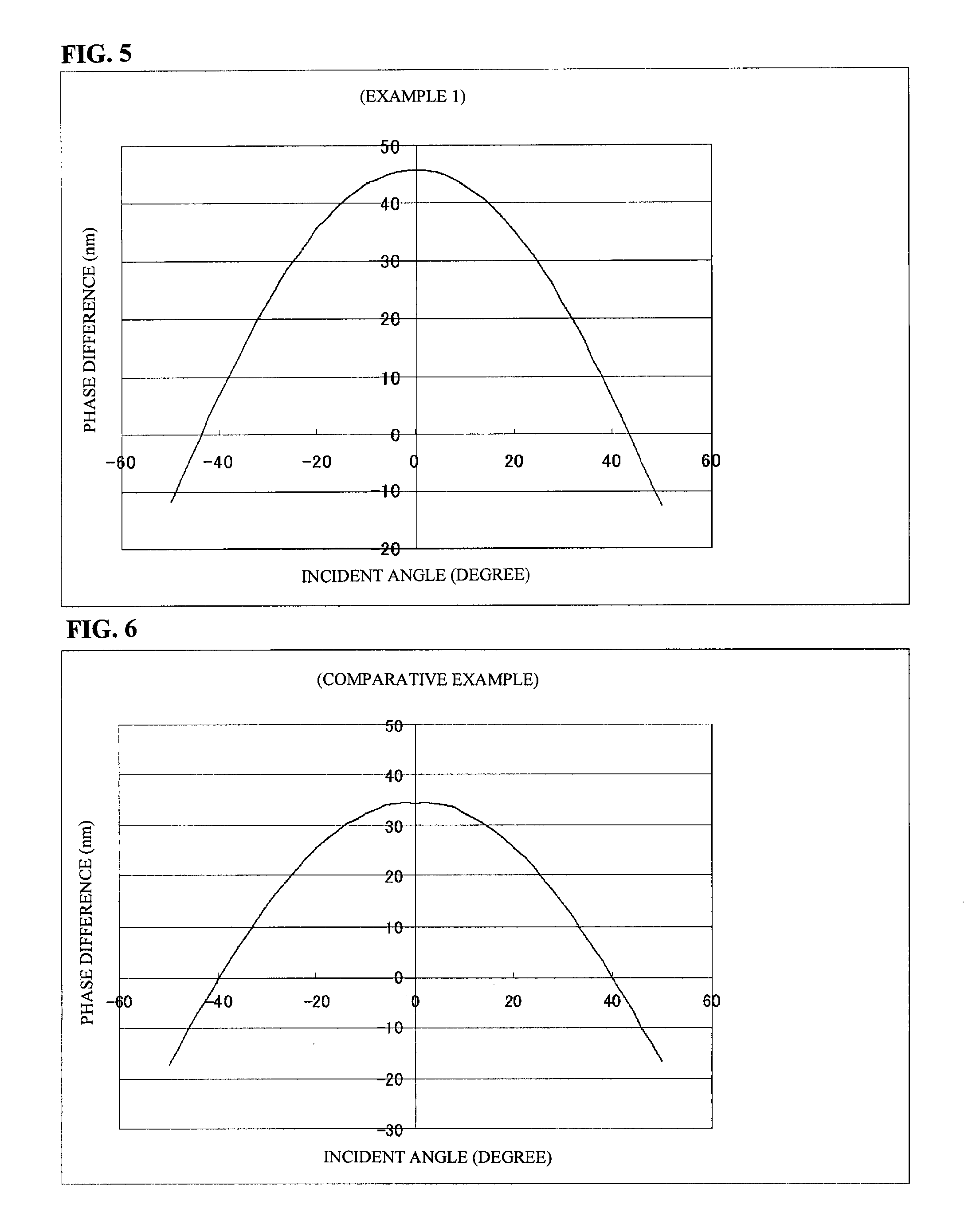

Polymerizable liquid crystal composition

ActiveUS20120056129A1Simple processIncrease process marginLiquid crystal compositionsOptical elementsPhase differenceUltraviolet

The present invention provides a polymerizable liquid crystal composition containing polymerizable liquid crystal compounds and a photoinitiator, wherein the photoinitiator has a light absorption band in a wavelength range of 280 to 400 nm; and at least one of the polymerizable liquid crystal compounds has a light absorption band in a wavelength range of 320 to 400 nm or a light-absorbing agent having a light absorption band in a wavelength range of 280 to 400 nm is contained. Thus, there is provided a material that can be cured in the air without replacing the atmosphere with an inert gas during irradiation with ultraviolet rays and that can achieve the characteristics required for a biaxial film, such as a sufficiently large front phase difference.

Owner:DAINIPPON INK & CHEM INC

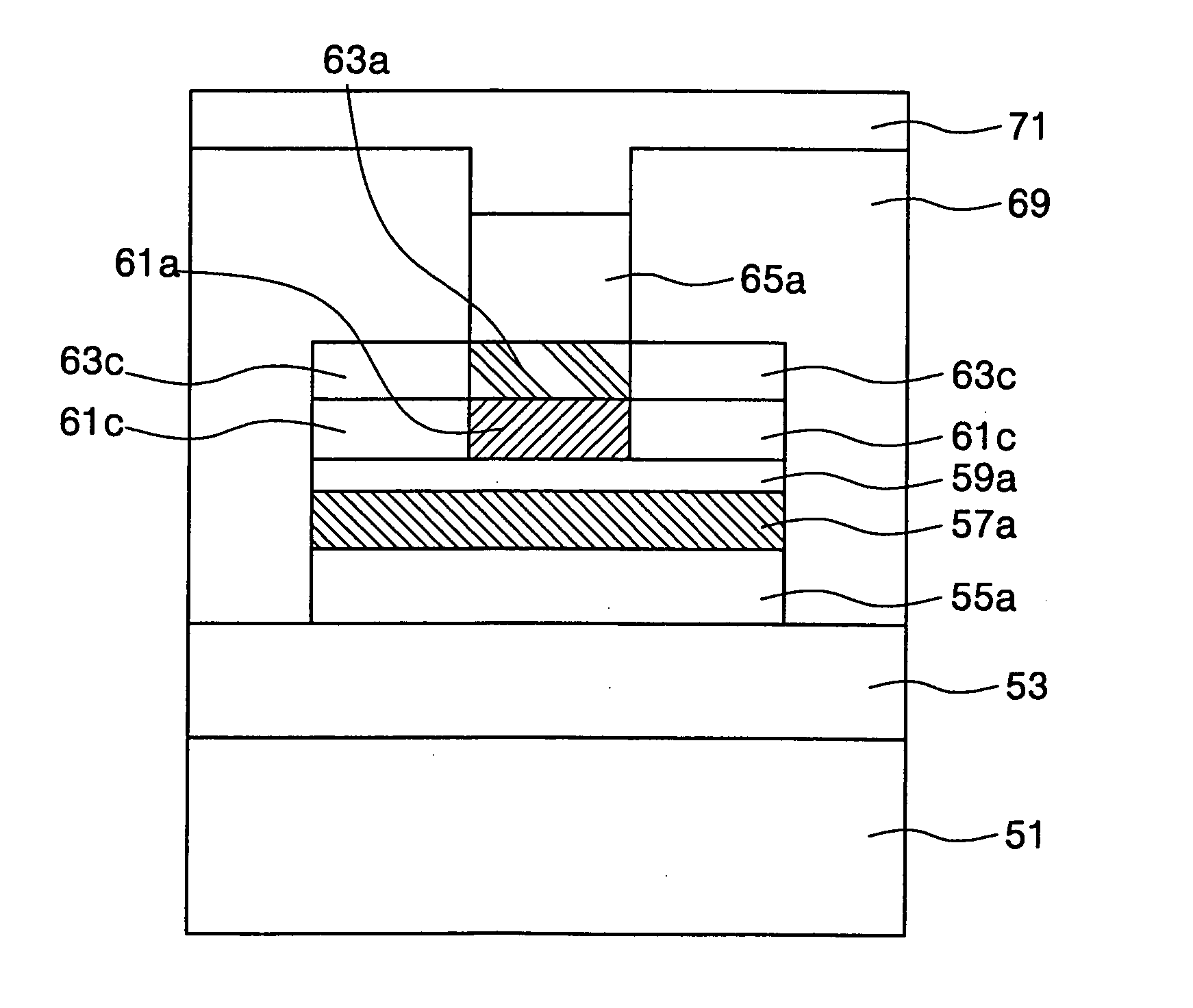

Memory with memory cells that include a MIM type capacitor with a lower electrode made for reduced resistance at an interface with a metal film

InactiveUS20070148896A1Reduce in quantityReduce resistanceTransistorSolid-state devicesCapacitanceEngineering

A semiconductor device includes memory cells each having an MISFET for memory selection formed on one major surface of a semiconductor substrate and a capacitive element comprised of a lower electrode electrically connected at a bottom portion to one of a source and drain of the MISFET for memory selection via a first metal layer and an upper electrode formed on the lower electrode via a capacitive insulating film. The lower electrode has a thickness of 30 nm or greater at the bottom portion thereof. Sputtering with a high ionization ratio and high directivity, such as PCM, is adapted to the formation of the lower electrode to make only the bottom portion of a capacitor thicker.

Owner:ELPIDA MEMORY INC

Magnetic tunnel junction structure having an oxidized buffer layer and method of fabricating the same

InactiveUS20050035386A1Inhibit deteriorationIncrease process marginTransistorMagnetic-field-controlled resistorsTunnel junctionMagnetic layer

There are provided a magnetic tunnel junction structure and a method of fabricating the same. The magnetic tunnel junction structure includes a lower electrode, a lower magnetic layer pattern and a tunnel layer pattern, which are sequentially formed on the lower electrode. The magnetic tunnel junction structure further includes an upper magnetic layer pattern, a buffer layer pattern, and an upper electrode, which are sequentially formed on a portion of the tunnel layer pattern. The sidewall of the upper magnetic layer pattern is surrounded by an oxidized upper magnetic layer, and the sidewall of the buffer layer pattern is surrounded by an oxidized buffer layer. The depletion of the upper magnetic layer pattern and the lower magnetic layer pattern in the magnetic tunnel junction region can be prevented by the oxidized buffer layer.

Owner:SAMSUNG ELECTRONICS CO LTD

Patterning process

ActiveUS20100178618A1High resolution performanceIncrease process marginSemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusResistSolubility

A pattern is formed by coating a chemically amplified positive resist composition comprising a resin comprising acid labile group-containing recurring units and a photoacid generator onto a substrate, drying to form a resist film, exposing the resist film to high-energy radiation through a phase shift mask having a lattice-like array of shifters, PEB, developing to form a positive pattern, illuminating or heating the positive pattern to eliminate acid labile groups for increasing alkaline solubility and to induce crosslinking for imparting solvent resistance, coating a reversal film, and dissolving away the positive pattern in an alkaline wet etchant to form a pattern by way of positive / negative reversal.

Owner:SHIN ETSU CHEM IND CO LTD

Method for fabricating mos device

ActiveUS20130183804A1Increase process marginDeep unitySemiconductor/solid-state device manufacturingSemiconductor devicesBiomedical engineeringHard mask

A method for fabricating a MOS device is described. A first hard mask layer is formed over a substrate. The first hard mask layer is patterned and a portion of the substrate removed to form a first patterned hard mask, and a fin structure surrounded by a trench and extending in a first direction. An insulating layer is formed at the trench bottom. A gate conductive layer is formed on the insulating layer, extending in a second direction. A first implant process is performed using the first patterned hard mask as a mask to form first S / D extension regions in the sidewalls of the fin structure. The first patterned hard mask is removed to expose the top of the fin structure, and then a second implant process is performed to form second S / D extension region therein.

Owner:UNITED MICROELECTRONICS CORP

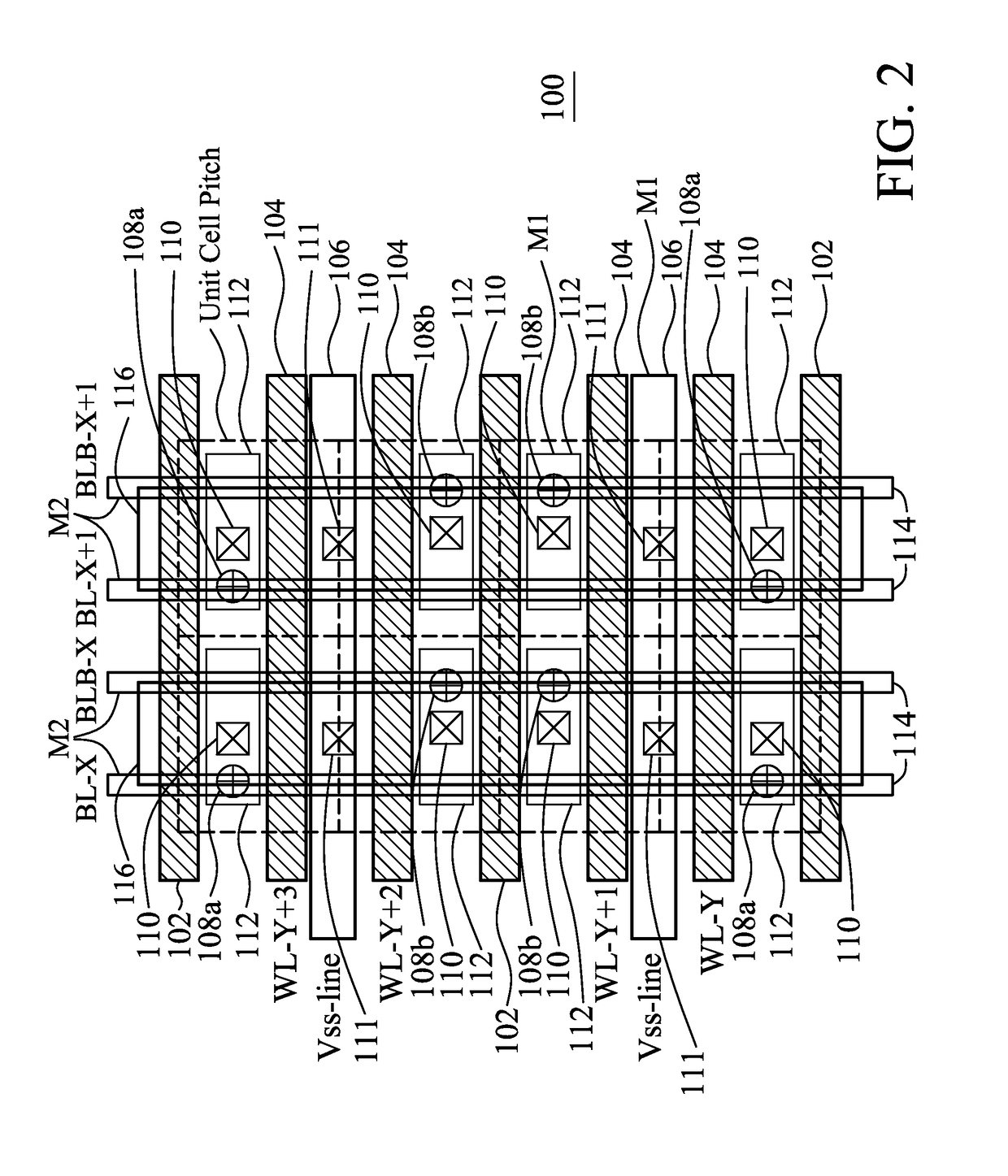

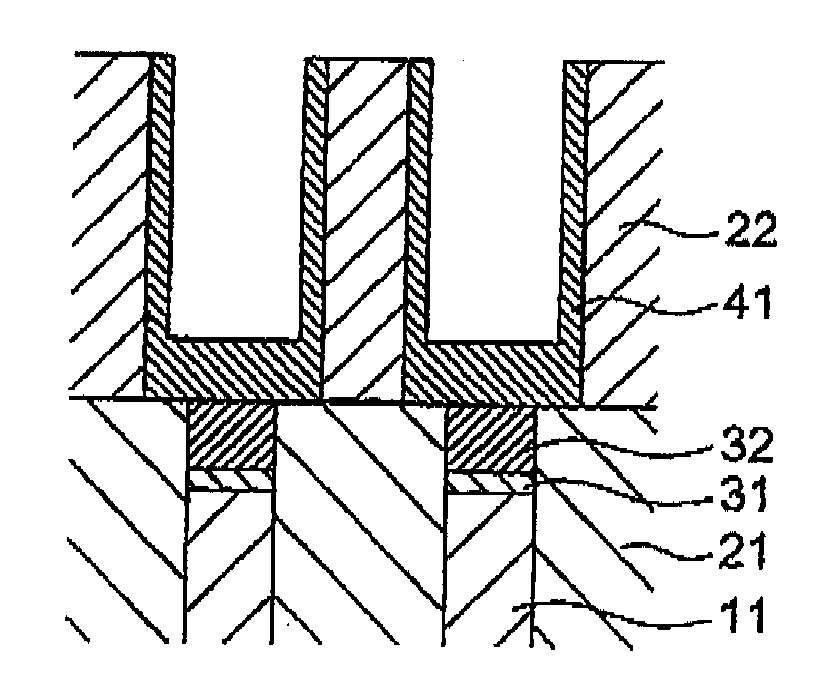

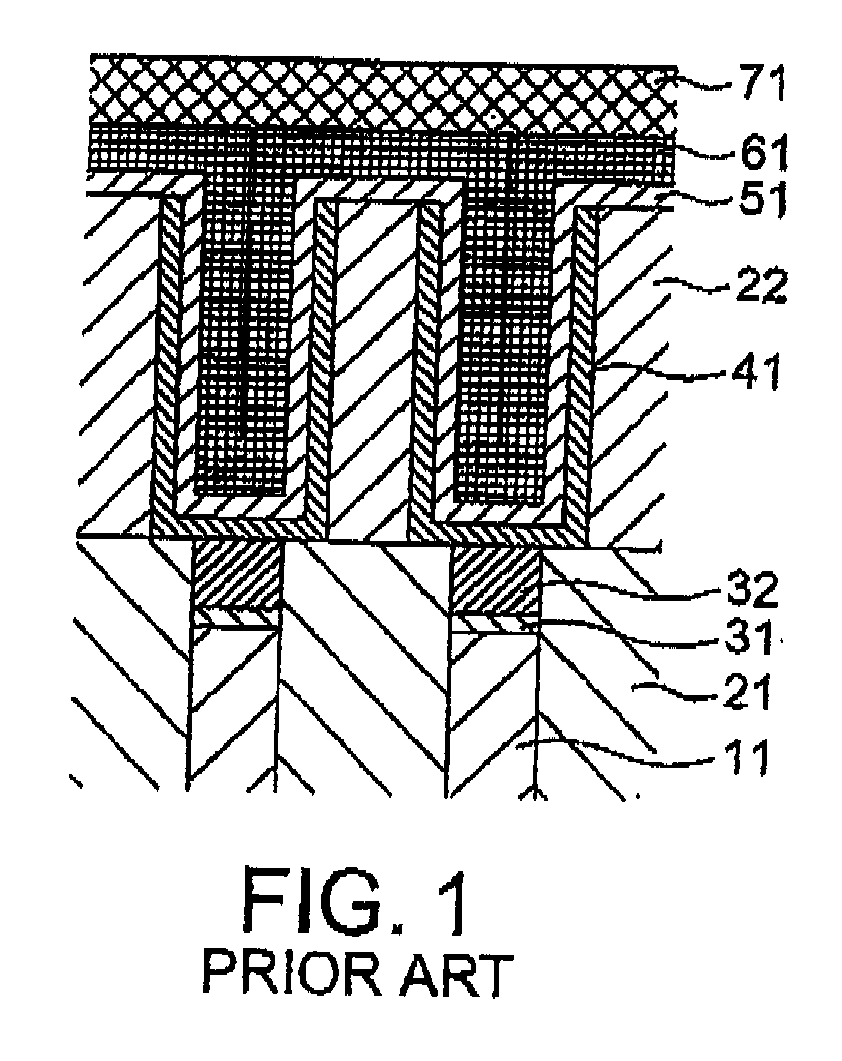

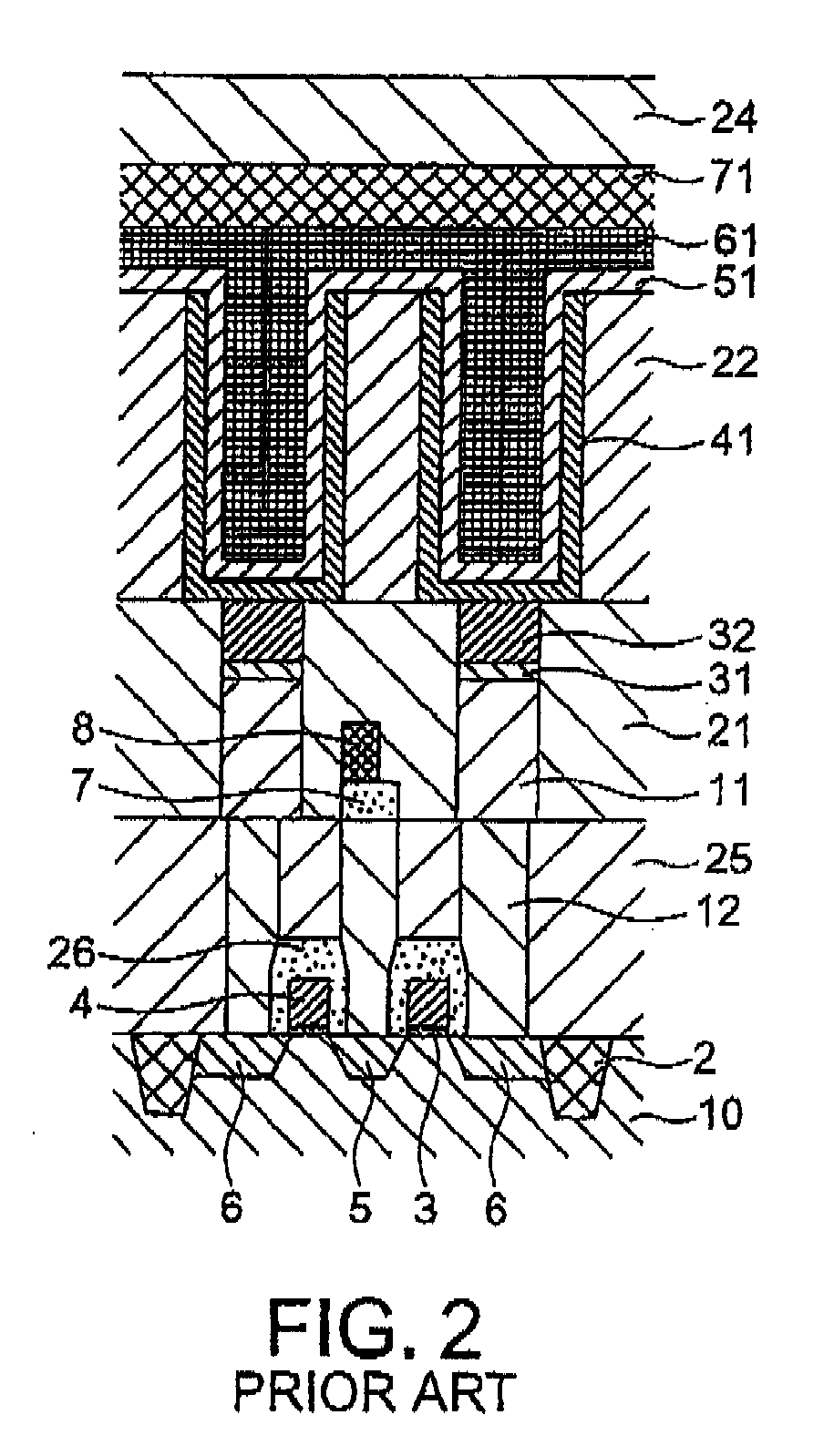

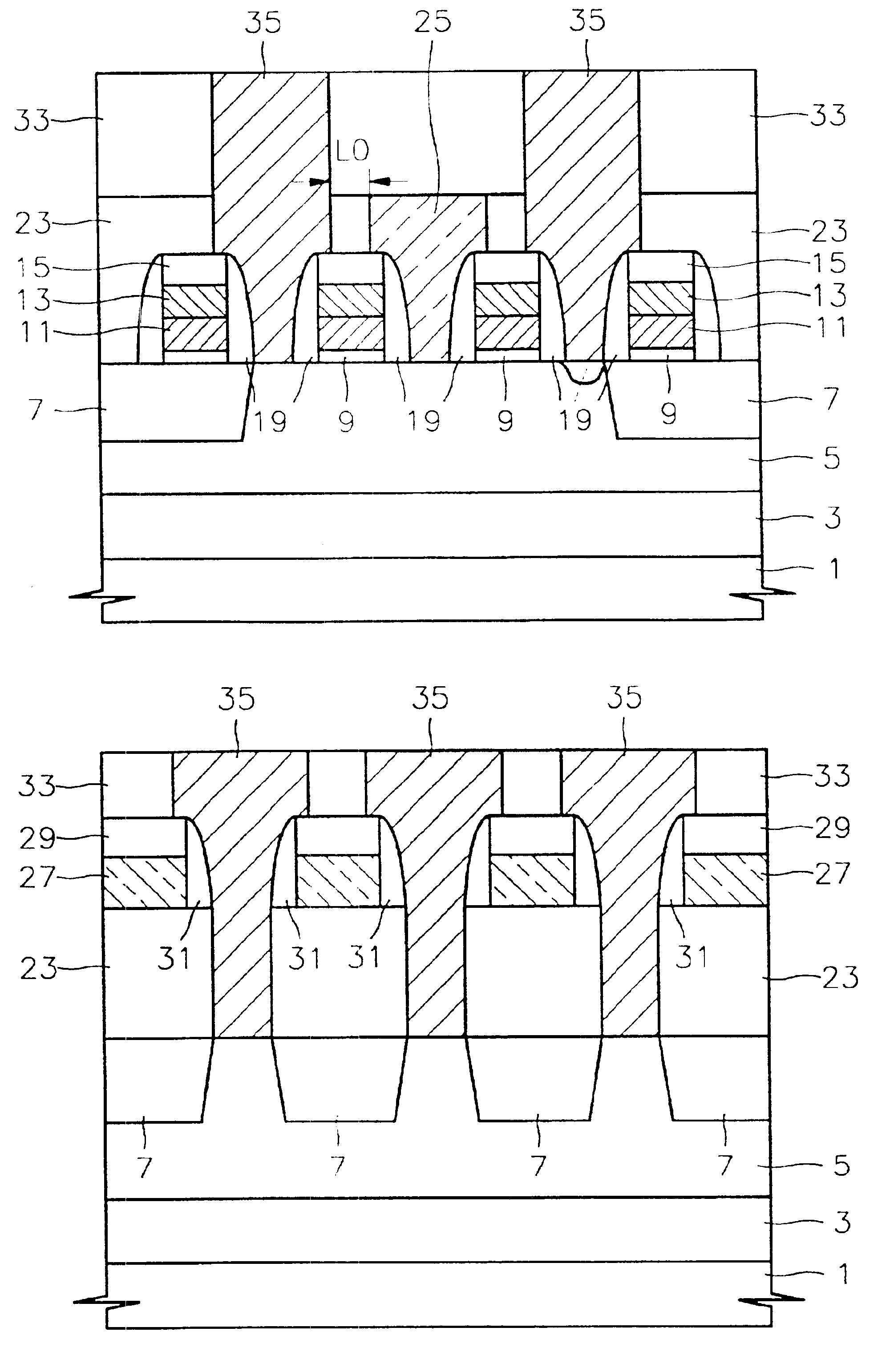

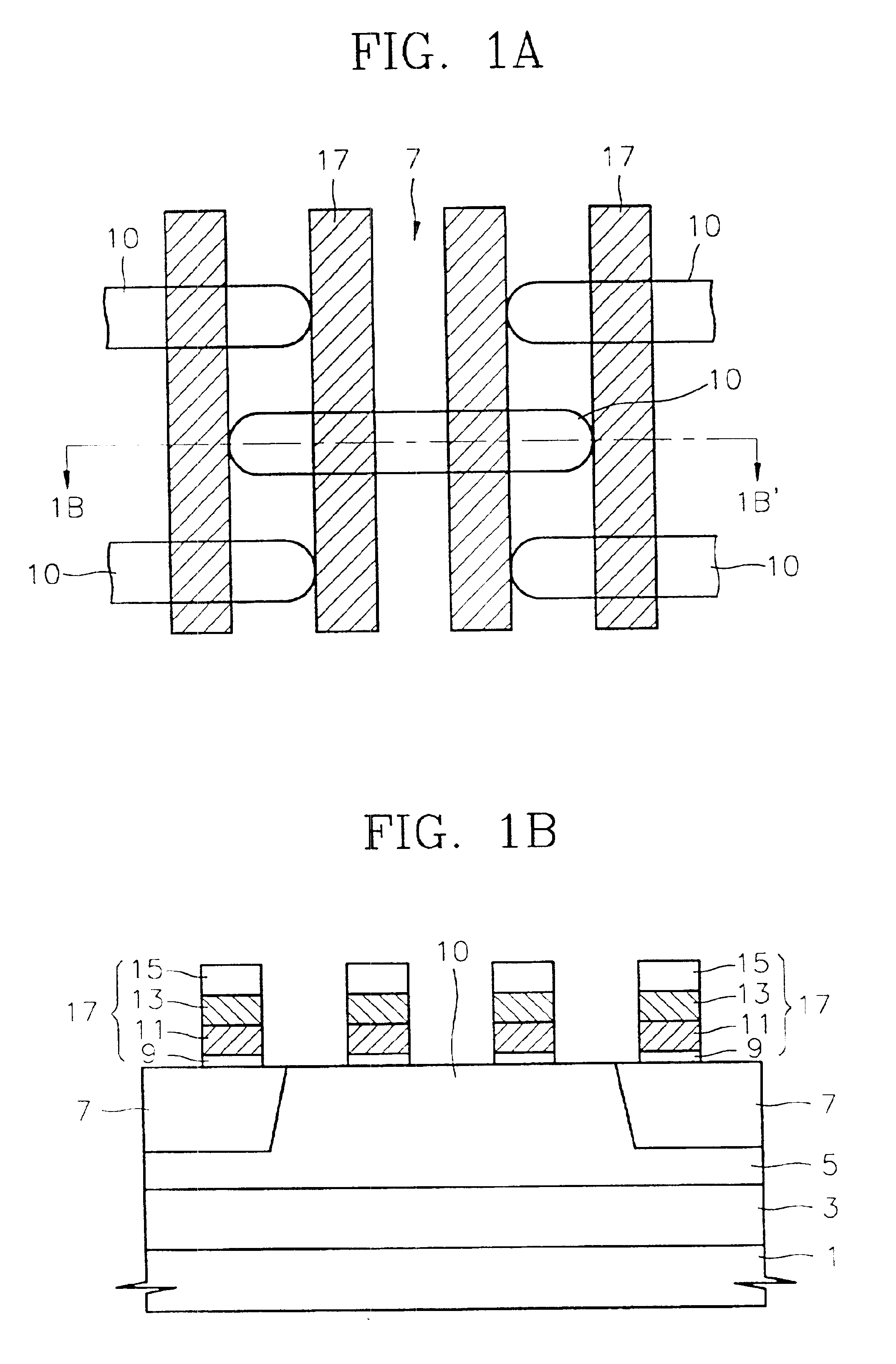

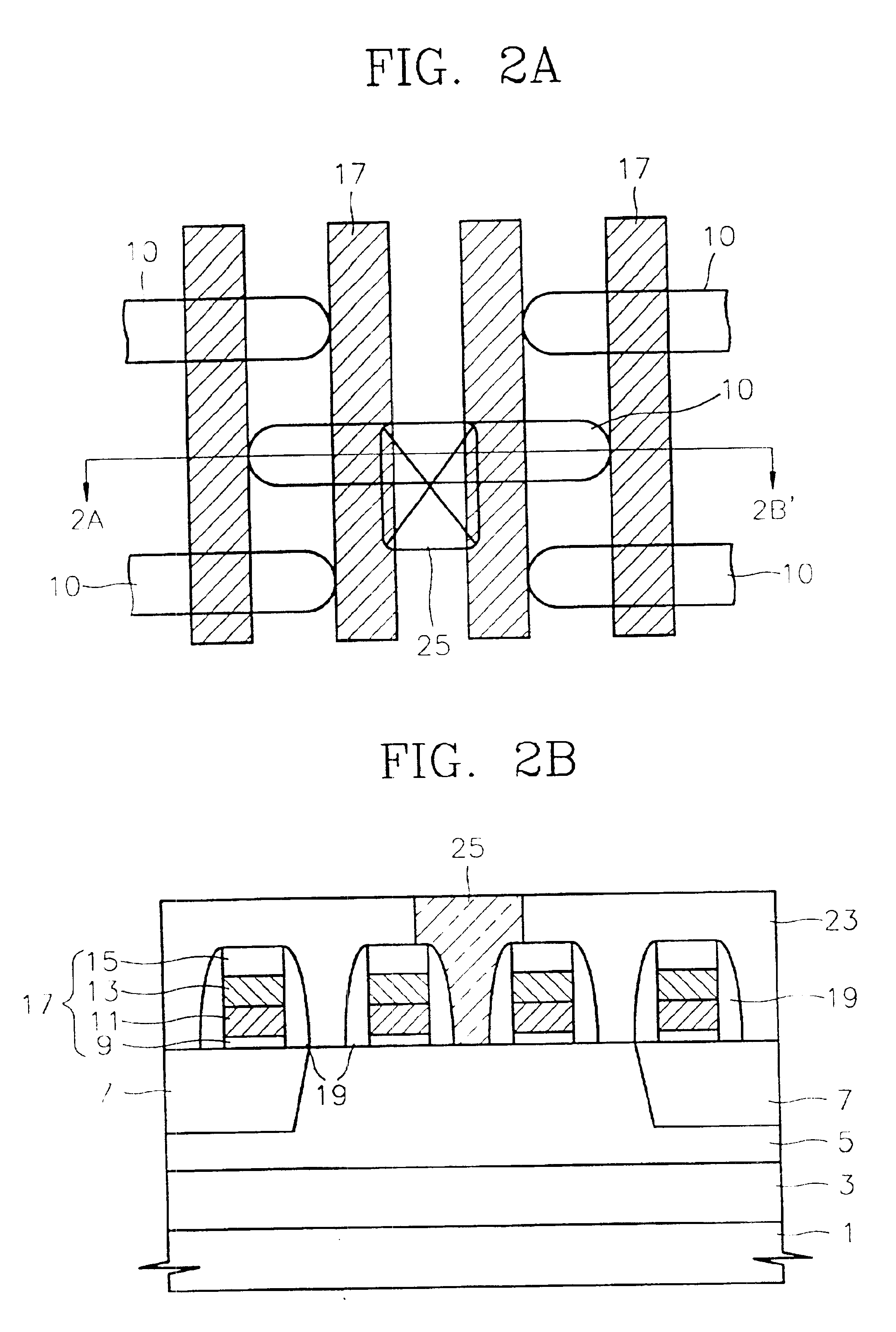

Semiconductor memory device having self-aligned contacts and method of fabricating the same

InactiveUS6885052B2Sufficient process marginSimple processTransistorSolid-state devicesBit lineEngineering

A semiconductor memory device having self-aligned contacts, capable of preventing a short-circuit between contacts for bit lines and contacts for storage electrodes and improving a process margin, and a method of fabricating the same are provided. The semiconductor memory device having self-aligned contacts includes a plurality of gate electrode patterns arranged in parallel on a semiconductor substrate, in which a plurality of first spacers are formed along the sidewalls of the gate electrode patterns, a first interdielectric layer formed on the entire surface of a resultant in which the first spacers are formed, a plurality of bit line patterns arranged in parallel on the first interdielectric layer to be perpendicular to the gate electrode patterns, in which a plurality of second spacers are formed along the sidewalls of the bit line patterns, a plurality of contacts for bit lines self-aligned with the first spacers, a second interdielectric layer formed on the entire surface of a resultant in which the second spacers are formed, and a plurality of contacts for storage electrodes simultaneously self-aligned with the second and first spacers.

Owner:SAMSUNG ELECTRONICS CO LTD