Patents

Literature

34results about How to "Sufficient process margin" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

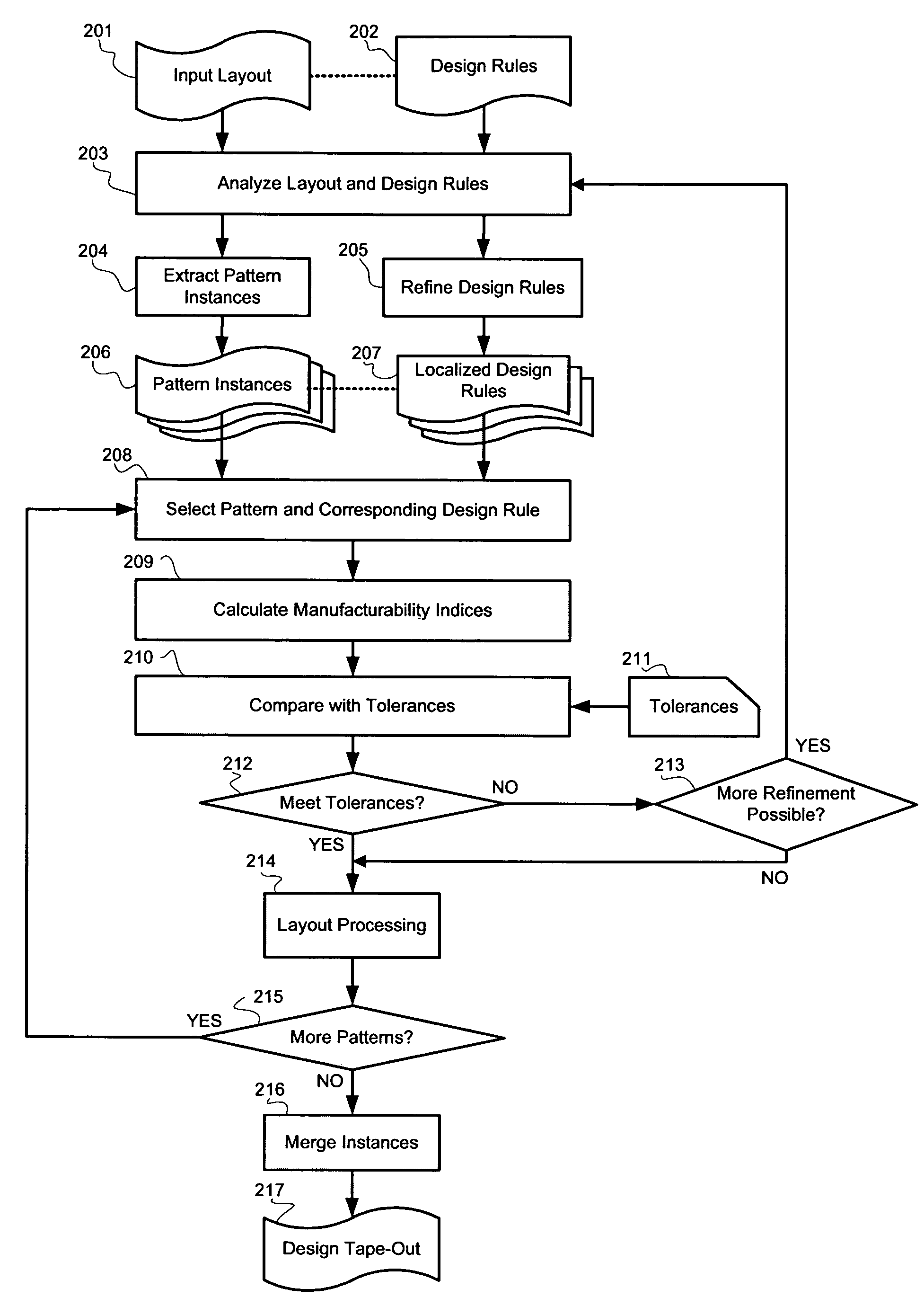

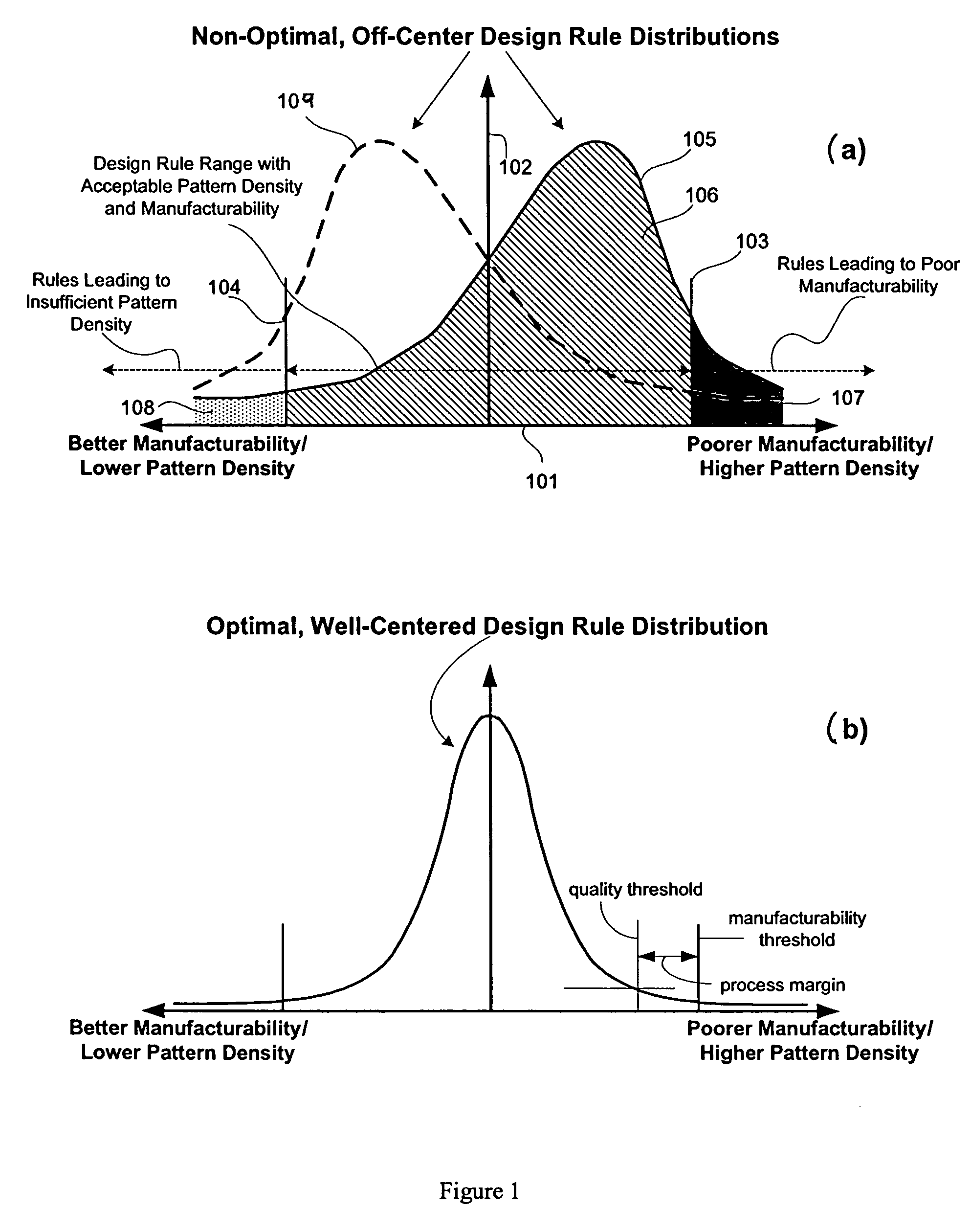

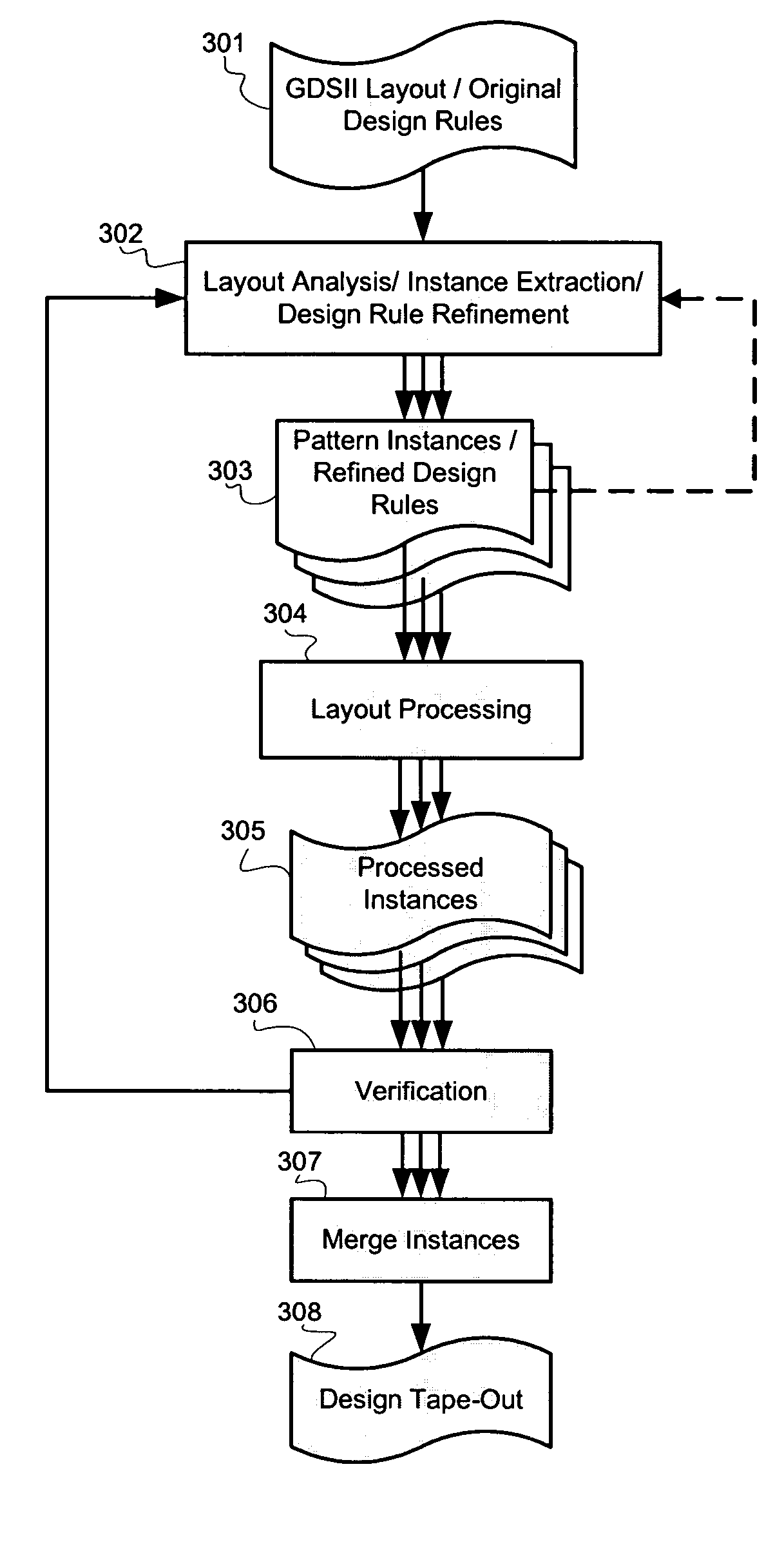

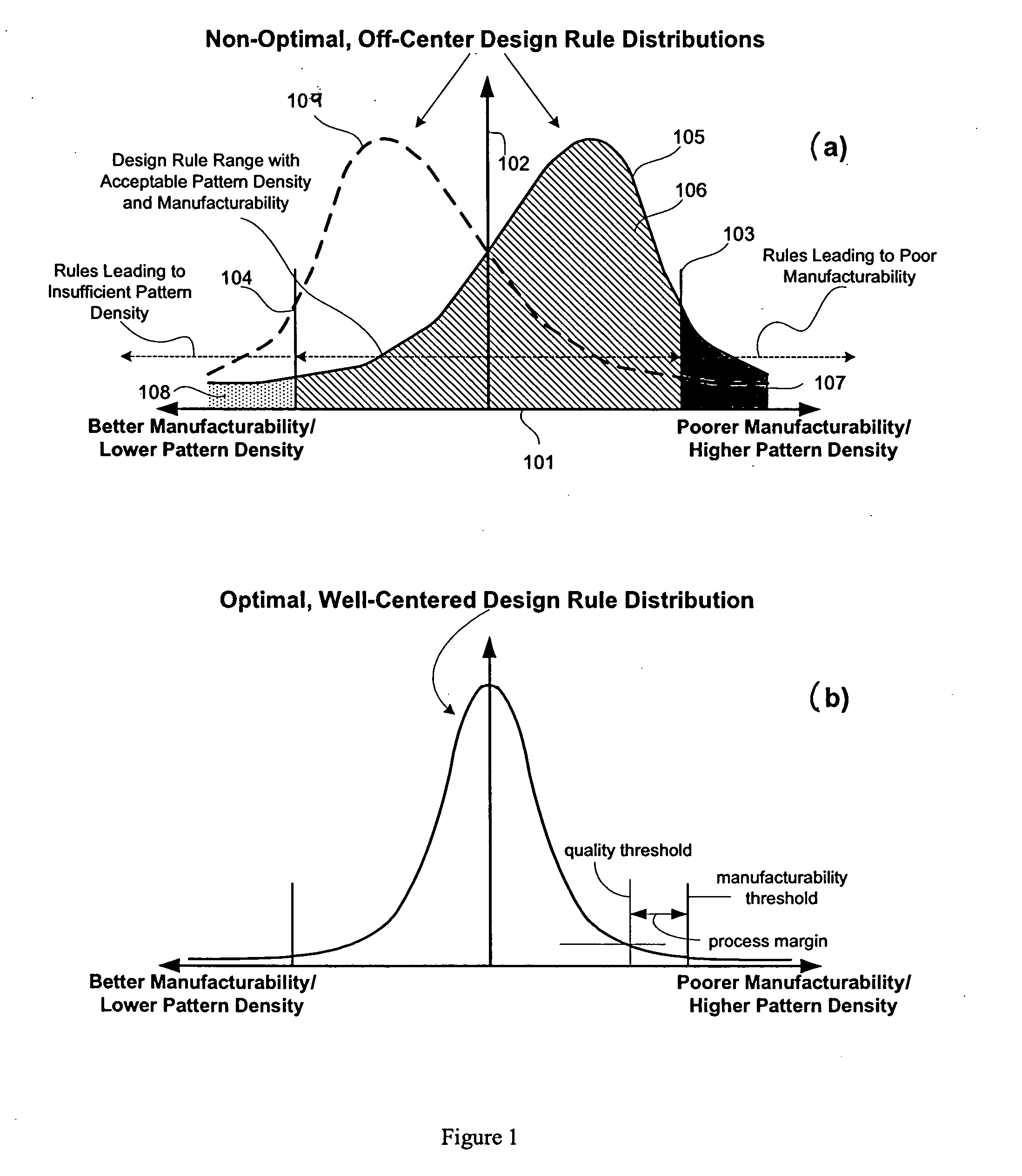

System for designing integrated circuits with enhanced manufacturability

ActiveUS7523429B2Improve manufacturabilityLittle interferencePressersMattress sewingGranularityEngineering

A system and method for integrated circuit design are disclosed to enhance manufacturability of circuit layouts through generation of hierarchical design rules which capture localized layout requirements. In contrast to conventional techniques which apply global design rules, the disclosed IC design system and method partition the original design layout into a desired level of granularity based on specified layout and integrated circuit properties. At that localized level, the design rules are adjusted appropriately to capture the critical aspects from a manufacturability standpoint. These adjusted design rules are then used to perform localized layout manipulation and mask data conversion.

Owner:APPLIED MATERIALS INC

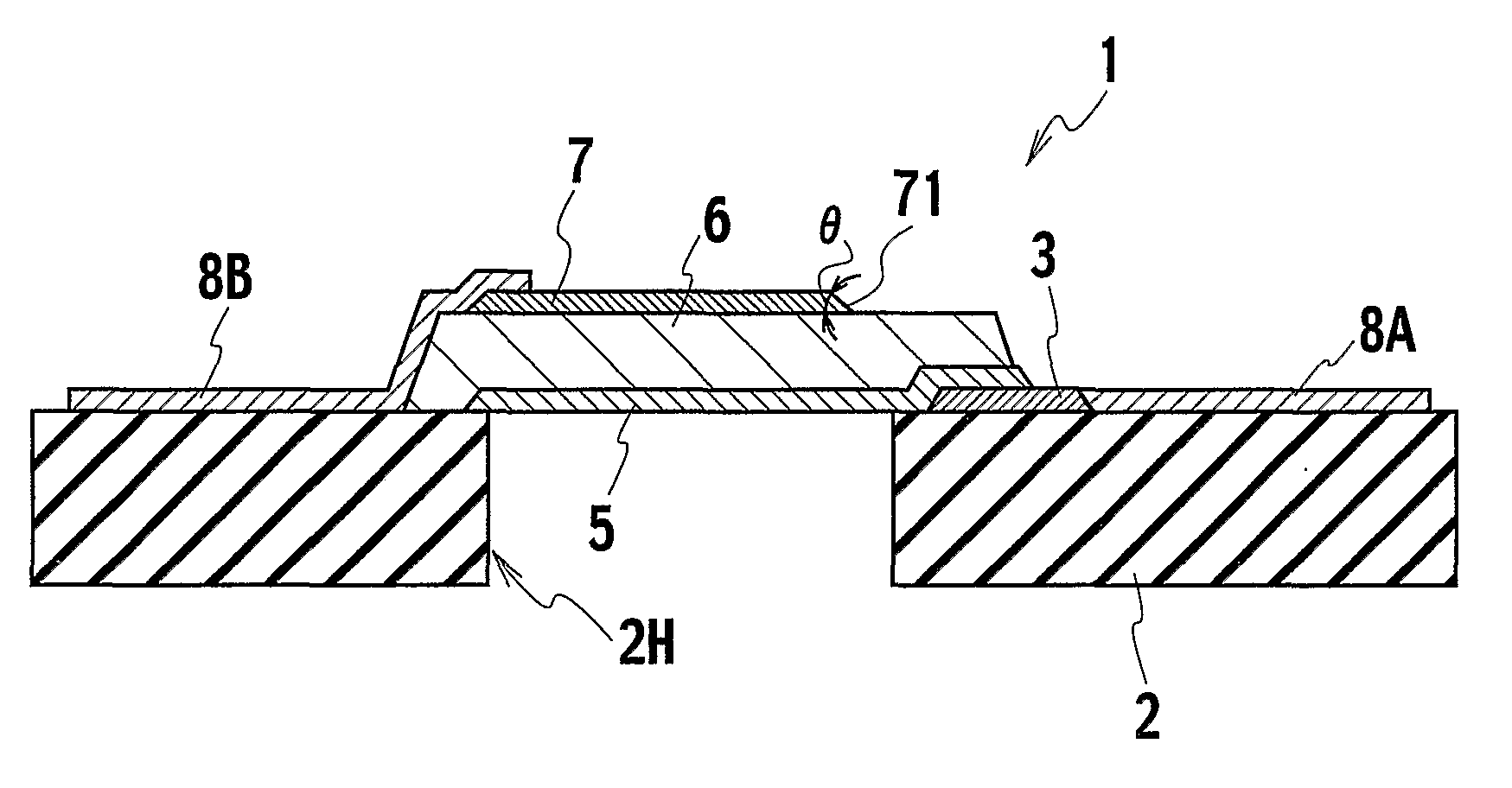

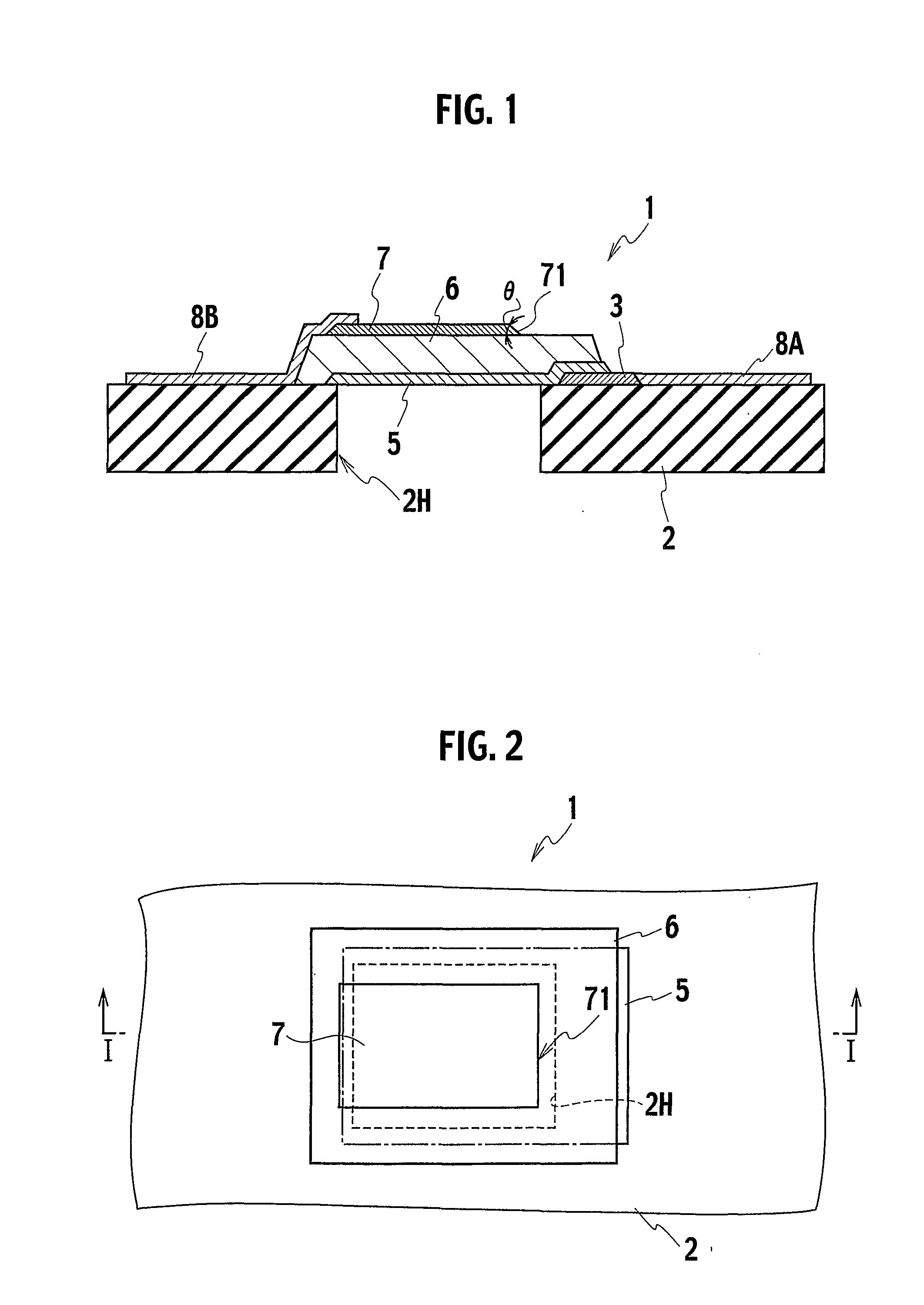

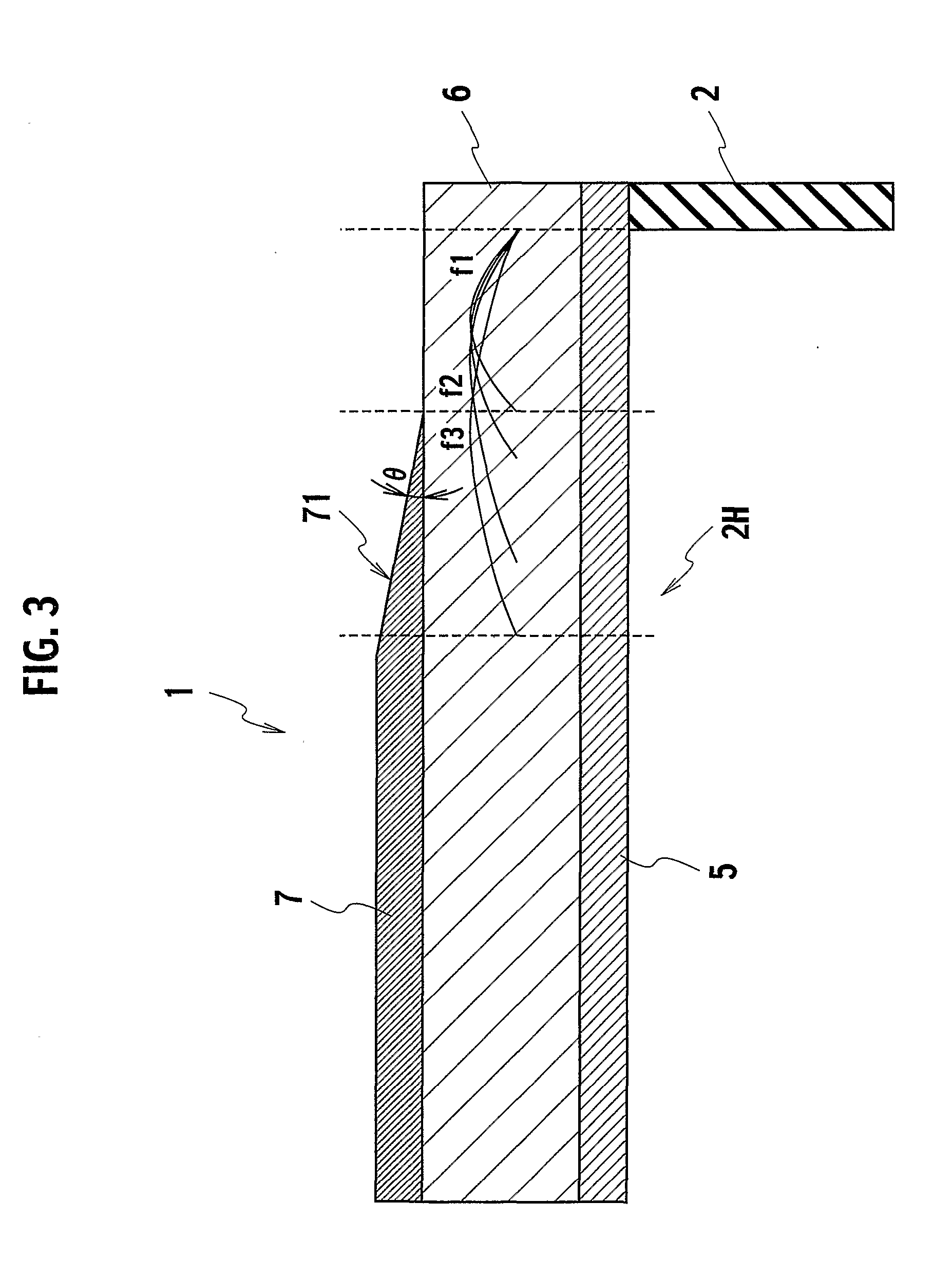

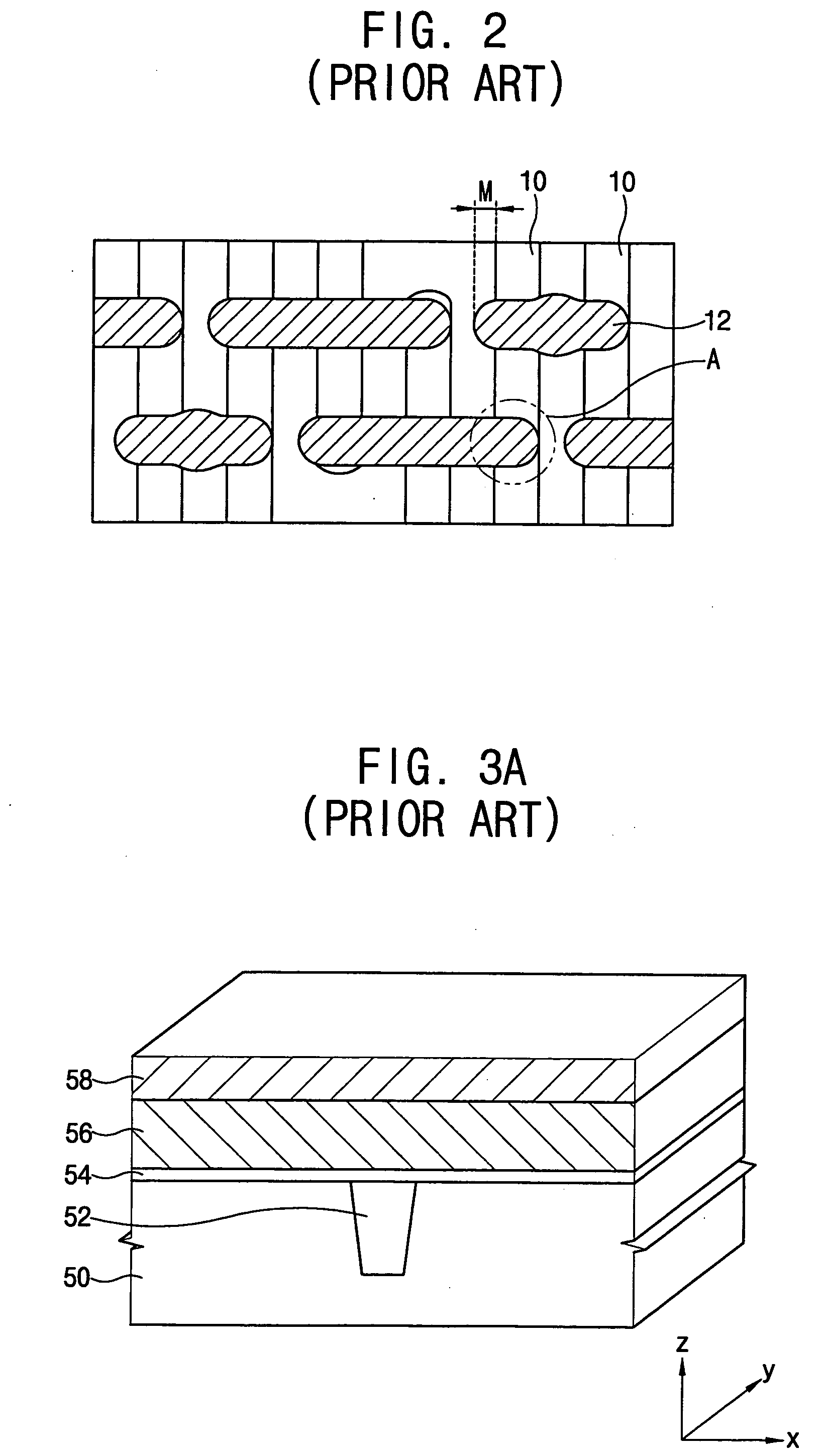

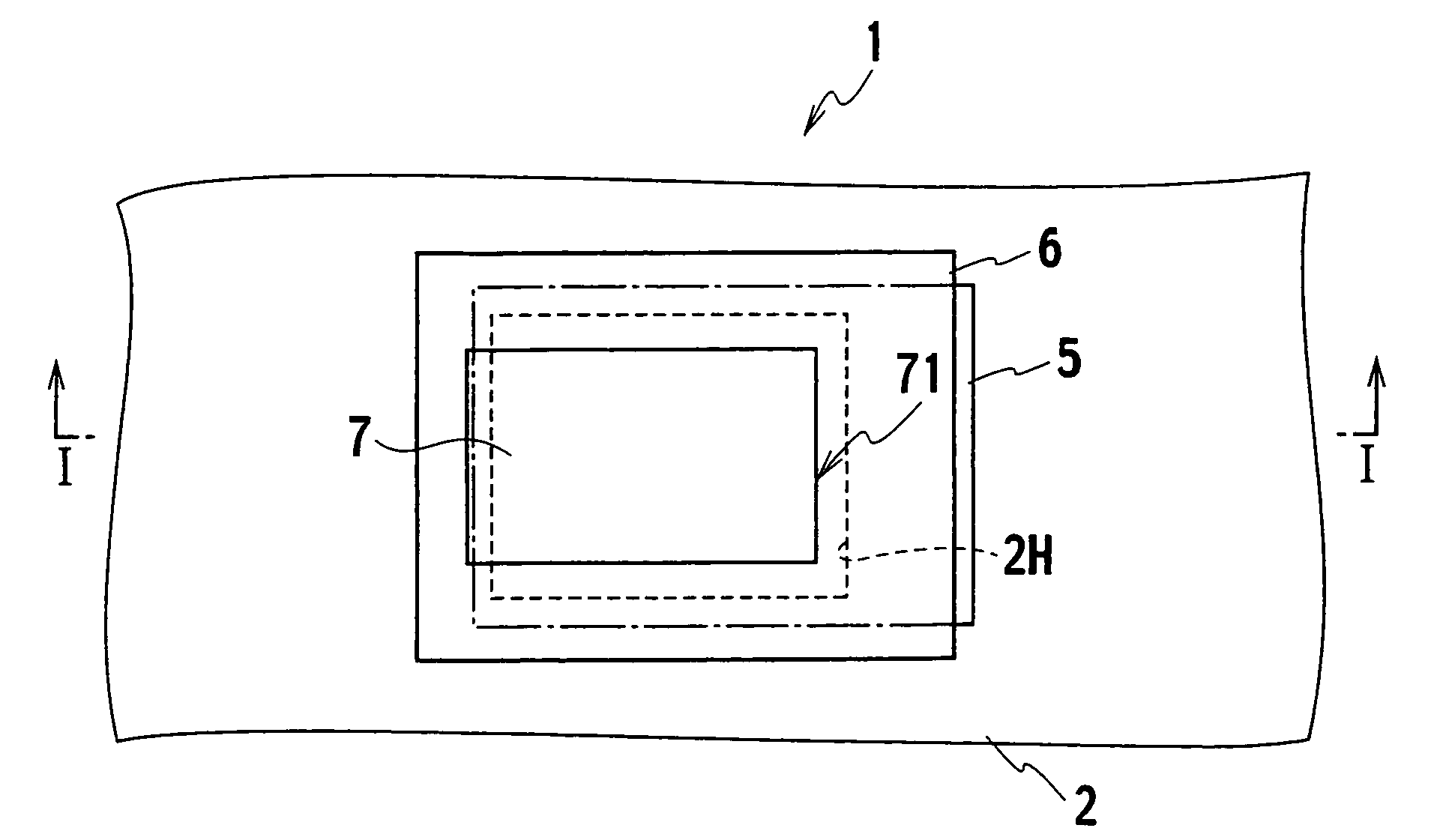

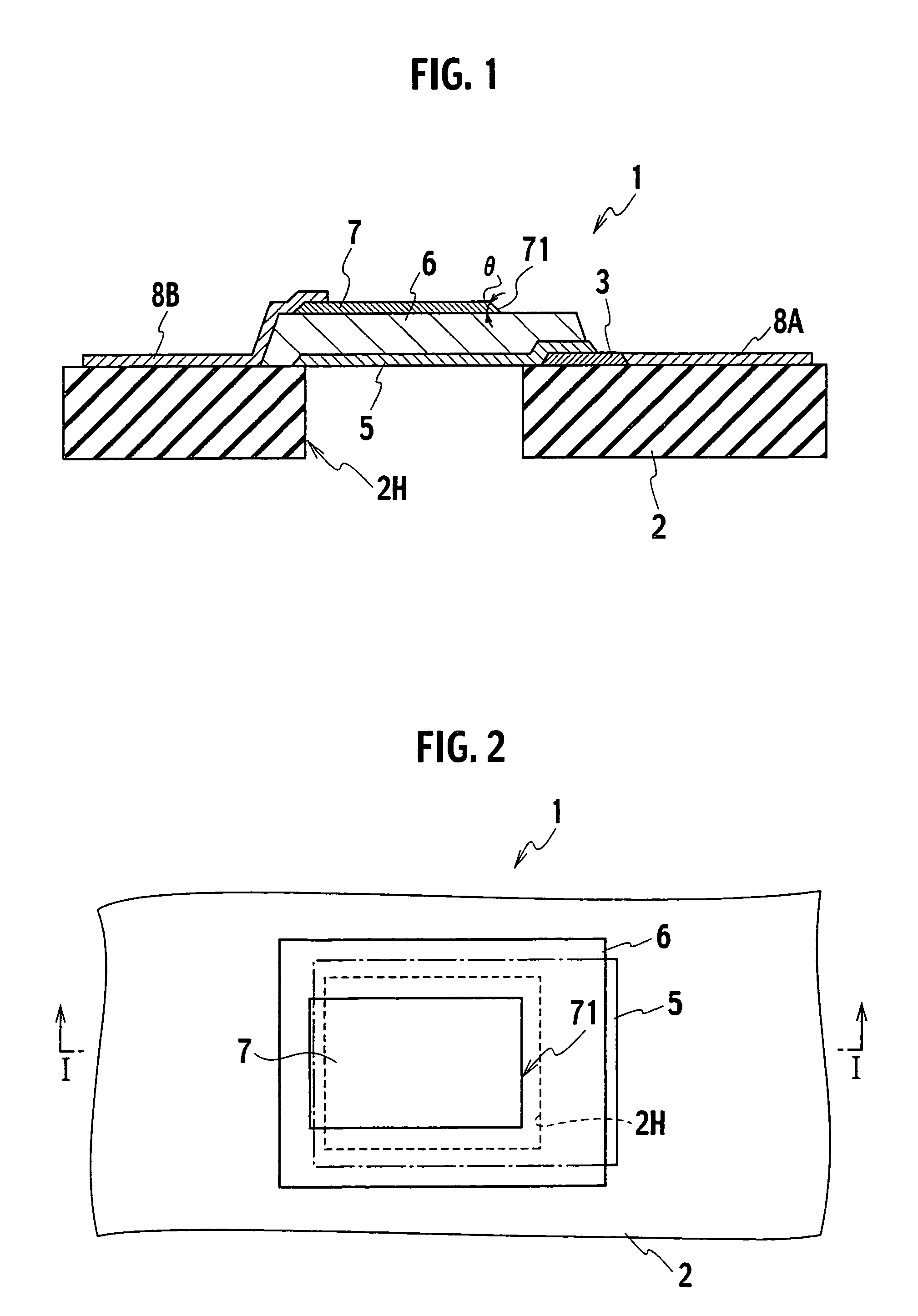

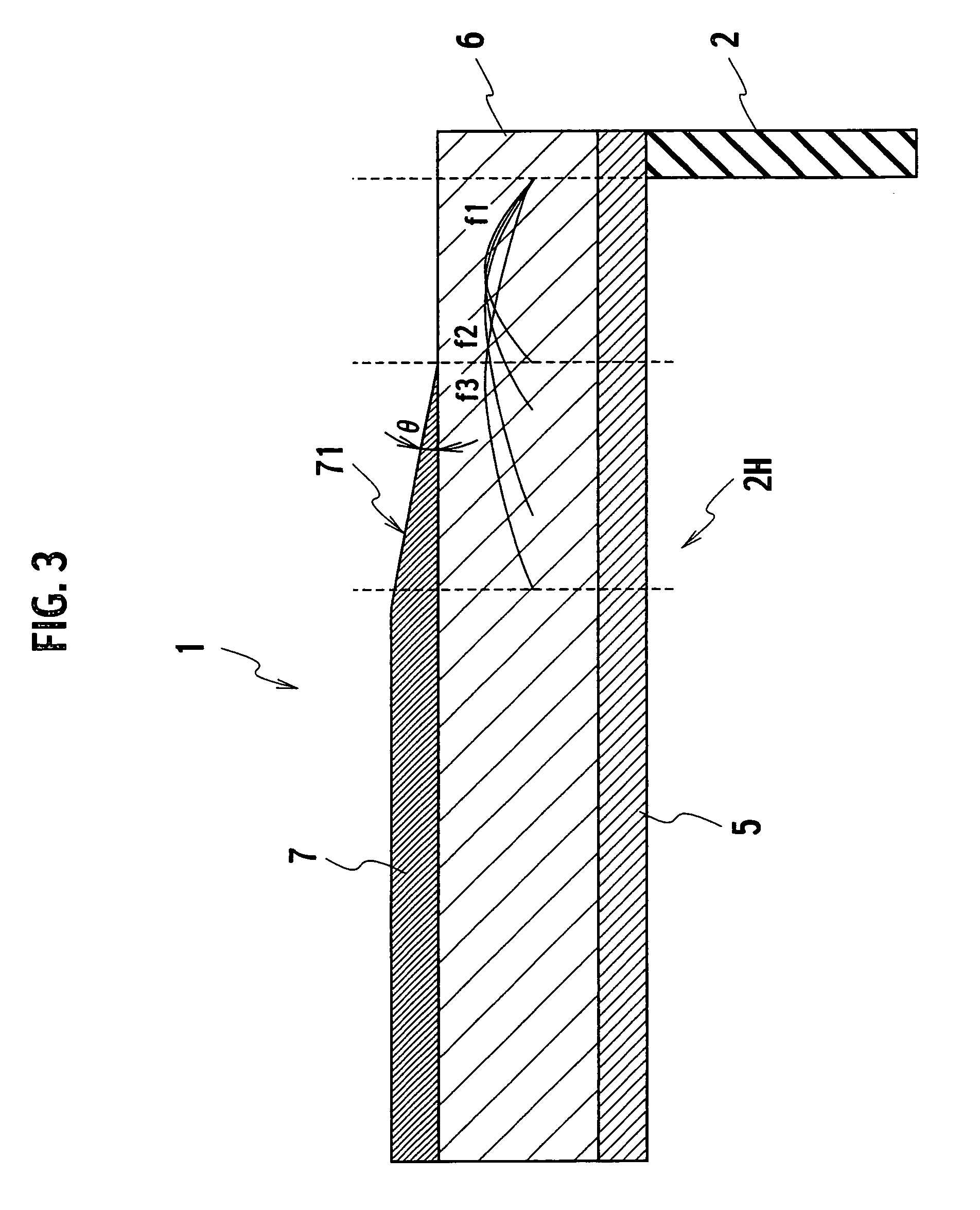

Thin film piezoelectric resonator and method of manufacturing the same

ActiveUS20090033177A1Good vibesOvercome problemsPiezoelectric/electrostrictive device manufacture/assemblyImpedence networksOptoelectronicsPiezoelectric thin films

A thin film piezoelectric resonator includes a substrate having a cavity; a first electrode extending over the cavity; a piezoelectric film placed on the first electrode; and a second electrode placed on the piezoelectric film, the second electrode having a periphery partially overlapping on the cavity and tapered to have an inner angle of 30 degrees or smaller defined by a part of the periphery thereof and a bottom thereof.

Owner:KK TOSHIBA

System for designing integrated circuits with enhanced manufacturability

ActiveUS20050188338A1Improve manufacturabilityLittle interferencePressersMattress sewingData conversionIntegrated circuit

A system and method for integrated circuit design are disclosed to enhance manufacturability of circuit layouts through generation of hierarchical design rules which capture localized layout requirements. In contrast to conventional techniques which apply global design rules, the disclosed IC design system and method partition the original design layout into a desired level of granularity based on specified layout and integrated circuit properties. At that localized level, the design rules are adjusted appropriately to capture the critical aspects from a manufacturability standpoint. These adjusted design rules are then used to perform localized layout manipulation and mask data conversion.

Owner:APPLIED MATERIALS INC

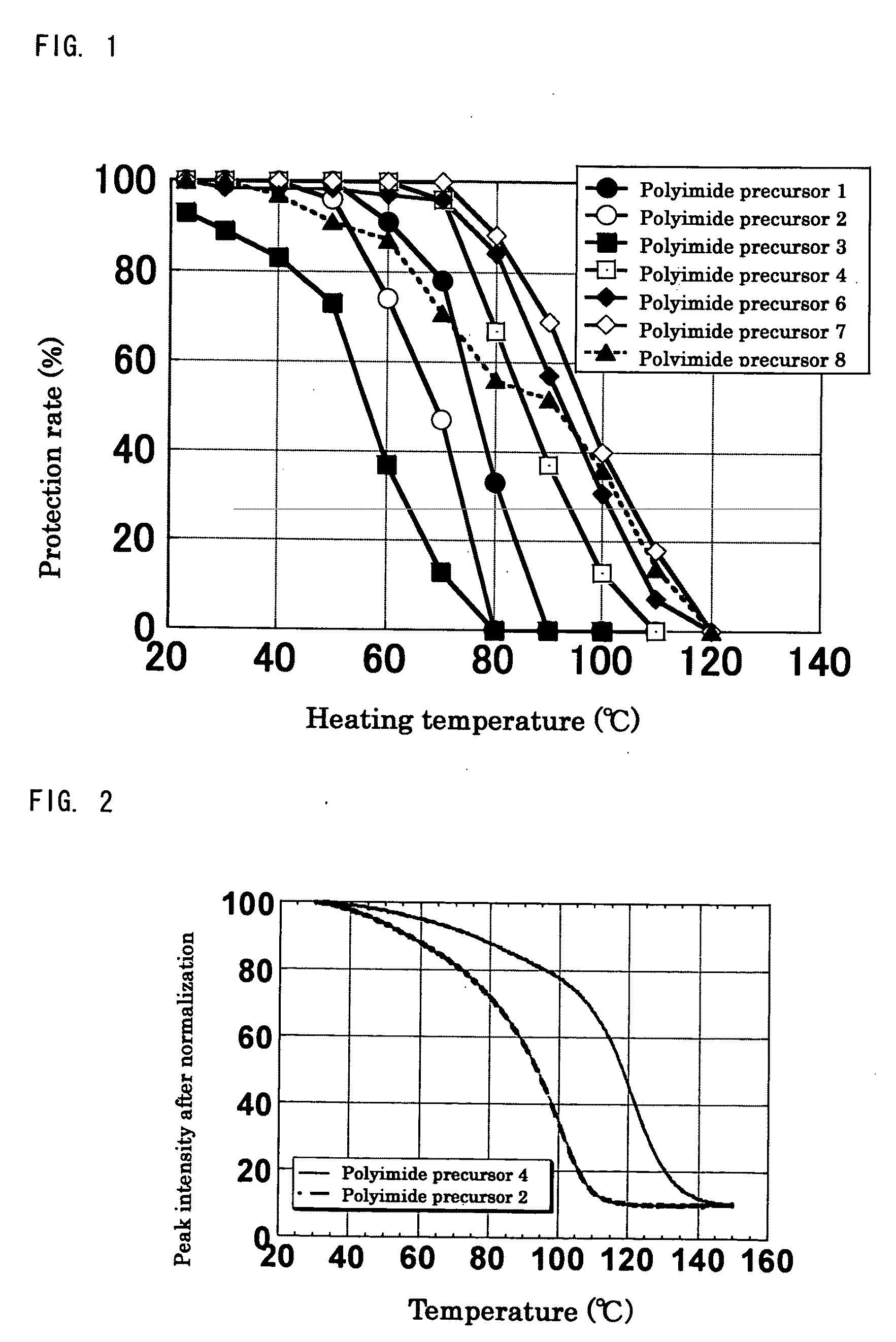

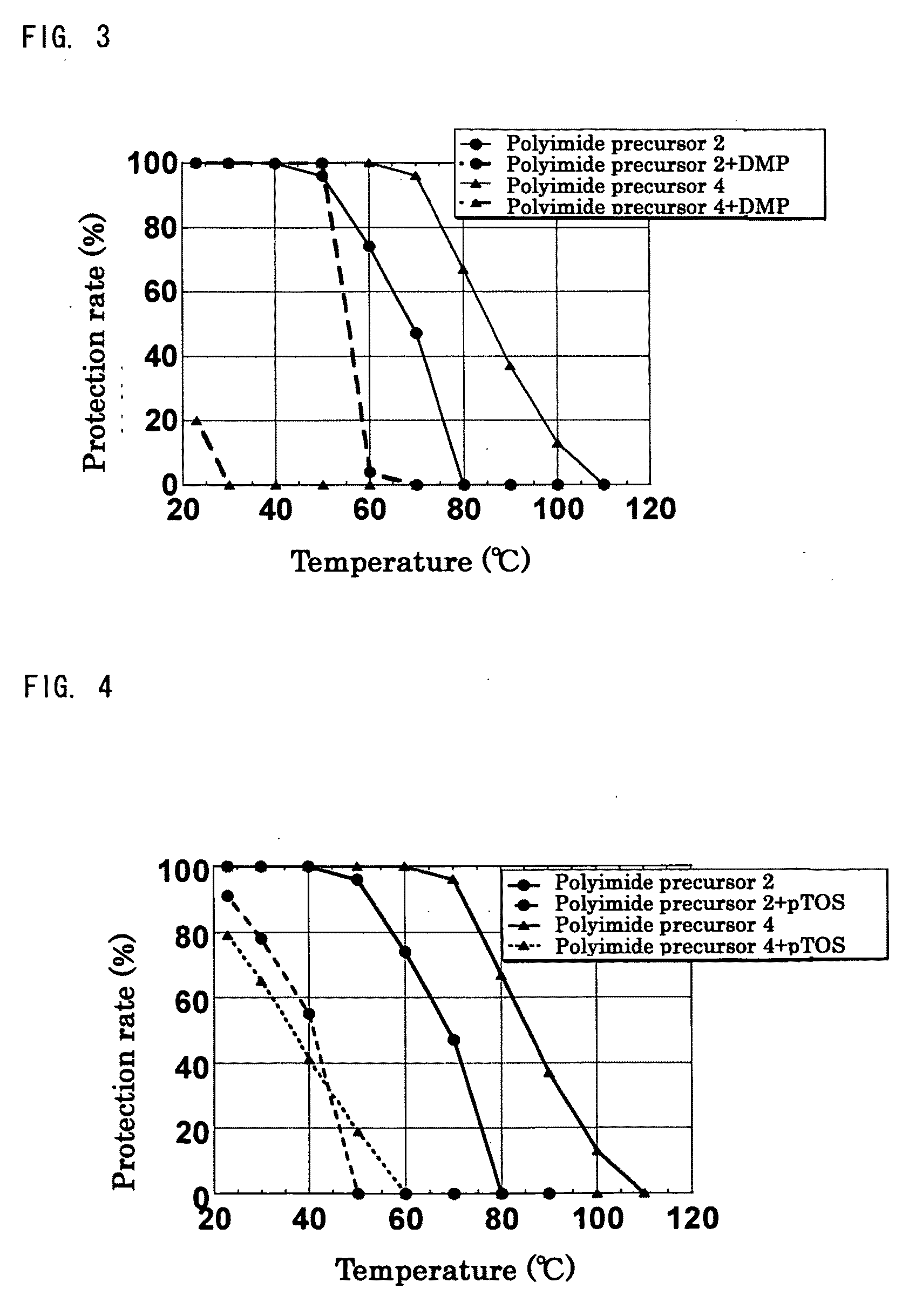

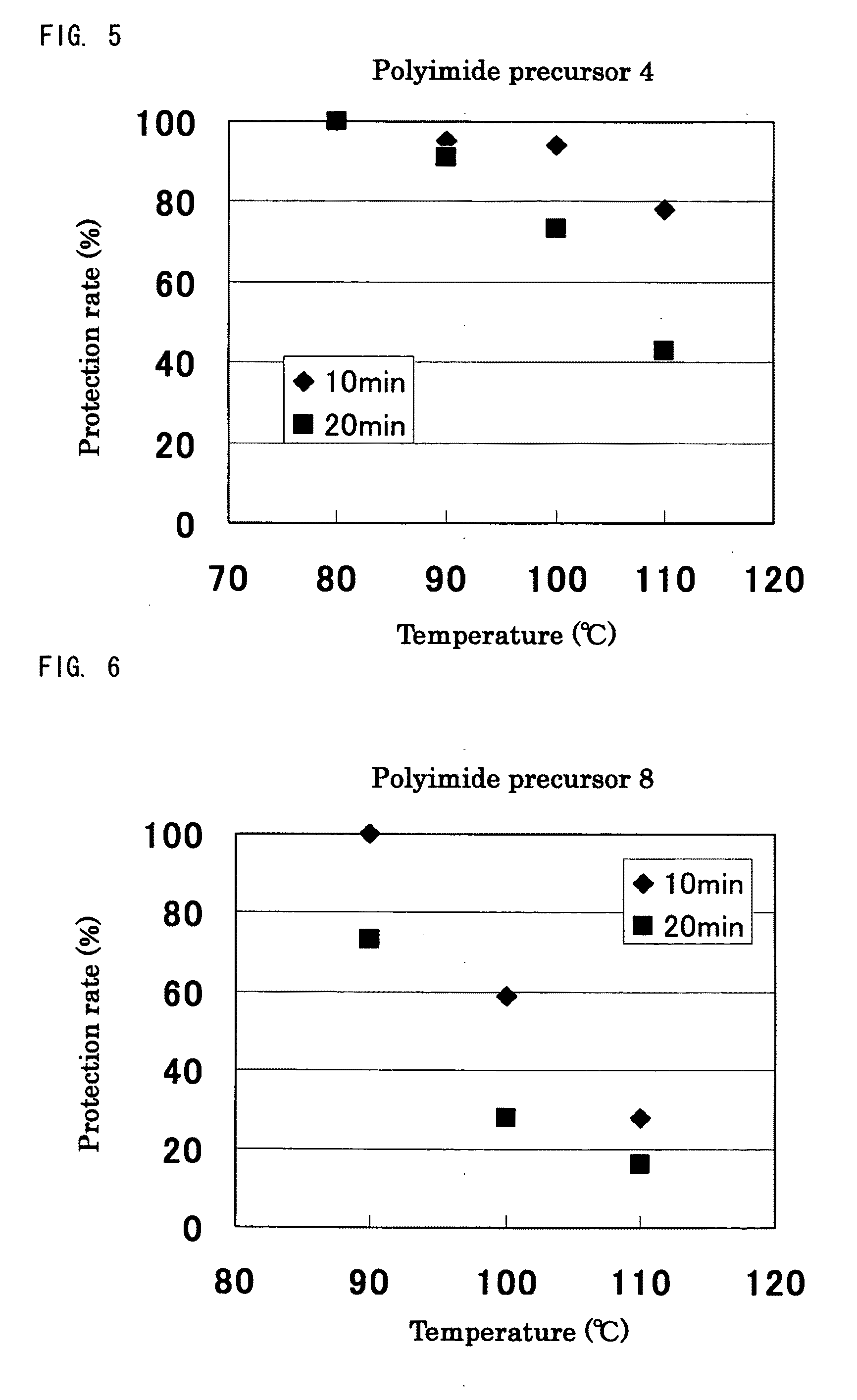

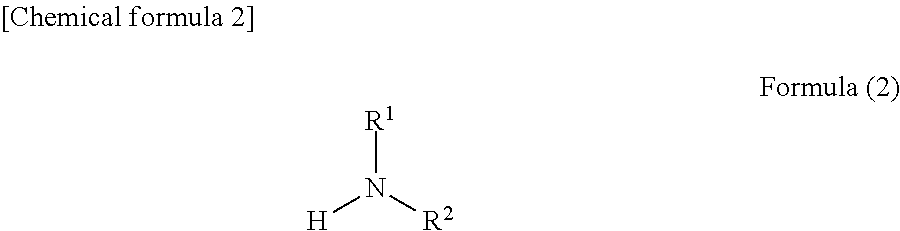

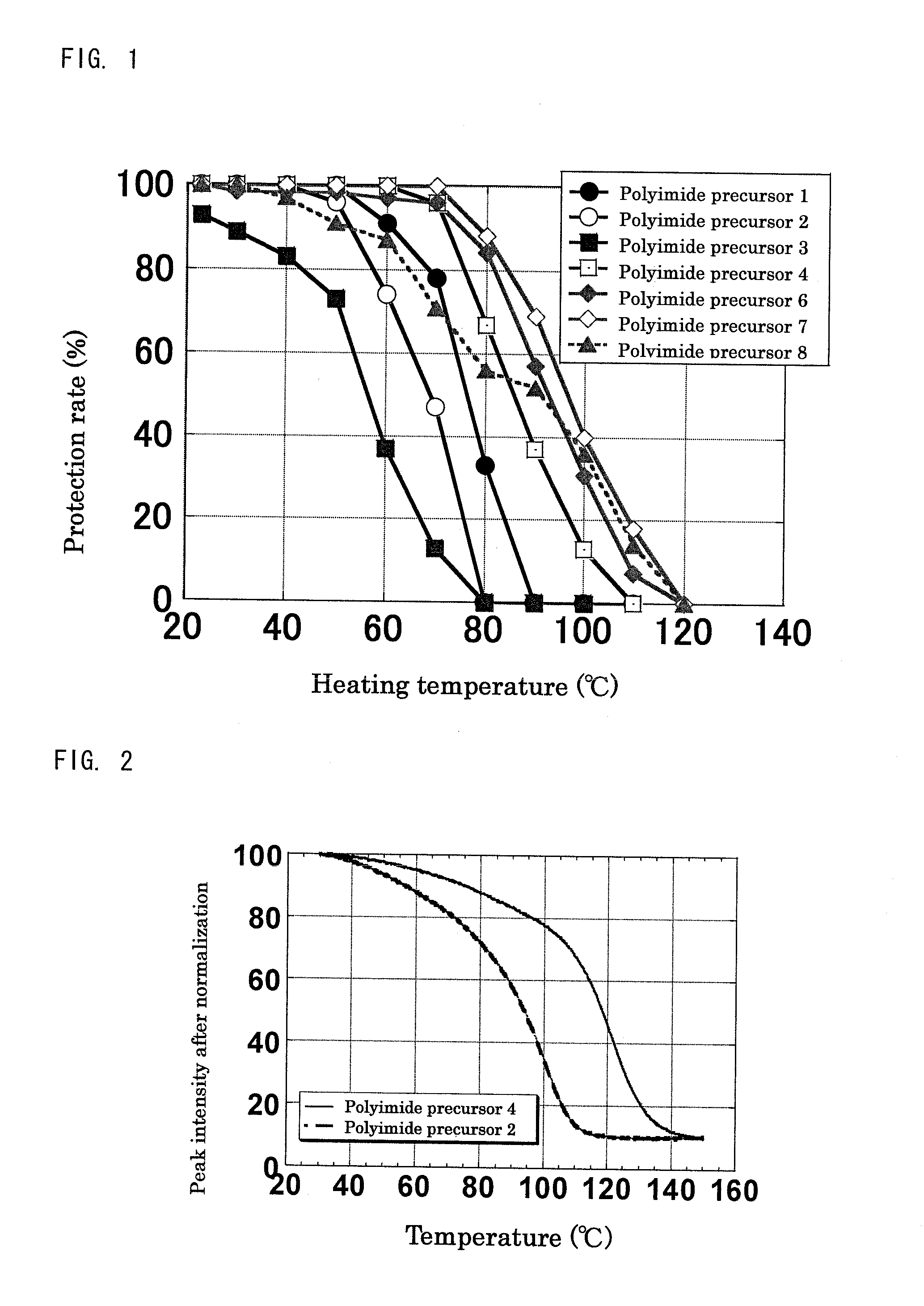

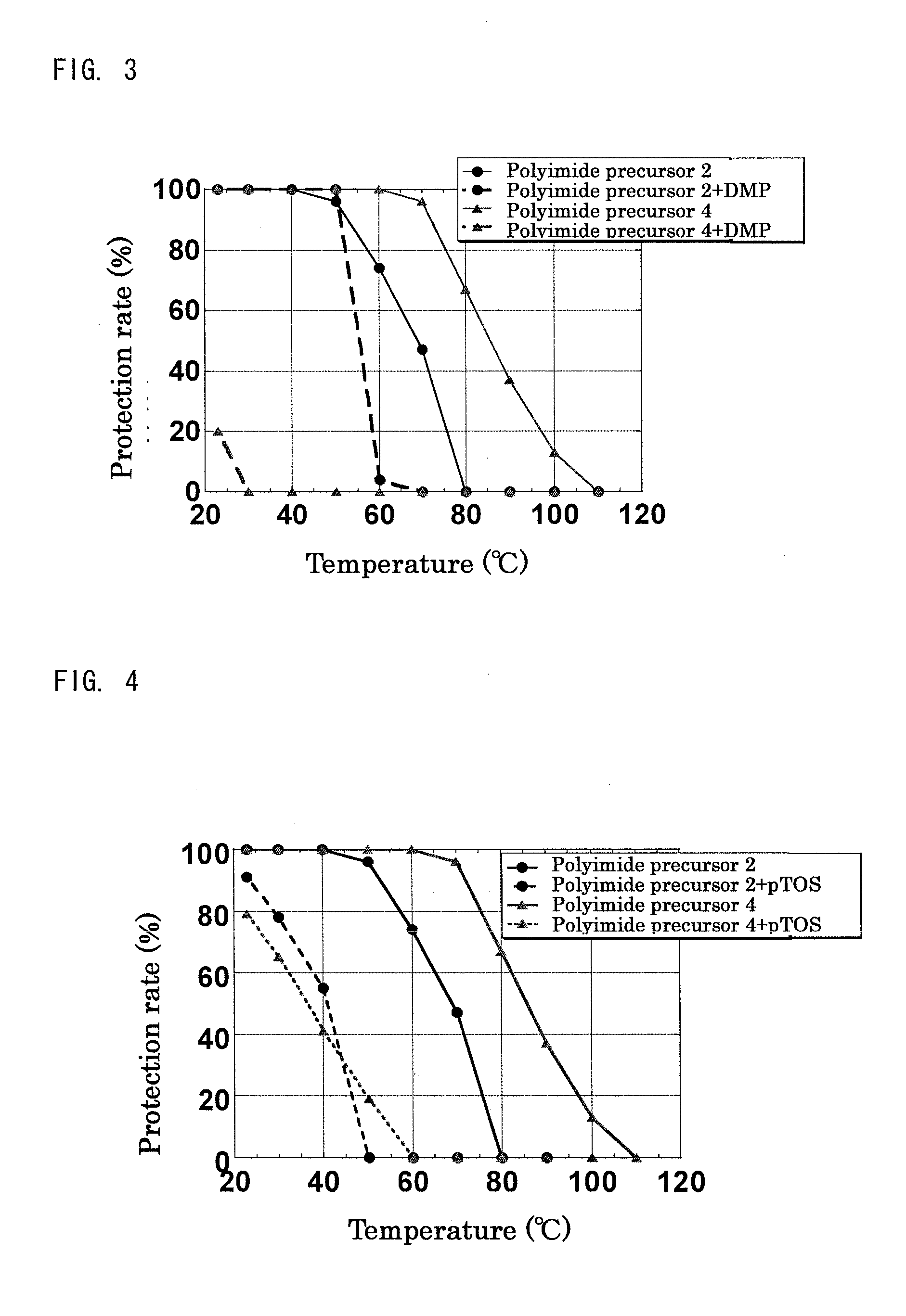

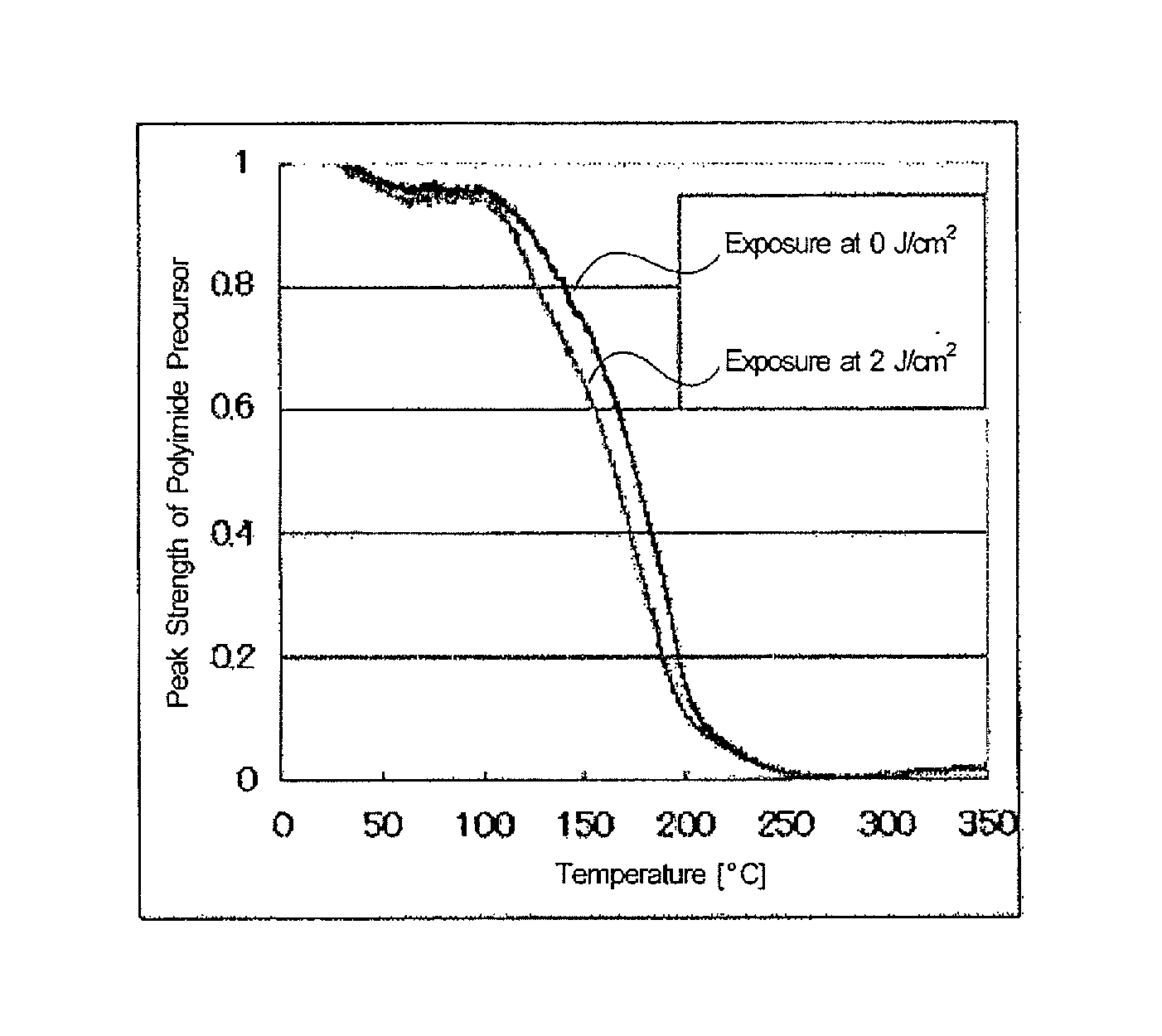

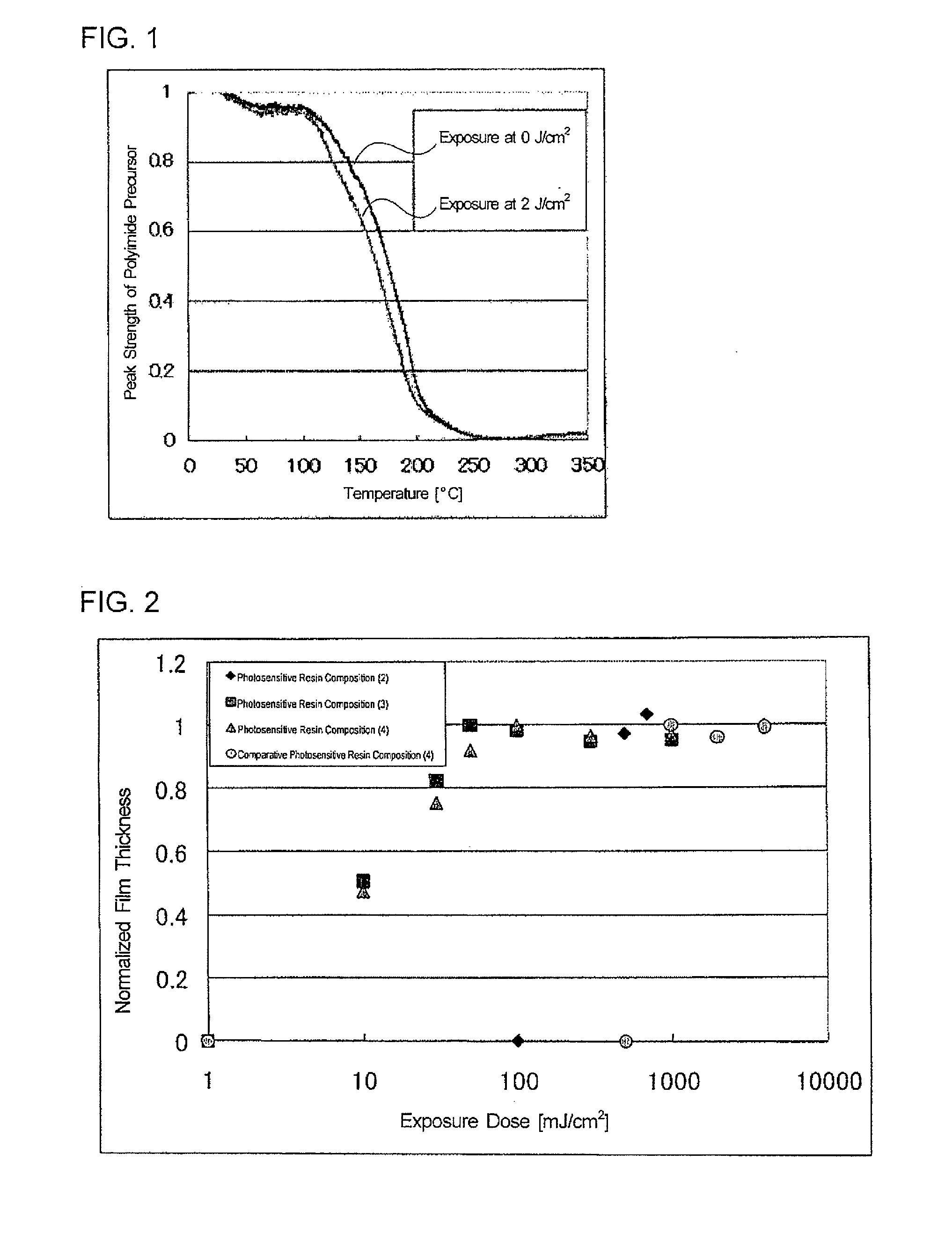

Polyimide precursor, resin composition comprising the polyimide precursor, pattern forming method using the resin composition, and articles produced by using the resin composition

ActiveUS20090263745A1Easy to synthesizeLow costOrganic chemistryPhotosensitive materialsChemical structureHalogen

It is a main object of the present invention to provide a polyimide precursor and a polyimide precursor resin composition, which precursor being easy to synthesize, available at low cost, excellent in storage and capable of giving polyimide that is low in impurities after imidization, irrespective of the chemical structure of the finally-obtained polyimide.It is another object of the present invention to provide a polyimide precursor having repeating units represented by the following formula (1) and a photosensitive resin composition comprising the polyimide precursor and a photoacid generator or photobase generator:In the formula (1), R1 is a tetravalent organic group; R2 is a divalent organic group; R1s may be the same or different from each other and R2s may be the same or different from each other in the repeating units; R3 and R4 respectively represent a monovalent organic group having a structure represented by the following formula (2) and may be the same or different from each other; and R3s and R4s in the repeating units may be the same or different from each other, respectively. In the formula (2), R5, R6 and R7 respectively represent a hydrogen atom, a halogen atom or a monovalent organic group; R8 is a monovalent organic group; R8s in the repeating units may be the same or different from each other; 35 mole % or less of R8s are organic groups having a reactive group; and R5, R6, R7 and R8 may be bonded to each other to form a ring structure.

Owner:DAI NIPPON PRINTING CO LTD

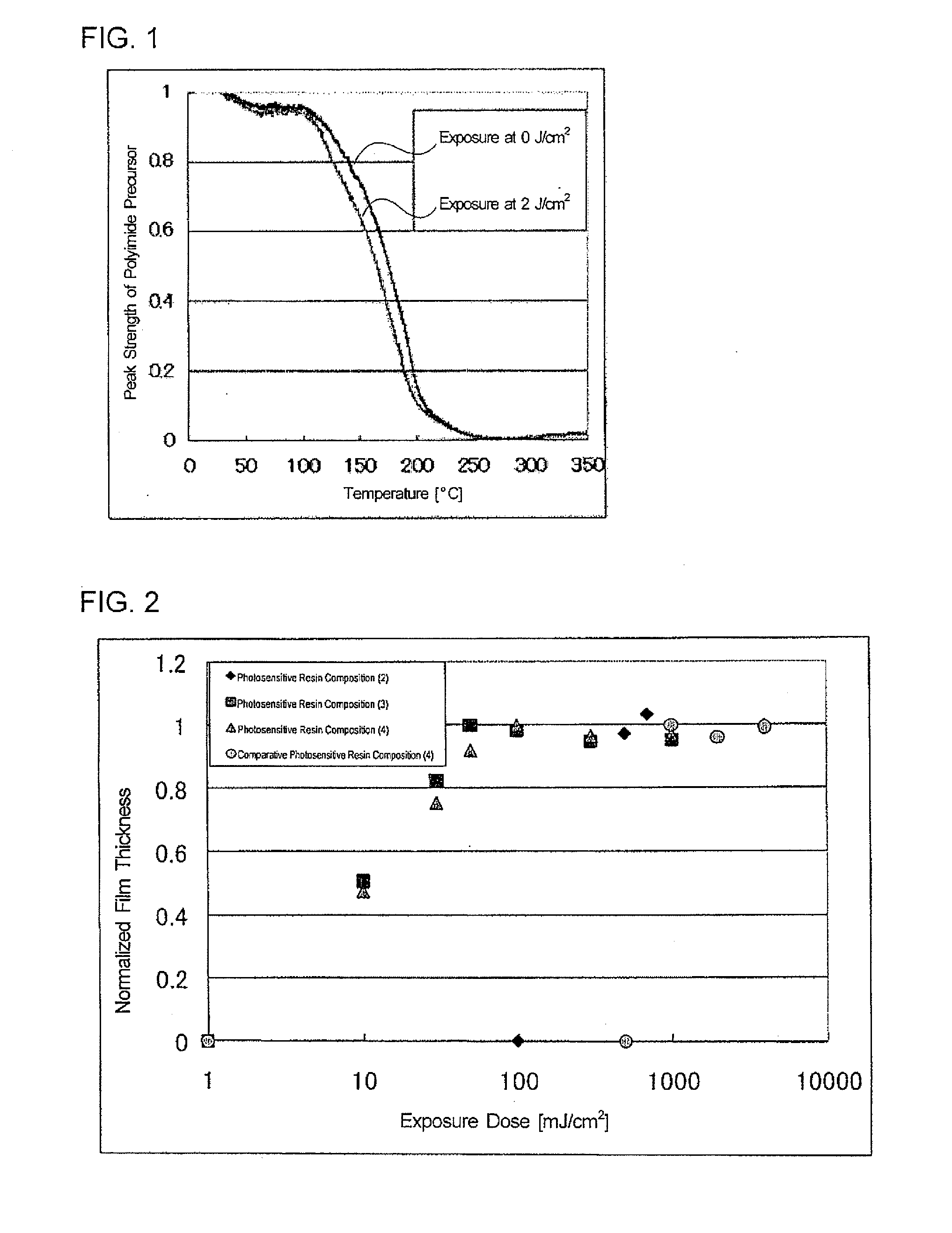

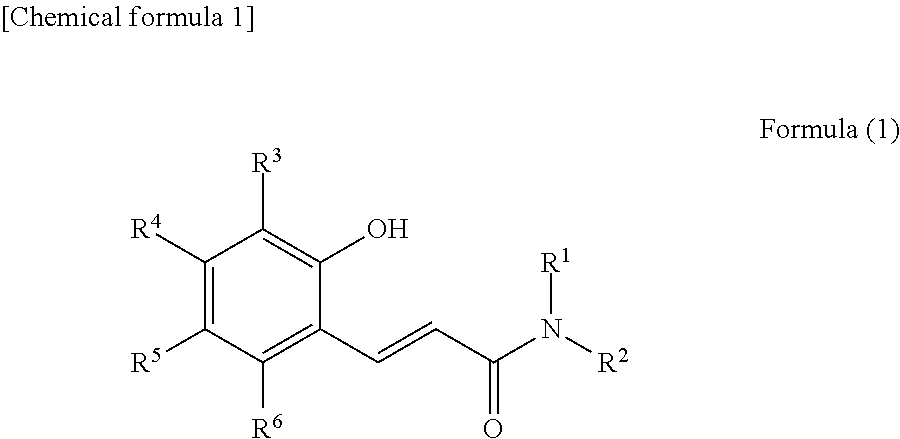

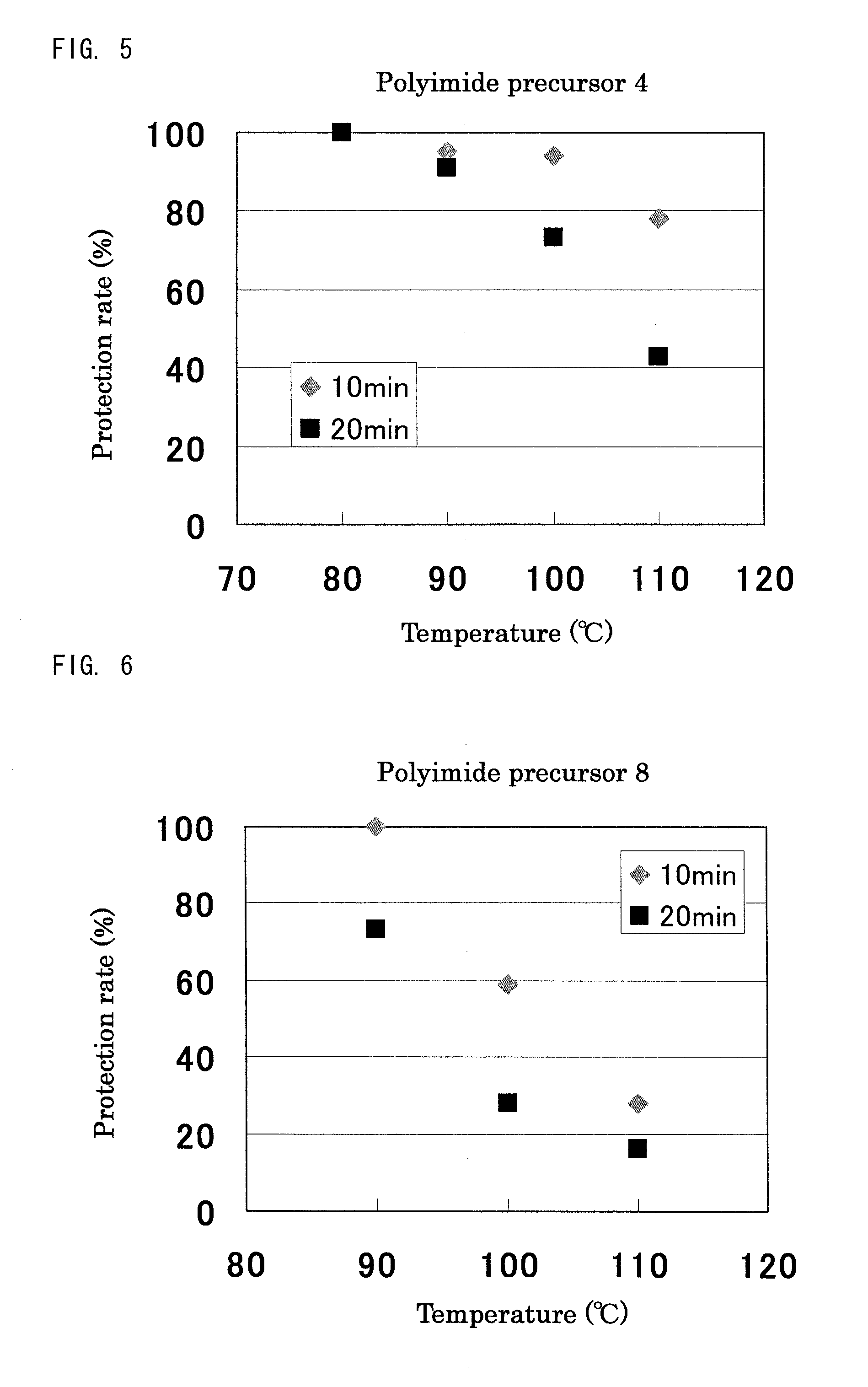

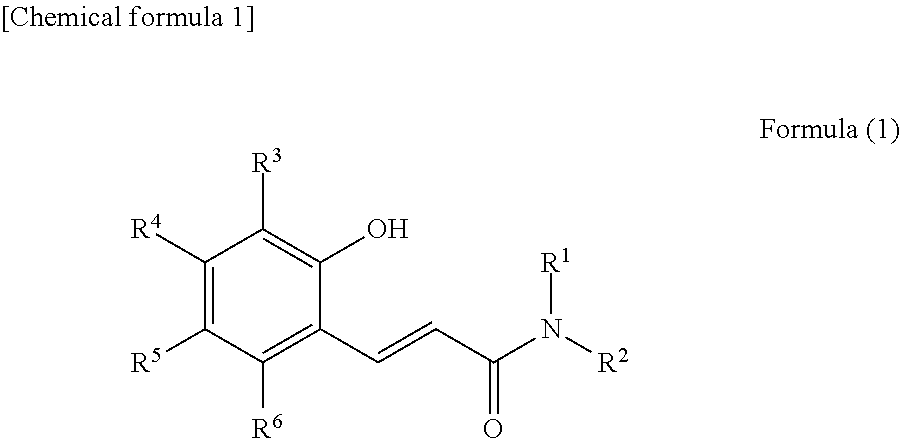

Base generator, photosensitive resin composition, pattern forming material comprising the photosensitive resin composition, and pattern forming method and article using the photosensitive resin composition

ActiveUS20110086311A1High sensitivityIncrease the differenceAdditive manufacturing apparatusOrganic chemistryImage resolutionElectromagnetic radiation

A photosensitive resin composition which is excellent in resolution, low in cost, and usable in a wide range of structures of polymer precursors each of which is reacted into a final product by a basic substance or by heating in the presence of a basic substance. The photosensitive resin composition includes a base generator which has a specific structure and generates a base by exposure to electromagnetic radiation and heating, and a polymer precursor which is reacted into a final product by the base generator and by a basic substance or by heating in the presence of a basic substance.

Owner:DAI NIPPON PRINTING CO LTD

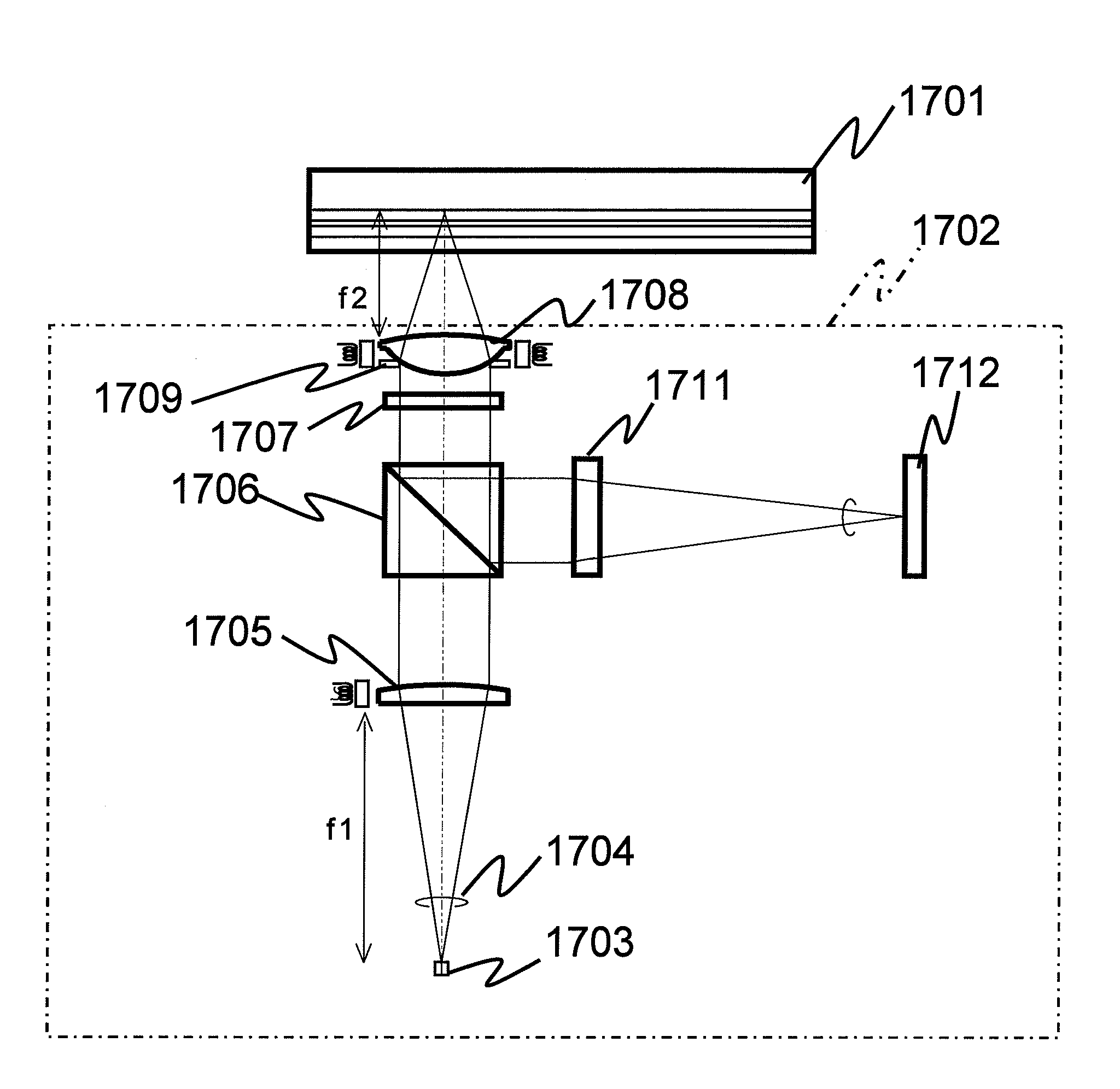

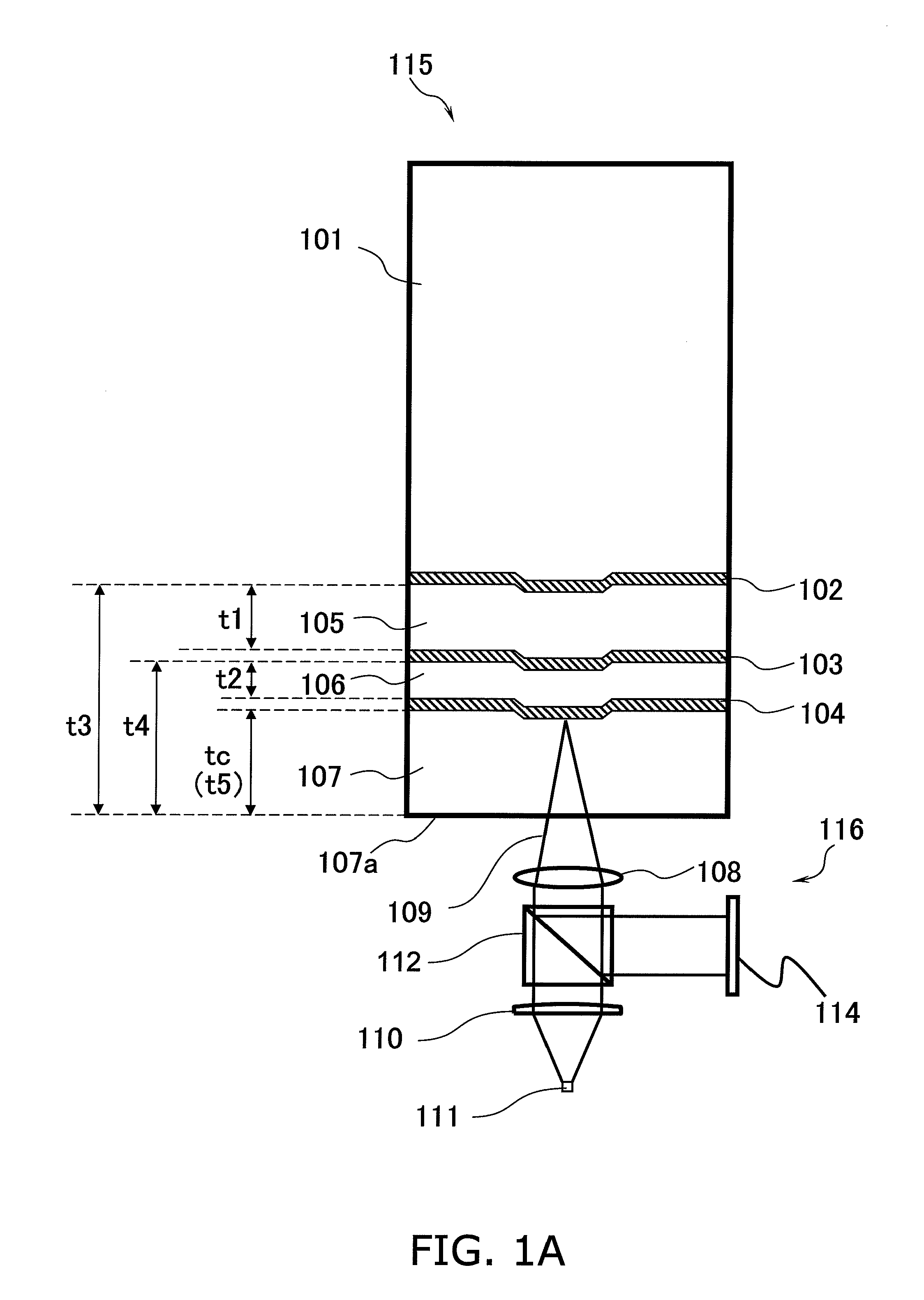

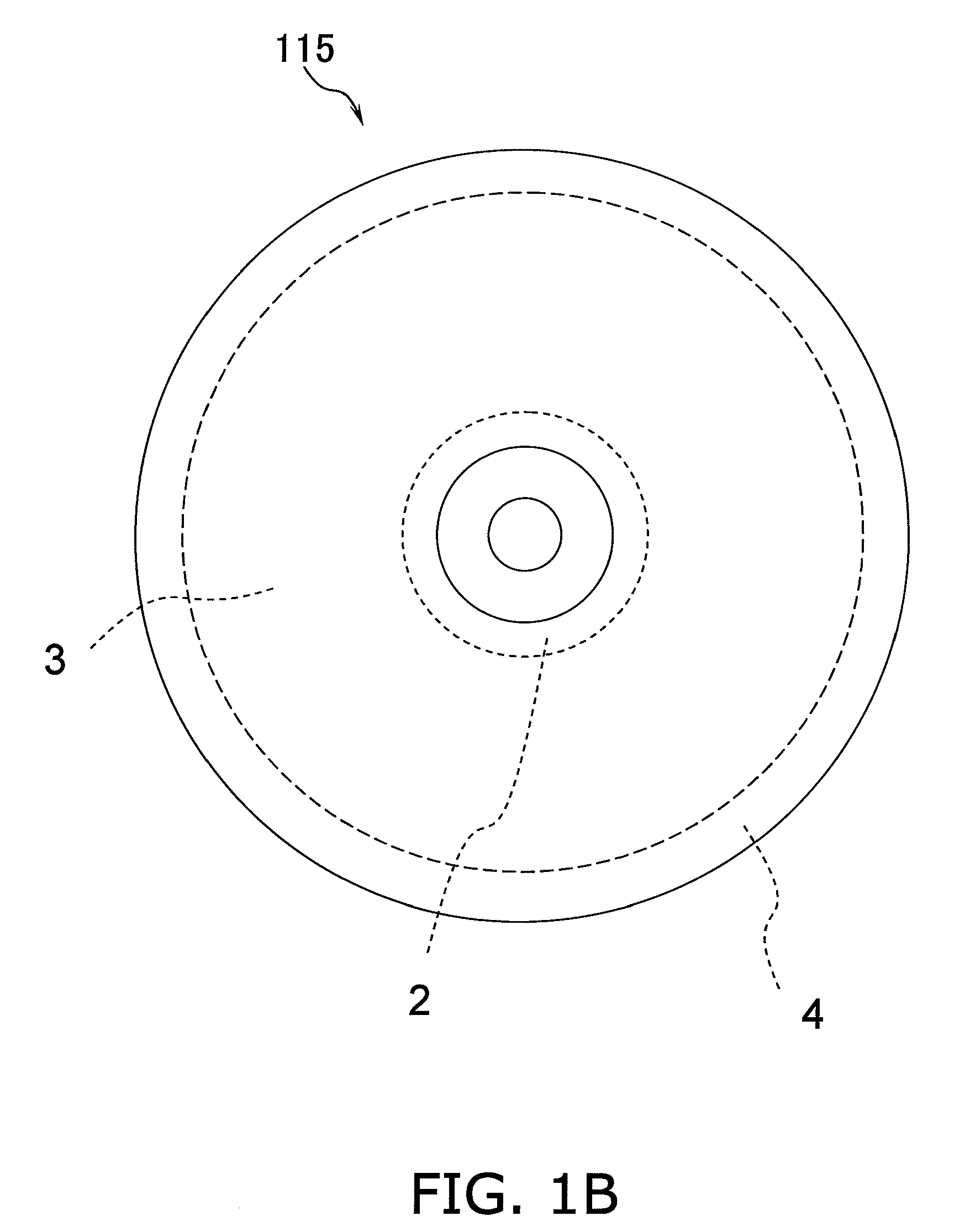

Optical information recording medium and recording and reproduction apparatus

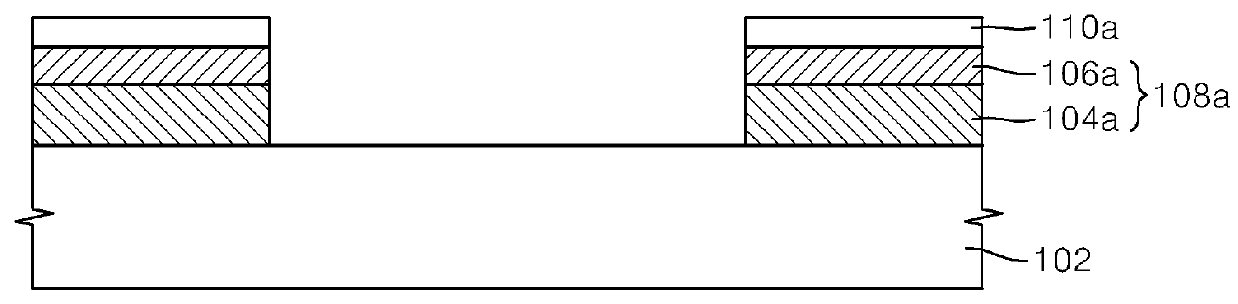

InactiveUS20100195474A1Sufficient process marginReduce impactMechanical record carriersRecord information storageInformation layerInter layer

A disk-shaped optical information recording medium (115) includes a substrate (101), first to nth information layers (102-104) layered upon the substrate (where n is an integer of 3 or more), kth intermediate layers (105, 106) provided between a kth information layer and a (k+1)th information layer (where k=1, 2, and so on up to n−1), and a protective layer (107) provided upon the nth information layer. The fluctuation range of the thicknesses from the protective layer surface (107a) to each of the information layers (102-104) is no more than ±3 μm relative to the average value of the thicknesses within a range from a radius of 23 mm to 24 mm from the center of the optical information recording medium.

Owner:PANASONIC CORP

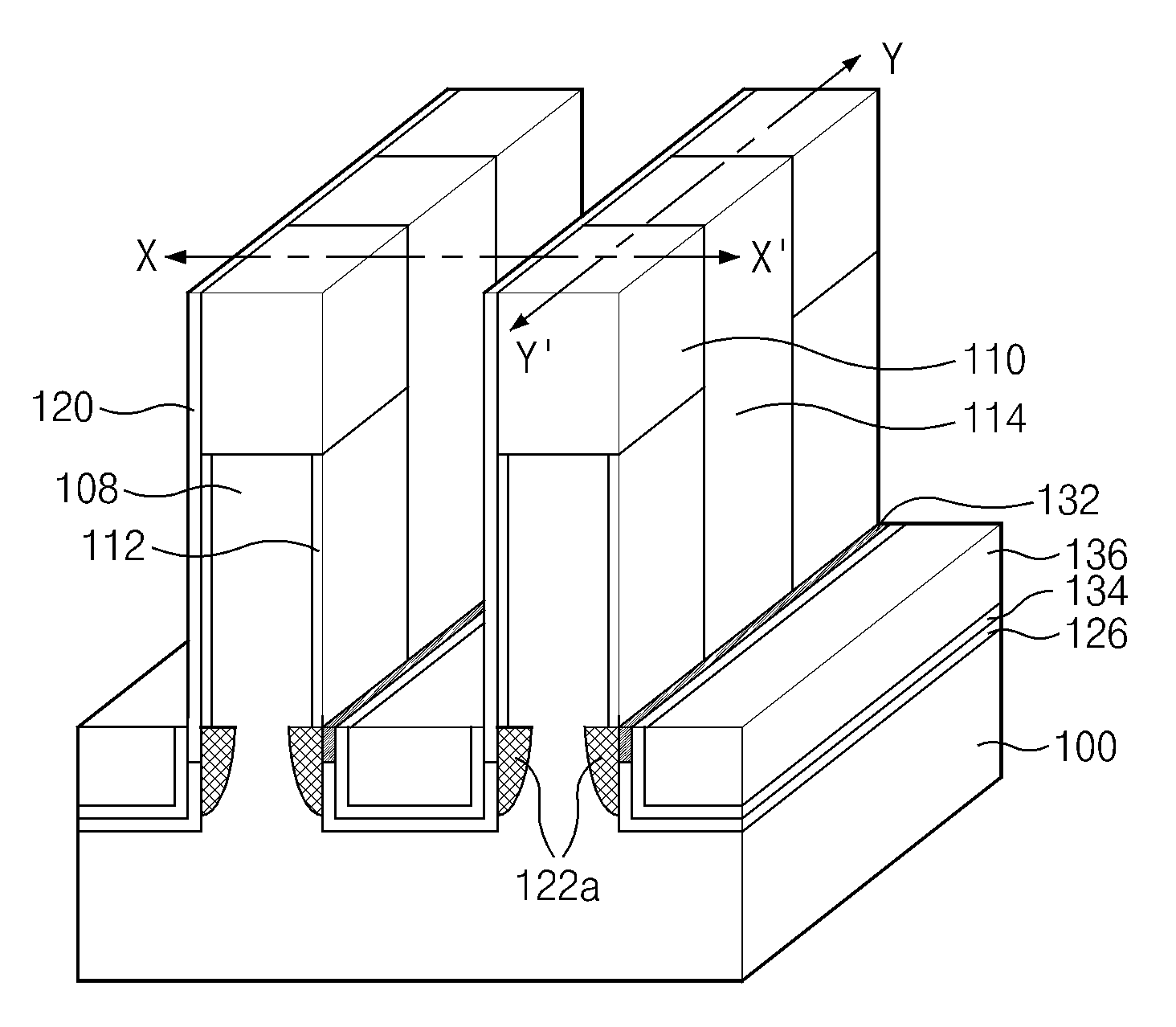

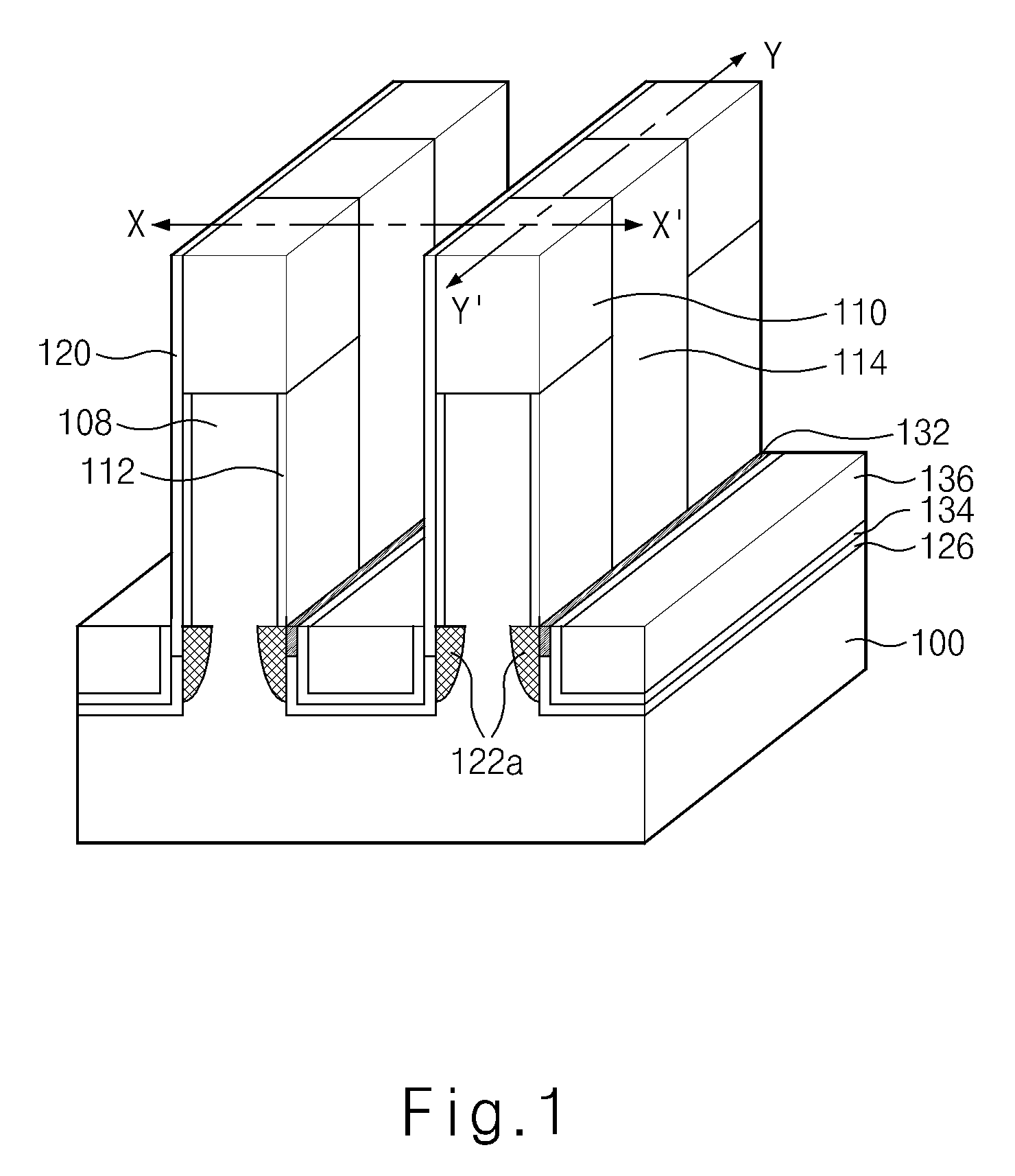

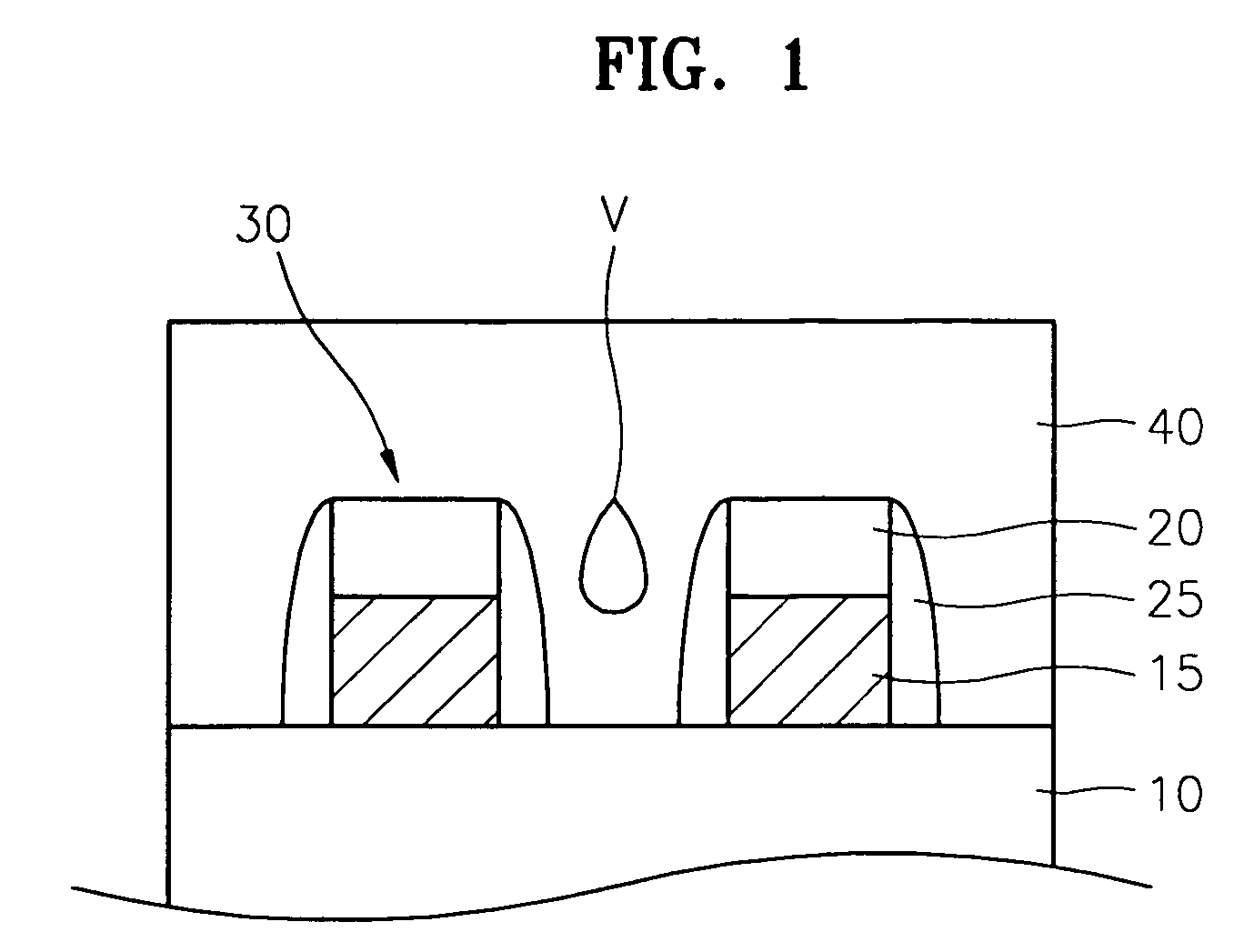

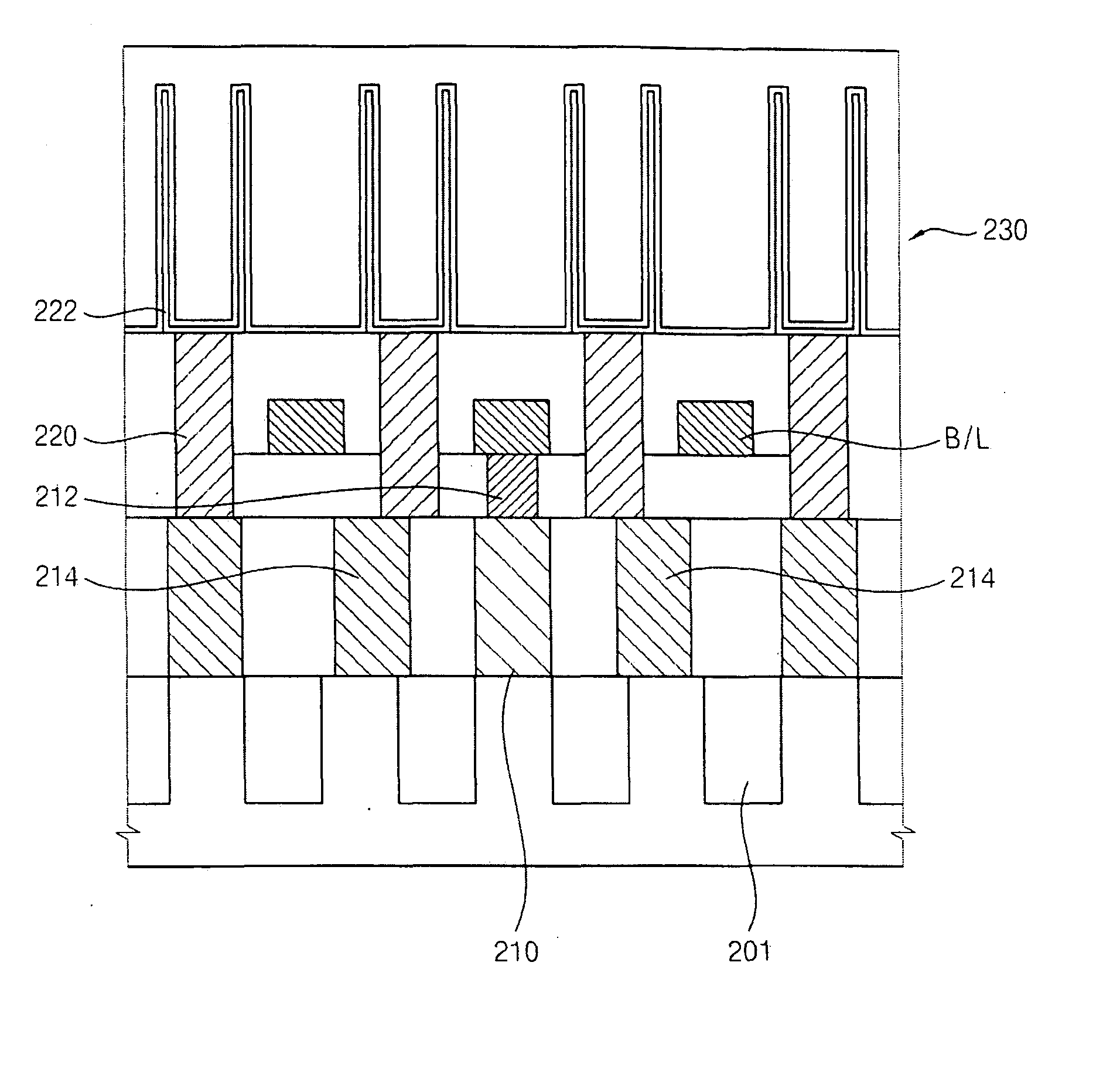

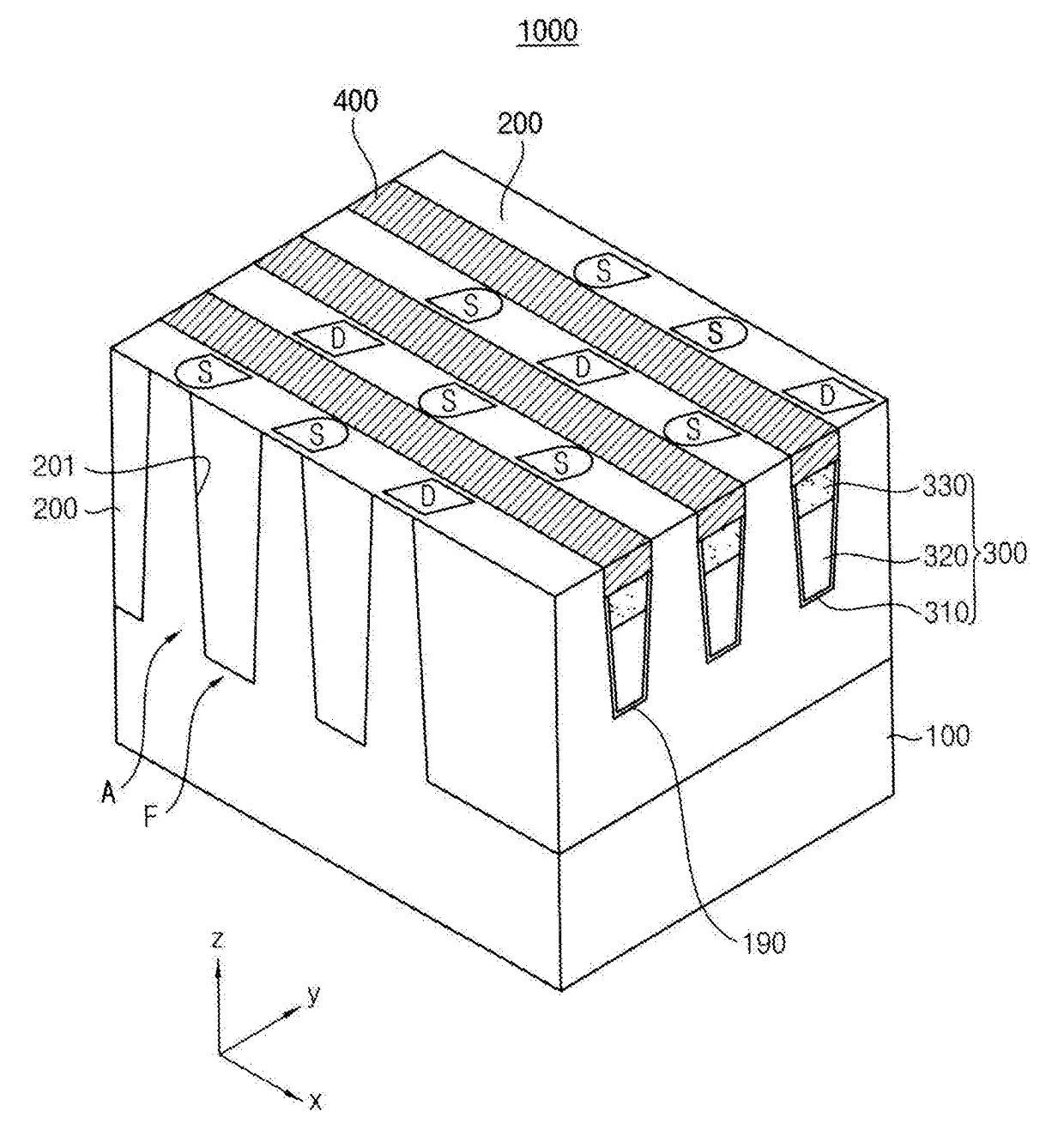

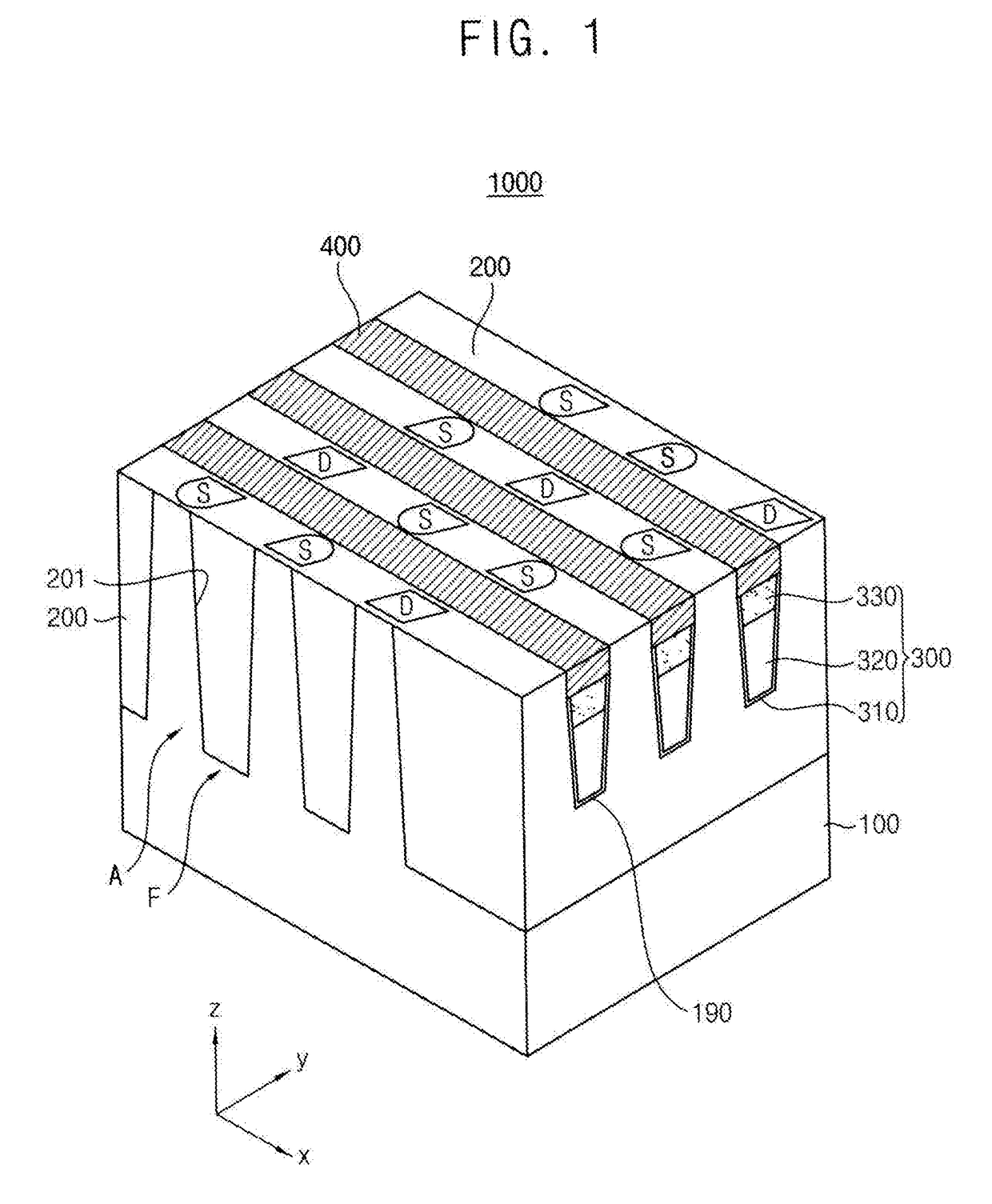

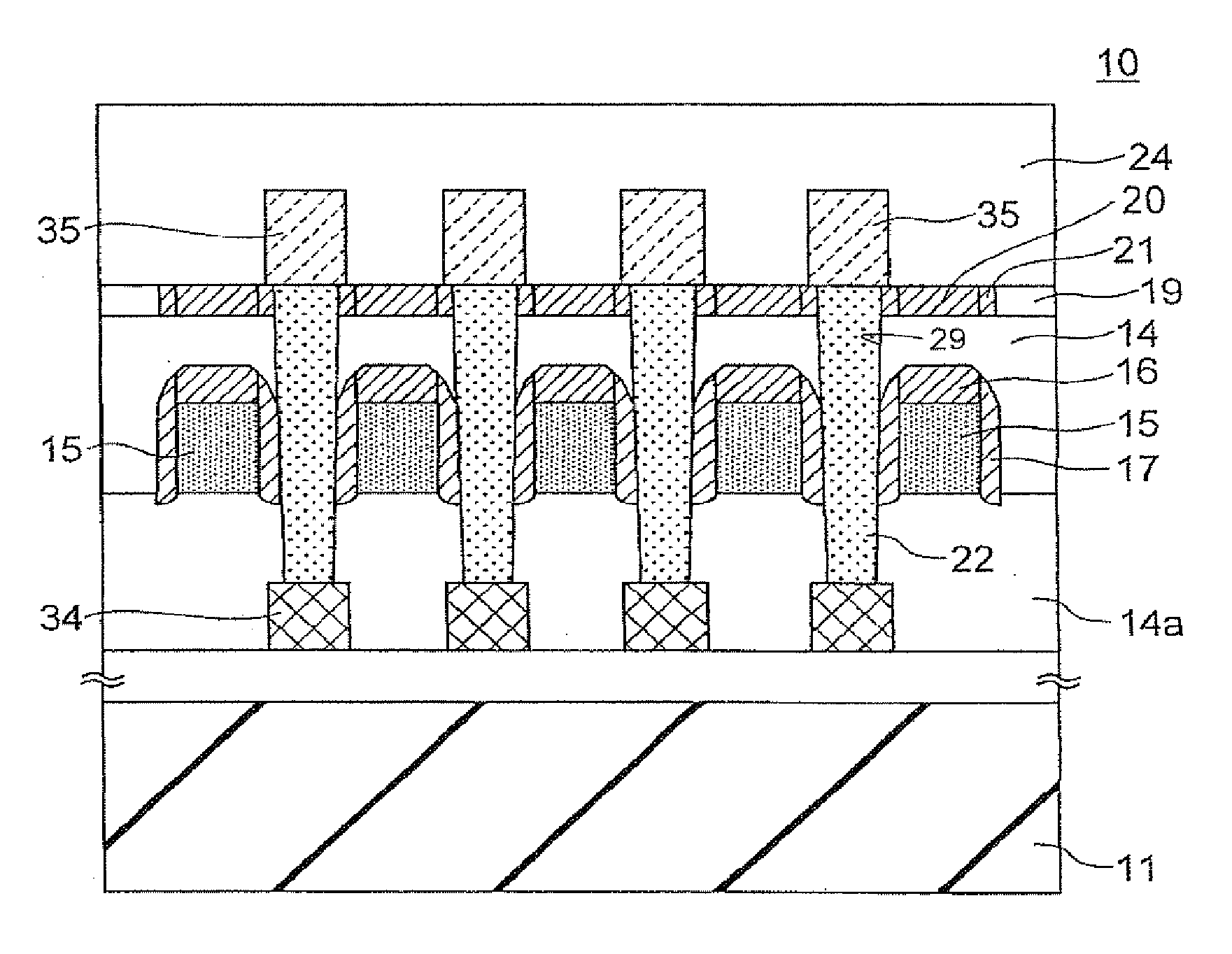

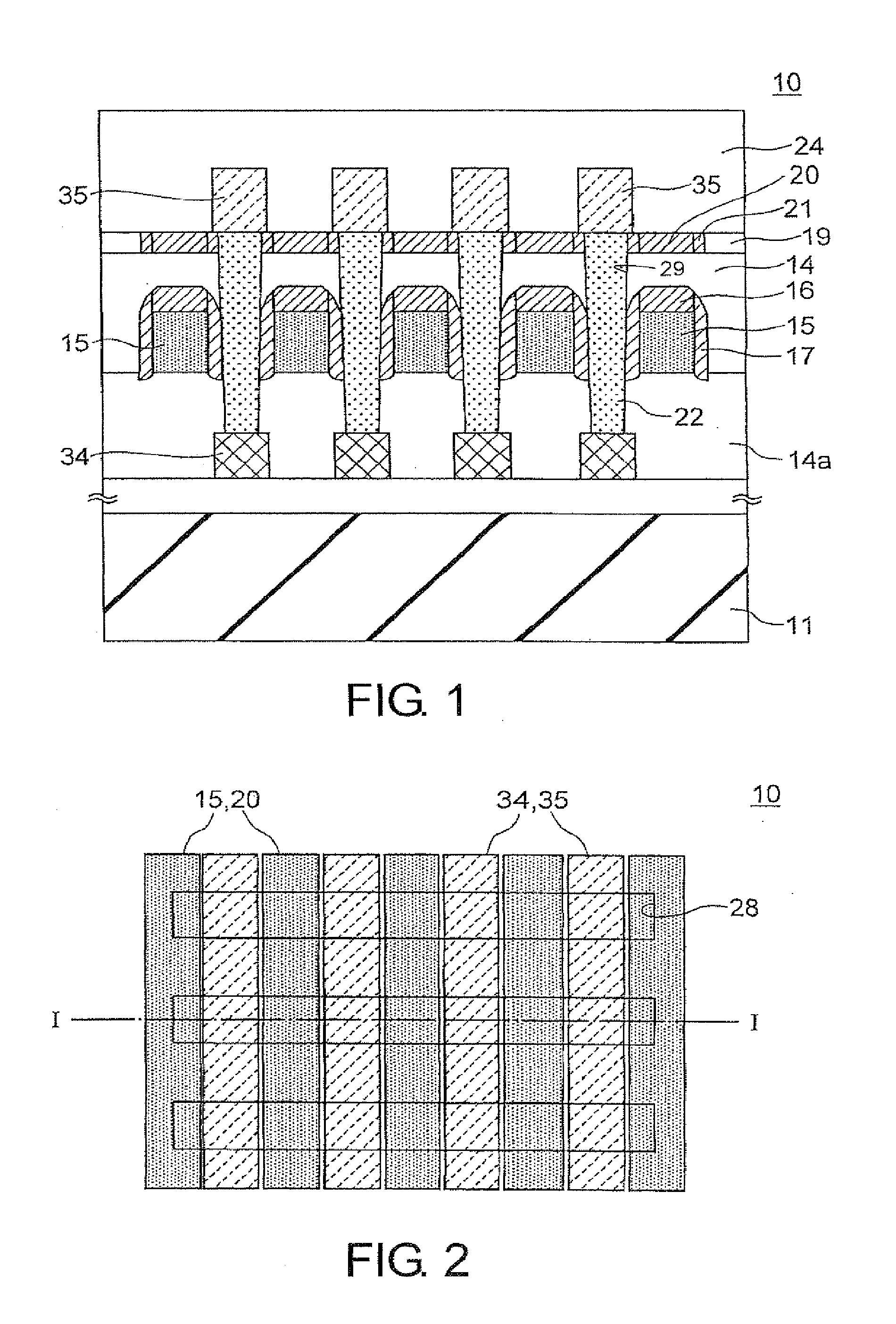

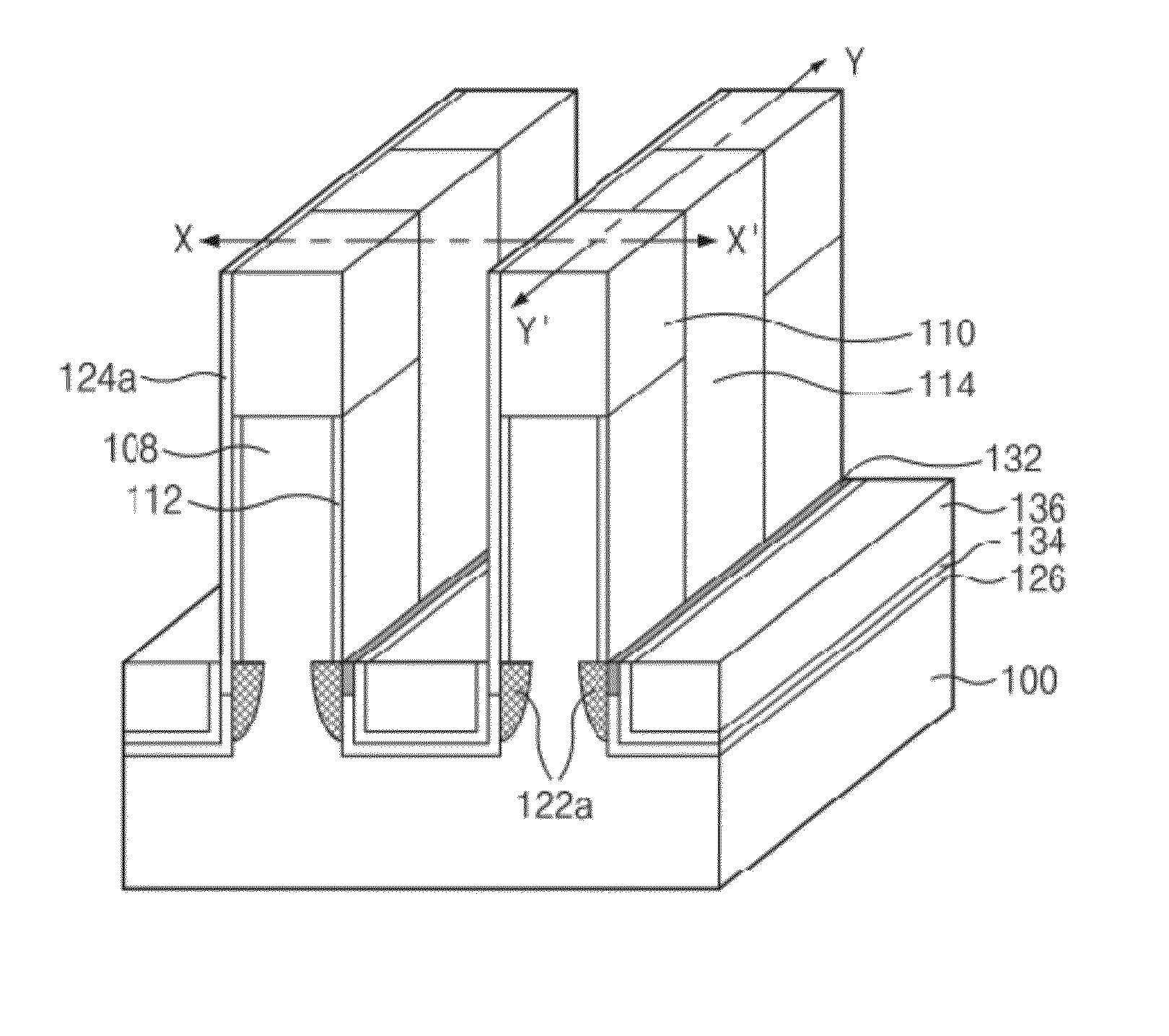

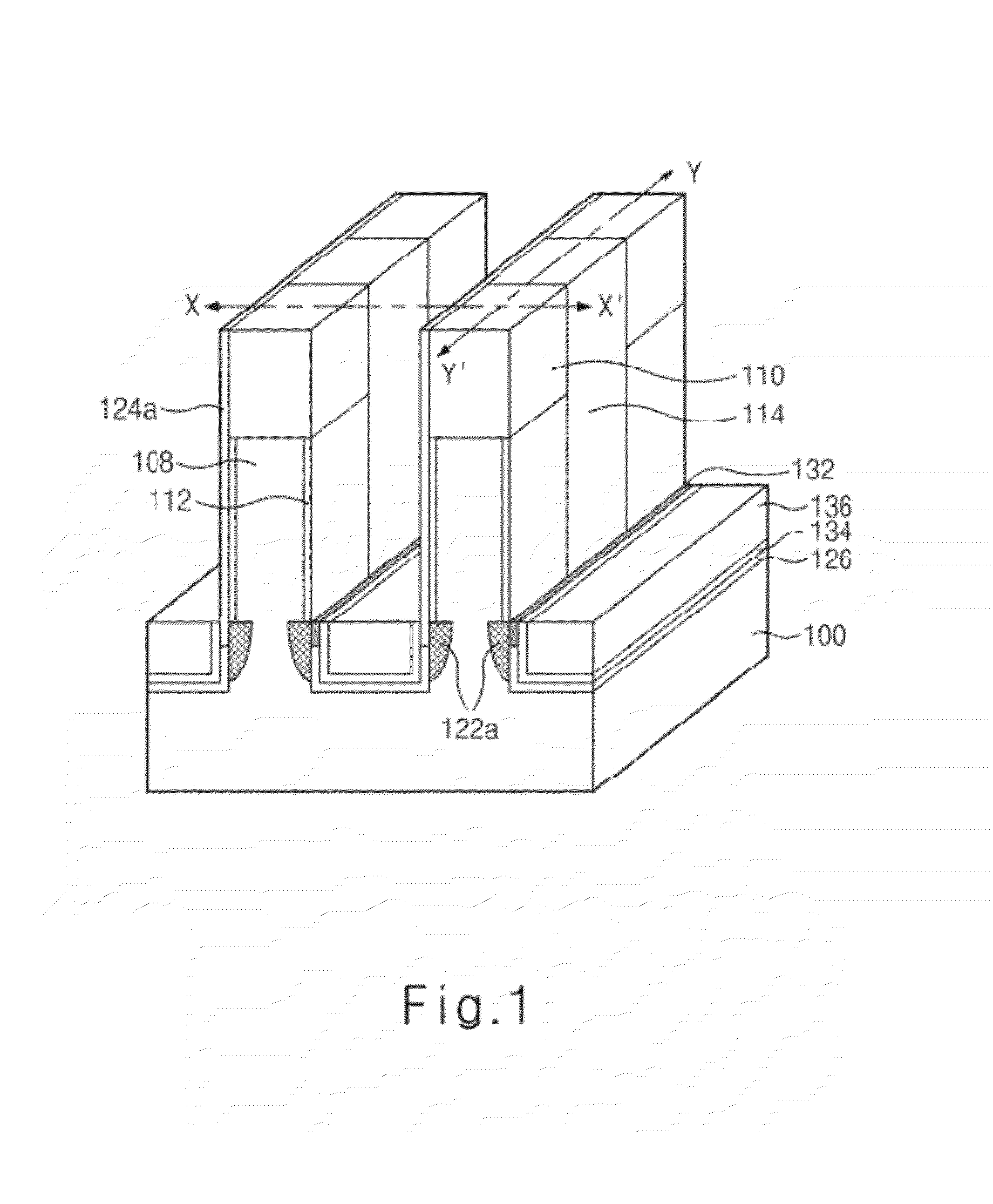

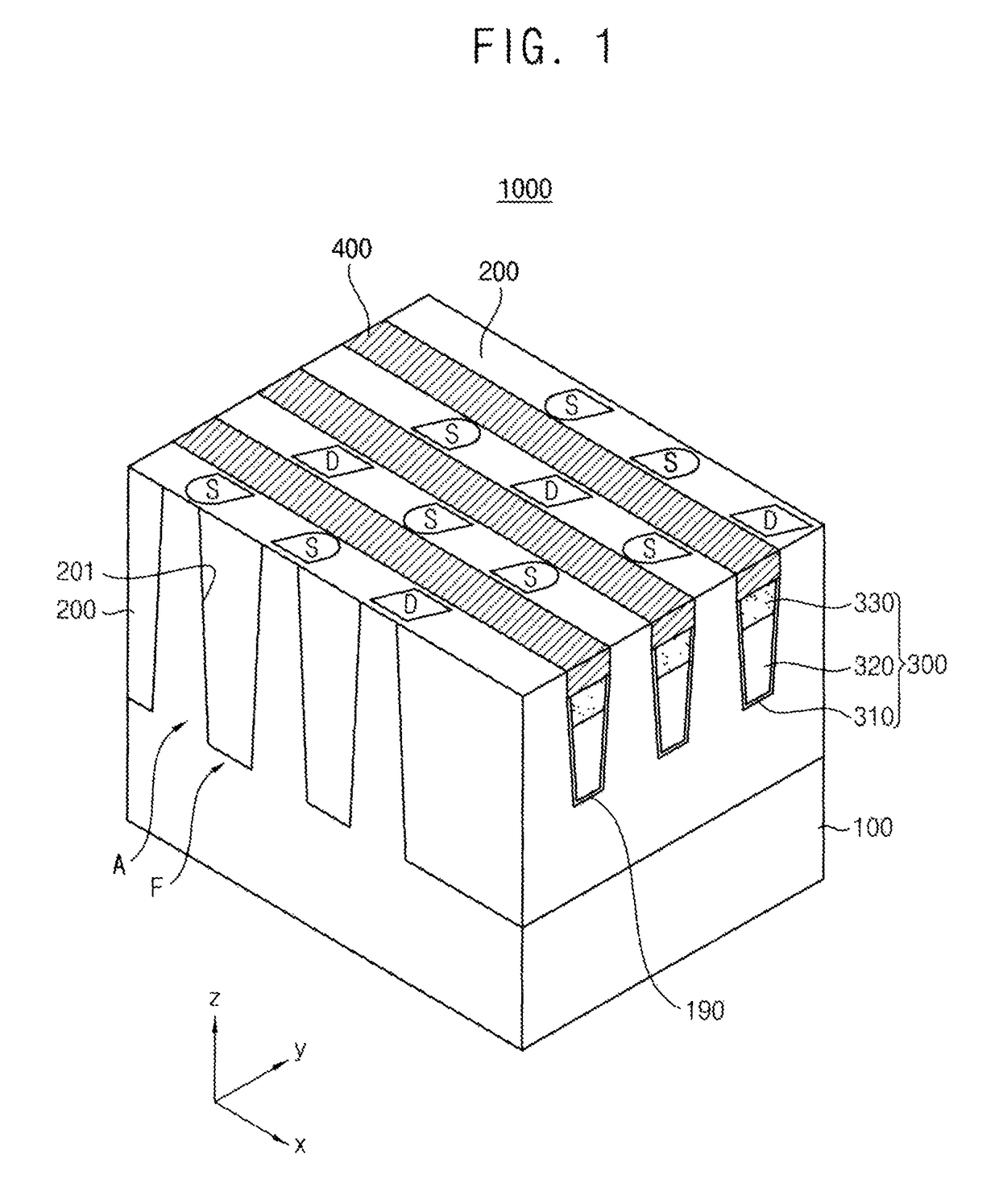

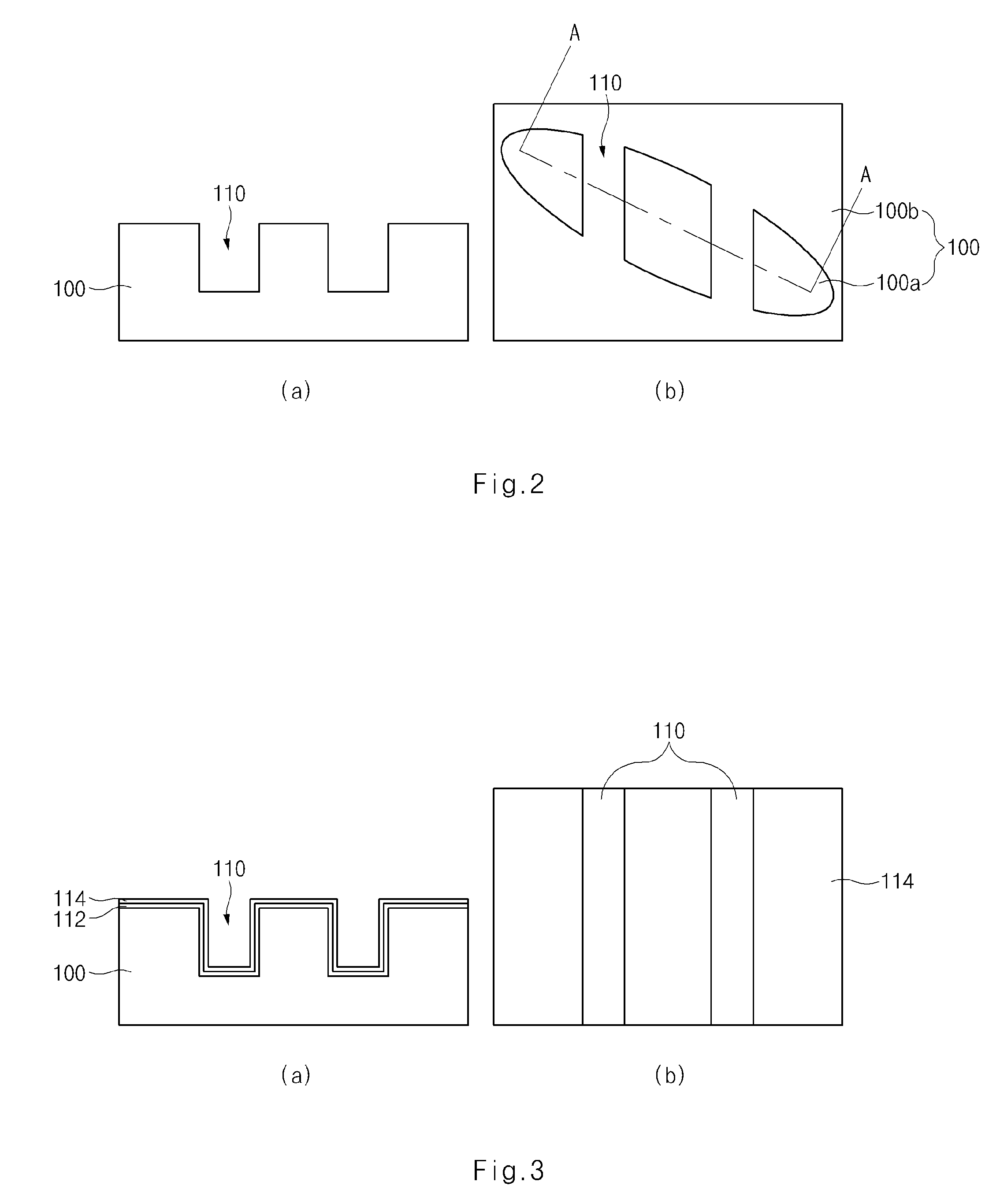

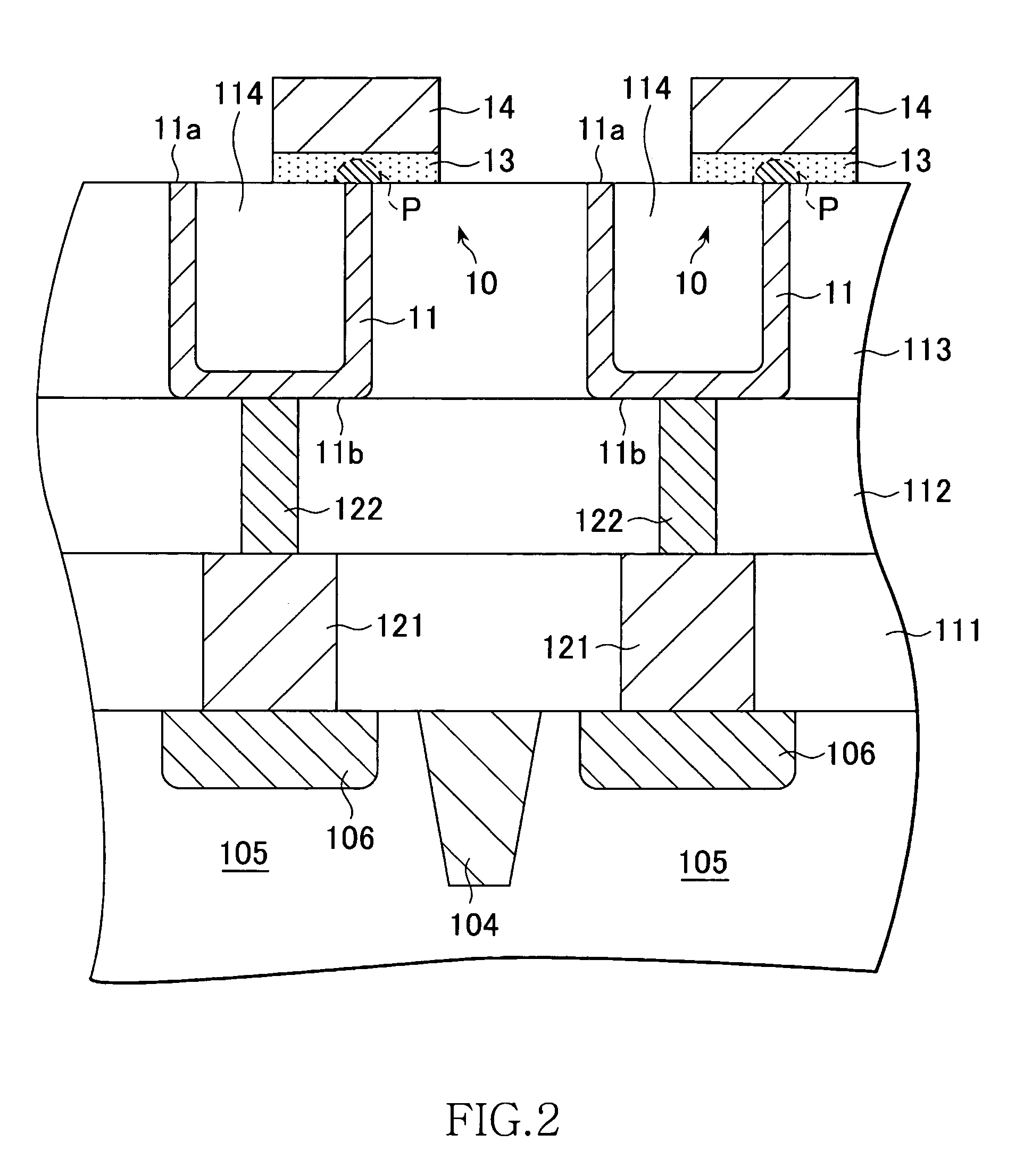

Semiconductor device having vertical channel transistor and manufacturing method of the same

ActiveUS20100301407A1Reduce resistanceReduction in design ruleSemiconductor/solid-state device manufacturingSemiconductor devicesBit lineNon symmetric

A semiconductor device having a vertical channel transistor and a method for manufacturing the same are provided. In the semiconductor device, a metal bit line is formed between vertical channel transistors, and the metal bit line is connected to only one of the vertical channel transistors through an asymmetric bit line contact. Through such a structure, the resistance of the bit line can be improved and the process margin for formation of the bit line can be secured.

Owner:SK HYNIX INC

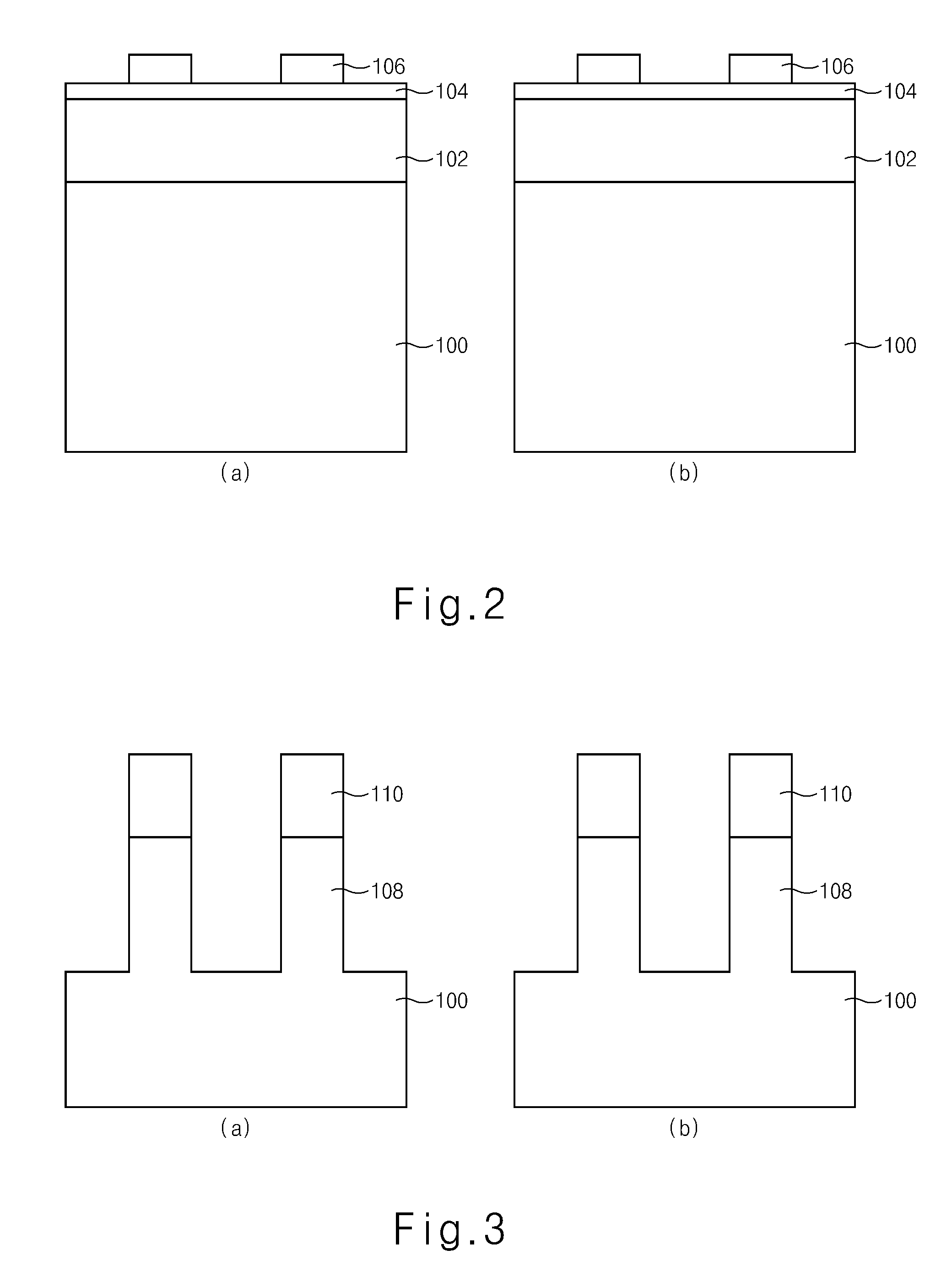

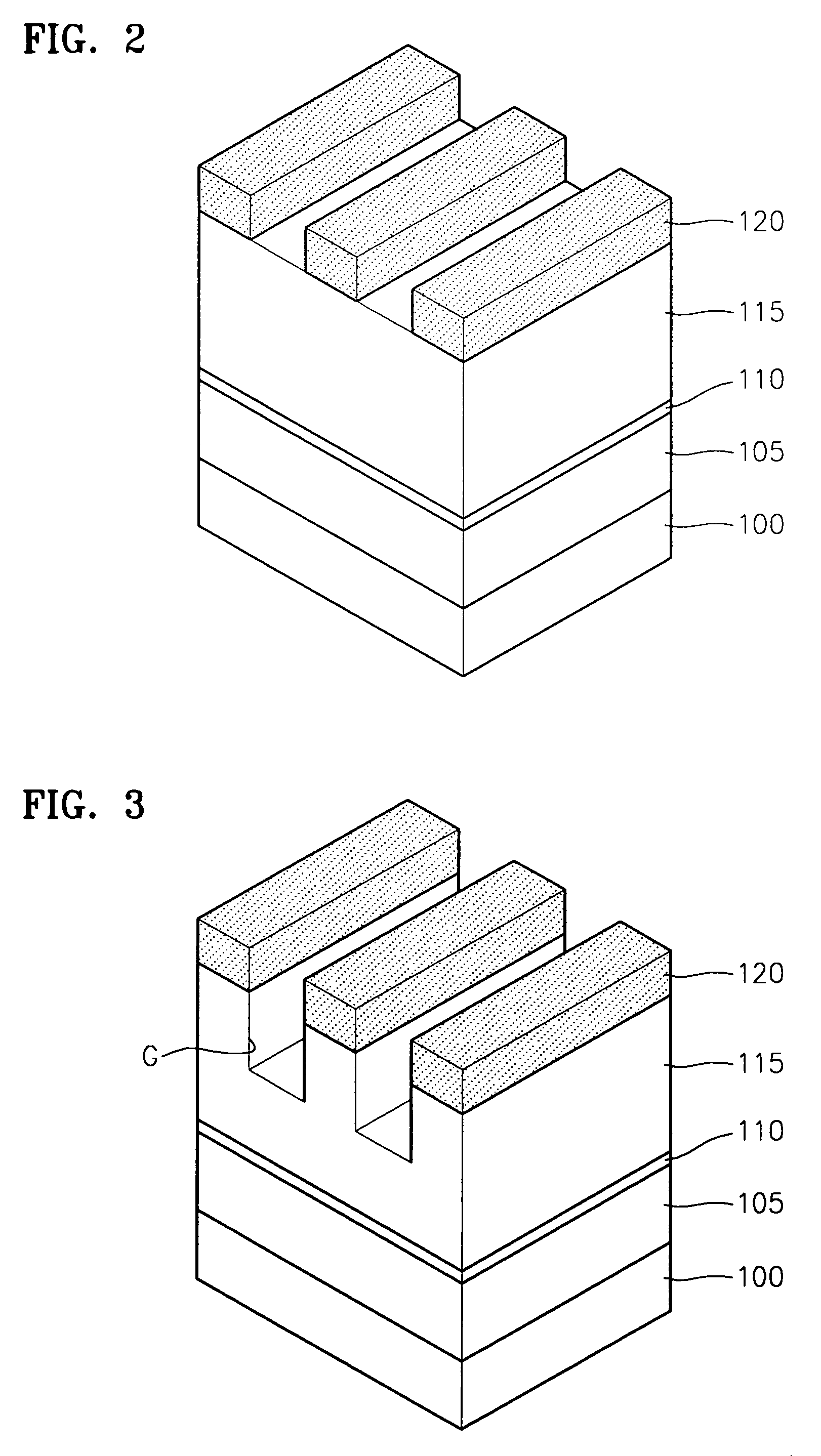

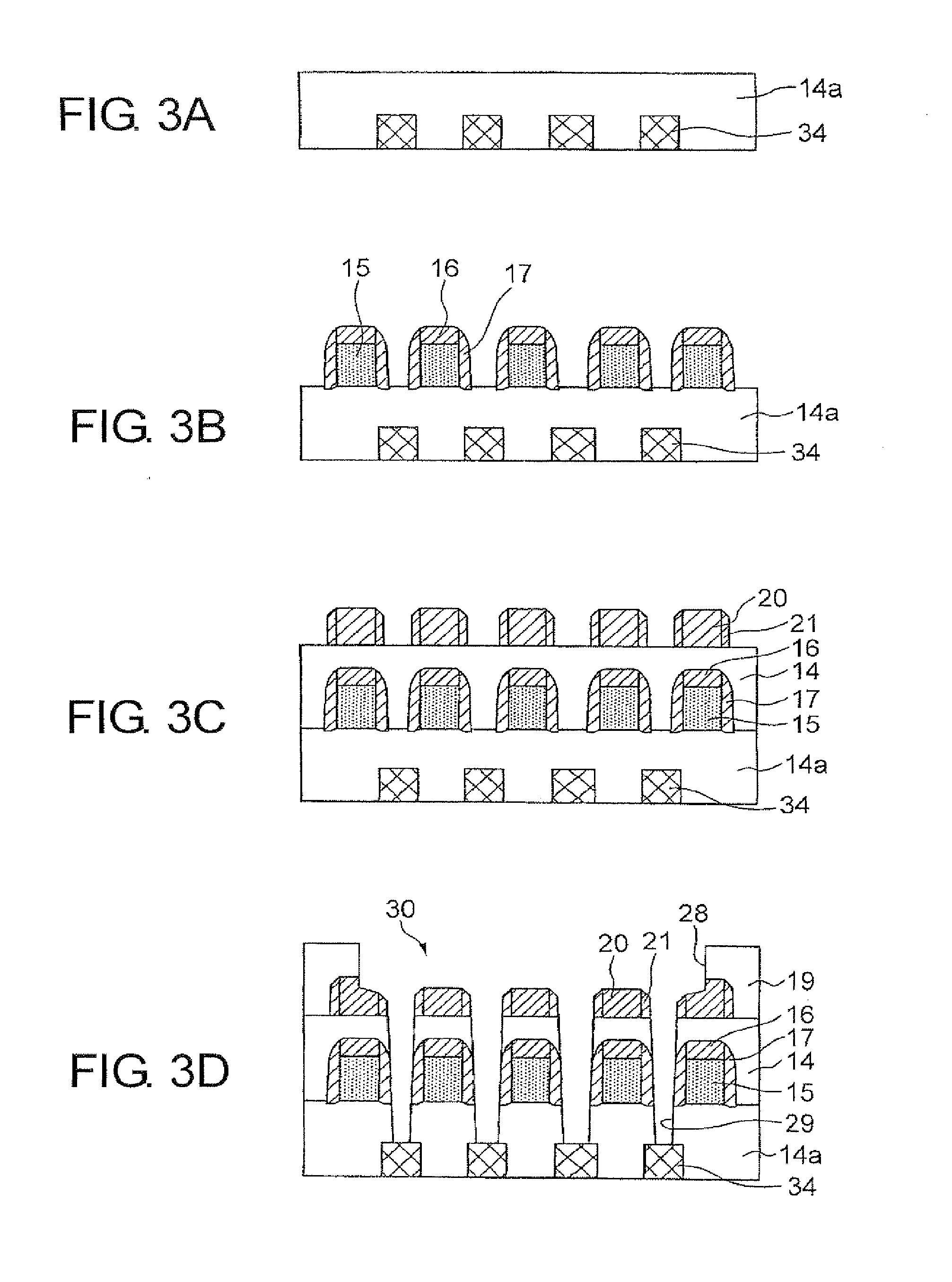

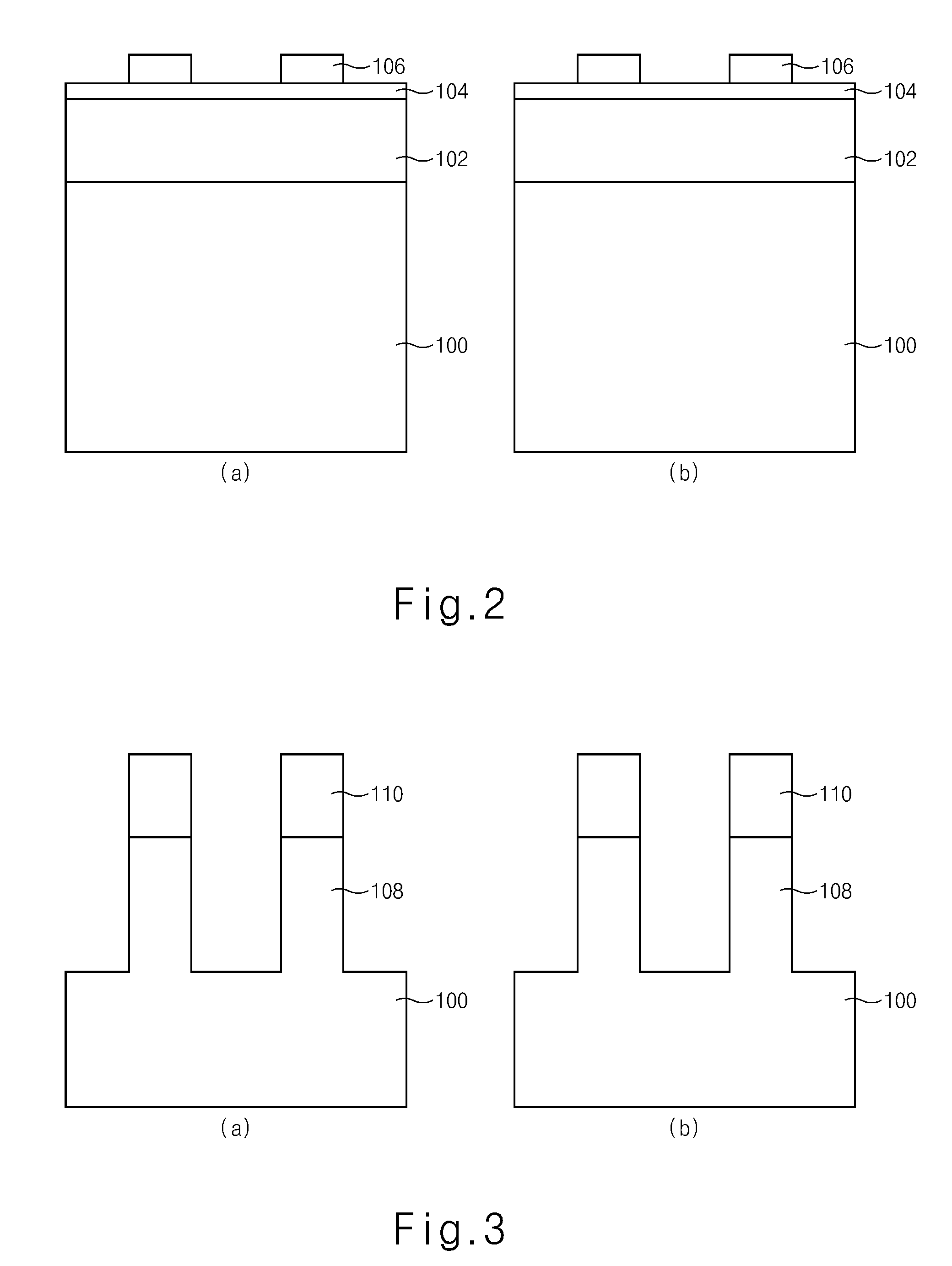

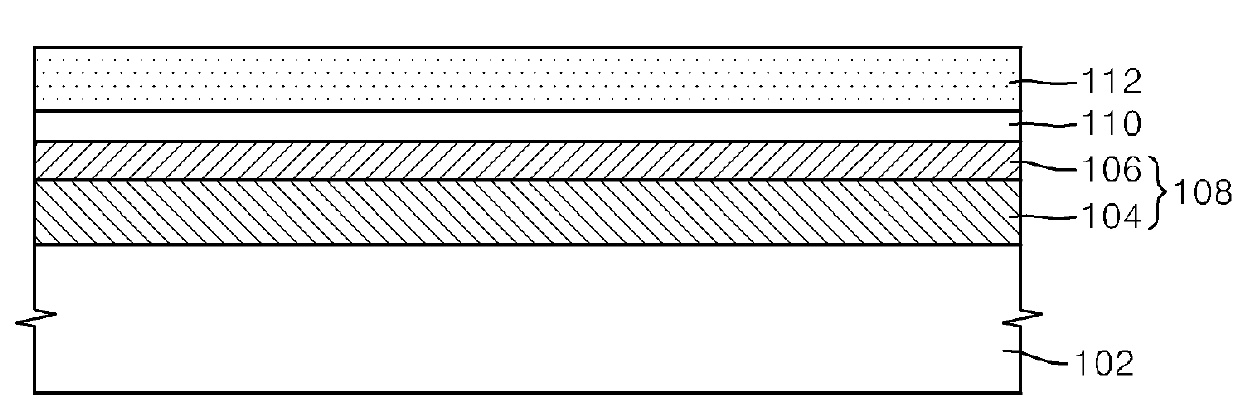

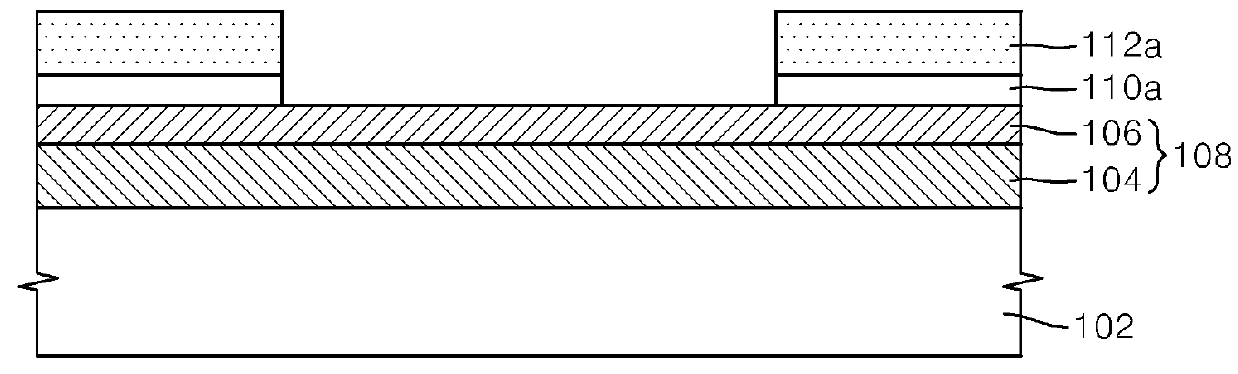

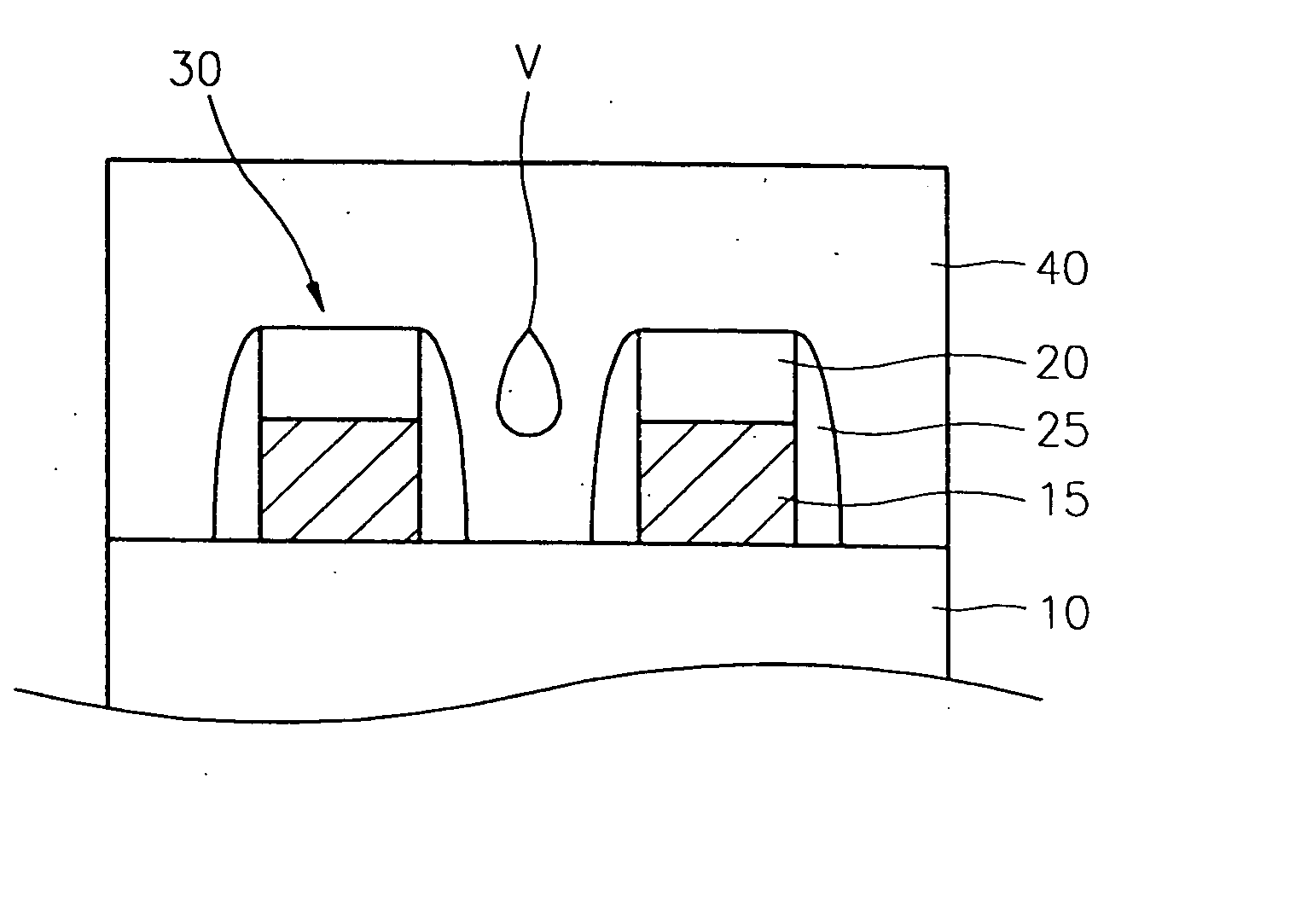

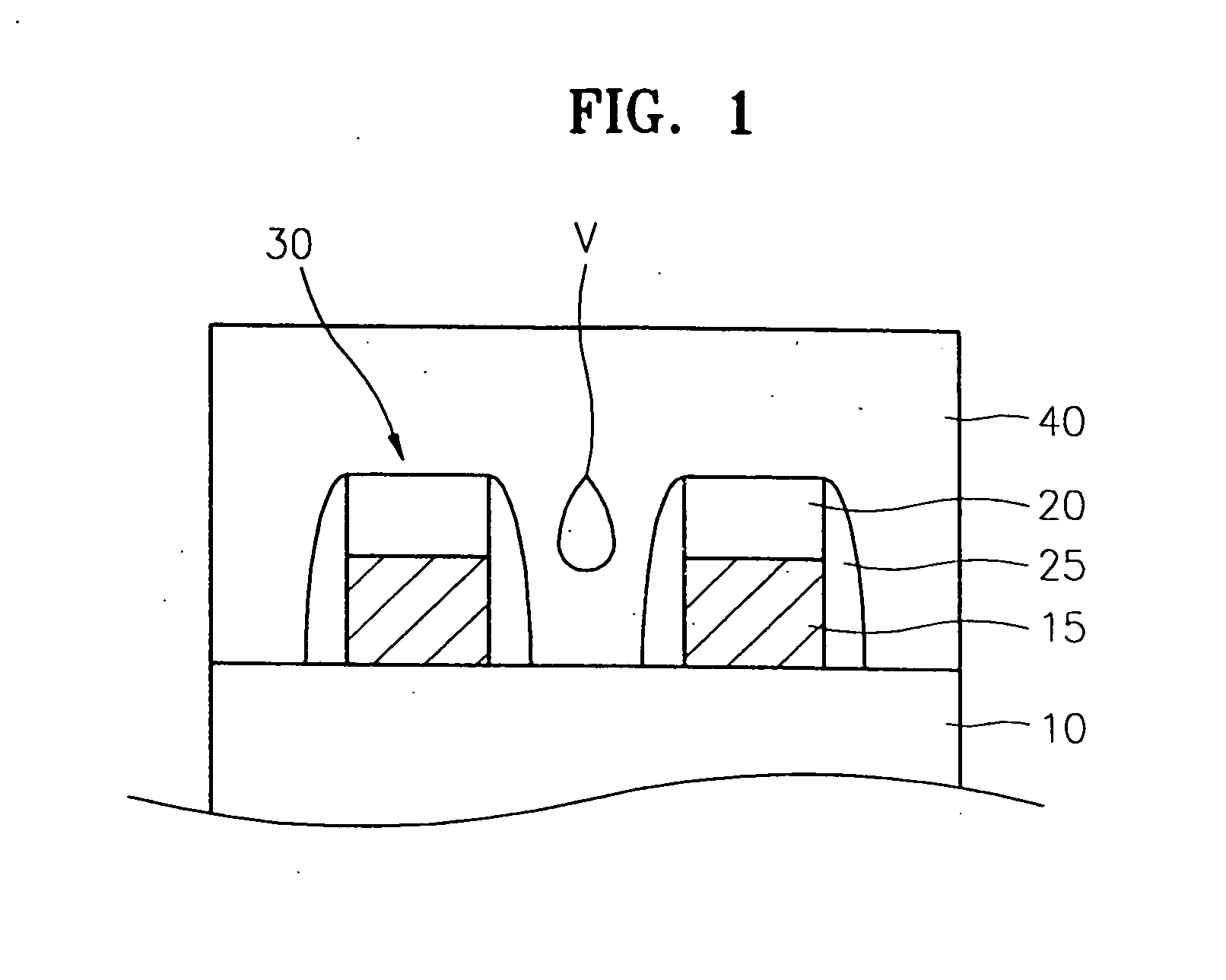

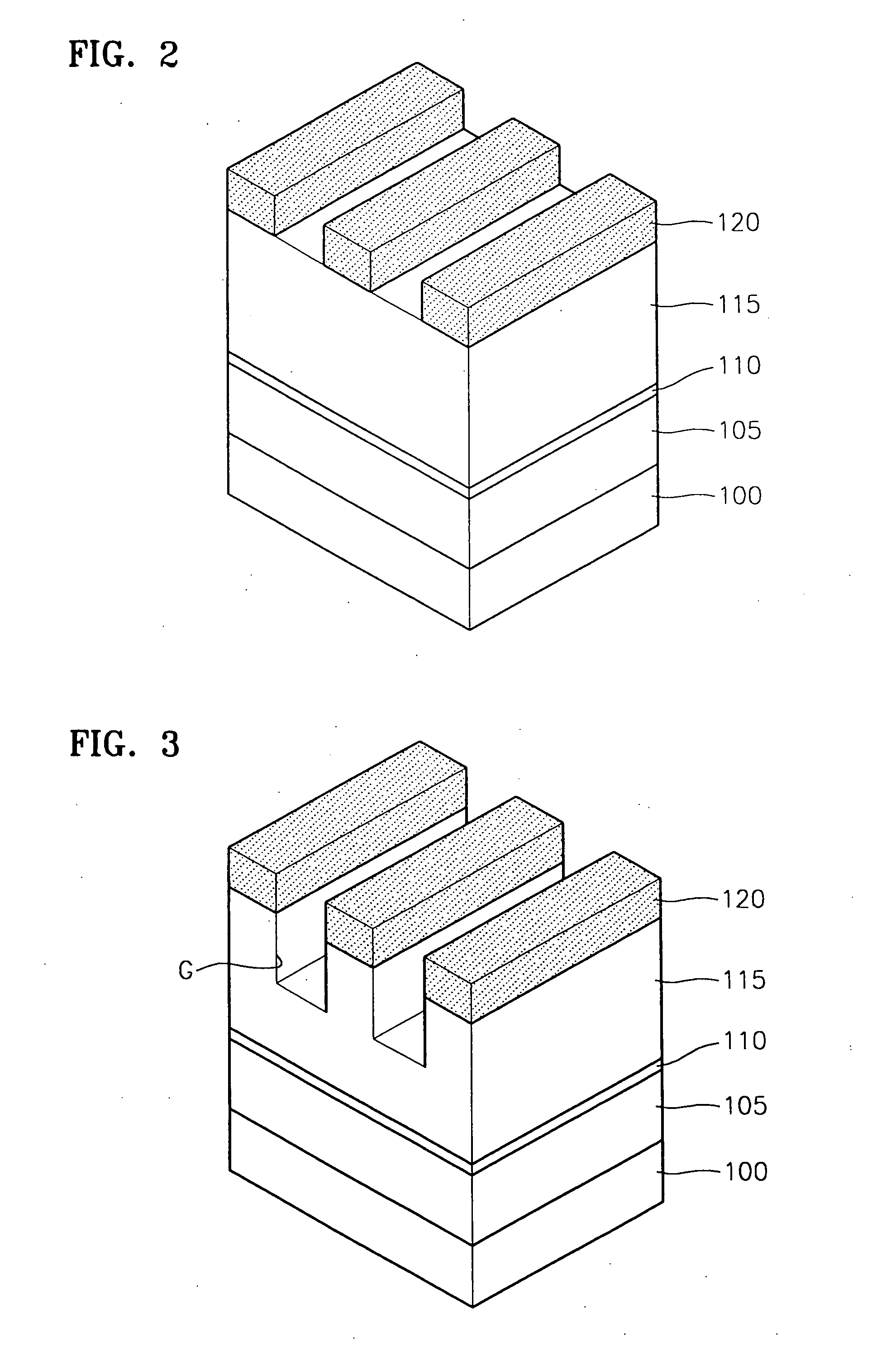

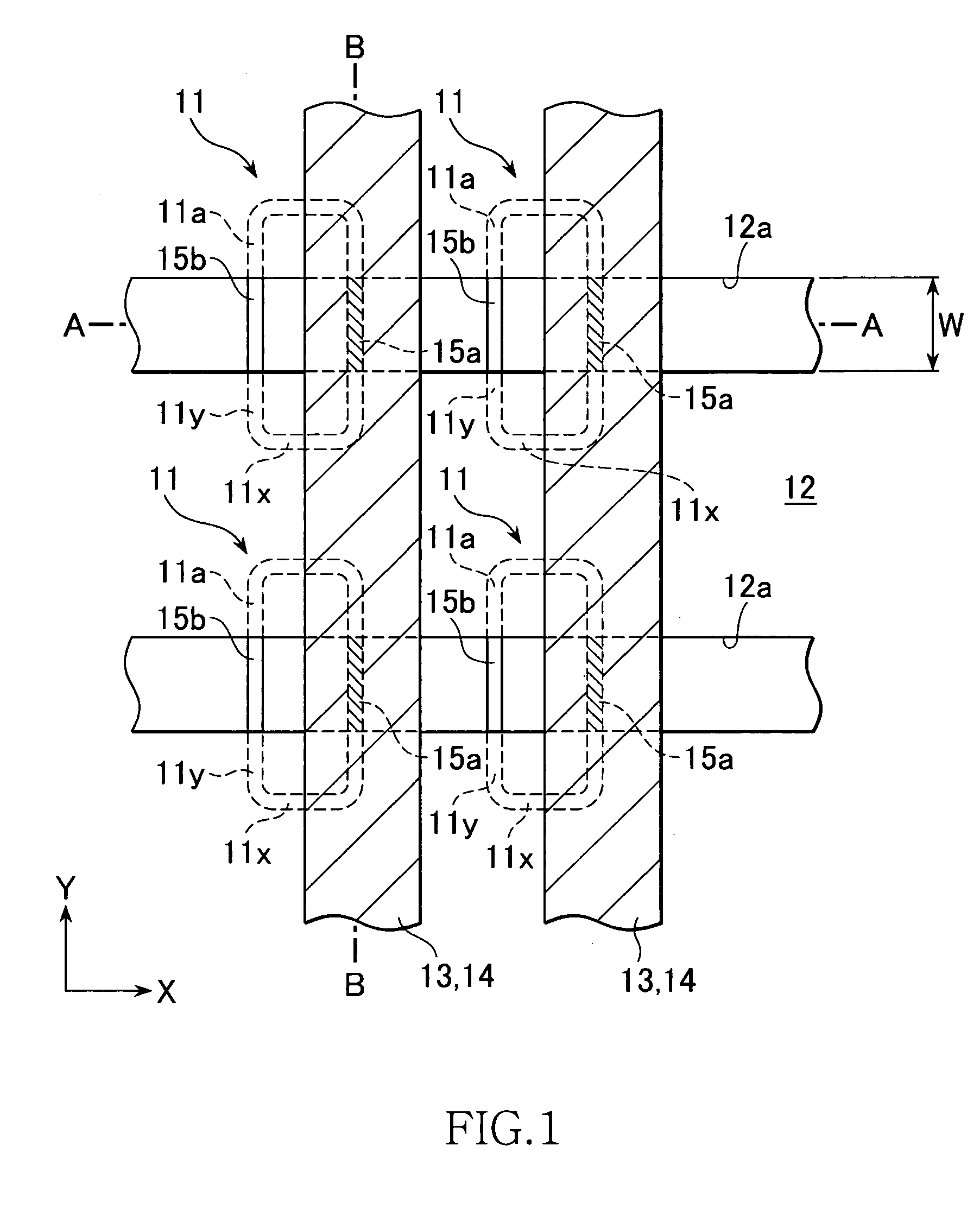

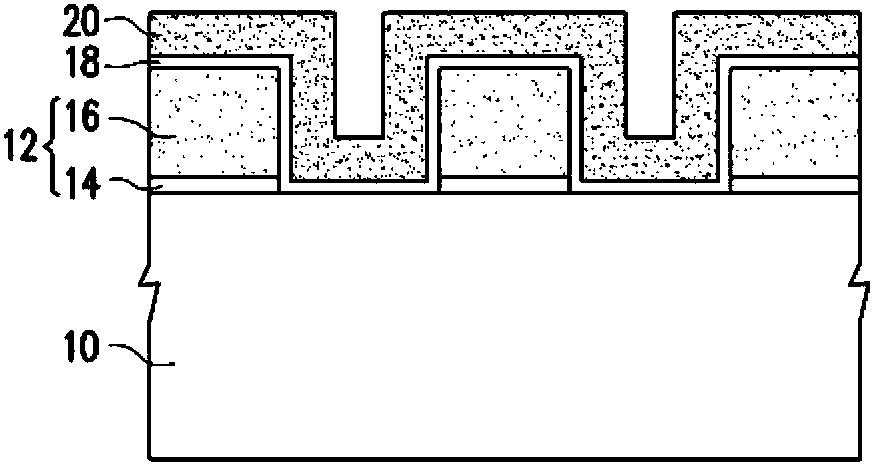

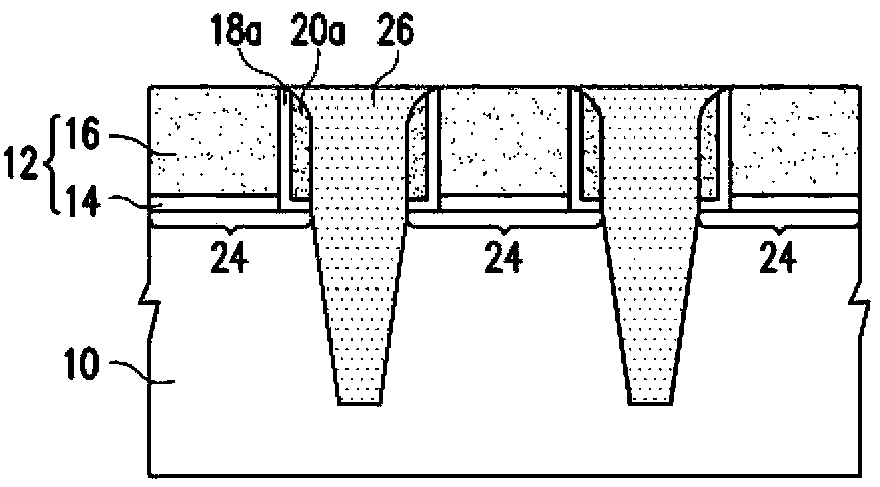

Method of manufacturing a semiconductor device

ActiveUS20050164455A1Prevent be breakSufficient process marginTransistorSolid-state devicesPolycrystalline siliconSemiconductor

In a method of manufacturing a semiconductor device including independent gate patterns separated from each other, an active region is defined by forming a field region on a substrate. A gate oxide layer and a polysilicon layer are formed on the substrate. A preliminary gate pattern is formed by partially removing the polysilicon layer along a first direction by a first etching process. A spacer is formed along a side surface of the preliminary gate pattern. A number of separated gate patterns is formed by partially removing the preliminary gate pattern along a second direction crossing the first direction by a second etching process. The gate patterns overlap with the active regions and are separated from each other. Therefore, the overlap margin is increased, and the polysilicon layer is prevented from being over-etched when it is patterned to form the gate pattern.

Owner:SAMSUNG ELECTRONICS CO LTD

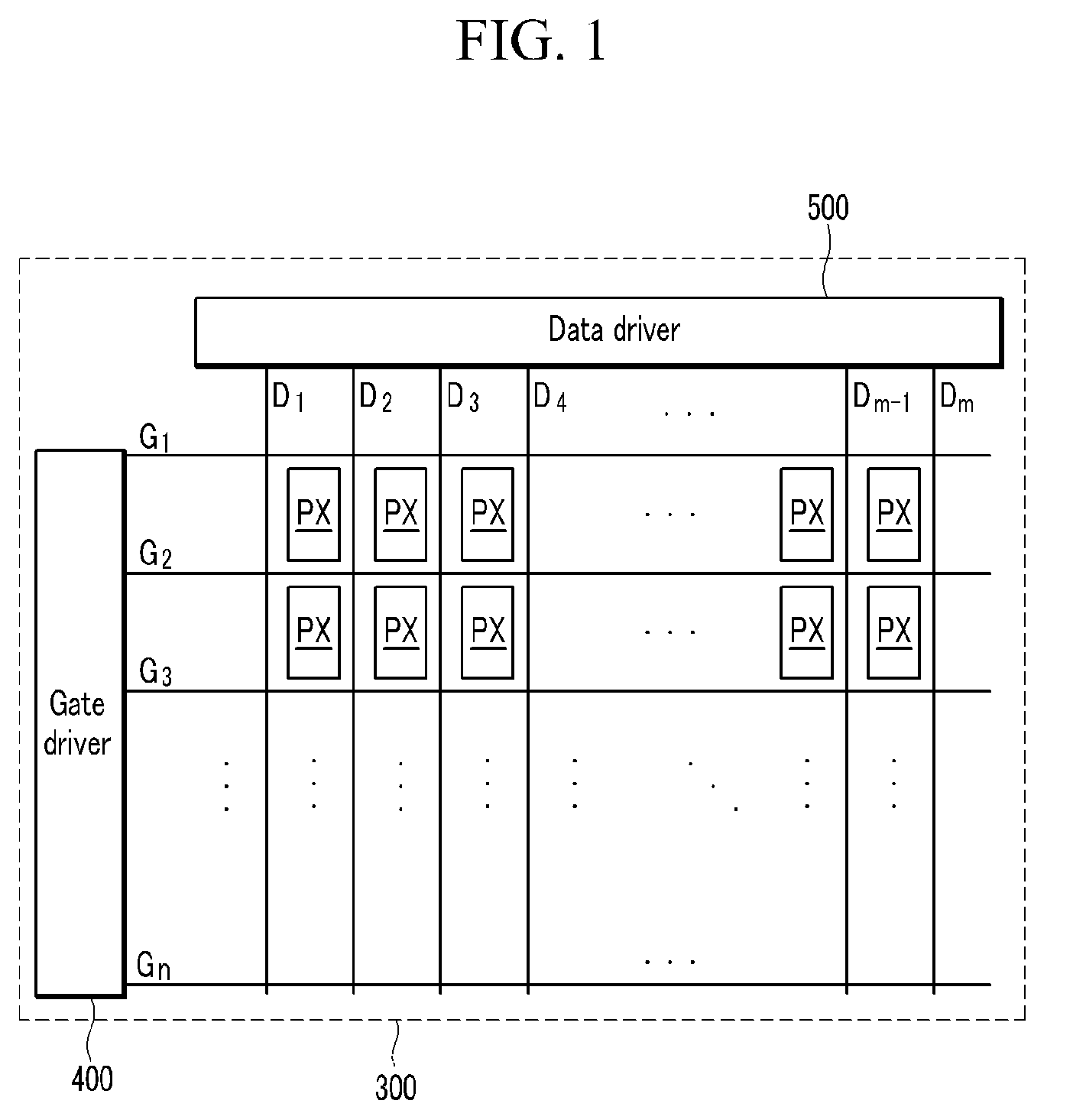

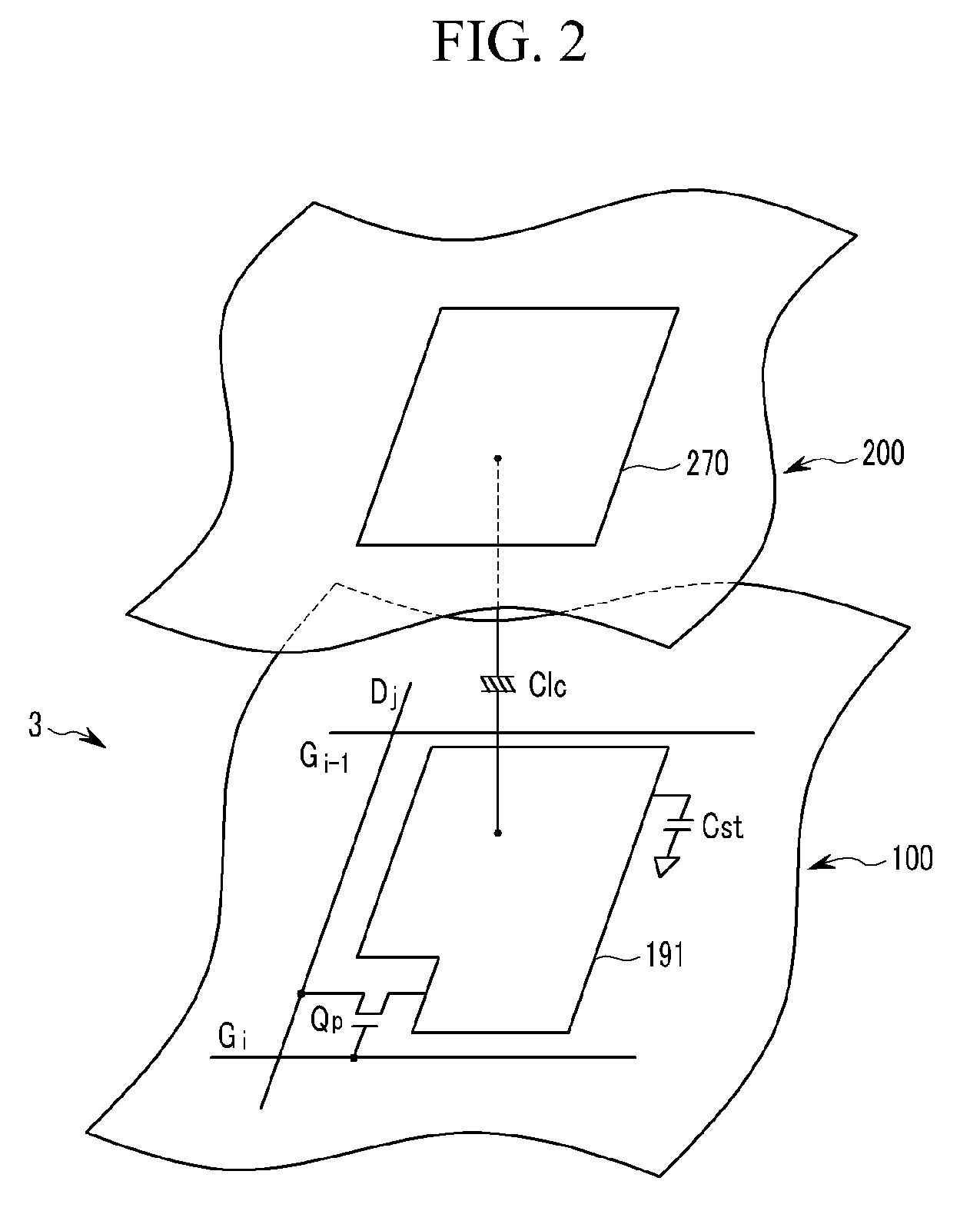

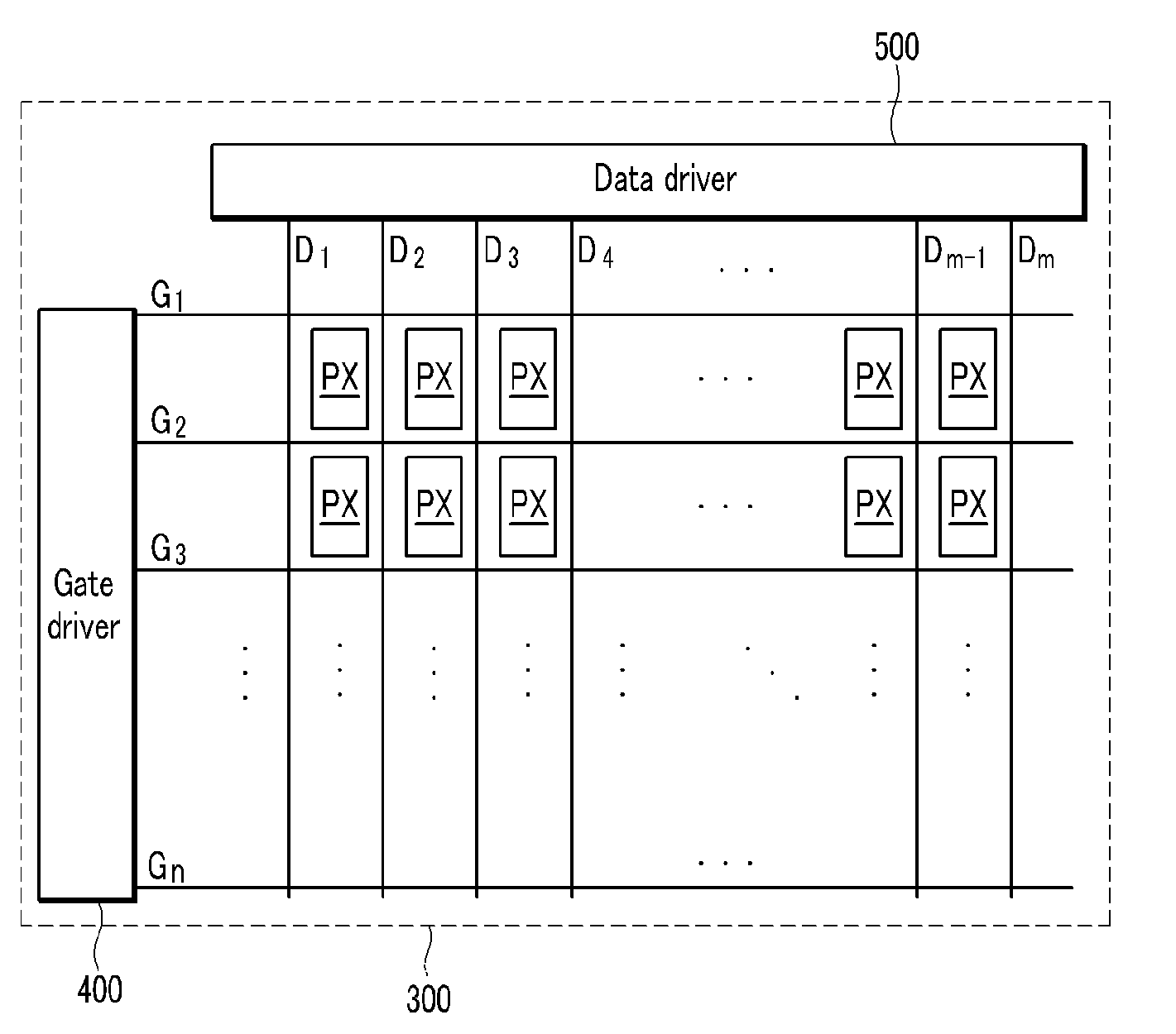

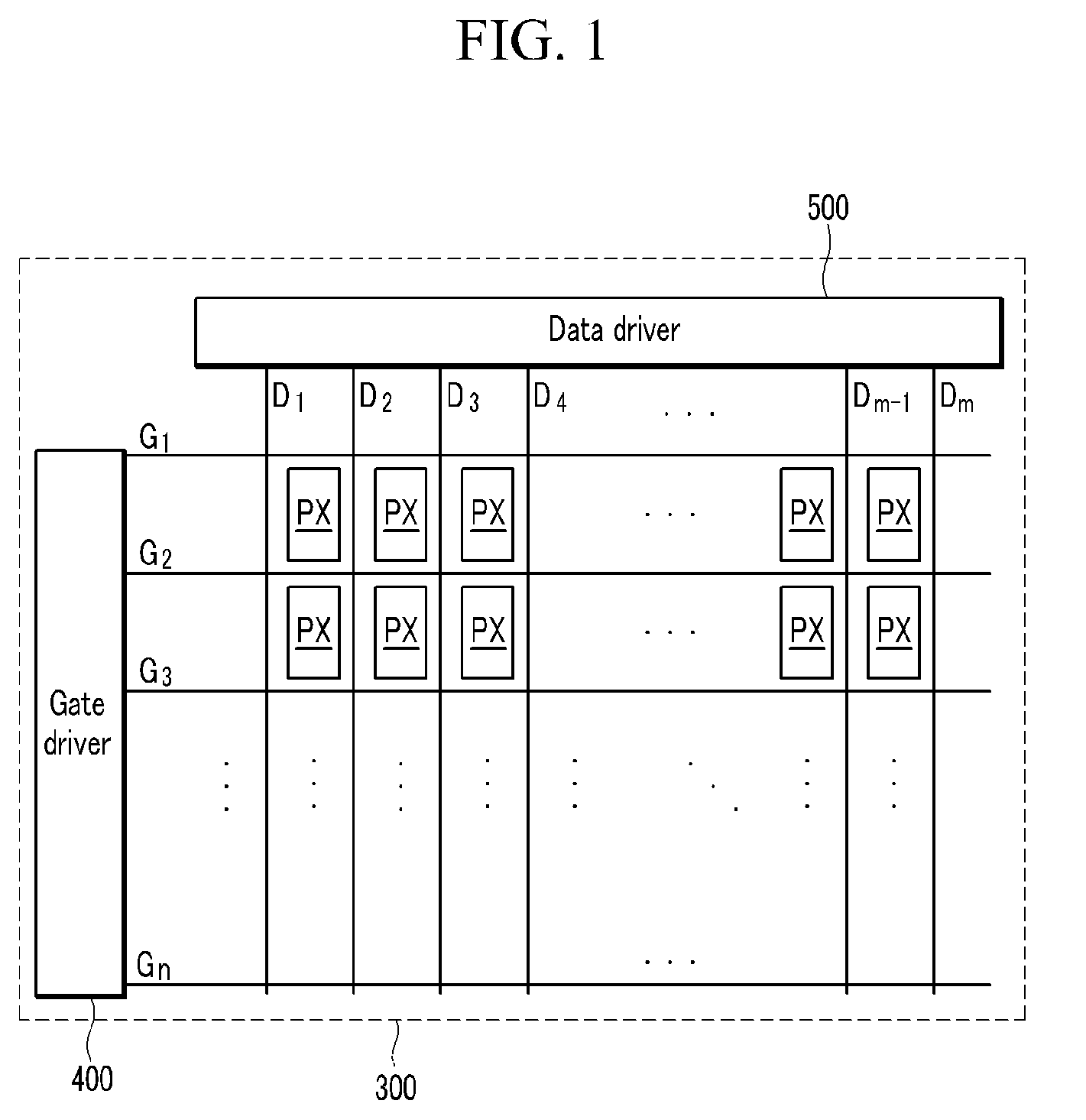

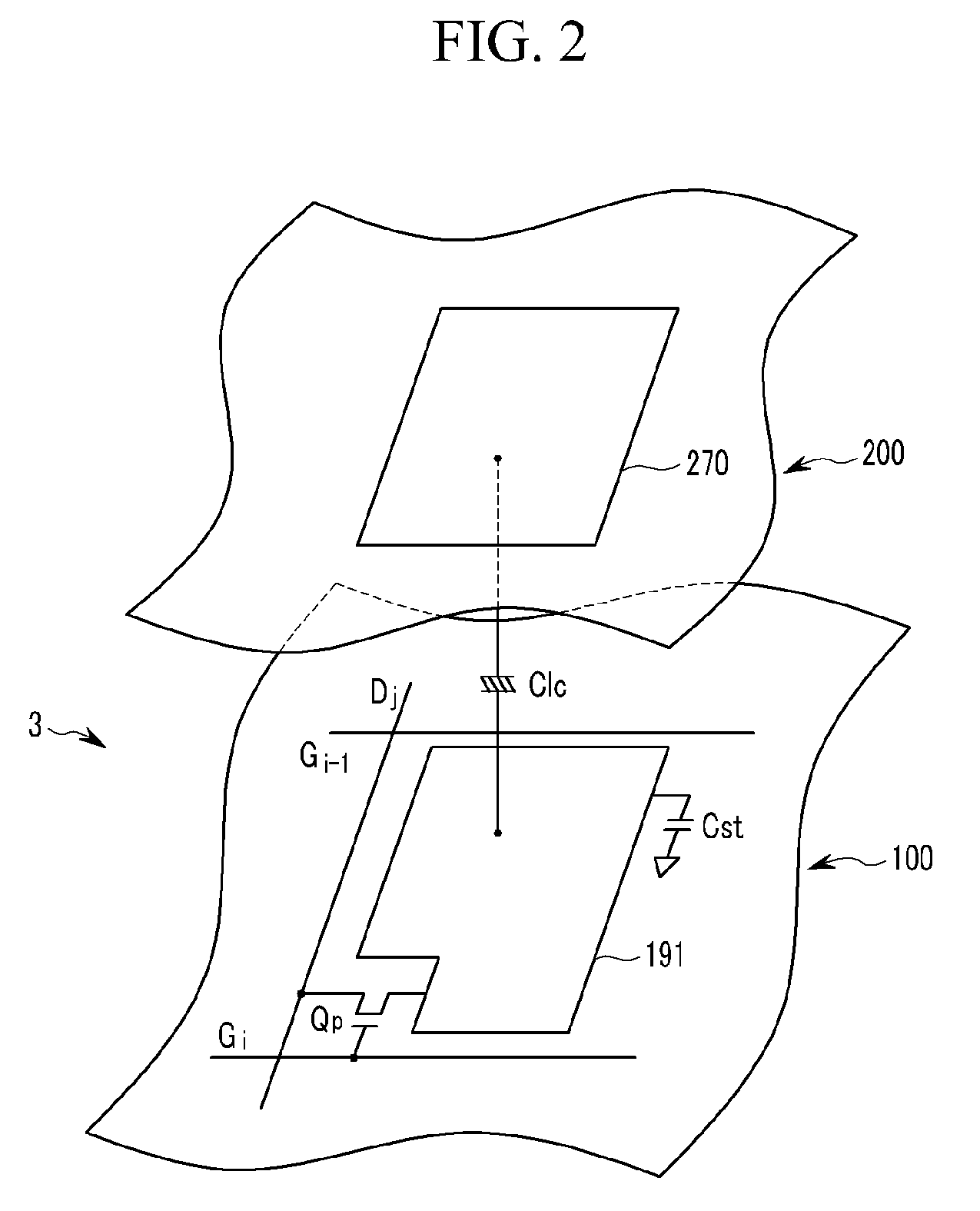

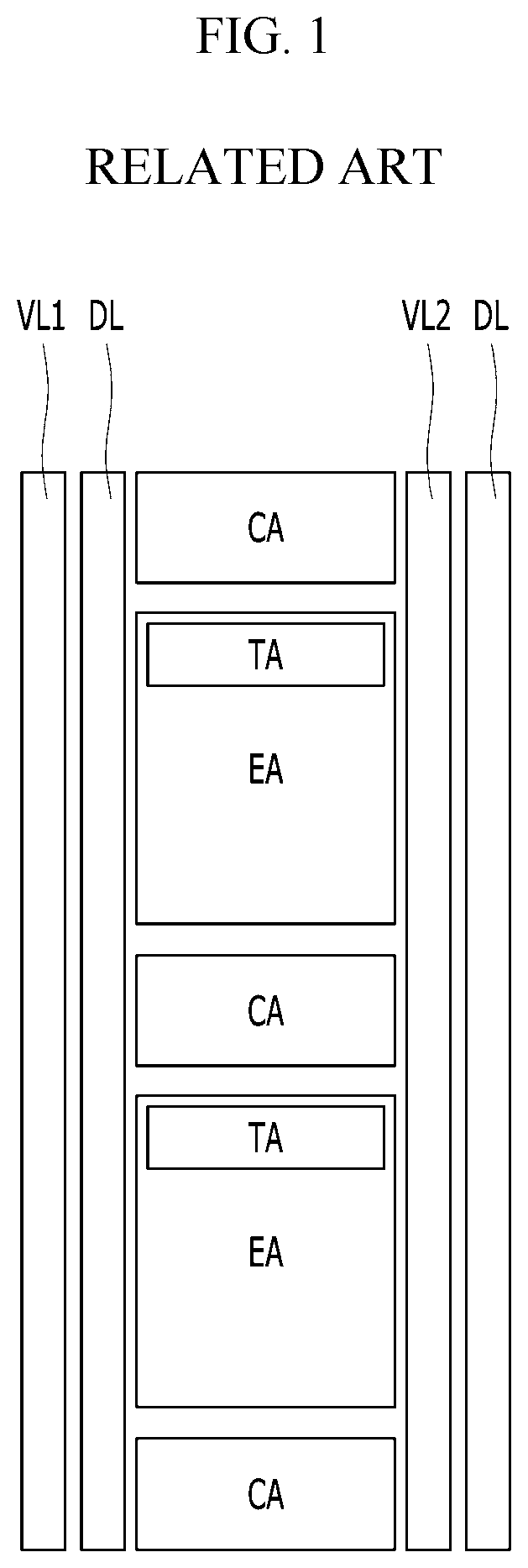

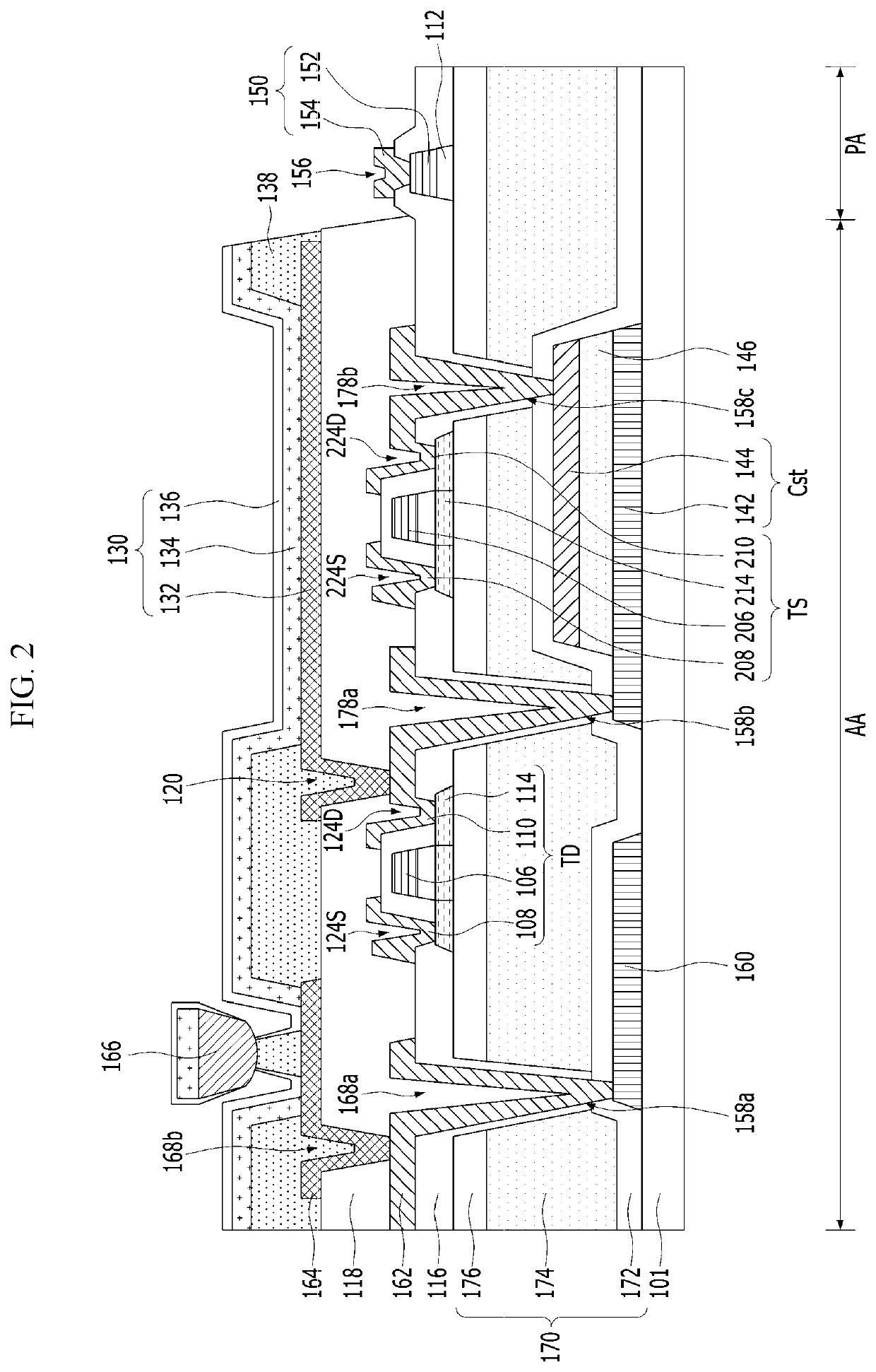

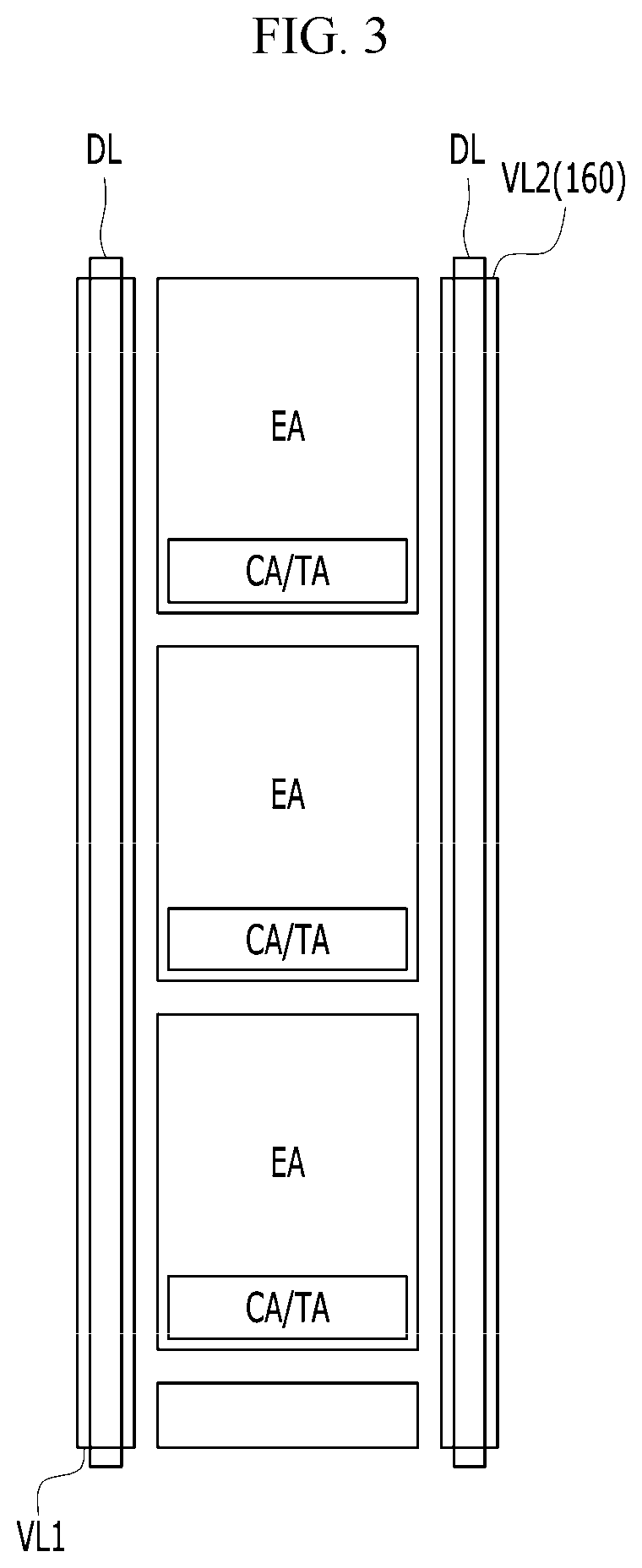

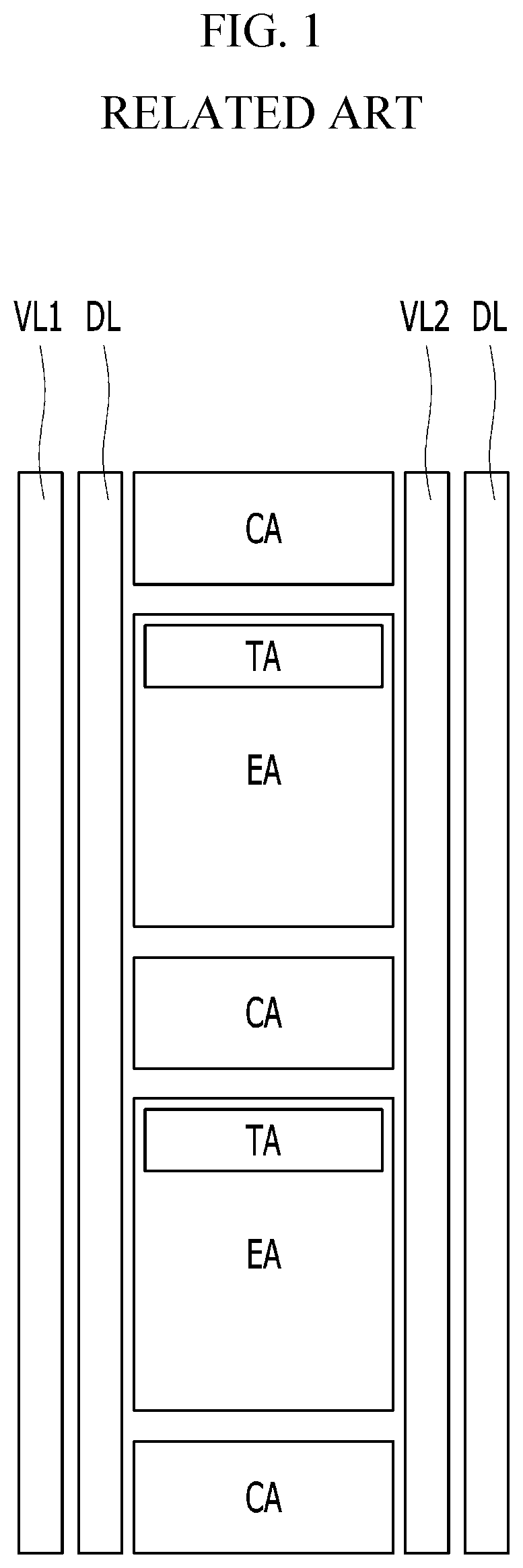

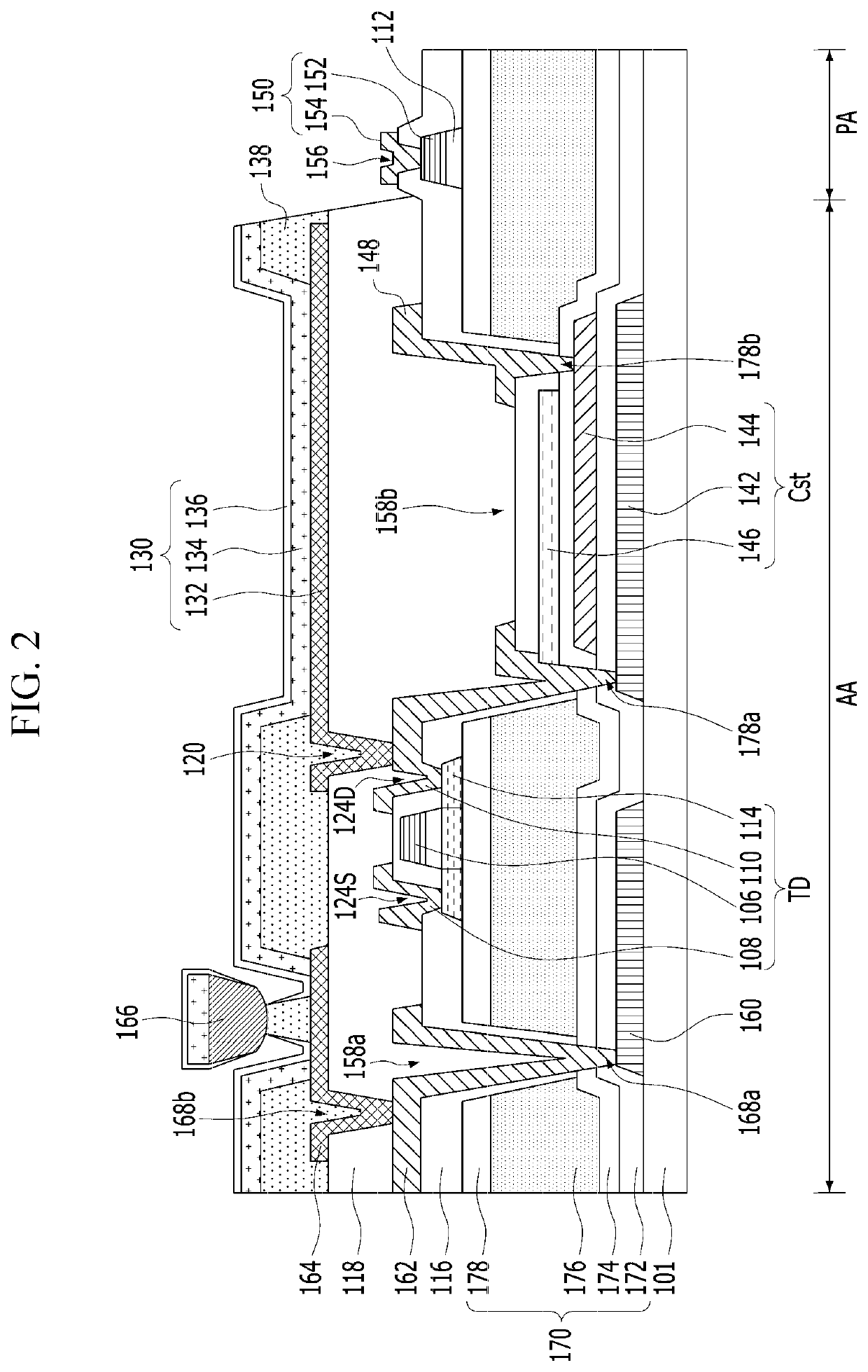

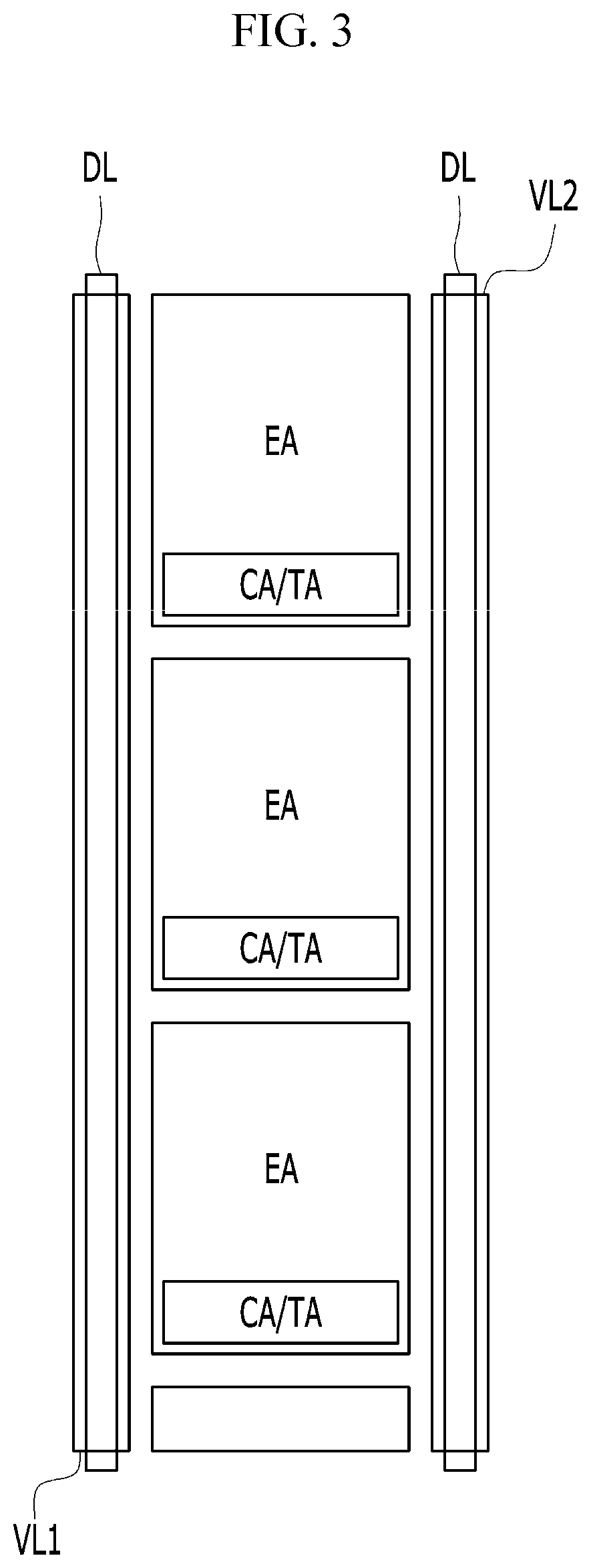

Display device

ActiveUS20180182836A1High resolutionSufficient process marginSolid-state devicesCapacitorsDisplay deviceComputer science

Disclosed is a display device with high resolution. The display device includes a substrate, a plurality of signal lines on the substrate, multiple buffer layers including at least one organic buffer layer and at least one inorganic buffer layer, and at least one transistor that overlaps one or more of the plurality of signal lines, with the multiple buffer layers interposed therebetween. Accordingly, it may be possible to ensure a sufficient process margin and consequently to realize a high resolution and improve production yield.

Owner:LG DISPLAY CO LTD

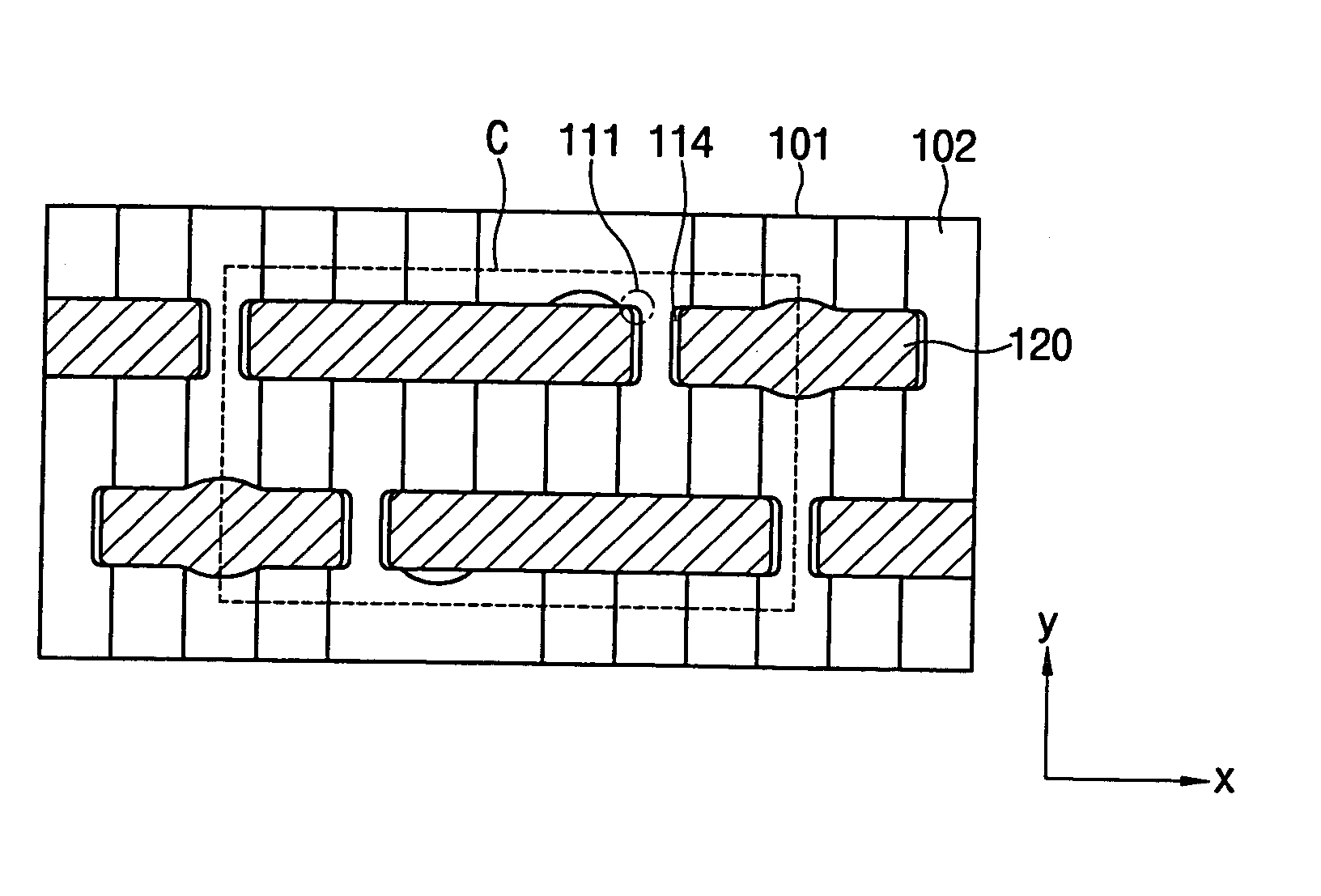

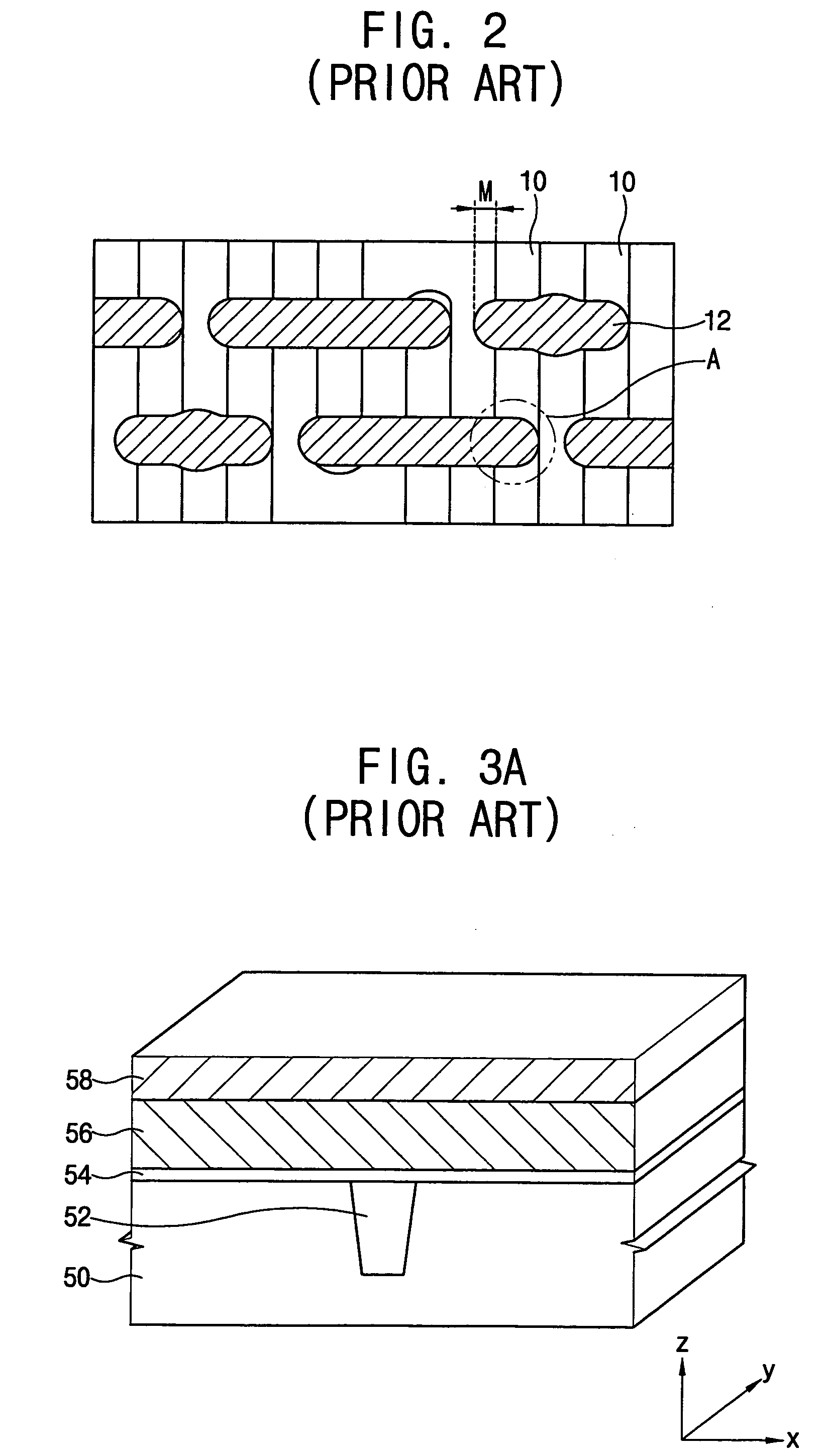

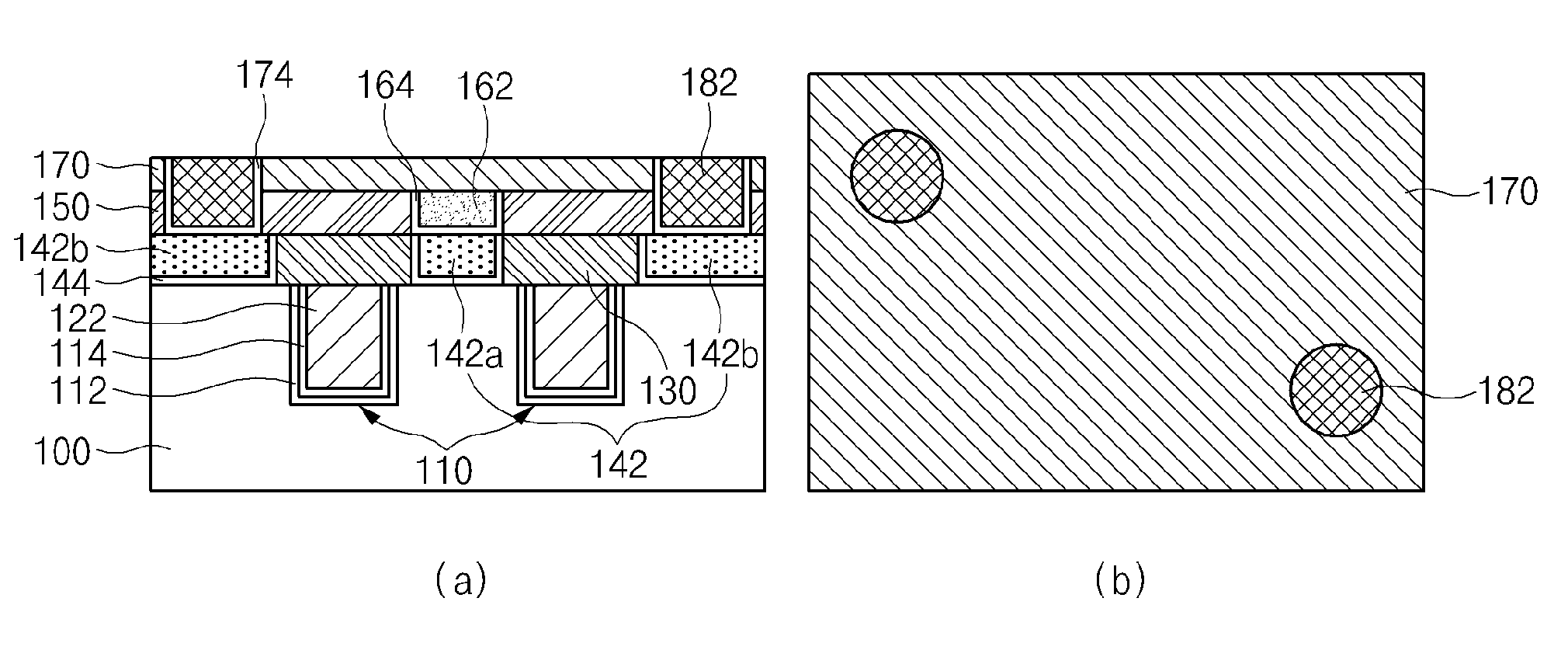

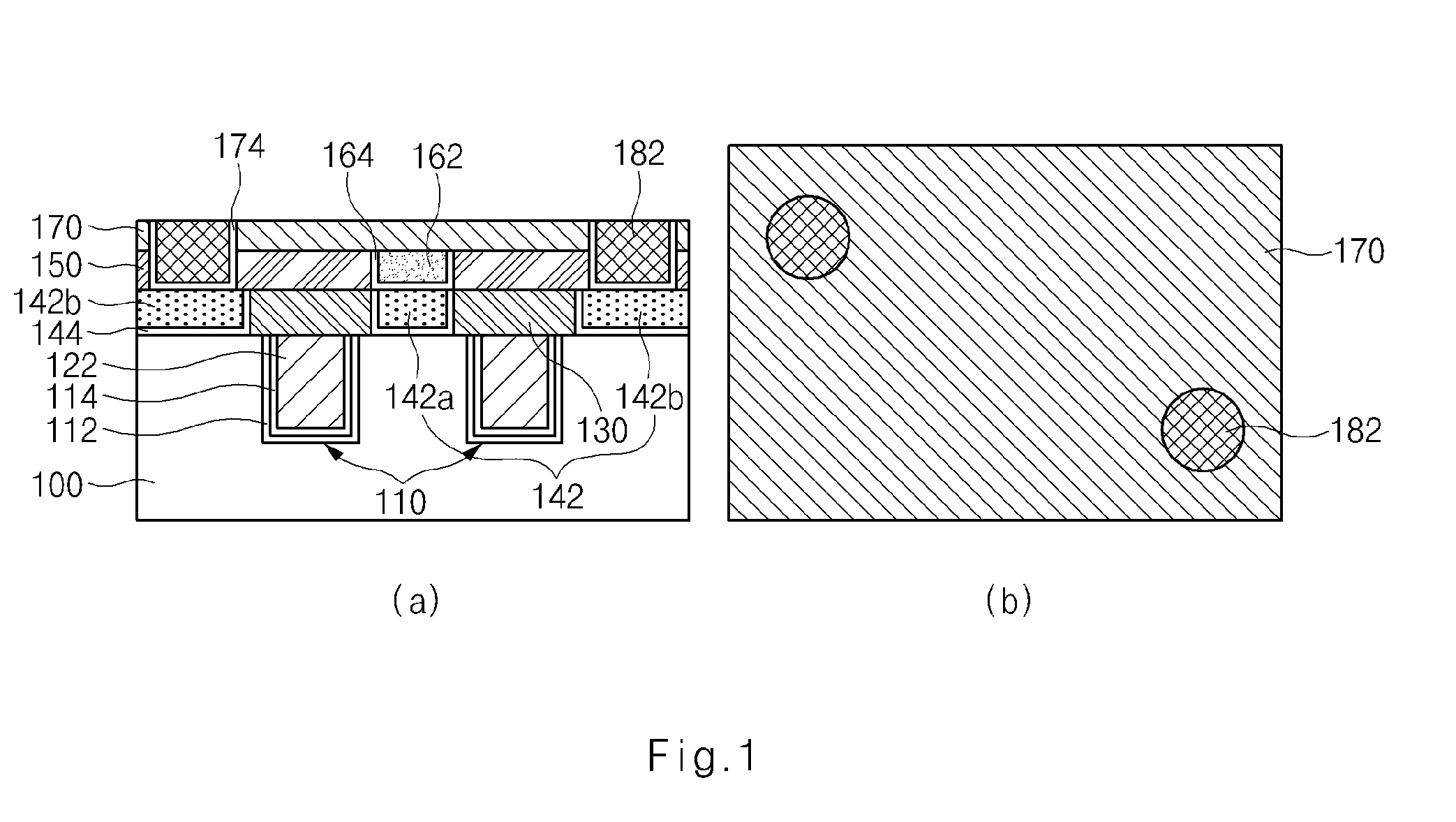

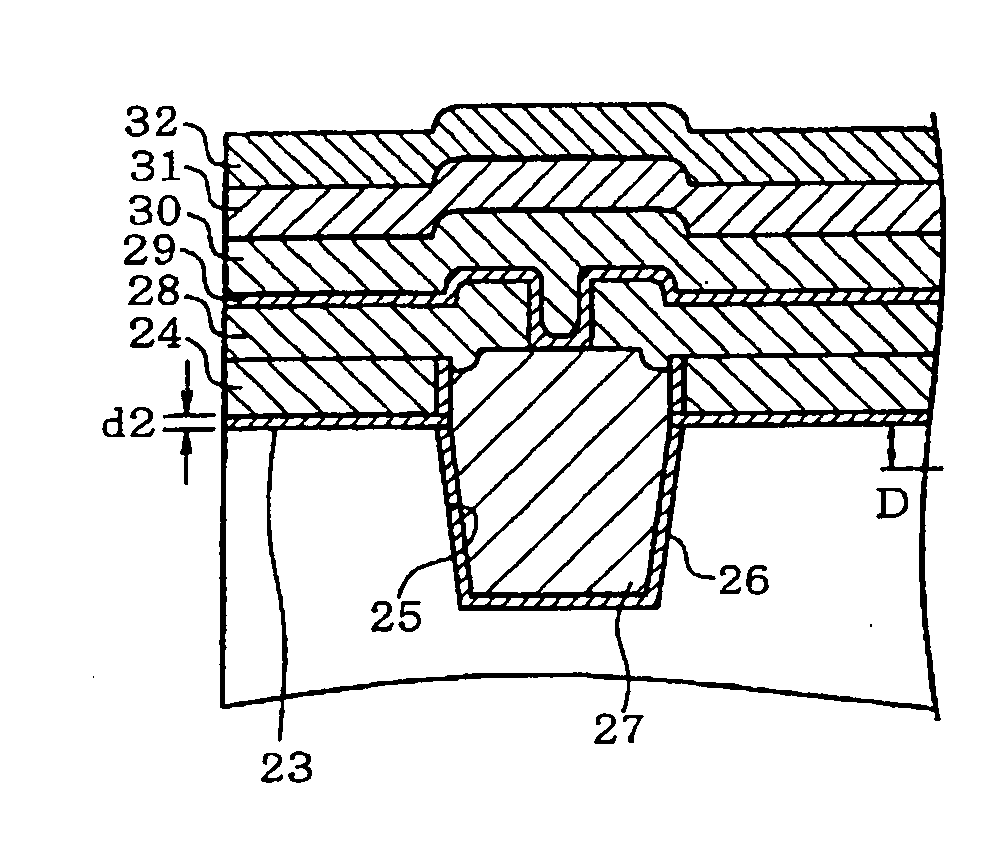

Semiconductor device including bit line formed using damascene technique and method of fabricating the same

ActiveUS7098135B2Well formedReduce designSolid-state devicesSemiconductor/solid-state device manufacturingBit lineDevice material

A semiconductor device including a bit line formed using a damascene technique and a method of fabricating the same. The method includes forming an insulating layer on a substrate, forming a groove by etching the insulating layer to a partial depth, and forming spacers on the inner walls of the groove. An opening is formed by etching the insulating layer disposed under the groove using the spacers as an etch mask. A conductive layer is formed to fill the opening. A capping layer is formed to fill the groove.

Owner:SAMSUNG ELECTRONICS CO LTD

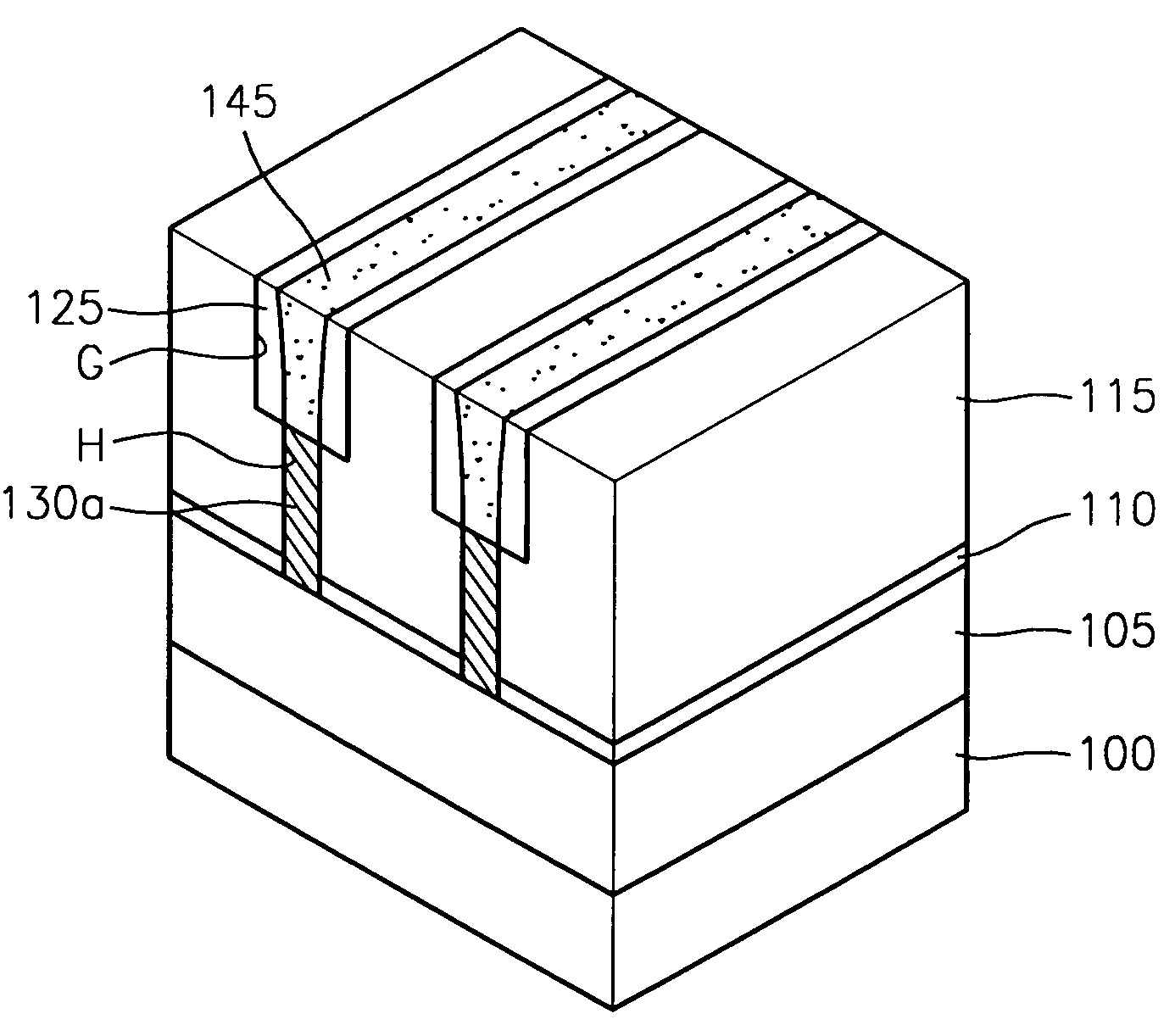

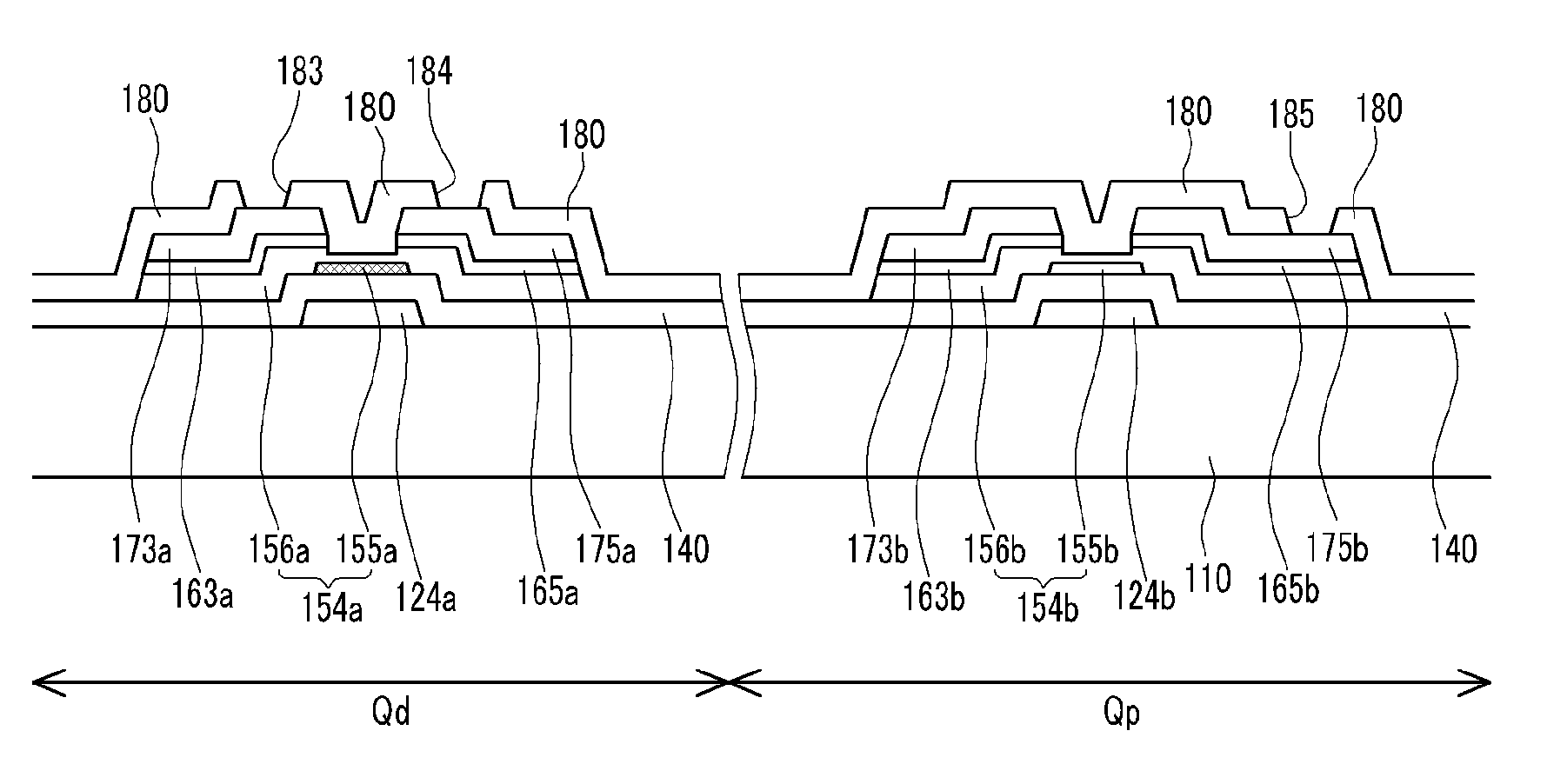

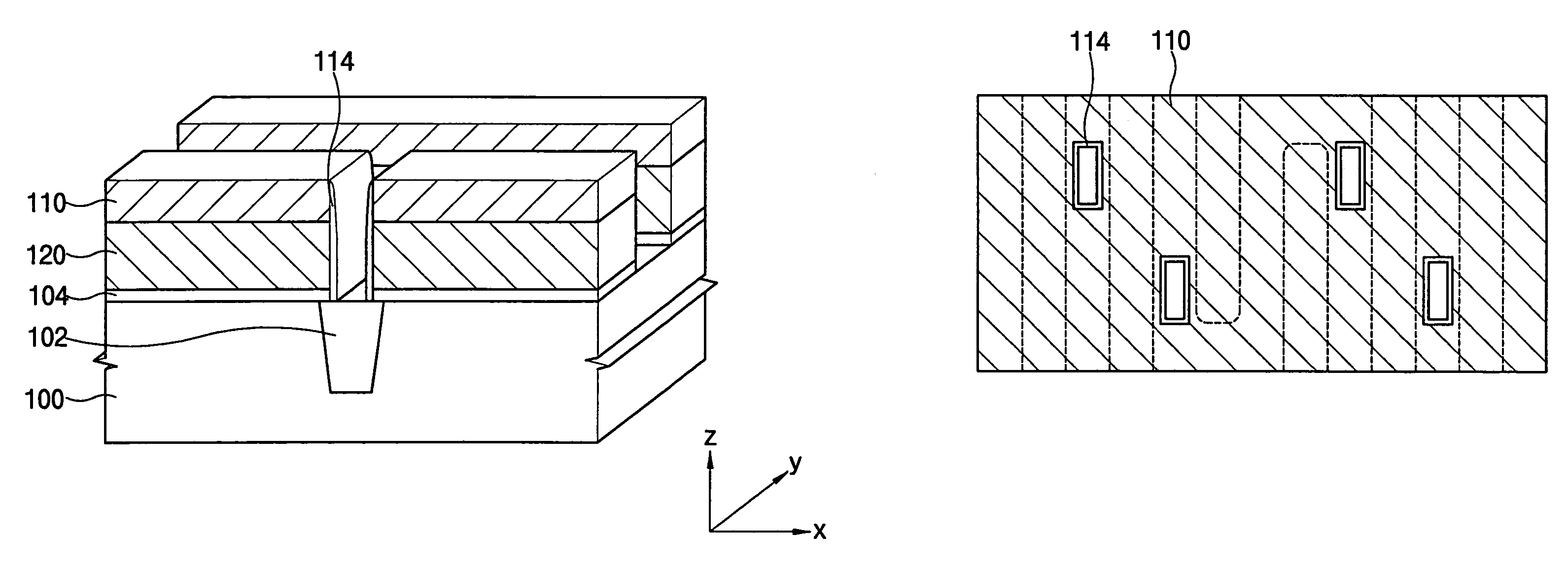

Thin film transistor, display device including the same, and method for manufacturing the same

ActiveUS8278661B2Effective energy densityHigh crystallinitySolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceAmorphous silicon

A display device and a manufacturing method thereof, include a first thin film transistor including a first control electrode, a first semiconductor disposed on the first control electrode, and a first input electrode and a first output electrode opposite to each other on the first semiconductor; and a second thin film transistor including a second control electrode, a second semiconductor disposed on the second control electrode, and a second input electrode and a second output electrode opposite to each other on the second semiconductor, wherein the first semiconductor includes a first lower semiconductor including polysilicon, and a first upper semiconductor disposed on the first lower semiconductor, the first upper semiconductor including amorphous silicon.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

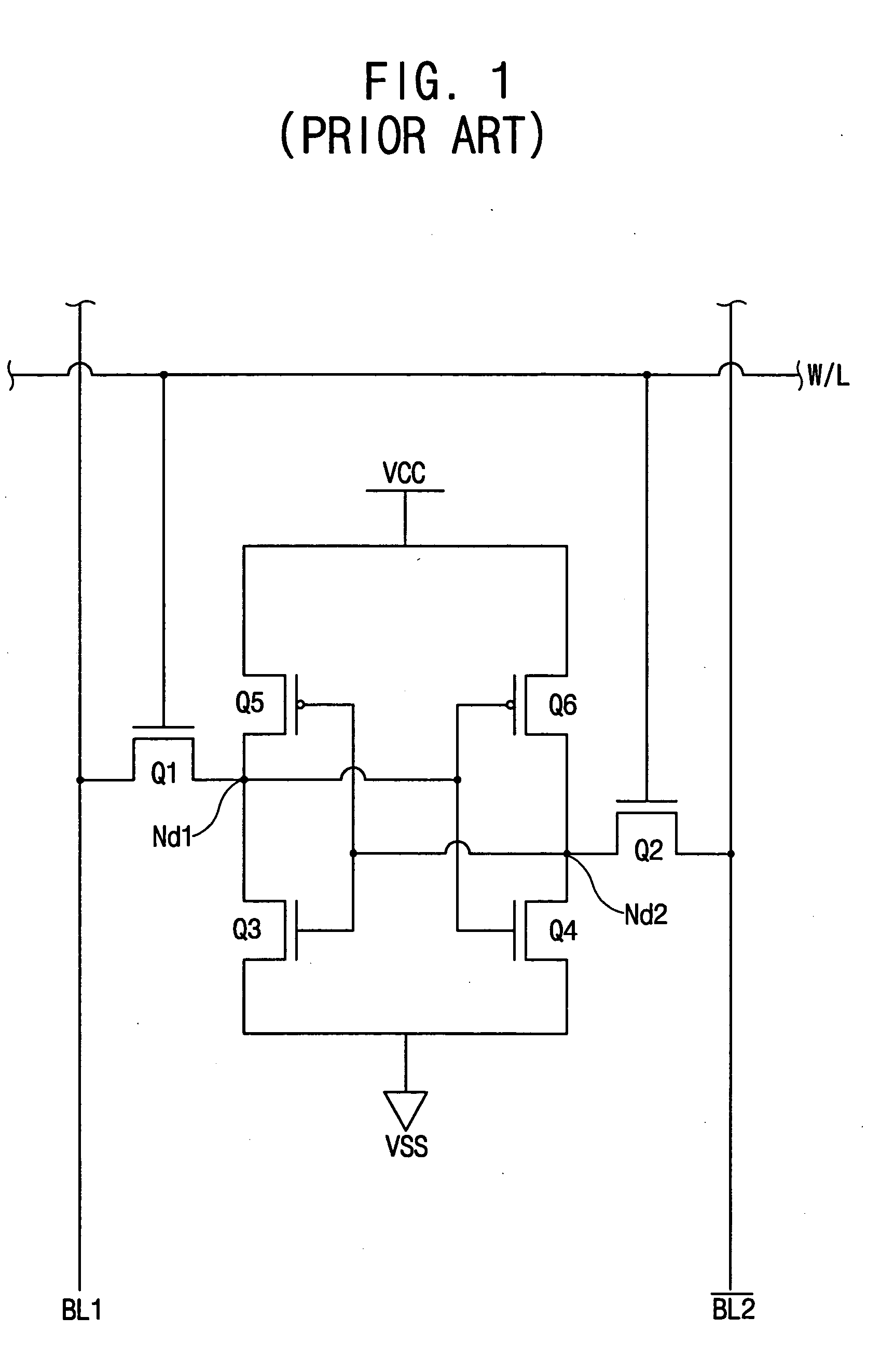

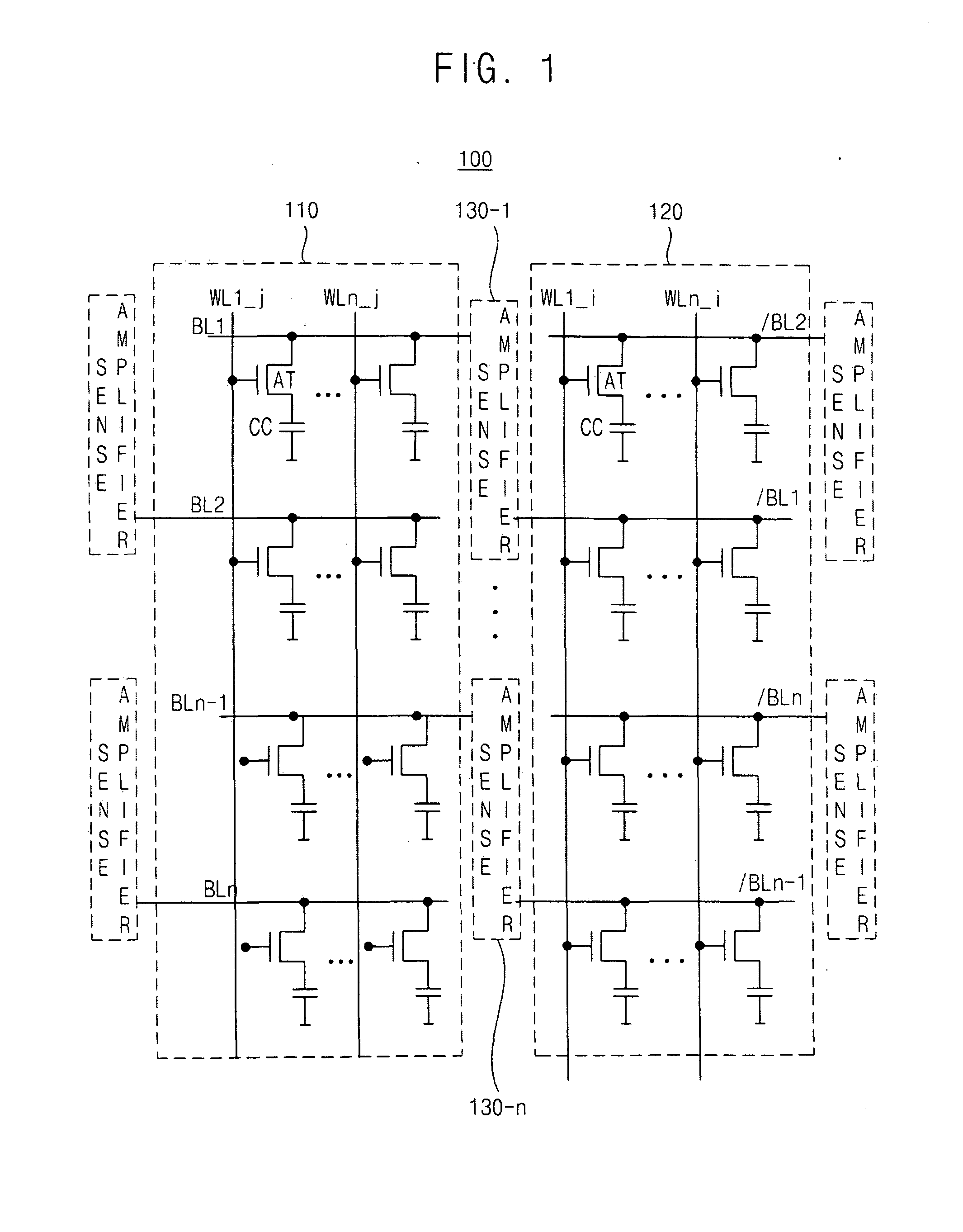

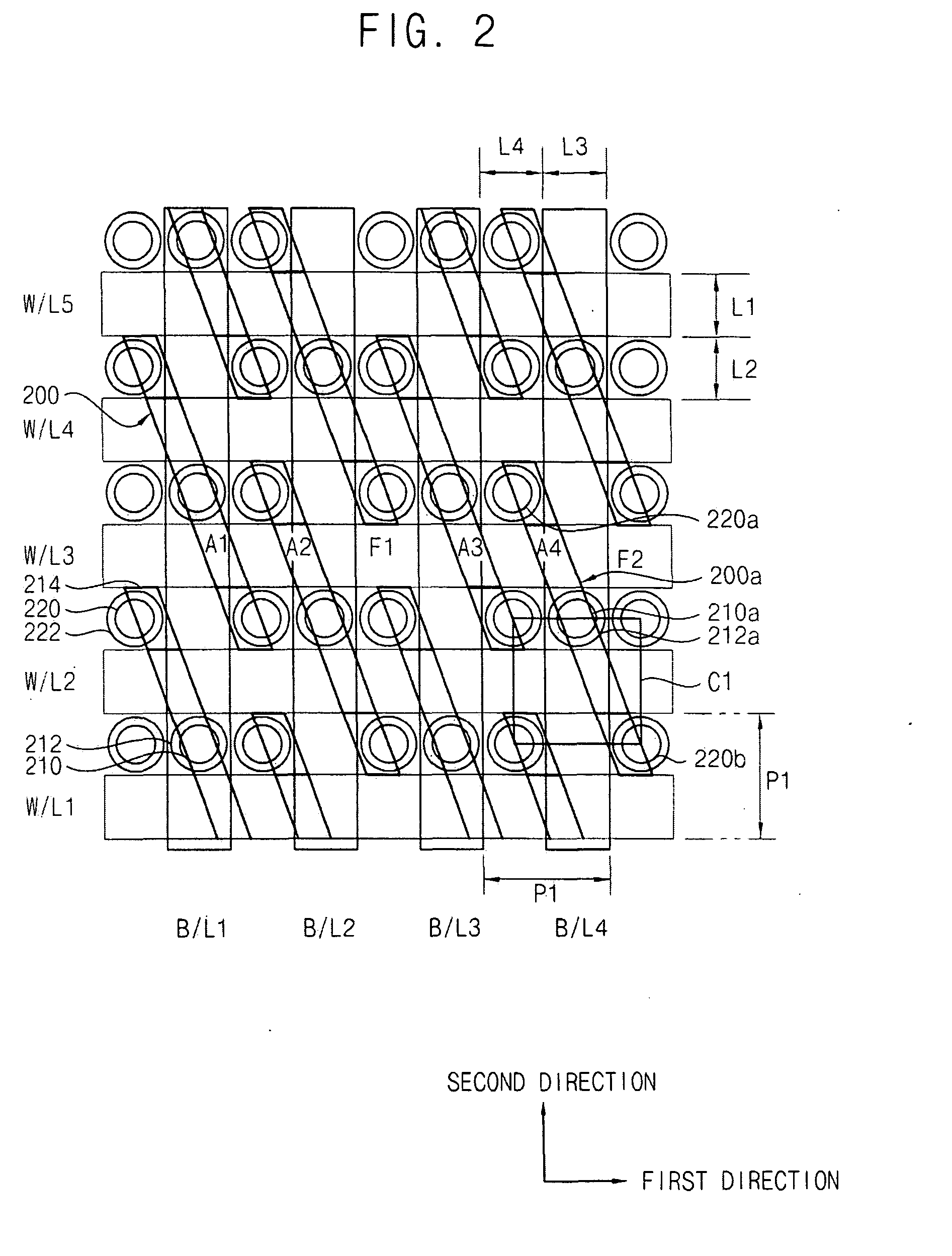

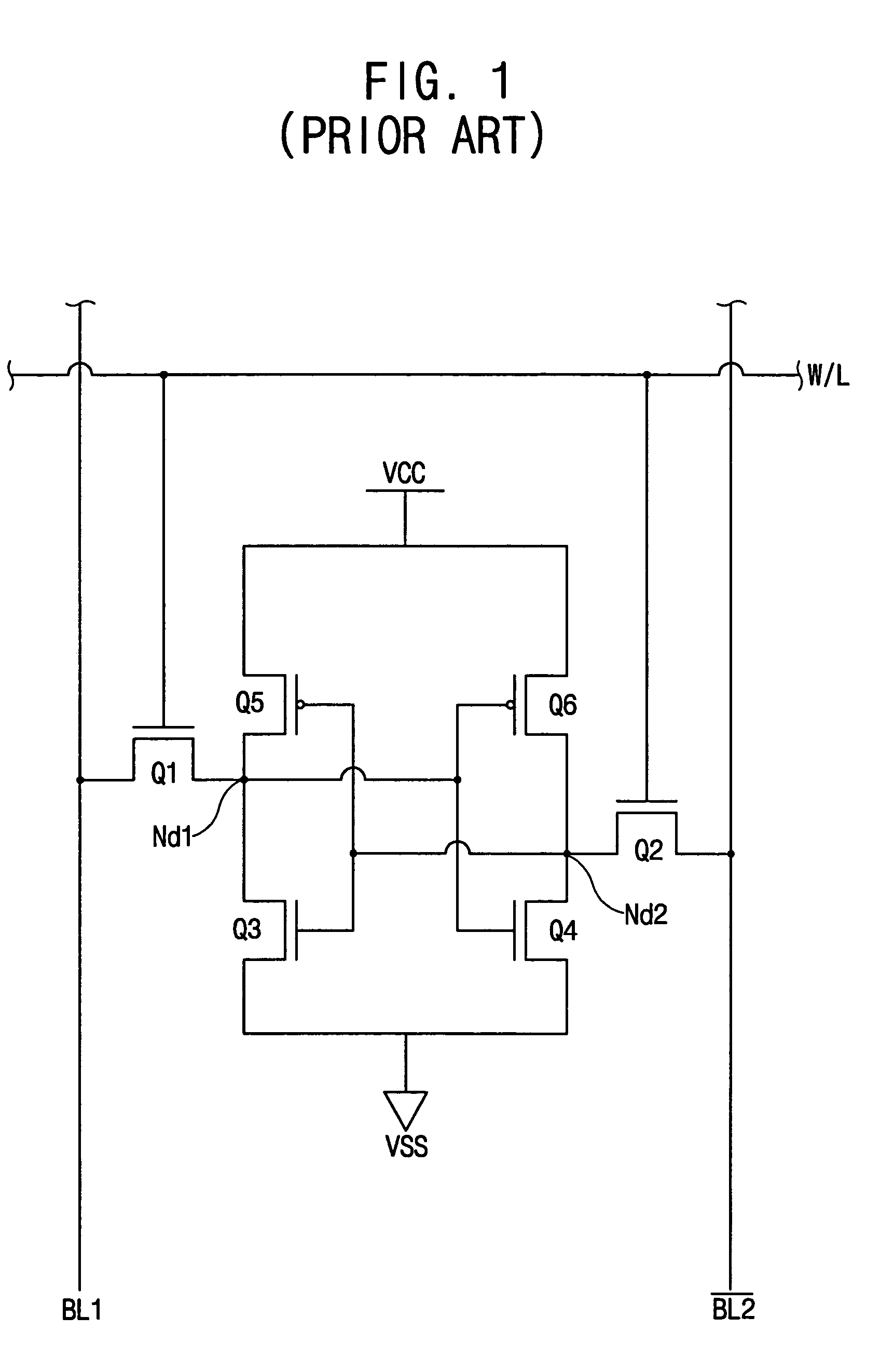

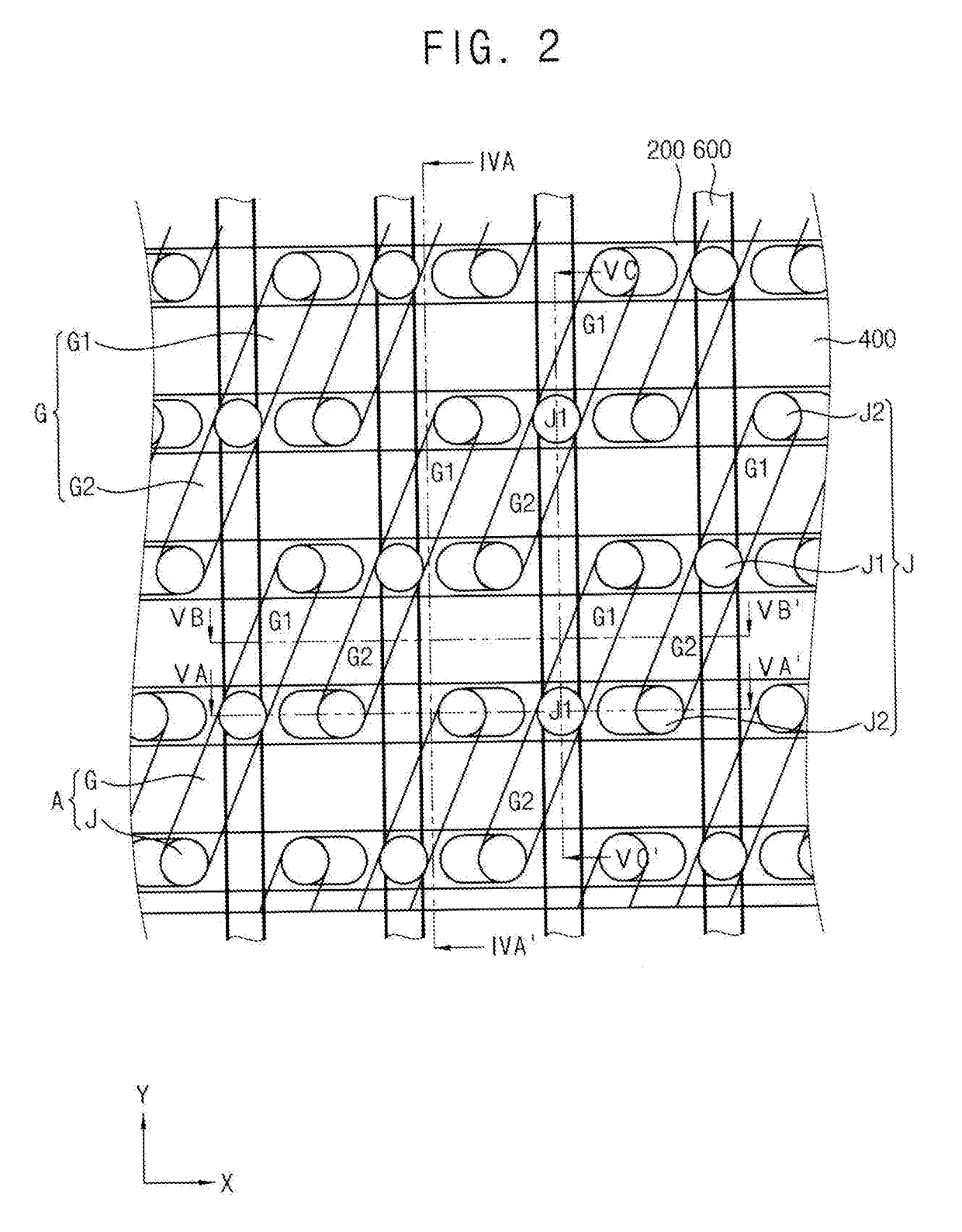

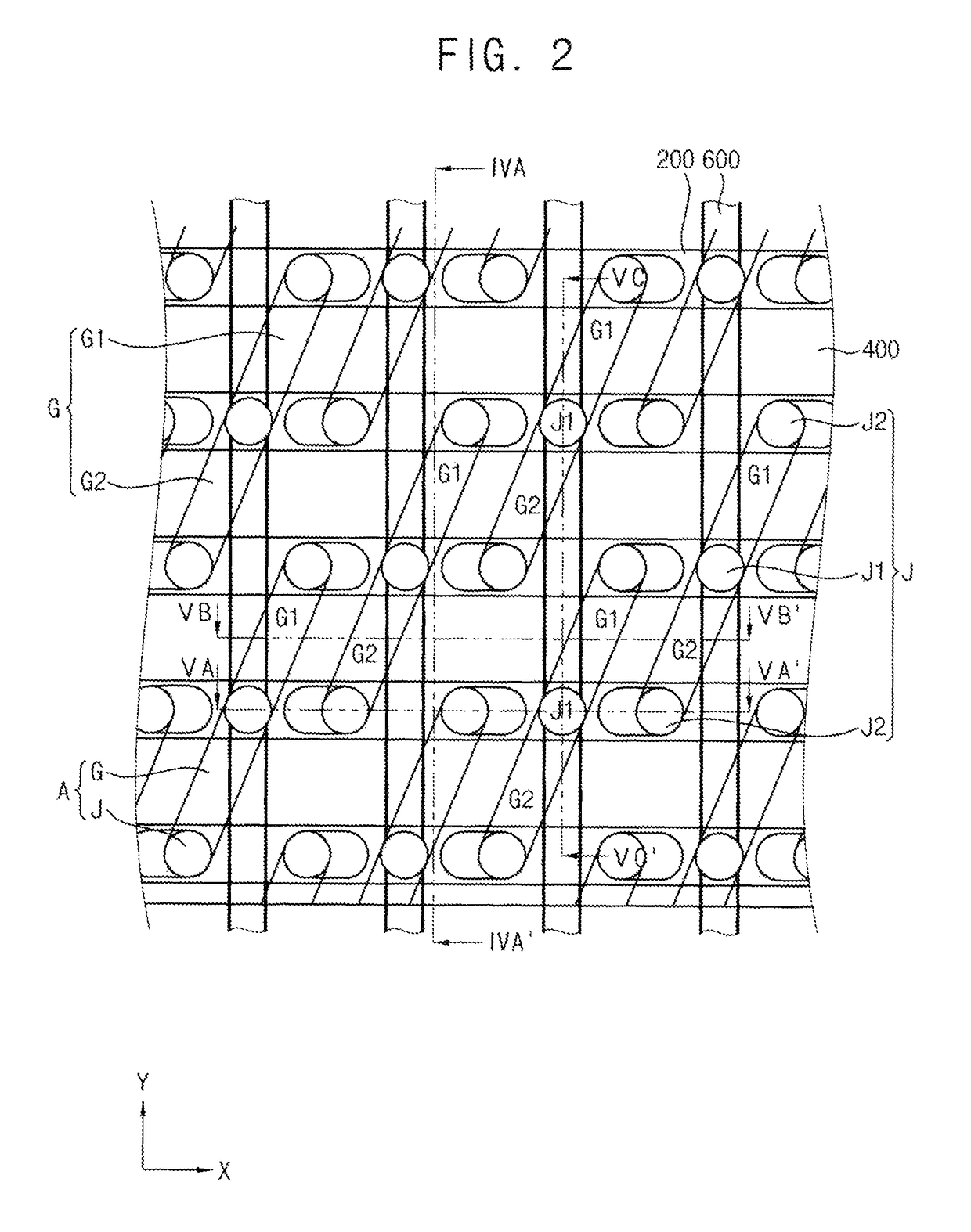

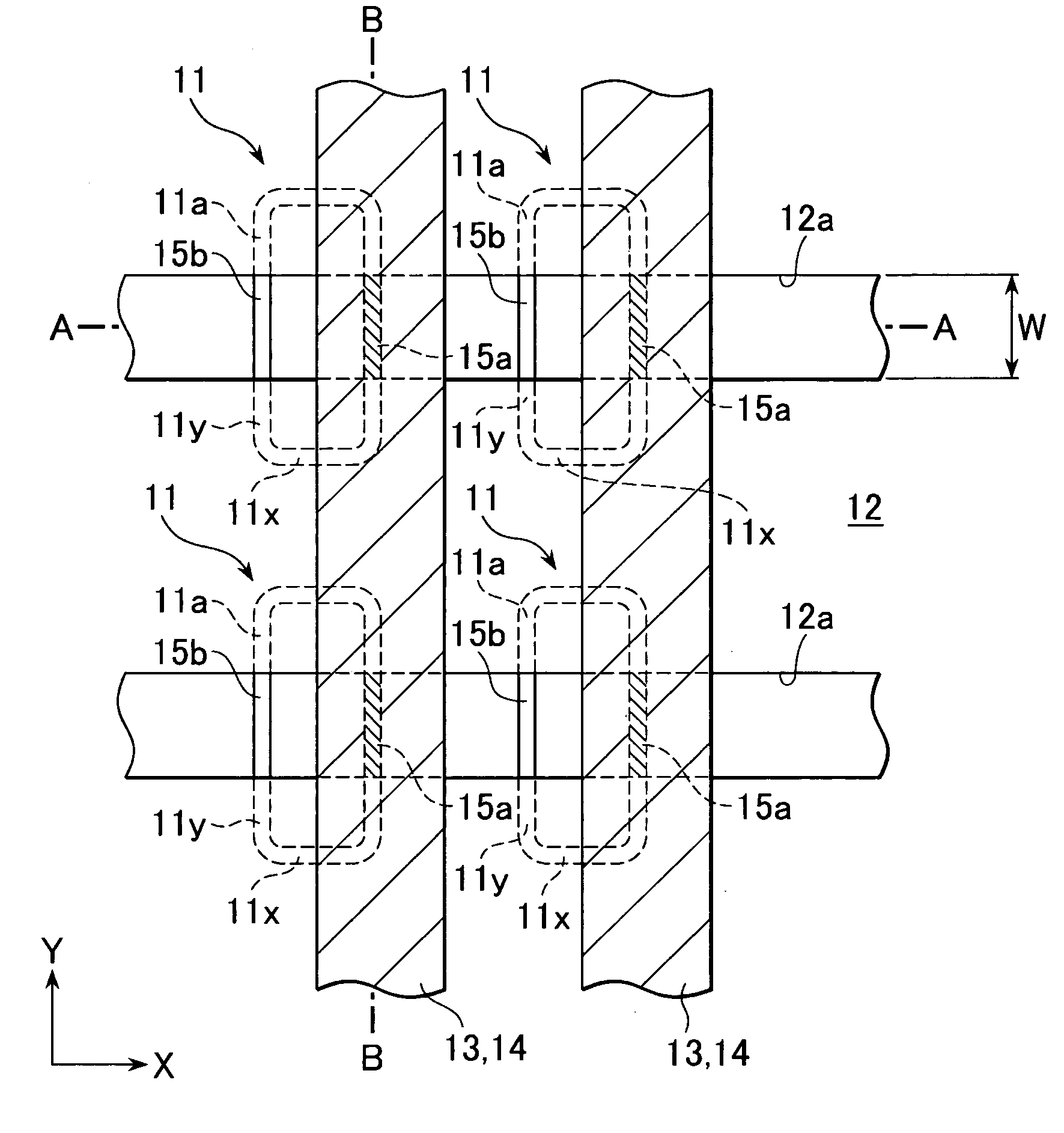

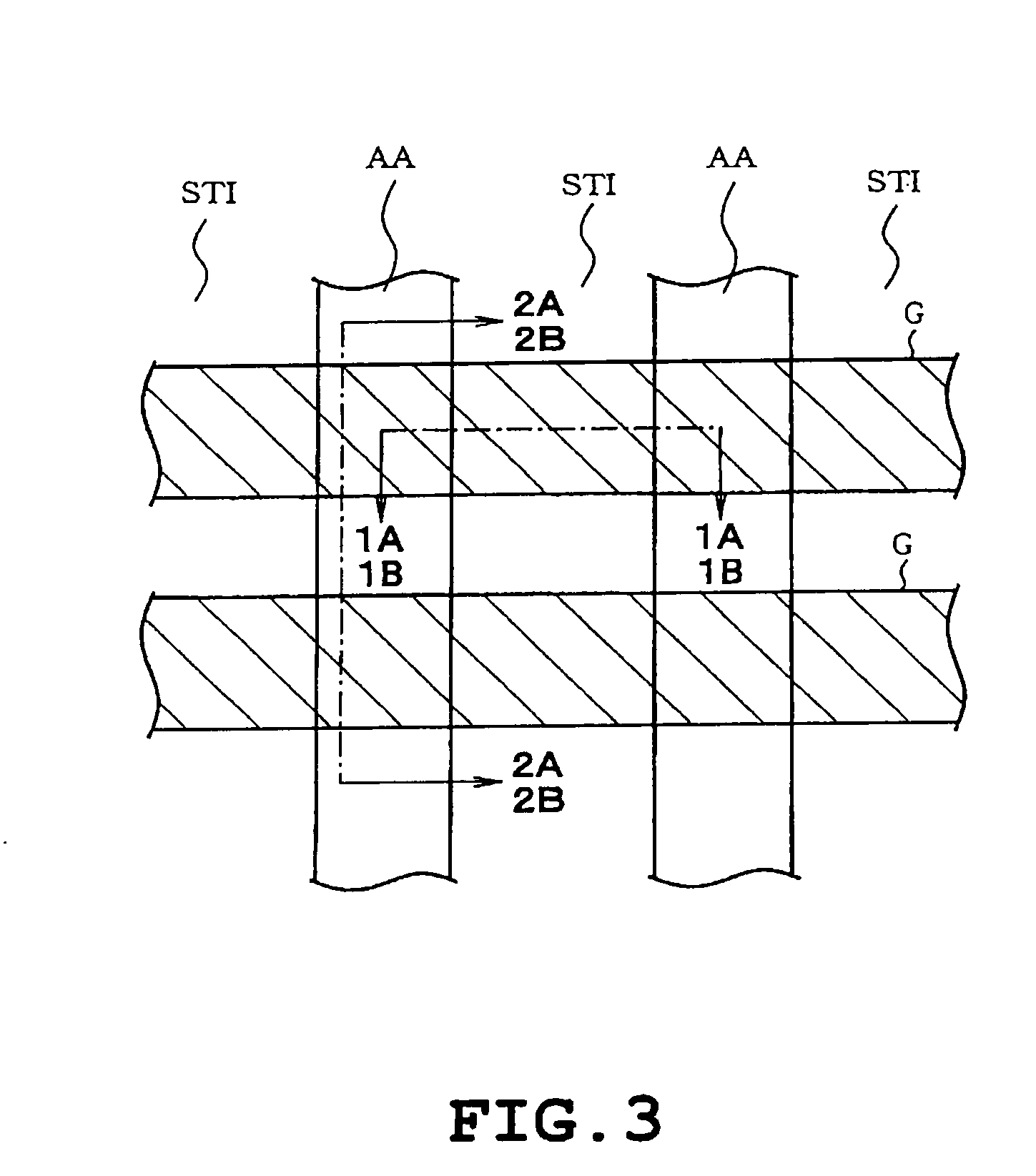

Semiconductor memory device

A semiconductor memory device includes unit active regions, word lines extending in a first direction over the unit active region, bit lines extending on the word lines in a second direction substantially perpendicularly to the first direction, first pad contacts in contact with central portions of the unit active regions, the first pad contacts being arranged between the word lines, direct contacts electrically connected between the first pad contacts and the bit lines, second pad contacts in contact with edge portions of the unit active regions, the second pad contacts being arranged between the word lines and between the bit lines, buried contacts electrically connected to the second pad contacts, and capacitors electrically connected to the buried contacts.

Owner:SAMSUNG ELECTRONICS CO LTD

Thin film transistor, display device including the same, and method for manufacturing the same

ActiveUS20090174690A1Increase charge mobilityEffective energy densitySolid-state devicesCathode-ray tube indicatorsAmorphous siliconDisplay device

A display device and a manufacturing method thereof, include a first thin film transistor including a first control electrode, a first semiconductor disposed on the first control electrode, and a first input electrode and a first output electrode opposite to each other on the first semiconductor; and a second thin film transistor including a second control electrode, a second semiconductor disposed on the second control electrode, and a second input electrode and a second output electrode opposite to each other on the second semiconductor, wherein the first semiconductor includes a first lower semiconductor including polysilicon, and a first upper semiconductor disposed on the first lower semiconductor, the first upper semiconductor including amorphous silicon.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

Method of manufacturing a semiconductor device

ActiveUS7049197B2Sufficient process marginAvoid breakingTransistorSolid-state devicesDevice materialEngineering

In a method of manufacturing a semiconductor device including independent gate patterns separated from each other, an active region is defined by forming a field region on a substrate. A gate oxide layer and a polysilicon layer are formed on the substrate. A preliminary gate pattern is formed by partially removing the polysilicon layer along a first direction by a first etching process. A spacer is formed along a side surface of the preliminary gate pattern. A number of separated gate patterns is formed by partially removing the preliminary gate pattern along a second direction crossing the first direction by a second etching process. The gate patterns overlap with the active regions and are separated from each other. Therefore, the overlap margin is increased, and the polysilicon layer is prevented from being over-etched when it is patterned to form the gate pattern.

Owner:SAMSUNG ELECTRONICS CO LTD

Thin film piezoelectric resonator and method of manufacturing the same

ActiveUS7709999B2Good vibesOvercome problemsPiezoelectric/electrostrictive device manufacture/assemblyPiezoelectric/electrostriction/magnetostriction machinesOptoelectronicsPiezoelectric thin films

A thin film piezoelectric resonator includes a substrate having a cavity; a first electrode extending over the cavity; a piezoelectric film placed on the first electrode; and a second electrode placed on the piezoelectric film, the second electrode having a periphery partially overlapping on the cavity and tapered to have an inner angle of 30 degrees or smaller defined by a part of the periphery thereof and a bottom thereof.

Owner:KK TOSHIBA

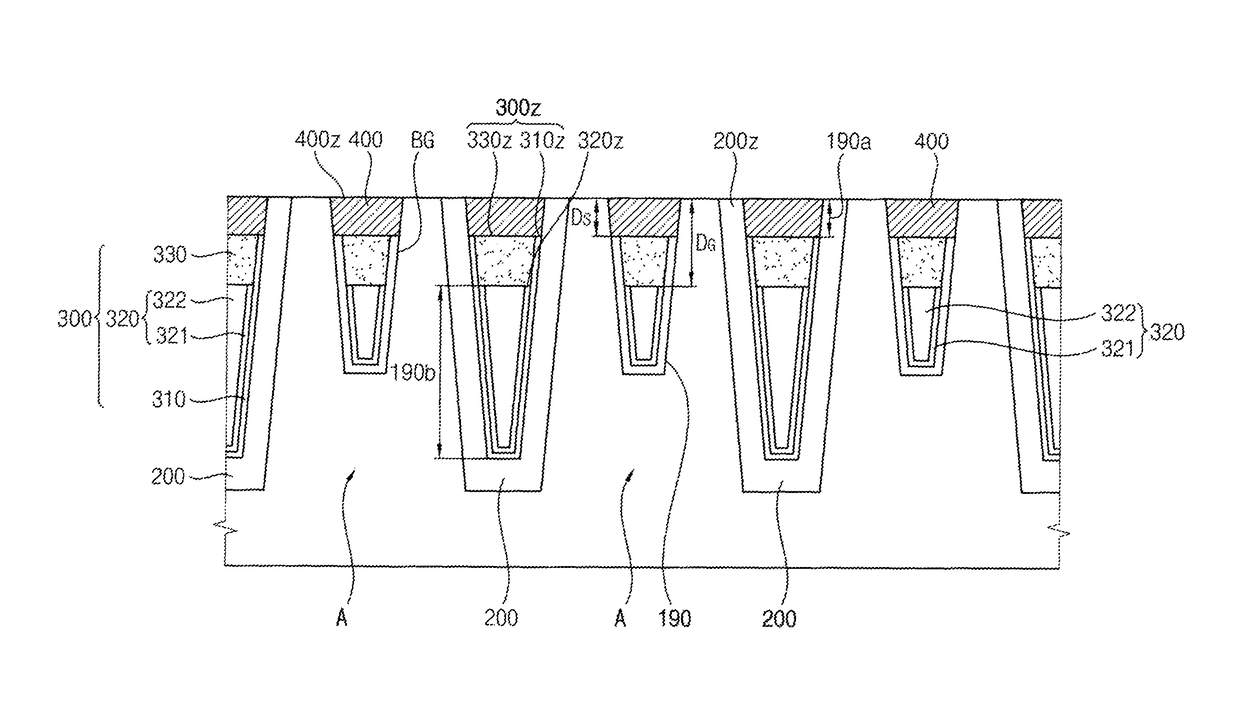

Semiconductor devices and methods of manufacturing the same

ActiveUS20170263723A1Sufficient process marginIncreasing thickness of insulationSemiconductor devicesSemiconductorDevice material

A semiconductor device may include a linear gate trench that crosses an active region of a substrate of the semiconductor device. The active region may include a plurality of gate areas at a bottom of the gate trench and junction areas at a surface of the substrate in a central portion and opposite end portions of the active region. A conductive line may be in a lower portion of the gate trench. The conductive line may include a gate line and a capping layer that at least partially isolates the gate line from an upper surface of the conductive line. A sealing line may be in an upper portion of the gate trench. The sealing line may cover the conductive line and a surface of the sealing line may be coplanar with the junction areas.

Owner:SAMSUNG ELECTRONICS CO LTD

Polyimide precursor, resin composition comprising the polyimide precursor, pattern forming method using the resin composition, and articles produced by using the resin composition

ActiveUS20110281218A1Easy to synthesizeLow costPhotosensitive materialsSemiconductor/solid-state device manufacturingChemical structureHydrogen atom

It is a main object of the present invention to provide a polyimide precursor and a polyimide precursor resin composition, which precursor being easy to synthesize, available at low cost, excellent in storage and capable of giving polyimide that is low in impurities after imidization, irrespective of the chemical structure of the finally-obtained polyimide.It is another object of the present invention to provide a polyimide precursor having repeating units represented by the following formula (1) and a photosensitive resin composition comprising the polyimide precursor and a photoacid generator or photobase generator:In the formula (1), R1 is a tetravalent organic group; R2 is a divalent organic group; R1s may be the same or different from each other and R2 s may be the same or different from each other in the repeating units; R3 and R4 respectively represent a monovalent organic group having a structure represented by the following formula (2) and may be the same or different from each other; and R3s and R4s in the repeating units may be the same or different from each other, respectively. In the formula (2), R5, R6 and R7 respectively represent a hydrogen atom, a halogen atom or a monovalent organic group; R8 is a monovalent organic group; R8s in the repeating units may be the same or different from each other; 35 mole % or less of R8s are organic groups having a reactive group; and R5, R6, R7 and R8 may be bonded to each other to form a ring structure.

Owner:DAI NIPPON PRINTING CO LTD

Base generator

ActiveUS8476444B2High sensitivityIncrease the differenceAdditive manufacturing apparatusOrganic chemistryImage resolutionElectromagnetic radiation

A photosensitive resin composition which is excellent in resolution, low in cost, and usable in a wide range of structures of polymer precursors each of which is reacted into a final product by a basic substance or by heating in the presence of a basic substance. The photosensitive resin composition includes a base generator which has a specific structure and generates a base by exposure to electromagnetic radiation and heating, and a polymer precursor which is reacted into a final product by the base generator and by a basic substance or by heating in the presence of a basic substance.

Owner:DAI NIPPON PRINTING CO LTD

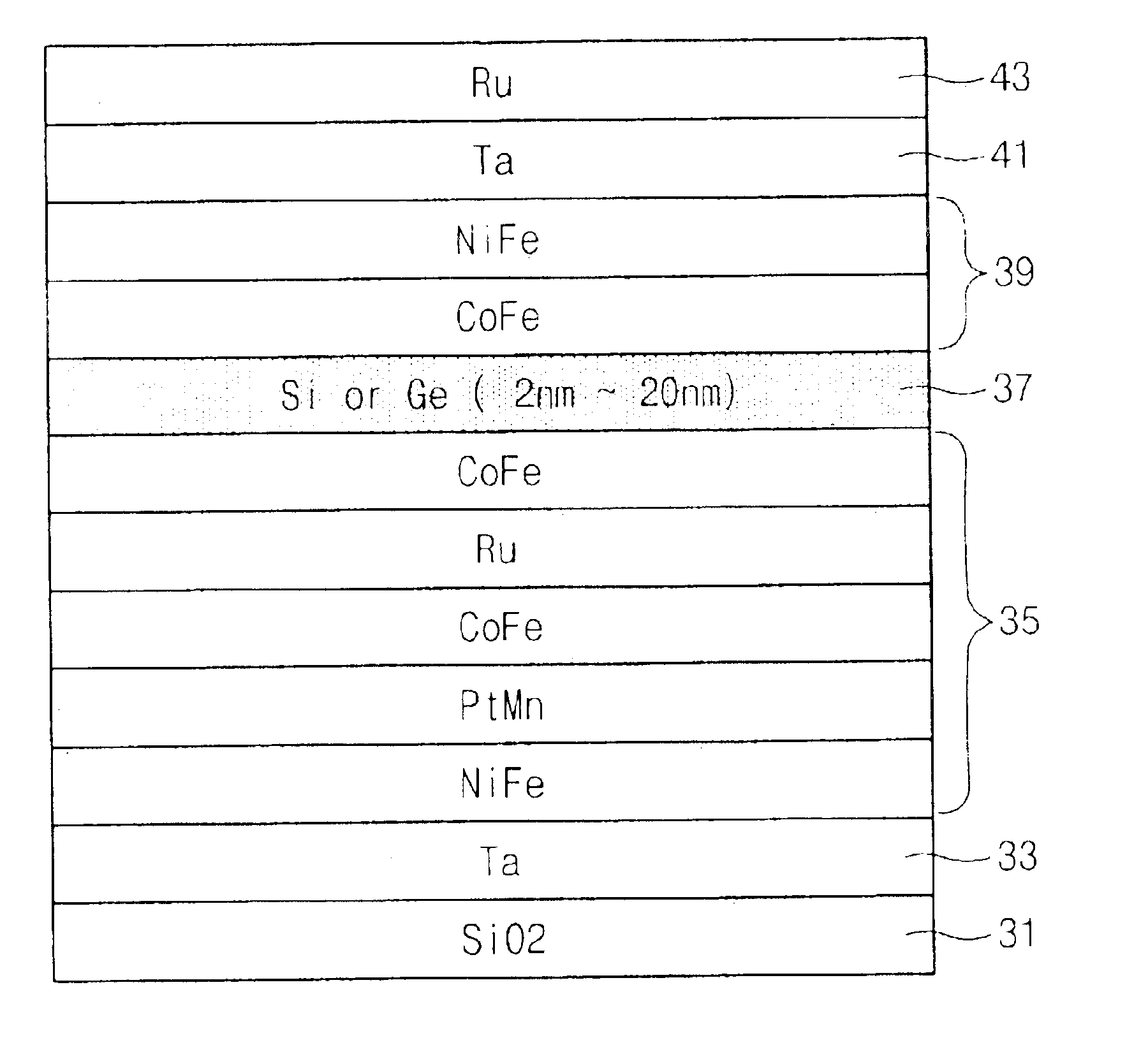

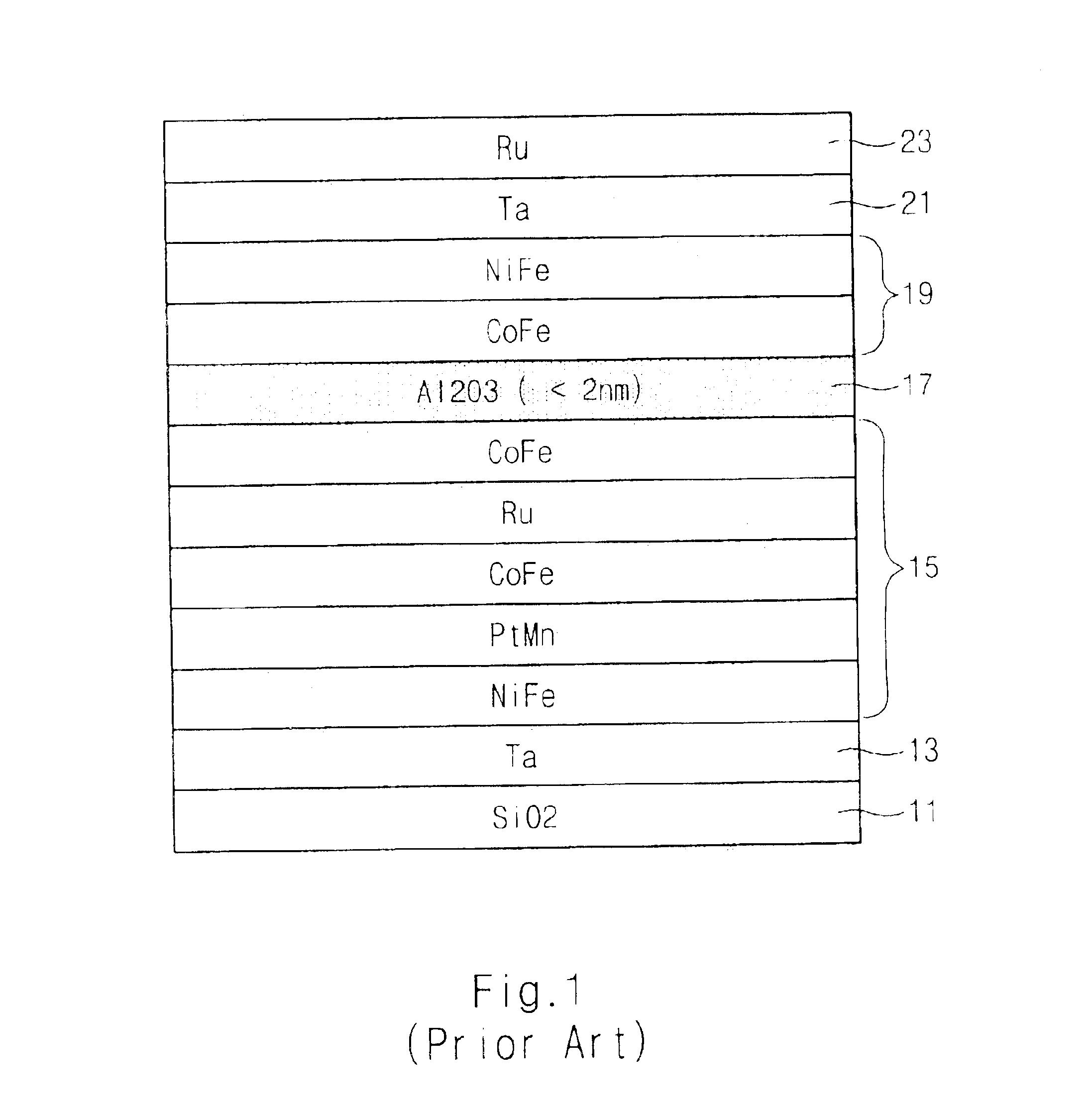

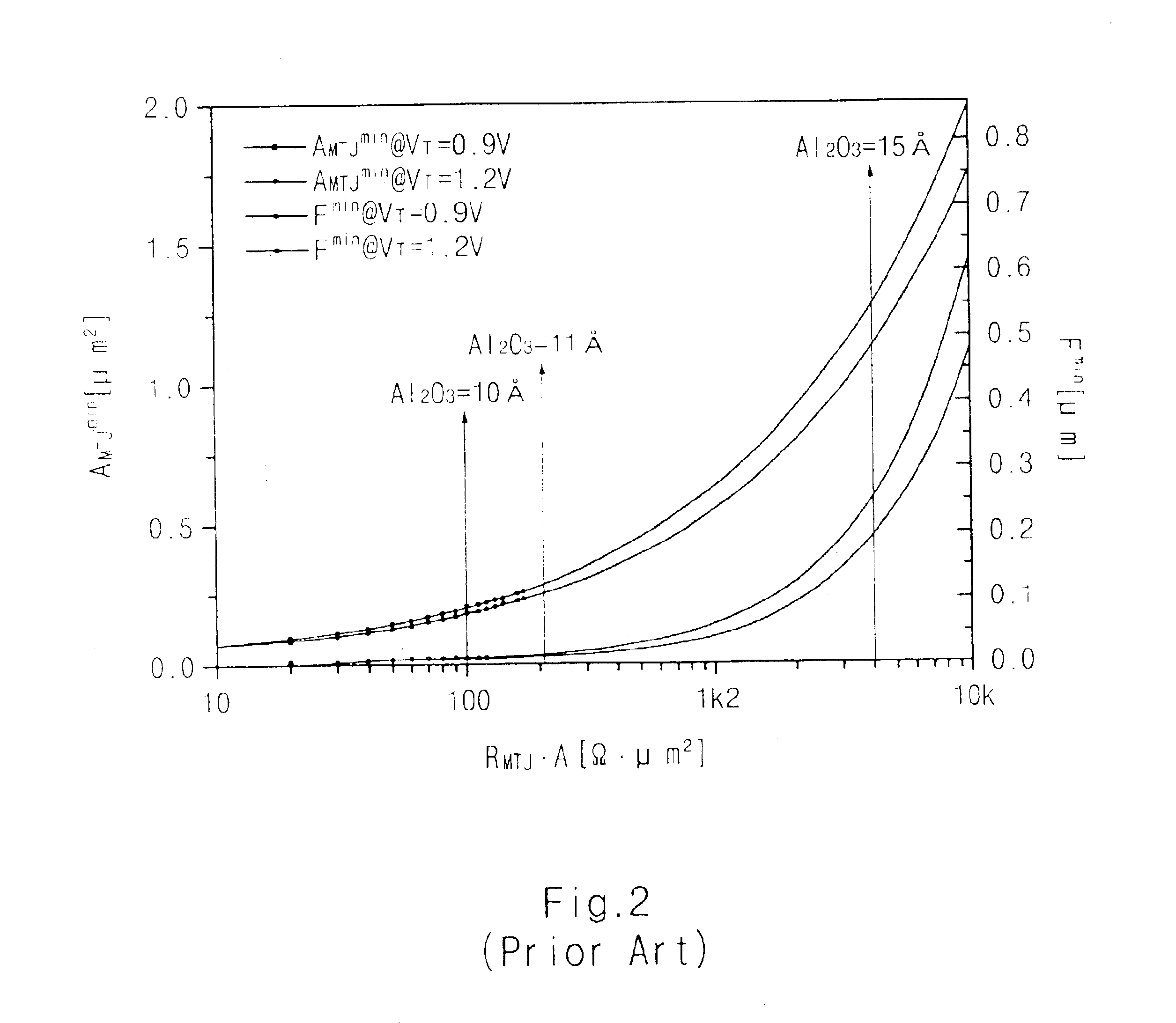

Method for manufacturing MTJ cell of magnetic random access memory

InactiveUS6849466B2Excellent characteristicsImprove reliabilityTransistorMagnetic-field-controlled resistorsRandom access memorySemiconductor

A method for fabricating a MTJ cell of a magnetic random access memory (MRAM) using a semiconductor film as a tunnel barrier layer is disclosed. The method comprises the steps of: forming a pinned ferromagnetic layer on a connection layer; forming a tunnel barrier layer using a semiconductor film on the pinned ferromagnetic layer; and forming a free ferromagnetic layer on the tunnel barrier layer.

Owner:SK HYNIX INC

Semiconductor device manufacturing method

ActiveUS20120070978A1Reduce the overall diameterAdd depthSolid-state devicesSemiconductor/solid-state device manufacturingMiniaturizationEngineering

A miniaturized semiconductor device is provided by reducing the design thickness of a wiring line protecting film covering the surface of a wiring layer, and reducing the distance between the wiring layer and via plugs formed by a self-aligning process. Dummy mask layers extending in the same layout pattern as the wiring layer is formed above the wiring layer covered with a protecting film composed of a cap layer and side wall layers. In the self-aligning process for forming via plugs in a self-aligned manner with the wiring layer and its protecting film, the thickness of the cap layer is reduced and the design interval between the via plugs is reduced, whereby the miniaturization of the semiconductor device is achieved.

Owner:LONGITUDE LICENSING LTD

Semiconductor device having vertical channel transistor and manufacturing method of the same

ActiveUS8357969B2Reduce resistanceReduce designSemiconductor/solid-state device manufacturingSemiconductor devicesBit lineEngineering

A semiconductor device having a vertical channel transistor and a method for manufacturing the same are provided. In the semiconductor device, a metal bit line is formed between vertical channel transistors, and the metal bit line is connected to only one of the vertical channel transistors through an asymmetric bit line contact. Through such a structure, the resistance of the bit line can be improved and the process margin for formation of the bit line can be secured.

Owner:SK HYNIX INC

Semiconductor devices and methods of manufacturing the same

ActiveUS9899487B2Preventing a bridge defectReduce the overall heightTransistorSemiconductor/solid-state device manufacturingSemiconductorSemiconductor device

A semiconductor device may include a linear gate trench that crosses an active region of a substrate of the semiconductor device. The active region may include a plurality of gate areas at a bottom of the gate trench and junction areas at a surface of the substrate in a central portion and opposite end portions of the active region. A conductive line may be in a lower portion of the gate trench. The conductive line may include a gate line and a capping layer that at least partially isolates the gate line from an upper surface of the conductive line. A sealing line may be in an upper portion of the gate trench. The sealing line may cover the conductive line and a surface of the sealing line may be coplanar with the junction areas.

Owner:SAMSUNG ELECTRONICS CO LTD

Blankmask and method for fabricating photomask using the same

ActiveUS9229317B2Sufficient process marginAdd featureOriginals for photomechanical treatmentEngineeringMaterials science

Provided is a blankmask with a light-shielding layer including a light block layer and an anti-reflective layer, and a hard mask film. The light block layer and the anti-reflective layer are formed by combining a layer formed of a MoSi compound and a layer formed of a MoTaSi compound. Thus, the blankmask enables formation of a pattern of 32 nm or less, since the light-shielding layer can be thinly formed to a thickness of 200 to 700 and a photomask having pattern fidelity corresponding to the resolution of the pattern can be formed. The light-shielding layer has an optical density of 2.0 to 4.0 at an exposure wavelength of 193 nm, chemical resistance, and a sufficient process margin for defect repair. Further, the hard mask film is formed to a thickness of 20 to 50 using a compound including tin (Sn) and chromium (Cr), thereby decreasing an etch rate of the hard mask film. Accordingly, a resist film can be formed as a thin film, thereby manufacturing a high-resolution blankmask.

Owner:S & S TECH

Semiconductor device including bit line formed using damascene technique and method of fabricating the same

InactiveUS20060284277A1Well formedReduce designSolid-state devicesSemiconductor/solid-state device manufacturingBit lineDevice material

A semiconductor device includes an insulating layer having a T-shaped groove formed by a wide opening overlapping a narrow opening, a bit line conductive layer that at least partially fills the narrow opening, and a bit line capping layer that fills the groove so that its top surface is as high as that of the insulating layer. Spacers are formed on the inner walls of the wide opening.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor device and method of manufacturing the same

InactiveUS20100270603A1Improve processing speedReduce power consumptionTransistorSolid-state devicesBit lineEngineering

A semiconductor device comprises gates comprising a first conductive layer, landing plug contacts formed adjacent to the gate and formed of a second conductive layer, a bit line formed over the landing plug contacts and formed of a third conductive layer, and storage electrode contacts formed over the landing plug contacts and the bit line and formed of a fourth conductive layer. The first conductive layer, the second conductive layer, the third conductive layer, and the fourth conductive layer are made of the same material.

Owner:SK HYNIX INC

Electrically rewritable non-volatile memory element

ActiveUS7528402B2Improve heating efficiencySufficient process marginTransistorSemiconductor/solid-state device detailsEngineeringRecording layer

A non-volatile semiconductor memory device includes a plurality of lower electrodes arranged in a matrix manner, a plurality of recording layer patterns, each being arranged on the lower electrode, that contain a phase change material, and an interlayer insulation film that is provided between the lower electrode and the recording layer pattern and that has a plurality of apertures for exposing one portion of the lower electrode. The lower electrode and the recording layer pattern are connected in each aperture. The apertures extend in the X direction in parallel to one another. The recording layer patterns extend in the Y direction in parallel to one another. Thus the aperture can be formed with higher accuracy as compared to forming an independent aperture. Accordingly, high heating efficiency can be obtained while effectively preventing occurrence of poor connection or the like.

Owner:MICRON TECH INC

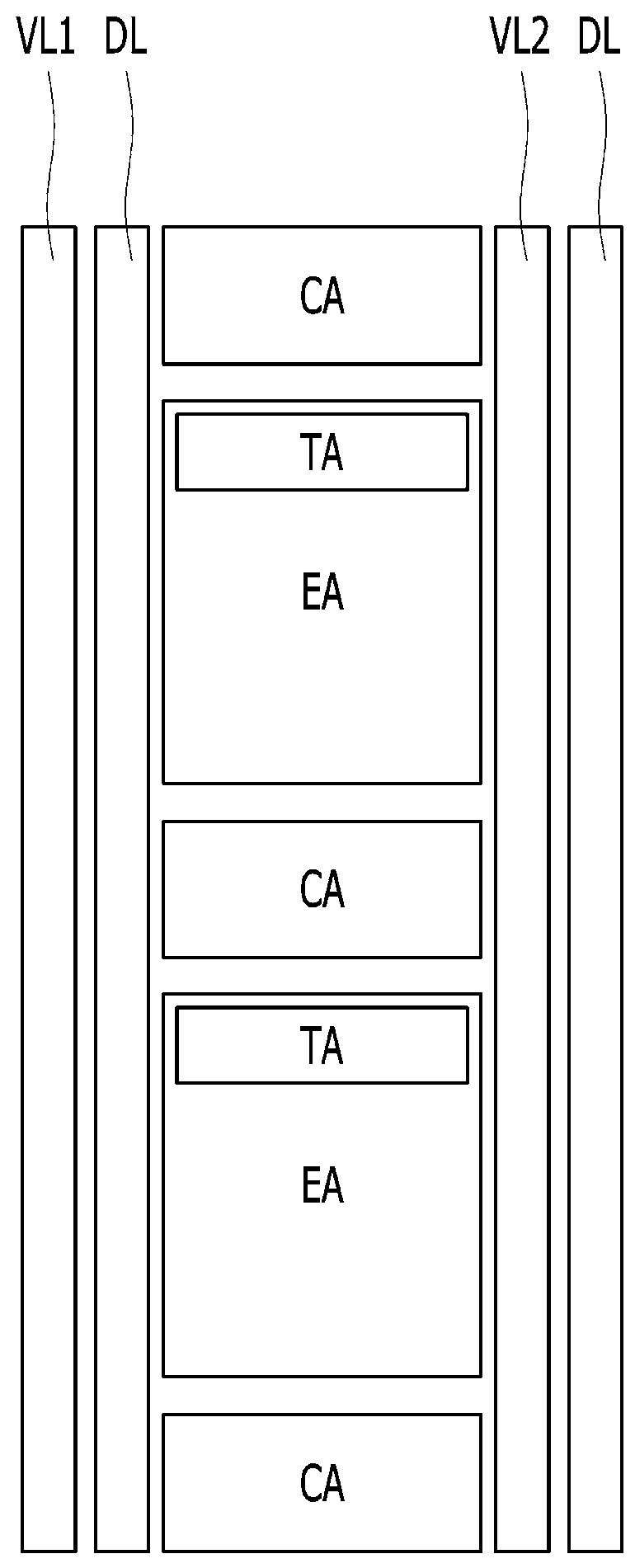

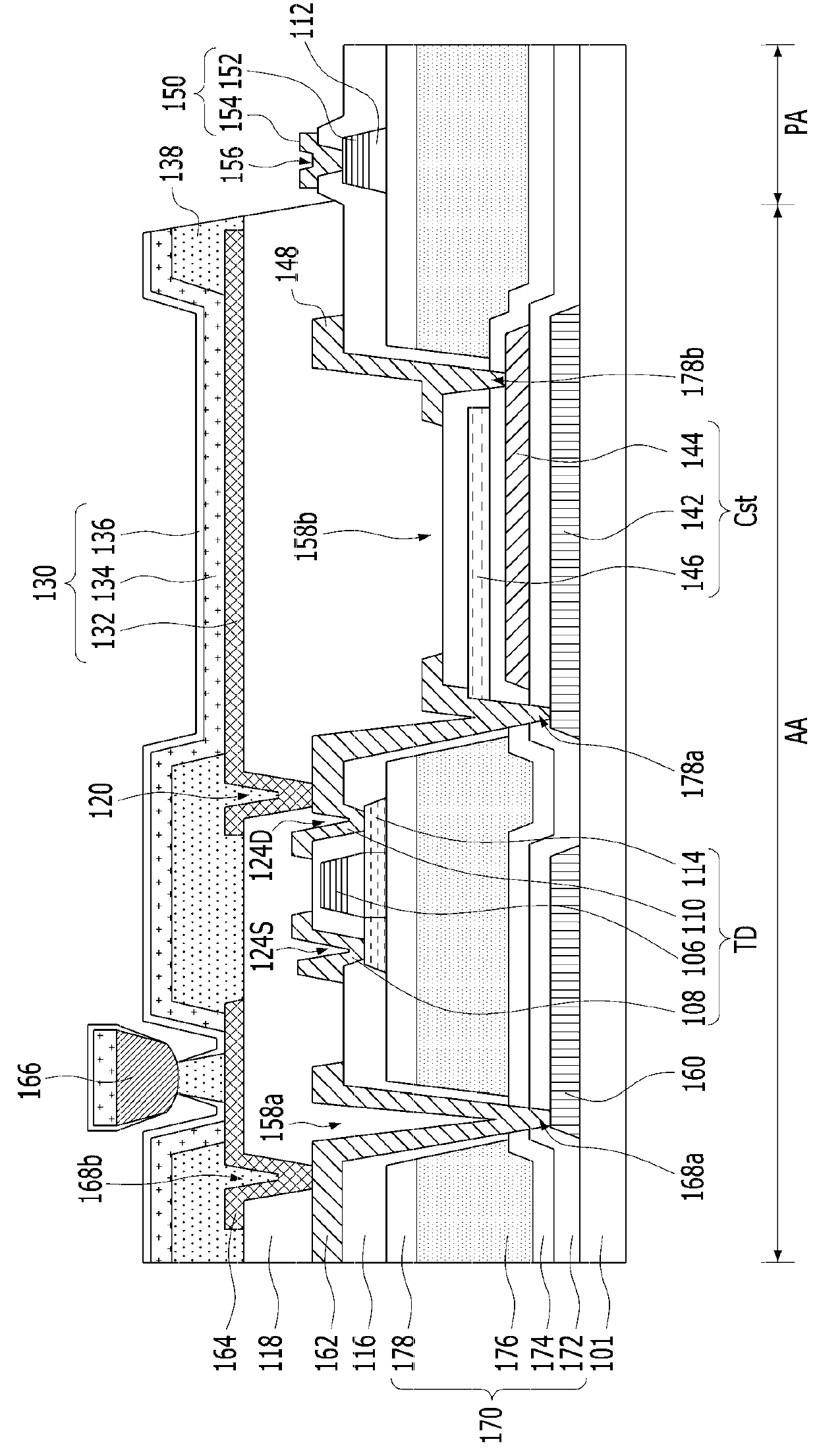

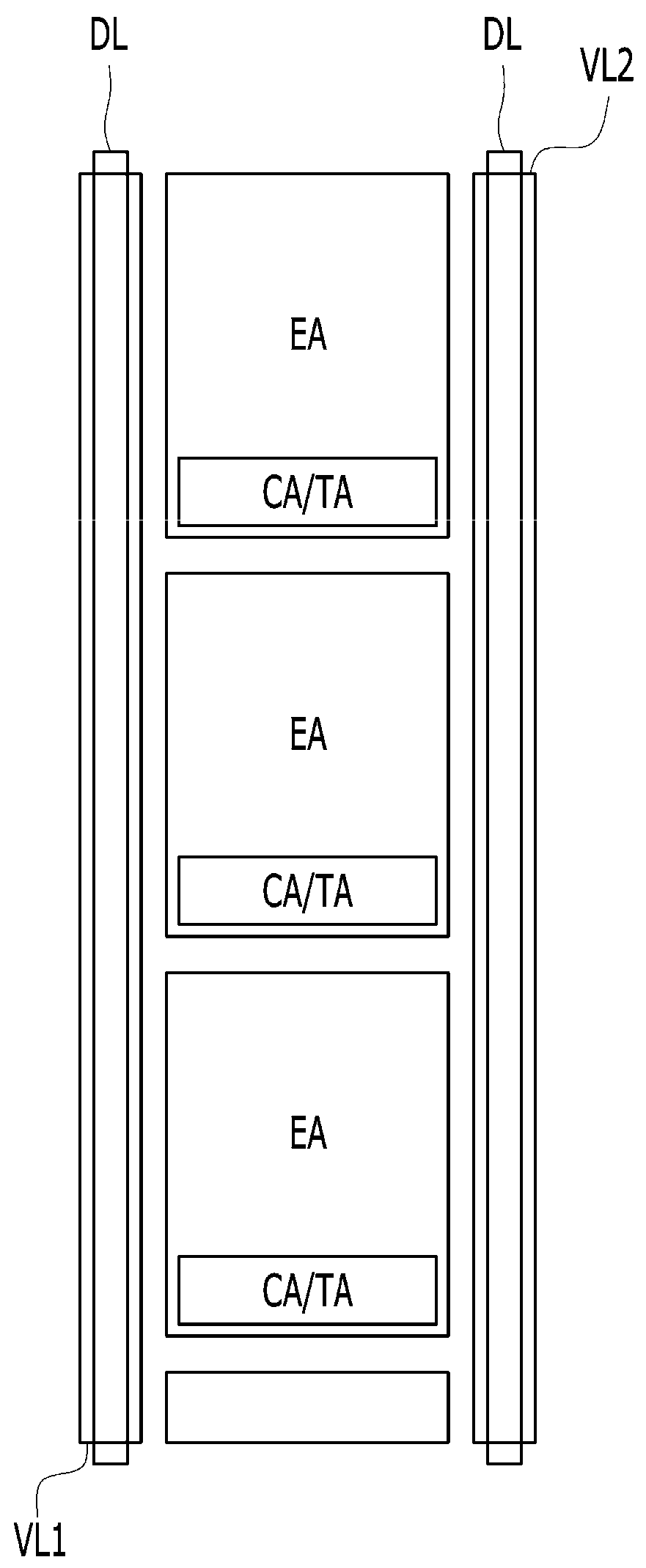

Organic light-emitting display device

ActiveUS10672339B2High resolutionSufficient process marginStatic indicating devicesSolid-state devicesImage resolutionDisplay device

Disclosed is an organic light-emitting display device capable of realizing a high resolution. The organic light-emitting display device includes a storage capacitor disposed on a substrate, which overlaps at least one transistor, with at least one buffer layer interposed therebetween, the at least one buffer layer disposed on the storage capacitor, and which includes a lower storage electrode and an upper storage electrode overlapping the lower storage electrode, with a storage buffer layer interposed therebetween, and a light-emitting diode connected to the transistor. One of the lower storage electrode and the upper storage electrode is formed to have the same line width and the same shape as the storage buffer layer, thereby ensuring a sufficient process margin and consequently realizing a high resolution and improving production yield.

Owner:LG DISPLAY CO LTD

Display device having multiple buffer layers

ActiveUS11158700B2High resolutionSufficient process marginSolid-state devicesCapacitorsImage resolutionDisplay device

Disclosed is a display device with high resolution. The display device includes a substrate, a plurality of signal lines on the substrate, multiple buffer layers including at least one organic buffer layer and at least one inorganic buffer layer, and at least one transistor that overlaps one or more of the plurality of signal lines, with the multiple buffer layers interposed therebetween. Accordingly, it may be possible to ensure a sufficient process margin and consequently to realize a high resolution and improve production yield.

Owner:LG DISPLAY CO LTD

Semiconductor device and method of fabricating the same

InactiveUS20080305612A1Improve the level ofSufficient process marginSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialSemiconductor

A semiconductor device such as a flash memory includes a semiconductor substrate, two gate insulating films formed on the substrate so as to have a first film thickness and a second film thickness smaller than the first film thickness respectively, and a polycrystalline silicon film formed on the gate insulating films so that parts of the polycrystalline silicon film on the respective gate insulating films are on a level with each other and serving as a gate electrode. The substrate is formed with a recess defined by a bottom and sidewalls substantially perpendicular to the bottom, the recess corresponding to the part of the gate insulating film with the first film thickness.

Owner:KK TOSHIBA

Nonvolatile memory cell and manufacturing method thereof

InactiveCN104143551AIncrease coupling areaImprove the coupling ratioSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringDielectric layer

The invention relates to a nonvolatile memory cell and a manufacturing method of the nonvolatile memory cell. The nonvolatile memory cell comprises a substrate, electric charge storage structures and a tunneling dielectric layer. An isolation structure is arranged in the substrate, active areas are defined, and the electric charge storage structures are arranged on the active areas respectively. The width of the bottom of each electric charge structure is equal to the width of the corresponding active area in essence, the first included angle between the side wall of each electric charge storage structure and the upper surface of the substrate is different from the second included angle between the side wall of each isolation structure and the upper surface of the substrate. The tunneling dielectric layer is arranged between the electric charge storage structures and the substrate, the lower surface of the tunneling dielectric layer is flat, and the upper surface of the tunneling dielectric layer is parallel to the upper surface of the substrate in essence.

Owner:MACRONIX INT CO LTD