Patents

Literature

280 results about "Hierarchical design" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

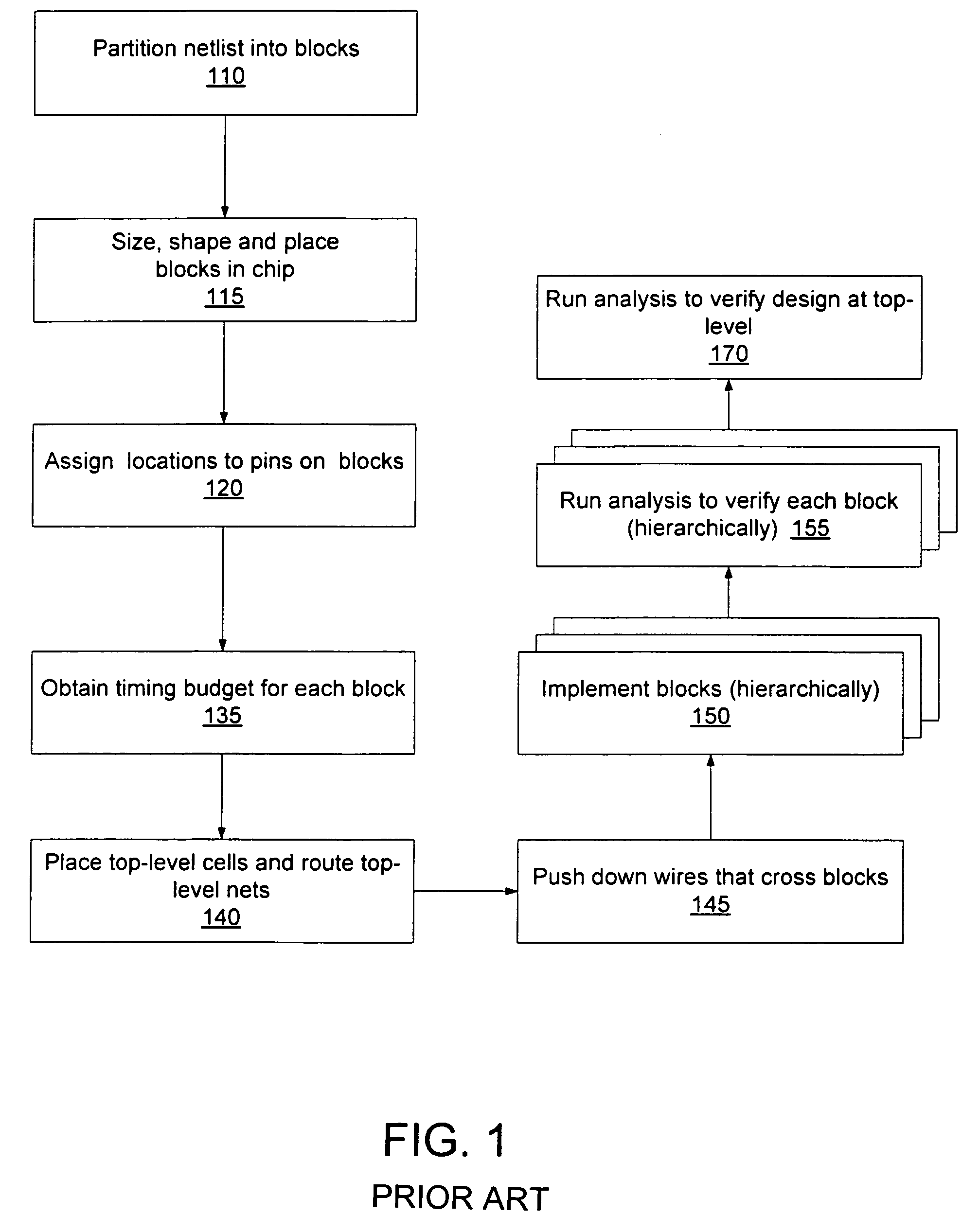

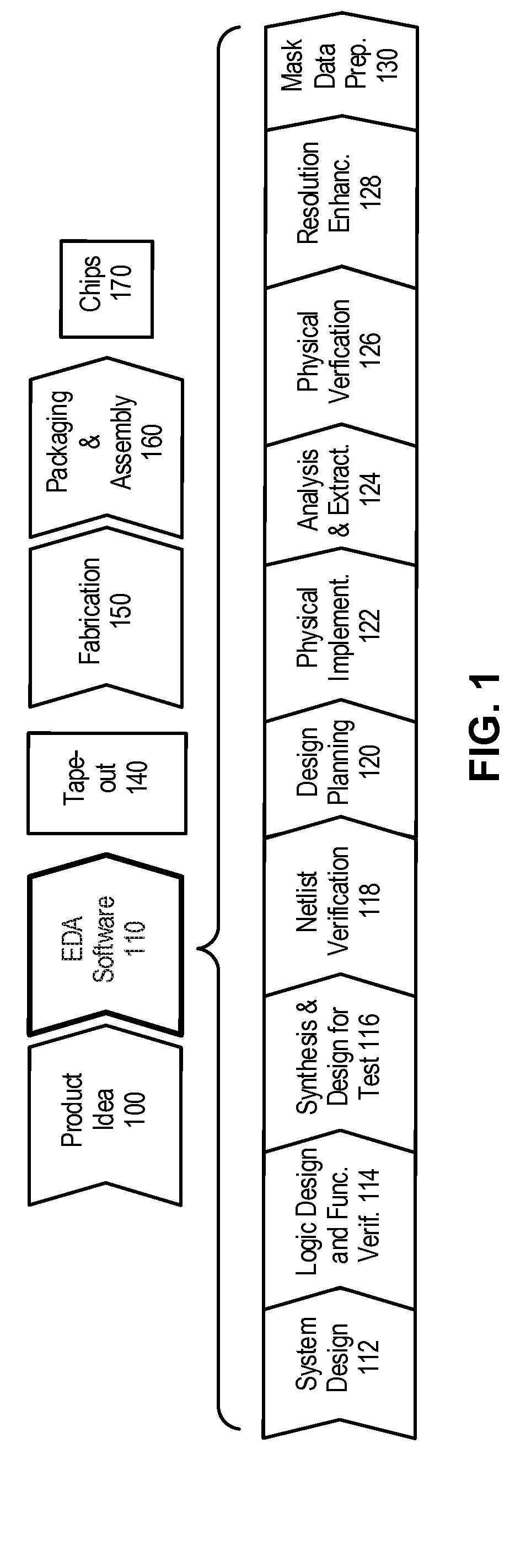

The basic flow of hierarchical design is simple…. Dividing a design into multiple blocks (sometimes referred to as sub-chips, sub-blocks, modules, hierarchical blocks, etc.). Designers can work on the blocks separately and in parallel from RTL through physical implementation.

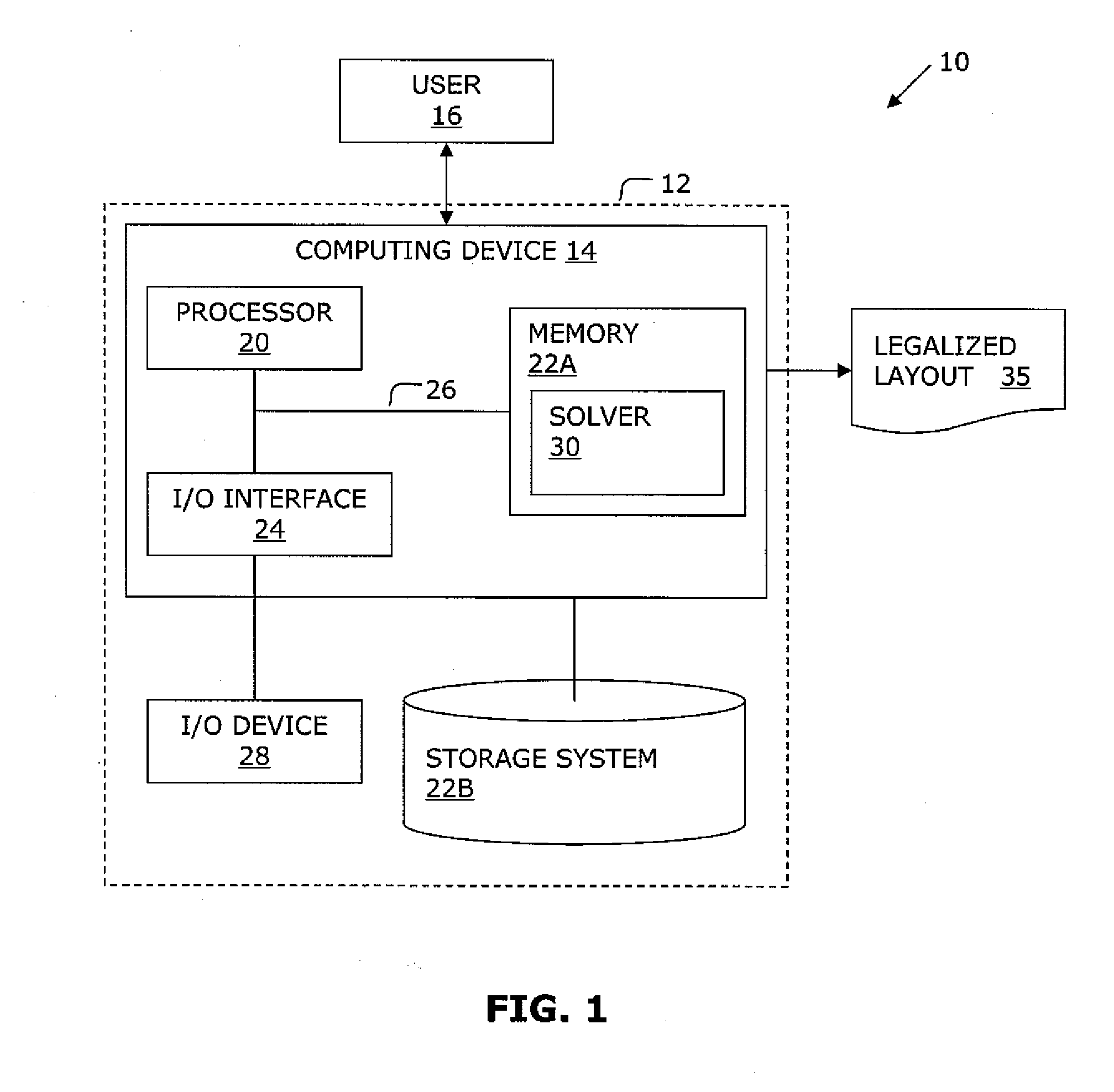

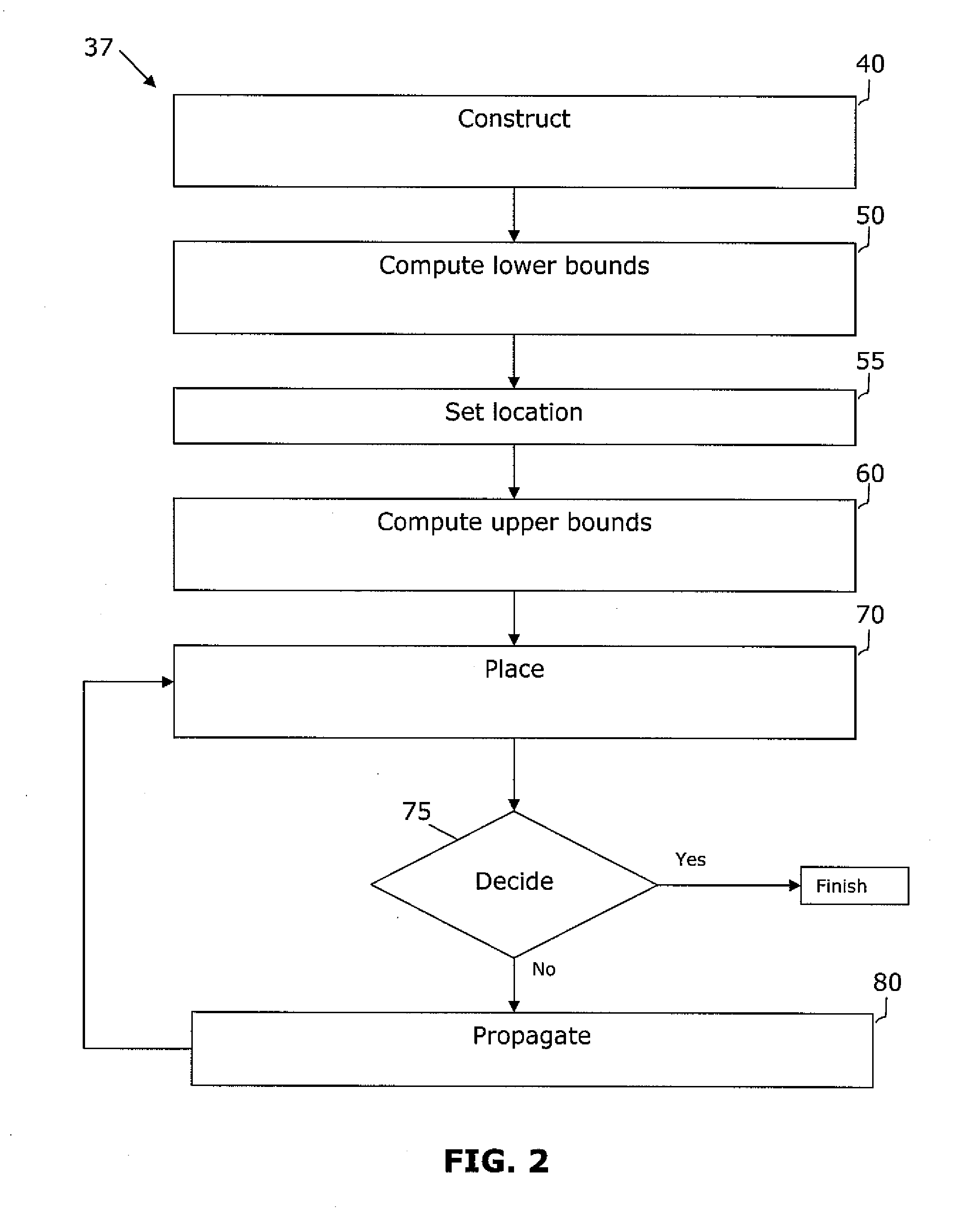

Minimum layout perturbation-based artwork legalization with grid constraints for hierarchical designs

InactiveUS7484197B2Computer aided designSoftware simulation/interpretation/emulationTheoretical computer scienceHierarchical design

A method comprises extracting a hierarchical grid constraint set and modeling one or more critical objects of at least one cell as a variable set. The method further comprises solving a linear programming problem based on the hierarchical grid constraint set with the variable set to provide initial locations of the critical objects of the at least one cell and determining target on-grid locations of the one or more critical objects in the at least one cell using the results of the linear programming solution.

Owner:GLOBALFOUNDRIES INC

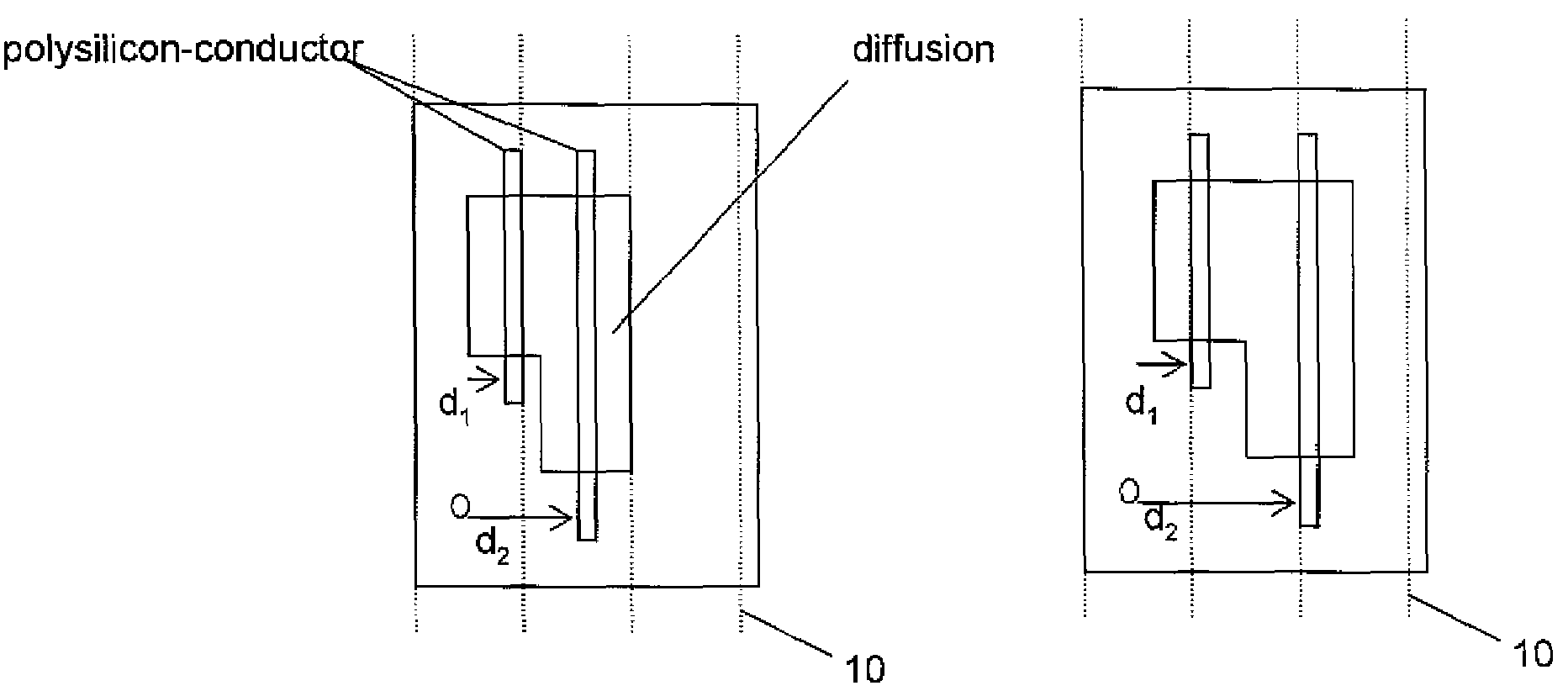

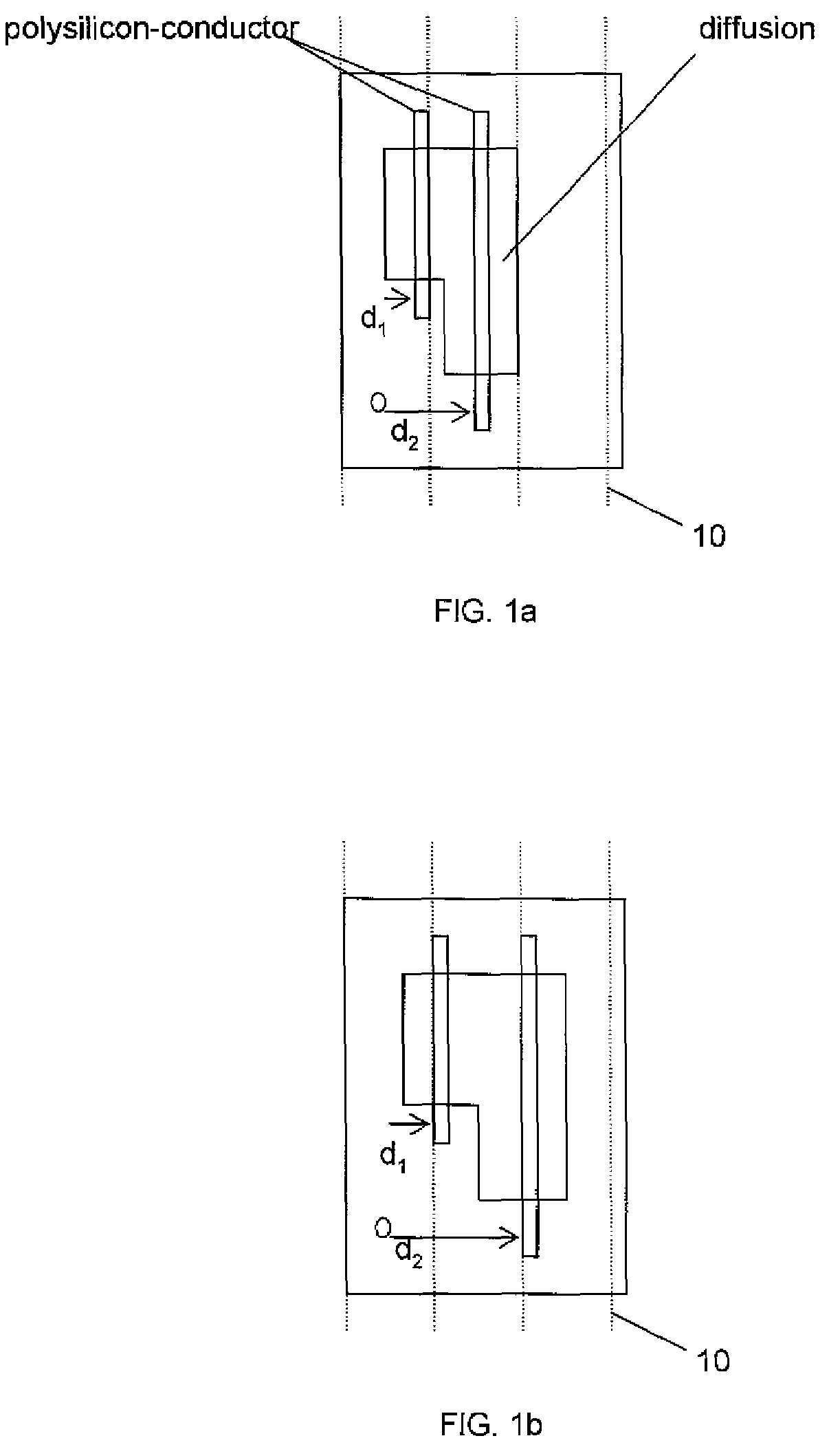

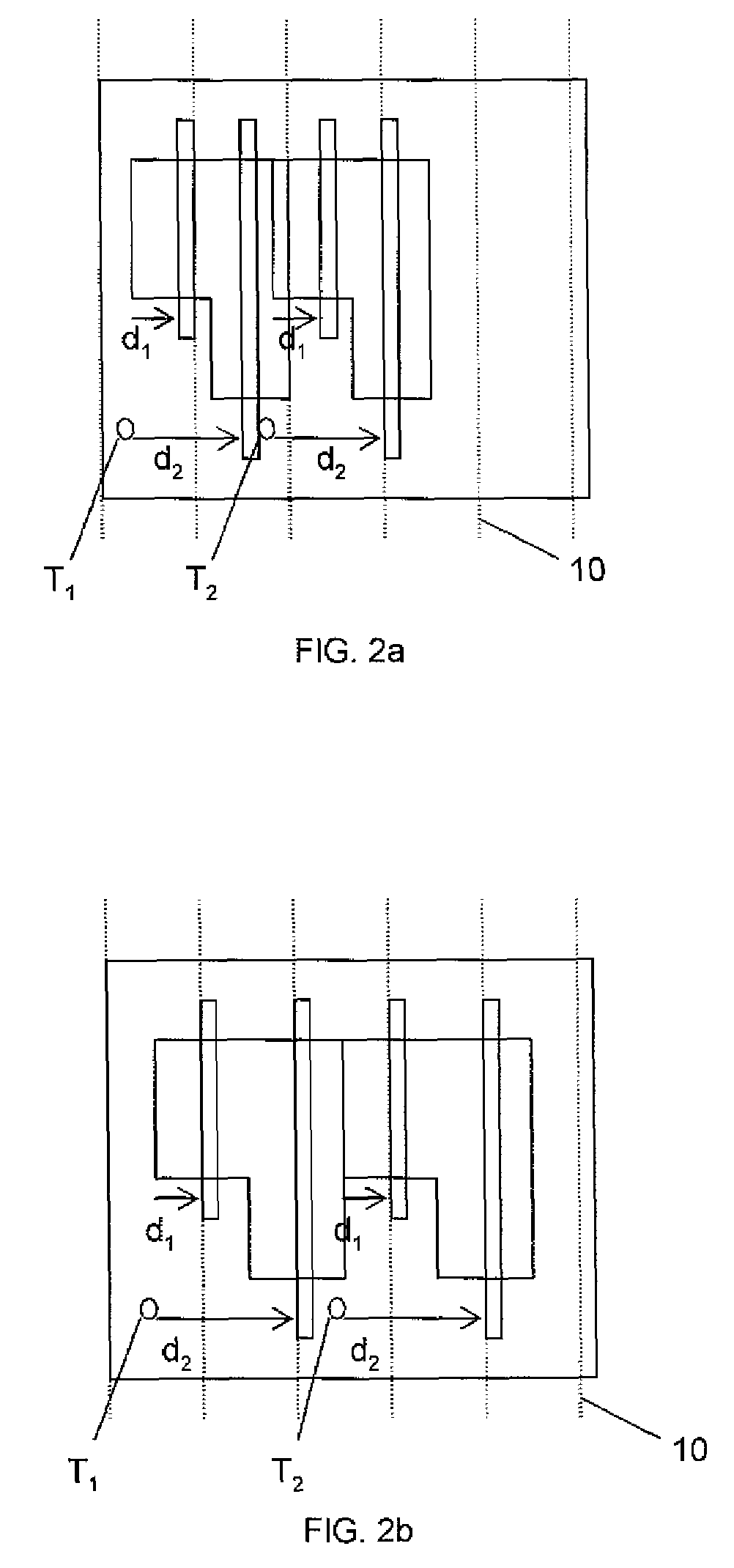

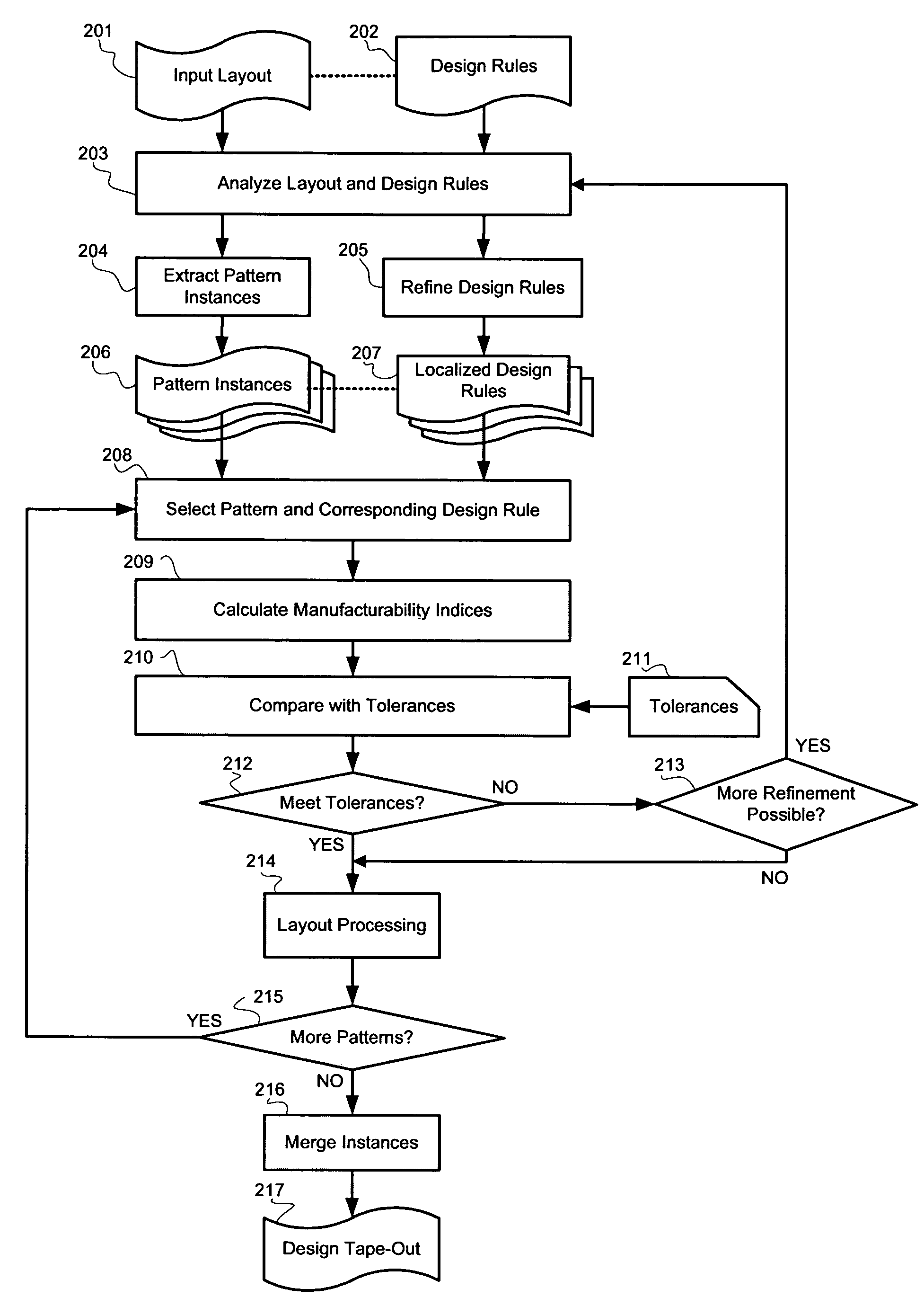

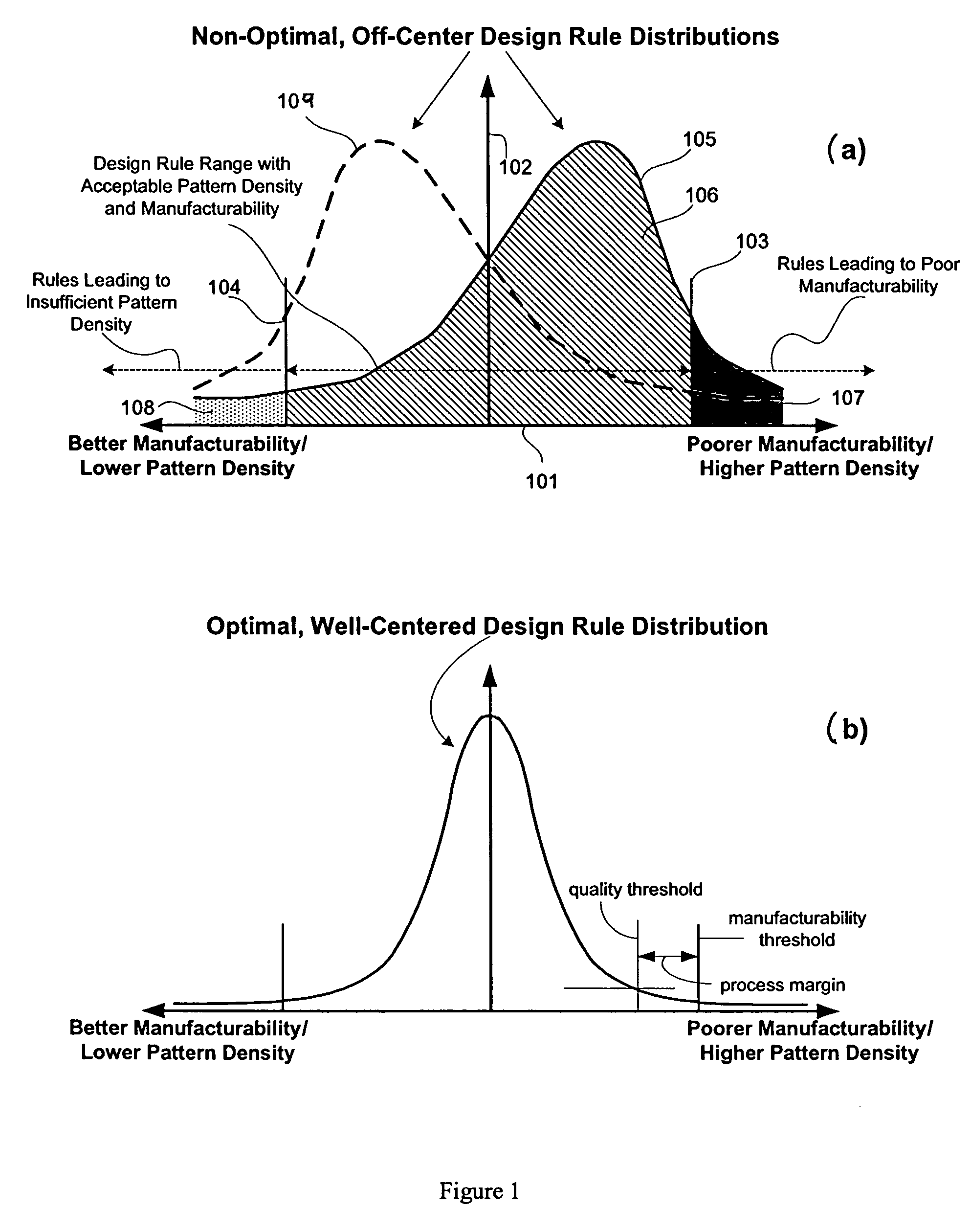

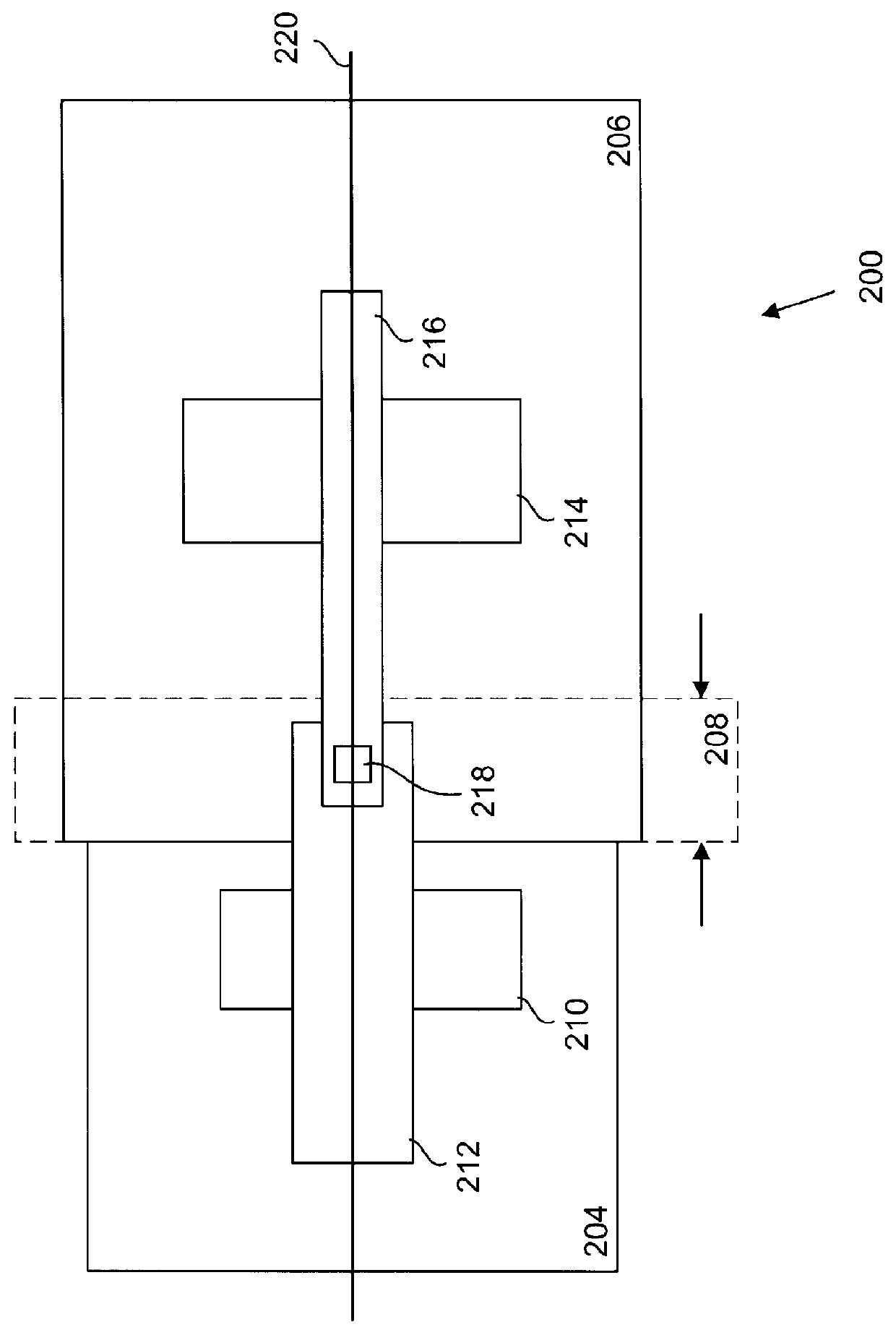

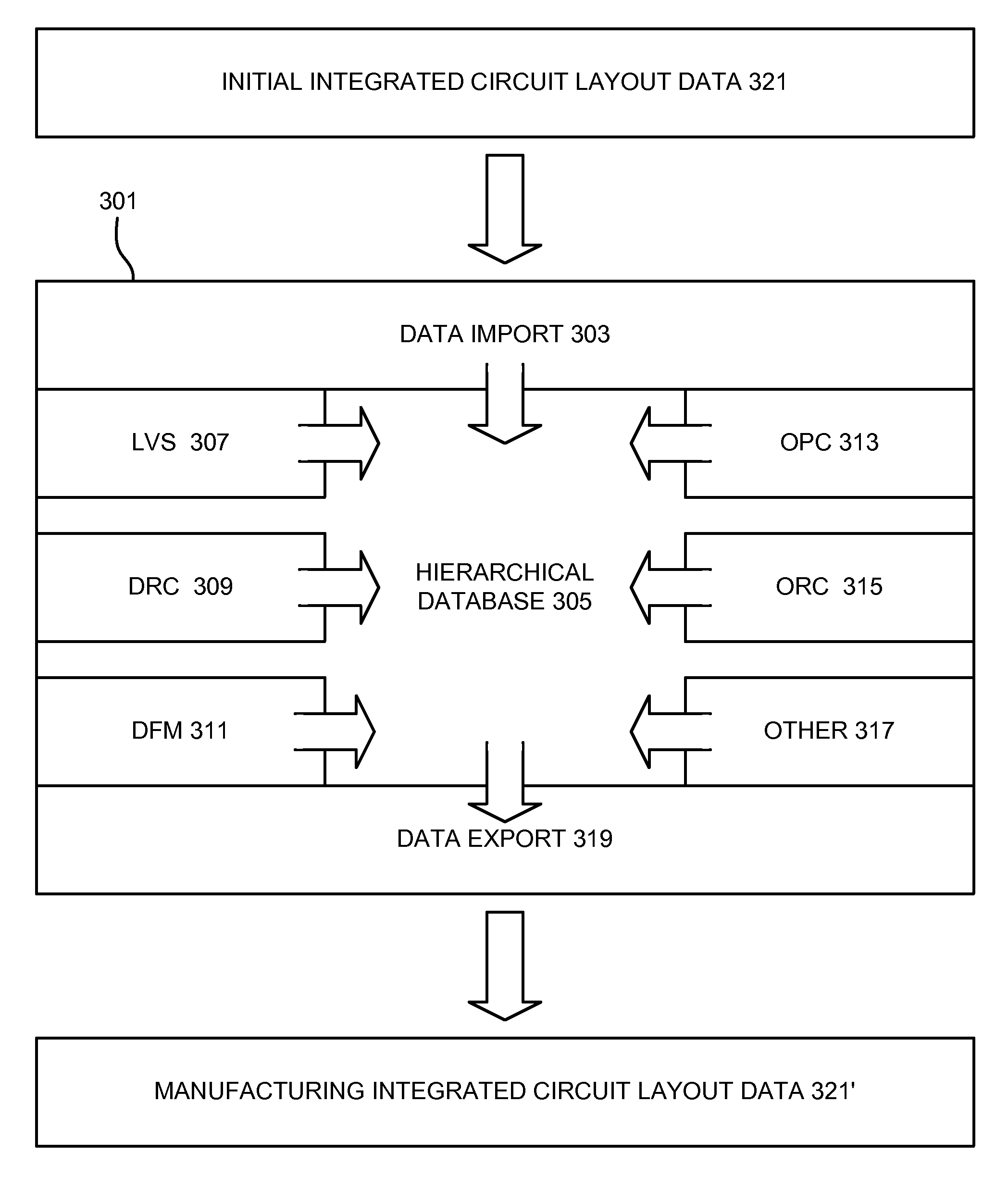

System for designing integrated circuits with enhanced manufacturability

ActiveUS7523429B2Improve manufacturabilityLittle interferencePressersMattress sewingGranularityEngineering

A system and method for integrated circuit design are disclosed to enhance manufacturability of circuit layouts through generation of hierarchical design rules which capture localized layout requirements. In contrast to conventional techniques which apply global design rules, the disclosed IC design system and method partition the original design layout into a desired level of granularity based on specified layout and integrated circuit properties. At that localized level, the design rules are adjusted appropriately to capture the critical aspects from a manufacturability standpoint. These adjusted design rules are then used to perform localized layout manipulation and mask data conversion.

Owner:APPLIED MATERIALS INC

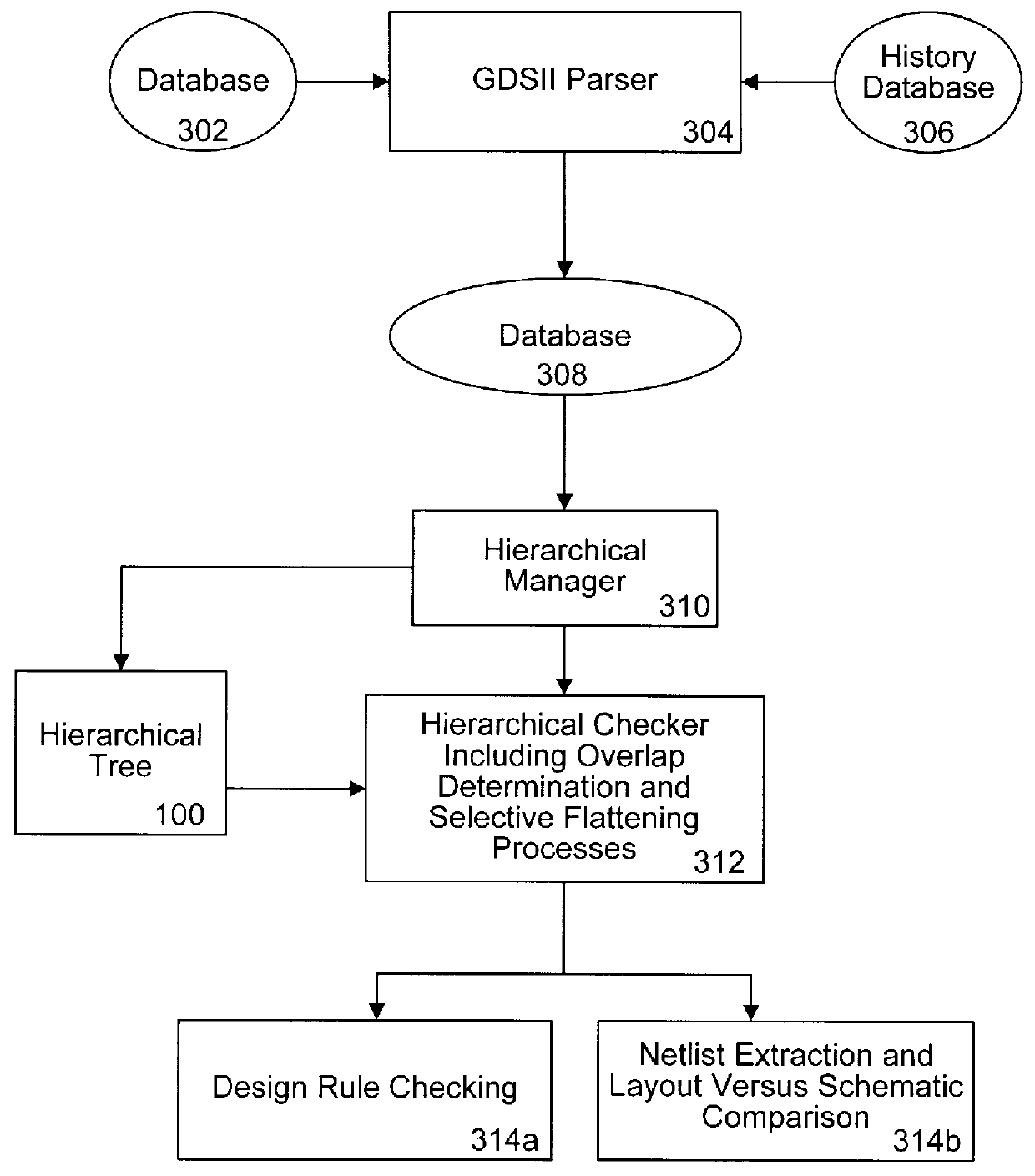

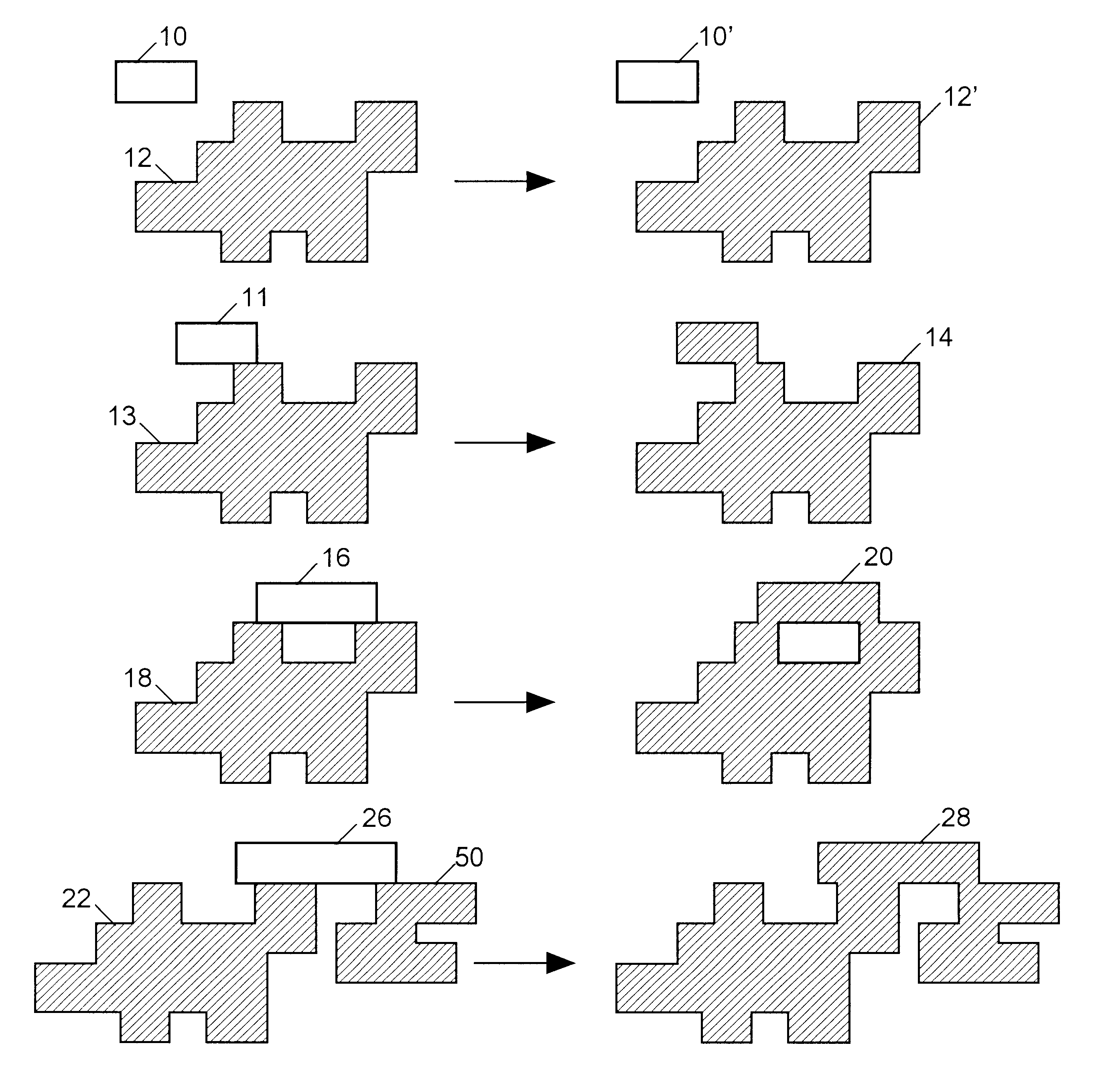

Layout overlap detection with selective flattening in computer implemented integrated circuit design

InactiveUS6011911AValid checkComputer aided designSoftware simulation/interpretation/emulationComputer architectureLayout Versus Schematic

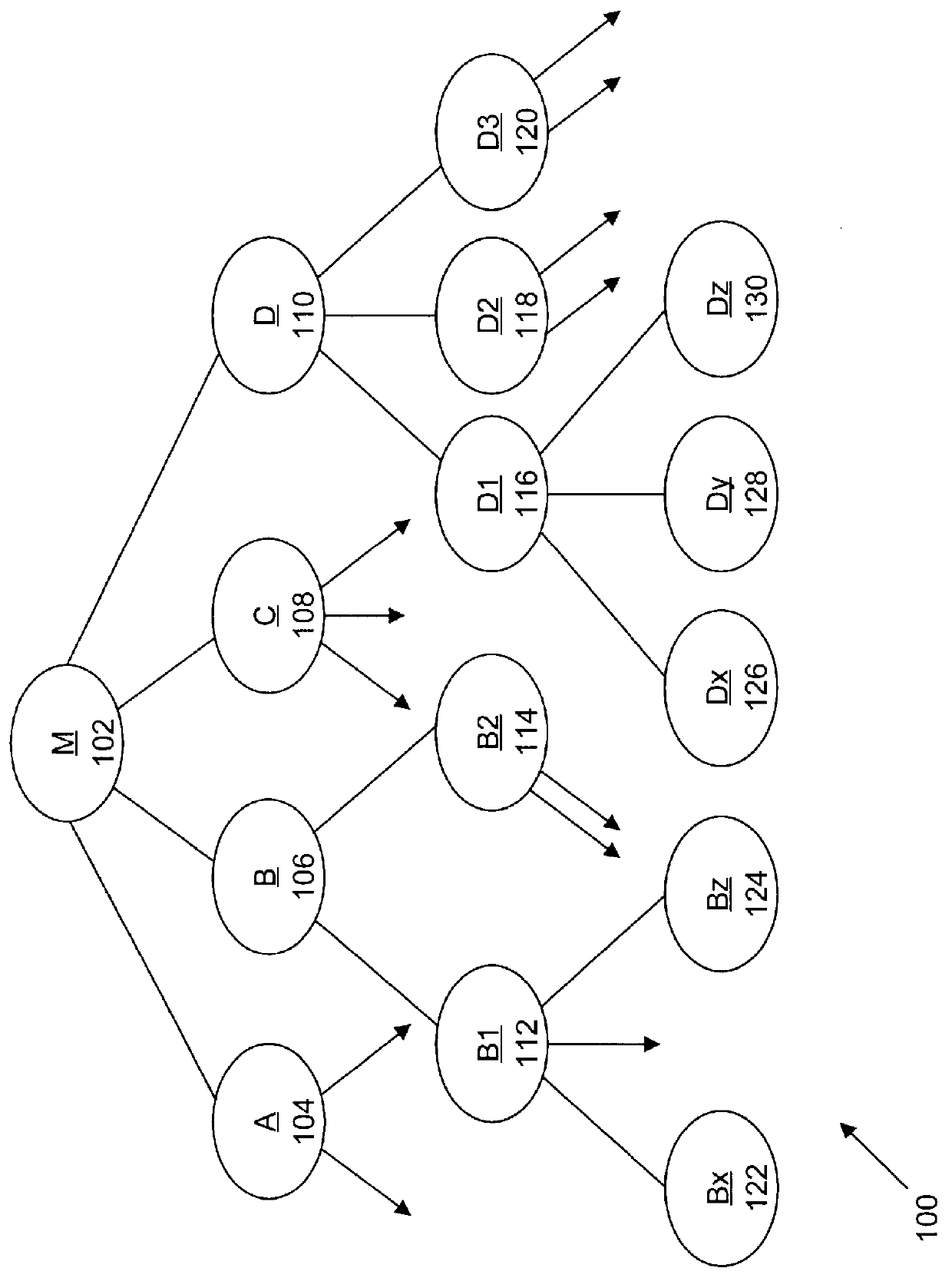

The present invention relates to a method for efficiently performing hierarchical design rules checks (DRC) and layout versus schematic comparison (LVS) on layout areas of an integrated circuit where cells overlap or where a cell and local geometry overlap. With the present invention, a hierarchical tree describes the integrated circuit's layout data including cells having parent-child relationships and including local geometry. The present invention performs efficient layout verification by performing LVS and DRC checking on the new portions of an integrated circuit design and layout areas containing overlapping cells. When instances of cells overlap, the present invention determines the overlap area using predefined data structures that divide each cell into an array of spatial bins. Each bin of a parent is examined to determine if two or more cell instances reside therein or if a cell instance and local geometry reside therein. Once overlap is detected, the areas of the layout data corresponding to the overlap areas are selectively flattened prior to proceeding to DRC and LVS processing. During selective flattening of the overlap areas, the hierarchical tree is traversed from the top cell down through intermediate nodes to the leaf nodes. Each time geometry data is located during the traversal, it is pushes directly to the top cell without being stored in intermediate locations. This provides an effective mechanism for selective flattening.

Owner:SYNOPSYS INC

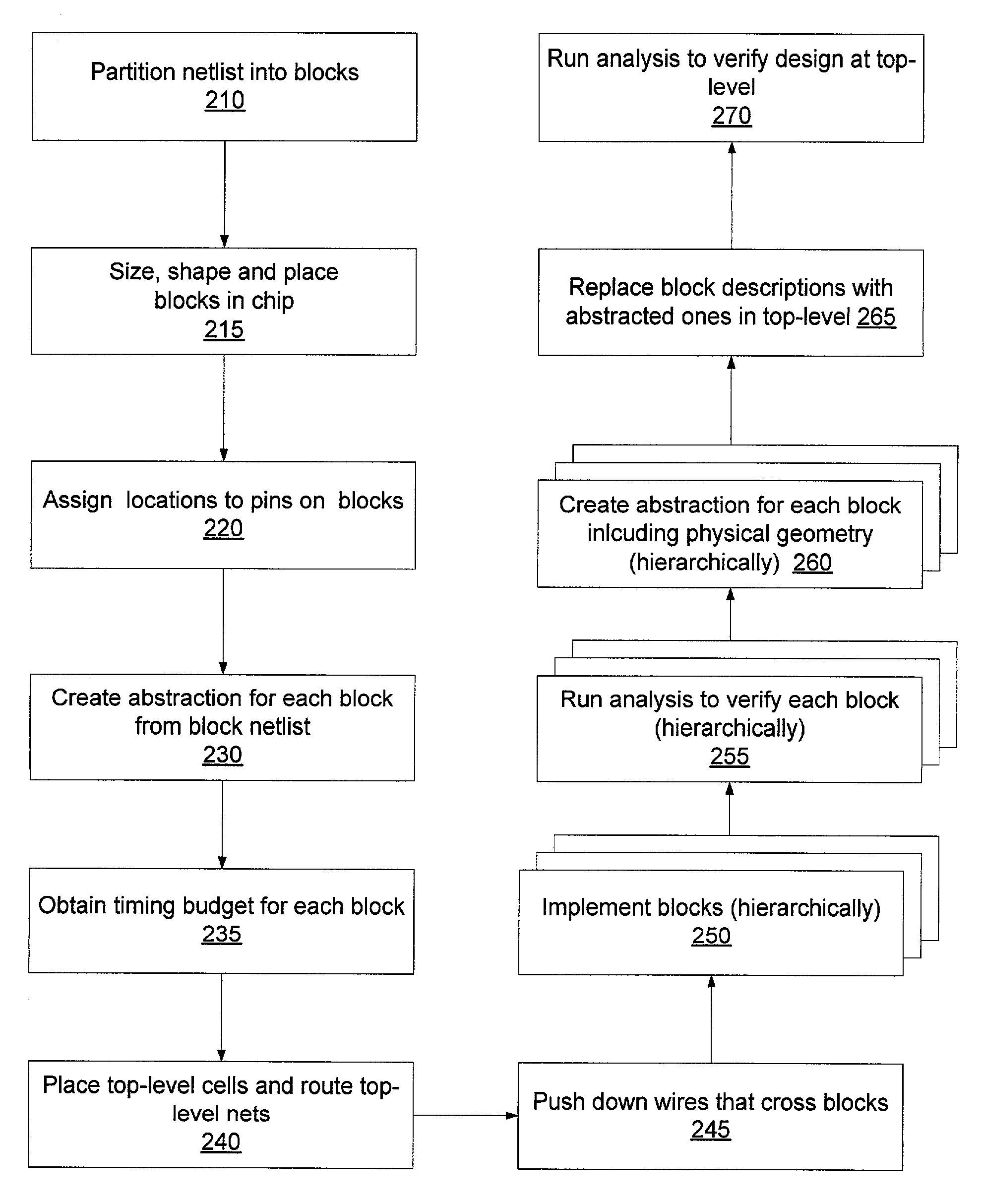

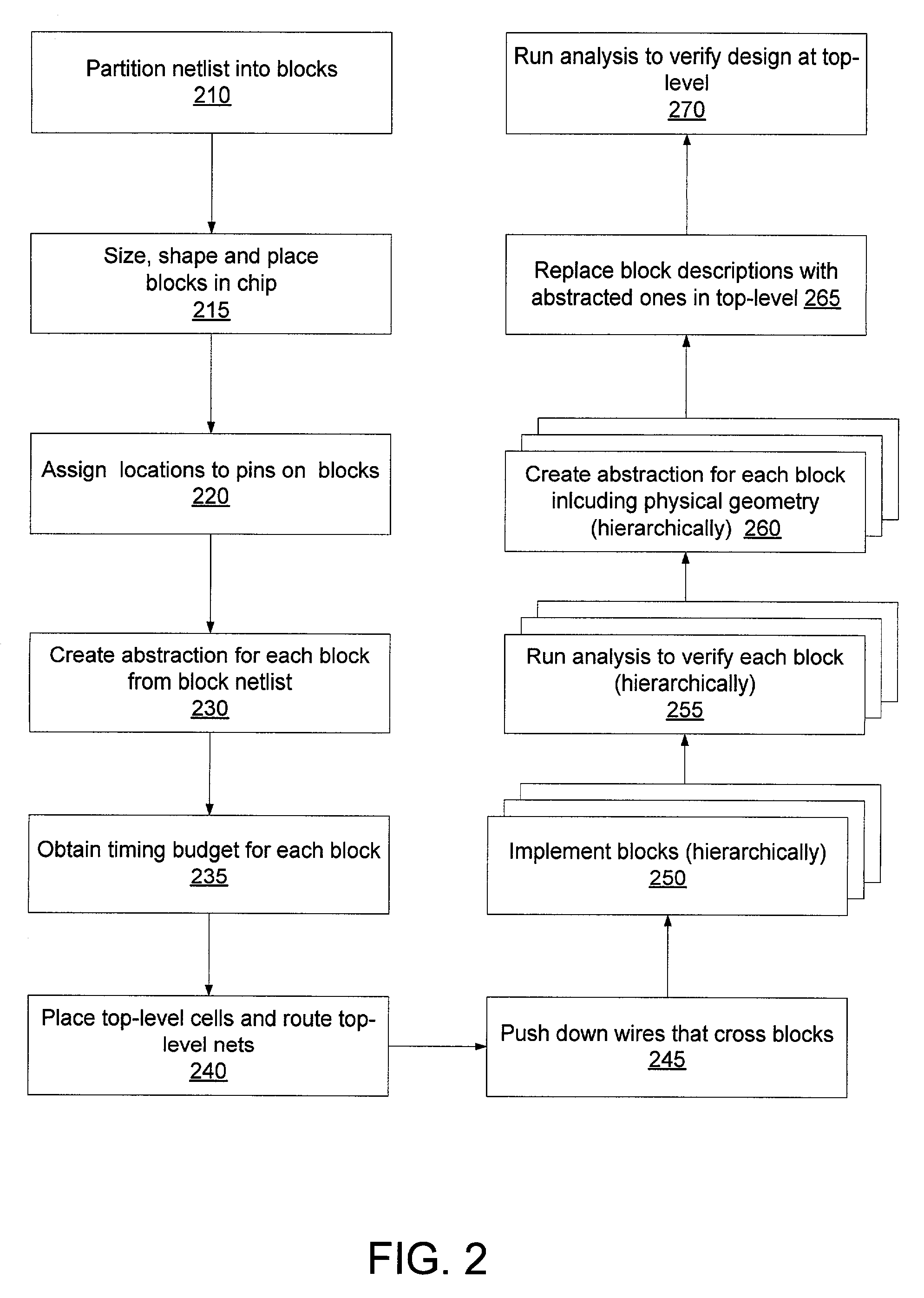

Representing the design of a sub-module in a hierarchical integrated circuit design and analysis system

InactiveUS7103863B2Reduce the amount of memoryReduce the amount requiredCAD circuit designSoftware simulation/interpretation/emulationComputer architectureHierarchical design

A method for modeling integrated circuit designs in a hierarchical design automation system which utilizes a block abstraction including therein set of all database objects (cells, nets, wires, vias, and blockages) that are necessary to achieve accurate placement, routing, extraction, simulation, and verification of the block's ancestors in the hierarchy.

Owner:SYNOPSYS INC

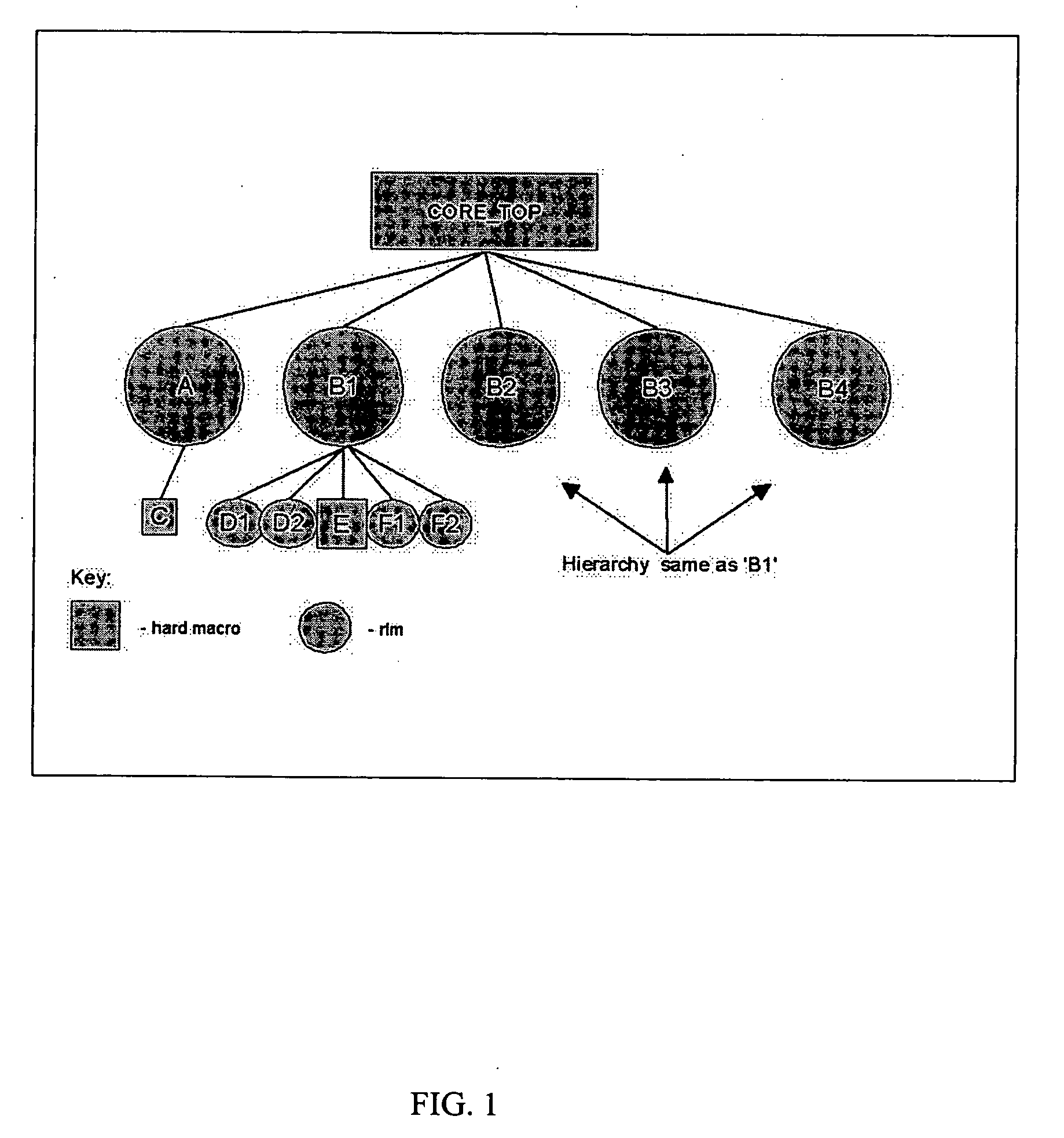

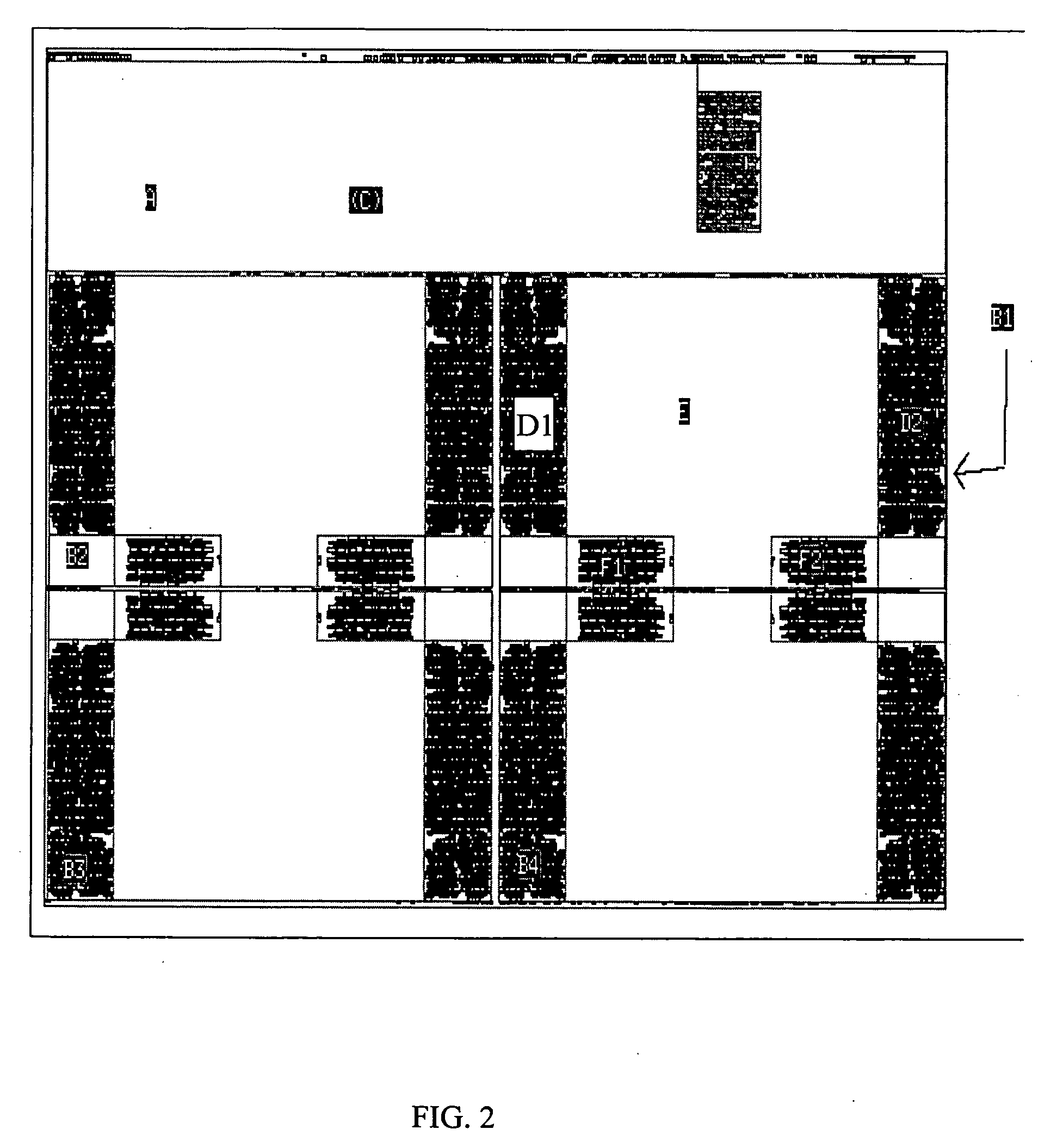

System and method to power route hierarchical designs that employ macro reuse

InactiveUS20070256044A1Computer aided designSpecial data processing applicationsHierarchical designLinearity

A method of routing a random logic macro (RLM) that is used multiple times in a hierarchical VLSI design without having to route each individual instantiation independently. Once an RLM has been routed and timed it can be copied and reused in a physical design as is, and does not require any wiring changes. This method is an advantage over existing art because it conserves area, improves wireability, and reduces the time required for routing and timing each RLM instance. Furthermore, each RLM possesses the same timing and power characteristics, which improves overall circuit performance.

Owner:IBM CORP

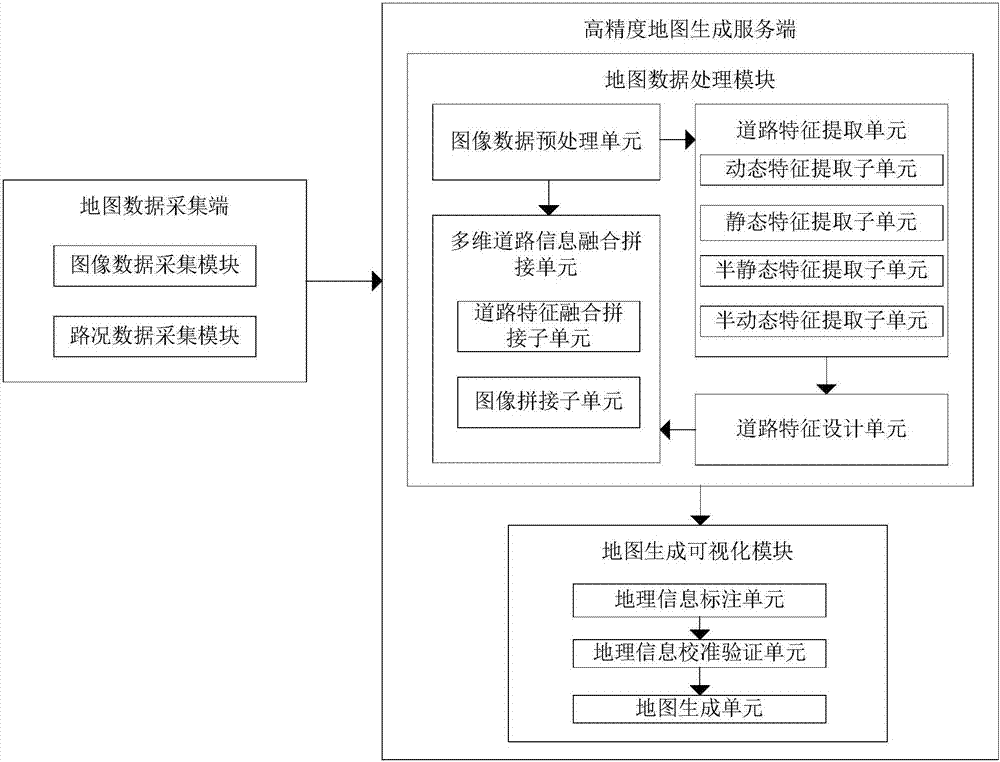

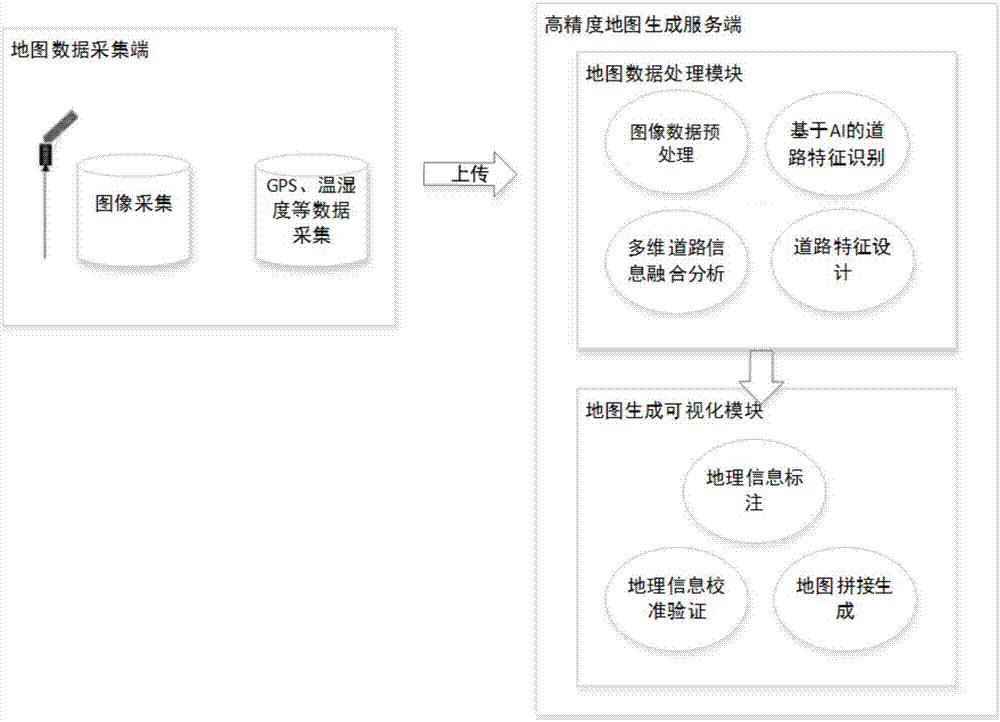

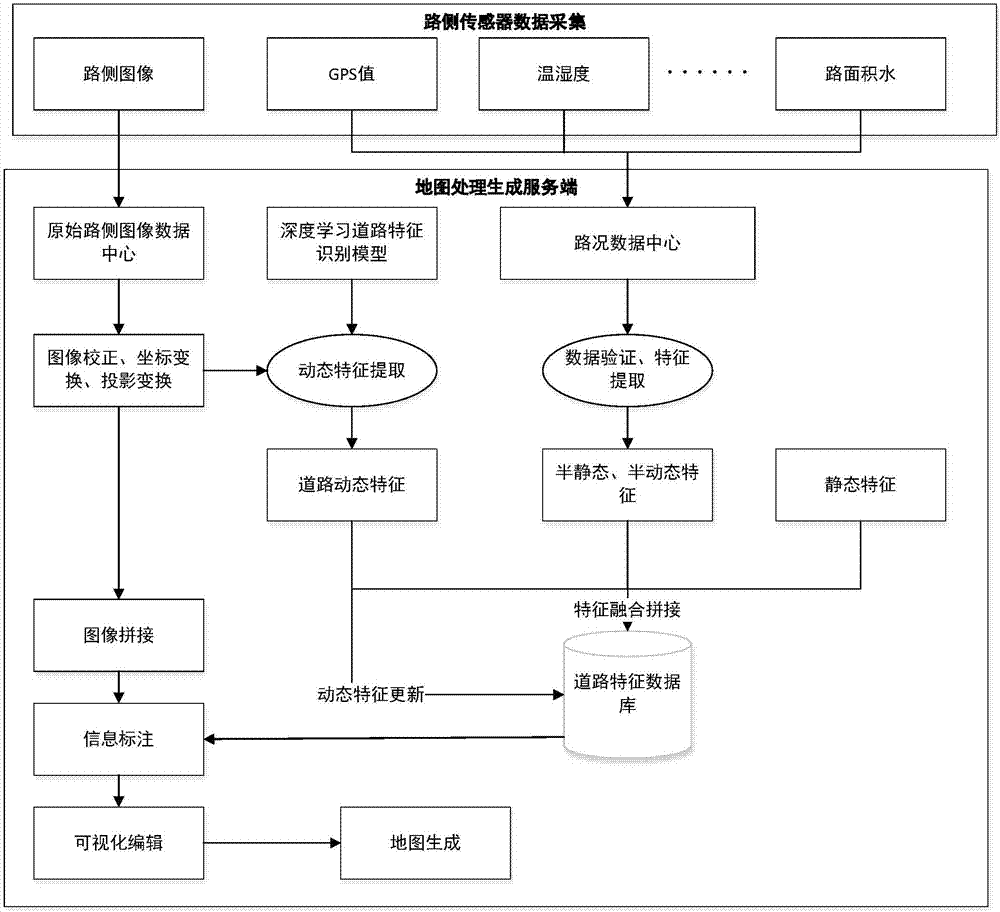

High-precision dynamic map data processing system and method based on road side sensors

ActiveCN107229690AWith real-time validityReal-time acquisitionRoad vehicles traffic controlCharacter and pattern recognitionData processing systemFeature extraction

The invention discloses a high-precision dynamic map data processing system and method based on road side sensors. The high-precision dynamic map data processing system comprises a map data acquisition terminal and a high-precision map generation service terminal. The map data acquisition terminal provides a bulk of diversified map road original data for the high-precision map generation service terminal; the high-precision map generation service terminal comprises a map data processing module and a map generation visual module; the map data processing module is used for extracting road features from the map road original data and carrying out hierarchical design on all the road features, splicing information of the same road, completing road feature data fusion on the road feature aspect first, finally completing image splicing on the image aspect, and generating a road downward projection drawing in dependence on the splicing result; and the map generation visual module is used for marking road information on the downward projection drawing, the marked road information and the downward projection drawing commonly form map data of a high-precision map, visual editing is carried out on the map data, and a high-precision dynamic map is generated. According to the invention, the generation cost of the high-precision map can be reduced, and the high-precision dynamic map can be updated quickly.

Owner:INST OF SOFTWARE APPL TECH GUANGZHOU & CHINESE ACAD OF SCI

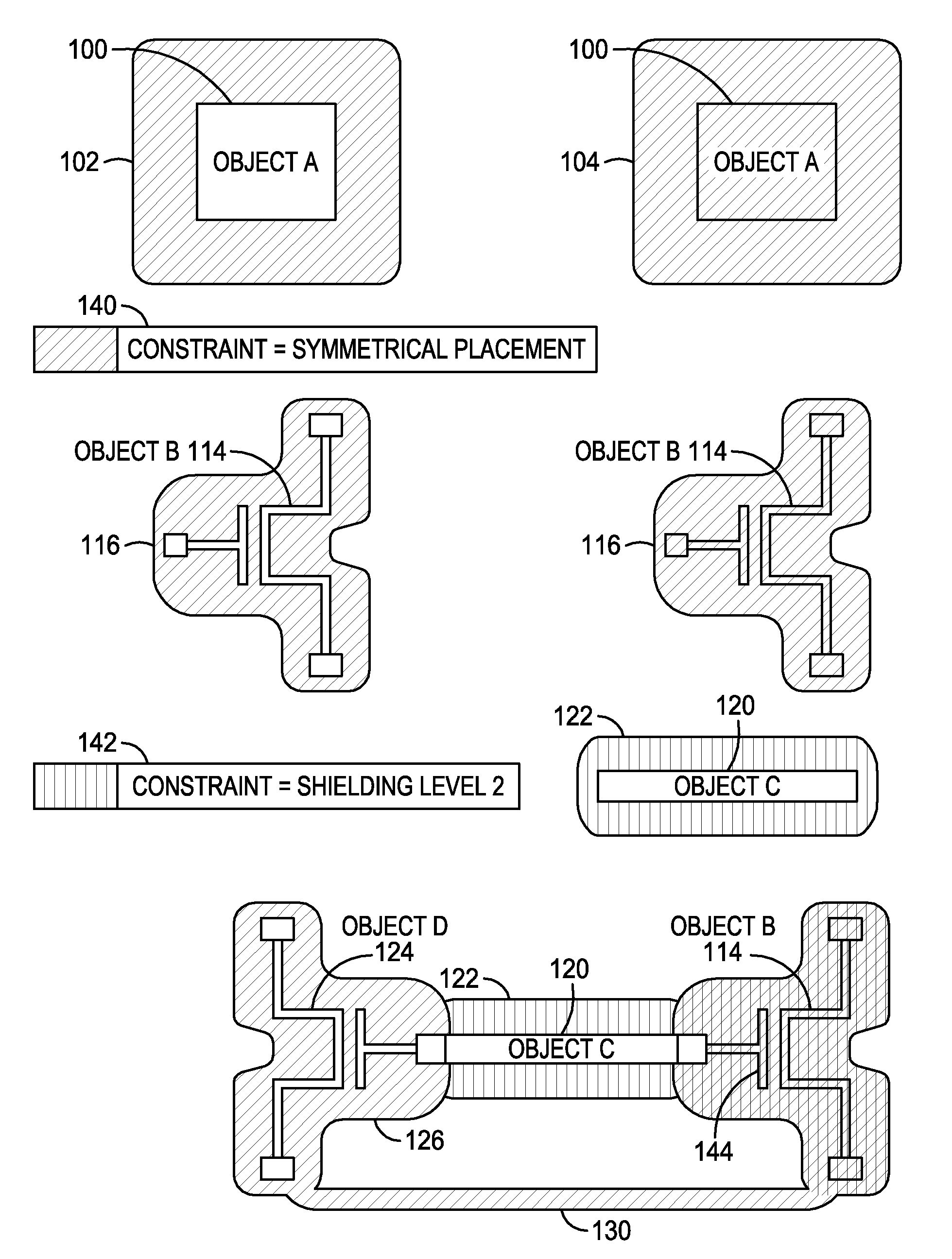

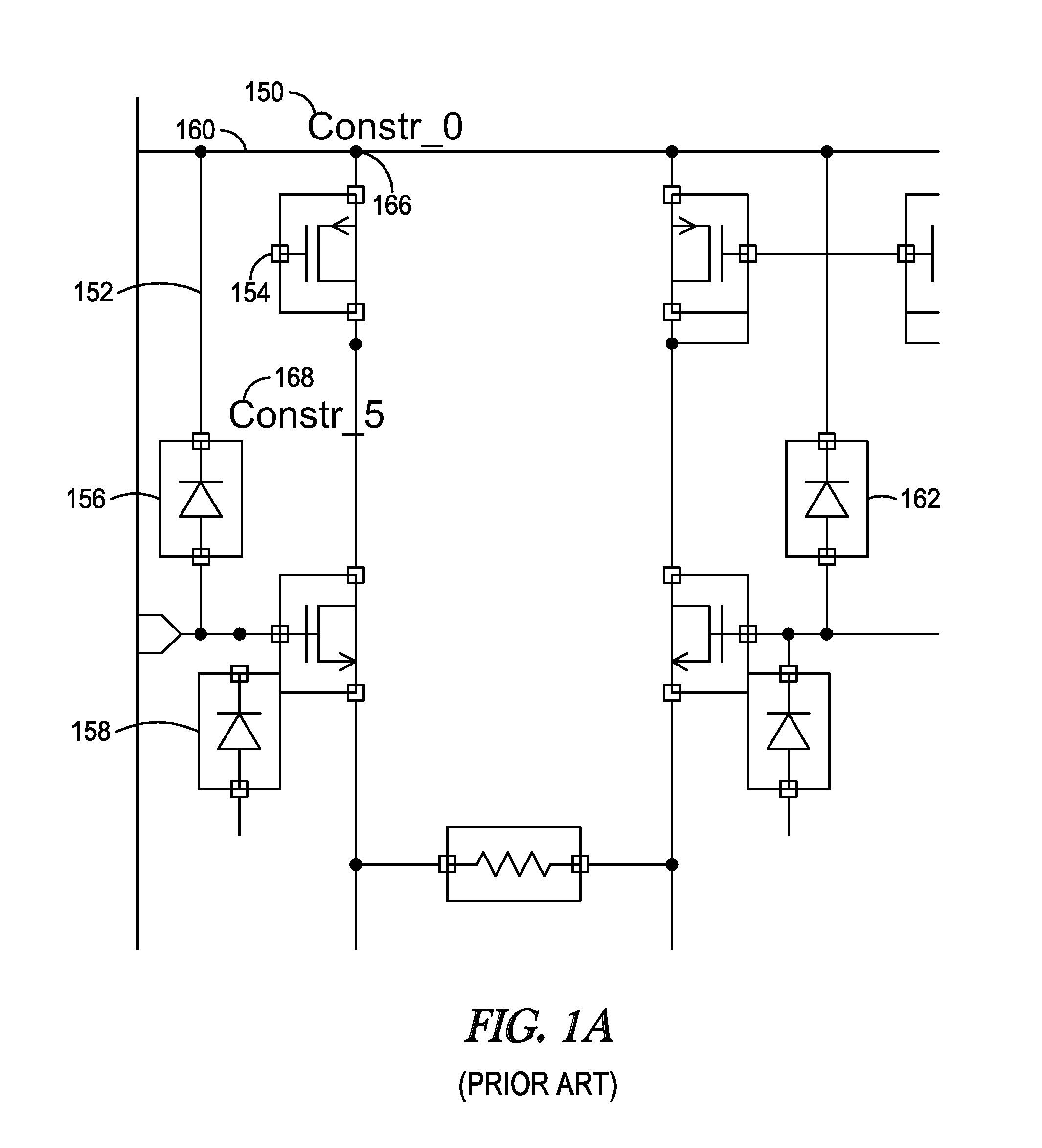

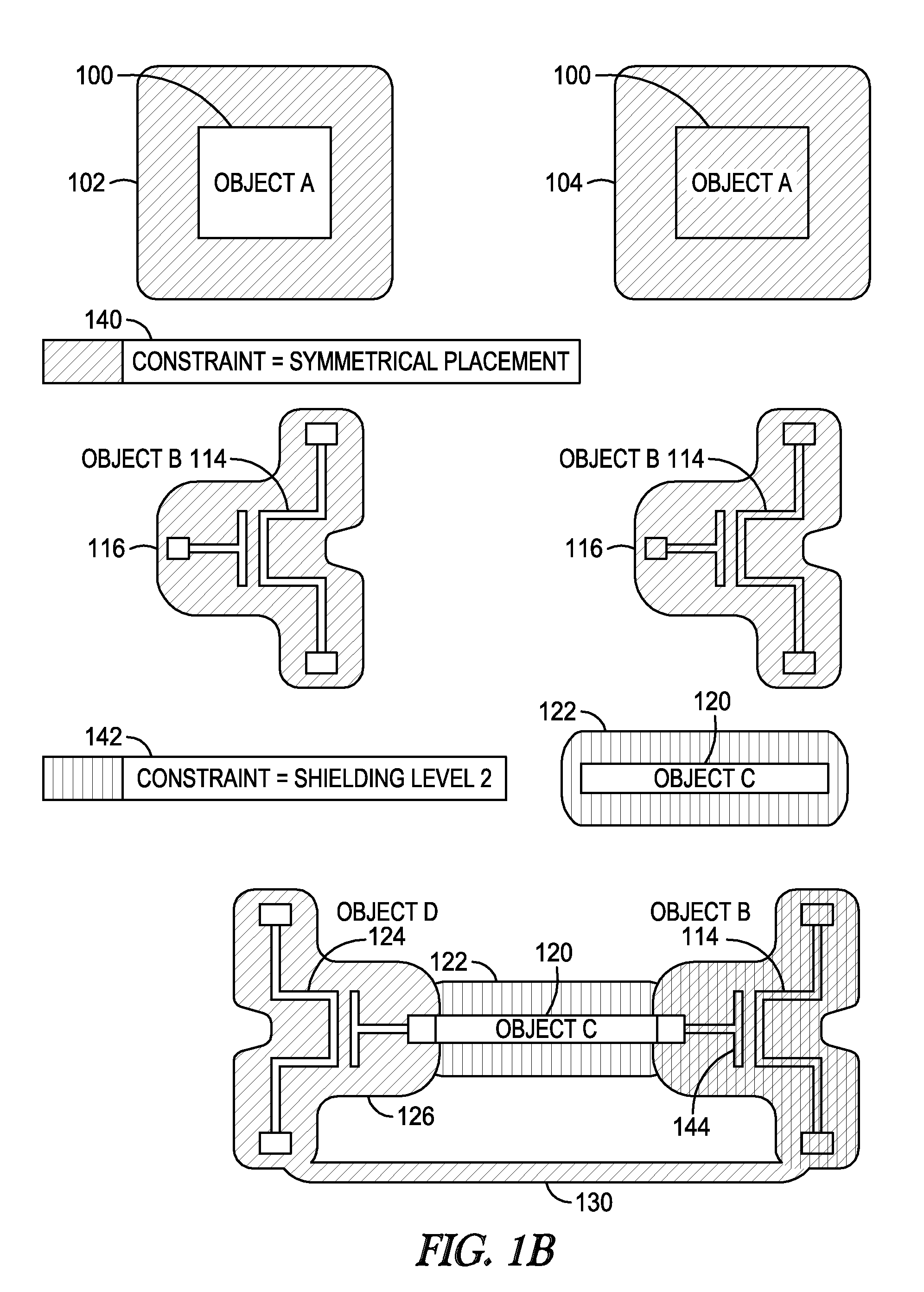

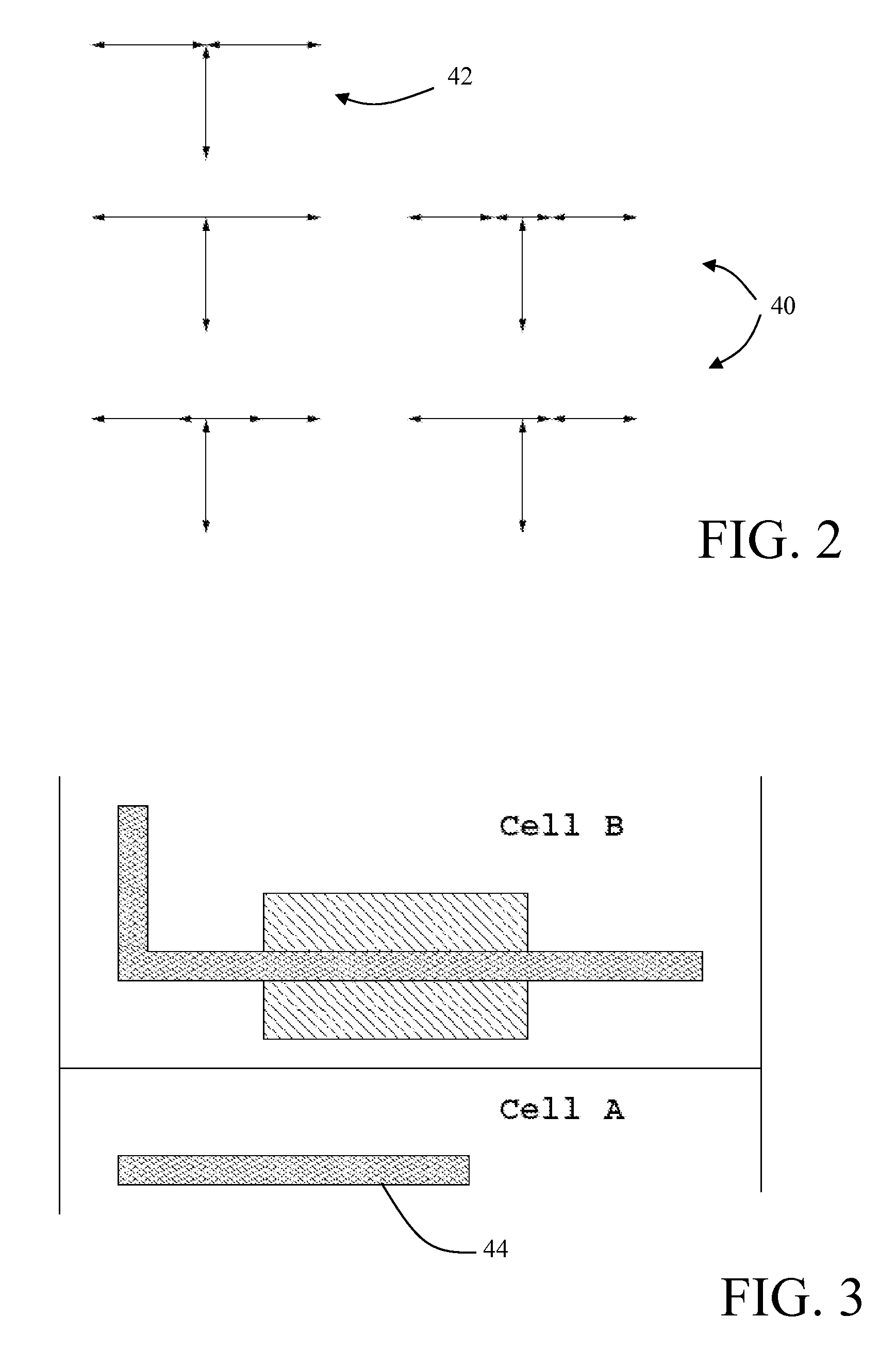

System and method for improved visualization and debugging of constraint circuit objects

Features are provided for graphically representing constraints on design objects in an Electronic Design Automation tool. A particular constraint on one or more circuit objects is displayed as a highlighted region that extends to each visible circuit object to which the constraint applies. Attributes of the highlighted region, such as density and thickness, may proportionally represent attributes of the constraint, such as a strength or distance specified by the constraint. The highlighted region is superimposed on or around circuit objects. The highlighted region may be a halo, which is a partially transparent region filled with a color. Multiple regions that represent the same type of constraint or relationship are connected by line segments, providing the ability to visualize groups of constrained objects, including groups that span levels of a hierarchical design. Intersecting highlighted regions are blended together using techniques such as alpha blending.

Owner:CADENCE DESIGN SYST INC

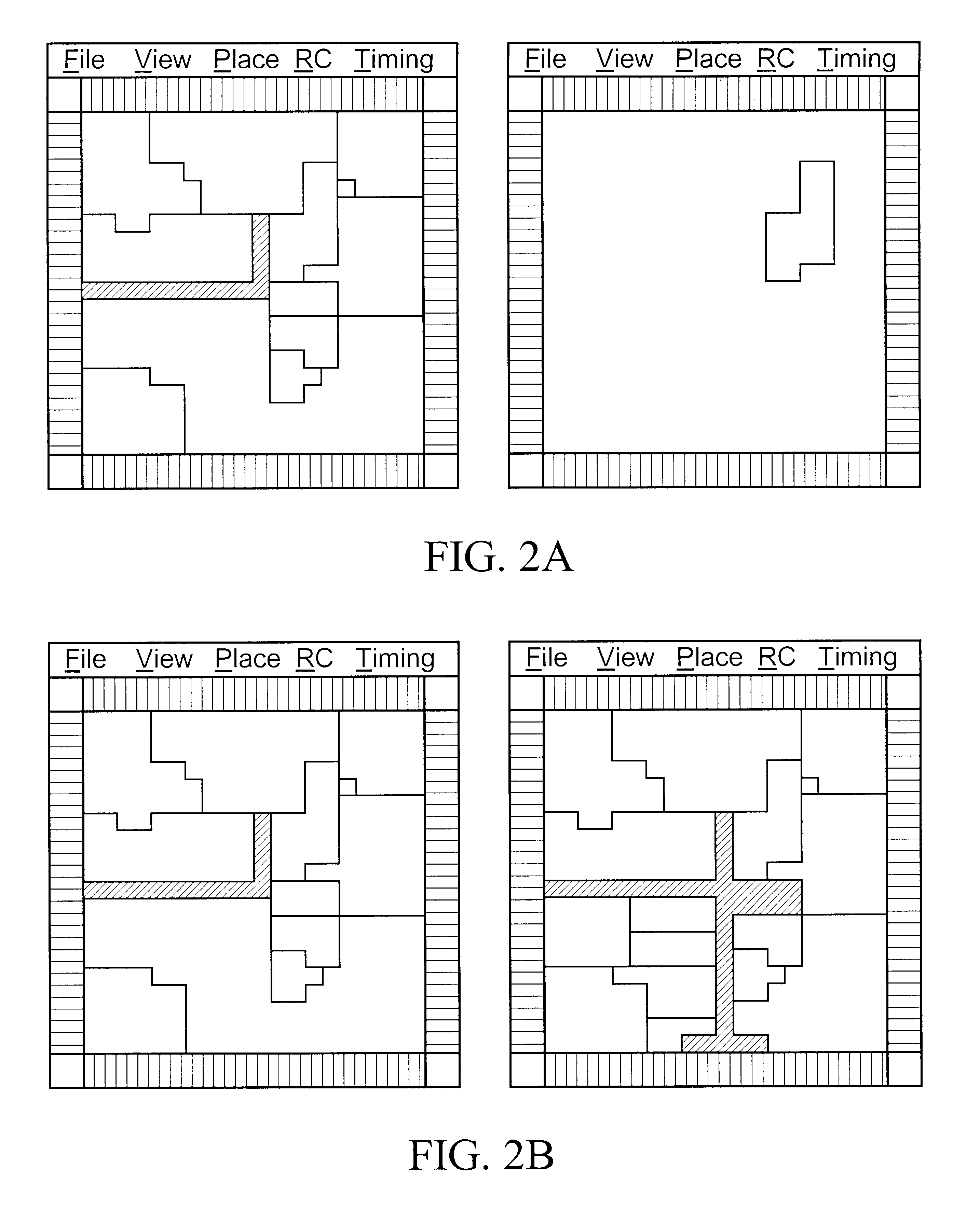

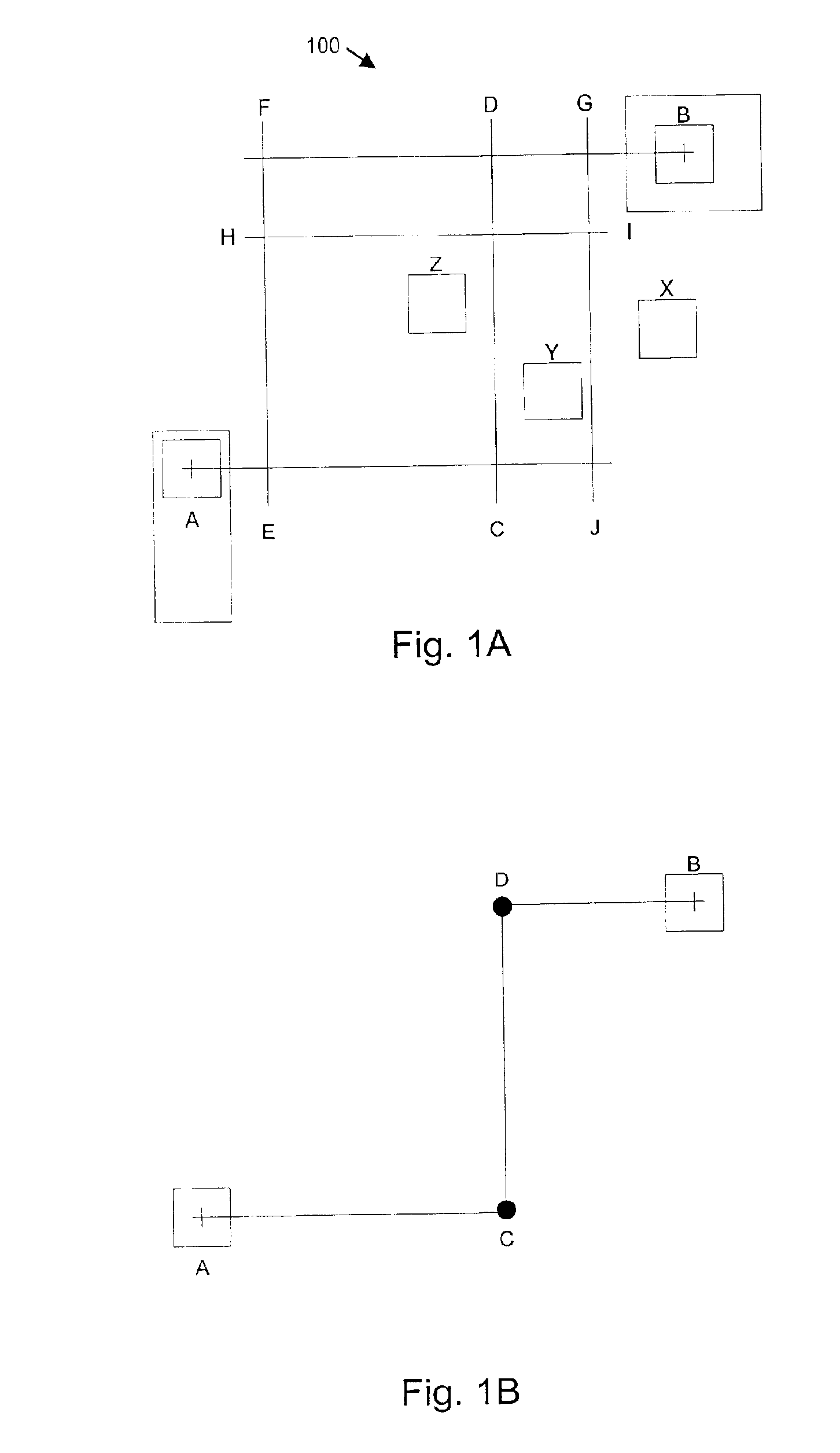

Amoeba display for hierarchical layout

InactiveUS6256768B1Computer programmed simultaneously with data introductionCAD circuit designComputer architectureLow speed

CAD software for automated circuit design provides improved display of hierarchical layout. Component placement perimeters are shown with "amoeba" characteristic for improved circuit floor-planning and analysis. Amoeba view of hierarchical design perimeter enables more intuitive observation of circuit floor-plan from actual component placement. Informational brevity conveyed by perimeters of hierarchies in design facilitates simpler interpretation of complex circuit layout, as well as distributed data access to remote sites through email or low-speed network.

Owner:CADENCE DESIGN SYST INC

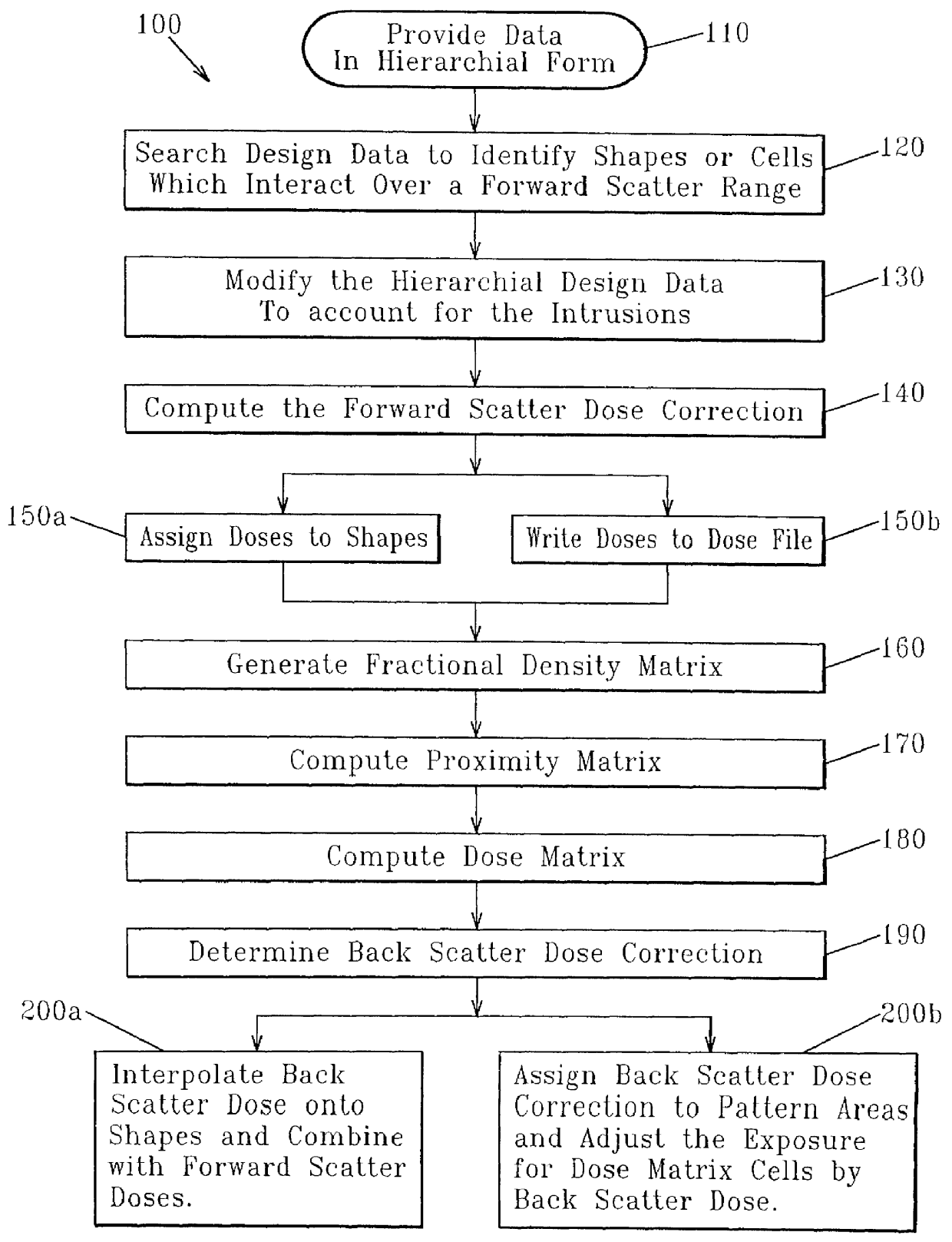

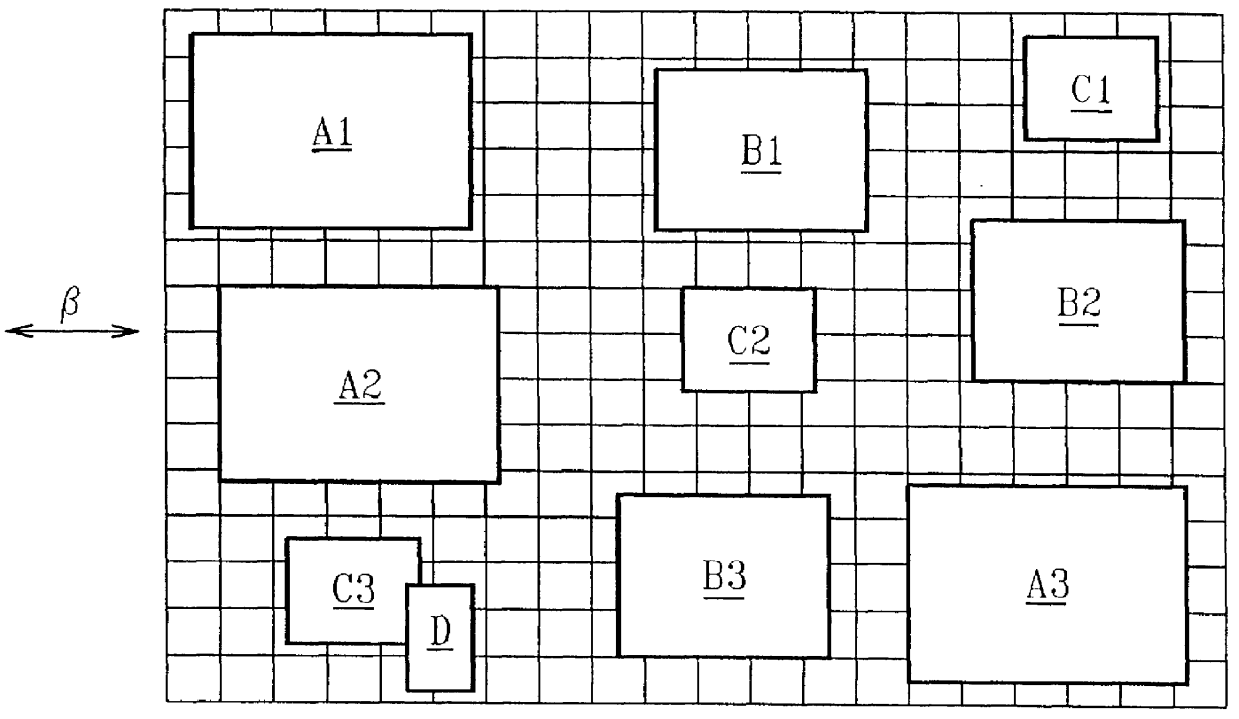

Electron beam proximity correction method for hierarchical design data

InactiveUS6035113AReduce proximity effectImprove computing efficiencyElectric discharge tubesSpecial data processing applicationsForward scatterResist

A method for formulating an exposure dose for an electron beam on a resist film for a pattern of geometric shapes which compensates for electron scattering effects utilizing hierarchial design data which is preserved to as great as an extent as possible in the computation of the exposure dose. The exposure dose is corrected for both the forward scatter and backscatter effects of the electron beam in which the design data is modified for interactions of shapes which are affected only over the forward scatter range. In another version of the method, a multiple Gaussian approximation is used where the short term Gaussian terms are treated as the forward scatter terms and the long term Gaussian terms are treated as the back scatter terms.

Owner:GLOBALFOUNDRIES INC

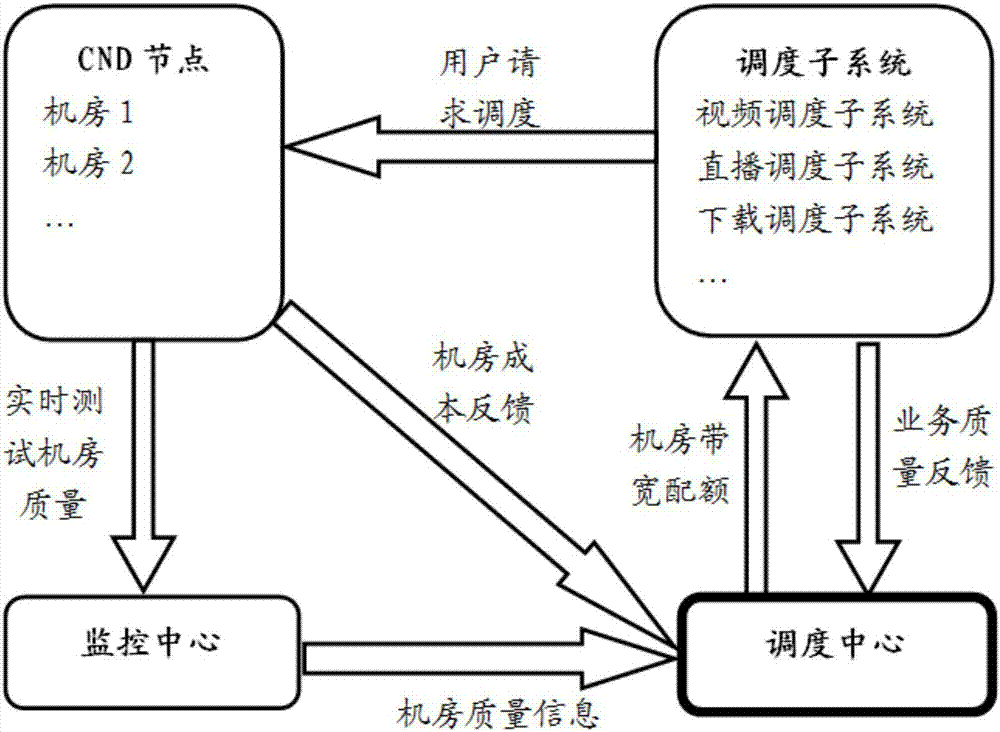

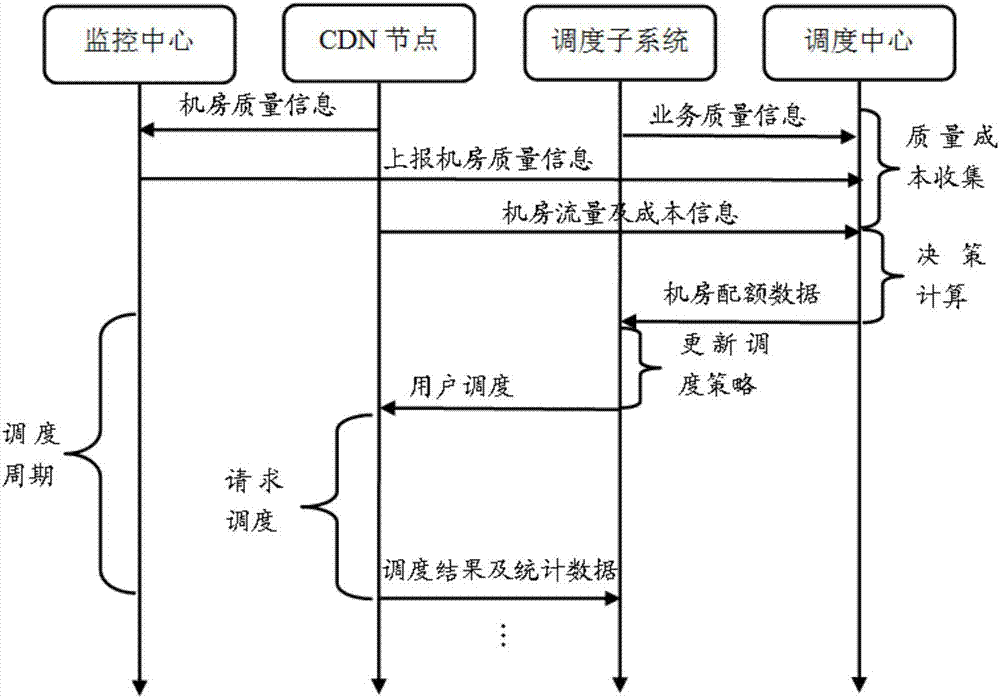

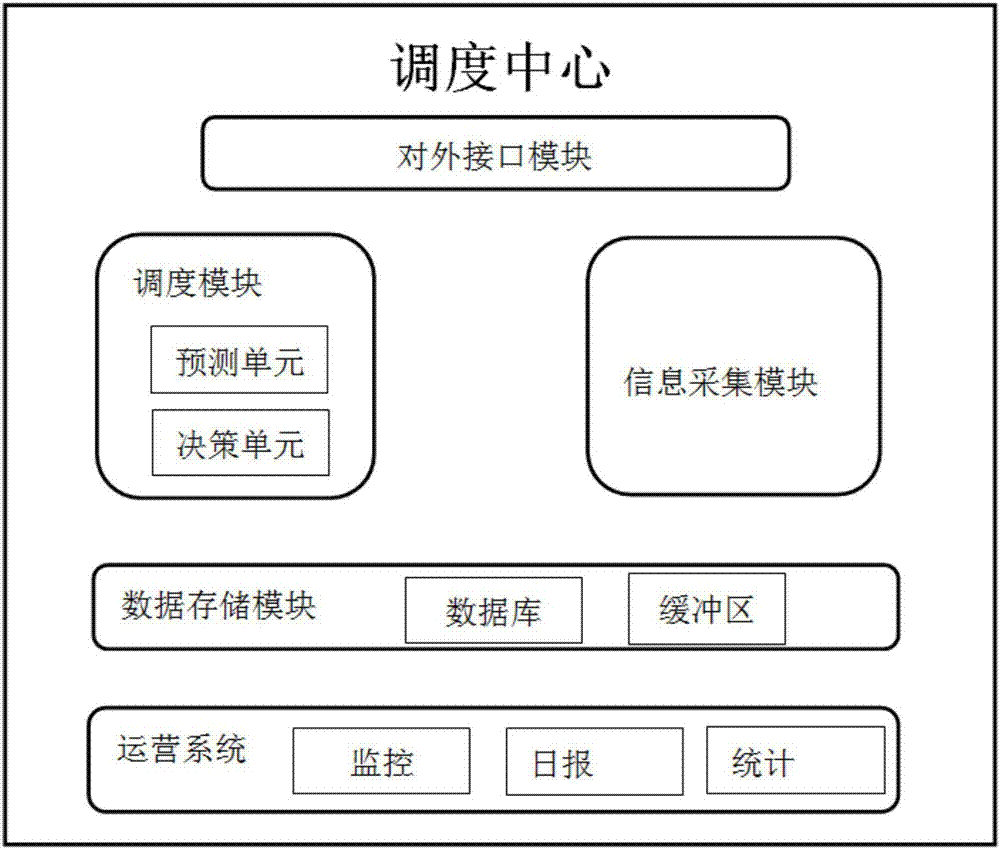

CDN bandwidth scheduling system and method

The invention discloses a CDN bandwidth scheduling system comprising a CDN node, a monitoring center, a scheduling subsystem and a scheduling center, wherein the monitoring center obtains machine room quality information of the CDN node and sends the machine room quality information to the scheduling center; the scheduling center calculates a machine room bandwidth quota of each machine room according to obtained machine room cost information, the machine room quality information and service quality information; and the scheduling subsystem updates a scheduling strategy according to a user request number, user bandwidth flow and the machine room bandwidth quota sent by the scheduling center. According to the CDN bandwidth scheduling system, the scheduling center is set to achieve the decoupling of CDN bandwidth scheduling and service scheduling via a hierarchical design, the scheduling subsystem provides the scheduling of service demands, the scheduling center controls the bandwidth quota of the scheduling subsystem while taking both of the quality and the cost into account, and thus the overall quality and cost are optimal.

Owner:TENCENT TECH (SHENZHEN) CO LTD

Method for routing connections in the display of a network topology

ActiveUS6880127B1Fast uniform and effective routingEffectively and uniformlyDrawing from basic elementsData processing applicationsProcess systemsHierarchical design

The present invention provides a systematic automated procedure for routing connections in display applications such as a network topology interface. In one embodiment, the invention first creates an “ideal routing” between two given nodes. The ideal routing includes three segments that join the nodes. If any obstructions exist on the original segments of the ideal routing then the procedure systematically reroutes the appropriate segments to achieve an efficient, visually cohesive and organized routing. The routing procedure operates at different layers, groups and subgroups of nodes. By using the procedure with a layered design it is possible to achieve fast, uniform and effective routing in very complex systems with many nodes and inter-node connections.

Owner:AVAGO TECH INT SALES PTE LTD

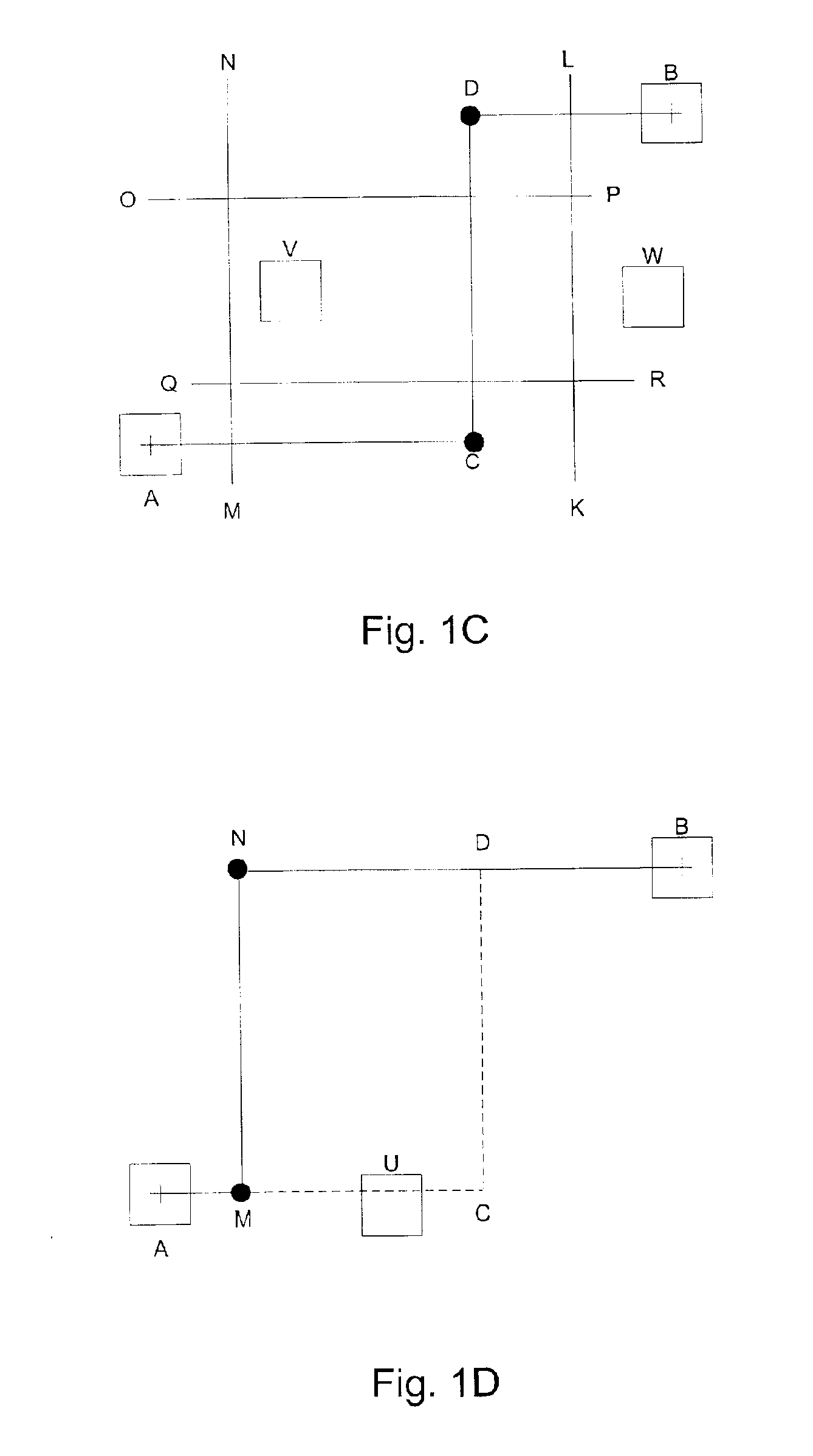

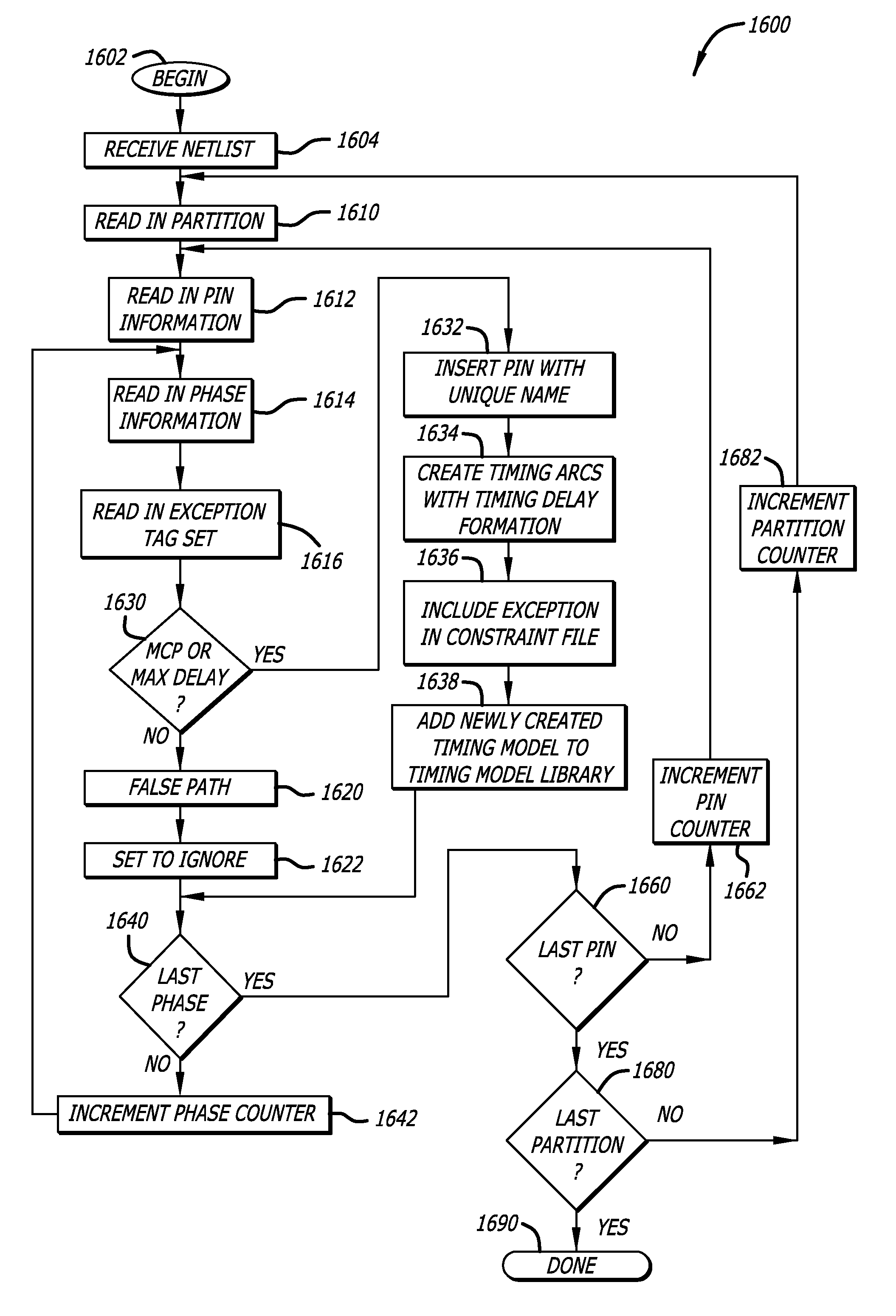

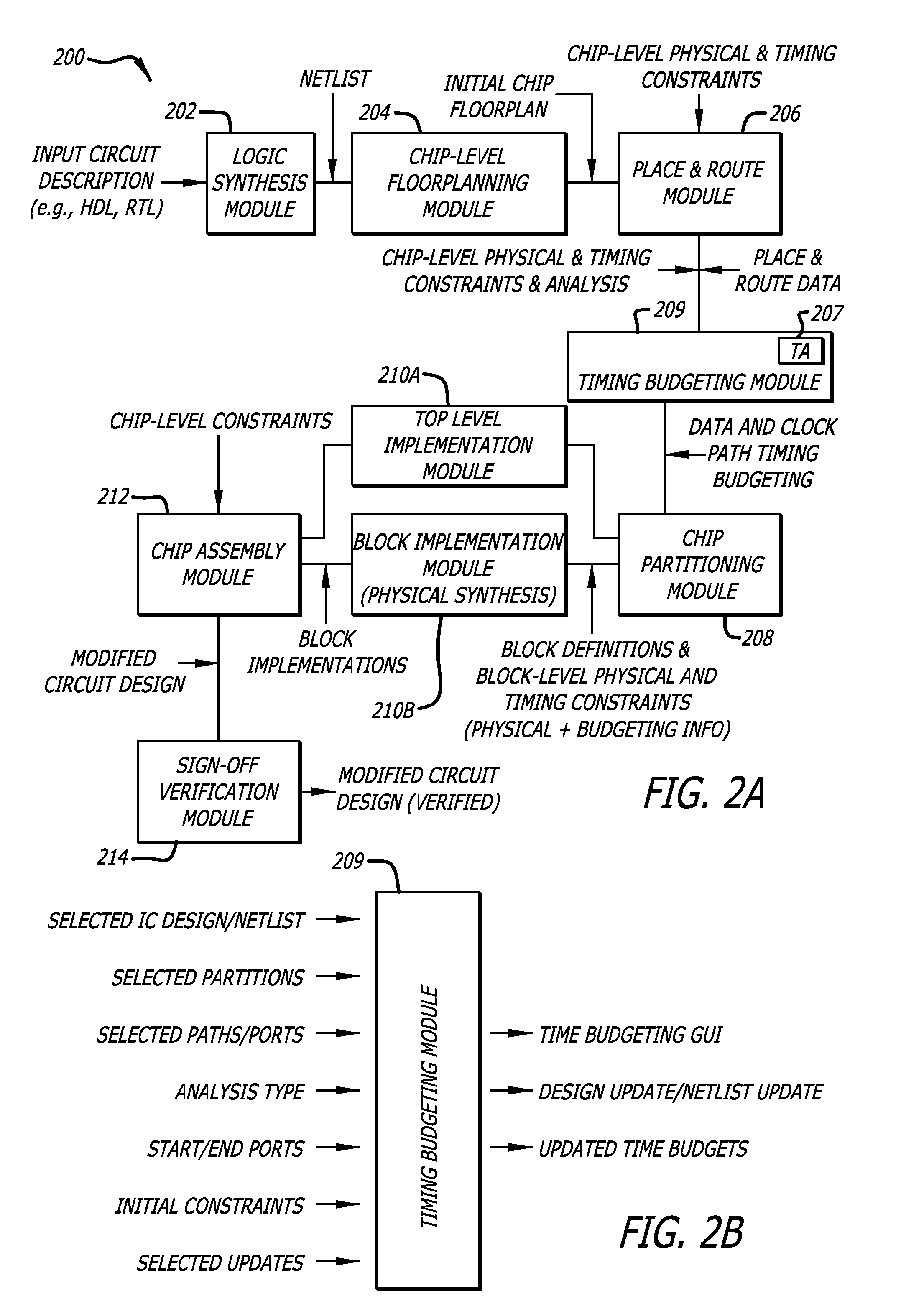

Multi-phase models for timing closure of integrated circuit designs

ActiveUS8640066B1Accurate modelingDetecting faulty computer hardwareComputer aided designFalse pathHierarchical design

In one embodiment, a method of designing an integrated circuit is disclosed, including receiving a first partition block for a top level of a hierarchical design of an integrated circuit; analyzing each pin of the first partition block for an attribute associated with the pin indicating a timing exception; and if a timing exception other than false path is indicated then generating an internal timing pin in a first timing graph model of the first partition block for each timing exception, and adding a timing arc and a dummy arc coupled to the internal timing pin in the first timing graph model of the first partition block. The internal timing pin adds a timing exception constraint for each timing exception. Timing of the top level may then be analyzed with the first timing graph model to determine if timing constraints, including the added timing exception constraints, are met.

Owner:CADENCE DESIGN SYST INC

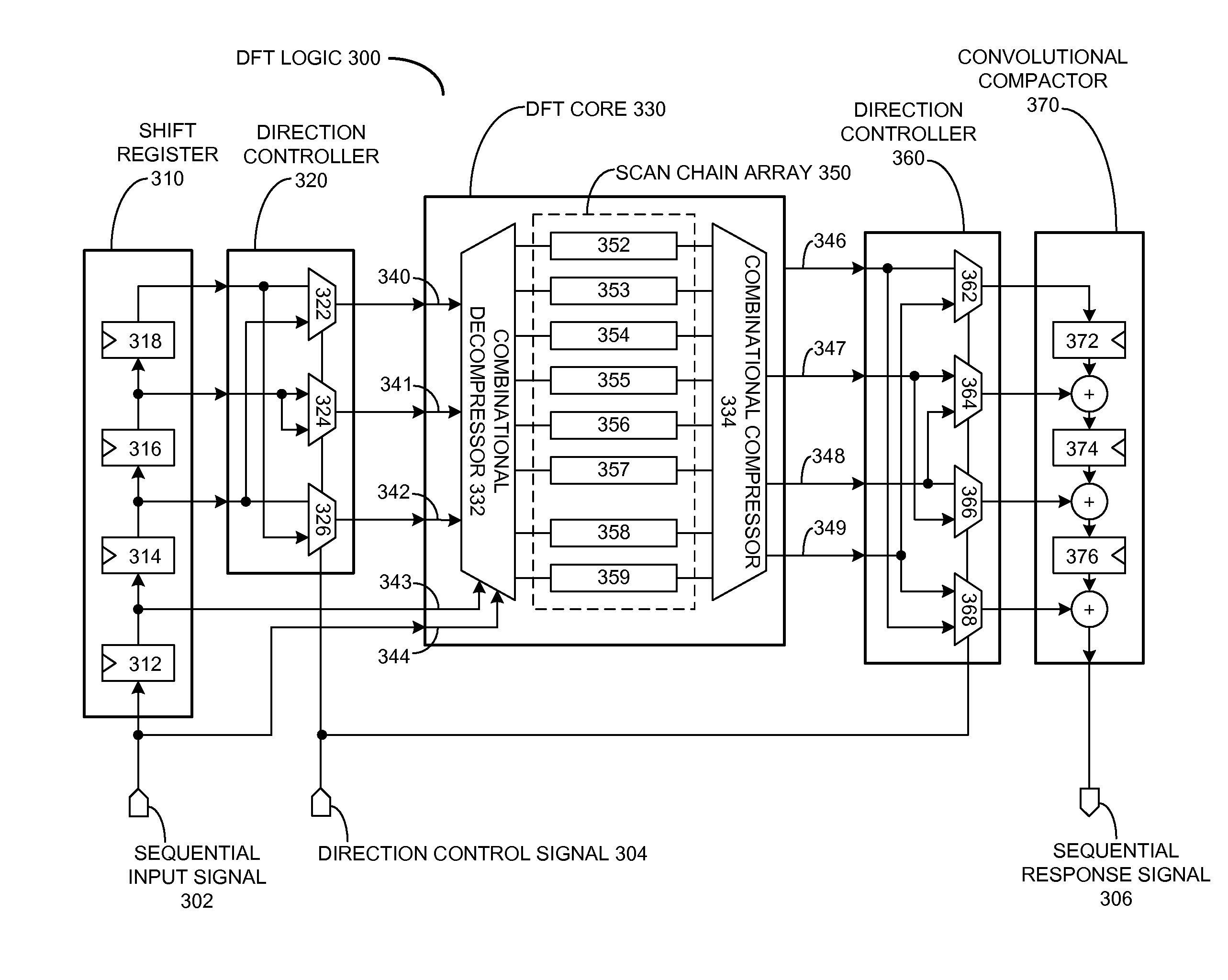

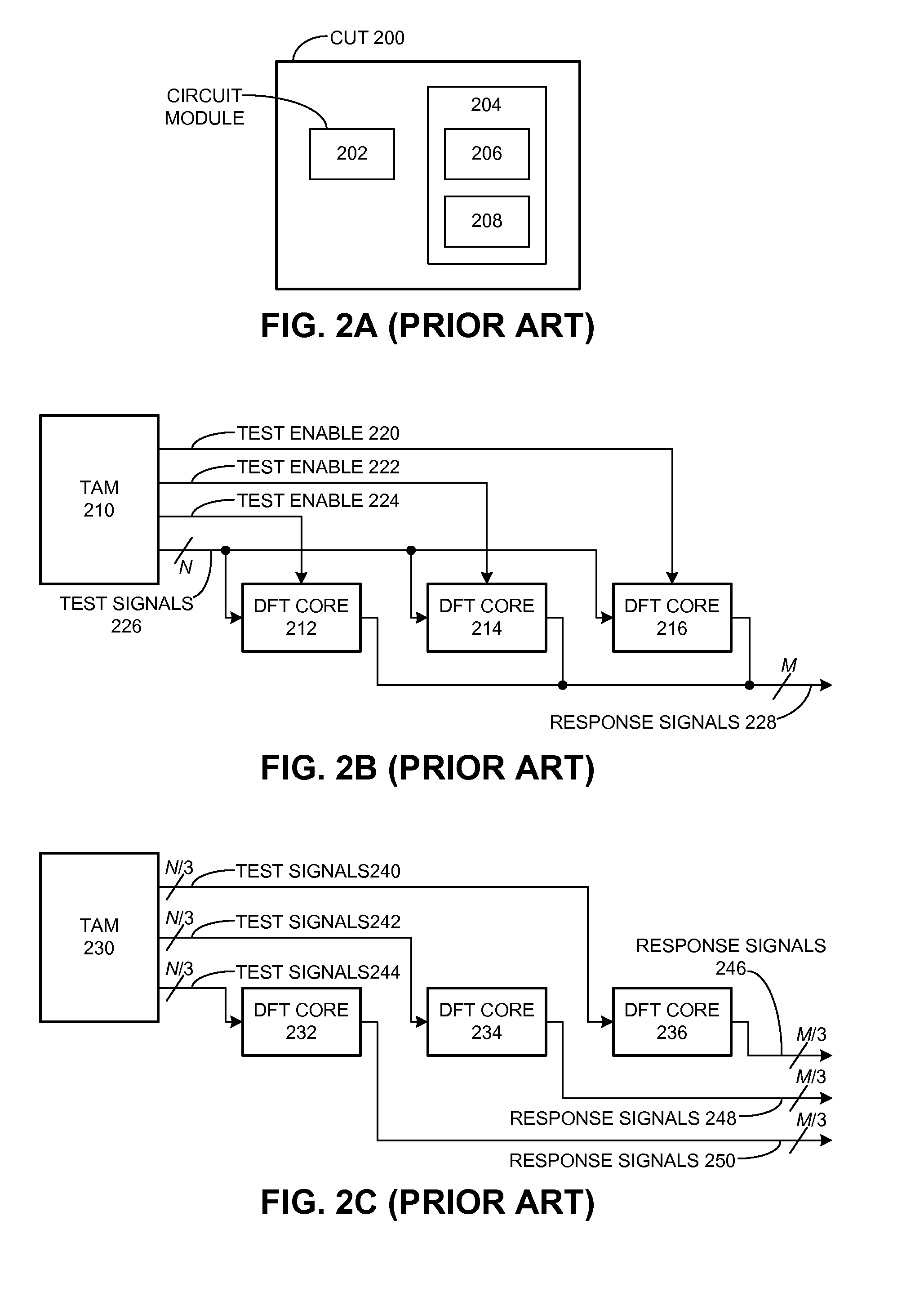

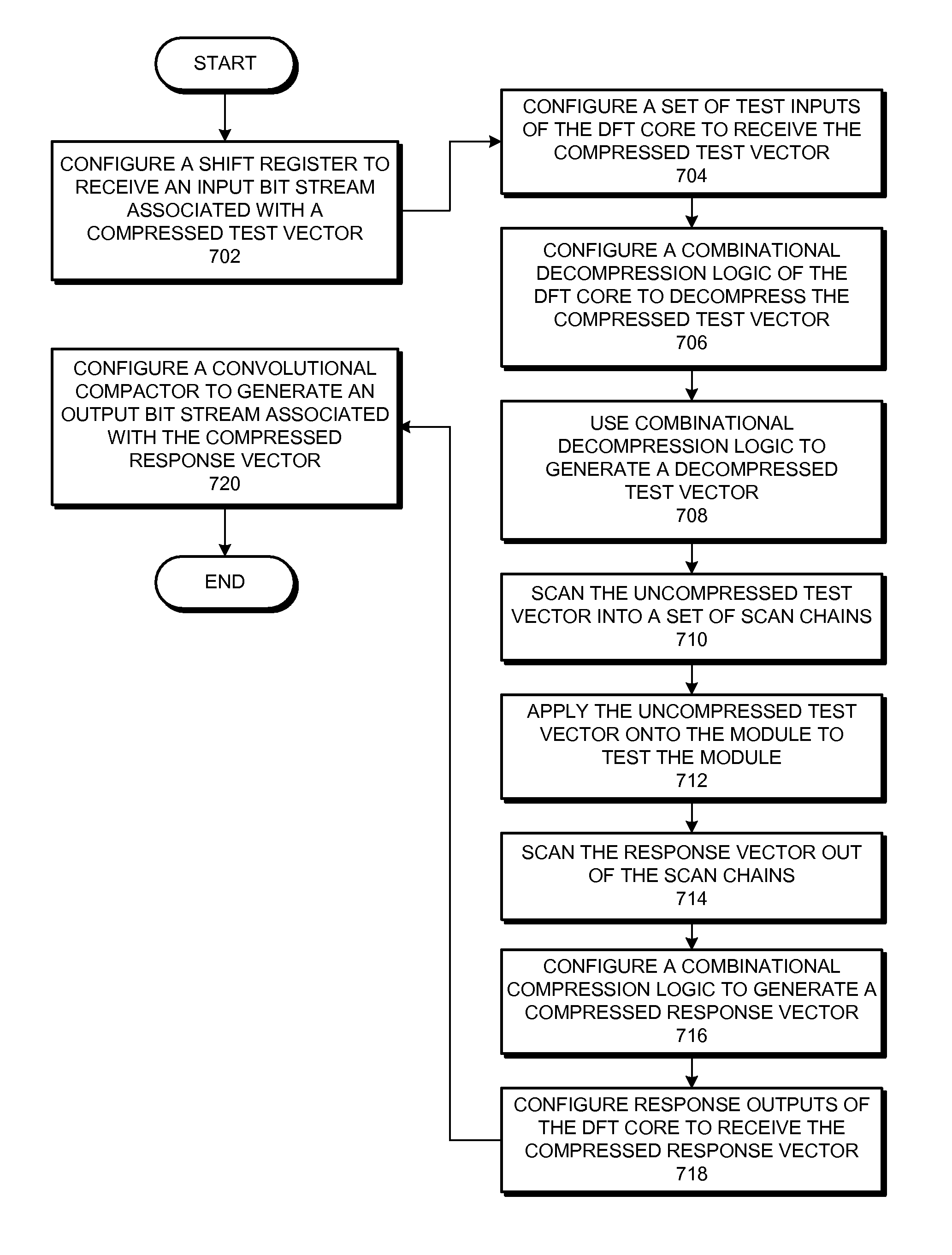

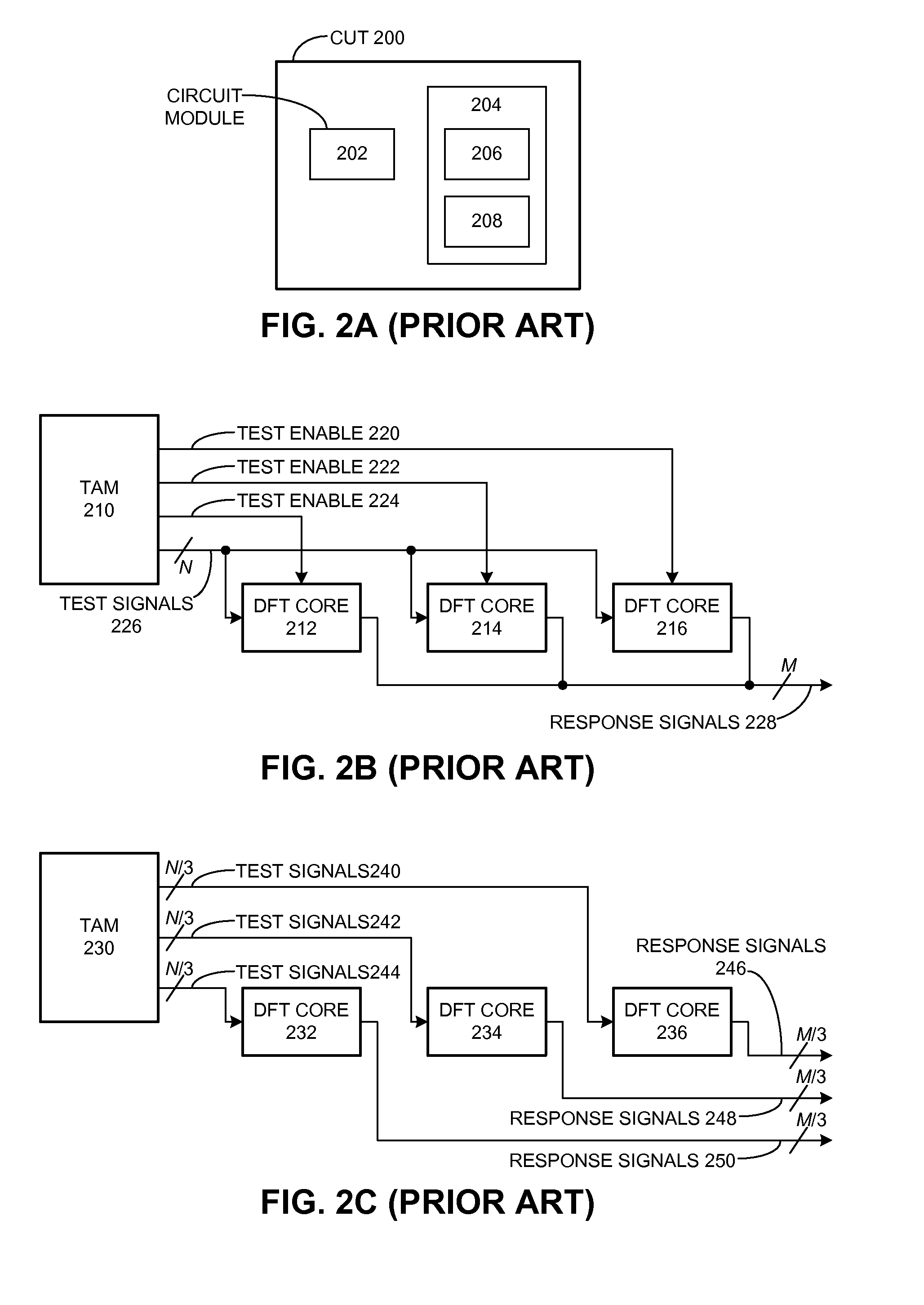

Method and apparatus for implementing a hierarchical design-for-test solution

ActiveUS20100192030A1Reduce test data testReduce test test application timeElectronic circuit testingLogical operation testingControl signalHierarchical design

Embodiments of the present invention provide methods and apparatuses for implementing hierarchical design-for-test (DFT) logic on a circuit. The hierarchical DFT logic implements DFT circuitry that can be dedicated to a module, and which can configure DFT circuitry for multiple modules to share a sequential input signal and / or to share a sequential output signal. During operation, the DFT circuitry for a first module can propagate a bit sequence from the sequential input signal to the DFT circuitry of a second module, such that the bit sequence can include a set of control signal values for controlling the DFT circuitry, and can include compressed test vectors for testing the modules. Furthermore, the DFT circuitry for the second module can generate a sequential response signal, which combines the compressed response vectors from the second module and a sequential response signal from the DFT circuitry of the first module.

Owner:SYNOPSYS INC

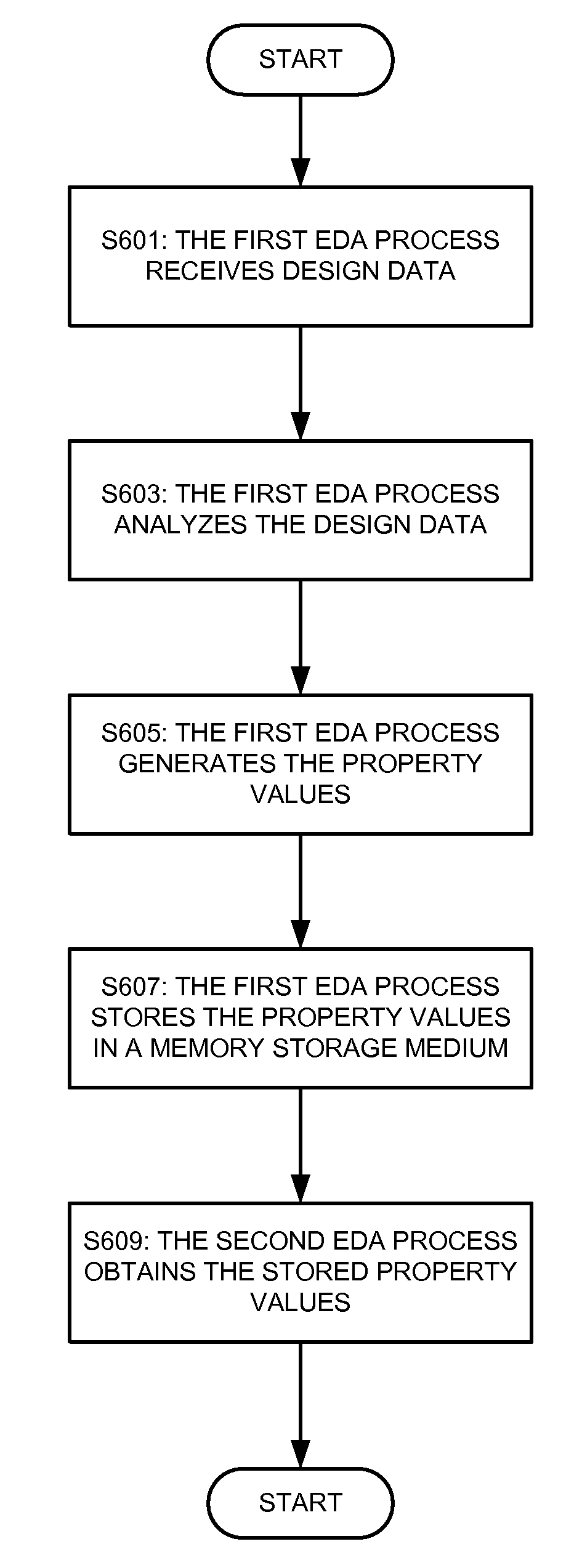

Properties In Electronic Design Automation

InactiveUS20080115096A1Easily calculateComputer aided designTotal factory controlComputer architectureLogic circuit design

One or more properties can be associated with a design object in a microdevice design. The design object may be an object in a physical layout design for a microdevice, such as a geometric element in a layout design. The design object also may be a collection of geometric elements in a layout design, such as a net, a cell in a hierarchical design, or even a collection of all of the geometric elements in a layer of a design. Still further, the design object may even be an item in a logical circuit design, such as a net in a logical circuit design for an integrated circuit. The values of one or more properties may be statically assigned for or dynamically generated during a design process performed by an electronic design automation tool. A property may be assigned a constant value or a value defined by an equation or other type of script that includes one or more variables. A property may be simple, where the definition of the property's value is not dependent upon the value of any other properties. Alternately, a property may be a compound property, where the definition of the property's value incorporates another, previously-determined property value. Still further, a property may be an alternative property, where the property is assigned one value definition under a first set of conditions and assigned another value definition under a second set of conditions. A first electronic design automation process may generate one or more property values. The generated property values then can be passed to another electronic design automation process in the design analysis flow for its use.

Owner:MENTOR GRAPHICS CORP

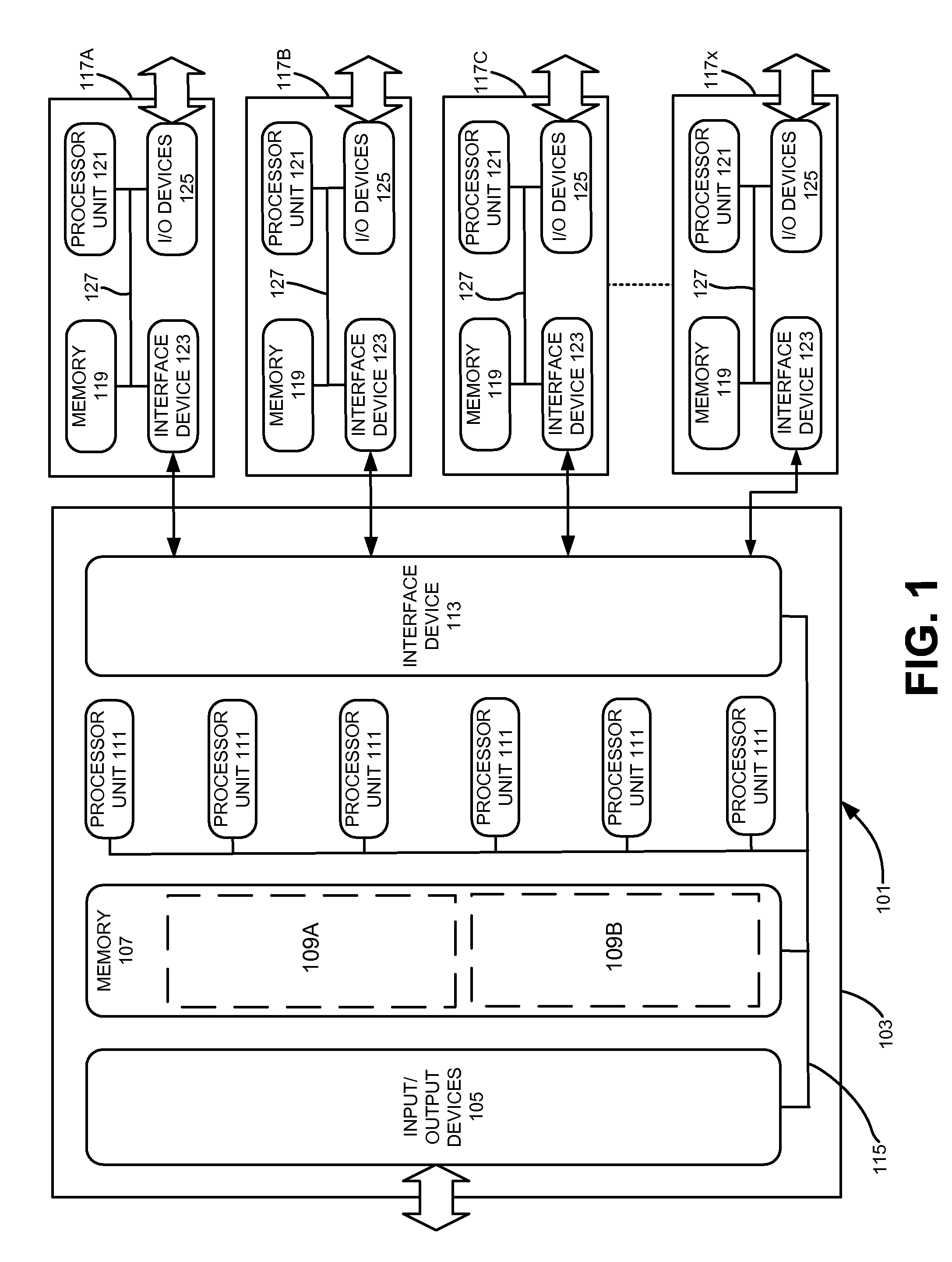

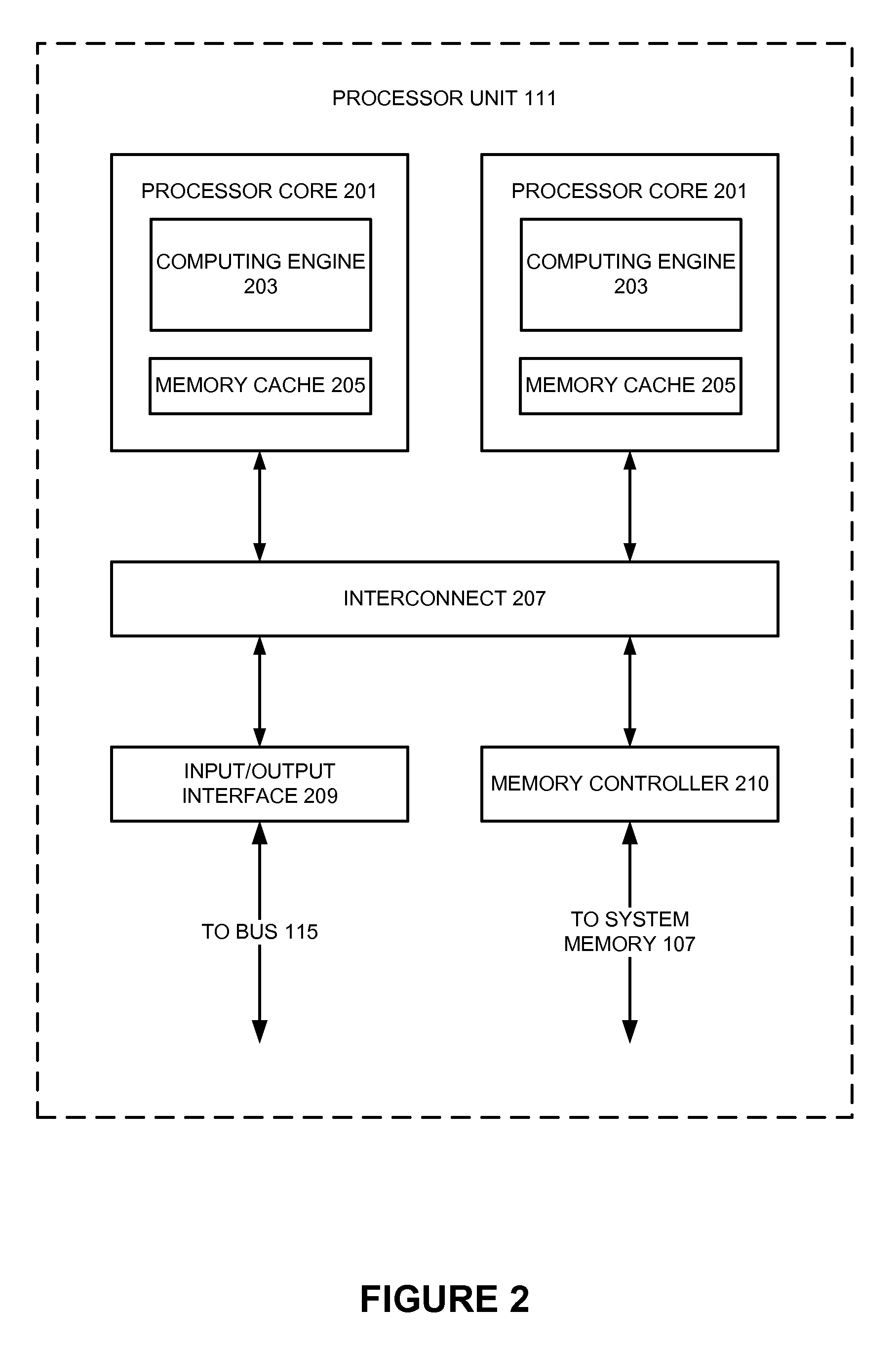

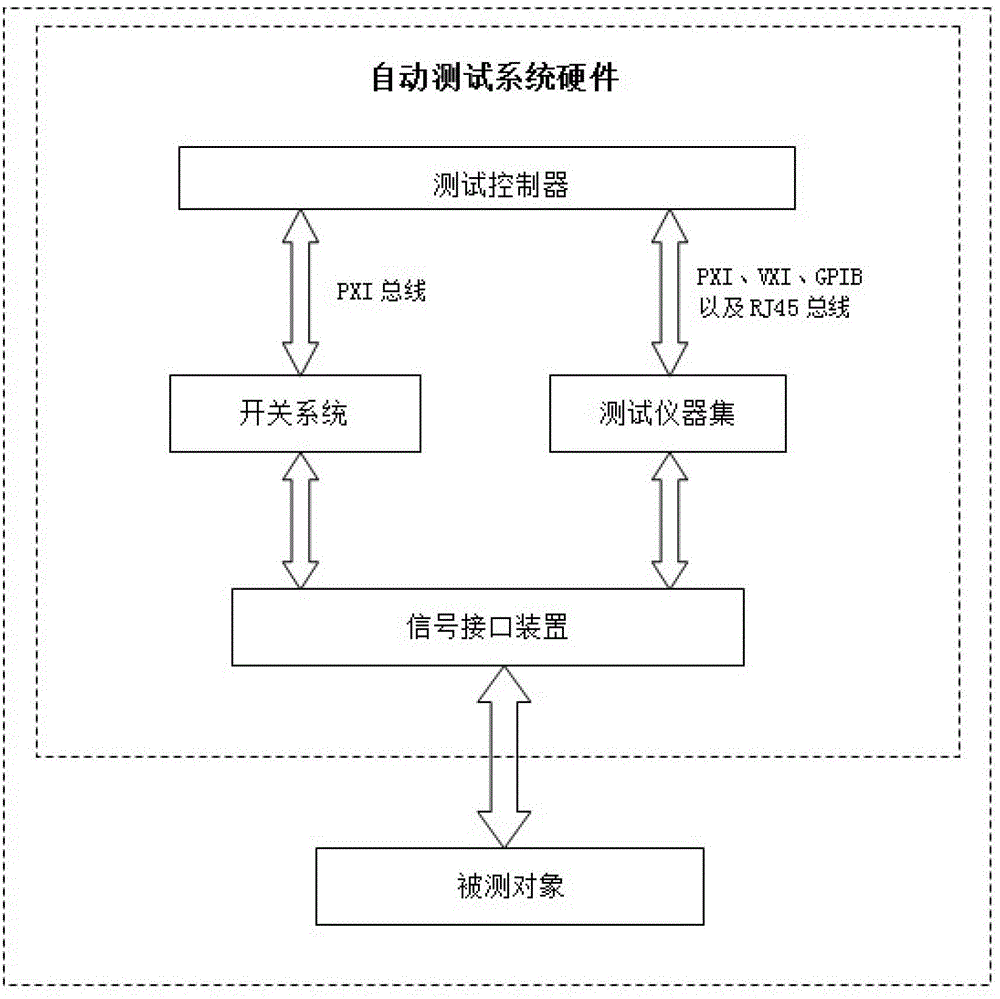

Integrated automatic test system of on-board computer of civilian airliner

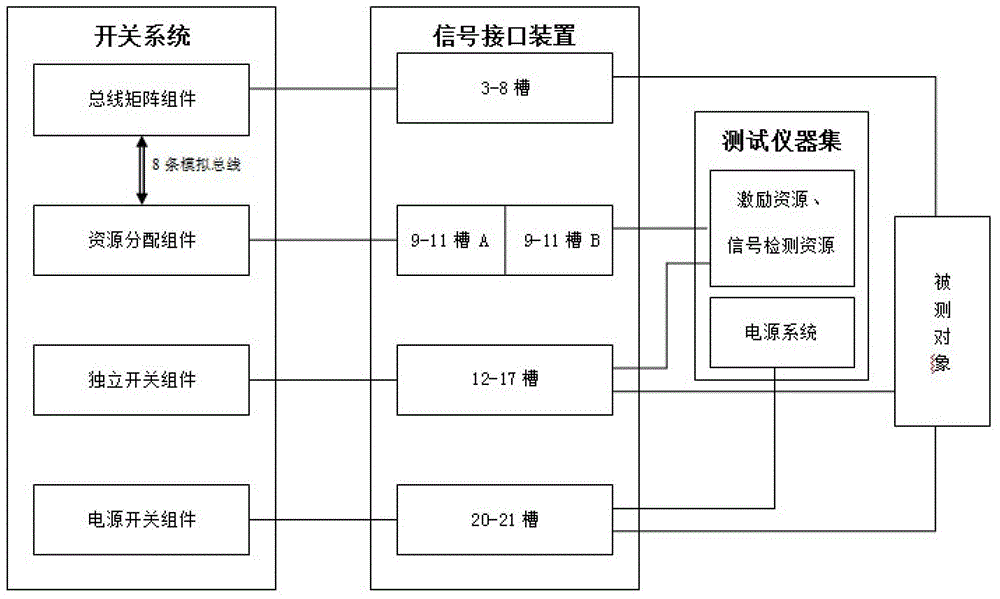

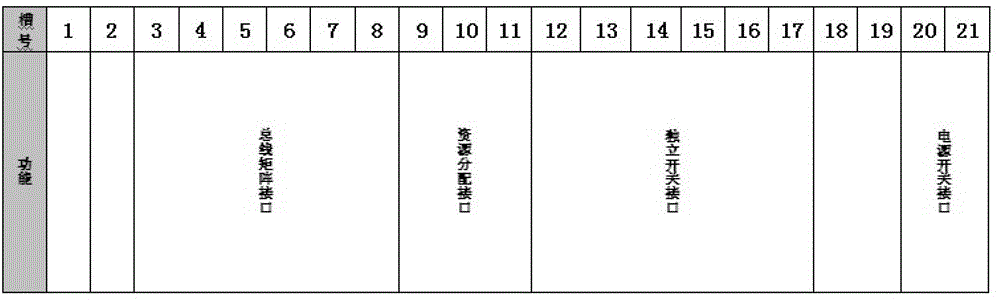

InactiveCN103336194ALow costImprove resource reusabilityElectrical testingOperational systemOn board

An integrated automatic test system of a on-board computer of a civilian airliner, which comprises a test controller, a test instrument collection, a switching system, and a signal interface device, wherein the test controller is connected with the test instrument collection and the switching system through an instrument control bus; the test instrument collection and the switching system are connected with the signal interface device; the signal interface device is used for being connected with a to-be-tested object of on-board electronic equipment of the to-be-tested civilian airliner; the test controller comprises a test module, a test management module, a test function library module, a driver module, and an operating system module; the test module, the test management module, the test function library module, the driver module, and the operating system module are classified into five levels during operation. The integrated automatic test system adopts the modularized design in the hardware architecture and the hierarchical design in the software architecture, so as to allow the modification and the extension of hardware and software to be more convenient, facilitate the improvement of resource reusability of the test system, and low the cost.

Owner:GUANGZHOU AIRCRAFT MAINTENANCE ENG

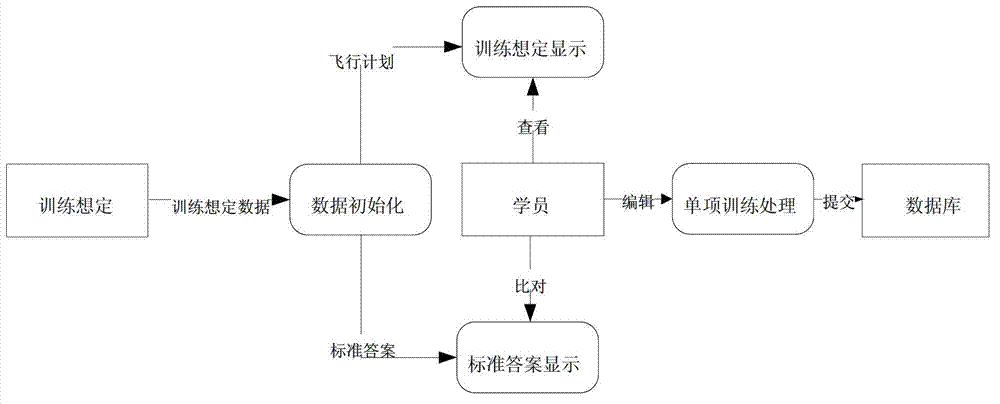

System and method for simulating and training program control of air traffic control

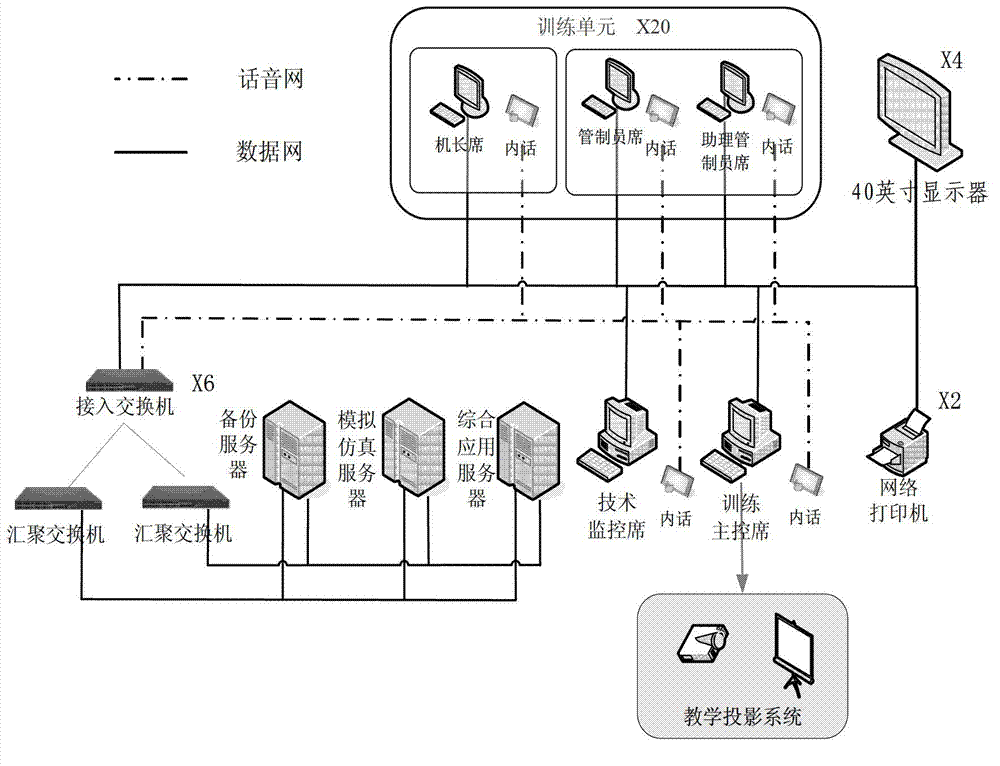

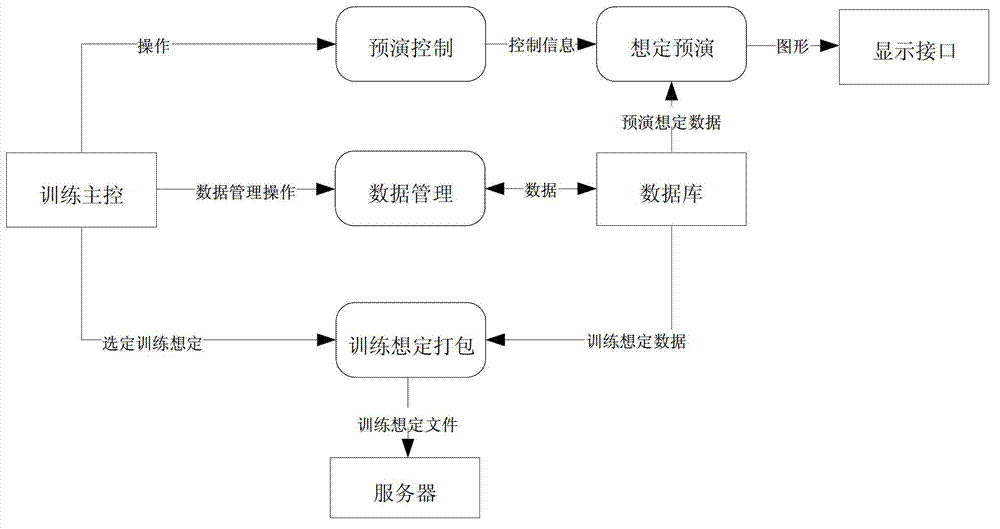

ActiveCN103050030AImprove understandingCreate a sense of spatial orientationCosmonautic condition simulationsSimulatorsDisplay deviceSimulation

The invention discloses a system for simulating and training the program control of an air traffic control. The system comprises a simulation server, a comprehensive application server, a switchboard, a technology monitoring position, a training master control position, at least one training unit, an inner telephone and a display device. By using the system disclosed by the invention, the control on-duty environment can be realistically simulated, the united simulation training of an area, a zone and an airport can be realized, the working procedure of each link of the program control can be fully trained, the control process can be comprehensively understood by a control person, and the control program can be comprehensively mastered by the control person. According to the system disclosed by the invention, a network adopts a hierarchical design, the network design is simplified, the detection and the removing of primary fault are realized; and a dual-network design of a voice network and a data network is adopted, the training command transmission is reliable, the data traffic of the data network is simultaneously reduced to a large extent, and the low-delay and less-vibration performance of voice transmission is solved by the independent voice network. The invention also provides a training method of a single training mode, a control on-duty mode and a united control on-duty mode of the system for simulating and training the program control of the air traffic control.

Owner:NO 15 INST OF CHINA ELECTRONICS TECH GRP +1

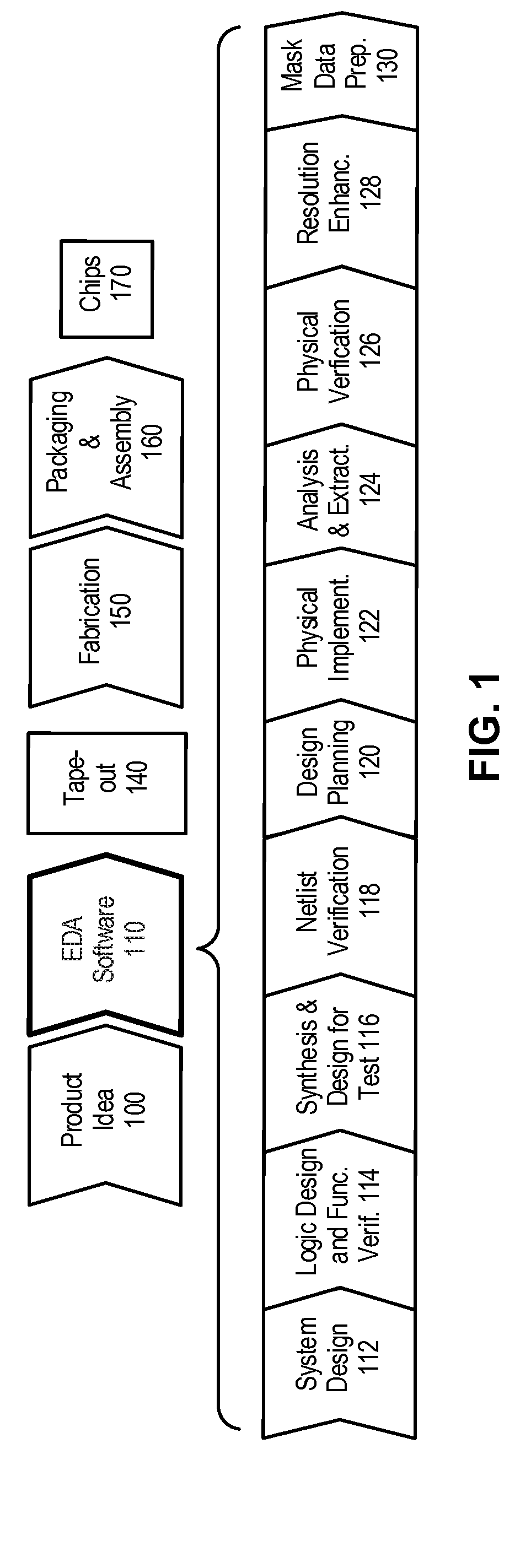

Implementing hierarchical design-for-test logic for modular circuit design

ActiveUS8065651B2Reduce dataReduce testingElectronic circuit testingDetecting faulty computer hardwareDesign testingControl signal

Embodiments of the present invention provide methods and apparatuses for implementing hierarchical design-for-test (DFT) logic on a circuit. The hierarchical DFT logic implements DFT circuitry that can be dedicated to a module, and which can configure DFT circuitry for multiple modules to share a sequential input signal and / or to share a sequential output signal. During operation, the DFT circuitry for a first module can propagate a bit sequence from the sequential input signal to the DFT circuitry of a second module, such that the bit sequence can include a set of control signal values for controlling the DFT circuitry, and can include compressed test vectors for testing the modules. Furthermore, the DFT circuitry for the second module can generate a sequential response signal, which combines the compressed response vectors from the second module and a sequential response signal from the DFT circuitry of the first module.

Owner:SYNOPSYS INC

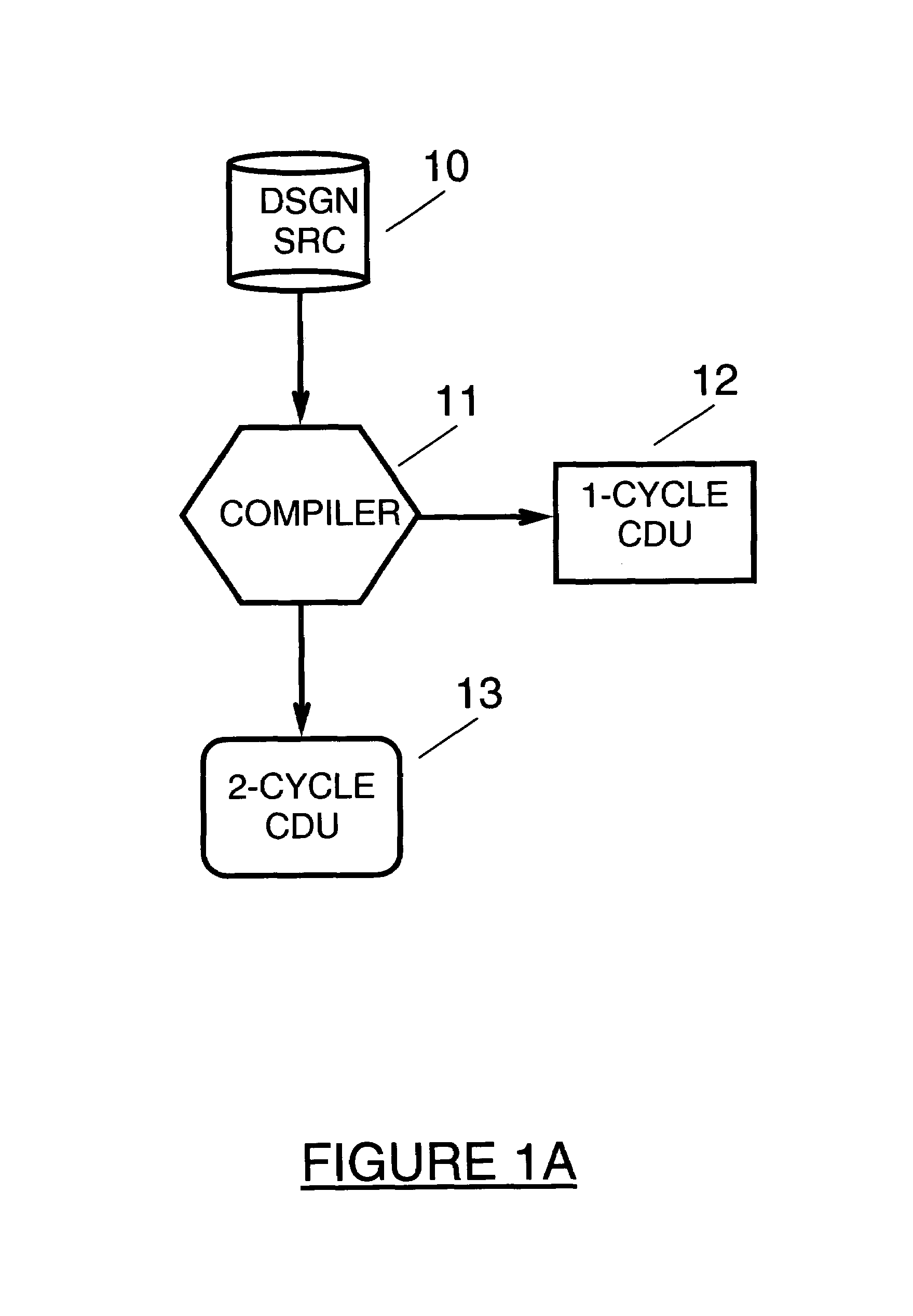

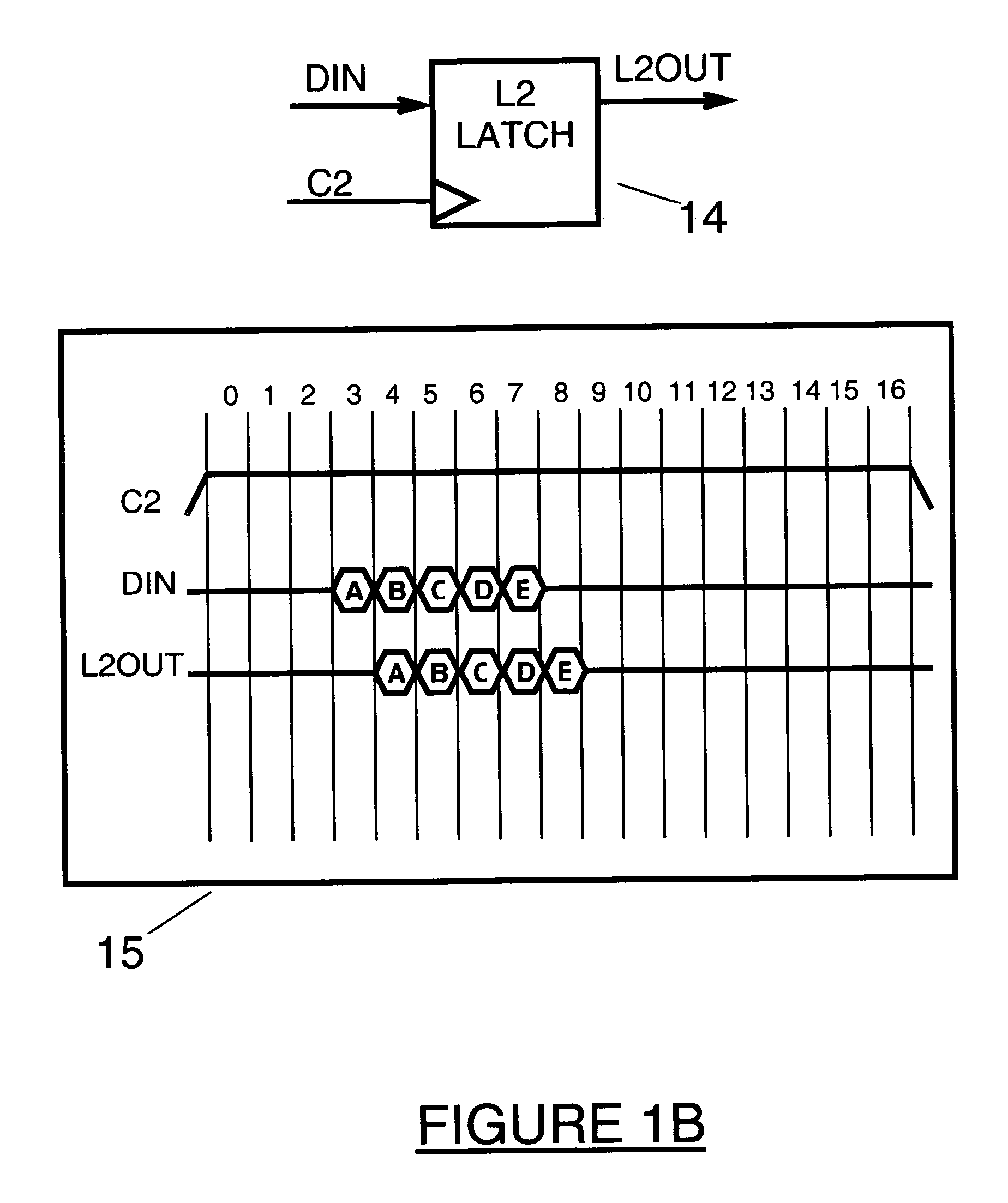

Method for the creation of a hybrid cycle simulation model

InactiveUS7483825B2Speed and size advantagePerformanceCAD circuit designSoftware simulation/interpretation/emulationHigh bandwidthParallel computing

Owner:GLOBALFOUNDRIES INC

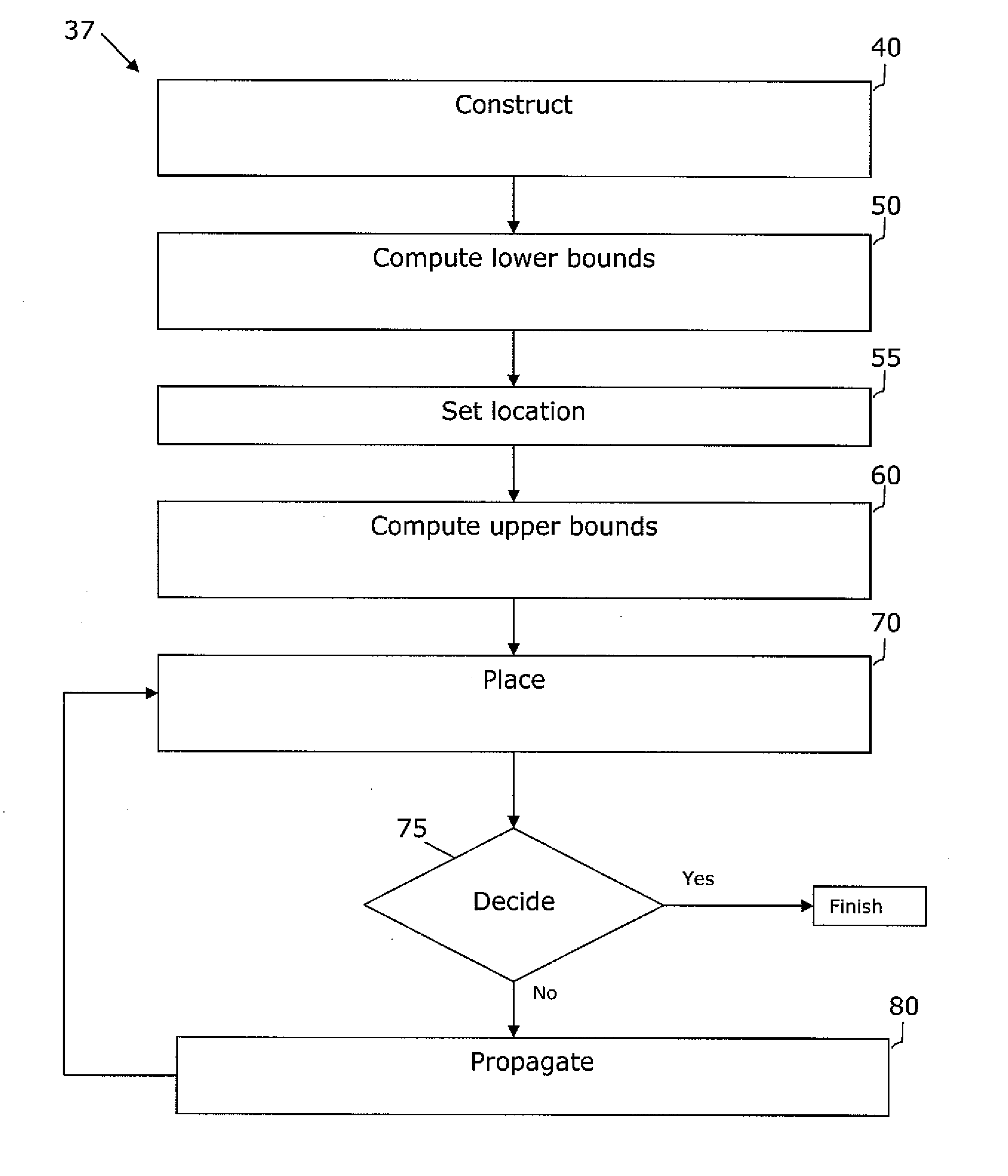

VLSI artwork legalization for hierarchical designs with multiple grid constraints

A system and method are disclosed for legalizing a flat or hierarchical VLSI layout to meet multiple grid constraints and conventional ground rules. Given a set of ground rules with multiple grid constraints and a VLSI layout (either hierarchical or flat) which is layout-versus-schematic (LVS) correct but may not be ground rule correct, the system and method provide a legalized layout which meets the multiple grid constraints while maintaining LVS correctness and fixing the ground rule errors as much as possible with minimum layout perturbation from the input design. The system and method support multiple grid pitch constraints for hierarchical design, and provide for LVS correctness to be maintained while an on-grid solution possibly with some spacing violations.

Owner:GLOBALFOUNDRIES US INC

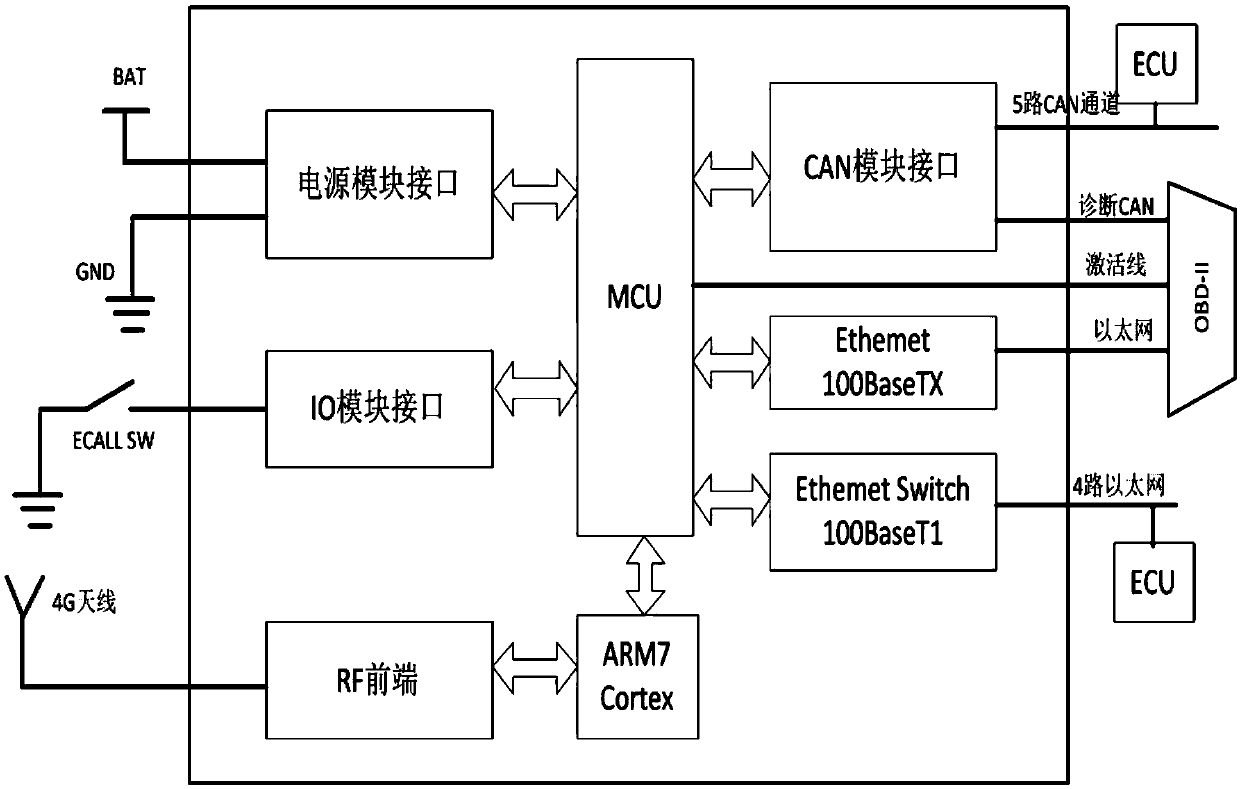

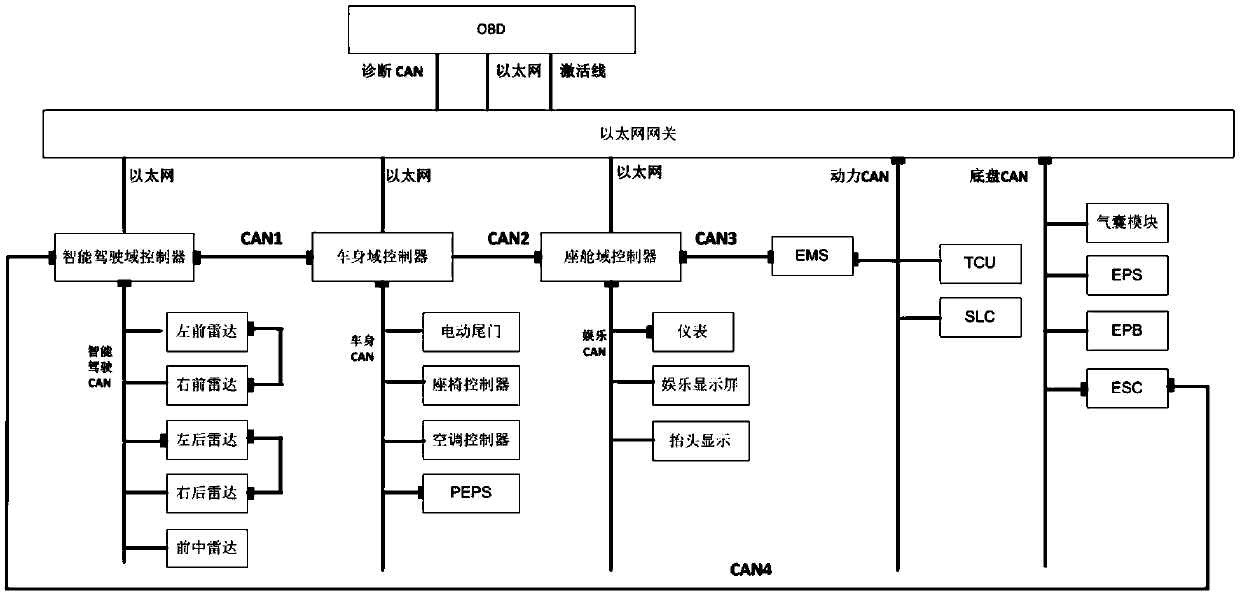

Smart car provided with Ethernet gateway with back configuration function

InactiveCN109532720AMeet big data transmissionFulfil requirementsNetwork connectionsElectric/fluid circuitRF front endHierarchical design

Owner:ANHUI JIANGHUAI AUTOMOBILE GRP CORP LTD

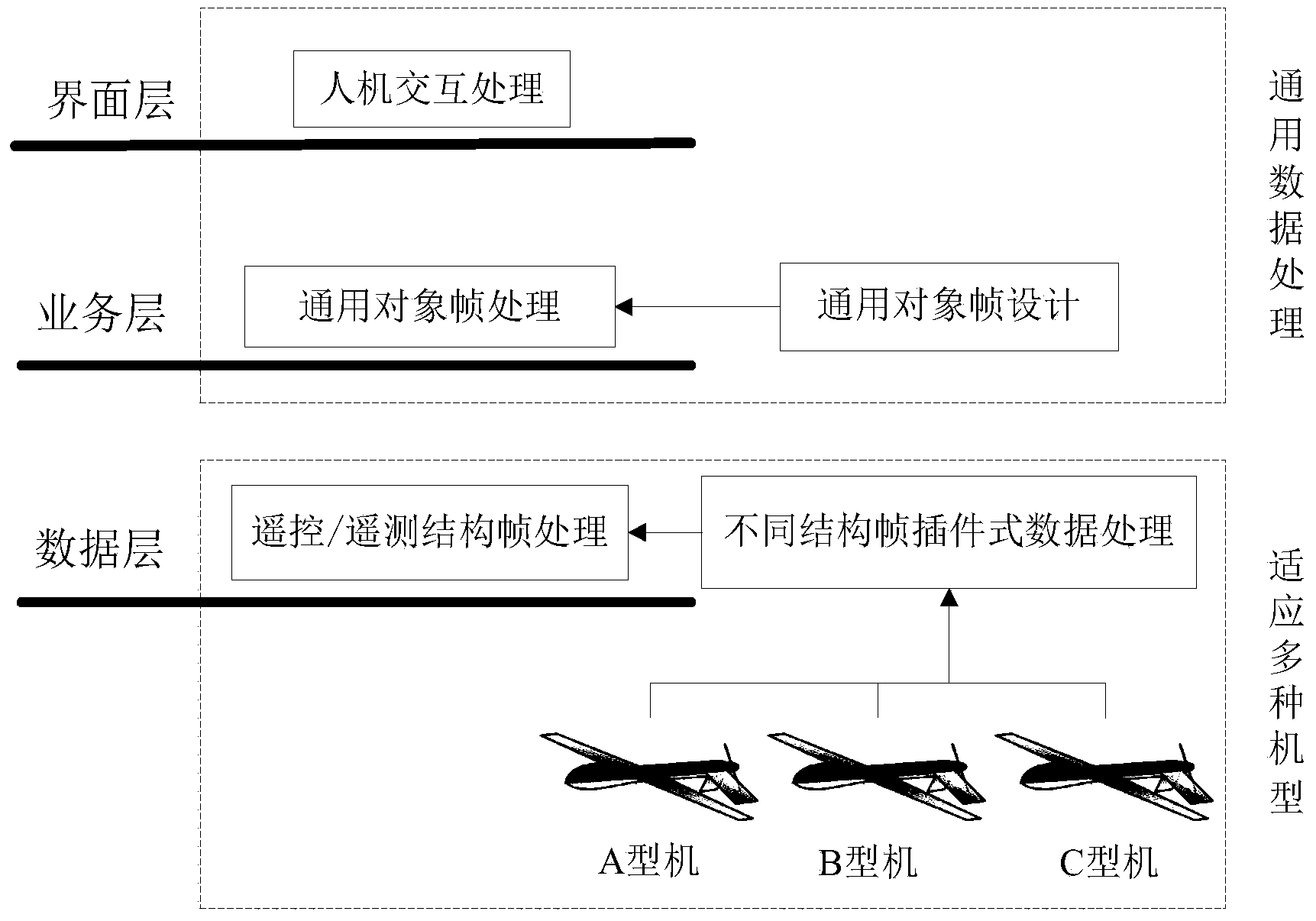

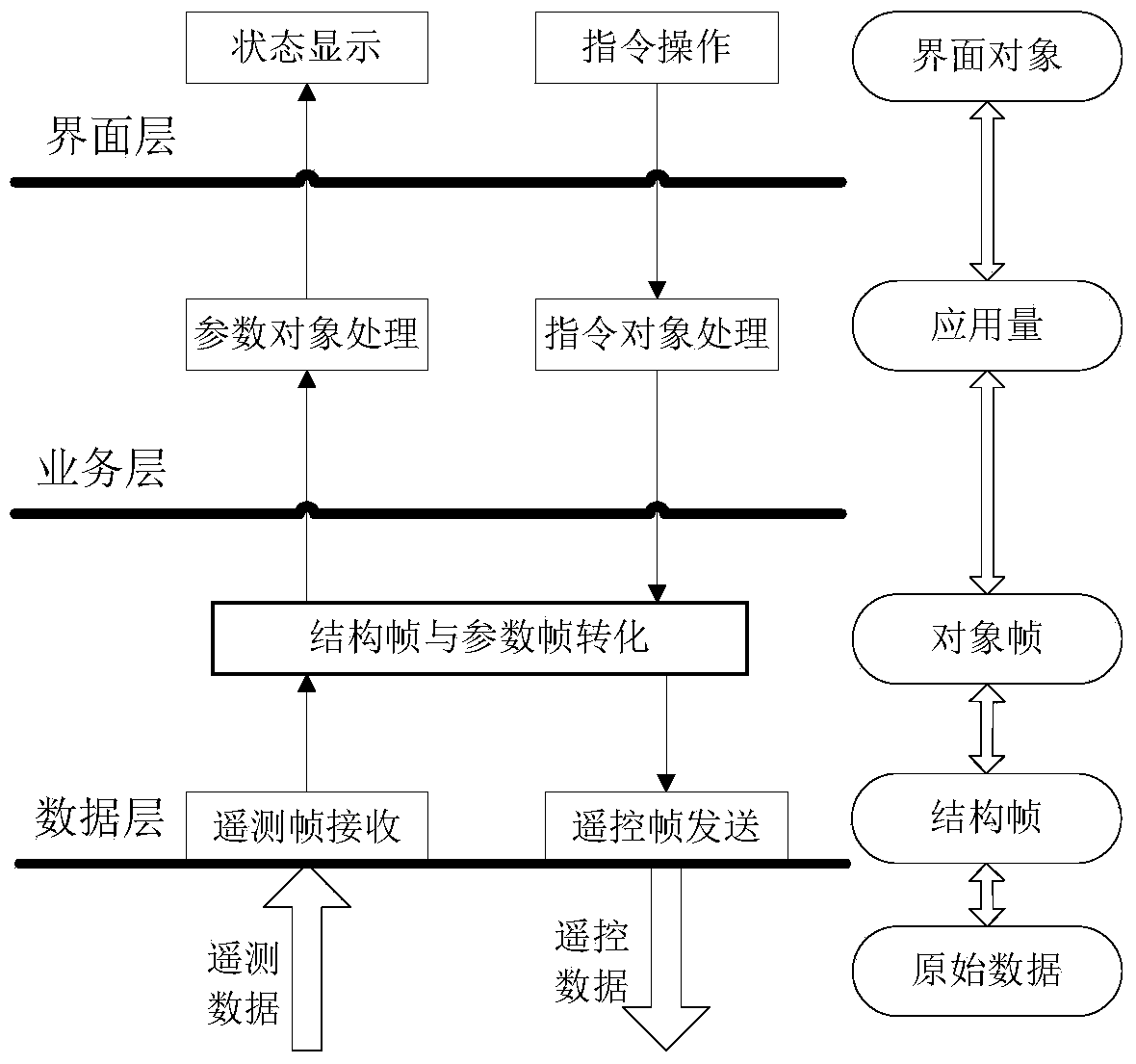

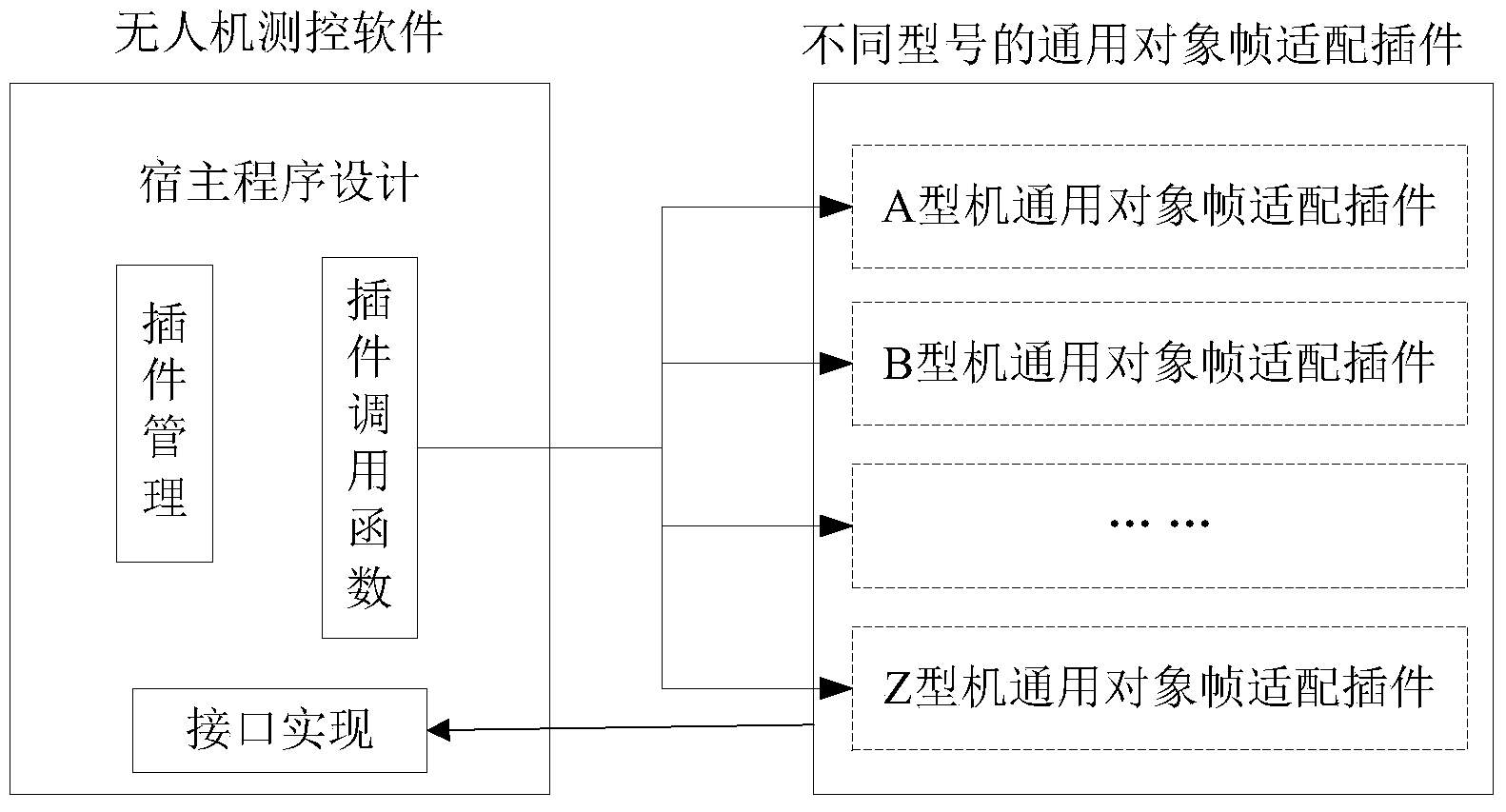

General hierarchical design method for unmanned aerial vehicle remote control command/telemetry parameter frame

ActiveCN103970044AImprove scalabilityAvoid duplication of software constructionTotal factory controlProgramme control in sequence/logic controllersCommand and controlUncrewed vehicle

The invention provides a general hierarchical design method for an unmanned aerial vehicle remote control command / telemetry parameter frame and belongs to the field of unmanned aerial vehicle command and control. According to the general hierarchical design method, a general command / parameter object frame is designed, all remote control command objects in the object frame are described according to a uniform form, all telemetry parameter objects are also described according to a uniform form, a measurement and control software data processing flow based on the general command / parameter object frame is designed, a telemetry structure frame is converted into a general parameter object frame on a software data layer, and the general command object frame is converted into a remote control structure frame; for unmanned aerial vehicles of different types, general object frame adaptive plug-ins corresponding to the types are designed, and when measurement and control software is suitable for the unmanned aerial vehicle of a certain type, the general object frame adaptive plug-in corresponding to the type is called for conversion of the object frame and the structure frame. According to the general hierarchical design method for the unmanned aerial vehicle remote control command / telemetry parameter frame, the coupling relationship between a software service layer and an interface layer and coupling relationship between the software service layer and the structure frame are eliminated, the generality of unmanned aerial vehicle ground station software is improved, and repeated software construction is also avoided.

Owner:北京北航天宇长鹰无人机科技有限公司

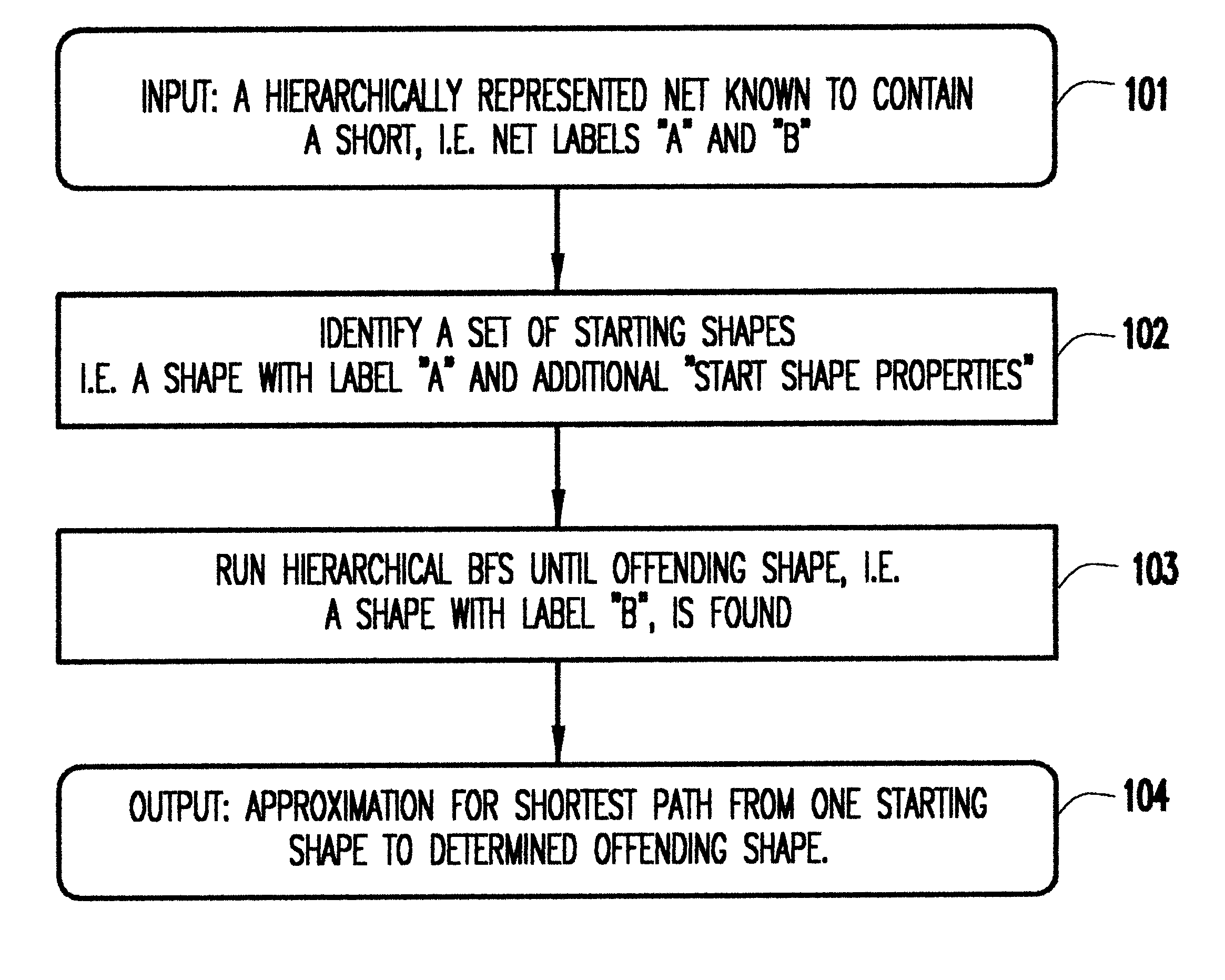

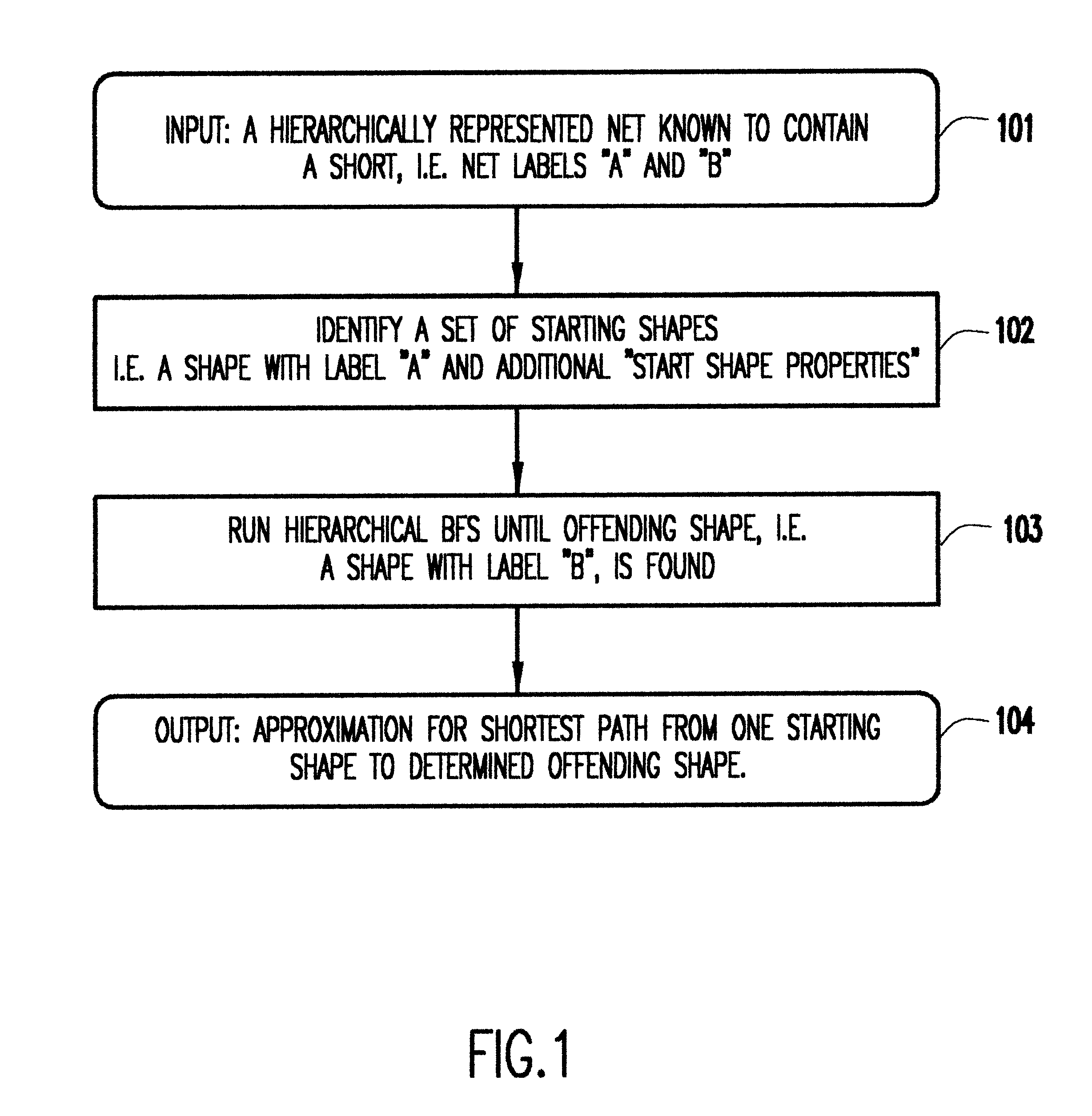

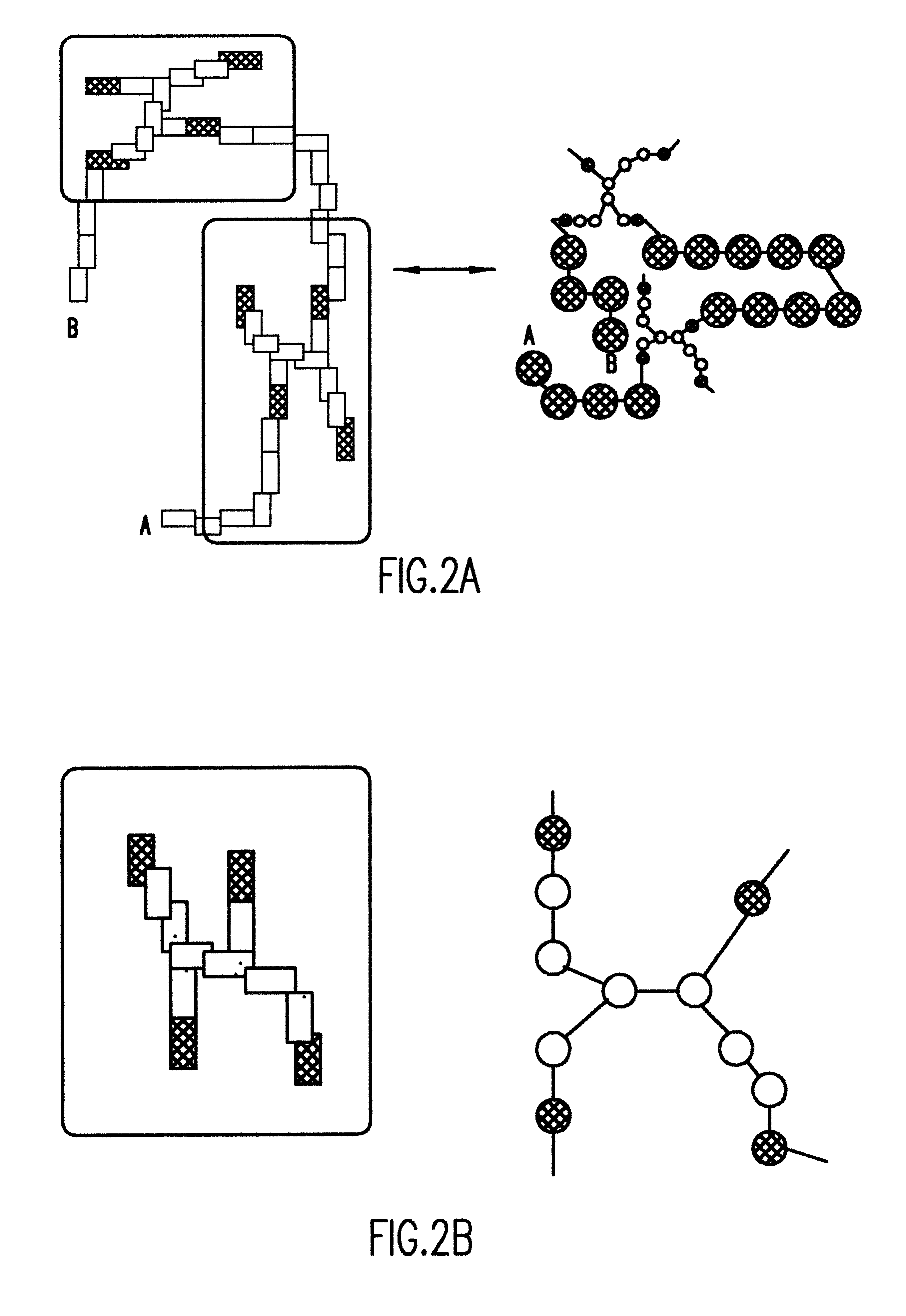

Efficient tracing of shorts in very large nets in hierarchical designs using breadth-first search with optimal pruning

InactiveUS6275974B1Effective trackingCAD circuit designSoftware simulation/interpretation/emulationTheoretical computer scienceHierarchical design

Tracing a short as a shortest path of explicit VLSI design component instances between two VLSI design component instances with different net names in a hierarchical design is a non-hierarchical problem. The method described in this document computes a shortest path of VLSI design leaf component instances containing at least one of the leaf design components causing the sort. To avoid exceeding available storage, the non-hierarchical instance information maintained during the process is pruned optimally. To achieve feasible performance, two methods to find "good" starting points are provided, based on geometrical distribution or based on connectivity information from the net build (if available).

Owner:IBM CORP

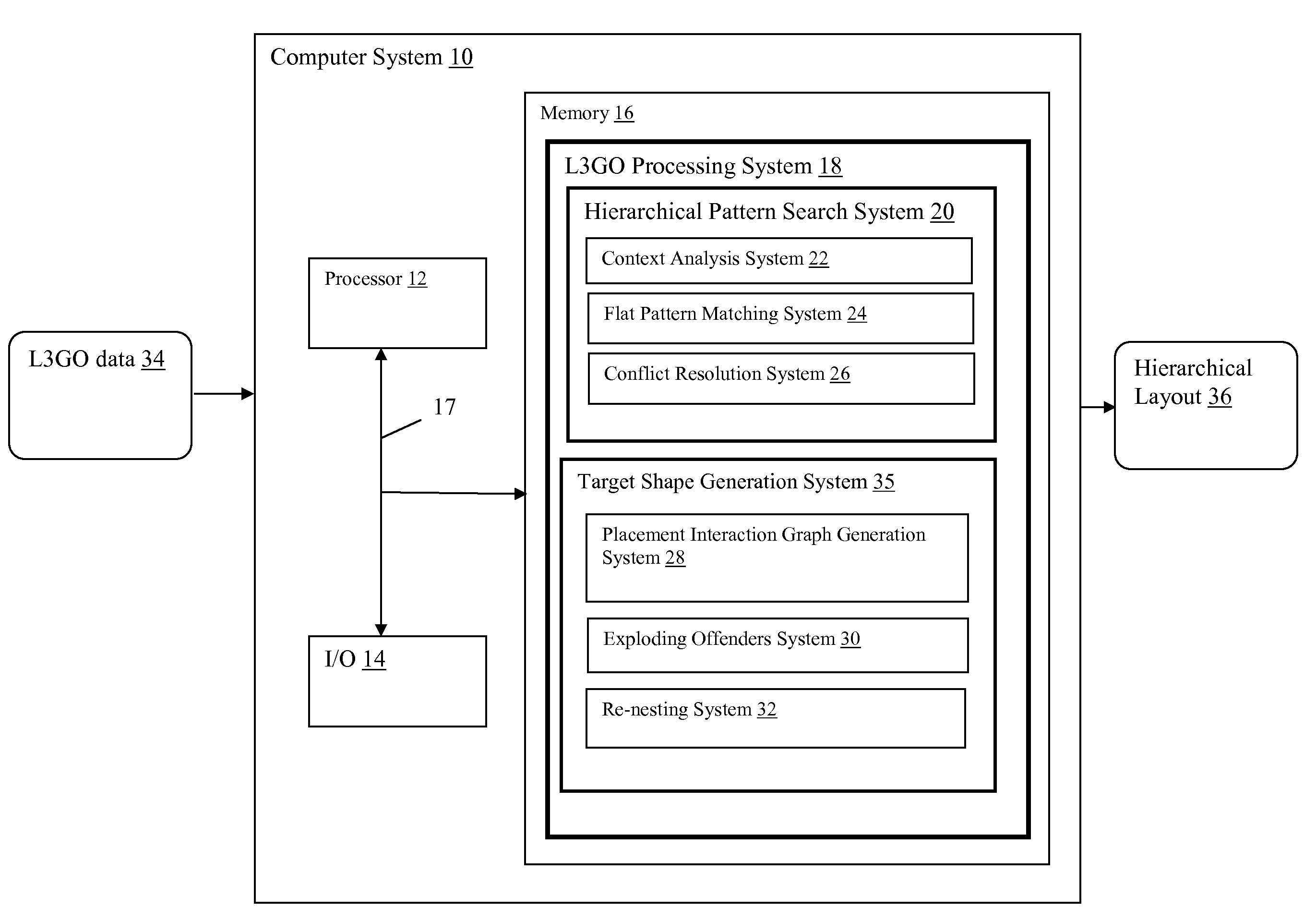

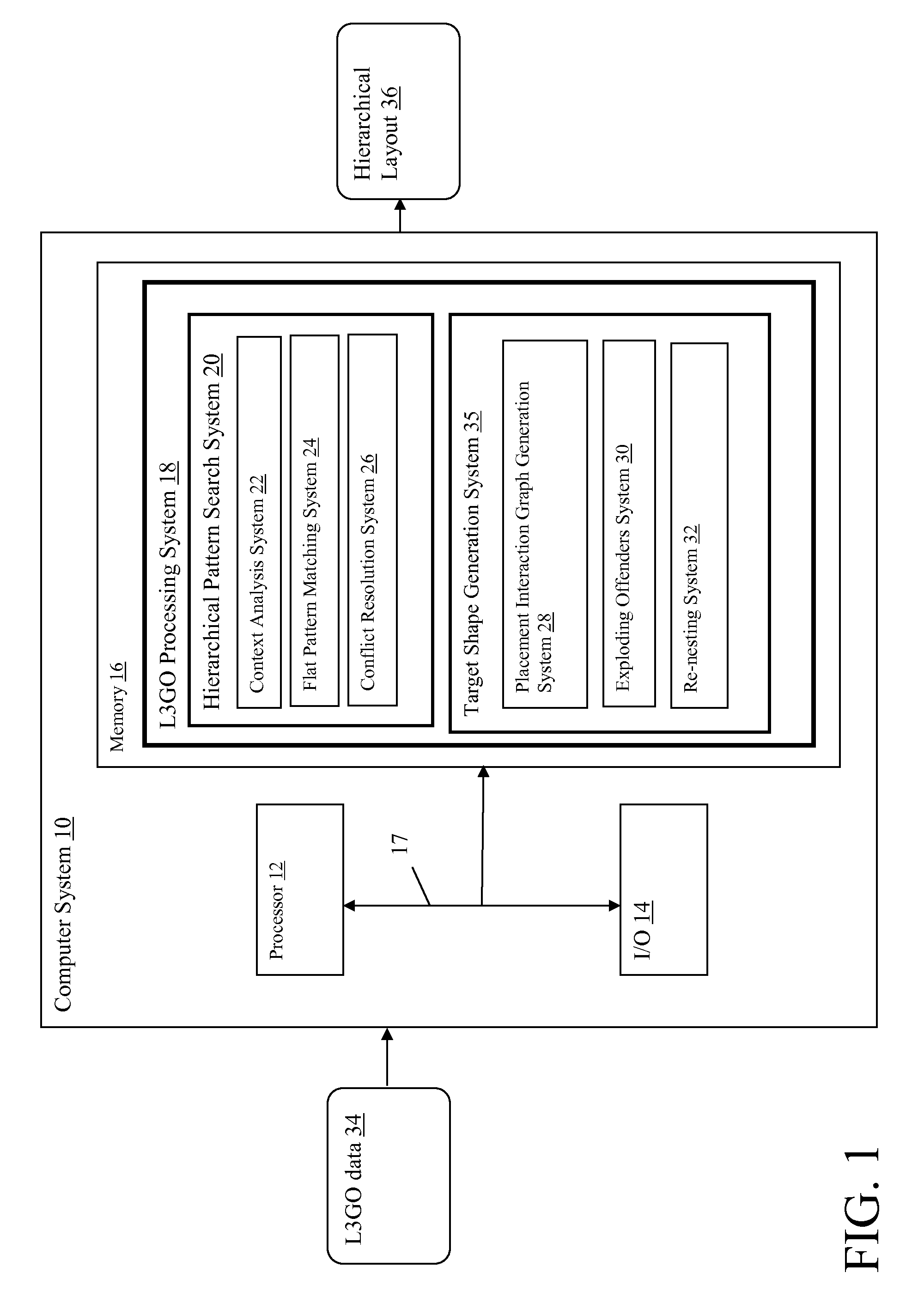

Pattern based elaboration of hierarchical l3go designs

InactiveUS20080244493A1The result is accurateCAD circuit designRecord carriers used with machinesGlyphHierarchical design

A system, method and program product that utilizes flat pattern based L3GO elaboration in a hierarchical environment to create a nested conventional layout. A system is provide for processing a glyph layout to generate shapes for use in a VLSI (very large scale integrated circuit) design process, including: a hierarchical pattern search system that matches patterns from a pattern library to a set of glyph data, wherein the patterns have dependencies that cross hierarchical design boundaries; and a target shape generation system that selects patterns from a set of matching patterns and generates associated shapes.

Owner:IBM CORP

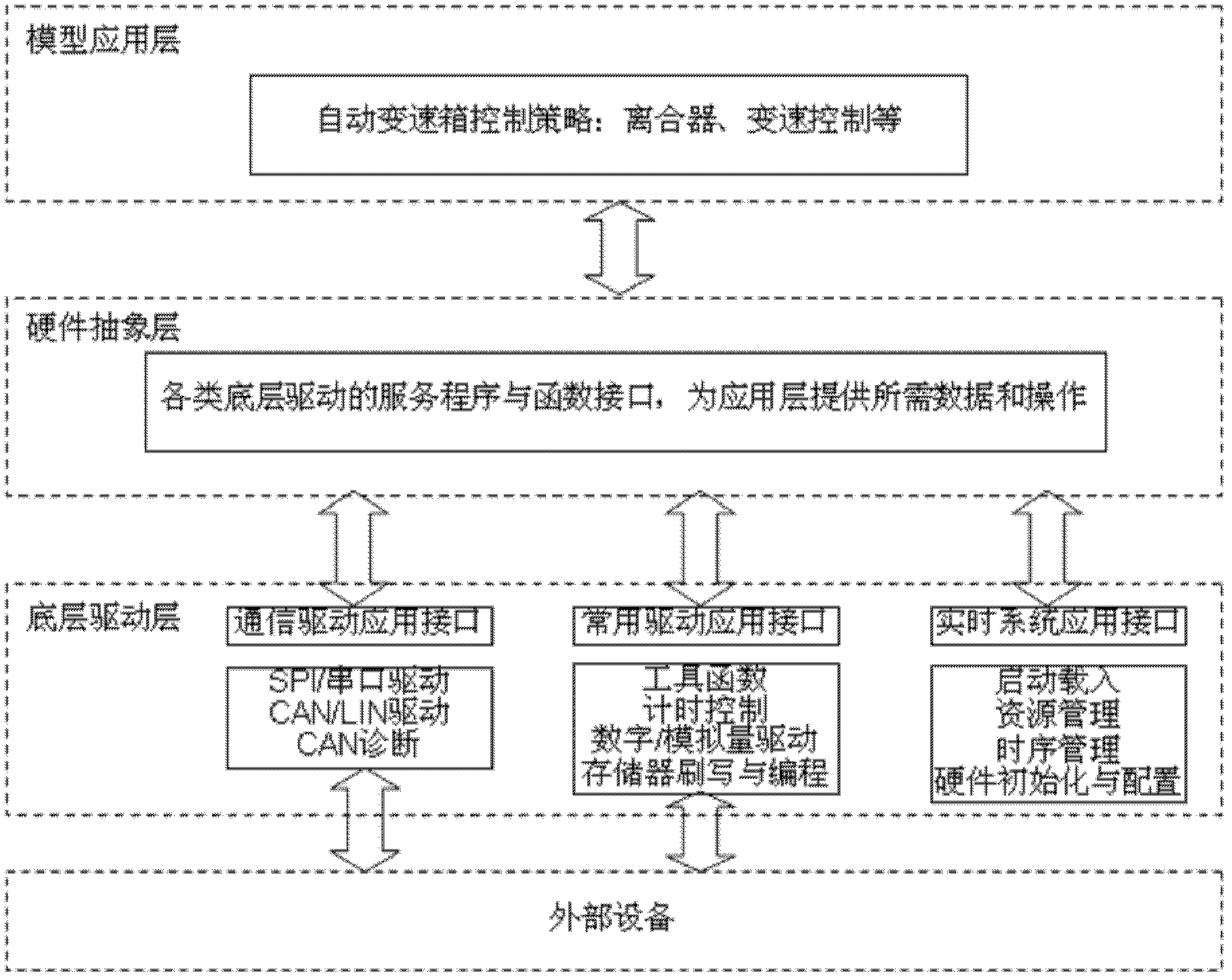

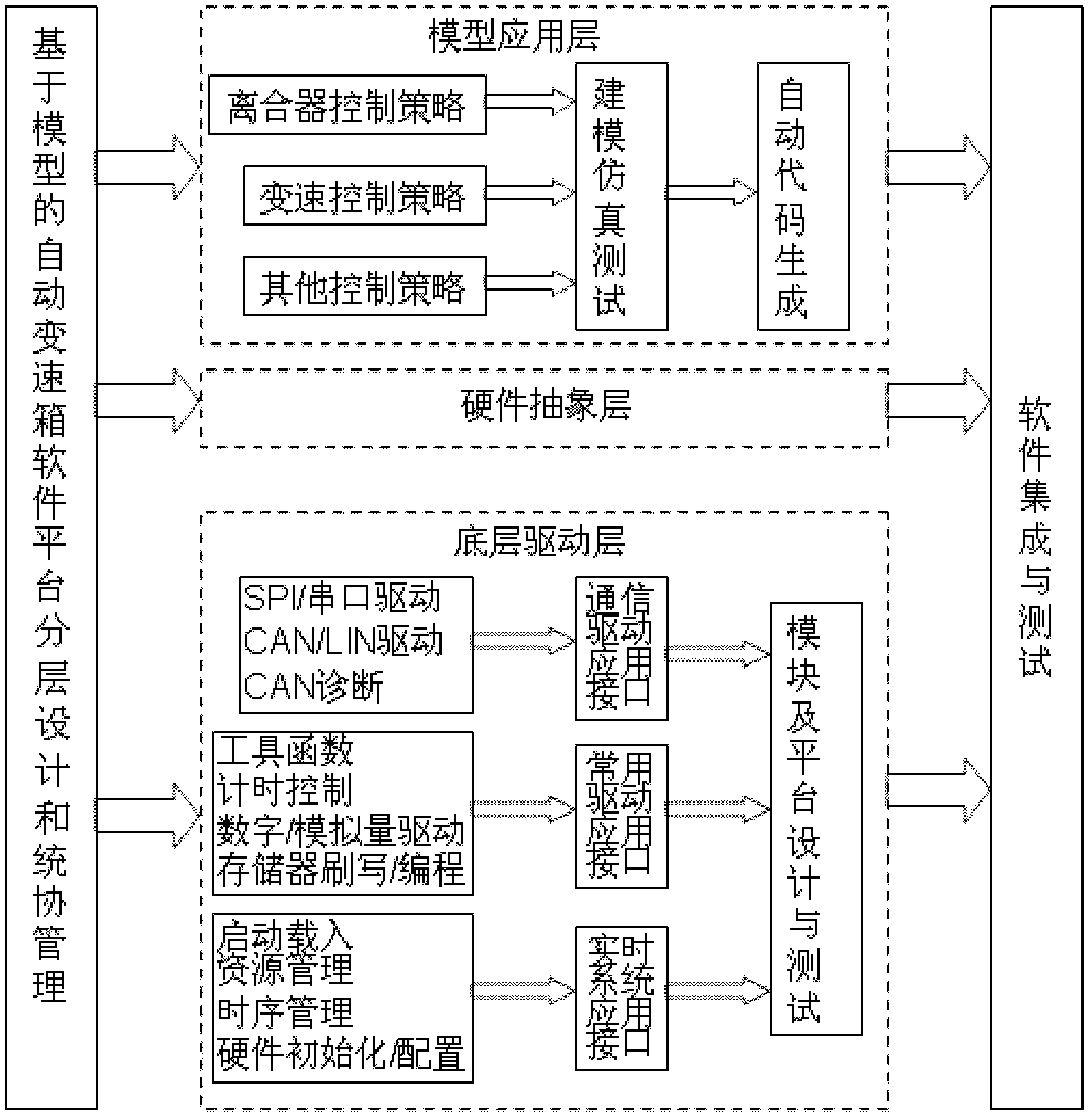

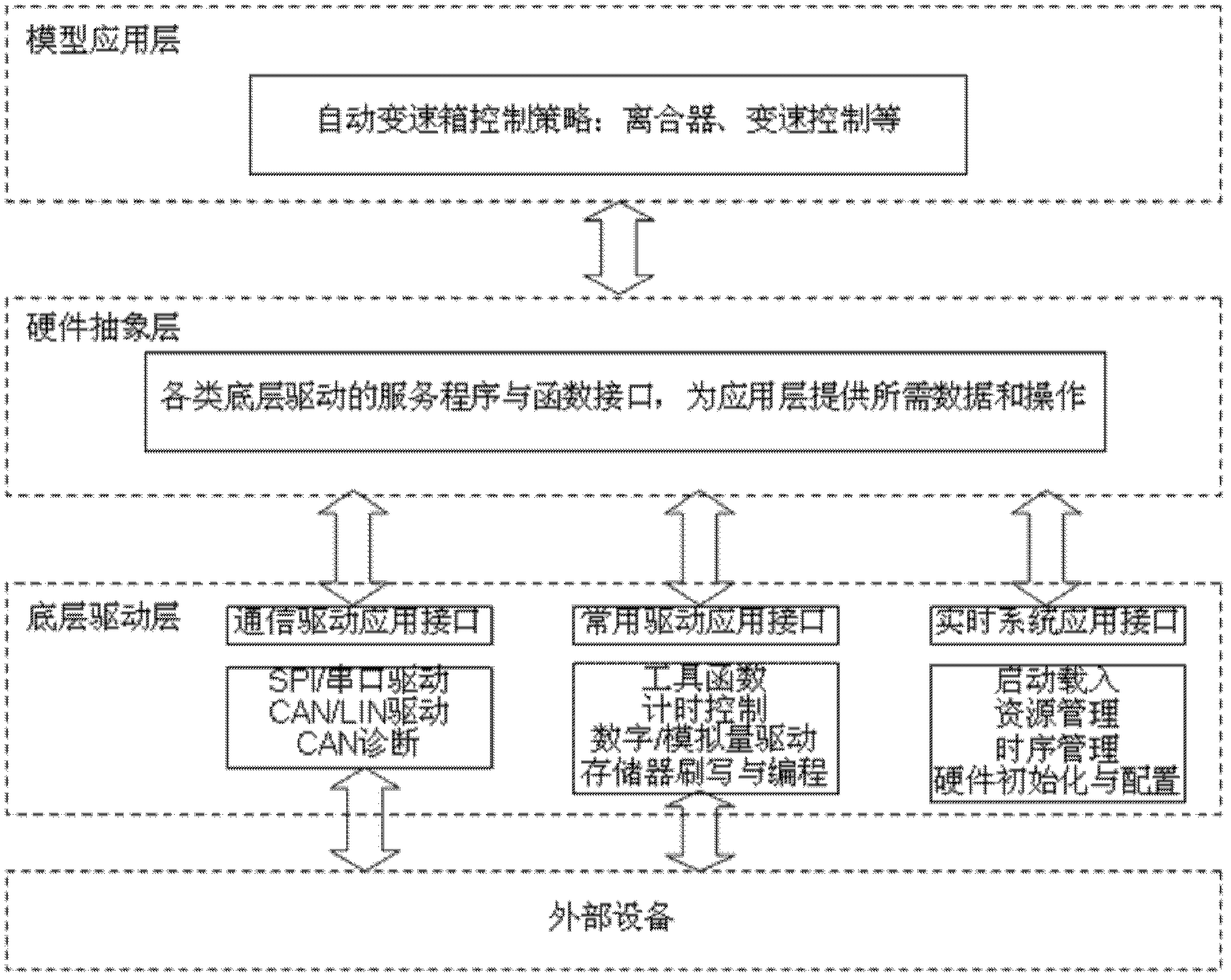

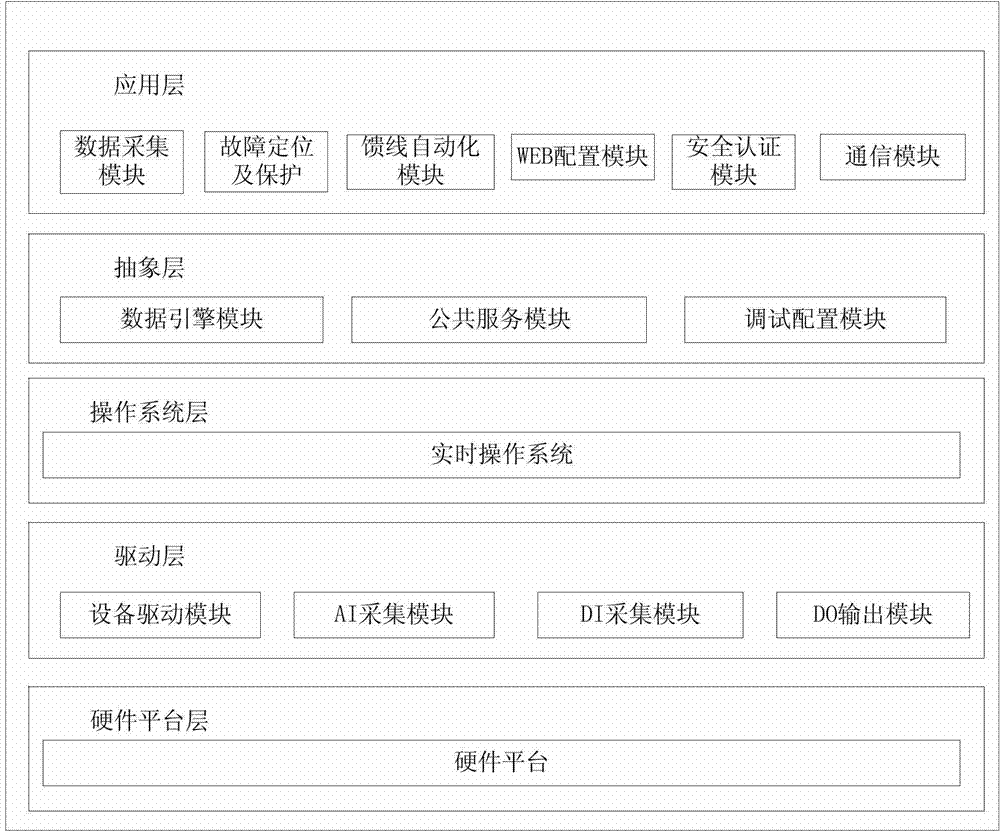

Layered design method of model-based automatic transmission software development platform

ActiveCN102200913AShorten and optimize development cyclesShorten and optimize development efficiencySpecific program execution arrangementsArea networkSoftware development

The invention relates to a layered design method of a model-based automatic transmission software development platform. The software development platform is divided into three layers, namely a model application layer, a hardware abstraction layer and a bottom-layer driving layer, wherein the hardware abstraction layer is used for jointing the model application layer and the bottom-layer driving layer; an automatic transmission control strategy is characterized by modelling, emulating and testing by a model development tool, automatically generating C codes and converting the C codes into an application layer software module to form the model application layer; the model application layer carries out data exchange by using the hardware abstraction layer and realizes access of bottom-layer platform data and corresponding operation by a joint function; the bottom-layer driving layer carries out controller area network (CAN) driving, analogue / digital conversion, digital input and output, and own function and state monitoring of the platform; and the bottom-layer driving layer executes the corresponding operation by function call of the hardware abstraction layer, and processes and updates data in real time.

Owner:WUHU WANLIYANG TRANSMISSION CO LTD

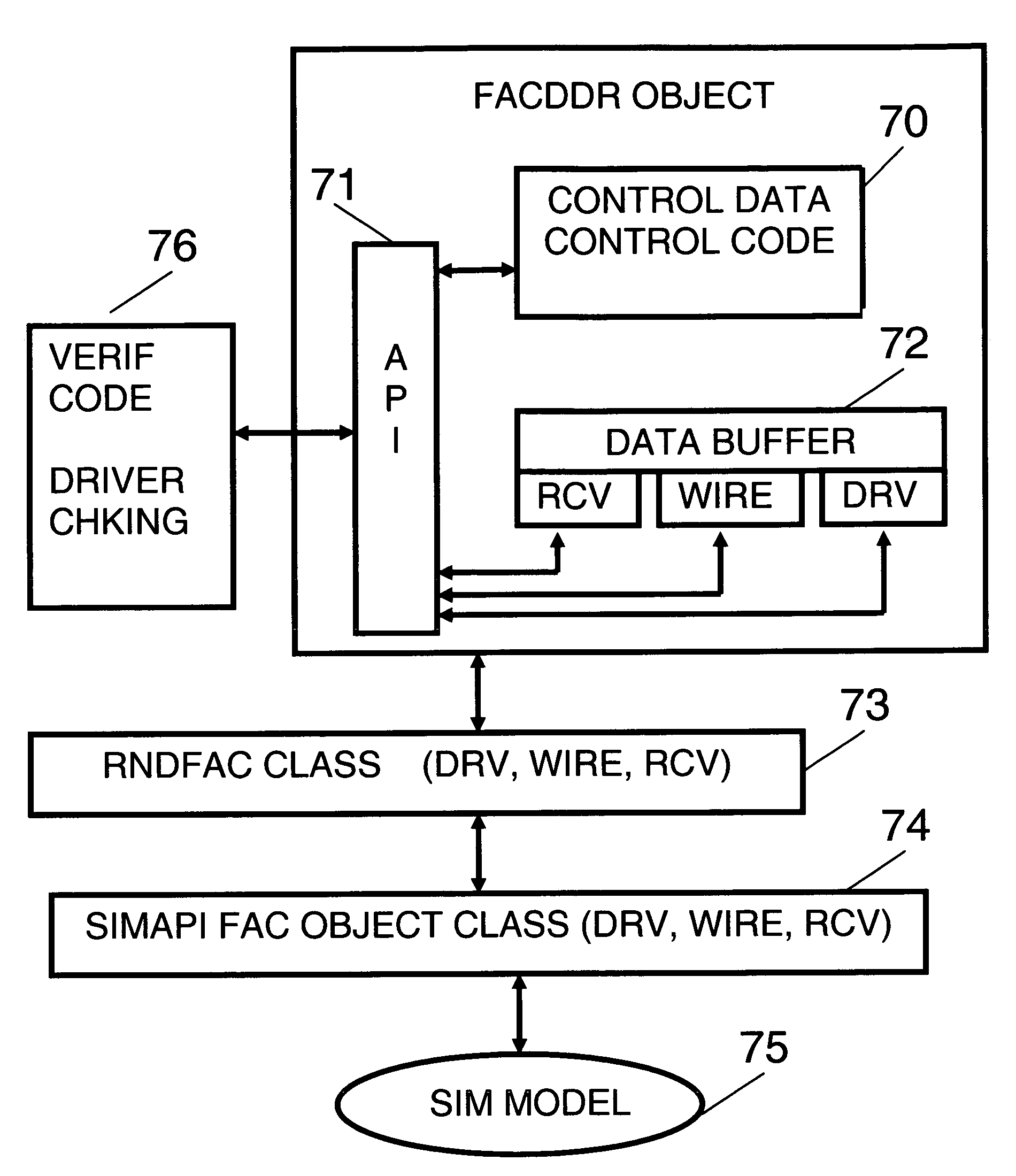

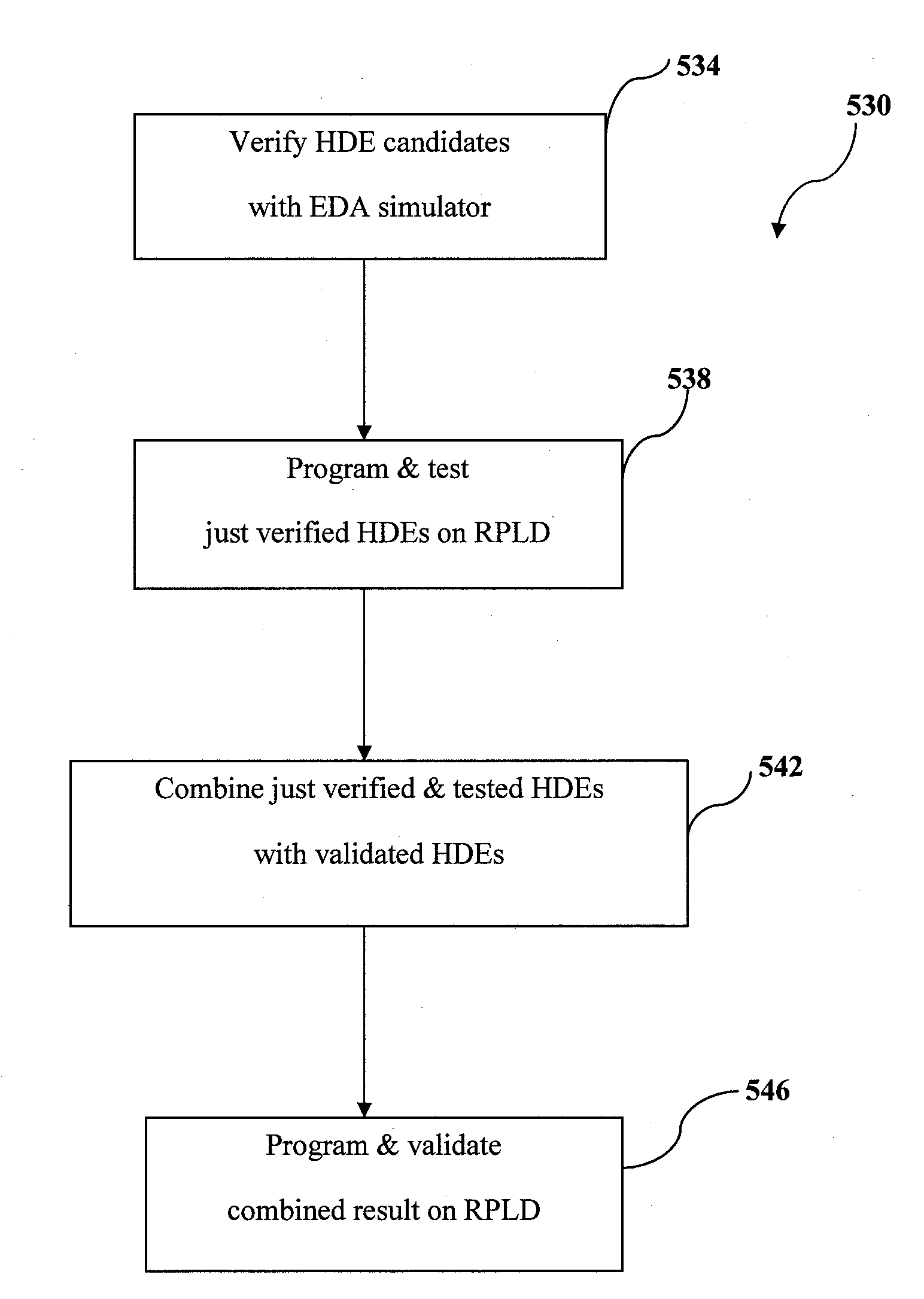

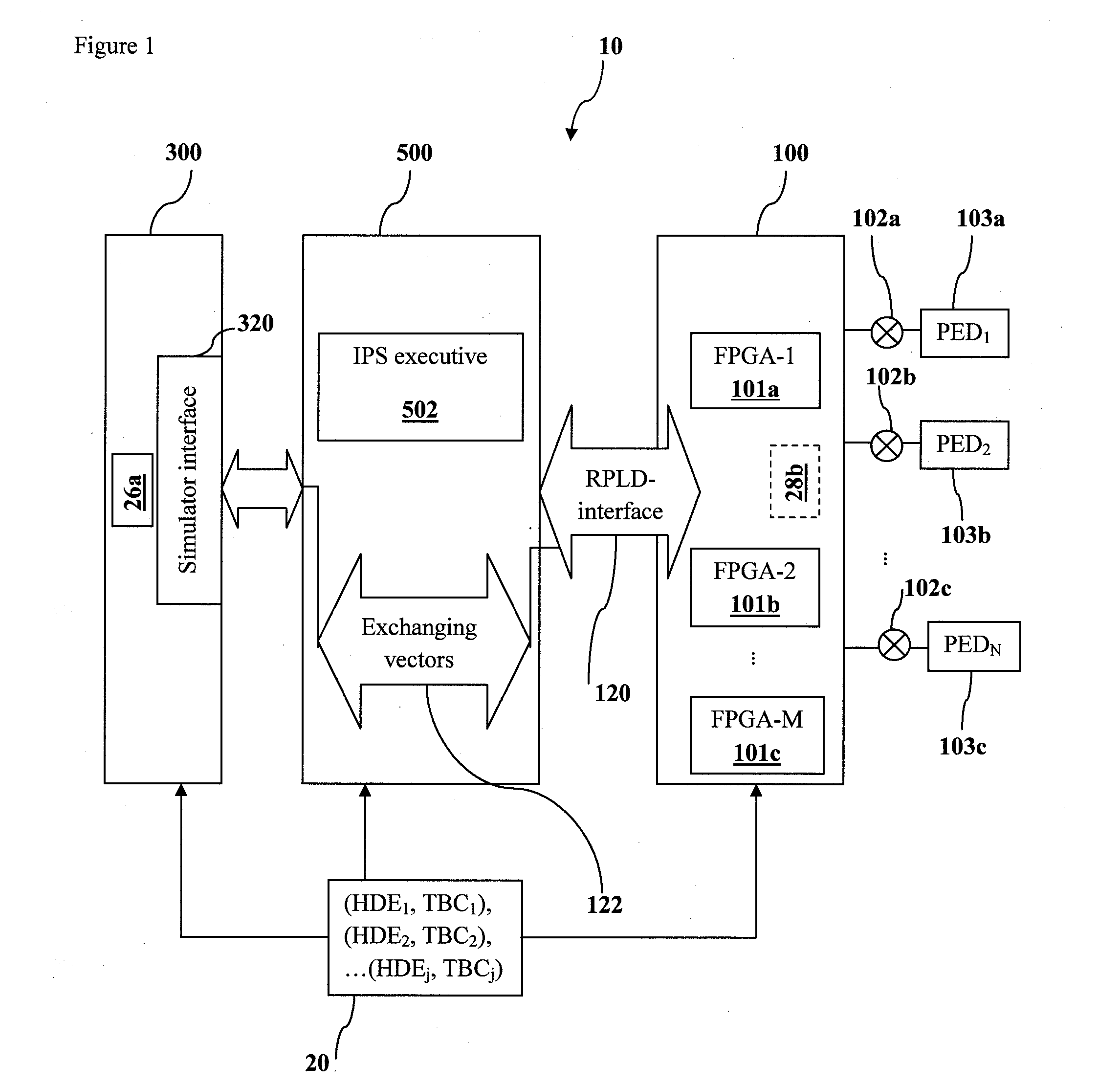

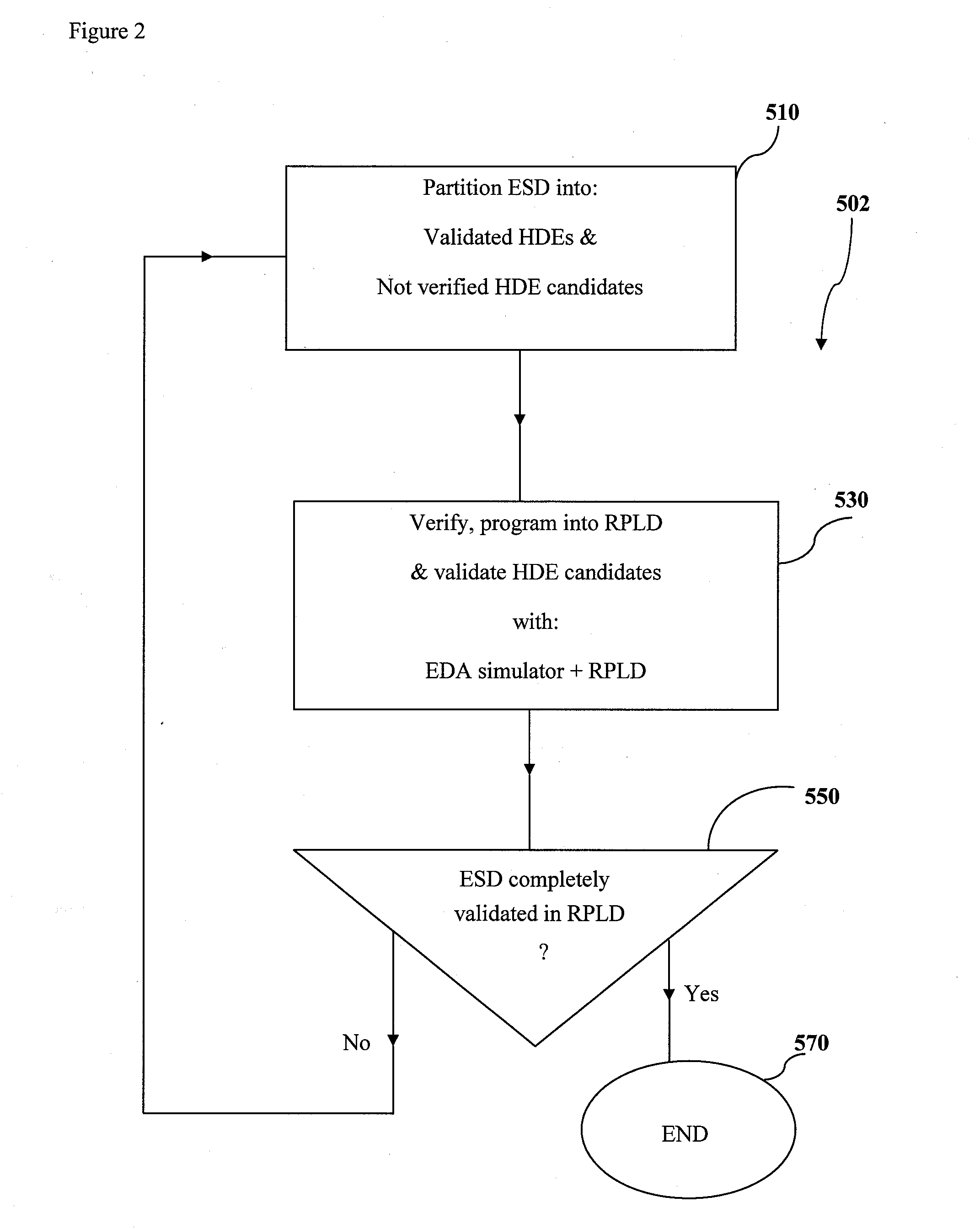

Integrated prototyping system for validating an electronic system design

InactiveUS20090150839A1Increases co-emulation throughputImprove throughputDetecting faulty computer hardwareCAD circuit designElectronic systemsCo-simulation

An integrated prototyping system (IPS) is proposed for verifying and validating an electronic system design (ESD) with hierarchical design elements (HDEs). The IPS has: a) A reprogrammable logic device (RPLD) having an emulation timing base and an RPLD-interface for programming and simulating HDEs under validation while transacting exchanging vectors. The RPLD is also switchably coupled to numerous external peripheral electronic devices (PED), b) An EDA simulator for simulating then verifying selected HDEs while transacting exchanging vectors. The EDA simulator also has a simulator interface; and c) An IPS controller bridging the RPLD and the EDA simulator. The IPS controller has an IPS executive for progressively verifying and validating the ESD. The IPS executive further includes a co-emulation software for jointly and simultaneously running the RPLD and the EDA simulator with an event-based synchronization scheme for interchanging exchanging vectors on demand between the RPLD and the EDA simulator.

Owner:INPA SYST

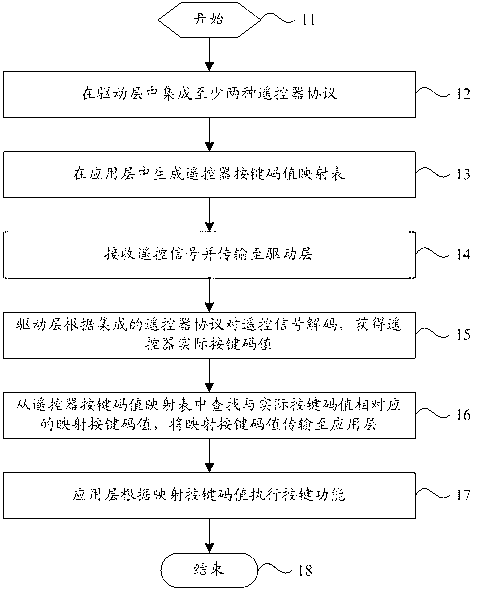

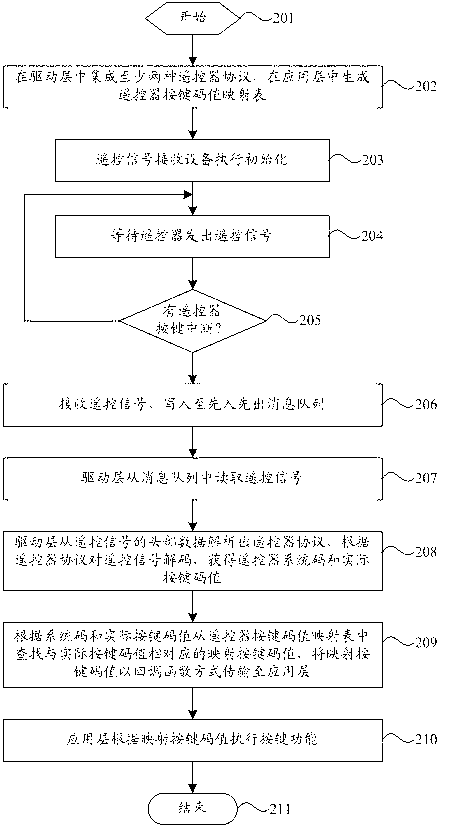

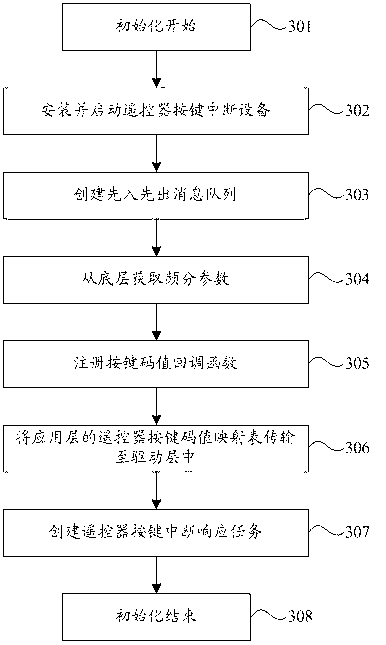

Method and apparatus for responding remote signals of remote receiving equipment

ActiveCN103000008AQuick responseAccurate responseTransmission systemsComputer hardwareSoftware development

The invention discloses a method and an apparatus for responding remote signals of remote receiving equipment. The method comprises the steps of integrating at least two remote controller protocols in a drive layer of remote signal receiving equipment; generating remote controller key code value mapping table in an application layer of the remote signal receiving equipment; decoding the remote signals by the drive layer according to the integrated remote controller protocols after the remote signal receiving equipment receives the remote signals, so as to obtain real key code value of the remote controller; then searching the mapping key code value corresponding to the real key code value in the remote controller key code value mapping table; and transmitting the mapping key code value to the application layer so as to execute a key function. With the hierarchical design of integrating a plurality of controller protocols in the drive layer and generating the remote controller key code value mapping table in the application layer, the apparatus can respond the remote signals with various protocols; and software in the drive layer is in no need of frequent modifications, so that the stability of the system is enhanced; and cost for software development and maintenance is reduced.

Owner:HISENSE BROADBAND MULTIMEDIA TECH

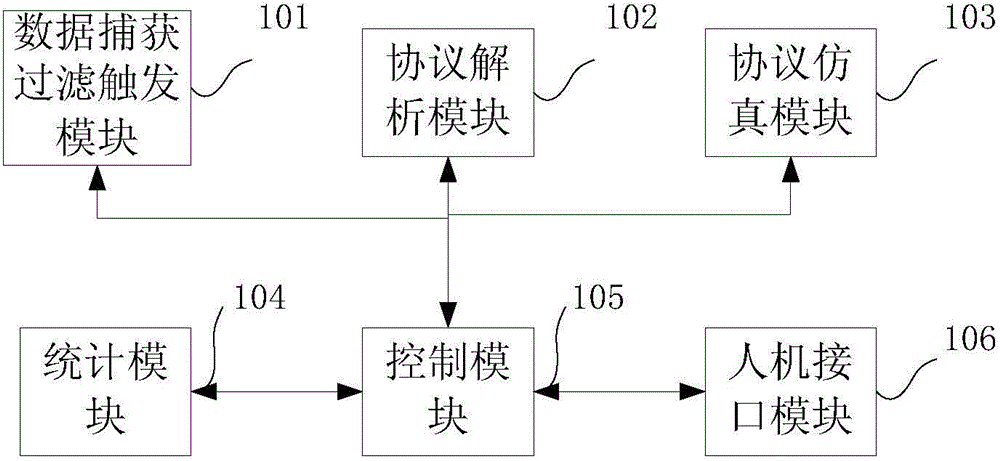

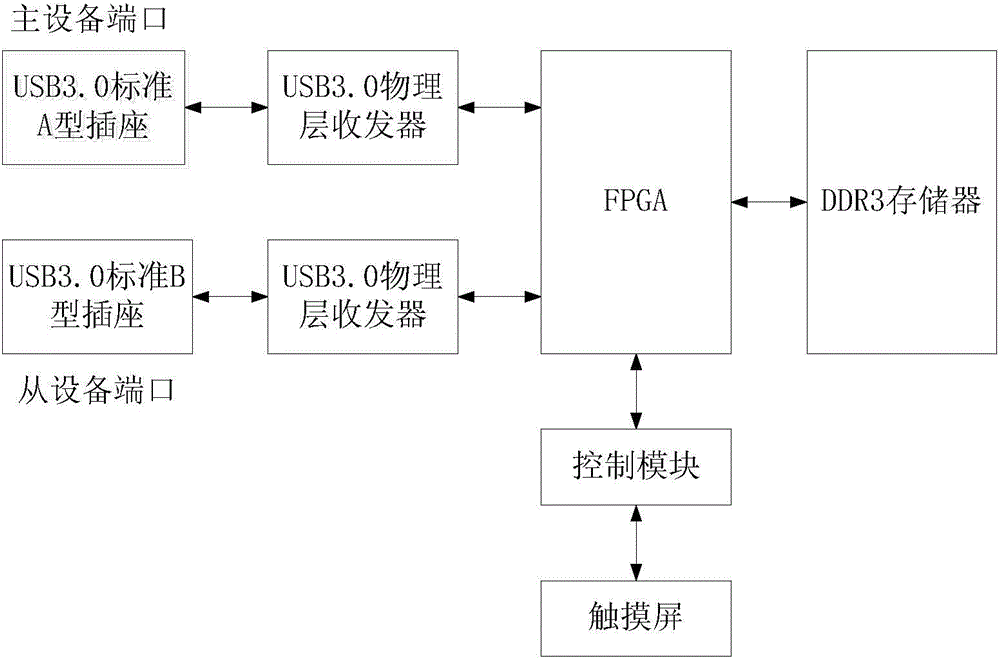

Handheld type USB3.0 protocol analyzer

InactiveCN104820637AMeet the needs of simulation testingEasy to carrySoftware testing/debuggingControl layerUsability

The invention relates to the technical field of testing, and in particular relates to a handheld type USB3.0 protocol analyzer. The handheld type USB3.0 protocol analyzer is characterized by comprising a data capturing, filtering and triggering module, a protocol analysis module, a protocol simulation module, a statistics module, a control module and a man-machine interface module; software of the handheld type USB3.0 protocol analyzer adopts a hierarchical design and is divided into a hardware control layer, a driver layer and an application layer; hardware adopts a high integrated design method, the problems that the existing testing instrument is bad in usability, non-portable and expensive in price are overcome; the handheld type USB3.0 protocol analyzer disclosed by the invention not only can meet a USB3.0 protocol analysis demand and a USB 3.0 protocol simulation testing demand, but also is simple and easy to use and convenient for carrying.

Owner:THE 41ST INST OF CHINA ELECTRONICS TECH GRP

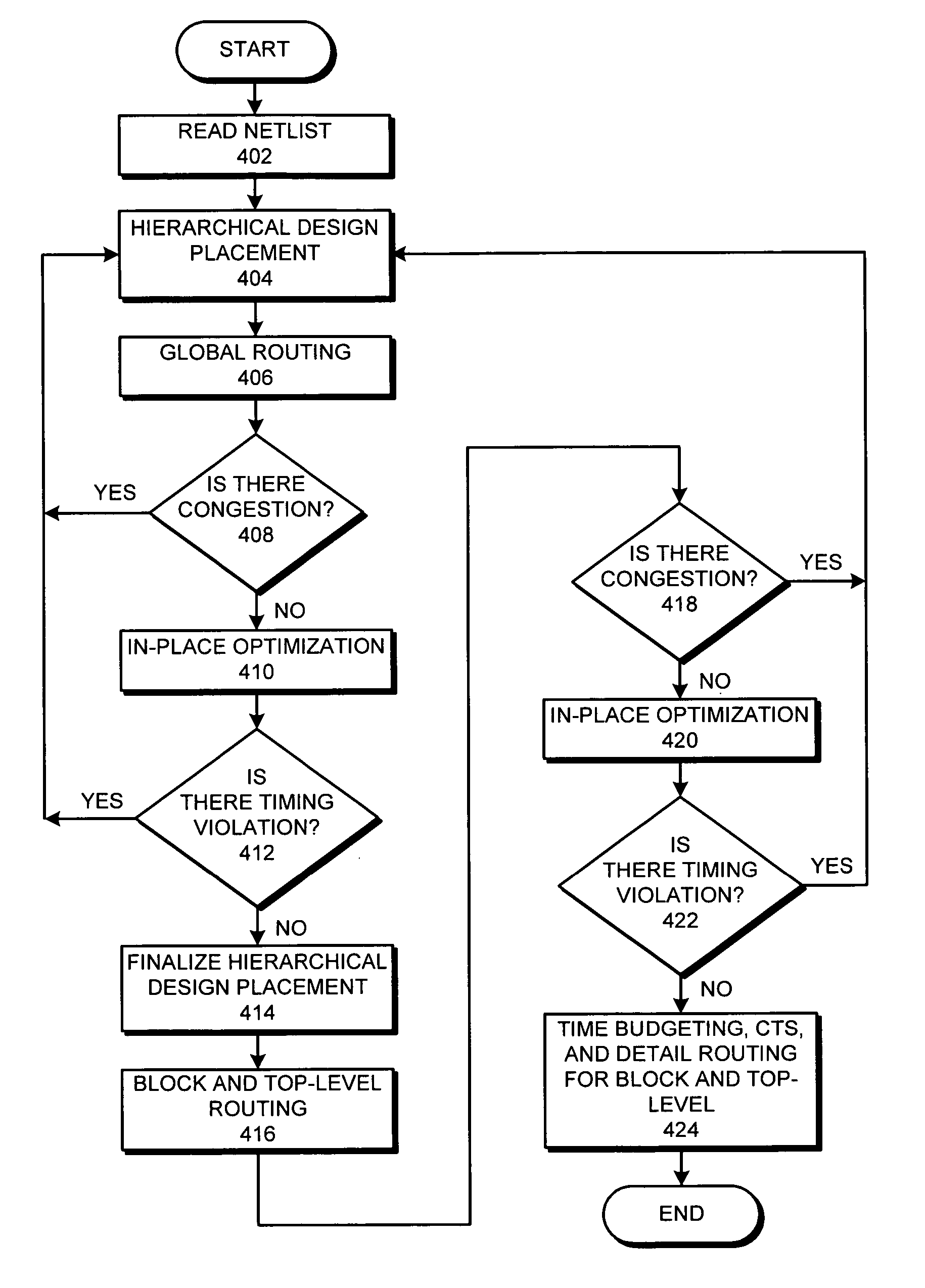

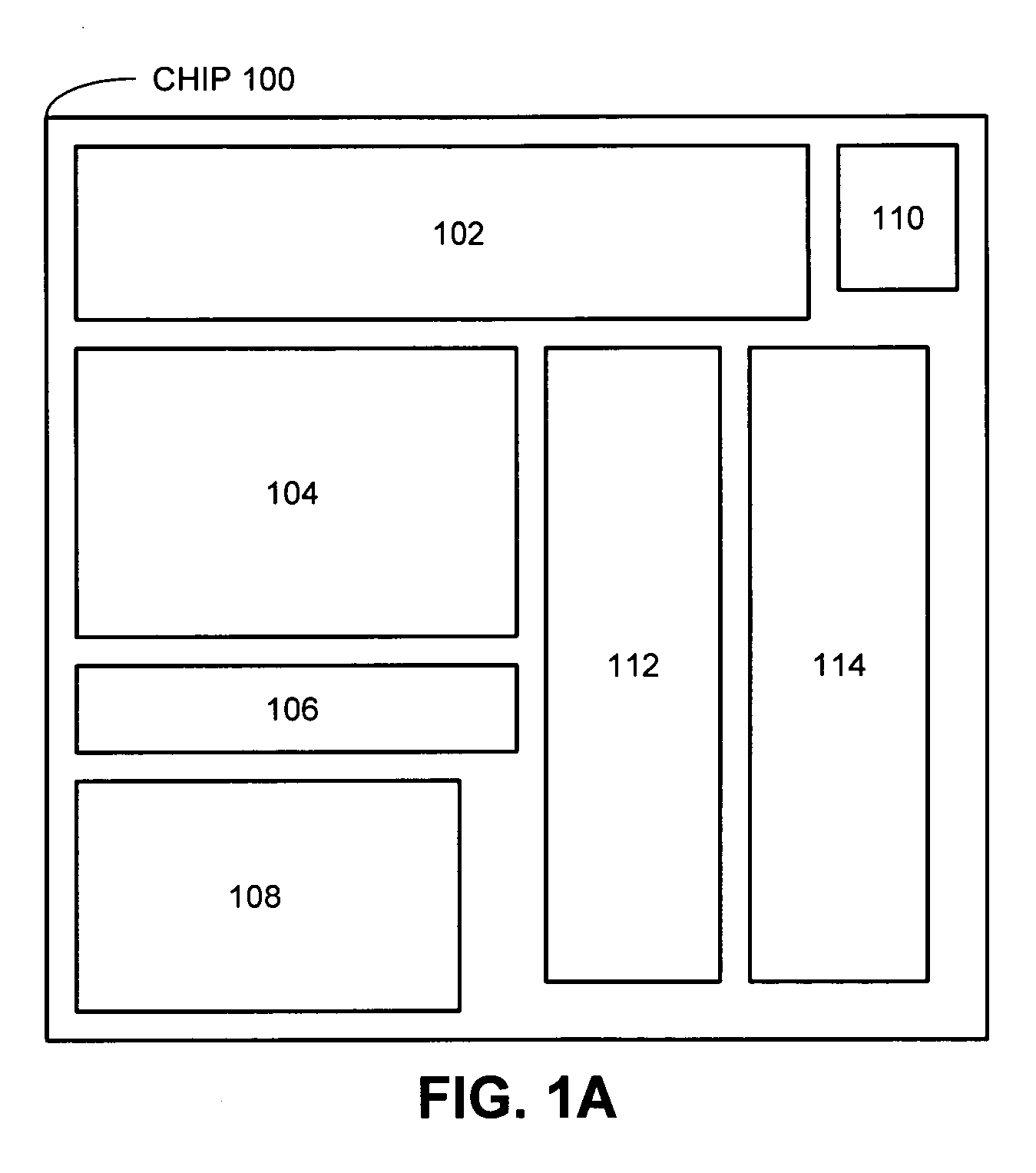

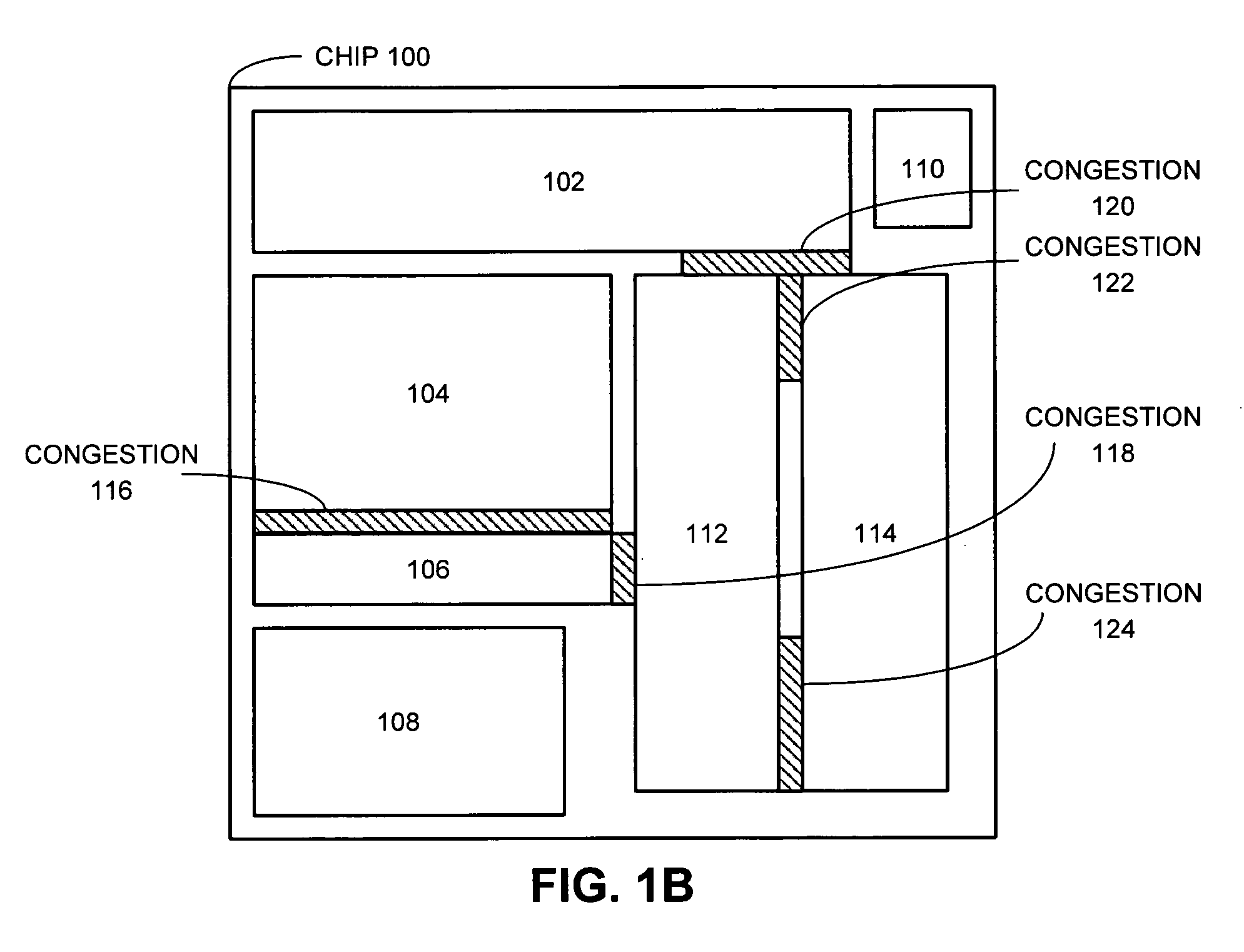

Method and apparatus for routing an integrated circuit

ActiveUS20060294485A1Facilitate early detectionComputer aided designSoftware simulation/interpretation/emulationComputer architectureNetwork generation

A system that routes nets within an integrated circuit. During operation, the system receives a representation for the integrated circuit, which includes block boundaries for physical partitions of the IC generated from a hierarchical design placement of the integrated circuit. The system then classifies each net in the integrated circuit based on the location of pins associated with the net. Next, the system generates routing constraints for each net based on the classification of the net and applies a feedthrough constraint to the physical partitions to restrict nets from feeding through physical partition boundaries. Finally, the system routes each net using the routing constraints for the net and the feedthrough constraints for the physical partitions. This routing is performed based on these block boundaries prior to finalizing the hierarchical design placement, thereby facilitating early detection of congestion or timing violations which can be corrected early in the design process.

Owner:SYNOPSYS INC

Properties In Electronic Design Automation

InactiveUS20080141193A1Easily calculateComputer aided designTotal factory controlComputer architectureLogic circuit design

One or more properties can be associated with a design object in a microdevice design. The design object may be an object in a physical layout design for a microdevice, such as a geometric element in a layout design. The design object also may be a collection of geometric elements in a layout design, such as a net, a cell in a hierarchical design, or even a collection of all of the geometric elements in a layer of a design. Still further, the design object may even be an item in a logical circuit design, such as a net in a logical circuit design for an integrated circuit. The values of one or more properties may be statically assigned for or dynamically generated during a design process performed by an electronic design automation tool. A property may be assigned a constant value or a value defined by an equation or other type of script that includes one or more variables. A property may be simple, where the definition of the property's value is not dependent upon the value of any other properties. Alternately, a property may be a compound property, where the definition of the property's value incorporates another, previously-determined property value. Still further, a property may be an alternative property, where the property is assigned one value definition under a first set of conditions and assigned another value definition under a second set of conditions. A first electronic design automation process may generate one or more property values. The generated property values then can be passed to another electronic design automation process in the design analysis flow for its use.

Owner:MENTOR GRAPHICS CORP

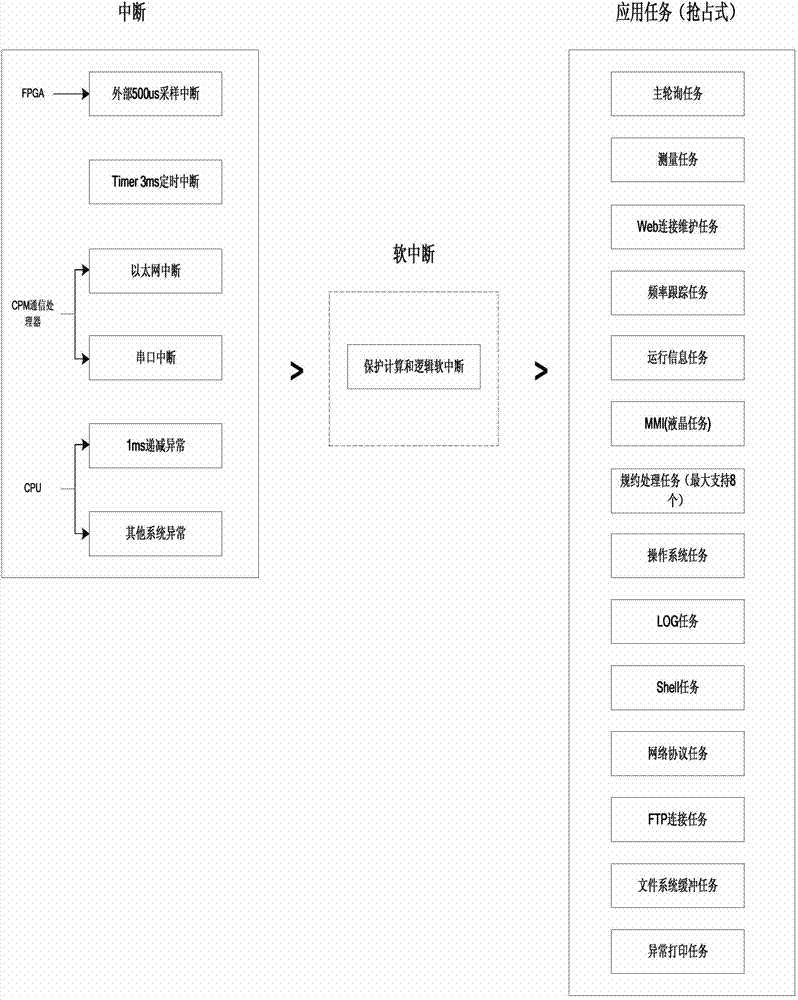

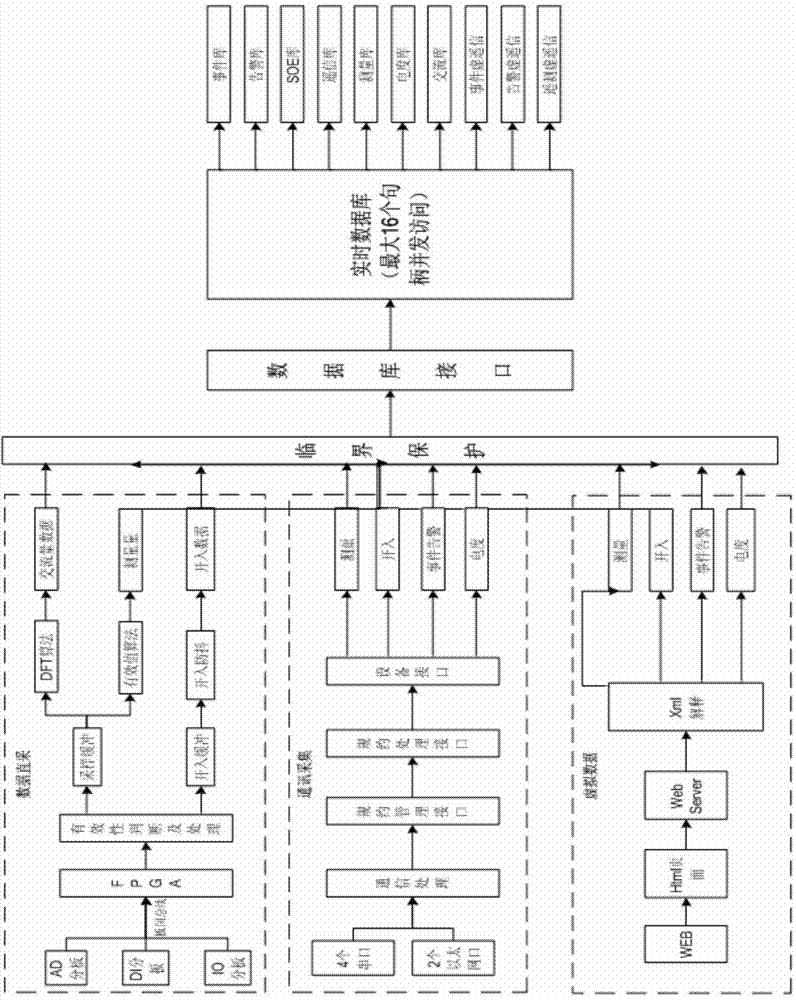

Control system used for power distribution terminal

InactiveCN103944259AEasy version upgradeFunction increaseCircuit arrangementsAbstraction layerPublic interface

Owner:STATE GRID CORP OF CHINA +3