Patents

Literature

1691 results about "Logical circuit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Logical Circuit is a comprehensive, practical and effective software solution whose main purpose is to help users design and simulate digital logic circuits.

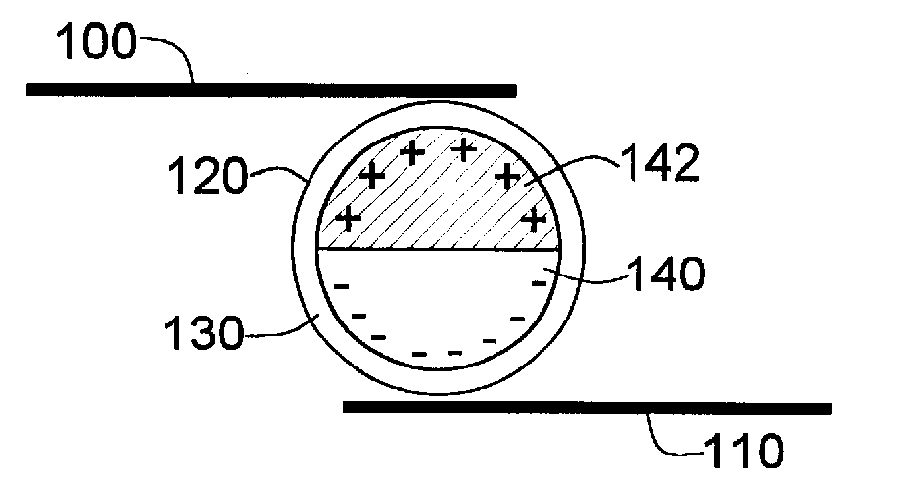

Electronically addressable microencapsulated ink and display thereof

InactiveUS7148128B2Inexpensive displayInking apparatusMechanical clocksSemiconductor materialsDisplay device

We describe a system of electronically active inks which may include electronically addressable contrast media, conductors, insulators, resistors, semiconductive materials, magnetic materials, spin materials, piezoelectric materials, optoelectronic, thermoelectric or radio frequency materials. We further describe a printing system capable of laying down said materials in a definite pattern. Such a system may be used for instance to: print a flat panel display complete with onboard drive logic; print a working logic circuit onto any of a large class of substrates; print an electrostatic or piezoelectric motor with onboard logic and feedback or print a working radio transmitter or receiver.

Owner:E INK CORPORATION

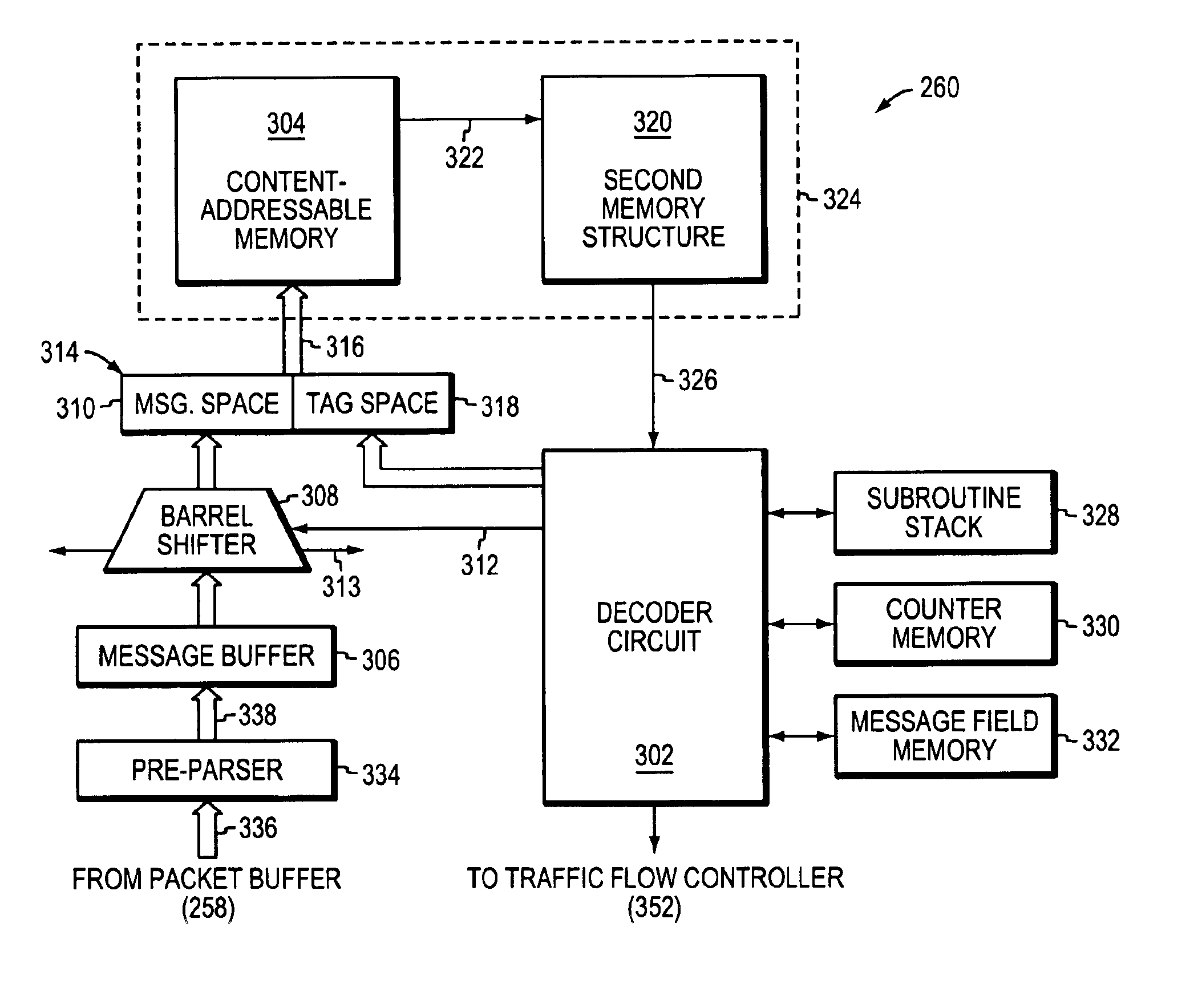

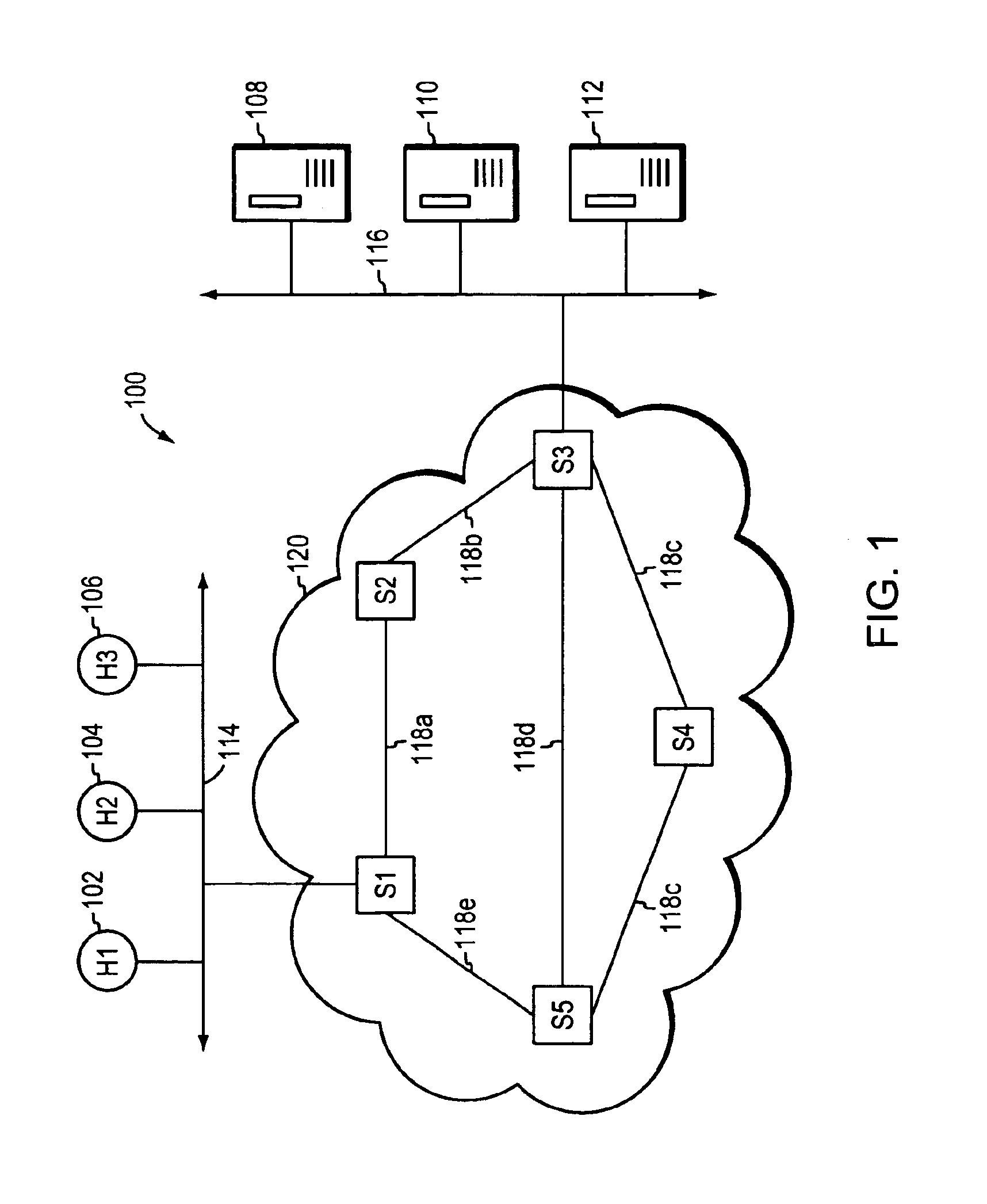

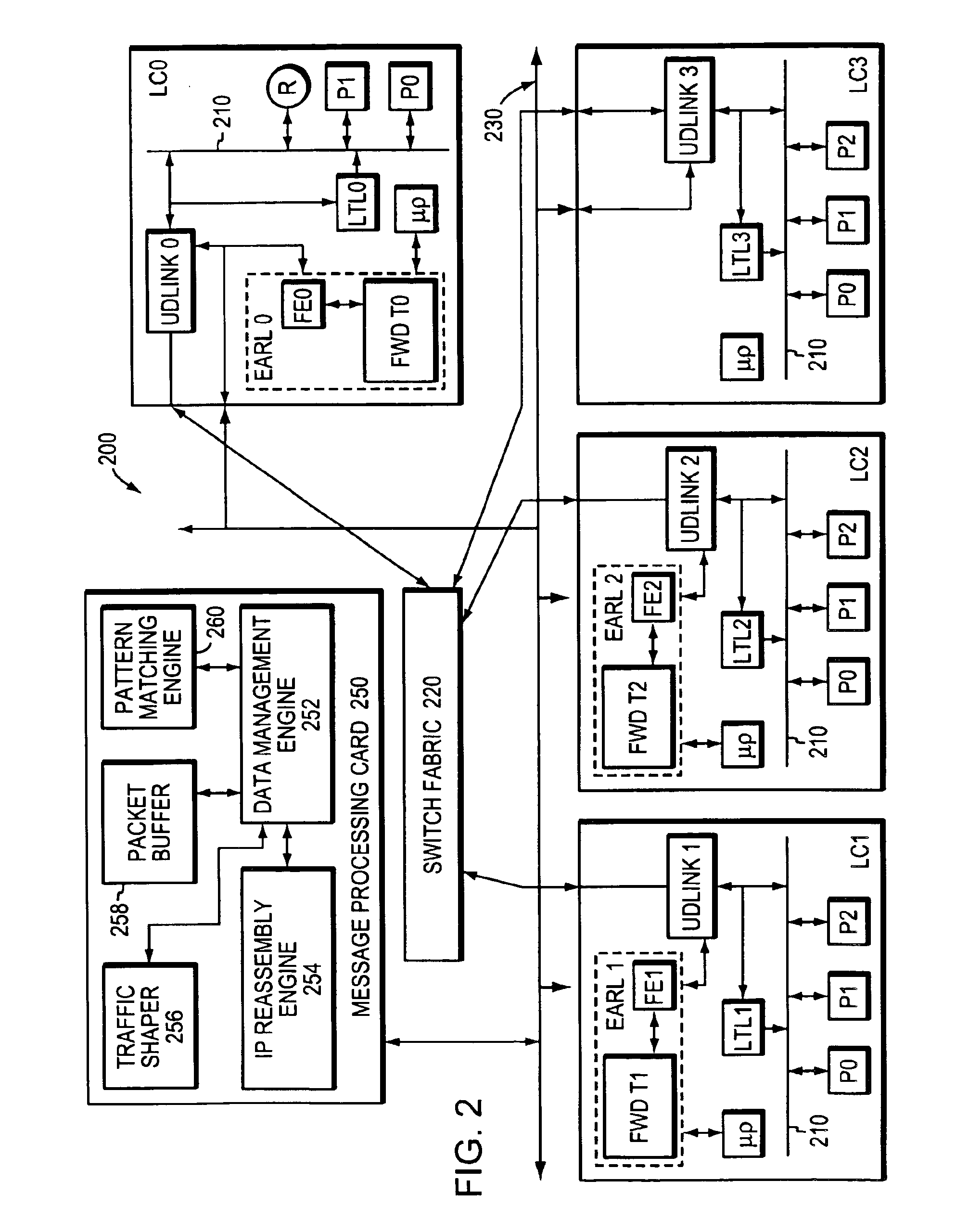

Method and apparatus for high-speed parsing of network messages

InactiveUS6892237B1Efficient analysisIncrease speedMultiple digital computer combinationsData switching networksPattern matchingRandom access memory

A programmable pattern matching engine efficiently parses the contents of network messages for regular expressions and executes pre-defined actions or treatments on those messages that match the regular expressions. The pattern matching engine is preferably a logic circuit designed to perform its pattern matching and execution functions at high speed, e.g., at multi-gigabit per second rates. It includes, among other things, a message buffer for storing the message being evaluated, a decoder circuit for decoding and executing corresponding actions or treatments, and one or more content-addressable memories (CAMs) that are programmed to store the regular expressions used to search the message. The CAM may be associated with a second memory device, such as a random access memory (RAM), as necessary, that is programmed to contain the respective actions or treatments to be applied to messages matching the corresponding CAM entries. The RAM provides its output to the decoder circuit, which, in response, decodes and executes the specified action or treatment.

Owner:CISCO TECH INC

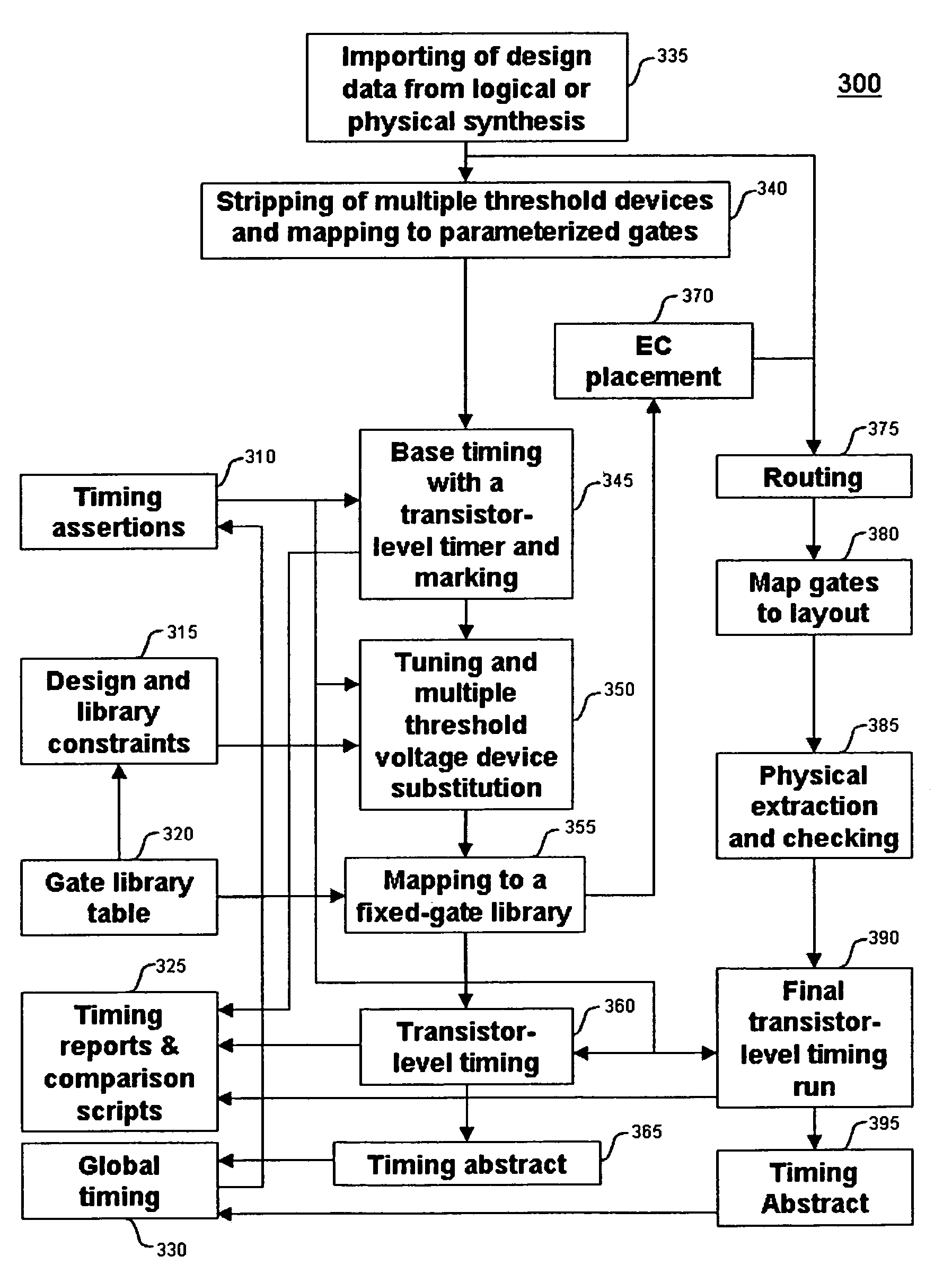

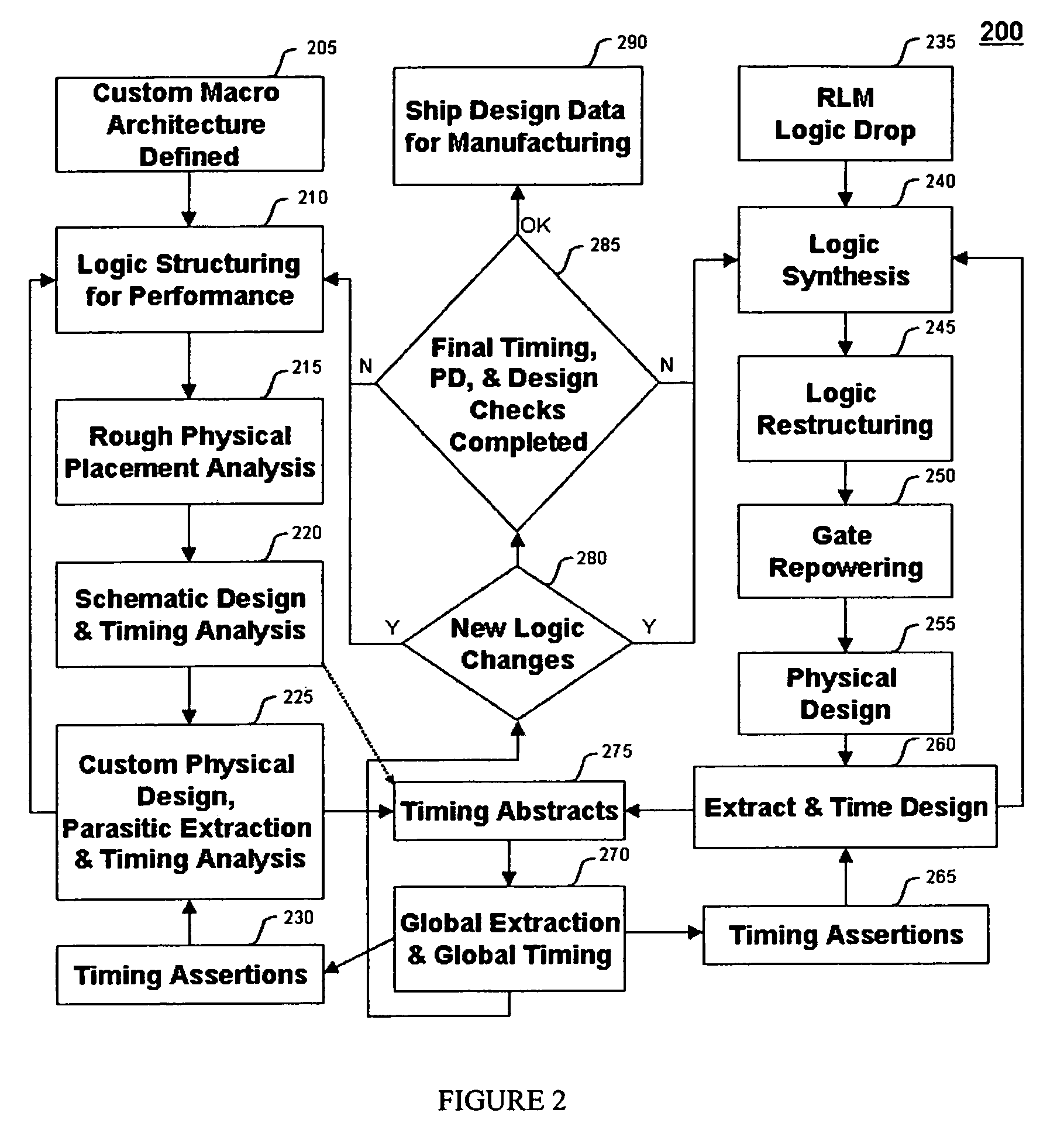

Method for tuning a digital design for synthesized random logic circuit macros in a continuous design space with optional insertion of multiple threshold voltage devices

InactiveUS7093208B2Efficient and effective methodologyError minimizationDigital storageComputer aided designContinuous designCritical section

A Digital Design Method which may be automated is for obtaining timing closure in the design of large, complex, high-performance digital integrated circuits. The methodincludes the use of a tuner on random logic macros that adjusts transistor sizes in a continuous domain. To accommodate this tuning, logic gates are mapped to parameterized cells for the tuning and then back to fixed gates after the tuning. Tuning is constrained in such a way as to minimize “binning errors” when the design is mapped back to fixed cells. Further, the critical sections of the circuit are marked in order to make the optimization more effective and to fit within the problem-size constraints of the tuner. A specially formulated objective function is employed during the tuning to promote faster global timing convergence, despite possibly incorrect initial timing budgets. The specially formulated objective function targets all paths that are failing timing, with appropriate weighting, rather than just targeting the most critical path. Finally, the addition of multiple threshold voltage gates allows for increased performance while limiting leakage power.

Owner:GLOBALFOUNDRIES INC

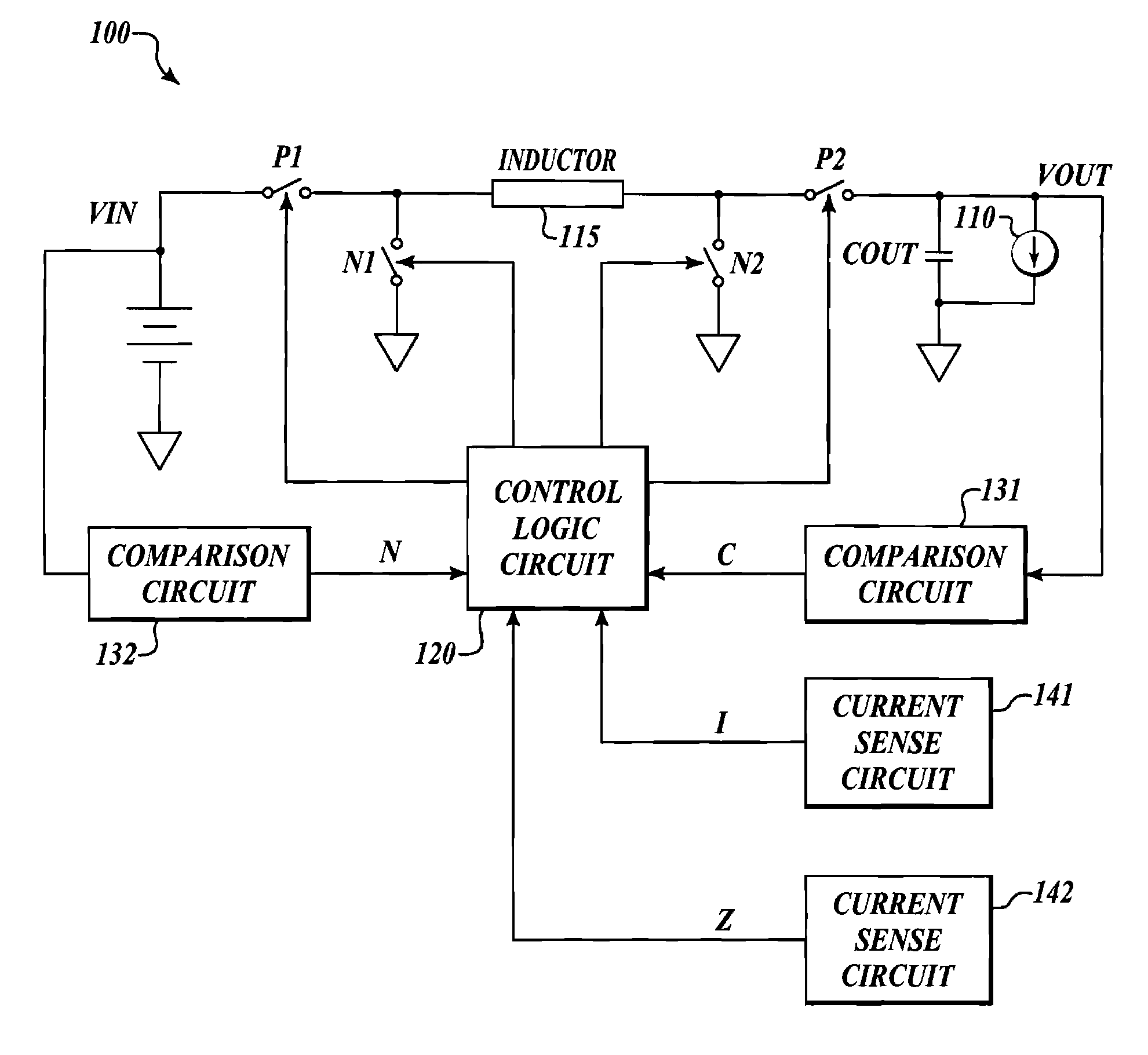

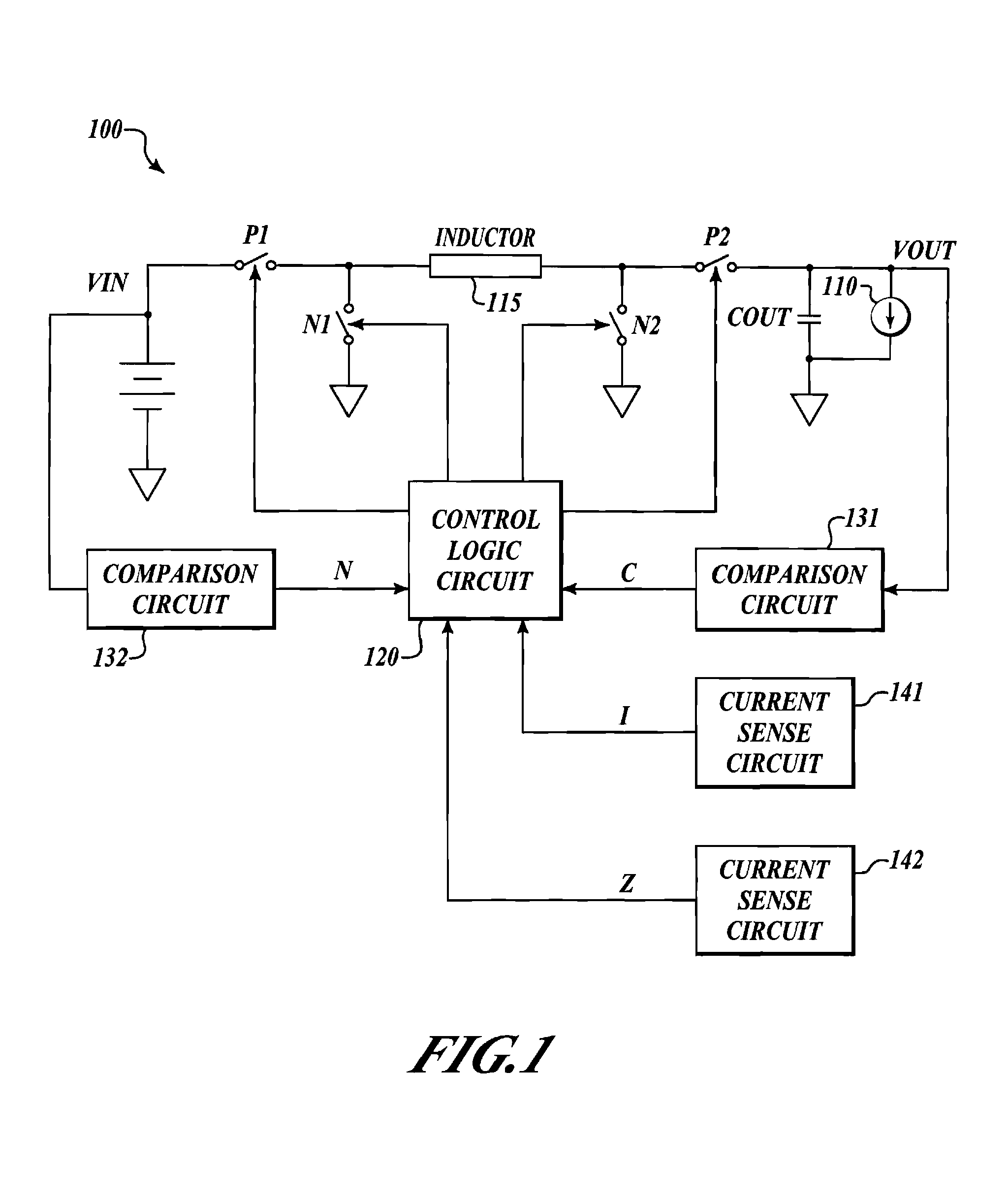

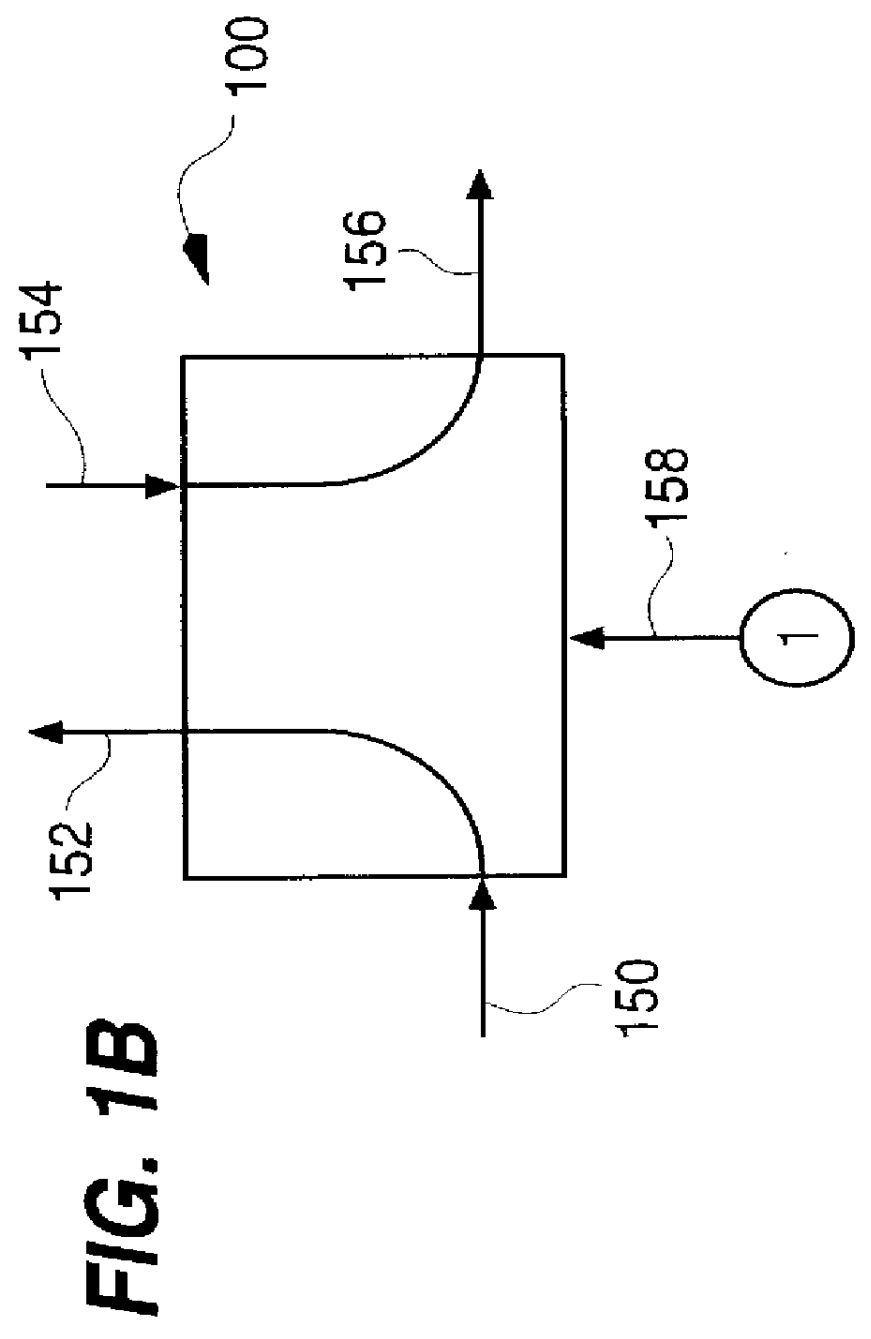

Apparatus and method for PFM buck-or-boost converter with smooth transition between modes

A PFM buck-or-boost converter is provided. The converter includes, inter alia, a hysteretic comparator, current sense circuitry, a logic circuit, drivers, current sense circuitry, a first buck switch, and a first boost switch. The current sense circuitry asserts signal Z if the current through the boost switch (from the load to the inductor) is greater than zero, and unasserts Z otherwise. Additionally, the current sense circuitry asserts signal I if the current through the buck switch is greater than a fixed current limit value, and unasserts I otherwise. The logic circuit employs the hysteretic comparator output, signal Z, and signal I to control the switches, and to determine whether to operate in buck regulation mode or boost regulation mode.

Owner:NAT SEMICON CORP

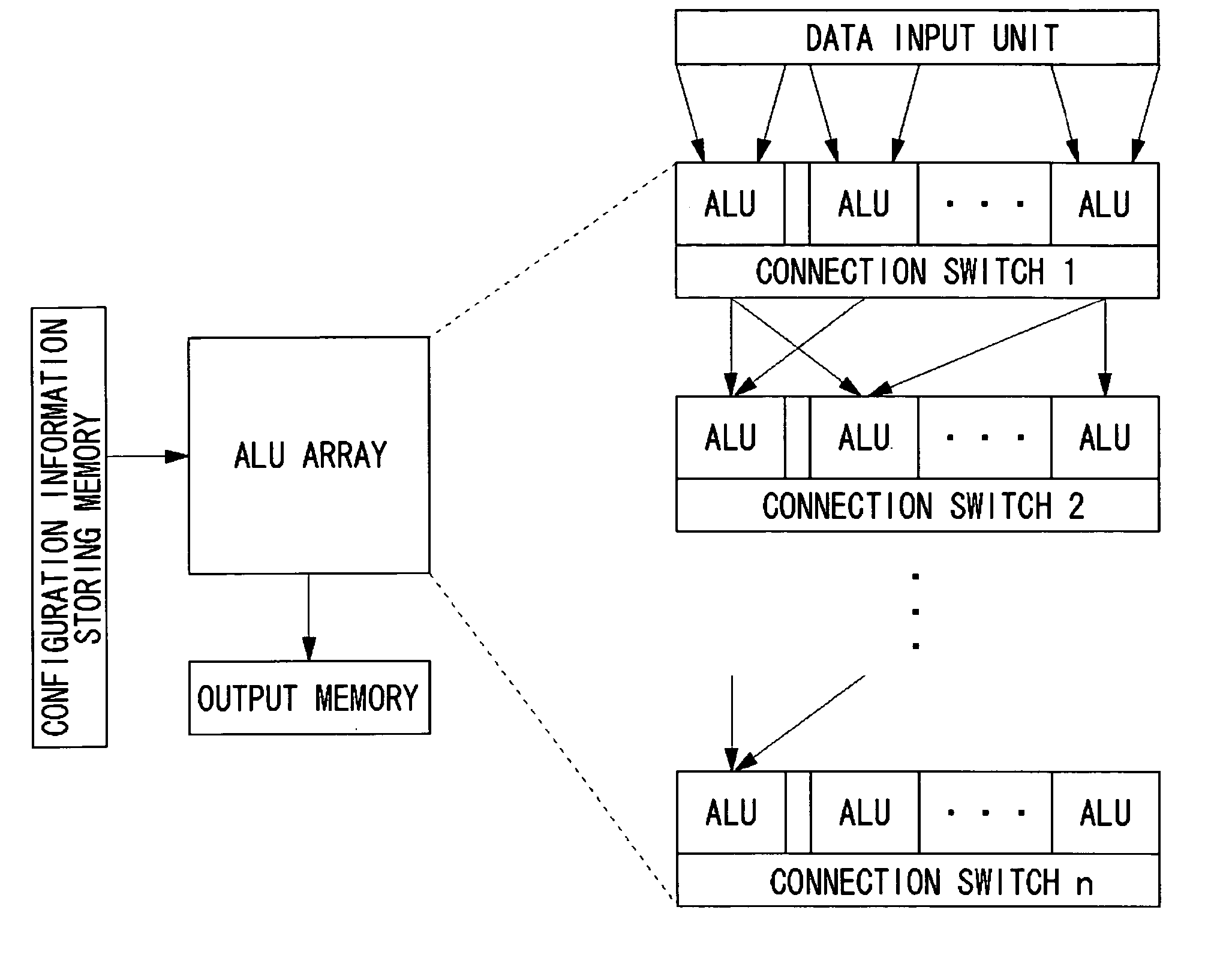

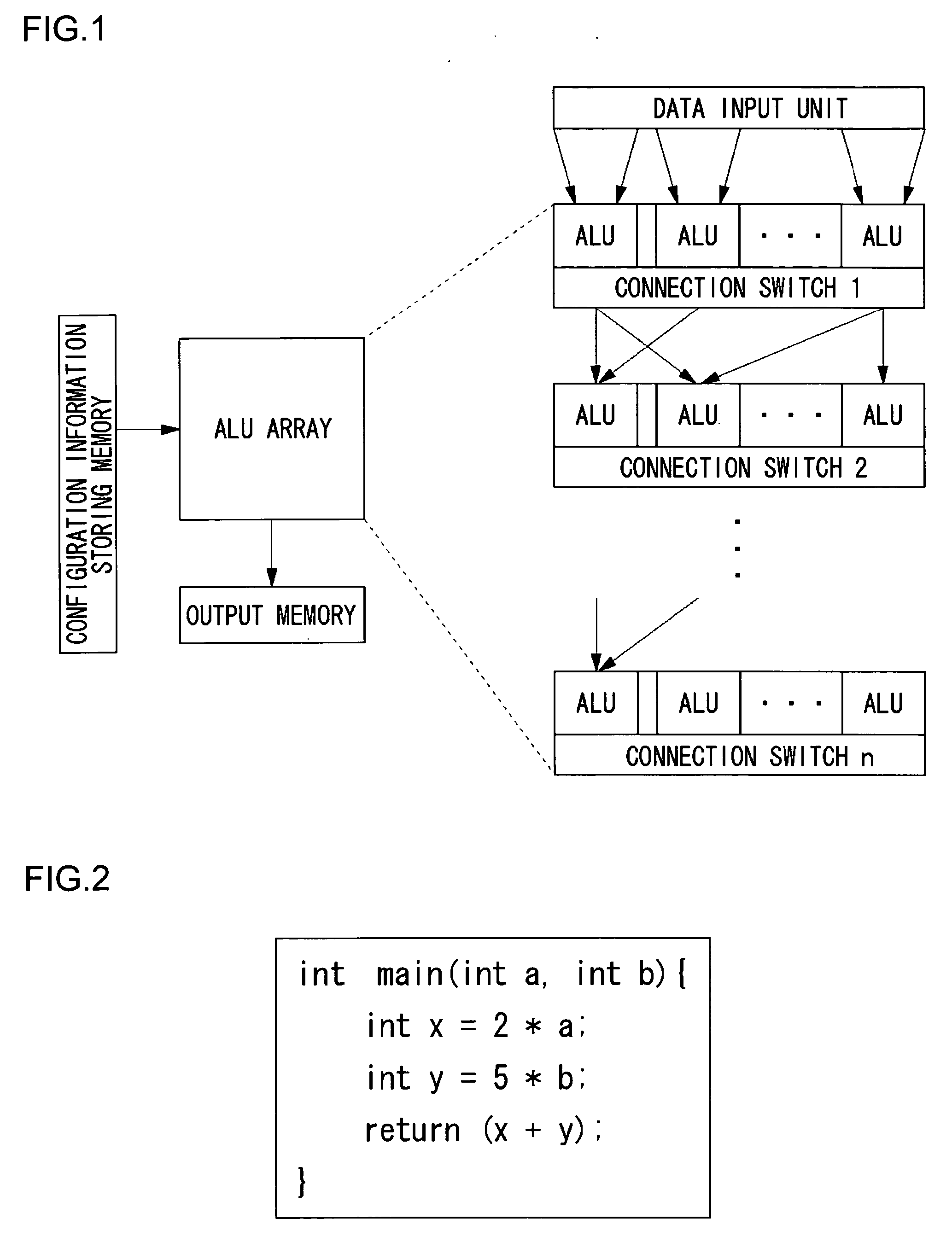

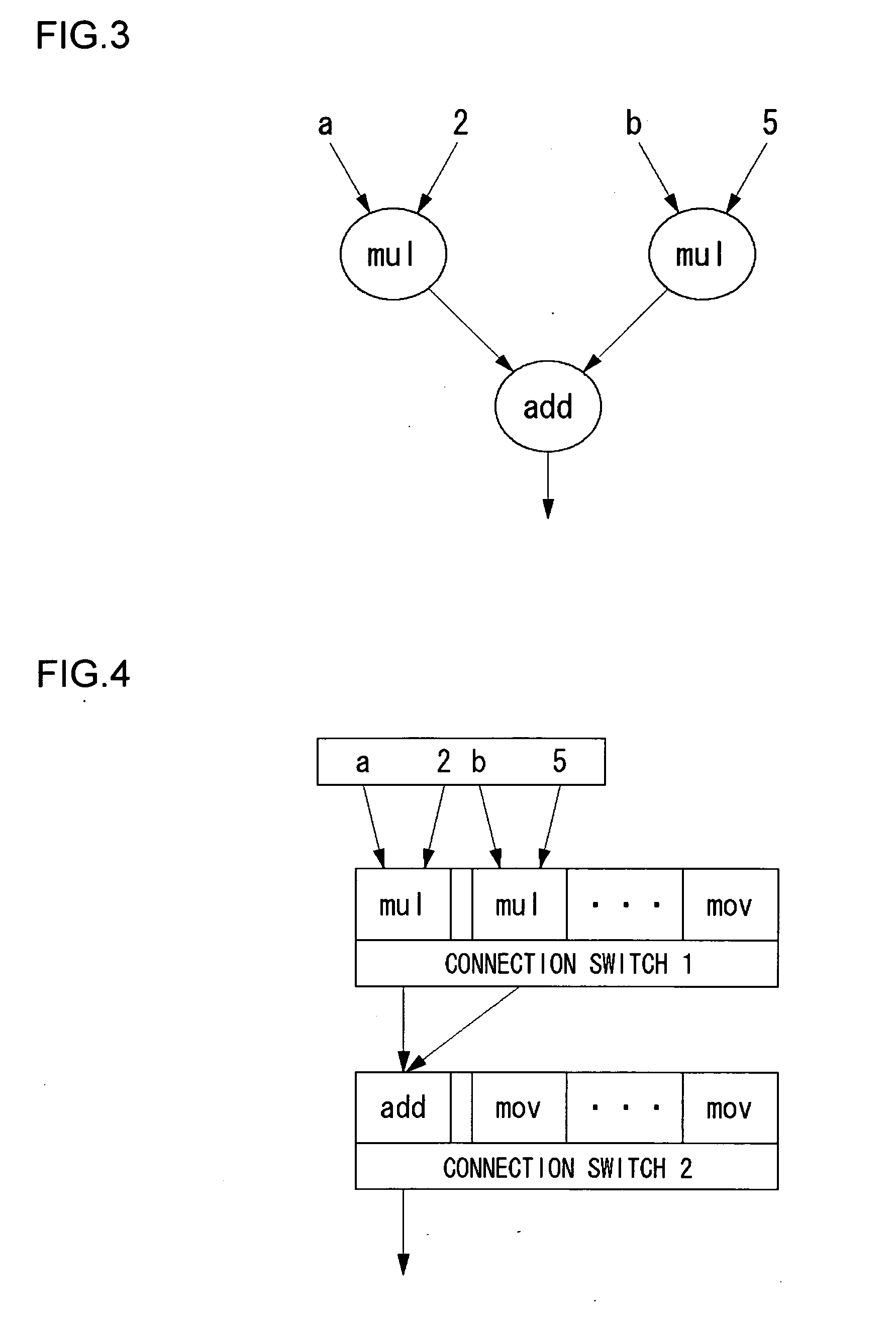

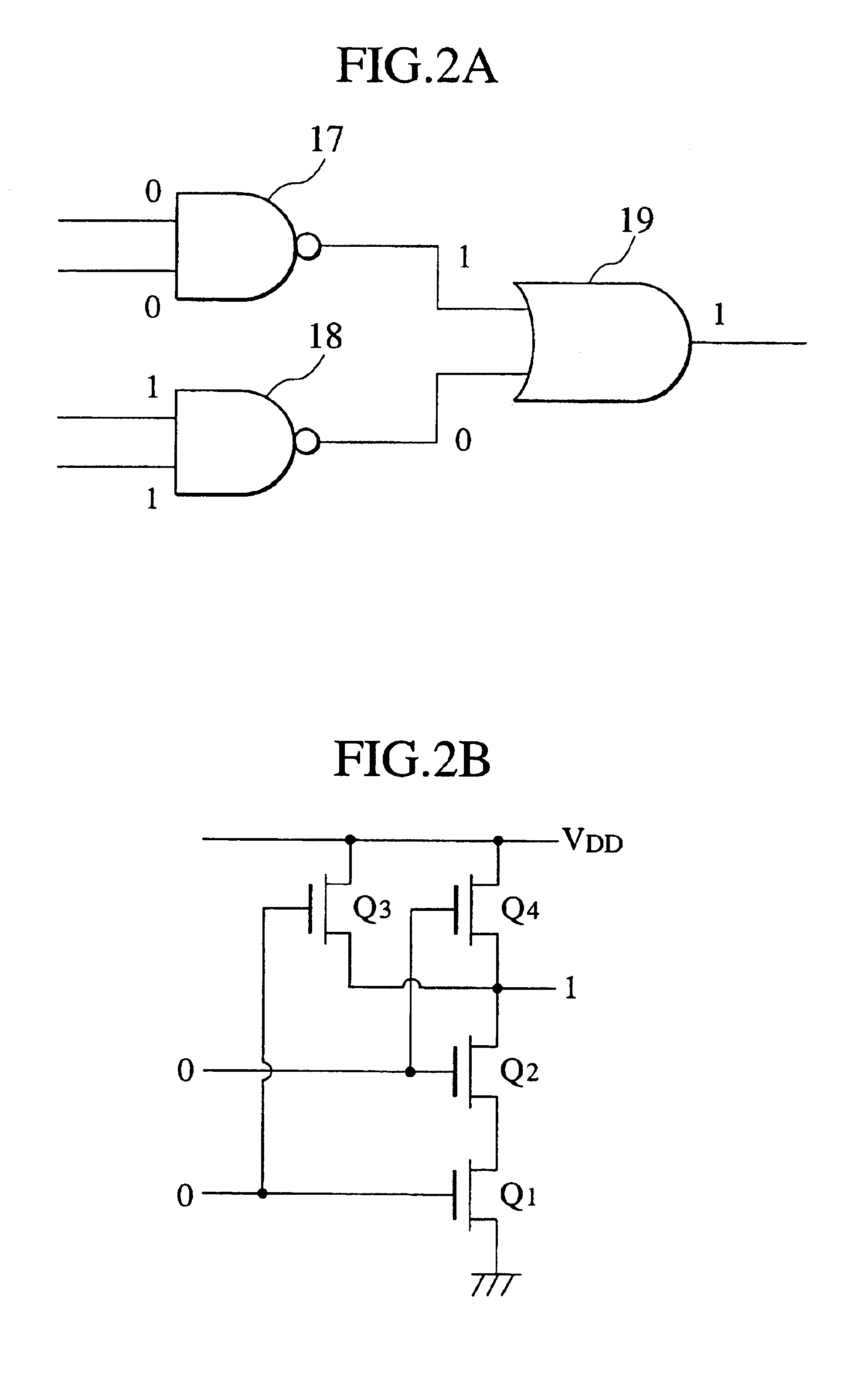

Reconfigurable circuit, processor having reconfigurable circuit, method of determining functions of logic circuits in reconfigurable circuit, method of generating circuit, and circuit

InactiveUS20050134308A1Reduce in quantityReduce switchingEnergy efficient ICTSemiconductor/solid-state device manufacturingLogical circuit

Owner:SANYO ELECTRIC CO LTD

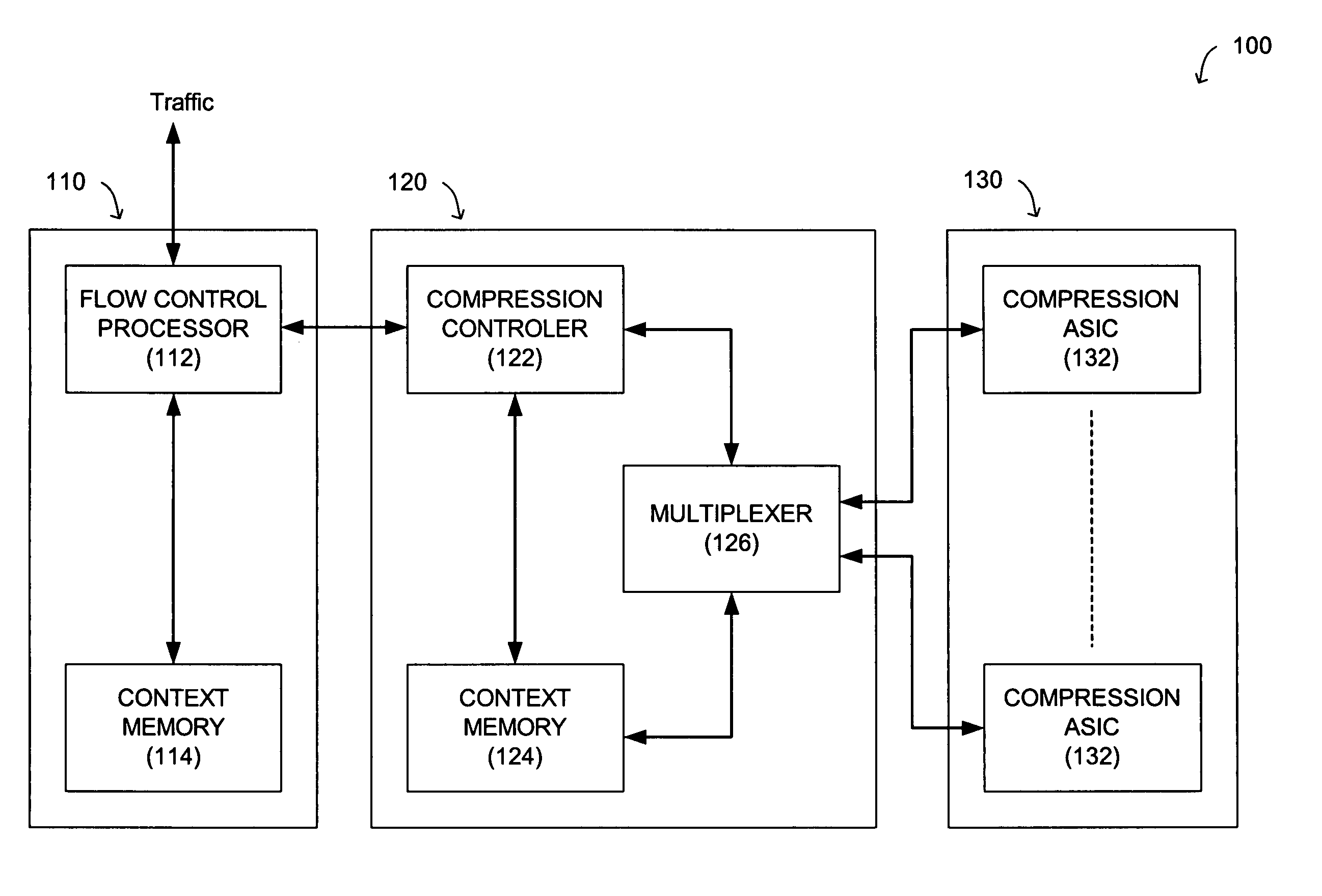

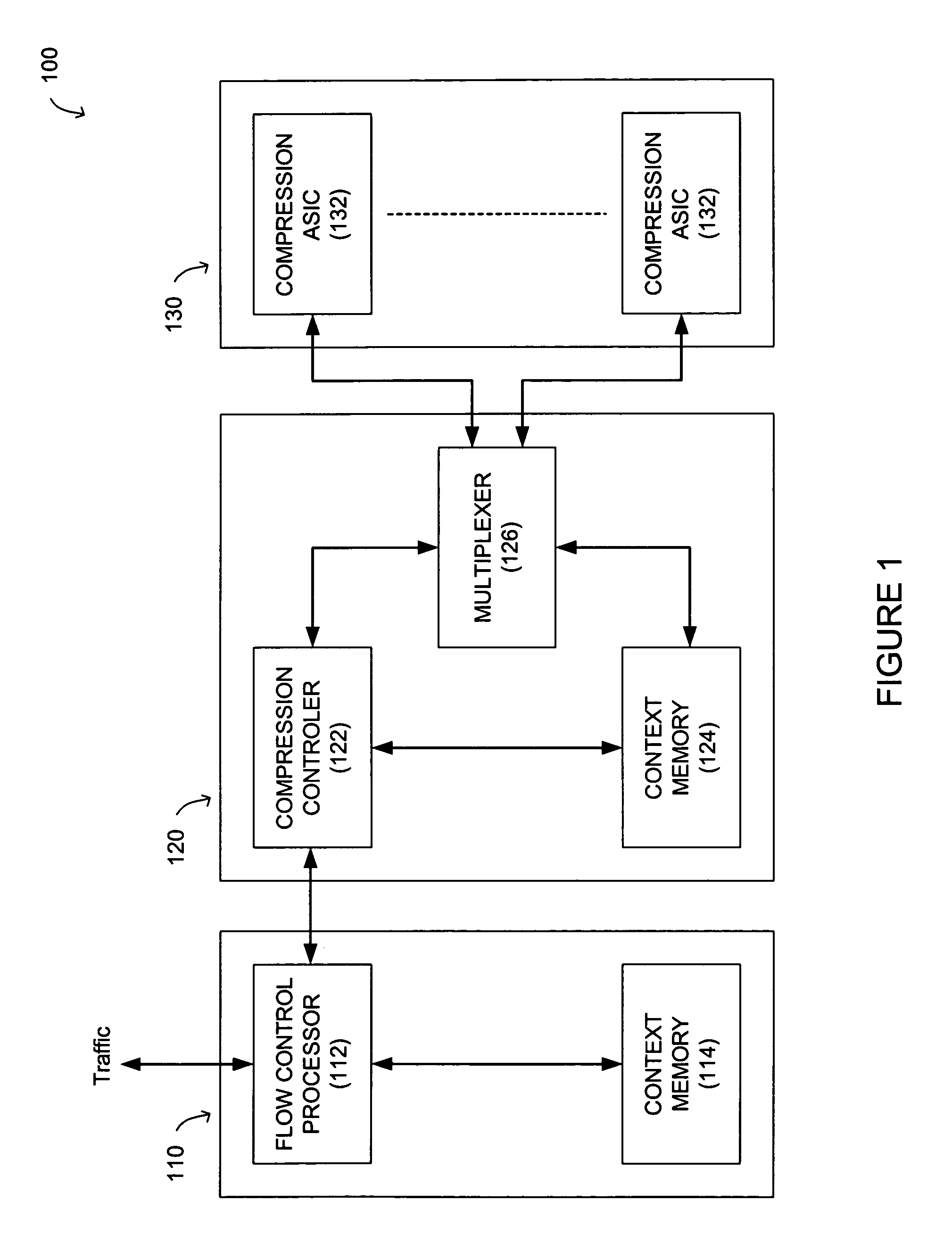

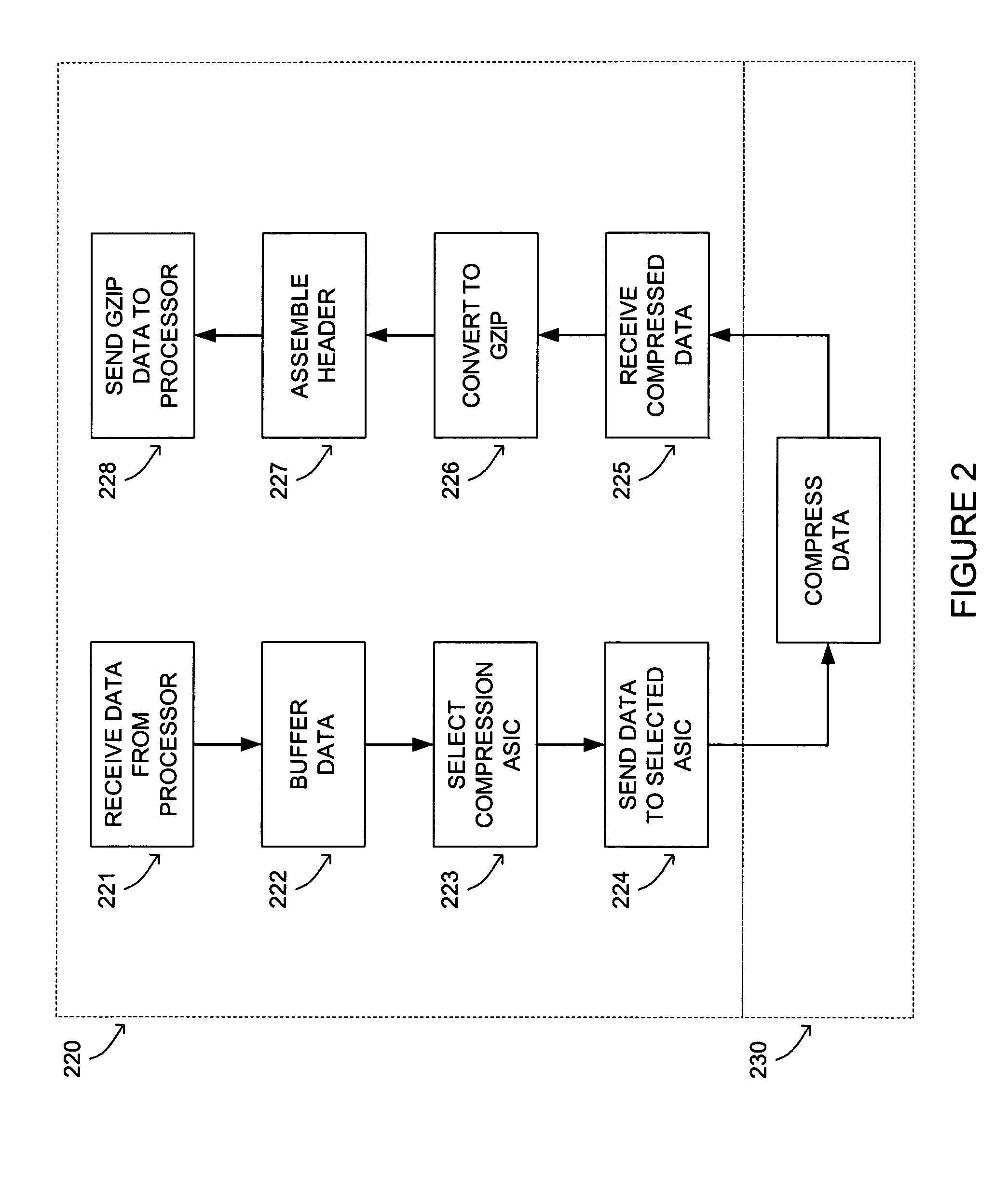

Hardware accelerated compression

ActiveUS7051126B1Improve compression speedImprove data throughputCode conversionMultiple digital computer combinationsData streamHardware acceleration

A compression system is arranged to use software and / or hardware accelerated compression techniques to increase compression speeds and enhance overall data throughput. A logic circuit is arranged to: receive a data stream from a flow control processor, buffer the data stream, select a hardware compressor (e.g., an ASIC), and forward the data to the selected hardware compressor. Each hardware compressor performs compression on the data (e.g., LZ77), and sends the compressed data back to the logic circuit. The logic circuit receives the compressed data, converts the data to another compressed format (e.g., GZIP), and forwards the converted and compressed data back to the flow control processor. History associated with the data stream can be stored in memory by the flow control processor, or in the logic circuit.

Owner:F5 NETWORKS INC

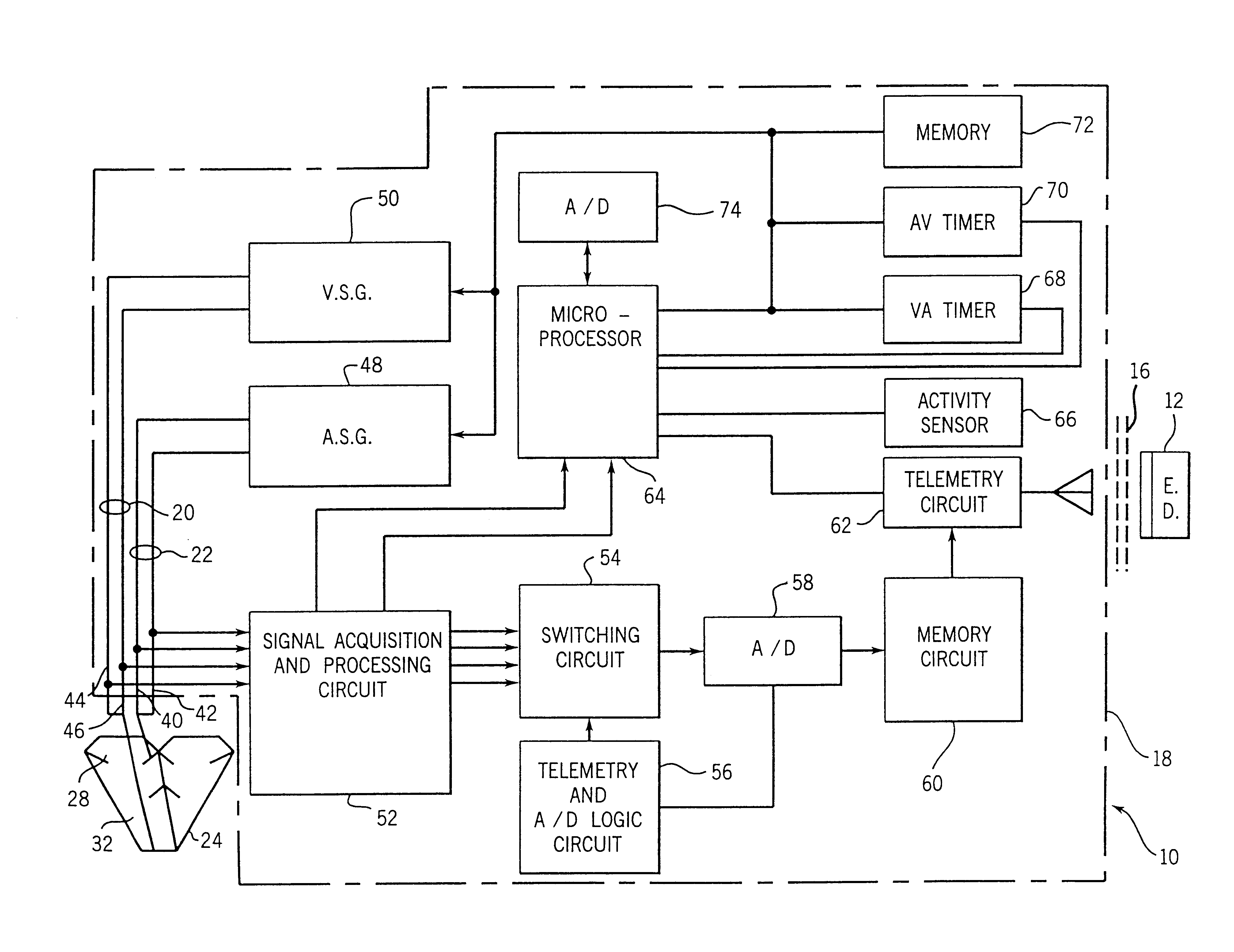

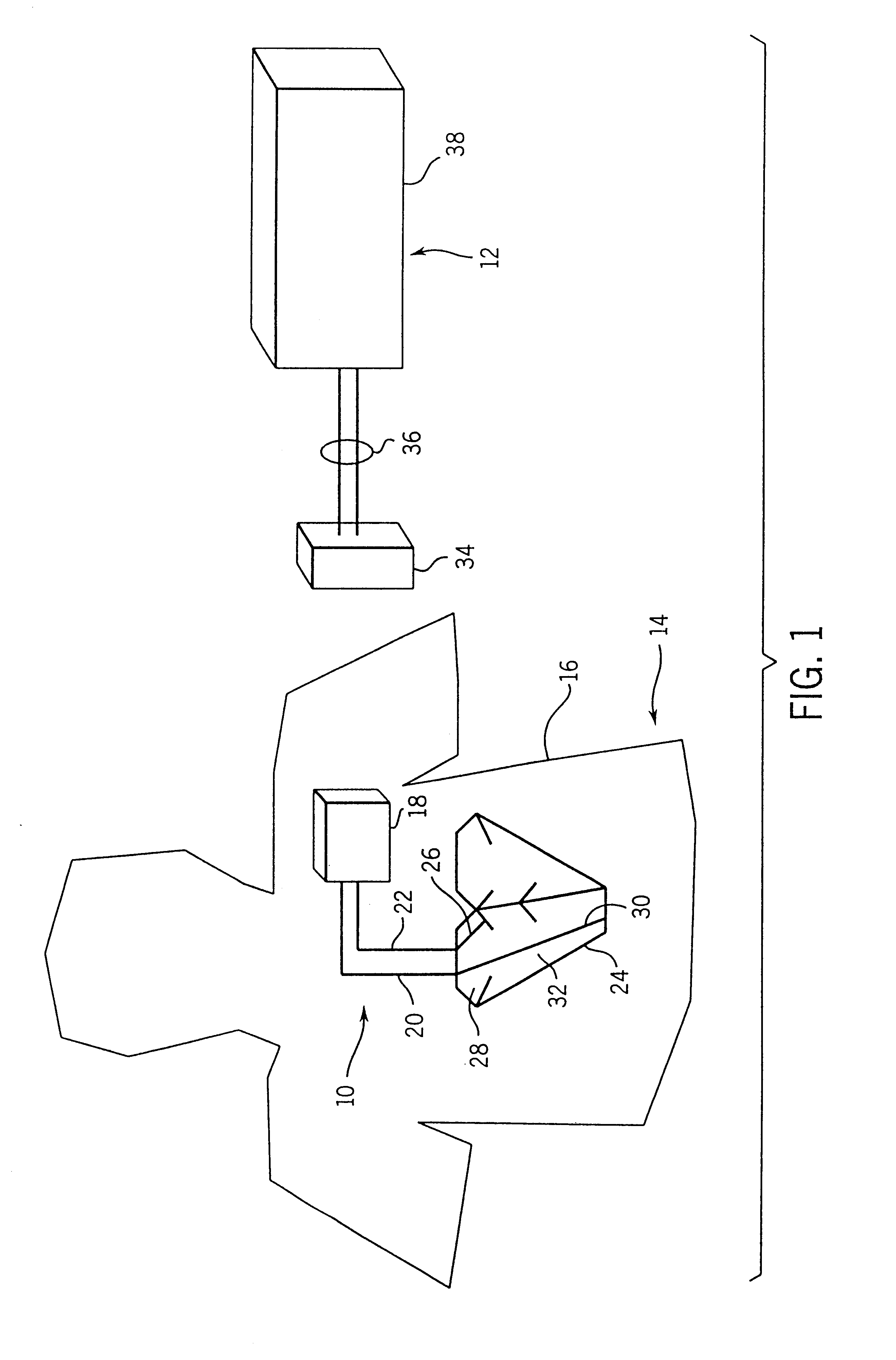

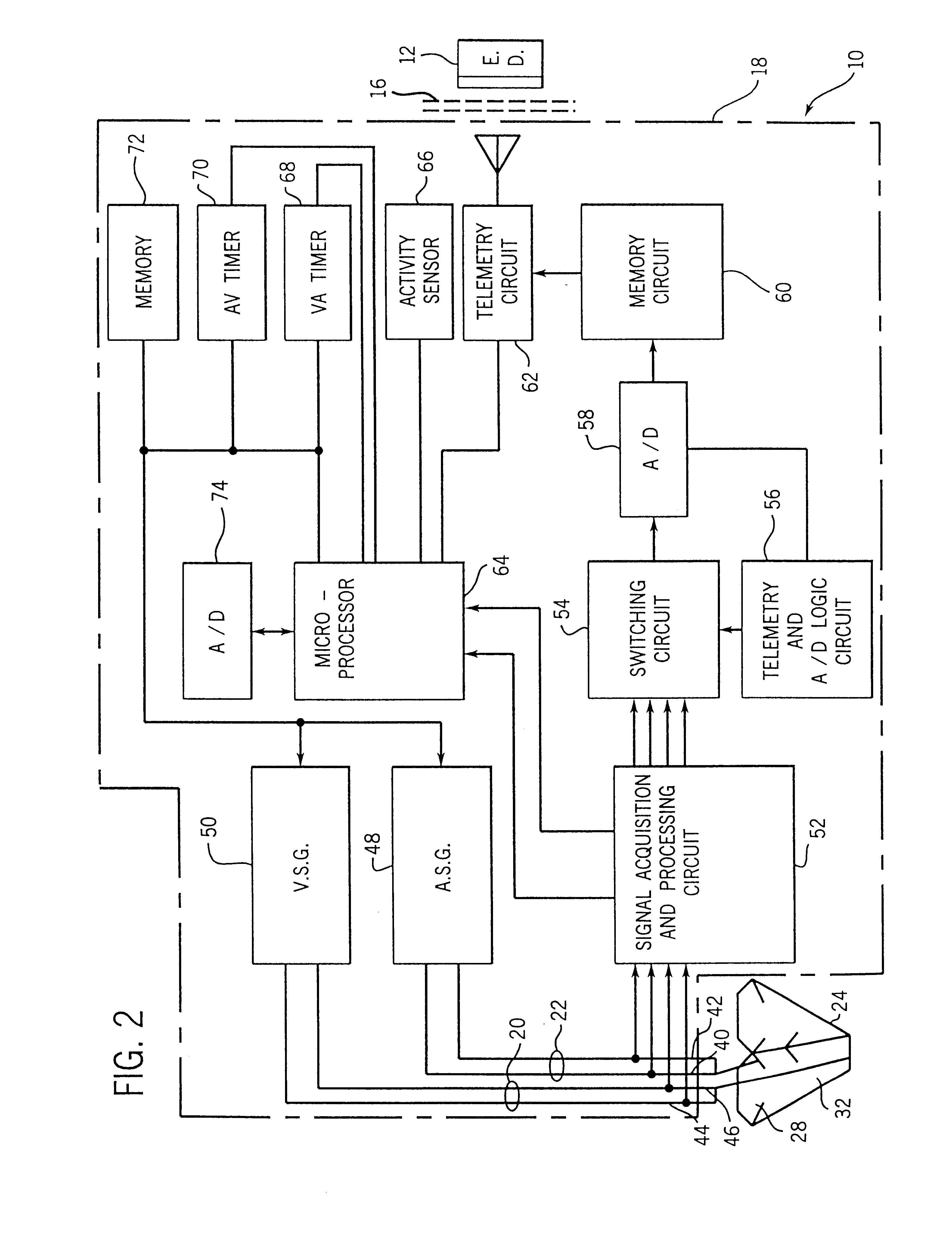

Implantable device with digital waveform telemetry

A technique for acquiring and accessing information from a medical implantable device is provided. Analog waveforms of interest are sensed and processed by signal acquisition circuitry. Analog parameters of interest are applied to selector switches which are controlled by a logic circuit. The logic circuit is also coupled an A / D converter for converting the analog signals to digital values. The digital values are stored in dedicated registers and are available for telemetry to an external device upon receipt of a request or prompt signal. When a digitized value is accessed and telemetered, the control logic circuit changes the conductive state of the selector switches to apply the corresponding analog signal to the A / D converter. The resulting digital value is applied to the corresponding register to refresh the accessed and telemetered value. The technique permits the external device to request and configure the implanted device to send only digitized values of interest. The technique also makes efficient use of the A / D converter, which consumes energy only as needed to refresh the memory when digital values are accessed and telemetered.

Owner:INTERMEDICS

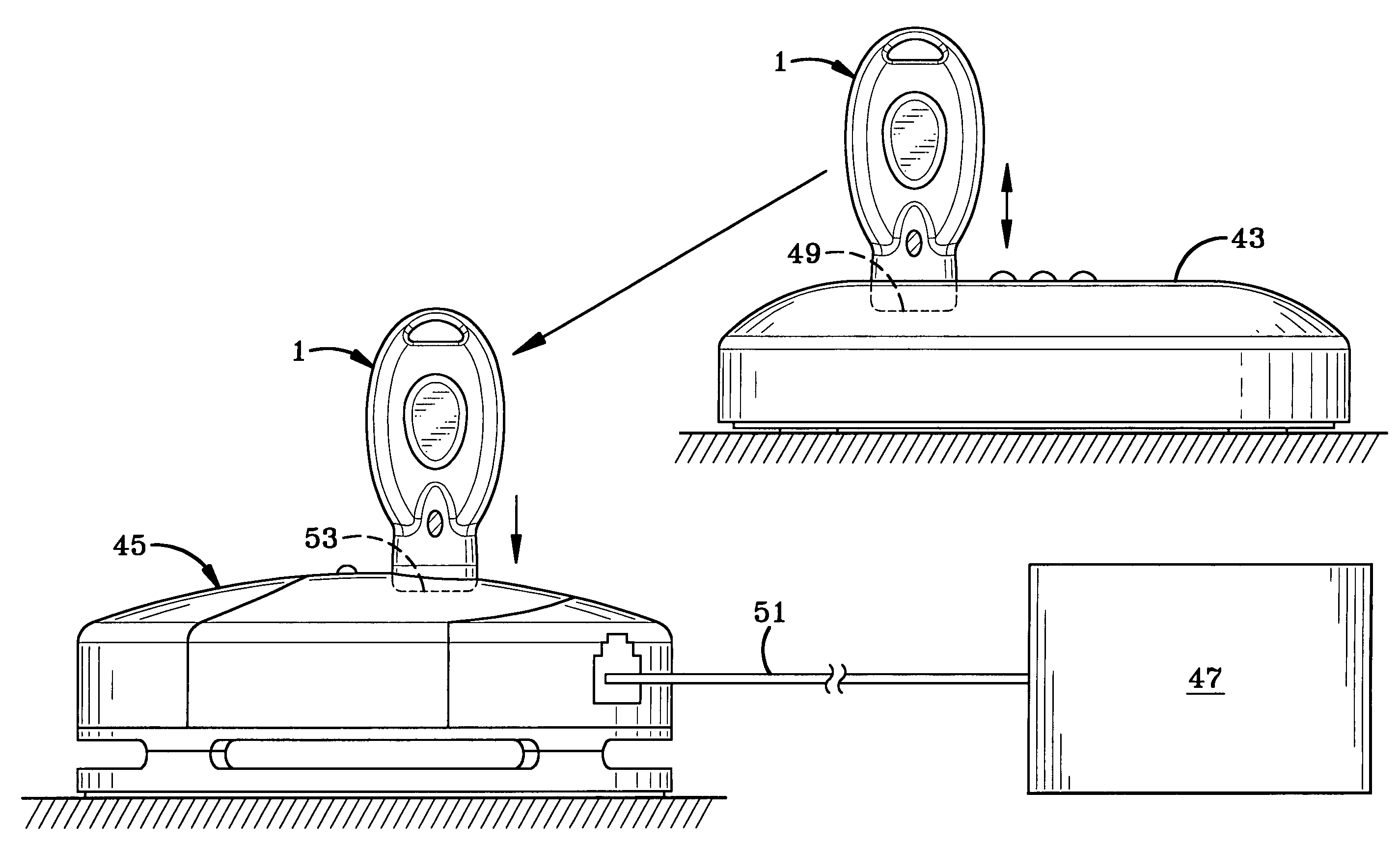

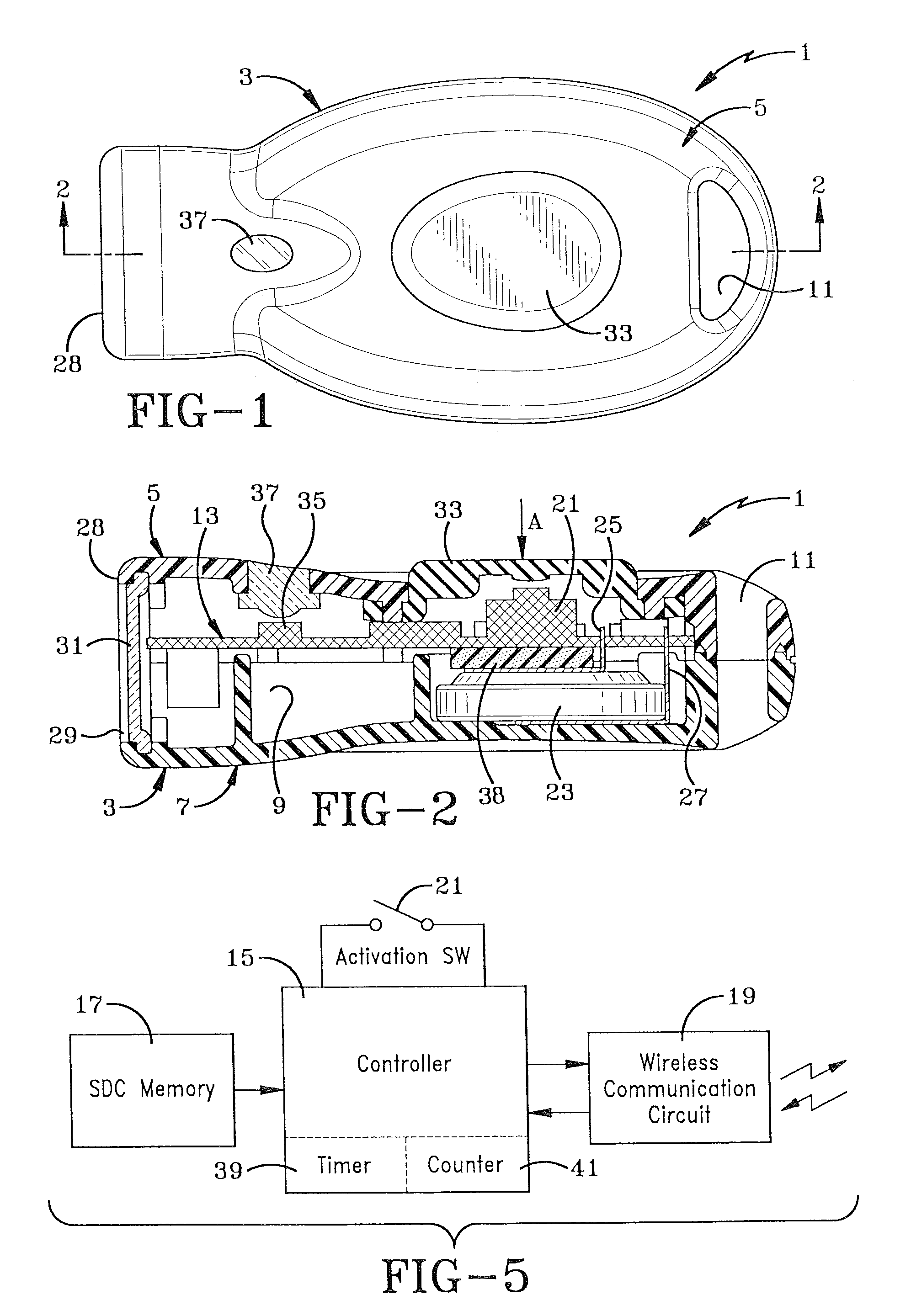

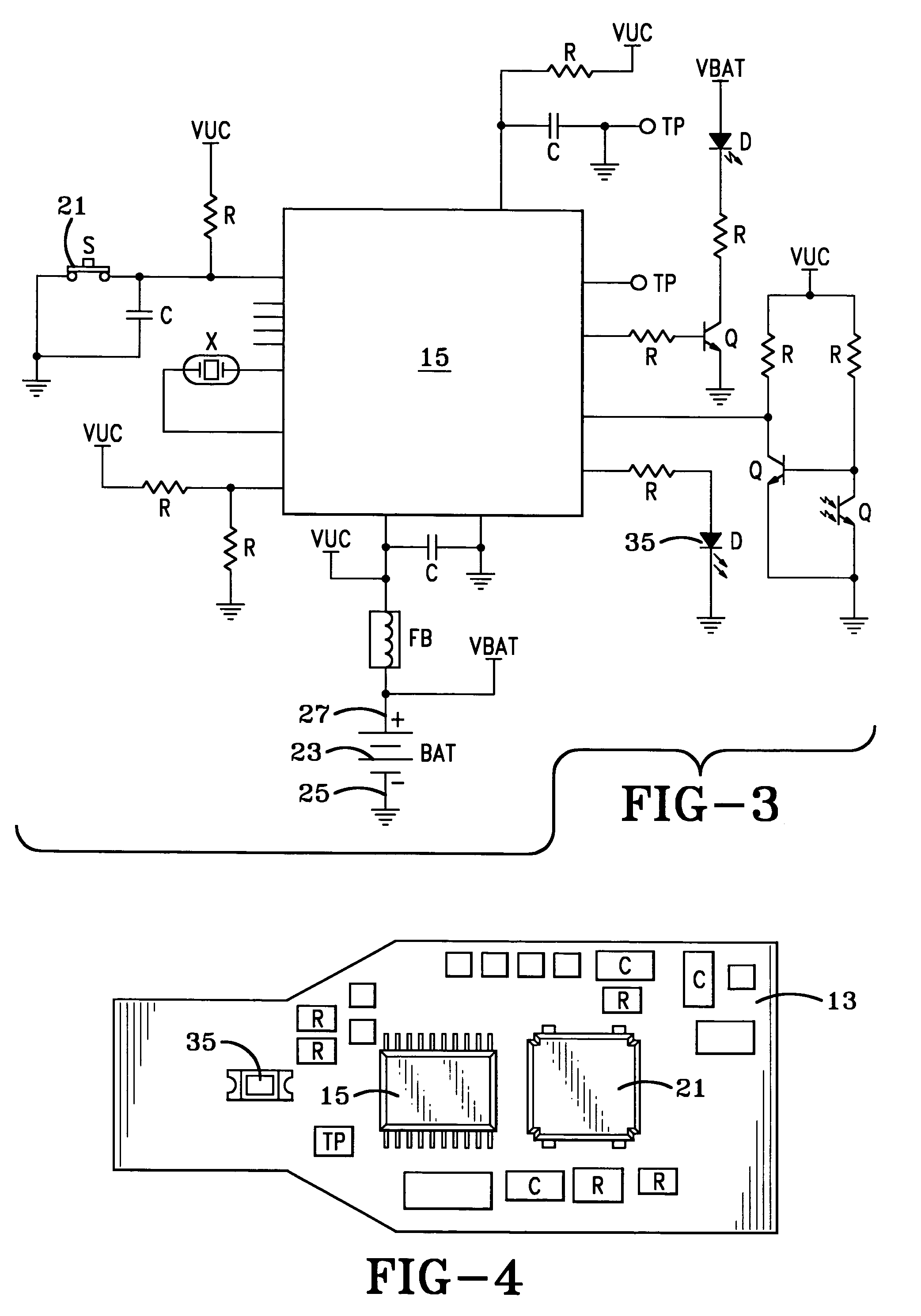

Programmable key for a security system for protecting merchandise

ActiveUS7737845B2Unauthorized useSufficient powerElectric signal transmission systemsMultiple keys/algorithms usageTime limitEngineering

Owner:INVUE SECURITY PROD INC

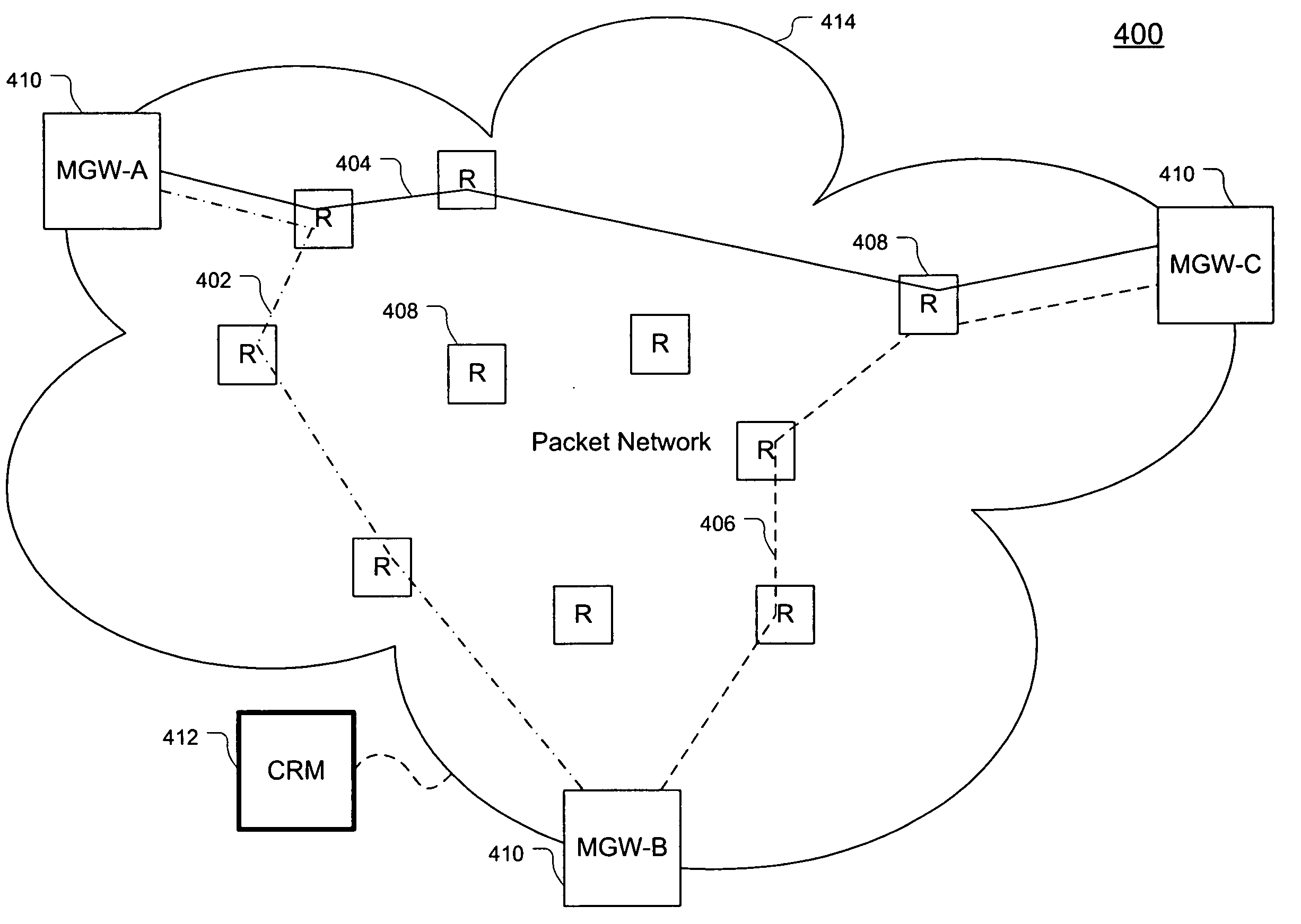

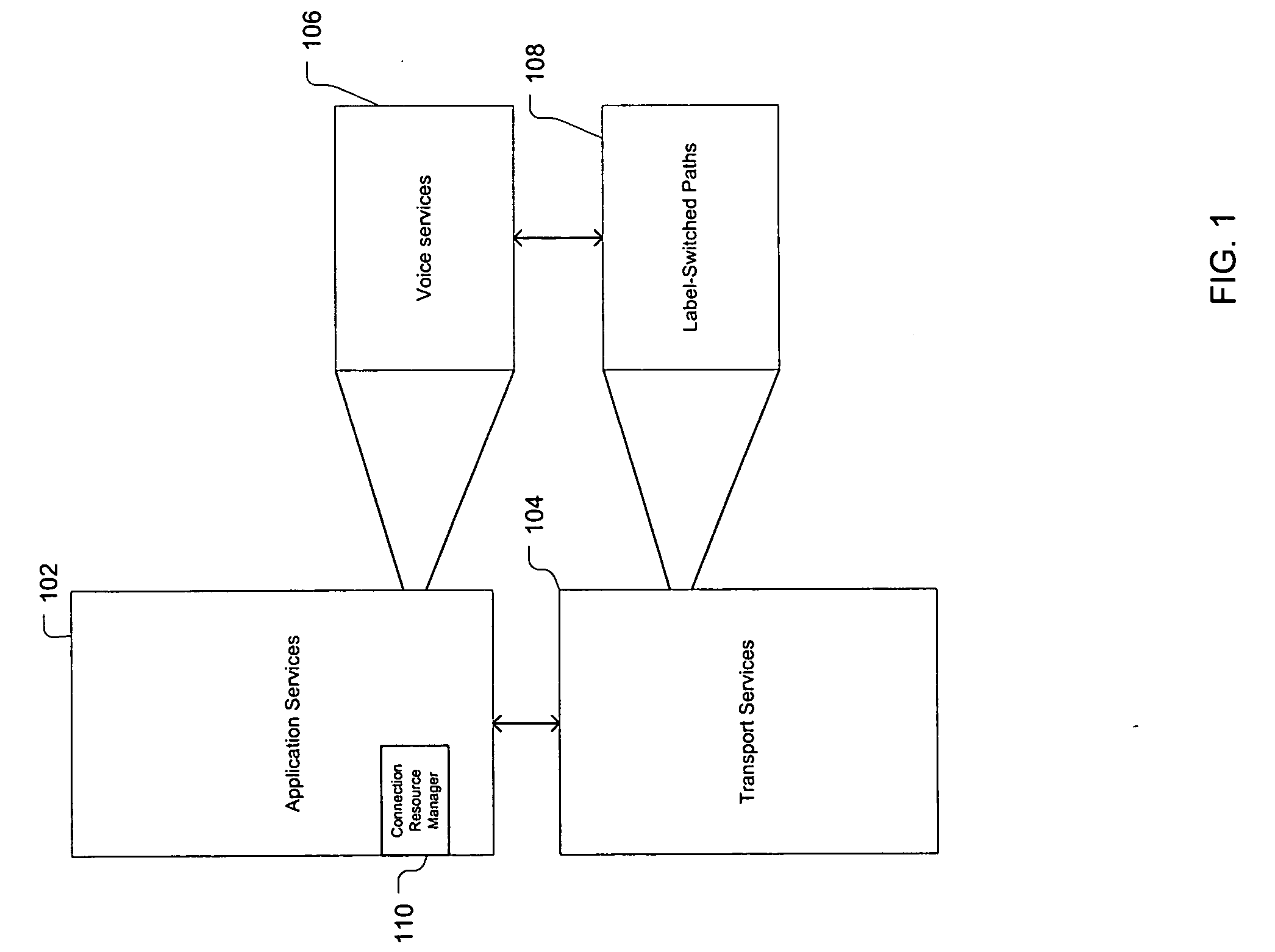

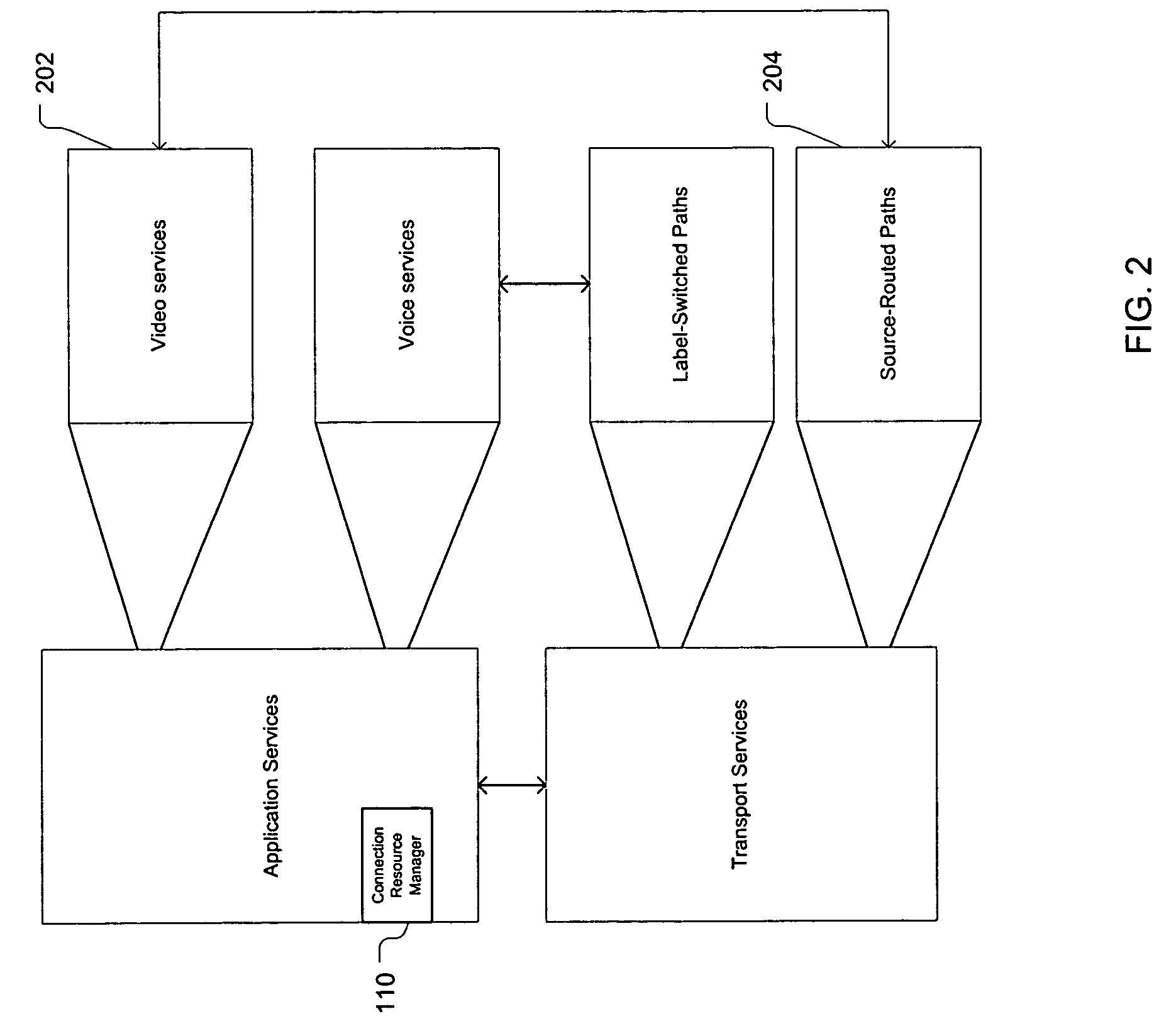

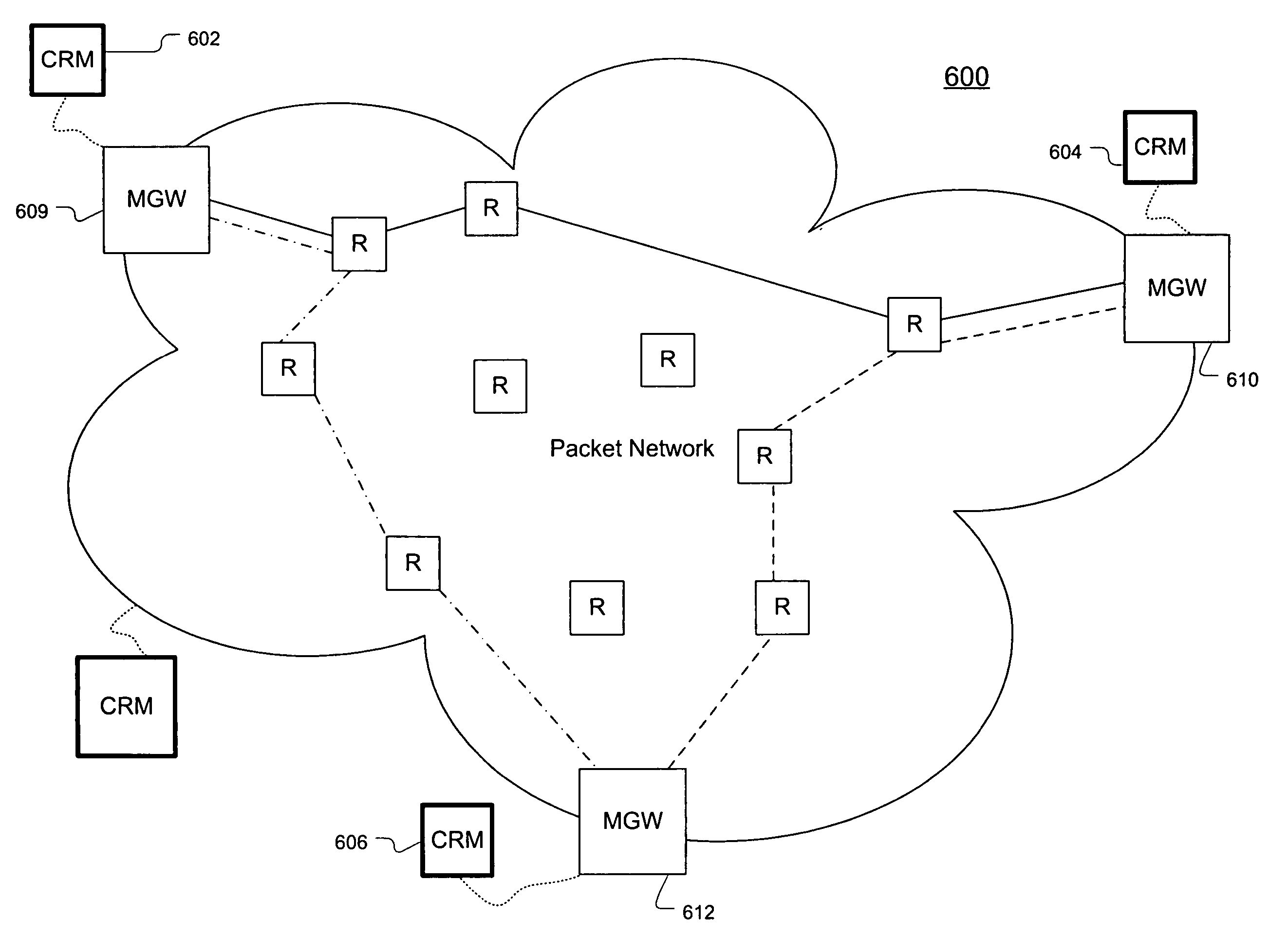

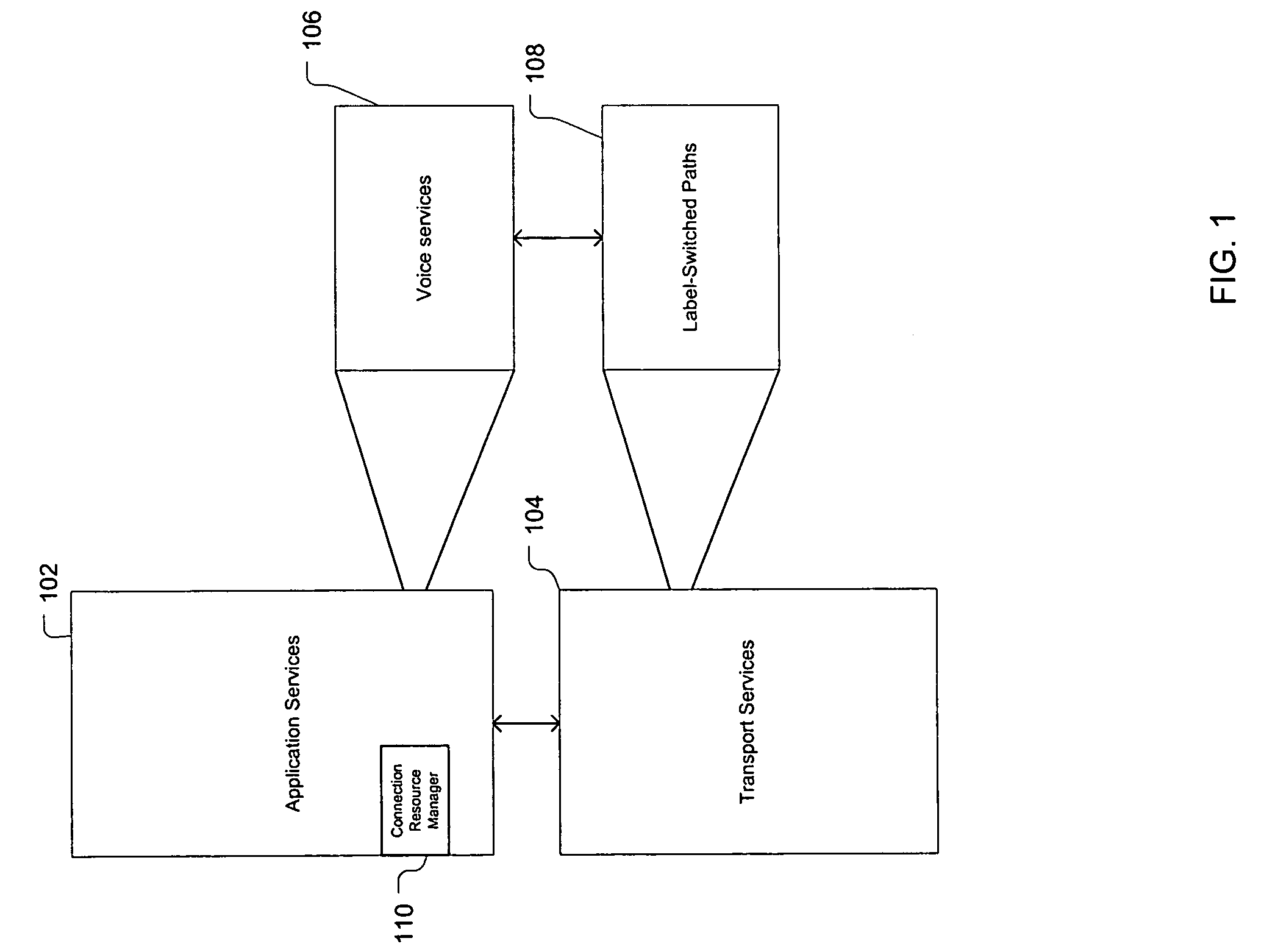

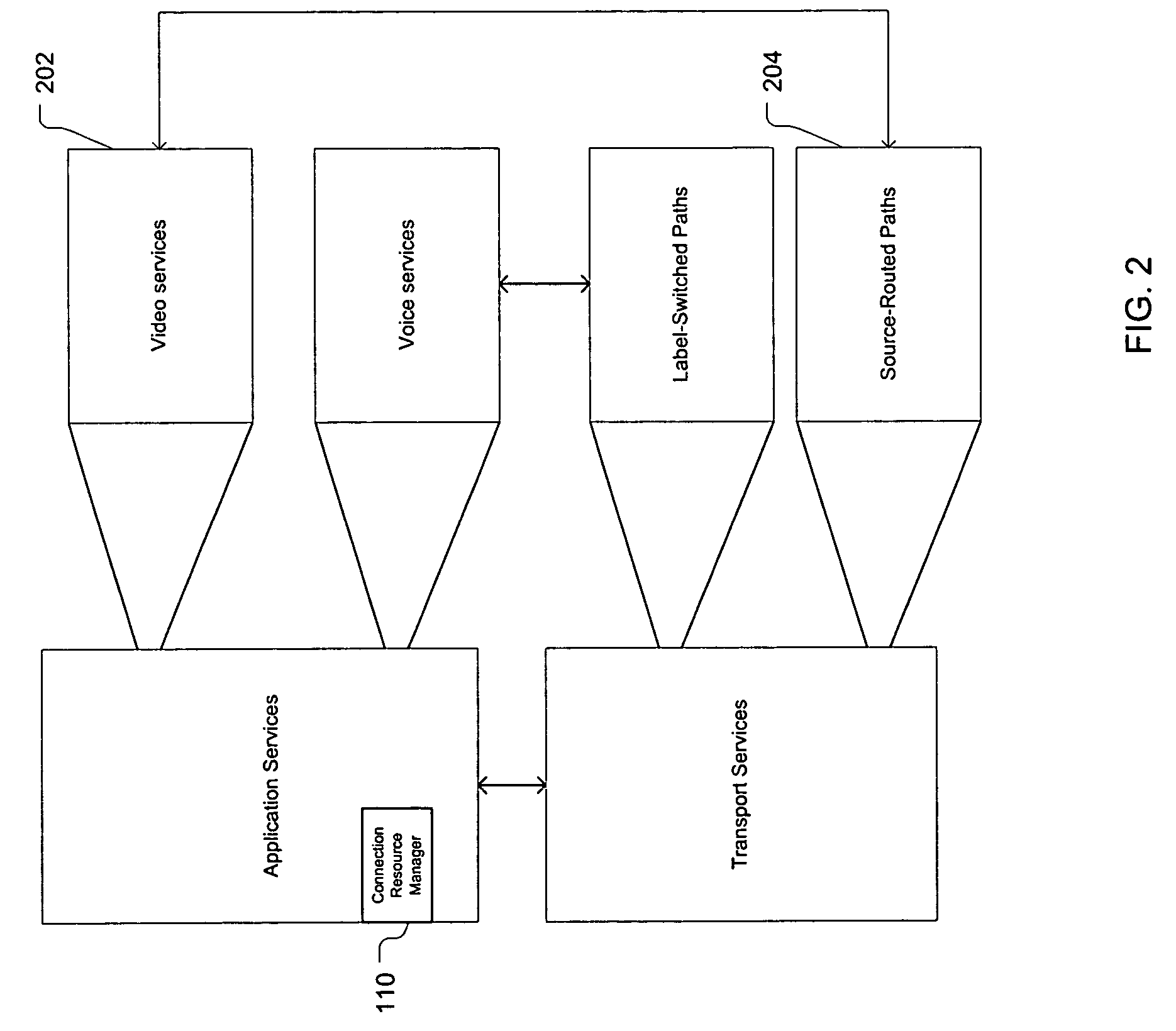

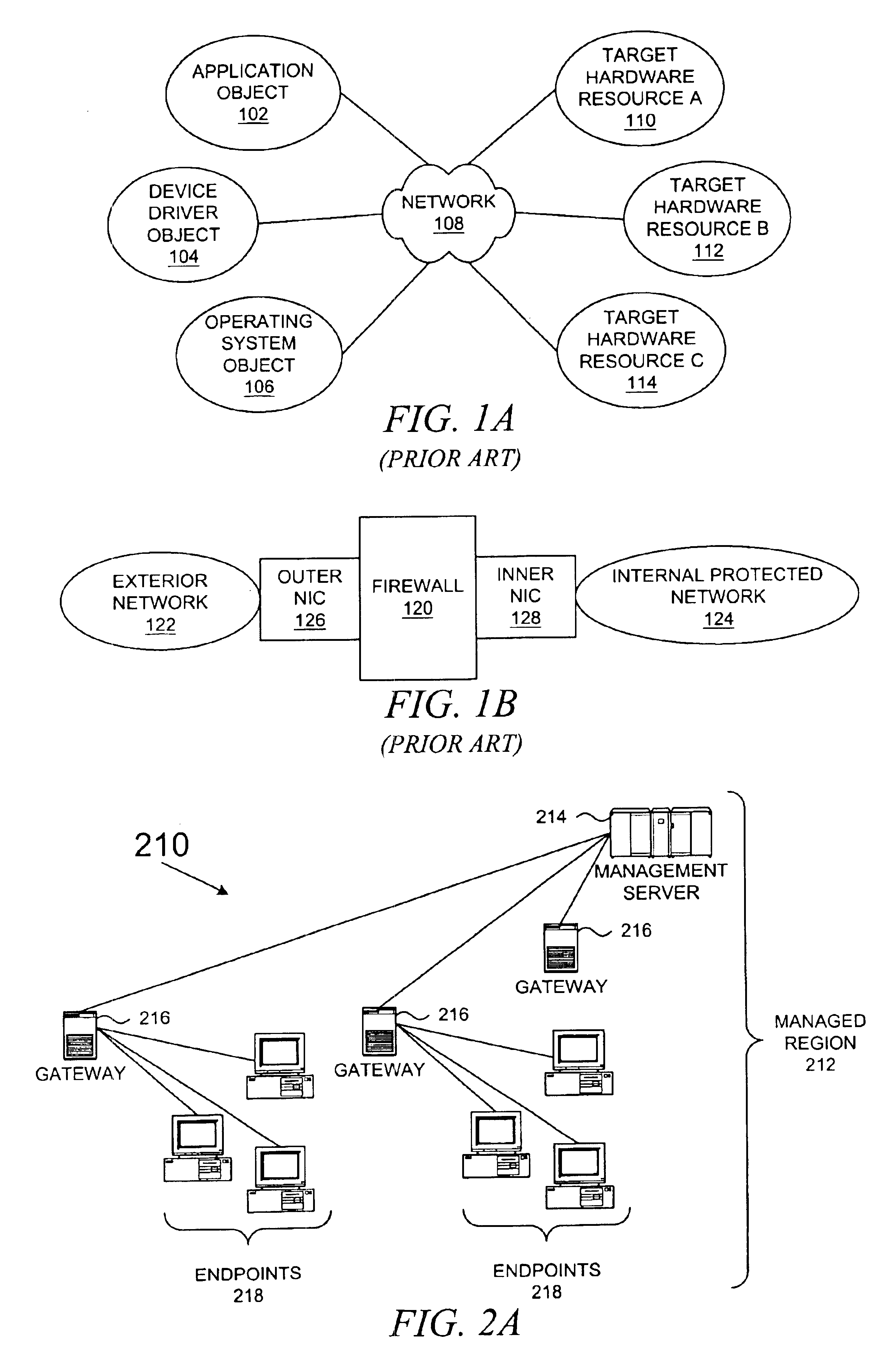

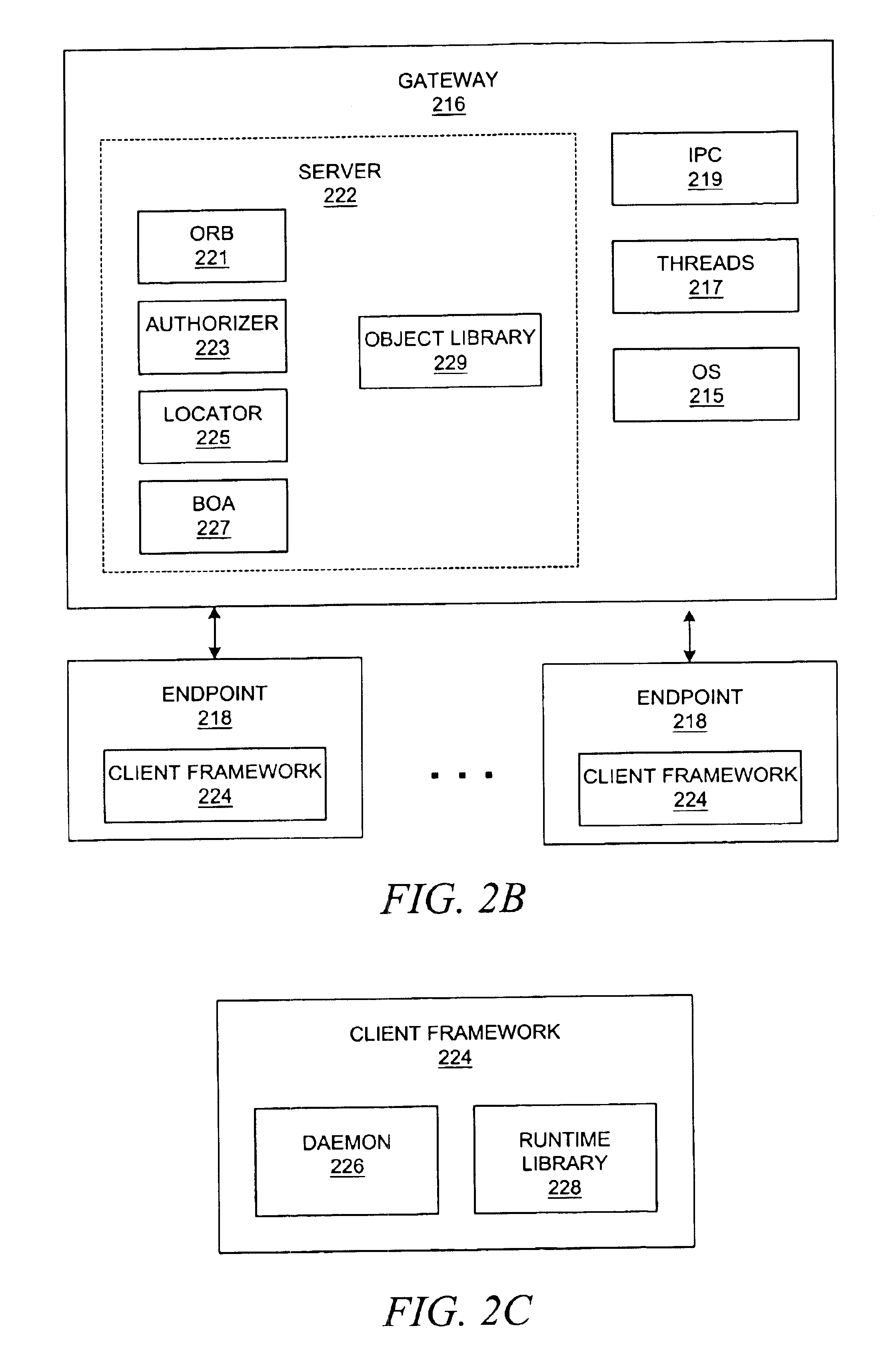

Network quality of service management

InactiveUS20050195741A1Fast response timeEfficient and reliableError preventionTransmission systemsQuality of serviceResource management

An architecture for quality-of-service (QoS) management creates a logical circuit-switched network within a packet network to support QoS-sensitive demands levied on the network. This QoS-managed network can serve to interwork, e.g., a PSTN with VoIP networks. The architecture can include a connection resource manager (CRM), which oversees bandwidth availability and demand admission / rejection on dynamically provisioned virtual trunk groups (VTGs) within the packet network, and a transport bandwidth controller (TBC). The VTGs serve to transport QoS-sensitive demands across the packet network. The TBC serves the CRM by providing an interface to routers and / or OAM systems of the packet network to size VTGs to meet QoS requirements. Media switches located at the packet network borders serve to mux / demux the demands into / from VTGs. CRMs and TBCs can be implemented as centralized, distributed, or hierarchical, and flat and aggregated variants of the architecture are supported. VTGs can be implemented using MPLS LSPs, VPNs, or source-based routing.

Owner:WSOU INVESTMENTS LLC

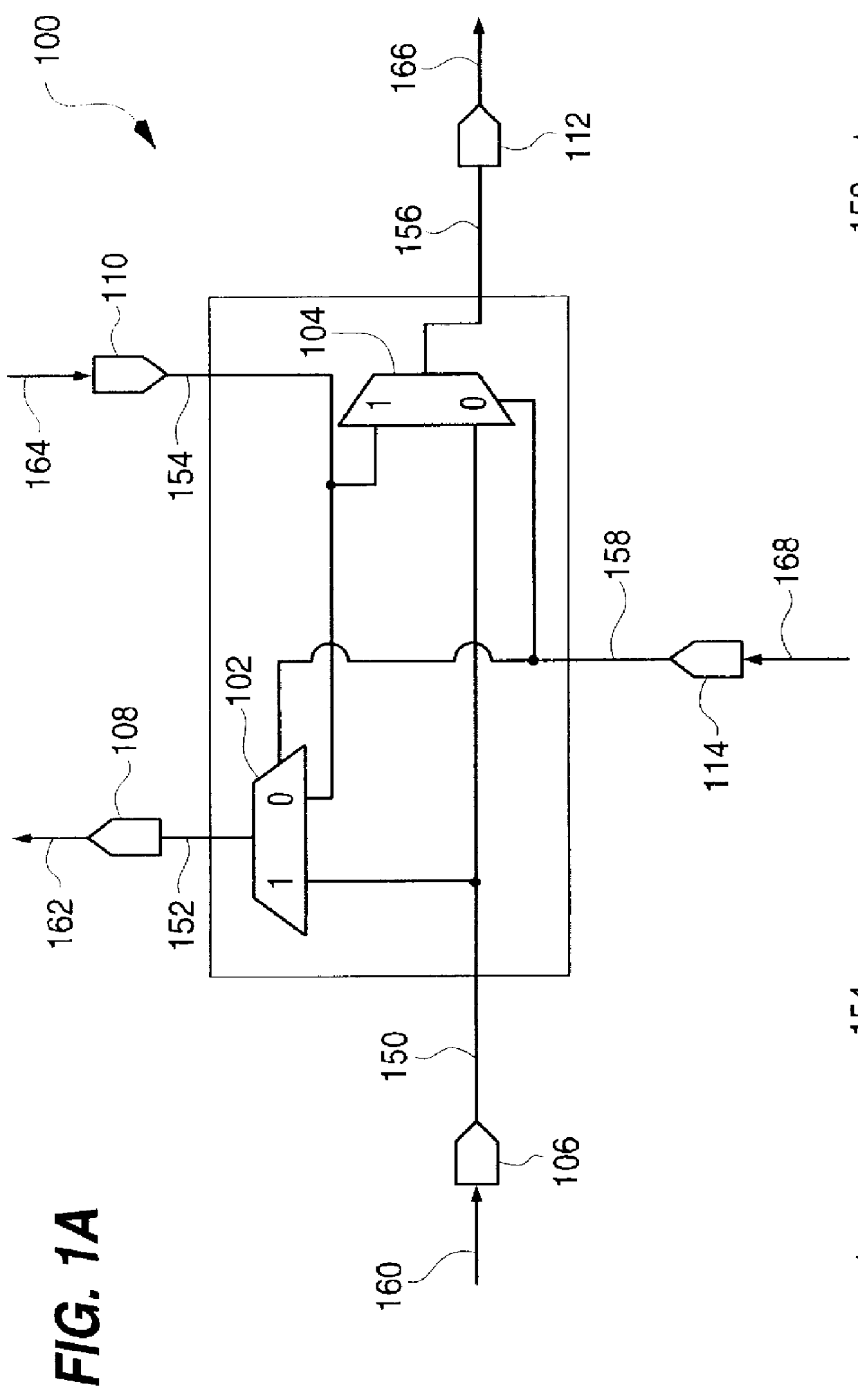

Methods and apparatus for dynamic topology configuration in a daisy-chained communication environment

InactiveUS6055228AImprove effective communication performanceDigital computer detailsNetworks interconnectionFiberCommunications system

A loop isolation circuit (LIC) to enable subdivision of a single daisy-chained communication loop (e.g., FC-AL) into smaller loops and to enable joining of smaller loops into a single larger loop. An LIC comprises essentially two multiplexors configured so as to permit controlled subdivision or joining of two loop portions. In a first selected state, the LIC subdivides a communication loop in which it is inserted into two loops. This configuration sacrifices accessibility among some devices previously on the larger loop for the benefit of enhanced bandwidth and reduced overhead due to node count. Bandwidth is enhanced by enabling simultaneous operation of two (or more) loop portions for establishing and communicating over logical circuit connections. However, when a failure of a redundant loop precludes access to devices, the LIC may be set to a second state to rejoin previously subdivided loops into a larger loop. This configuration restores access among all devices sharing common access to the larger loop. The LIC of the present invention therefore enables communication loop controllers to dynamically reconfigure a daisy-chained loop communication system to enhance performance in normal operation. The LIC of further enables restoration of the larger loop to restore redundant loop configurations. The LIC of the present invention is applicable in many daisy-chained loop communication environments including, but not limited to, Fiber Channel Arbitrated Loop (FC-AL).

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

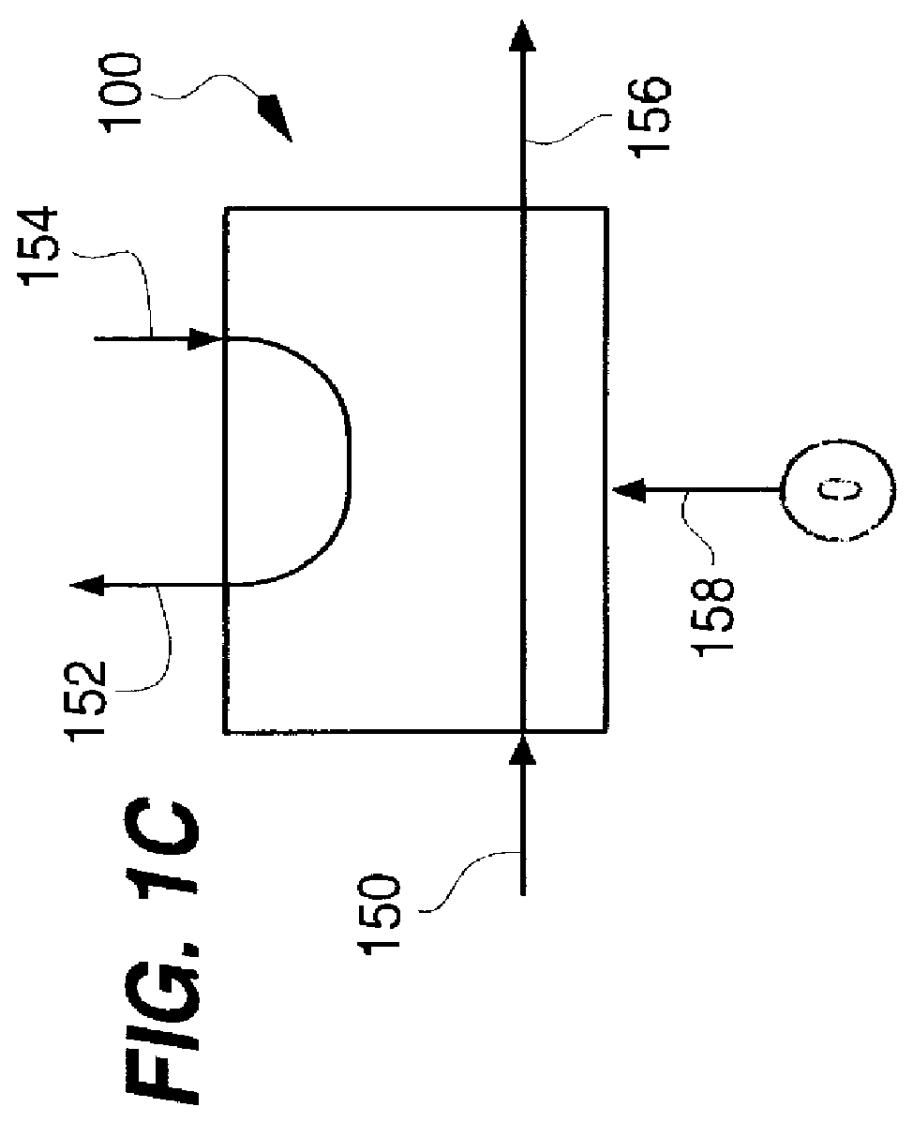

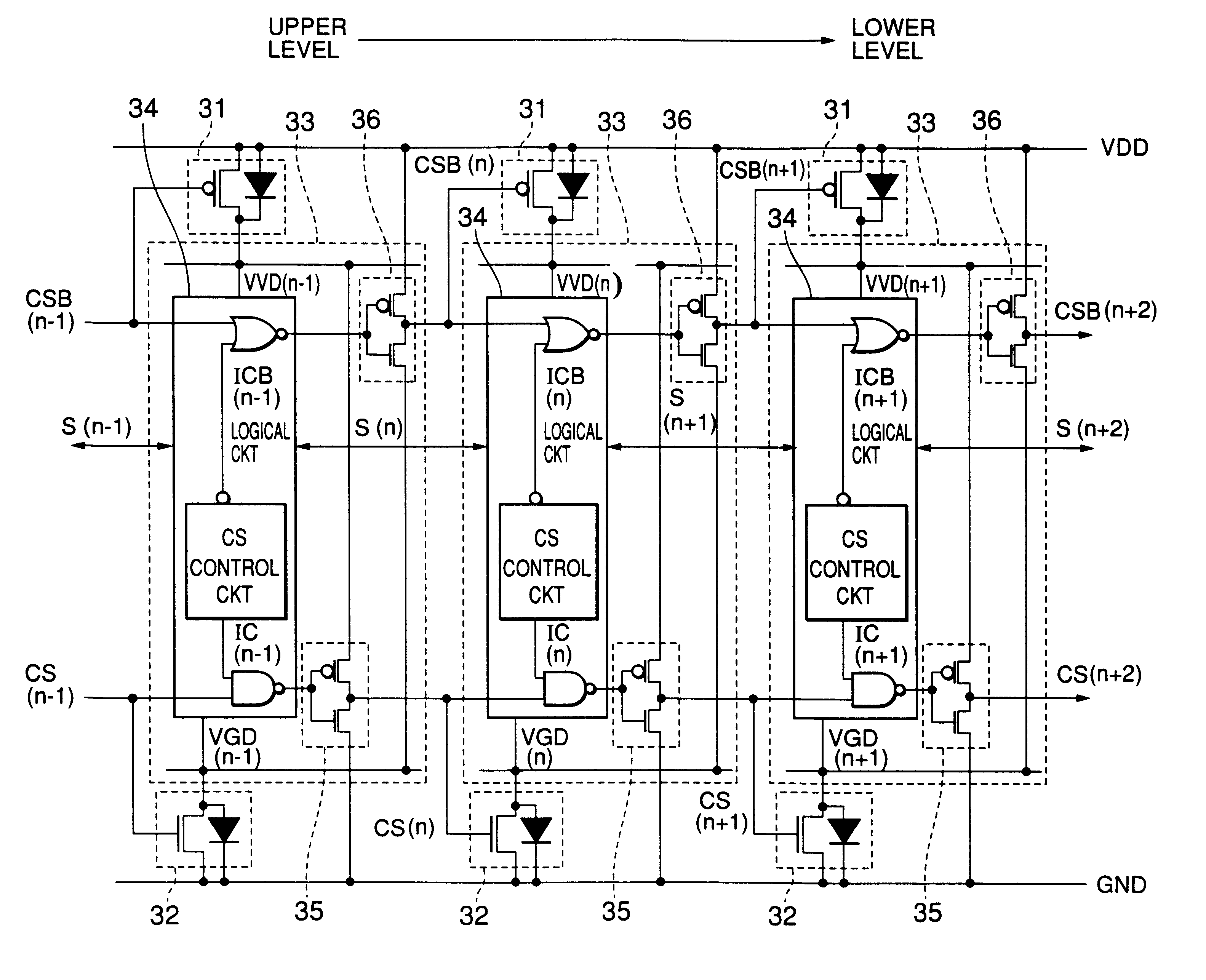

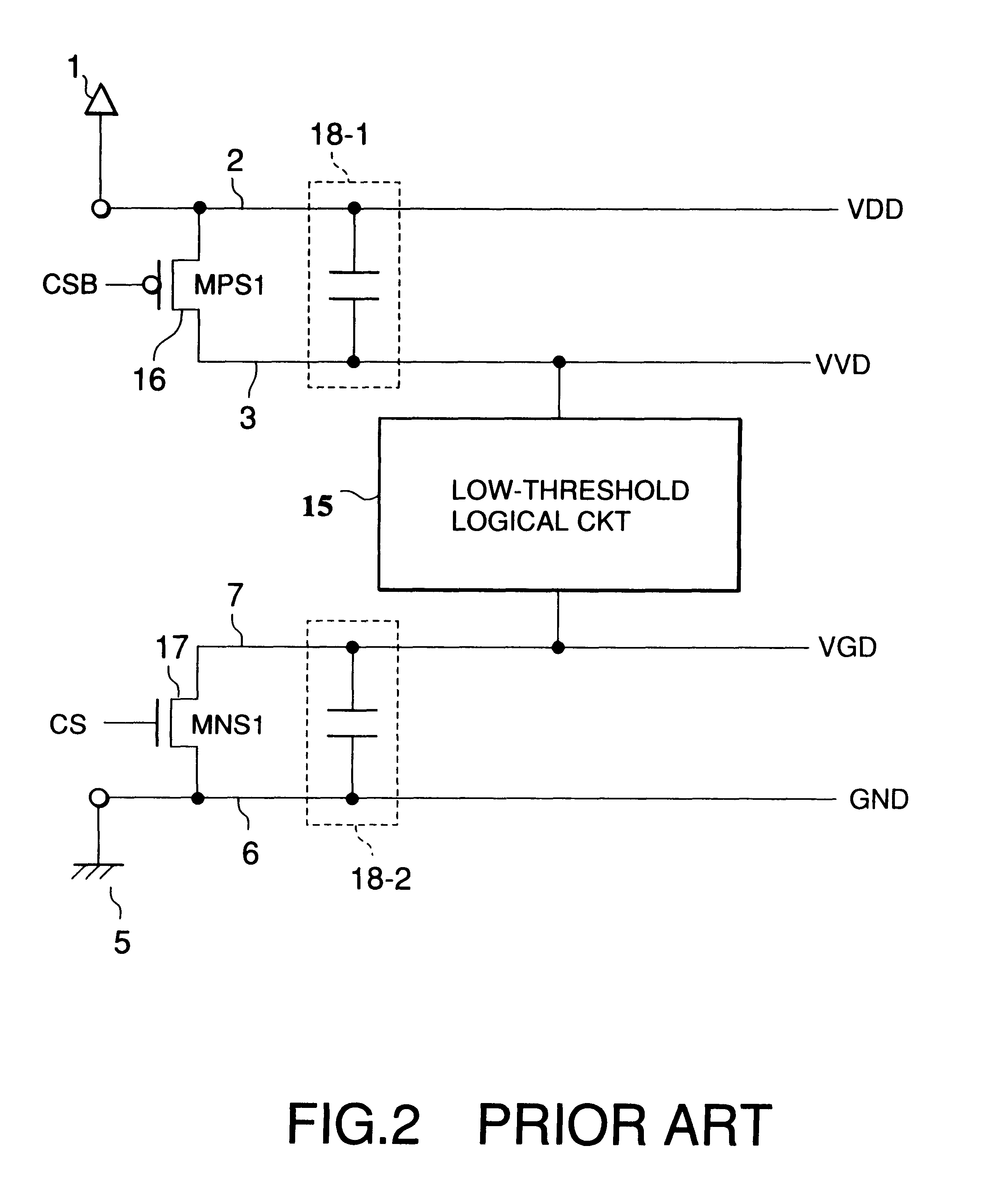

Semiconductor integrated circuit device with low power consumption and simple manufacturing steps

InactiveUS6208171B1Reduce manufacturing stepsProduction costPower reduction by control/clock signalLogic circuits characterised by logic functionPotential clampBack bias

In a semiconductor integrated circuit, a control transistor 4 and a potential clamp circuit 9 are arranged between a power supply line 2 and a virtual power supply line 3. Even in a sleeve mode where the control transistor 4 is turned off, the potential clamp circuit 9-1 clamps the virtual power supply line 3 at a certain potential to hold a potential state (high level or low level) of each node of a logical circuit. At this time, each FET forming the logical circuit is applied with a back bias so that a threshold voltage Vt becomes higher than that in an active mode. Therefore, a leakage current can be decreased. In the semiconductor integrated circuit, the threshold voltage Vt of the control transistor 4 can be selected to be equal to that of one FET of the complementary FET forming the logical circuit. Therefore, the layout area and the number of manufacturing steps can be reduced.

Owner:NEC CORP

Network quality of service management

InactiveUS7609637B2Fast response timeEfficient and reliableError preventionTransmission systemsQuality of serviceQos management

Owner:WSOU INVESTMENTS LLC

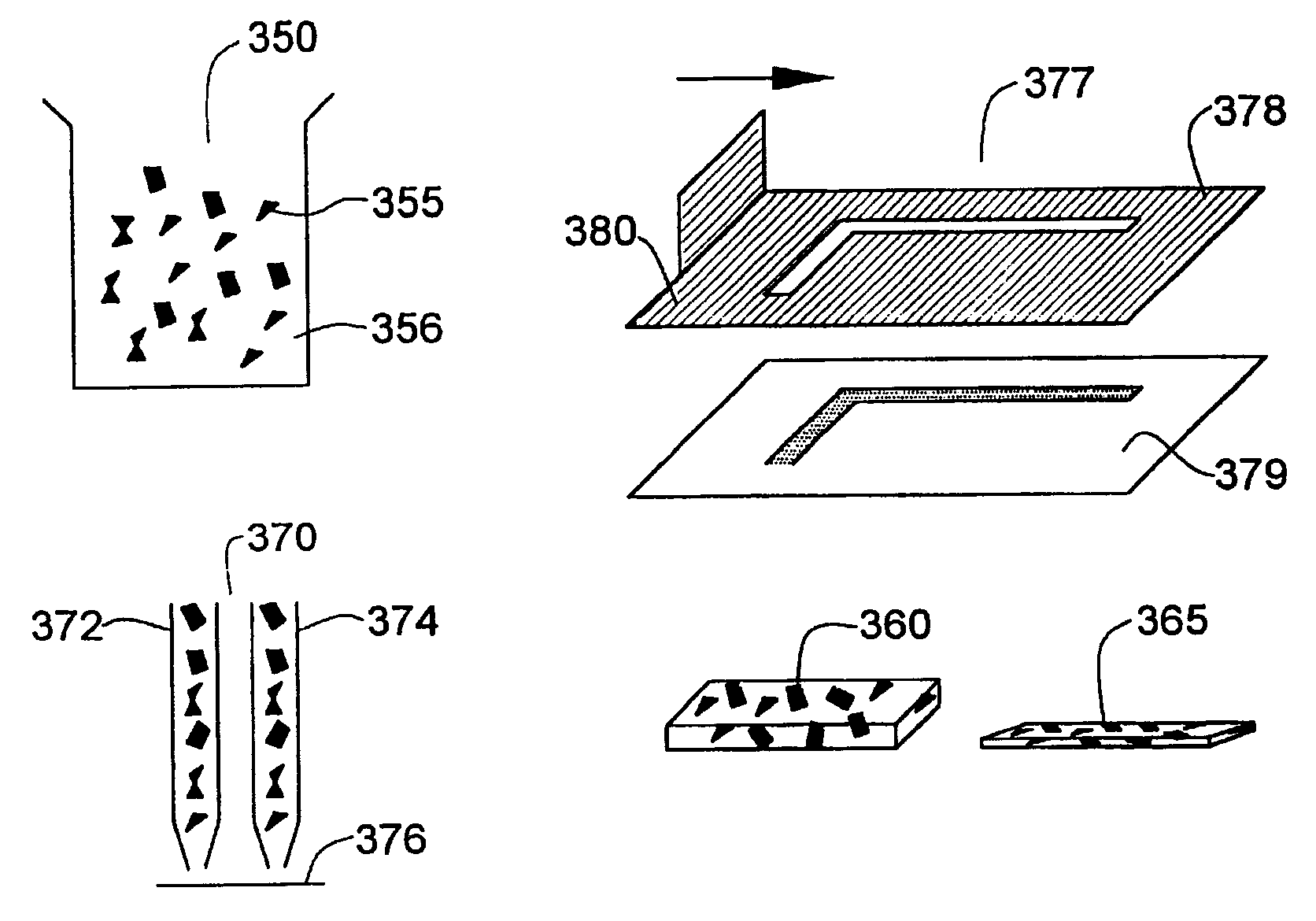

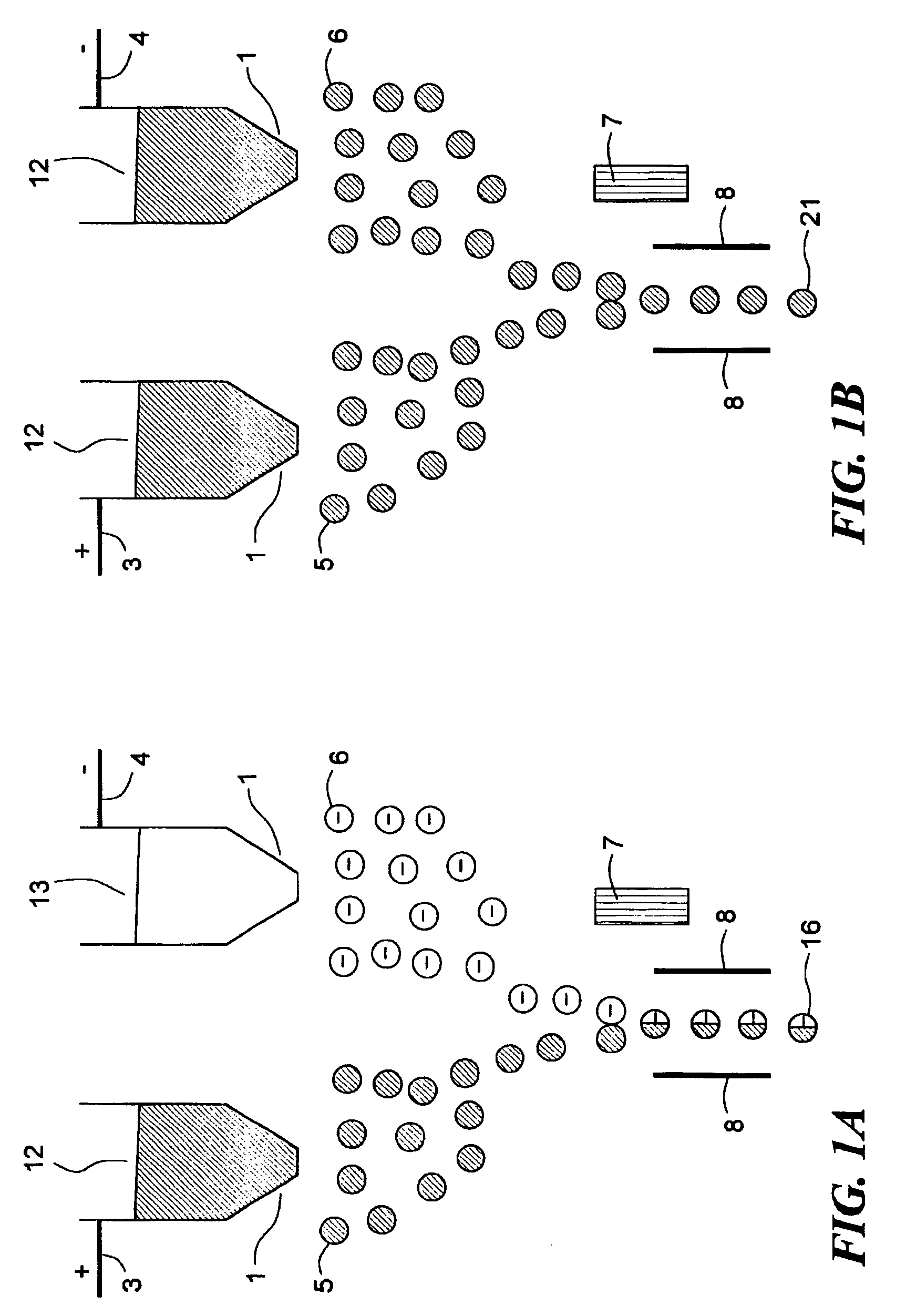

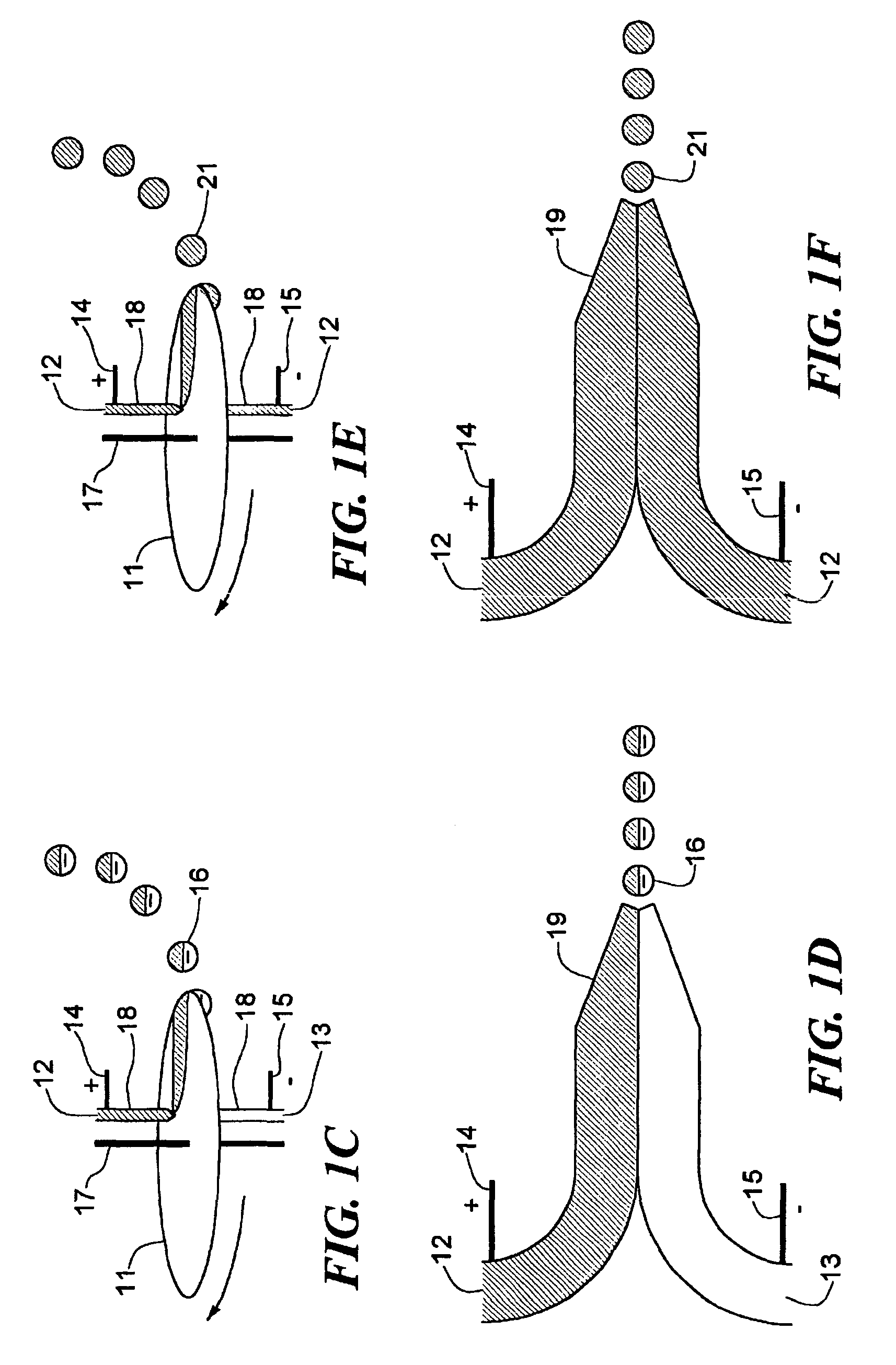

Electronically addressable microencapsulated ink and display thereof

InactiveUS20070057908A1Inexpensive displayMechanical clocksVisual indicationsElectrical conductorSemiconductor materials

A system of electronically active inks is described which may include electronically addressable contrast media, conductors, insulators, resistors, semiconductive materials, magnetic materials, spin materials, piezoelectric materials, optoelectronic, thermoelectric or radio frequency materials. We further describe a printing system capable of laying down said materials in a definite pattern. Such a system may be used for instance to: print a flat panel display complete with onboard drive logic; print a working logic circuit onto any of a large class of substrates; print an electrostatic or piezoelectric motor with onboard logic and feedback or print a working radio transmitter or receiver.

Owner:E INK CORPORATION

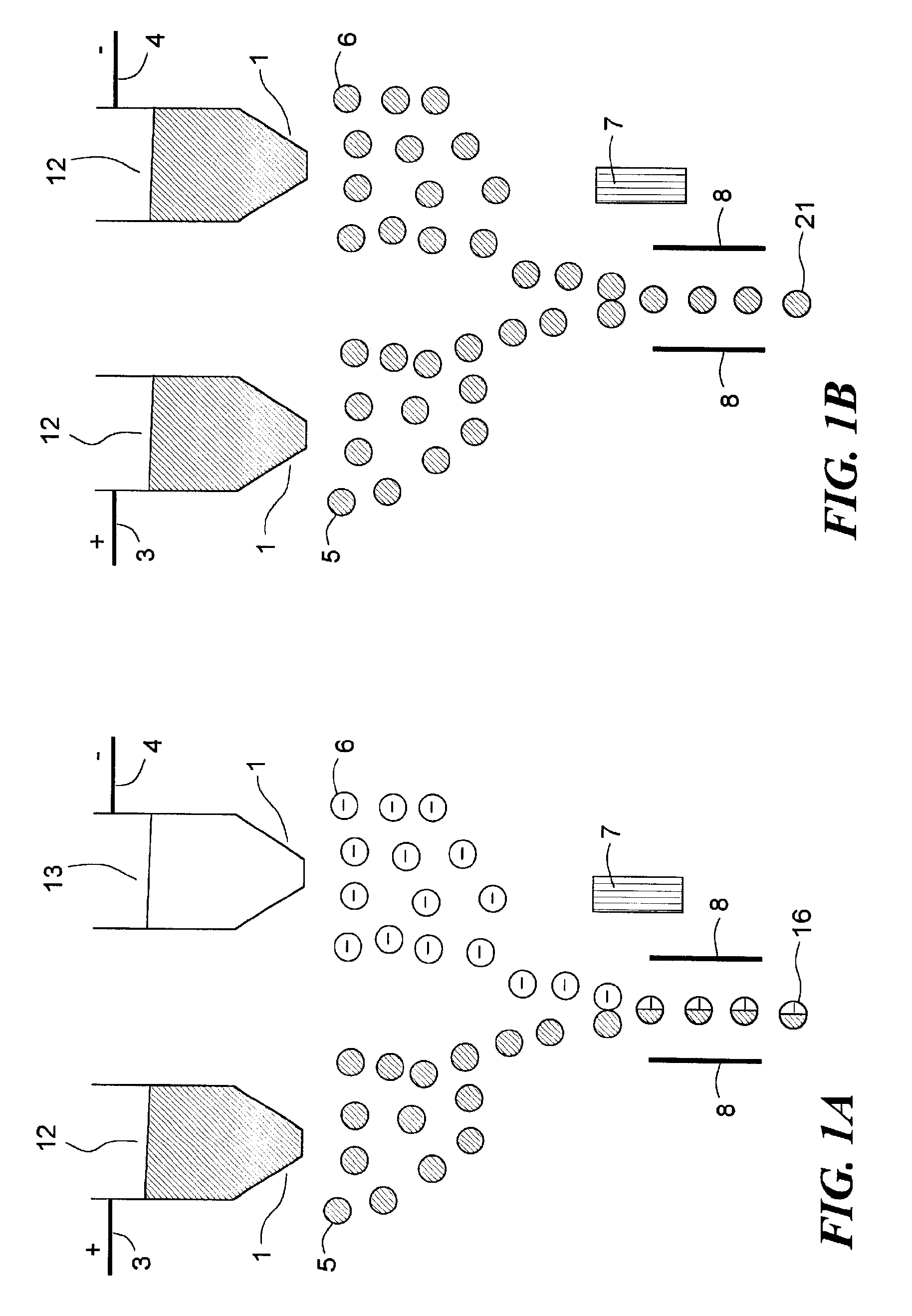

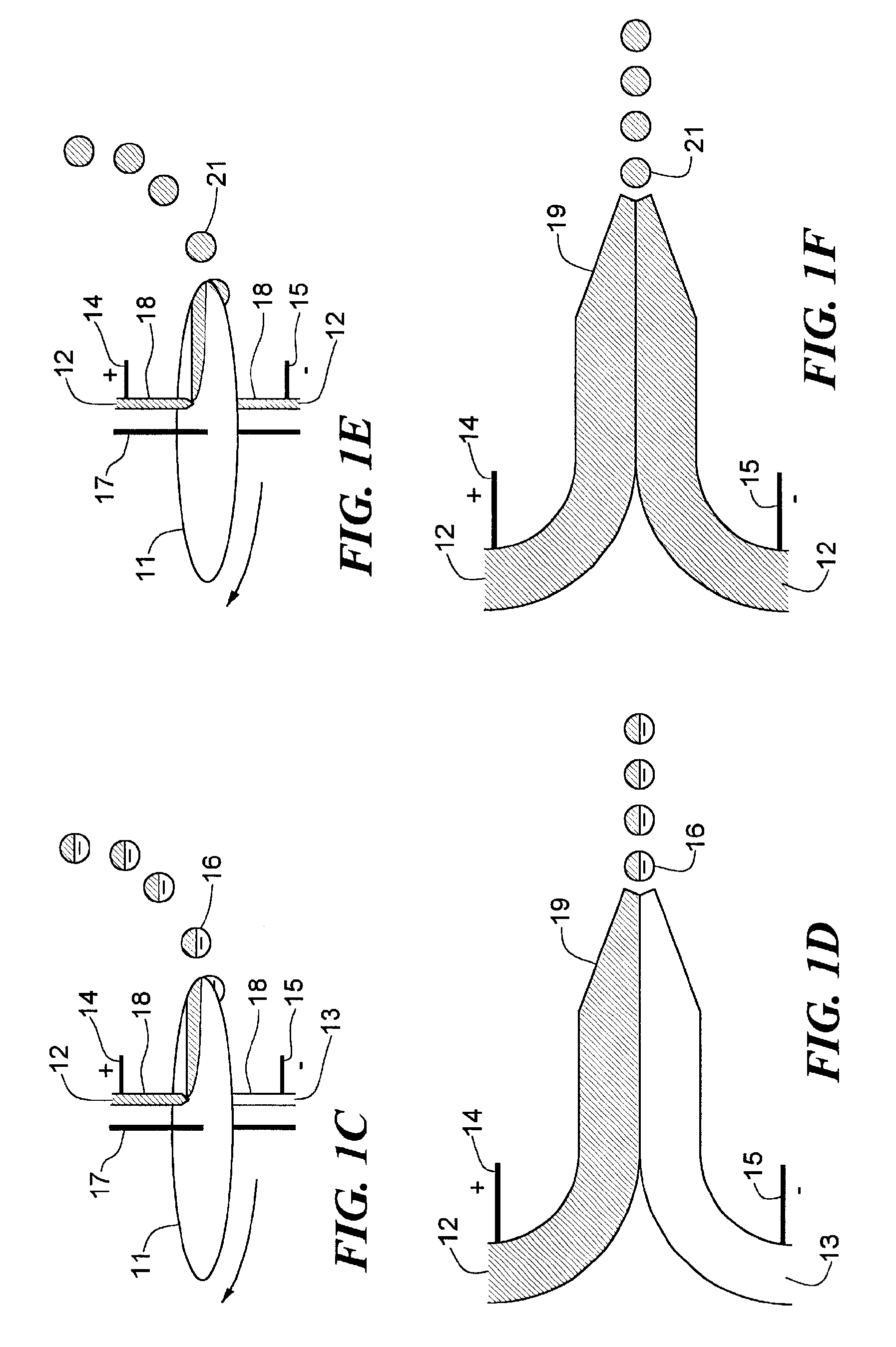

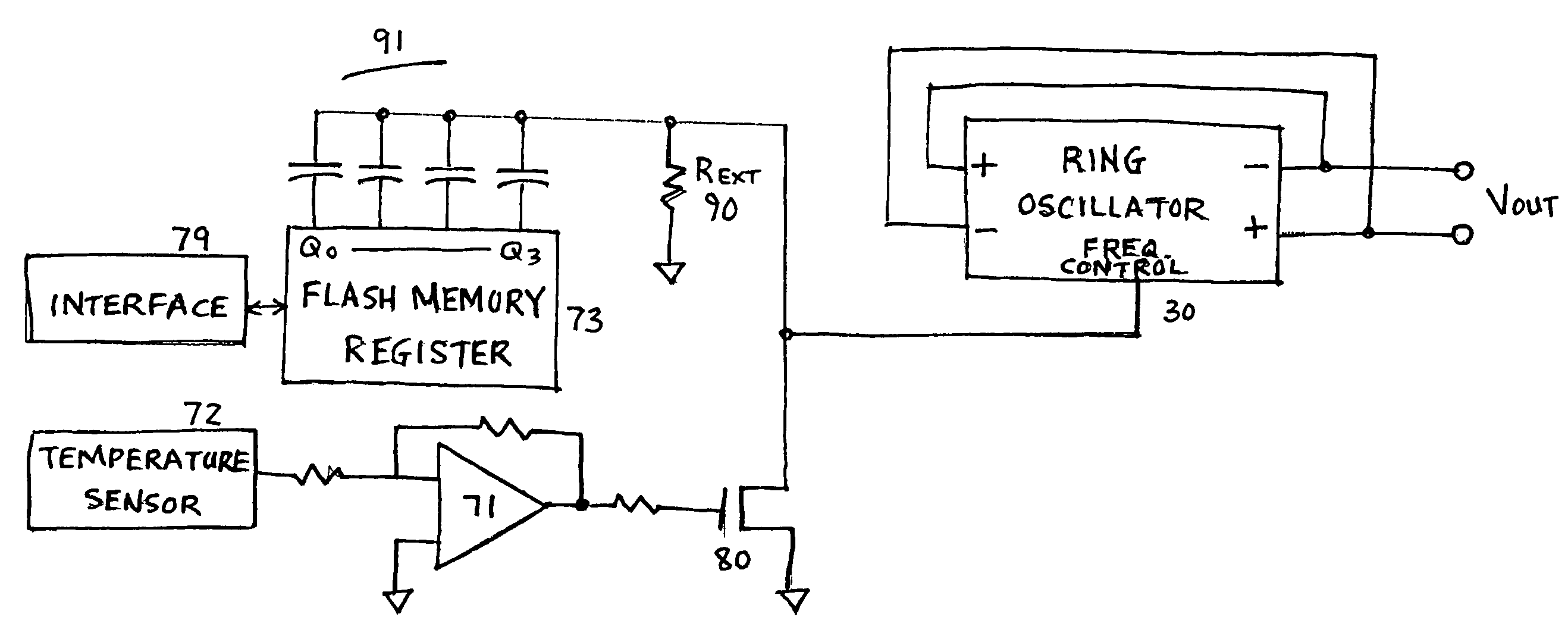

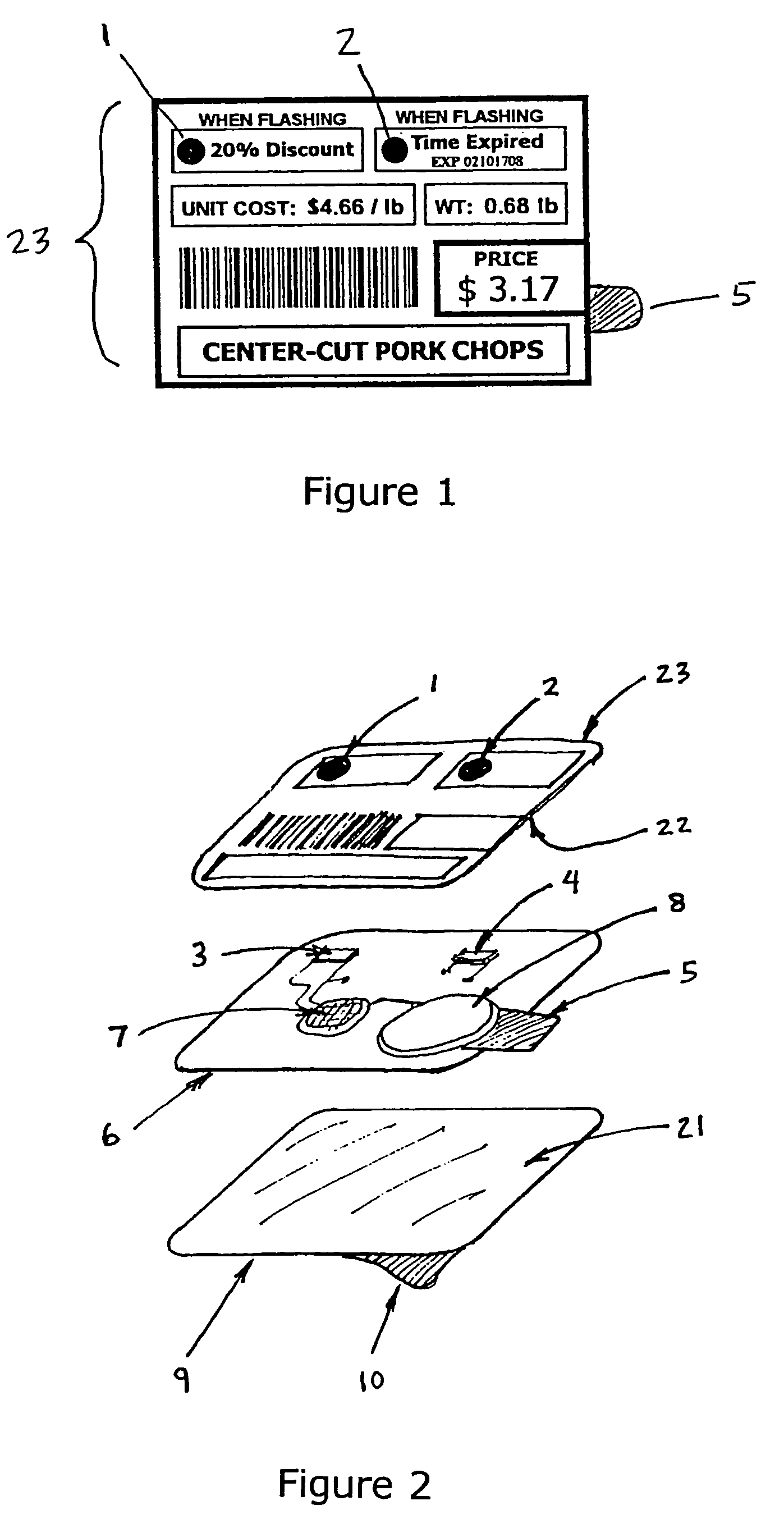

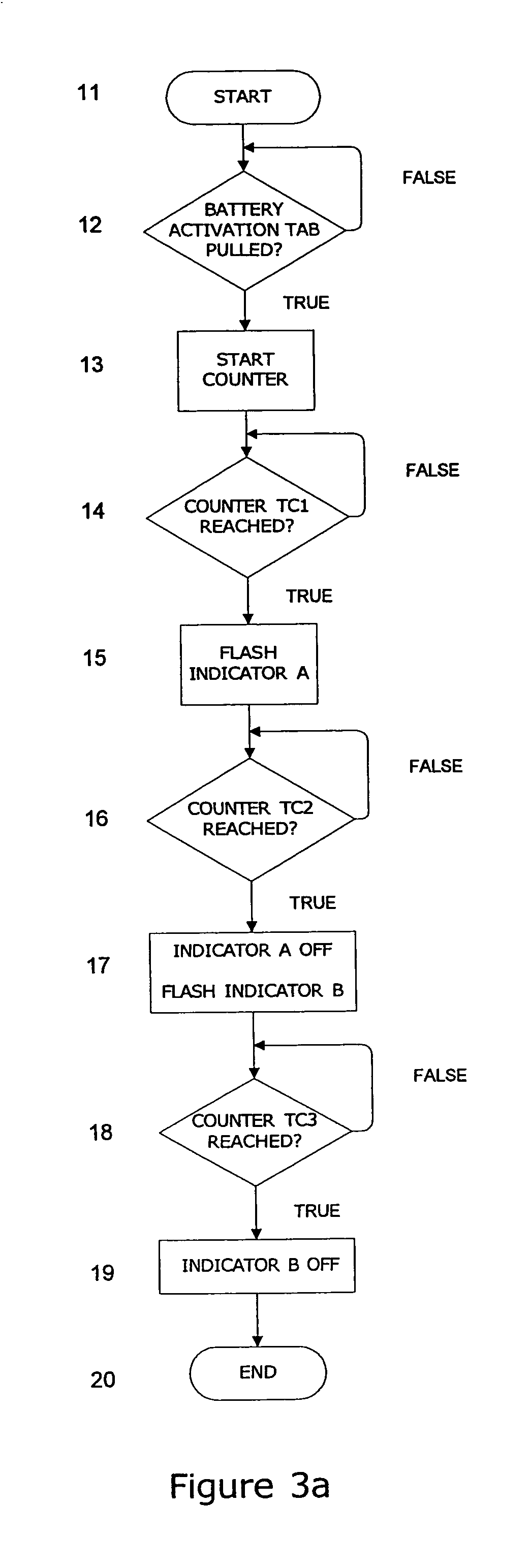

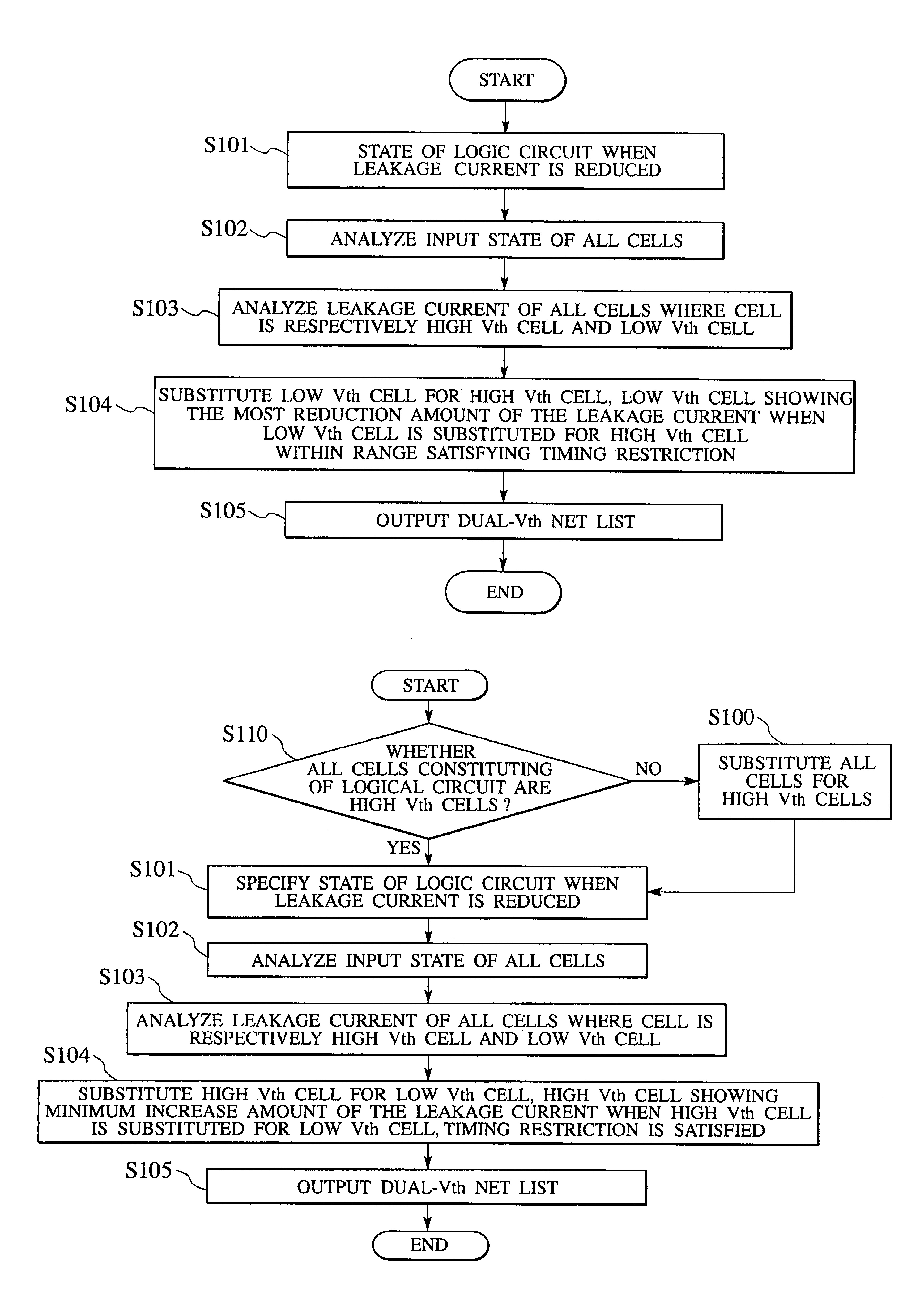

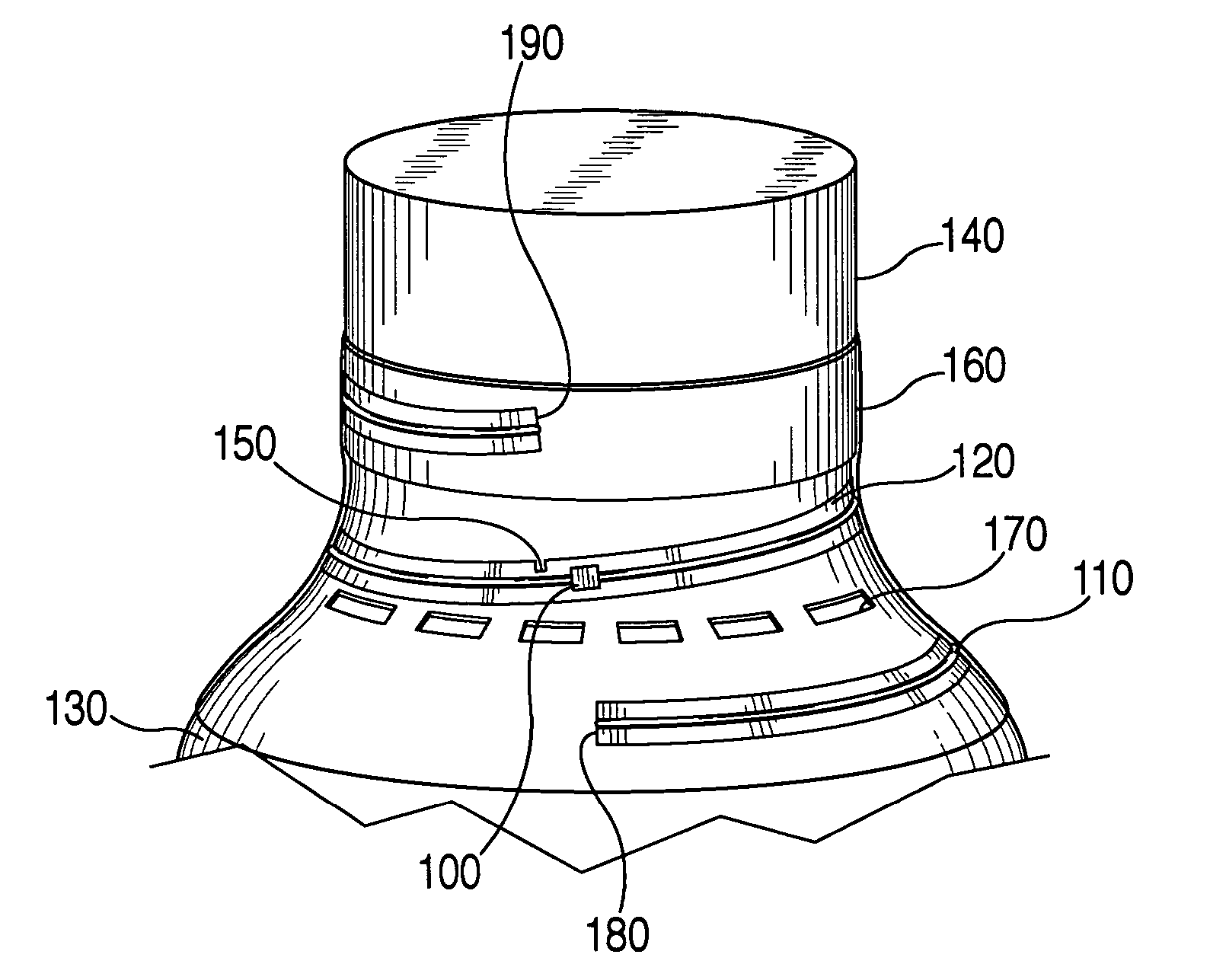

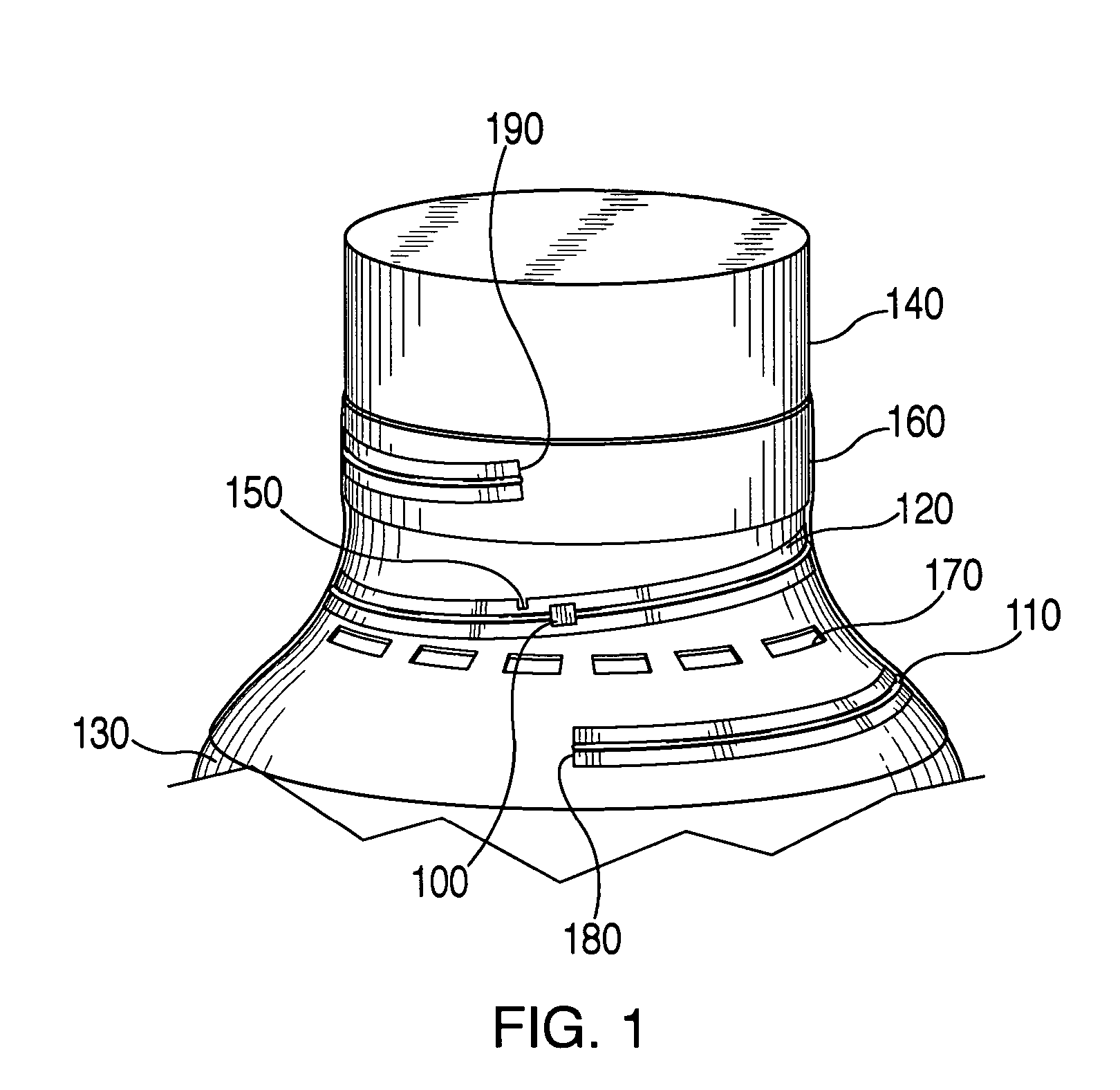

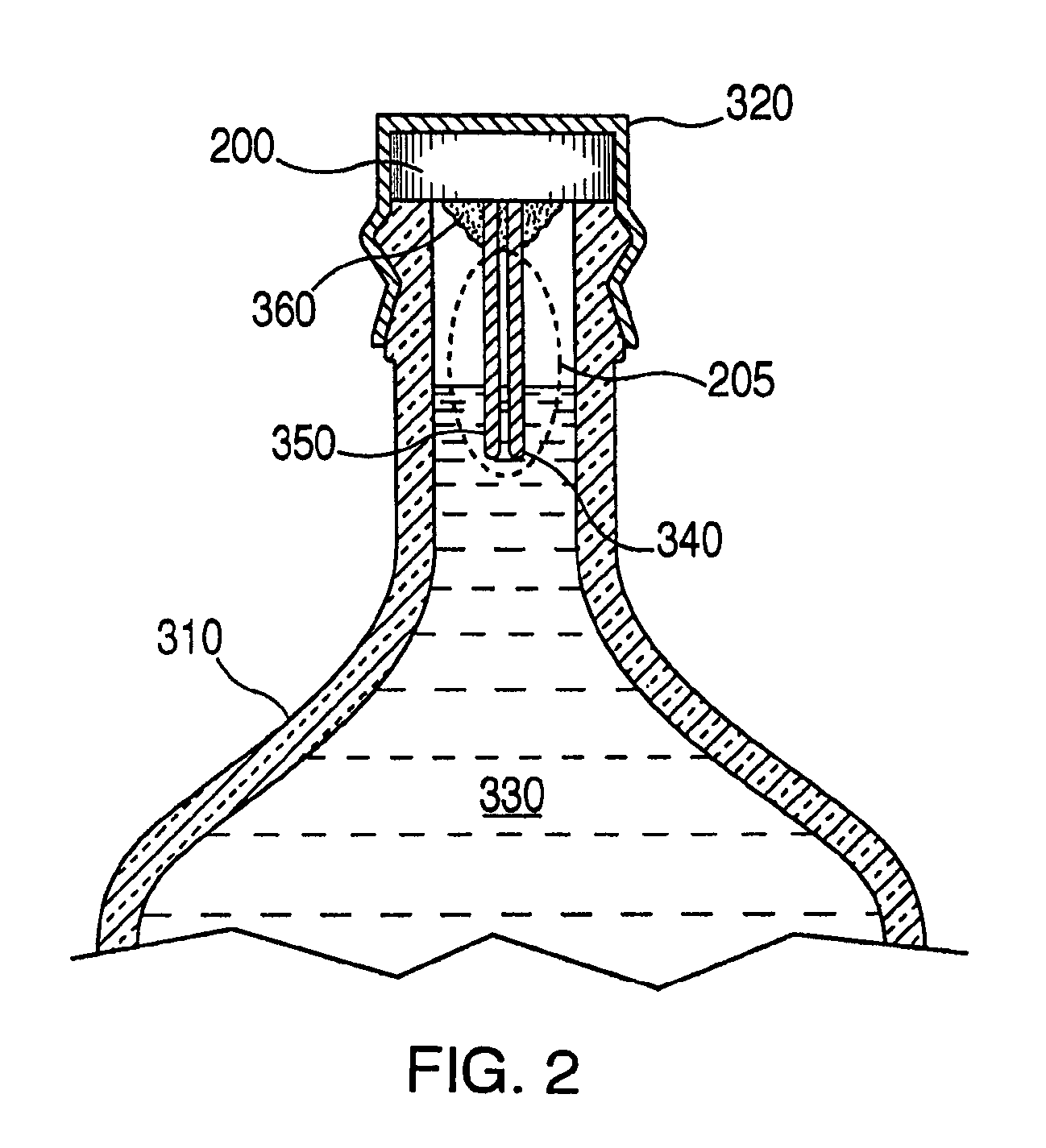

Perishable product electronic label including time and temperature measurement

ActiveUS7057495B2Informed decisionSimpler and more complex calculationStampsElectric signal transmission systemsEngineeringElectronic assemblies

An electronic assembly may be contained in a label that performs time-temperature integration (TTI) and indicates that time and / or temperature levels have been reached that may compromise the quality, shelf life, or safety of the item to which the label is affixed. The label may be used on a wide variety of objects that require careful handling in terms of temperature and / or time elapsed before use. The labeling system includes circuitry that measures and calculates, and indictor(s) that signal that the time has come for discounted sale, and, later, that the time has come for disposal rather than sale. Optionally, the circuitry may act as an “over-temperature alarm” system, to measure, calculate, and indicate when a one-time temperature violation has occurred that is of such a magnitude that the item is immediately considered compromised or spoiled. The label may take the form of a flexible, disposable label that is typically powered by a small battery. Methods may include providing a temperature-variable oscillator or time-base, counting cycles of said oscillator within a logic circuit to determine when one or more preset total cycle counts is / are reached, and signaling when said total cycle count(s) is / are reached.

Owner:COPELAND COLD CHAIN LP

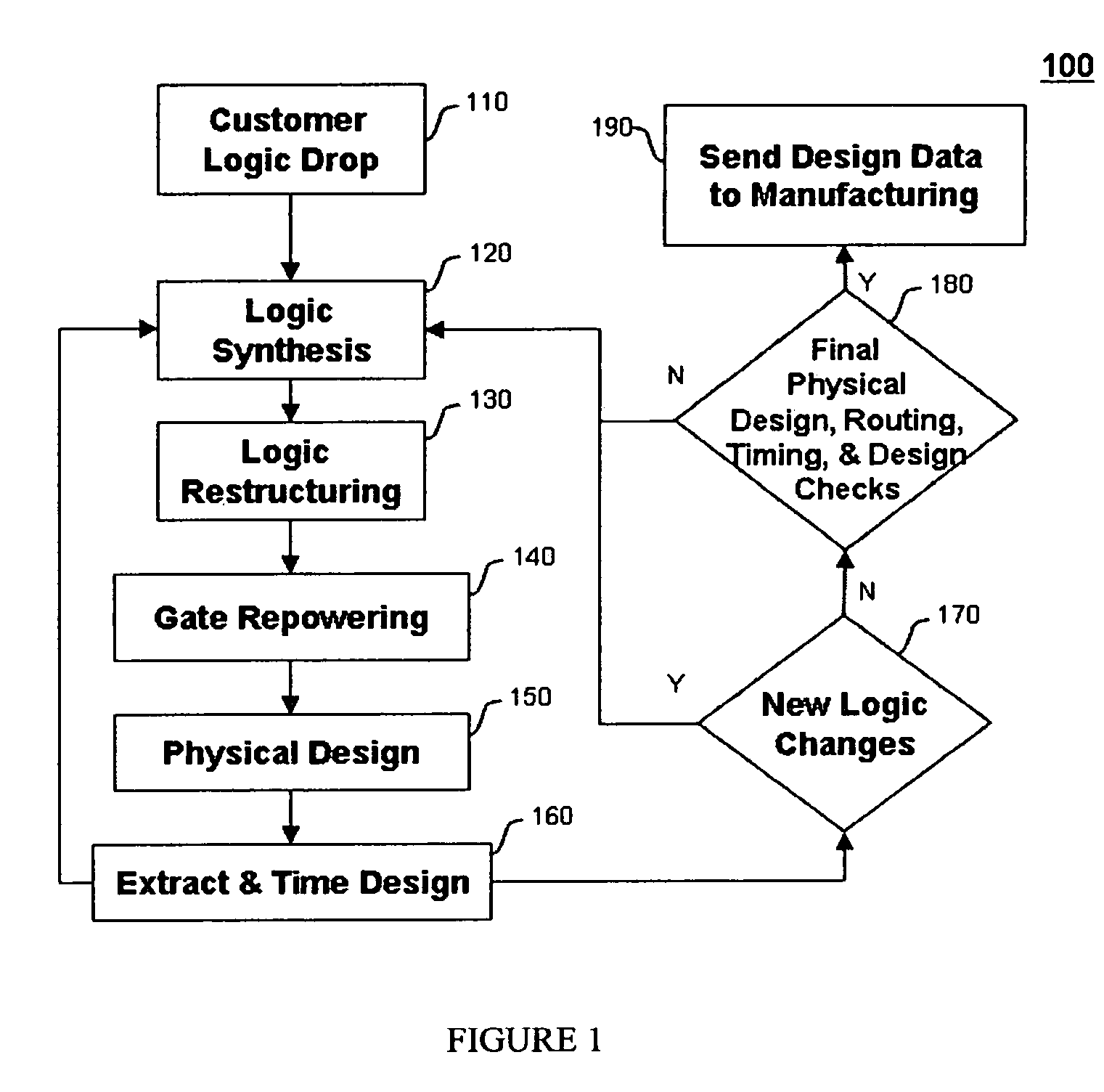

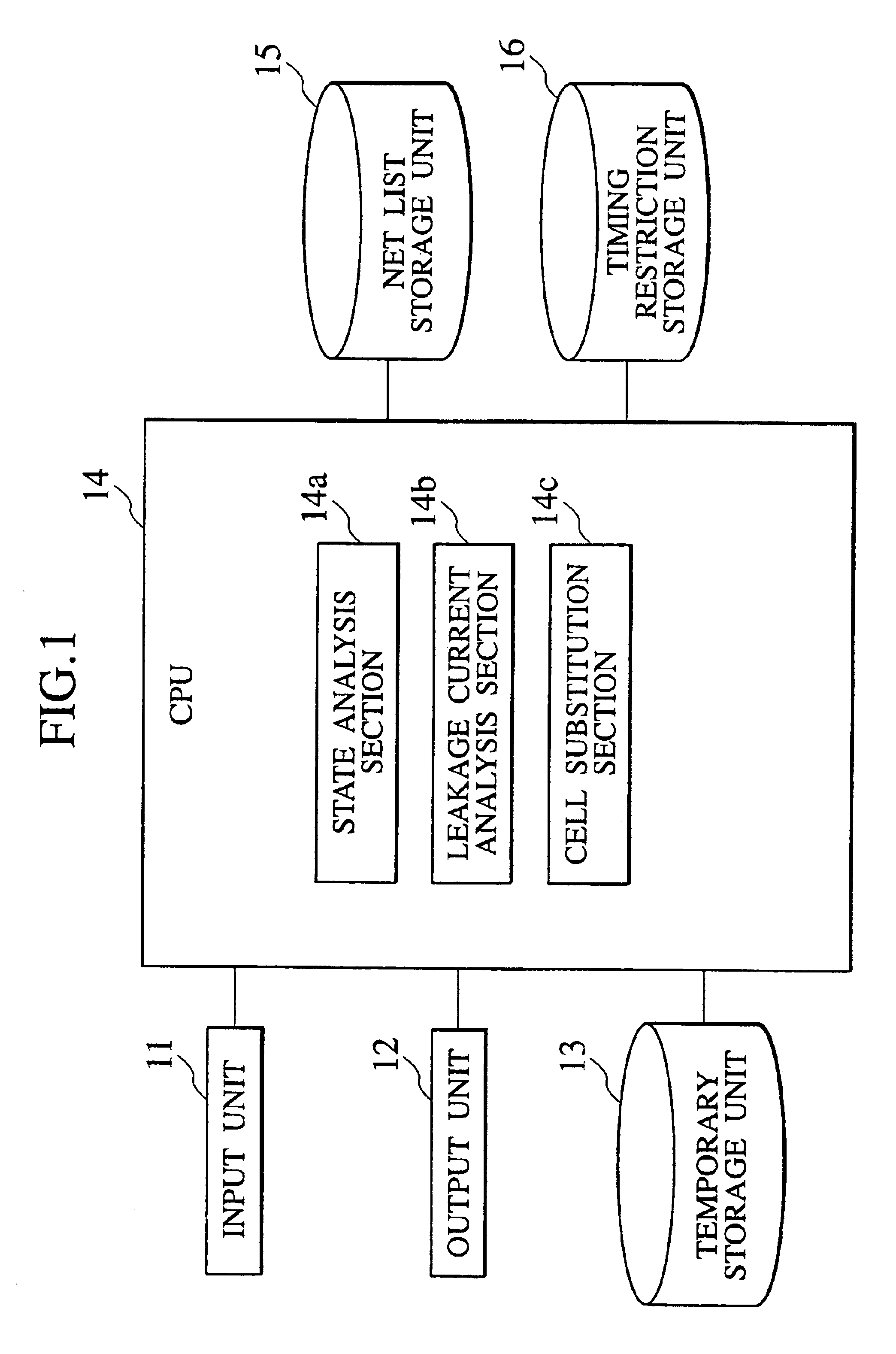

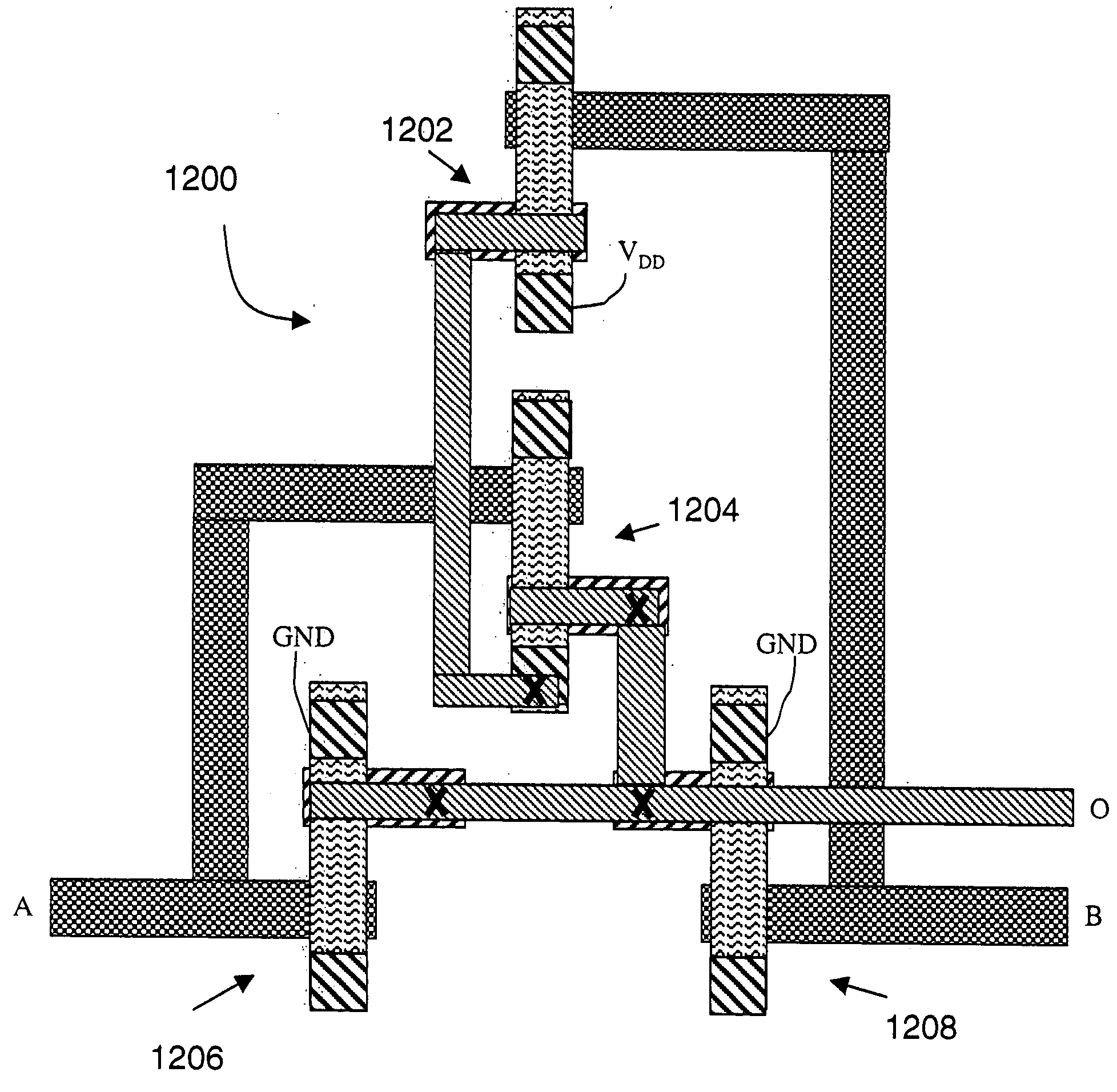

Logic circuit design equipment and method for designing logic circuit for reducing leakage current

A logic circuit design equipment and a logic circuit design method include analyzing input states of all of first cells, respectively, analyzing leakage currents of all of first cells in a case where each first cell is high Vth cell showing a small leakage current at a low speed operation and low Vth cell showing a large leakage current at a high speed operation, respectively, and substituting the first cells for second cells within a range satisfying a timing restriction. Herein, a threshold of the second cell is different from a threshold of the first cell.

Owner:KK TOSHIBA

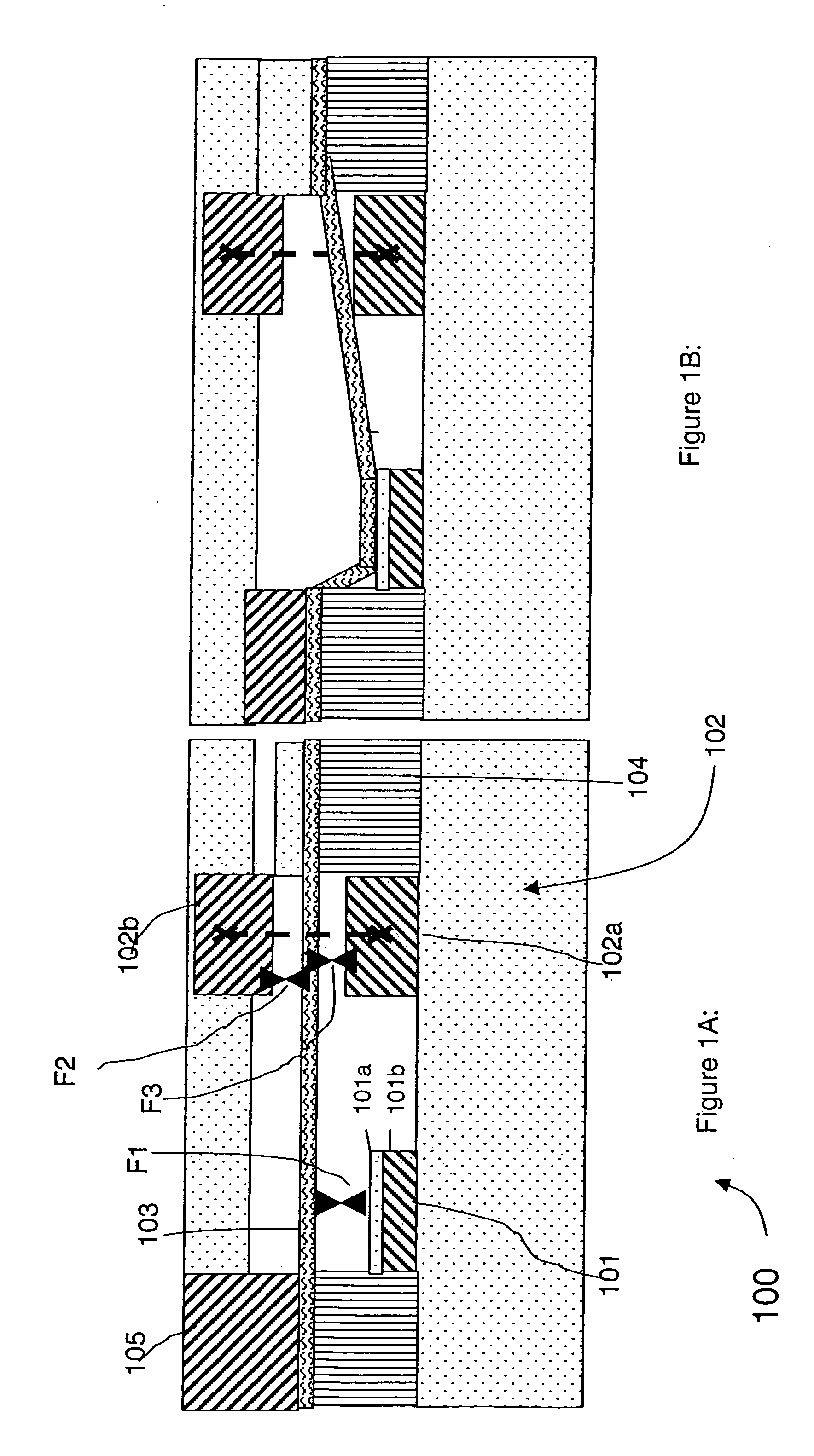

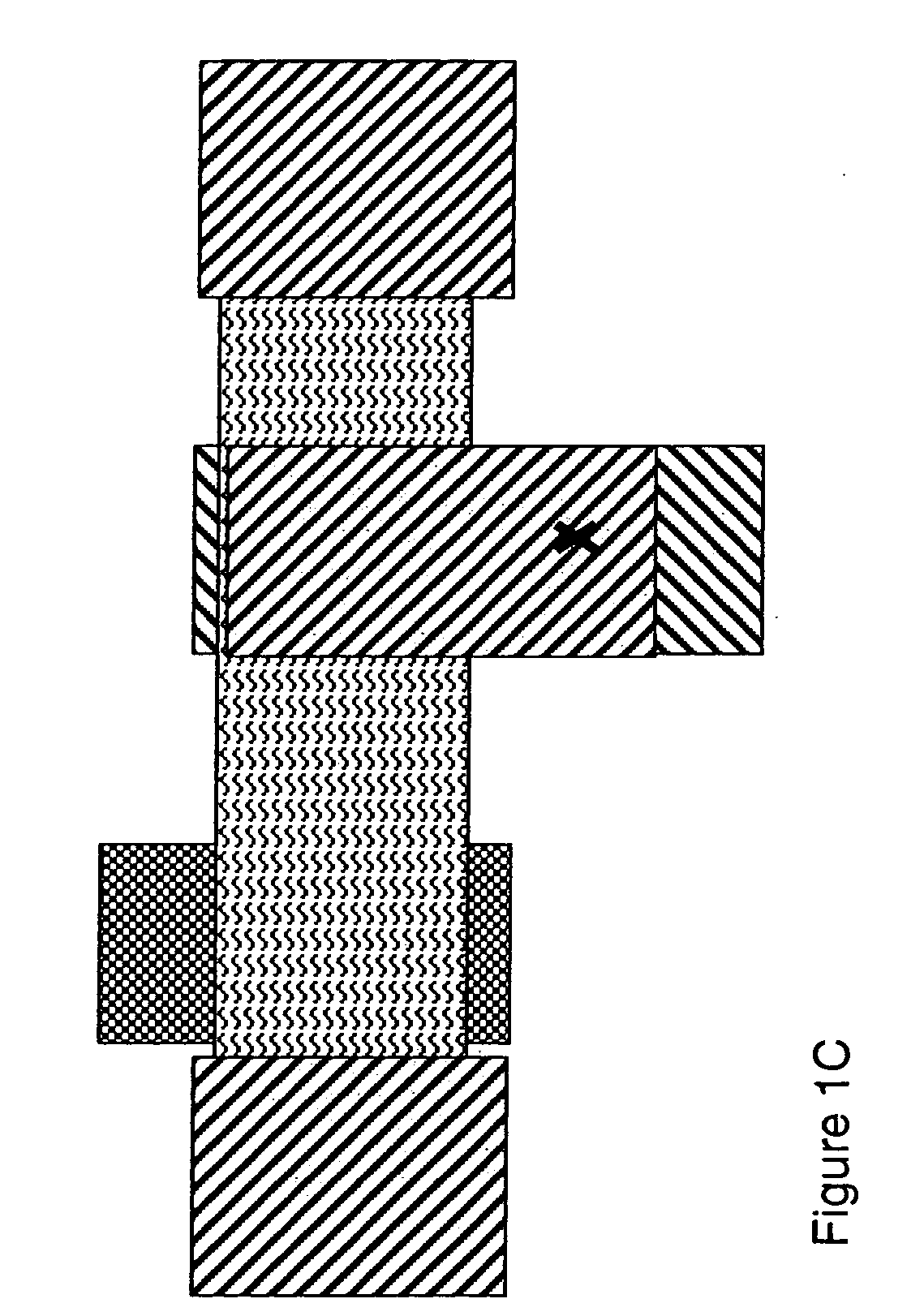

Circuits made from nanotube-based switching elements with multiple controls

InactiveUS20050035786A1TransistorLogic circuits characterised by logic functionNanotubeElectrically conductive

Nanotube-based switching elements with multiple controls and circuits made from such. A switching element includes an input node, an output node, and a nanotube channel element having at least one electrically conductive nanotube. A control structure is disposed in relation to the nanotube channel element to controllably form and unform an electrically conductive channel between said input node and said output node. The output node is constructed and arranged so that channel formation is substantially unaffected by the electrical state of the output node. The control structure includes a control electrode and a release electrode, disposed on opposite sides of the nanotube channel element. The control and release may be used to form a differential input, or if the device is constructed appropriately to operate the circuit in a non-volatile manner. The switching elements may be arranged into logic circuits and latches having differential inputs and / or non-volatile behavior depending on the construction.

Owner:NANTERO

Method and system for management of resource leases in an application framework system

InactiveUS6950874B2Optimize data processingHighly distributed service management architectureError preventionFrequency-division multiplex detailsData processing systemResource management

A method, system, apparatus, and computer program product are presented for management of resource leases within a distributed data processing system. A resource manager receives a lease request from a requester for a resource in which the lease request has a requested lease period. In response to receiving the lease request, the resource manager secures leases along a logical circuit of resources through the distributed data processing system. The resource manager requests leases from other resource managers along the data path that comprises the logical circuit because use of the requested resource requires use of other resources. After securing leases on a logical circuit of resources, the resource manager returns a lease grant for the resource to the requester. If the system detects oversubscribed conditions and / or error conditions, the system can adjust the pending leases in an appropriate manner, such as terminating a lease, adjusting the lease period of a lease, and the like.

Owner:IBM CORP

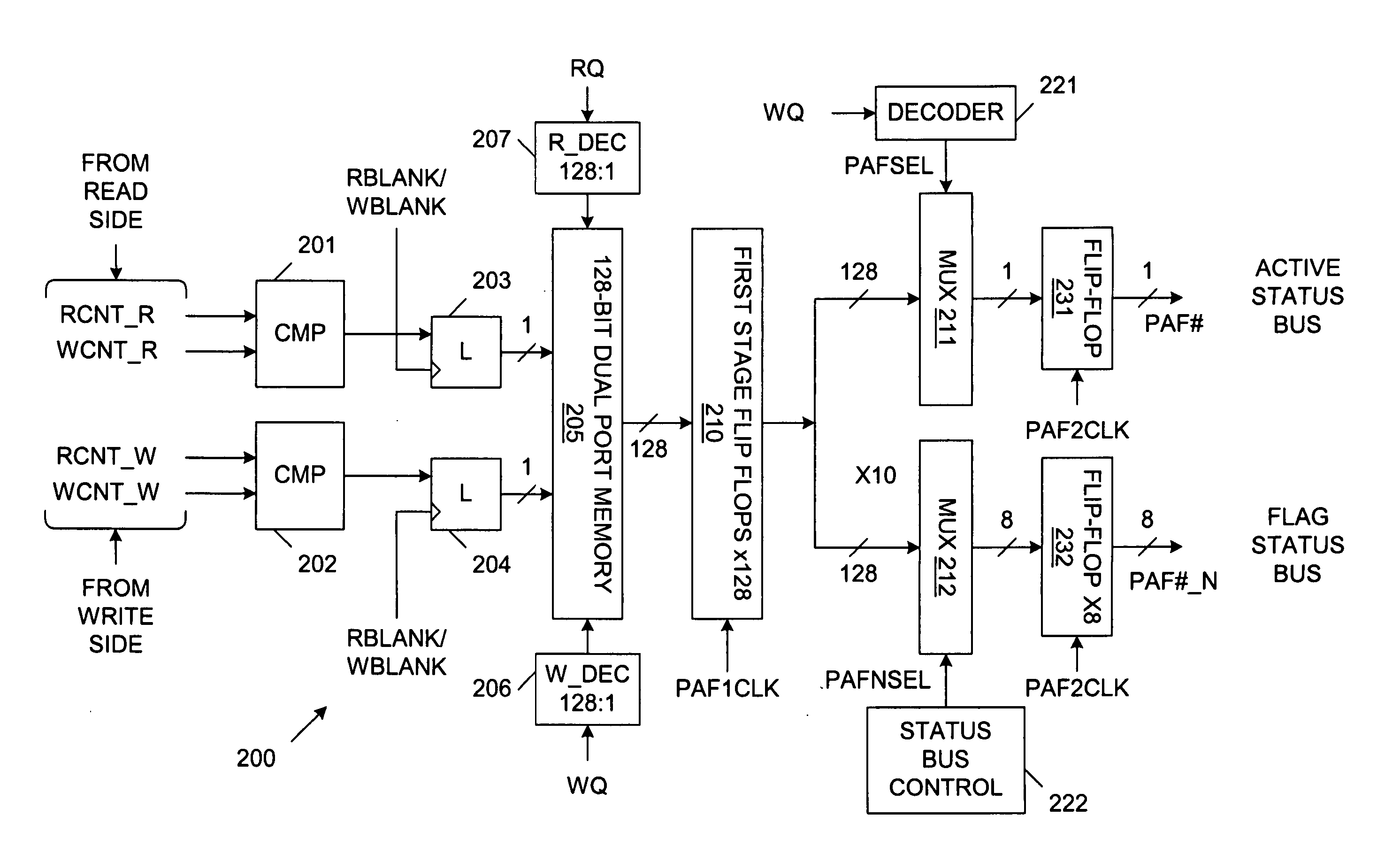

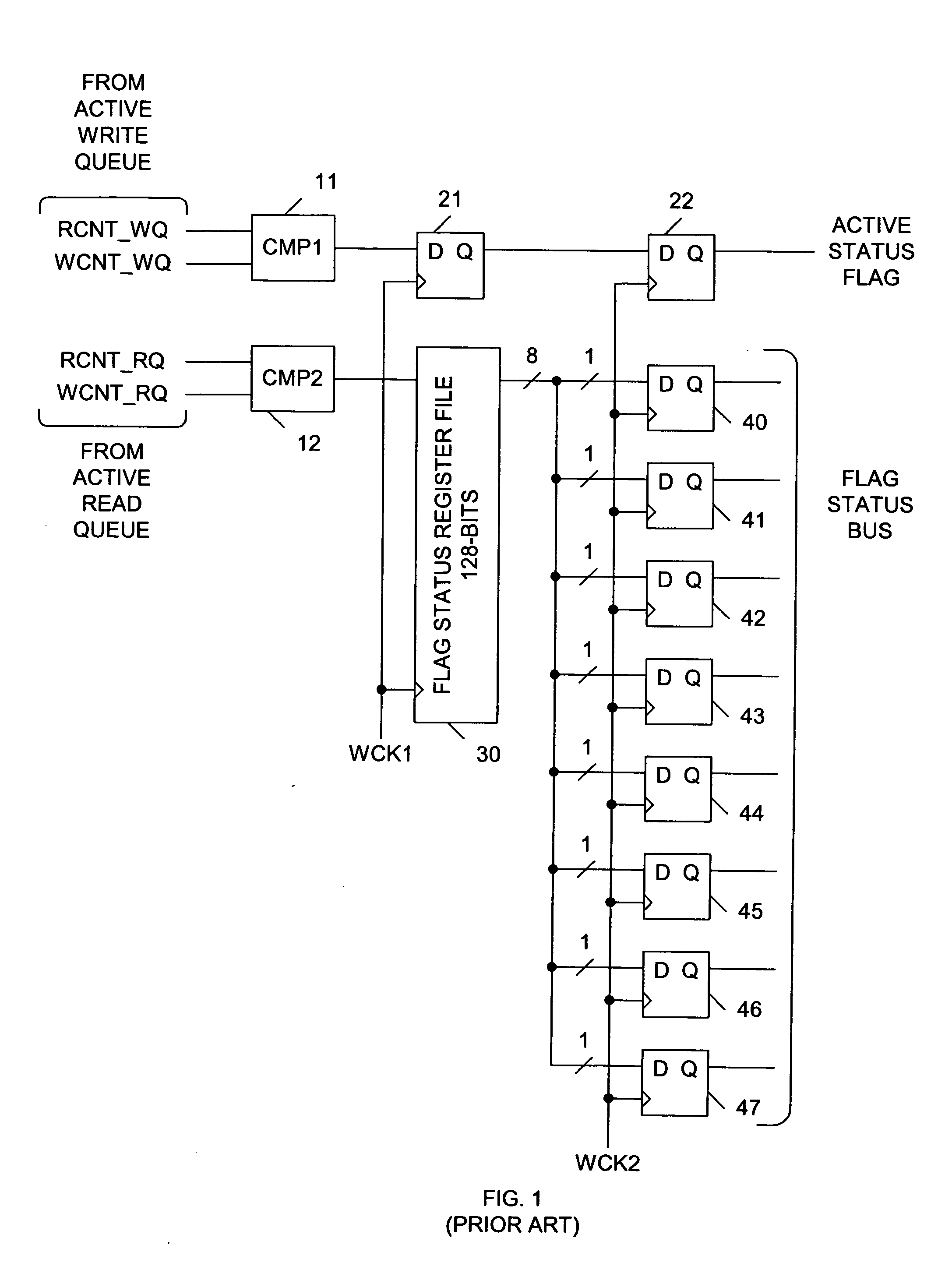

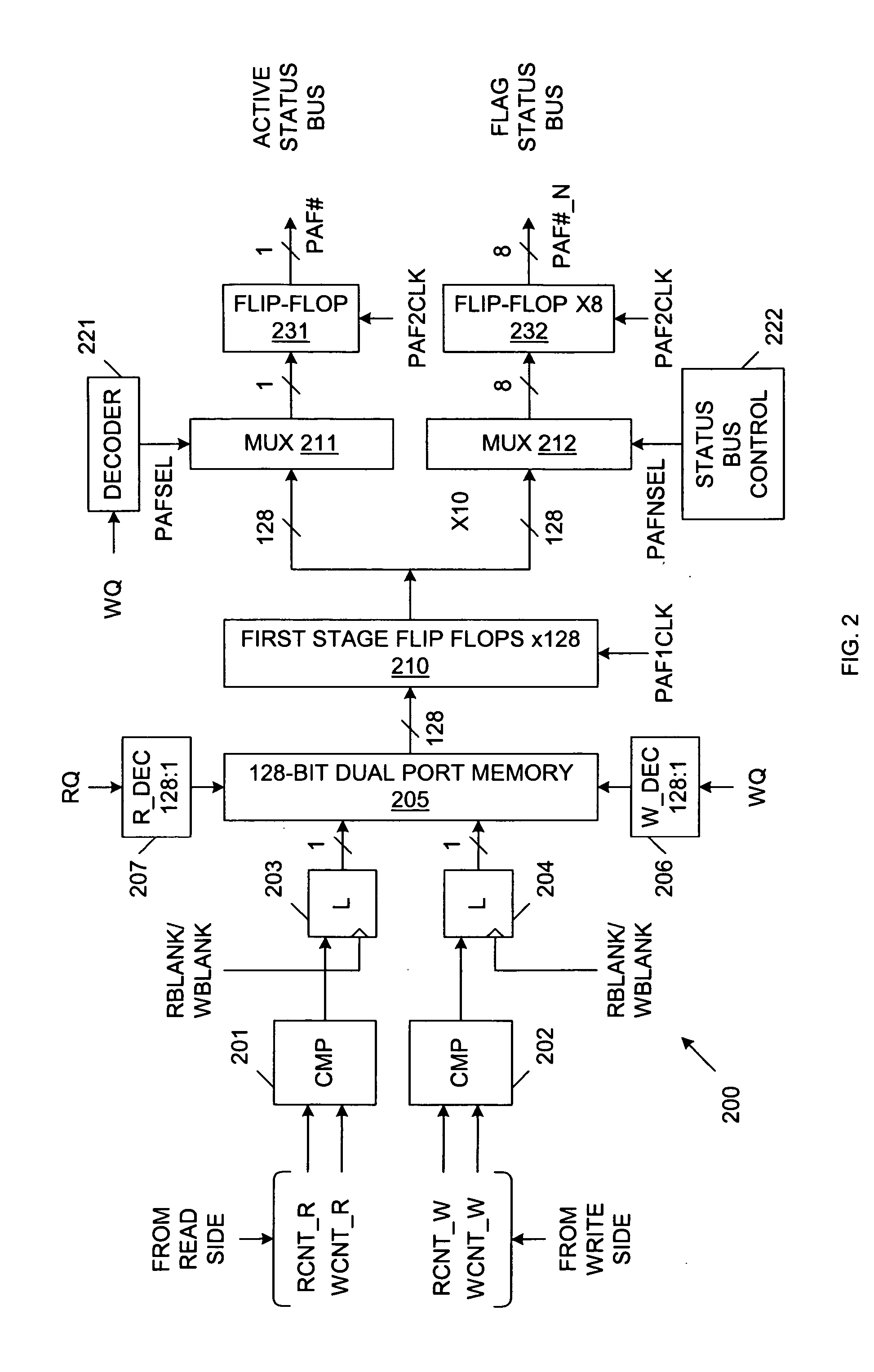

Status bus accessing only available quadrants during loop mode operation in a multi-queue first-in first-out memory system

ActiveUS20060020742A1Efficient routingMemory systemsInput/output processes for data processingBus masteringControl circuit

A flag logic circuit is provided for use in a multi-queue memory device having a plurality of queues. A first stage memory stores a flag value for each of the queues in the multi-queue memory device. Flag values are routed from the first stage memory to a flag status bus having a width N in the manner described below. A status bus control circuit receives a signal that identifies the number of queues M actually used by the multi-queue memory device, and in response, generates a repeating pattern of X control values, wherein X is equal to (M−(M mod N)) / N+1. A selector circuit sequentially routes X sets of N flag values from the first stage memory to the flag status bus in response to the repeating pattern of X control values. The X sets of N flag values include the flag values associated with the queues actually used.

Owner:INTEGRATED DEVICE TECH INC

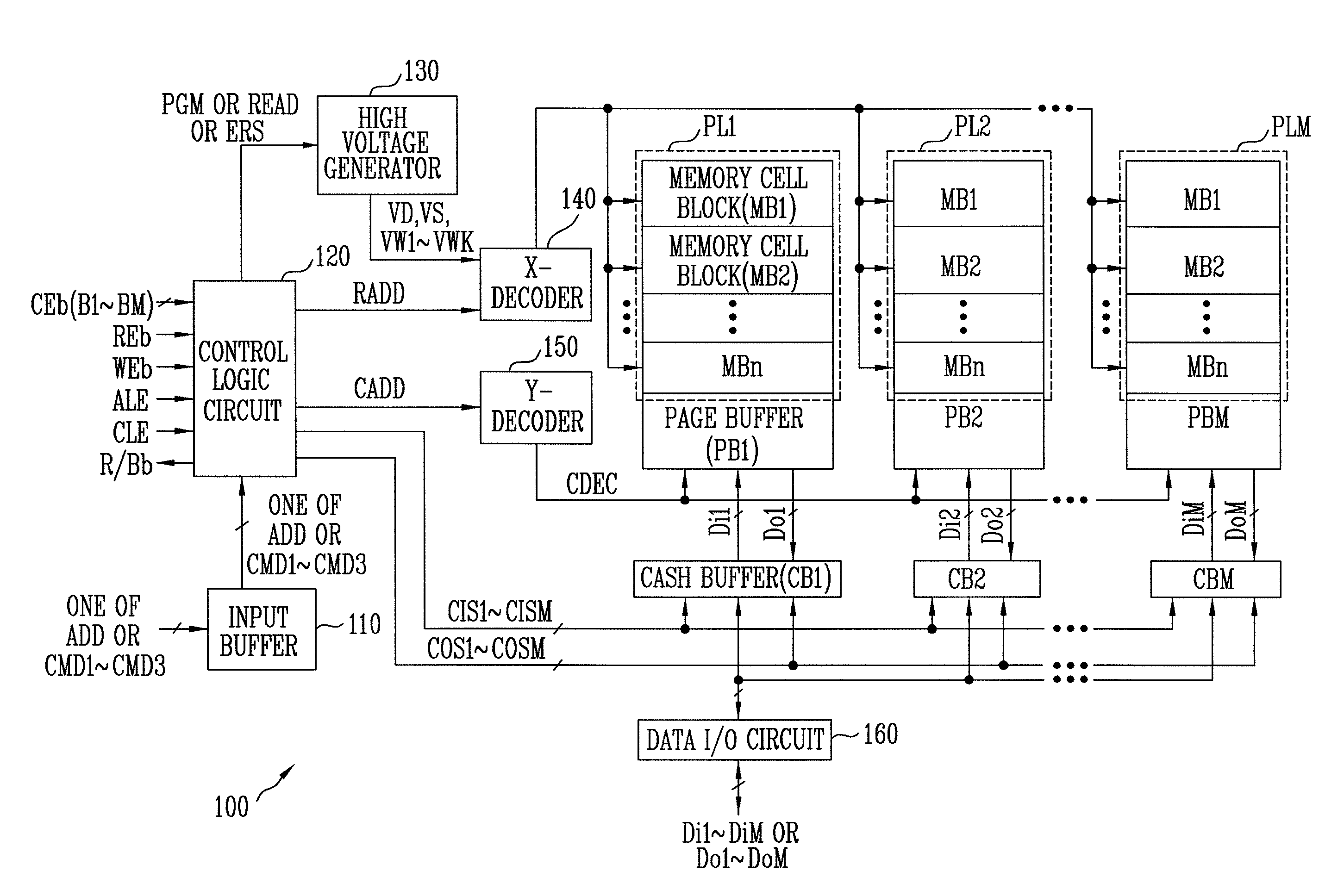

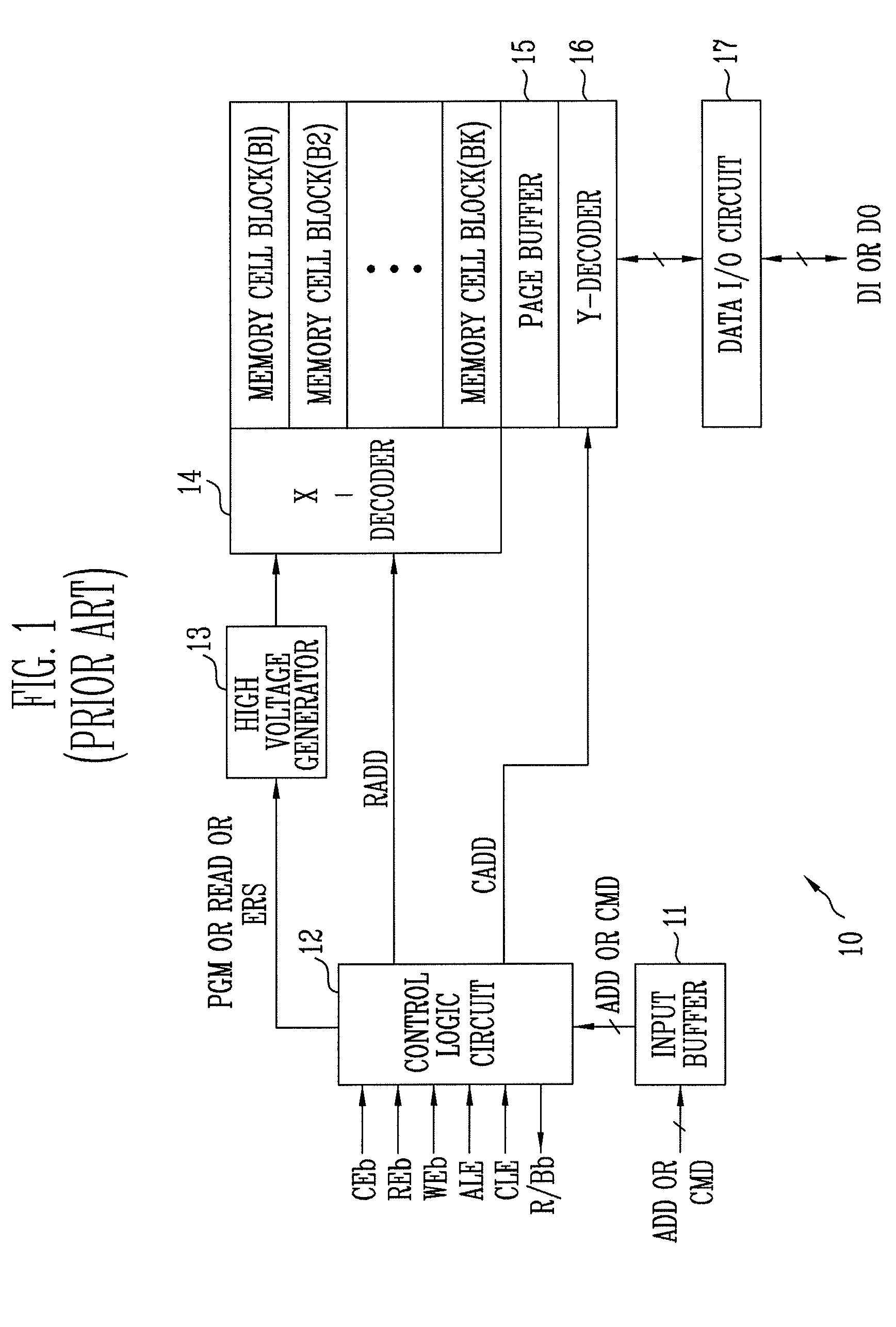

Multi-plane type flash memory and methods of controlling program and read operations thereof

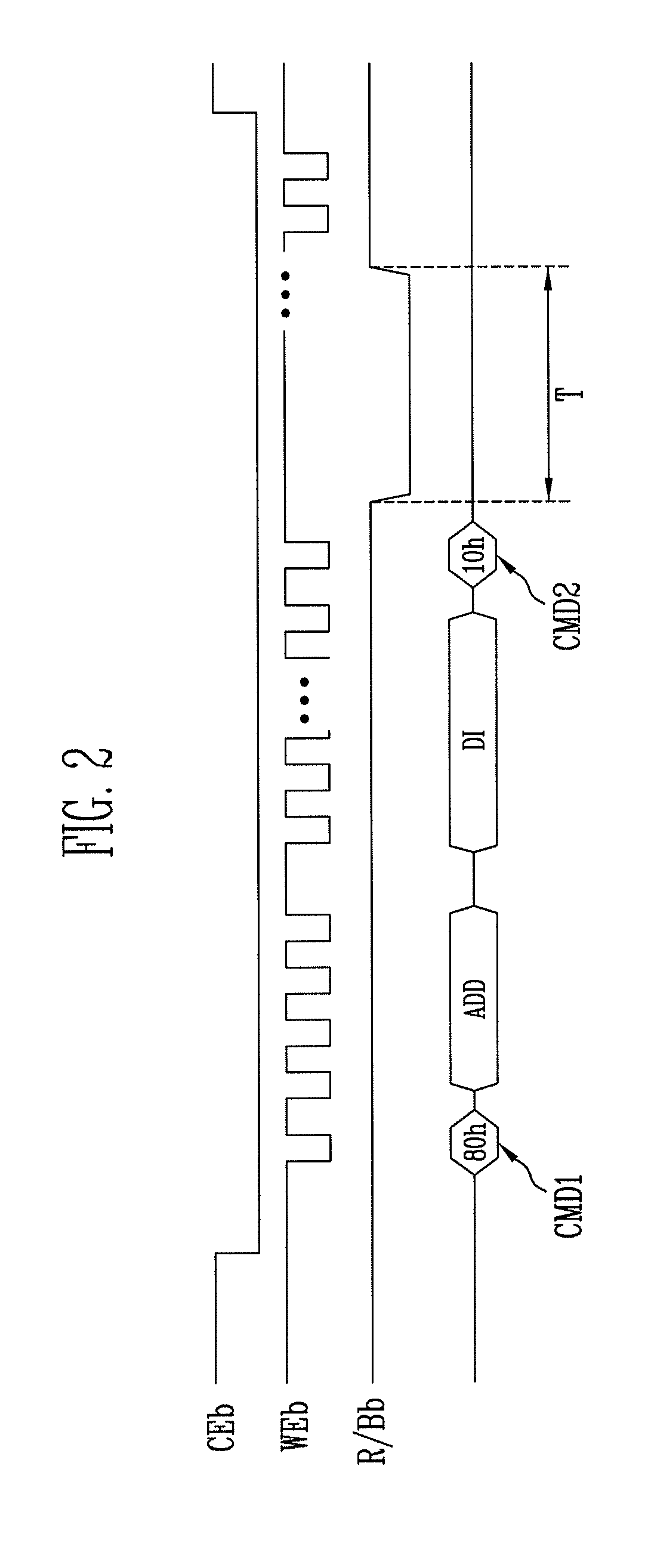

ActiveUS8347042B2Data augmentationIncrease speedRead-only memoriesDigital storageControl signalInput control

A multi-plane type flash memory device comprises a plurality of planes each including a plurality of memory cell blocks, page buffers each latching an input data bit to be output to its corresponding plane or latching an output data bit to be received from the corresponding plane, cache buffers each storing an input or output data bits in response to one of cache input control signals and each transferring the stored data bit to the page buffer or an external device in response to one of cache output control signals, and a control logic circuit generating the cache input and output control signals in response to command and chip enable signals containing plural bits. The program and read operations for the plural planes are conducted simultaneously in response to the chip enable signal containing the plural bits, which increases an operation speed and data throughput processed therein.

Owner:SK HYNIX INC

Apparatus and method for detecting tampering with containers and preventing counterfeiting thereof

An apparatus for detecting tampering with a container sealed with a cap. The apparatus includes a radio frequency transceiver for transmitting a signal upon receipt of a transmit command and an antenna attached thereto. In a first embodiment, the radio frequency transceiver and the antenna are mounted on a substrate attached to the container and the cap. The radio frequency transceiver is disabled when the antenna is separated into two portions upon breaking the seal between the container and the cap. In a second embodiment, the apparatus is mounted within a cap and includes a logic circuit and a probe that detects changes in the level of contents within the container. The probe produces an output relative to the level of contents in the container. The logic circuit then either prevents the radio frequency transceiver form communicating or causes it to transmit an alternative signal.

Owner:CLAESSENS FRANCIS M +1

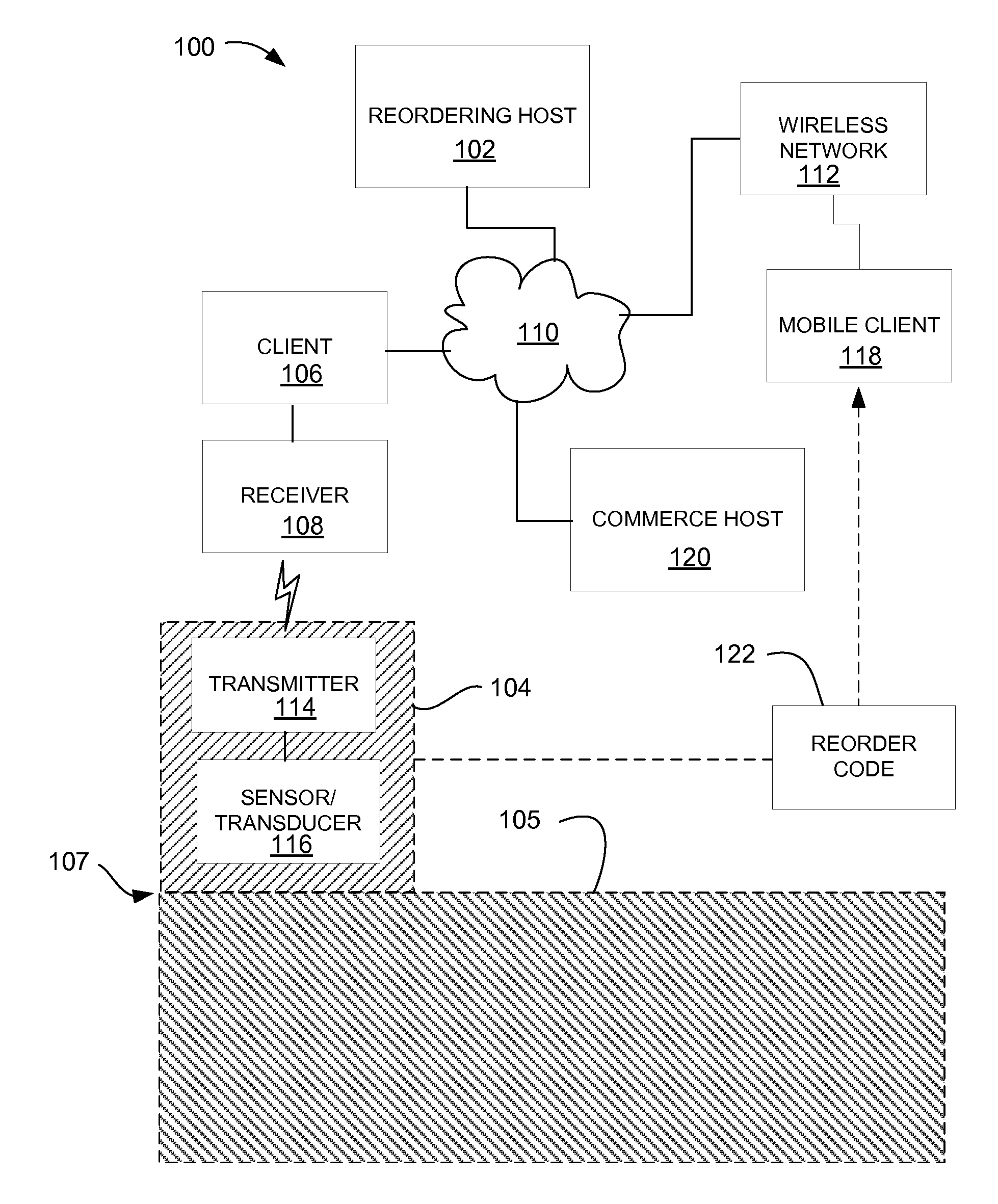

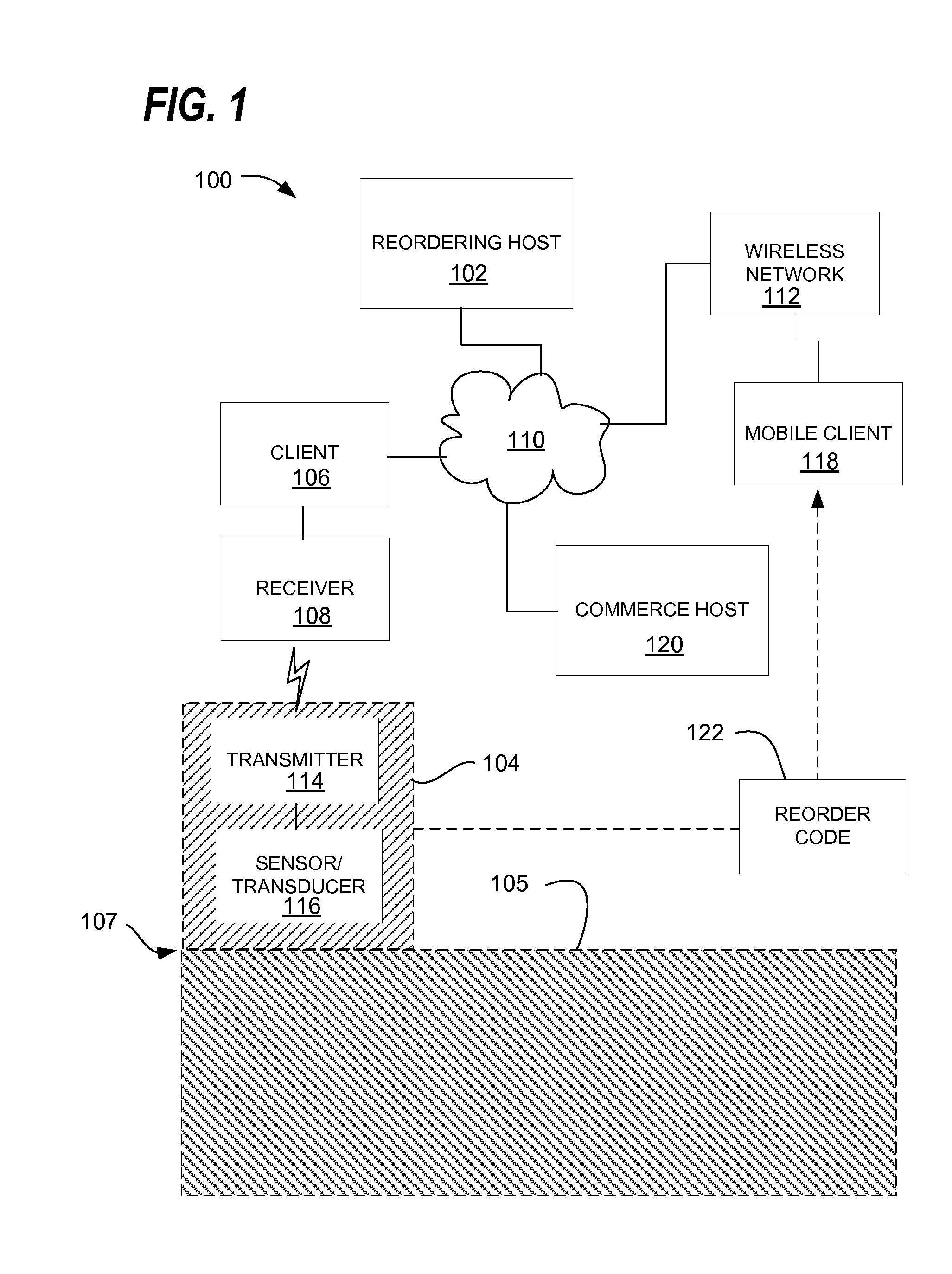

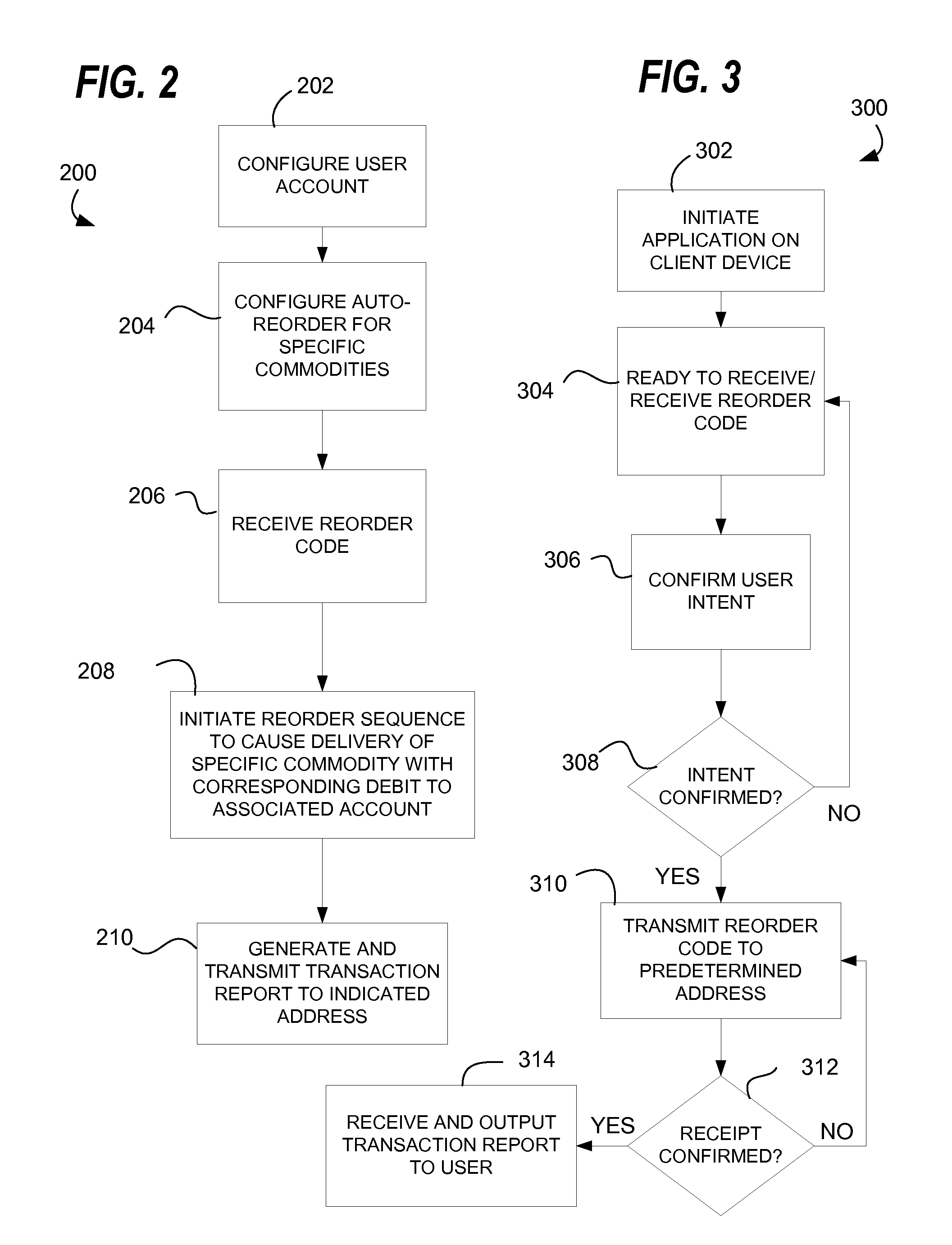

Automatic resupply of consumable commodities

Methods and systems for facilitating initiation of resupply orders for consumable commodities include using a stand-alone electronic or audio-generating device incorporated into retail product packaging. The stand-alone device is equipped with a rudimentary processor or logic circuit, a memory, and a wireless transmitter. A simple user interface / activation device such as a push button or membrane switch is coupled to the logic circuit or processor. The stand-alone device is incorporated into or with product packaging, and may be configured with a resupply code at or after a point of sale. A user may activate the user interface of the device when the product needs resupplying, causing the resupply code to be transmitted to an access point or terminal that initiates a reorder sequence for the product.

Owner:SHUSTER GARY STEPHEN

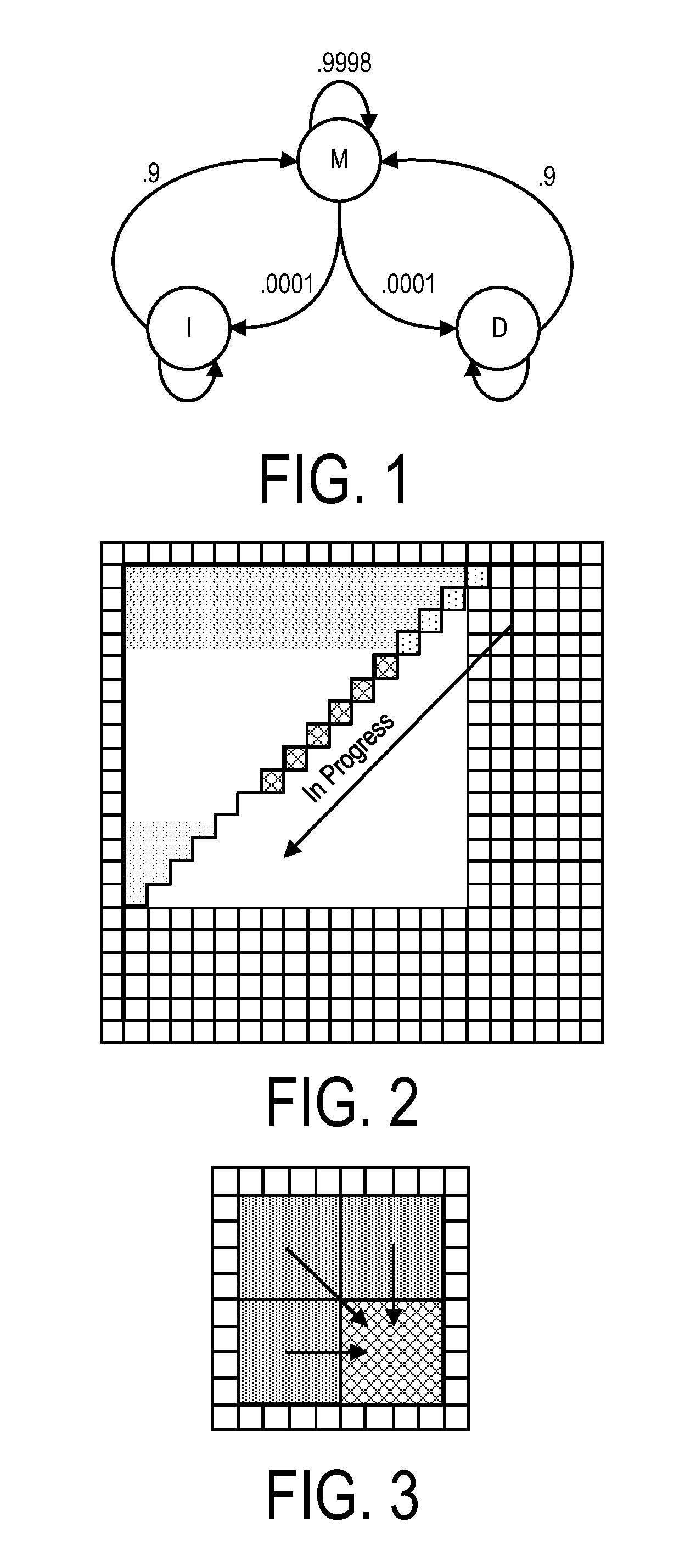

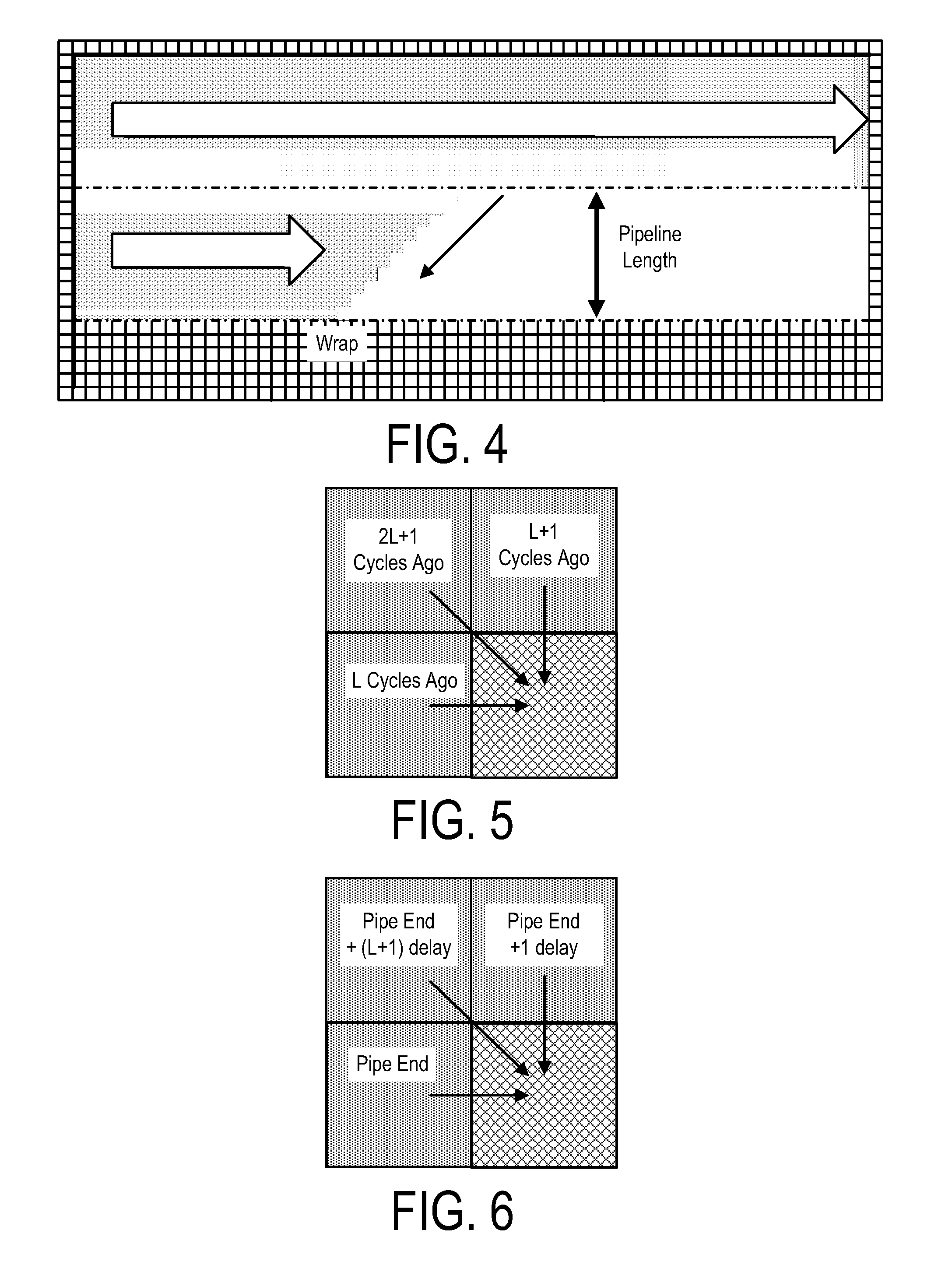

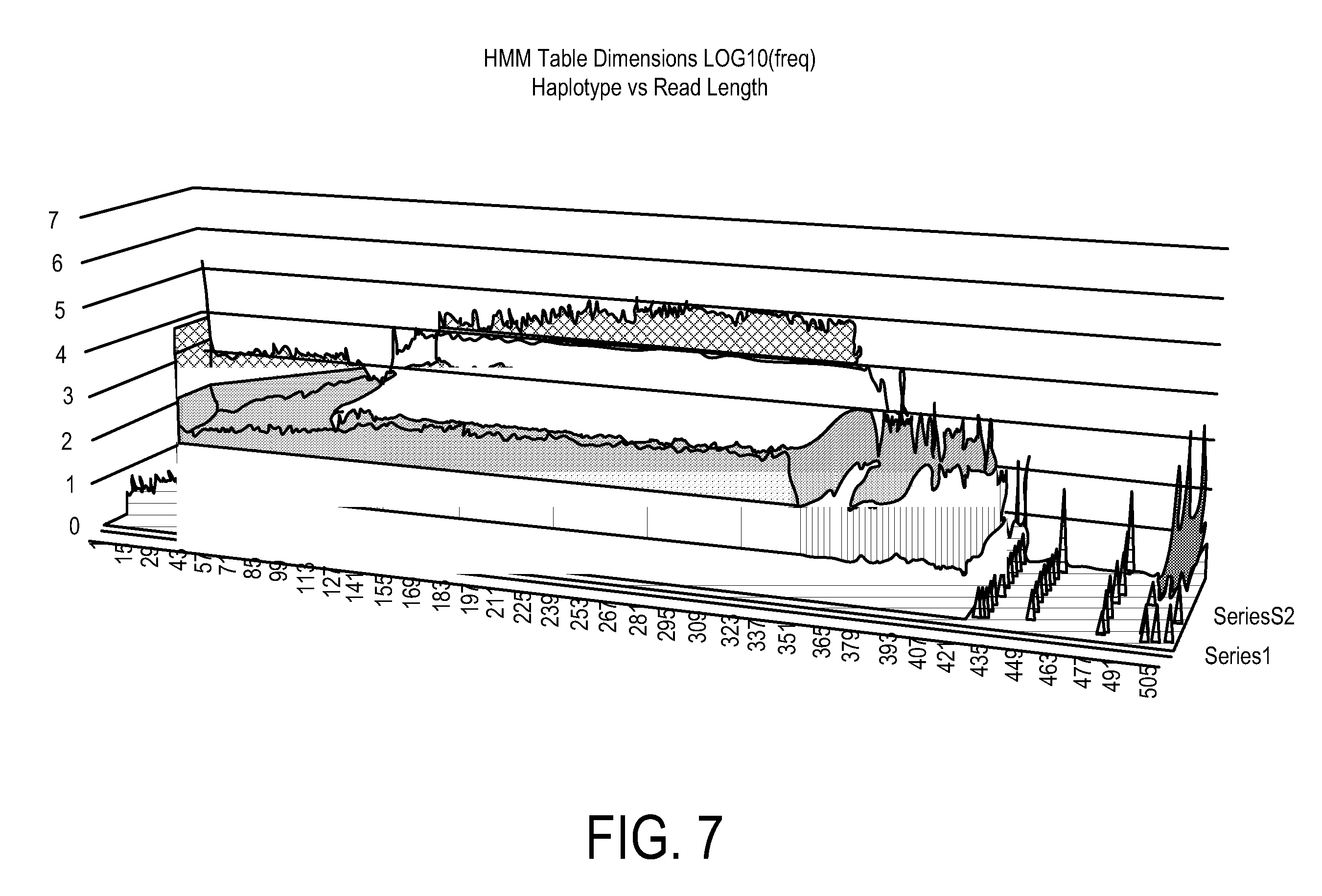

Bioinformatics systems, apparatuses, and methods executed on an integrated circuit processing platform

ActiveUS20160306923A1Processing speedProcessed result accuracyMemory architecture accessing/allocationMathematical modelsData sourceGenomic data

A system, method and apparatus for executing a bioinformatics analysis on genetic sequence data includes an integrated circuit formed of a set of hardwired digital logic circuits that are interconnected by physical electrical interconnects. One of the physical electrical interconnects forms an input to the integrated circuit that may be connected with an electronic data source for receiving reads of genomic data. The hardwired digital logic circuits may be arranged as a set of processing engines, each processing engine being formed of a subset of the hardwired digital logic circuits to perform one or more steps in the bioinformatics analysis on the reads of genomic data. Each subset of the hardwired digital logic circuits may be formed in a wired configuration to perform the one or more steps in the bioinformatics analysis.

Owner:EDICO GENOME

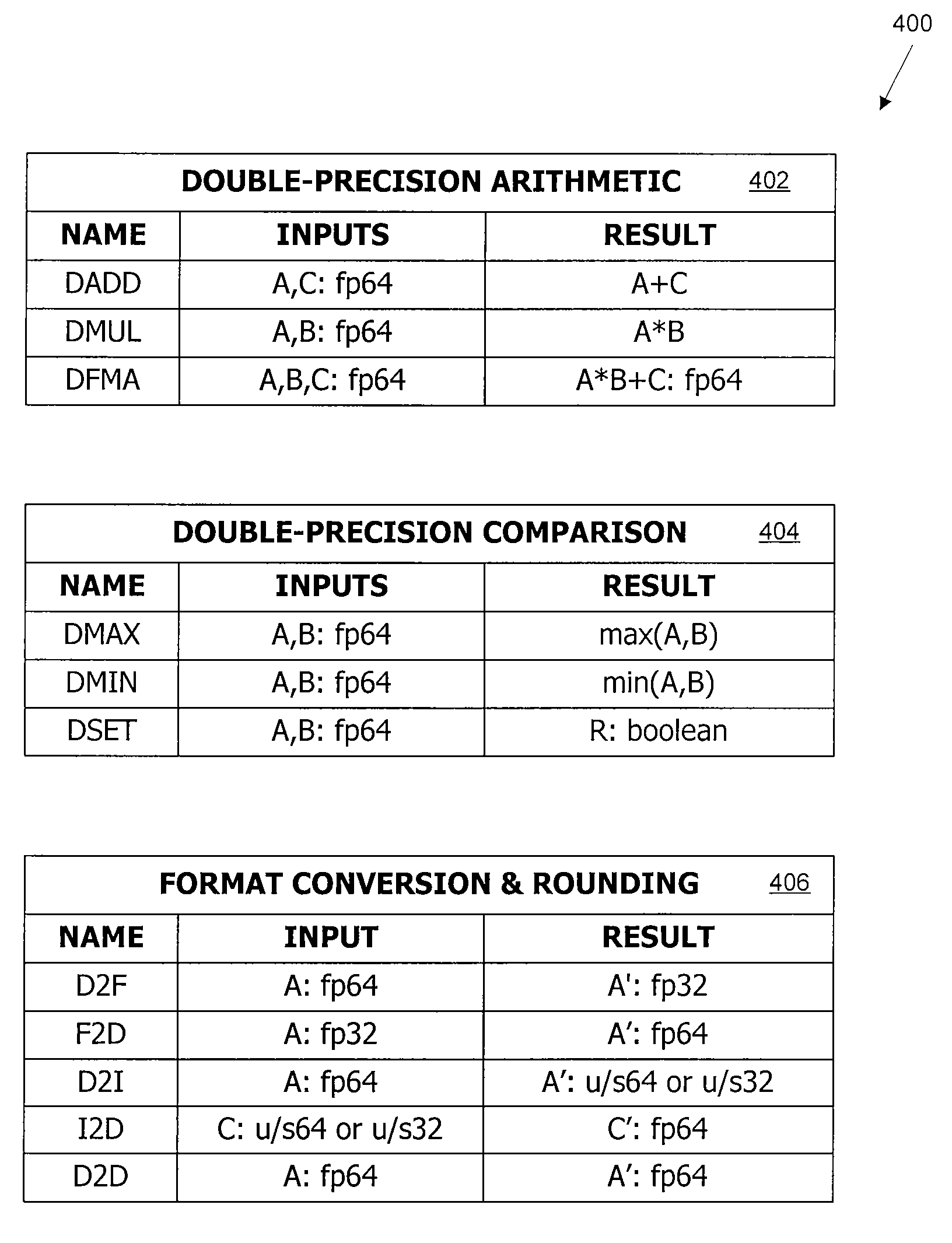

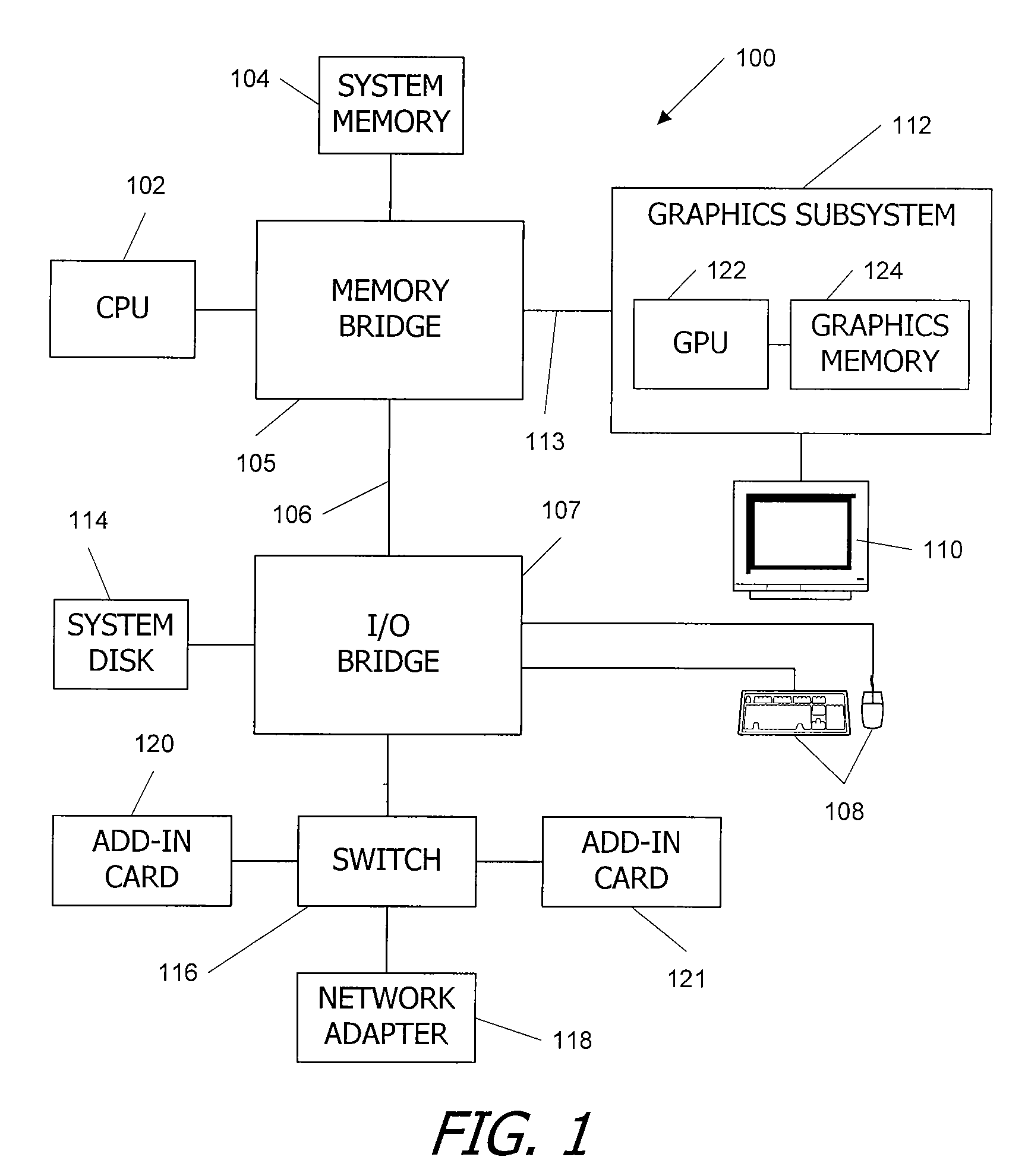

Fused multiply-add functional unit

ActiveUS20090150654A1Reduce the impactReduce impactRegister arrangementsComputation using non-contact making devicesGraphicsDatapath

A functional unit is added to a graphics processor to provide direct support for double-precision arithmetic, in addition to the single-precision functional units used for rendering. The double-precision functional unit can execute a number of different operations, including fused multiply-add, on double-precision inputs using data paths and / or logic circuits that are at least double-precision width. The double-precision and single-precision functional units can be controlled by a shared instruction issue circuit, and the number of copies of the double-precision functional unit included in a core can be less than the number of copies of the single-precision functional units, thereby reducing the effect of adding support for double-precision on chip area.

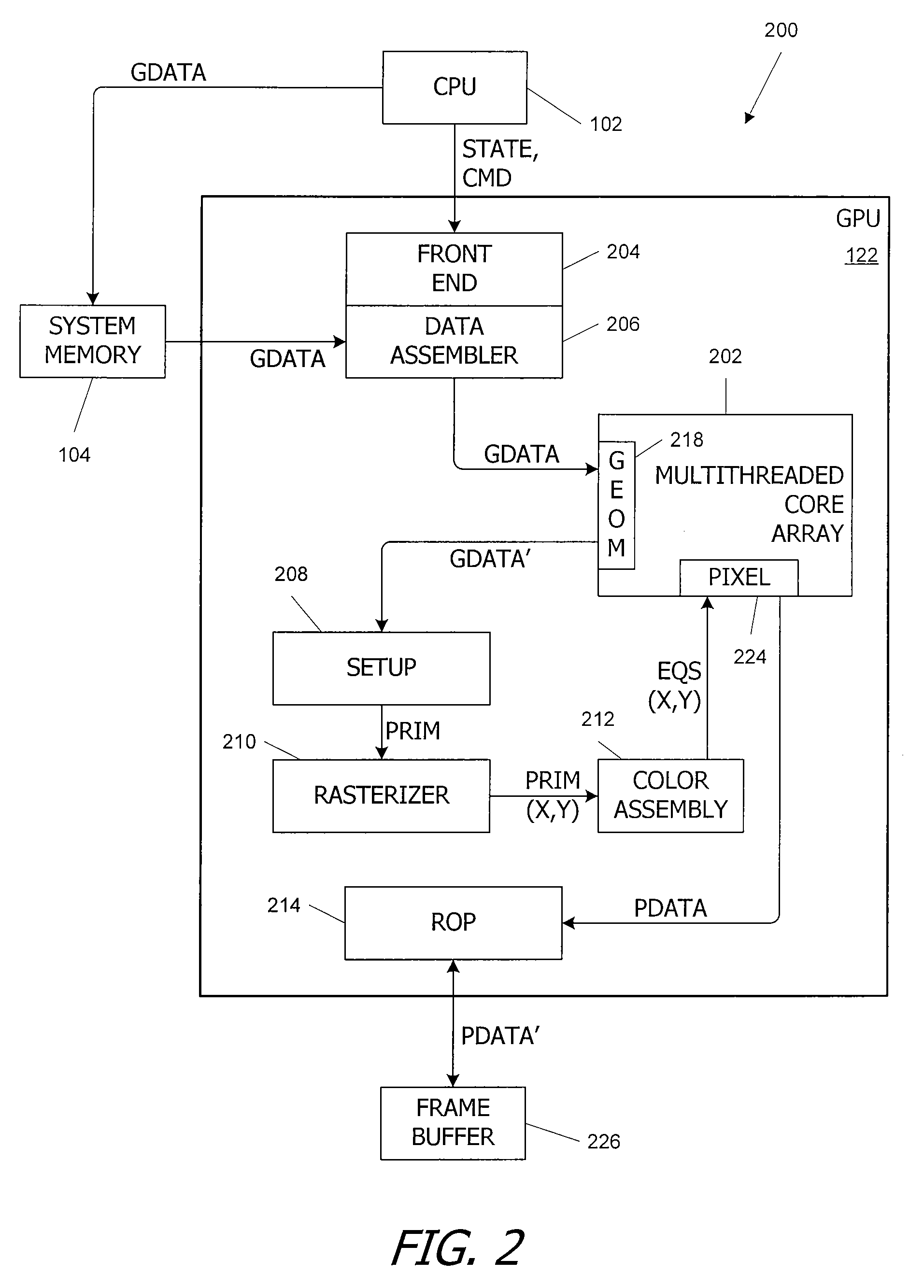

Owner:NVIDIA CORP

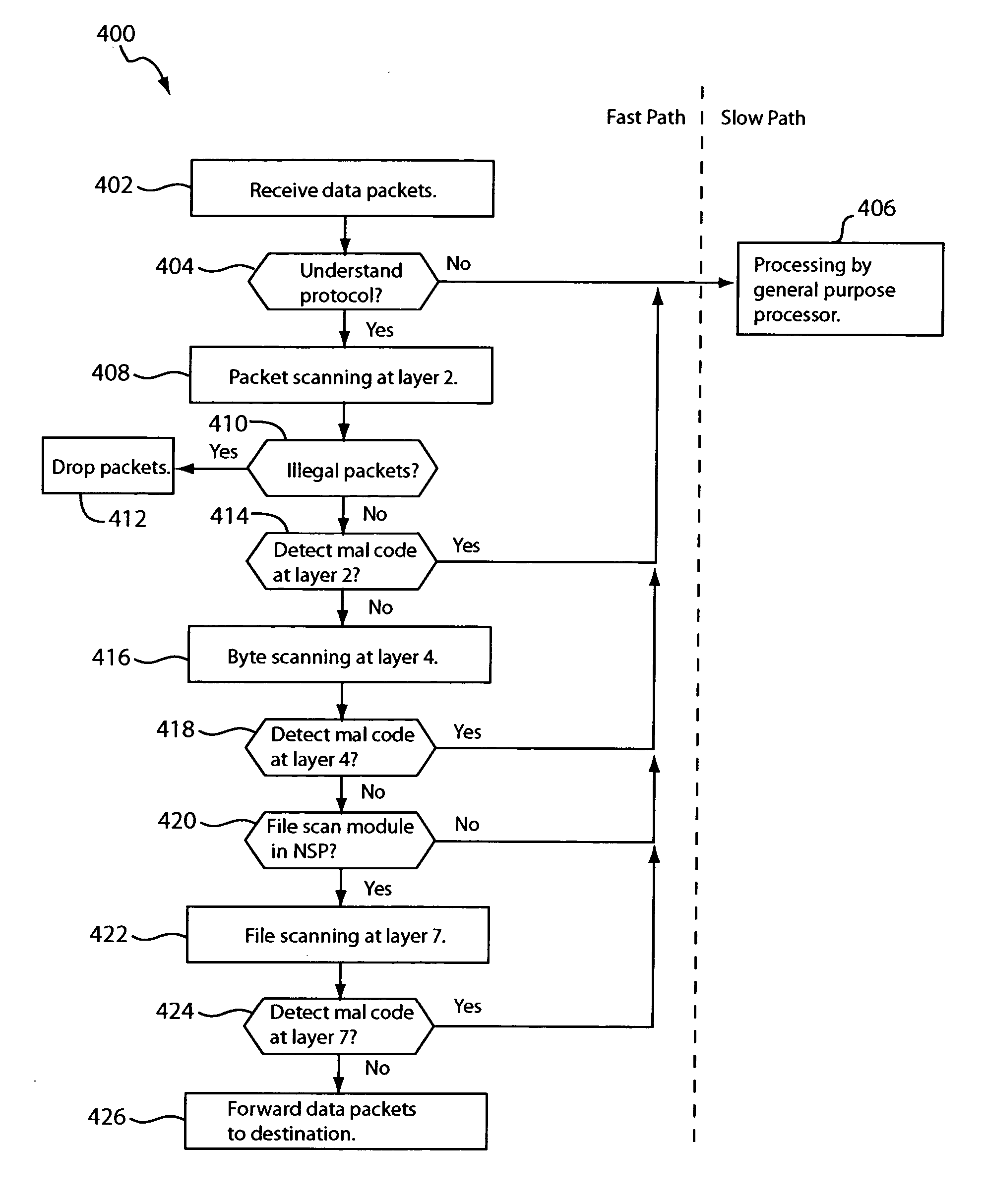

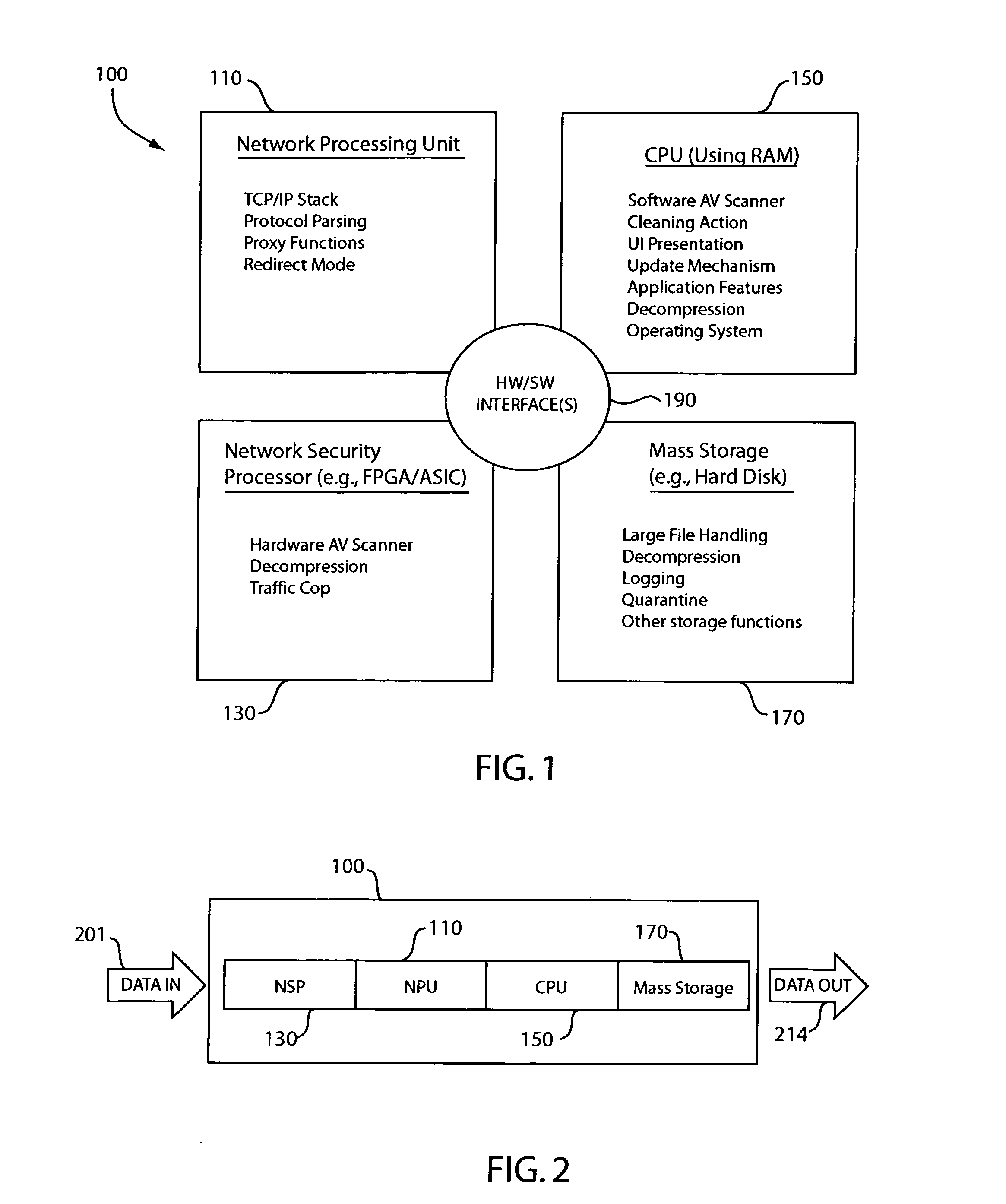

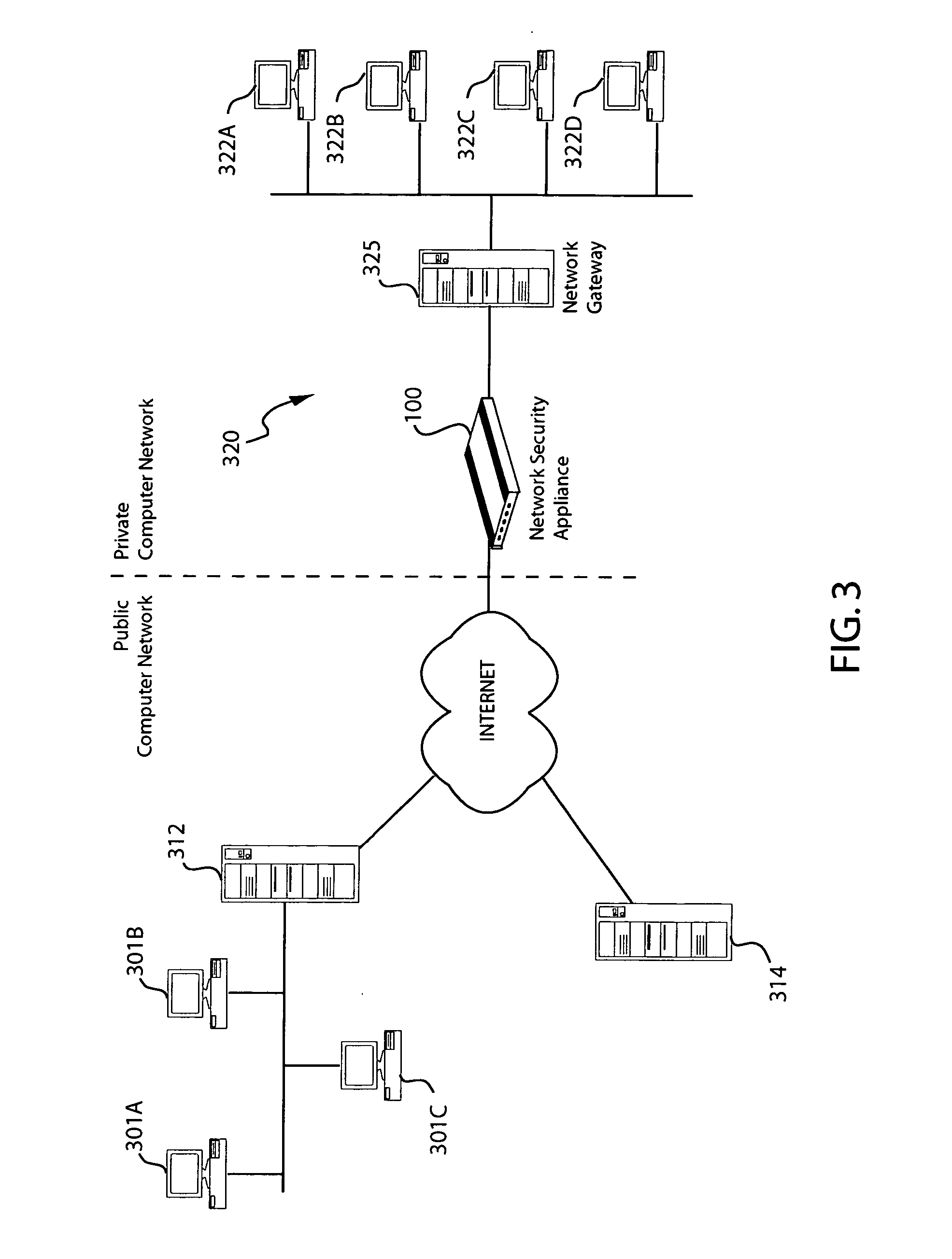

Method and apparatus for securing a computer network

ActiveUS20060206936A1Minimize impactMemory loss protectionError detection/correctionData packGeneral purpose

In one embodiment, a network security appliance includes a logic circuit, a network processing unit, and a general purpose processor to protect a computer network from malicious codes, unauthorized data packets, and other network security threats. The logic circuit may include one or more programmable logic devices configured to scan incoming data packets at different layers of a multi-layer protocol, such as the OSI-seven layer model. The network processing unit may work in conjunction with the logic circuit to perform protocol parsing, to form higher layer data units from the data packets, and other network communications-related tasks. The general purpose processor may execute software for performing functions not available from the logic circuit or the network processing unit. For example, the general purpose processor may remove malicious code from infected data or perform malicious code scanning on data when the logic circuit is not configured to do so.

Owner:TREND MICRO INC

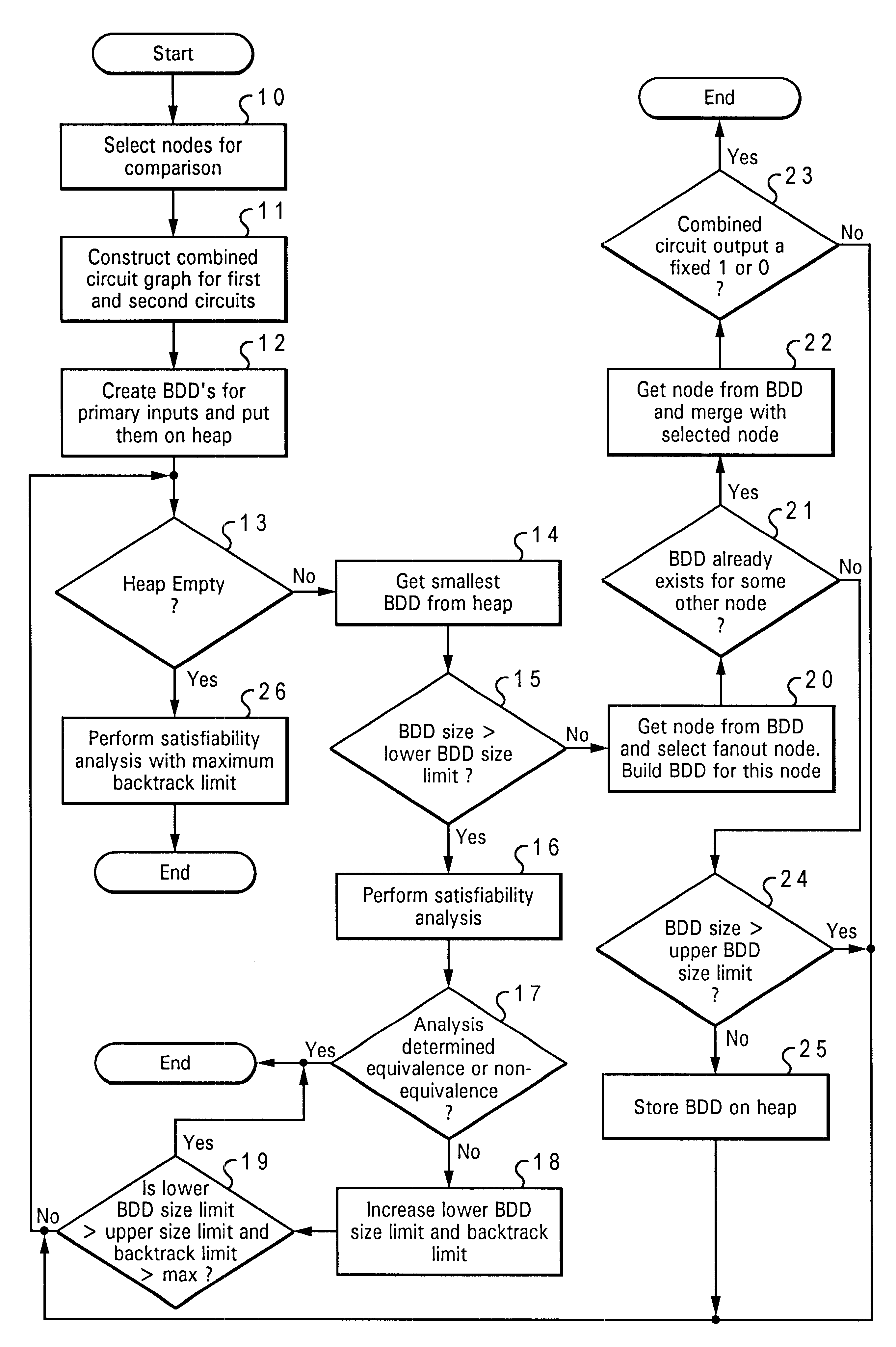

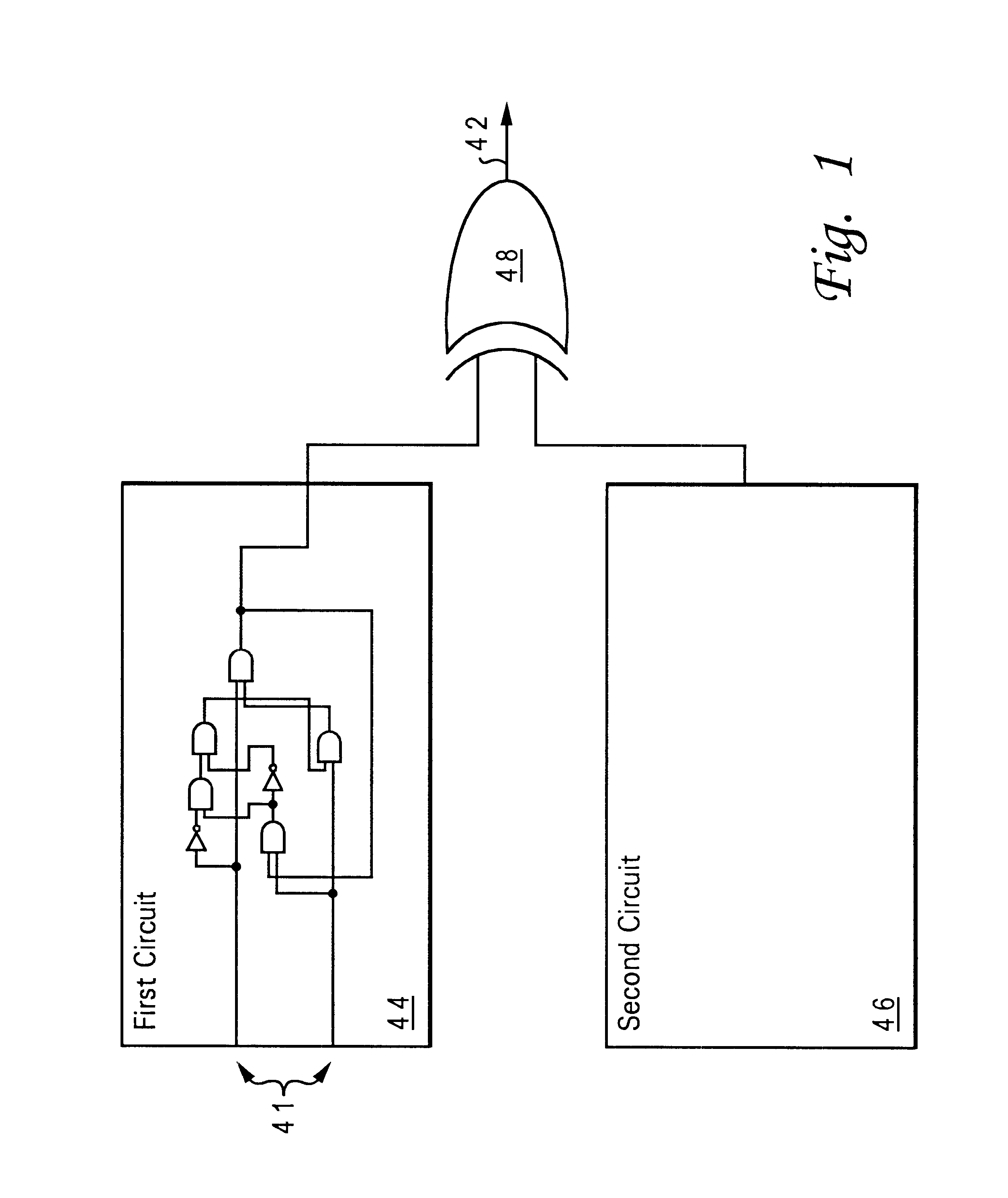

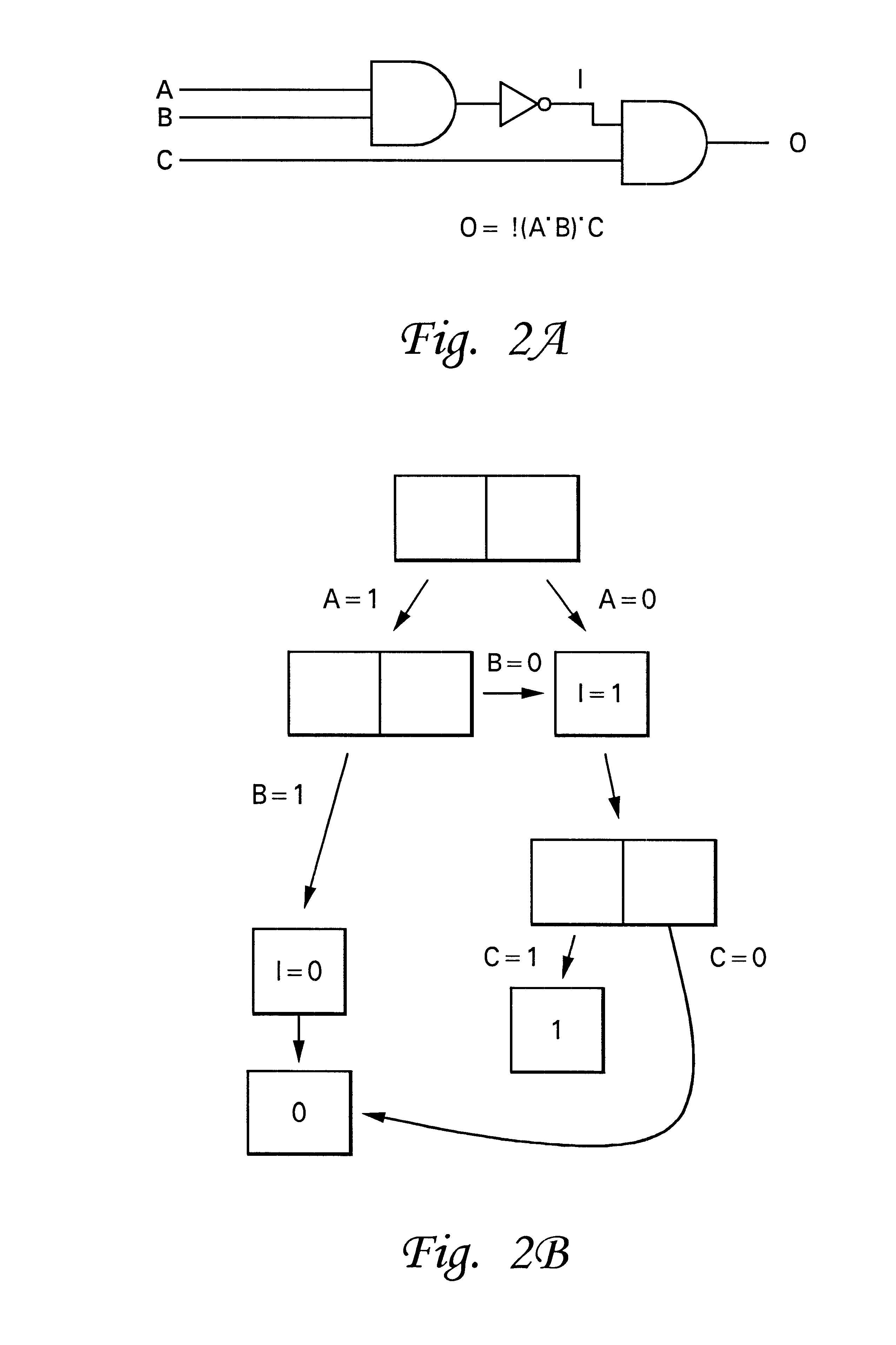

Method and system for equivalence-checking combinatorial circuits using interative binary-decision-diagram sweeping and structural satisfiability analysis

InactiveUS6473884B1Computer aided designSoftware simulation/interpretation/emulationBinary decision diagramLogical network

A method and system for equivalence checking of logical circuits using iterative circuit reduction and satisfiability techniques provide improved performance in computer-based verification and design tools. By intertwining a structural satisfiability solver and binary decision diagram functional circuit reduction method, computer-based tools can make more efficient use of memory and decrease computation time required to equivalence check large logical networks. Using the circuit reduction technique back-to-back with the simulation technique, optimum local and global circuit reduction are simultaneously achieved. By iterating between the structural and functional techniques, and adjusting the size of sub-networks being analyzed within a larger network, sub-networks can be reduced or eliminated, decreasing the amount of memory required to represent the next larger inclusive network.

Owner:IBM CORP

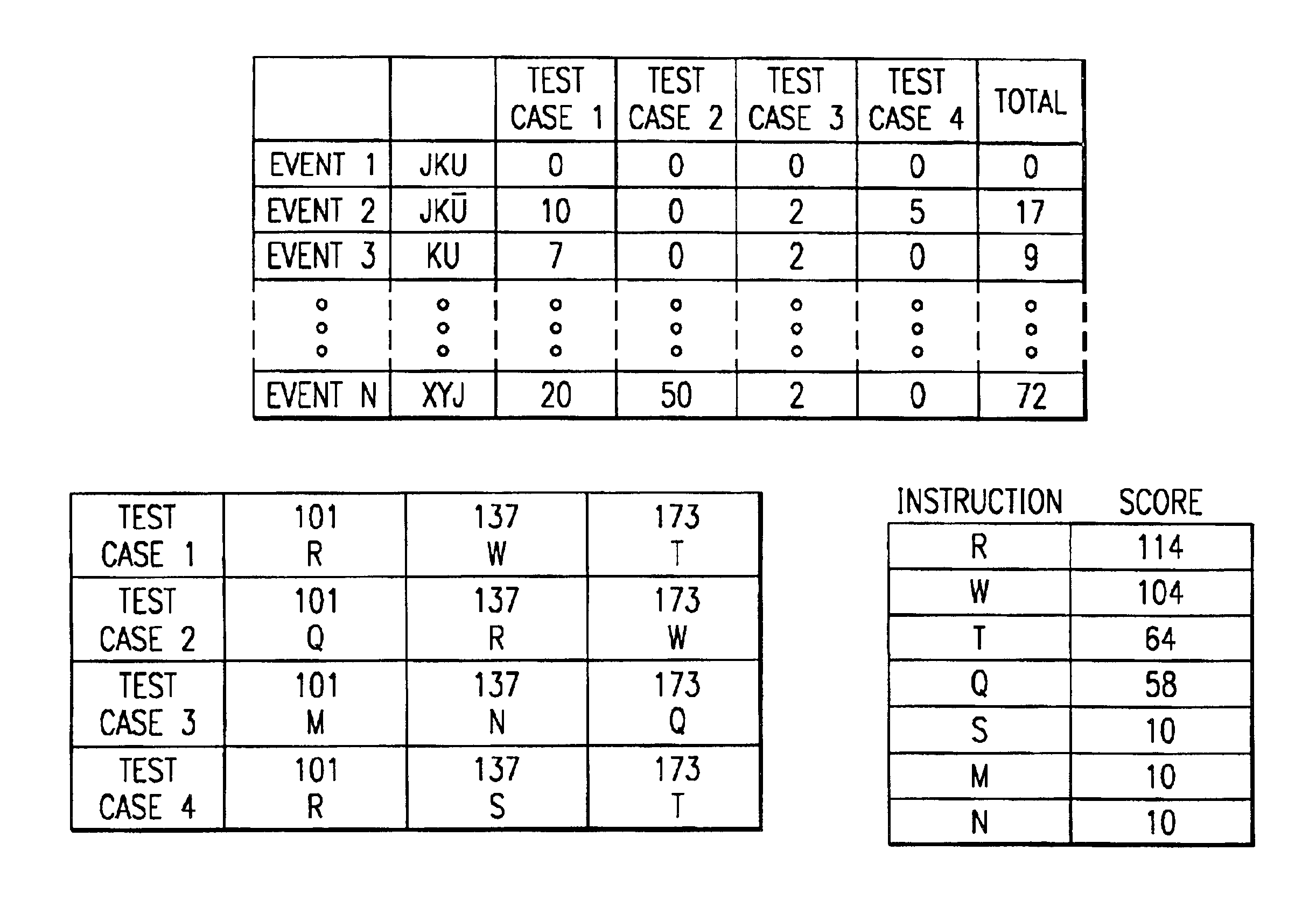

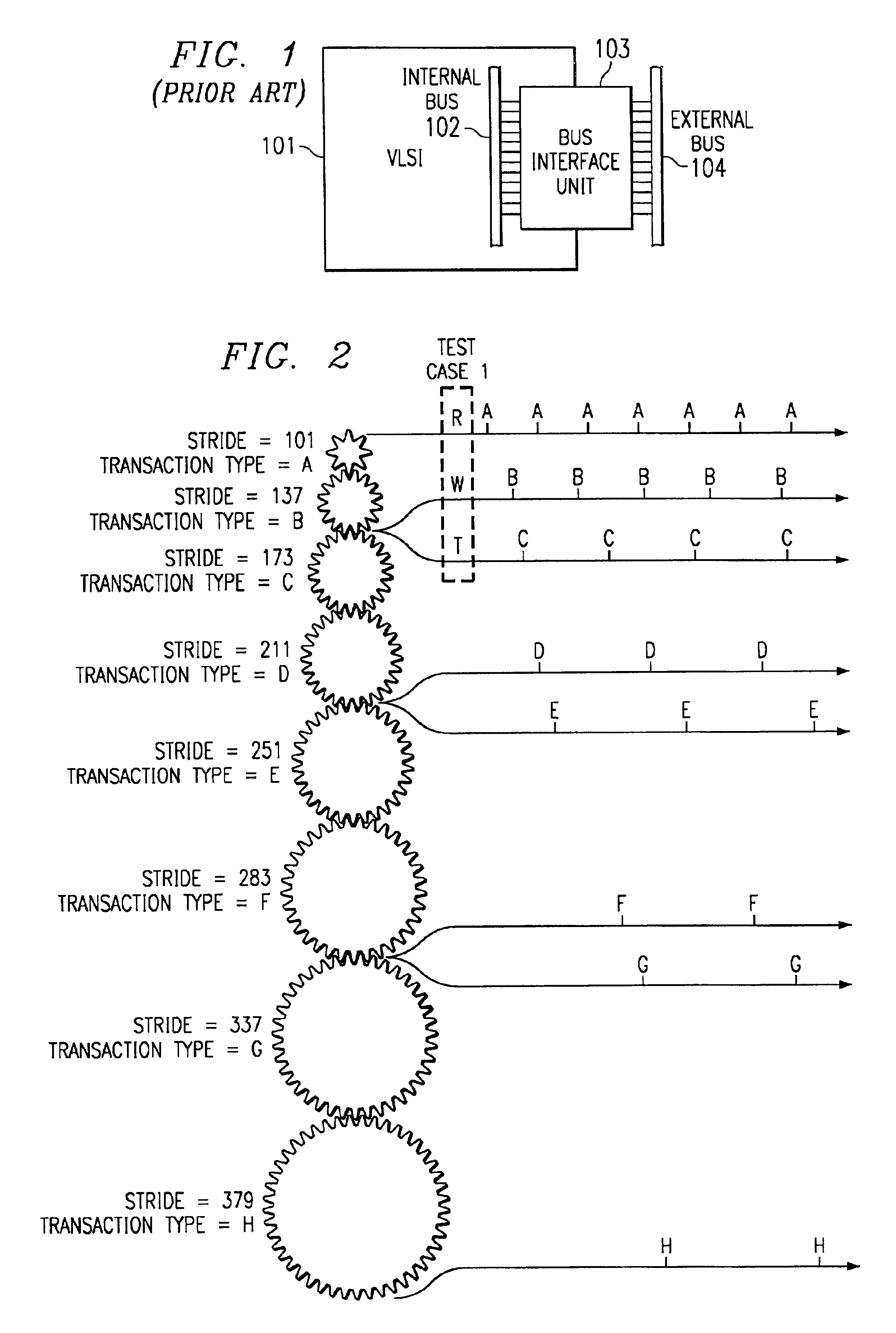

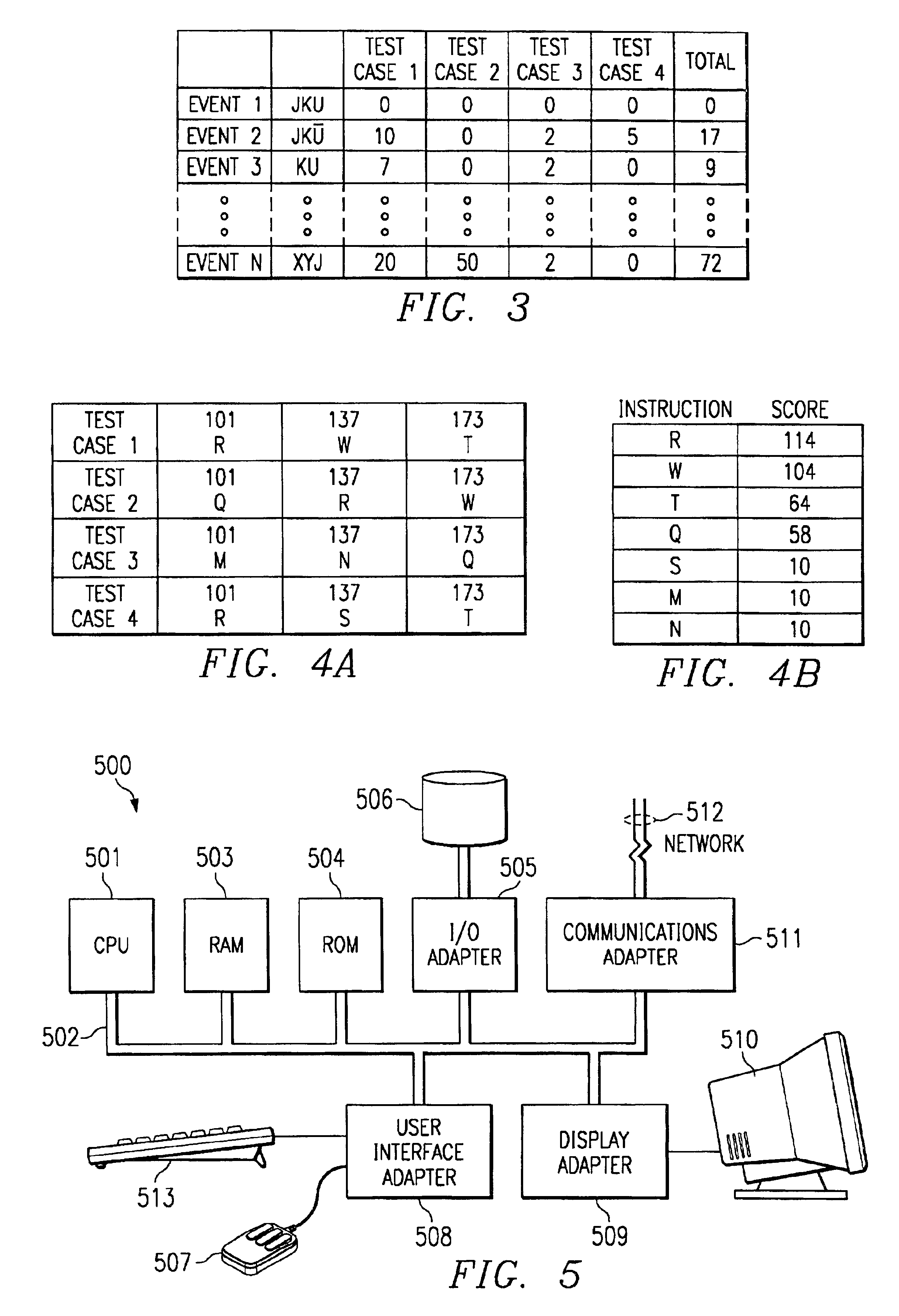

Method and apparatus for generating transaction-based stimulus for simulation of VLSI circuits using event coverage analysis

InactiveUS6859770B2Improve trustElectronic circuit testingAnalogue computers for electric apparatusSpecific testAlgorithm

The present invention applies genetic algorithmic generation of test cases the simulation of VLSI logic circuit blocks. The present invention generates a number of original test cases. This aggregate of solutions is provided to a circuit simulator. The results of the simulator are maintained in a matrix or table. The results detail the number of times that particular logic states or events associated with the VLSI block have been stimulated by particular test cases. The aggregate of solutions and the simulation results are then analyzed by the genetic algorithm. The genetic algorithm preferably identifies states associated with the circuit simulation that have not been produced by the original test cases. The genetic algorithm then combines characteristics of various test cases to generate new test cases. The new test cases are provided to the circuit simulator thereby providing a higher degree of confidence that the entire VLSI chip design has been simulated.

Owner:SAMSUNG ELECTRONICS CO LTD

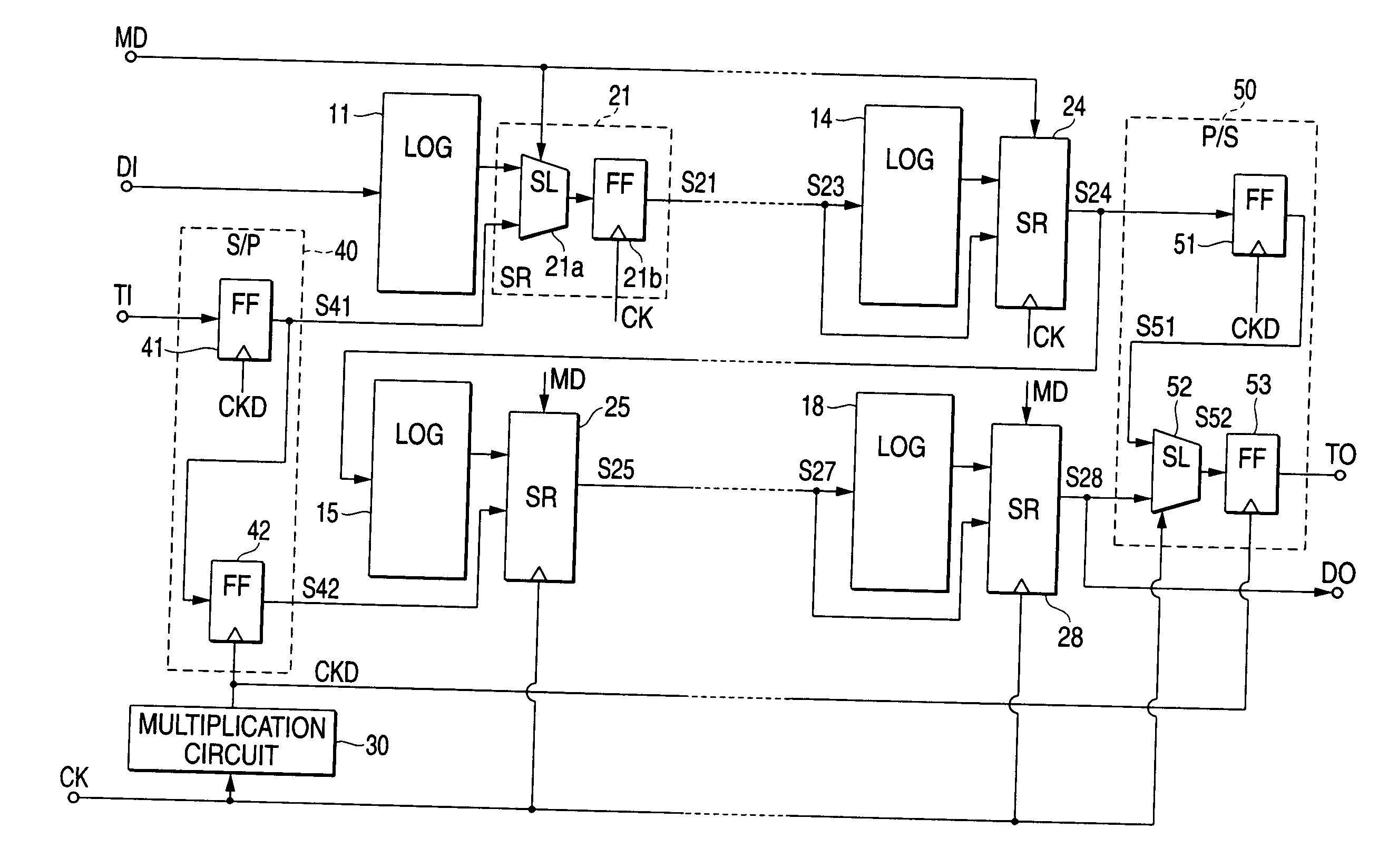

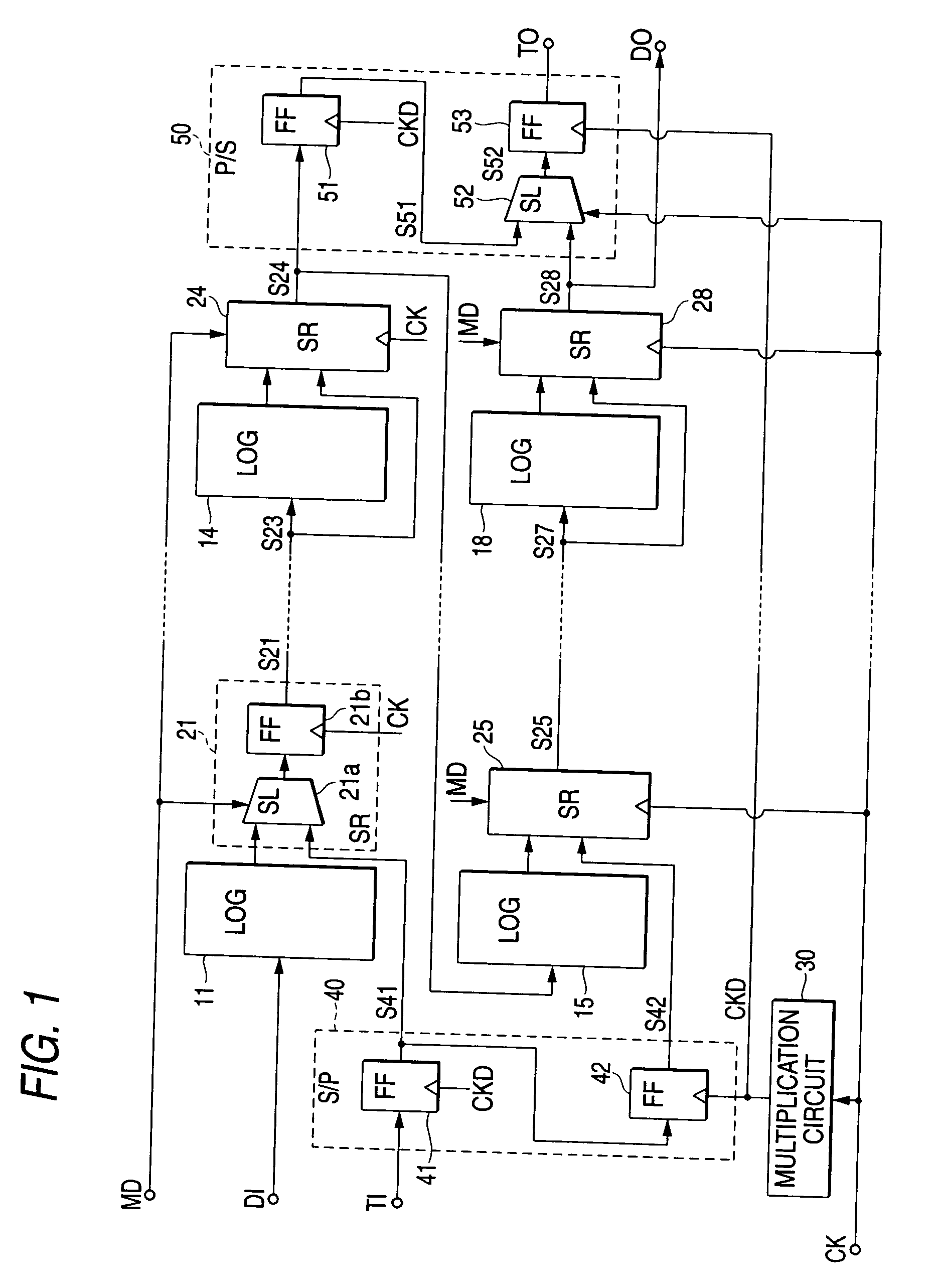

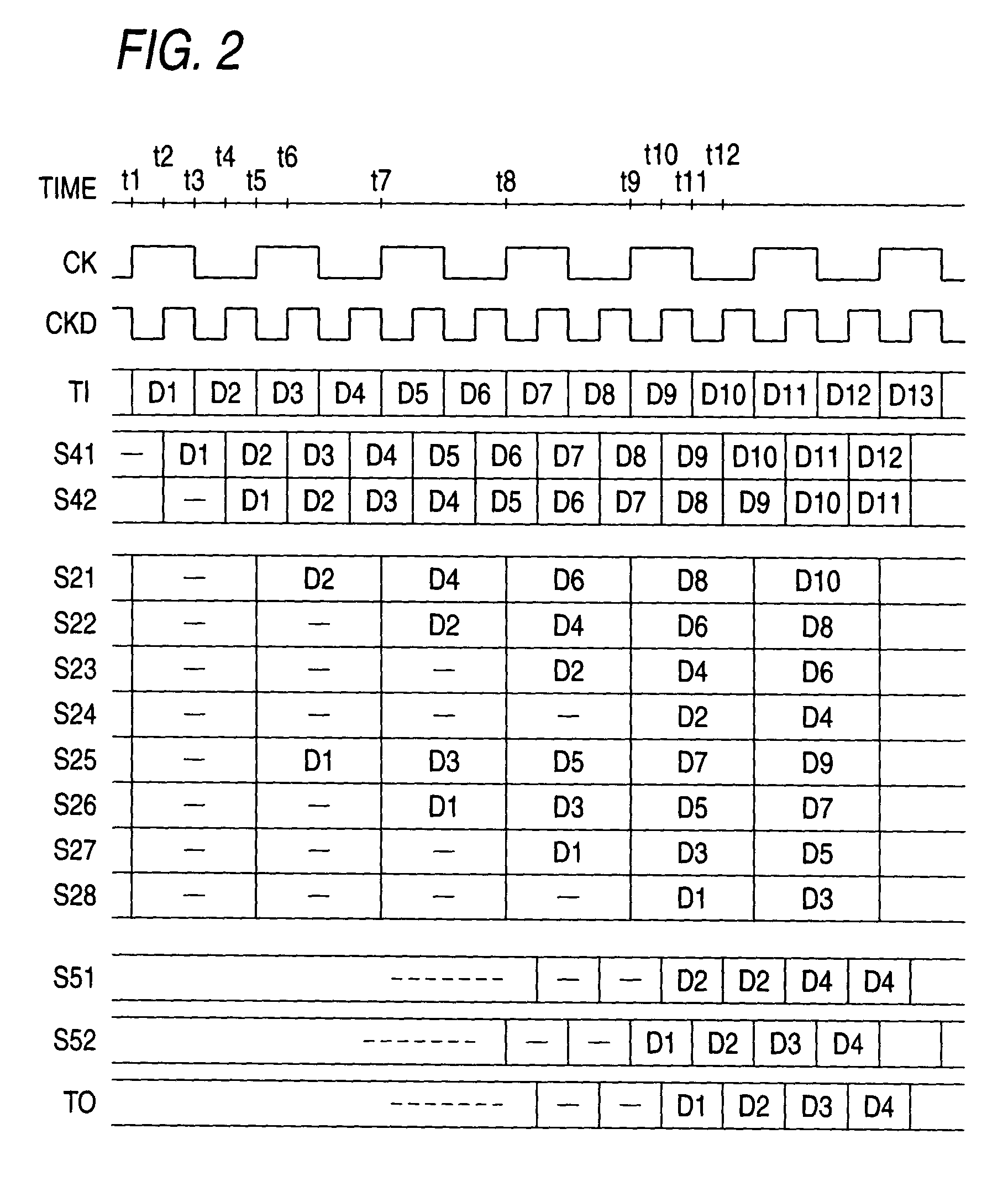

Semiconductor integrated circuit with a test circuit

A shift scan chain includes logic circuit blocks 11-18 and scan registers 21-28 connected at stages succeeding them. The shift chain is divided into divisional chains including the scan registers 21-24 and the scan registers 25-28. In the test operation mode of a semiconductor integrated circuit, test input data TI are supplied in synchronism with a multiplied clock signal CKD at a frequency twice of that of a clock signal CK. The test input data TI are converted by a serial / parallel conversion circuit 40 into parallel data S41 and S42, which are respectively supplied to the head scan registers 21 and 25 of the corresponding divisional chains. The length of each divisional chains becomes ½, and a test time period can be shortened.

Owner:LAPIS SEMICON CO LTD

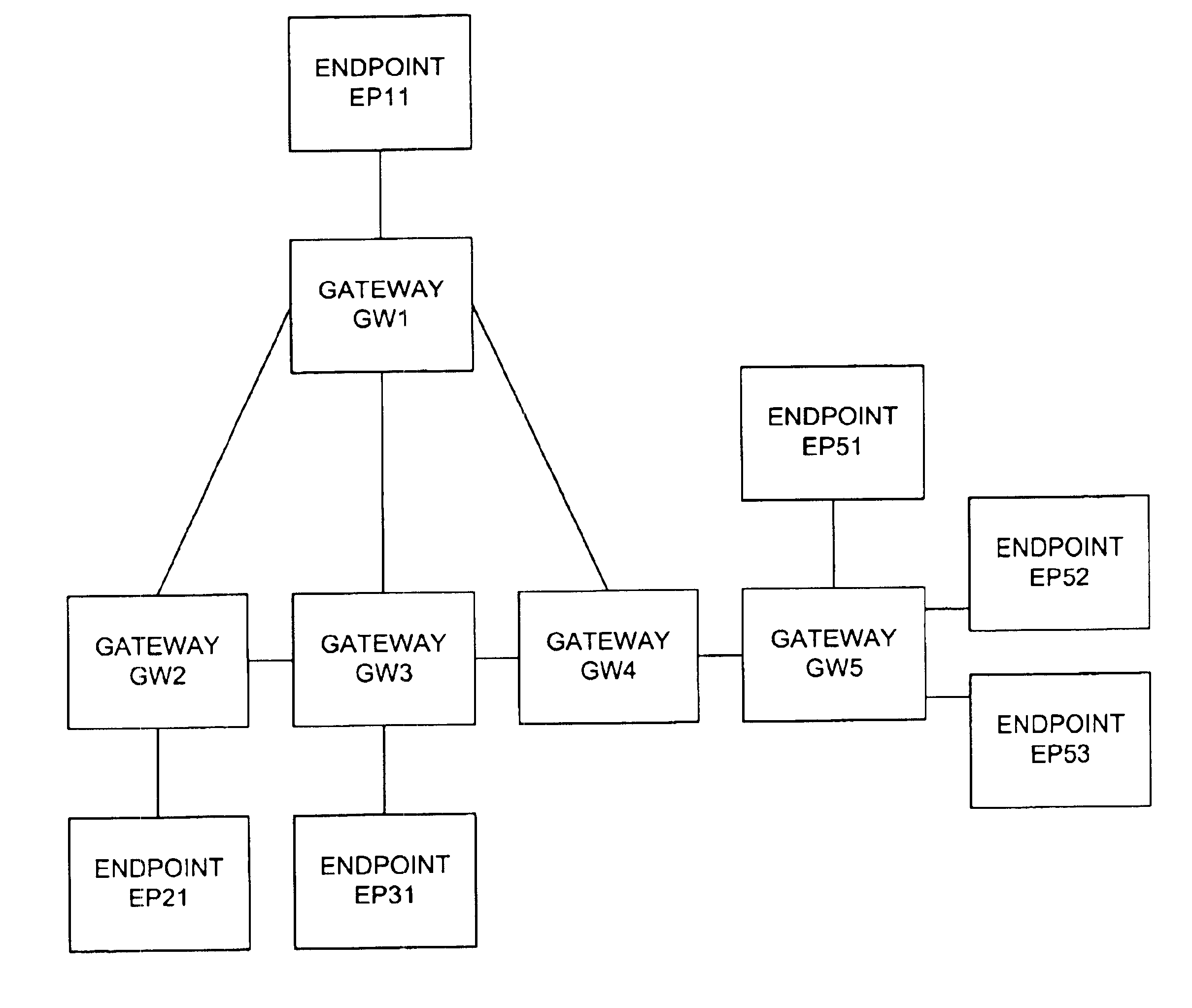

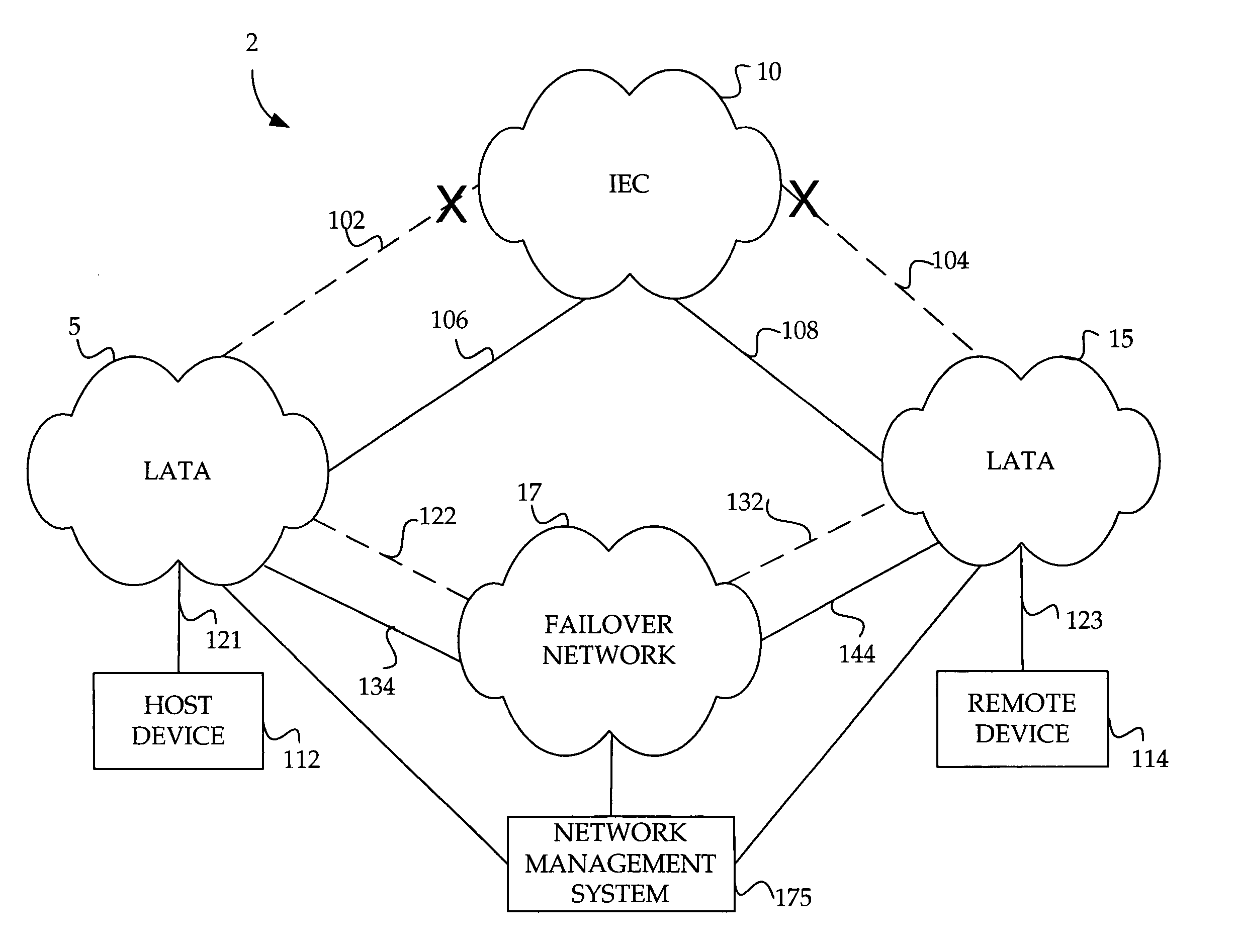

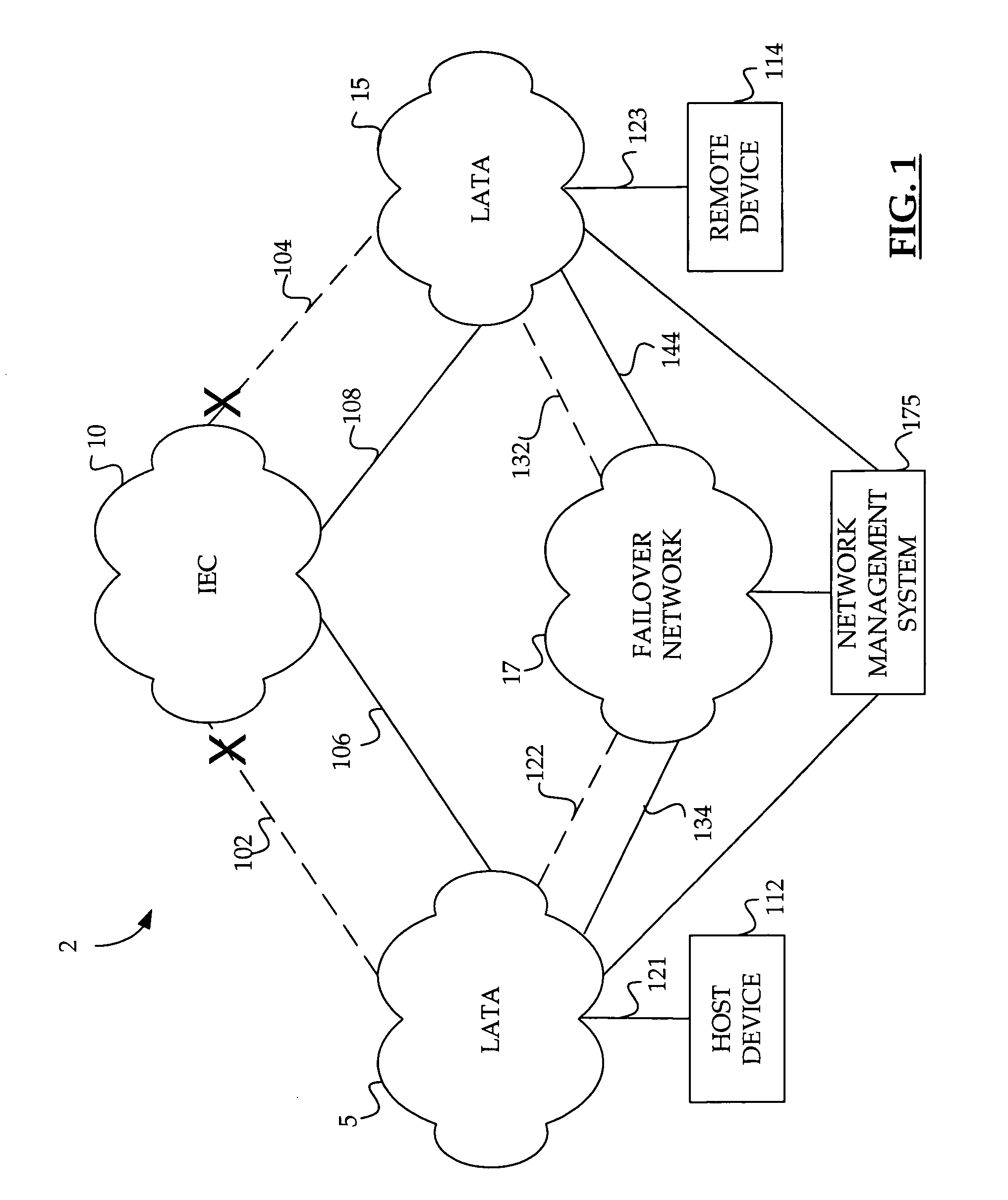

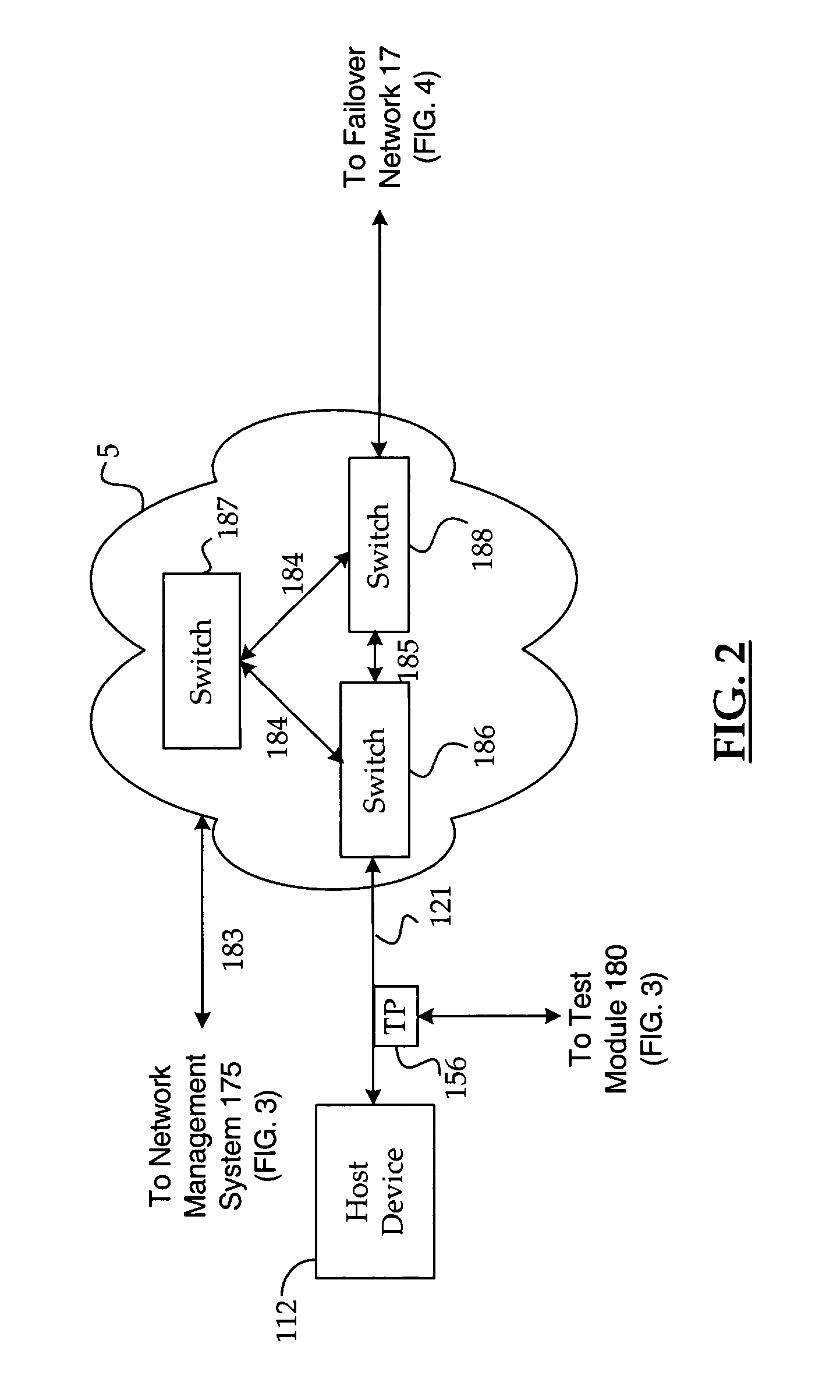

Method and system for prioritized rerouting of logical circuit data in a data network

A method and system are provided for prioritized rerouting of logical circuit data in a data network. A logical circuit failure is identified in the data network. Following the identification of the logical circuit failure, a quality of service parameter for the communication of data in the failed logical circuit is determined. The quality of service parameter may include a traffic descriptor indicating the quality of the data communicated in the logical circuit. Then, a logical failover circuit comprising an alternate communication path for communicating the data in the failed logical circuit is identified. Next, a quality of service parameter for the communication of data in the logical failover circuit is determined. If the quality of service parameter for the failed logical circuit is equal to the quality of service parameter for the logical failover circuit, then the data from the failed logical circuit is rerouted to the logical failover circuit. In this manner, the quality of the data in the logical failover circuit is communicated at the same level of service provisioned for the failed logical circuit.

Owner:RAKUTEN GRP INC

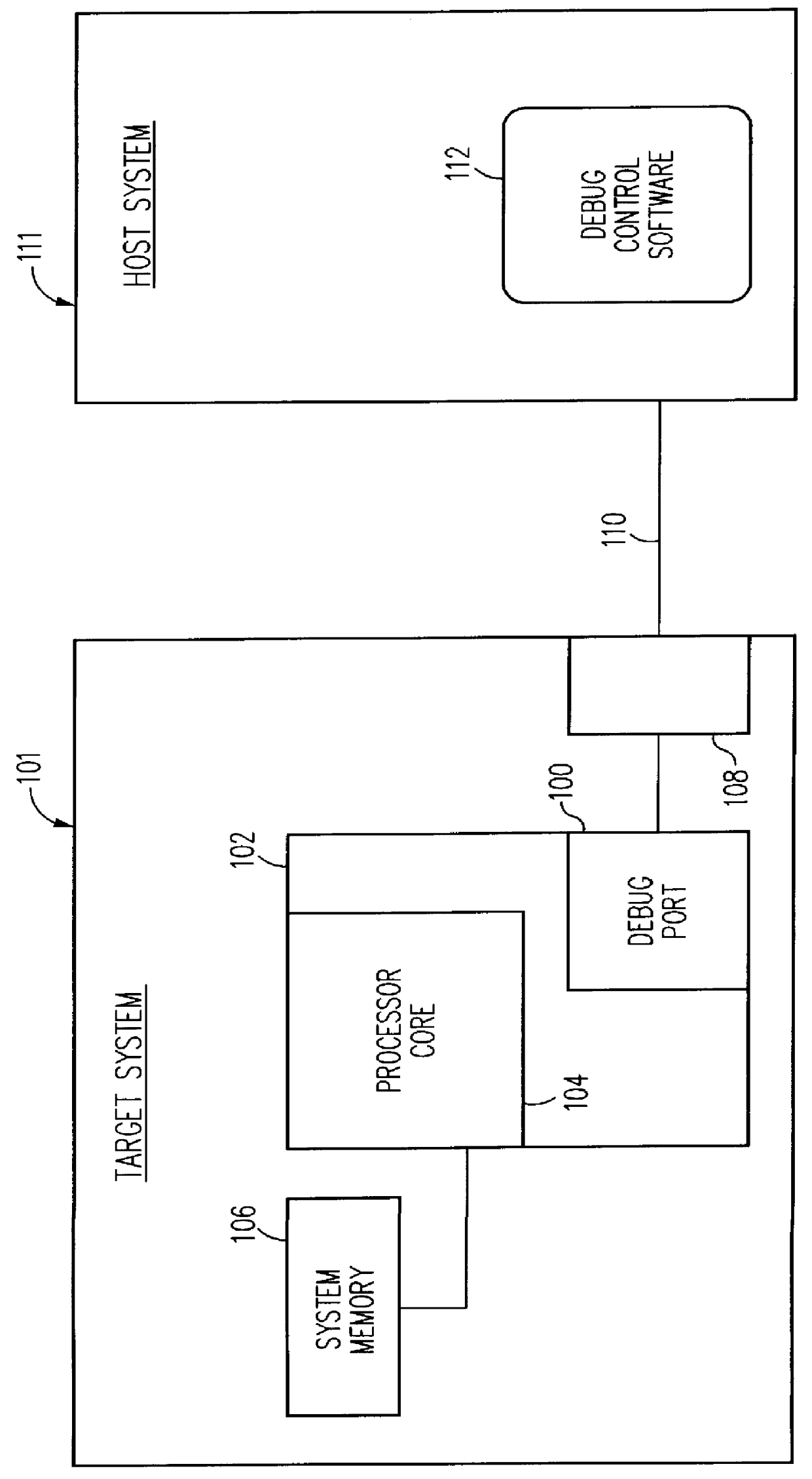

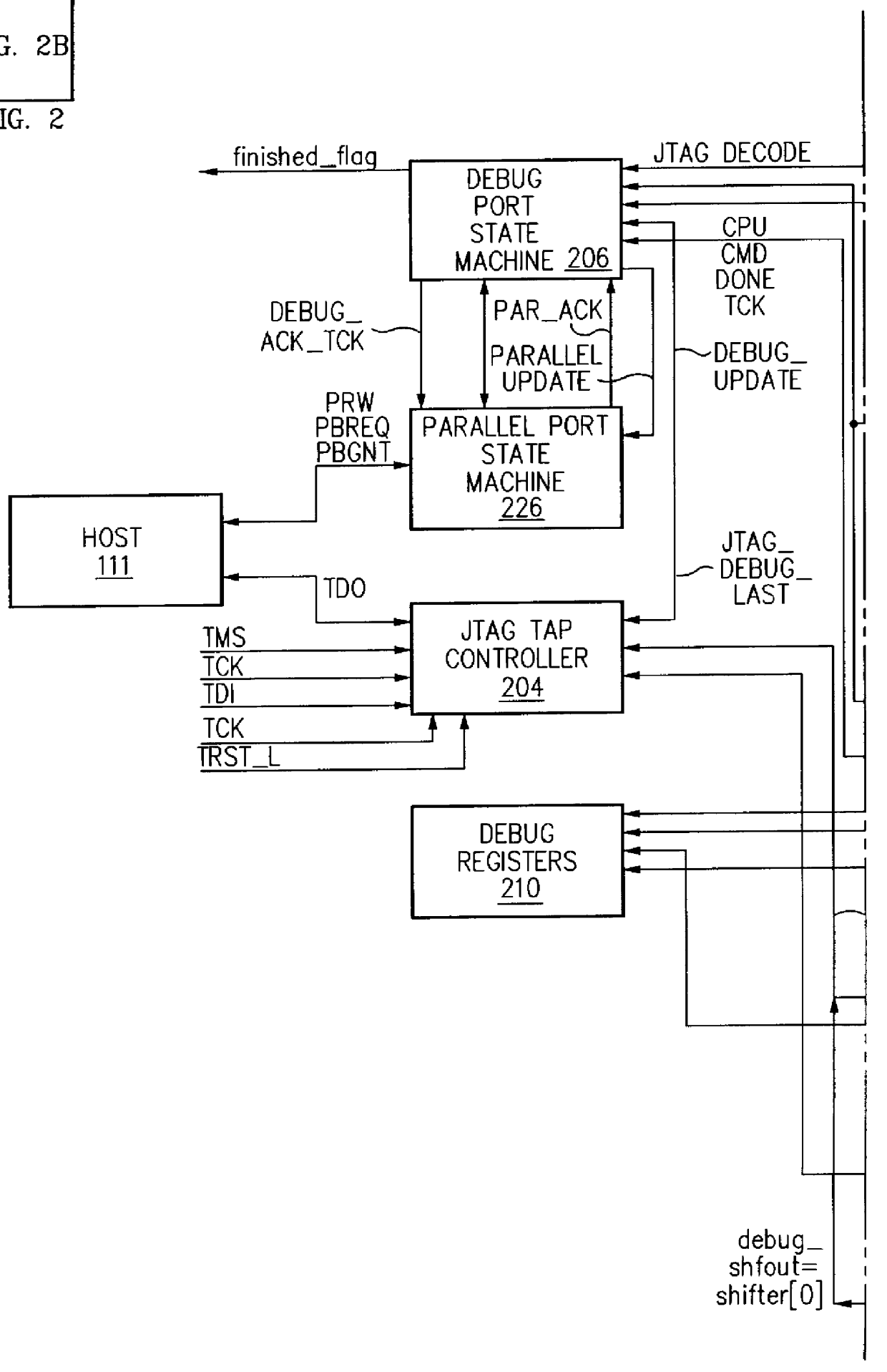

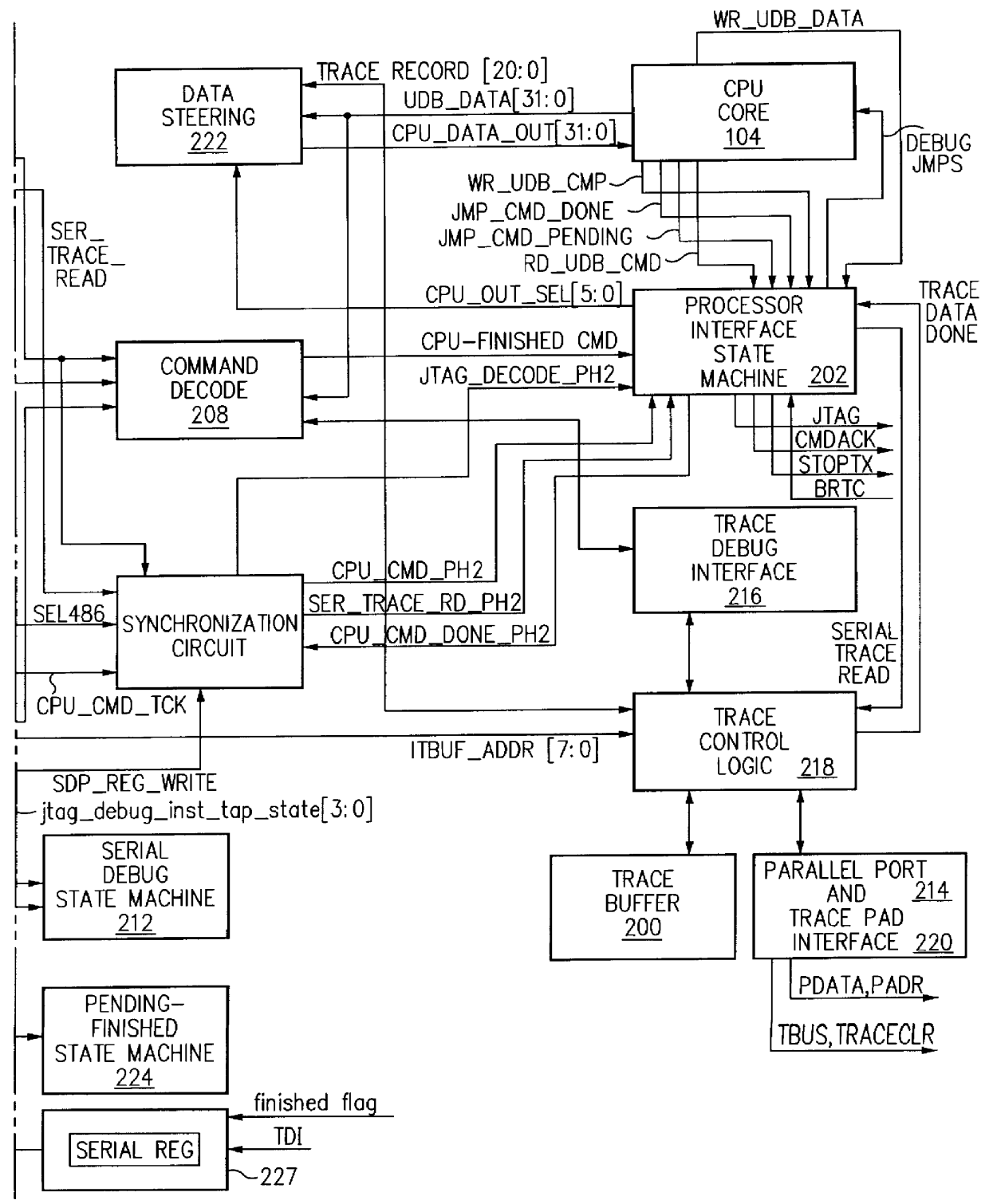

Debug interface including state machines for timing synchronization and communication

A system for debugging a processor includes logic circuits for communicating commands and data between a serial input / output port, a trace logic, and the processor. Some embodiments of the debugging system also include a parallel input / output port so that the logic circuits also communicate commands and data between the parallel input / output port, the trace logic, and the processor. The debug system includes a plurality of state machines that read the commands and data from the serial input / output ports. The commands are decoded by a decode logic. Some of the commands, such as commands for reading data from memory, utilize processor intervention and are transferred to the processor for execution. The state machines operate only on a single command at one time so that an active state machine does not accept additional commands until completion of the command that is currently executed. Once execution of the command is complete, the state machines generate an indication of the completion event or condition, typically by setting a flag in a debug register or by asserting a readable output pin. The completion event or condition is accessed by a debug tool such as a host processor, a monitoring tool, or the like.

Owner:ADVANCED MICRO DEVICES INC

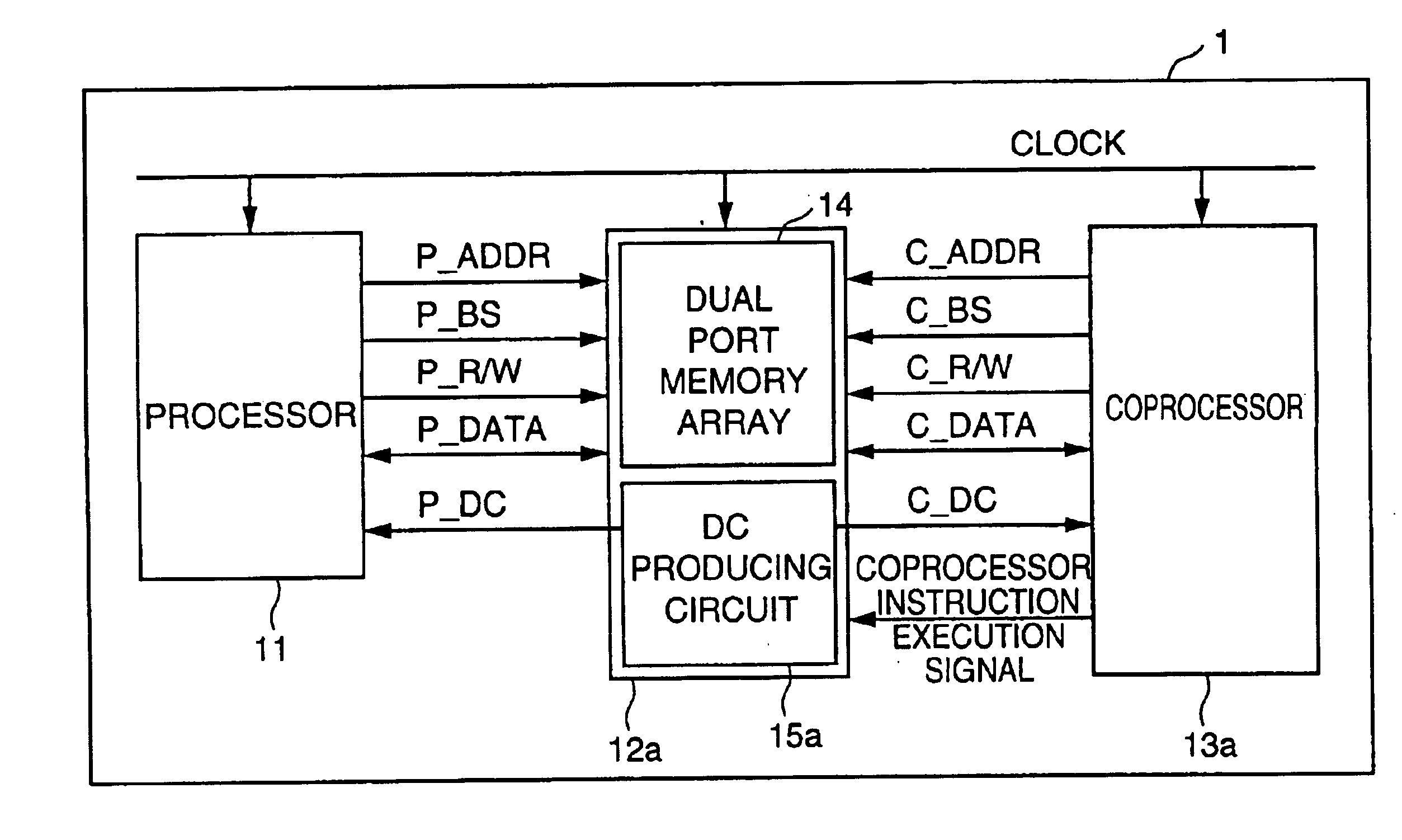

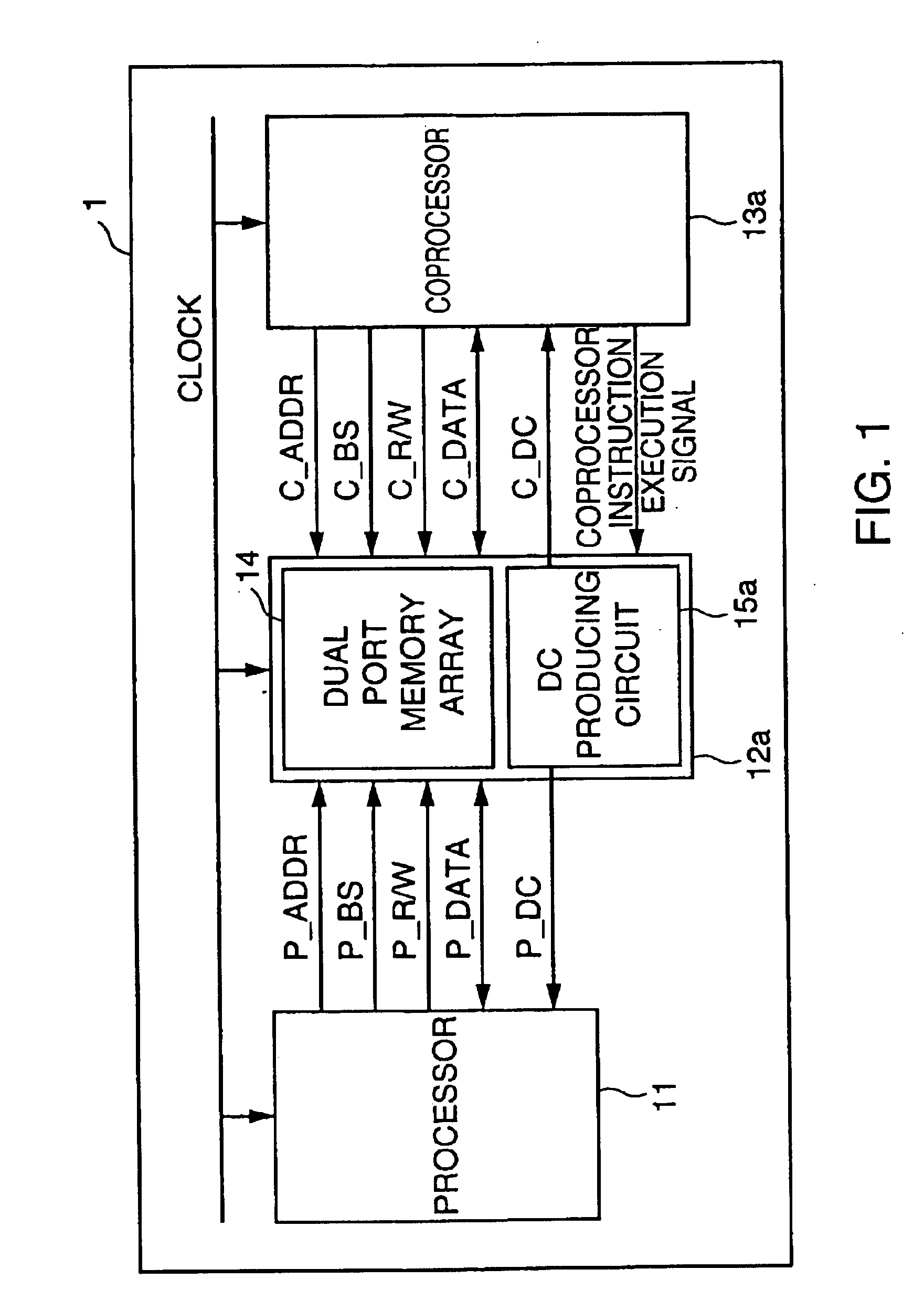

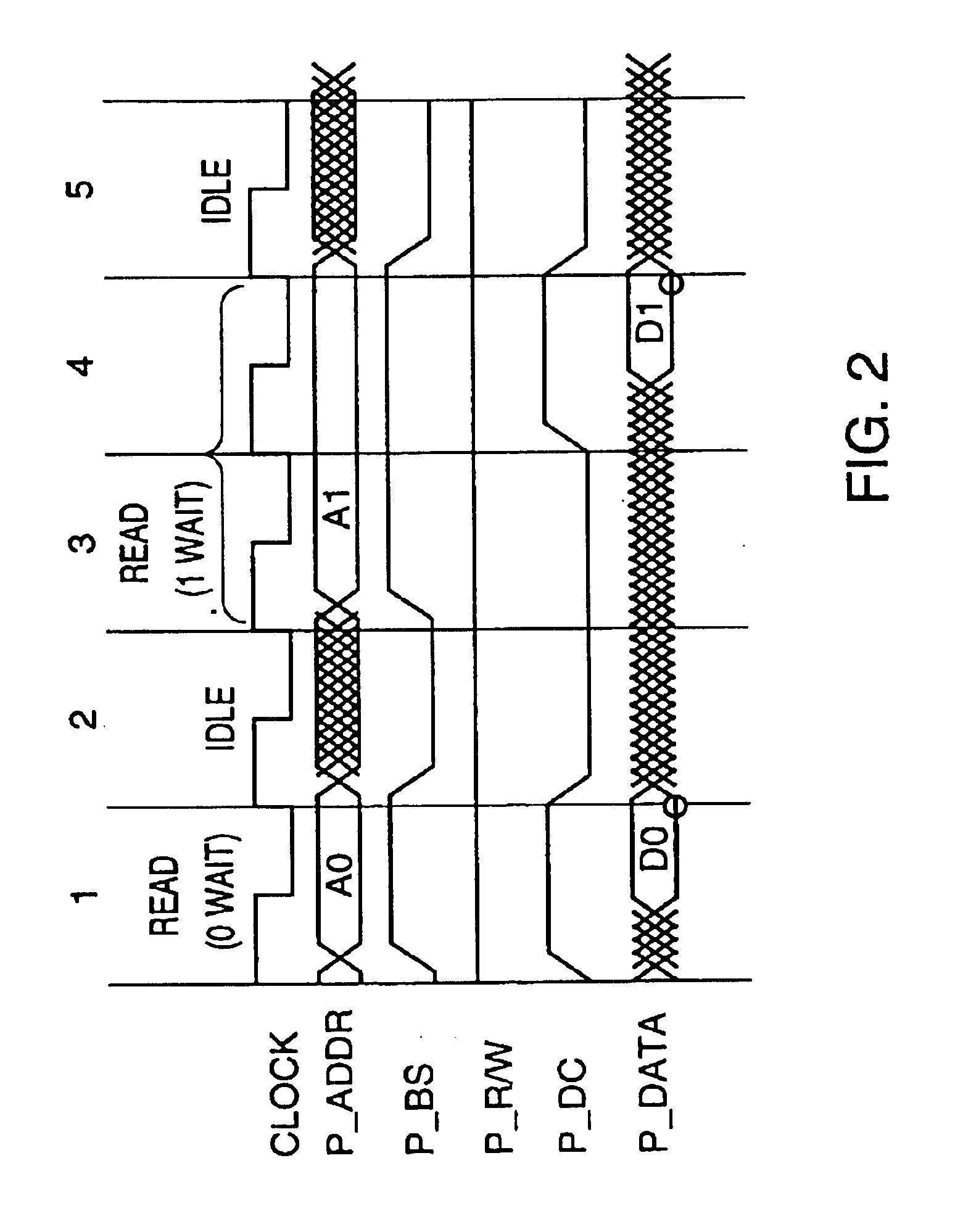

Synchronous signal producing circuit for controlling a data ready signal indicative of end of access to a shared memory and thereby controlling synchronization between processor and coprocessor

InactiveUS6928523B2Reduce overheadReduce power consumptionProgram synchronisationGeneral purpose stored program computerCoprocessorProcessor register

A synchronous signal producing circuit includes an access inhibit region register for designating an access inhibit region for a processor in a shared memory, a comparing circuit for detecting the access by the processor to the access inhibit region designated in the access inhibit region register, and a logic circuit for issuing a P_DC signal setting the processor to a wait state based on a coprocessor instruction execution signal and a result of the comparison by the comparing circuit.

Owner:RENESAS TECH CORP