Patents

Literature

372 results about "Digital integrated circuits" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

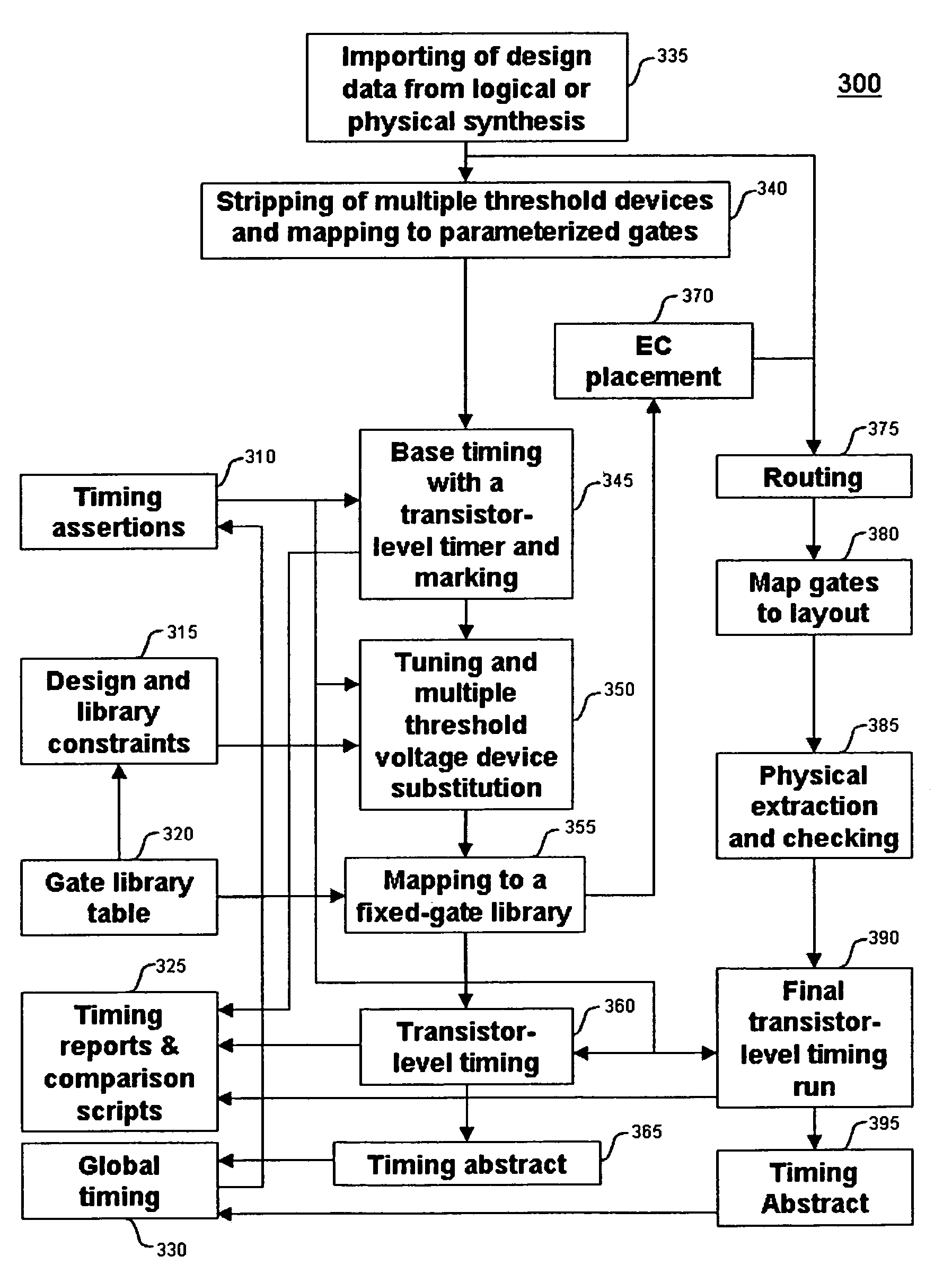

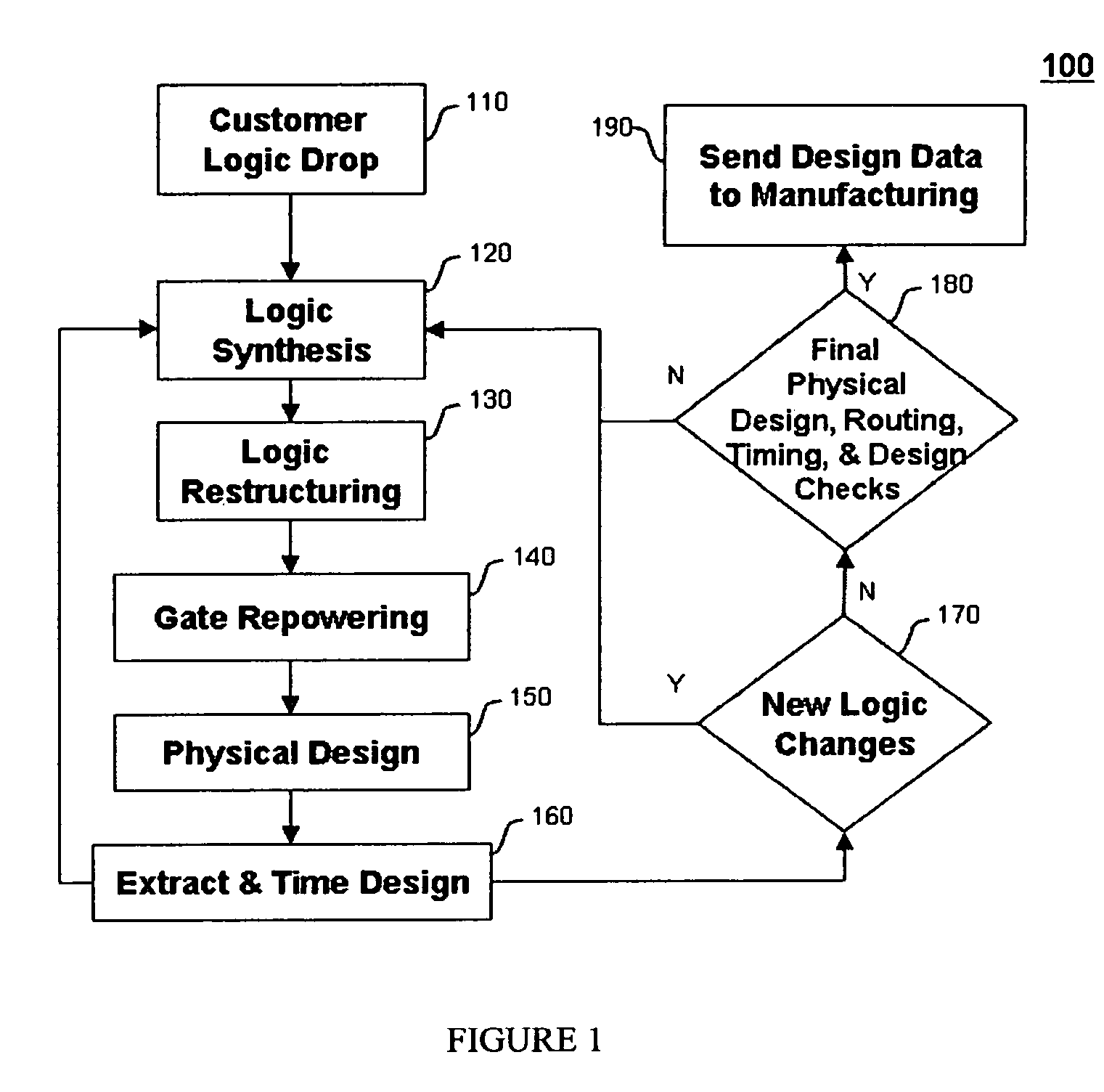

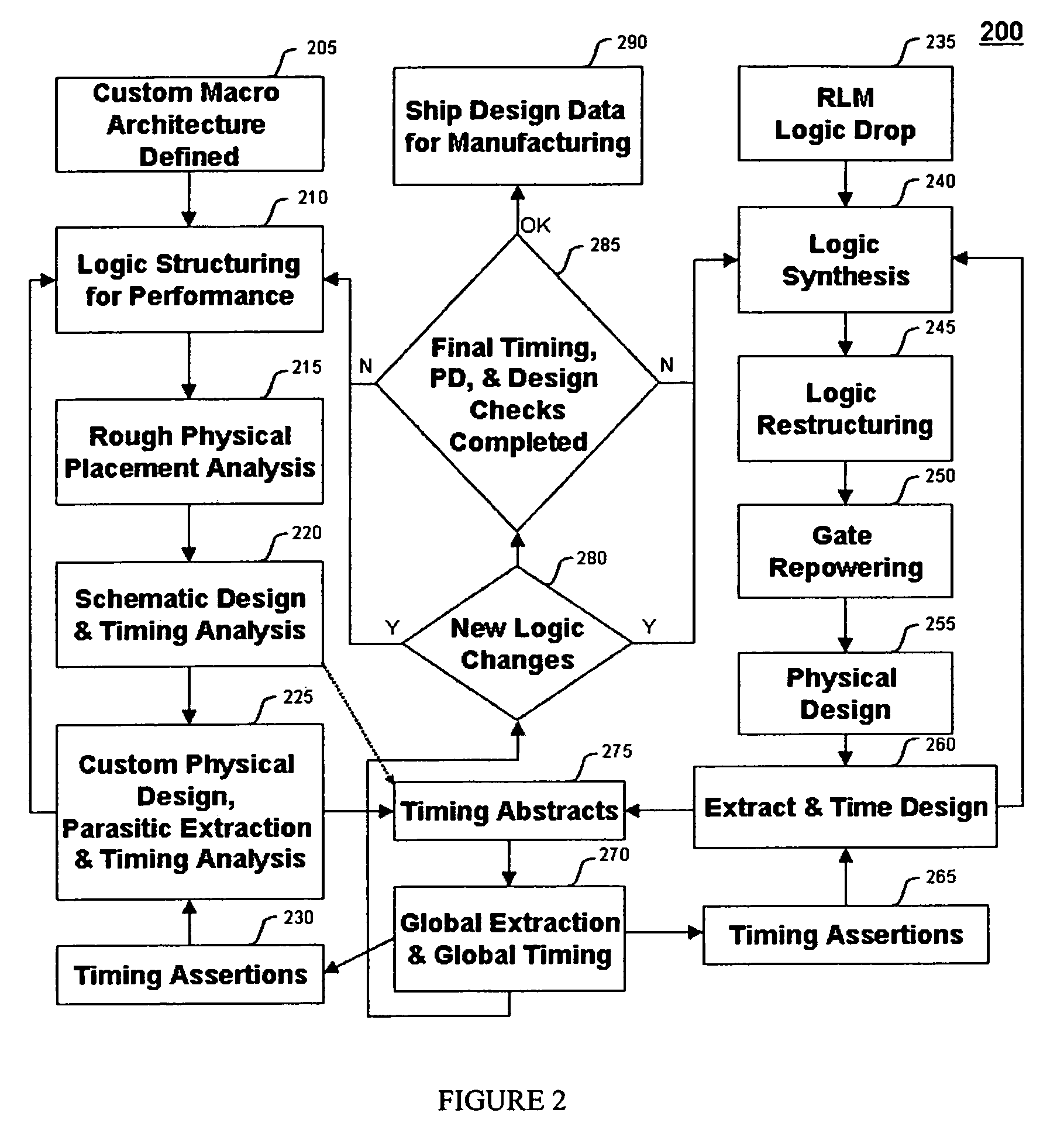

Method for tuning a digital design for synthesized random logic circuit macros in a continuous design space with optional insertion of multiple threshold voltage devices

InactiveUS7093208B2Efficient and effective methodologyError minimizationDigital storageComputer aided designContinuous designCritical section

A Digital Design Method which may be automated is for obtaining timing closure in the design of large, complex, high-performance digital integrated circuits. The methodincludes the use of a tuner on random logic macros that adjusts transistor sizes in a continuous domain. To accommodate this tuning, logic gates are mapped to parameterized cells for the tuning and then back to fixed gates after the tuning. Tuning is constrained in such a way as to minimize “binning errors” when the design is mapped back to fixed cells. Further, the critical sections of the circuit are marked in order to make the optimization more effective and to fit within the problem-size constraints of the tuner. A specially formulated objective function is employed during the tuning to promote faster global timing convergence, despite possibly incorrect initial timing budgets. The specially formulated objective function targets all paths that are failing timing, with appropriate weighting, rather than just targeting the most critical path. Finally, the addition of multiple threshold voltage gates allows for increased performance while limiting leakage power.

Owner:GLOBALFOUNDRIES INC

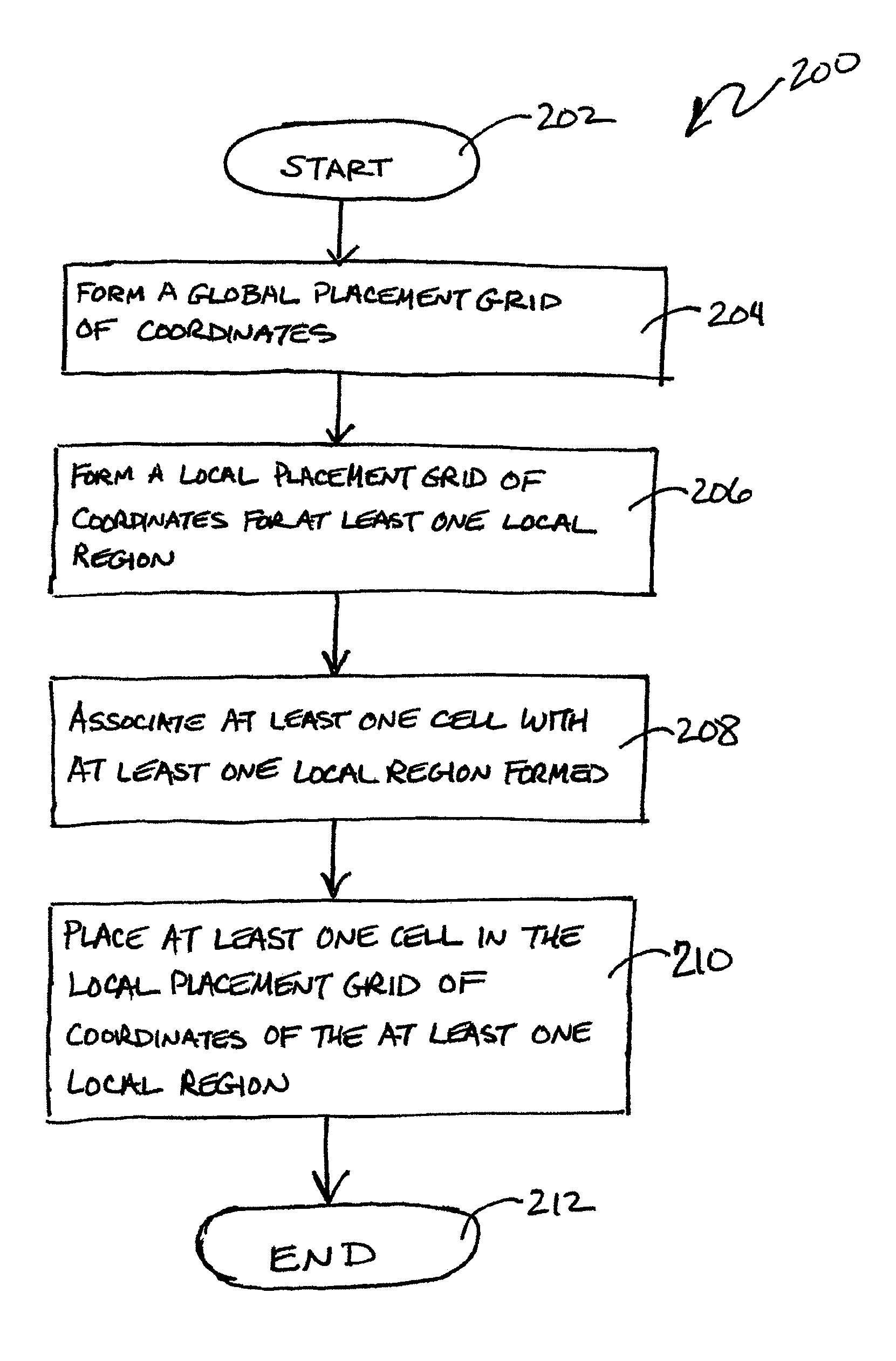

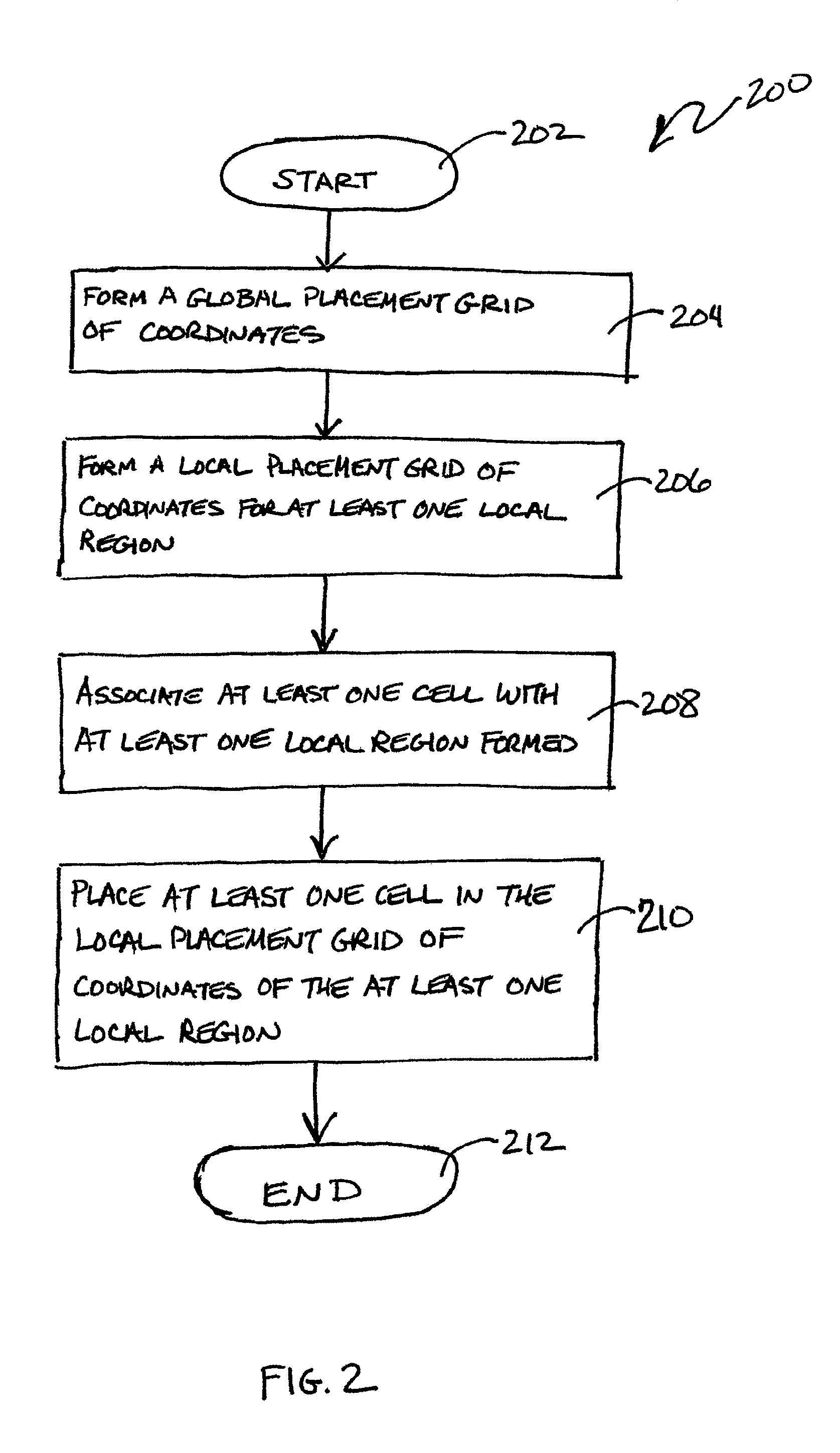

Flat placement of cells on non-integer multiple height rows in a digital integrated circuit layout

ActiveUS7802219B2Reduce the amount requiredExtension of timeComputer programmed simultaneously with data introductionComputer aided designIntegrated circuit layoutHorizontal and vertical

The various embodiments of the present invention generally relate to systems, methods, and computer program products for placement of at least one cell in a digital integrated circuit layout. A global placement grid of coordinates is formed, where the coordinates represent horizontal and vertical directions. A local placement grid of coordinates is also formed for at least one local region, where the local placement grid of coordinates represent horizontal and vertical directions, and where the at least one local region is adapted to support non-integer multiple height rows. At least one cell is associated with the at least one local region formed, and the cell can be placed in the local placement grid of the local region.

Owner:CADENCE DESIGN SYST INC

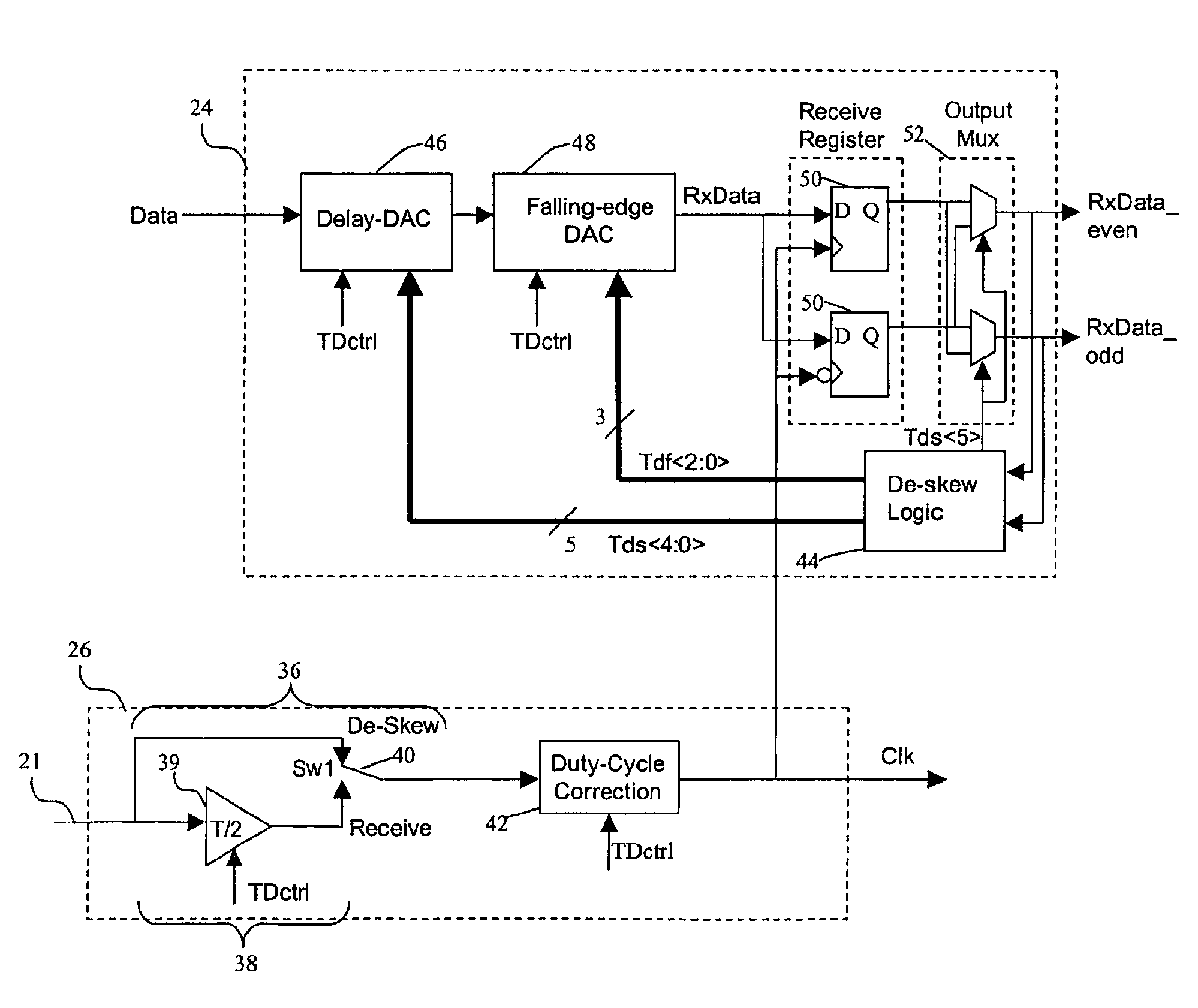

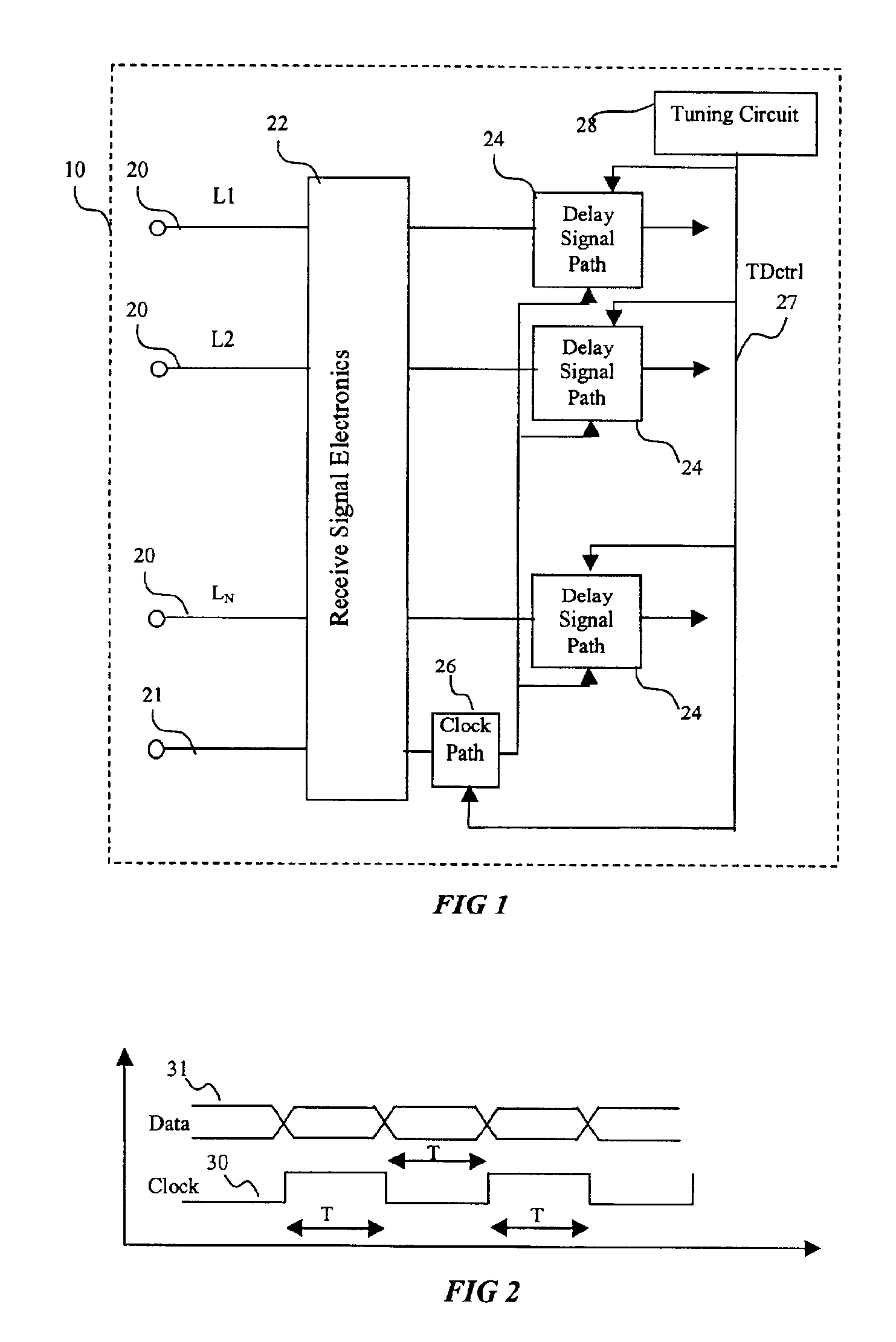

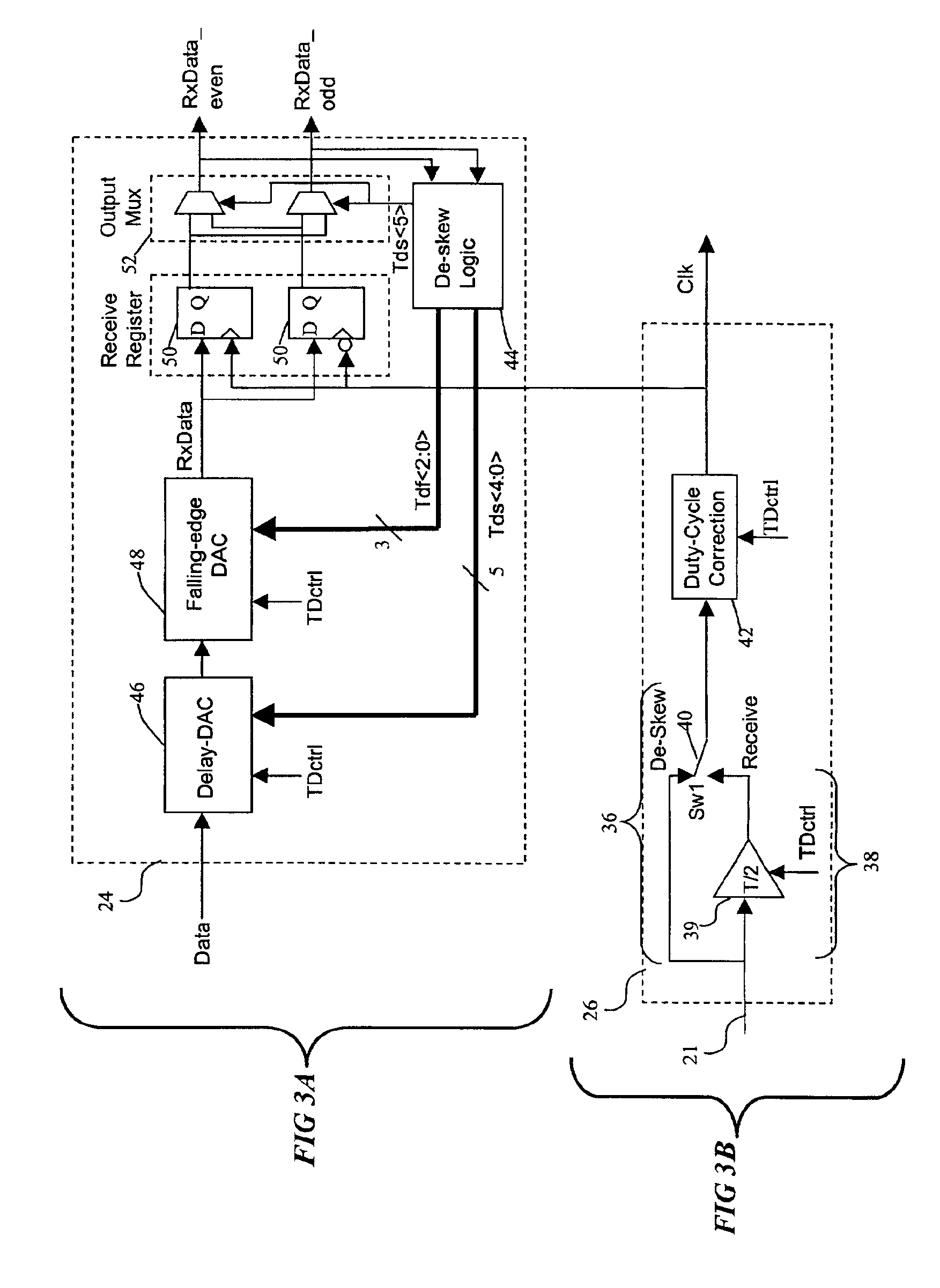

Timing skew compensation technique for parallel data channels

InactiveUS6874097B1OperateGenerating/distributing signalsTransmission path multiple useTransport systemSCSI

A method and apparatus for correcting the timing skew of data signals in a parallel data transmission system, such as Small Computer System Interface (SCSI) data bus, relative to a receive clock in the data bus. The system separately corrects the receive clock duty cycle, and also features independent de-skewing of the rising and falling edges of a data waveform to improve timing accuracy of transmitted signals. The method and apparatus can be used without substantial changes to existing transmission system protocols, and can be implemented on an all-digital integrated circuit.

Owner:MAXTOR

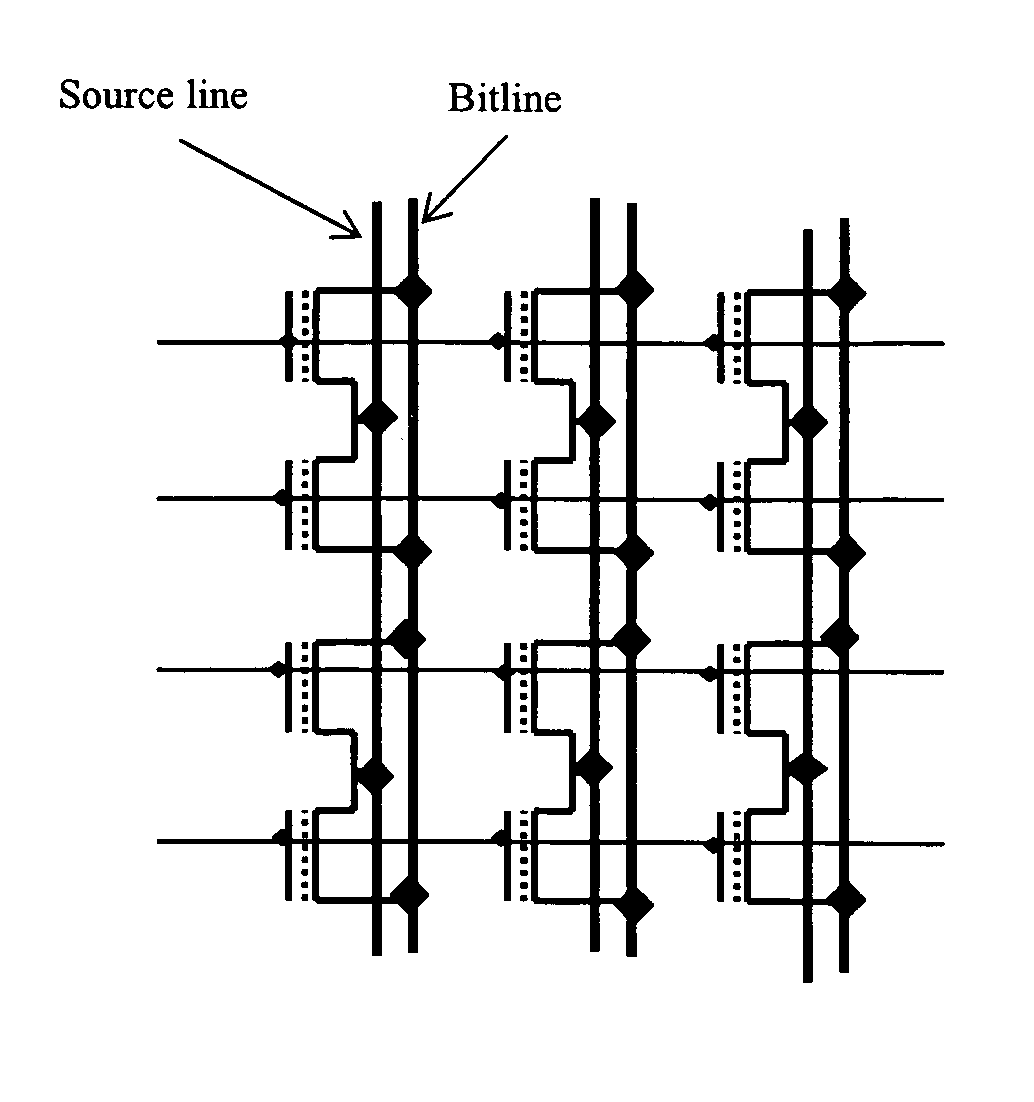

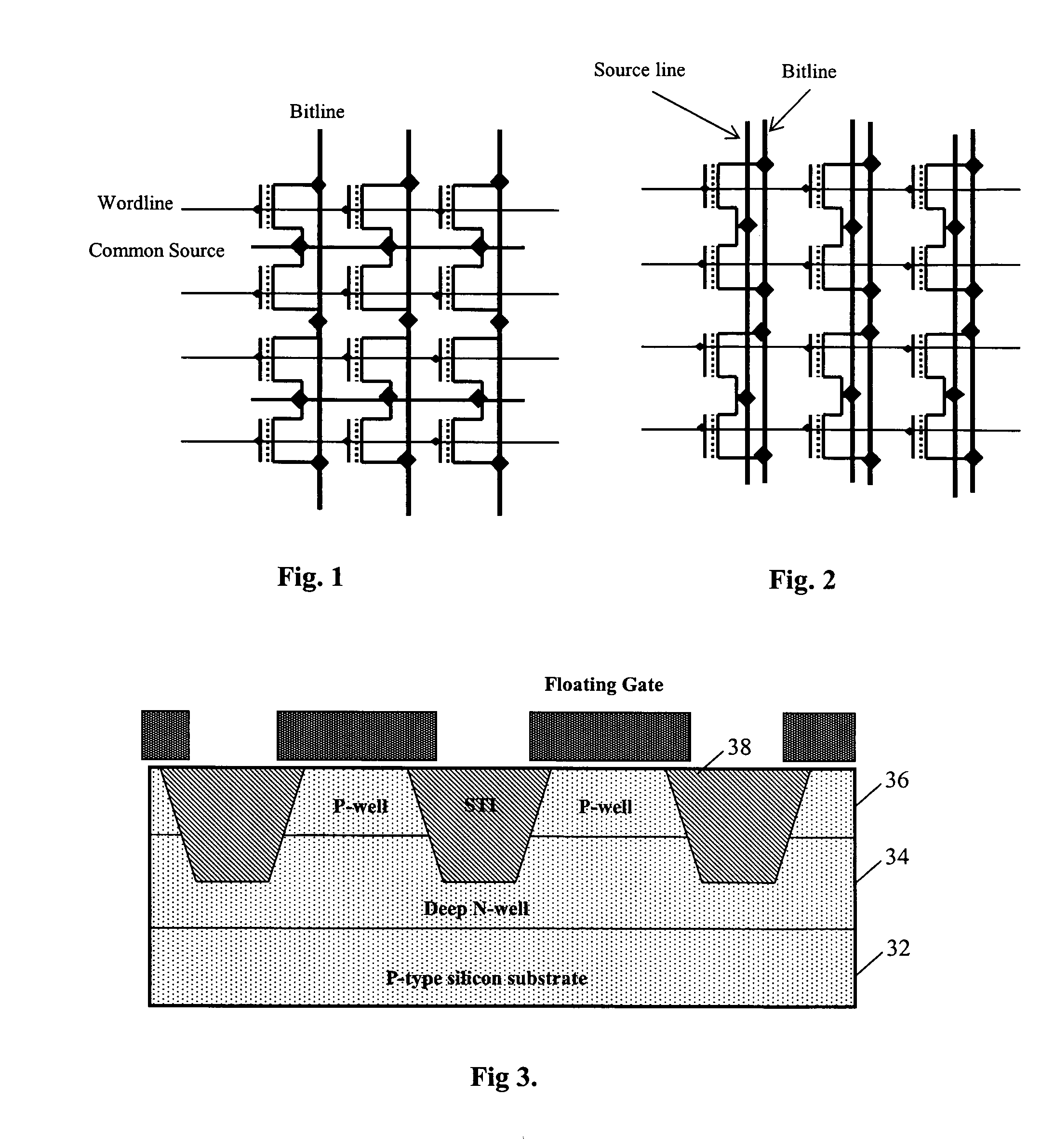

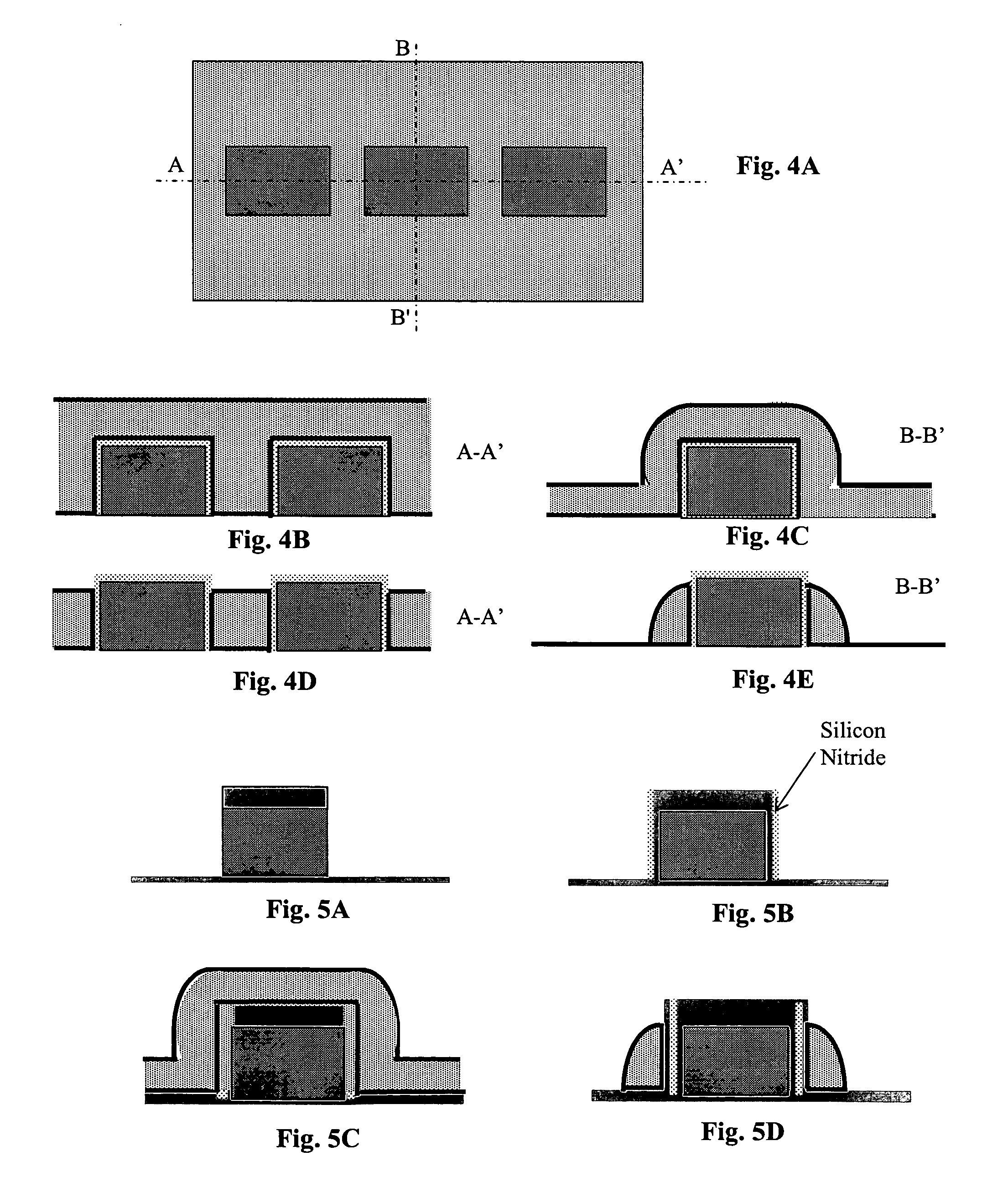

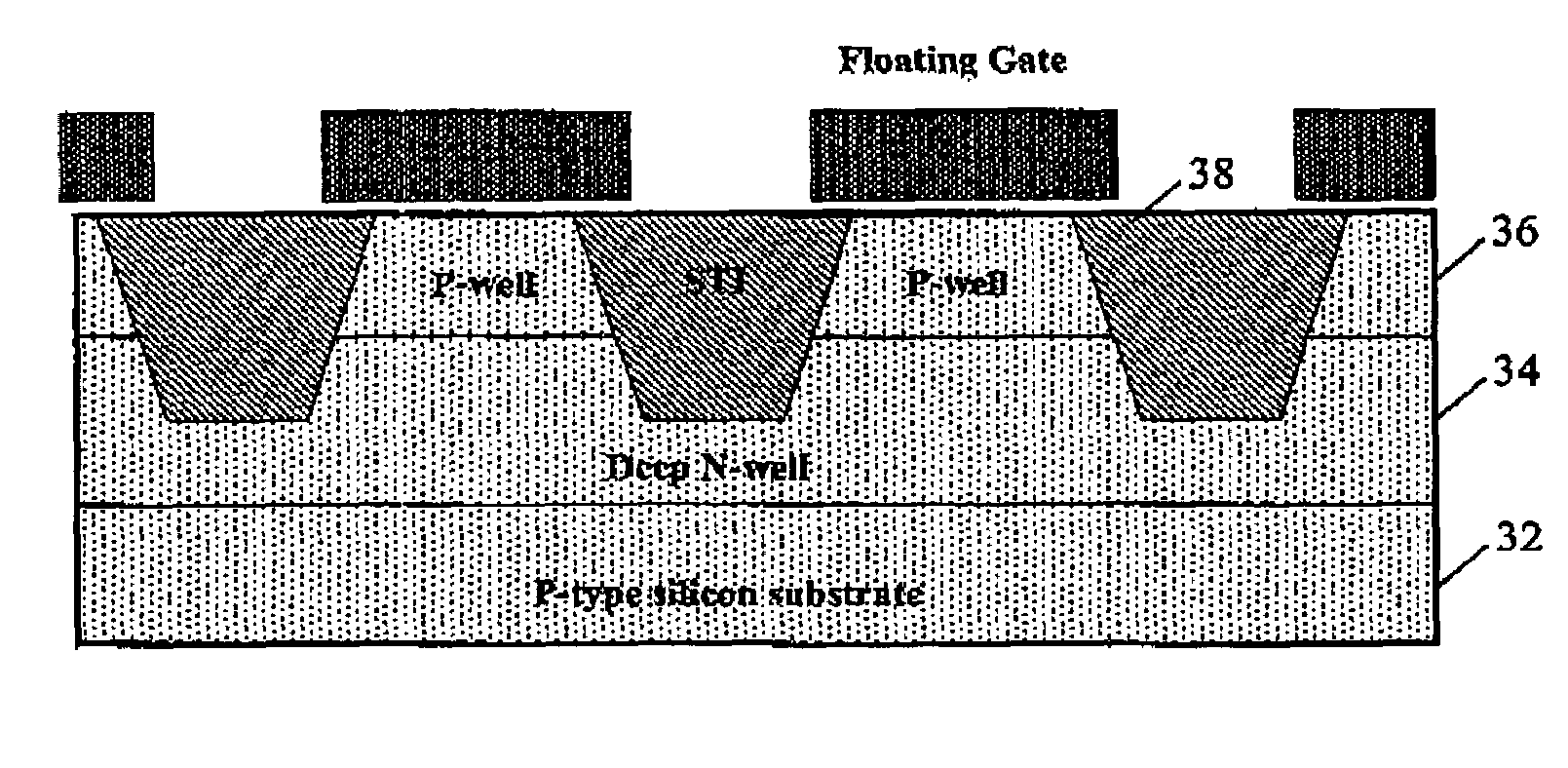

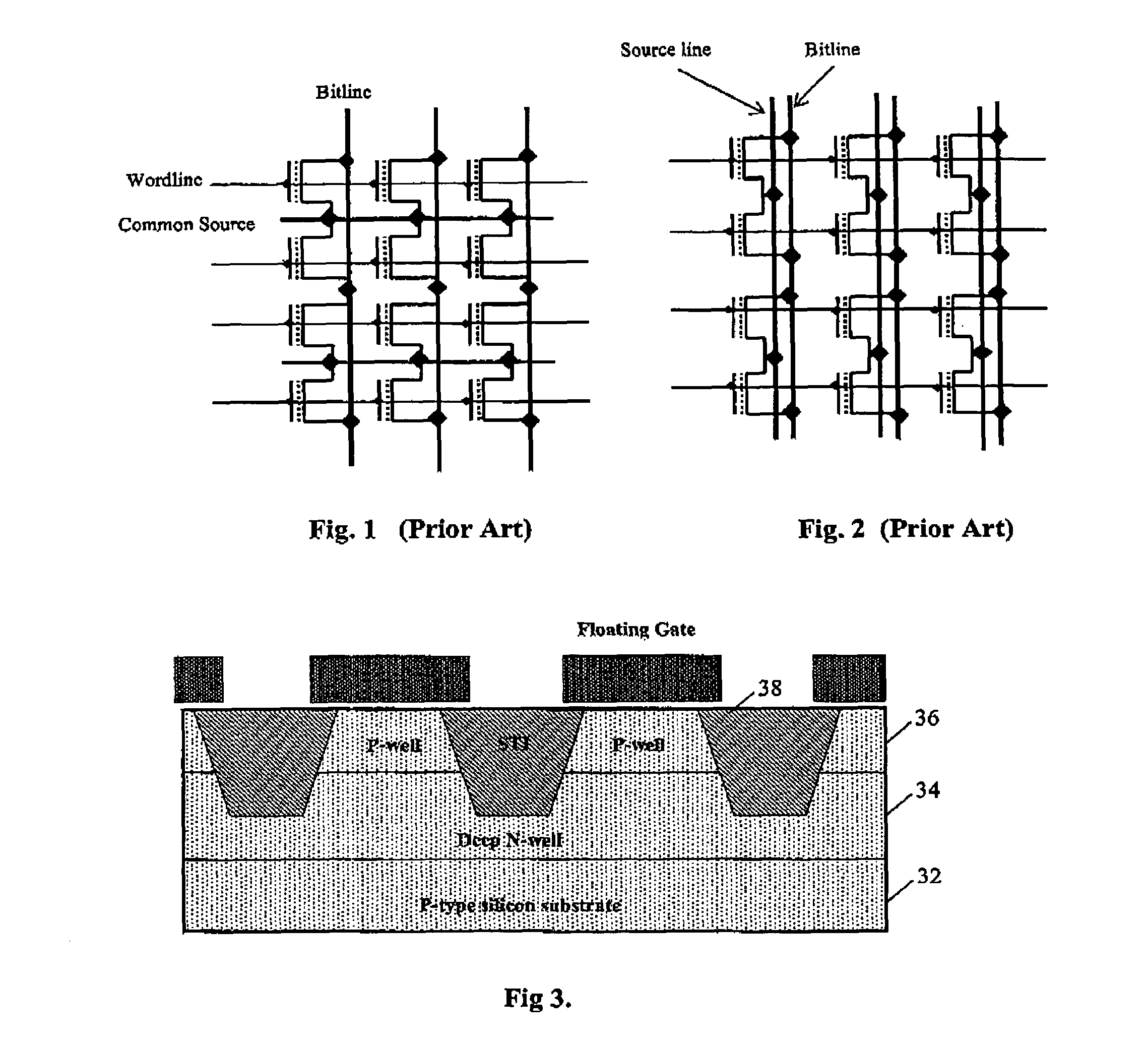

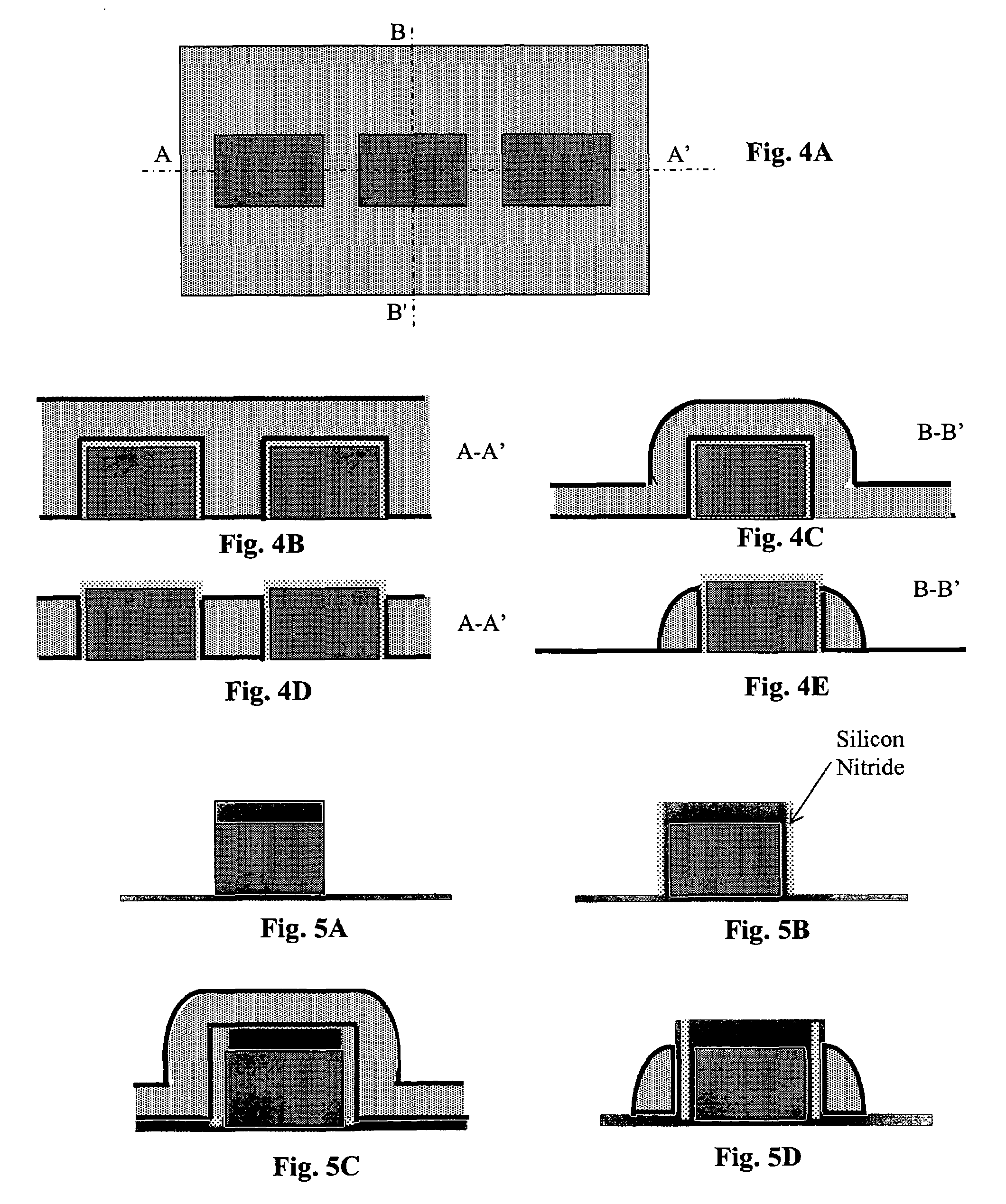

Low voltage EEPROM memory arrays

InactiveUS20050110073A1Increase cell read currentReduce voltageTransistorSolid-state devicesLow voltageFowler nordheim

A non-volatile memory array includes memory cells connected in a common source arrangement and formed in columns of isolated well regions so that Fowler-Nordheim tunneling is used for both write and erase operations of the memory cells. The memory arrays can be formed as NOR arrays or NAND arrays. In one embodiment, the memory array of the present invention is formed as a byte alterable EEPROM with parallel access. In another embodiment, an insulated gate bipolar transistor (IGBT) is coupled to the memory cells to increase the cell read current of the memory array. When the memory array incorporates IGBTs on the bitlines, the cell read current becomes independent of the wordline voltages. Thus, the memory array of the present invention can be operated at low voltages. The use of IGBTs in the memory array of the present invention enables formation of embedded non-volatile memories in low-voltage digital integrated circuits.

Owner:SPADEA GREGORIO

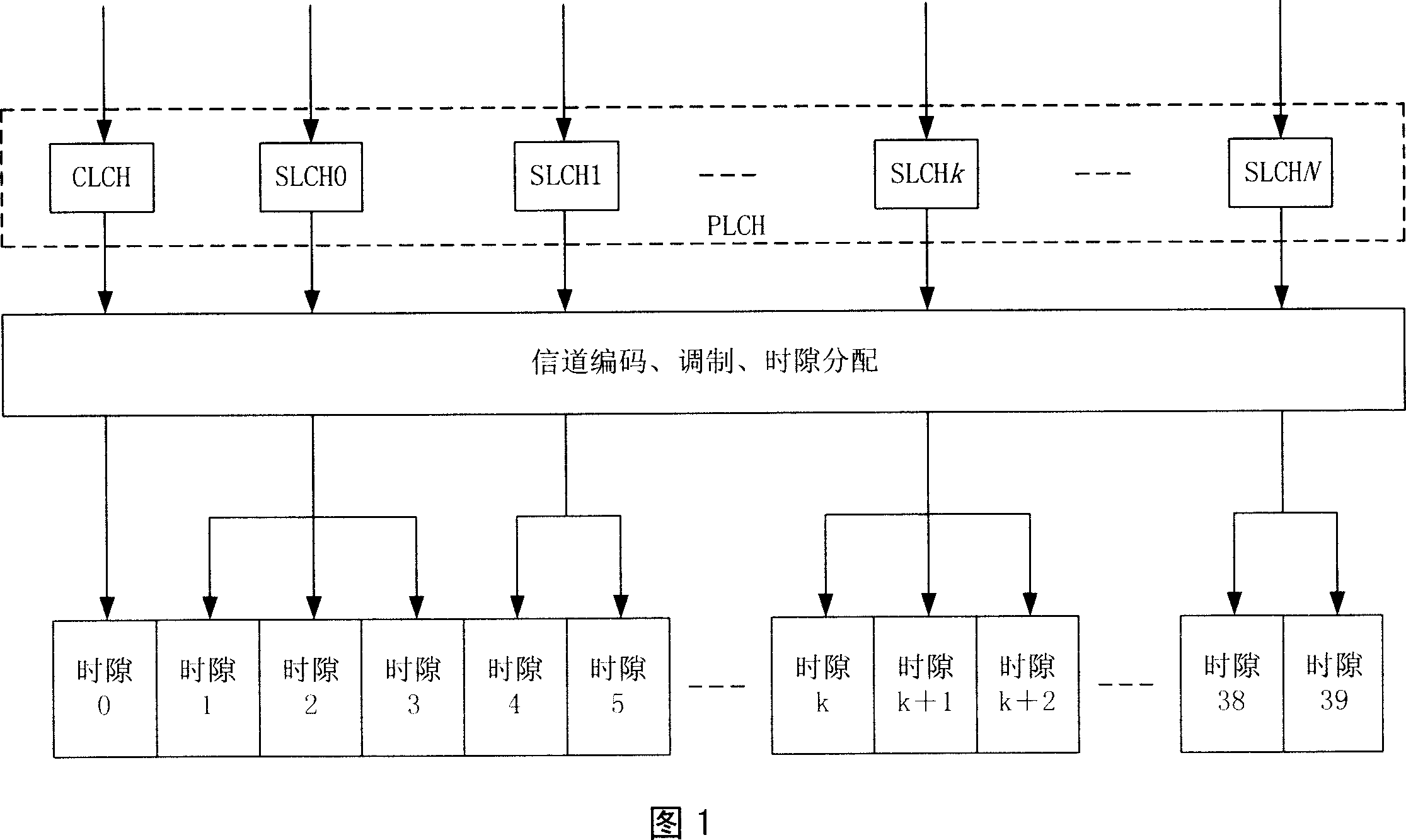

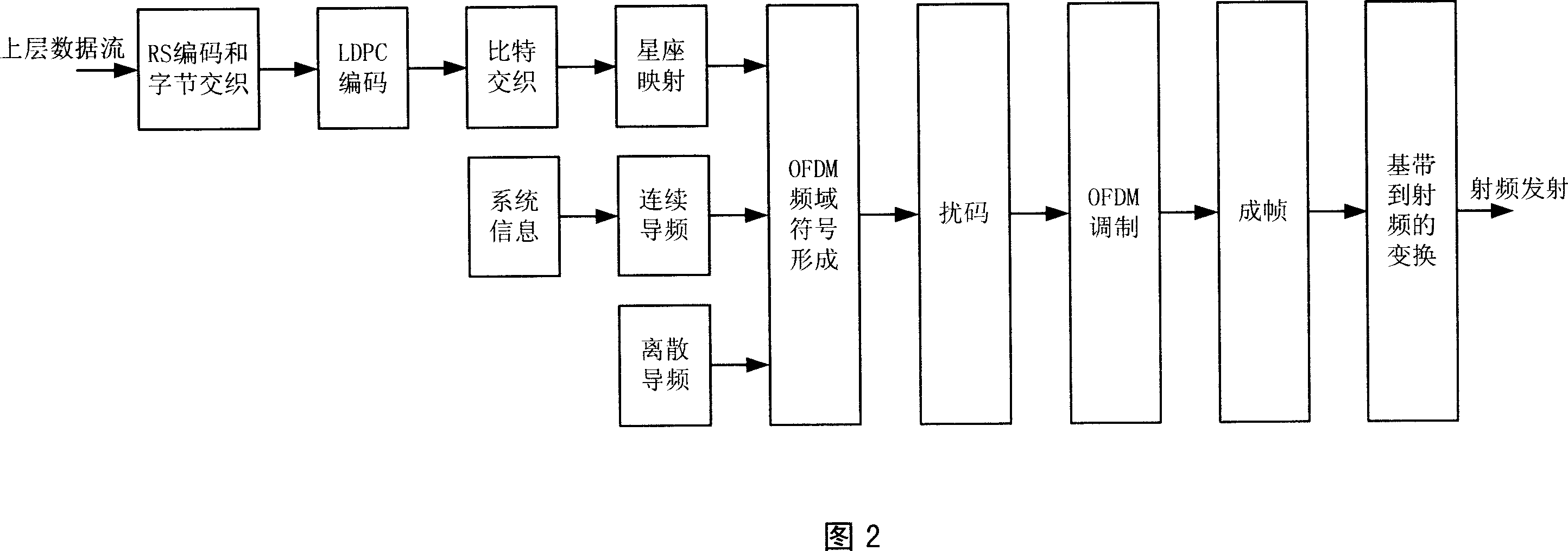

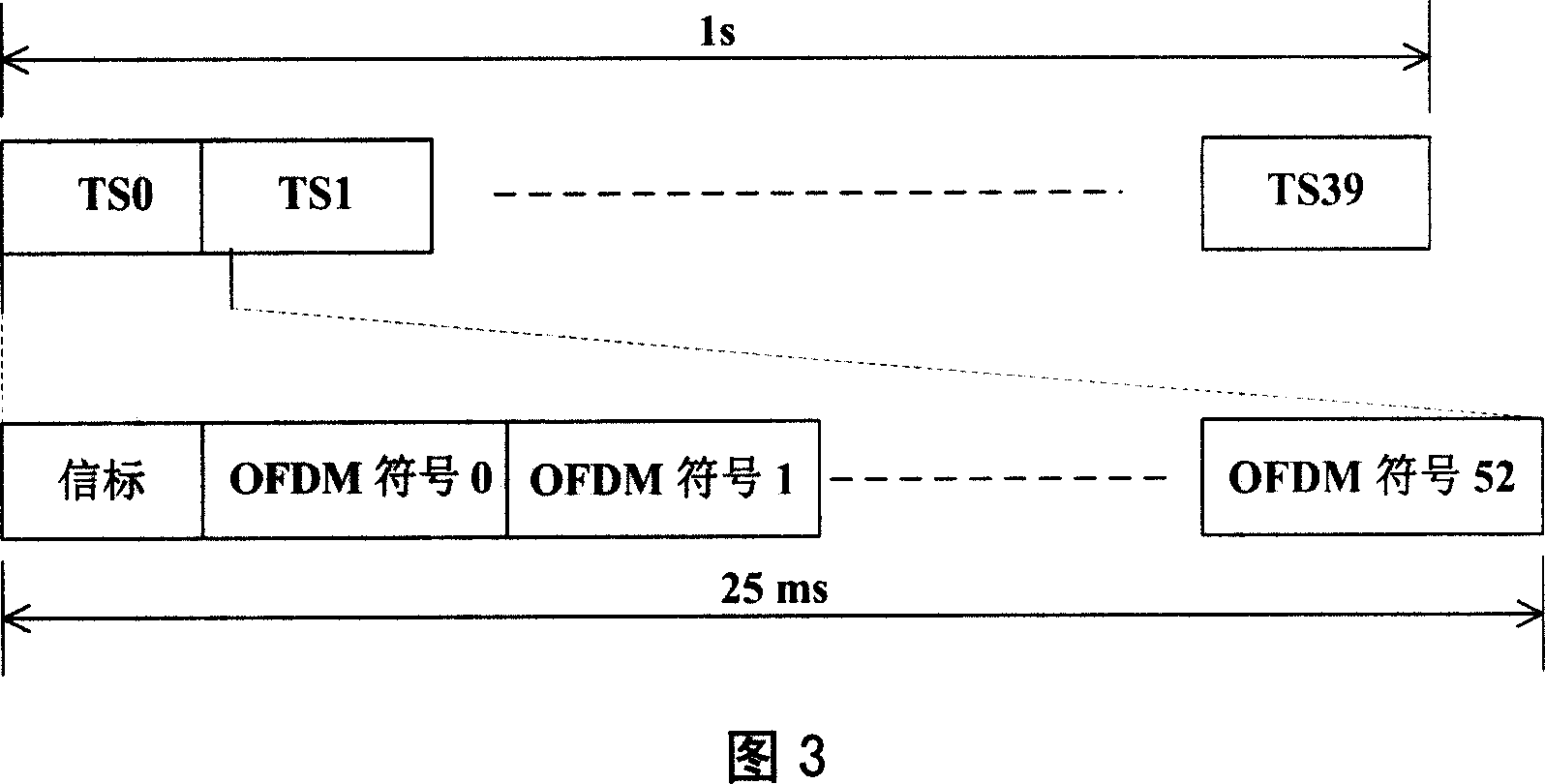

Multicarrier digital mobile multimedia broadcast system, and digital information transmission method

InactiveCN1960357AImprove performanceBroadcast with distributionCode division multiplexLow-pass filterCarrier signal

The method comprises: after sequentially making RS coding and byte interlace, LDPC coding, bit interlace and constellation mapping for the upper layer data, the acquired data symbol, discrete pilot frequency and the continuous polite frequency are multiply connected to form OFDM polite frequency and make scrambling; generating OFDM symbol through IFFT transformation, and after forming time slot through inserting frame head, they are connected to form signal frame of physical layer; after making low pass filter and quadrature up-conversion for the physical layer signal frame, they are sent out. The invention can provide radio broadcast such as audio, video and multicast for mobile, fixed and portable receiver. The system thereof uses micro wave and large-scale IC technology. The method adopts OFDM of LDPC solution.

Owner:TIMI TECH

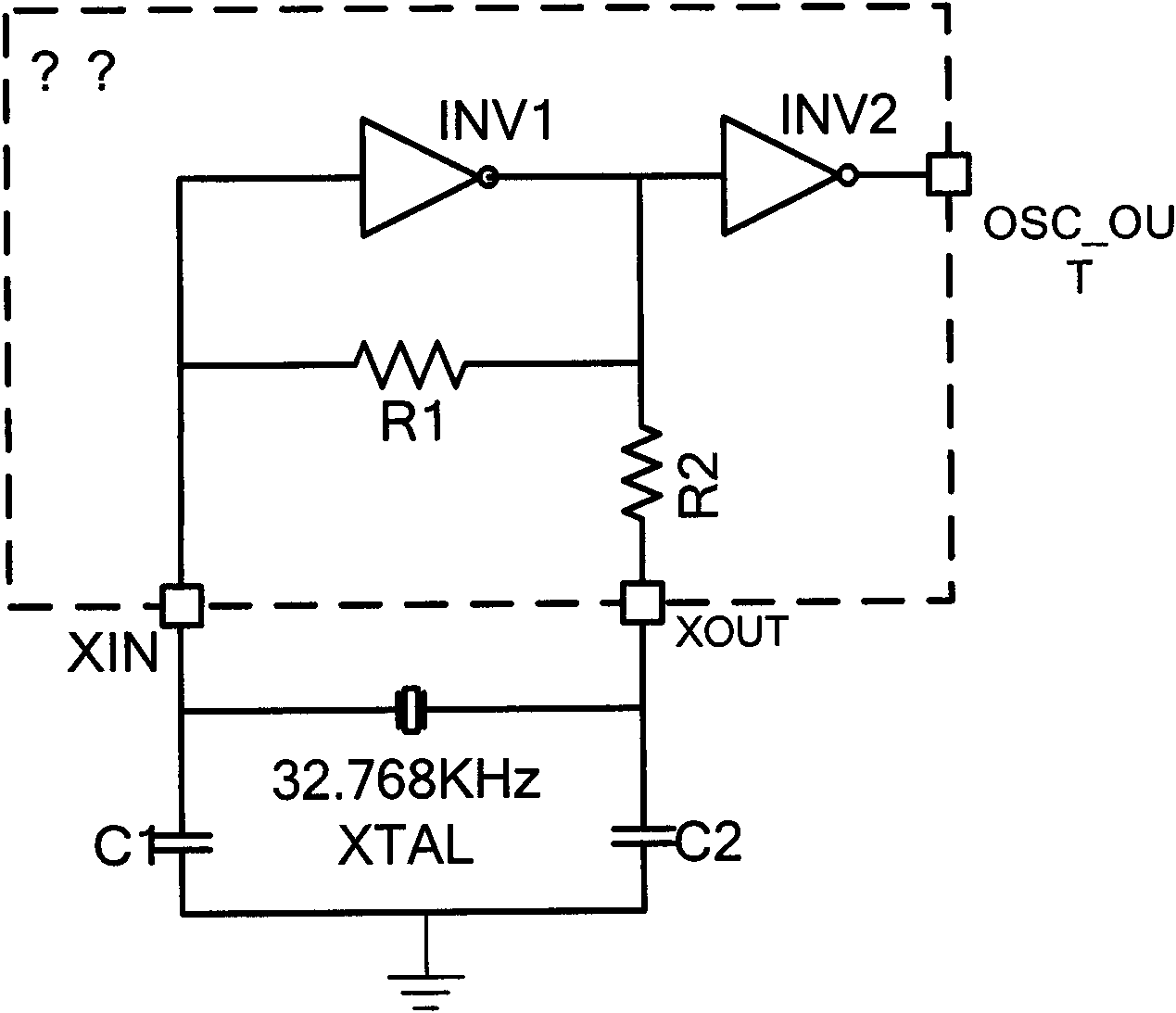

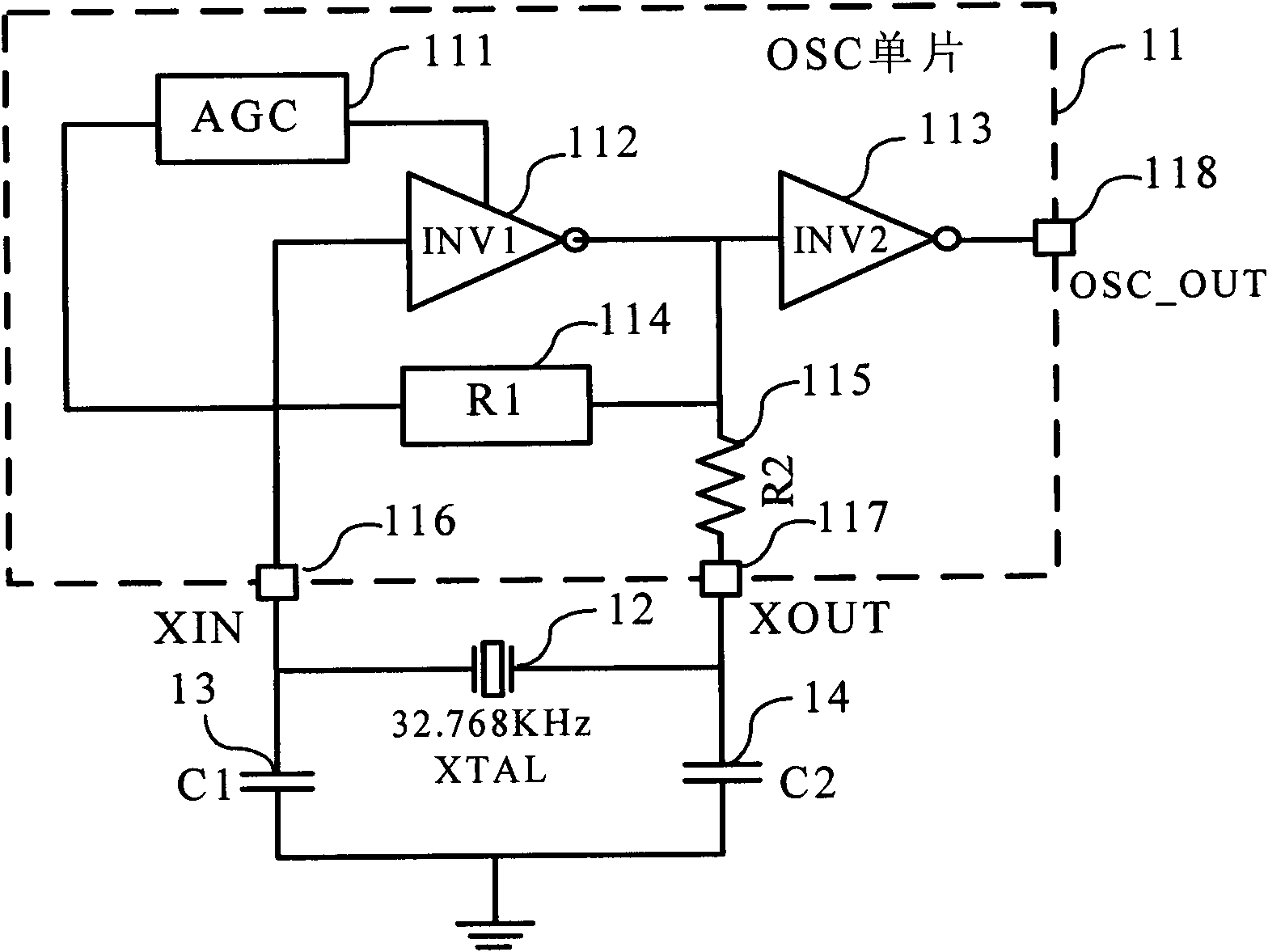

Low power consumption and rapid oscillation starting crystal oscillator module with programmable adjusting start-oscillation condition

The invention discloses a low power consumption and rapid oscillation starting crystal oscillator module with a transposable start oscillation condition, which consists of an inverting amplifier, an inverting reshaper chain, an automatic gain control loop (AGC), a feedback resistor, a power limitation resistor, and an external passive crystal oscillator and an external load capacitor. The inverting amplifier is provided with a transposable feedback resistor R1, and the transposable start oscillation condition of the crystal oscillator is realized; and the automatic gain control loop (AGC) is inserted between an input end and a bias end of the inverting amplifier, and the contradiction between the oscillation starting time and power consumption is solved. The invention also provides a highresistor realizing IC (integrated circuit) by adopting a transconductance amplifier of micro current source, and a transposable feedback resistor R1 for the oscillator amplifier branch circuit and a high resistor in a pi-shaped filter. The resistance value of the high resistance can be controlled by programming, the start oscillation condition of the oscillator can be adjusted through adjusting the feedback resistance R1, and reliable and quick start oscillation of the oscillator can be realized; and lower phase noise can be realized through adjusting the high resistor in the pi-shaped filter. The crystal oscillator circuit has the characteristics of low power consumption and rapid start oscillation, and can be used for the digital integrated circuit, such as a base band of various of satellite navigation allocation receptors, real time clocks (RTC).

Owner:杭州中科微电子有限公司

Low voltage EEPROM memory arrays

InactiveUS7075140B2Increase cell read currentReduce voltageTransistorSemiconductor/solid-state device testing/measurementLow voltageFowler nordheim

A non-volatile memory array includes memory cells connected in a common source arrangement and formed in columns of isolated well regions so that Fowler-Nordheim tunneling is used for both write and erase operations of the memory cells. The memory arrays can be formed as NOR arrays or NAND arrays. In one embodiment, the memory array of the present invention is formed as a byte alterable EEPROM with parallel access. In another embodiment, an insulated gate bipolar transistor (IGBT) is coupled to the memory cells to increase the cell read current of the memory array. When the memory array incorporates IGBTs on the bitlines, the cell read current becomes independent of the wordline voltages. Thus, the memory array of the present invention can be operated at low voltages. The use of IGBTs in the memory array of the present invention enables formation of embedded non-volatile memories in low-voltage digital integrated circuits.

Owner:SPADEA GREGORIO

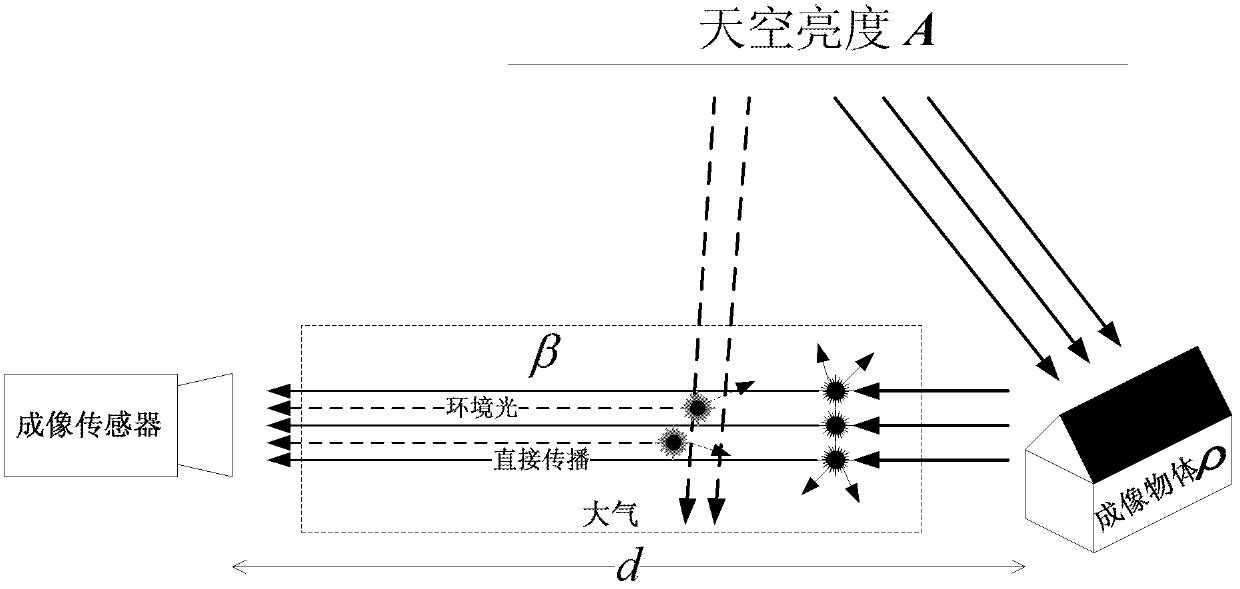

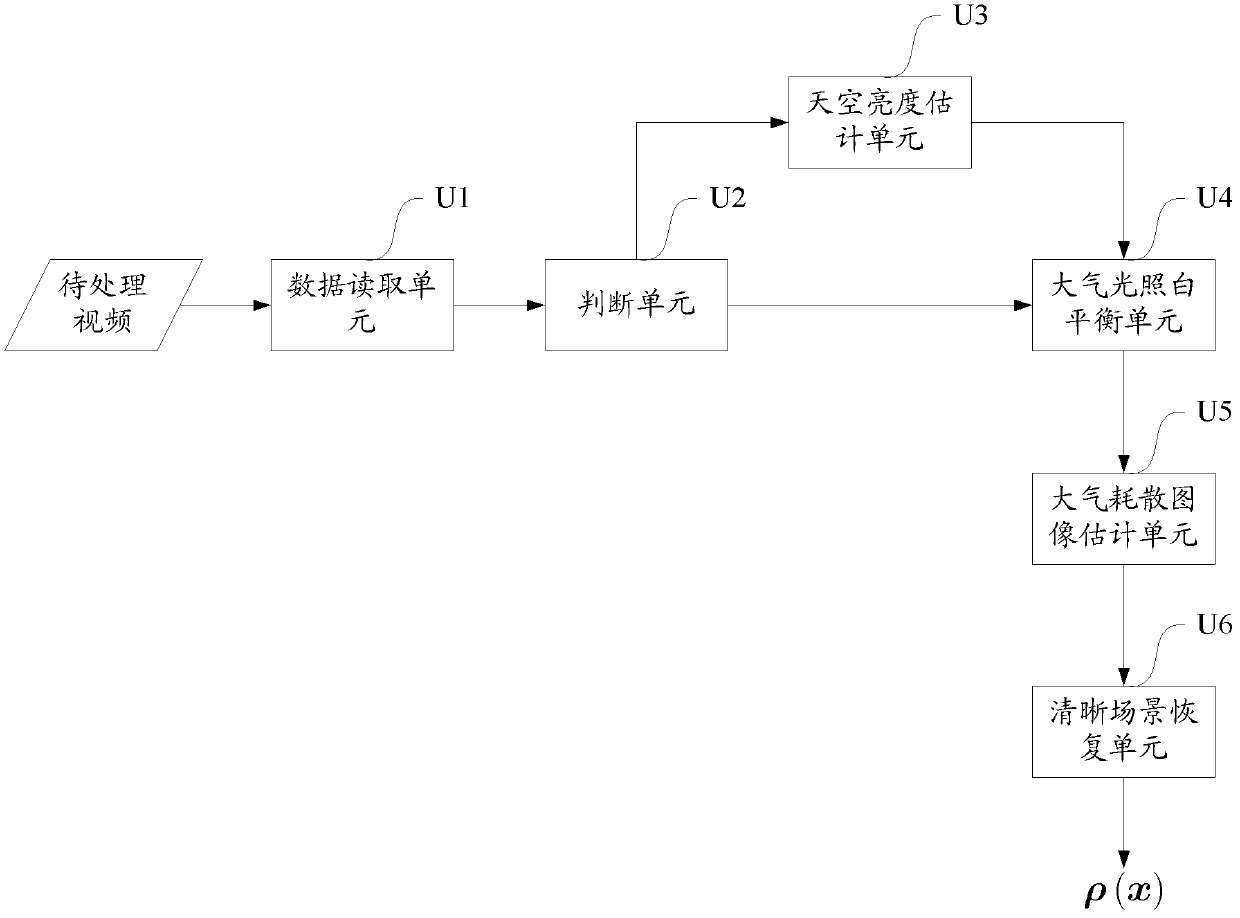

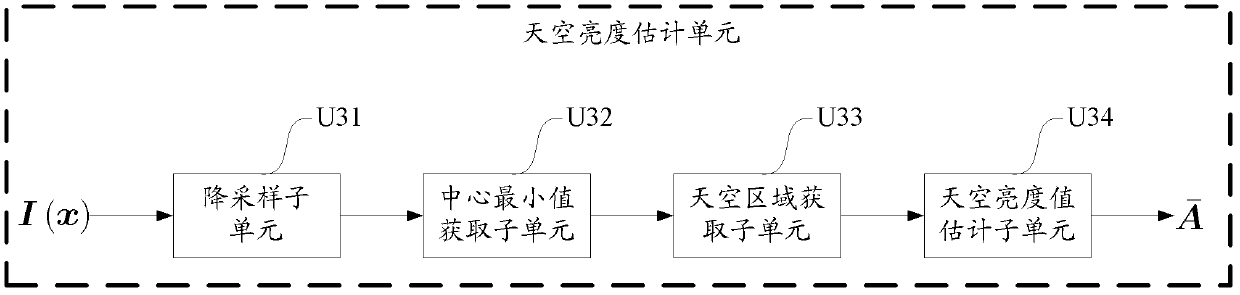

Real-time video defogging system

InactiveCN102170574AAcceleration of defogging processingImprove defogging effectImage enhancementColor signal processing circuitsSky brightnessImage estimation

The invention provides a real-time video defogging system which belongs to the field of image processing and is characterized by being realized in a digital integrated circuit and comprising a data reading unit, a judgment unit, a sky brightness estimation unit, an atmosphere illumination white balance unit, an atmosphere dissipation image estimation unit and a clear scene recovery unit. As for the former K frames in the current lens of a video to be processed, the sky region thereof is estimated so that the sky brightness value is calculated; then the atmosphere illumination color of an image to be processed is corrected according to the sky brightness value by utilizing a white balance algorithm and a white balance image is normalized, the minimum values, minimum values of various colorcomponent are solved out so as to serve as rough estimated image; and based on the minimum values, an refined atmosphere dissipation image is calculated by utilizing an edge maintained flatting method, and the atmosphere scene albedo is calculated based on the atmosphere dissipation image, so that defogging recovery processing is carried out. As for a common-intermediate-format (CIF) video with the resolution of 288*352, the processing speed can be up to 60 fps (frames per second); and as for a D1-format video with the resolution of 578*720, the processing speed can be up to 15 fps, thus the system provided by the invention can be applied to monitoring systems and meet the requirement on real-time performance.

Owner:BEIJING UNIV OF TECH

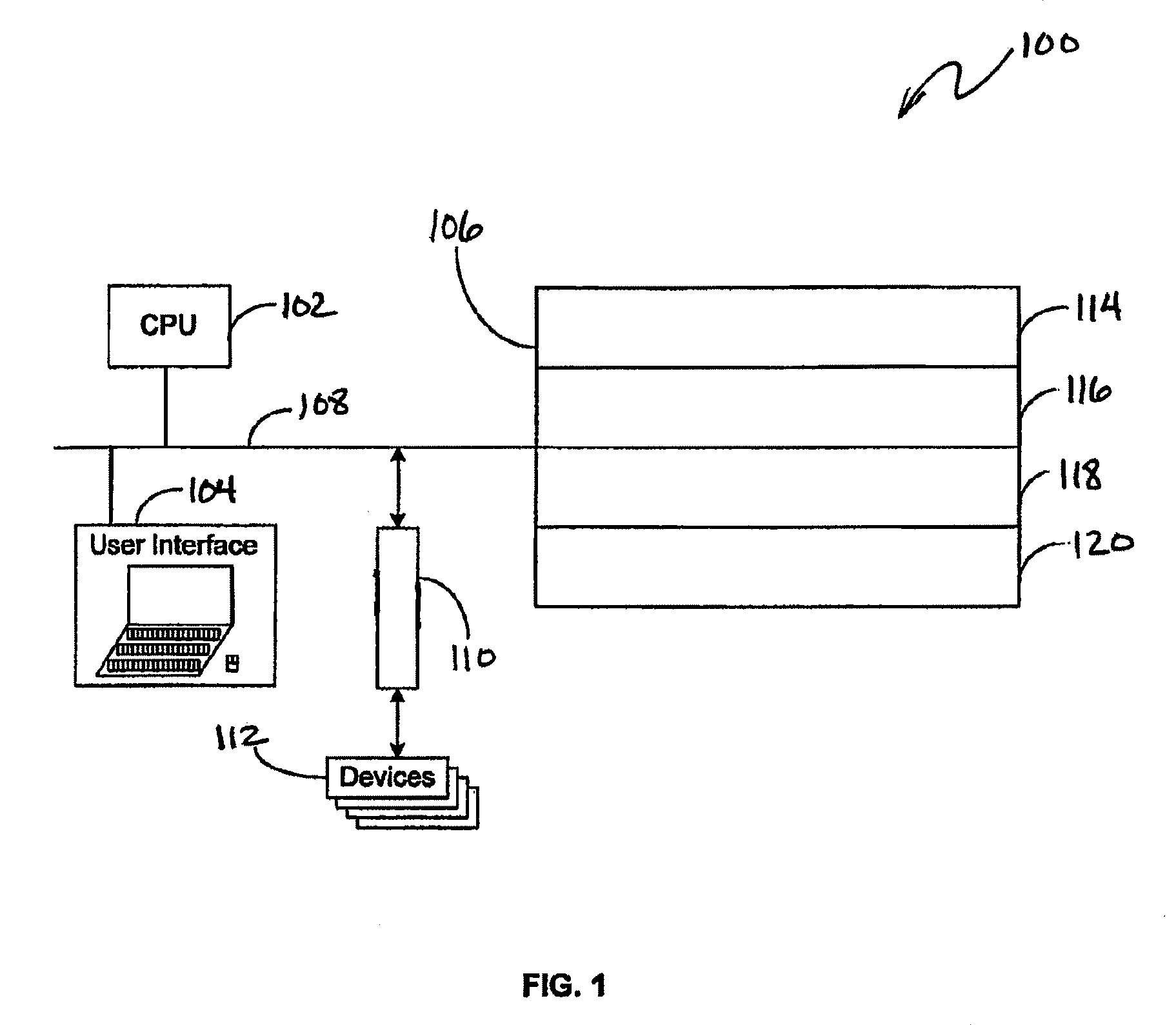

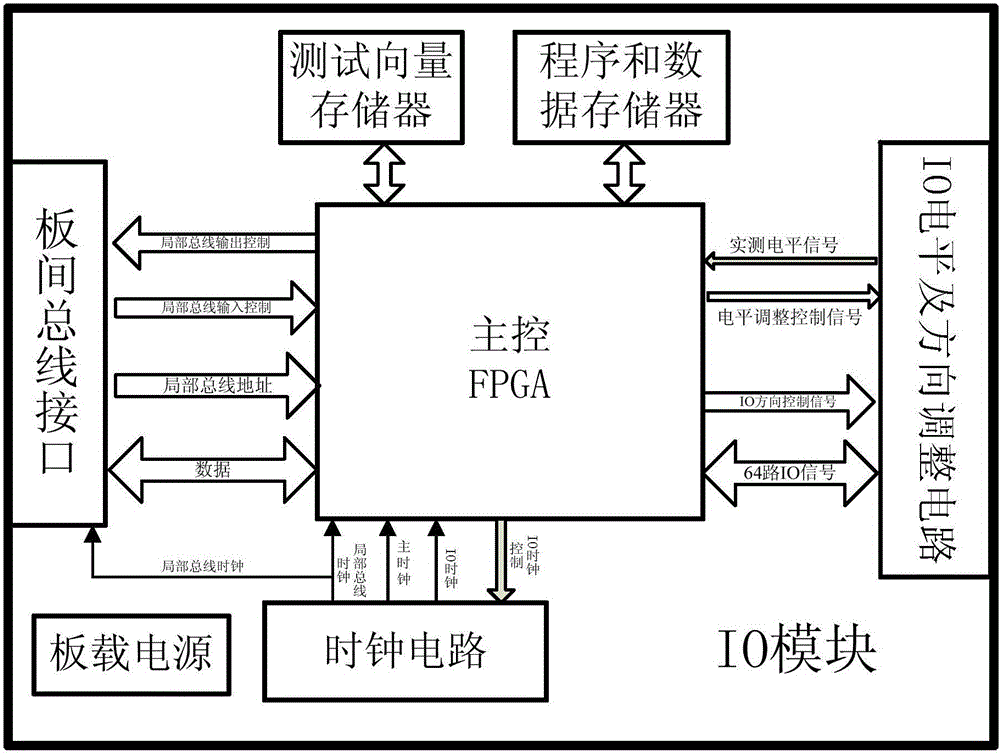

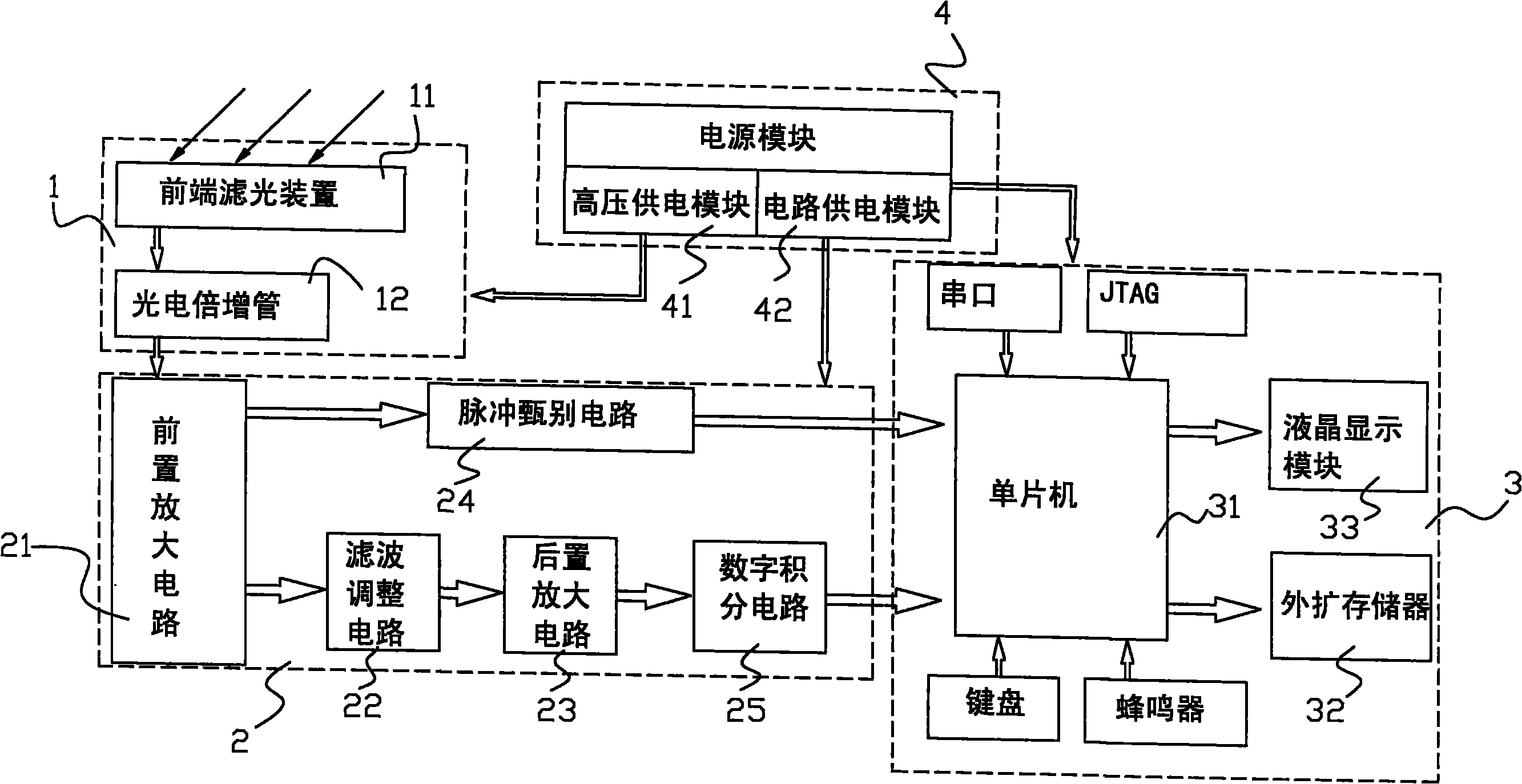

Digital integrated circuit chip testing system

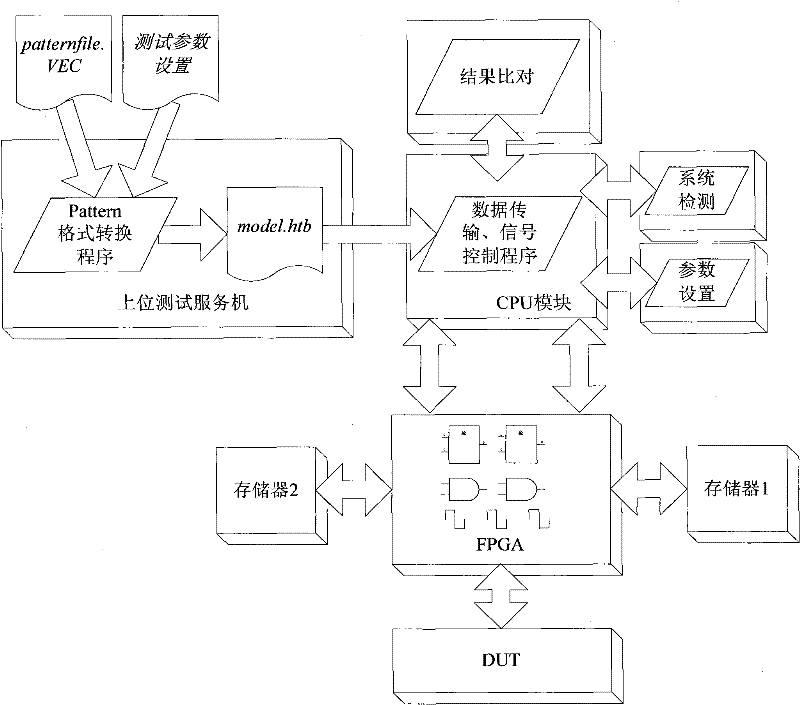

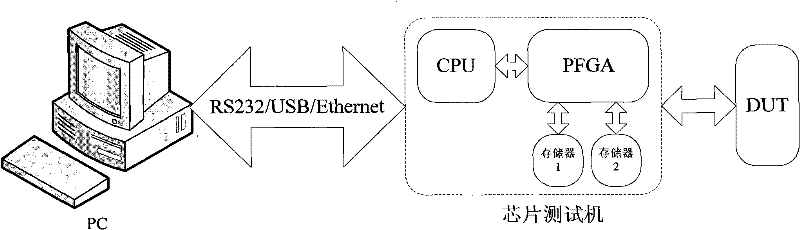

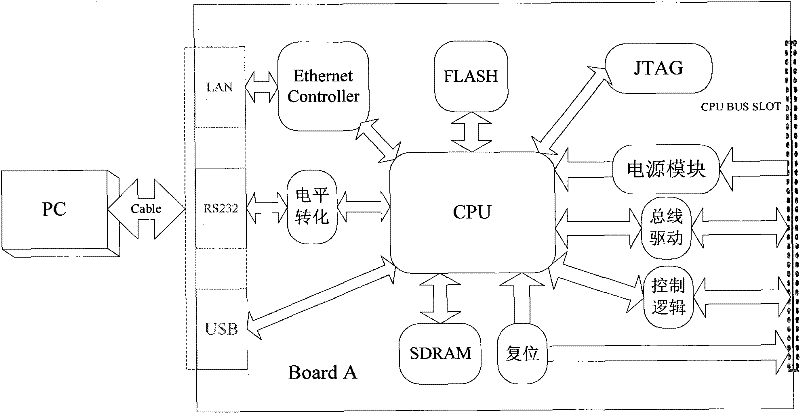

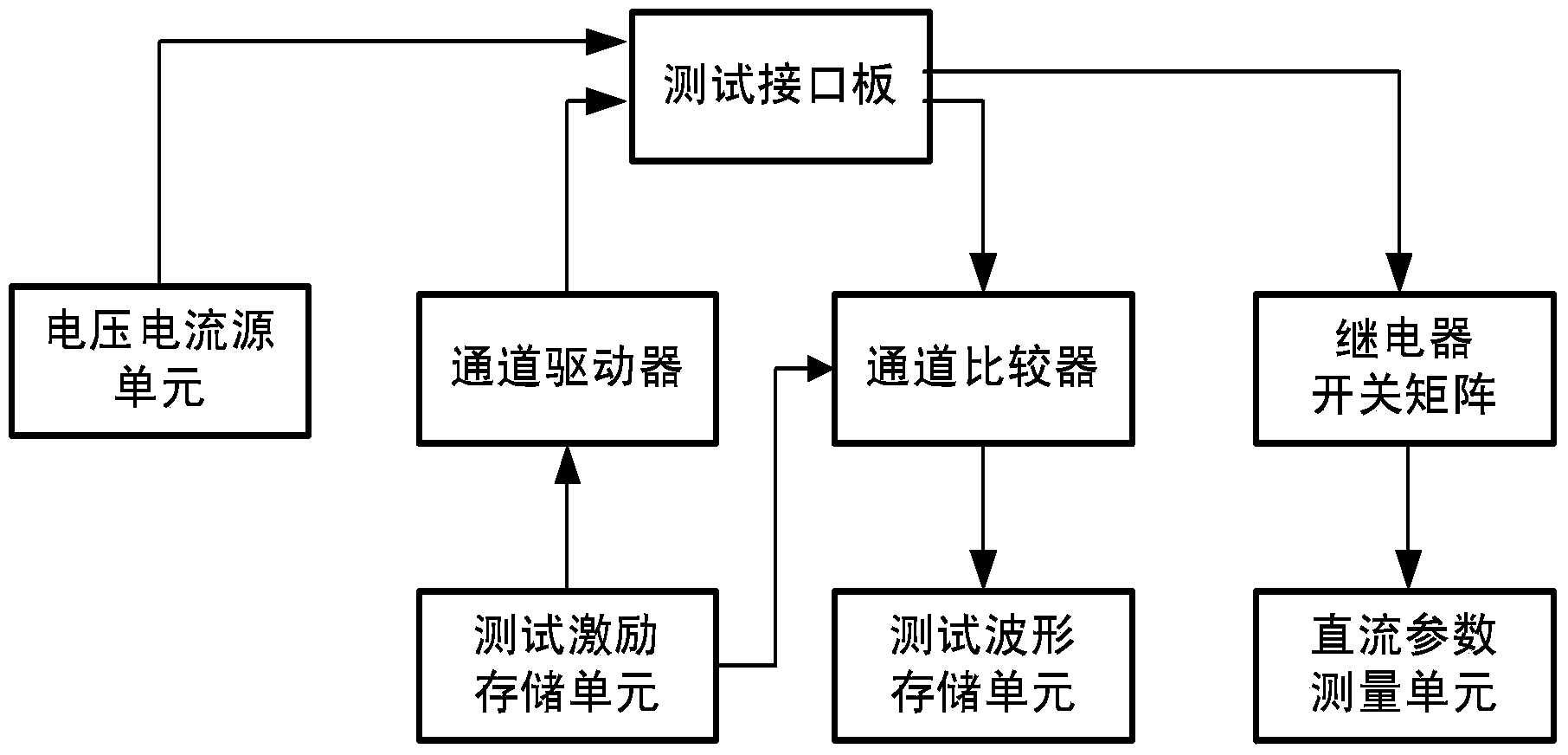

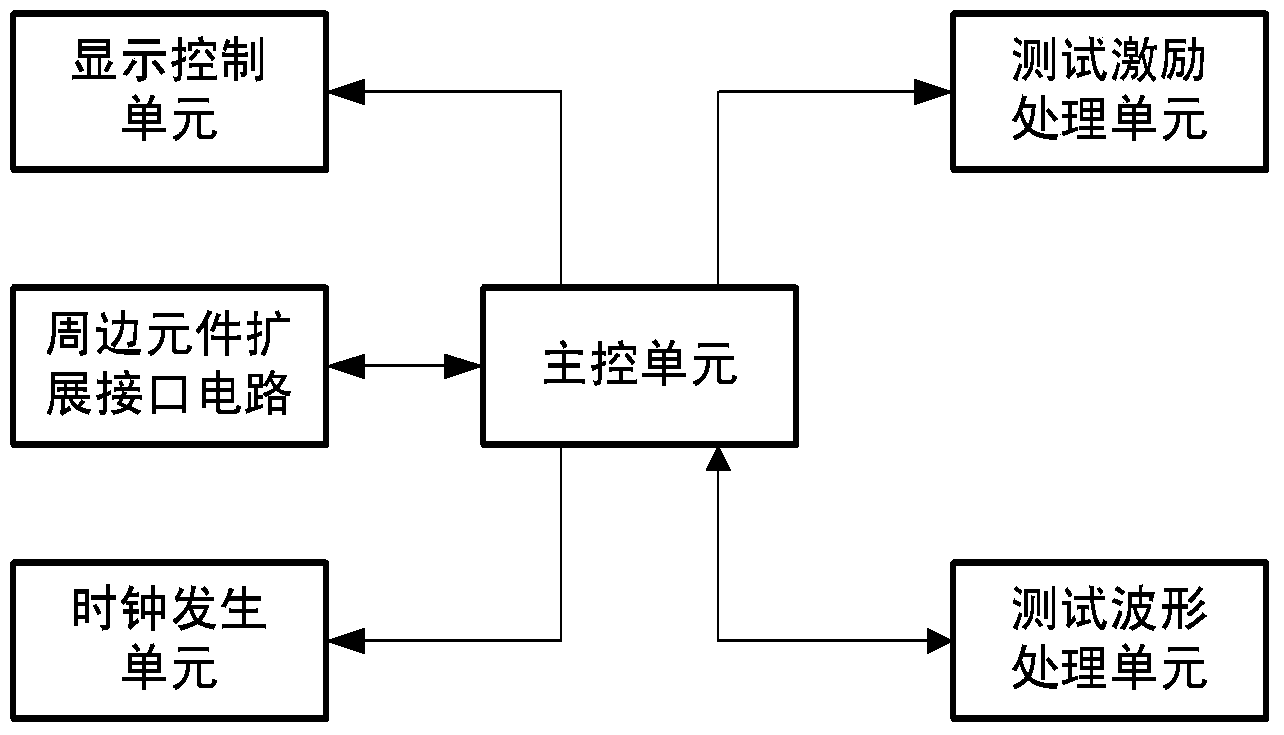

InactiveCN102540060AImprove stabilityImprove mean time between failuresElectrical testingFpga implementationsTest object

The invention provides a test pattern-based testing system for realizing a functional test on a digital integrated circuit. The functional test is mainly used for testing logical functions of a chip under a certain timing sequence, and a basic principle is that the chip is excited by means of test patterns and whether the response of the chip is consistent with expected response is observed. The functional test can cover failure models of extremely high proportion logic circuits. A debugging technology supported one-step testing system comprises two parts, namely test pattern file conversion software applied to a personal computer (PC) and a digital integrated circuit chip testing machine, wherein the digital integrated circuit chip testing machine consists of architectures of a central processing unit (CPU) and a field programmable gate array (FPGA); the CPU is used for storing and converting pattern files, controlling the testing process, communicating with a host, and the like. A pattern controlling logic circuit is realized by an FPGA, the waveform generation, the control of Pattern random access memory (RAM) and sampling control are finished through the FPGA, and a drive and a comparator are controlled so as to test and control a tested object.

Owner:BEIJING CEC HUADA ELECTRONIC DESIGN CO LTD

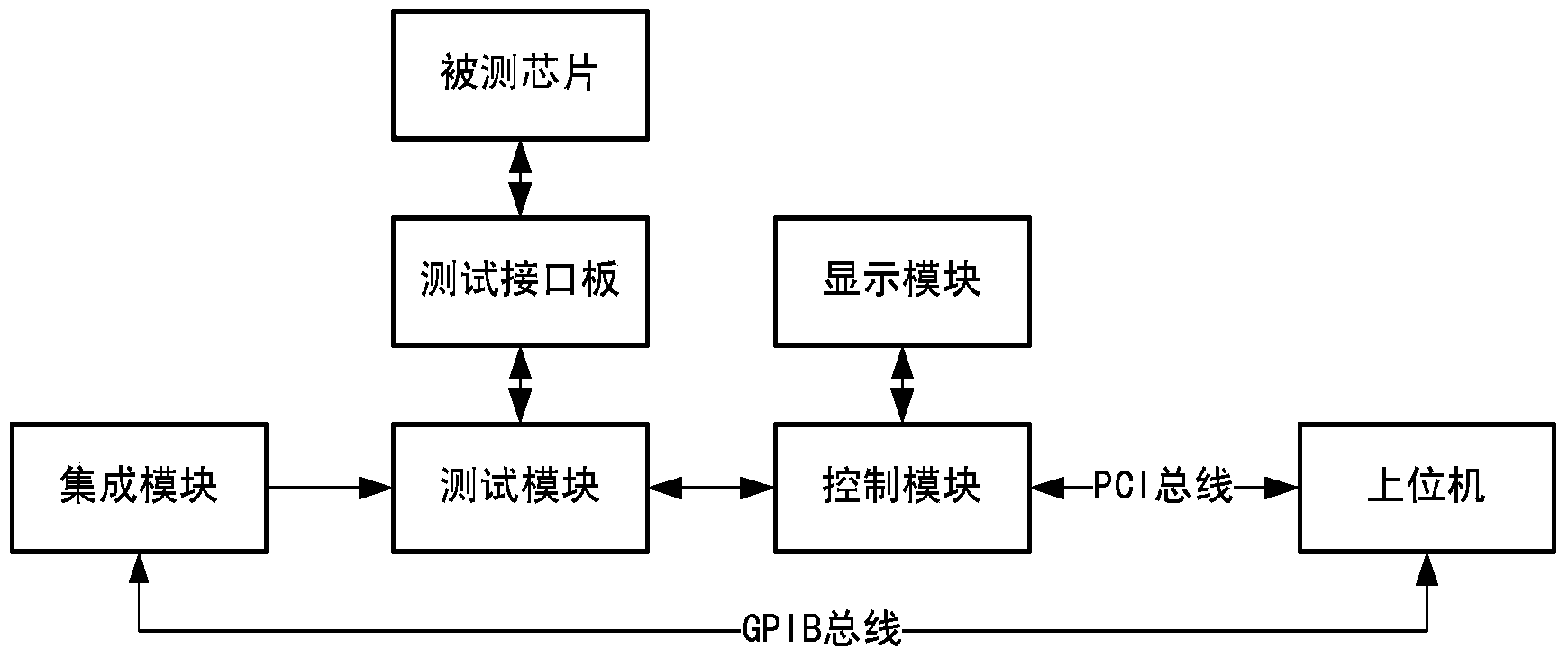

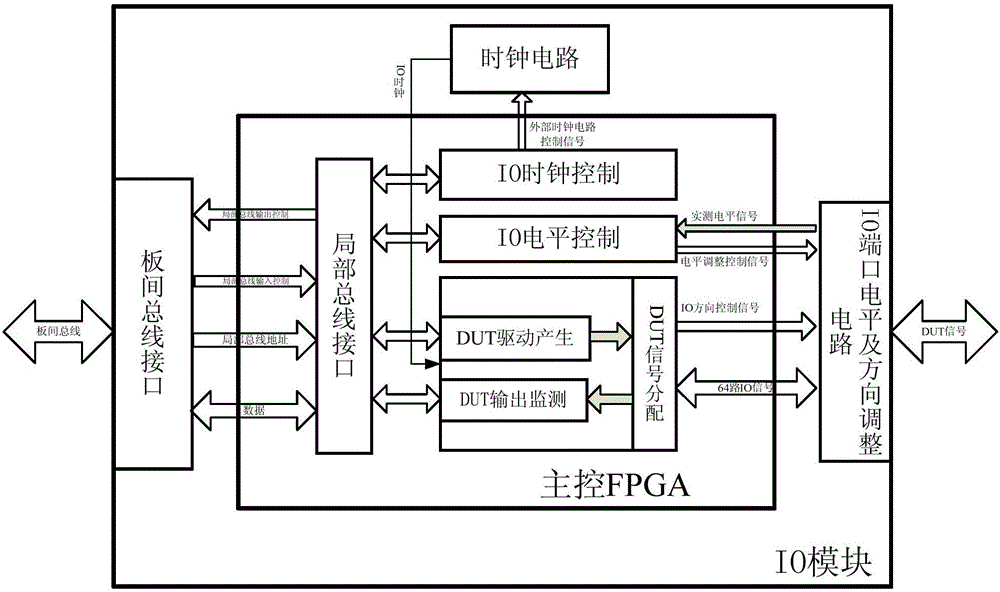

Automatic test system for digital integrated circuit

ActiveCN103837824AMeet testing needsSolve complex operationsDigital circuit testingTest efficiencyTest quality

The invention discloses an automatic test system for a digital integrated circuit. The automatic test system is composed of a tested chip, a test interface board, an integration module, a test module, a control module, a display module and an upper computer. The control module is connected with the upper computer. The test module is connected with the control module. A base pin of the tested chip is connected with the test interface board which is connected with the test module. The integration module is connected with the test module and the upper computer. The display module is connected with the control module and displays a waveform after final comparison by the aid of upper computer software, so that the automatic test for functions and performance of the chip is completed. The automatic test system is low in cost, easy to implement under laboratory conditions, easy and convenient to operate, high in development rate and capable of meeting the test requirements of small-batch products. According to the system, through an automatic test, the problem that operation is complex due to the fact that the number of test items is large in a manual test is solved, the test efficiency is enhanced, a misjudgment caused by artificial factors in the manual test is avoided, and therefore test quality is improved.

Owner:INST OF ELECTRONICS CHINESE ACAD OF SCI

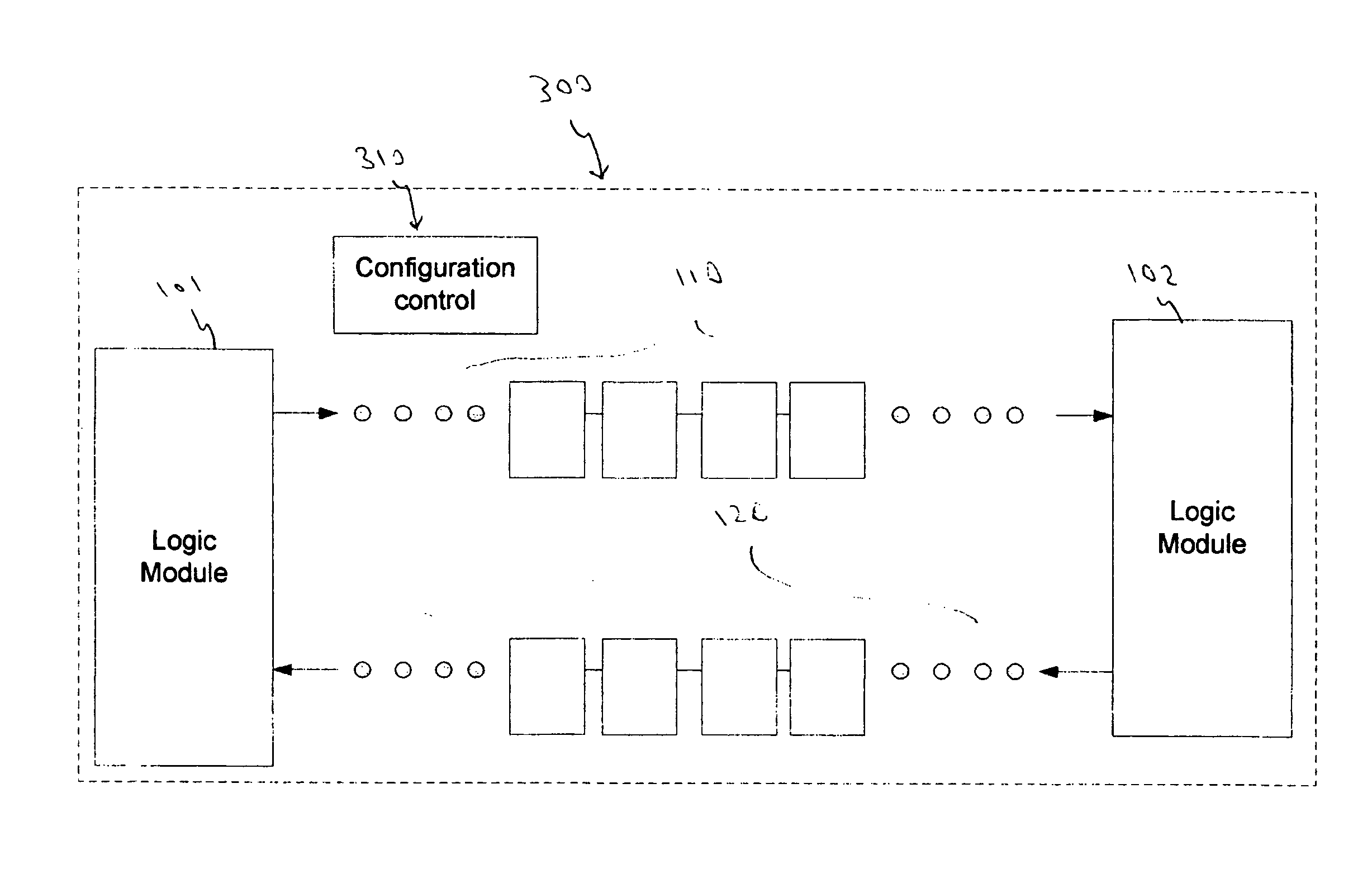

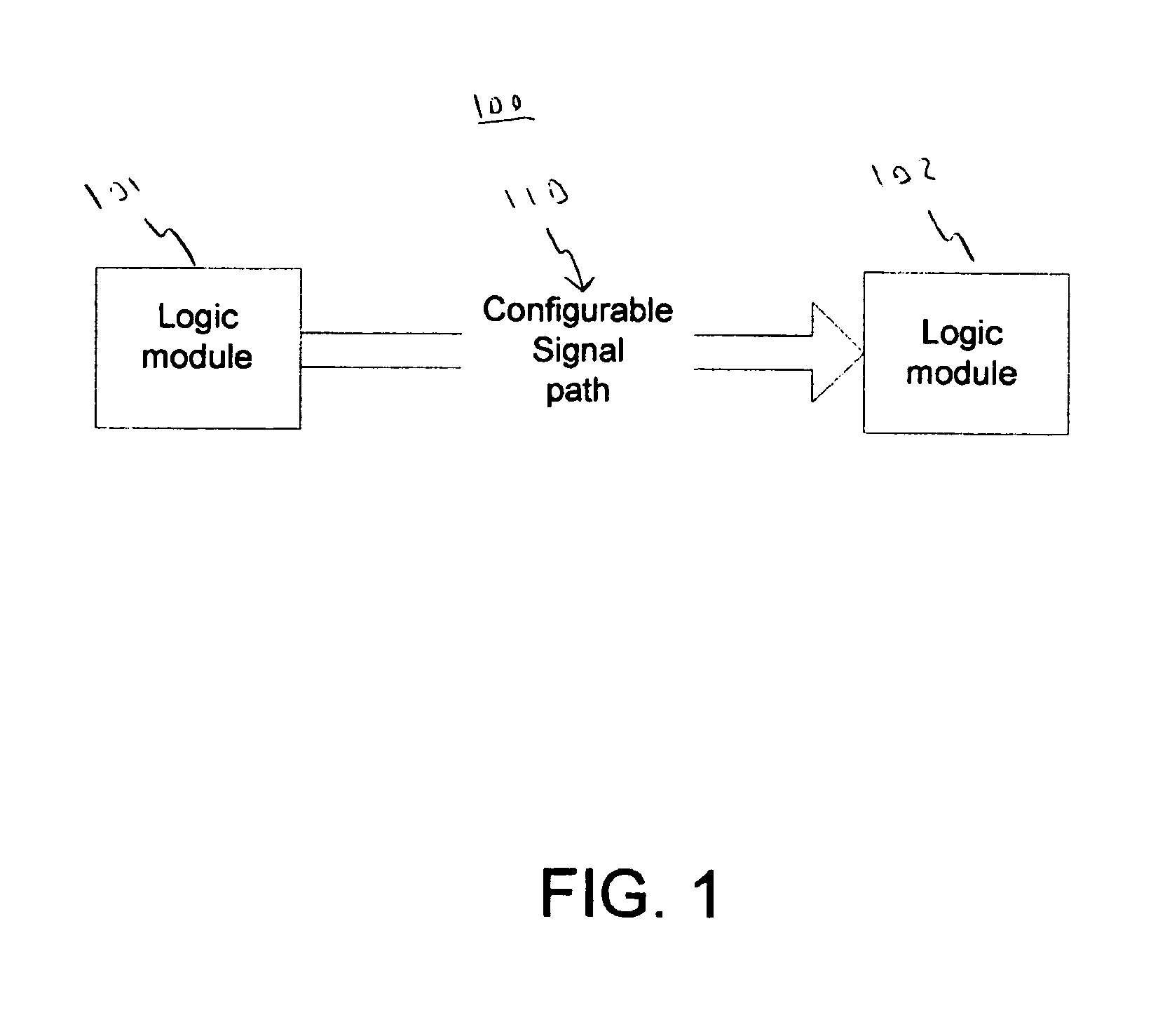

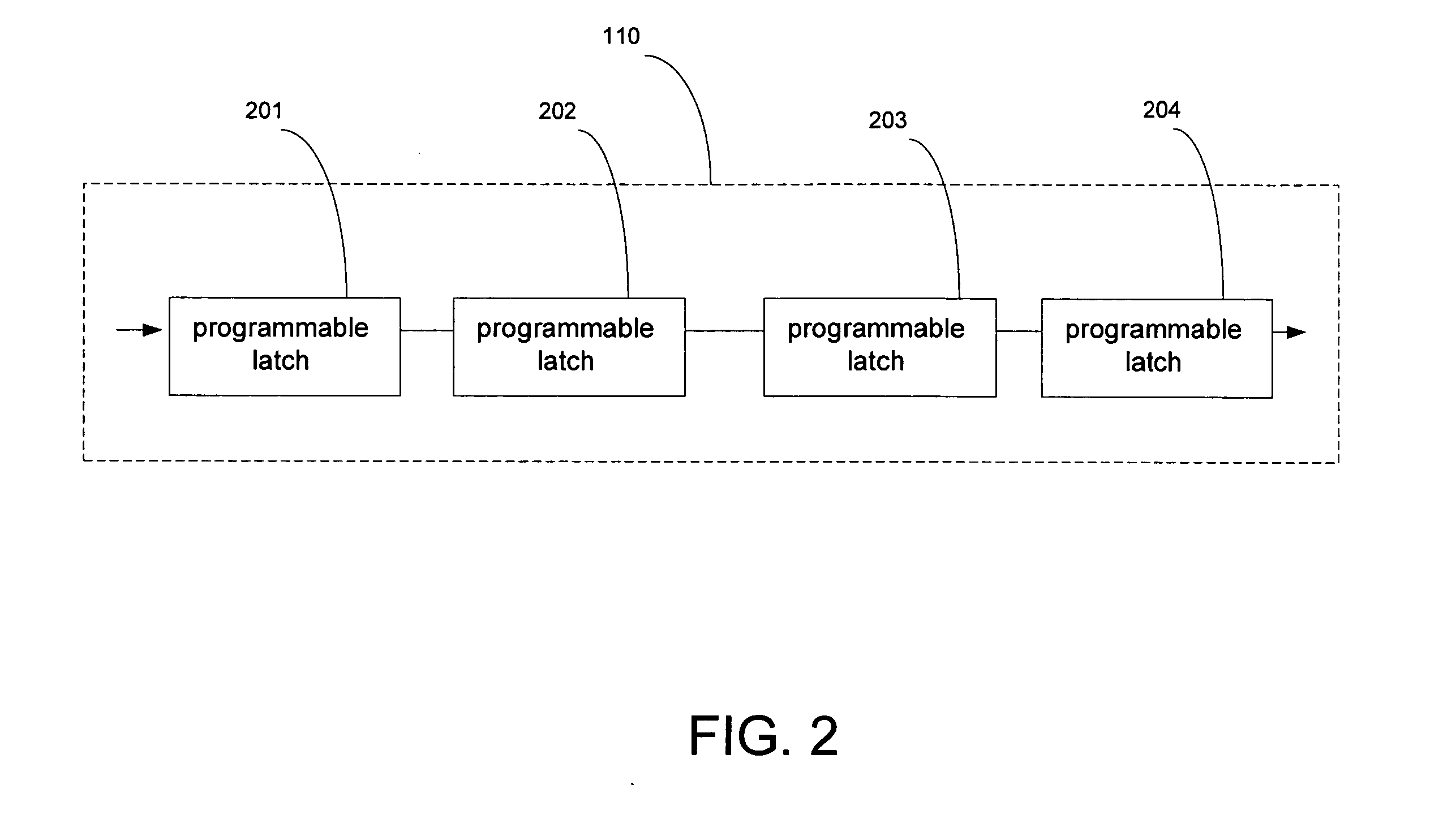

Method and system for elastic signal pipelining

Owner:INTELLECTUAL VENTURES HOLDING 81 LLC

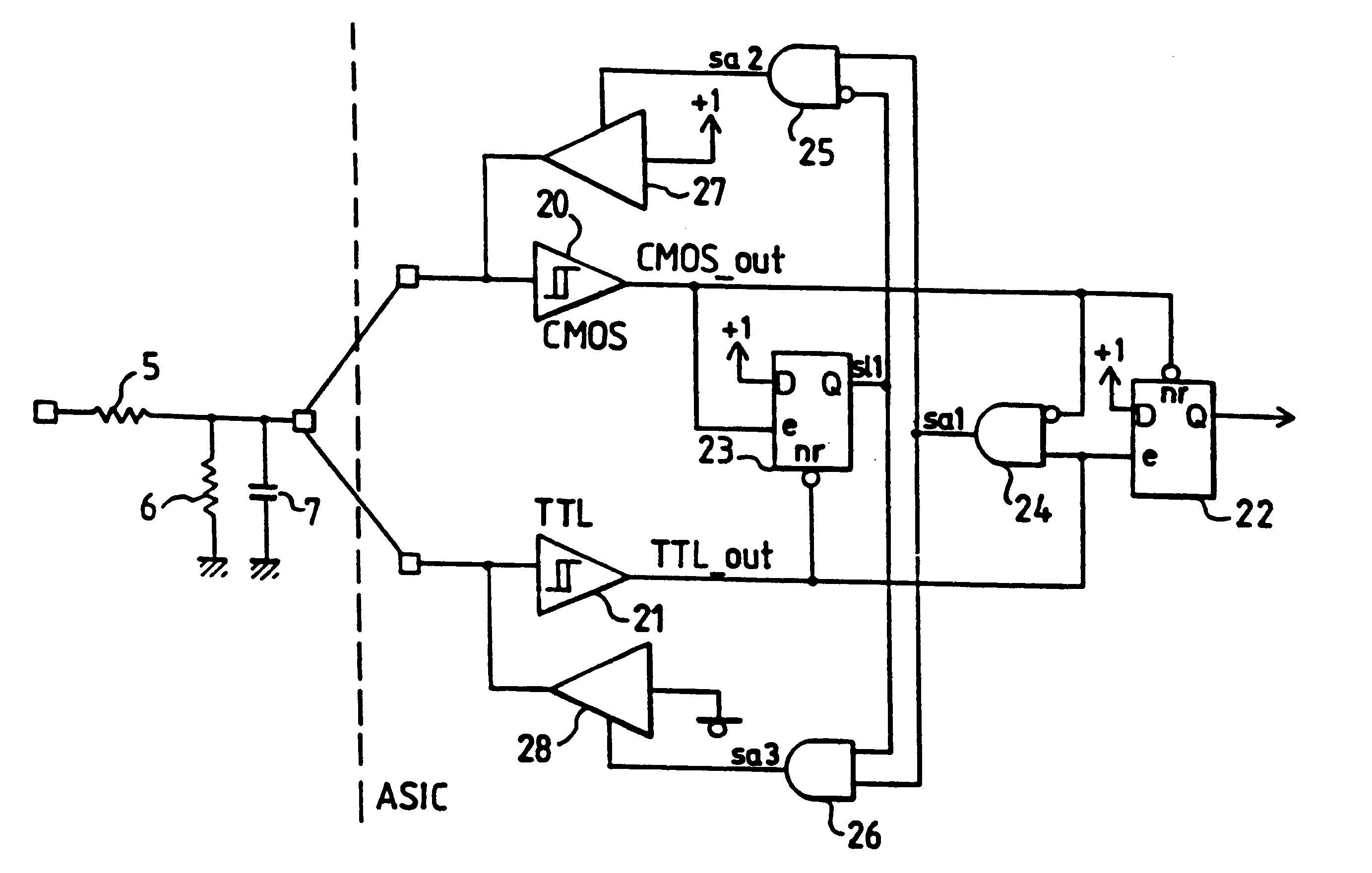

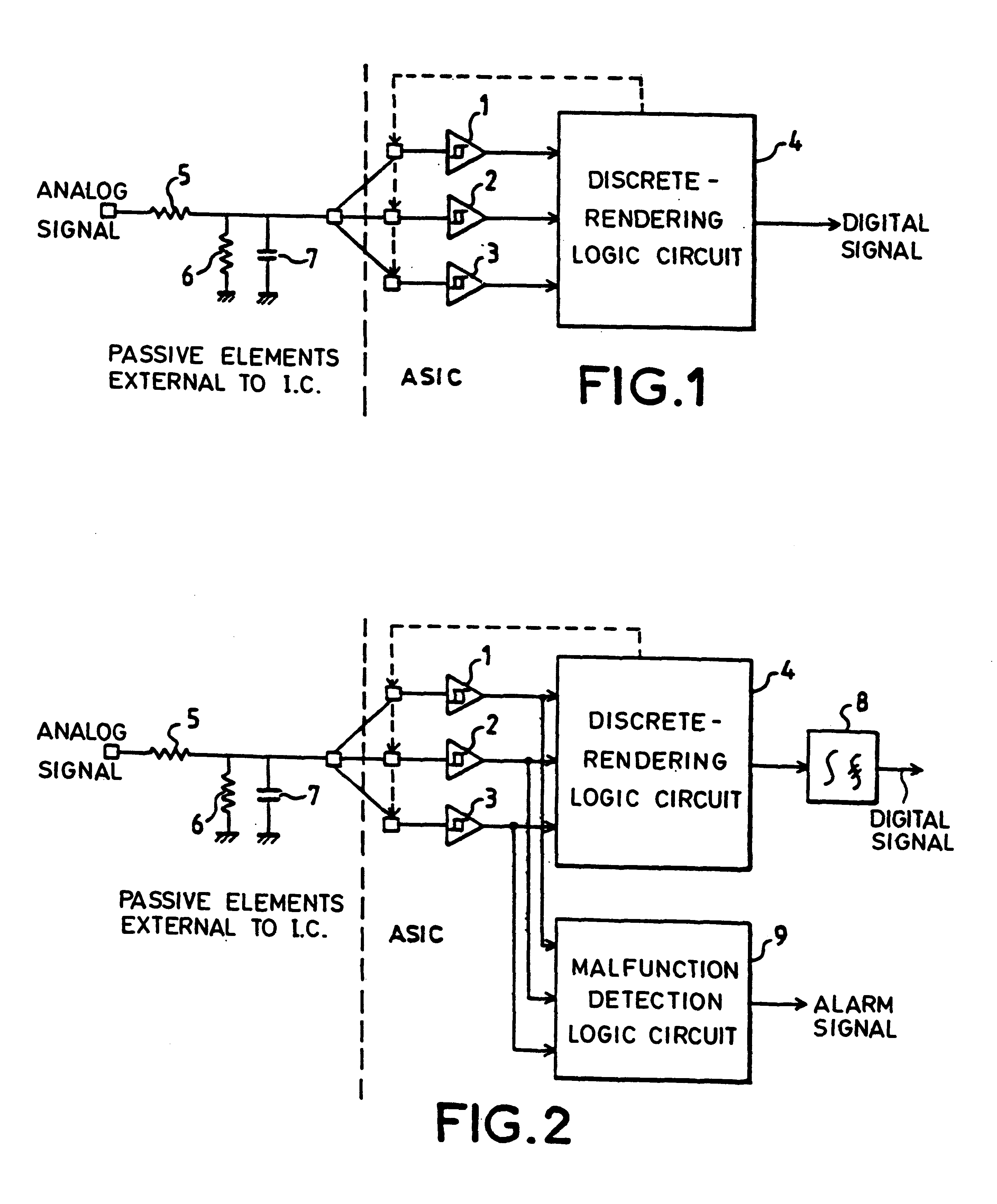

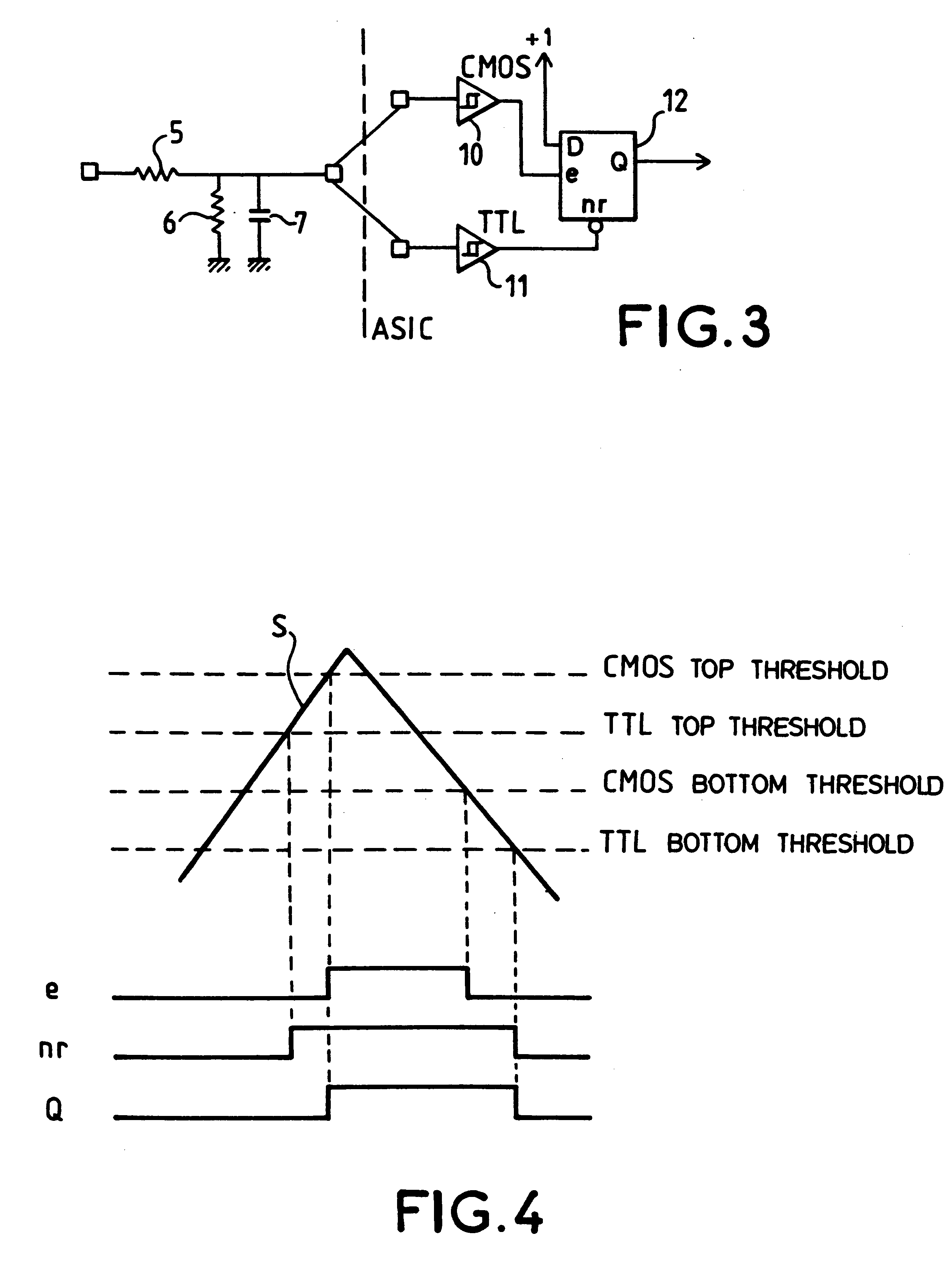

Circuit for the acquisition of binary analog signals

InactiveUS6204786B1Increase the number ofAnalogue/digital conversionElectric signal transmission systemsSchmitt triggerAnalog signal

The disclosure relates to the acquisition of a binary analog signal at input of a digital integrated circuit after its range of voltage variation has been matched with that acceptable by the digital integrated circuit by means of a resistive divider bridge. It is usual to define the architecture of an ASIC digital integrated circuit on the basis of libraries of pre-characterized cells. The disclosed device is designed to increase the possibilities of choice open to the integrated circuit designer, in enabling him to one pre-characterized cell of a Schmitt trigger for its top switching threshold and another for its bottom switching threshold. It consists of a circuit comprising, at input, a bank of Schmitt triggers of different types, followed by a discrete-rendering logic circuit deducing the logic state of the binary input analog signal of the combination of the output states of the input Schmitt triggers.

Owner:SEXTANT AVIONIQUE

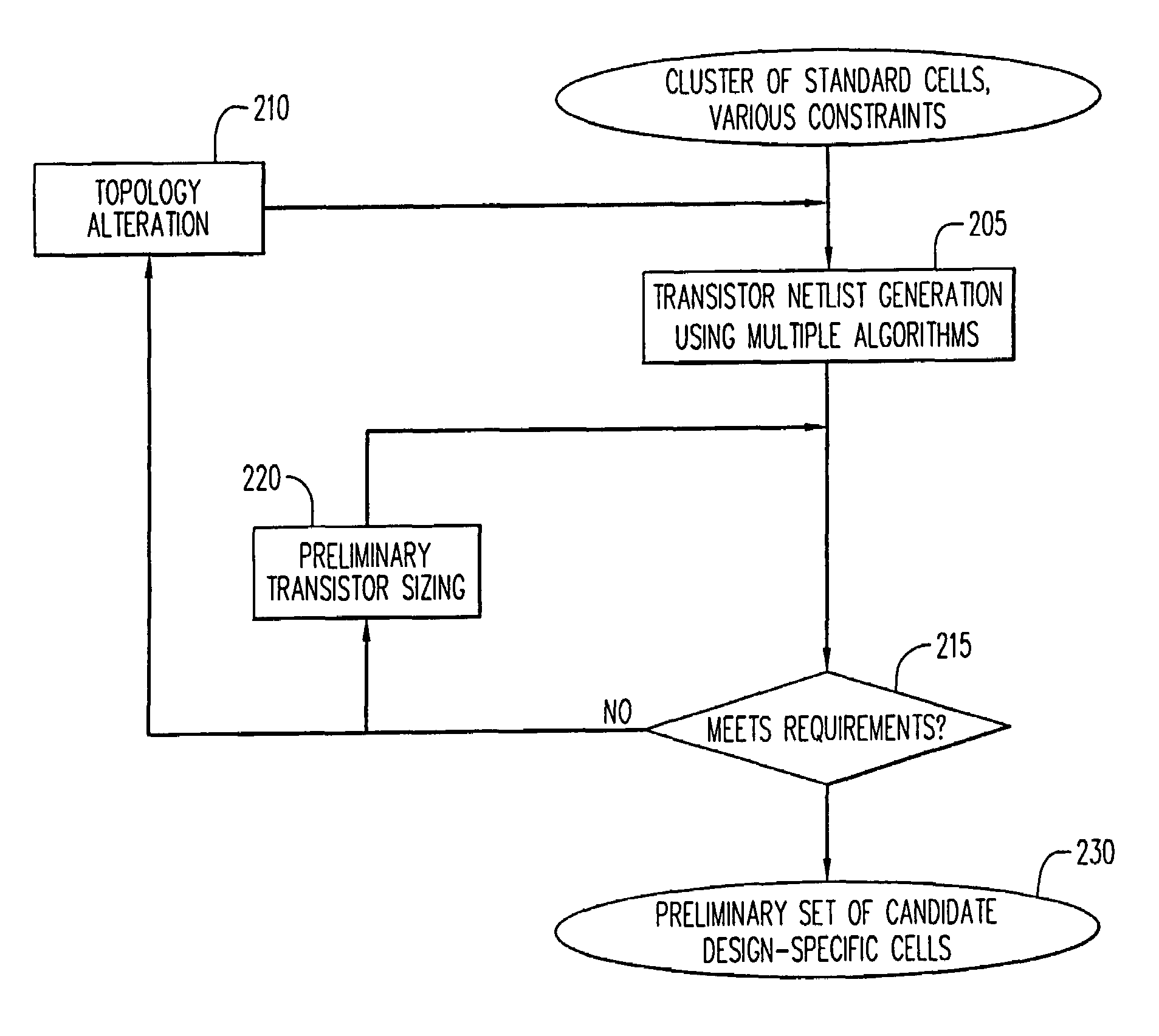

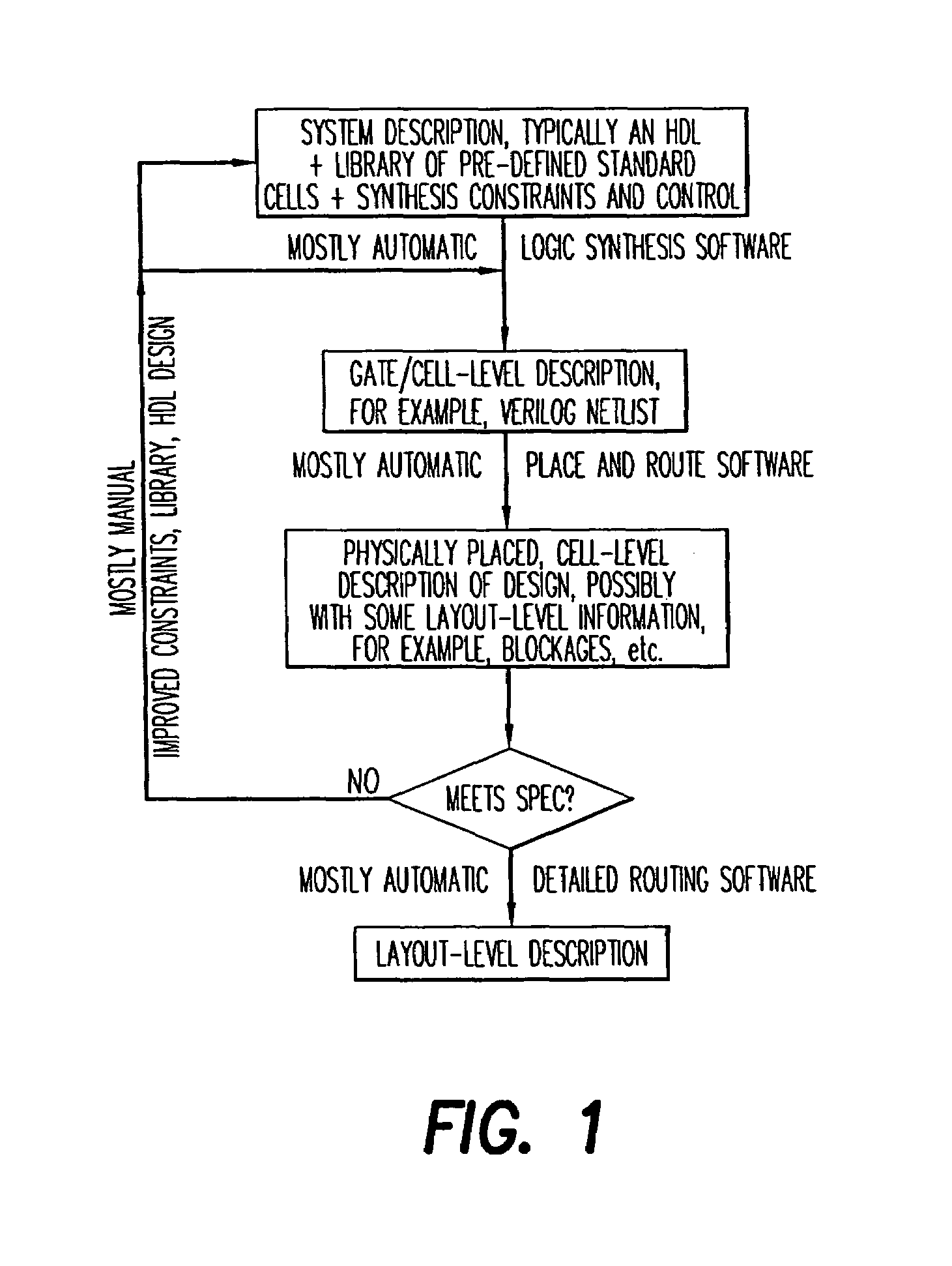

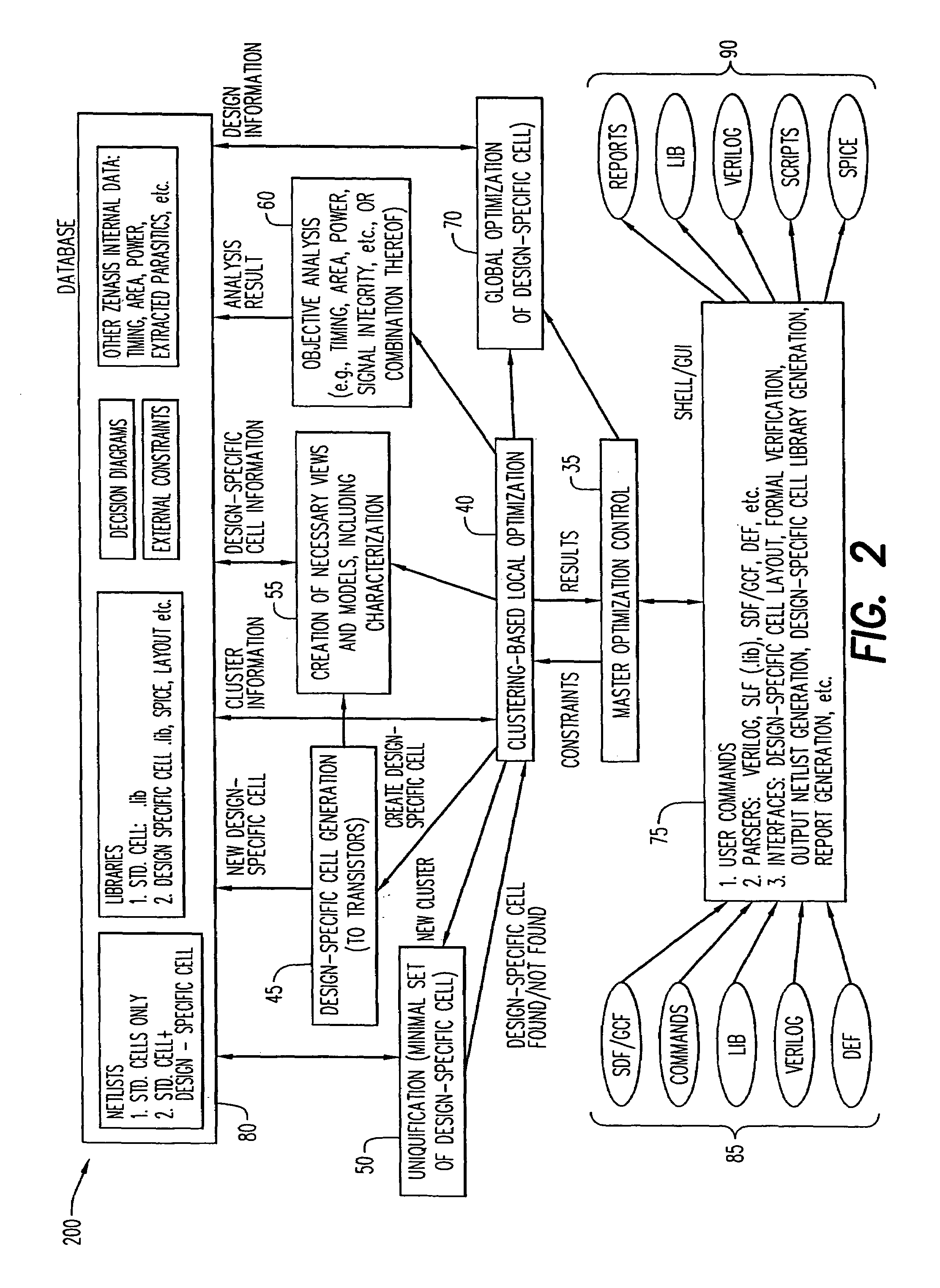

Process for automated generation of design-specific complex functional blocks to improve quality of synthesized digital integrated circuits in CMOS using altering process

InactiveUS7003738B2Small sizeCAD circuit designSoftware simulation/interpretation/emulationCMOSGenerative Design

The present invention pertains to an automated method for designing a integrated circuit (IC) design-specific cell, the method includes the steps of receiving a design specification for the design-specific cell, mapping a transistor-level representation of the design-specific cell, wherein the mapping is based on at least one, but perhaps plural design specifications, and evaluating the transistor-level representation of the design-specific cell for satisfaction of the design specification.

Owner:OPEN-SILICON

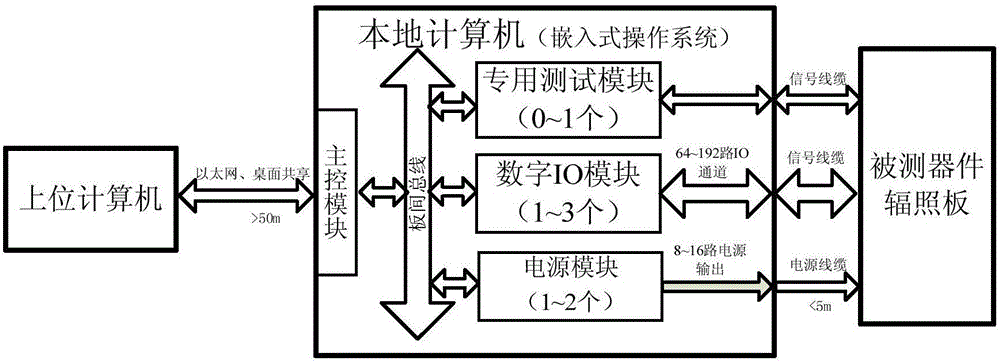

System and method for online testing of radiation effect of modular digital integrated circuit

ActiveCN105911454AImprove standardizationImprove scalabilityElectronic circuit testingComputer moduleModularity

The invention relates to a system and method for the online testing of a radiation effect of a modular digital integrated circuit, and the system enables all needed function circuits in the effect testing to be divided into relatively independent modules on the basis of summarizing the similarities and differences of conventional digital integrated circuit radiation effect online testing systems. The electrical and mechanical connection among the modules, the design in the modules and the mechanical structure of a system board respectively employ conventional industrial standards, thereby achieving a purpose that a system can employ a commercial module or an independently developed modular for quick connection, enabling the system to be better in expandability, and saving the design time and cost of hardware. The method can be used for the majority of the online testing of the radiation effect of digital integrated circuits of bullets and satellites. The system plays an important role in standardizing a national radiation effect online testing system.

Owner:NORTHWEST INST OF NUCLEAR TECH

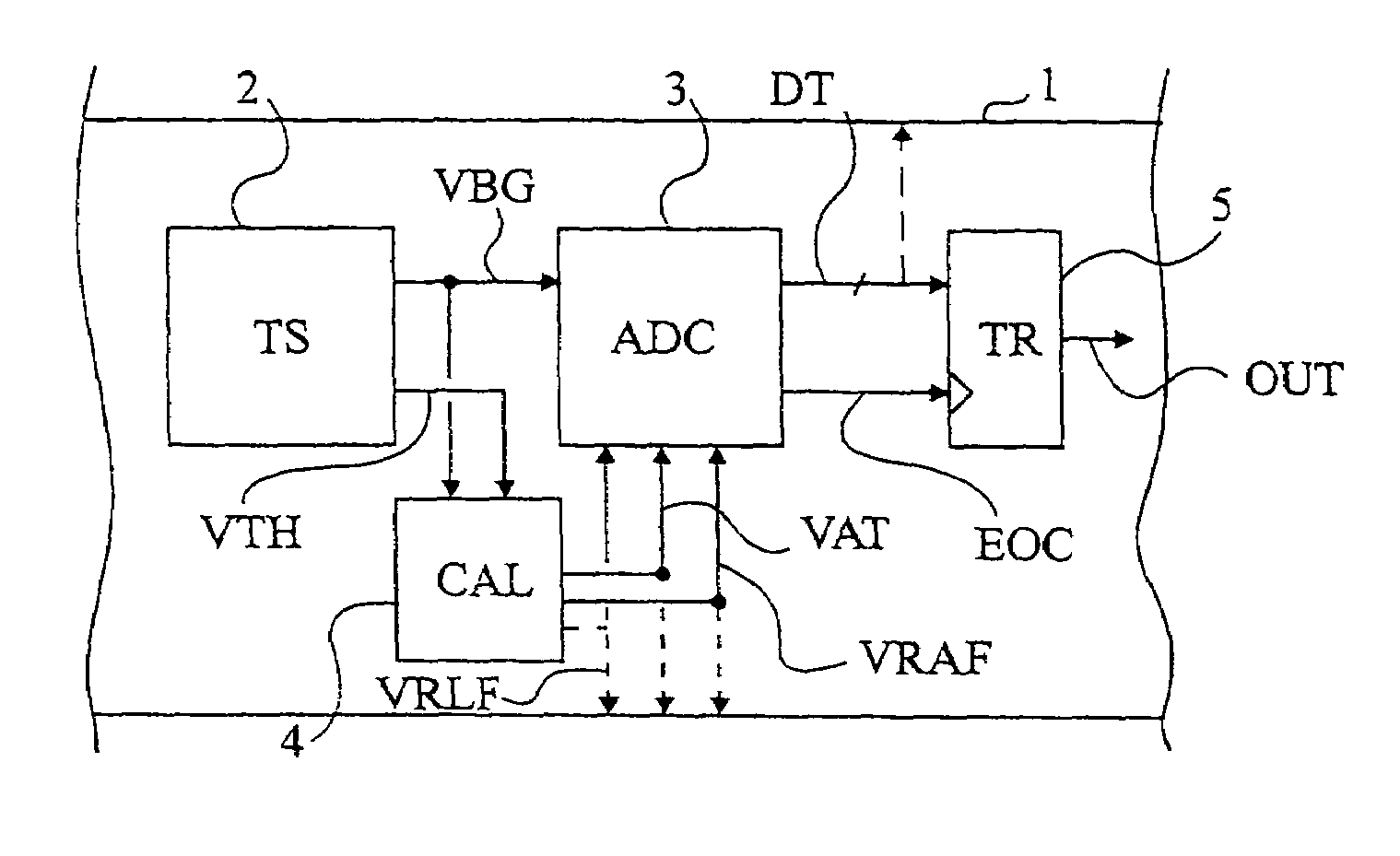

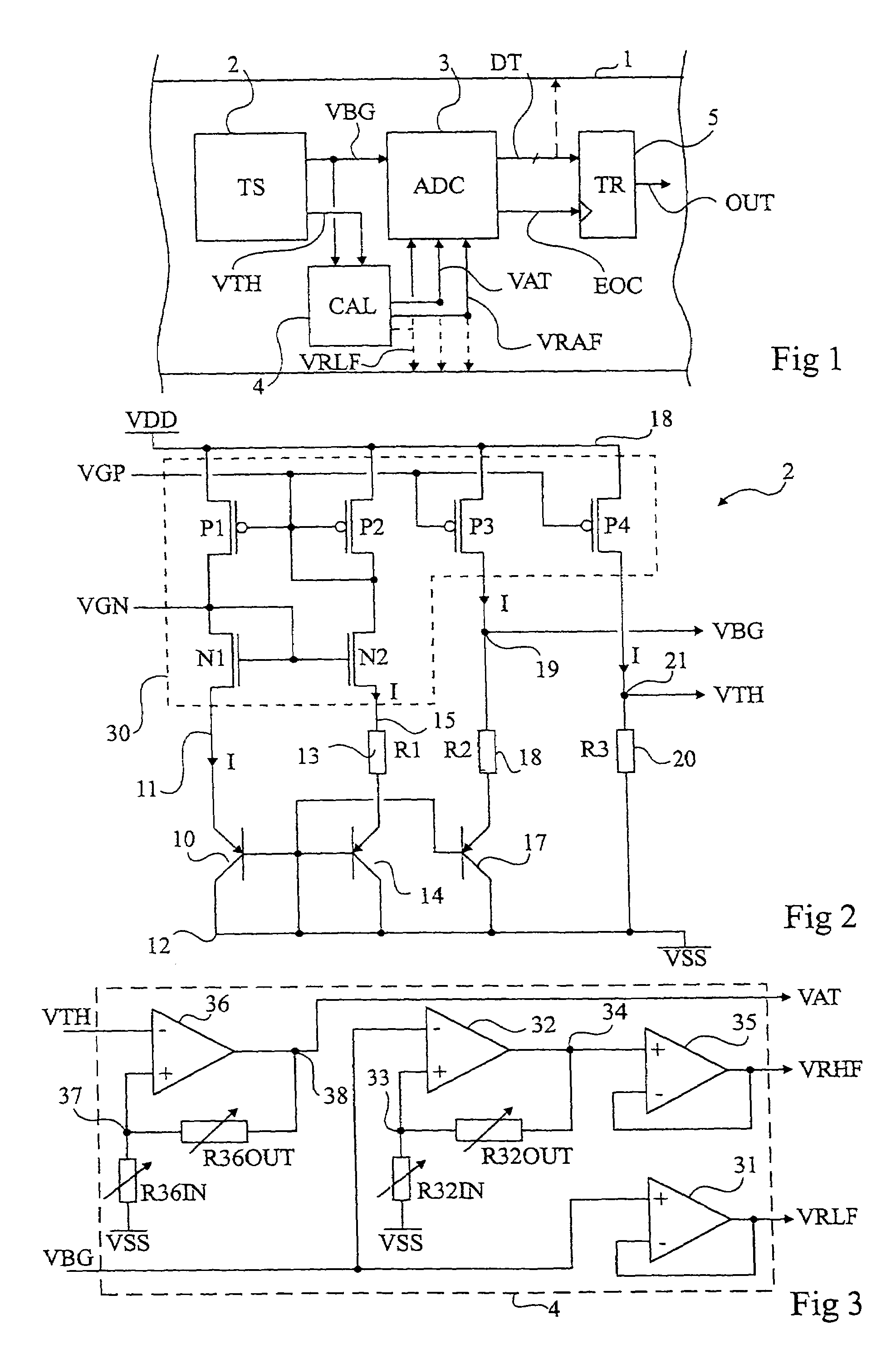

Integrated digital temperature sensor

InactiveUS7029171B2Reduce mistakesThermometer detailsThermometers using material expansion/contactionVoltage referenceDigital converter

A digital integrated circuit temperature sensor including an analog-to-digital converter providing a binary word representative of a temperature internal to the integrated circuit, and a circuit for providing an analog voltage representative of the circuit temperature and for generating a reference voltage for the analog-to-digital converter. The present invention especially applies to the testing of integrated circuits and to the control of their frequency and / or of their operating temperature according to their internal temperature.

Owner:STMICROELECTRONICS SRL

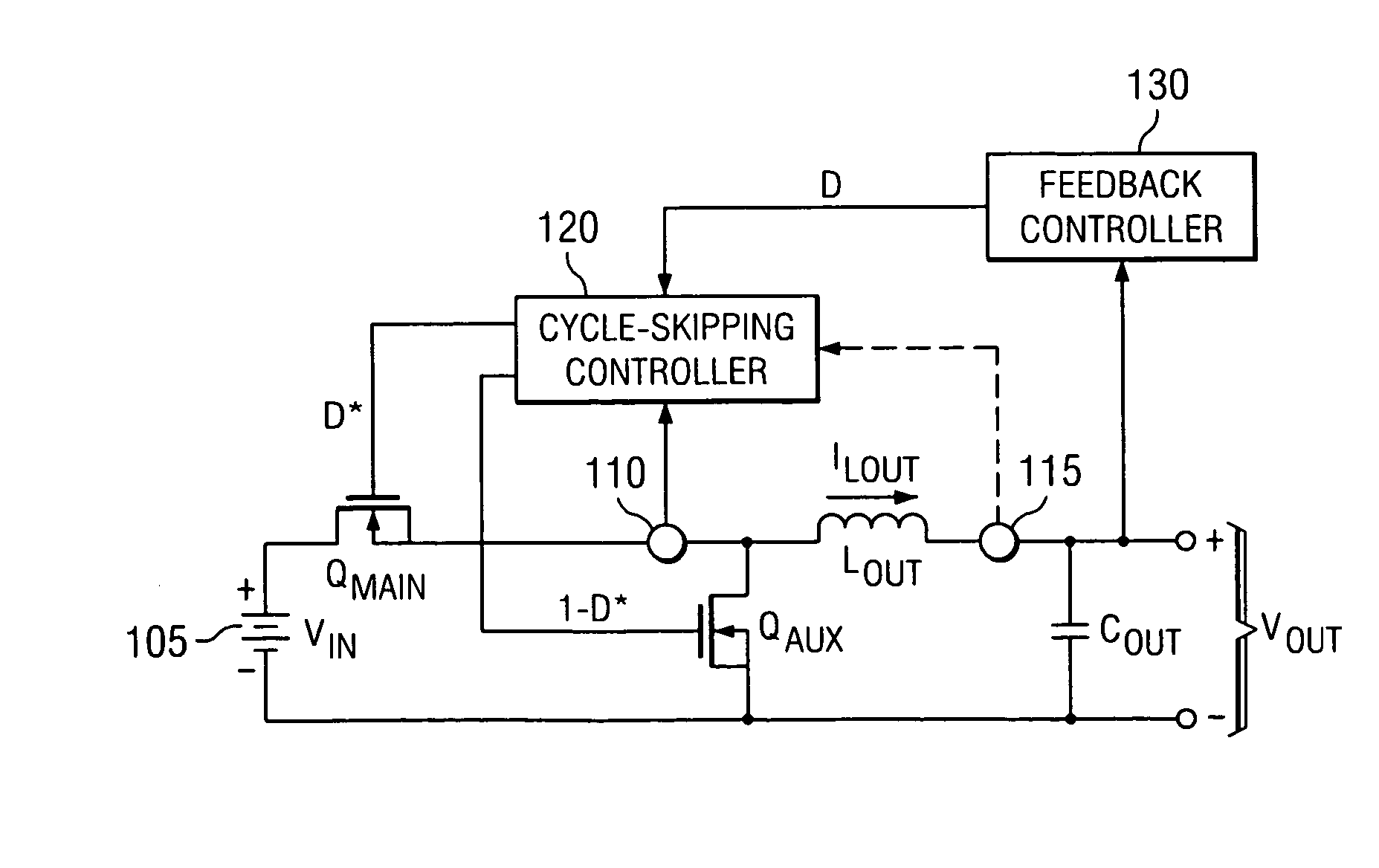

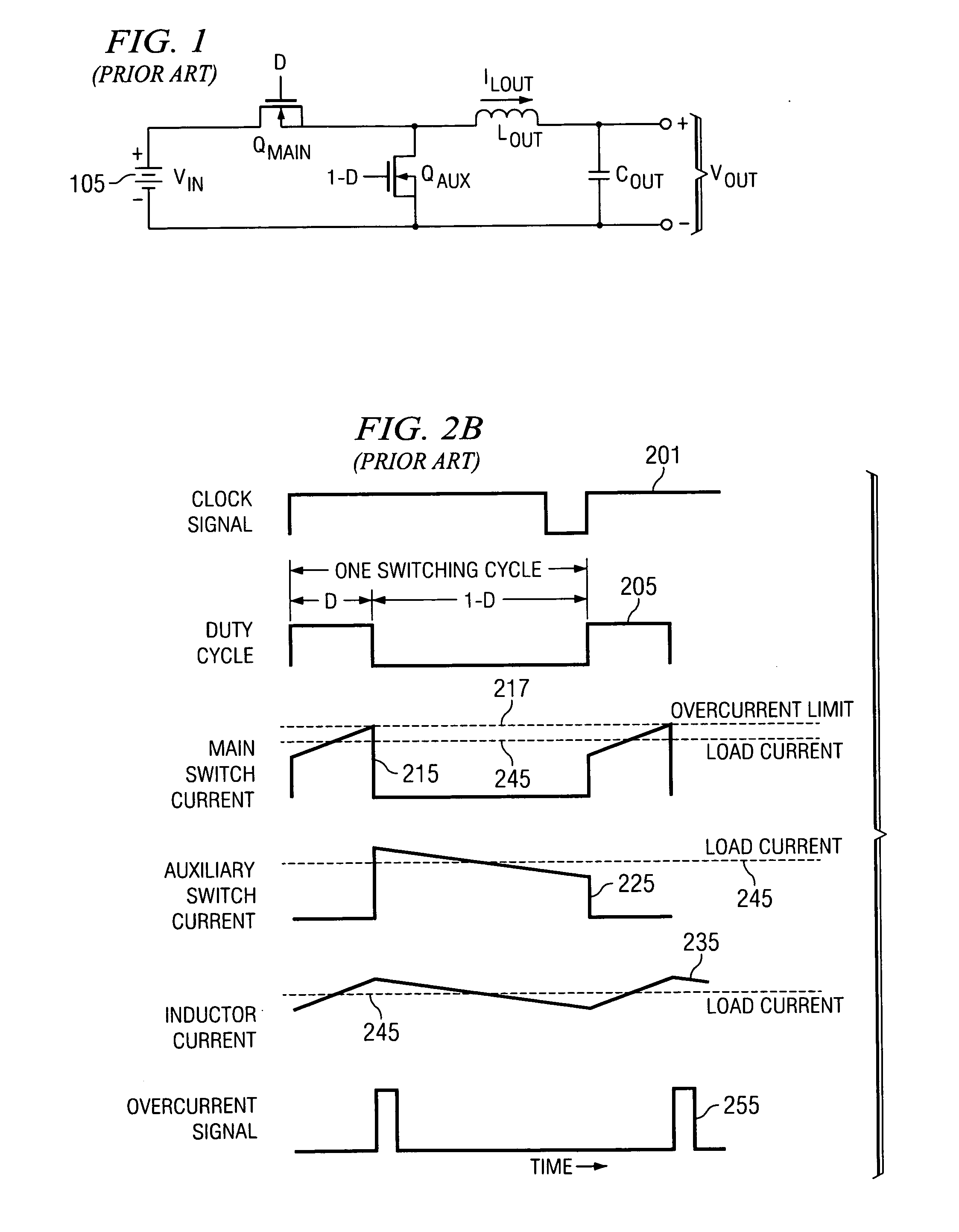

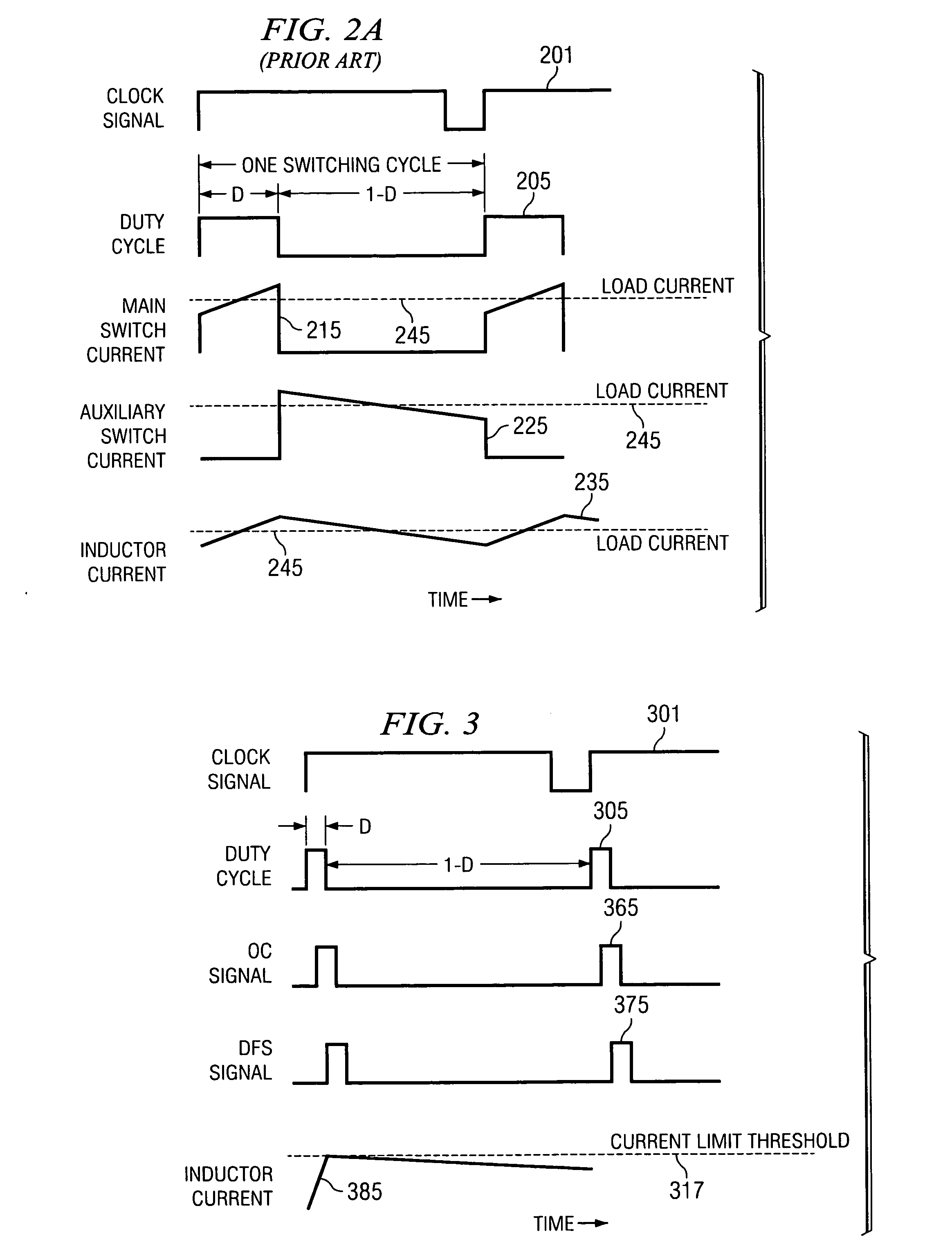

Method and apparatus for overcurrent protection in DC-DC power converters

ActiveUS20070008748A1Easy to implementWide rangeDc-dc conversionEmergency protective arrangements for limiting excess voltage/currentSwitching cycleEngineering

Owner:TEXAS INSTR INC

Device for detecting power equipment discharge based on ultraviolet method

InactiveCN101813730AImprove securityReduce workloadElectrical testingPhotometry electrical circuitsUltravioletPower equipment

The invention discloses a device for detecting power equipment discharge based on an ultraviolet method, comprising a sensor unit, a signal processing unit, a processor unit and a power supply unit, wherein the sensor unit comprises a front-end light-filtering device and a photomultiplier which are correspondingly arranged; the signal processing unit comprises a front-end amplifying circuit, a wave-filtering adjustment circuit, a post amplifying circuit, a pulse discriminating circuit and a digital integrating circuit; the power supply unit comprises a high-voltage power supply module and a circuit power supply module; the high-voltage power supply module is connected with the power end of the photomultiplier; and the circuit power supply module is connected with the related power ends of the signal processing unit and the processor unit. The device not only can qualitatively analyze the discharge condition, but also can quantitatively detect the discharge capacity of the equipment, is convenient for the operators to understand the discharge trend of the equipment and simultaneously provides the basis for evaluating the insulation state of the operating equipment. The device adopts non-contact measurement, thereby greatly improving the security of power detection.

Owner:CHONGQING UNIV

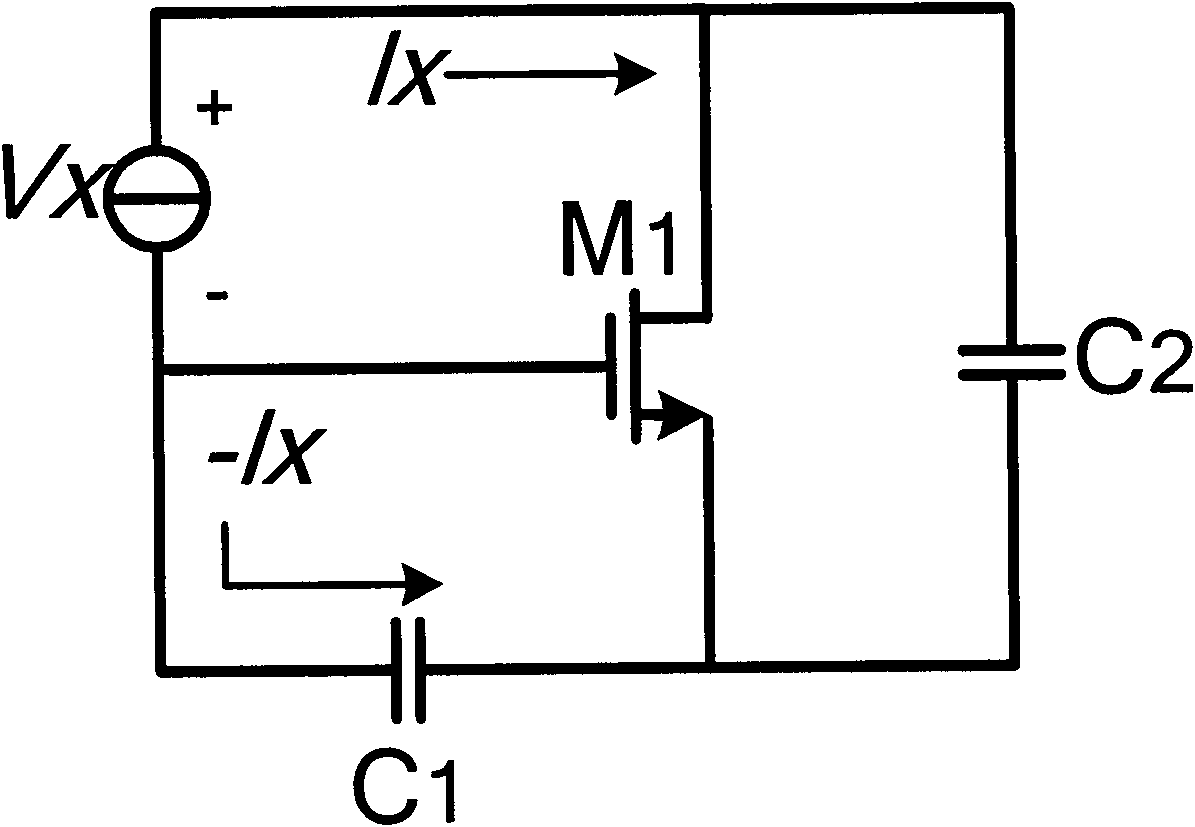

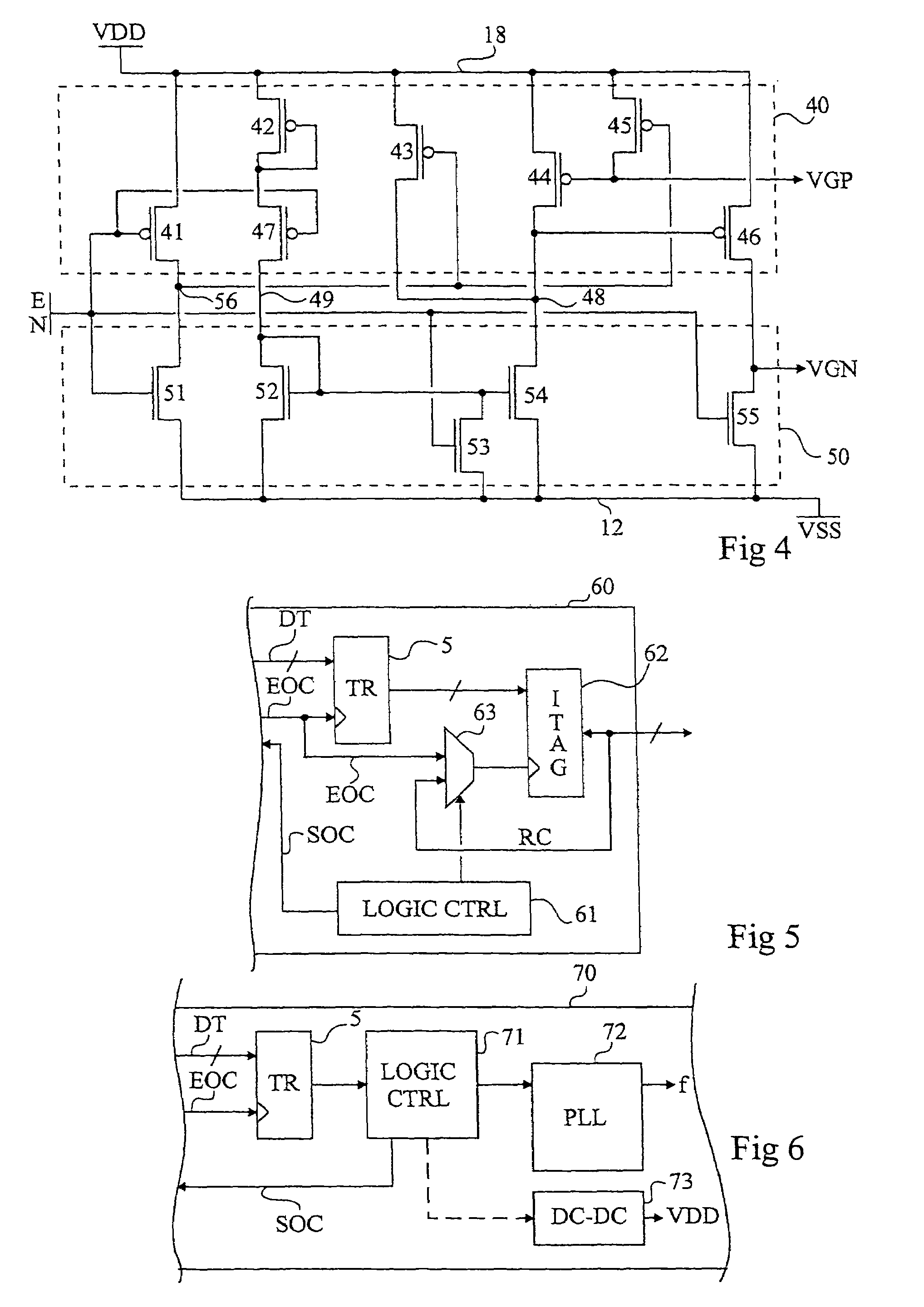

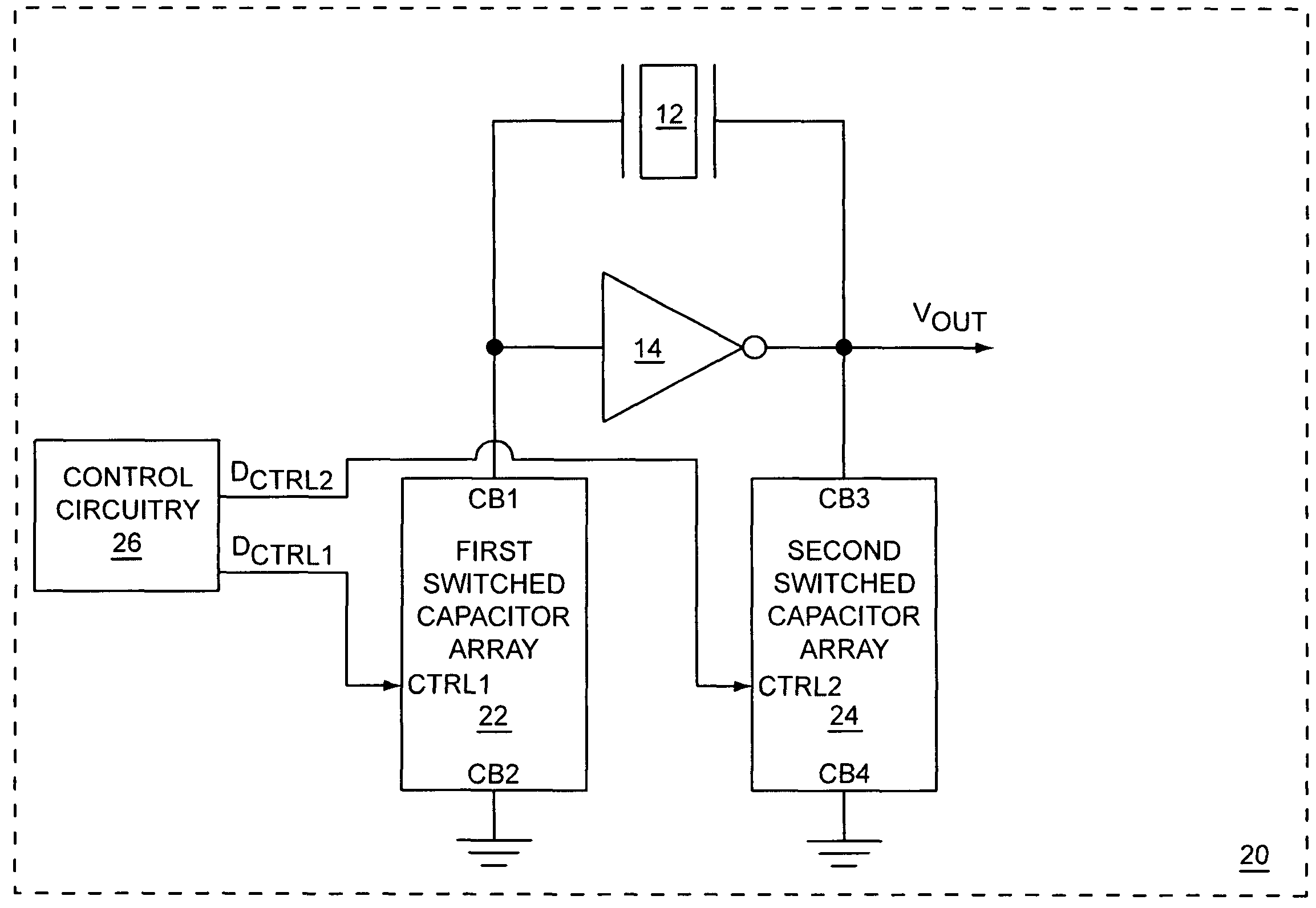

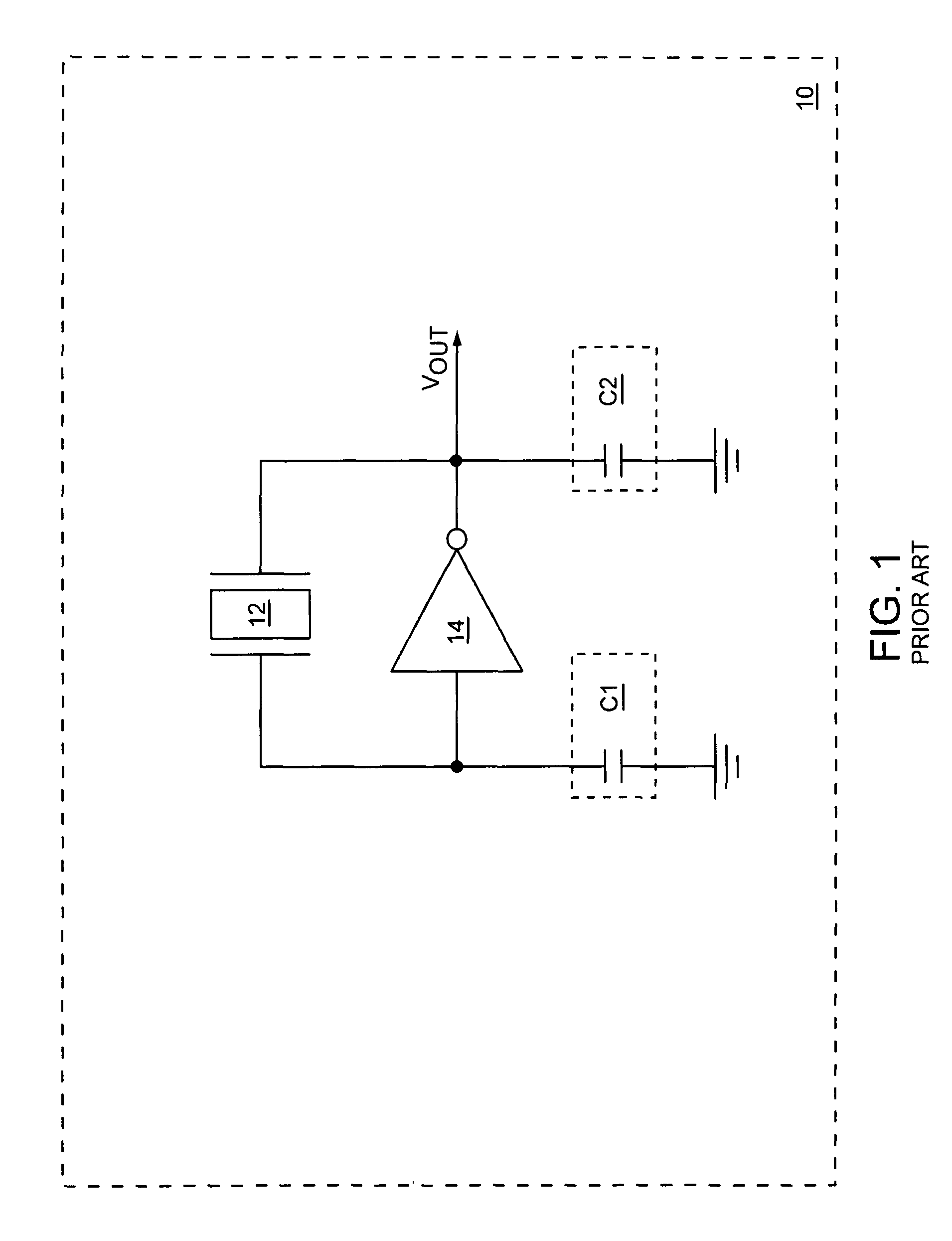

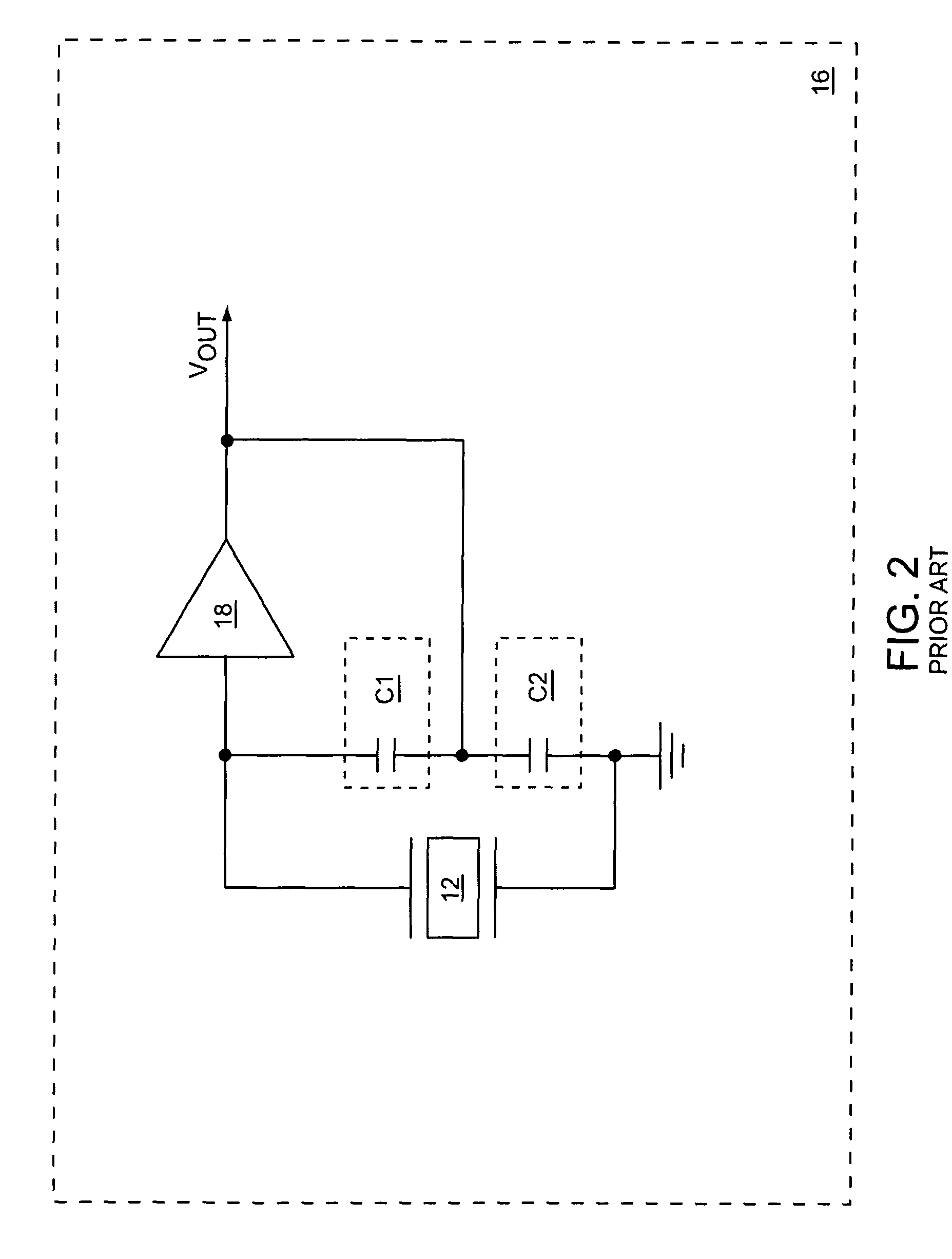

Digitally-controlled crystal oscillator circuit

ActiveUS7868710B1High gainImprove reliabilityAngle modulation by variable impedenceOscillations generatorsCapacitanceControl signal

The present invention relates to a digitally-controlled crystal oscillator (DCXO) circuit having control circuitry, an active core, and a pair of thermometer-coded switched-capacitor circuits (TCSCCs), each of which is coupled to the active core and to a crystal. The active core, the crystal, and the pair of TCSCCs form a DCXO, which provides an output signal having an output frequency. Each TCSCC includes multiple capacitive elements, which are selected by a respective control signal from the control circuitry to control the output frequency. The DCXO circuit may be integrated into a digital integrated circuit (IC) without need for a digital-to-analog converter (DAC), and may be used with a wide range of crystal types. By using thermometer-coding, the pair of TCSCCs provides monotonic frequency tuning behavior. Further, by utilizing different types of tuning steps, the DCXO may have a wide tuning range with high resolution.

Owner:QORVO US INC

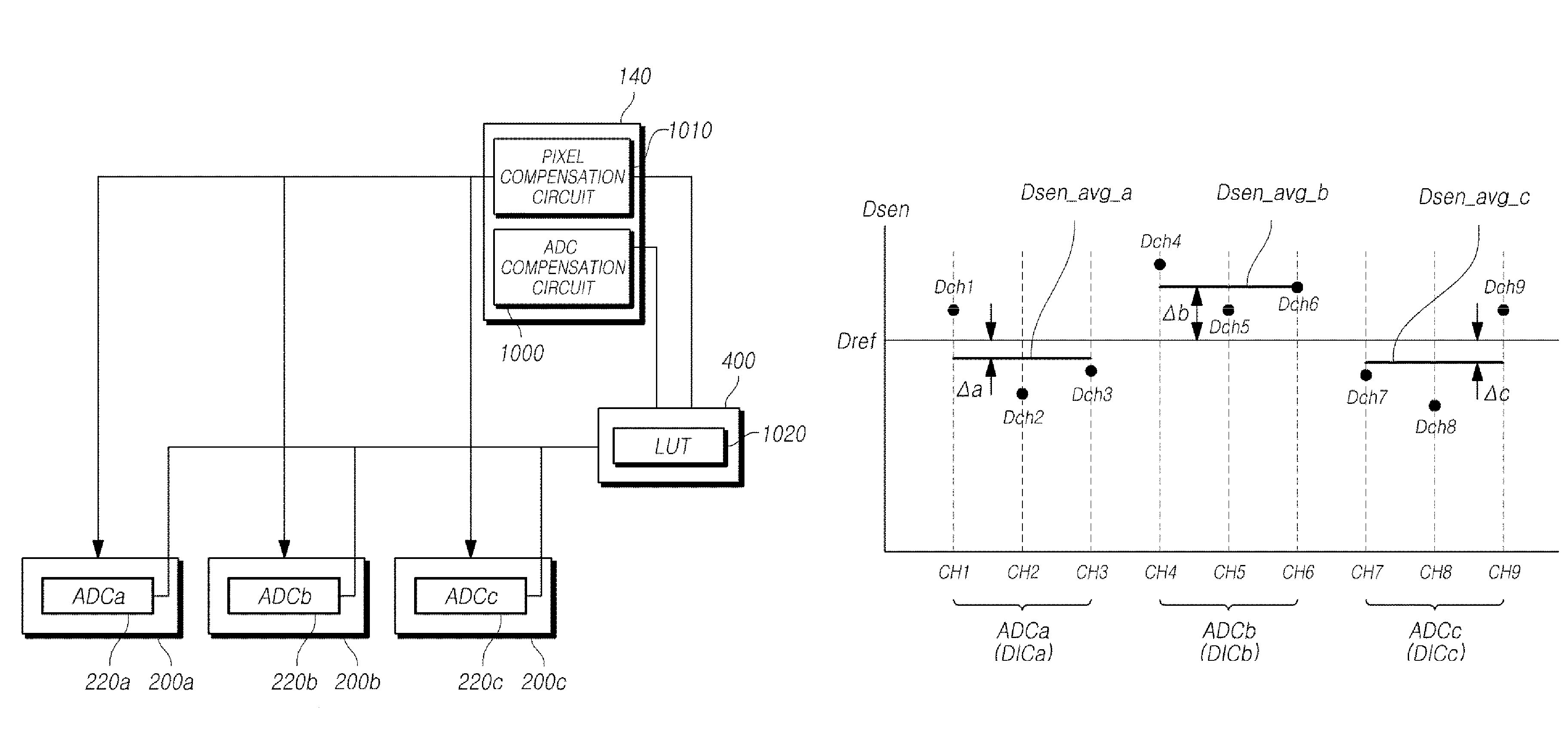

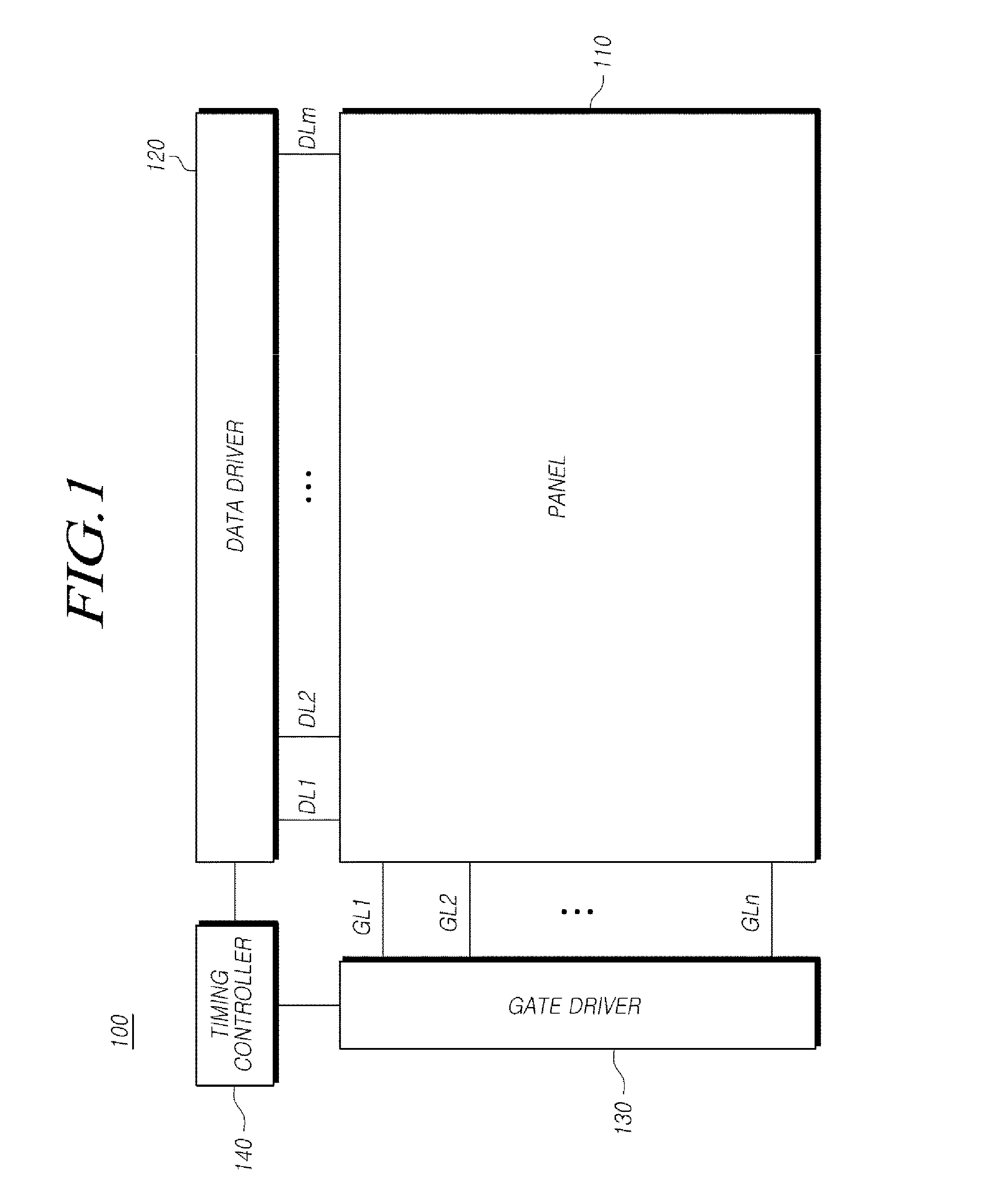

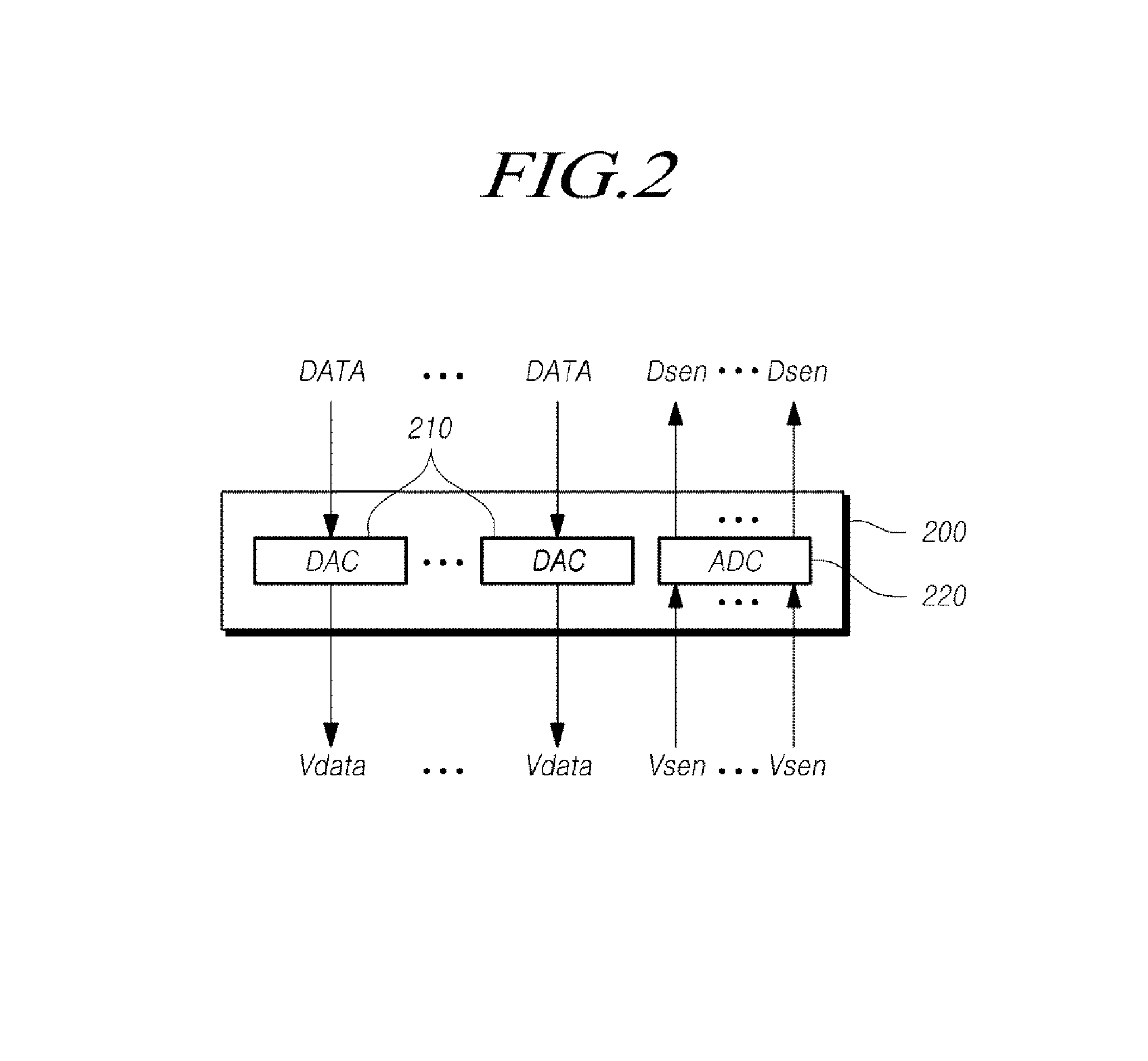

Display device with ADC and pixel compensation

ActiveUS9076387B1Prevent and reduce non-uniformityImprove image qualityStatic indicating devicesAnalogue-digital convertersDisplay deviceEngineering

A display device includes a display panel having data lines, gate lines and a plurality of subpixels. Each of the plurality of subpixels are defined by the data lines and the gate lines, and each of the plurality of subpixels includes a circuit having a transistor. A plurality of Digital Integrated Circuits (DICs) where a digital to analog converter (DAC) is disposed within each of the plurality of DICs. An analog to digital converter (ADC) is disposed within each of the plurality of DICS, where the ADC disposed in each of the plurality of DICs includes a plurality of sensing channels. The display device includes a pixel compensation circuit to compensate a characteristic of the transistor within each of the plurality of subpixels and an ADC compensation circuit to compensate a characteristic of the ADC within each of the plurality of DICs.

Owner:LG DISPLAY CO LTD

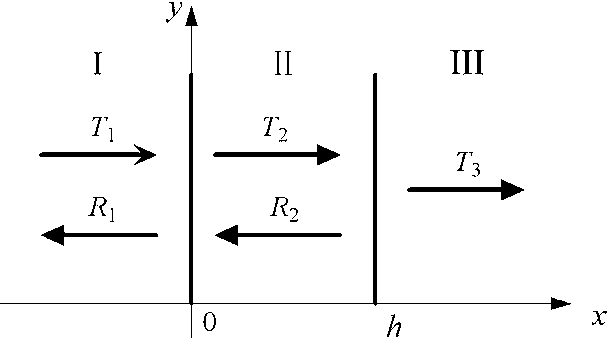

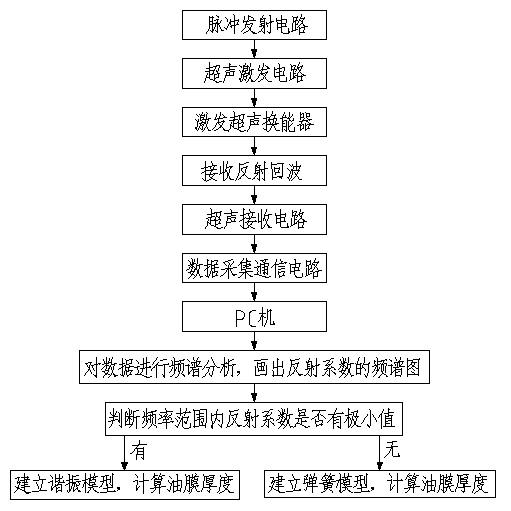

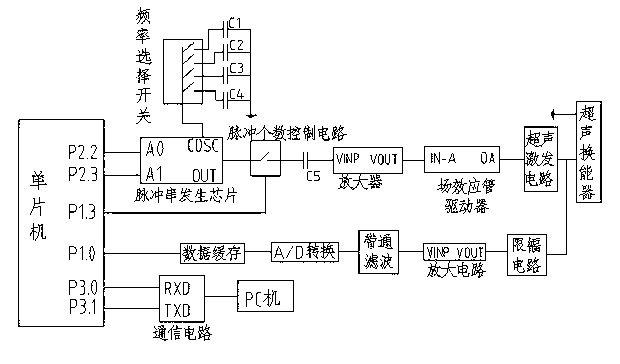

Ultrasonic film thickness measuring instrument and measuring method thereof

InactiveCN103308011AReduce volumeWill not cause missingUsing subsonic/sonic/ultrasonic vibration meansMicrocontrollerMeasuring instrument

The invention provides an ultrasonic measuring instrument and a measuring method for monitoring the thickness of an oil film between two contacted surfaces. The ultrasonic measuring instrument comprises a pulse transmission circuit, an ultrasonic excitation circuit, an ultrasonic receiving circuit, a data acquisition communication circuit and a personal computer (PC) which are sequentially connected, wherein the ultrasonic excitation circuit is further connected with an ultrasonic transducer; and the pulse transmission circuit and the data acquisition communication circuit share the same single-chip microcomputer. Compared with a traditional ultrasonic thickness measuring instrument, the size of the ultrasonic thickness measuring instrument is smaller due to a digital integrated circuit, the analog-to-digital (A / D) sampling rate is very high, radio frequency sampling is directly carried out to an ultrasonic signal, and the information is not lost. A circuit design is simpler, and corresponding data can be processed. The designed instrument adopts a new oil film thickness calculation method, can measure oil film thicknesses of nano level, and is more applicable to measuring the thicknesses of lubricating oil films.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

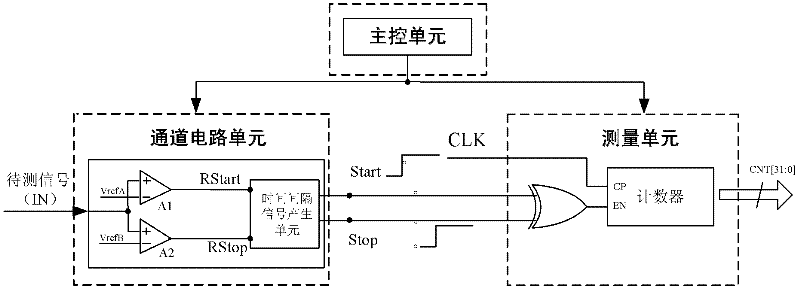

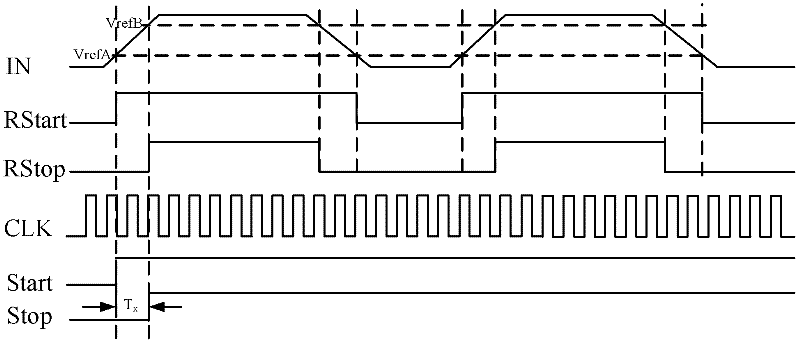

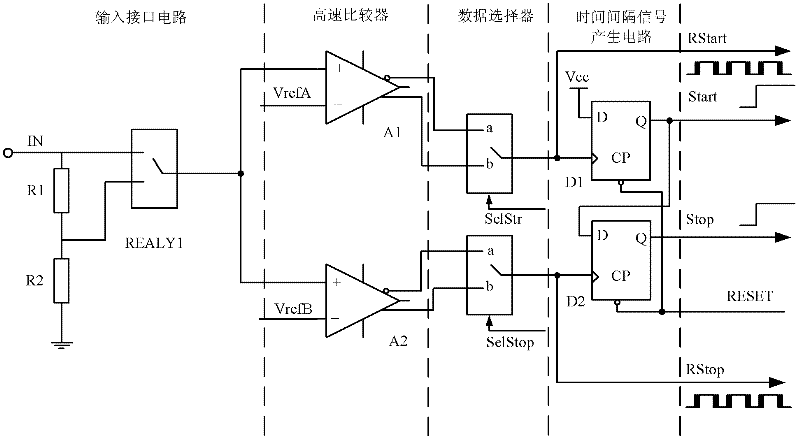

Time parameter measurement system

InactiveCN102346236ATo overcome the shortcomings that are not easy to achieveOvercoming the limitations of measurement bandwidthDigital circuit testingImage resolutionOperating frequency

The invention discloses a time parameter measurement system for digital integrated circuits. The system is implemented by converting a to-be-measured signal IN into a time interval start signal Start and a stop signal Stop as well as pulse signals RStart and RStop by a channel circuit unit; then, the four signals are respectively provided for an accurate time measurement unit and a coarse time measurement unit to carry out measurement, wherein the accurate time measurement unit is composed of a multi-stage delay line and a calibration unit, and used for carrying out measurement under the condition that the rising edge of the to-be-measured signal is steep; and the coarse time measurement unit is composed of a jittering shielding circuit, a counter 1 and a counter 2 (the operating frequencies of the counter 1 and the counter 2 are complementary), and used for carrying out measurement under the condition that the rising edge of the to-be-measured signal is slow. By using the system disclosed by the invention, the difficulty of improving the resolution ratio of a time parameter measurement system for high-precision digital integrated circuits in the prior art is overcome, and the technical difficulty that the measurement bandwidth of a time parameter measurement system is limited caused by the jitter of output signals of a comparator for channel circuits.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

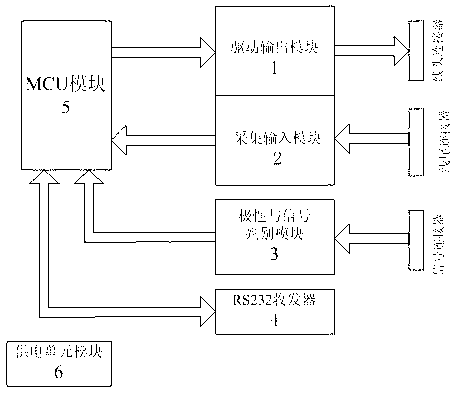

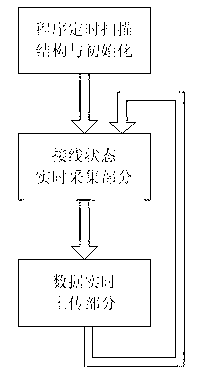

Wiring judgement control machine for wiring simulation system for verification on power transformer

InactiveCN102798834AFully electronicReal-time judgmentProgramme controlComputer controlEffective solutionTransceiver

The invention discloses a wiring judgement control machine for a wiring simulation system for verification on a power transformer. The wiring judgement control machine is composed of a drive output module, an acquisition input module, a polarity and signal discrimination module, an RS232 transceiver, an MCU (microprogrammed control unit) module, a power supply unit, etc; the MCU module is in one-way connection with the drive output module, the acquisition input module, and the polarity and signal discrimination module, and is in two-way connection with the RS232 transceiver; and the whole controller adopts a digital integrated circuit, and is used for rapidly judging the wiring relationships of 48 connecting wires under the management of embedded software, and uploading the result to an upper PC (personal computer) continuously and in real time, so as to perform further processing such as a judgement about right or wrong. Via the wiring judgement control machine disclosed by the invention, an effective solution is provided for a wiring judgement for the conductor terminal of each simulator in the wiring simulation system for verification on the power transformer.

Owner:ELECTRIC POWER RES INST OF GUANGXI POWER GRID CO LTD

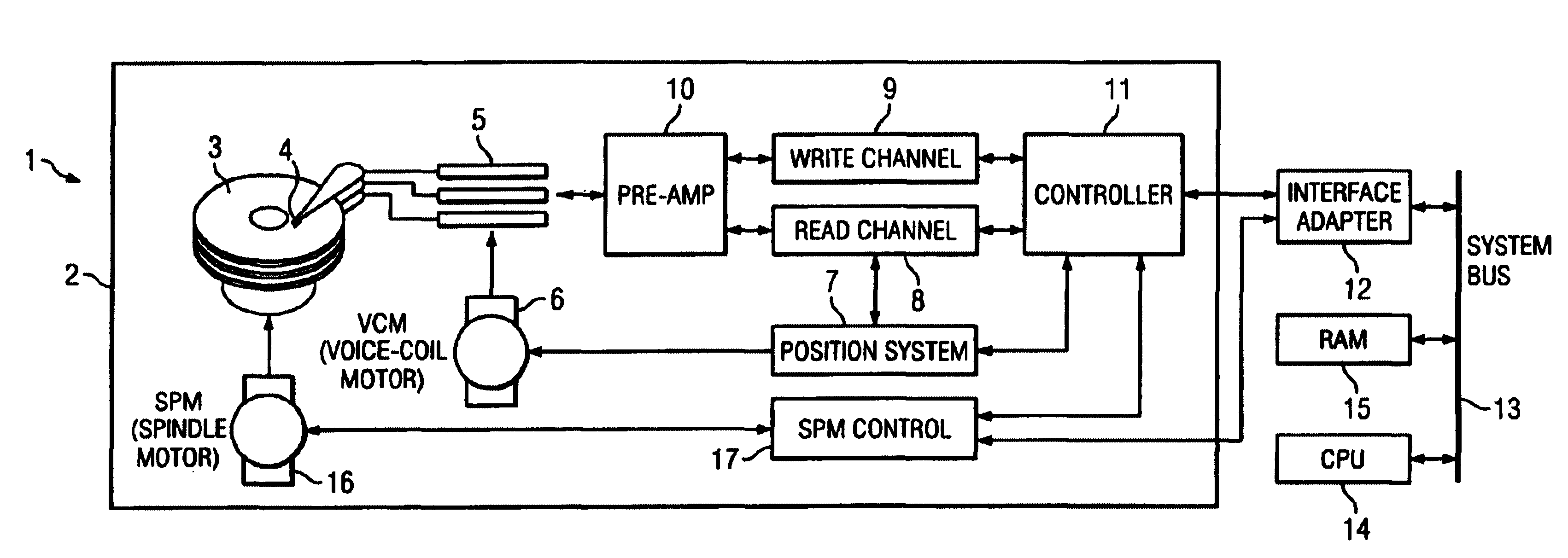

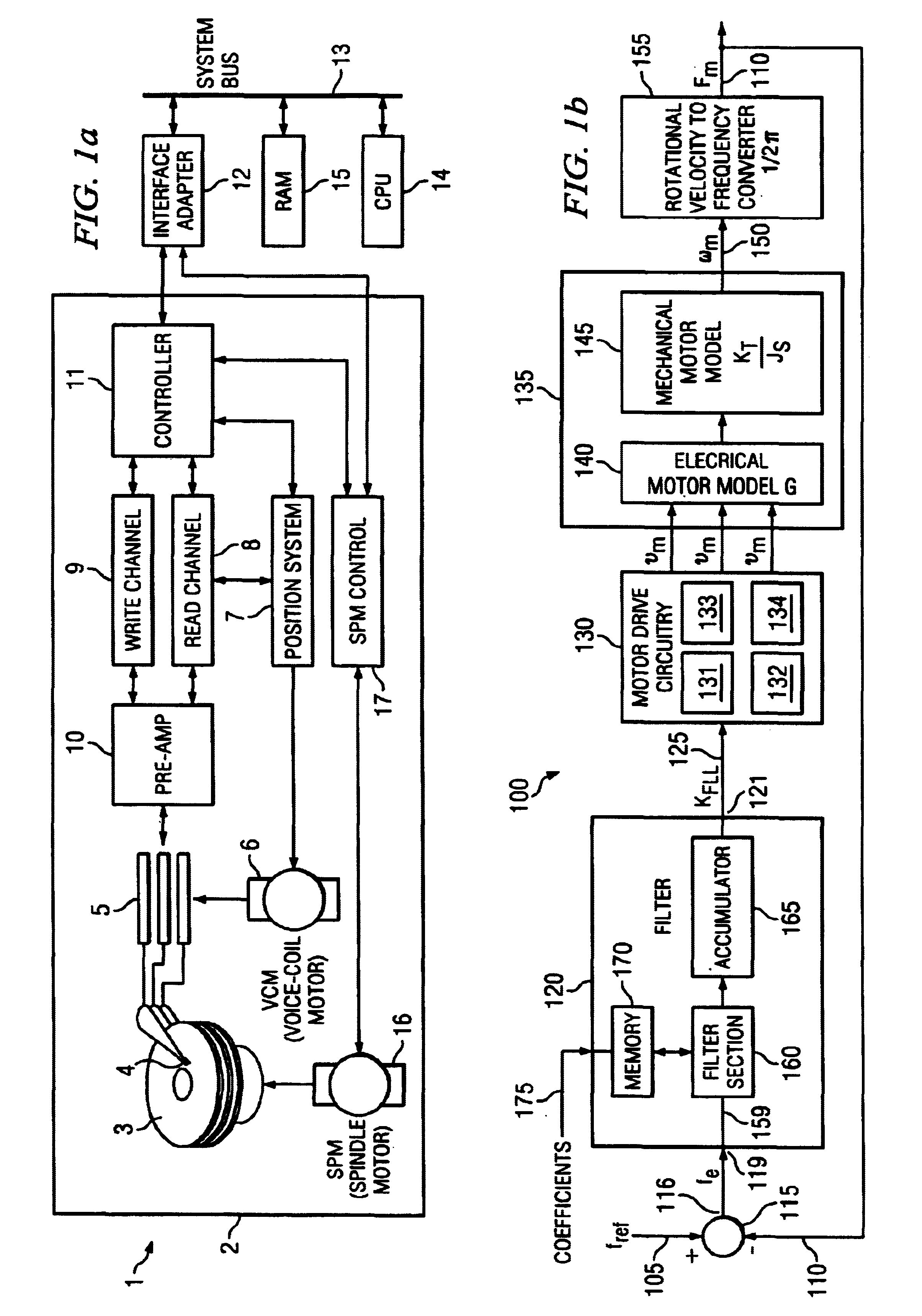

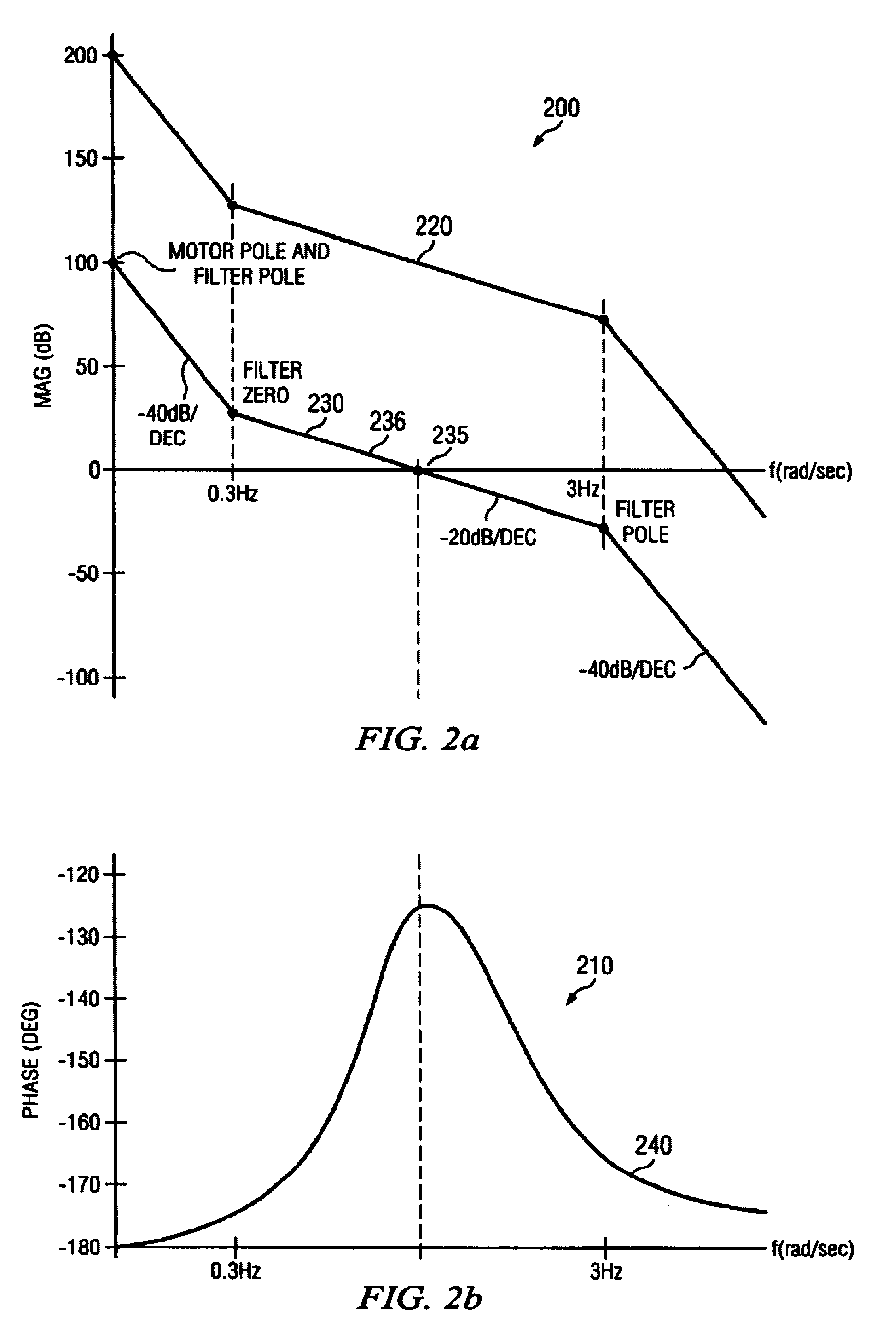

Embedded programmable filter for disk drive velocity control

A disk drive having a motor and a velocity control loop, which includes a frequency detector and a filter. The filter includes a filter section and an accumulator. The filter is programmable in that filter coefficient(s) are dynamically received by the filter section. One embodiment of the filter section is an infinite impulse response filter. One embodiment of the filter is a digital integrated circuit. A method for compensating a control loop by infinite impulse response filtering and accumulating. The control loop may be a position, velocity, acceleration or force control loop. A programmable digital integrated circuit for compensating a velocity control loop having a filter section cascaded with an accumulator. The integrated circuit may include memory for storing filter coefficient(s) for the filter section, thereby not requiring external components.

Owner:STMICROELECTRONICS SRL

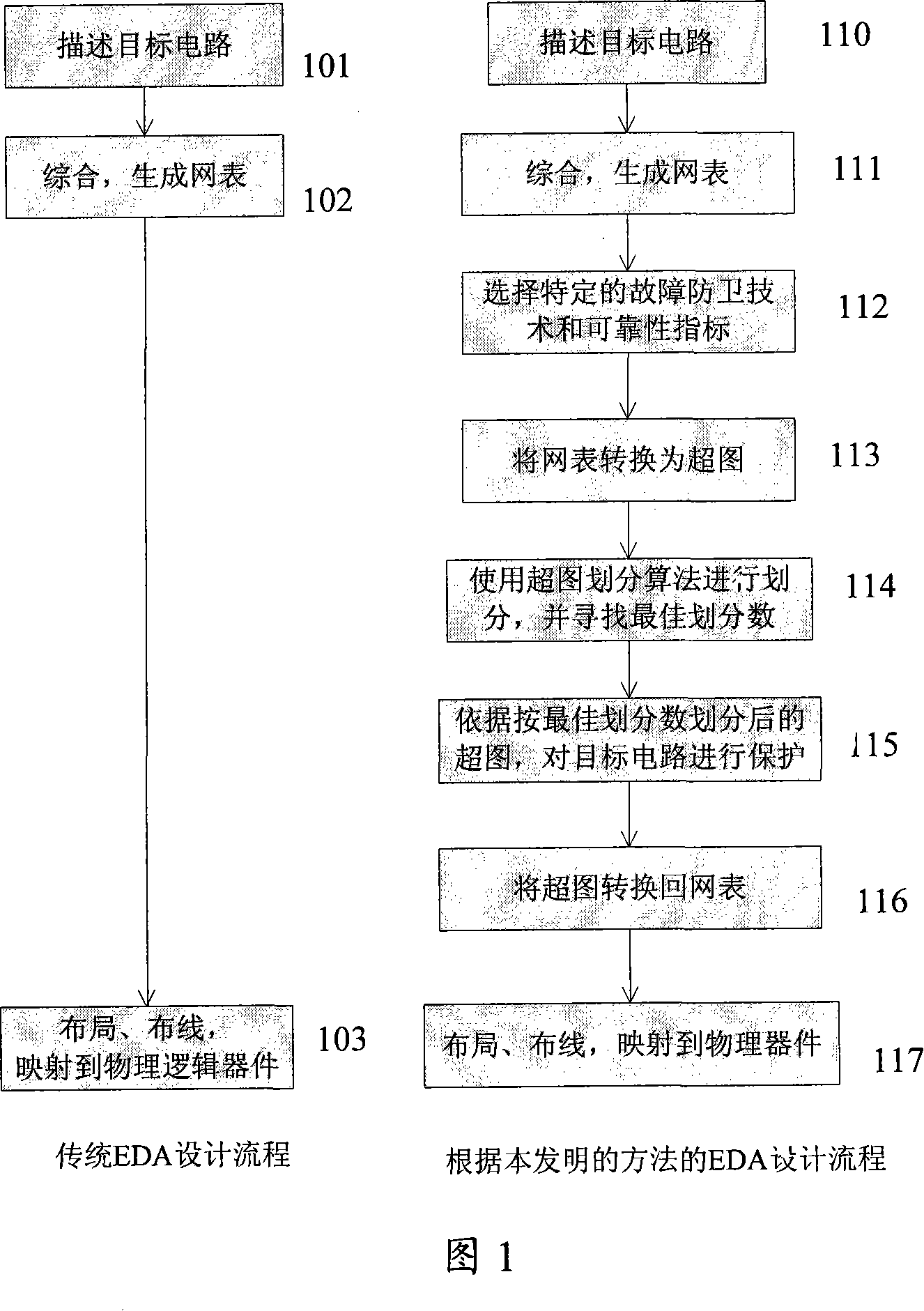

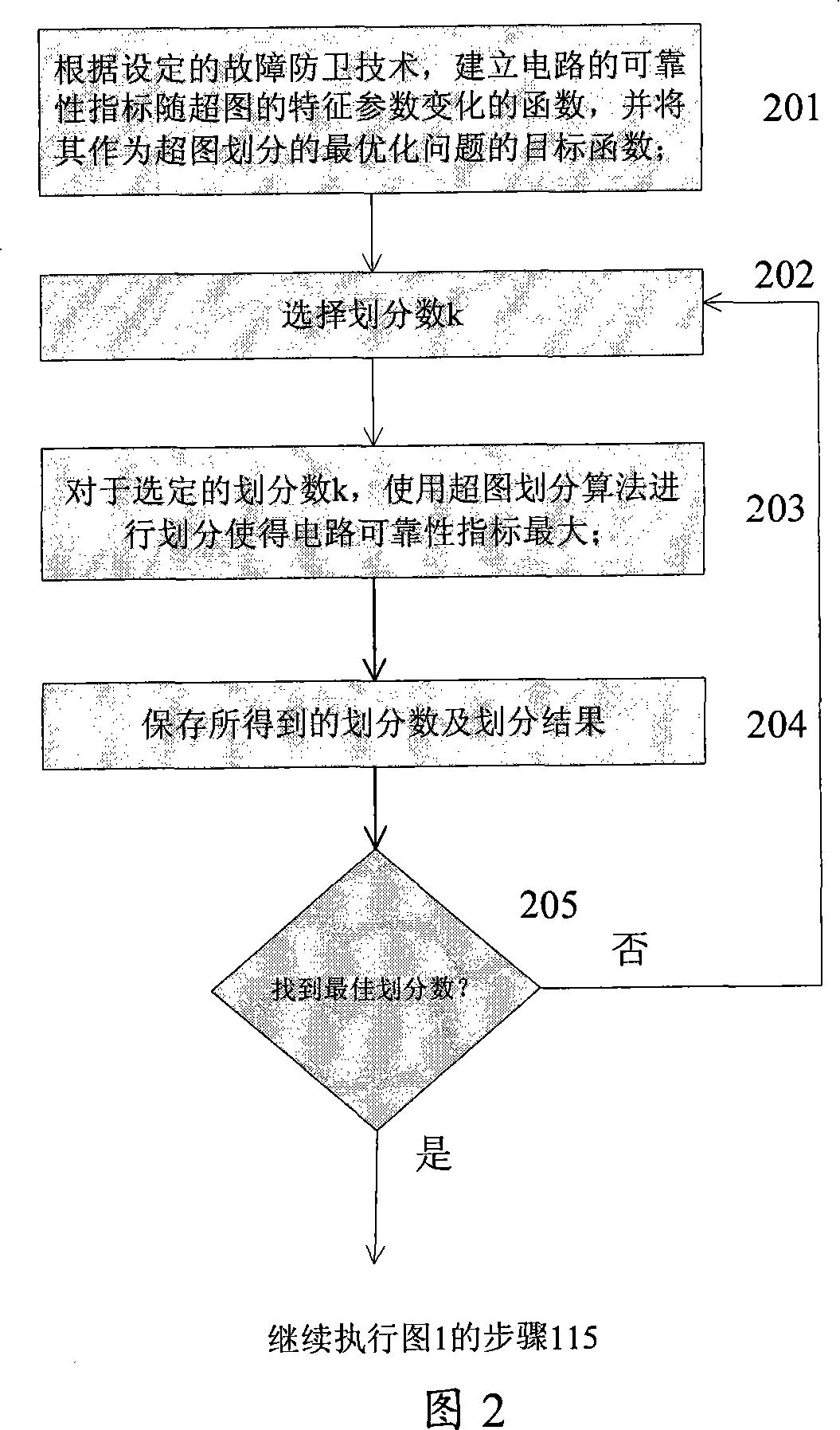

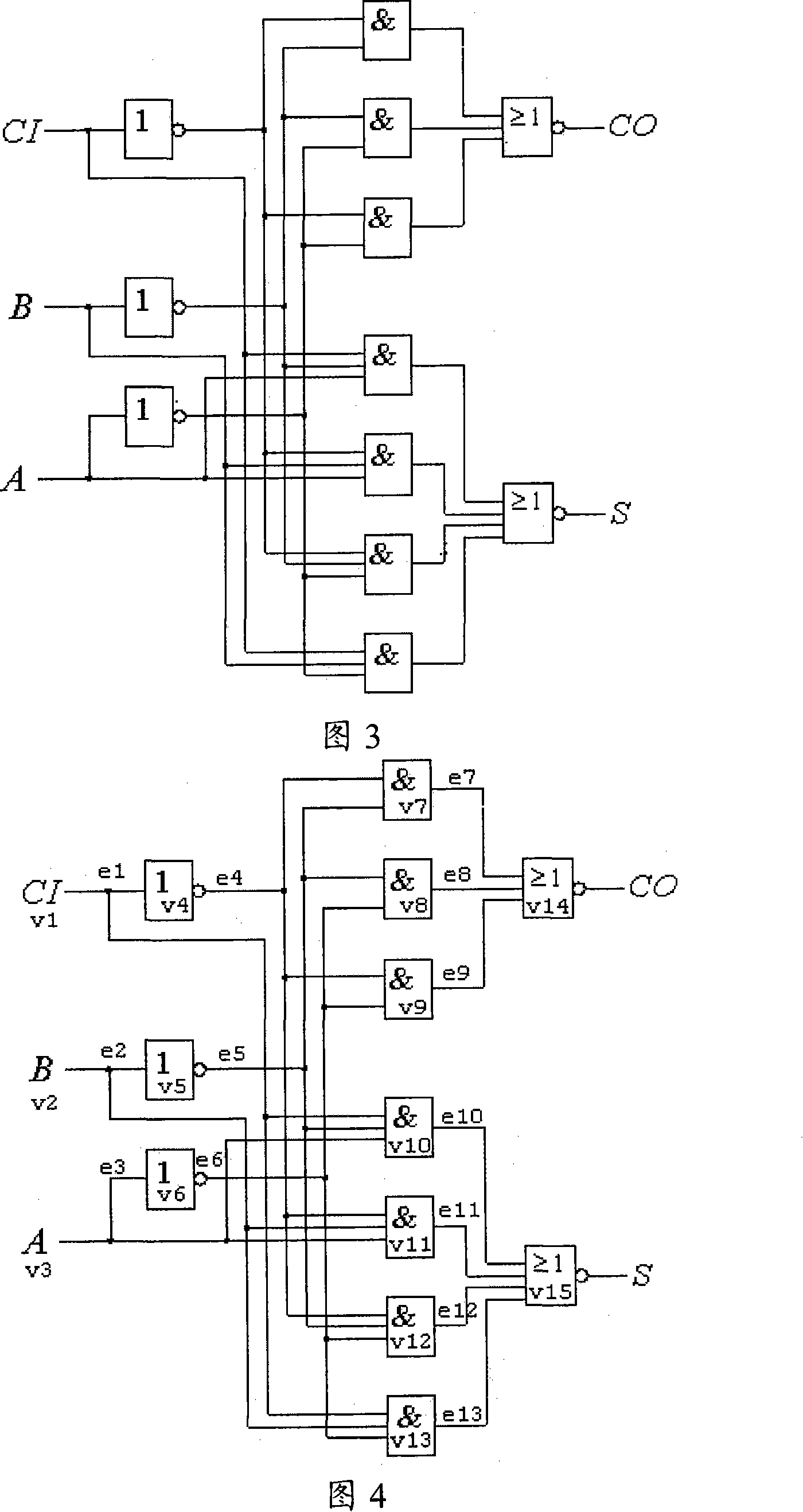

High reliability digital integrated circuit design method

InactiveCN101149765AAvoid overheadReduce manufacturing costSpecial data processing applicationsNetlistDesign methods

A design method of high reliability digital circuit, convert netlist into hypergraph after getting netlist documents using traditional EDA design flow, a fine-grained division method based on hypergraph, allow designers describe circuit only through traditional EDA method, and allocate all kinds of fault defense technologies and all kinds of reliability index, namely add specified fault defense technology to the circuit automatically in order to get a digital integrated circuits of high reliability fault-tolerant circuit.

Owner:BEIHANG UNIV

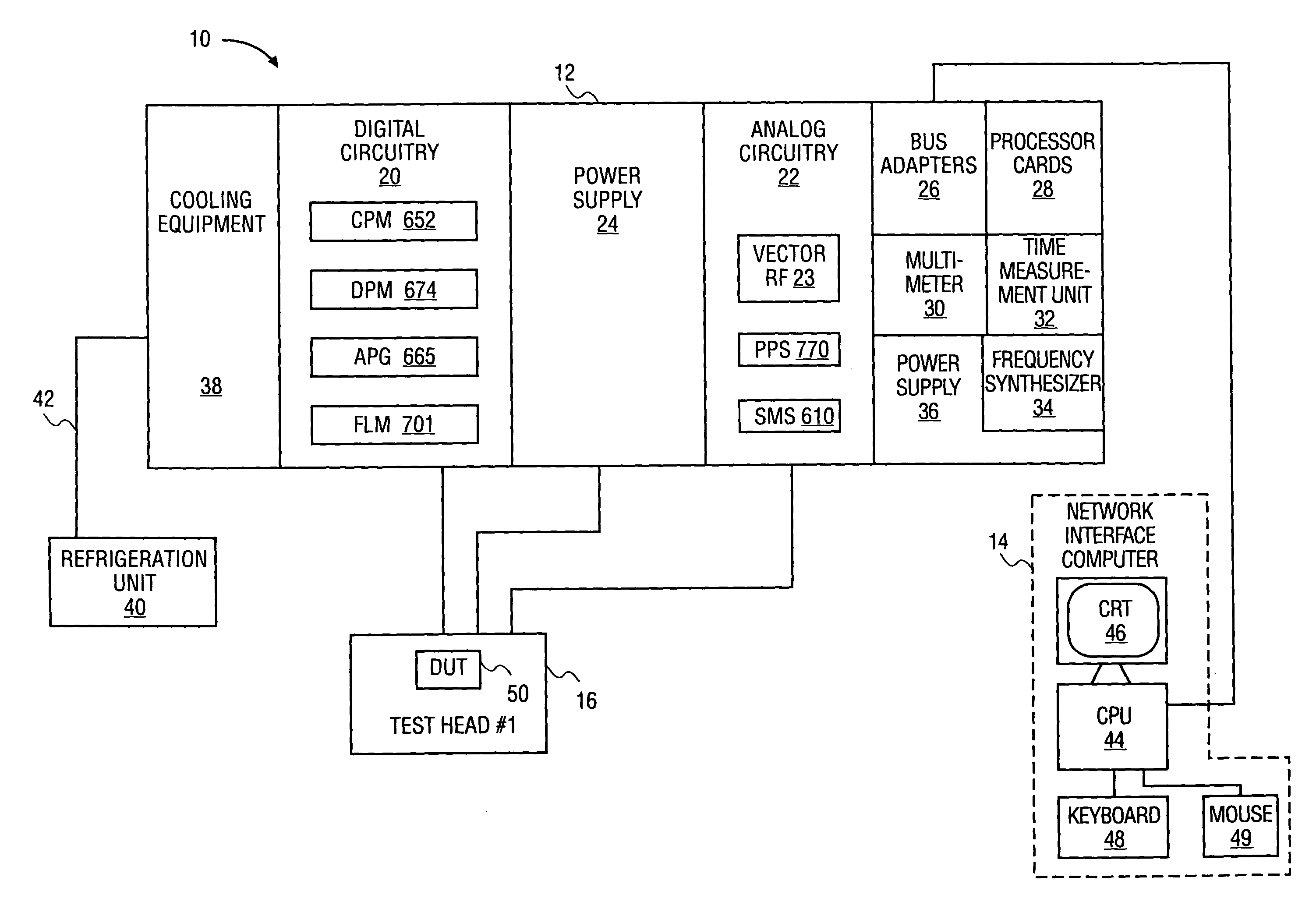

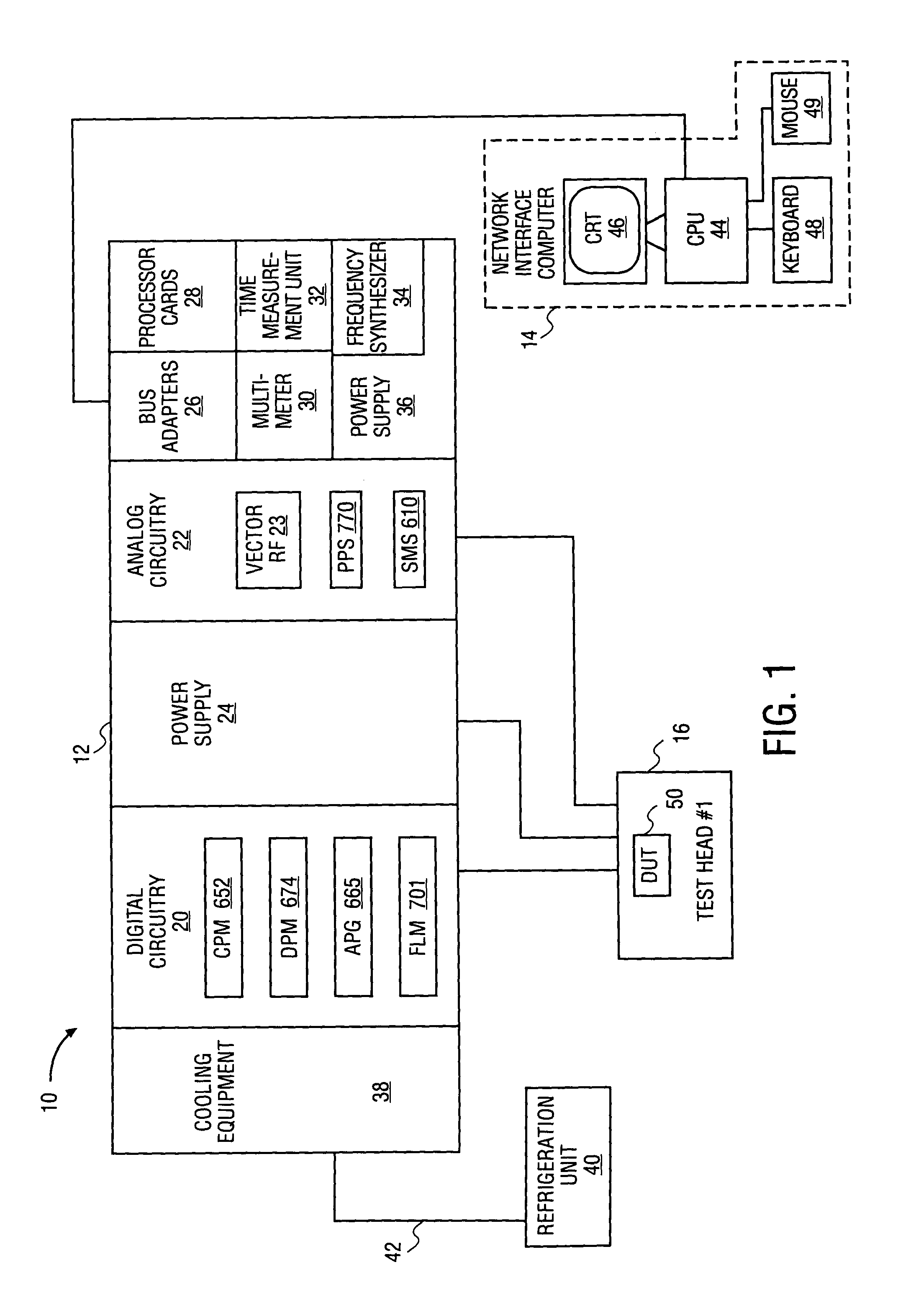

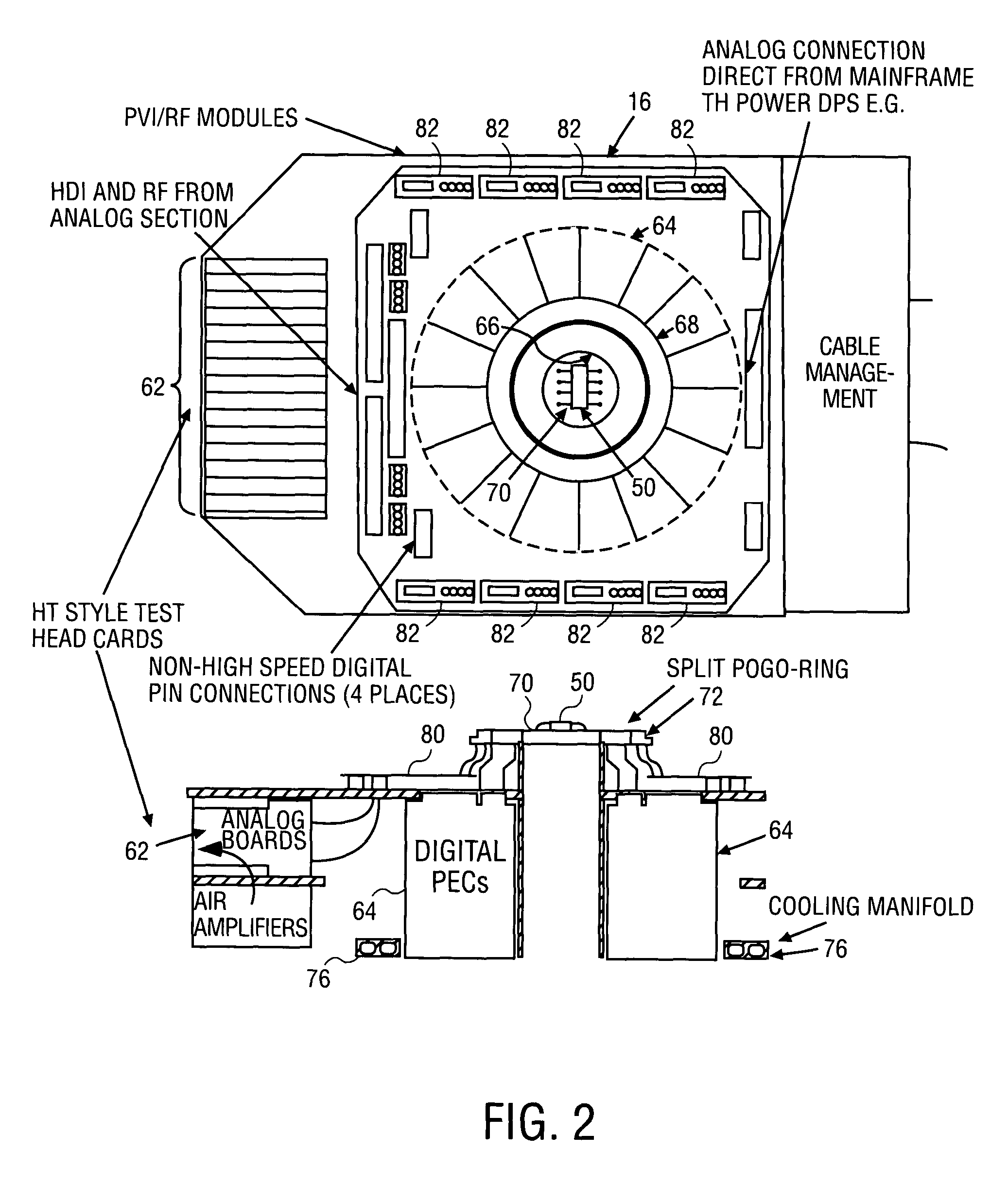

Single platform electronic tester

InactiveUS7092837B1Resistance/reactance/impedenceTesting/calibration of speed/acceleration/shock measurement devicesEquipment under testTester device

An electronic tester with digital, and analog, and memory test circuitry on a single platform. A test head is coupled to a device under test. The device under test can be a system-on-a-chip integrated circuit, a mixed signal integrated circuit, a digital integrated circuit, or an analog integrated circuit. Digital test circuitry applies digital test signals to the device under test coupled to the test head and receives digital outputs from the device under test in response to the digital test signals. Analog test circuitry applies analog test signals to the device under test coupled to the test head and receives analog outputs from the device under test in response to the analog test signals. Memory test circuitry applies memory test patterns to the device under test coupled to the test head and receives memory outputs from the device under test in response to the memory test patterns. A tester computer supervises the application of digital, analog, and memory test signals from the digital, analog, and memory test circuitry to the device under test such that signals applied to the device under test can be solely digital test signals, solely analog test signals, solely memory test signals, or mixed digital, analog, and memory test signals. The test head, the digital test circuitry, the analog test circuitry, the memory test circuitry, and the computer are operable as a single platform.

Owner:LTX CORP

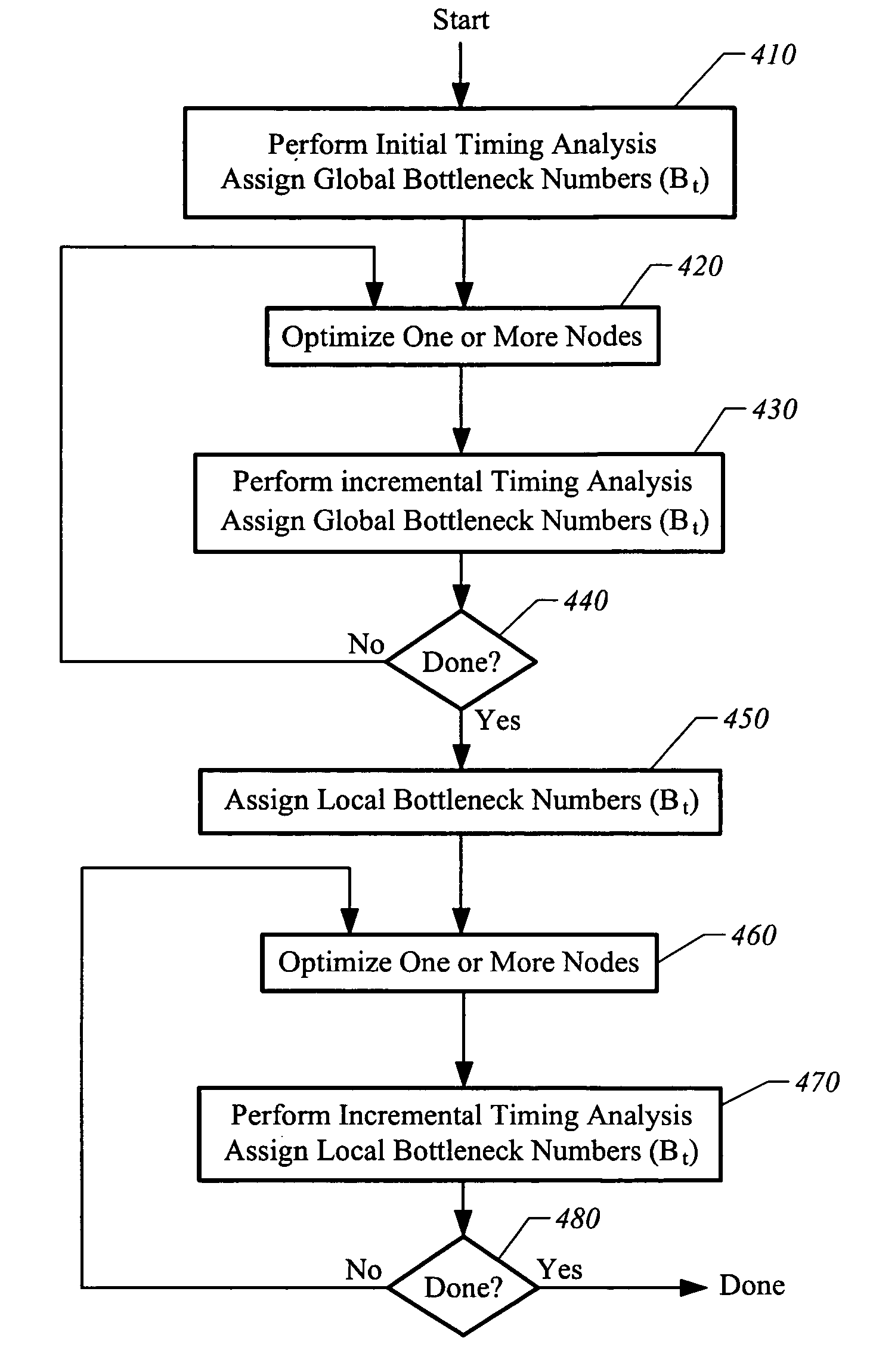

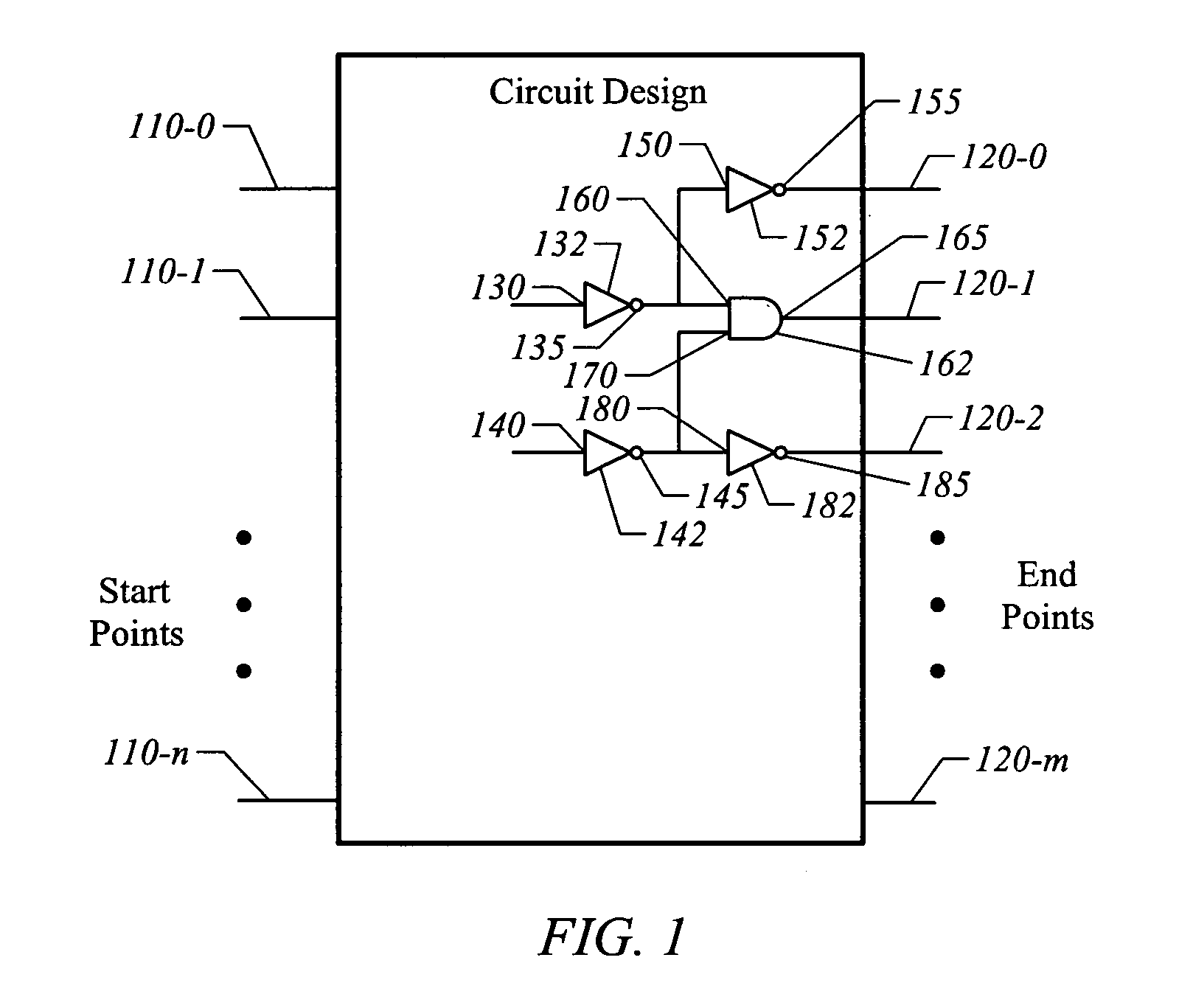

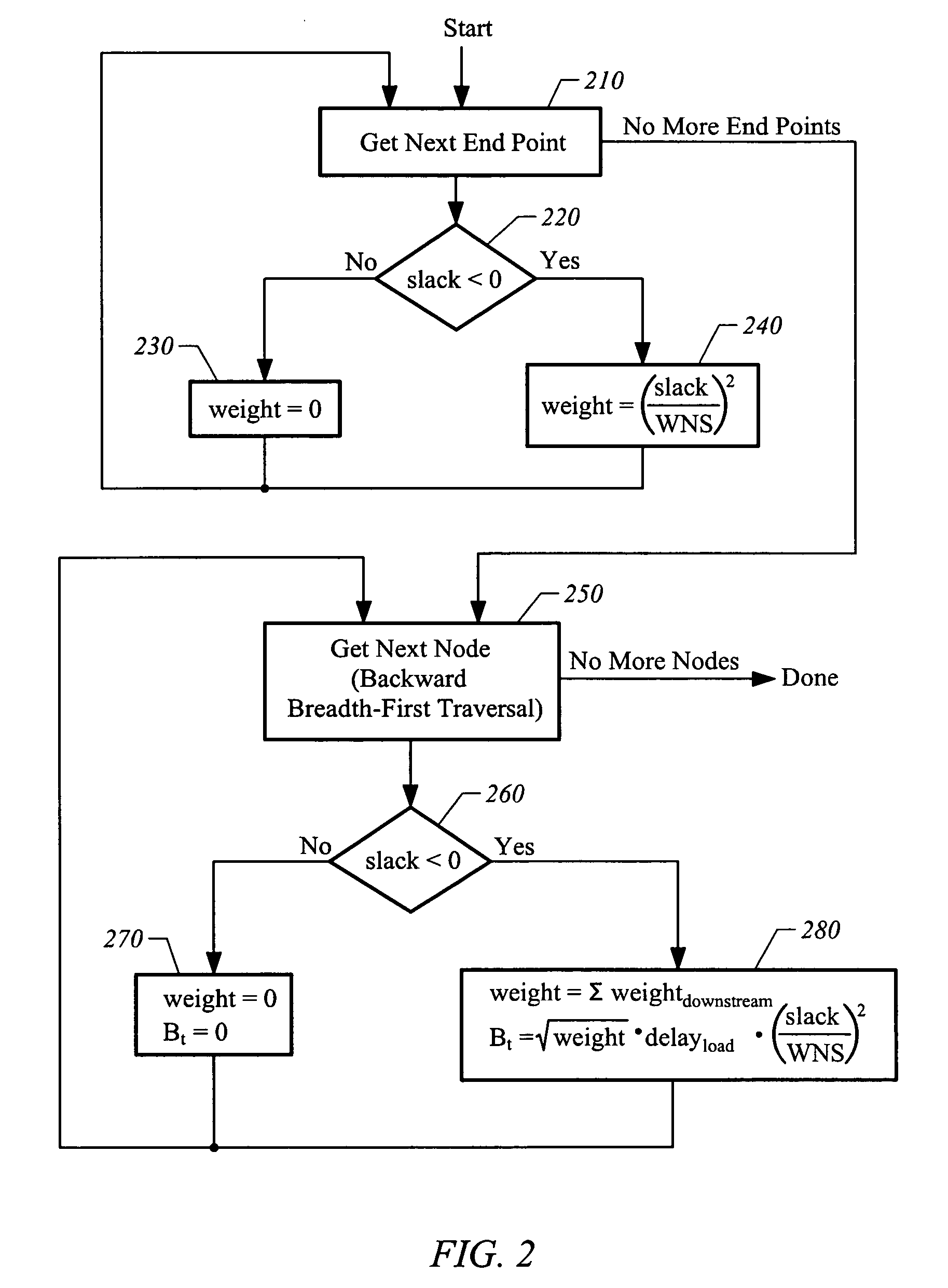

Method and apparatus for optimization of digital integrated circuits using detection of bottlenecks

ActiveUS7191417B1Reduce the amount of calculationHigh return on investmentDetecting faulty computer hardwareCAD circuit designTheoretical computer scienceObject function

A method and apparatus is described which allows efficient optimization of integrated circuit designs. By performing a global analysis of the circuit and identifying bottleneck nodes, optimization focuses on the nodes most likely to generate the highest return on investment and those that have the highest room for improvement. The identification of bottleneck nodes is seamlessly integrated into the timing analysis of the circuit design. Nodes are given a bottleneck number, which represents how important they are in meeting the objective function. By optimizing in order of highest bottleneck number, the optimization process converges quickly and will not get side-tracked by paths that cannot be improved.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

Direct-current arc fault detection protection method and method and detection circuit

ActiveCN103812081ASimple methodThe implementation process is simpleElectrical testingEmergency protective arrangements for automatic disconnectionLow voltageHigh-voltage direct current

The invention discloses a direct-current arc fault detection protection method and method and a detection circuit. Accumulated energy of high-frequency component in alternating component of arc current in a specific time period is adopted as a basis for judging whether an arc fault occurs or not. The direct-current arc fault detection protection device comprises a solid-state switch or a mechanical relay, an alternating component detection circuit and a first AND gate and direct-current arc fault detection circuit. The direct-current arc fault detection protection method is simple, quick in detection speed and high in reliability, a direct-current arc fault detection function is conveniently achieved by adopting an analog-digital integrated circuit, and the achieving and manufacturing cost is low. The direct-current arc fault detection protection method and method can be widely applied to low-voltage and high-voltage power systems of airplanes, ships and warships, photovoltaic cell systems and civilian high-voltage direct-current power transmission and distribution systems.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

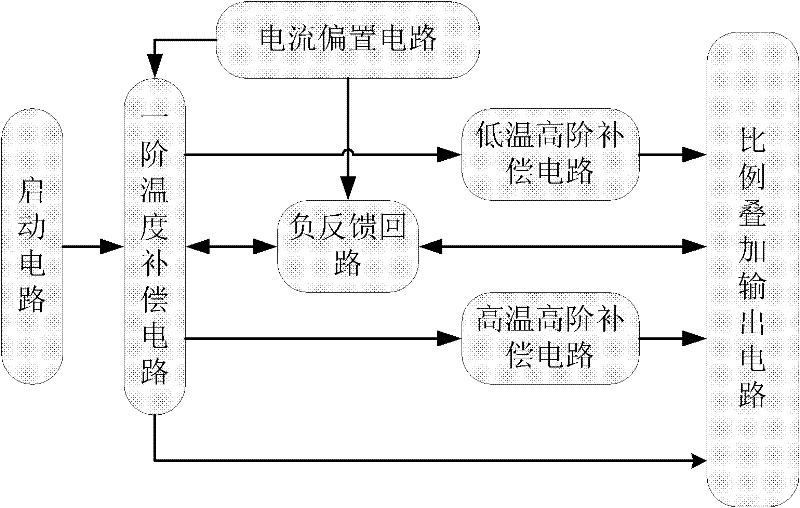

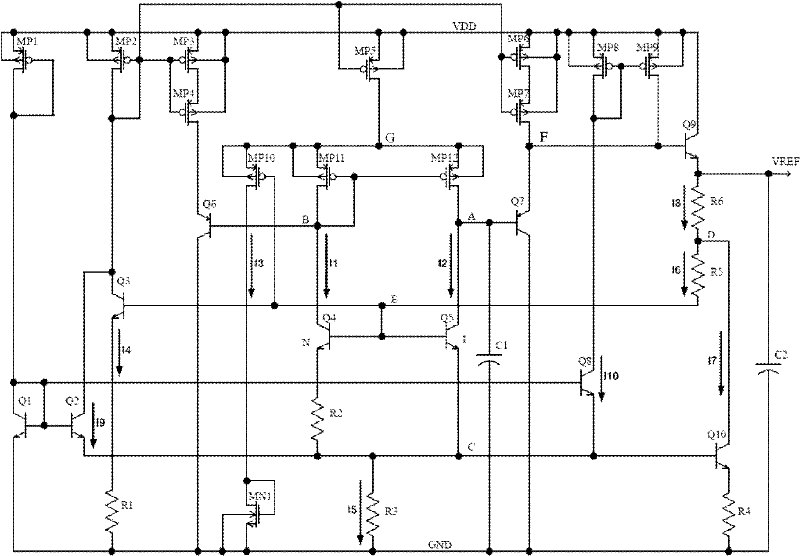

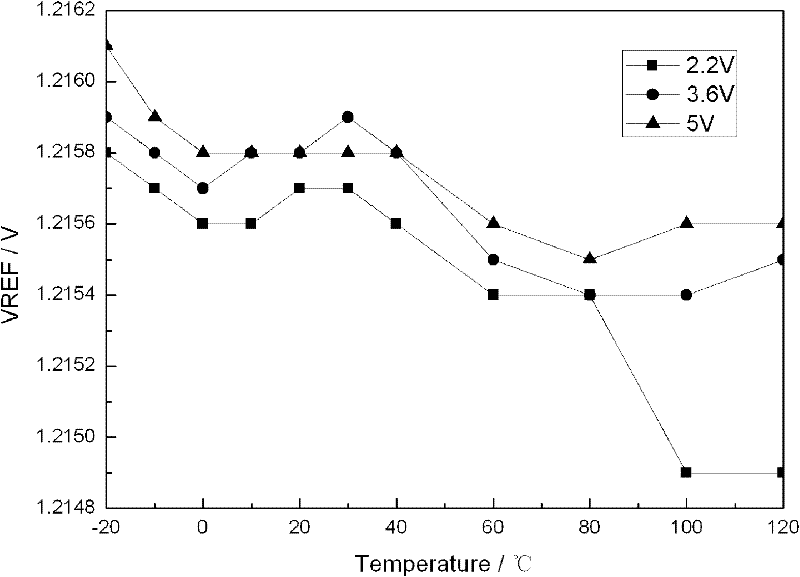

Voltage reference source capable of compensation in full temperature range

InactiveCN102541133ASmall temperature coefficientImprove temperature stabilityElectric variable regulationNegative feedbackVoltage reference

The invention discloses a voltage reference source capable of compensating in a full-temperature range, which particularly comprises a start-up circuit, a first-order temperature-compensation circuit, a proportional superposition output circuit and a current bias circuit, and is characterized by further comprising a low-temperature high-order compensation circuit, a high-temperature high-order compensation circuit and a negative feedback circuit. The voltage reference source adopts index curvature compensation at the low temperature, adopts piecewise linear curvature compensation at the high temperature, has extremely good temperature stability and extremely low temperature coefficient and can be applied to an analogue integrated circuit, a high-precision digital-to-analogue conversion circuit and a pure digital integrated circuit.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

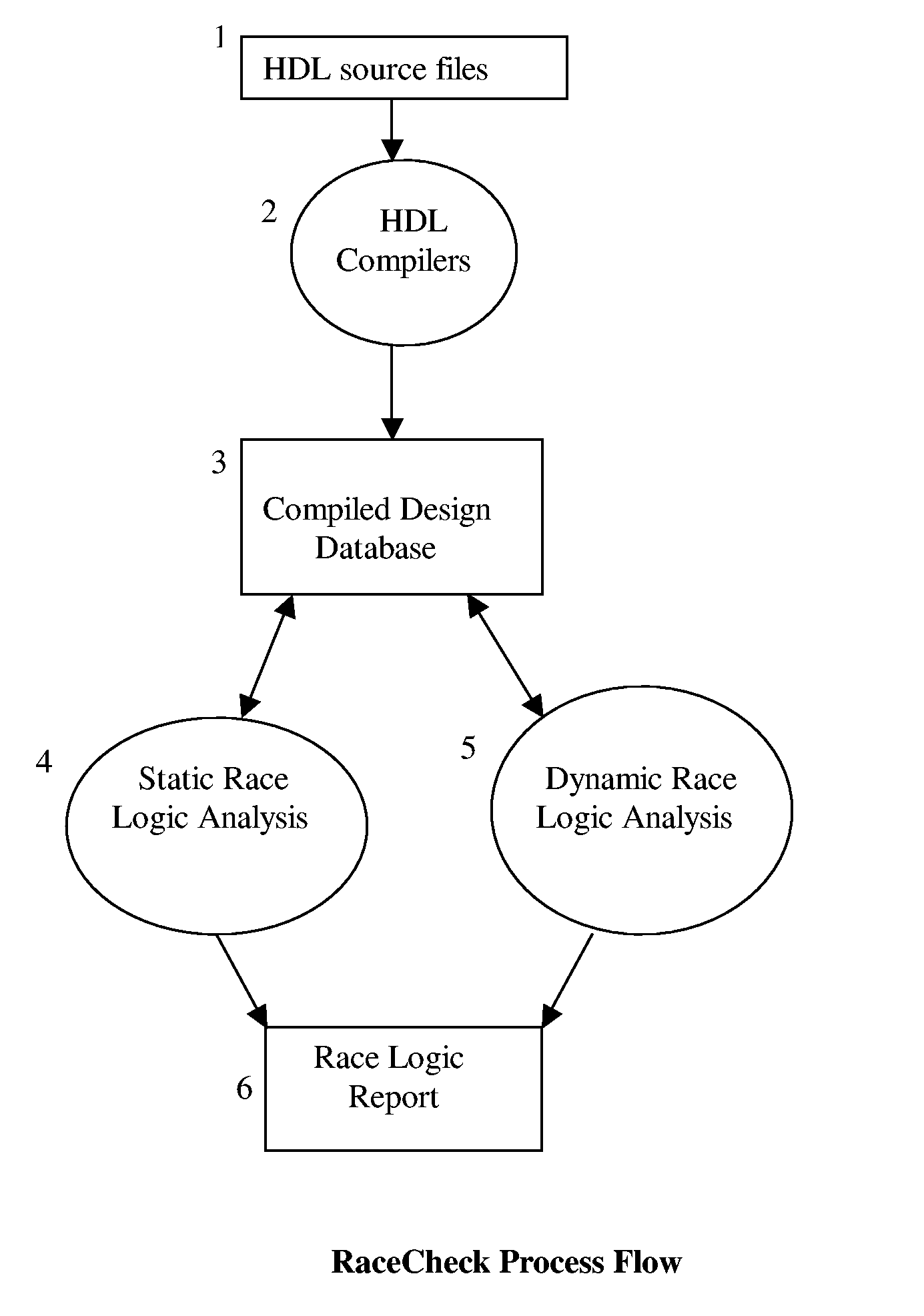

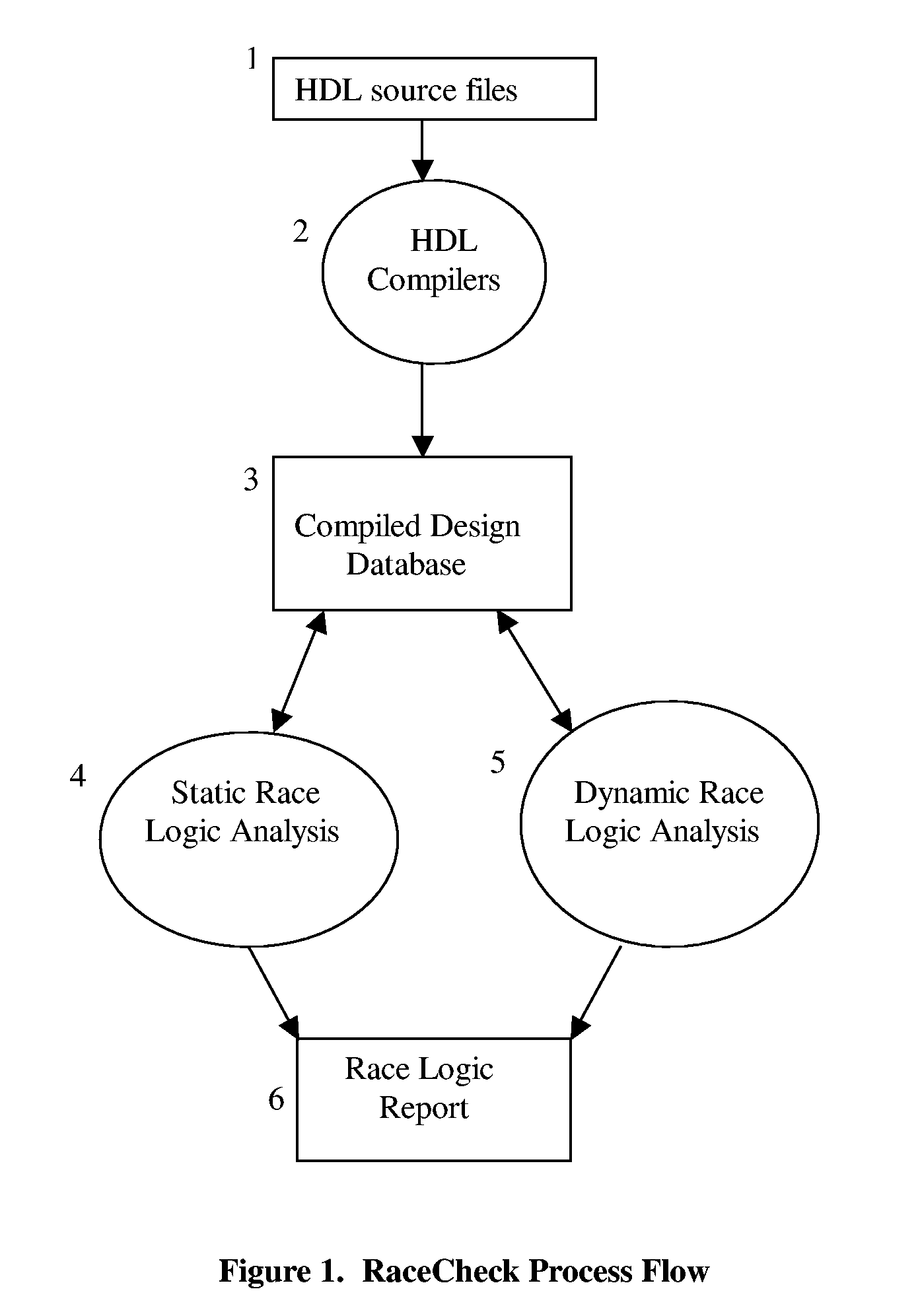

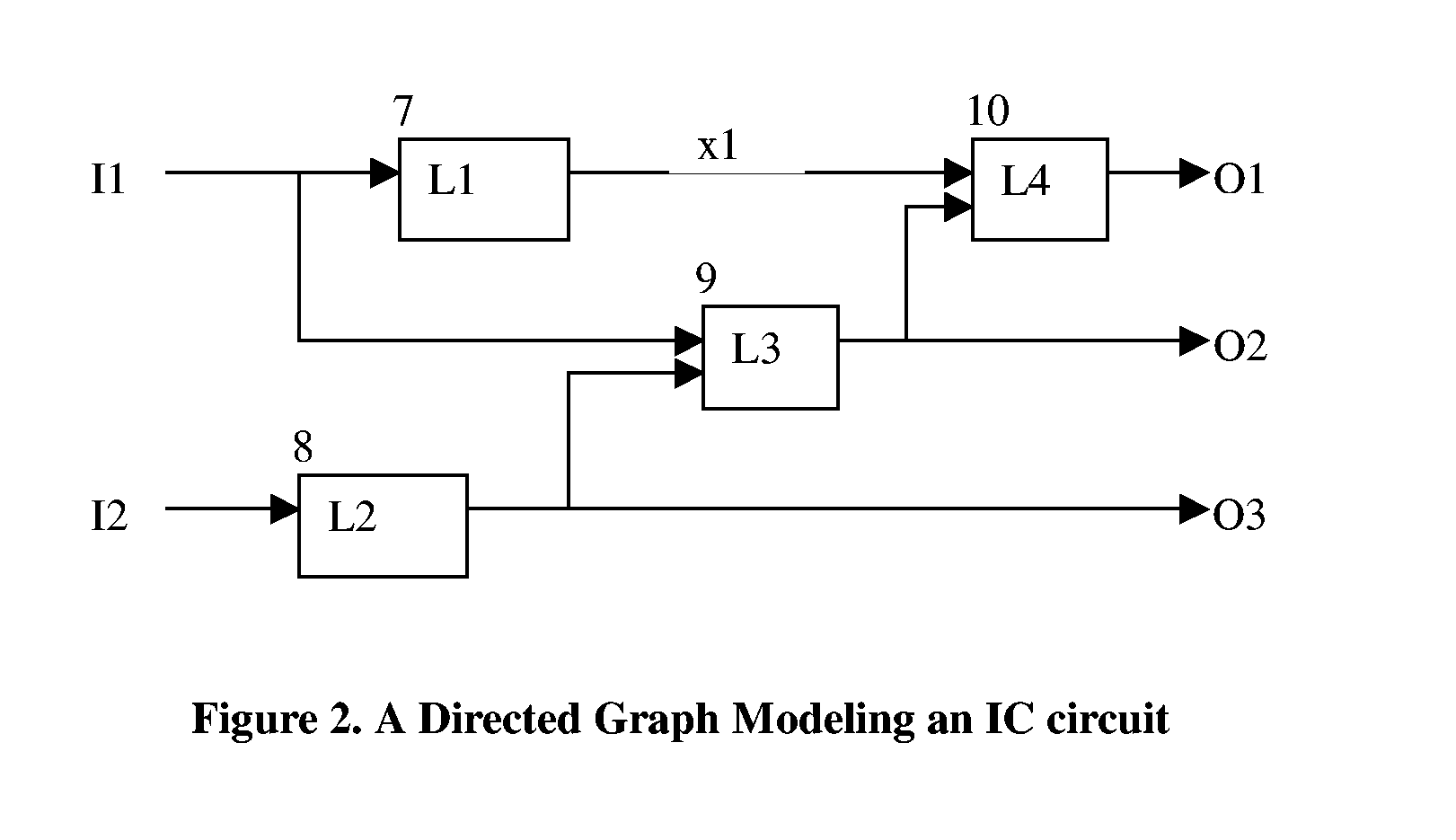

RaceCheck: A Race Logic Ana,yzer Program for Digital Integrated Circuits

ActiveUS20060075367A1Reduce effortShorten the timeElectrical testingDesign optimisation/simulationTime informationSystemC

This invention describes a race logic audit program, RaceCheck, which is unique from the prior arts. Specifically, RaceCheck can perform both static and dynamic race logic analysis, and it works with a plurality of hardware description languages (HDL), which include but not limited to: VHDL, Verilog, SystemVerilog, and SystemC. Furthermore, RaceCheck makes use of both structural and timing information of IC designs, as well as binary-decision diagram (BDD) and automatic test pattern generation (ATPG) techniques to derive accurate race logic analysis results with few false violations. Finally, RaceCheck can detect concurrent invocation races of the $random system function, concurrent invocation races of user-defined tasks and functions, zero-delay combination loops, and RaceCheck's dynamic analysis engine uses a HDL simulation kernel to perform timing-accurate race logic analysis. All these aforementioned features are unique for the invention and have not been reported in any prior arts.

Owner:DYNETIX DESIGN SOLUTIONS

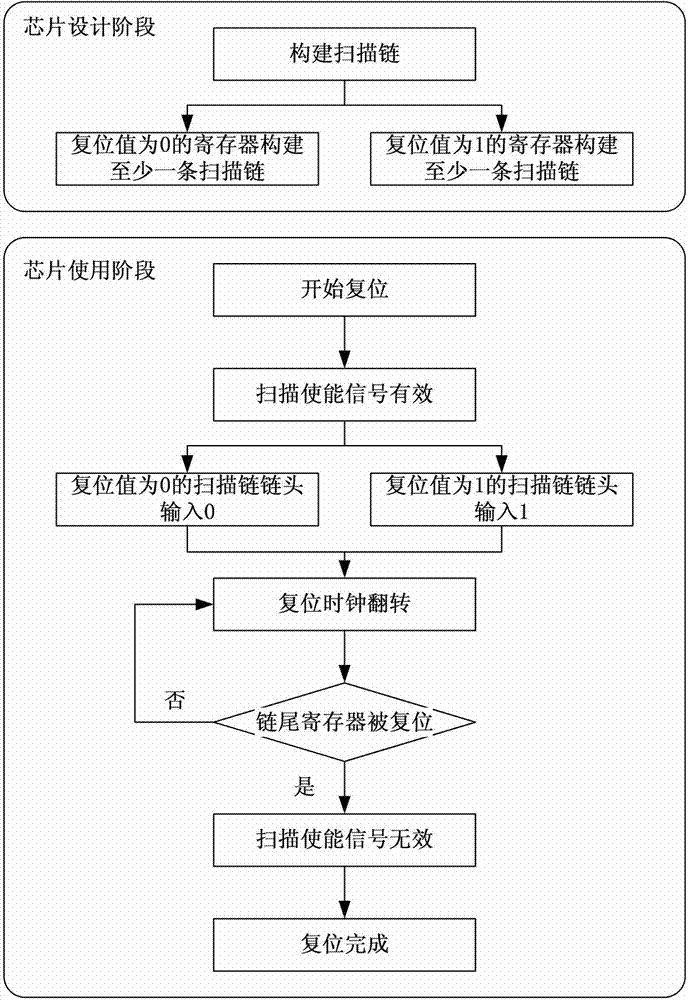

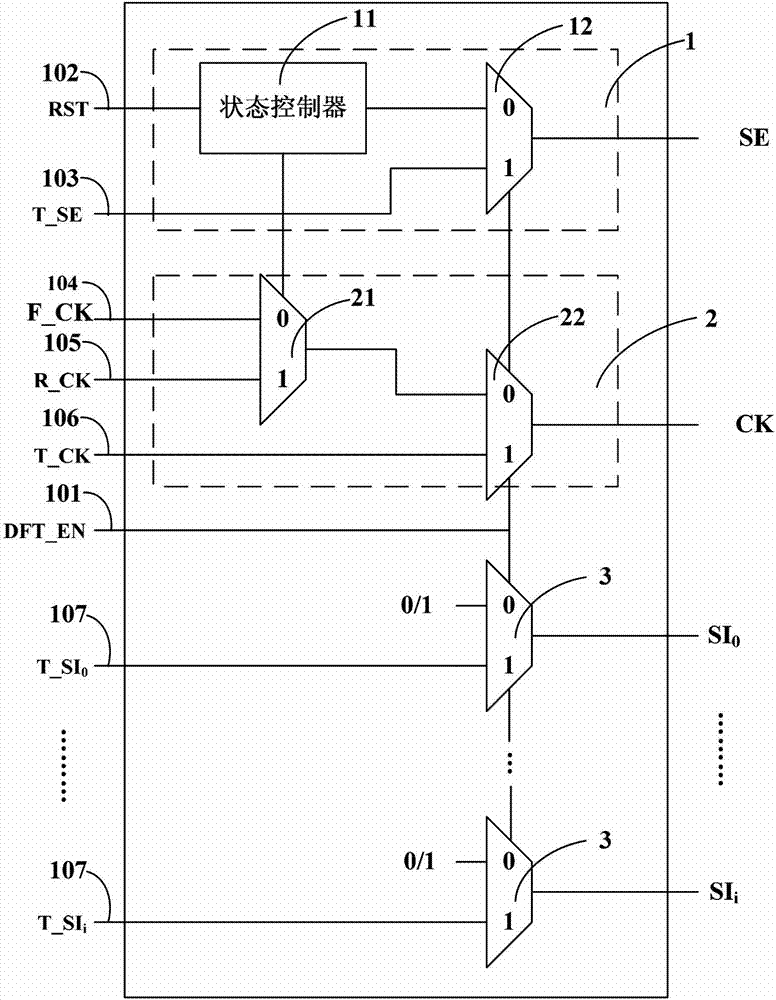

Resetting method and resetting control device of register inside chip based on scanning chain

ActiveCN102970013AEasy resetReset is simply and conveniently achievedElectronic switchingProcessor registerDesign stage

The invention discloses a resetting method and a resetting control device of a register inside a chip based on a scanning chain. The resetting method comprises the steps of: 1) respectively building at least one scanning chain for the register according to a resetting value 0 or 1 in a chip design stage; and 2) setting a scanning enabling signal of each register as valid and writing the resetting value into a head of the scanning chain in a chip use stage. The resetting control device comprises a scanning chain enabling control unit, a scanning chain clock control module and an input data selector which respectively outputs test data or the resetting value to the head of the scanning chain. The input terminal of the resetting control device comprises a test enabling terminal, a resetting signal input end, a test scanning enabling signal / work clock / resetting clock / test clock input end and a plurality of test data input terminals. According to the invention, the inner register of the chip can be efficiently reset so that influence on the performance of a digital integrated circuit chip is low, and the resetting method and the resetting control device have the advantages of high stability, small power consumption, simple structure and is convenient to implement.

Owner:NAT UNIV OF DEFENSE TECH