Patents

Literature

1433 results about "Equipment under test" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

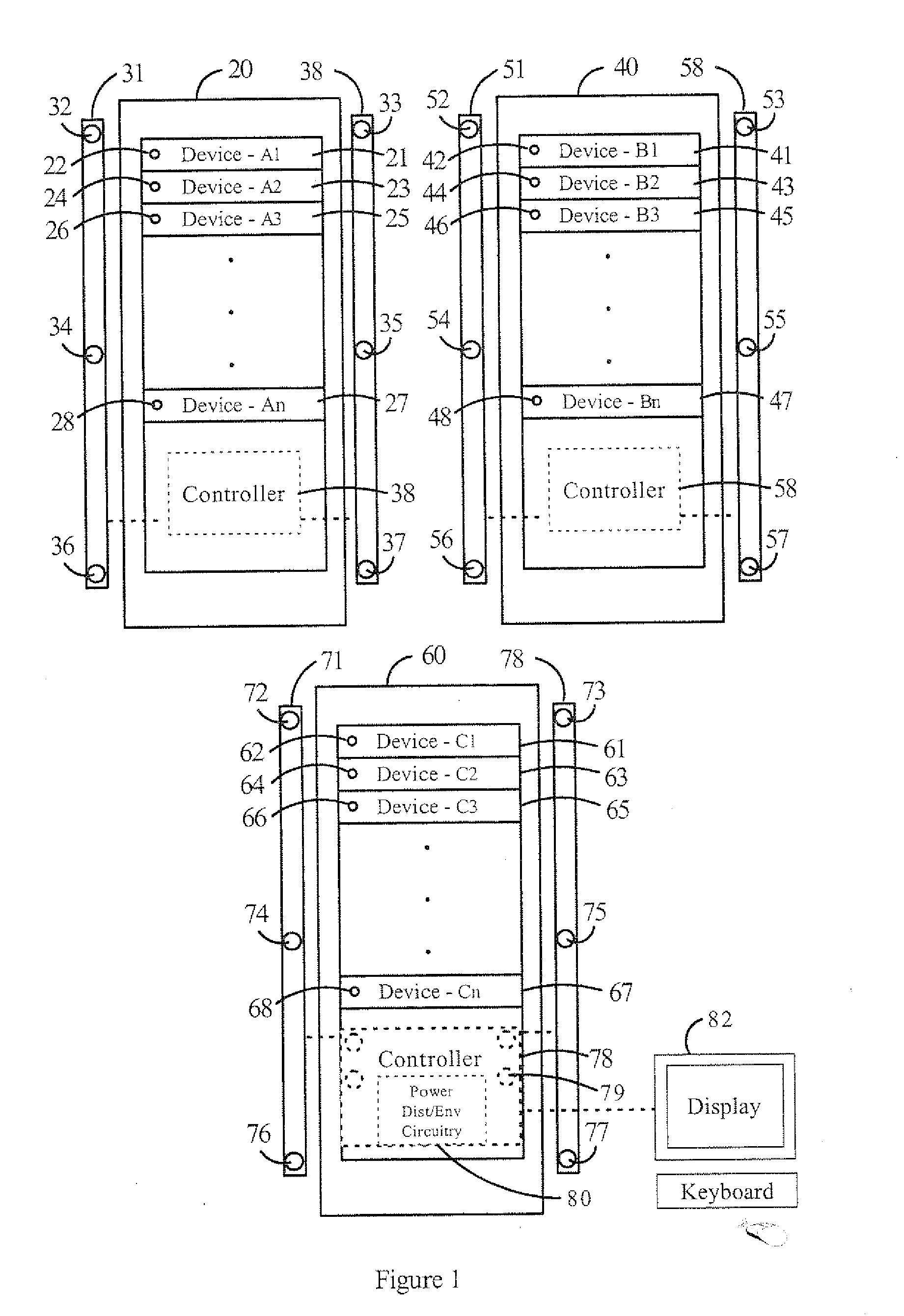

Location-based testing for wireless data communication networks

ActiveUS7539489B1Easy to optimizeFacilitate data communicationError preventionFrequency-division multiplex detailsTest stimulusSystem under test

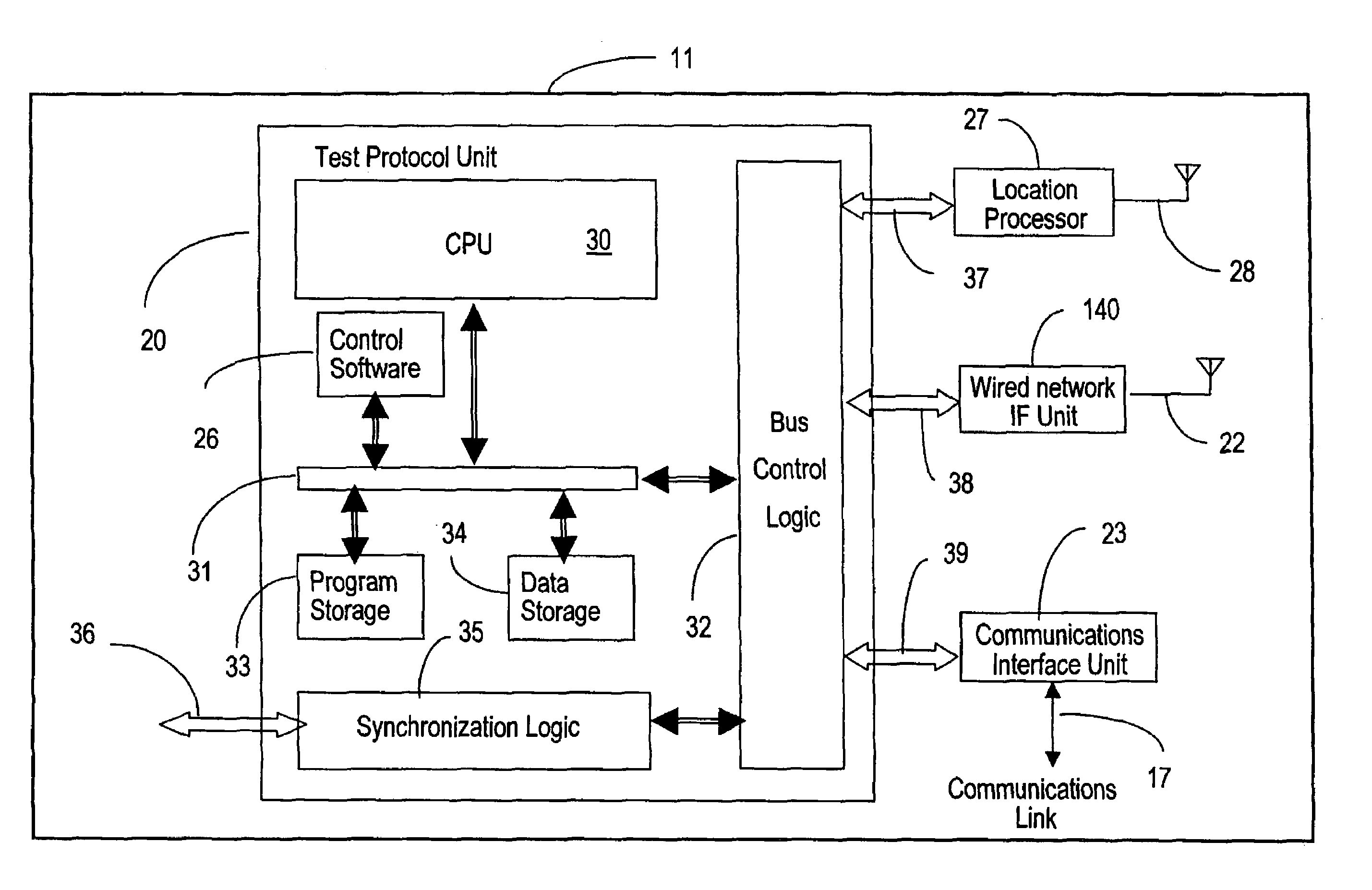

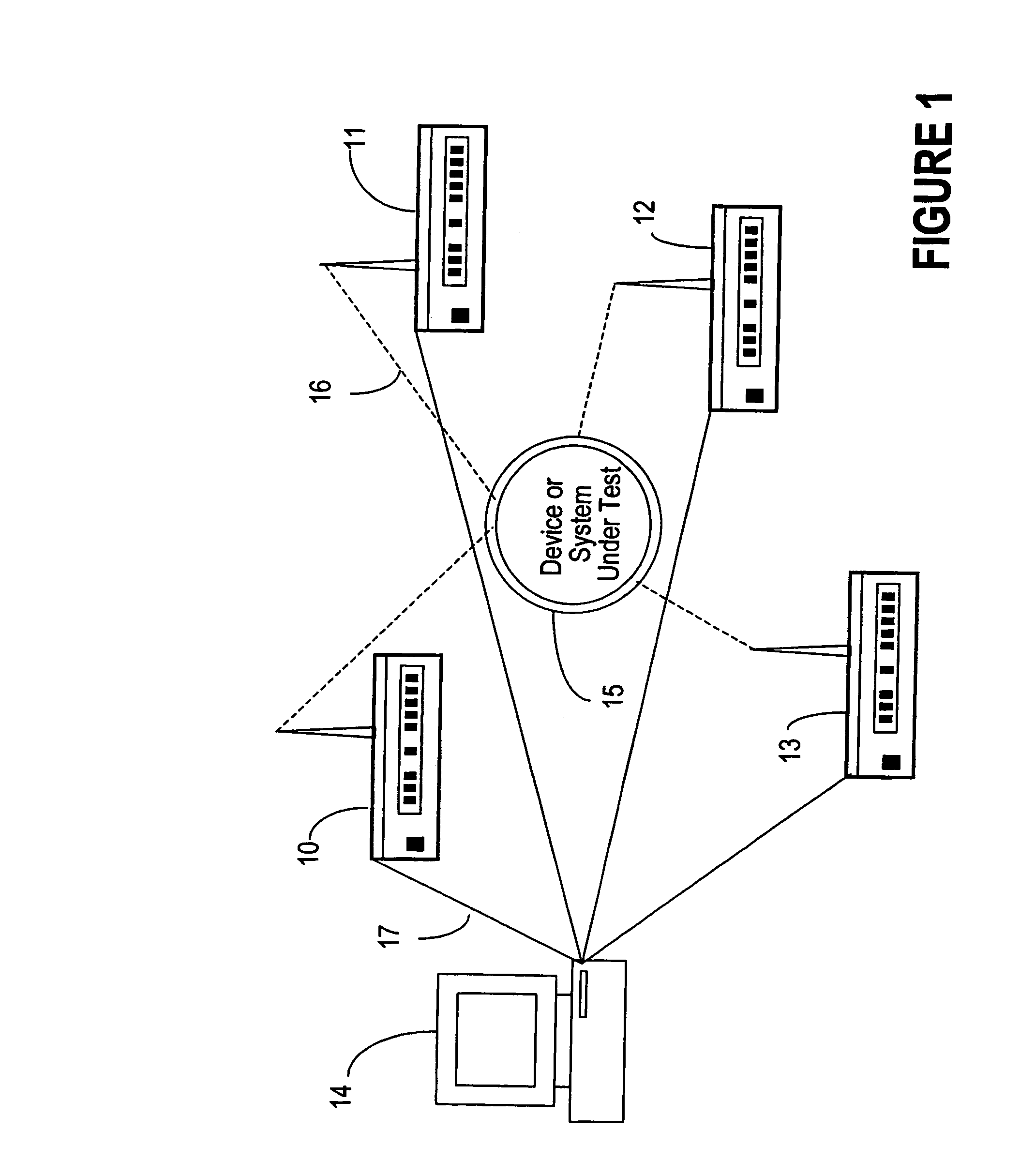

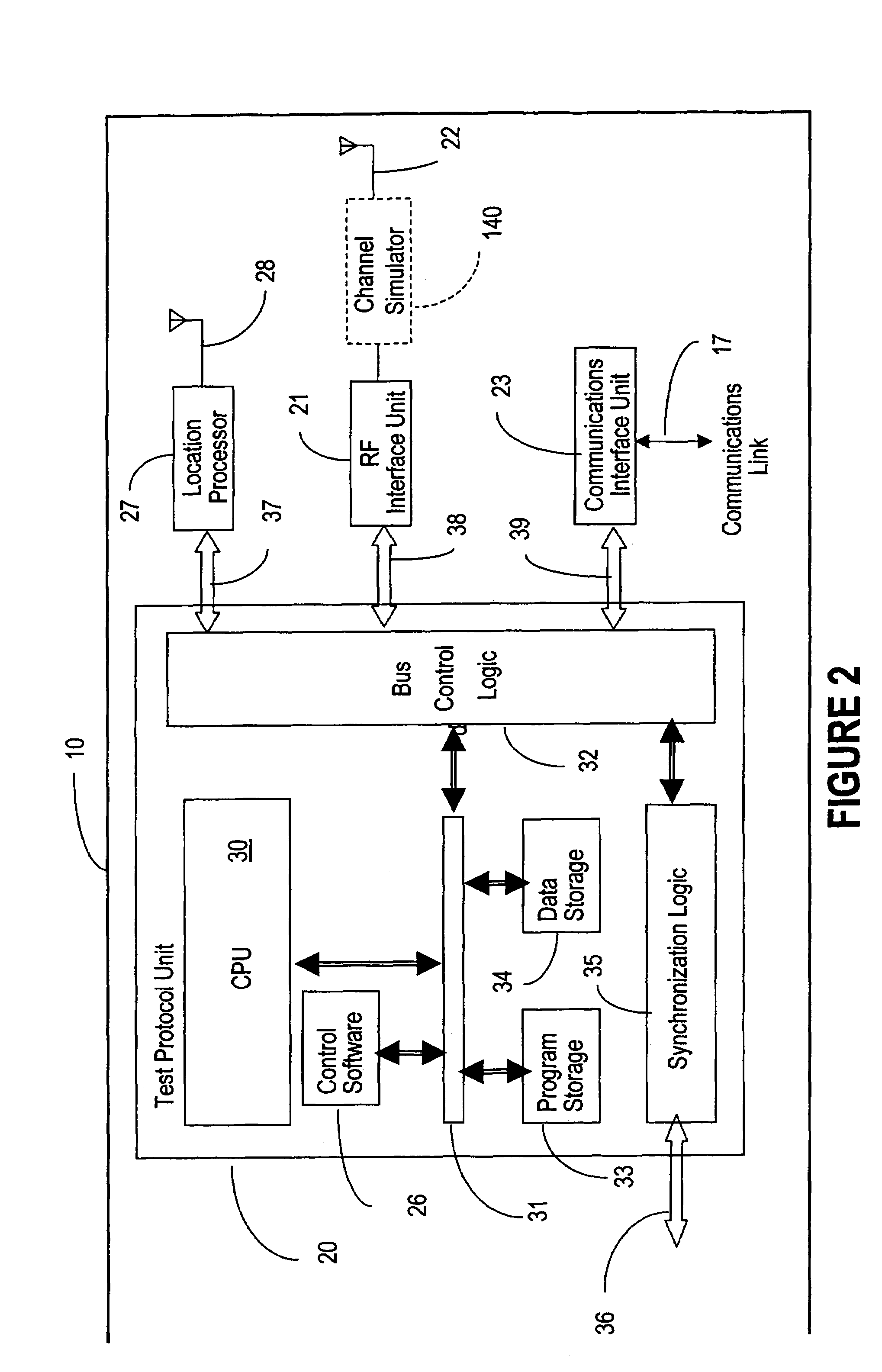

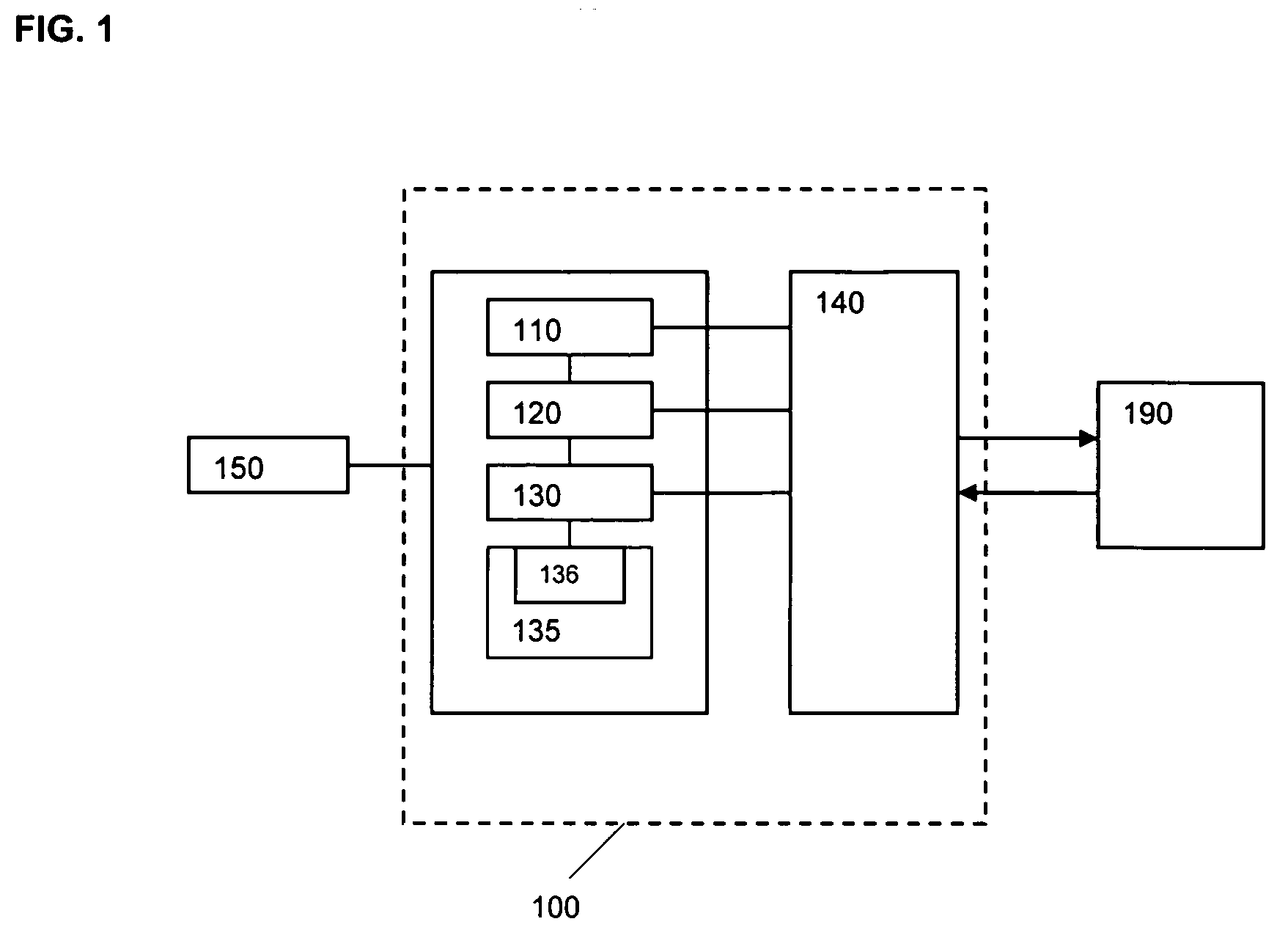

Apparatus and methods facilitating a distributed approach to performance and functionality testing of location-sensitive wireless data communication systems and equipment are described. A plurality of test units, geographically distributed at arbitrary points in a three-dimensional volume surround the system or equipment under test. Each test unit generates test stimuli and records responses from the device under test, and emulates the effects of changes in spatial location within an actual wireless network environment. A central controller co-ordinates the set of test units to ensure that they act as a logical whole, and enables testing to be performed in a repeatable manner in spite of the variations introduced by the location sensitive characteristics of wireless data communication networks. The central controller also maintains a user interface that provides a unified view of the complete test system, and a unified view of the behavior of the system or equipment under test. For diagnostic purposes, the recorded responses may be regenerated to view any defects as many times as necessary to correct them. Alternatively, each test unit may have either wired network interface units, instead of a wireless interface unit to test systems or equipment forming part of a wired network portion in the wireless data communication system.

Owner:KEYSIGHT TECH SINGAPORE (SALES) PTE LTD

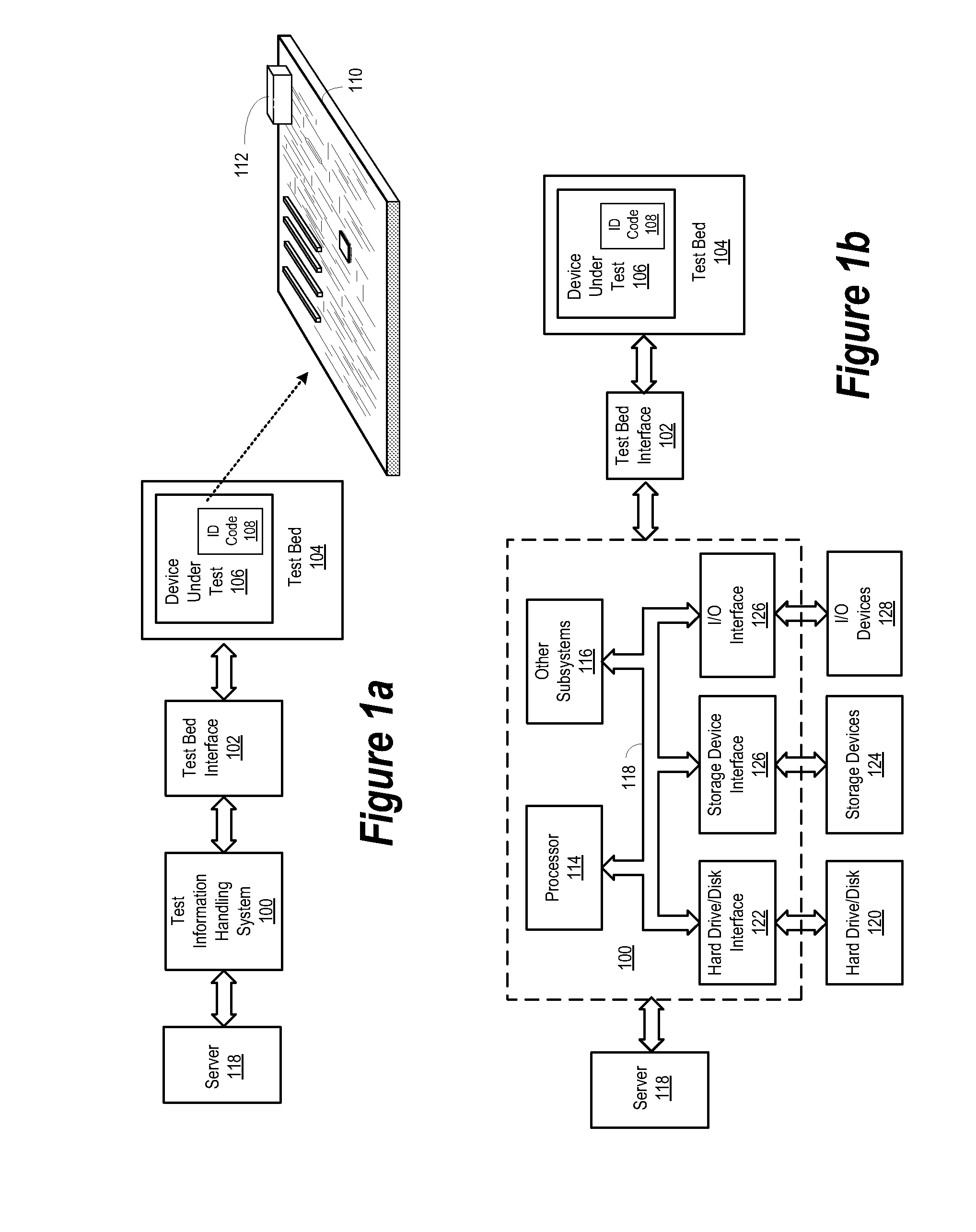

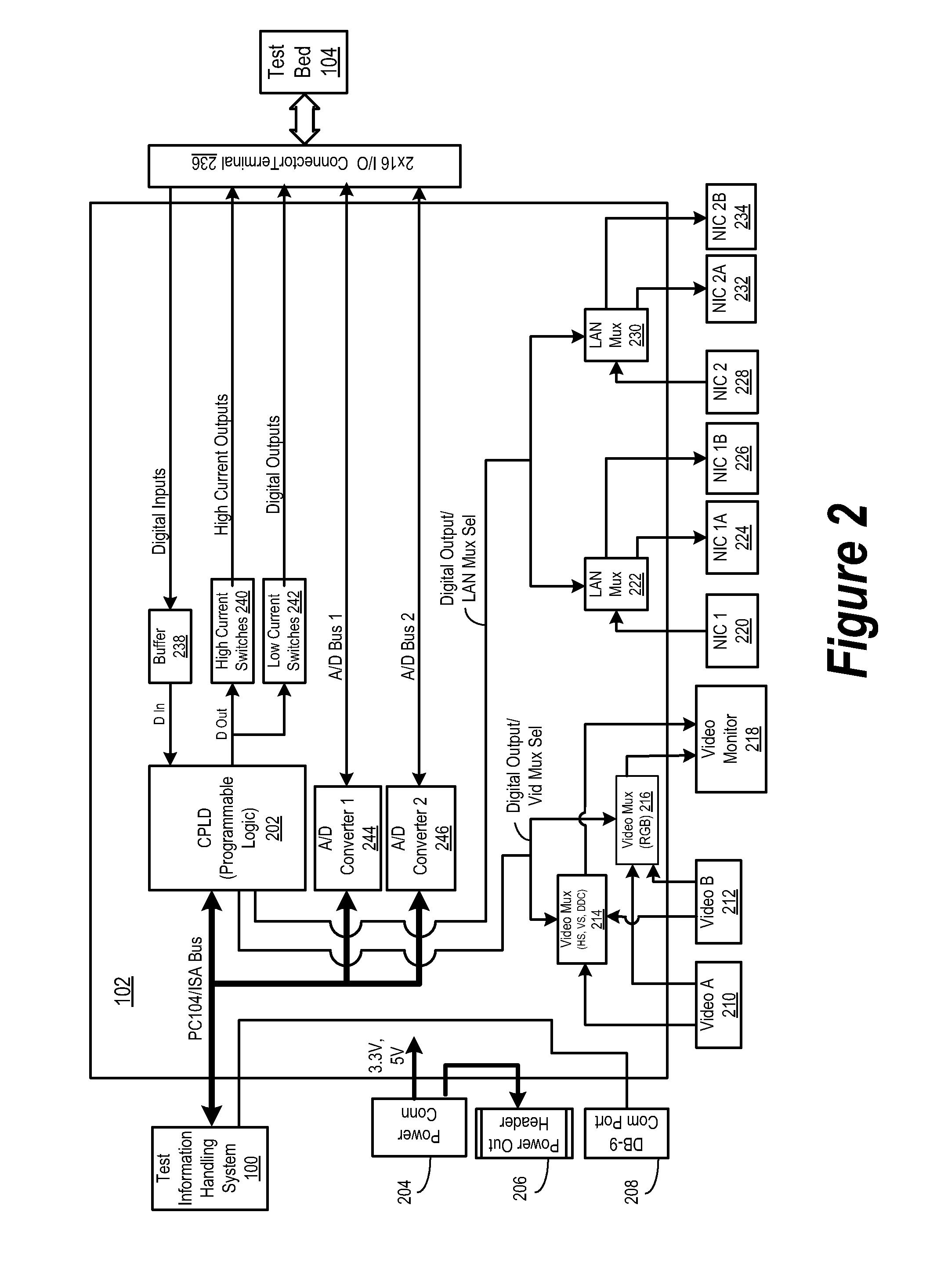

System and method for testing information handling system components

InactiveUS20080262759A1Quickly and easily swappedElectrical testingSpecial data processing applicationsControl signalHandling system

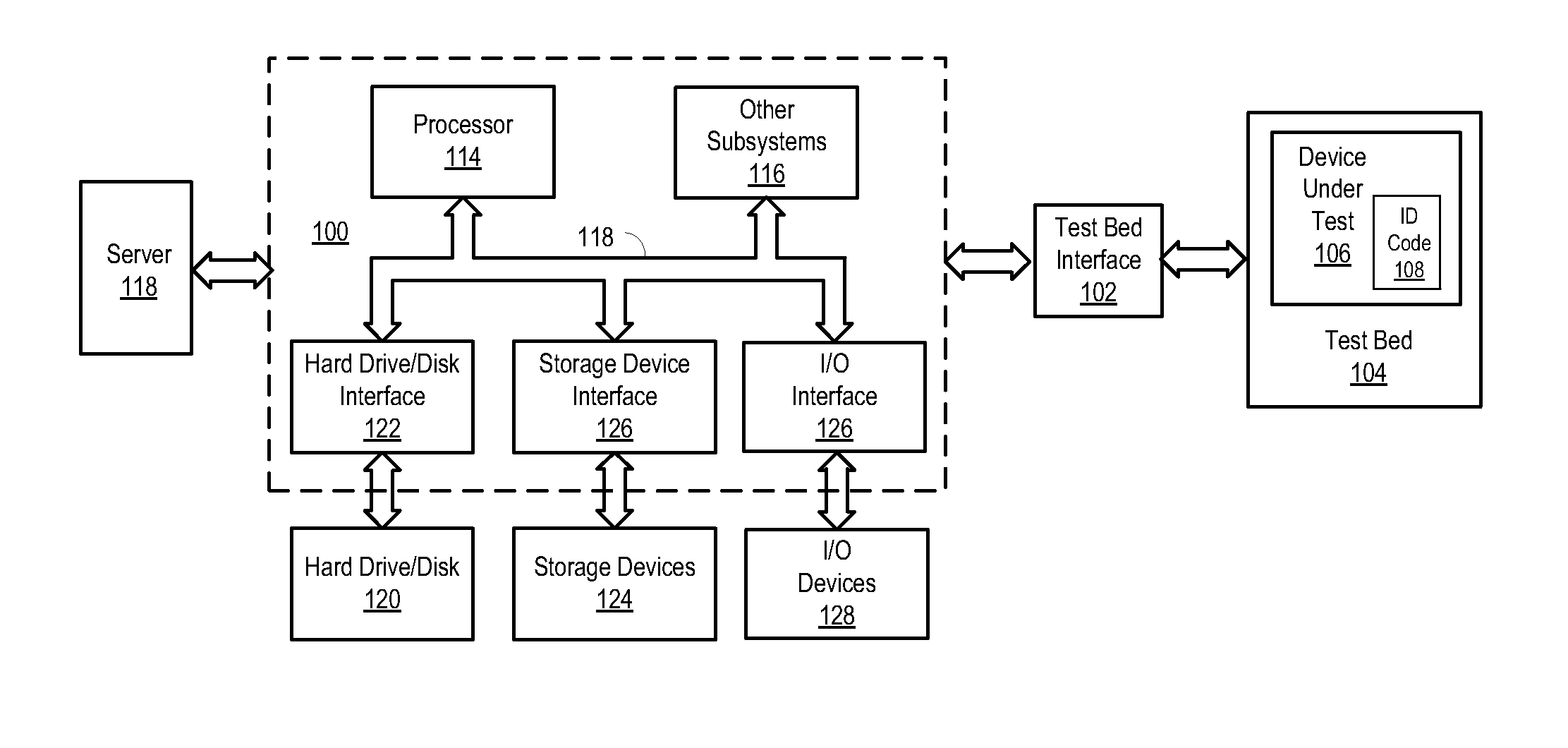

A system and method is disclosed for testing components used in the manufacture of information handling systems. In embodiments of the invention, a device-under-test (DUT) comprises a DUT identifier code. The DUT is operably coupled to a test bed. An information handling system is operable to use the identifier code to select and execute a predetermined test program to generate a plurality of test commands. A test bed interface is operable to receive the test commands and to generate a plurality of test control signals therefrom to perform a predetermined set of tests of said DUT.

Owner:DELL PROD LP

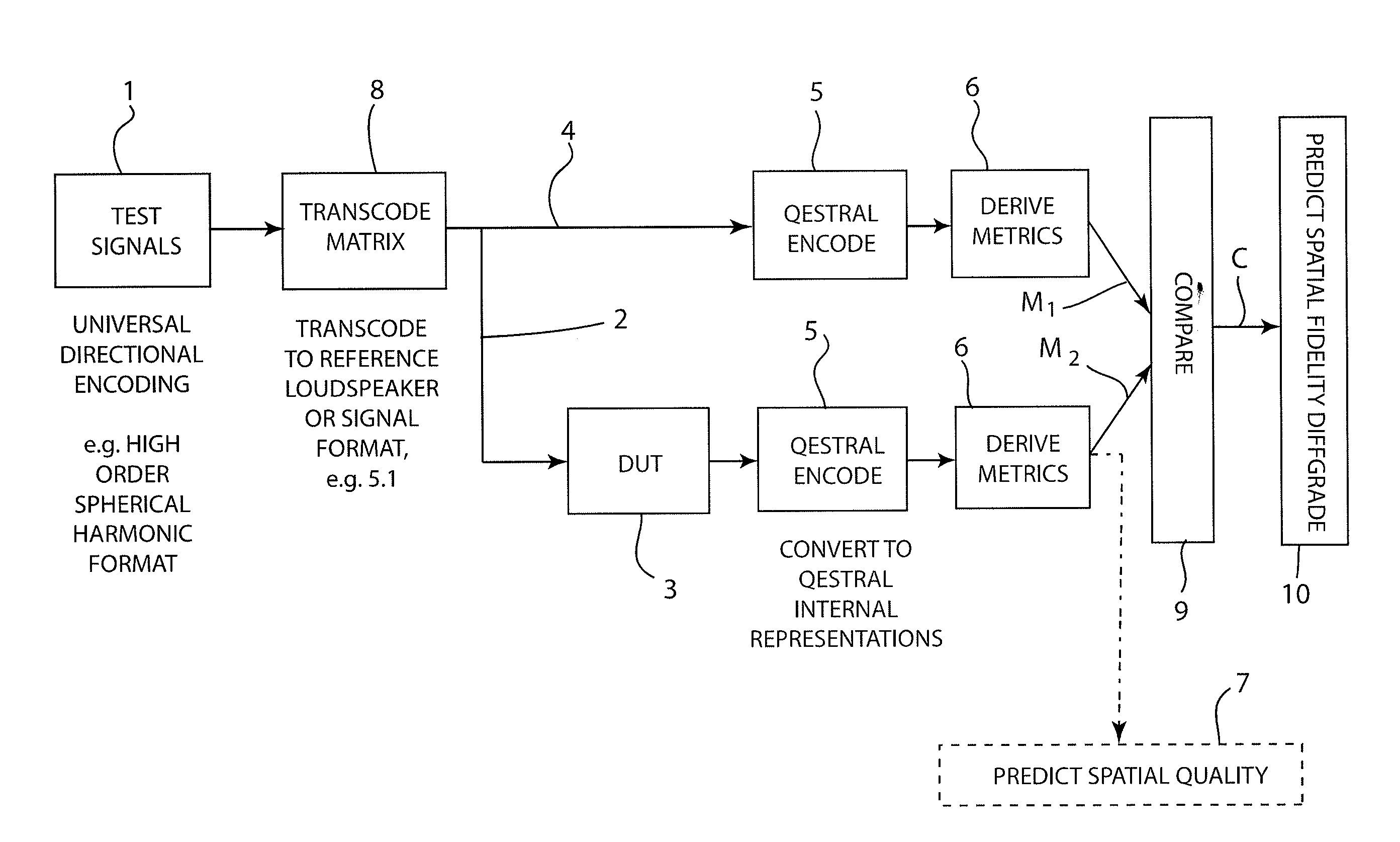

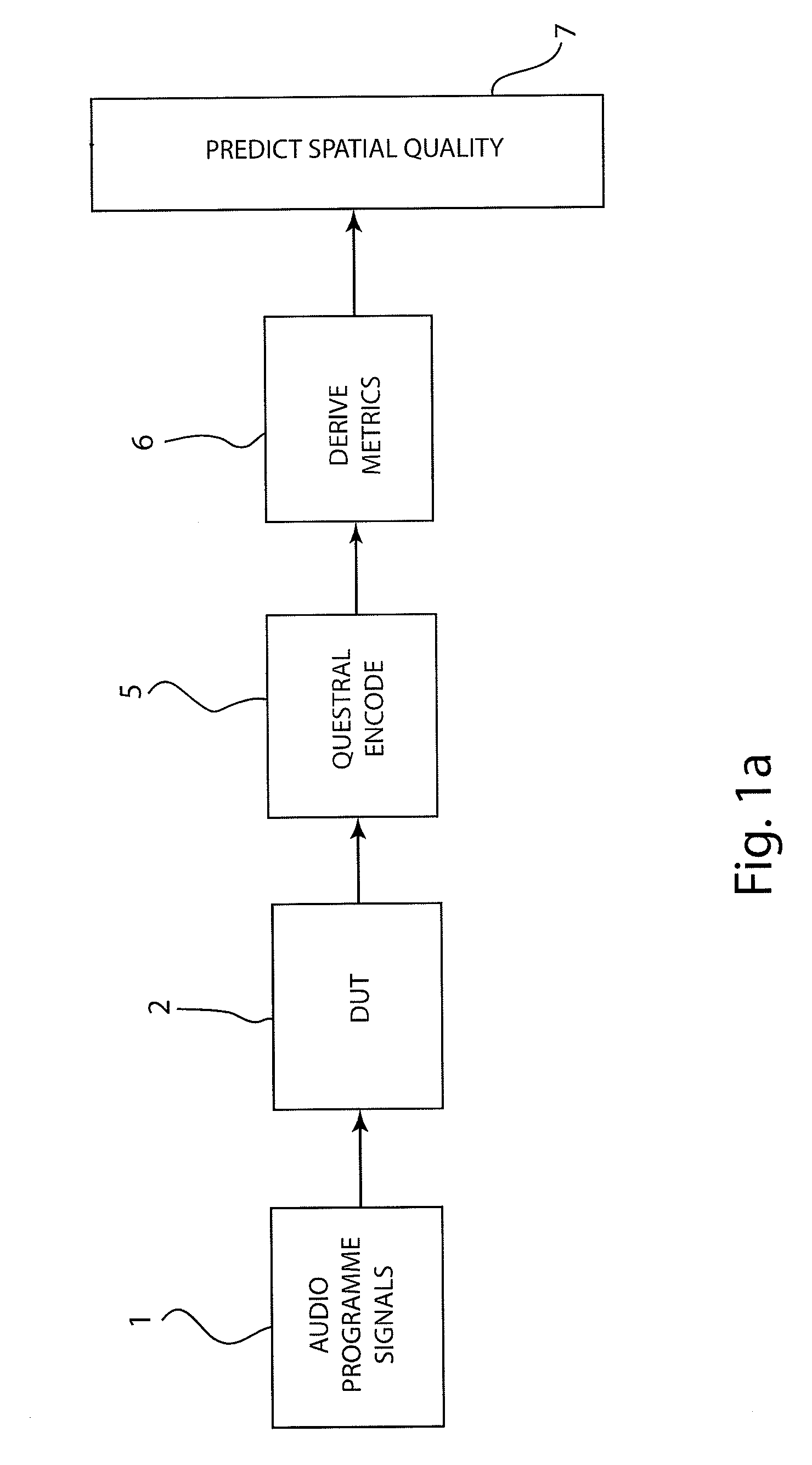

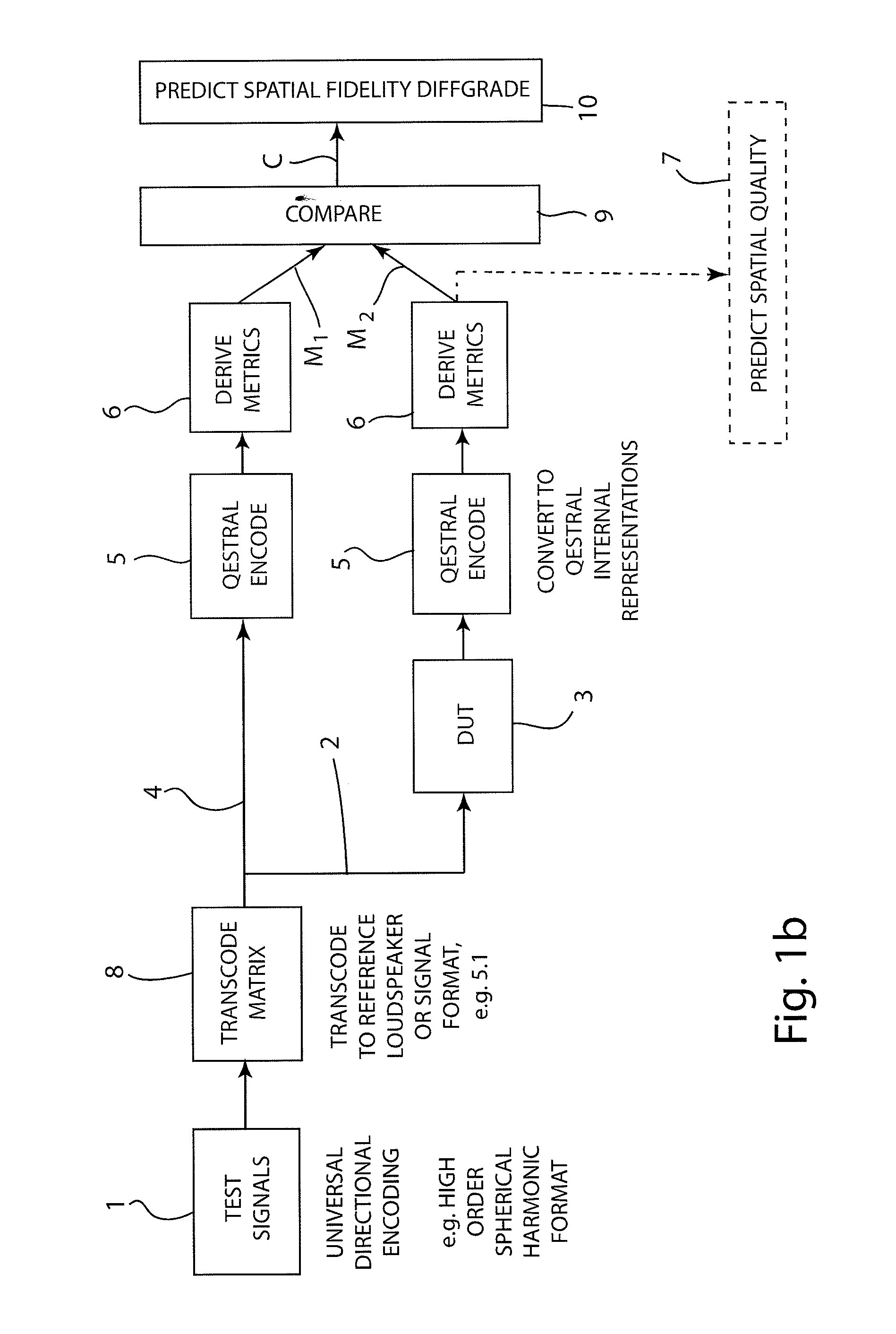

System, devices and methods for predicting the perceived spatial quality of sound processing and reproducing equipment

The present invention relates to a method and corresponding system for predicting the perceived spatial quality of sound processing and reproducing equipment. According to the invention a device to be tested, a so-called device under test (DUT), is subjected to one or more test signals and the response of the device under test is provided to one or more means for deriving metrics, i.e. a higher-level representation of the raw data obtained from the device under test. The derived one or more metrics is / are provided to suitable predictor means that “translates” the objective measure provided by the one or more metrics to a predicted perceived spatial quality. To this end said predictor means is calibrated using listening tests carried out on real listeners. By means of the invention there is thus provided an “instrument” that can replace expensive and time consuming listening tests for instance during development of various audio processing or reproduction systems or methods.

Owner:UNIVERSITY OF SURREY

GUI implementations on central controller computer system for supporting protocol independent device testing

InactiveUS20140237292A1Quick configurationError detection/correctionComputer hardwareGraphical user interface

Owner:ADVANTEST CORP

Probe head having a membrane suspended probe

ActiveUS7368927B2Semiconductor/solid-state device testing/measurementElectrical measurement instrument detailsEngineeringRestoring force

A probe head including an elastic membrane capable of exerting a restoring force when one of the surfaces of the elastic membrane is distorted. A conductive probe includes a beam having a first end and a second end, with a probe tip proximate the first end for contacting a device under test. A beam contact proximate the second end of the beam. The beam being movable to deform at least one surface of the elastic membrane.

Owner:FORMFACTOR INC

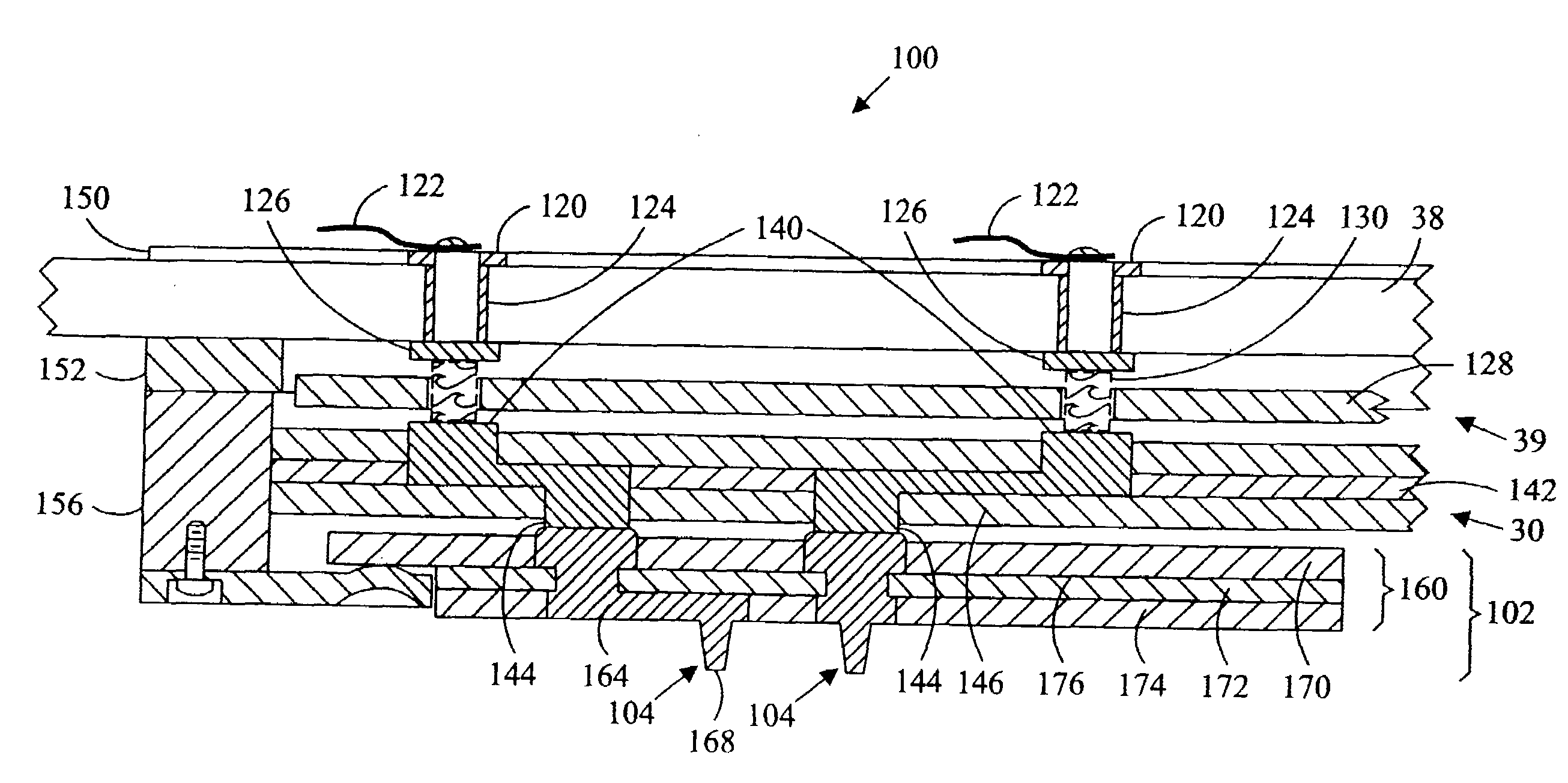

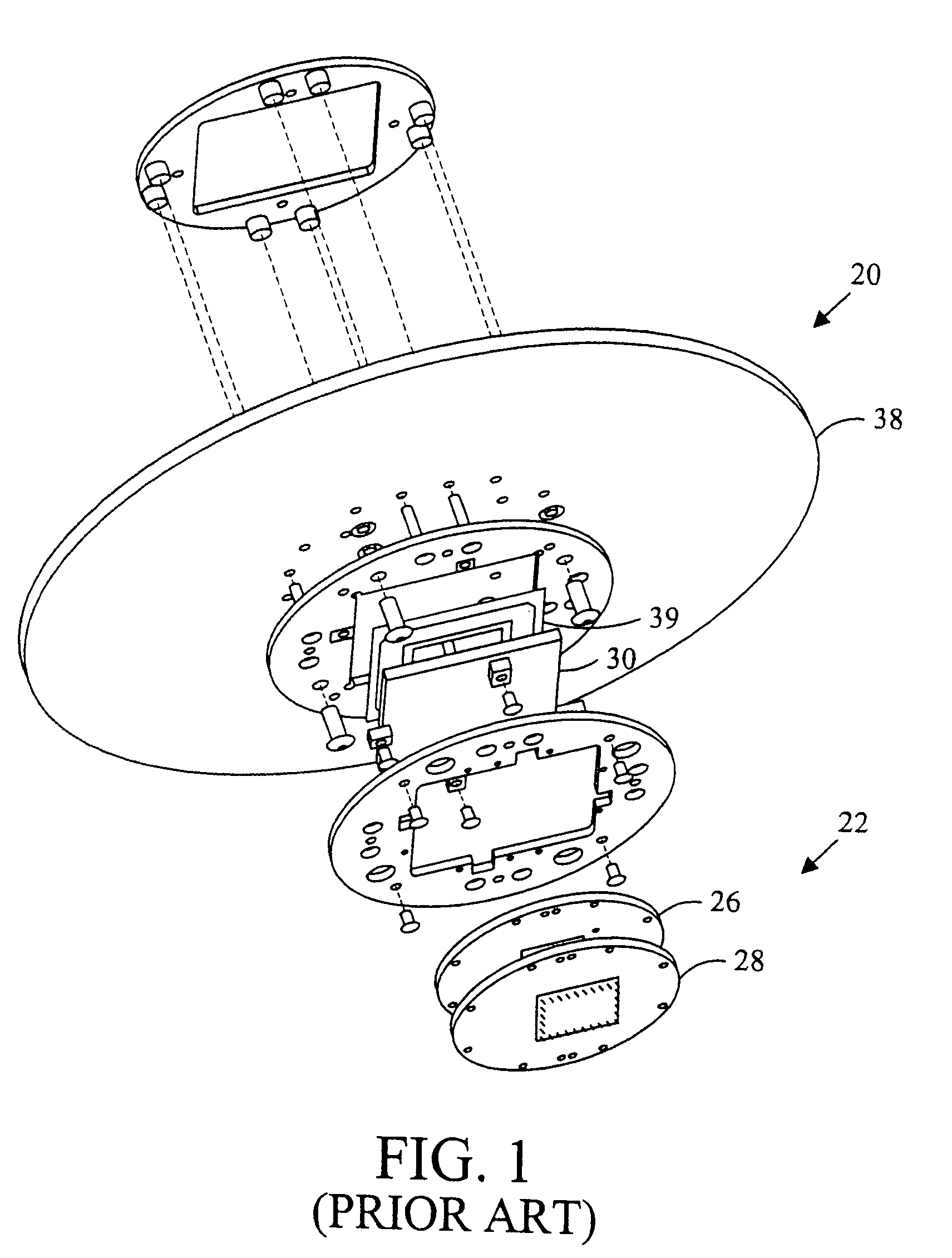

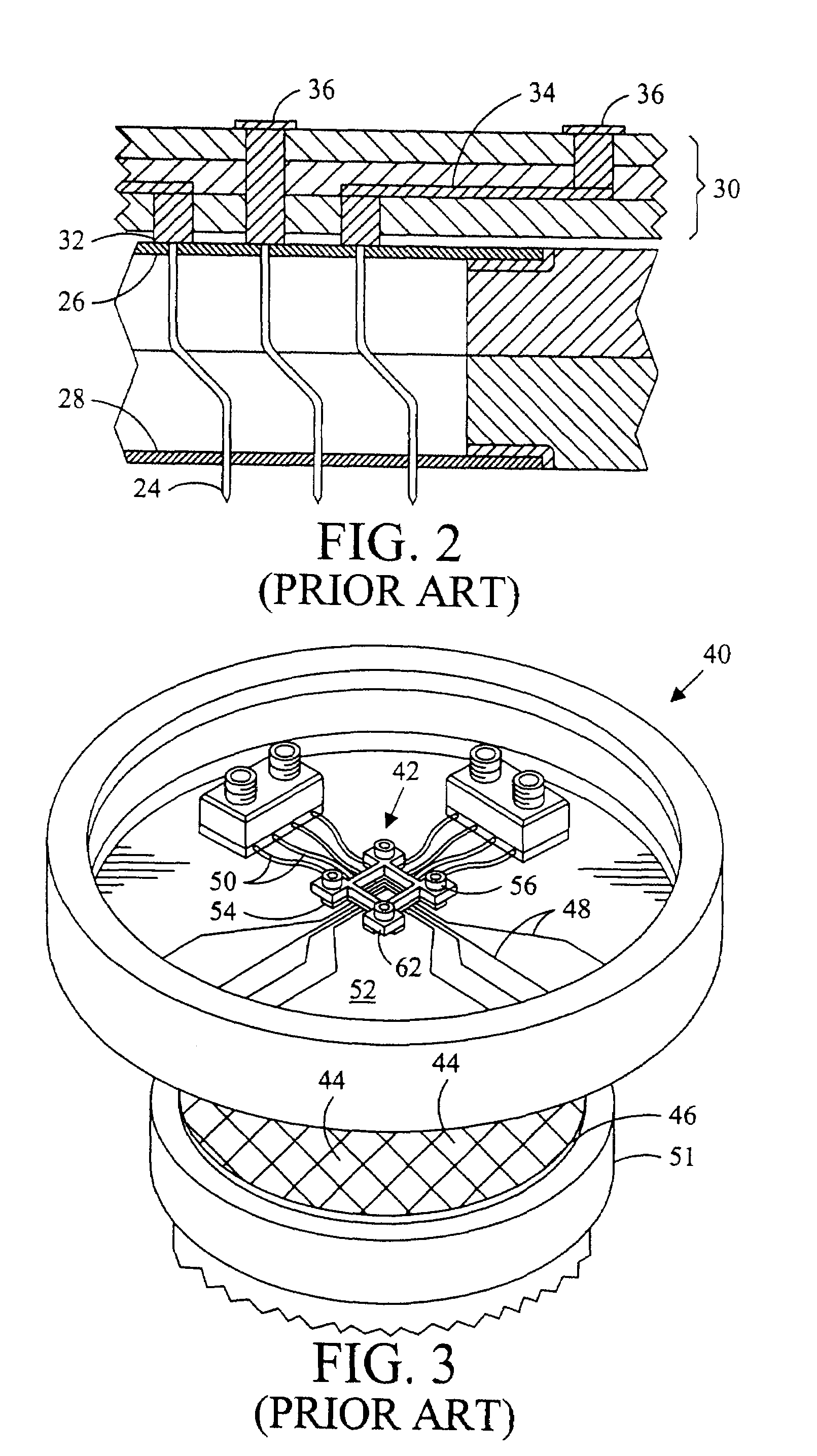

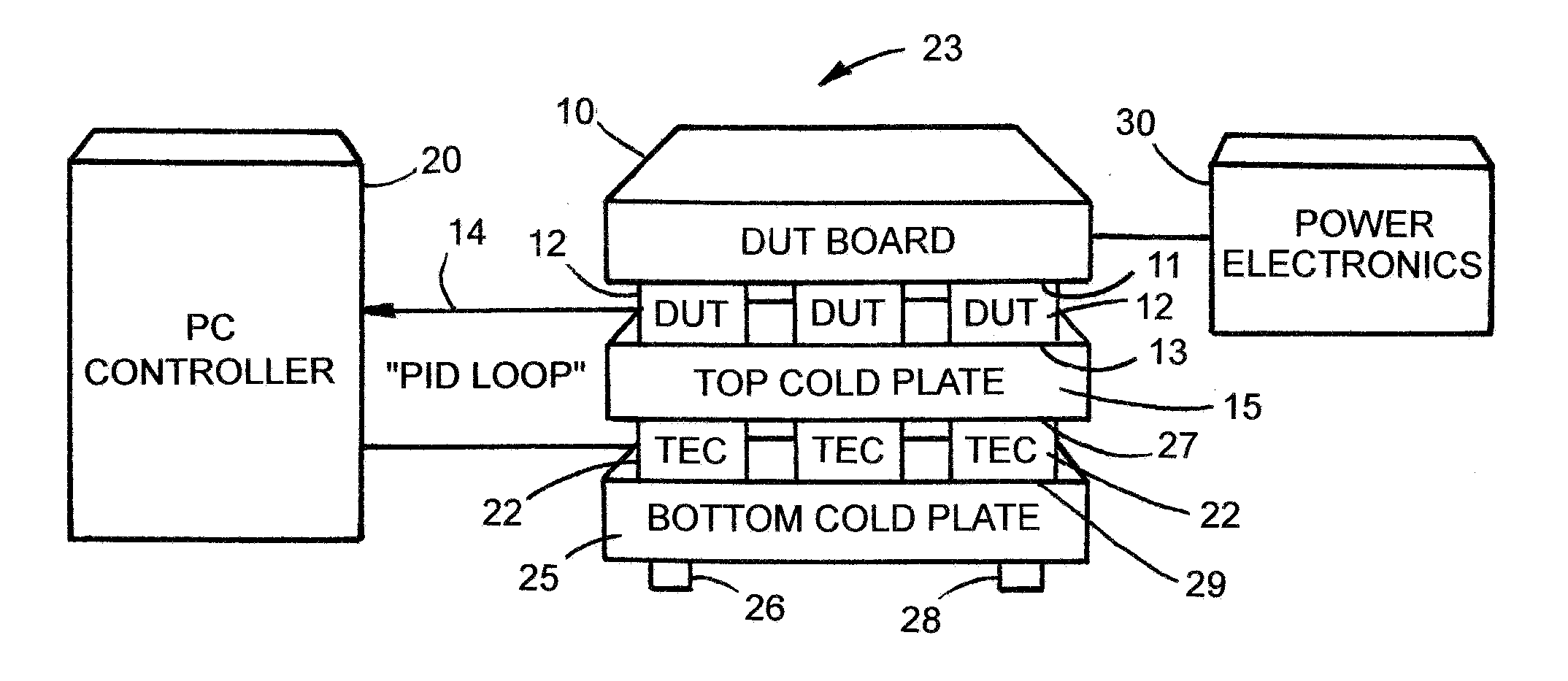

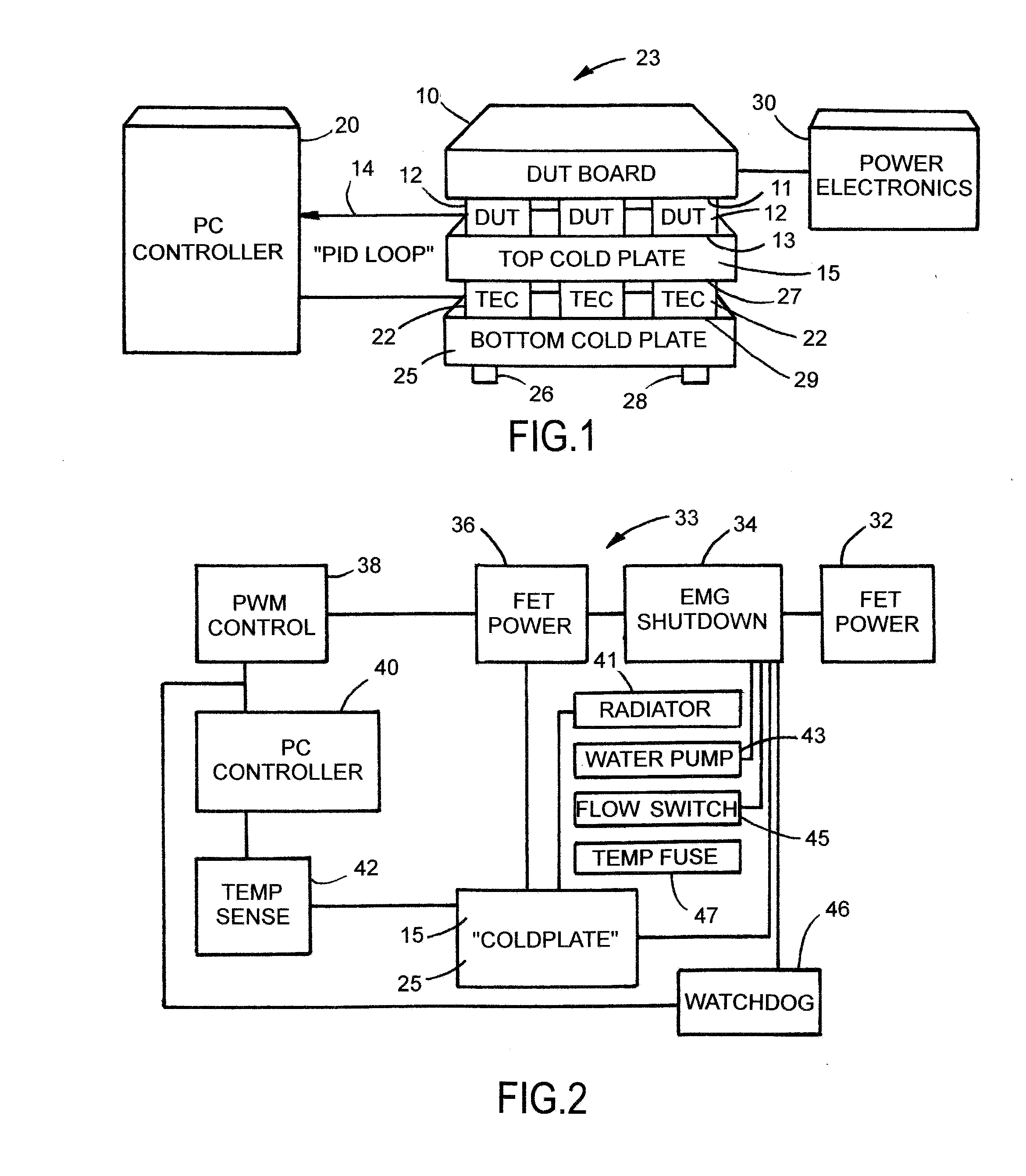

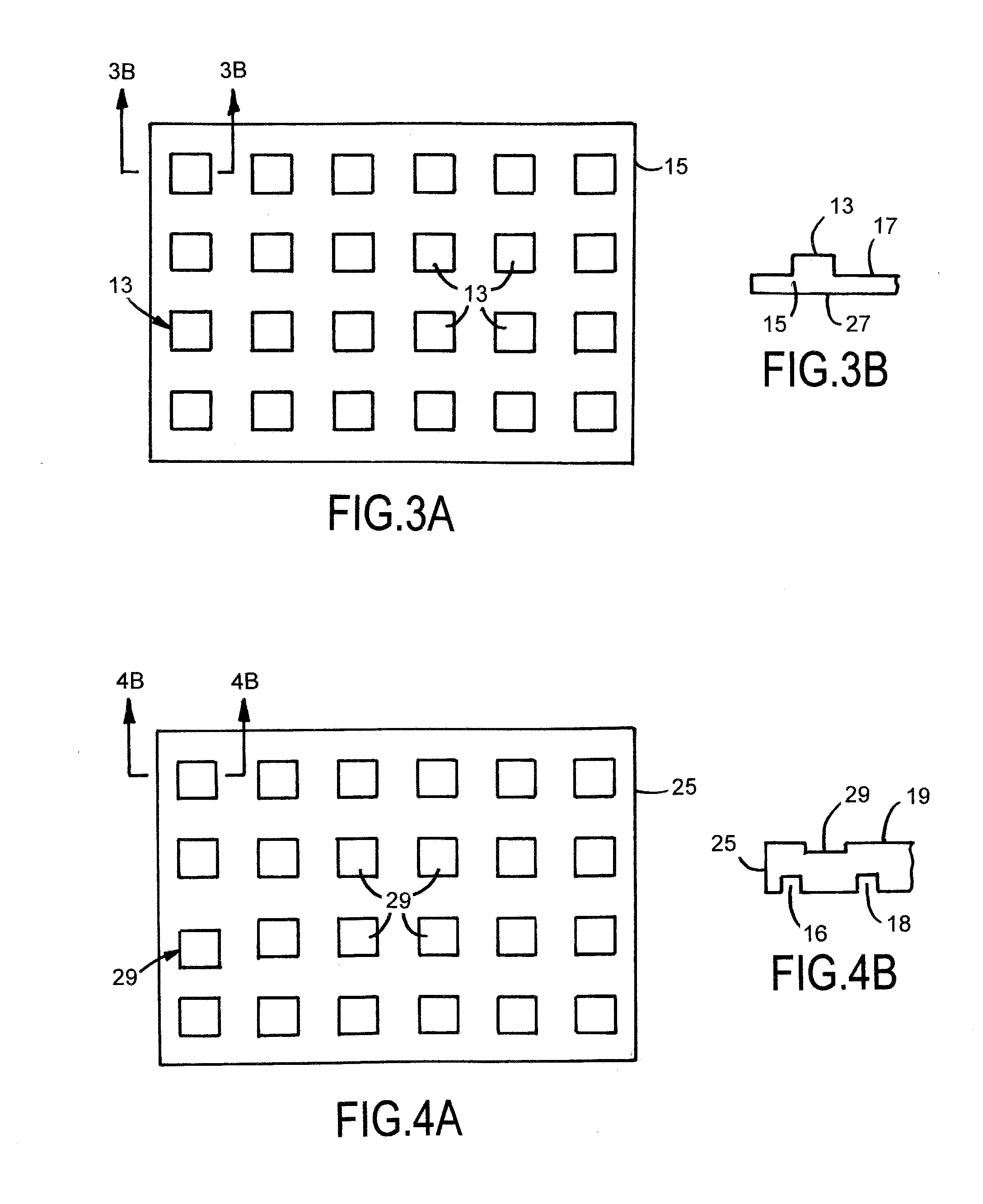

Systems and Methods for Thermal Control

ActiveUS20130285686A1Electronic circuit testingFault location by increasing destruction at faultDevice under testThermoelectric element

The present invention relates generally to a system and a method for thermal control. More particularly, the invention encompasses an apparatus for thermal control and management of at least one device under test (DUT). The inventive thermal control and management apparatus also allows for the management of a plurality of devices under test, and with each device under test having its own testing regimen. The thermal control and management of the device under test (DUT) is managed using at least one thermoelectric element or cooler (TEC), which can be used to either heat or cool the corresponding device under test (DUT).

Owner:SILICON TURNKEY SOLUTIONS

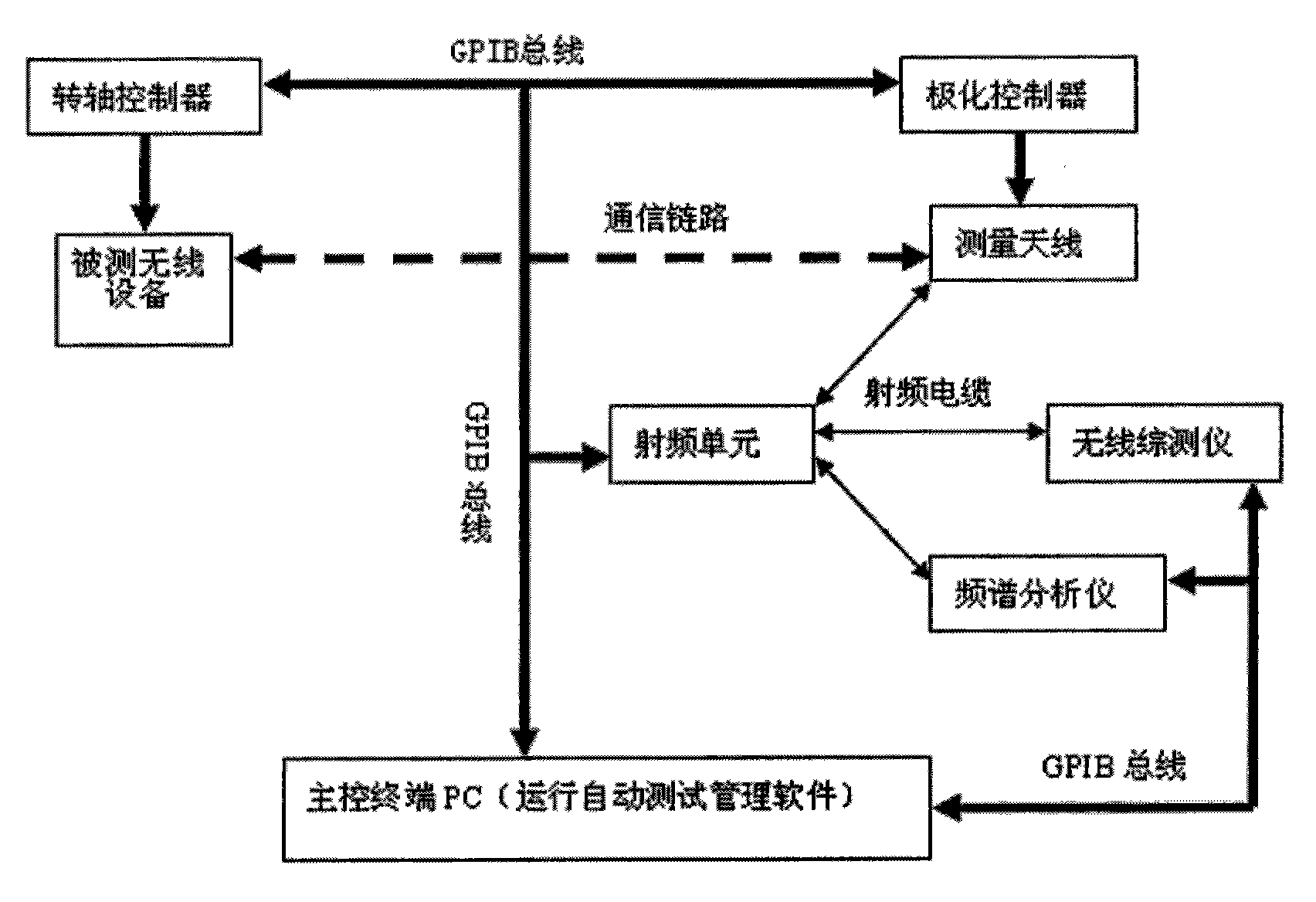

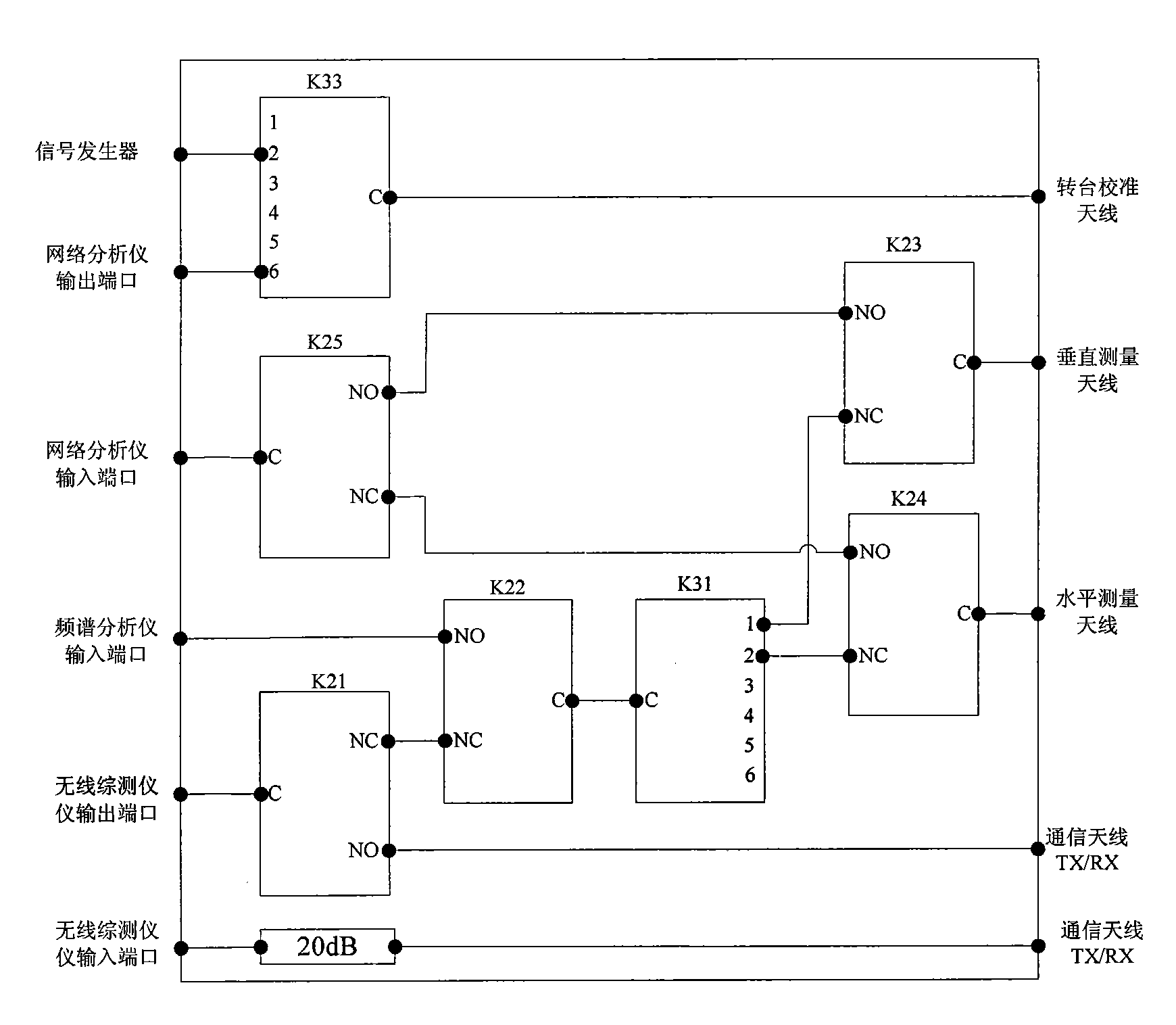

Multi-wireless access technology based over-the-air test system and test method thereof

InactiveCN101605350AAll test typesWide coverageEnergy efficient ICTTransmission monitoringTelecommunications linkSpectrum analyzer

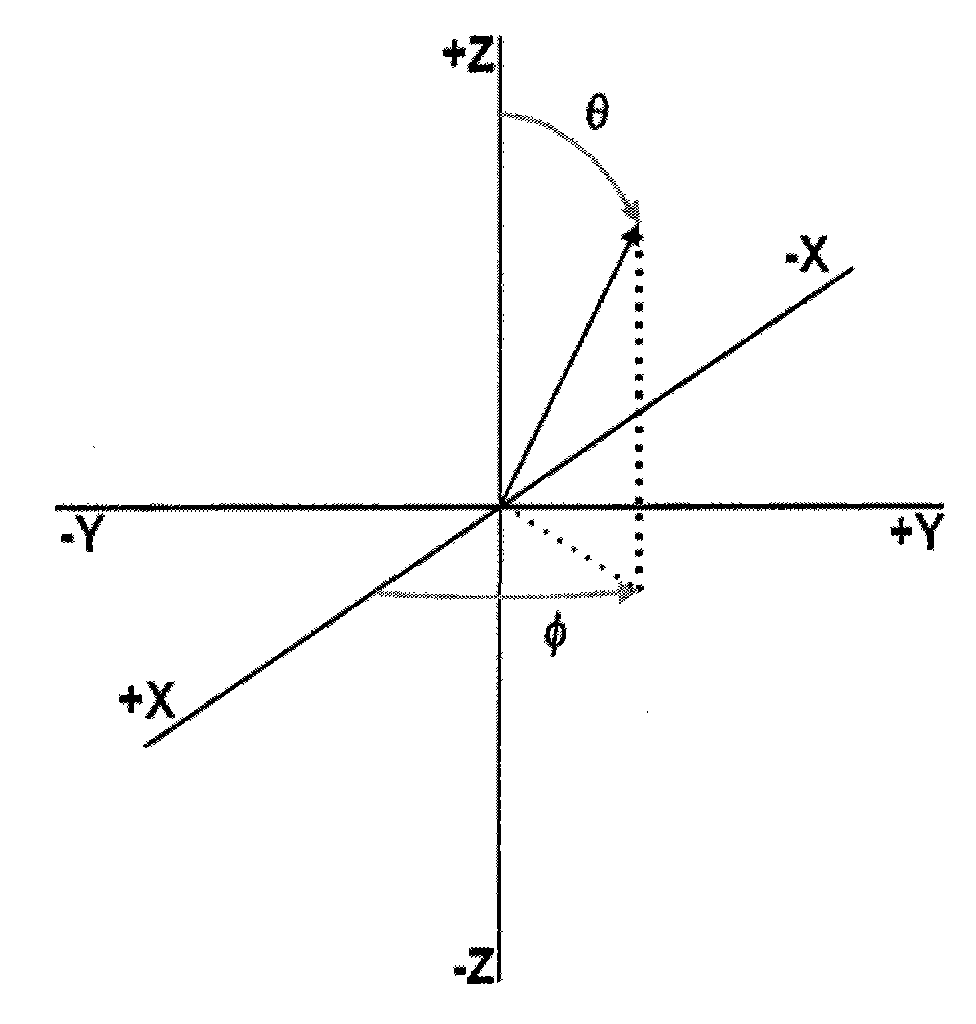

A multi-wireless access technology based over-the-air test system, used for evaluating over-the-air index of a wireless terminal device, has the principle of putting a device to be tested in a three-dimensional space, and establishing a communication link with a base station simulator (namely wireless communications test set); controlling Phi, Theta axles (two axles perpendicular to each other) to rotate according to set step, performing measurement on various angle positions; measuring spherical effective Total Radiated Power of a moving station in the three-dimensional space and Total Isotropic Sensitivity of a receiver. The system mainly comprises a darkroom, a high-accuracy positioning system and its controller(including a rotating axle controller and a polarization controller), a radio frequency test instrument and a main control terminal computer with automatic test program, wherein the radio frequency instruments comprises a wireless communications test set, a spectrum analyzer, a network analyzer and a radio frequency unit.

Owner:TELECOMM METROLOGY CENT OF MINIST OF IND & INFORMATION TECH

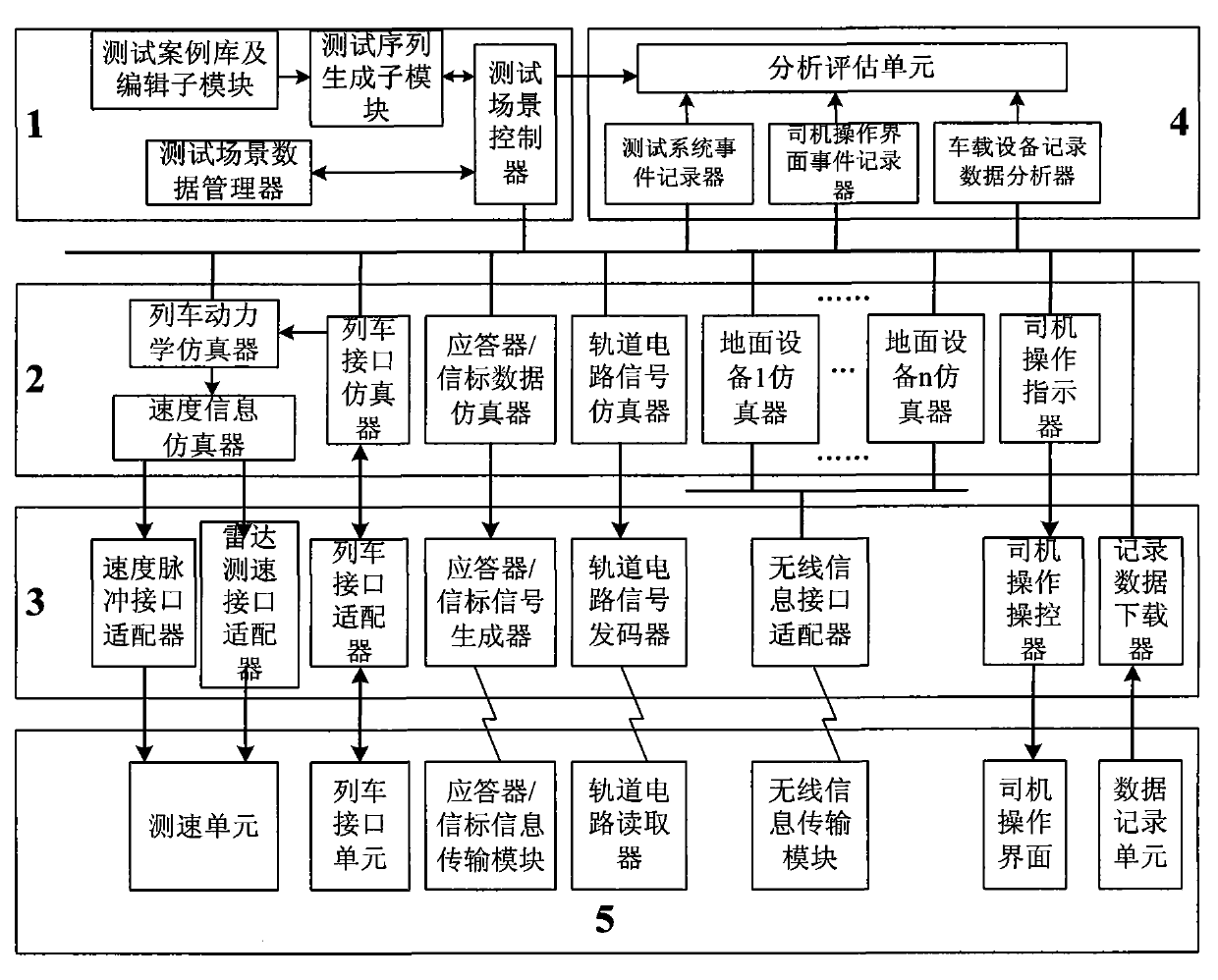

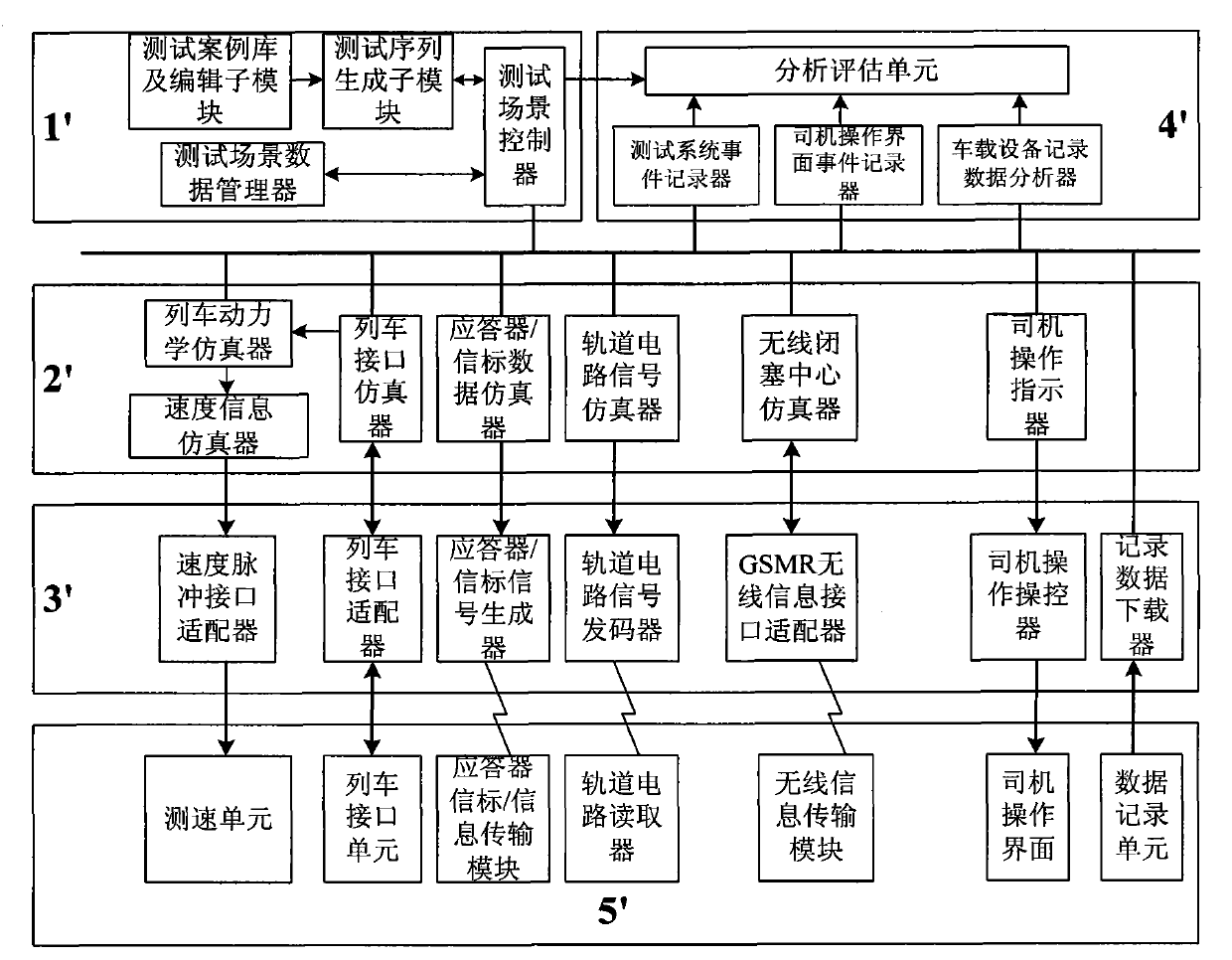

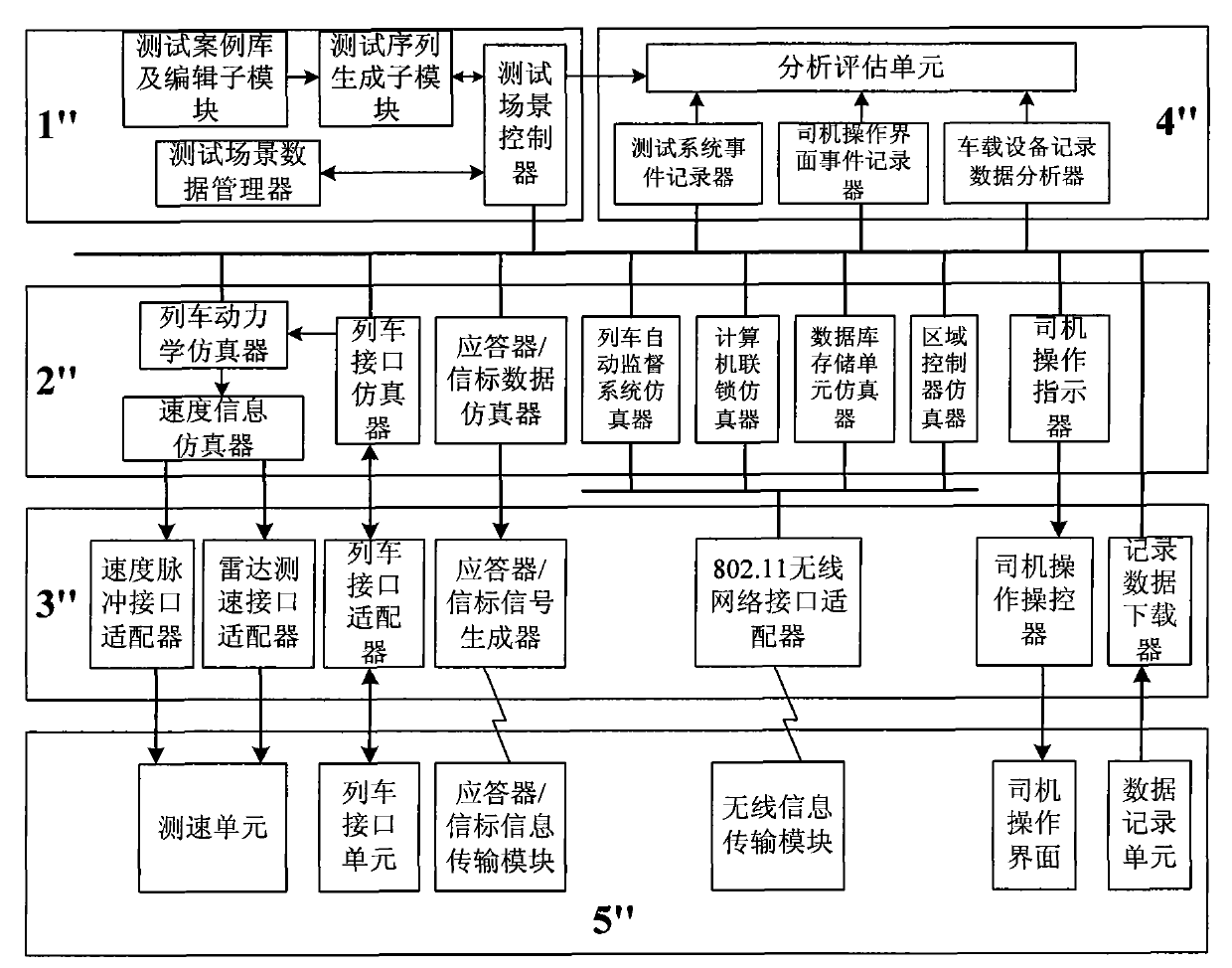

Test system and method of data-driven vehicle-mounted operation control system

InactiveCN102004489AImprove adaptabilityFlexible and convenient testingElectric testing/monitoringTest executionEmbedded system

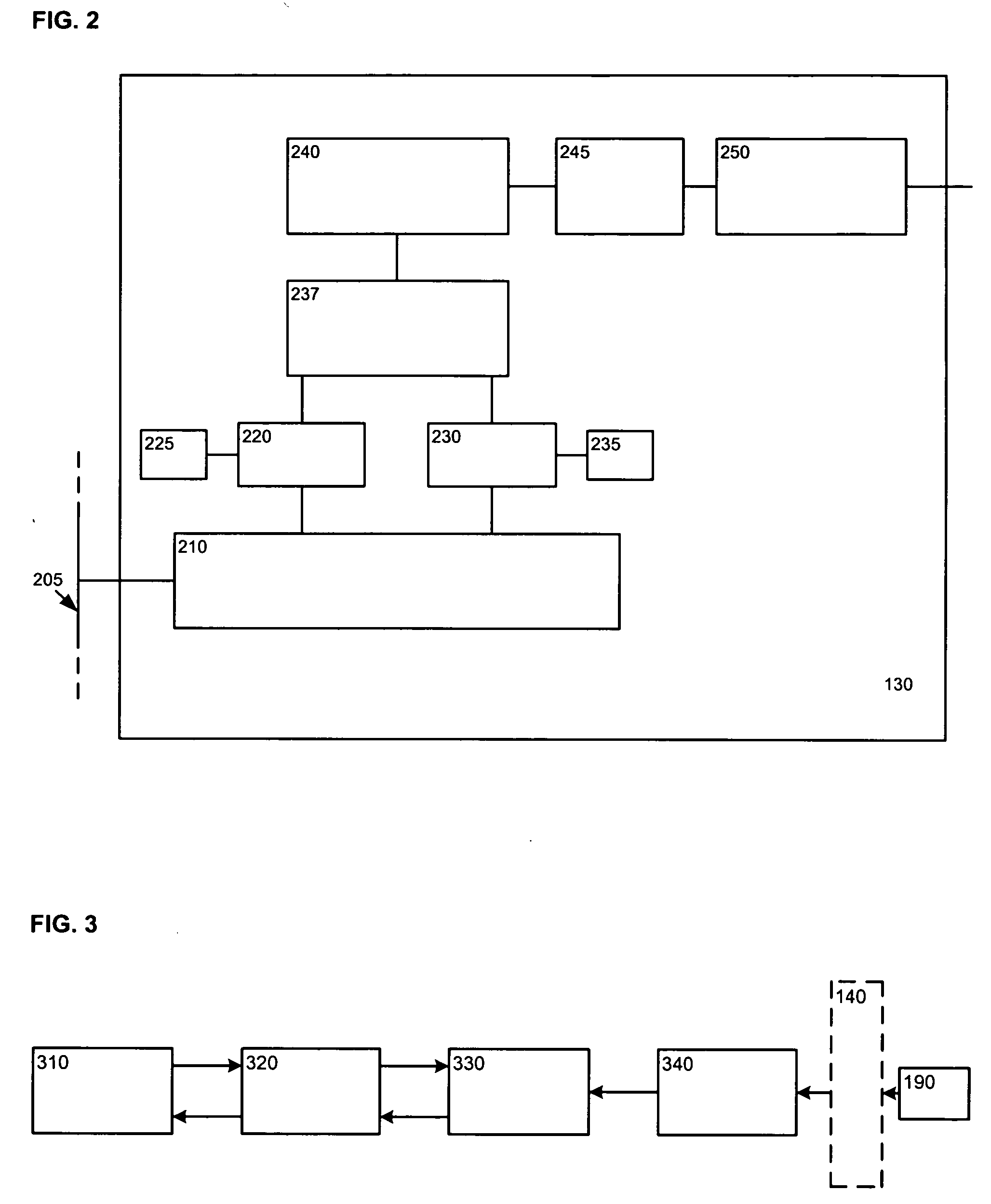

The invention discloses a test system and method of a data-driven rail traffic vehicle-mounted operation control system, belonging to the technical field of rail traffic signal system test. The test system comprises a test management module, a test execution module, a test interface adaption module and a test analysis and assessment module and is connected with a tested vehicle-mounted operation control system by the test interface adaption module, wherein the test management module finishes the functions of storing, modifying and configuring test data, the test execution module finishes the function of executing the test data, the test analysis and assessment module finishes the functions of recording, treating, analyzing and assessing the test data, and the test interface adaption module finishes the functions of adapting to the interface characteristics of real tested vehicle-mounted equipment and interacting practical information with the tested equipment. The invention can be conveniently used for various types of tests on the vehicle-mounted equipment of a train operation control system, wherein the tests comprise function test, interconnection test and the like; and in addition, the invention has good popularity and flexibility.

Owner:BEIJING JIAOTONG UNIV

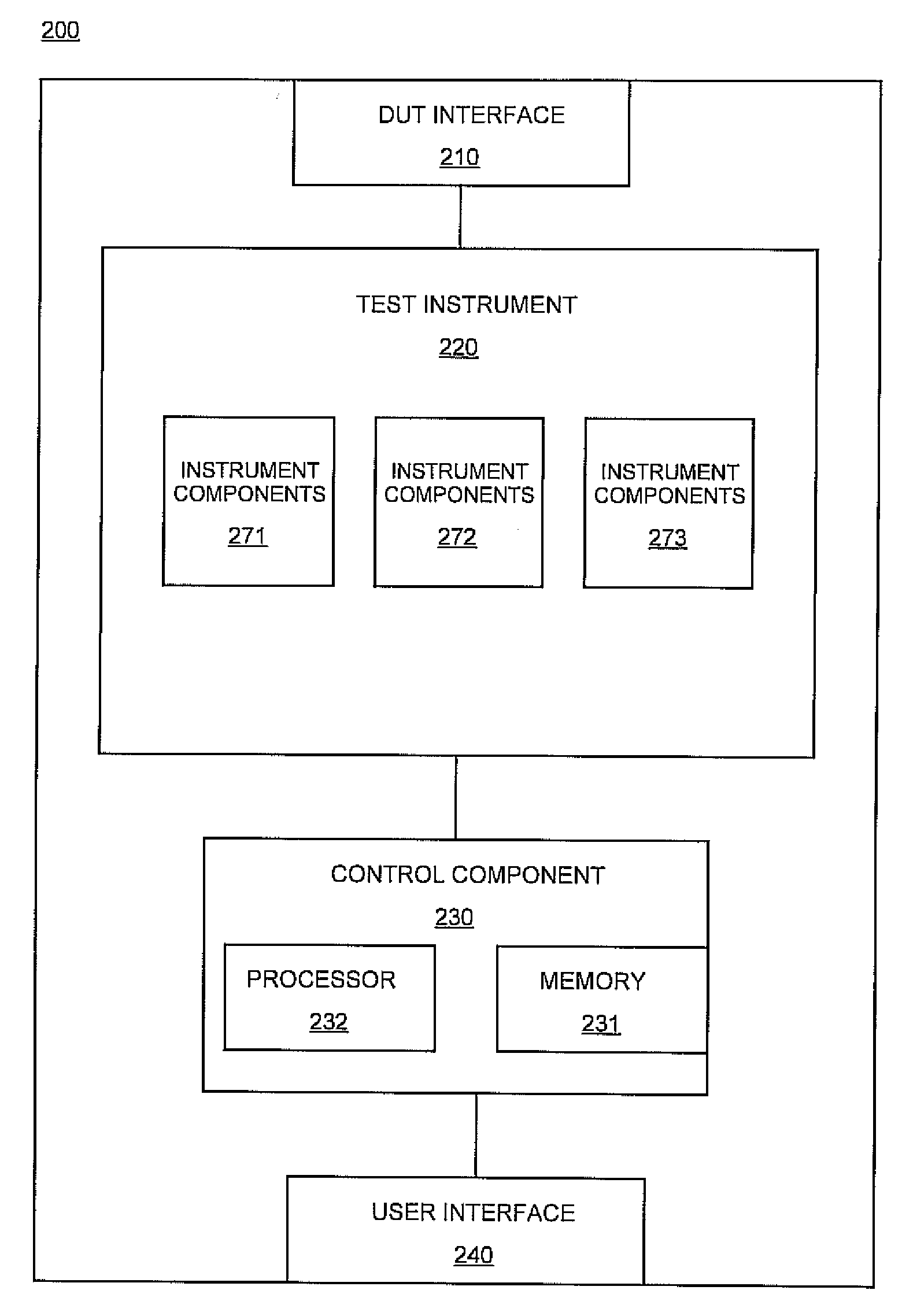

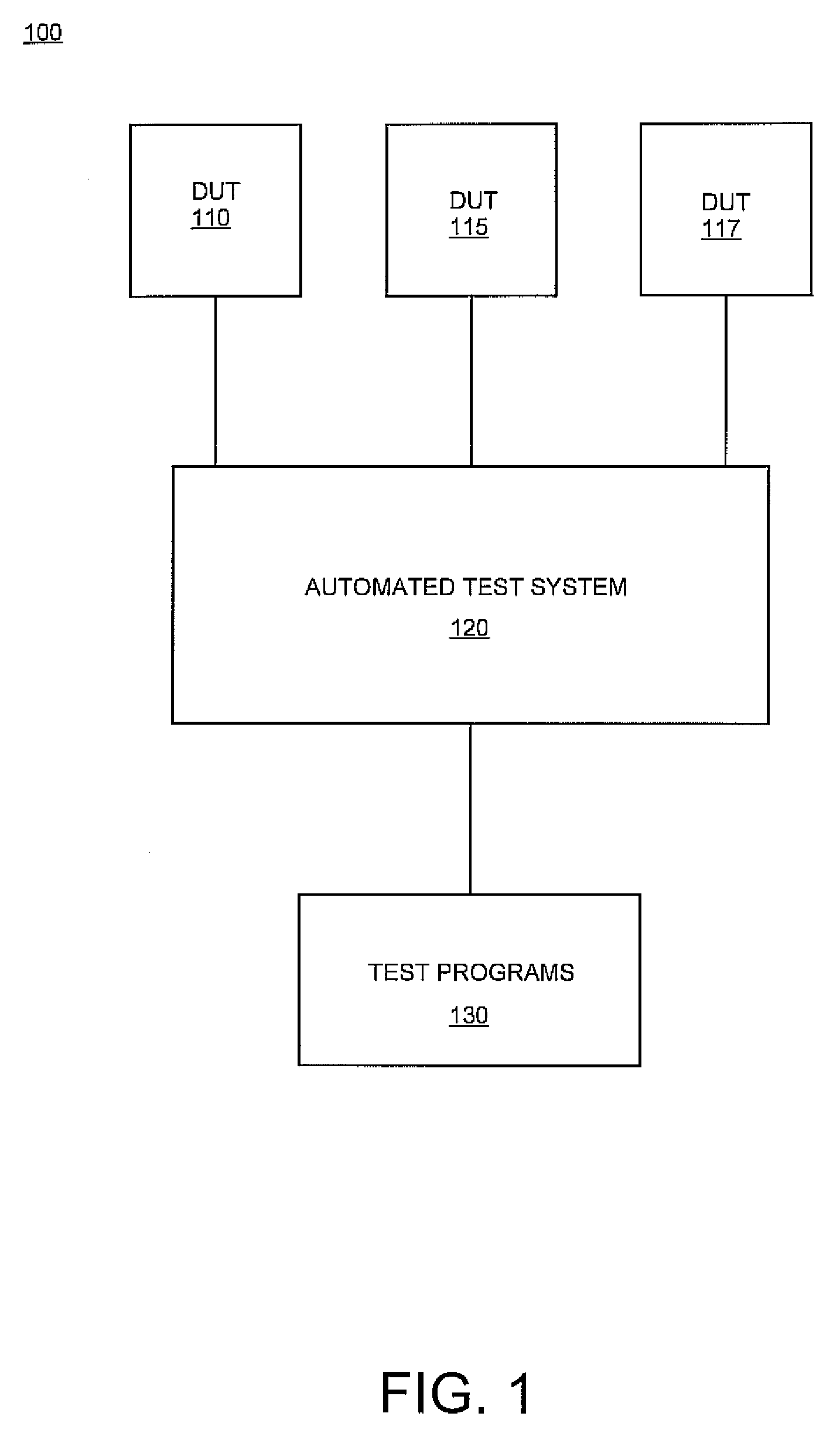

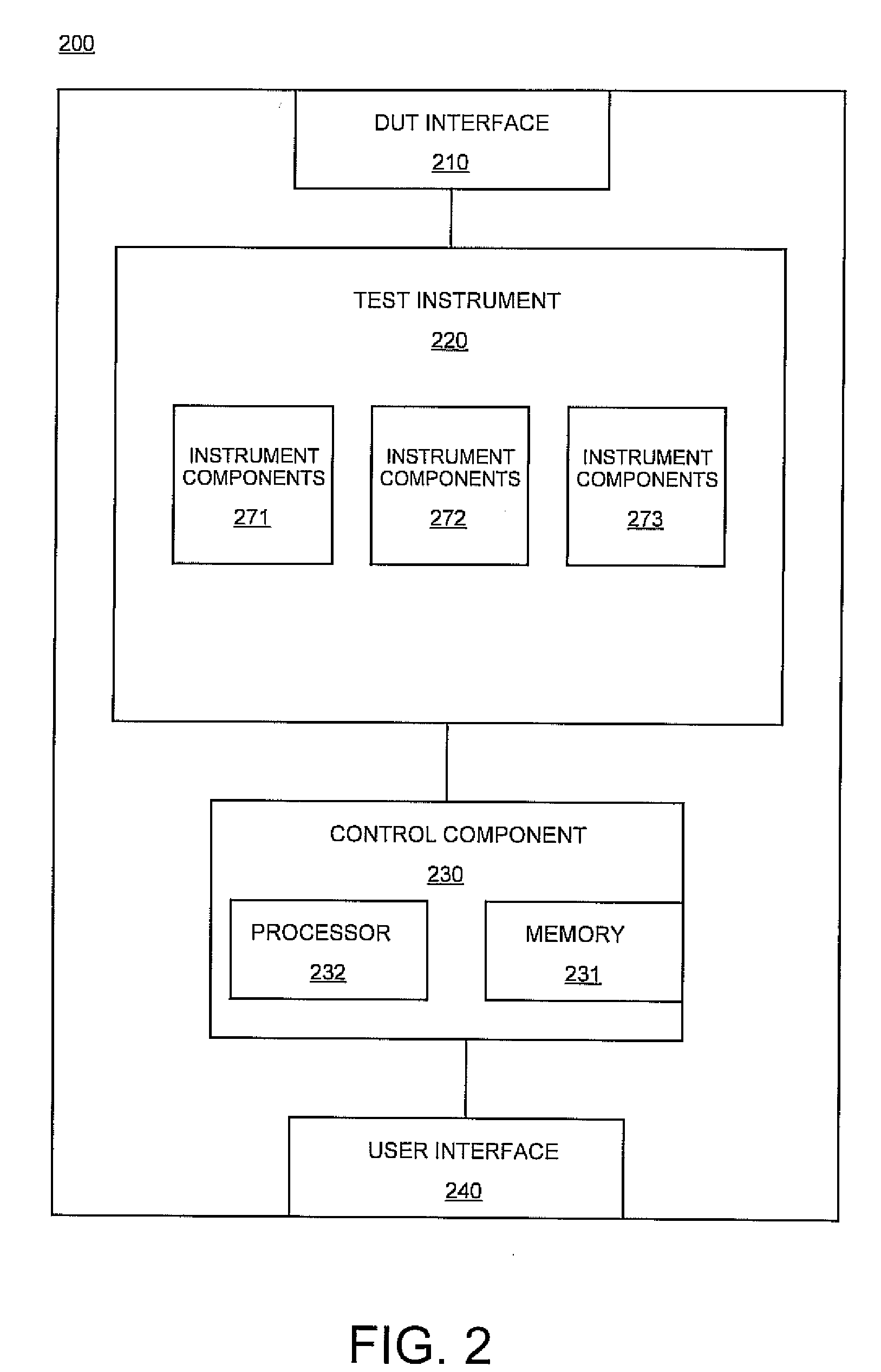

Automated test system and method

InactiveUS20100023294A1Special data processing applicationsAutomated test systemsComputer hardwareEquipment under test

An efficient automated testing system and method are presented. In one embodiment, an automated testing system includes a control component and an automated test instrument for testing a device or a plurality of devices (e.g., packages or wafers containing multiple independent different devices) under test. The automated test instrument component performs testing operation on the device or devices under test (DUT). The control component manages testing activities of a test instrument testing the device under test, including managing implementation of a plurality of test programs loaded as a group. In one exemplary implementation, the automated test system also includes a DUT interface and a user interface. The device under test interface interfaces with a device or devices under test.

Owner:CREDENCE SYSTEMS

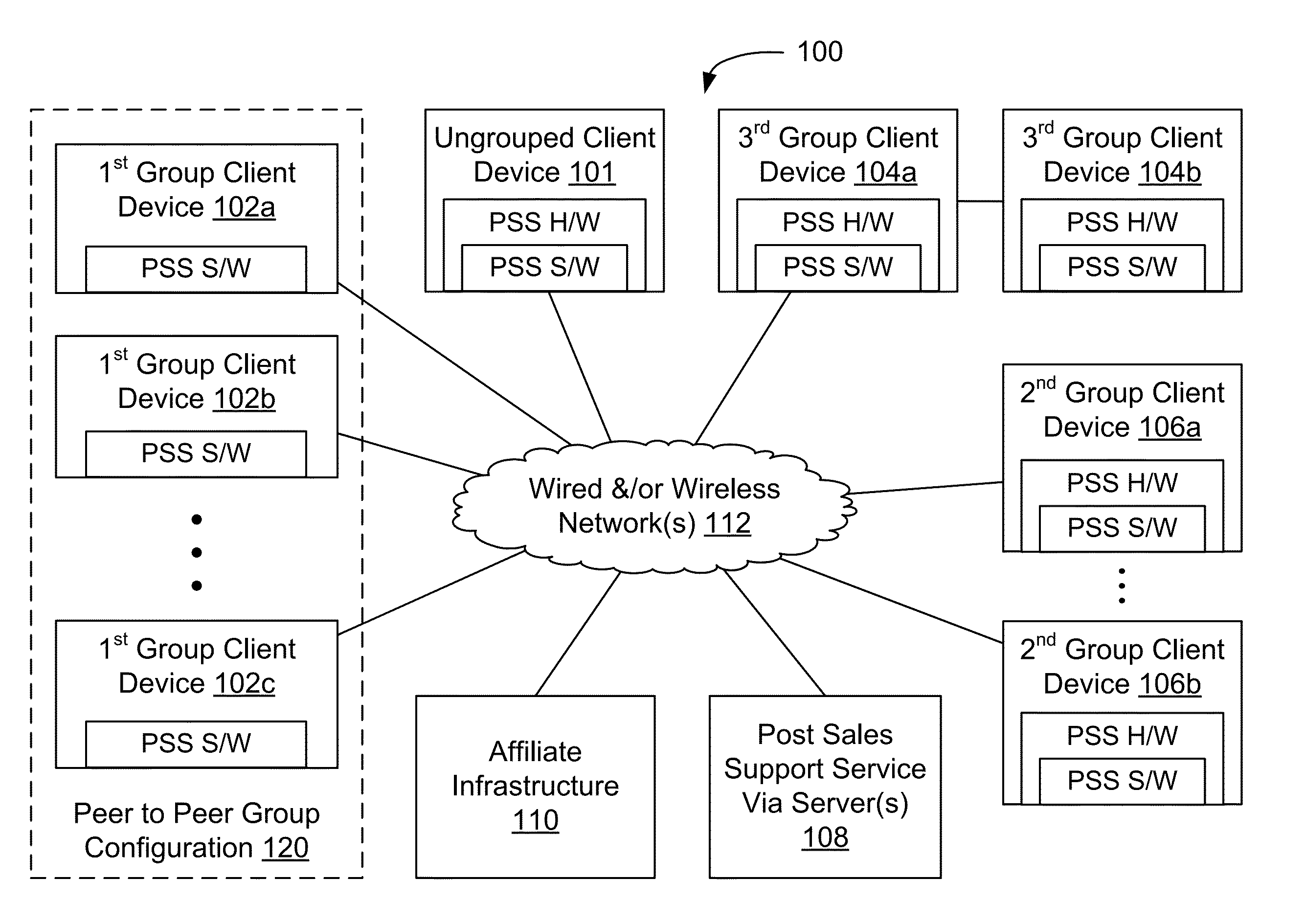

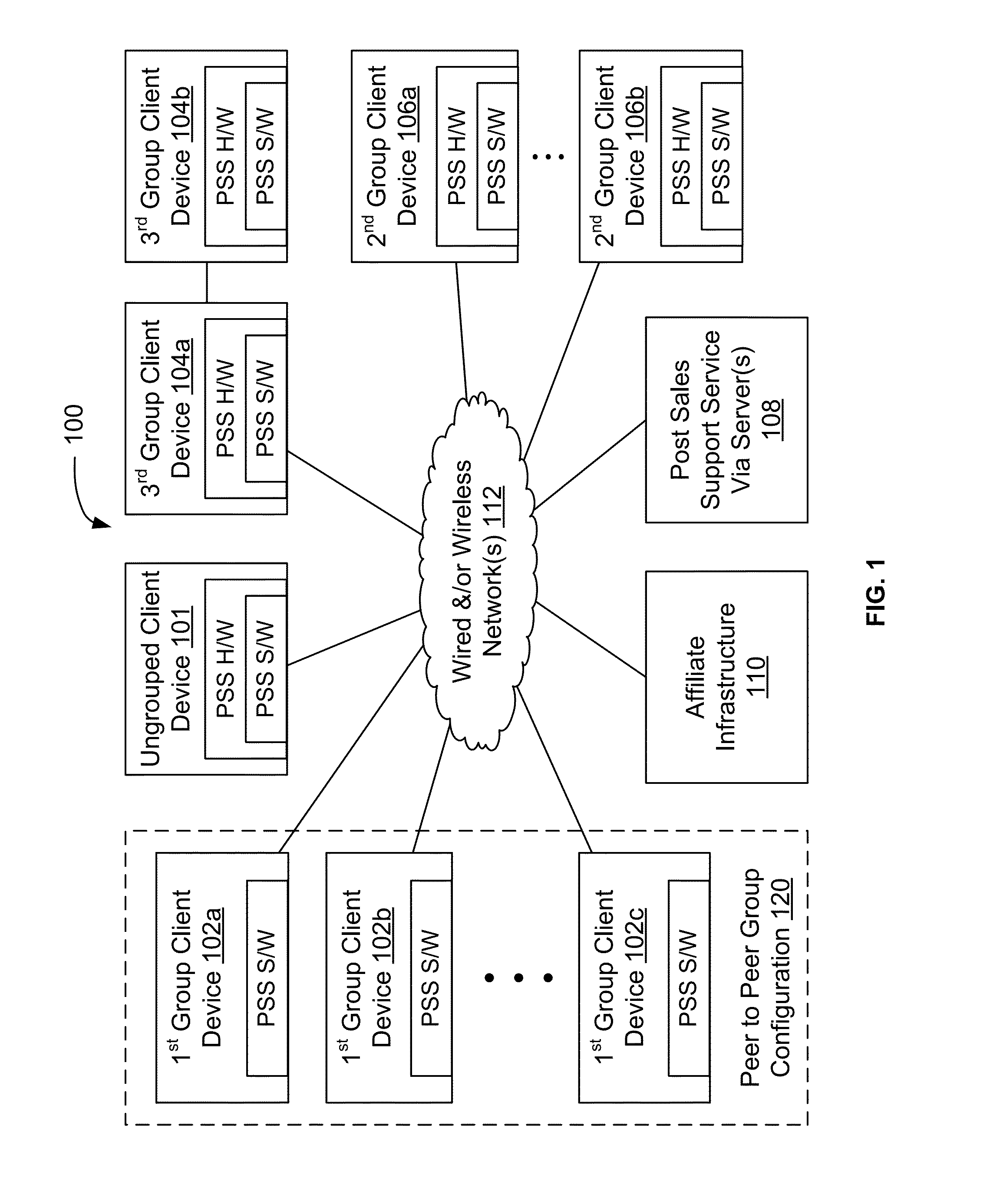

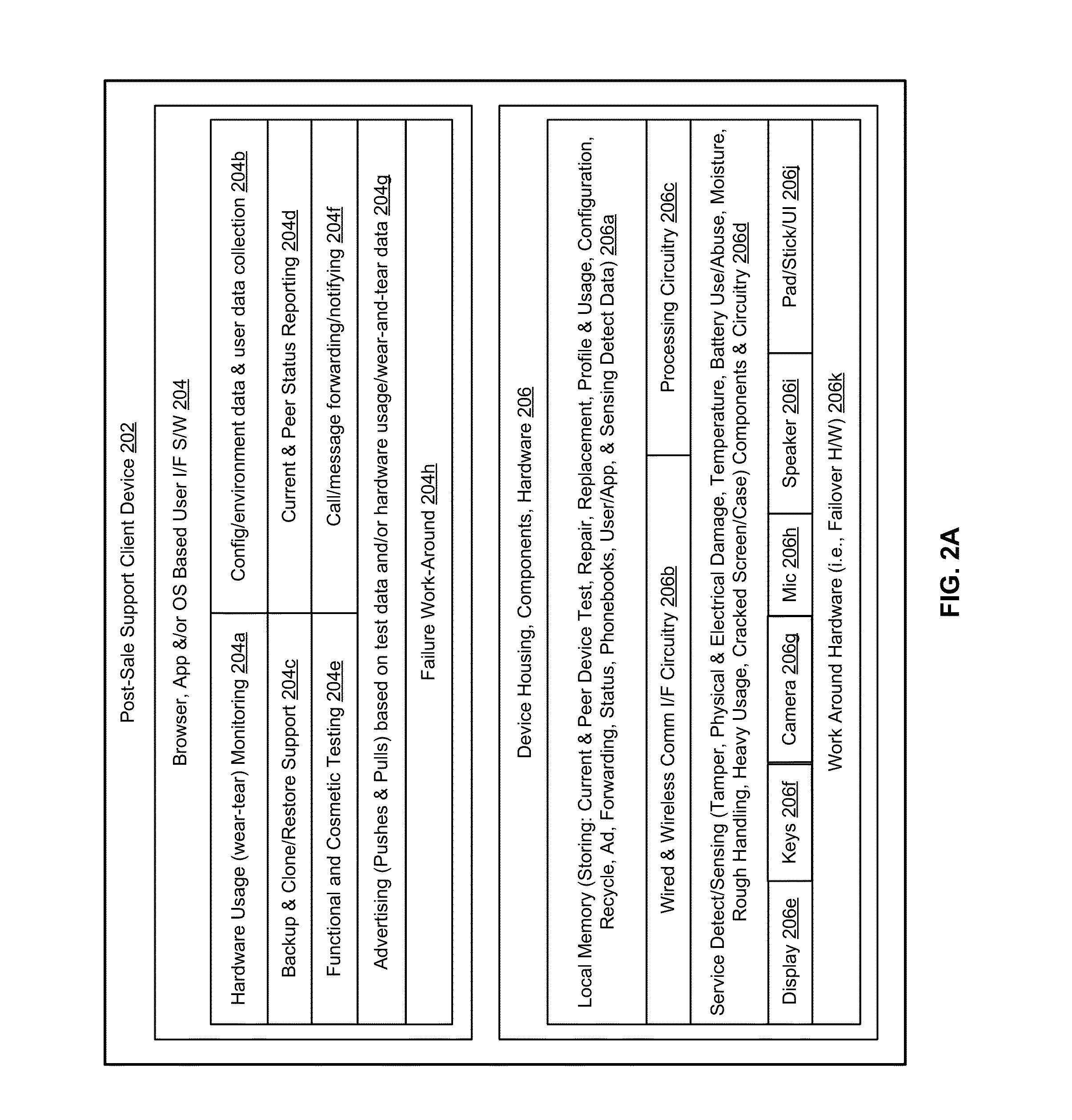

Electronic device post-sale support system

A system comprises a device under test, a testing device coupled to said device under test via a direct connection, and a post-sales support server communicatively coupled to said testing device via a wide area network connection. The testing device is operable to collect, from said device under test via said direct connection, responses to test stimuli generated in accordance with test code. The testing device is operable to provide said responses to said post-sale support server. The post-sale support server is operable to generate a valuation of said device under test based on said responses, and make said valuation available to a user of said device under test. The valuation may comprise a monetary value based offer associated with third party repair, resale and recycling.

Owner:BENNETT JAMES DUANE

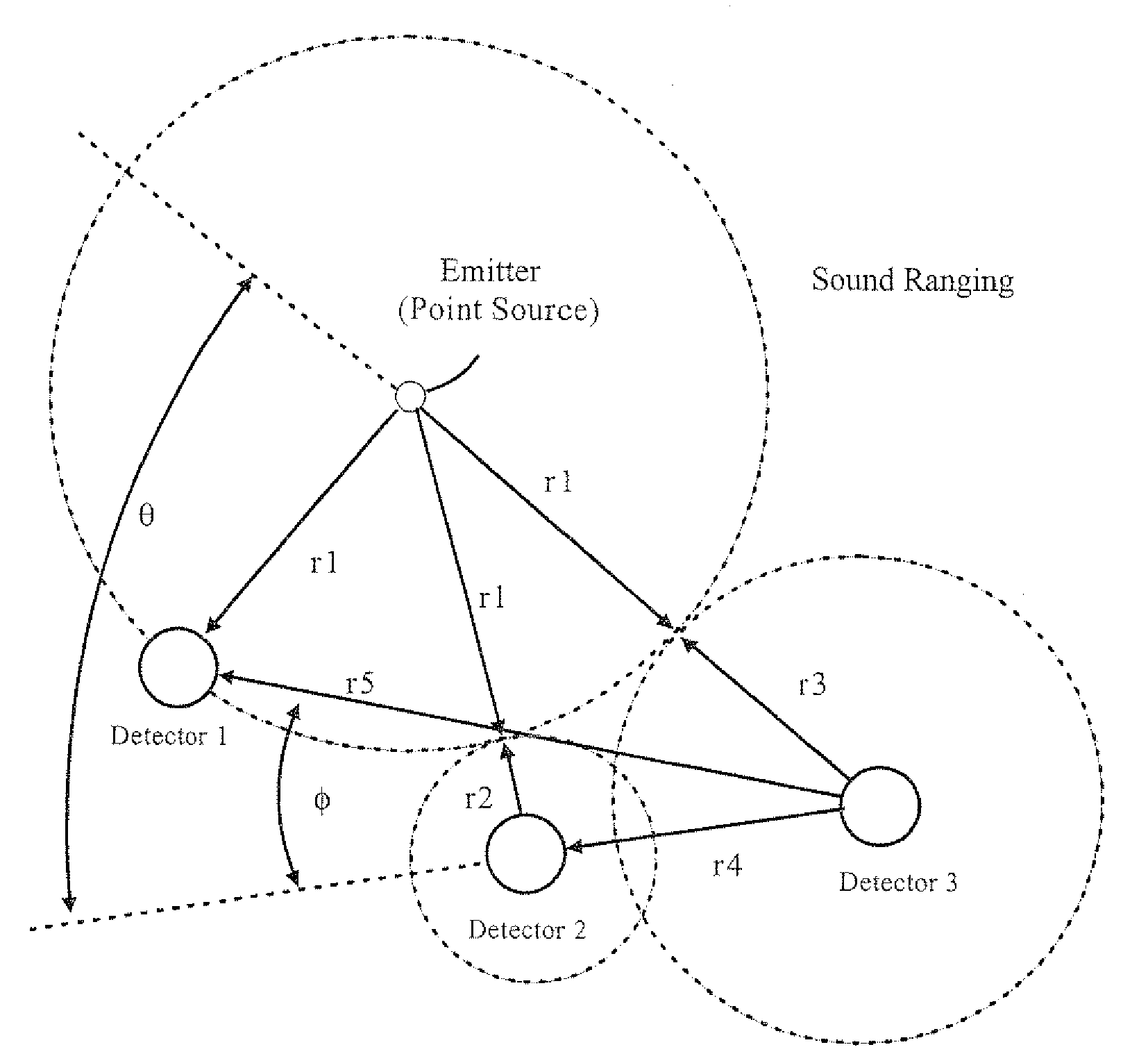

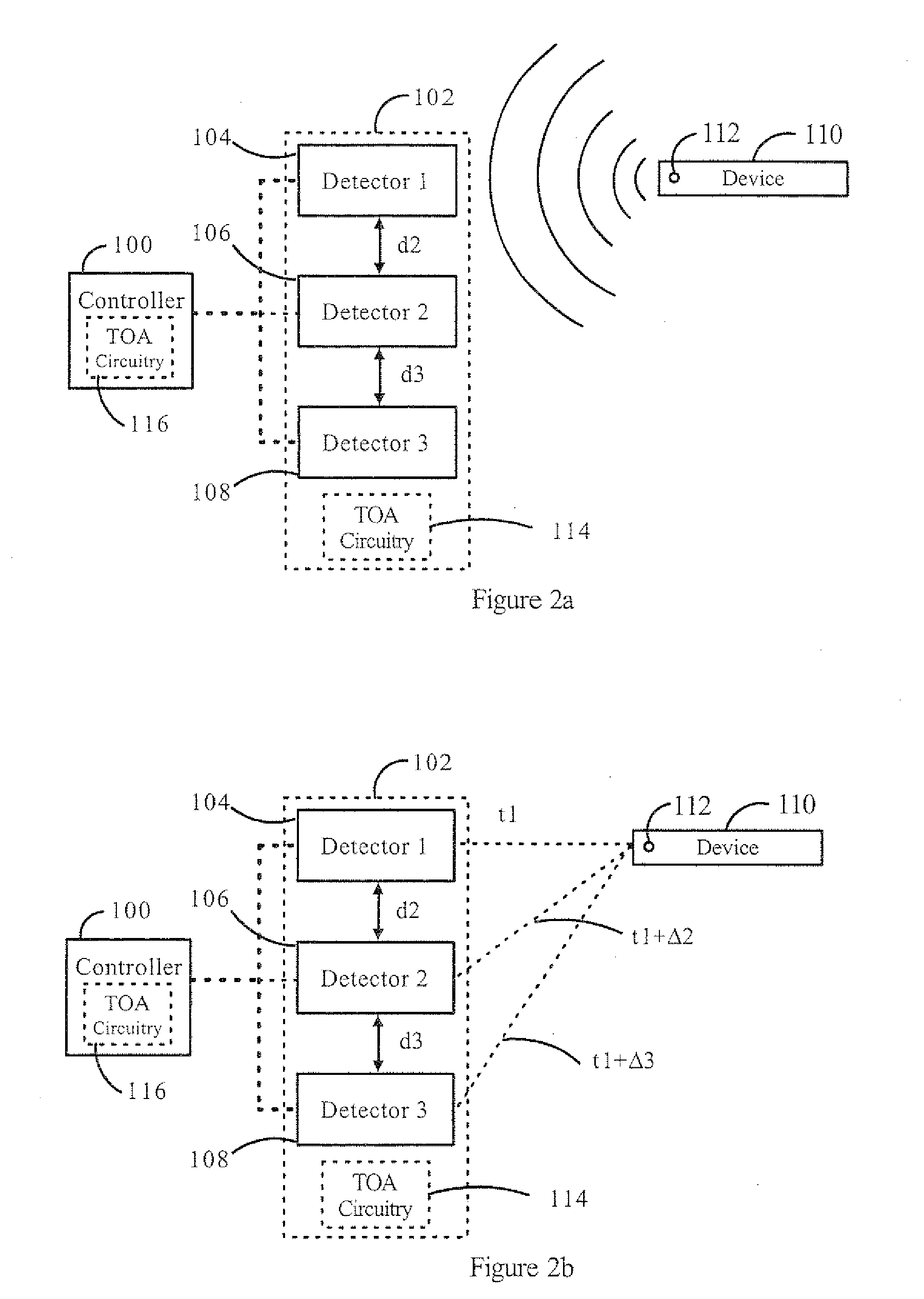

System and method for automatic determination of the physical location of data center equipment

The invention is directed to a system and method for automatic discovery of the physical location of at least one device in a data center, the device having an associated ultrasonic emitter. The system generally includes a plurality of ultrasonic detectors having known locations in the data center. A controller initiates the generation of an ultrasonic signal from an ultrasonic emitter associated with a device under test. Time of arrival circuitry generates time of arrival information associated with each ultrasonic detector based on the time of receipt of the ultrasonic signal. The controller determines the location of the device under test based on the known location of the ultrasonic detectors within the data center and the time of arrival information associated with each ultrasonic detector.

Owner:SUNBIRD SOFTWARE INC

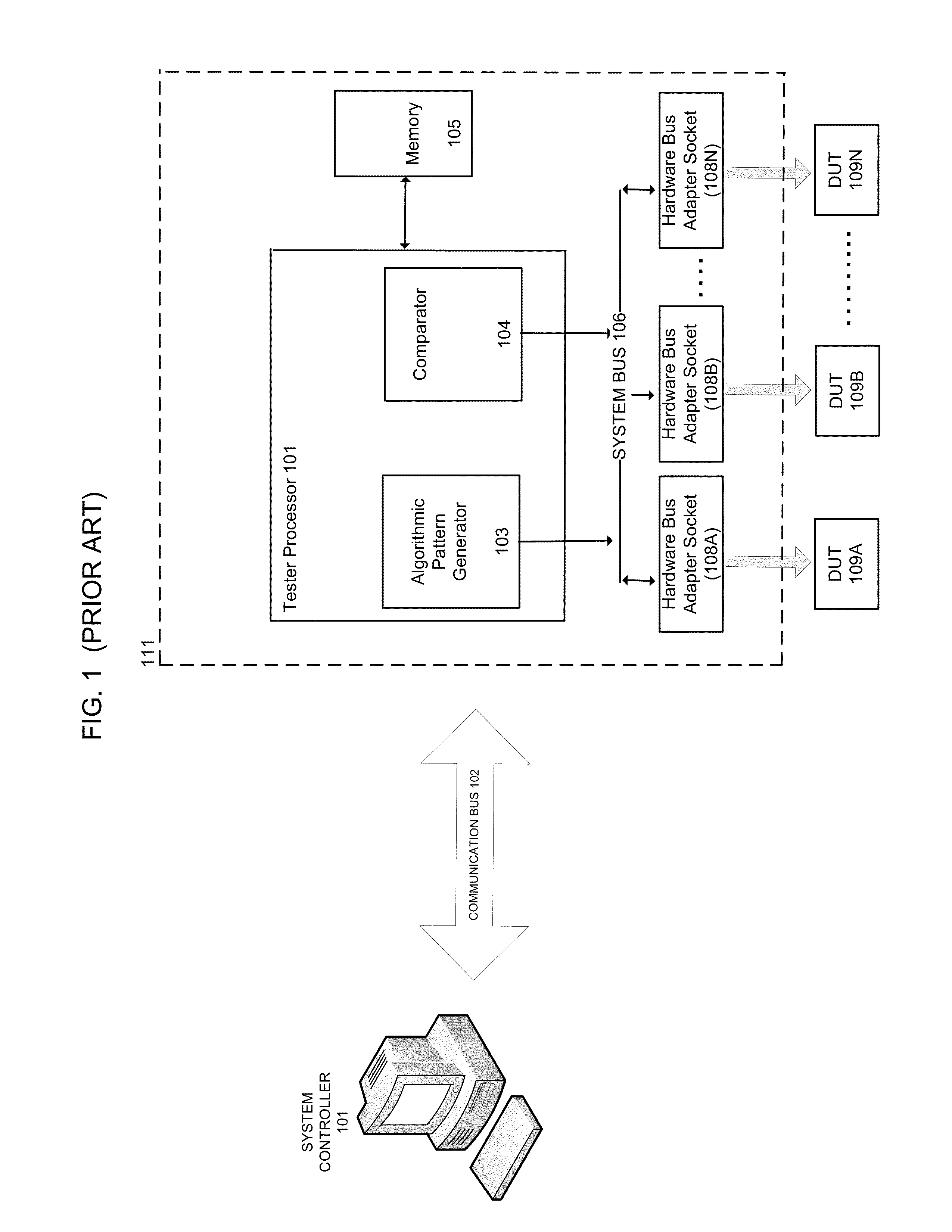

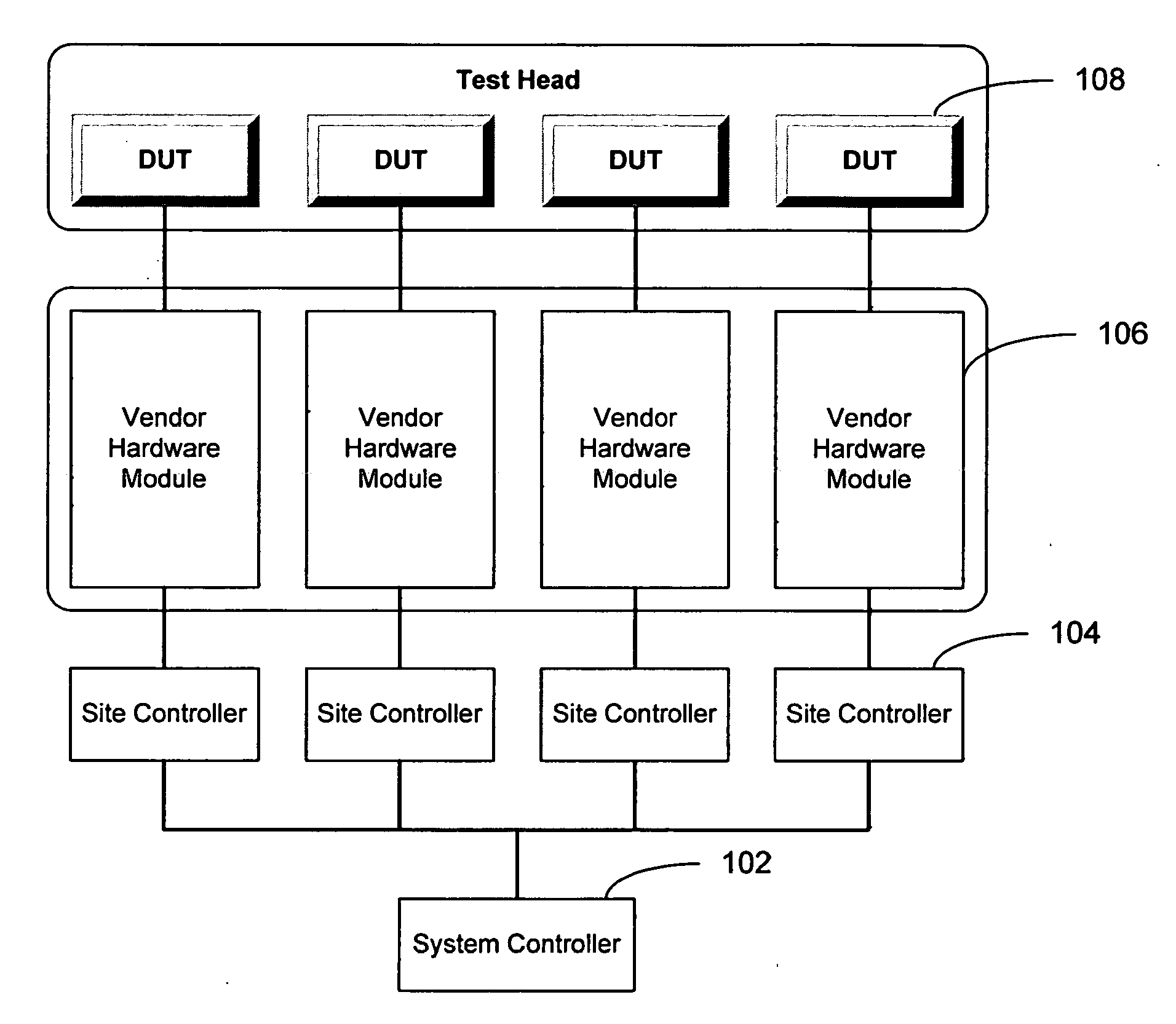

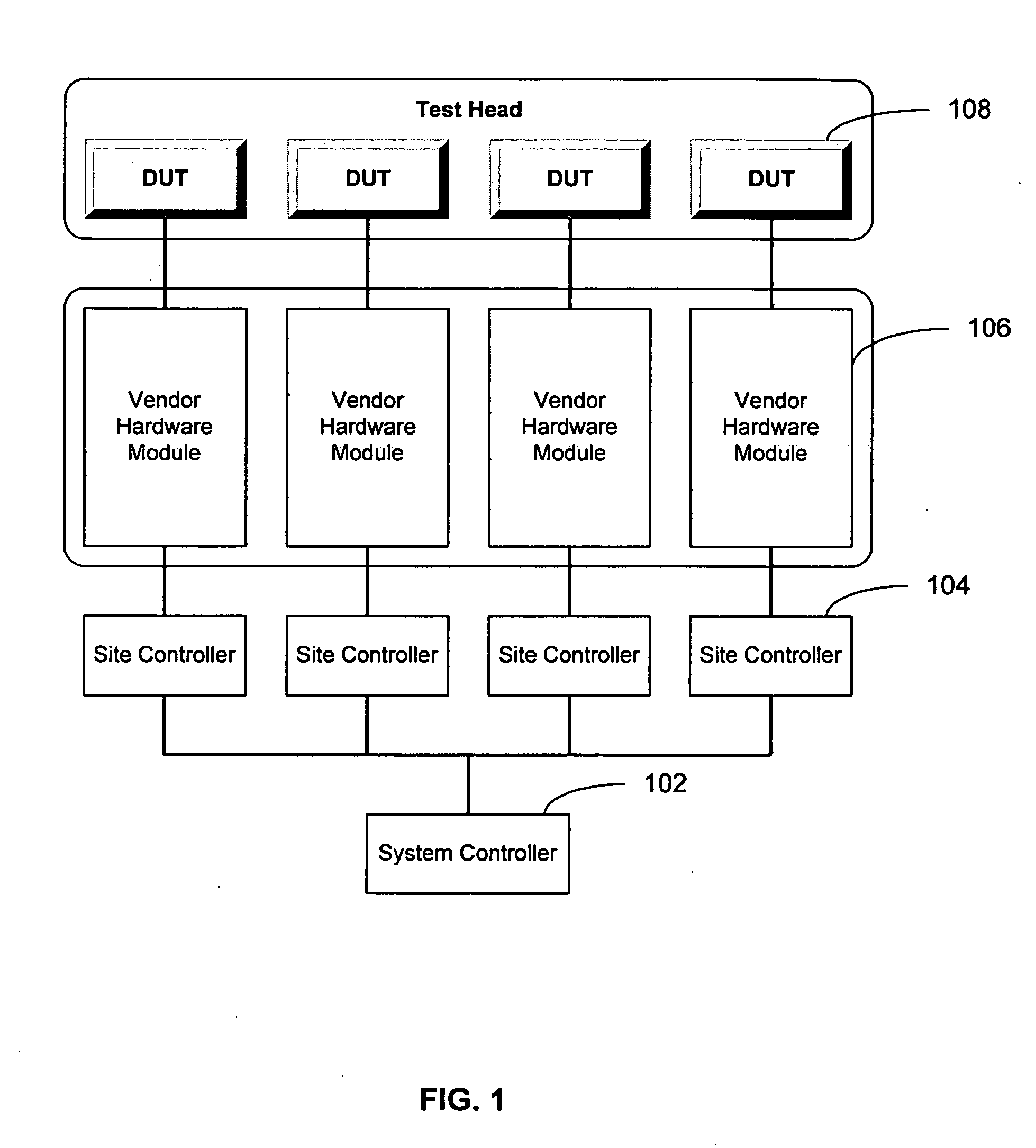

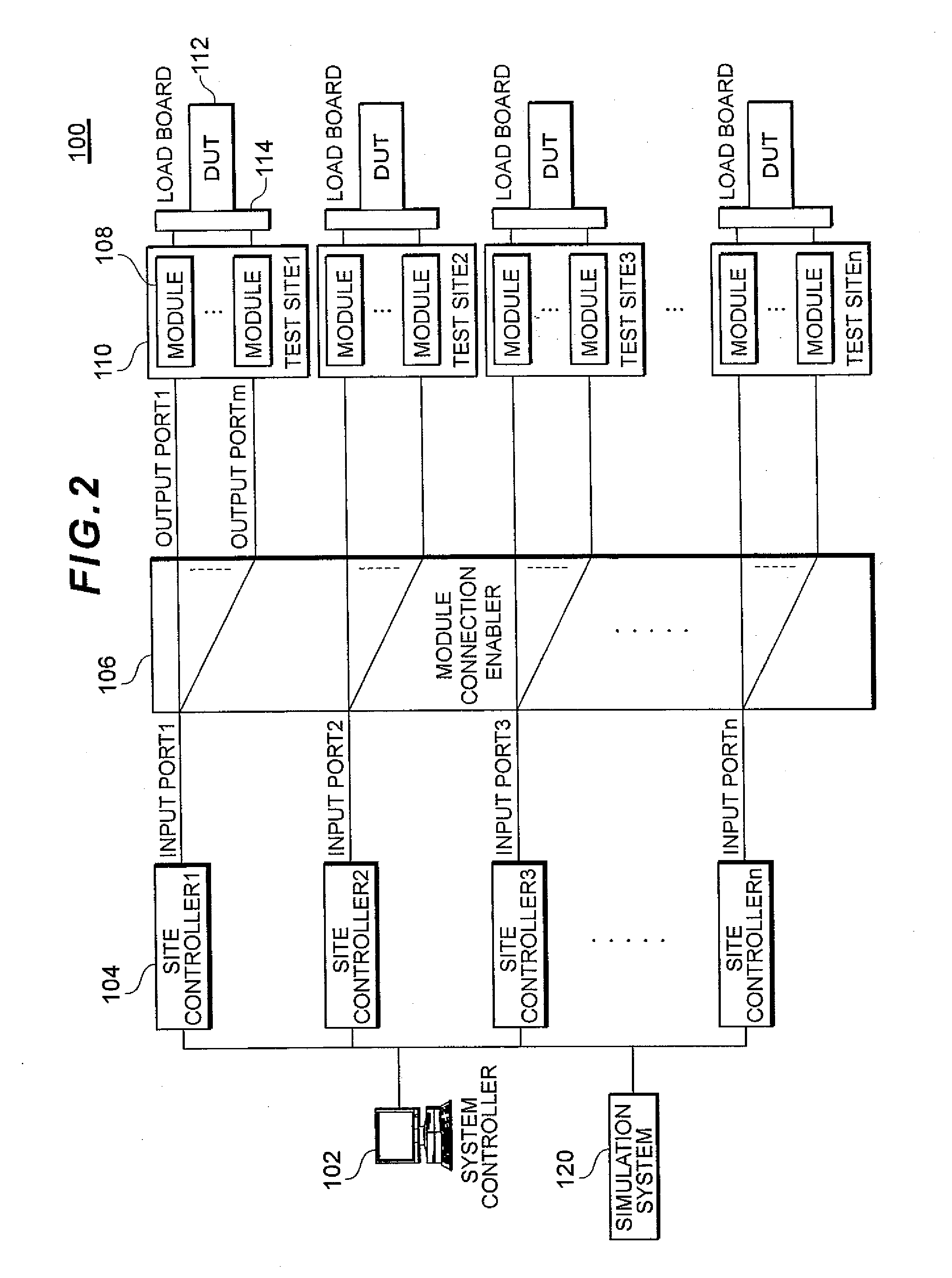

Method and system for scheduling tests in a parallel test system

An efficient and low-cost method for testing multiple DUTs in a parallel test system is disclosed. In one embodiment, a method for scheduling tests in a parallel test system having at least two devices-under-test (DUTs) coupled to a test controller through one or more vendor hardware modules includes receiving a test plan comprising a plurality of tests arranged in a predetermined test flow, where the predetermined test flow comprises a plurality of tests arranged in a directed graph and each test is arranged as a vertex in the directed graph, determining a test execution schedule in accordance with the test plan at runtime, where the test execution schedule identifies a set of next tests to be executed according to current states of the at least two DUTs and where the set of next tests include different tests to be performed on different DUTs, and testing the at least two DUTs using the test execution schedule.

Owner:ADVANTEST CORP

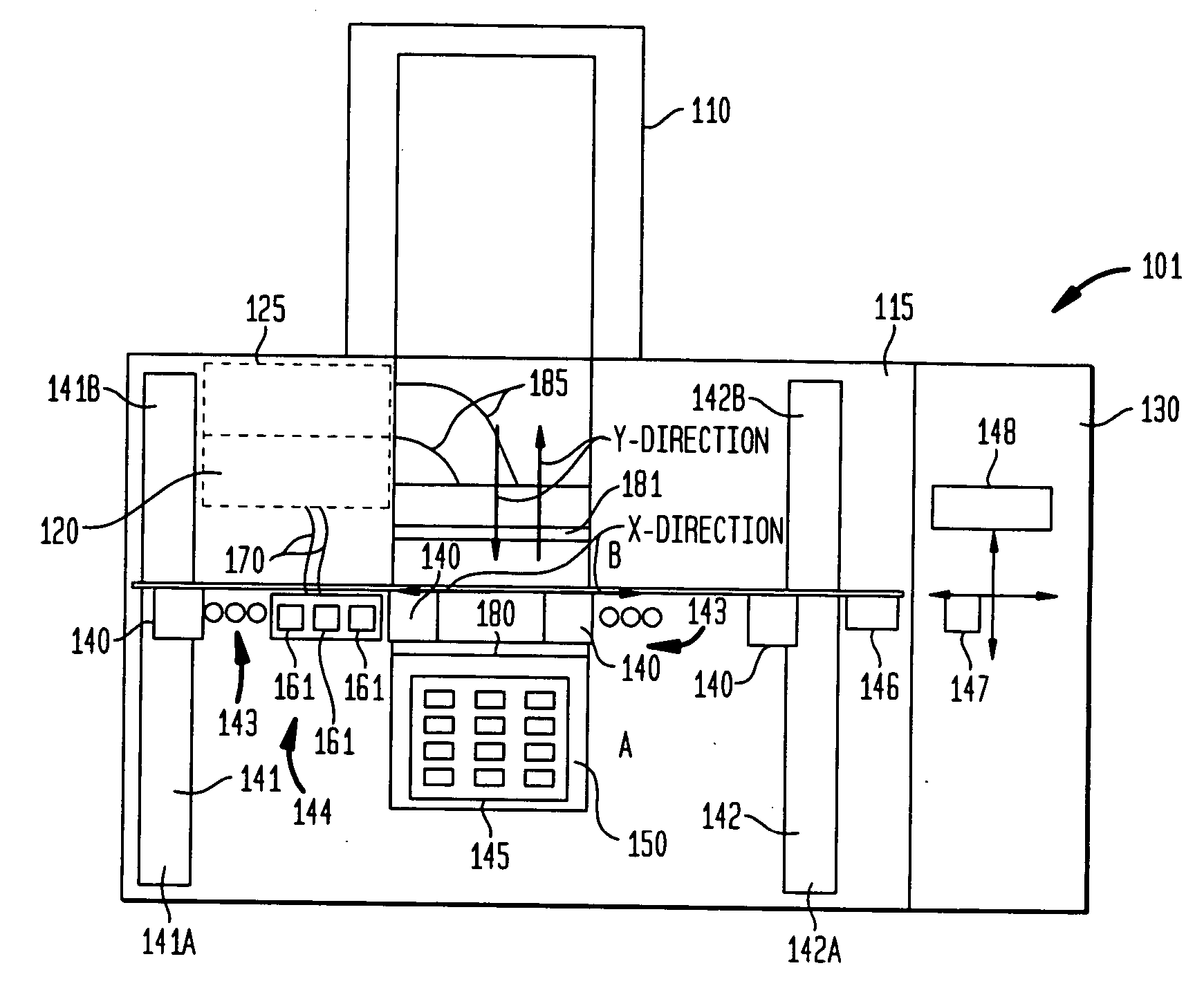

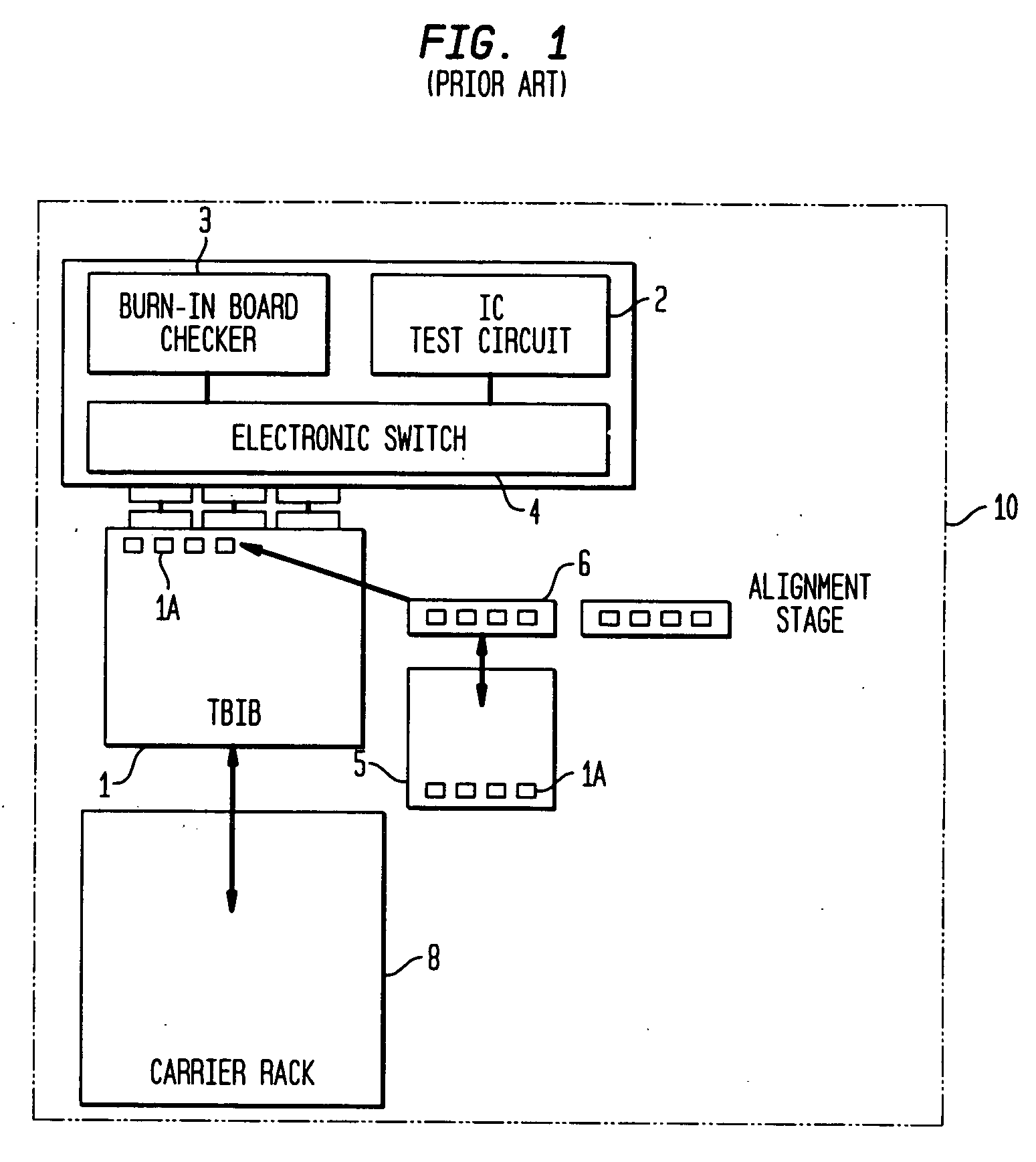

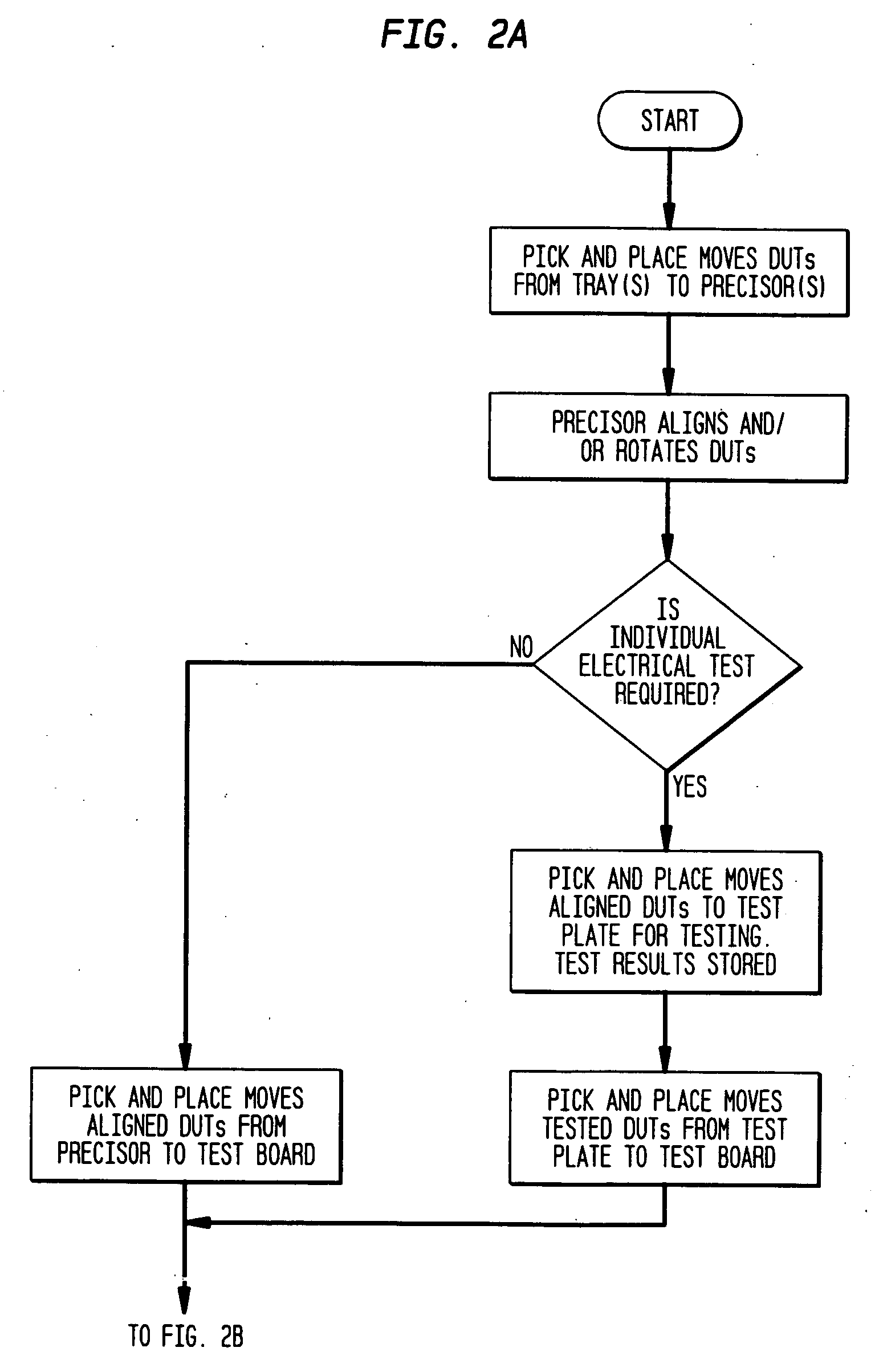

Method for testing semiconductor devices and an apparatus therefor

InactiveUS20060066293A1Good flexibilityEfficient loadingSemiconductor/solid-state device testing/measurementElectronic circuit testingElectricityEngineering

A method for testing integrated circuit devices and loading such devices into a test board for further testing and an apparatus therefor is disclosed. The method allows for selection between two modes of operation. In a first mode, the integrated circuit devices are subjected to an electrical test before being placed into the test board for further testing. In a second mode, the integrated circuit devices are tested after being placed in the test board. The apparatus allows for the selection between the first mode and the second mode. In either mode, information about the tested devices and the sockets in the test board is used to load the test boards intelligently. Intelligent loading means that devices under test (DUTs) are not placed in bad sockets and devices that do test bad are removed from the test board, with an option of replacing the failed DUT with another DUT before subsequent environmental testing of the DUTs in the test board is carried out.

Owner:KES SYST

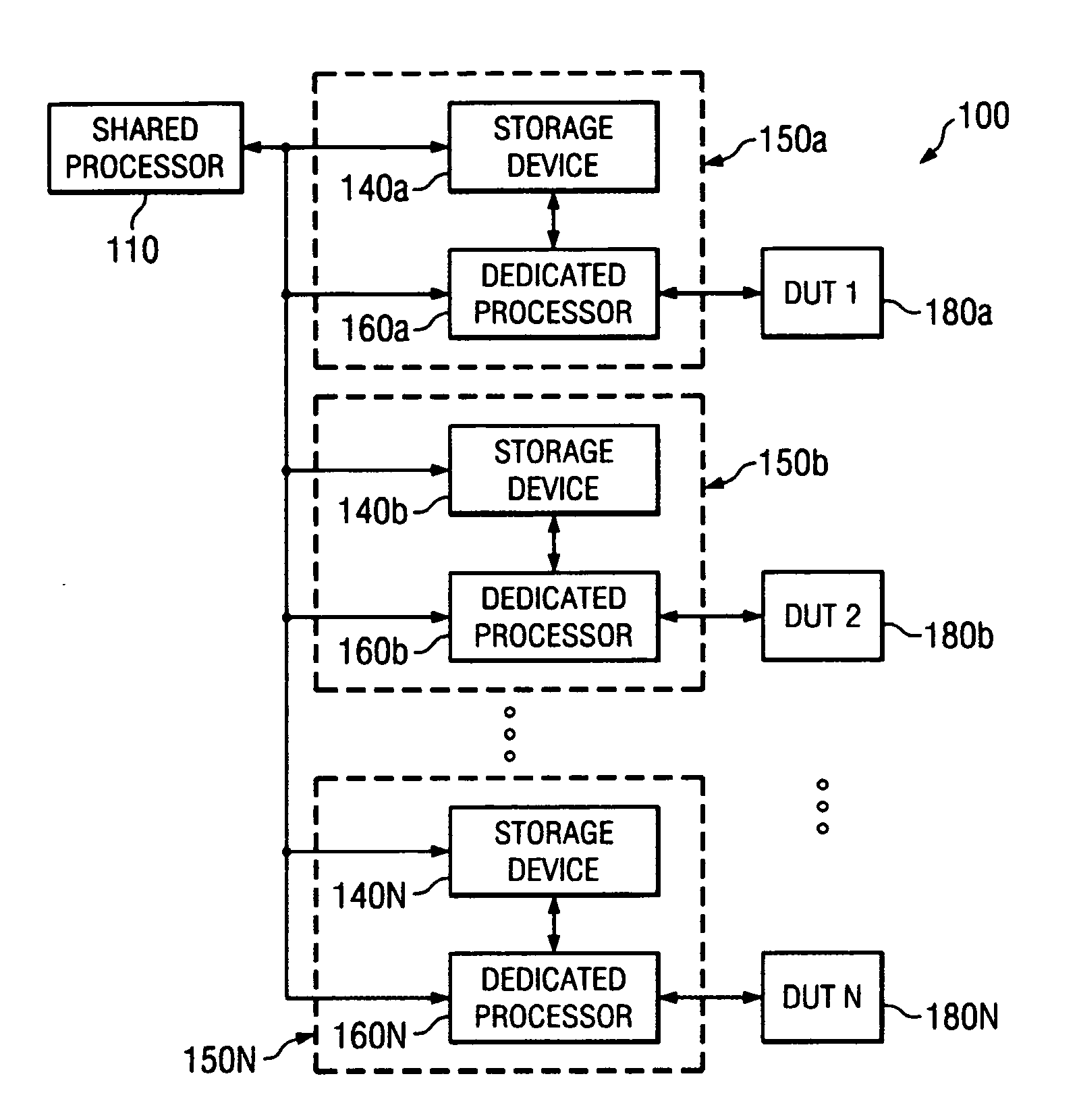

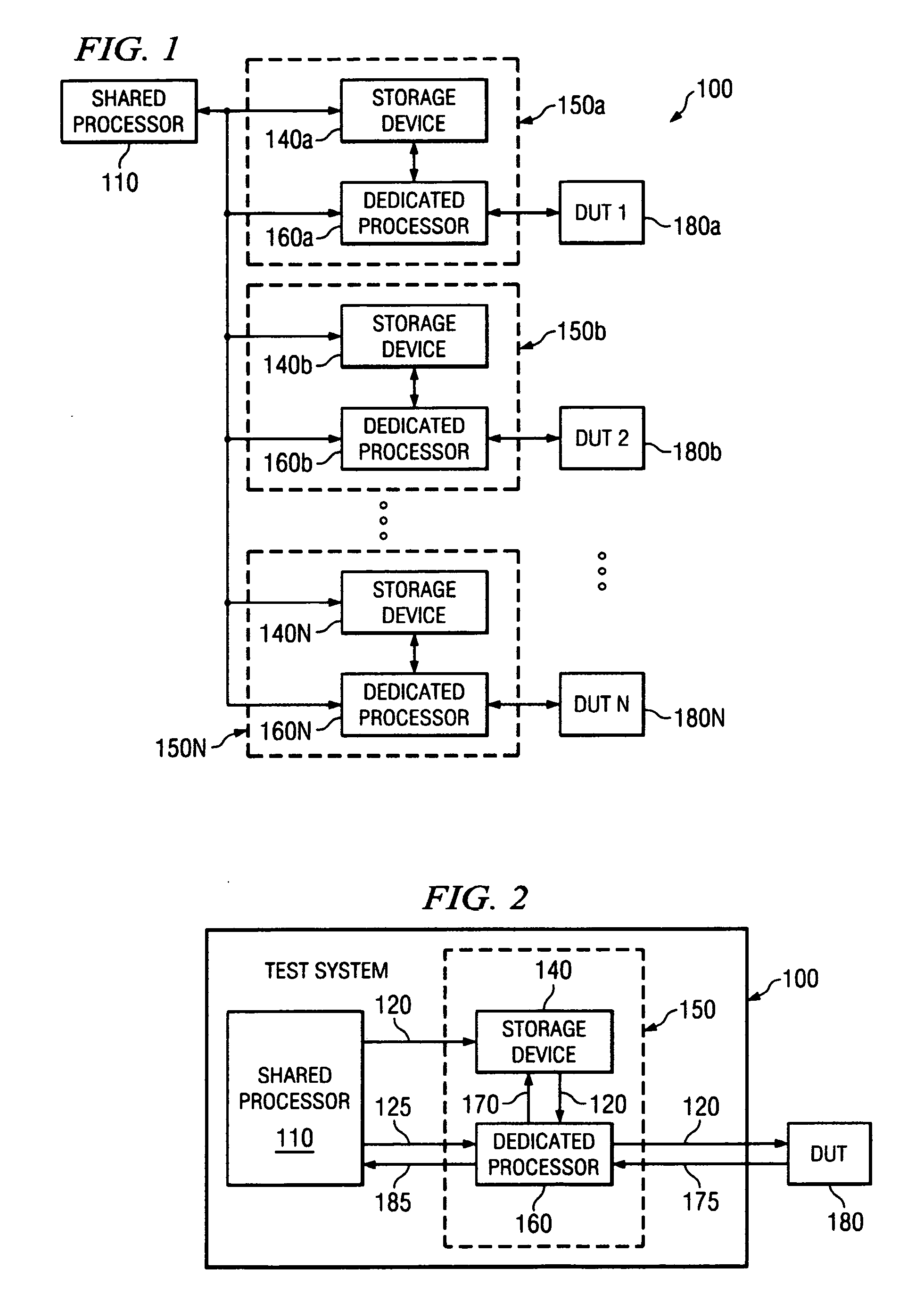

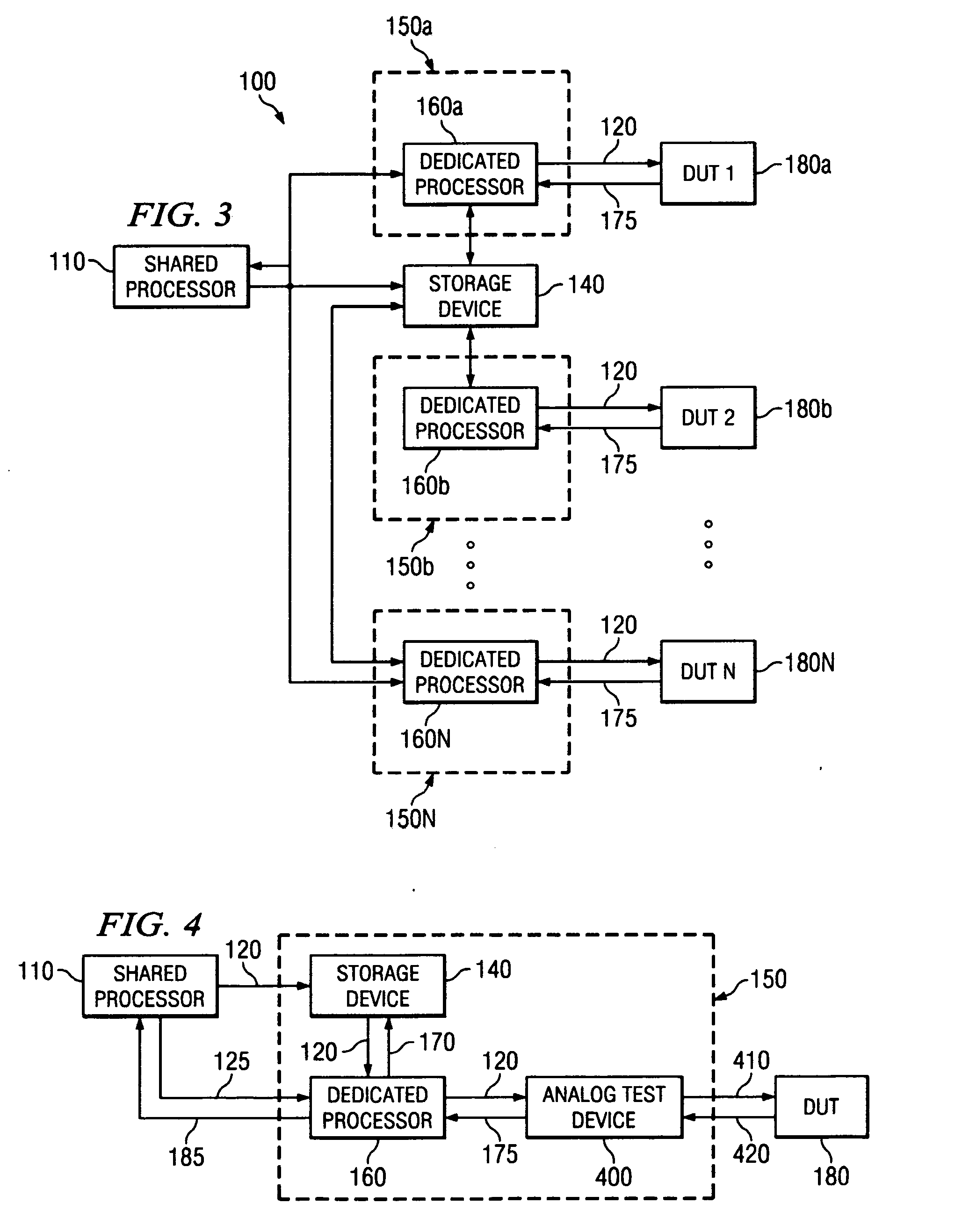

Test system and method for testing electronic devices using a pipelined testing architecture

ActiveUS20070198881A1Improve throughputLow costElectronic circuit testingError detection/correctionComputer hardwareControl signal

A test system for performing tests on devices under test (DUTs) includes a storage device storing test data for performing the tests on the DUTs, a shared processor for generating the test data, storing the test data in the storage device and generating a test control signal including one or more test instructions for executing the tests, and, for each DUT, a dedicated processor configured to receive a test control signal from the shared processor, and in response to the test control signal, transfer the test data for one of the test instructions to the DUT to execute that test instruction and verify the completion of that test instruction.

Owner:ADVANTEST CORP

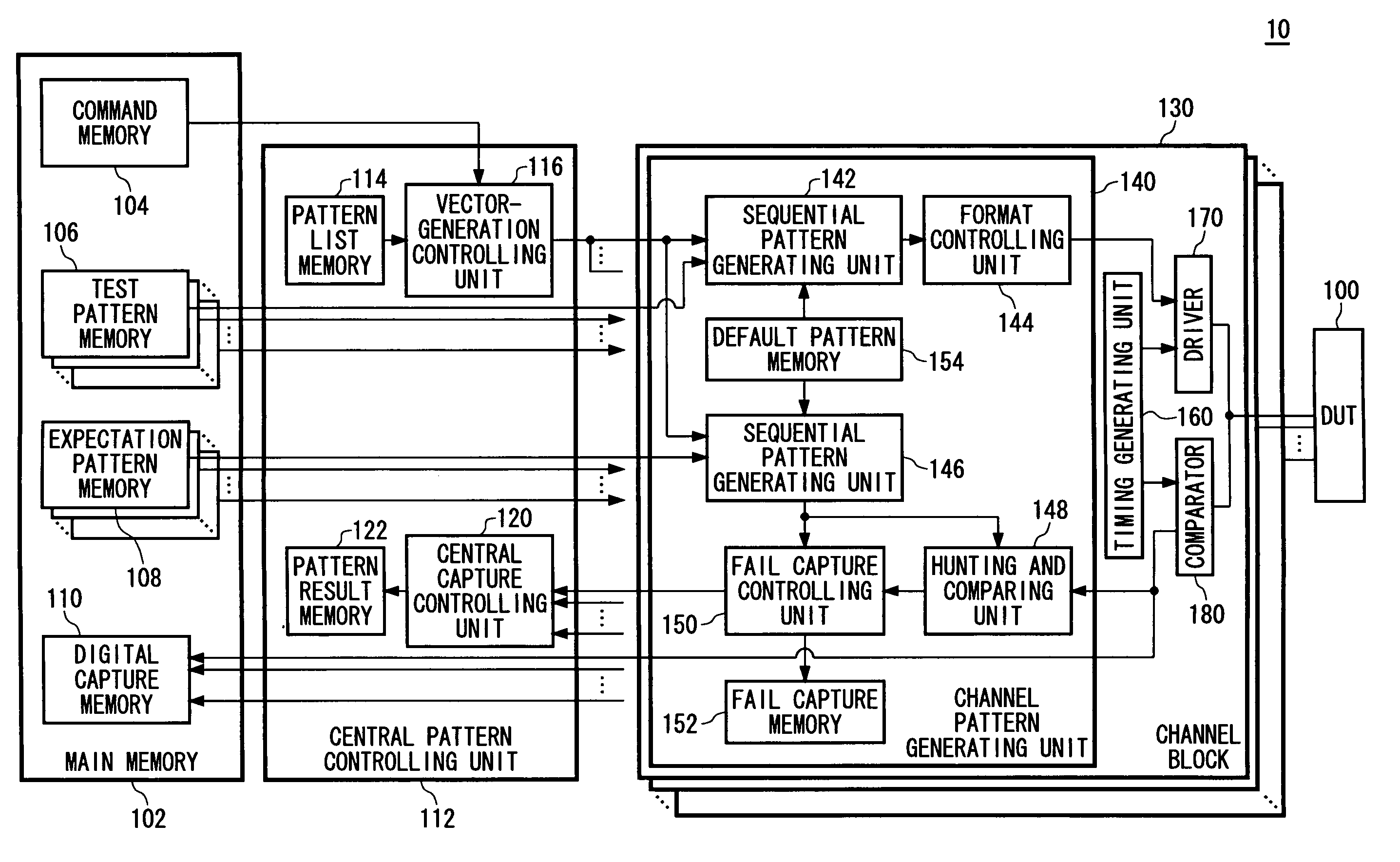

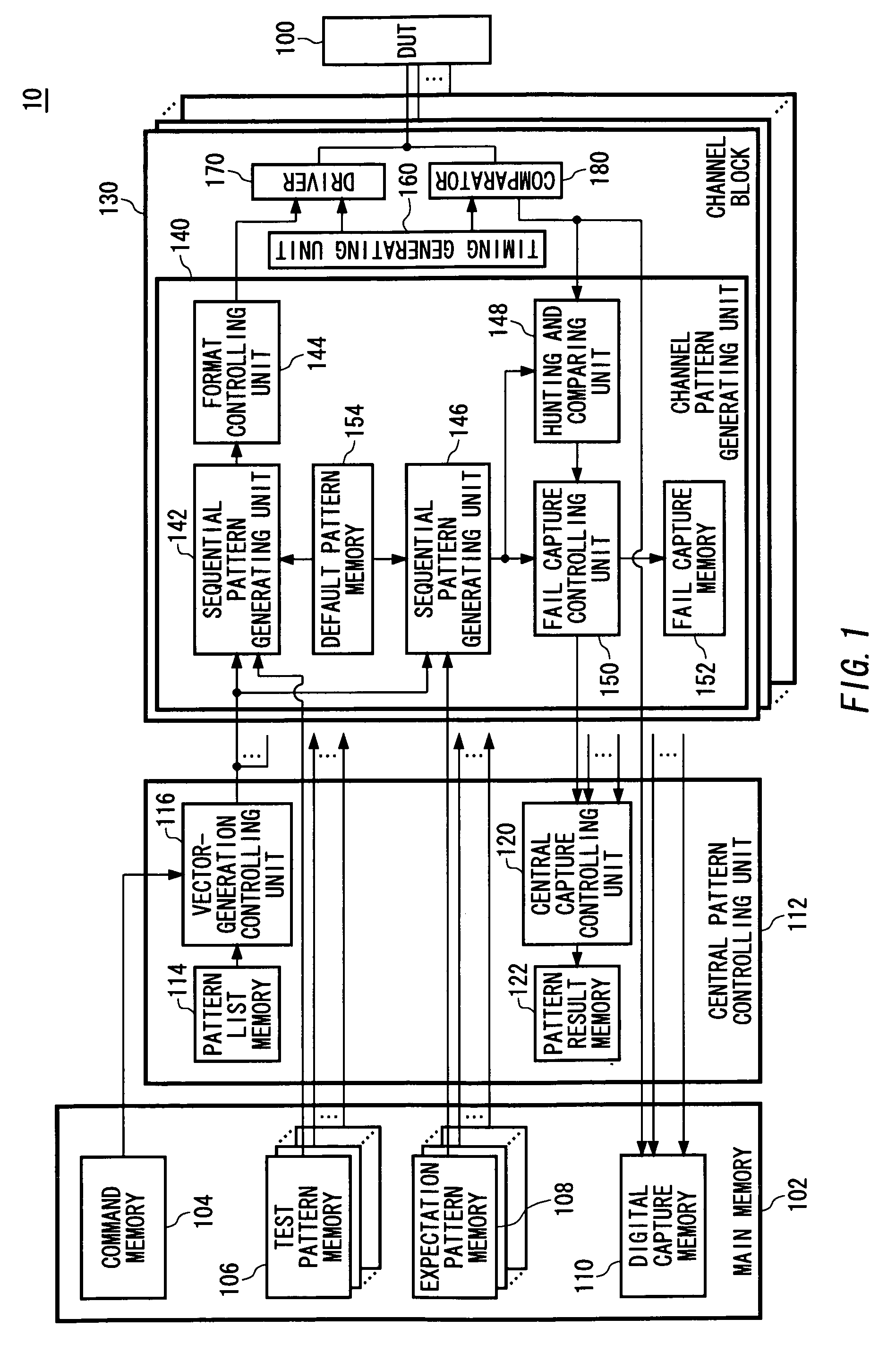

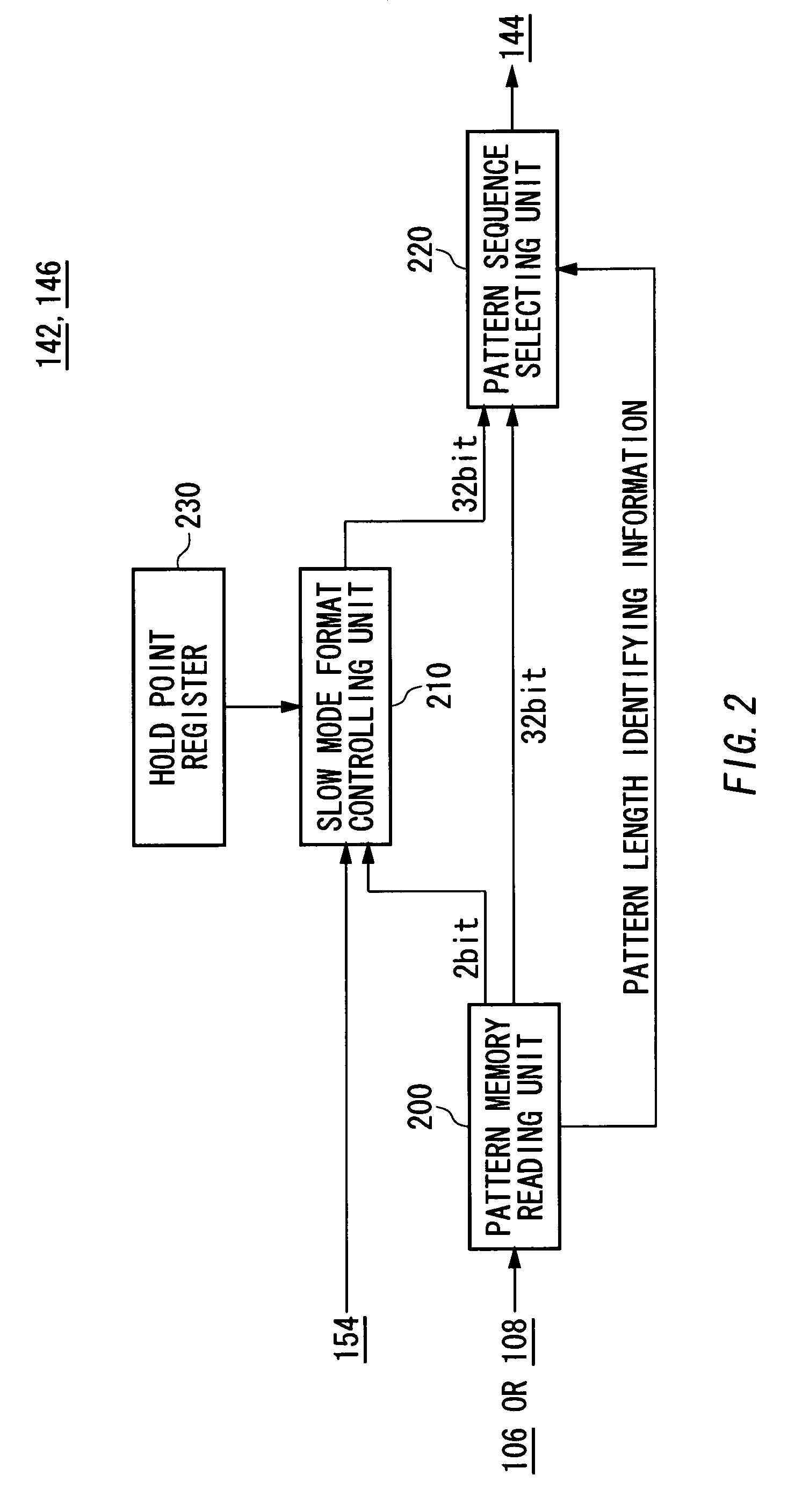

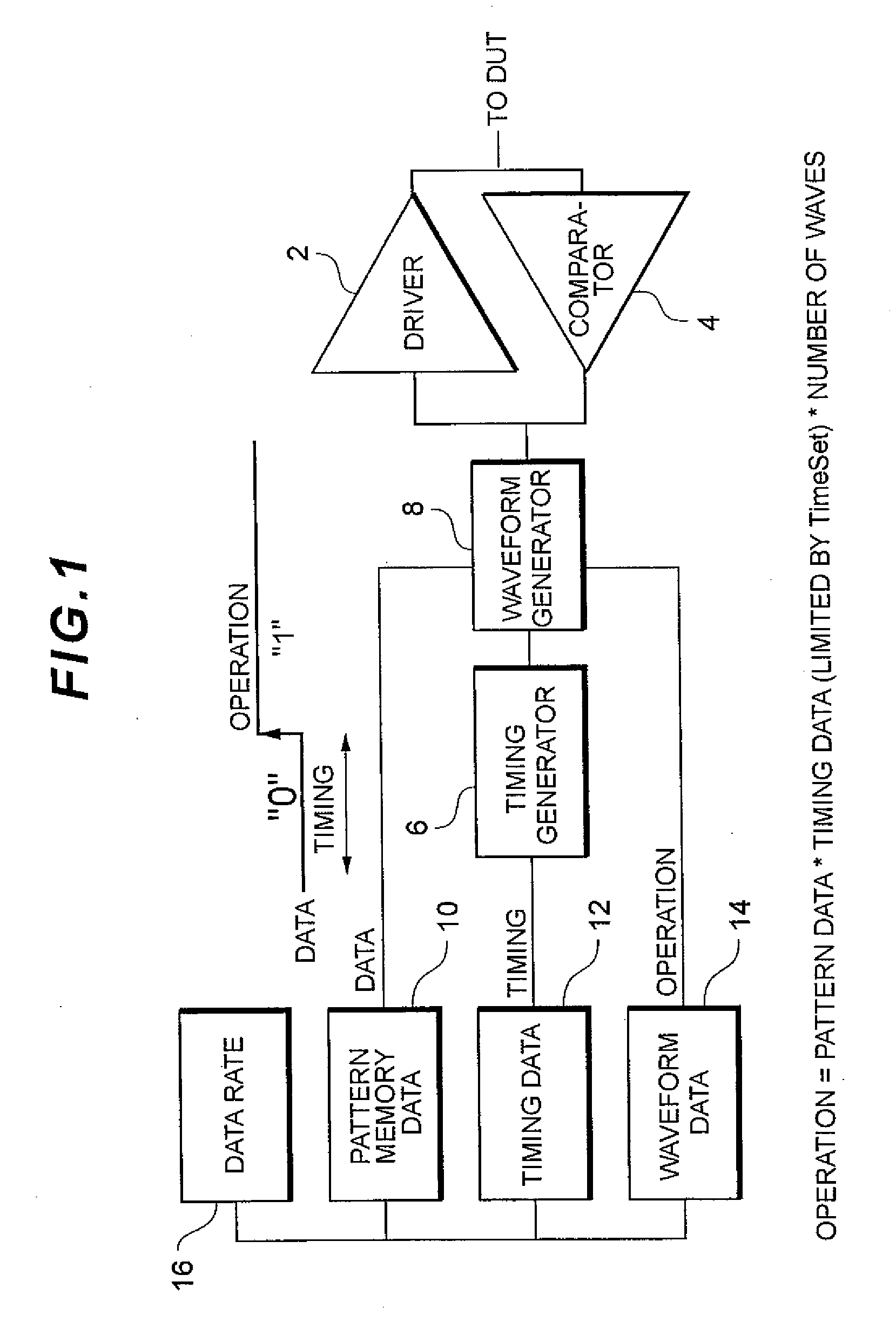

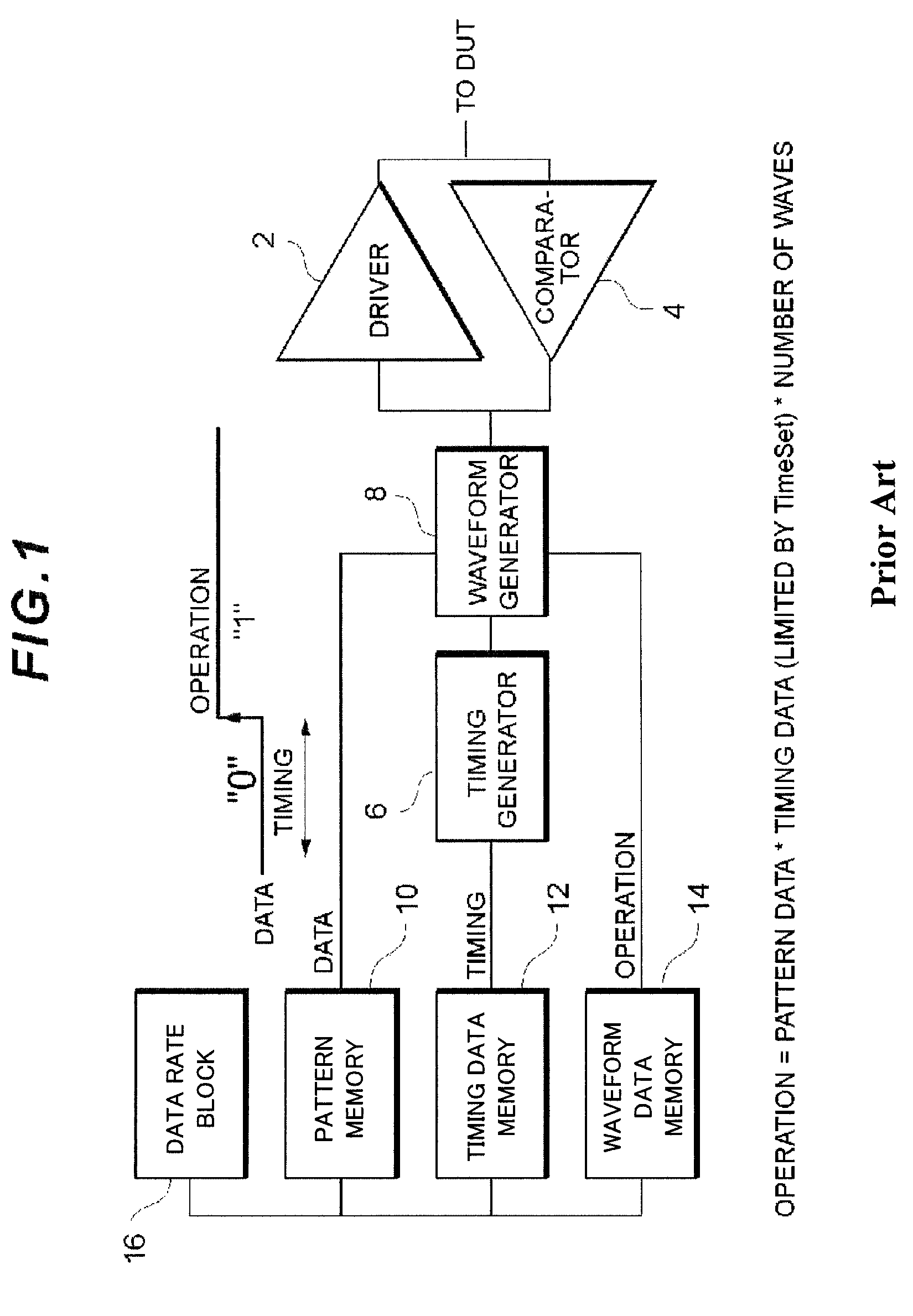

Test apparatus and testing method

ActiveUS20060190794A1Efficient use ofElectronic circuit testingError detection/correctionPattern sequenceEquipment under test

There is provided a testing apparatus that tests a device under test. The testing apparatus includes: a command executing unit operable to sequentially execute commands included in a test program for the device under test every command cycle; a test pattern memory operable to store pattern length identifying information identifying a pattern length of a test pattern sequence being output during a command cycle period executing the command and the test pattern sequence, in association with each command; a test pattern memory reading unit operable to read a test pattern sequence of a length corresponding to the pattern length identifying information stored on the test pattern memory in association with one command from the test pattern memory when the one command is executed; and a test pattern outputting unit operable to output the test pattern sequence read by the test pattern memory reading unit in association with the one command to a terminal of the device under test during a command cycle period executing the one command.

Owner:ADVANTEST CORP

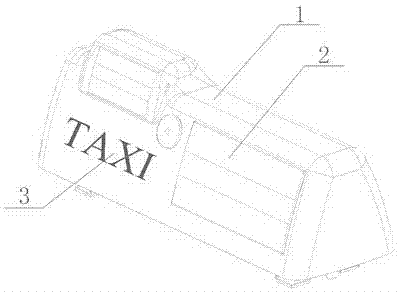

Atmospheric particulate online monitoring equipment based on taxi toplight

PendingCN107340212AReduce energy consumptionReduce occupancyTransmission systemsSatellite radio beaconingParticulatesEquipment under test

The invention discloses atmospheric particulate online monitoring equipment based on a taxi toplight and belongs to the technical field of environmental monitoring. The atmospheric particulate online monitoring equipment comprises a monitoring module, a master control module, a communication module, a positioning module, the taxi toplight and a power supply module, wherein the taxi toplight is fixed at the top of the taxi, and internal electric equipment of the taxi toplight is powered by the power supply module; the monitoring module comprises a PM2.5 sensor, a PM10 sensor and a PM100 sensor, and air inlets of the sensors are connected with one ends of air distribution valves fixed in the taxi toplight through air inlet hoses; the master control module is electrically connected with the other modules; the positioning module is used for positioning the taxi; the communication module is used for realizing connection between equipment under test and the online monitoring system. The equipment utilizes the taxi to carry the particulate sensors to execute measurement in real time, so that the mounting cost of gridding equipment is reduced, maintenance cost is reduced, and data accuracy is improved.

Owner:NOVA FITNESS CO LTD

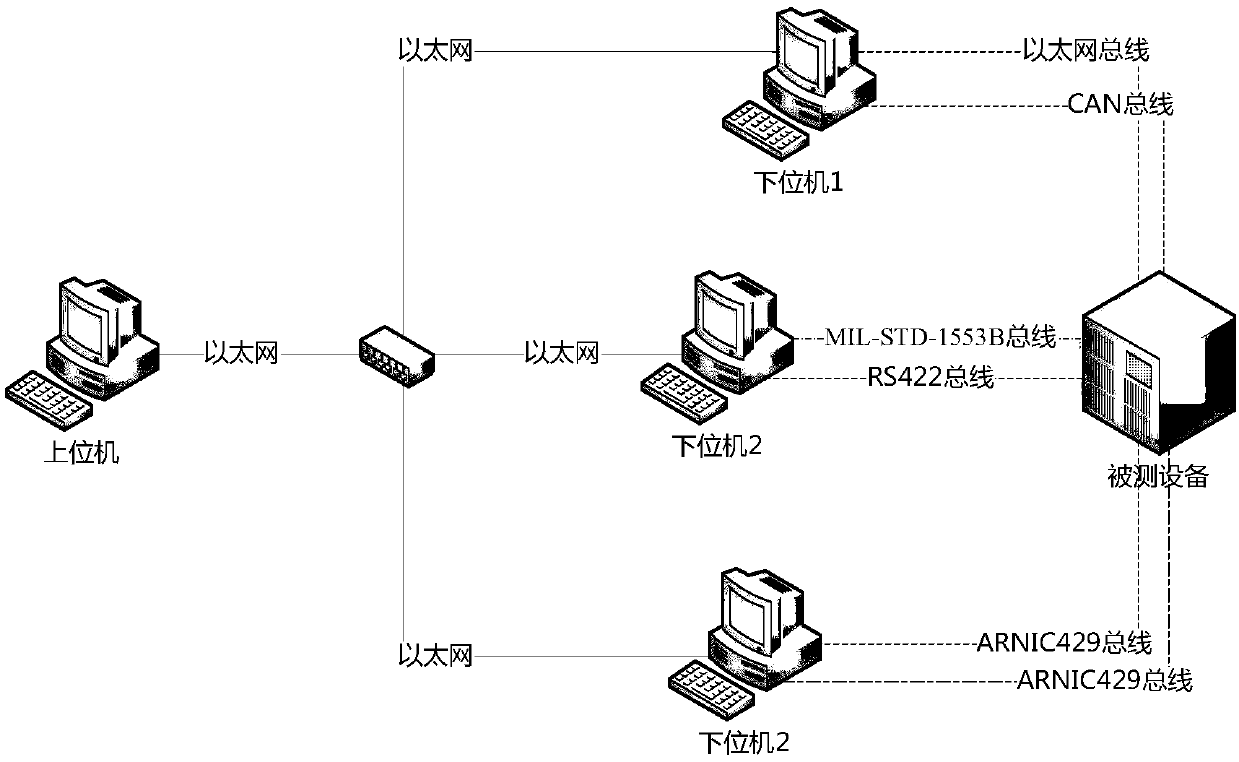

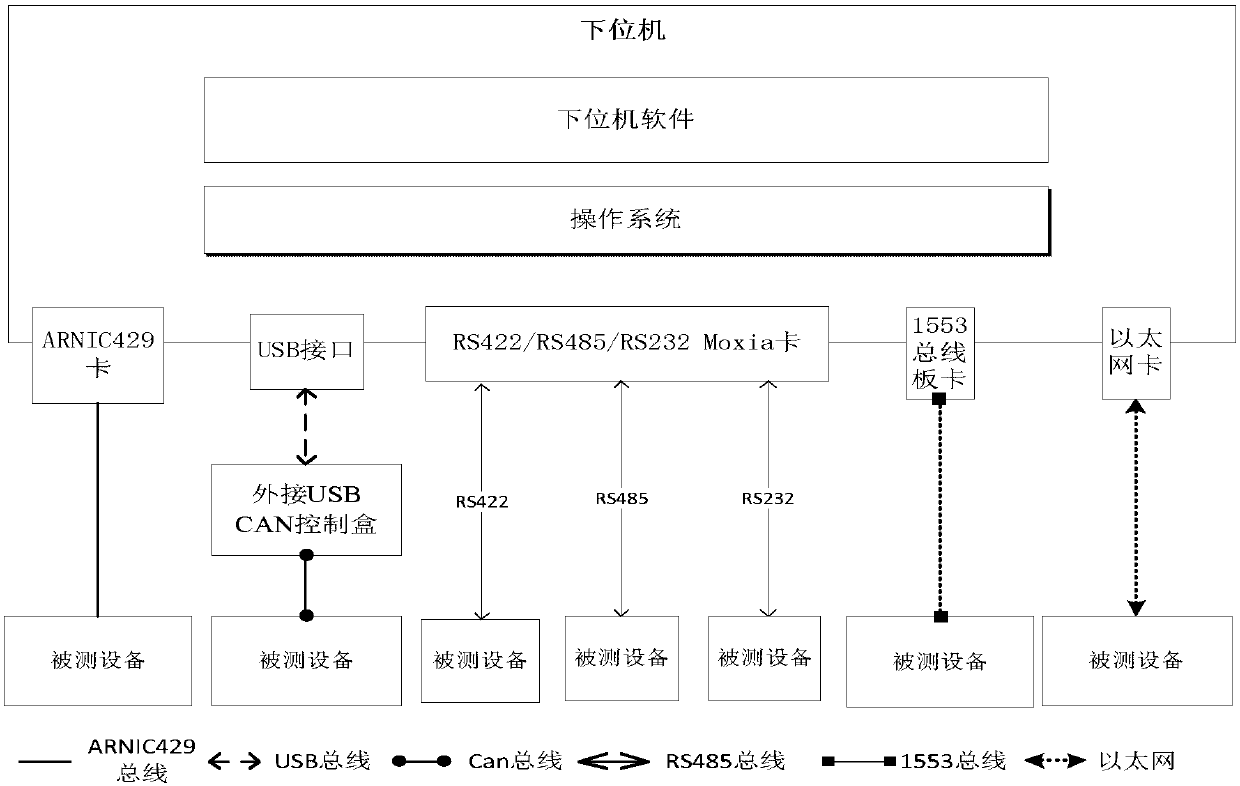

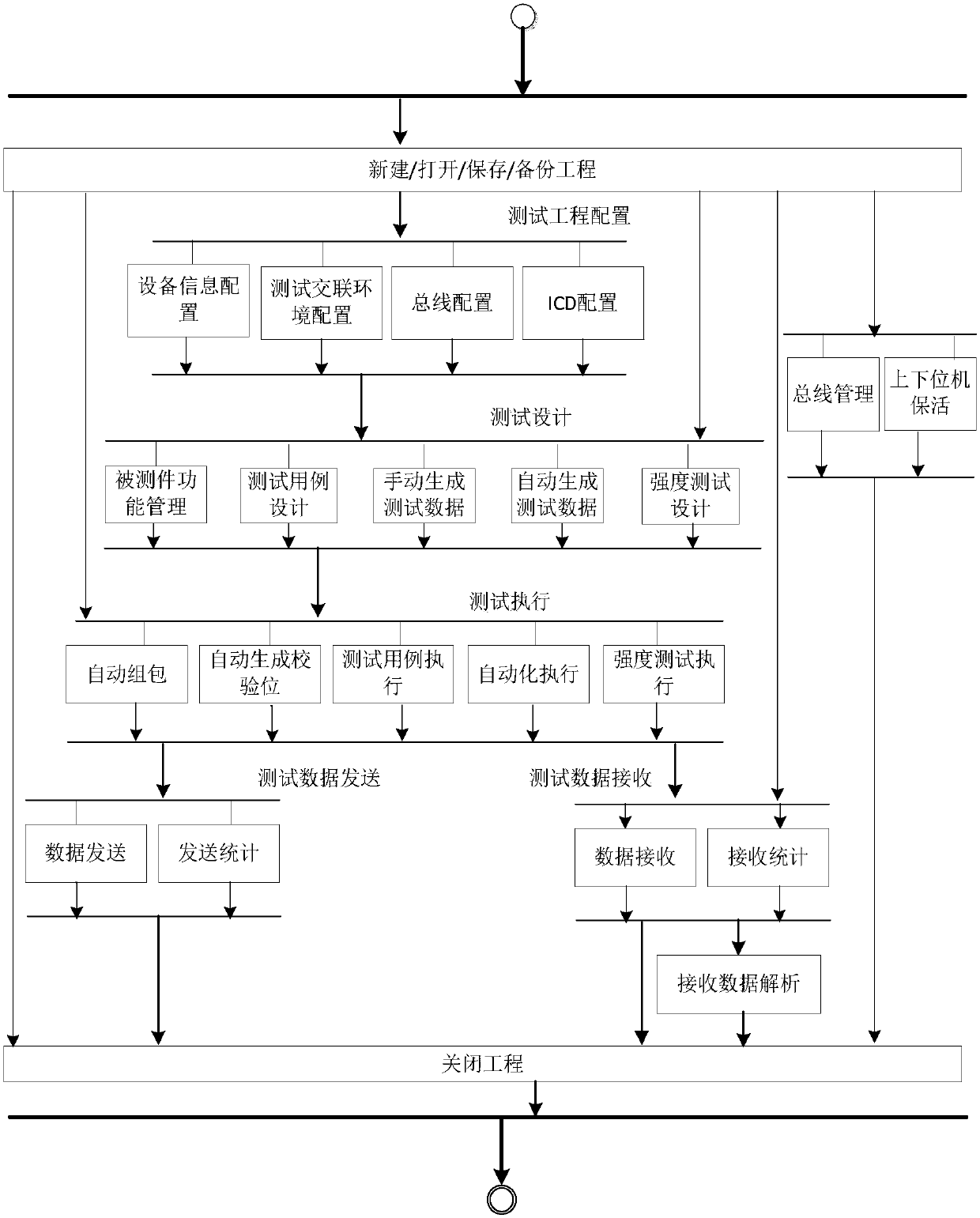

Embedded software testing auxiliary system

ActiveCN107562635AImprove construction efficiencyRealize simulationSoftware testing/debuggingTransceiverUsability

The invention provides an embedded software testing auxiliary system, and aims at providing a software testing auxiliary system which can improve the efficiency of building a testing environment, lower the operation difficulty and improve the usability. According to the technical scheme, an upper computer constructs a testing crosslinking environment of tested equipment and testing equipment, describes bus attributes, an interface control document ICD, testing case preconditions and testing steps, forms control law data according to the preconditions and the testing steps to dispatch testing data, sends, judges and receives the data, and conducts reverse analysis on the received data according to an ICD format; a lower computer cooperates with the upper computer to send the data through adetailed bus, then the data is received, testing cases and design constructed by data simulation and receiving-sending procedure control are automatically executed, and simulation of embedded softwareperipheral equipment and monitoring and detecting of the interaction process of peripheral equipment data are achieved. According to the embedded software testing auxiliary system, the testing casesof controlling a construction testing scene are executed based on the data receiving-sending procedure, and the time for developing a simulation system is shortened.

Owner:10TH RES INST OF CETC

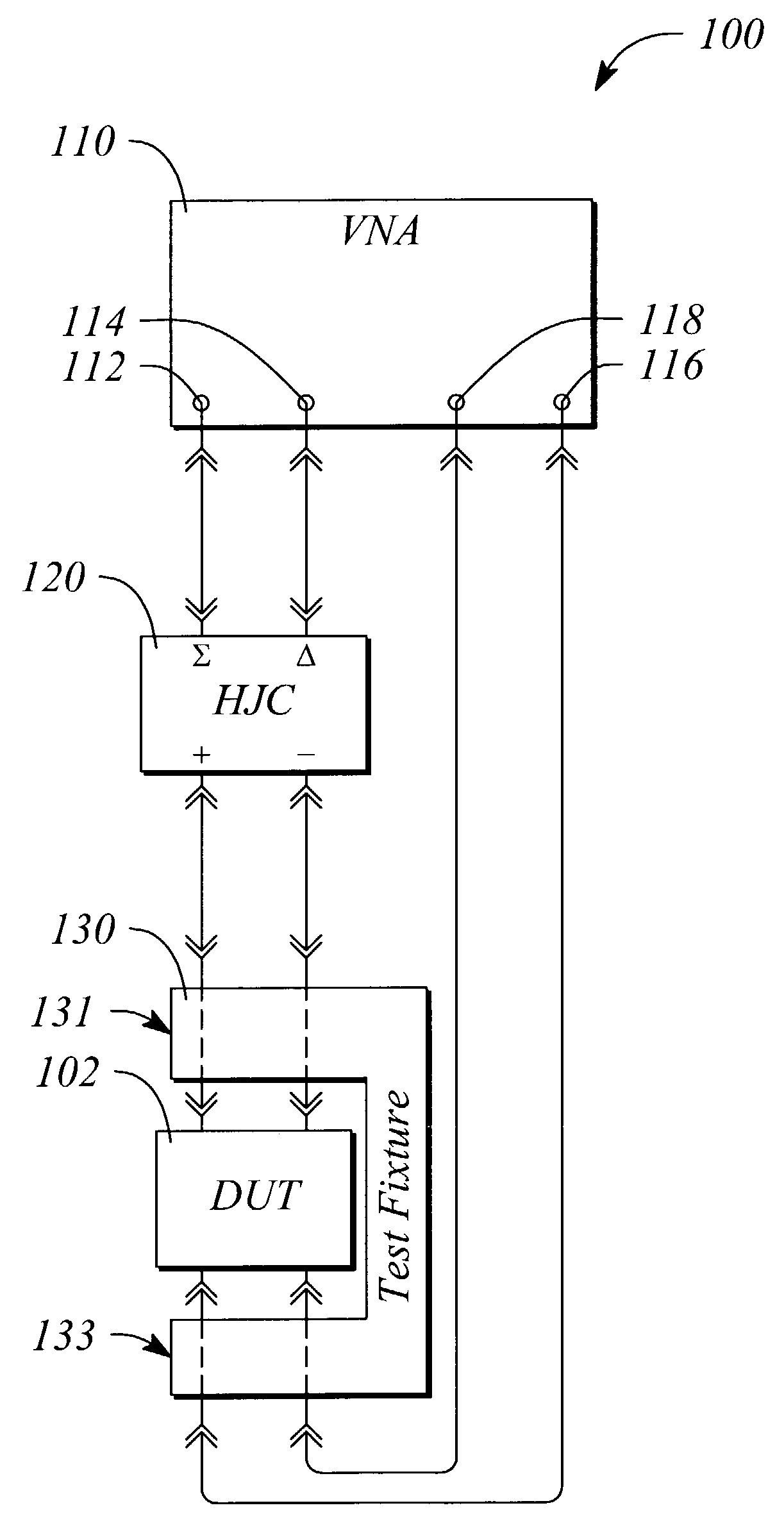

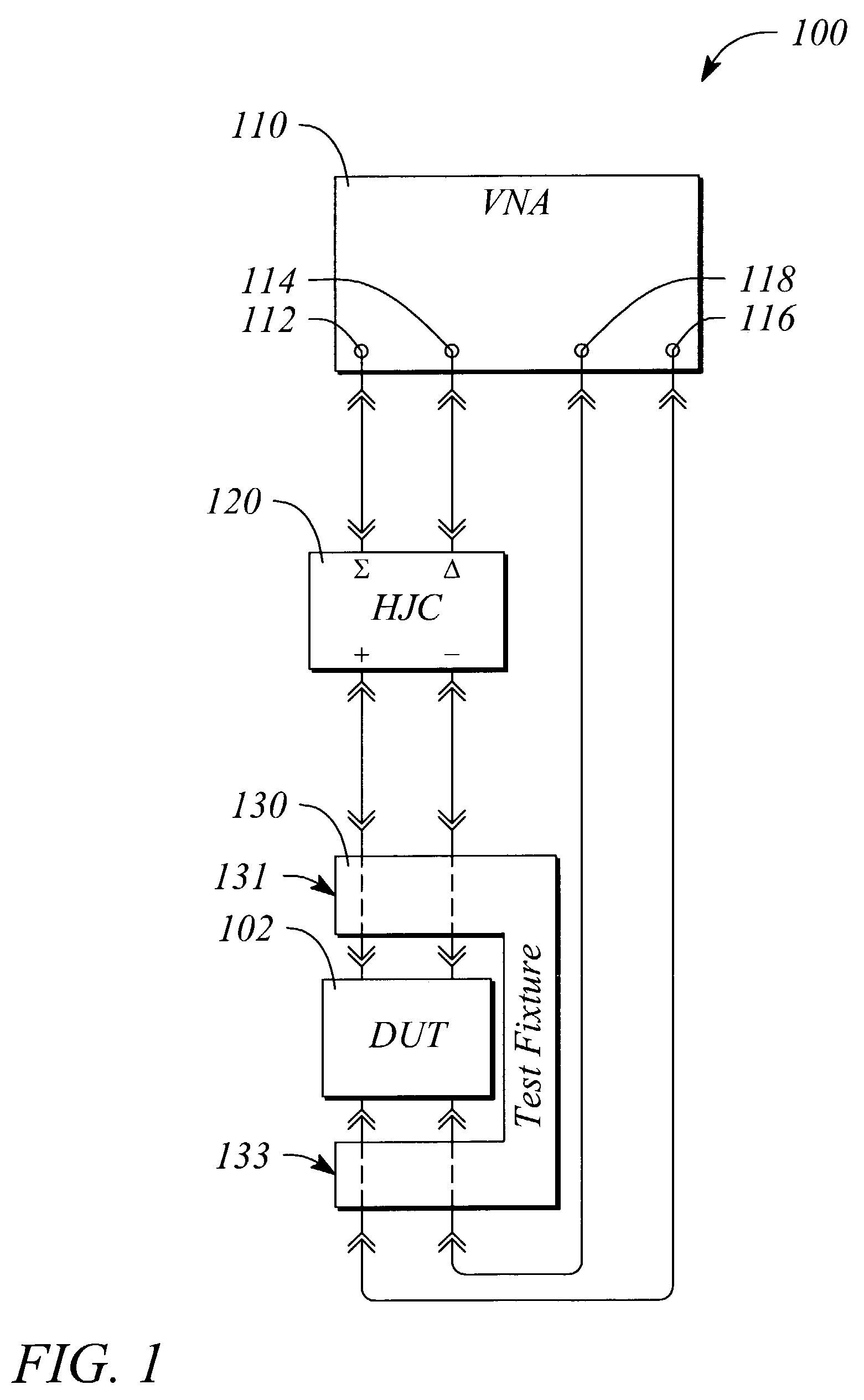

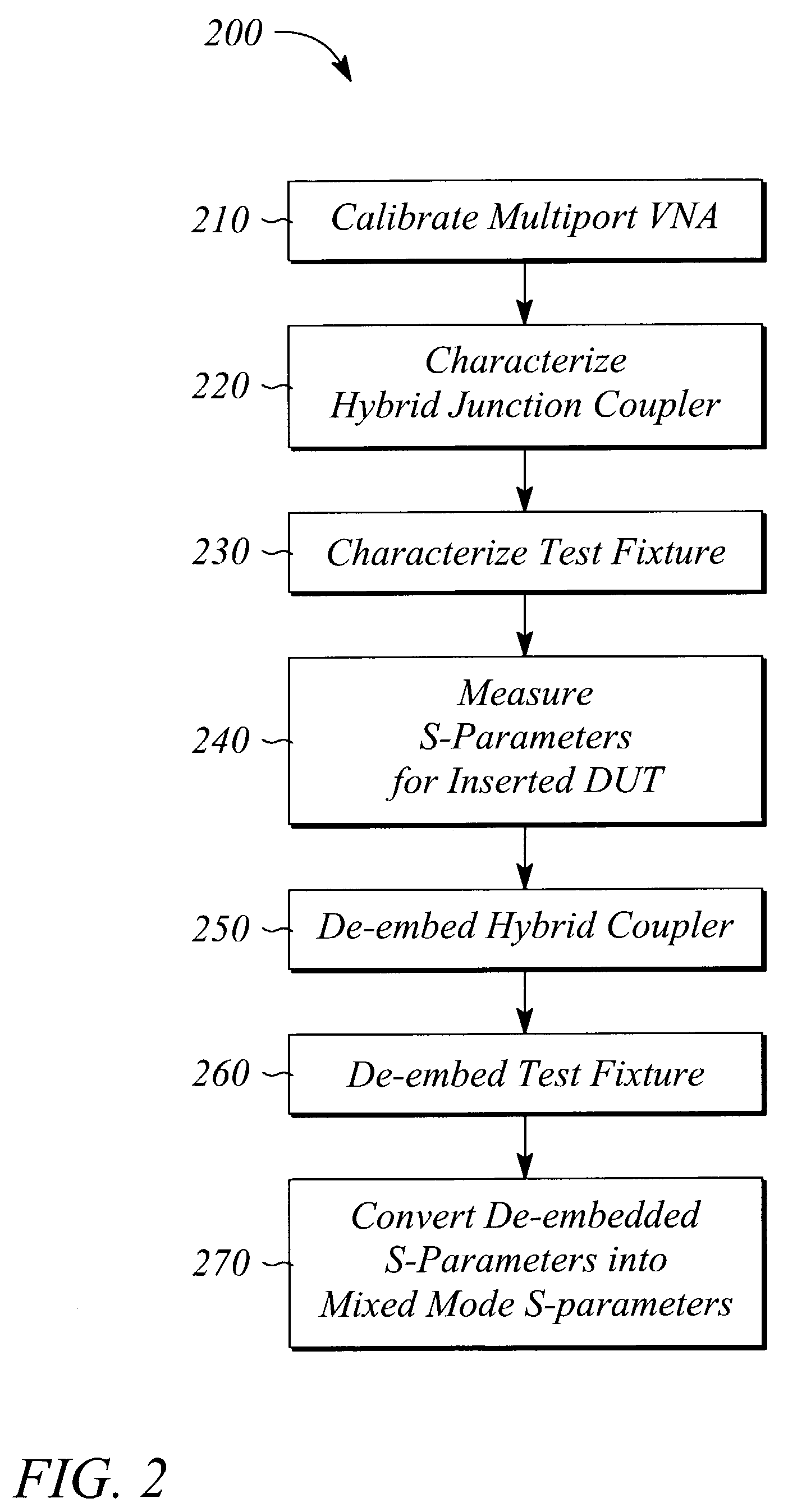

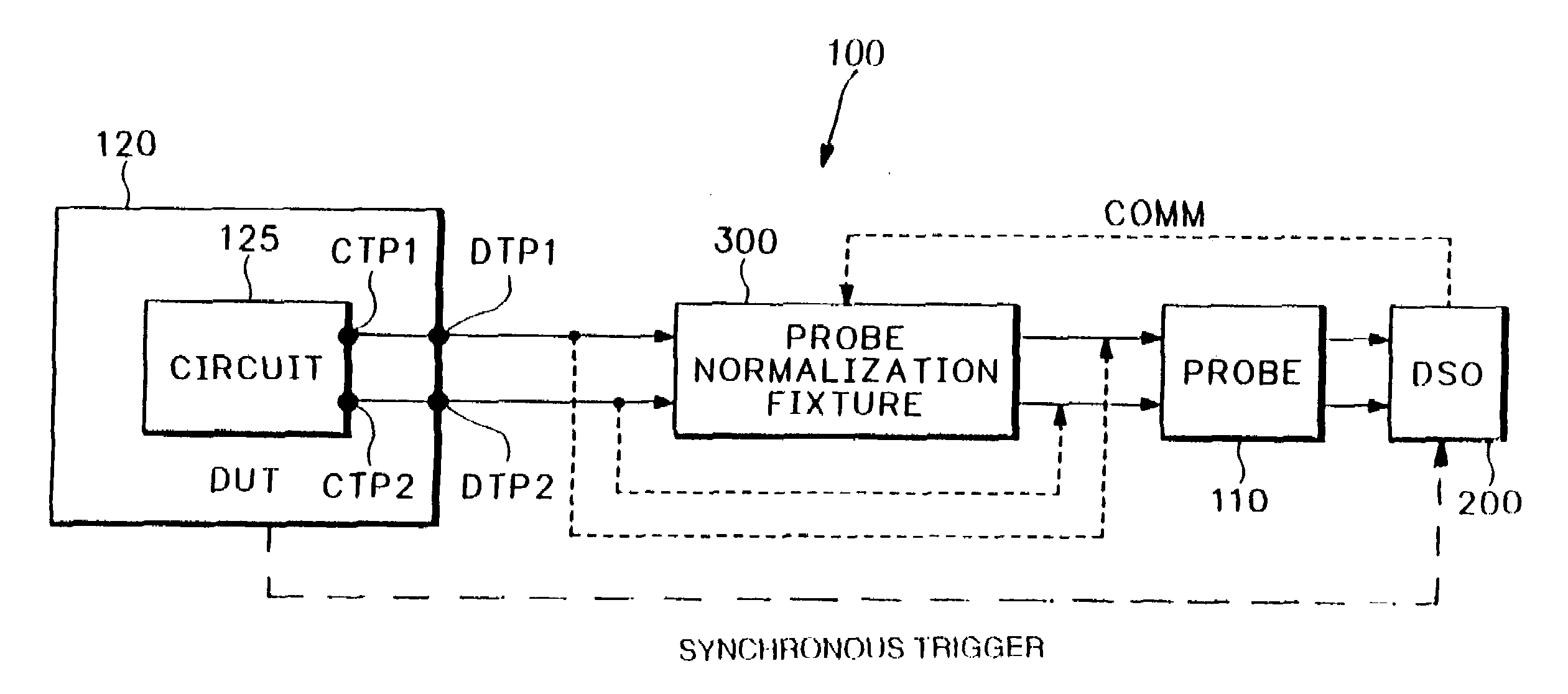

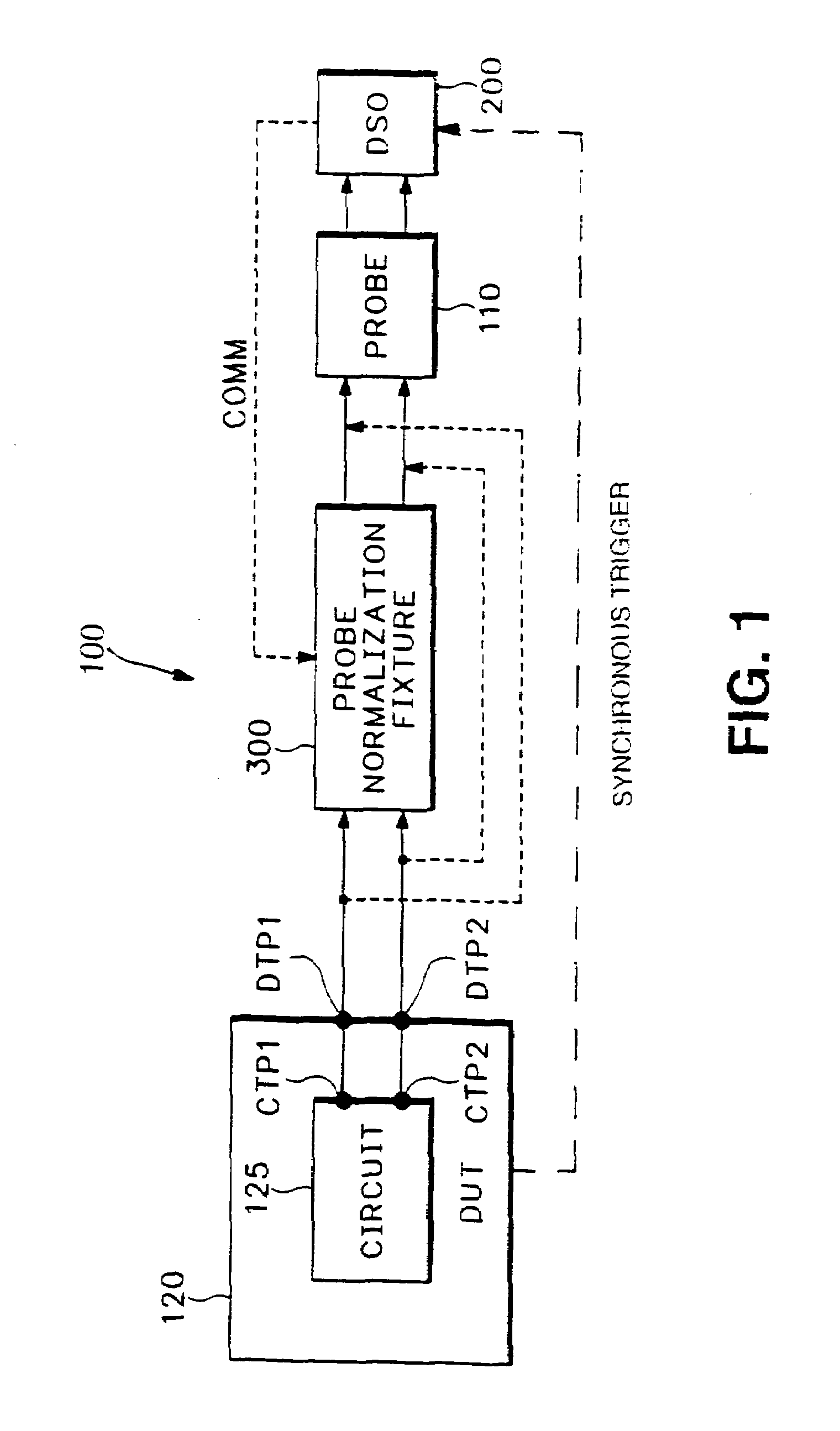

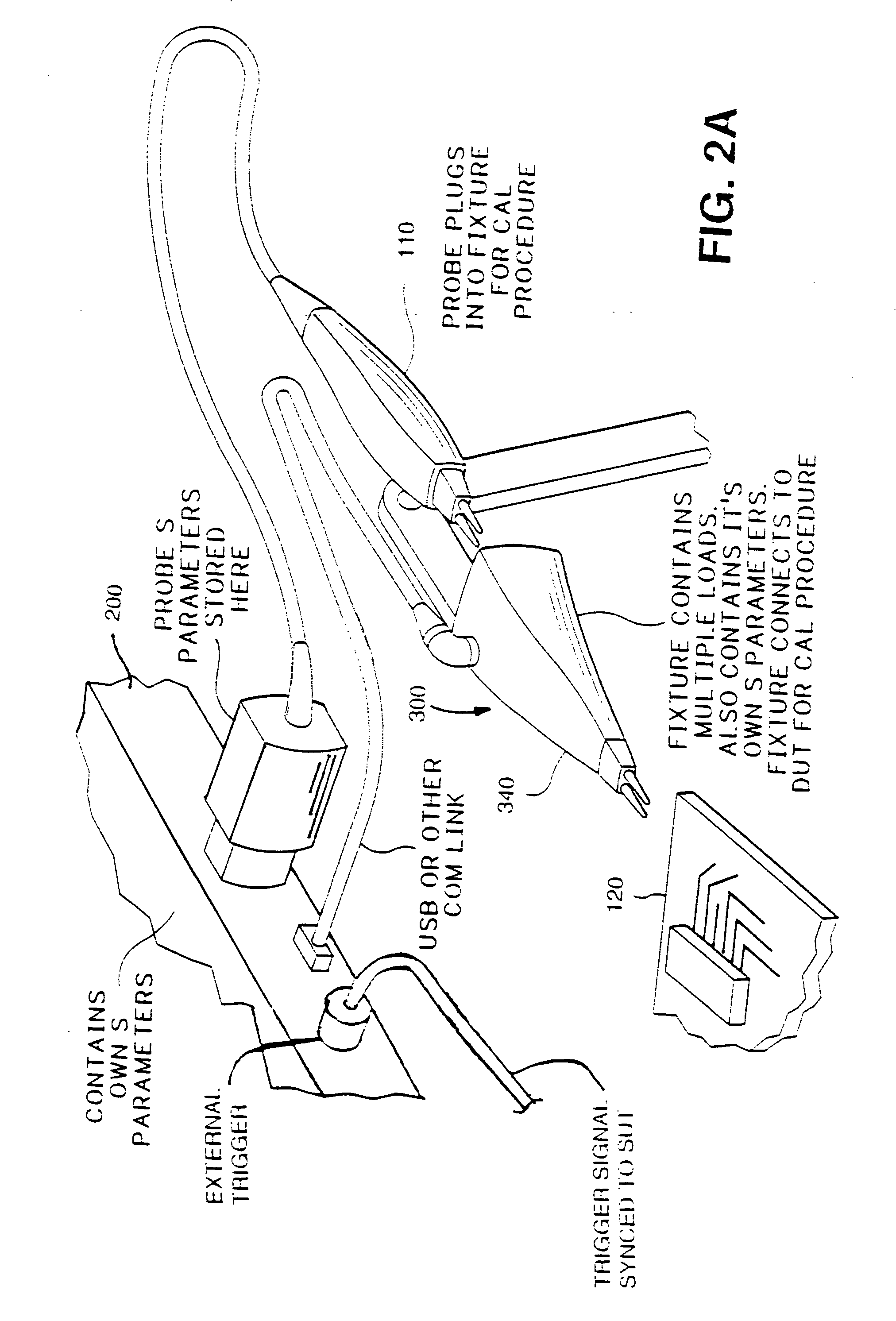

Balanced device characterization including test system calibration

A test system and method characterize a balanced device under test (DUT) with a vector network analyzer (VNA) measurement system using a differential or balanced stimulus signal and further calibrate the VNA using conventional calibration standards. An effect of errors introduced by an uncalibrated portion of the measurement system, such as test fixturing and hybrid junction coupling, is de-embedded from measured S-parameters for the DUT. The method includes calibrating the VNA, characterizing the uncalibrated portion, measuring S-parameters for the DUT with the calibrated VNA, and de-embedding the uncalibrated portion characterization from the S-parameter measurements. The test system includes a multiport VNA measurement system that includes a hybrid coupler, an optional test fixture, and a computer program. A processor executes the computer program. Instructions of the computer program implement the method.

Owner:KEYSIGHT TECH

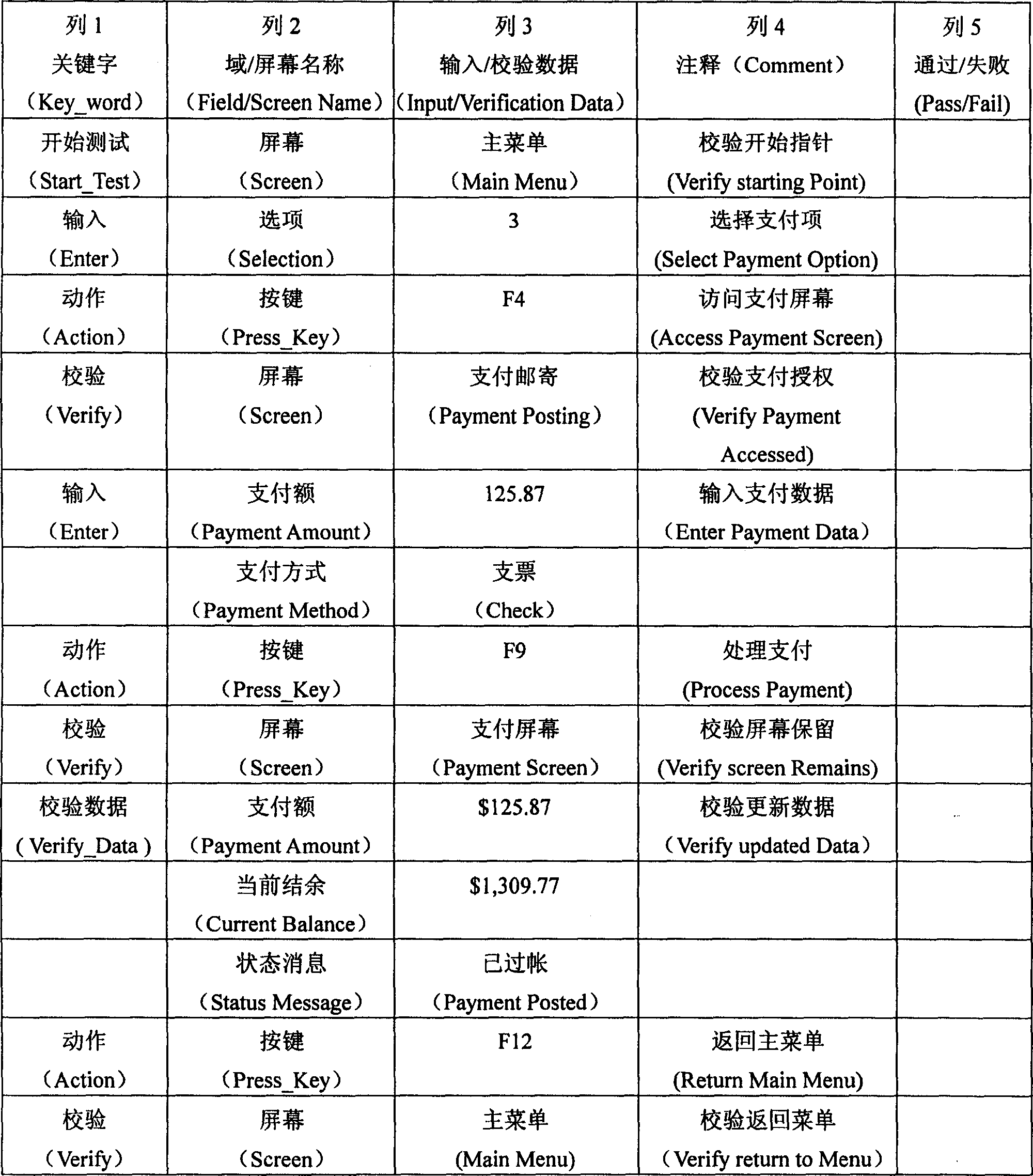

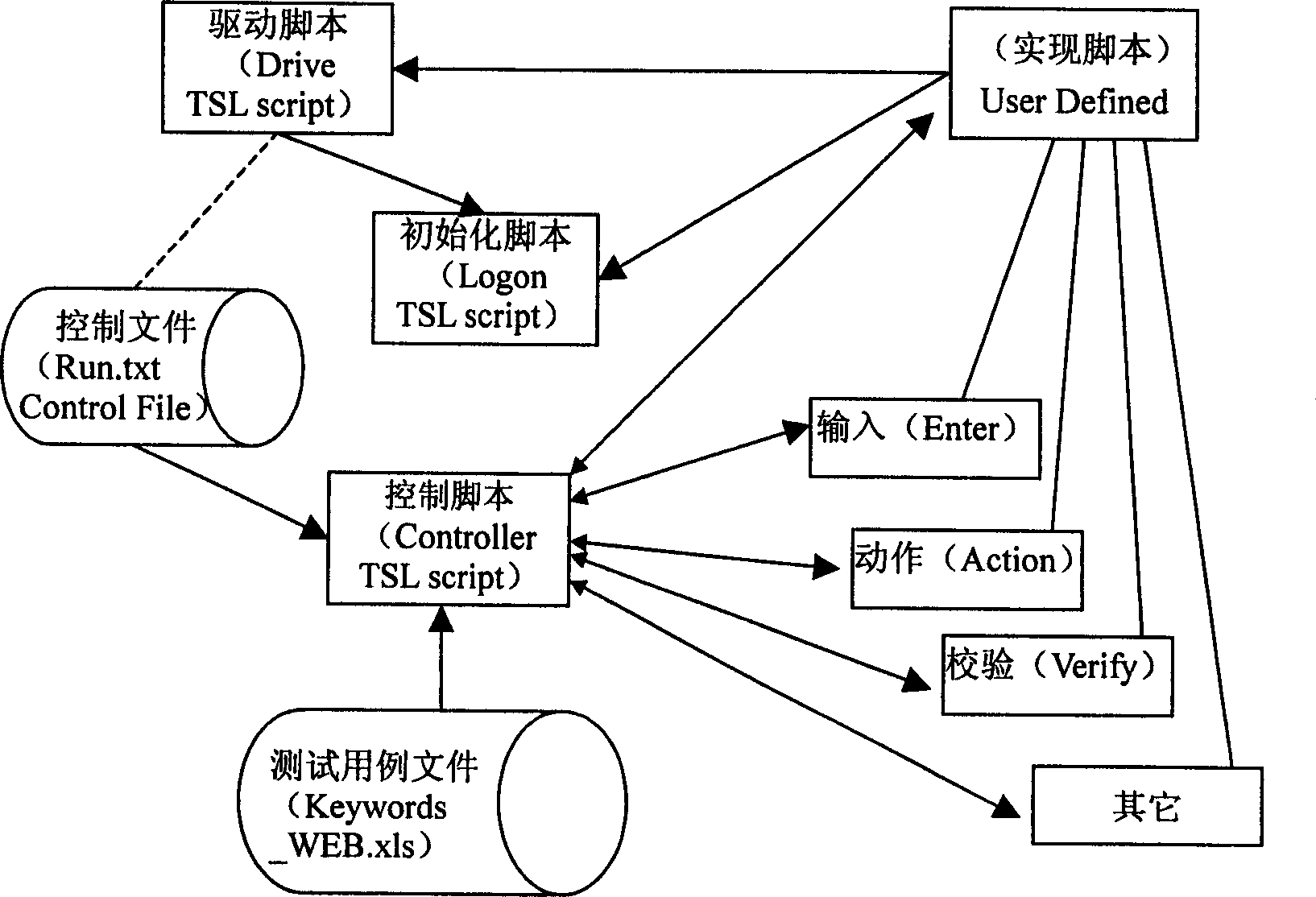

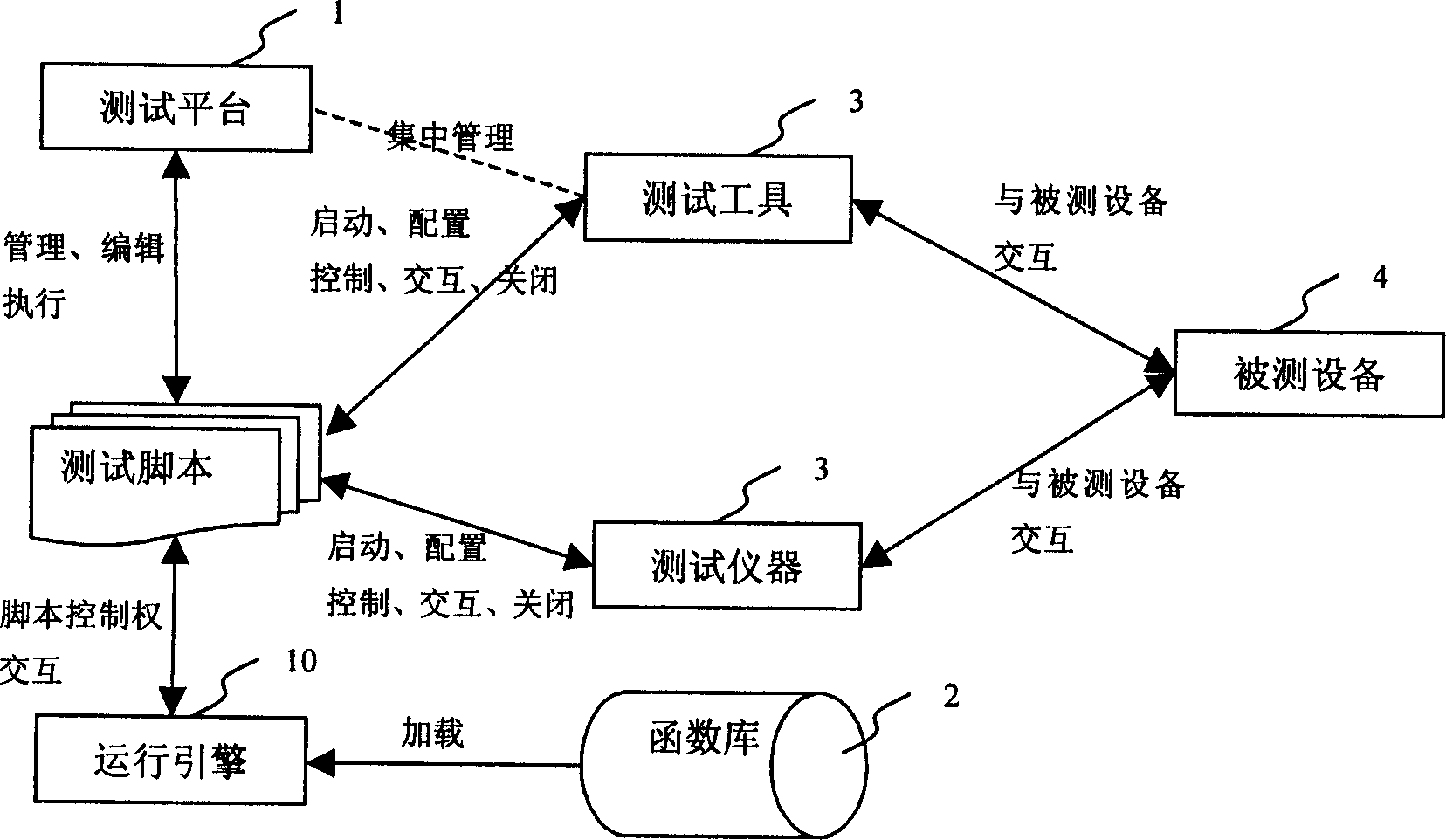

Data-driven automatic testing system and method

InactiveCN1877543AImprove loading efficiencyReduce maintenance costsSoftware testing/debuggingEquipment under testTest platform

Disclosed is a data-driving automatic testing system which comprises testing tools and testing instruments, devices to be tested, testing platform and function library connected with the testing platform. The function library includes a product function library, a testing tool function library and a testing instrument library; the testing platform includes a testing environment generating module, a test cases generating module, an operation engine, a testing logic generation module and a testing suite generating module. The invention also provides a data-driving automatic testing method. The invention is characterized in that the inventive system and method can be transmitted among platforms and tool platforms; testing environment and testing logic can be shared and overloaded. The invention has the advantages that the function library has high loading efficiency; has low maintain cost; employing testing suite to improve testing efficiency.

Owner:GLOBAL INNOVATION AGGREGATORS LLC

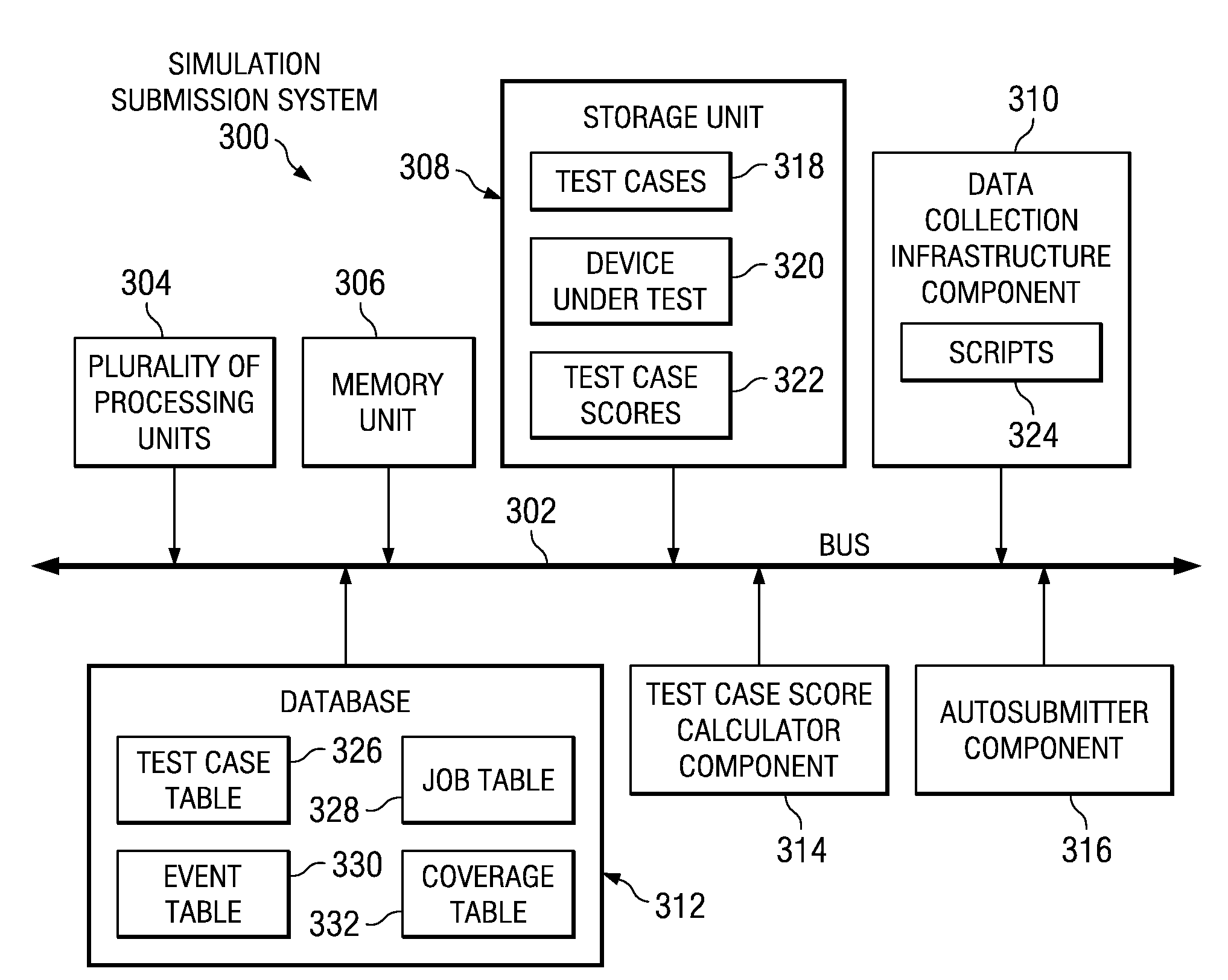

Method and System for Automatic Selection of Test Cases

InactiveUS20090006066A1Error detection/correctionCAD circuit designComputer architectureEquipment under test

A system for selecting a test case. A test case with a high score is selected. A simulation job is run on a device under test on a plurality of processors using the selected test case. Simulation performance and coverage data is collected for the selected test case and the collected simulation performance and coverage data is stored in a database.

Owner:IBM CORP

Signal analysis system and calibration method for measuring the impedance of a device under test

ActiveUS20080048677A1Resistance/reactance/impedenceTesting/calibration of speed/acceleration/shock measurement devicesEquipment under testSpectral domain

A method and apparatus adapted to calibrate a signal path of a signal analysis system such that digital samples of a signal under test acquired by the system are processed for representing the impedance of a device under test. The method and apparatus calibrates the signal path to characterize transfer parameters of the device under test within a spectral domain. A reference impedance (Zref) is retrieved that is associated with the signal analysis system. The transfer parameters of the device under test and the reference impedance (Zref) are processed to effect thereby a representation of the device under test impedance (Zeq) as a function of frequency.

Owner:TEKTRONIX INC

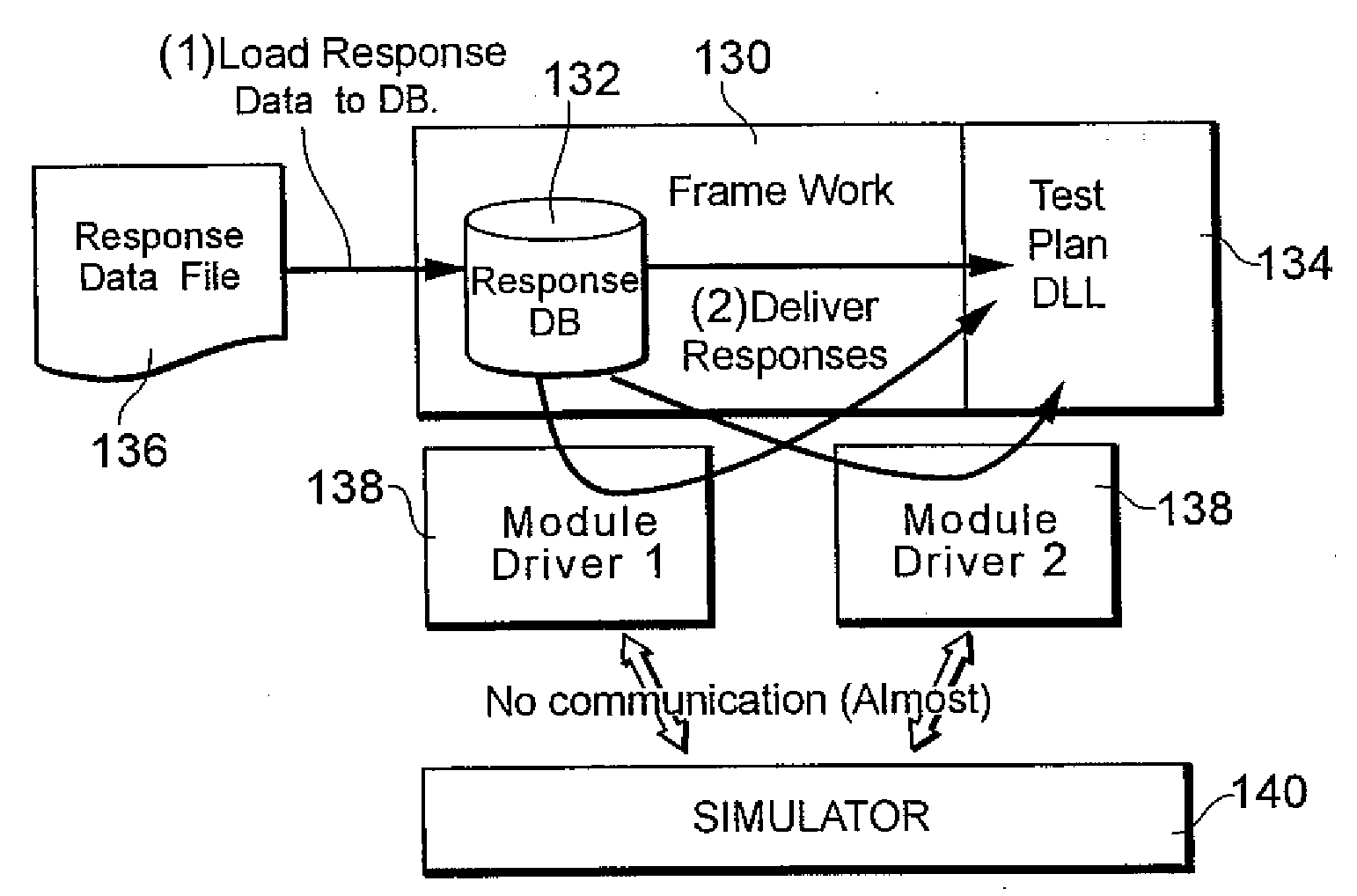

System, method, and program product for simulating test equipment

The simulation method includes a step of measuring a predetermined characteristic from a real device by using test equipment that supplies a test signal to a device-under-test (DUT); a step of saving Response Data generated from measurements obtained by measuring in a file; and a step of verifying activities of a test plan program in a simulation system that simulates the test equipment by using the Response Data saved in the file.

Owner:ADVANTEST CORP

Method and system for wafer and device level testing of an integrated circuit

InactiveUS20030076125A1Needless expense associatedDefective assemblyDigital circuit testingResistance/reactance/impedenceEquipment under testComputer module

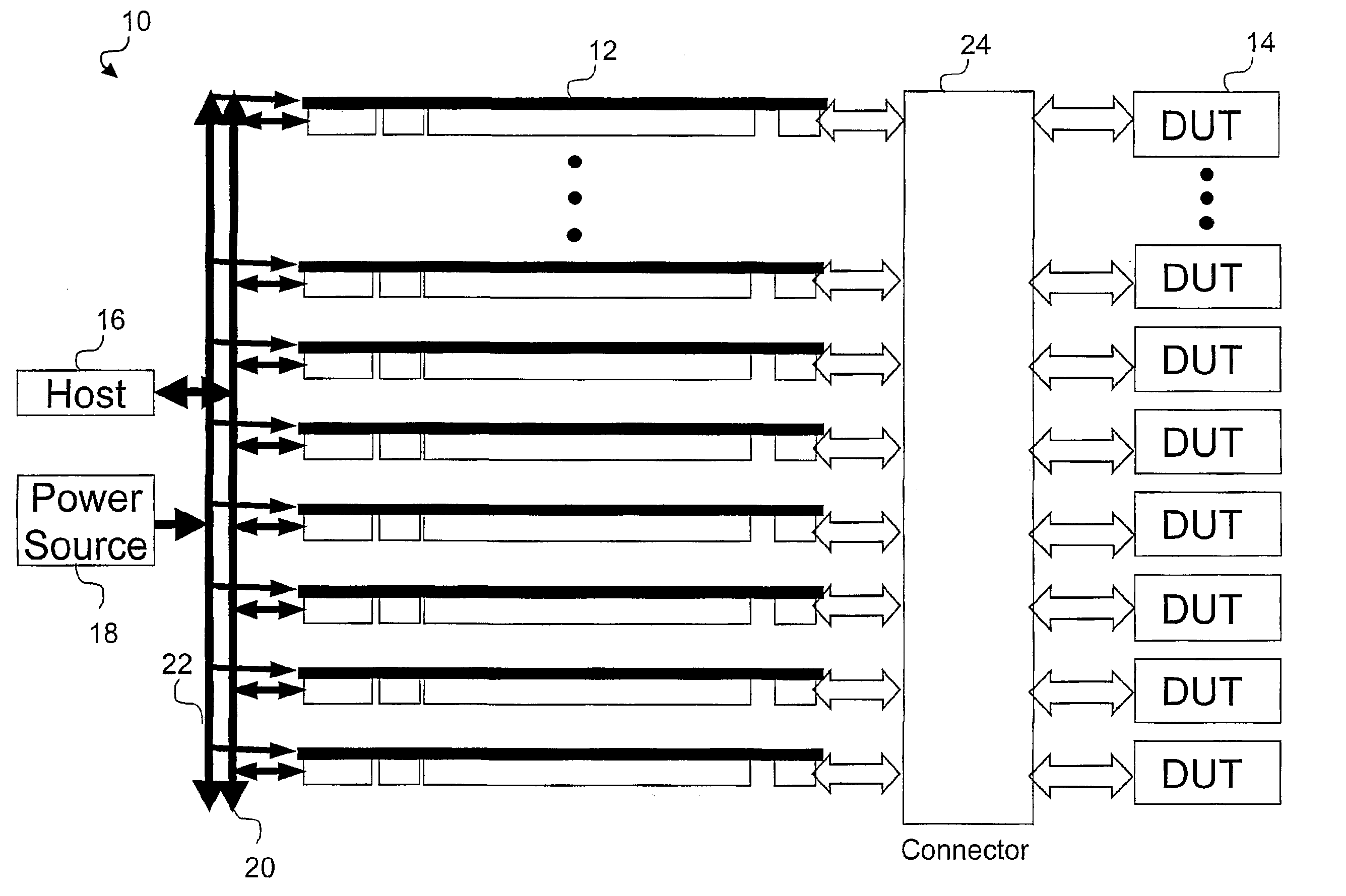

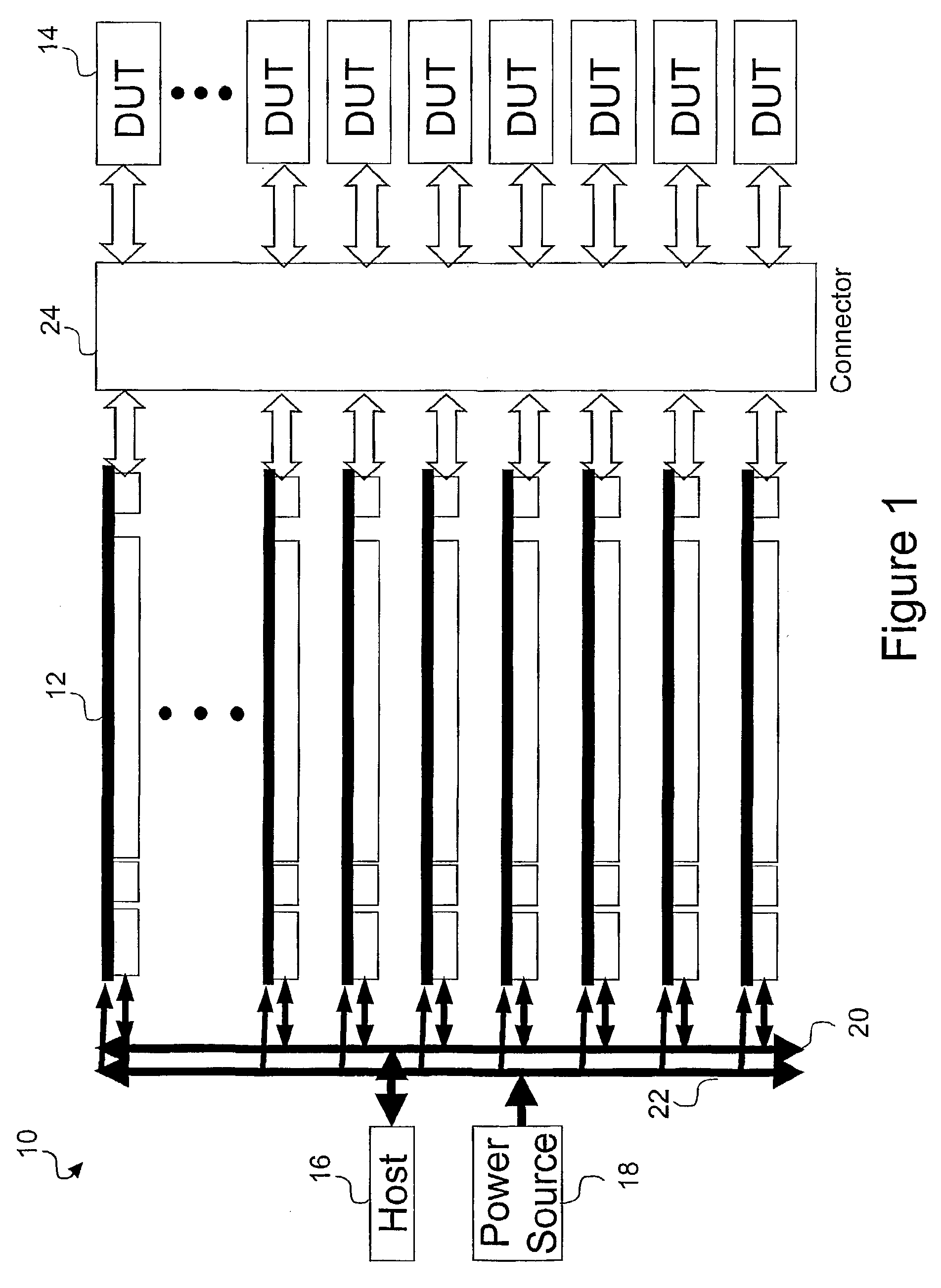

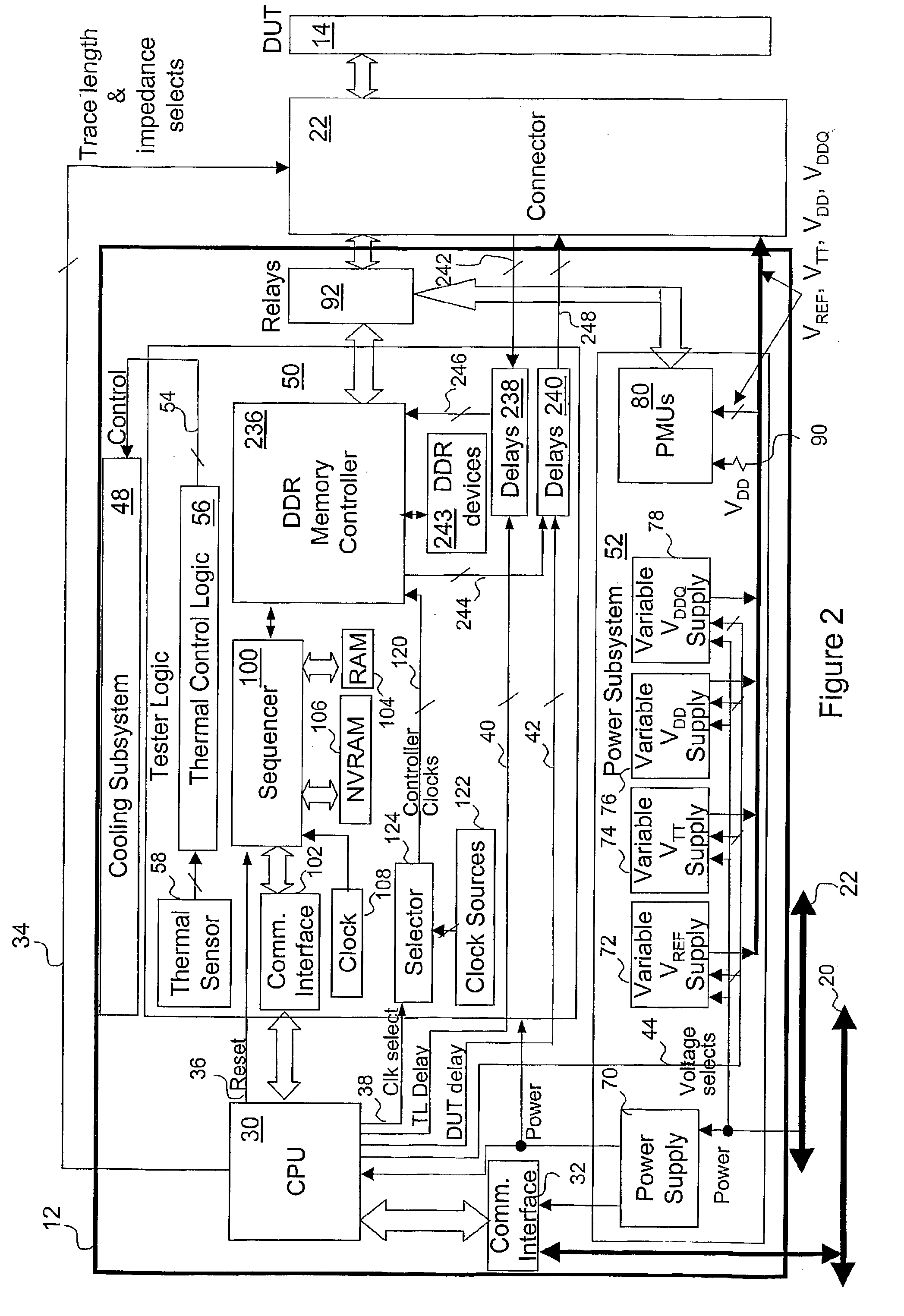

A tester comprises test logic and a connector for at least one device under test. The connector, which may comprise a wafer probe for dice on a wafer or a test fixture or either packaged integrated circuit devices or circuit board modules, has connections for the device under test that present an impedance selected to emulate the characteristic impedance of an end-use environment of the device under test. For example, in an embodiment in which the device under test comprises DDR memory and the end-use environment is a DDR memory module, the characteristic impedance is approximately 60 ohms. Thus, the tester of the present invention can accurately simulate operational behavior in an end-use environment of the device under test. Because this accurate simulation is available even for dice on a wafer, the needless expense associated with packaging defective dies and assembling defective dies into modules can be avoided. The test logic, which is couplet to the connector for communication with the device under test, transfers test commands and test data to (tic device under test. The test data and commands are utilized to perform multiple types of tests, including tests of the memory core and internal logic of the device under test. In this manner, the need for multiple types of testers is reduced or eliminated.

Owner:MCCORD DON

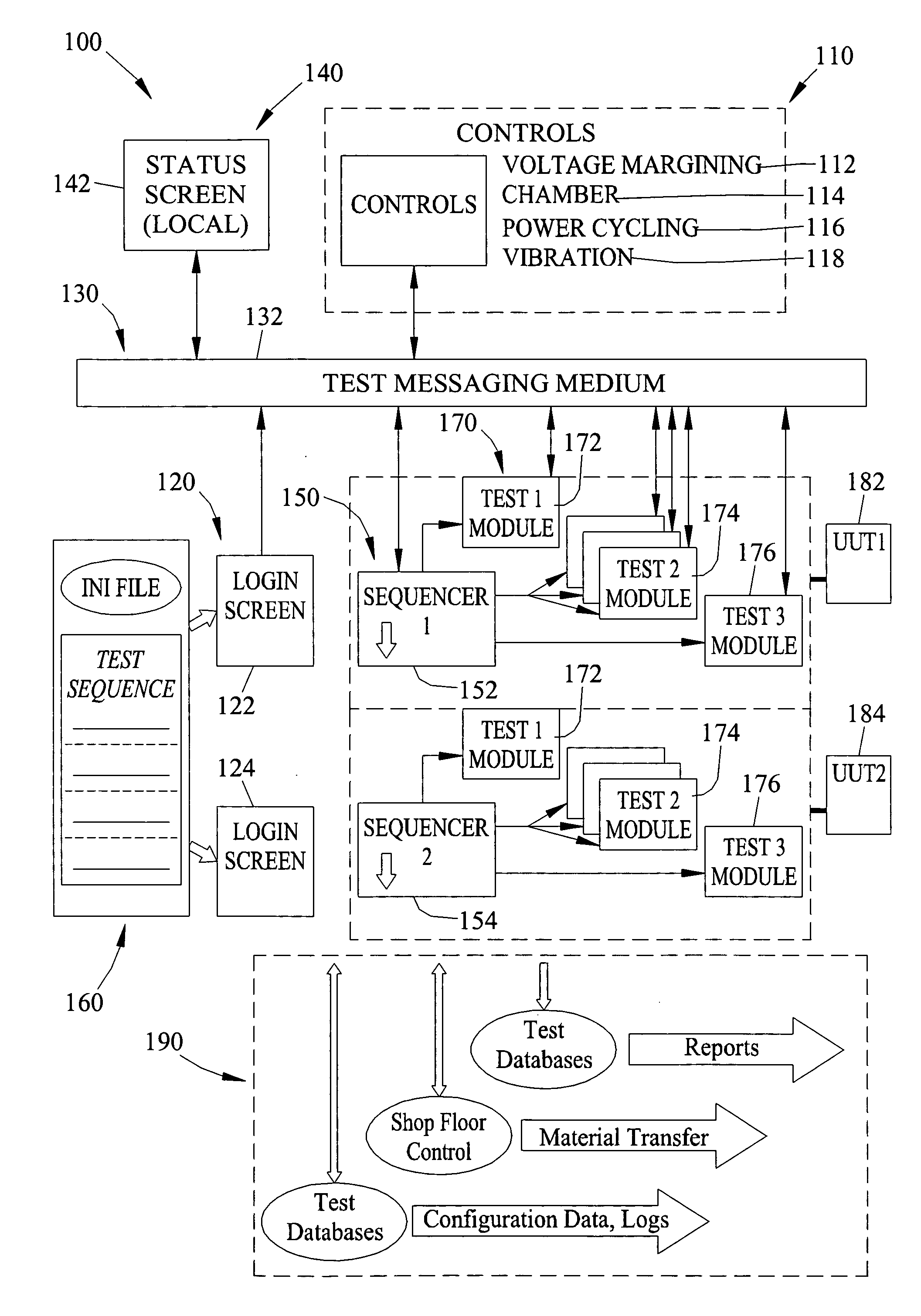

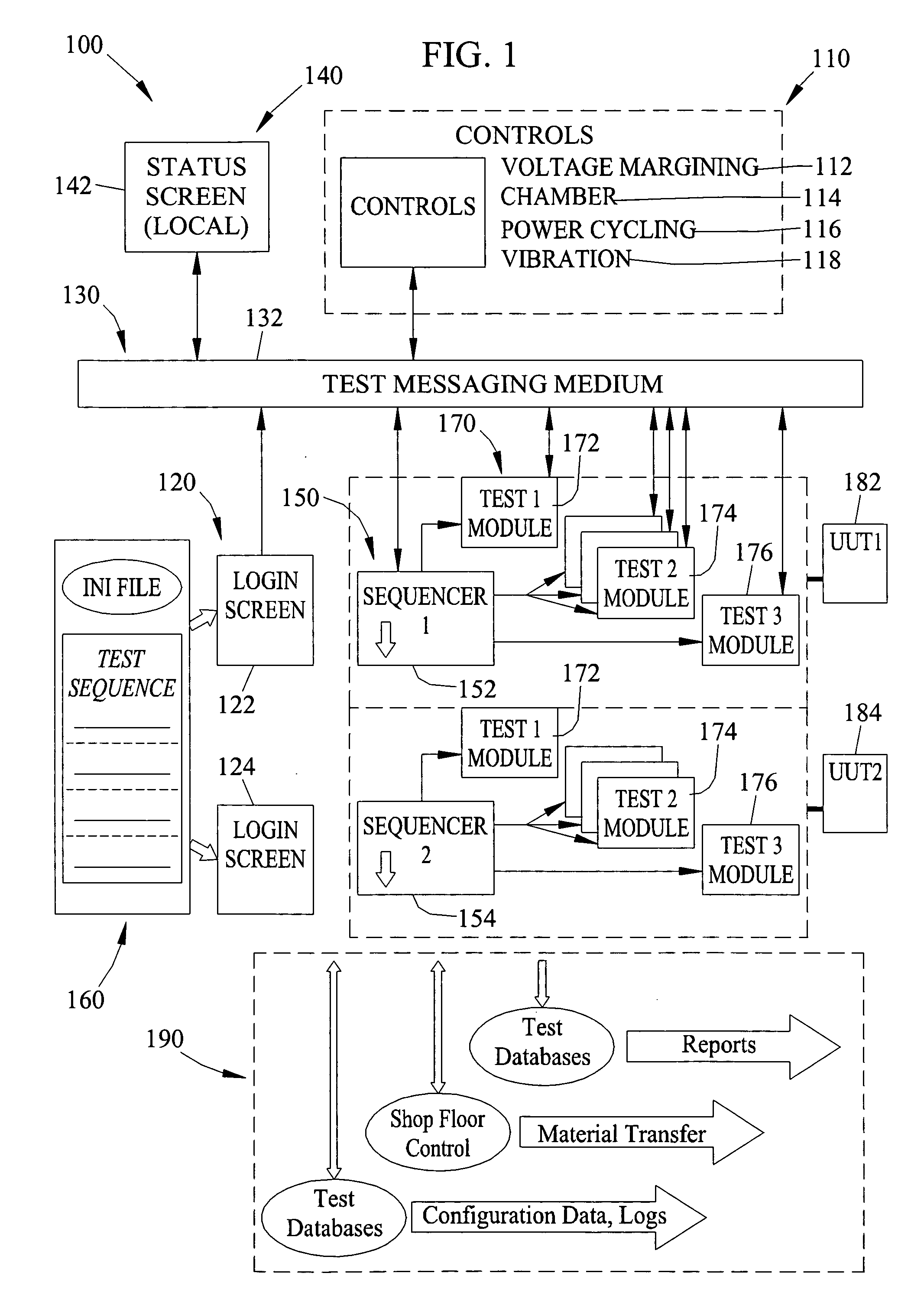

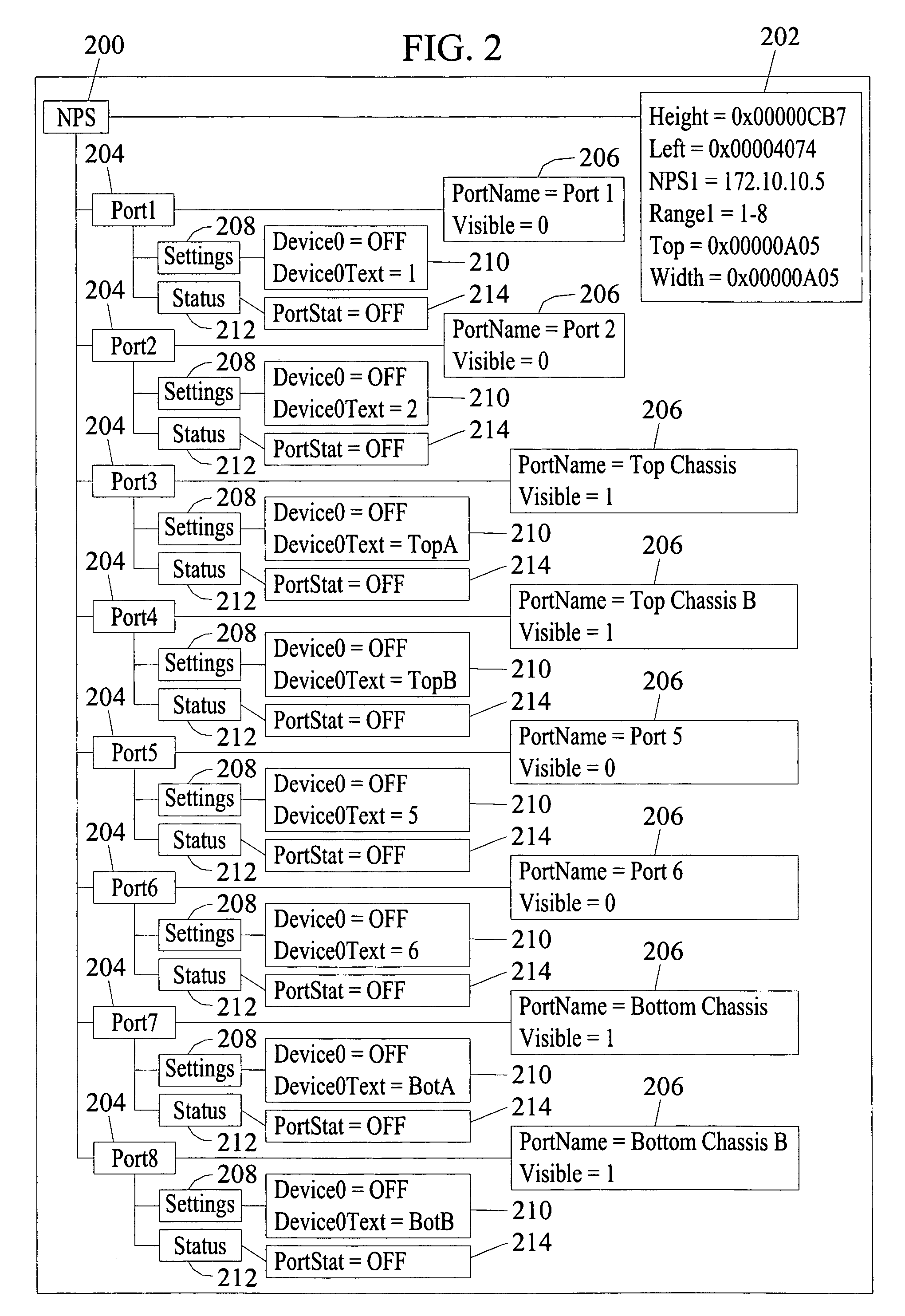

Area-and product-independent test automation system and method for automatically synchronizing tests of multiple devices

InactiveUS20060036907A1Limited scalabilityError detection/correctionScripting languageComputer hardware

An area- and product-independent test automation system and a method for synchronizing testing of multiple devices are disclosed. The test automation system may include a test sequence being written in a script language common to different products or test areas in an electronic component manufacturing or testing facility. Executable test modules control the testing of individual devices under test. The test sequence includes commands that reference the test modules. A sequencer reads the commands in the test sequence and executes the corresponding test modules. A test messaging medium receives commands from the modules and stores test status information. Device-specific controllers monitor the test messaging medium for commands and communicate with test hardware to execute the commands. The device-specific controllers also write test status information to the test messaging medium.

Owner:EMC CORP

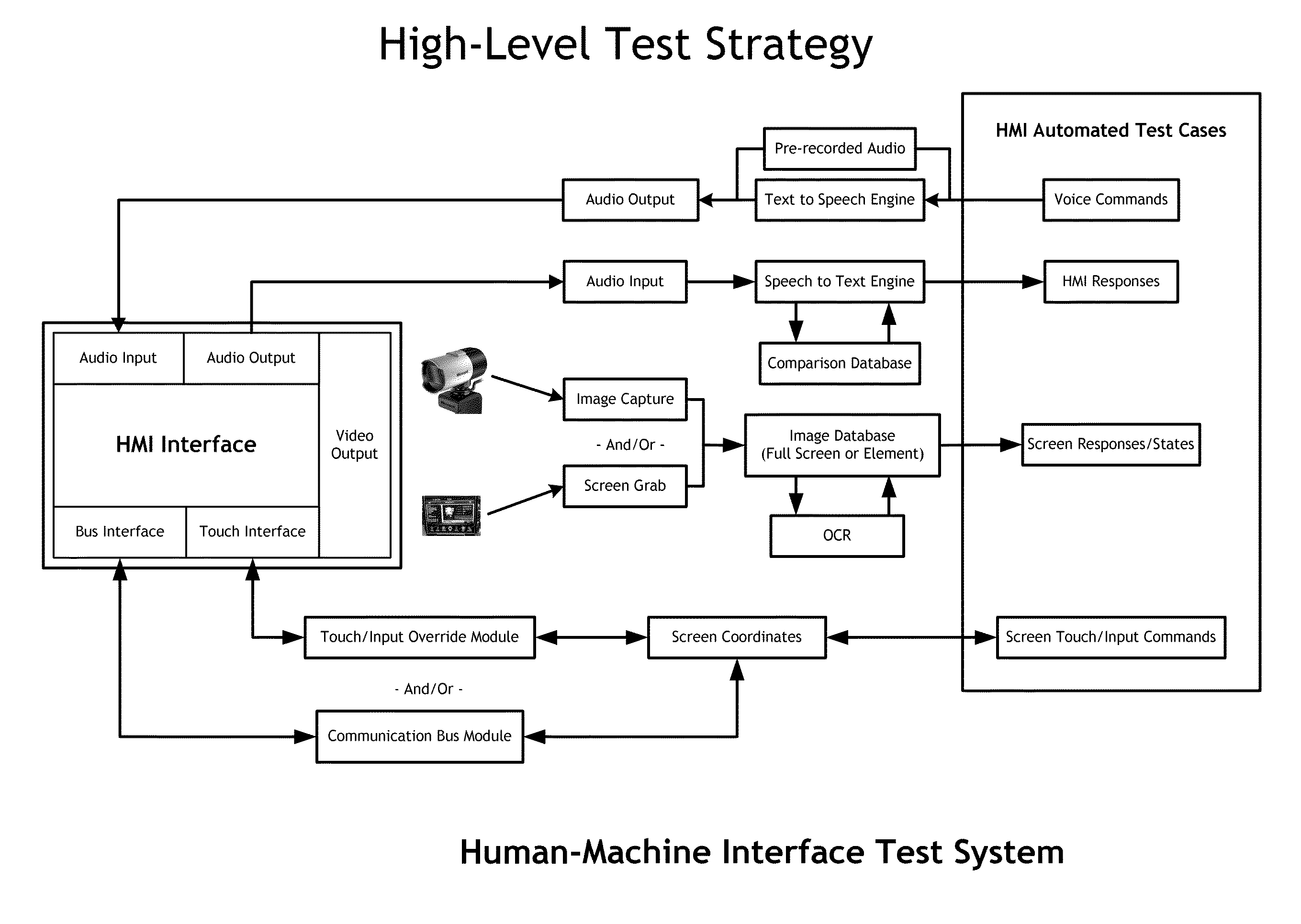

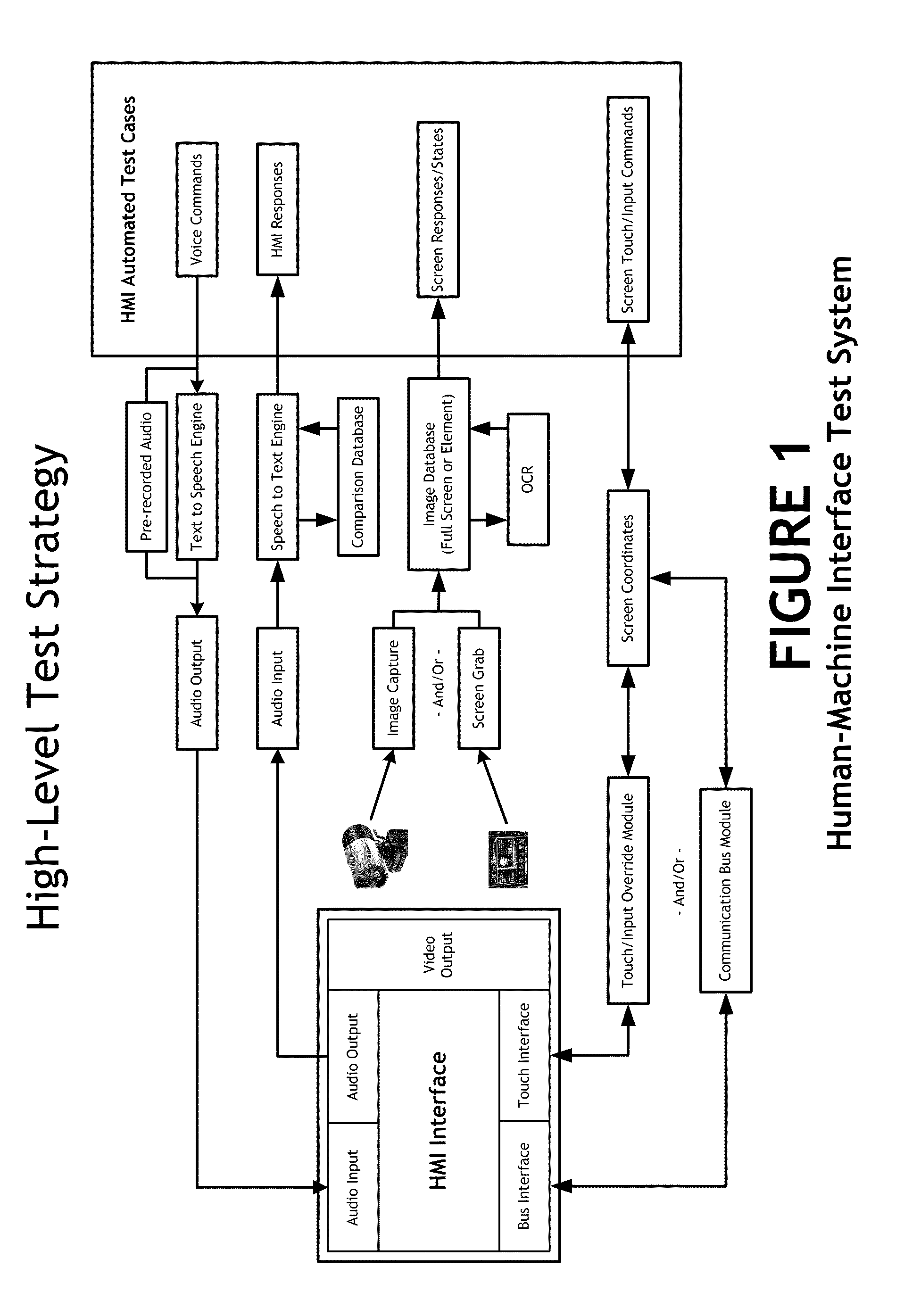

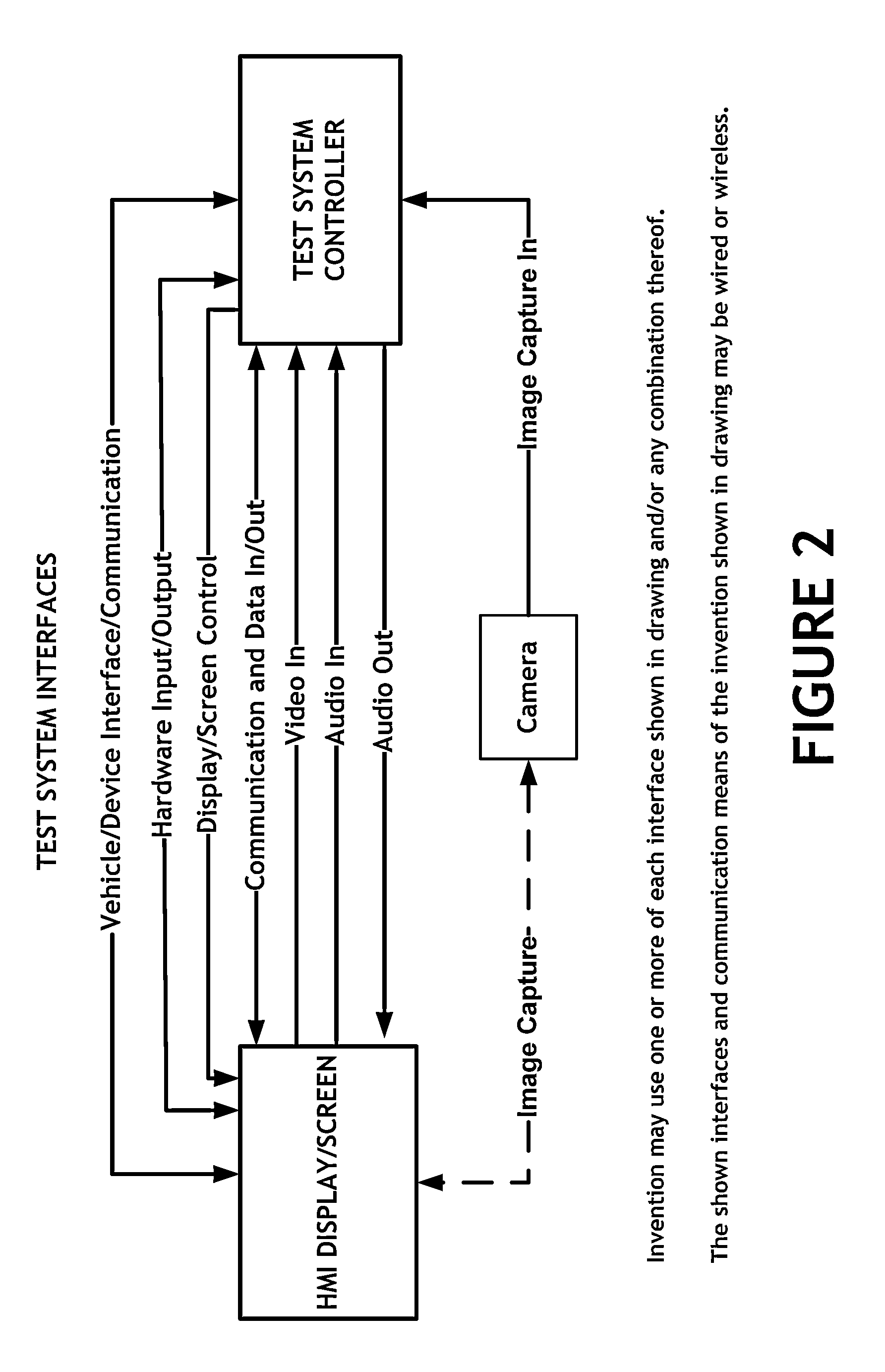

Human-Machine Interface Test System

ActiveUS20140303756A1Complete testFully testedComputer controlError detection/correctionHuman interactionComputer hardware

The human-machine interface test system enables the automated testing of vehicle interface systems and consumer electronics devices, replacing testing and validation that previously had required human interaction. The human-machine interface device (HMI test object or device under test) does not need to be altered (via hardware or software modifications or additions) to be able to be tested using the human-machine interface test system. The HMIts involves the automated audio input generation and output analysis, visual verification of a display screen with graphics and texts display, including touch and gesture interface control and feedback, external device interface, as well as data logging for communication between the HMI device and the rest of the system, that will replace the testing and validation that previously required human interaction. The HMIts provides more accurate and reliable results from the conducted tests, increasing repeatability and consistency in a controlled environment, while significantly decreasing test time.

Owner:FEV NORTH AMERICA INC

Test equipment, method for loading test plan and program product

InactiveUS7809520B2Resistance/reactance/impedenceTesting circuitsEquipment under testSystem controller

Test equipment includes a memory to which a test plan that includes a plurality of sub-test plans is loaded and a system controller that, when the test equipment actually examines a device-under-test (DUT), loads the test plan to the memory by the unit of the sub-test plan and supplies a test signal to the DUT by interpreting the loaded test plan.

Owner:ADVANTEST CORP

Test component and method of operation thereof

ActiveUS20040243334A1Many timesShorten the timeElectronic circuit testingError detection/correctionReal systemsEquipment under test

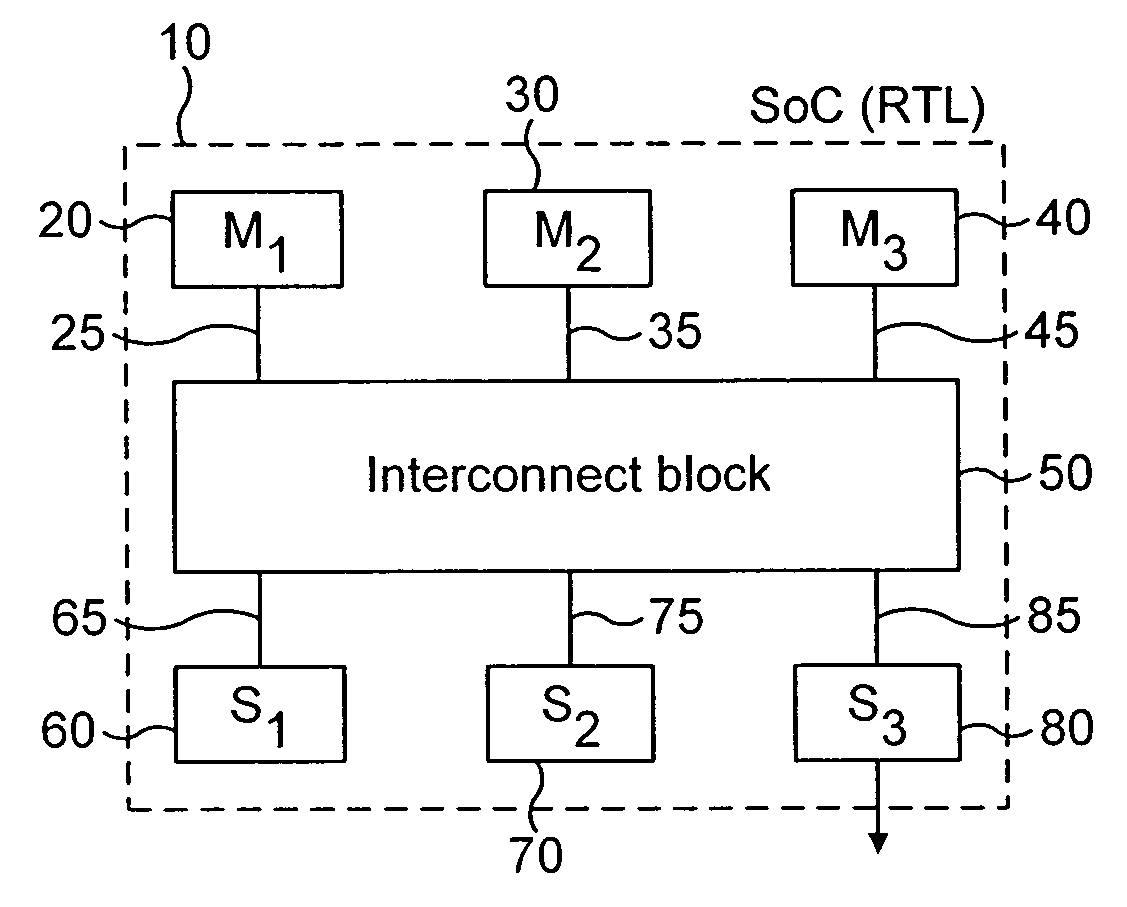

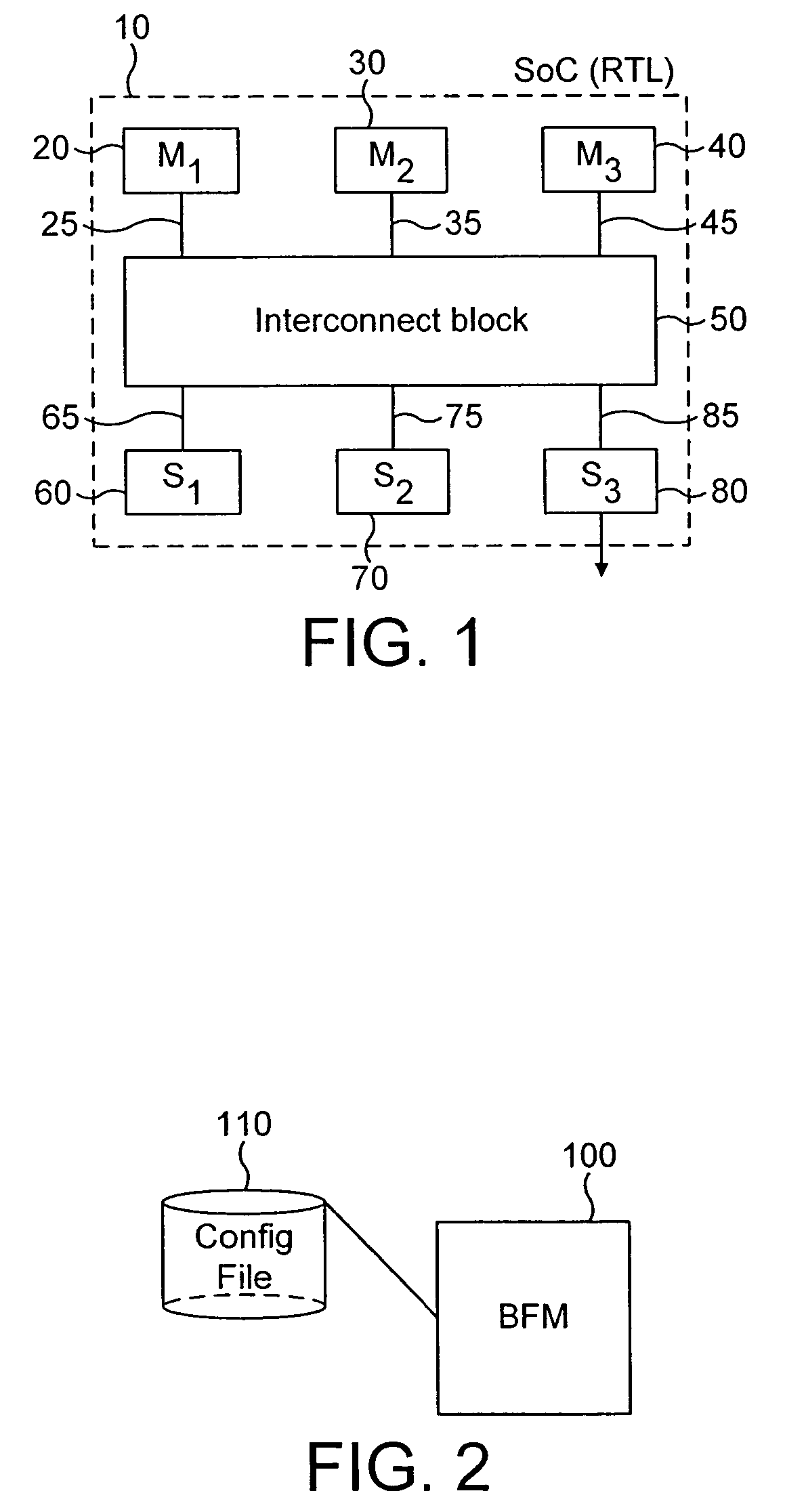

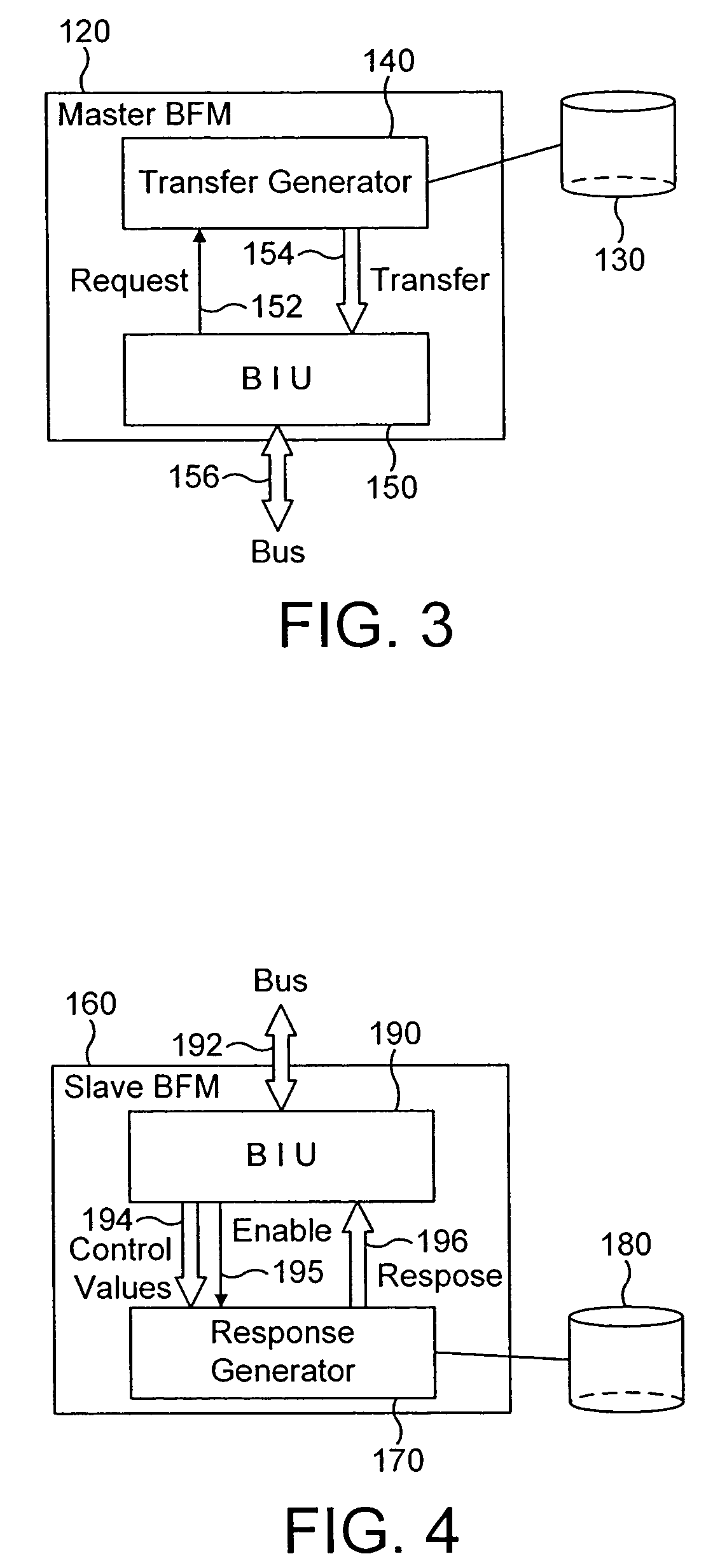

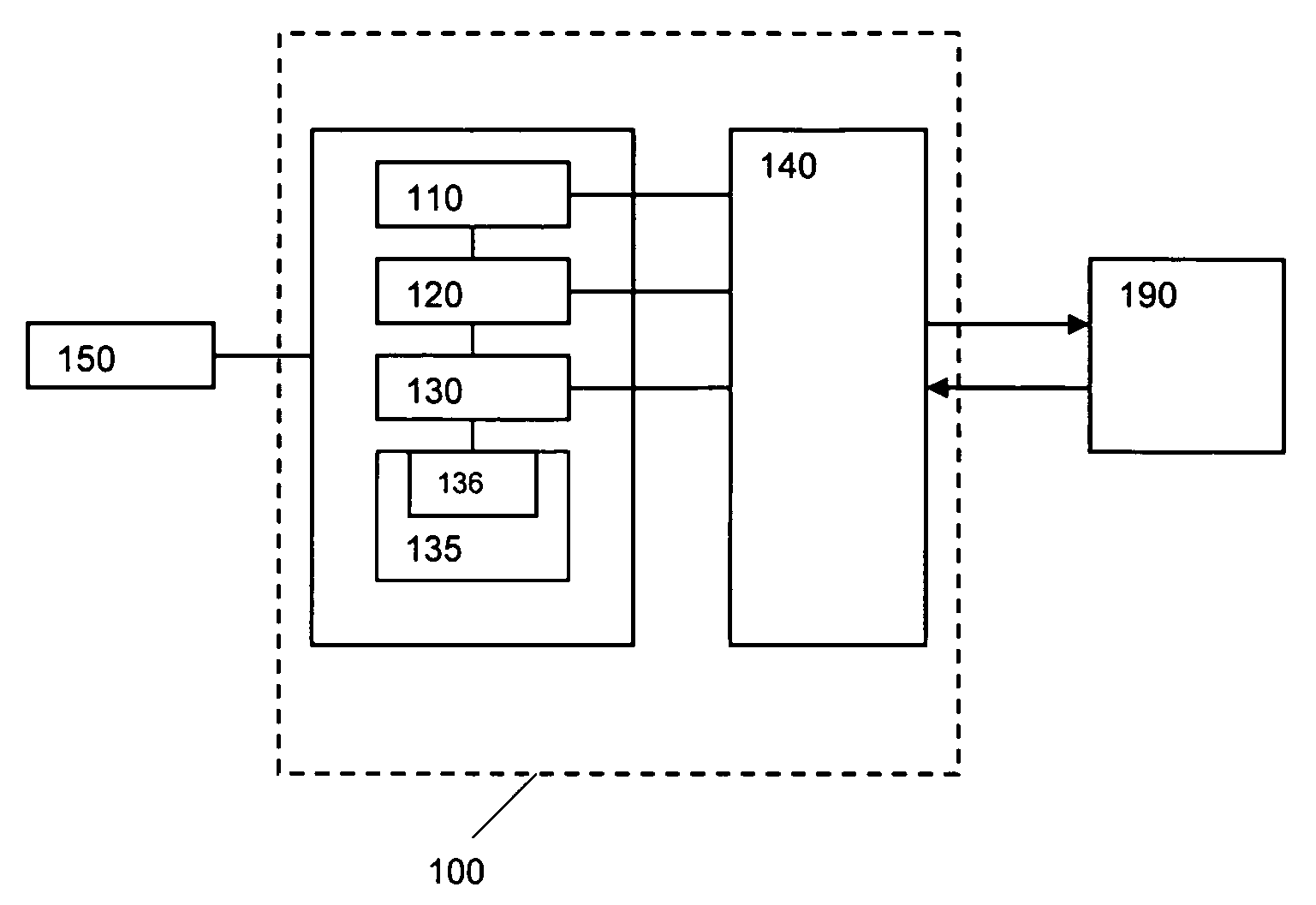

A test component and method of operation thereof are provided, the test component being arranged in a test environment to issue a test sequence over a bus to a device under test. A configuration file is provided to specify the behaviour of the test component, the configuration file comprising a plurality of regions with each region specifying attributes for use in determining the test sequence. A number of the regions specify constraint attributes defining allowable test sequences. The method of the present invention comprises the steps of: (a) when a test sequence is required to be issued, causing the test component to select, based on predetermined criteria, one of a number of regions provided by the configuration file; and (b) using the constraint attributes for that selected region to generate the test sequence to be issued on to the bus. It has been found that such an approach provides an efficient technique for enabling the test component to be configured to emulate the actual component which in the real system will interact with the device being tested. It has also been found that the time taken to write the tests required for the device under test is significantly reduced compared to prior art techniques.

Owner:ARM LTD

Bit synchronization for high-speed serial device testing

ActiveUS20060245291A1Difficult for be differenceElectronic circuit testingError detection/correctionComputer hardwareComputer science

An apparatus for testing electronic devices employs a programmable device to adjust the timing of the strobes such that the strobes sample the bit stream from a device under test at or near the center of the bit position. The strobe time adjustment is performed based on pairs of strobe readings made around a number of different bit positions. The programmable device examines the pairs of strobe reading made around each of the different bit positions to determine whether or not a bit transition has occurred there. The programmable device selects the bit positions around which a bit transition has not occurred as eye candidates, and defines the center of the largest contiguous region of eye candidates as the center of the bit position.

Owner:CREDENCE SYSTEMS

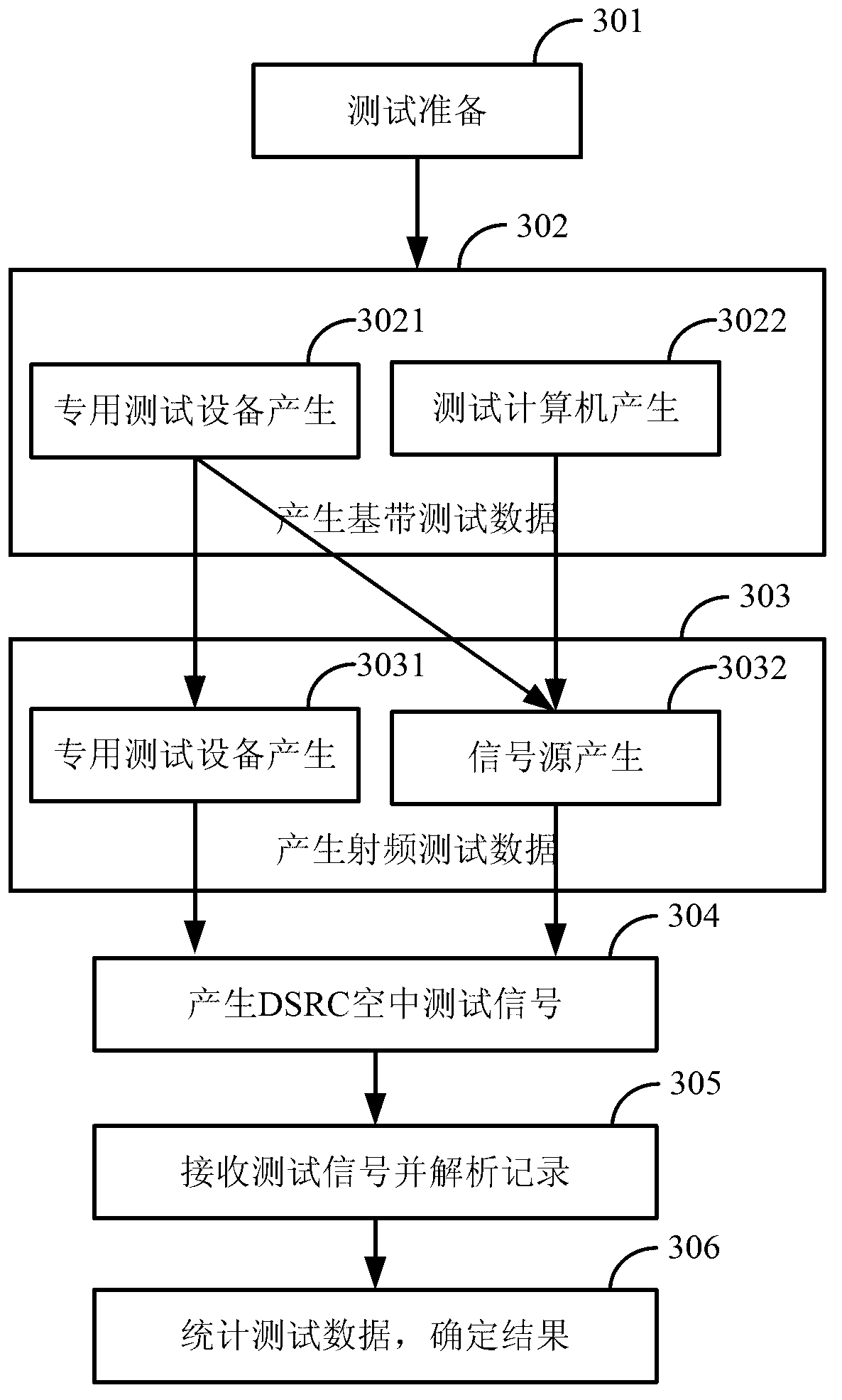

System and method for testing dedicated short range communication (DSRC) equipment

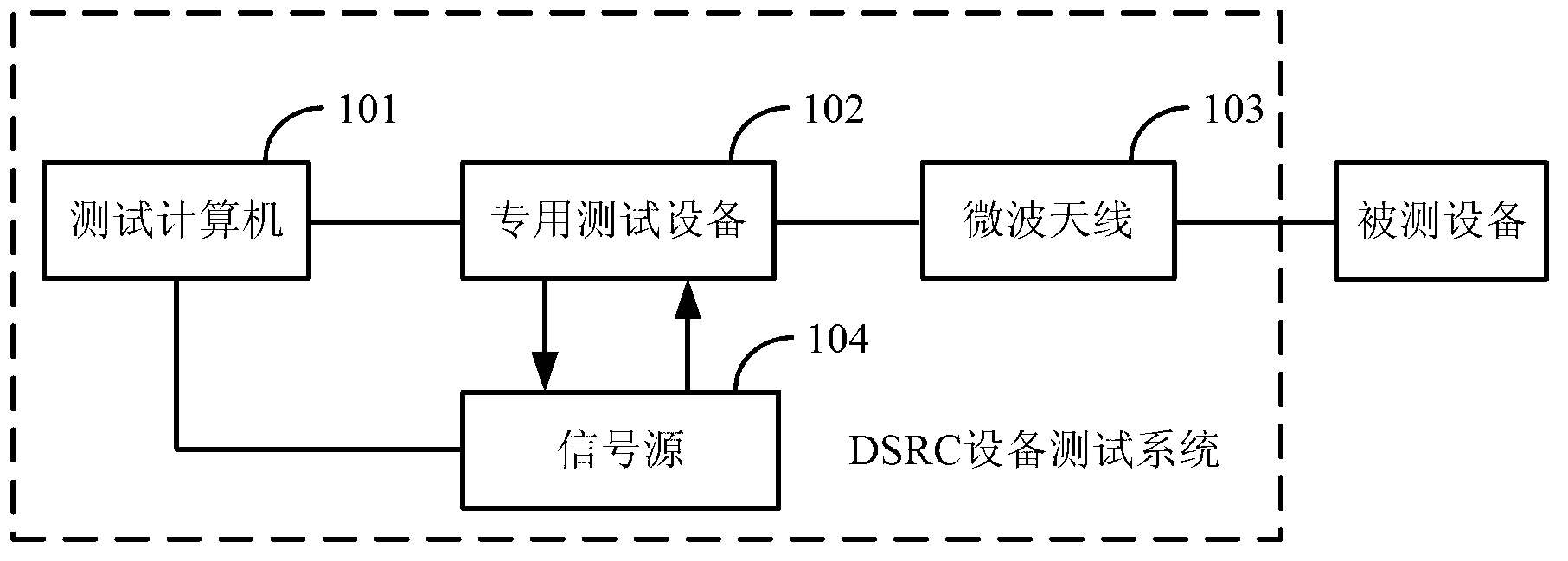

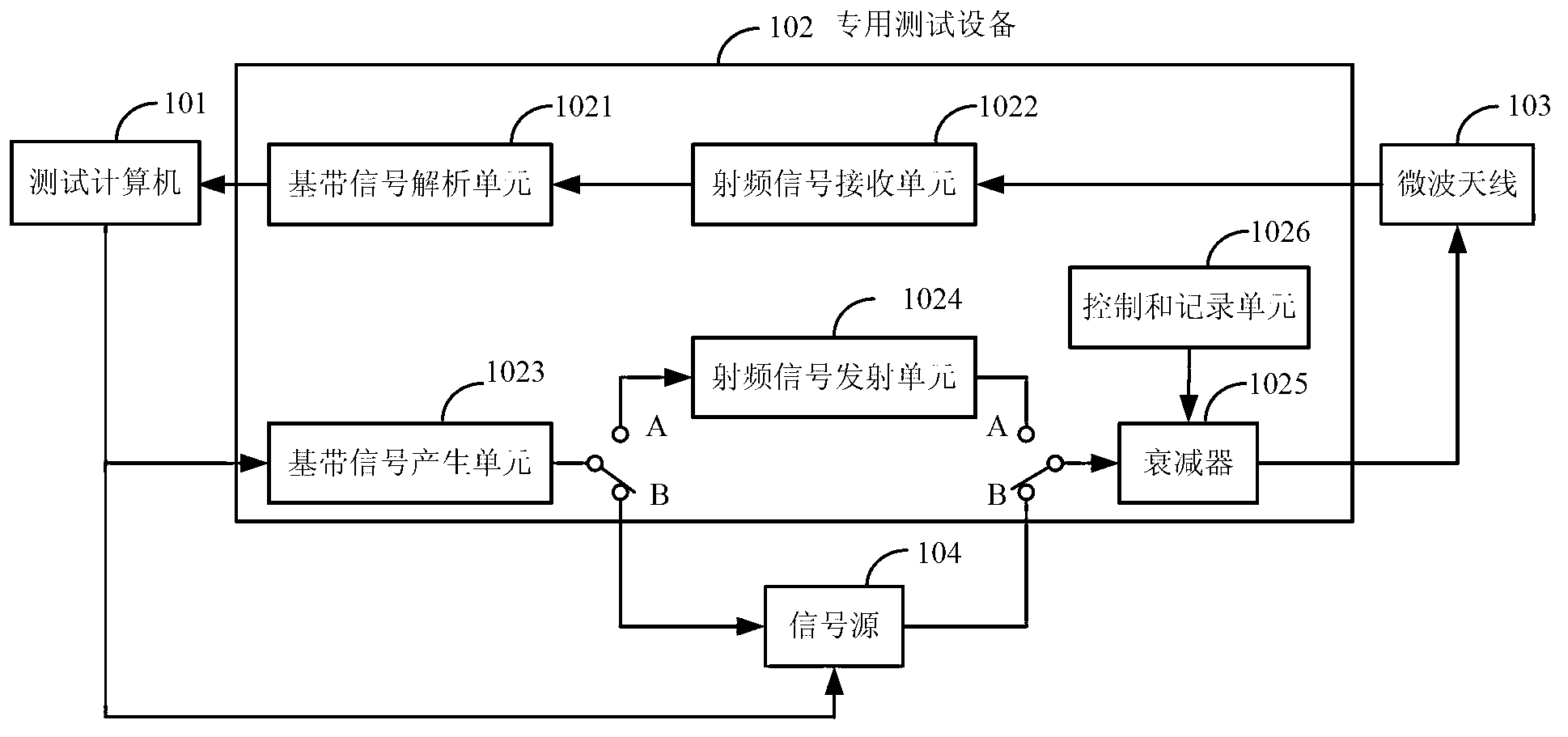

ActiveCN103236891AGuarantee product qualityLow costTransmitters monitoringReceivers monitoringComputer hardwarePerformance index

The invention discloses a system and a method for testing dedicated short range communication (DSRC) equipment. The system comprises a testing computer, special testing equipment, a signal source and a microwave antenna, testing software is installed in the testing computer, the testing computer chooses test content and configure test parameters according to tested equipment and controls testing processes according to the test content and the text parameters, the special testing equipment generates DSRC test data under the control of the testing computer, receives response data returned by the tested equipment and sends the data after being analyzed to the testing computer, the signal source outputs the DSRC test data according to input data of the special testing equipment or programming instructions of the testing computer, the microwave antenna emits the DSRC test data provided by the special testing equipment or the signal source to the tested equipment, receives response returned by the tested equipment and provides the response to the special testing equipment, and the testing computer further determines test results according to the test data provided by the special testing equipment. By the system and the method, testing of protocol uniformity of a link layer and an application layer and key parameters and receiving performance indexes of a physical layer of the DSRC equipment can be realized, and product quality of the tested equipment can be guaranteed.

Owner:北京易路行技术有限公司 +1

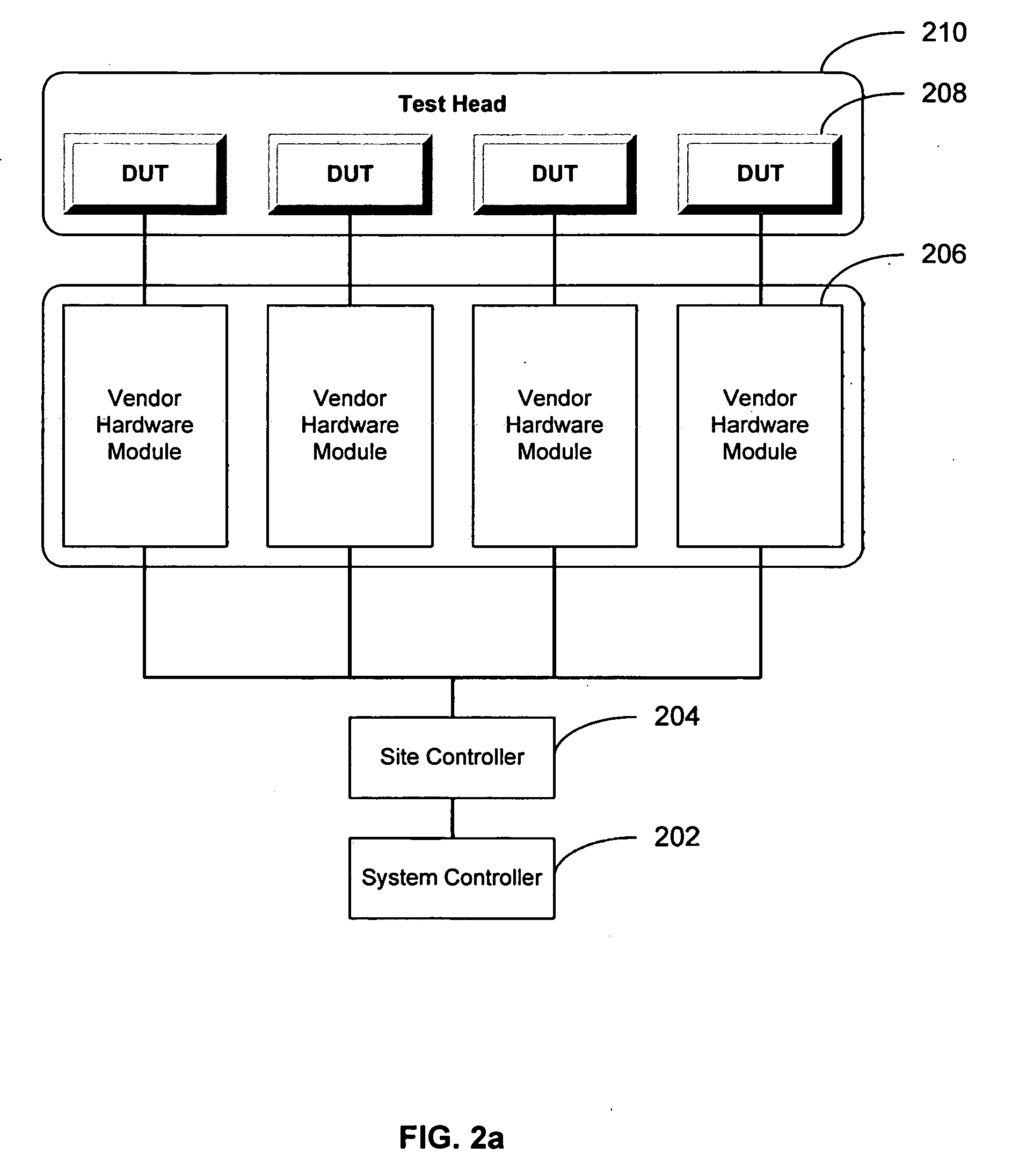

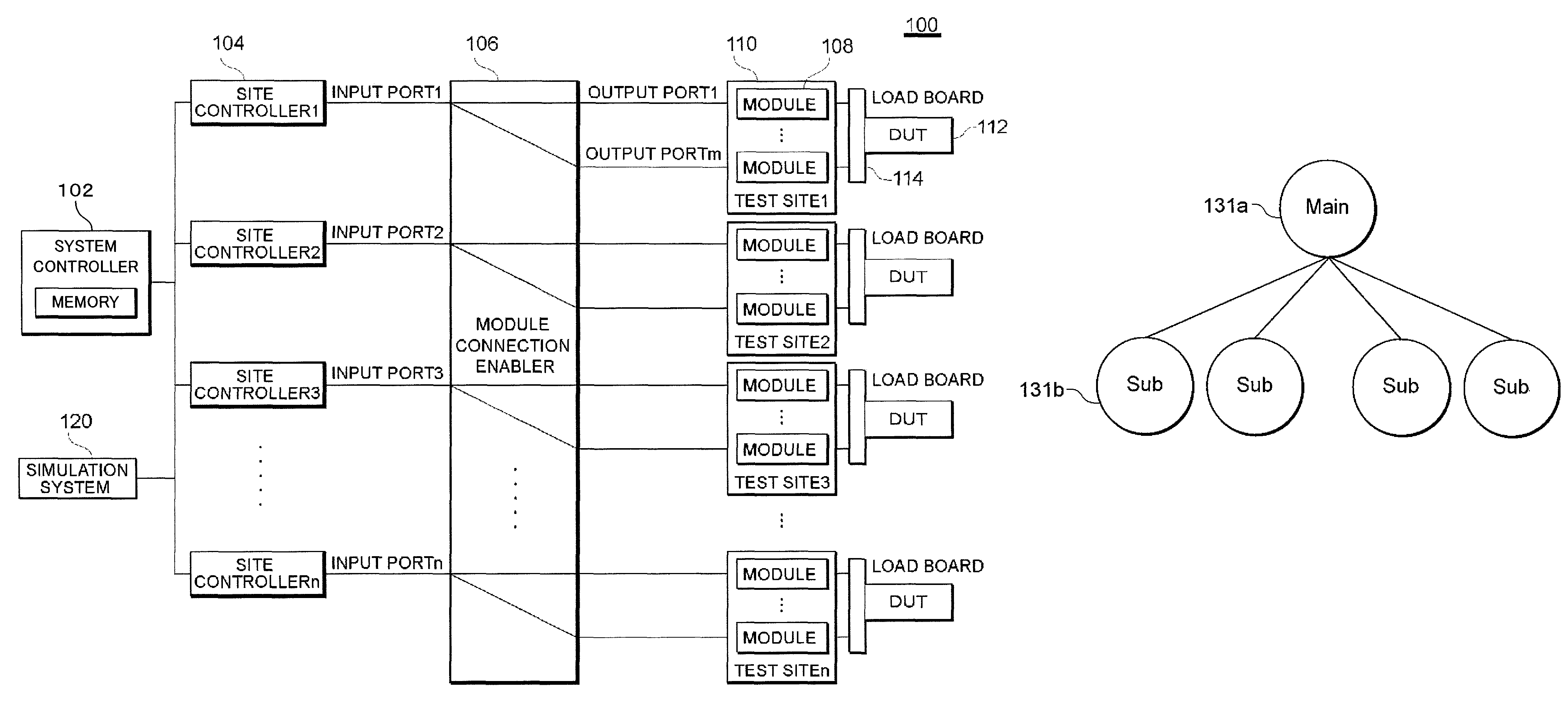

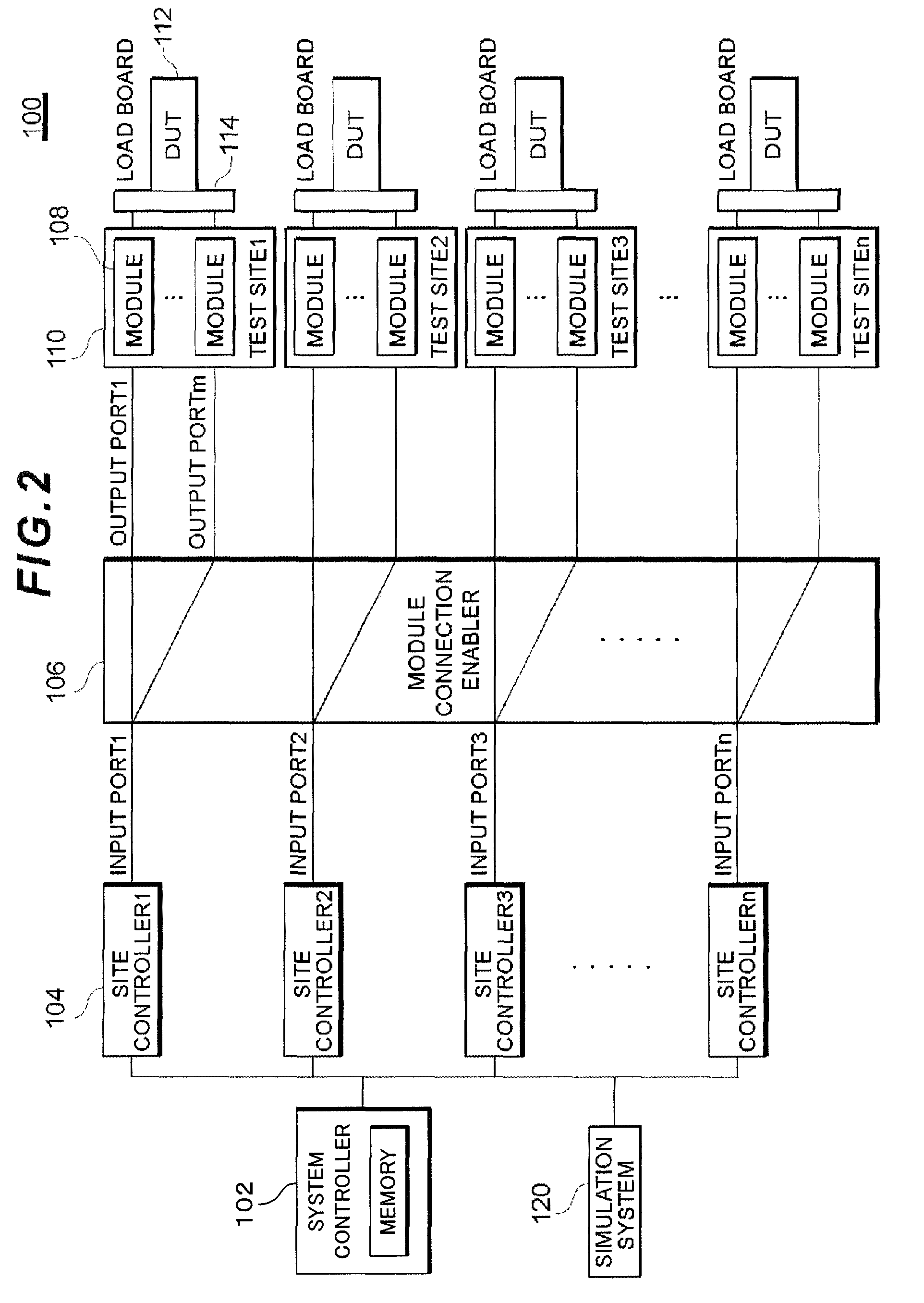

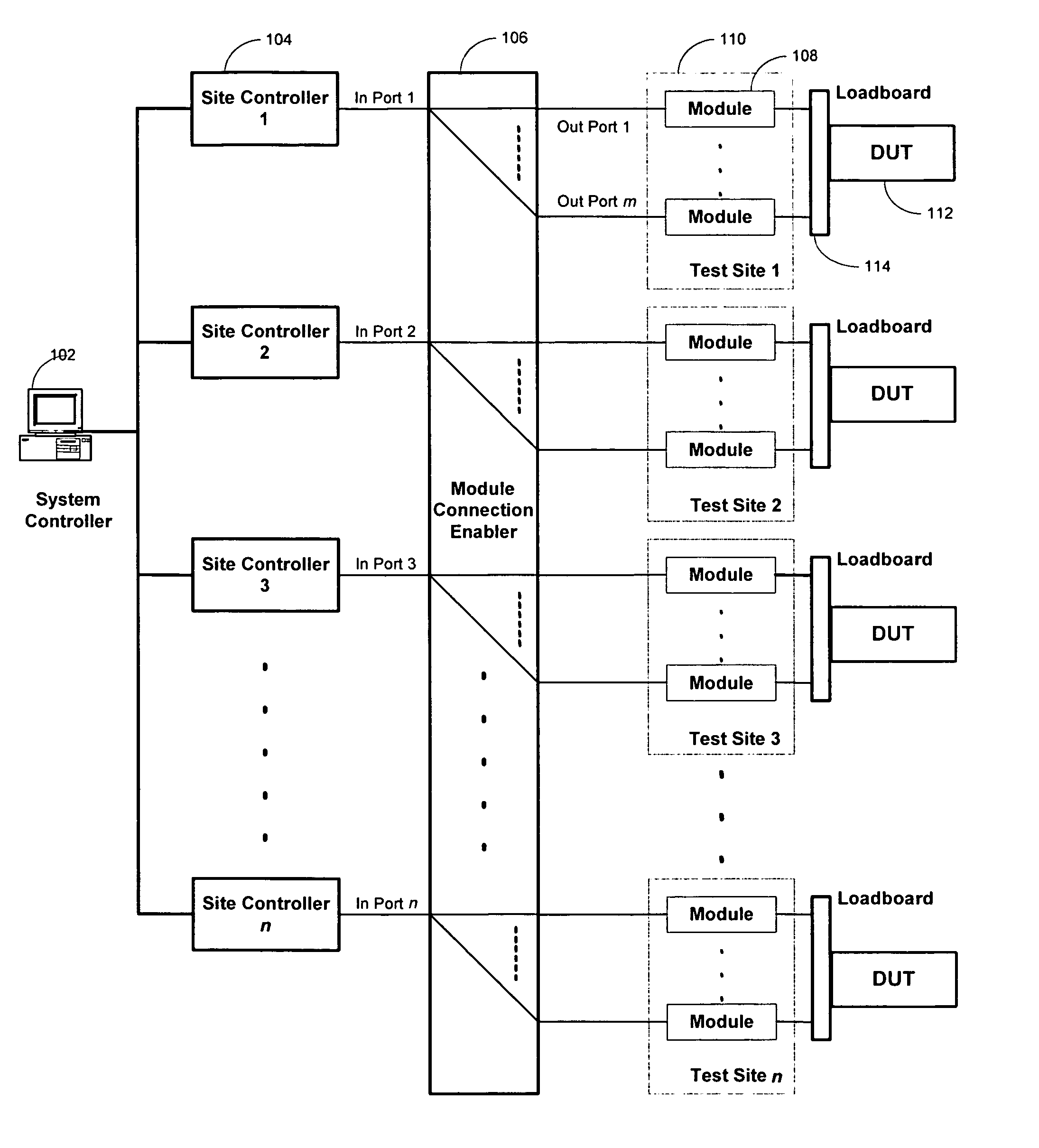

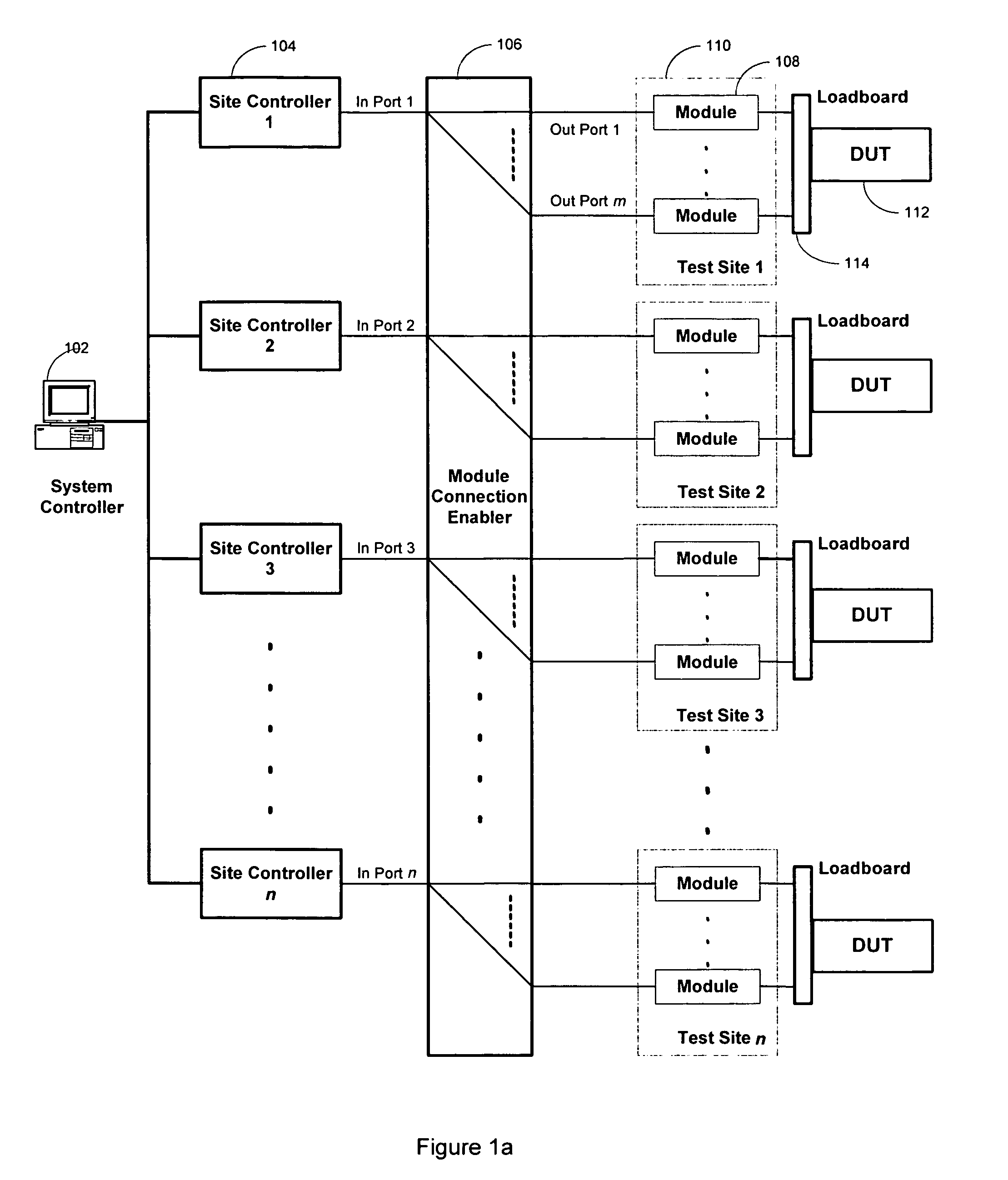

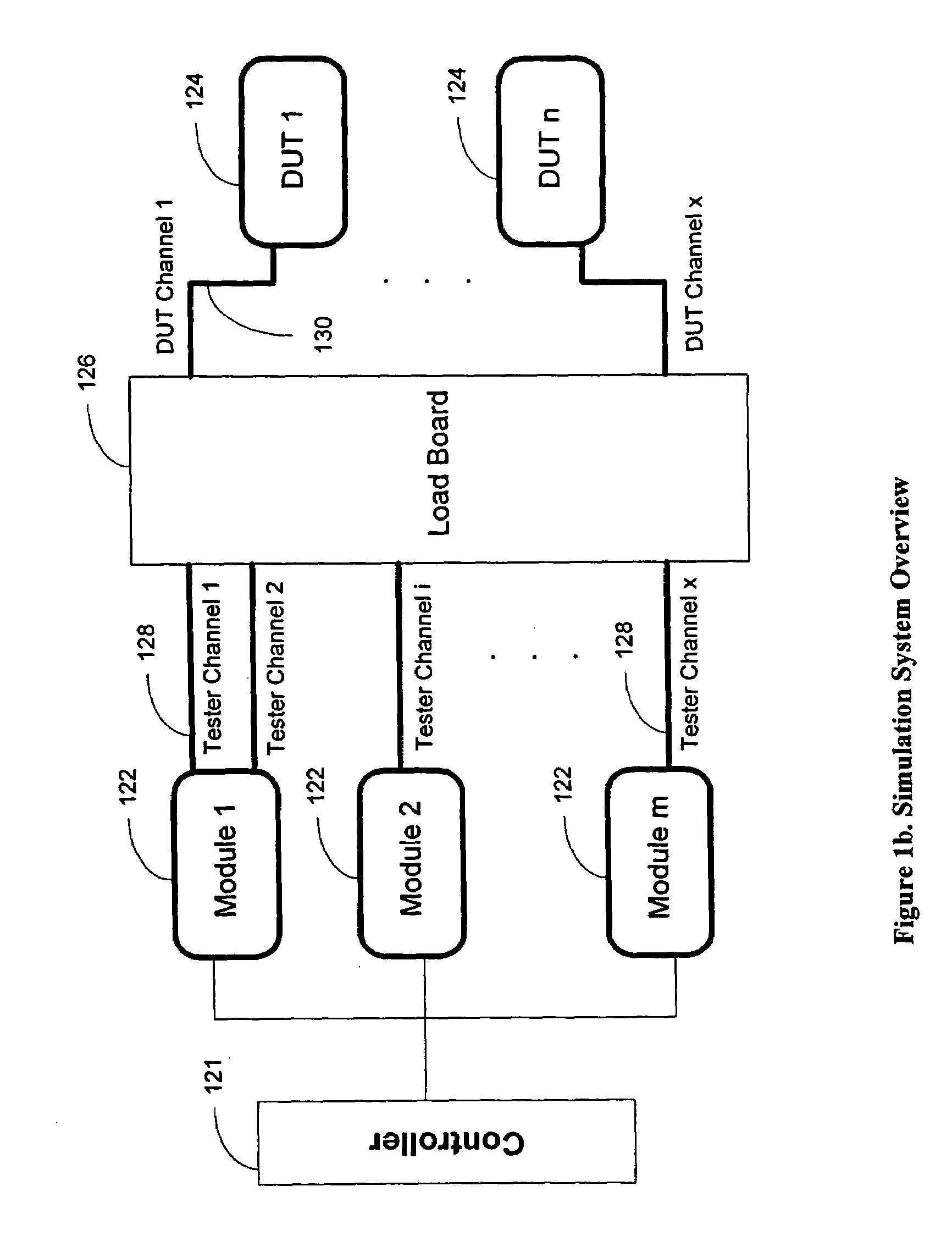

Method and system for simulating a modular test system

InactiveUS7210087B2Use minimizedDigital circuit testingFunctional testingEquipment under testModularity

A method for simulating a modular test system is disclosed. The method includes providing a controller, where the controller controls at least one vendor module and its corresponding device under test (DUT) model, creating a simulation framework for establishing standard interfaces between the at least one vendor module and its corresponding DUT model, configuring the simulation framework, and simulating the modular test system using the simulation framework.

Owner:ADVANTEST AMERICA R & D CENT