Patents

Literature

508 results about "Internal logic" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

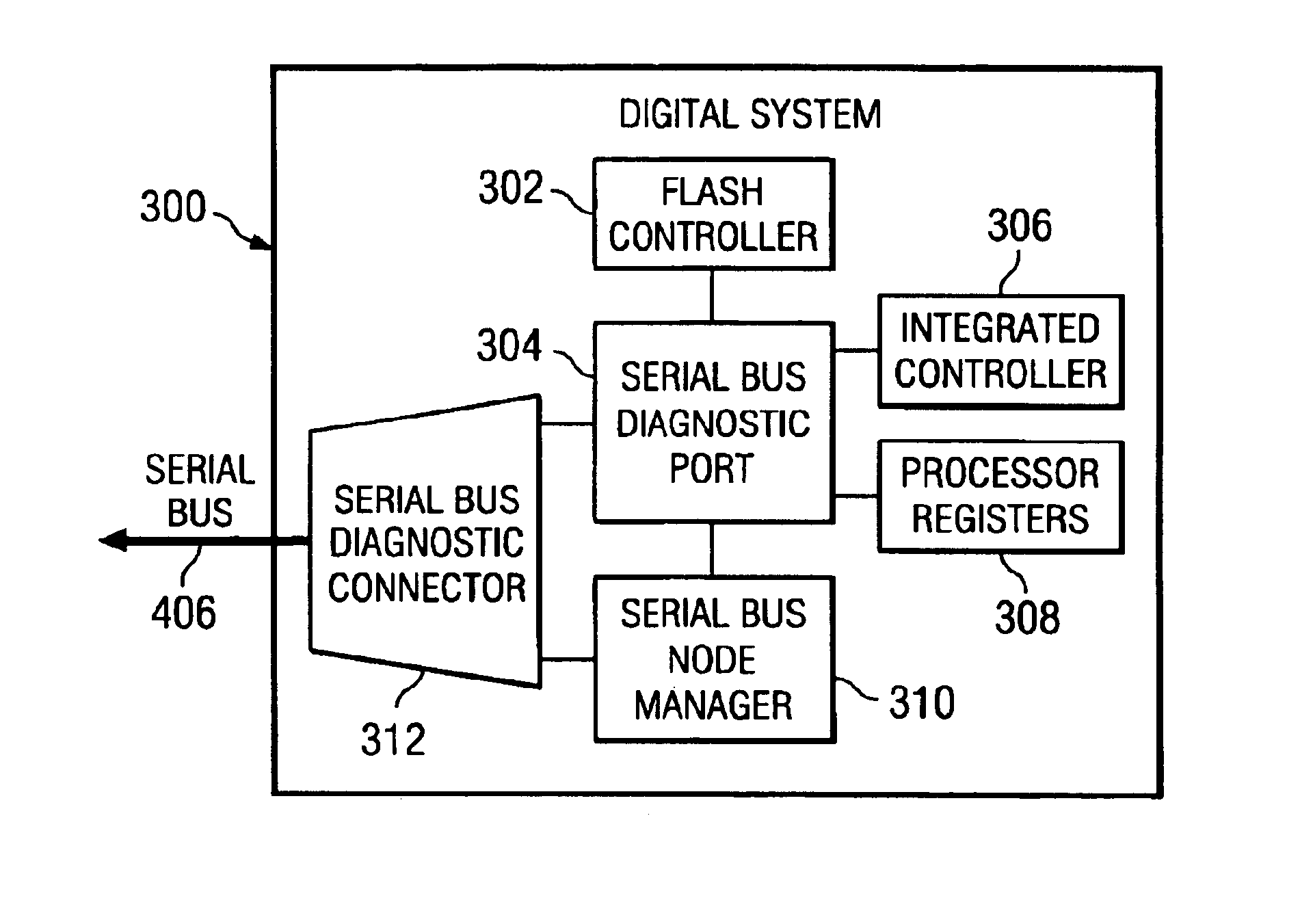

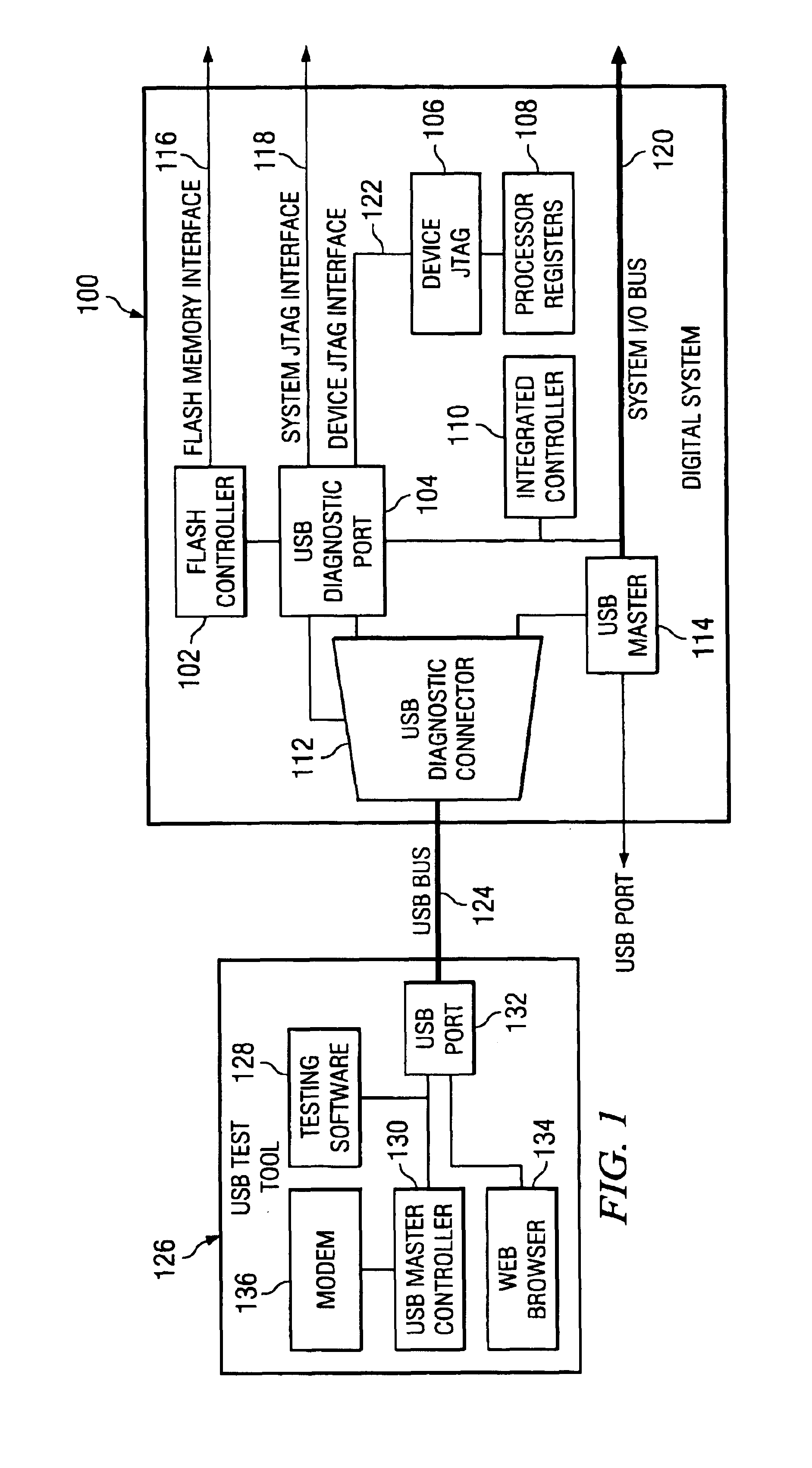

Serial bus diagnostic port of a digital system

InactiveUS6732301B1Error detection/correctionEmergency protective arrangements for automatic disconnectionSoftware developmentFlash memory controller

A digital system provides a serial bus diagnostic port such as, for example, a universal serial bus (USB) diagnostic port. The USB diagnostic port can include a USB slave device operable to interface to a universal serial bus, a flash memory controller interface coupled to the USB slave device and operable to interface to a flash memory controller, and a test access port controller coupled to the USB slave device and operable to interface to a test access port. The diagnostic port can further include a system interface coupled to the USB slave device and operable to interface to an integrated controller independently of an operating system. Via the diagnostic port, a USB testing tool with testing software can access and debug internal logic of the digital system. As an alternative to a USB diagnostic port, the serial bus diagnostic port can be implemented in a variety of wired or wireless implementations such as, for example, an I.E.E.E. 1394 diagnostic port, an Ethernet diagnostic port, or a wireless Internet diagnostic port. Further, the serial bus diagnostic port can, for example, be used for software development, in-factory testing or in-field diagnostics of the digital system.

Owner:HEWLETT PACKARD DEV CO LP

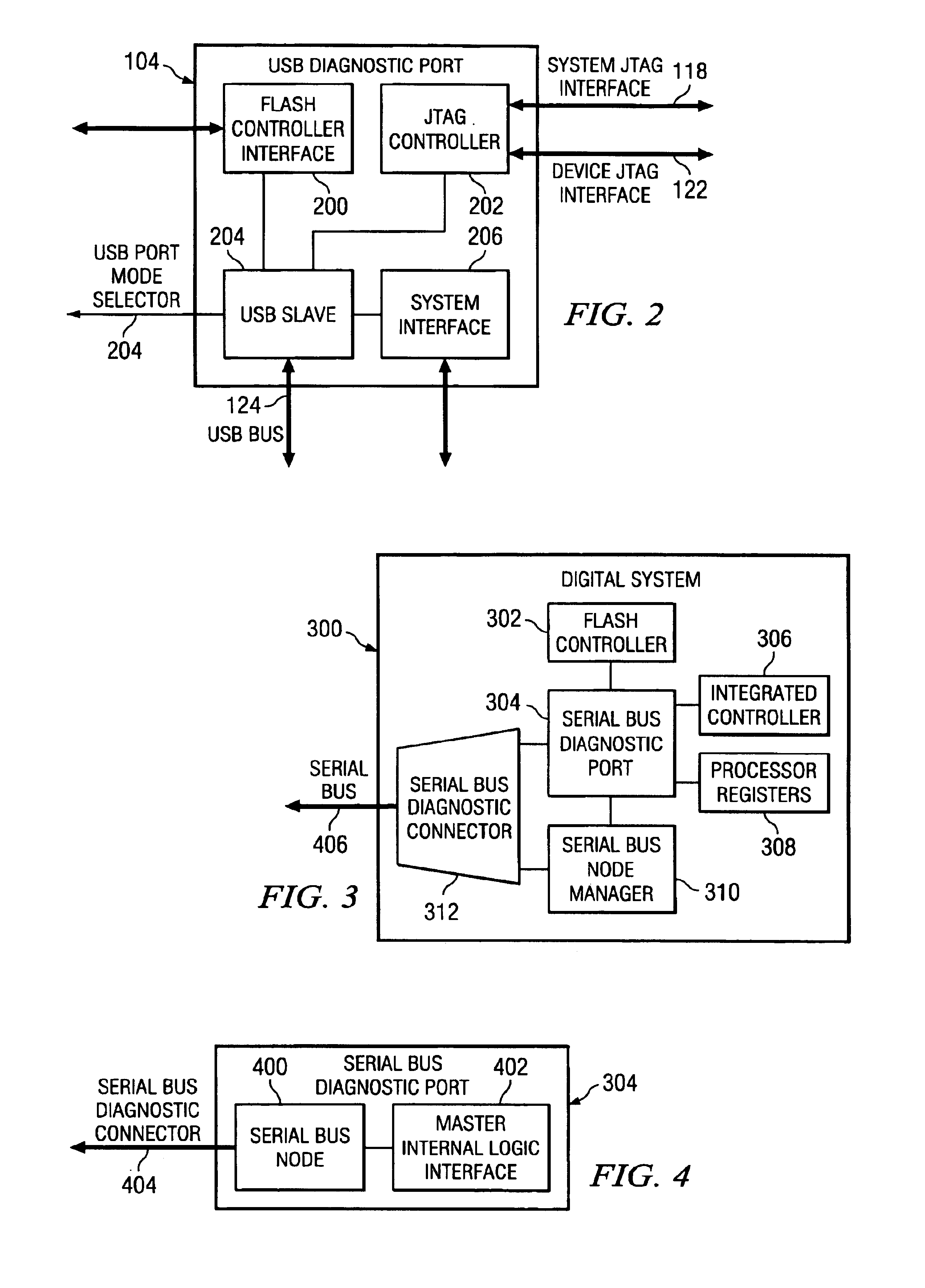

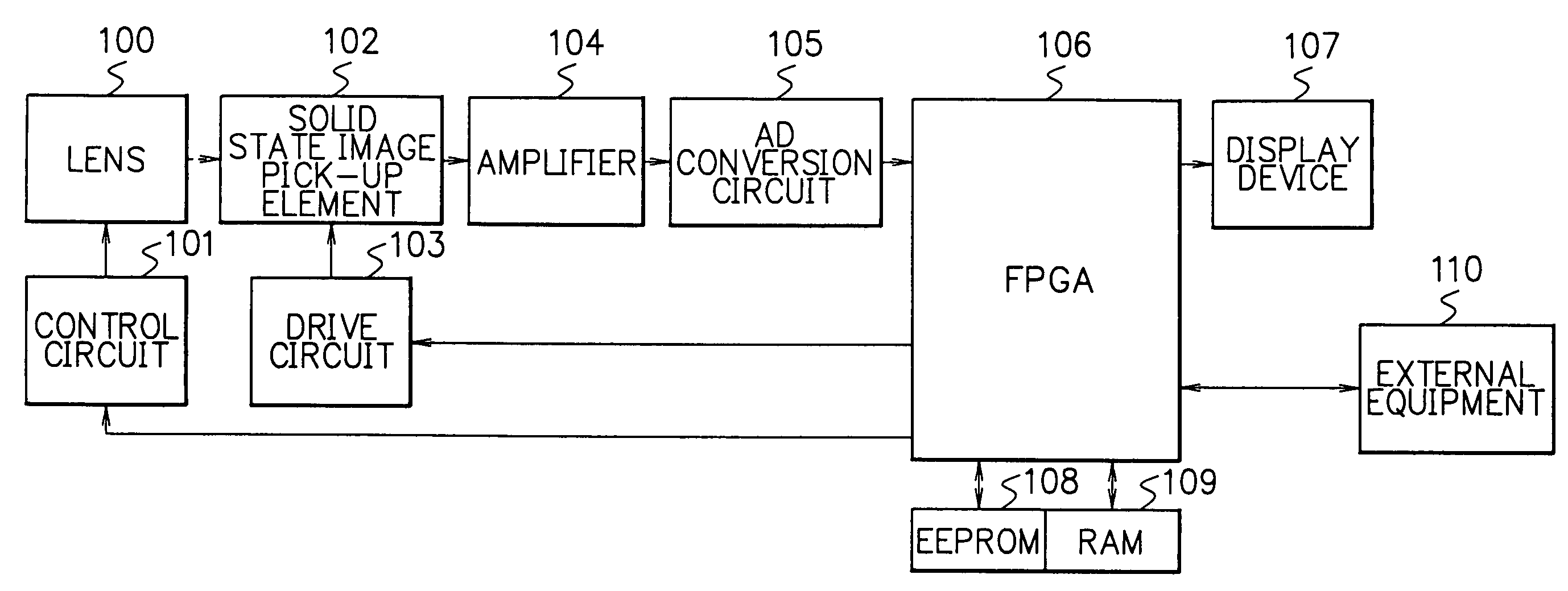

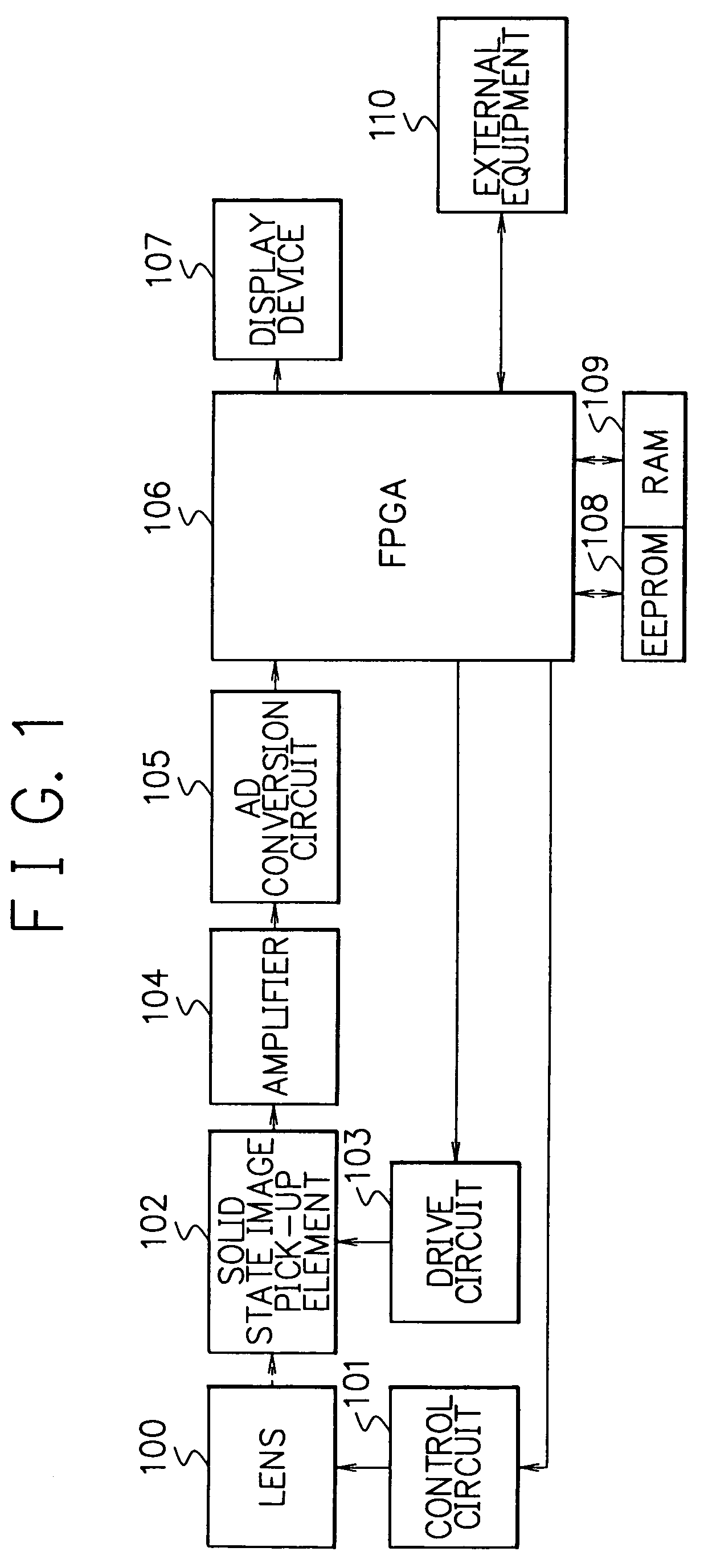

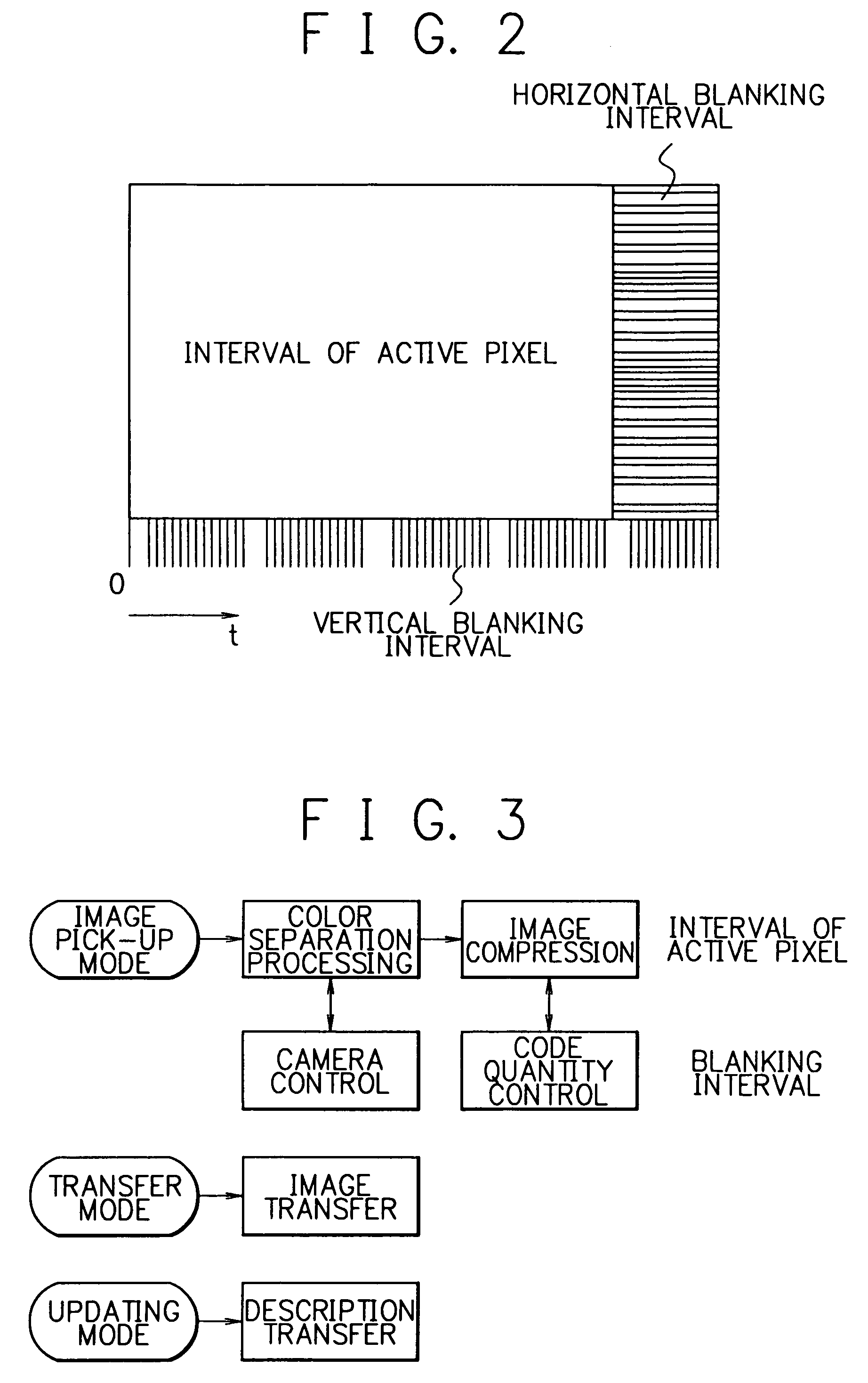

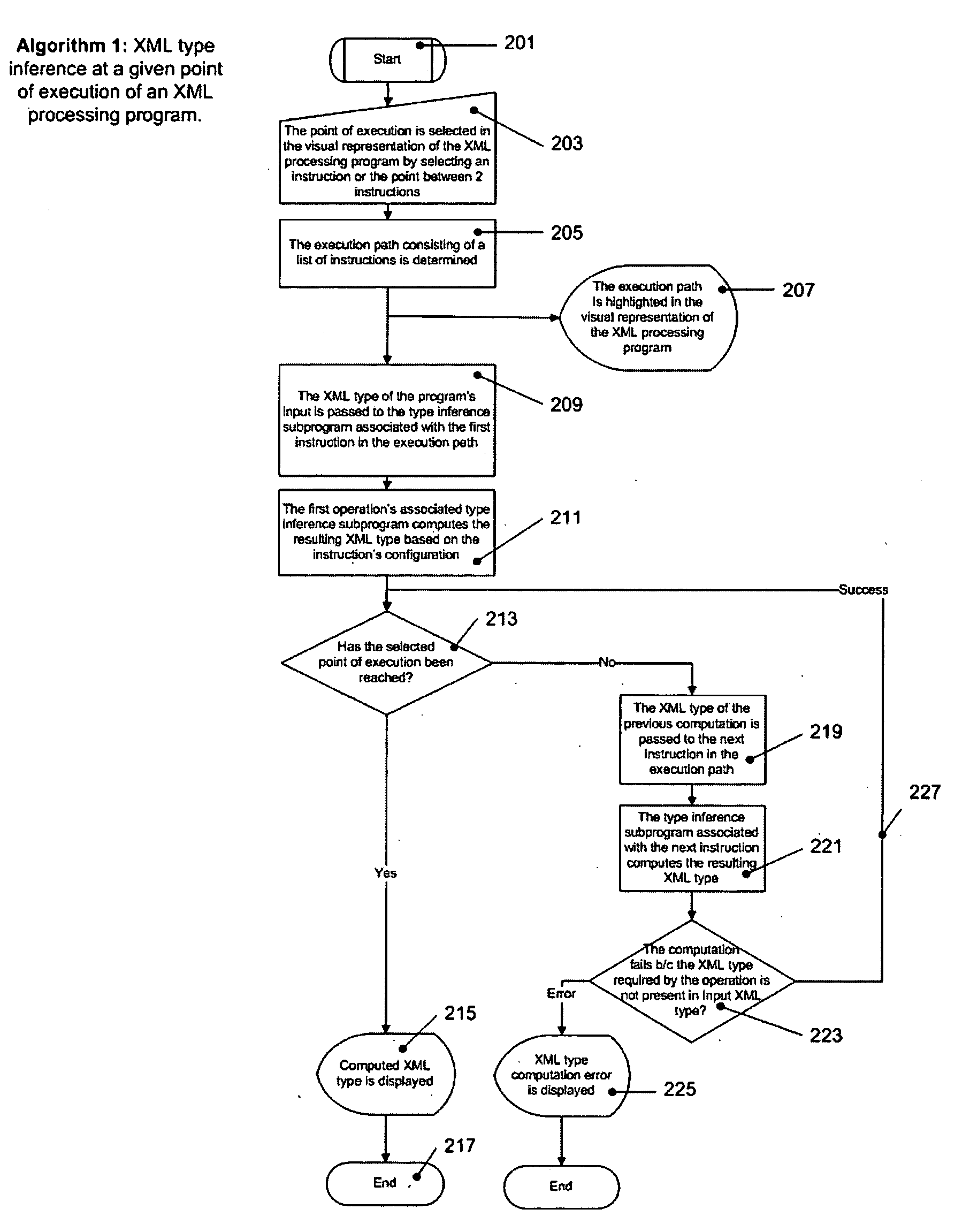

Image processing system

InactiveUS7142731B1Dissipation power is smallTelevision system detailsPulse modulation television signal transmissionDigital signal processingImaging processing

An image processing system whose circuit size is small, and whose dissipation power is small is provided. The image processing system executes digital image processing of an interval of active pixel in the condition that a first internal logic description is written in a field programmable gate array. Subsequently, in interval of non-active pixel with the exception of the interval of active pixel, the image processing system executes digital control processing in the condition that the first internal logic description of the field programmable gate array is rewritten to a second internal logic description. The image processing system executes again the digital image processing in the condition that the second internal logic description of the field programmable gate array is rewritten to the first internal logic description.

Owner:NEC CORP

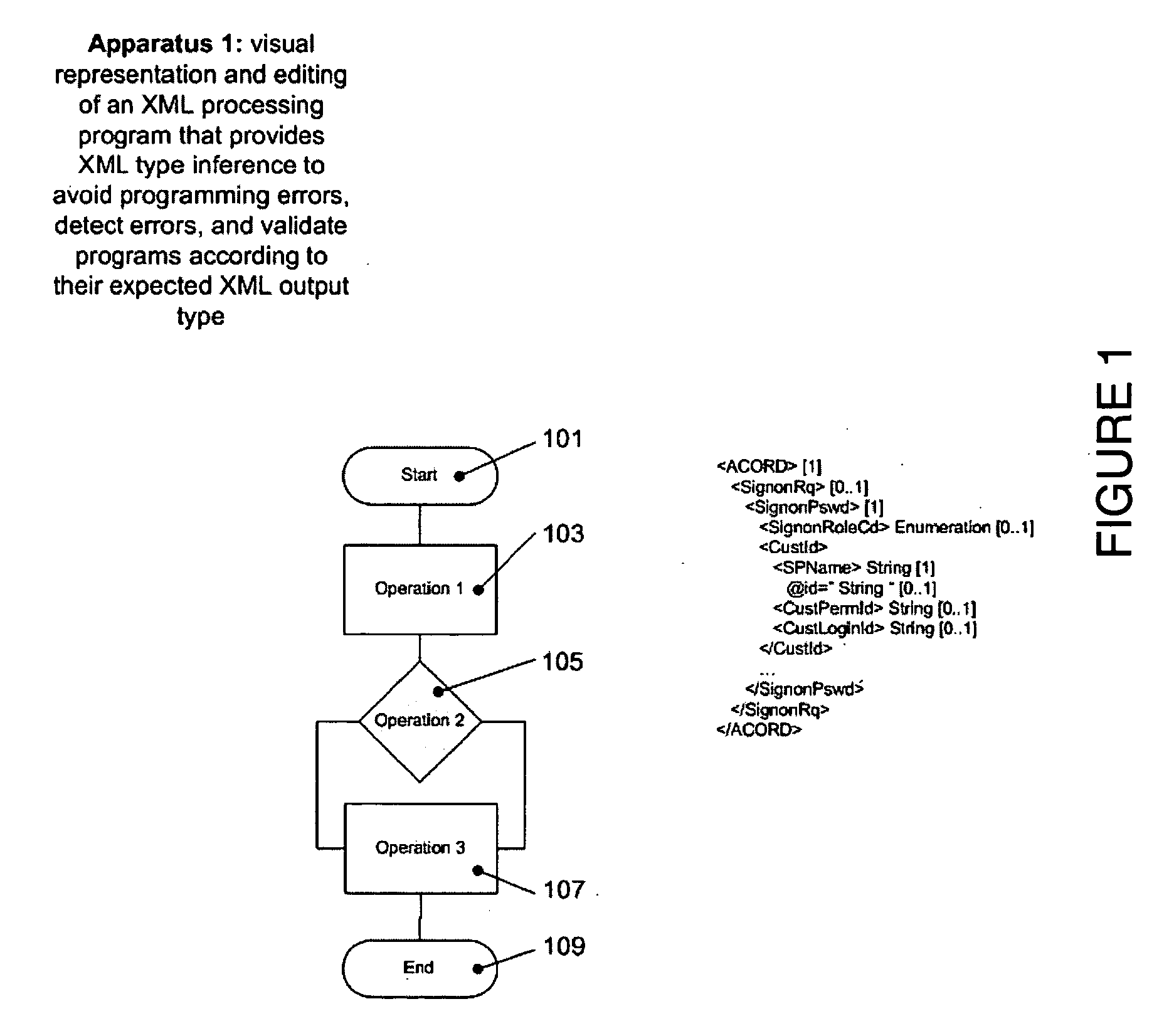

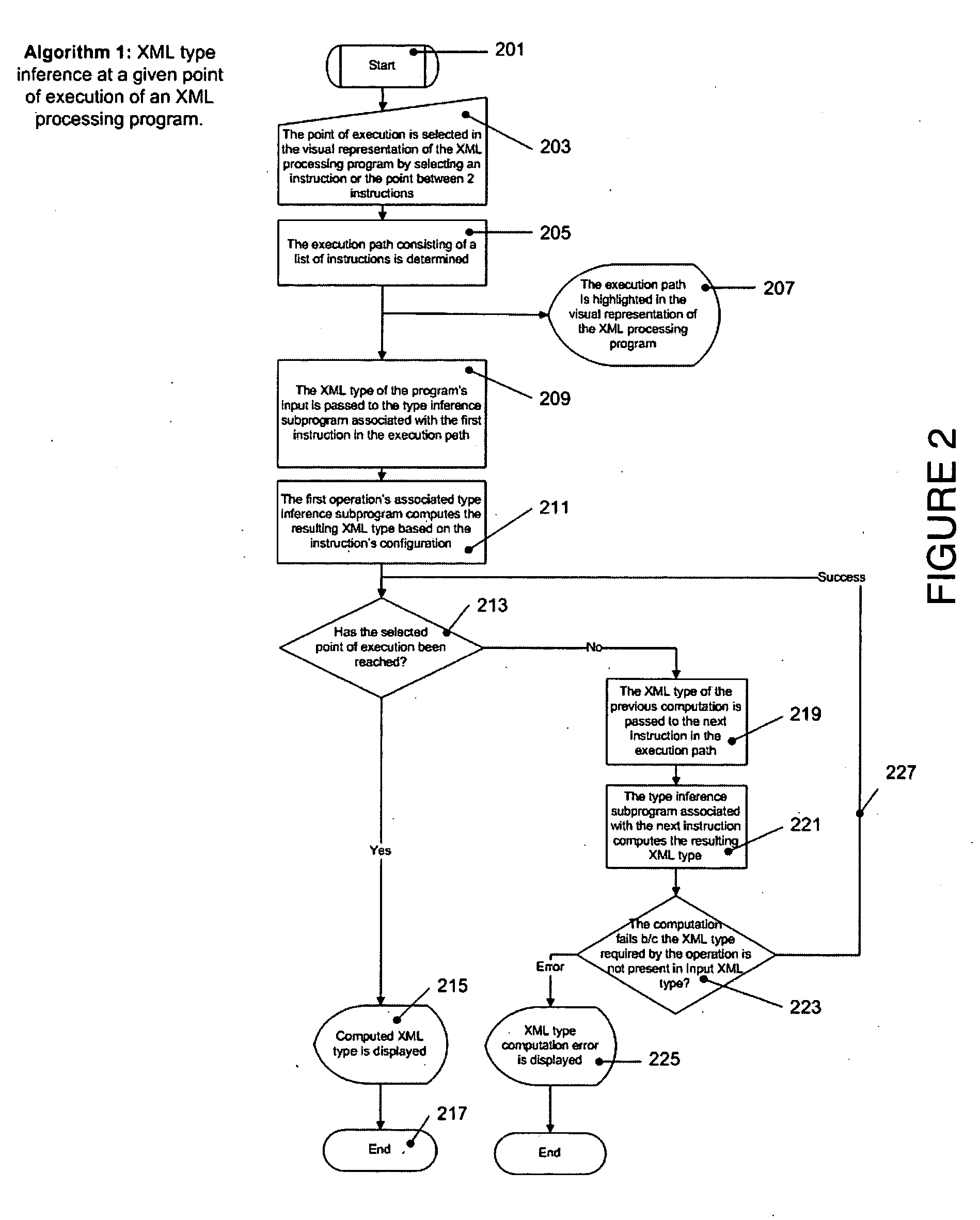

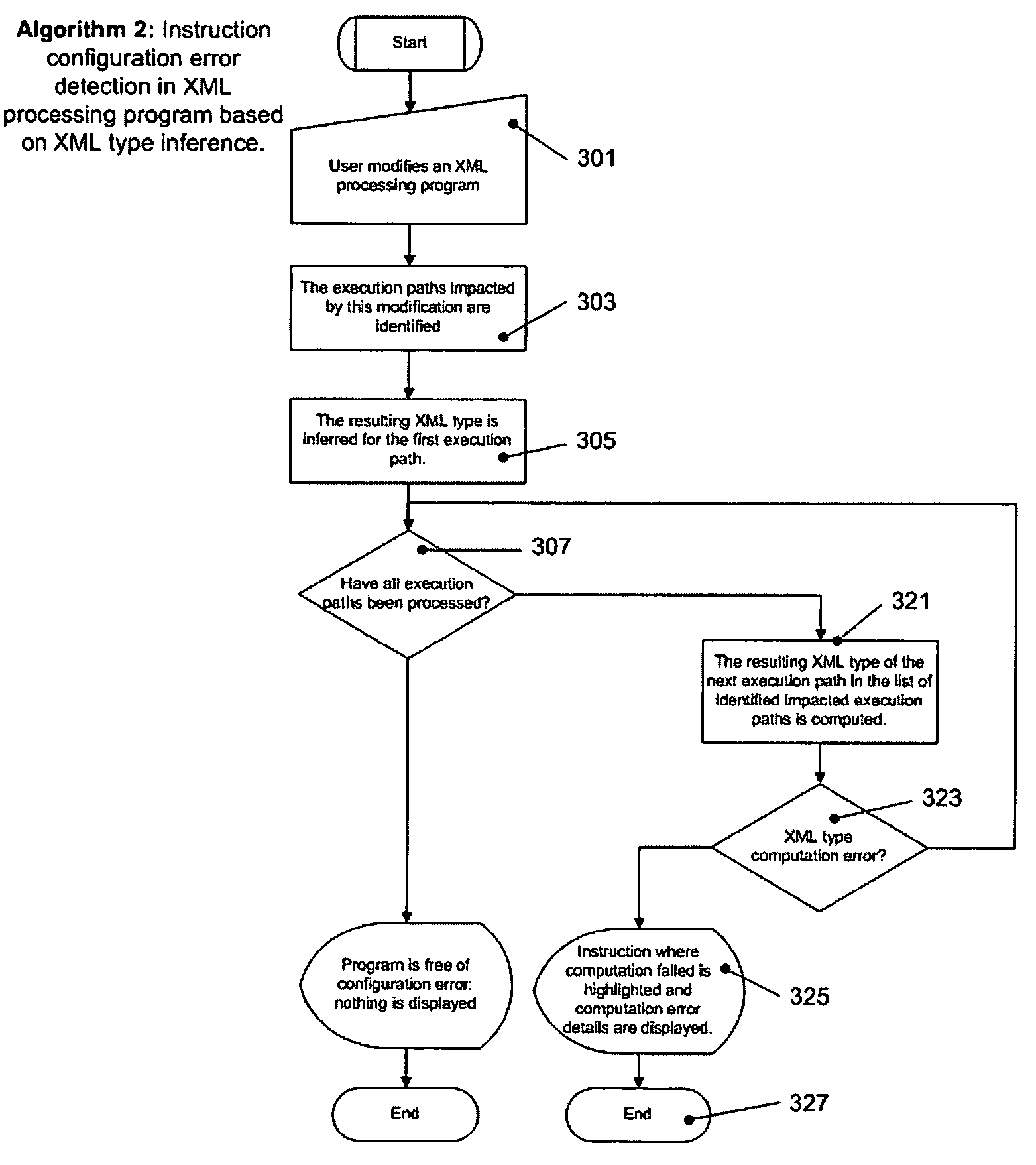

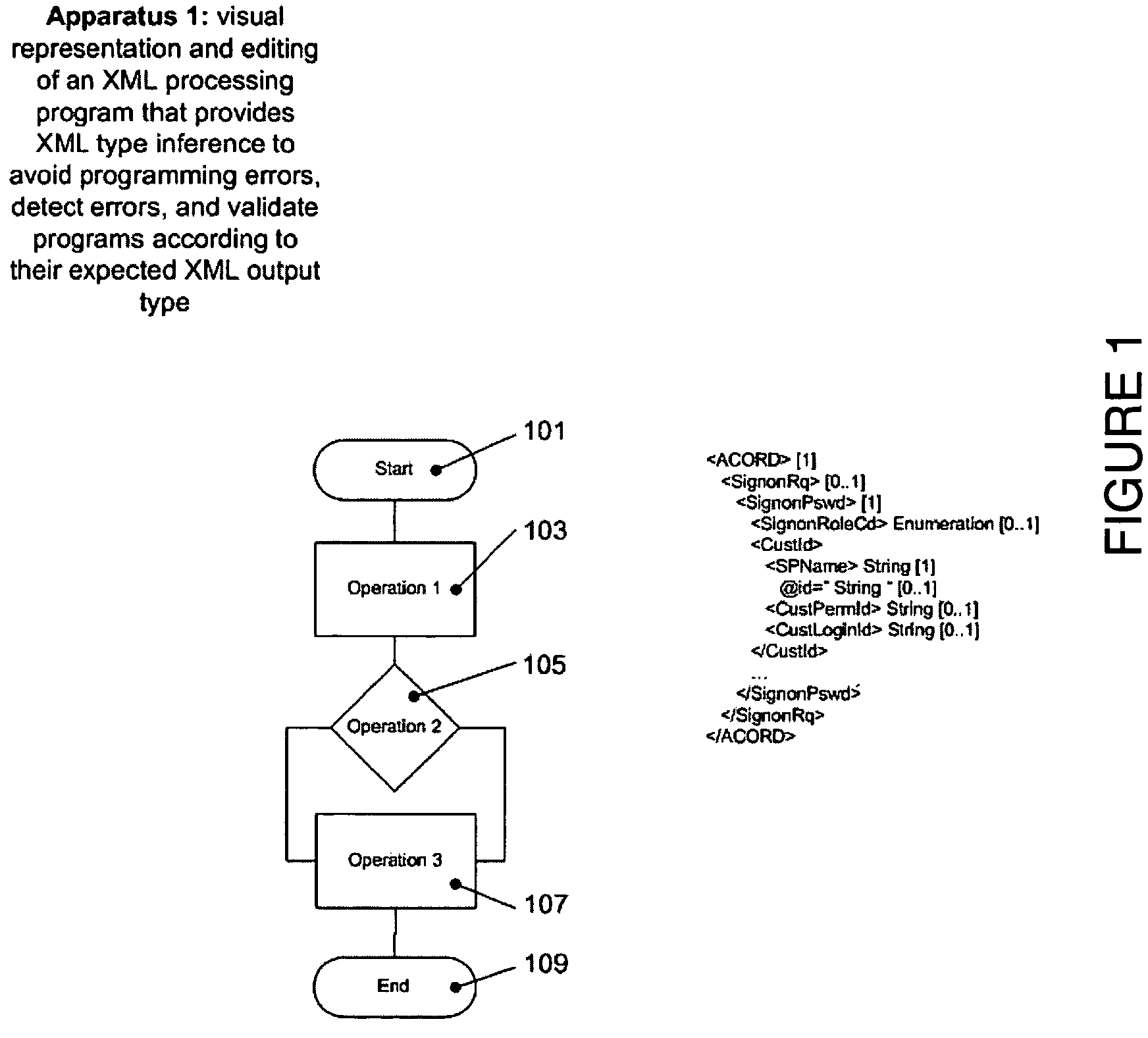

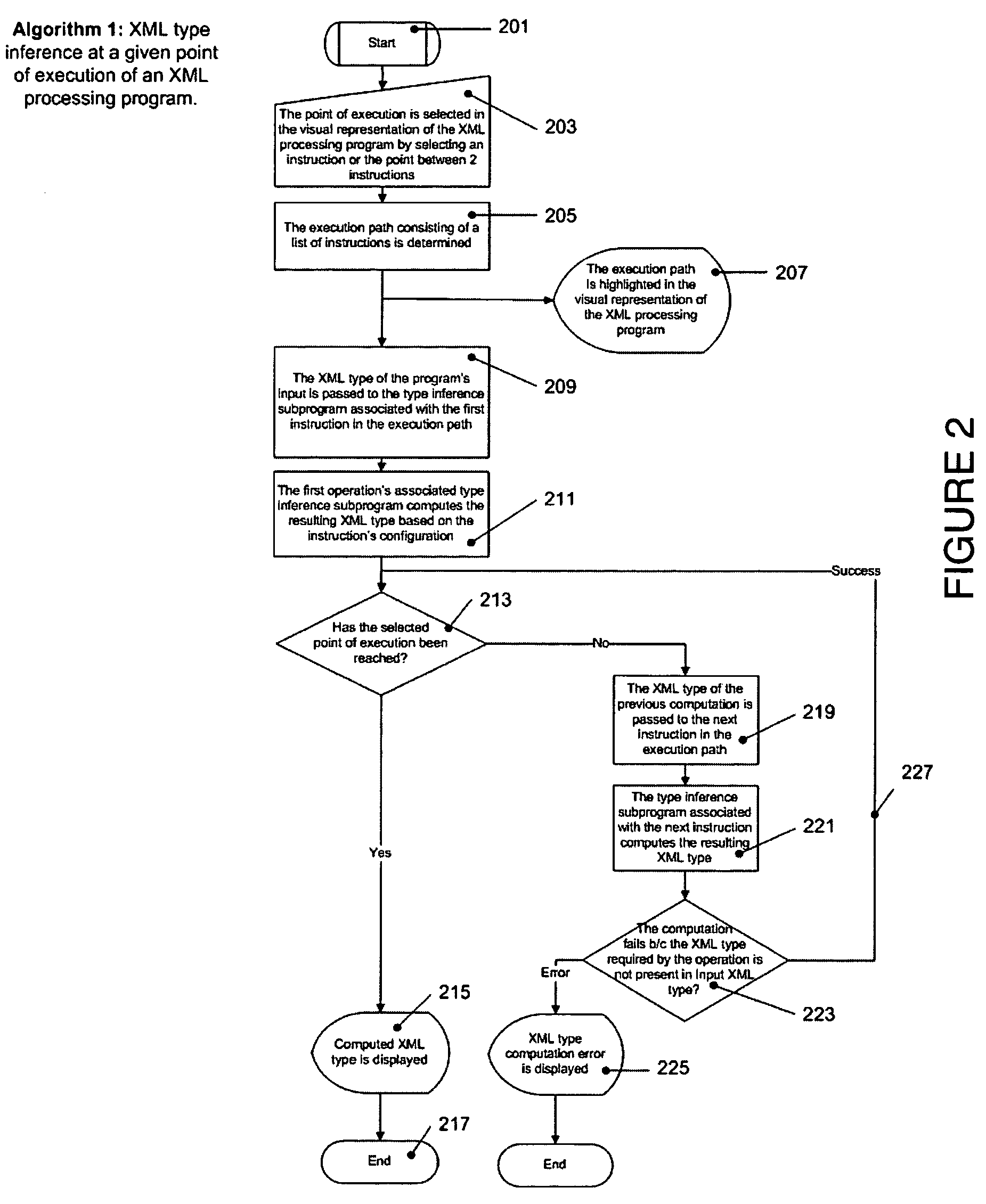

Graphical XML programming system and engine where XML processing programs are built and represented in a graphical fashion

ActiveUS20060075387A1Fix bugsDesign errorNatural language data processingVisual/graphical programmingChange managementWeb service

A system and methods are provided for operating and building graphically XML processing programs, guiding the user in development of the program, preventing and detecting development errors as the program is being designed, ensuring that the program is valid, i.e. satisfies required input and output constraints at all times, i.e. from the time it is developed to when it is deployed in a production environment, ensuring the automated change management if the internal logic of the Web service, or data sources called by the service or the schema that underlies the Web service are modified. The system includes a graphical XML Programming system where XML processing programs are built and represented in a graphical fashion, a real-time metadata computation and visualization method for each selected execution point in the visual program that provides guided programming, error prevention and detection, and change impact analysis and change management, and, an automated execution path exploration method that enables overall program validation and error identification. The system and methods allow a user to reduce by at least a factor of 2 the costs of development and maintenance of reliable XML processing programs such as Web Services.

Owner:DIEBOLD NIXDORF

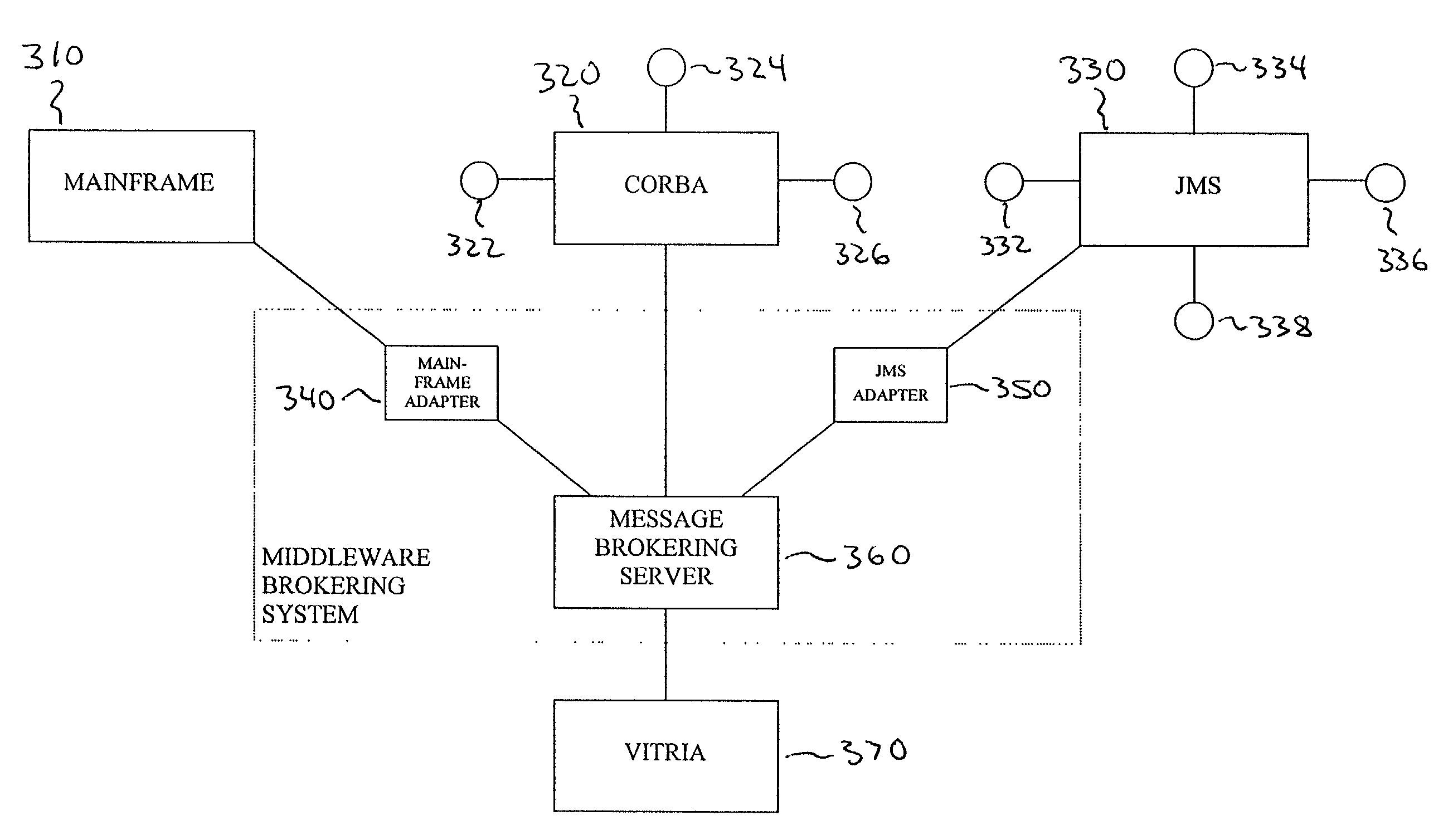

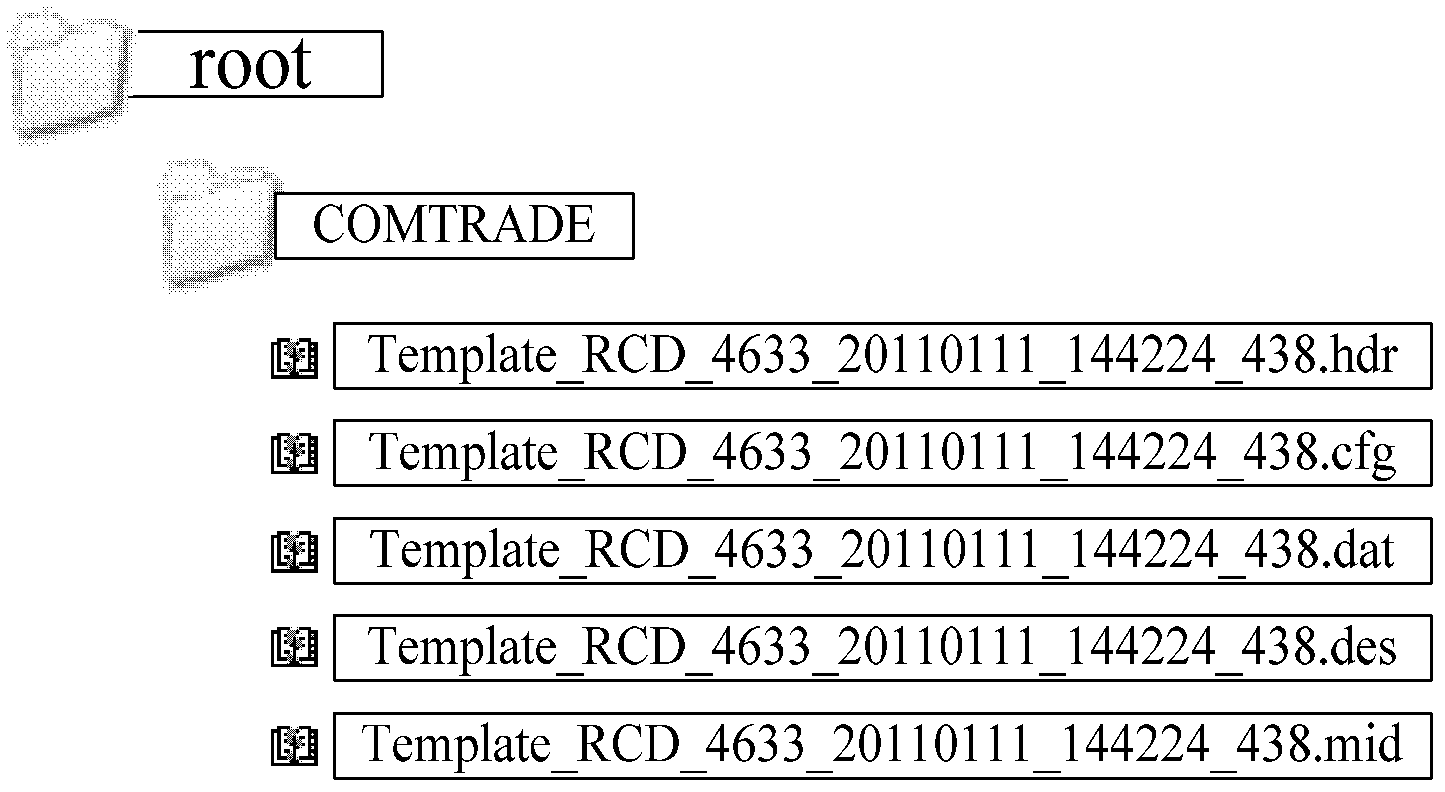

Middleware brokering system

InactiveUS7216181B1Minimize the numberReduces vendor dependencyMultiple digital computer combinationsData switching networksPublish–subscribe patternSyntax

The present invention, known as the Middleware Brokering System, brokers messages between middleware computing products. Each middleware service can send data to the Middleware Brokering System in its native data format and programming syntax. The Middleware Brokering System converts the data transmitted from the different platforms into a standard format known as a structured event. Messages are then transmitted to and stored in an underlying, commercially available publish / subscribe engine. The Middleware Brokering System contains internal logic that determines whether any subscribers are interested in the messages. If an interested subscriber is found, the Middleware Brokering System retrieves the message from the publish / subscribe engine, converts the data from the structured event into the native format of the receiving application, and sends the message to the appropriate application.

Owner:T MOBILE INNOVATIONS LLC

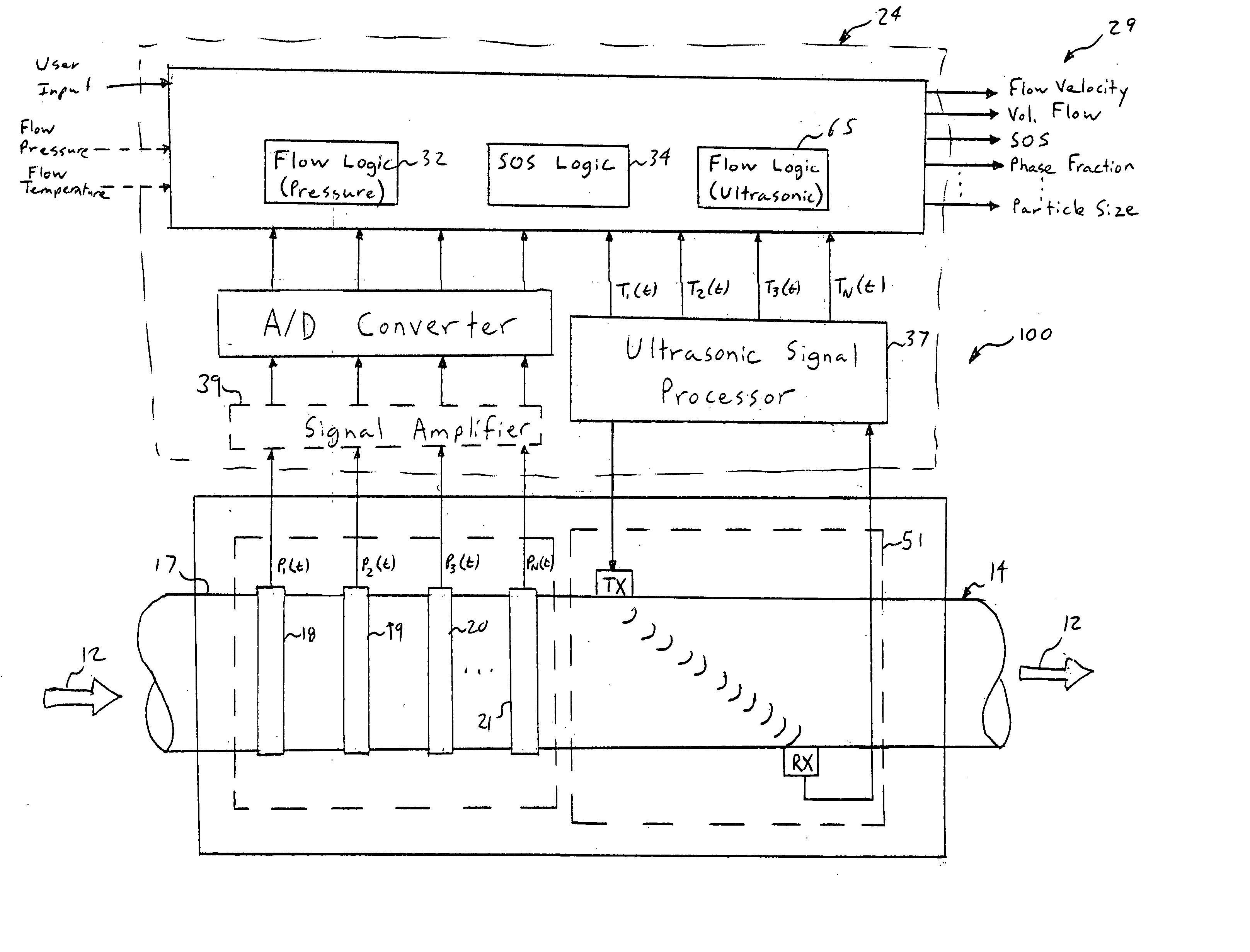

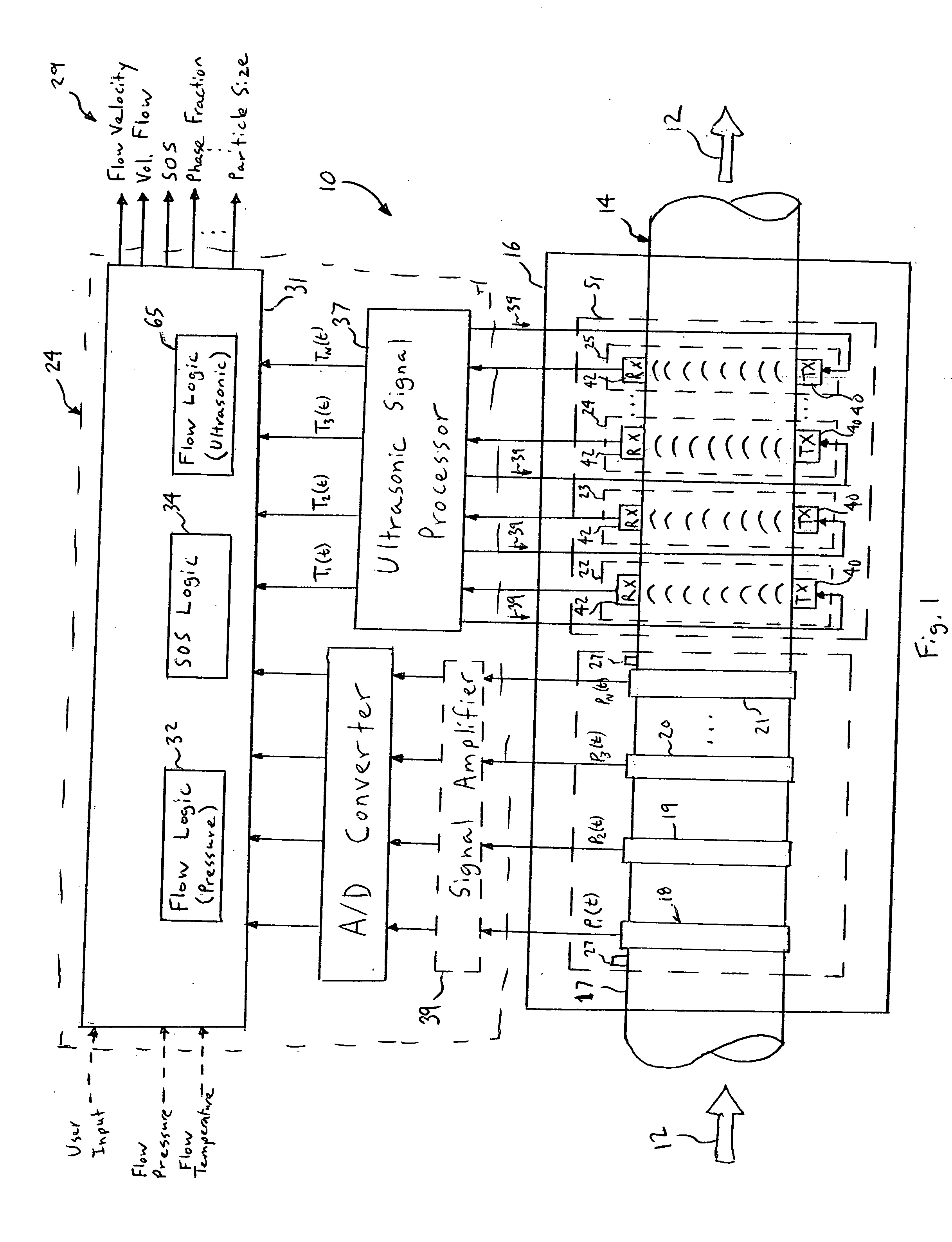

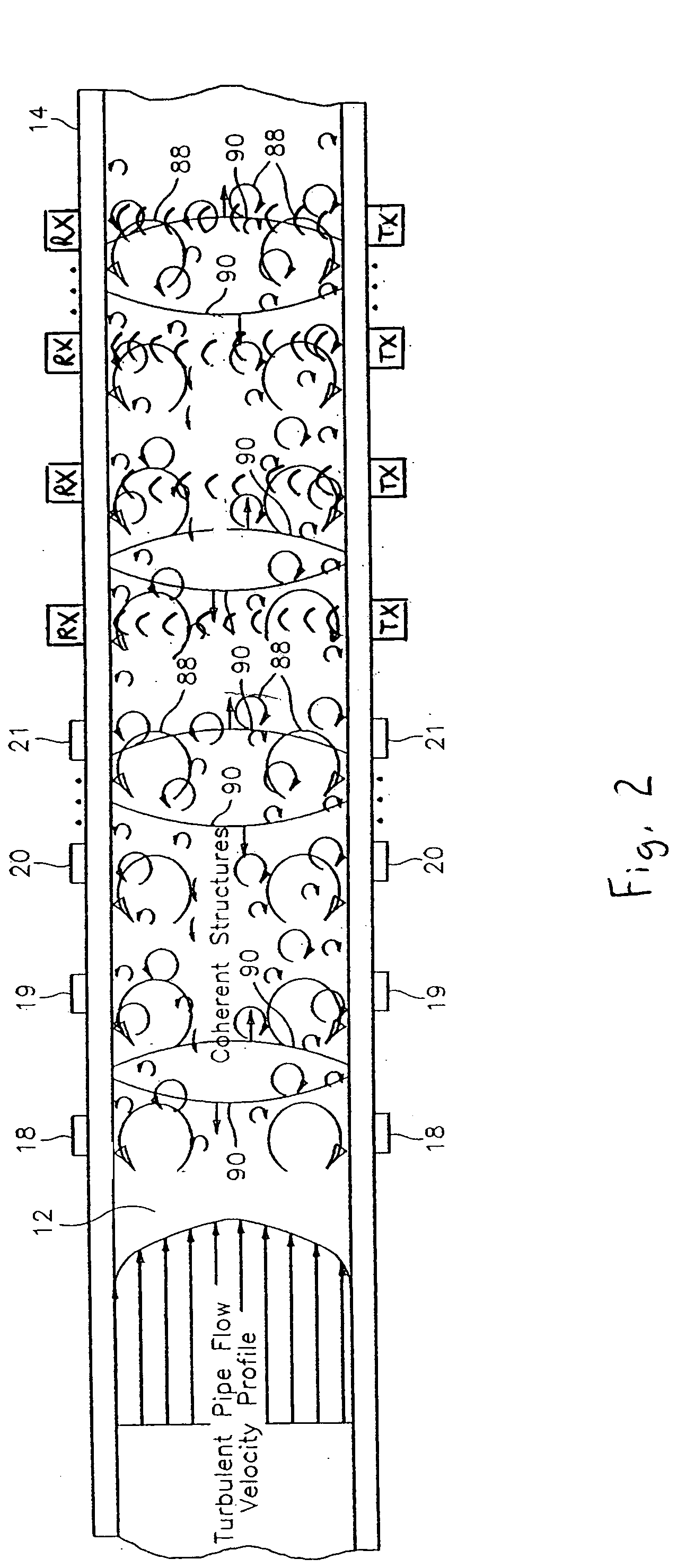

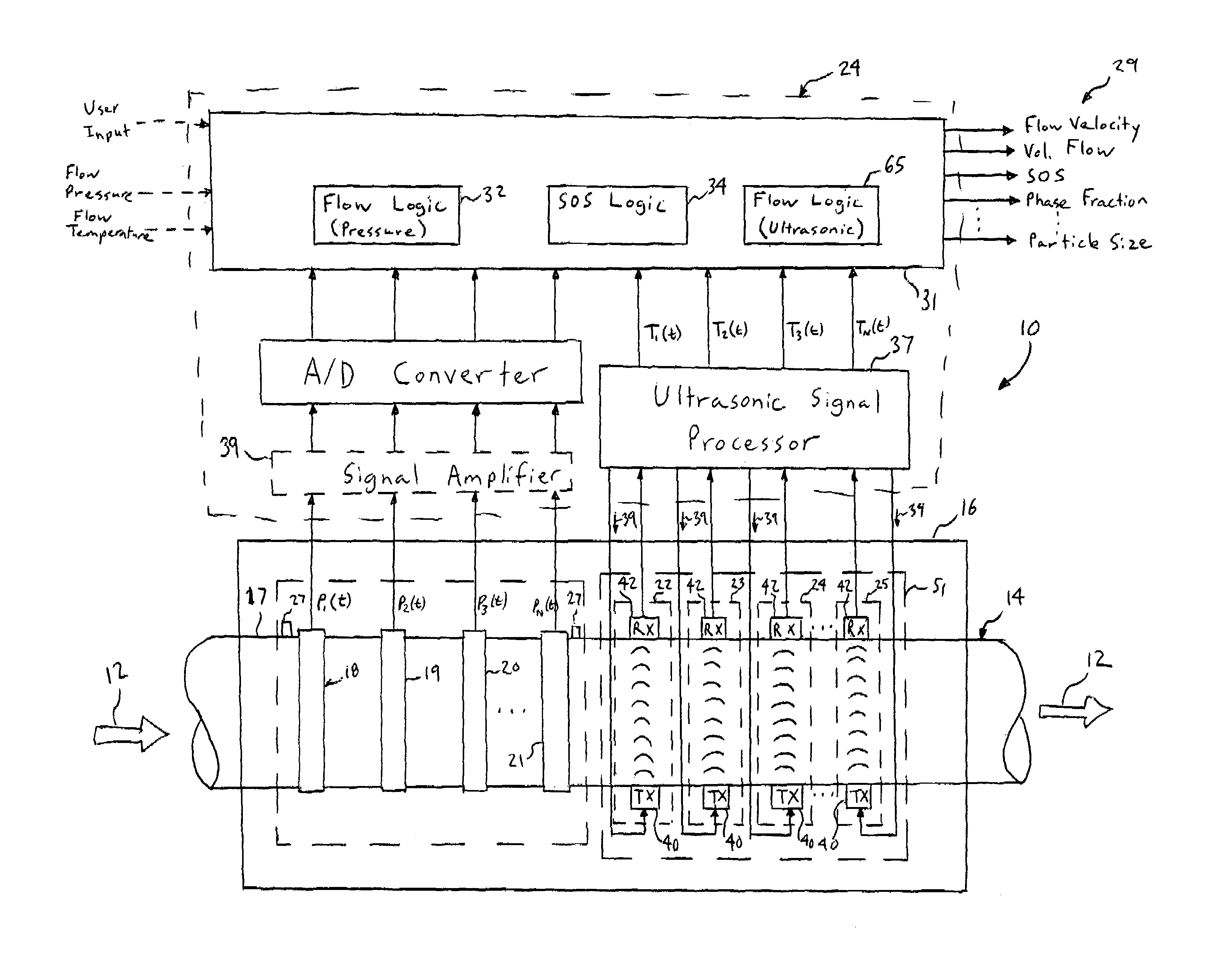

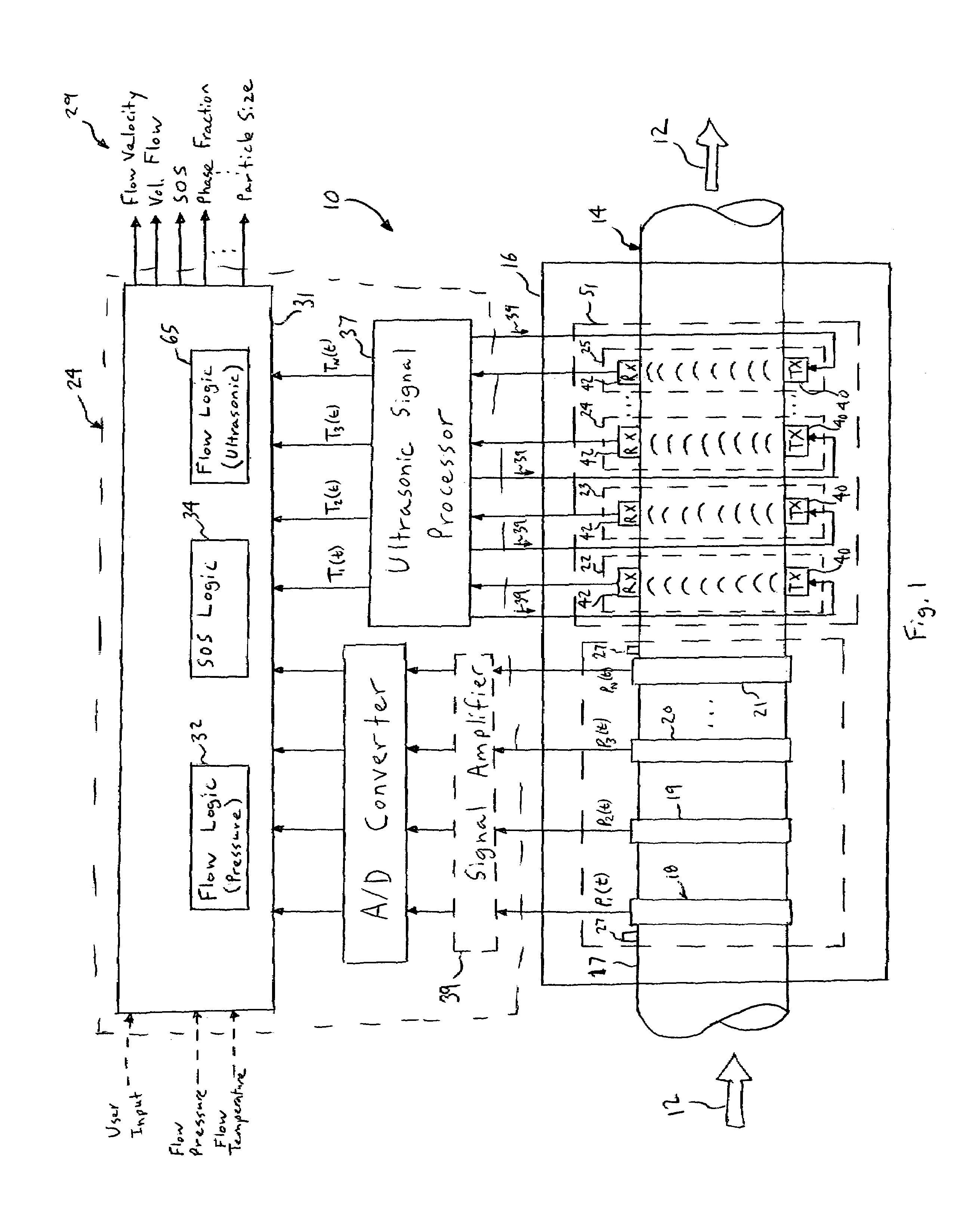

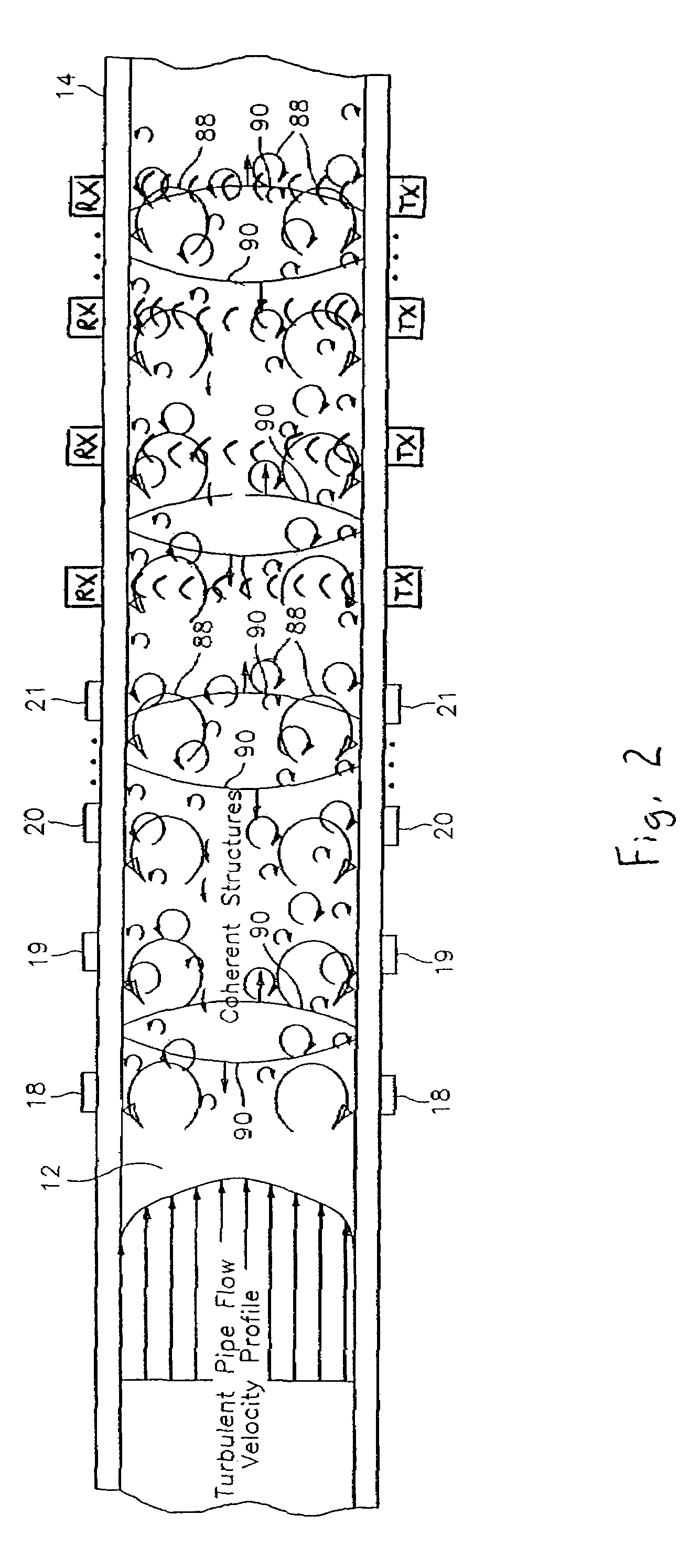

Flow measurement apparatus having strain-based sensors and ultrasonic sensors

ActiveUS20050125170A1More robustMaterial analysis using sonic/ultrasonic/infrasonic wavesVolume/mass flow measurementUltrasonic sensorMeasurement device

A flow measurement apparatus is provided that combines the functionality of an apparatus that uses strain-based sensors and ultrasonic sensors to measure the speed of sound propagating through a fluid flowing within a pipe, and measure pressures disturbances (e.g. vortical disturbances or eddies) moving with a fluid to determine respective parameters of the flow propagating through a pipe. The apparatus includes a sensing device that includes an array of pressure sensors used to measure the acoustic and convective pressure variations in the flow to determine desired parameters and an ultrasonic meter portion to measure the velocity and volumetric flow of the fluid. In response to an input signal or internal logic, the processor can manually or dynamically switch between the pressure sensors and ultrasonic sensors to measure the parameters of the flow. The flow measurement apparatus thereby provides a robust meter capable of measuring fluid flows having a wide range of different characteristics and flows exposed to different environmental conditions.

Owner:EXPRO METERS

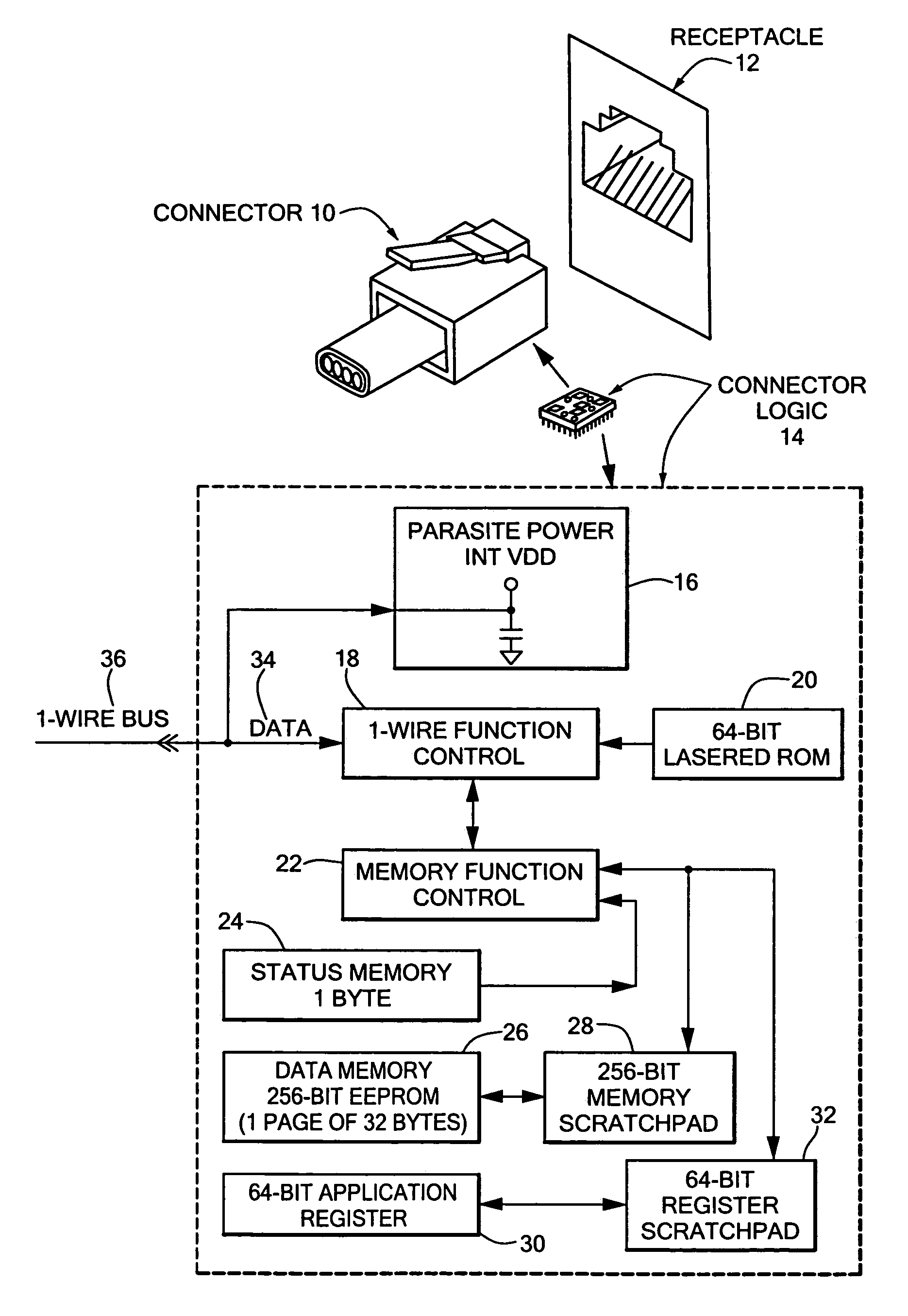

Smart cables

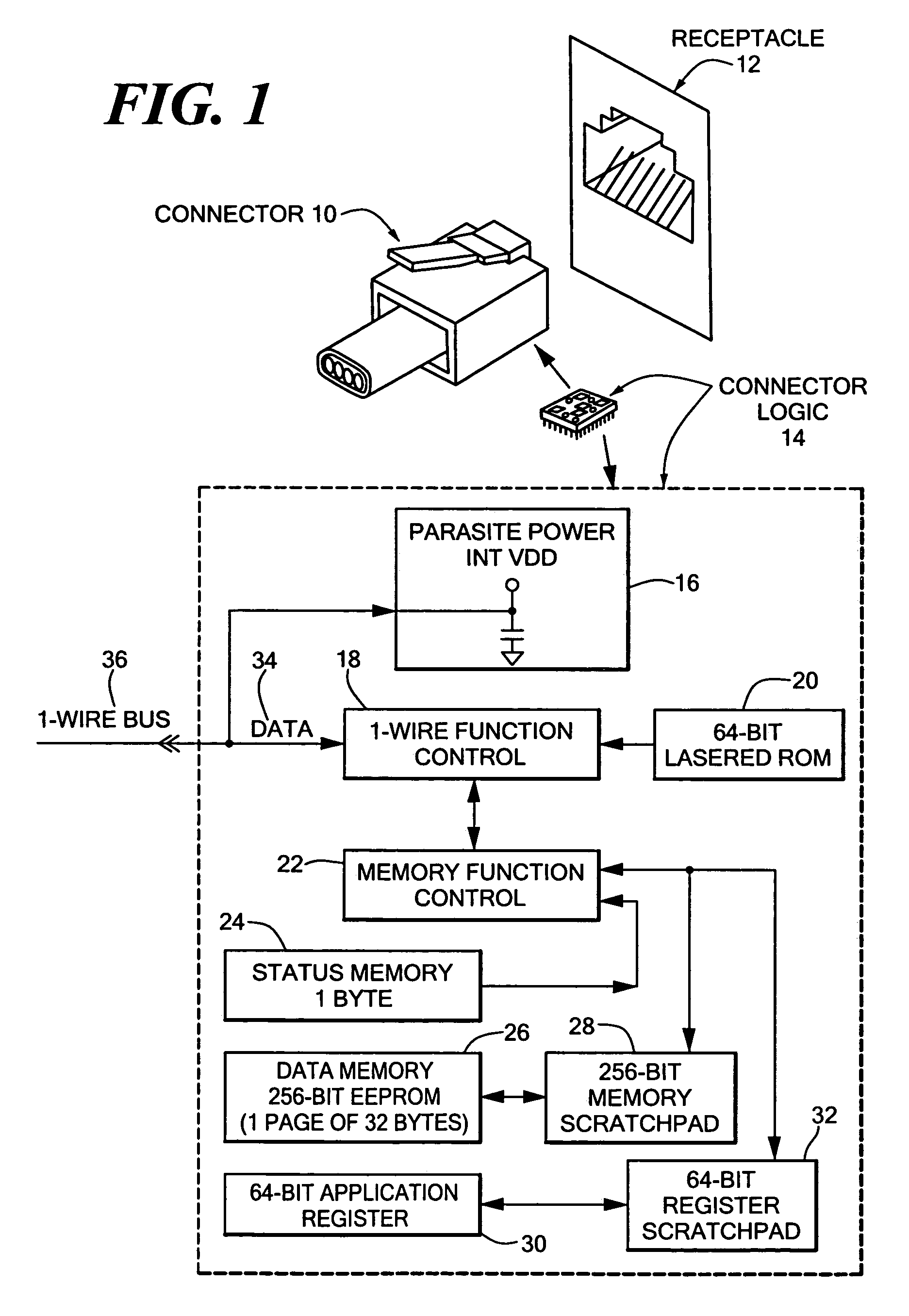

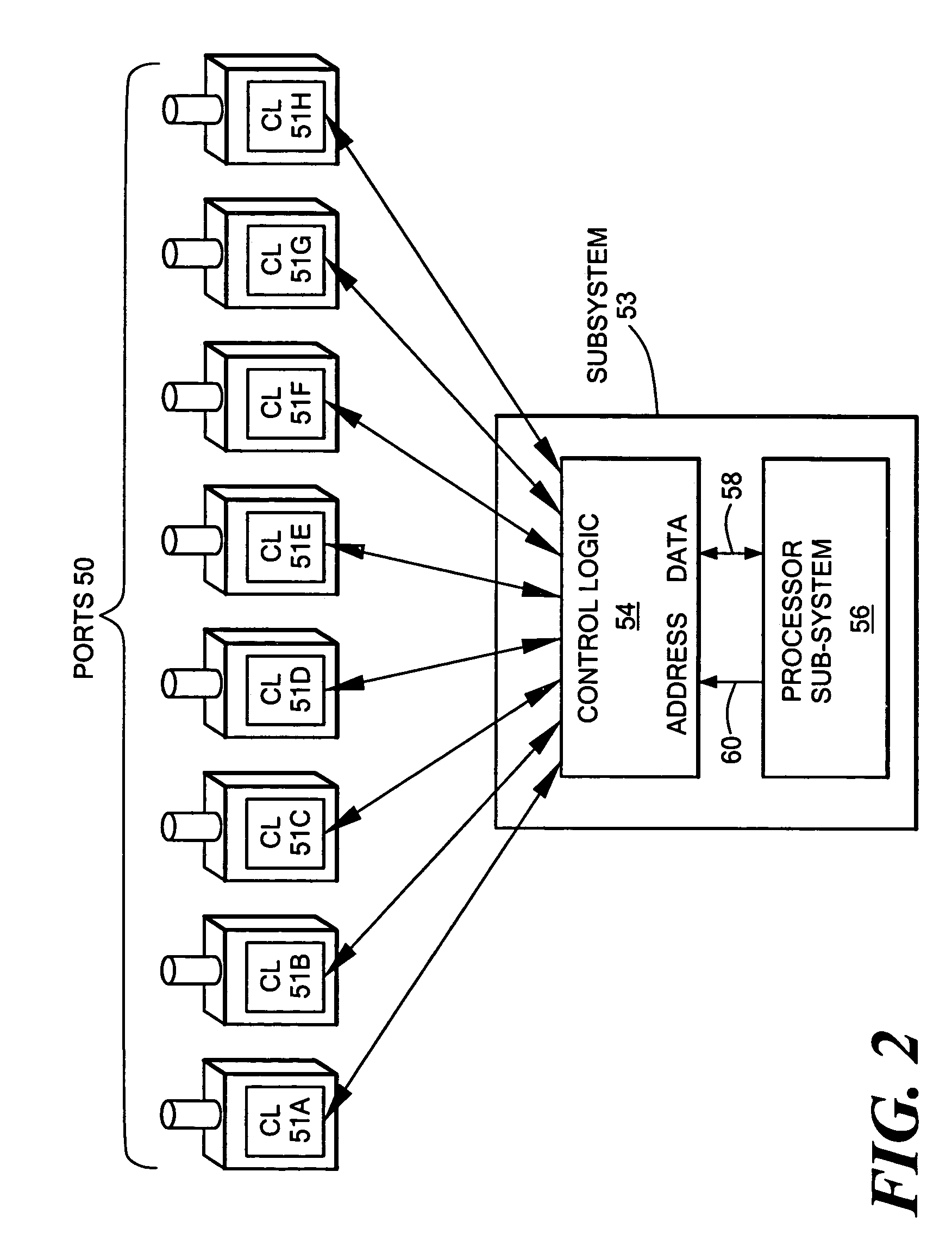

A system for connecting an I / O device to a central system including a cable connector having a memory for storing configuration information such as the type of the I / O device, characteristics of the I / O device, and / or the identity or characteristics of a user associated with the I / O device. Multiple universal slots are each capable of accepting the disclosed cable connector. When the disclosed connector is inserted into one of the slots, the central system operates to automatically detect the presence of the associated I / O device, and to read configuration information from the memory in the connector into memory within the central system. Configuration information read from the connector is used to configure the central system. The central system may use the configuration information from the connector memory to direct data and / or signals between the multiple universal slots and separate internal logic blocks associated with different types of I / O devices. User specific configuration information read by the central system from the connector memory may be used to configure user specific functions, such as, for example, speech recognition. The central system may further write various types of configuration information to the memory in the cable connector. Such information may include user specific characteristics determined during operation of the device, such as user specific speech characteristics.

Owner:QUARTET TECH

Self-directing node

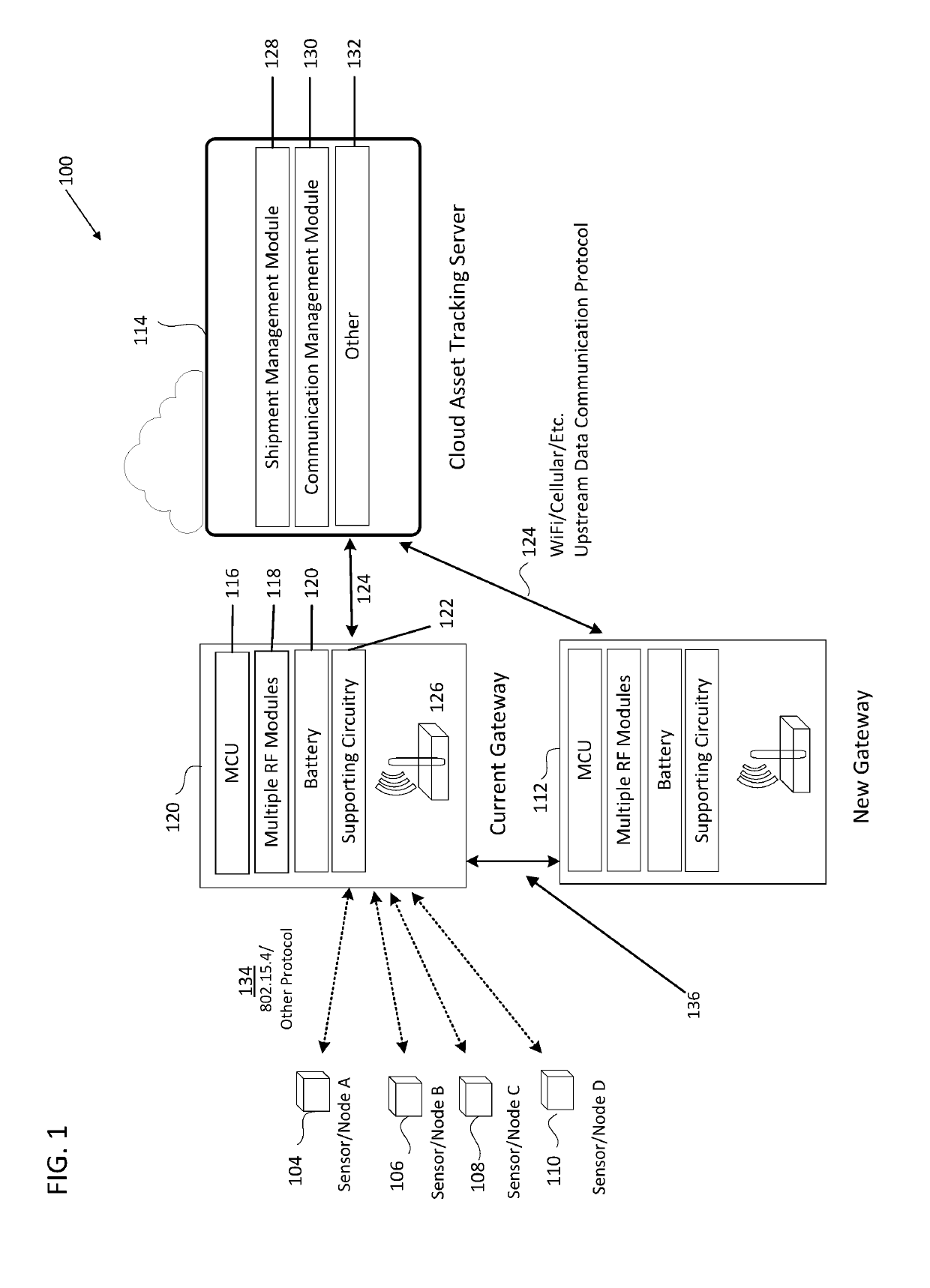

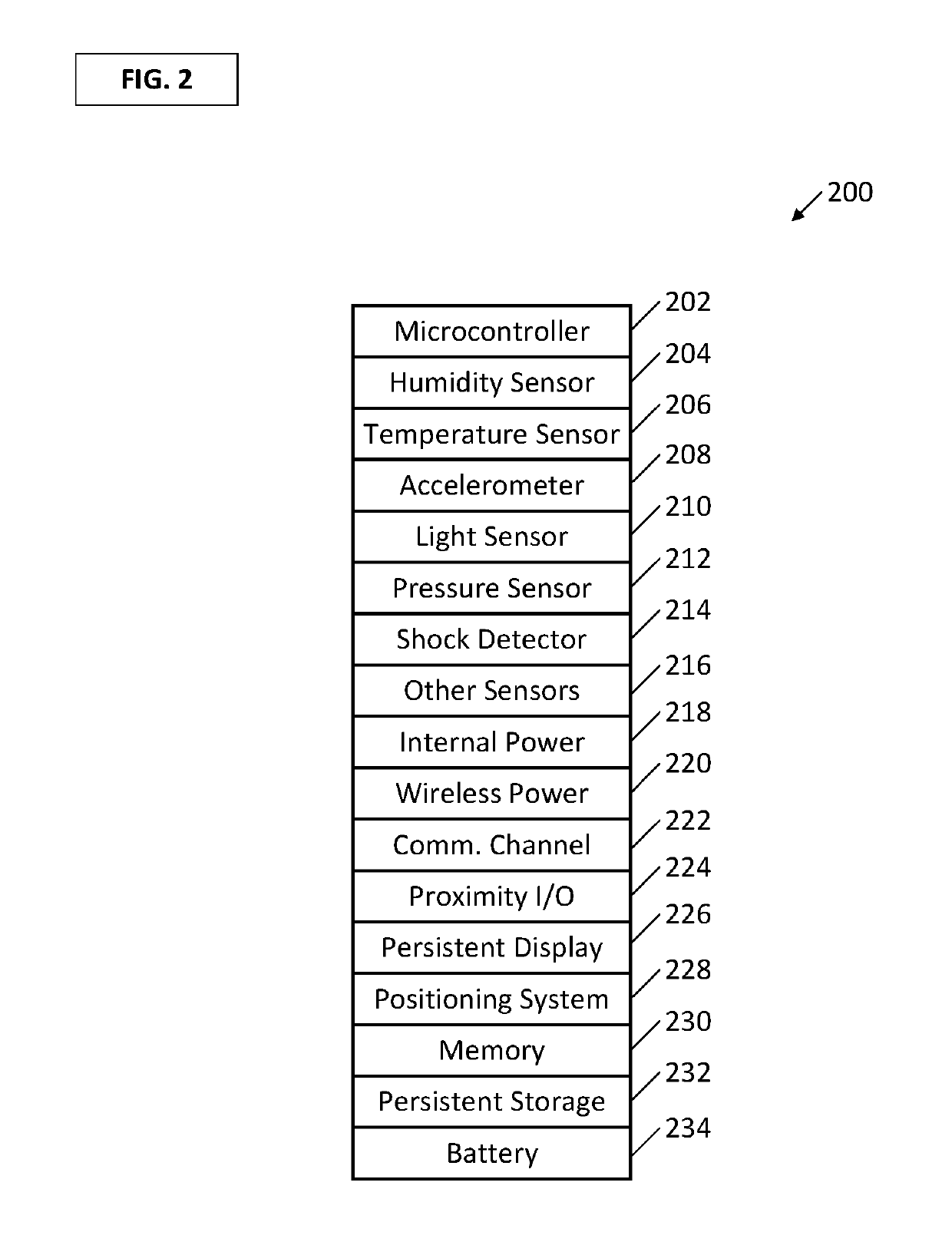

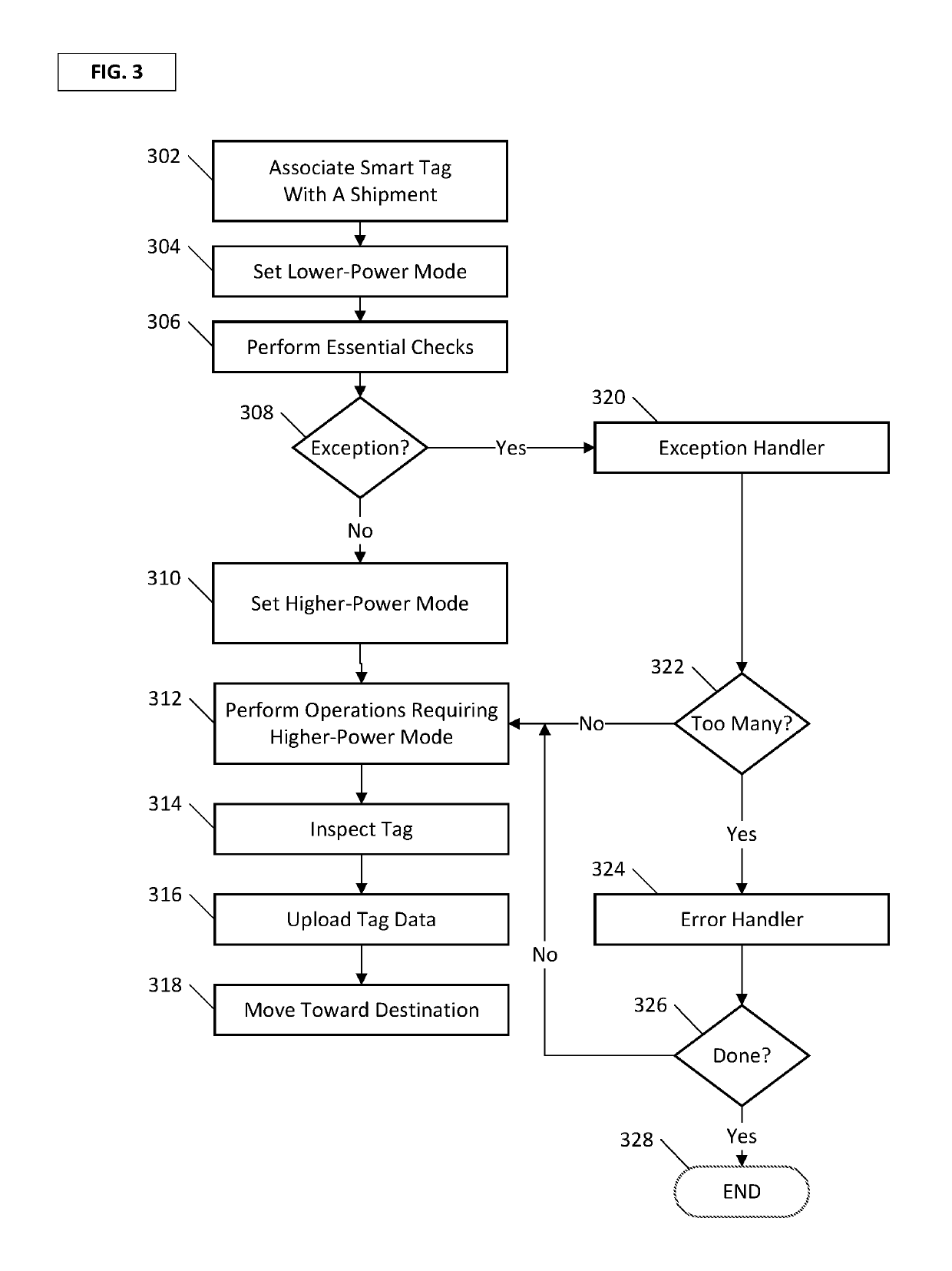

Lost, misplaced, incorrectly delivered, and damaged assets are a common occurrence in shipment or asset tracking. Disclosed are various embodiments concerning a battery-less or intermittent battery use environments in which a node uses internal logic (e.g., circuitry and / or software) that, based at least in part on sensor information and stored information regarding the history of the node, may track events that have occurred to the node. The node may be responsive to events and determine whether exceptions have occurred that require attention. For example, detecting damage might cause the node to update an output to indicate the node and associated material, if any, needs to be rerouted to address the exception.

Owner:INTEL CORP

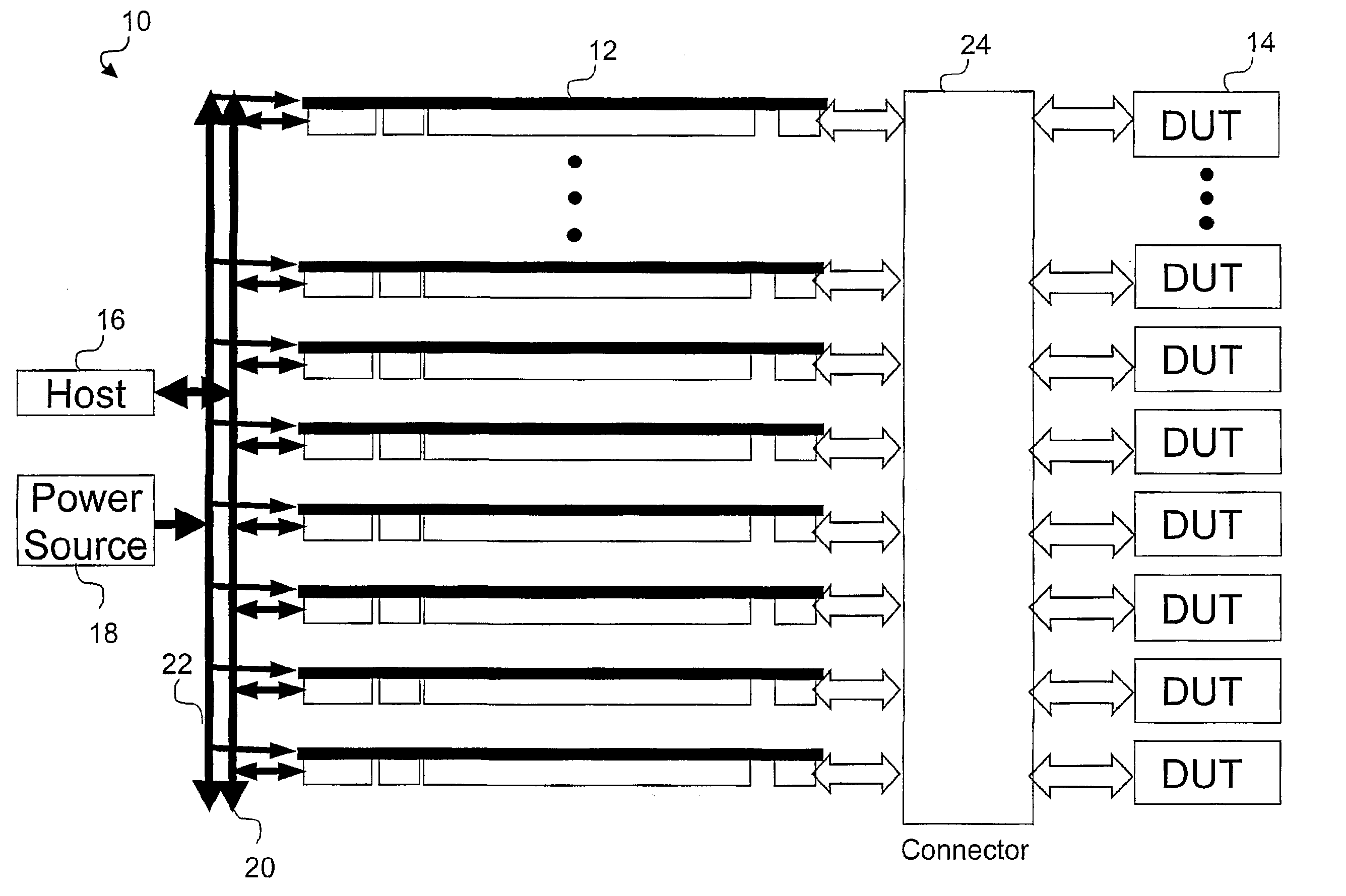

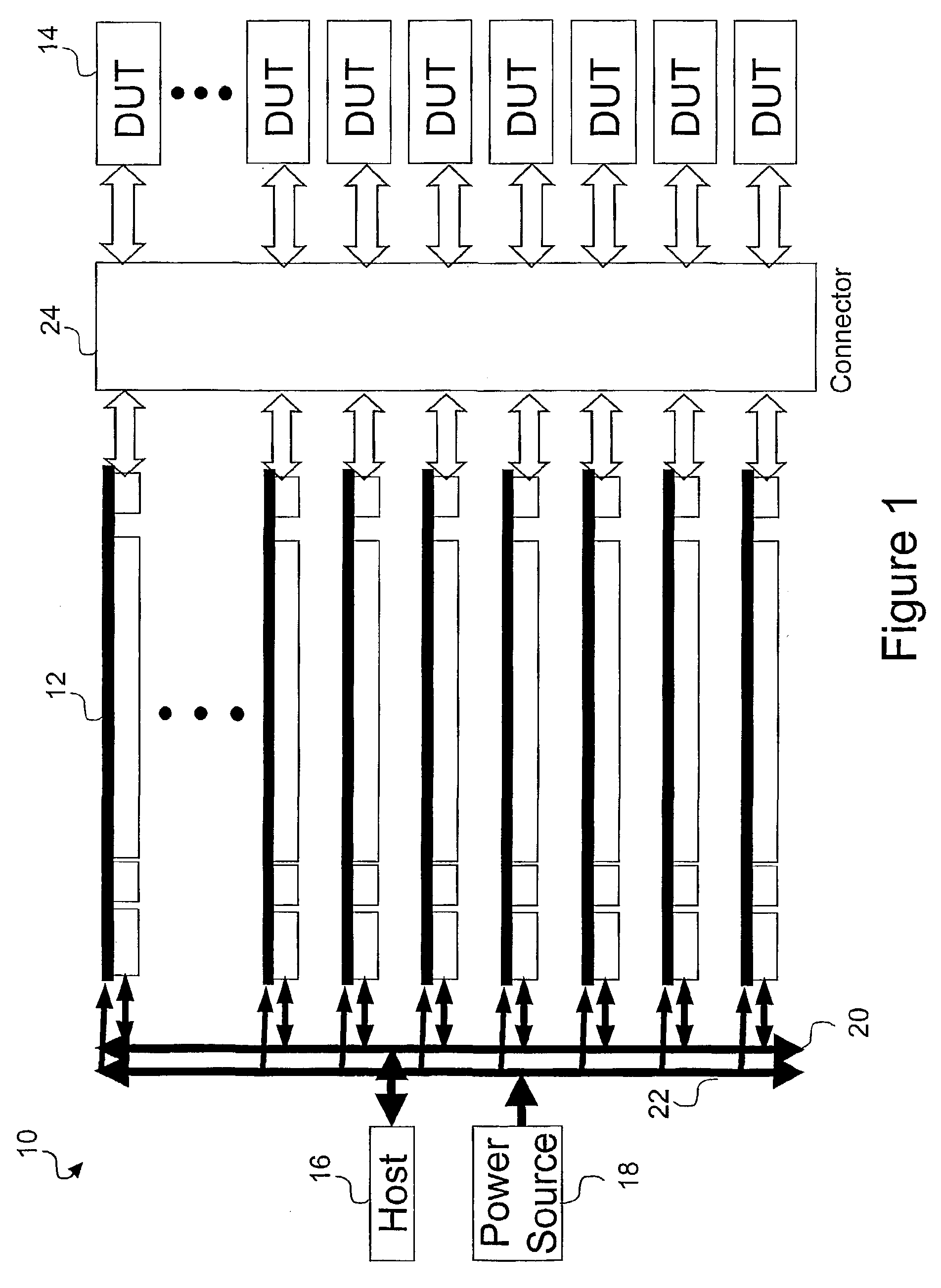

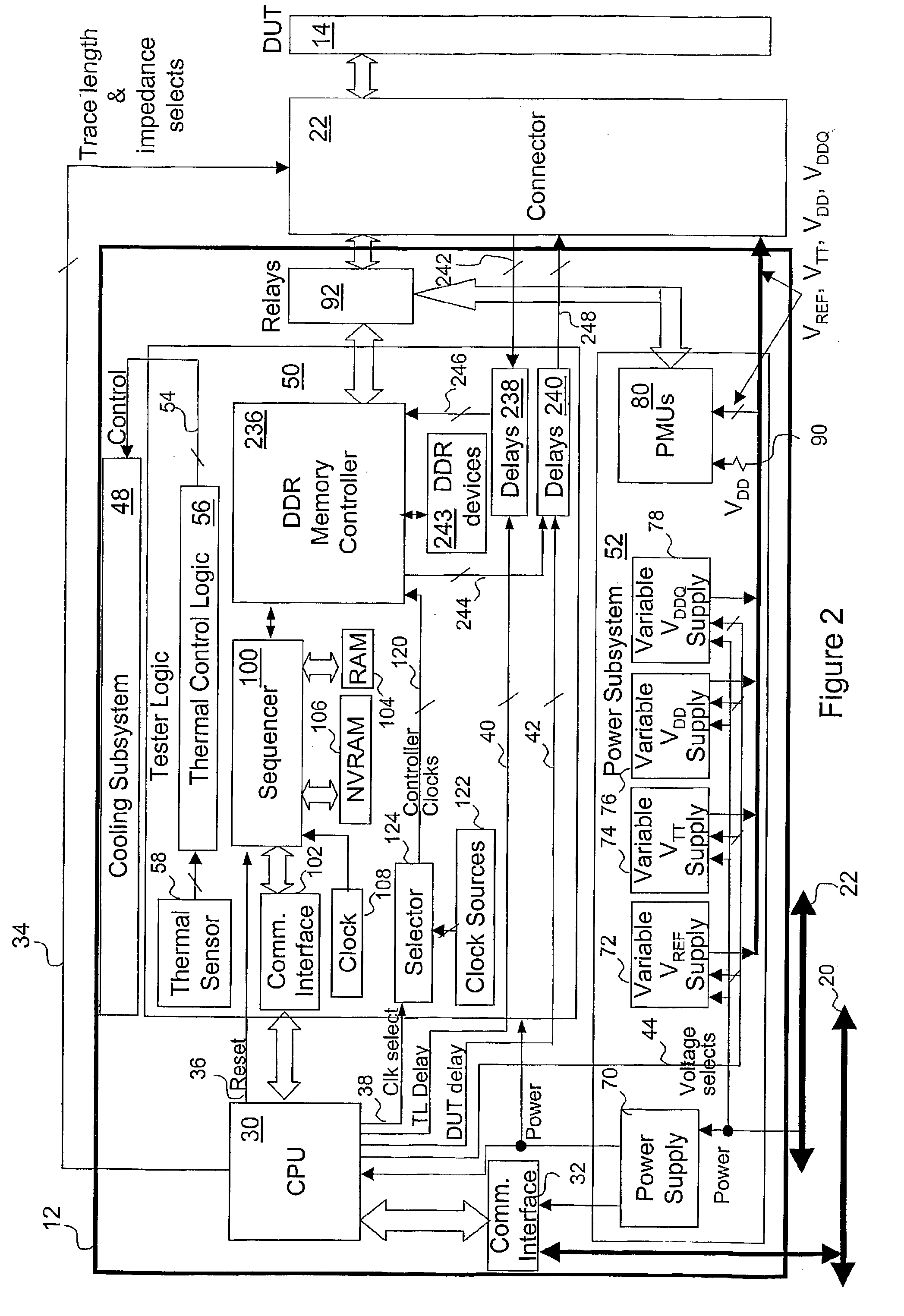

Method and system for wafer and device level testing of an integrated circuit

InactiveUS20030076125A1Needless expense associatedDefective assemblyDigital circuit testingResistance/reactance/impedenceEquipment under testComputer module

A tester comprises test logic and a connector for at least one device under test. The connector, which may comprise a wafer probe for dice on a wafer or a test fixture or either packaged integrated circuit devices or circuit board modules, has connections for the device under test that present an impedance selected to emulate the characteristic impedance of an end-use environment of the device under test. For example, in an embodiment in which the device under test comprises DDR memory and the end-use environment is a DDR memory module, the characteristic impedance is approximately 60 ohms. Thus, the tester of the present invention can accurately simulate operational behavior in an end-use environment of the device under test. Because this accurate simulation is available even for dice on a wafer, the needless expense associated with packaging defective dies and assembling defective dies into modules can be avoided. The test logic, which is couplet to the connector for communication with the device under test, transfers test commands and test data to (tic device under test. The test data and commands are utilized to perform multiple types of tests, including tests of the memory core and internal logic of the device under test. In this manner, the need for multiple types of testers is reduced or eliminated.

Owner:MCCORD DON

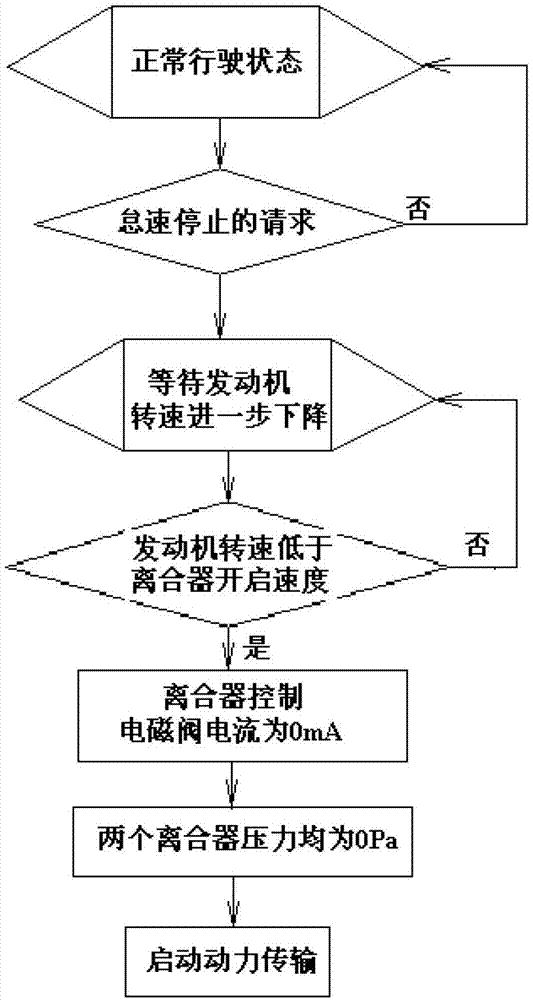

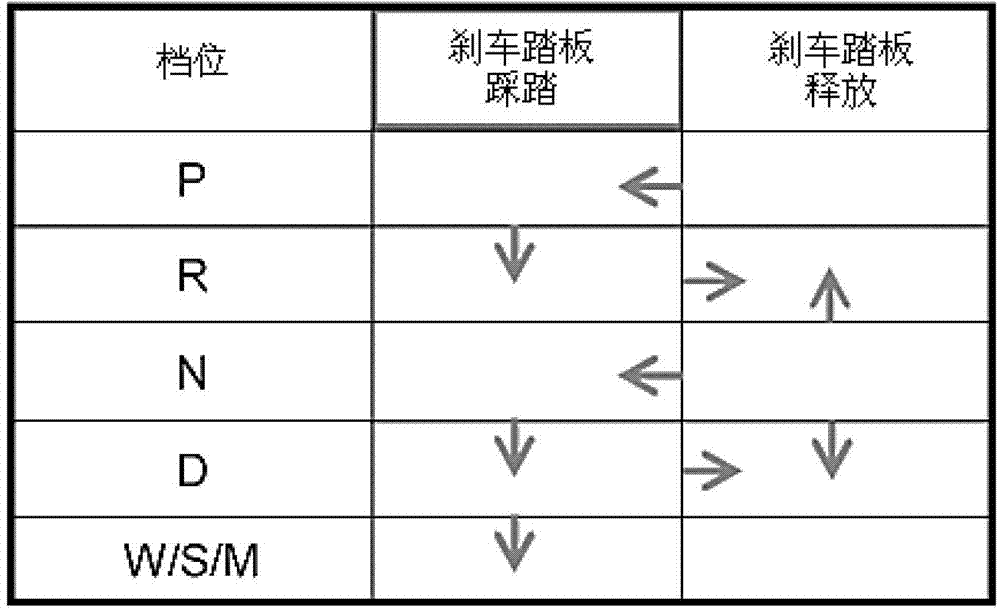

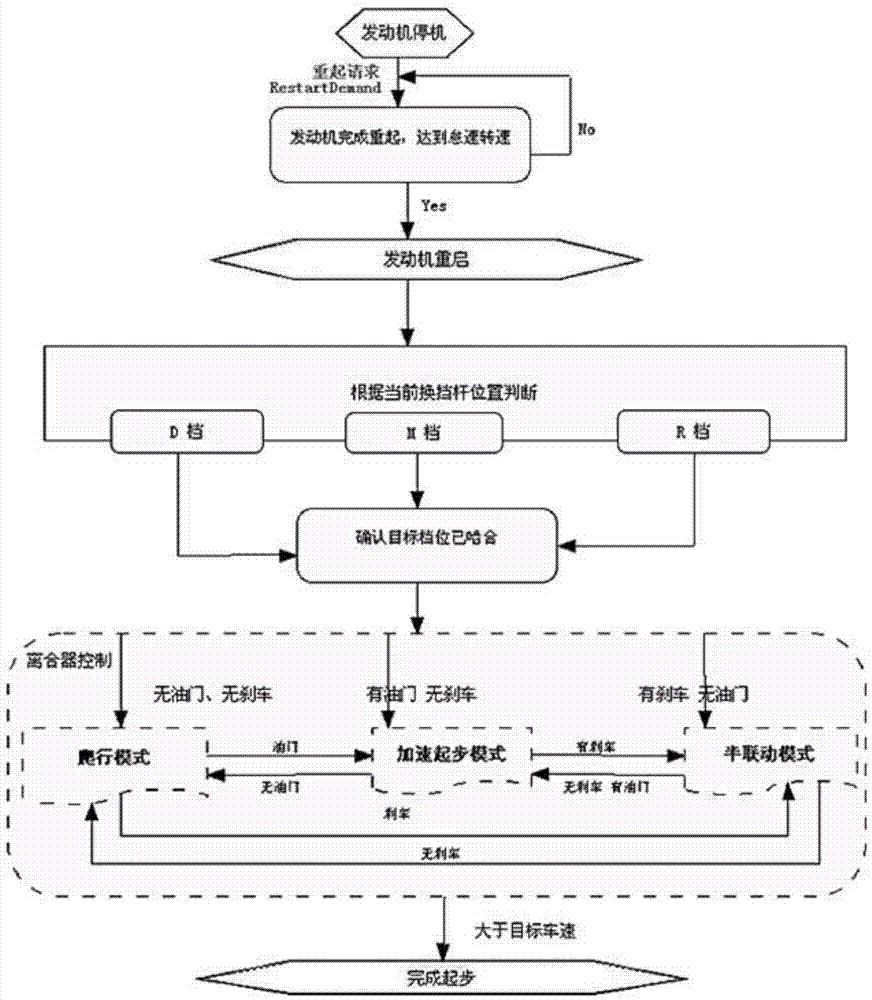

Control method based on engine starting and stopping and system thereof

A control method for a gearbox based on engine starting and stopping and a system thereof belong to the field of automotive transmissions. The judgment and the predictive analysis for an engine state are implemented according to engine control signals acquired by a CAN (Controller Area Network) high-speed bus and gear signals of a gear shift mechanism; and the sliding friction degree of a wet clutch is adjusted by comprehensive judgment and predictive analysis through acquiring gearbox signals and diagnosis results of TCU (Transmission Control Unit) internal logic to present driving working conditions, so that the automobile starting control after engine restarting, the engine stopping time judgment and the start-stop feedback signal sending are realized. The method and the system implement optical control for the working state of the gearbox of the automobile in the mutual change process between movement state and stationary state in the start-stop technology, and solve the problem of wearing the clutch mechanical body caused by needing two clutches for sliding friction starting in the prior art.

Owner:SHANGHAI AUTOMOBILE GEAR WORKS

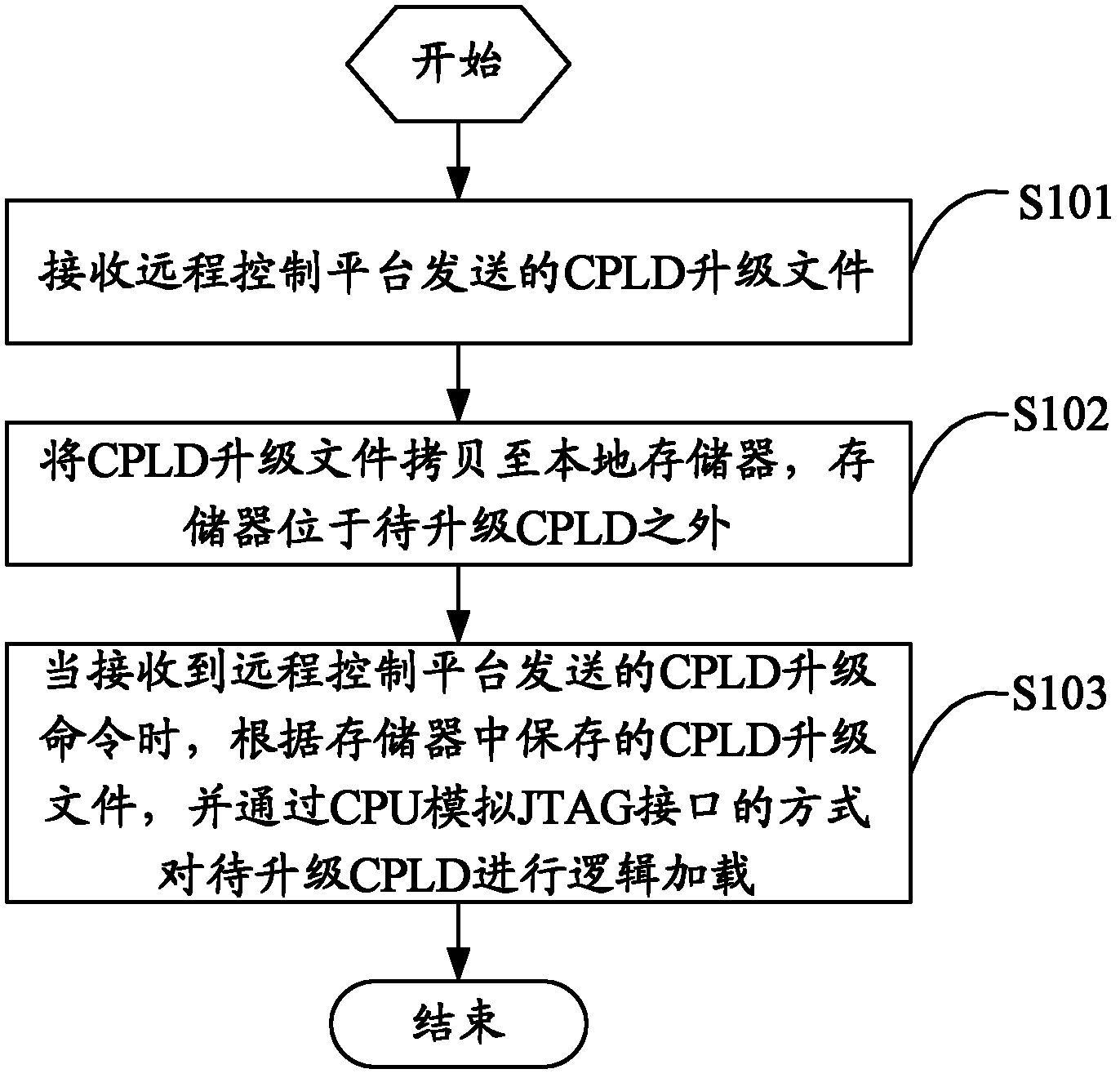

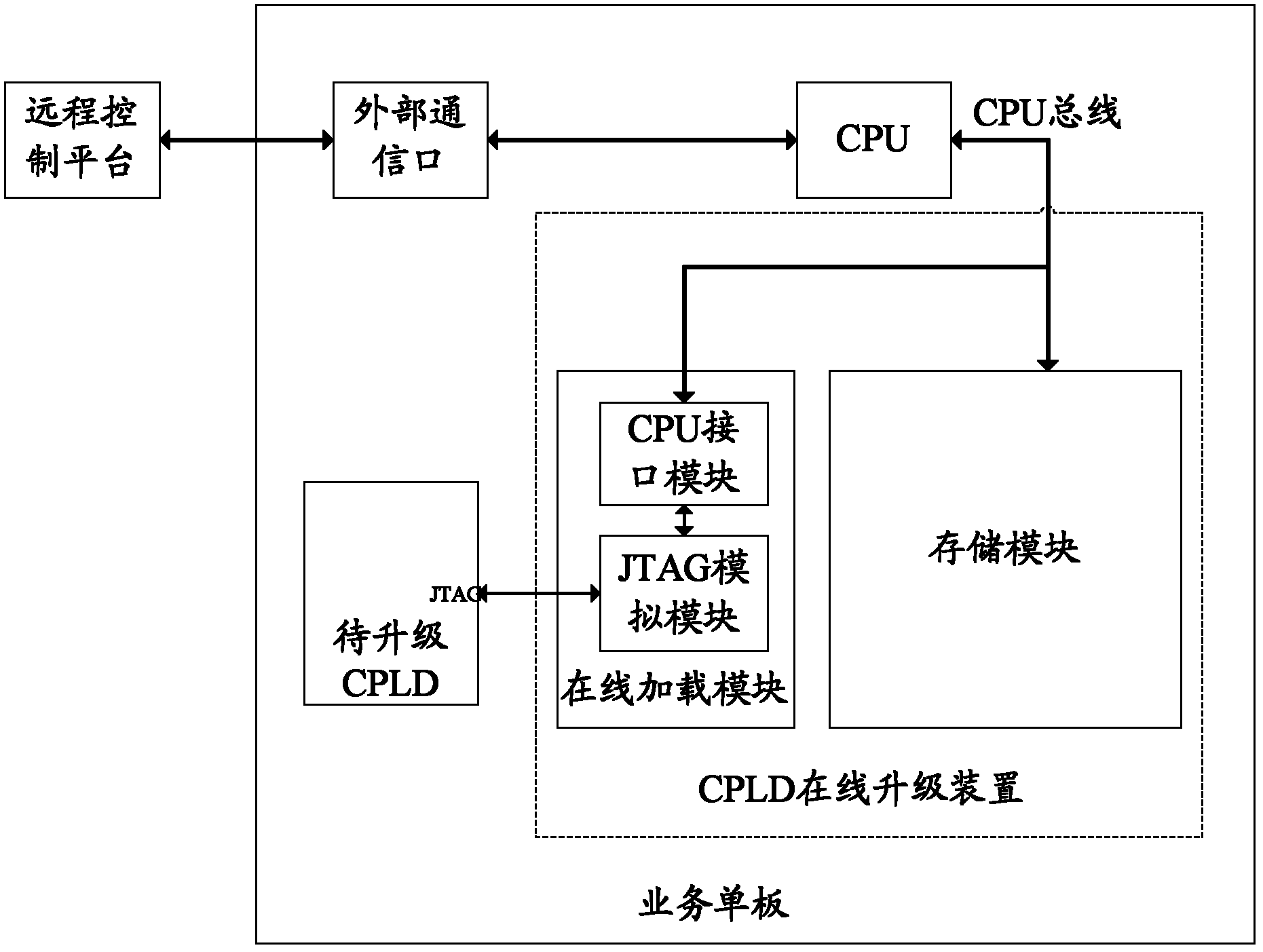

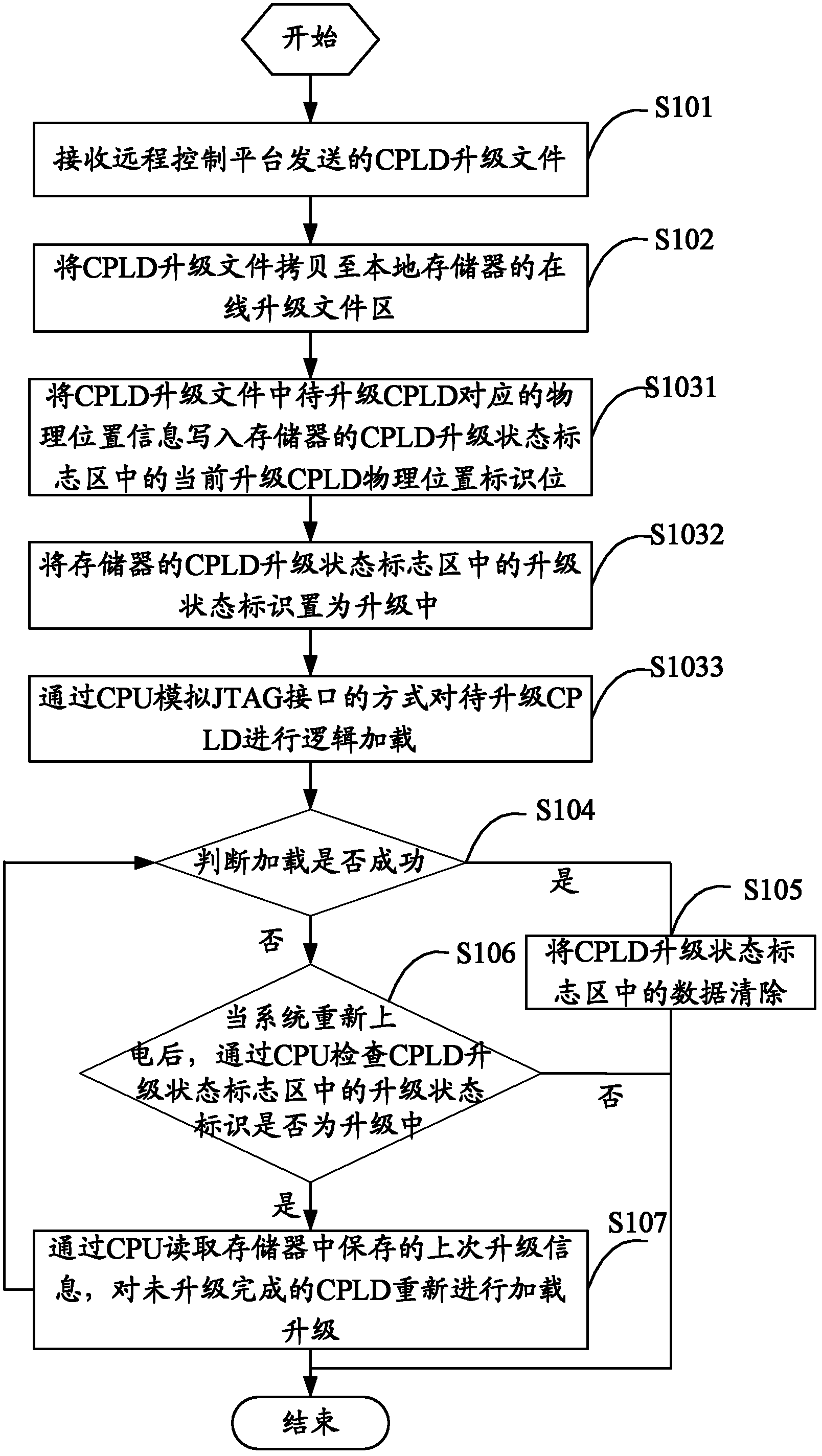

Online CPLD (Complex Programmable Logic Devices) upgrading method, device and business veneer

InactiveCN102662701AImprove reliabilitySimple methodProgram loading/initiatingRemote controlComplex programmable logic device

The invention relates to an online CPLD (Complex Programmable Logic Devices) upgrading method, an online CPLD upgrading device and a business veneer. The method comprises the following steps: receiving a CPLD upgrading file sent by a remote control platform; and copying the CPLD upgrading file to a local storage, and when receiving the CPLD upgrading instruction sent by the remote control platform, logically loading a CPLD to be upgraded through a CPU (Central Processing Unit) in a manner of simulating a JTAG (Joint Test Action Group) interface according to the CPLD upgrading file stored in the storage. According to the invention, remote upgrading on on-site equipment CPLD can be realized without depending on the internal logics of the CPLD to be upgraded, and CPLD of all factories can be compatible by adopting the upgrading manner of simulating the JTAG interface, so that the universality is good; furthermore, in the online upgrading process, if the abnormal conditions of reset or power failure of the CPU occur, the CPLD, whose online upgrading is not completed, can still be reloaded for upgrading when the system is restarted, so that the online upgrading reliability of the CPLD is improved.

Owner:ZTE CORP

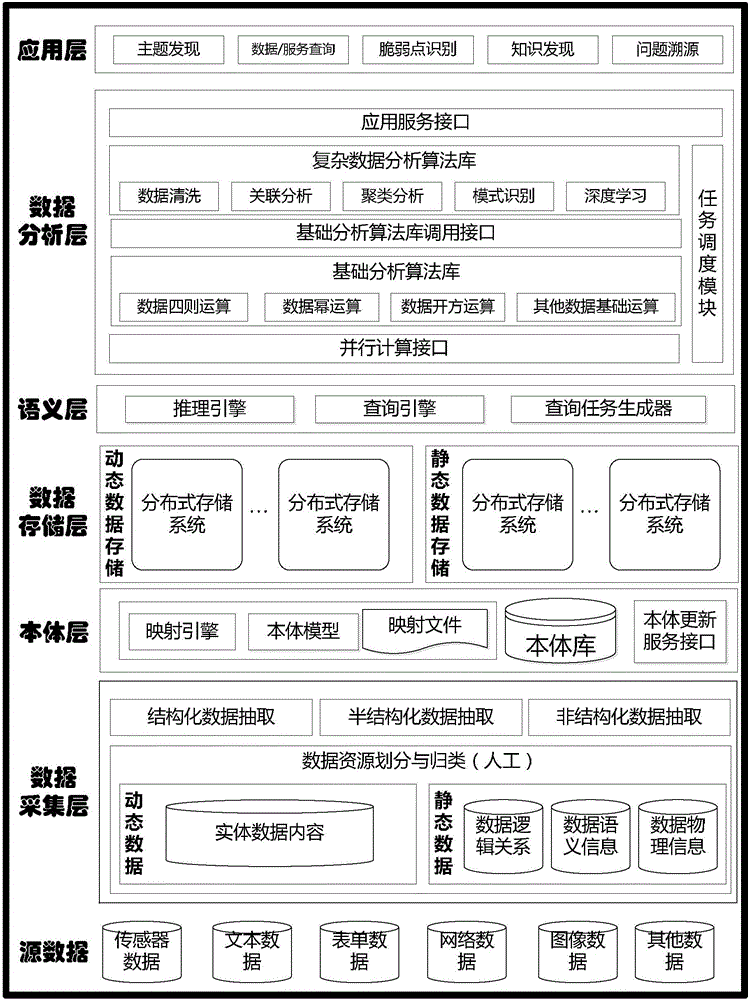

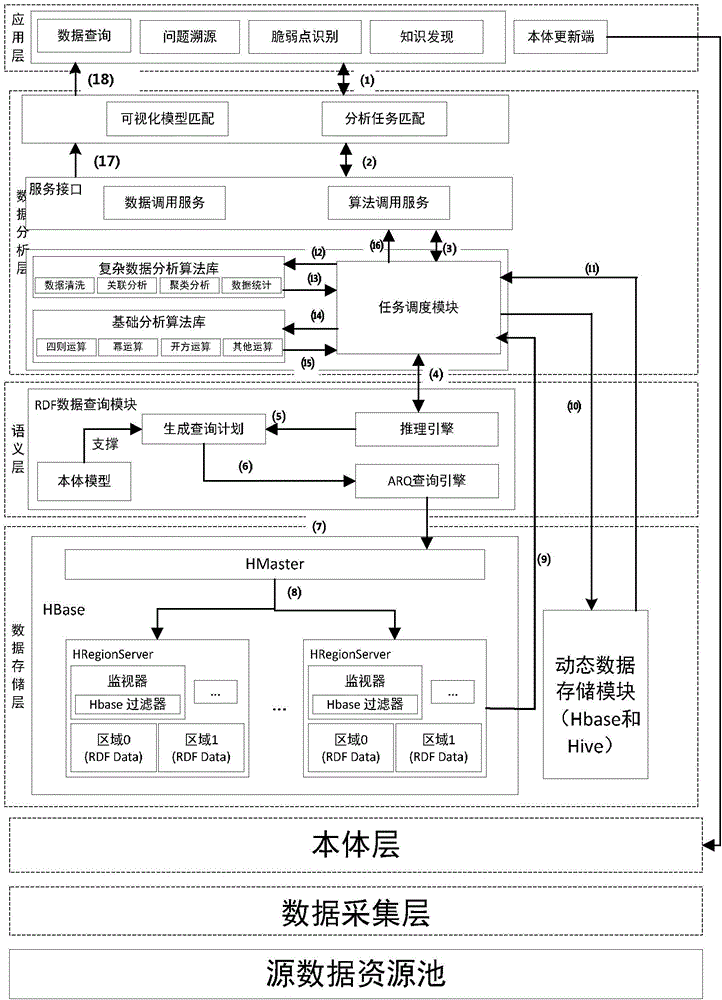

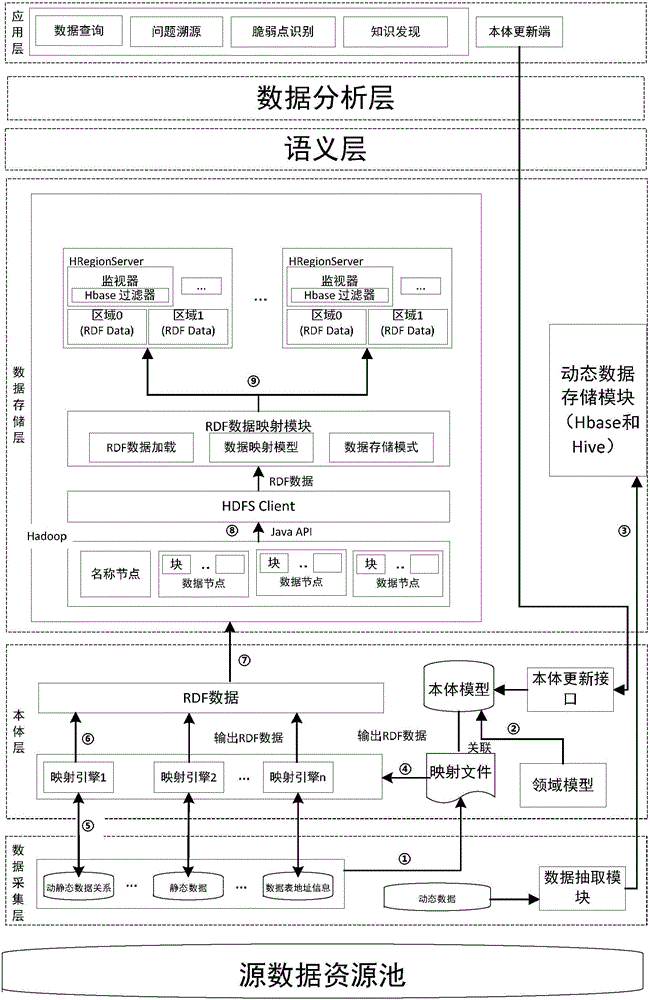

Semantic net based large scale offline data analysis framework

InactiveCN106570081AGood organizational performanceValid updateDatabase updatingSpecial data processing applicationsData informationData acquisition

The invention relates to a semantic net based large scale offline data analysis framework. The large scale offline data analysis framework includes a data acquisition layer, a body layer, a data storage layer, a semantic layer, a data analysis layer and an application layer. A data source includes dynamic data and static data, and the static data includes data and database internal logic semantic and structure type. The static data is established into a body model in the analysis framework; the static data is extracted and modeled, and then the static data orients a user or an upper analysis task in a semantic service manner. The large scale offline data analysis framework can effectively improve the ability to organizing multi-source heterogeneous offline data and has a uniform interface to upper data; and application users or data analysis workers can access a lower data source through a semantic interface without knowing all the information of different data sources, and relevant data information is acquired. The large scale offline data analysis framework can effectively update the whole data source from a global perspective by correction of the body structure having changed content and update and inference service built in an application tool.

Owner:TONGJI UNIV

PCI system and adapter requirements following reset

InactiveUS6035355AComponent plug-in assemblagesProgram loading/initiatingOperational systemComputerized system

A method of registering a newly added peripheral device with a computer system by responding with a status message from the device to a bus of the computer system, in response to an access attempt, and within a predetermined time period from the deasserting of the reset signal applied to device, so as to avoid stalling and thereby avoid the need to reboot the system in order to initialize the new peripheral device with the operating system. The device may be allowed to initially send a retry response, provided the response occurs during an initial latency period which is less than the predetermined time period. The invention also enables the peripheral device to respond to non-configuration cycles immediately following configuration completion. Internal logic of the peripheral device can be initialized after responding with the status message. Non-configuration access to the peripheral device can be prevented until it is ready to respond, by setting a bit (in the configuration space of the peripheral device to indicate that the peripheral device is ready.

Owner:IBM CORP

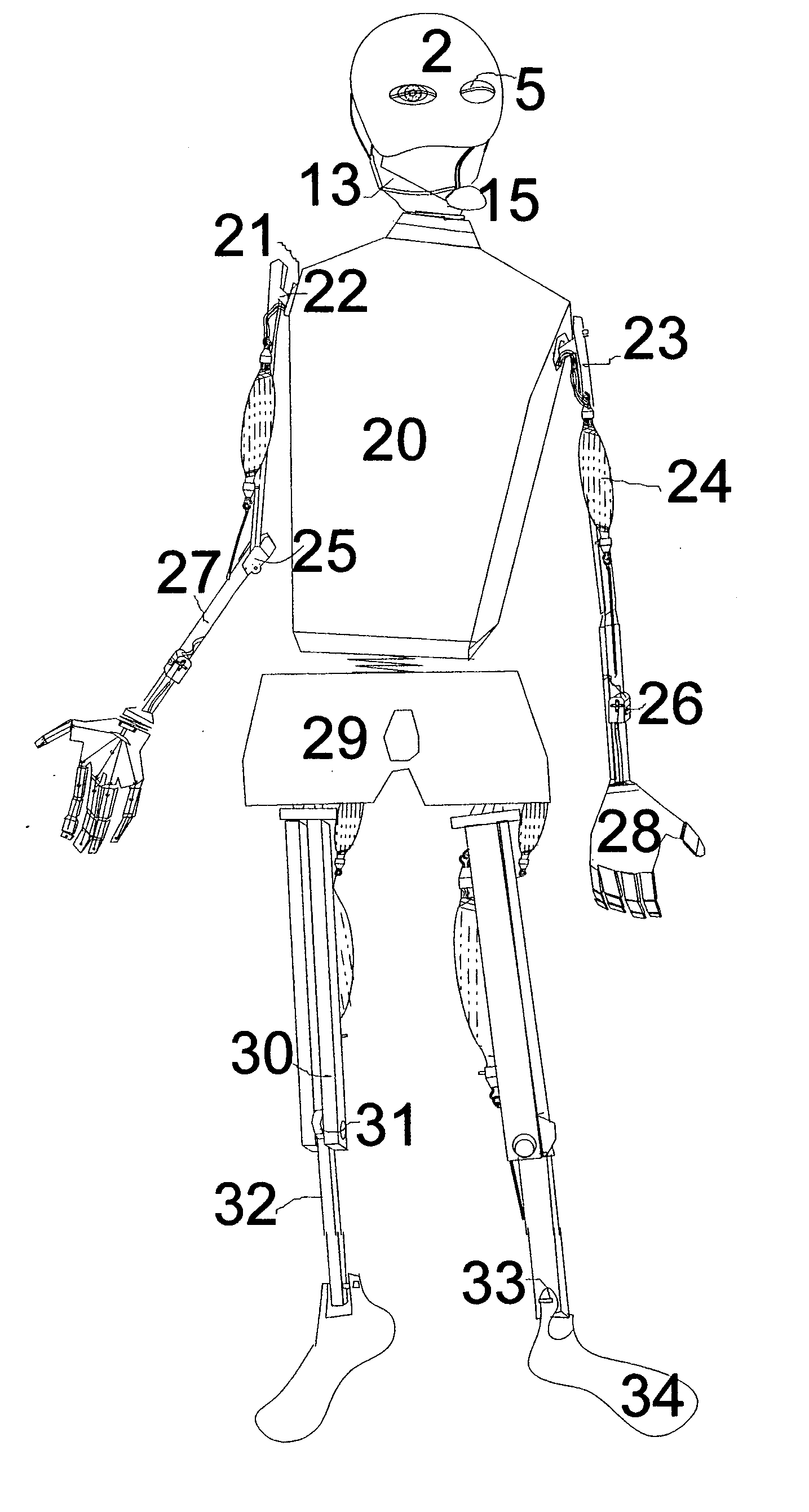

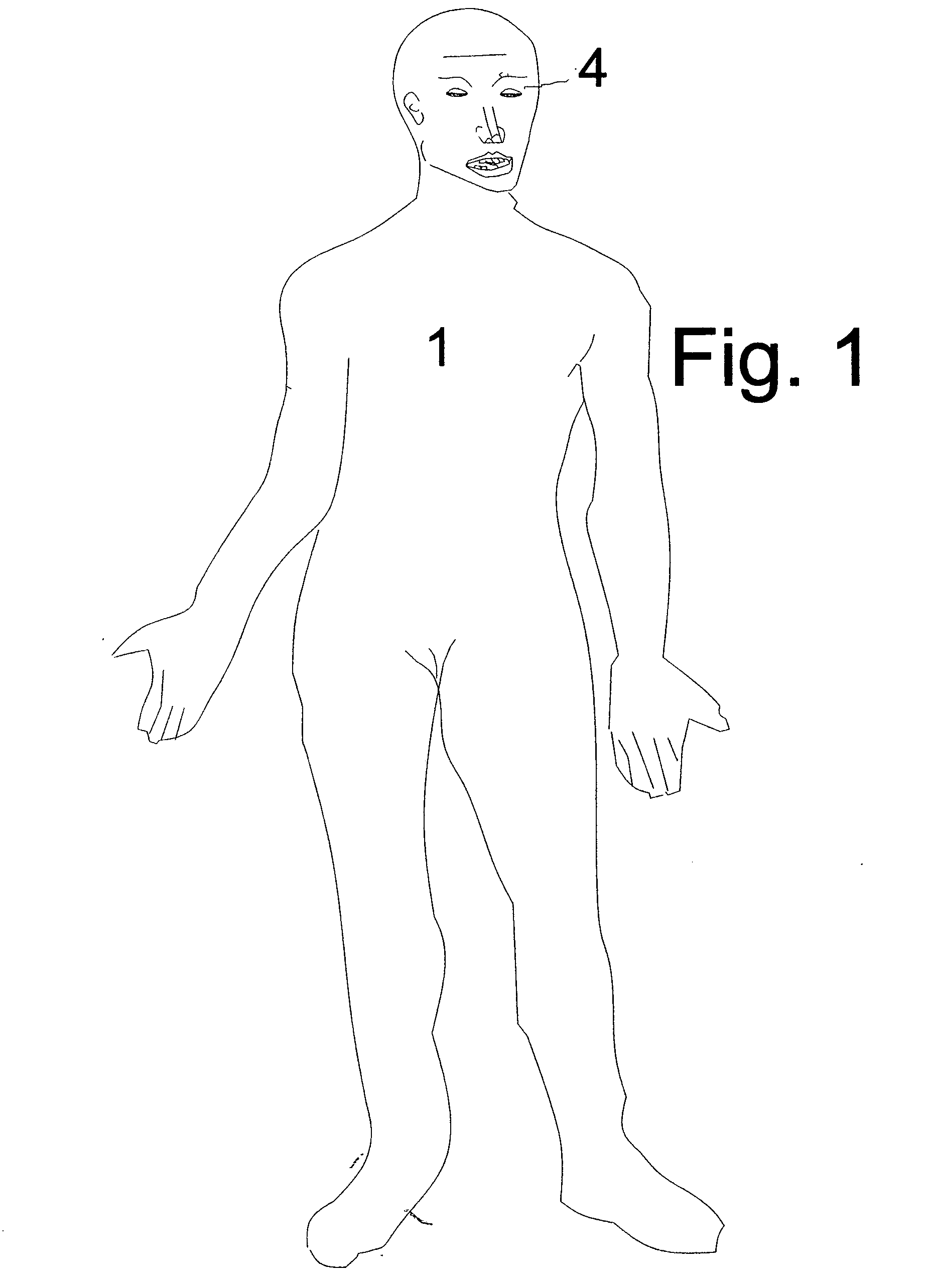

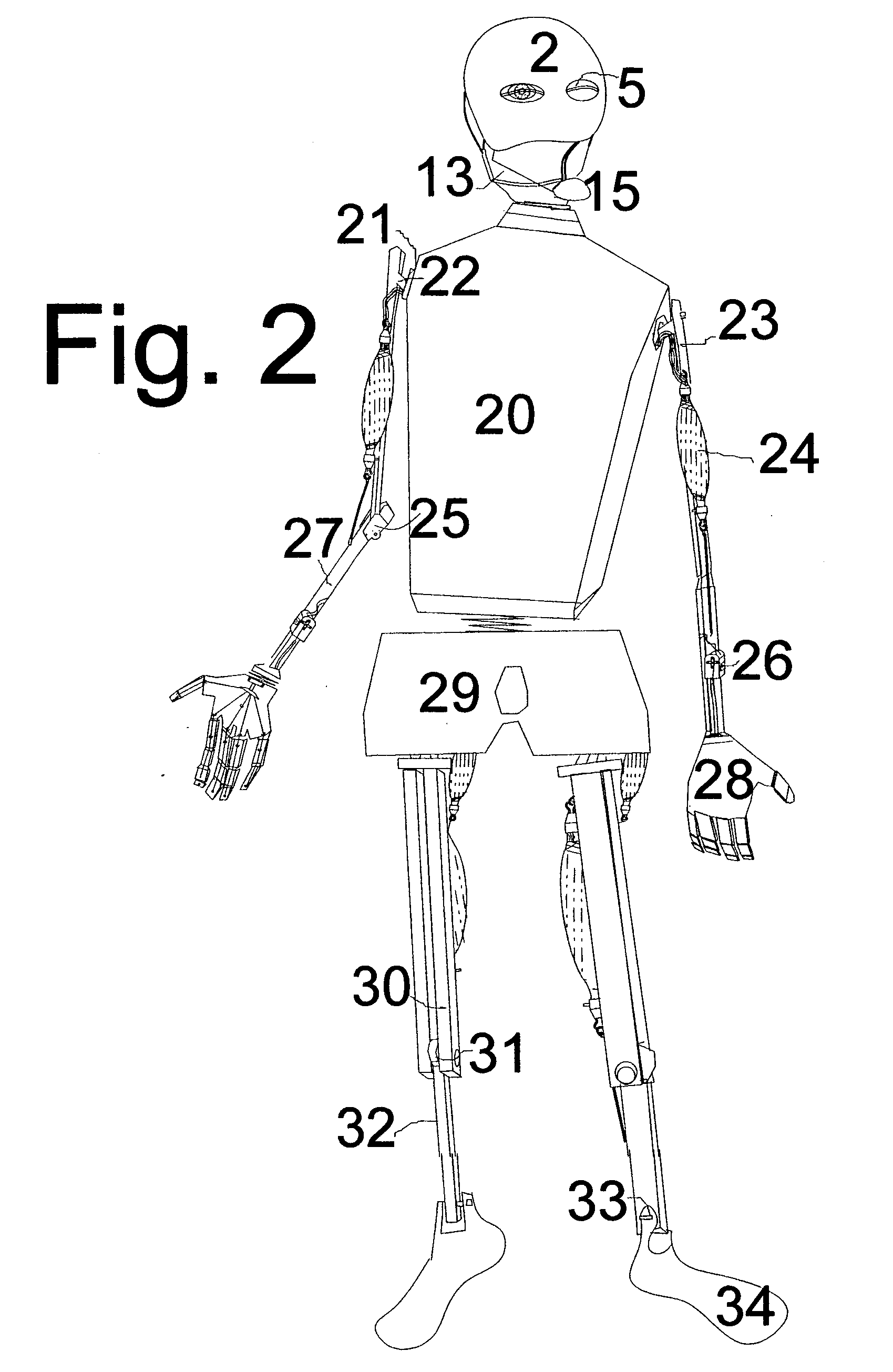

Self-contained, submersible, autonomous, speaking android

A self-contained anthropomorphic robot for erotic entertainment, stunt work, and commercial display. The robot has a contiguous, anatomically correct, lifecast outer skin. The outer skin is elastic, pigmented, and translucent, and is colored with superficial layers of translucent coloring agent to achieve a highly human appearance. In the preferred embodiment, the elastic skin is translucent silicone. This skin overlies soft padding and an articulated endoskeleton. The robot runs on its own internal power supply, and does not require an external power source. The robot can understand spoken commands and phrases, and can choose and speak its replies, according to internal logic. It generates its own body warmth, and is capable of operation under water.

Owner:SISK BRADLEY G

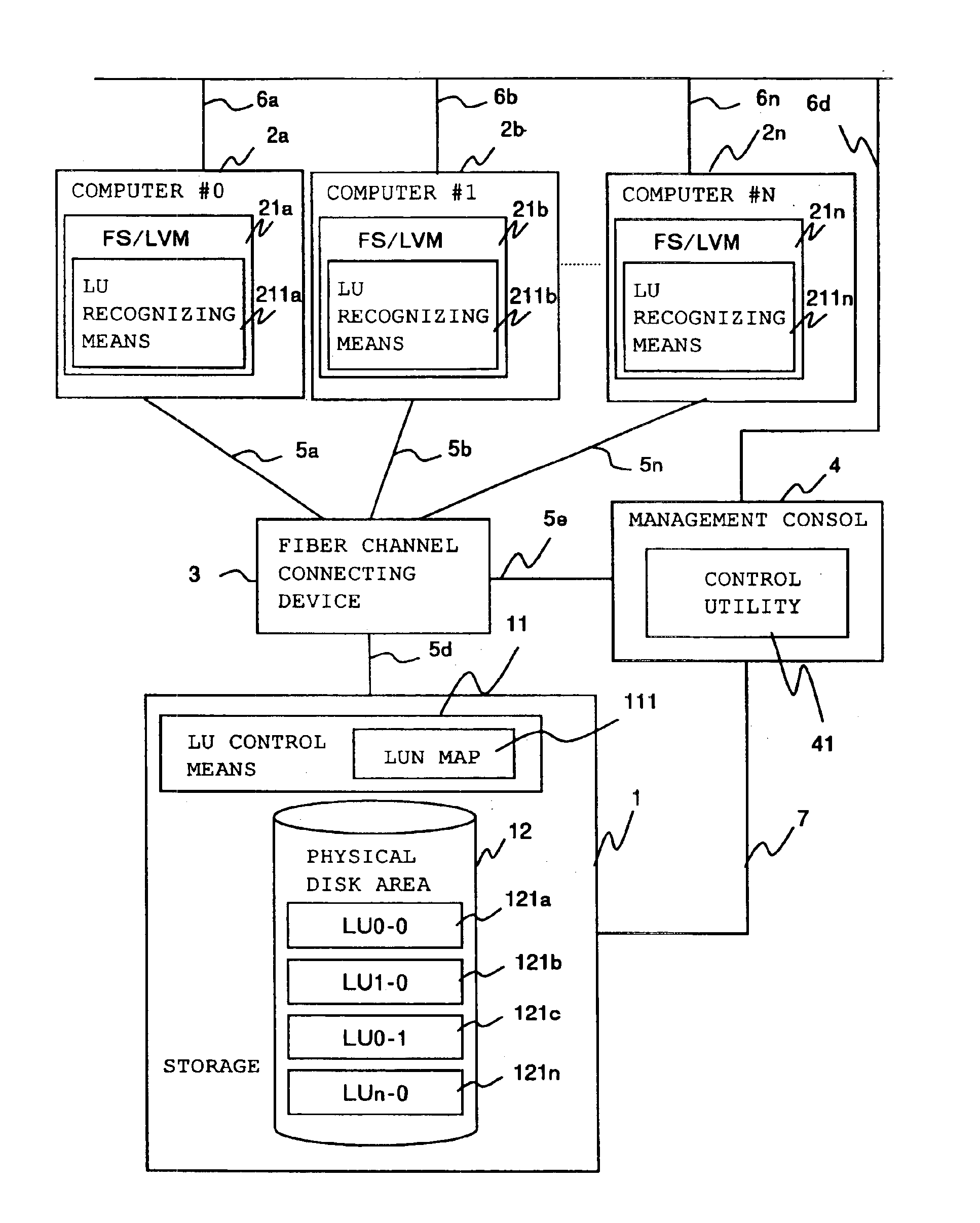

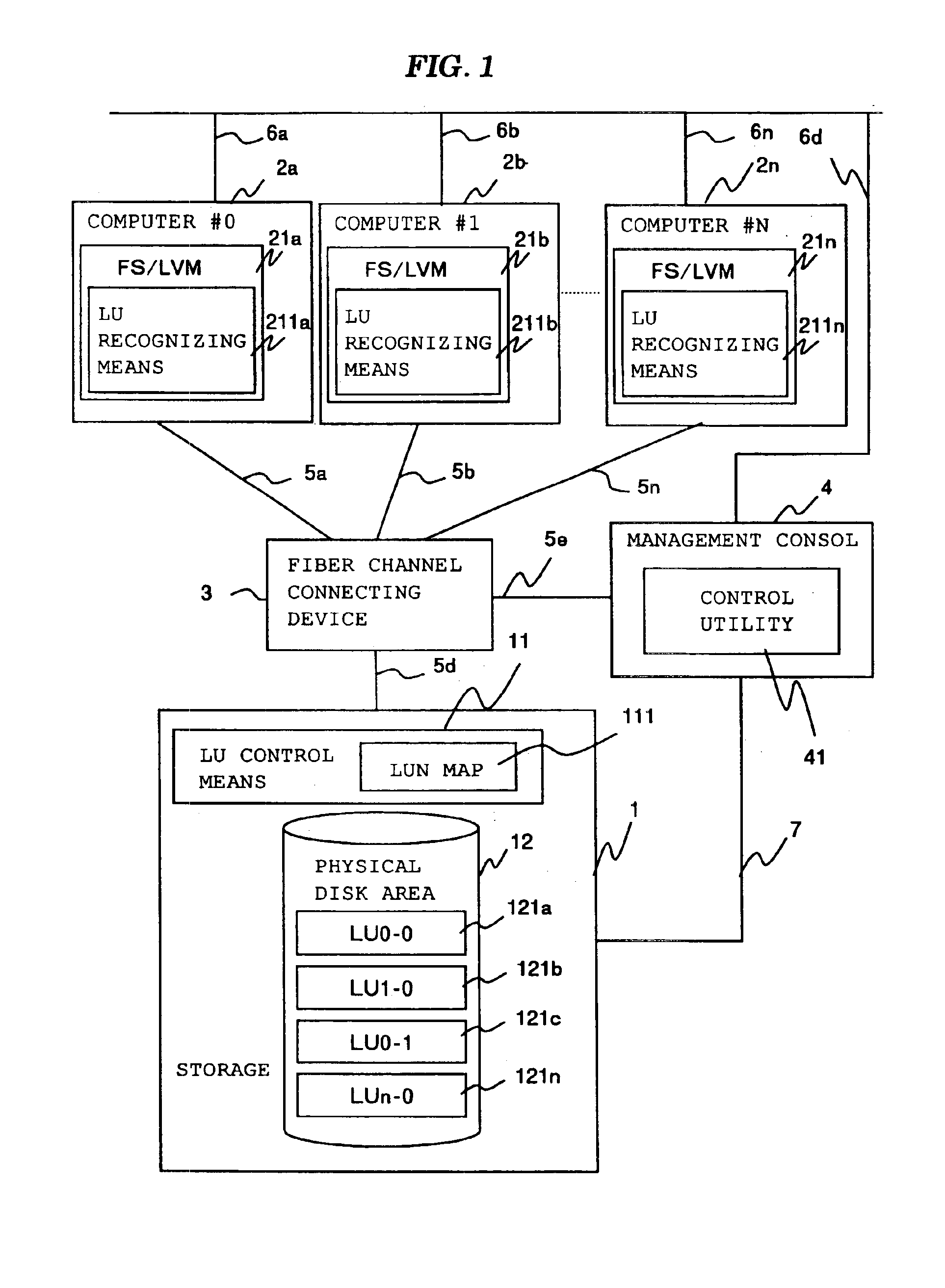

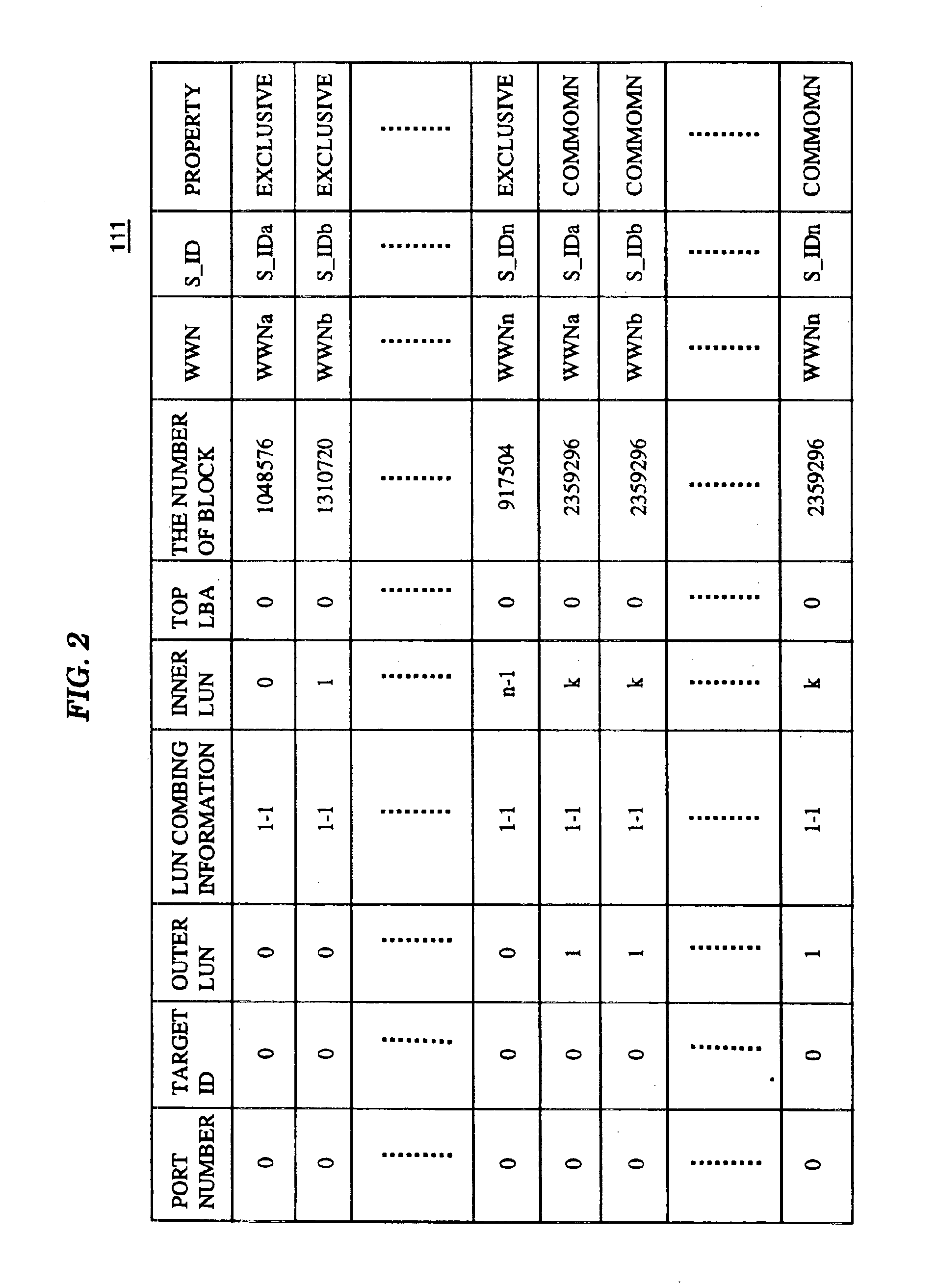

Computer system with storage system having re-configurable logical volumes

InactiveUS6880058B2Logical volume is facilitatedEasy to manageInput/output to record carriersError detection/correctionContinuous useComputerized system

In order to enable an area of each logical volume to be expanded while continuously using the logical volume and to integrate separate logical volumes in a single continuous area, a storage has logical volume control means for controlling the construction of a logical volume, a logical volume number map in which logical volume construction information is described, and copy means for copying the logical volume. By allowing two or more inner logical numbers to be described per external logical number in the logical volume number map, improved flexibility in combining the logical volumes in the storage is achieved. By copying a plurality of separate logical volumes into a physical continuous area by the copy means, the logical volumes are integrated.

Owner:HITACHI LTD

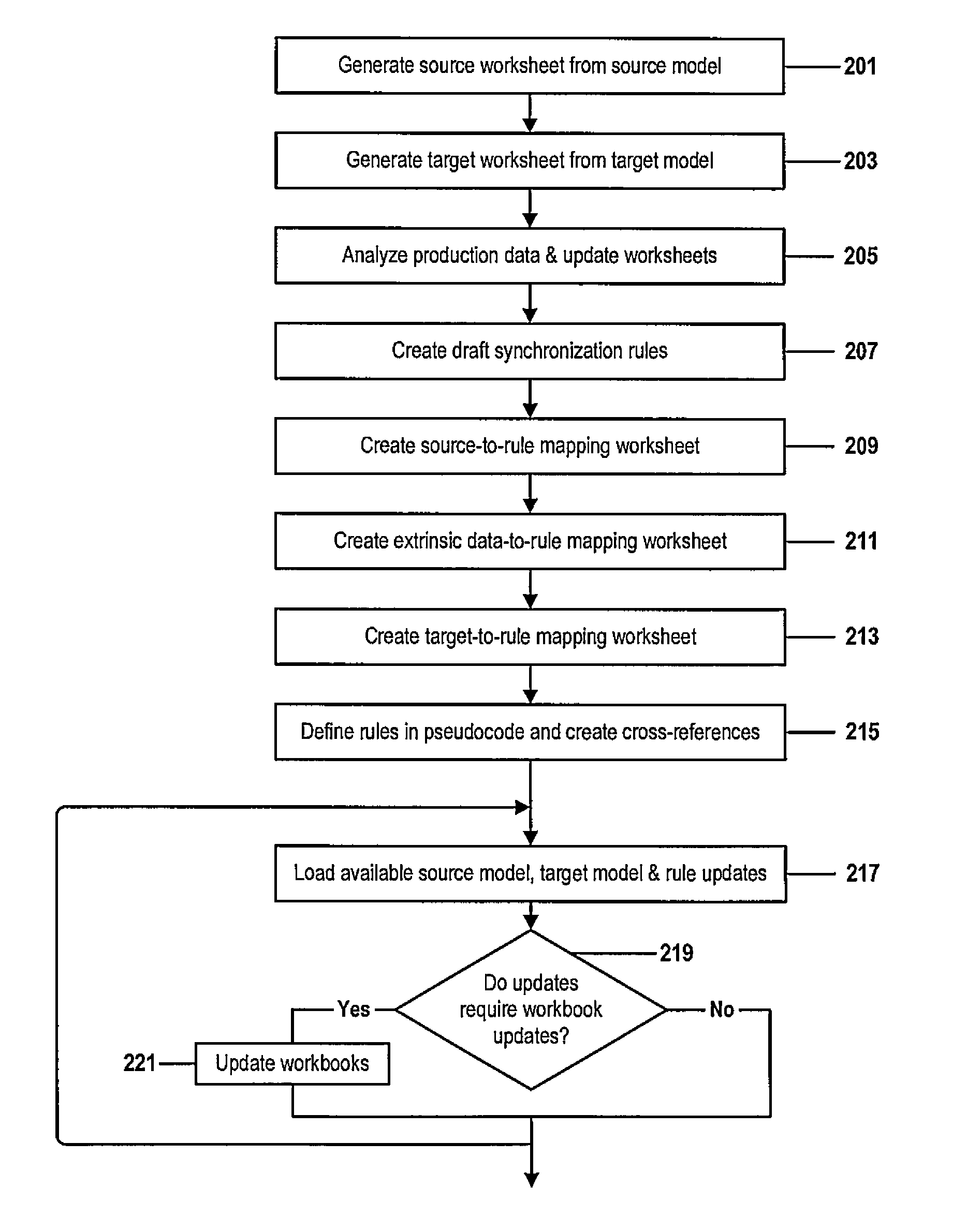

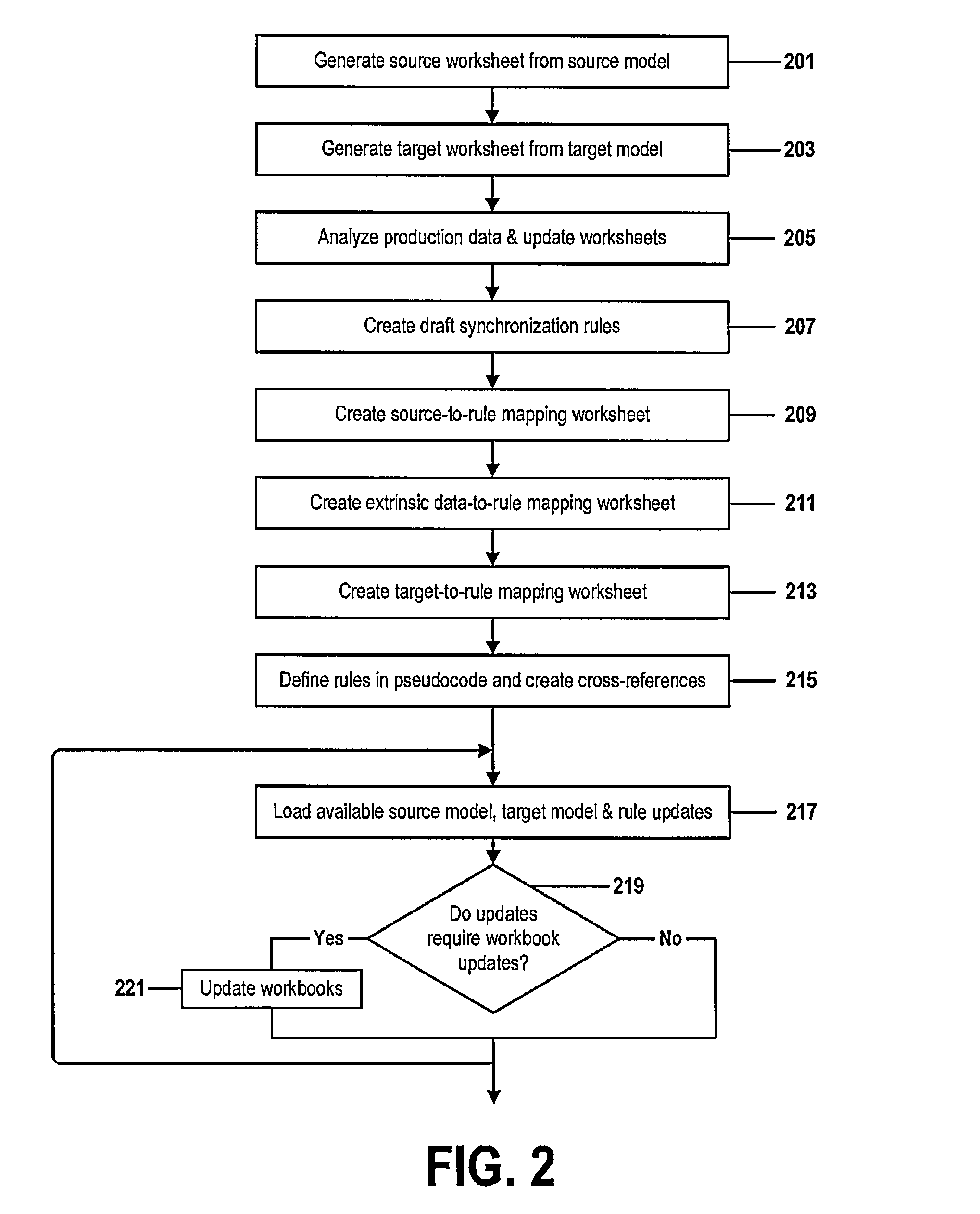

Automatically managing mapping and transform rules when synchronizing systems

A method and associated system for managing rules that synchronize operations of a source system and a target system. A set of linked worksheets is generated as a function of the internal logic of the synchronization rules and of worksheets that represent data models of the source and target systems. These generated worksheets describe and relate data elements of the data models, extrinsic data that is stored externally to the source and target systems, and logical procedures performed by the synchronization rules. When the source data model, the target data model, or a logical procedure is revised, the linked worksheets are updated in response to the revision and these updates automatically propagate across the synchronization rules and across other components of the source system, the target system, and the synchronization mechanism.

Owner:IBM CORP

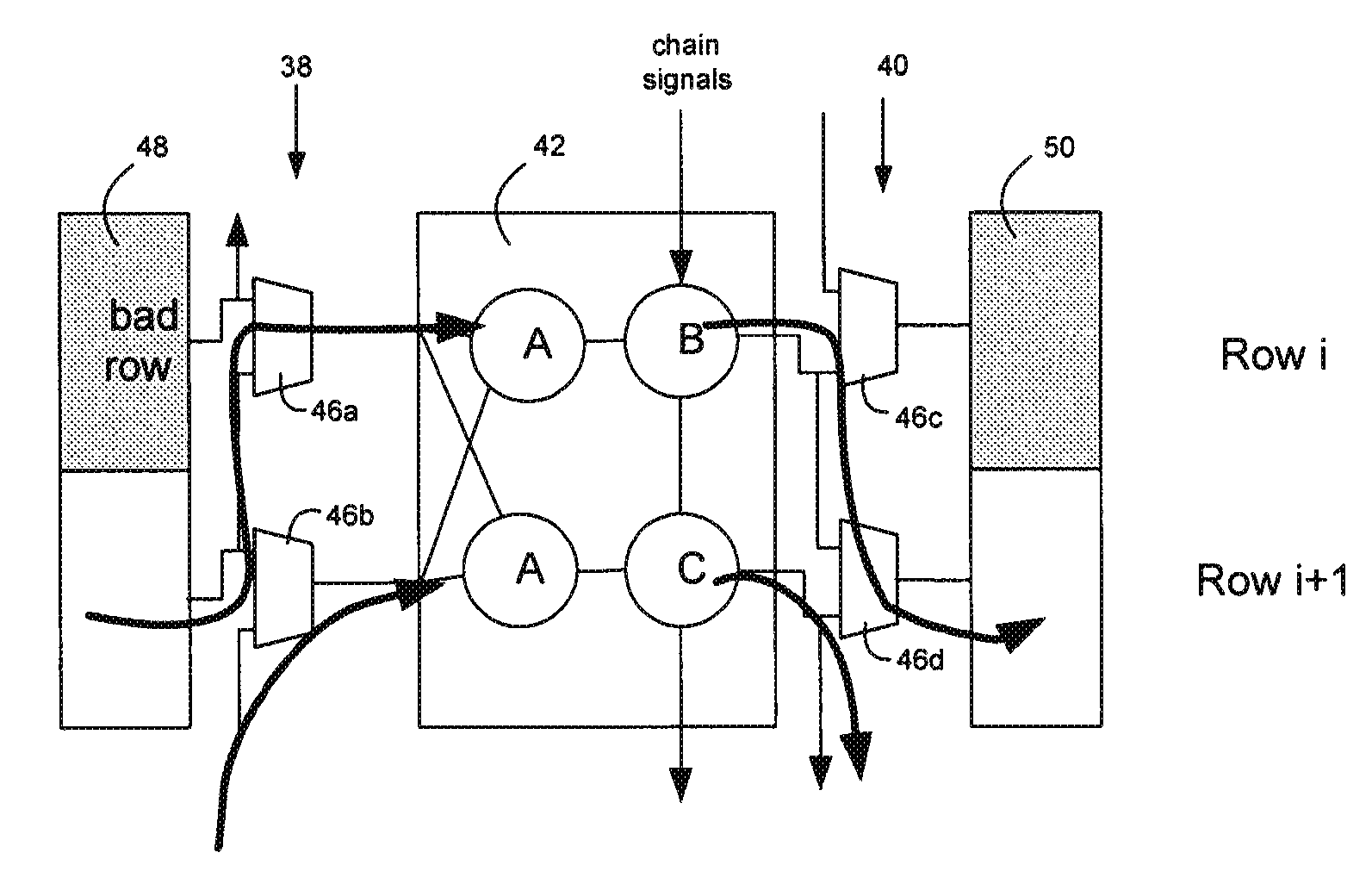

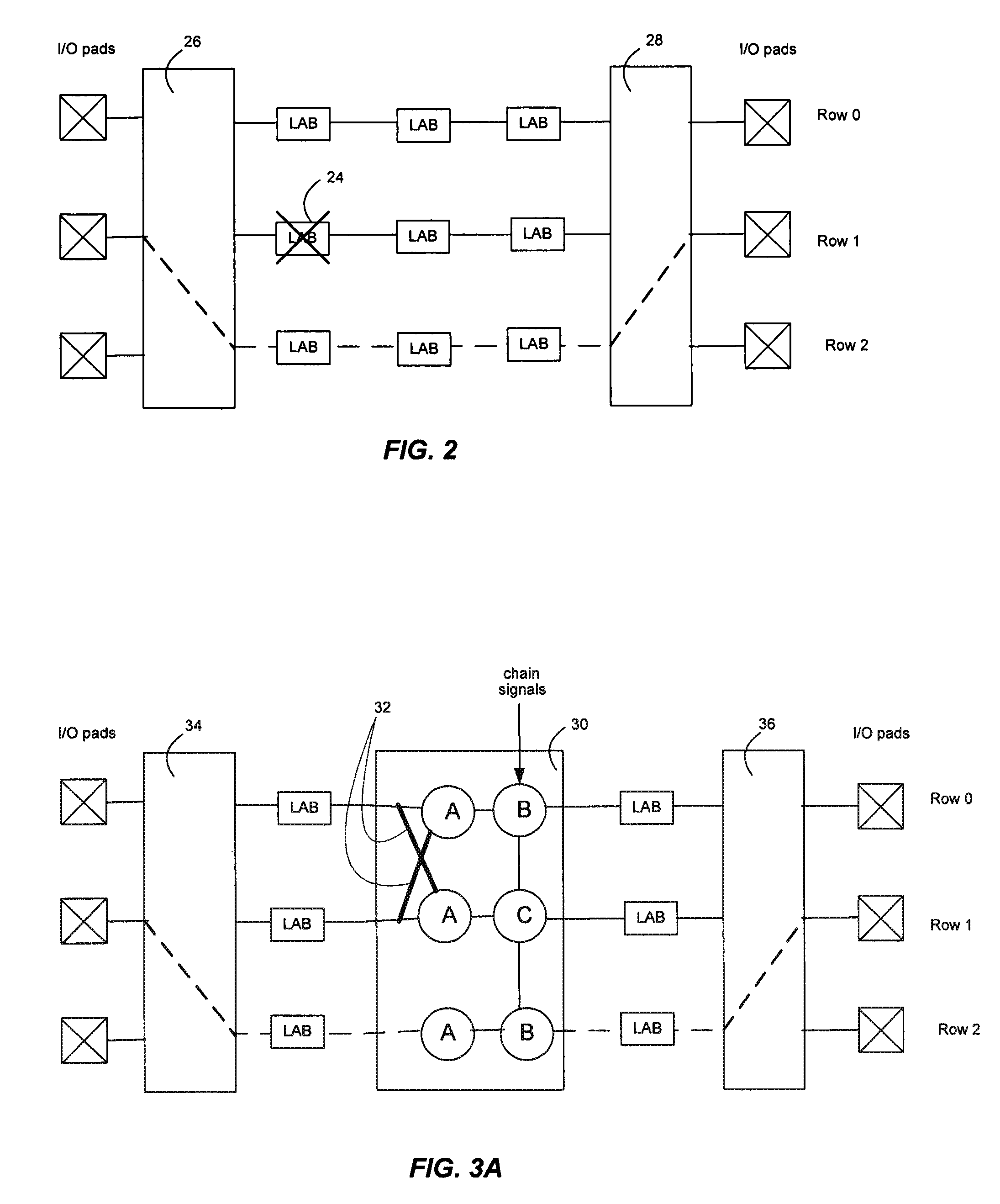

Multi-row block supporting row level redundancy in a pld

InactiveUS20100060309A1Solid-state devicesReliability increase by circuit redundancyComputer architectureProgrammable logic device

In a Programmable Logic Device (PLD), a multi-row block that has internal logic connections between rows has redundant internal connections between rows to replace the internal logic connections when a fault occurs. The redundant internal logic connections extend through a row, linking the row above a defective row with a row below the defective row. Elements in a multi-row block are configurable to perform a default function and a function of an element in a neighboring row, if the functions are different.

Owner:ALTERA CORP

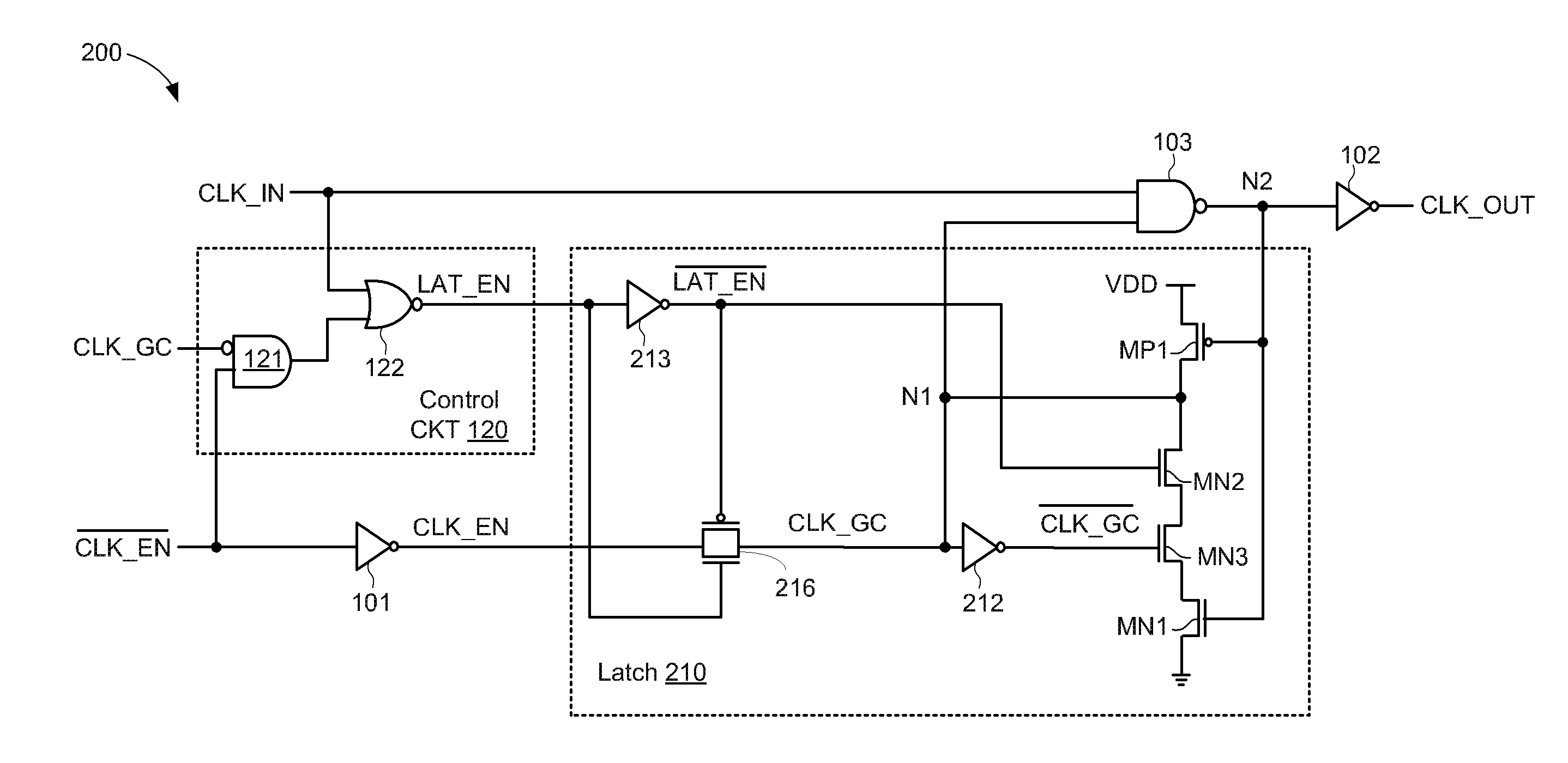

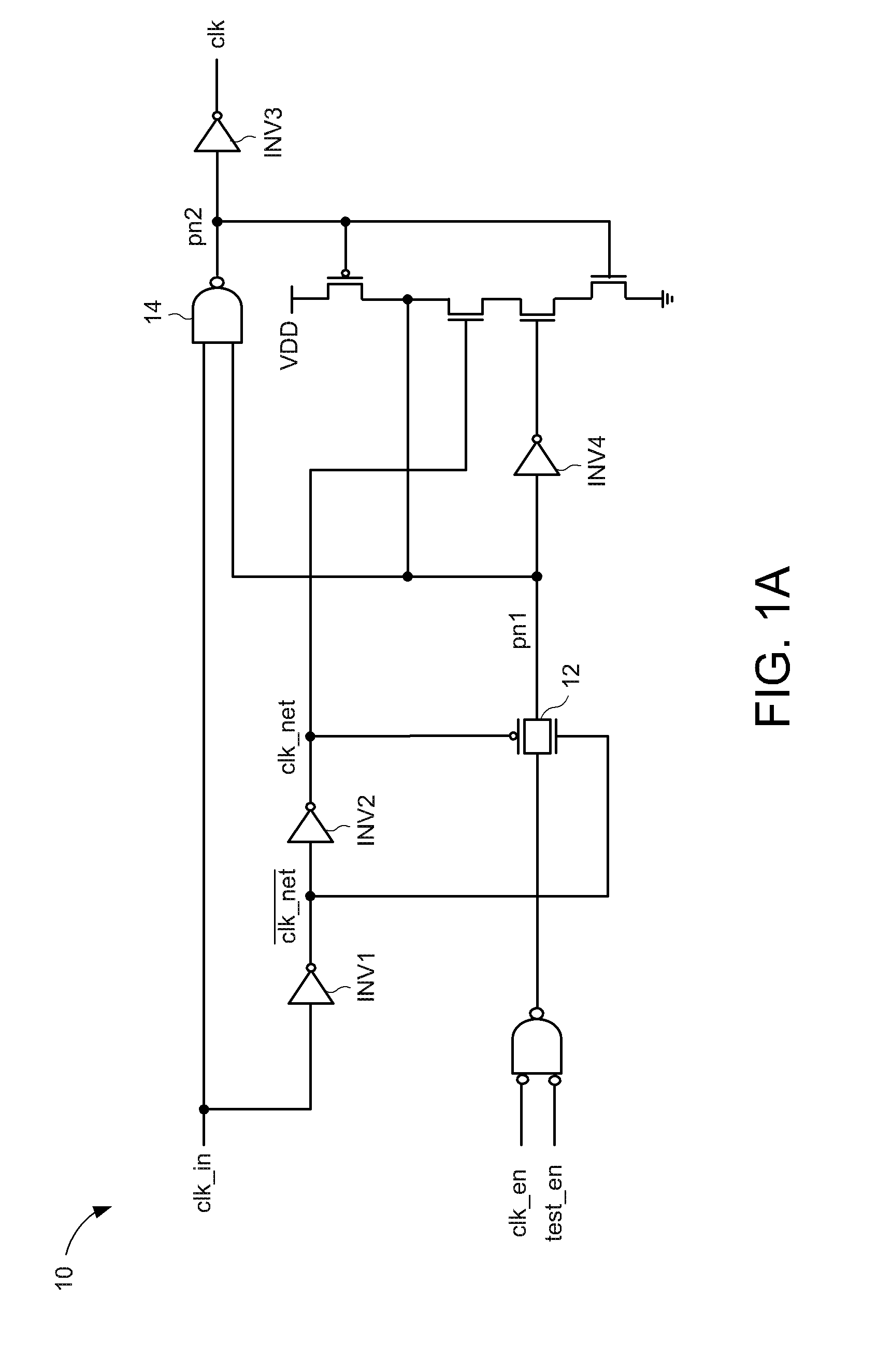

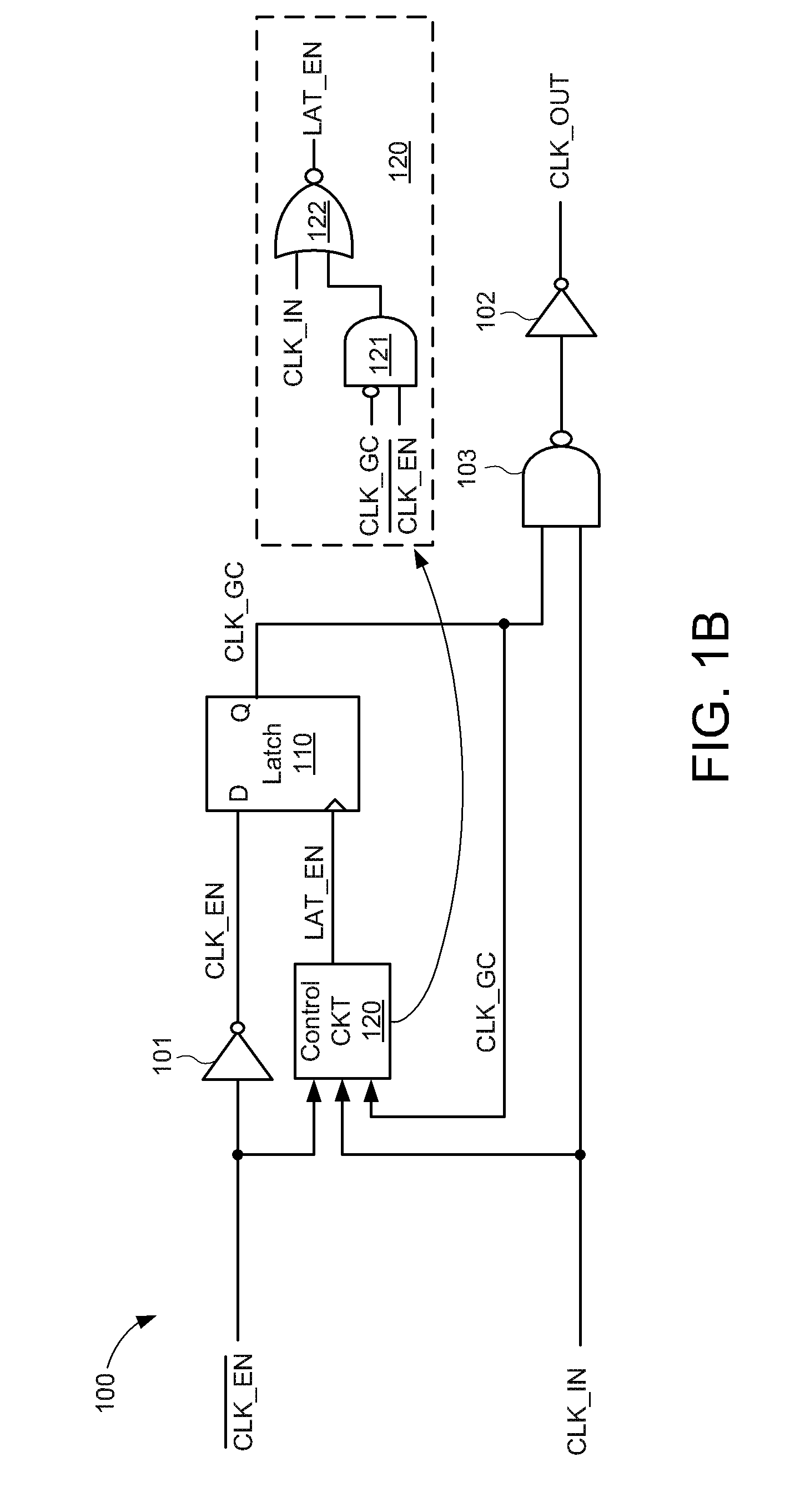

Clock gating circuit for reducing dynamic power

ActiveUS20150200669A1Power reduction by control/clock signalElectric pulse generatorData terminalControl signal

A clock-gating circuit is disclosed that may reduce unnecessary power consumption associated with clock distribution networks. For some embodiments, the clock-gating circuit includes a latch control circuit, a storage latch, and a logic gate. The control circuit has inputs to receive an input clock signal, a clock enable signal, and a clock gating control signal, and has an output terminal to generate a latch enable signal. The latch has a data terminal responsive to the clock enable signal, a latch enable terminal responsive to the latch enable signal, and an output to generate the clock gating control signal. The logic gate has inputs to receive the input clock signal and the clock gating control signal, and has an output terminal to generate an output clock signal. The clock-gating circuit may reduce power consumption during an enabled state by maintaining the latch enable signal at a constant logic state, thereby reducing dynamic power consumption by preventing internal logic gates from dynamically switching logic states while the input clock signal is gated.

Owner:QUALCOMM INC

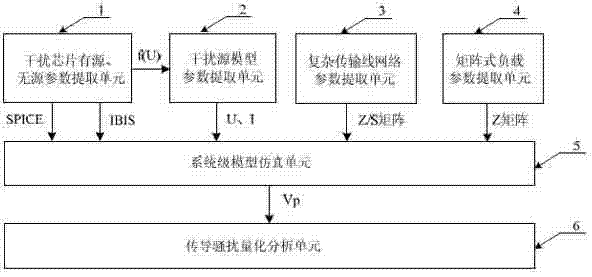

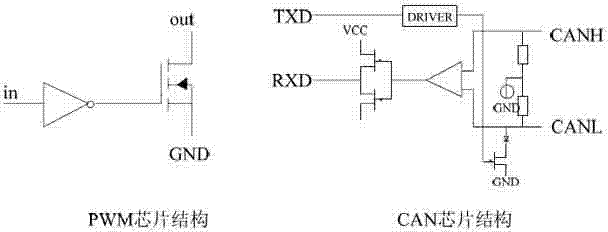

System and method for modeling printed circuit board level conducted electromagnetic interference

ActiveCN103488840ASimulation is accurateGuaranteed to workSoftware simulation/interpretation/emulationSpecial data processing applicationsCapacitanceHemt circuits

The invention relates to the field of electromagnetic compatibility, in particular to a system and a method for modeling printed circuit board level conducted electromagnetic interference. Conducted interference of a power wire port of a certain control circuit board is quantitatively analyzed by extraction through a circuit model and modular modeling. Interference noise sources, equivalent resistance R, inductance L, capacitance C, conductance G parameters and internal logic circuits of devices are acquired by respectively calculating and equalizing circuits, main interference chips, power modules and the like on the circuit board, modular package is performed, so that an equivalent circuit model of the whole power system is built, and conducted interference waveforms and quantitative spectra of points on a power wire can be obtained by circuit simulation. Conducted electromagnetic interference frequency and amplitude of key circuits on the printed circuit board can be quantitatively analyzed at a pre-design phase, portions with poor electromagnetic compatibility are found and optimized, the electromagnetic interference degree of the whole circuit board is reduced, and research and development cycle and cost can be reduced.

Owner:DONGFANG ELECTRIC CORP LTD

Flow measurement apparatus having strain-based sensors and ultrasonic sensors

ActiveUS7237440B2More robustMaterial analysis using sonic/ultrasonic/infrasonic wavesVolume/mass flow by dynamic fluid flow effectUltrasonic sensorEngineering

Owner:EXPRO METERS

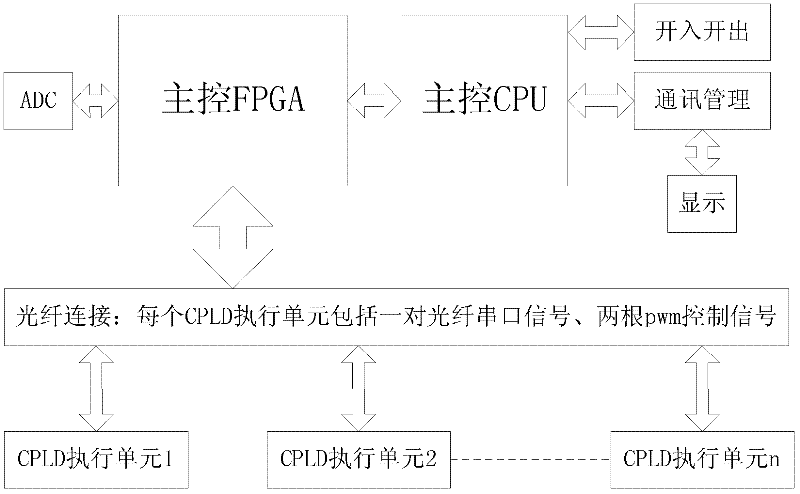

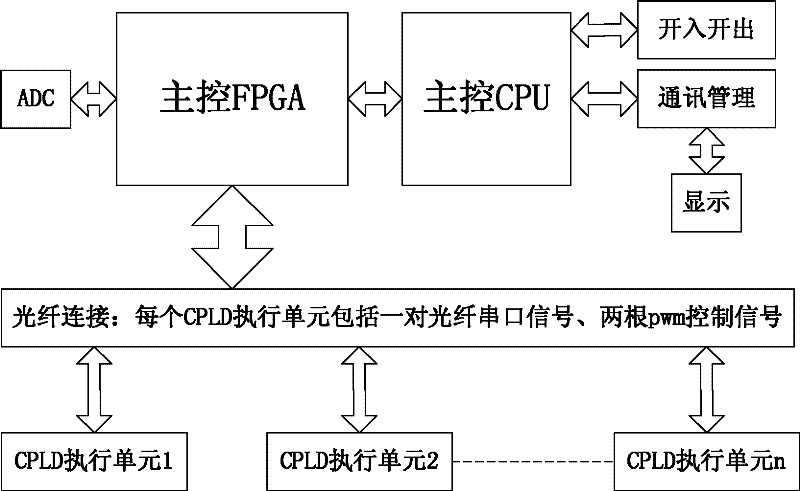

Control system of chain type current transformer

ActiveCN102403880AImprove scalabilityGive full play to the functions of FPGA+CPLDAc-dc conversionHuman–machine interfaceComplex programmable logic device

This invention discloses a control system for realizing a chain type current transformer; the system disclosed by this invention uses a distributed control method so as to satisfy a multi-chain-link expandable control demand in the chain type current transformer; a FPGA (Field Programmable Gate Array) utilizes a parallel processing function, abundant I / O (Input / Output) pins and an expandable internal logic unit so as to realize the operational processing for a plenty of data and the chain type expansion control of the current transformer; a CPU (Central Processing Unit) utilizes own abundant internal resources so as to realize the protection function of a current transformer system; an input / output is capable of controlling and collecting each switching value; communication management provides abundant communication interfaces; a display provides a personalized man-machine interface; CPLD (Complex Programmable Logic Device) executing units realize a branched chain link control function and are connected with the FPGA by optical fibers; the reliability thereof is ensured; the quantity of the CPLD executing units can be increased according to the chain link requirement of the current transformer system; this design completely satisfies the demand of the control system of the current chain type current transformer; in addition, the expandability and the reliability of the currenttransformer chain link are improved greatly.

Owner:BEIJING SIFANG JIBAO AUTOMATION +1

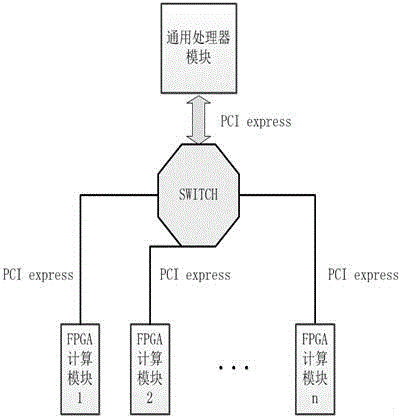

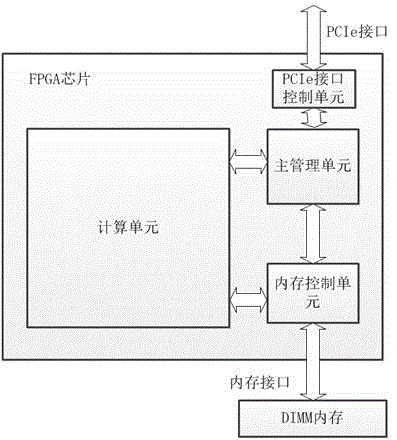

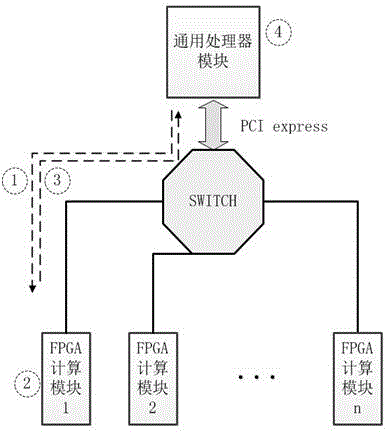

High-performance heterogeneous computing platform based on x86 architecture processor and FPGA (Field Programmable Gate Array)

InactiveCN104657330AFast transmissionImprove programmabilityGeneral purpose stored program computerConcurrent instruction executionComputer architectureInterconnection

The invention discloses a high-performance heterogeneous computing platform based on an x86 architecture processor and an FPGA (Field Programmable Gate Array). The high-performance heterogeneous computing platform belongs to the technical field of computer construction, and comprises a universal processor module with the x86 architecture processor, a PCIe SWITCH module and an FPGA computing module on the basis of a current platform, wherein the universal processor module is responsible for high-performance task distributing and dispatching, flow control and computing result collecting summarizing; an FPGA chip is built in the PCIe SWITCH module; the PCIe SWITCH module is responsible for interconnection and a data transmission task between the universal processor module and the FPGA computing module; the FPGA computing module is used for converting data to be operated into a computing result through internal logic, and processing and storing. According to the high-performance heterogeneous computing platform based on the x86 architecture processor and the FPGA, the expandability of a computing system is strong; appropriate FPGA computing module quantity is designed according to the application of different scales, so that higher computing parallelism is achieved, and the aim of improving the whole computing performance is achieved.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

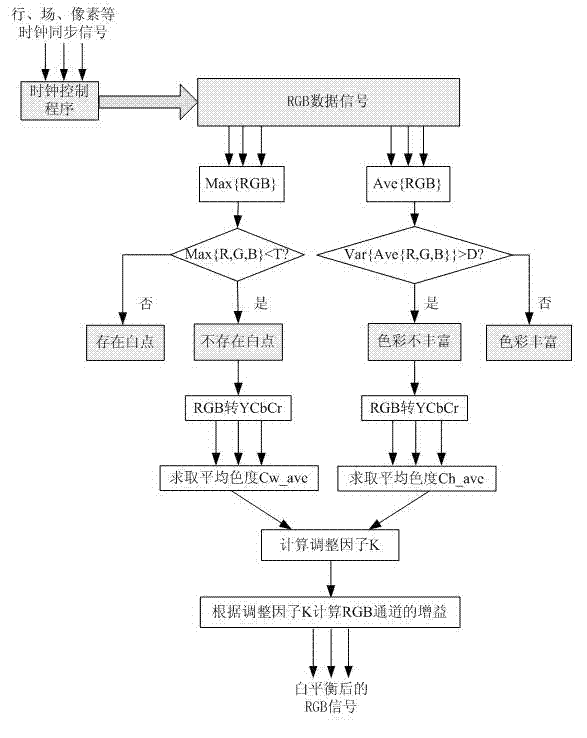

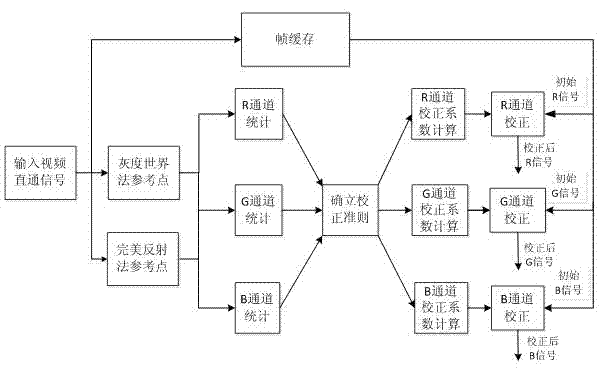

White balance processing method directed towards atypical-feature image

InactiveCN102883168AVersatileExtensive processing effectsColor signal processing circuitsInternal memoryBright spot

The invention relates to a white balance processing method directed towards an atypical-feature image. The method comprises the following steps: (1) acquiring the brightest spot RGB (Red, Green and Blue) information of a frame of images as well as an RGB mean through a Camera Link industrial camera; (2) scanning the frame of video images, setting a white spot brightness threshold value and an RGB channel difference threshold, and determining whether current images contain a white area or not and color is rich or not; (3) performing color space conversion on the current images if the current images are determined that the white region is not contained and the color is not rich, and respectively calculating an average chromaticity Cw_ave of a reference point of a perfect reflection method and an average chromaticity Ch_ave of a reference point of a gray world method; and (4) calculating an average chromaticity Cw_ave obtained by the perfect reflection method and an average chromaticity Ch_ave obtained by the gray world method directed towards the current images, and performing white balance correction combined with two classic algorithms on the current frame of images by using the ratio of the Cw_ave and (the Cw_ave plus the Ch_ave) as an adjustment factor K. The method can be realized by using the recourses of an FPGA (Field Programmable Gata Array) internal logic unit, an internal memory, a multiplier and the like.

Owner:SHANGHAI UNIV

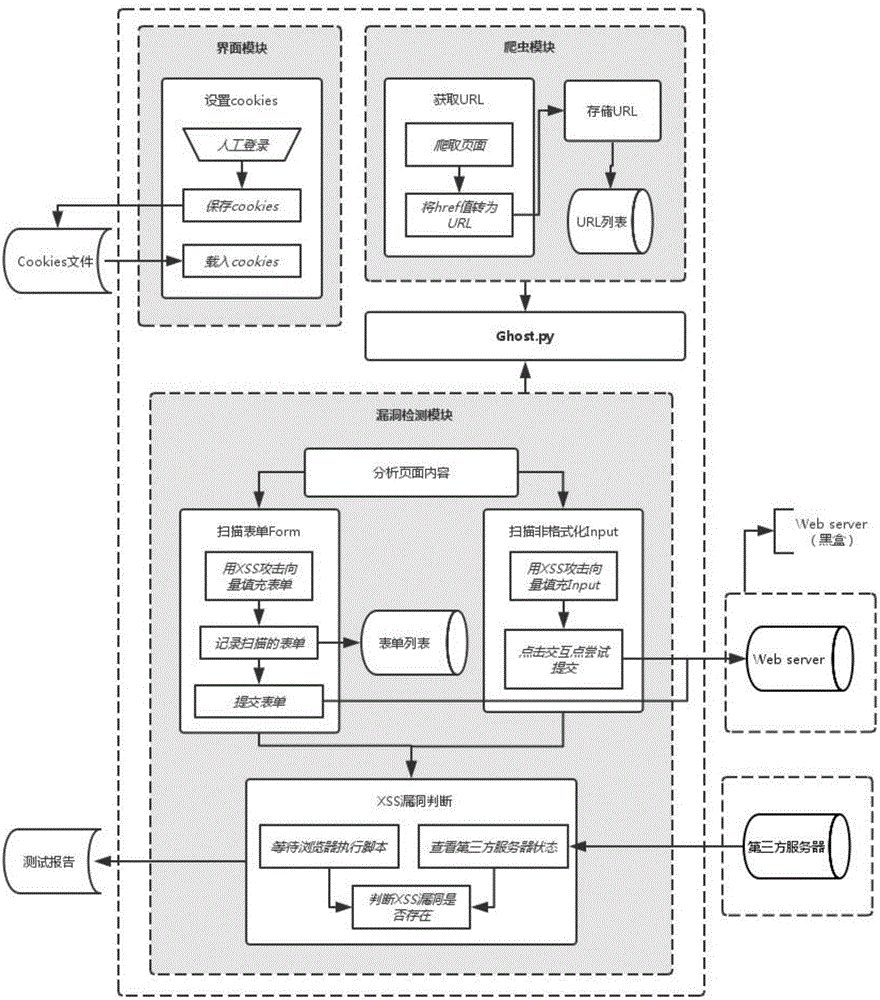

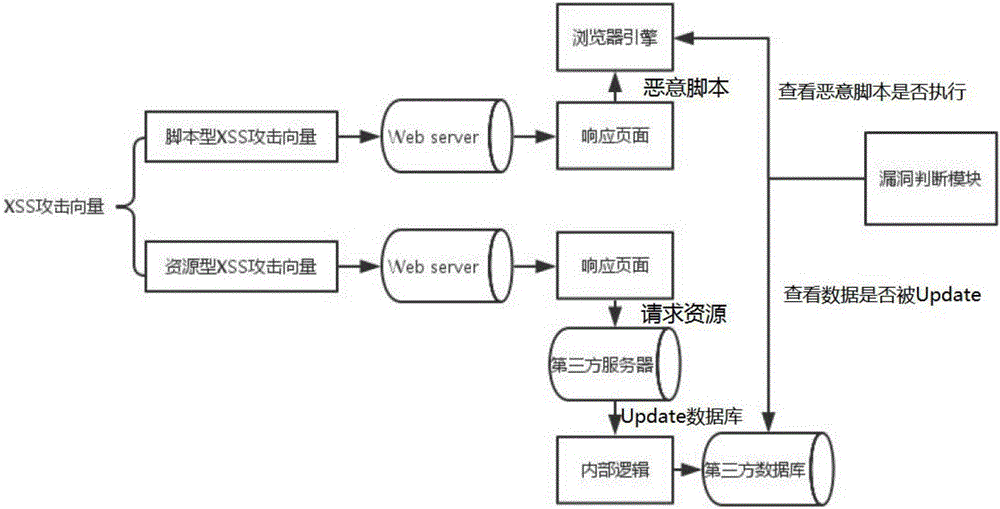

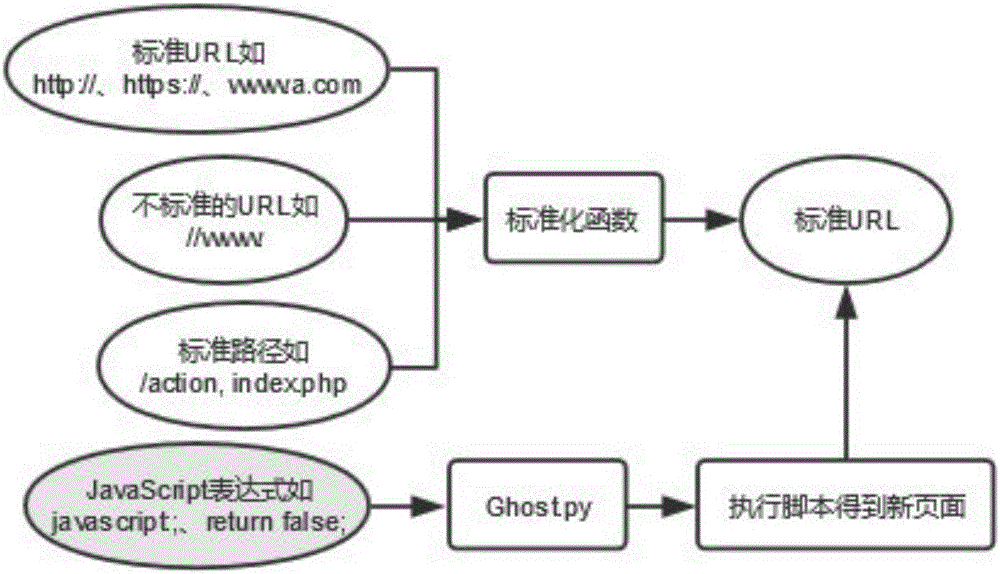

Automatic detection system capable of dynamically determining XSS vulnerability

An automatic detection system capable of dynamically judging XSS vulnerabilities, the system is composed of a crawler module, a dynamic vulnerability detection module and a user interaction interface. The software system introduces a library containing the browser kernel, which can simulate browser behavior to parse JavaScript and load Ajax to obtain hidden injection points and interaction points in the page, and find unconventional web submission request methods through static analysis of the page structure. Compared with the traditional static method and the method without dynamic judgment module, the coverage rate of injection point identification is greatly improved. The injection point test uses a black-box method without considering the internal logic of the server. After submitting the attack vector, it can detect whether there is any abnormality on the page by simulating the behavior of the browser, that is, it can detect whether the browser has executed the web script, and can directly judge It is more accurate to find out whether the current injection point is vulnerable. In addition, the system is completely developed in Python language, which is easy to maintain and carry out secondary development.

Owner:BEIJING UNIV OF TECH

System and method for providing graphical representation and development of a processing application

ActiveUS7512840B2Good serviceError detection/correctionNatural language data processingChange managementWeb service

A system and methods are provided for operating and building graphically XML processing programs, guiding the user in development of the program, preventing and detecting development errors as the program is being designed, ensuring that the program is valid, i.e. satisfies required input and output constraints at all times, i.e. from the time it is developed to when it is deployed in a production environment, ensuring the automated change management if the internal logic of the Web service, or data sources called by the service or the schema that underlies the Web service are modified. The system includes a graphical XML Programming system where XML processing programs are built and represented in a graphical fashion, a real-time metadata computation and visualization method for each selected execution point in the visual program that provides guided programming, error prevention and detection, and change impact analysis and change management, and, an automated execution path exploration method that enables overall program validation and error identification. The system and methods allow a user to reduce by at least a factor of 2 the costs of development and maintenance of reliable XML processing programs such as Web Services.

Owner:DIEBOLD NIXDORF

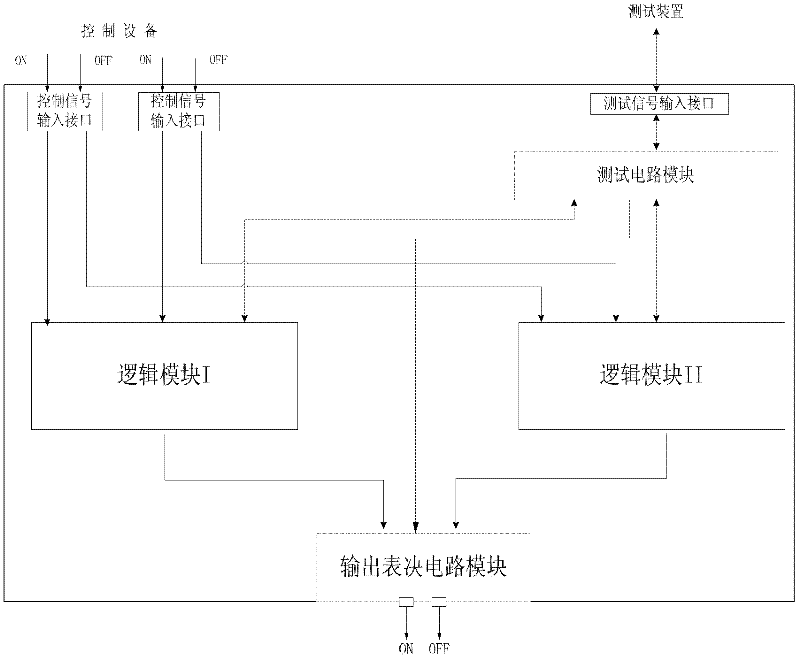

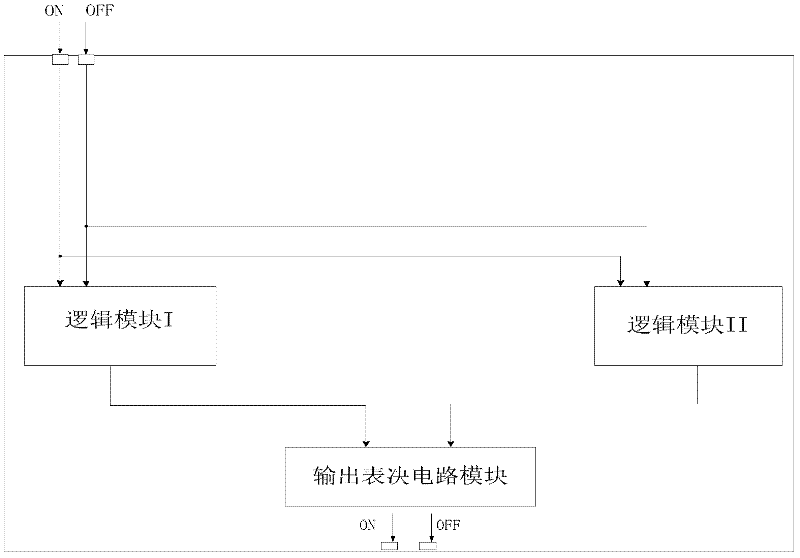

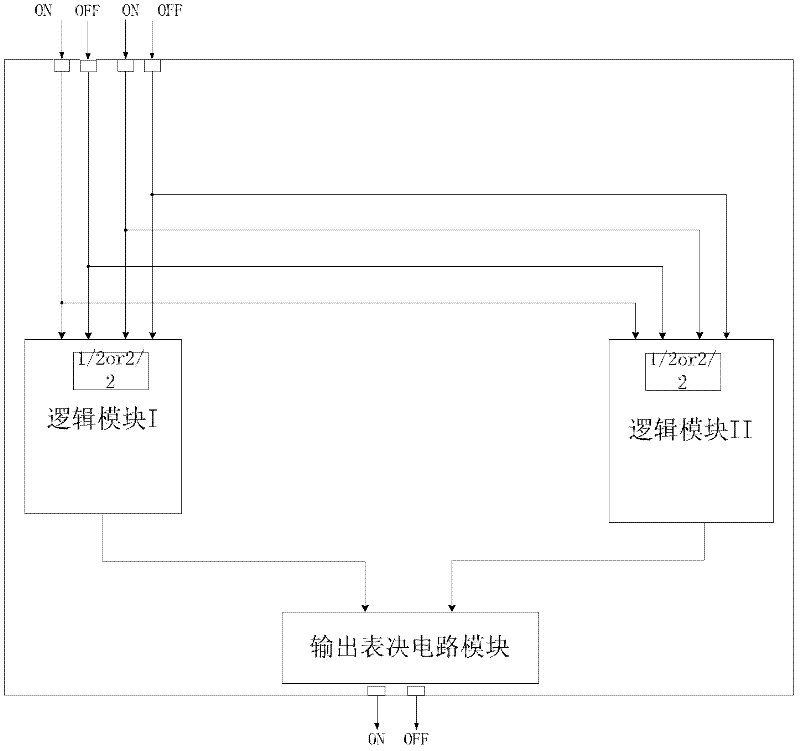

Multifunctional driving module

ActiveCN102394117AImprove reliabilitySimple logicNuclear energy generationNuclear power plant controlAutomatic controlControl signal

The invention discloses a multifunctional driving module, and relates to the field of nuclear power plants. The multifunctional driving module comprises an input interface and an output interface; a testing circuit module, a functional logic circuit module and an output voting circuit module are arranged in the driving module; and the input interface comprises a control signal input interface anda testing signal input interface. The driving module employs programmable hardware (such as a CPLD (Complex Programmable Logic Device) or an FPGA (Field Programmable Gate Array) chip) to design the functional logic circuit, and the internal logic can be compiled according to the practical use, for example, the redundant voting (such as AND or NOT) logic and the priority processing logic for a received control signal are realized. The driving module is designed by a hardware circuit without operating software, and is high in reliability; and all the interfaces are in the form of hard wiring and can undergo interface application with automatic control platforms such as DCS (Distributed Control System), PLC (Programmable logic controller), etc.

Owner:CHINA TECHENERGY +1

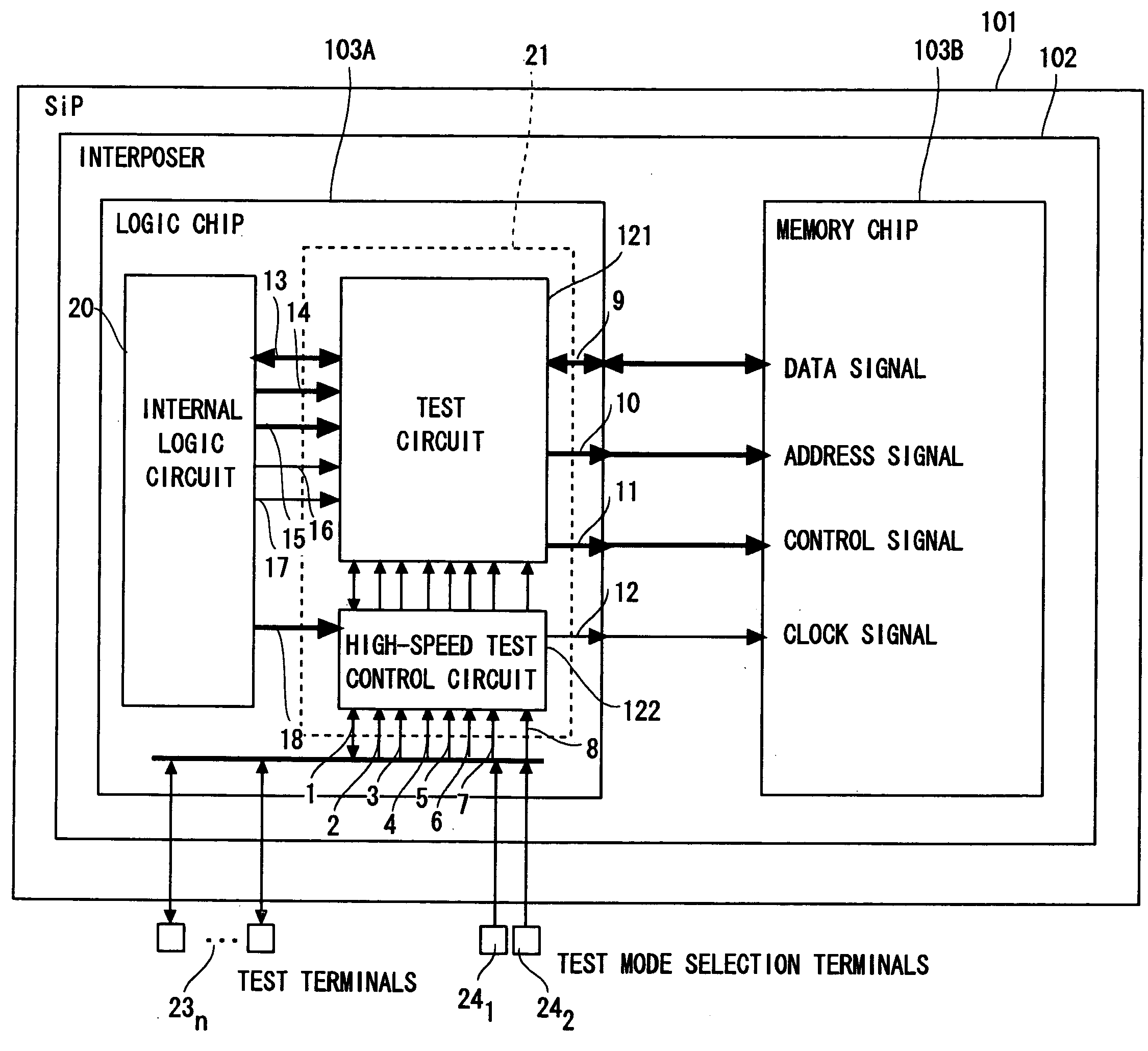

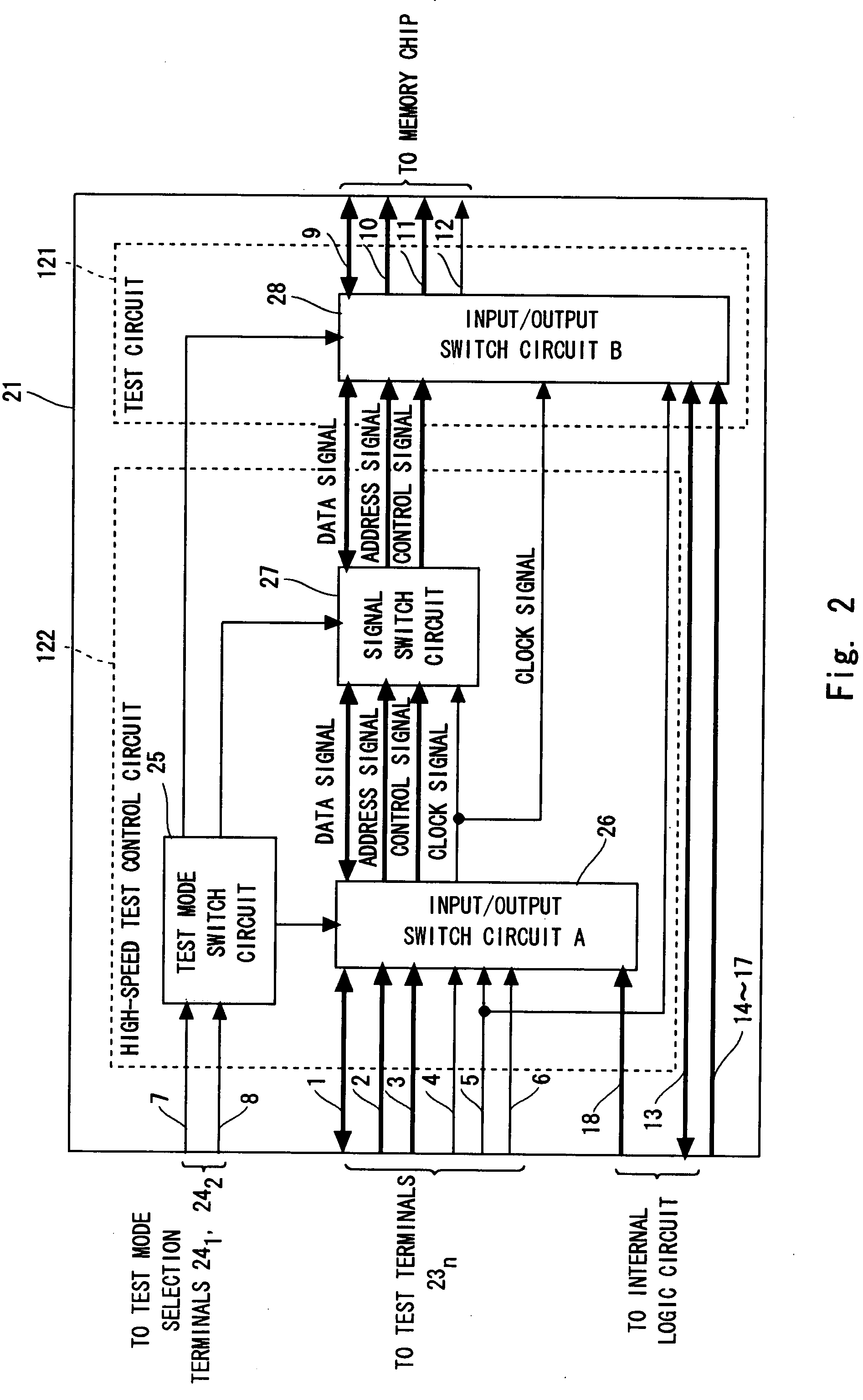

Semiconductor apparatus and test method therefor

InactiveUS20070245200A1Increase speedElectronic circuit testingError detection/correctionElectricityMemory chip

A SiP includes a logic chip and a memory chip. The memory chip includes a memory circuit to be tested, and the logic chip includes an internal logic circuit and a test processor electrically connected therewith. The test processor is connected with an access terminal of the memory circuit and supplies a test signal input from an external terminal to the access terminal to thereby test the memory circuit. The test processor includes a high-speed test control circuit to adjust signal delay and supplies a test signal from the external terminal to the access terminal through the high-speed test control circuit when performing high-speed test at an actual operation speed.

Owner:RENESAS ELECTRONICS CORP

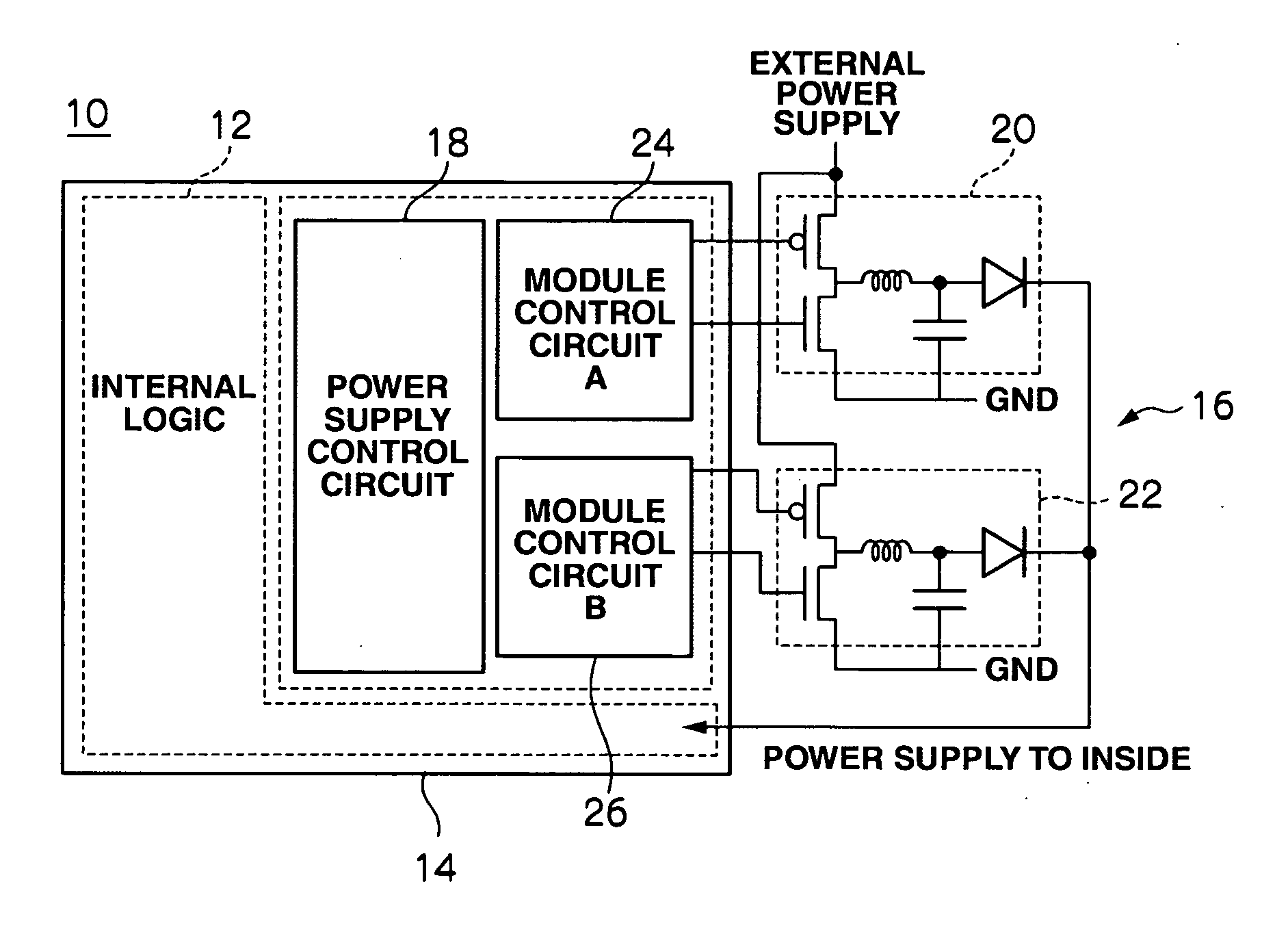

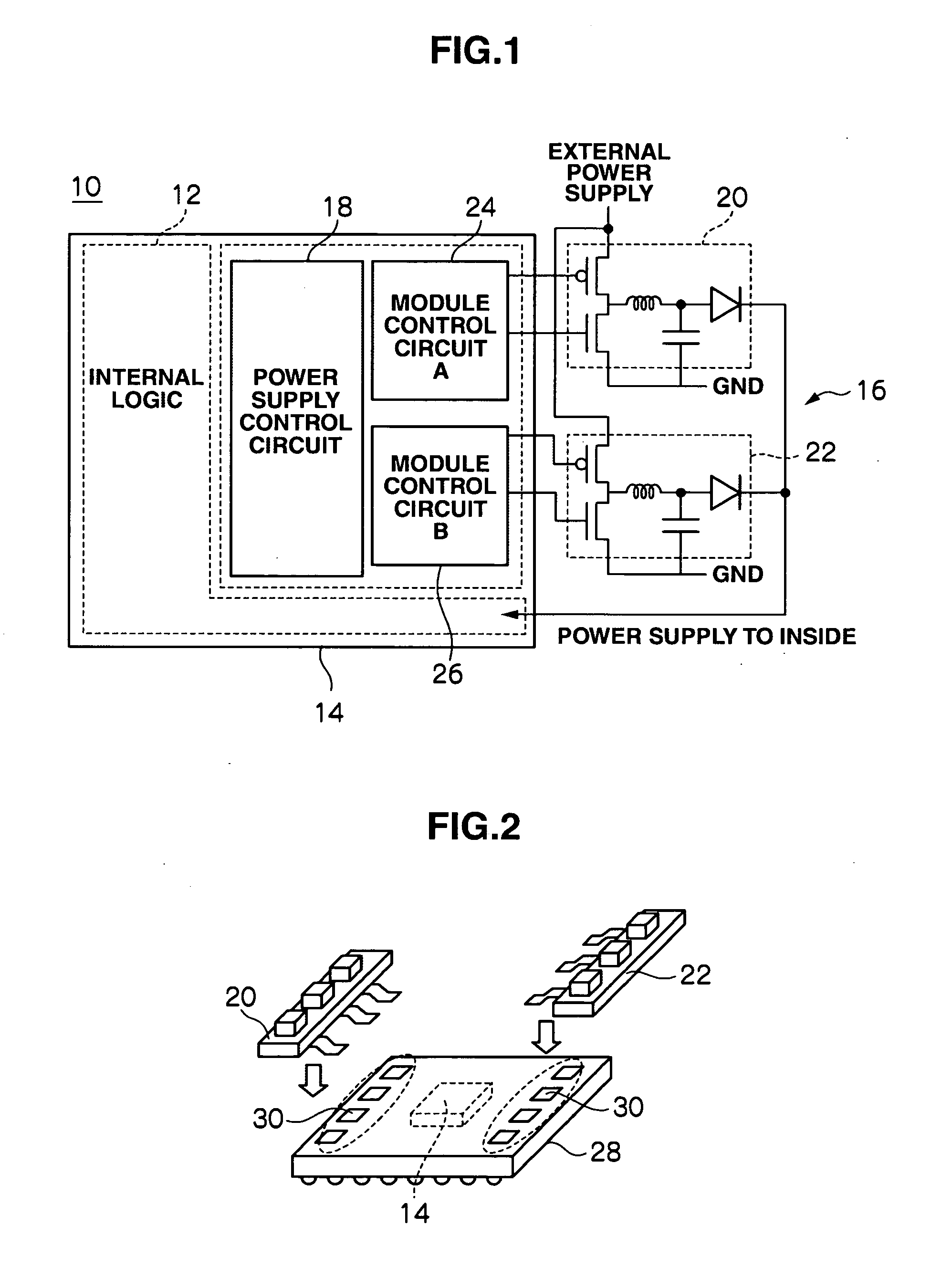

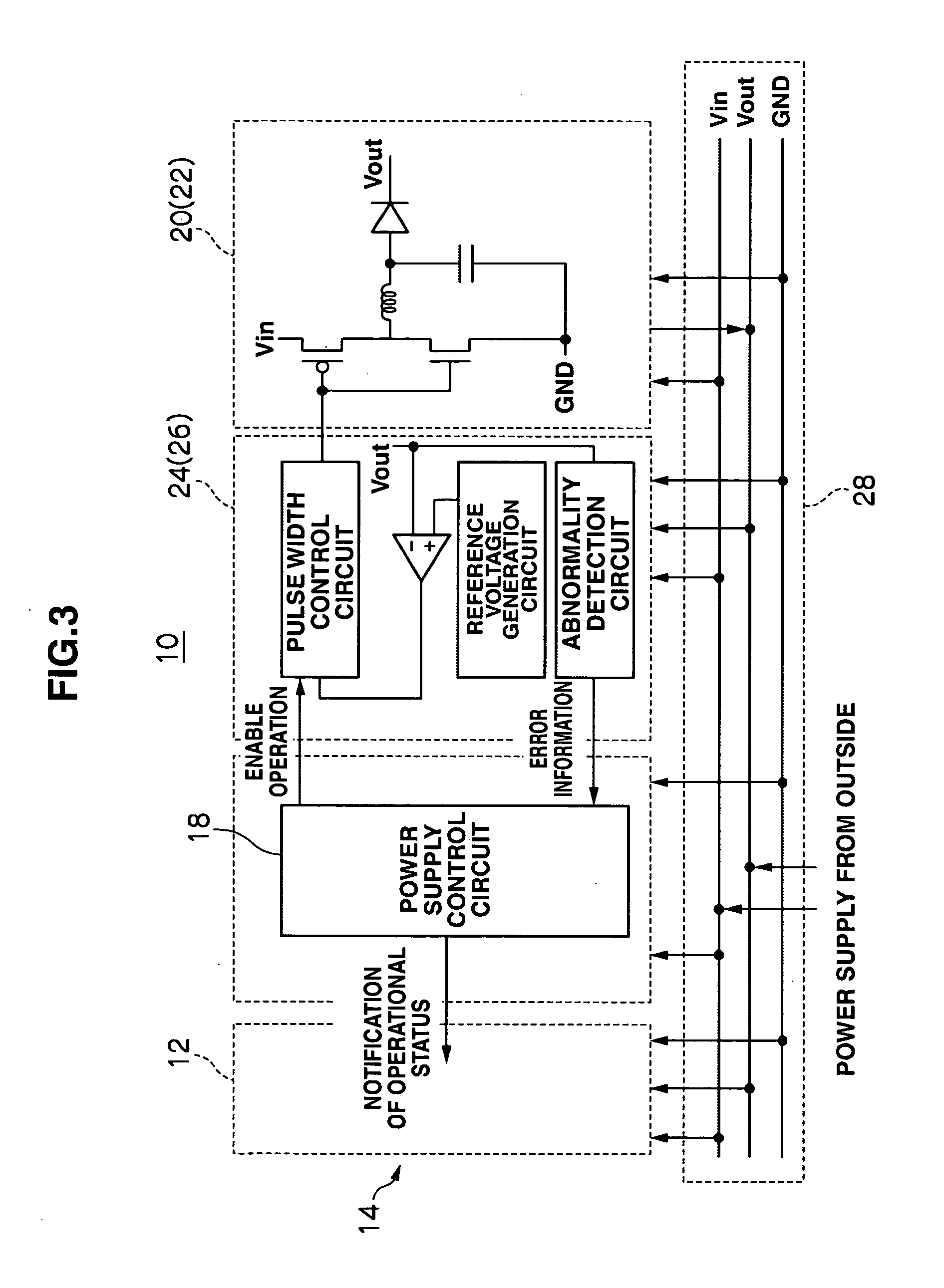

Semiconductor integrated circuit and semiconductor integrated circuit device

InactiveUS20070226557A1Improve reliabilityElectronic circuit testingDigital data processing detailsMultiplexingControl circuit

An LSI chip has an internal logic, power supply control circuit and module control circuits, mounted thereon. External modules are provided outside the LSI chip. A power supply circuit for supplying power to the internal logic is composed of the module control circuits and external modules, that is, the power supply circuit is multiplexed, so that if a failure occurs in one of the power supplies, a different normally-operating power supply supplies power to the internal logic. Accordingly, the reliability of the LSI chip is improved.

Owner:GOOGLE LLC

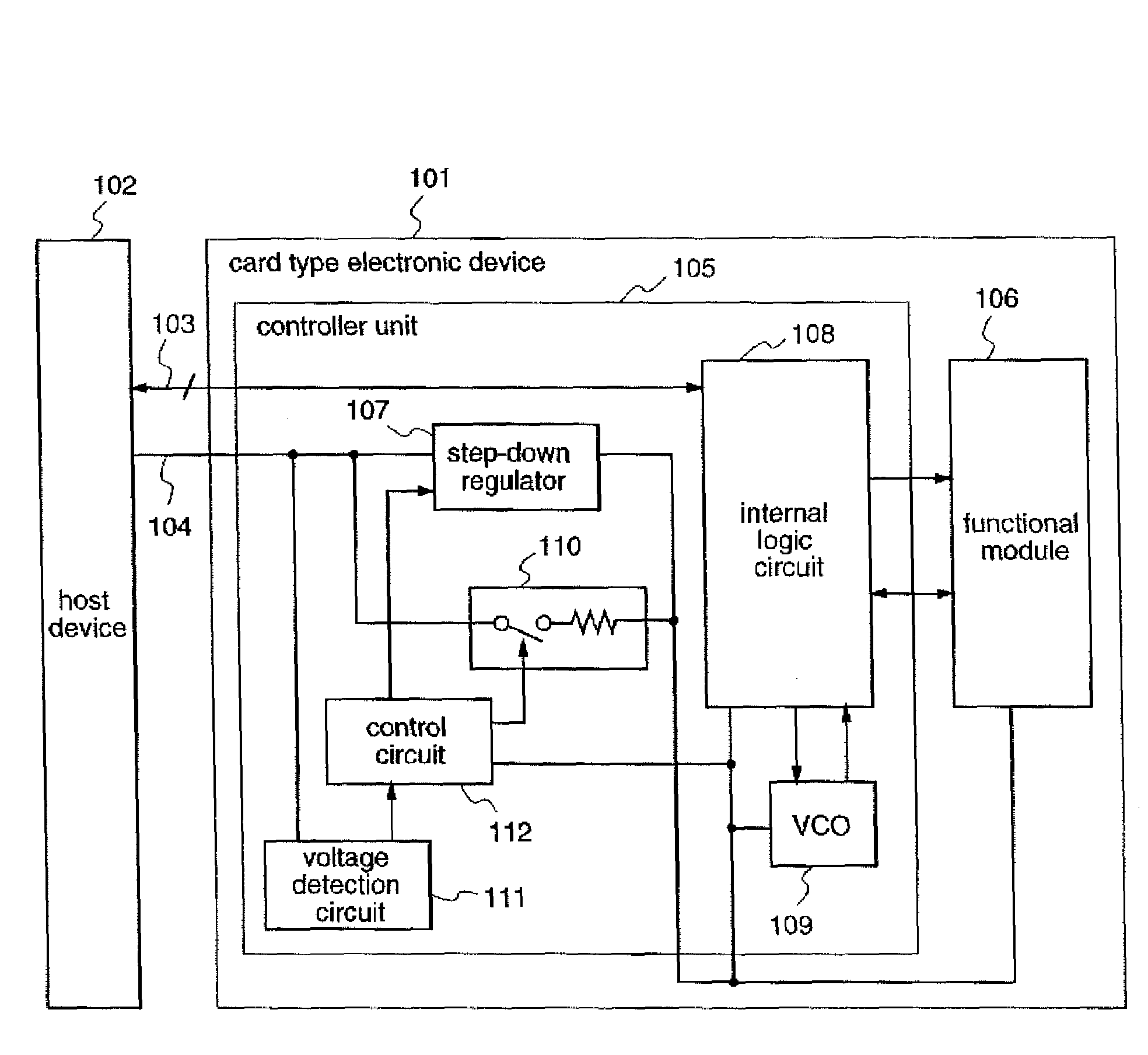

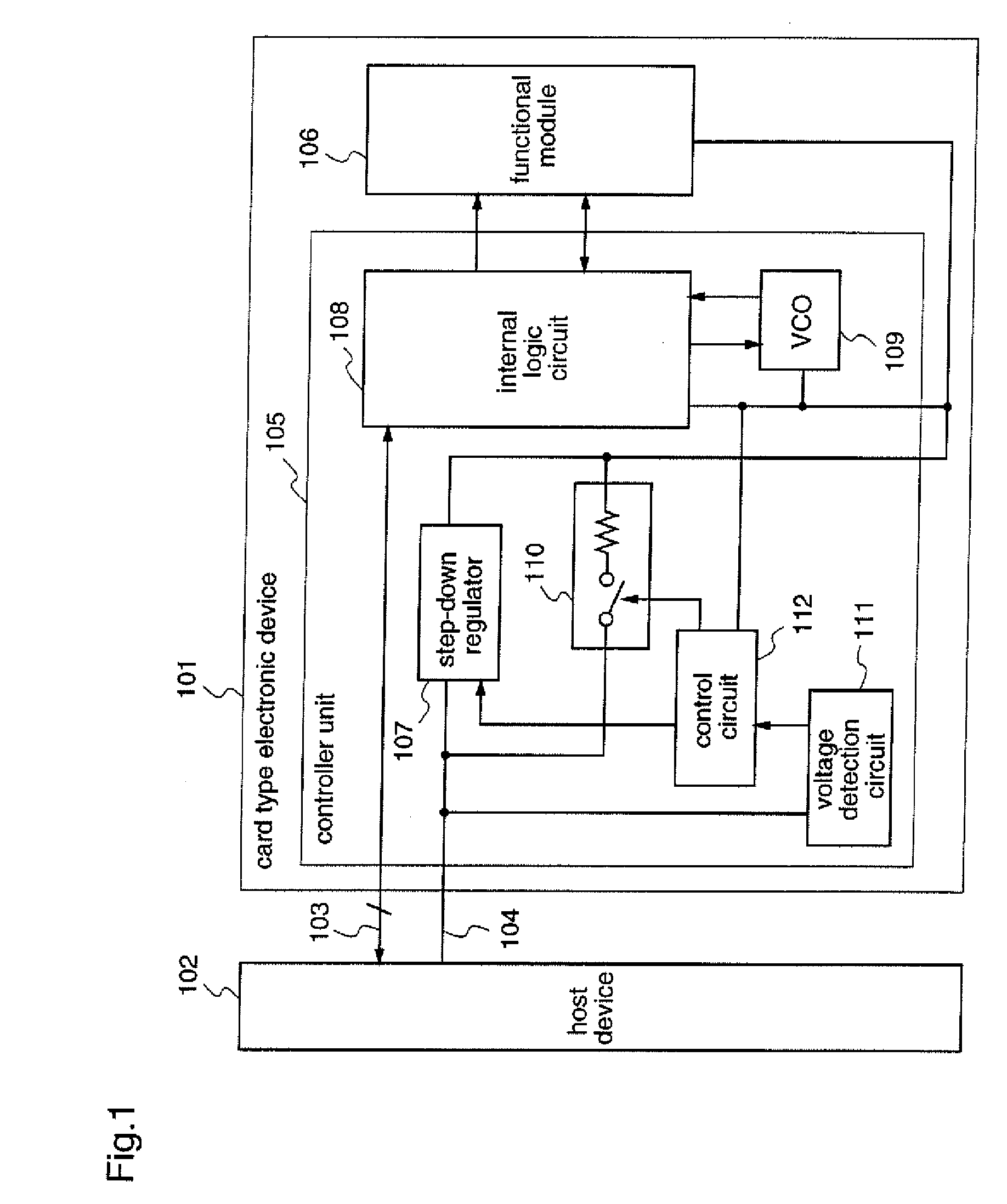

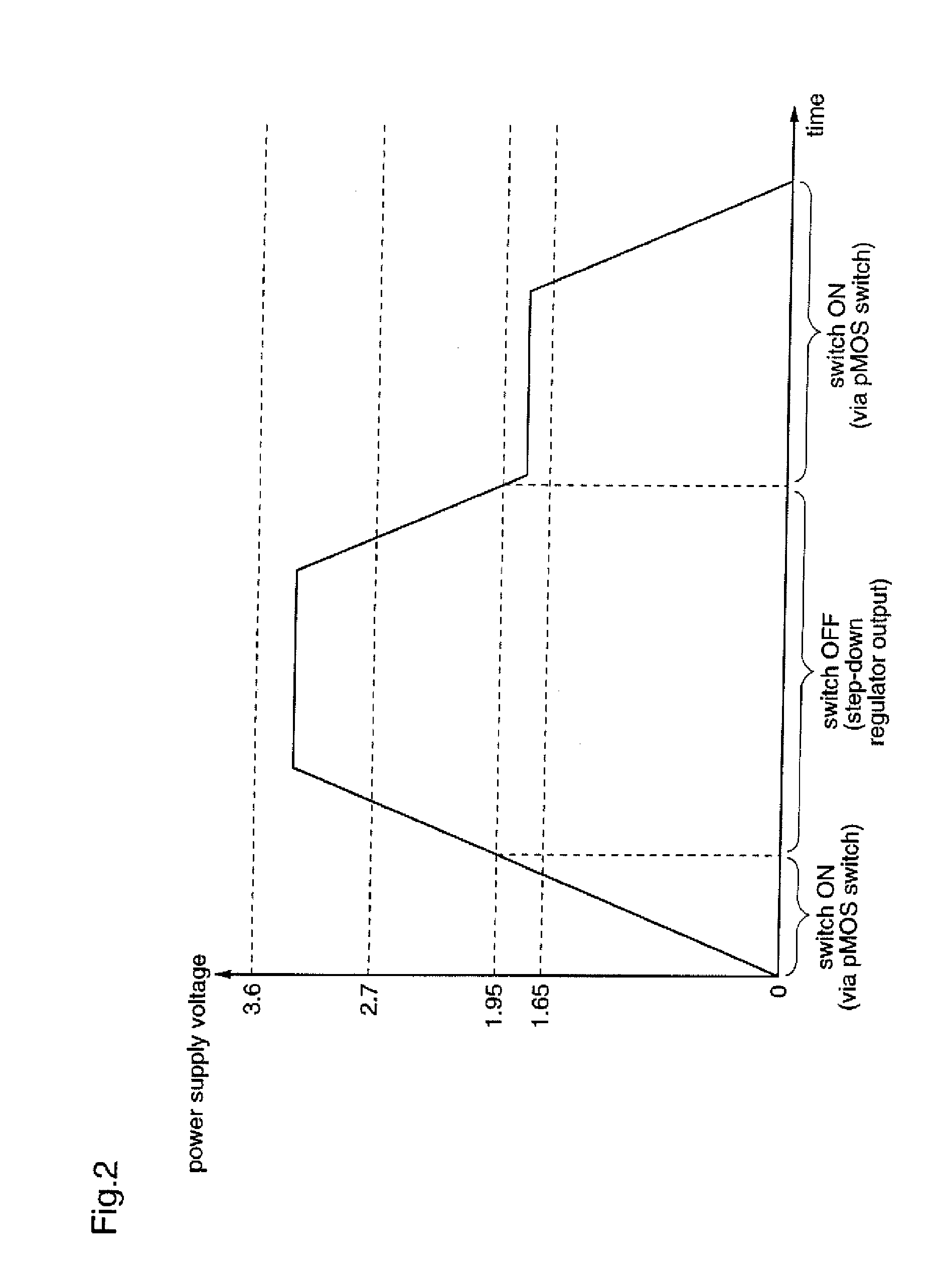

Card-type electronic device and host device

InactiveUS20090077393A1Reduce power consumptionSimple designVolume/mass flow measurementPower supply for data processingComputer moduleEngineering

A card type electronic device according to the present invention comprises a p MOS switch (110) connected to a power supply line (104), a step-down regulator (107) for stepping down a power supply voltage, a voltage detection circuit (111) for detecting a power supply voltage value and outputting information as to whether the value exceeds a predetermined voltage value or not, a control circuit (112) for turning on the pMOS switch (110) to halt the step-down regulator (107) when the power supply voltage of the power supply line (104) is equal to or lower than the predetermined voltage value, and turning off the pMOS switch (110) to activate the step-down regulator (107) when the power supply voltage exceeds the predetermined voltage value, and an internal logic circuit (108) which is operated with the power supply voltage supplied via the pMOS switch (110) or the output voltage supplied from the step-down regulator (107), and performs control for a functional module (106) and communication control with external devices. Accordingly, even when the power supply voltages within two kinds of voltage ranges are supplied from the host device, power supply voltages within appropriate voltage ranges can be applied to the respective internal blocks.

Owner:PANASONIC CORP

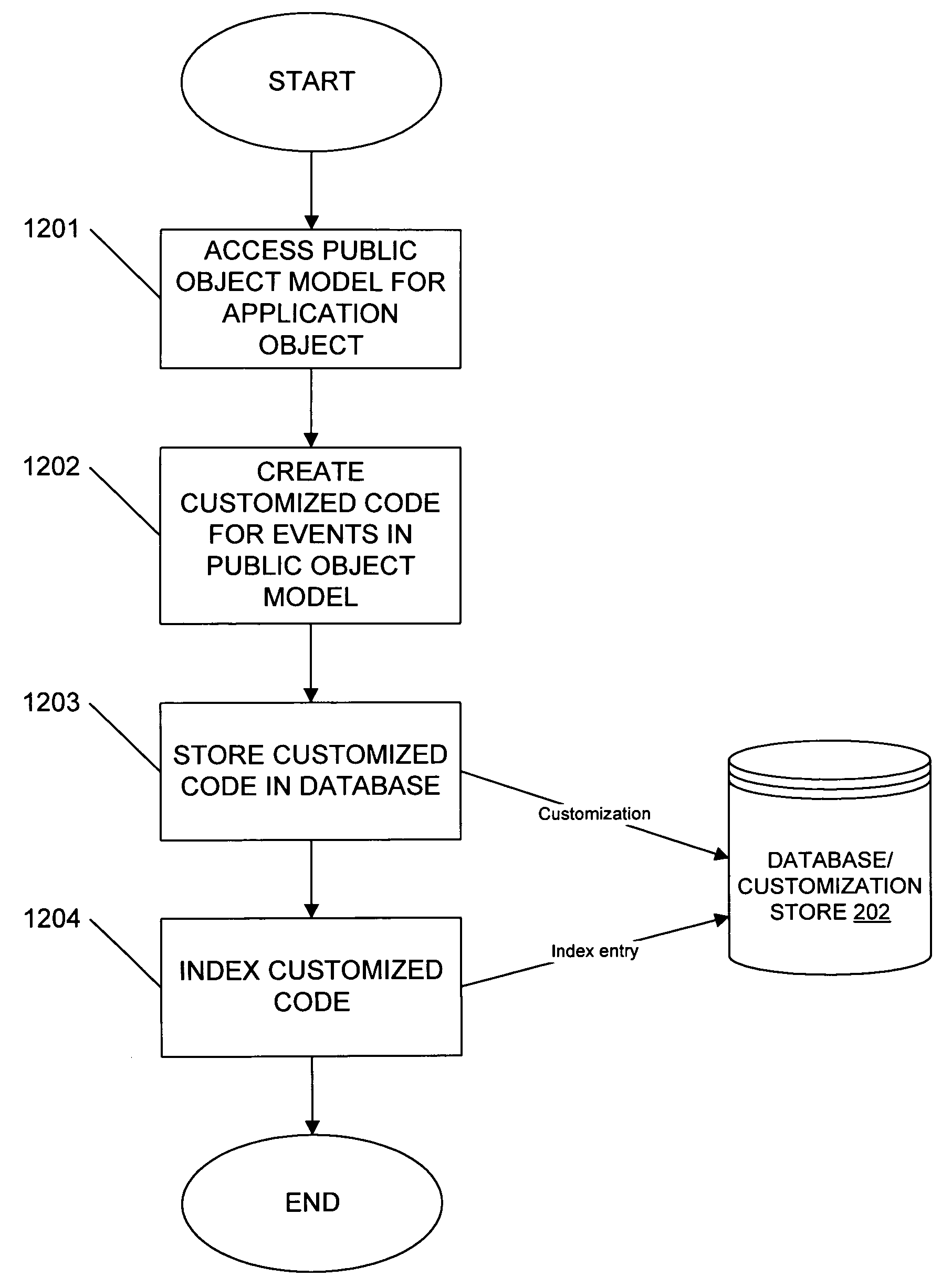

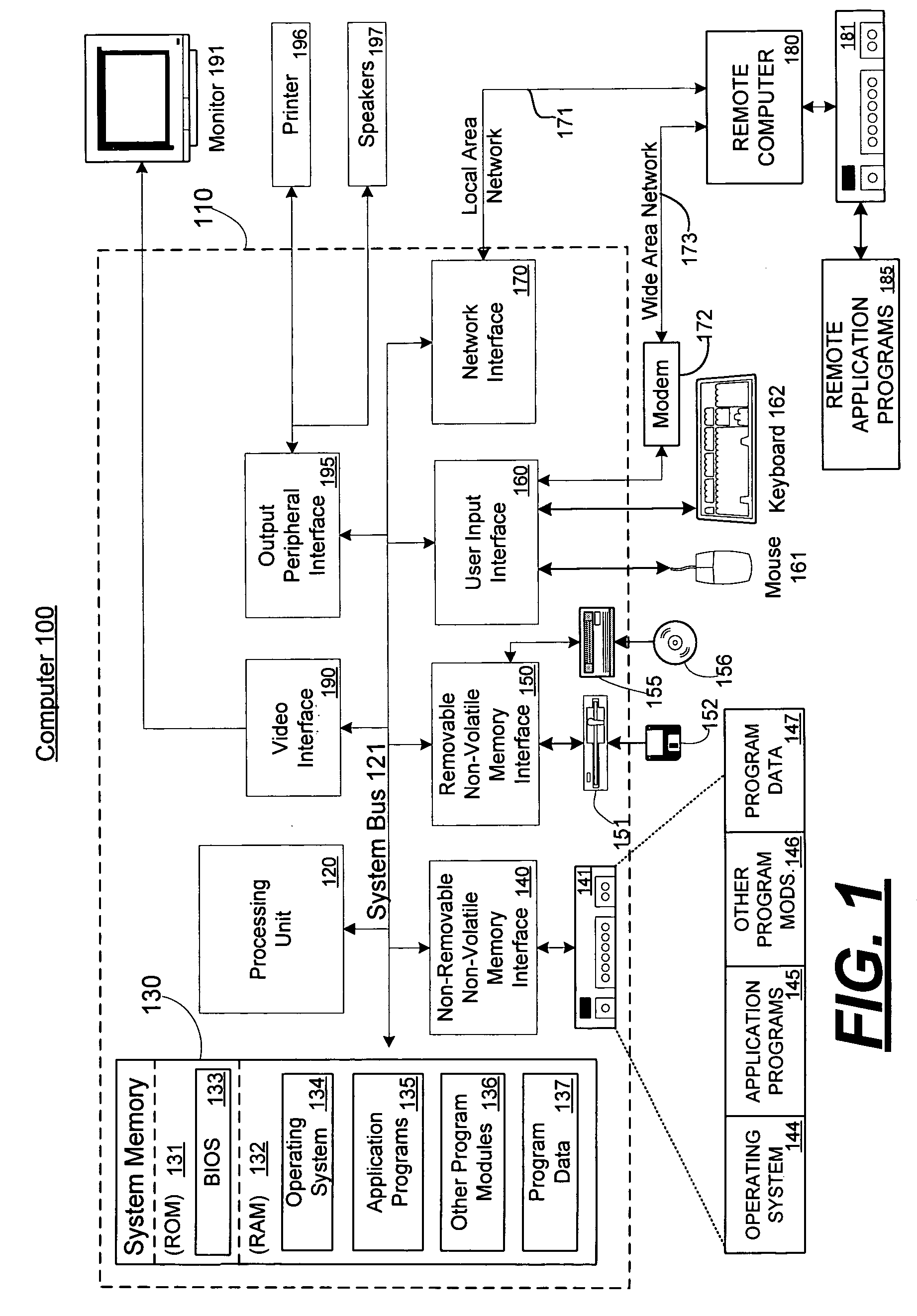

Architecture for customizable applications

InactiveUS20050251797A1Convenient and efficient retrievalFast executionSoftware maintainance/managementProgram loading/initiatingRunning timeApplication object

An architecture for customizable applications includes an application object and a customization object. The application object has internal logic that performs a set of fixed or predetermined actions, and a public object model. The public object model includes a set of public methods that are invocable on the application object, and a set of event source which are methods that can be implemented by a programmer and are called by the internal logic of the application object. By implementing methods invocable by the event sources, it is possible to extend and customize the functionality of the application object. The customizations are stored in a customization database for retrieval during the dynamic operation of the application object. Each customization may be identified by a “moniker,” which is a string having a hierarchical format. The moniker is derived partly from fixed data known to the application object, and partly from environmental data that is ascertained by the application object at run time.

Owner:MICROSOFT TECH LICENSING LLC

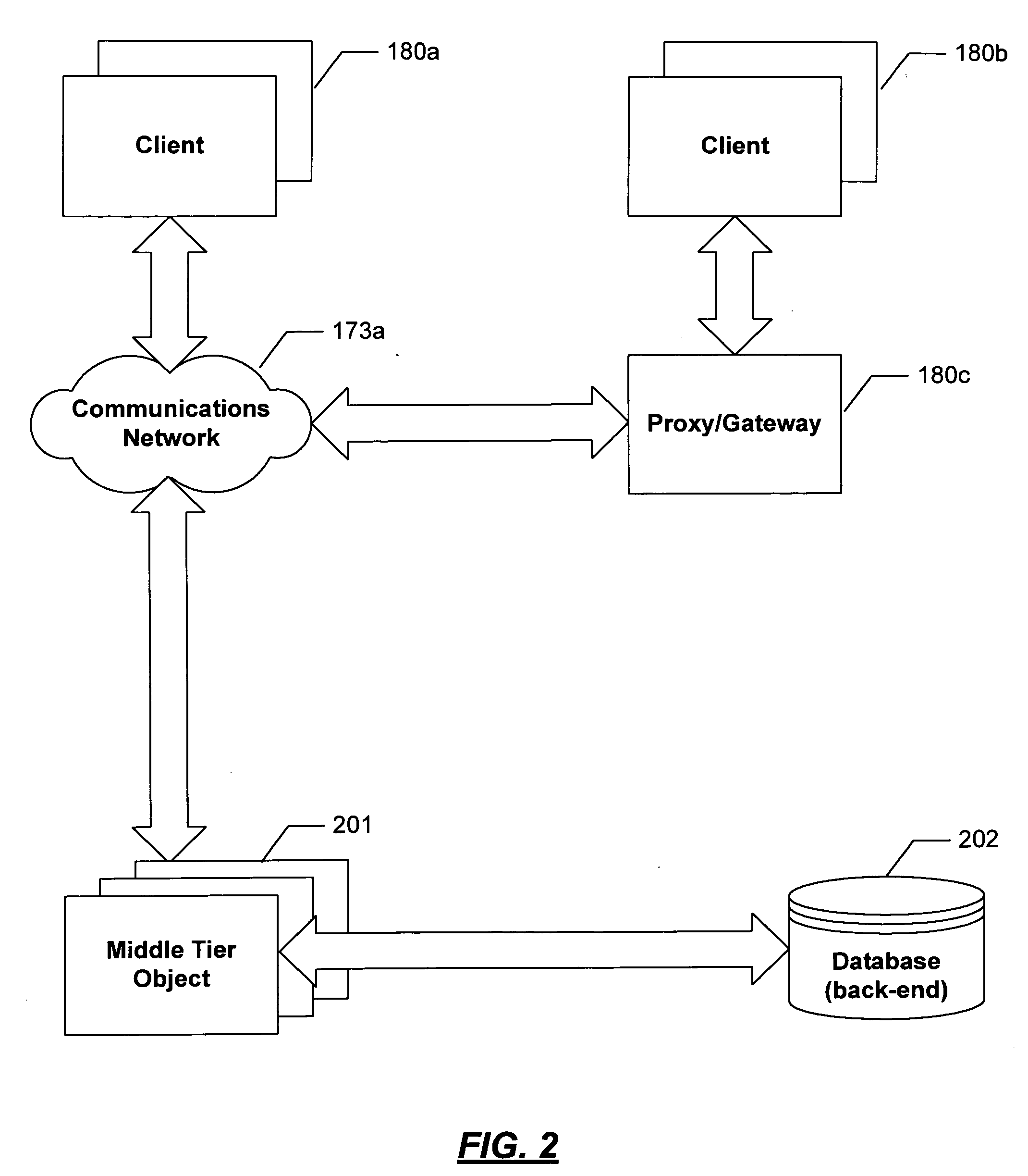

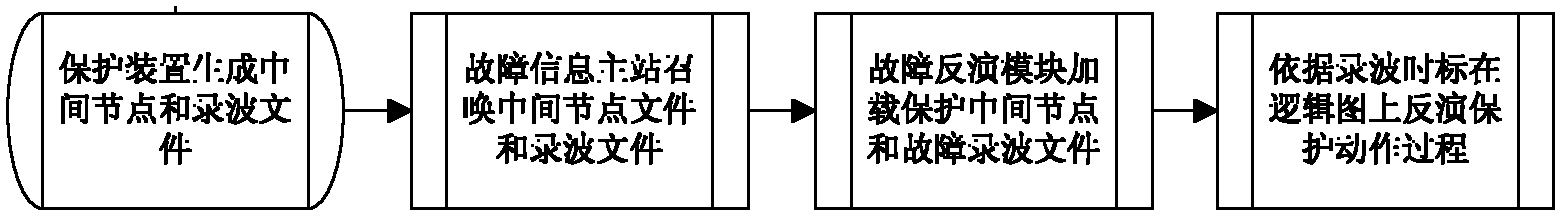

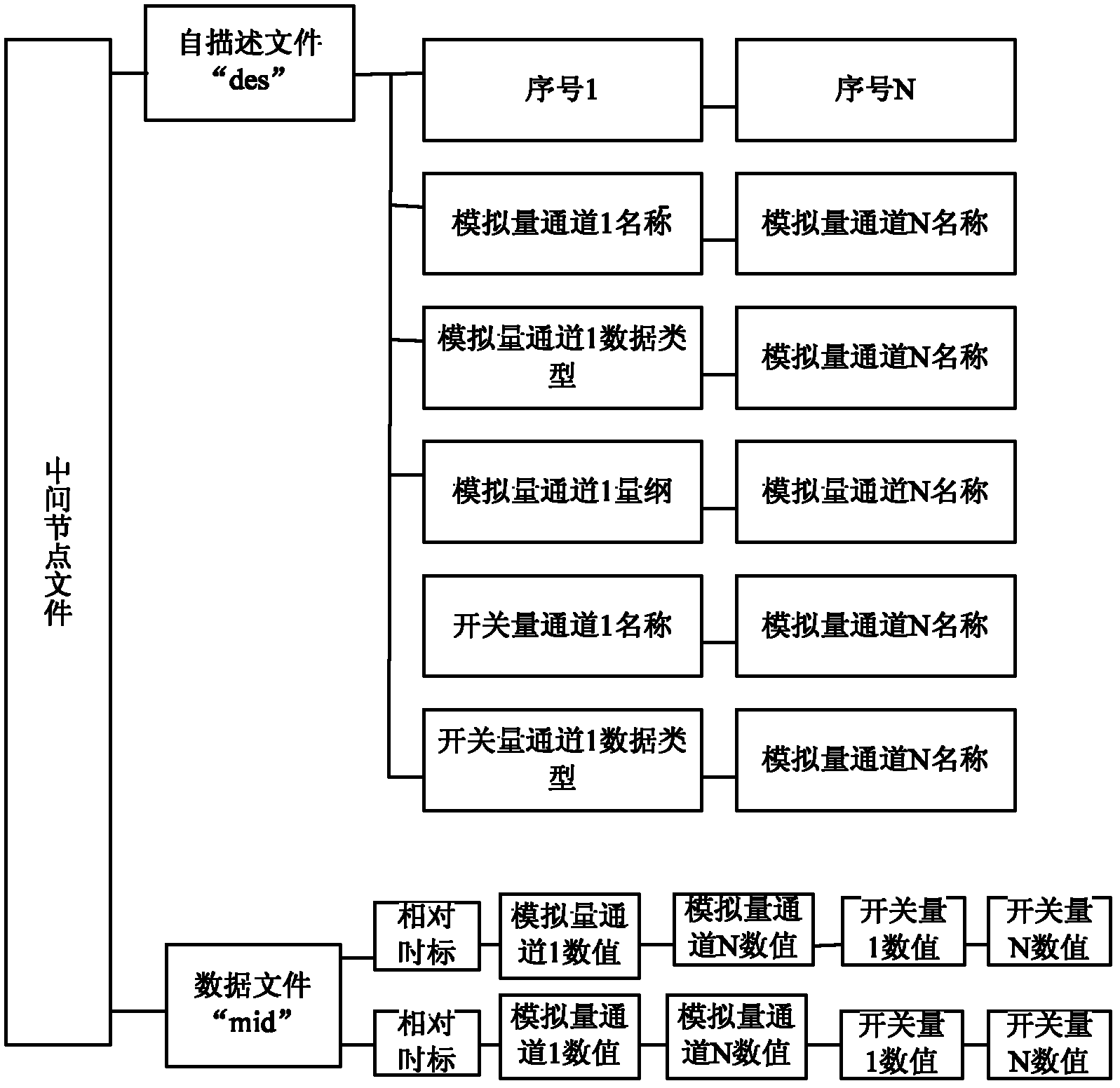

Remote inversion method of internal action logic of protection device

ActiveCN102496930AFast information routeAccurate Information ApproachInformation technology support systemAc network circuit arrangementsElectric power systemLogical process

The invention provides a realization method in which intermediate node information correlated to an internal action logic of a relay protection device is uploaded and a visual logic diagram is combined to invert a protection process of the internal logic when there is a fault at a power grid. The provided method can be applied to a power grid fault information system. And the method comprises the following steps that: when there is a fault at a power grid, internal logic operation information of a relay protection device is processed to generate an intermediate node file that can describe the fault in detail; according to an IEC61850-8-1 protocol, the relay protection device uploads the intermediate node file and a fault wave-recording COMTRADE file to a remote fault information master station; and a visual application module loads the intermediate node file, the protection logic diagram file and the COMTRADE fault wave-recording file to demonstrate a protection logic operation situation in the whole fault process. According to the invention, a visual observation means is provided for inversion of an accident in a power system; and a rapid, accurate, and high efficient informational way is provided for accident localization and a fault analysis; therefore, an action process of a relay protection device is hyalinized and the visibility is realized.

Owner:STATE GRID ZHEJIANG ELECTRIC POWER +1