Patents

Literature

3399 results about "Equivalent circuit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In electrical engineering and science, an equivalent circuit refers to a theoretical circuit that retains all of the electrical characteristics of a given circuit. Often, an equivalent circuit is sought that simplifies calculation, and more broadly, that is a simplest form of a more complex circuit in order to aid analysis. In its most common form, an equivalent circuit is made up of linear, passive elements. However, more complex equivalent circuits are used that approximate the nonlinear behavior of the original circuit as well. These more complex circuits often are called macromodels of the original circuit. An example of a macromodel is the Boyle circuit for the 741 operational amplifier.

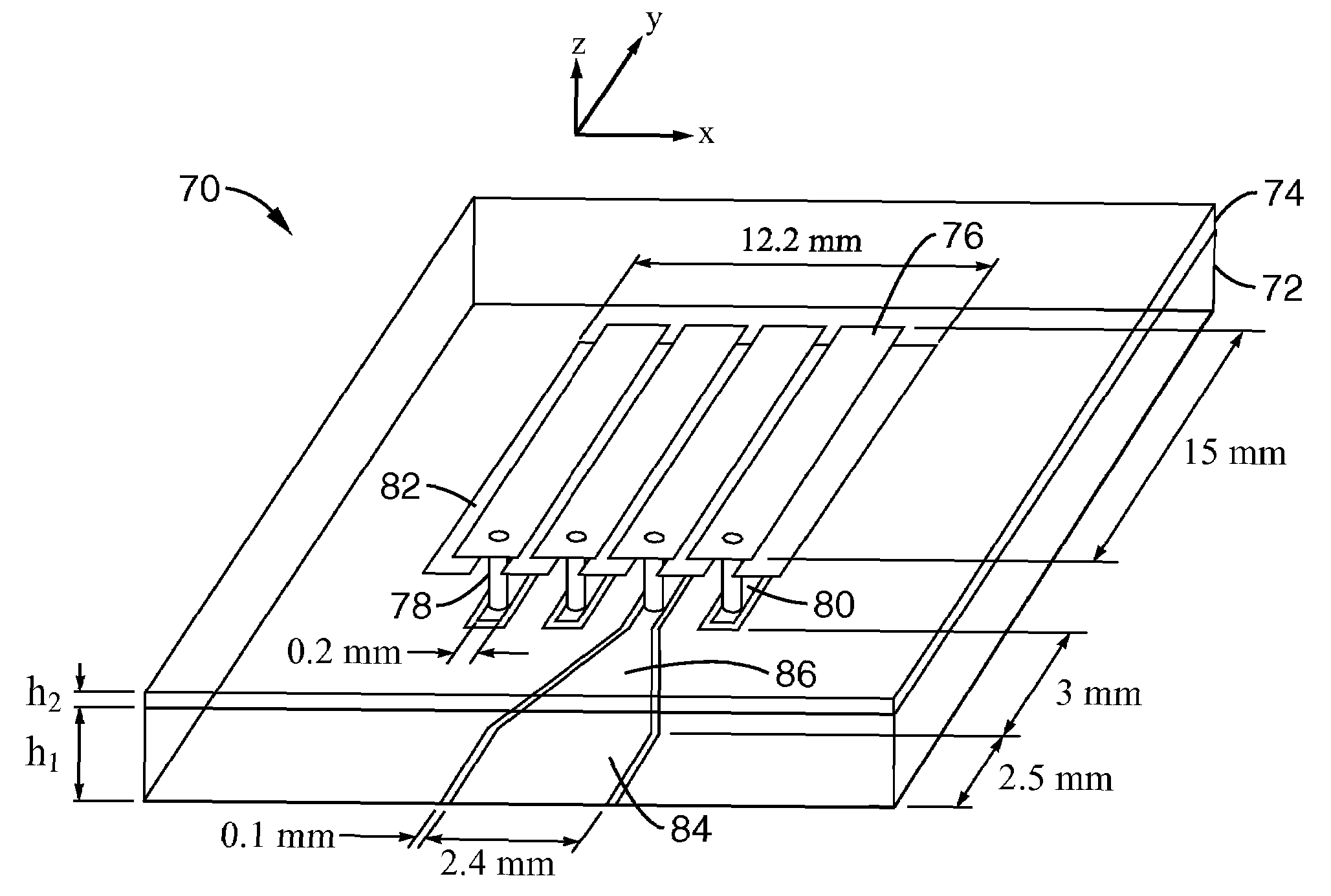

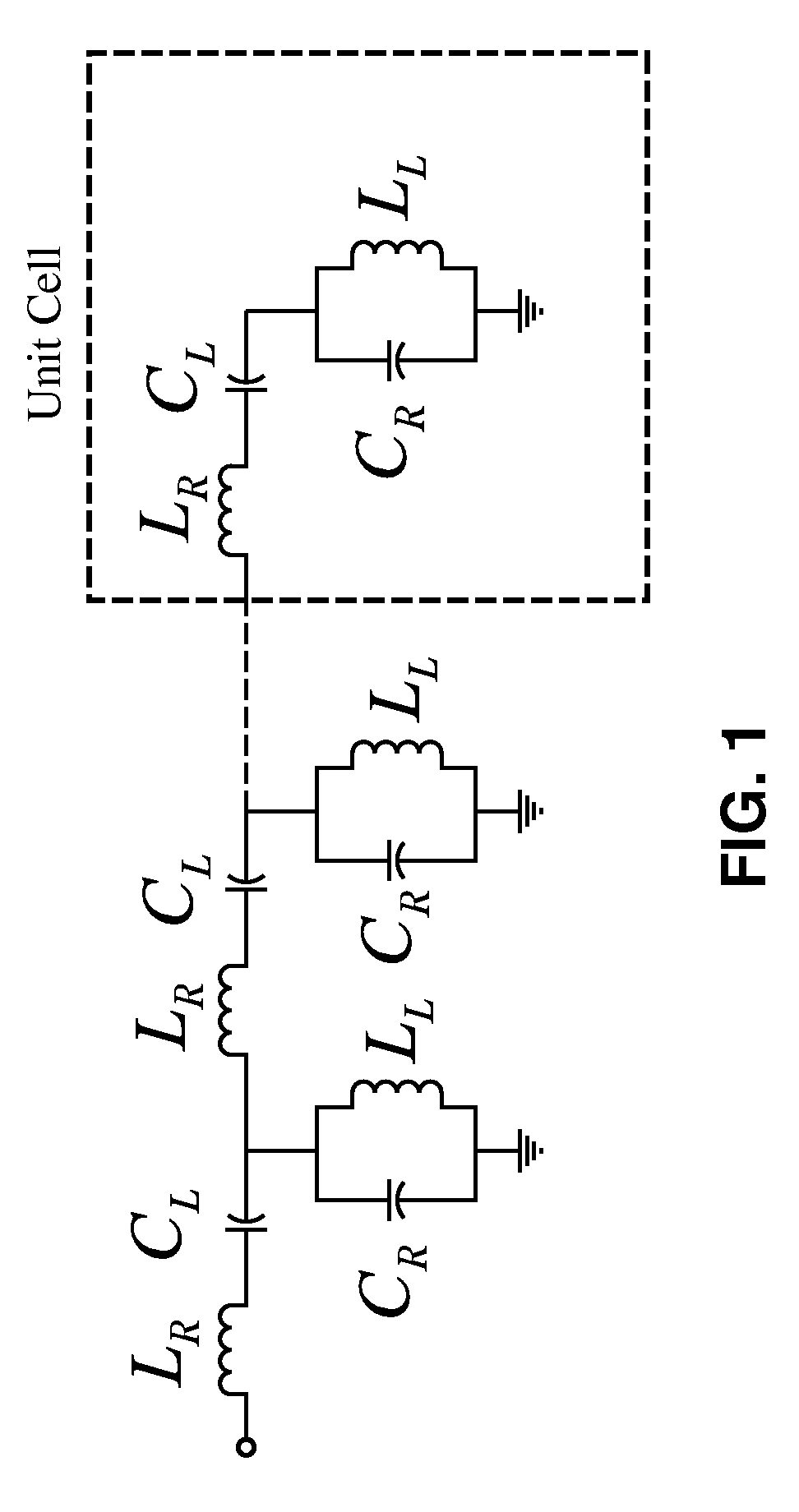

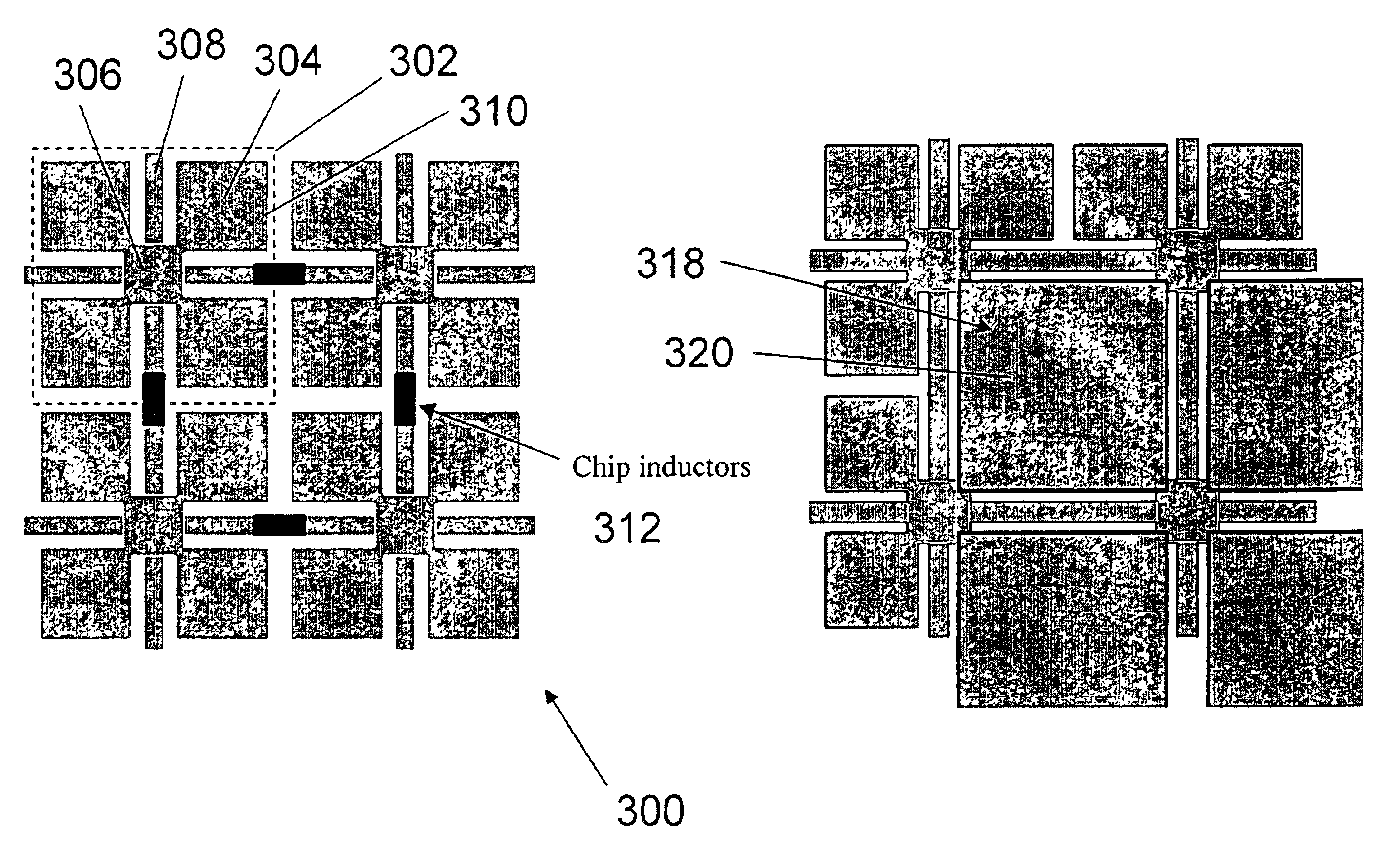

Composite right/left-handed transmission line based compact resonant antenna for RF module integration

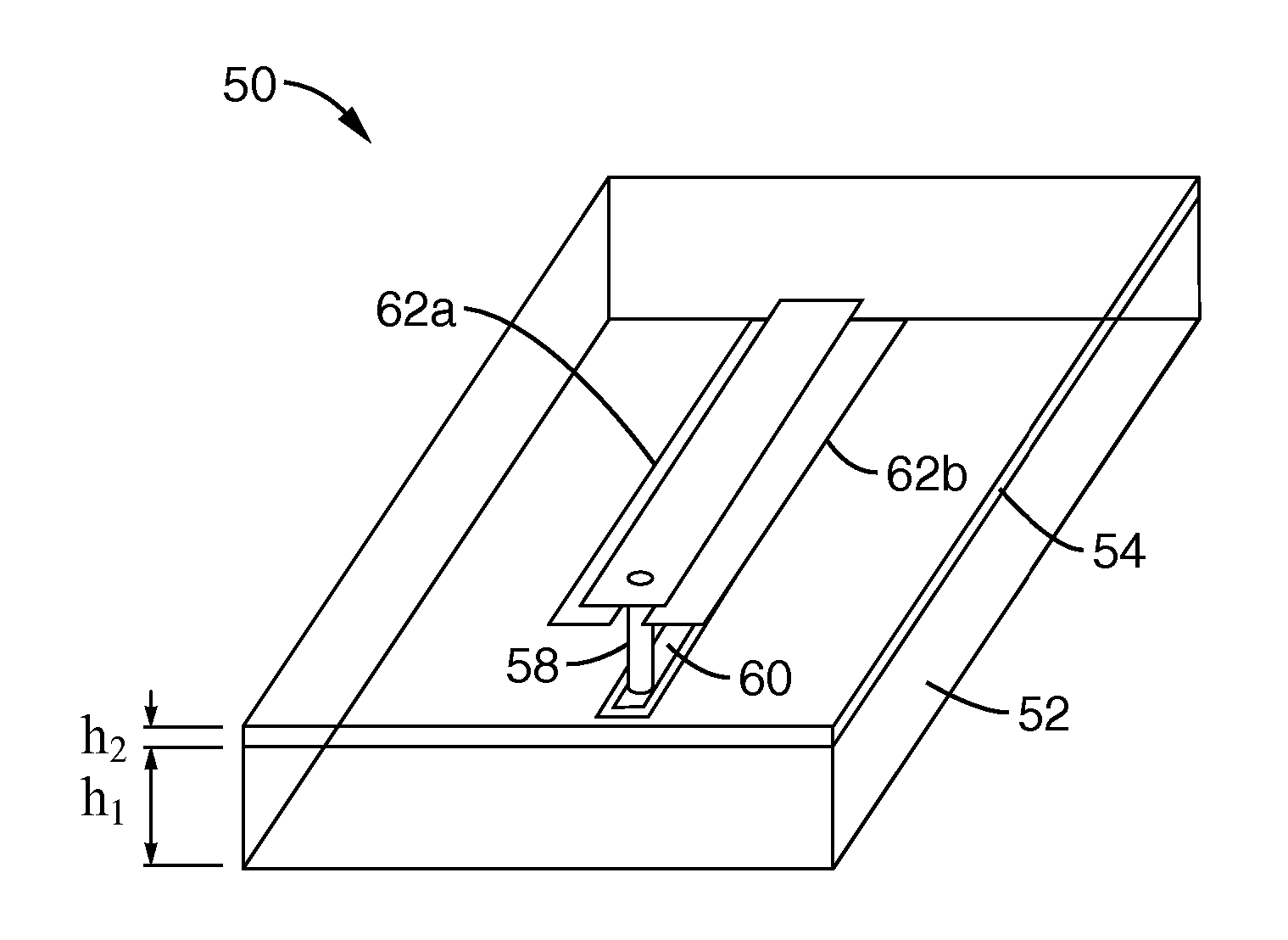

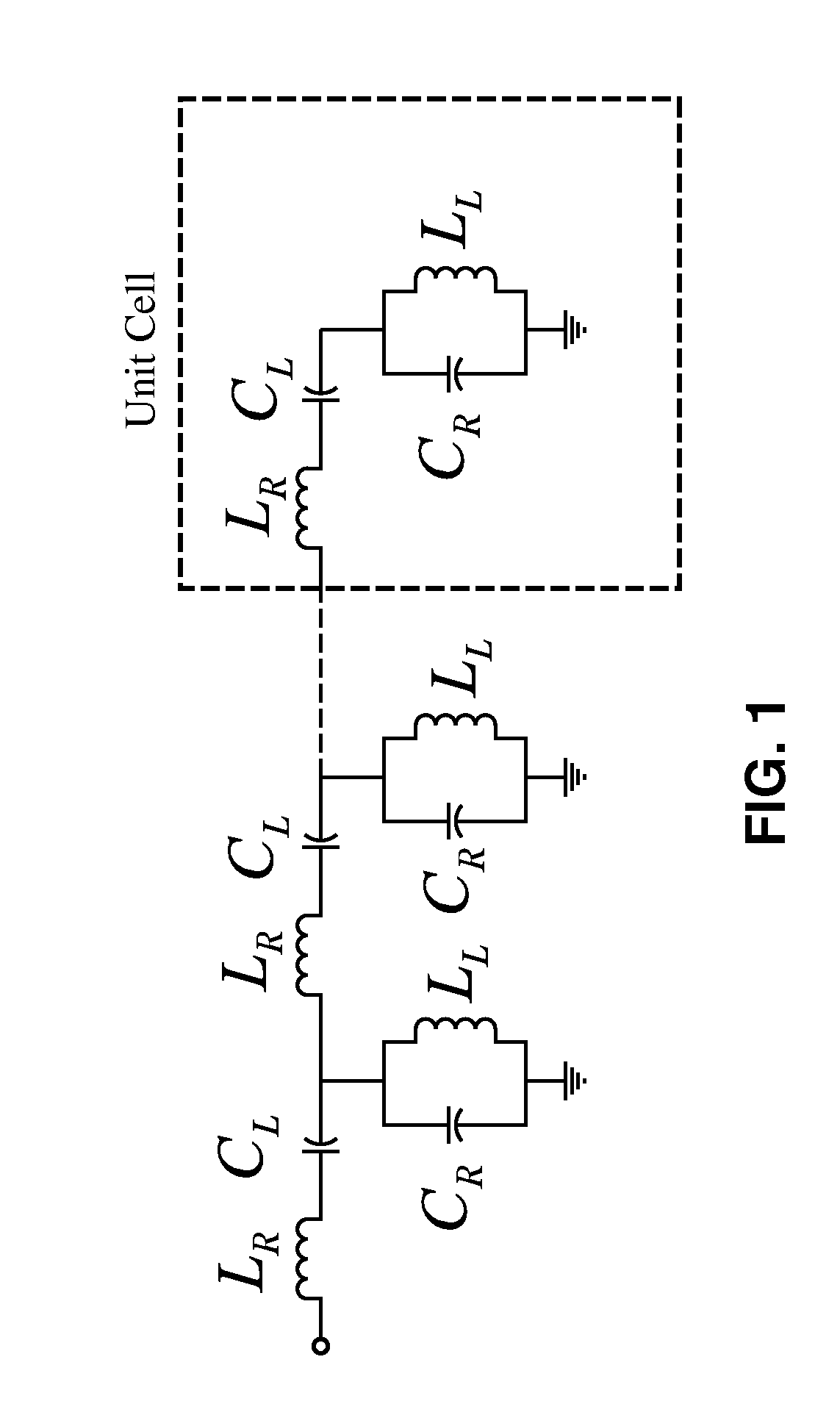

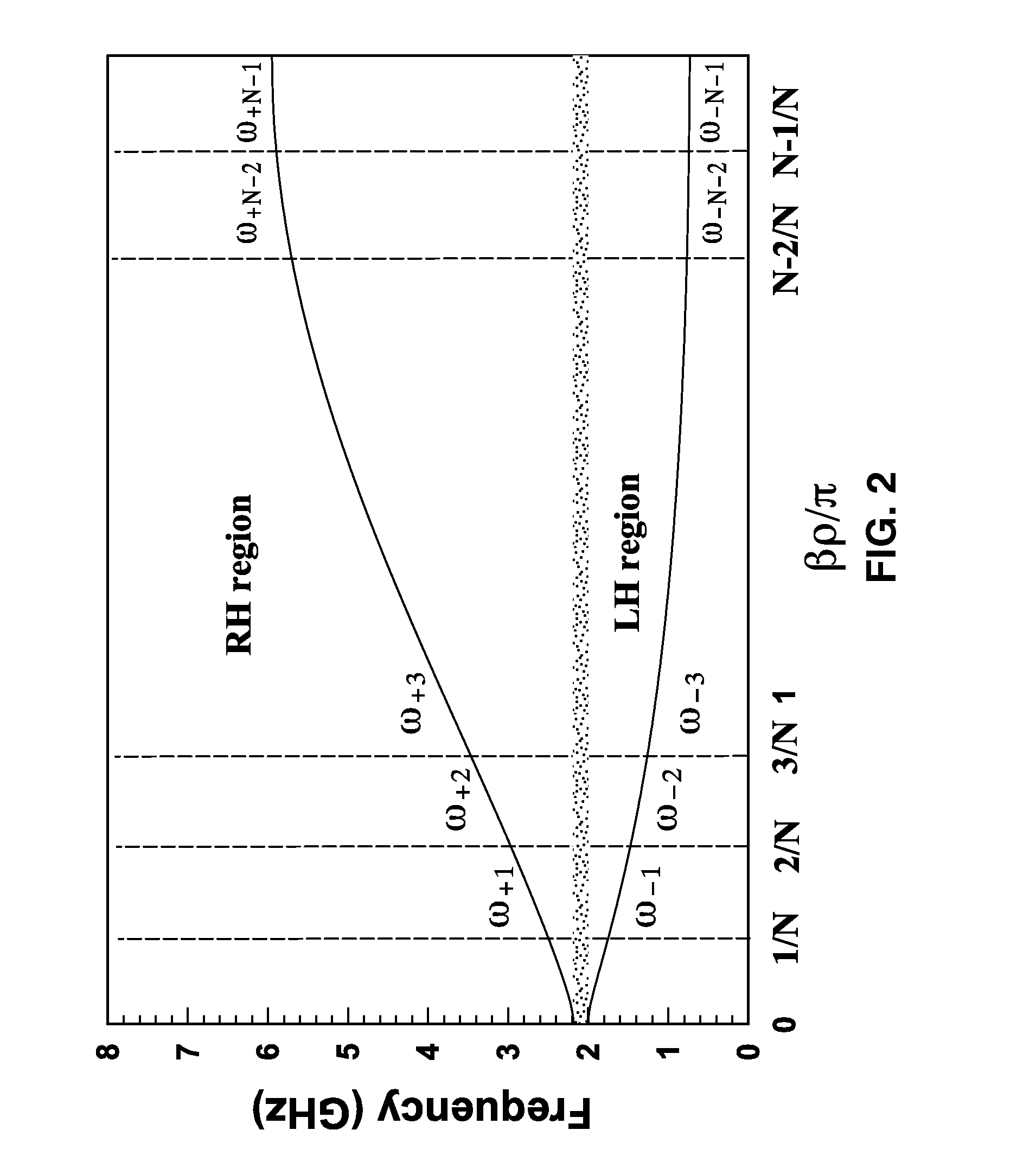

ActiveUS20070176827A1Improve efficiencyAccurate manufacturing capabilitySimultaneous aerial operationsRadiating elements structural formsMetal-insulator-metalShunt capacitors

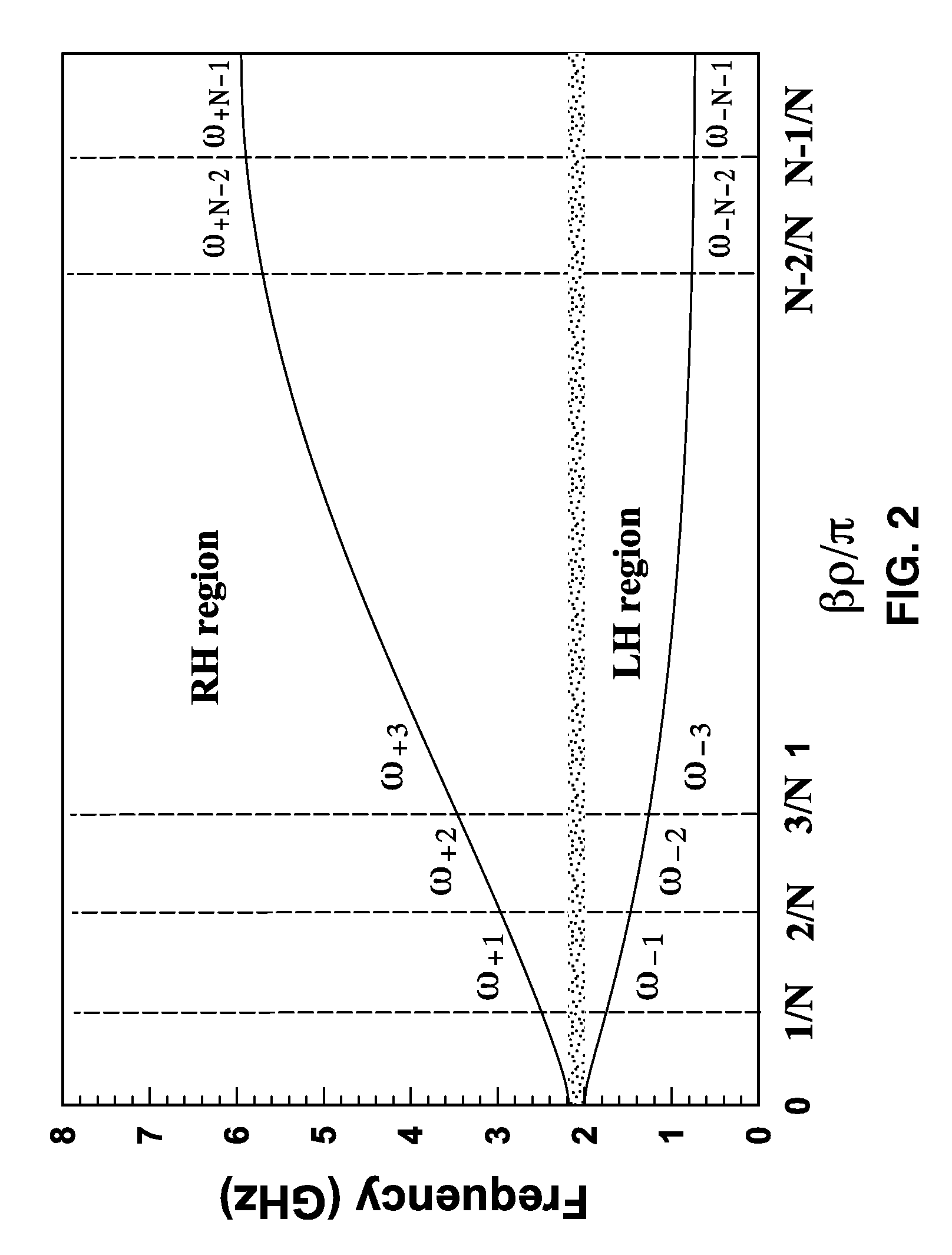

An apparatus based on composite right-handed or left-handed (CRLH) principles to provide a transmission line or antenna structure having a plurality of cells to which one or more feed ports are attached. The apparatus is based on an equivalent circuit Right-Hand (RH) series induction (LR) and shunt capacitor (CR), and Left-Hand (LH) series capacitor (CL) and induction (LL), in which effective permittivity (e) and permeability (m) of the structure are manipulated by the choice of CR, LR, CL, and LL. One embodiment describes mushroom antenna cells (1D or 2D array) in which vias extend up from a feed network on a ground plane through at least one dielectric region to each of a first plurality of conductive elements (plates or strips). Optionally, a second plurality of conductive elements are disposed between first and second dielectric layers to form metal-insulator-metal (MIM) capacitors to lower resonance frequency.

Owner:RGT UNIV OF CALIFORNIA

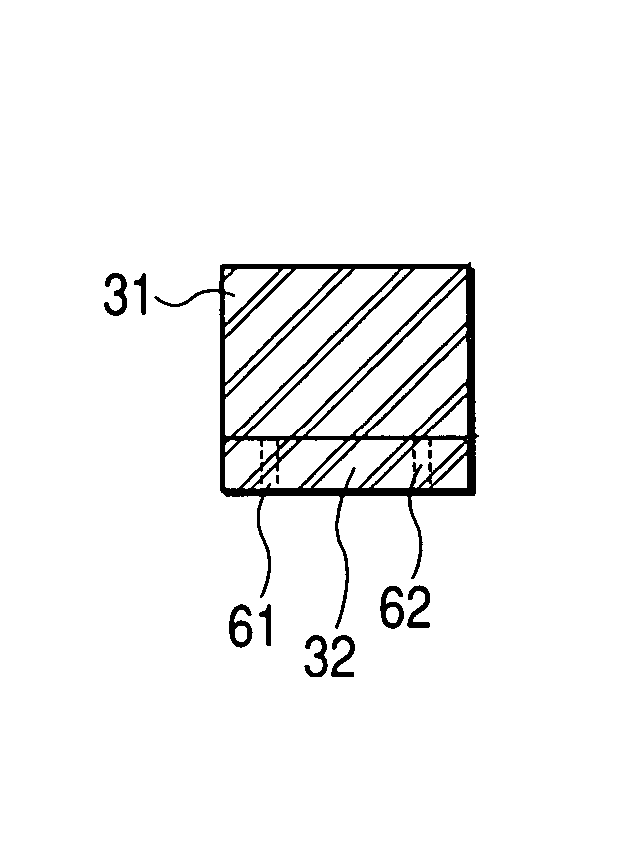

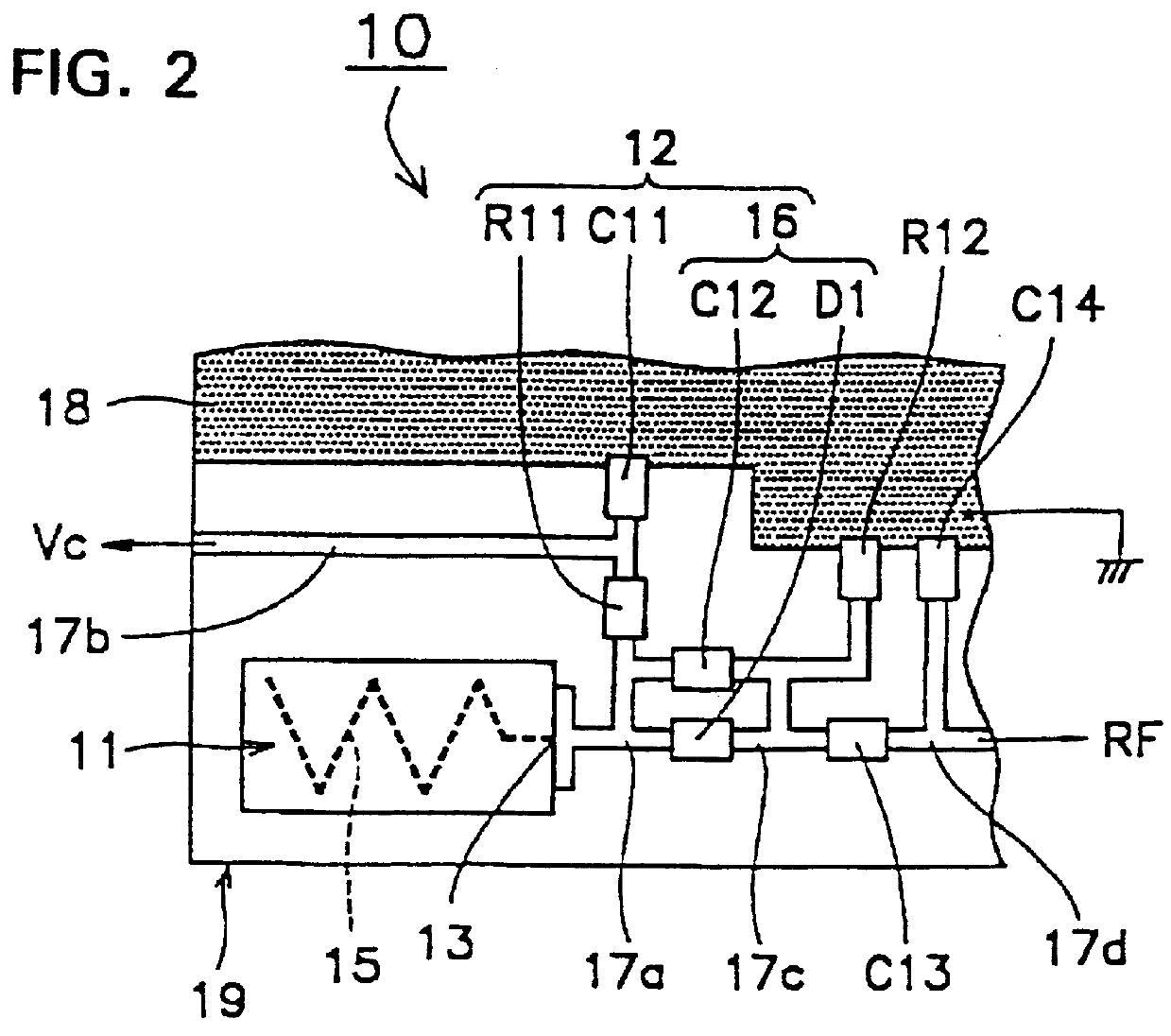

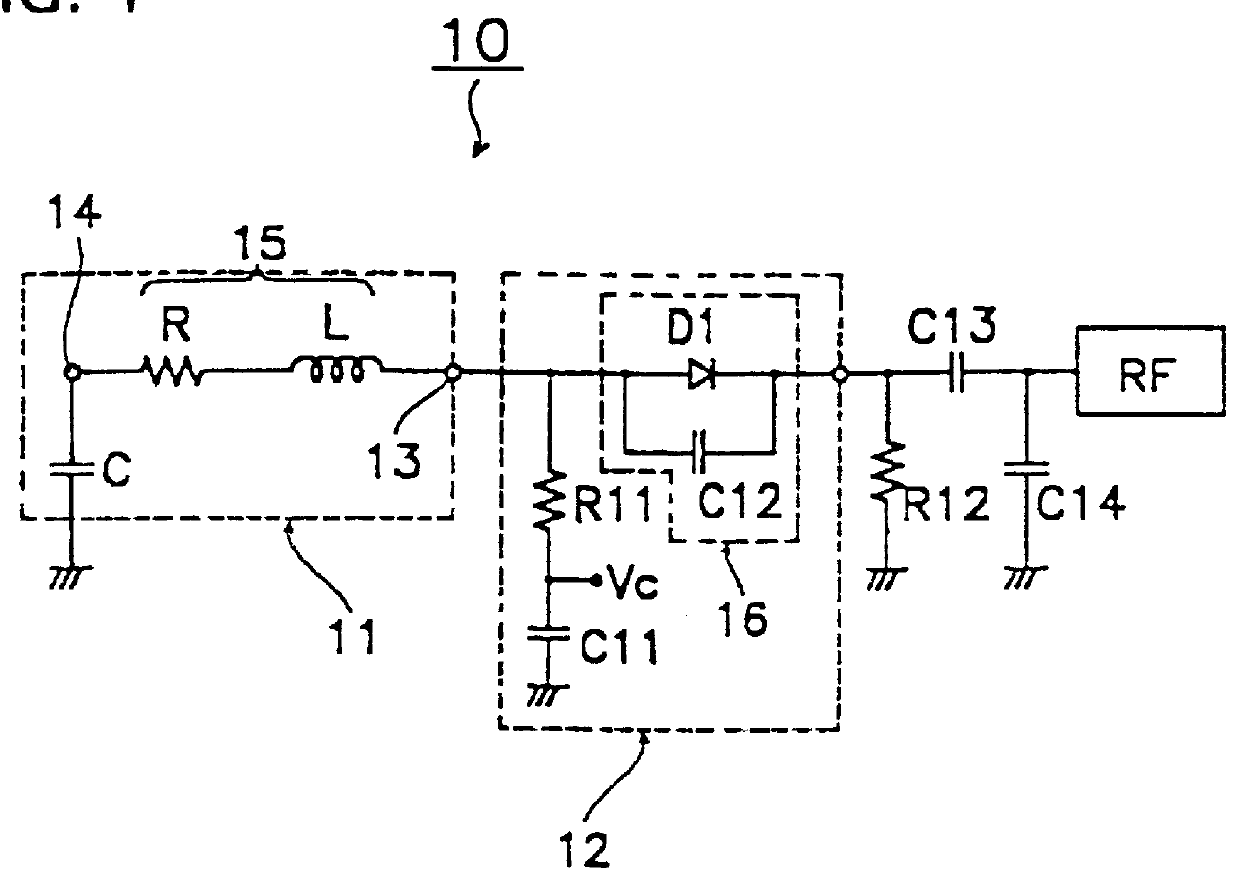

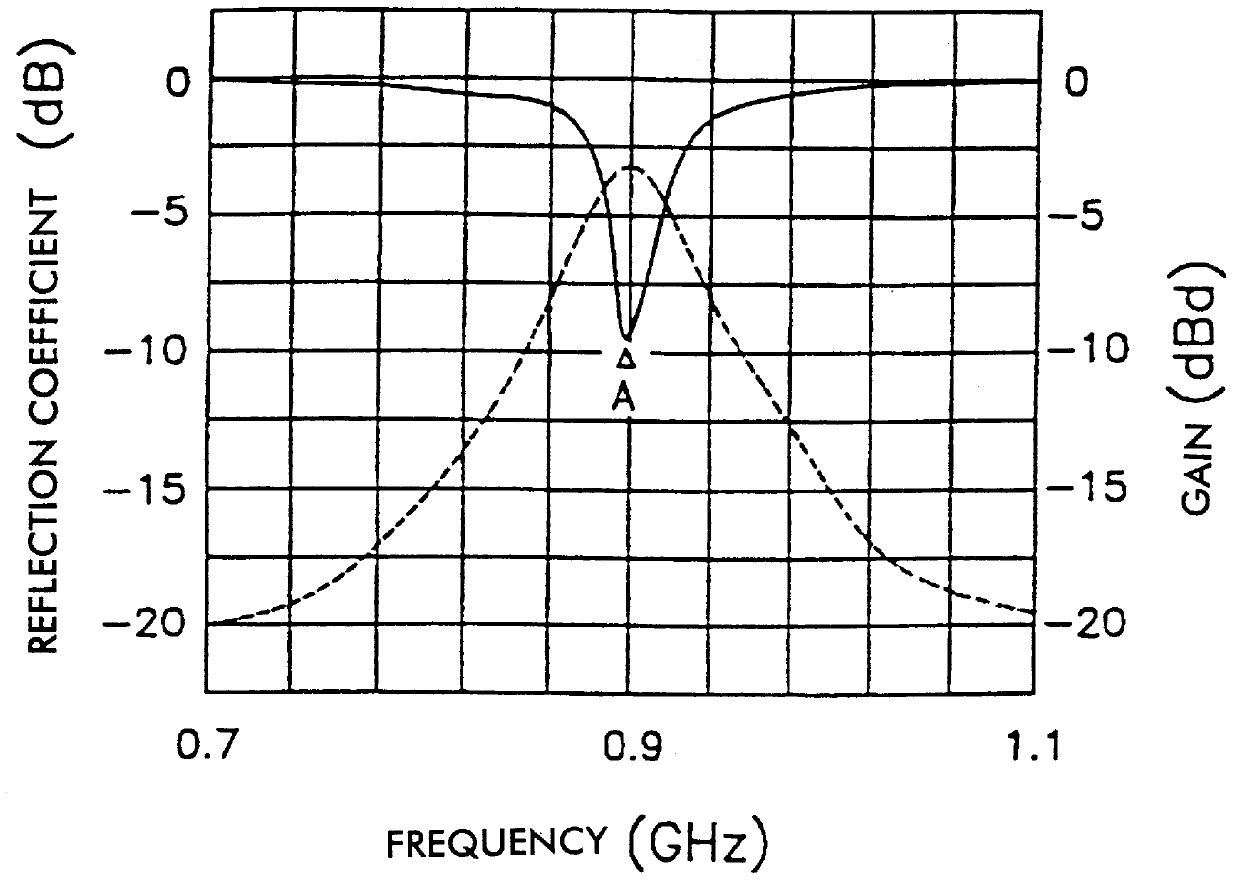

Antenna, method for manufacturing the antenna, and communication apparatus including the antenna

InactiveUS20050099337A1Small sizeSmall and inexpensiveSimultaneous aerial operationsAntenna supports/mountingsElectrical conductorImpedance matching

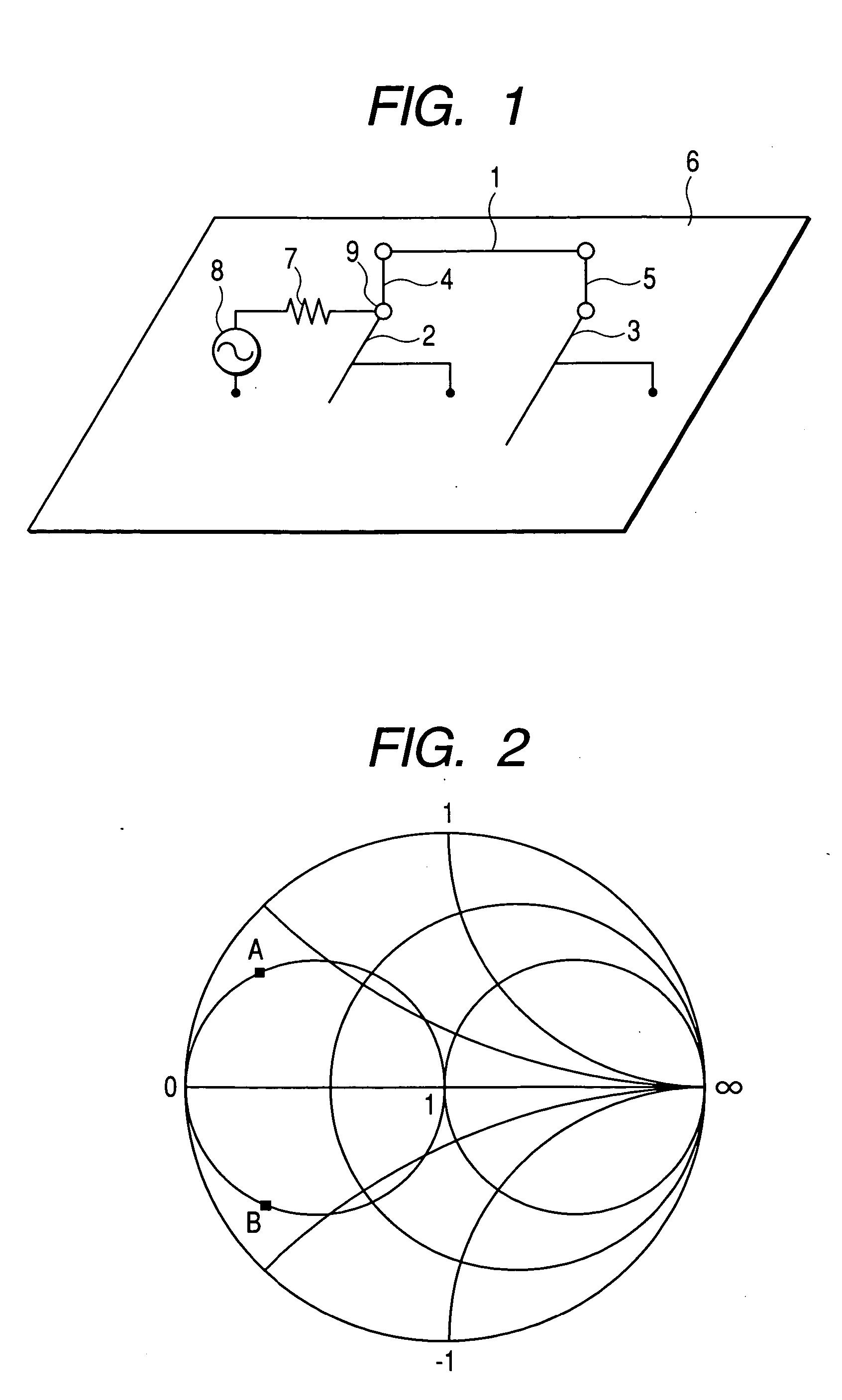

The invention provides a small multimode antenna capable of commonly using a single feeding point at a plurality of frequencies. The antenna includes a radiating conductor 1 disposed above a ground conductor 6 and distributed-constant circuits 2 and 3 coupled to the radiating conductor. Each of the distributed-constant circuits is constructed by a transmission line and has a branch. One end of the radiating conductor and one end of the distributed-constant circuit 2 are connected to each other to be a connection point and, further, the other end of the radiating conductor and one end of the distributed-constant circuit 3 are connected to each other. The connection point is a single feeding point 9 using the ground conductor as an earth. The distributed-constant circuits 2 and 3 are designed as an equivalent circuit in which different stubs are connected in parallel with a transmission line, and impedance matching at a plurality of frequencies is realized at the feeding point.

Owner:HITACHI LTD +1

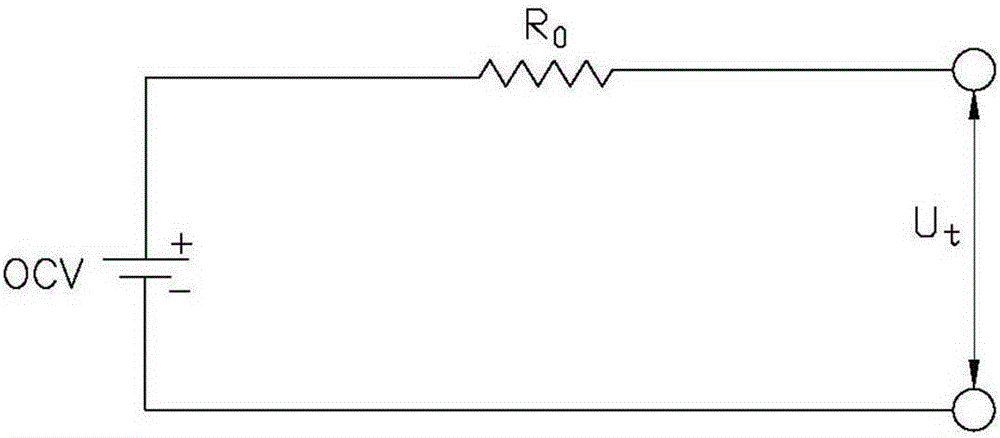

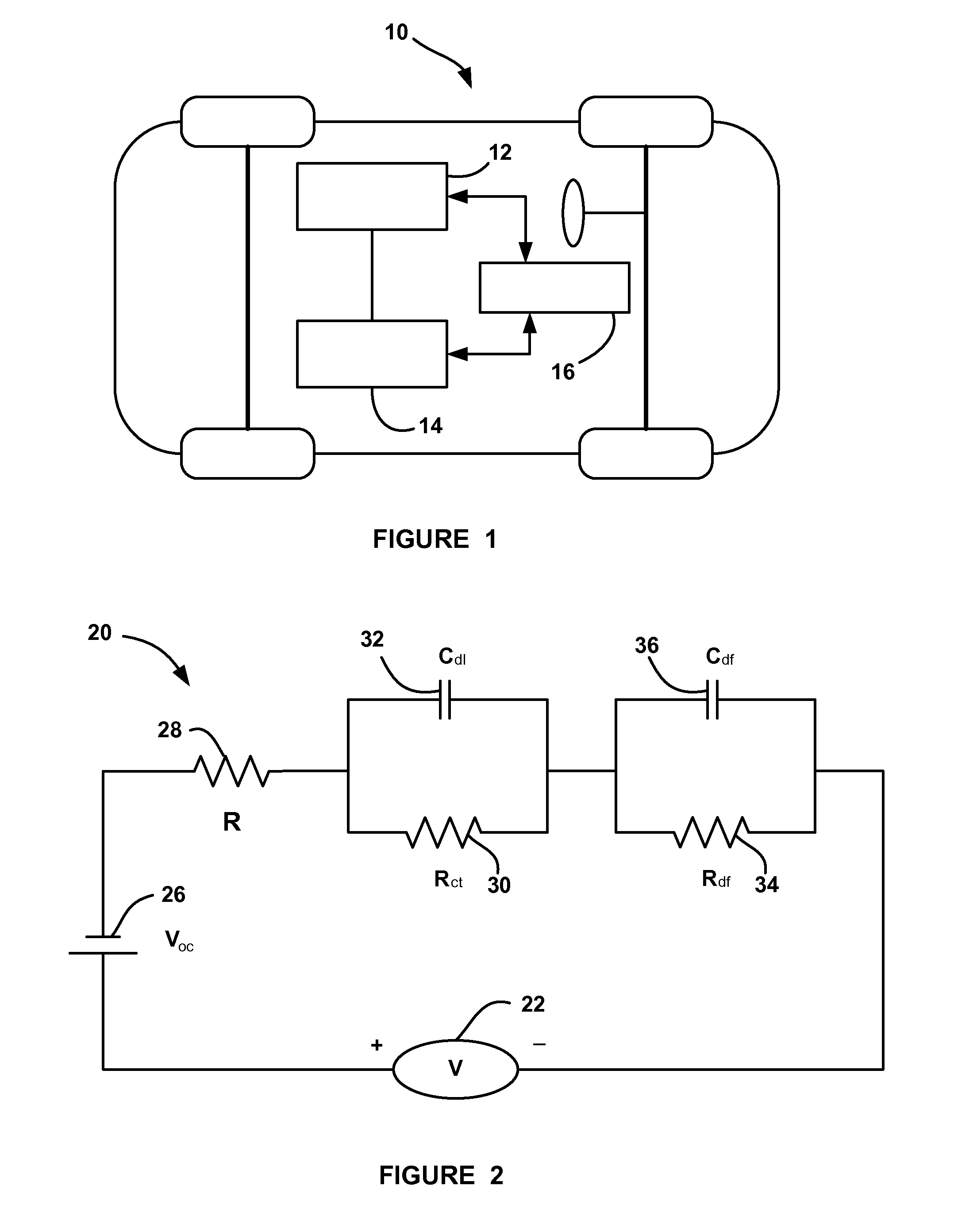

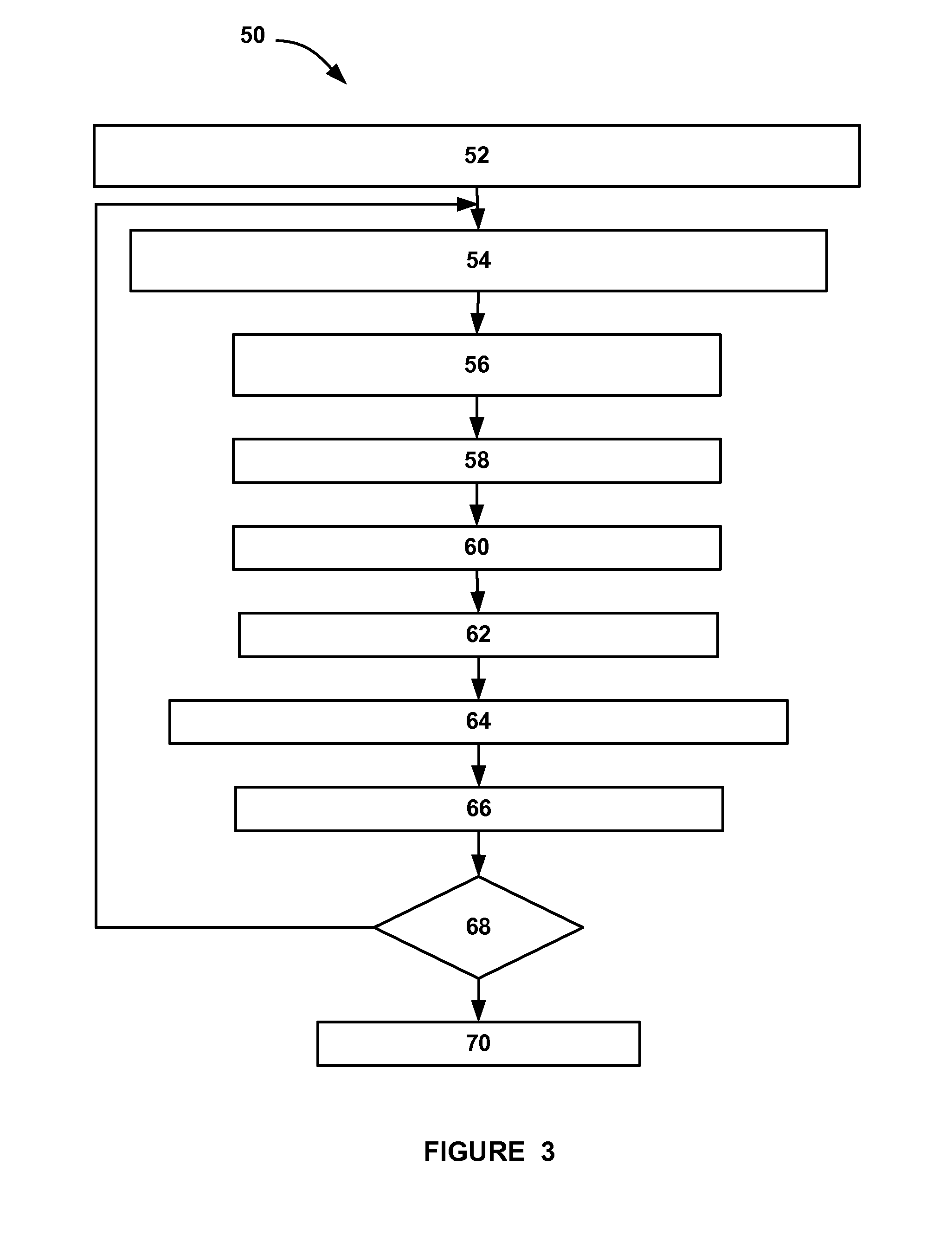

Systems and methods for estimation and prediction of battery health and performance

ActiveUS20180143257A1Testing/monitoring control systemsElectrical testingMoving averageState of health

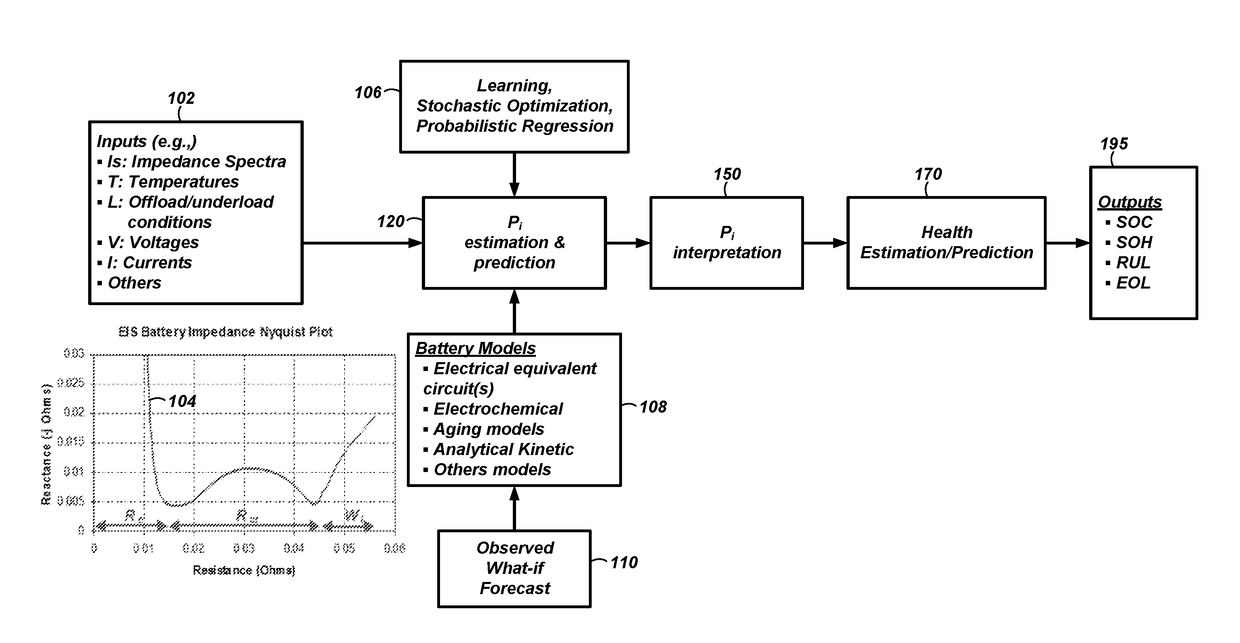

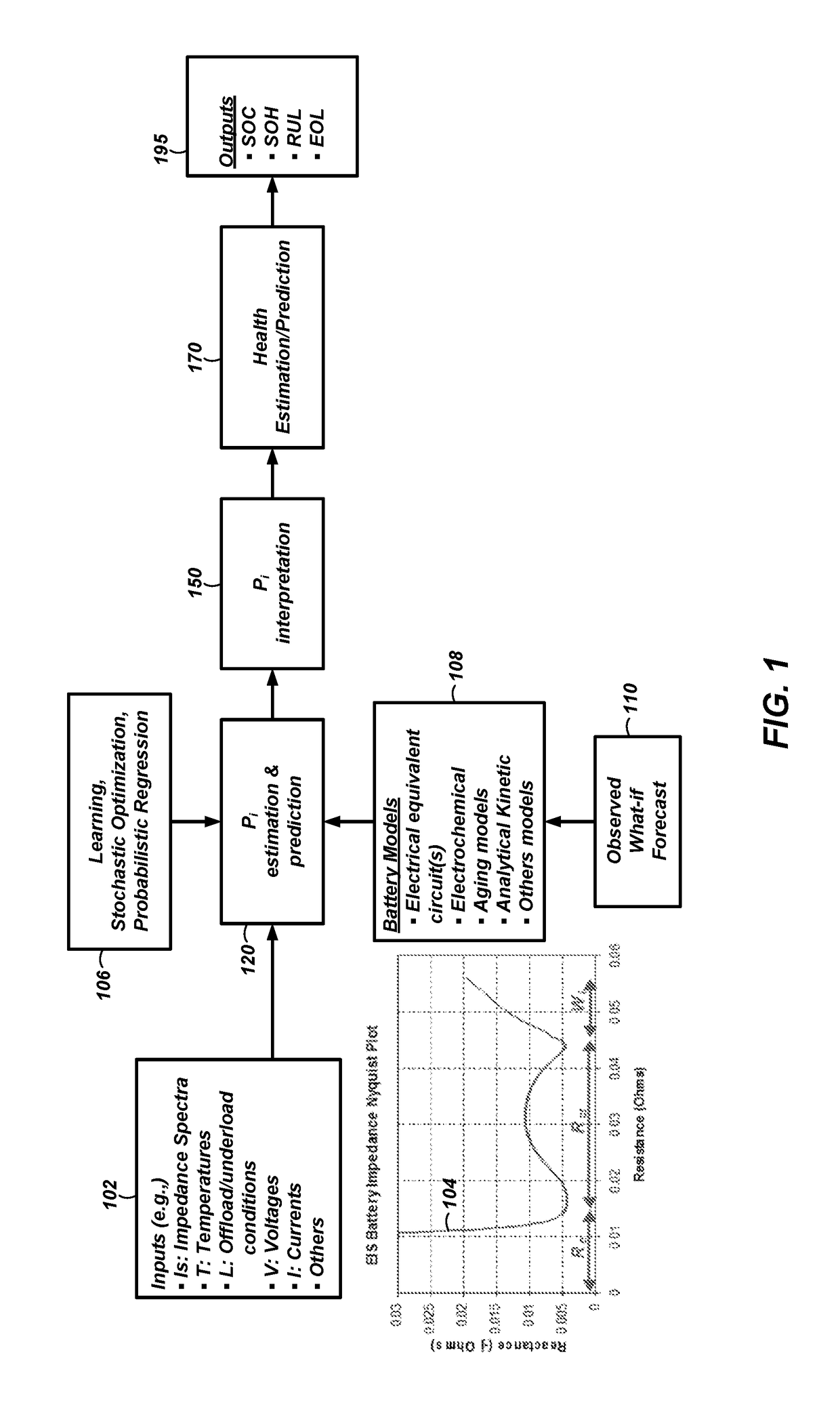

Systems and computer-implemented methods are used for analyzing battery information. The battery information may be acquired from both passive data acquisition and active data acquisition. Active data may be used for feature extraction and parameter identification responsive to the input data relative to an electrical equivalent circuit model to develop geometric-based parameters and optimization-based parameters. These parameters can be combined with a decision fusion algorithm to develop internal battery parameters. Analysis processes including particle filter analysis, neural network analysis, and auto regressive moving average analysis can be used to analyze the internal battery parameters and develop battery health metrics. Additional decision fusion algorithms can be used to combine the internal battery parameters and the battery health metrics to develop state-of-health estimations, state-of-charge estimations, remaining-useful-life predictions, and end-of-life predictions for the battery.

Owner:BATTELLE ENERGY ALLIANCE LLC

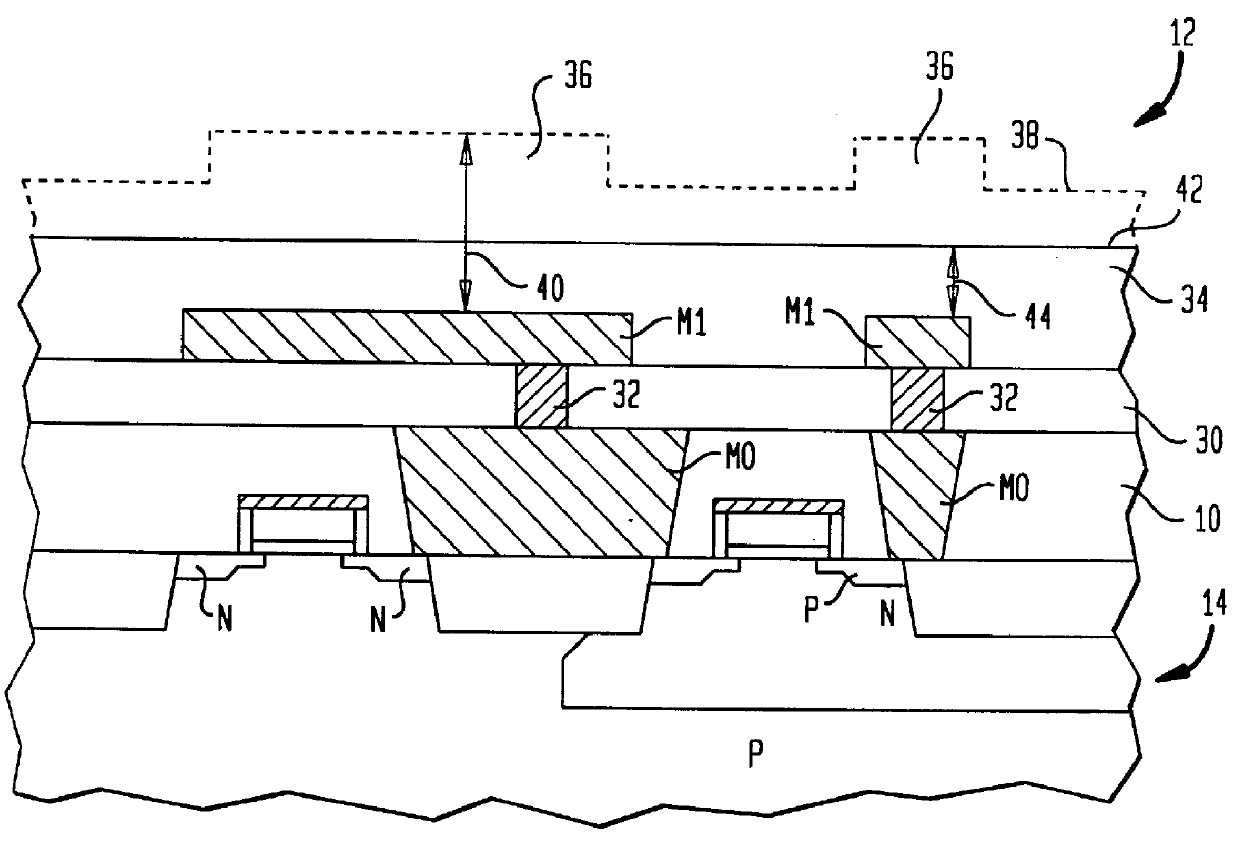

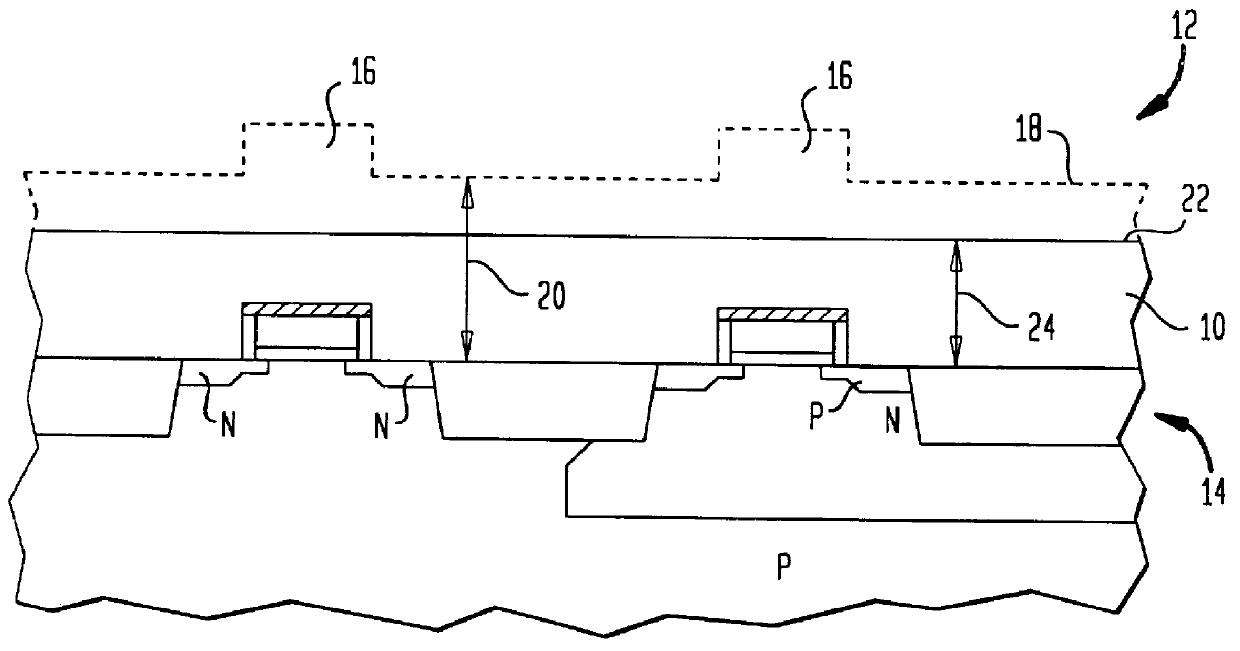

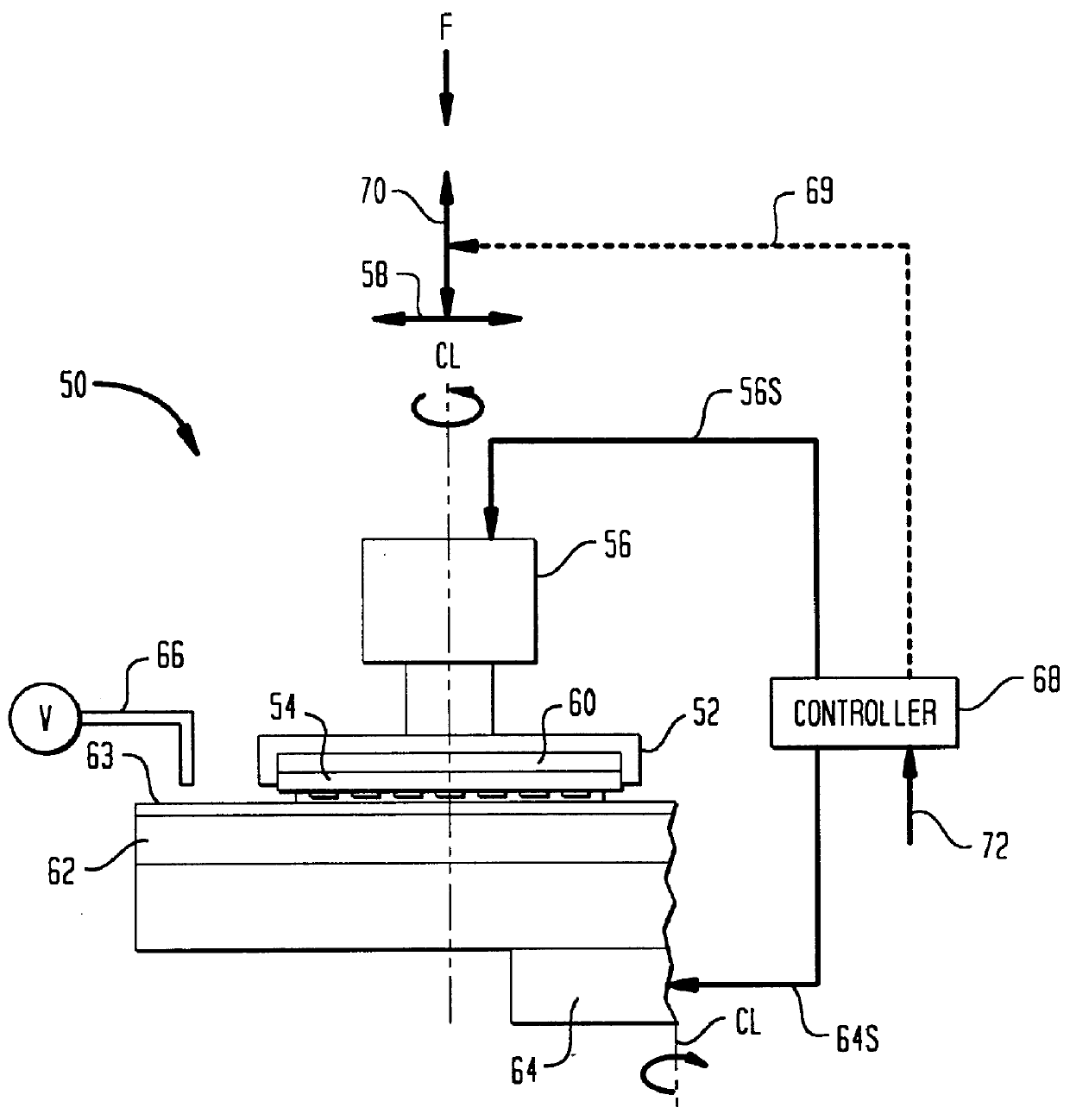

Method and apparatus for in-line oxide thickness determination in chemical-mechanical polishing

InactiveUS6020264ASemiconductor/solid-state device testing/measurementResistance/reactance/impedenceElectrical resistance and conductanceEngineering

In-line thickness measurement of a dielectric film layer on a surface of a workpiece subsequent to a polishing on a chemical-mechanical polishing machine in a polishing slurry is disclosed. The workpiece includes a given level of back-end-of-line (BEOL) structure including junctions. The measurement apparatus includes a platen and an electrode embedded within the platen. A positioning mechanism positions the workpiece above the electrode with the dielectric layer facing in a direction of the electrode. A slurry dam is used for maintaining a prescribed level of a conductive polishing slurry above the electrode, the prescribed level to ensure a desired slurry coverage of the workpiece. A capacitance sensor senses a system capacitance C in accordance with an RC equivalent circuit model, wherein the RC equivalent circuit includes a resistance R representative of the slurry and workpiece resistances and the system capacitance C representative of the dielectric material and junction capacitances. Lastly, a capacitance-to-thickness converter converts the sensed capacitance to a dielectric thickness in accordance with a prescribed system capacitance / optical thickness calibration, wherein the prescribed calibration corresponds to the given level of BEOL structure of the workpiece.

Owner:IBM CORP

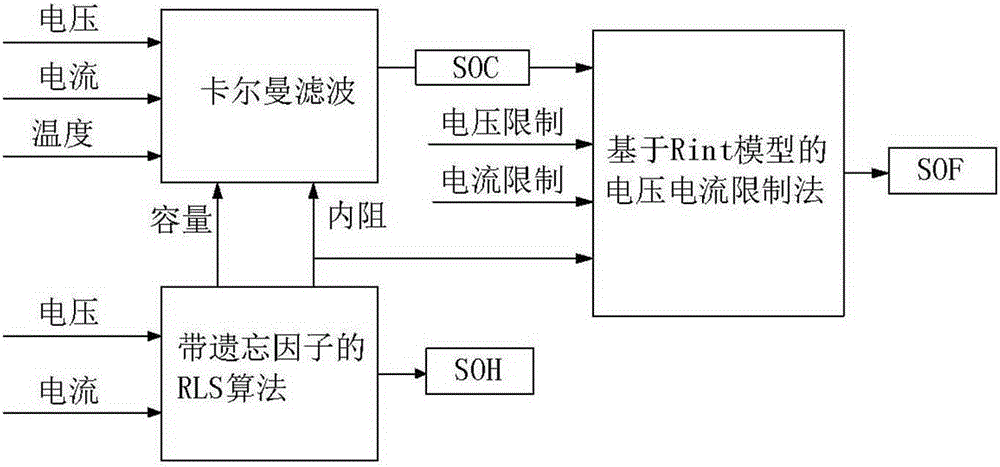

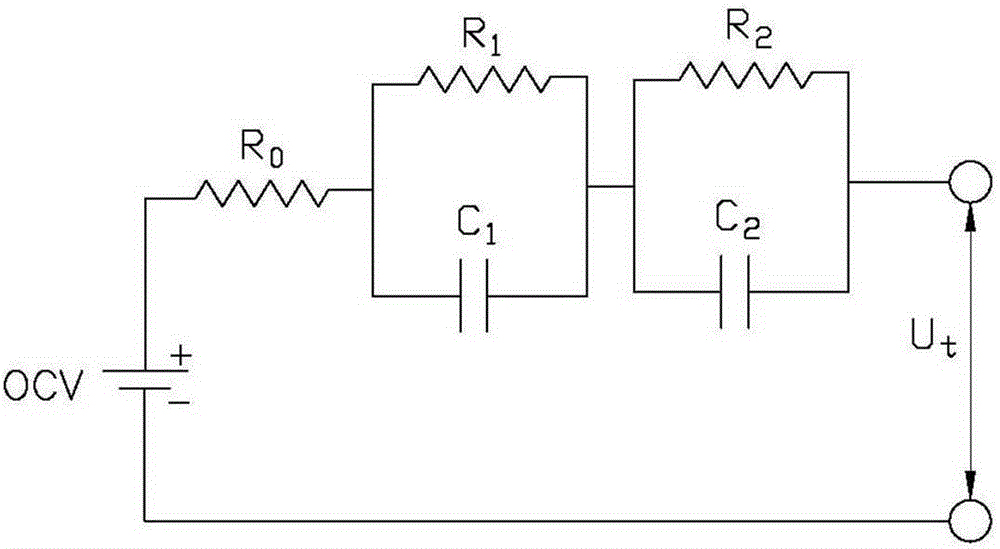

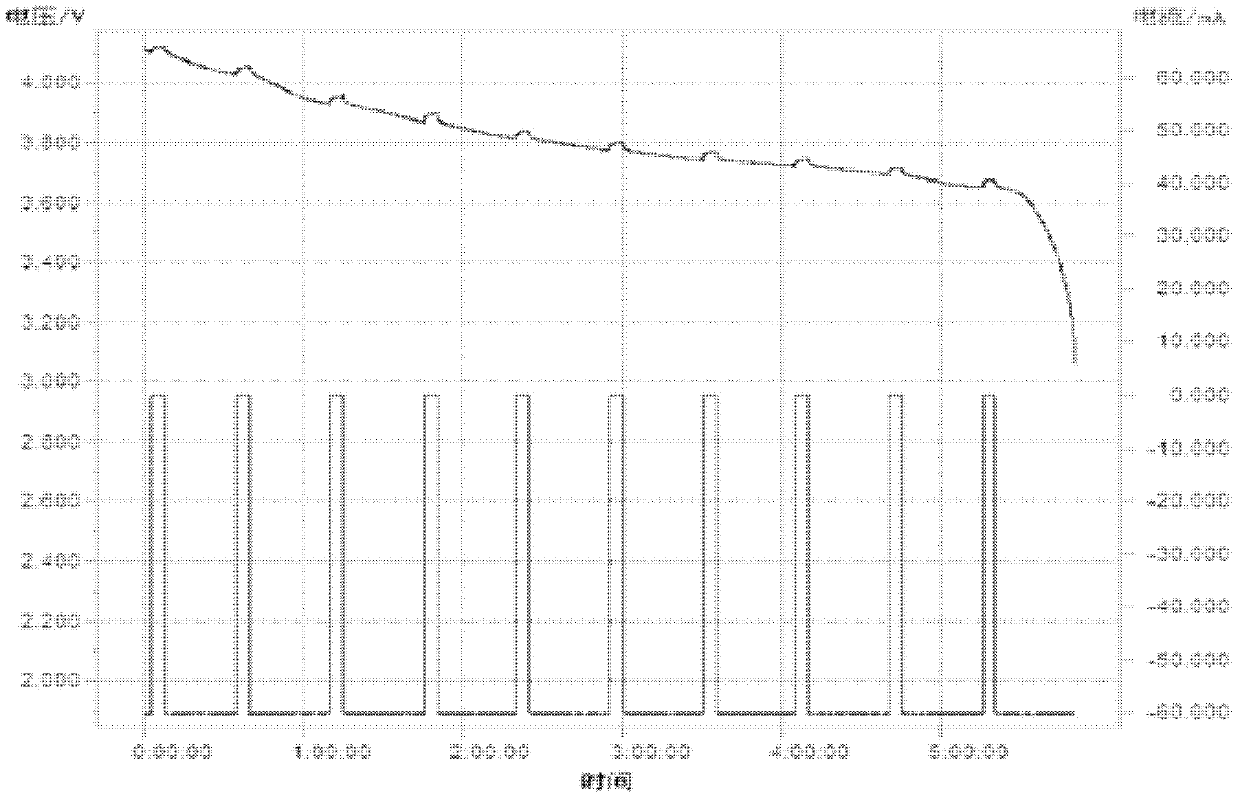

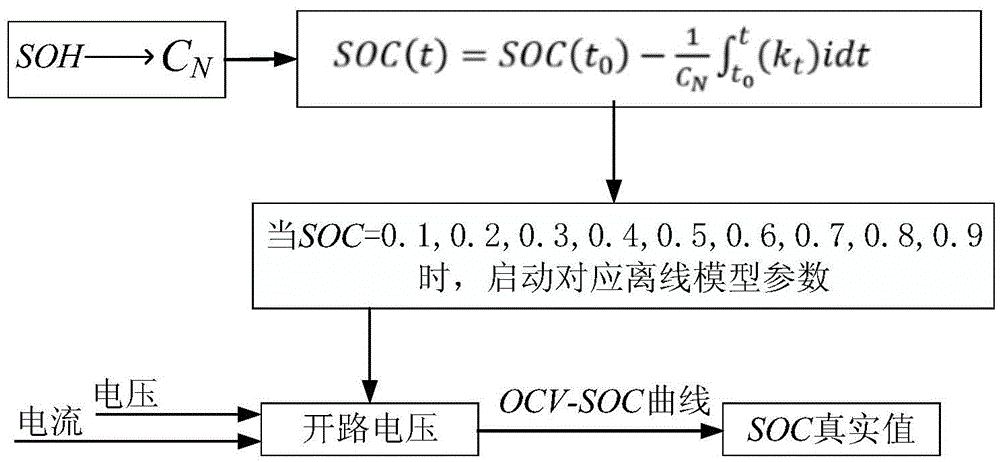

Combined estimation method for lithium ion battery state of charge, state of health and state of function

ActiveCN105301509AGuaranteed estimation accuracyImprove state estimation performanceElectrical testingInternal resistanceState of health

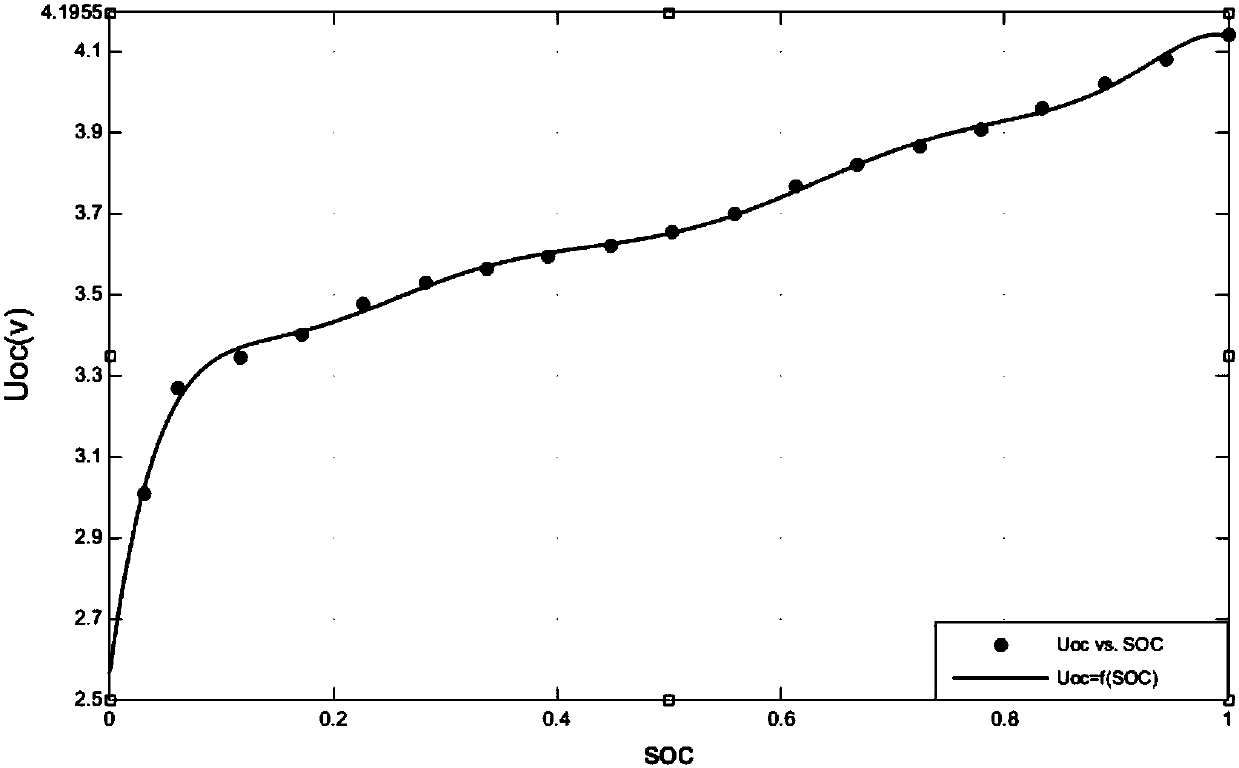

The invention provides a combined estimation method for lithium ion battery state of charge, state of health and state of function. The combined estimation method comprises the steps that the state of he---alth of a battery is estimated online: open circuit voltage and internal resistance are identified online by adopting a recursive least square method with a forgetting factor, the state of charge is indirectly acquired according to a pre-established OCV-SOC corresponding relation, and then the size of battery capacity is estimated according to cumulative charge and discharge electric charge between two SOC points; the state of charge of the battery is estimated online: the state of charge of the battery is estimated by adopting the Kalman filter algorithm based on a two-order RC equivalent circuit model, and the battery capacity parameter in the Kalman filter algorithm is updated according to the estimation result of battery capacity; and the state of function of the battery is estimated online: the maximum chargeable and dischargeable current is calculated based on the voltage limit and the current limit of the battery according to internal resistance obtained by online identification, and then the maximum chargeable and dischargeable function can be obtained through further calculation.

Owner:TSINGHUA UNIV

Composite right/left-handed transmission line based compact resonant antenna for RF module integration

ActiveUS7446712B2Improve efficiencyAccurate manufacturing capabilitySimultaneous aerial operationsRadiating elements structural formsMetal-insulator-metalShunt capacitors

Owner:RGT UNIV OF CALIFORNIA

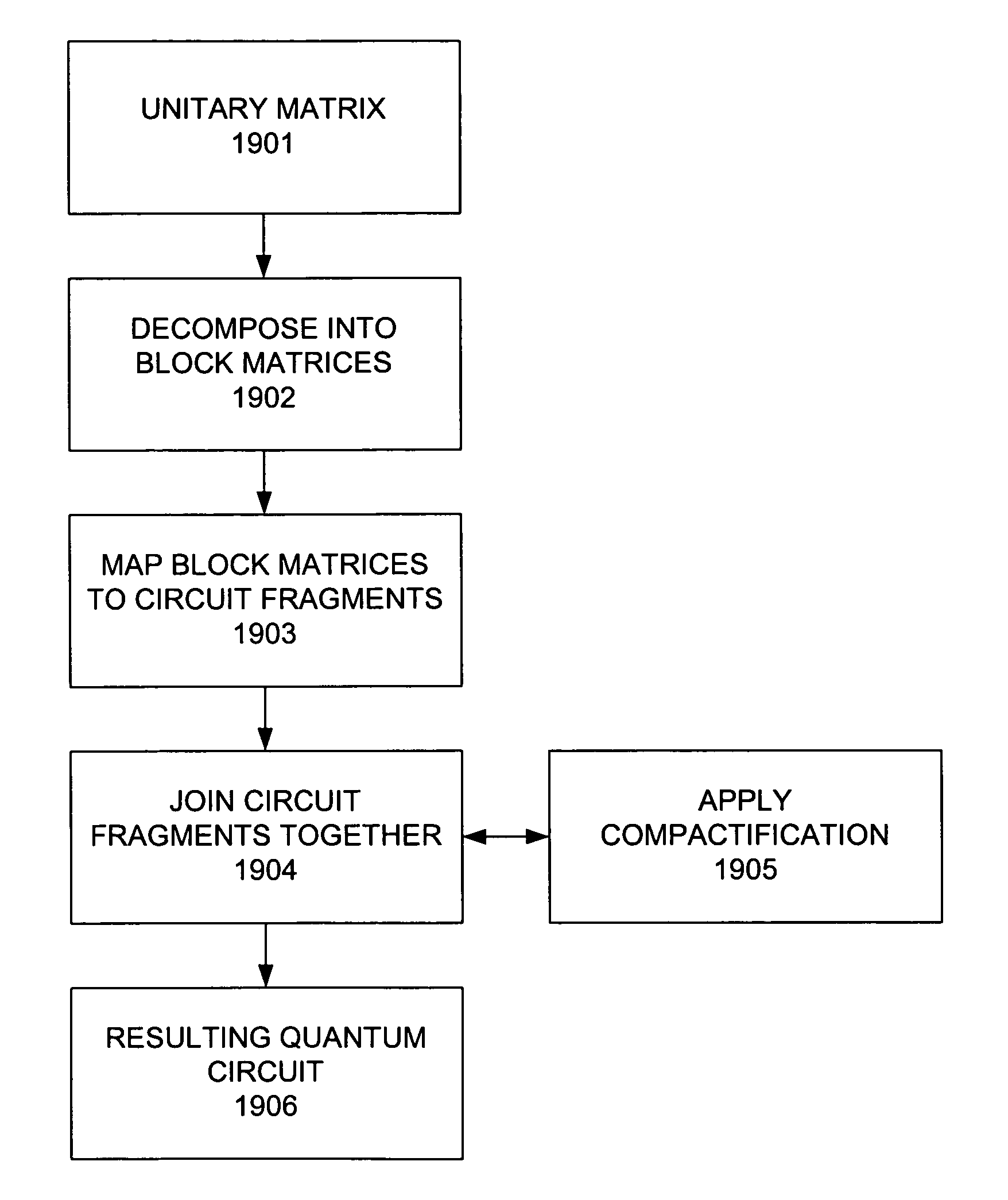

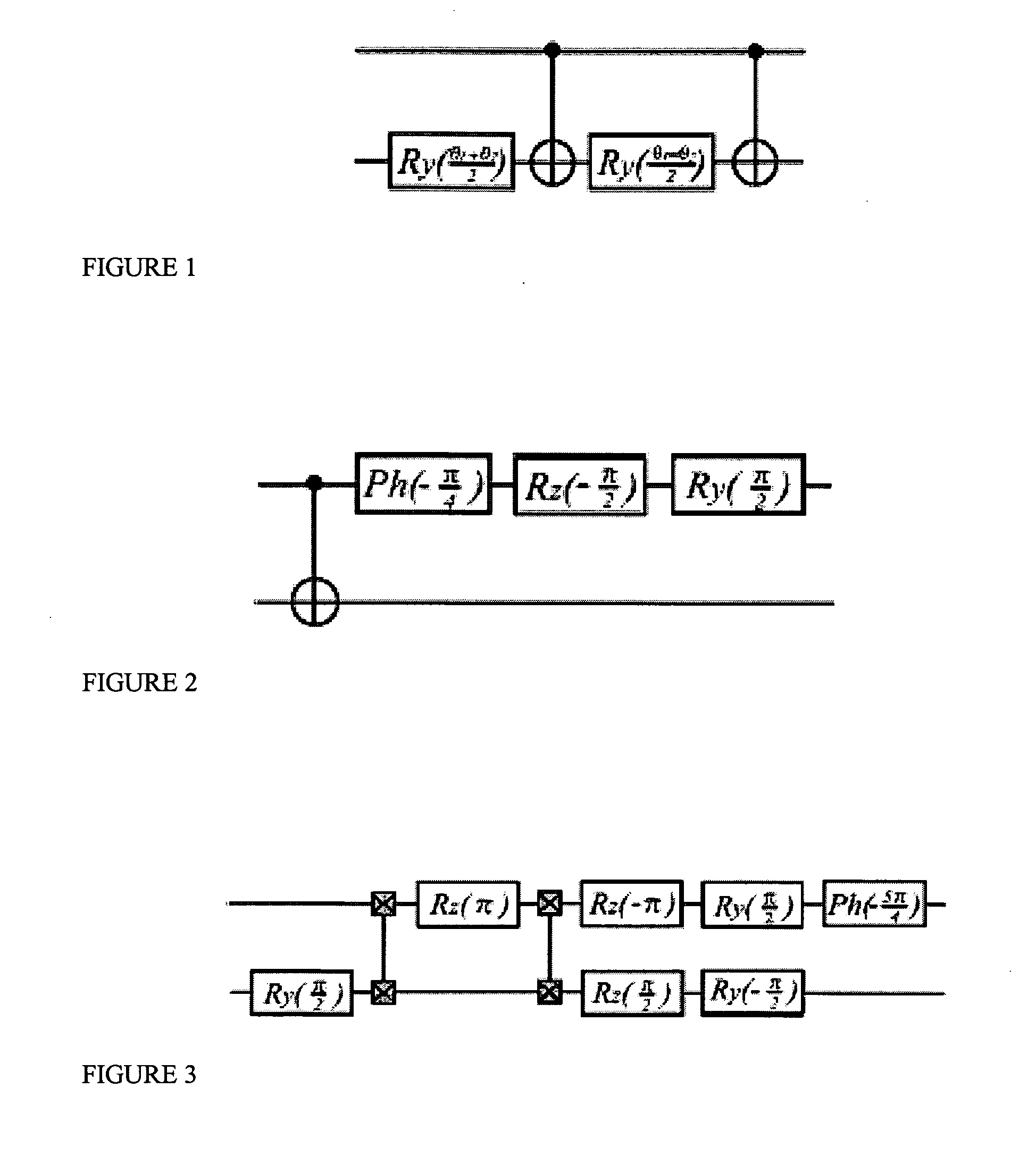

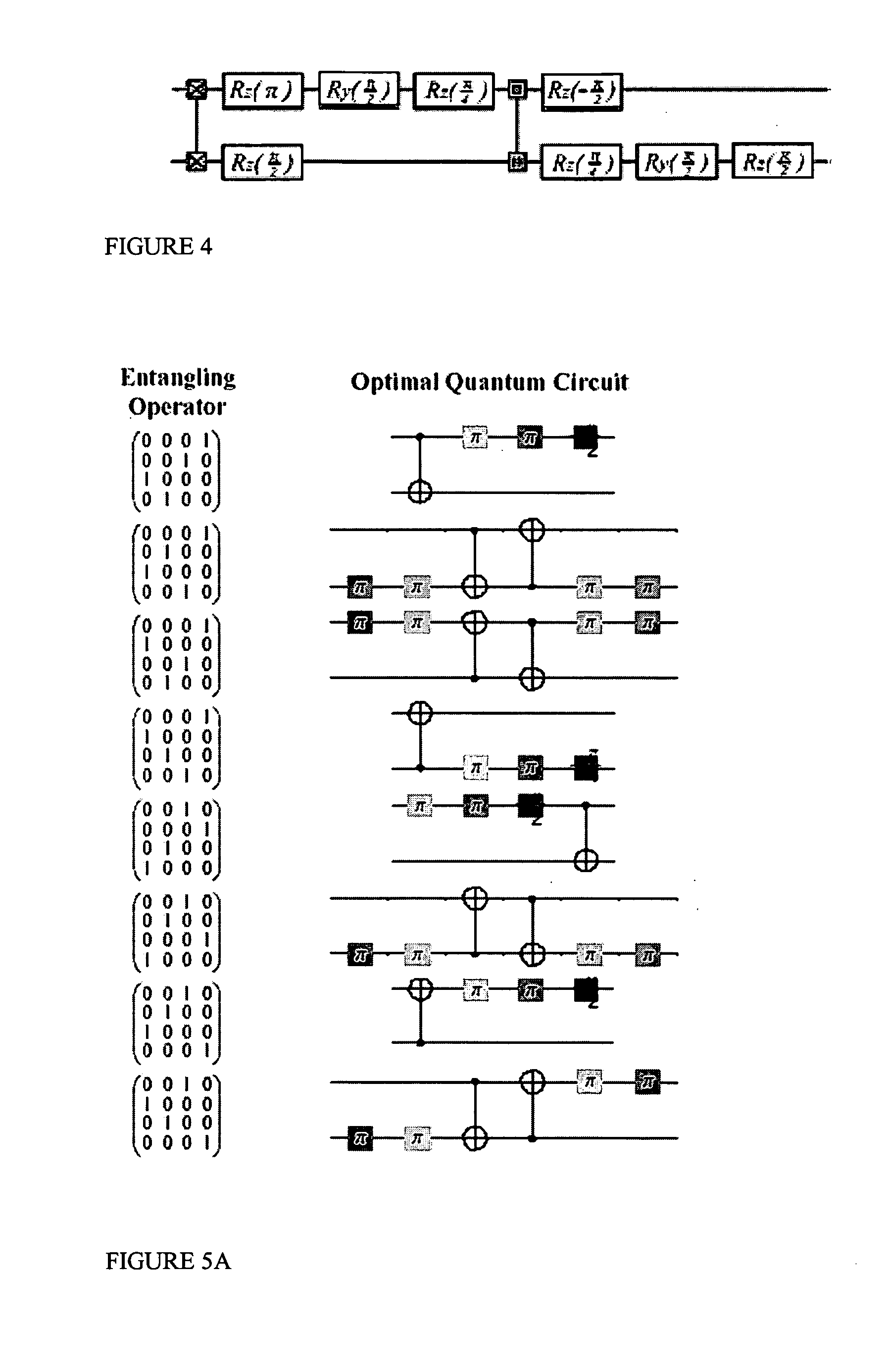

Method and apparatus for automated design of quantum circuits

The present invention provides an algebraic approach to quantum circuit design based on using a GSVD (Generalized Singular Value Decomposition) to map a unitary matrix, representing a desired quantum computation, into a product of block diagonal unitary matrices, each of which can then be mapped into equivalent circuit fragments. The invention describes a number of rules allowing such circuits to be compactified.

Owner:CALIFORNIA INST OF TECH

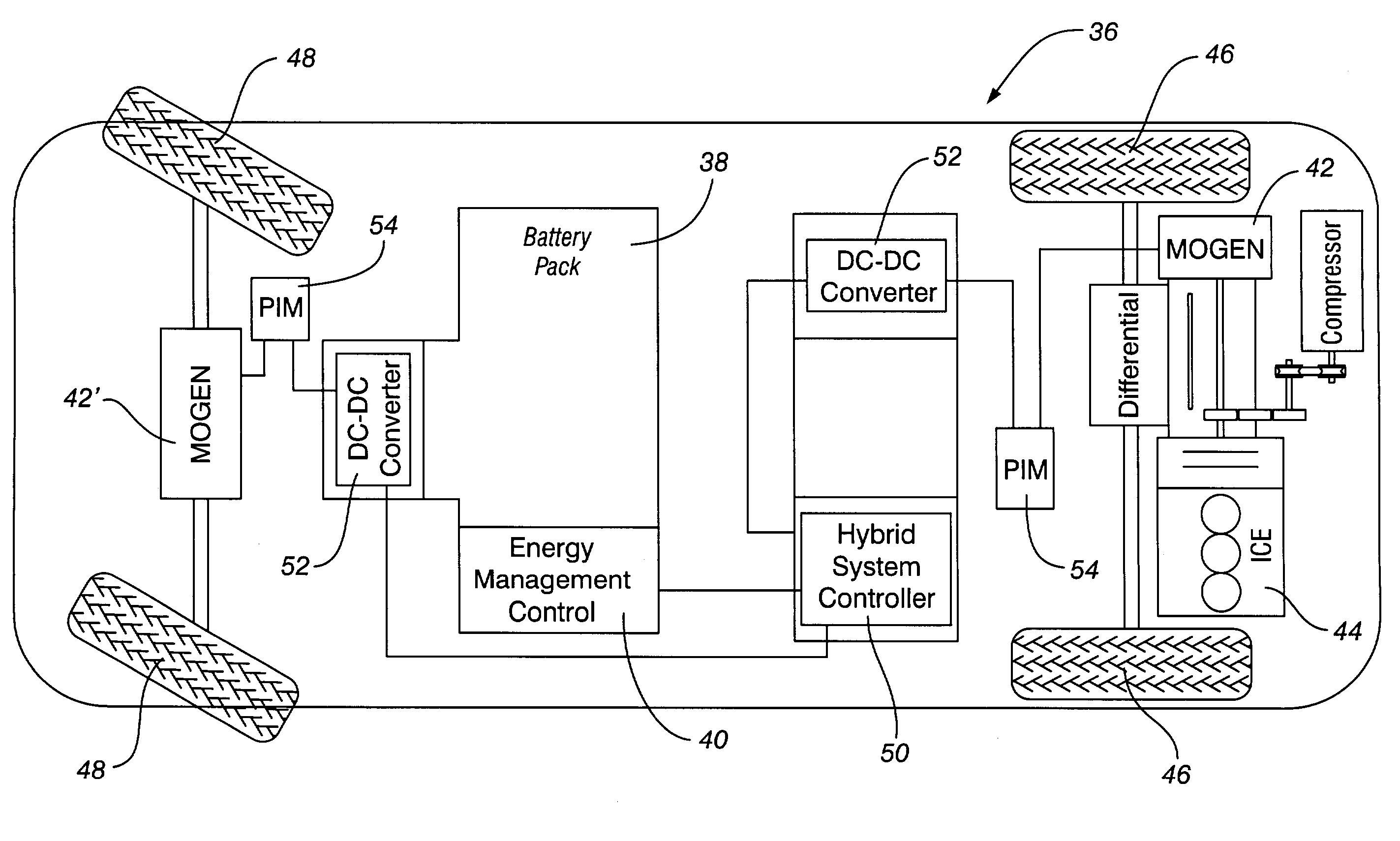

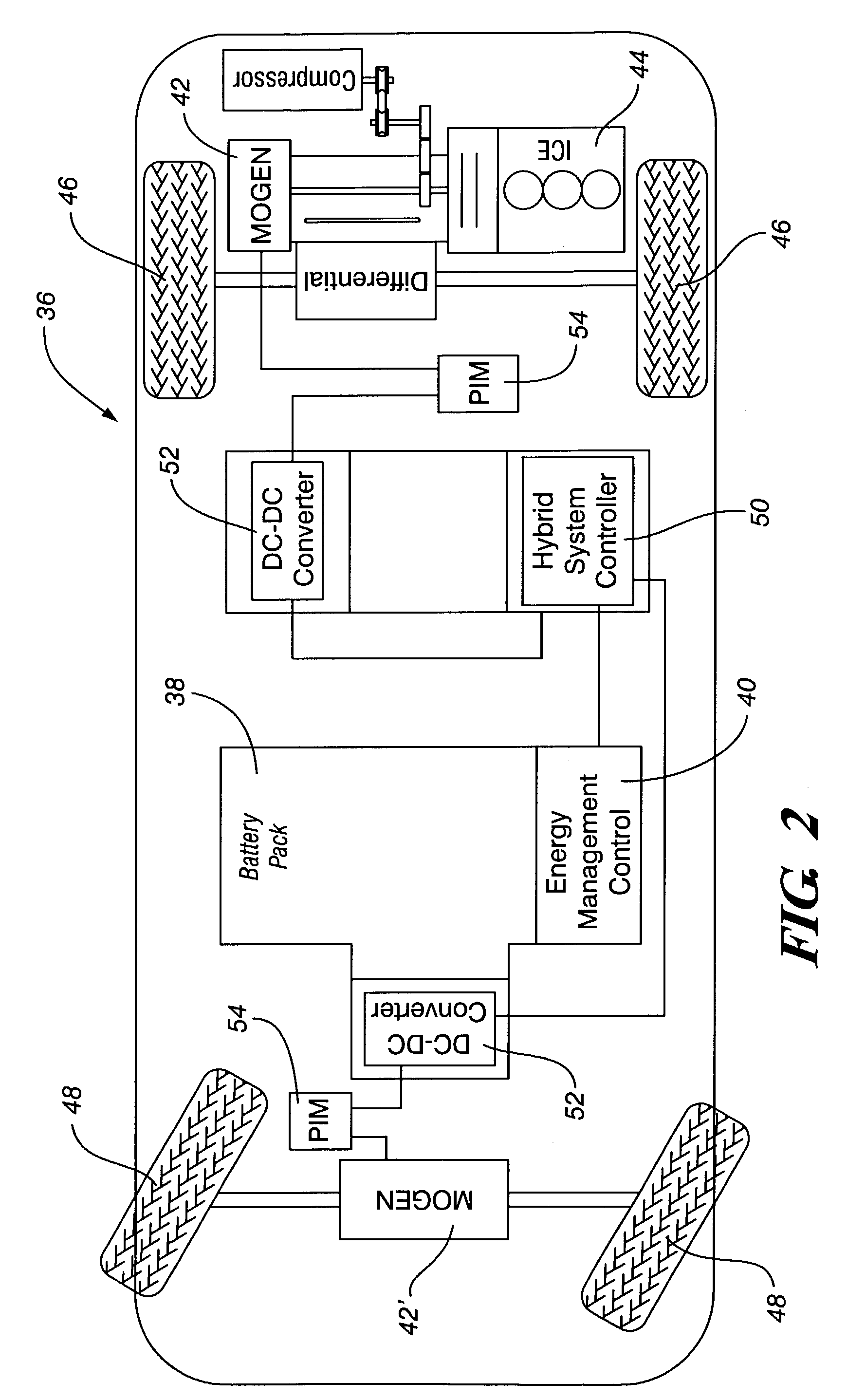

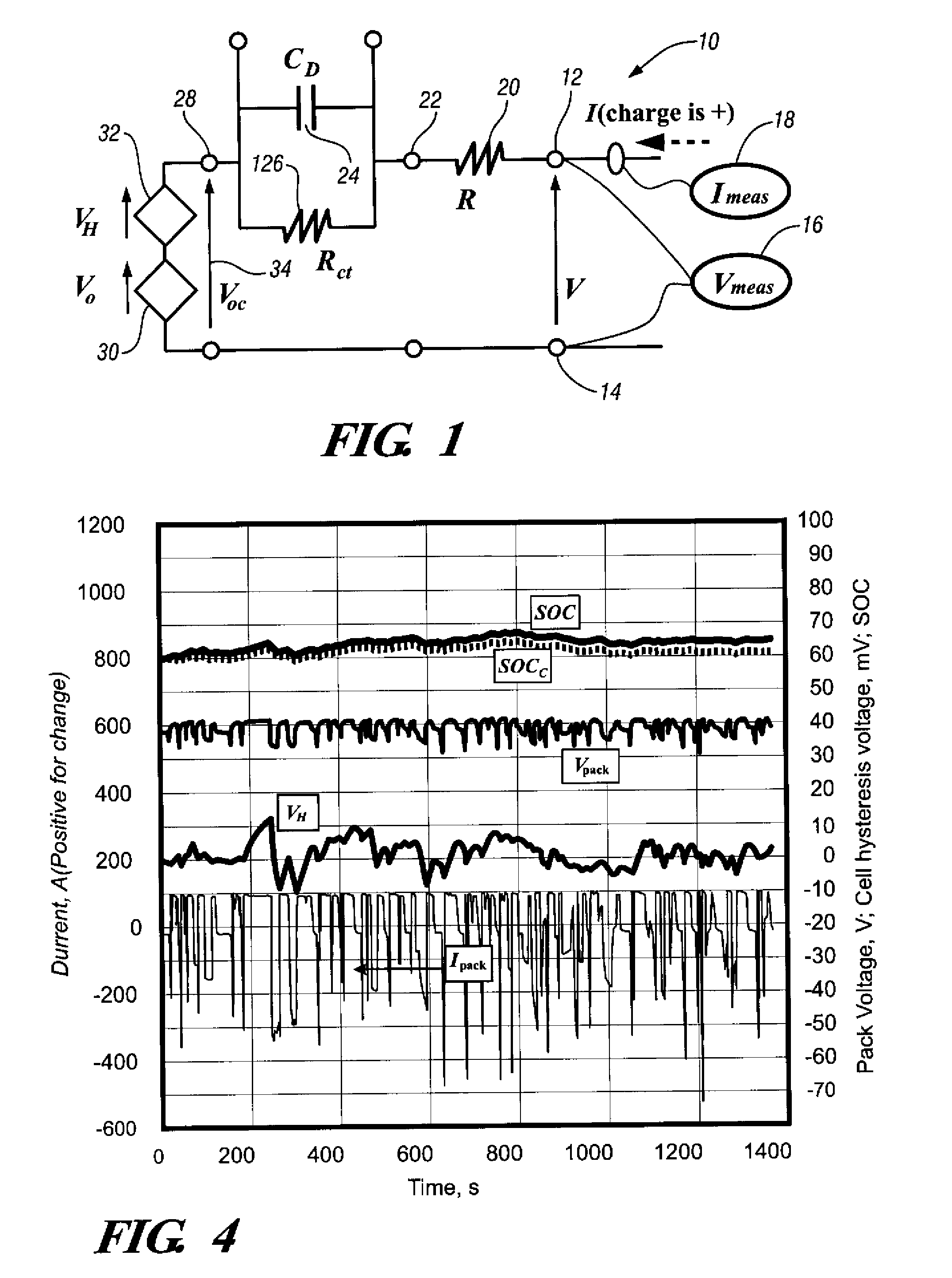

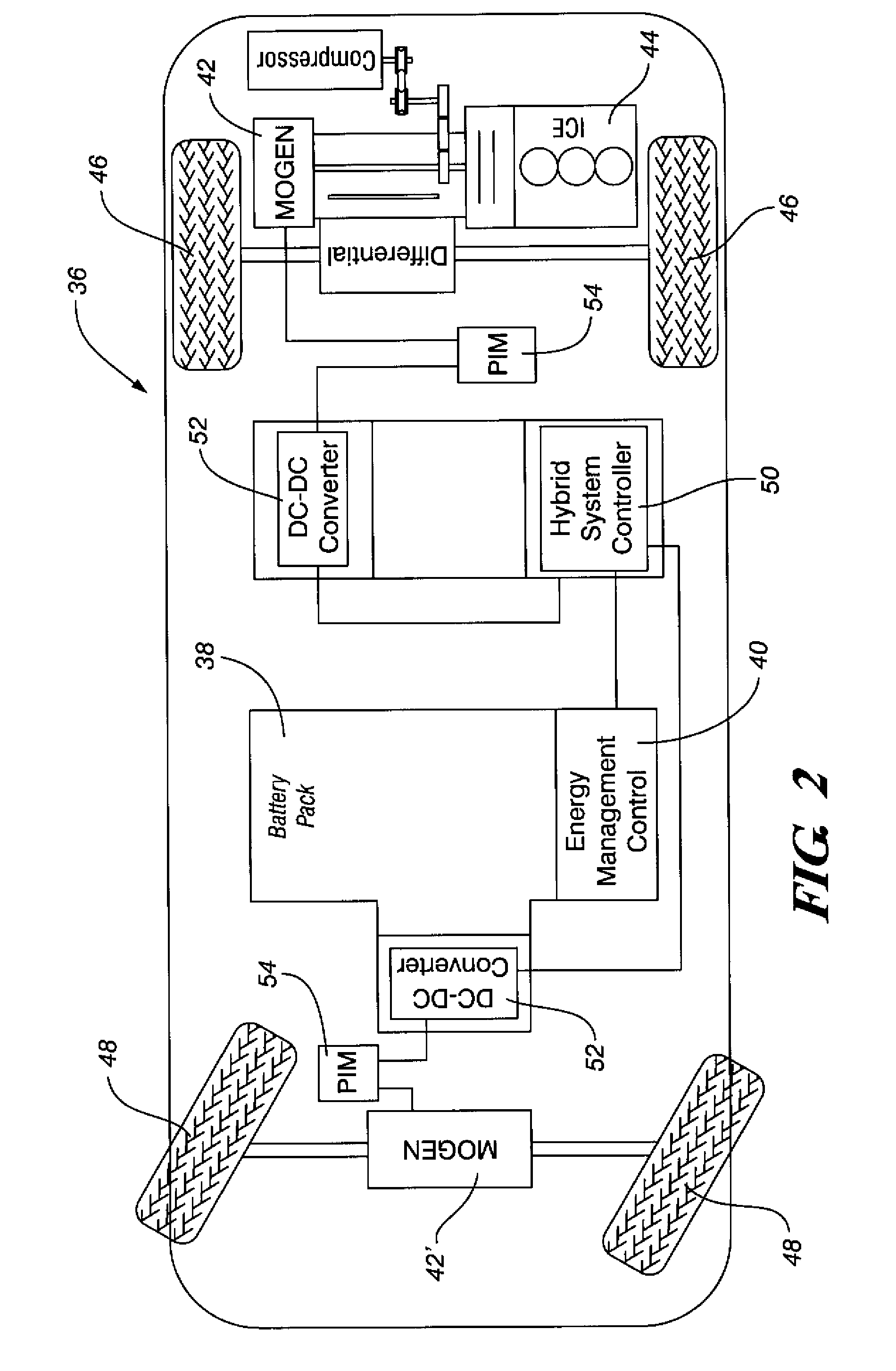

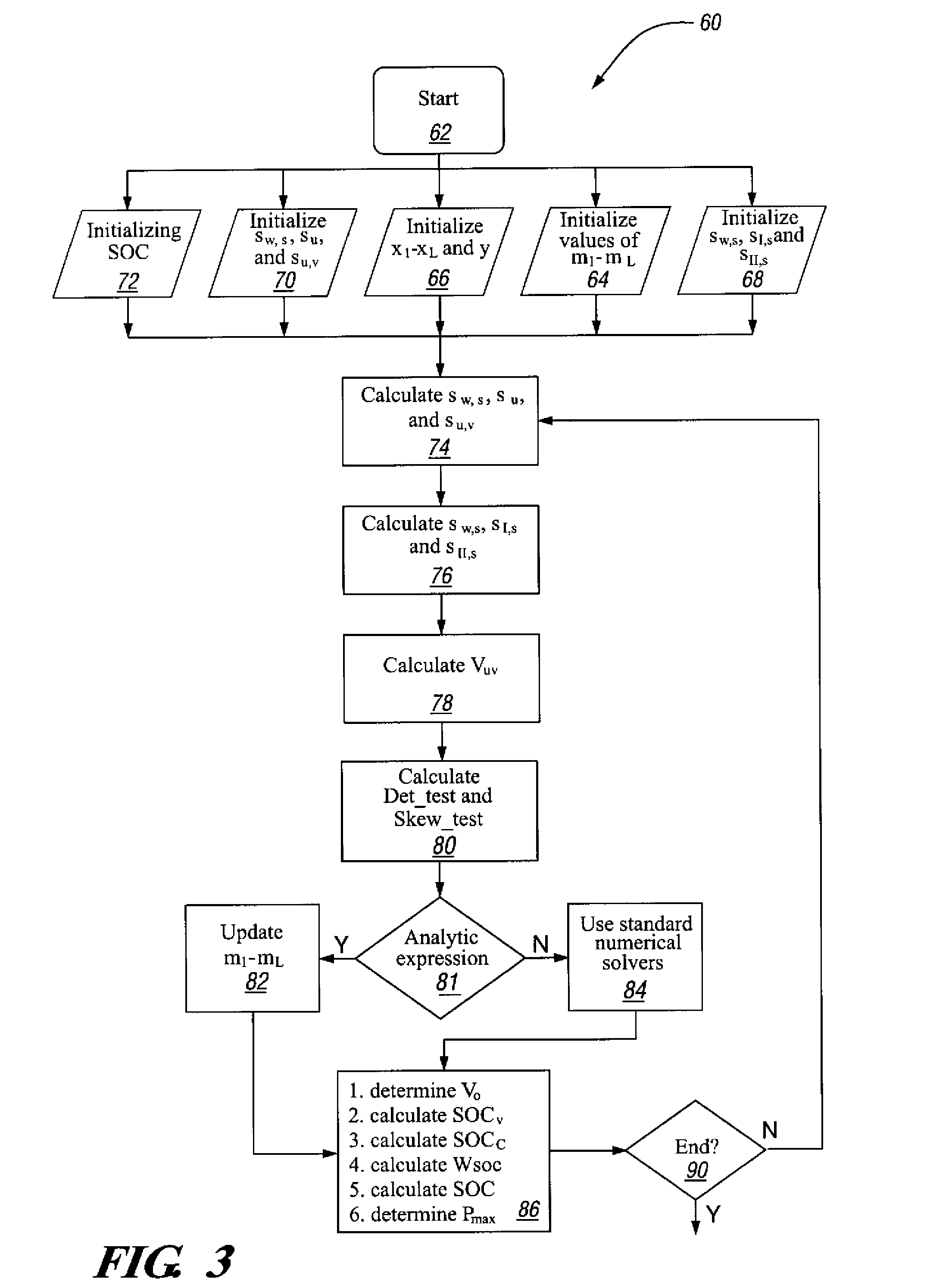

Method and apparatus for generalized recursive least-squares process for battery state of charge and state of health

InactiveUS7324902B2Current/voltage measurementTesting electric installations on transportBattery state of chargeState of health

Owner:GM GLOBAL TECH OPERATIONS LLC

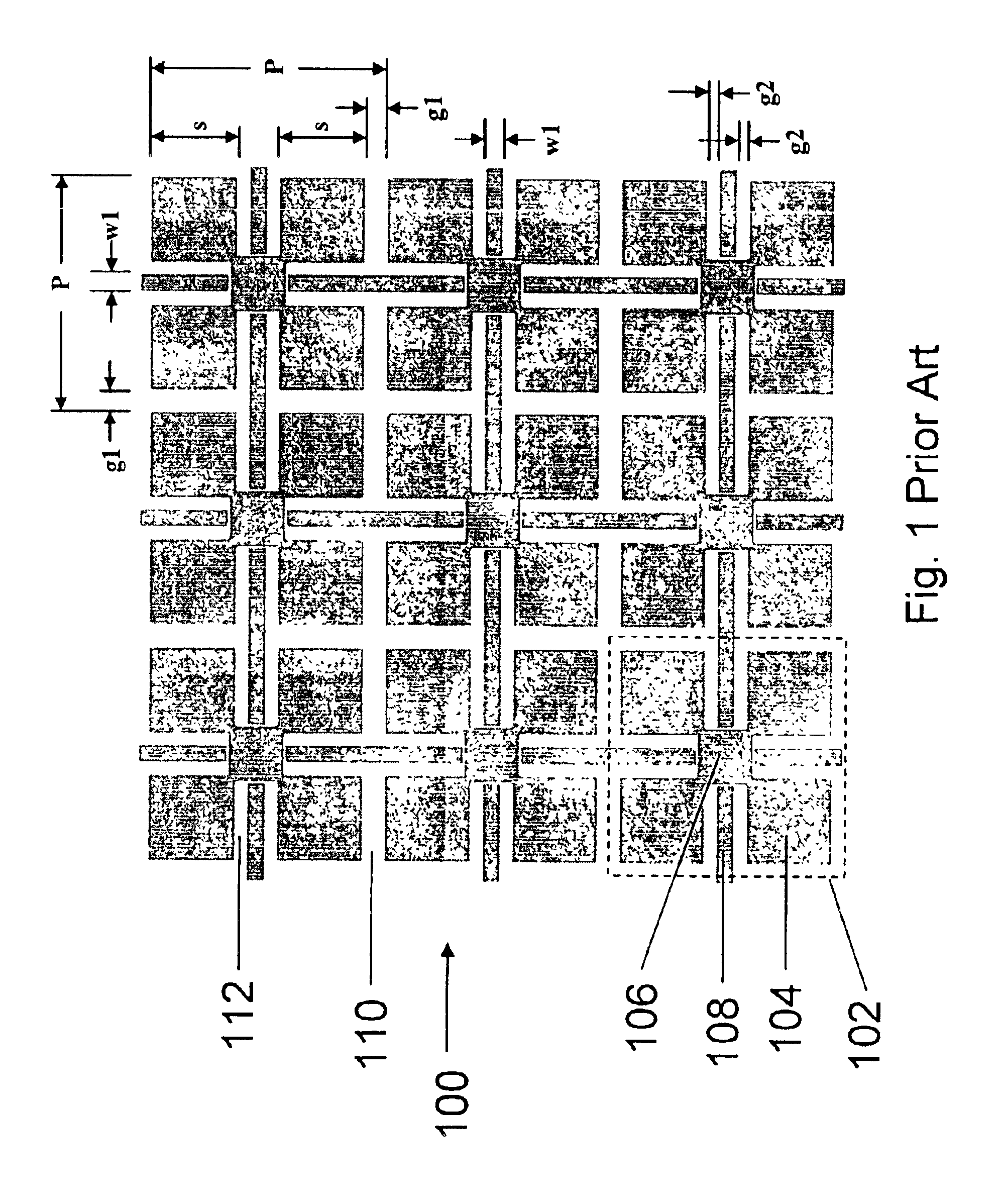

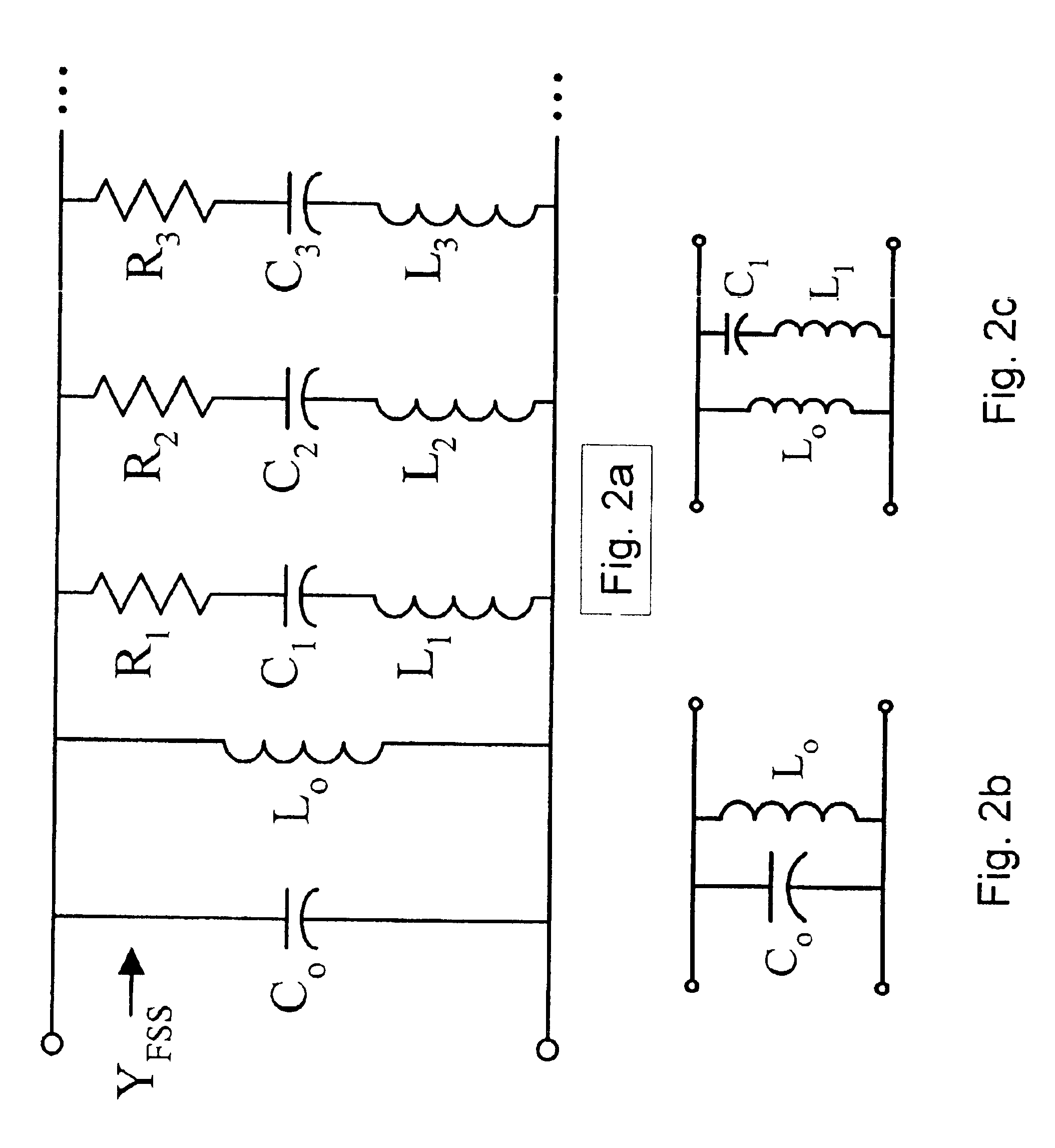

Low frequency enhanced frequency selective surface technology and applications

ActiveUS7071889B2Reduce physical sizeHigh surfaceSimultaneous aerial operationsRadiating elements structural formsWave structureCapacitance

DC inductive FSS technology is a printed slow wave structure usable for reduced size resonators in antenna and filter applications of wireless applications. It is a dispersive surface defined in terms of its parallel LC equivalent circuit that enhances the inductance and capacitance of the equivalent circuit to obtain a pole frequency as low as 300 MHz. The effective sheet impedance model has a resonant pole whose free-space wavelength can be greater than 10 times the FSS period. A conductor-backed DCL FSS can create a DC inductive artificial magnetic conductor (DCL AMC), high-impedance surface with resonant frequencies as low as 2 GHz. Lorentz poles introduced into the DCL FSS create multi-resonant DCL AMCs. Antennas fabricated from DCL FSS materials include single-band elements such as a bent-wire monopole on the DCL AMC and multi-band (dual and triple) shorted patches, similar to PIFAs with the patch / lid being a DCL FSS.

Owner:OAE TECH INC

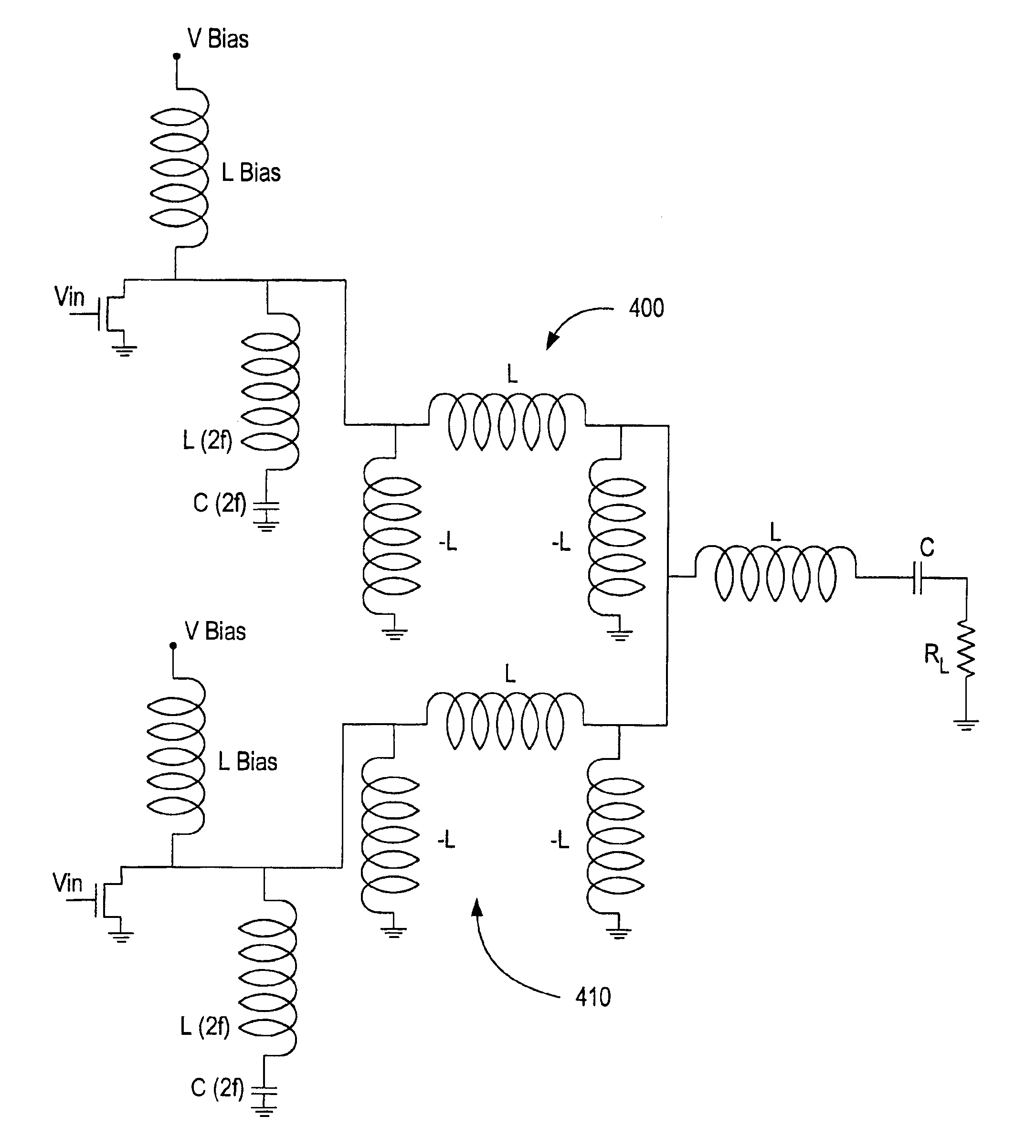

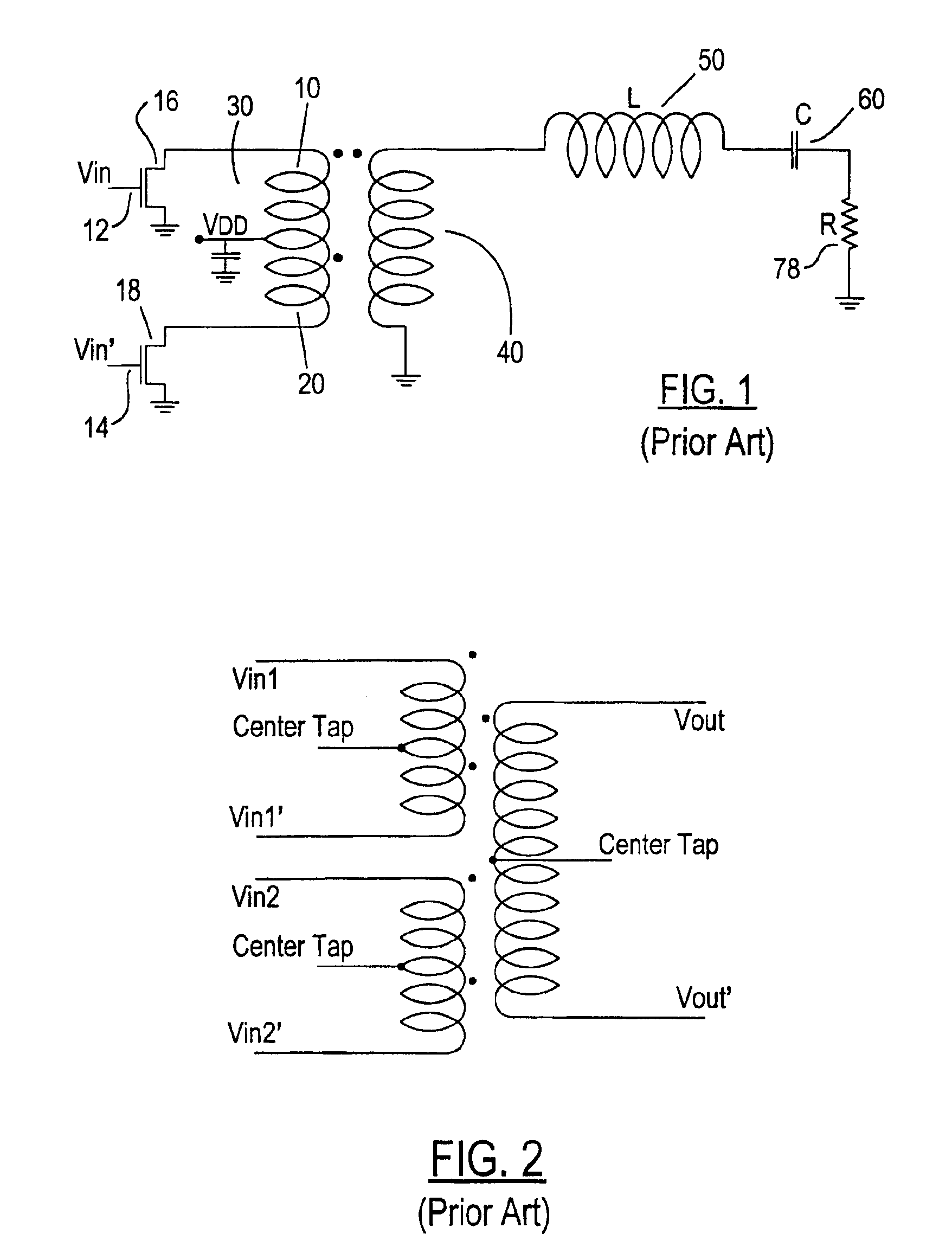

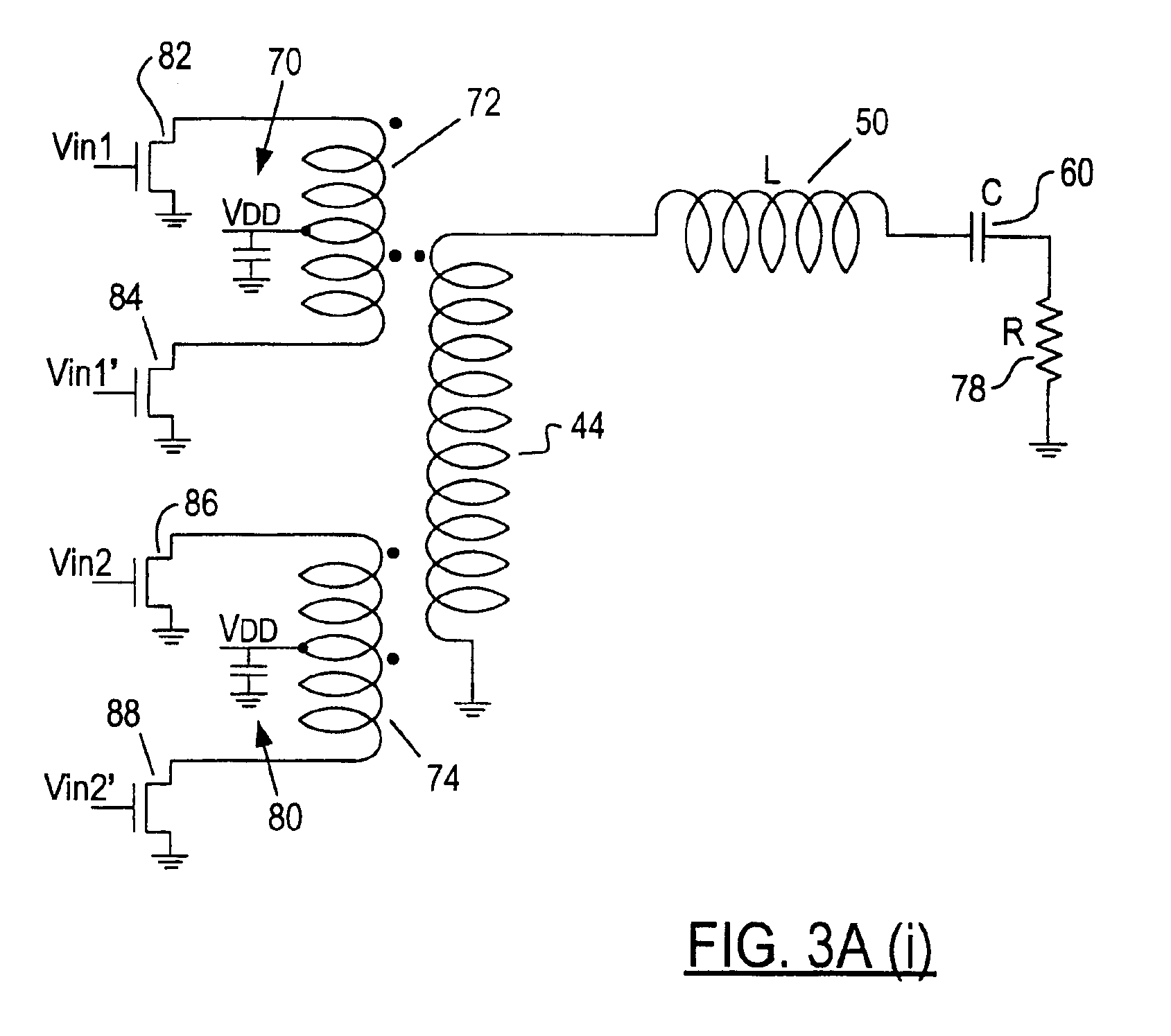

Switched-mode power amplifier integrally performing power combining

InactiveUS6937096B2Negative-feedback-circuit arrangementsPower amplifiersAudio power amplifierImpedance transformer

A switched-mode power amplifier is configured for performing power amplification of a plurality of signals input thereto and integrally summing (combining) those signals. Conceptually, this is achieved by replacing the input winding of the transformer component of a transformer-coupled voltage switching amplifier with separate input components, one for each input signal, in similar manner to the configuration of the input components of a three-port combiner (trifilar). In a first transformer-containing category of embodiments of the invention, the input winding of the amplifier's transformer is comprised of a plurality of series-coupled windings, one for each of the plurality of input components / signals such that the input components constitute a series connection of low output impedance sources applied to the amplifier's resonator and load. This, in turn, provides a high level of isolation between the amplifier input components and results in a low level of loss. In a second non-transformer-containing category of embodiments of the invention, the transformer component is replaced by a transmission line impedance transformer, or a lumped element equivalent circuit, which transforms the low output impedance sources to high output impedance sources and those sources are connected in parallel (rather than in series per the first category of embodiments).

Owner:ZARBANA DIGITAL FUND

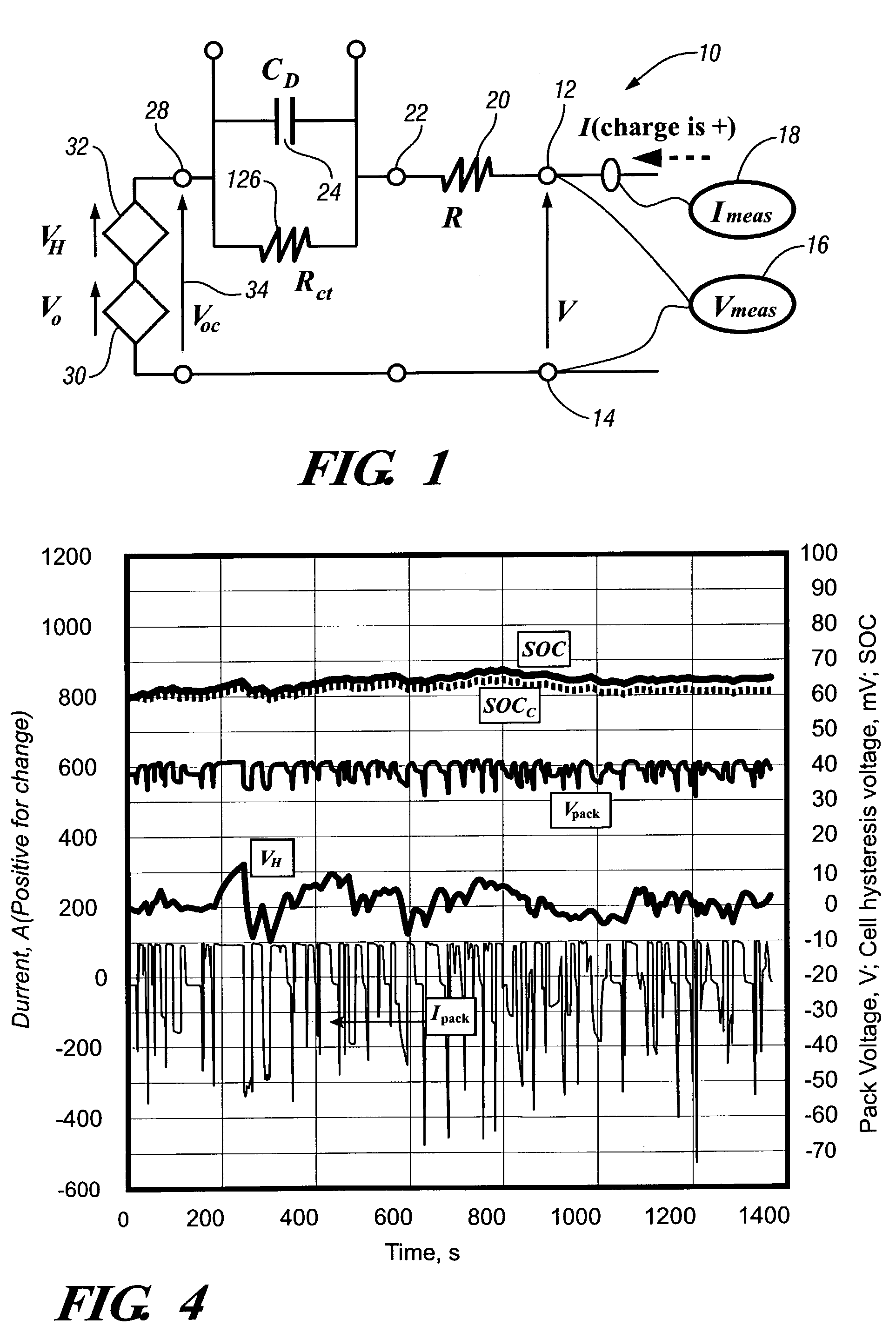

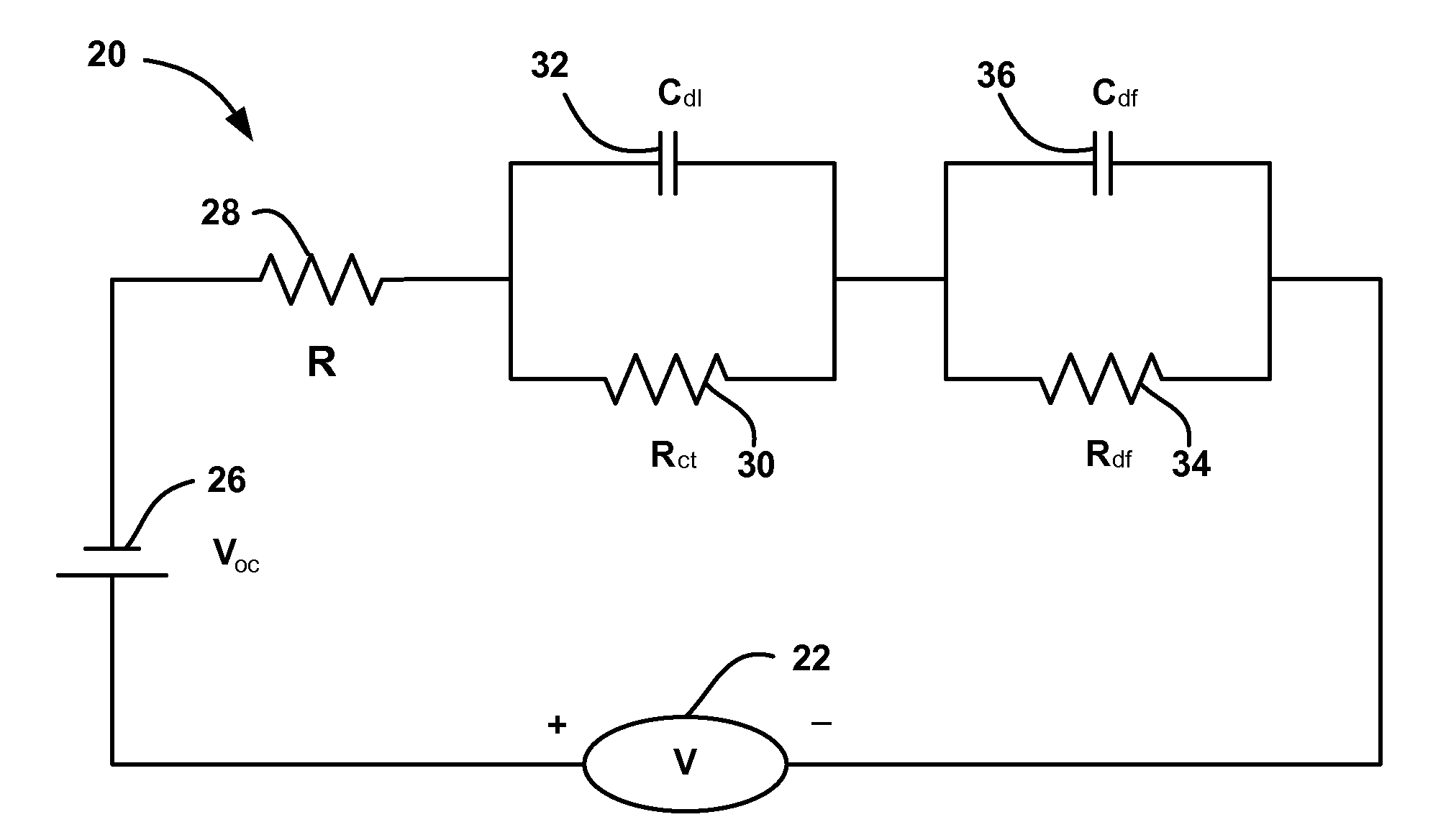

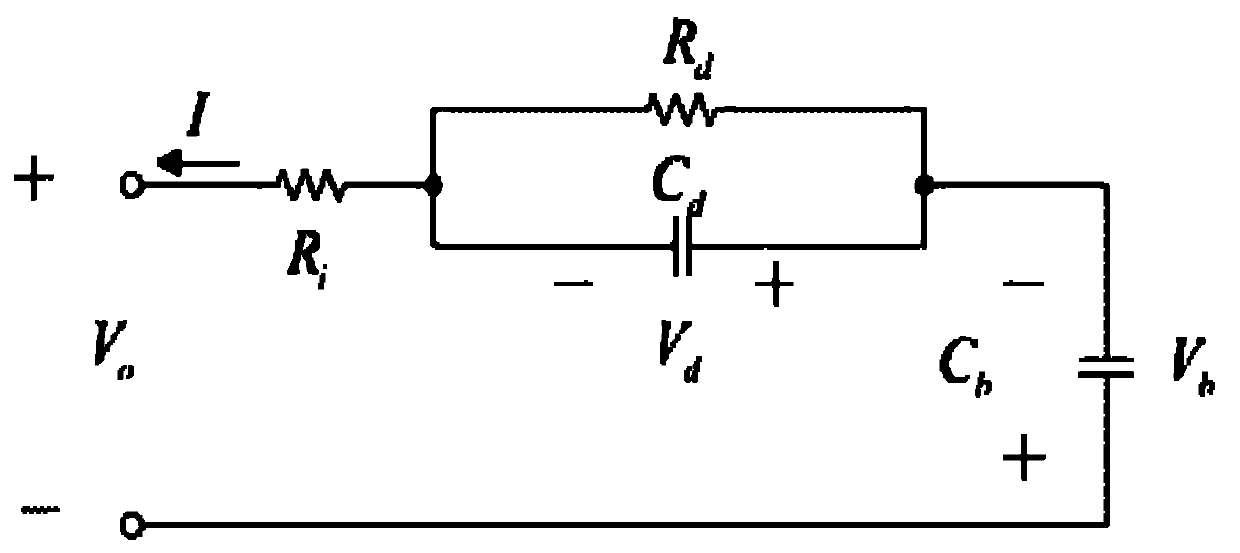

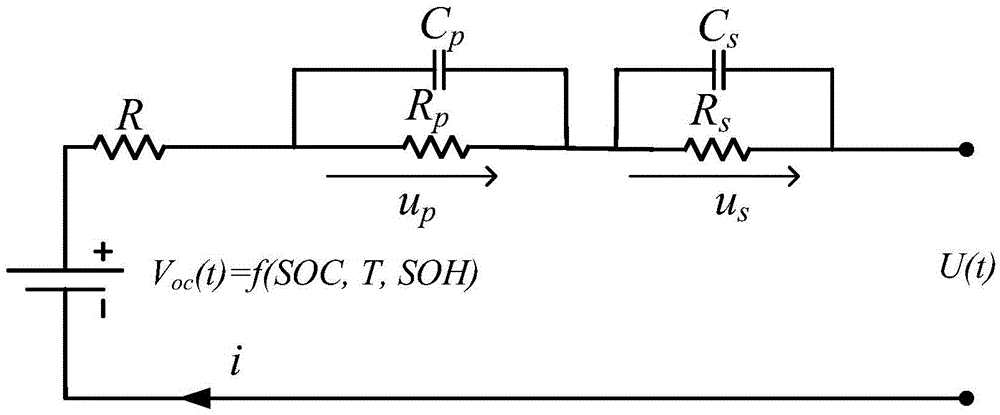

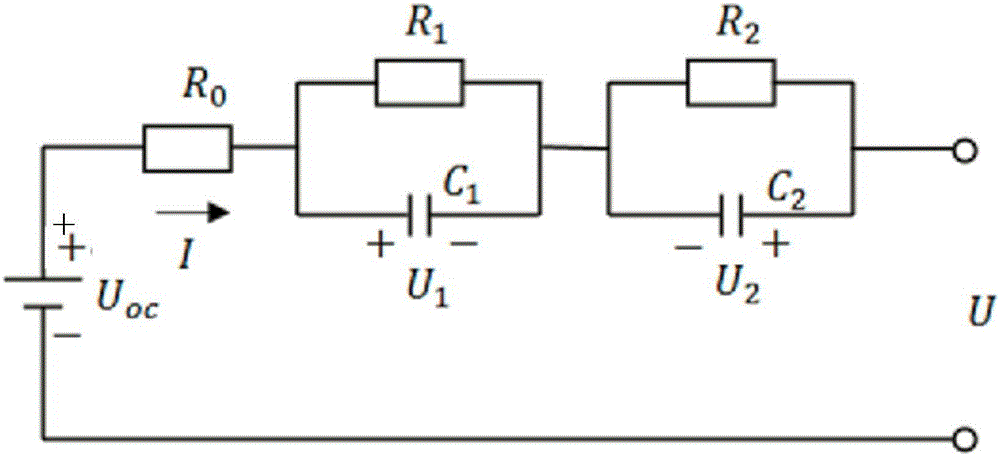

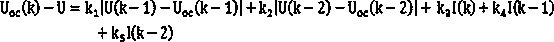

Adaptive battery parameter extraction and soc estimation for lithium-ion battery

ActiveUS20110309838A1Reliable battery state-of-charge estimateMaterial analysis by electric/magnetic meansElectrical testingBattery state of chargeElectrical battery

A system and method for estimating internal parameters of a lithium-ion battery to provide a reliable battery state-of-charge estimate. The method uses a two RC-pair equivalent battery circuit model to estimate the battery parameters, including a battery open circuit voltage, an ohmic resistance, a double layer capacitance, a charge transfer resistance, a diffusion resistance and a diffusion capacitance. The method further uses the equivalent circuit model to provide a difference equation from which the battery parameters are adapted, and calculates the battery parameters from the difference equation.

Owner:GM GLOBAL TECH OPERATIONS LLC

Method and apparatus for generalized recursive least-squares process for battery state of charge and state of health

InactiveUS20070159137A1Batteries circuit arrangementsCurrent/voltage measurementBattery state of chargeState of health

A method for determining a voltage based or current based state of charge (SOC) and state of health (SOH) of a battery system is provided. The method includes: providing a model of the battery system including an equivalent circuit having both low frequency and high frequency elements; establishing a plurality of functional relationships comprising relationship of the equivalent circuit with SOC; reducing at least part of the plurality of functional relationships into a set of time segmented recursive functional relationships, wherein a state at a first time t can be modeled by a functional presentation of a state at a second time t−Δt that occurred before the first time t; and computing a set of data points based upon the set of time segmented recursive functional relationships using a matrix for operation in matrix algebra.

Owner:GM GLOBAL TECH OPERATIONS LLC

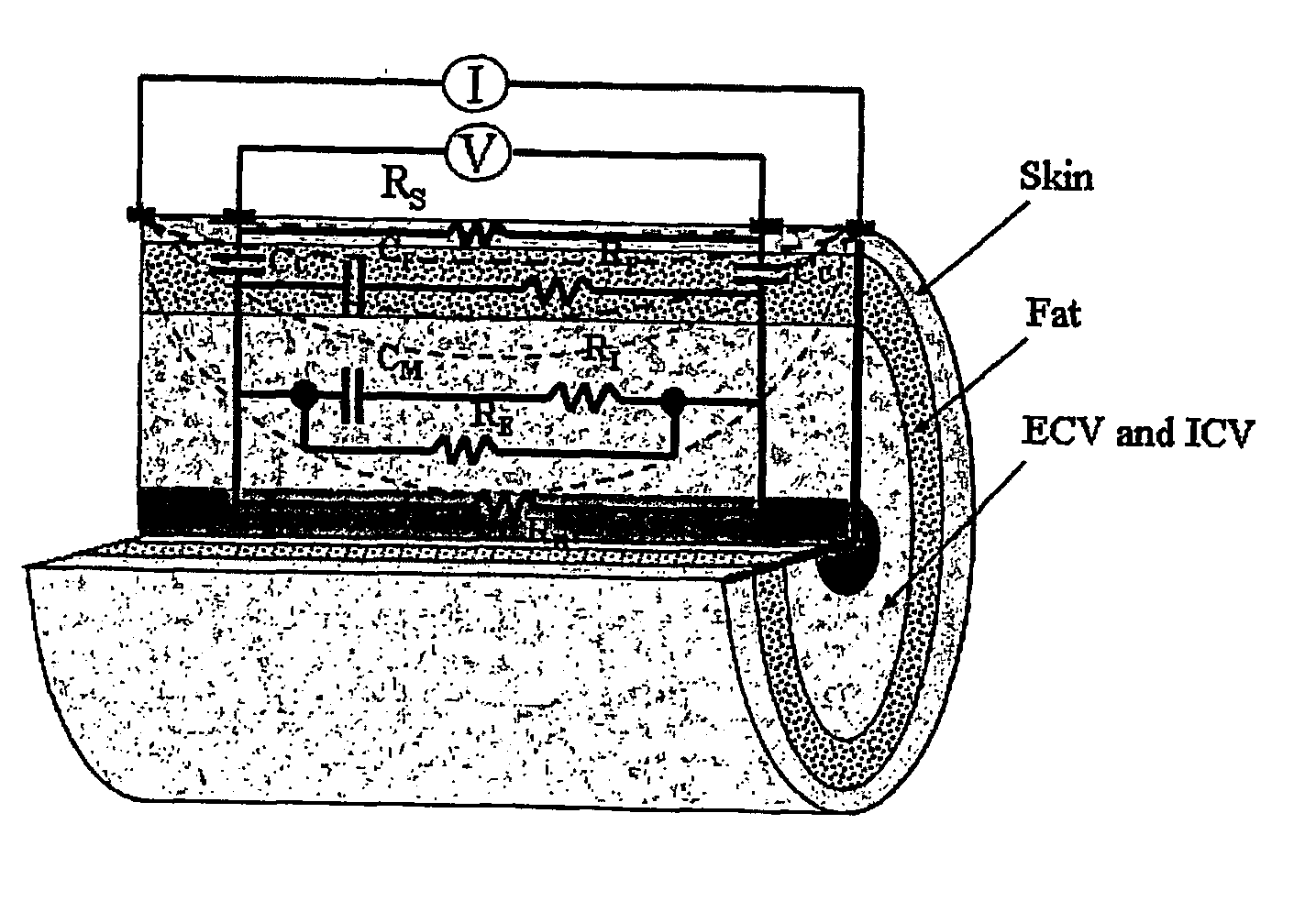

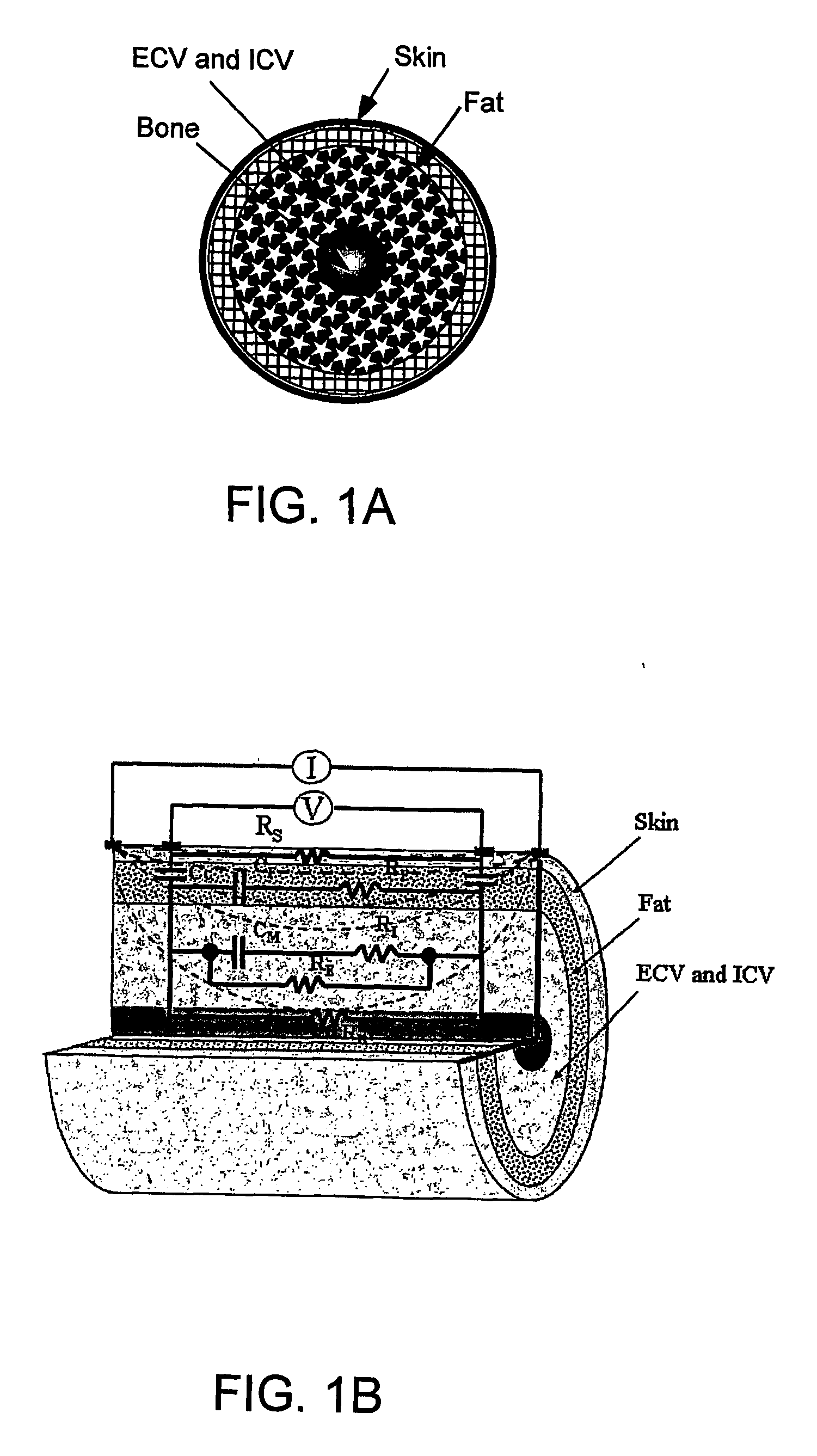

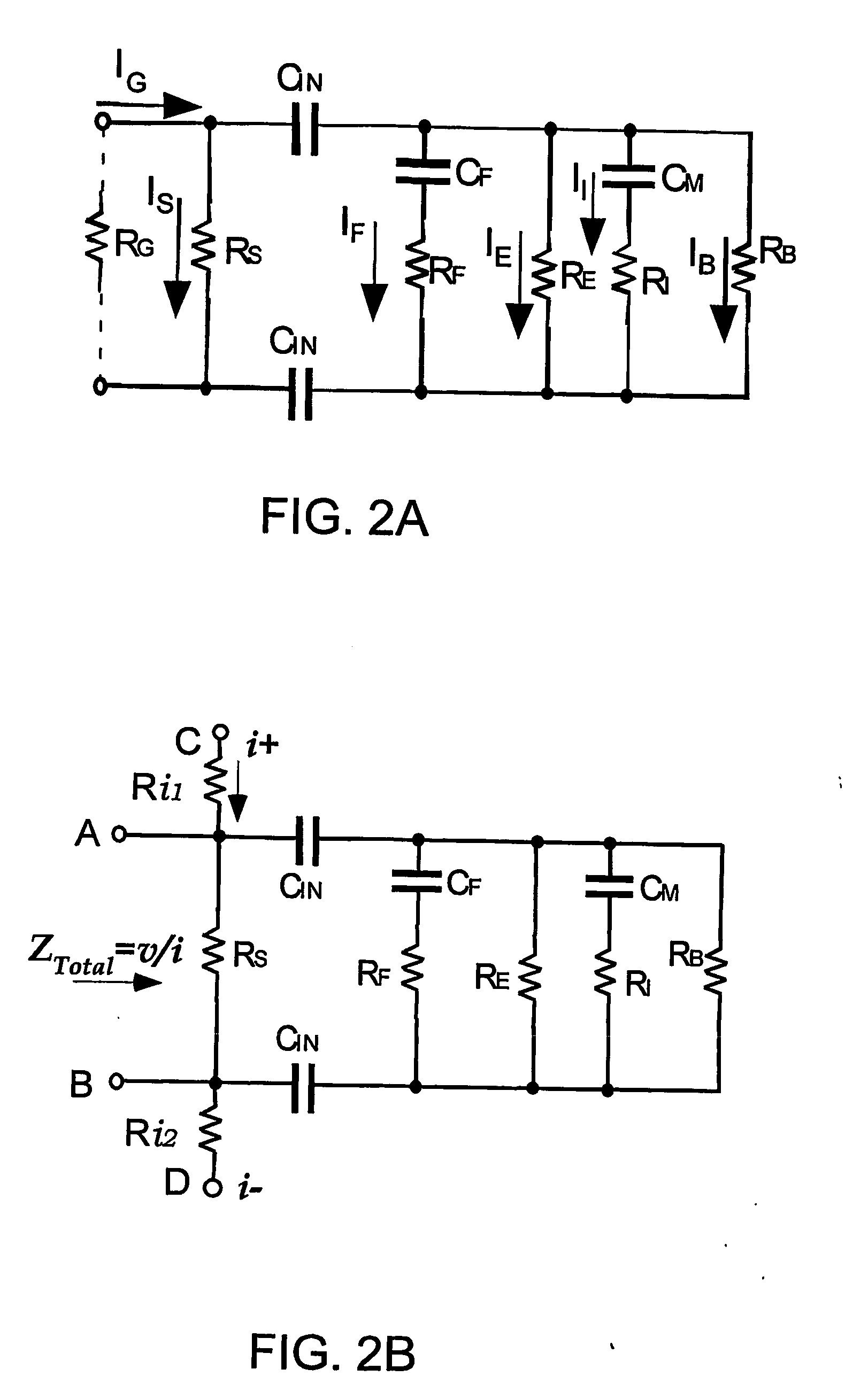

Bioimpedance methods and apparatus

InactiveUS20070027402A1Significant differenceDiagnostic recording/measuringSensorsMedicineBioimpedance spectroscopy

Methods and apparatus for providing bioimpedance analysis are provided. In certain aspects, equivalent circuit frequency response models are provided which lead to improved correlations with MRI data. The frequency response models take account of body composition, including the fat component of a body segment. Data obtained by performing bioimpedance spectroscopy (BIS) and MRI on the calves of subjects illustrates the improved correlations achieved compared to single frequency analyses at 50 kilohertz and analyses performed using the conventional Cole-Cole model.

Owner:RENAL RES INST +1

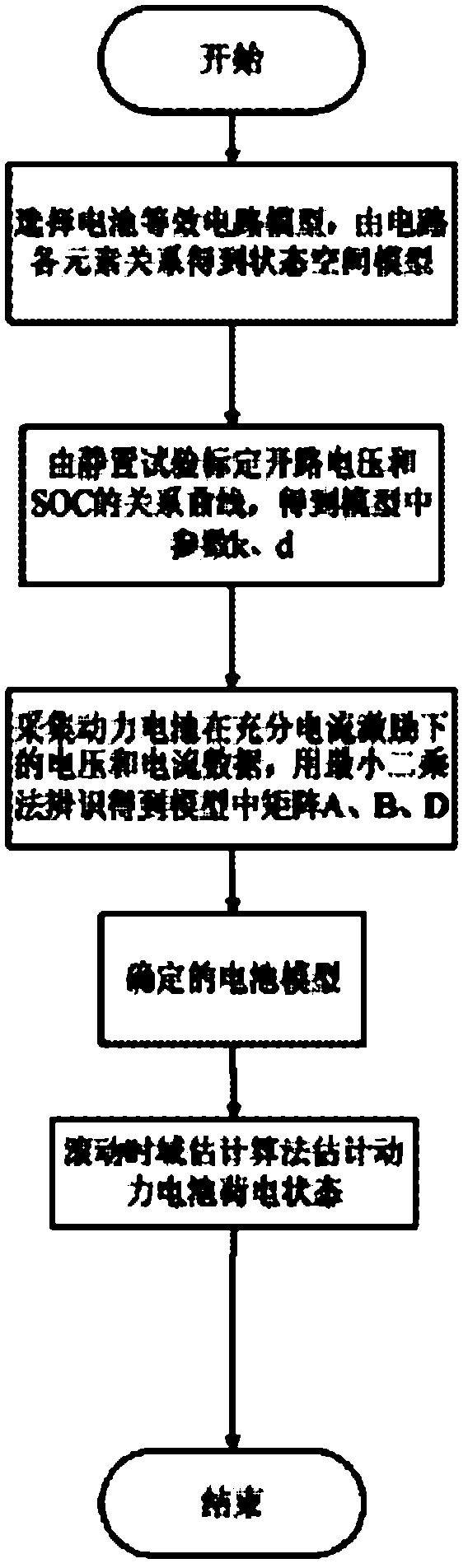

Method for estimating charge state of power cell

InactiveCN102608542AIn line with the actual useReduce estimation errorElectrical testingDiscretizationData system

The invention discloses a method for estimating the charge state of a power cell, which comprises the following steps that: 1. a continuous state space model capable of expressing the relationship of each element in an expression circuit is obtained by an equivalent circuit model of a power cell; the relationship between the open-circuit voltage and the cell charge state is obtained through the standing experiment of the power cell, and the cell charge state is introduced into the continuous state space model of the power cell as a state variable; the power battery model under the noise environment is obtained by combining the noise information; and finally the continuous state space model is subjected to linearization and discretization so as to obtain a linear discrete state space model; 2. a relationship curve of the open-circuit voltage and the cell charge state is obtained through the standing experiment of the power cell, and a parameter k and a parameter d in the power cell model are obtained approximately; 3. parameters of the power cell model are obtained through the identification of current and voltage data collected by a data collecting system; and 4. the power cell charge state is estimated by utilizing a moving horizon estimation method based on the determined power cell model.

Owner:JILIN UNIV

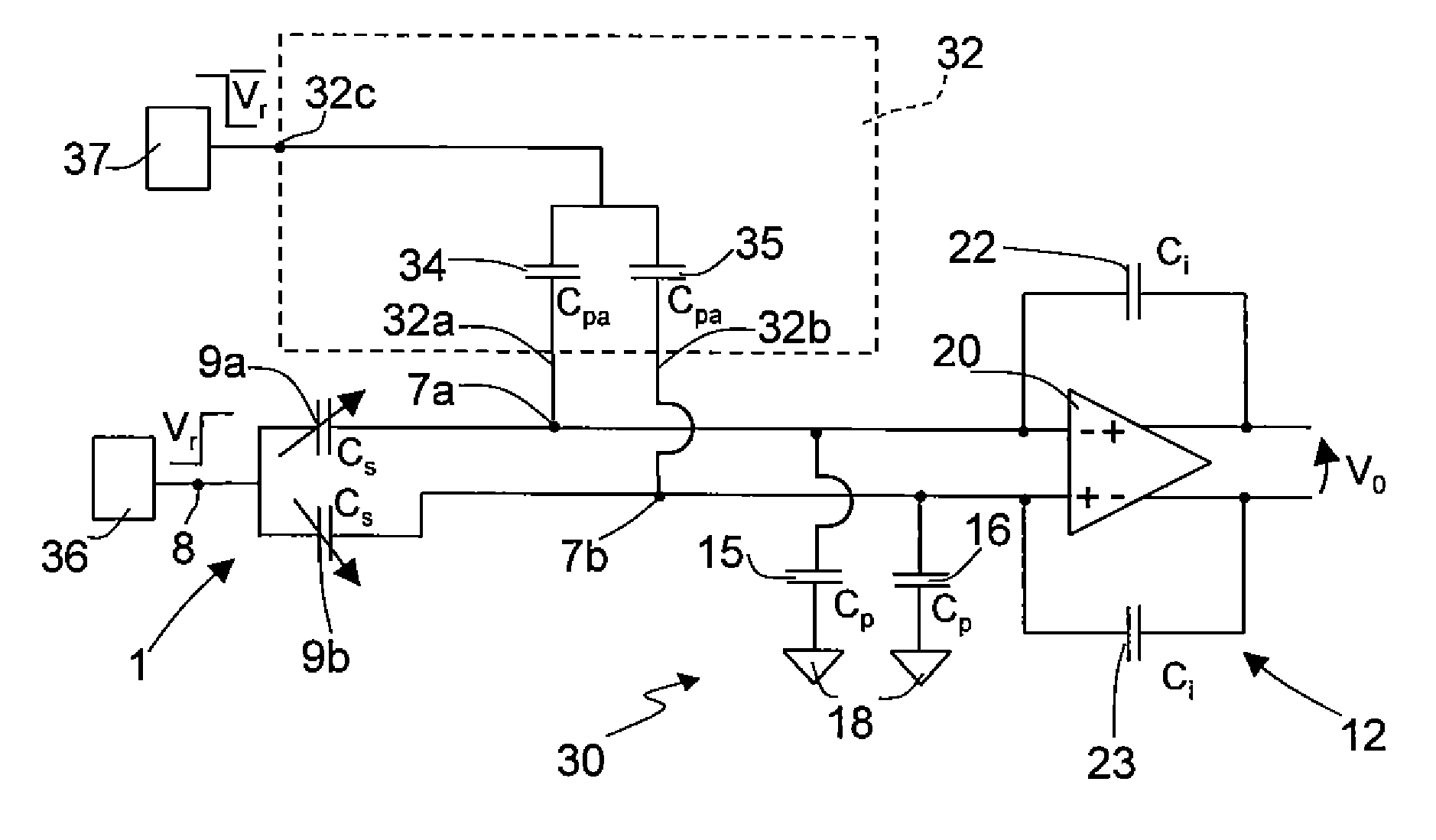

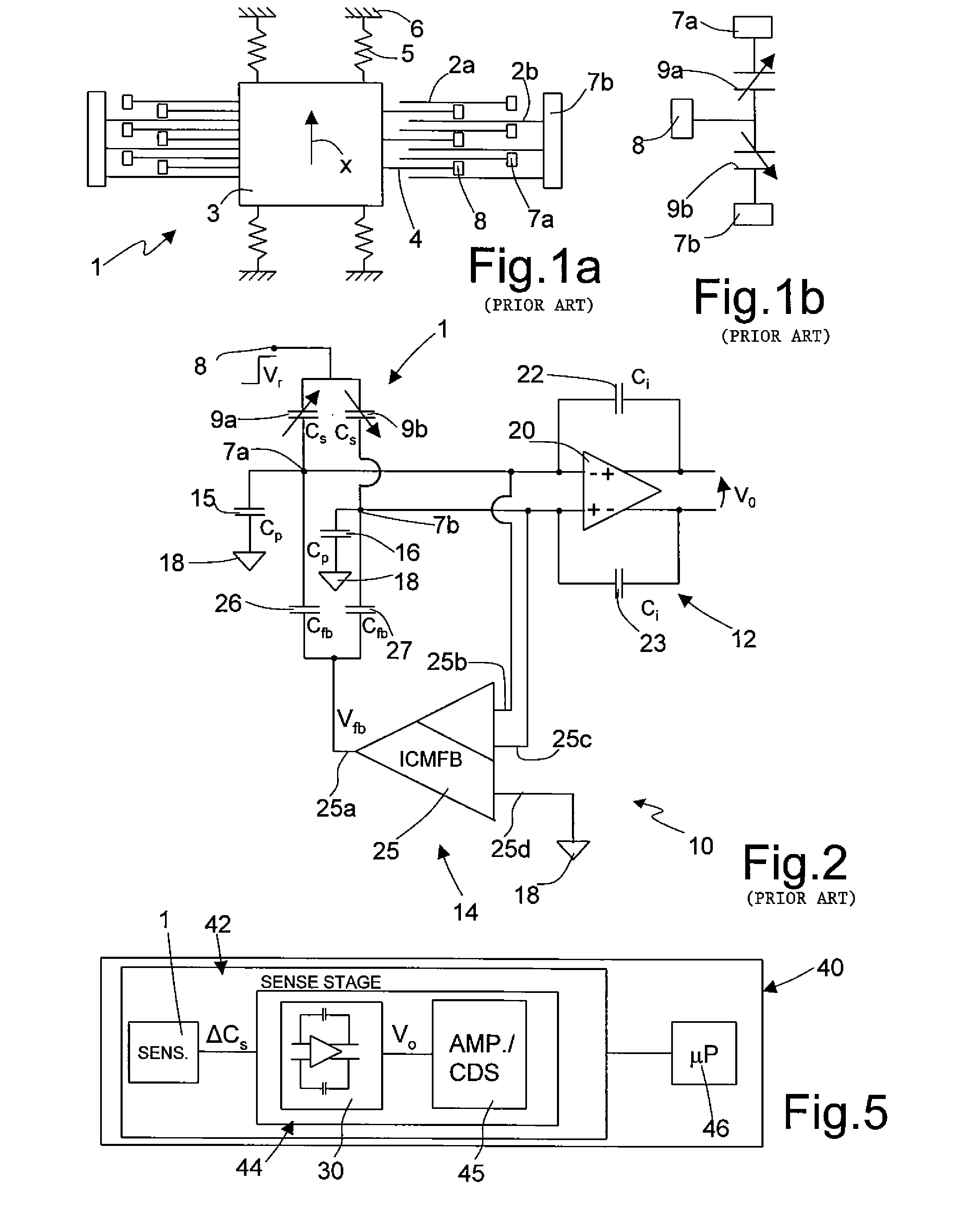

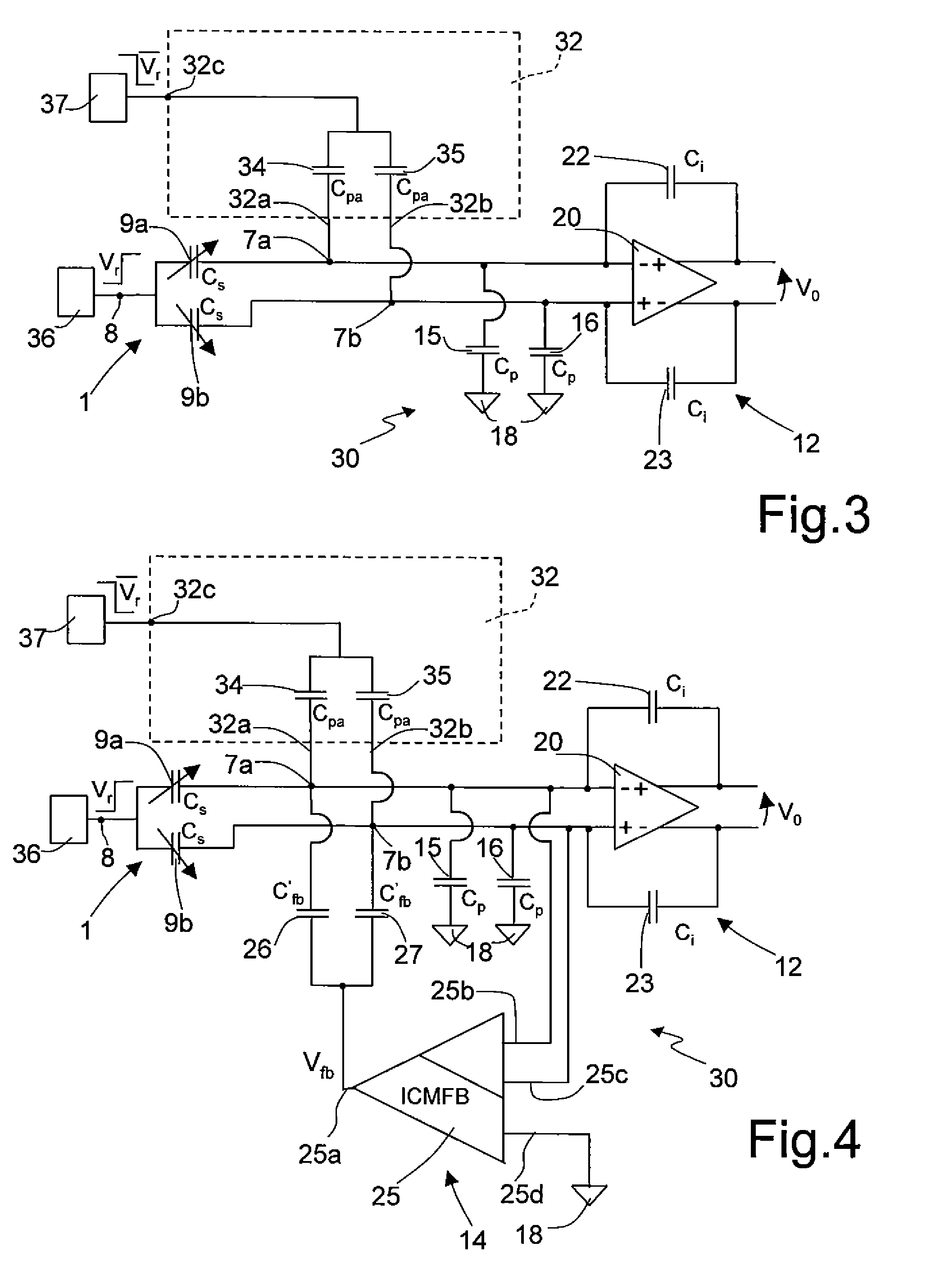

Detection circuit using a differential capacitive sensor with input-common-mode control in a sense interface

ActiveUS20070163815A1Overcome disadvantagesOvercome problemsTransmission systemsAcceleration measurementElectricityAudio power amplifier

A detection circuit is provided with a differential capacitive sensor and with an interface circuit having a first sense input and a second sense input, electrically connected to the differential capacitive sensor. Provided in the interface circuit are: a sense amplifier connected at input to the first sense input and to the second sense input and supplying an output signal related to a capacitive unbalancing of the differential capacitive sensor; and a common-mode control circuit, connected to the first sense input and to the second sense input and configured to control a common-mode electrical quantity present on the first sense input and on the second sense input. The common-mode control circuit is of a totally passive type and is provided with a capacitive circuit, which is substantially identical to an equivalent electrical circuit of the differential capacitive sensor and is driven with a driving signal in phase opposition with respect to a read signal supplied to the differential capacitive sensor.

Owner:STMICROELECTRONICS SRL

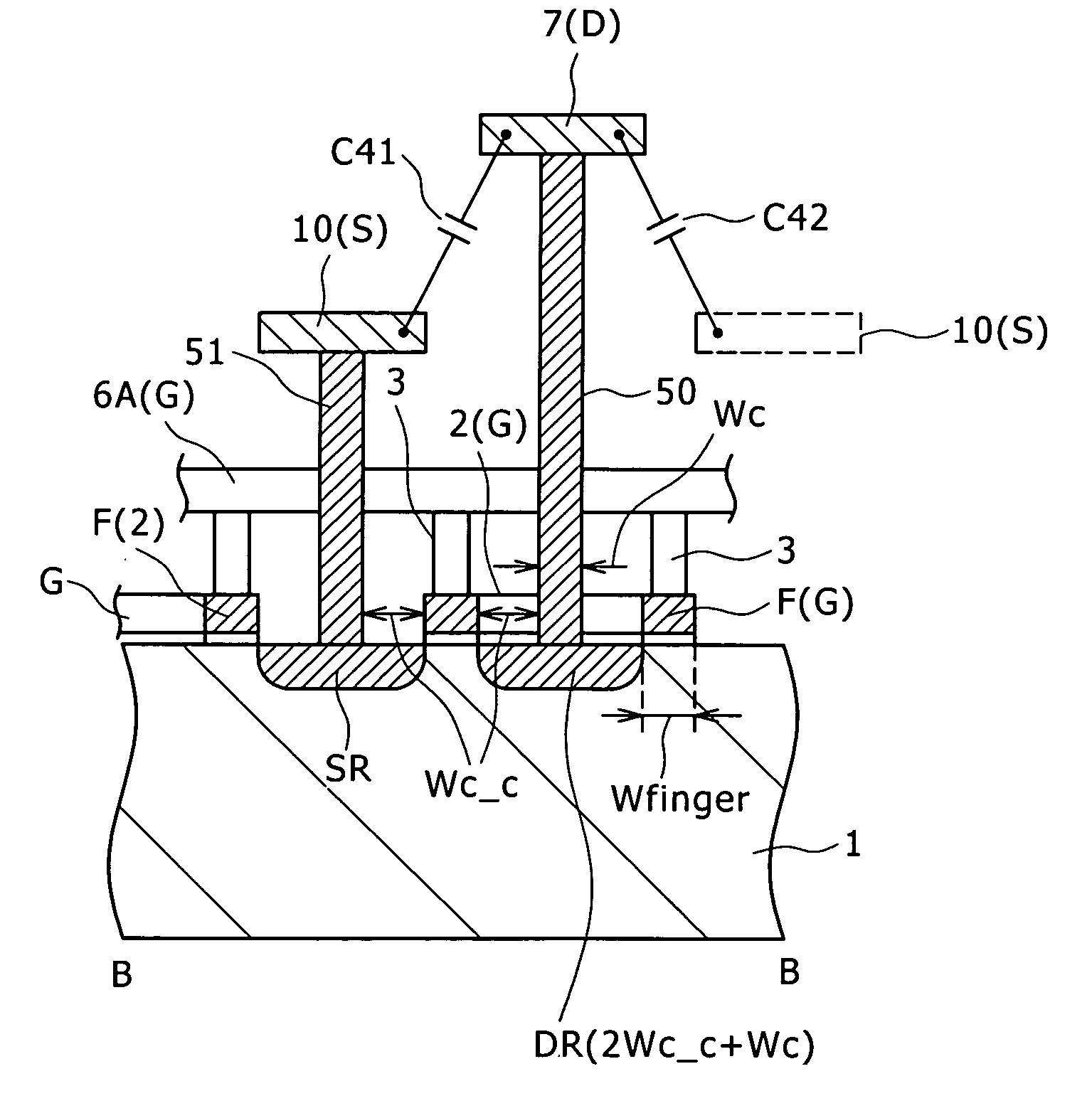

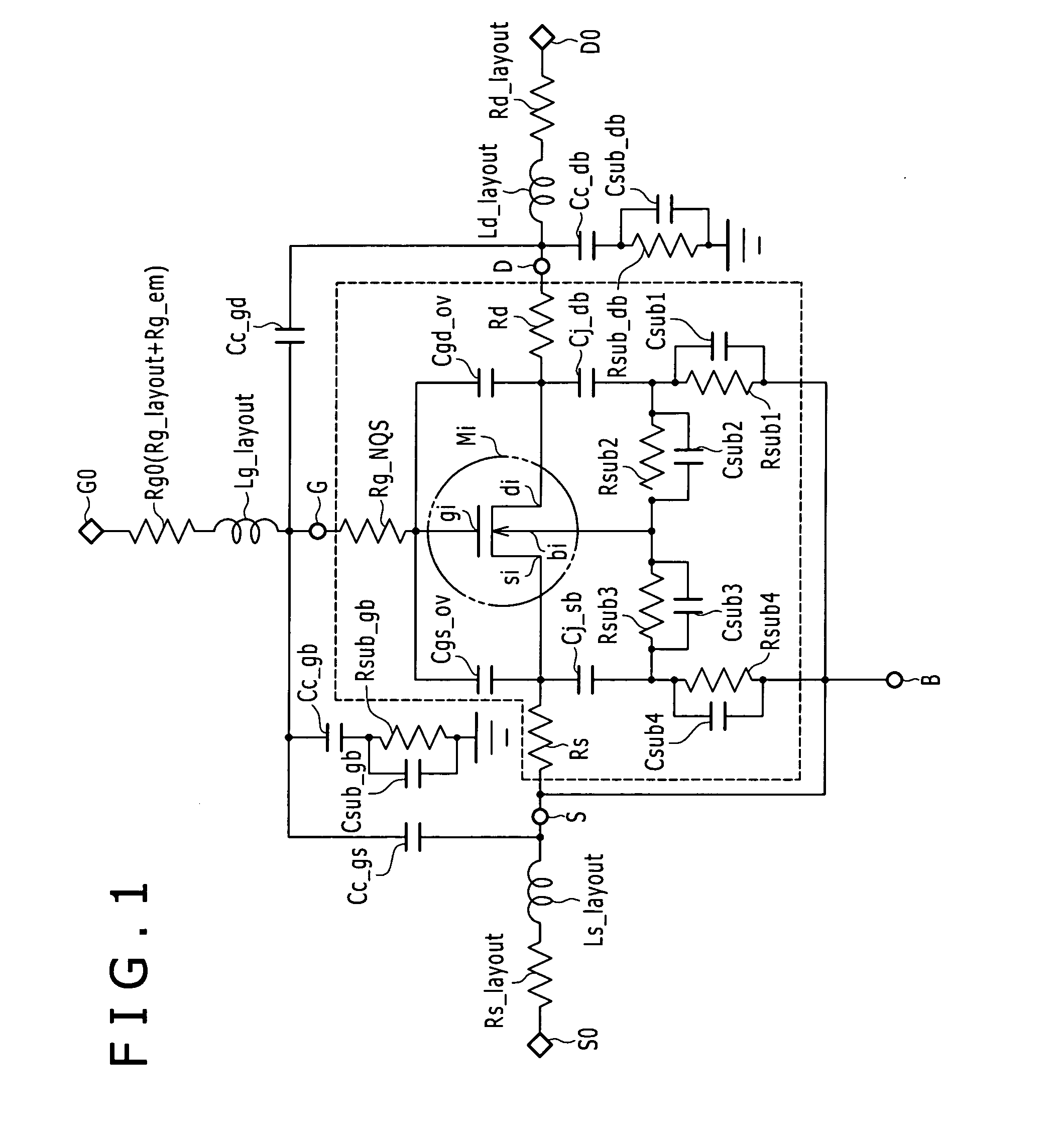

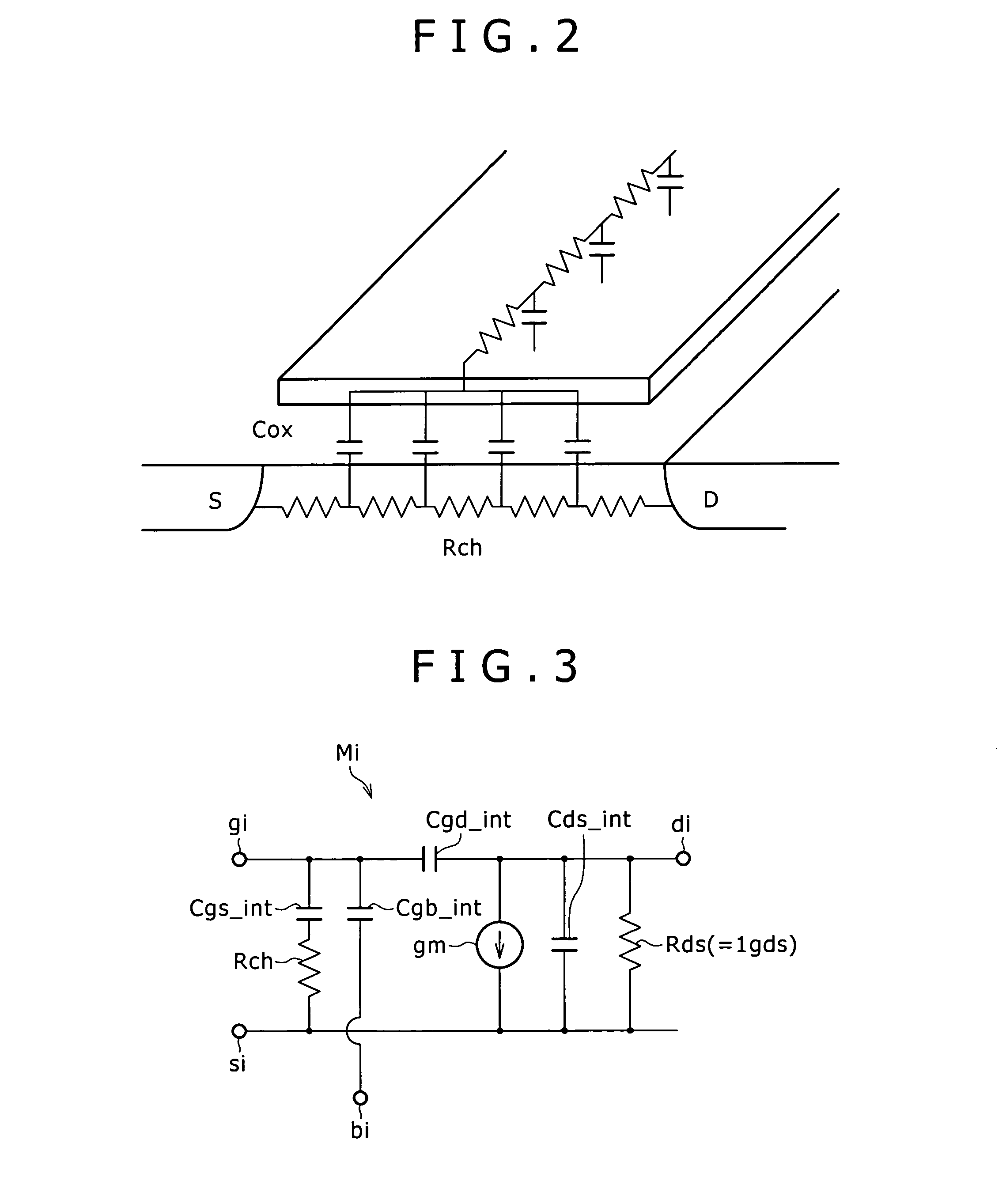

Designing method for high-frequency transistor and high-frequency transistor having multi-finger gate

InactiveUS20060107246A1Reduce coupling capacitanceWell representedCAD circuit designSoftware simulation/interpretation/emulationCapacitanceEngineering

The present invention provides a designing method for a high-frequency transistor, which includes a transistor section, a drain region, and a gate electrode, a source wiring line, a drain wiring line, and a gate wiring line, for optimizing wiring lines and contacts from voltage supplying nodes to electrode lead nodes. The method includes the steps of measuring a sensitivity to a high-frequency characteristic of the high-frequency transistor regarding coupling capacities between the wiring lines and coupling capacities between the wiring lines and the semiconductor substrate from among equivalent circuit parameters which vary in response to a configuration of the wiring lines and the contacts; deciding layered levels individually of the gate wiring line, source wiring line, and drain wiring line based on the measured sensitivities; and designing patterns of the gate wiring line, source wiring line, and drain wiring line in the individually decided layered levels and the positions and the sizes of the wiring lines and the contacts for connecting the wiring lines and the transistor section to each other.

Owner:SONY CORP

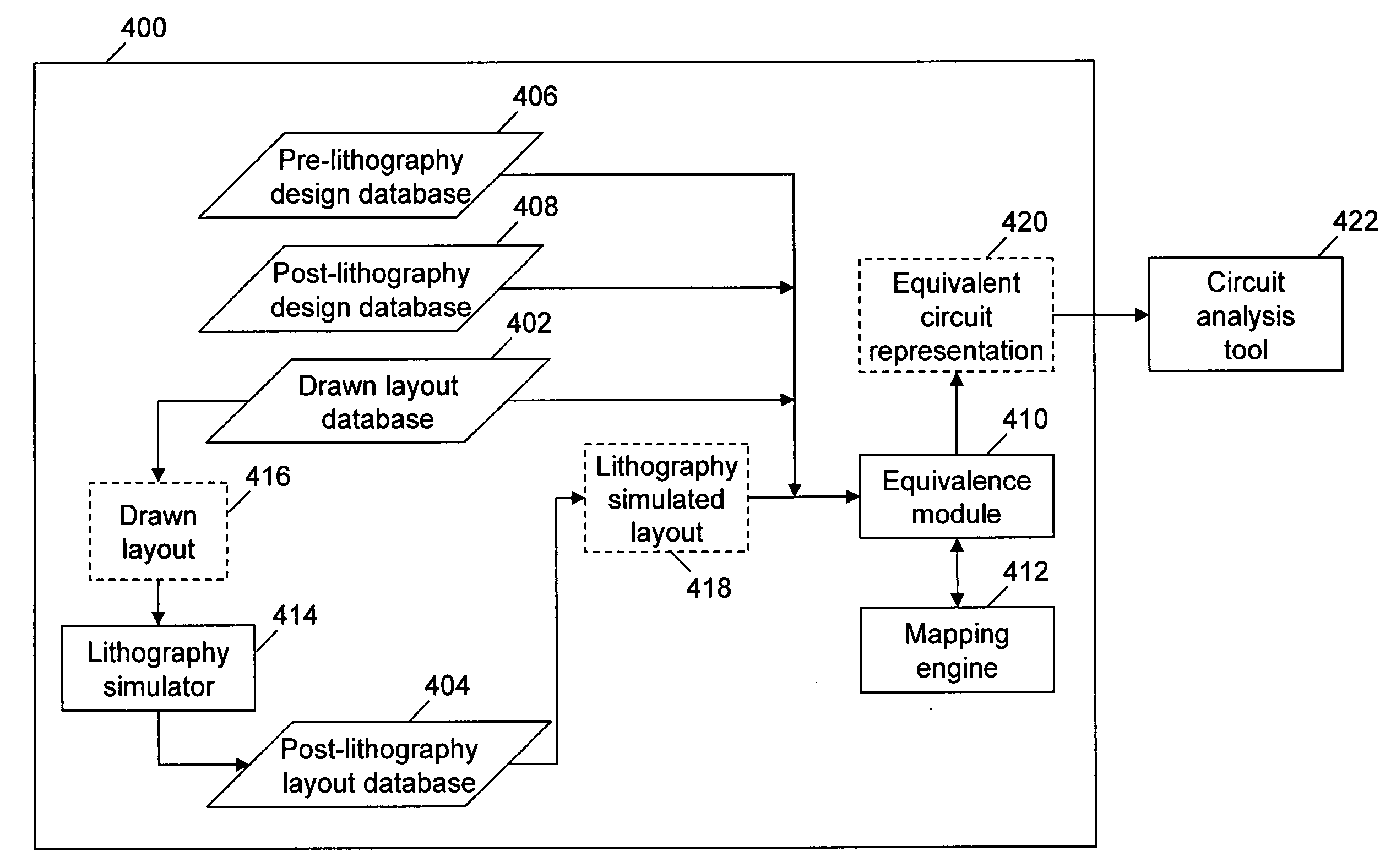

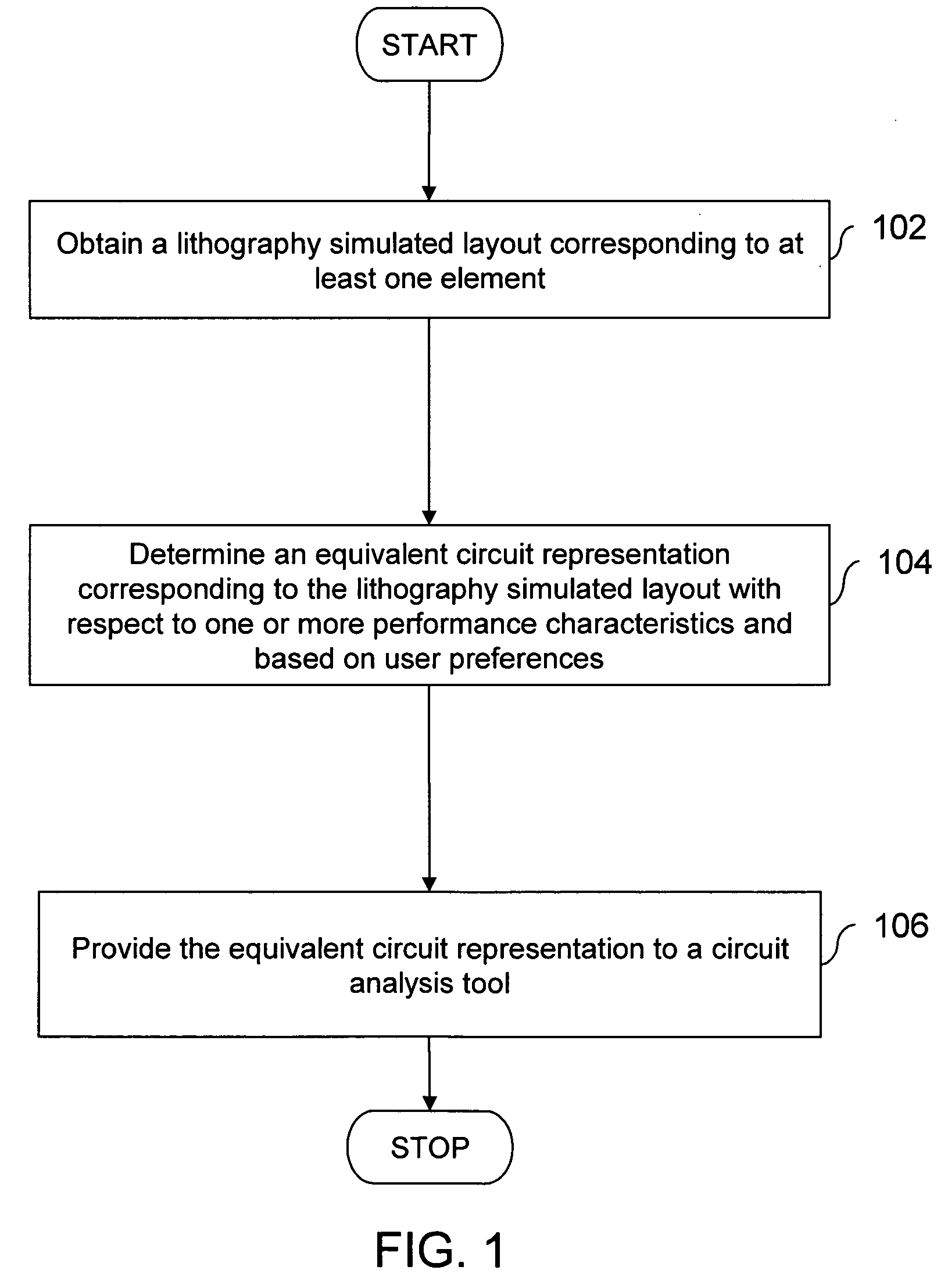

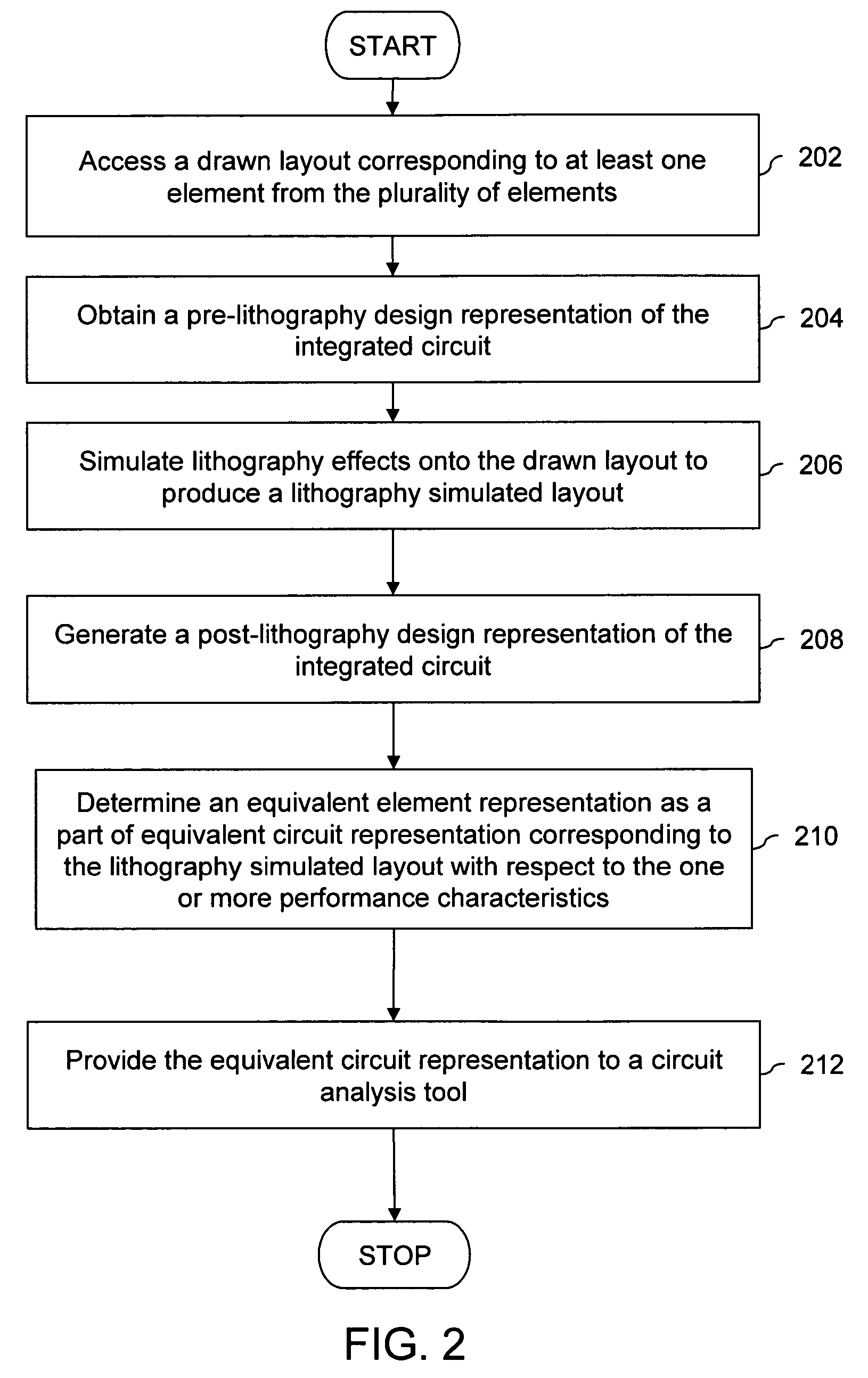

Method and system for finding an equivalent circuit representation for one or more elements in an integrated circuit

InactiveUS20060150132A1Reduce processing timeAnalogue computers for electric apparatusDetecting faulty computer hardwareLithographic artistEngineering

The present invention provides a method and a system for designing an integrated circuit comprising a plurality of elements. The method includes obtaining a lithography-simulated layout corresponding to at least one element. The lithography-simulated layout accounts for lithography effects on the element. The method further includes determination of an equivalent circuit representation that is compatible to a circuit analysis tool, corresponding to the lithography-simulated layout with respect to one or more performance characteristics and based on user preferences. The method also provides equivalent circuit representation to the circuit analysis tool that analyzes one or more performance characteristics of the elements.

Owner:RPX CORP

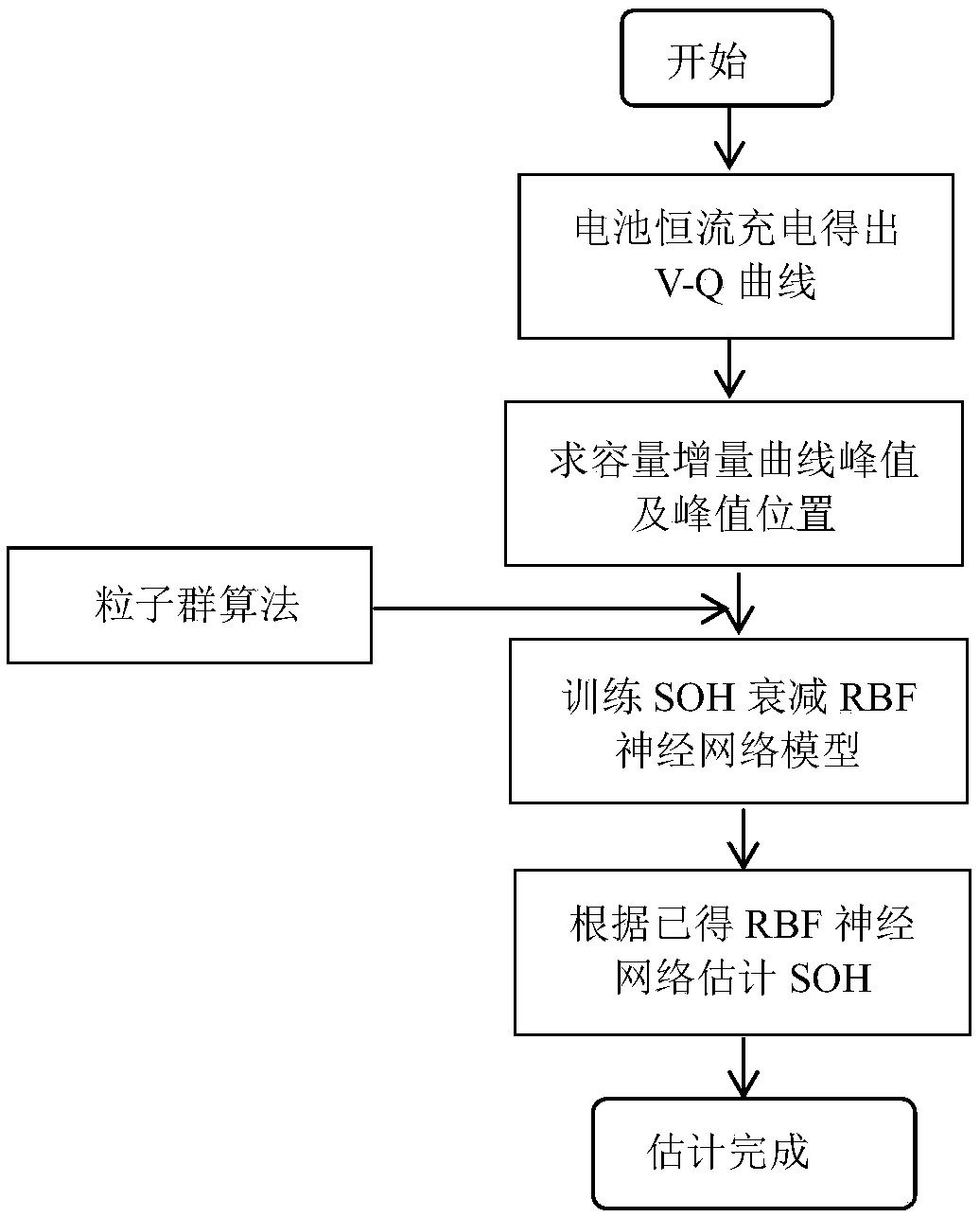

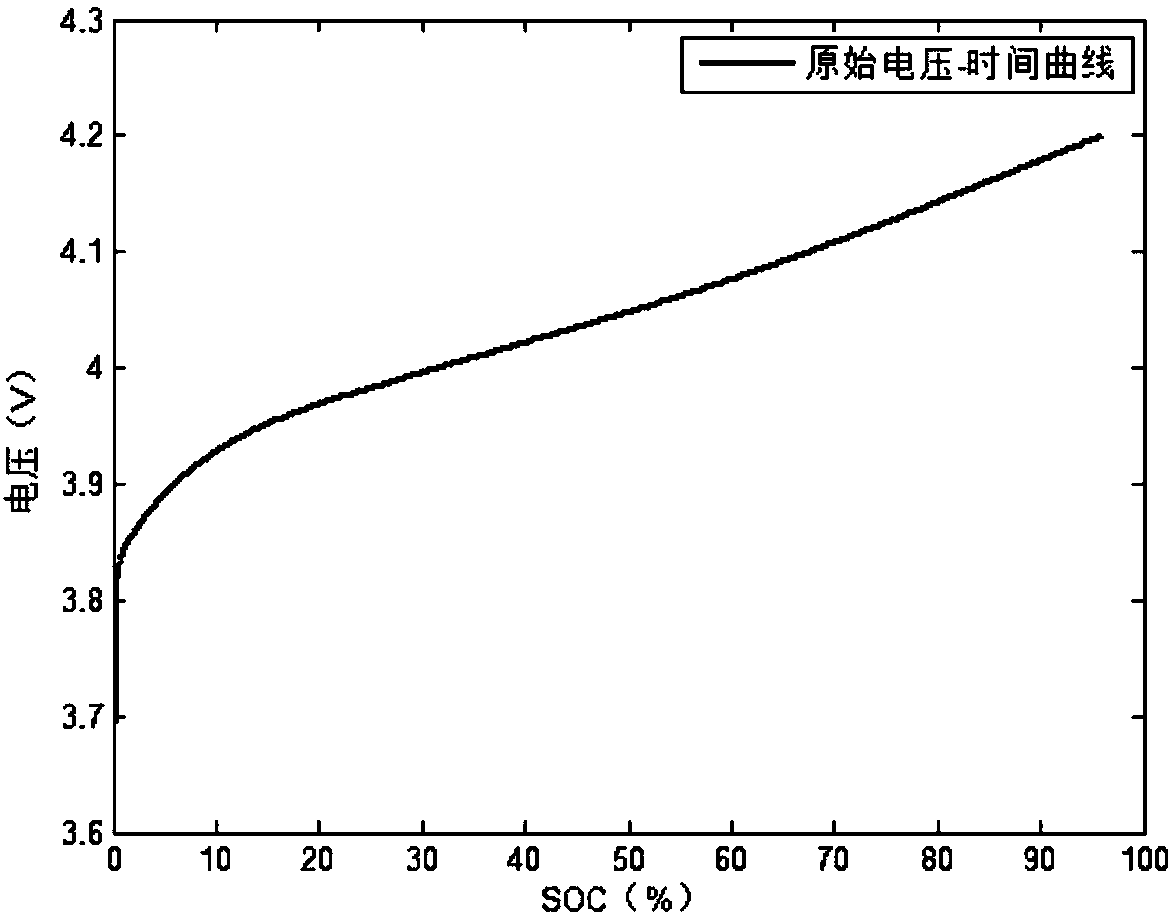

Method for estimating health state of power battery

InactiveCN108445406ARealize online estimationImprove fitting abilityElectrical testingPower batteryInformation gain

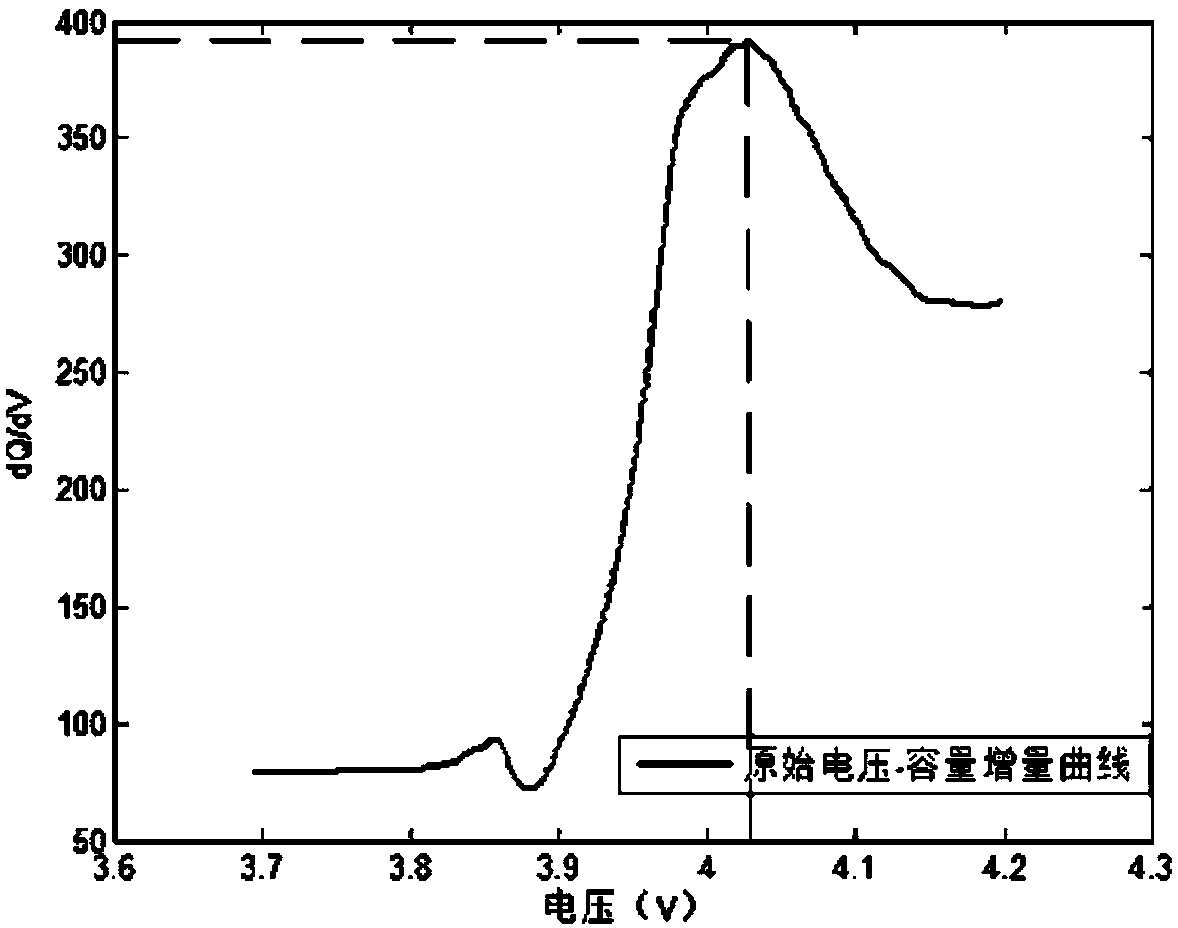

The invention discloses a method for estimating the health state of a power battery. The method comprises steps of acquiring the constant-current charging voltage V, current I and time t of a batteryto obtain charging capacity Q, establishing a V-Q relationship curve, acquiring a capacity increment curve peak value and peak position information, establishing a RBF neural network, training a RBF neural network model by a particle swarm optimization algorithm, and estimating the health state of the battery by using the generated RBF neural network. The method establishes a mapping relationshipamong the constant-current charging capacity increment curve peak value, the peak position and the health state of the battery by means of a data driving mode without establishing an equivalent circuit of the electric vehicle power battery, thereby improving estimation accuracy and realizing online real-time estimation for the overall estimation of a battery pack.

Owner:GUILIN UNIV OF ELECTRONIC TECH

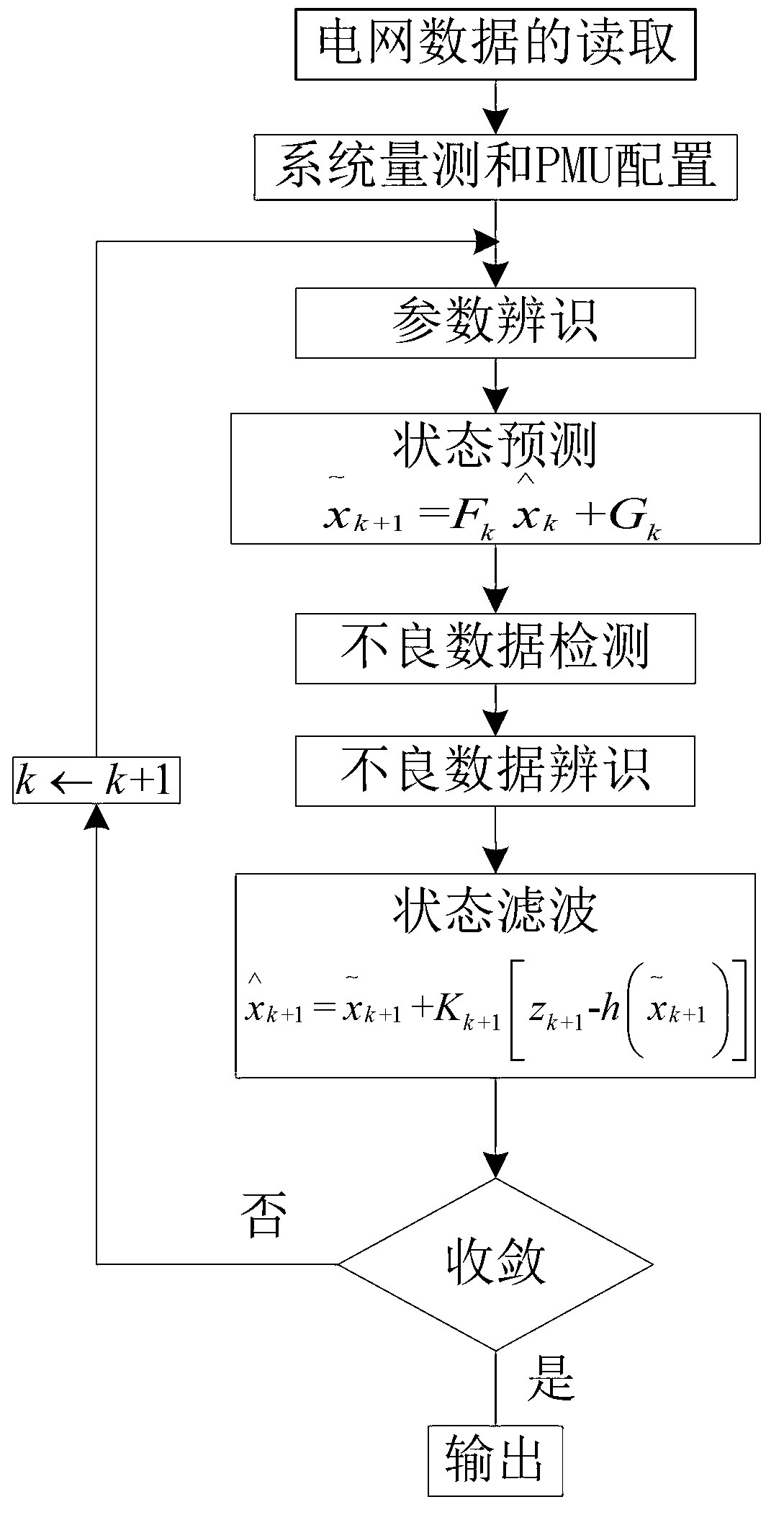

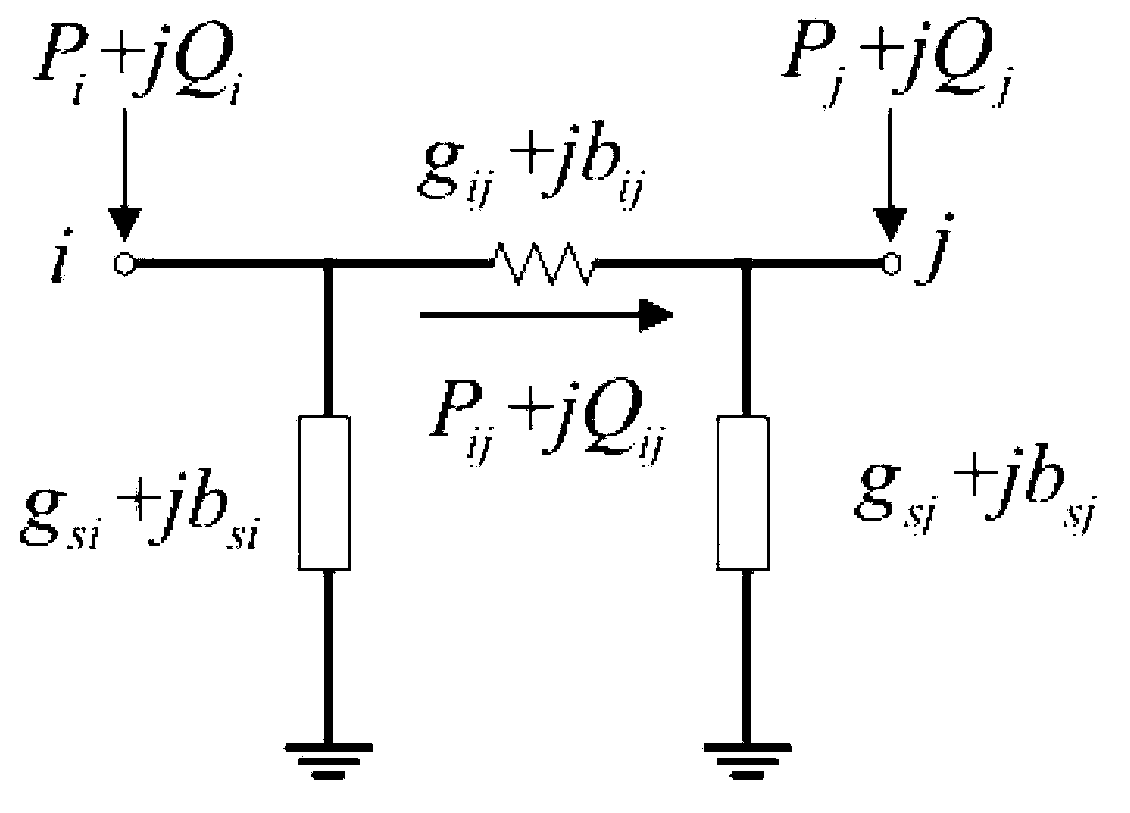

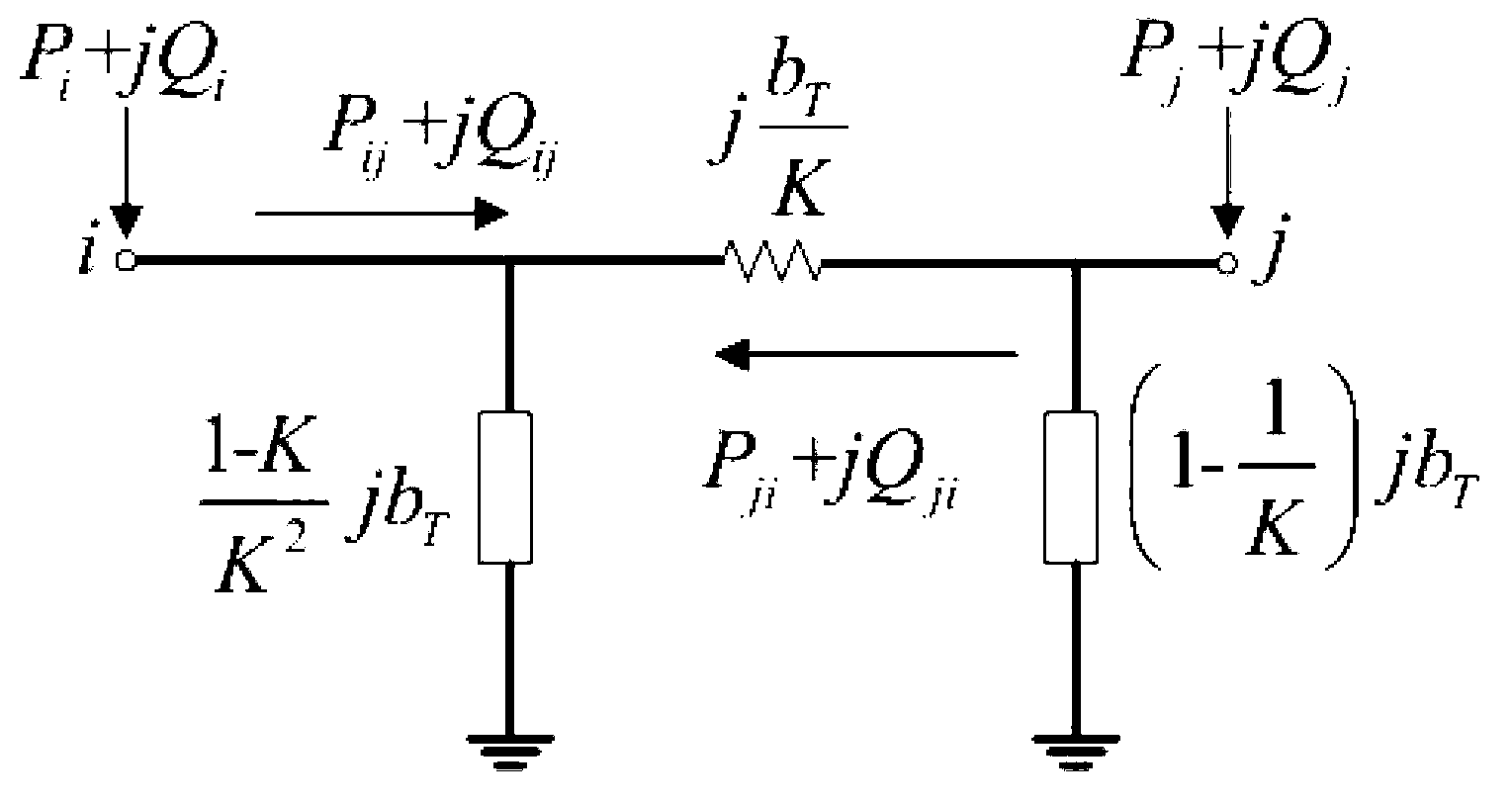

Method for detecting and identifying dynamic bad data of electric power system

InactiveCN103324847AMeet development requirementsEfficient Economic DispatchSpecial data processing applicationsVoltage amplitudeElectric power system

The invention relates to the technical field of operation and control of an electric power system and discloses a method for detecting and identifying dynamic bad data of the electric power system. The method comprises the steps of A, reading a current network parameter and a network topology of the electric power system and forming a node admittance matrix and a branch circuit-node incidence matrix; B, establishing an equivalent circuit according to the network topology of the electric power system and configuring measurement functions and a power management unit (PMU) of the electric power system, wherein system measurement includes node voltage amplitude measurement, node current amplitude measurement, node power injection measurement and node trend measurement; C, detecting and identifying the dynamic bad data of the electric power system; D, judging the convergence condition. By means of the method, accidentally arisen bad data from a supervisory control and data acquisition (SCADA) system and in the PMU measurement can be found and eliminated, and accordingly an accurate operation state, voltage amplitude and phase angles of nodes of a power grid are obtained.

Owner:SOUTHWEST JIAOTONG UNIV

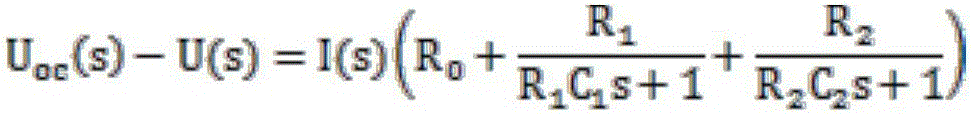

Online lithium ion battery SOC (state of charge) estimation method based on extended Kalman filter

InactiveCN103529398AEstimates are accurate and reliableReliable convergenceElectrical testingCapacitanceEstimation methods

The invention discloses an online lithium ion battery SOC estimation method based on extended Kalman filter, belongs to the technical field of SOC prediction of a lithium ion battery, and aims to solve the problem that the reliability of the online estimation of a conventional lithium ion battery SOC is low due to influence of initial value selection. The method comprises the steps as follows: a voltage and current relation of a first-order RC (resistance / capacitance) equivalent circuit of a detected lithium ion battery and a voltage and current relation of a second-order RC equivalent circuit are established firstly; a charge-discharge experiment is performed on the detected lithium ion battery to establish a polynomial fitting function of a Kalman filter initial value SOC 0 of the detected lithium ion battery; a covariance P (0) of the Kalman filter initial value SOC 0 and a Kalman filter initial error of the detected lithium ion battery is obtained; and then, battery SOC estimation based on extended Kalman filter is performed, so that the online estimation of the lithium ion battery SOC is realized. The method is used for online estimation of the lithium ion battery SOC.

Owner:HARBIN INST OF TECH

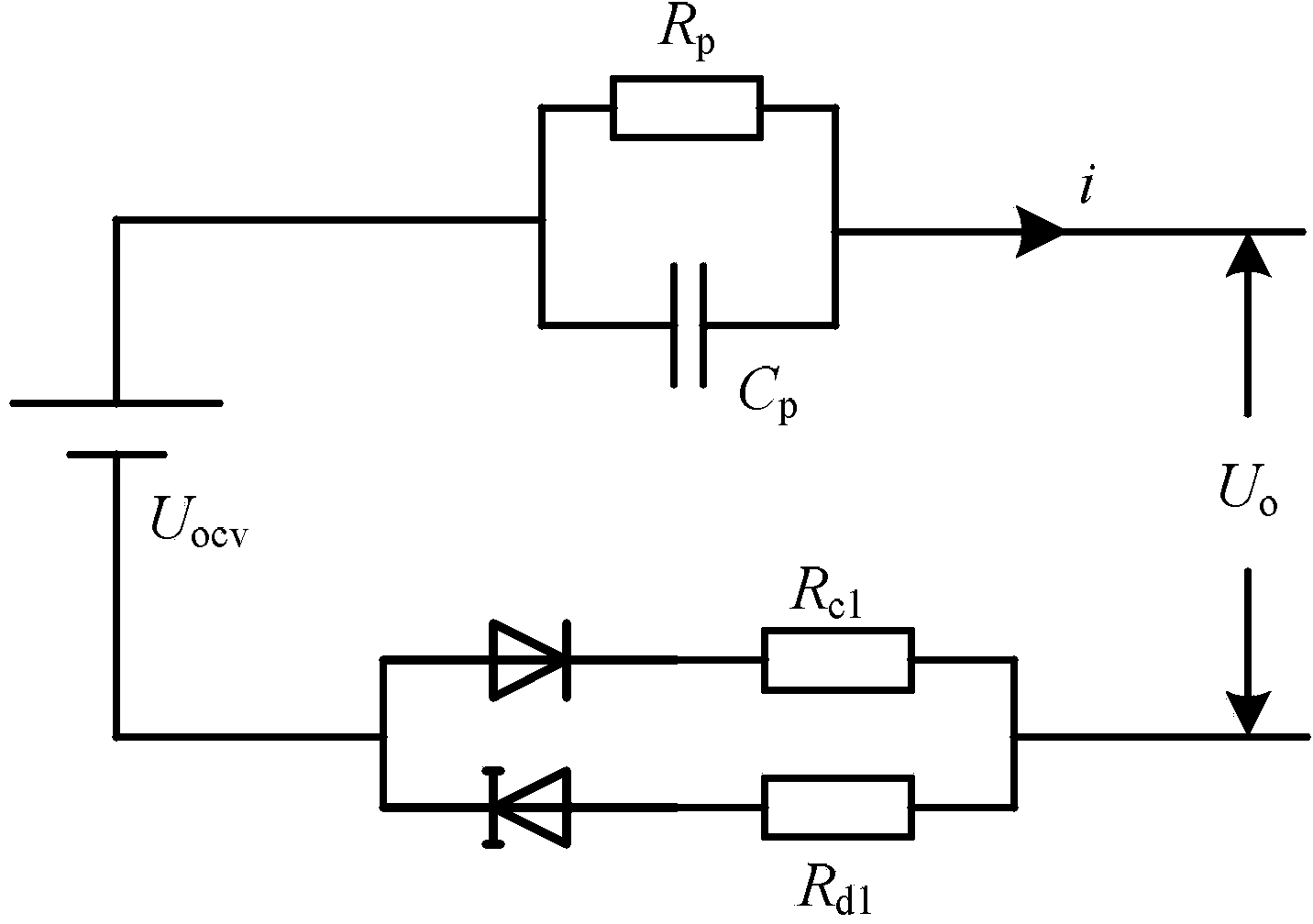

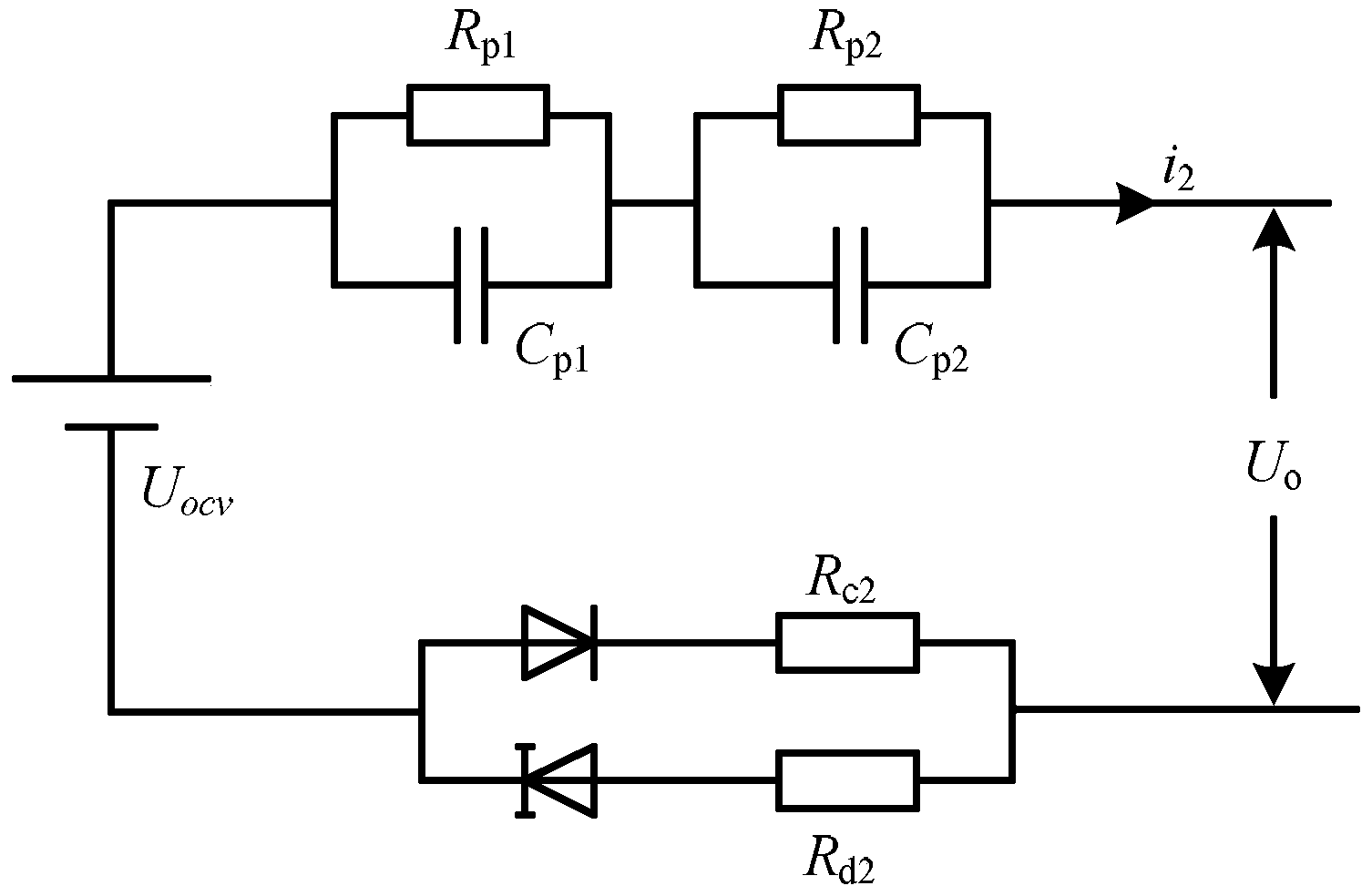

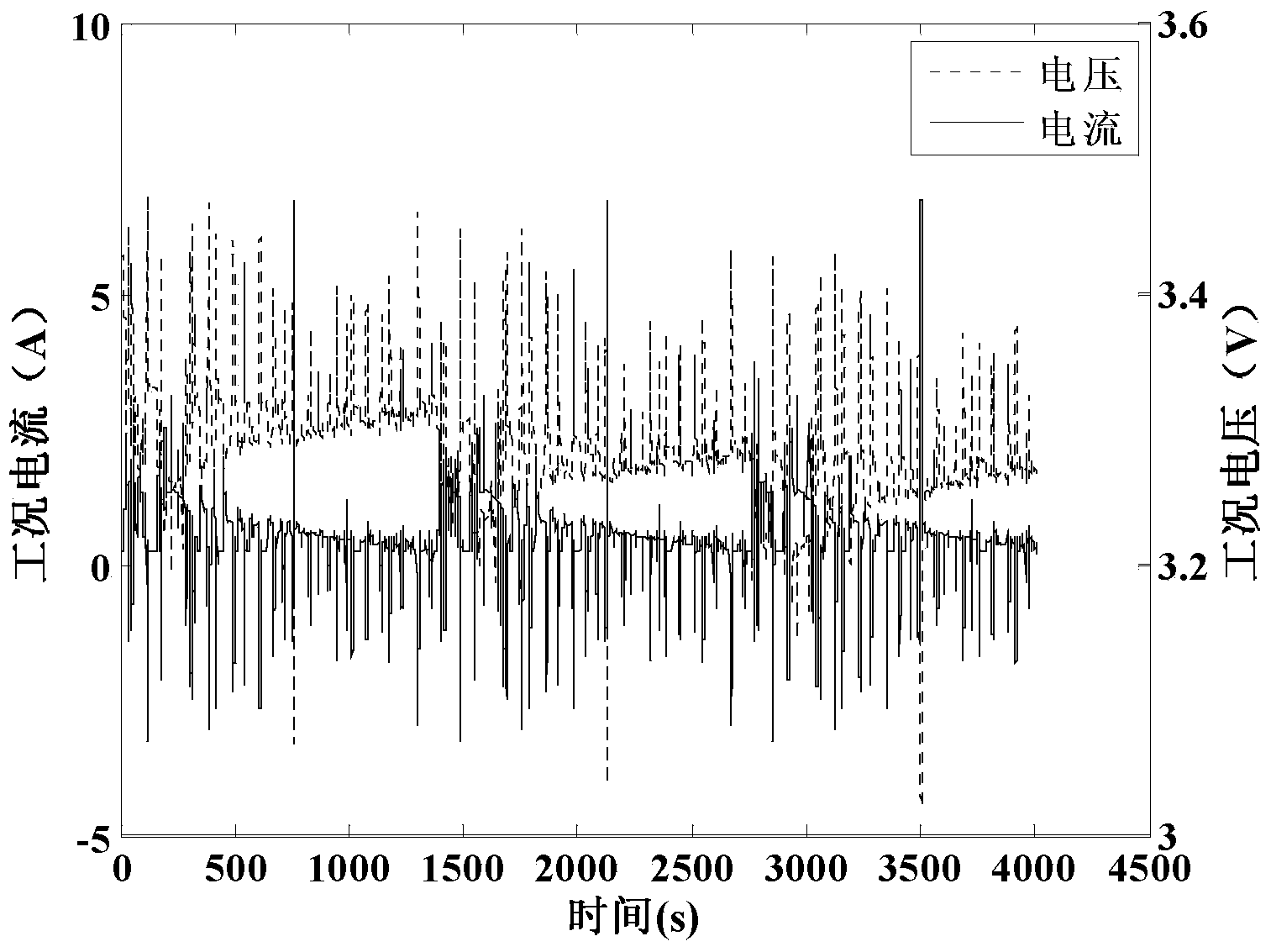

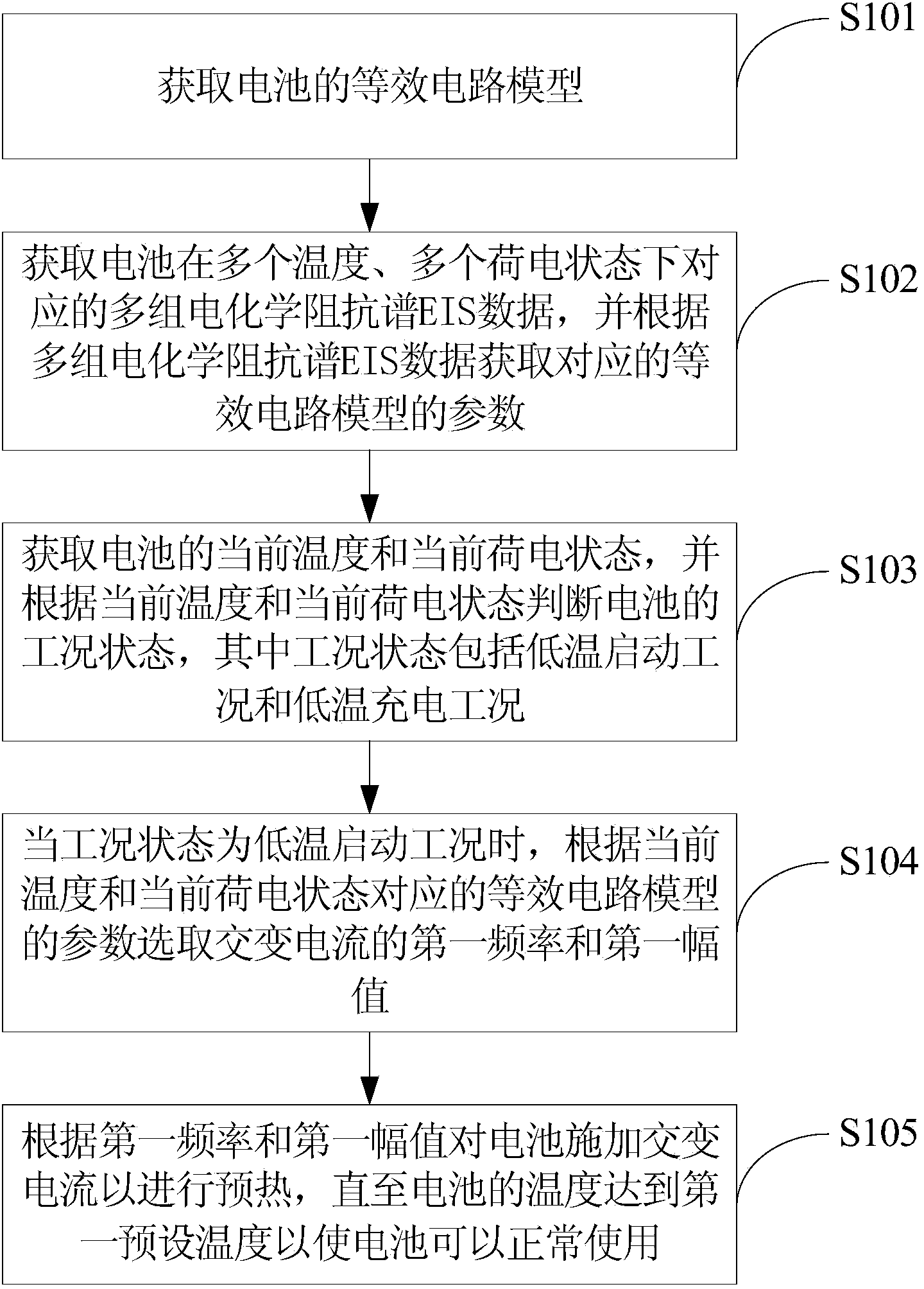

Battery low-temperature preheating and charging method

ActiveCN103825060AWarm up fastAvoid it happening againSecondary cells charging/dischargingLithiumProduction rate

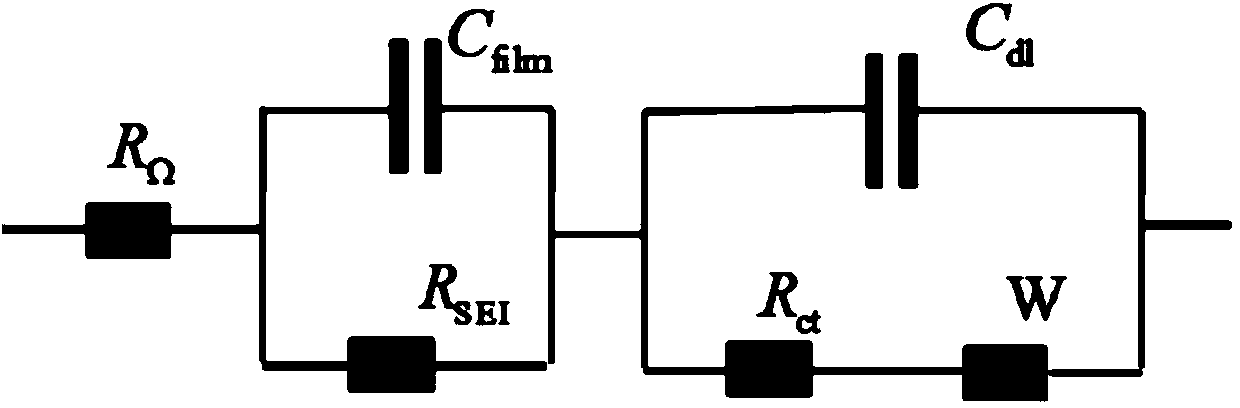

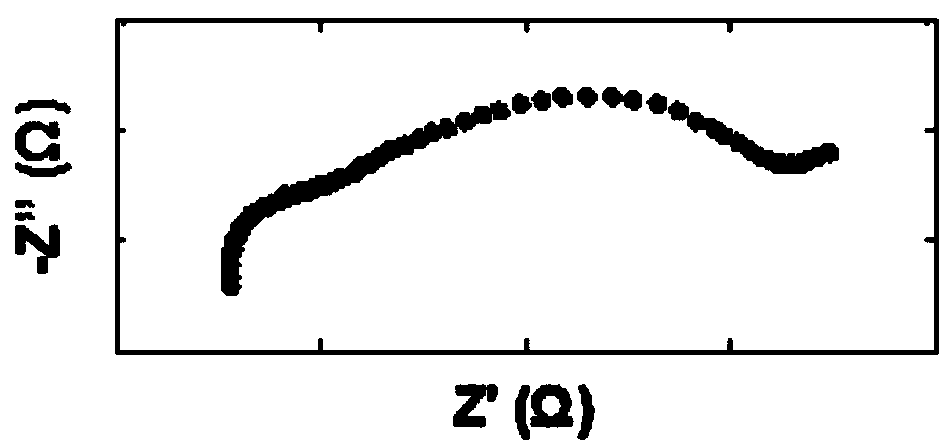

The invention brings forward a battery low-temperature preheating and charging method which comprises the following steps: an equivalent circuit model of a battery is obtained; multiple electrochemical impedance spectroscopy EIS data corresponding to multiple temperatures and multiple charged states are obtained, and corresponding parameters of the equivalent circuit model are obtained according to the multiple electrochemical impedance spectroscopy EIS data; current temperature and current charged state of the battery are obtained, and the working condition state of the battery, including low-temperature starting condition and low-temperature charging condition, is judged according to the current temperature and the current charged state; when the working condition state is the low-temperature starting condition, first frequency and a first amplitude of alternating current are selected according to parameter values of the equivalent circuit model corresponding to the current temperature and the current charged state; alternating current is applied on the battery according to the first frequency and the first amplitude for preheating until the temperature of the battery reaches a first preset temperature so as to make the battery to be normally used. By the method of the embodiment, lithium precipitation is avoided, and heat production rate inside the battery is raised.

Owner:TSINGHUA UNIV

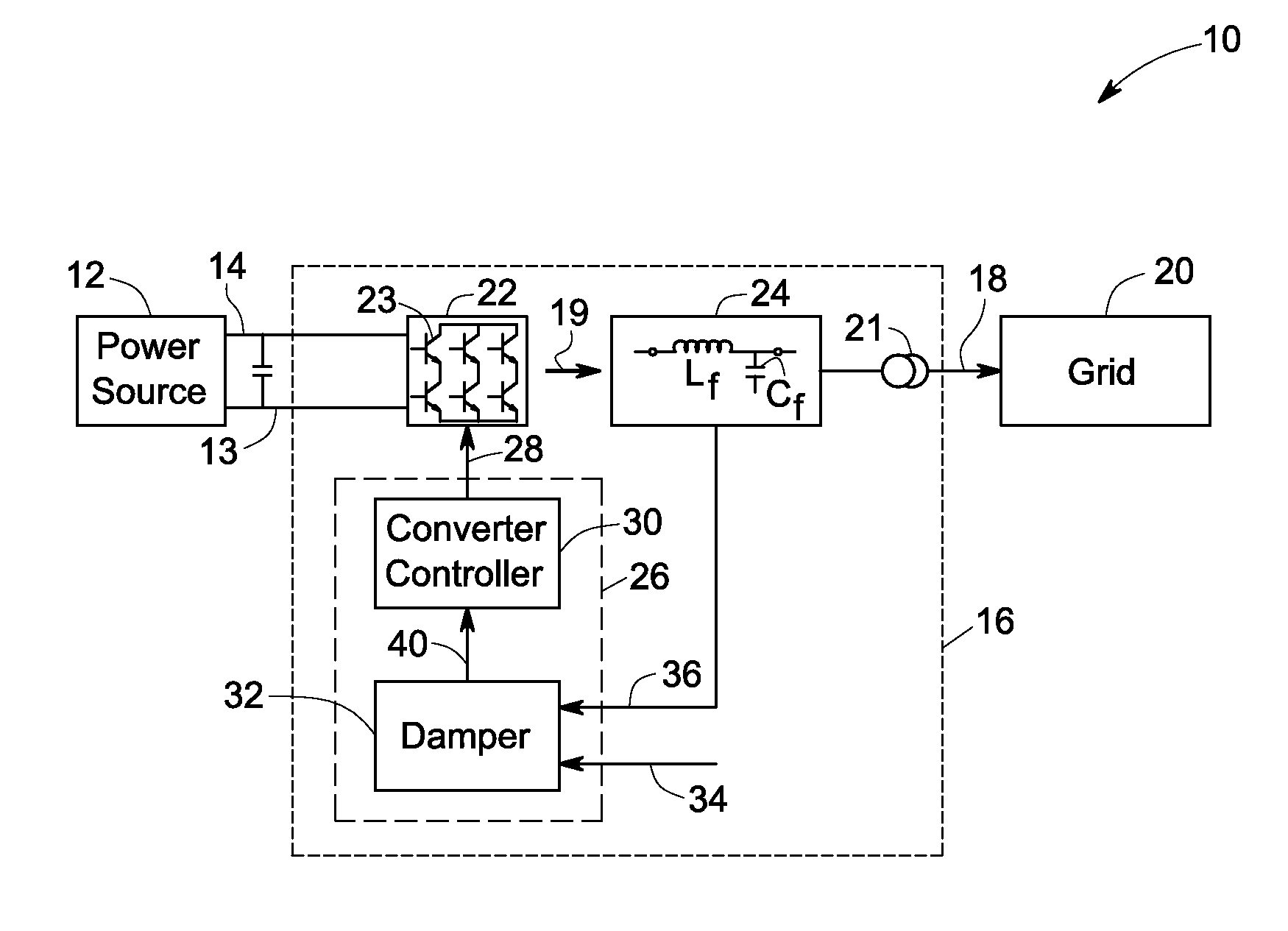

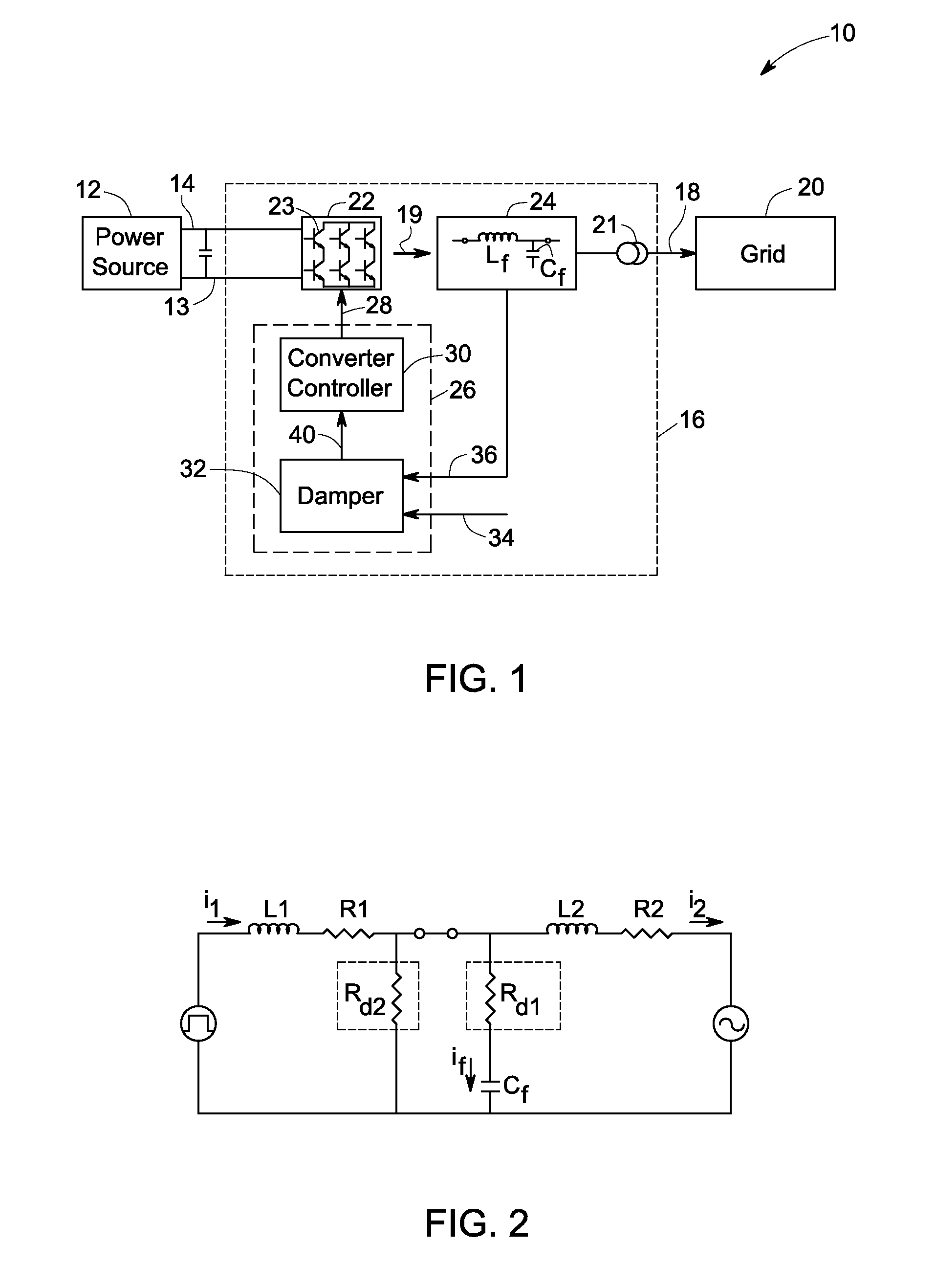

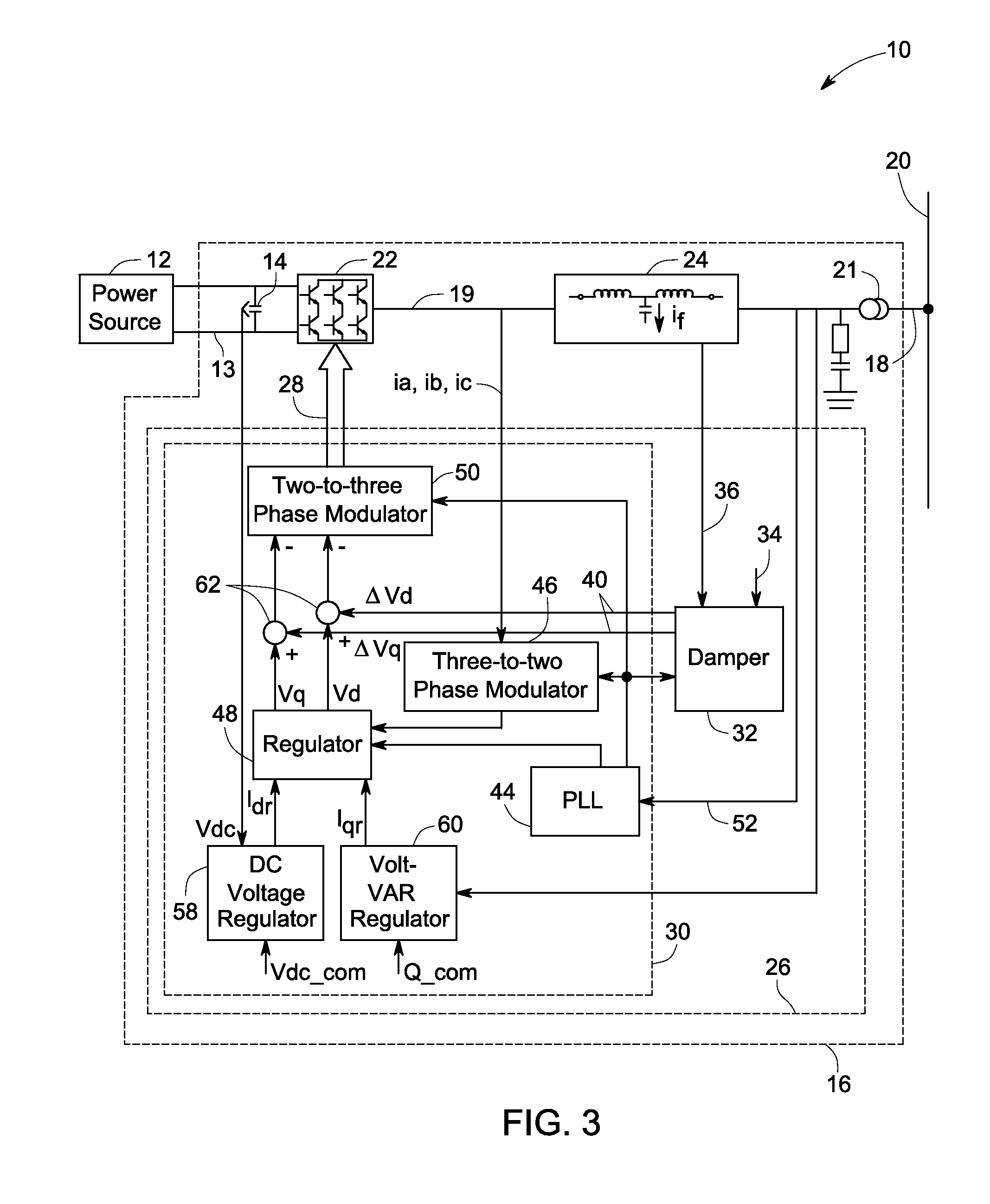

System and method for damping lc circuits in power conversion systems

ActiveUS20120063179A1Single network parallel feeding arrangementsWind energy generationControl signalEngineering

A power conversion system comprises a power converter comprising a plurality of semiconductor power switches, an LC filter coupled between an output of the power converter and an electric grid, and a power conversion control system. The LC filter comprises an inductor coupled in series to the electric grid, and a capacitor. The LC filter and the grid result in an equivalent LC circuit comprising an impedance of the LC filter and an impedance of the electric grid. The power conversion control system comprises a damper and a converter controller. The damper receives an LC filter signal and an equivalent LC circuit impedance signal and generates a damping signal. The converter controller receives a current or voltage reference signal, a current or voltage command signal, and the damping signal to generate control signals for driving switching operations of the semiconductor power switches.

Owner:GENERAL ELECTRIC CO

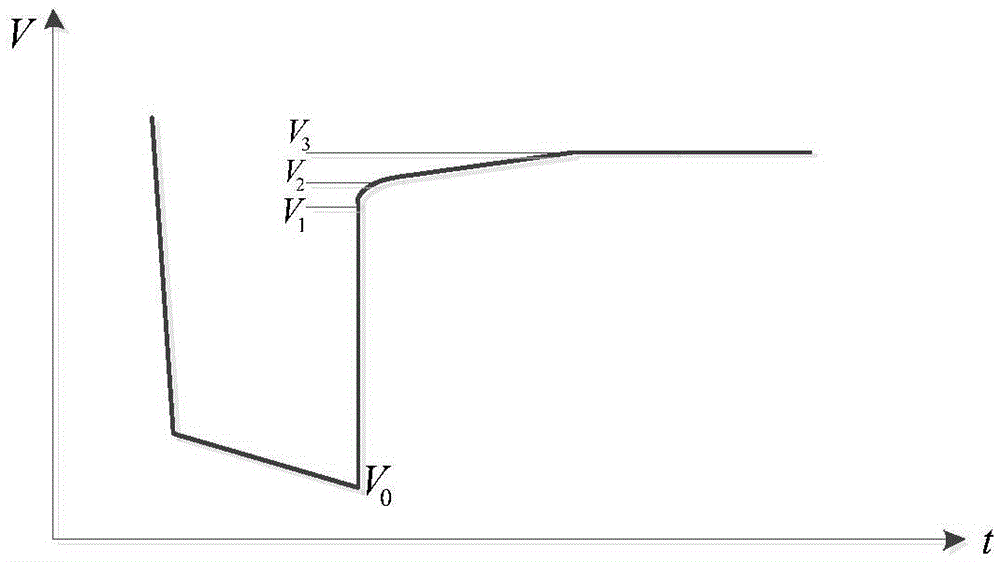

Lithium battery SOC estimation method of off-line data segmentation correction

InactiveCN105548898AAccurate estimateEliminate cumulative errorsElectrical testingTerminal voltageEstimation methods

The invention discloses a lithium battery SOC estimation method of off-line data segmentation correction. The method is mainly applied to a battery management system of an electric vehicle and is used for correcting an actual capacity of a lithium battery and eliminating an accumulation error of a traditional ampere-hour integral method. The method comprises the following steps of establishing a battery equivalence circuit model; acquiring an OCV-SOC curve; using a terminal voltage response curve at the time that battery discharging is ended to carry out off-line parameter identification on the equivalence circuit model; calculating a battery health state SOH; using an ampere-hour integral method to calculate a current value of the SOC in real time; using the battery health state to correct a SOC value; using off-line data to carry out segmentation elimination on the accumulation error in the ampere-hour integral method. By using the method of the invention, the battery SOC can be accurately estimated and the accumulation error of battery SOC estimation performed through using the ampere-hour integral method is eliminated.

Owner:SOUTH CHINA UNIV OF TECH

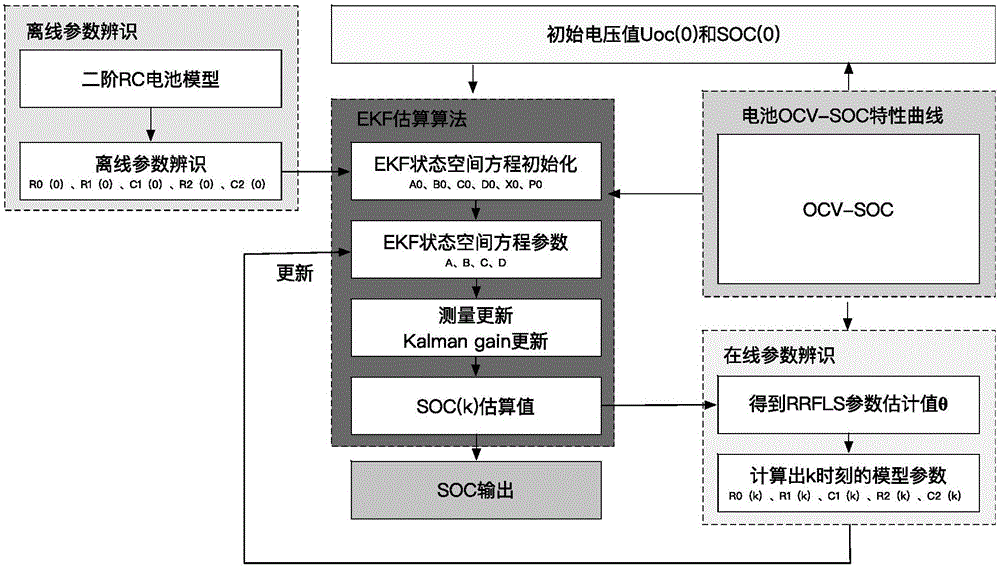

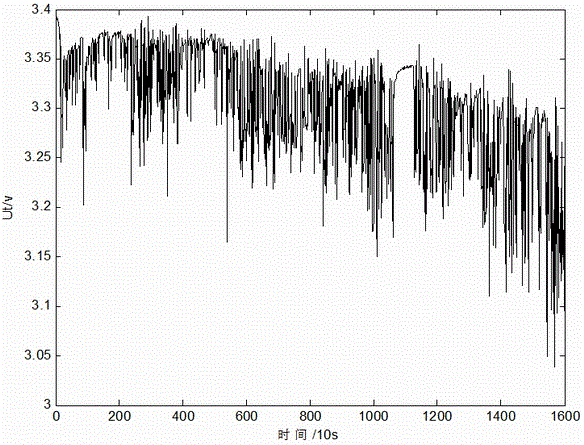

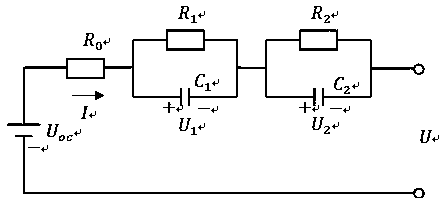

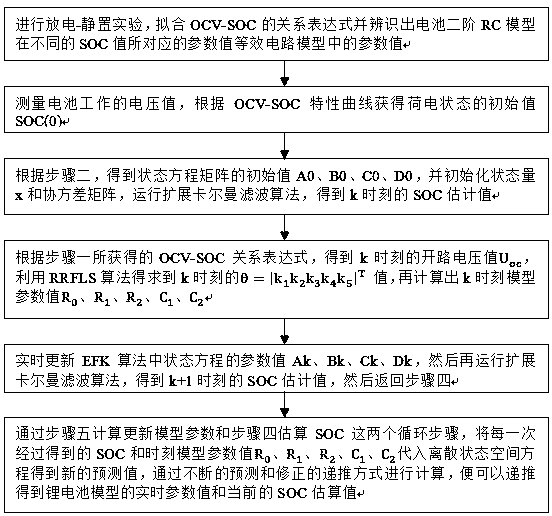

Method and system for estimating SOC (State-of-Charge) of power battery based on dynamic parameters

The invention discloses a method and system for estimating SOC (State-of-Charge) of a power battery based on dynamic parameters. The method comprises the following steps: carrying out a discharge-standing experiment on the battery, obtaining OCV (Open Circuit Voltage)-SOC characteristic curves of the battery at different temperatures, and fitting out an OCV-SOC relational expression; carrying out a constant current pulse discharge-standing experiment on the battery, recording voltage response during the experiment, and identifying the initial value of the parameter of a battery second-order RC equivalent circuit model by an offline method; carrying out dynamic parameter identification on the second-order RC equivalent circuit model by using a forgetting factor-containing recursive least squares method RRFLS; carrying out online estimation on the SOC of the battery by using an EKF (Extended Kalman Filter) algorithm. The estimation method overcomes the defects of inaccuracy and cumulative error of the initial value of SOC in an ampere-hour integral method, and adapts to the dynamic change of battery characteristics, the battery model is high in precision and convergence speed, and is stable and reliable, and the precision of SOC online estimation is improved. The method and system can be widely used in fields of electric vehicles and energy storage battery management systems.

Owner:SHENZHEN HYUTEEN NEW ENERGY CO LTD

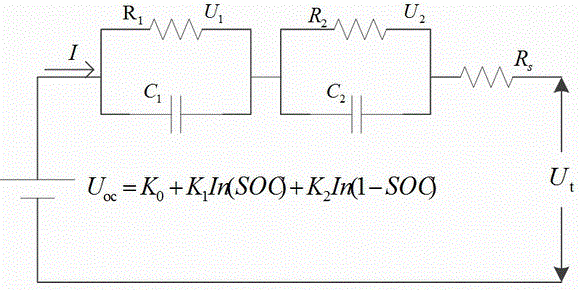

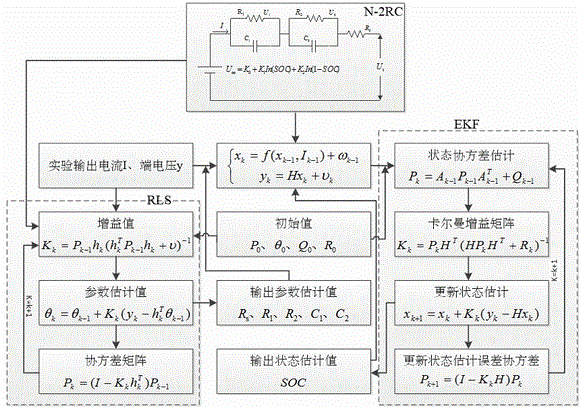

Power-cell SOC online closed-loop estimation method based on N-2RC model

The invention discloses a power-cell SOC online closed-loop estimation method based on an N-2RC model. In the invention, an electrochemical model and an equivalent circuit model are combined and a novel power cell model is provided. The N-2RC model uses a Nernst electrochemical model to replace an electromotive force portion of a second-order RC equivalent circuit model so that one to one correspondence of a cell electromotive force and SOC can be accurately reflected. Based on the model, a recursive least-square method based on a forgetting factor is used to identify a model parameter, and then an expansion Kalman filtering algorithm is used to realize on-line closed loop estimation of the cell SOC. The electrochemical model can well describe a cell characteristic on an electrochemical aspect, but the structure is complex and the model is not suitable for individually individual usage. And the equivalent circuit model belongs to an external characteristic model and can well express a volt-ampere characteristic relationship of the cell, but can not reflect an internal characteristic of the cell. By using the method in the invention, the above problems are overcome.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

SOC (state of charge) estimation method

InactiveCN107390127AFast convergenceOvercome errorElectrical testingModel parametersElectric vehicle

The present invention discloses an SOC (state of charge) estimation method. According to the method, a battery OCV-SOC relationship module, a parameter acquisition module, an offline identification parameter value, a parameter discrete state space model, a battery parameter online identification module, a battery dynamic parameter update module and a battery SOC estimation module. The method includes the following specific steps that: 1, a discharge-standing experiment is performed, an OCV-SOC relationship expression is obtained through fitting, parameter values in an equivalent circuit model are identified; 2, a battery second-order RC system discrete state space model is established, and the battery model parameters are identified online and dynamically updated; and 3, the SOC of a battery is estimated online. With the method of the invention adopted, the defects of inaccuracy and accumulative error of the initial value of the SOC of a battery of in an ampere-hour integration method can be eliminated. The method is applicable to the dynamic change of the characteristics of the battery, can improve the accuracy of SOC online estimation and can be widely applied to the electric vehicles and storage battery management system field. The method has the advantages of high battery model precision, fast convergence, high stability and high reliability.

Owner:SUNWODA ELECTRIC VEHICLE BATTERY CO LTD

Antenna device

InactiveUS6034640AWide rangeLess affectedSimultaneous aerial operationsAntenna supports/mountingsElectrical conductorInductor

The invention provides an antenna device, comprising: an antenna body including a conductor, an equivalent circuit of said conductor comprising an inductive component and a resistive component in a series connection, wherein a frequency adjusting circuit including at least a parallel circuit of a switching element and a passive element is connected to said conductor of said antenna body. The antenna body is connected in series with said frequency adjusting circuit. The invention enable to provide a compact antenna device for use in a mobile communication apparatus that performs transmission and reception on frequencies in a wide range.

Owner:MURATA MFG CO LTD

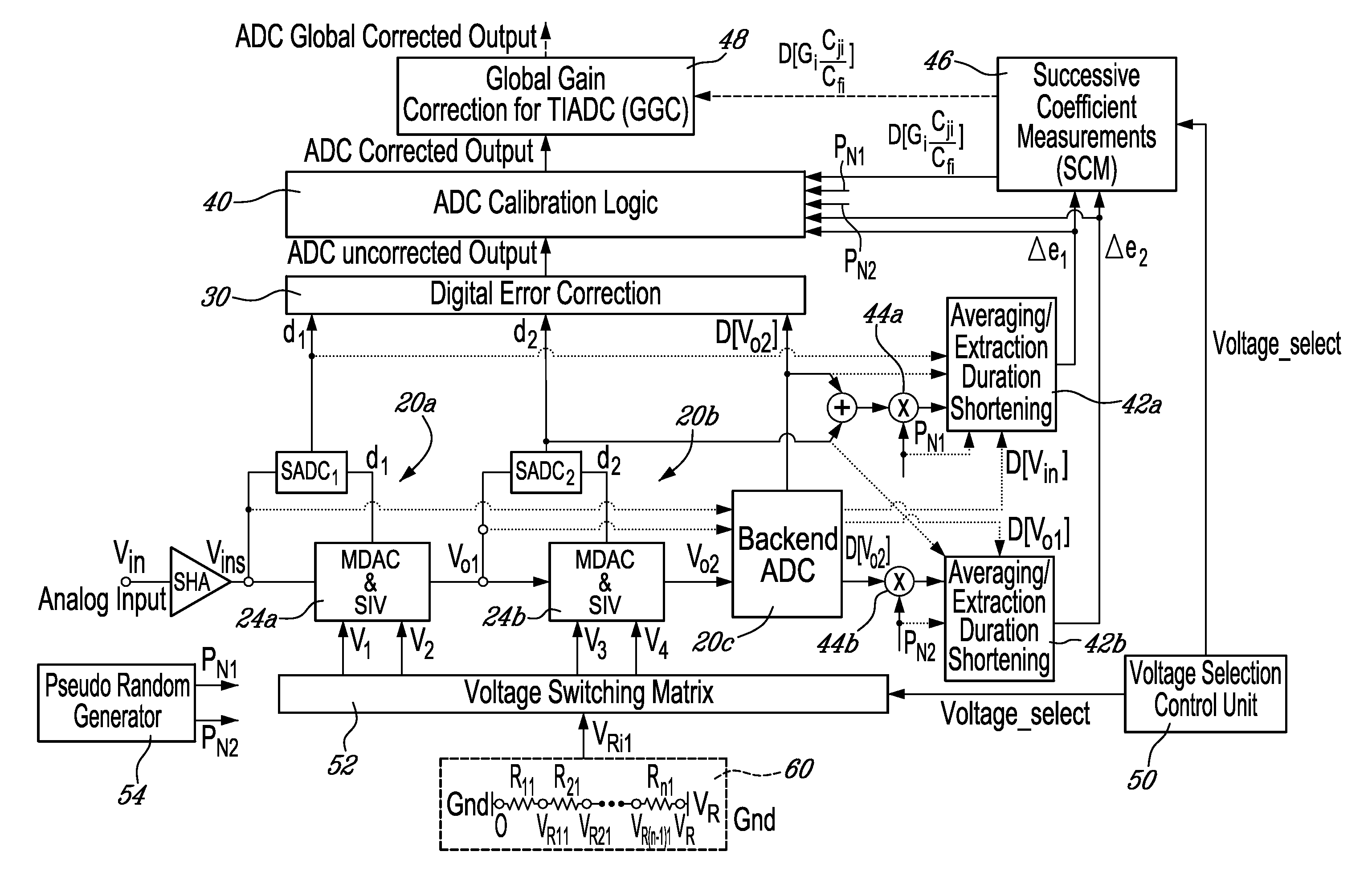

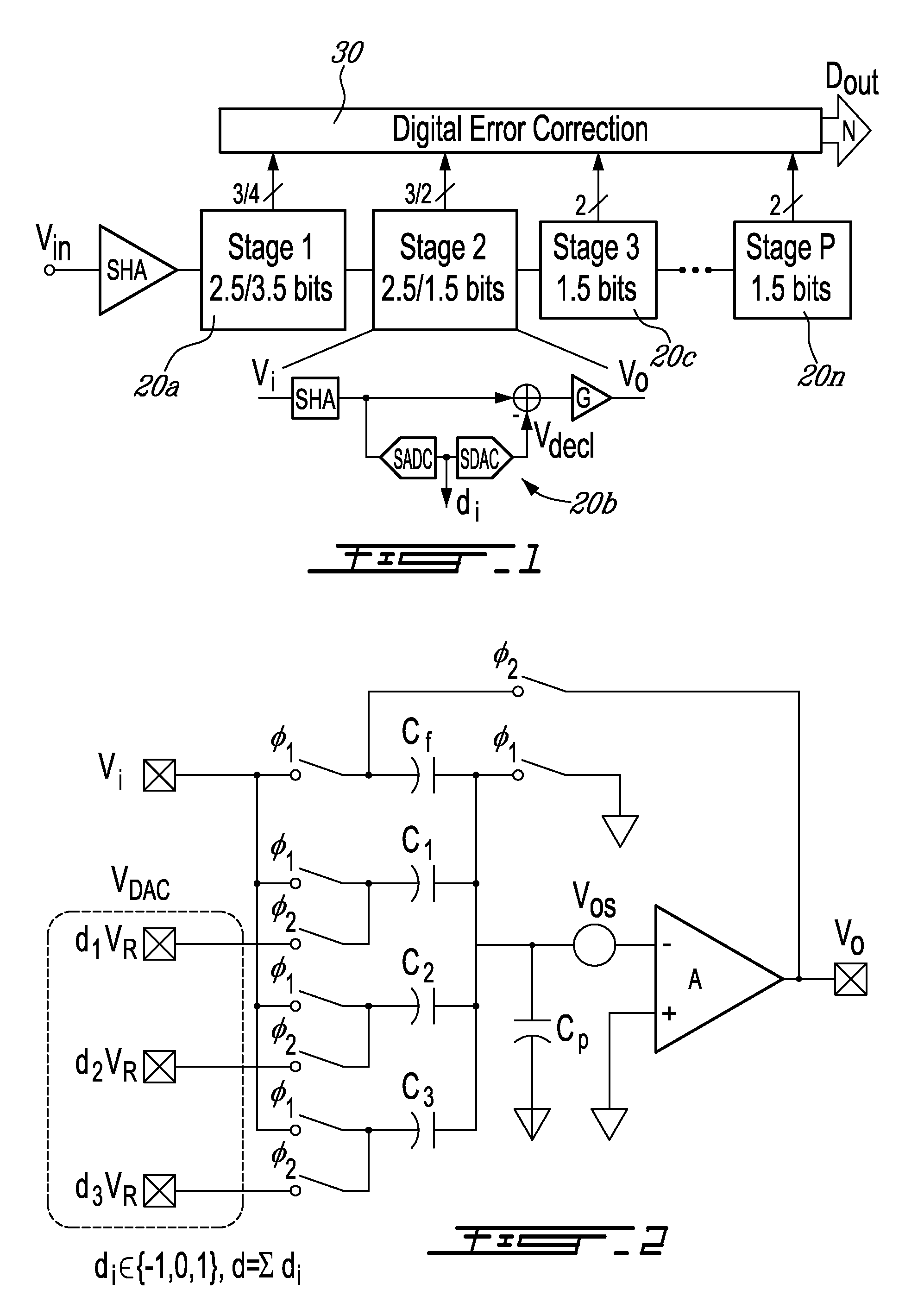

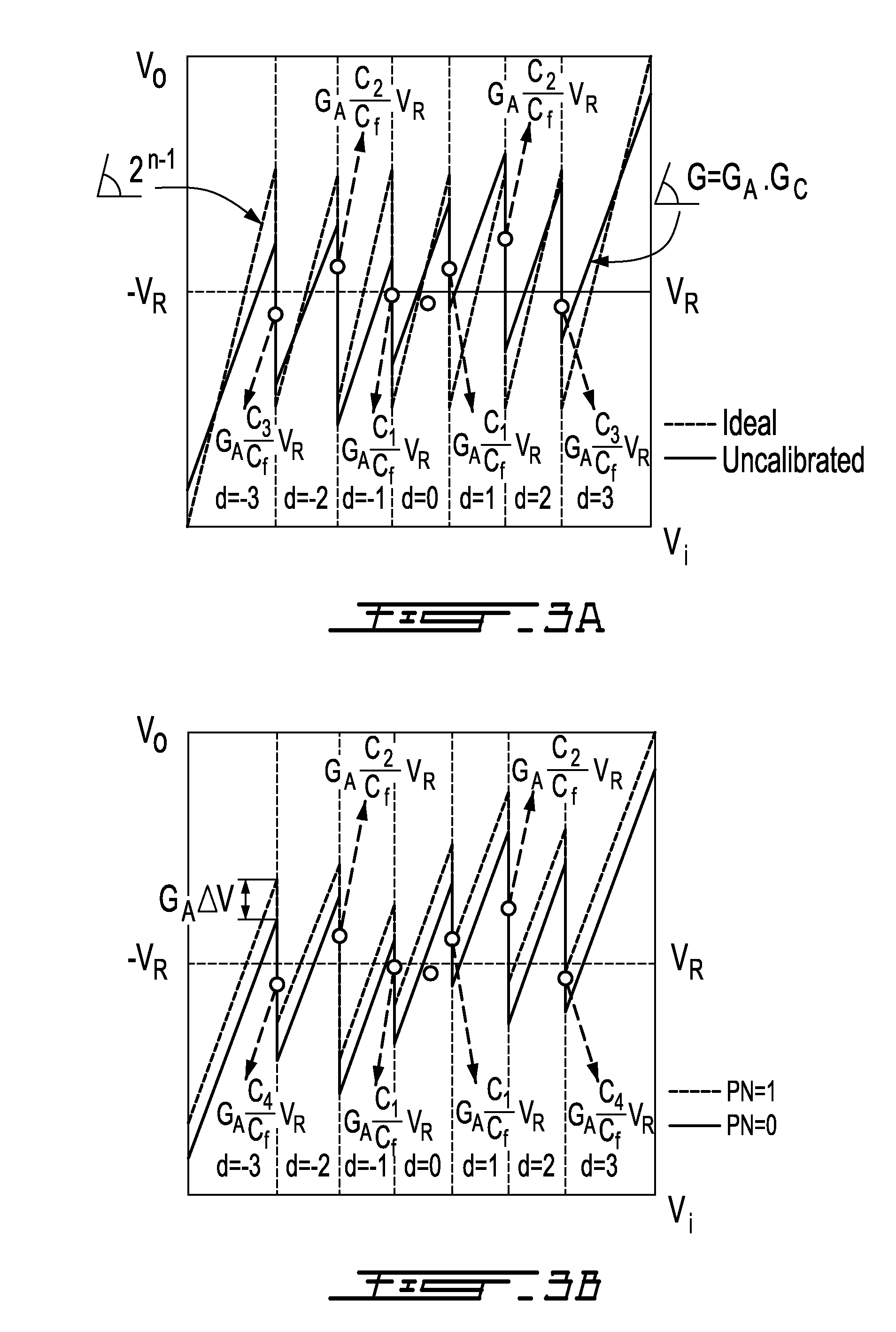

Circuit calibration using voltage injection

InactiveUS7187310B2High resolutionReduce calibration timeElectric signal transmission systemsAnalogue-digital convertersEngineeringVoltage

Efficient calibration of circuits is performed using injection imprecise voltage by using different voltages in a subtractive manner to be able to calibrate with respect to a voltage that is out of a desirable measurable range using measuring circuitry. Efficient background calibration of circuits is also achieved by providing an equivalent circuit element to circuit elements receiving an injected calibration signal, and switching circuit elements. Such imprecise voltages can be determined through such calibration, and then used to calibrate a second circuit generating the imprecise voltages.

Owner:EL SANKARY KAMAL +1

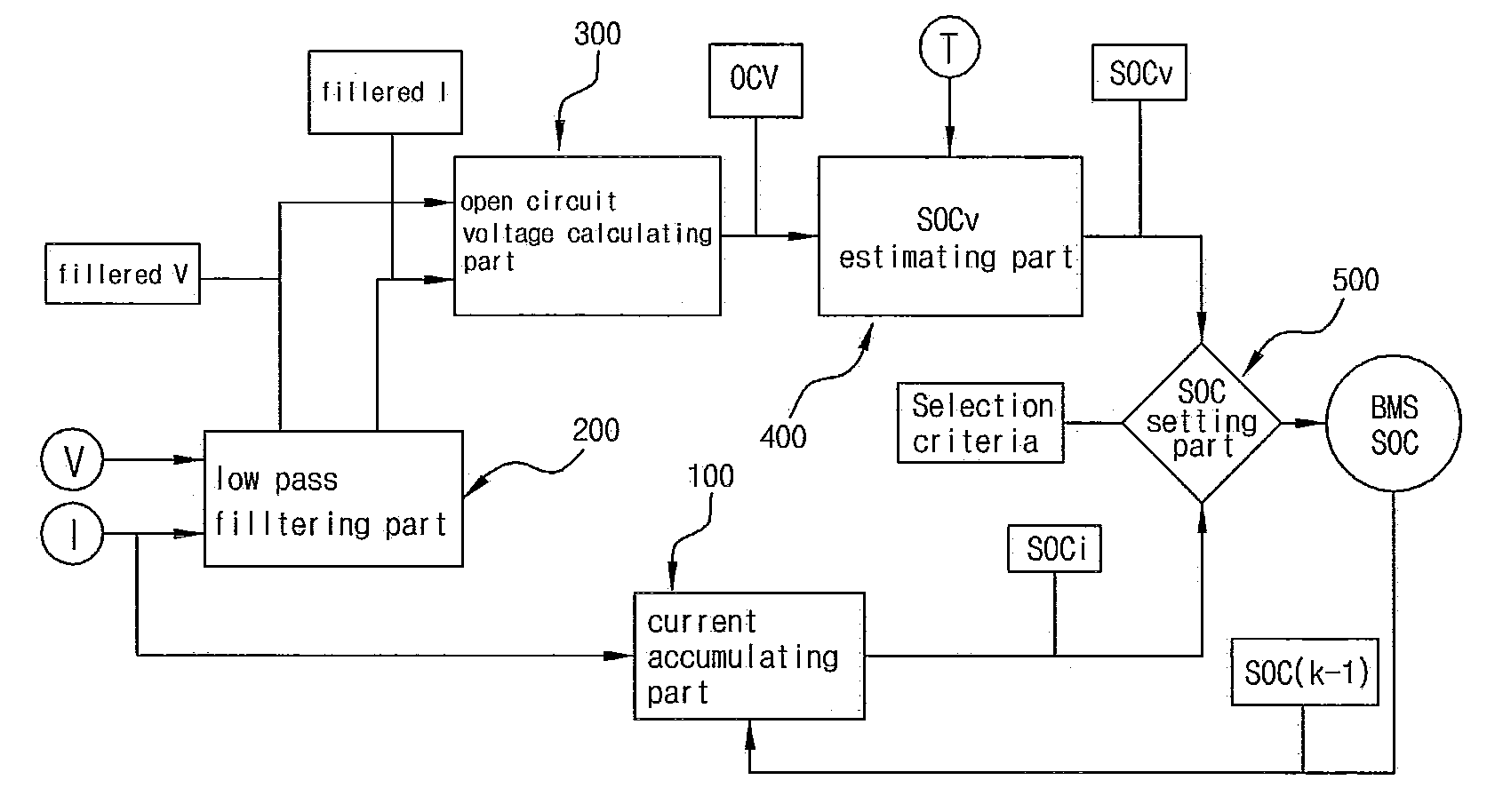

Method for Measuring SOC of a Battery in a Battery Management System and the Apparatus Thereof

InactiveUS20100280777A1Accurate measurementEasily and precisely measuringElectric devicesOperating modesElectrical batteryState of charge

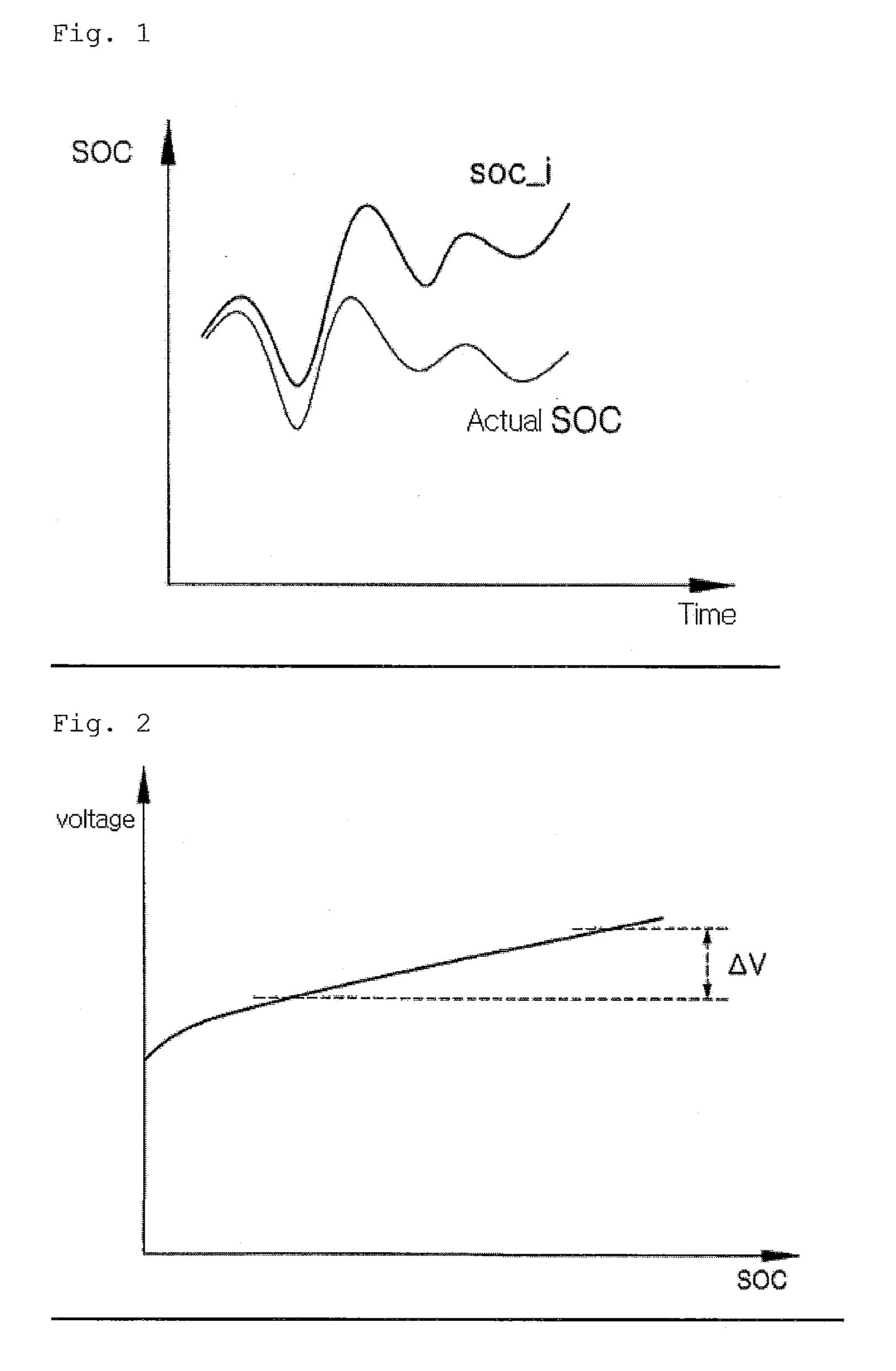

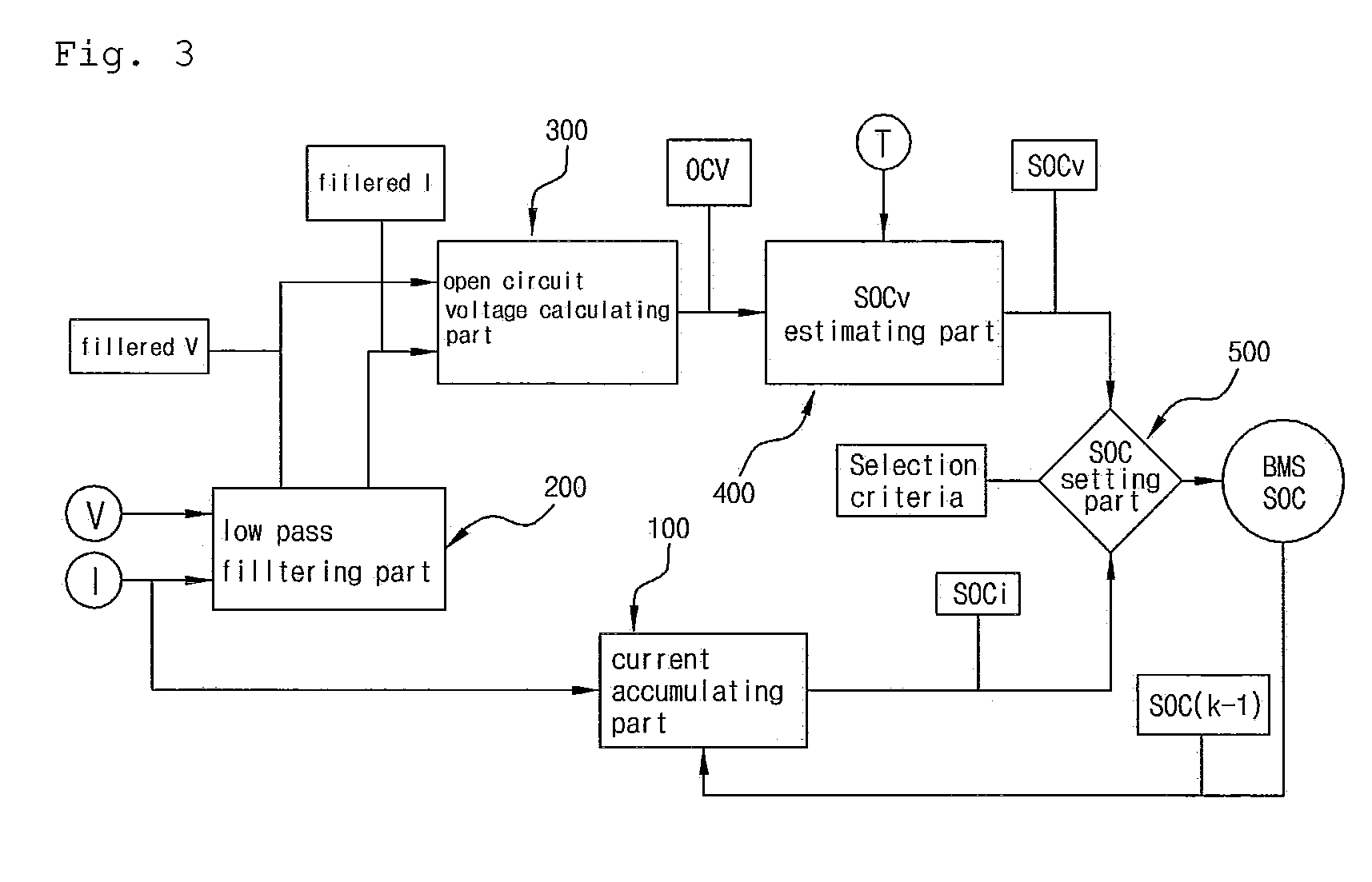

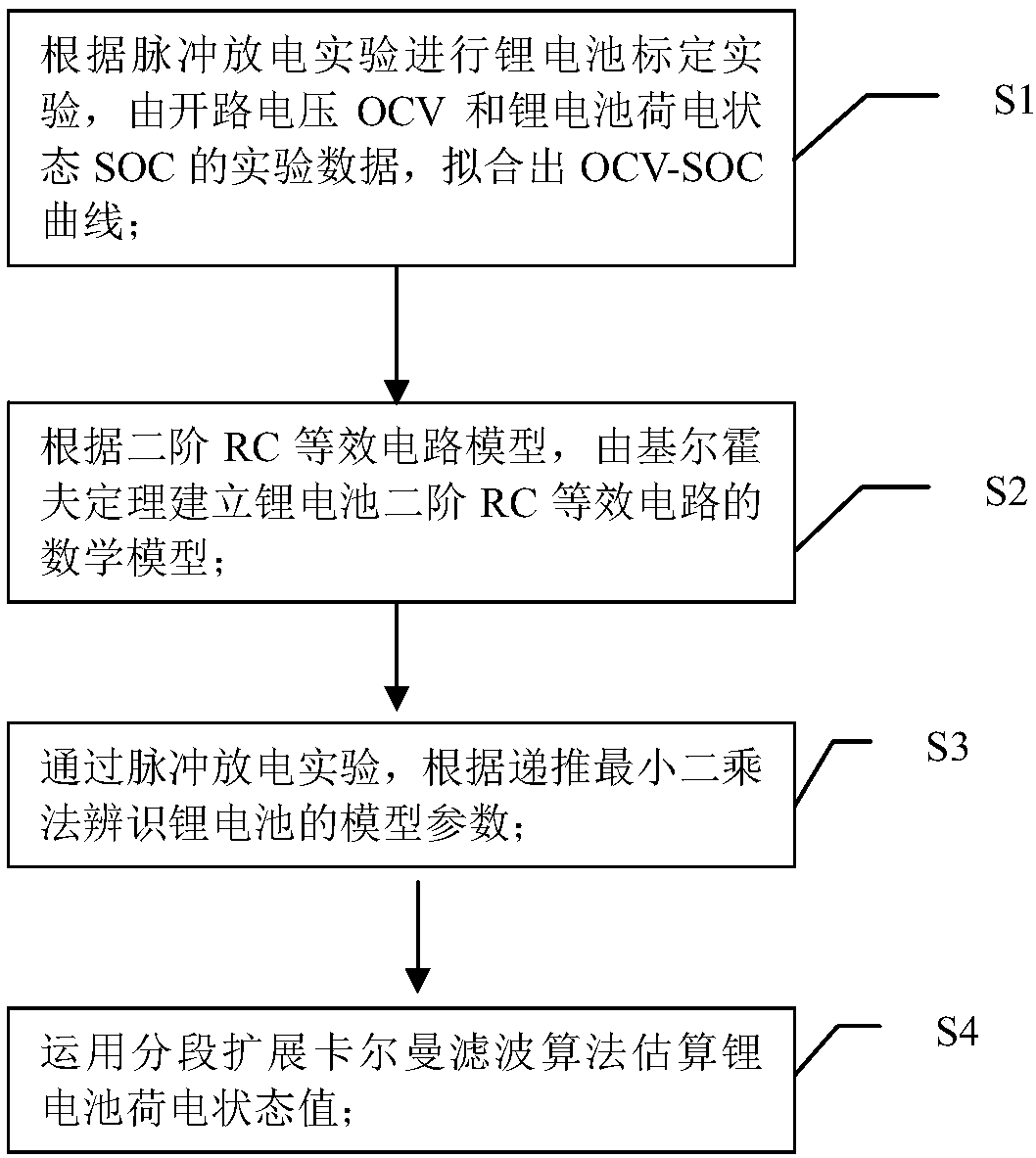

According to an embodiment of this invention, a method for measuring SOC (State Of Charge) of a battery comprises the steps of: obtaining current data, voltage data and temperature by measuring the current, the voltage and the temperature of a battery; calculating SOCi (State Of Charge based on current) by accumulating the current data; calculating open circuit voltage by using an equivalent circuit model which simply presents the current data, the voltage data and the battery through an electric circuit; calculating SOCv (State Of Charge based on voltage) by using the temperature data and the open circuit voltage; and choosing at least one of the SOCi and the SOCv as SOC of the battery by using the SOCi and the SOCv based on the judgment on the current state of the battery for a certain time interval.

Owner:SK INNOVATION CO LTD

Method based on segmented expansion Kalman filtering for estimating state of charge of lithium battery

InactiveCN107741569AEmbody dynamic characteristicsImprove estimation accuracyElectrical testingModel parametersEngineering

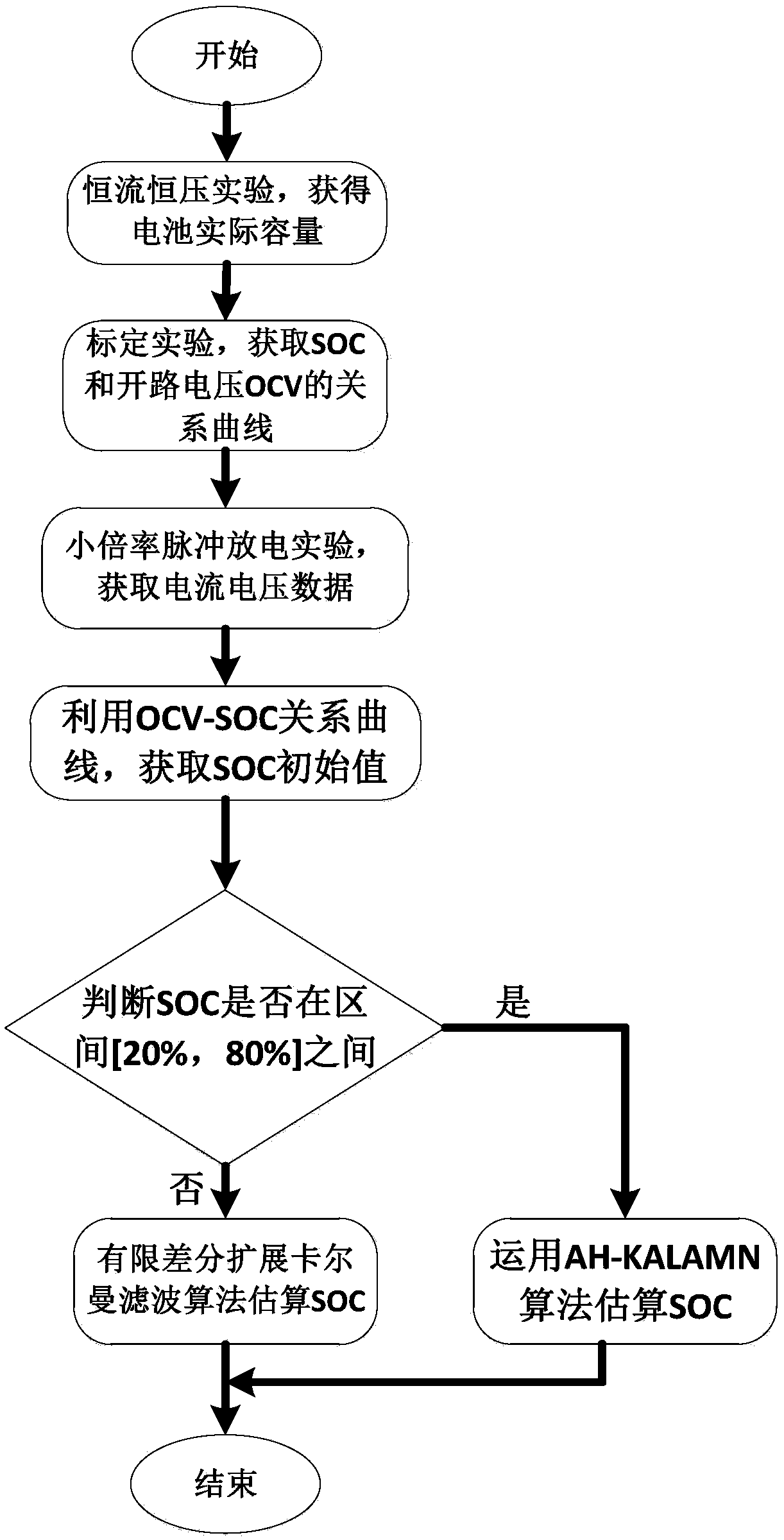

The invention discloses a method based on segmented expansion Kalman filtering for estimating the state of charge of a lithium battery. The method mainly comprises the steps of firstly, establishing asecond-order RC equivalent circuit model according to a working mechanism of the lithium battery; secondly, according to experimental data of pulse discharge responses of the lithium battery, utilizing a recursive least square method (RLS) to identify model parameters; thirdly, establishing a state space model of lithium battery discretization, adopting a segmented EKF algorithm to estimate the SOC of the lithium battery. According to the method, the suitable expansion Kalman filtering algorithm is utilized while an intensity nonlinearization process is distinguished from the working processof the lithium battery, and the robustness in the process of adopting a traditional EKF algorithm to estimate SOC is effectively improved; the problem is solved that decrease of filtering precision and possible filtering divergence are caused by Taylor series expansion linearization.

Owner:WENZHOU UNIVERSITY