Patents

Literature

108 results about "Dielectric thickness" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Any specimen thickness can be used, however the most common thickness is between 0.8 to 3.2 mm (0.032 to 0.125 inch). Specimens over 2 mm thick are typically tested in oil to decrease the chance of flashover before breakdown. Data: Dielectric strength is calculated by dividing the breakdown voltage by the thickness of the sample.

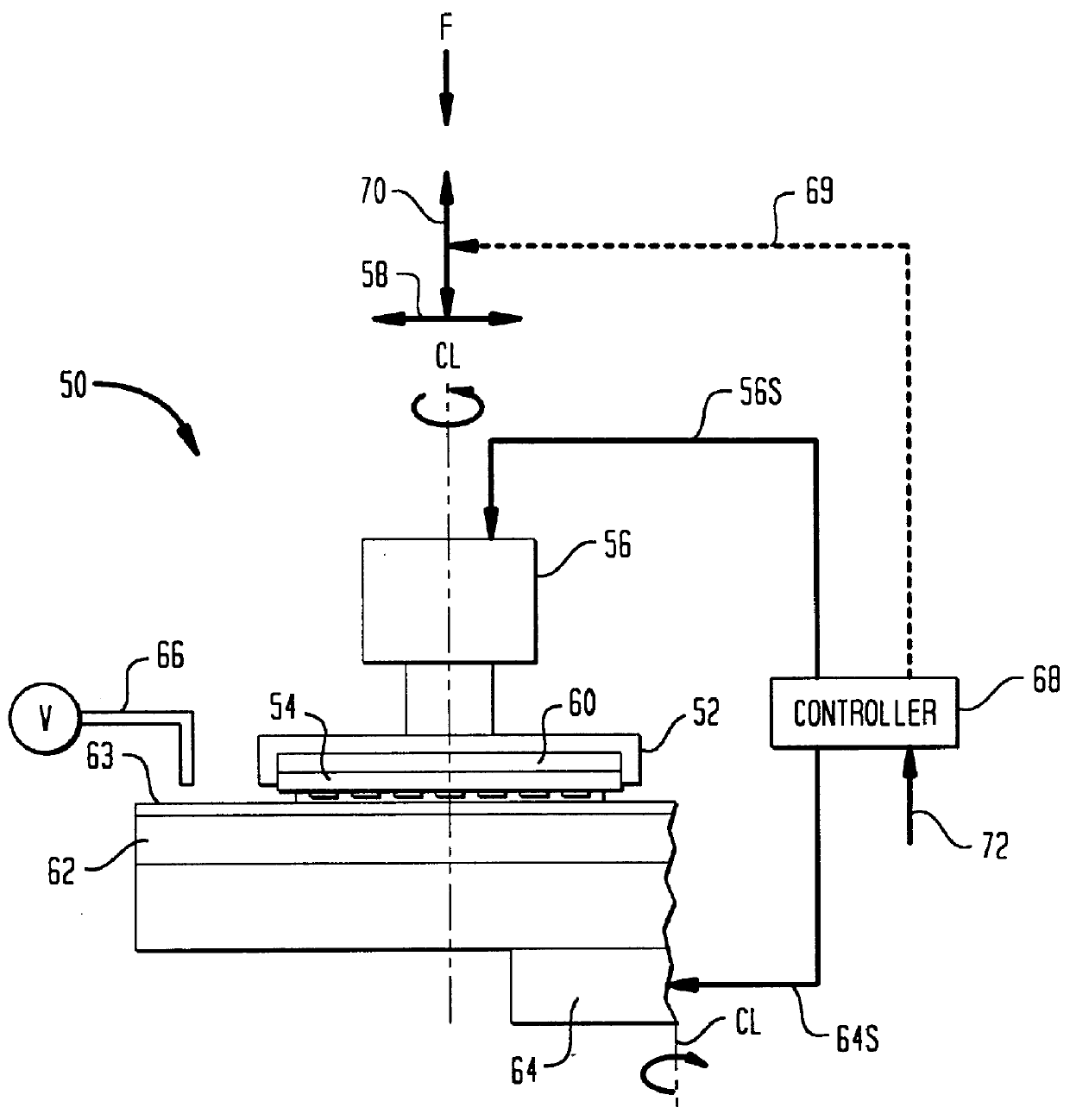

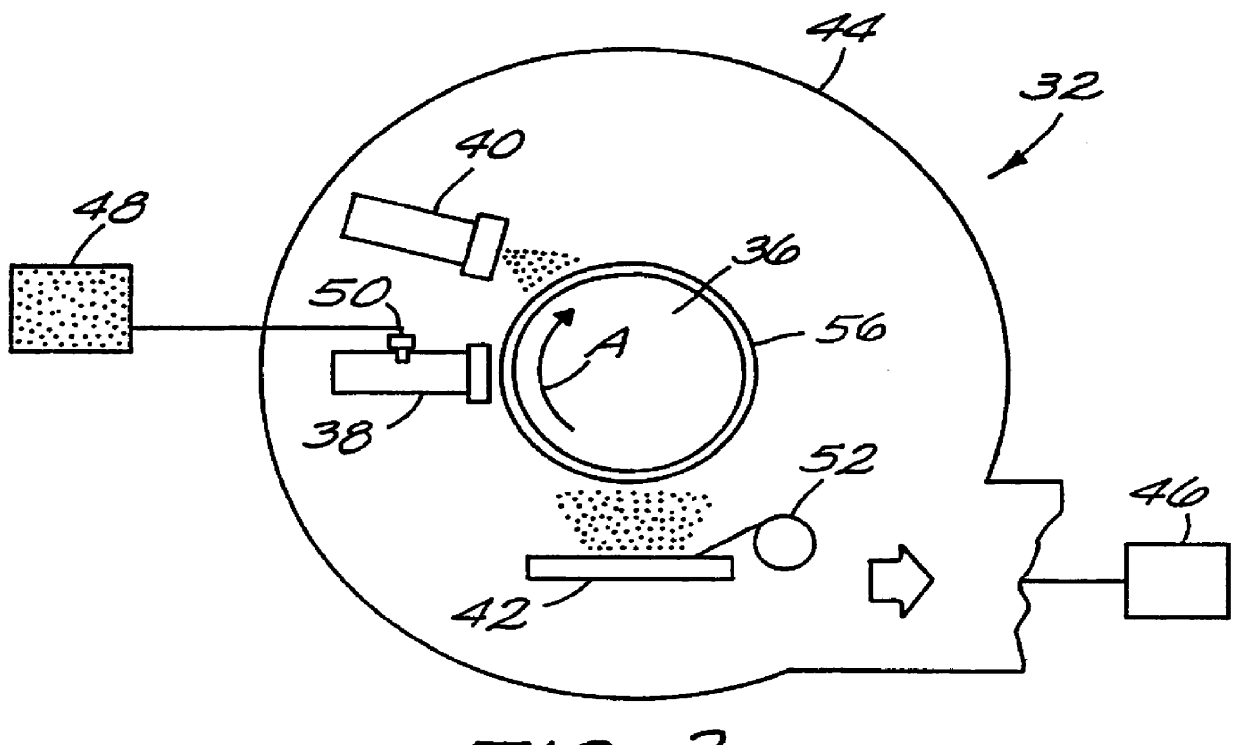

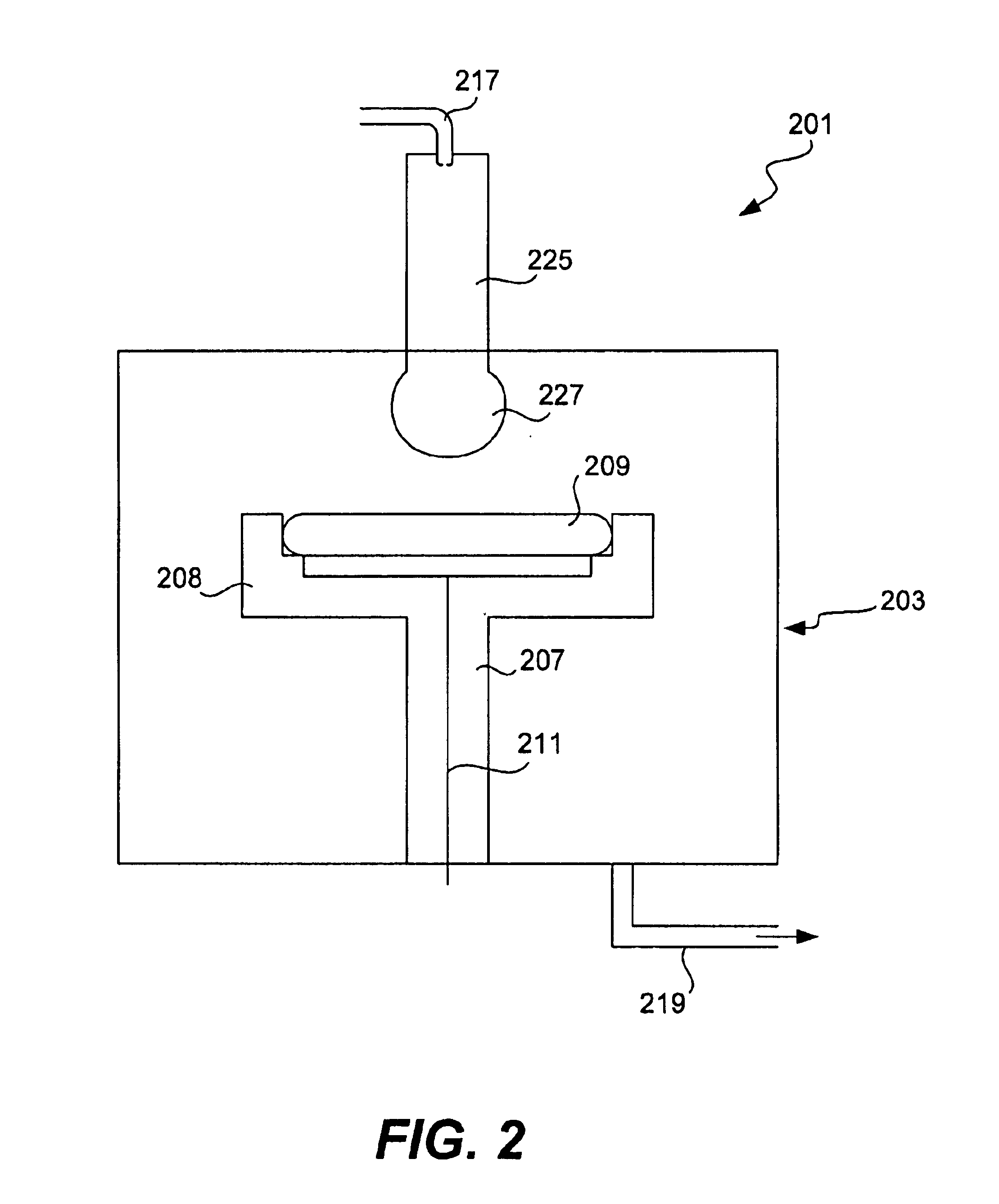

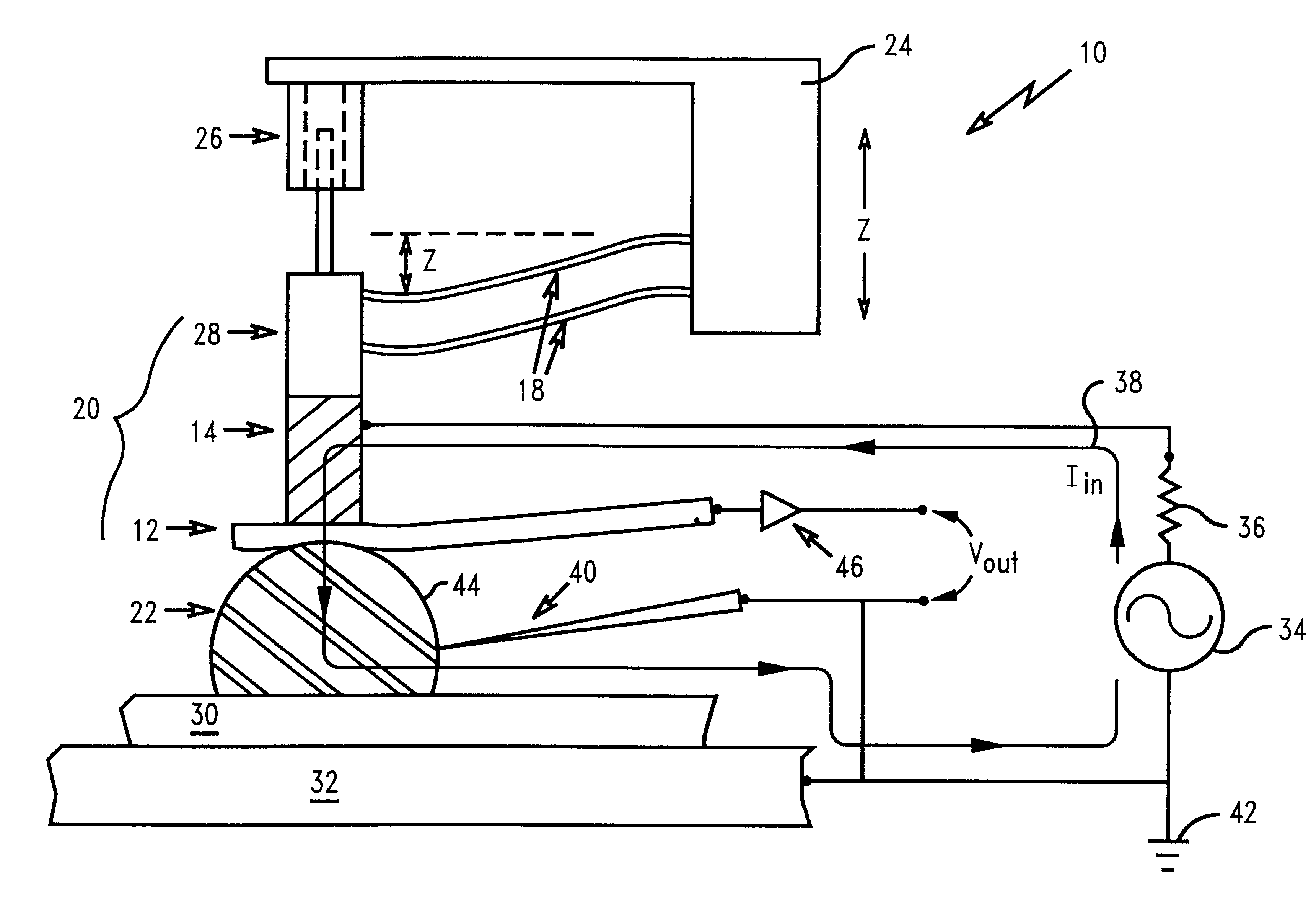

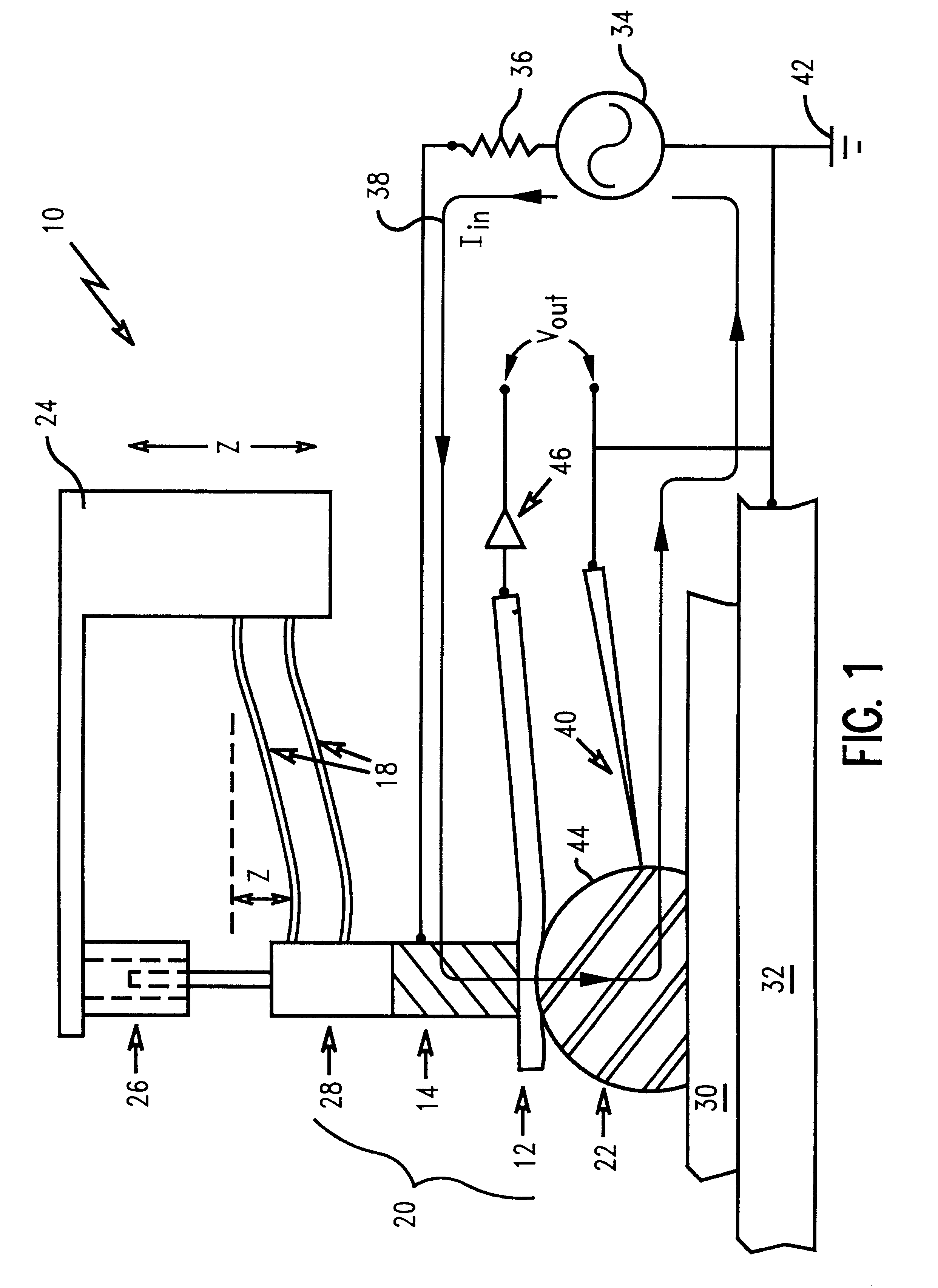

Method and apparatus for in-line oxide thickness determination in chemical-mechanical polishing

InactiveUS6020264ASemiconductor/solid-state device testing/measurementResistance/reactance/impedenceElectrical resistance and conductanceEngineering

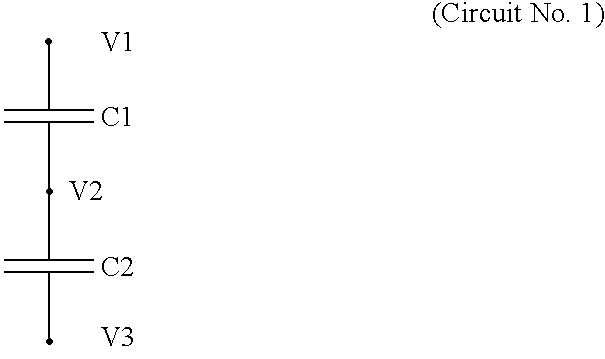

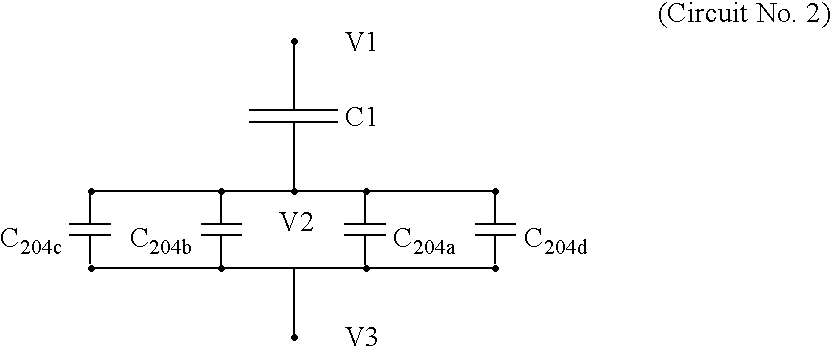

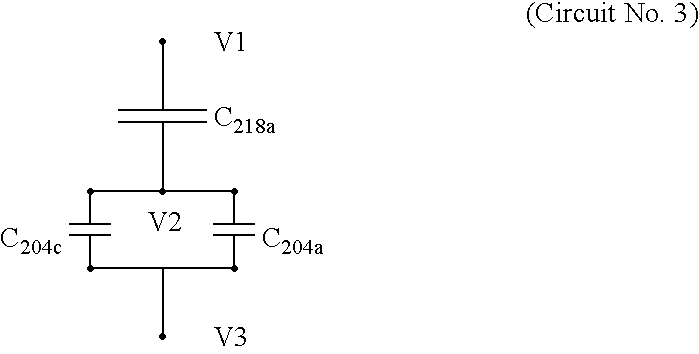

In-line thickness measurement of a dielectric film layer on a surface of a workpiece subsequent to a polishing on a chemical-mechanical polishing machine in a polishing slurry is disclosed. The workpiece includes a given level of back-end-of-line (BEOL) structure including junctions. The measurement apparatus includes a platen and an electrode embedded within the platen. A positioning mechanism positions the workpiece above the electrode with the dielectric layer facing in a direction of the electrode. A slurry dam is used for maintaining a prescribed level of a conductive polishing slurry above the electrode, the prescribed level to ensure a desired slurry coverage of the workpiece. A capacitance sensor senses a system capacitance C in accordance with an RC equivalent circuit model, wherein the RC equivalent circuit includes a resistance R representative of the slurry and workpiece resistances and the system capacitance C representative of the dielectric material and junction capacitances. Lastly, a capacitance-to-thickness converter converts the sensed capacitance to a dielectric thickness in accordance with a prescribed system capacitance / optical thickness calibration, wherein the prescribed calibration corresponds to the given level of BEOL structure of the workpiece.

Owner:IBM CORP

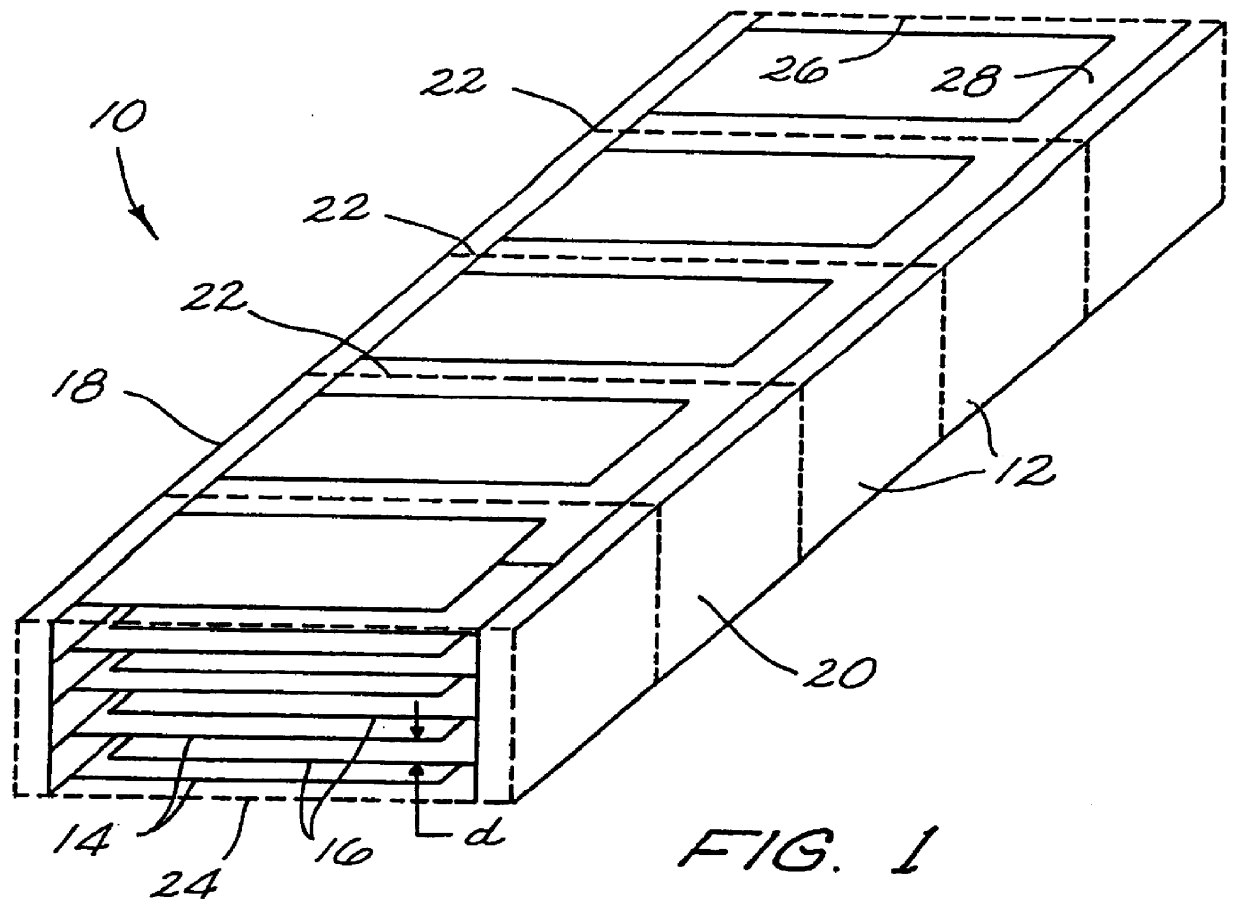

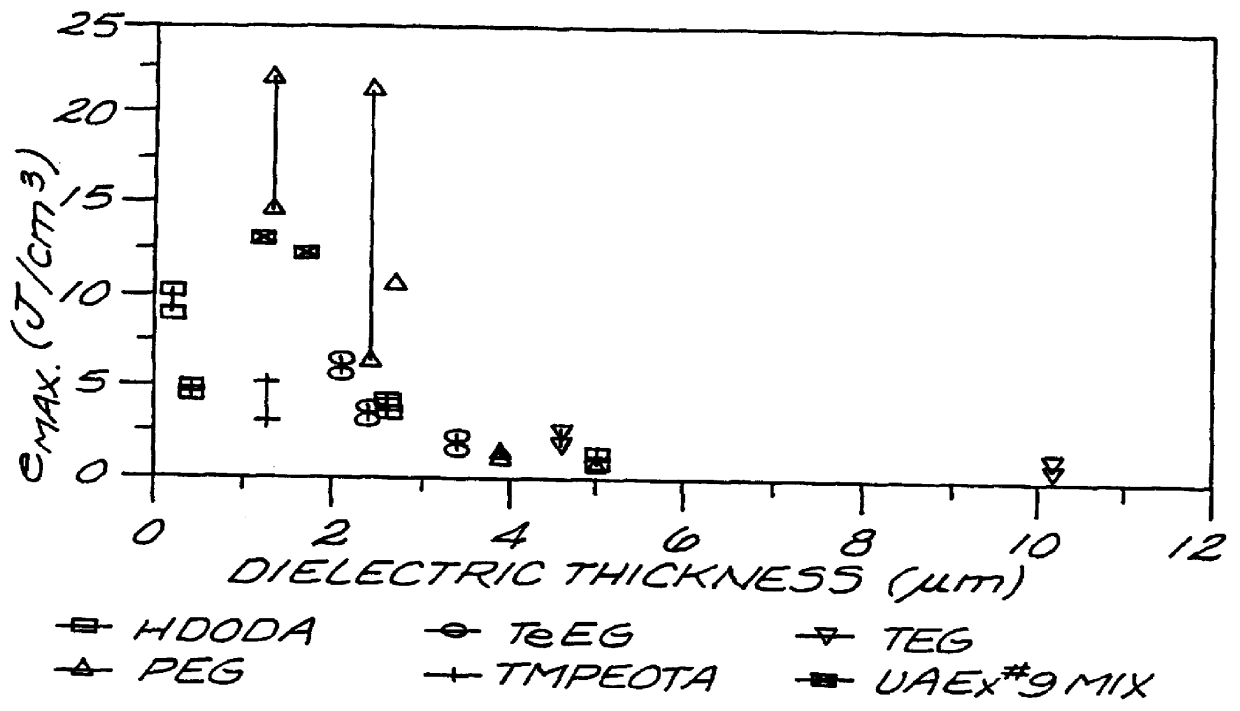

High energy density capacitor

A high energy density, high power density capacitor having an energy density of at least about 0.5 J / cm3 is provided. The capacitor comprises a plurality of interleaved metal electrode layers separated by a polymer layer. The interleaved metal electrode layers terminate at opposite ends in a solder termination strip. The high energy density aspect of the capacitors of the invention is achieved by at least one of the following features: (a) the dielectric thickness between the interleaved metal electrode layers is a maximum of about 5 mu m; (b) the polymer is designed with a high dielectric constant kappa of at least about 3.5; (c) the metal electrode layers within the polymer layer are recessed along edges orthogonal to the solder termination strips to prevent arcing between the metal electrode layers at the edges; and (d) the resistivity of the metal electrode layers is within the range of about 10 to 500 ohms per square, or a corresponding thickness of about 200 to 30 ANGSTROM .

Owner:SIGMA LAB OF ARIZONA

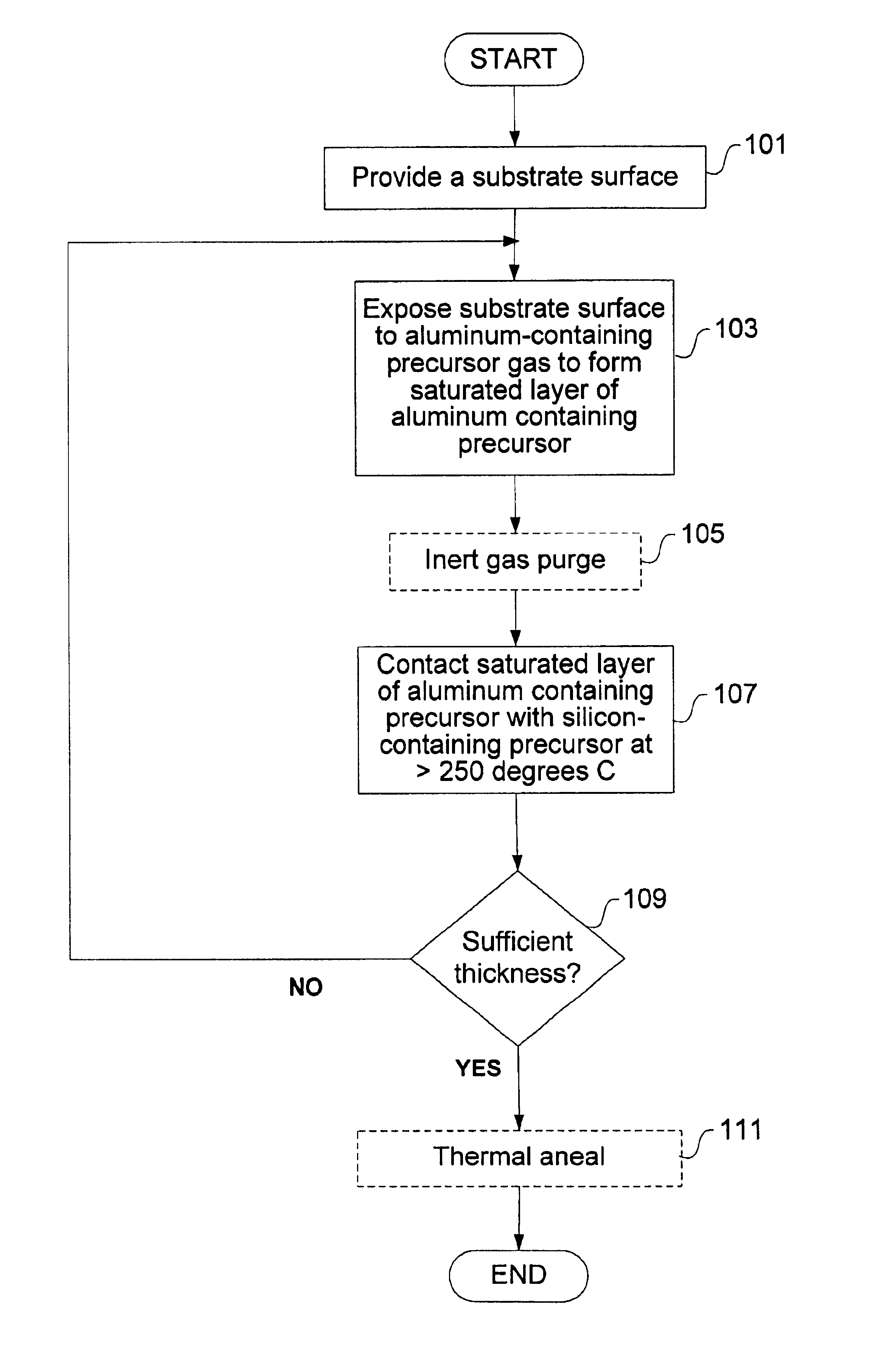

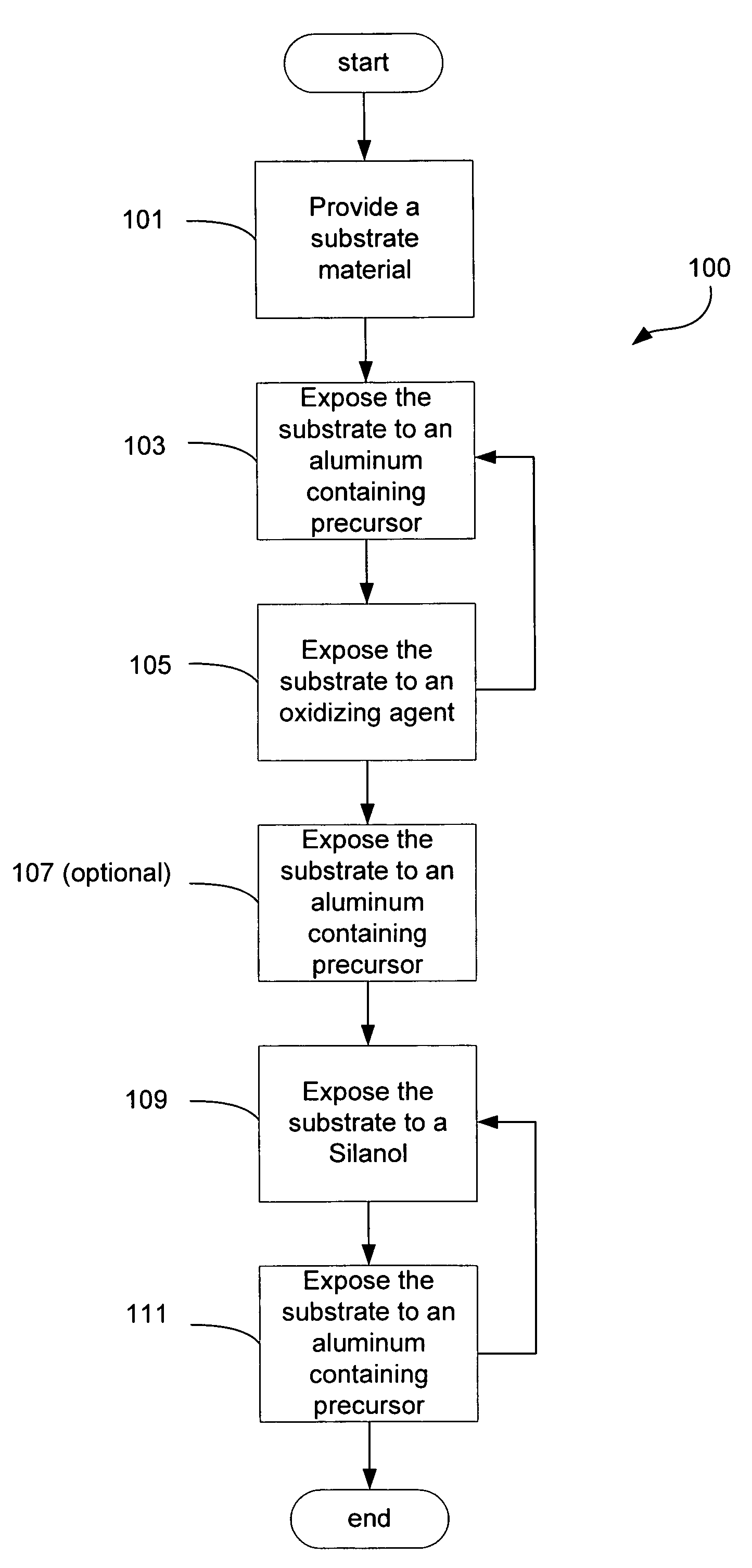

Properties of a silica thin film produced by a rapid vapor deposition (RVD) process

InactiveUS6867152B1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingHysteresisSilicon dioxide

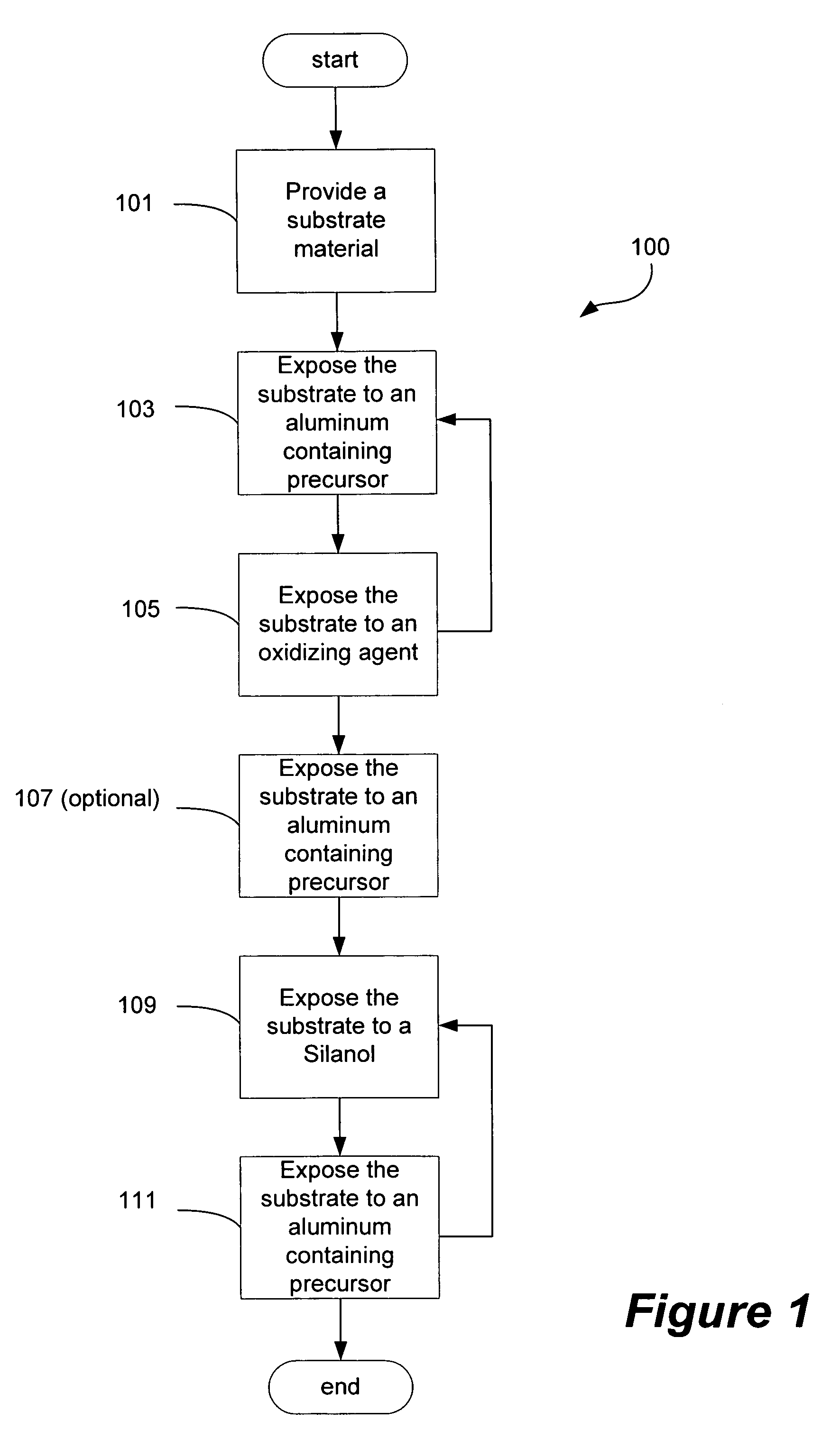

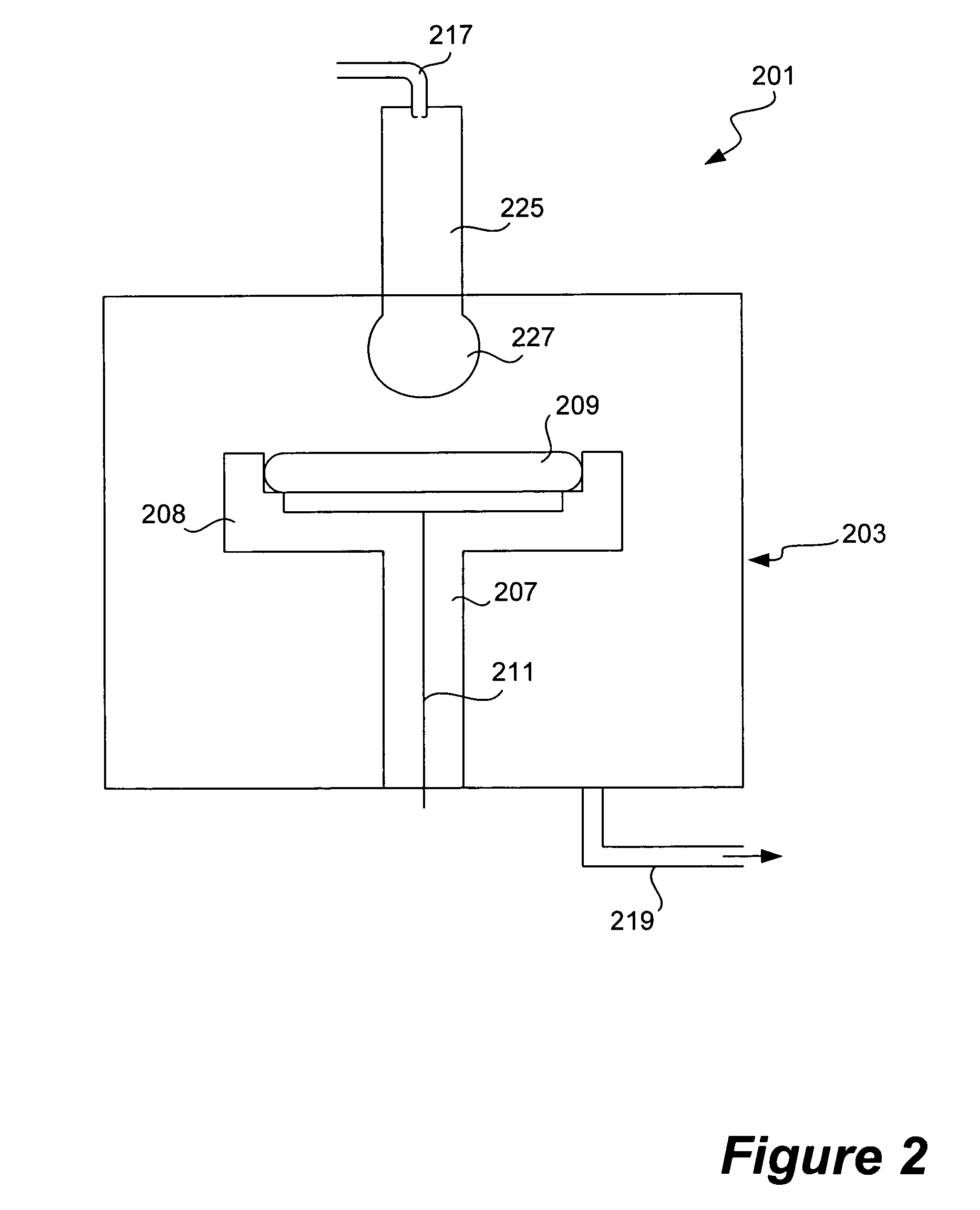

A rapid vapor deposition (RVD) method conformally deposits a dielectric material on small features of a substrate surface. The resulting dielectric film has a low dielectric constant, low wet etch rate, low film shrinkage and low stress hysteresis, appropriate for various integrated circuit dielectric gap fill applications such as shallow trench isolation. The method includes the following two principal operations: depositing a thin conformal and saturated layer of aluminum-containing precursor over some or all of the substrate surface; and exposing the saturated layer of aluminum-containing precursor to a silicon-containing precursor gas to form a dielectric layer. In some cases, the substrate temperatures during contact with silicon-containing precursor are greater than about 250 degree Celsius to produce an improved film. In other cases, post-deposition anneal process may be used to improve properties of the film. Generally an inert gas purge is employed between the introduction of reactant gases to remove byproducts and unused reactants. These operations can be repeated to deposit multiple layers of dielectric material until a desired dielectric thickness is achieved.

Owner:NOVELLUS SYSTEMS

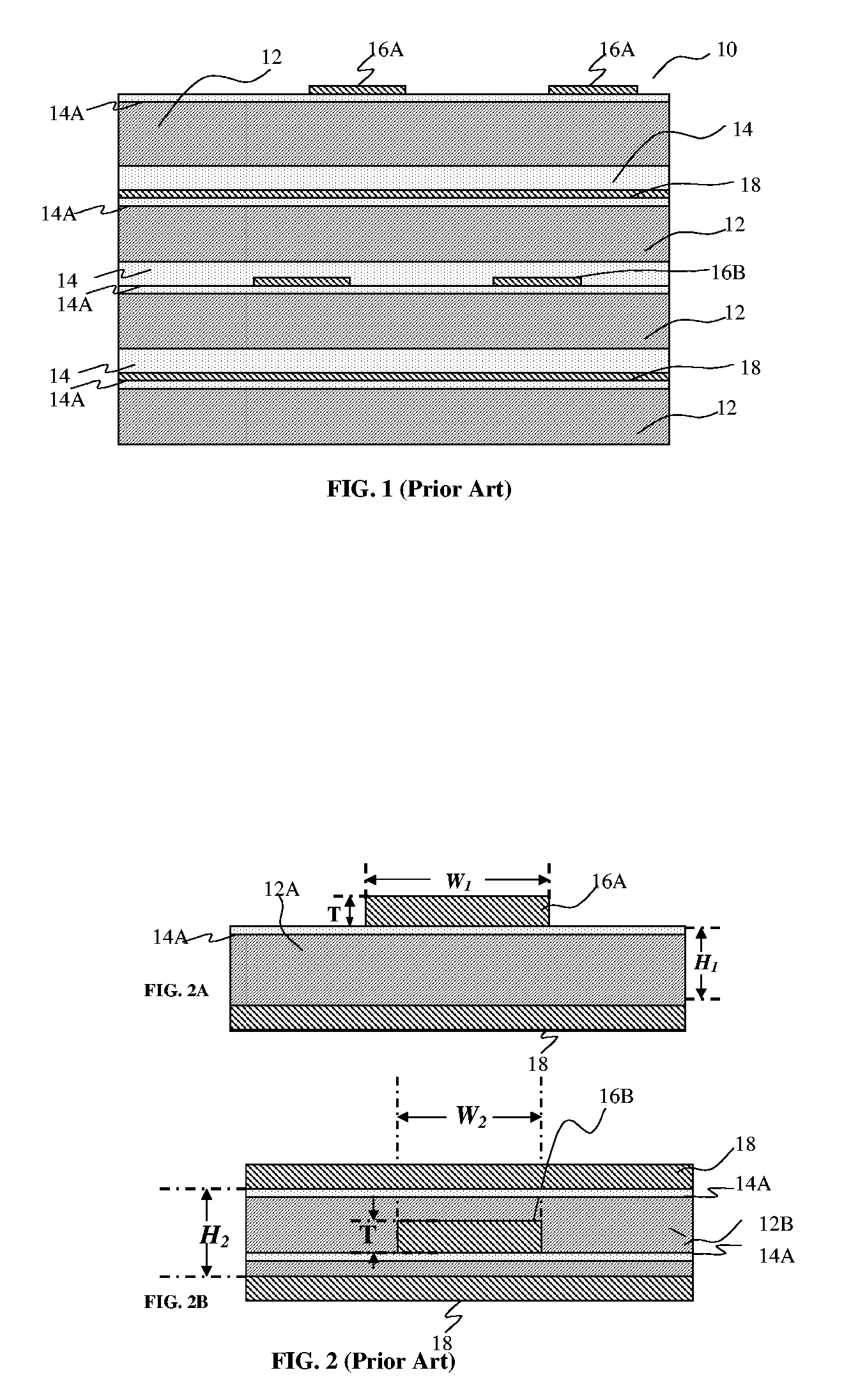

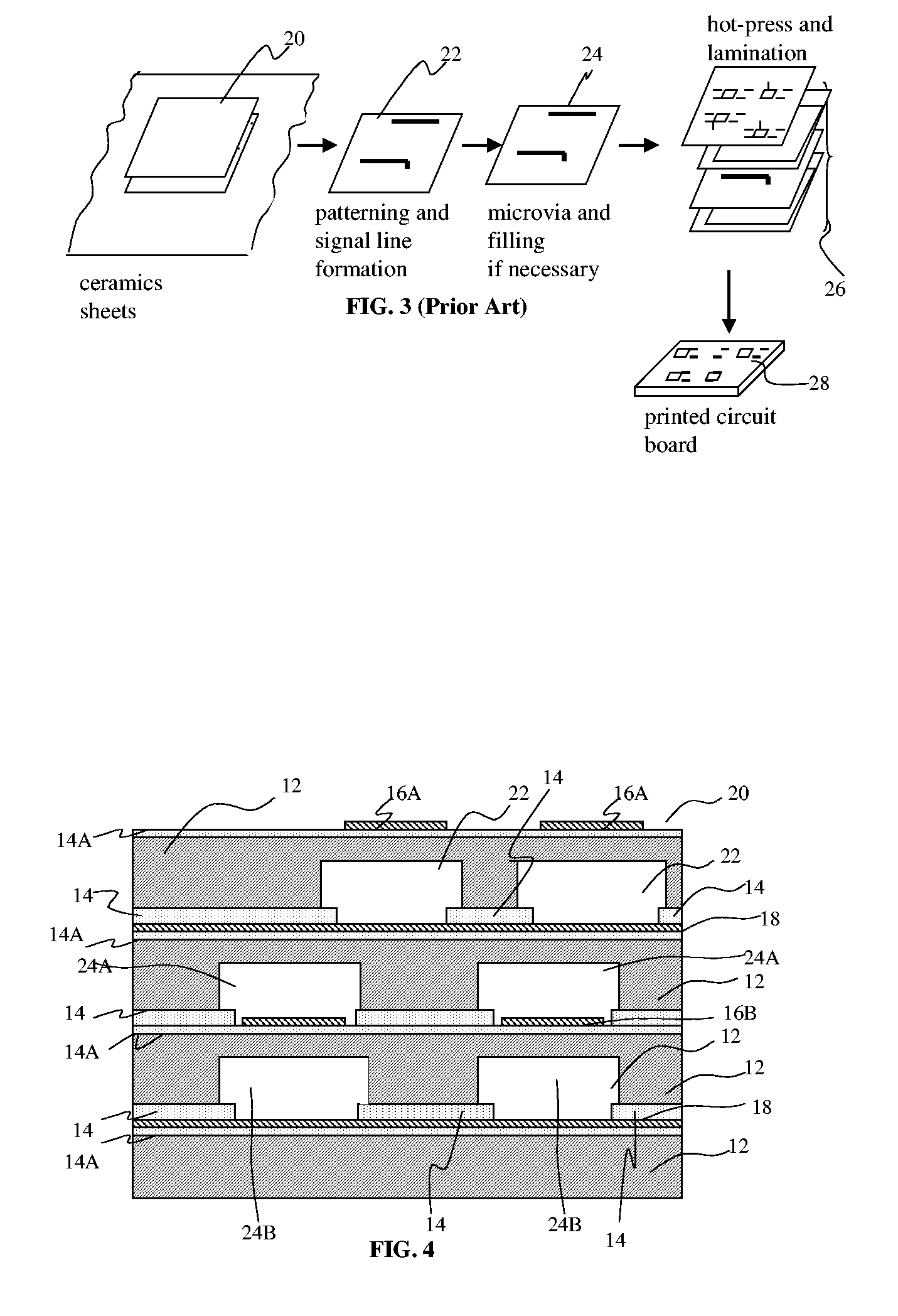

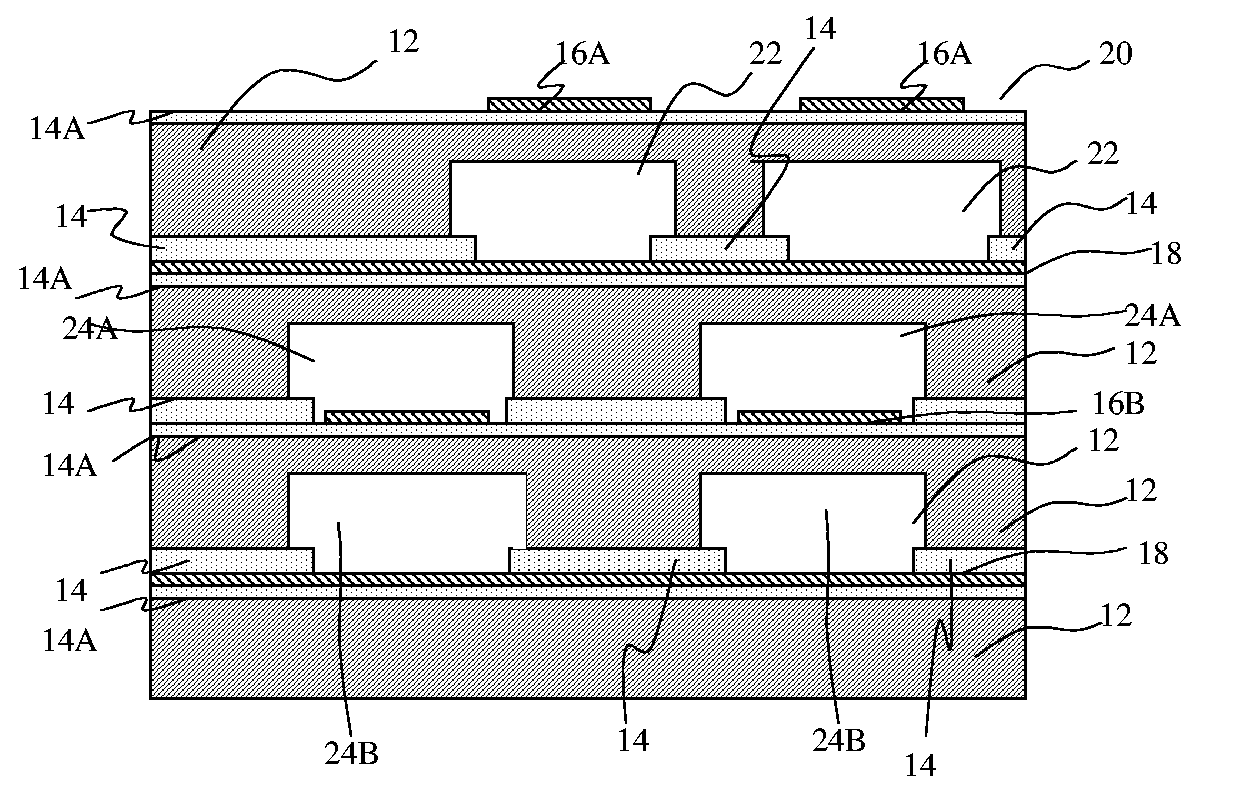

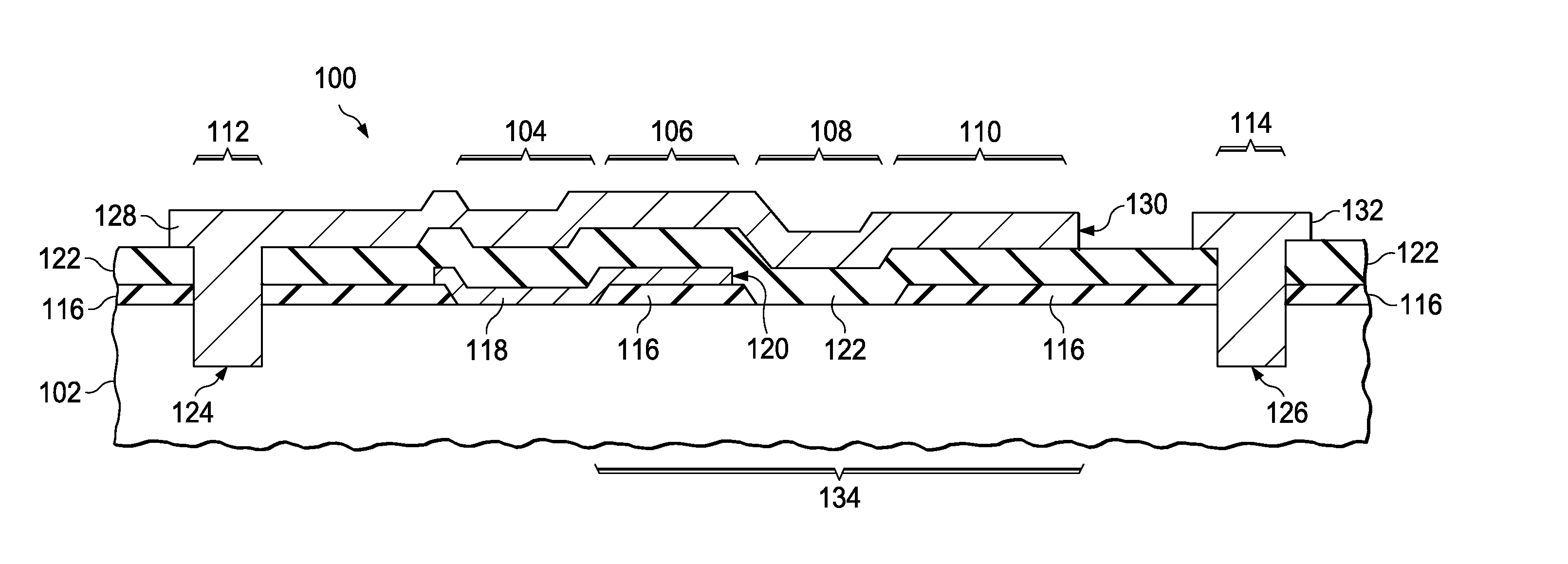

High-speed flex printed circuit and method of manufacturing

ActiveUS7663064B2Reduce effective dielectric constant and effective dielectric lossHigh bandwidthPrinted circuit assemblingPrinted circuit aspectsElectricityMicrowave

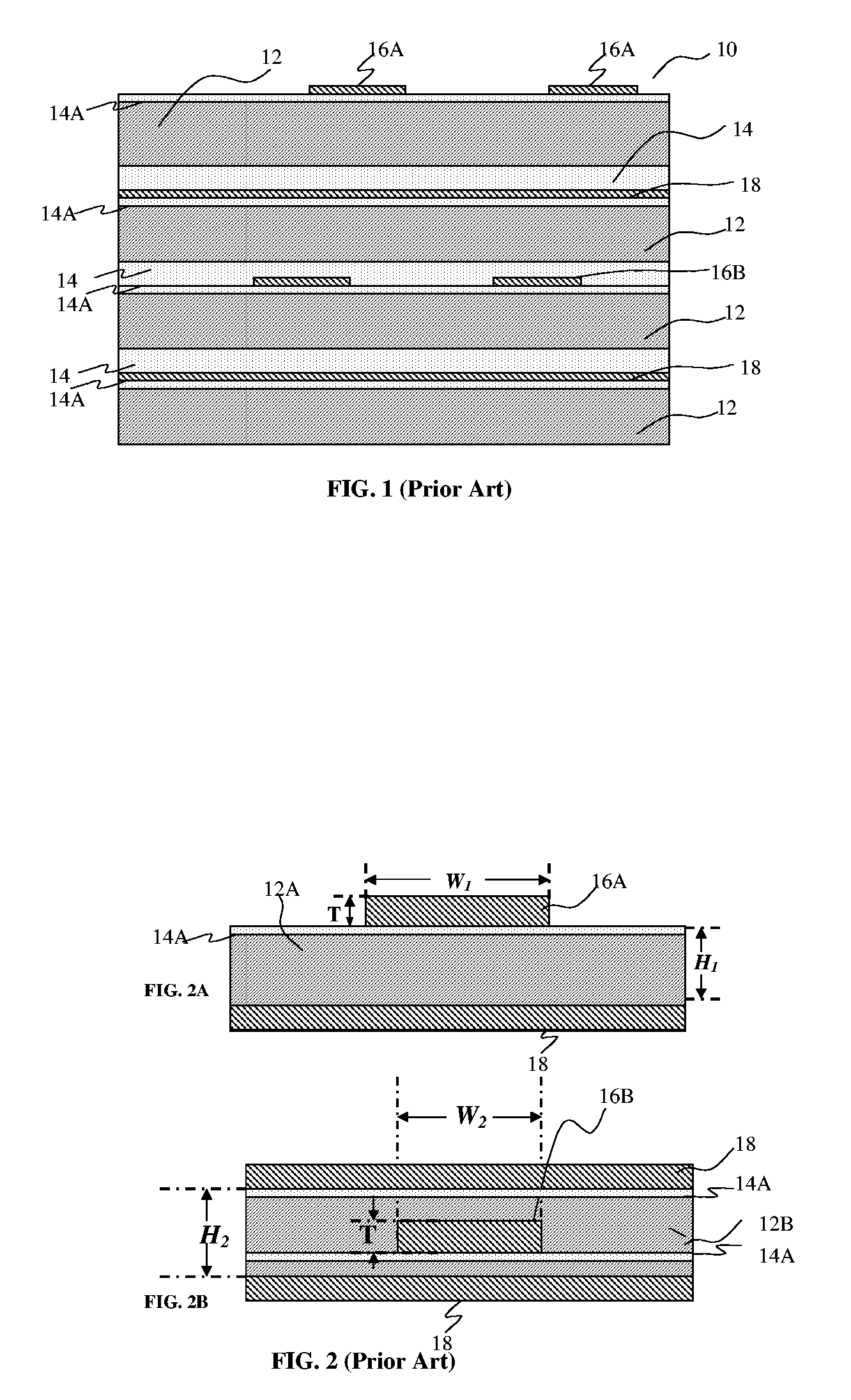

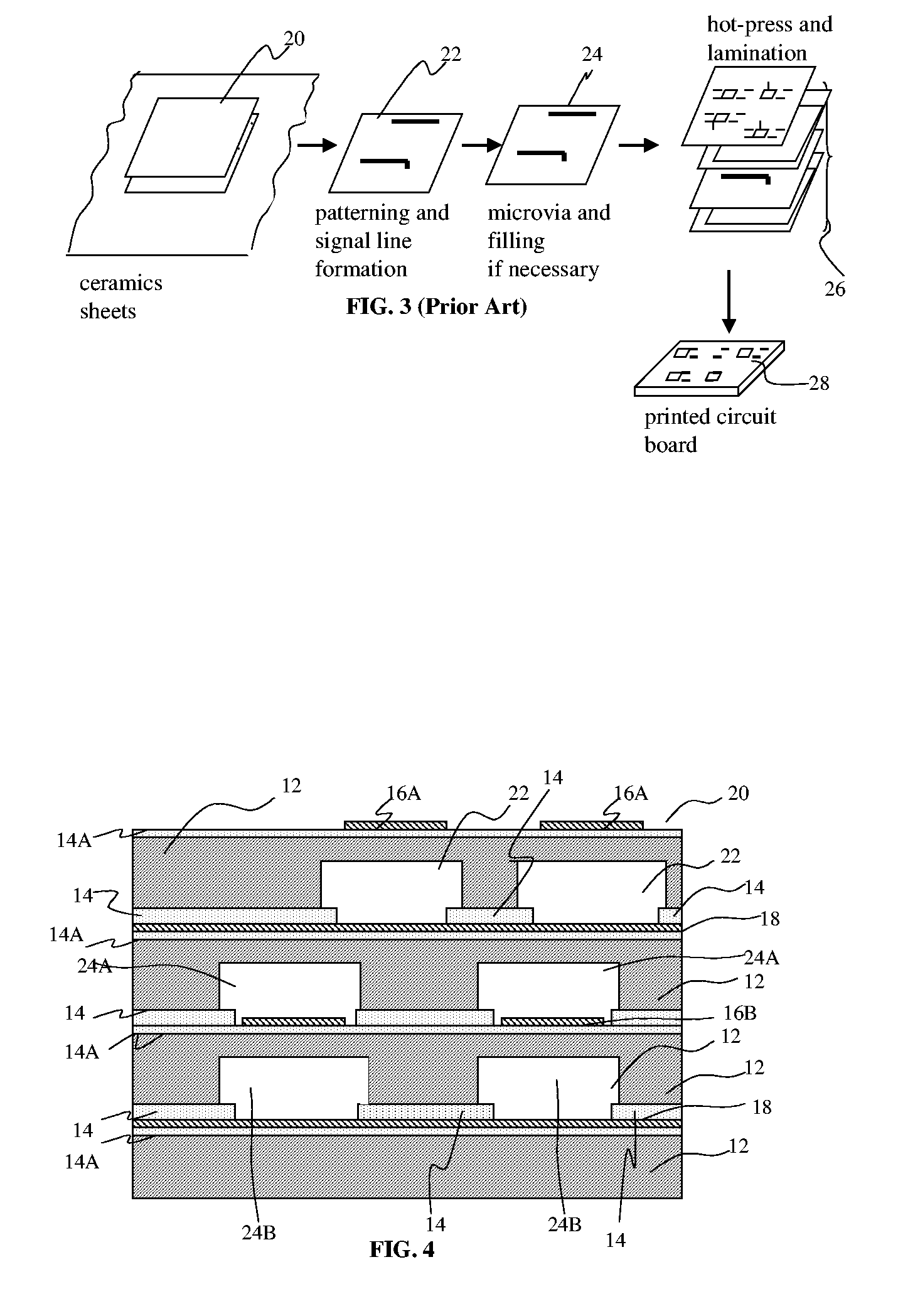

Multilayer high speed flex printed circuit boards (FLEX-PCBs) are disclosed including a dielectrics systems with the back-side trenches, adhesives, signal lines and ground planes, wherein the signal line and ground plane lane are located on the dielectrics. Using of the open trenches in the substrate help to reduce the microwave loss and dielectric constant and thus increasing the signal carrying speed of the interconnects. Thus, according to the present invention, it is possible to provide a simply constructed multiplayer high speed FLEX-PCB using the conventional material and conventional FLEX-PCB manufacturing which facilitates the design of circuits with controlled bandwidth based on the trench opening in the dielectrics, and affords excellent connection reliability. As the effective dielectric constant is reduced, the signal width is required to make wider or the dielectric thickness is required to make thinner keeping fixed characteristics impedance. The fundamental techniques disclosed here can also be used for high-speed packaging.

Owner:BANPIL PHOTONICS

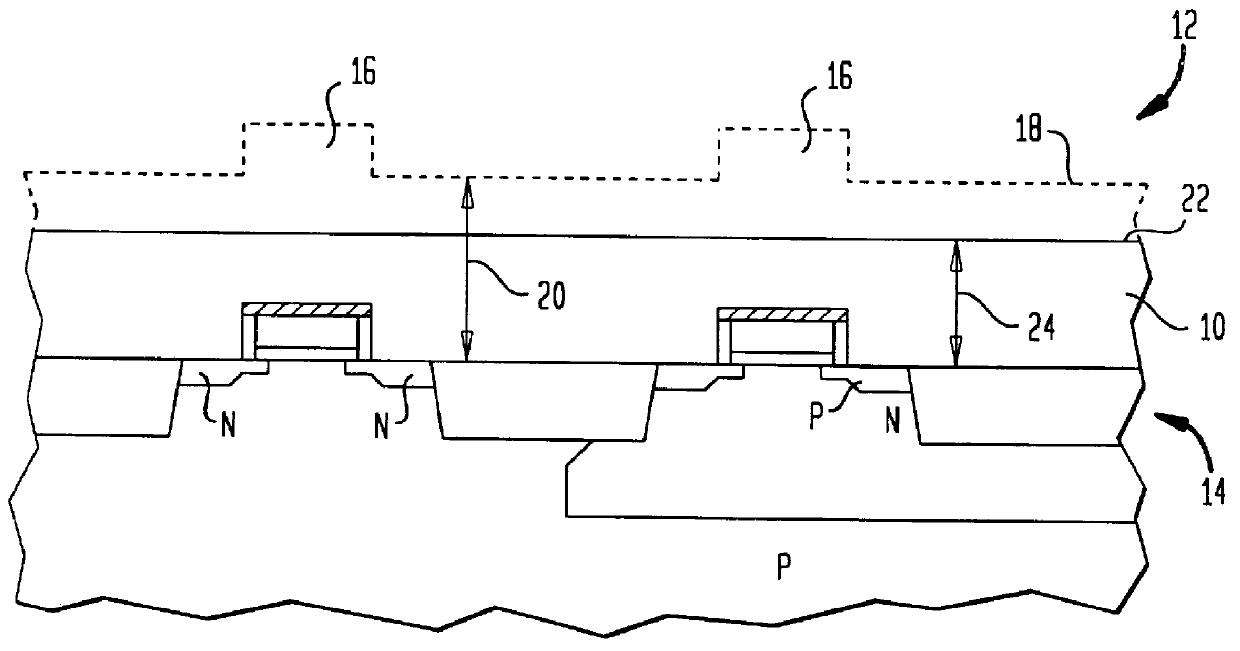

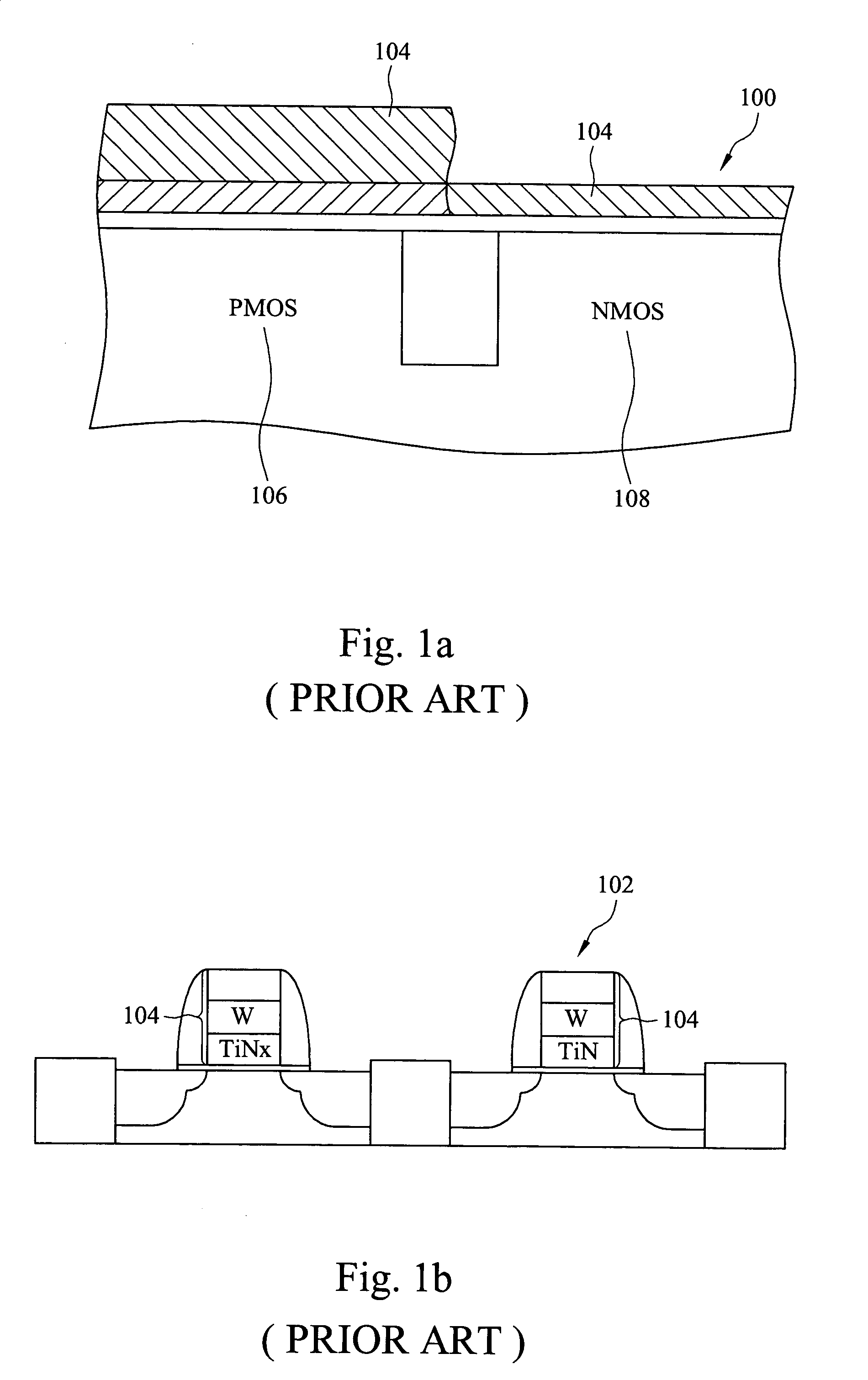

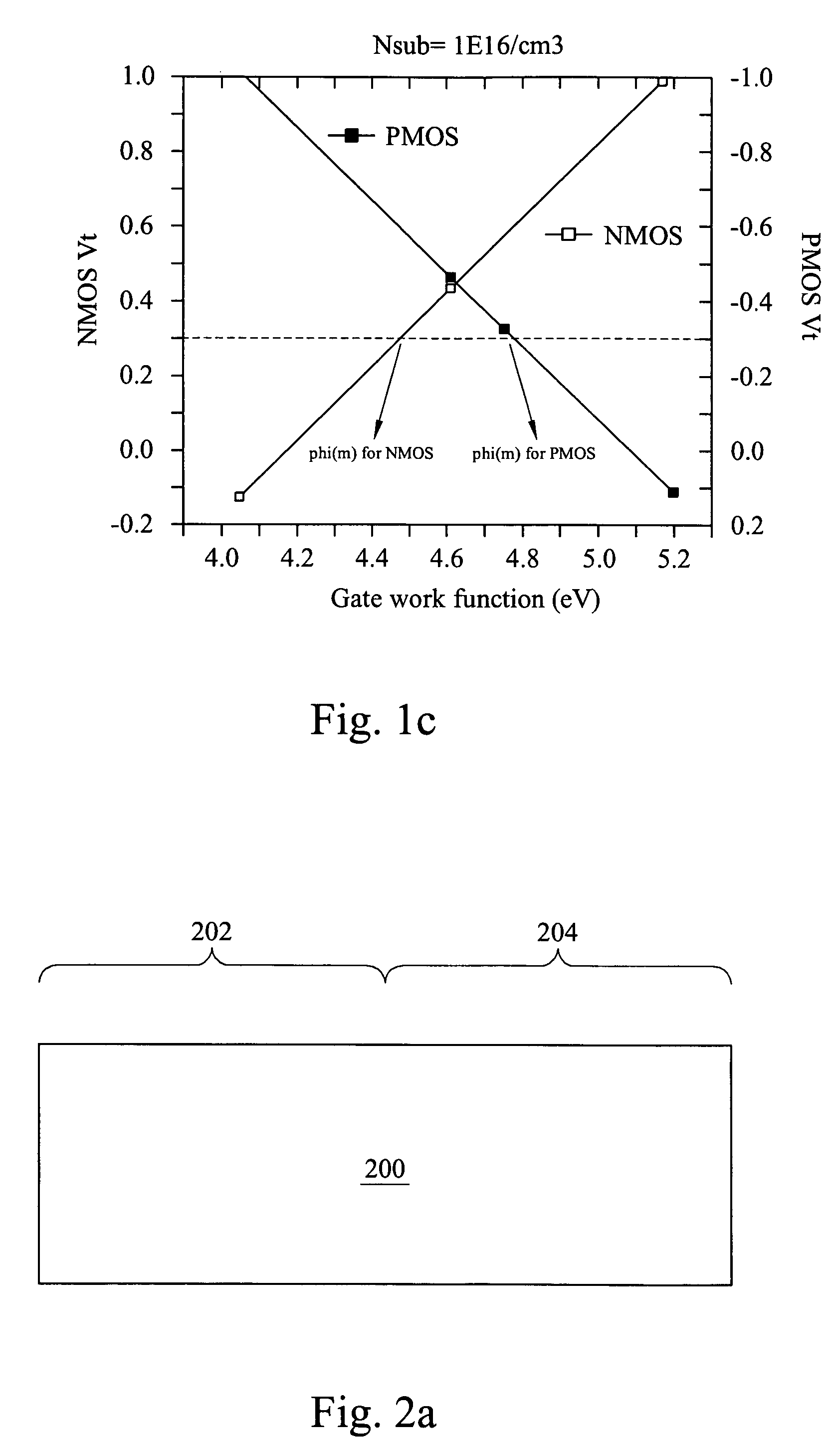

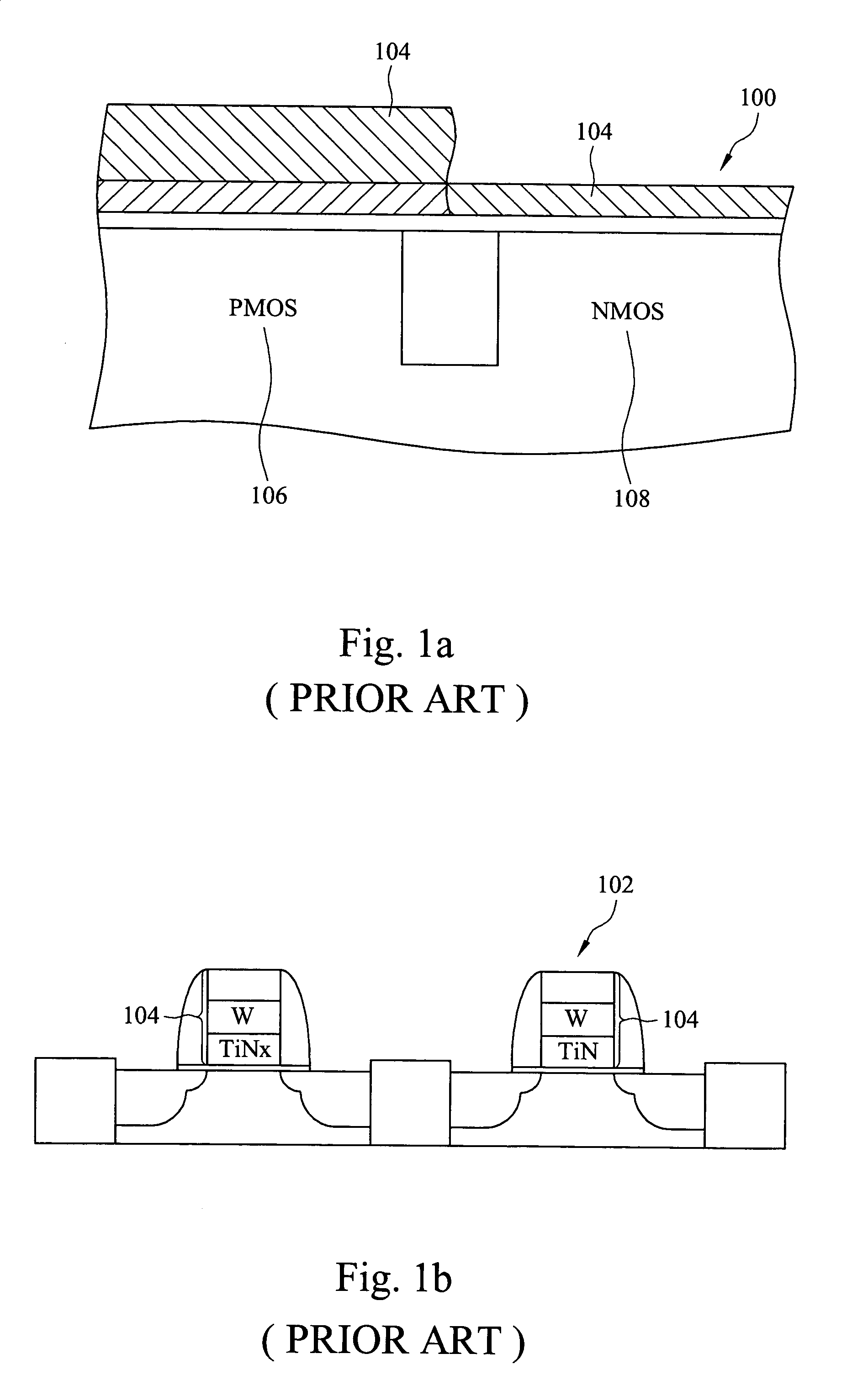

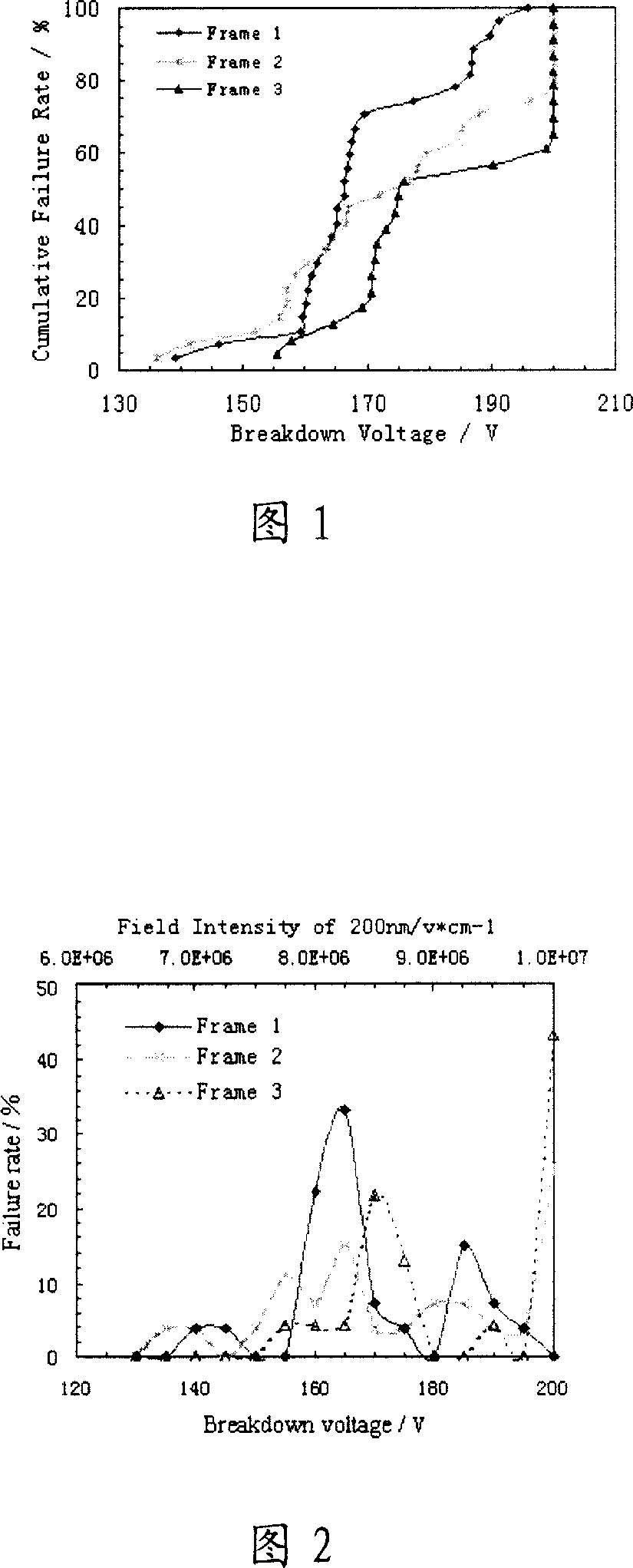

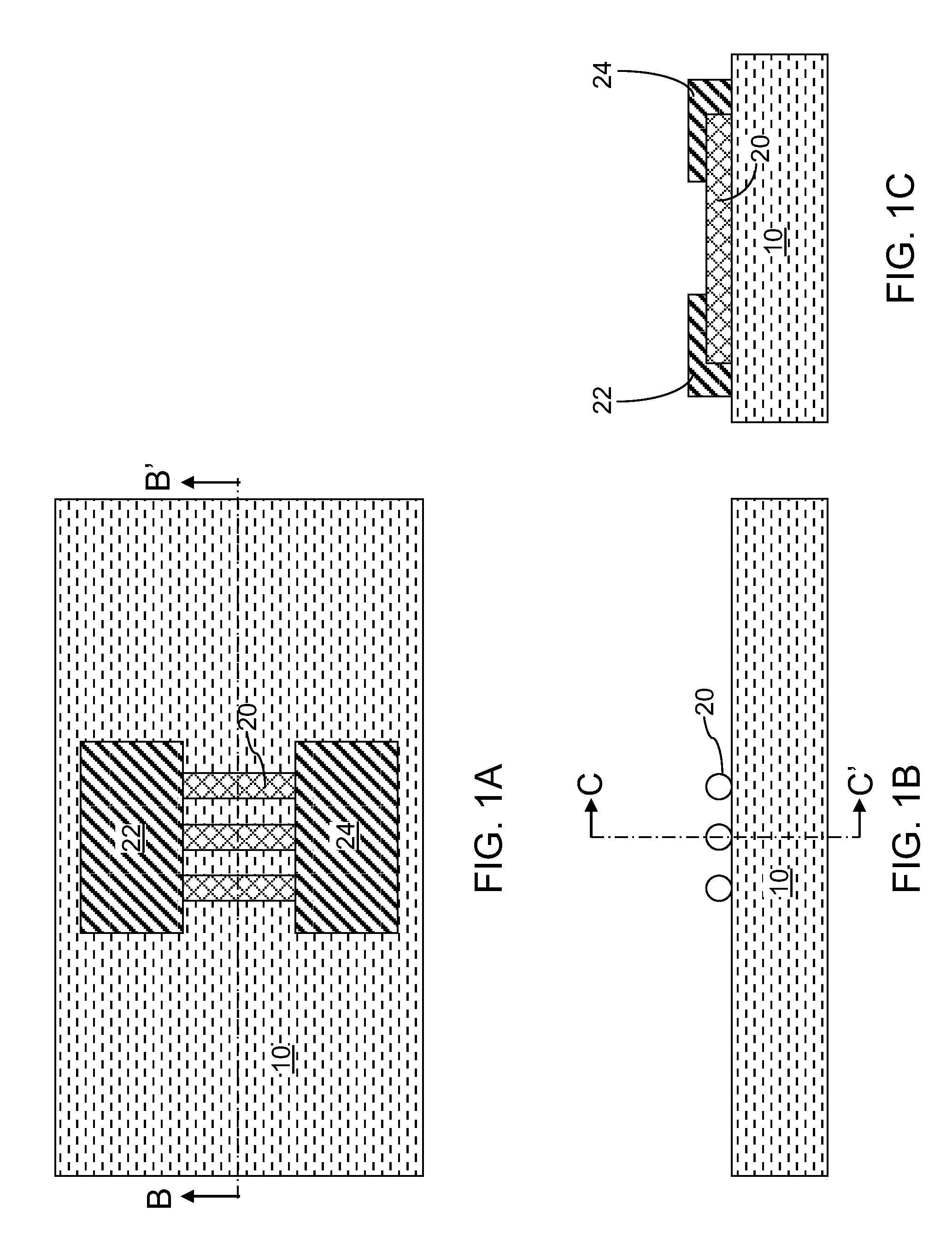

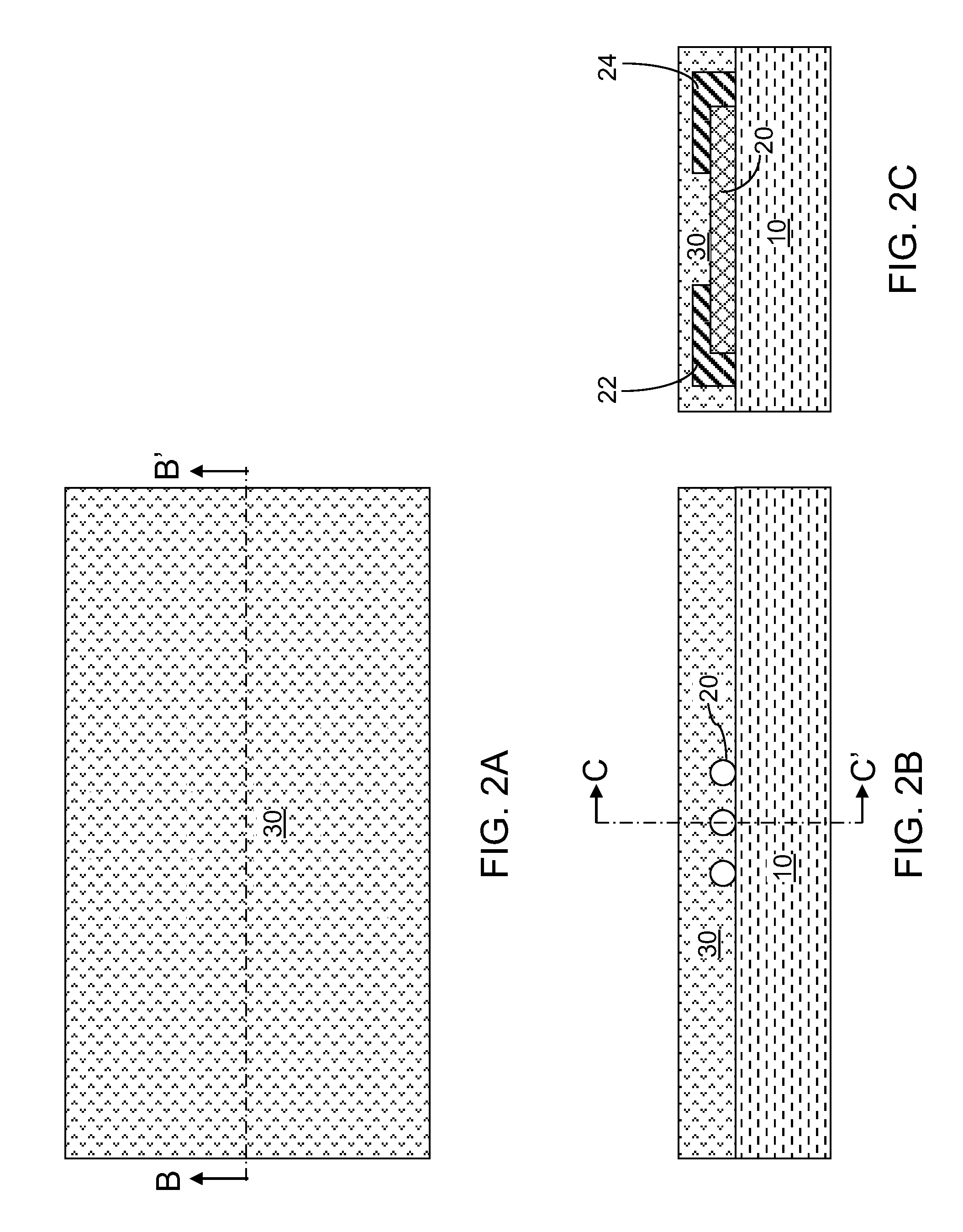

Fully depleted SOI multiple threshold voltage application

An integrated circuit comprises a substrate and a buried dielectric formed in the substrate. The buried dielectric has a first thickness in a first region, a second buried dielectric thickness in a second region, and a step between the first and second regions. A semiconductor layer overlies the buried dielectric.

Owner:TAIWAN SEMICON MFG CO LTD

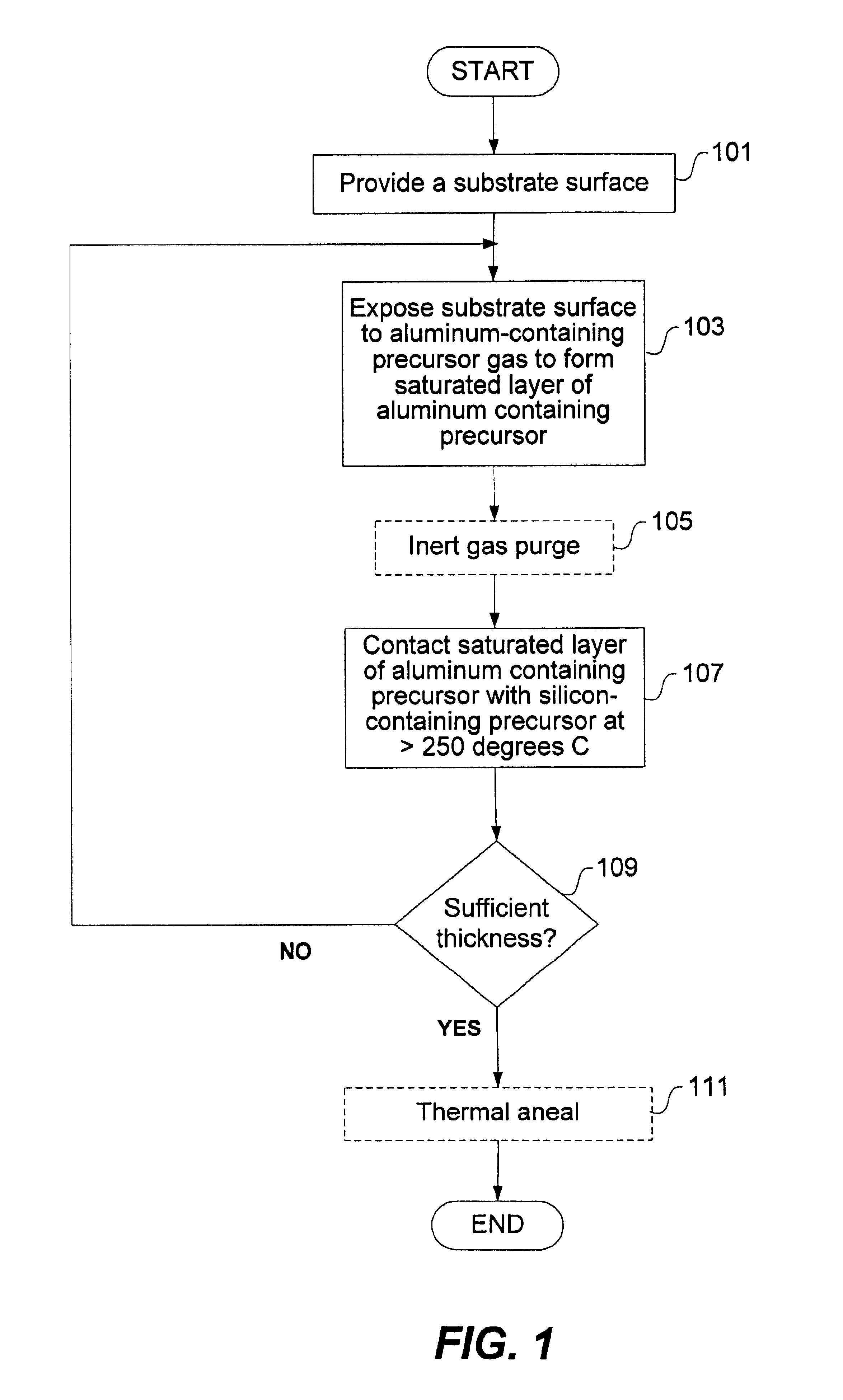

Silica thin films produced by rapid surface catalyzed vapor deposition (RVD) using a nucleation layer

ActiveUS7202185B1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingOxygenSilicon dioxide

An method employing atomic layer deposition (ALD) and rapid vapor deposition (RVD) techniques conformally deposits a dielectric material on small features of a substrate surface. The resulting dielectric film has a low dielectric constant and a high degree of surface smoothness. The method includes the following three principal operations: exposing a substrate surface to an aluminum-containing precursor gas to form a saturated layer of aluminum-containing precursor on the substrate surface; exposing the substrate surface to an oxygen-containing gas to oxidize the layer of aluminum-containing precursor; and exposing the substrate surface to a silicon-containing precursor gas to form the dielectric film. Generally an inert gas purge is employed between the introduction of reactant gases to remove byproducts and unused reactants. These operations can be repeated to deposit multiple layers of dielectric material until a desired dielectric thickness is achieved.

Owner:NOVELLUS SYSTEMS

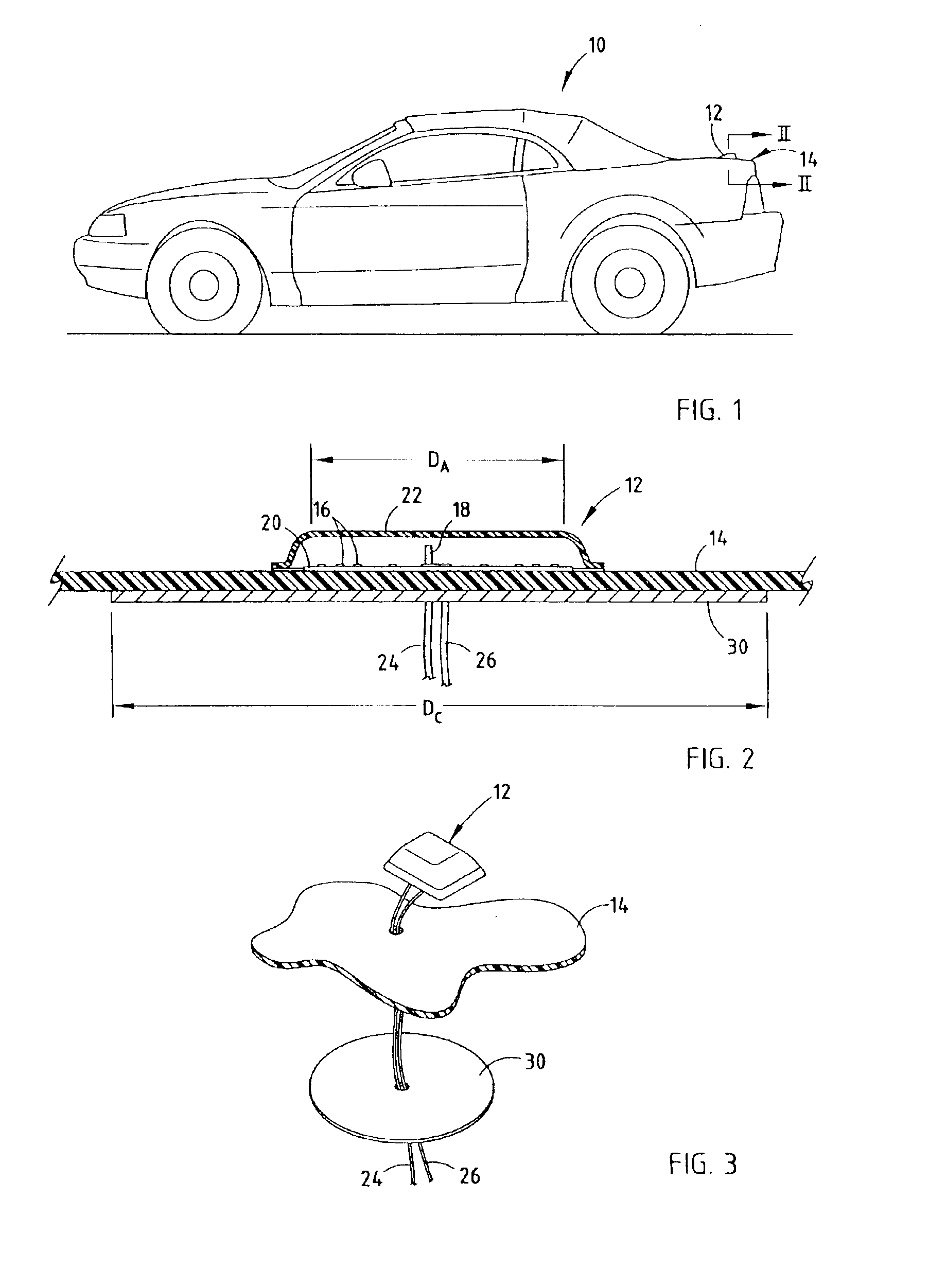

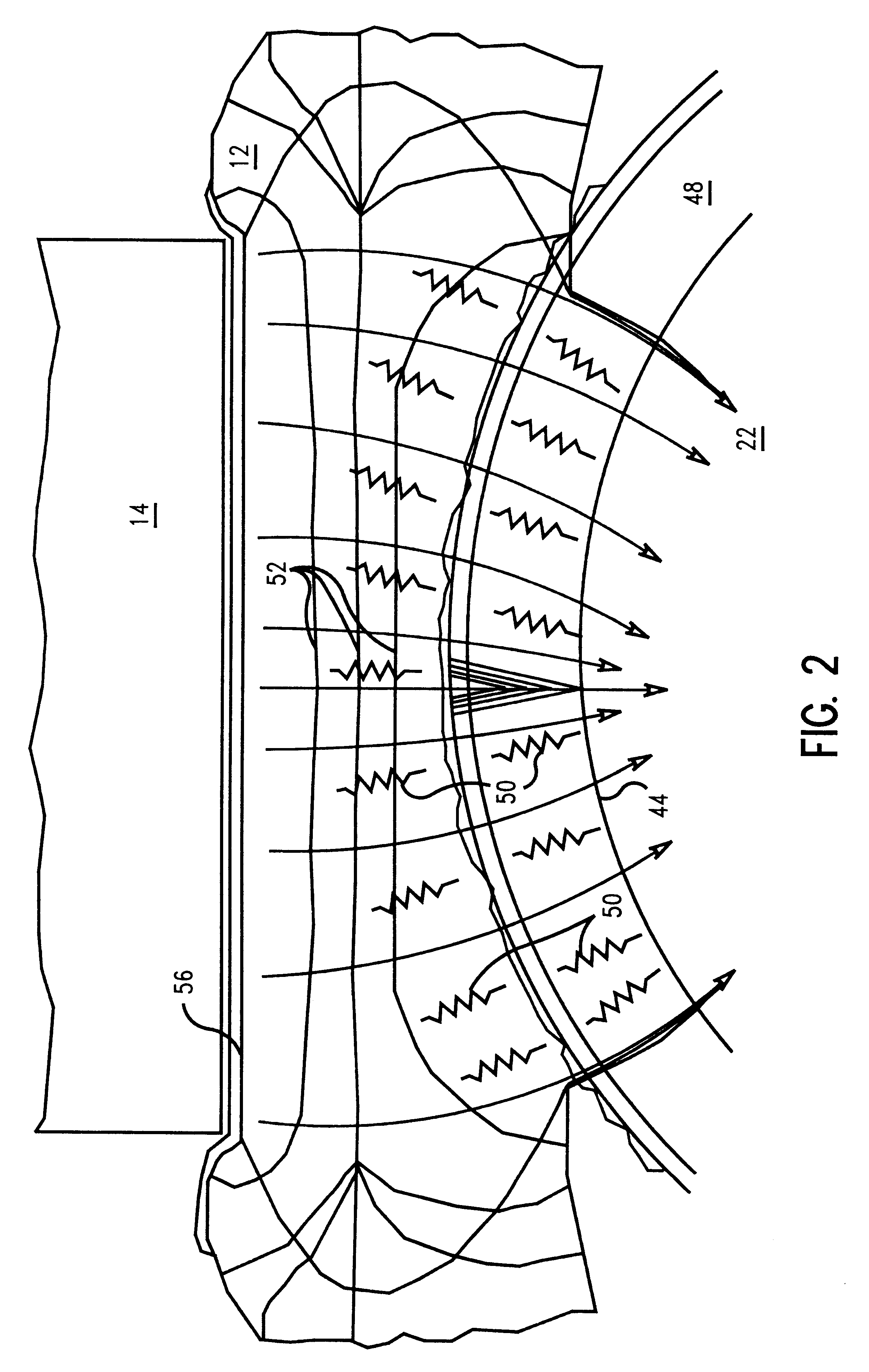

Antenna system employing floating ground plane

InactiveUS6999032B2Improve antenna performanceImpedance stabilitySimultaneous aerial operationsAntenna adaptation in movable bodiesCapacitanceCapacitive coupling

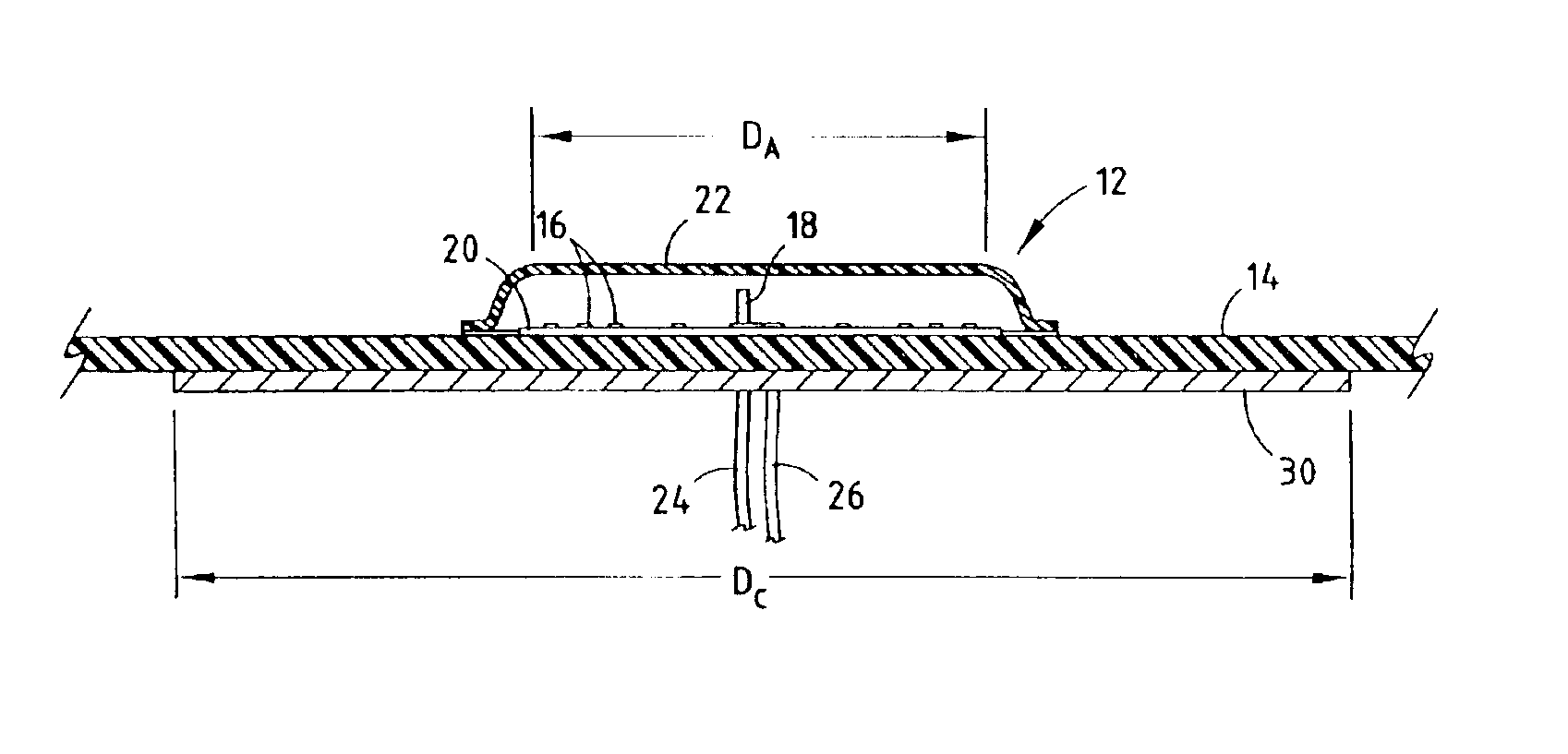

An antenna system is assembled to a dielectric medium on a vehicle and is spaced from an electrically conductive member so as to allow for enhanced antenna performance. The dielectric medium has first and second surfaces and a dielectric thickness between the first and second surfaces. An antenna is mounted to the first surface of the dielectric medium for receiving and / or transmitting signals. An electrically conductive member is mounted to the second surface of the dielectric medium for providing a floating ground that forms a capacitive coupling with the antenna. The electrically conductive member is dielectrically isolated from vehicle electrical ground.

Owner:DELPHI TECH INC

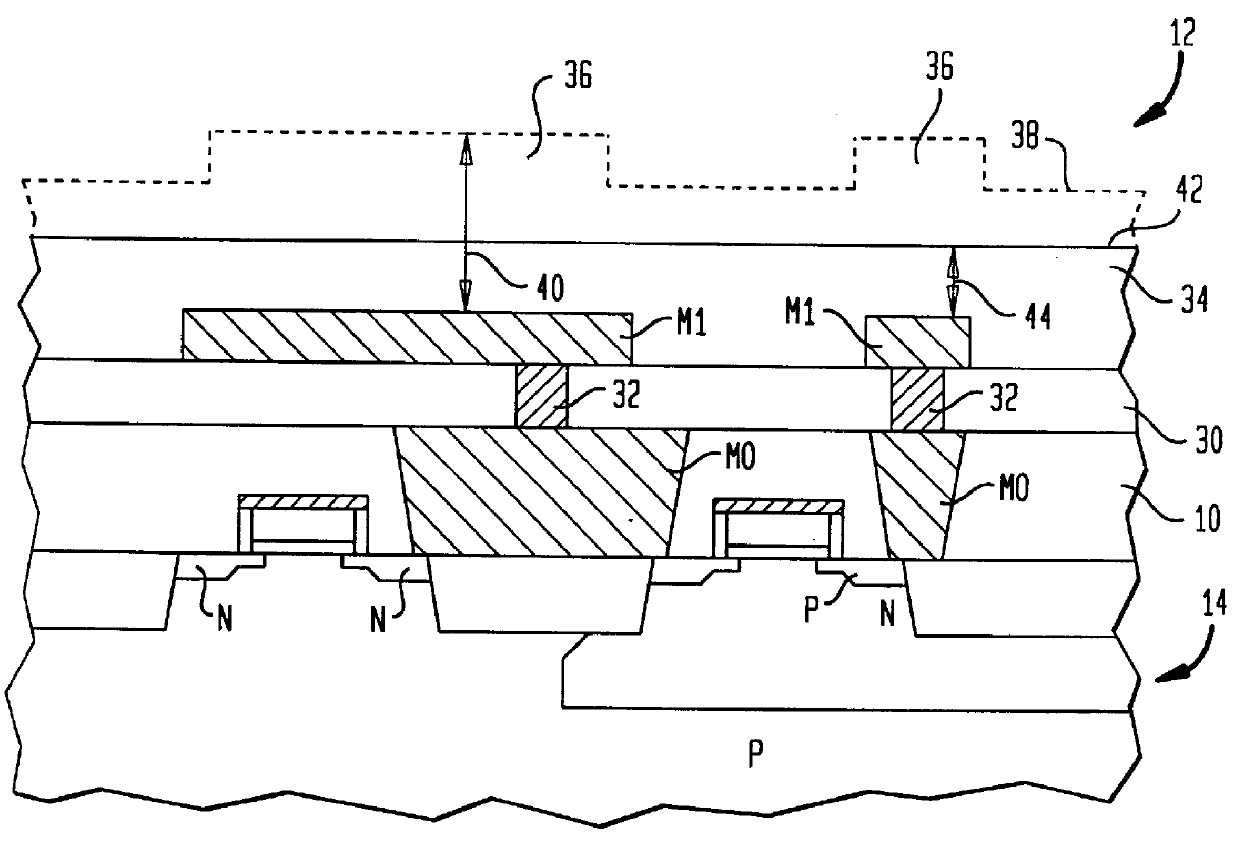

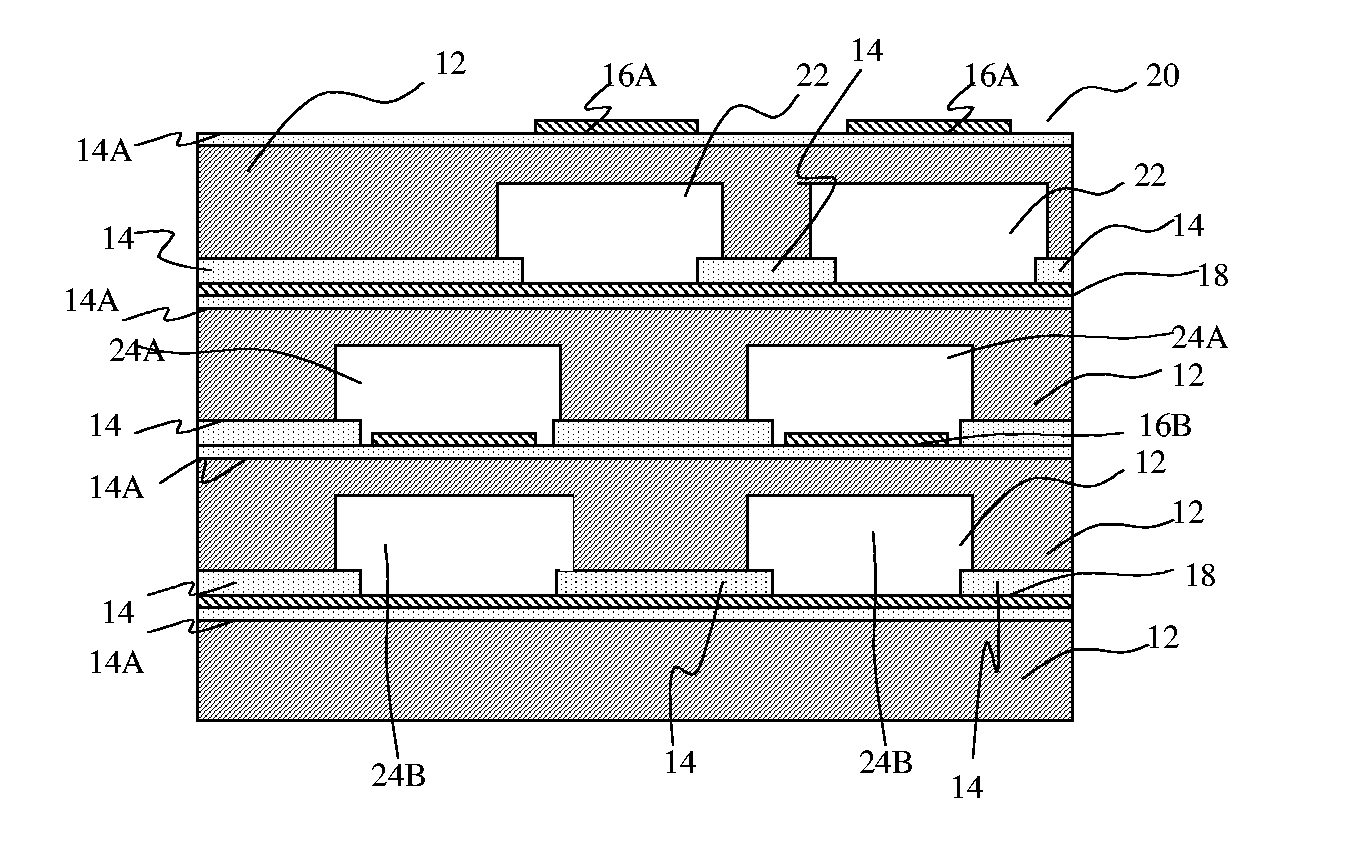

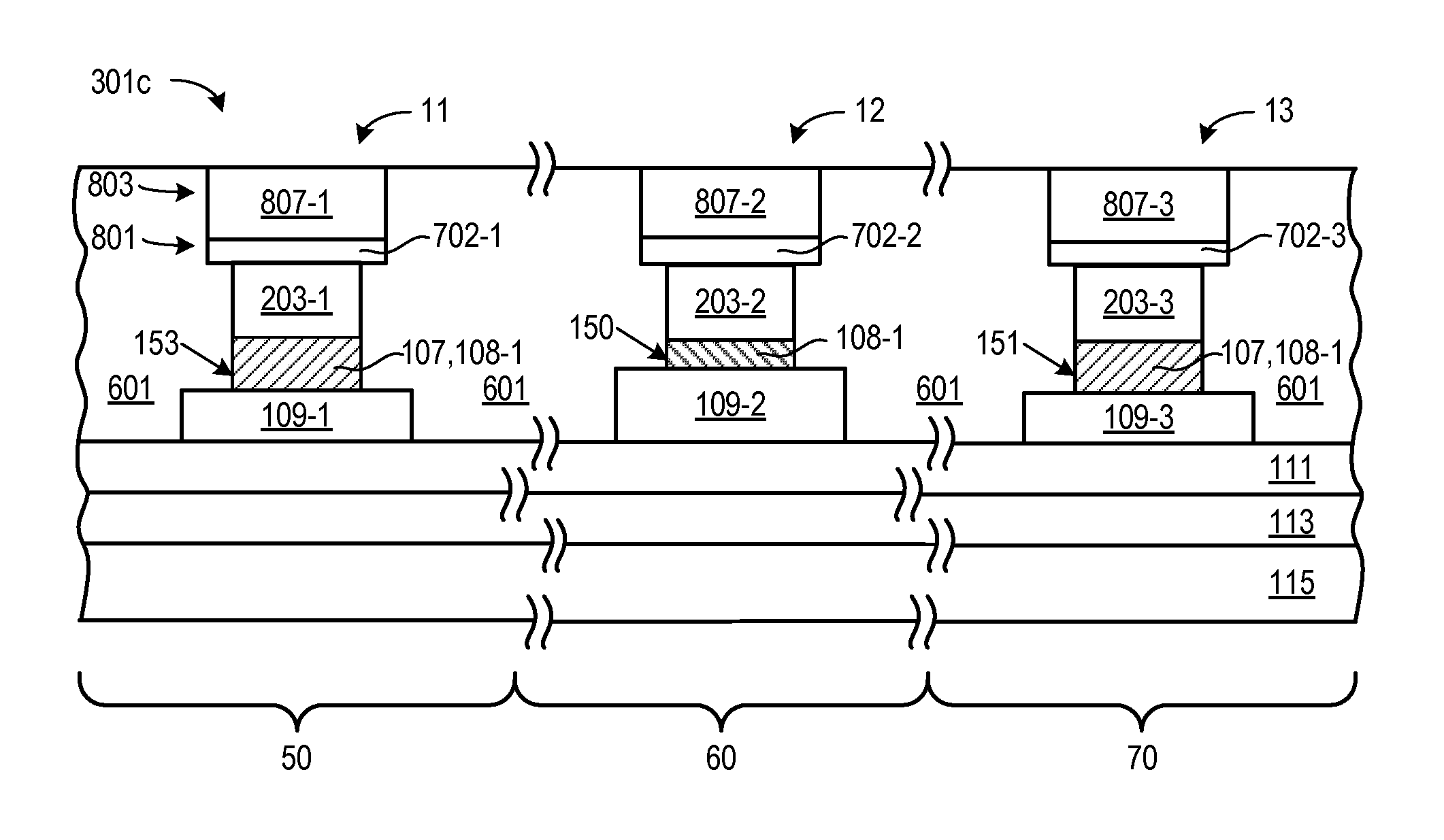

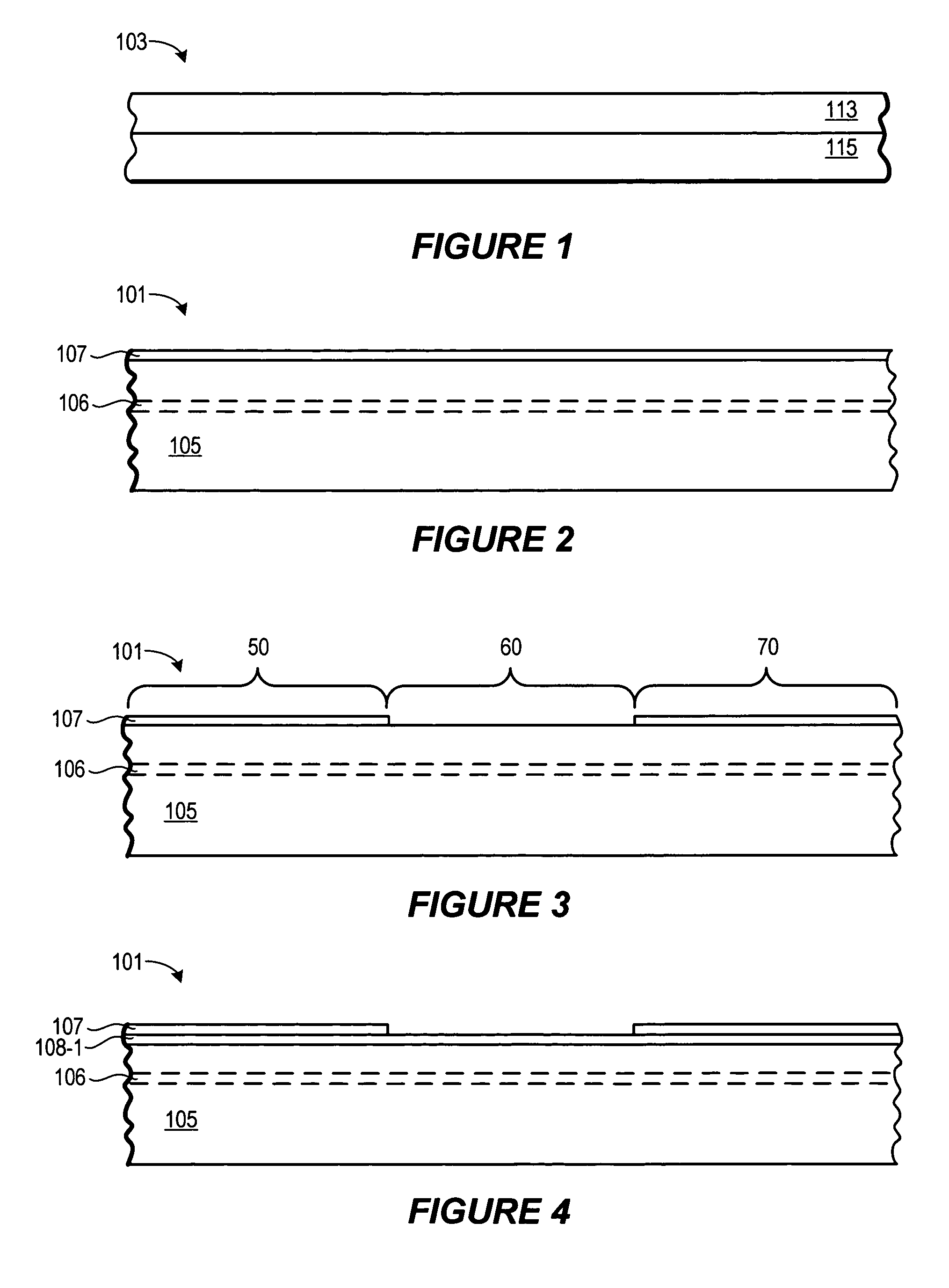

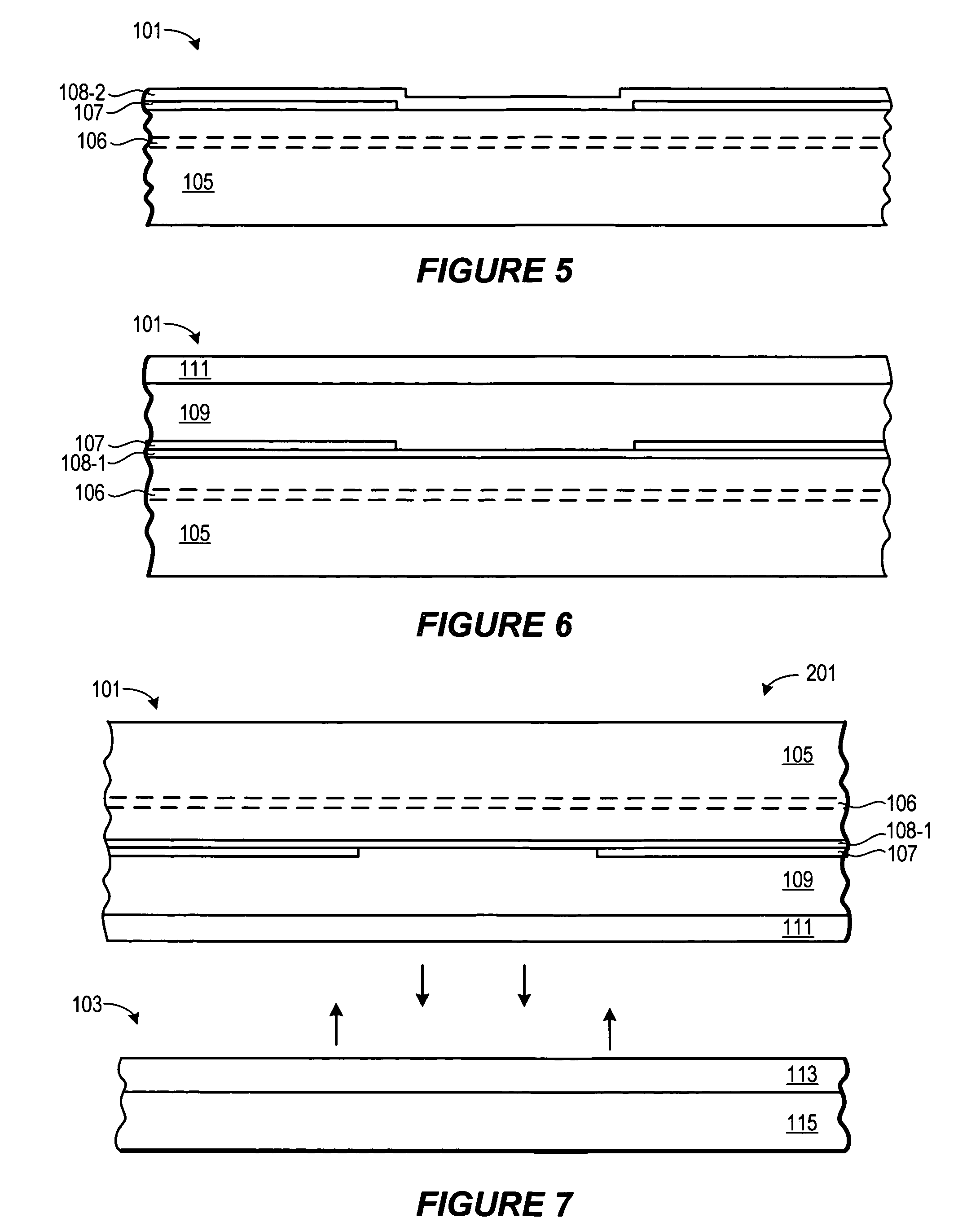

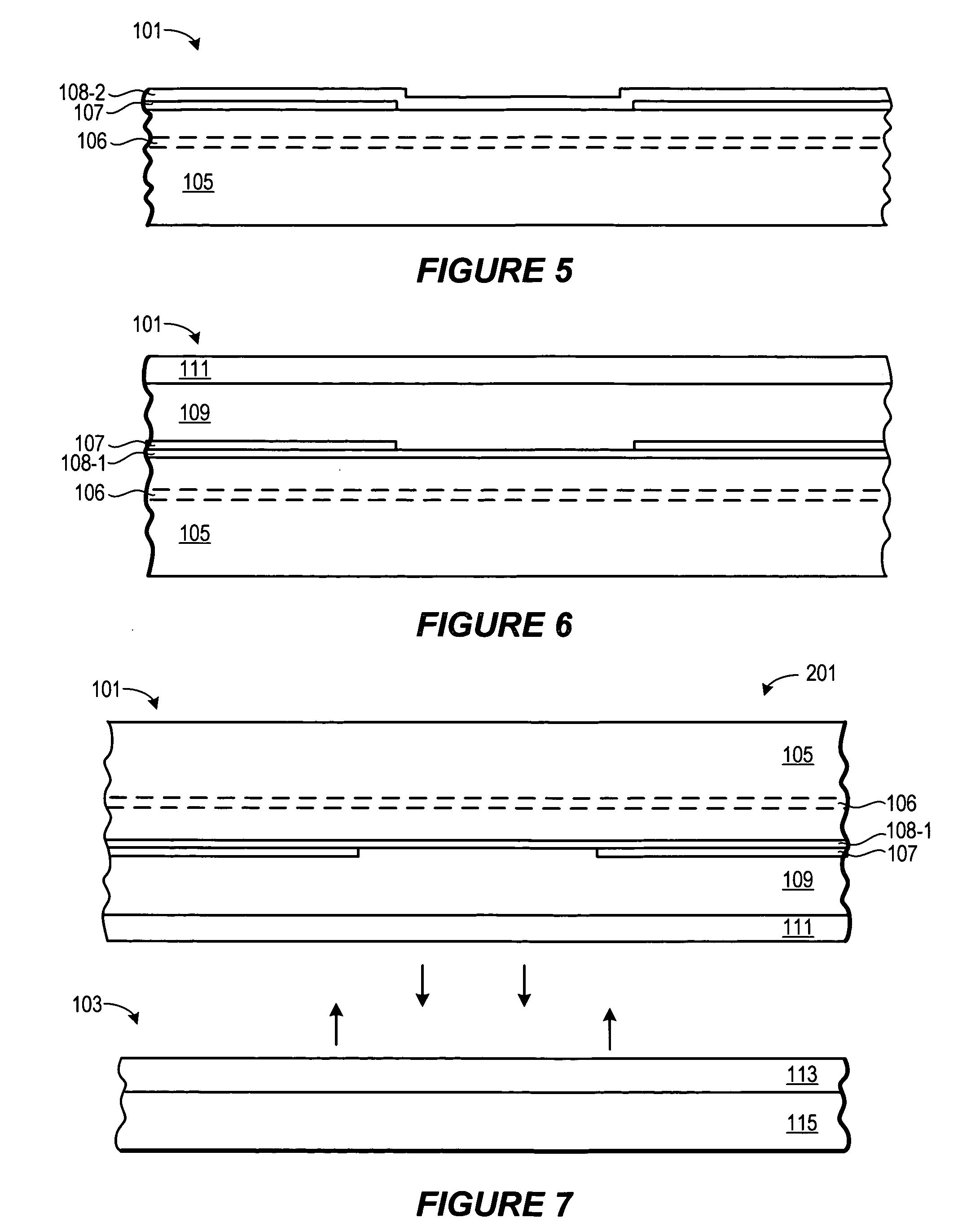

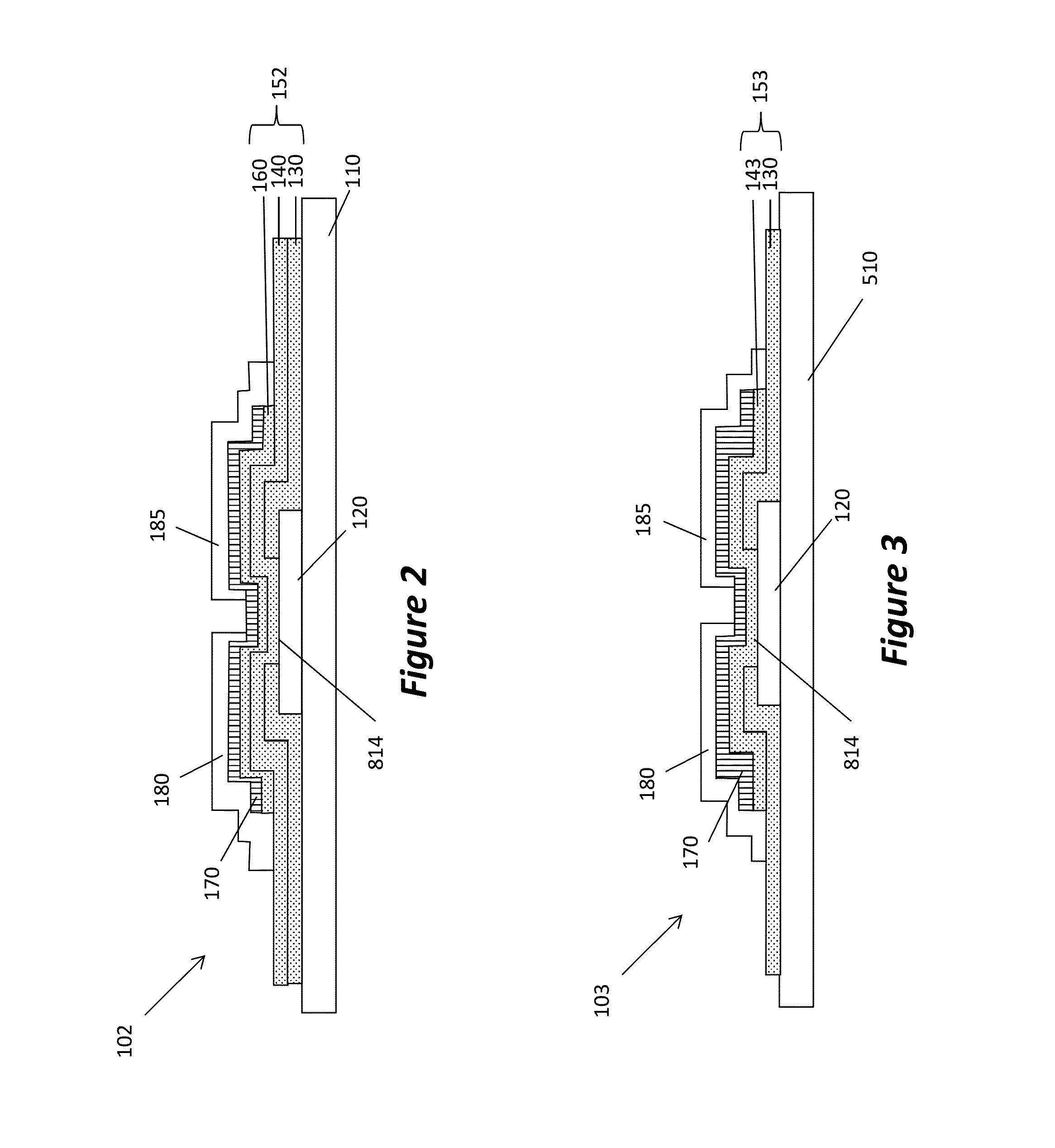

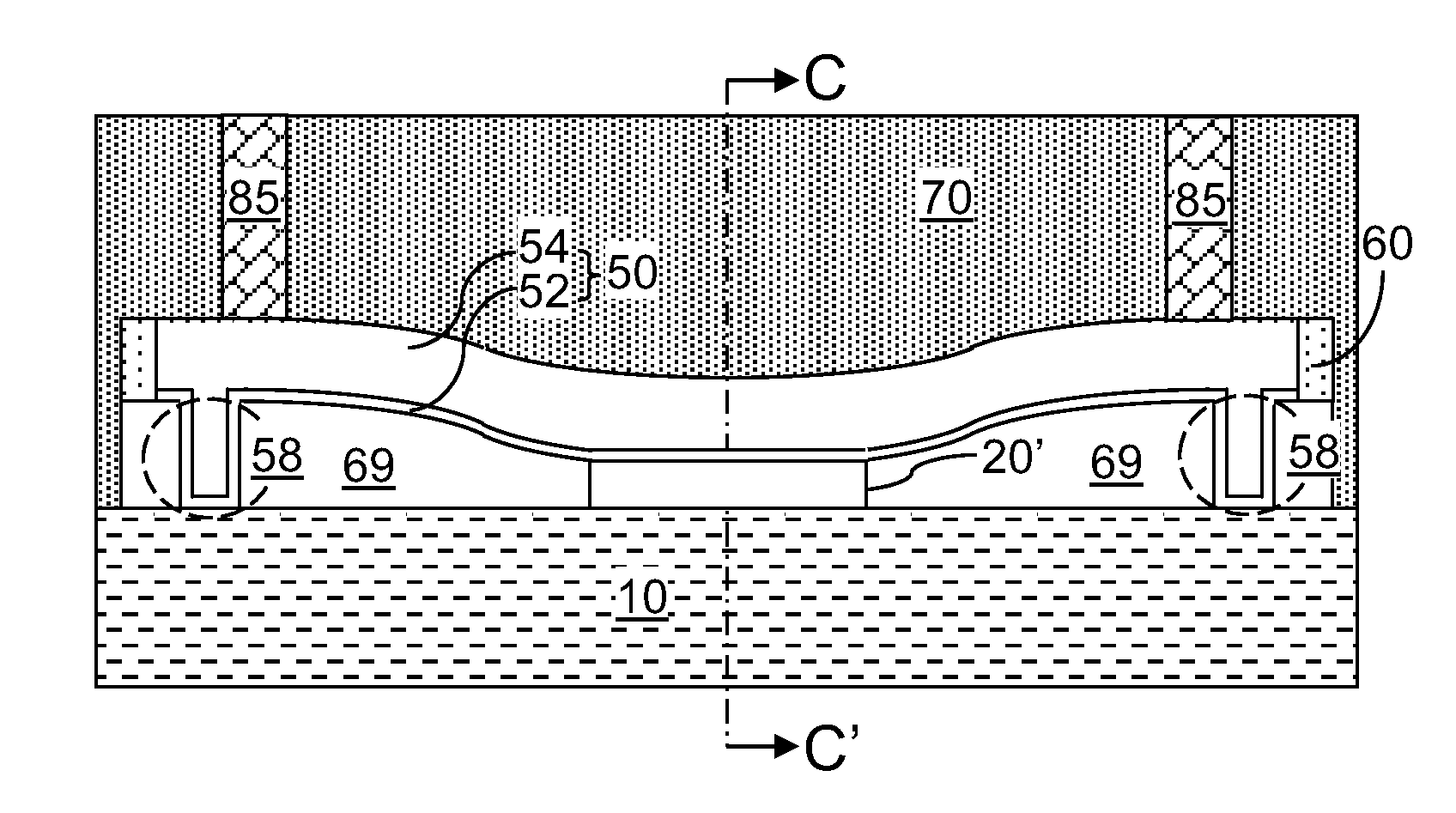

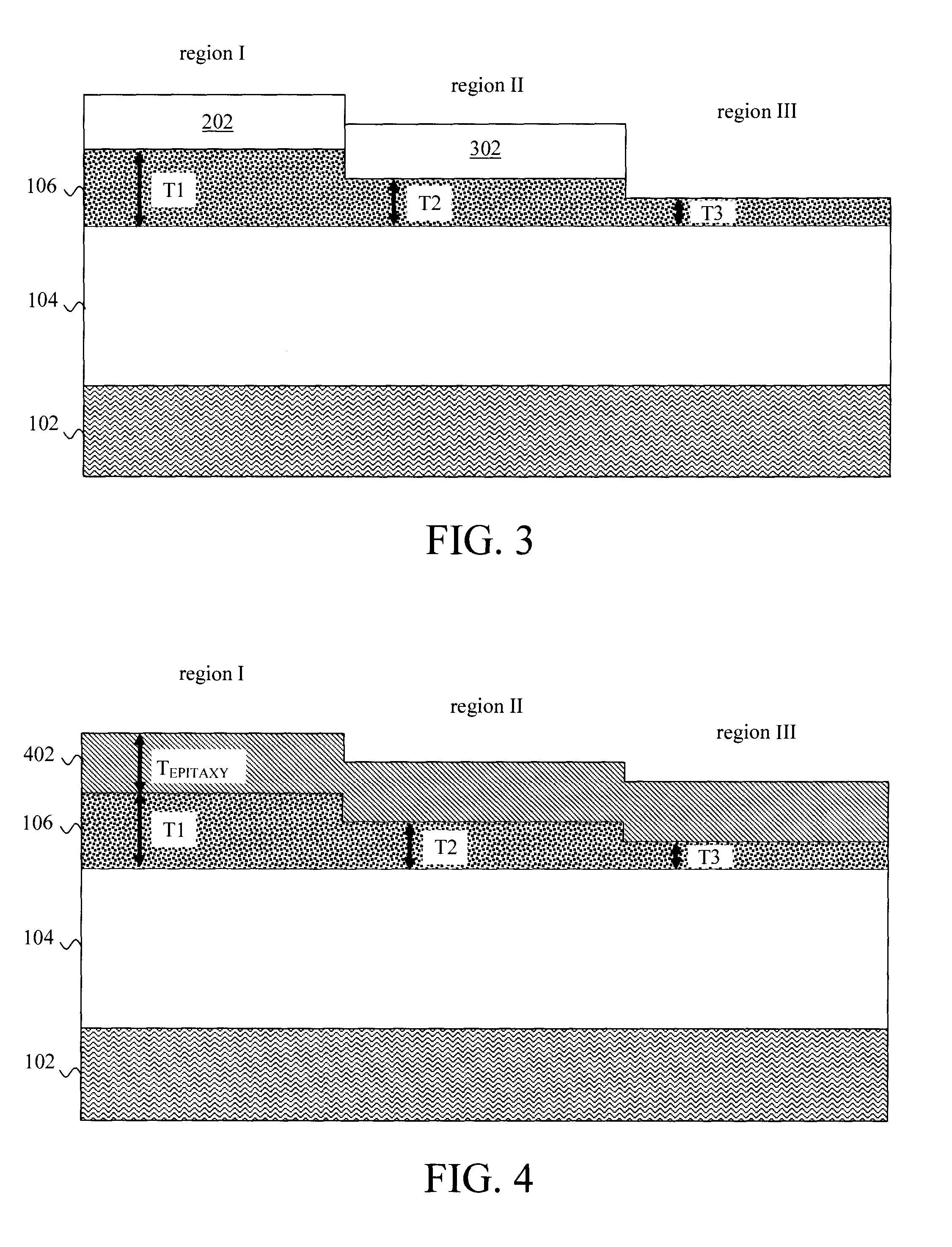

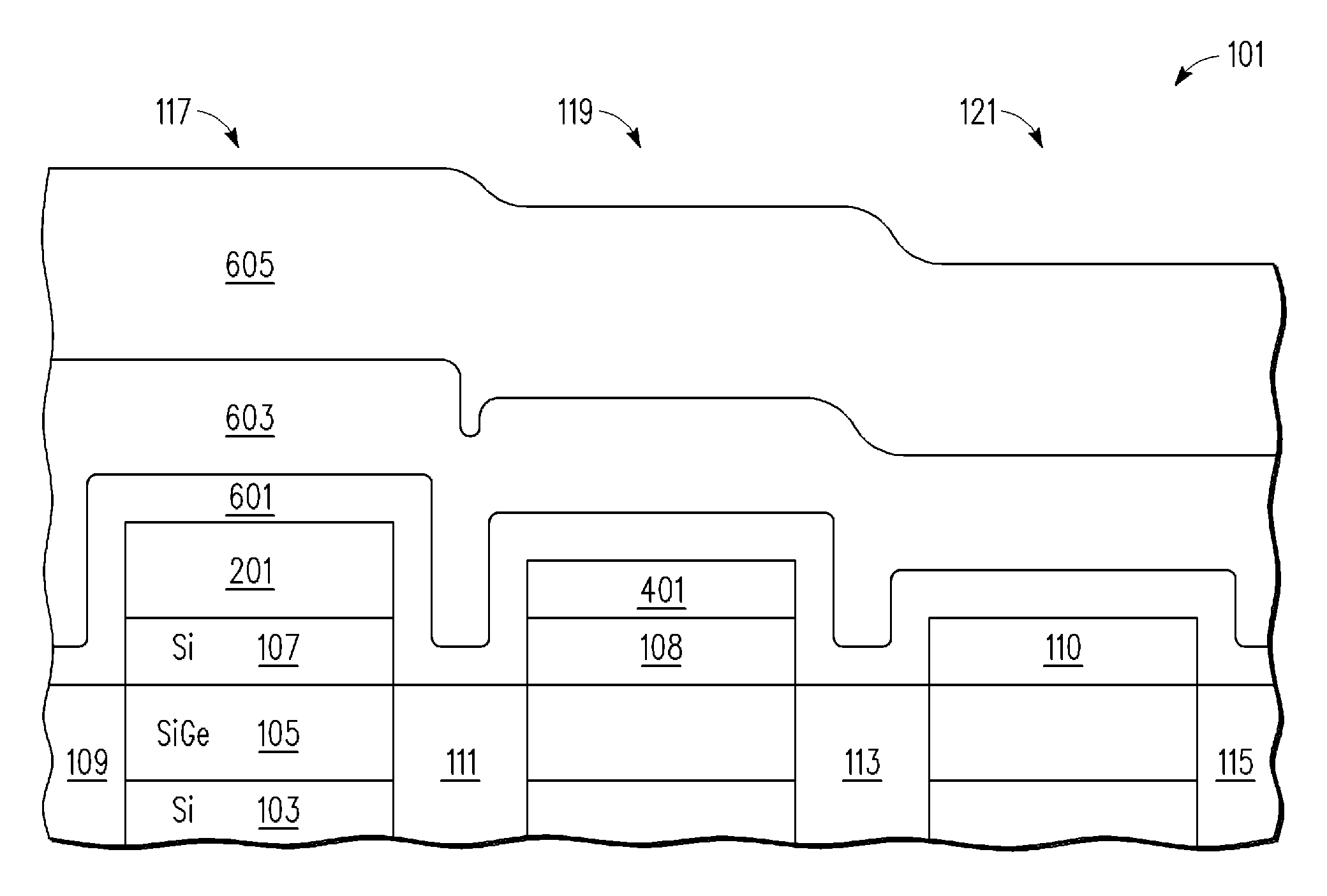

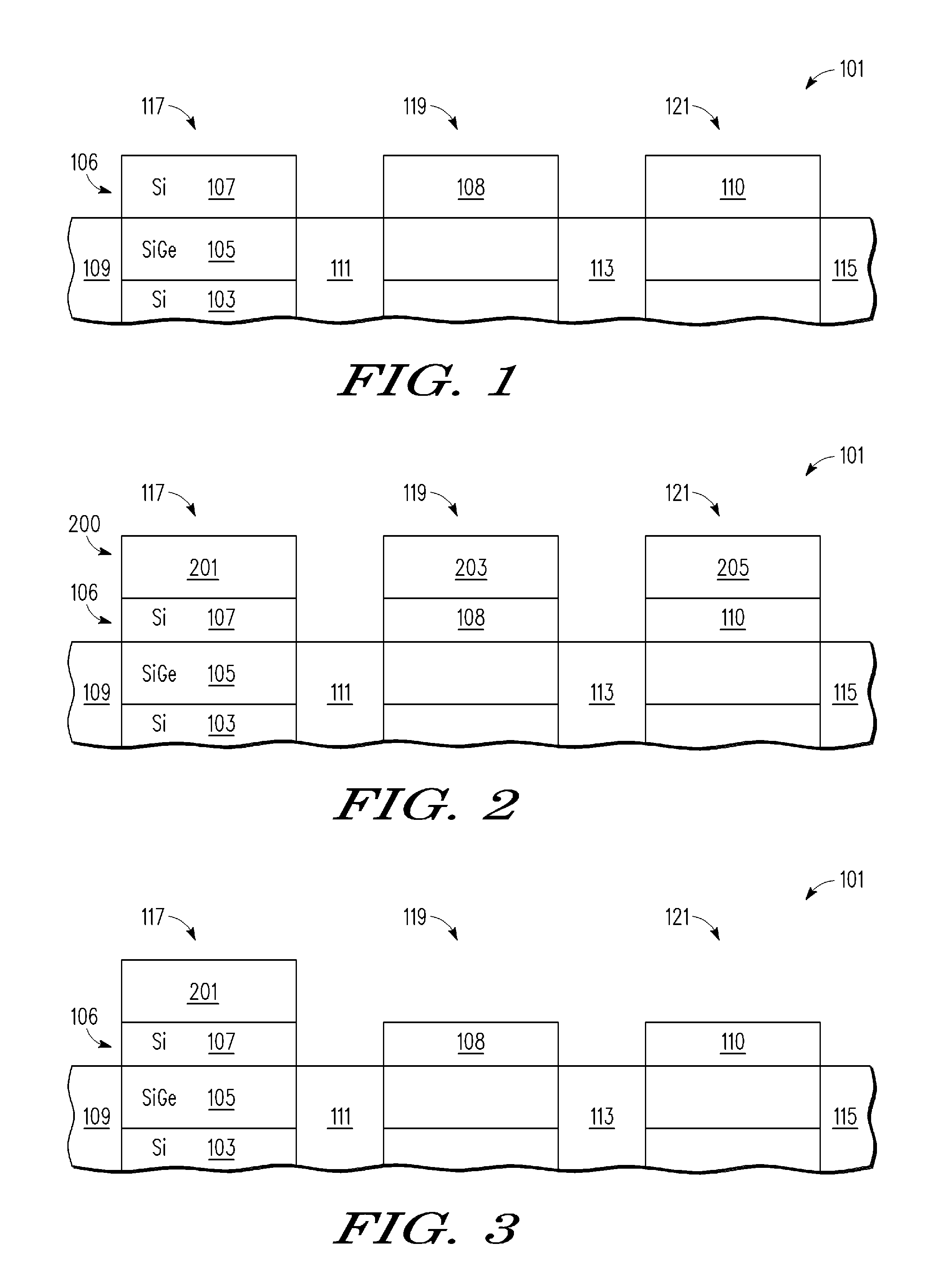

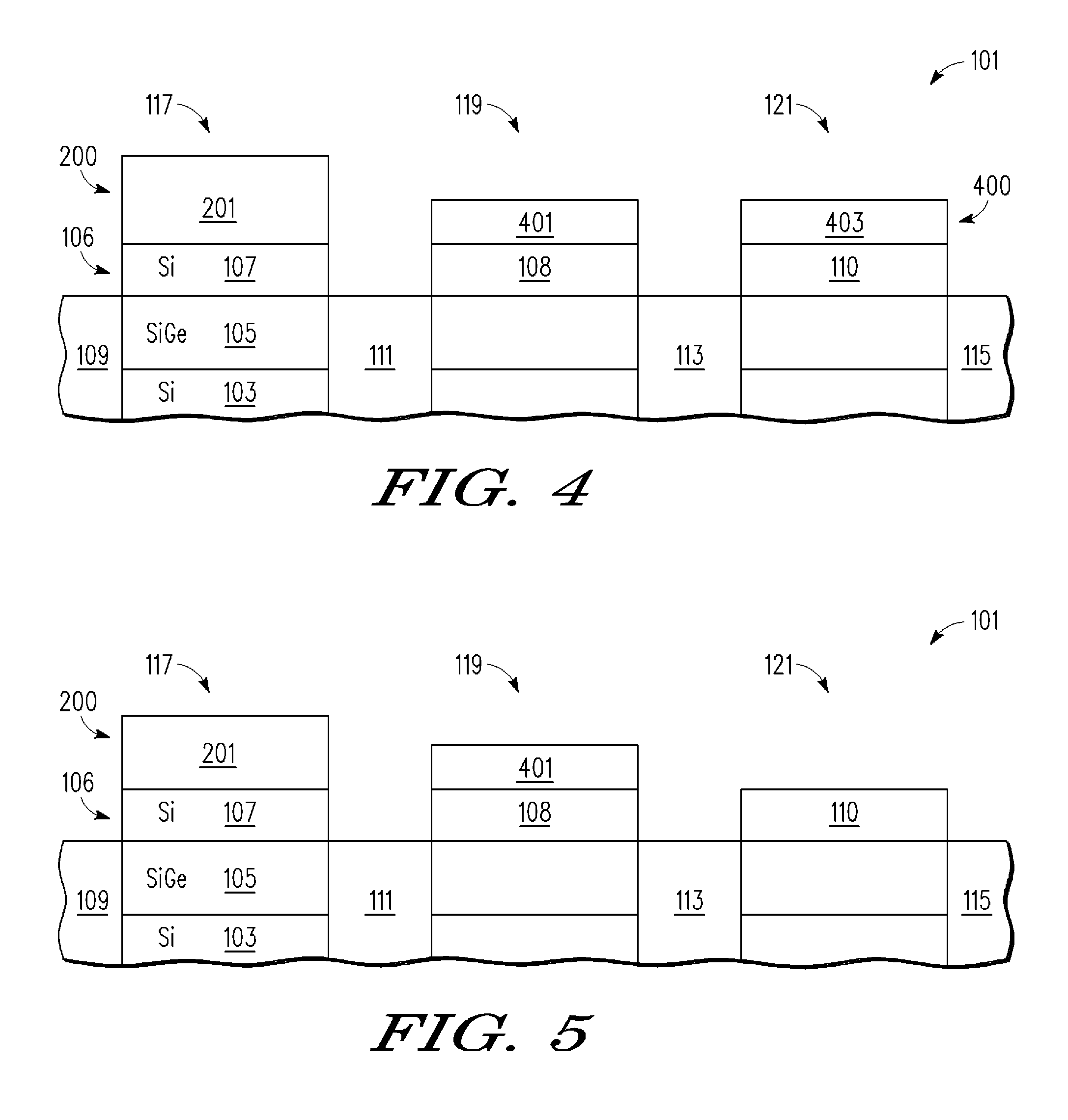

Method of forming double gate transistors having varying gate dielectric thicknesses

ActiveUS7538000B2Solid-state devicesSemiconductor/solid-state device manufacturingGate dielectricBottom gate

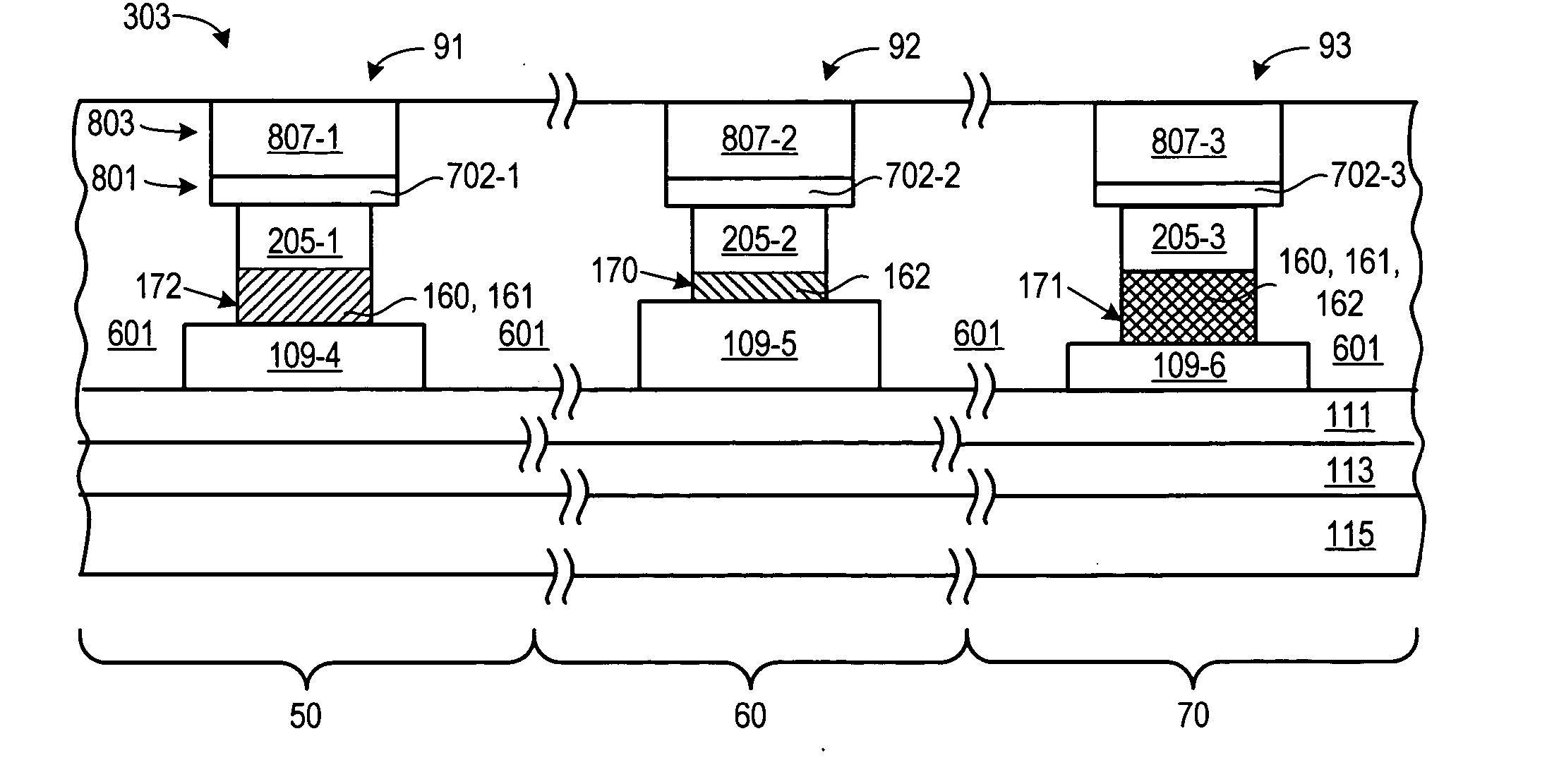

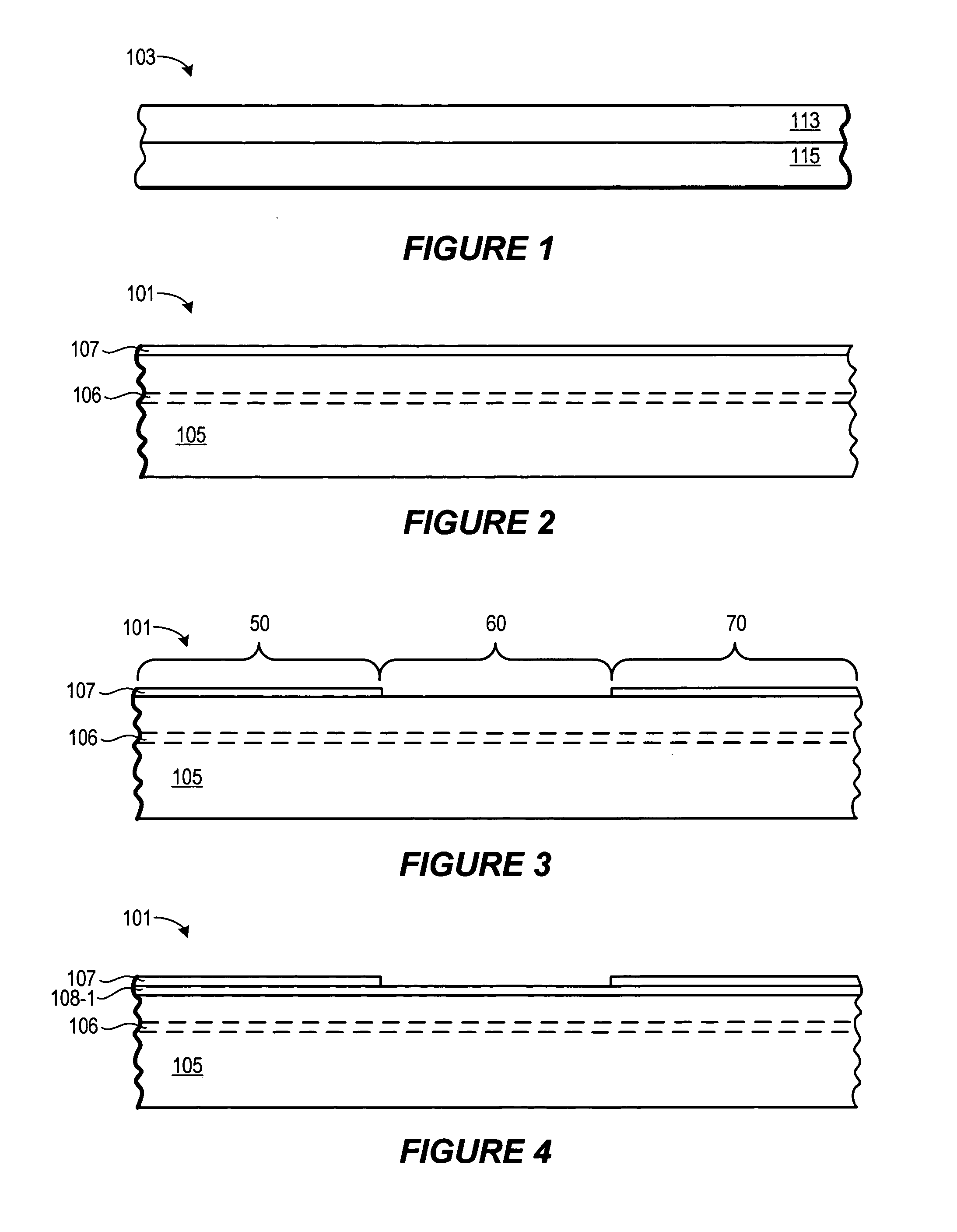

Double gate transistors (12, 13) having different bottom gate dielectric thicknesses are formed on a first wafer (101) by forming a first gate dielectric layer (107); removing part of the first gate dielectric layer (107) from a first area (60); forming a second gate dielectric layer (108) to obtain a thinner bottom gate dielectric layer (150) over the first area (60) and a thicker bottom gate dielectric layer (151) over the second area (70); and forming a planar bottom gate layer (109) over first and second gate dielectric layers. After inverting and bonding the first wafer (101) to a second wafer (103), the bottom gate electrodes (109-2, 109-3), bottom gate dielectric layers (107, 108) and channel regions (203-2, 203-3) for the first and second double gate transistors (12, 13) are selectively etched prior to formation of the top gate structures.

Owner:TAIWAN SEMICON MFG CO LTD

High-speed flex printed circuit and method of manufacturing

ActiveUS20070066126A1Reduce effective dielectric constant effective dielectricReduce effective dielectric effective dielectric lossPrinted circuit assemblingHigh frequency circuit adaptationsAdhesiveEngineering

High speed flex printed circuit boards (FLEX-PCBs) are disclosed comprising a dielectrics systems with the back-side trenches, adhesives, signal lines and ground-plans, wherein the signal line and ground-plan are located on the dielectrics. Using of the open trenches in the substrate help to reduce the microwave loss and dielectric constant and thus increasing the signal carrying speed of the interconnects. Thus, according to the present invention, it is possible to provide a simply constructed high speed FLEX-PCB using the conventional material and conventional FLEX-PCB manufacturing which facilitates the design of circuits with controlled bandwidth based on the trench opening in the dielectrics, and affords excellent connection reliability. As the effective dielectric constant is reduced, the signal width is required to make wider or the dielectric thickness is required to make thinner keeping fixed characteristics impedance. The fundamental techniques disclosed here can also be used for high-speed packaging.

Owner:BANPIL PHOTONICS

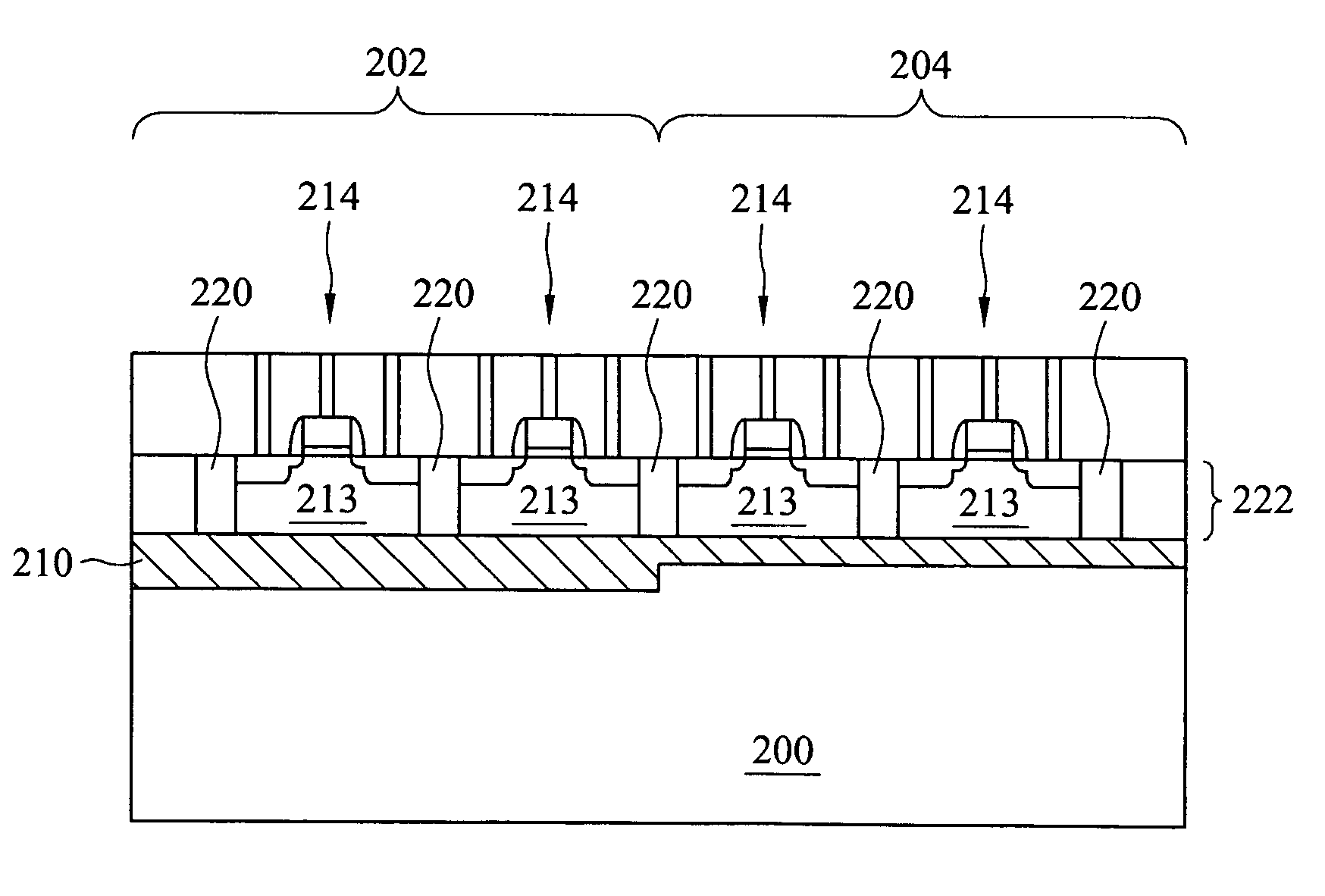

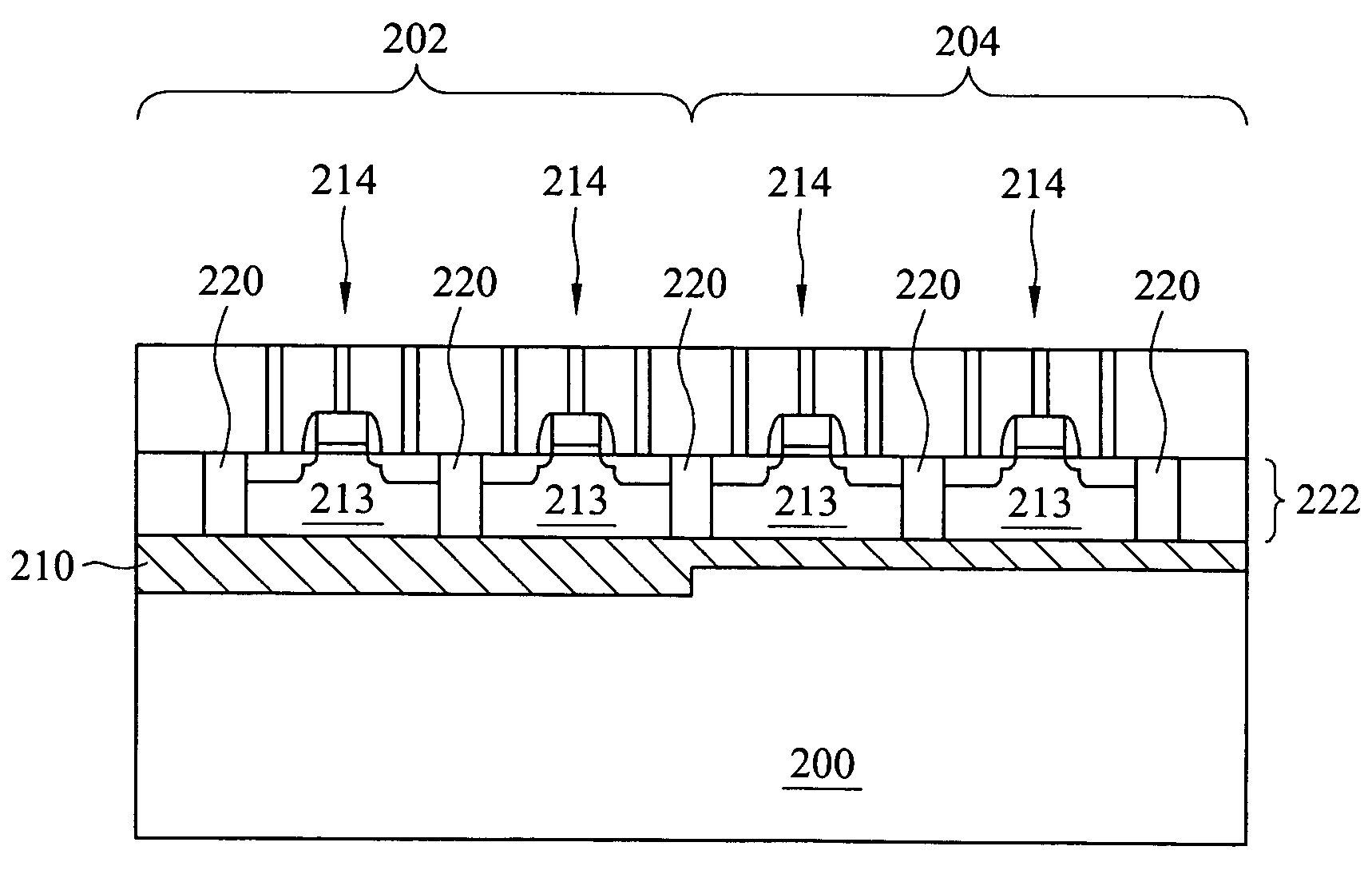

Structure and manufacturing method of multi-gate dielectric thicknesses for planar double gate device having multi-threshold voltages

Double gate transistors (12, 13) having different bottom gate dielectric thicknesses are formed on a first wafer (101) by forming a first gate dielectric layer (107); removing part of the first gate dielectric layer (107) from a first area (60); forming a second gate dielectric layer (108) to obtain a thinner bottom gate dielectric layer (150) over the first area (60) and a thicker bottom gate dielectric layer (151) over the second area (70); and forming a planar bottom gate layer (109) over first and second gate dielectric layers. After inverting and bonding the first wafer (101) to a second wafer (103), the bottom gate electrodes (109-2, 109-3), bottom gate dielectric layers (107, 108) and channel regions (203-2, 203-3) for the first and second double gate transistors (12, 13) are selectively etched prior to formation of the top gate structures.

Owner:TAIWAN SEMICON MFG CO LTD

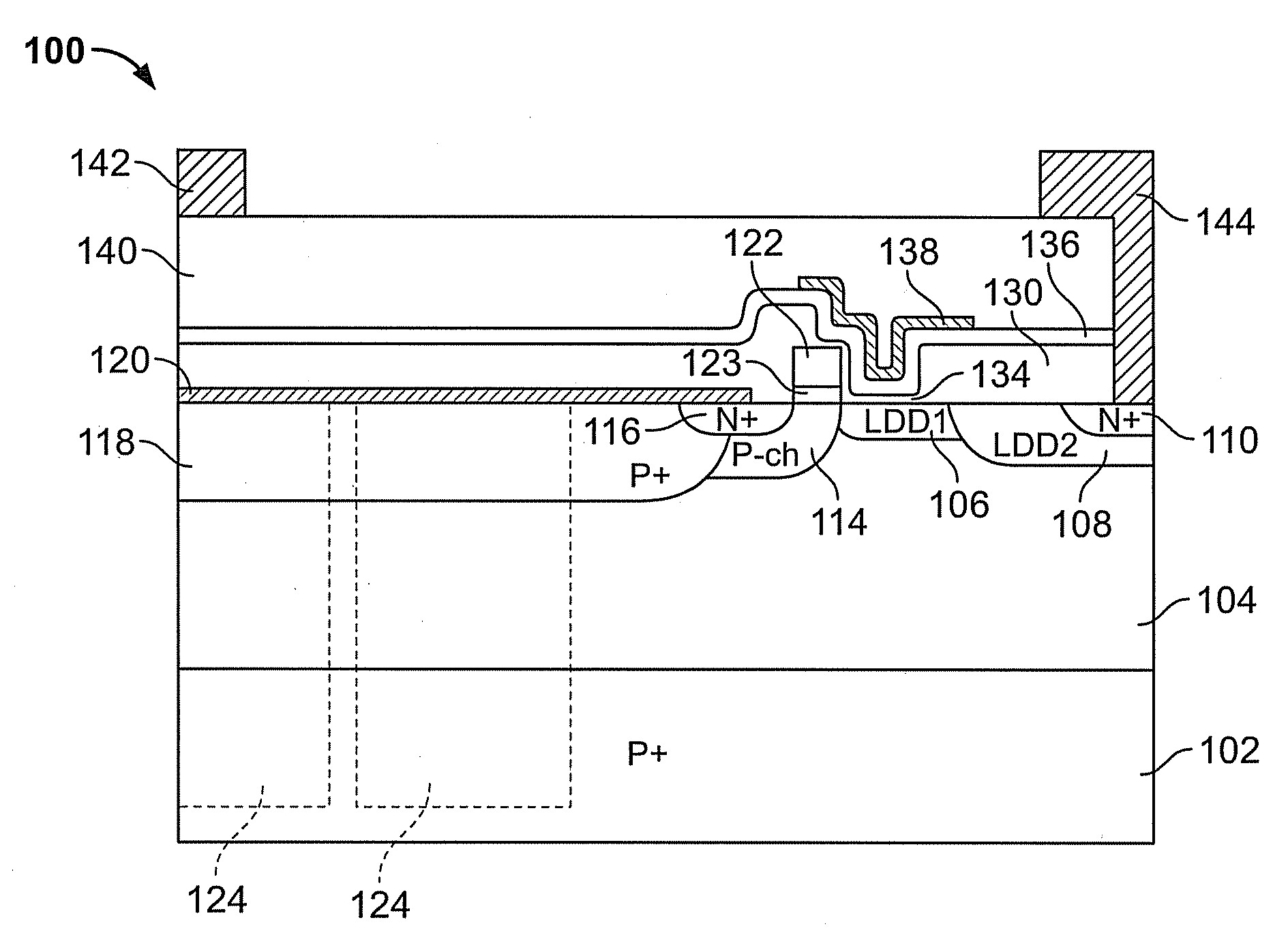

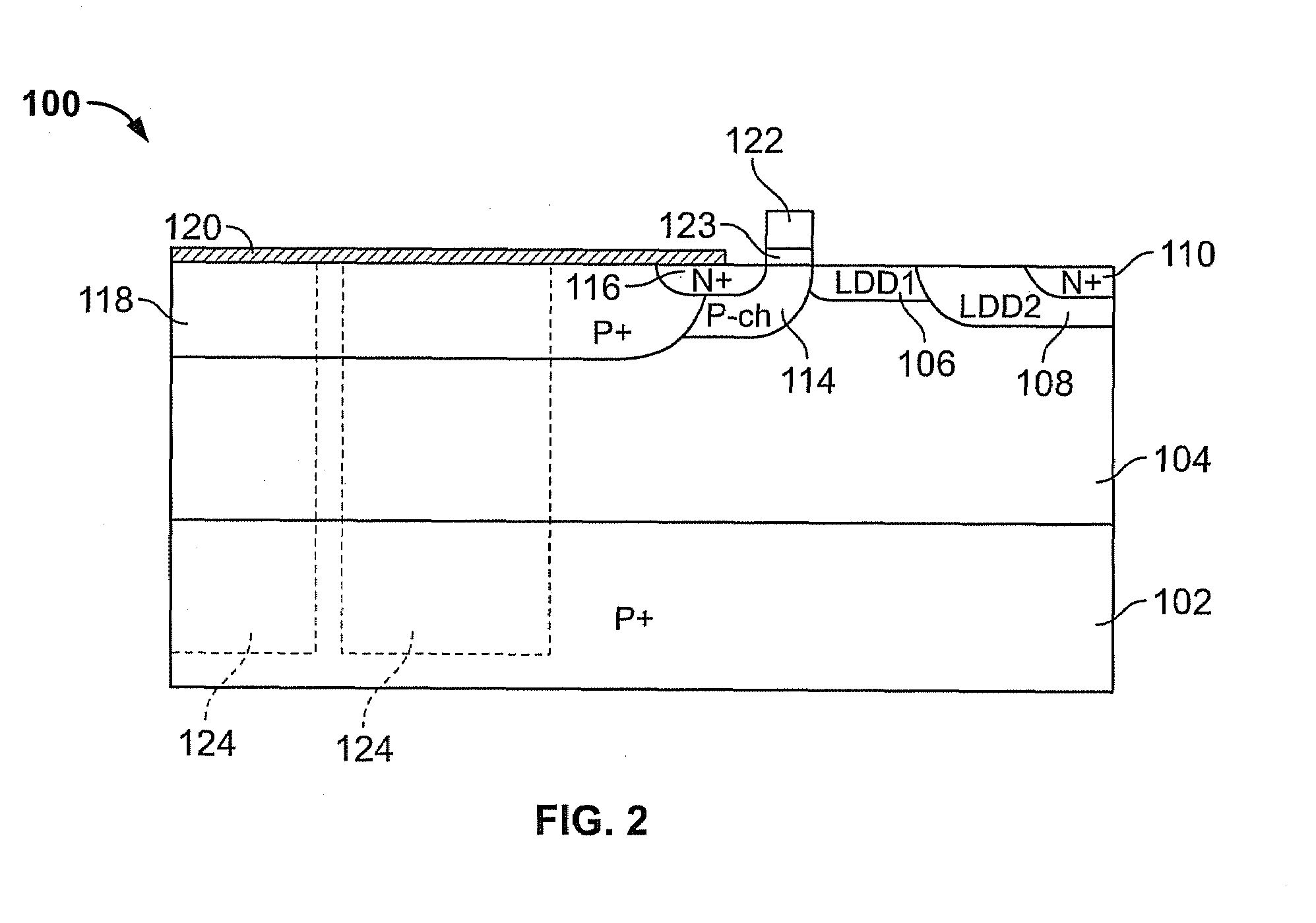

Mosfet device having dual interlevel dielectric thickness and method of making same

InactiveUS20090267145A1Reduce hot carrier injectionReduce injectionSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETDielectric layer

A method of forming a metal-oxide-semiconductor (MOS) device includes the following steps: forming a semiconductor layer of a first conductivity type having source and drain regions of a second conductivity type, a channel region and a lightly-doped drain region formed therein; forming a gate over the channel region proximate an upper surface of the semiconductor layer; after the forming steps, depositing a first dielectric layer having a first thickness over an upper surface of the semiconductor layer; etching the first dielectric layer in a region over the lightly-doped drain proximate to the gate to reduce its thickness; conformably depositing a second dielectric layer having a second thickness over the first dielectric layer, including in the etched region, the second thickness being less than the first thickness; and forming a shielding electrode over the second dielectric layer.

Owner:CICLON SEMICON DEVICE

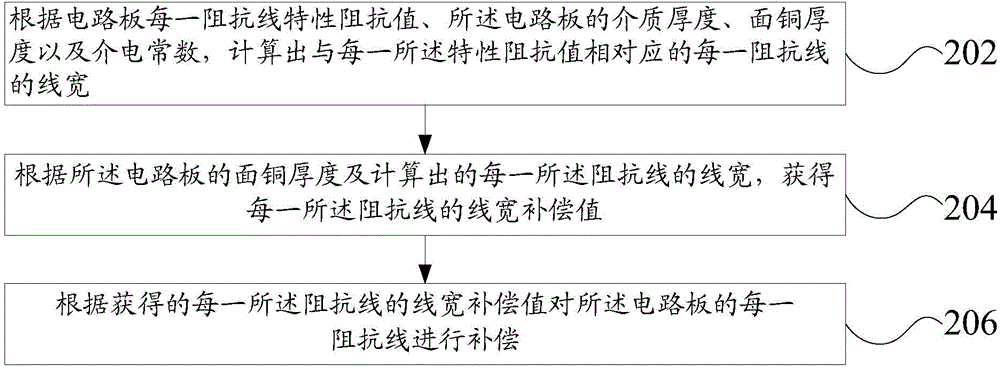

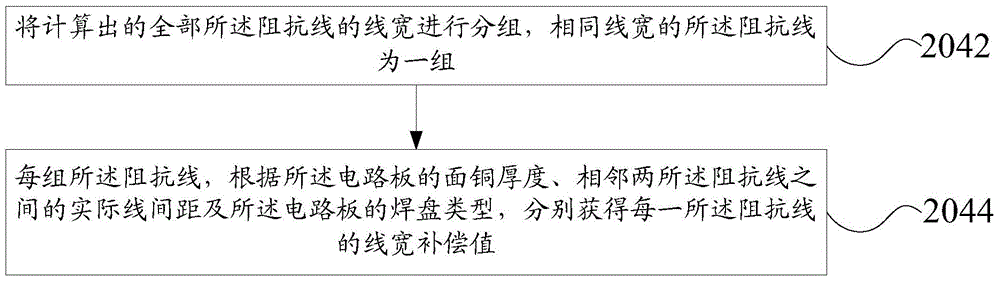

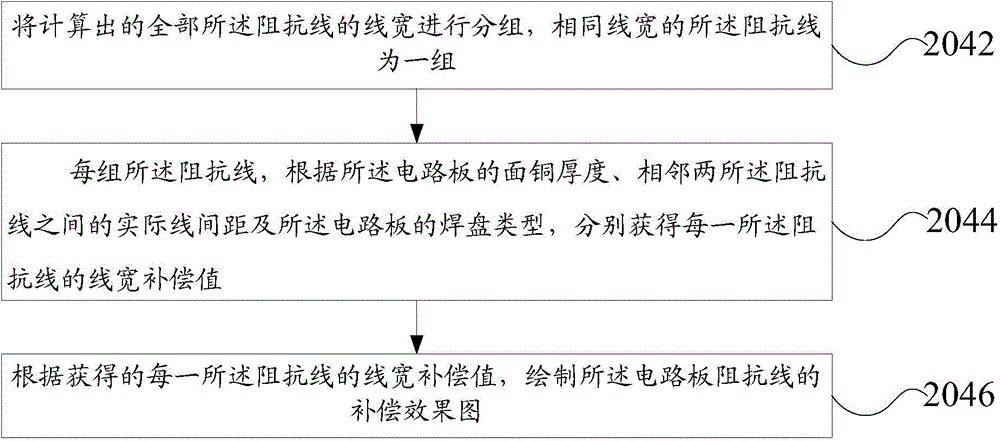

Circuit board impedance line compensation method and device

ActiveCN104470212AAvoid situations where the transmitted signal is distortedEasy to operateHigh frequency circuit adaptationsComputer designed circuitsEngineeringCharacteristic impedance

The invention provides a circuit board impedance line compensation method and device. The circuit board impedance line compensation method includes the following steps that 202, the line width of each impedance line corresponding to each characteristic impedance value is calculated according to the characteristic impedance value of each impedance line of a circuit board, the dielectric thickness of the circuit board, the thickness of face copper and a dielectric constant; 204, the line width compensation value of each impedance line is obtained according to the thickness of the face copper of the circuit board and the calculated line width of each impedance line; 206, compensation is conducted on the impedance lines of the circuit board according to the obtained line width compensation value of each impedance line. According to the circuit board impedance line compensation method, the corresponding line width compensation values of all the impedance lines can be obtained at the same time, the circuit board compensation device can be used for fast conducting compensation on the line widths of all the impedance lines of the circuit board, and the production efficiency is improved effectively.

Owner:ZHUHAI FOUNDER TECH HI DENSITY ELECTRONICS +1

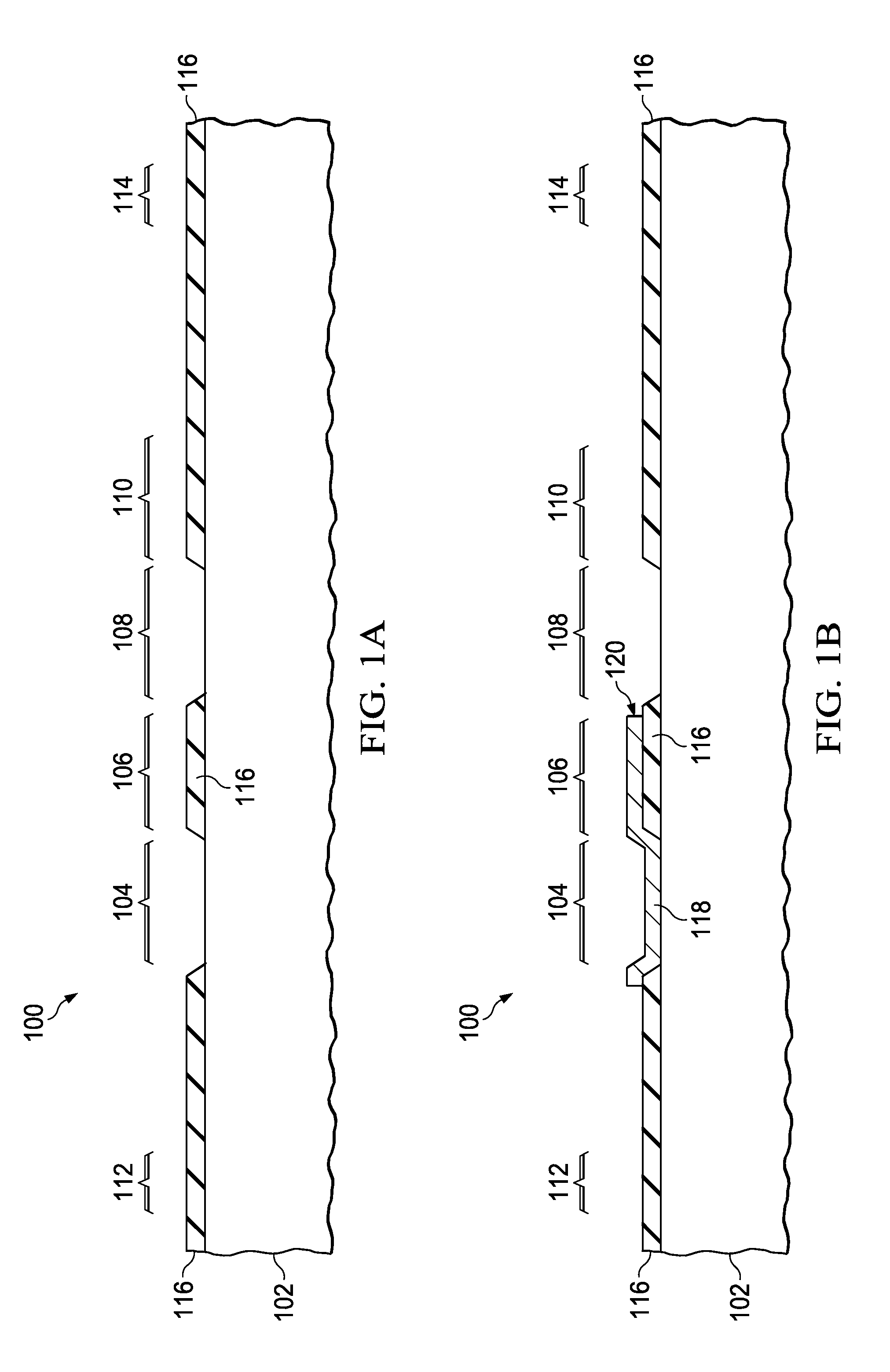

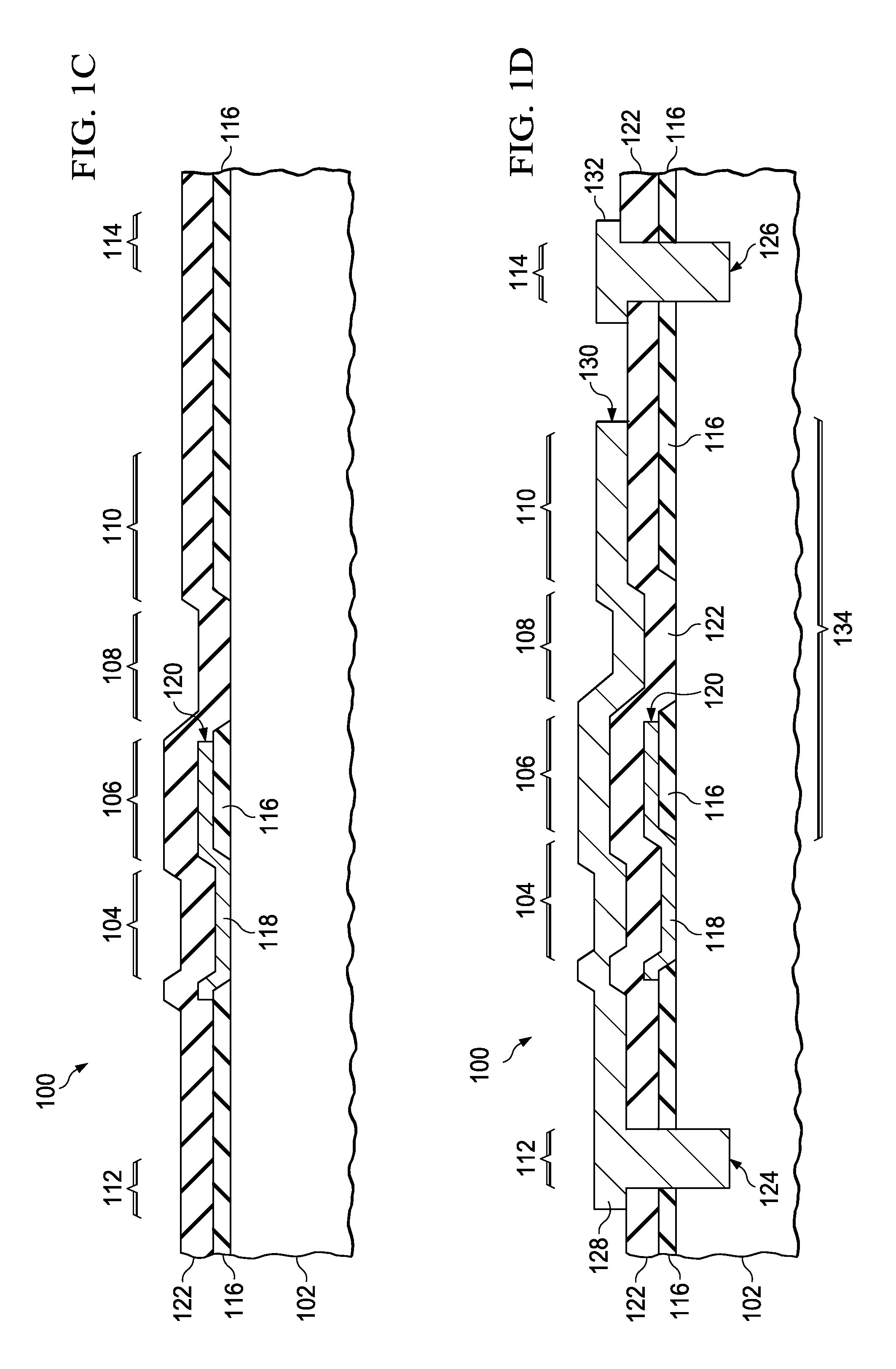

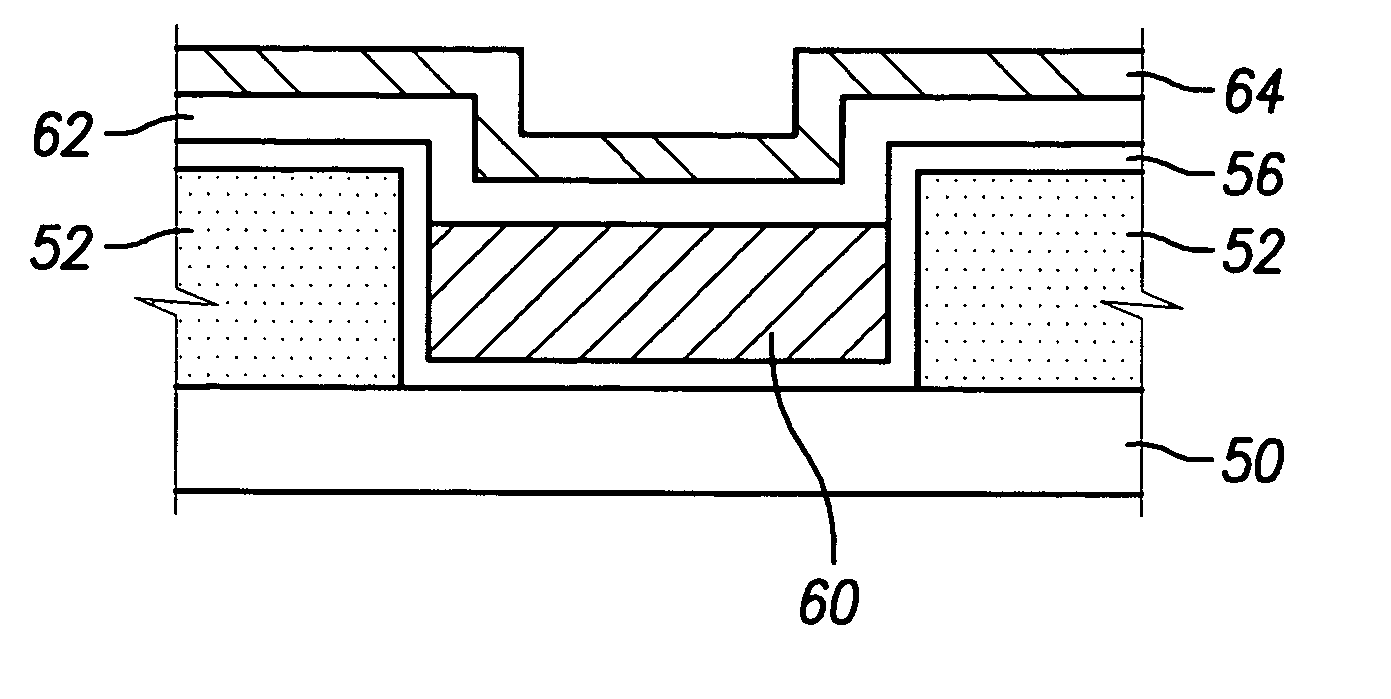

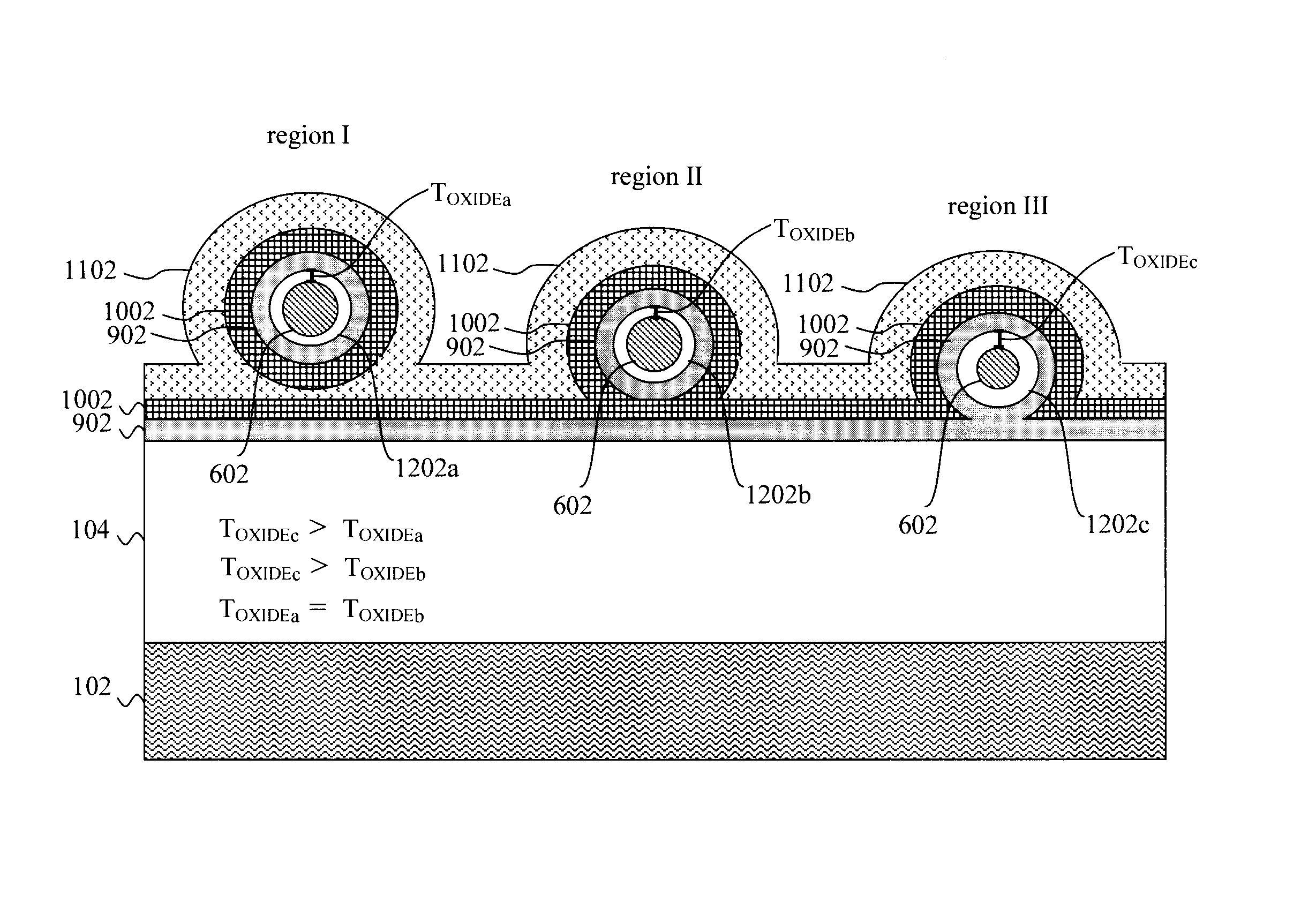

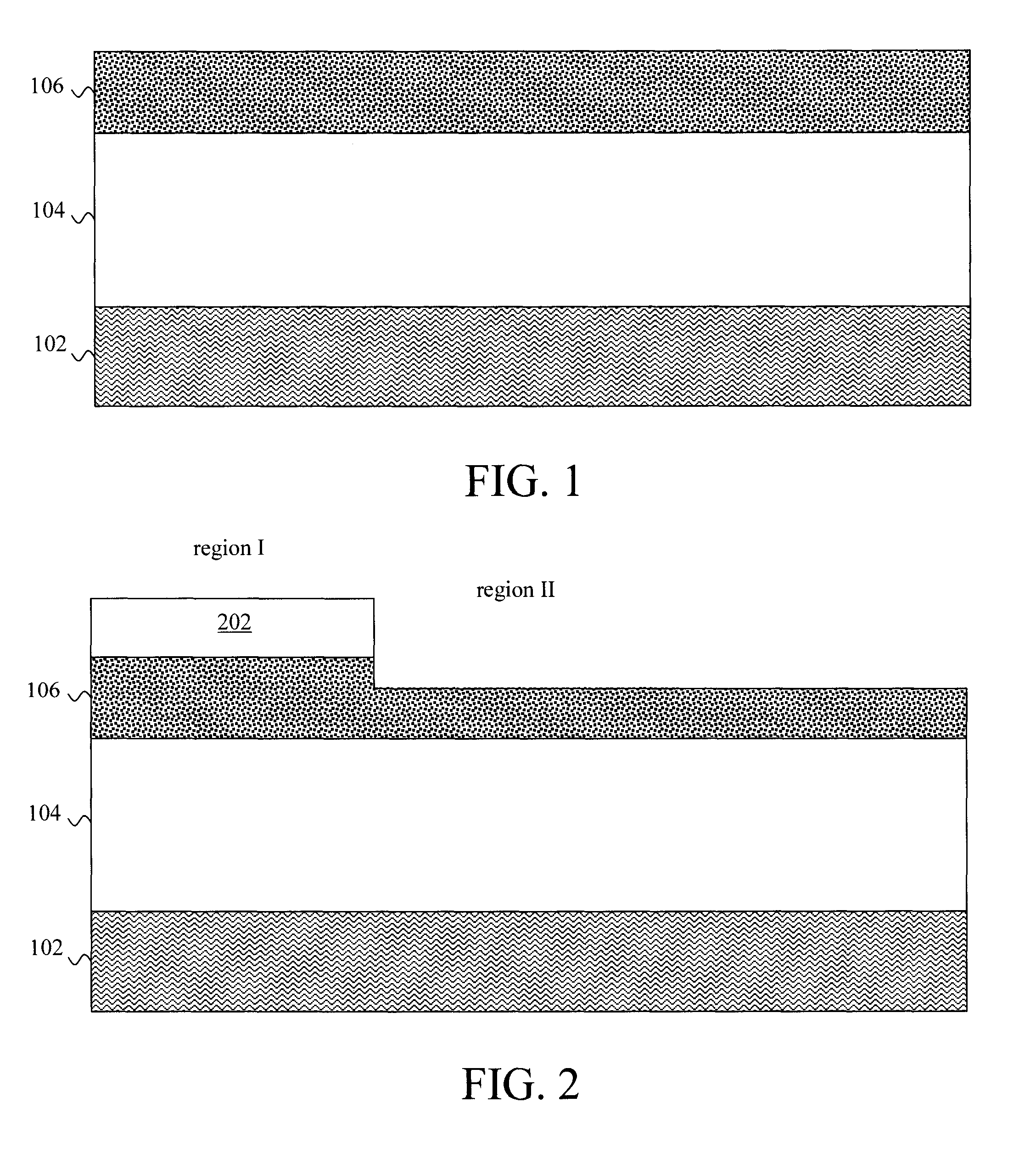

Stepped dielectric for field plate formation

ActiveUS8829613B1Semiconductor/solid-state device manufacturingSemiconductor devicesDielectric layerSemiconductor

A semiconductor device is formed with a stepped field plate over at least three sequential regions in which a total dielectric thickness under the stepped field plate is at least 10 percent thicker in each region compared to the preceding region. The total dielectric thickness in each region is uniform. The stepped field plate is formed over at least two dielectric layers, of which at least all but one dielectric layer is patterned so that at least a portion of a patterned dielectric layer is removed in one or more regions of the stepped field plate.

Owner:TEXAS INSTR INC

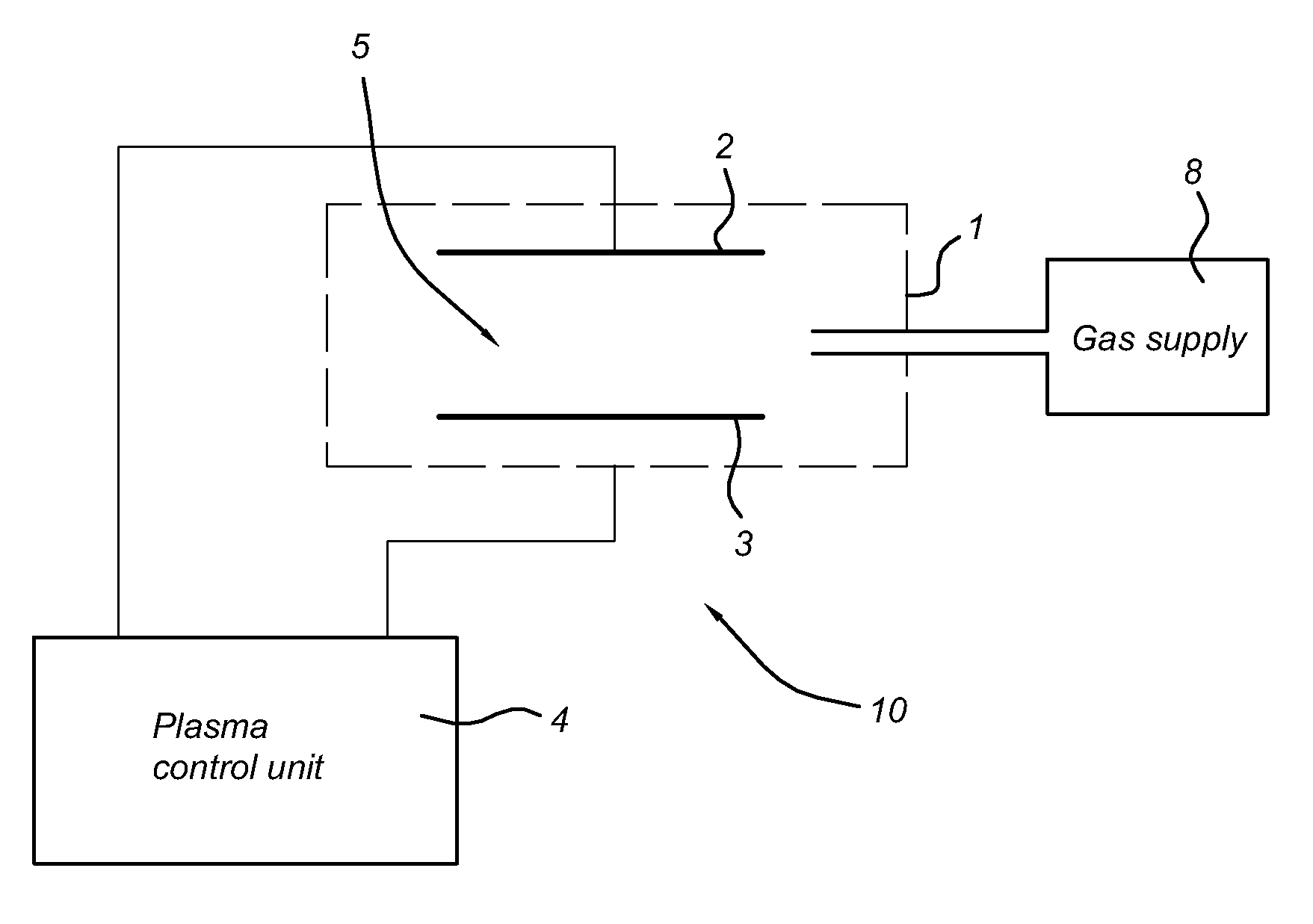

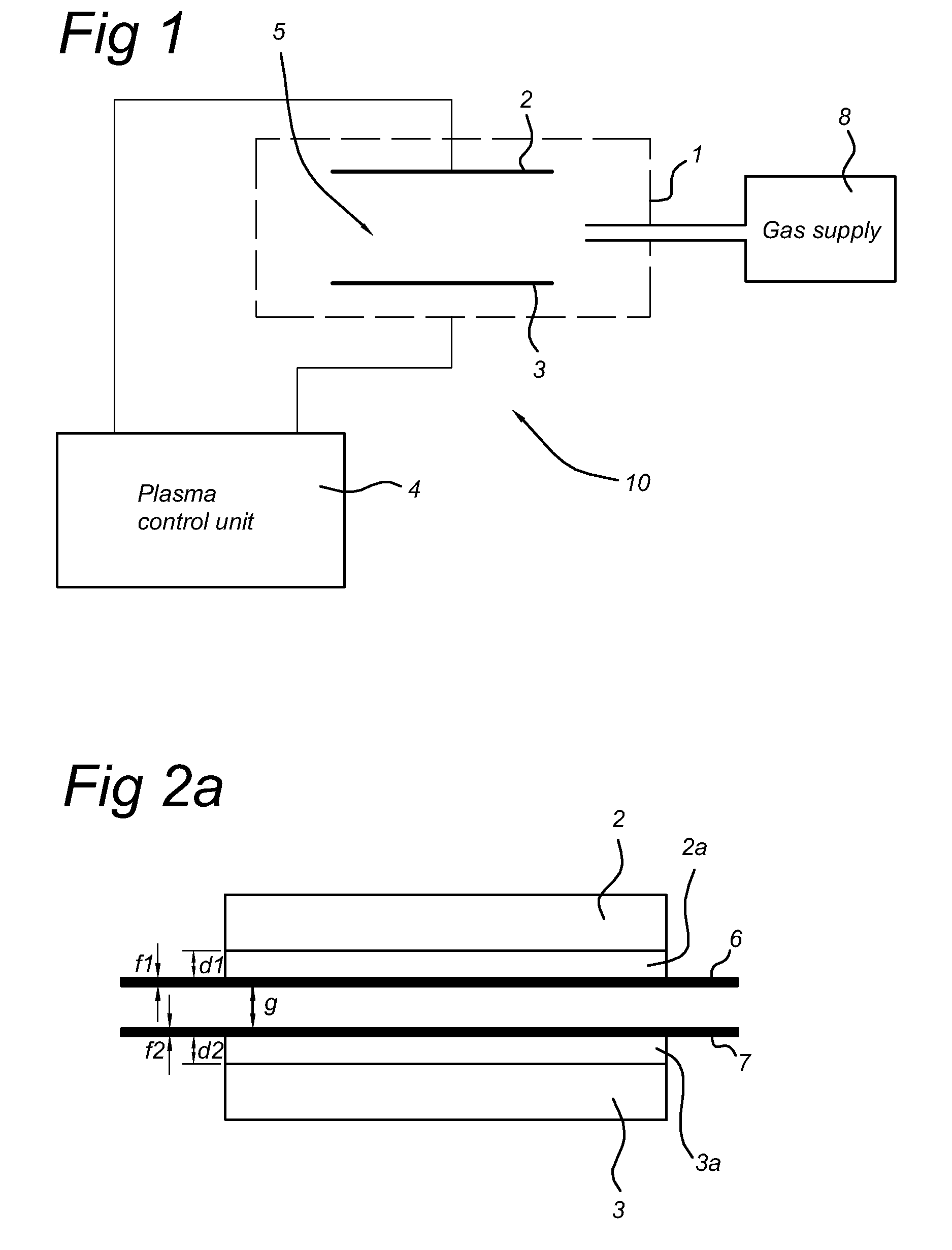

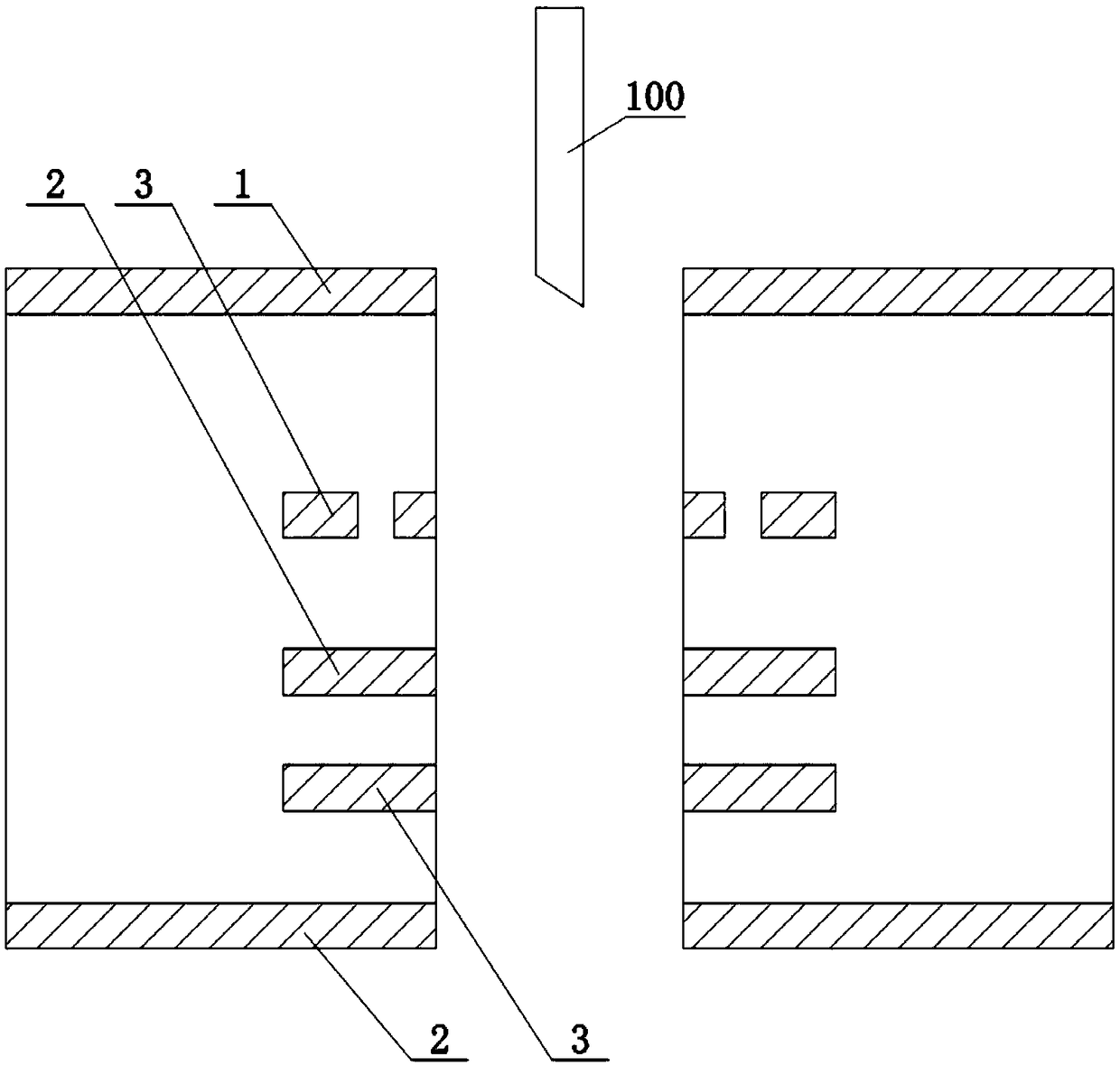

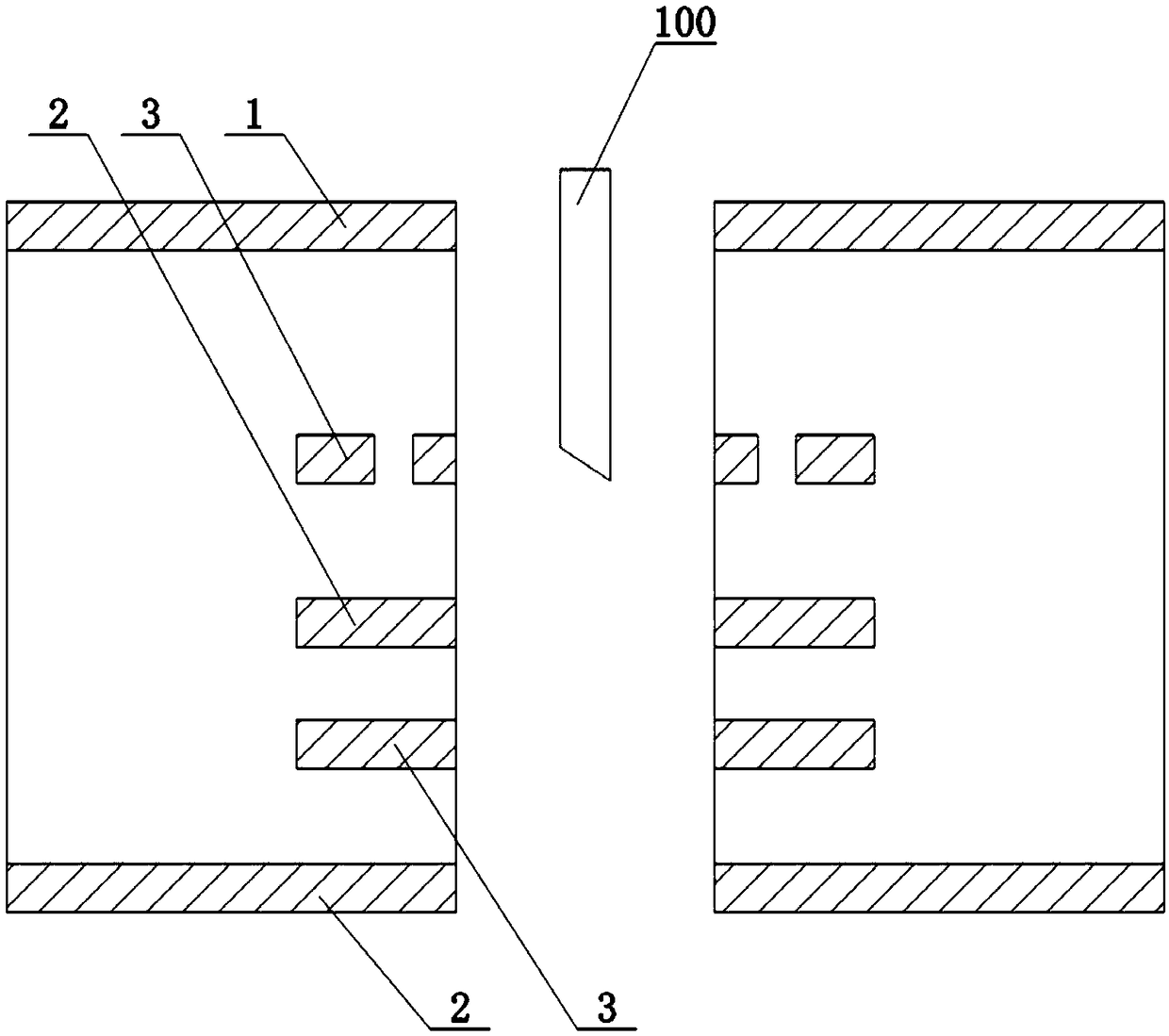

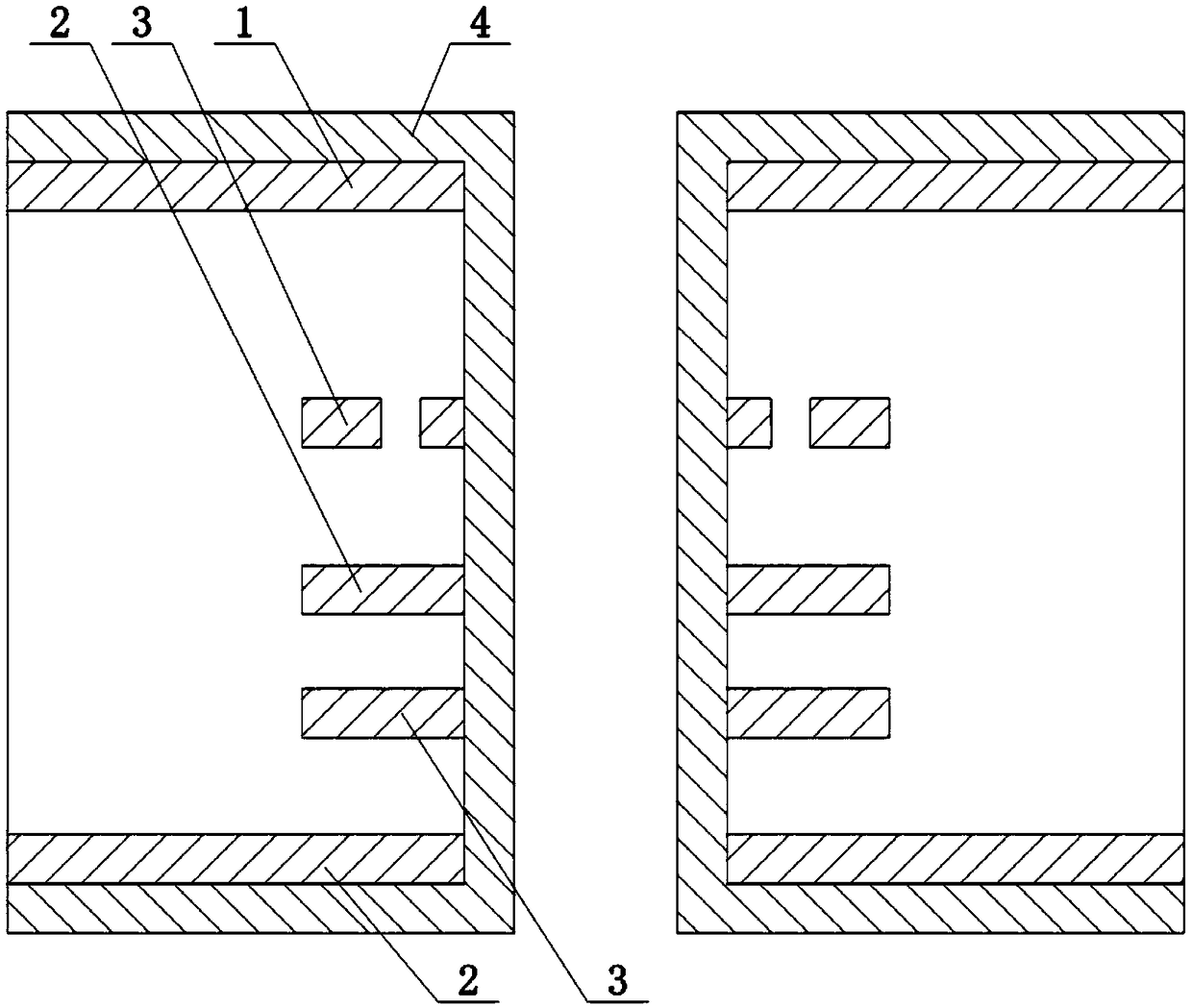

Plasma treatment apparatus and method for treatment of a substrate with atmospheric pressure glow discharge electrode configuration

InactiveUS20110014424A1Increase plasma stabilityImprove stabilityElectric discharge tubesLayered productsFree distanceEngineering

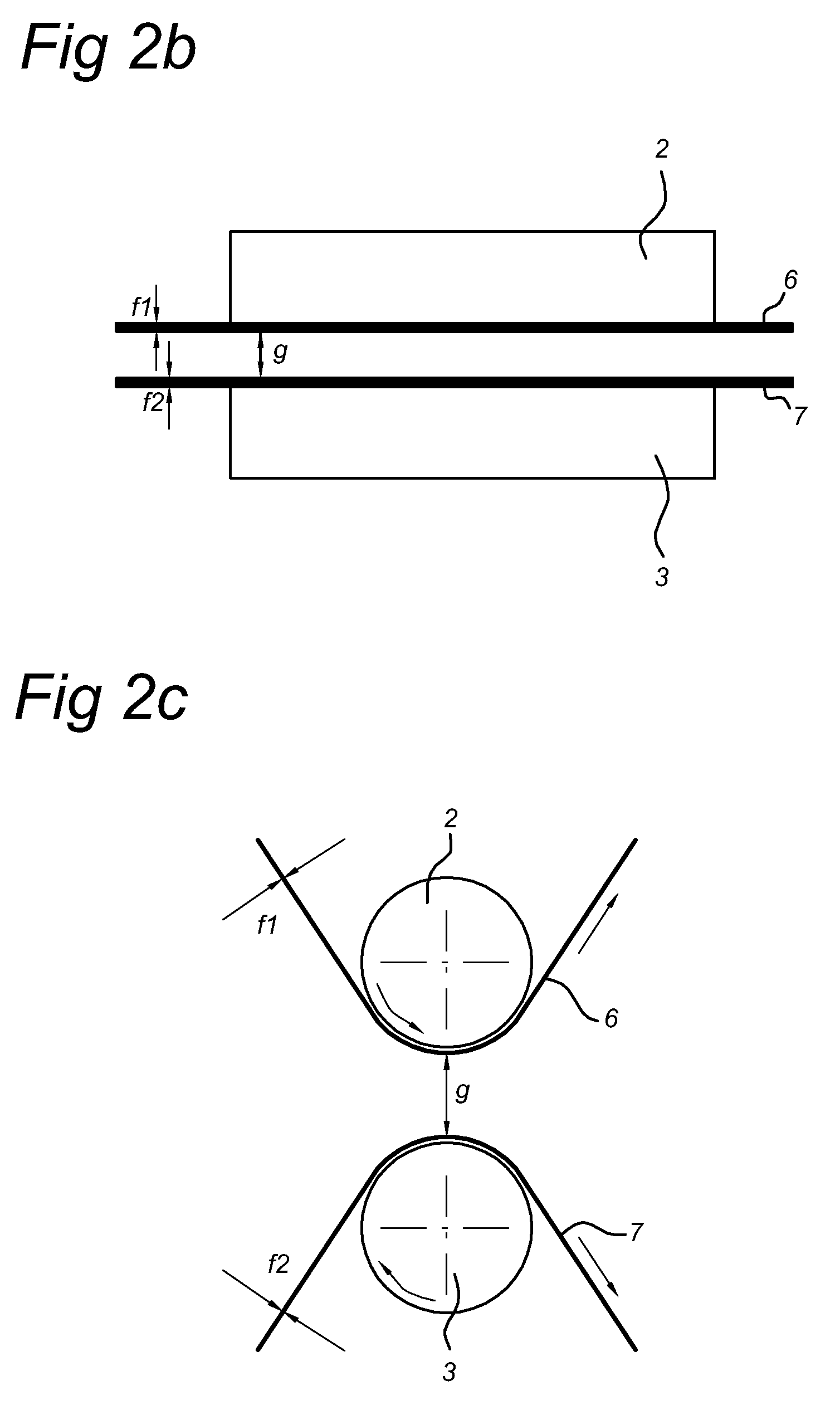

Plasma treatment apparatus and method for treating a substrate (6, 7) e.g. for deposition of a layer on the substrate (6, 7). Two opposing electrodes (2, 3) and a treatment space (5) are provided. A dielectric barrier (6, 7; 2a, 3a), comprising in operation the substrate, is provided in the treatment space (5) between the at least two opposing electrodes (2, 3) which are connected to a plasma control unit (4). A gap distance (g) is the free distance in the treatment space (5) of a gap between the at least two opposing electrodes (2, 3) in operation. A total dielectric distance (d) is the sum of the dielectric thickness of the dielectric layers (2a, 3a) and the substrate (6, 7). The product of gap distance (g) and total dielectric distance (d) is controlled to a value less than or equal to 1.0 mm2.

Owner:FUJIFILM MFG EURO

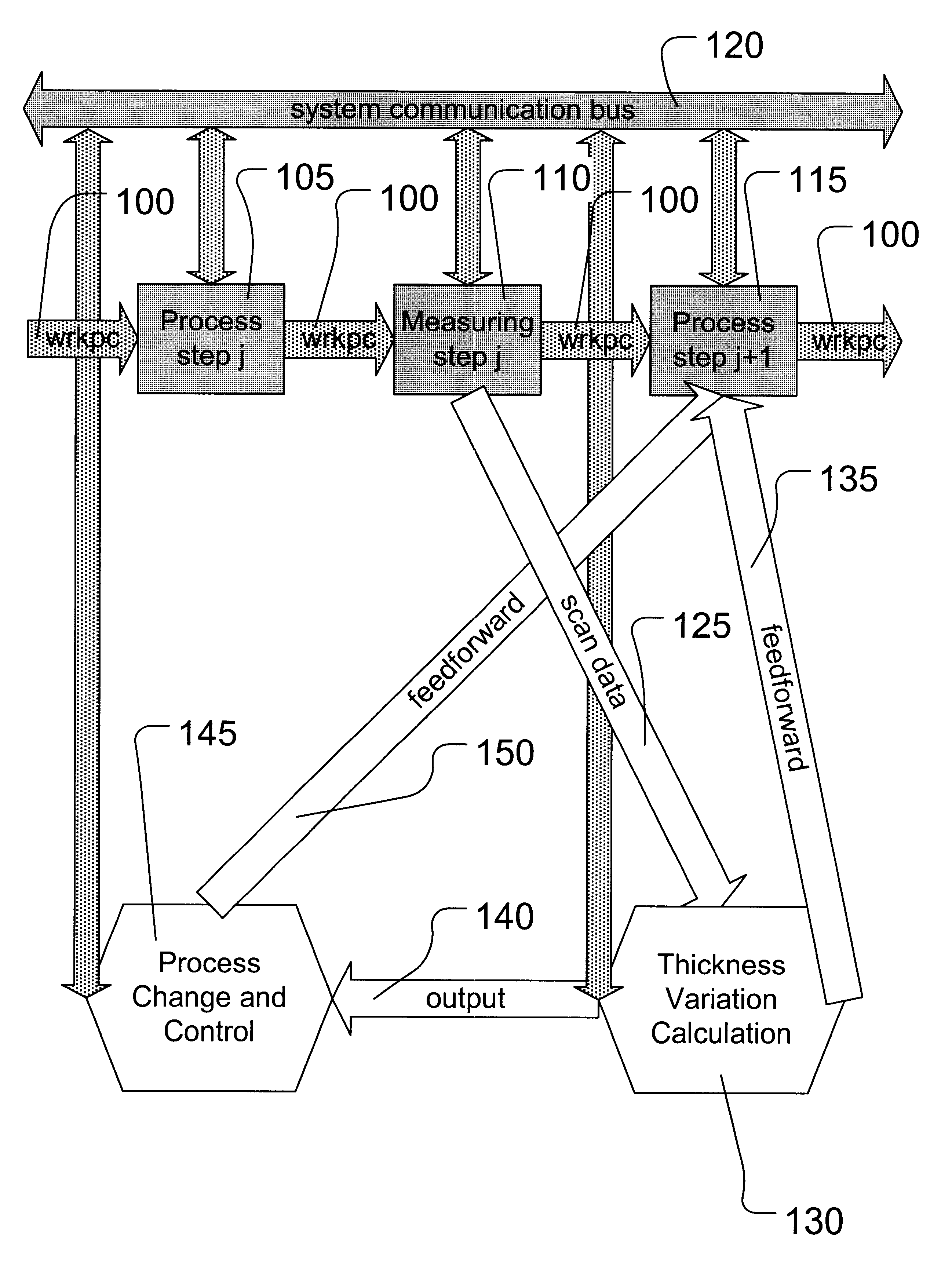

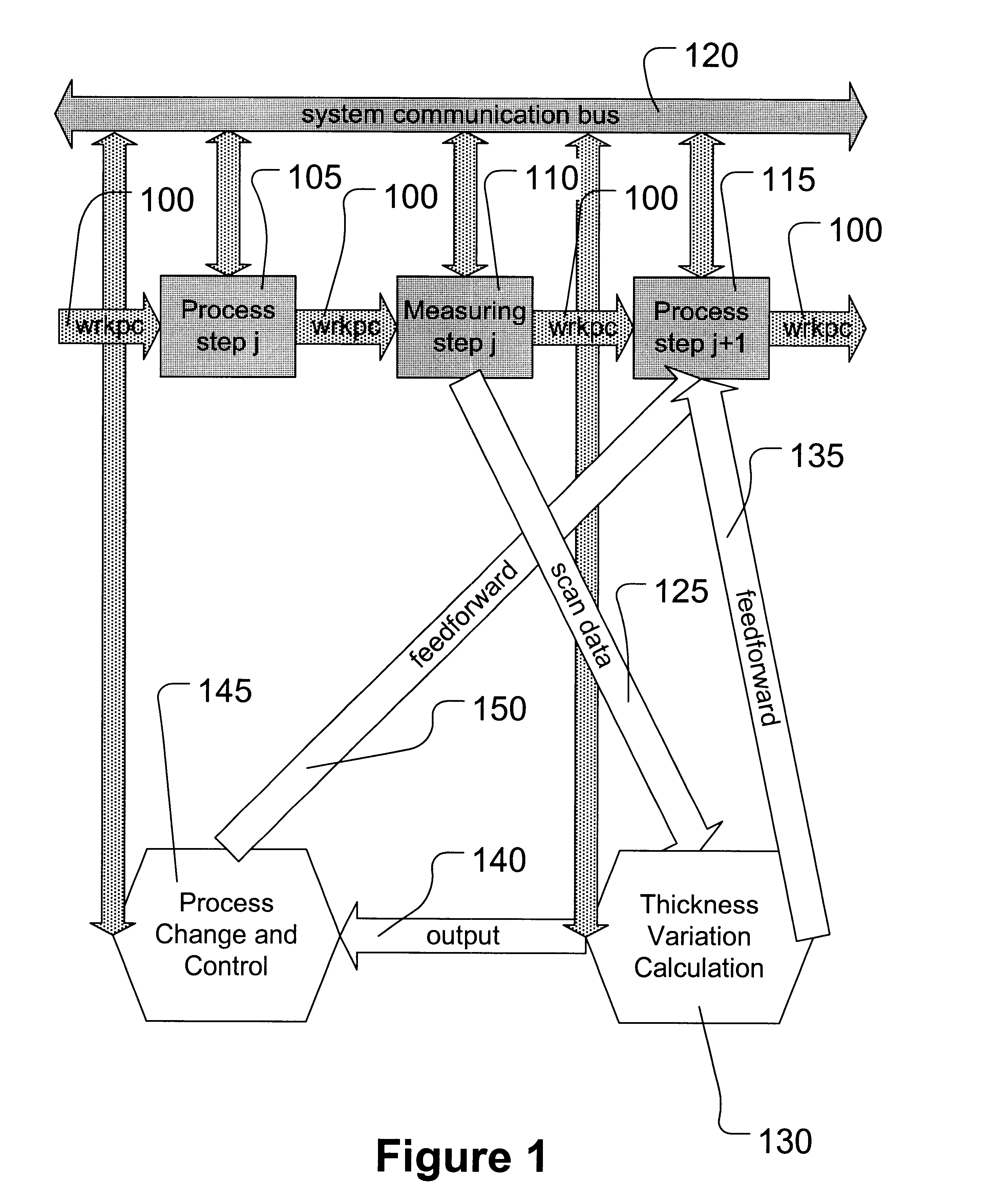

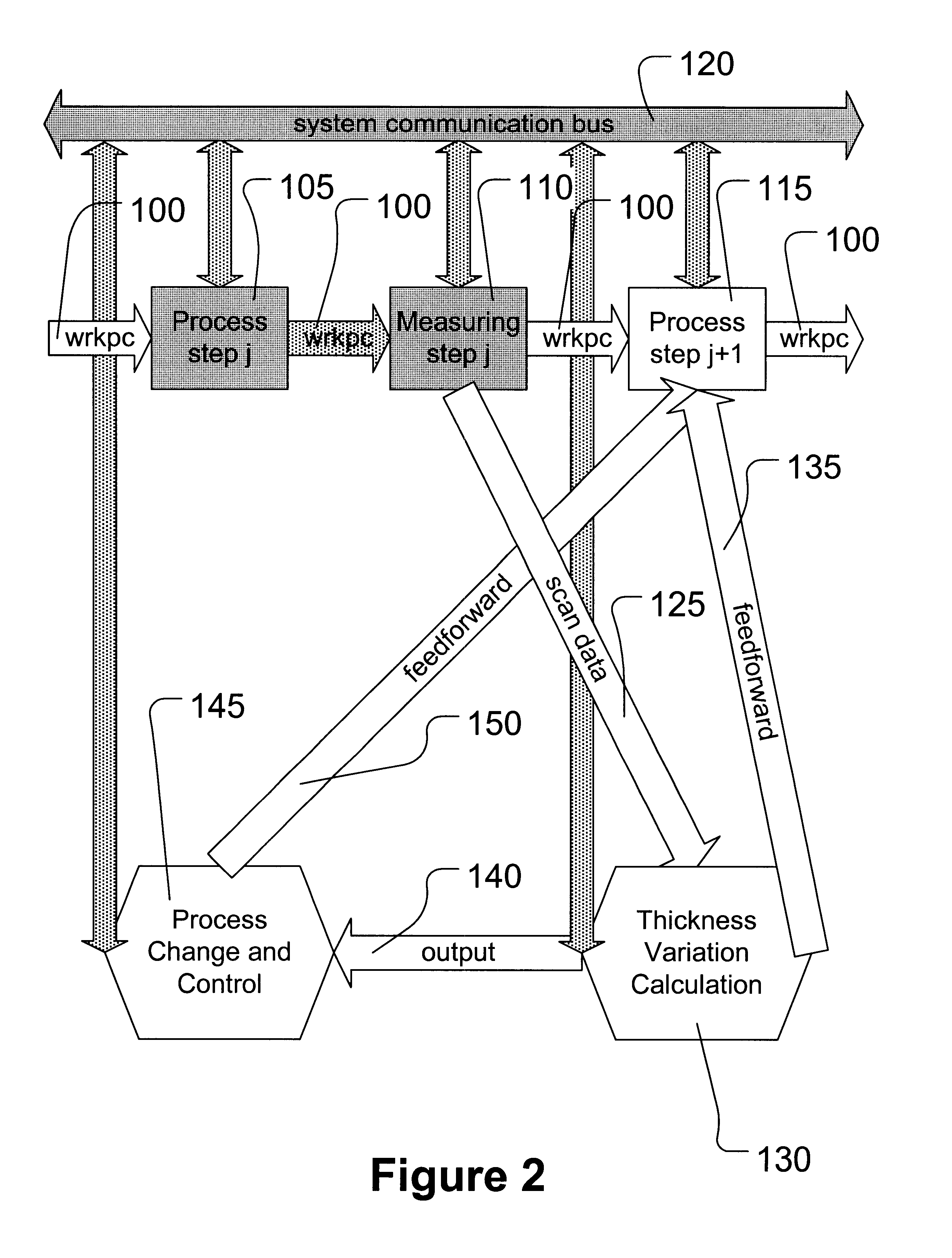

Method of reducing interlayer dielectric thickness variation feeding into a planarization process

InactiveUS6514865B1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingDielectric layerMaterials science

A method is provided that comprises forming a first dielectric layer on a workpiece, measuring a thickness of the first dielectric layer, and forming a second dielectric layer above the first dielectric layer, the second dielectric layer being formed to a thickness that is determined based upon the measured thickness of the first dielectric layer.

Owner:GLOBALFOUNDRIES INC

Method of measuring oxide thickness during semiconductor fabrication

InactiveUS6228665B1TransistorSemiconductor/solid-state device testing/measurementLinear correlationWafer fabrication

A measurement of thickness of a metal oxide layer on a solder ball connection during semiconductor fabrication is demonstrated by an in-situ capacitance measurement of the oxide layer. A linear relationship is shown between the reactance of the metal oxide and its thickness. This linearity is derived empirically, and correlated to Auger Spectroscopy test results for accuracy. The linear relationship demonstrated with these measurements exhibits a linear correlation coefficient, R2, greater than or equal to 0.974. This close, linear relationship allows for accurate testing of the oxide thickness using standard electrical parameter measurements during wafer fabrication.The method requires the determination of an analytical relationship between dielectric thickness and dielectric capacitance; the performance of an in-situ test of the dielectric layer capacitance including measuring the dielectric layer capacitance; and, the calculation of the dielectric layer thickness by using reactance values, calculated from the measured dielectric layer capacitance, as a variable within the analytical relationship.

Owner:IBM CORP

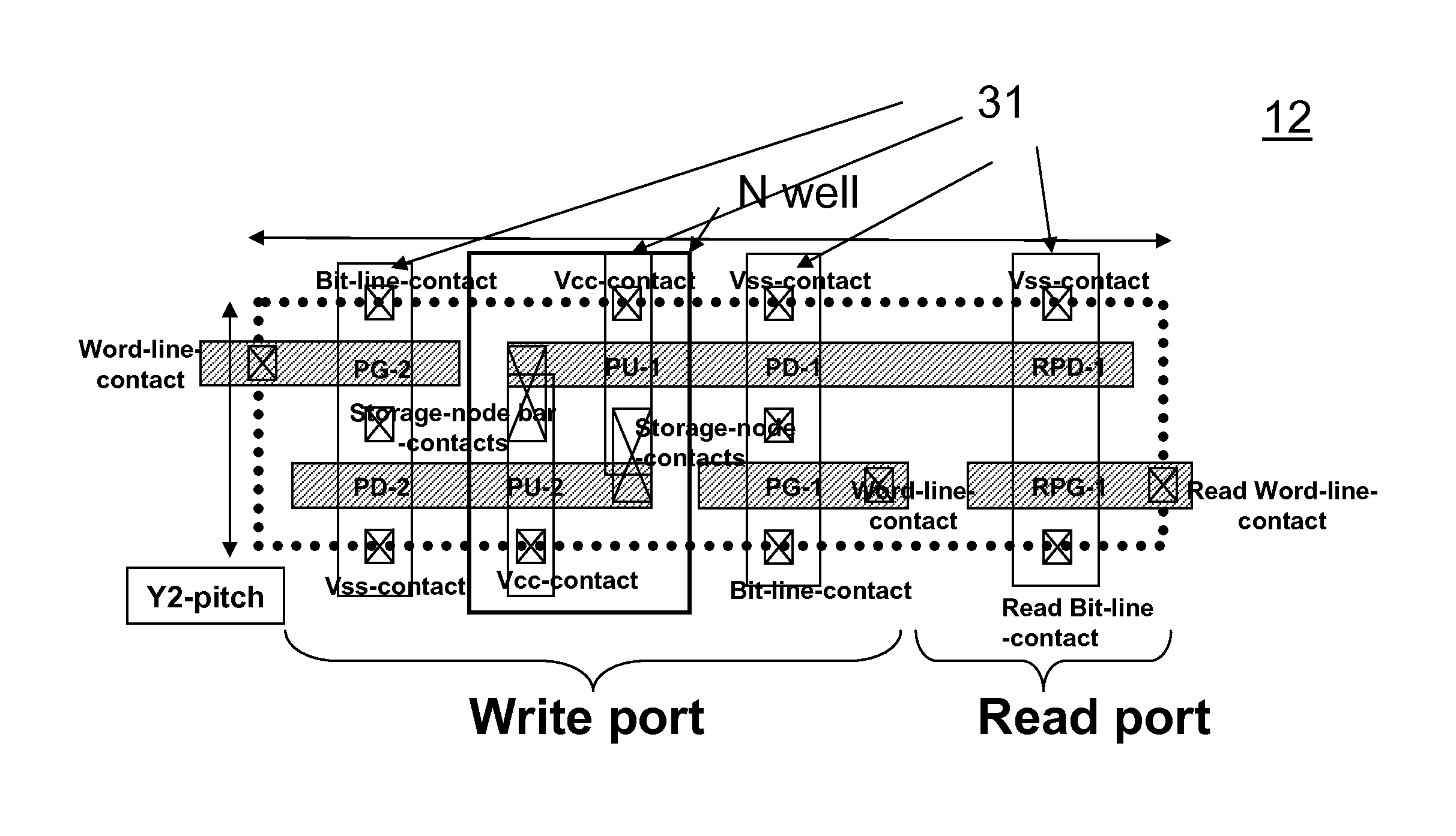

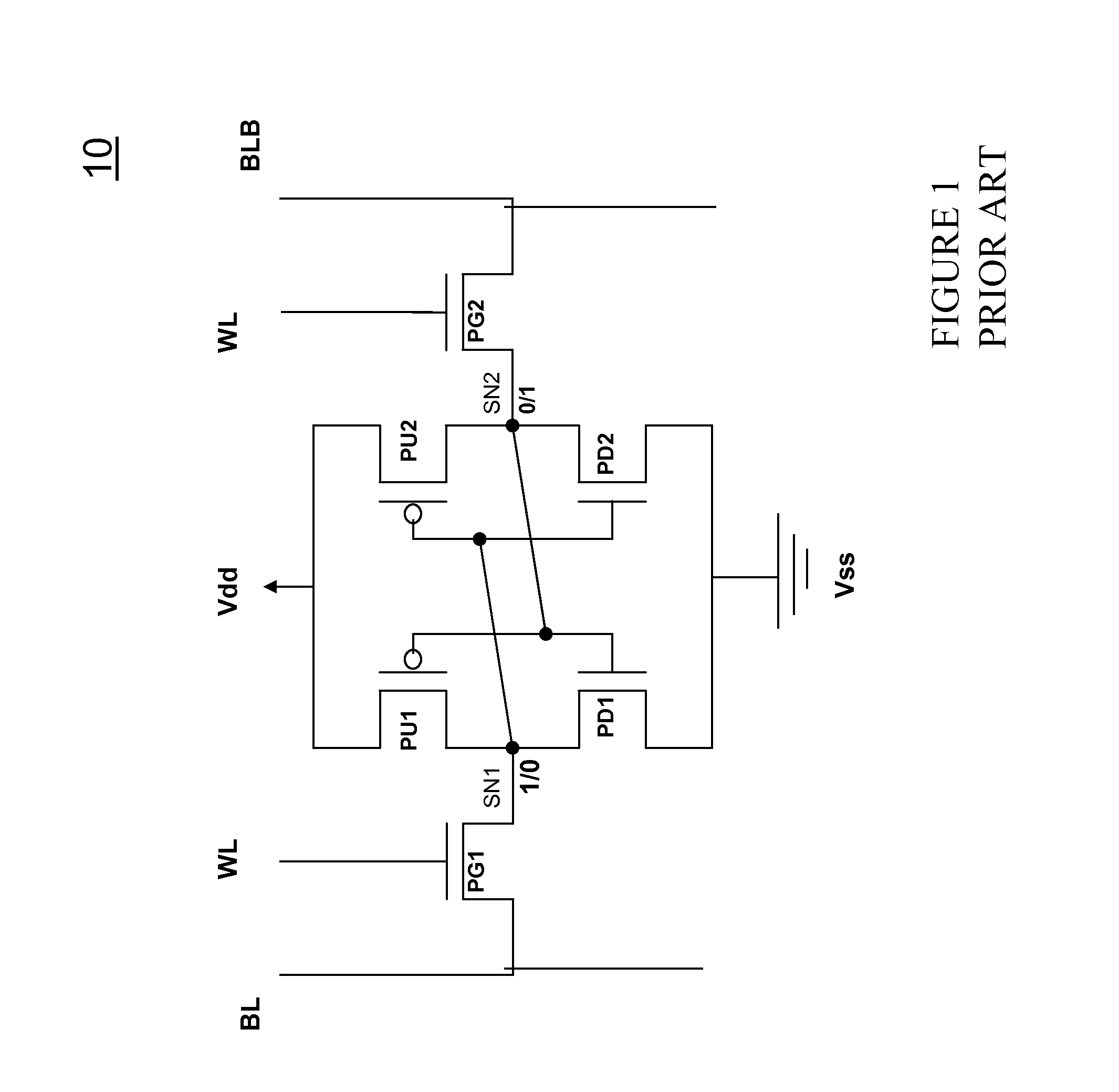

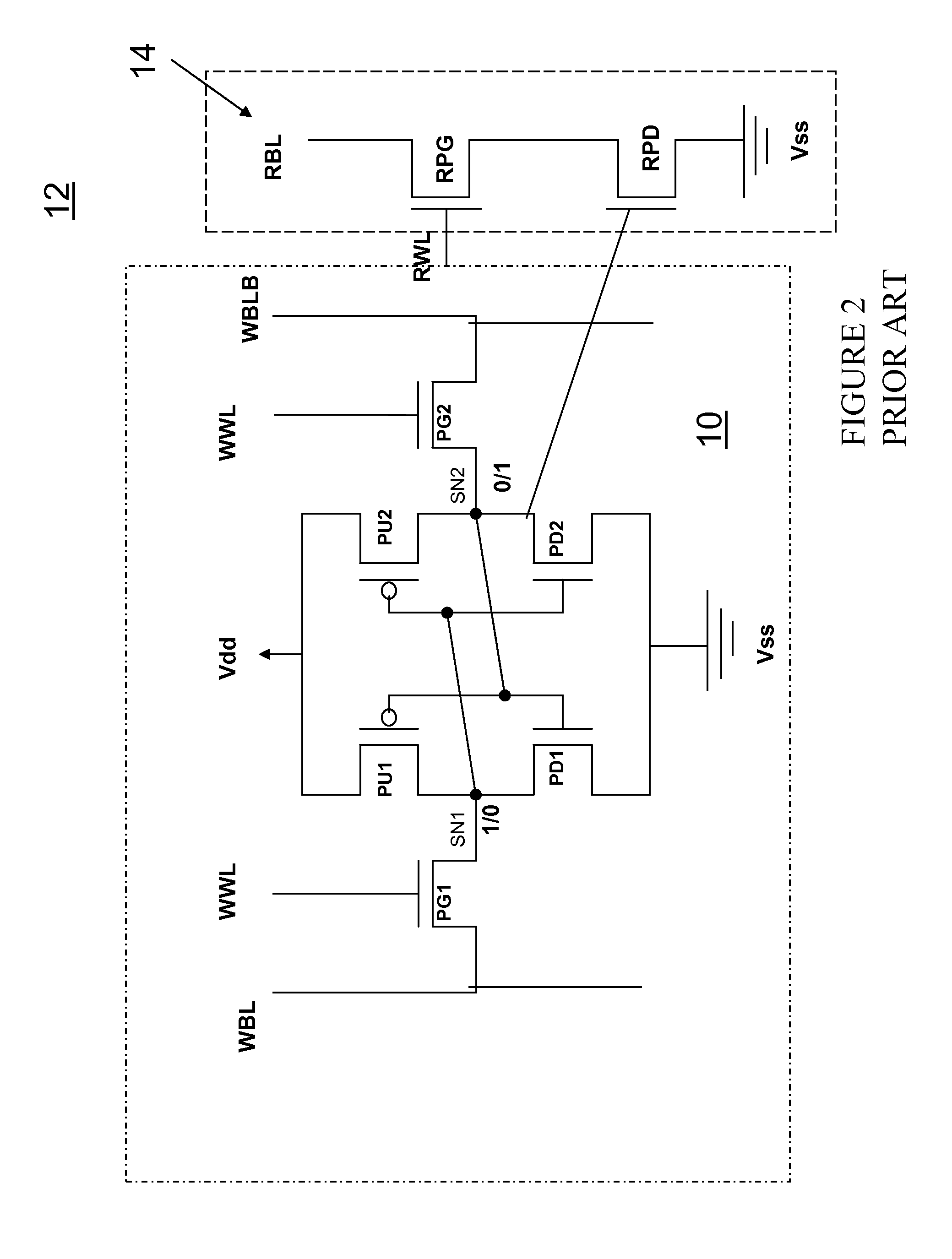

Embedded SRAM Memory for Low Power Applications

ActiveUS20110068413A1Reduce standby power consumptionReduce leakage currentTransistorSolid-state devicesPower applicationDual core

Circuits and methods for providing a dual gate oxide (DGO) embedded SRAM with additional logic portions, where the logic and the embedded SRAM have NMOS transistors having a common gate dielectric thickness but have different lightly doped drain (LDD) implantations formed using different LDD masks to provide optimum transistor operation. In an embodiment, a first embedded SRAM is a single port device and a second embedded SRAM is a dual port device having a separate read port. In certain embodiments, the second SRAM includes NMOS transistors having LDD implants formed using the logic portion LDD mask. Transistors formed with the logic portion LDD mask are faster and have lower Vt than transistors formed using a SRAM LDD mask. Dual core devices having multiple embedded SRAM arrays are disclosed. Methods for making the embedded SRAM are also disclosed.

Owner:TAIWAN SEMICON MFG CO LTD

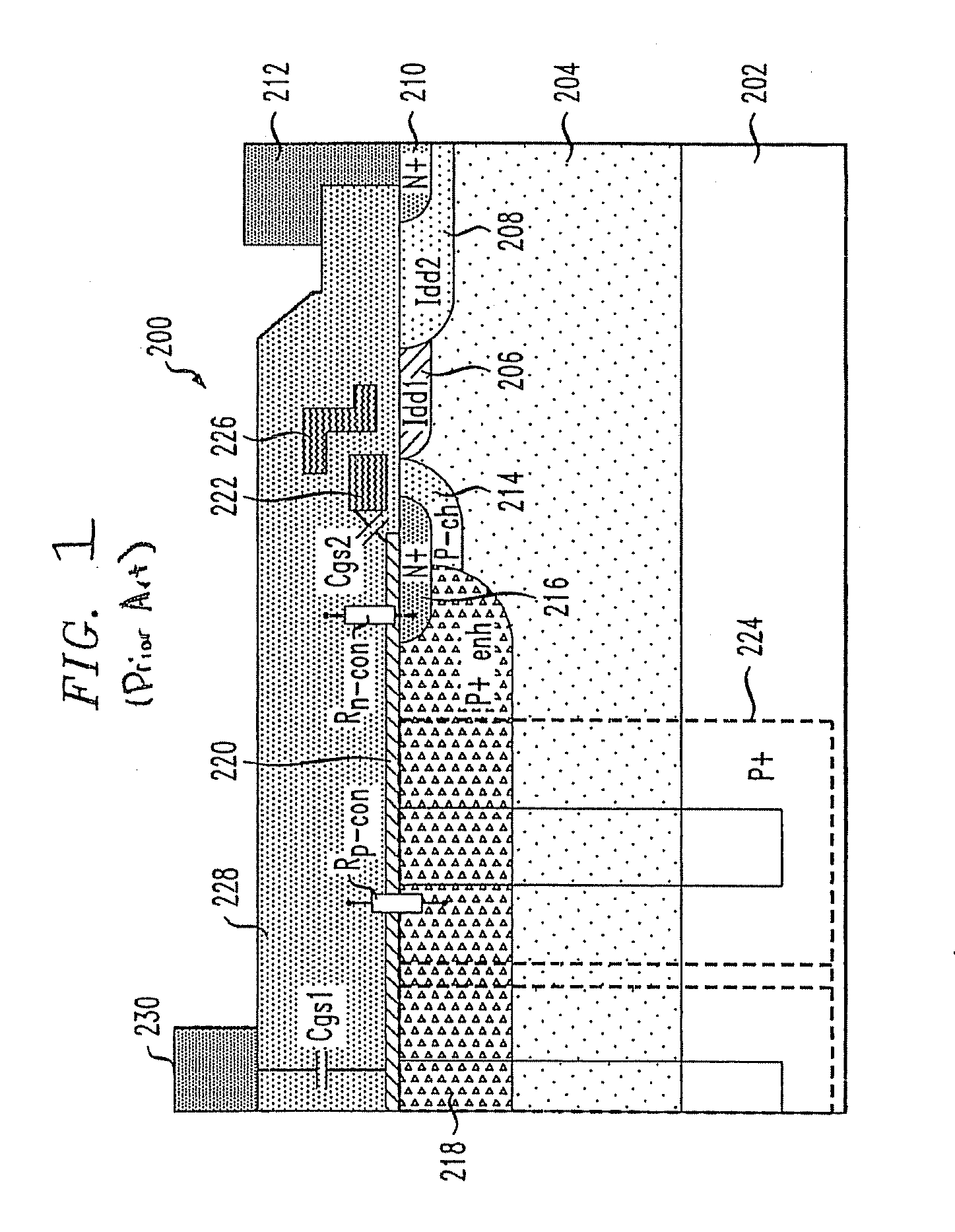

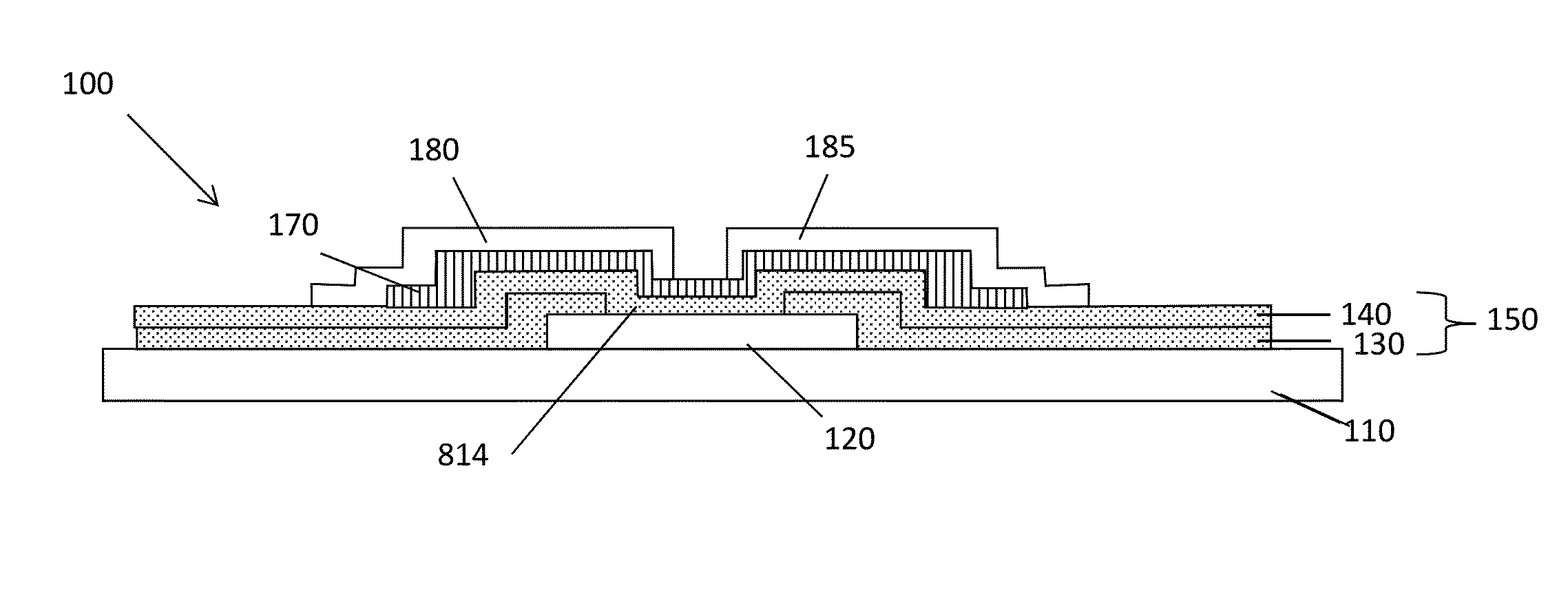

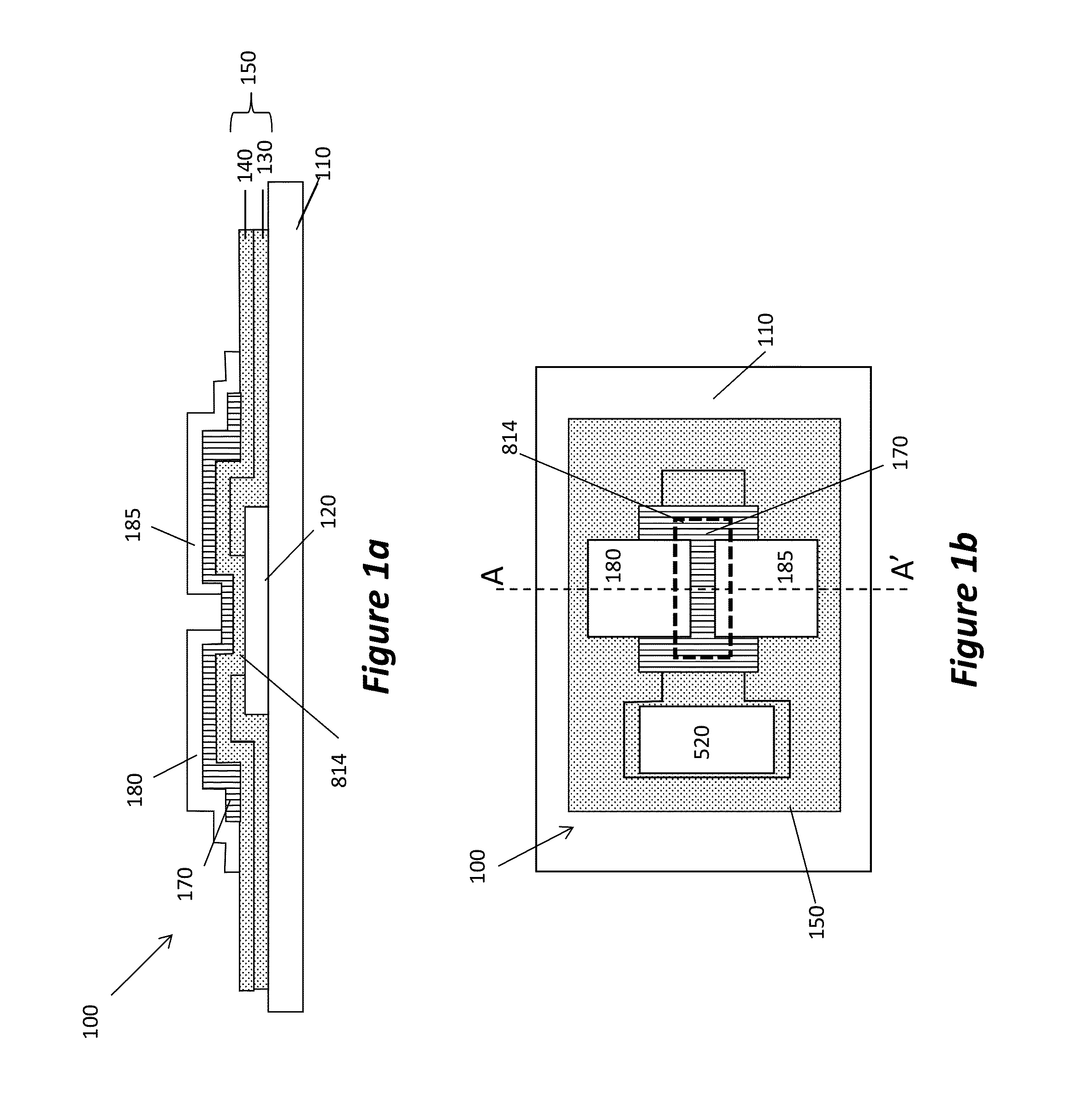

Enhancement-depletion mode inverter with two transistor architectures

ActiveUS20160126241A1Easy injectionReduces the possibility of short circuitsTransistorSolid-state devicesGate dielectricElectrical conductor

An enhancement-depletion-mode inverter includes a load transistor and a drive transistor. The load transistor has a top gate architecture with a first source, a first drain, a load channel region, a first semiconductor layer, and a first gate electrode. A load gate dielectric is in the load channel region, and has a load dielectric thickness. The load transistor is configured to operate in a depletion mode. The drive transistor has a bottom gate architecture with a second source, a second drain, a drive channel region, a second semiconductor layer, and a second gate electrode. A drive gate dielectric is in the drive channel region, and has a drive dielectric thickness that is different from the load dielectric thickness. The drive transistor is configured to operate in a normal mode or an enhancement mode. The first source is electrically connected to the second drain and the first gate.

Owner:EASTMAN KODAK CO

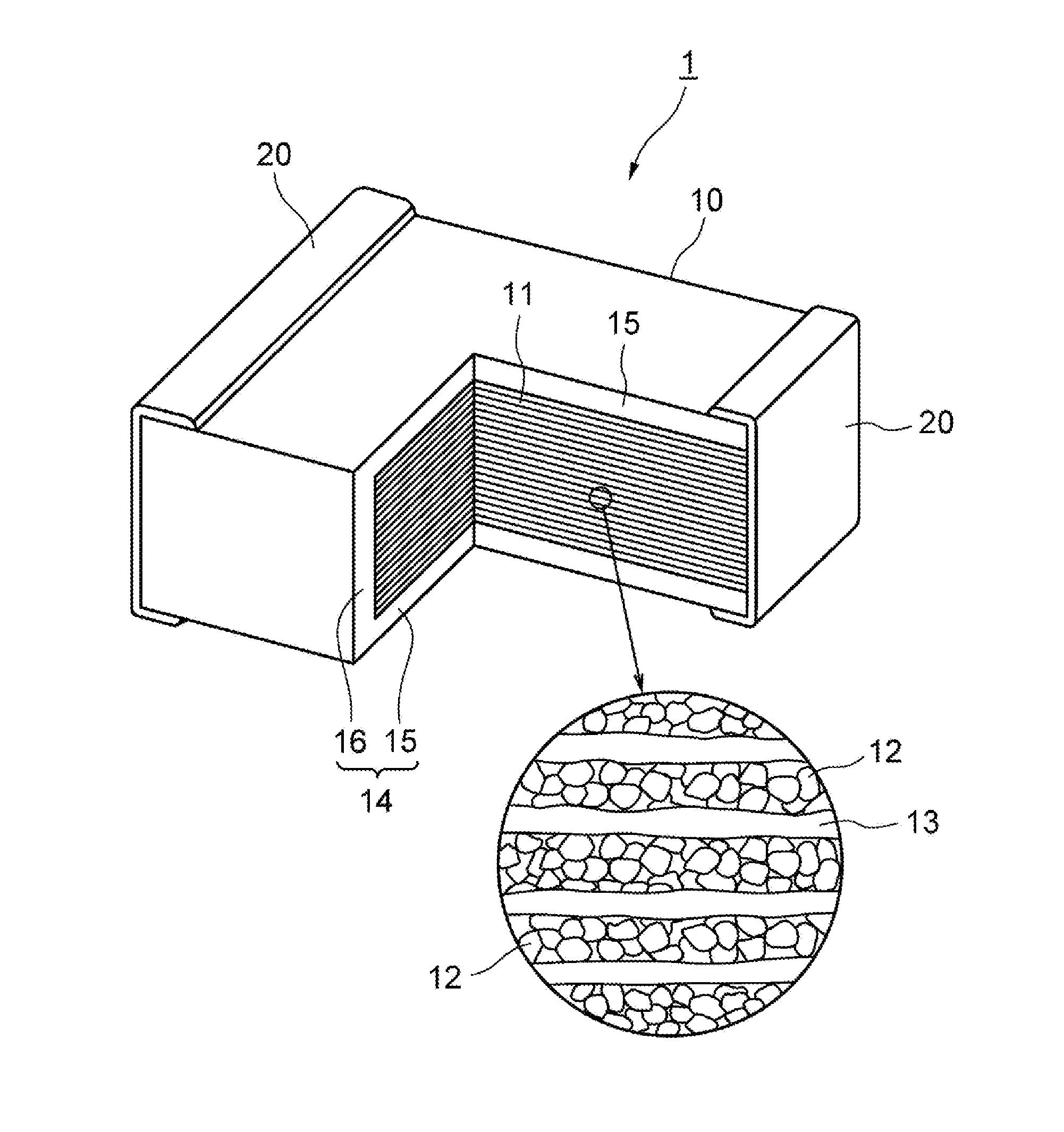

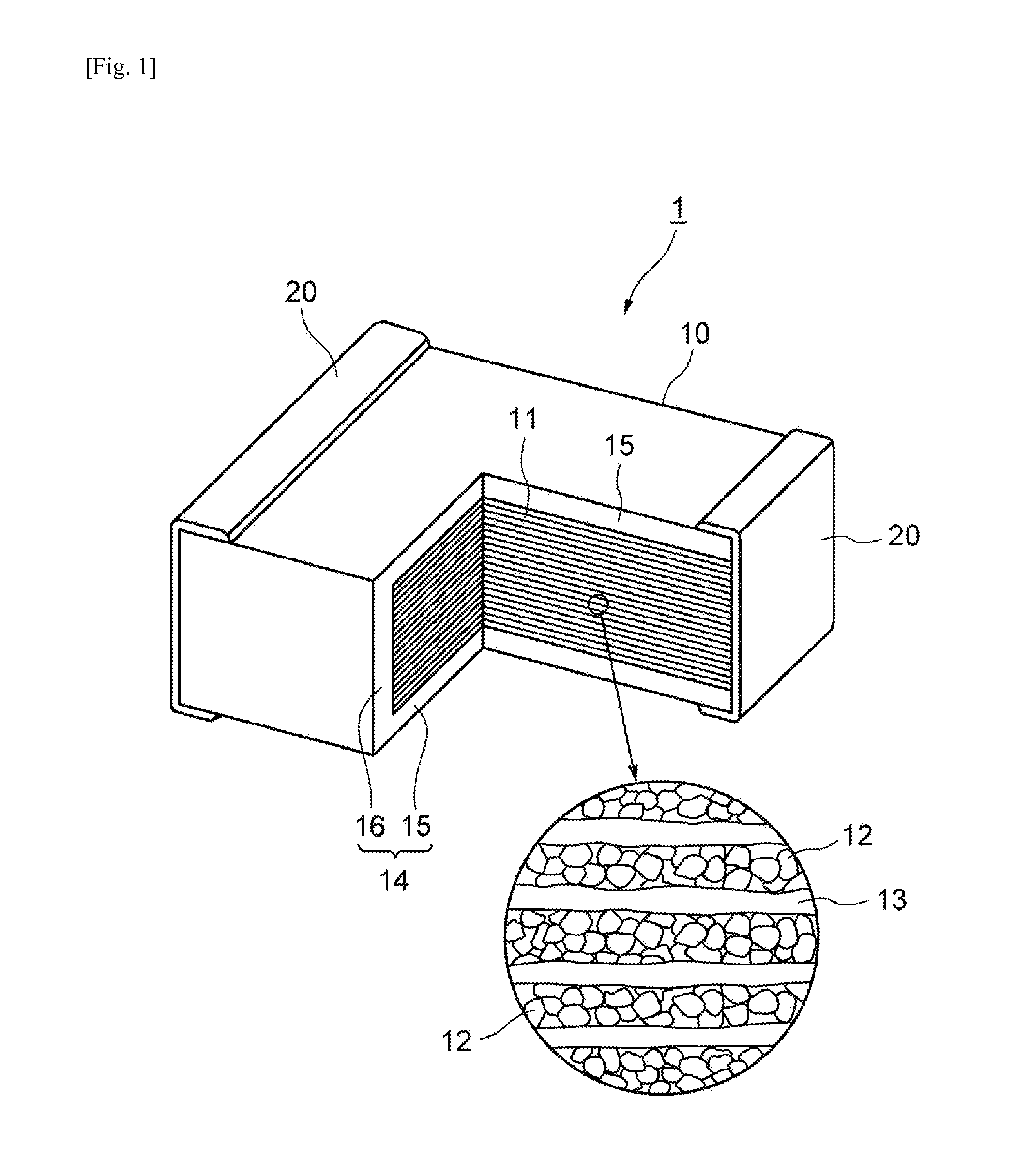

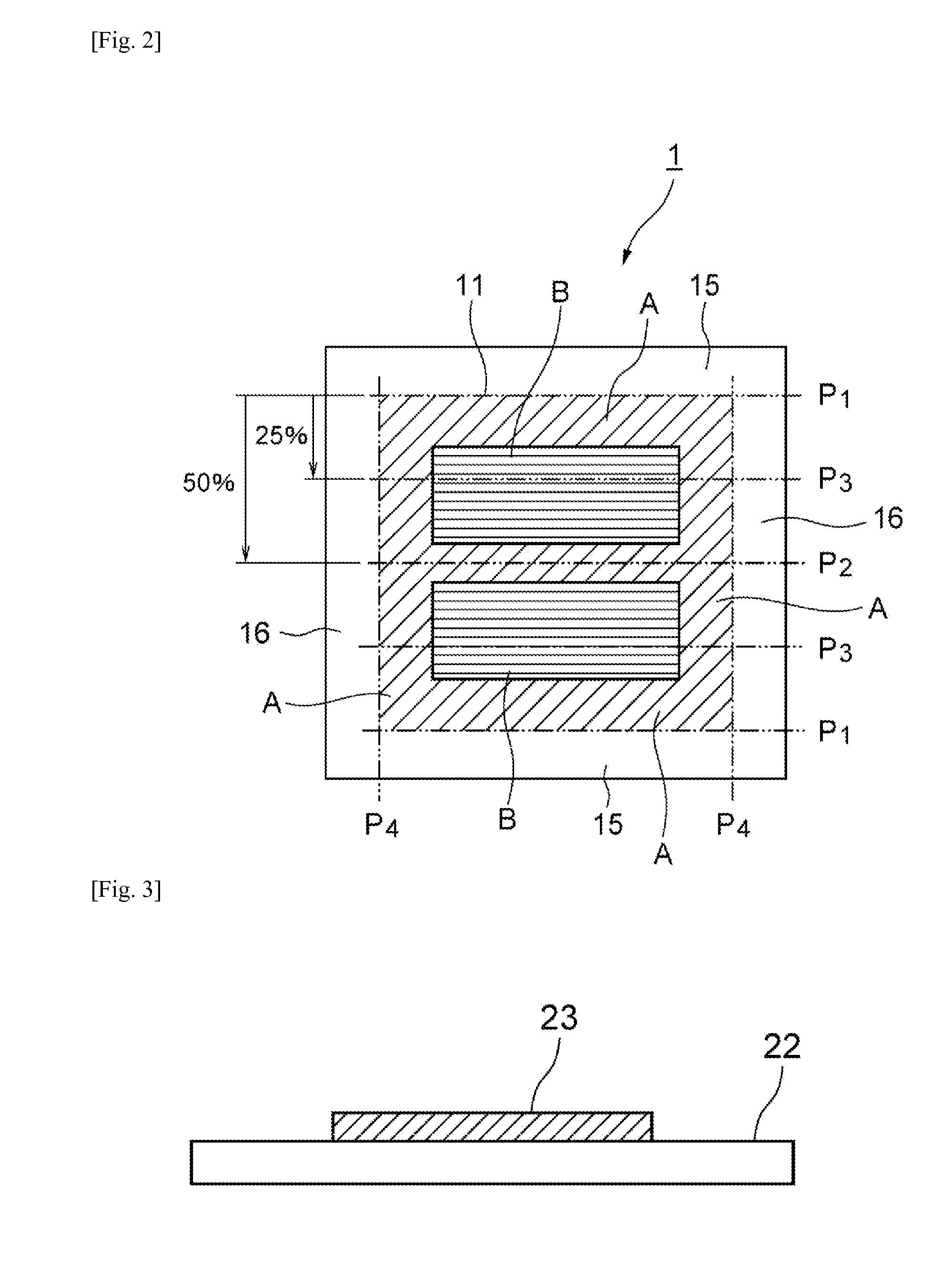

Multilayer ceramic capacitor

ActiveUS20140211367A1Sufficient CR productSmall sizeFixed capacitor dielectricStacked capacitorsCeramic capacitorCrystallite

With a multilayer ceramic capacitor whose average grain size of the dielectric grains present at the outermost layer position P1 in the laminate is given by D1, average grain size of the dielectric grains present at the center position P2 in the laminate is given by D2, and average grain size of the dielectric grains present at the 25%-penetrated position P3 which is a position penetrated into the laminate by 25% is given by D3, growth of the dielectric grains occurring as a result of sintering is partially suppressed in such a way that the relationships of average grain sizes D1, D2, and D3 satisfy the conditions of 1.5×D1<D3 and 1.2×D2<D3. This way, a sufficient CR product can be obtained even with a dielectric thickness of 1 μm or less.

Owner:TAIYO YUDEN KK

Fully depleted SOI multiple threshold voltage application

An integrated circuit comprises a substrate and a buried dielectric formed in the substrate. The buried dielectric has a first thickness in a first region, a second buried dielectric thickness in a second region, and a step between the first and second regions. A semiconductor layer overlies the buried dielectric.

Owner:TAIWAN SEMICON MFG CO LTD

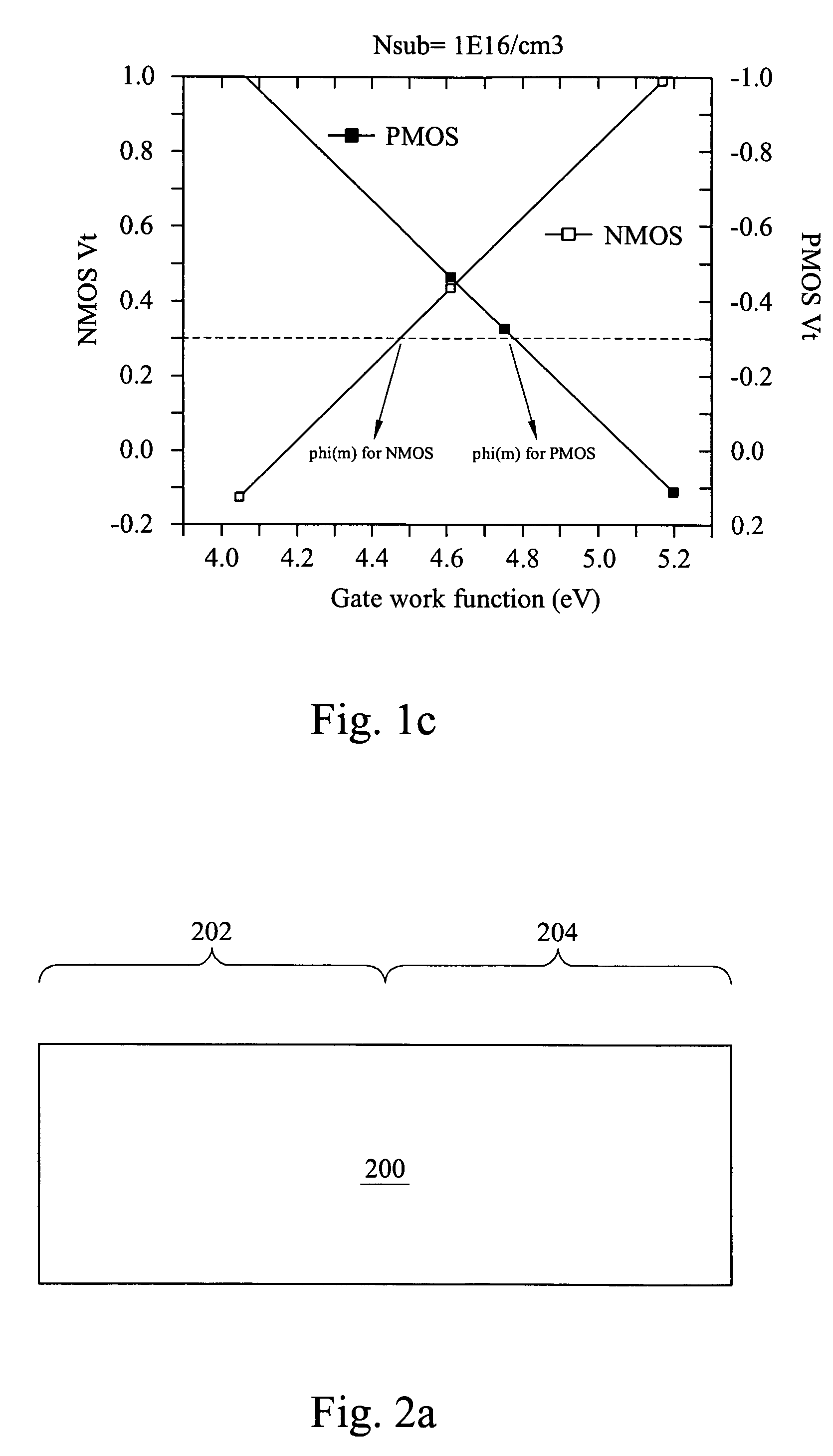

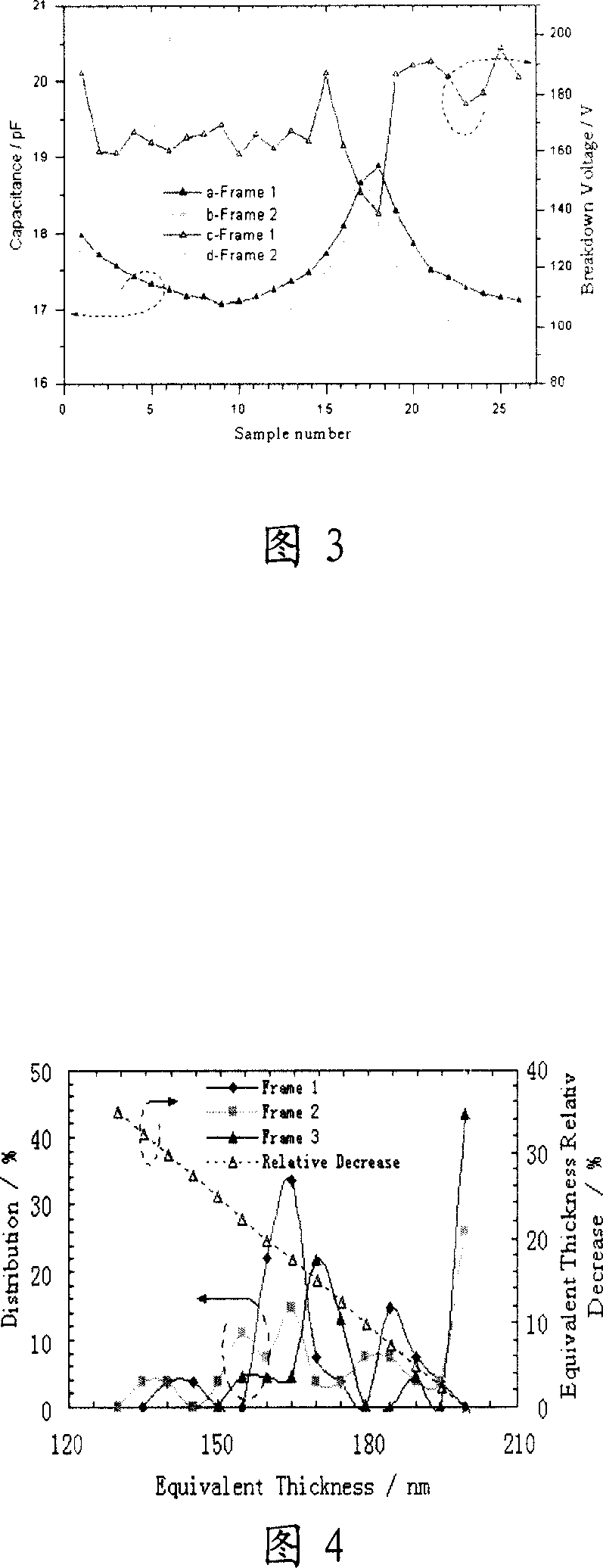

Method for estimating and monitoring dielectric film quality and reliability

InactiveCN101017153AReflect thinningMaterial breakdown voltageTesting dielectric strengthElectricityProcess conditions

This invention discloses one method to estimate and monitor dielectric layer quality and reliability, which comprises the following steps: first setting deficiency to result the puncture of dielectric layer; exerting field onto tested dielectric layer to get puncture voltage of VBD; setting the tested dielectric intensity as EDS as certain value under process condition; getting tested dielectric thickness dEQ for comparison between puncture voltage with dielectric intensity; comparing the thickness with the tested dielectric layer production to get real dielectric thickness and design.

Owner:信息产业部电子第五研究所

Collapsable gate for deposited nanostructures

A disposable material layer is first deposited on a graphene layer or a carbon nanotube (CNT). The disposable material layer includes a material that is less inert than graphene or CNT so that a contiguous dielectric material layer can be deposited at a target dielectric thickness without pinholes therein. A gate stack is formed by patterning the contiguous dielectric material layer and a gate conductor layer deposited thereupon. The disposable material layer shields and protects the graphene layer or the CNT during formation of the gate stack. The disposable material layer is then removed by a selective etch, releasing a free-standing gate structure. The free-standing gate structure is collapsed onto the graphene layer or the CNT below at the end of the selective etch so that the bottom surface of the contiguous dielectric material layer contacts an upper surface of the graphene layer or the CNT.

Owner:GLOBALFOUNDRIES INC

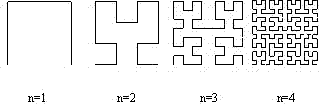

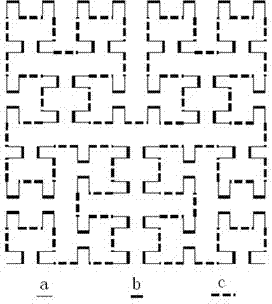

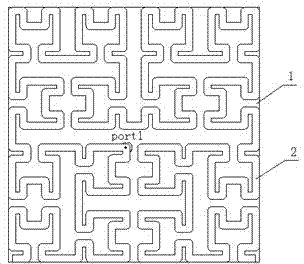

Method for designing Hilbert fractal ultrahigh frequency antenna

ActiveCN103793573AImprove collection effectSensitive receptionRadiating elements structural formsSpecial data processing applicationsDielectric substrateEngineering

The invention discloses a method for designing a Hilbert fractal ultrahigh frequency antenna. The method includes the steps of arranging a grounding board and a Hilbert fractal wire layer on the two sides of a dielectric substrate respectively, enabling the lengths of parallel dual wires, short circuit terminals and additional wire sections to serve as parameters when the sizes of all parts of wire sections inside the wire layer are determined, meanwhile, considering the wire width, the dielectric thickness and the dielectric constant to build calculation equations of the resonance frequency and the standing-wave ratio of the antenna, carrying out simulating optimization on the parameters within the available ranges of the resonance frequency and the standing-wave ratio to obtain optimal values of the lengths of the three kinds of wire sections and the widths of the wire sections, and finally manufacturing the Hilbert fractal ultrahigh frequency antenna according to the simulation results. According to the method, the Hilbert fractal ultrahigh frequency antenna is optimized by changing the lengths of the parallel dual wires, the short circuit terminals and the additional wire sections, and the collecting effect of the antenna on partial discharge ultrahigh frequency signals of electrical equipment is greatly improved.

Owner:NORTH CHINA ELECTRIC POWER UNIV (BAODING)

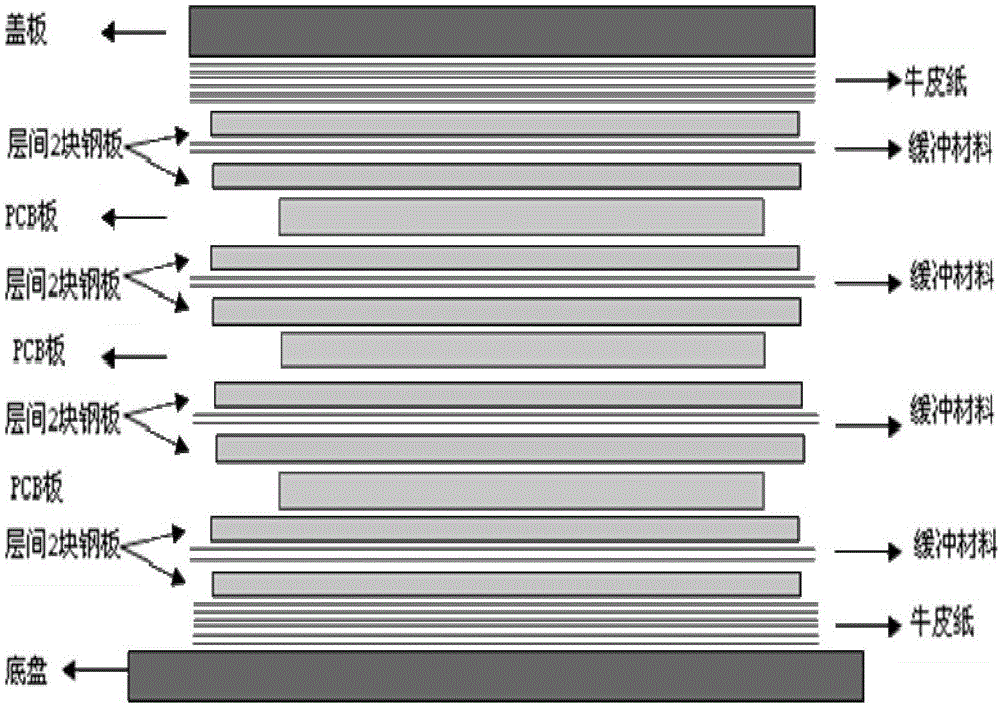

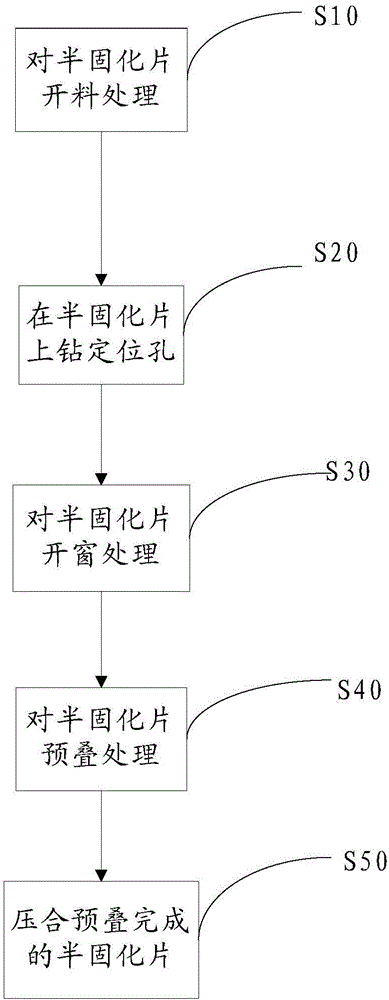

Method for producing copper-free area between layers of printed board

InactiveCN106659000AEfficient fillingLow costMultilayer circuit manufactureDielectric thicknessElectrical and Electronics engineering

The invention relates to a method for producing a copper-free area between layers of a printed board, comprising subjecting a prepreg to a blanking treatment; drilling a positioning hole in the prepreg; subjecting the prepreg to windowing treatment; subjecting the prepreg to pre-stacking treatment; and press fitting the pre-stacked prepreg. The method, by opening a window at a position close to a core board and then performing thepre-stacking and the lamination operations, guarantees that the laminated PCB has no empty edge, fills the recess position of the copper-free area, fills the cavity at a low level, reduces the cost, improves the production capacity, and does not affect the dielectric thickness.

Owner:SHENZHEN SUNTAK MULTILAYER PCB

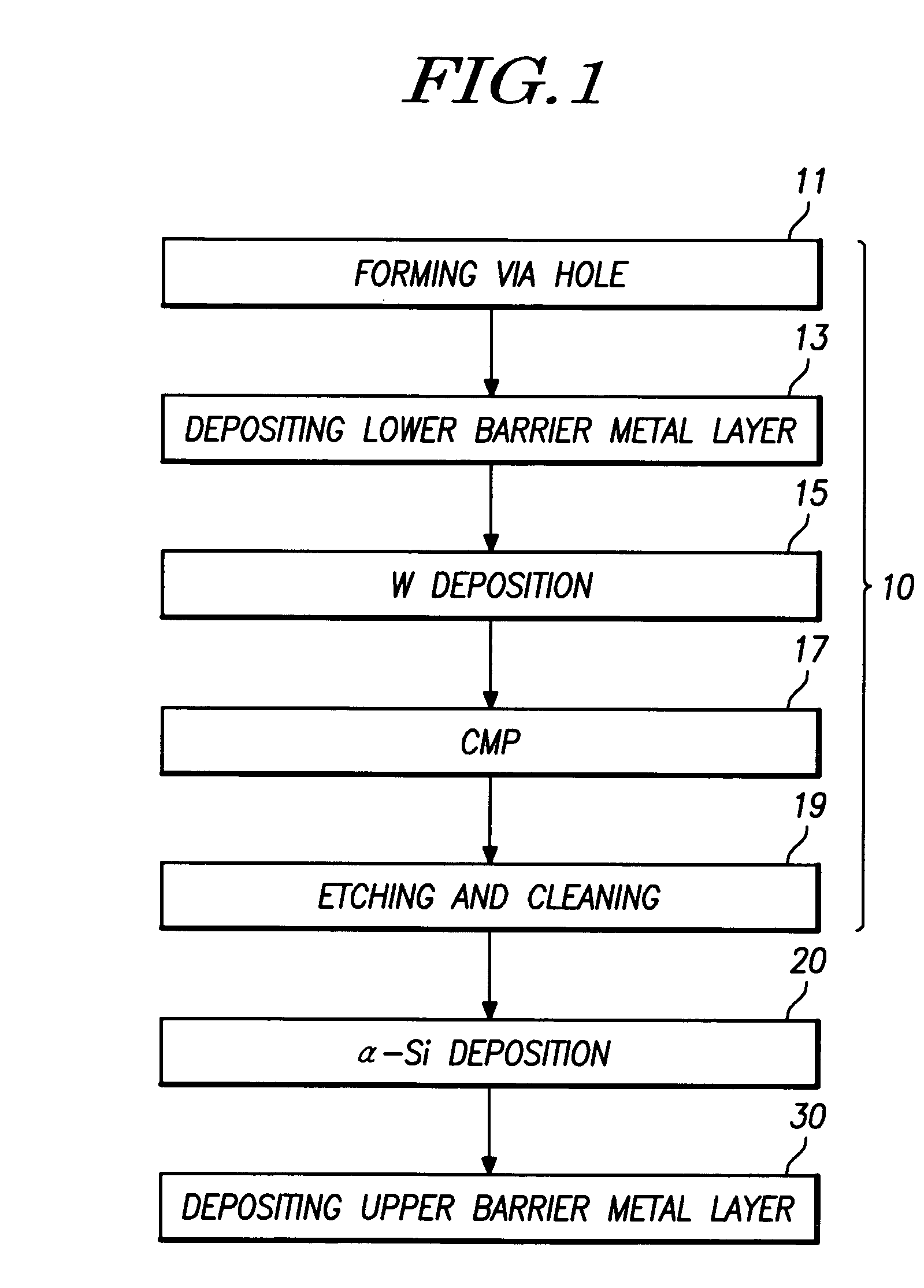

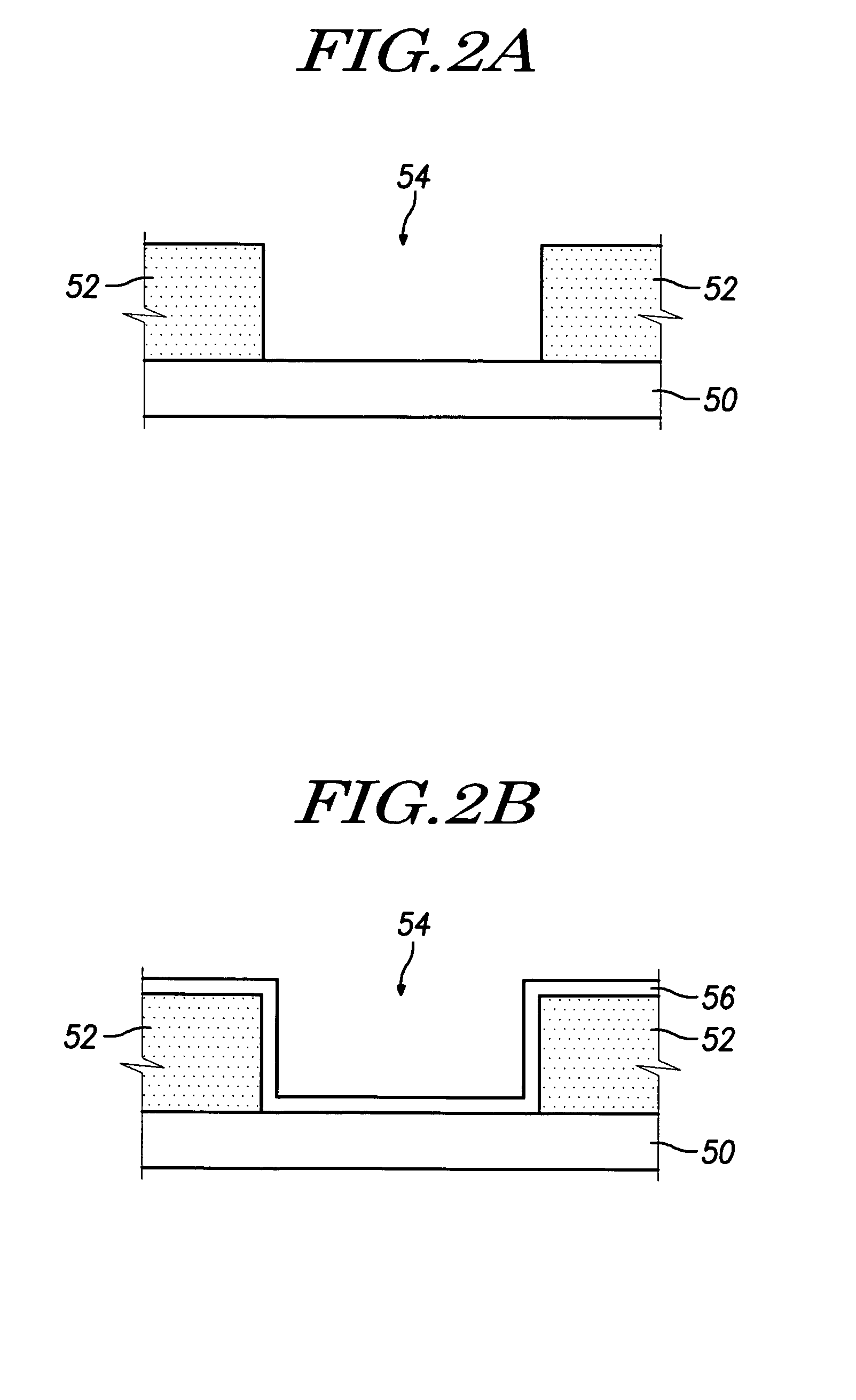

Antifuse having uniform dielectric thickness and method for fabricating the same

InactiveUS20060145292A1Facilitate formation of silicideImprove uniformitySemiconductor/solid-state device detailsSolid-state devicesAmorphous siliconAntifuse

Disclosed are an antifuse having a uniform amorphous silicon (antifuse material) thickness and a method for fabricating such an antifuse device. The antifuse is located between overlying and underlying conductive layers, and includes: a contact and / or via hole in an insulating layer on the underlying conductive layer; a lower metal layer contacting inner surfaces of the contact and / or via hole and a top surface of the insulating layer; a filling layer contacting the lower barrier metal layer and at least partially filling the contact and / or via hole; an antifuse material layer contacting a top surface of the filling layer and a part of the lower metal layer; and an upper metal layer on the antifuse material layer.

Owner:DONGBU ELECTRONICS CO LTD

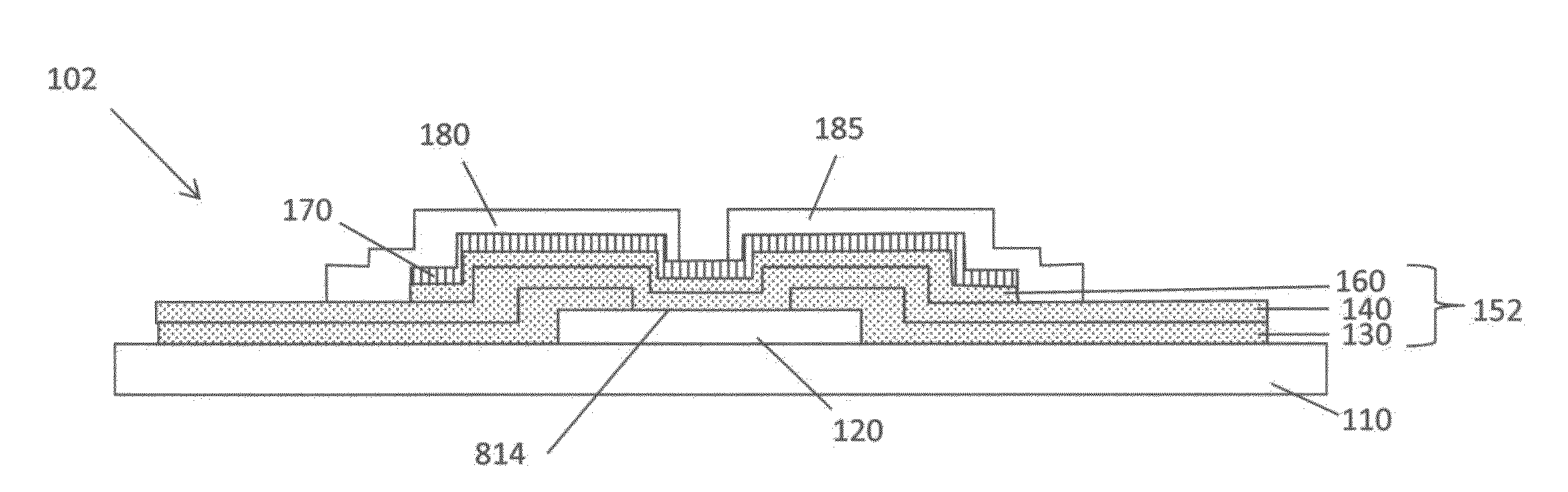

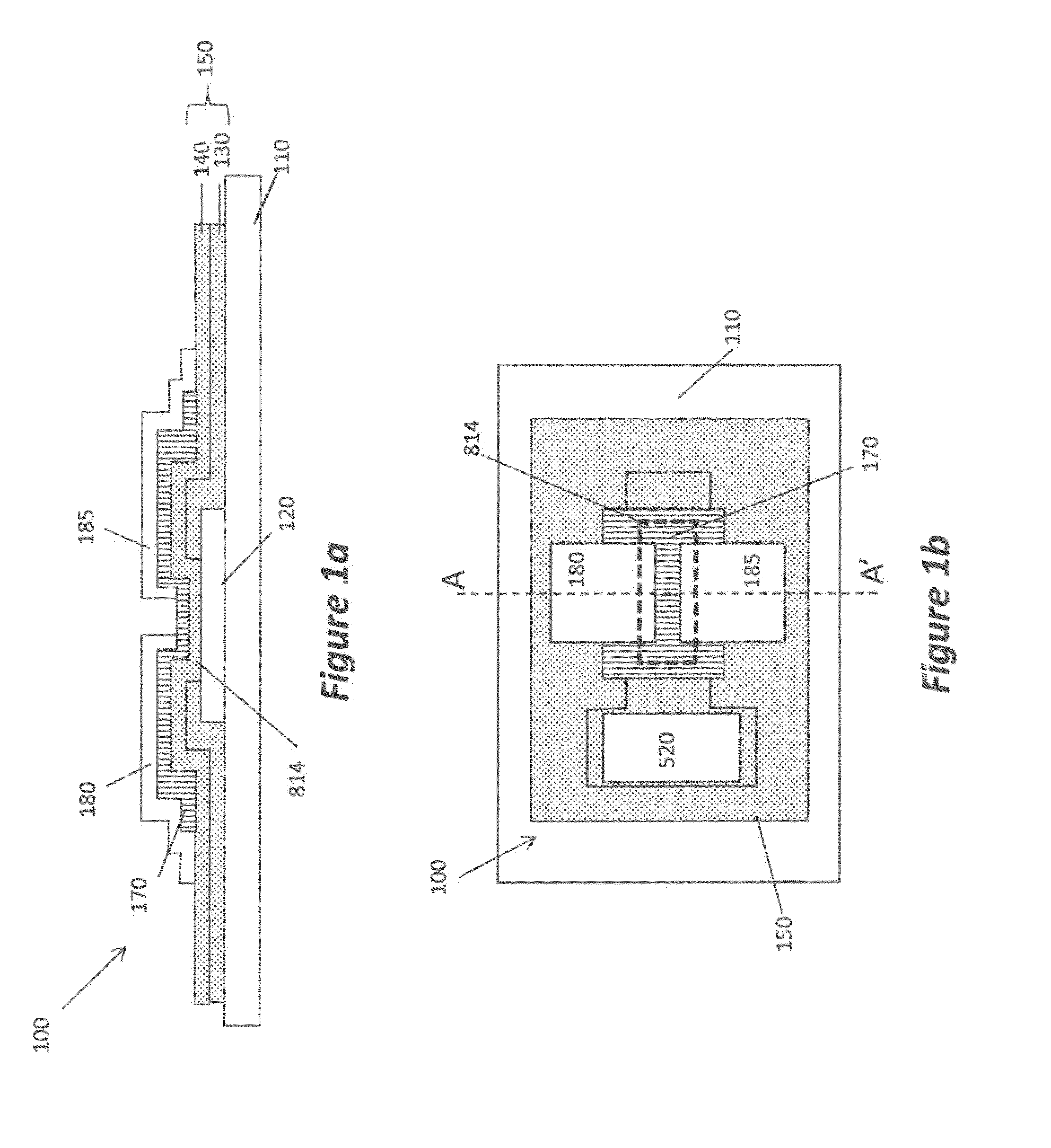

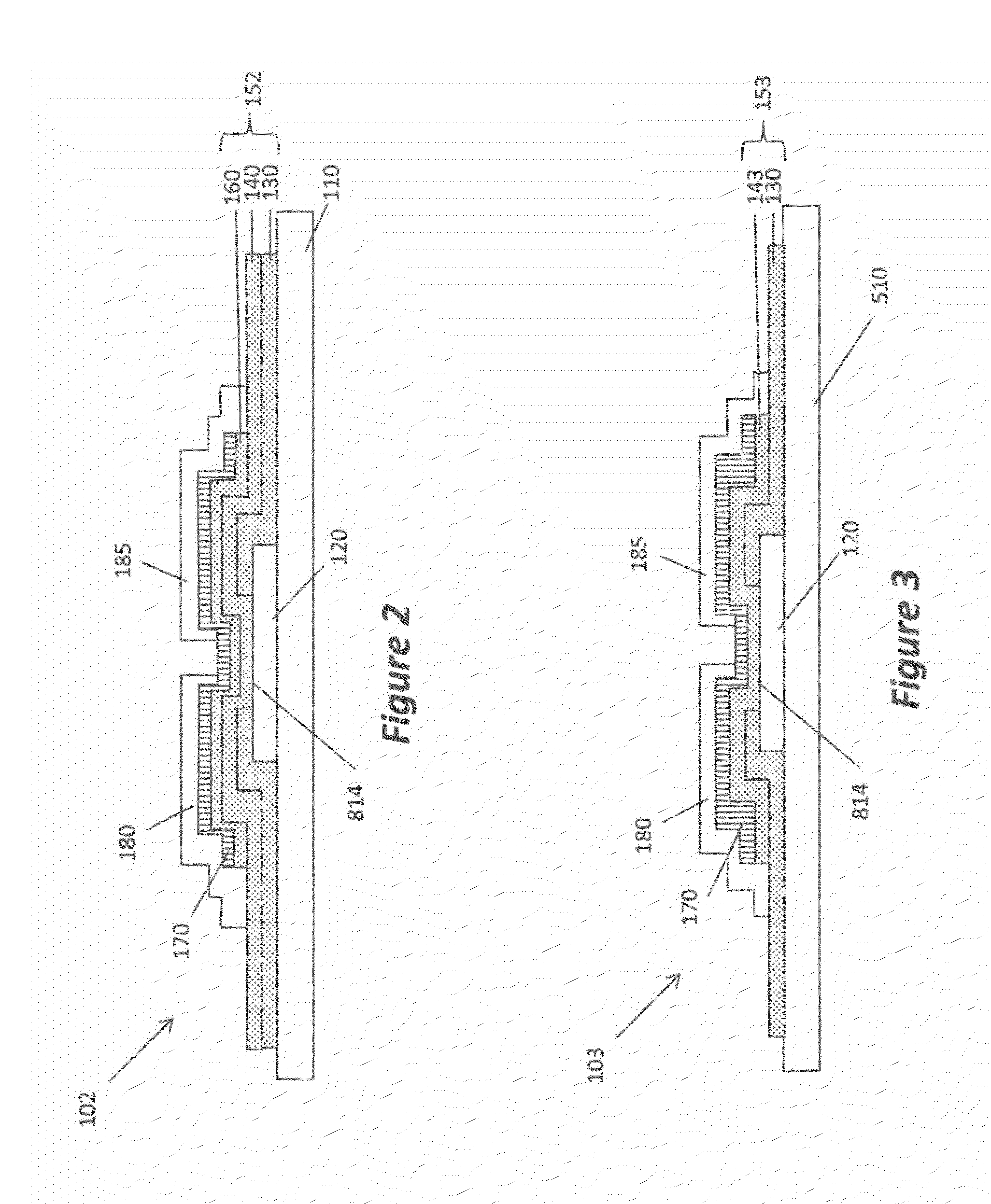

TFT substrate with variable dielectric thickness

A transistor includes a substrate and an electrically conductive gate over the substrate. The gate has a gate length. A source electrode and a drain electrode are over the substrate, and are separated by a gap defining a channel region. The channel region has a channel length that is less than the gate length. A semiconductor layer is in contact with the source electrode and drain electrode. A dielectric stack is in contact with the gate, and has first, second, and third regions. The first region is in contact with the semiconductor layer in the channel region, and has a first thickness. The second region is adjacent to the first region that has the first thickness. The third region is adjacent to the second region, and has a thickness that is greater than the first thickness.

Owner:EASTMAN KODAK CO

Techniques for dual dielectric thickness for a nanowire CMOS technology using oxygen growth

In one aspect, a method of forming a CMOS device includes forming nanowires suspended over a BOX, wherein a first / second one or more of the nanowires are suspended at a first / second suspension height over the BOX, and wherein the first suspension height is greater than the second suspension height; depositing a conformal gate dielectric on the BOX and around the nanowires wherein the conformal gate dielectric deposited on the BOX is i) in a non-contact position with the conformal gate dielectric deposited around the first one or more of the nanowires, and ii) is in direct physical contact with the conformal gate dielectric deposited around the second one or more of the nanowires such that the BOX serves as an oxygen source during growth of a conformal oxide layer at the interface between the conformal gate dielectric and the second one or more of the nanowires.

Owner:IBM CORP

Semiconductor devices with different dielectric thicknesses

Owner:NXP USA INC

PCB back drilling control method and PCB

The invention belongs to the technical field of PCB manufacturing and discloses a PCB back drilling control method and a PCB. The PCB back drilling control method comprises steps: a through hole is opened in the PCB; with the drilling surface of back drilling as an upper surface, the distance L between an upper surface copper layer to a reference layer is measured; the PCB is electroplated; the thickness T of an electroplating layer on the upper surface copper layer is measured; and back drilling with a depth of L+T is carried out from one side of the upper surface copper layer on the throughhole. The PCB is manufactured by using the above PCB back drilling control method. The distance between the upper surface copper layer and the reference layer is measured before electroplating, the thickness of the electroplating layer on the upper surface copper layer is measured after electroplating, the sum of the two is used as a reference index for the depth of the back drilling, high-precision nondestructive detection on the dielectric thickness is realized, the back drilling depth can be accurately controlled in the case of back drilling, and the setting precision of a through hole residual pile can be improved.

Owner:DONGGUAN SHENGYI ELECTRONICS

EEPROM cell structures having non-uniform channel-dielectric thickness and methods of making the same

An EEPROM cell structure, having varied gate-dielectric thickness, can include: a semiconductor substrate; a memory transistor and a select transistor on the substrate; and a floating junction formed in the substrate between the transistors and extending partially underneath the memory transistor; a gate-dielectric layer in the memory transistor, along a lateral direction, being arranged into a tunnel region having thickness Ttunnel and overlying a portion of the floating junction, a near-channel region having thickness Tnear>Ttunnel and located at a side of the tunnel region opposite the select transistor, and a far-channel region having thickness Tfar<Tnear and located at a side of the near-channel-region opposite the tunnel-region. A related method making such an EEPROM cell structure has corresponding steps.

Owner:SAMSUNG ELECTRONICS CO LTD