Patents

Literature

747results about "Computer designed circuits" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

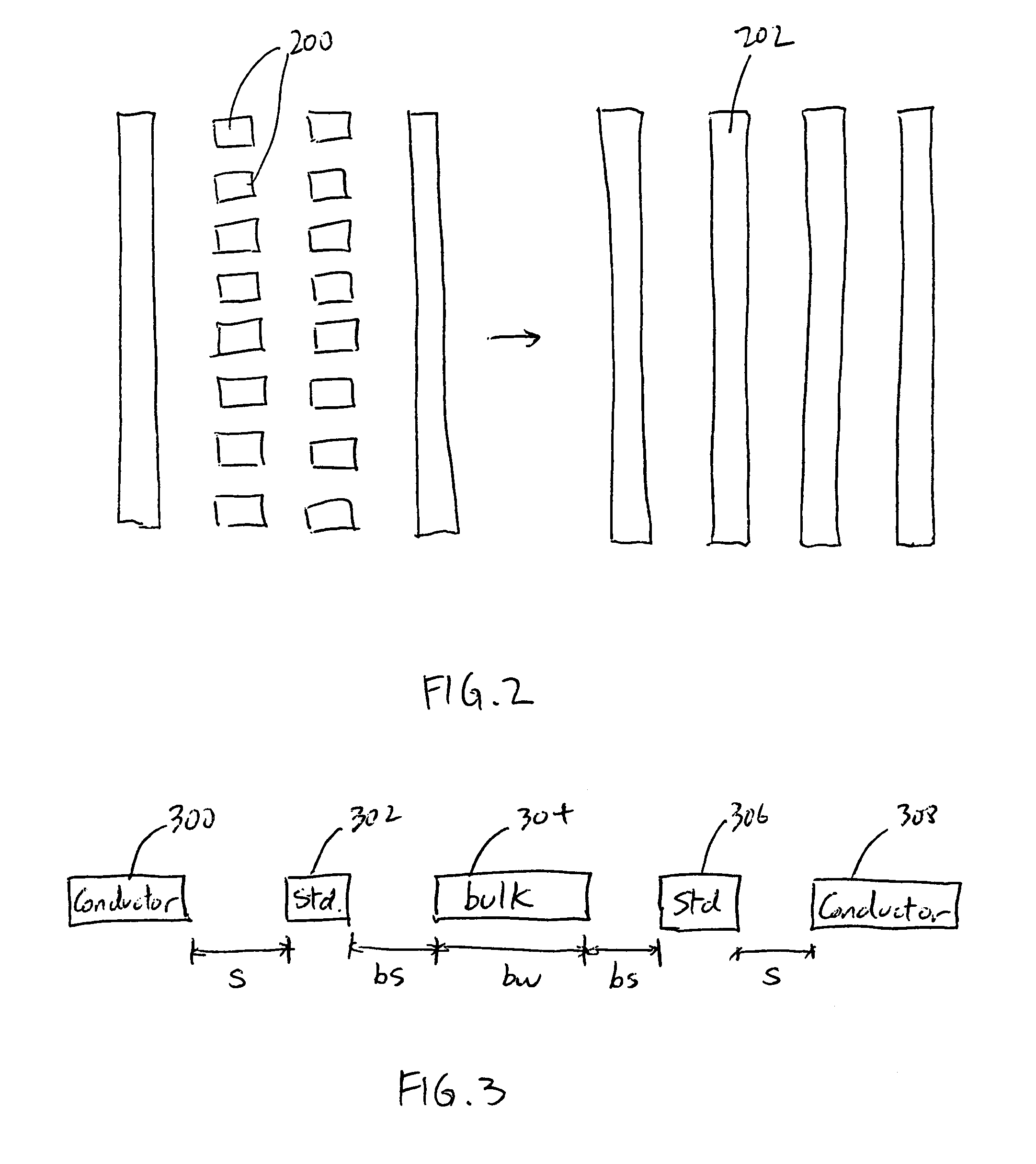

Methods and mechanisms for inserting metal fill data

A method for implementing virtual metal fill includes obtaining a layout record for a circuit design, and inserting metal fill data into the layout record based on one or more rules, wherein the metal fill data represents a consolidation of actual metal fill. A method for implementing virtual metal fill includes obtaining a layout record for a circuit design, and inserting metal fill data into the layout record, the metal fill data representing a virtual metal fill having a configuration that is different from a configuration of actual metal fill.

Owner:CADENCE DESIGN SYST INC

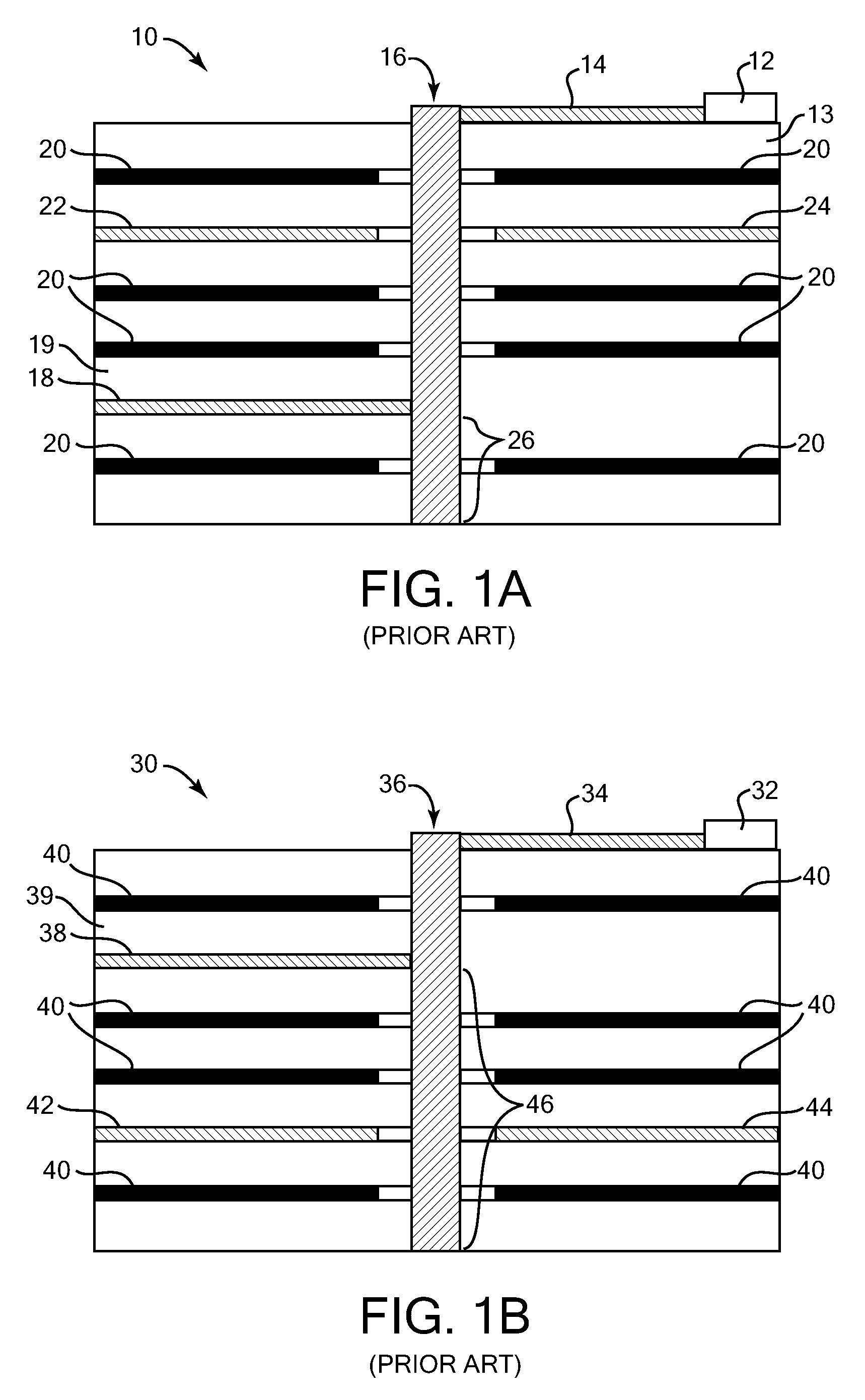

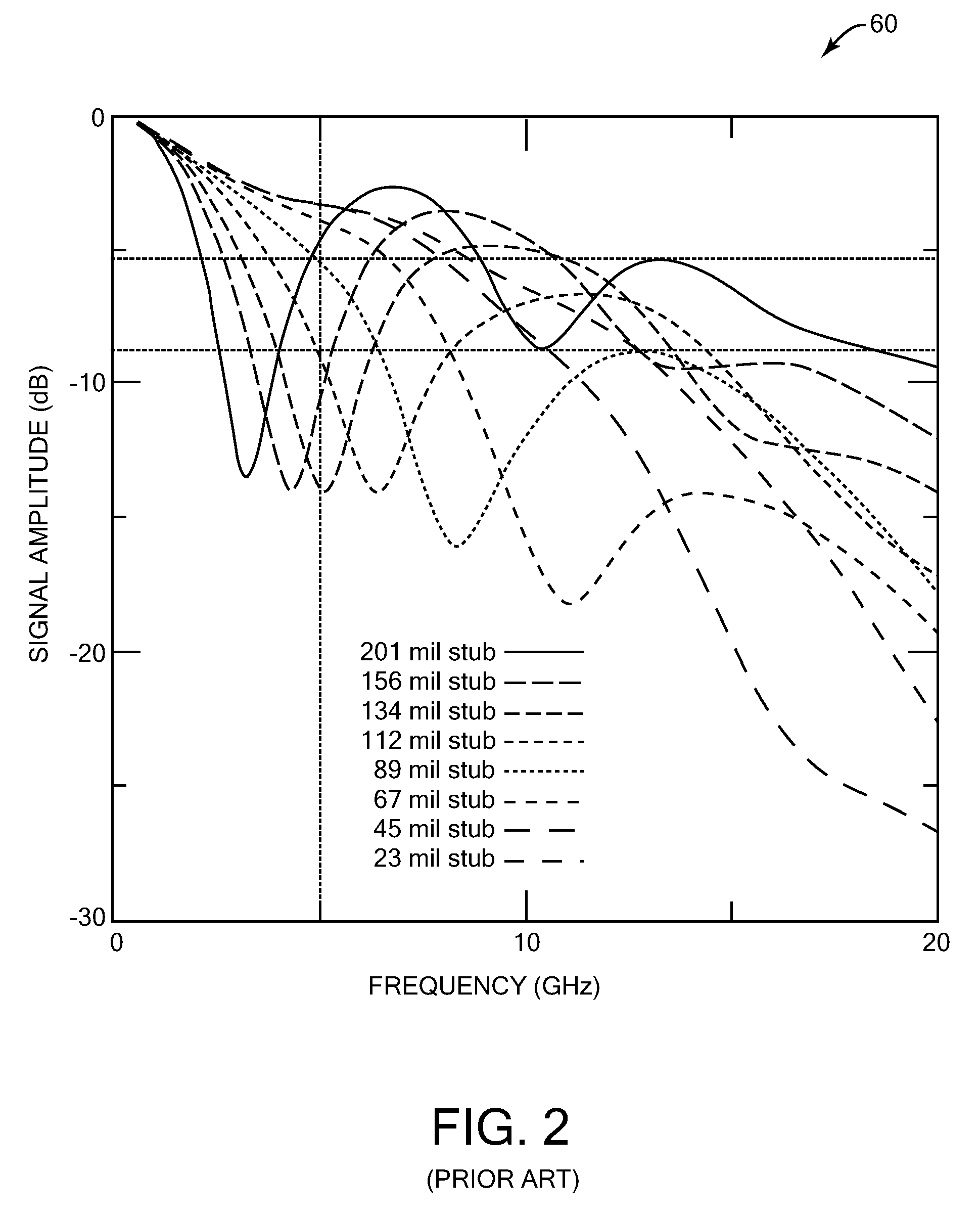

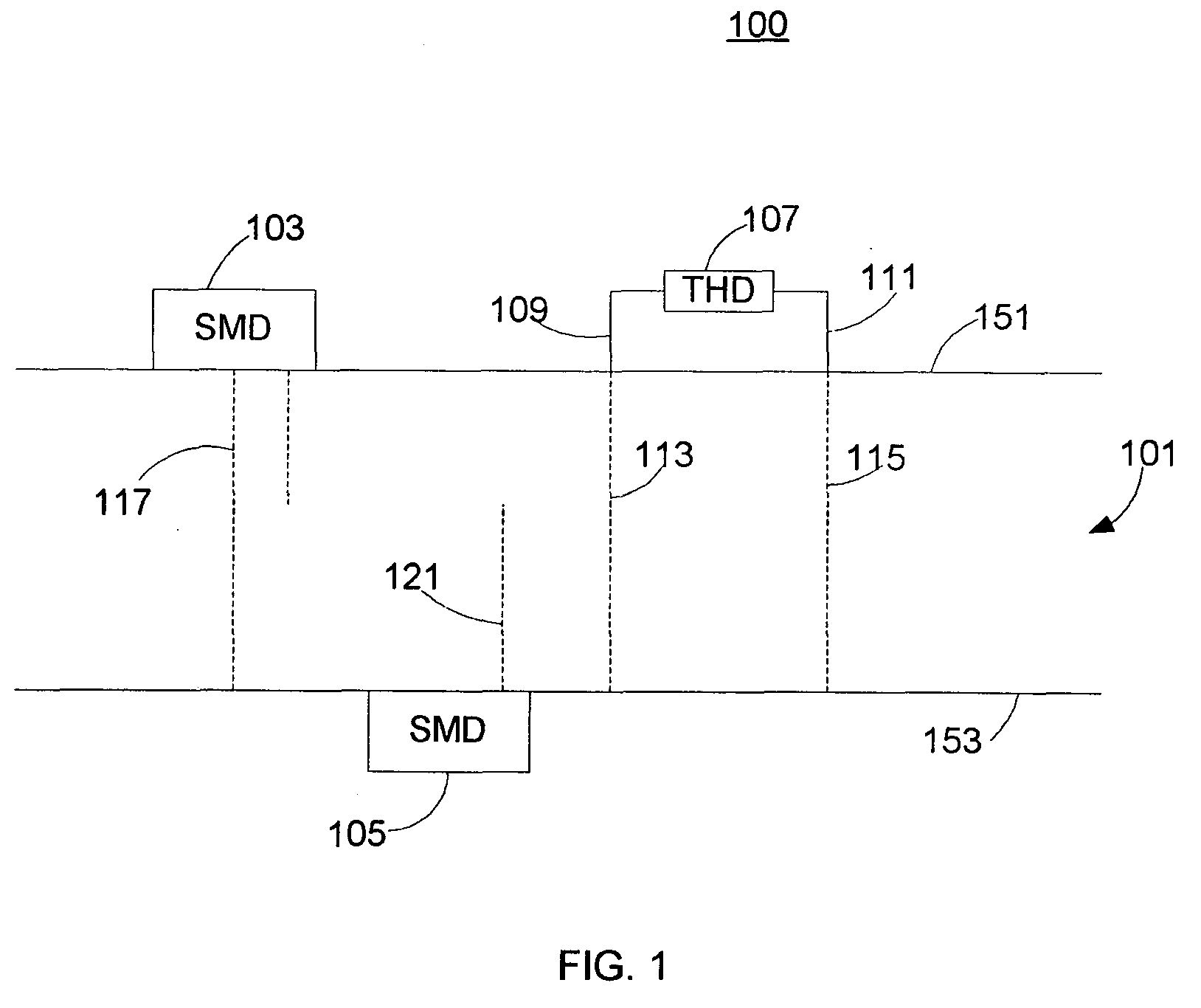

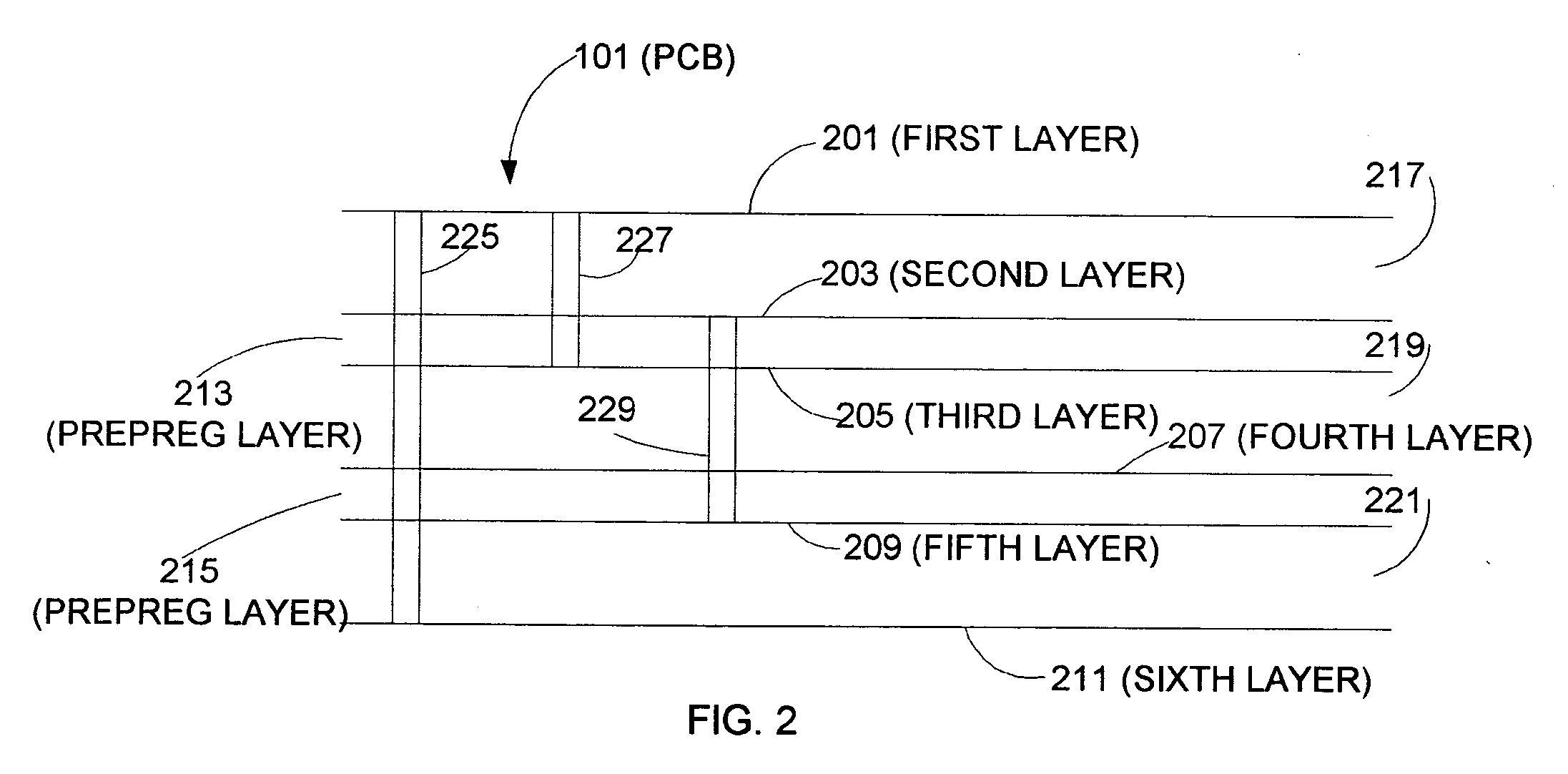

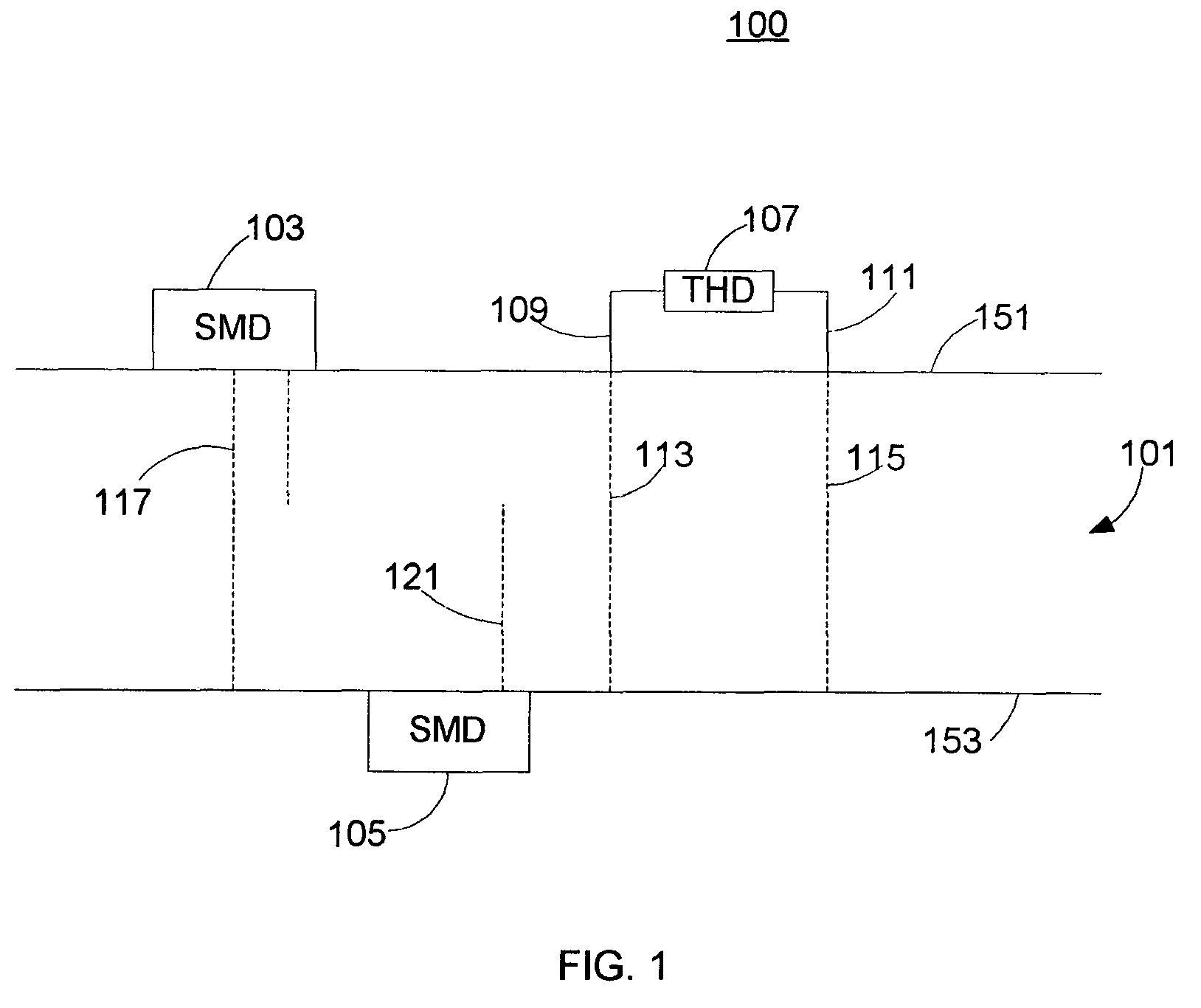

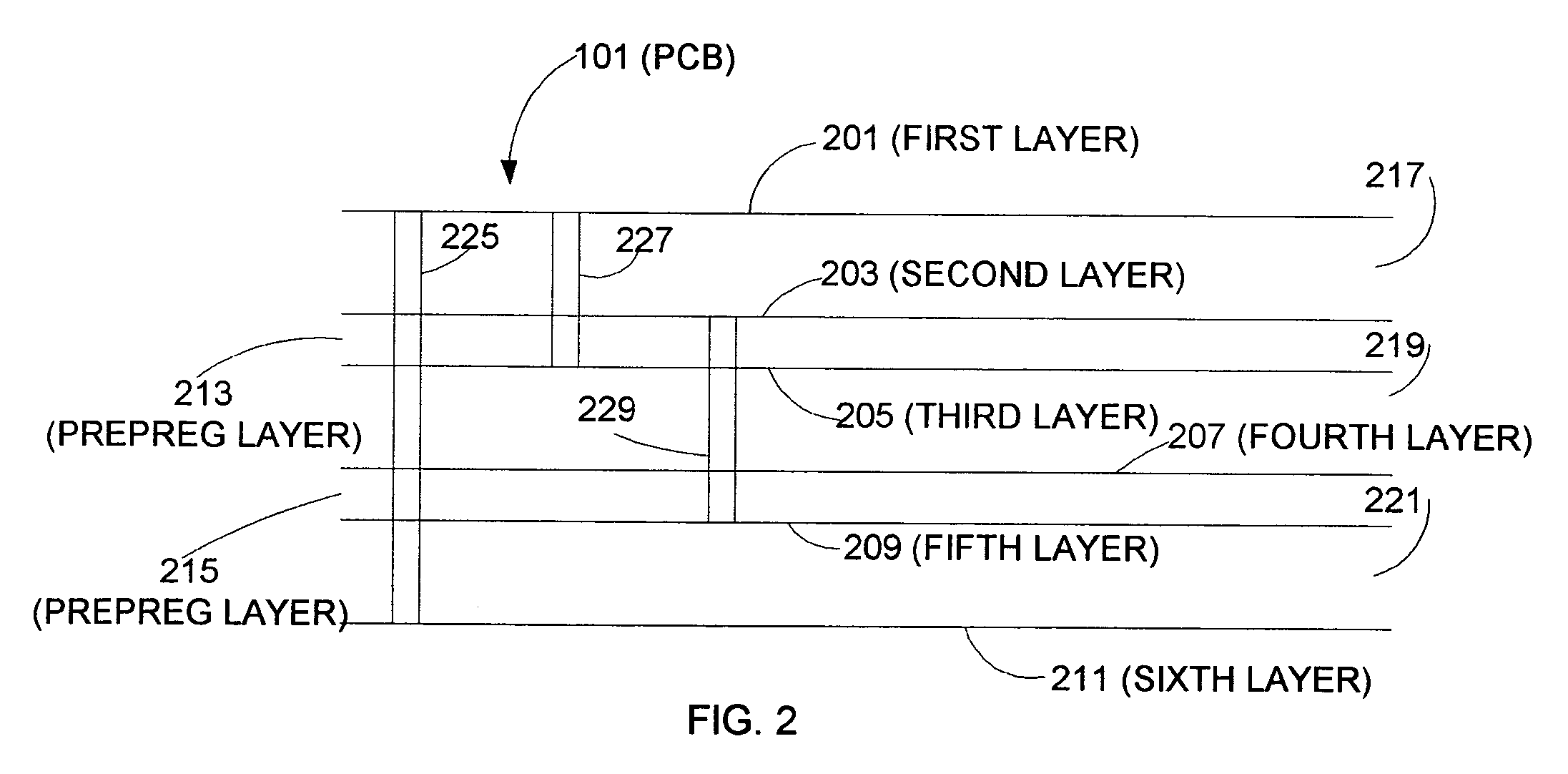

Method and system for reducing via stub resonance

InactiveUS20090049414A1Increase signal strengthReduce decreasePrinted circuit aspectsHigh frequency circuit adaptationsResonanceEngineering

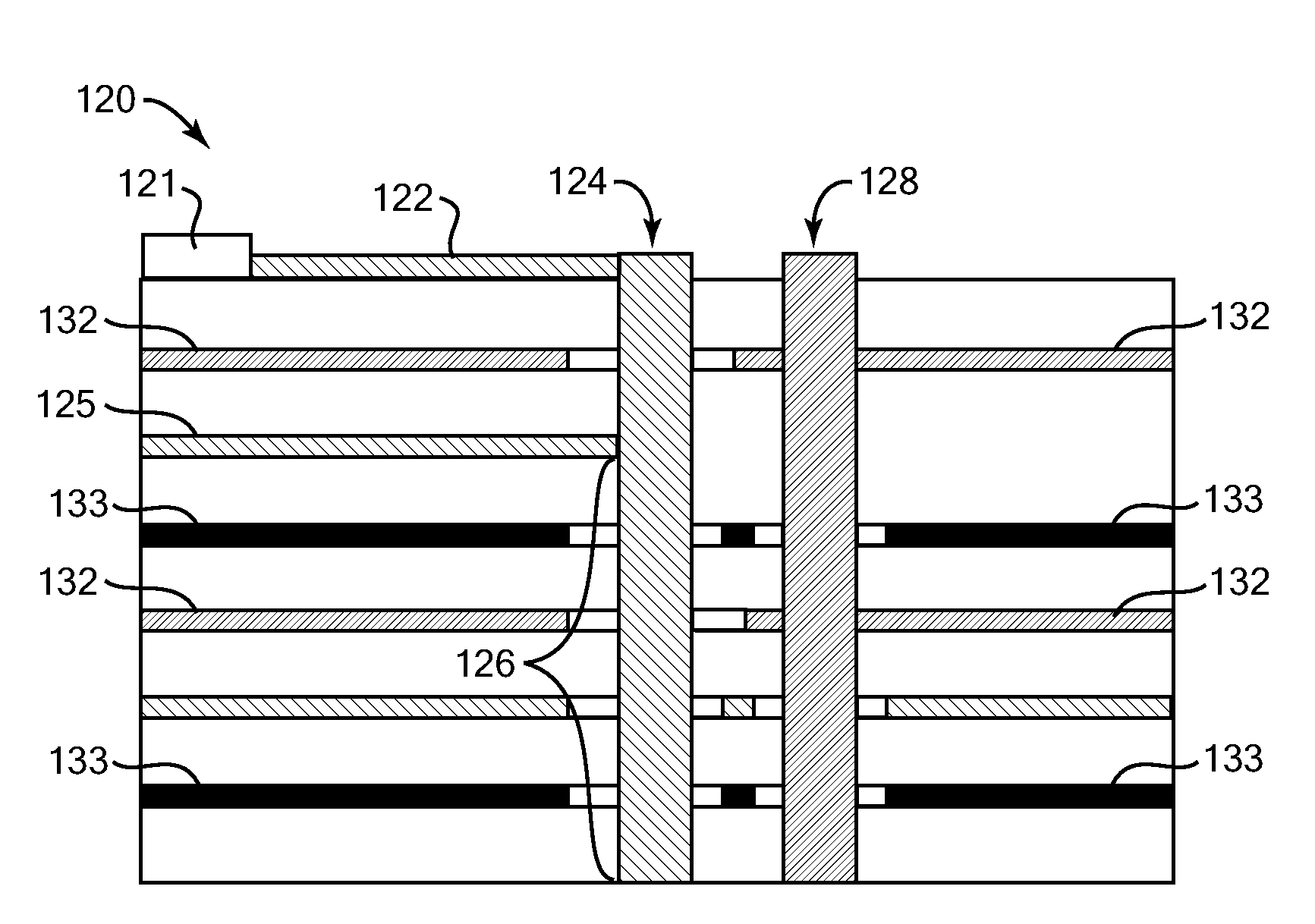

Reducing via stub resonance in printed circuit boards. In one aspect, a method for reducing via stub resonance in a circuit board includes determining that resonance exists for a signal to be transmitted through a signal via extending across a plurality of layers in the circuit board. The resonance is caused by a via stub of the signal via, the via stub extending past a layer connected to the signal via. A location is determined for a ground via to be placed relative to the signal via, the location of the ground via being determined based on reducing the resonance for the signal to be transmitted in the signal via.

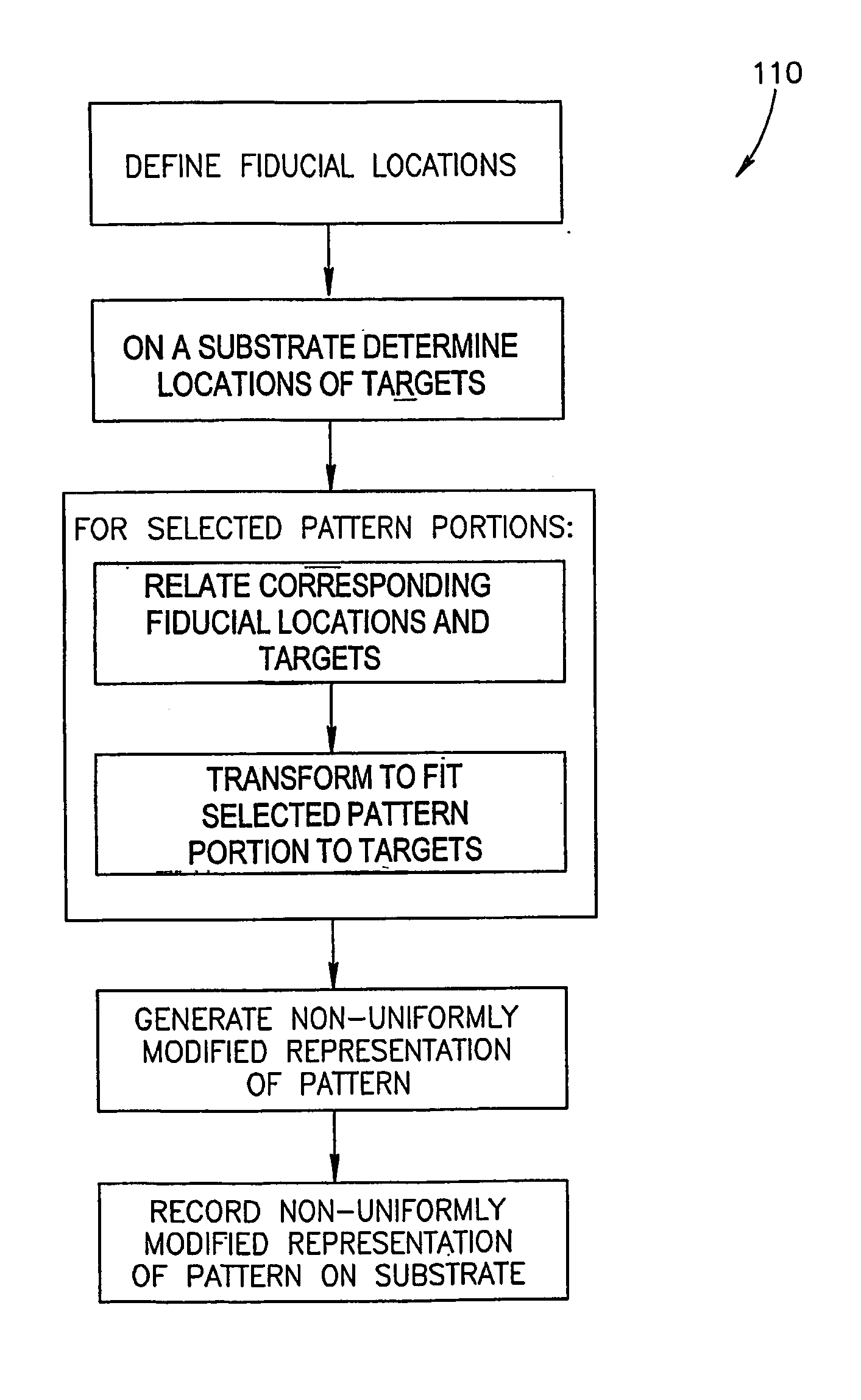

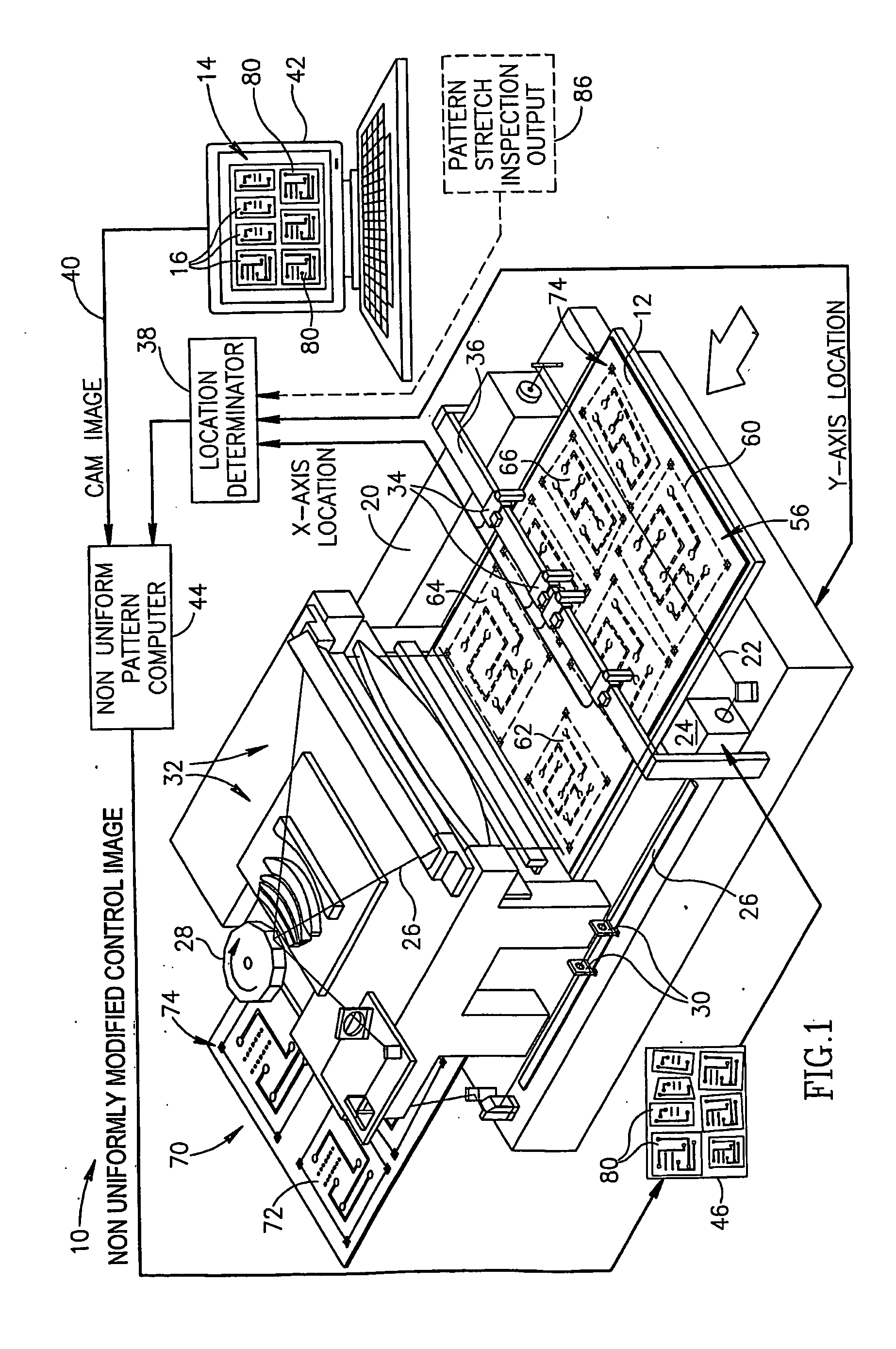

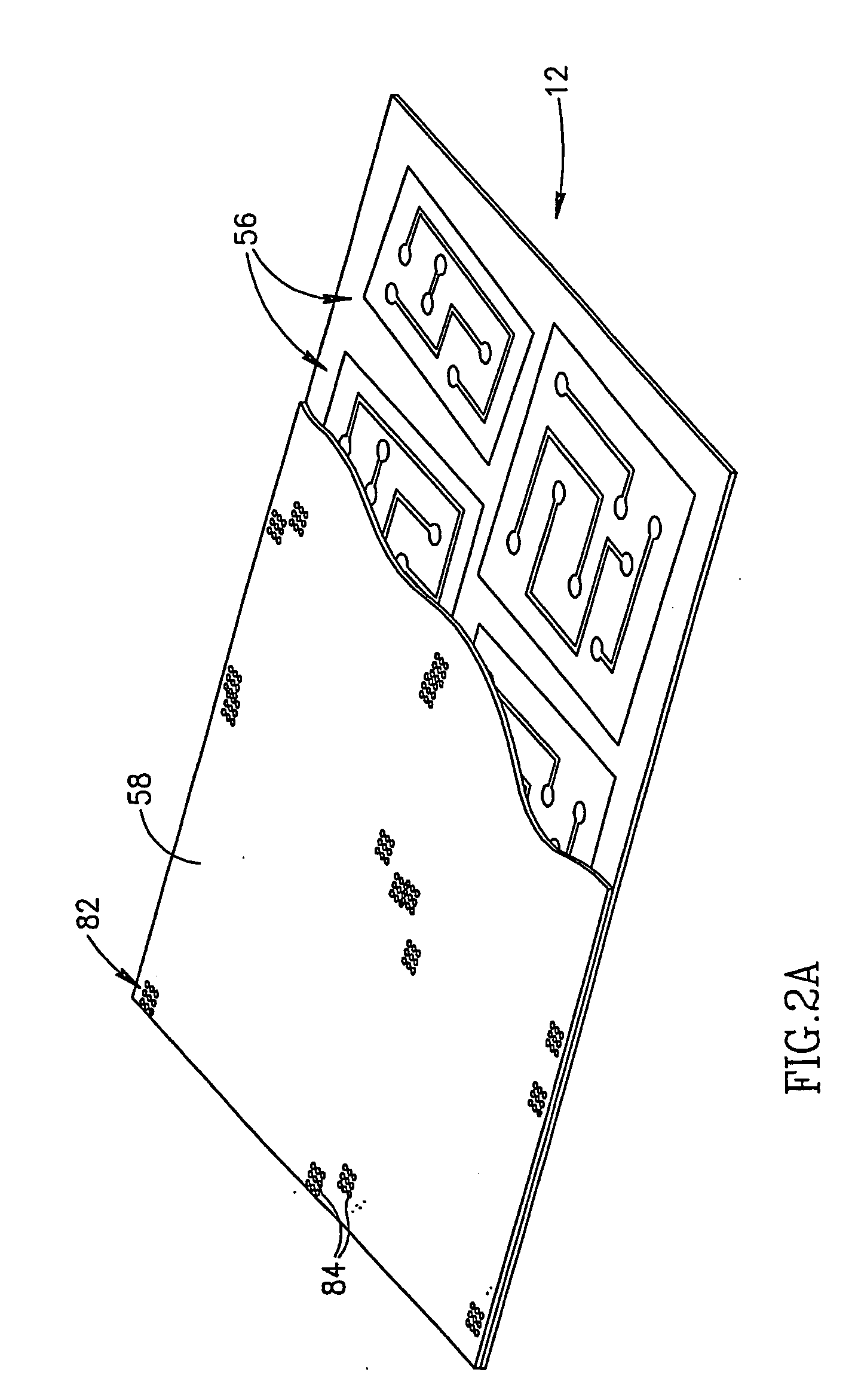

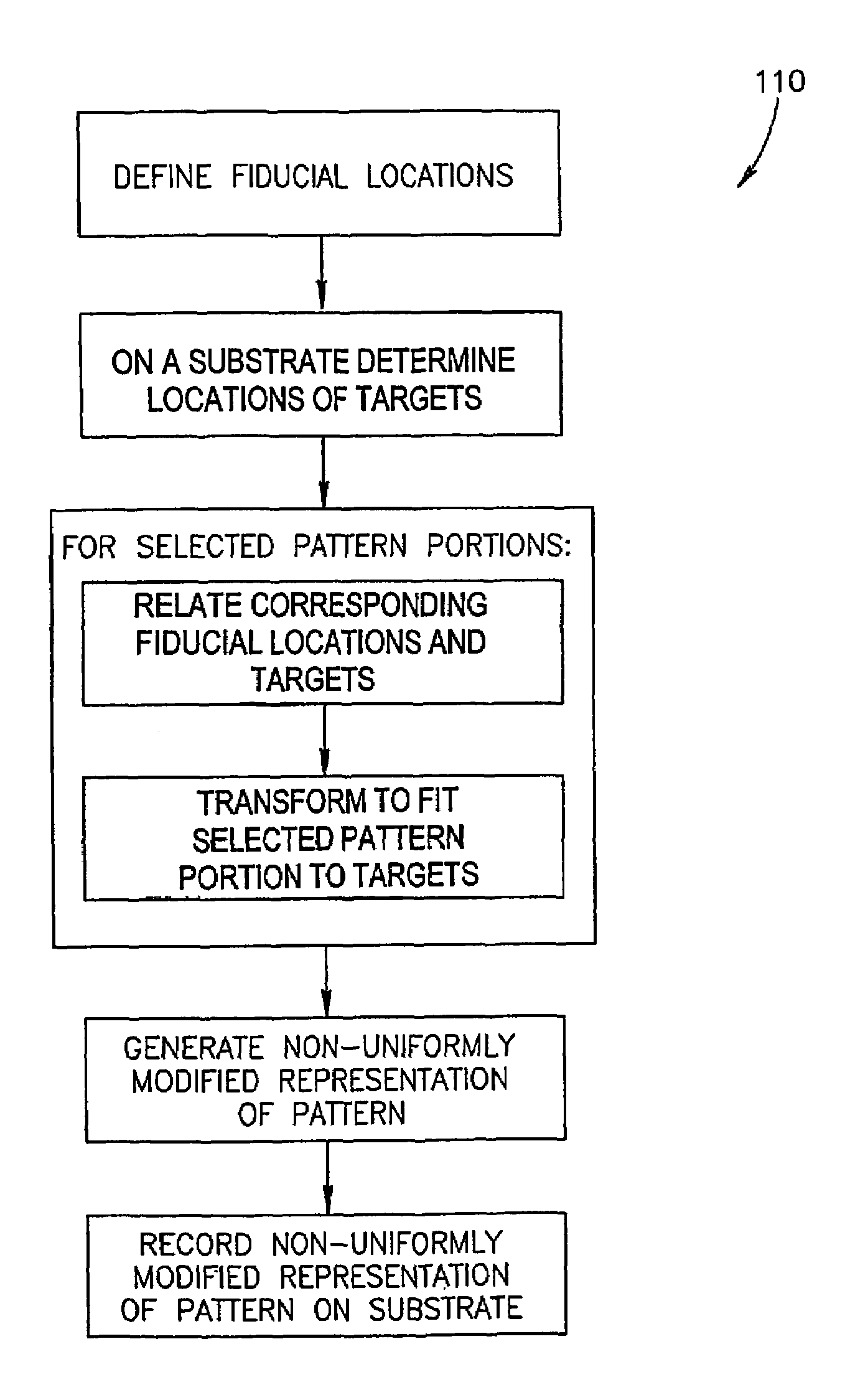

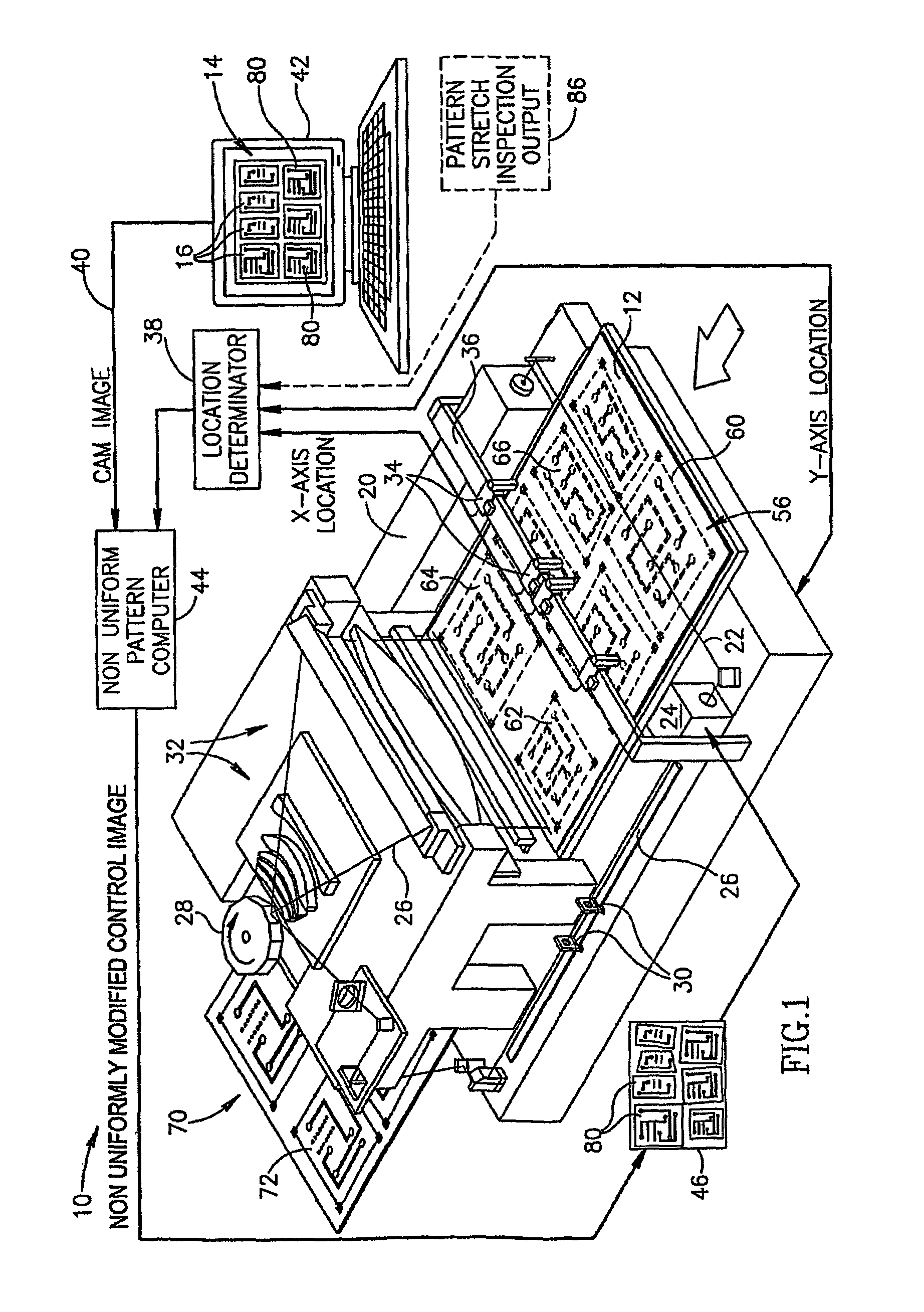

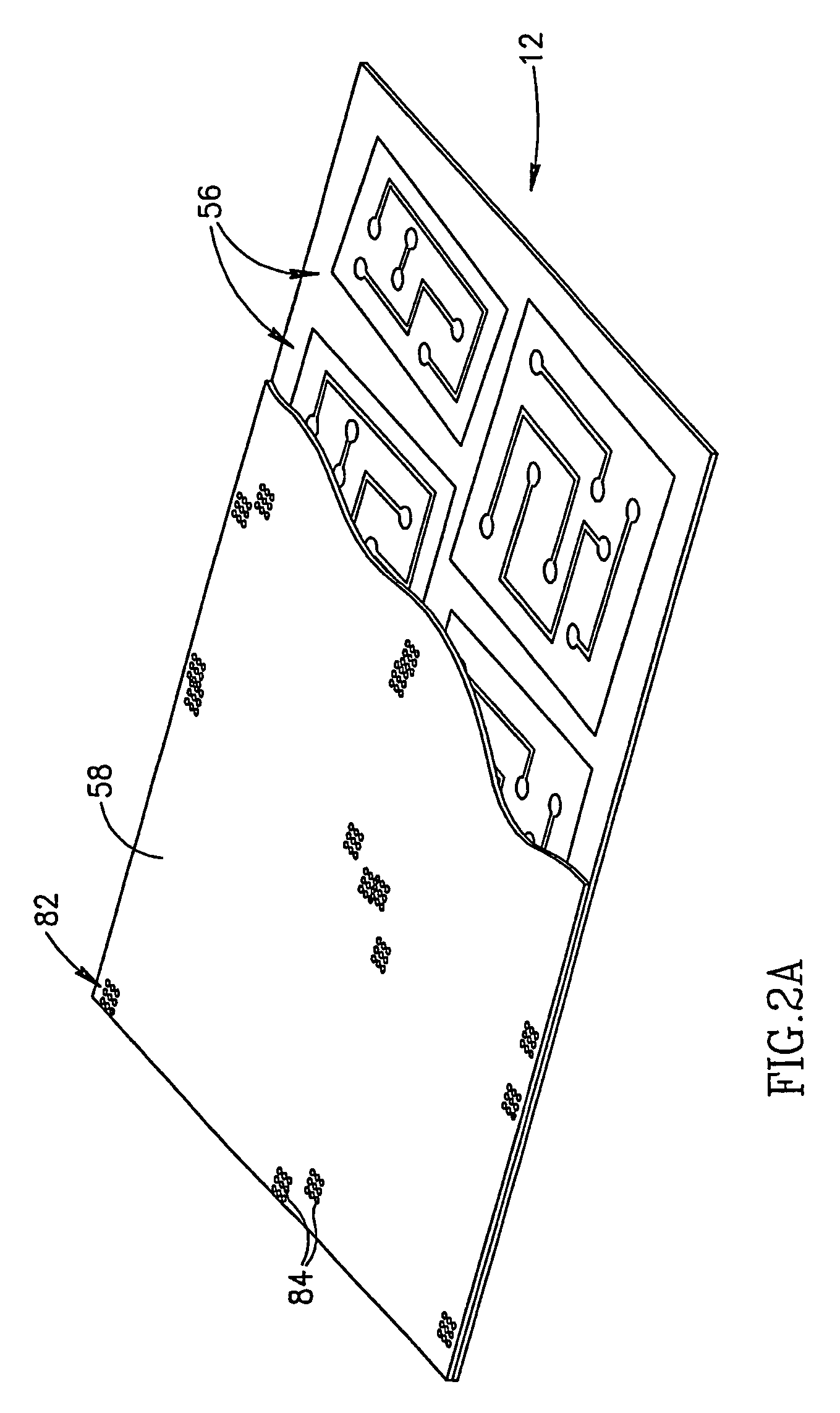

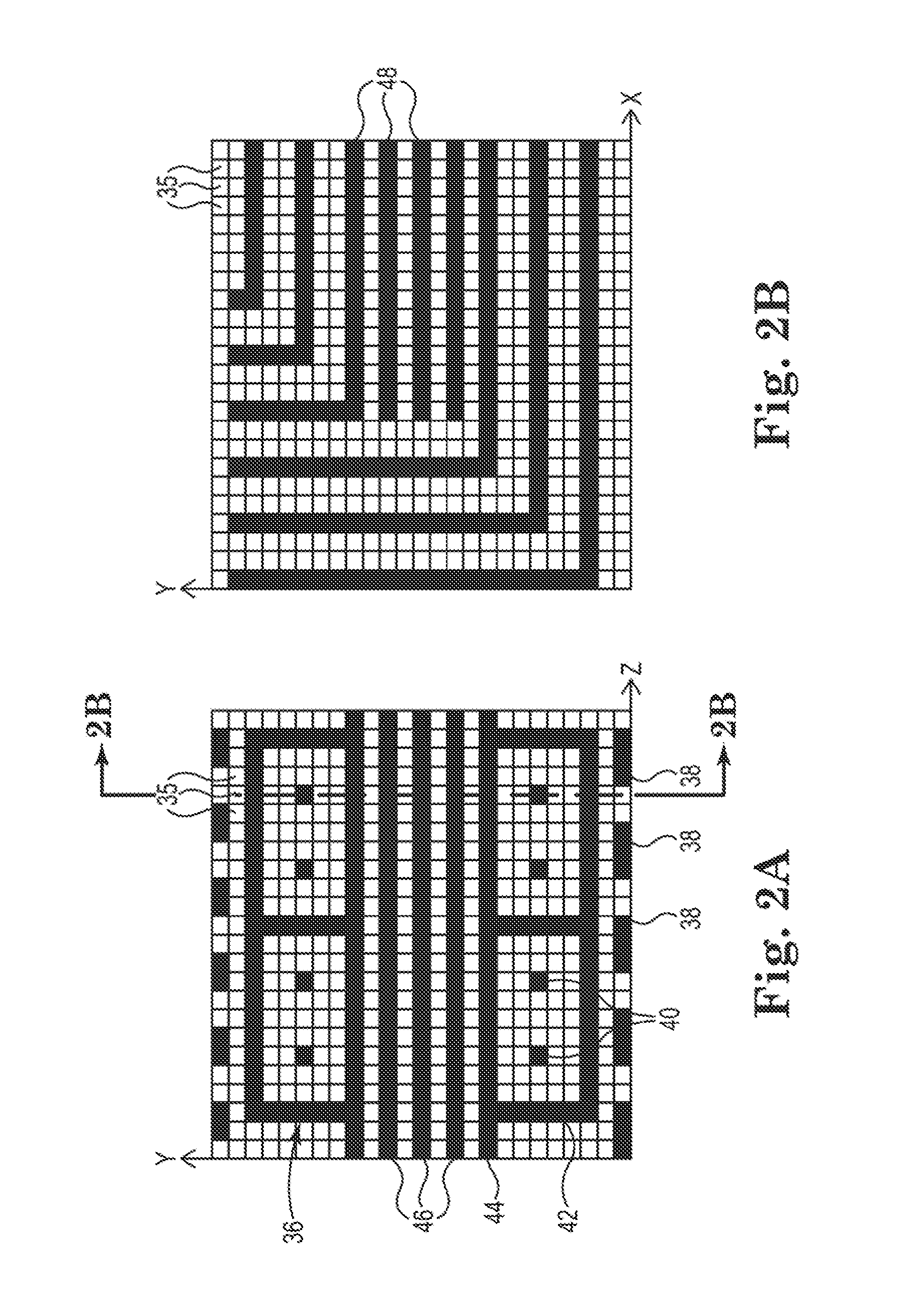

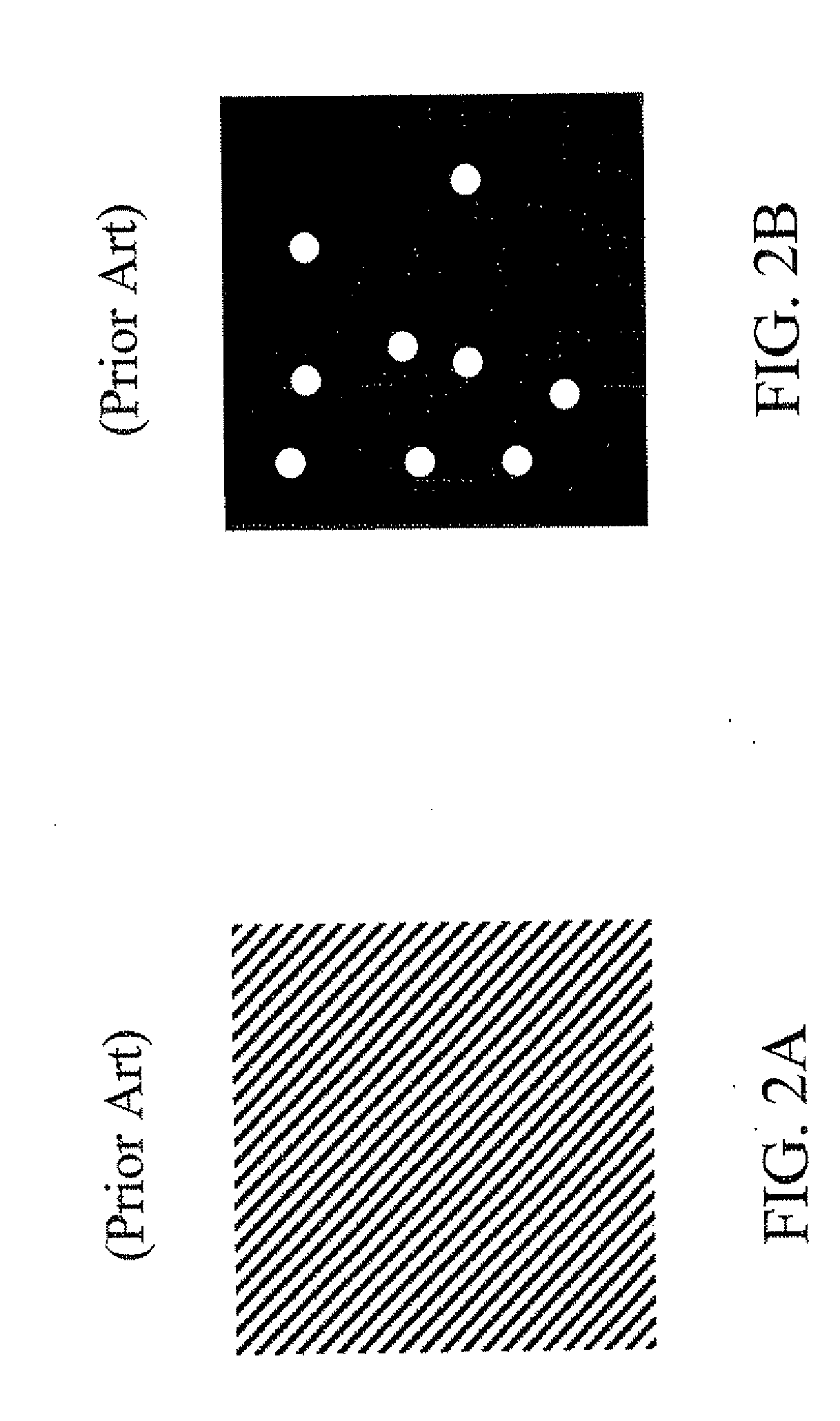

System and method for manufacturing printed circuit boards employing non-uniformly modified images

ActiveUS20050213806A1Non uniformCharacter and pattern recognitionCircuit board tools positioningEngineeringDigital control

A system and method for fabricating an electrical circuit in which a digital control image (46) is generated by non-uniformly modifying (44) a representation of an electrical circuit (40), such that an electrical circuit pattern (72) recorded on a substrate (12) using the digital control image (46) precisely fits an already formed electrical circuit portion (62).

Owner:ORBOTECH LTD

System and method for manufacturing printed circuit boards employing non-uniformly modified images

ActiveUS7508515B2Circuit board tools positioningCharacter and pattern recognitionEngineeringDigital control

A system and method for fabricating an electrical circuit in which a digital control image (46) is generated by non-uniformly modifying (44) a representation of an electrical circuit (40), such that an electrical circuit pattern (72) recorded on a substrate (12) using the digital control image (46) precisely fits an already formed electrical circuit portion (62).

Owner:ORBOTECH LTD

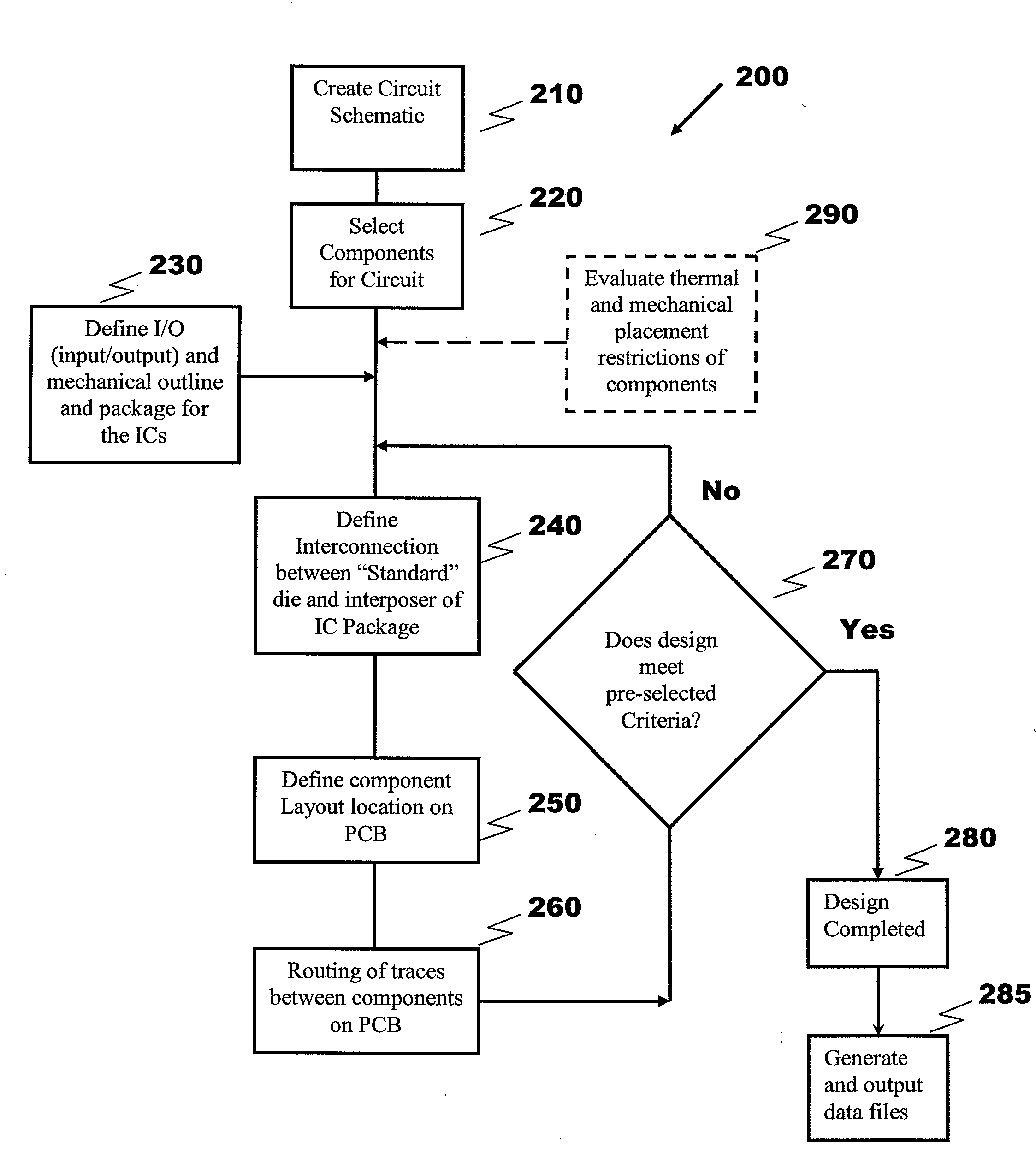

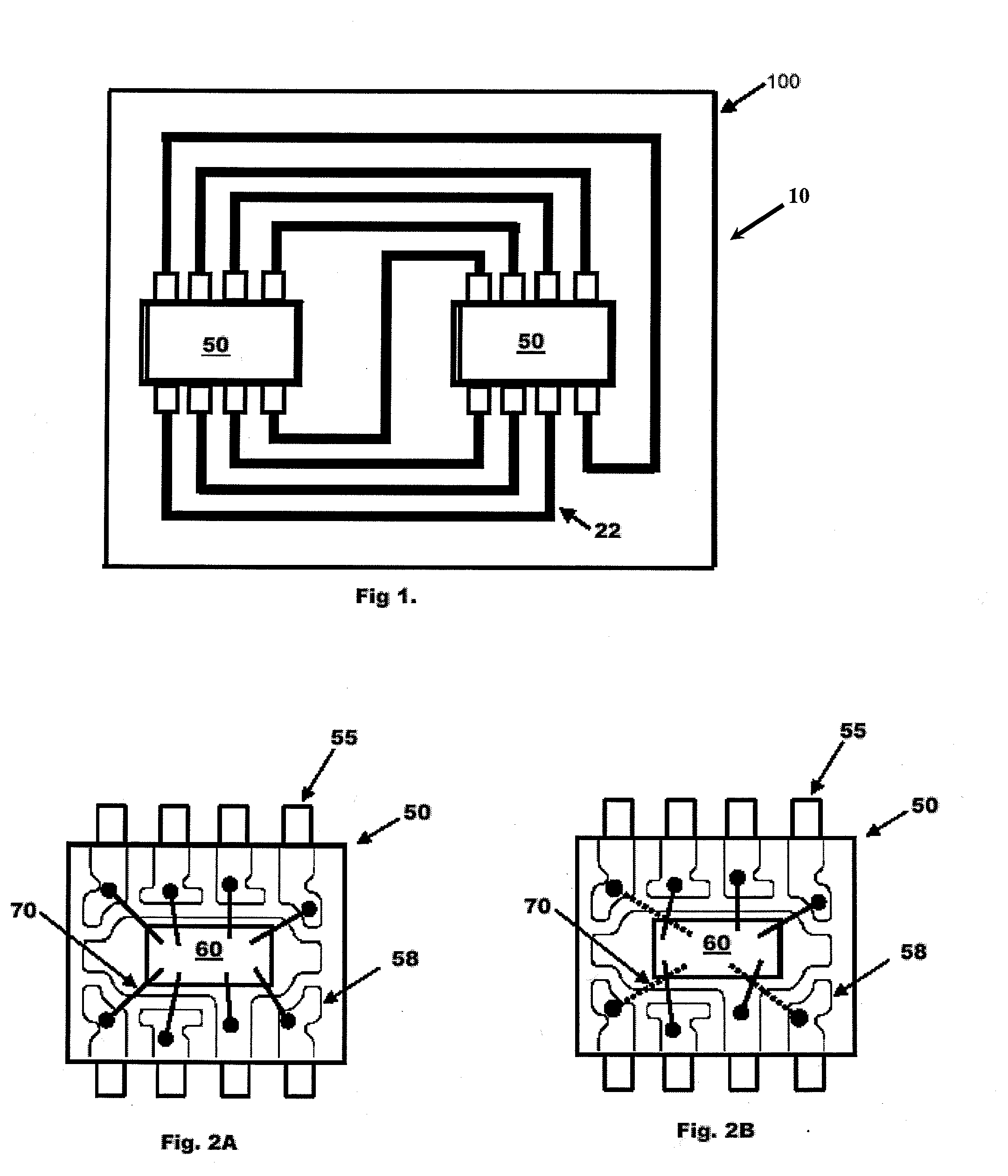

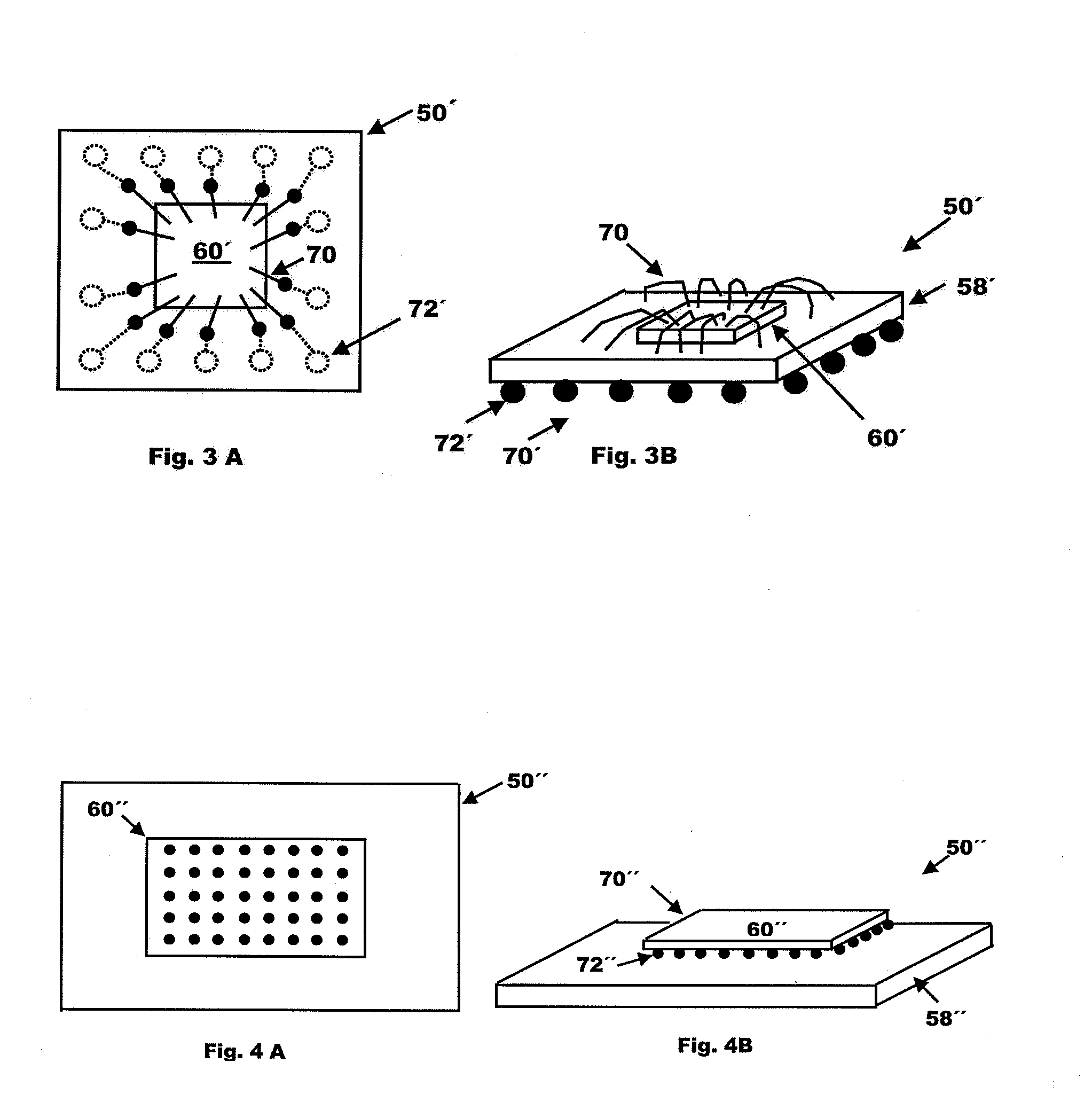

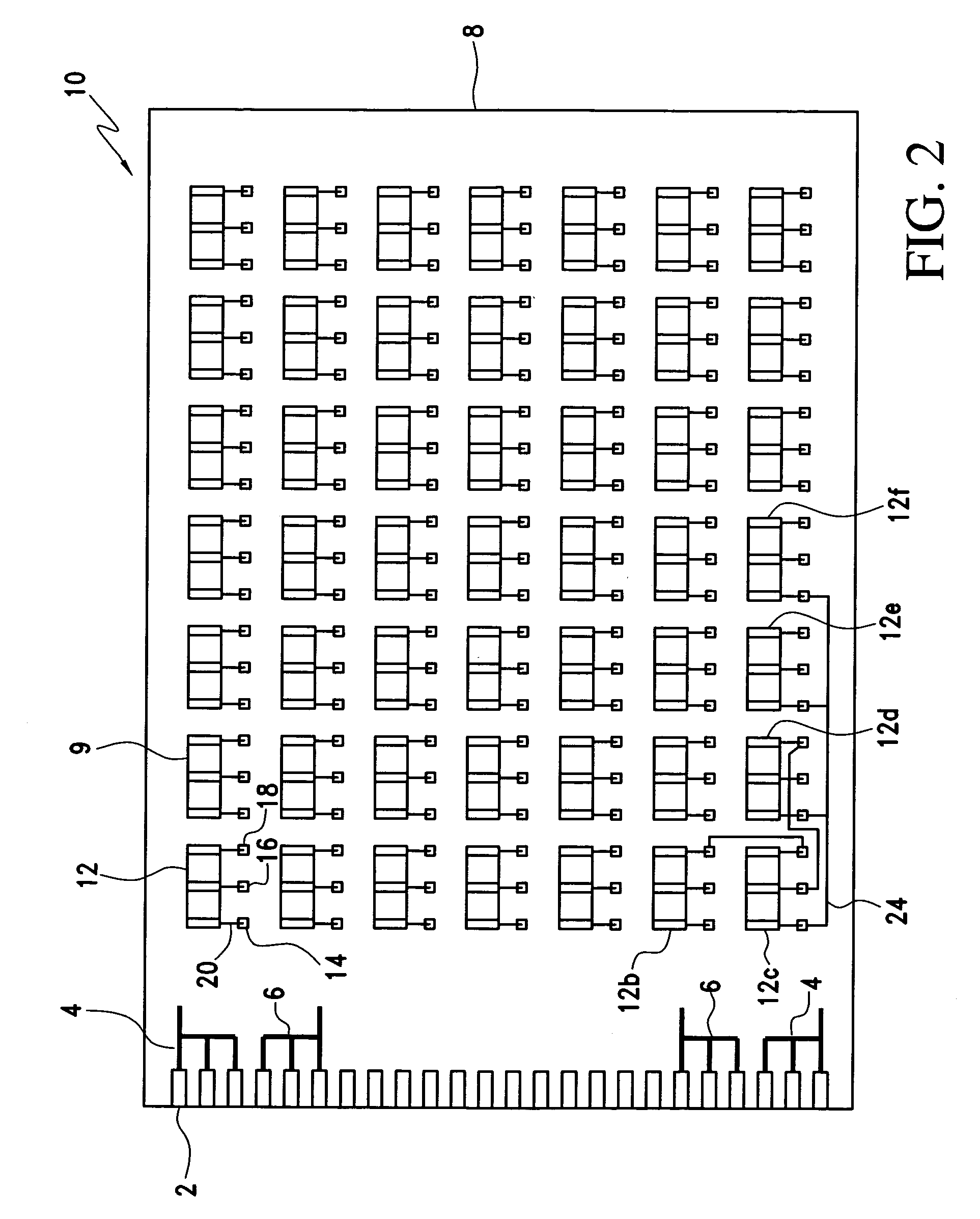

Simultaneous design of integrated circuit and printed circuit board

InactiveUS20080288908A1Optimal PCB circuit assembly designPrinted circuit aspectsSolid-state devicesInterconnectionIntegrated circuit layout

A printed circuit board (PCB) circuit assembly is designed utilizing software to create the best performing “total design” by selecting component layout locations, optimizing the circuit routing of the PCB copper (or other metallic) traces, and simultaneously optimizing the interconnections between a “standard” die inside an integrated circuit (IC) package and an interposer substrate of the IC package.

Owner:MIRROR SEMICON

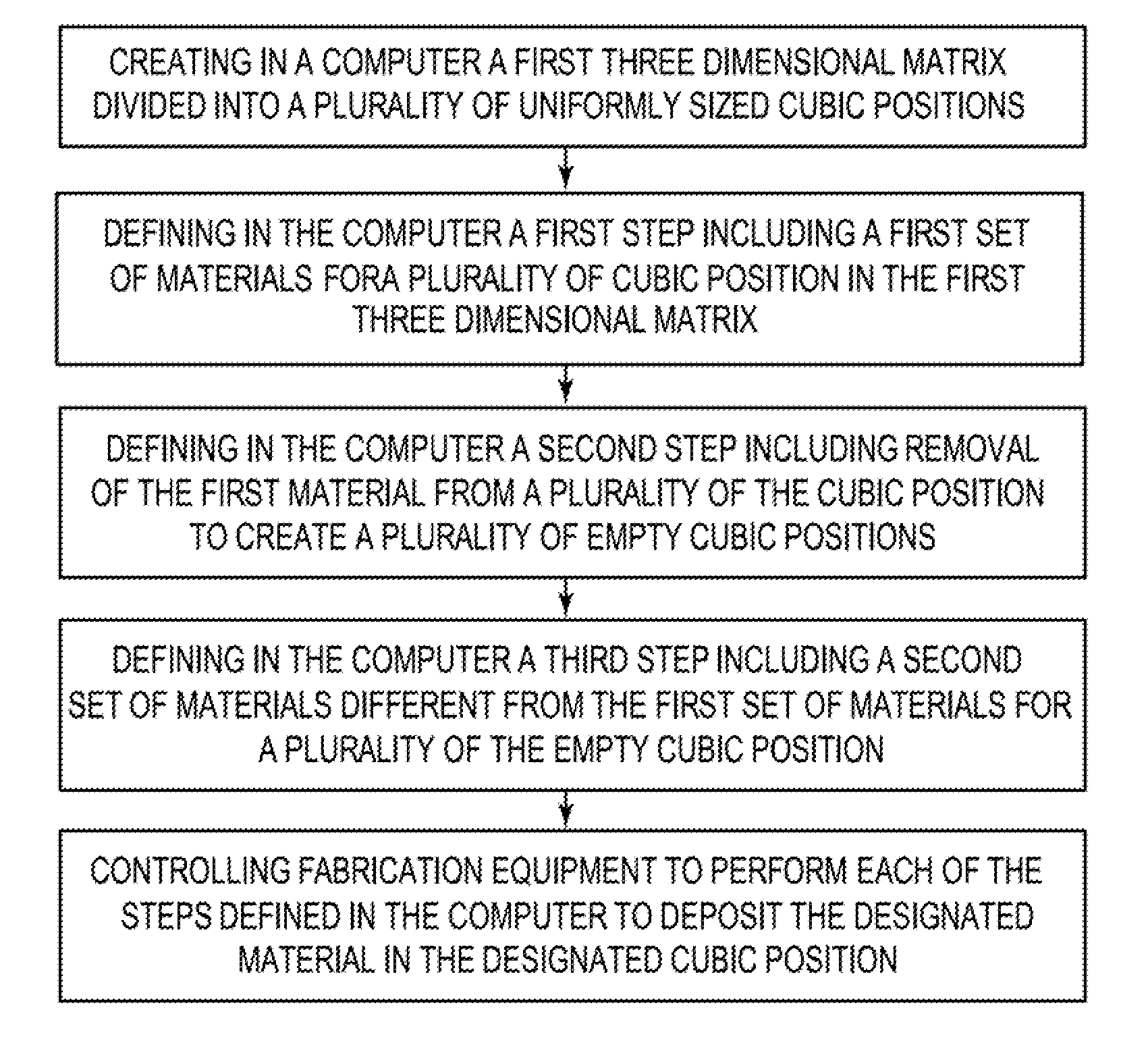

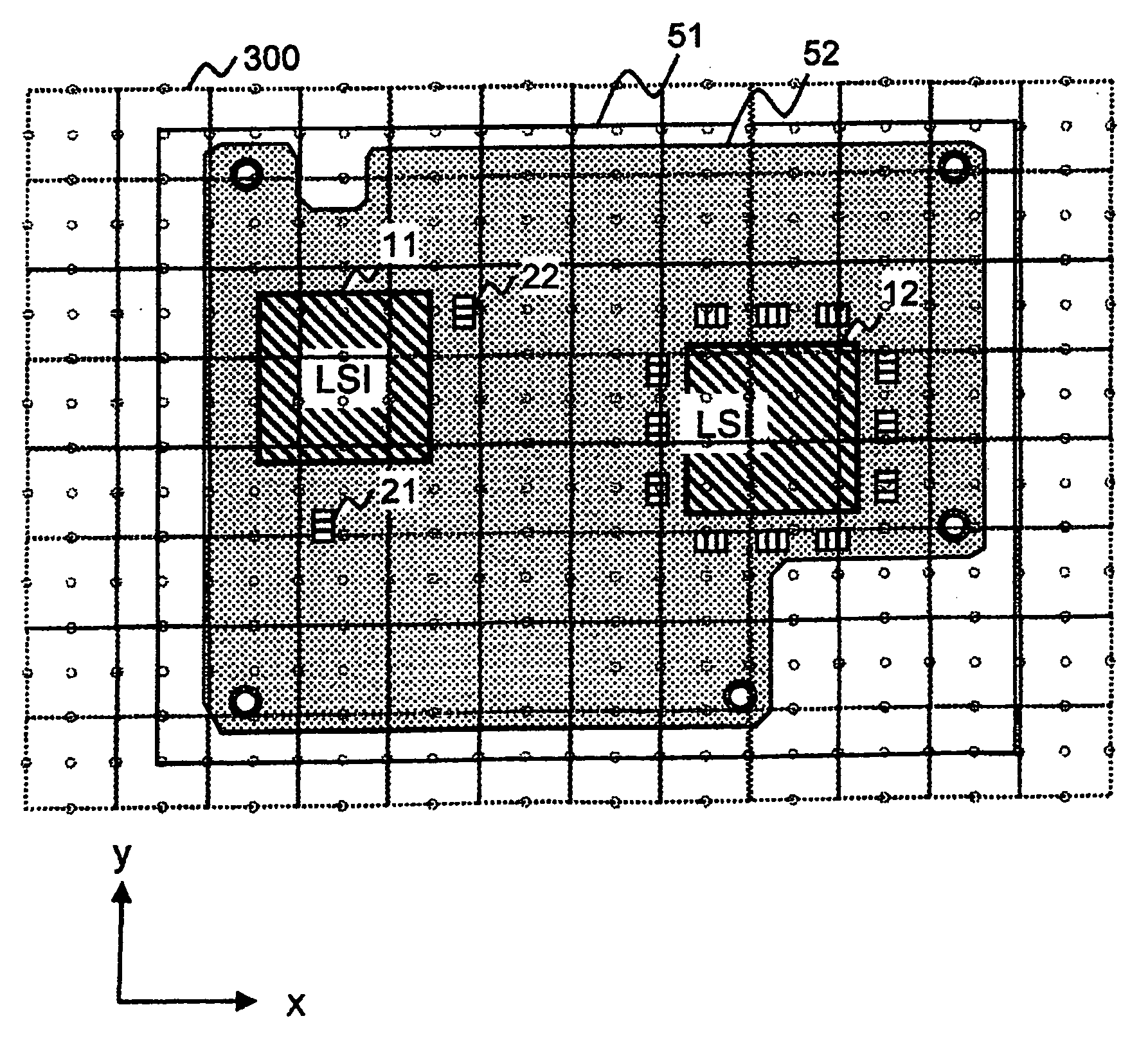

Matrix defined electrical circuit structure

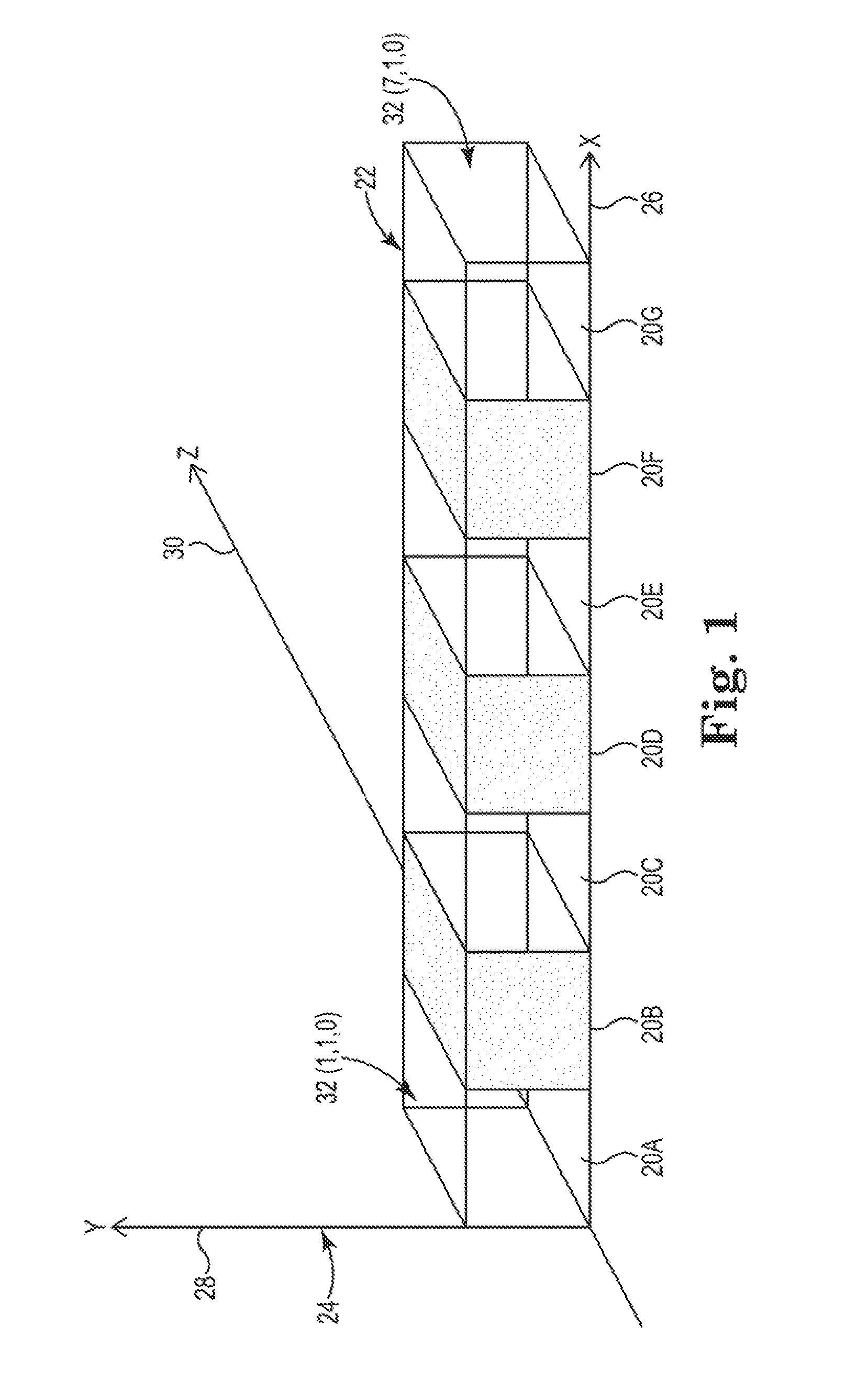

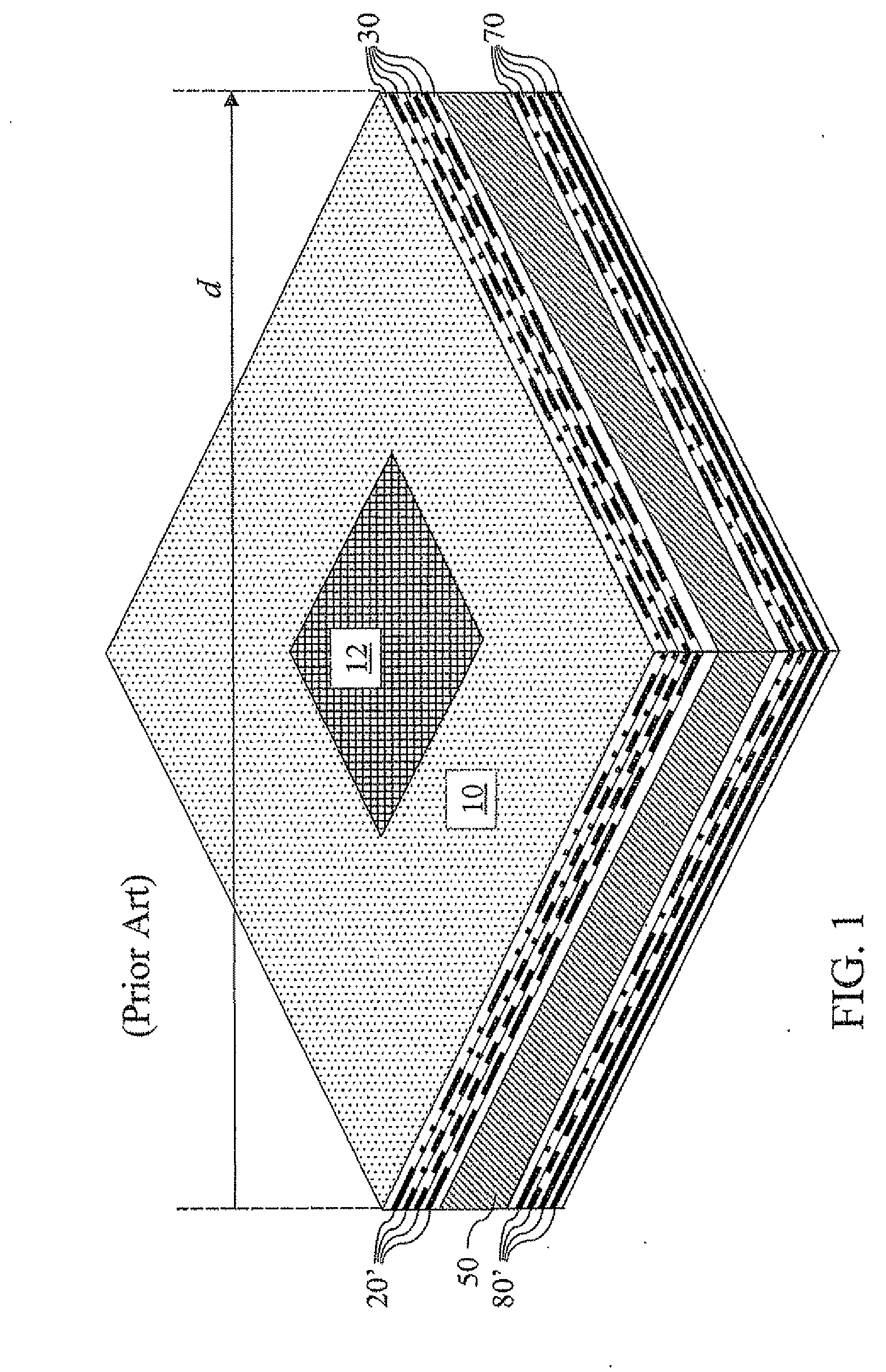

InactiveUS20150013901A1Without tooling or costly artworkReduce environmental problemsSolid-state devicesSemiconductor/solid-state device manufacturingComputer Aided DesignThree dimensional matrix

A system and method for “pixelating” a three-dimensional circuit structure into a three-dimensional matrix of cubes that are located with respect to a coordinate system. The design step is typically performed on a conventional computer using computer aided design software that pixelates the proposed circuit structure into an array of uniformly sized cube. The fabrication process involves adding and subtracting bulk materials from the individual cubic positions within the pixelated representation of the circuit structure. Various existing and new techniques can be used to add or subtract bulk materials as the cubic positions within the matrix to construct the circuit structure.

Owner:HSIO TECH

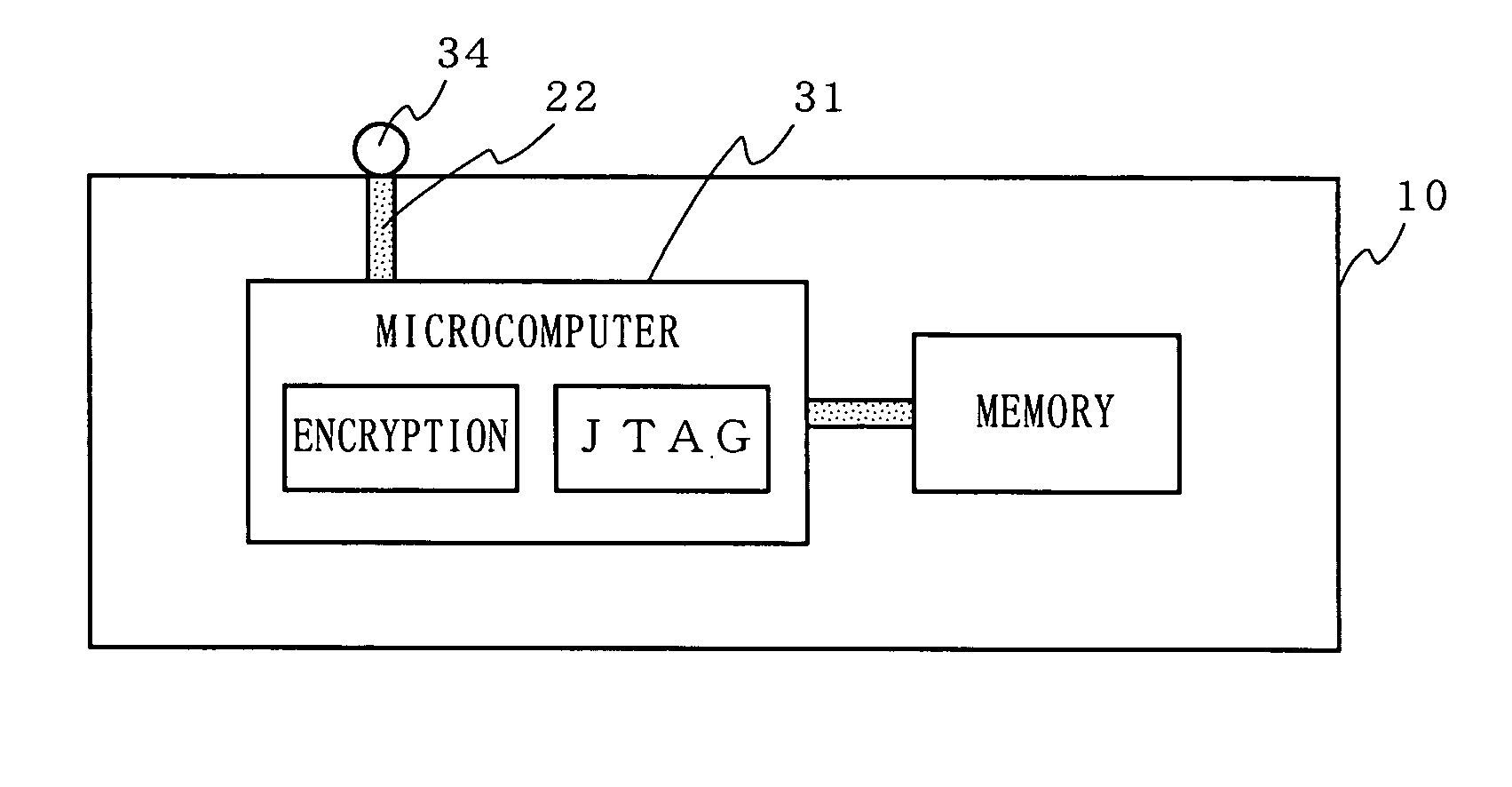

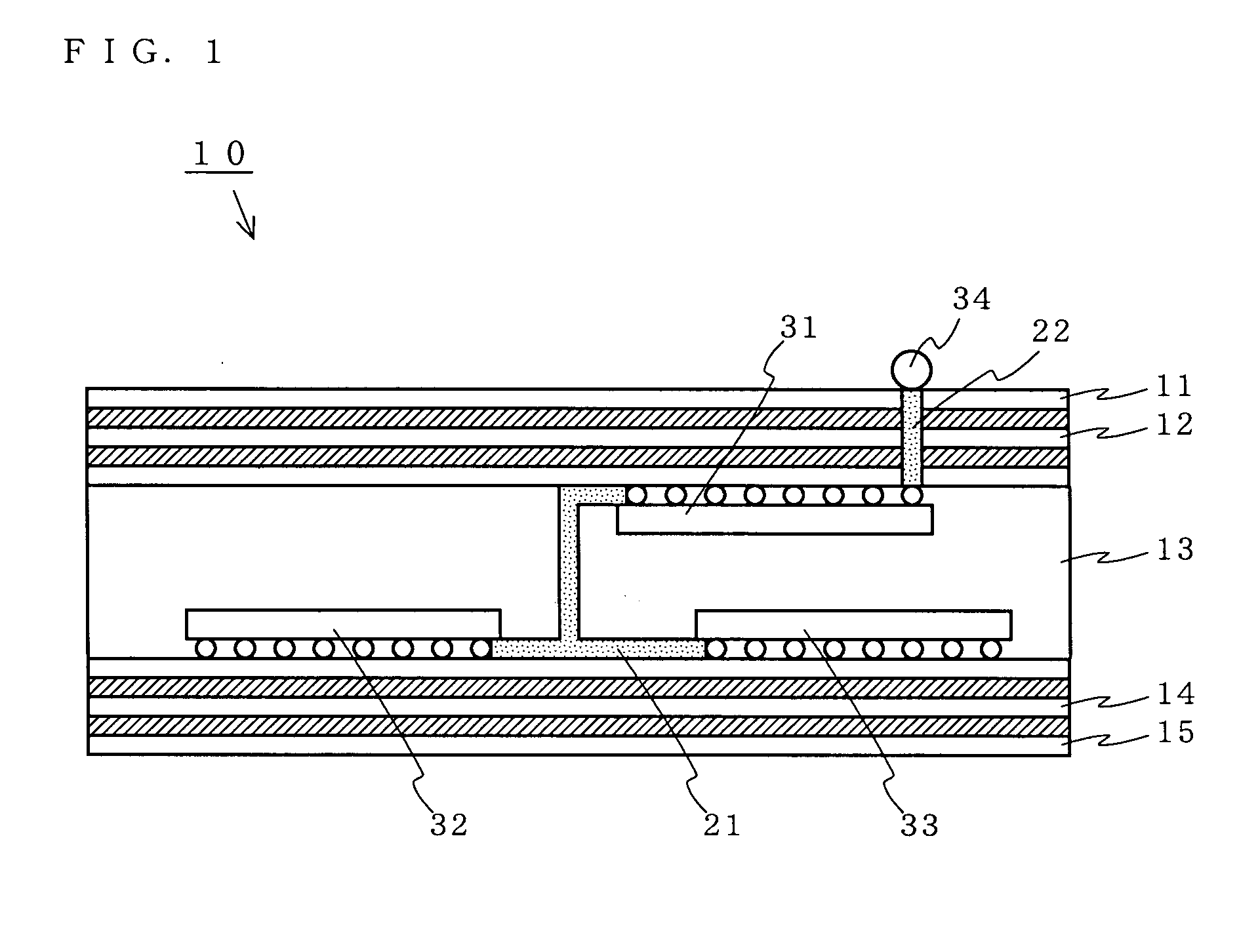

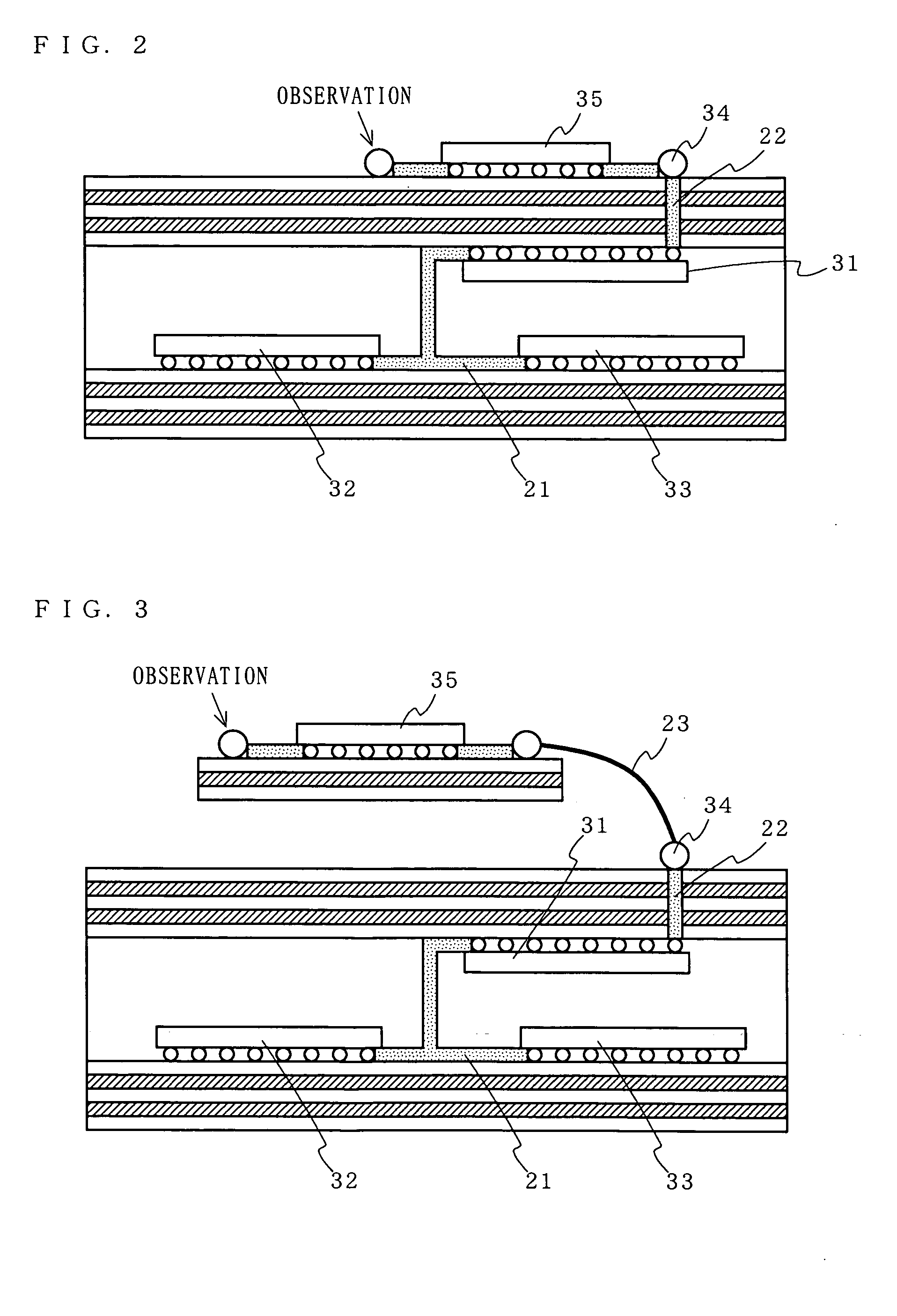

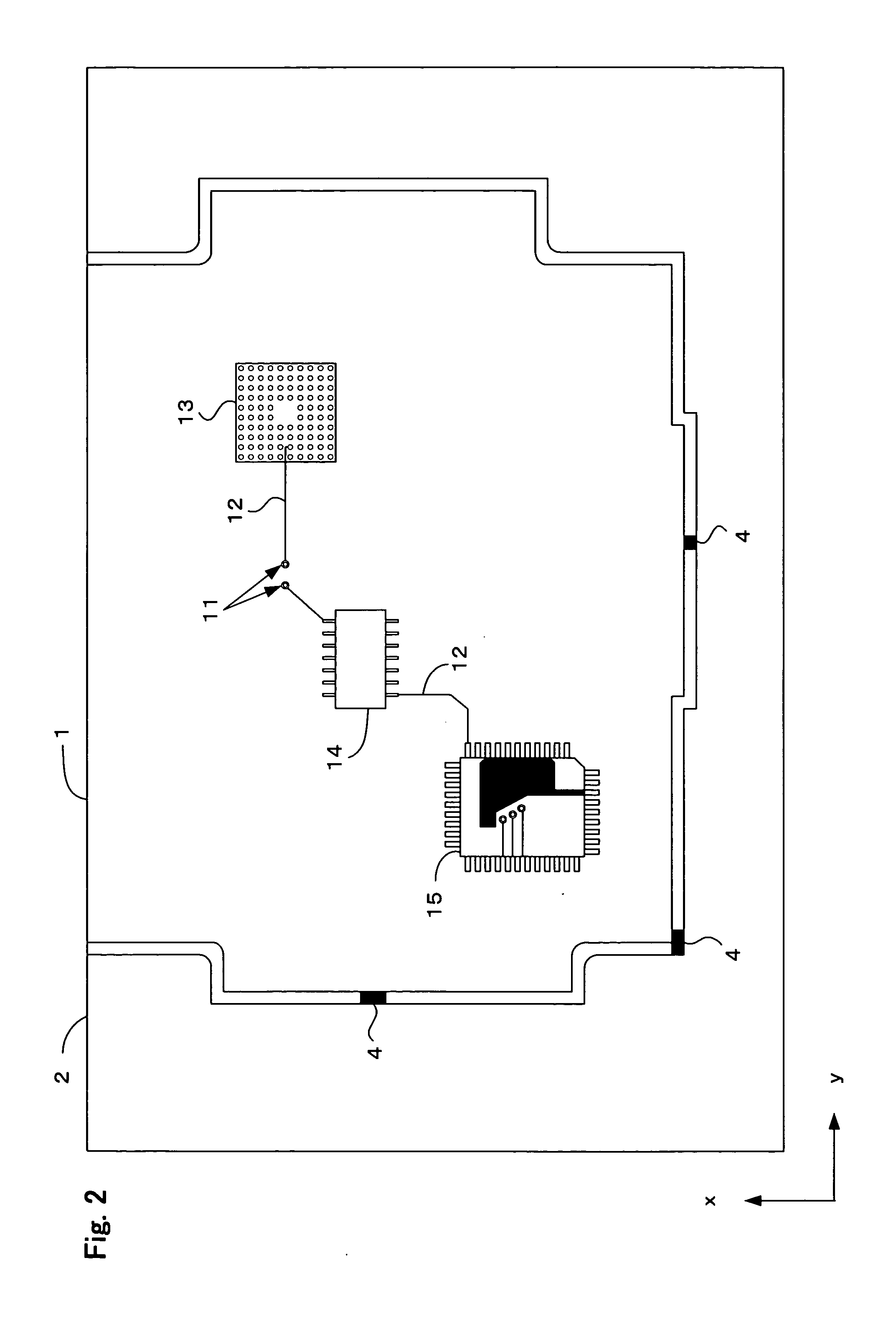

Mobile terminal, circuit board, circuit board design aiding apparatus and method, design aiding program, and storage medium having stored therein design aiding program

InactiveUS20050081049A1Improve tamper resistanceSolve the real problemSolid-state devicesAnalogue computers for electric apparatusThird partyTamper resistance

A circuit board is provided in which tamper resistance is improved by making probing by third parties difficult, while solving problems associated with the current techniques and manufacturing costs. A signal line through which a confidential signal requiring tamper resistance flows and components 32 and 33 connected to the signal line 21 by the terminals thereof, are laid out in a component-containing layer 13 of a circuit board 10. Only a confidential signal having been encrypted through a predetermined component 31 is outputted to an observation point 34 provided on a surface of the circuit board 10. External observation and control of the confidential signal is performed by decoding a cipher provided by the component 31 to the signal which appears at the observation point 34.

Owner:PANASONIC CORP

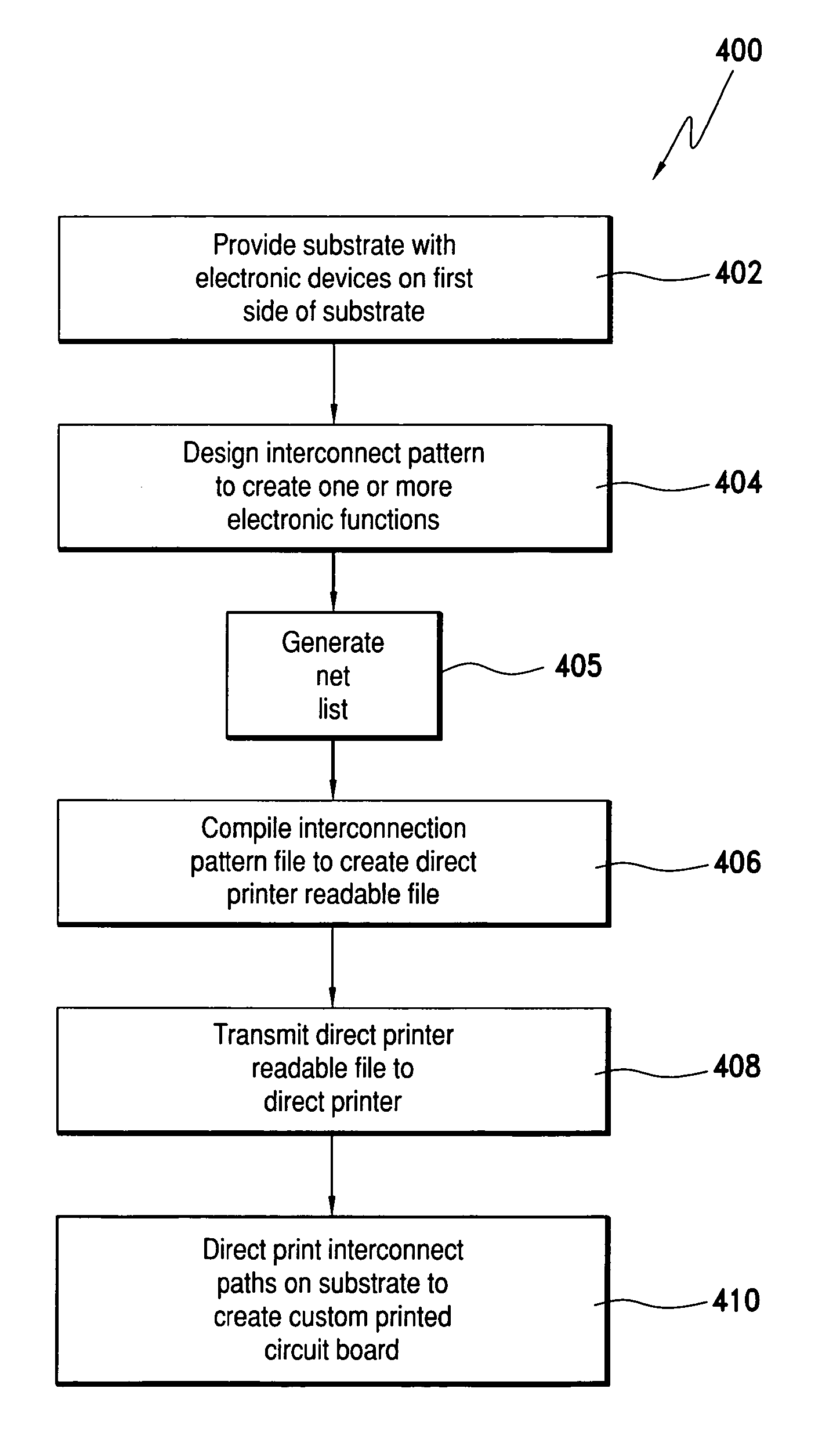

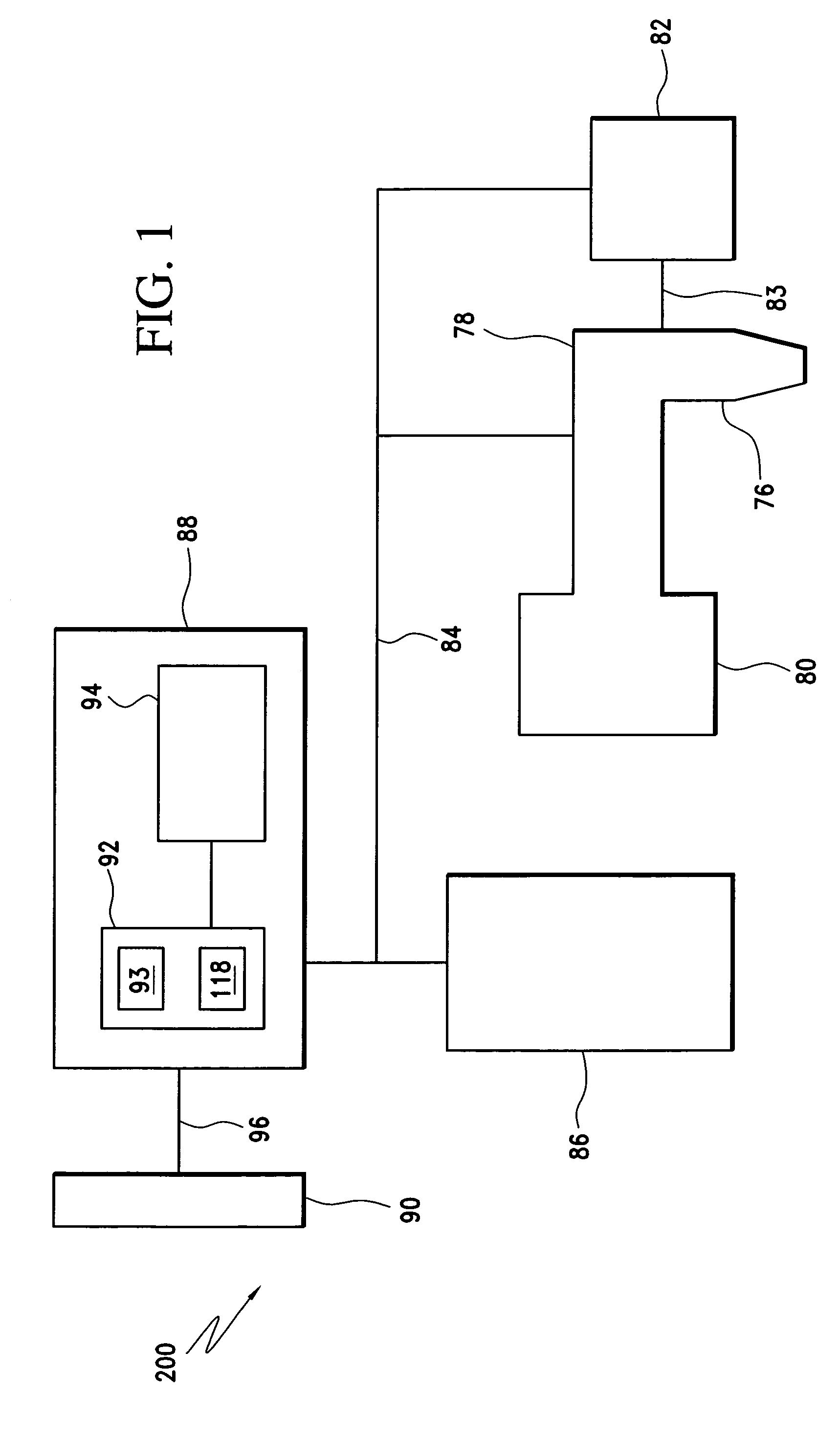

System and process for manufacturing custom electronics by combining traditional electronics with printable electronics

InactiveUS7533361B2Easily and inexpensively modifyPrinted circuit assemblingSemiconductor/solid-state device detailsDisplay deviceAutomotive industry

A system and process for manufacturing custom printed circuit boards on pre-provided substrates, wherein the substrate is pre-provided with standard integrated circuits. The standard integrated circuits are pre-provided on the substrate in a conventional manner, such as by standard integrated circuit technologies, in many different packing technologies. The user designs the custom printed circuit board using a design tool to perform one or more specific electronic functions, based on the pre-provided electronic devices, and / or custom designed and direct printed electronic devices. The electronic devices includes transistors, resistors, capacitors, among other types of devices. The system and process allows users to customize standard “generic” circuit boards with some known electronic functions for their own particular application. Examples of such uses include displays, the automotive industry and many others.

Owner:CABOT CORP

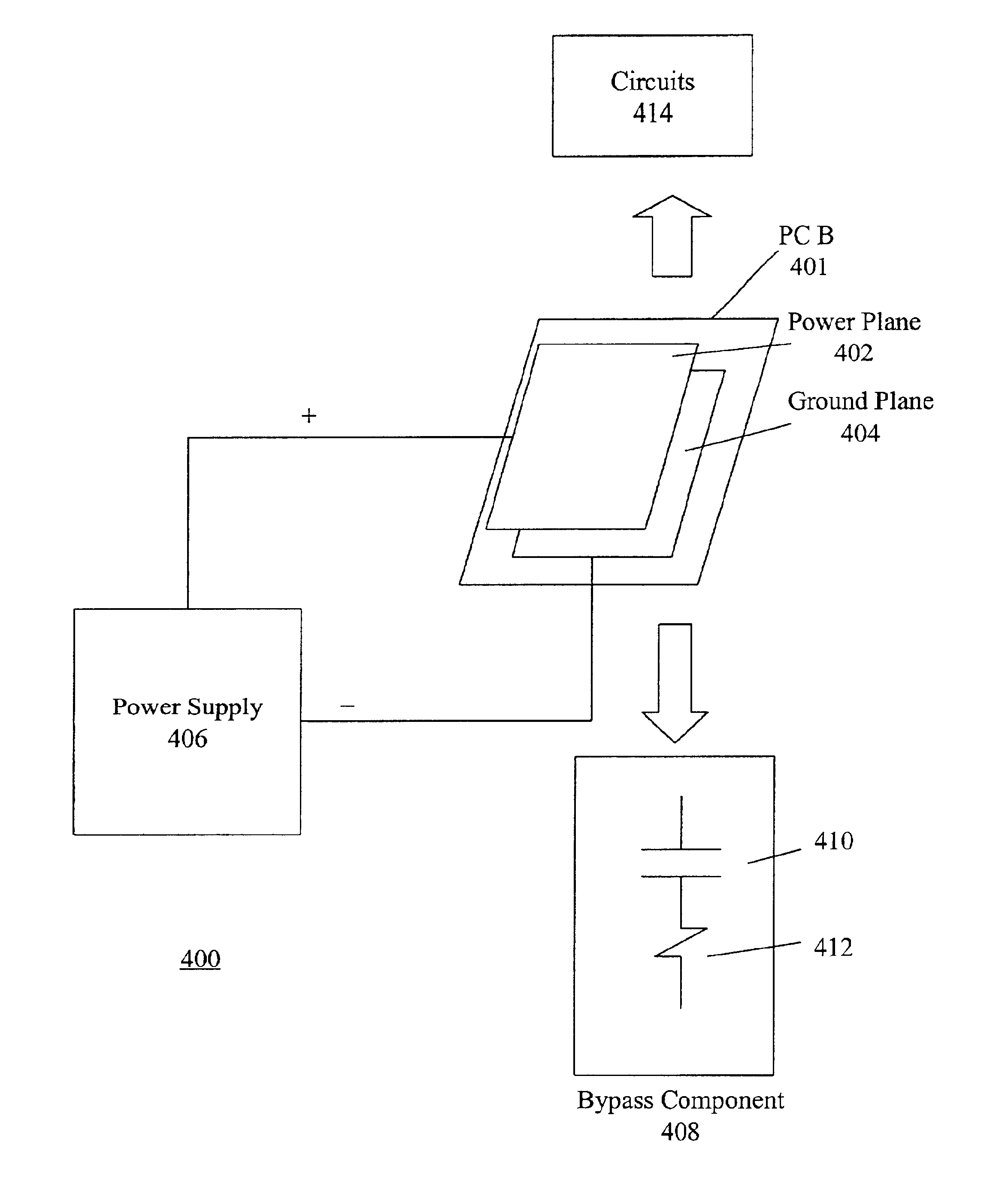

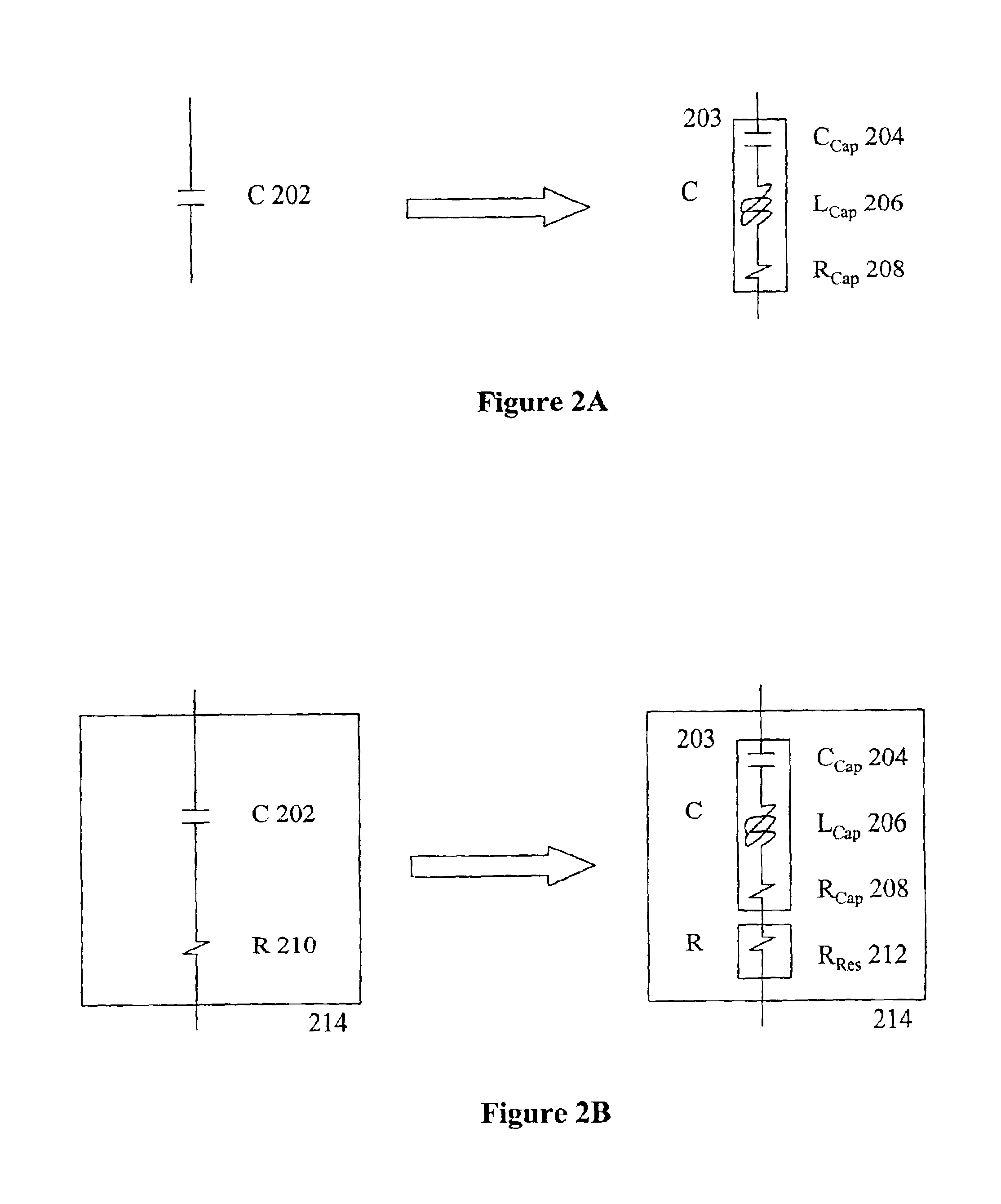

Method and apparatus to attenuate power plane noise on a printed circuit board using high ESR capacitors

InactiveUS6870436B2Reduce and minimize noiseMultiple-port networksMagnetic/electric field screeningElectrical resistance and conductanceNegative power

In a method of the present invention, performance characteristics of a printed circuit board are analyzed. The printed circuit board, bypass components and an applied stimulus are modeled. Each of the bypass components includes a capacitor and a resistor in series with each other. Alternatively, a second capacitor is coupled in parallel to the above capacitor and resistor. A simulation of the circuit model is then performed. In this embodiment of the invention, the simulation is responsive to the stimulus as is performed over a range of bypass resistor values. In another embodiment of the invention, a printed circuit board is described with components and characteristics that reduce noise. Such a printed circuit board includes a power plane and a plurality of bypass components. Moreover, the plurality of bypass components include bypass capacitors and bypass resistors coupled in series between the positive power plane and the negative power plane.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP +1

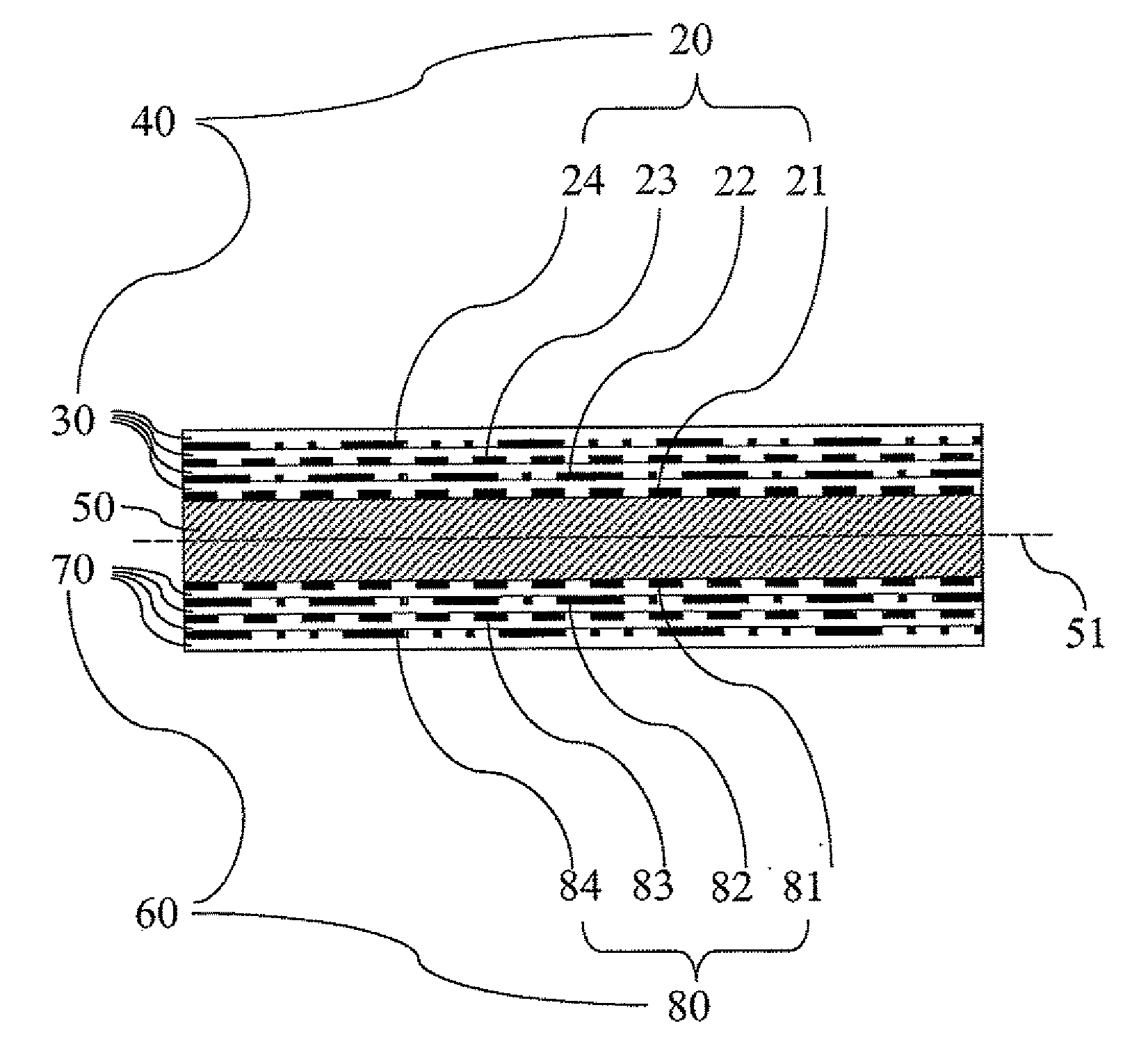

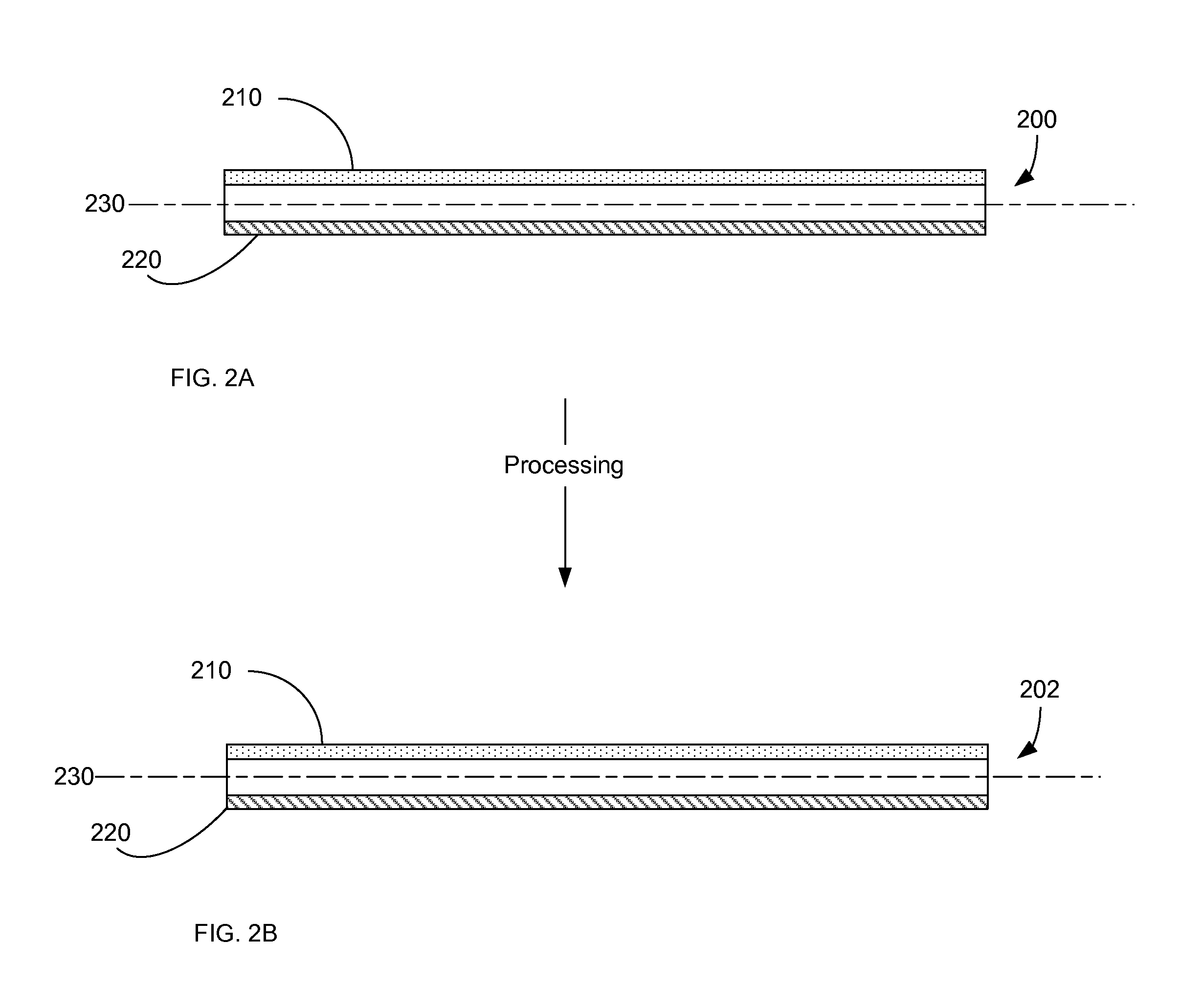

Packaging substrate having pattern-matched metal layers

InactiveUS20090114429A1Maximum flexibilitySemiconductor/solid-state device detailsPrinted circuit aspectsElectricityMetal interconnect

A pattern matched pair of a front metal interconnect layer and a back metal interconnect layer having matched thermal expansion coefficients are provided for a reduced warp packaging substrate. Metal interconnect layers containing a high density of wiring and complex patterns are first developed so that interconnect structures for signal transmission are optimized for electrical performance. Metal interconnect layers containing a low density wiring and relatively simple patterns are then modified to match the pattern of a mirror image metal interconnect layer located on the opposite side of the core and the same number of metal interconnect layer away from the core. During this pattern-matching process, the contiguity of electrical connection in the metal layers with a low density wiring may become disrupted. The disruption is healed by an additional design step in which the contiguity of the electrical connection in the low density is reestablished.

Owner:GLOBALFOUNDRIES INC

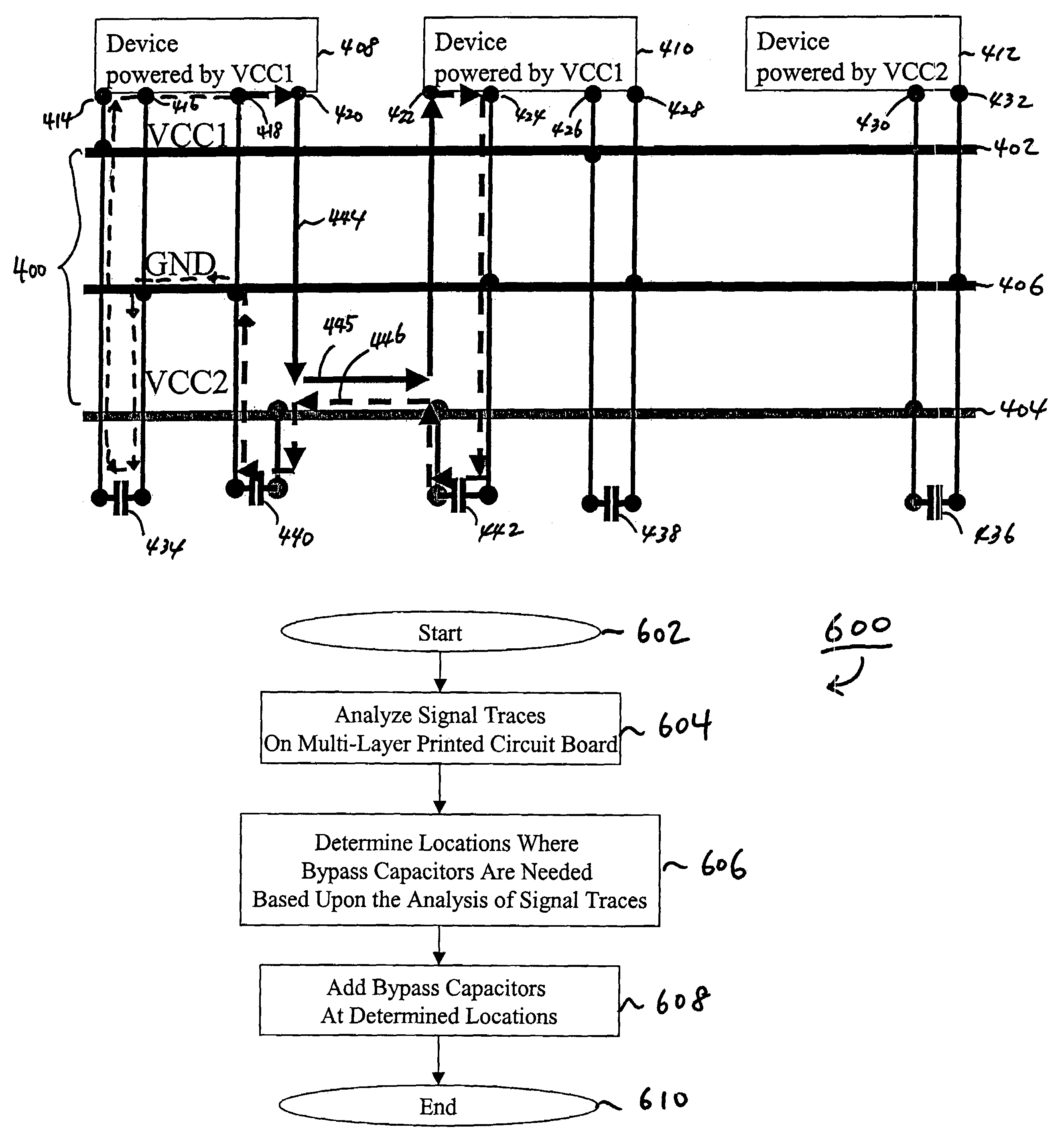

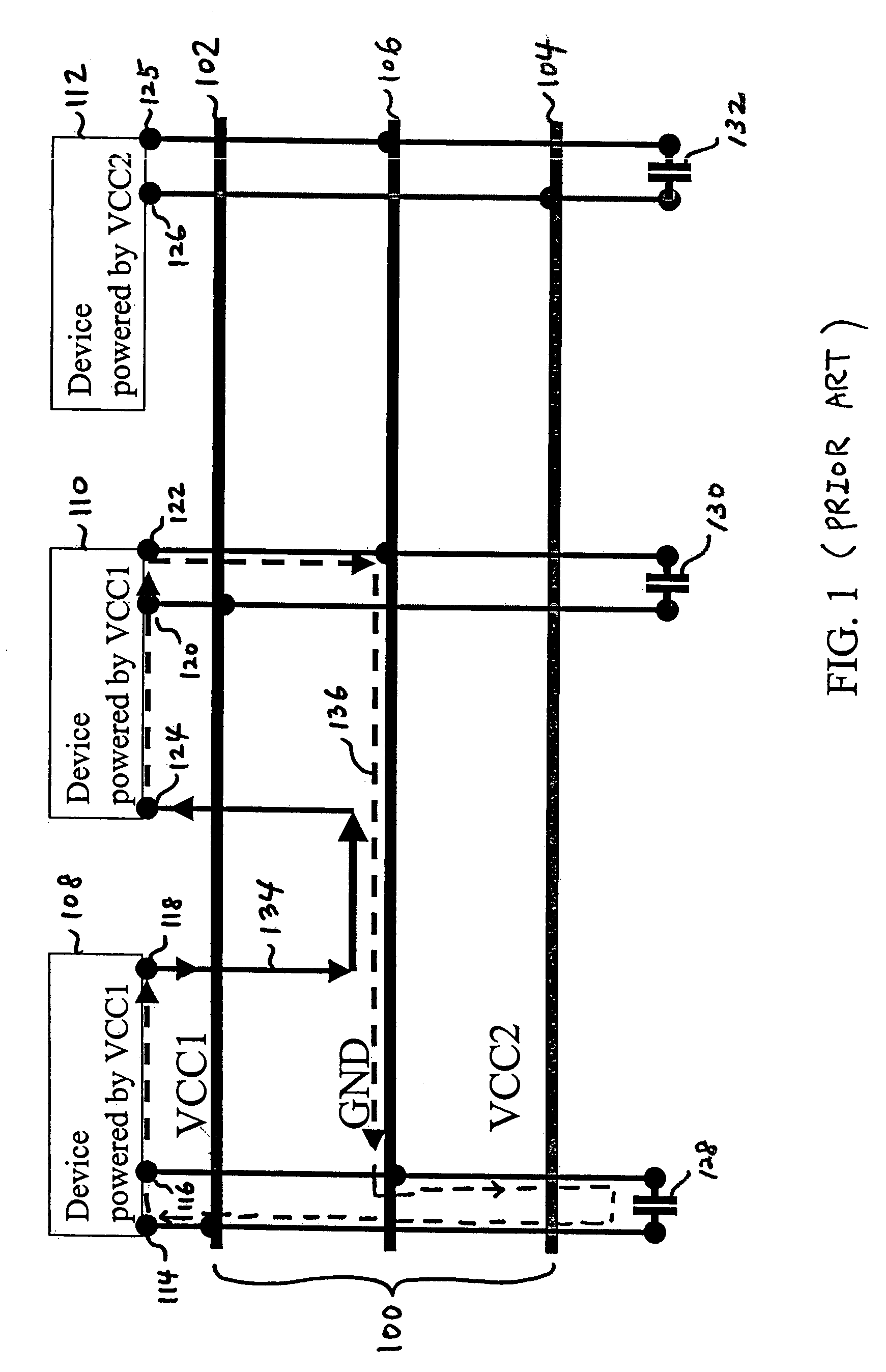

Method for selecting and placing bypass capacitors on multi-layer printed circuit boards

ActiveUS7047515B1Signal transmission reflectionEasy to controlCross-talk/noise/interference reductionPrinted circuit aspectsMethod selectionEngineering

A method places bypass capacitors for controlling the signal integrity of a signal routed between devices on a multi-layer printed circuit board by analysis of the routing of the signal and the signal characteristics. In general, when an interconnecting signal between devices is routed adjacent to an impedance control plane that does not serve as the circuit supply voltage plane or the reference voltage plane for all devices interconnected by the signal trace, the method selects locations for addition of bypass capacitors based upon the routing of the interconnecting signal trace to improve signal integrity.

Owner:EXTREME NETWORKS INC

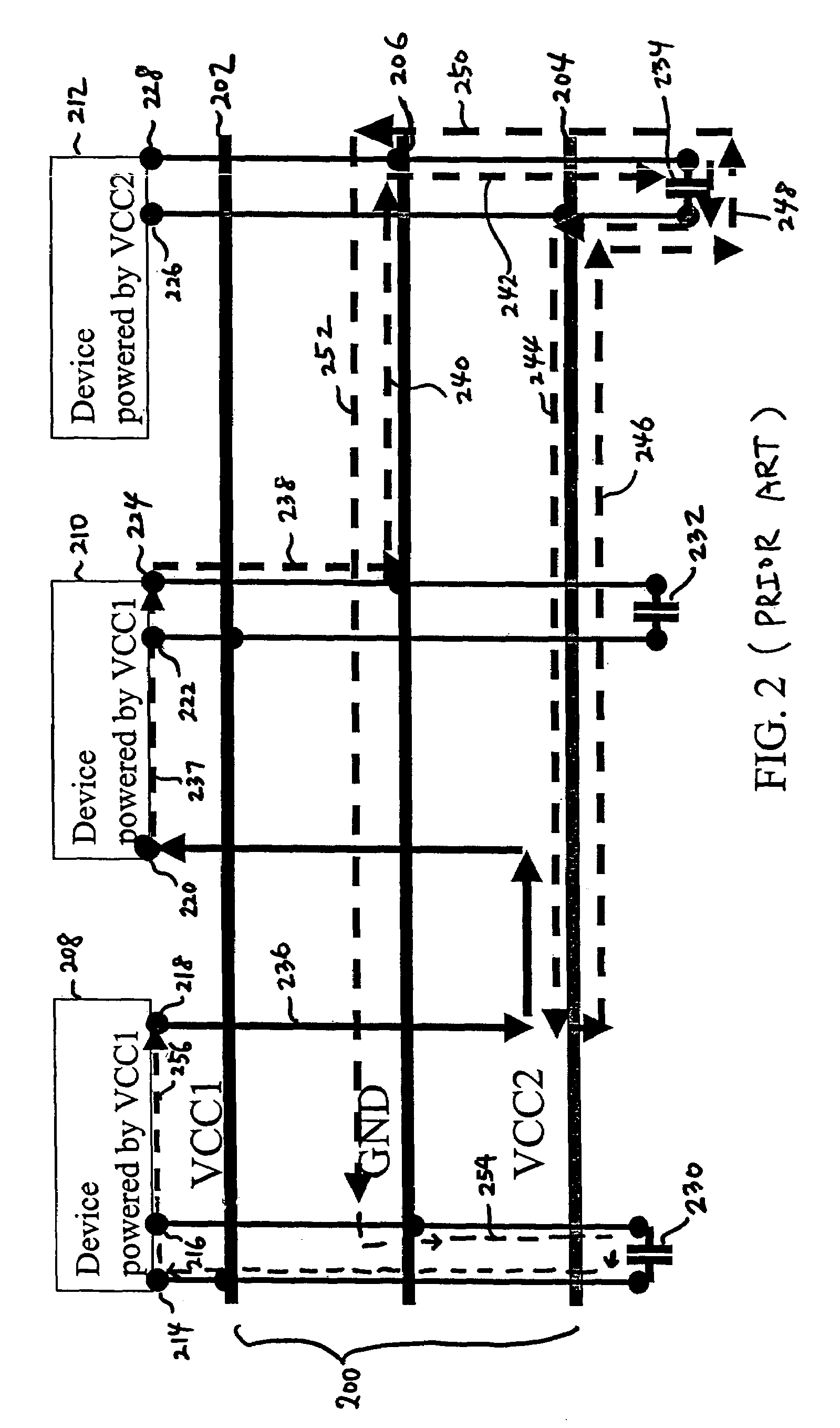

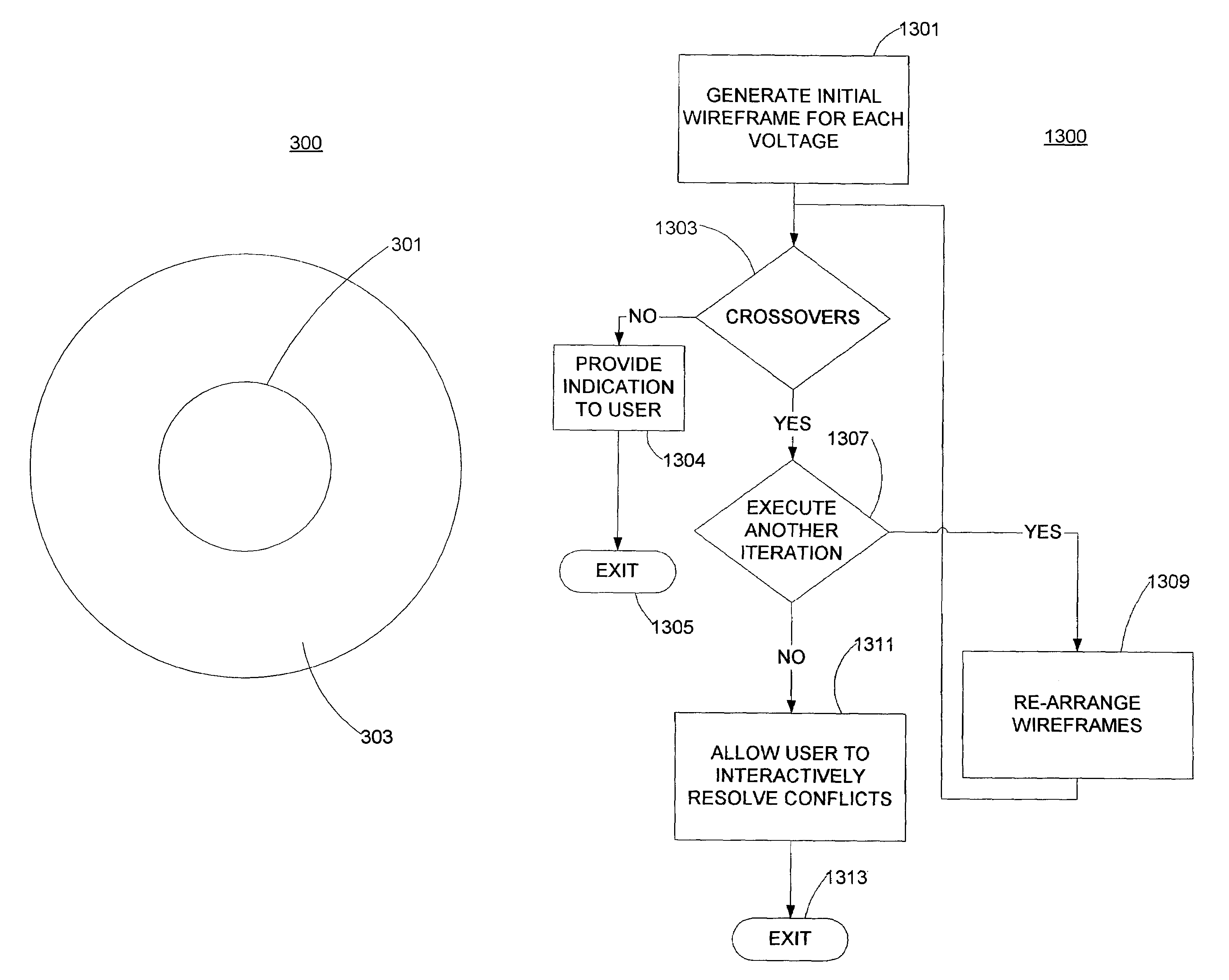

Generating a split power plane of a multi-layer printed circuit board

ActiveUS20050022149A1Printed circuit aspectsHigh voltage circuit adaptationsAverage currentEngineering

Methods and apparatuses generate a split power plane for a multiplayer printed circuit board (PCB). An aspect of the invention supports the generation of a split power plane by constructing wireframes corresponding to each of the power voltages. If a crossover between different voltage wireframes exists, at least one of the voltage wireframes may be modified in order to eliminate the crossover. With another aspect of the invention, a trace layout, corresponding to the wireframe, is constructed in accordance with electrical current requirements, e.g. average electrical current and peak electrical current, of the associated components. With another aspect of the invention, a plane that contain the traces that associated with a power voltage may be enhanced by increasing the associated area of the layout in accordance with the available area of the split power plane. The enhancement of a plane may be prioritized in accordance with peak electrical current that is associated with the plane.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

High performance printed circuit board

InactiveUS20140326495A1Reduce in quantitySimple designPrinted circuit aspectsHigh frequency circuit adaptationsEngineeringImpedance matching

Owner:AMPHENOL CORP

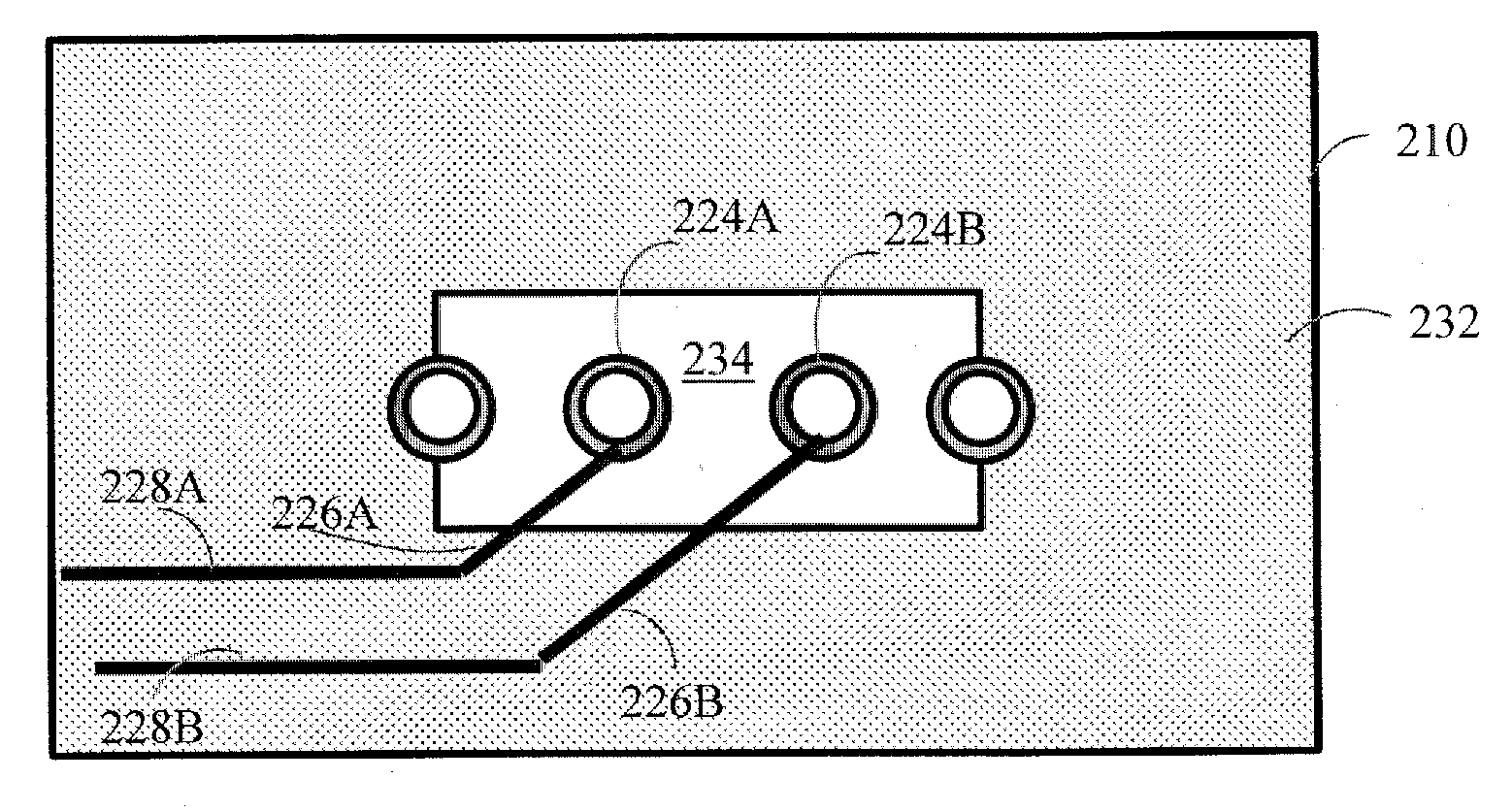

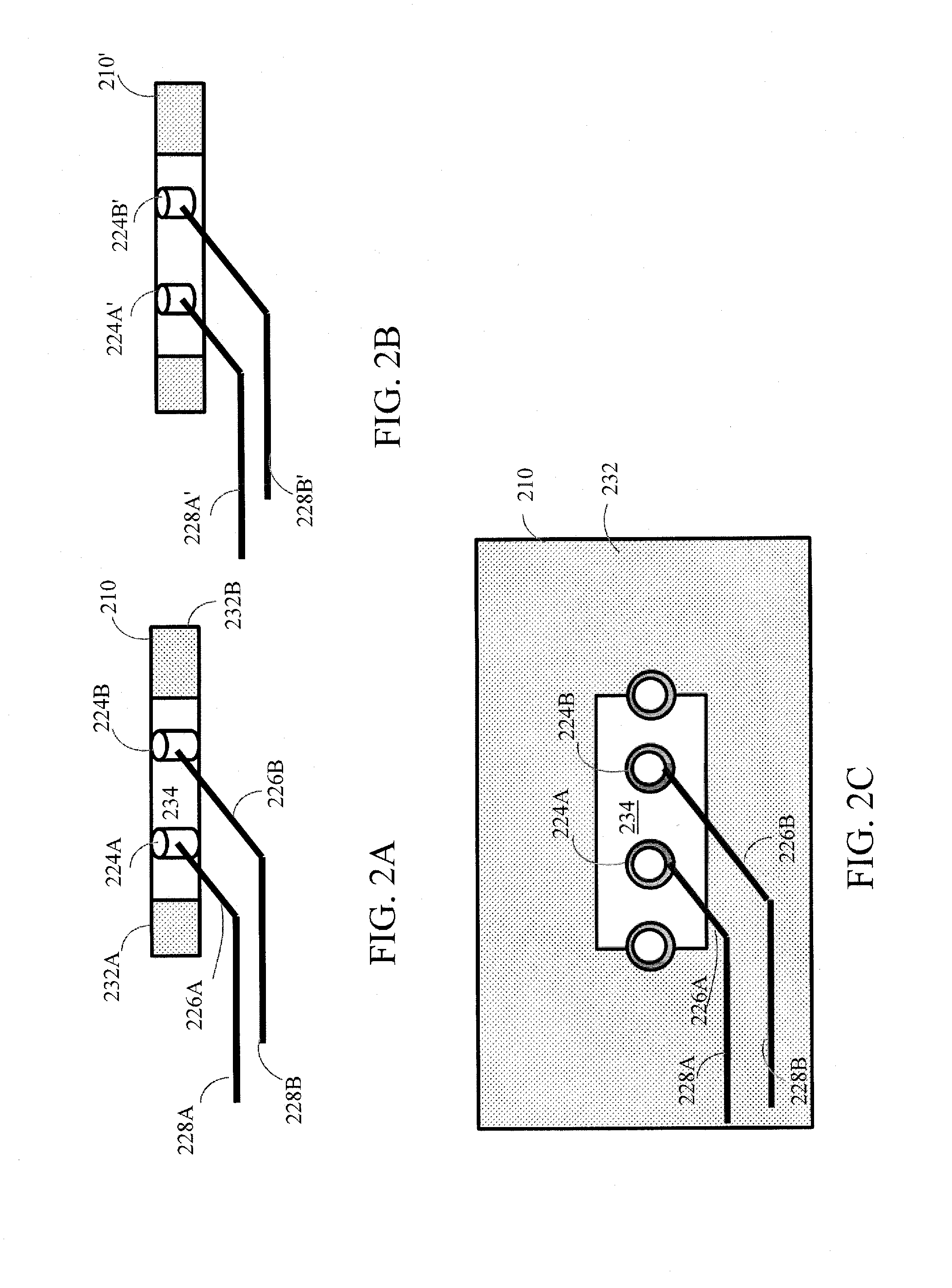

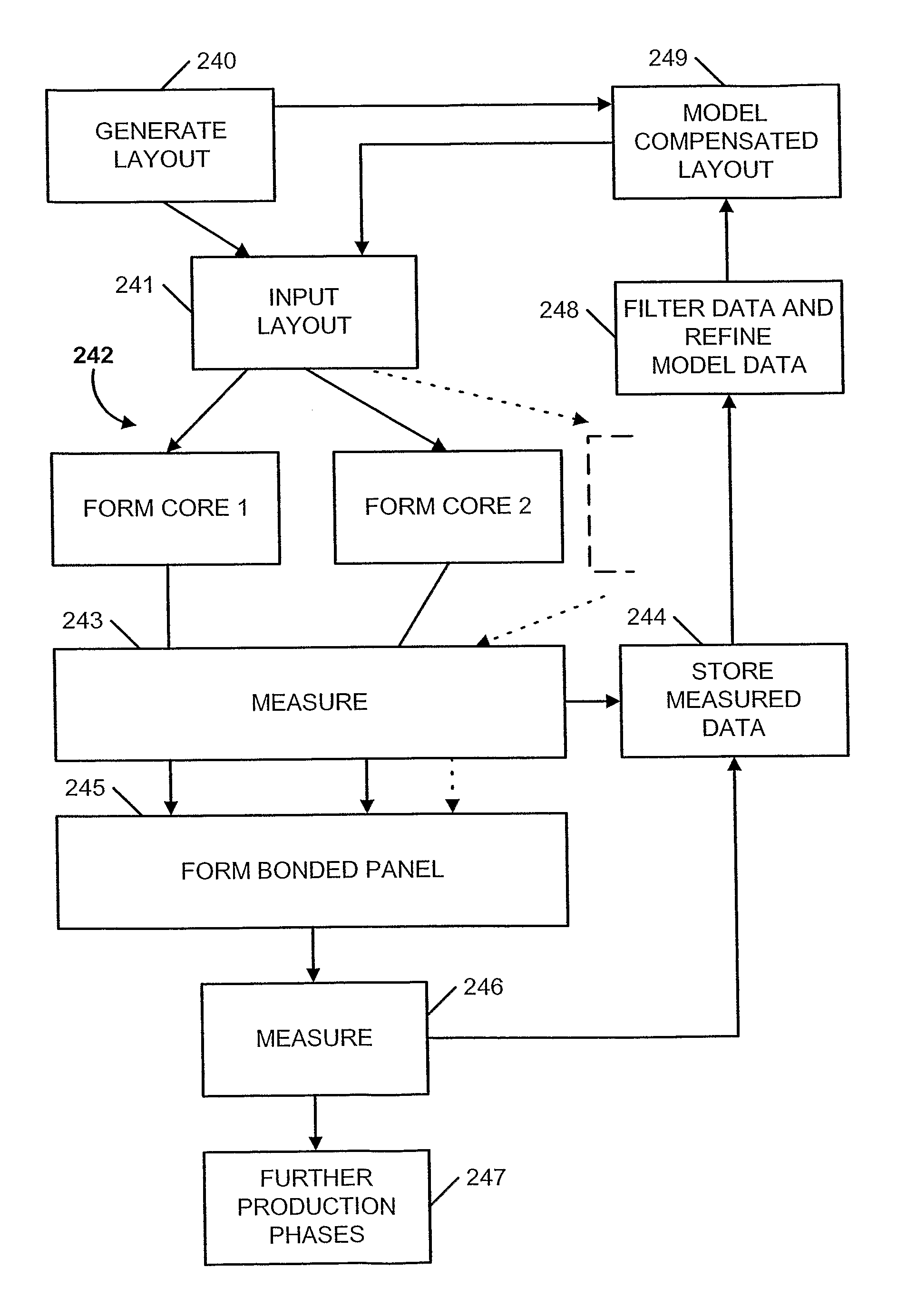

Registration System and Method

ActiveUS20110130860A1Precise positioningPrinted circuit aspectsSemiconductor/solid-state device manufacturingNonlinear distortionElement model

Printed circuit boards are manufactured by forming a composite layer using a control system which models a production process to generate data using non-linear compensation techniques to compensate for non-linear distortion occurring in a circuit layout applied to a constituent layer. Measurement data of actual circuit layouts is used to update stored values of parameters used in the modelling process. In one form of the model, the desired layout in the composite layer is represented by an array of cells and cell sizes corresponding to an initial stage of the production process are calculated, the model working backwards from the final state of the production process to the initial state, and a finite element model used to determine corresponding positions of cells, taking account of interaction between cells, from which the compensation data is calculated.

Owner:XACTPCB LTD

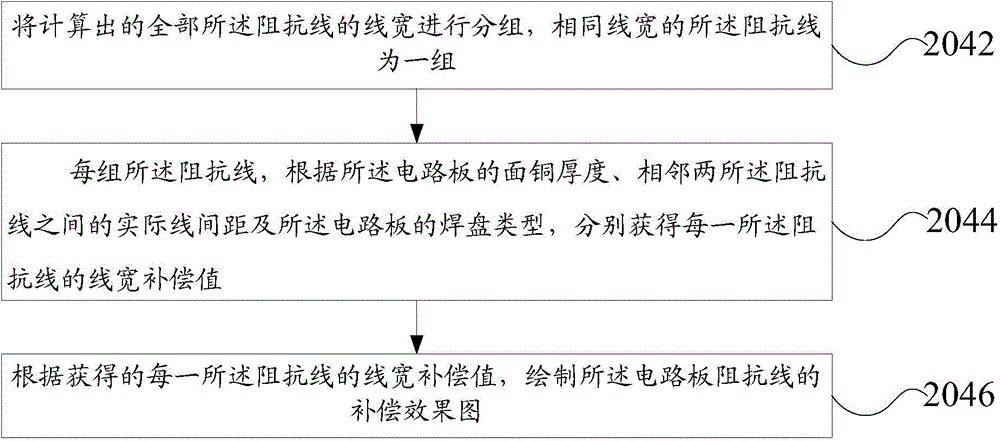

Circuit board impedance line compensation method and device

ActiveCN104470212AAvoid situations where the transmitted signal is distortedEasy to operateHigh frequency circuit adaptationsComputer designed circuitsEngineeringCharacteristic impedance

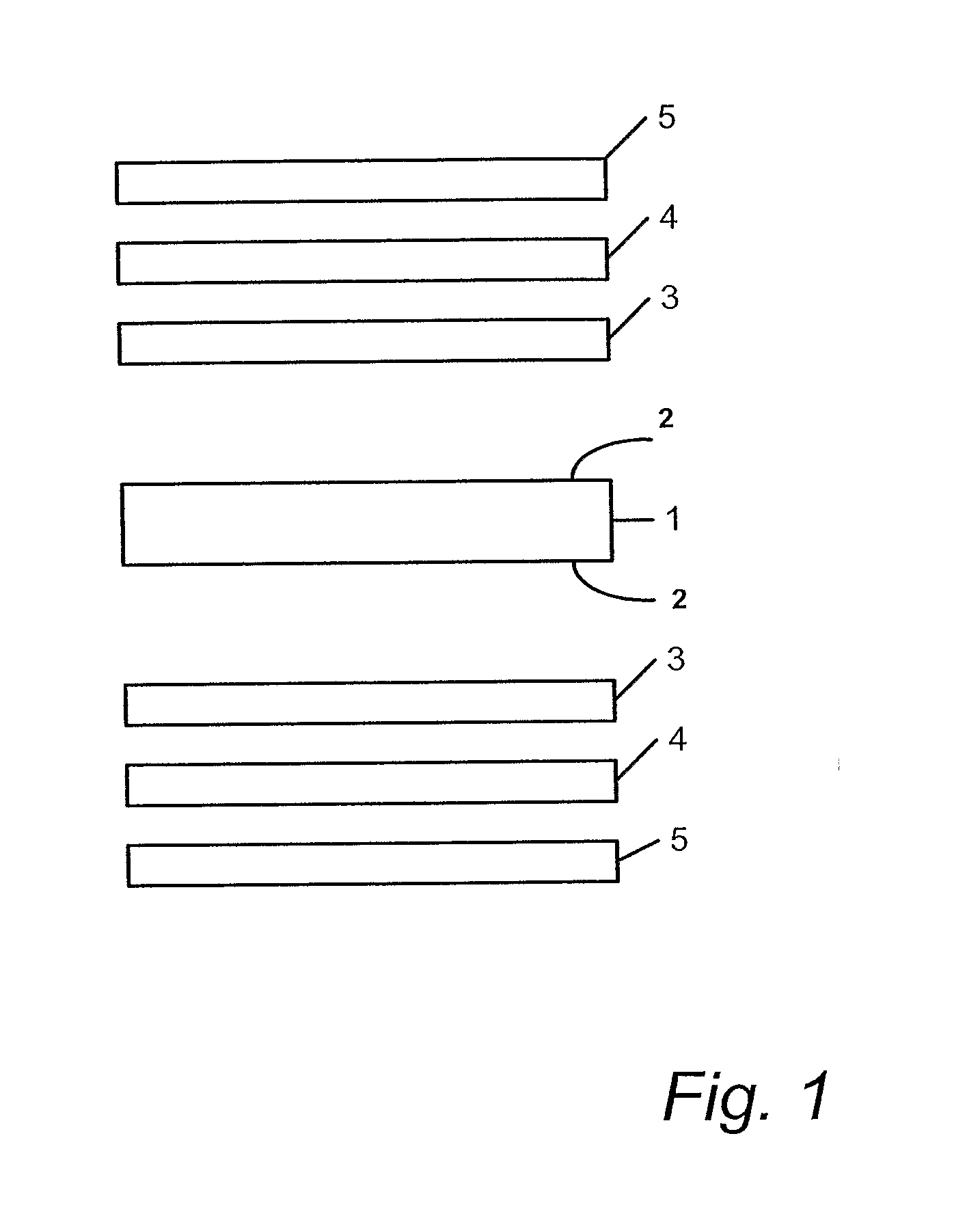

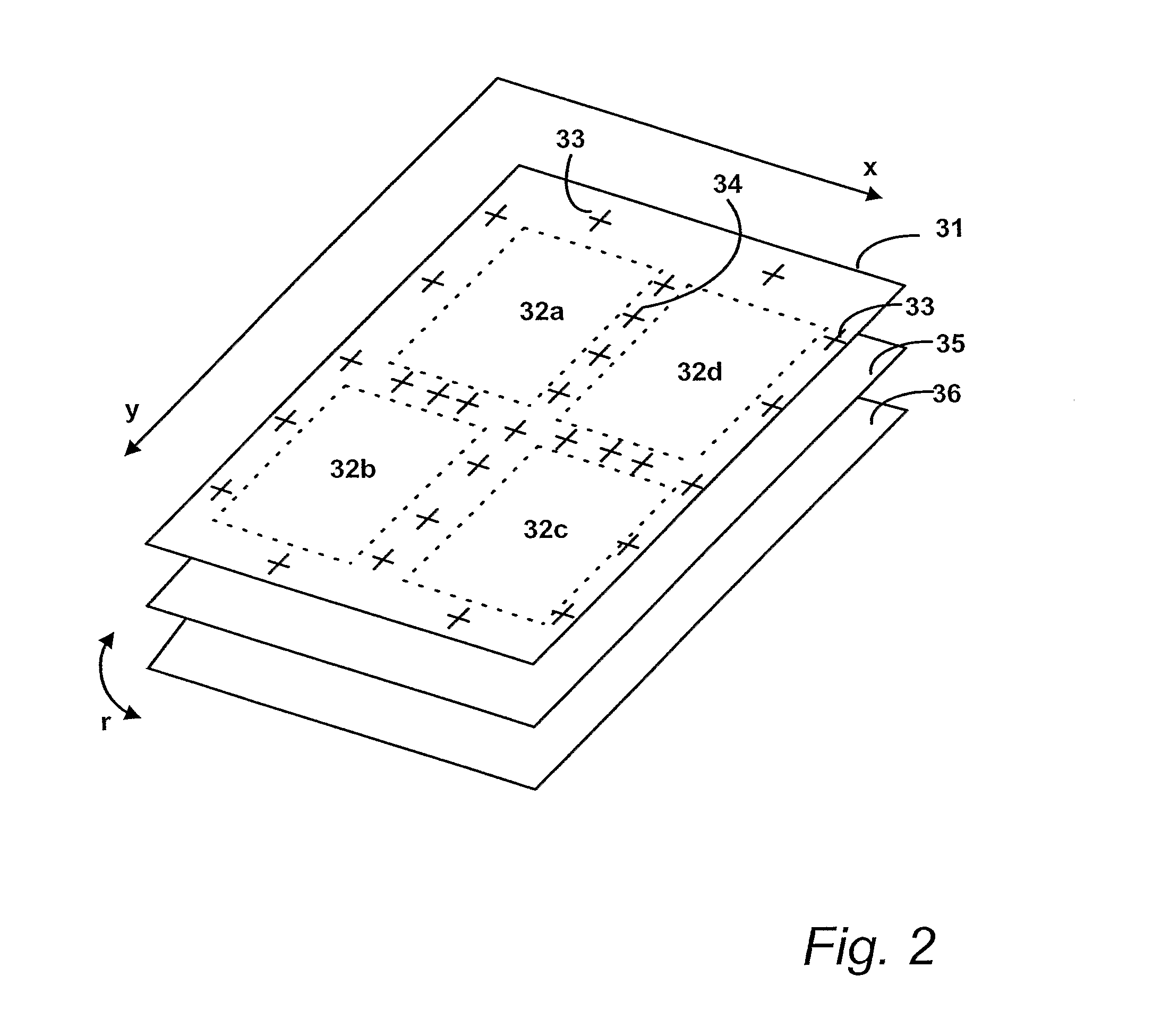

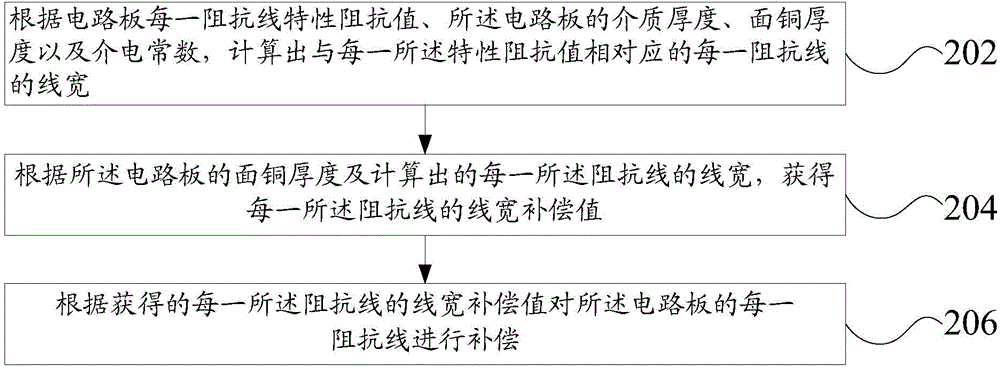

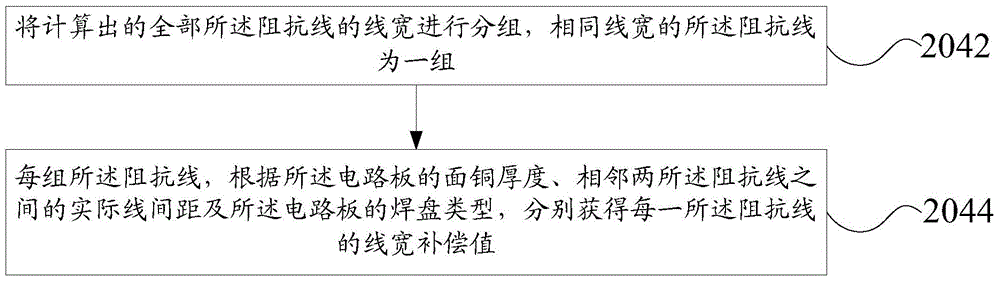

The invention provides a circuit board impedance line compensation method and device. The circuit board impedance line compensation method includes the following steps that 202, the line width of each impedance line corresponding to each characteristic impedance value is calculated according to the characteristic impedance value of each impedance line of a circuit board, the dielectric thickness of the circuit board, the thickness of face copper and a dielectric constant; 204, the line width compensation value of each impedance line is obtained according to the thickness of the face copper of the circuit board and the calculated line width of each impedance line; 206, compensation is conducted on the impedance lines of the circuit board according to the obtained line width compensation value of each impedance line. According to the circuit board impedance line compensation method, the corresponding line width compensation values of all the impedance lines can be obtained at the same time, the circuit board compensation device can be used for fast conducting compensation on the line widths of all the impedance lines of the circuit board, and the production efficiency is improved effectively.

Owner:ZHUHAI FOUNDER TECH HI DENSITY ELECTRONICS +1

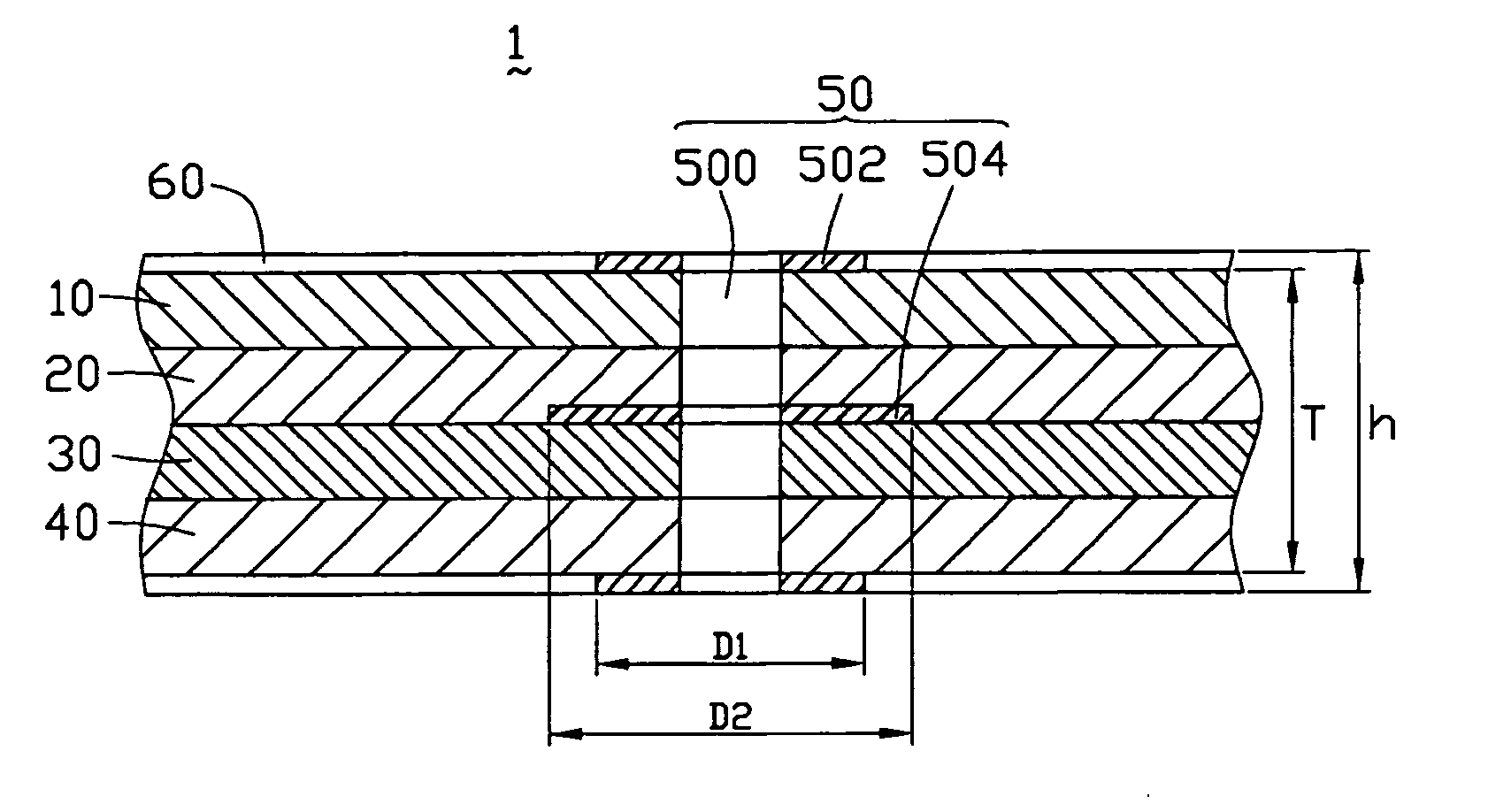

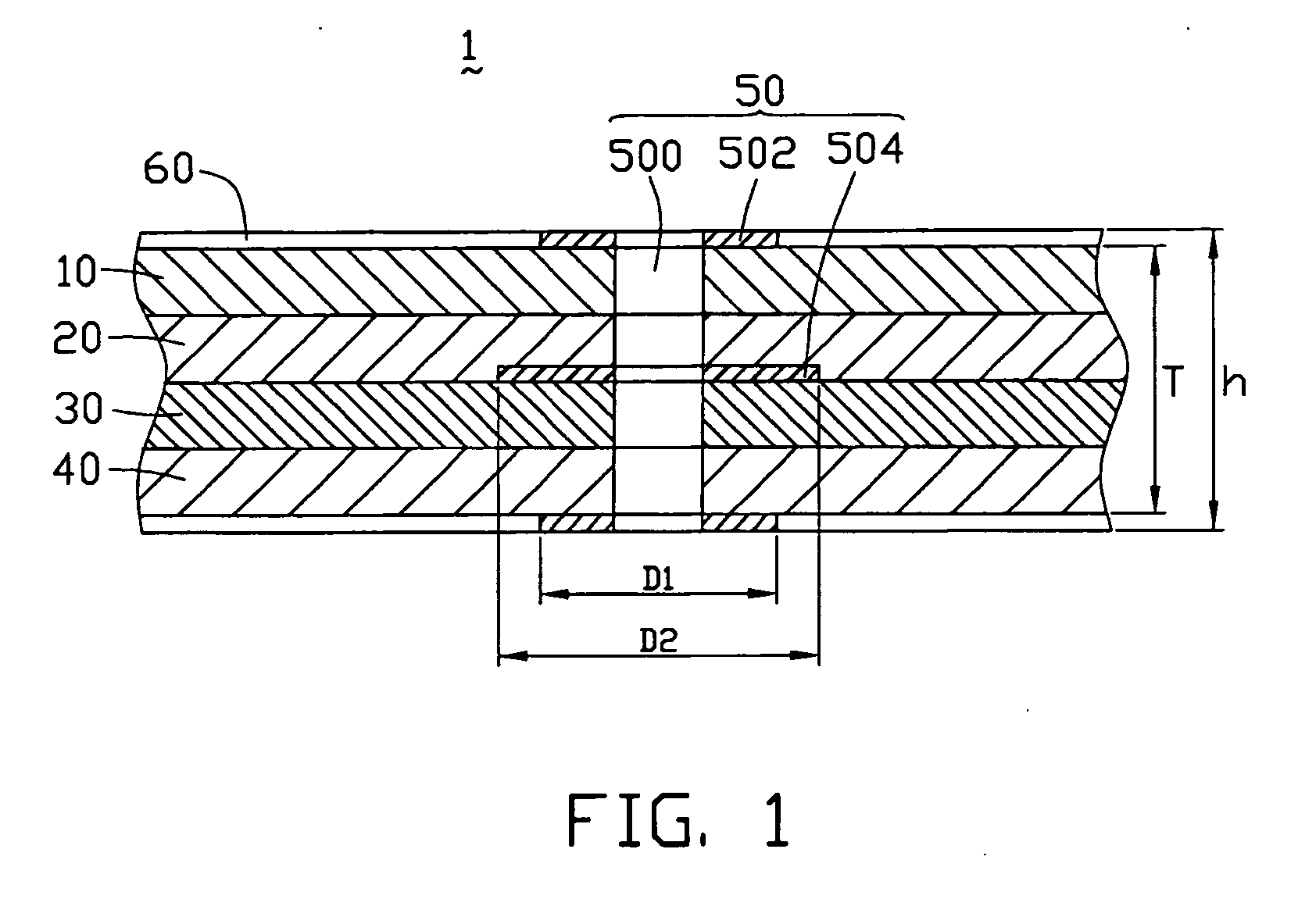

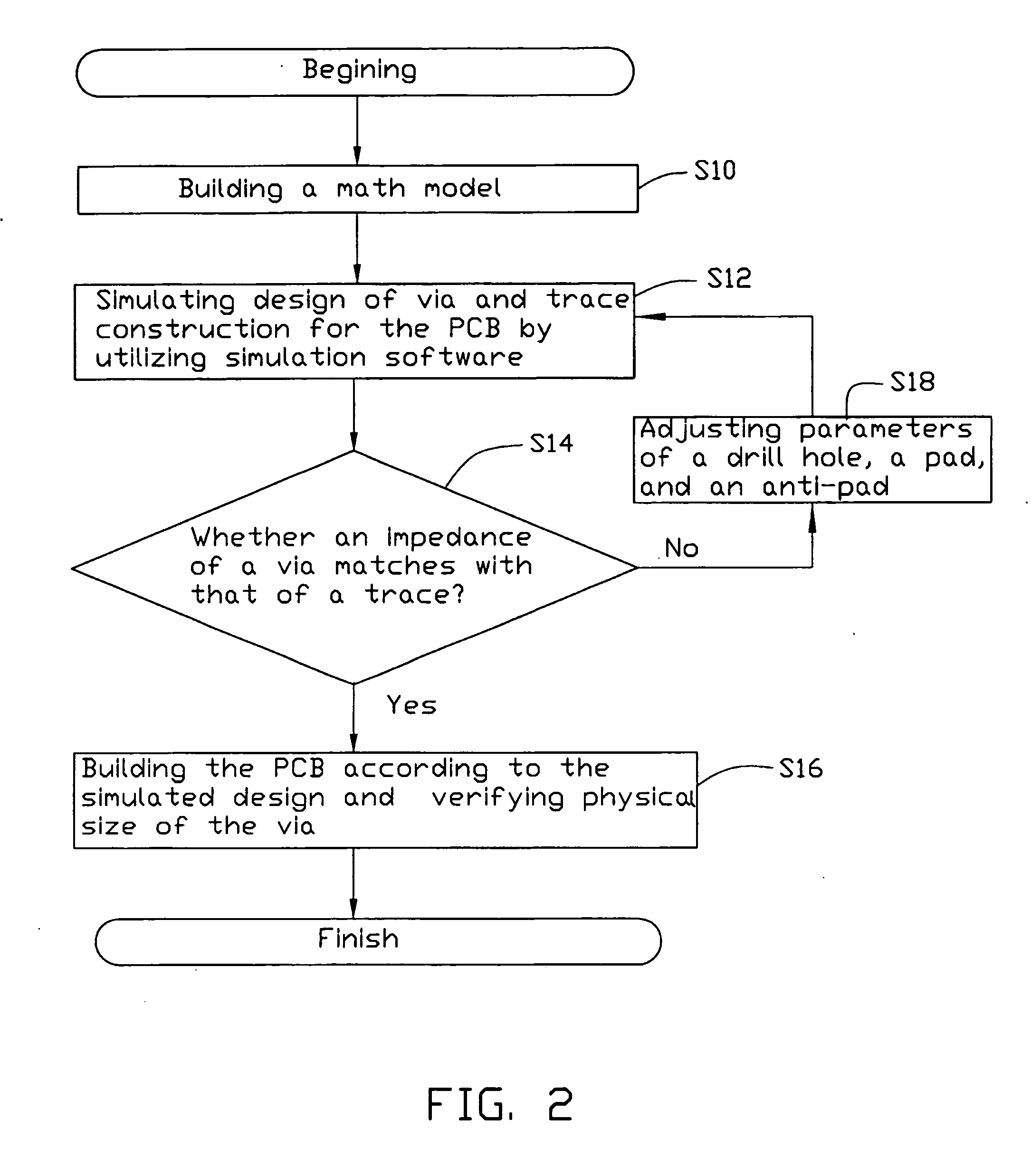

Method for improving via's impedance

InactiveUS20070074905A1Efficiently signal integrityIncrease transfer speedHigh frequency circuit adaptationsPrinted circuit aspectsMathematical modelEngineering

A method is for controlling an impedance of a via of a printed circuit board. The Via is connected with a trace and includes a drill hole, a pad and an anti-pad. The method includes steps of: building a math model; testing whether an impedance of the via matching with an impedance of the trace; analyzing the impedance of the via if passing the testing; and adjusting parameters of the pad, the anti-pad, and the drill hole if fails testing, and returning to the simulating step, till impedance matching achieved. The method which can efficiently keep signals integrality and increase signal transmission speed.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

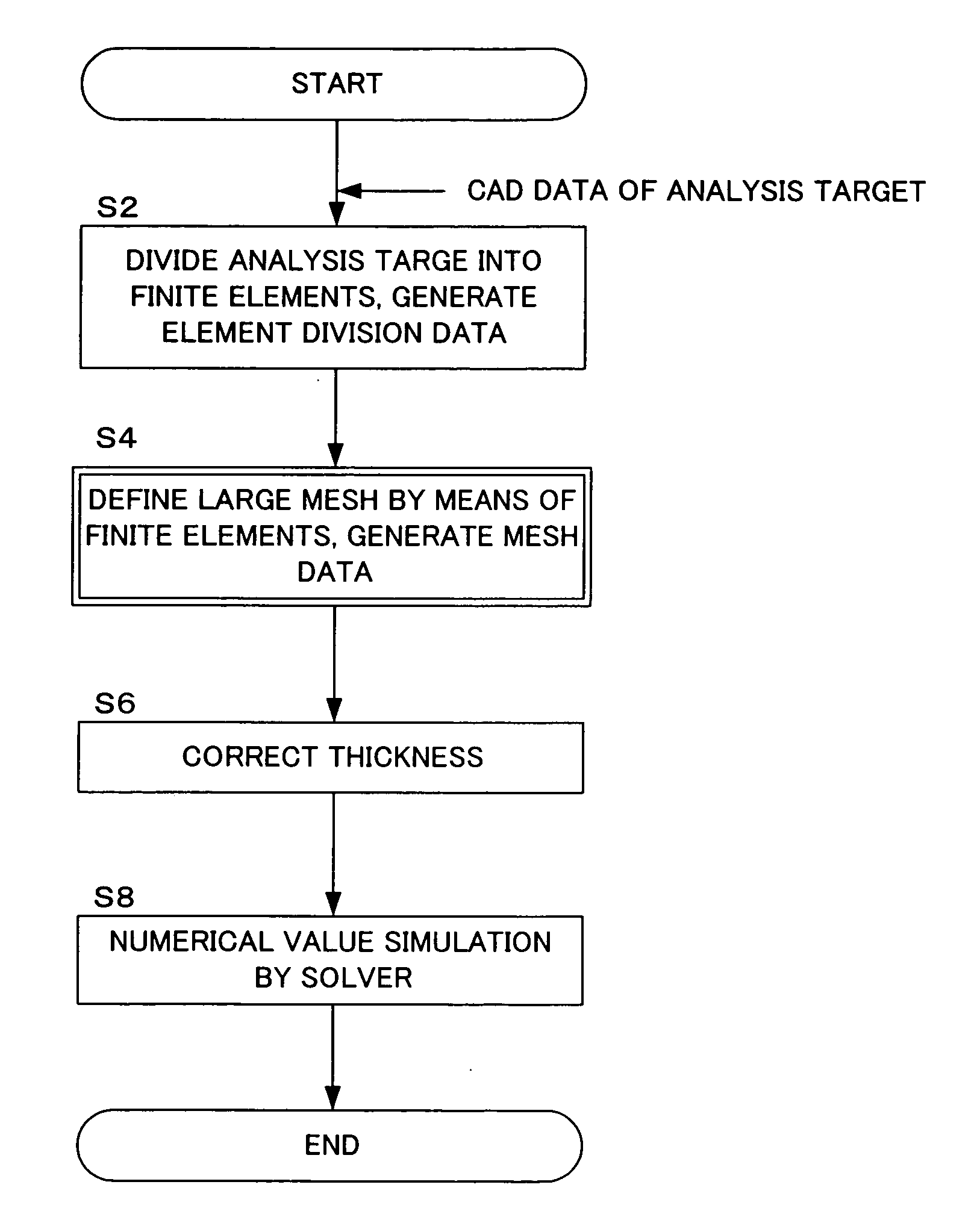

Structural analysis method employing finite element method

InactiveUS20060173660A1Shorten structural analysis timeLowering prediction accuracyPrinted circuits stress/warp reductionComputation using non-denominational number representationMulti materialFinite element method

A structural analysis method that saves analysis time without lowering the prediction accuracy is provided. The structural analysis method has dividing up the analysis target into a plurality of finite elements; defining a plurality of meshes that divide up the analysis target into units larger than the finite elements and calculating, for each mesh, the proportion of one material among the plurality of materials that occupy the finite element contained in the mesh; specifying a mesh in which the calculated proportion of the one material exceeds a predetermined threshold value and generating mesh data by substituting material information specifying materials other than the one material with material information of the materials of the finite elements contained in the specified mesh; and calculating the physical amount yielded in the analysis target on the basis of the generated mesh data.

Owner:FUJITSU LTD

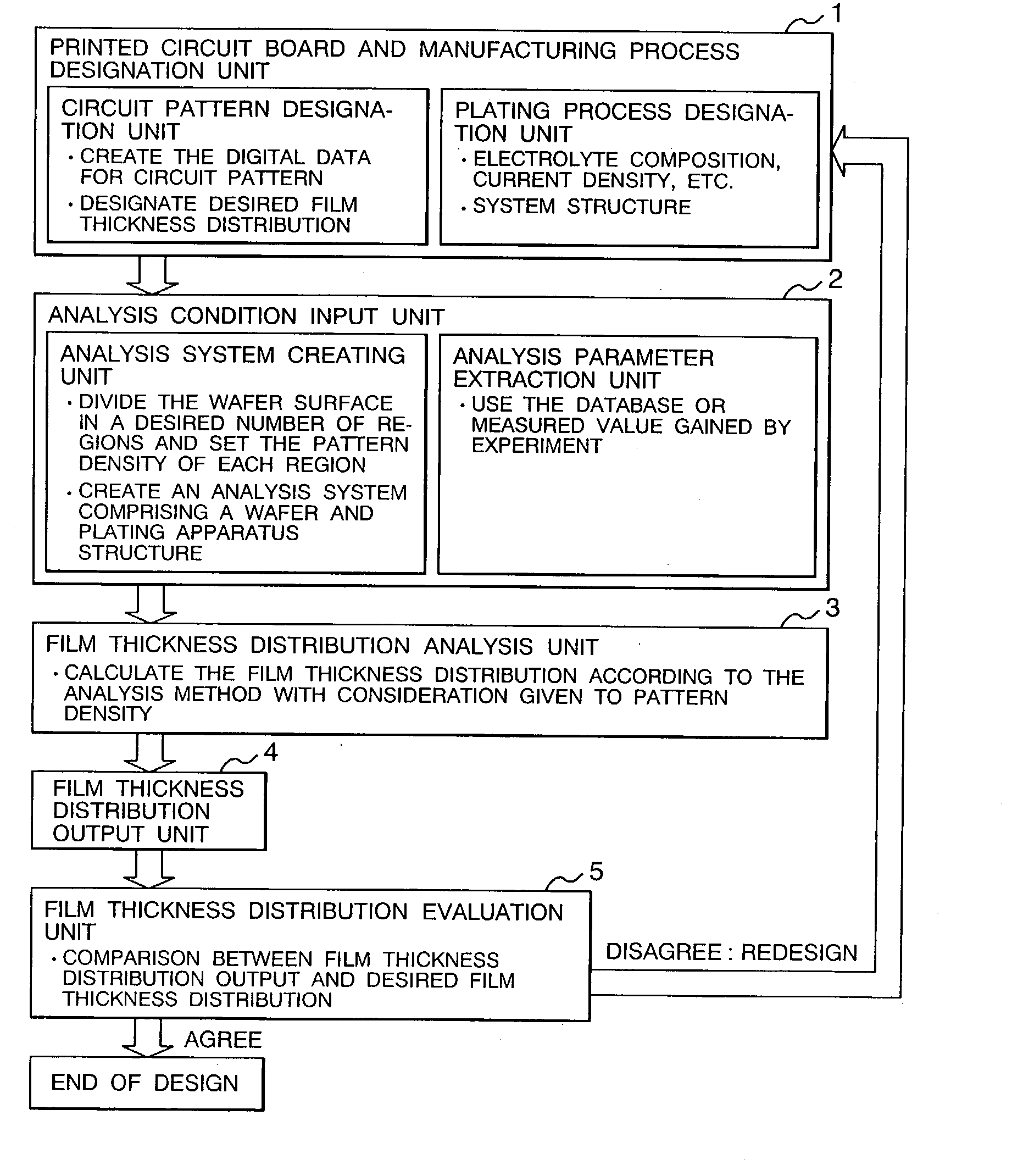

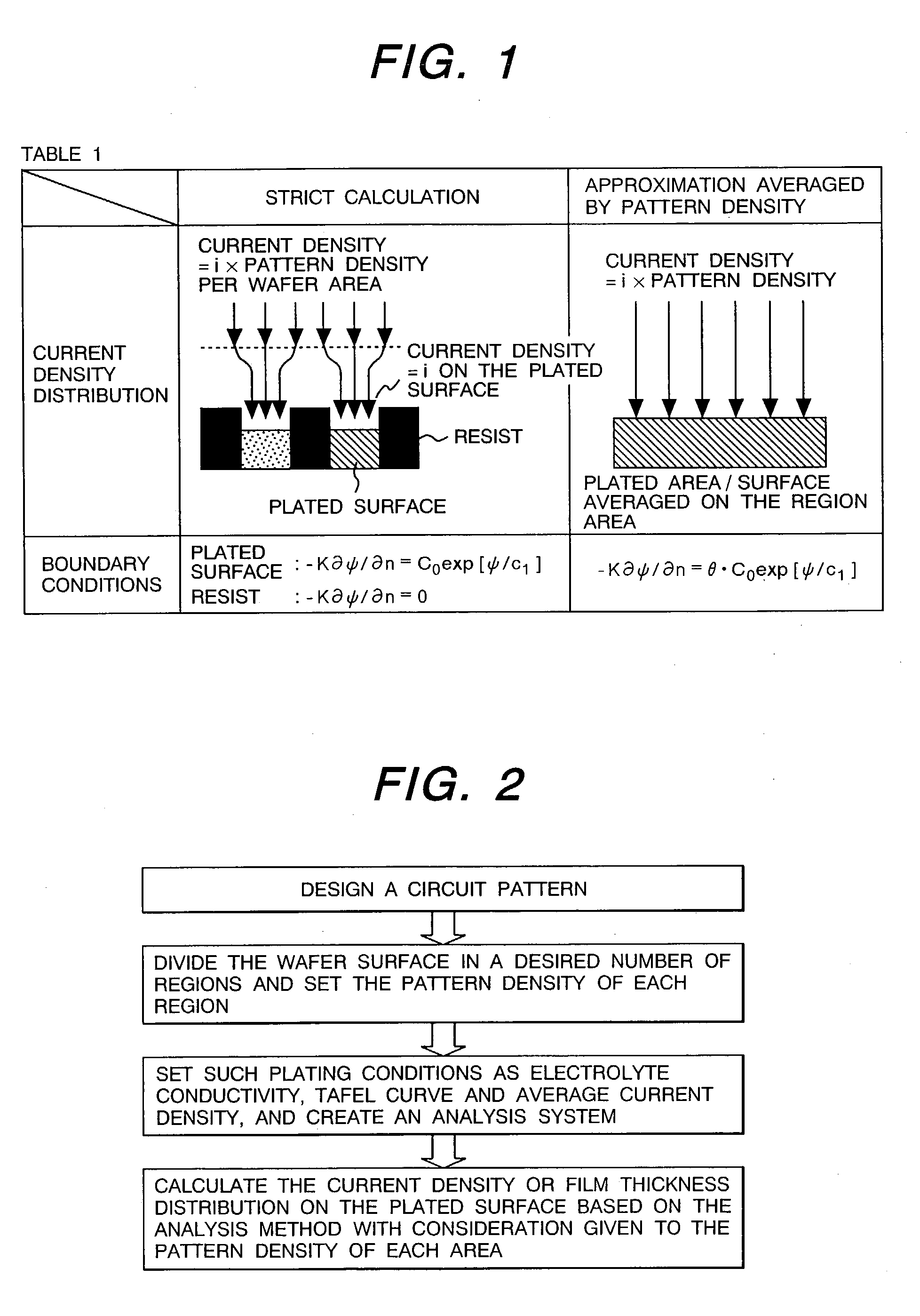

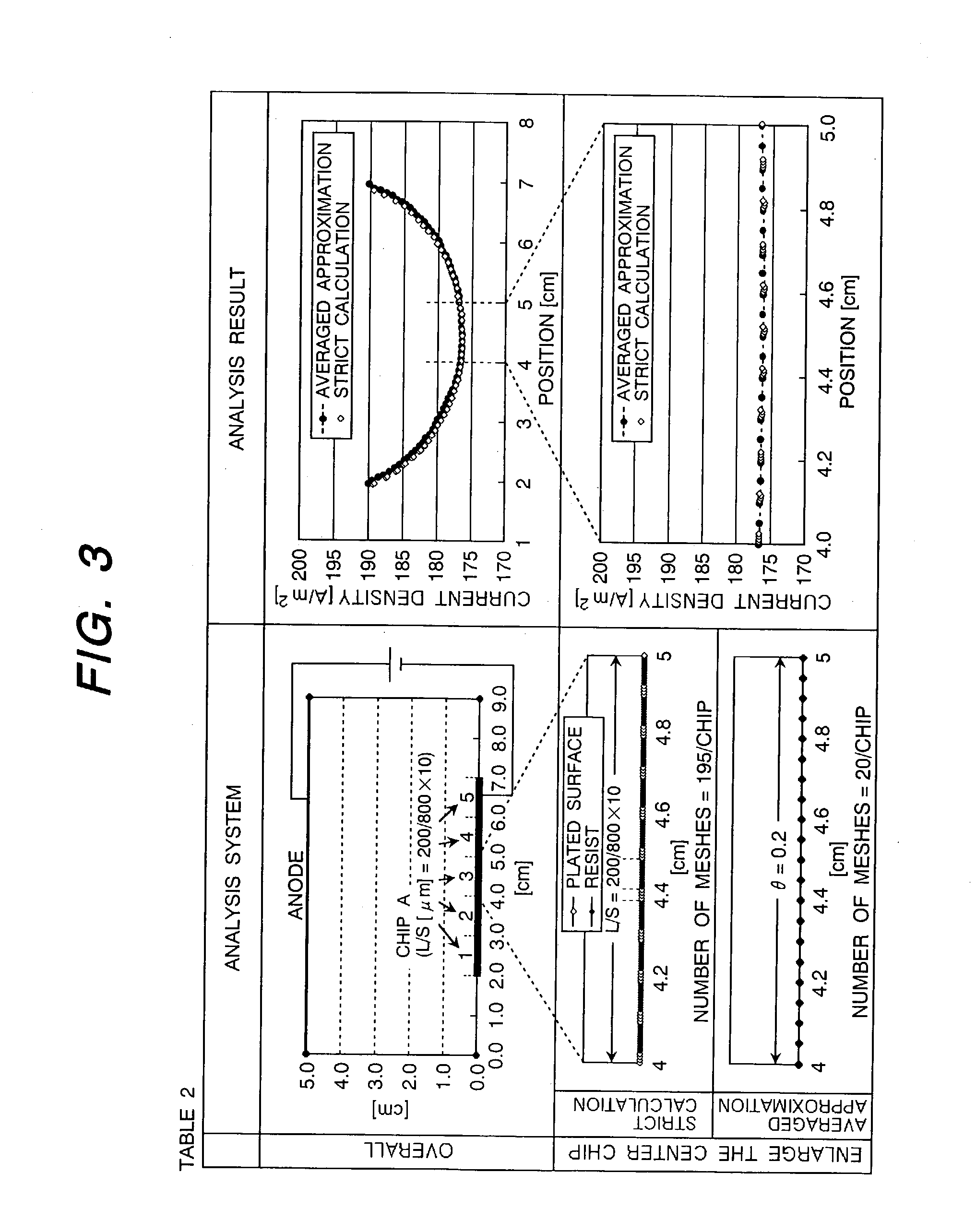

Analysis method of film thickness distribution and design system of printed circuit board and manufacturing processes

ActiveUS20030196181A1Short-time and efficient predictionCellsSemiconductor/solid-state device testing/measurementAverage currentVolumetric Mass Density

The object of the present invention is to provide a film thickness distribution analysis method that ensures quick and effective prediction of film thickness distribution by computer simulation in the pattern plating process. On the circuit pattern of a printed circuit board, in the method for analyzing the thickness distribution of metal film plated selectively, hypothetically dividing the printed circuit board into one or more regions, introducing pattern density .theta.j=Aj / Sj (Sj: the area Sj of a desired region j, and Aj: the area of the plated surface inside the area j), and calculating the approximate average current density or film thickness distribution based on "approximation averaged by pattern density".

Owner:HITACHI LTD

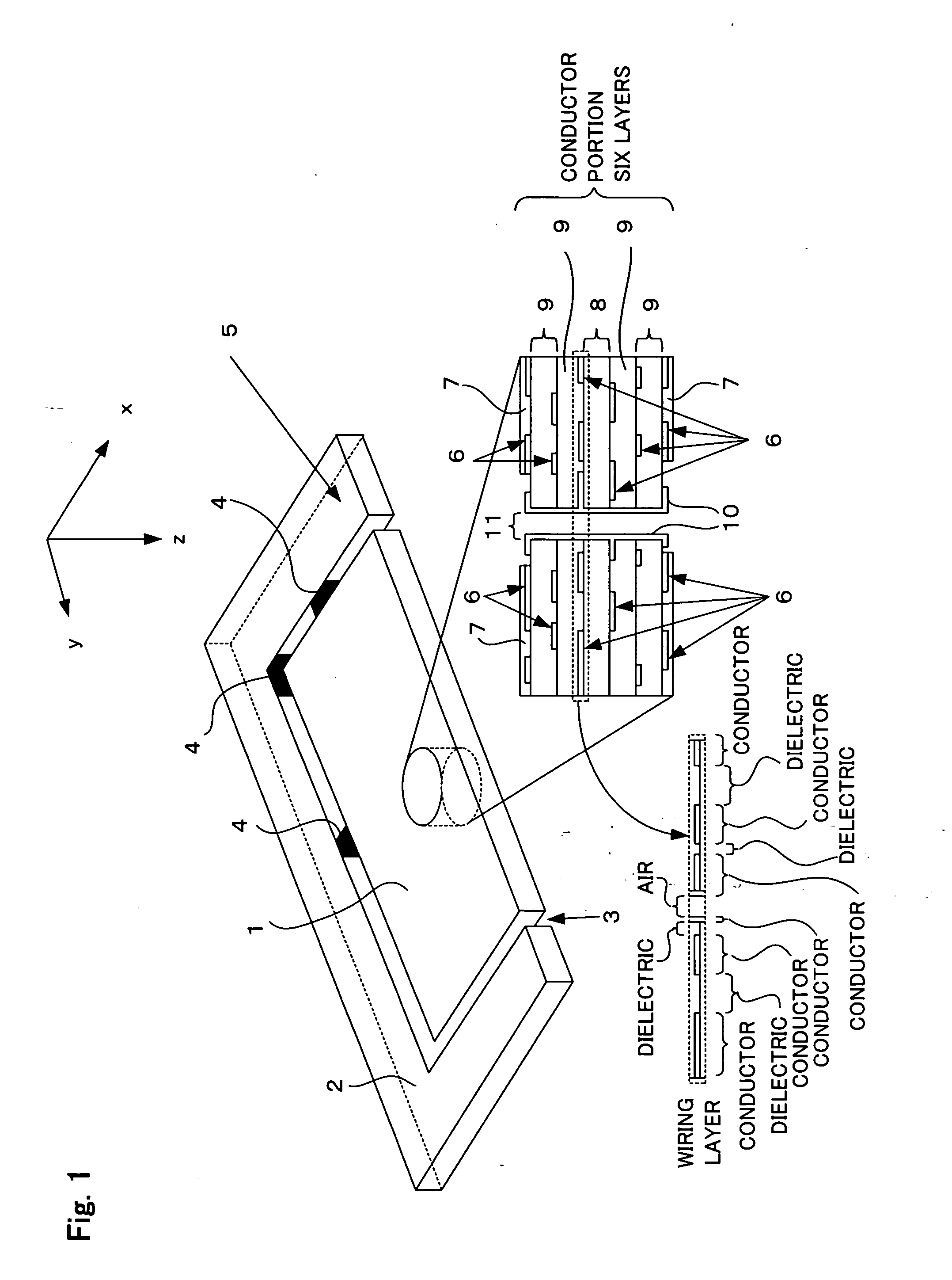

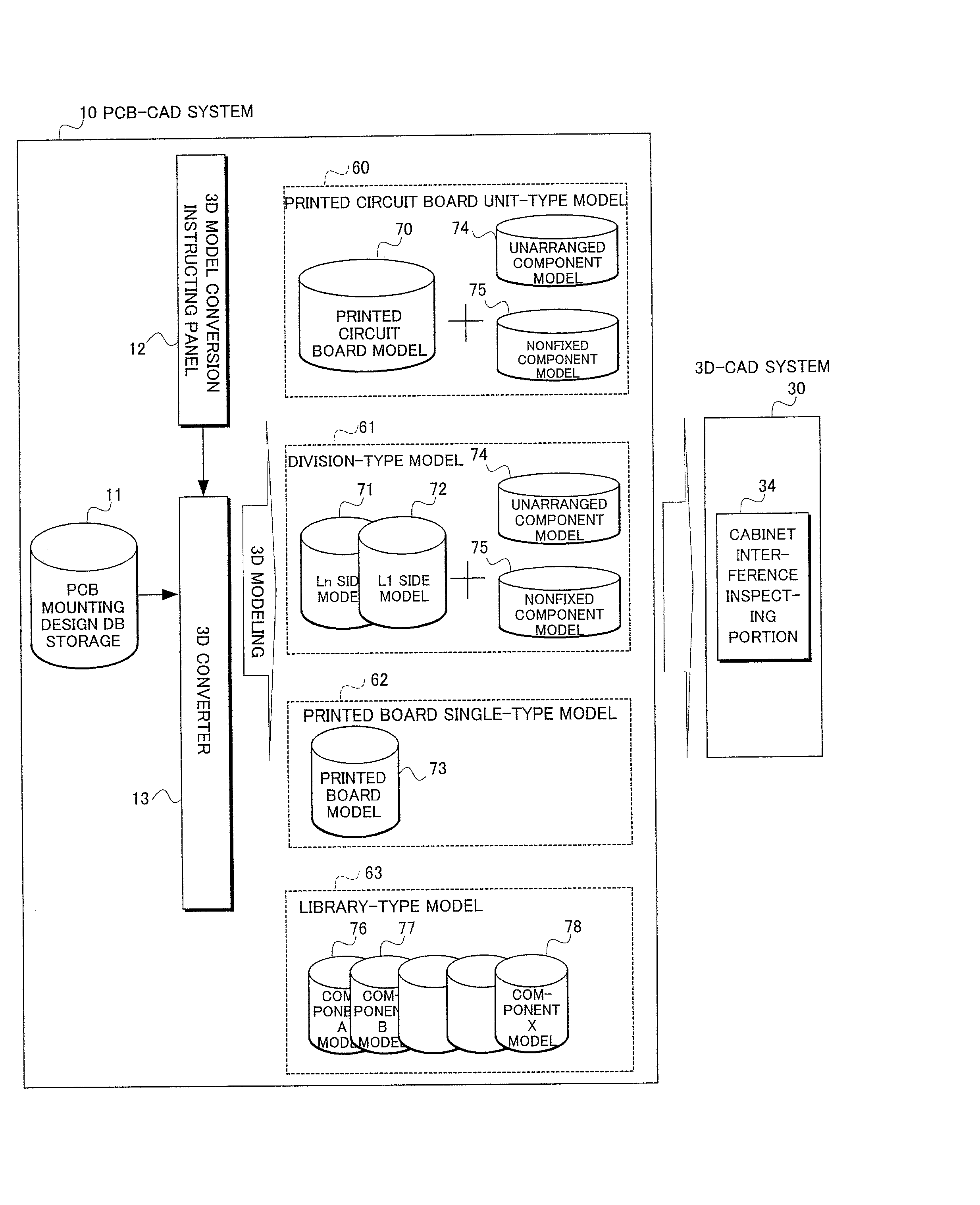

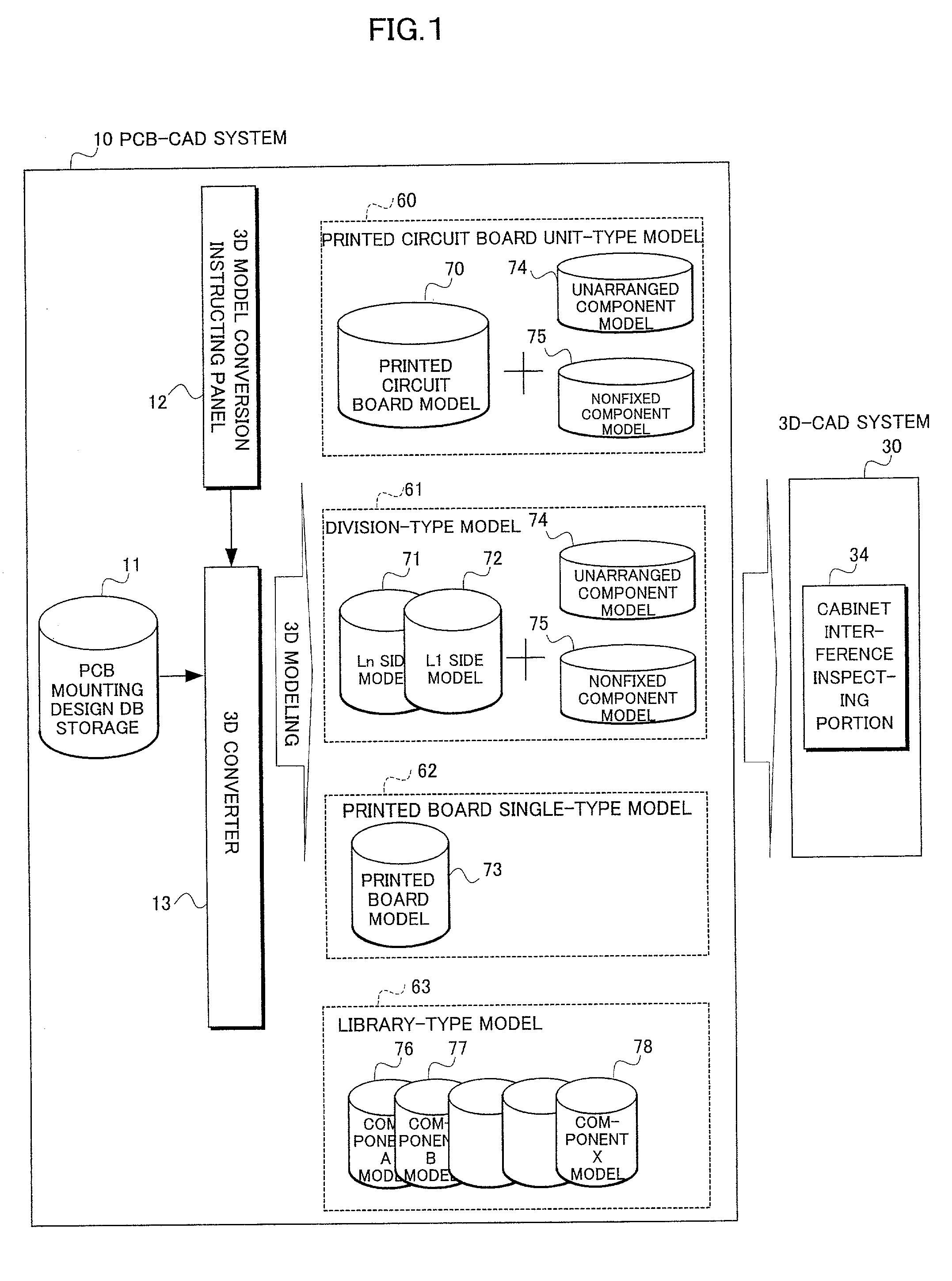

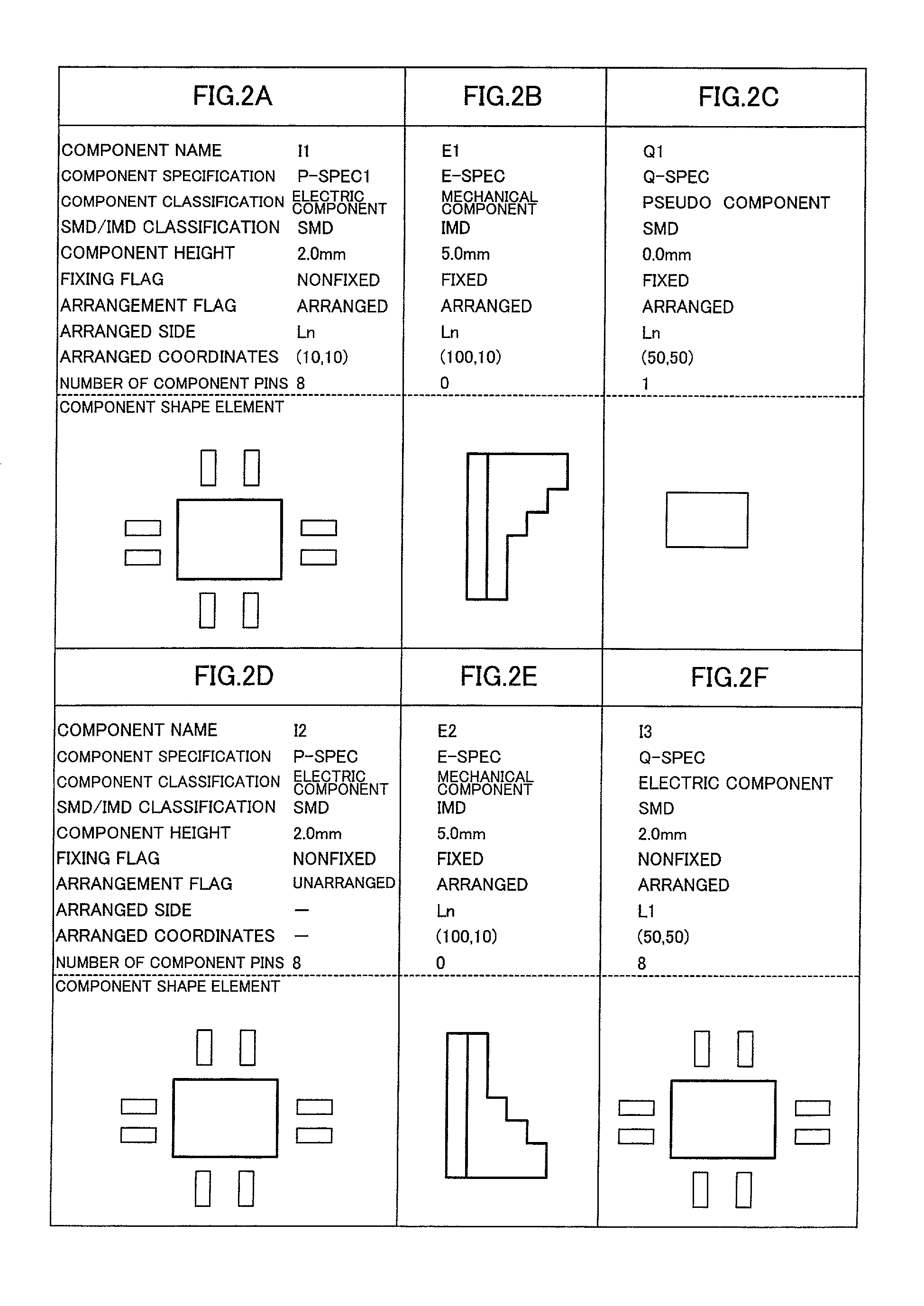

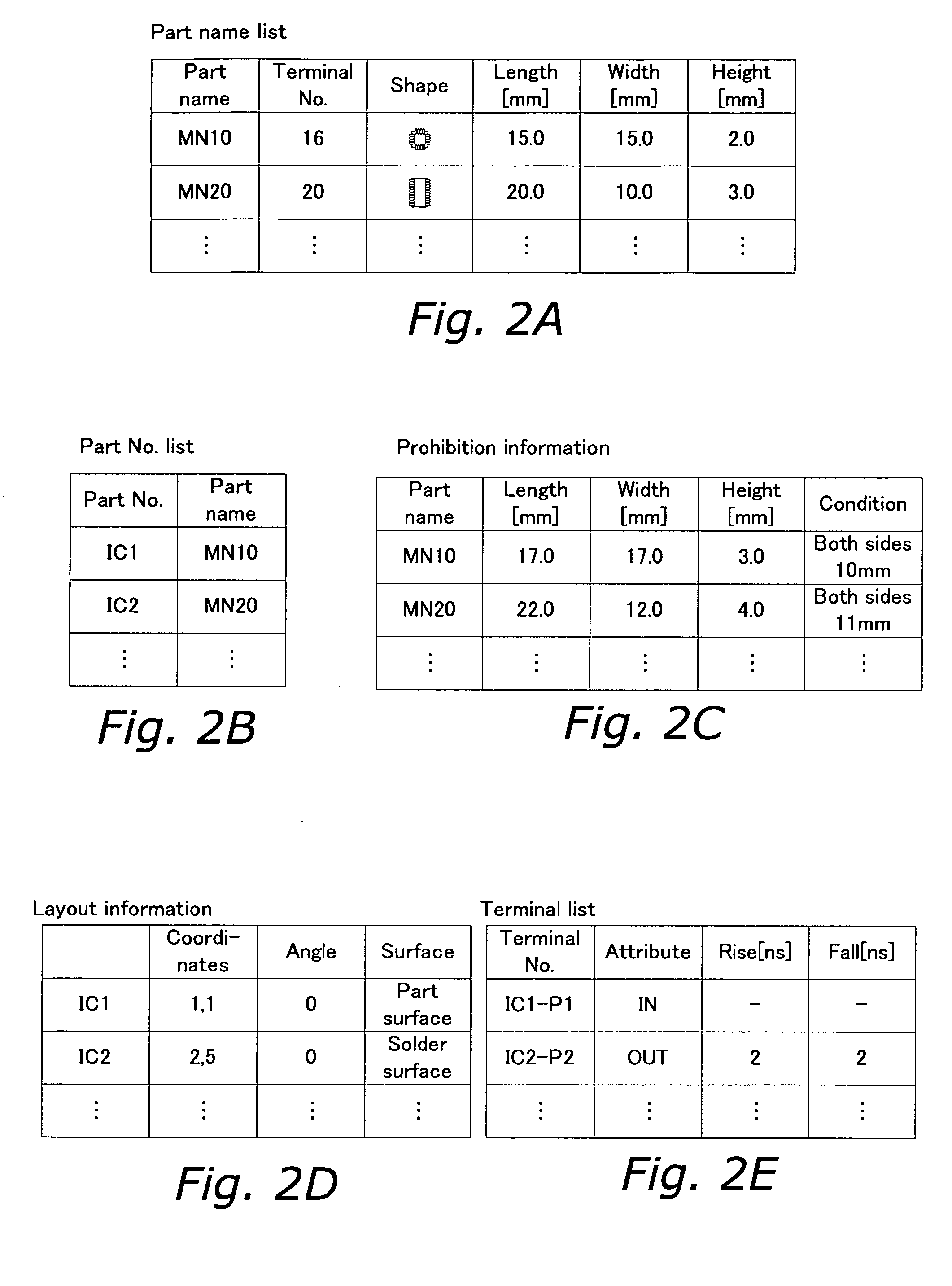

Printed circuit board design system

A printed circuit board design system performs, with a 3D-CAD system, a mounting design including a cabinet. In order to prepare, without mistakes in less man-hours, an accurate 3D model of a printed circuit board provided to the 3D-CAD system, a converter converts the printed circuit board into a unit-type model, a division-type model, a single-type model, and a library-type model composed of one or more models based on attributes preliminarily added to a mounting component stored in a mounting design DB storage.

Owner:FUJITSU LTD

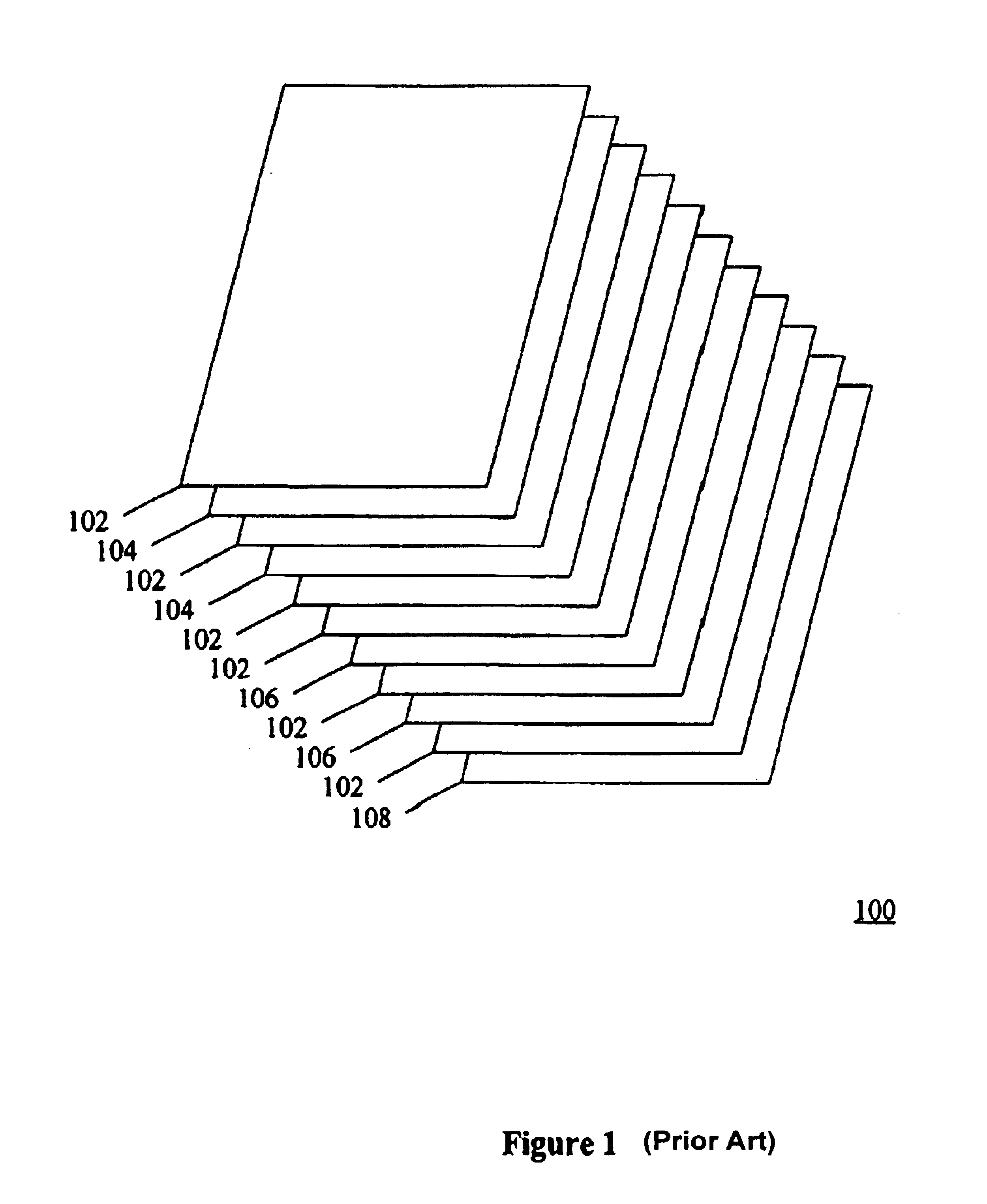

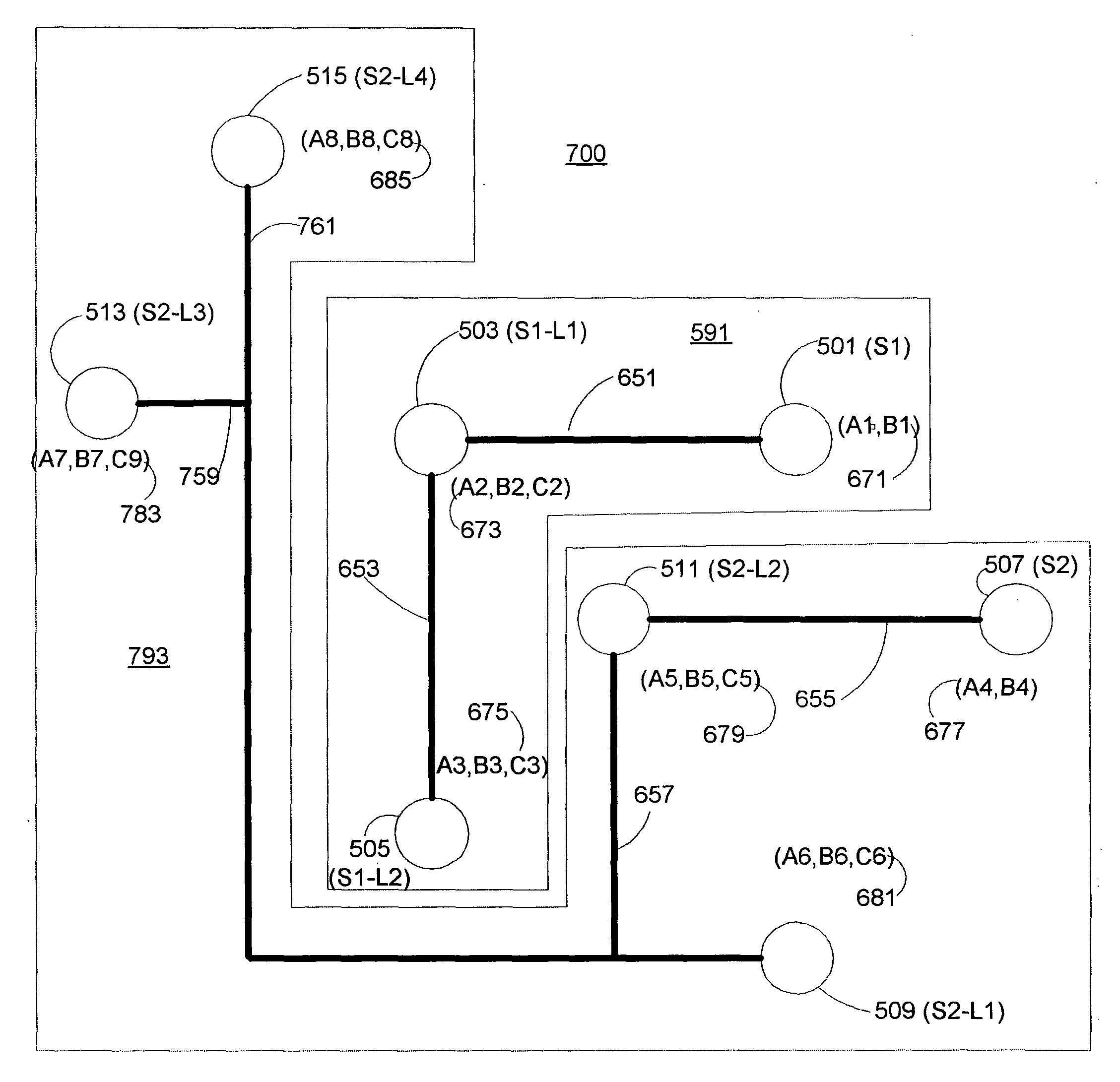

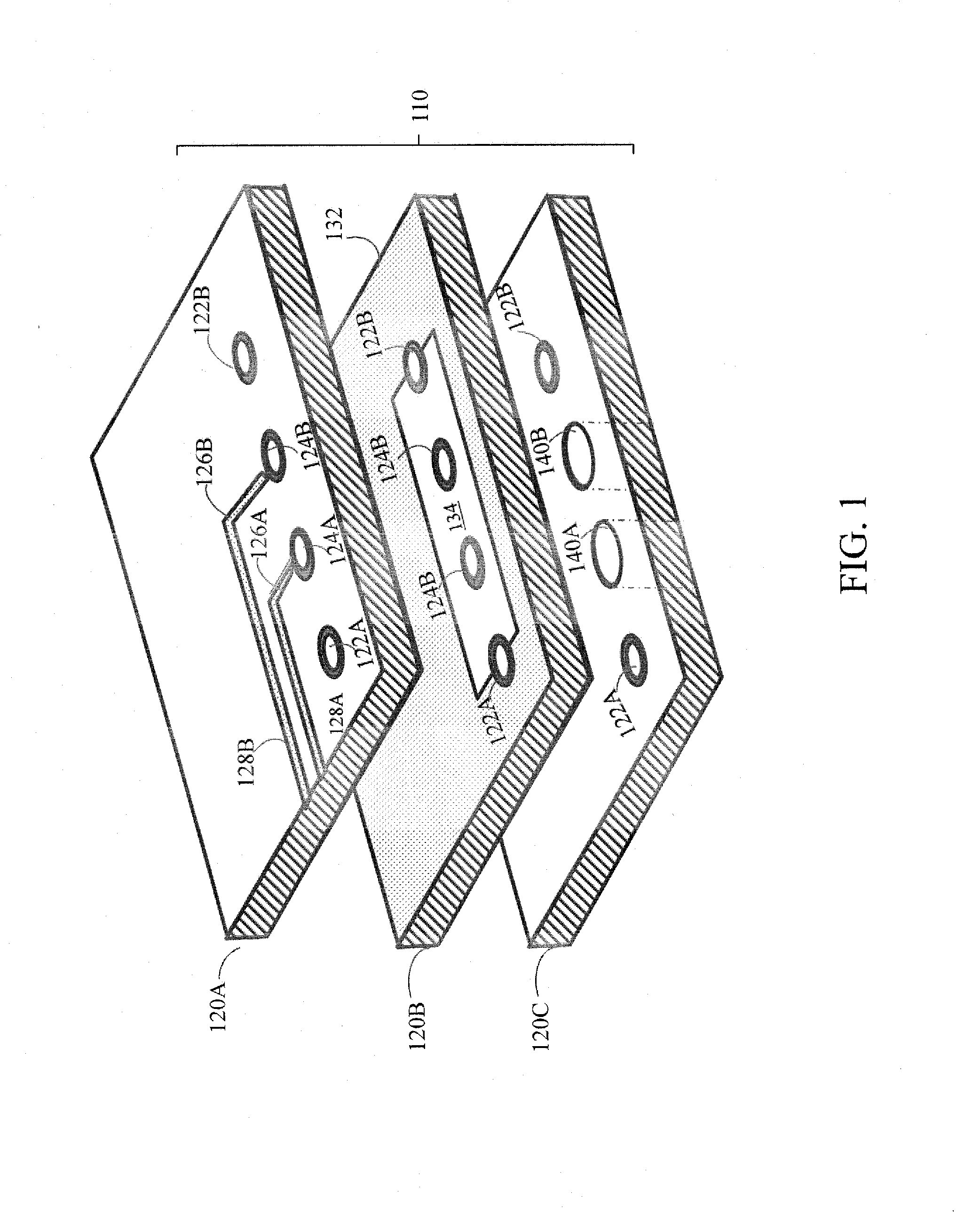

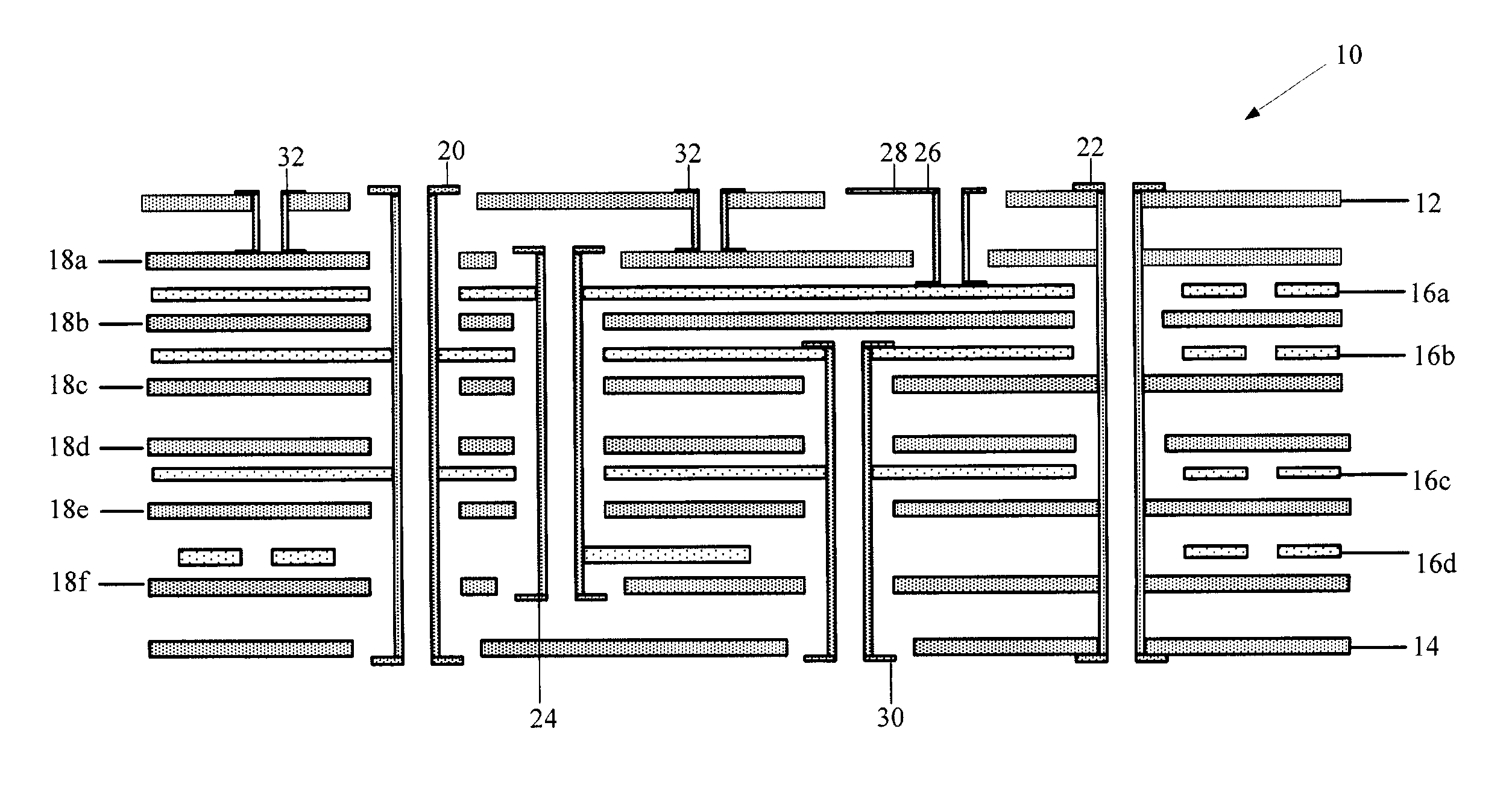

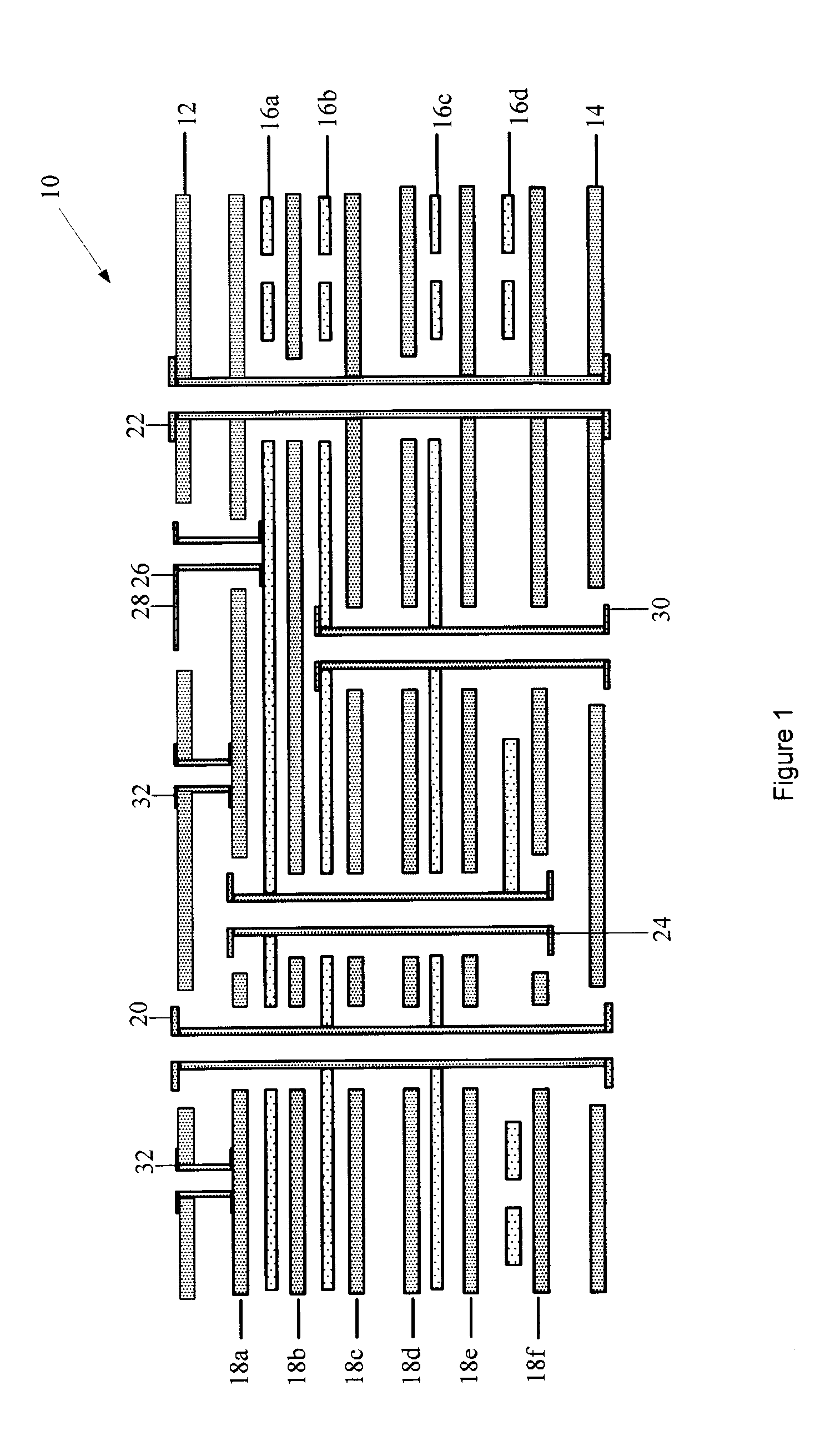

Techniques for reducing the number of layers in a multilayer signal routing device

InactiveUS7069646B2Reduce in quantityEfficient routingComputer designed circuitsElectrical connection printed elementsSignal routingEngineering

Techniques for reducing the number of layers in a multilayer signal routing device are disclosed. In one particular exemplary embodiment, the techniques may be realized as a method wherein the multilayer signal routing device has a plurality of electrically conductive signal path layers for routing a plurality of electrical signals thereon. The method may comprise forming a plurality of electrically conductive vias in the multilayer signal routing device for electrically connecting at least two of the plurality of electrically conductive signal path layers, wherein the plurality of vias are arranged so as to form at least one channel in at least one other of the plurality of electrically conductive signal path layers. The method may also comprise grouping at least a portion of the plurality of electrical signals based at least in part upon their proximity to the at least one channel so that they may be efficiently routed therein.

Owner:RPX CLEARINGHOUSE

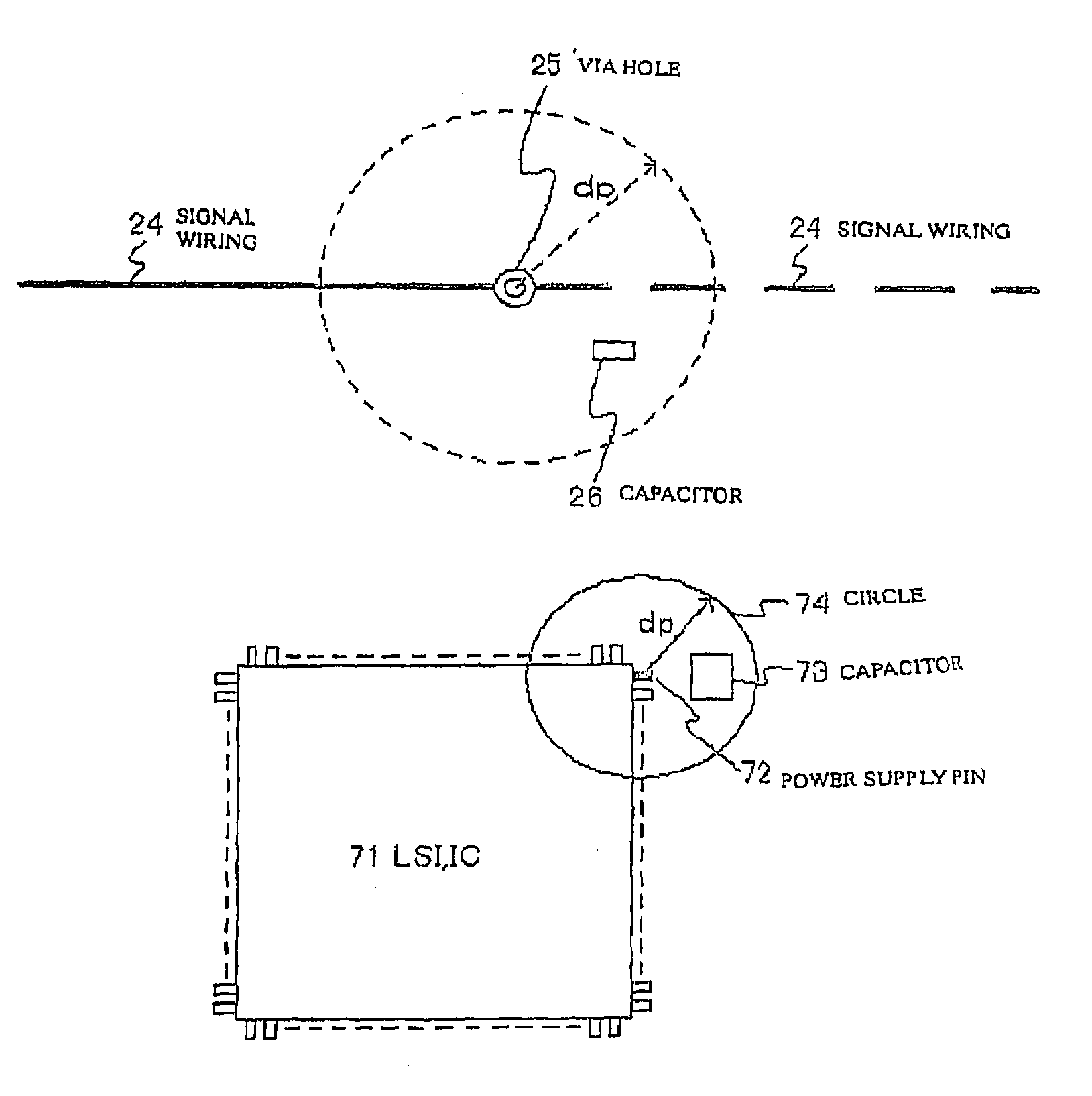

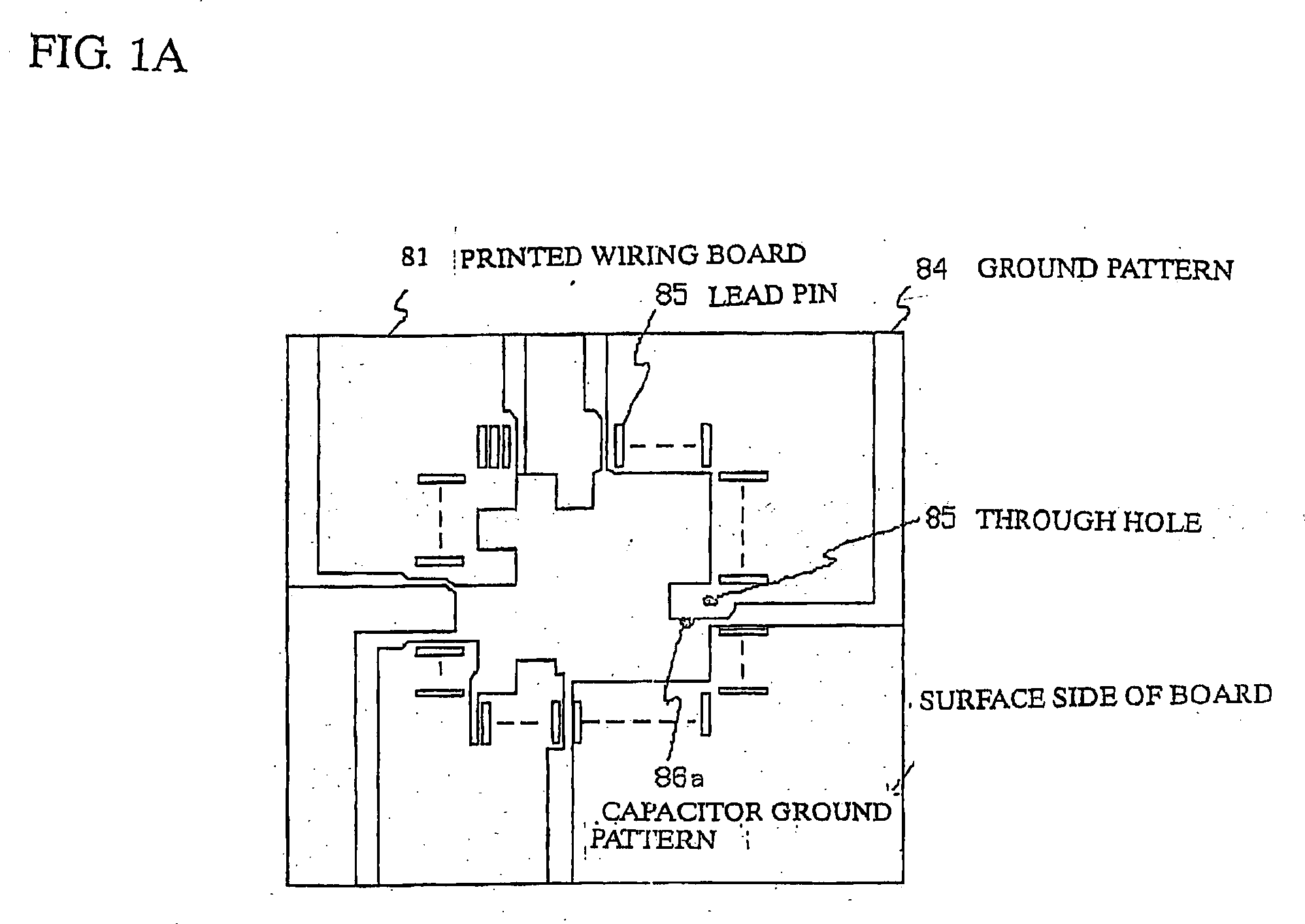

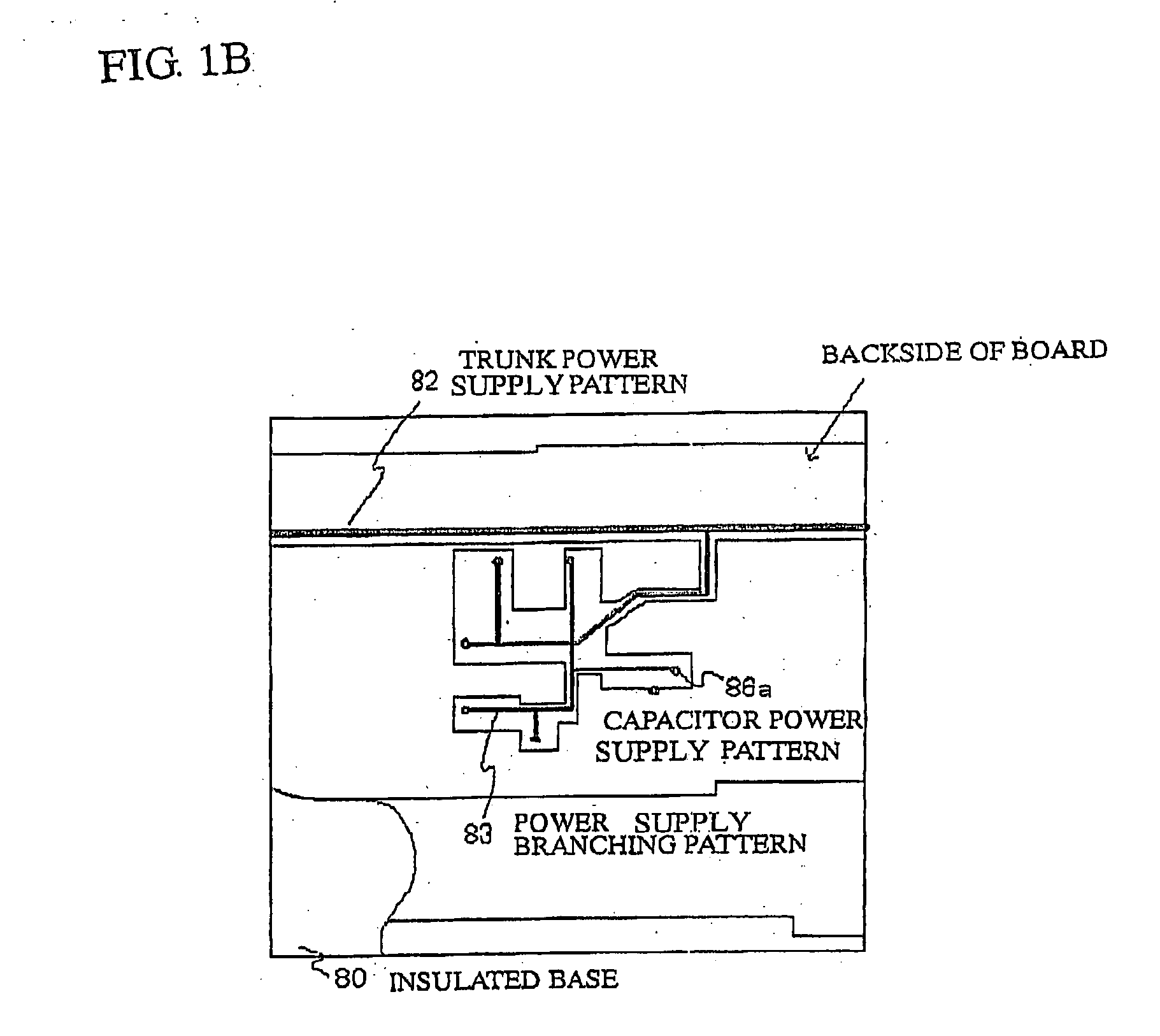

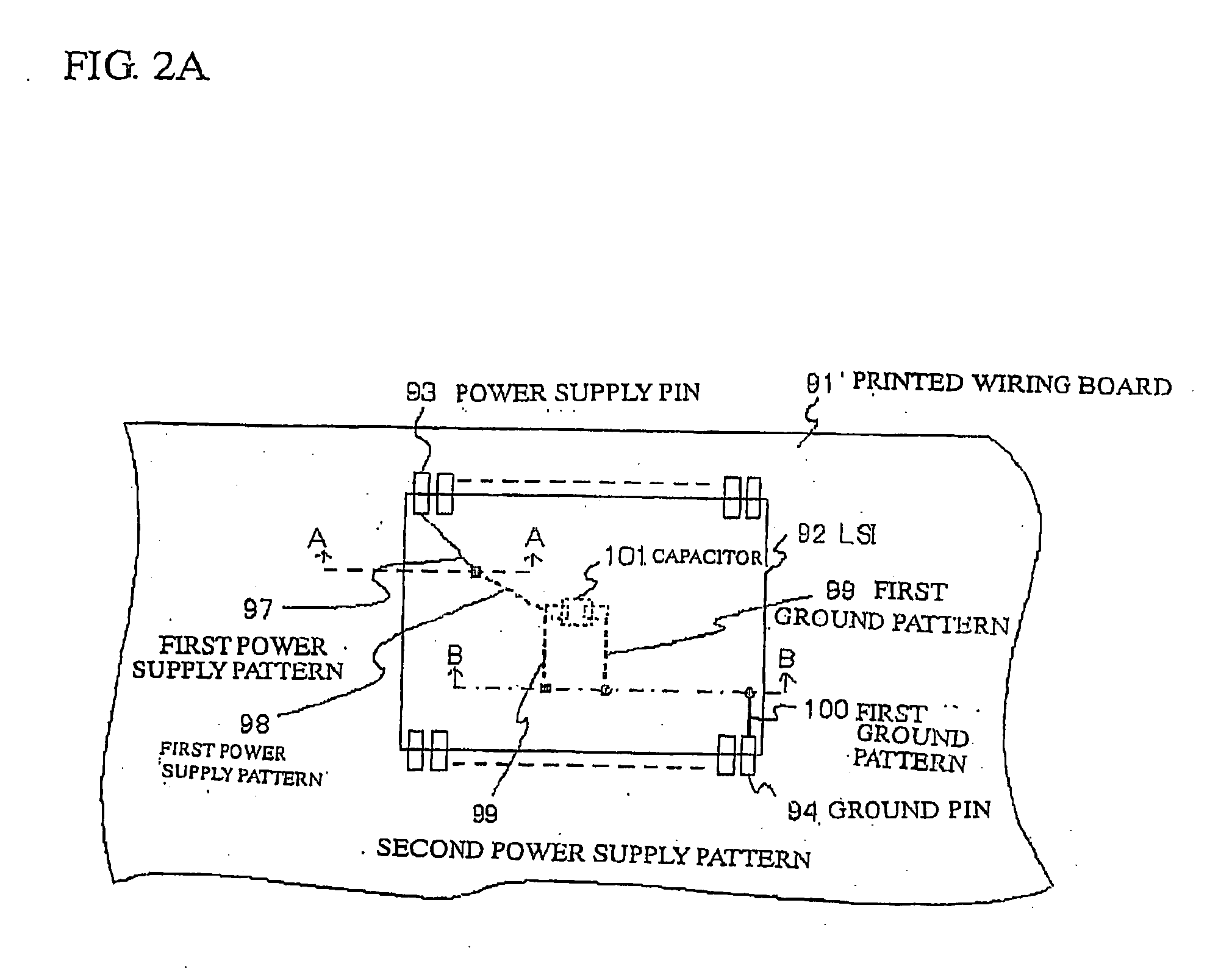

Printed circuit wiring board designing support device, printed circuit board designing method, and its program

ActiveUS7168058B2Easy to optimizeCross-talk/noise/interference reductionPrinted circuit aspectsGround planeCapacitor

Owner:NEC CORP

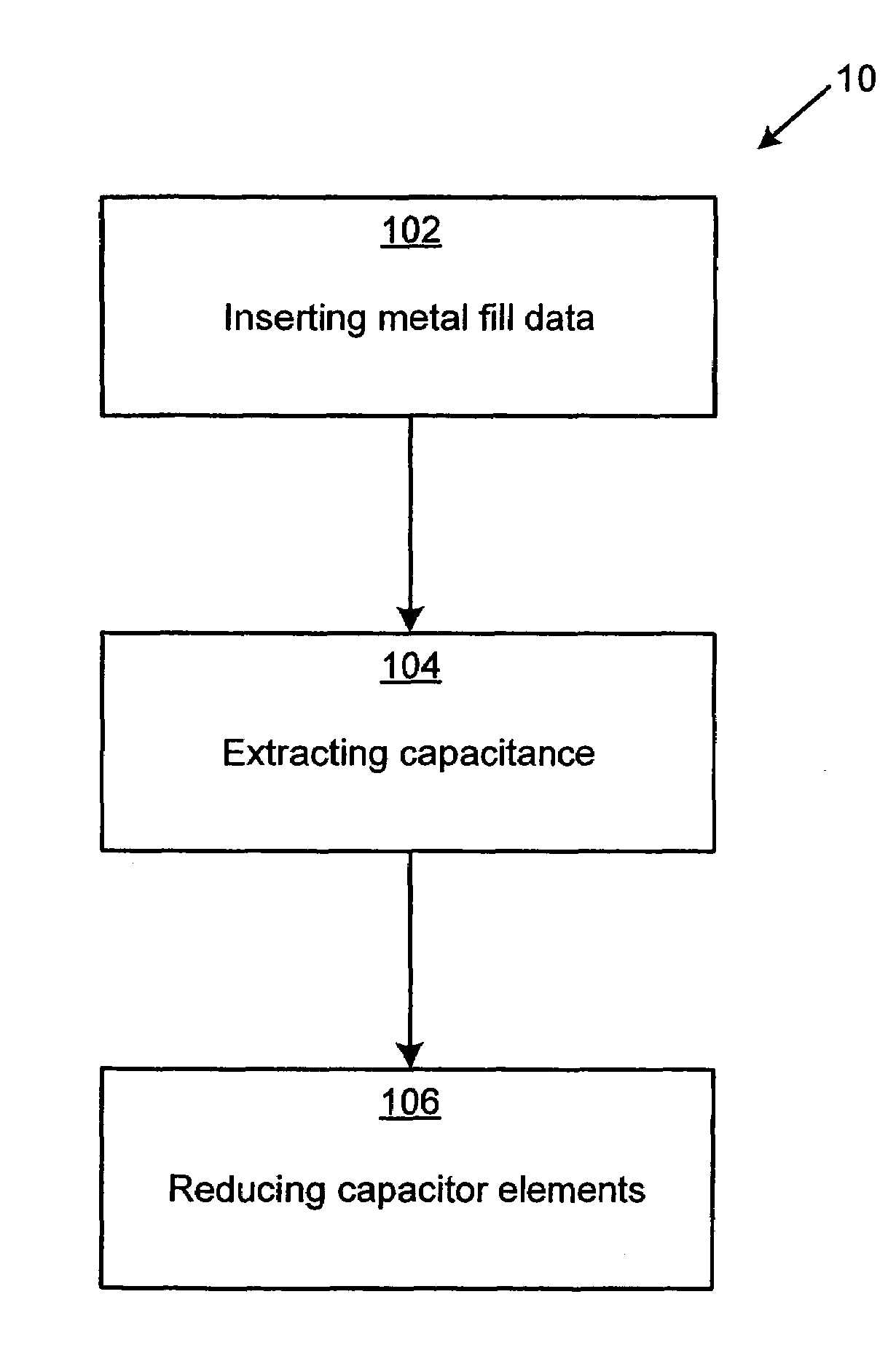

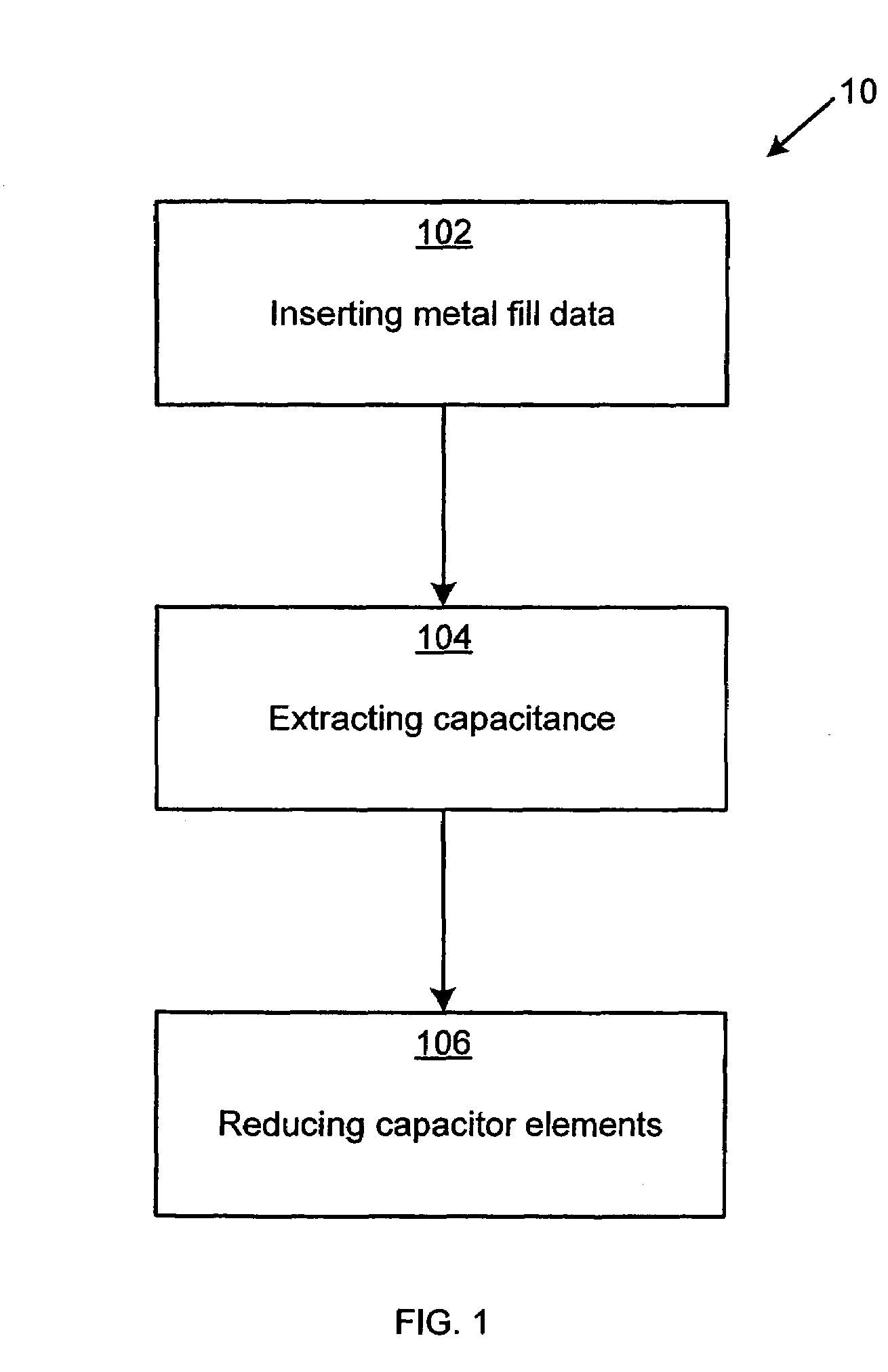

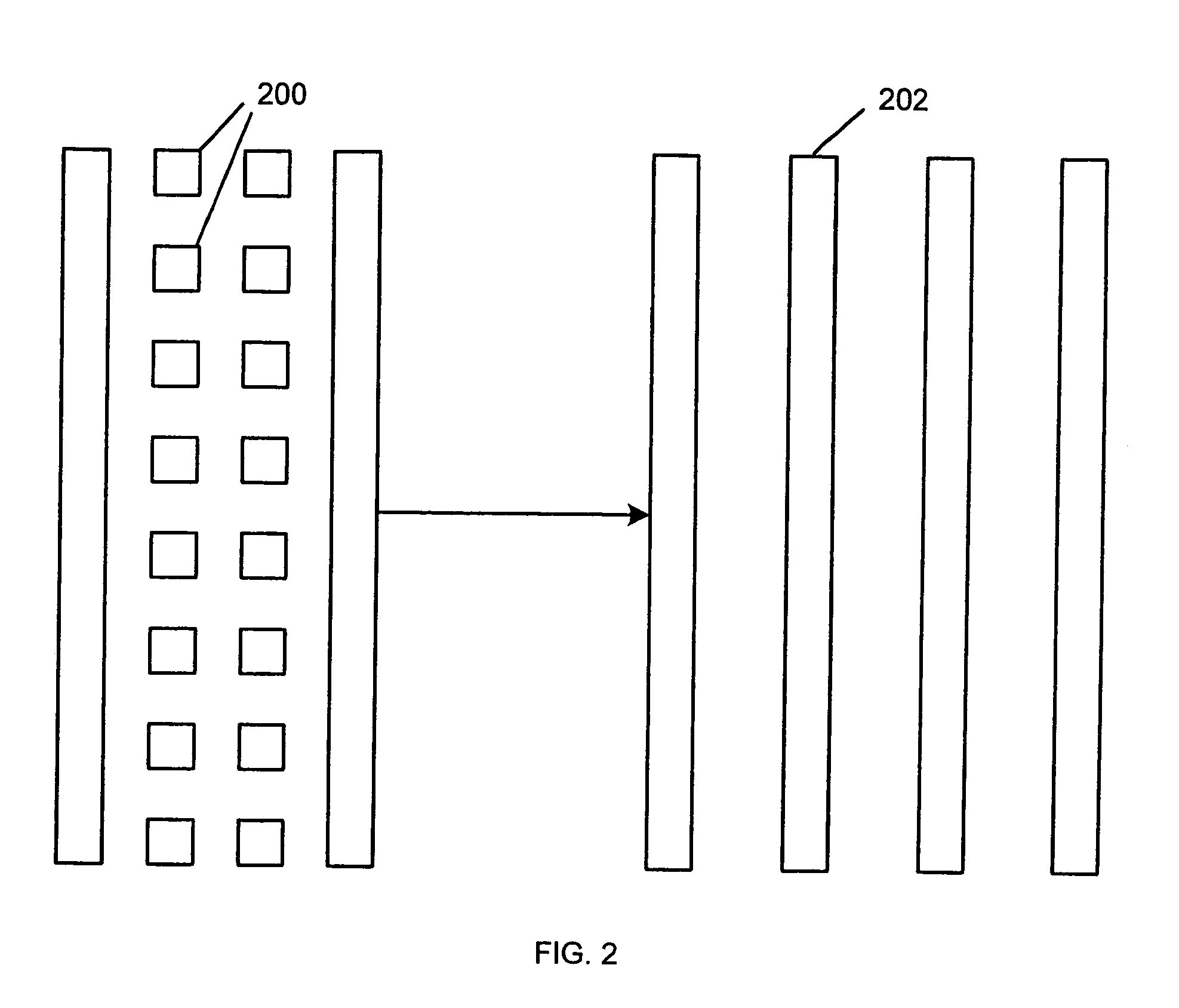

Methods and mechanisms for implementing virtual metal fill

ActiveUS7448010B1Extract capacitancePrinted circuit aspectsComputer designed circuitsCapacitanceEngineering

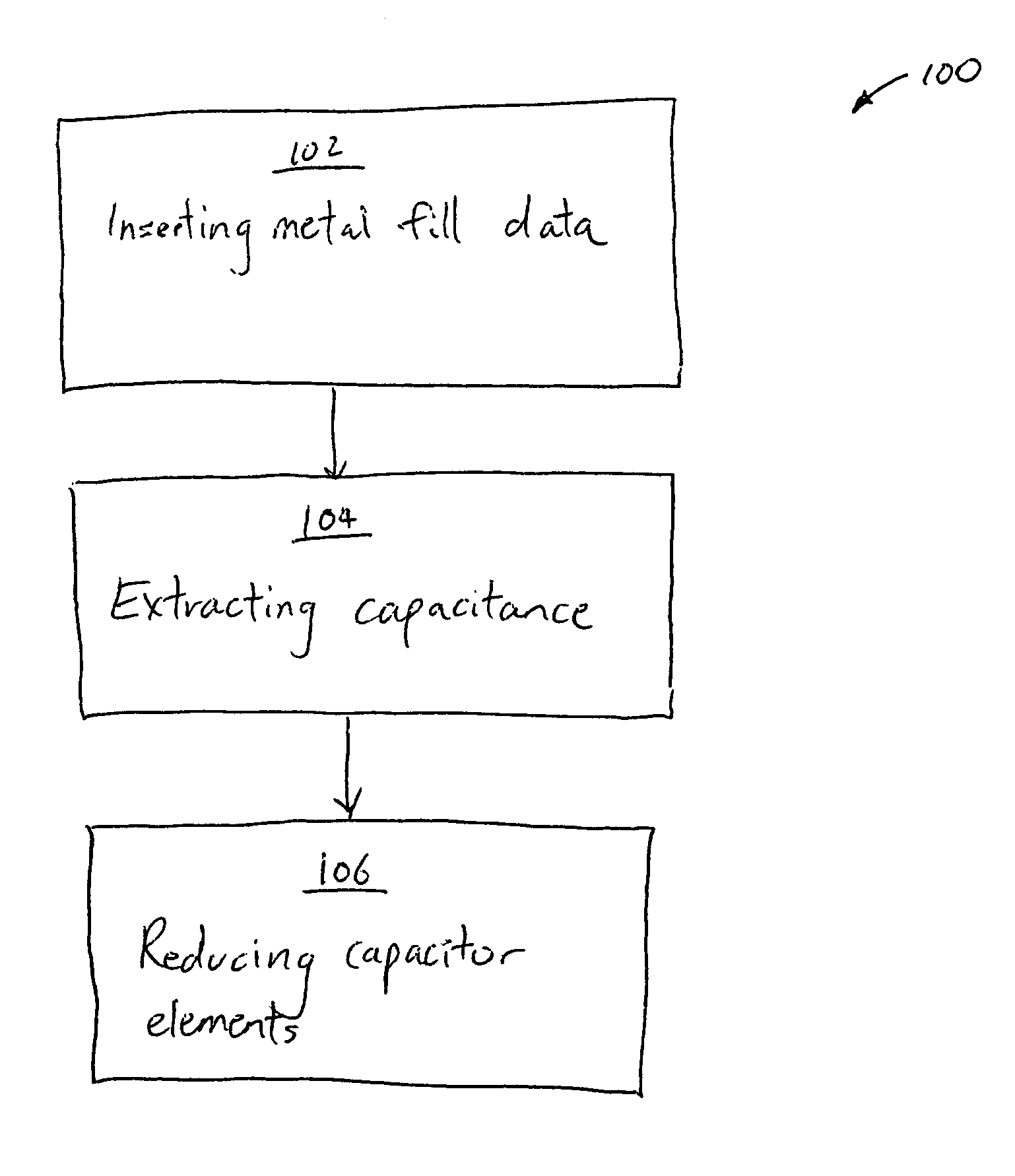

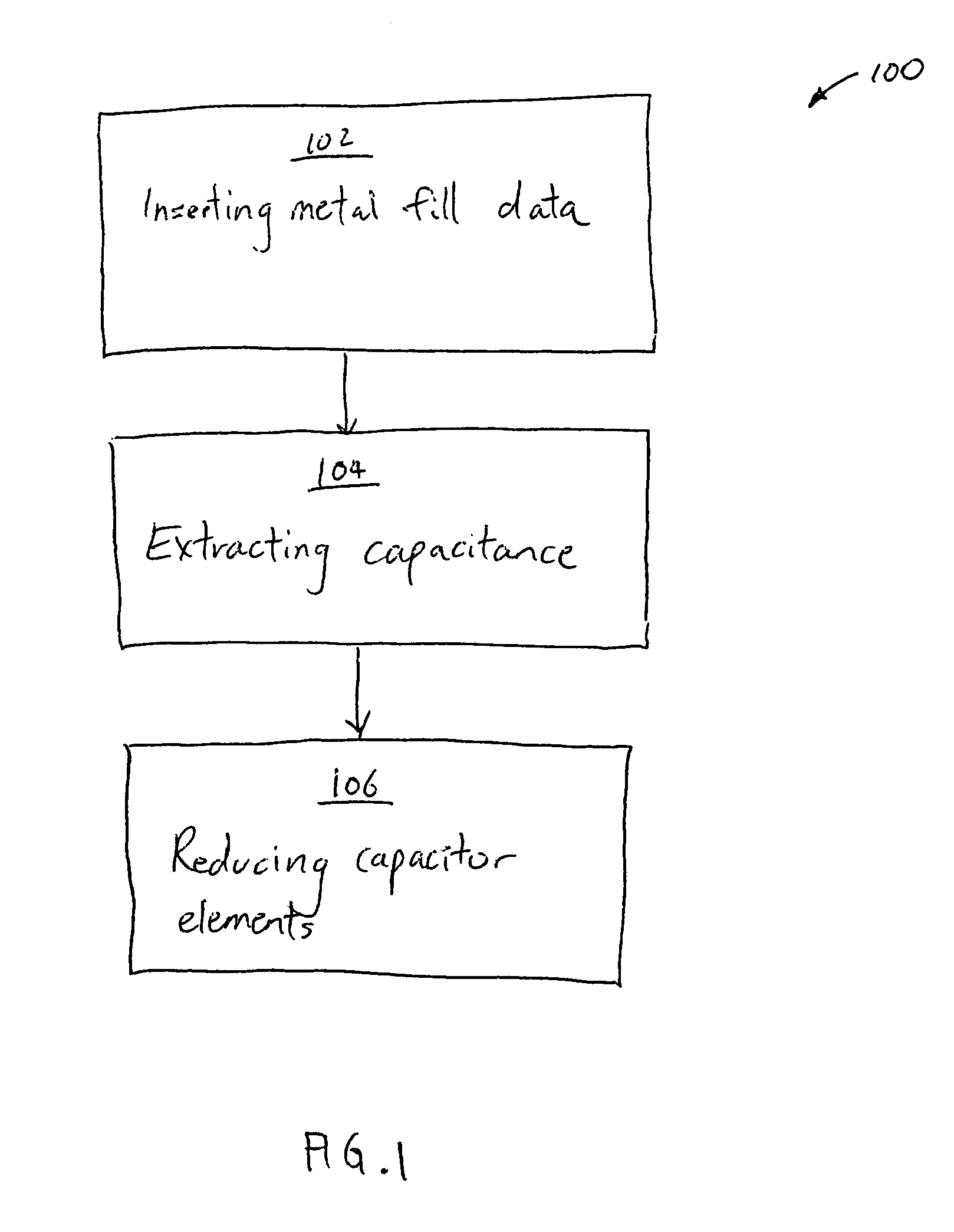

A method for implementing virtual metal fill includes inserting metal fill data into a layout record based on one or more rules, extracting capacitance from the layout record to create a capacitance network, and reducing the capacitance network.

Owner:CADENCE DESIGN SYST INC

Substrates Having Voltage Switchable Dielectric Materials

Owner:LITTELFUSE INC

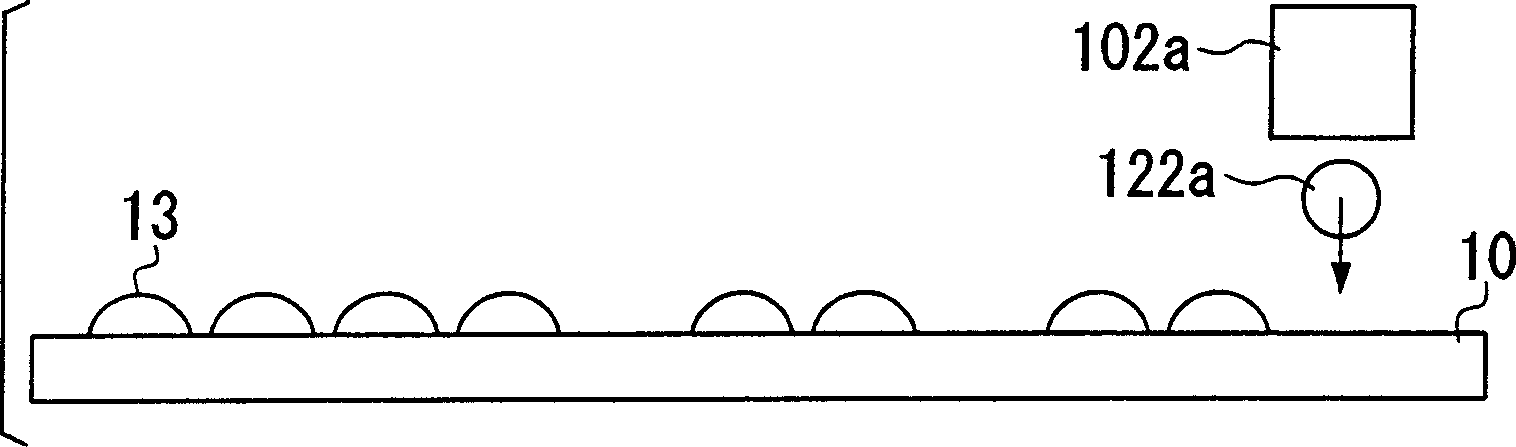

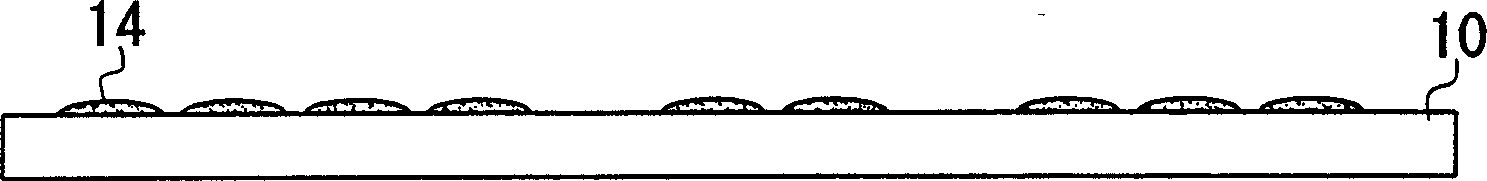

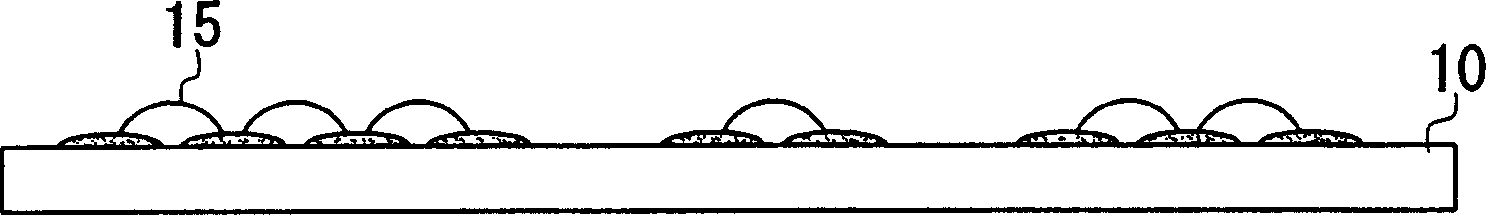

Multi-layer distribution board and mfg method, electronic device and electronic apparatus

InactiveCN1503338AAdjust injection volumePrevent breakdownSemiconductor/solid-state device detailsPrinted circuit aspectsInter layerEngineering

A multilayer circuit board and a manufacturing method for producing the board via simple manufacturing processes employing a droplet jetting method, where the inter-layer insulating film can be easily made flat. The multilayer circuit board includes at least two wiring layers, an inter-layer insulating film provided between every adjacent two of the wiring layers, and conductive posts for providing electrical conductivity between the wiring layers. The manufacturing method includes the step of forming the inter-layer insulating film by changing the film thickness of the inter-layer insulating film according to a concavo-convex shape of an area where the inter-layer insulating film is formed, so as to level an upper surface of the inter-layer insulating film. The concavo-convex shape may be computed based on design data of a circuit pattern for forming the wiring layers and the conductive posts, or may be measured before the inter-layer insulating film is formed.

Owner:SEIKO EPSON CORP

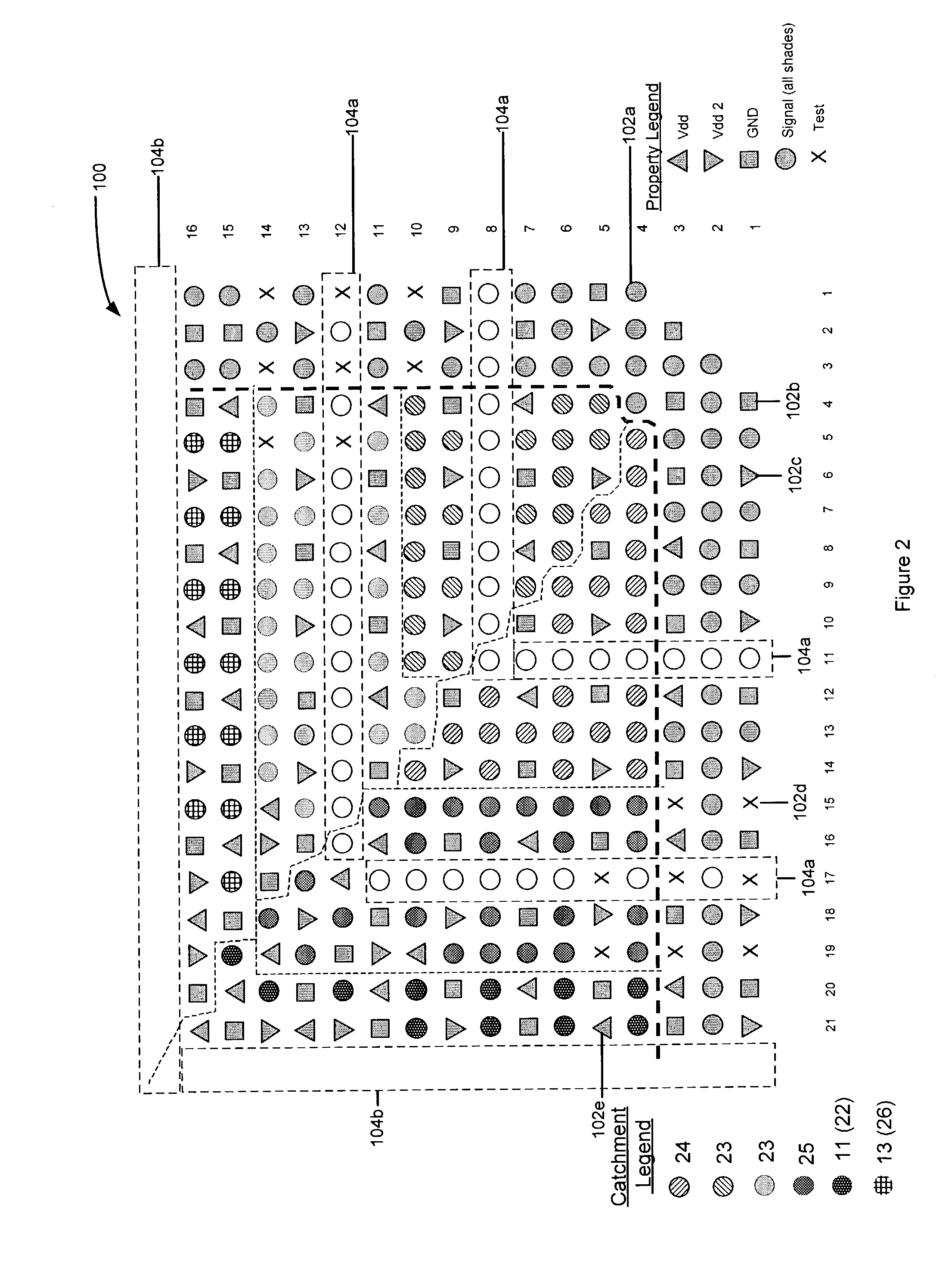

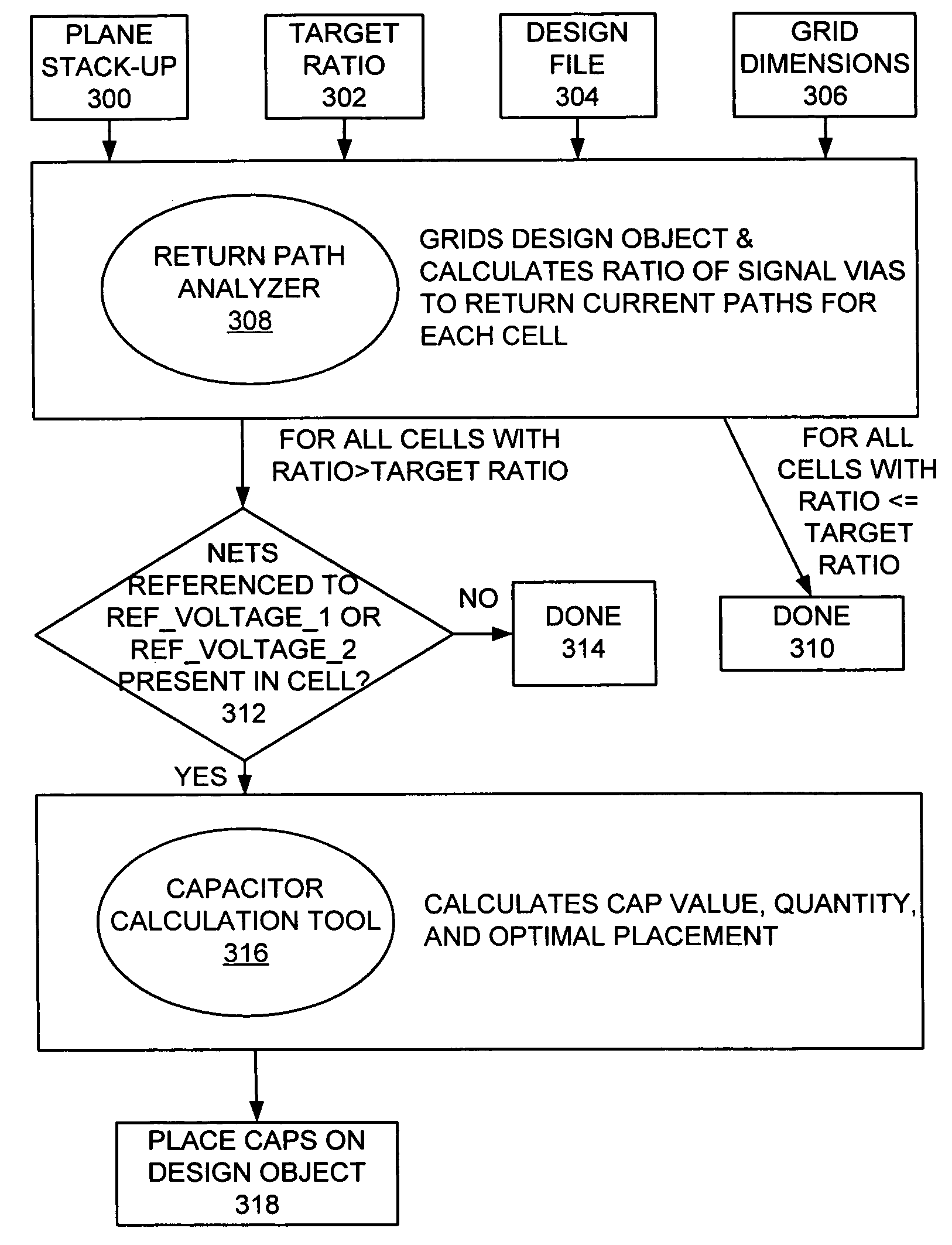

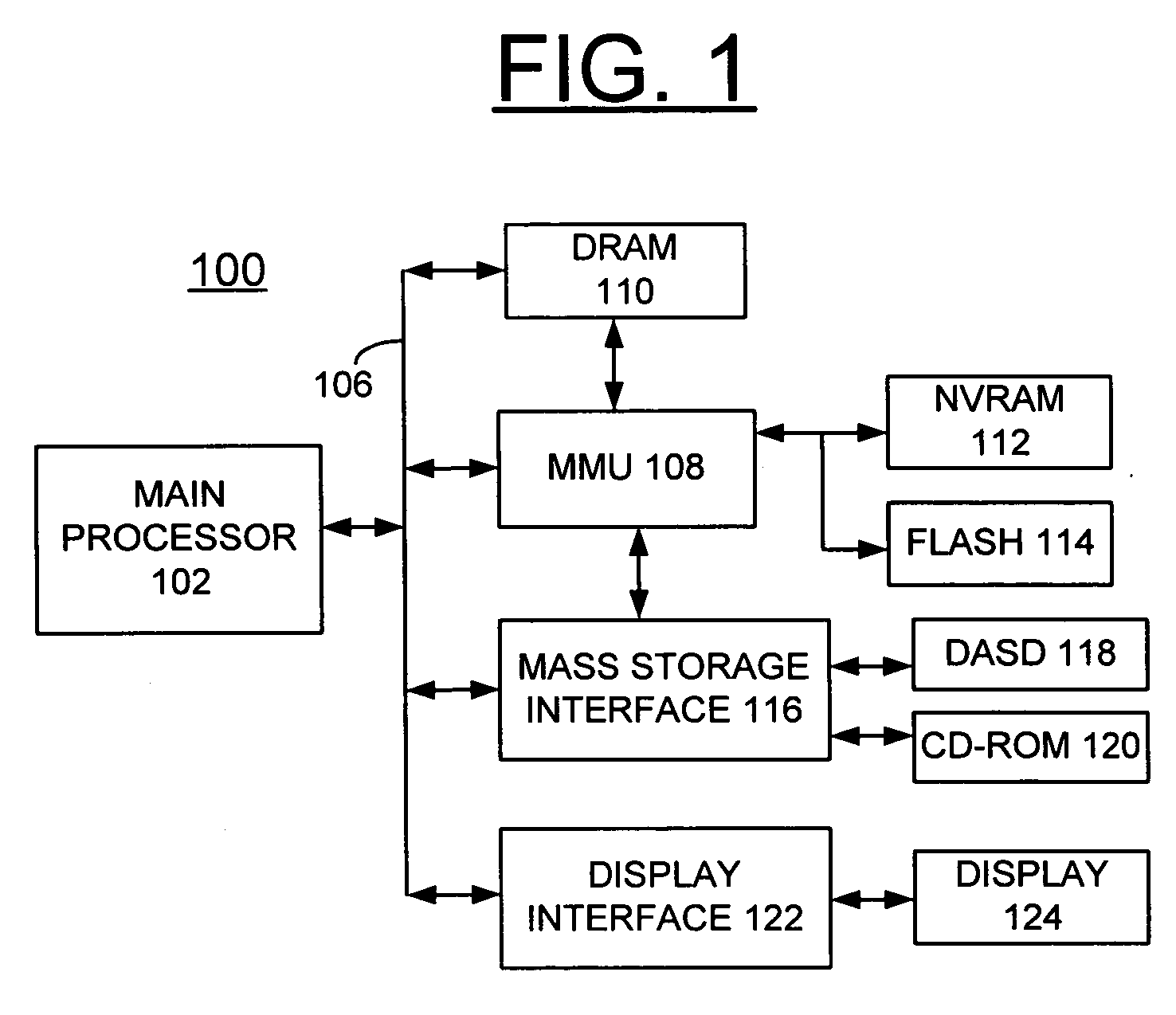

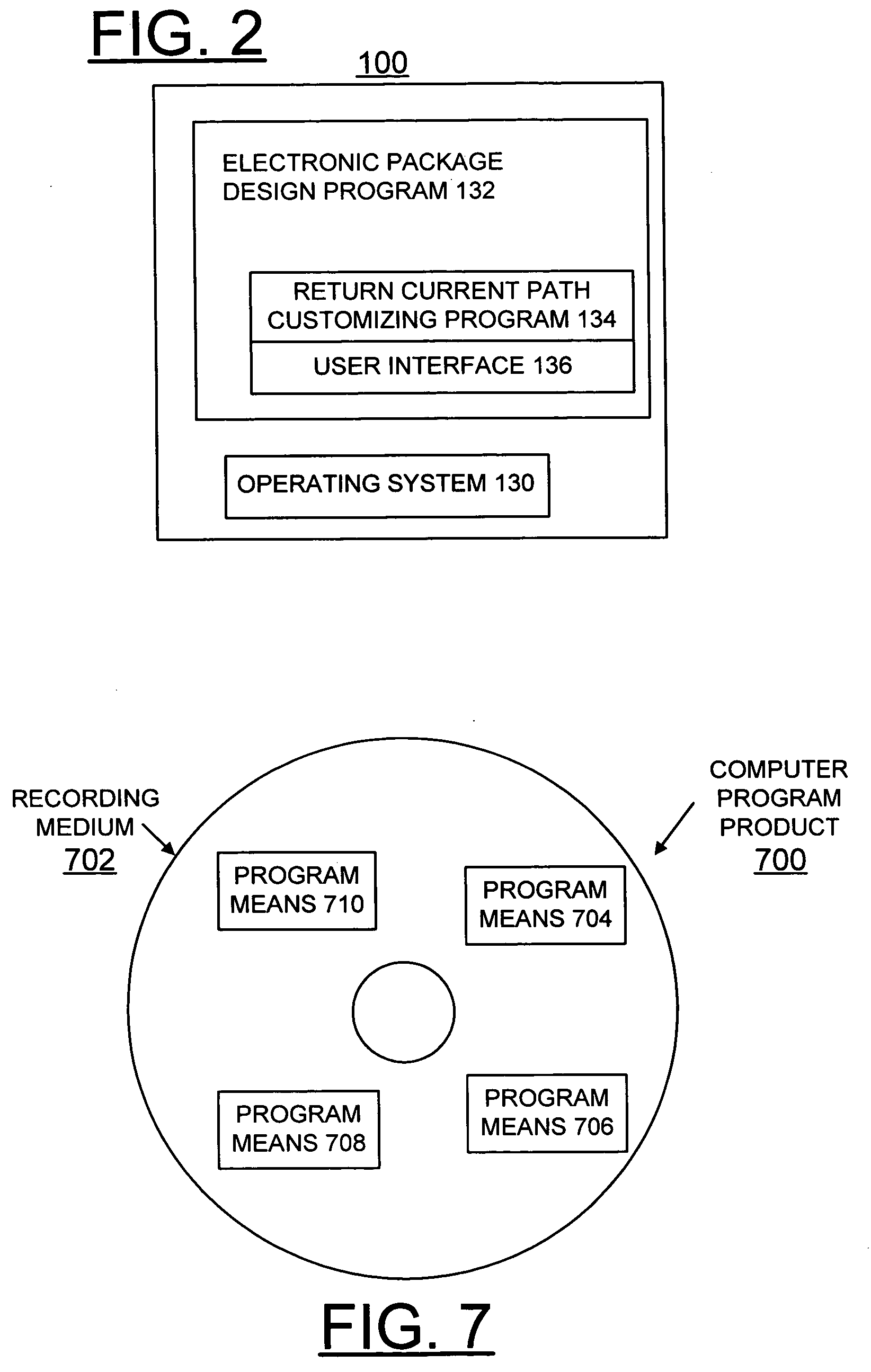

Method, apparatus and computer program product for implementing enhanced high frequency return current paths utilizing decoupling capacitors in a package design

InactiveUS20050108671A1Cross-talk/noise/interference reductionHigh voltage circuit adaptationsReturn currentPackage design

A method, apparatus and computer program product are provided for implementing high frequency return current paths utilizing decoupling capacitors within electronic packages. Electronic package physical design data are received for identifying a board layout. For each of a plurality of cells in a grid of a set cell size within the identified board layout, a respective number of signal vias are identified. A ratio of signal vias to return current paths is calculated for each of the plurality of cells. Each cell having a calculated ratio greater than a target ratio is identified. One or more decoupling capacitors are selectively added within each of the identified cells to provide high frequency return current paths.

Owner:GOOGLE LLC

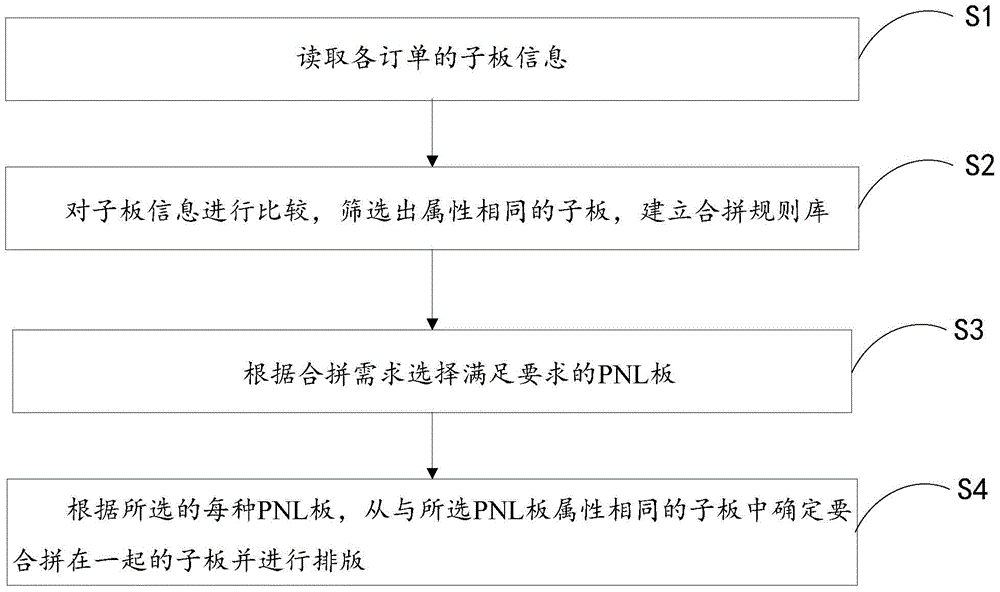

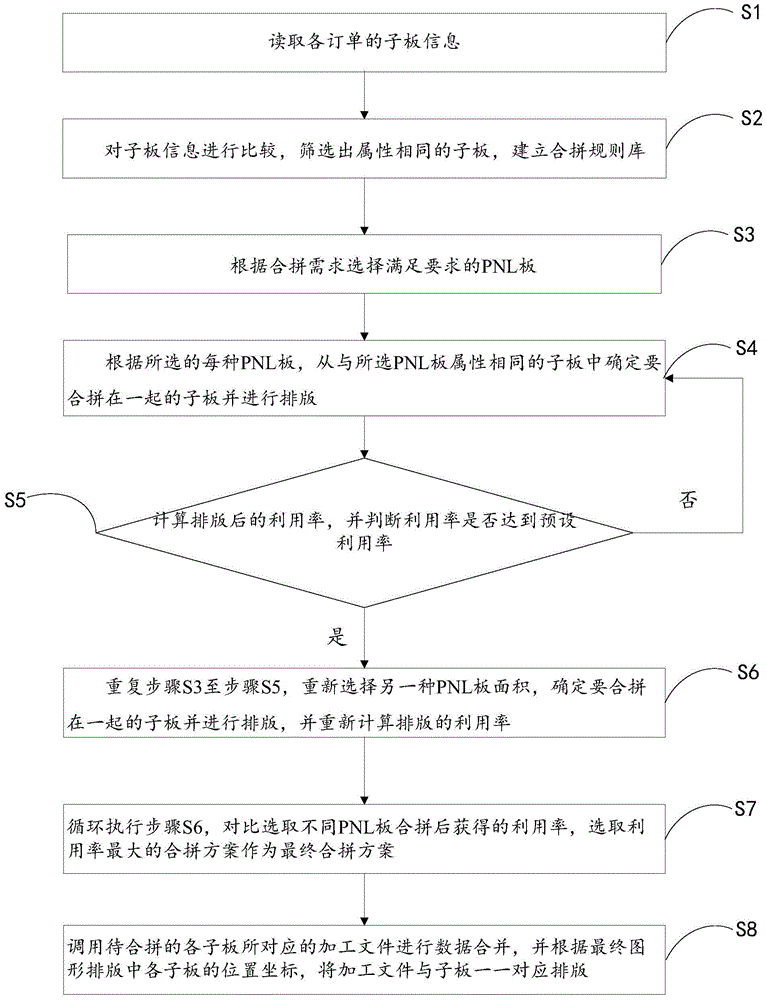

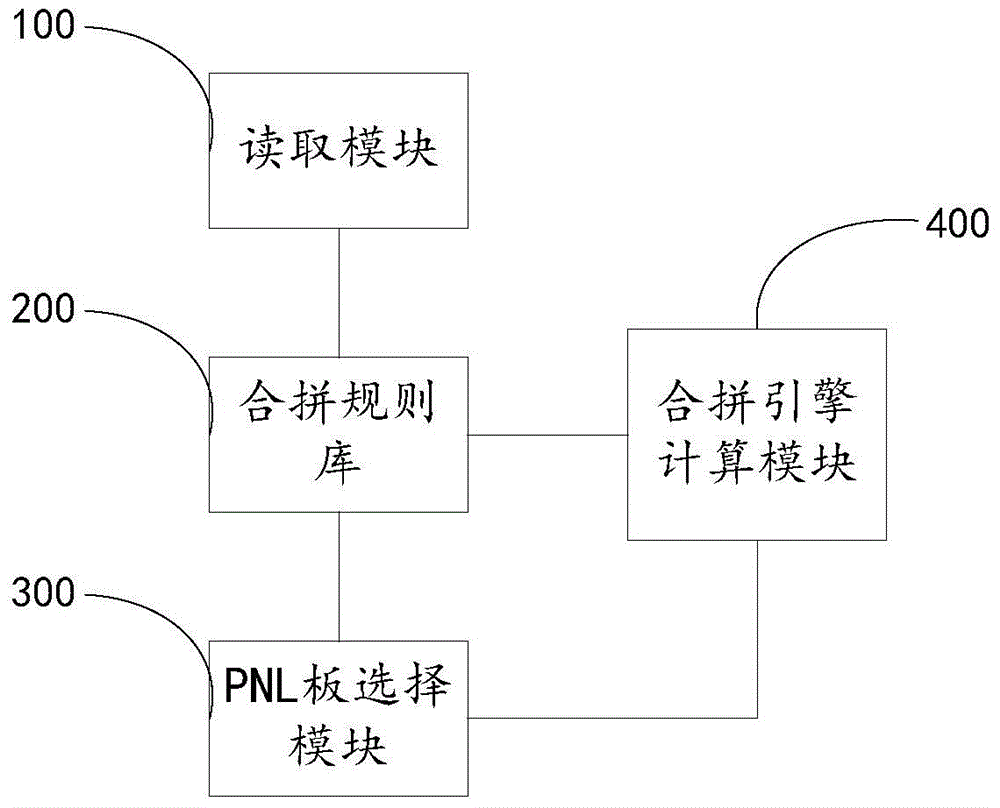

Printed circuit board (PCB) combining and joining method and system

InactiveCN105678408AIncrease the number of varietiesReduce dependencePrinted circuit assemblingForecastingPrinted circuit boardComputer science

The present invention discloses a PCB combining and joining method. The method comprises the steps of S1 reading the daughter board information of orders, wherein the daughter board information comprises the respective areas, delivery quantities and attributes of the daughter boards; S2 comparing the daughter board information, screening the daughter boards of same attributes, and establishing a combining and joining rule database; S3 selecting the panels (PNL) satisfying requirements according to the combining and joining demands; S4 according to the PNL, determining the daughter boards which are combined and joined together from the daughter boards having the same attribute with the PNL, and carrying out typesetting. The present invention also discloses a PCB combining and joining system. The system comprises a reading module used for reading the daughter board information in the orders; the combining and joining rule database for storing the information of the screened daughter boards of same attribute; a PNL selecting module used for selecting the PNL satisfying requirements according to the combining and joining demands; and a combining and joining engine calculating module used for selecting the daughter boards according to a sequence from large to small, determining whether the daughter boards can be combined and joined, determining whether the typesetting is successful, determining the daughter boards which are combined and joined together finally, and carrying out the typesetting.

Owner:GUANGZHOU FASTPRINT CIRCUIT TECH +2

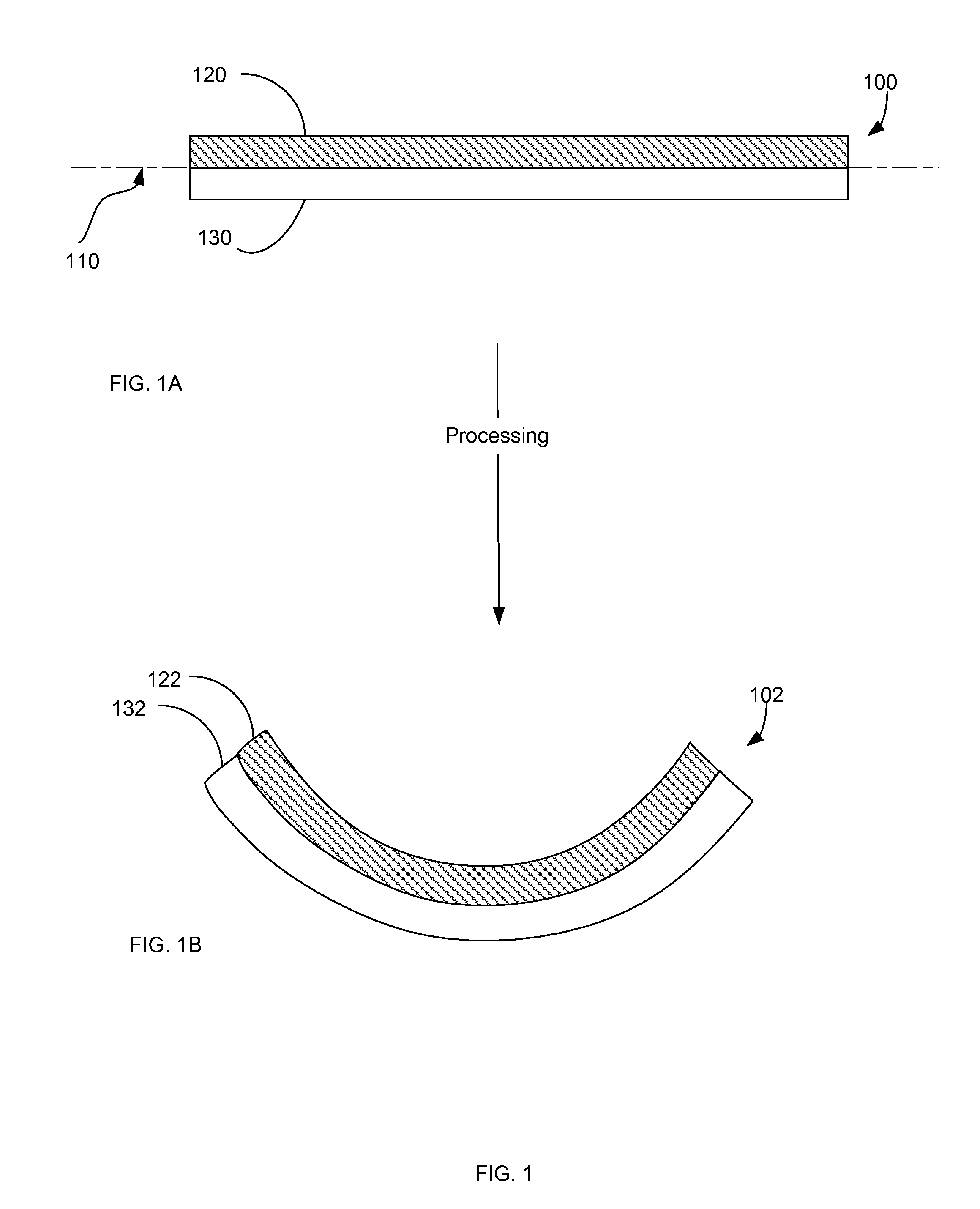

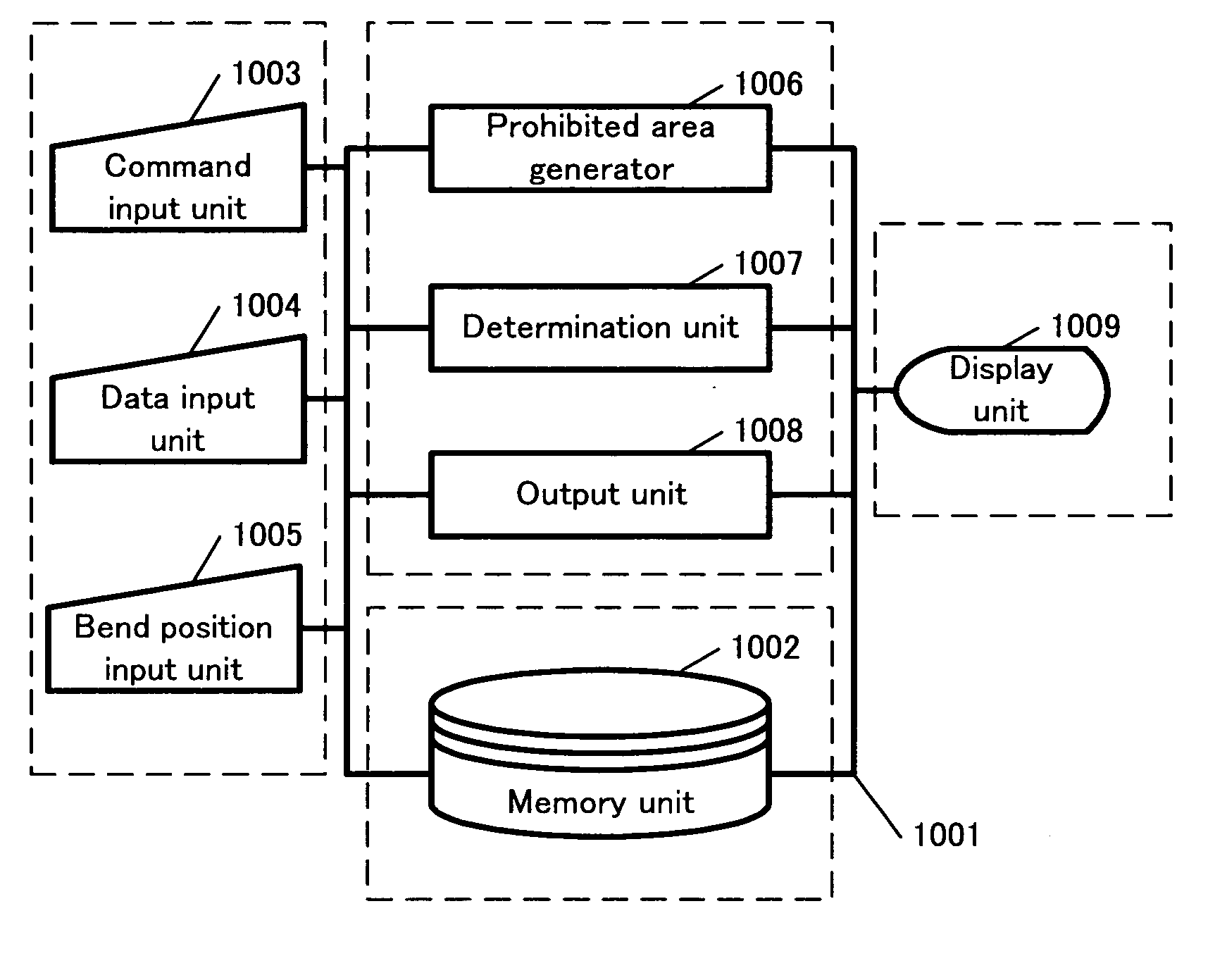

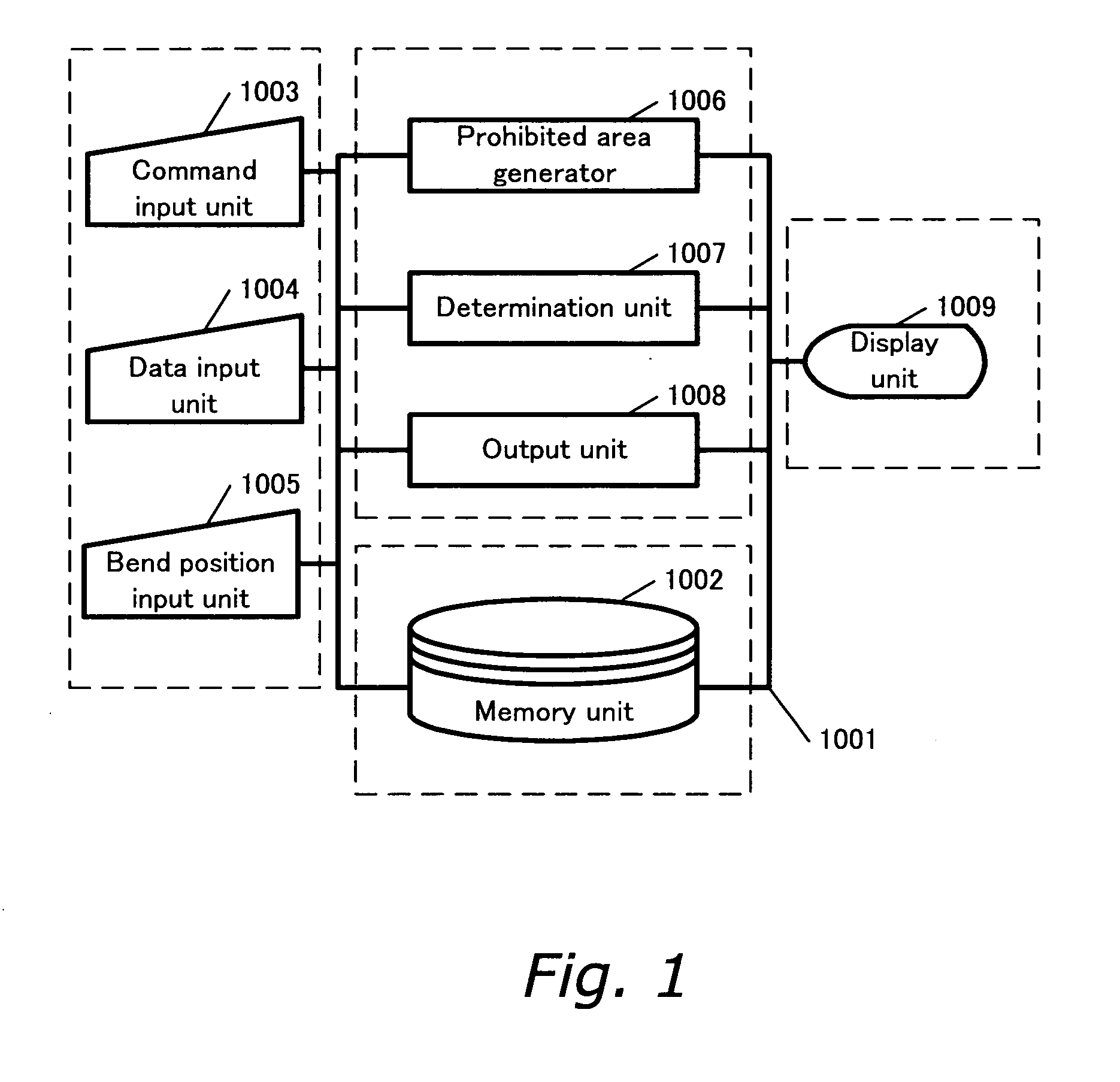

Device, method, and program for computer aided design of flexible substrates

InactiveUS20050287871A1Easily consideredCoupling device connectionsElectric discharge tubesComputer Aided DesignEngineering

A device, method, and program too facilitate the design of flexible printed circuit boards is disclosed which generates, as a prohibited space, a position assumed to be occupied by a part on an opposing printed circuit board when the printed circuit board is bent from a bend position. Design preparation of a bendable flexible printed circuit board can be efficiently checked by checking for the presence / absence of interference between parts and prohibited spaces.

Owner:PANASONIC CORP

Generating a split power plane of a multi-layer printed circuit board

Methods and apparatuses generate a split power plane for a multiplayer printed circuit board (PCB). An aspect of the invention supports the generation of a split power plane by constructing wireframes corresponding to each of the power voltages. If a crossover between different voltage wireframes exists, at least one of the voltage wireframes may be modified in order to eliminate the crossover. With another aspect of the invention, a trace layout, corresponding to the wireframe, is constructed in accordance with electrical current requirements, e.g. average electrical current and peak electrical current, of the associated components. With another aspect of the invention, a plane that contain the traces that associated with a power voltage may be enhanced by increasing the associated area of the layout in accordance with the available area of the split power plane. The enhancement of a plane may be prioritized in accordance with peak electrical current that is associated with the plane.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

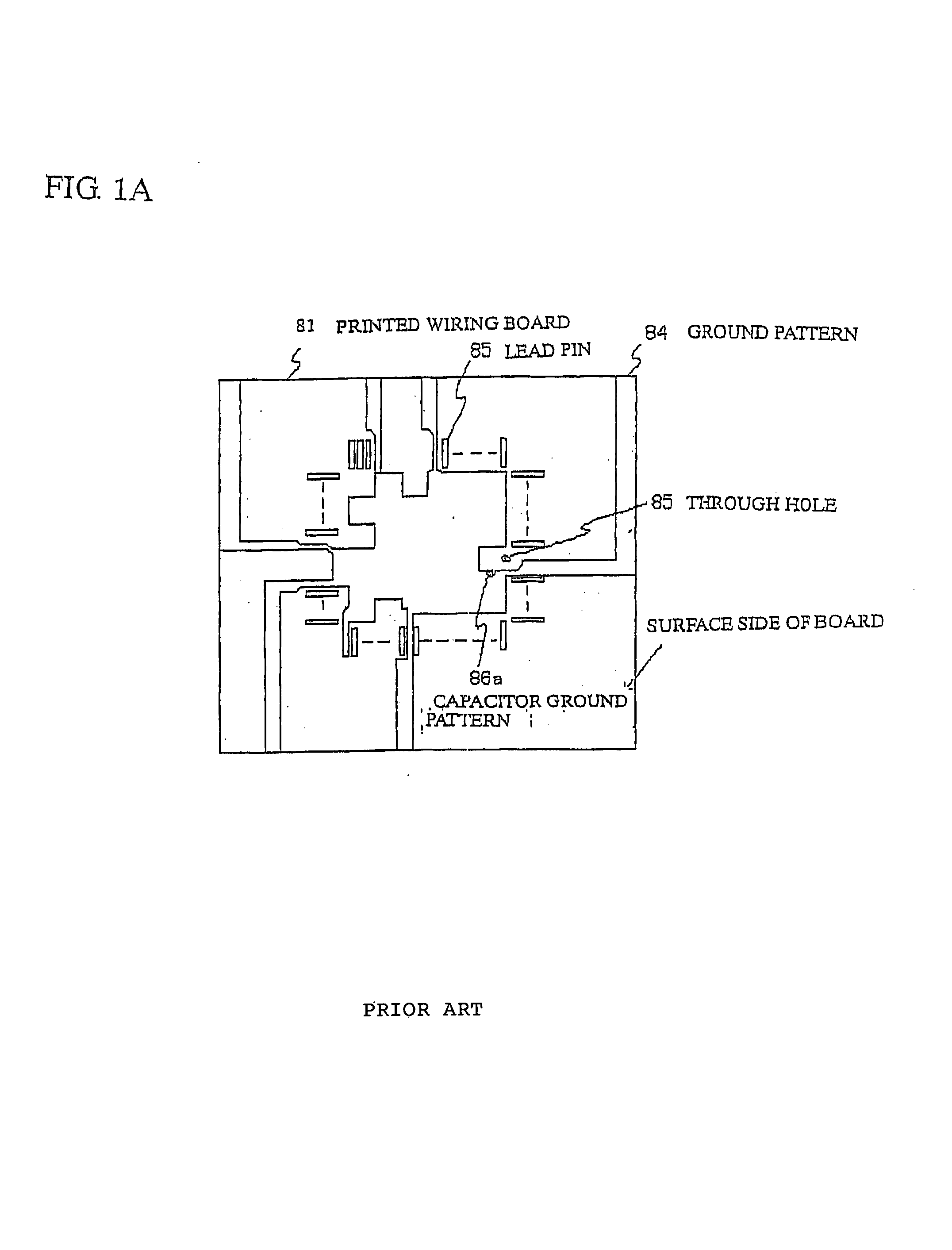

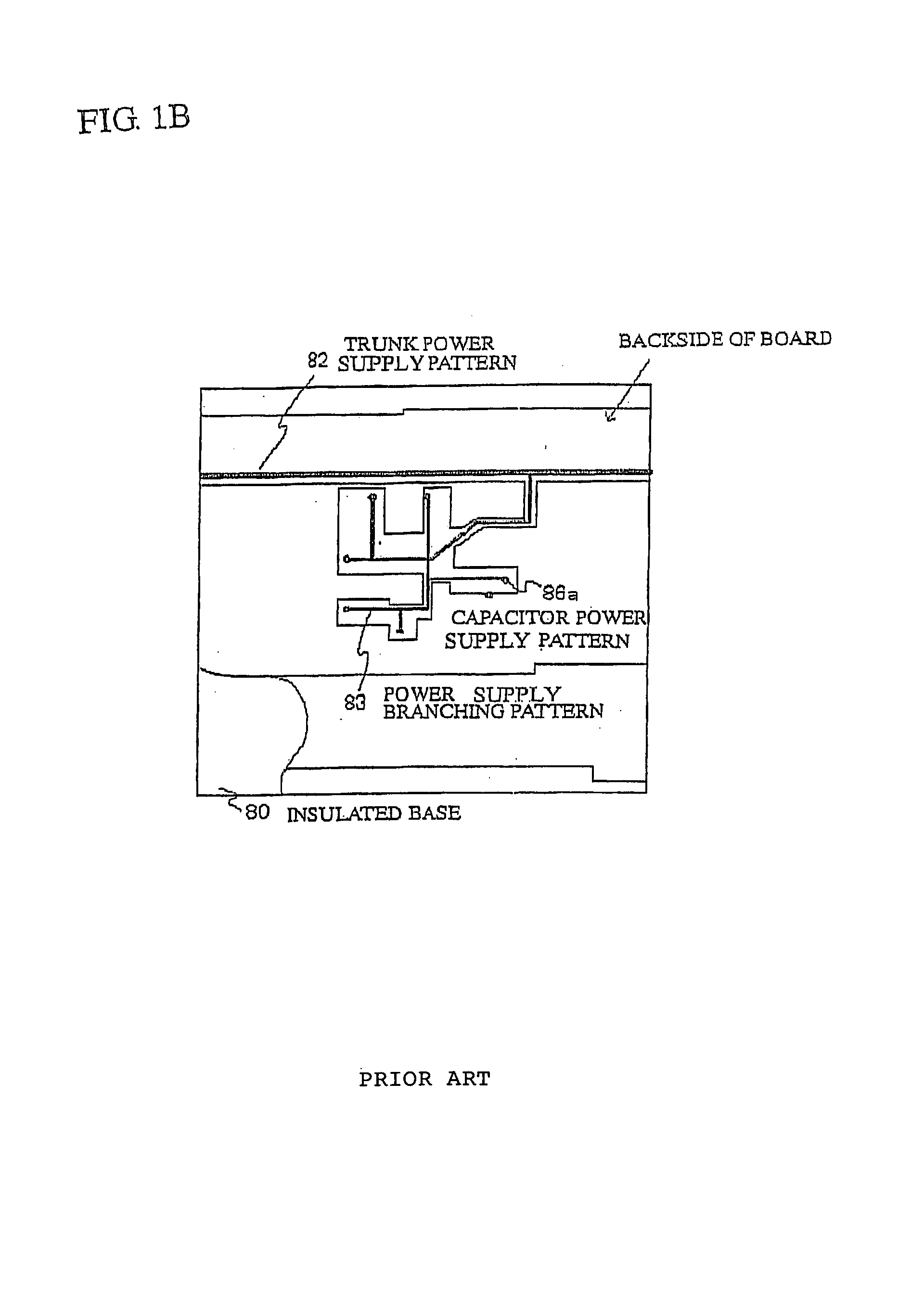

Printed circuit wiring board designing support device, printed circuit board designing method, and its program

ActiveUS20060161874A1Easy to optimizeCross-talk/noise/interference reductionPrinted circuit aspectsCapacitanceEngineering

A printed circuit wiring board designing support device includes a layout data receiving section receiving printed circuit board layout data through an input / output section, a section for extracting structures of power supply / ground planes, a via hole extracting section for extracting a via hole interconnecting the wirings extending over power supply / ground planes, a capacitor extracting section for extracting a capacitor connected between power supply / ground planes, a distance measuring section for measuring the distance between the via hole and the capacitor, a database where the allowable distance value between the via hole and the capacitor in respect to the distance between the power supply and ground planes is recorded, an examination section for comparing the capacitor / via hole distance with the allowable distance value, and a warning section for issuing a warning when the distance between the via hole and the capacitor is larger than the allowable distance value.

Owner:NEC CORP

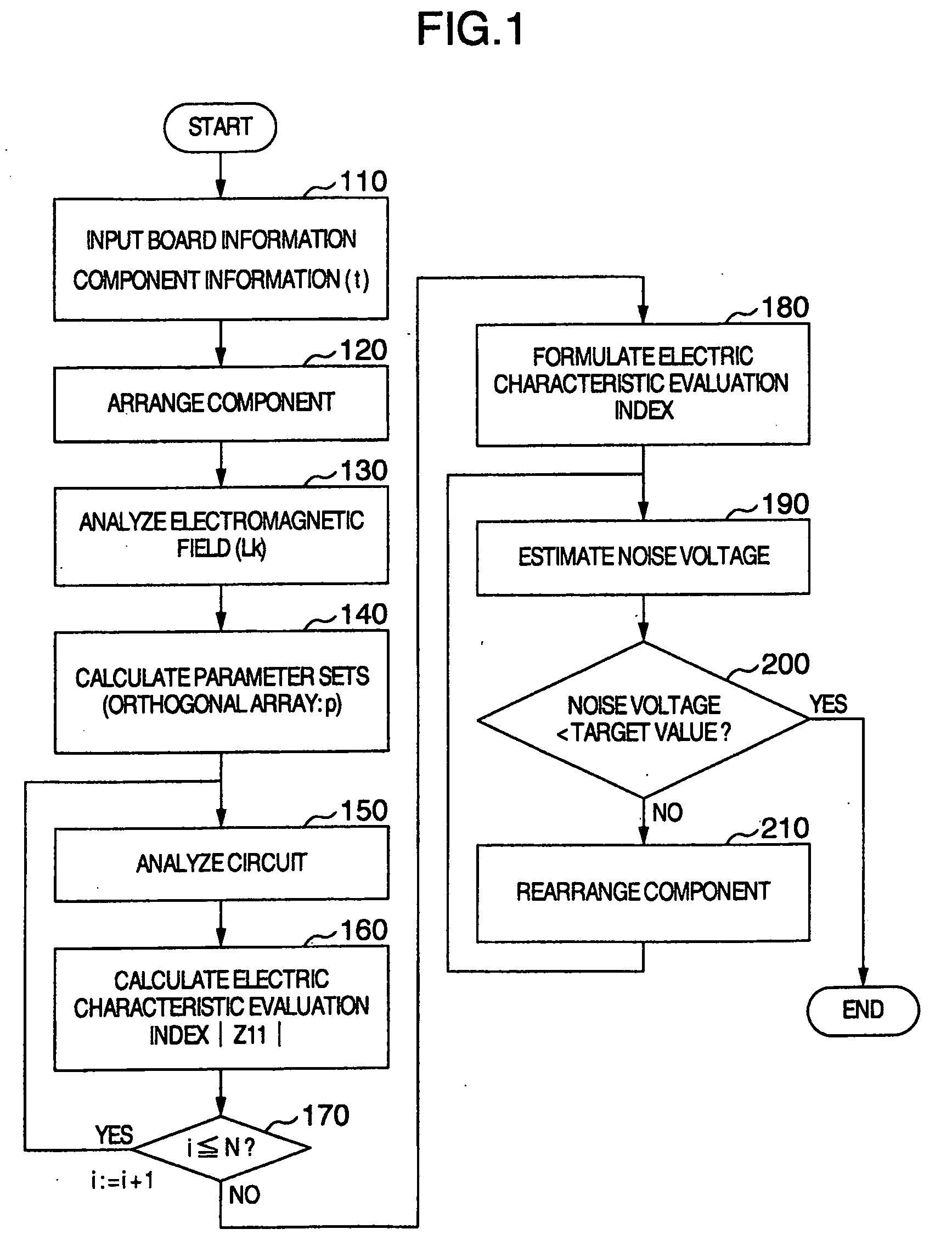

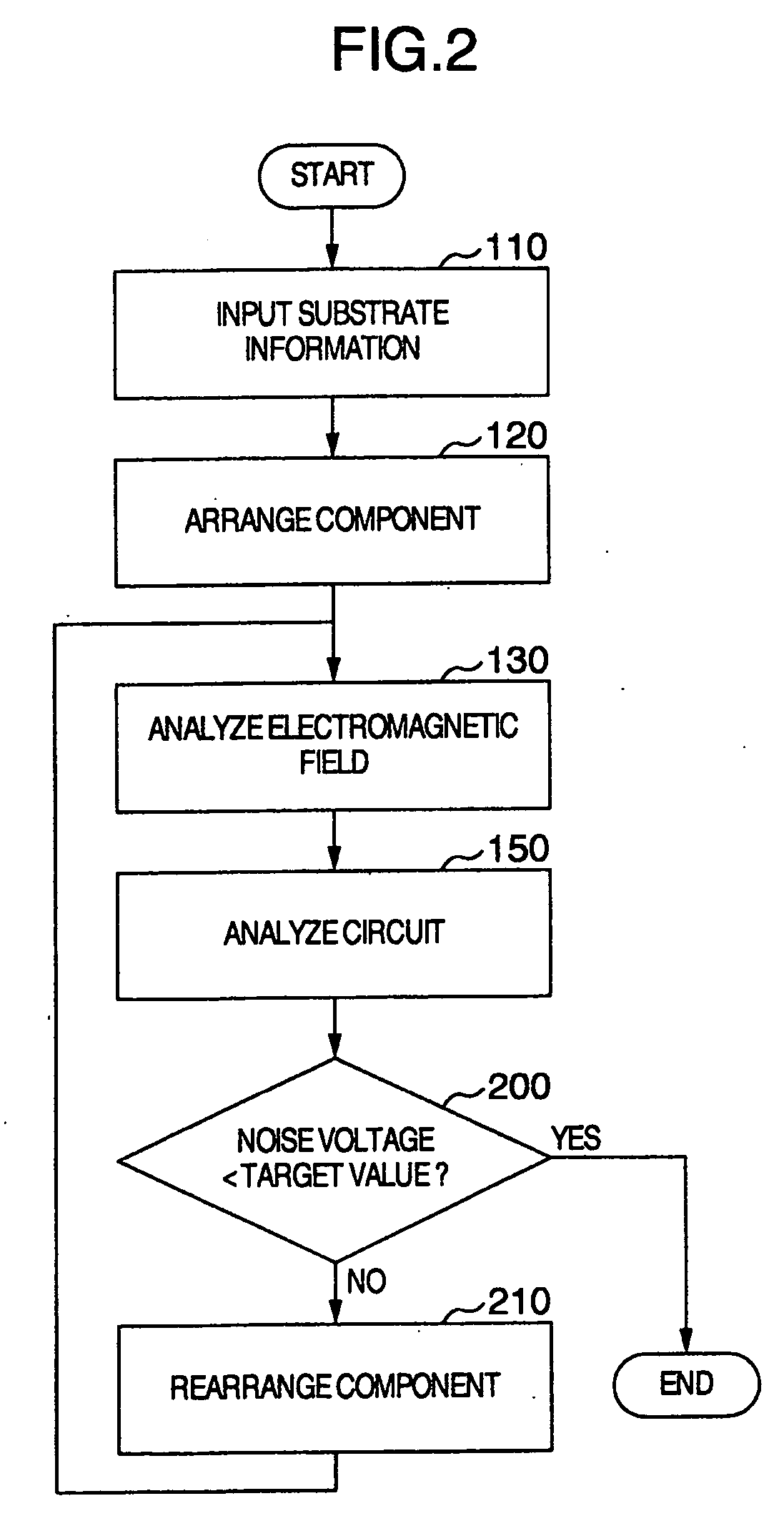

Support method and apparatus for printed circuit board

InactiveUS20090213558A1Guaranteed uptimeReduce design costResistance/reactance/impedenceCross-talk/noise/interference reductionOrthogonal arrayElectromagnetic field

An orthogonal array is formed by performing electromagnetic field analysis only once and determining a range by using the mount position and type of a capacitor and the number of capacitors as parameters to perform circuit analysis a small number of times. An estimation equation is formed by using as an index a result of the absolute value of the calculated power source impedance, and a capacitor is disposed to reduce noises by using the estimation equation.

Owner:HITACHI LTD