Patents

Literature

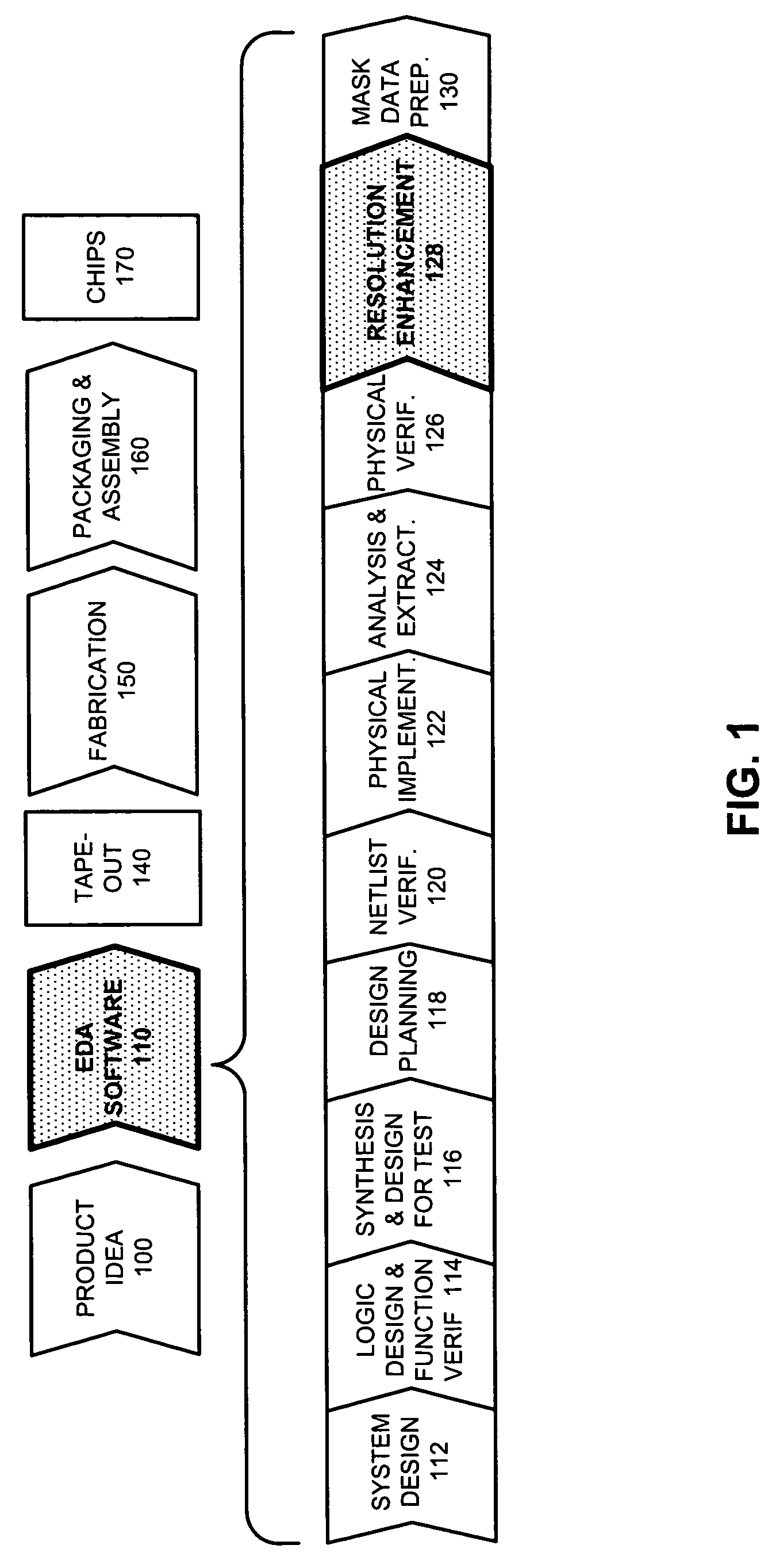

4978results about "Photographic processes" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

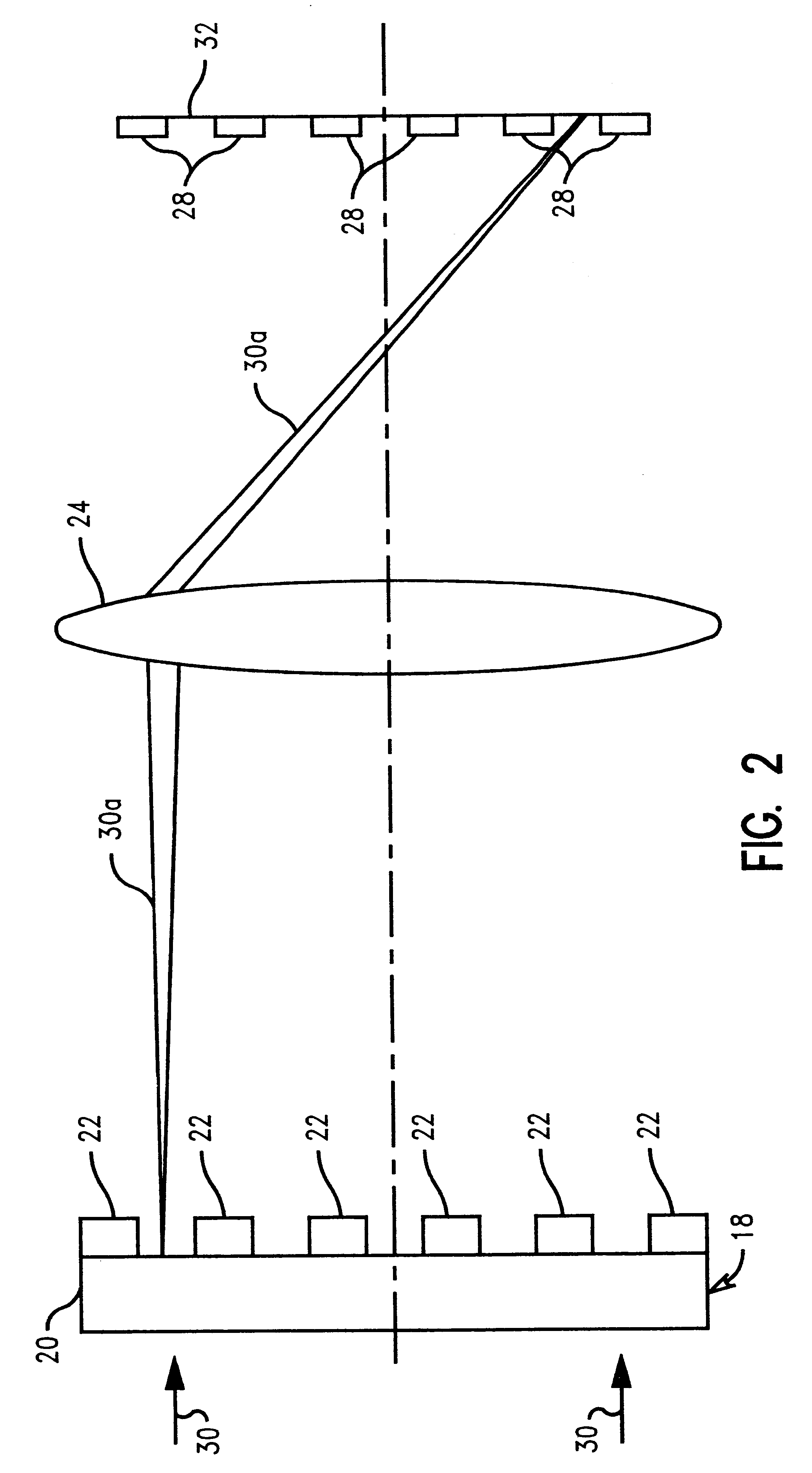

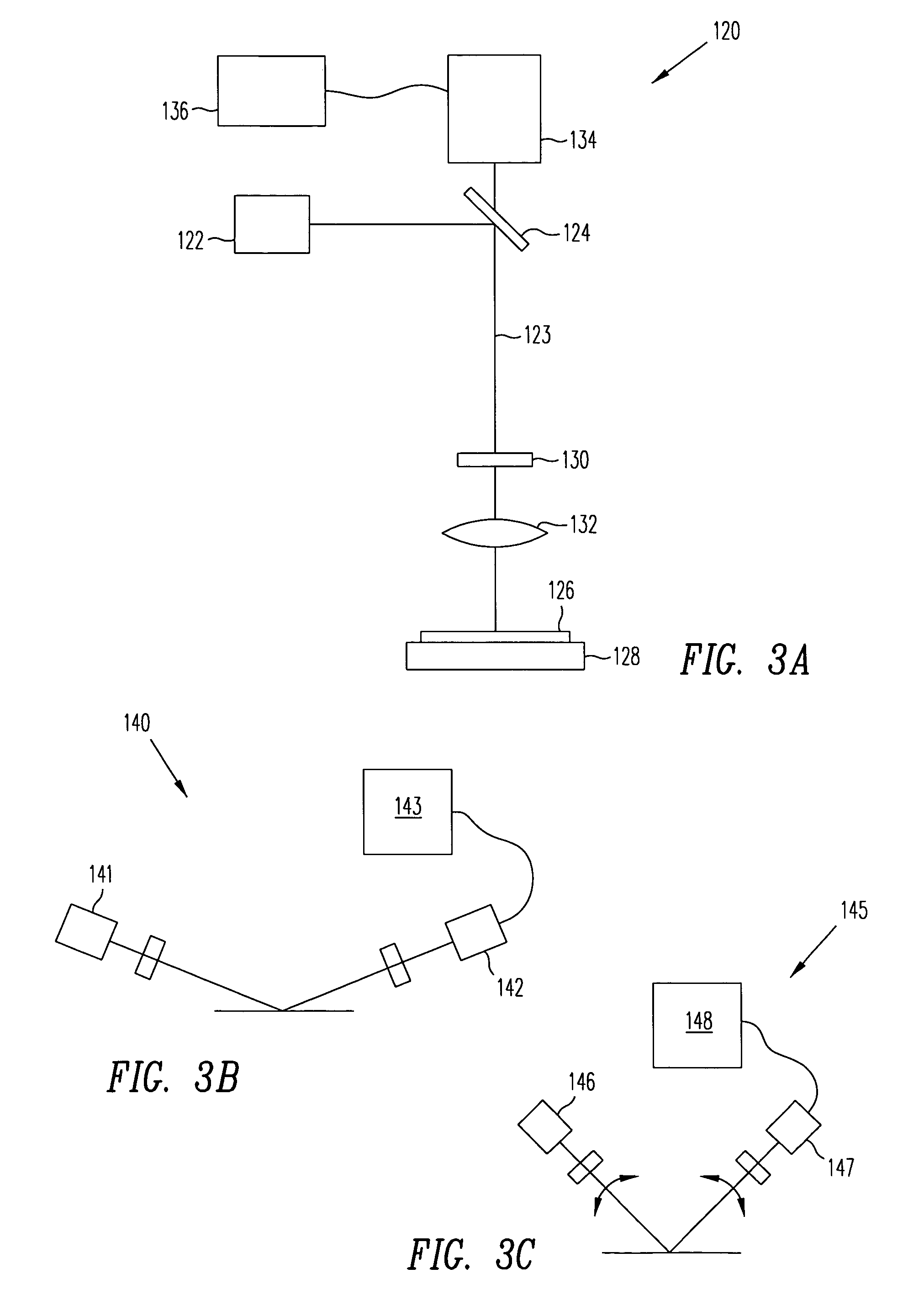

Methods and Scatterometers, Lithographic Systems, and Lithographic Processing Cells

ActiveUS20110027704A1Scattering properties measurementsSemiconductor/solid-state device manufacturingScatterometerEngineering

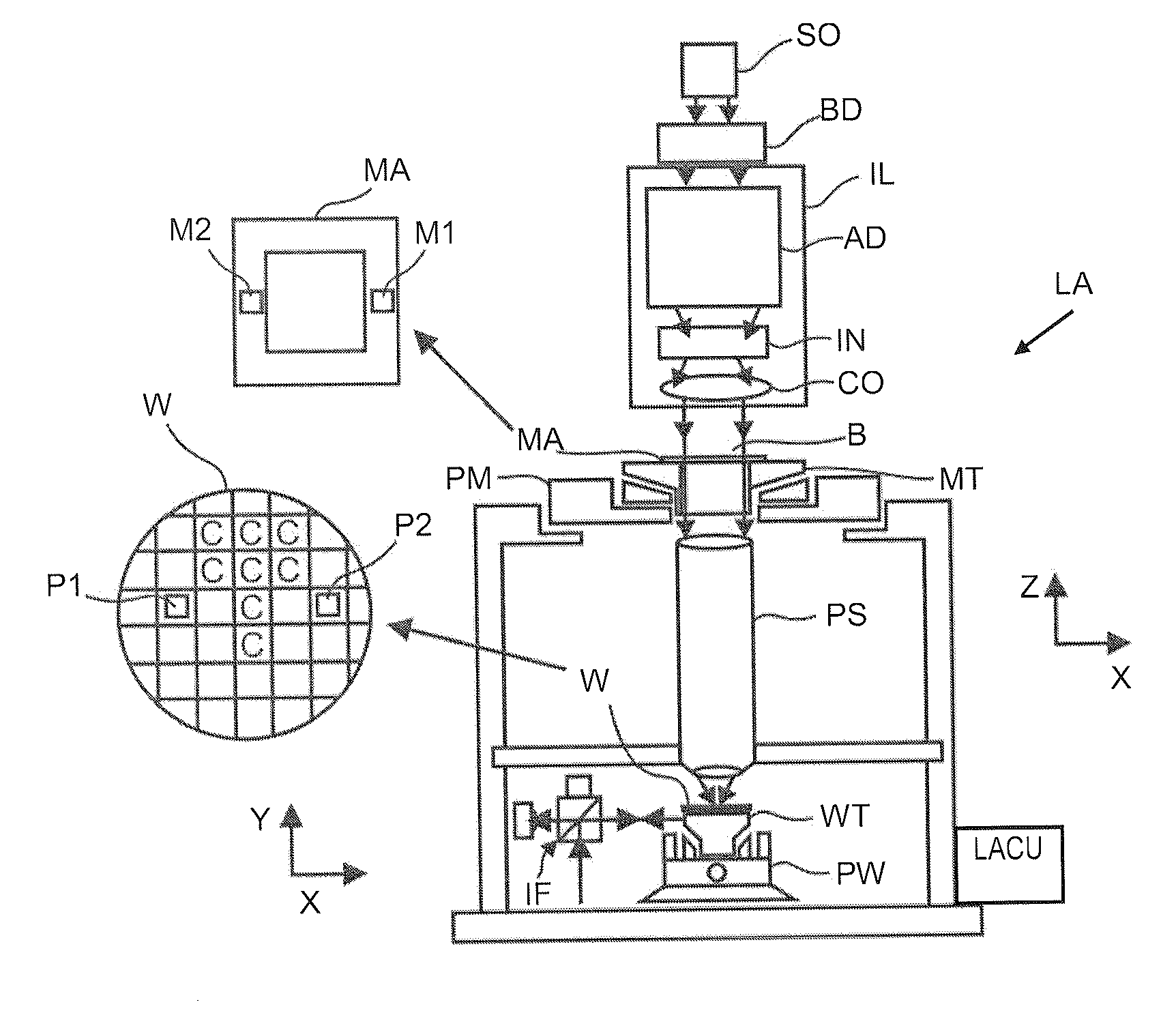

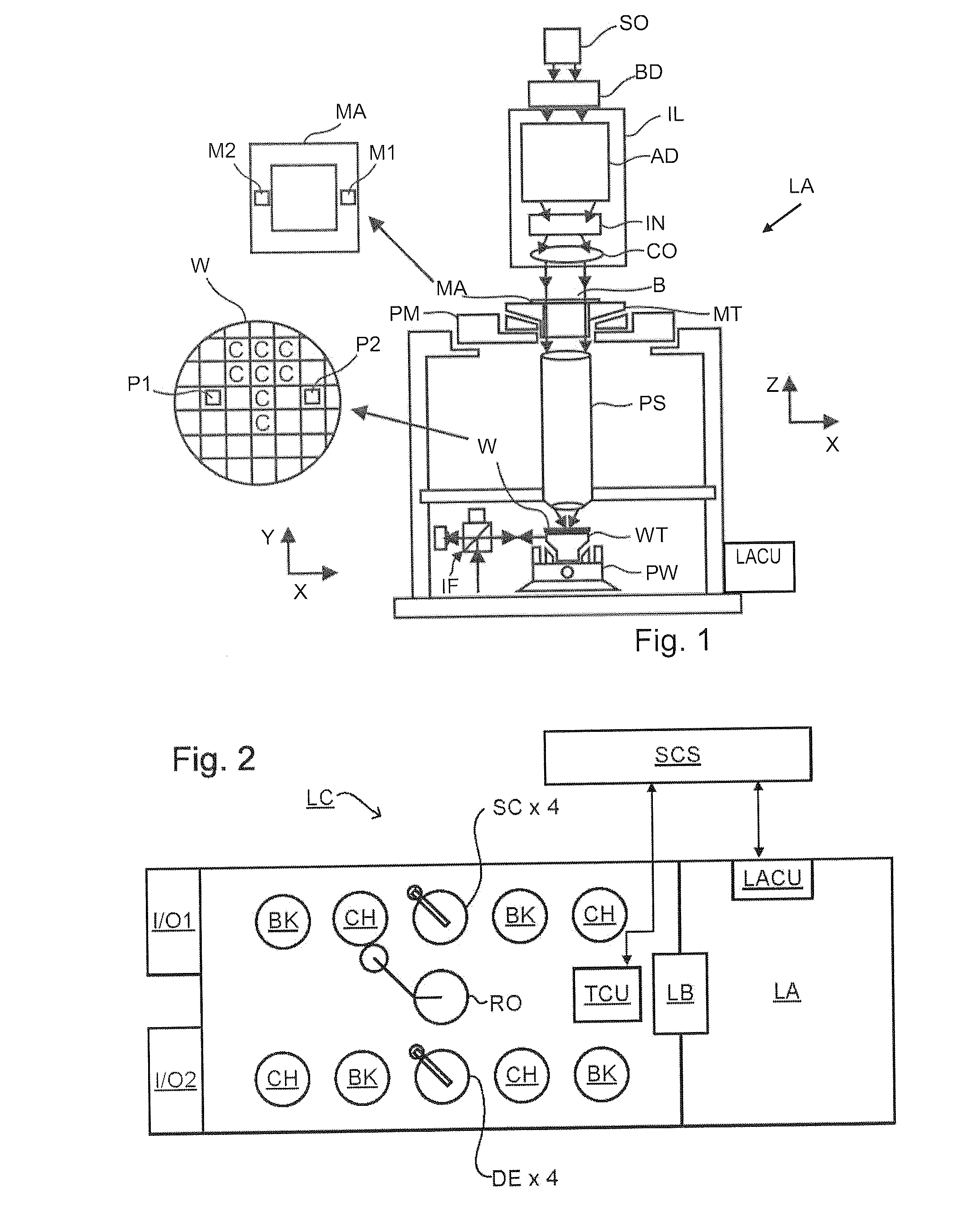

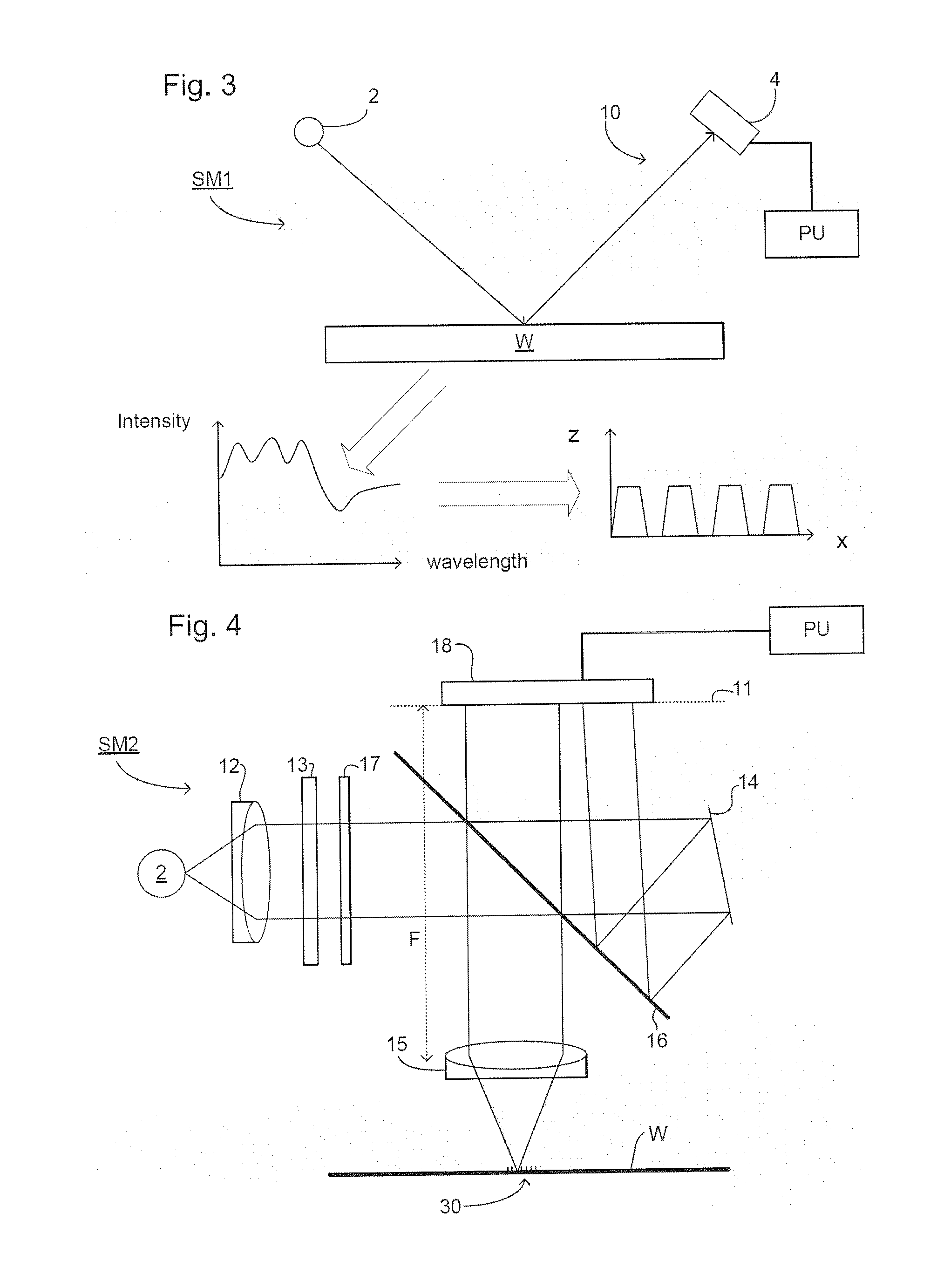

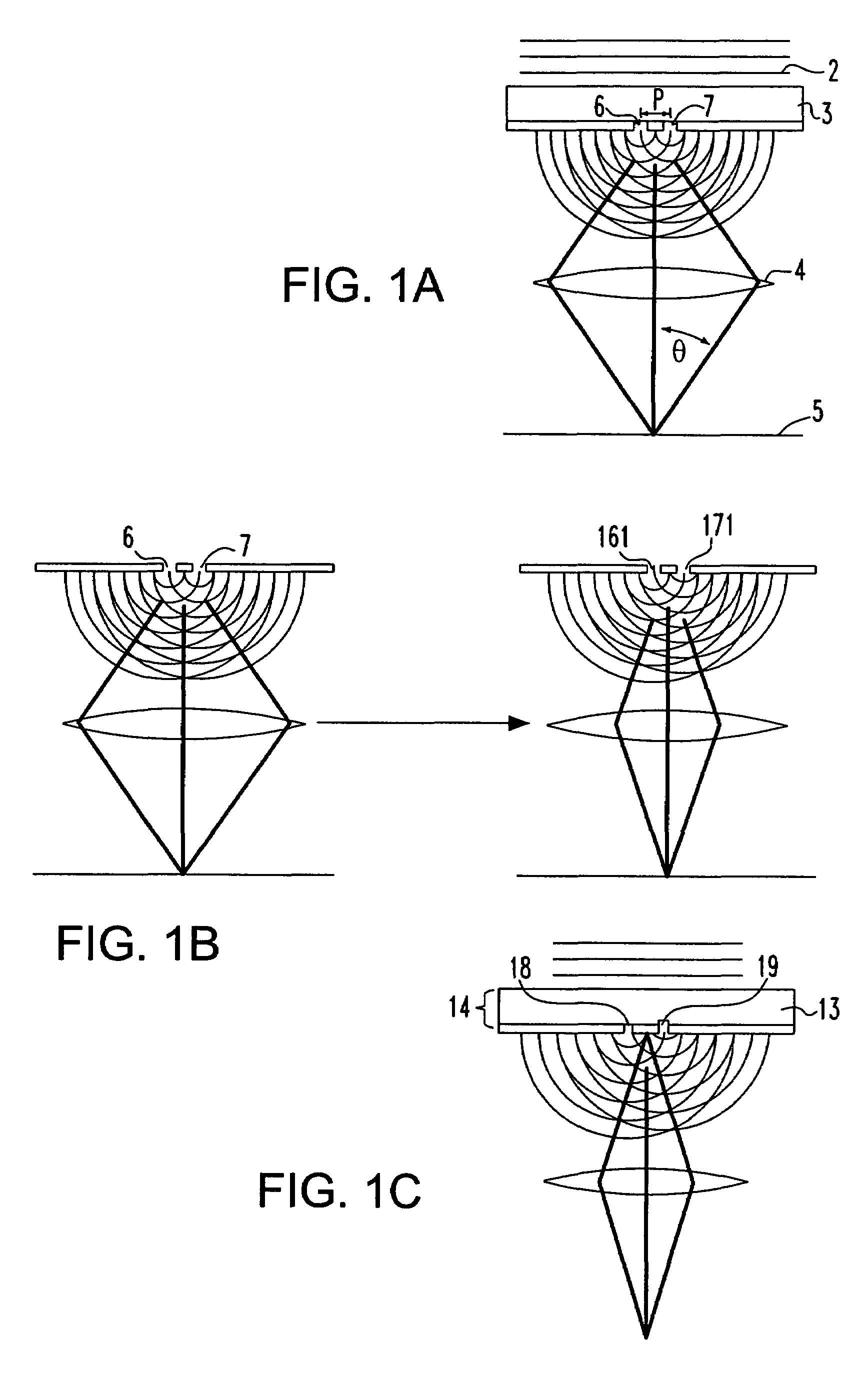

In a method of determining the focus of a lithographic apparatus used in a lithographic process on a substrate, the lithographic process is used to form a structure on the substrate, the structure having at least one feature which has an asymmetry in the printed profile which varies as a function of the focus of the lithographic apparatus on the substrate. A first image of the periodic structure is formed and detected while illuminating the structure with a first beam of radiation. The first image is formed using a first part of non-zero order diffracted radiation. A second image of the periodic structure is foamed and detected while illuminating the structure with a second beam of radiation. The second image is formed using a second part of the non-zero order diffracted radiation which is symmetrically opposite to the first part in a diffraction spectrum. The ratio of the intensities of the measured first and second portions of the spectra is determined and used to determine the asymmetry in the profile of the periodic structure and / or to provide an indication of the focus on the substrate. In the same instrument, an intensity variation across the detected portion is determined as a measure of process-induced variation across the structure. A region of the structure with unwanted process variation can be identified and excluded from a measurement of the structure.

Owner:ASML NETHERLANDS BV

Method and system for drying a substrate

ActiveUS20050046934A1Good pattern uniformityImprove uniformityMicroscopesPhotomechanical exposure apparatusCooking & bakingThin membrane

A method and system is described for drying a thin film on a substrate following liquid immersion lithography. Drying the thin film to remove immersion fluid from the thin film is performed prior to baking the thin film, thereby reducing the likely hood for interaction of immersion fluid with the baking process. This interaction has been shown to cause non-uniformity in critical dimension for the pattern formed in the thin film following the developing process.

Owner:TOKYO ELECTRON LTD

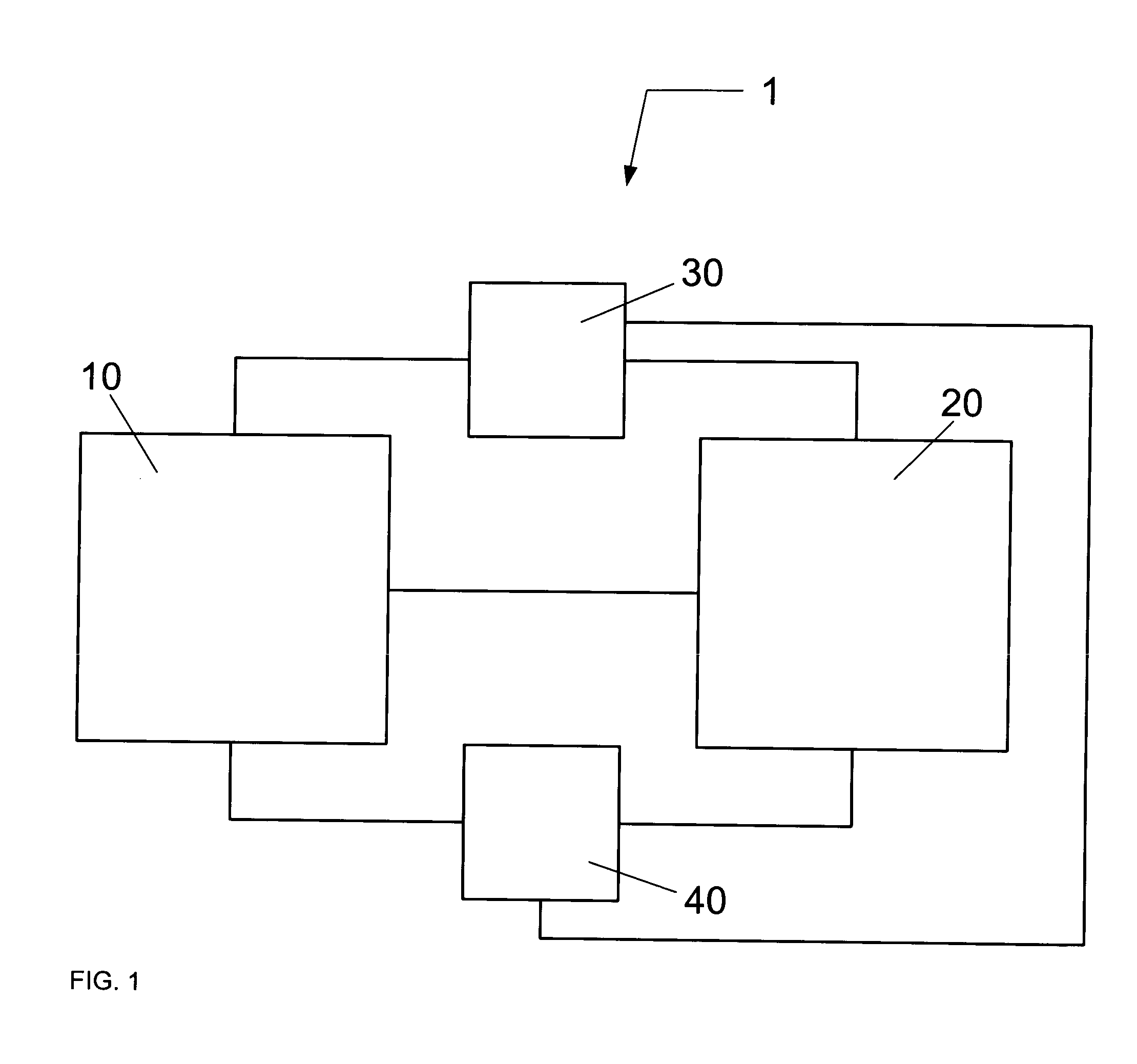

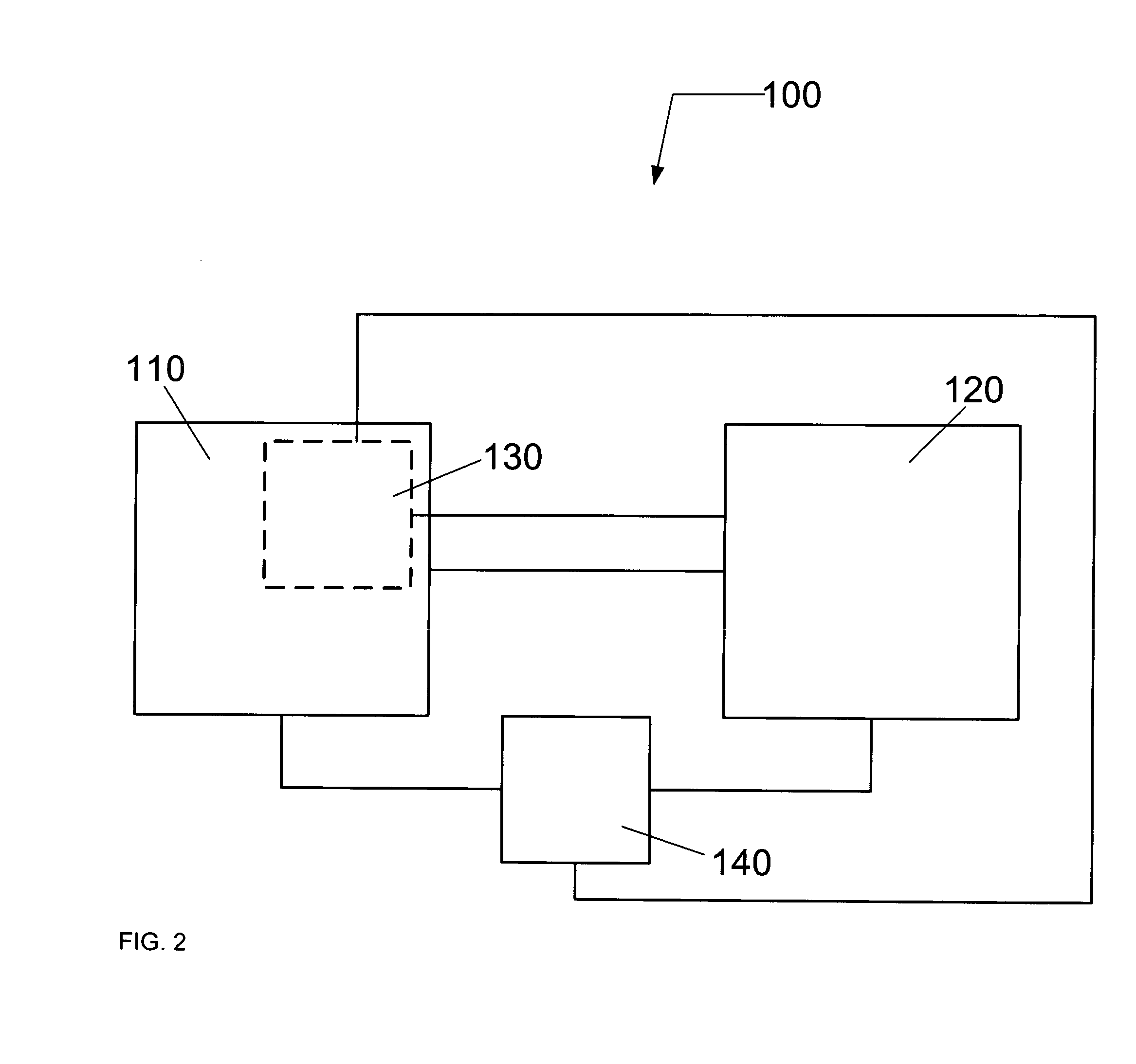

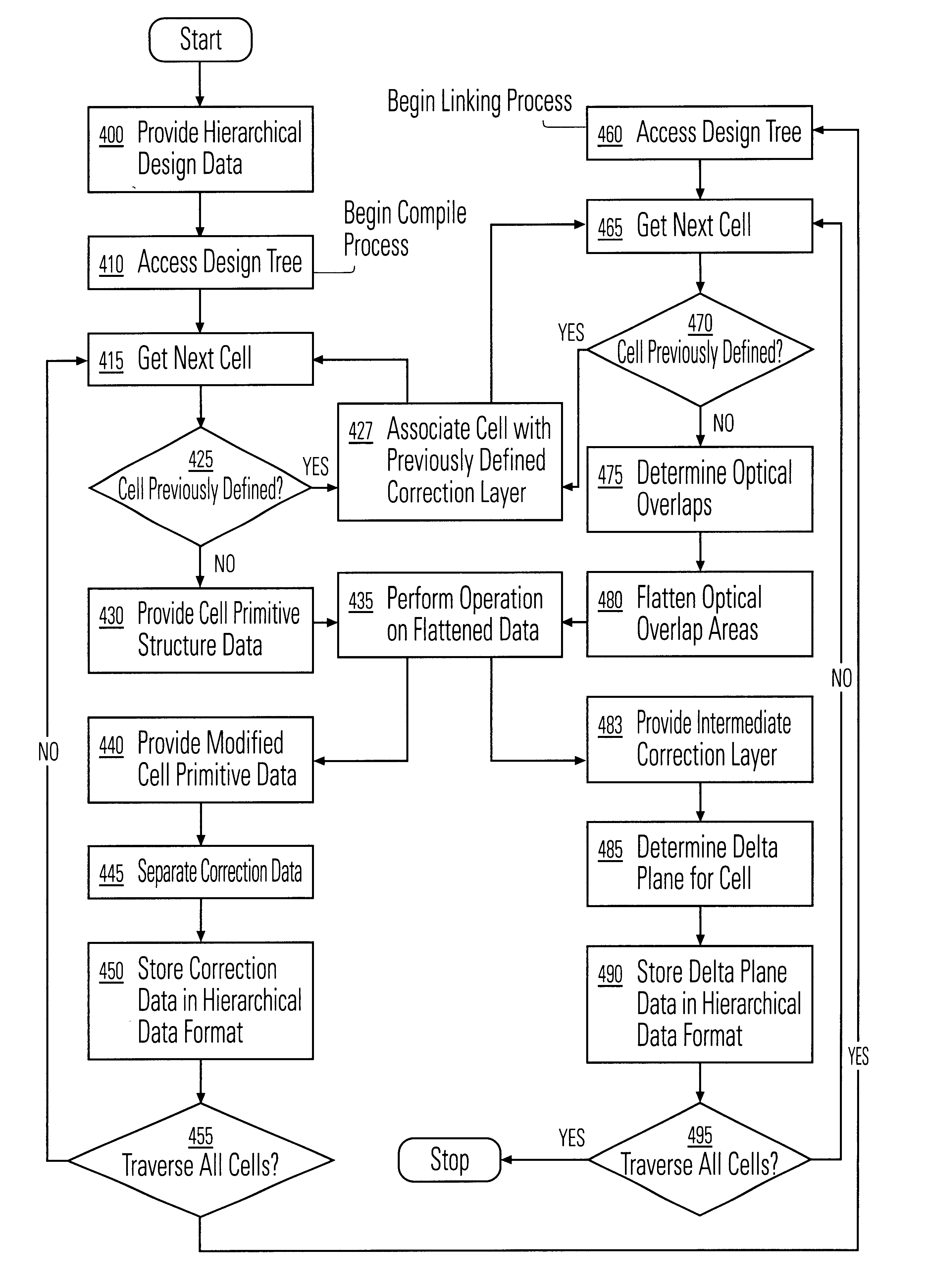

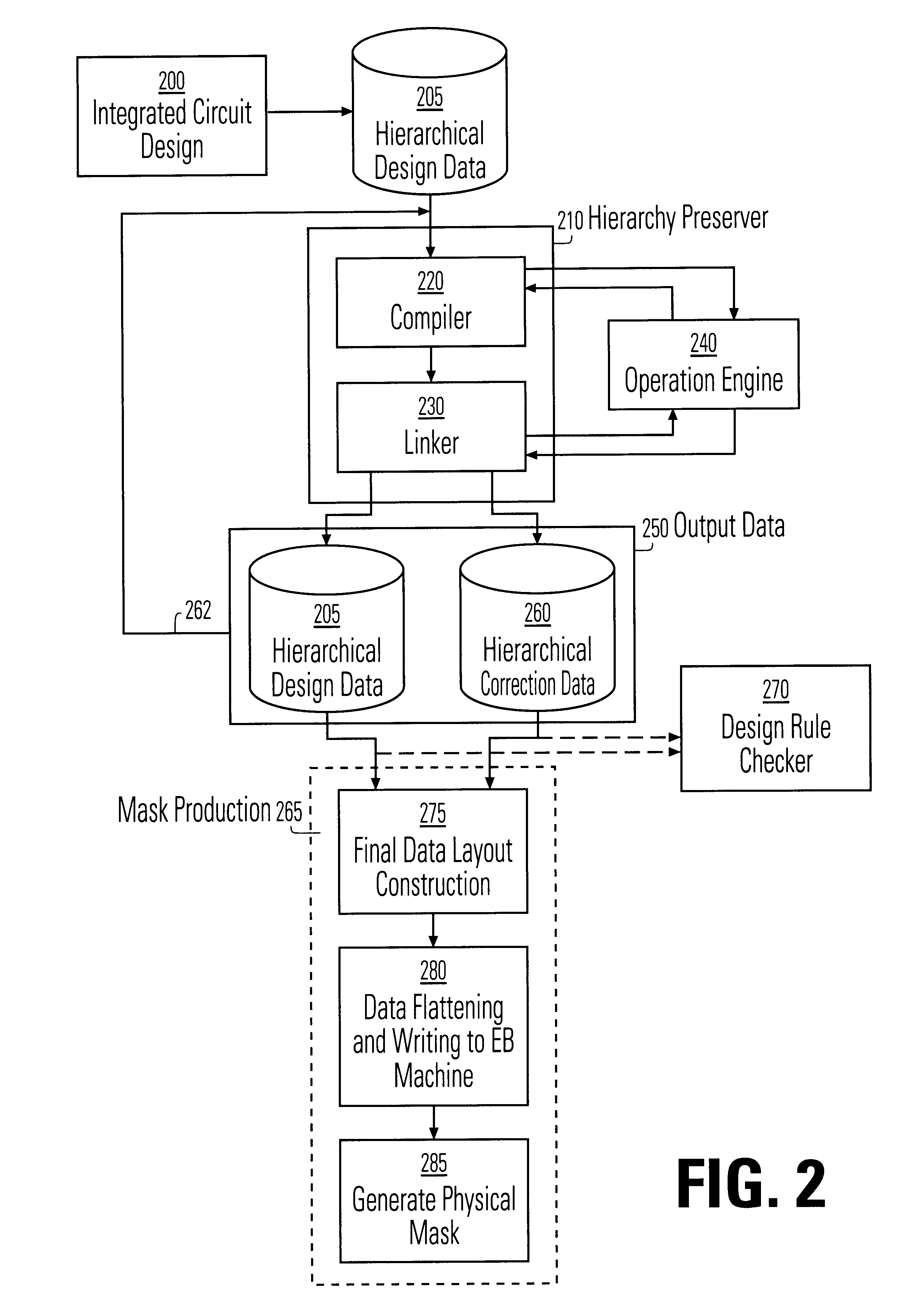

Data hierarchy layout correction and verification method and apparatus

InactiveUS6370679B1Computation using non-denominational number representationOriginals for photomechanical treatmentComputer architectureValidation methods

A method and apparatus for the correction of integrated circuit layouts for optical proximity effects which maintains the original true hierarchy of the original layout is provided. Also provided is a method and apparatus for the design rule checking of layouts which have been corrected for optical proximity effects. The OPC correction method comprises providing a hierarchically described integrated circuit layout as a first input, and a particular set of OPC correction criteria as a second input. The integrated circuit layout is then analyzed to identify features of the layout which meet the provided OPC correction criteria. After the areas on the mask which need correction have been identified, optical proximity correction data is generated in response to the particular set of correction criteria. Finally, a first program data is generated which stores the generated optical proximity correction data in a hierarchical structure that corresponds to the hierarchical structure of the integrated circuit layout. As the output correction data is maintained in true hierarchical format, layouts which are OPC corrected according to this method are able to be processed through conventional design rule checkers with no altering of the data.

Owner:SYNOPSYS INC

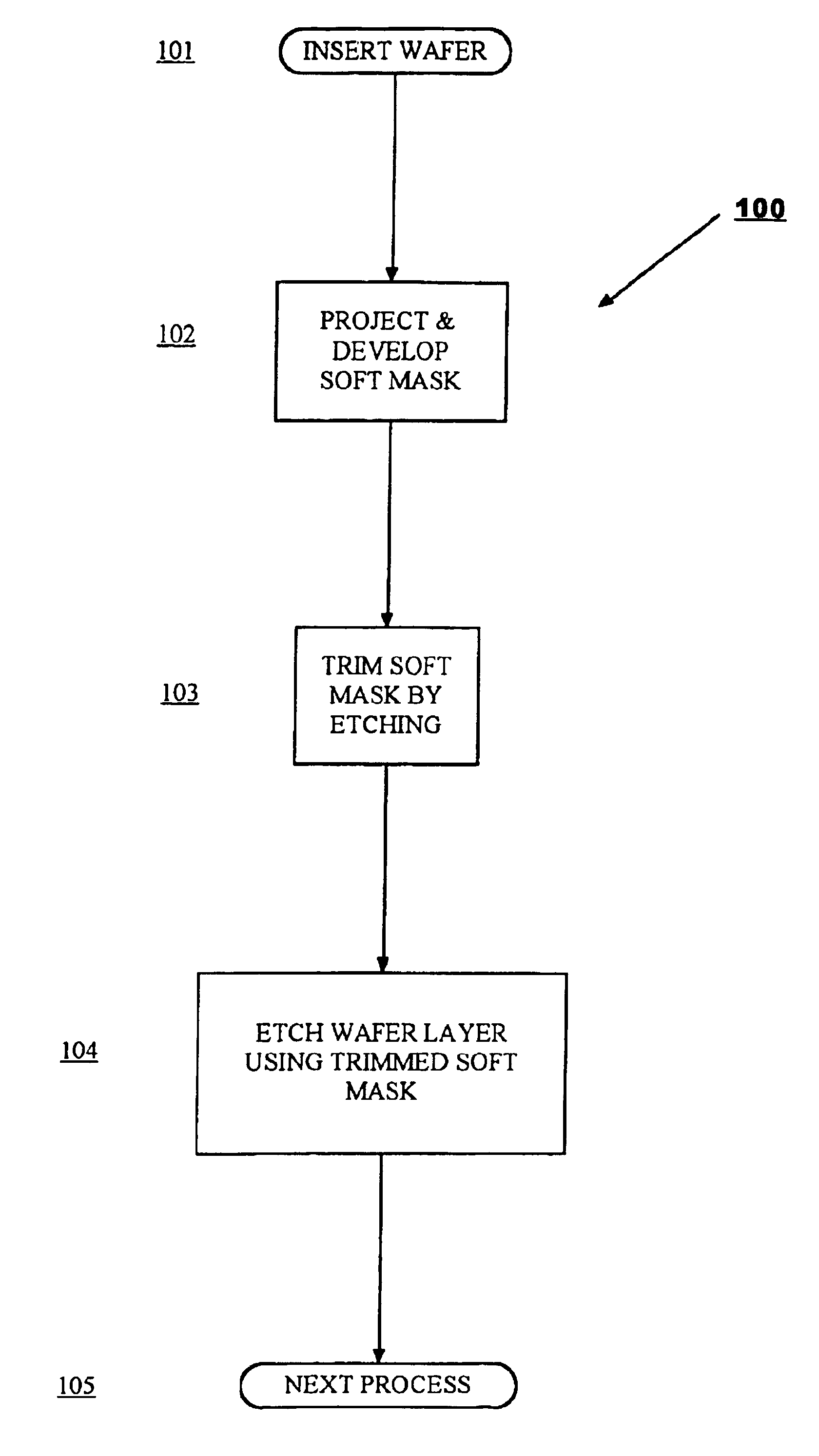

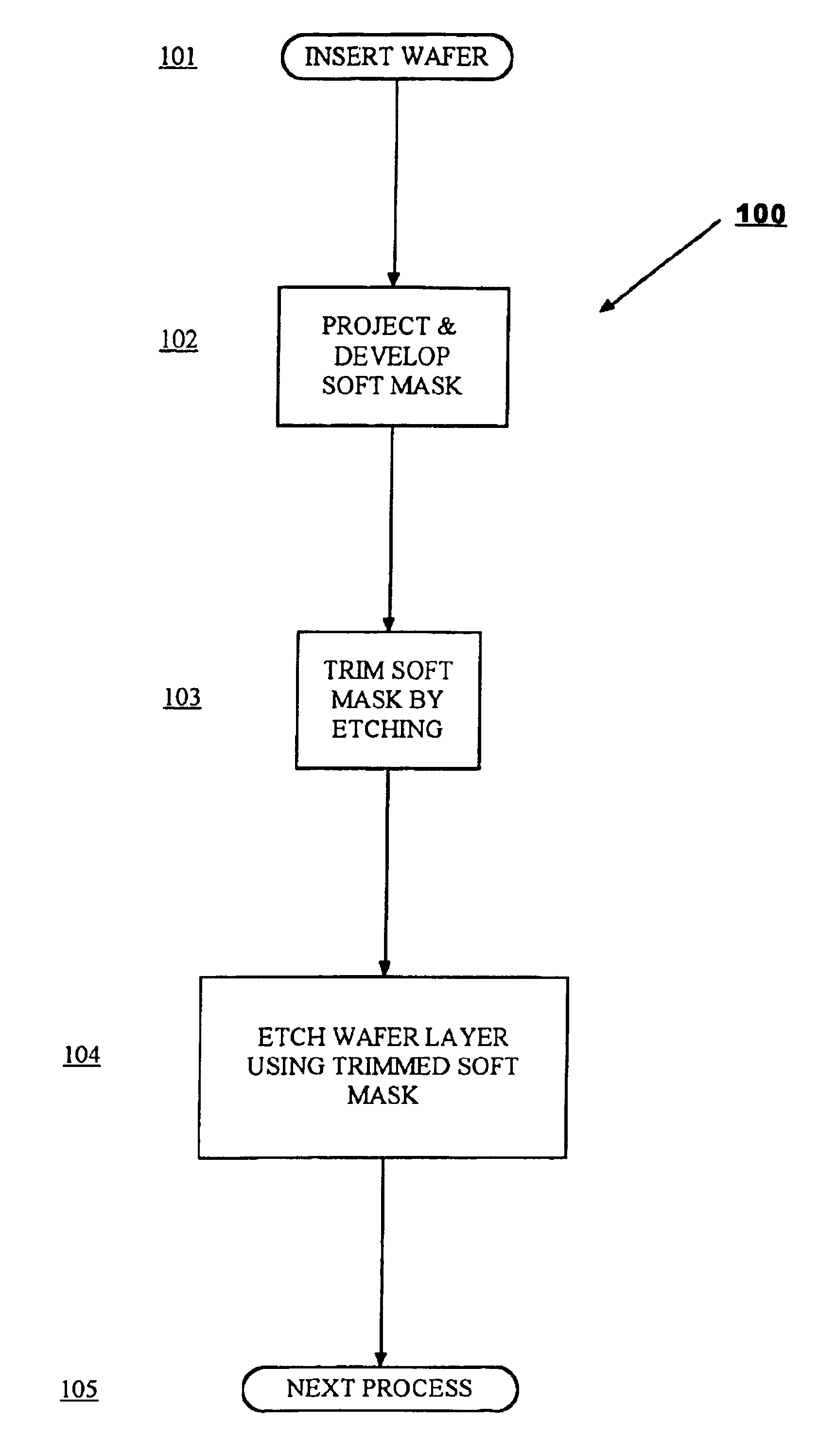

Gate linewidth tailoring and critical dimension control for sub-100 nm devices using plasma etching

InactiveUS6864041B2Tight tolerance variationMinimal variationVacuum gauge using ionisation effectsDecorative surface effectsImage resolutionLine width

A method of fabricating an electronic chip on a wafer in which a first mask at a predetermined lower resolution is developed on the wafer and then etched under a first set of conditions for a predetermined period to achieve a mask that is below the resolution limit of current lithography. The etched mask is then used as a hard mask for etching material on a lower layer.

Owner:INT BUSINESS MASCH CORP

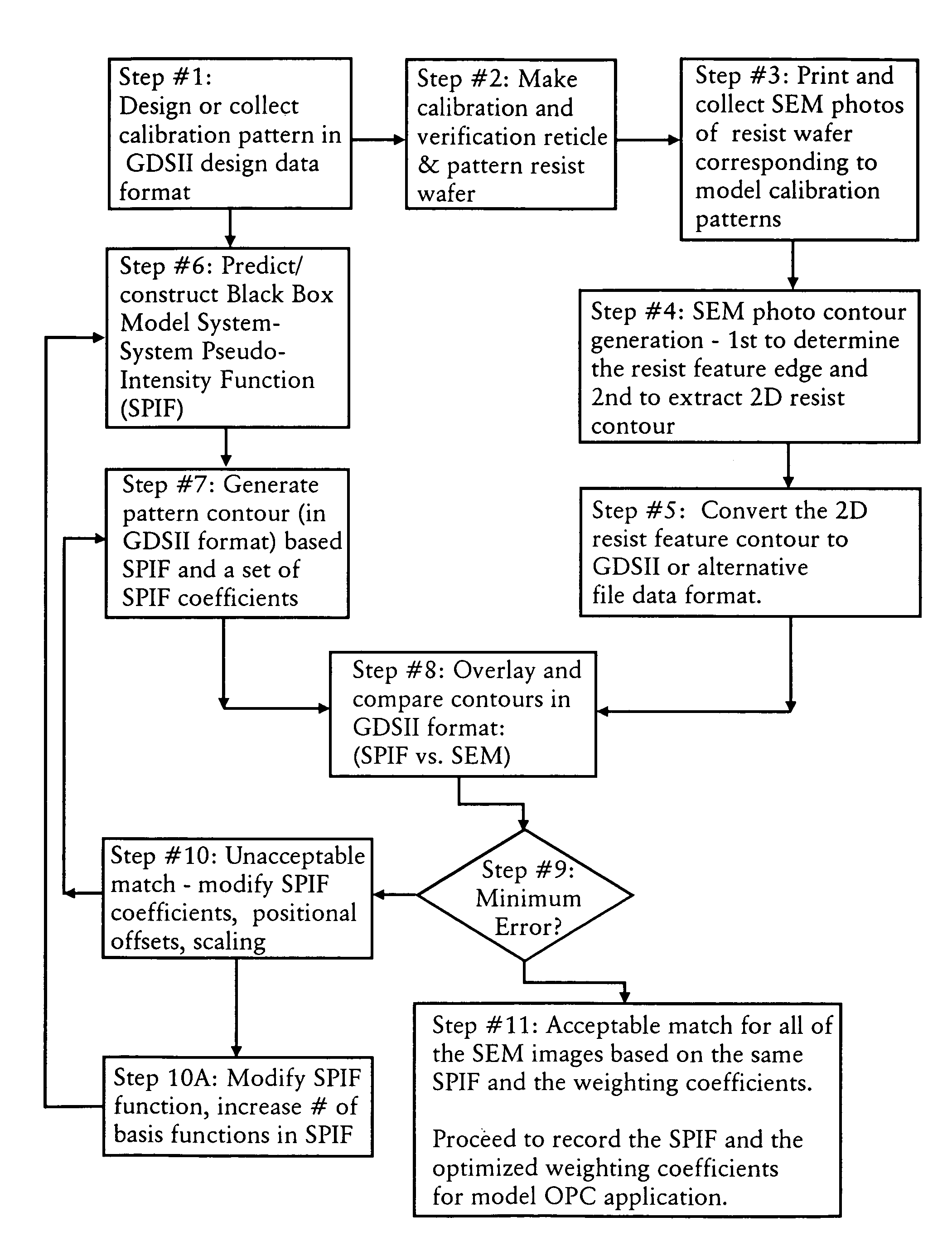

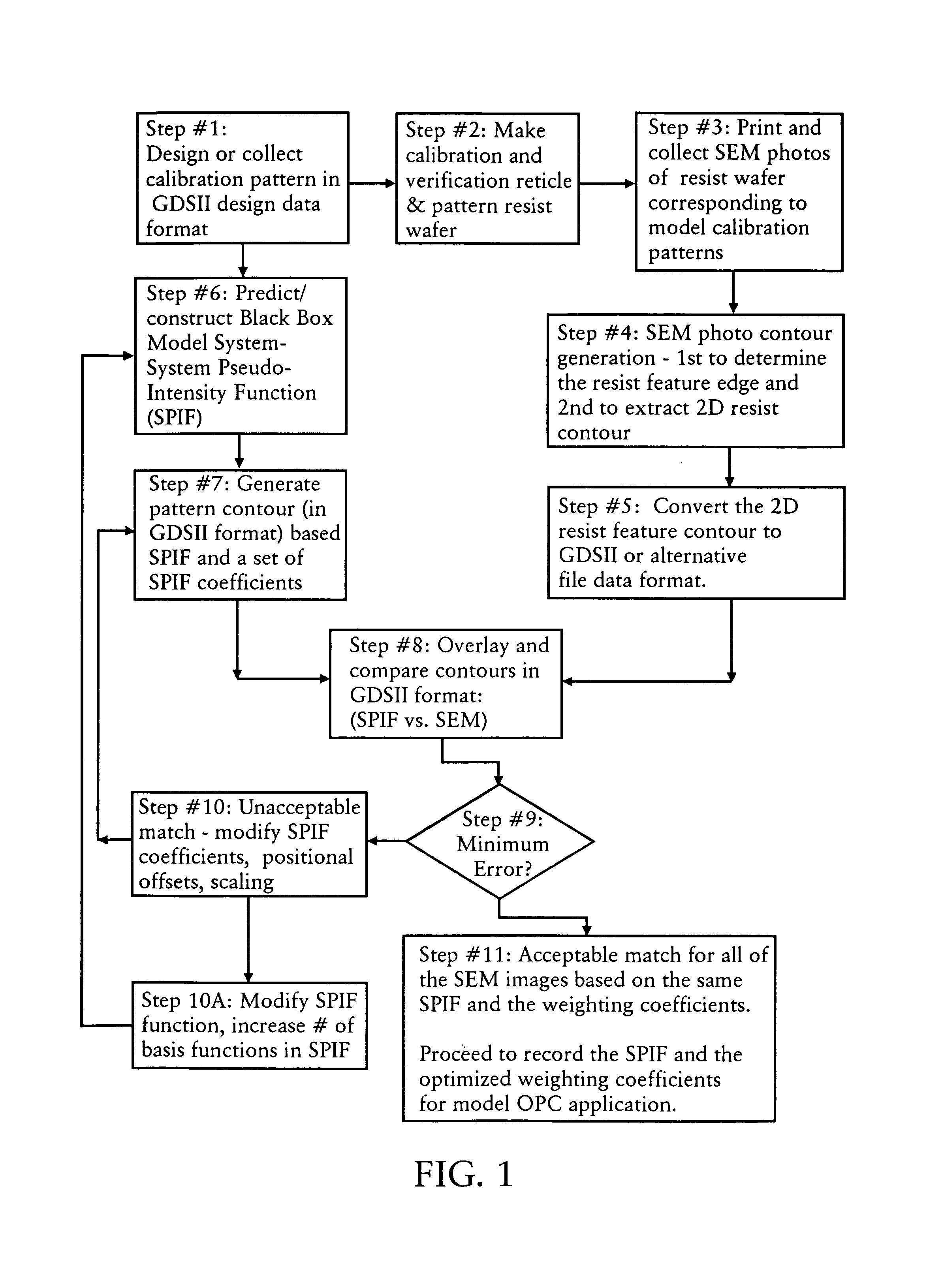

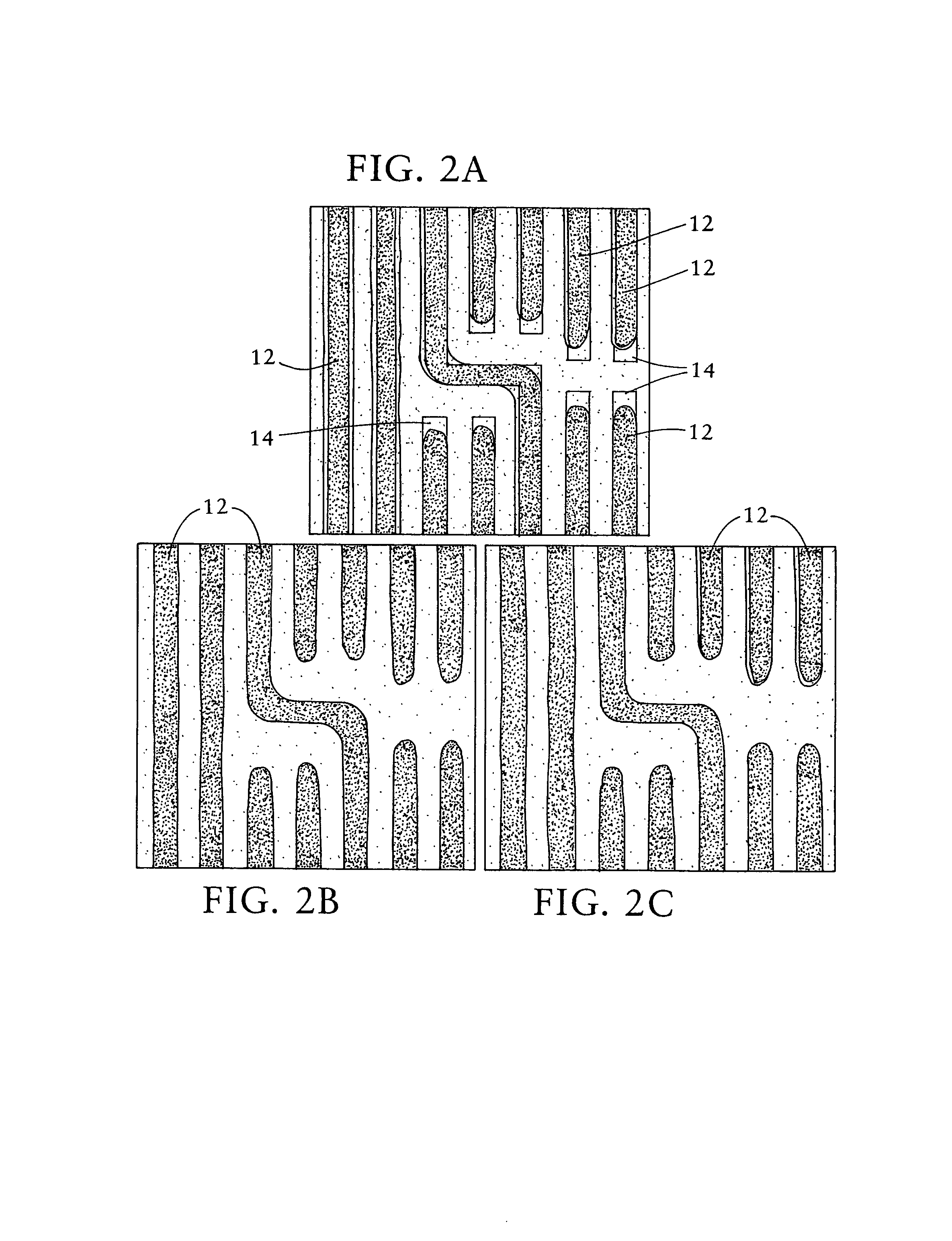

Method of two dimensional feature model calibration and optimization

InactiveUS7175940B2Minimize proximity effectAccurate performanceSemiconductor/solid-state device manufacturingCharacter and pattern recognitionPattern recognitionData format

A method for generating a photolithography mask for optically transferring a pattern formed in the mask onto a substrate utilizing an imaging system. The method includes the steps of: (a) defining a set of calibration patterns, which are represented in a data format; (b) printing the calibration patterns on a substrate utilizing the given imaging system; (c) determining a first set of contour patterns corresponding to the calibration patterns imaged on the substrate; (d) generating a system pseudo-intensity function, which approximates the imaging performance of the imaging system; (e) determining a second set of contour patterns by utilizing the system pseudo-intensity function to define how the calibration patterns will be imaged in the substrate; (f) comparing the first set of contour patterns and the second set of contour patterns to determine the difference therebetween; (g) adjusting the system pseudo-intensity function until the difference between the first set of contour patterns and the second set of contour patterns is below a predefined criteria; and (h) utilizing the adjusted system pseudo-intensity function to modify the mask so as to provide for optical proximity correction.

Owner:ASML NETHERLANDS BV

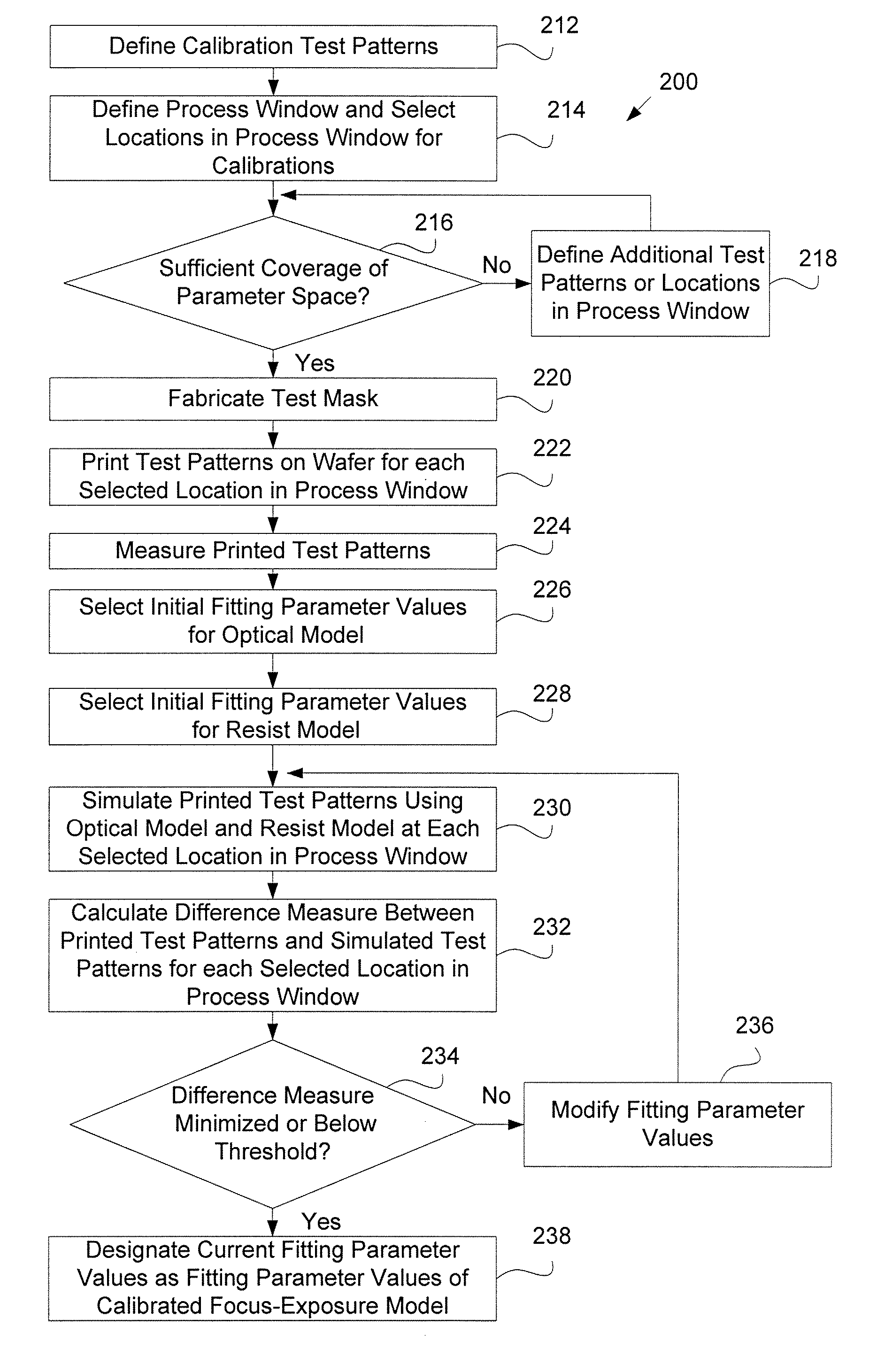

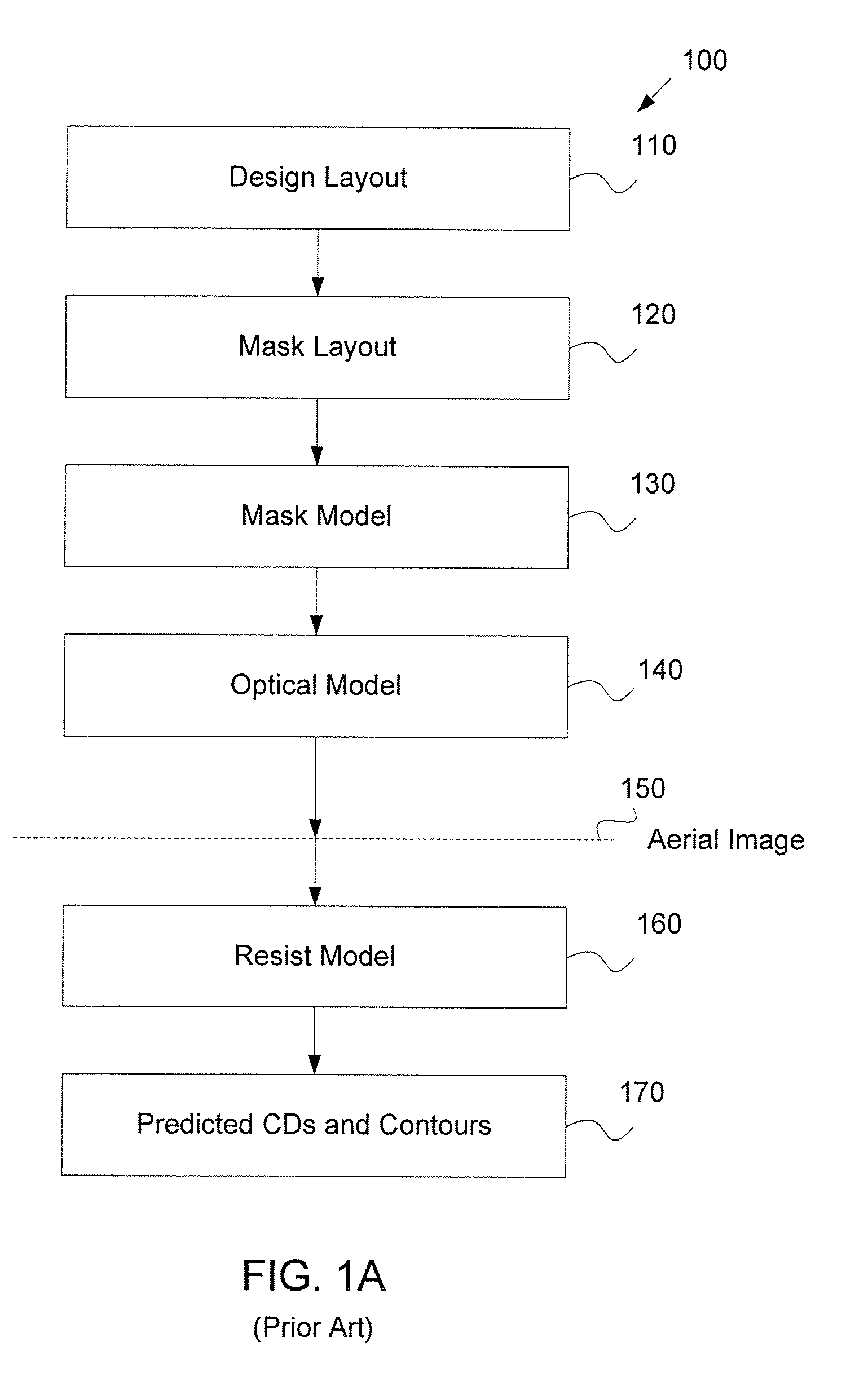

System and method for creating a focus-exposure model of a lithography process

ActiveUS20070031745A1Good accuracy and robustnessPhotomechanical apparatusOriginals for photomechanical treatmentLithography processAlgorithm

A system and a method for creating a focus-exposure model of a lithography process are disclosed. The system and the method utilize calibration data along multiple dimensions of parameter variations, in particular within an exposure-defocus process window space. The system and the method provide a unified set of model parameter values that result in better accuracy and robustness of simulations at nominal process conditions, as well as the ability to predict lithographic performance at any point continuously throughout a complete process window area without a need for recalibration at different settings. With a smaller number of measurements required than the prior-art multiple-model calibration, the focus-exposure model provides more predictive and more robust model parameter values that can be used at any location in the process window.

Owner:ASML NETHERLANDS BV

Isosorbide containing polyesters and methods for making same

InactiveUS6063464AHigher inherent viscosityInherent viscosityBottlesSynthetic resin layered productsPolyesterDiol

A polyester polymer and method for making the polyester, wherein the polyester is prepared by (1) combining in a reactor a monomer containing a diacid moiety; a monomer comprising a diol moiety; and a monomer containing an isosorbide moiety; with a condensation catalyst suitable for condensing aromatic diacids and diols; and (2) heating the monomers and catalyst to polymerize the monomers to yield a polyester having an inherent viscosity of at least about 0.15 dL / g.

Owner:EI DU PONT DE NEMOURS & CO

Cleaning solution for photoresist and method for forming pattern using the same

ActiveUS7238653B2Use cleanOrganic detergent compounding agentsTransportation and packagingResistAlcohol

Cleaning solutions for photoresist are disclosed which are useful for cleaning a semiconductor substrate in the last step of development when photoresist patterns are formed. Also, methods for forming photoresist patterns using the same are disclosed. The disclosed cleaning solution comprises H2O as a solution, a surfactant which is phosphate-alcoholamine salt represented by Formula 1, and an alcohol compound. The disclosed cleaning solution has lower surface tension than that of distilled water which has been used for conventional cleaning solutions, thereby improving resistance to photoresist pattern collapse and stabilizing the photoresist pattern formation.wherein R, x, y, z, a and b are as defined in the specification.

Owner:SK HYNIX INC

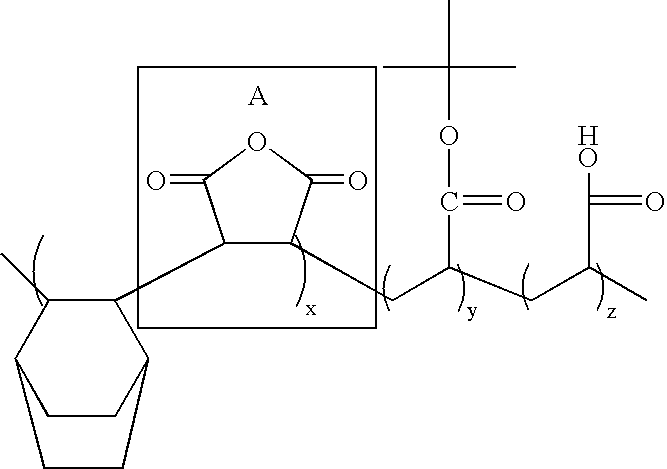

Photoresist monomers, polymers and photoresist compositions for preventing acid diffusion

Photoresist monomers, polymers thereof, photoresist compositions containing the same for preventing acid generated in the exposed area during the course of a photolithography process from being diffused to the unexposed area. The line edge roughness and slope pattern are improved when an ultrafine photoresist pattern is formed using photoresist copolymer having a multi-oxygen-containing compound as a repeating unit such as an ethyleneoxy moiety represented by Formula 1 with at least one polymerizable carbon-carbon double bond. In addition, the shape of pattern is improved by eliminating top loss and the adhesion of pattern to the substrate is improved. wherein n is an integer ranging from 1 to 5.

Owner:SK HYNIX INC +1

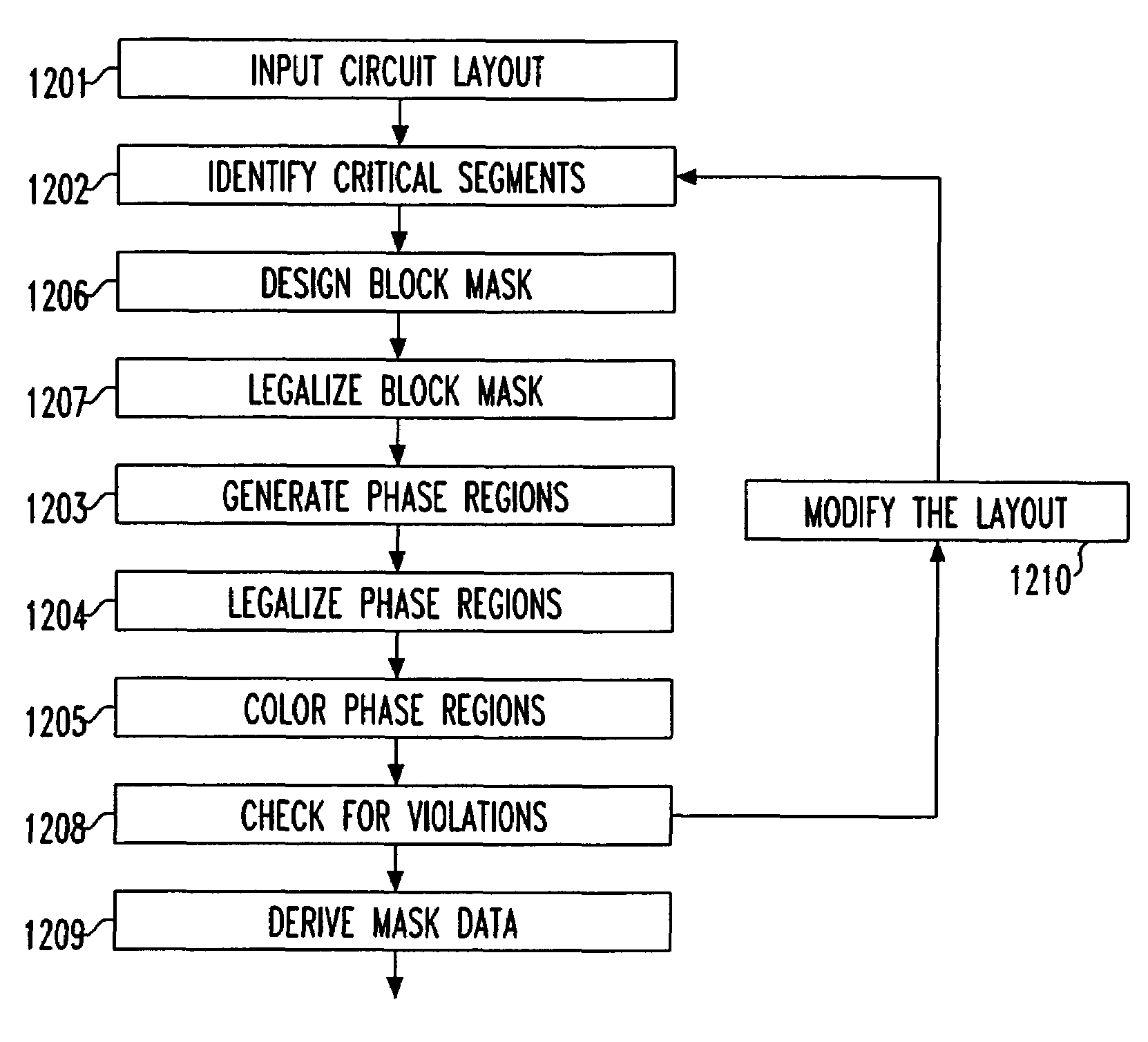

Generating mask patterns for alternating phase-shift mask lithography

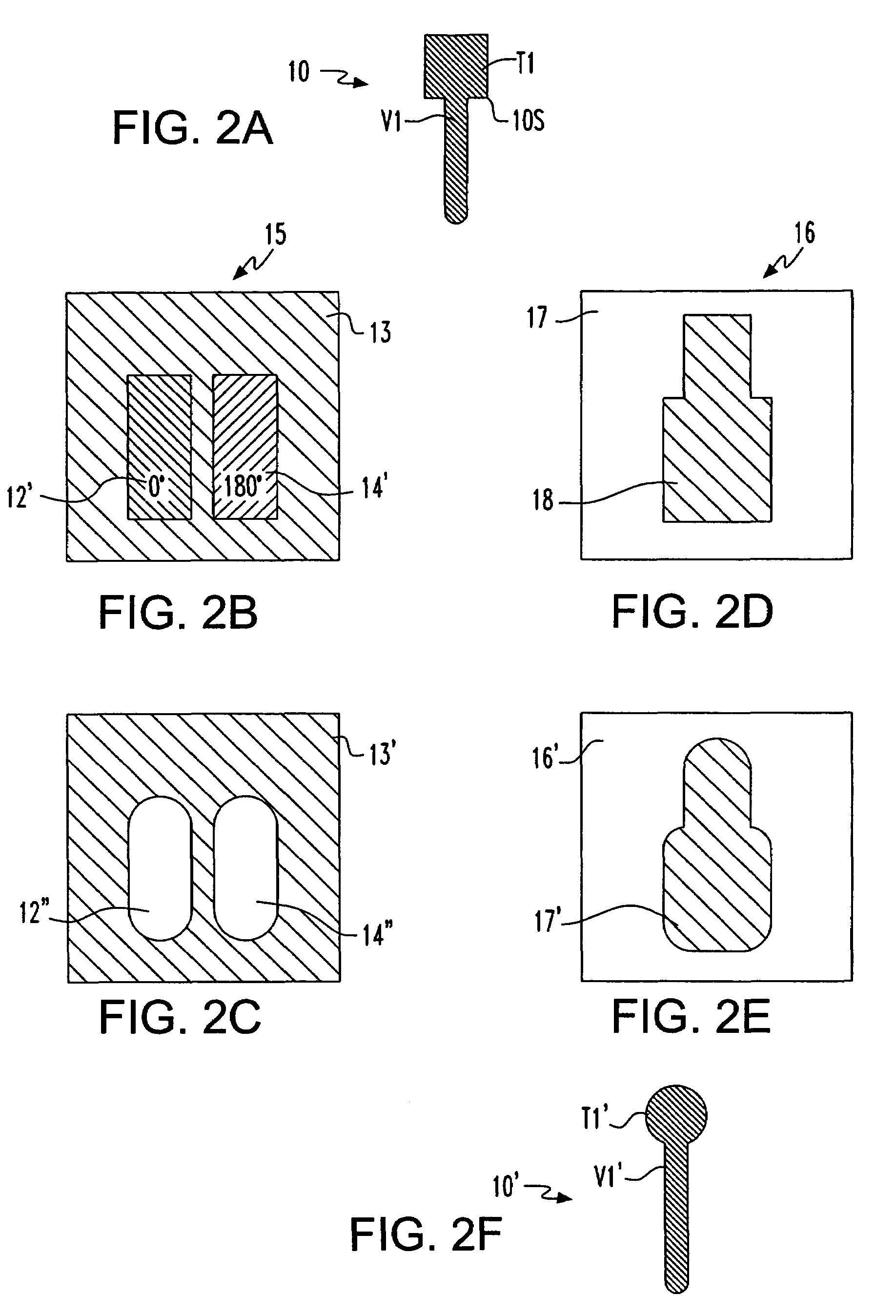

InactiveUS6993741B2Photosensitive materialsSemiconductor/solid-state device manufacturingResistEngineering

A method of generating patterns of a pair of photomasks from a data set defining a circuit layout to be provided on a substrate includes identifying critical segments of the circuit layout to be provided on the substrate. Block mask patterns are generated and then legalized based on the identified critical segments. Thereafter, phase mask patterns are generated, legalized and colored. The legalized block mask patterns and the legalized phase mask patterns that have been colored define features of a block mask and an alternating phase shift mask, respectively, for use in a dual exposure method for patterning features in a resist layer of a substrate.

Owner:GLOBALFOUNDRIES INC

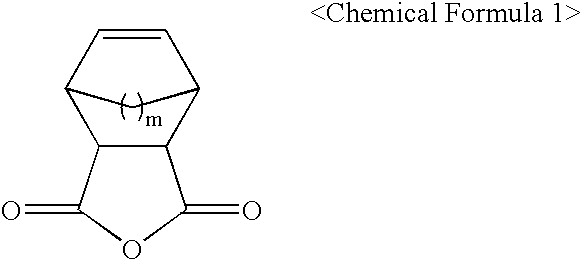

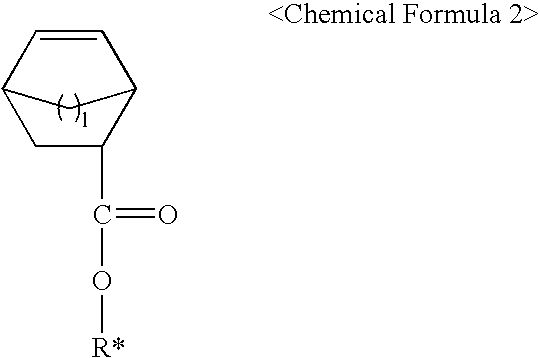

Polymers for photoresist and photoresist compositions using the same

InactiveUS6987155B2Improve the immunityExcellent etching resistance and adhesiveness and photosensitivityElectric discharge tubesPhotomechanical exposure apparatusResistX-ray

The present invention relates to photoresist monomers, polymers formed therefrom and photoresist compositions suitable for photolithography processes employing a DUV light source, such as KrF (249 nm) and ArF(193 nm); EUV; VUV; E-beam; ion-beam; and X-ray. Photoresist monomers of the present invention are represented by the following Chemical Formula 1: wherein, m is 1 or 2.Polymers of the present invention comprise repeating units derived from the comonomer of Chemical Formula 1, preferably together with monomers of the following Chemical Formula 2: wherein,R* is an acid-labile group, andl is 1 or 2.

Owner:HYUNDAI ELECTRONICS IND CO LTD

Uniform surfaces for hybrid material substrate and methods for making and using same

Devices, systems and methods of using same where hybrid substrate materials are provided with a substantially uniform surface to provide uniformity of properties, including interaction with their environments. Uniform surfaces are applied as coatings over, e.g., hybrid metal / silica, metal / polymer, metal / metal surfaces to mask different chemical properties of differing regions of the surface and to afford a protective surface for the hybrid structure.

Owner:PACIFIC BIOSCIENCES

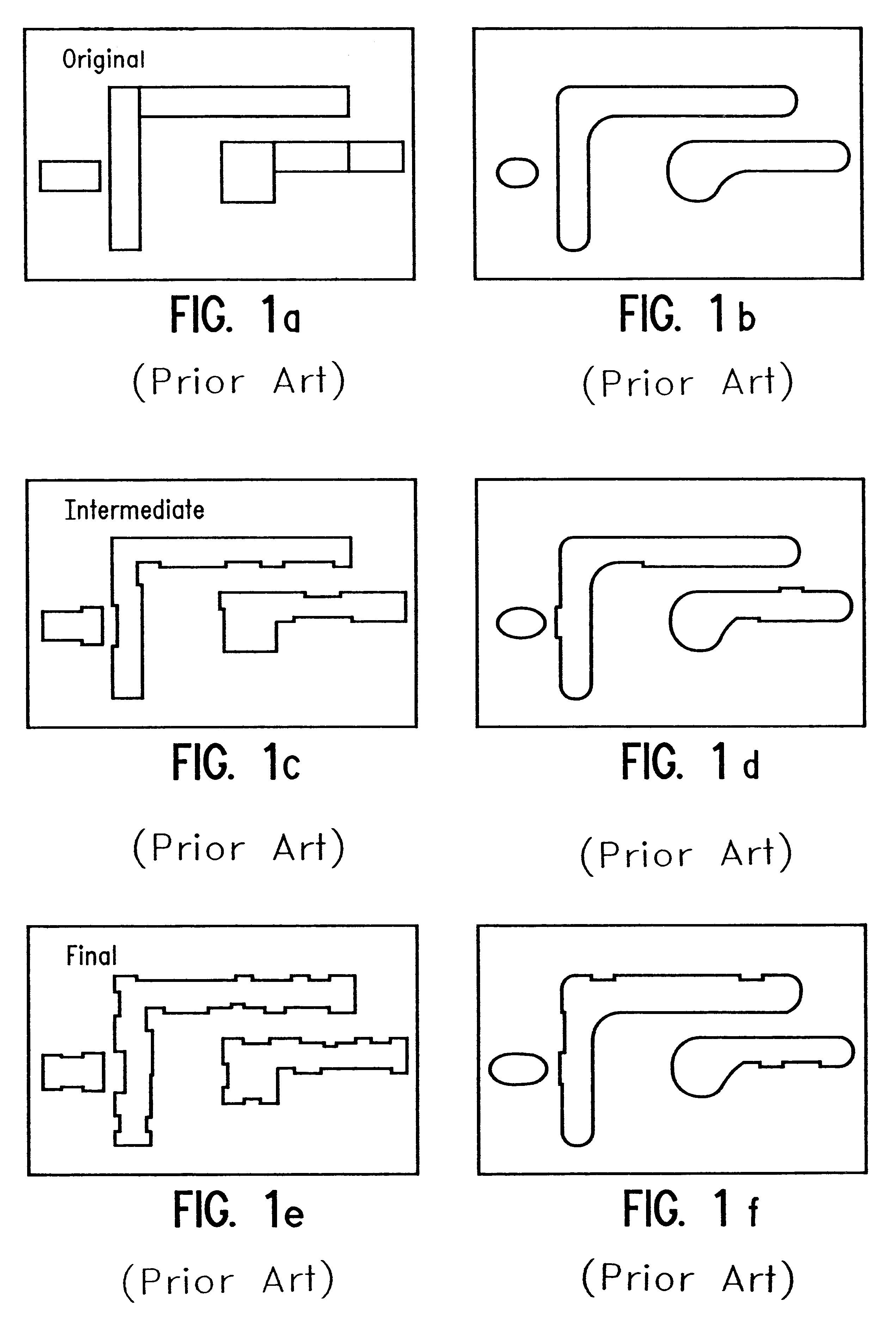

Process window based optical proximity correction of lithographic images

InactiveUS6578190B2Maximize rangeCharacter and pattern recognitionPhotomechanical exposure apparatusProcess windowPlanographic printing

Owner:GLOBALFOUNDRIES U S INC

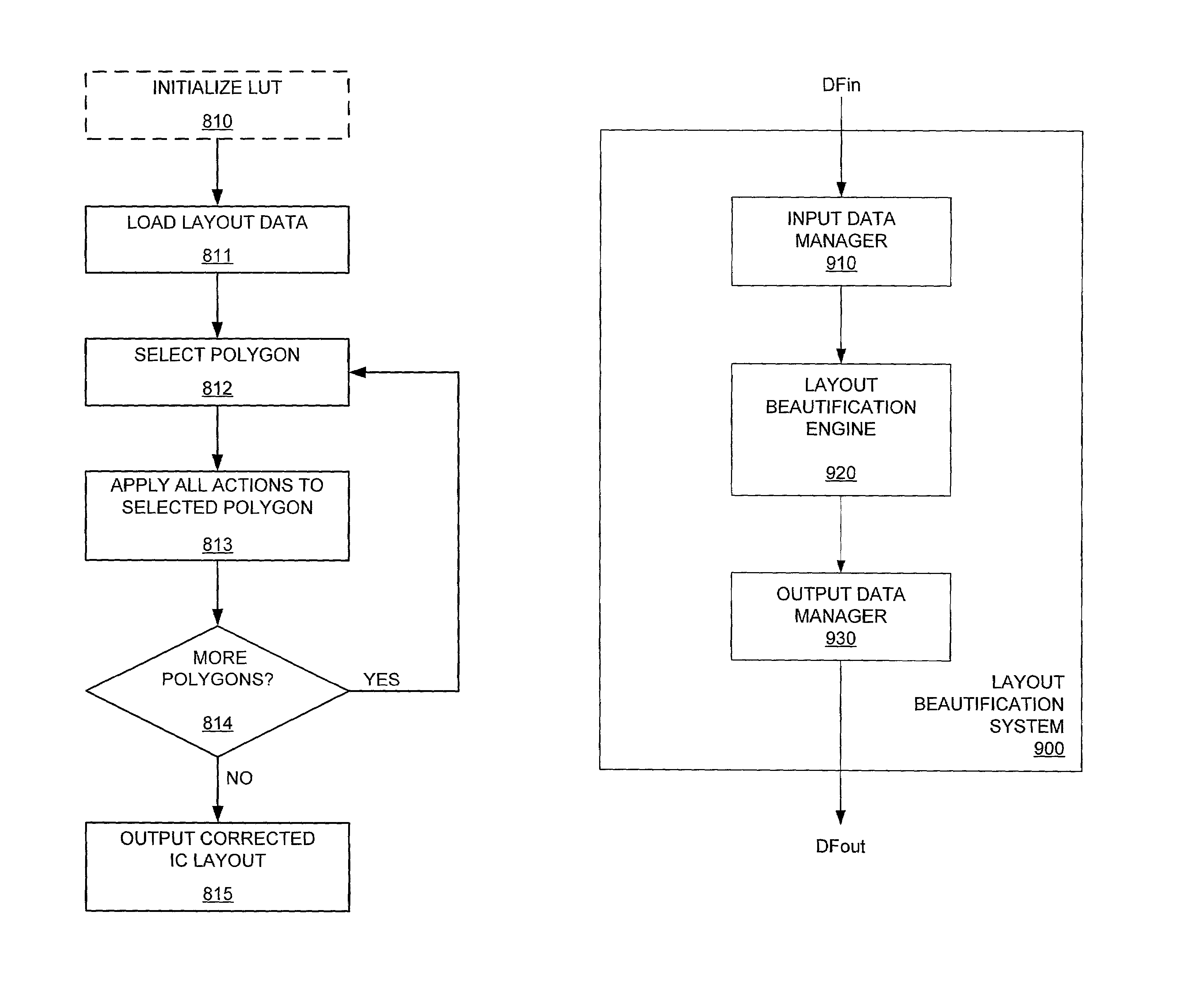

Shape-based geometry engine to perform smoothing and other layout beautification operations

ActiveUS7159197B2Efficient executionData be eliminatedOriginals for photomechanical treatmentComputer aided designData fileEngineering

A shape-based layout beautification operation can be performed on an IC layout to correct layout imperfections. A shape is described by edges (and vertices) related according to specified properties. Each shape can be configured to match specific layout imperfection types. Corrective actions can then be associated with the shapes, advantageously enabling efficient formulation and precise application of those corrective actions. Corrective actions can include absolute, adaptive, or replacement-type modifications to the detected layout imperfections. A concurrent processing methodology can be used to minimize processing overhead during layout beautification, and the actions can also be incorporated into a lookup table to further reduce runtime. A layout beautification system can also be connected to a network across which shapes, actions, and IC layout data files can be accessed and retrieved.

Owner:SYNOPSYS INC

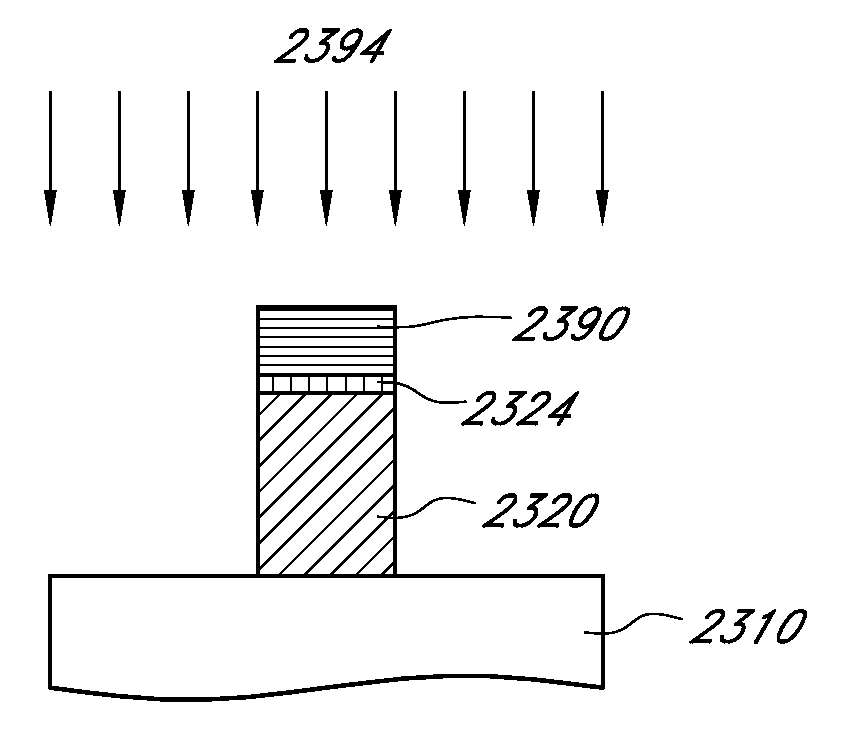

Radiation patternable CVD film

InactiveUS8465903B2Electric discharge tubesSemiconductor/solid-state device manufacturingCross-linkGas phase

Methods for forming photoresists sensitive to radiation on a substrate are provided. Described are chemical vapor deposition methods of forming films (e.g., silicon-containing films) as photoresists using a plasma which may be exposed to radiation to form a pattern. The deposition methods utilize precursors with cross-linkable moieties that will cross-link upon exposure to radiation. Radiation may be carried out in the with or without the presence of oxygen. Exposed or unexposed areas may then be developed in an aqueous base developer.

Owner:APPLIED MATERIALS INC

Antireflective coatings comprising poly(oxyalkylene) colorants

InactiveUS6048662AReduce the amplitudeImprove anti-reflectionPhotosensitive materialsRadiation applicationsCounterionThin layer

This invention relates to antireflective coatings comprising polymeric polyoxyalkylenated colorants. More particularly, the present invention relates to antireflective coatings for utilization in forming thin layers between reflective substrates and photoresist coatings. Such antireflective coatings are very useful and beneficial within the production and fabrication of semiconductors through photolithographic procedures due to the liquid, non-crystallizing nature of polyoxyalkylenated colorants, and the lack of potentially damaging counterions, metals, and / or electrolytes within the inventive antireflective colored coatings. The inventive coatings may also be applied on lenses, mirrors, and other optical components. Methods of forming such antireflective coatings are also contemplated within this invention.

Owner:MILLIKEN & CO

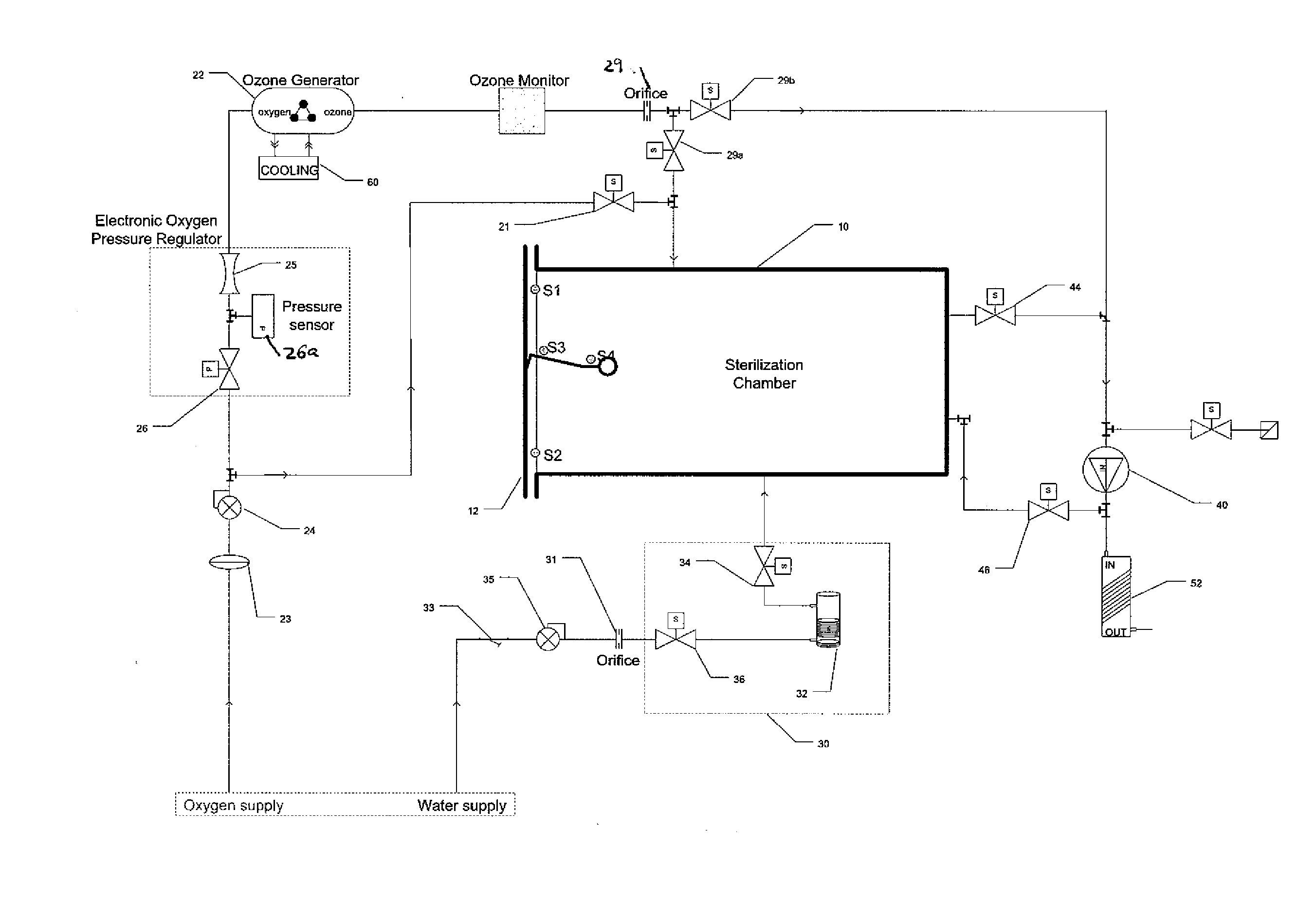

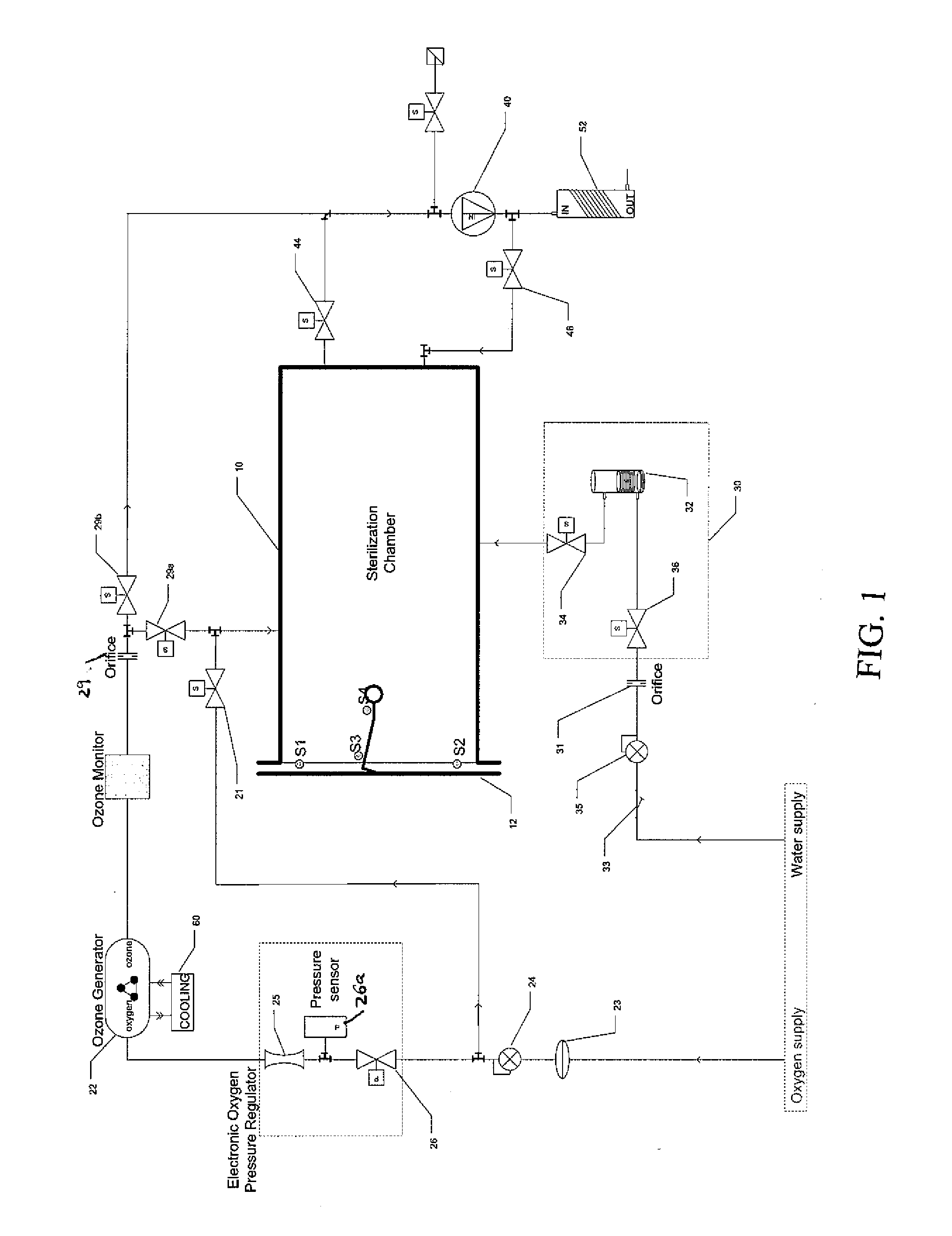

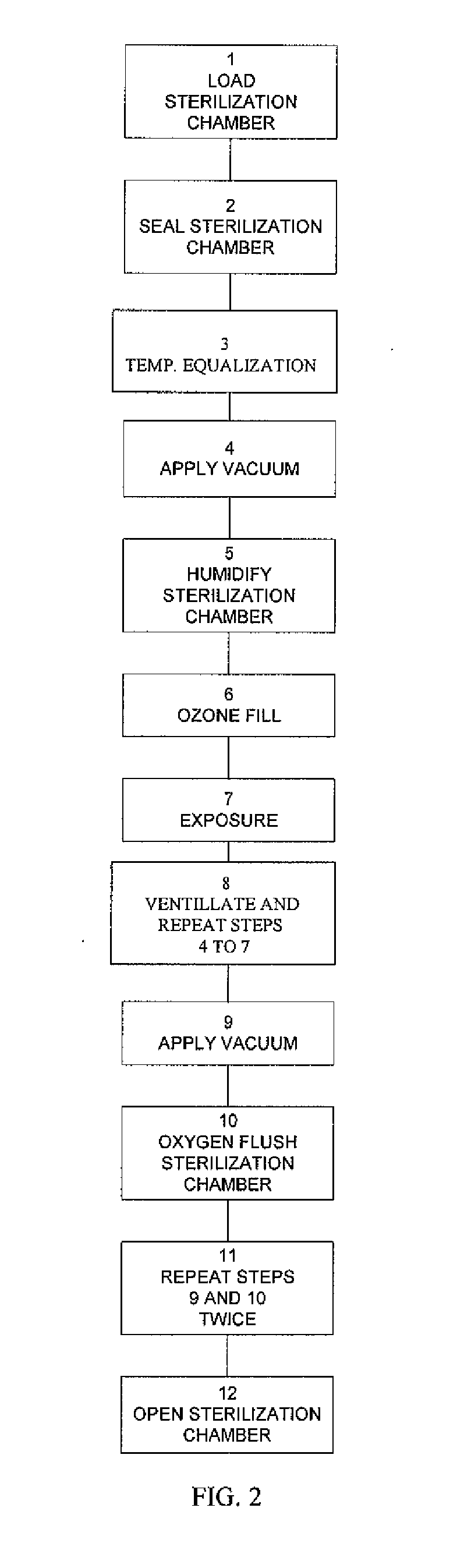

Method and apparatus for ozone sterilization

InactiveUS20070258855A1Avoid condensationPrevent water condensationElectrolysis componentsExhaust apparatusVacuum pressureWater vapor

The present invention provides a method and apparatus for sterilizing articles using an ozone-containing gas, where condensation of water from the sterilization atmosphere during the sterilization process is substantially prevented. The inventive sterilization method includes providing a sterilization chamber and placing an article into the sterilization chamber. The sterilization chamber is sealed prior to equalizing the temperature of the article and the atmosphere in the sterilization chamber. A vacuum is applied to achieve a preselected vacuum pressure in the sterilization chamber. Once the vacuum pressure is set, water vapour is supplied to the sterilization chamber. Ozone-containing gas is then supplied to the sterilization chamber and the sterilization chamber remains sealed for a preselected treatment period, where the sterilization chamber remains sealed throughout the whole process. Finally, vacuum in the sterilization chamber is released.

Owner:STRYKER CORP

Organic devices, organic electroluminescent devices and organic solar cells

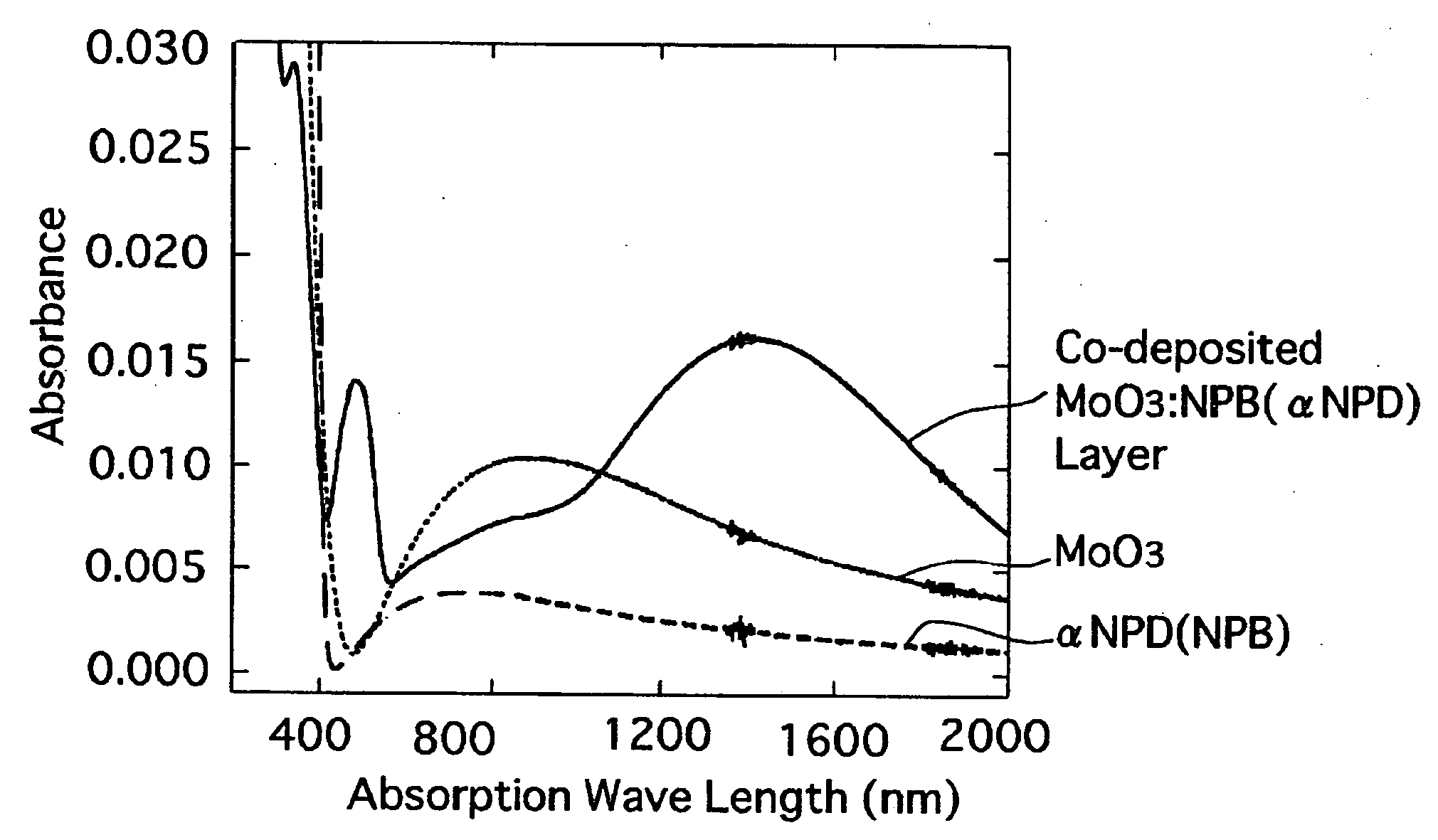

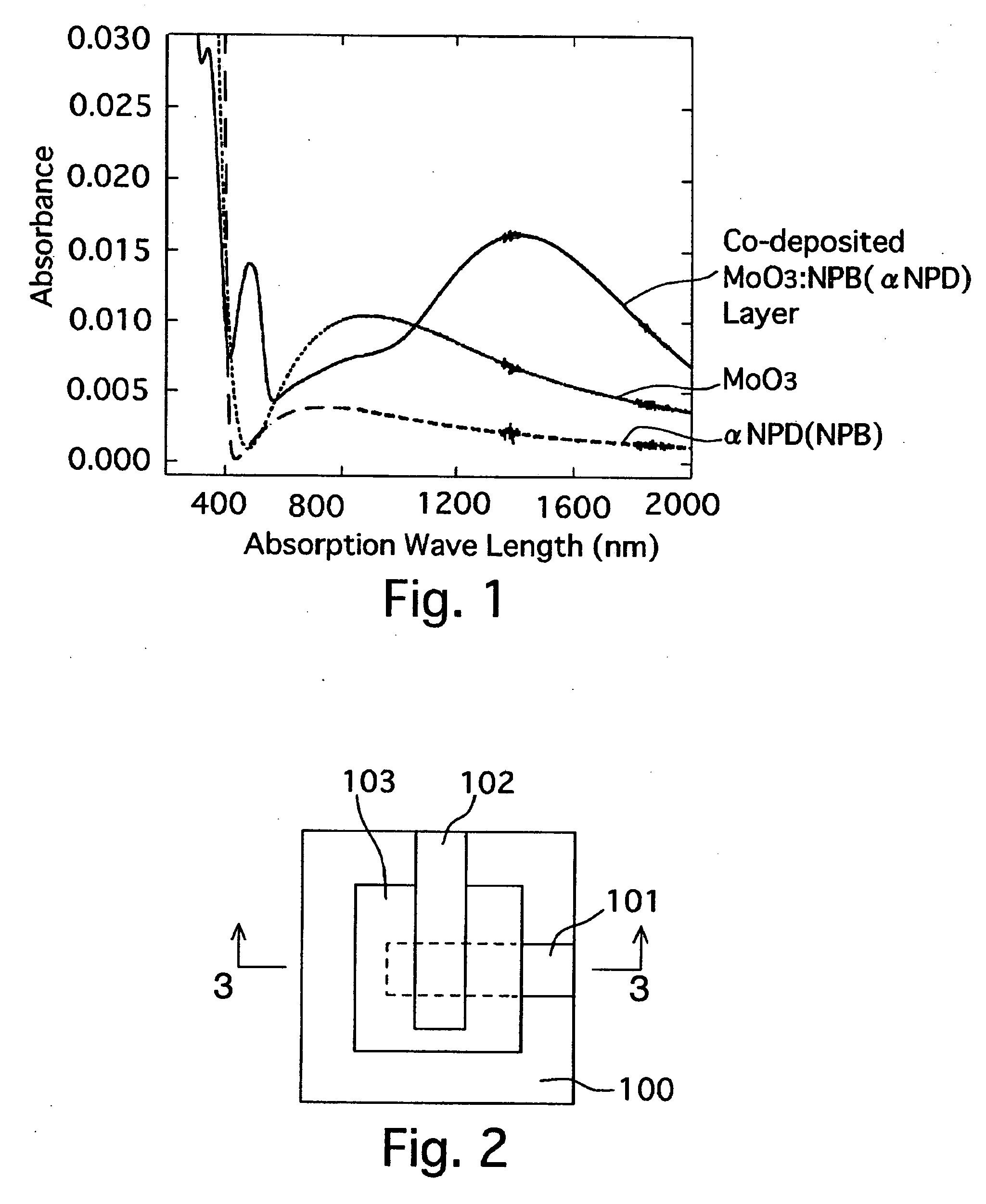

ActiveUS20060008740A1Reduce harmLower barrier heightElectric discharge tubesElectroluminescent light sourcesOrganic solar cellSimple Organic Compounds

An organic device, including an organic compound having charge-transporting ability (i.e., transporting holes and / or electrons) and / or including organic light emissive molecules capable of emitting at least one of fluorescent light or phosphorescent light, has a charge transfer complex-contained layer including a charge transfer complex formed upon contact of an organic hole-transporting compound and molybdenum trioxide via a manner of lamination or mixing thereof, so that the organic hole-transporting compound is in a state of radical cation (i.e., positively charged species) in the charge transfer complex-contained layer.

Owner:MITSUBISHI HEAVY IND LTD +1

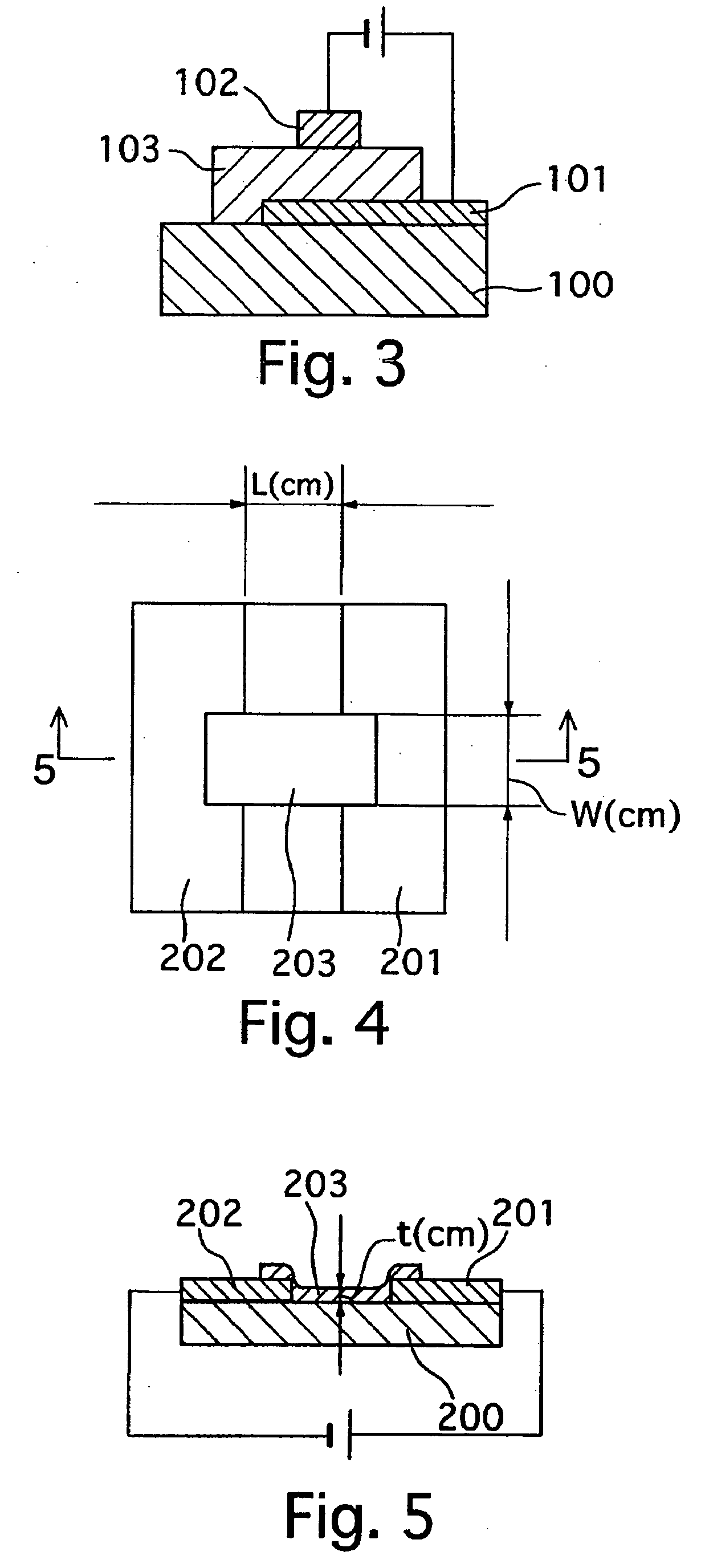

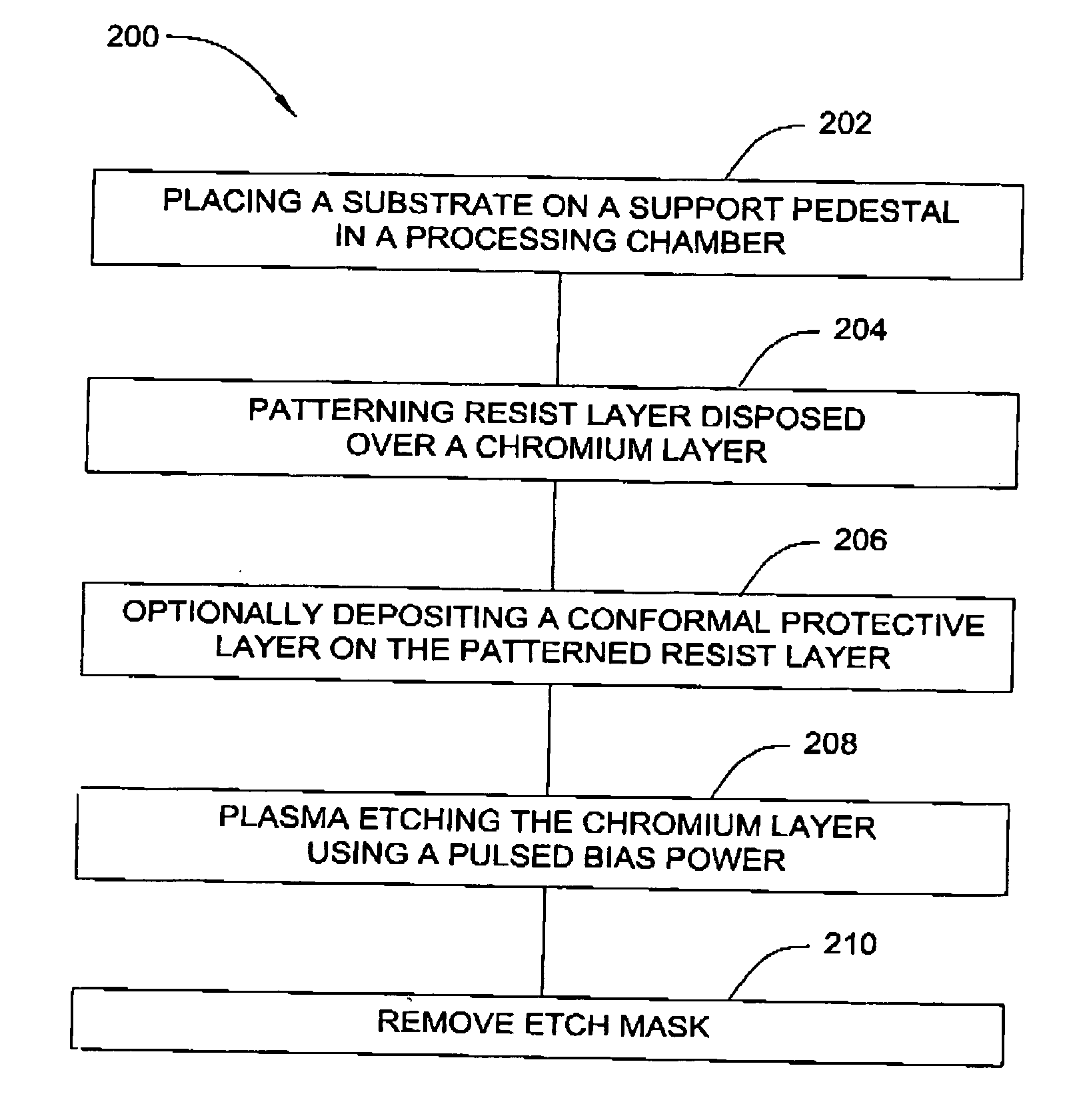

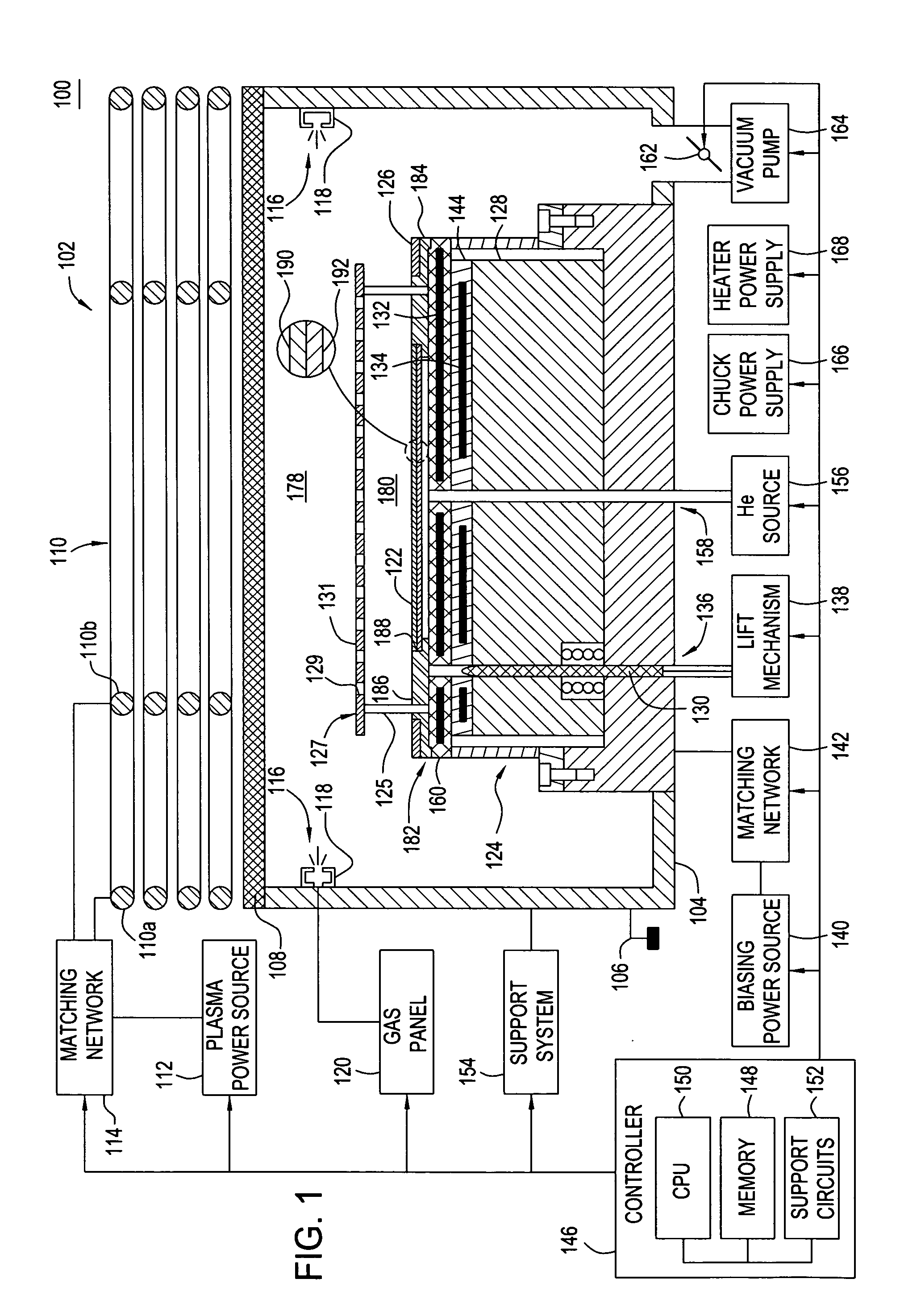

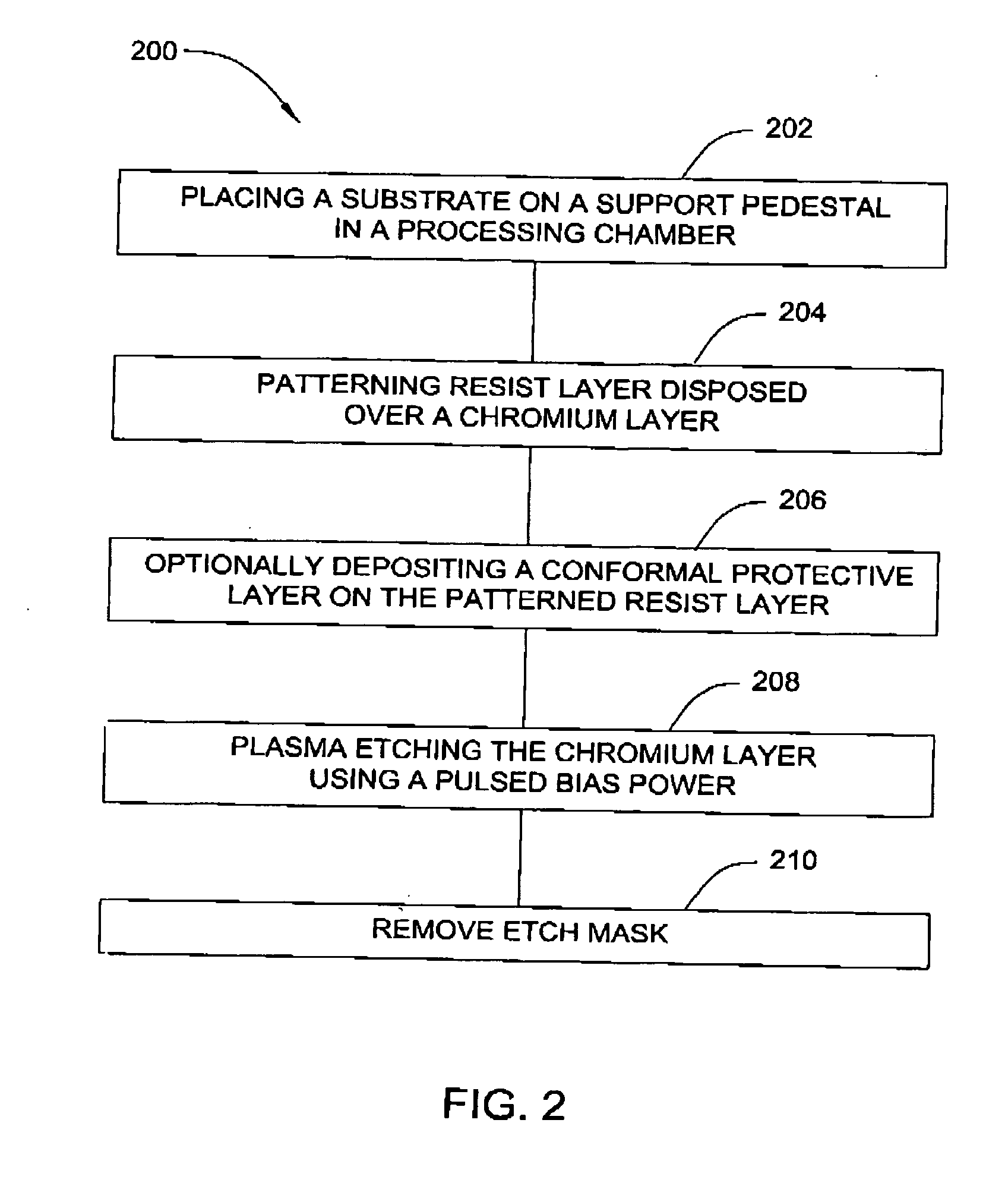

Method for plasma etching a chromium layer suitable for photomask fabrication

A method for etching a chromium layer is provided herein. In one embodiment, a method for etching a chromium layer includes providing a filmstack in an etching chamber, the filmstack having a chromium layer partially exposed through a patterned layer, providing at least one halogen containing process gas to a processing chamber, biasing the layer disposed on a substrate support in the processing chamber with a plurality of power pulses less than 600 Watts, and etching the chromium layer through a patterned mask. The method for plasma etching a chromium layer described herein is particularly suitable for fabricating photomasks.

Owner:APPLIED MATERIALS INC

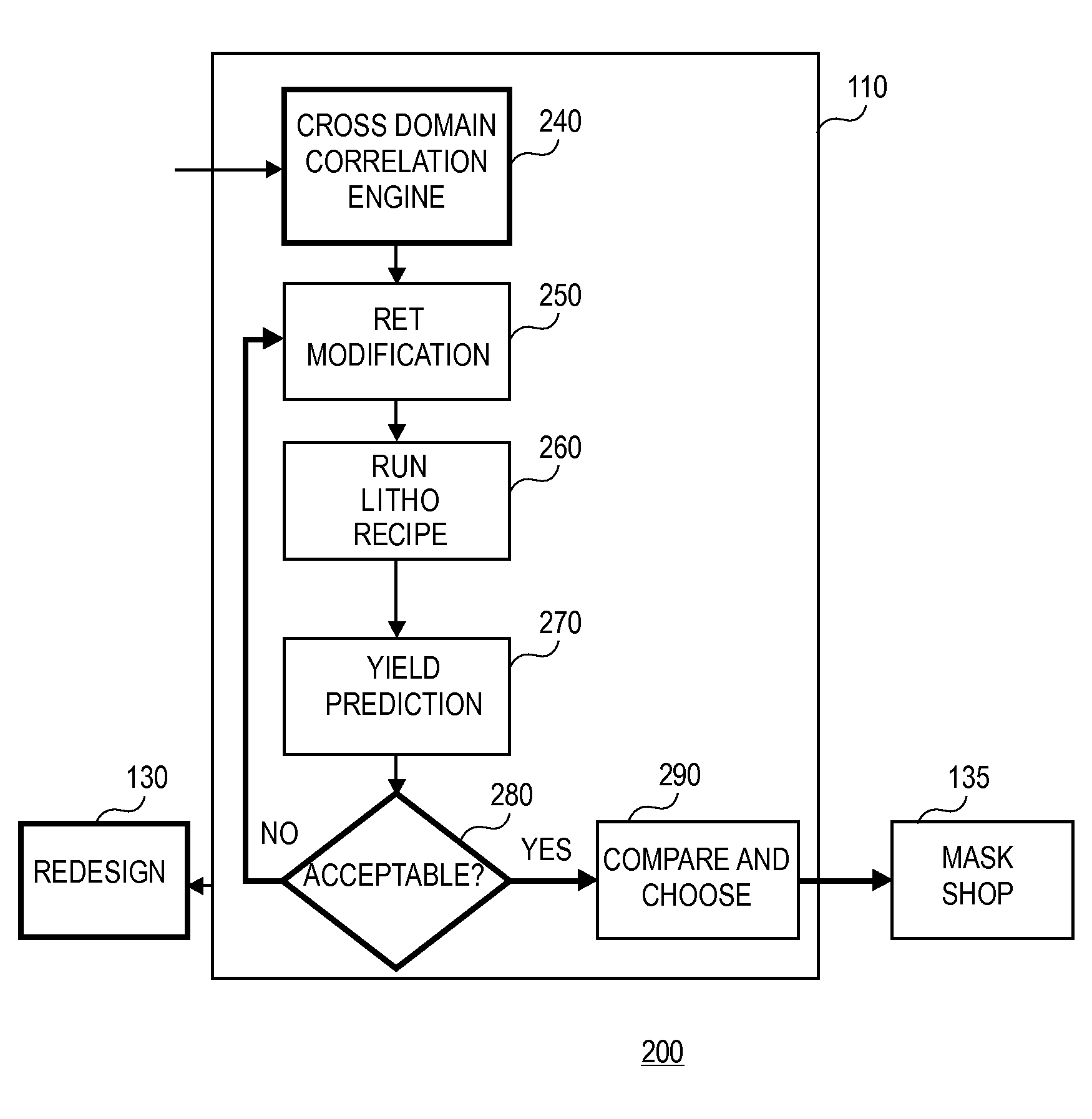

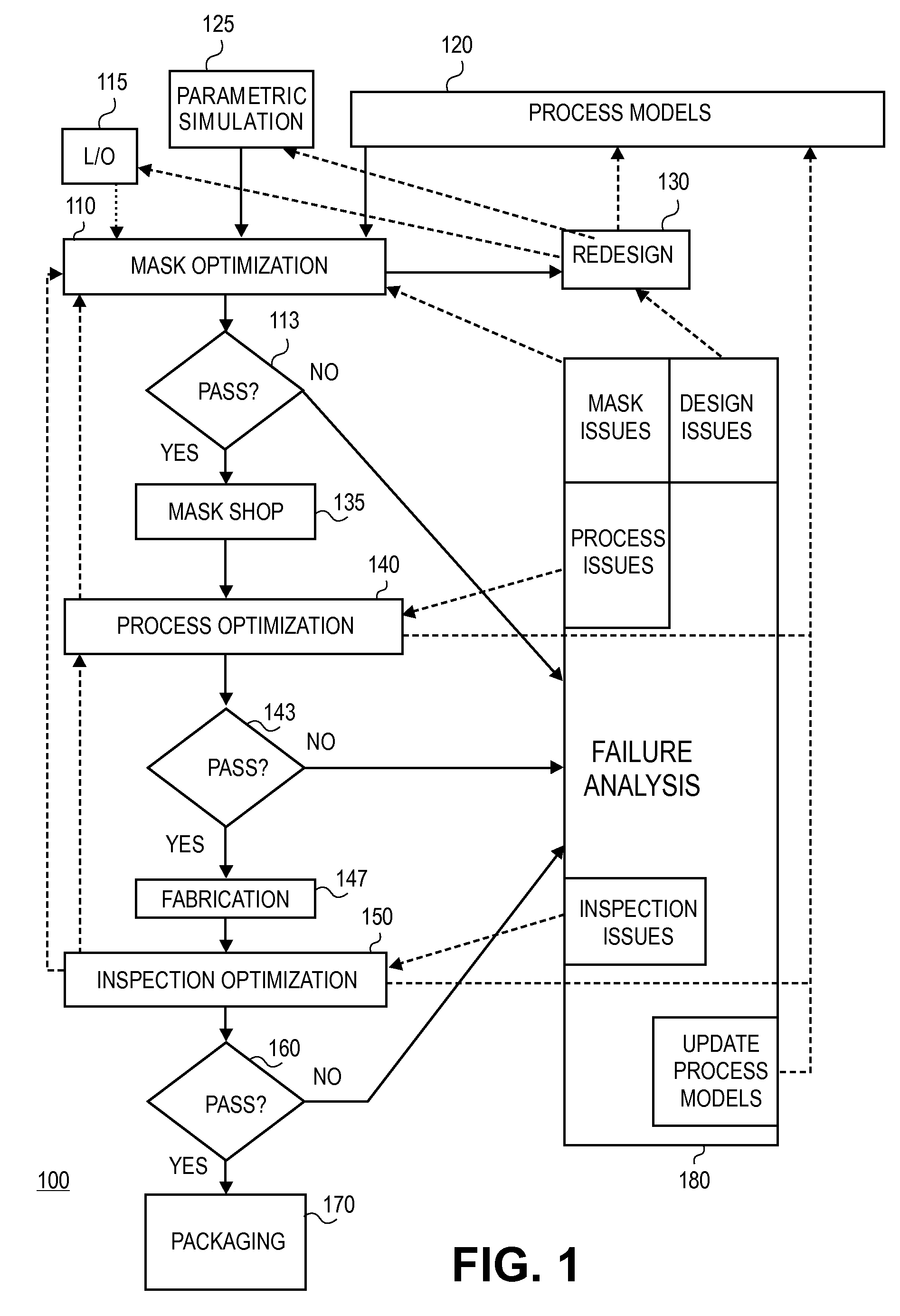

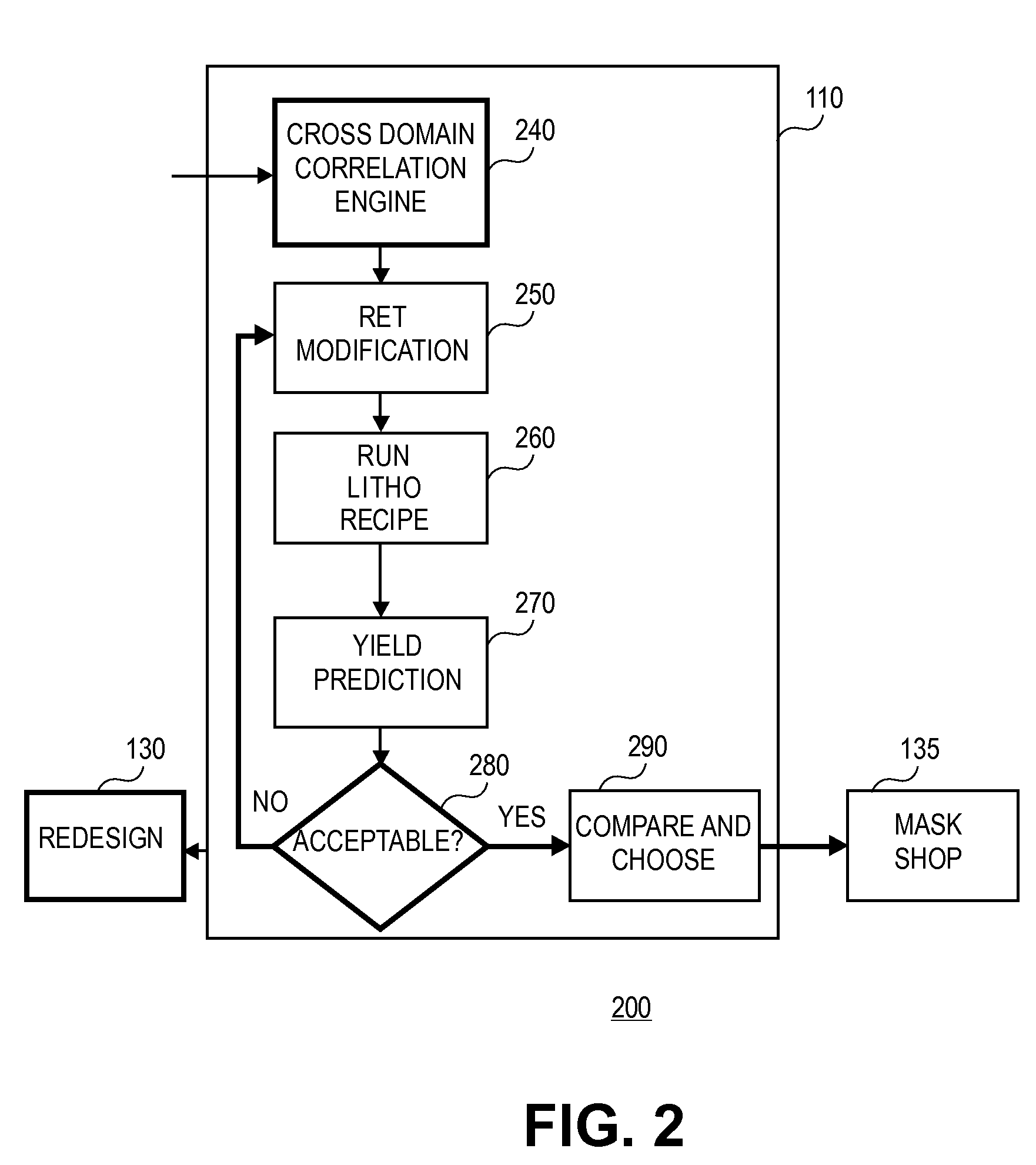

Method and system for mask optimization

ActiveUS20080148216A1Originals for photomechanical treatmentComputer aided designProcess engineering

Owner:CADENCE DESIGN SYST INC

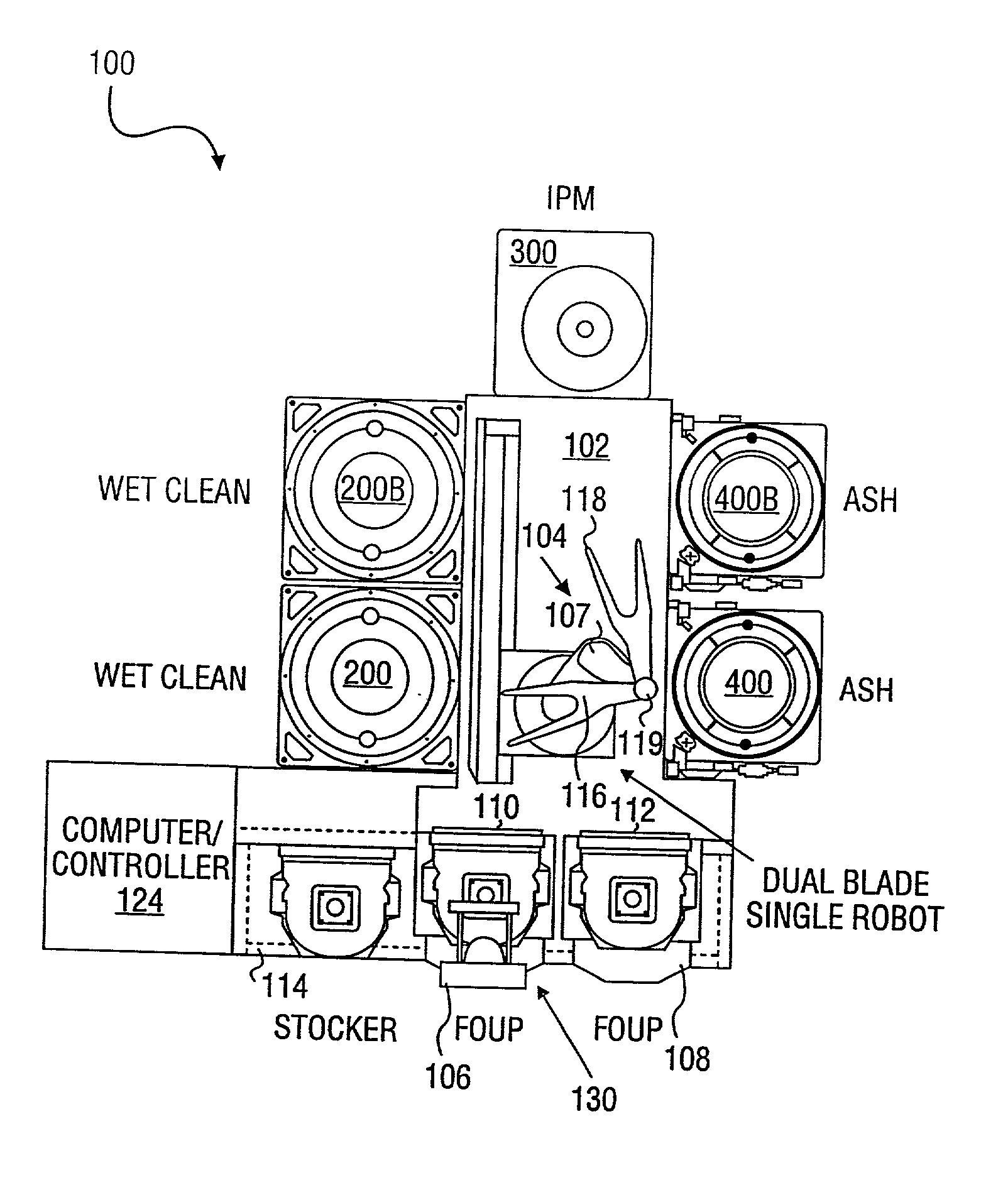

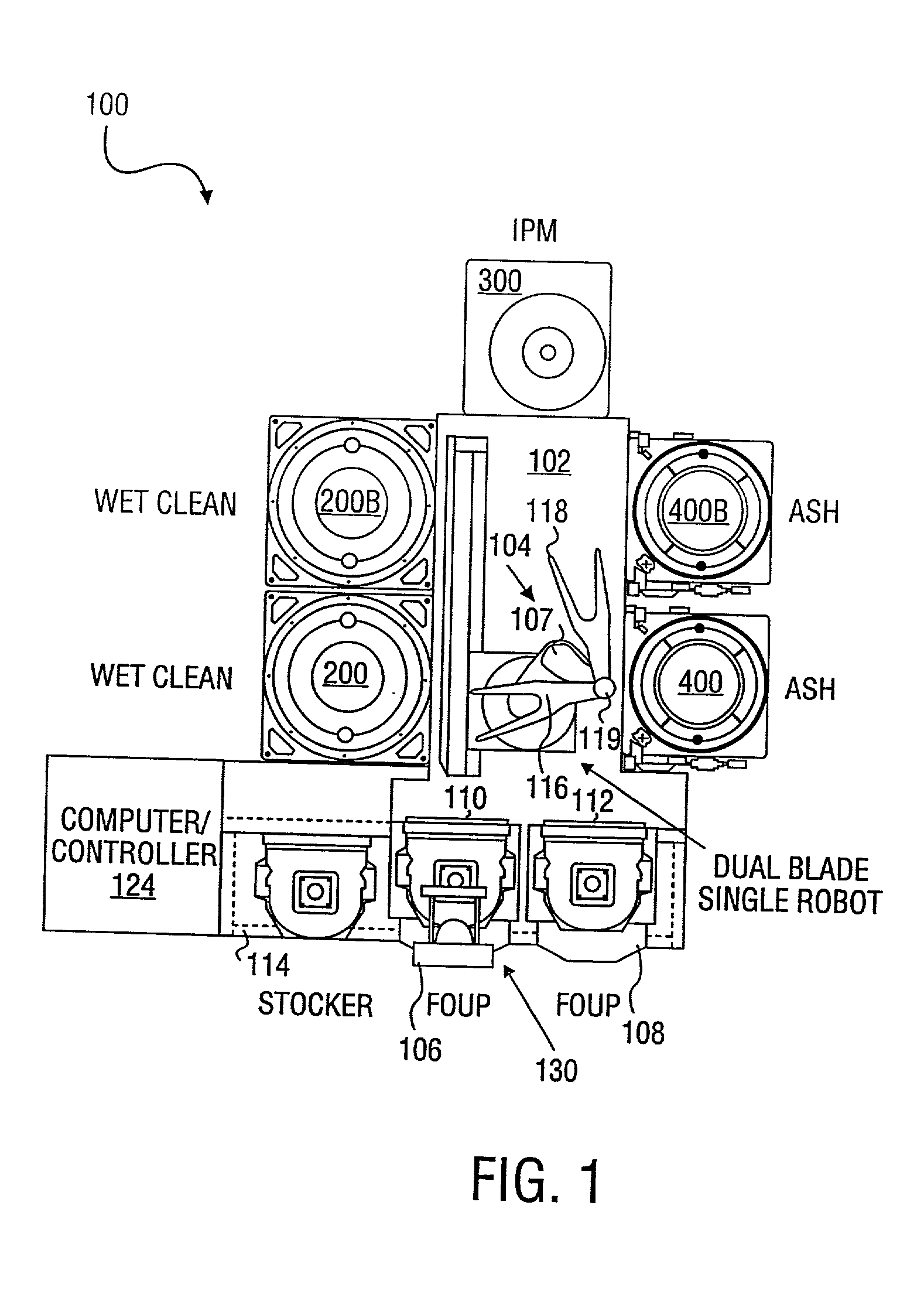

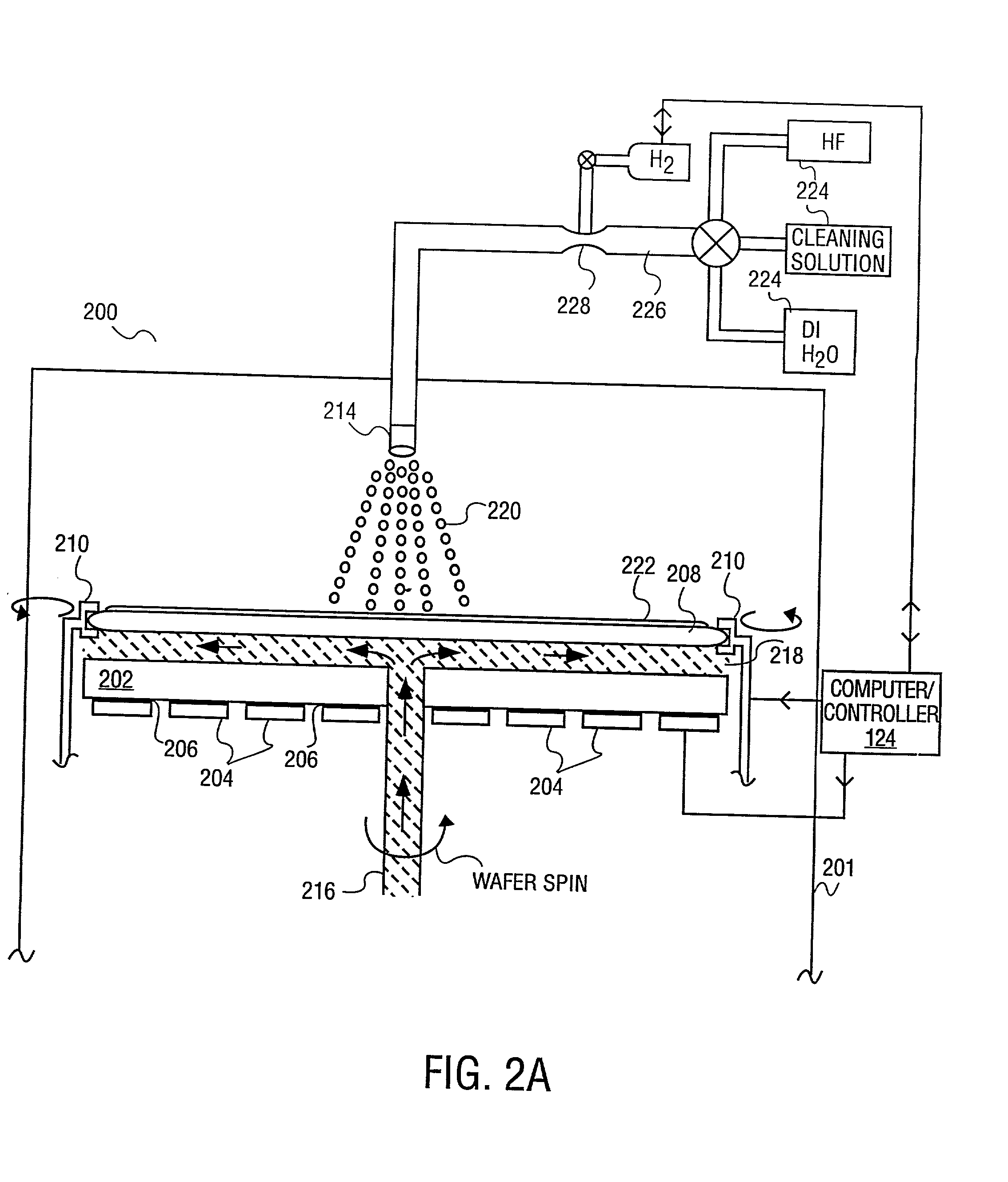

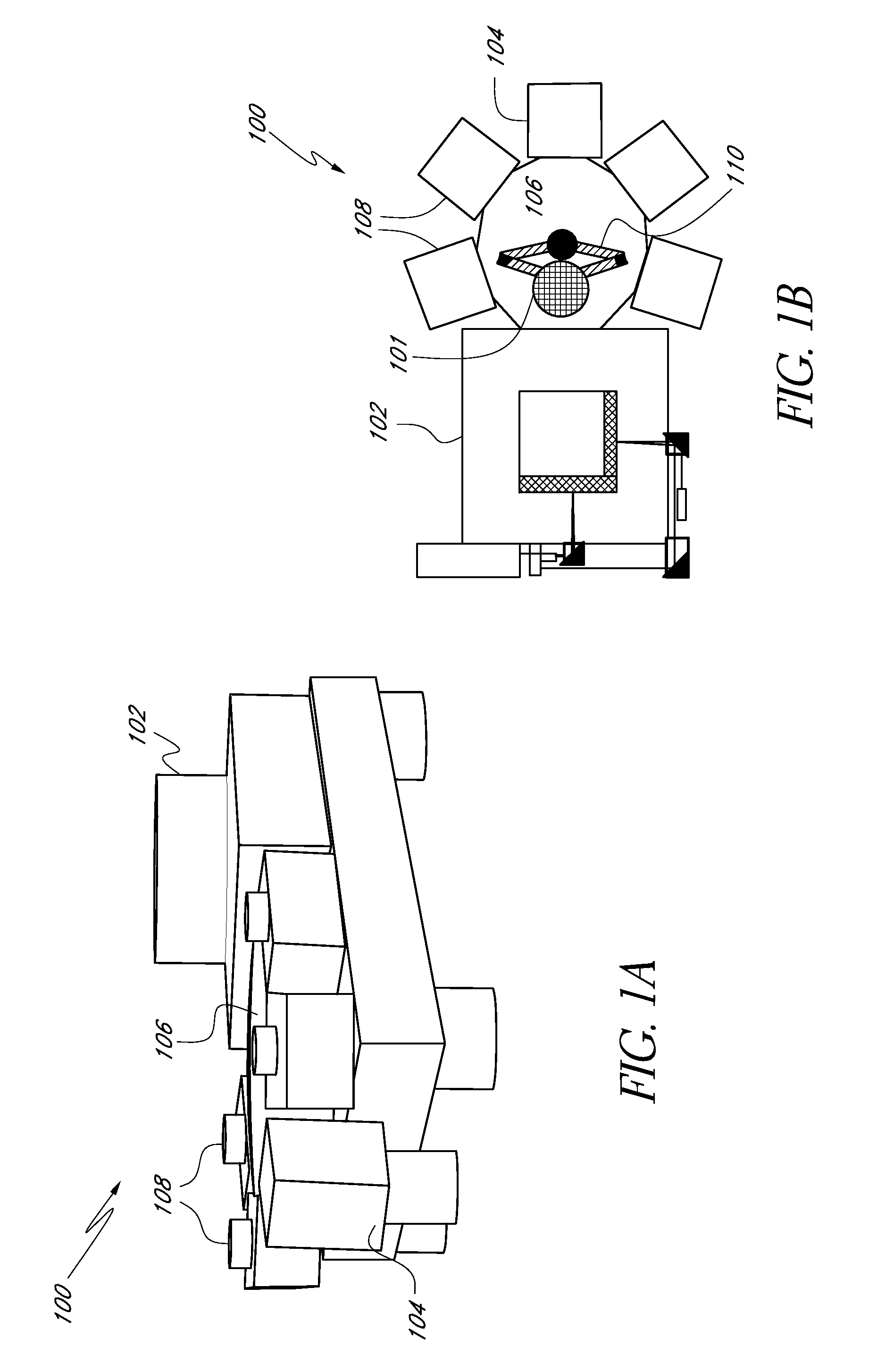

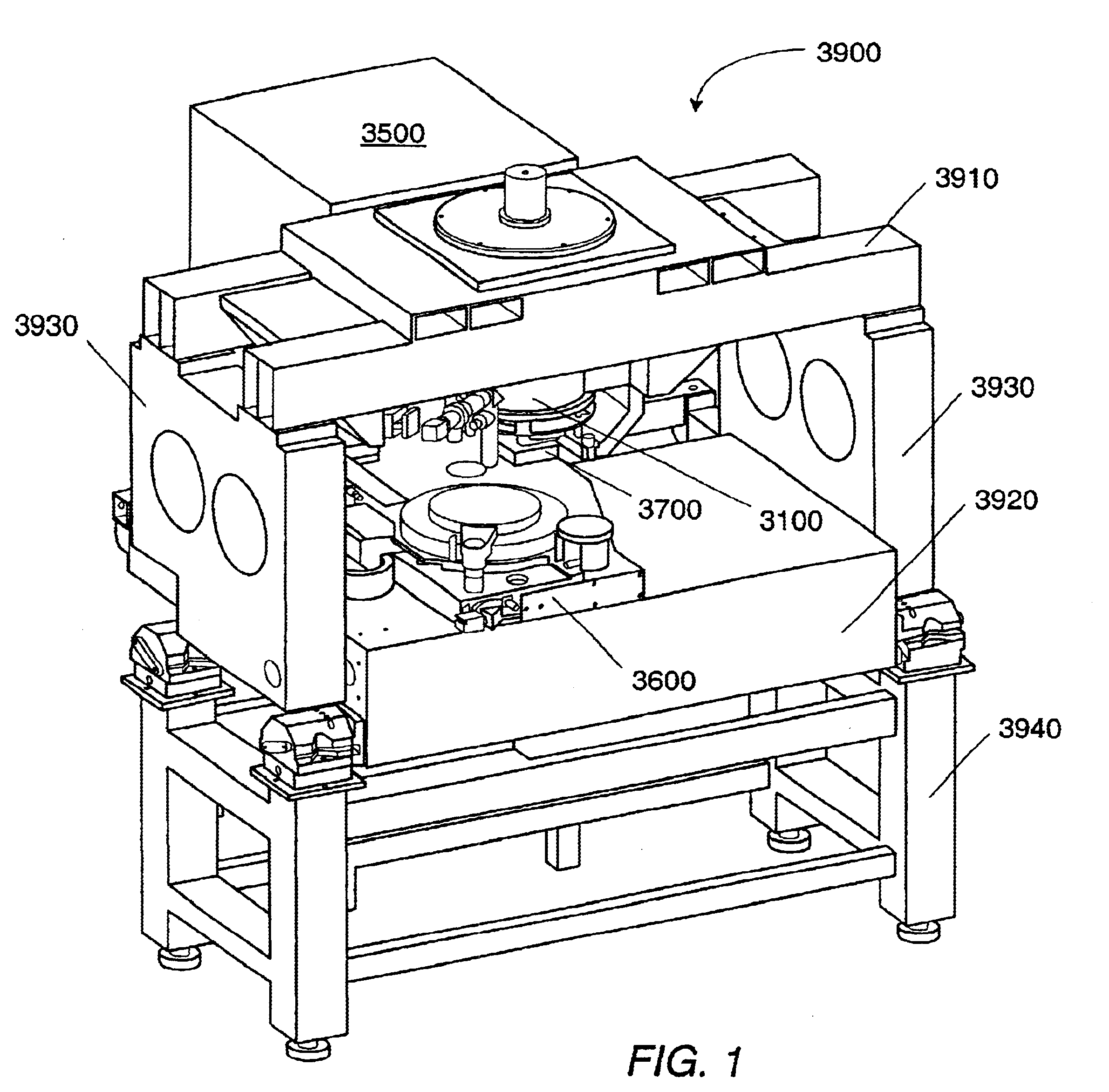

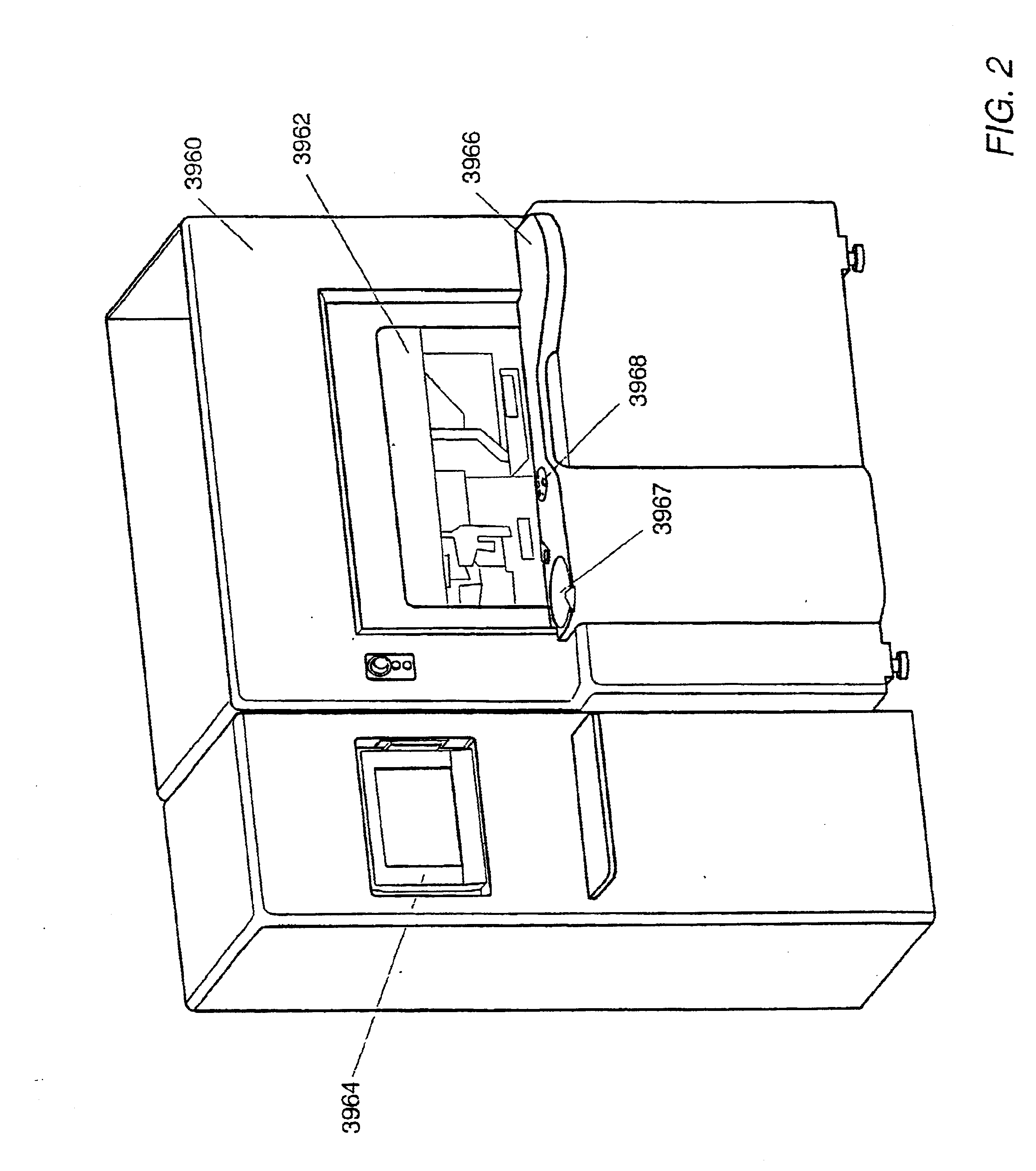

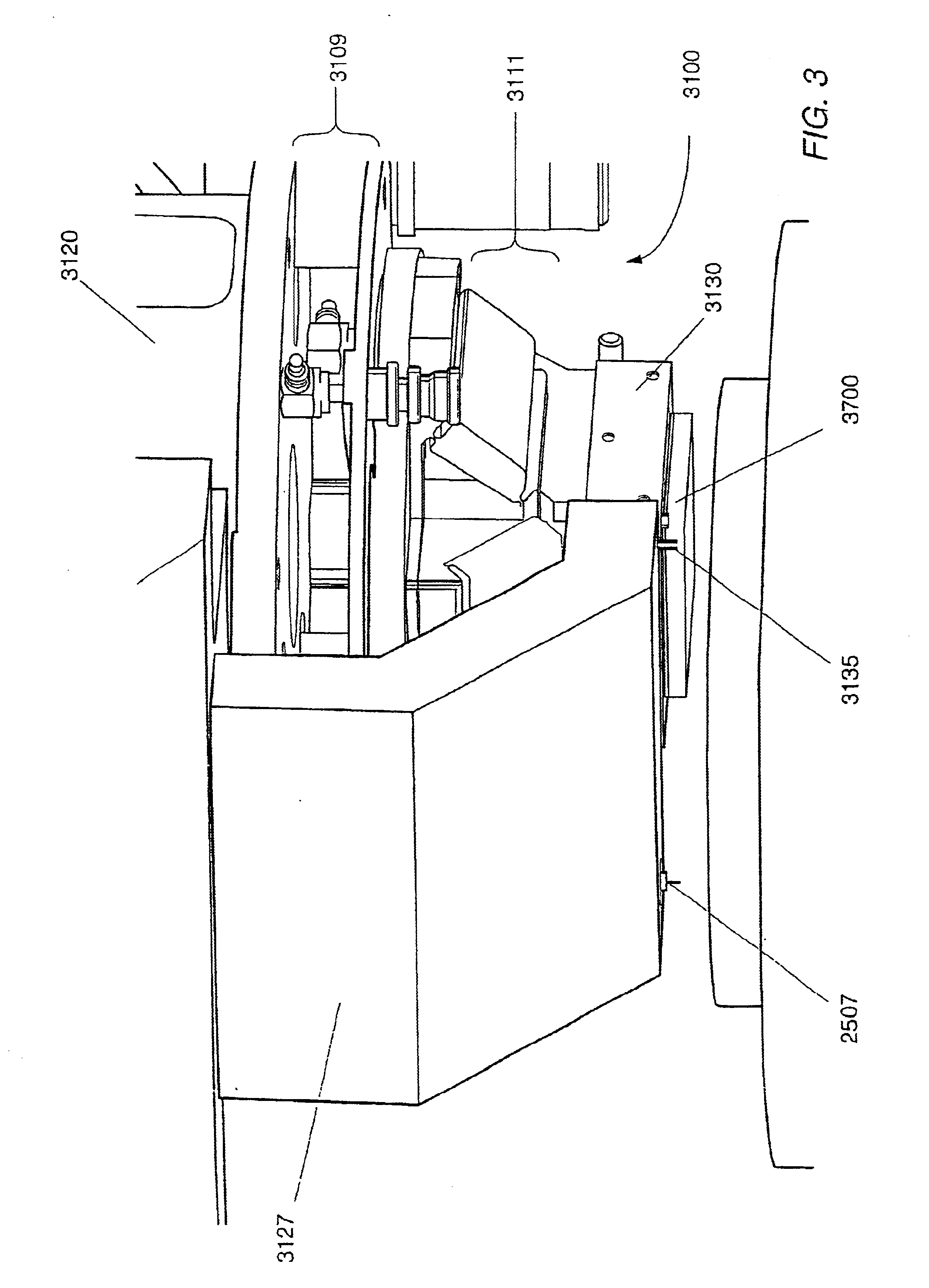

Method and apparatus for processing a wafer

InactiveUS20030045098A1Vacuum evaporation coatingPhotomechanical apparatusEngineeringMechanical engineering

A method of a single wafer wet / dry cleaning apparatus comprising: a transfer chamber having a wafer handler contained therein; a first single wafer wet cleaning chamber directly coupled to the transfer chamber; and a first single wafer ashing chamber directly coupled to the transfer chamber.

Owner:APPLIED MATERIALS INC

Photoresist composition for deep UV radiation containing an additive

InactiveUS6723488B2Reduce impactPrevent degradationPhotosensitive materialsElectric discharge tubesUltravioletAqueous solution

Owner:AZ ELECTRONICS MATERIALS USA CORP

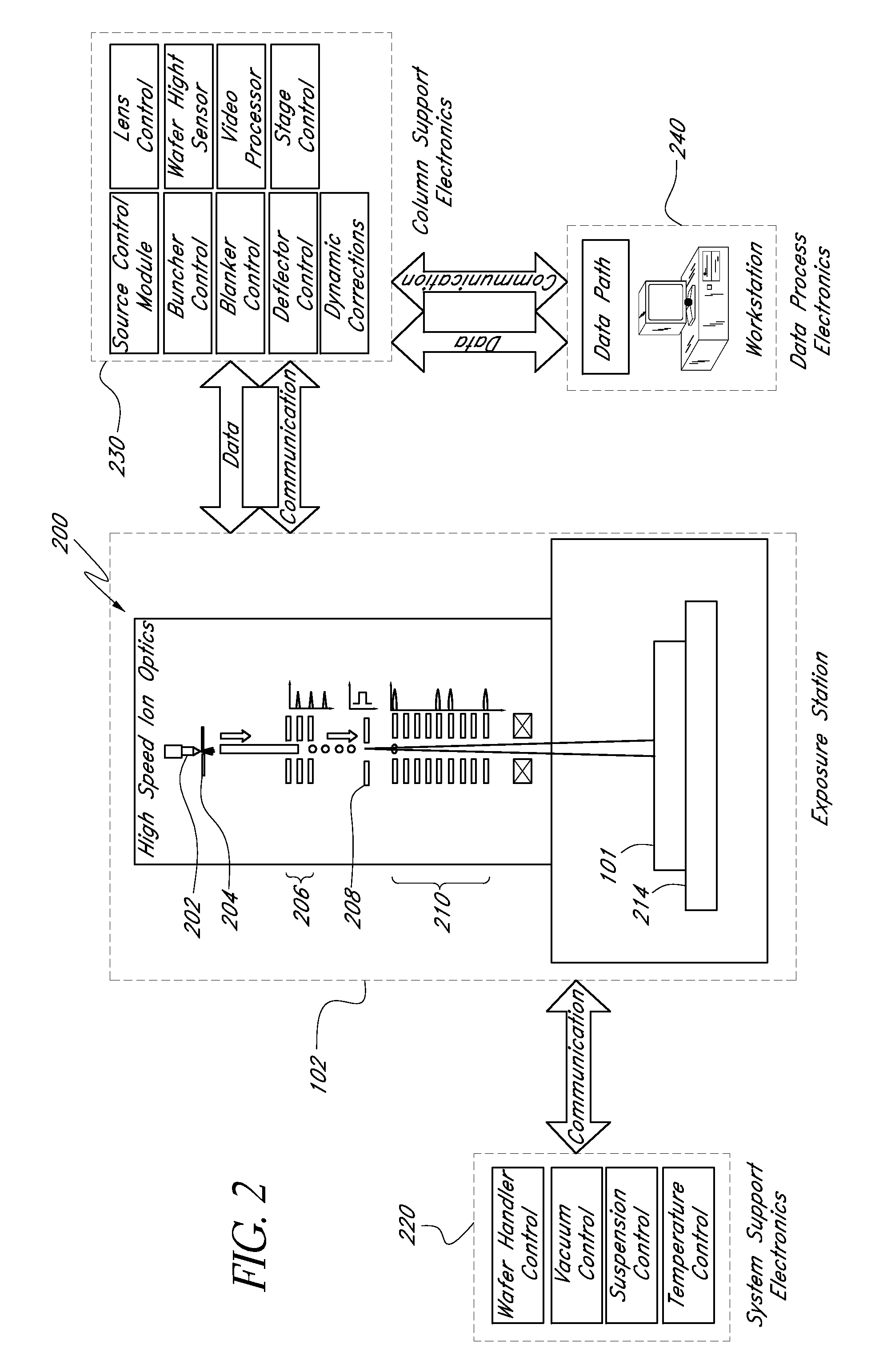

Apparatus and method for conformal mask manufacturing

ActiveUS20080160431A1Electric discharge tubesPhotosensitive materialsComputational physicsIrradiation

A manufacturing process technology creates a pattern on a first layer using a focused ion beam process. The pattern is transferred to a second layer, which may act as a traditional etch stop layer. The pattern can be formed on the second layer without irradiation by light through a reticle and without wet chemical developing, thereby enabling conformal coverage and very fine critical feature control. Both dark field patterns and light field patterns are disclosed, which may enable reduced or minimal exposure by the focused ion beam.

Owner:NEXGENSEMI HLDG INC

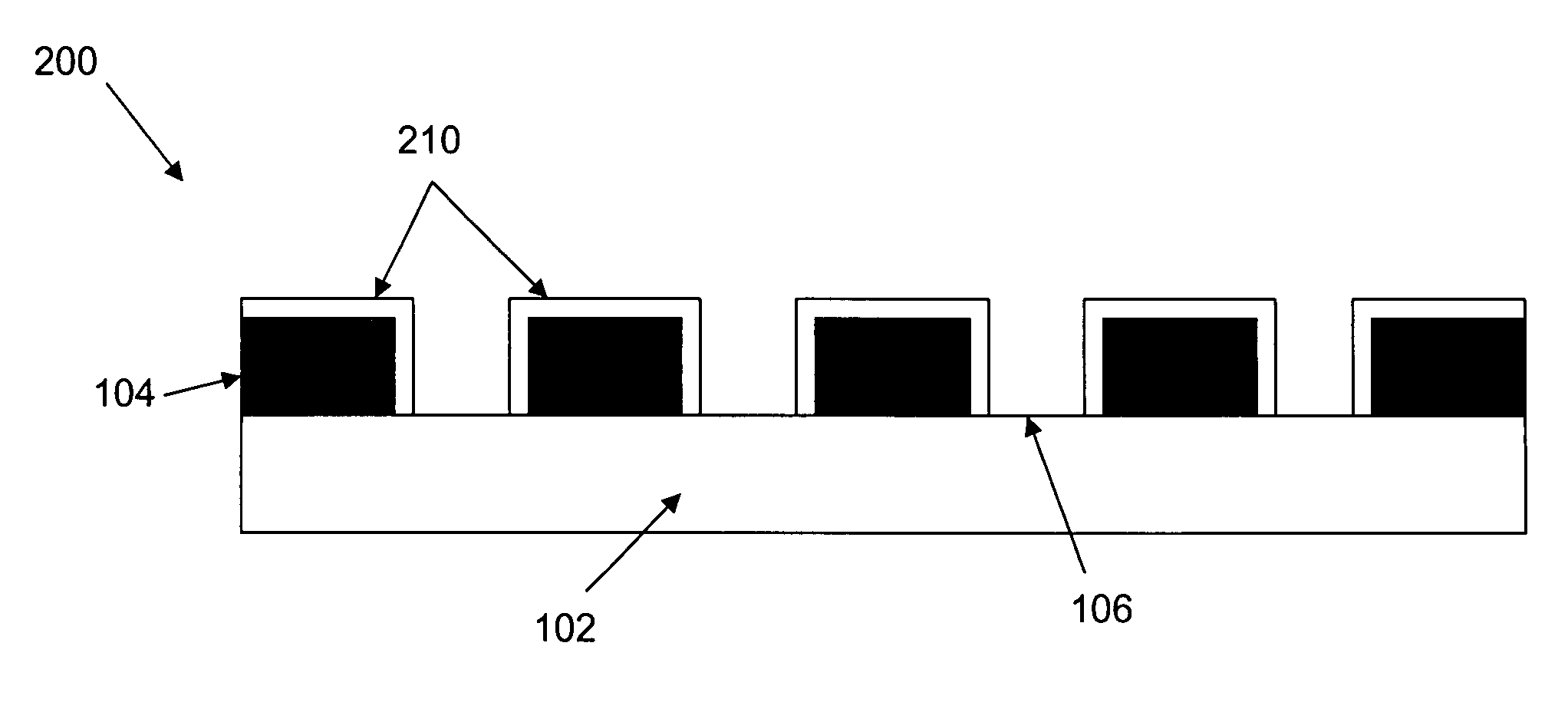

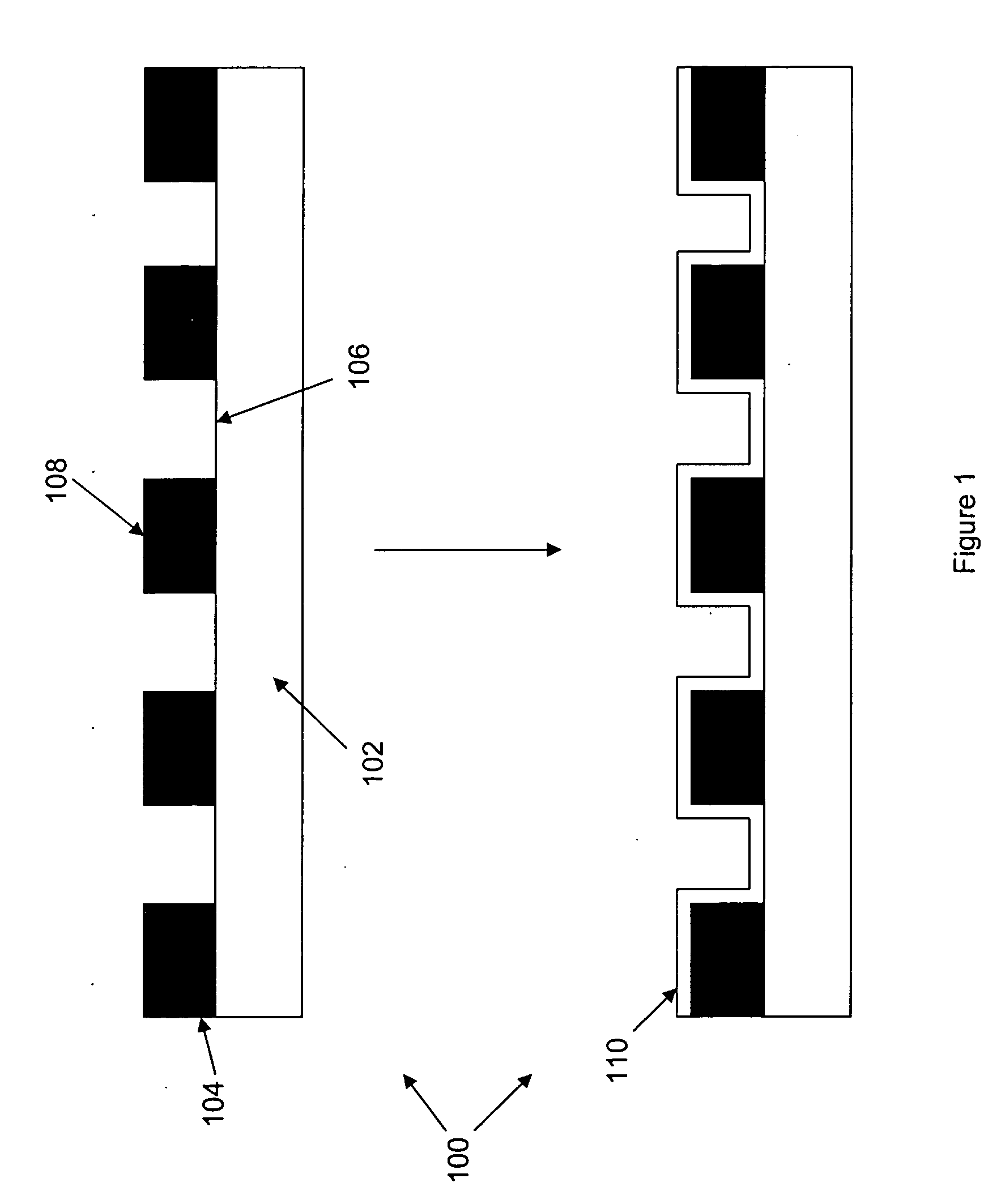

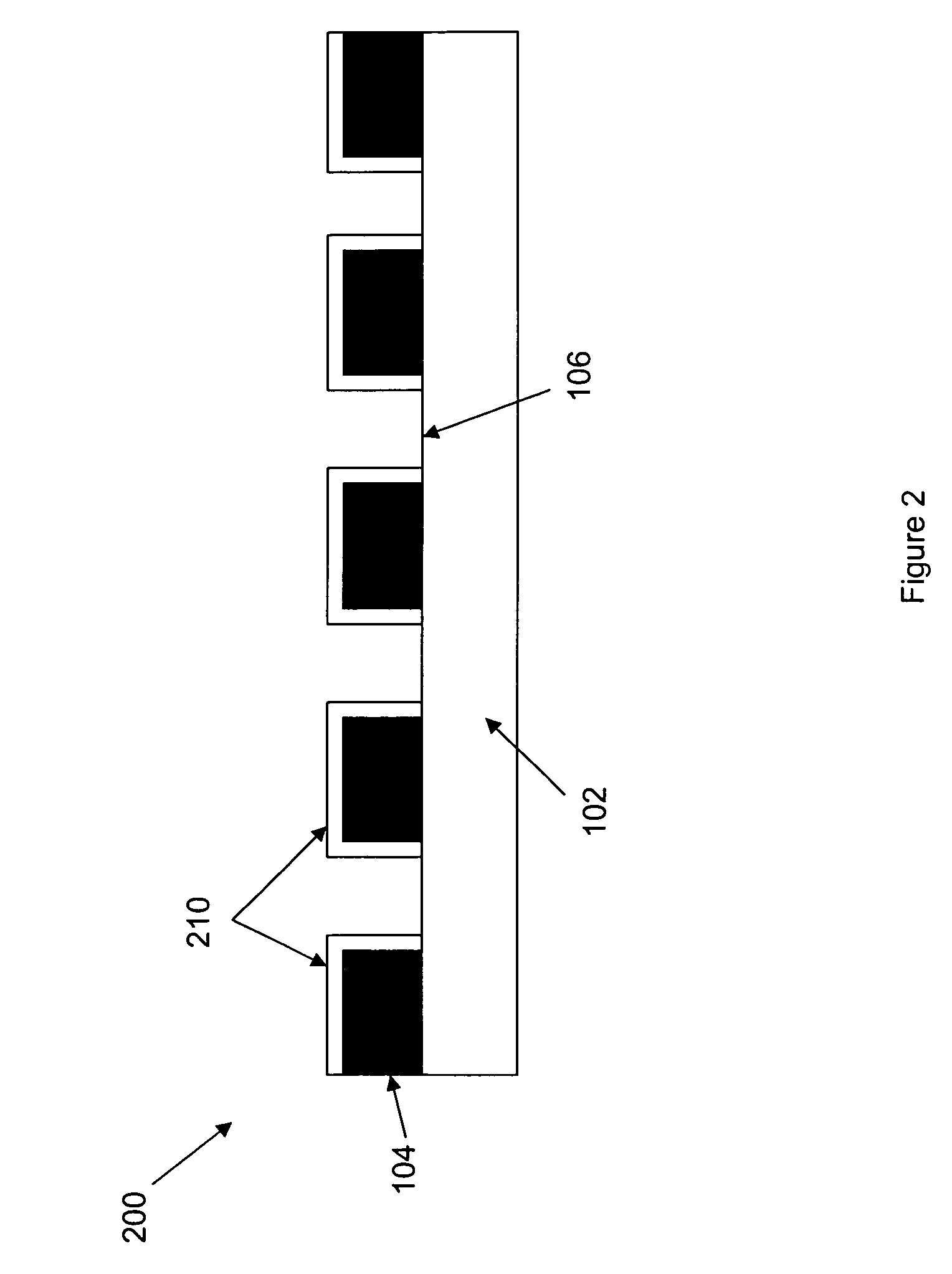

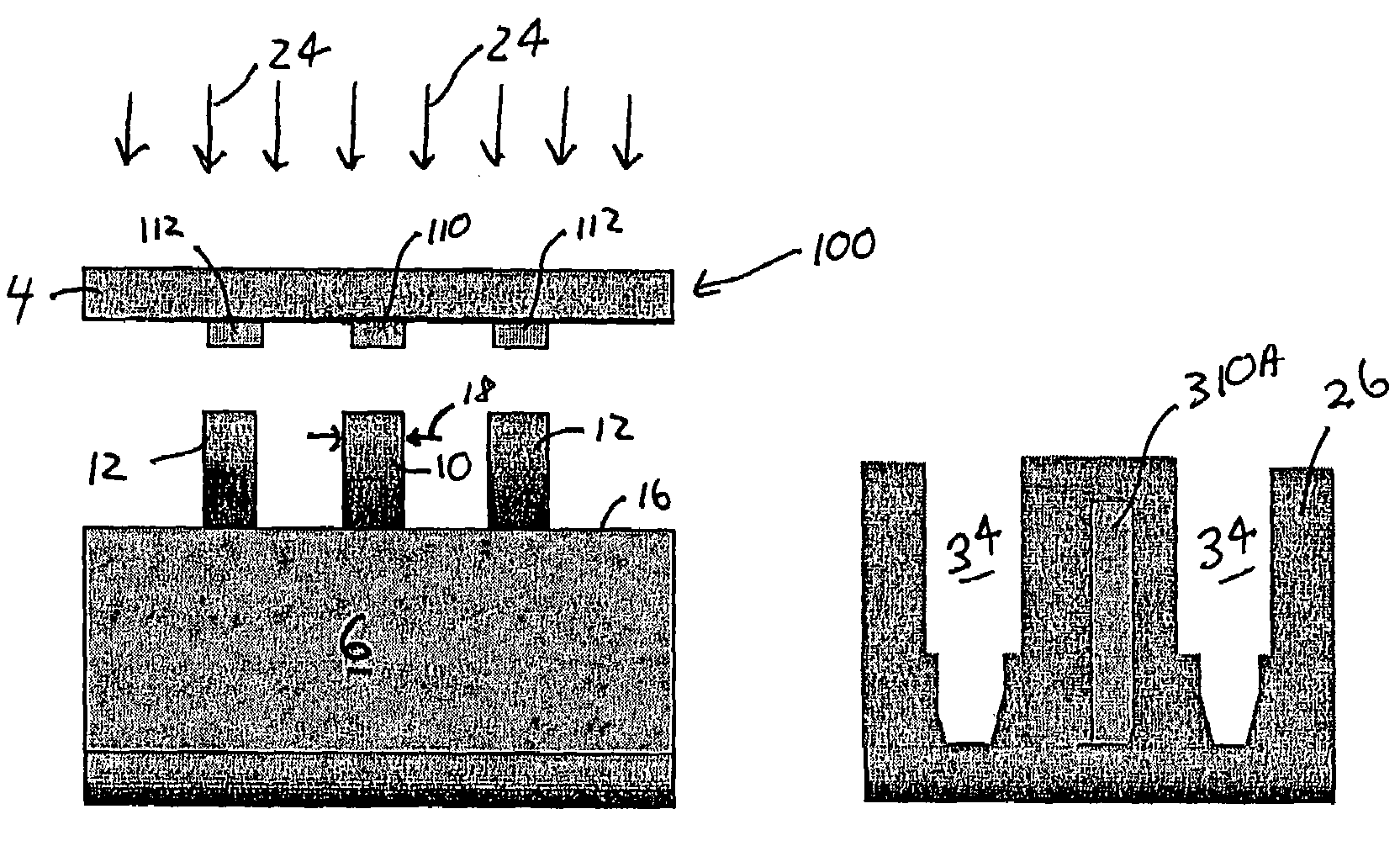

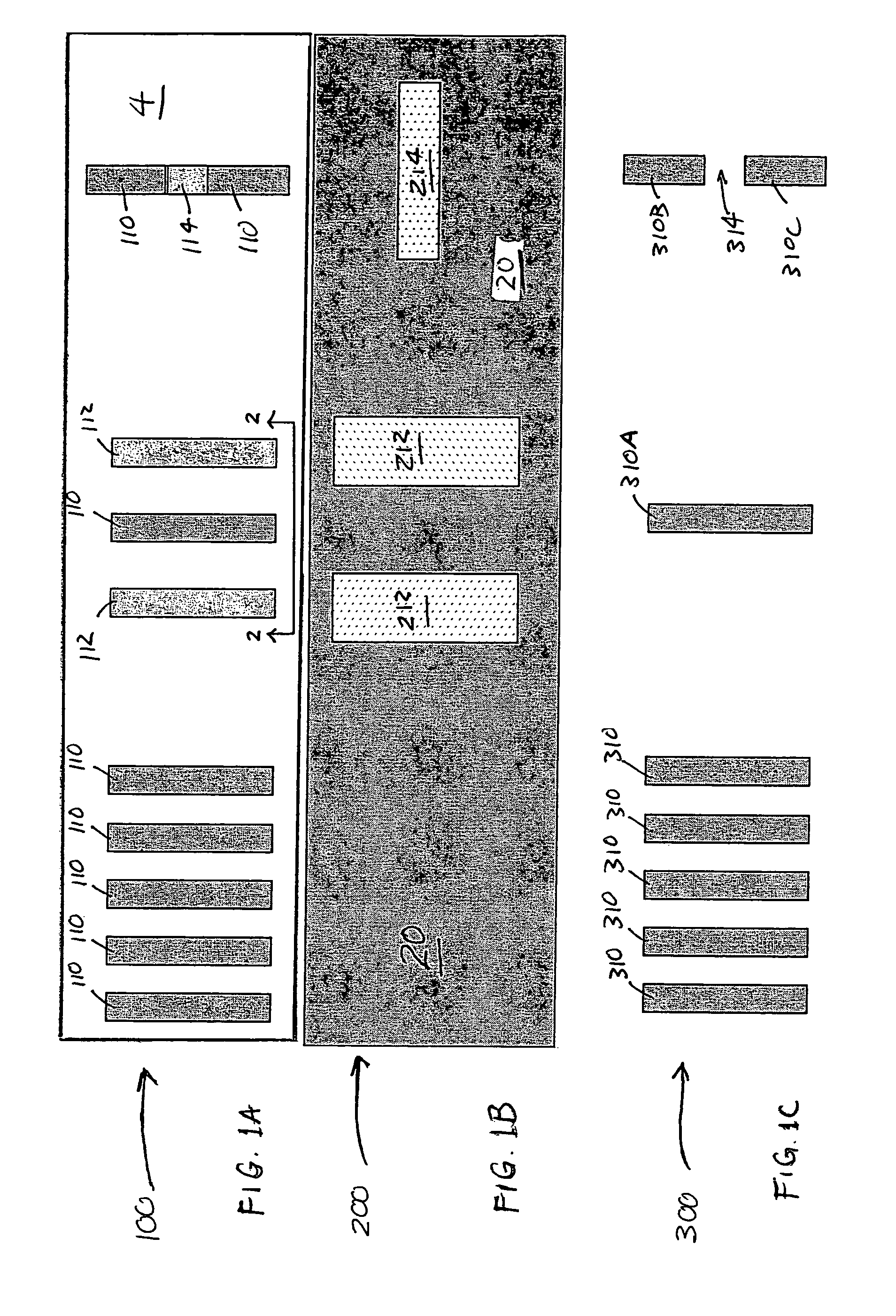

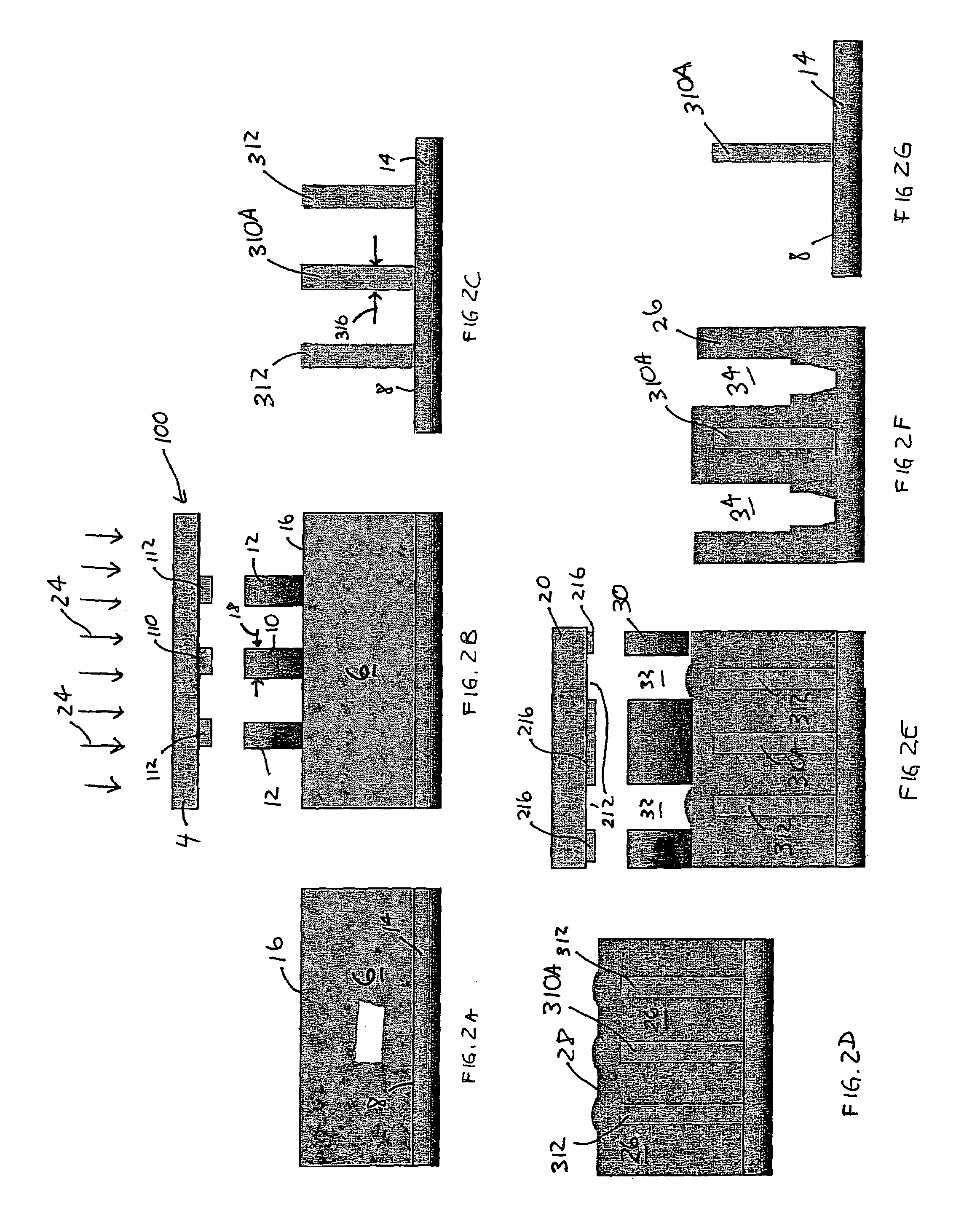

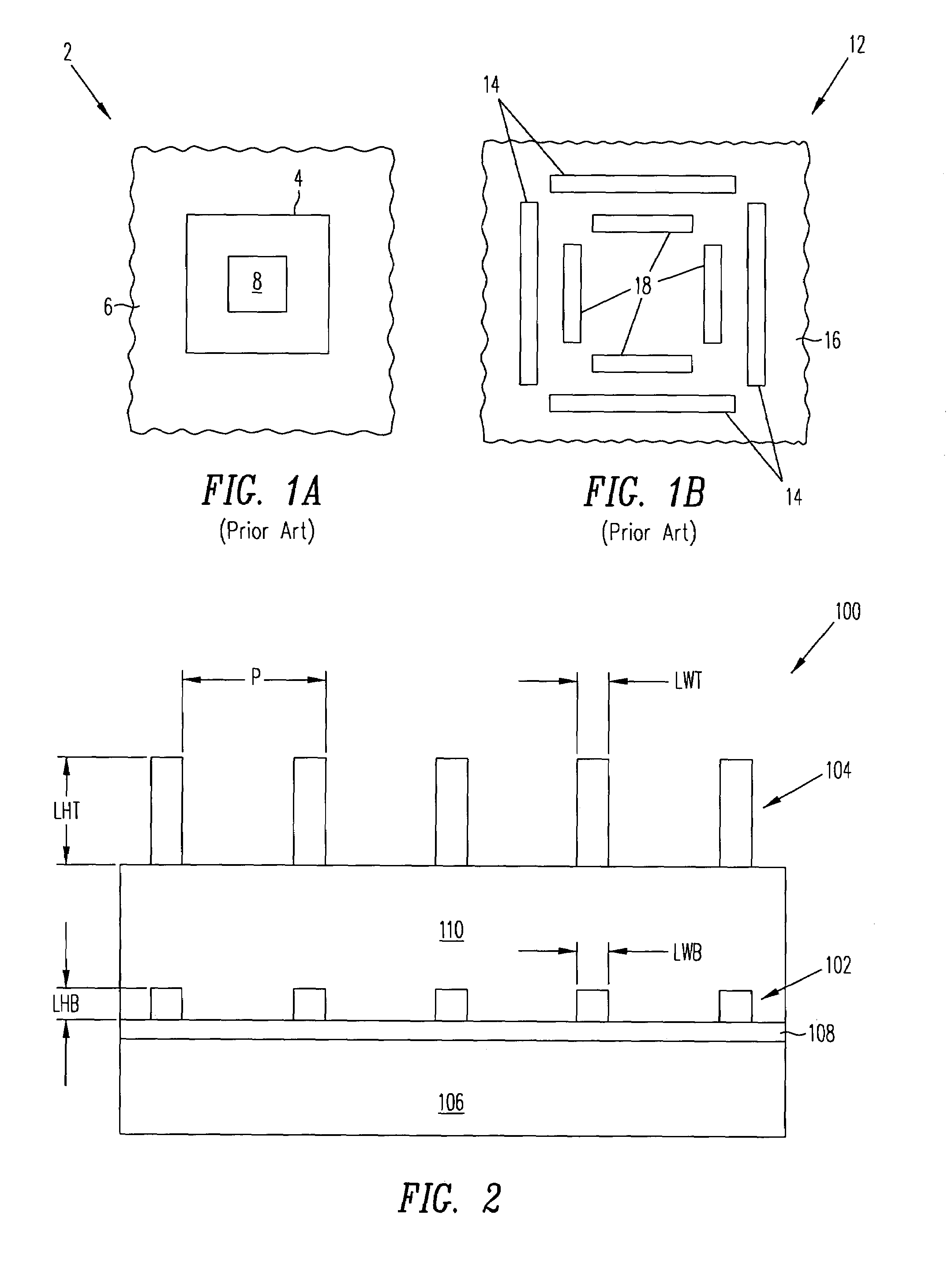

Method utilizing compensation features in semiconductor processing

InactiveUS7202148B2Increased process windowReduce depthRadiation applicationsSemiconductor/solid-state device manufacturingEngineeringFlare

A photolithography and etch process sequence includes a photomask having a pattern with compensation features that alleviate patterning variations due to the proximity effect and depth of focus concerns during photolithography. The compensation features may be disposed near isolated or outermost lines of a device pattern. A photoresist pattern is formed to include the compensation features and the pattern etched to form a corresponding etched pattern including the compensation features. After etching, a protection material is formed over the layer and a trim mask is used to form a further photoresist pattern over the protection material. A subsequent etching pattern etches the protection material and removes the compensation features and results in the device lines being formed unaffected by proximity effects. Flare dummies may additionally be added to the mask pattern to increase pattern density and assist in endpoint detection. Flare dummies, like the compensation features, are subsequently removed by a photolithography and etching process sequence.

Owner:TAIWAN SEMICON MFG CO LTD

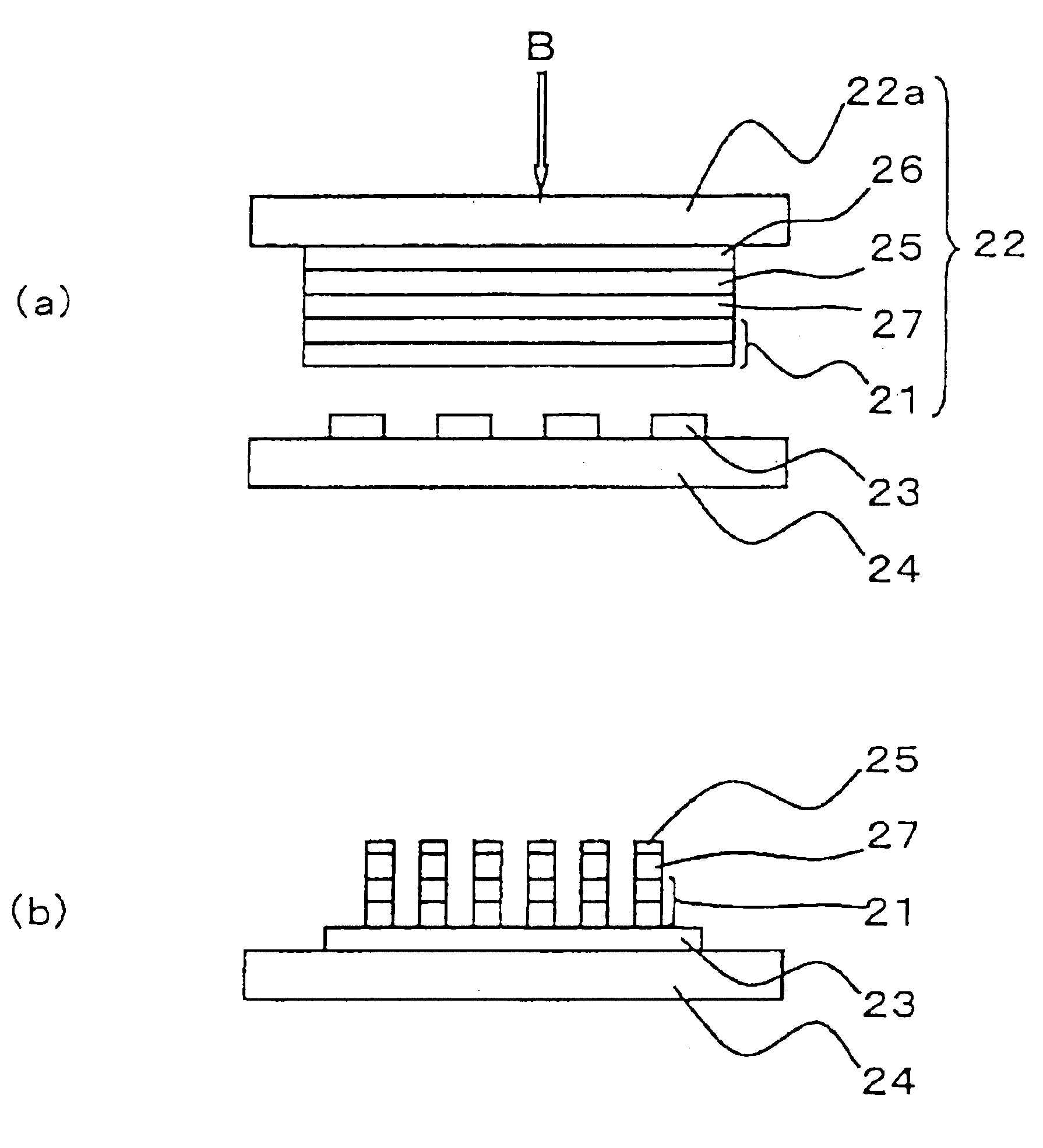

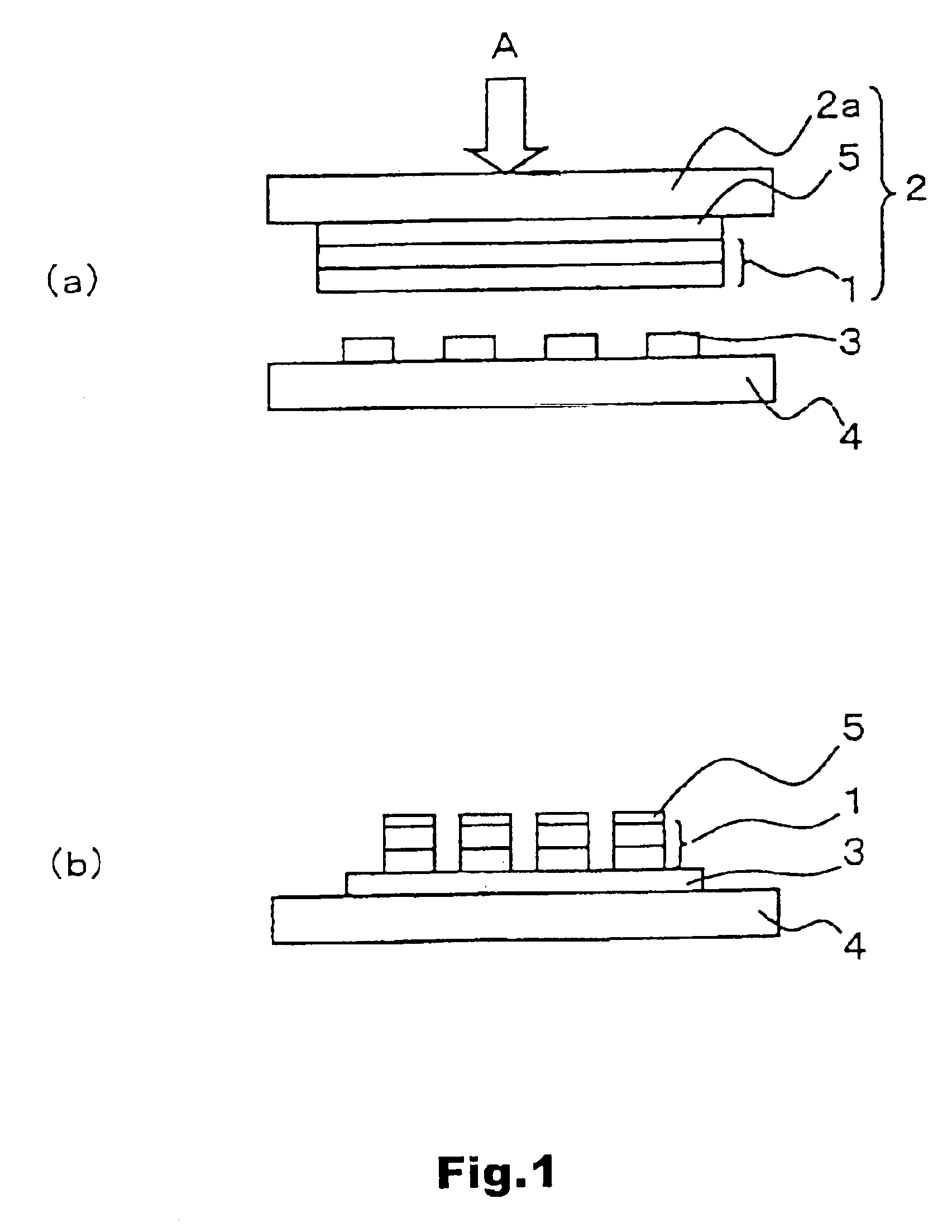

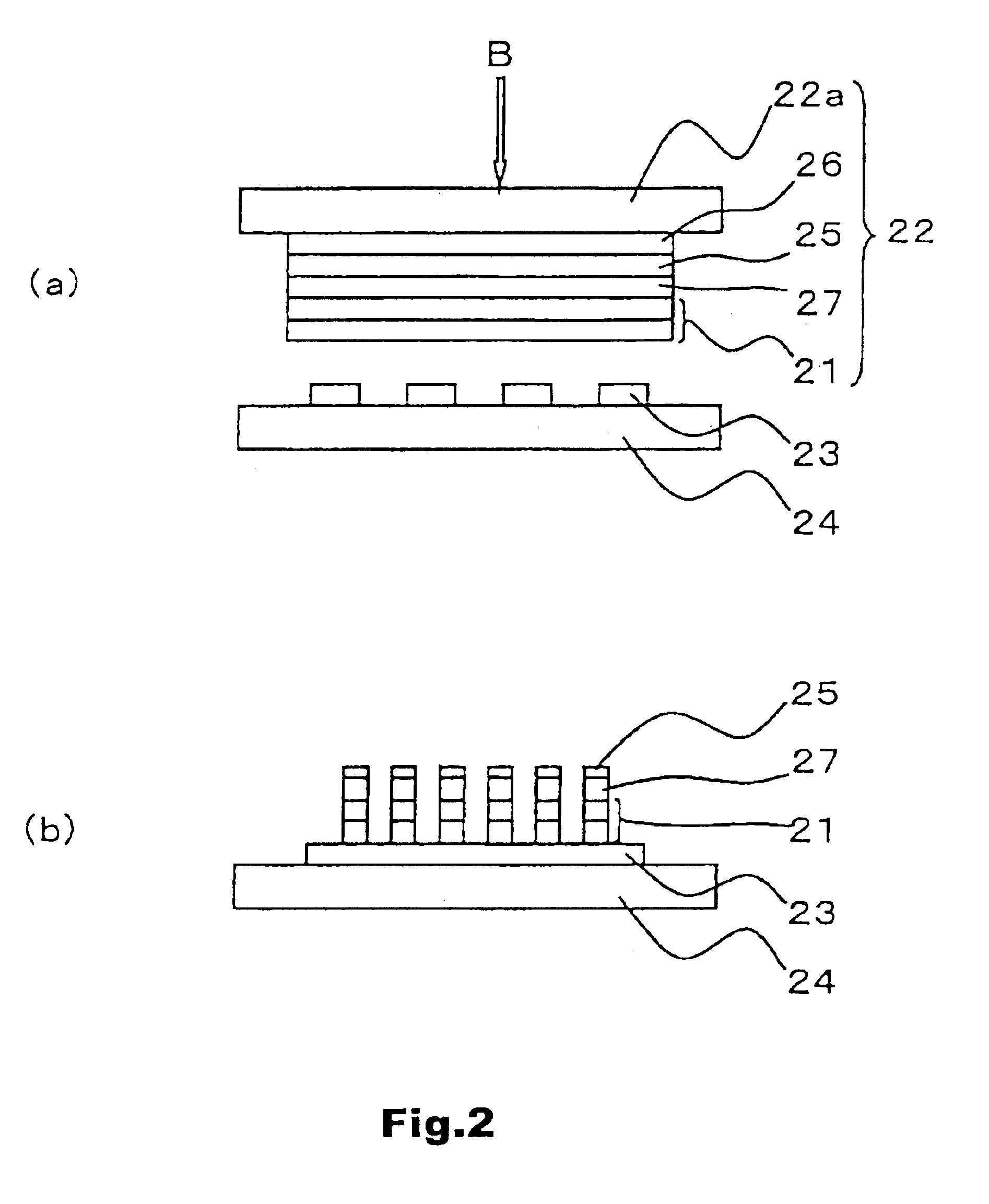

Alignment methods for imprint lithography

InactiveUS6916584B2Enhance lithography processLow viscosity liquidNanoinformaticsSemiconductor/solid-state device manufacturingEngineeringRotational alignment

Described are methods for patterning a substrate by imprint lithography. Imprint lithography is a process in which a liquid is dispensed onto a substrate. A template is brought into contact with the liquid and the liquid is cured. The cured liquid includes an imprint of any patterns formed in the template. Alignment of the template with the substrate is performed prior to curing the liquid. Alignment of the template with the substrate includes rotational alignment of the template with respect to the substrate.

Owner:CANON KK

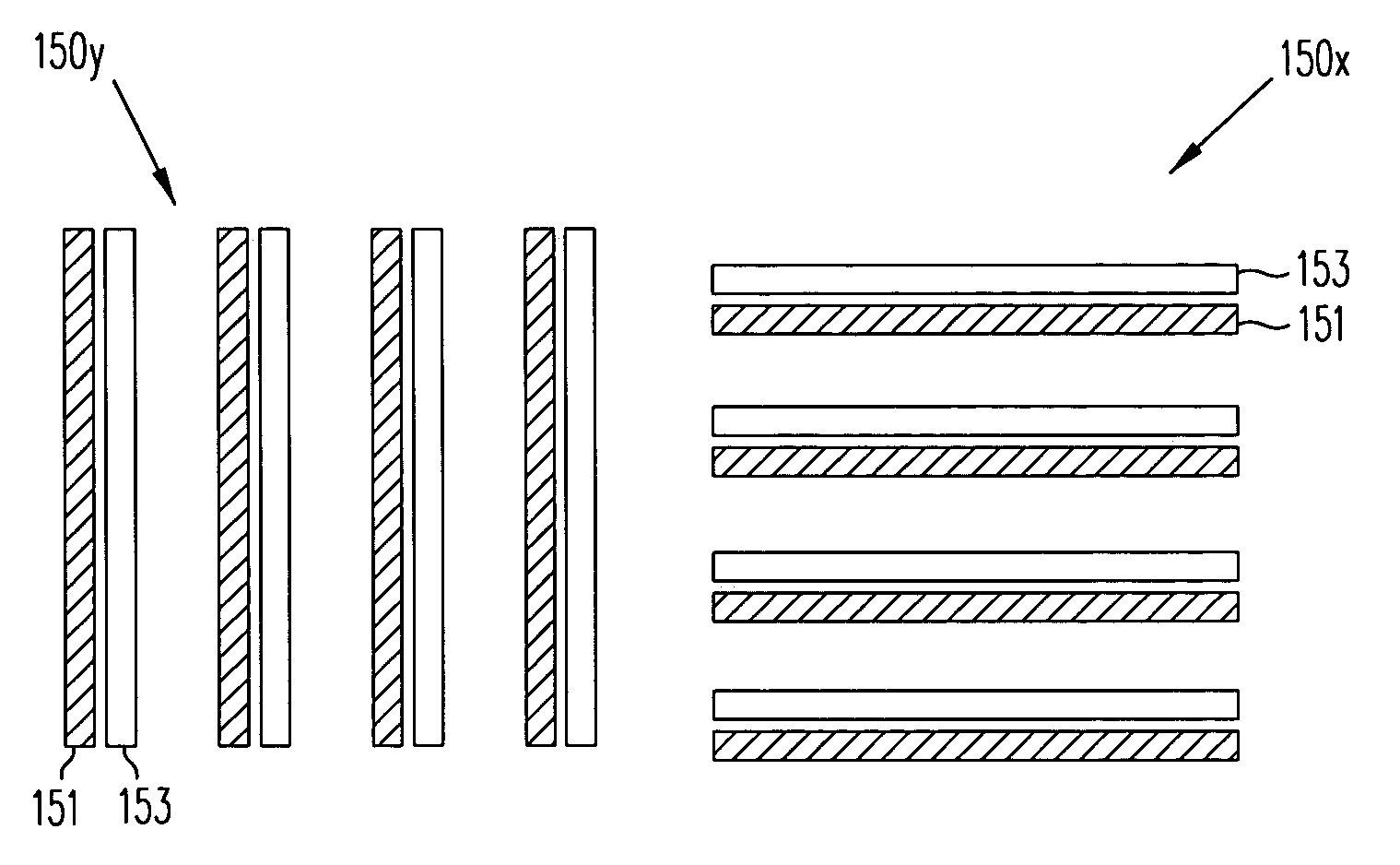

Spectroscopically measured overlay target

InactiveUS7061615B1Adequate fitEasy to measureSemiconductor/solid-state device detailsSolid-state devicesImage resolutionLine width

An overlay target for spectroscopic measurement includes at least two diffraction gratings, one grating overlying the other. The diffraction gratings may include an asymmetry relative to each other in order to improve resolution of the presence as well as the direction of any mis-registration. For example, the asymmetry between the two diffraction gratings may be a phase offset, a difference in pitch, line width, etc. The overlay target may be spectroscopically measuring, for example, using an optical model and a best fit analysis. Moreover, the overlay target may be optimized by modeling the overlay target and adjusting the variable parameters and calculating the sensitivity of the overlay target to changes in variable parameters.

Owner:ONTO INNOVATION INC

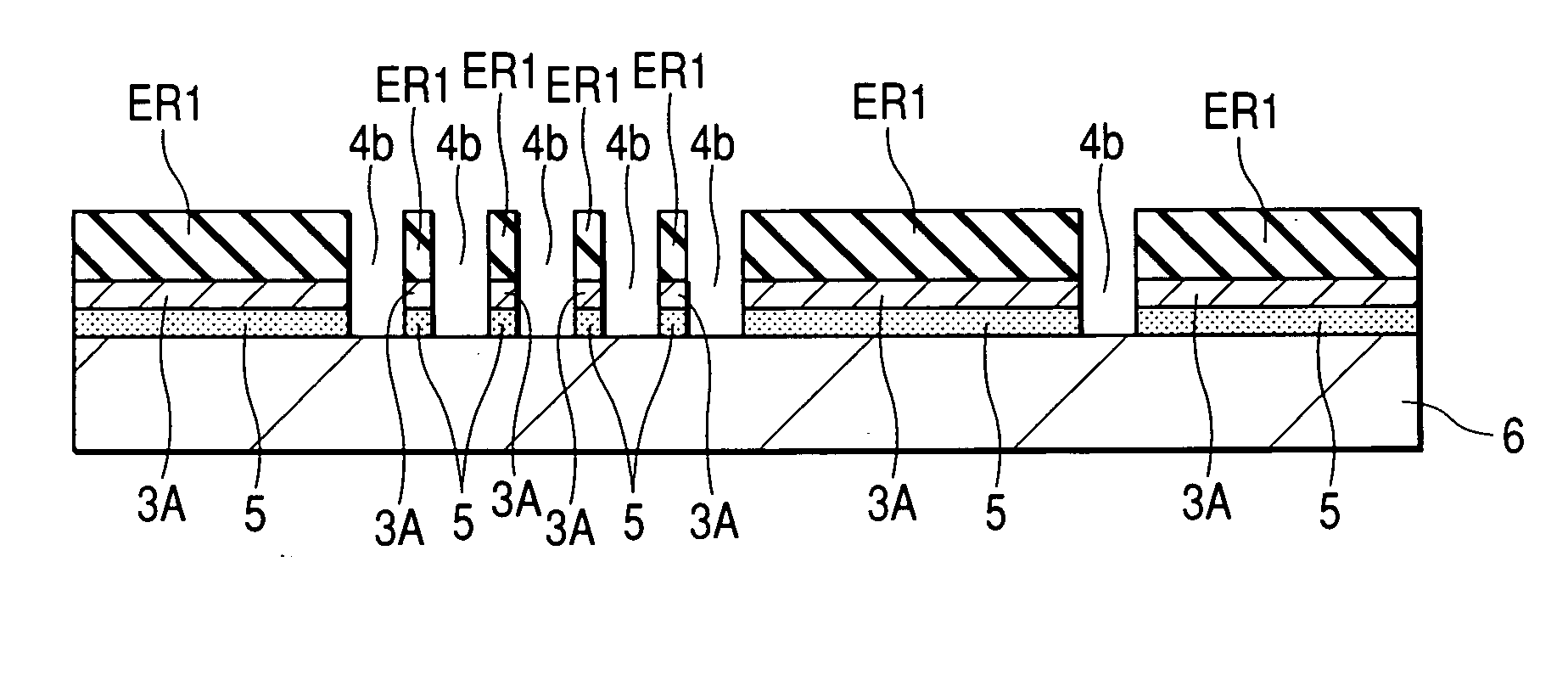

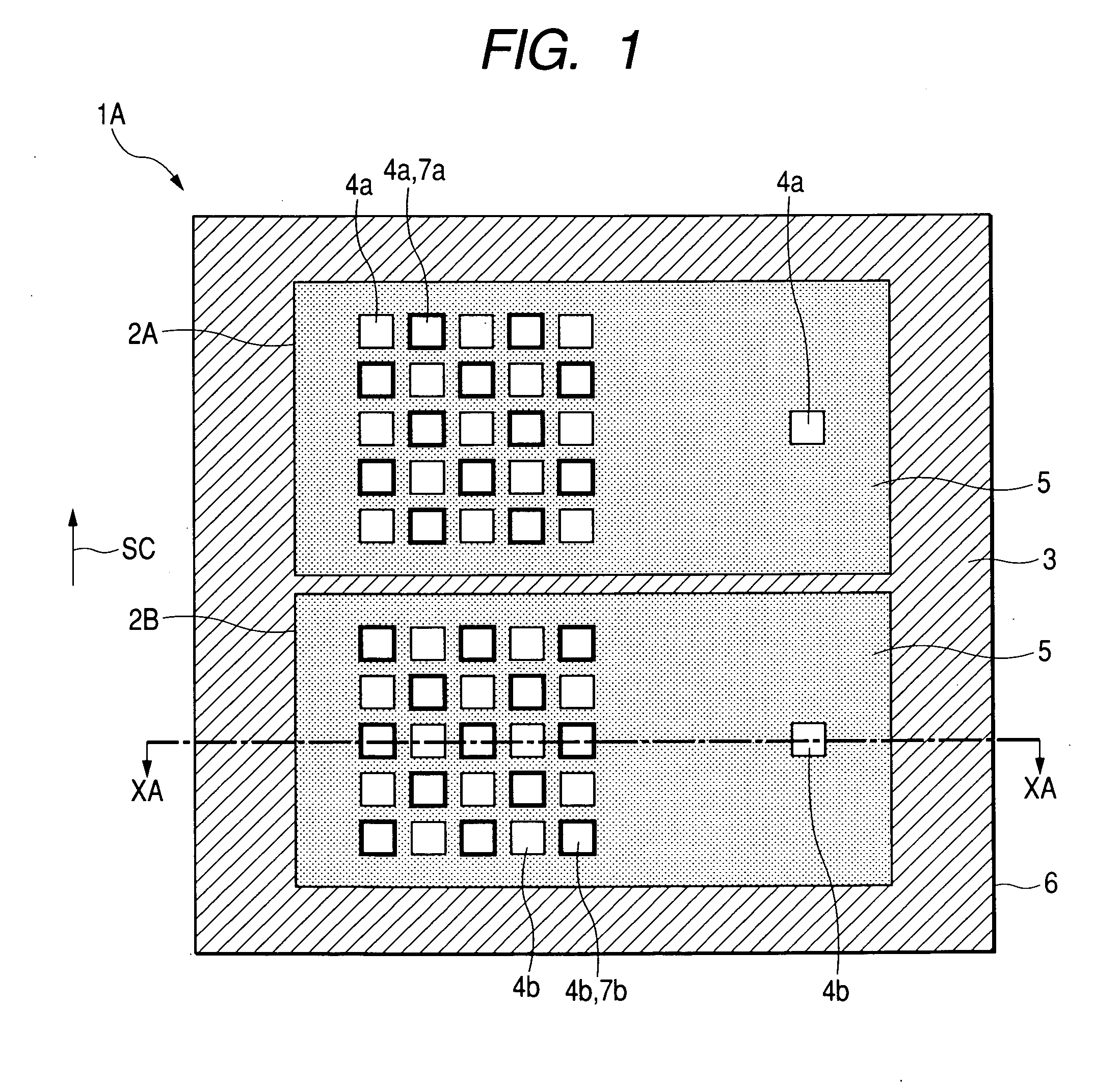

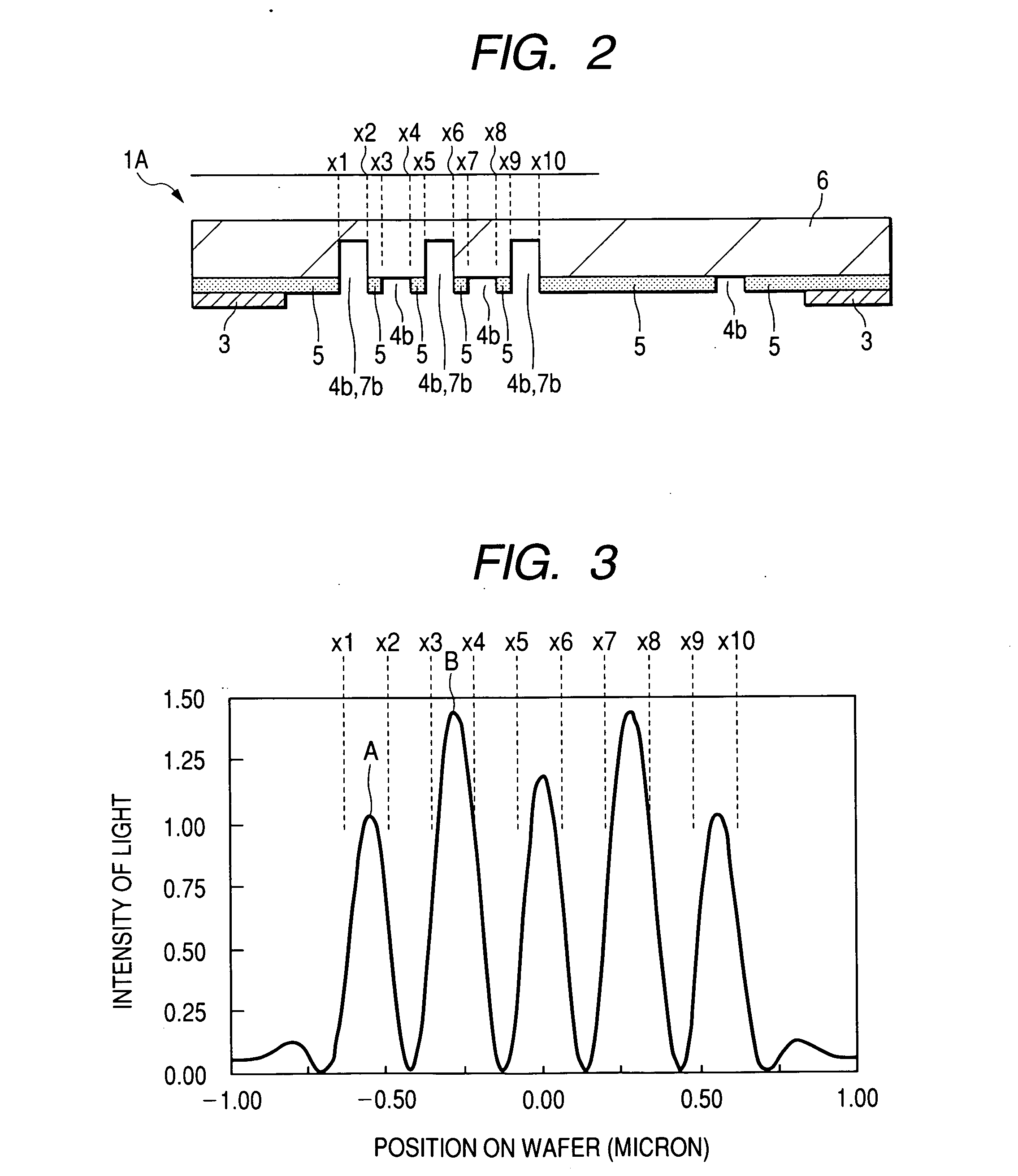

Manufacturing method of semiconductor integrated circuit device

InactiveUS20050090120A1Reduce dataSemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusSemiconductorLight transmission

In a massed region of each of a plurality of transfer areas of a mask a plurality of light transmission patterns are formed by opening a half-tone film. A phase shifter is disposed in each of the light transmission patterns so that a 180° phase inversion occurs between the lights that transmit through adjacent light transmission patterns. In a sparse region of the plurality of transfer areas a solitary light transmission pattern is formed by opening the half-tone film. Both shape and size are the same among the light transmission patterns, which are disposed symmetrically in both the massed and sparse regions about the center between the transfer areas. The phase shifters in the massed regions are disposed so that the phase of each phase shifter in one of the transfer areas comes to be opposed to that of its counterpart in the other transfer area. In the exposure process, those transfer areas are overlaid one upon another in the same chip region.

Owner:HITACHI LTD

Transfer film and process for producing organic electroluminescent device using the same

InactiveUS6805979B2Decorative surface effectsCathode ray/electron stream lampsEngineeringOrganic electroluminescence

Owner:SHARP KK

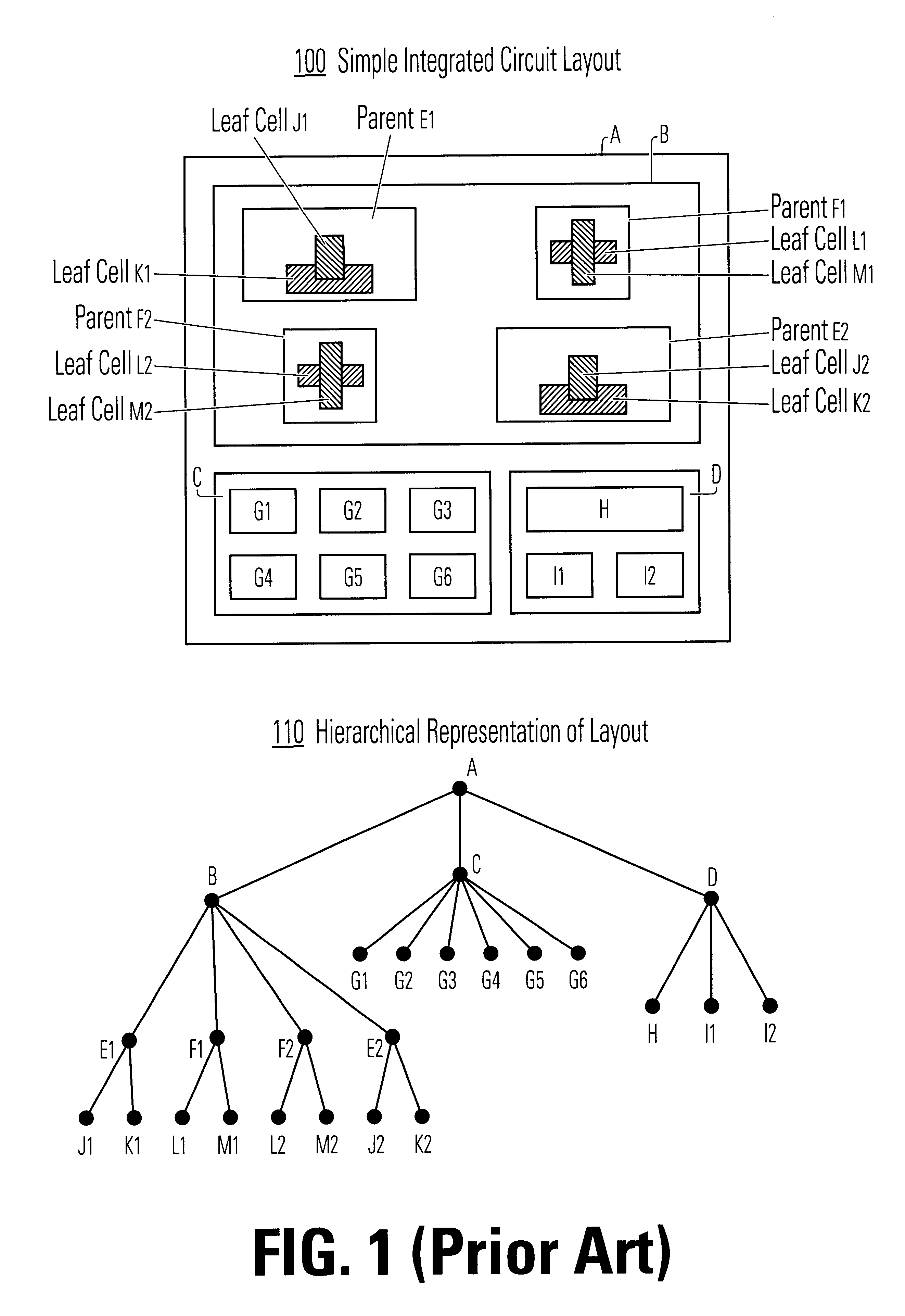

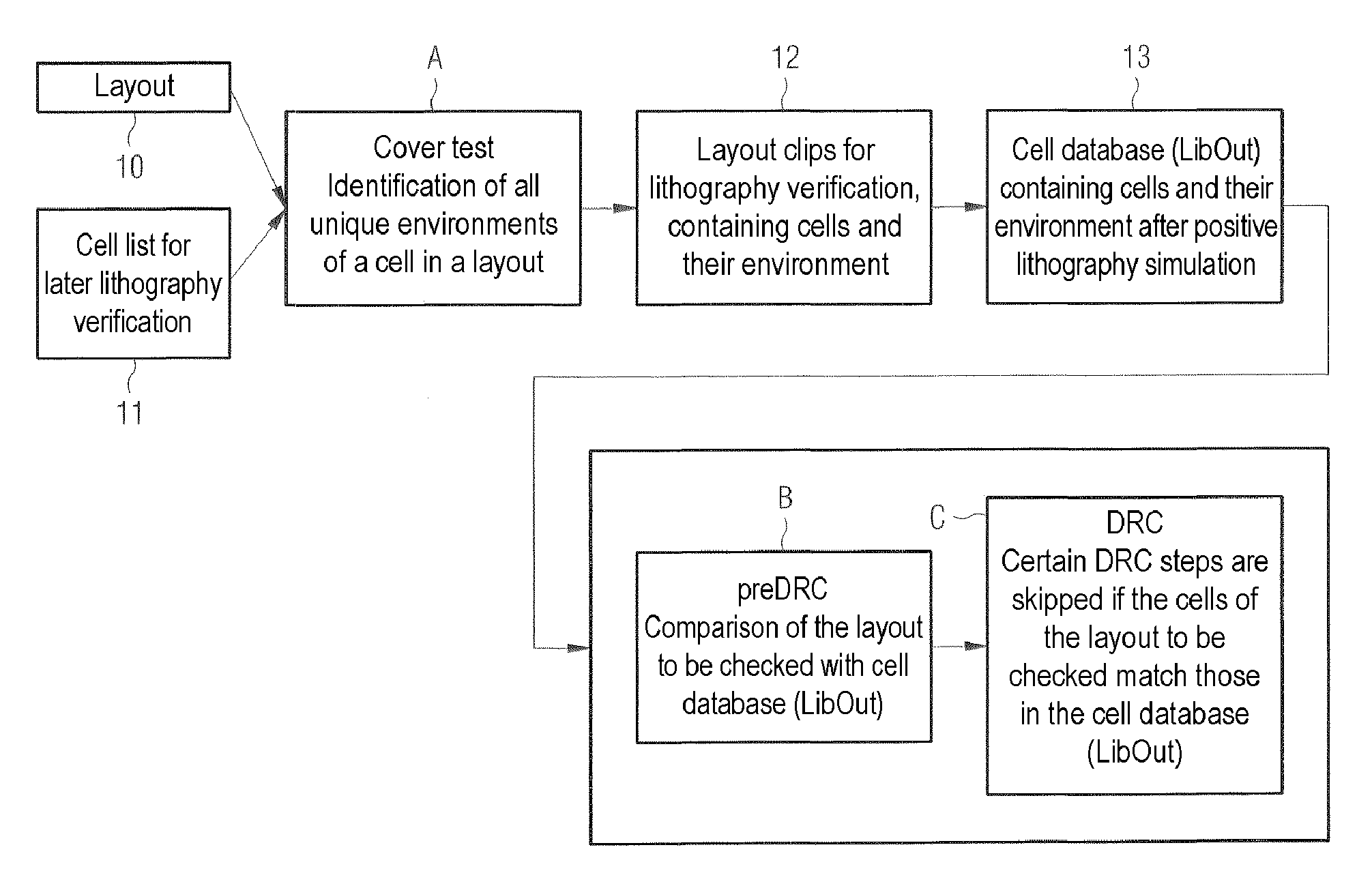

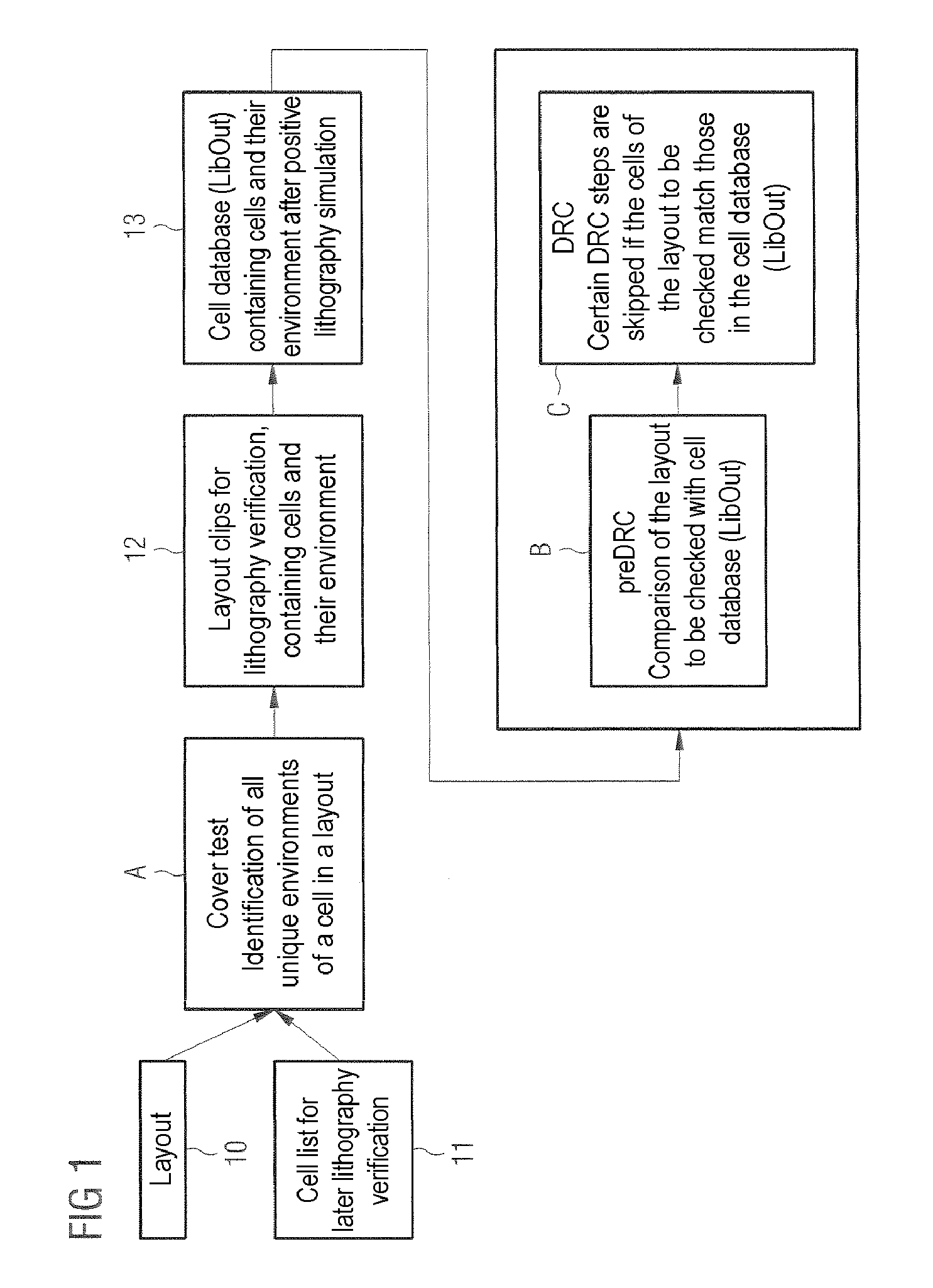

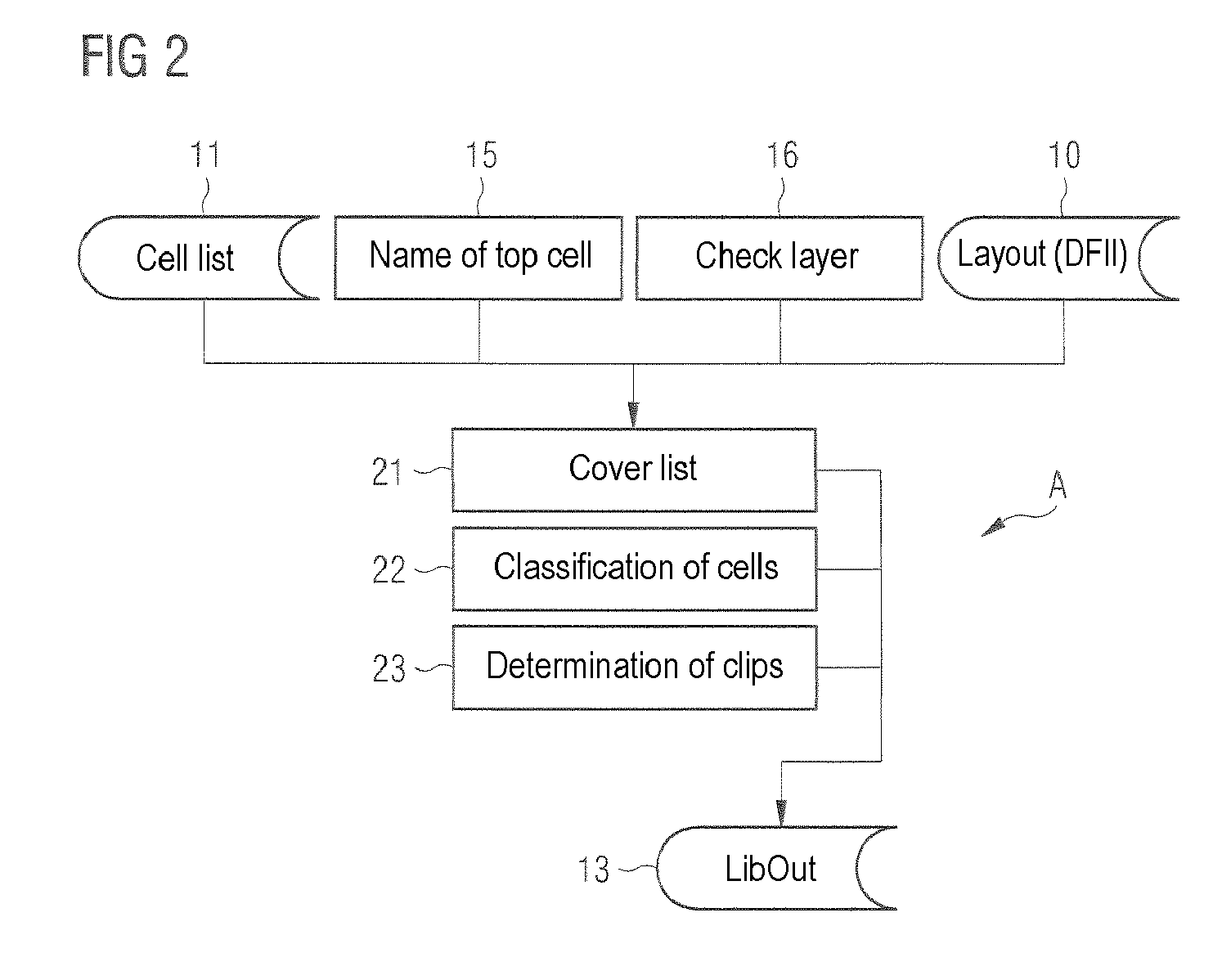

Method and device for classifying cells in a layout into a same environment and their use for checking the layout of an electronic circuit

InactiveUS7665051B2Originals for photomechanical treatmentComputer aided designComputer scienceSemiconductor components

A method and a device can be used for checking the layout of an electronic circuit of a semiconductor component. For example, the method includes an automatic classification of cells in at least one layout into a cell database, and an automatic layout checker comparing the cell database to a layout to be checked.

Owner:POLARIS INNOVATIONS LTD

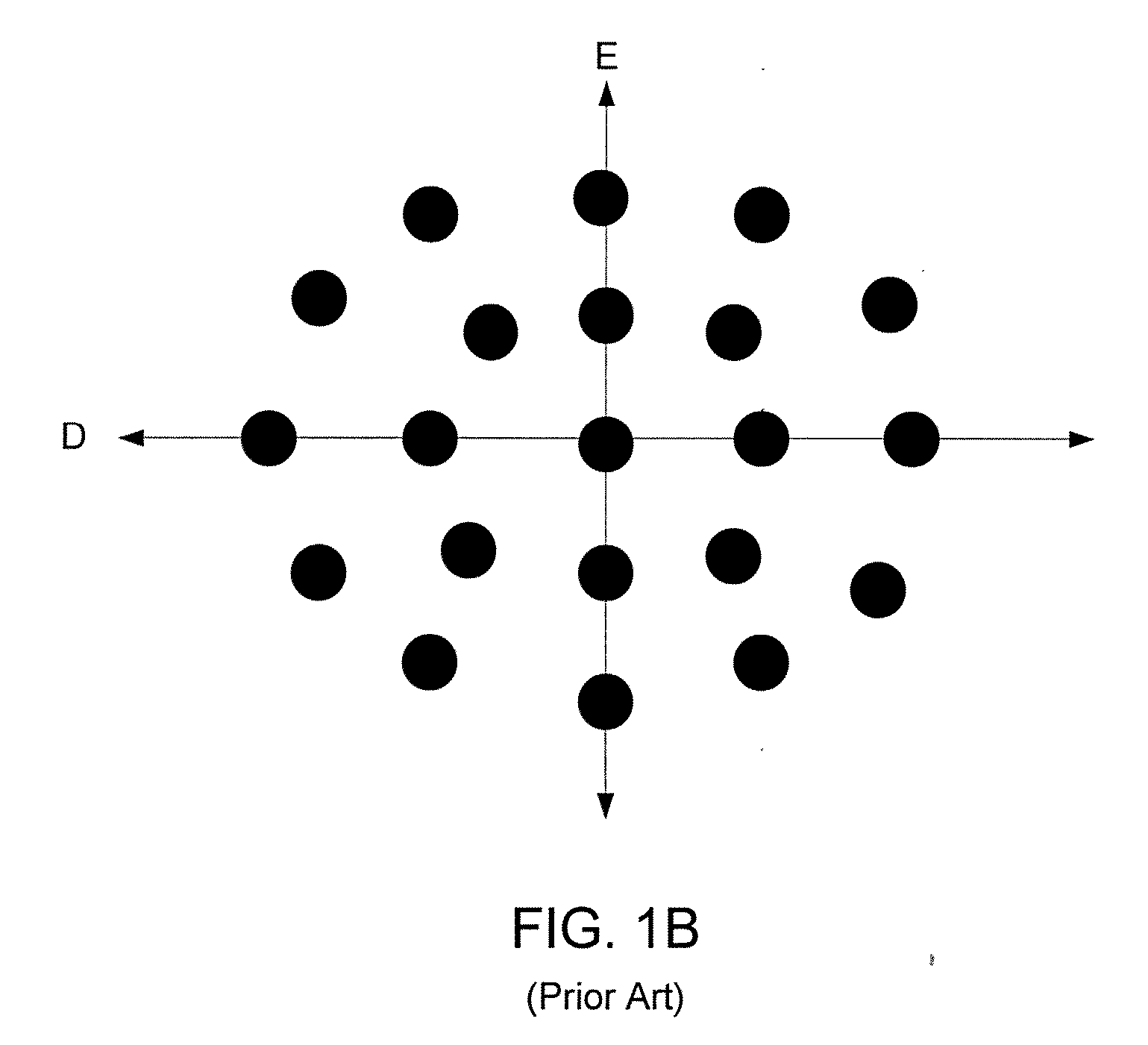

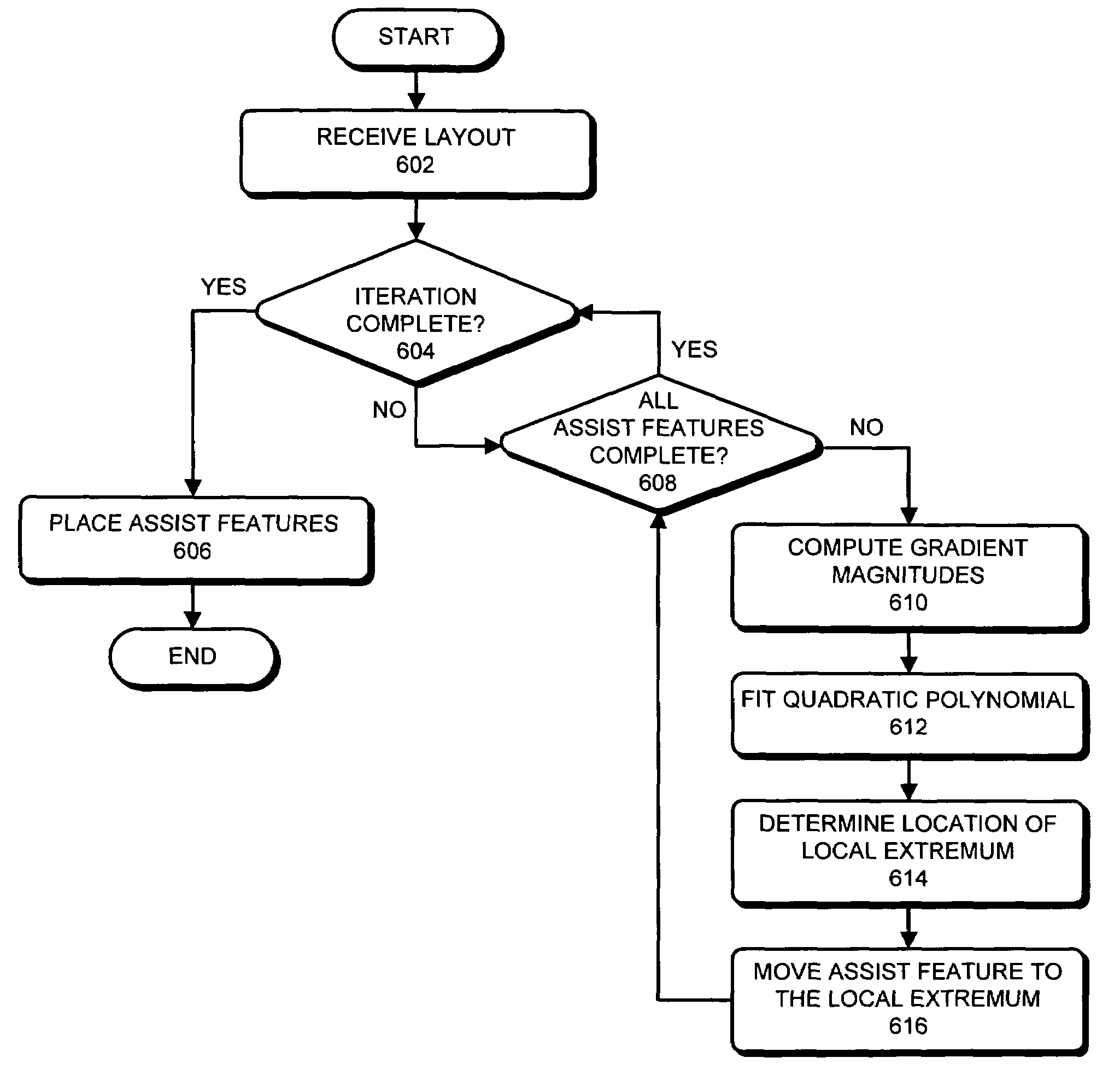

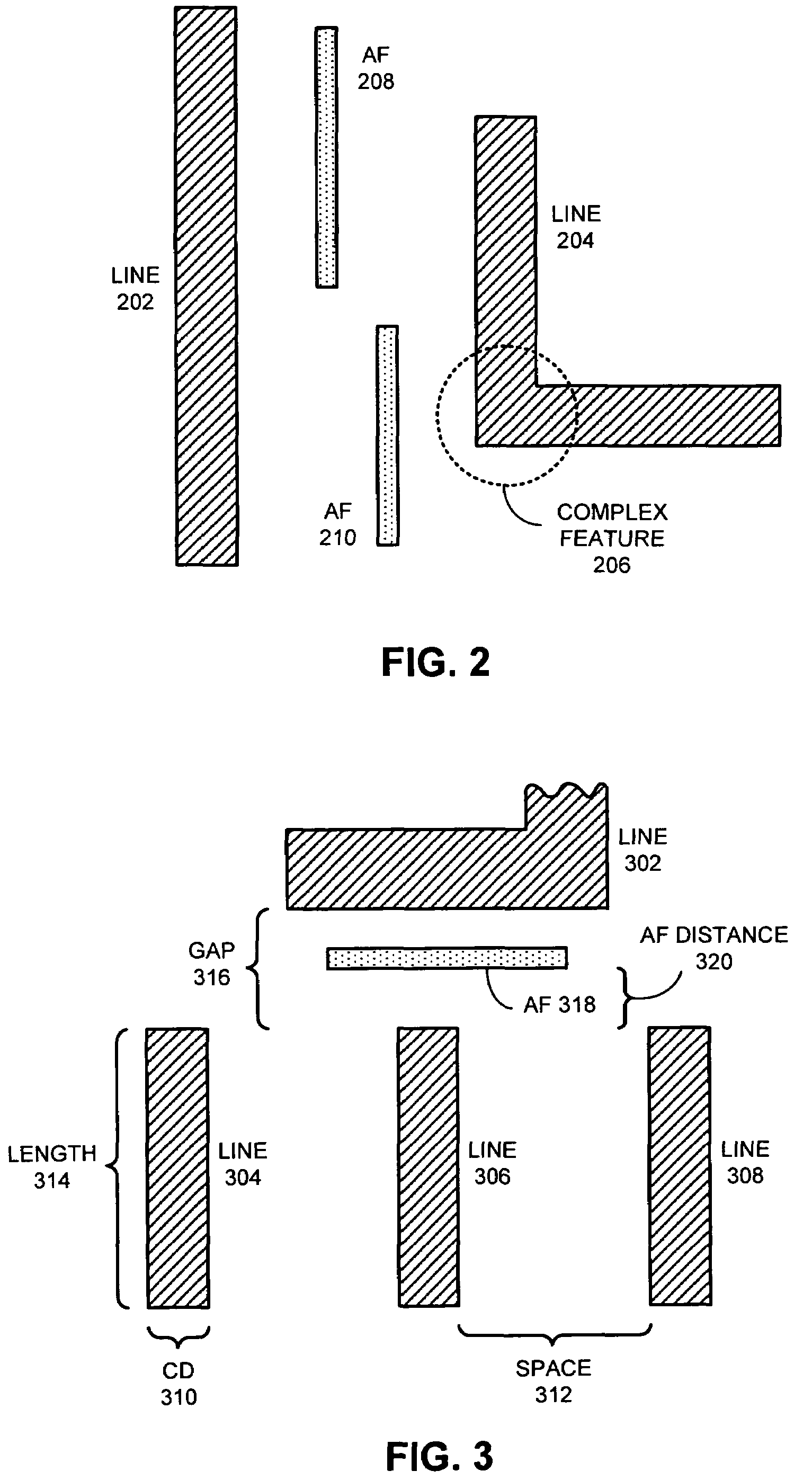

Method and apparatus for placing assist features by identifying locations of constructive and destructive interference

One embodiment of the present invention provides a system that determines a location in a layout to place an assist feature. During operation, the system receives a layout of an integrated circuit. Next, the system selects an evaluation point in the layout. The system then chooses a candidate location in the layout for placing an assist feature. Next, the system determines the final location in the layout to place an assist feature by, iteratively, (a) selecting perturbation locations for placing representative assist features in the proximity of the candidate location, (b) computing aerial-images using an image intensity model, the layout, and by placing representative assist features at the candidate location and the perturbation locations, (c) calculating image-gradient magnitudes at the evaluation point based on the aerial-images, and (d) updating the candidate location for the assist feature based on the image-gradient magnitudes.

Owner:SYNOPSYS INC