Patents

Literature

110results about How to "Lower barrier height" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

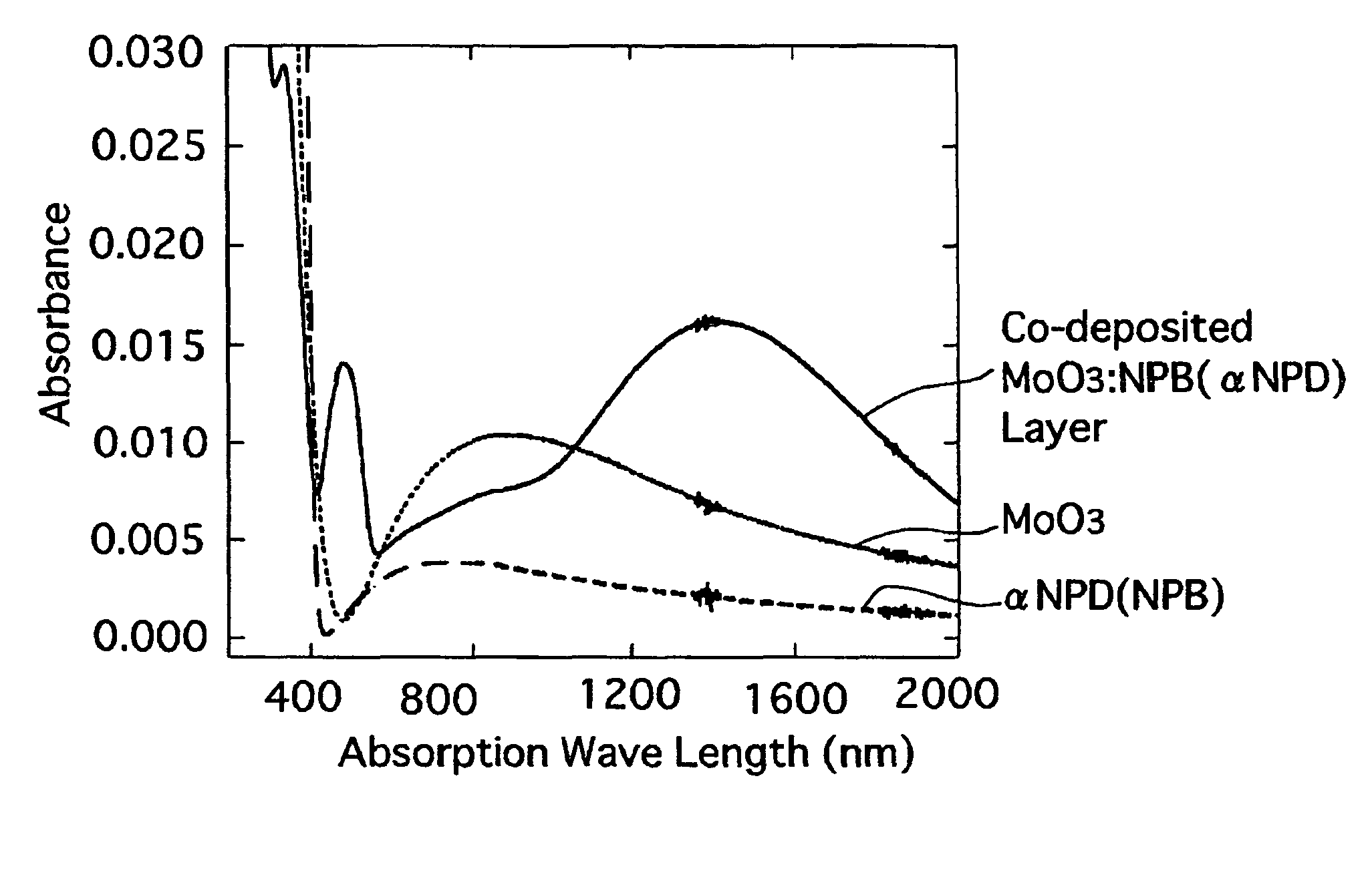

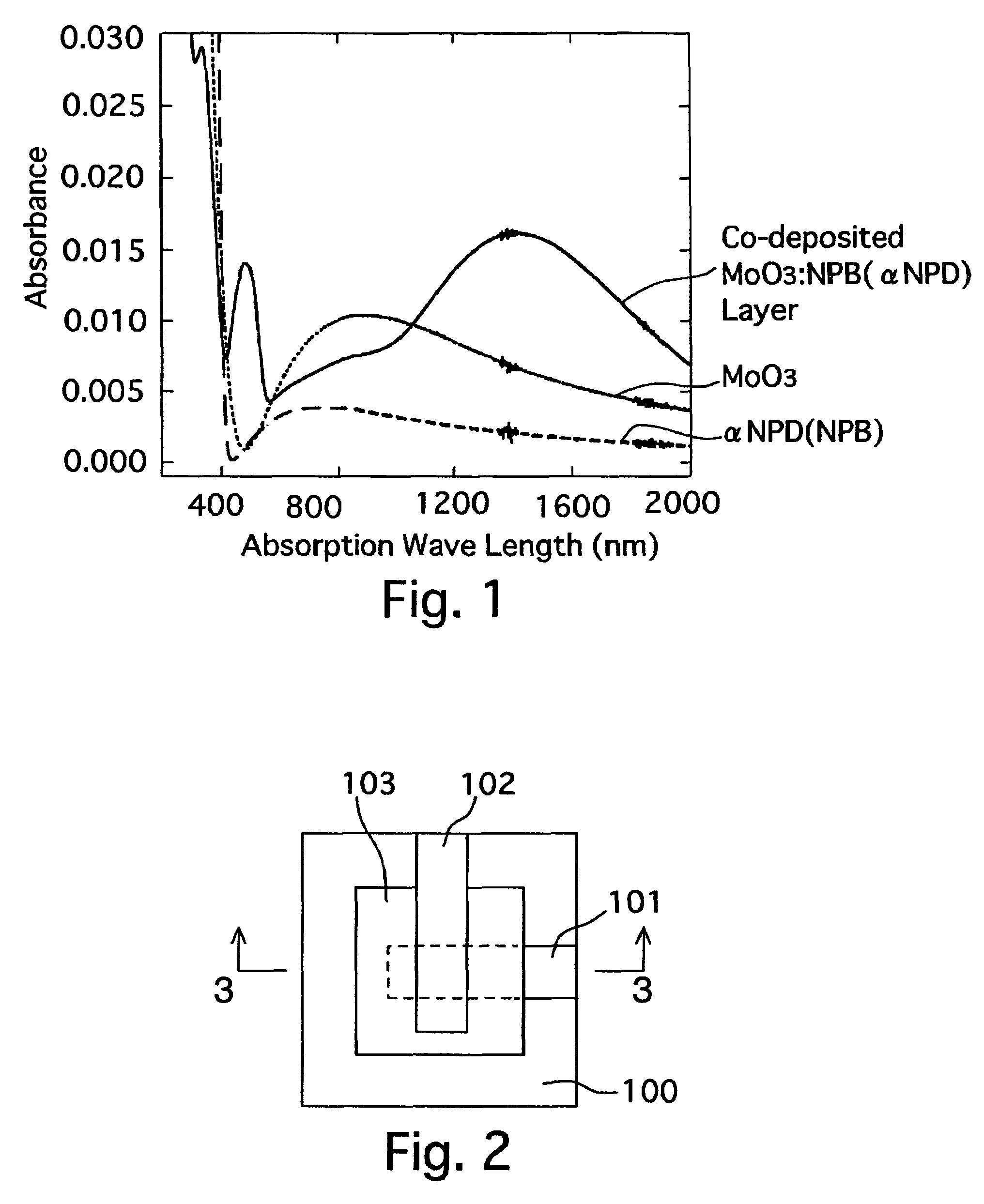

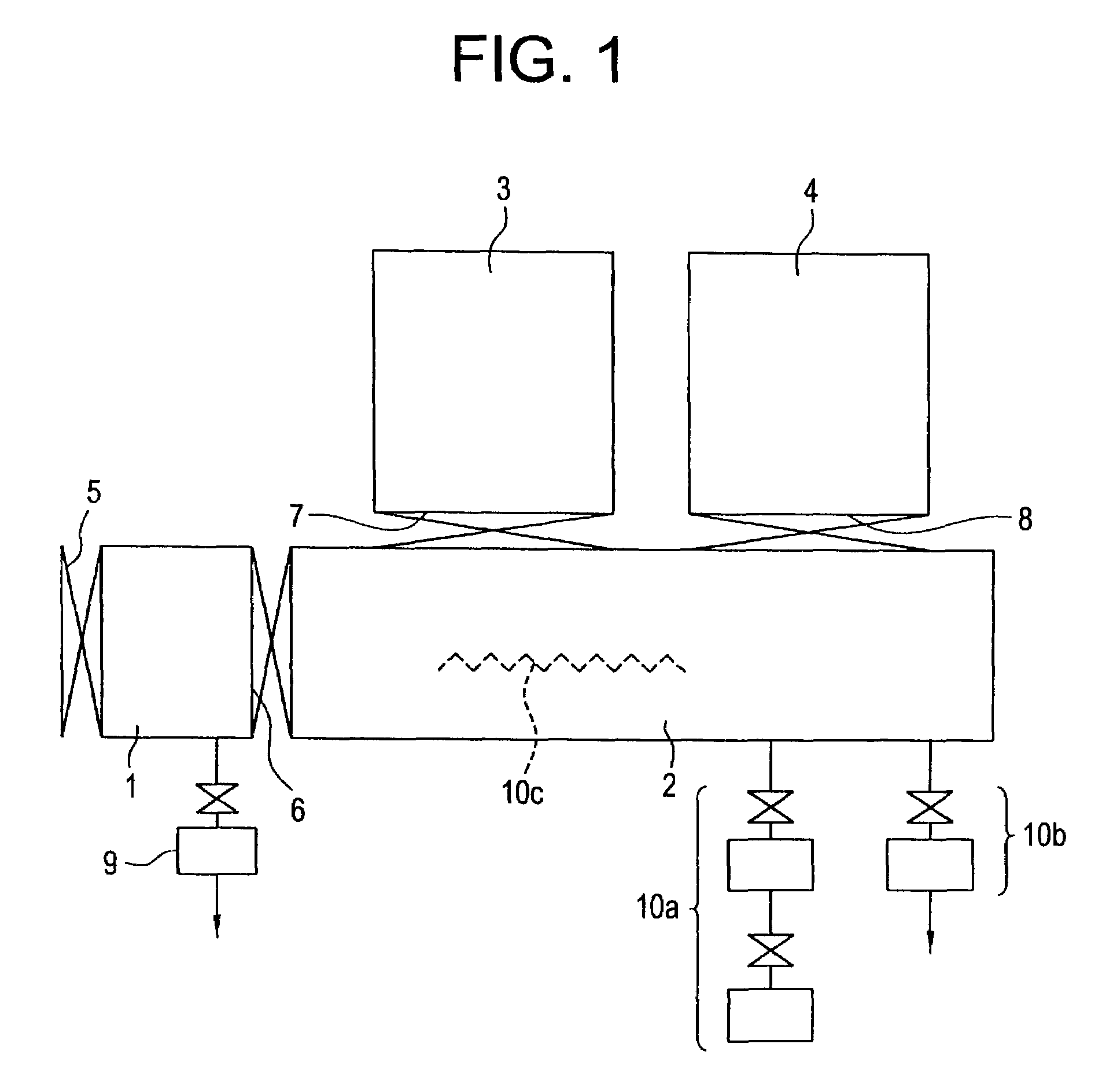

Organic devices, organic electroluminescent devices and organic solar cells

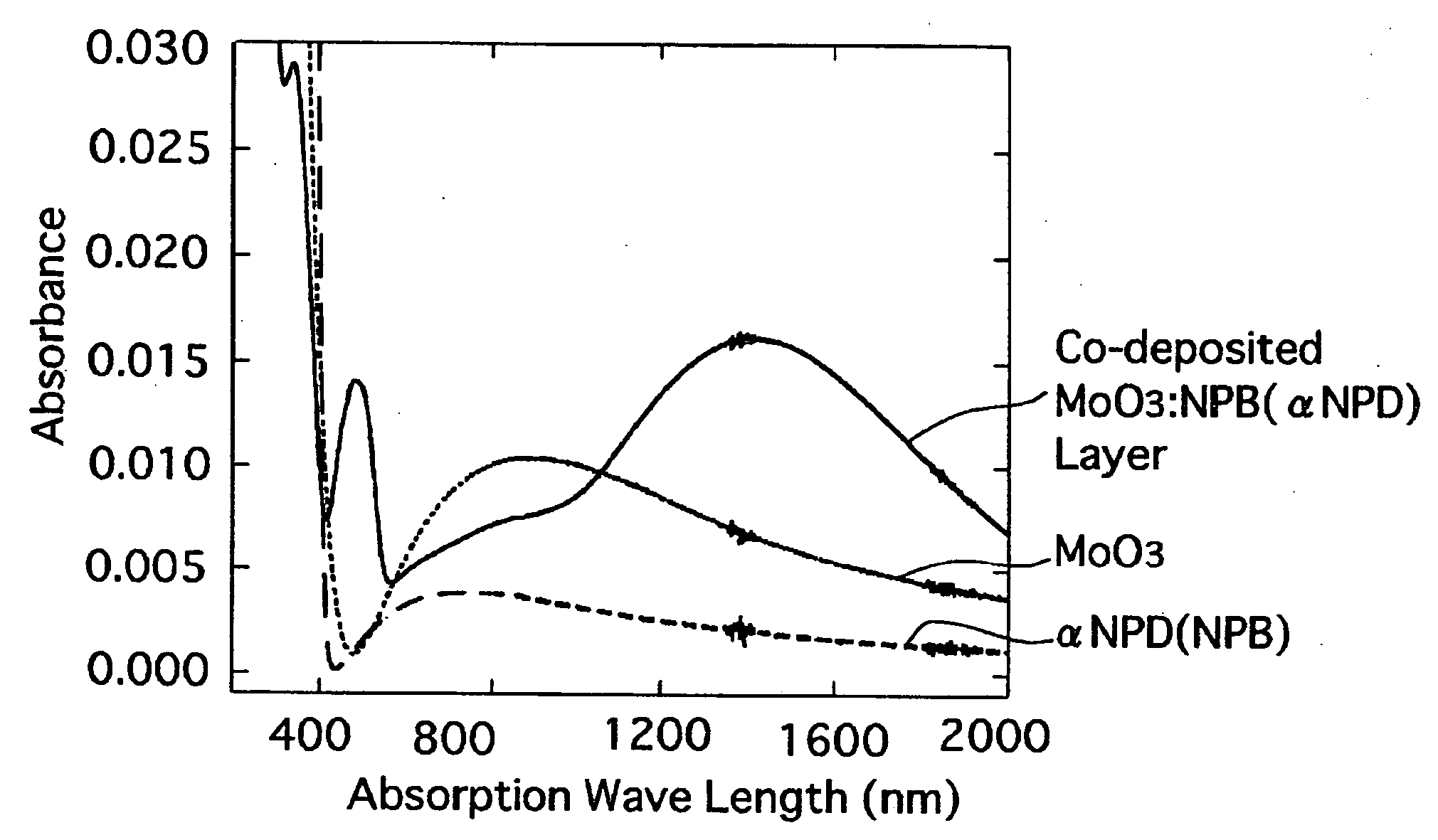

ActiveUS20060008740A1Reduce harmLower barrier heightElectric discharge tubesElectroluminescent light sourcesOrganic solar cellSimple Organic Compounds

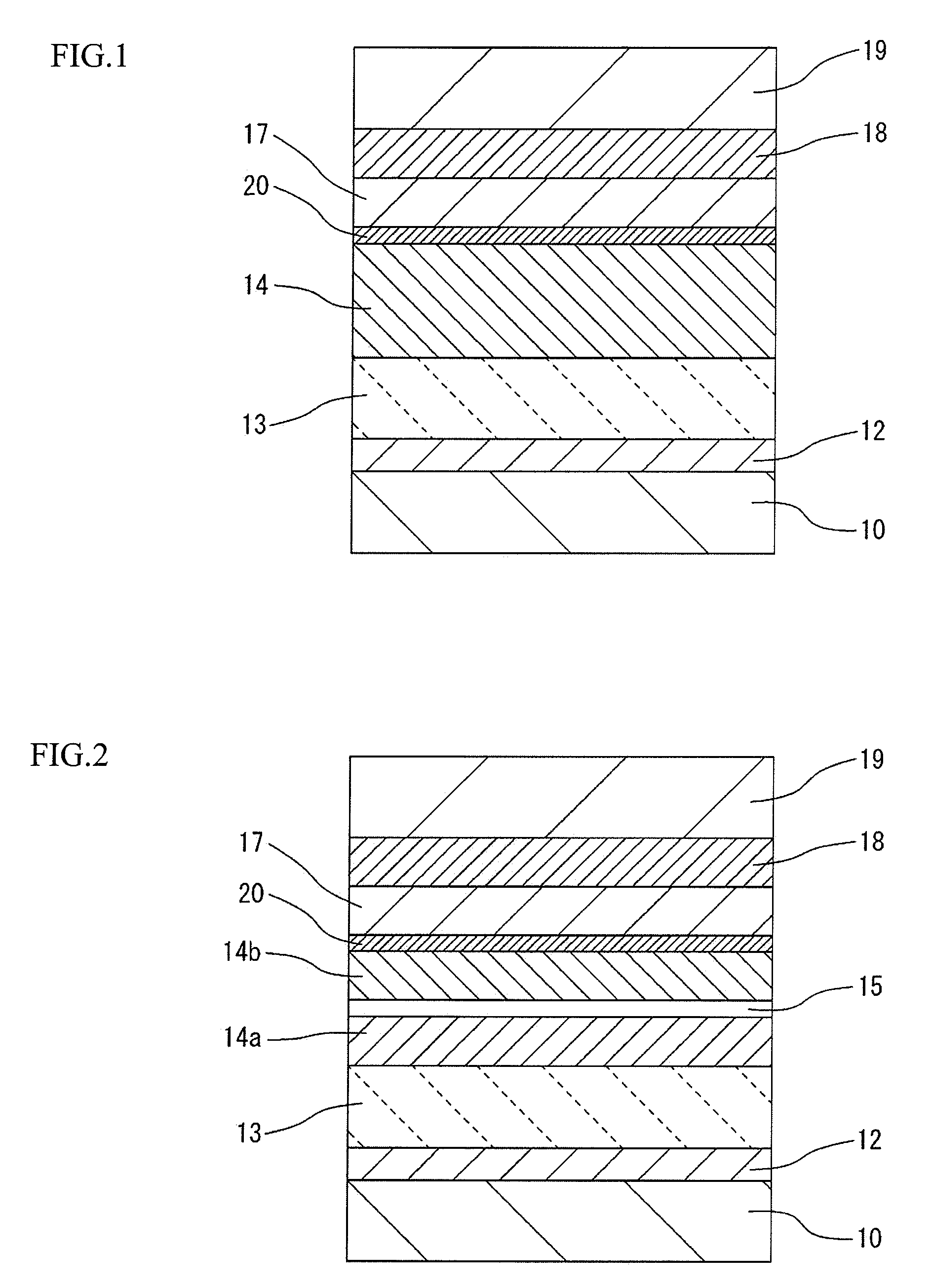

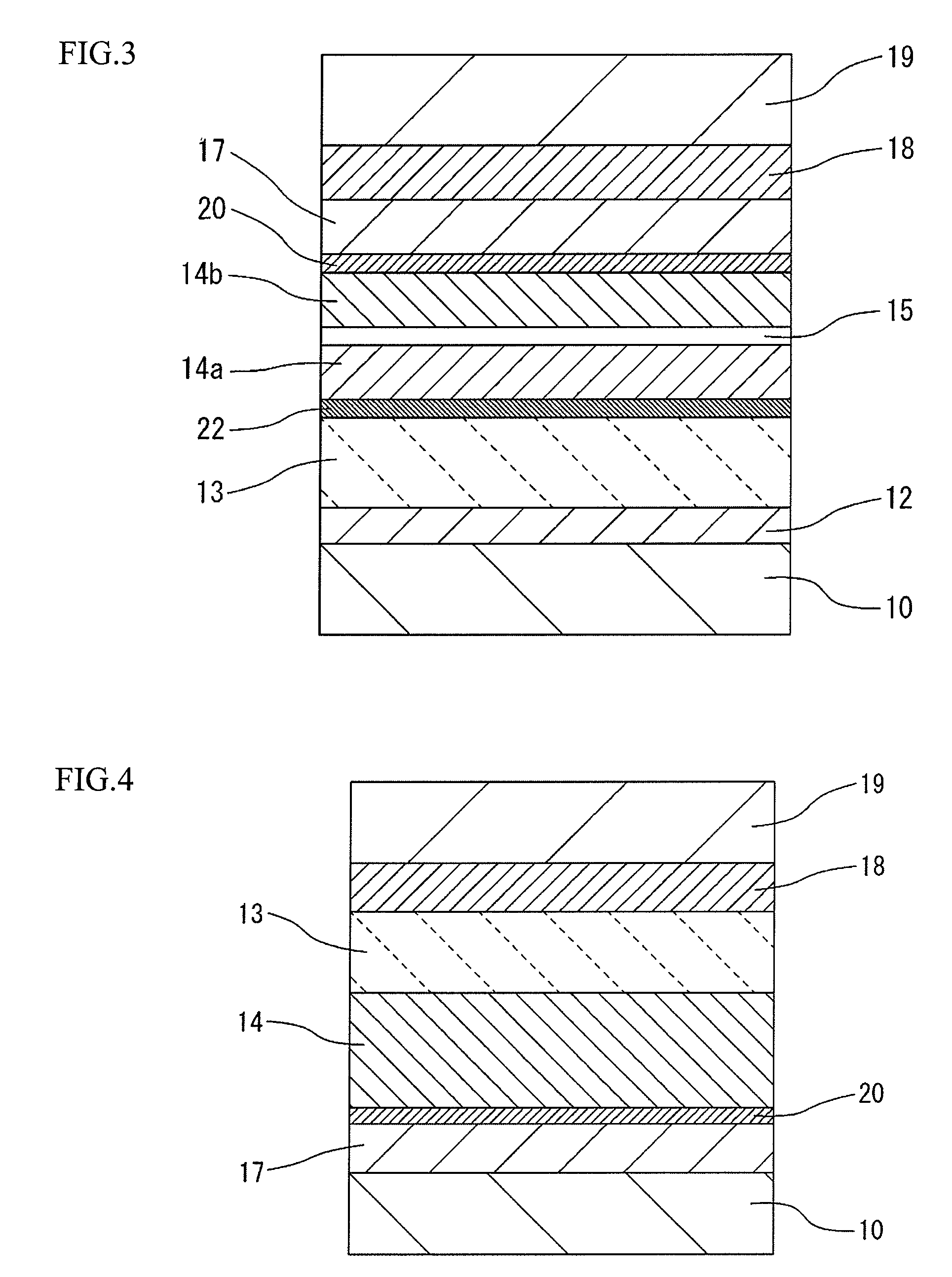

An organic device, including an organic compound having charge-transporting ability (i.e., transporting holes and / or electrons) and / or including organic light emissive molecules capable of emitting at least one of fluorescent light or phosphorescent light, has a charge transfer complex-contained layer including a charge transfer complex formed upon contact of an organic hole-transporting compound and molybdenum trioxide via a manner of lamination or mixing thereof, so that the organic hole-transporting compound is in a state of radical cation (i.e., positively charged species) in the charge transfer complex-contained layer.

Owner:MITSUBISHI HEAVY IND LTD +1

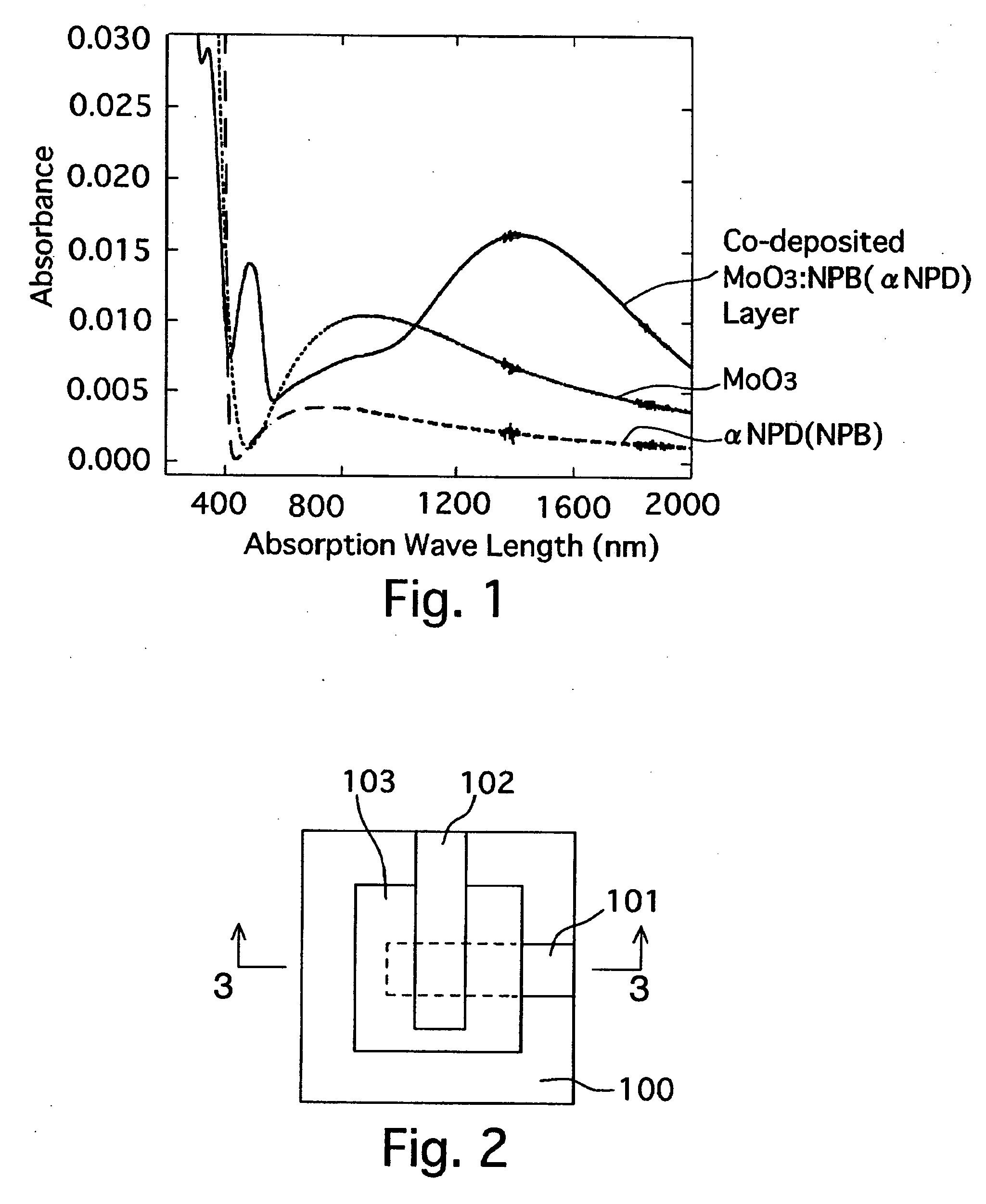

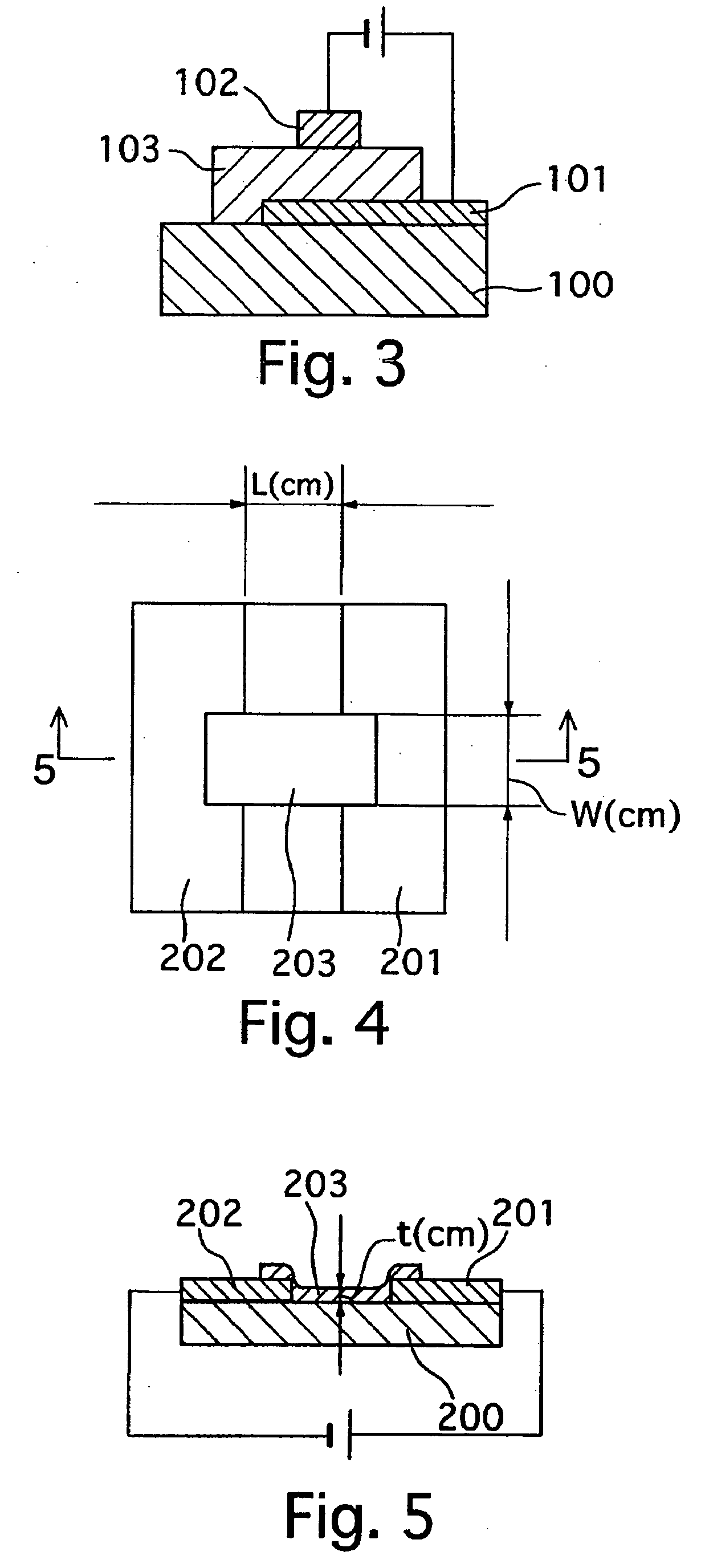

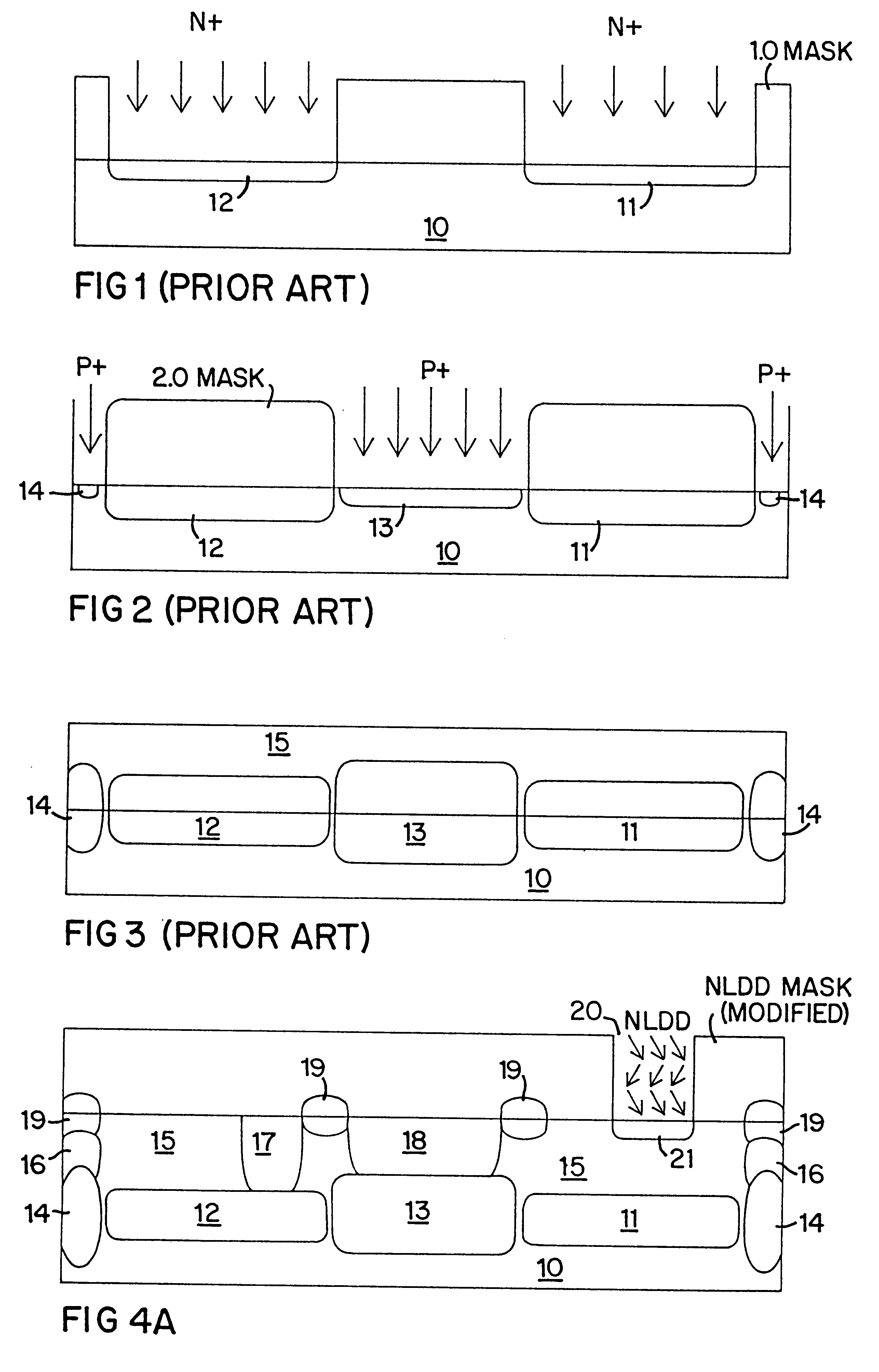

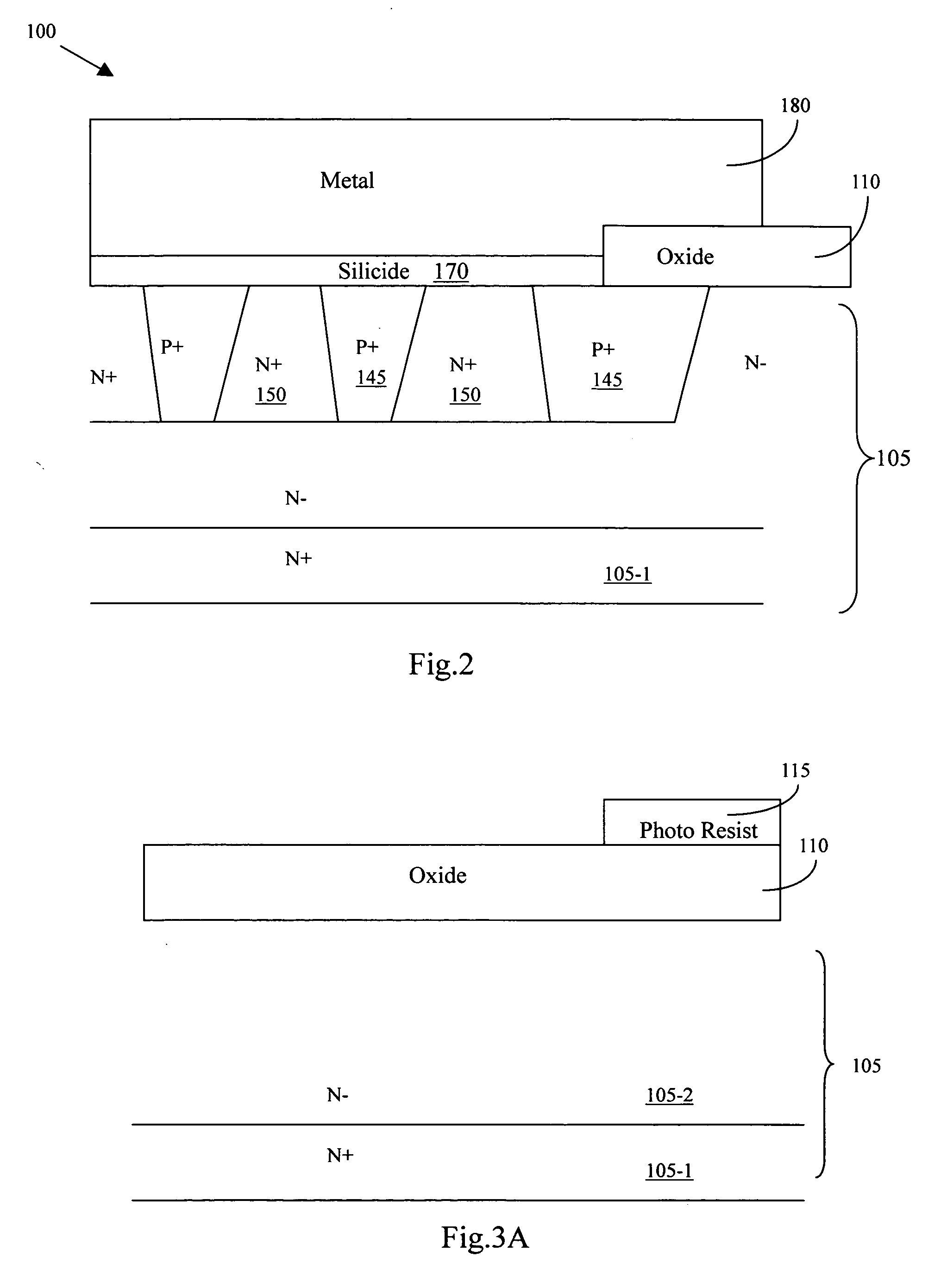

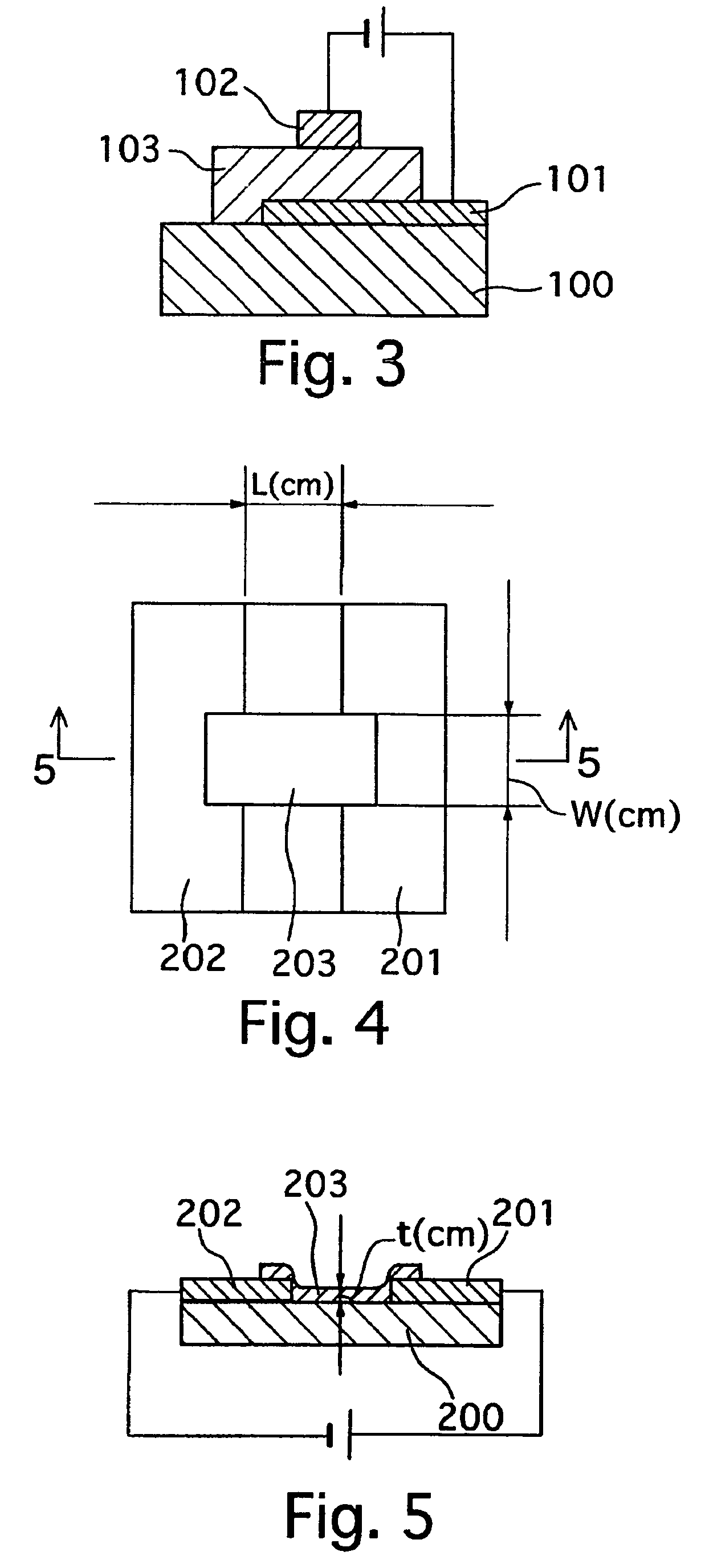

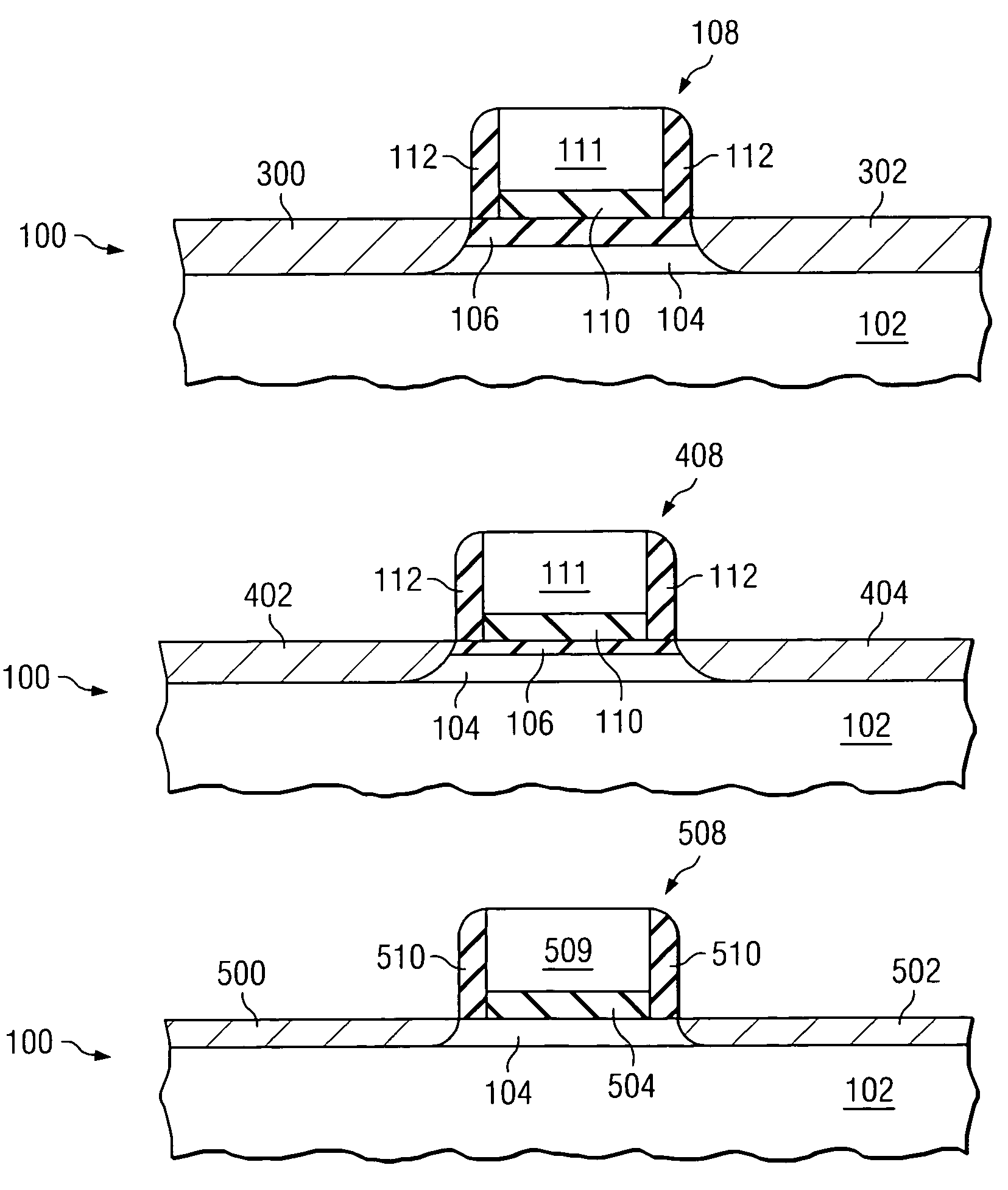

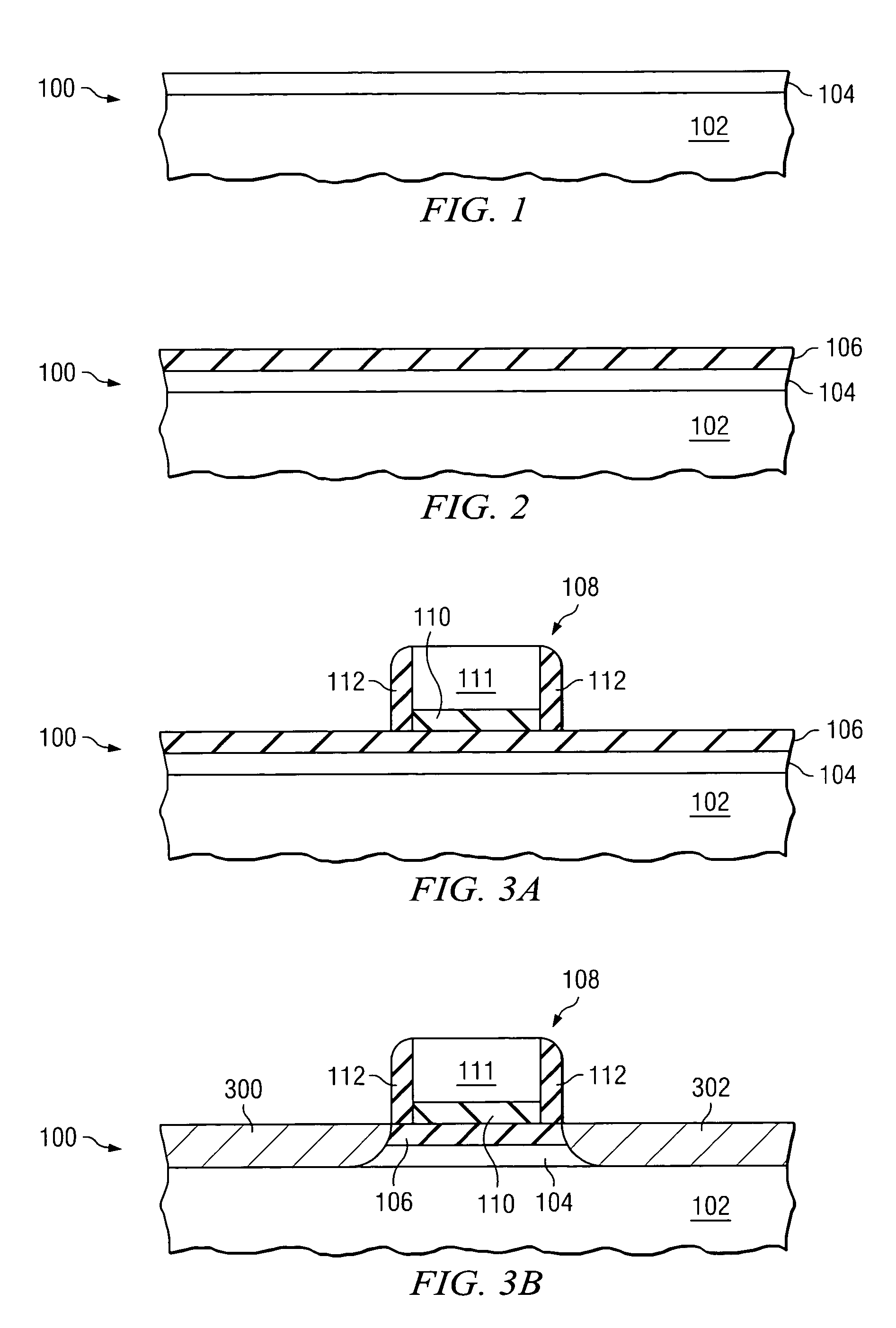

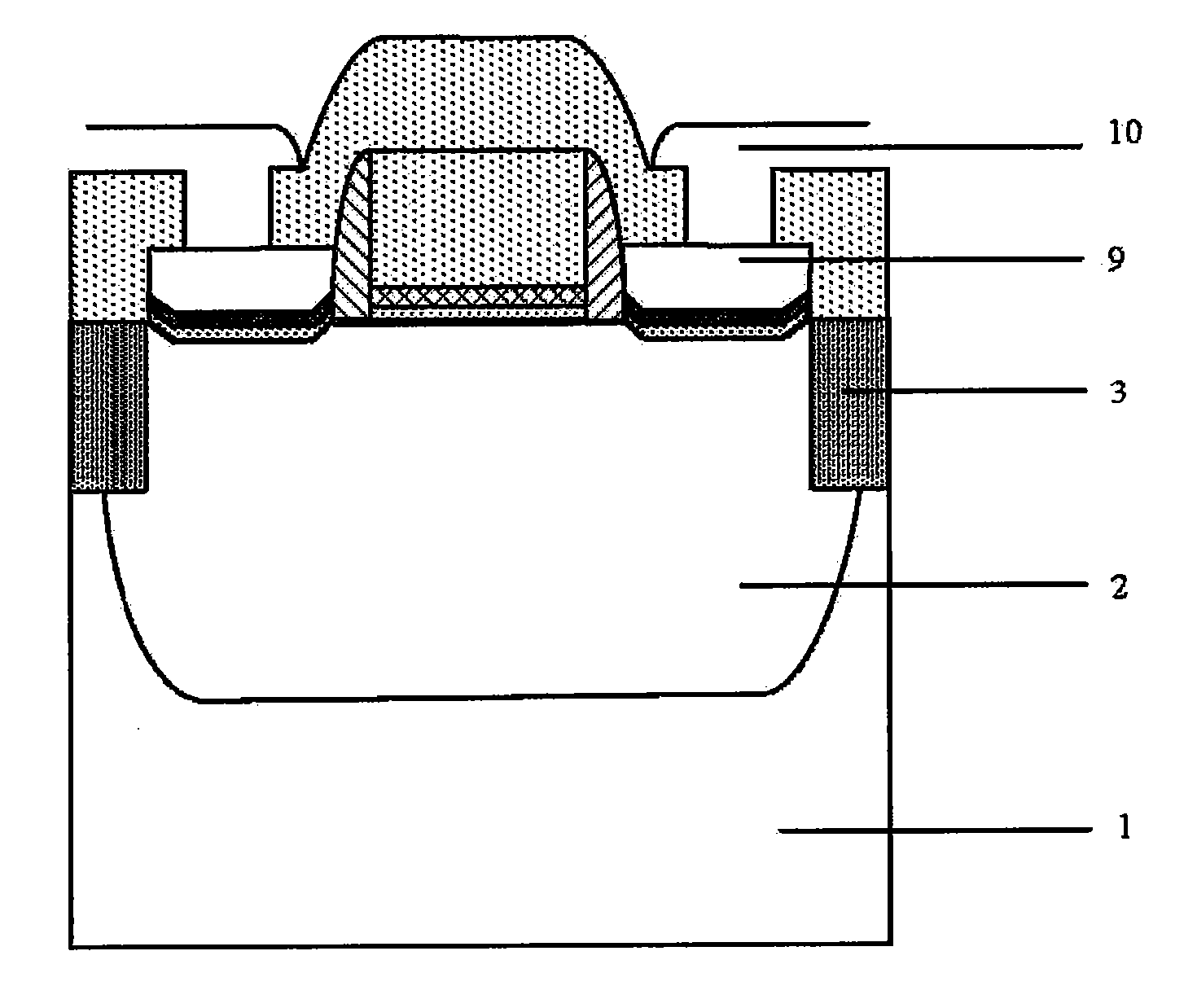

Method of fabricating Schottky diode and related structure

InactiveUS6261932B1Easy to optimizeReduce parasitic capacitanceTransistorSolid-state devicesDopantMetal silicide

A method of forming an improved Schottky diode structure as part of an integrated circuit fabrication process that includes the introduction of a selectable concentration of dopant into the surface of an epitaxial layer so as to form a barrier-modifying surface dopant layer. The epitaxial layer forms the cathode of the Schottky diode and a metal-silicide layer on the surface of the epitaxial layer forms the diode junction. The surface dopant layer positioned between the cathode and the diode junction is designed to raise or lower the barrier height between those two regions either to reduce the threshold turn-on potential of the diode, or to reduce the reverse leakage current of the transistor. The particular dopant conductivity used to form the surface dopant layer is dependent upon the conductivity of the epitaxial layer and the type of metal used to form the metal-silicide junction.

Owner:SEMICON COMPONENTS IND LLC

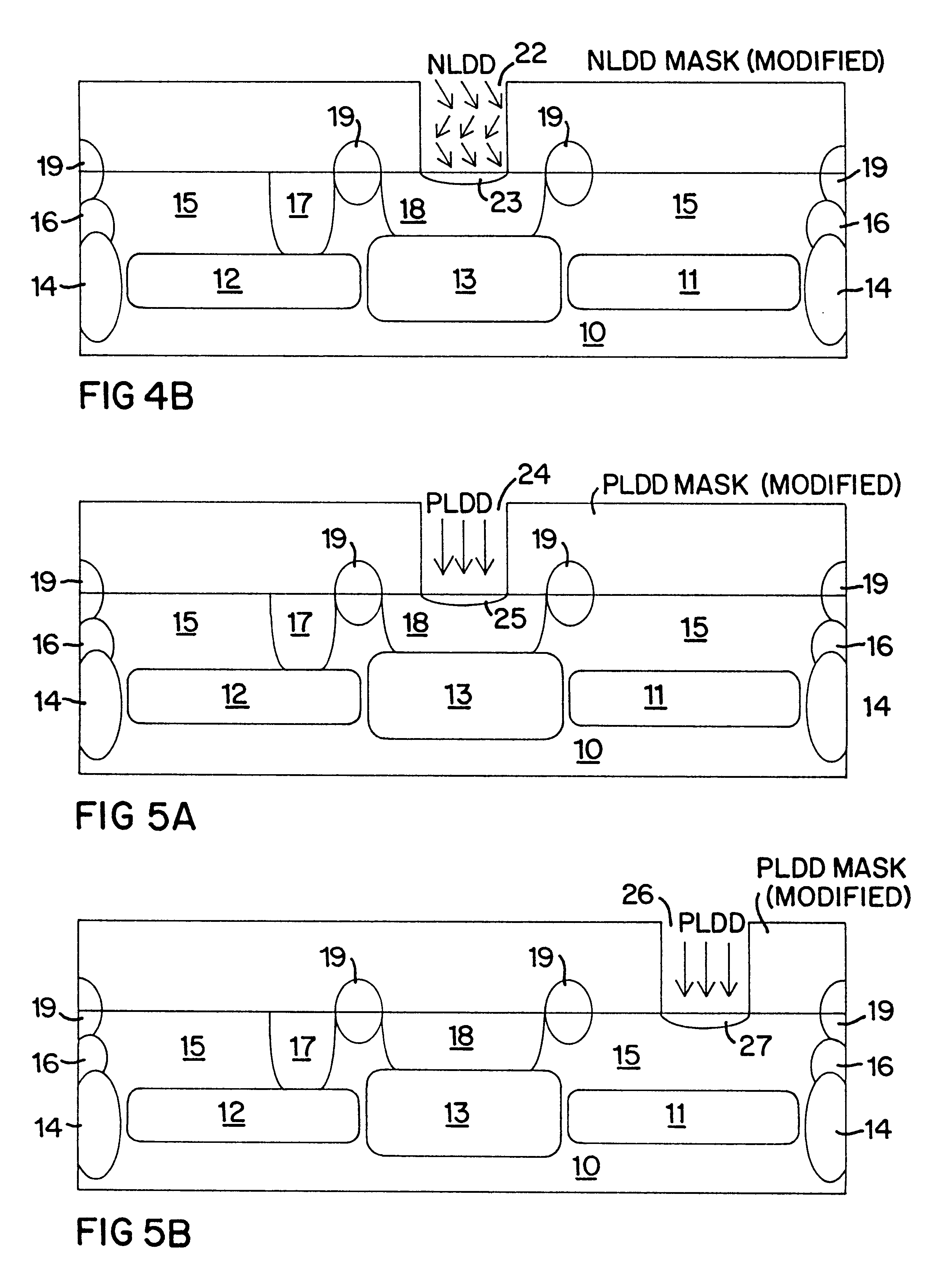

Junction barrier schottky with low forward drop and improved reverse block voltage

InactiveUS20060237813A1Improve performanceReduce horizontal sizeSemiconductor devicesEngineeringDrain current

This invention discloses a junction barrier Schottky device supported on a substrate that has a first conductivity type. The Schottky device includes a first diffusion region of a fist conductivity type for functioning as a forward barrier height reduction region. The Schottky device further includes a second diffusion region of a second conductivity type disposed immediately adjacent to the first diffusion region for functioning as a backward blocking enhancement region to reduce the backward leakage current.

Owner:TAURUS MICROPOWER

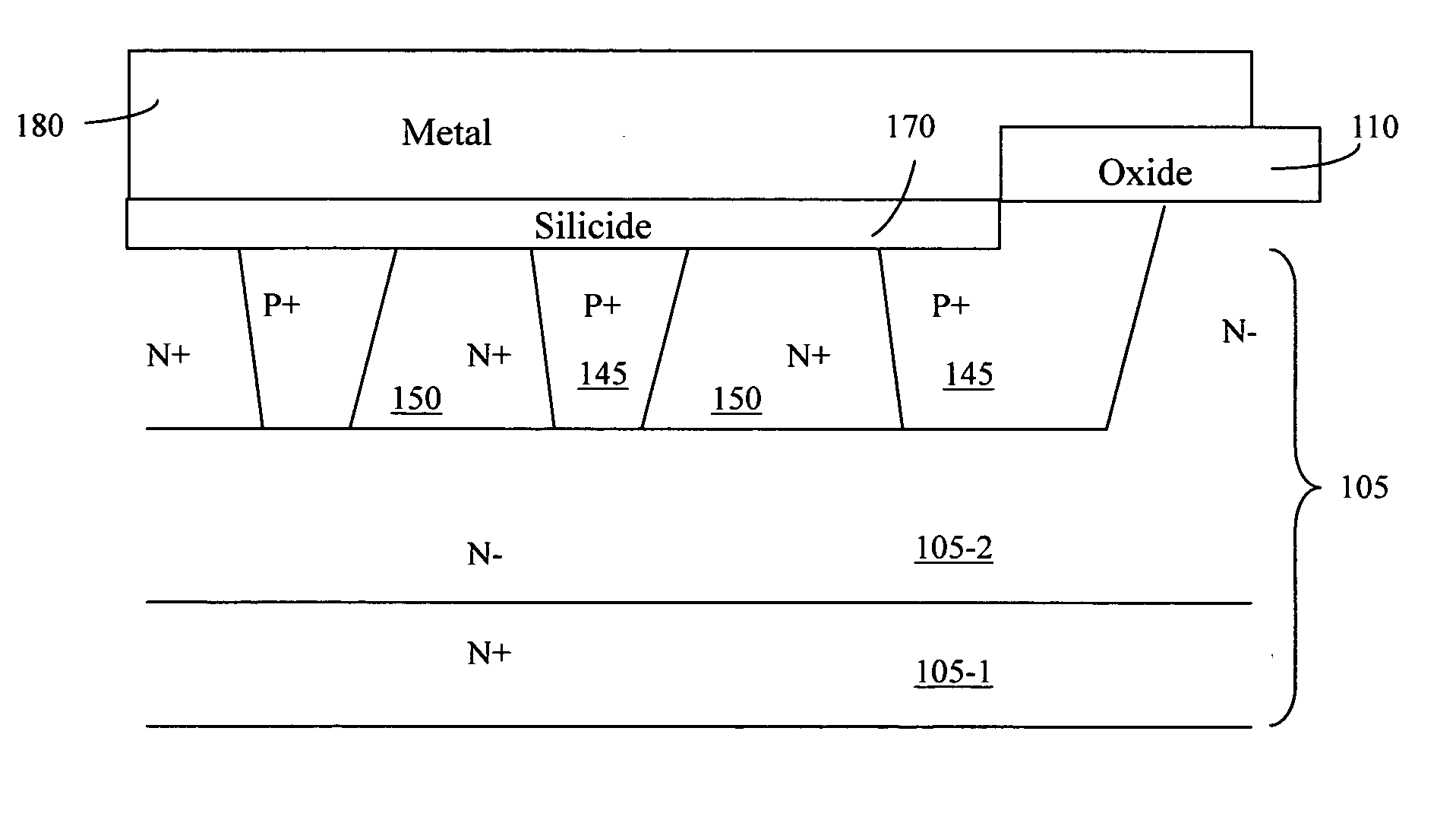

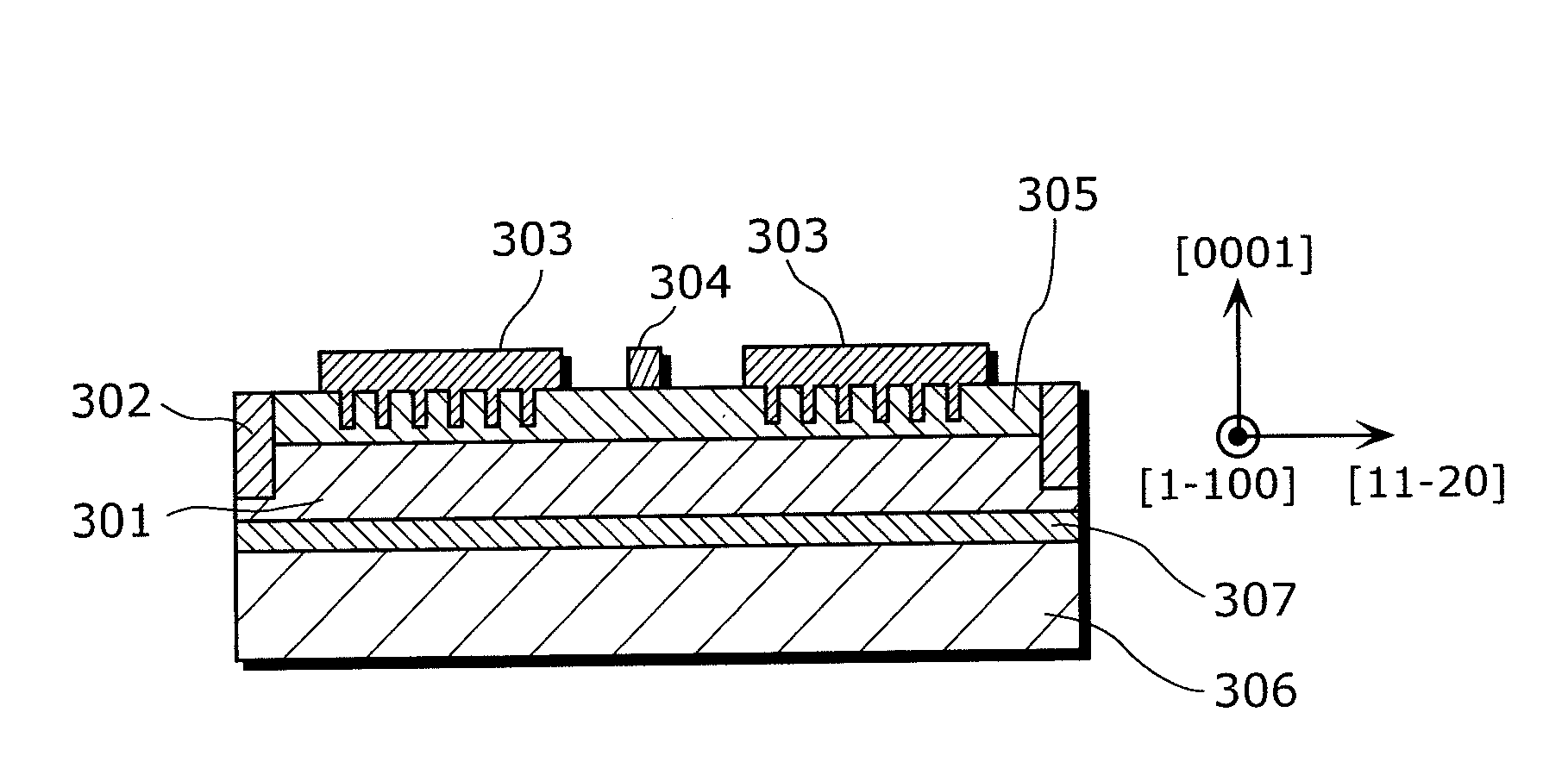

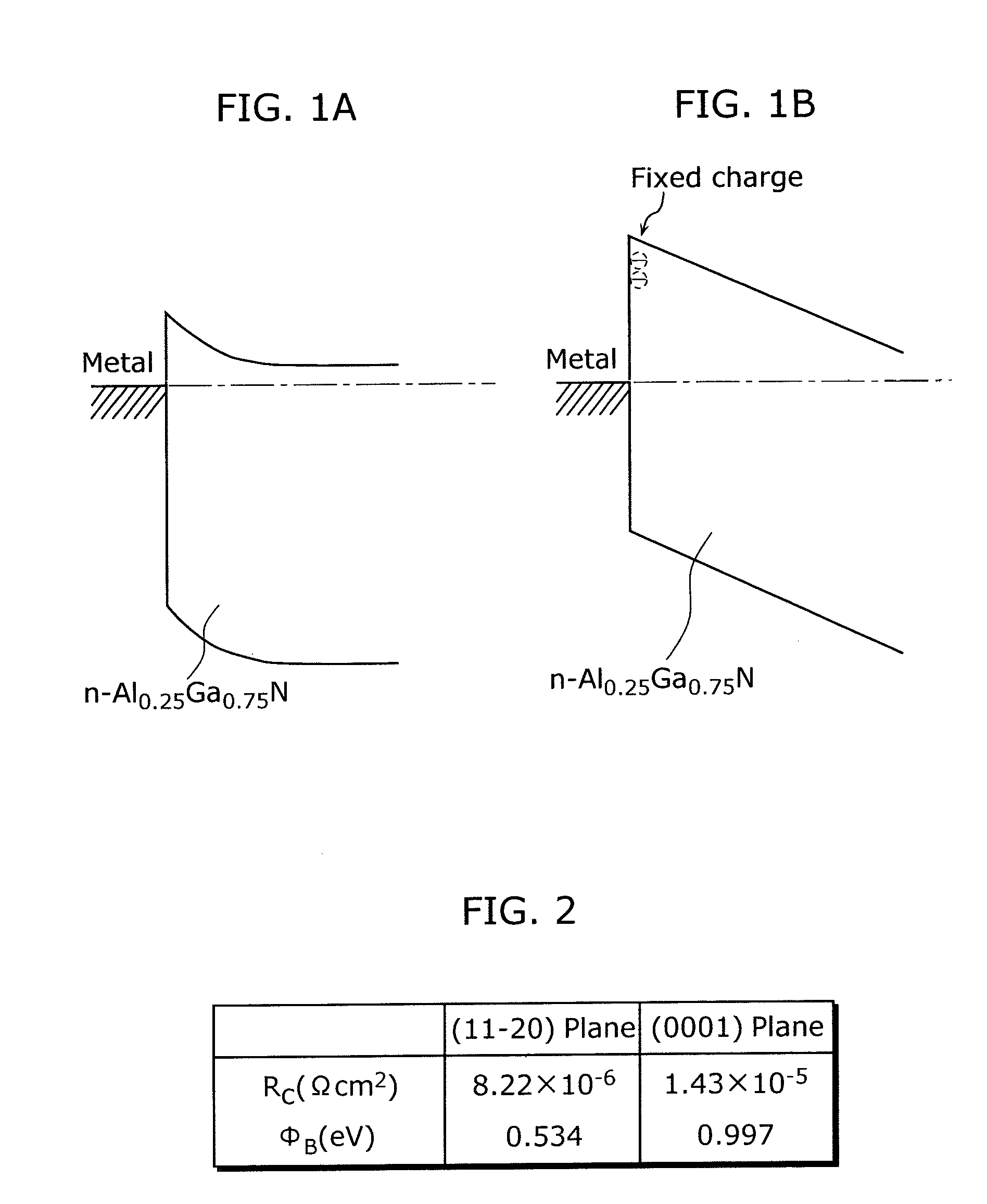

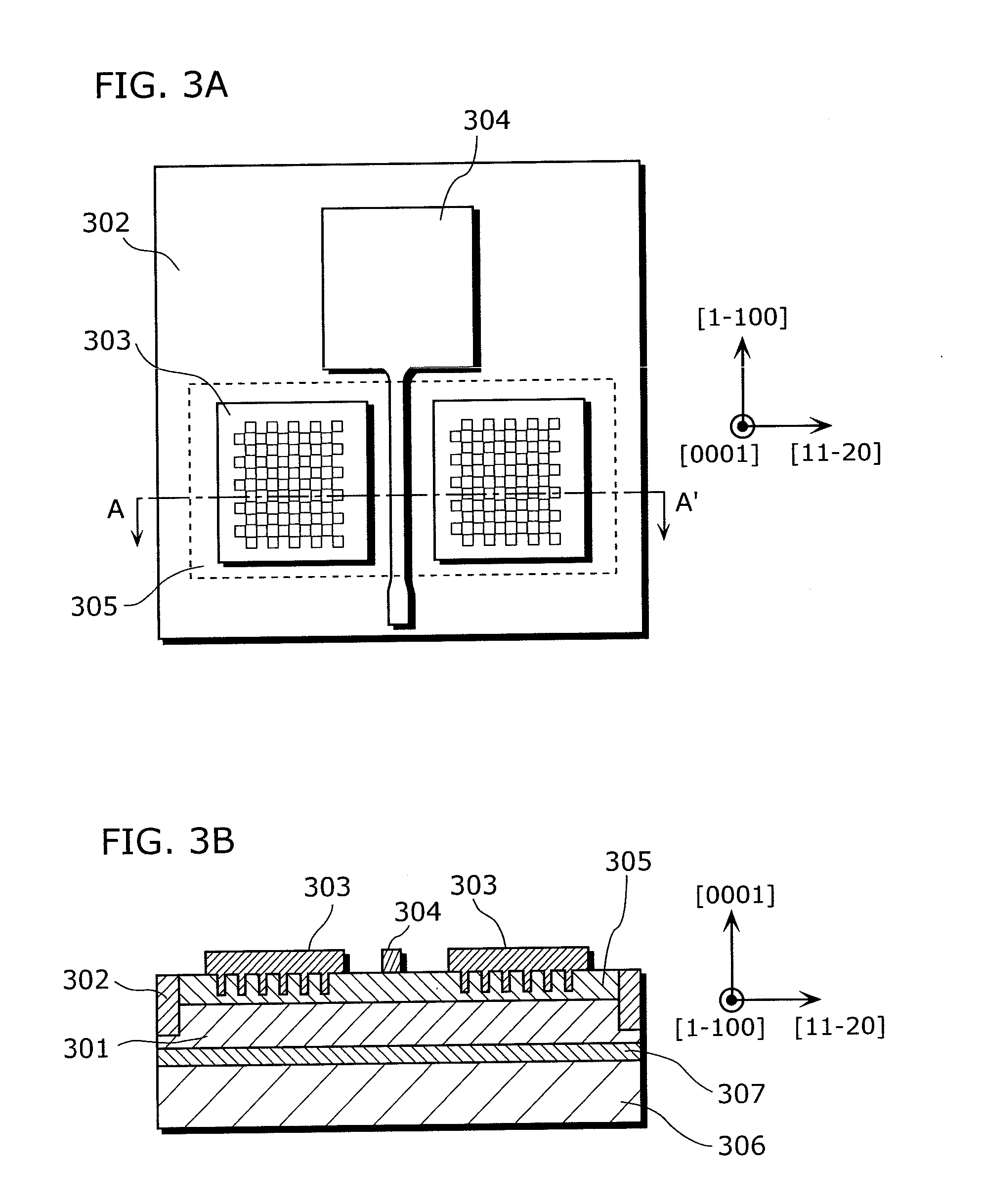

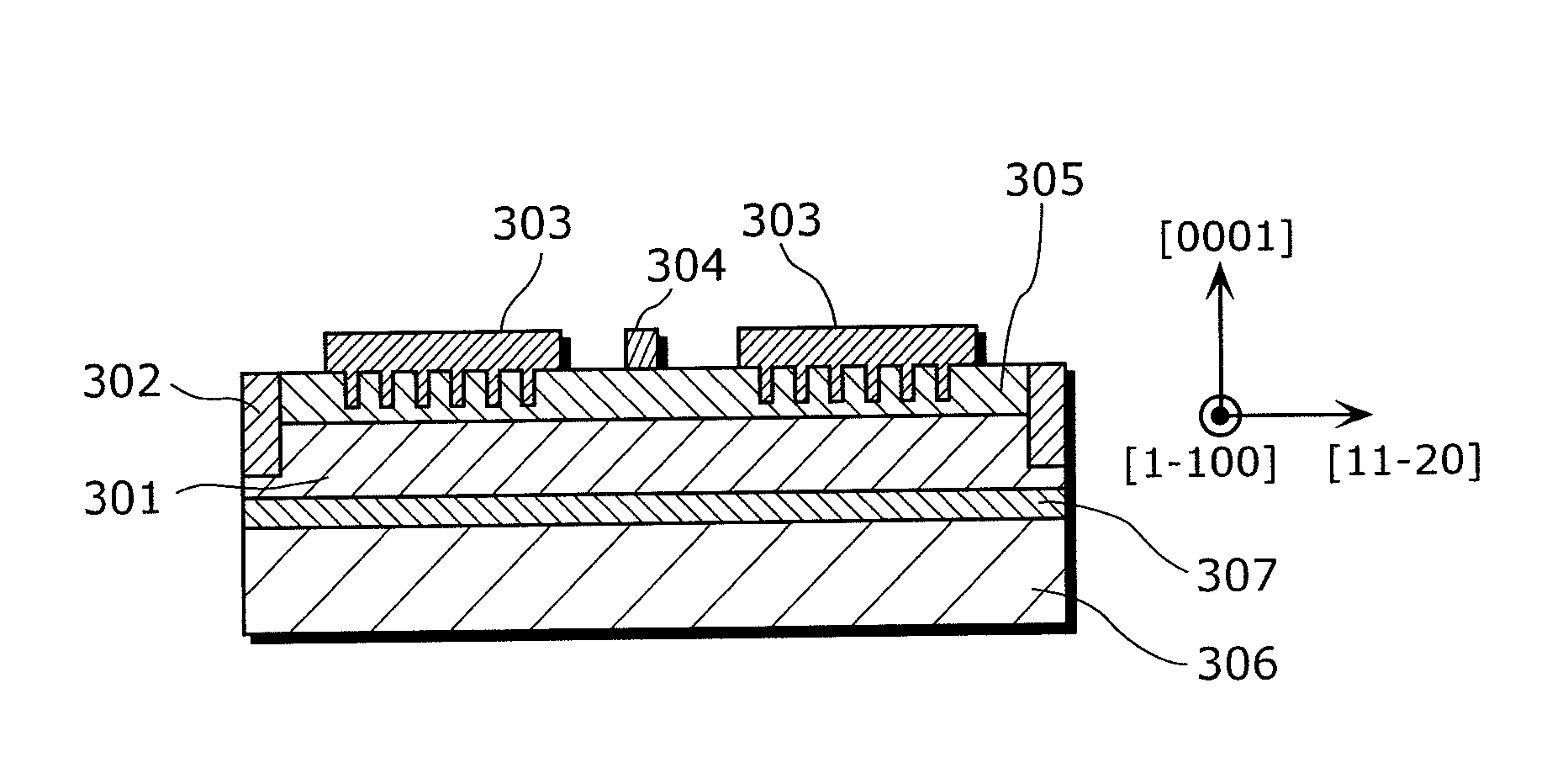

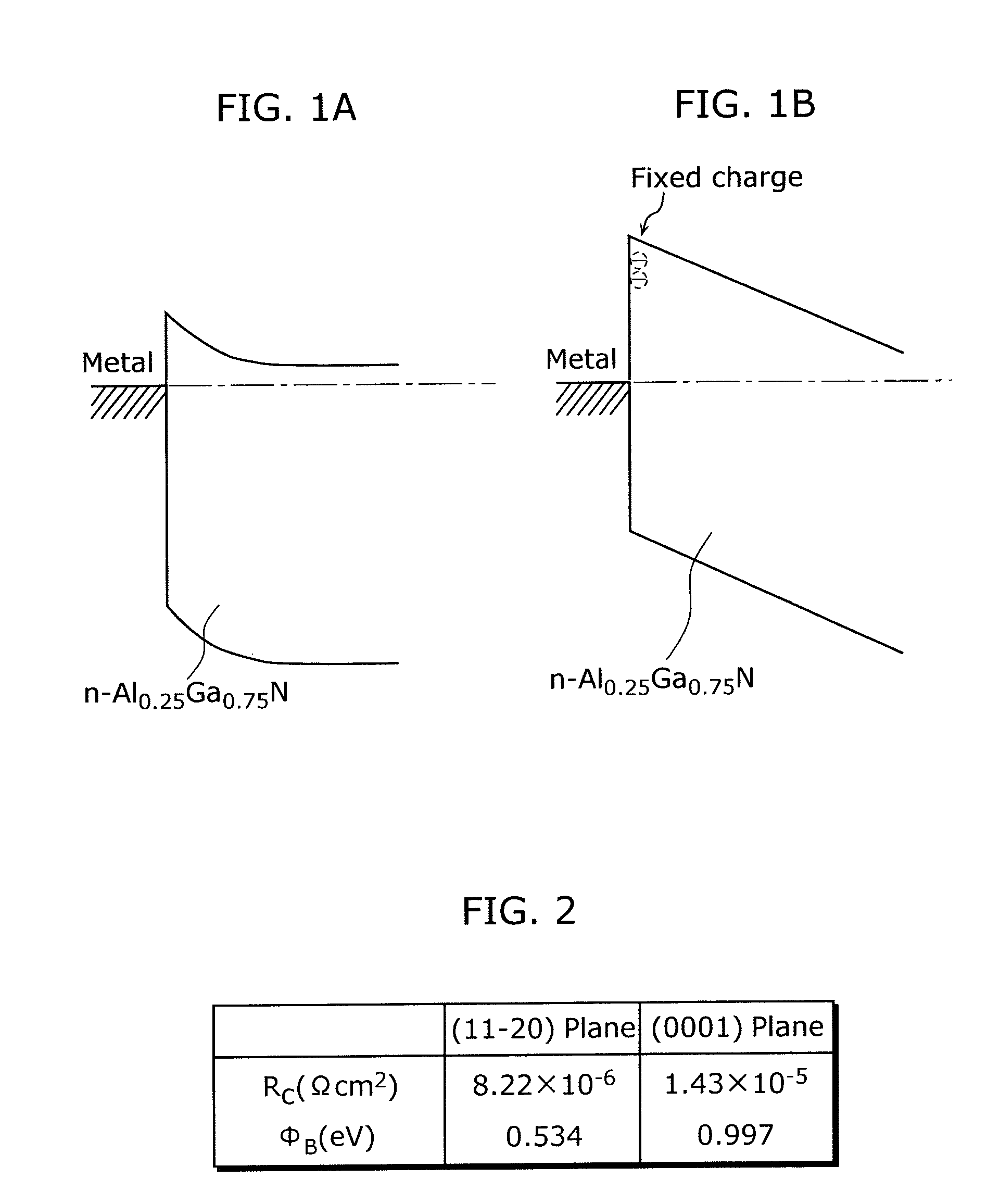

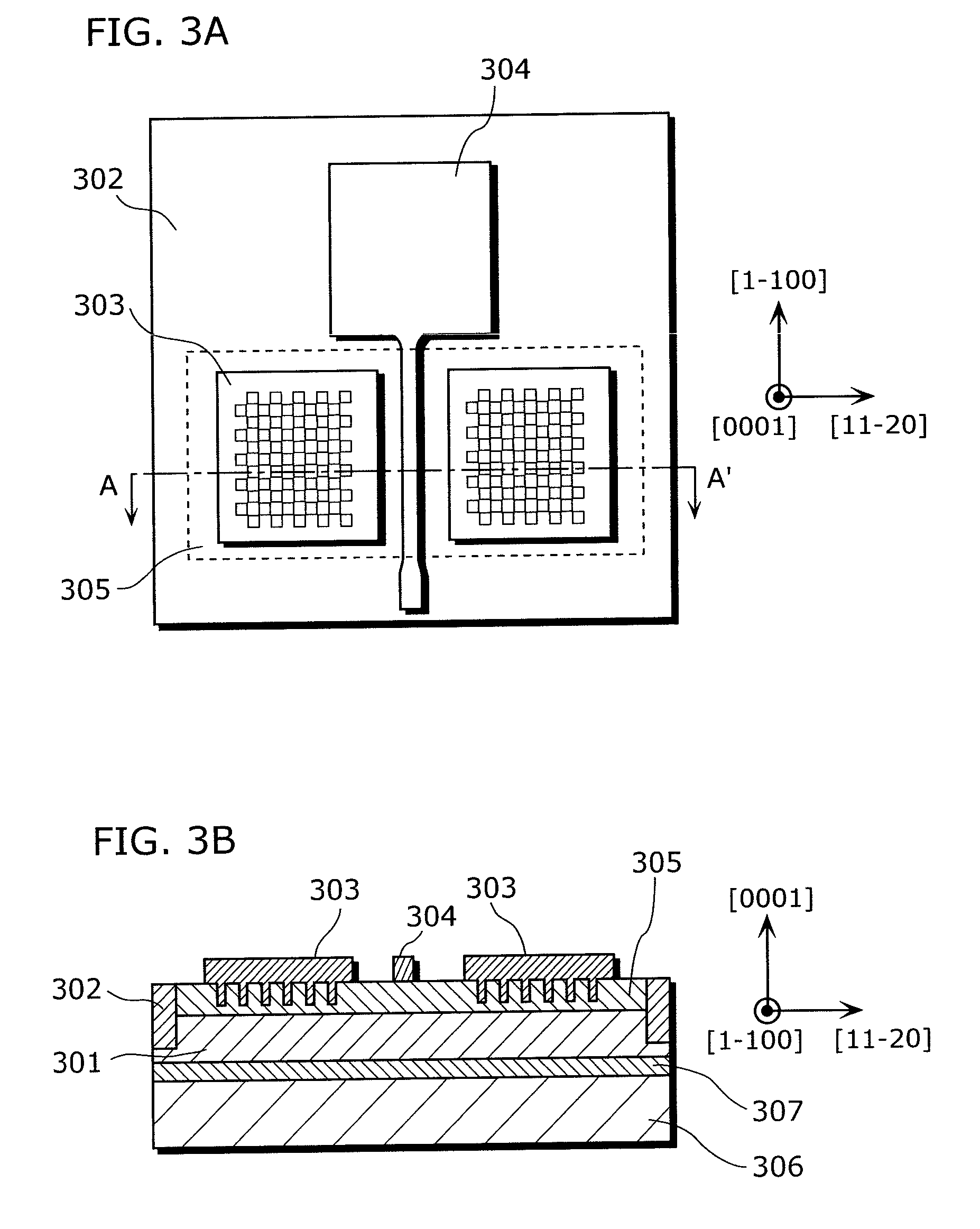

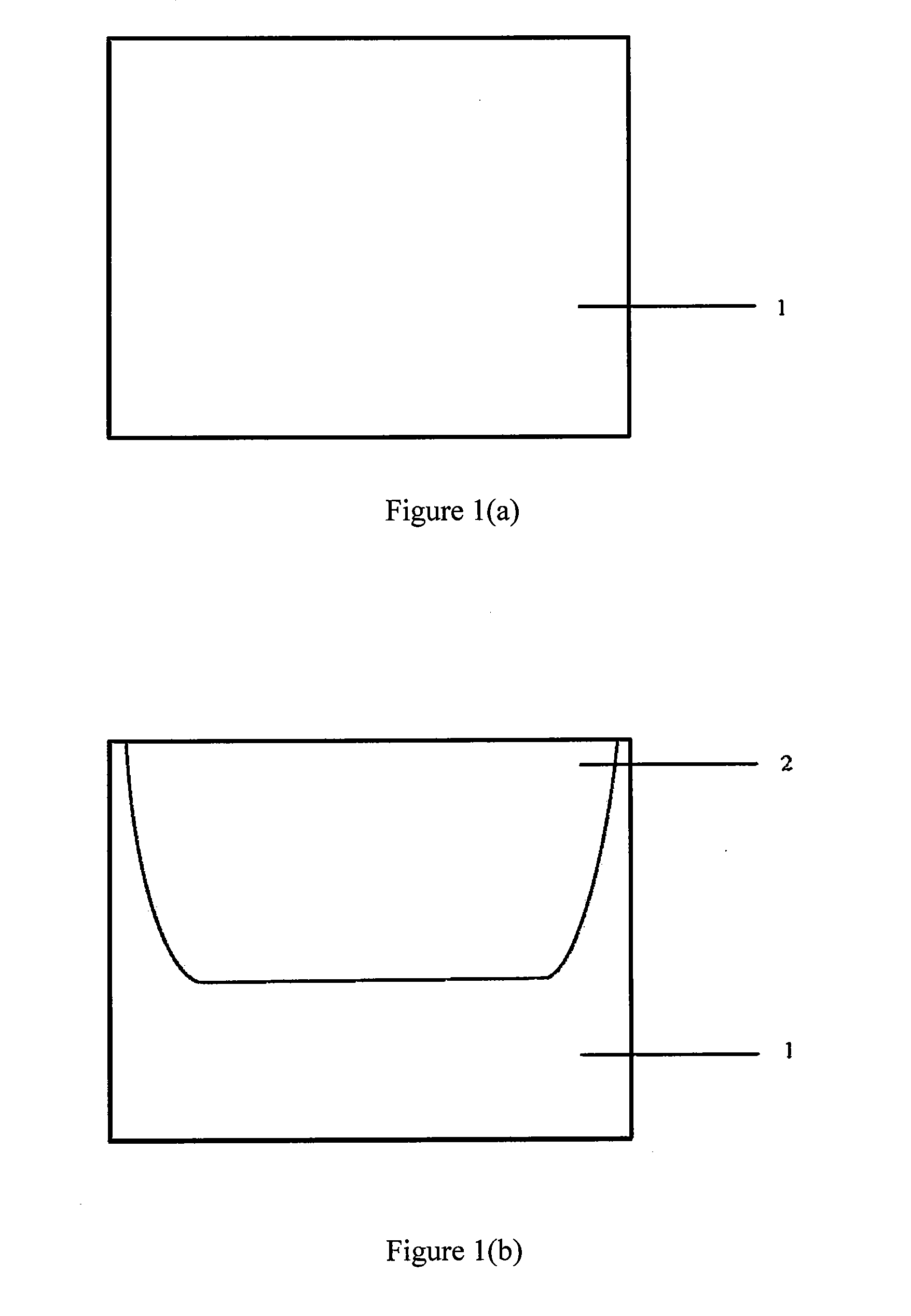

Nitride semiconductor device and manufacturing method thereof

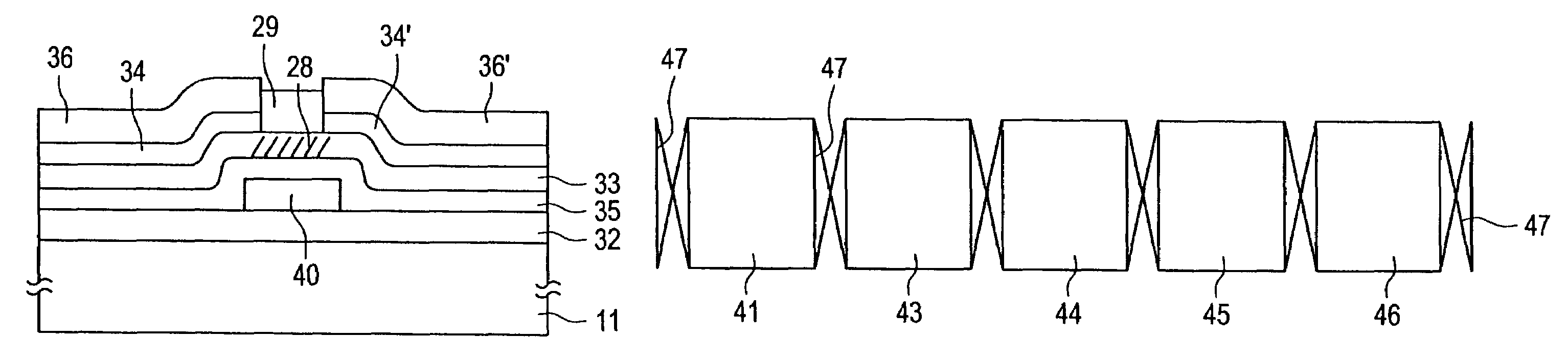

ActiveUS20080217625A1Reduce parasitic resistanceLower barrier heightSemiconductor/solid-state device manufacturingSemiconductor devicesCheckerboard patternIsolation layer

It is an object of the present invention to provide a nitride semiconductor device with low parasitic resistance by lowering barrier height to reduce contact resistance at an interface of semiconductor and metal. The nitride semiconductor device includes a GaN layer, a device isolation layer, an ohmic electrode, an n-type Al0.25Ga0.75N layer, a sapphire substrate, and a buffer layer. A main surface of the n-type Al0.25Ga0.75N layer is on (0001) plane as a main surface, and concaves are arranged in a checkerboard pattern on the surface. The ohmic electrode contacts the sides of the concaves of the n-type Al0.25Ga0.75N layer, and the sides of the concaves are on non-polar surfaces such as (11-20) plane or (1-100) plane.

Owner:PANASONIC CORP

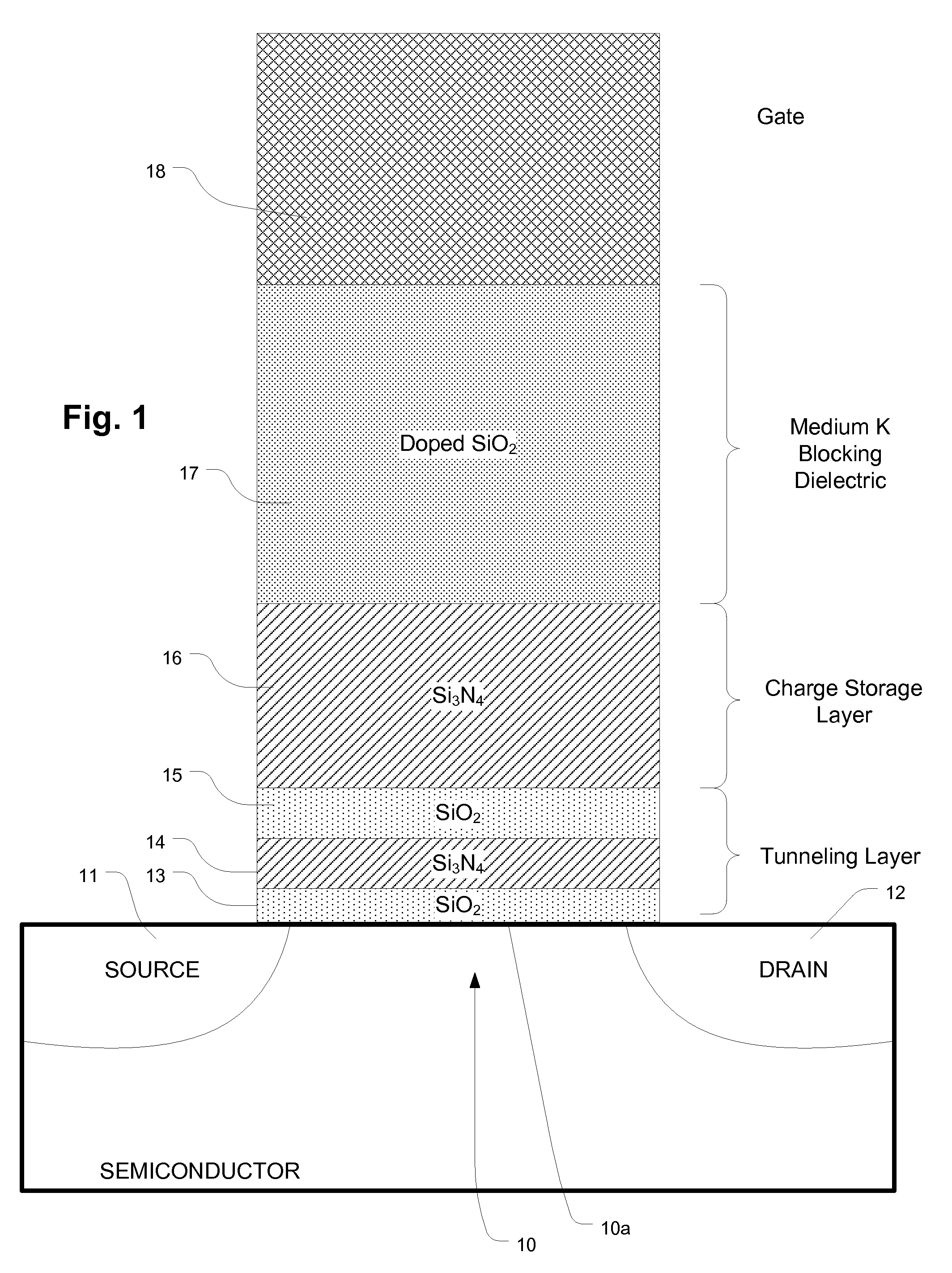

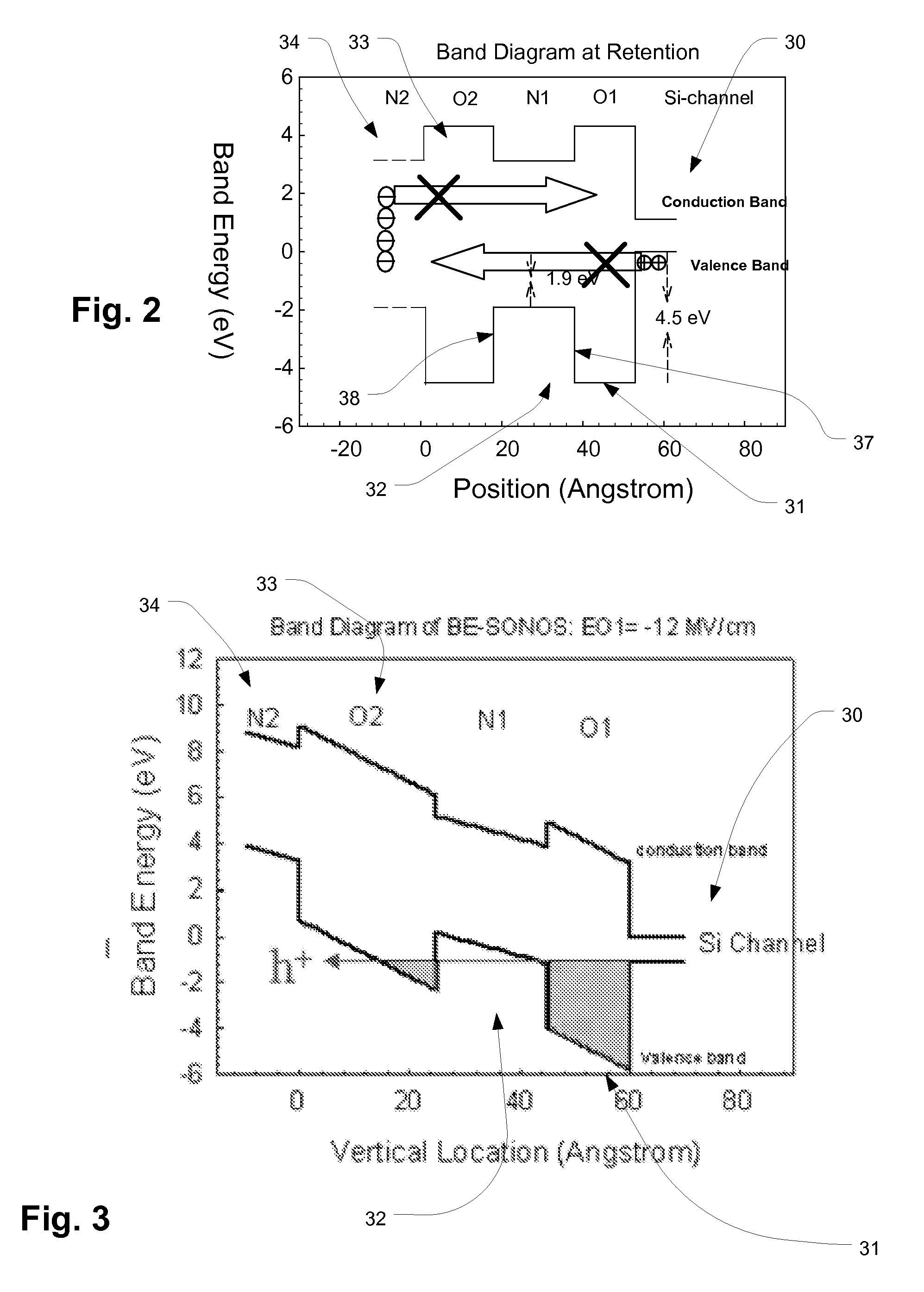

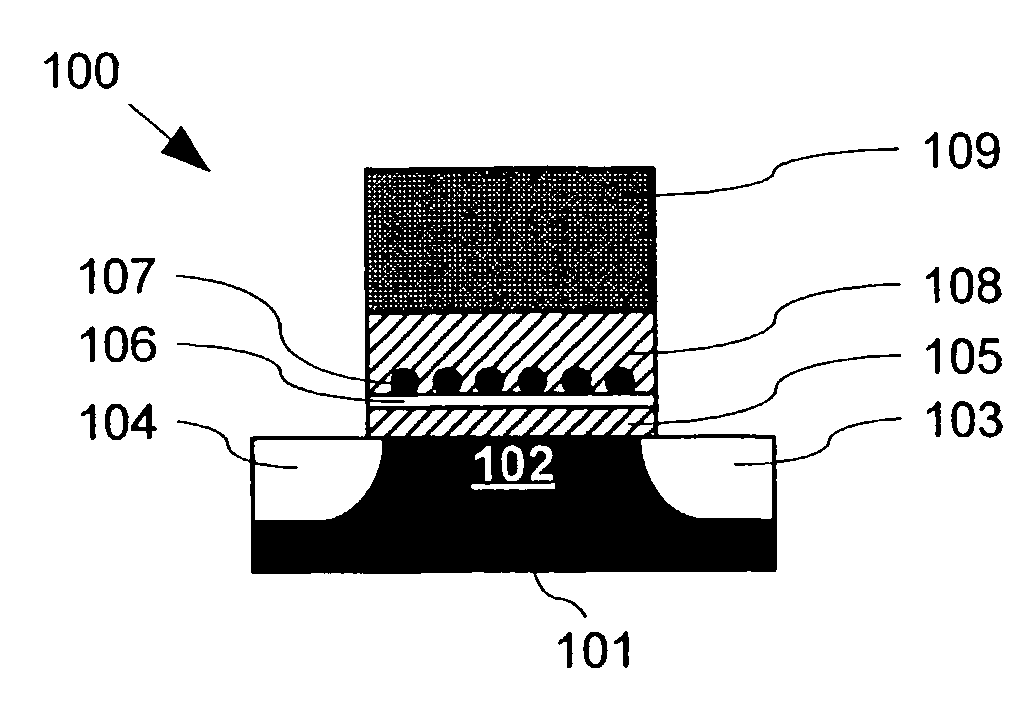

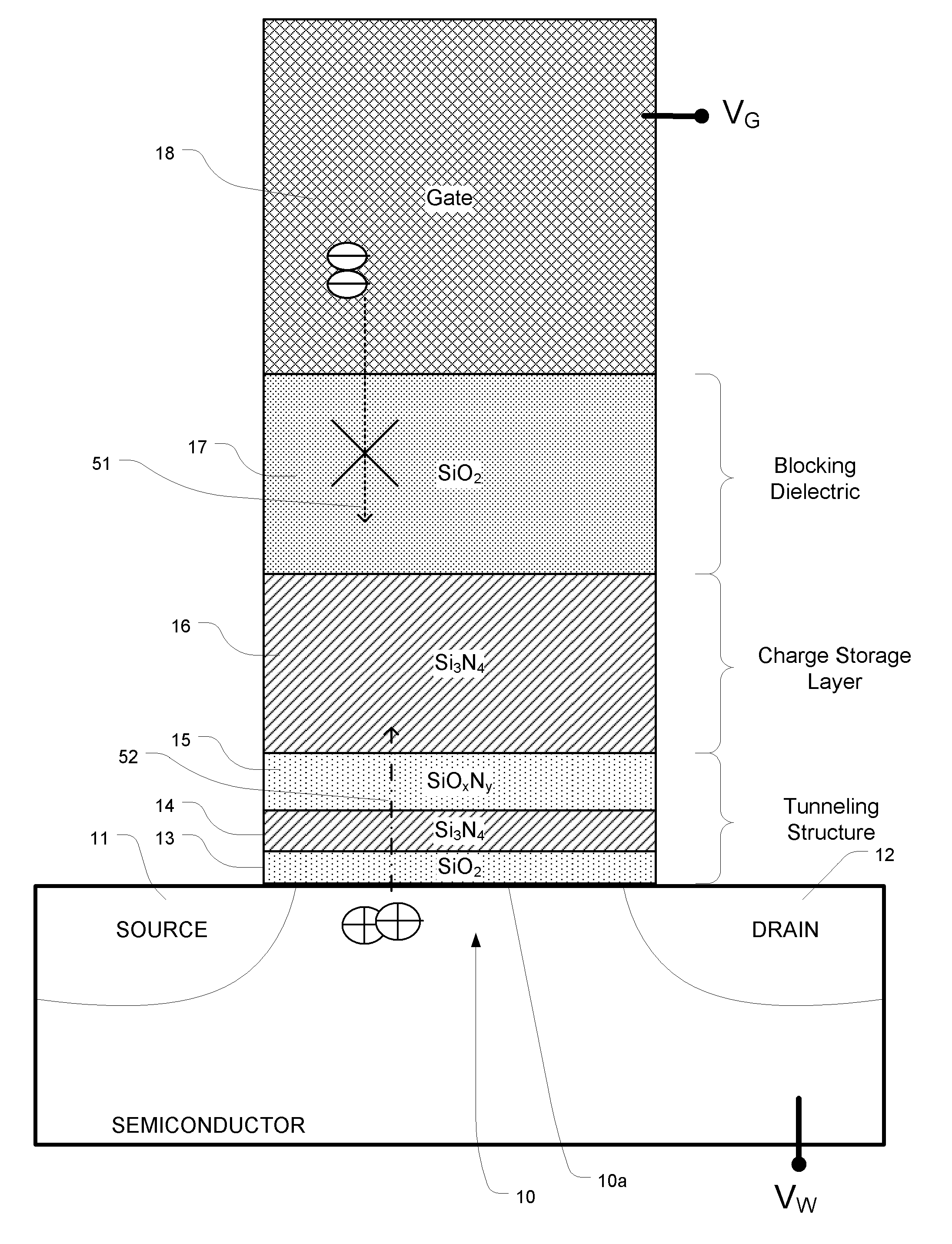

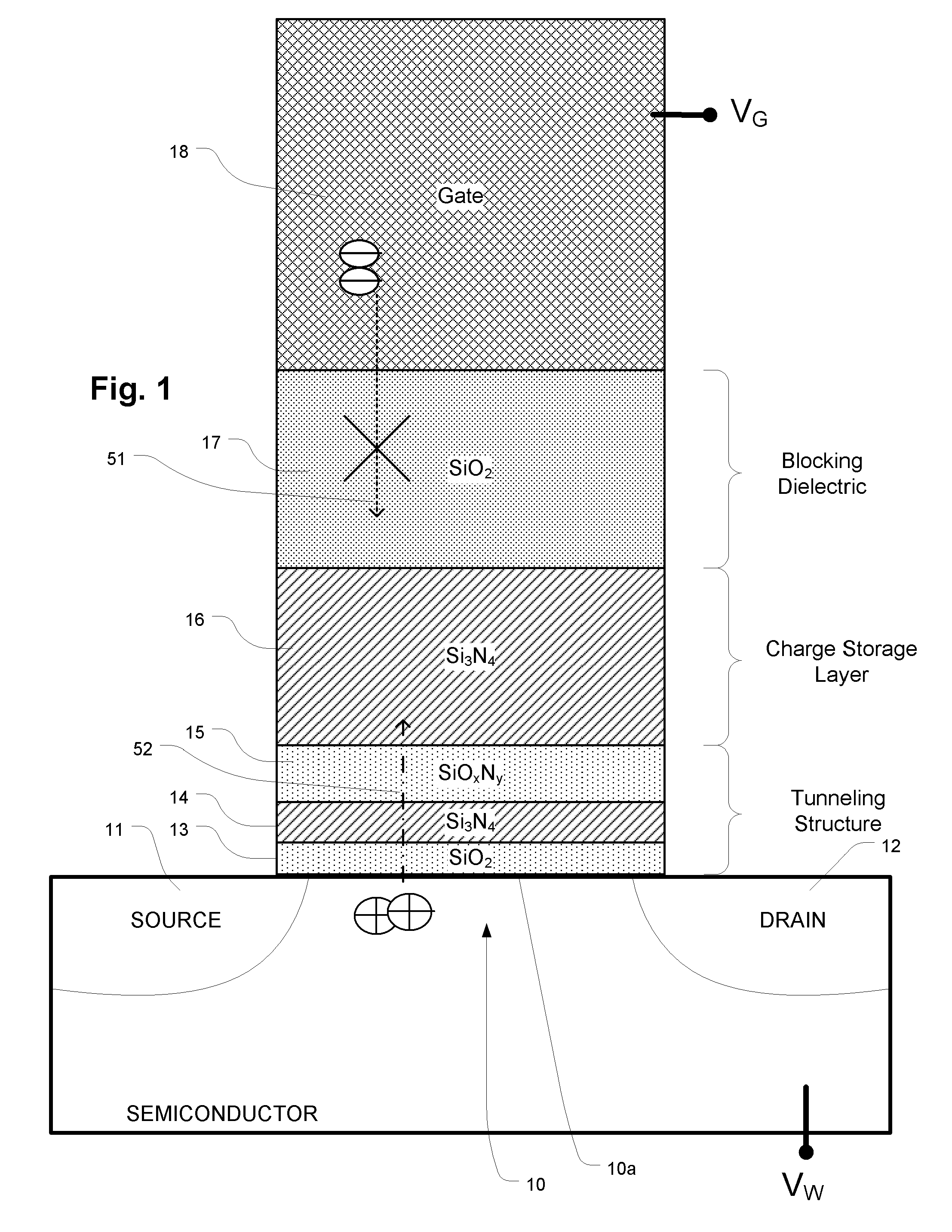

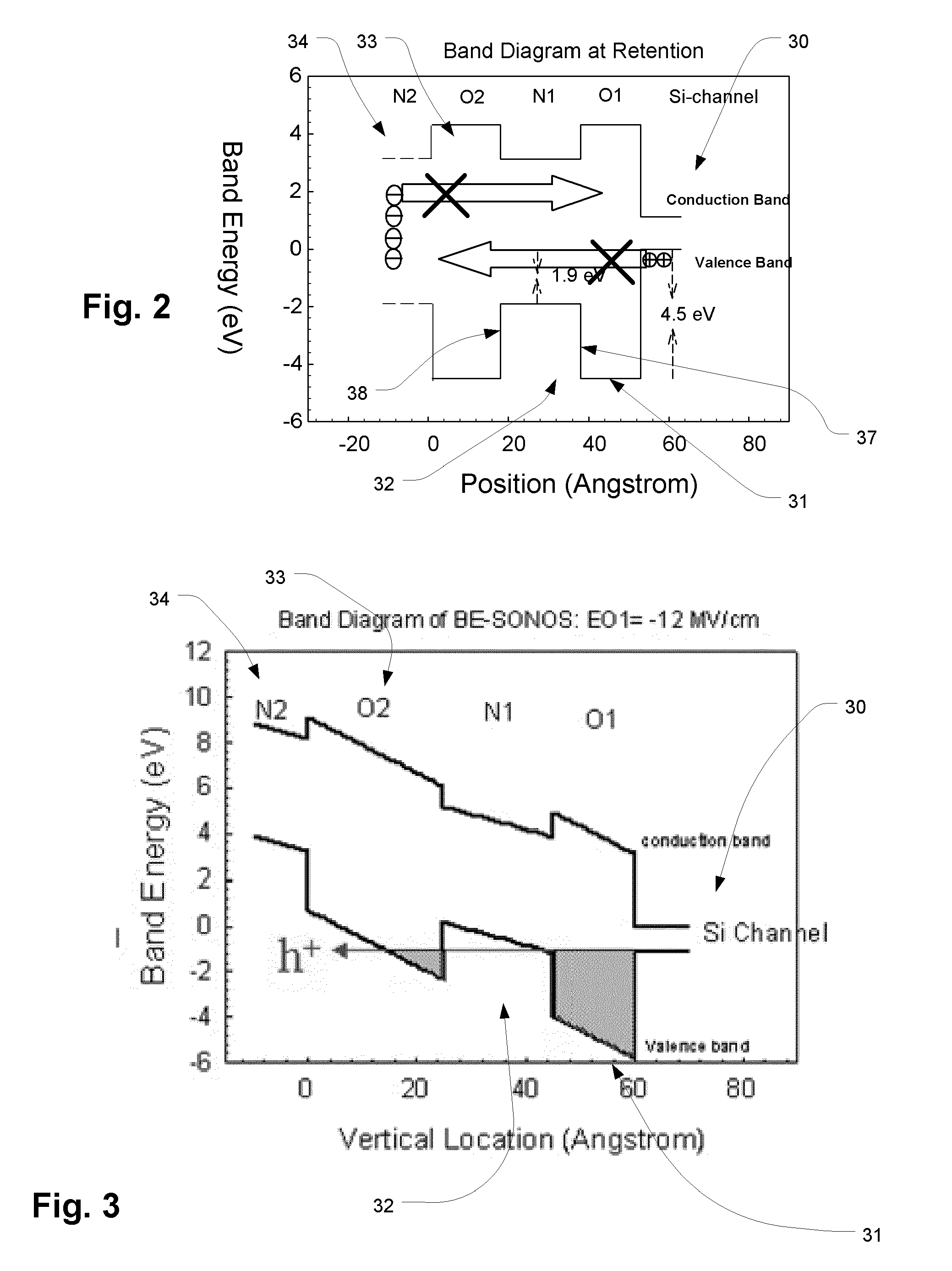

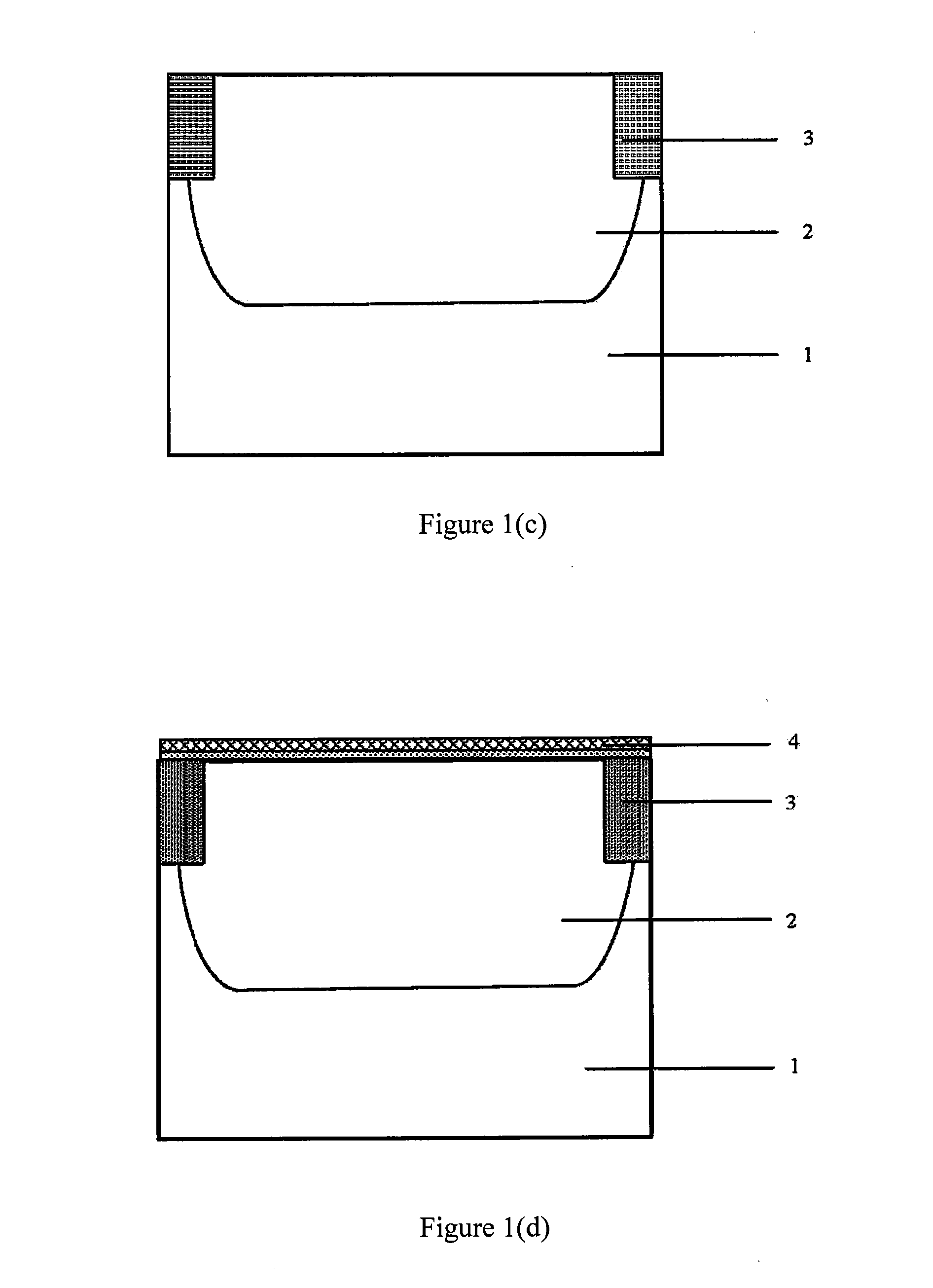

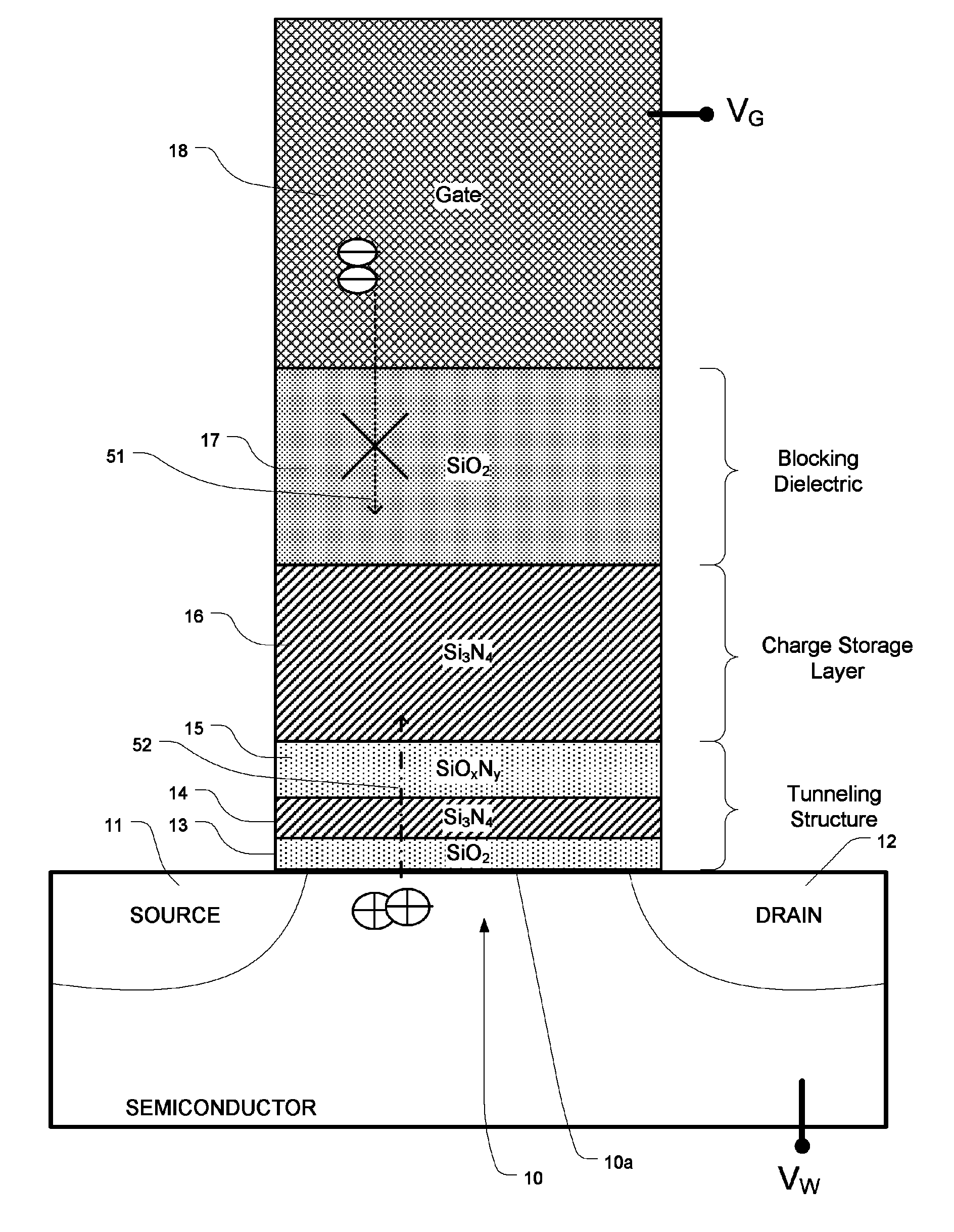

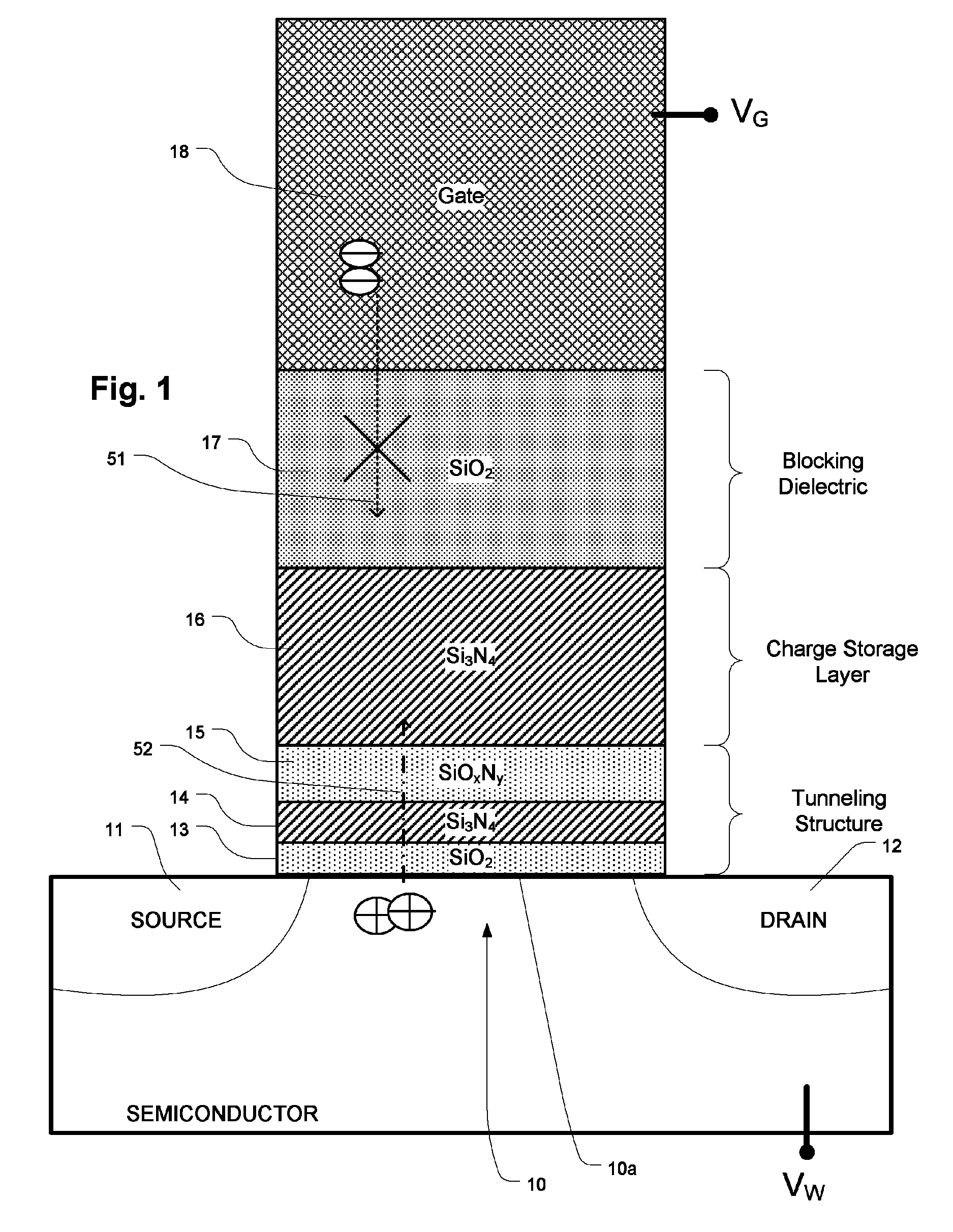

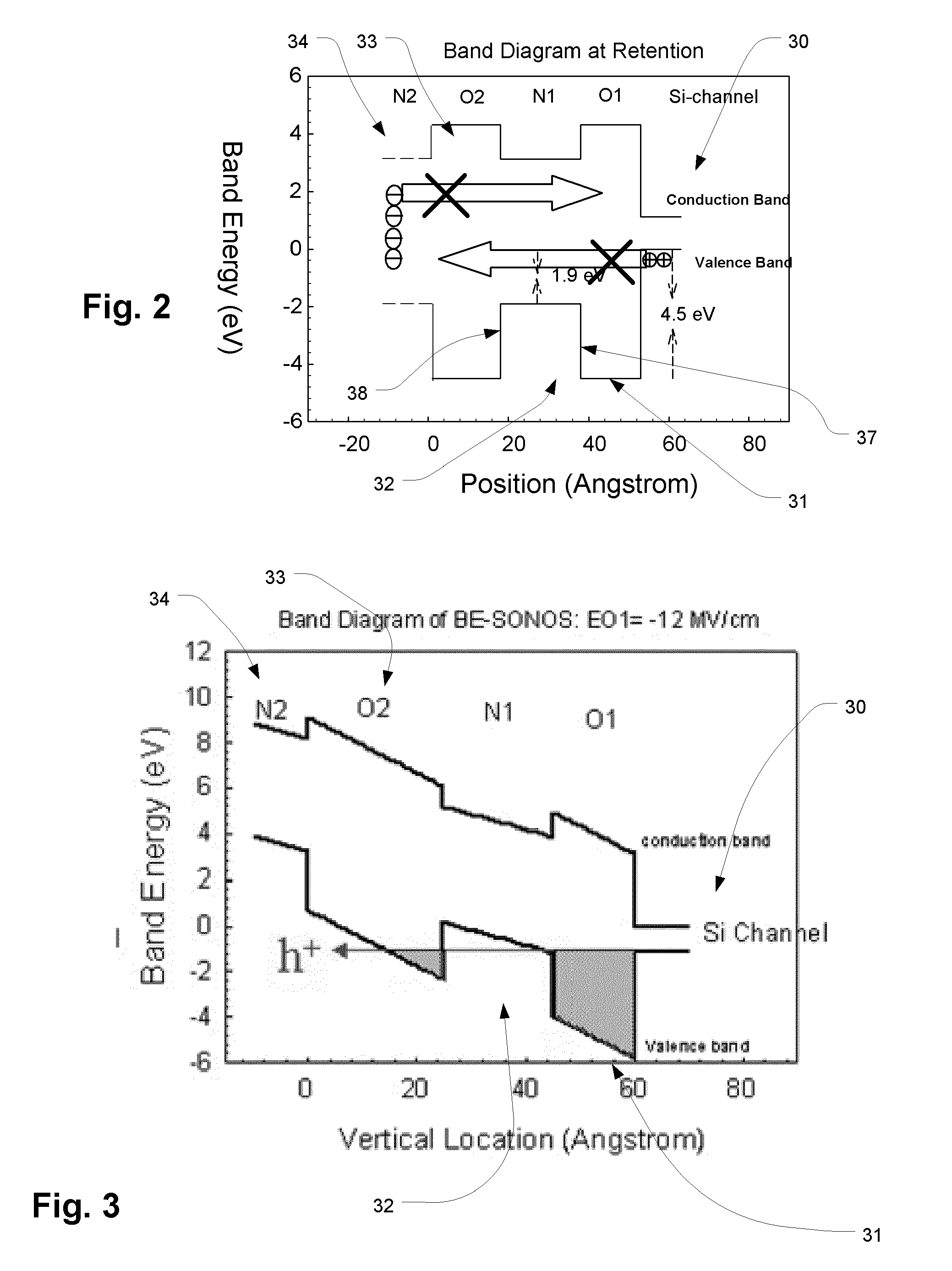

Blocking dielectric engineered charge trapping memory cell with high speed erase

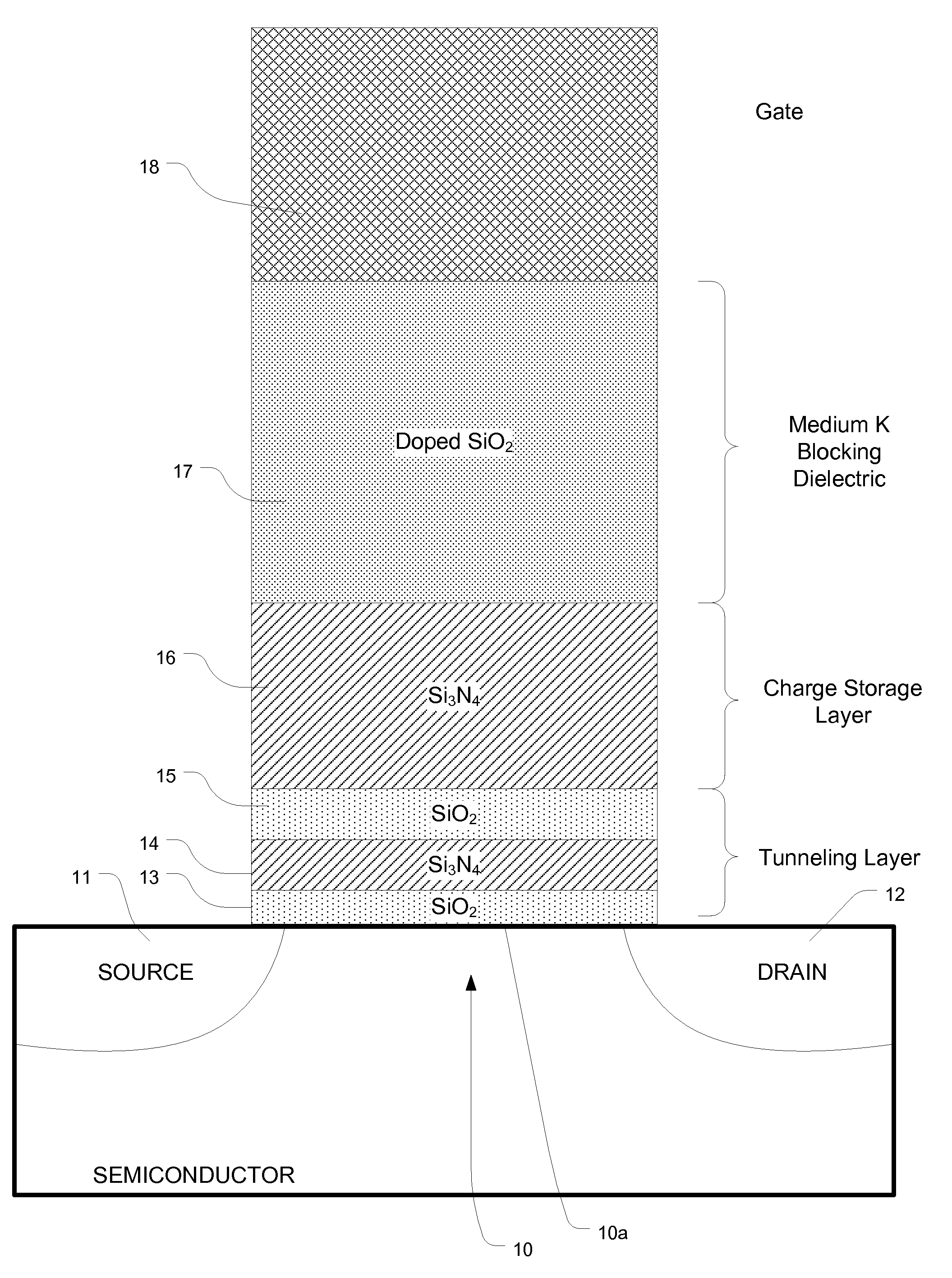

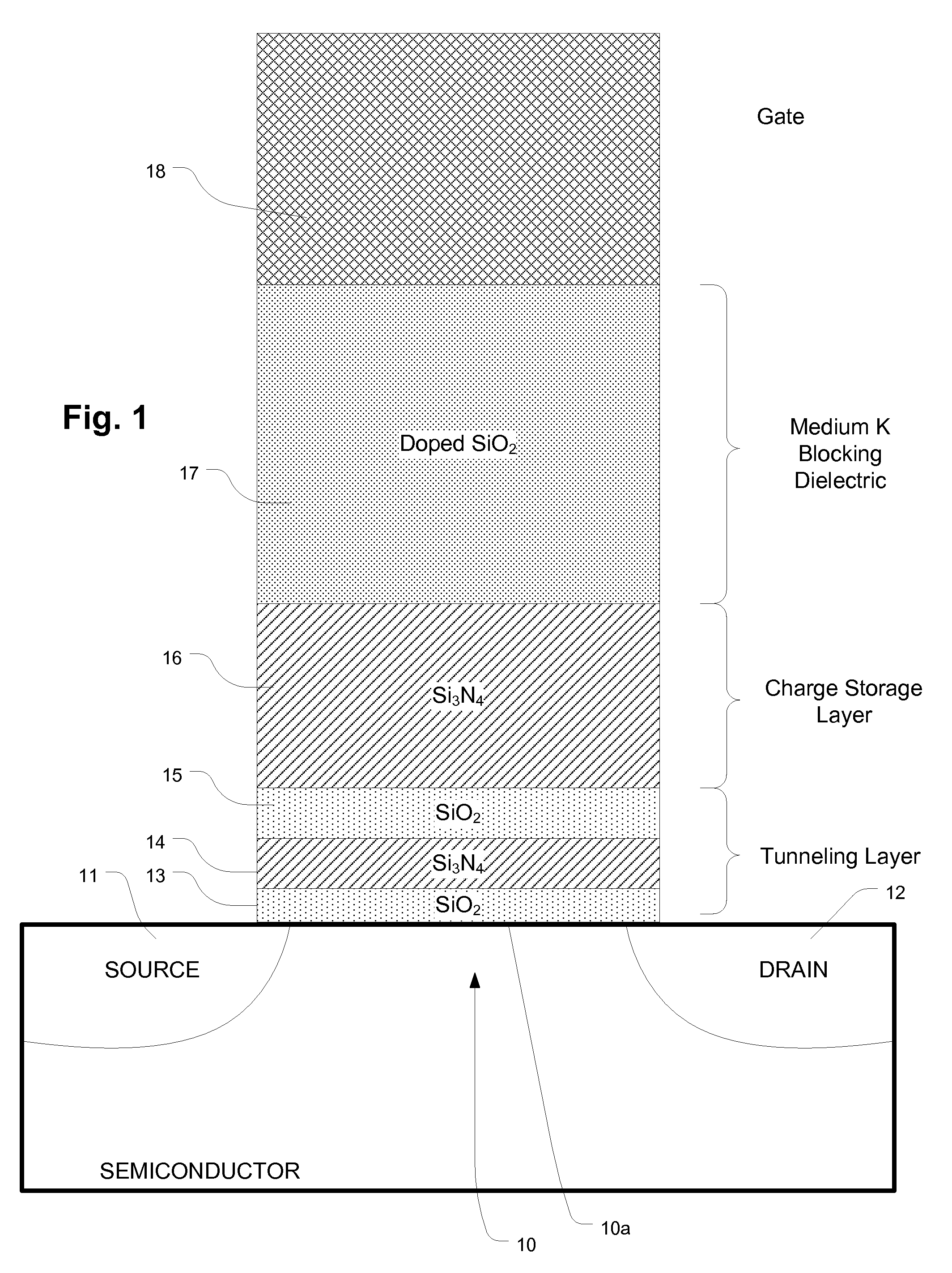

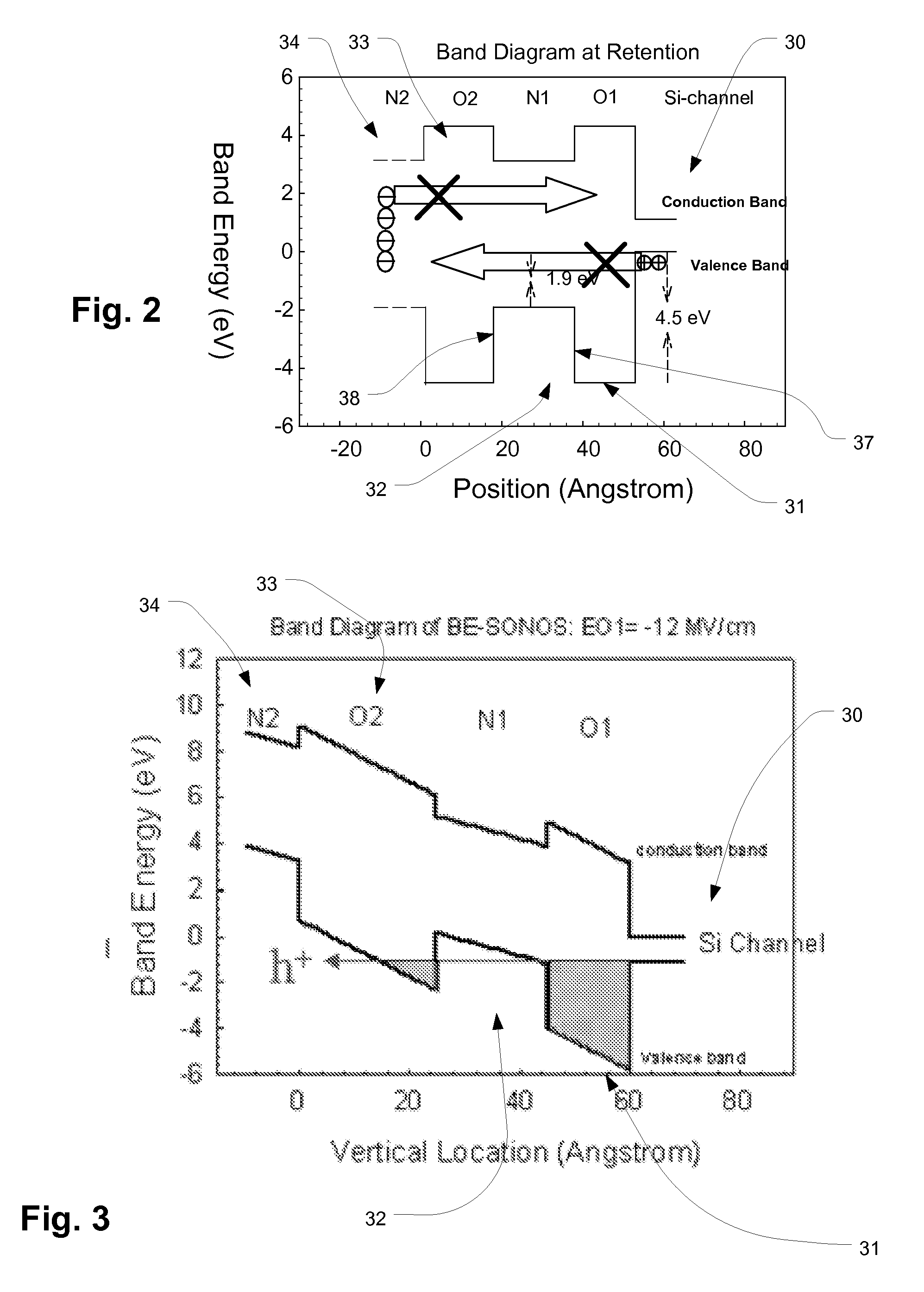

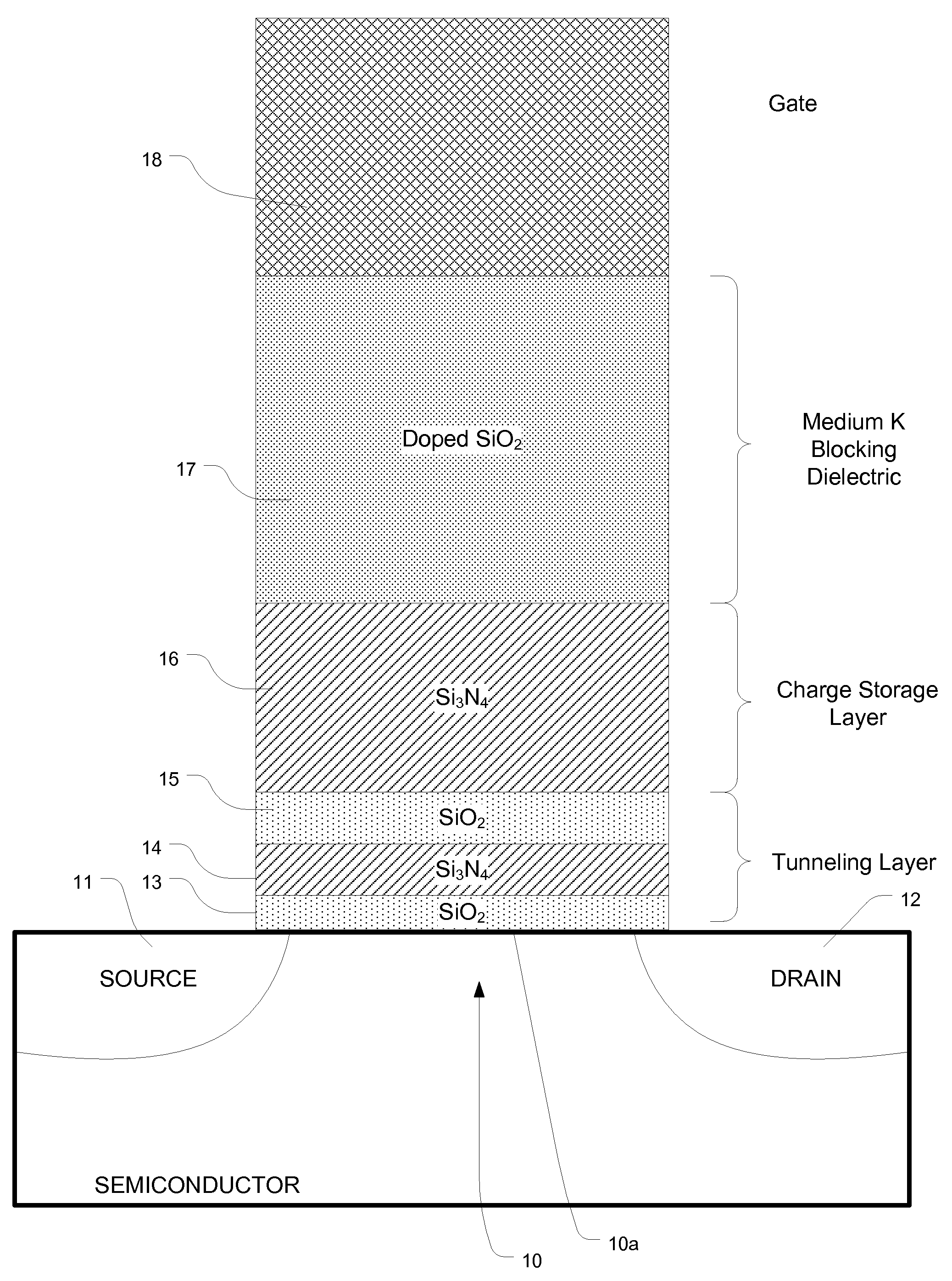

ActiveUS7737488B2High barrier heightFast programmingSolid-state devicesRead-only memoriesDielectricTrapping

A band gap engineered, charge trapping memory cell includes a charge trapping element that is separated from a gate by a blocking layer of metal doped silicon oxide material having a medium dielectric constant, such as aluminum doped silicon oxide, and separated from the semiconductor body including the channel by an engineered tunneling dielectric.

Owner:MACRONIX INT CO LTD

Blocking dielectric engineered charge trapping memory cell with high speed erase

ActiveUS20090039416A1Fast programmingImprove reliabilitySolid-state devicesRead-only memoriesDielectricTrapping

A band gap engineered, charge trapping memory cell includes a charge trapping element that is separated from a gate by a blocking layer of metal doped silicon oxide material having a medium dielectric constant, such as aluminum doped silicon oxide, and separated from the semiconductor body including the channel by an engineered tunneling dielectric.

Owner:MACRONIX INT CO LTD

Organic devices, organic electroluminescent devices and organic solar cells

ActiveUS8101857B2Lower barrier heightSolid-state devicesSemiconductor/solid-state device manufacturingOrganic devicesOrganic solar cell

An organic device, including an organic compound having charge-transporting ability (i.e., transporting holes and / or electrons) and / or including organic light emissive molecules capable of emitting at least one of fluorescent light or phosphorescent light, has a charge transfer complex-contained layer including a charge transfer complex formed upon contact of an organic hole-transporting compound and molybdenum trioxide via a manner of lamination or mixing thereof, so that the organic hole-transporting compound is in a state of radical cation (i.e., positively charged species) in the charge transfer complex-contained layer.

Owner:MITSUBISHI HEAVY IND LTD +1

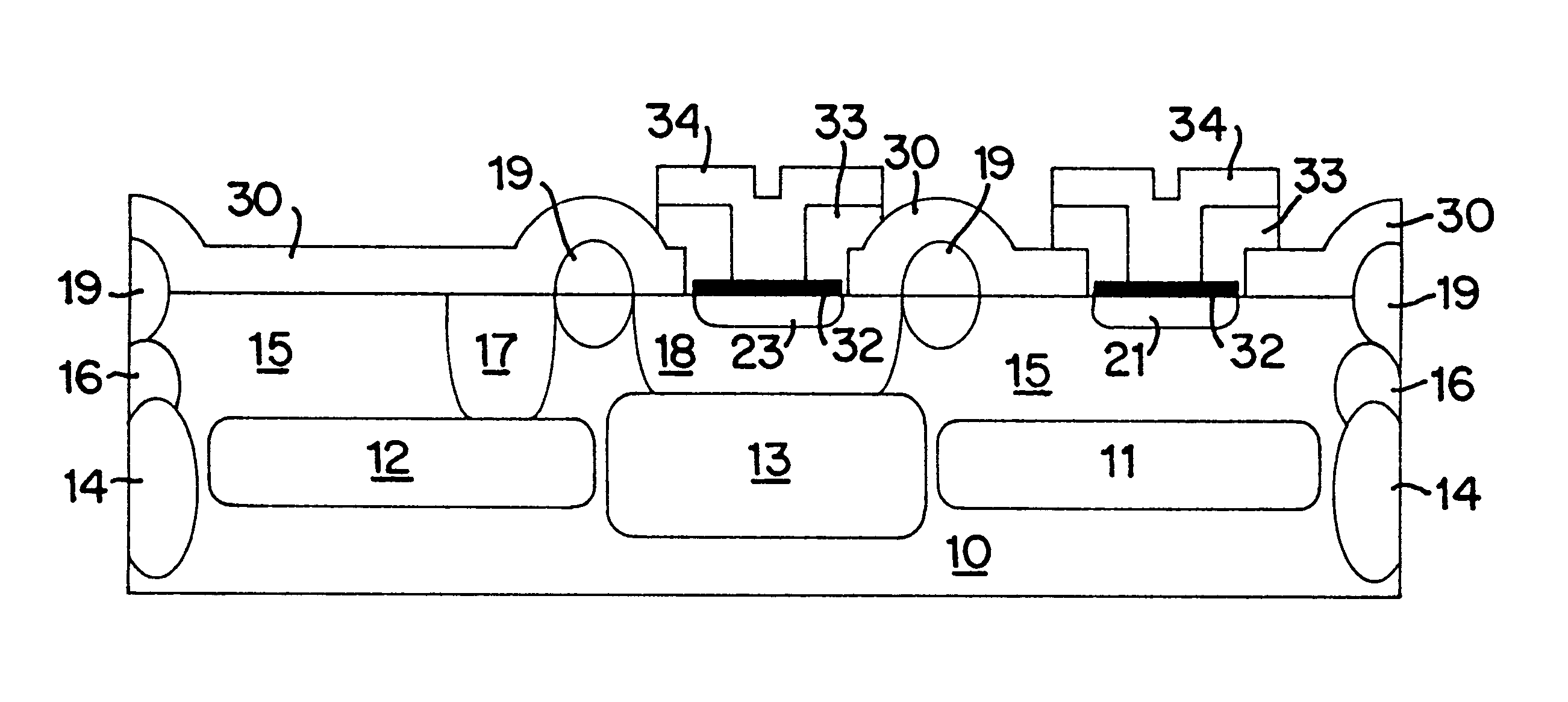

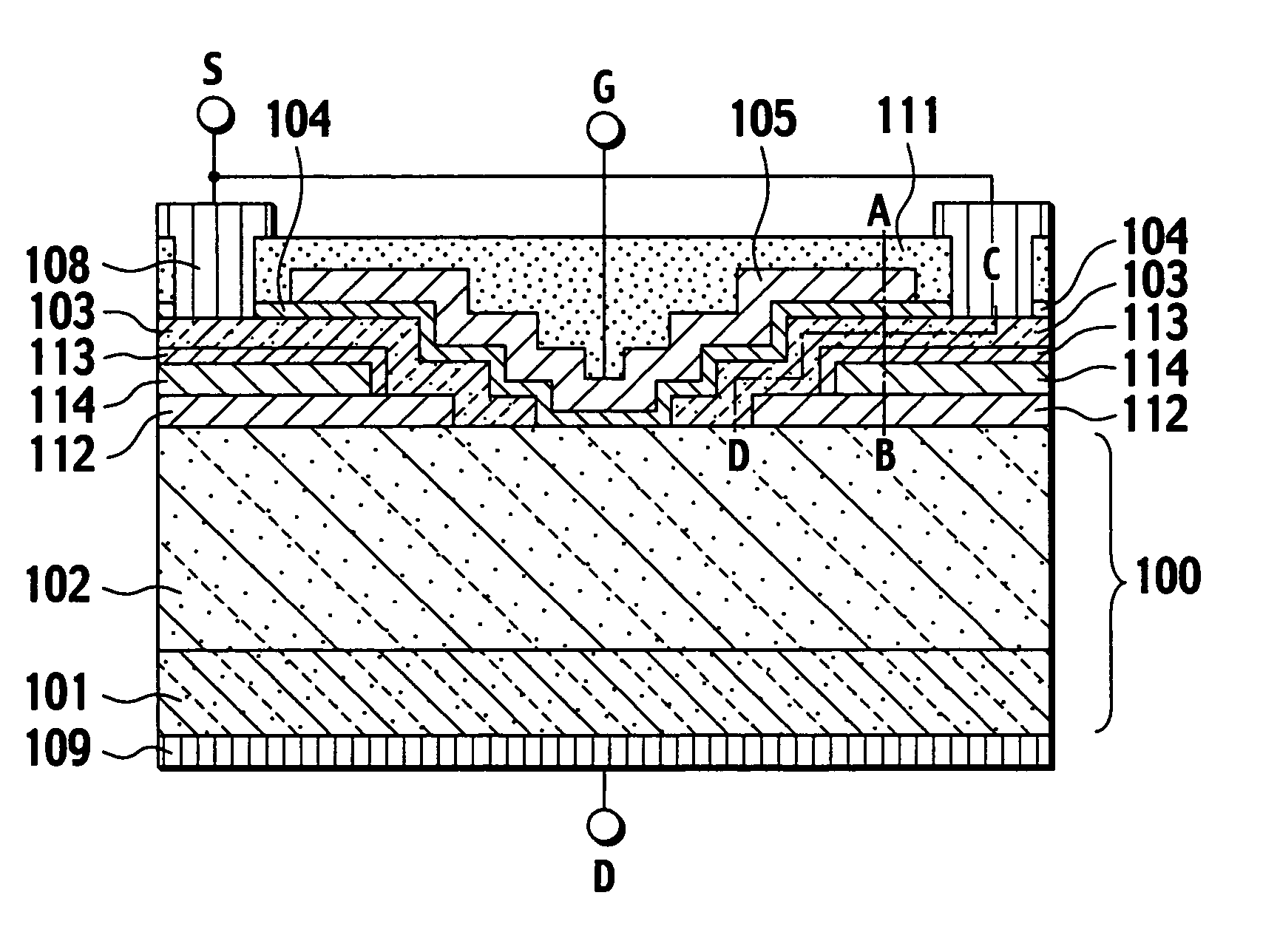

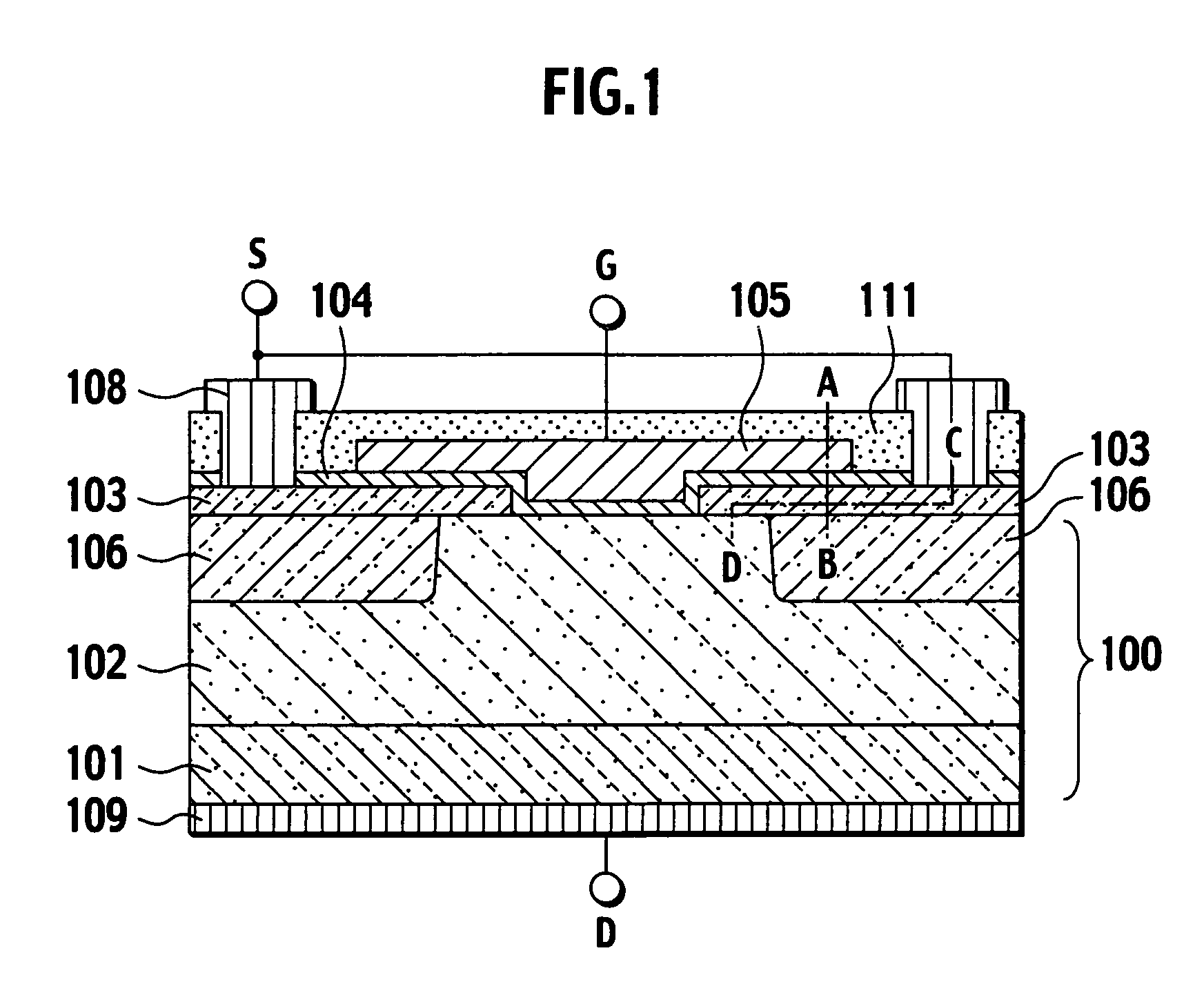

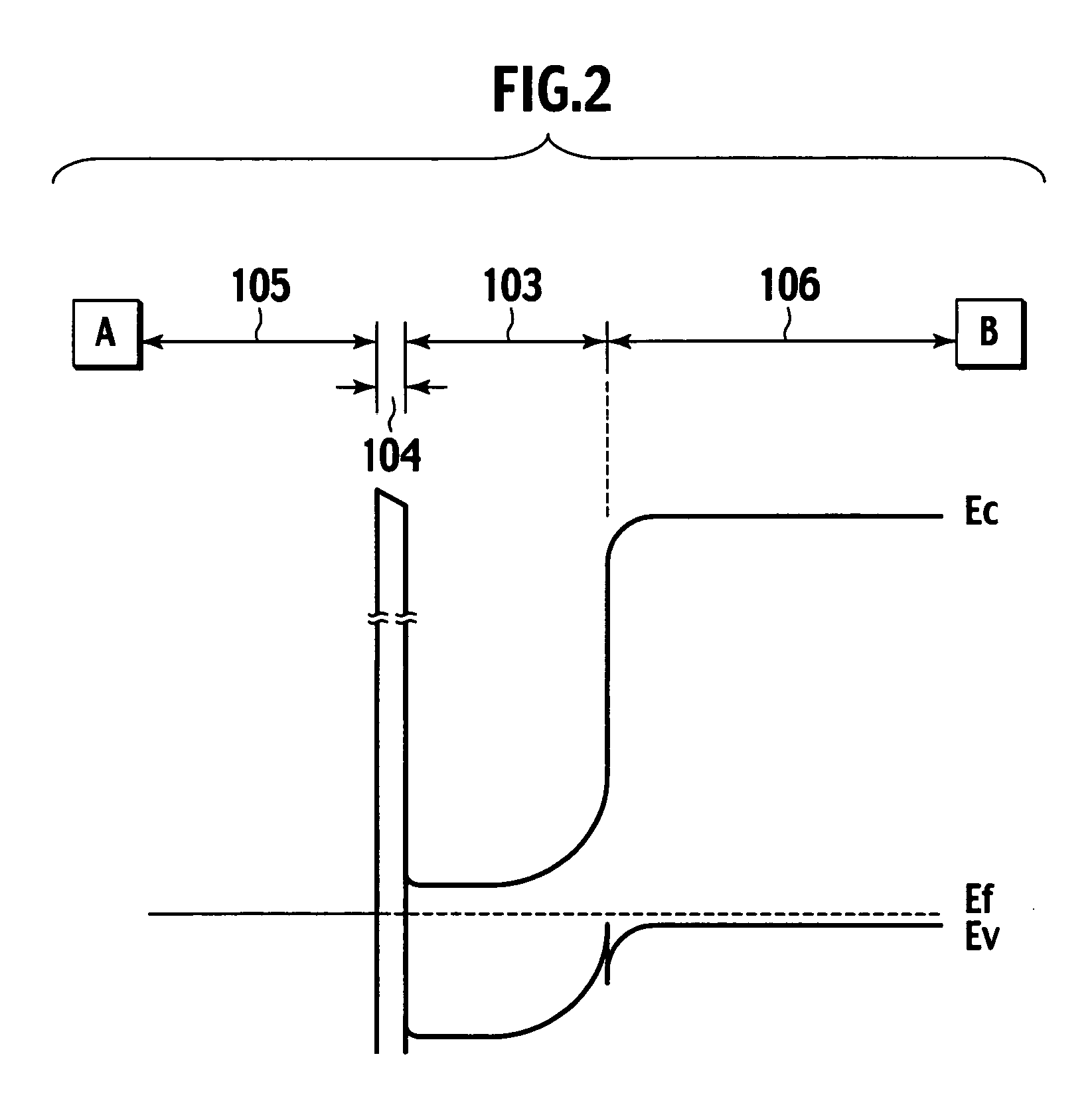

Semiconductor device with heterojunction

ActiveUS20050199873A1Lower barrier heightImprove transistor driving forceSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionContact formation

An aspect of the present invention provides a semiconductor device that includes a semiconductor base made of a first semiconductor material of a first conductivity type, a hetero-semiconductor region forming a heterojunction with the semiconductor base and made of a second semiconductor material having a different band gap from the first semiconductor material, a first gate electrode arranged in the vicinity of the heterojunction, a first gate insulating film configured to insulate the first gate electrode from the semiconductor base, a source electrode formed in contact with the hetero-semiconductor region, a dram electrode formed in contact with the semiconductor base, and an electric field extending region partly facing the first gate electrode, the first gate insulating film and hetero-semiconductor region interposed between the electric field extending region and the first gate electrode, the electric field extending region extending a built-in electric field into the hetero-semiconductor region.

Owner:NISSAN MOTOR CO LTD

Nitride semiconductor device and manufacturing method thereof

ActiveUS7777305B2Reduce parasitic resistanceLower barrier heightSemiconductor/solid-state device manufacturingSemiconductor devicesIsolation layerElectrode Contact

It is an object of the present invention to provide a nitride semiconductor device with low parasitic resistance by lowering barrier height to reduce contact resistance at an interface of semiconductor and metal. The nitride semiconductor device includes a GaN layer, a device isolation layer, an ohmic electrode, an n-type Al0.25Ga0.75N layer, a sapphire substrate, and a buffer layer. A main surface of the n-type Al0.25Ga0.75N layer is on (0 0 0 1) plane as a main surface, and concaves are arranged in a checkerboard pattern on the surface. The ohmic electrode contacts the sides of the concaves of the n-type Al0.25Ga0.75N layer, and the sides of the concaves are on non-polar surfaces such as (1 1 −2 0) plane or (1 −1 0 0) plane.

Owner:PANASONIC CORP

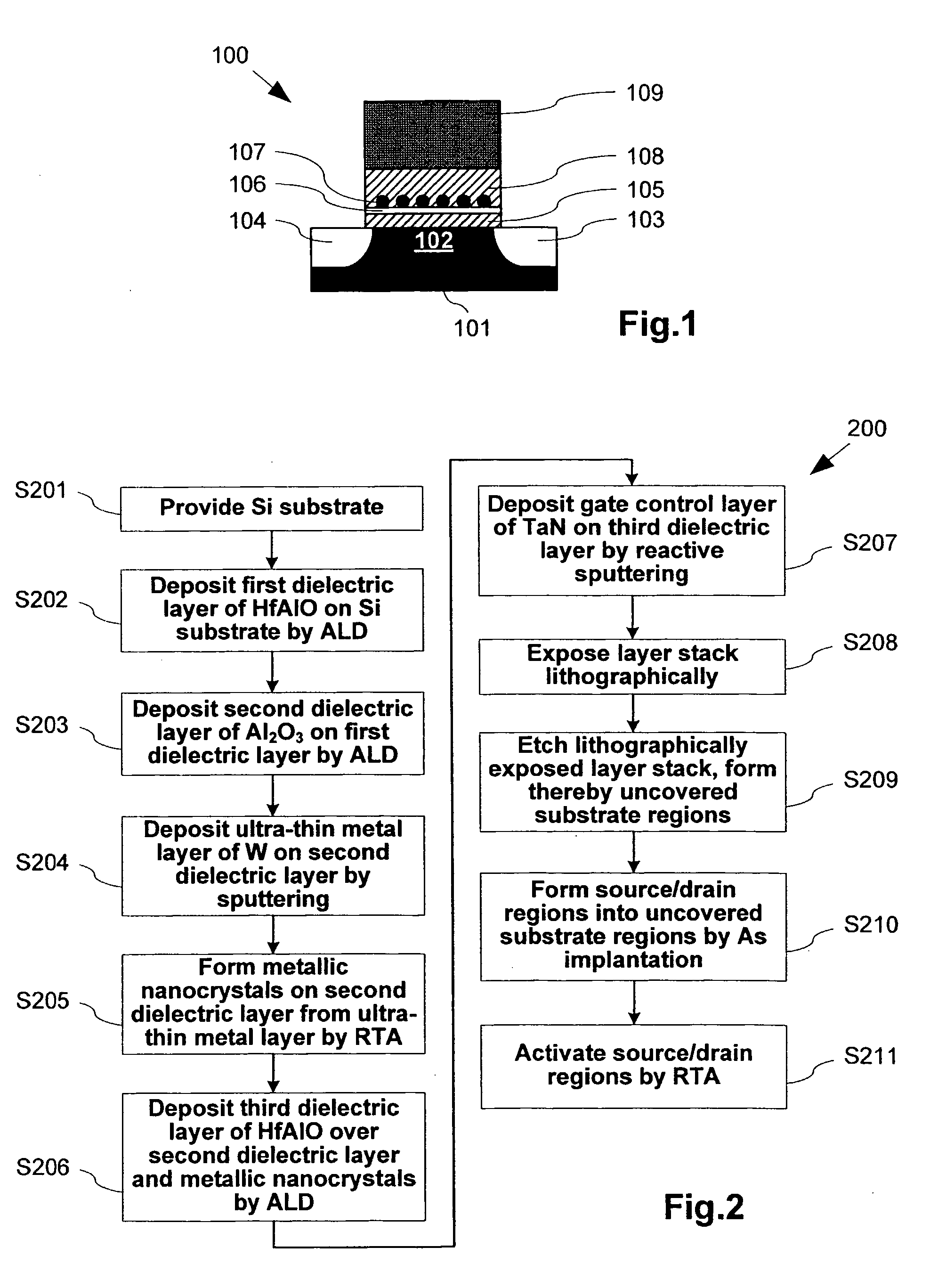

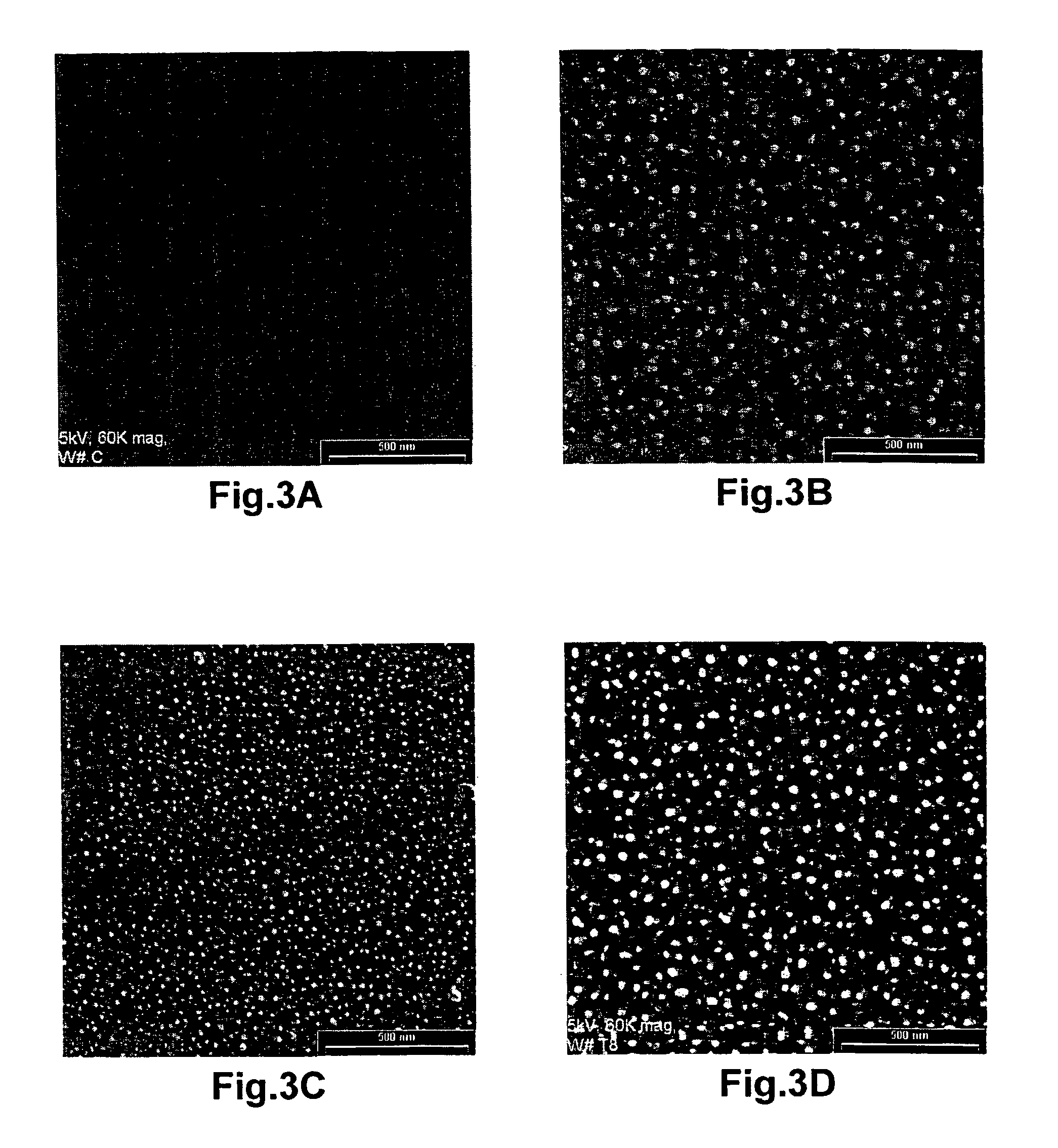

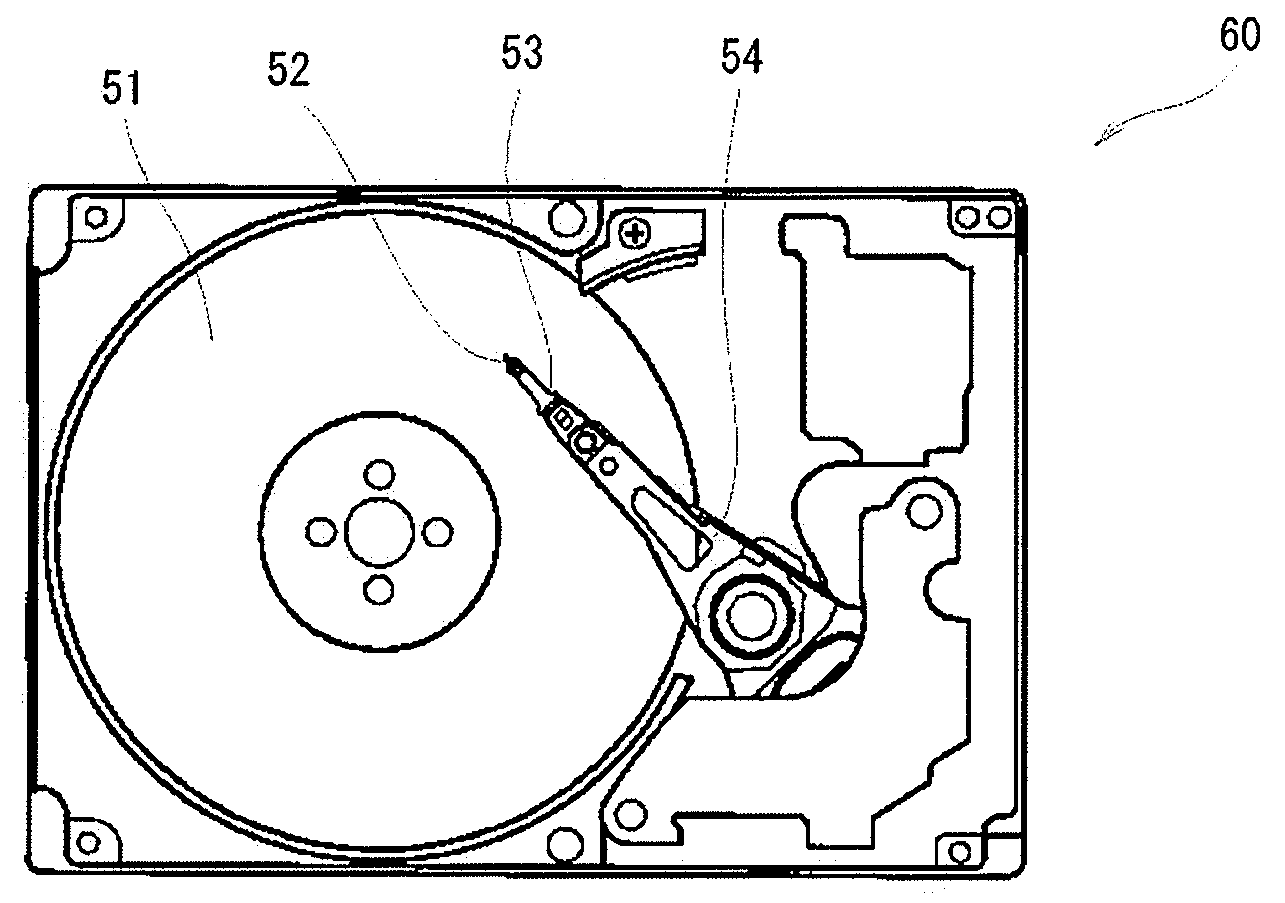

Nonvolatile flash memory device and method for producing the same

InactiveUS20090189215A1Improve programming efficiencyRestrain charge lossNanoinformaticsSemiconductor/solid-state device manufacturingThin metalCharge carrier

Owner:NAT UNIV OF SINGAPORE

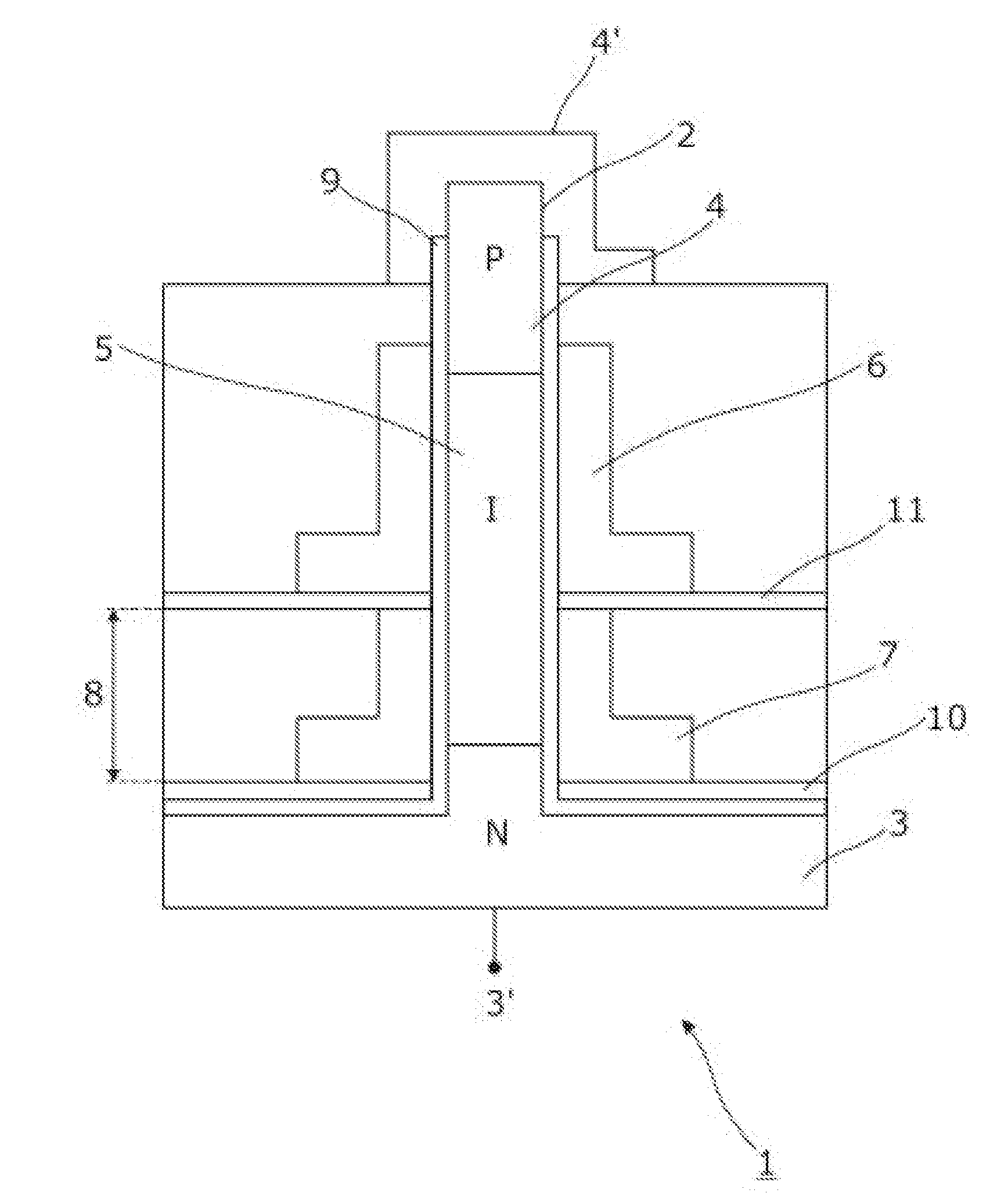

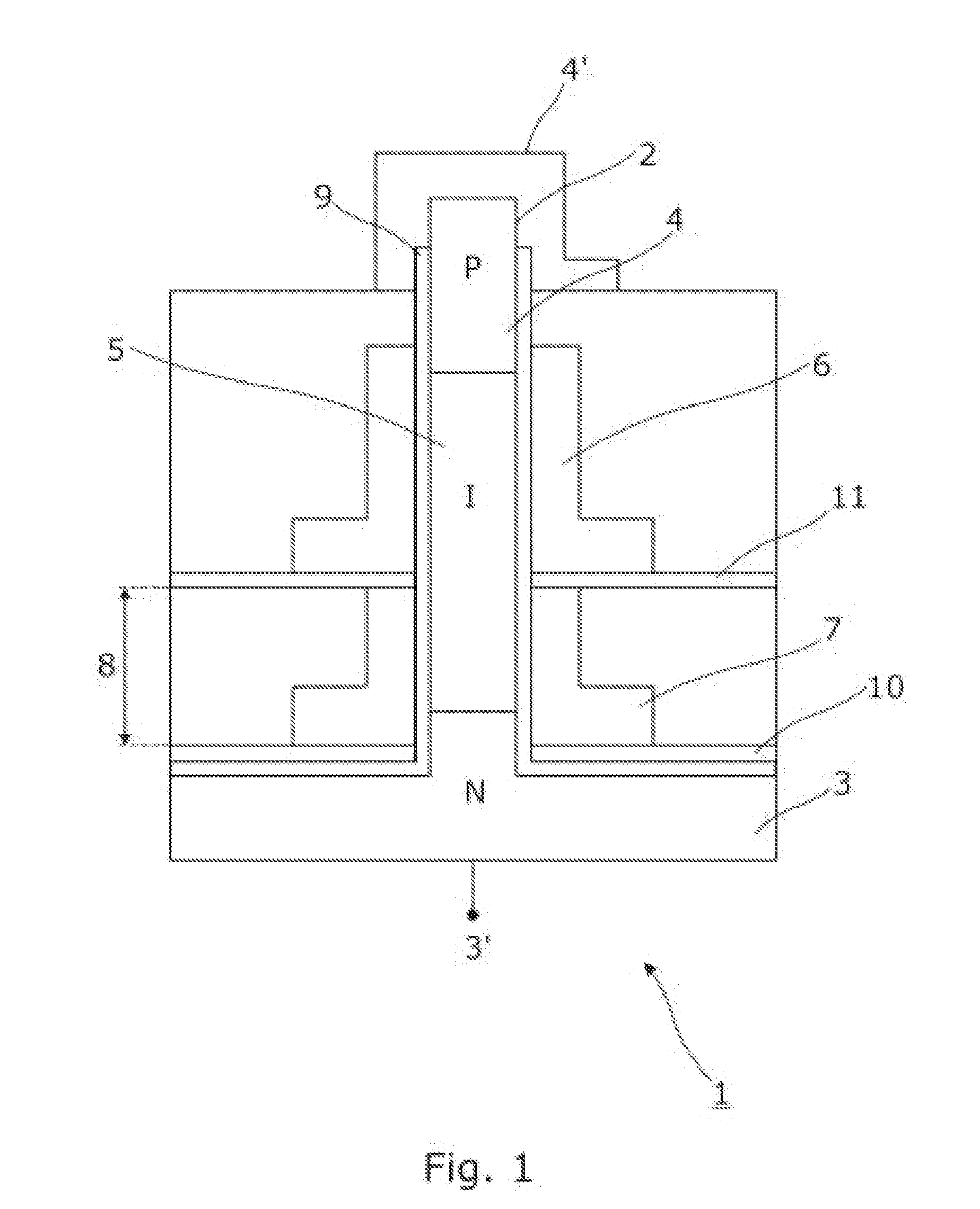

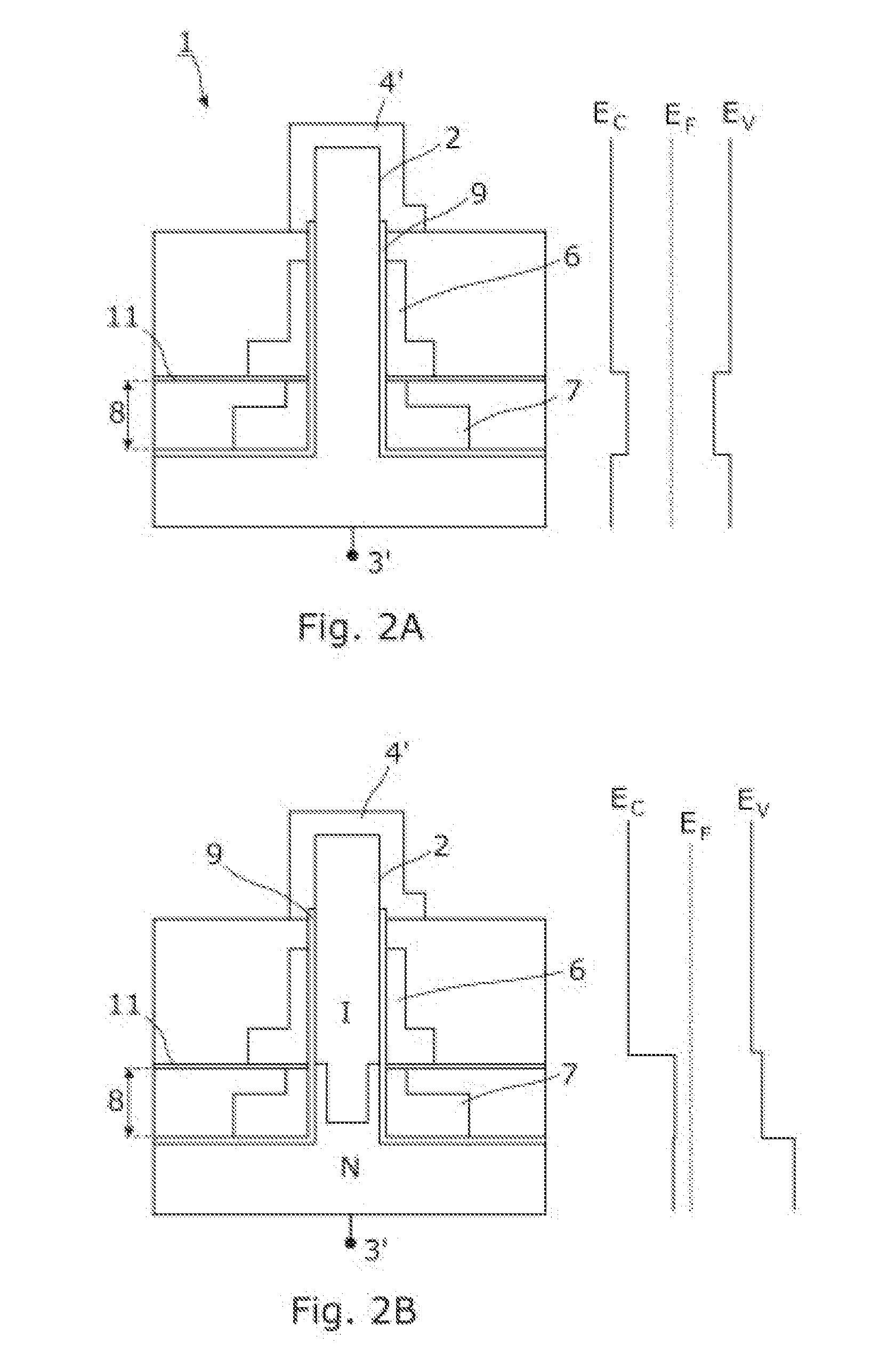

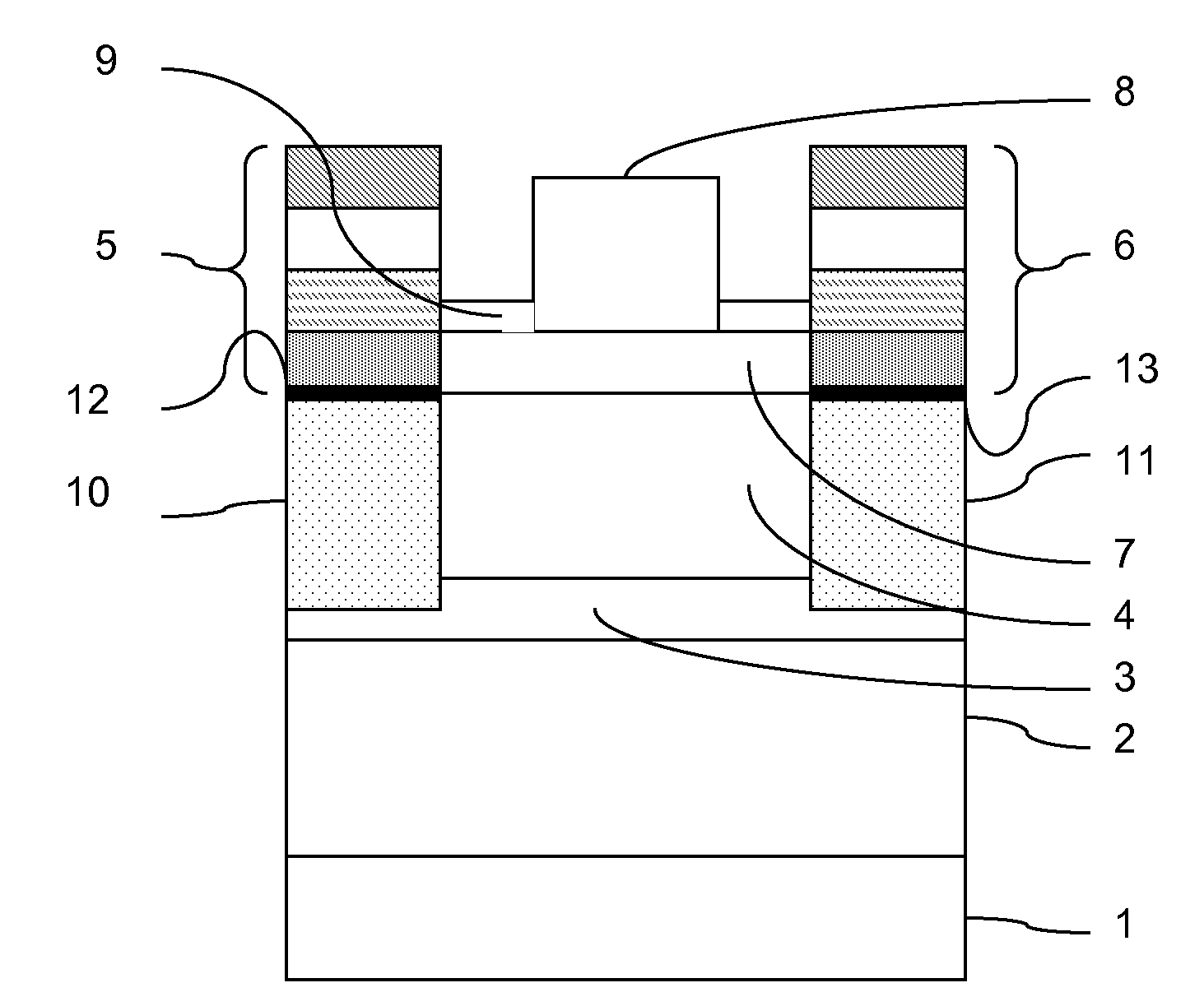

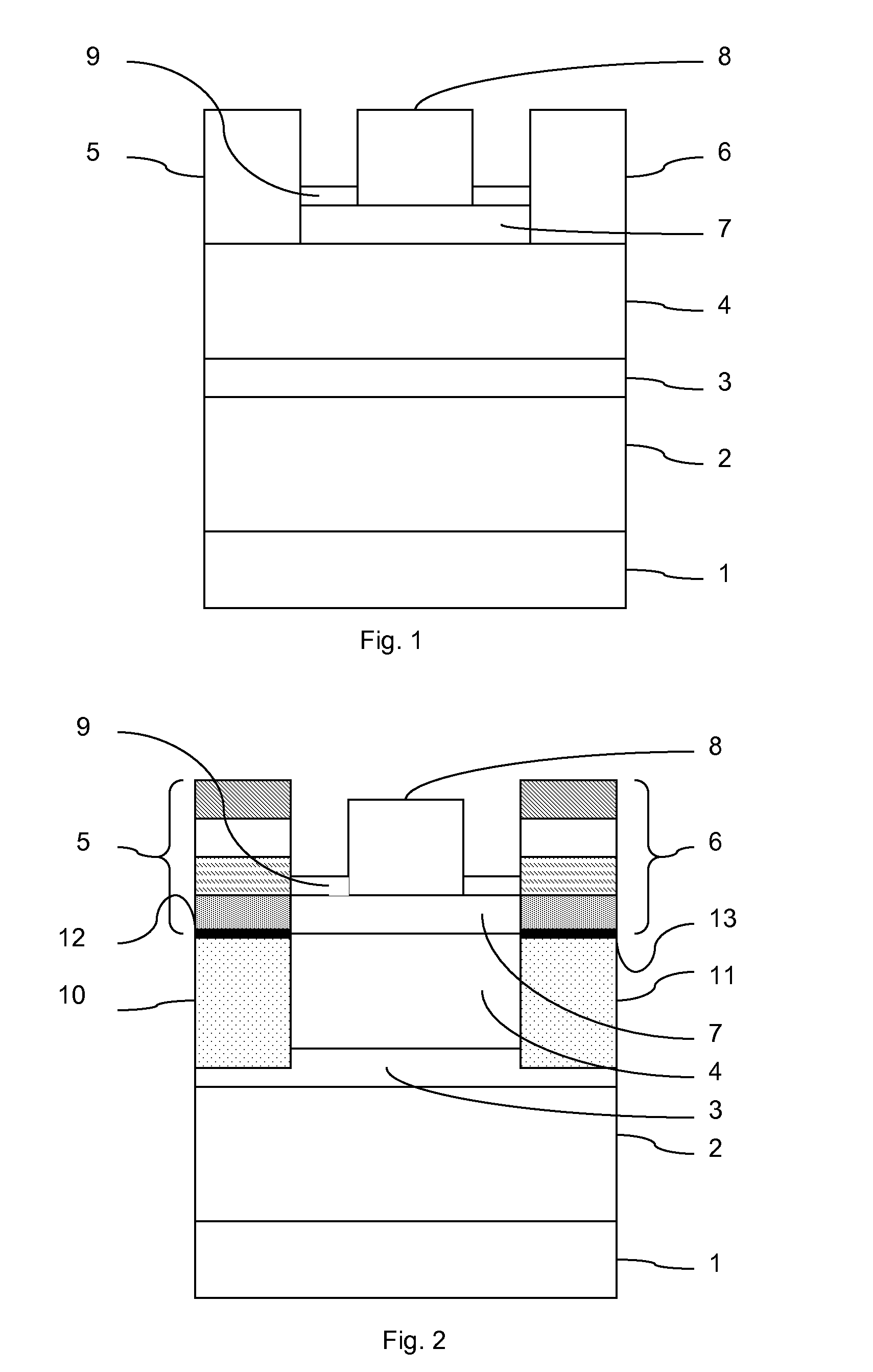

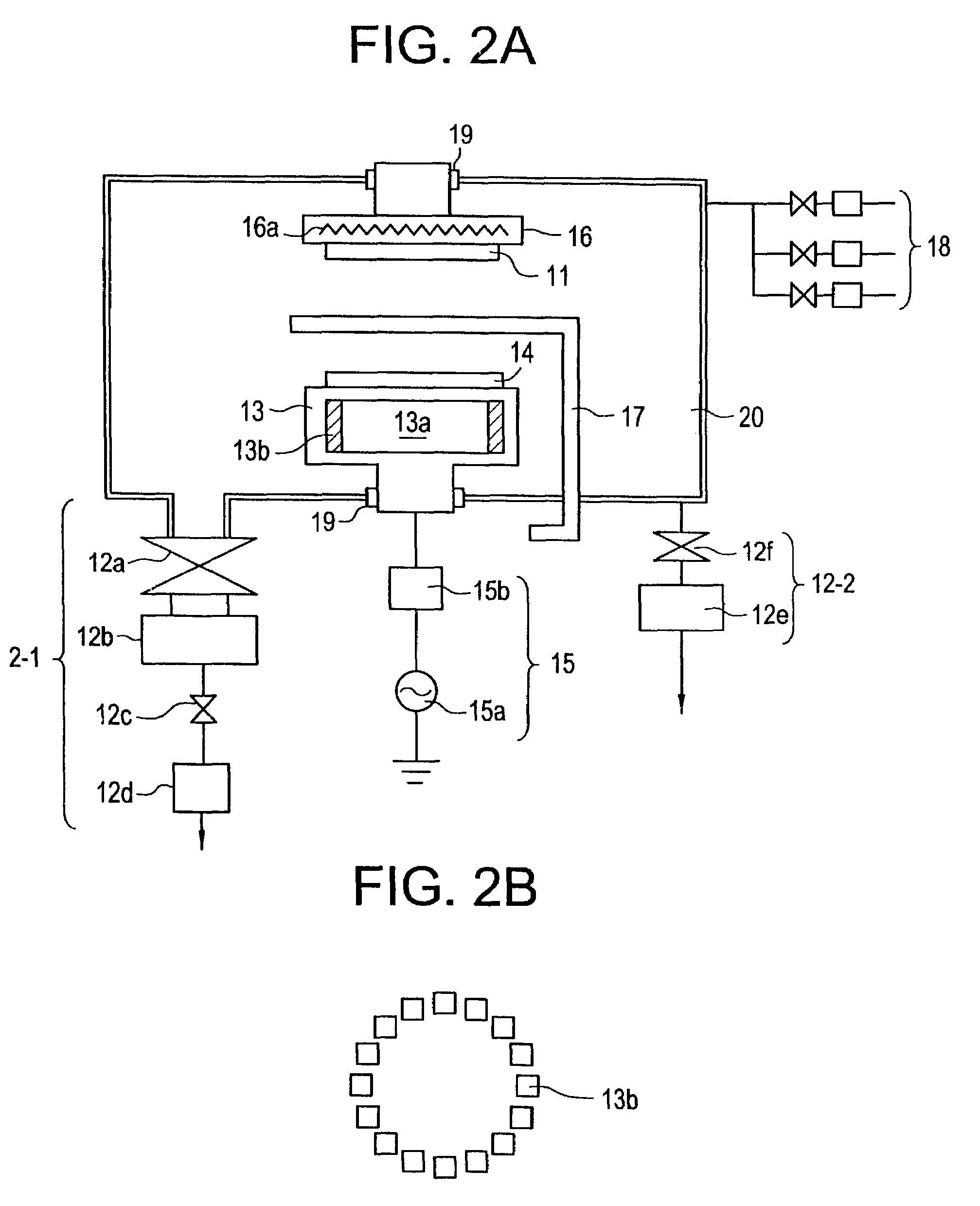

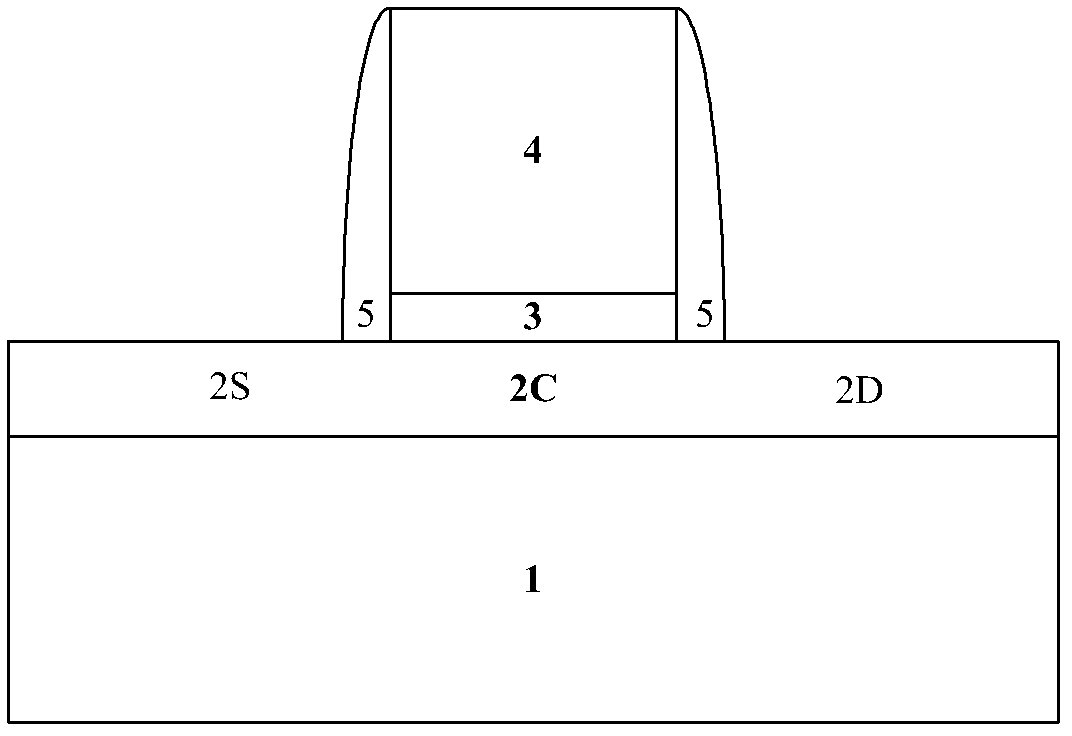

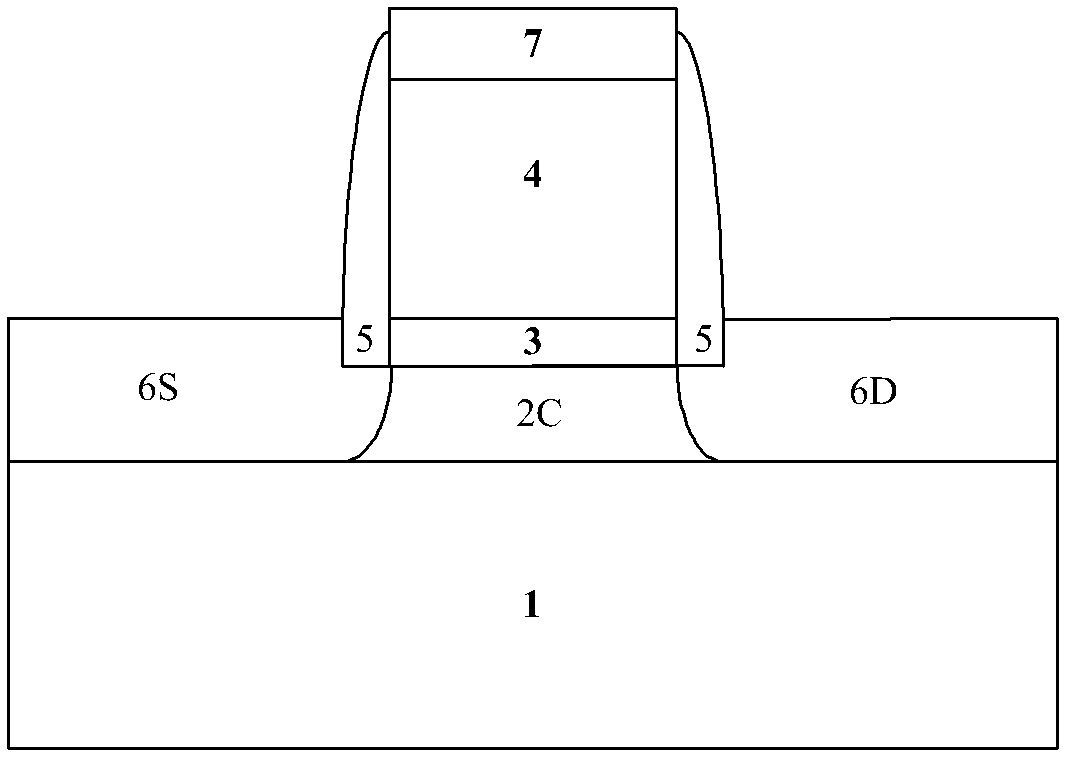

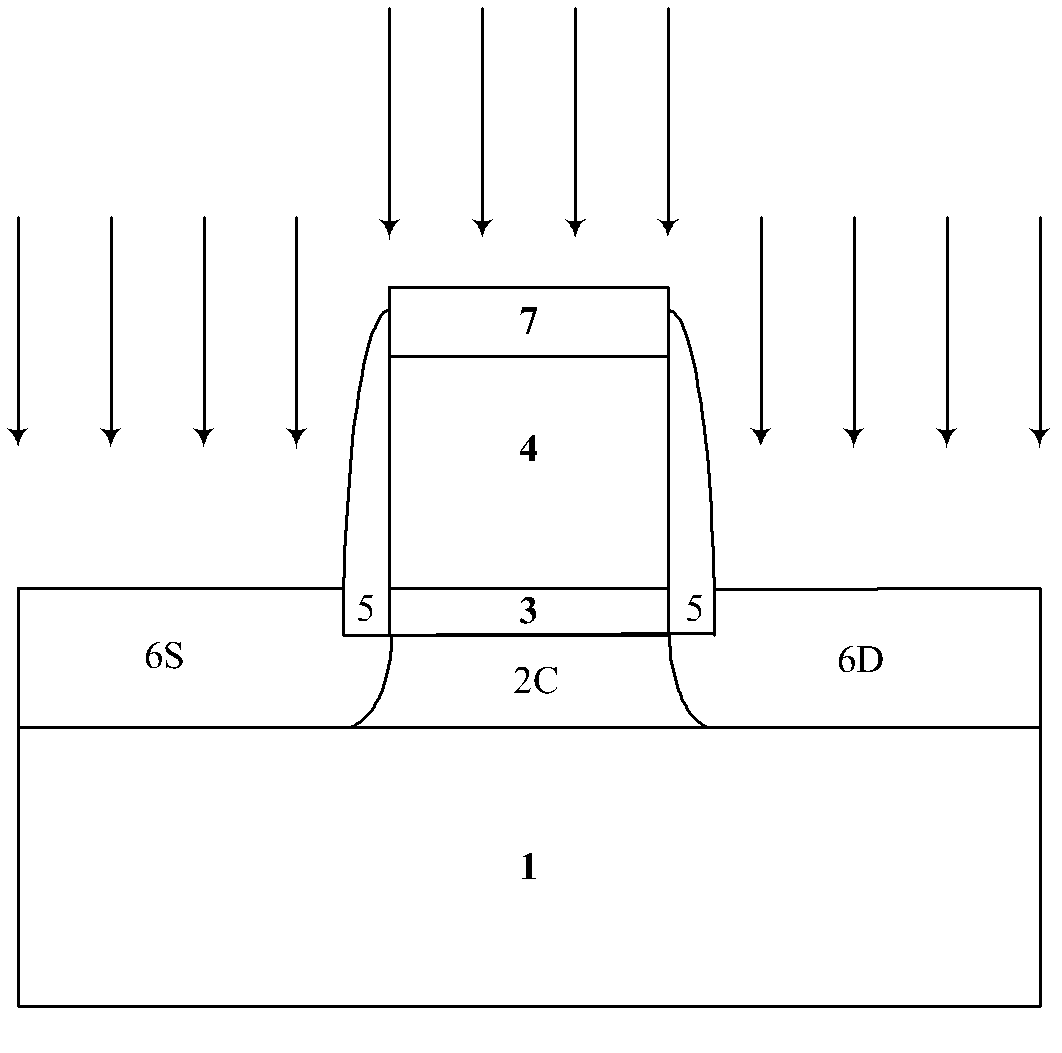

Nanowire field-effect device with multiple gates

InactiveUS20130264544A1Improve tunneling efficiencyIncrease ratingsNanoinformaticsSemiconductor/solid-state device manufacturingSemiconductor materialsNanowire

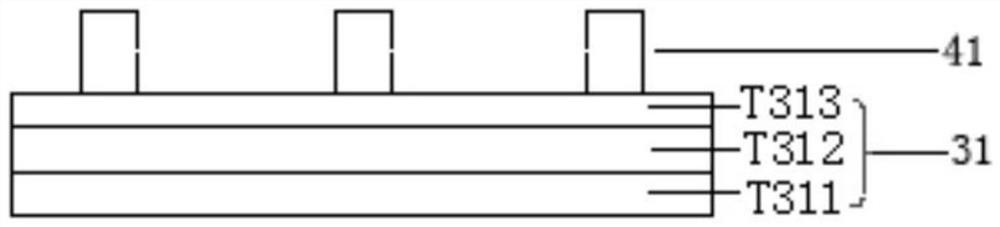

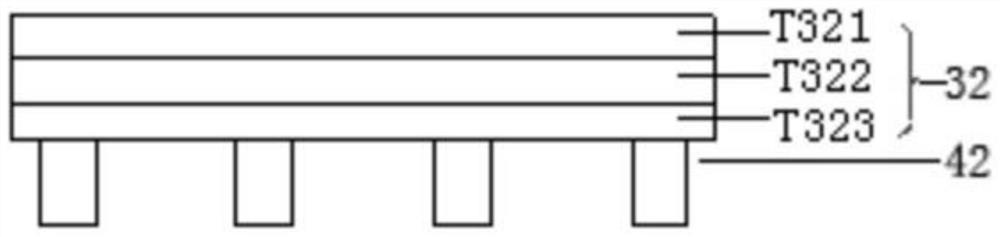

The present invention relates to a semiconductor device (1) comprising: at least a nanowire (2) configured to comprise: at least a source region (3) comprising a corresponding source semiconductor material, at least a drain region (4) comprising a corresponding drain semiconductor material and at least a channel region (5) comprising a corresponding channel semiconductor material, the channel region (5) being arranged between the source region (3) and the drain region (4), at least a gate electrode (6) that is arranged relative to the nanowire (2) to circumferentially surround at least a part of the channel region (5), and at least a strain gate (7) that is arranged relative to the nanowire (2) to circumferentially surround at least a part of a segment of the nanowire (2), the strain gate (7) being configured to apply a strain to the nanowire segment (8), thereby to facilitate at least an alteration of the energy bands corresponding to the source region (3) relative to the energy bands corresponding to the channel region (5).

Owner:IBM CORP

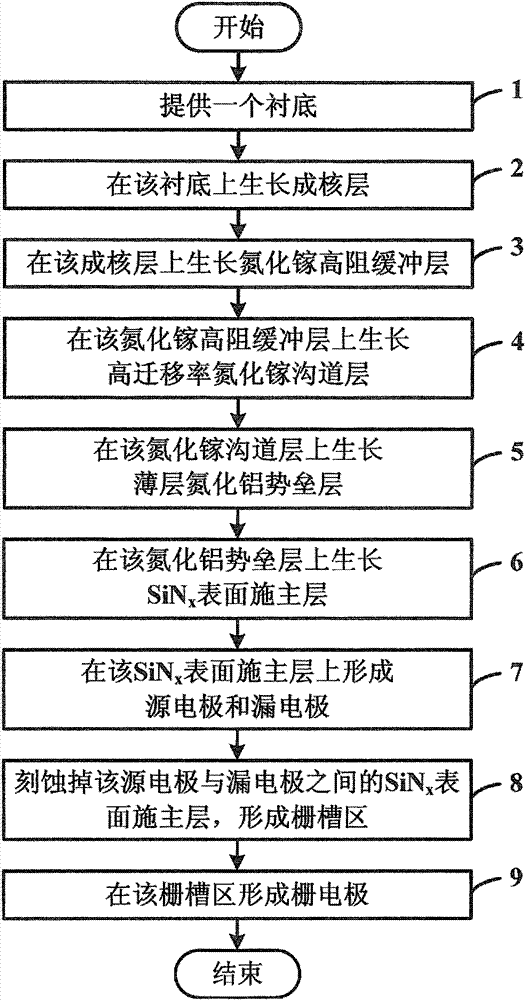

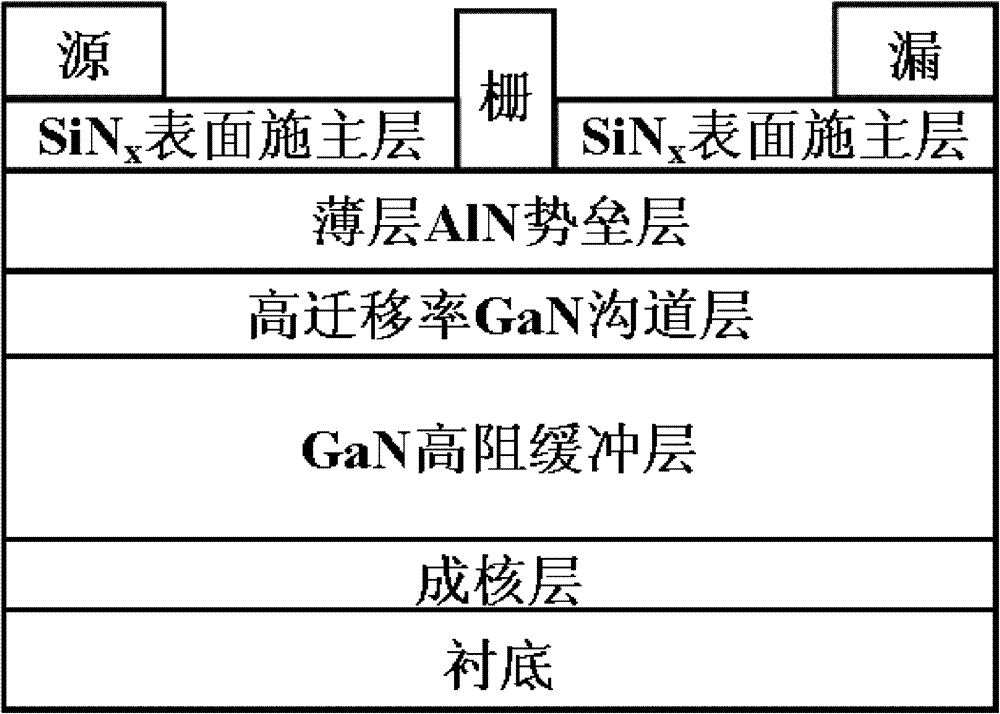

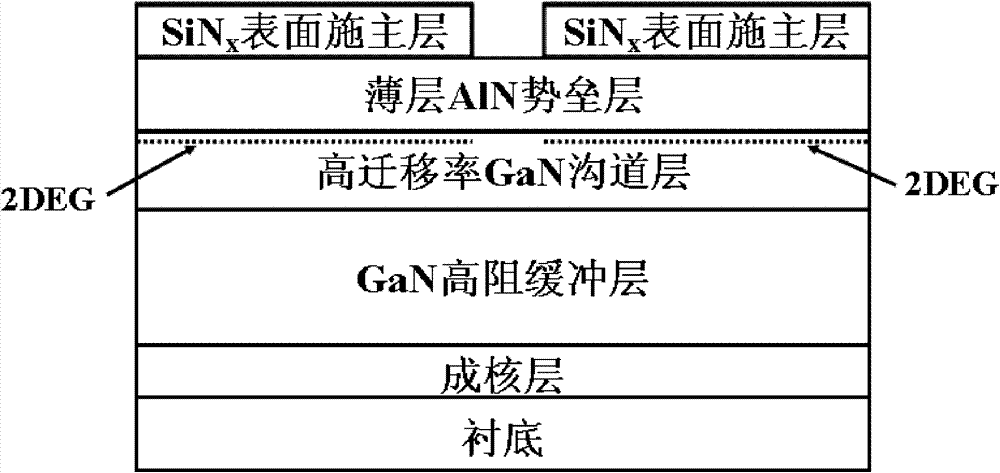

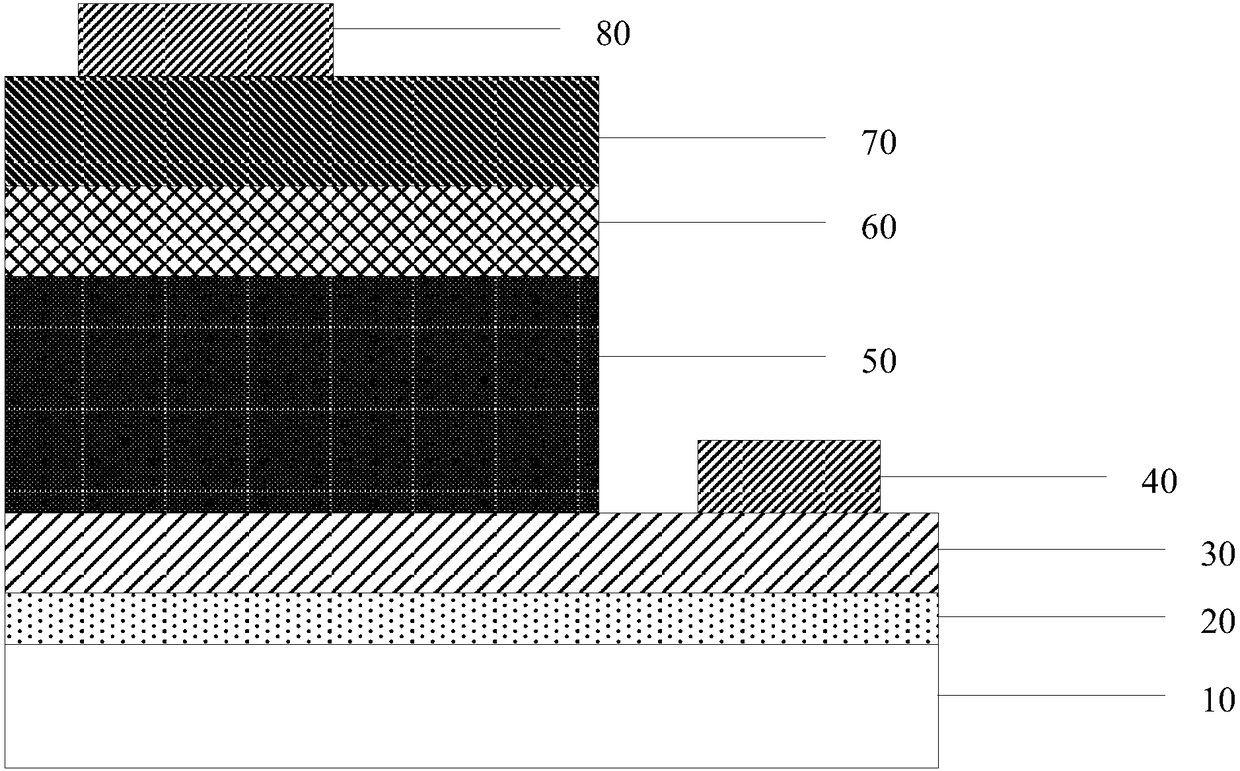

Enhanced A1N/GaN high-electron mobility transistor and fabrication method thereof

InactiveCN102789982ALow costSimple processSemiconductor/solid-state device manufacturingSemiconductor devicesGallium nitrideElectron mobility

The invention relates to the technical field of a semiconductor, and discloses an enhanced A1N / GaN high-electron mobility transistor and a fabrication method of the enhanced A1N / GaN high-electron mobility transistor. The fabrication method comprises the steps of: providing a substrate, planting a nucleating layer on the substrate; planting a gallium nitride high-resistance buffer layer on the nucleating layer; planting a high-mobility gallium nitride groove layer on the gallium nitride high-resistance buffer layer; planting a thin-layer aluminum nitride barrier layer on the gallium nitride groove layer; planting a SiNx surface donor layer on the aluminum nitride barrier layer; forming a source electrode and a drain electrode on the SiNx surface donor layer; and etching the SiNx surface donor layer between the source electrode and the drain electrode to form a grid groove area, and forming a grid electrode in the grid groove area. The ultra-thin A1N barrier layer under the grid can not form two-dimensional electronic gas in the groove, so that the overall groove is cut off, and an enhanced HEMT (high electron mobility transistor) apparatus is formed. The enhanced A1N / GaN high-electron mobility transistor can be applied to the fields such as a high-power power switch, a micro-wave switch and a digital circuit.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

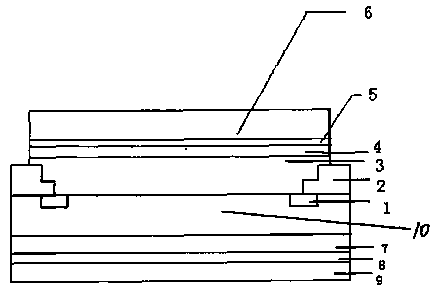

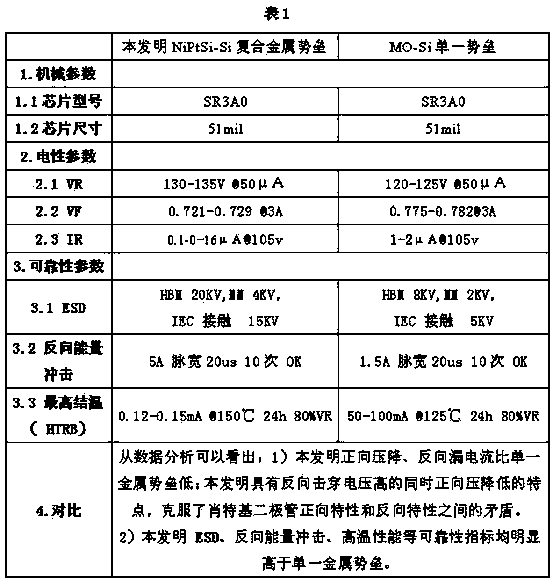

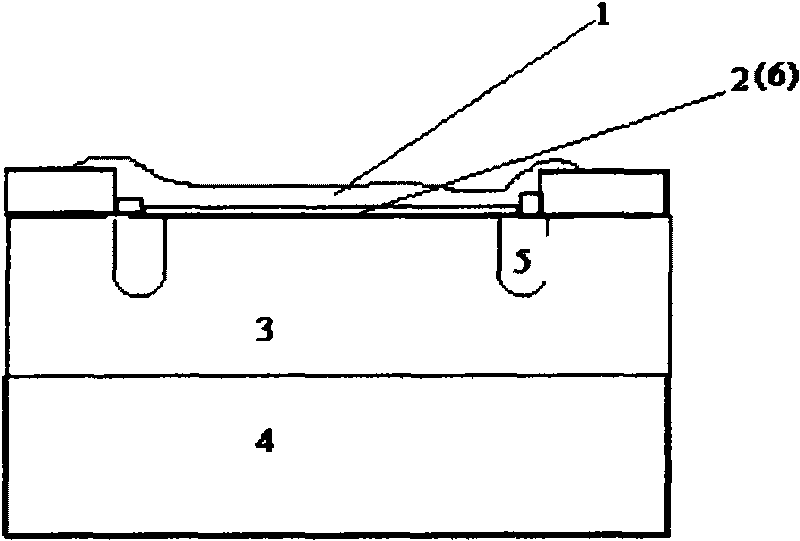

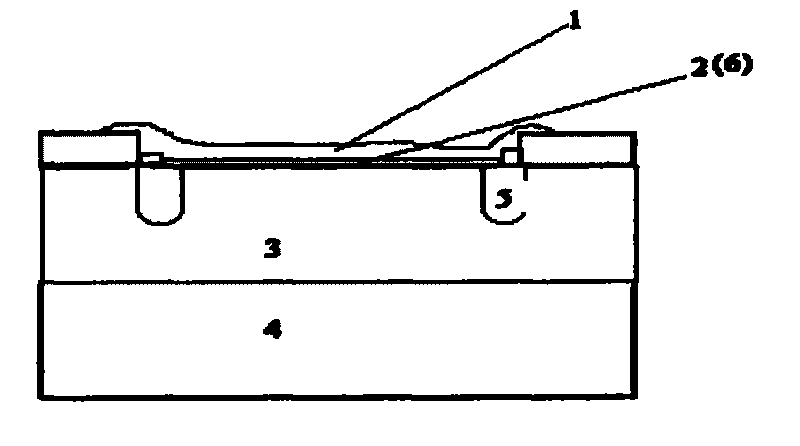

Schottky diode chip, Schottky diode device and manufacturing method for Schottky diode chip-composite barrier

ActiveCN103681885ABlocking mutual expansionImprove fatigue resistanceSemiconductor/solid-state device manufacturingDiodeSchottky barrierMetal silicide

The invention discloses a Schottky diode chip, a Schottky diode device and a manufacturing method for a Schottky diode chip-composite barrier. The Schottky diode chip comprises an N-type silicon semiconductor substrate; the obverse side of the semiconductor substrate is provided with a NiPtSi barrier layer, and the barrier layer makes direct contact with the semiconductor substrate to form a NiPtSi-Si barrier. The manufacturing method is simple, low in cost, practical and effective; NiPt alloy is adopted as Schottky barrier metal, and the composite metal silicide-silicon contact barrier (NiPtSi-Si) is formed; the obtained chip and the device eliminate the contradiction between forward voltage drop and reverse electric leakage with regard to a single-metal barrier, the reverse electric leakage and the forward voltage drop are both low, and meanwhile high-temperature resistant performance, antistatic performance, reverse energy impact performance and the like are well improved.

Owner:济南市半导体元件实验所

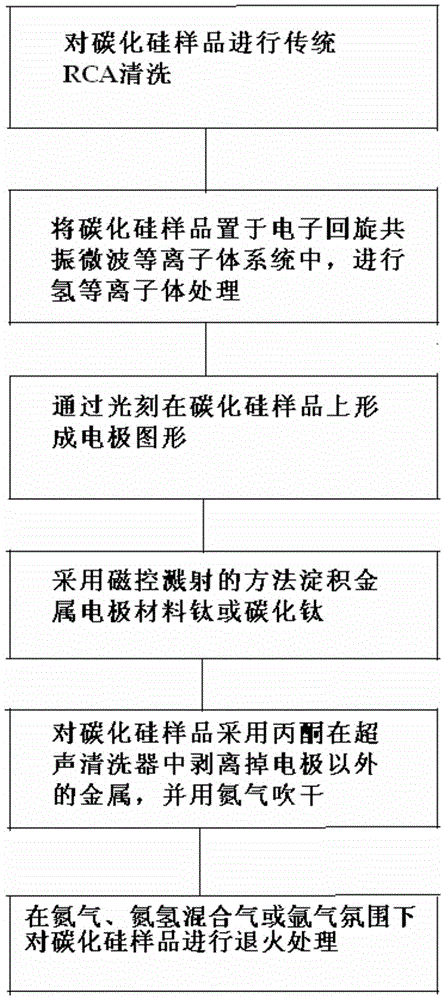

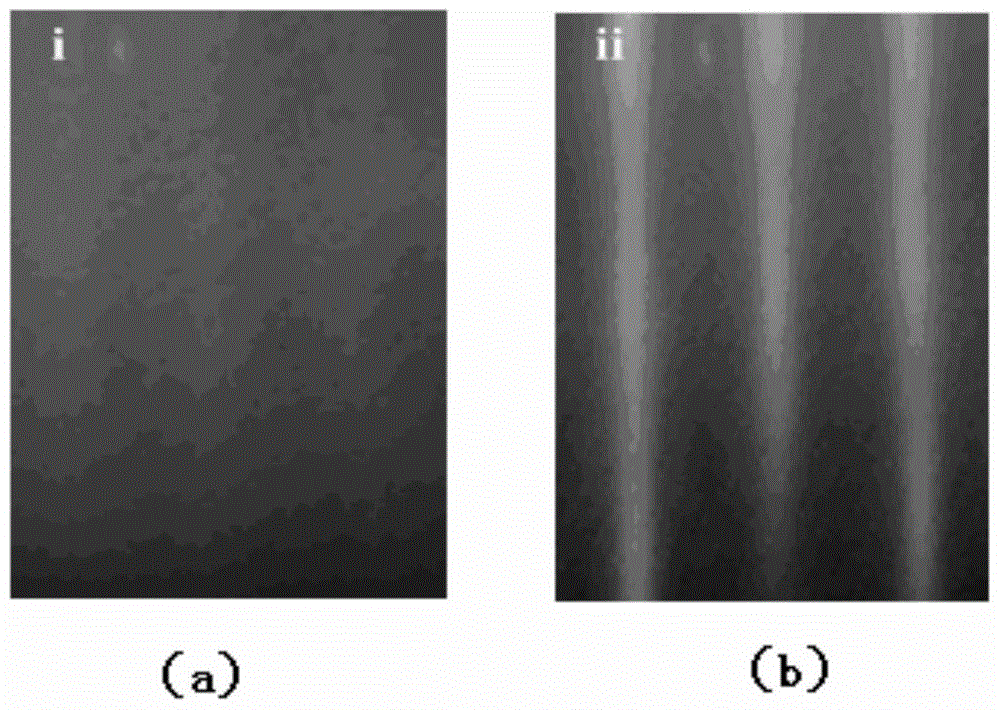

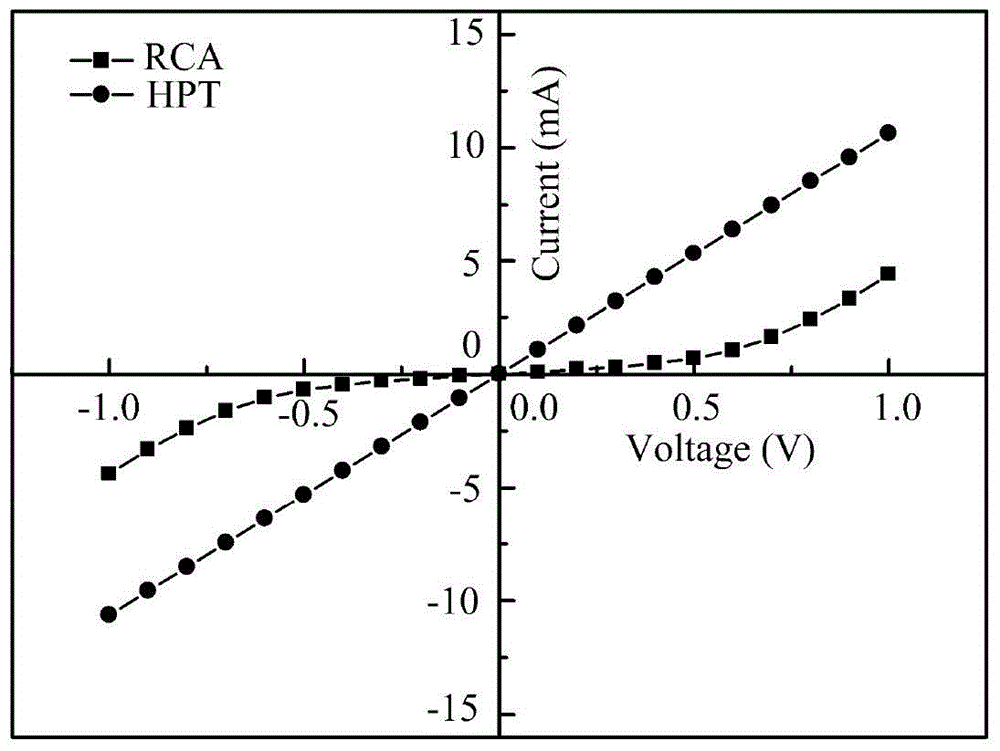

Method for increasing ohmic contact characteristic of silicon carbide semiconductor

InactiveCN105702712AEffective cleaning and passivationDecrease the density of surface statesSemiconductor devicesRCA cleanTitanium carbide

The invention relates to the field of microelectronic technology, a method for improving the ohmic contact characteristics of a silicon carbide semiconductor, comprising the following steps: (1) performing traditional RCA cleaning on a silicon carbide sample; (2) placing the silicon carbide sample in electron cyclotron resonance microwave plasma In the bulk system, hydrogen plasma treatment is carried out; (3) electrode pattern is formed on the silicon carbide sample by photolithography; (4) metal electrode material titanium or titanium carbide is deposited by magnetron sputtering; (5) The silicon sample was stripped of metal other than the electrodes in an ultrasonic cleaner with acetone, and dried with nitrogen; (6) the silicon carbide sample was annealed in a nitrogen atmosphere. In the present invention, after pre-treating the surface of silicon carbide with hydrogen plasma generated by an electron cyclotron resonance system, the surface of silicon carbide is effectively cleaned and passivated, and the surface state density is significantly reduced, and combined with low work function metal titanium or titanium carbide and relatively The silicon carbide substrate with high doping concentration has a low barrier height of Ti / SiC contact, and good ohmic contact can be formed under low temperature annealing conditions.

Owner:DALIAN UNIV OF TECH

Charge trapping memory cell having bandgap engineered tunneling structure with oxynitride isolation layer

ActiveUS20110075486A1Increase erasing speedSolve the lack of heightSolid-state devicesRead-only memoriesTrappingIsolation layer

A band gap engineered, charge trapping memory cell includes a charge storage structure including a trapping layer. a blocking layer, and a dielectric tunneling structure including a thin tunneling layer, a thin bandgap offset layer and a thin isolation layer comprising silicon oxynitride. The memory cell is manufactured using low thermal budget processes.

Owner:MACRONIX INT CO LTD

System and method for integrating low schottky barrier metal source/drain

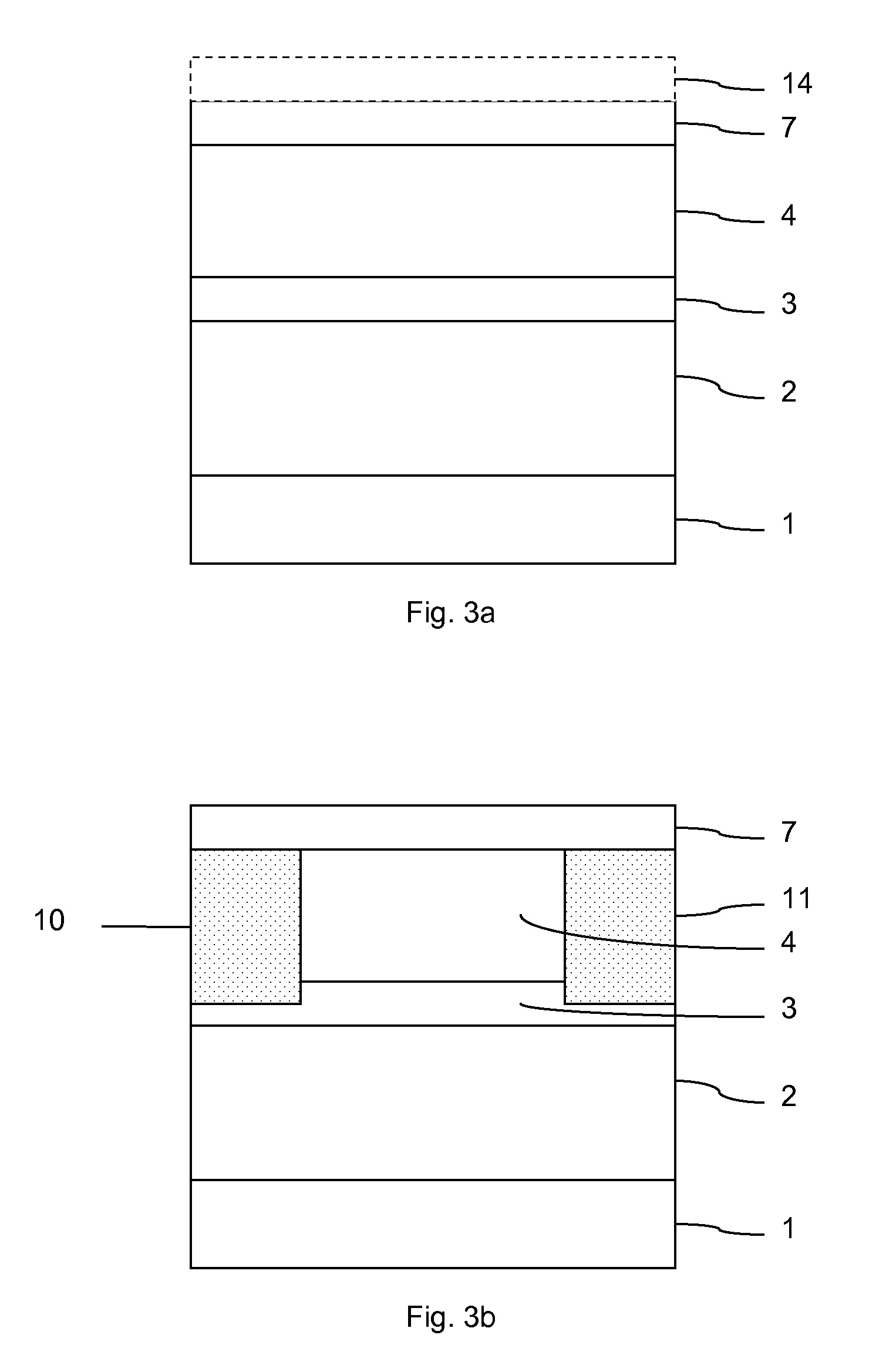

ActiveUS7238567B2Lower Schottky Barrier HeightLower barrier heightTransistorSolid-state devicesSchottky barrierOptoelectronics

According to one embodiment of the invention, a method for integrating low Schottky barrier metal source / drain includes providing a substrate, forming an epitaxial SiGe layer outwardly from the substrate, forming an epitaxial Si layer outwardly from the SiGe layer, and forming a metal source and a metal drain.

Owner:TEXAS INSTR INC

Electronic devices with improved ohmic contact

ActiveUS20100038682A1Lower barrier heightReduce overall heightSemiconductor/solid-state device detailsSolid-state devicesPhysicsOhm

In one embodiment, the disclosure relates to an electronic device successively comprising from its base to its surface: (a) a support layer, (b) a channel layer adapted to contain an electron gas, (c) a barrier layer and (d) at least one ohmic contact electrode formed by a superposition of metallic layers, a first layer of which is in contact with the barrier layer. The device is remarkable in that the barrier layer includes a contact region under the ohmic contact electrode(s). The contact region includes at least one metal selected from the metals forming the superposition of metallic layers. Furthermore, a local alloying binds the contact region and the first layer of the electrode(s).

Owner:S O I TEC SILICON ON INSULATOR THECHNOLOGIES

Schottky barrier diode and preparation method thereof

InactiveCN101697357AEasy to prepareEasy to operateSemiconductor/solid-state device manufacturingSemiconductor devicesThin oxideSchottky barrier

The invention provides a schottky barrier diode and a preparation method thereof. The schottky barrier diode has a structure that an N-type semiconductor is used as a substrate, an N-epitaxial layer is formed on the substrate and a positive electrode is a (blocking layer) metallic material. The preparation method comprises the following steps: cleaning for 10 to 30 minutes with a cleaning reagent of 75 degrees between a silicon epitaxial wafer and a metal to grow a layer of thin oxide layer, wherein the thickness of the oxide layer is between 20 and 100 angstroms; and sputtering or evaporating the metal to ensure that an alloy forms a silicide which servers as a barrier layer so as to form the schottky barrier diode. The preparation method is simple and reduces the barrier height through the participation of the thin oxide layer under the condition with a low cost, the efficient preparation obtains a low forward voltage drop schottky barrier diode, and compared with the conventional diode structure, the schottky barrier diode has a more extensive application range.

Owner:上海芯石微电子有限公司

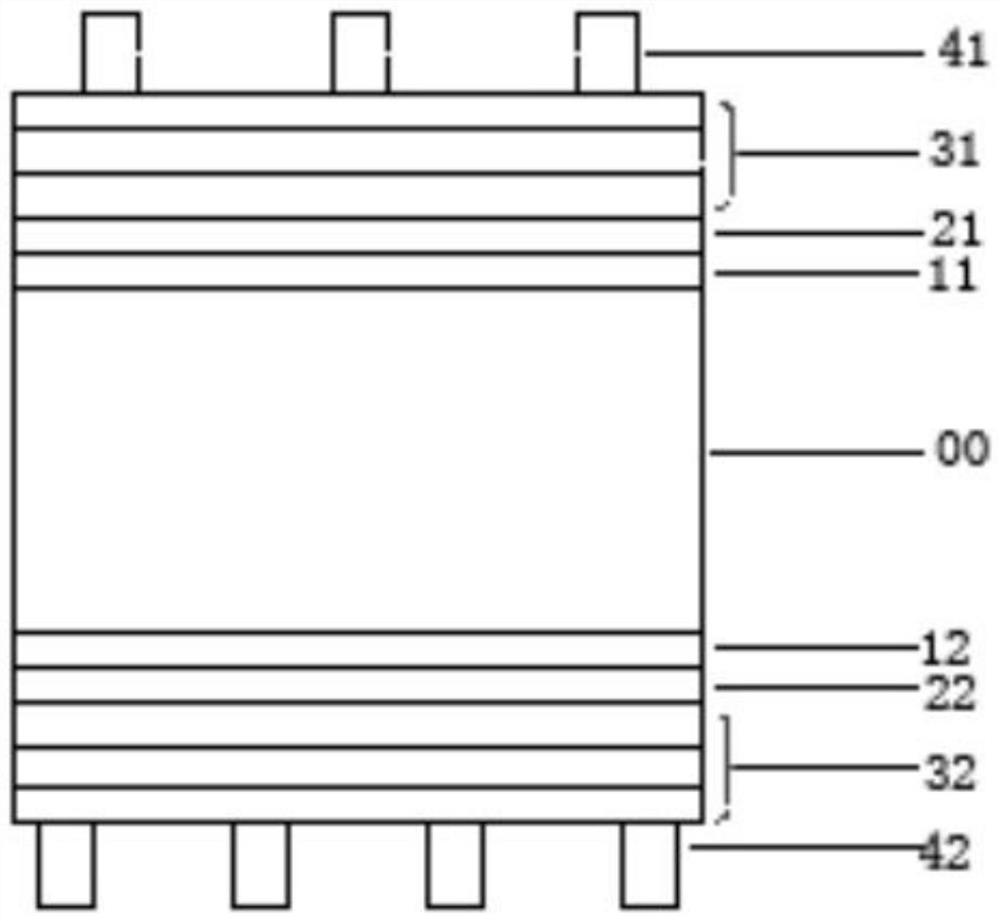

Silicon-based heterojunction solar cell and preparation method thereof

PendingCN111653644AImprove conversion efficiencyReduce manufacturing stepsFinal product manufacturePhotovoltaic energy generationHeterojunctionEngineering

The invention discloses a silicon-based heterojunction solar cell. The silicon-based heterojunction solar cell comprises a crystalline silicon substrate; a first intrinsic amorphous silicon layer, a first doping layer, a first TCO layer and a first metal electrode are sequentially arranged on the upper surface of the crystalline silicon substrate; a second intrinsic amorphous silicon layer, a second doping layer, a second TCO layer and a second metal electrode are sequentially arranged on the lower surface of the crystalline silicon substrate. The preparation method comprises the following steps: (1), obtaining a crystalline silicon substrate; (2), carrying out plasma chemical vapor deposition on a first intrinsic amorphous silicon layer, a second intrinsic amorphous silicon layer, a firstdoping layer and a second doping layer ; (4), depositing a first TCO layer and a second TCO layer, and performing plasma treatment at the same time; and (5), forming a first metal electrode and a second metal electrode through silk-screen printing. The method is rapid, practical and easy to implement, the functional interface contact of TCO and doped amorphous silicon can be optimized, and the conversion efficiency of the heterojunction solar cell is remarkably improved.

Owner:晋能光伏技术有限责任公司

Surface corrosion of CdTe film and CdTe solar cell preparing by the process

InactiveCN101335310AImprove performanceLower barrier heightFinal product manufactureSemiconductor/solid-state device manufacturingSchottky barrierTe element

The invention relates to a method for surface corrosion of a CdTe film and preparation of a CdTe solar cell by adopting the method, pertaining to the processing field of semiconductor devices. An mixed liquid of nitric acid, glacial acetic acid, NaAc and deionized water is served as corrosive liquid, wherein, the NaAc is served as a buffering agent to keep the pH value of the intermixture unchanged and lead the reaction to be more stable; CdTe and the nitric acid react to generate a layer rich in tellurium; after washing and blow-drying, a back contact layer containing Cu or without Cu is sedimented; finally, a back electrode is sedimented for preparing the CdTe solar cell. Sedimentation of back contact material can increase carrier concentration near a pn junction, reduce the height of Schottky potential barrier and avoid direct sedimentation of Cu from forming a comparatively complex CuxTe structure. By adopting the method for corrosion and the preparation of the CdTe solar cell, the performance of the solar cell can be obviously improved and the stability and the repeatability of the device can be ensured.

Owner:SICHUAN UNIV

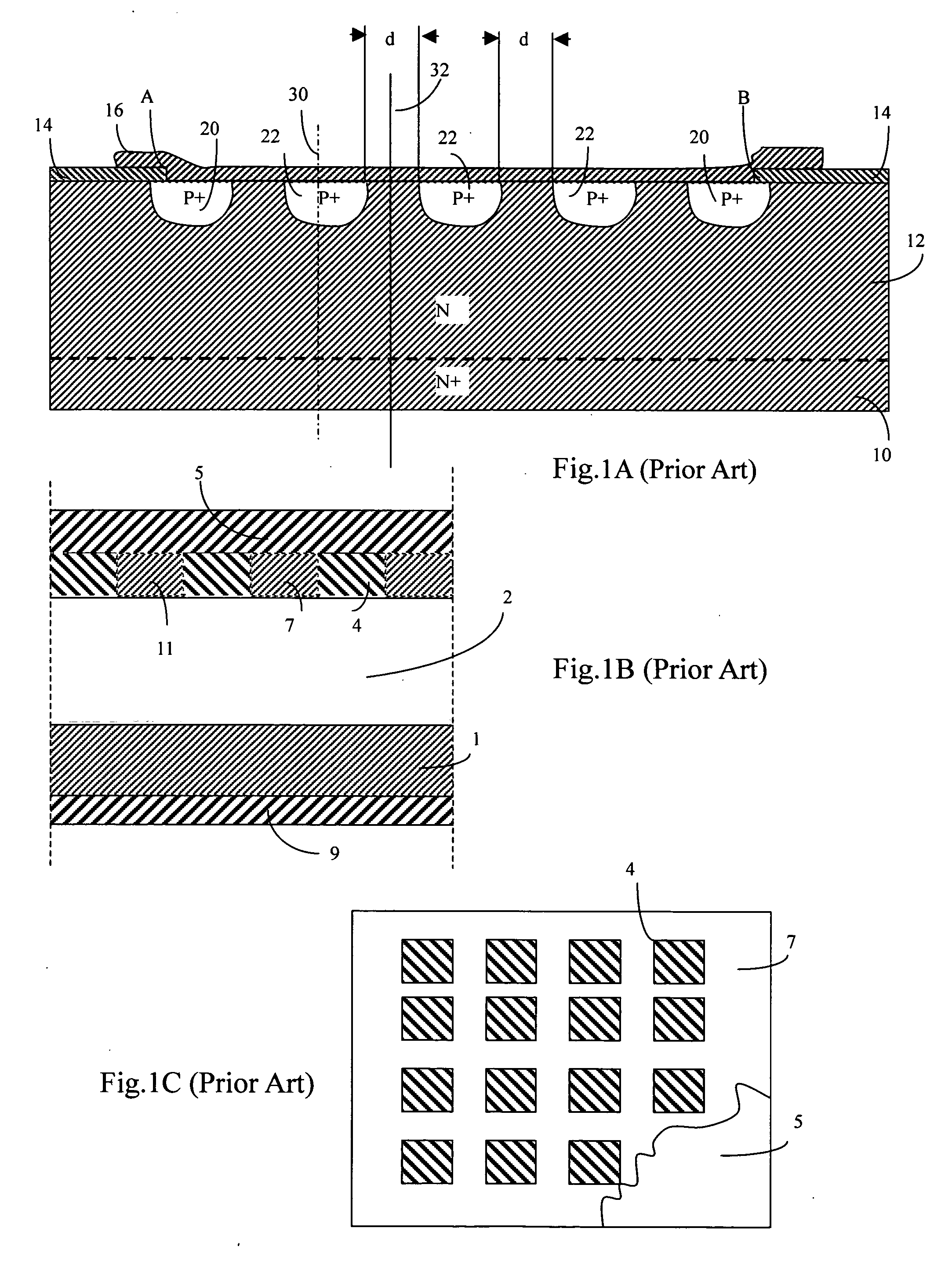

Method of manufacturing gate insulated field effect transistors

InactiveUS7507615B2Stable characteristicsLower barrier heightVacuum evaporation coatingSputtering coatingSputteringHydrogen

A method of manufacturing thin film field effect transistors is described. The channel region of the transistors is formed by depositing an amorphous semiconductor film in a first sputtering apparatus followed by thermal treatment for converting the amorphous phase to a polycrystalline phase. The gate insulating film is formed by depositing an oxide film in a second sputtering apparatus connected to the first apparatus through a gate valve. The sputtering for the deposition of the amorphous semiconductor film is carried out in an atmosphere comprising hydrogen in order to introduce hydrogen into the amorphous semiconductor film. On the other hand the gate insulating oxide film is deposited by sputtering in an atmosphere comprising oxygen.

Owner:SEMICON ENERGY LAB CO LTD

Germanium-based nmos device and method for fabricating the same

InactiveUS20130069126A1On-off ratio can be increasedLittle resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesSilicon oxideHafnium

An embodiment of the invention provides a germanium-based NMOS device and a method for fabricating the same, which relates to fabrication process technology of an ultra-large-scale-integrated (ULSI) circuit. The germanium-based NMOS device has two dielectric layer interposed between a metal source / drain and a substrate. The bottom dielectric layer includes a dielectric material having a high pinning coefficient S such as hafnium oxide, silicon nitride, hafnium silicon oxide or the like, and the top dielectric layer includes a dielectric material having a low conduction band offset ΔEC such as titanium oxide, gallium oxide, strontium titanium oxide or the like. According to the method, Fermi level pinning effect can be alleviated, electron barrier height can be lowered, and thus performance of the germanium-based Schottky NMOS device can be improved. Compared with a conventional single dielectric layer such as aluminum oxide (Al2O3), Schottky barrier height can be lowered while low source / drain resistances can be maintained, and thus performance of the device can be significantly improved.

Owner:PEKING UNIV

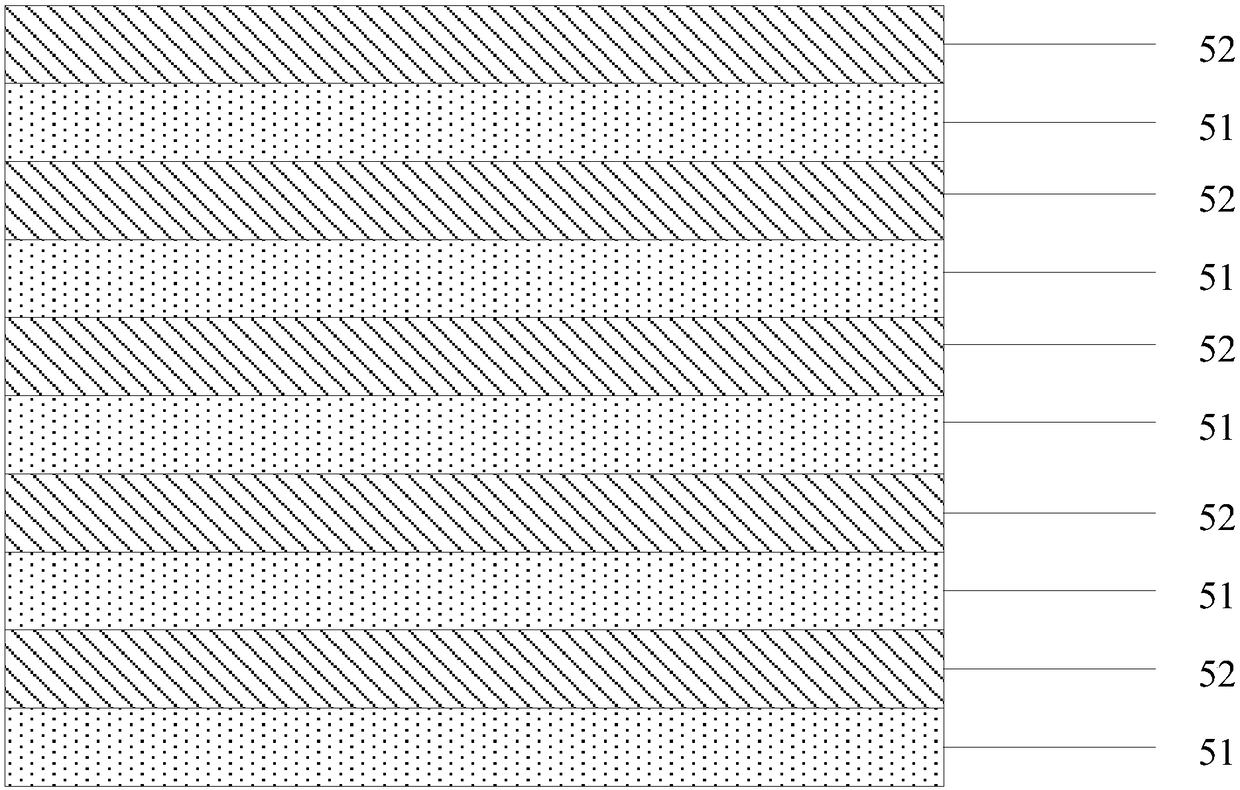

Light emitting diode and preparation method thereof

ActiveCN108110104AIncreased electron-hole wavefunction overlapConducive to radiative recombination luminescenceSemiconductor devicesContact layerBlocking layer

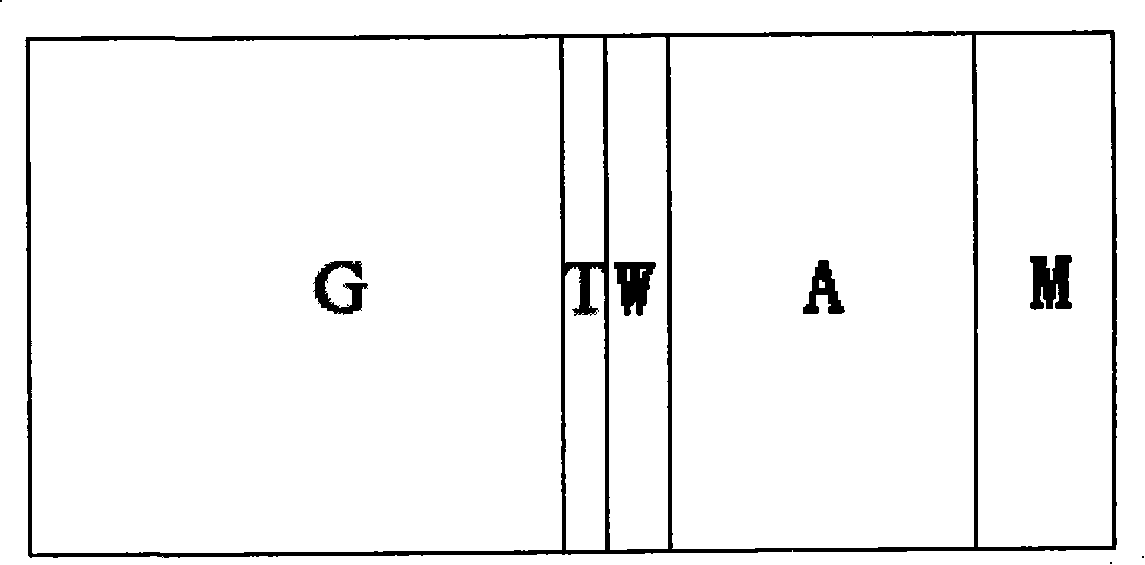

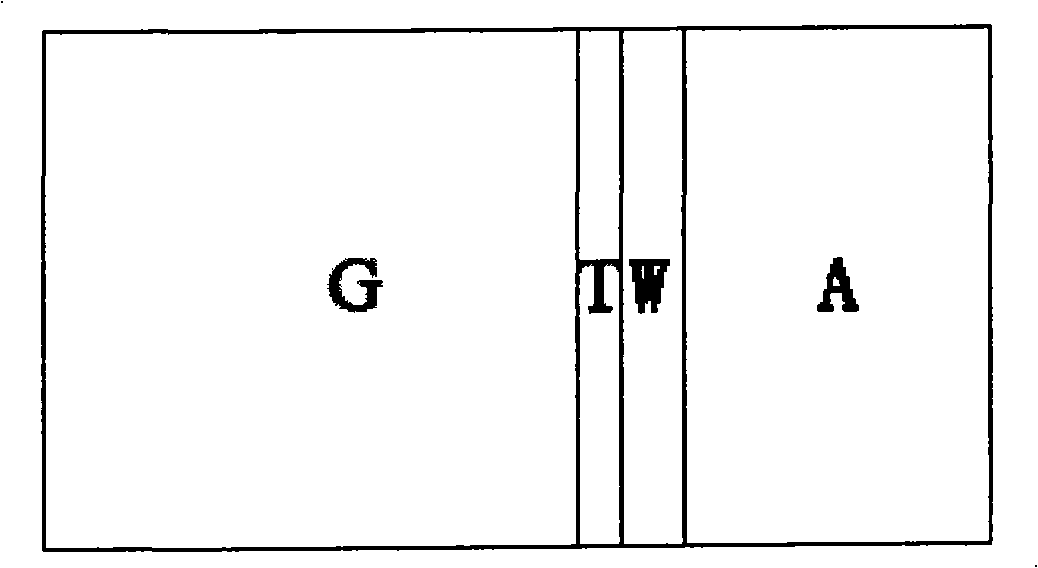

The application discloses a light emitting diode and a preparation method thereof. According to the light emitting diode, the last quantum barrier layer of a plurality of quantum well layers and an electron blocking layer in a conventional structure are replaced with a super lattice structure comprising a plurality of first-type super lattice layers and a plurality of second-type super lattice layers; the super lattice structure reduces polarization electric field intensity of the last quantum barrier layer, improves an electron hole wave function overlapping degree of the light emitting diodeand is beneficial to radiation composite light emitting of the light emitting diode; and the super lattice structure not only reduces the preparation difficulty of the light emitting diode, but alsoenables growth of the high-quality super lattice structure and second-type contact layer to be possible. In addition, existence of the super lattice structure also enables a electronic barrier heightof a conduction band of the integral second-type structural layer to be further increased, greatly reduces electron leakage, meanwhile, reduces a barrier height of a valence band hole, promotes transmission of the hole, greatly promotes internal quantum efficiency of multiple quantum well layers, reduces sudden reduction of efficiency, and greatly promotes integral light emitting power of the light emitting diode.

Owner:XIAMEN CHANGELIGHT CO LTD

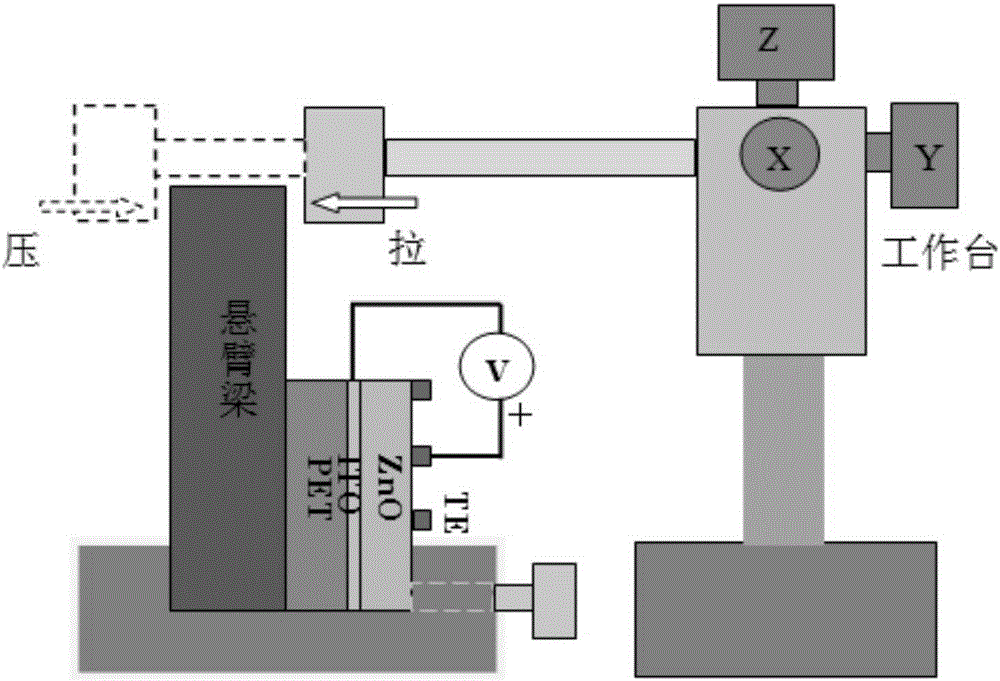

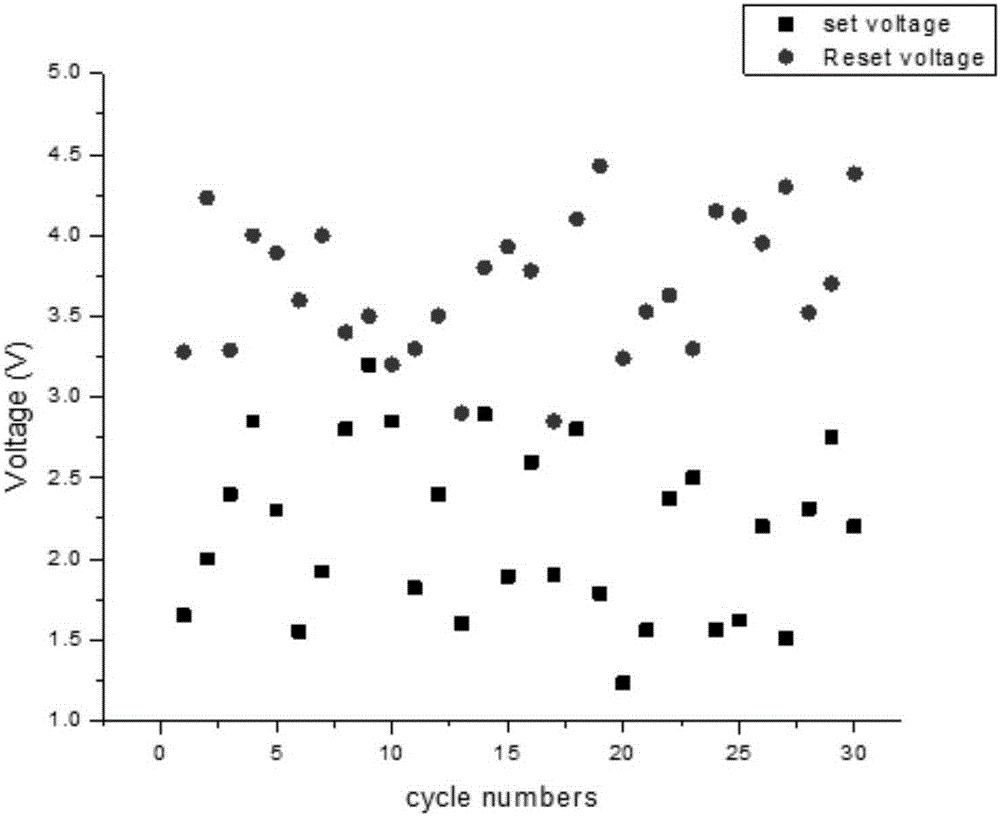

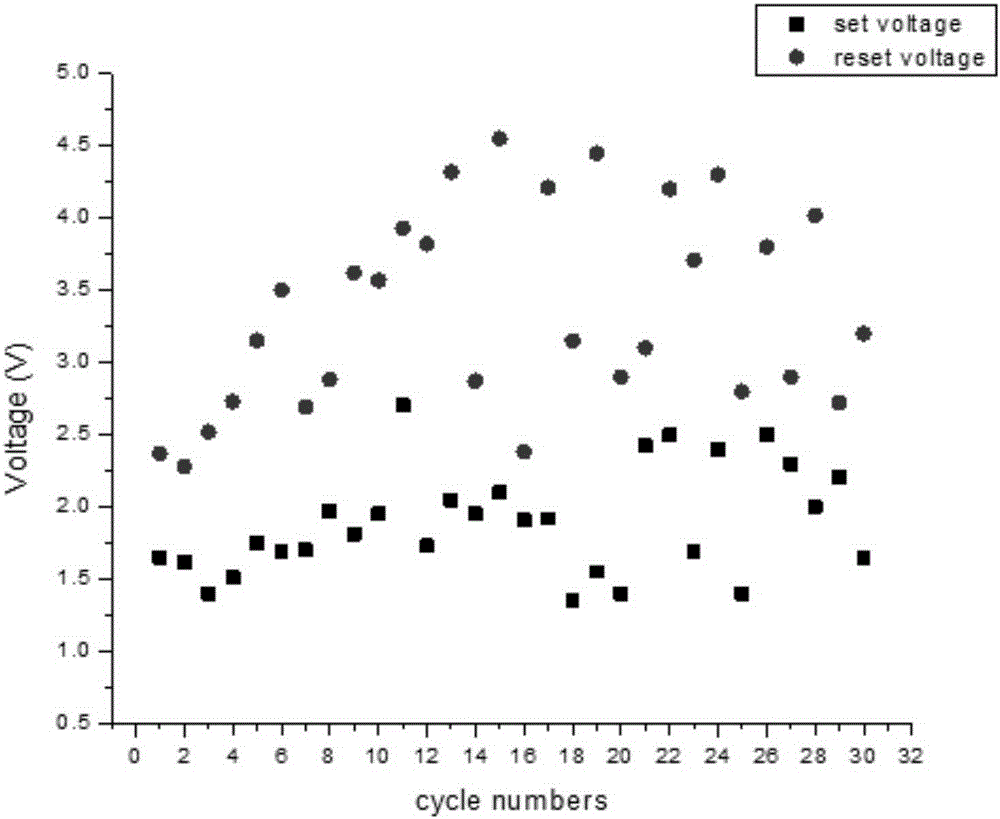

ZnO piezoelectric effect-based low-power consumption flexible resistance-variable memory and preparation method thereof

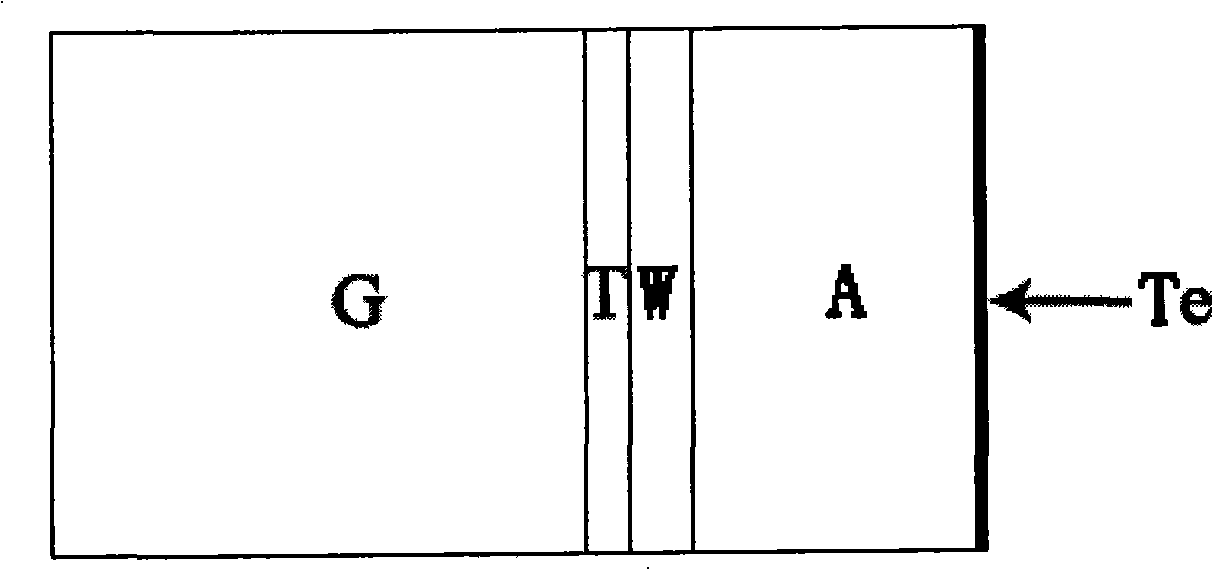

ActiveCN105244362AReduce operating voltageReduce power consumptionSolid-state devicesSemiconductor devicesRandom access memoryEvaporation

The invention discloses a ZnO piezoelectric effect-based low-power consumption flexible resistance-variable memory and a preparation method thereof. The low-power consumption flexible resistance variable random-access memory (RAM) of the invention comprises a TE layer, a ZnO layer and an ITO / PET layer which are sequentially distributed from top to bottom, wherein the TE layer is made of Pt, Cu or Au of which the function is greater than a ZnO function. The method includes the following steps that: with an ITO / Pet flexible substrate adopted as a bottom electrode, a ZnO thin film is prepared through a sputtering method, and ZnO / ITO / PET can be obtained; and the ZnO / ITO / PET base body is arranged in a deposition chamber, and a metal upper electrode can be obtained through electron beam evaporation and by means of a mask method, so that a metal thin film electrode can be deposited on the ZnO thin film, and finally a flexible TE / ZnO / ITO / PET device can be obtained. According to the ZnO piezoelectric effect-based low-power consumption flexible resistance-variable memory and the preparation method thereof of the invention, set and reset voltage of the ZnO thin film layer can be adjusted and controlled through the piezoelectric effect of the ZnO thin film layer itself, and therefore, the operating voltage of the device can be decreased, and the power consumption of the device can be reduced, and the service life of the device can be prolonged.

Owner:芜湖启博知识产权运营有限公司

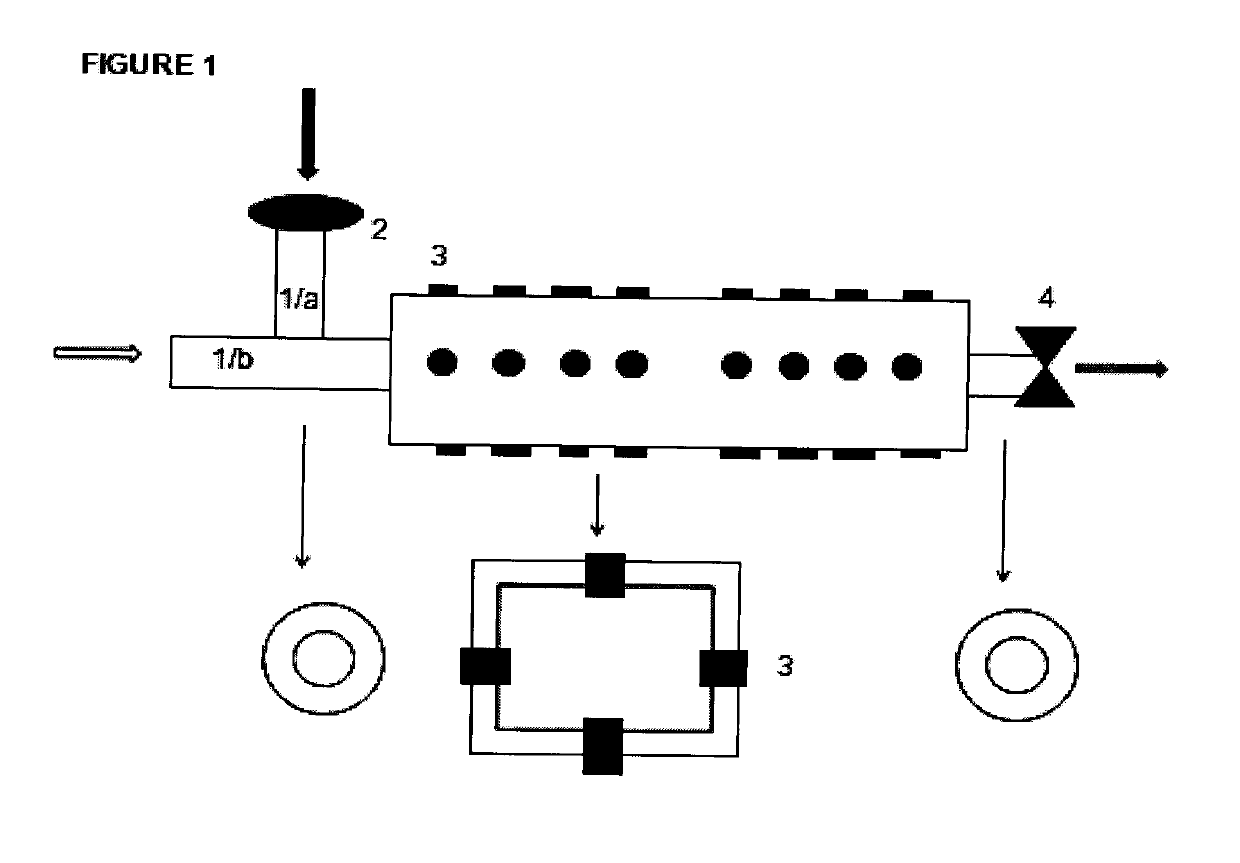

Olfactory detector for early diagnosis of ovarian cancer

ActiveUS20190317073A1Lower barrier heightLow densityWithdrawing sample devicesPreparing sample for investigationAbnormal tissue growthBlood plasma

The invention relates to a device and a method for cancer detection and screening, based on analysis of Volatile Organic Compounds emitted by certain cancerous tumors. The device and method provide high sensitivity and specificity analyses. The sample to be analysed may be e.g. blood or blood plasma. In one aspect, the invention is directed towards detection of or screening for gynaecological cancers, e.g. ovarian cancer. Particularly, the device comprises the following parts: a sample holder for a fluid or solid body sample; an air inlet; a detector tube comprising 4×4-16×4 sensors; optionally an individual potentiometer connected to each sensor of the detector tube; an analogue to digital signal converter; four control cards; a computer-based program for the registration and statistical calculation of results; and an electricity source.

Owner:VOC DIAGNOSTICS AB

Magnetoresistance effect element and magnetoresistive device

InactiveUS20090080123A1Improve the magnetoresistance effectQuality improvementNanomagnetismMagnetic measurementsSemiconductorMagnetic layer

The high quality magnetoresistance effect element is capable of reducing resistance in the perpendicular-plane direction and preventing performance deterioration of a barrier layer. The magnetoresistance effect element comprises: a free layer; a pinned magnetic layer; and a barrier layer being provided between the free layer and the pinned magnetic layer, and the barrier layer is composed of a semiconductor.

Owner:FUJITSU LTD +1

Schottky diode and manufacturing method thereof

InactiveCN103311316ALower barrier heightImprove driving abilitySemiconductor/solid-state device manufacturingSemiconductor devicesDopantSalicide

The invention discloses a Schottky diode and a manufacturing method thereof. The Schottky diode comprises a substrate and a metal silicide on the substrate. The Schottky diode is characterized in that an interface between the substrate and the metal silicide also comprises a dopant ion segregation area which is formed by being injected with the dopant ion, and then segregated and annealed. According to the novel Schottky diode and the manufacturing method thereof, the dopant ion is injected into the electrodes of the metal silicide and a drive is annealed so that the dopant ion is segregated on the interface between the substrate and the metal silicide. Therefore, a Schottky barrier height is effectively reduced (e.g. the Schottky barrier height is enabled to be lower than 0.1 eV) and then a drive capacity is enhanced.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

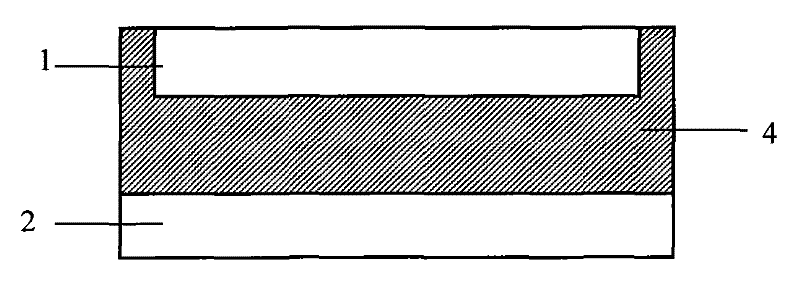

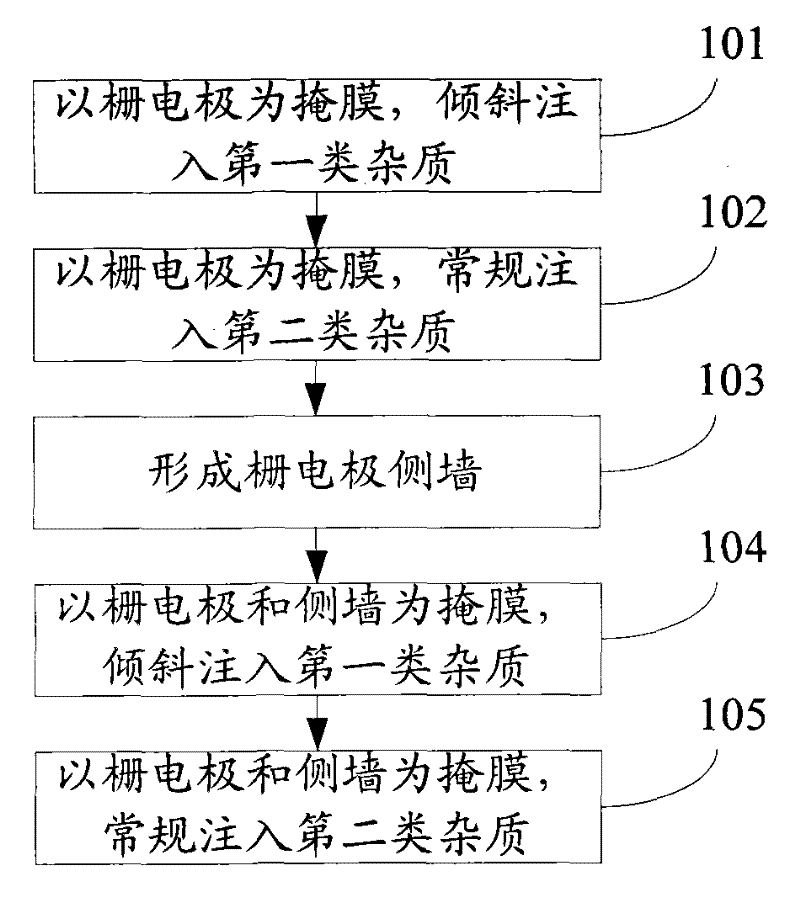

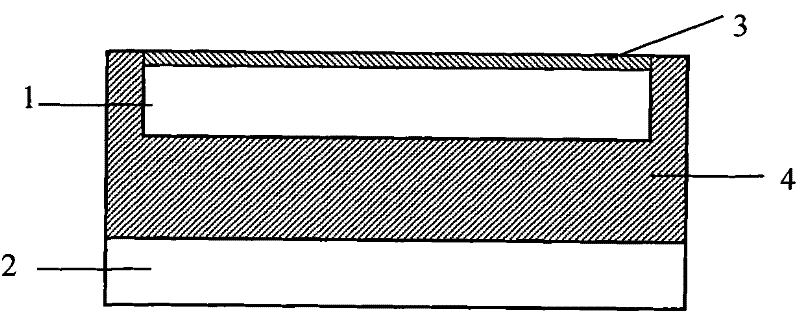

Manufacturing method of silicon MOS transistor on partially consumed insulating layer

InactiveCN101661889BImproving the ability to resist short channel effectEnhanced ability to resist short channel effectsSemiconductor/solid-state device manufacturingSilicon chipIon implantation

The invention discloses a manufacturing method of a PD SOI MOS transistor, which comprises the processes of defining an active area on an SOI silicon chip and doping after a gate electrode is formed, wherein the processes comprise the steps of: A. implanting angled ions by taking the gate electrode as a masking film, wherein the type of the implanted impurity is a first type of impurity with the same type as that of the impurity at the bottom inside the silicon film layer of the SOI silicon chip; B. implanting conventional ions by taking the gate electrode as the masking film, wherein the type of the implanted impurity is a second type of impurity with the type opposite to that of the first type of impurity; C. forming side wall layers at two sides of the gate electrode; D. implanting theangled ions by taking the gate electrode and the side wall layers as the masking film, wherein the type of the implanted impurity is the first type of impurity, and the ion implantation energy is setto be higher than that of the angled ions in step A; and E, implanting the conventional ions by taking the gate electrode and the side wall layers as the masking film, wherein the type of the implanted impurity is the second type of impurity. The method effectively inhibits the punch-through of DIBL effect and source leakage deep areas, thus greatly promoting the short channel effect resistant capability of the device.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

Fin FET (field effect transistor) and manufacturing method of fin FET

ActiveCN103311294ALow source-drain resistanceLower the altitudeSemiconductor/solid-state device manufacturingSemiconductor devicesIonDrain resistance

The invention discloses a fin FET (field effect transistor), which comprises an SOI (silicon on insulator) substrate, a fin-shaped grid electrode stack structure and a channel region, wherein the fin-shaped grid electrode stacking structure is arranged on the SOI substrate, the channel region is arranged between a source drain region and a source drain region arranged at the two sides of the grid electrode stacking structure in the SOI substrate, the source drain regions and the channel region extend in the first direction, and the grid electrode stacking structure extends in the second direction vertical to the first direction. The fin FET is characterized in that the source drain regions are metal silicide, the interface part between the source drain regions and the channel region also comprises doping ion segregation regions. According to the novel fin FET device and a manufacturing method of the novel fin FET device provided by the invention, doping ions are filled into the source drain of the metal silicide of the Fin FET, in addition, the annealing driving is carried out so that the doping ions are segregated at the interface part of the channel region, the fin FET source and drain resistance is effectively reduced, and meanwhile, the Schottky barrier height is also reduced, so the driving capability is improved.

Owner:锐立平芯微电子(广州)有限责任公司

Charge trapping memory cell having bandgap engineered tunneling structure with oxynitride isolation layer

ActiveUS8169835B2Solve the lack of heightAvoid insufficient thicknessSolid-state devicesRead-only memoriesTrappingIsolation layer

A band gap engineered, charge trapping memory cell includes a charge storage structure including a trapping layer. a blocking layer, and a dielectric tunneling structure including a thin tunneling layer, a thin bandgap offset layer and a thin isolation layer comprising silicon oxynitride. The memory cell is manufactured using low thermal budget processes.

Owner:MACRONIX INT CO LTD