Patents

Literature

430 results about "Thin oxide" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

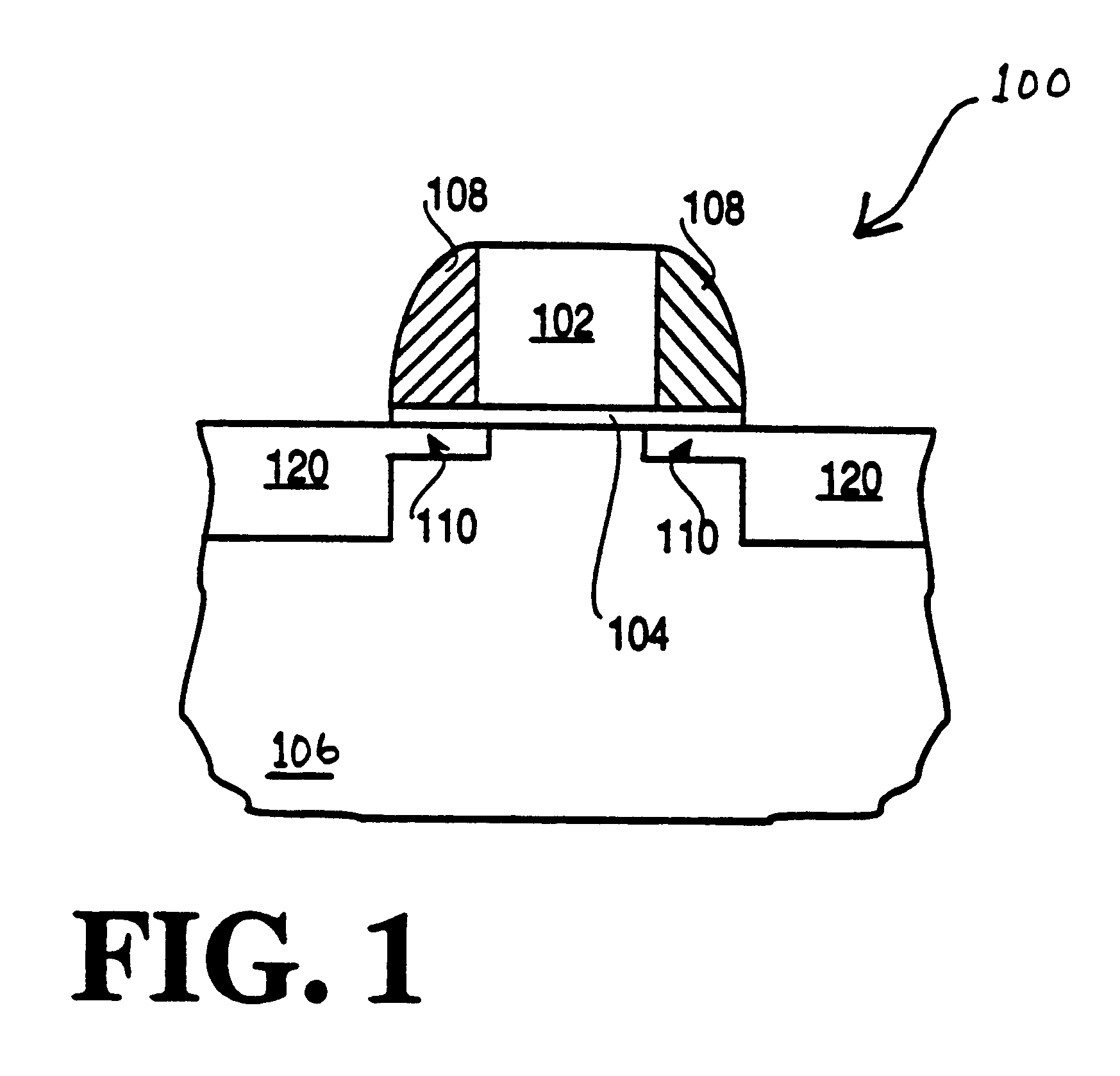

Semiconductor device having deposited silicon regions and a method of fabrication

InactiveUS6235568B1Semiconductor/solid-state device manufacturingSemiconductor devicesThin oxideSilicon alloy

The present invention describes an MOS device having deposited silicon regions and its a method of fabrication. In one embodiment of the present invention a substrate having a thin oxide layer formed on a silicon surface is heated and exposed to an ambient comprising germane (GeH4) to remove the thin oxide from the silicon surface. A silicon or silicon alloy film can then be deposited onto the silicon surface of the substrate.

Owner:INTEL CORP

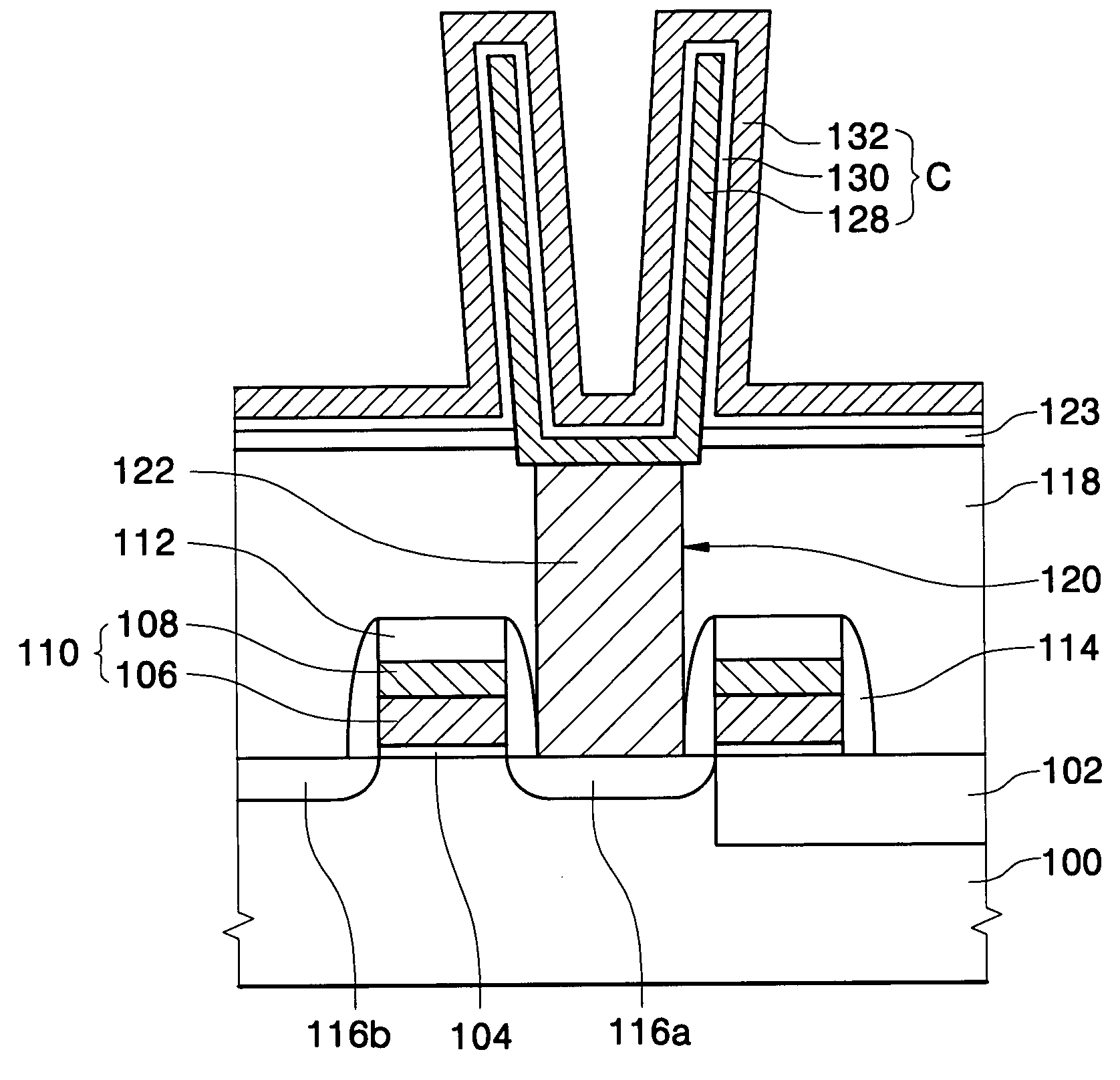

Method of forming oxide layer using atomic layer deposition method and method of forming capacitor of semiconductor device using the same

In a method of forming an oxide layer using an atomic layer deposition and a method of forming a capacitor of a semiconductor device using the same, a precursor including an amino functional group is introduced onto a substrate to chemisorb a portion of the precursor on the substrate. Then, the non-chemisorbed precursor is removed. Thereafter, an oxidant is introduced onto the substrate to chemically react the chemisorbed precursor with the oxidant to form an oxide layer on the substrate. A deposition rate is fast and an oxide layer having a good deposition characteristic may be obtained. Also, a thin oxide film having a good step coverage and a decreased pattern loading rate can be formed.

Owner:SAMSUNG ELECTRONICS CO LTD

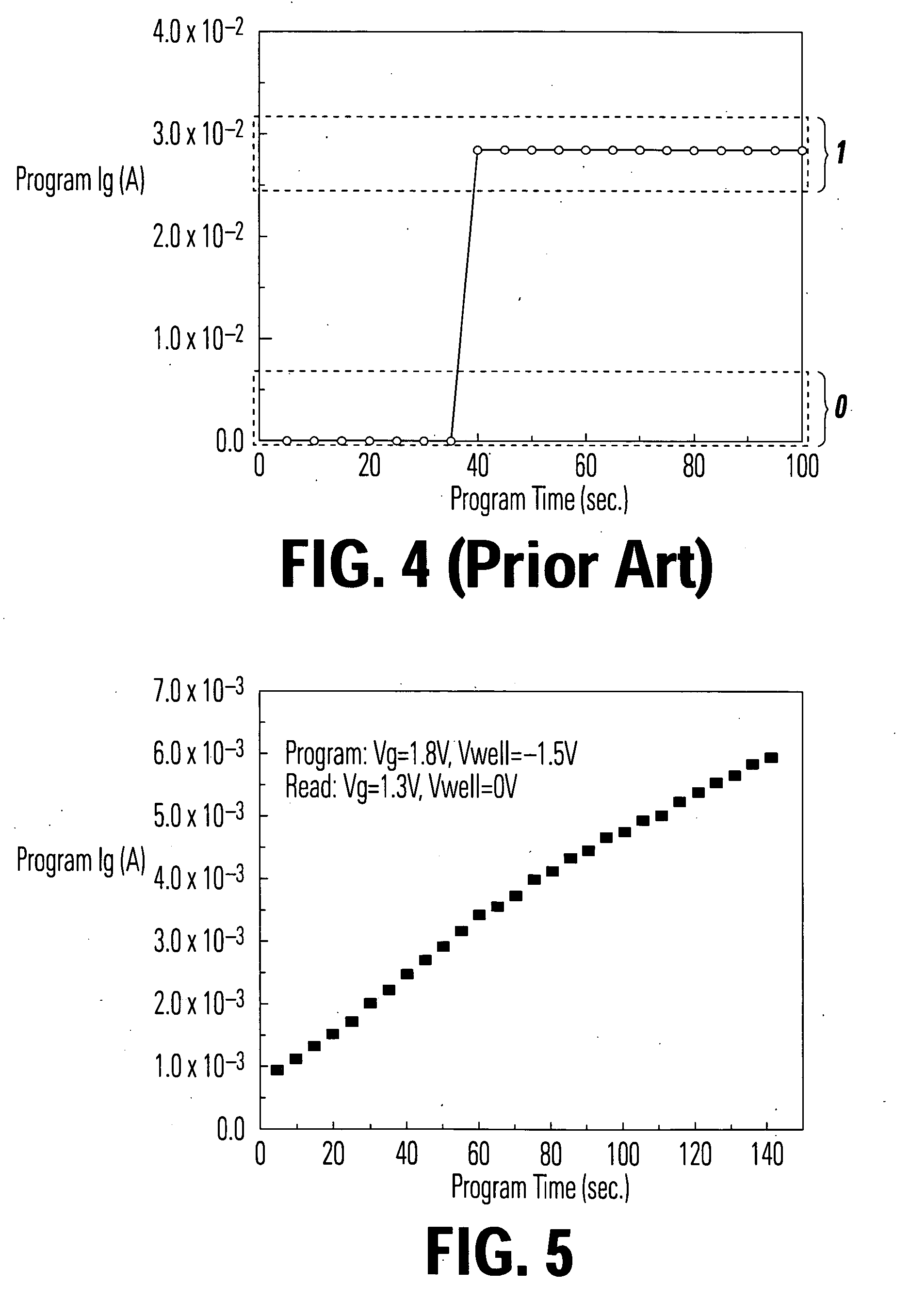

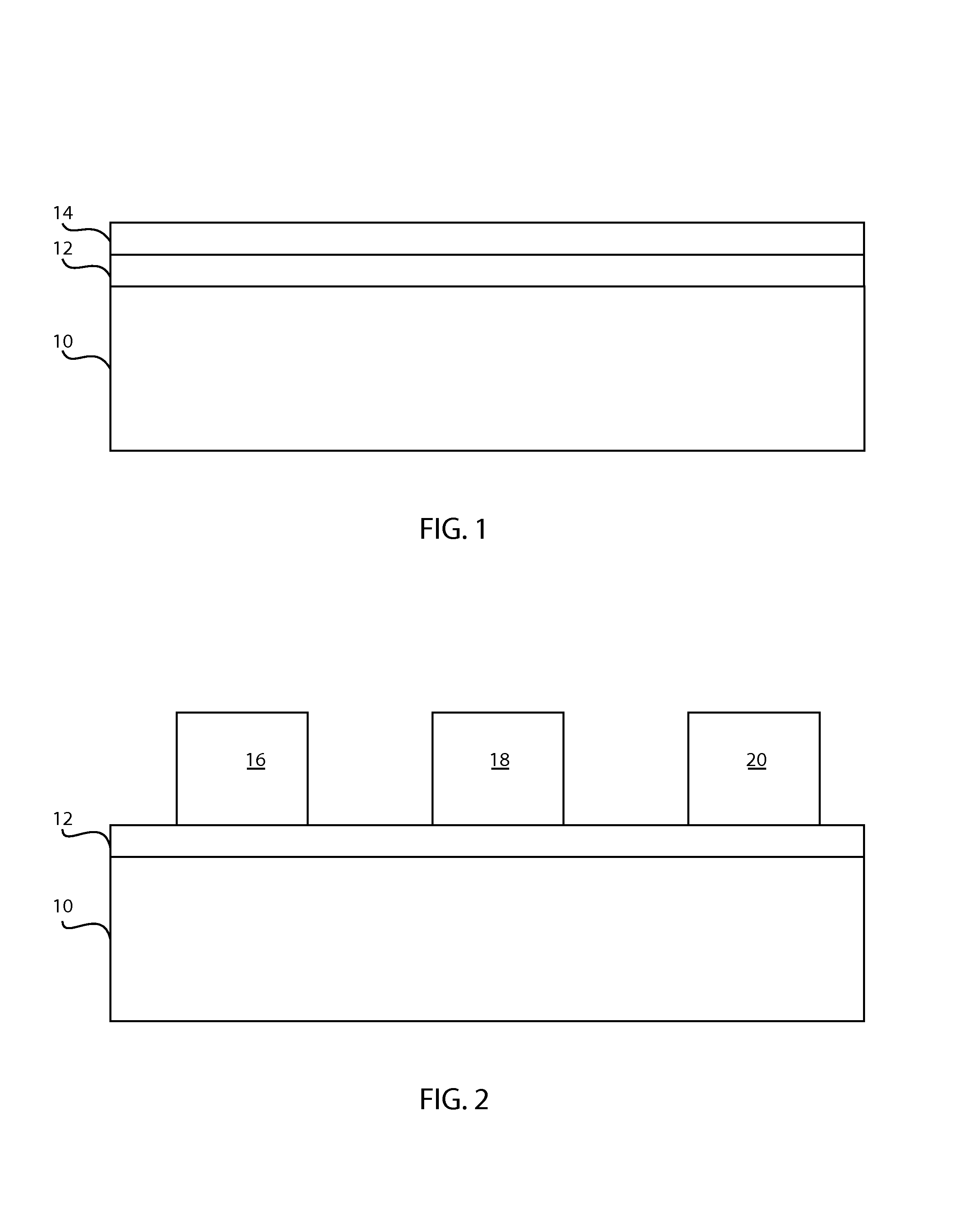

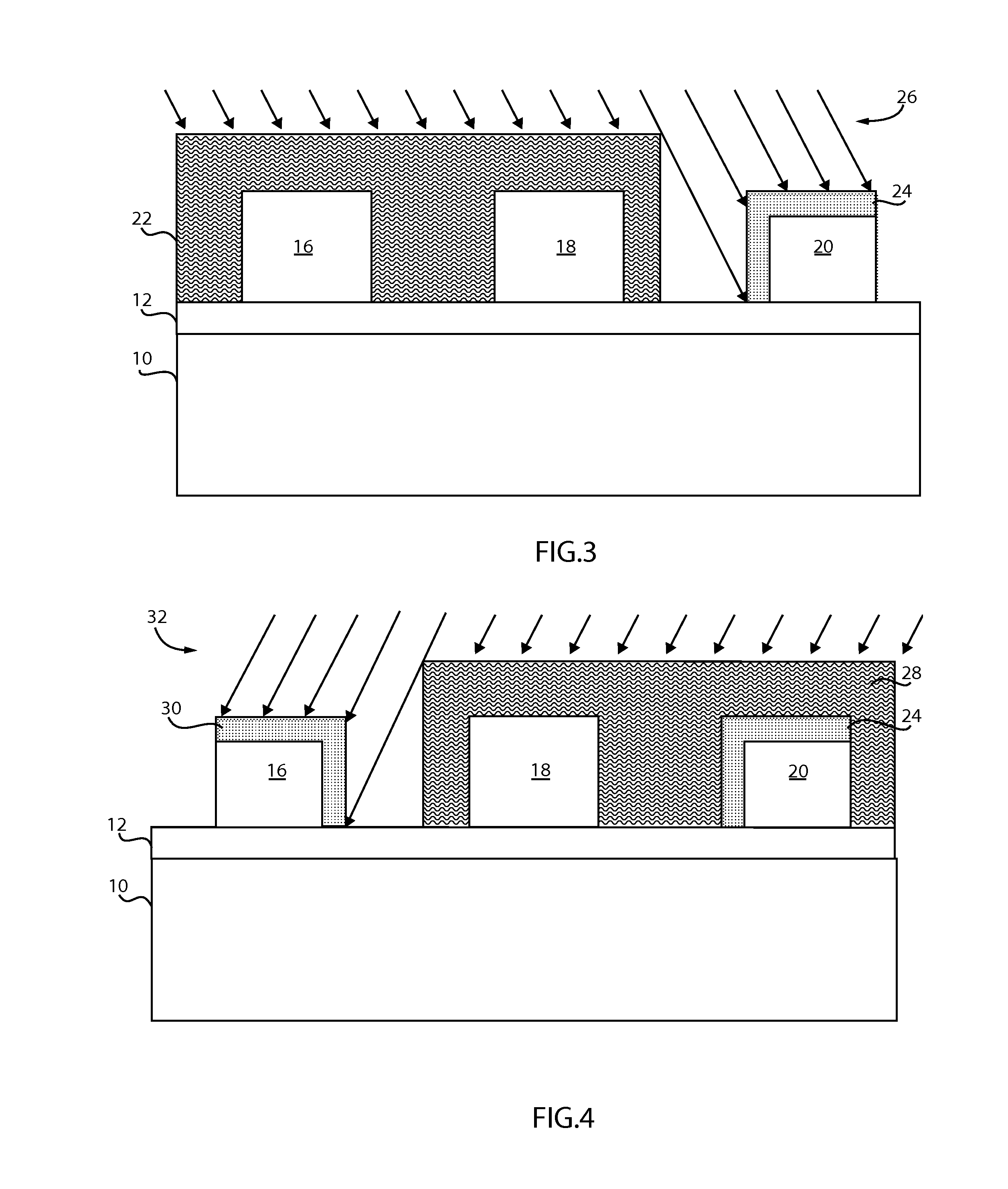

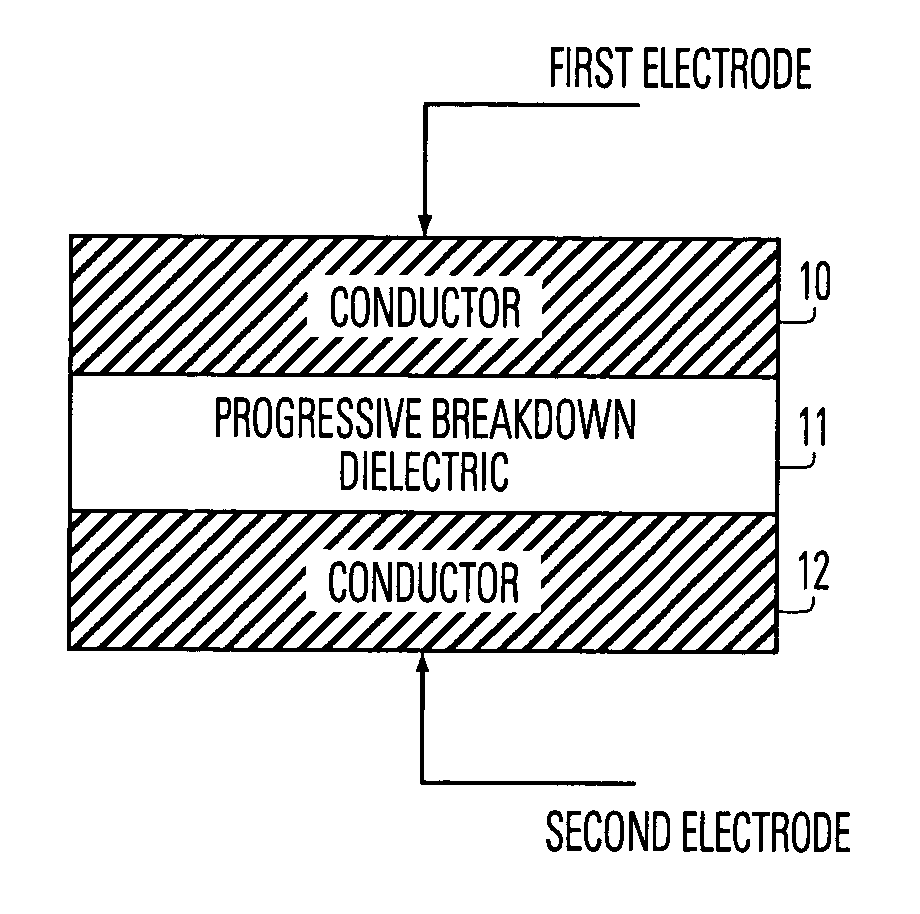

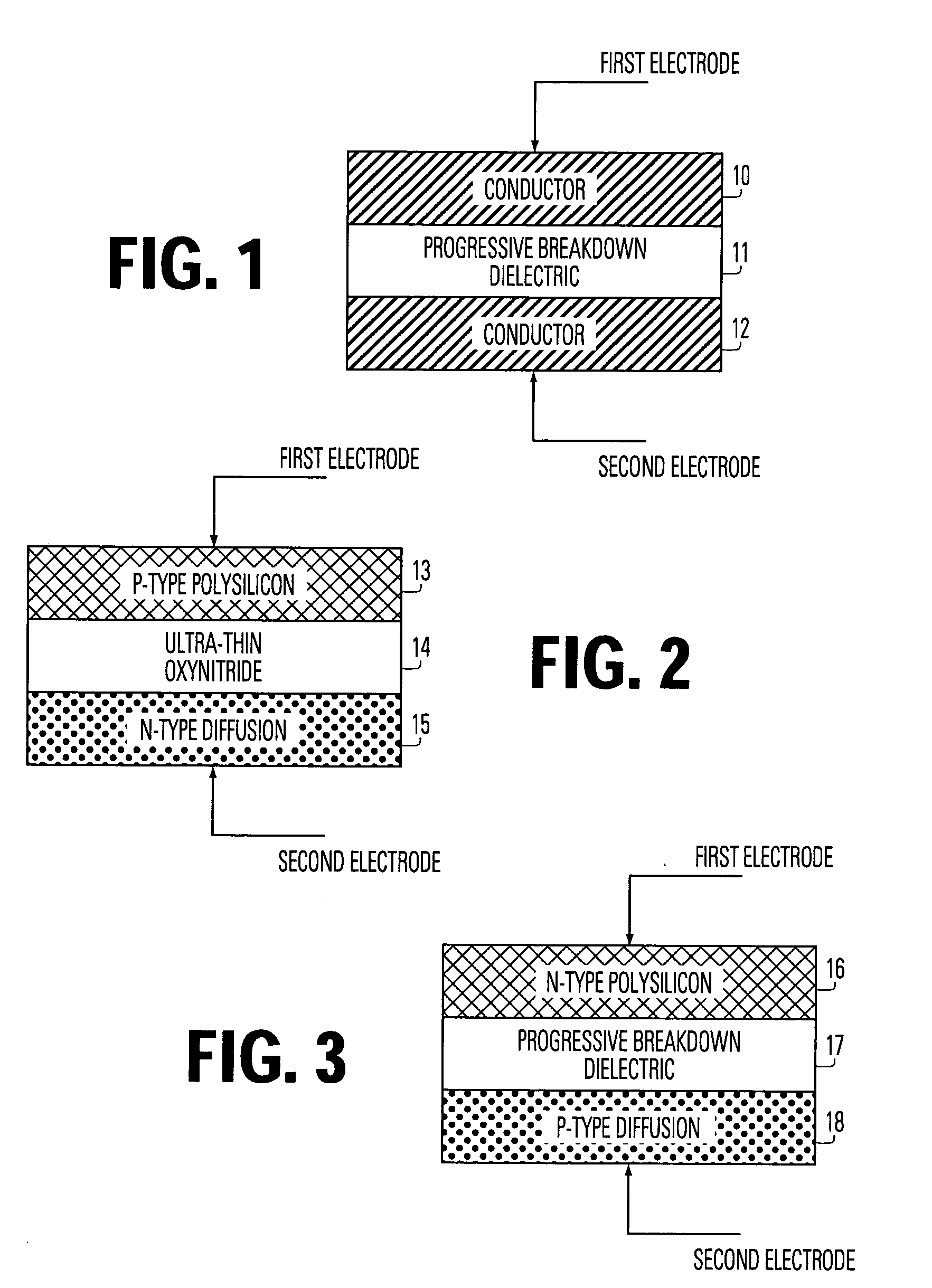

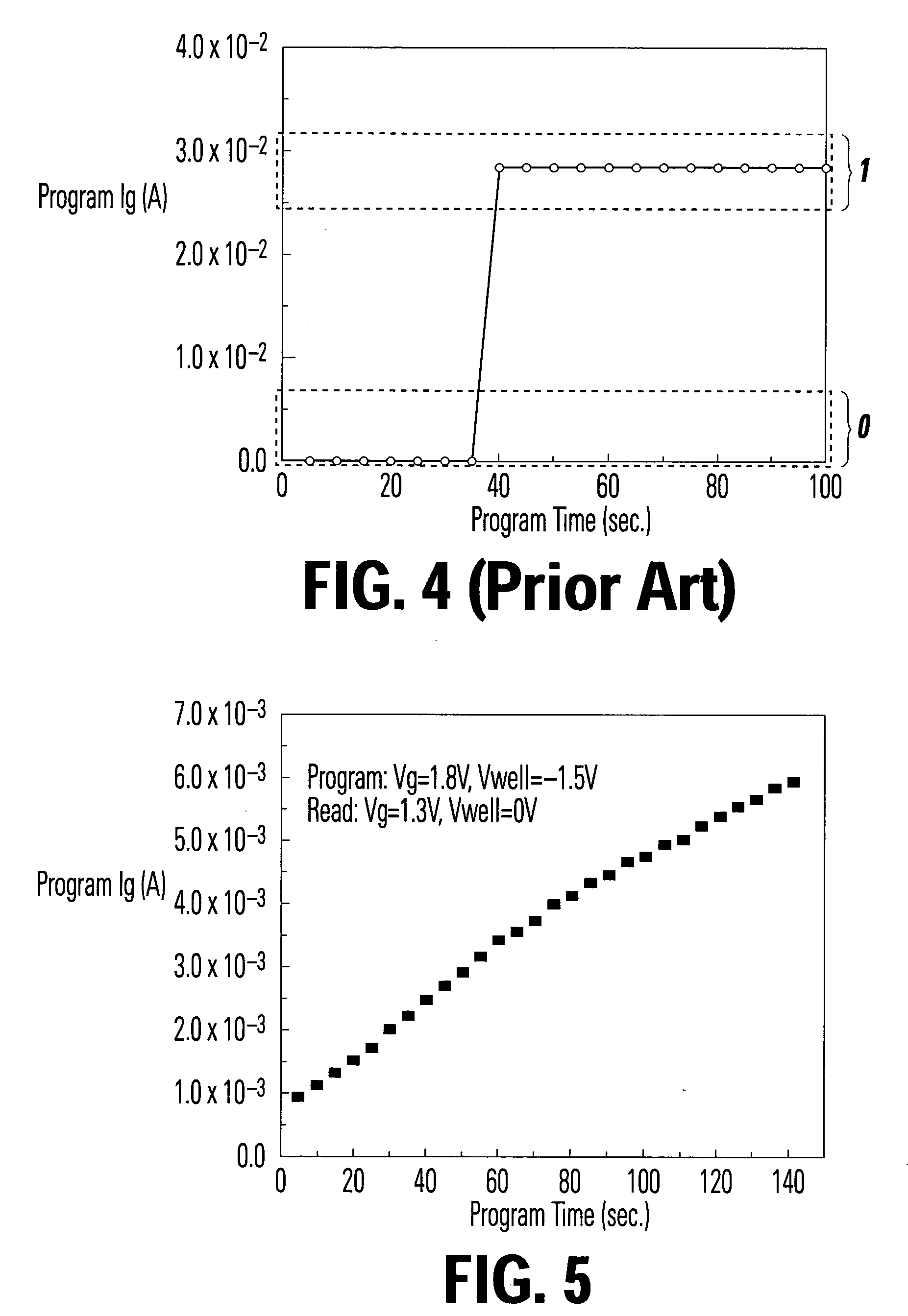

Method for manufacturing a multiple-bit-per-cell memory

ActiveUS20060073642A1Easy to manufactureSolid-state devicesSemiconductor/solid-state device manufacturingThin oxideOptoelectronics

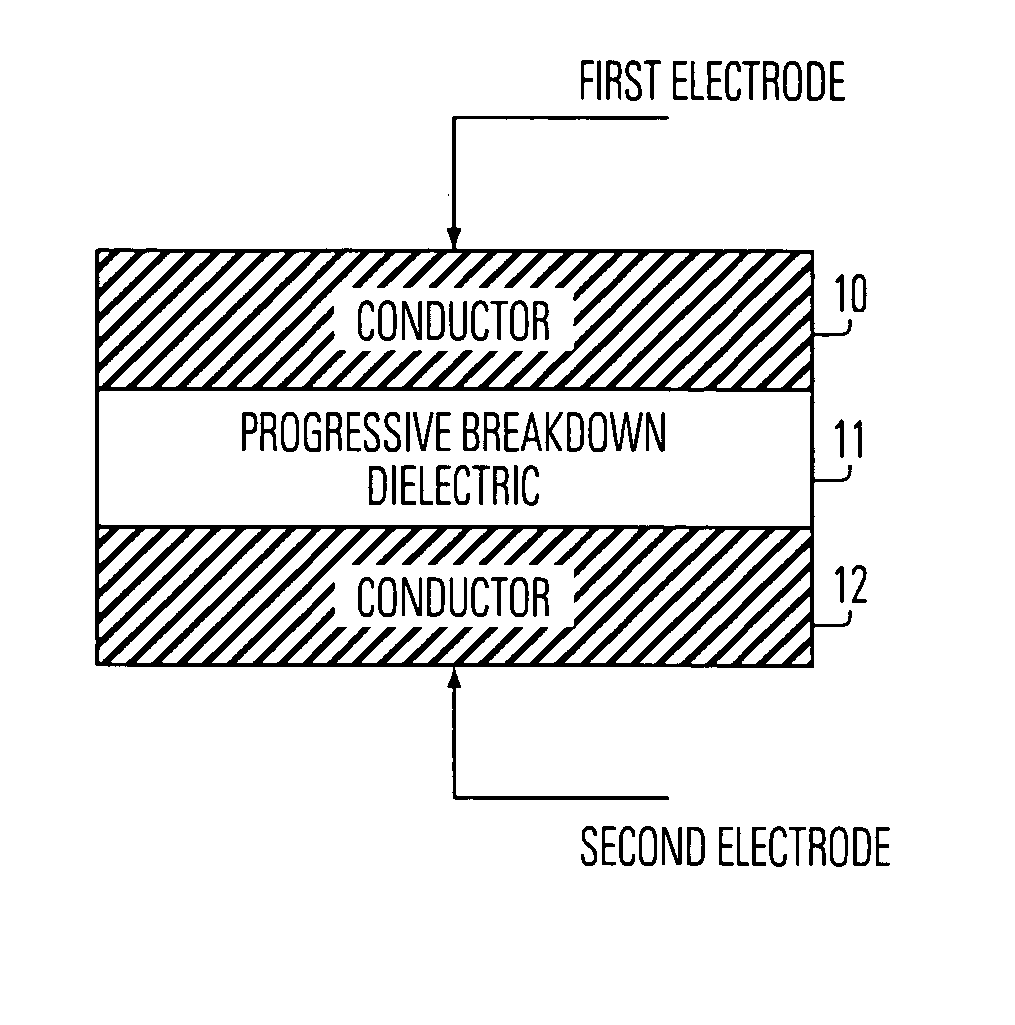

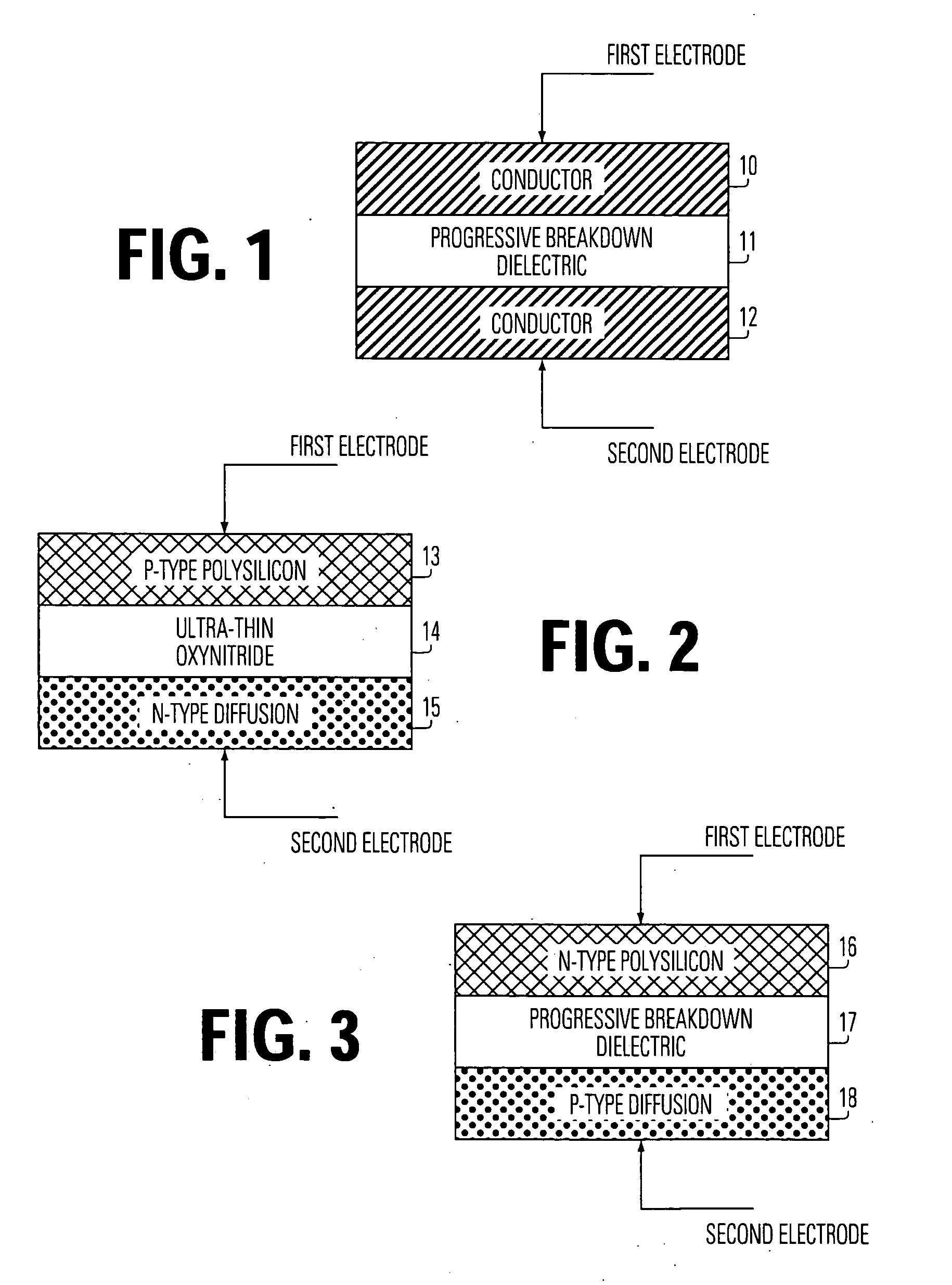

A method for manufacturing an electrically programmable non-volatile memory cell comprises forming a first electrode on a substrate, forming an inter-electrode layer of material on the first electrode having a property which is characterized by progressive change in response to stress, and forming a second electrode over the inter-electrode layer of material. The inter-electrode layer comprises a dielectric layer, such as ultra-thin oxide, between the first and second electrodes. A programmable resistance, or other property, is established by stressing the dielectric layer, representing stored data. Embodiments of the memory cell are adapted to store multiple bits of data per cell and / or adapted for programming more than one time without an erase process.

Owner:MACRONIX INT CO LTD

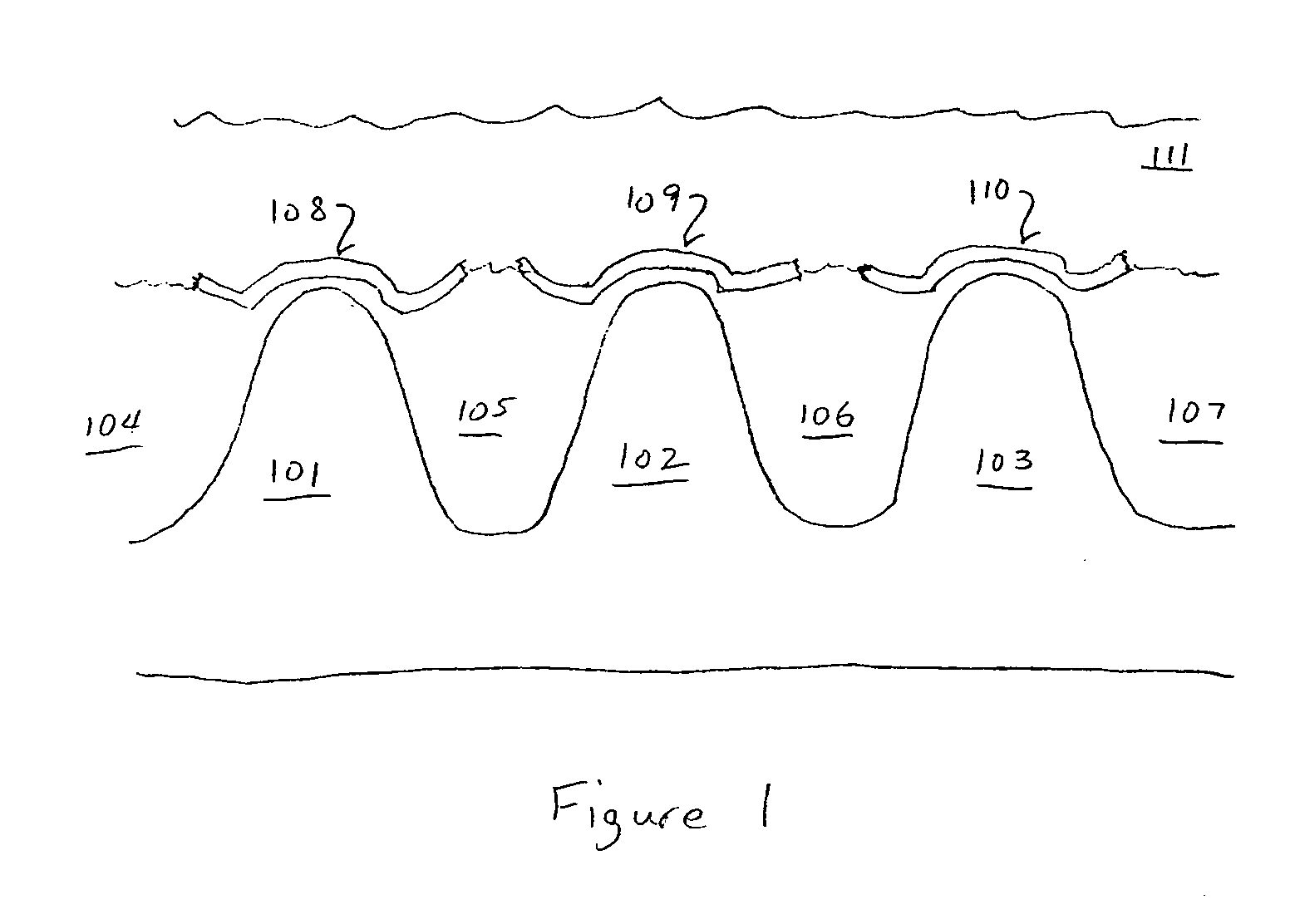

Method of making an ultra thin silicon nitride film

InactiveUS6150286ASemiconductor/solid-state device manufacturingSemiconductor devicesSelf limitingThin oxide

Various methods of fabricating a circuit structure utilizing silicon nitride are provided. In one aspect, a method of fabricating a circuit structure is provided that includes forming a silicon nitride film on a silicon surface, annealing the silicon nitride film in an ammonia ambient and annealing the silicon nitride film in a nitrous oxide ambient to form a thin oxide layer at an interface between the silicon nitride film and the silicon surface. The process of the present invention enables the manufacture of thin silicon nitride films with highly uniform morphology for use as gate dielectrics or other purposes. The thin oxide film is self-limiting in thickness and improves differential mechanical stresses.

Owner:GLOBALFOUNDRIES INC

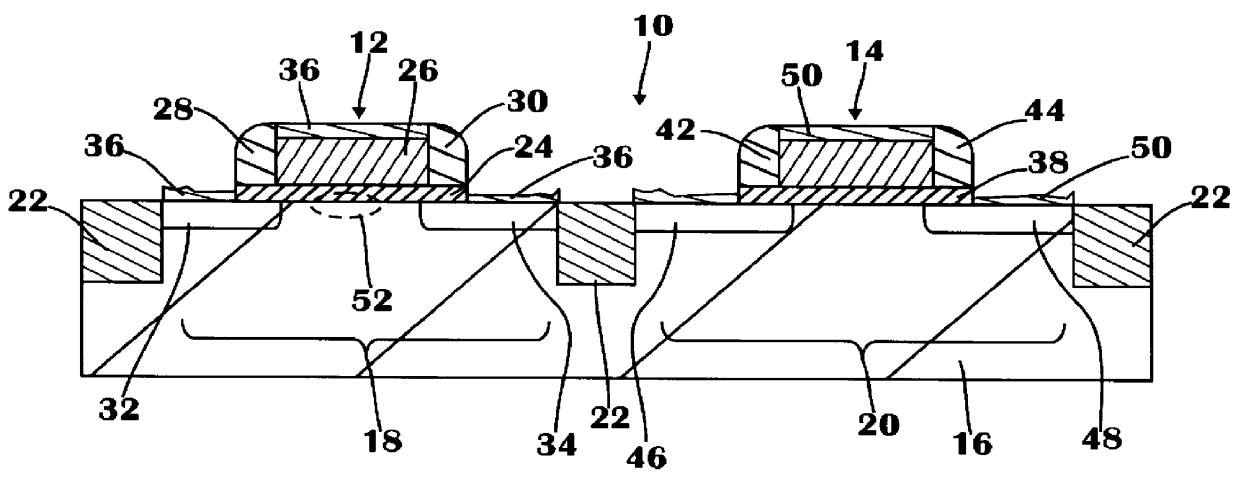

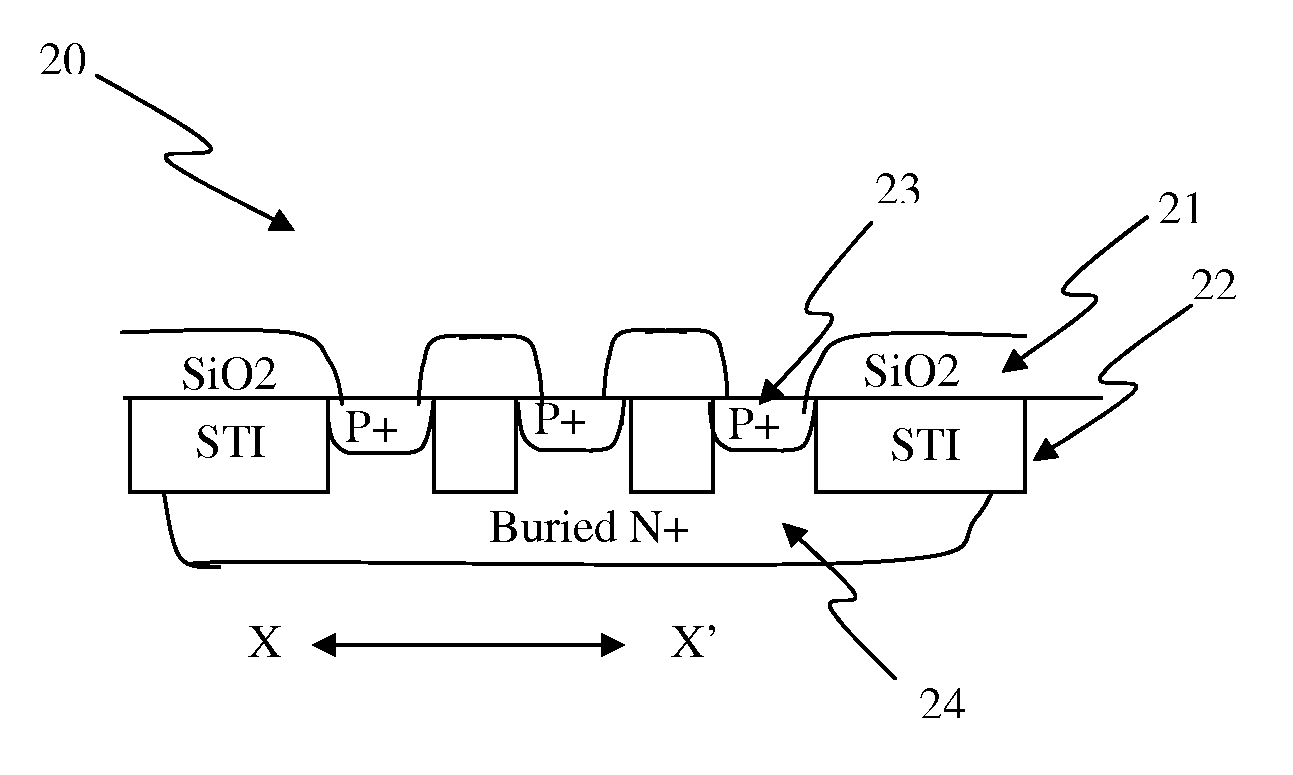

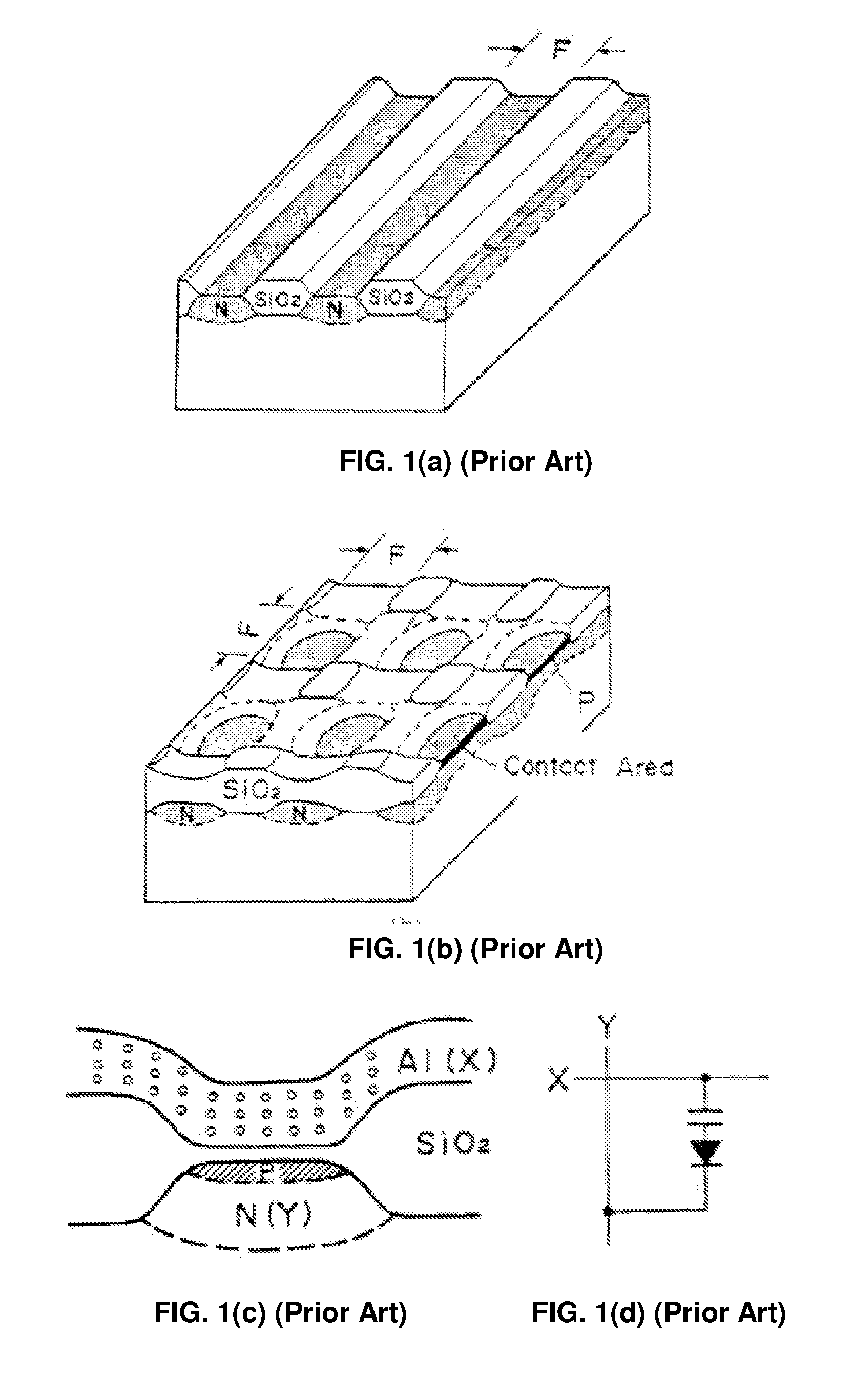

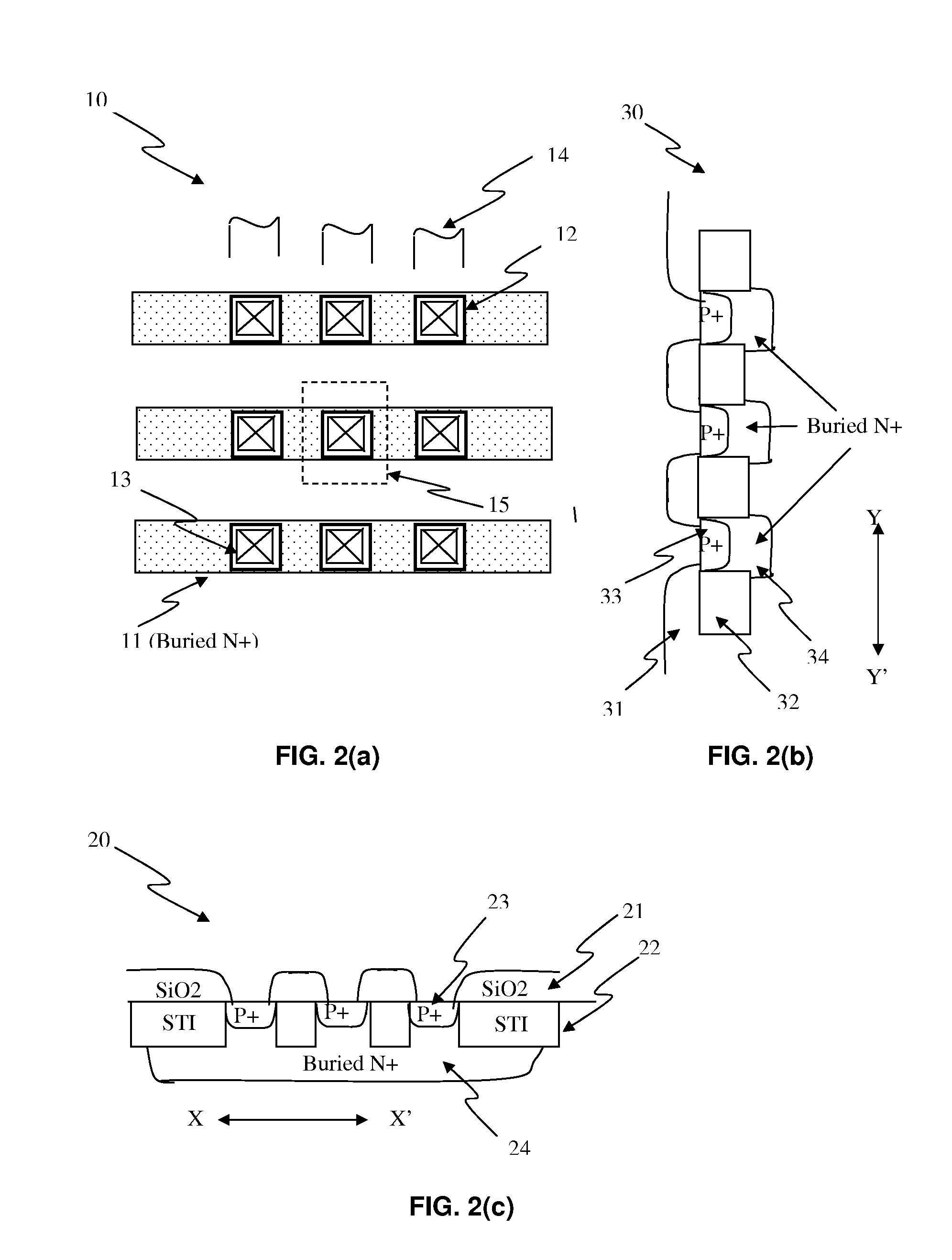

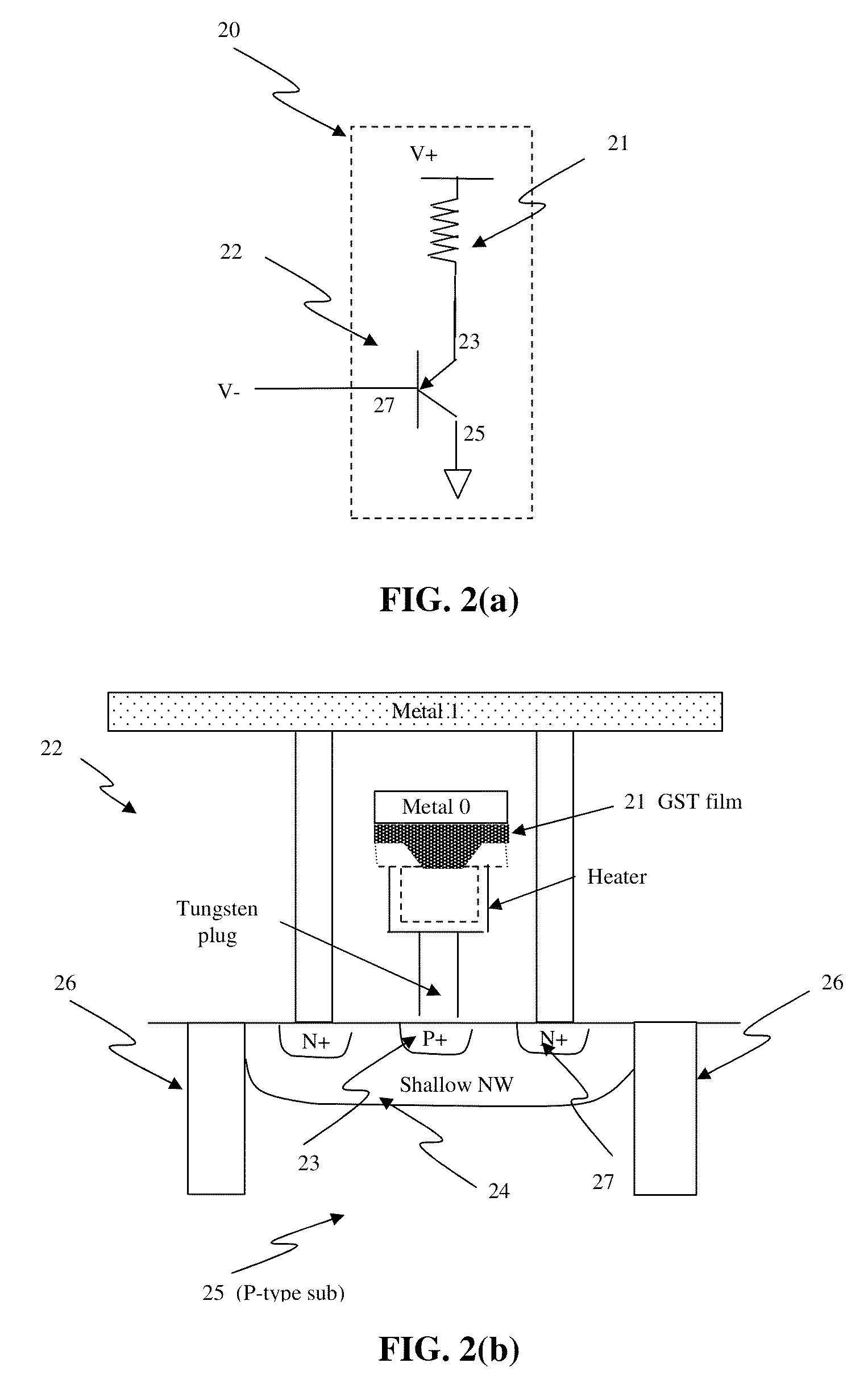

Circuit and system of a high density Anti-fuse

ActiveUS20120147653A1Eliminate needHigh voltageSemiconductor/solid-state device detailsSolid-state devicesThin oxideHigh density

A high density anti-fuse cell can be built at the cross points of two perpendicular interconnect lines, such as active region lines, active and polysilicon lines, active and metal lines, or polysilicon and metal lines. The cell size can be very small. At least one of the anti-fuse cells have a thin oxide fabricated before, after, or between a diode in at least one contact holes at the cross points of the interconnect lines. The thin oxide of the anti-fuse cells at the cross points can be selected for rupture by applying supply voltages in the two perpendicular lines. In some embodiments, a diode can be created after thin oxide is ruptured so that explicitly fabricating a diode or opening a contact hole at the cross-point may not be necessary.

Owner:ATTOPSEMI TECH CO LTD

Mobile ionic contamination detection in manufacture of semiconductor devices

InactiveUS6348808B1Efficient detectionElectronic circuit testingIndividual semiconductor device testingEngineeringSemiconductor device fabrication

A test transistor structure formed in a semiconductor device has a thick-oxide transistor with an elongated serpentine-shaped metal gate. The gate is used to first measure the threshold voltage of the thick-oxide test structure. Then, a current is passed through the elongated metal line which forms the serpentine gate to heat the area of the test structure. While being heated, a stress voltage is applied between the substrate and one end of the gate electrode, this stress voltage being much larger than the logic voltage used in operating thin-oxide transistors on the chip. After a selected time, the current is removed, the stress voltage is removed, and the threshold voltage of the thick-oxide transistor is again measured and compared to the original value. Any reduction in threshold voltage can be attributed to the migration of positive charge to the silicon-to-oxide interface beneath the gate, and is proportional to the area between the source and drain regions of the test transistor.

Owner:BELL SEMICON LLC

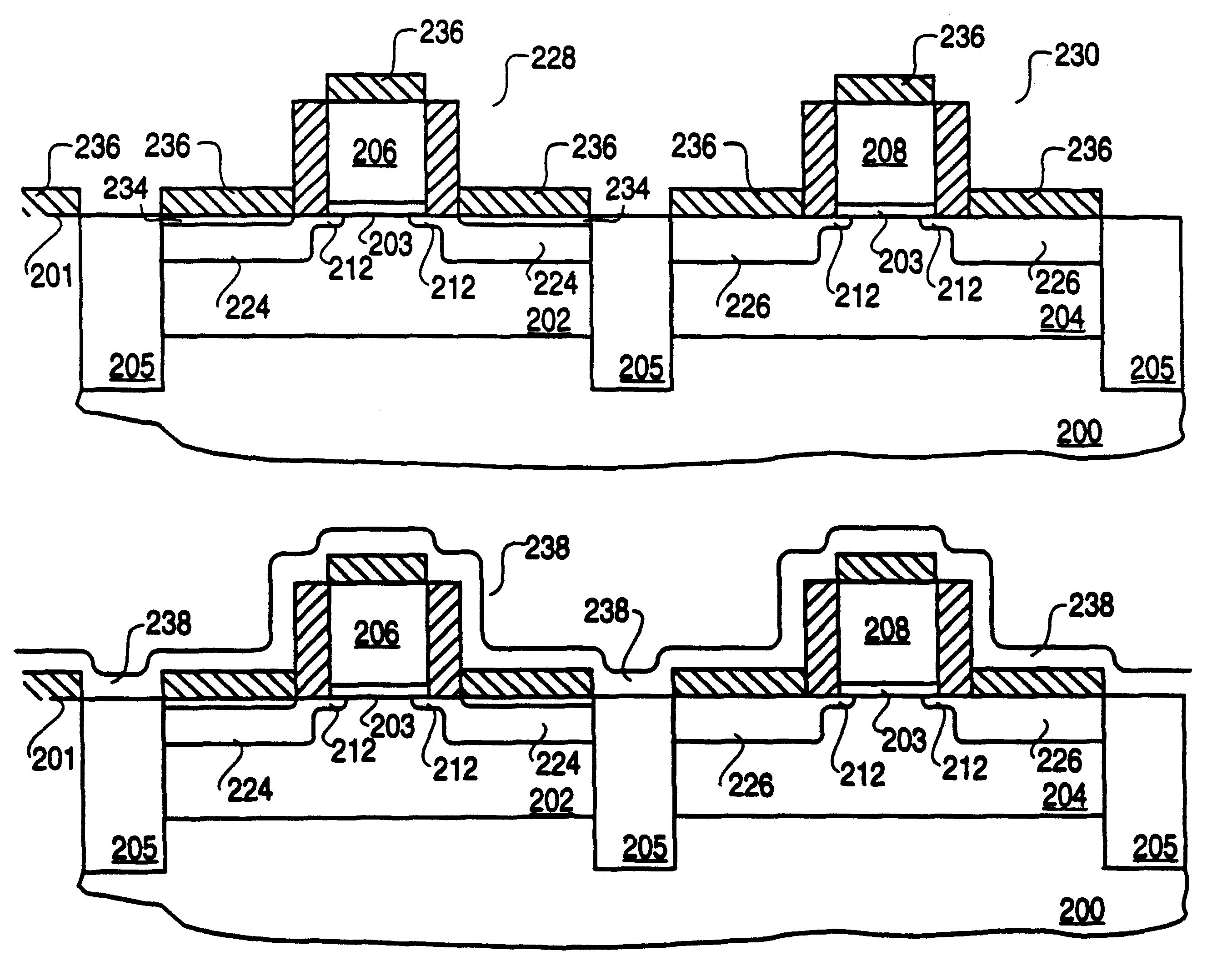

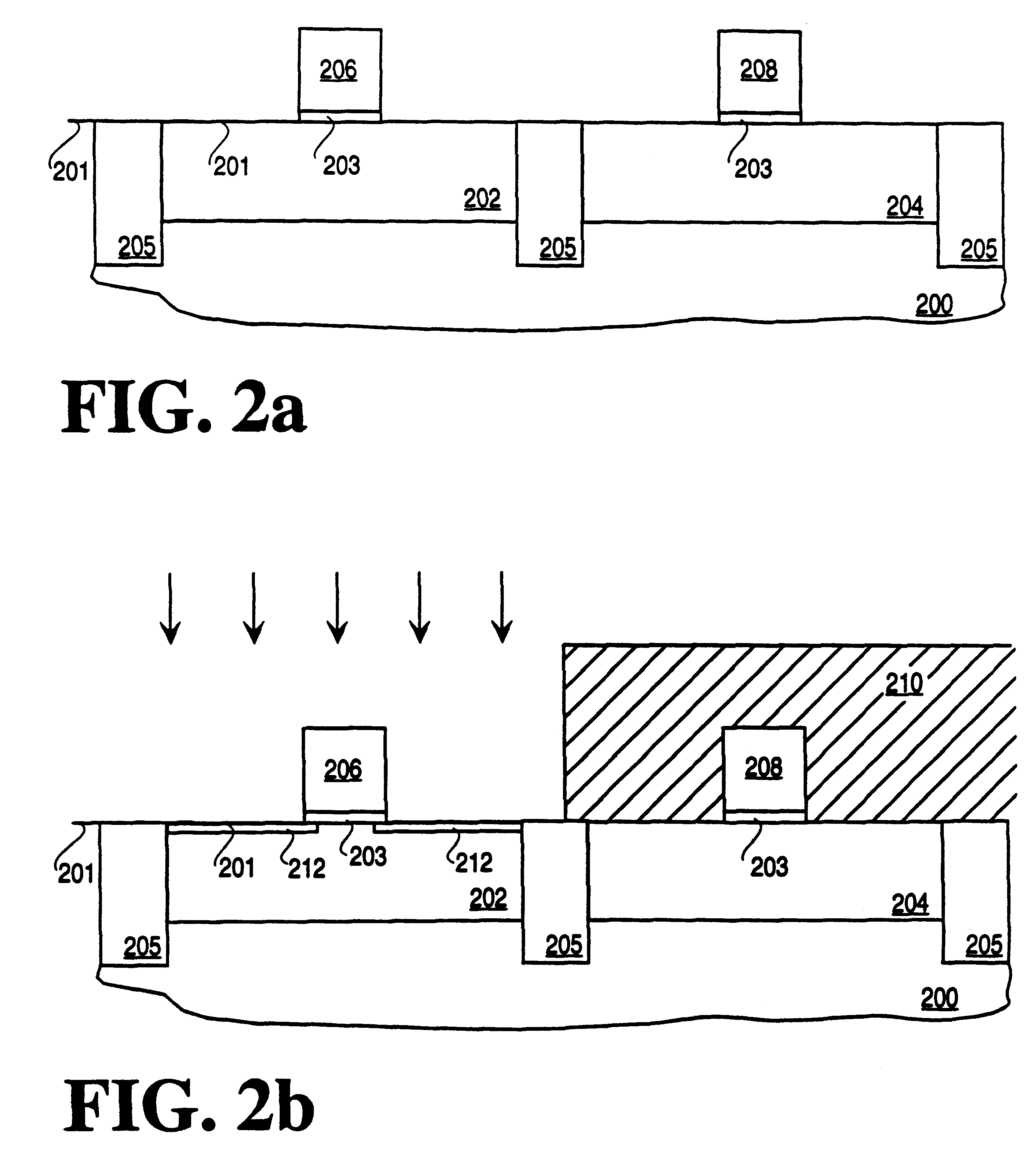

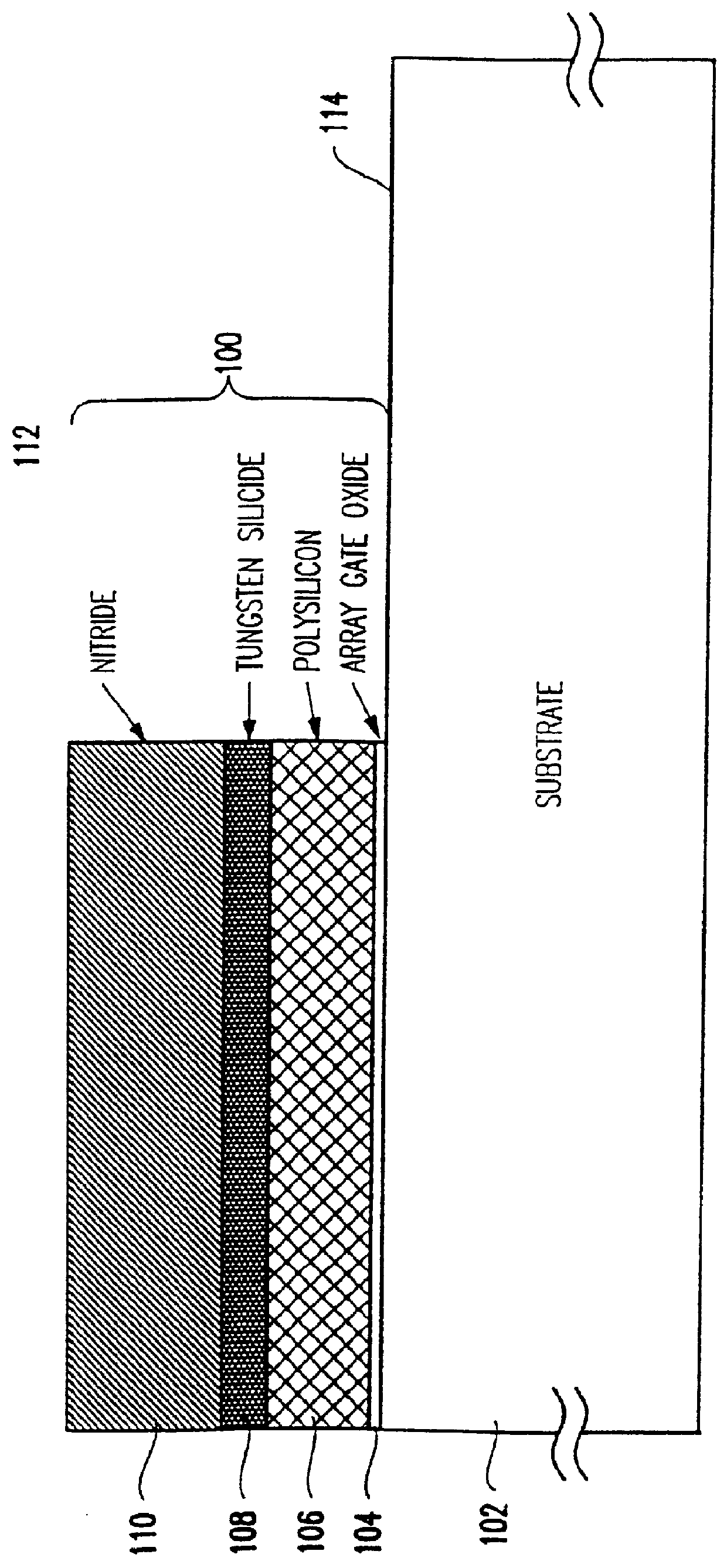

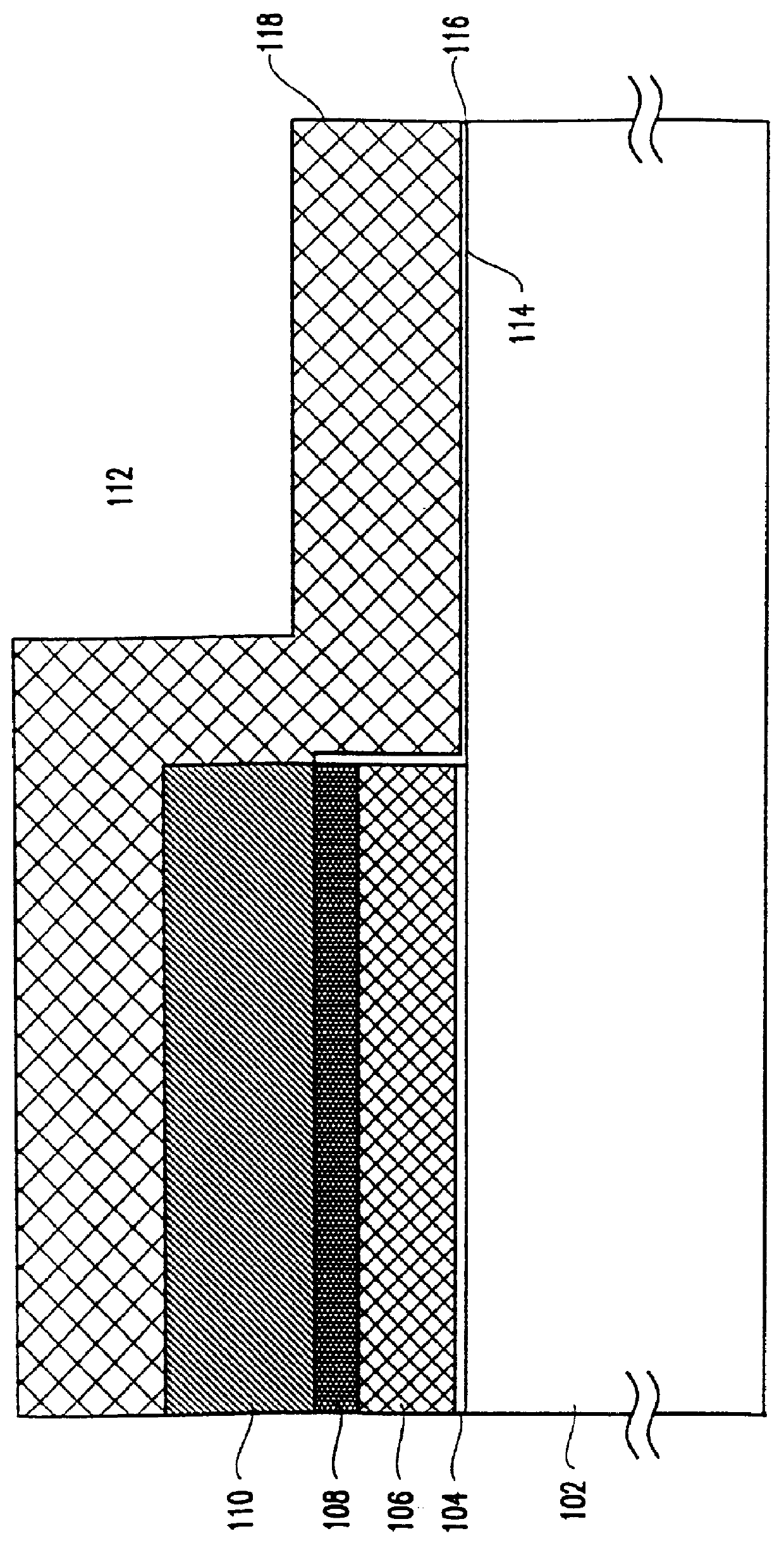

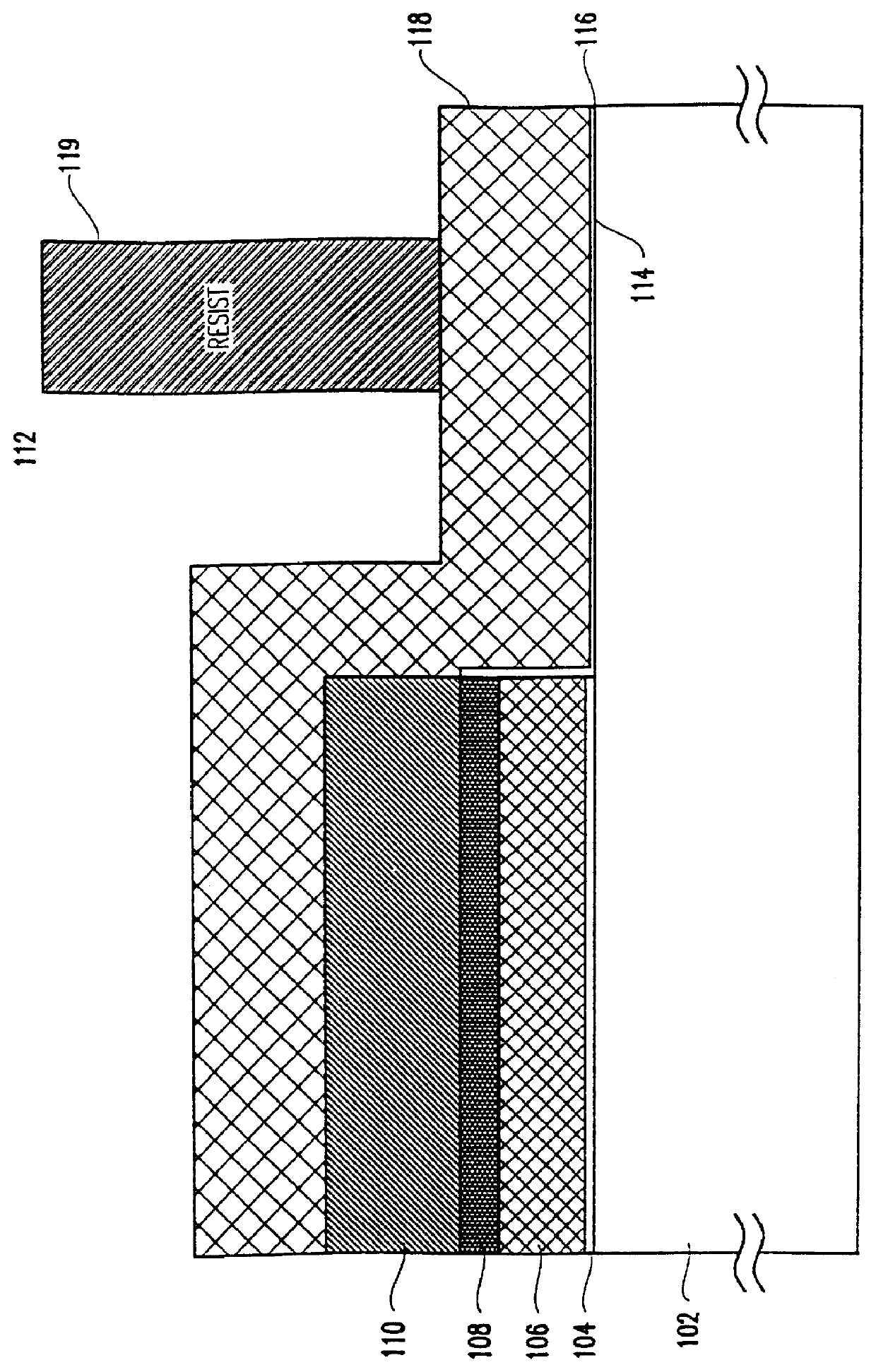

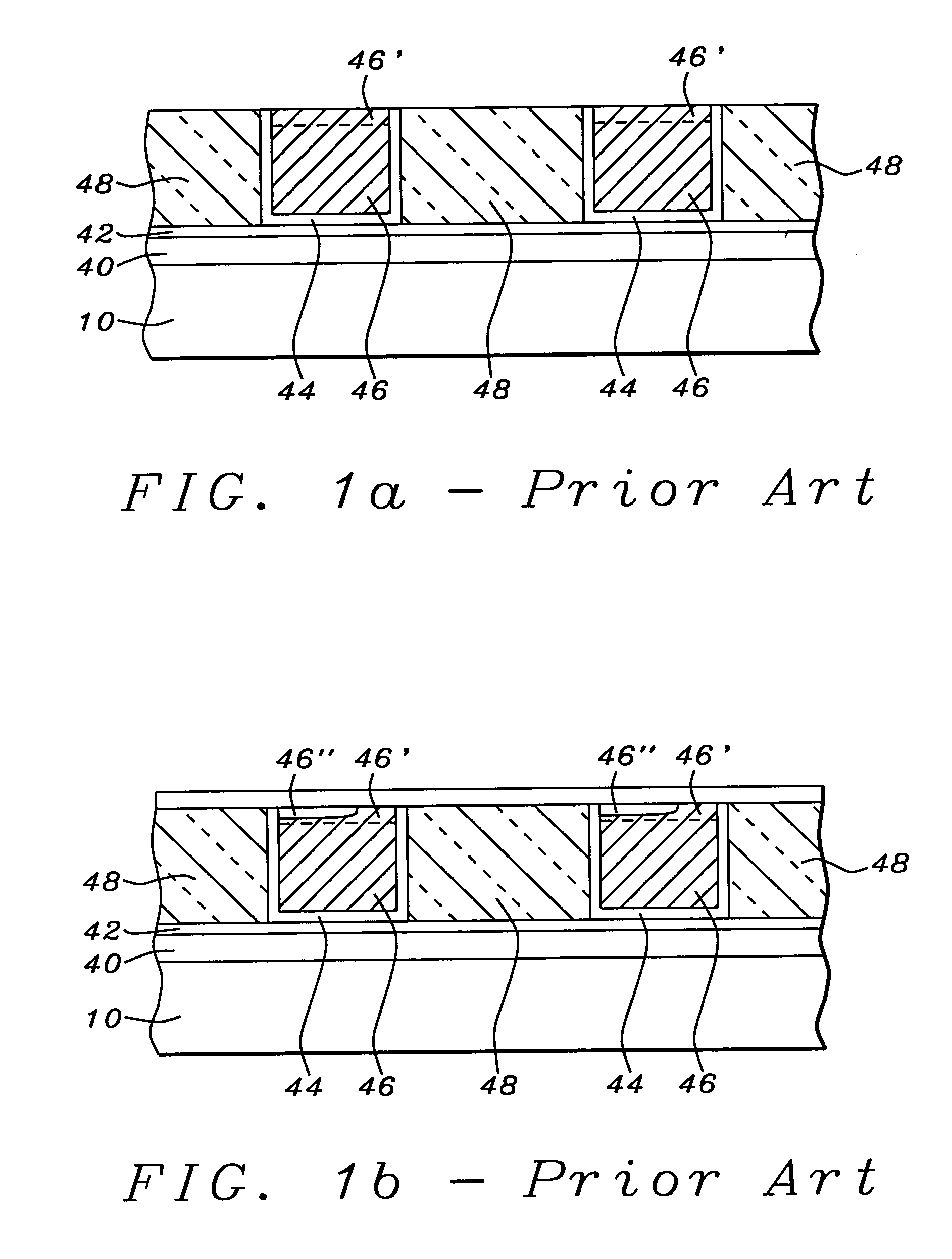

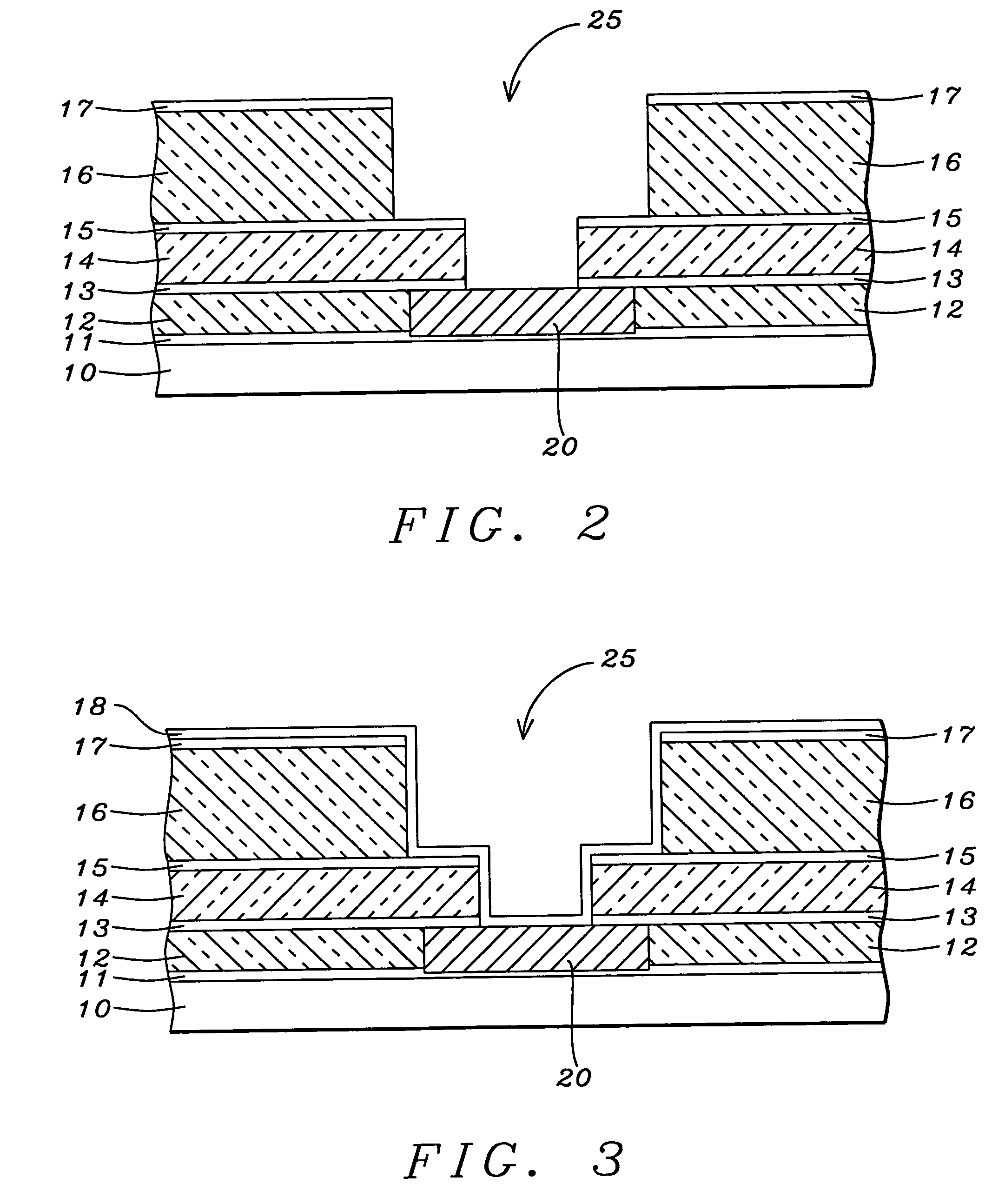

Method for dual gate oxide dual workfunction CMOS

InactiveUS6087225AIncrease flexibilityIncrease junction formation flexibilityTransistorSolid-state devicesThin oxideCMOS

A method of forming integrated circuit chips including two dissimilar type NFETs and / or two dissimilar type PFETs on the same chip, such as both thick and thin gate oxide FETs. A DRAM array may be constructed of the thick oxide FETs and logic circuits may be constructed of the thin oxide FETs on the same chip. First, a gate stack including a first, thick gate SiO2 layer is formed on a wafer. The stack includes a doped polysilicon layer on the gate oxide layer, a silicide layer on the polysilicon layer and a nitride layer on the silicide layer. Part of the stack is selectively removed to re-expose the wafer where logic circuits are to be formed. A thinner gate oxide layer is formed on the re-exposed wafer. Next, gates are formed on the thinner gate oxide layer and thin oxide NFETs and PFETs are formed at the gates. After selectively siliciding thin oxide device regions, gates are etched from the stack in the thick oxide device regions. Finally, source and drain regions are implanted and diffused for the thick gate oxide devices.

Owner:GOOGLE LLC

Method of forming oxide layer using atomic layer deposition method and method of forming capacitor of semiconductor device using the same

InactiveUS7151039B2Increase deposition rateImprove featuresTransistorSolid-state devicesThin oxideChemical reaction

In a method of forming an oxide layer using an atomic layer deposition and a method of forming a capacitor of a semiconductor device using the same, a precursor including an amino functional group is introduced onto a substrate to chemisorb a portion of the precursor on the substrate. Then, the non-chemisorbed precursor is removed. Thereafter, an oxidant is introduced onto the substrate to chemically react the chemisorbed precursor with the oxidant to form an oxide layer on the substrate. A deposition rate is fast and an oxide layer having a good deposition characteristic may be obtained. Also, a thin oxide film having a good step coverage and a decreased pattern loading rate can be formed.

Owner:SAMSUNG ELECTRONICS CO LTD

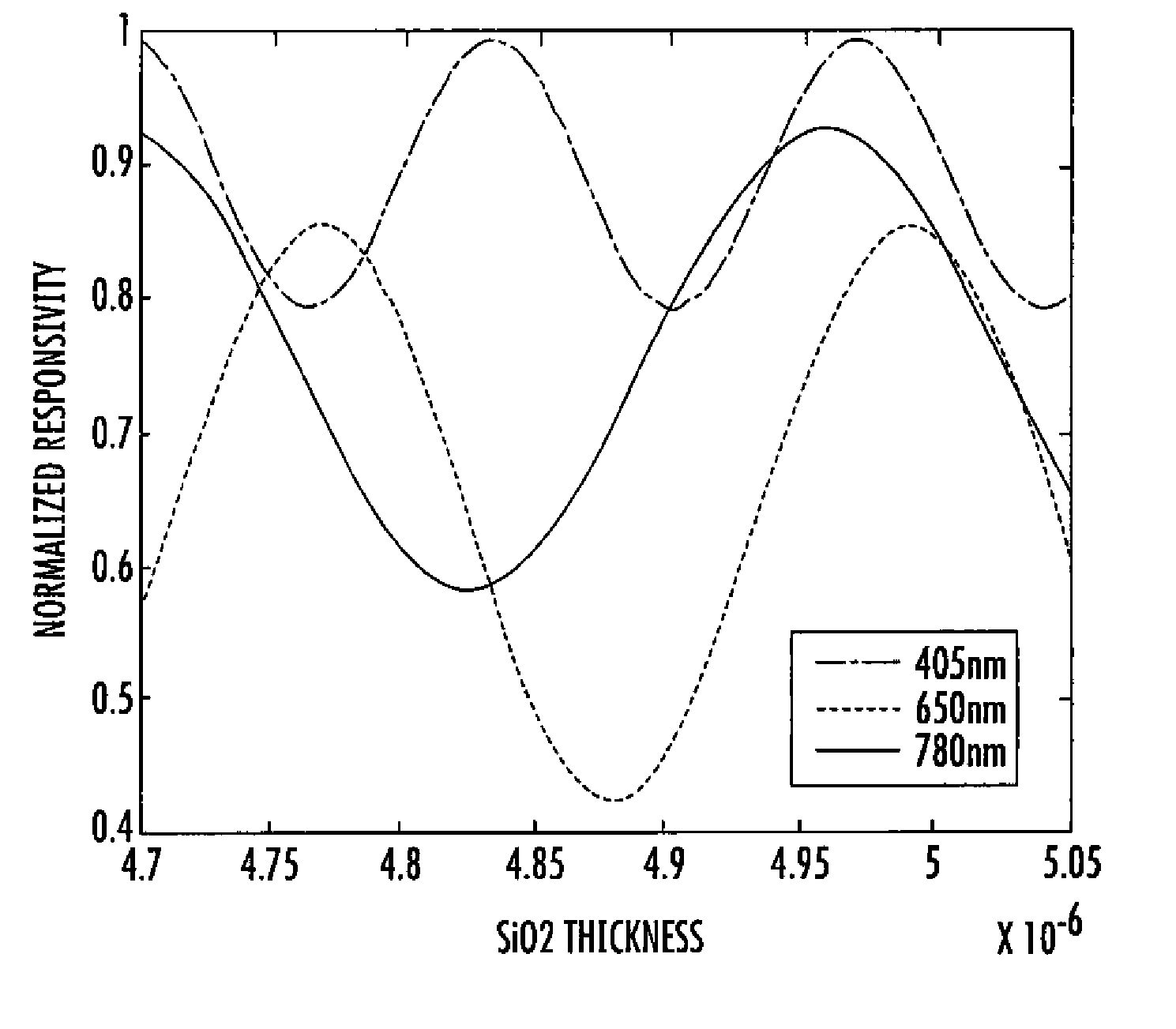

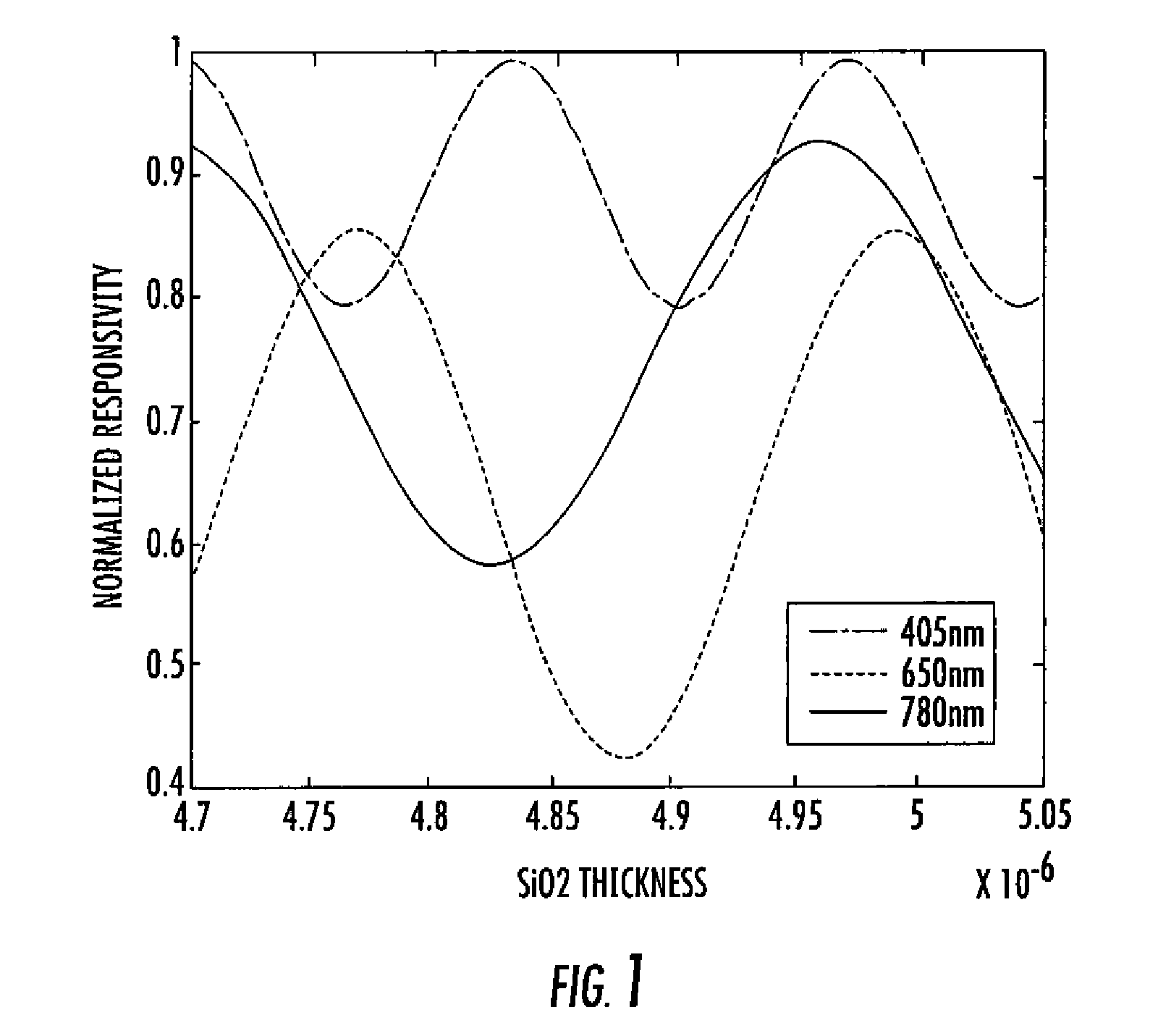

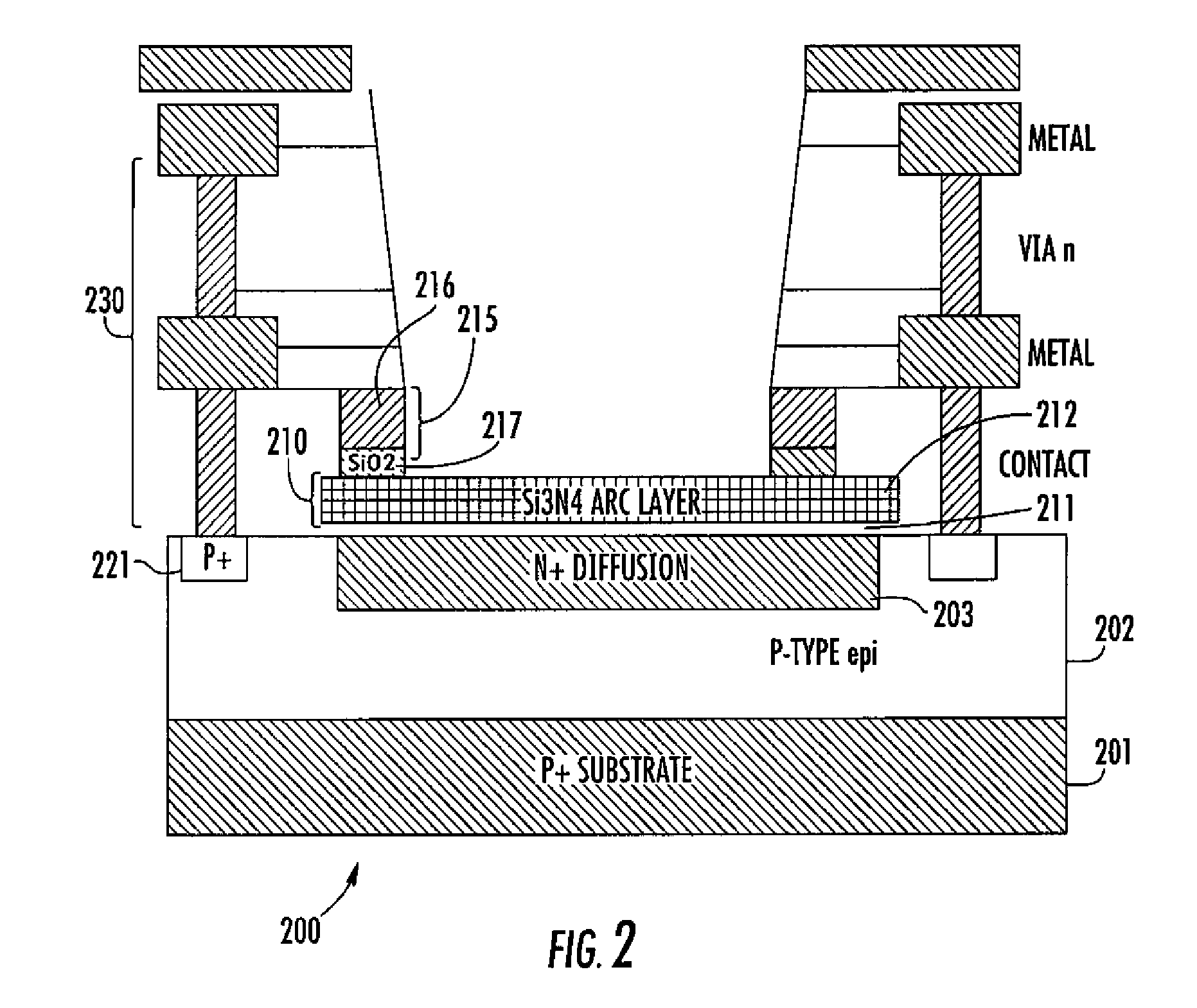

Photodiode for multiple wavelength operation

InactiveUS20070072326A1Solid-state devicesSemiconductor/solid-state device manufacturingAnti-reflective coatingThin oxide

A method of a fabricating a multiple wavelength adapted photodiode and resulting photodiode includes the steps of providing a substrate having a first semiconductor type surface region on at least a portion thereof, implanting and forming a second semiconductor type shallow surface layer into the surface region, and forming a multi-layer anti-reflective coating (ARC) on the shallow surface layer. The forming step includes depositing or forming a thin oxide layer on the shallow surface layer and depositing a second dielectric layer different from the thin oxide layer on the thin oxide layer. An etch stop is formed on the second dielectric, wherein the etch stop includes at least one layer resistant to oxide etch. At least one oxide including layer (e.g. ILD) is then deposited on the etch stop. The oxide including layer and etch stop are then removed to expose at least a portion of the ARC to the ambient.

Owner:INTERSIL INC

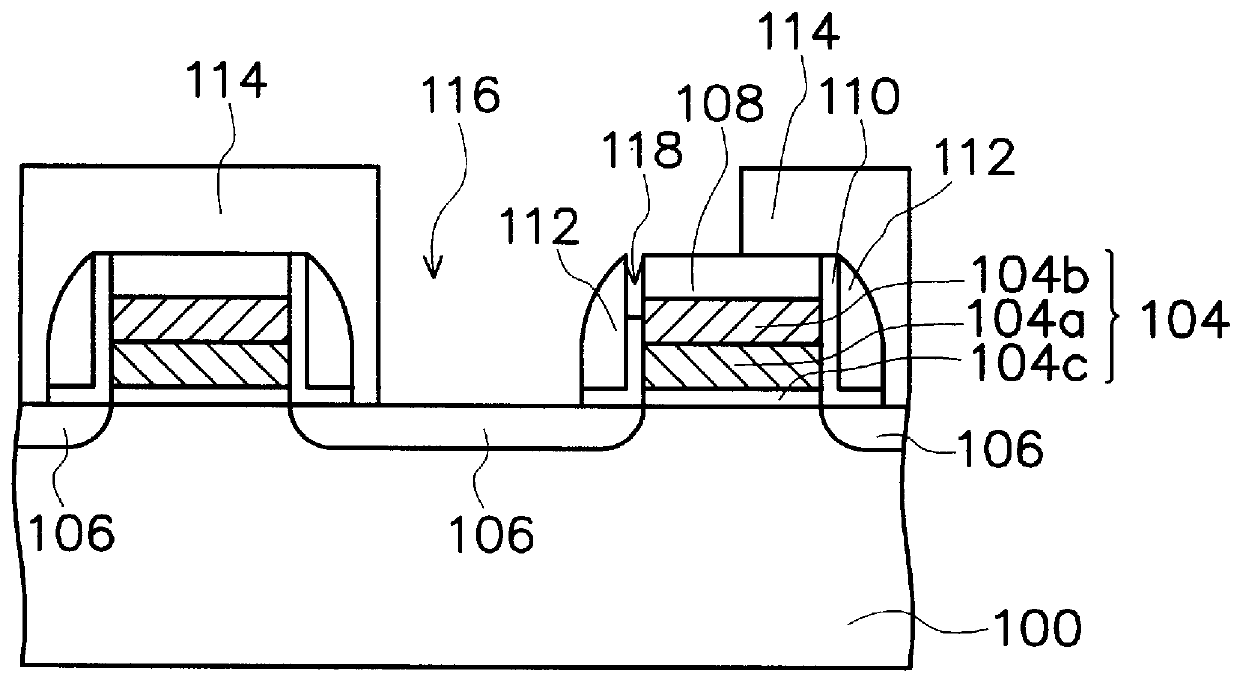

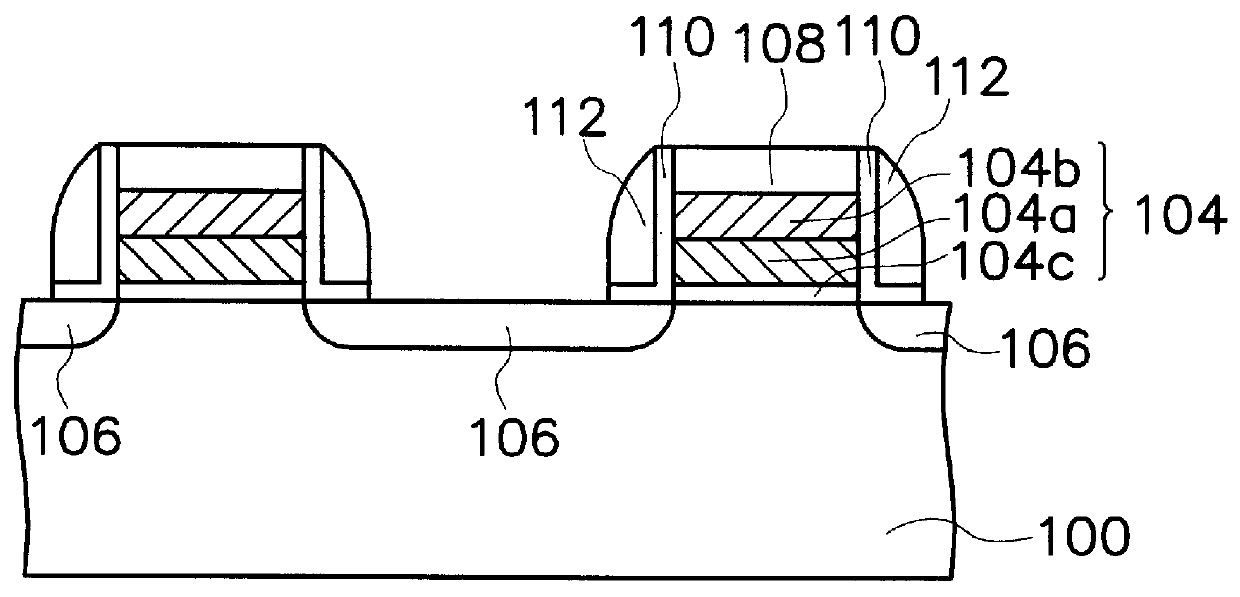

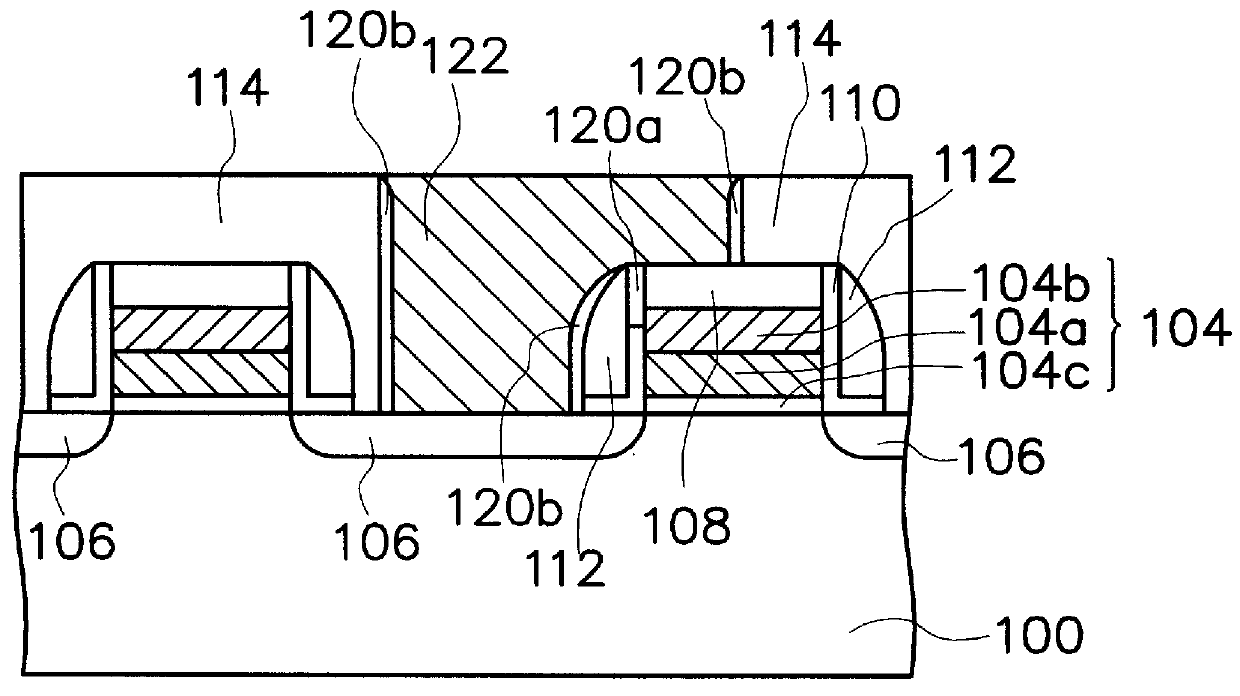

Method for forming a self-aligned contact

A method for forming a SAC opening is provided. As a self-aligned contact (SAC) opening is formed in a dielectric layer on a semiconductor substrate to expose one of source / drain regions in the substrate, a misalignment of the SAC opening may occur to expose a portion of the gate structure. The gate structure has a gate, which is covered by a cap layer on the top, a thin oxide layer on each sidewall of the gate and the cap layer, and a spacer on the thin oxide layer. The SAC opening causes a clearance between the spacer and the gate since a portion of the thin oxide layer is removed. The method contains forming an insulating layer over the substrate to fill the clearance. An etching back process is performed to remove the insulating layer so that a remaining portion of the insulating layer fills the clearance to fully isolate the gate.

Owner:UNITED MICROELECTRONICS CORP

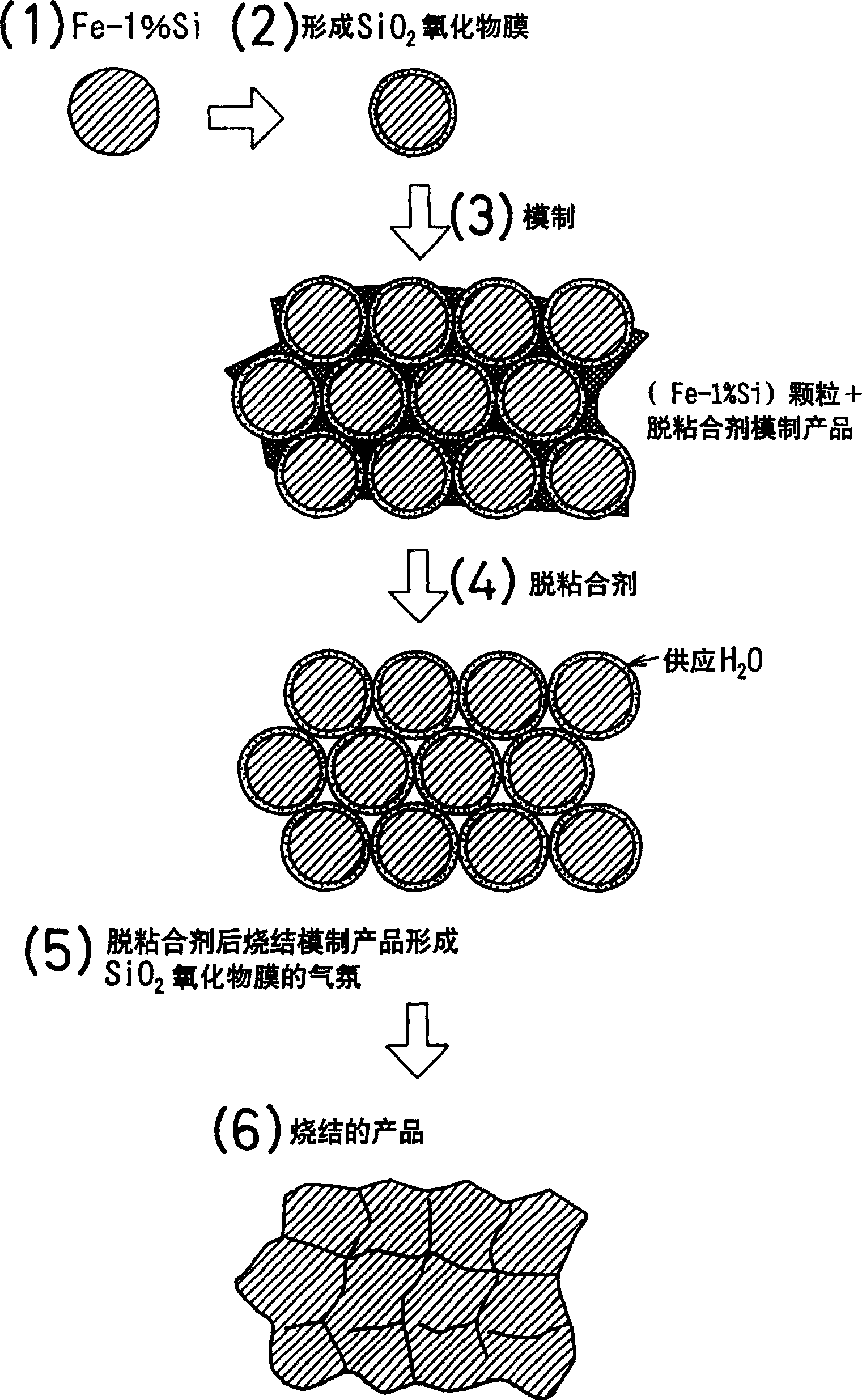

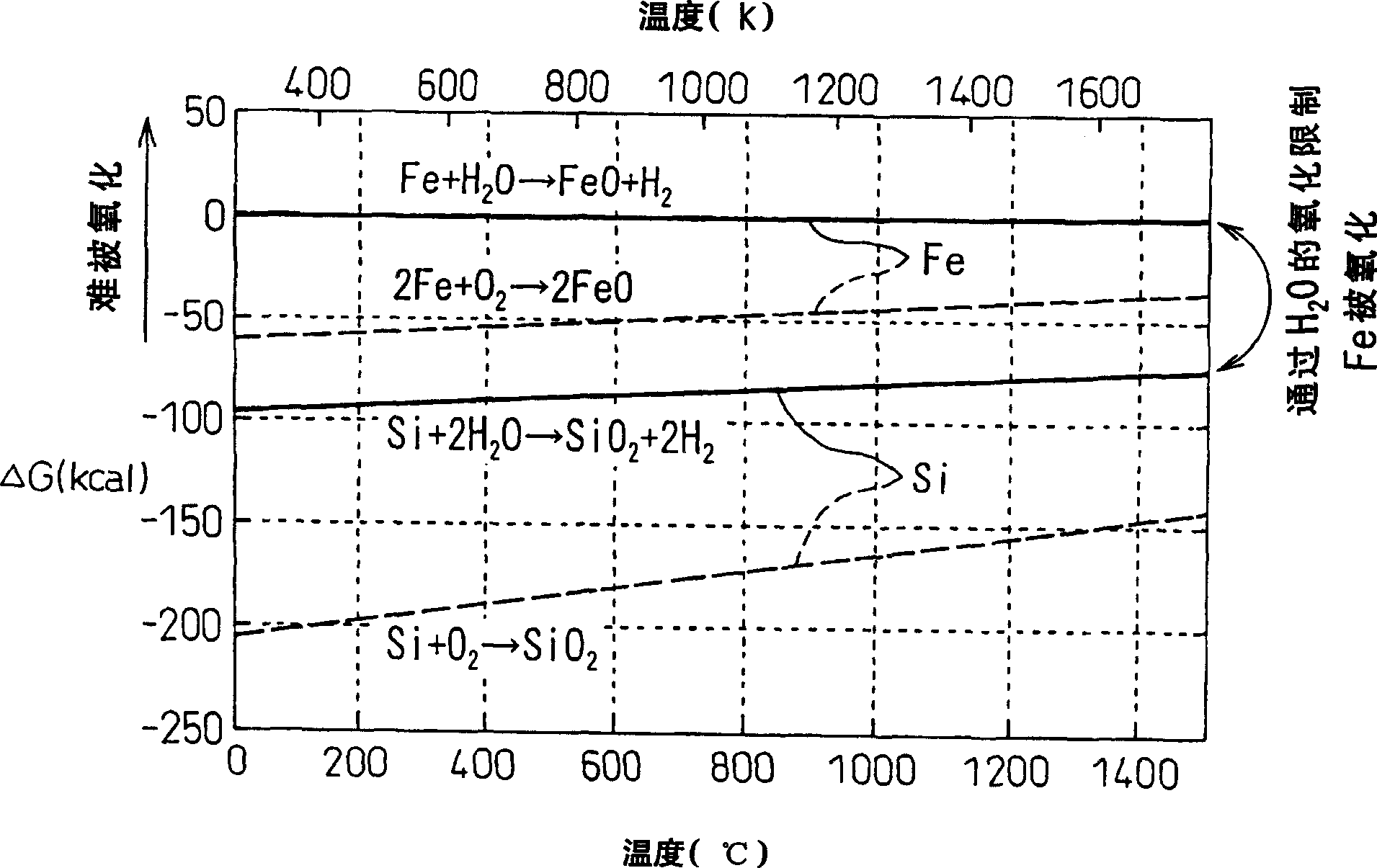

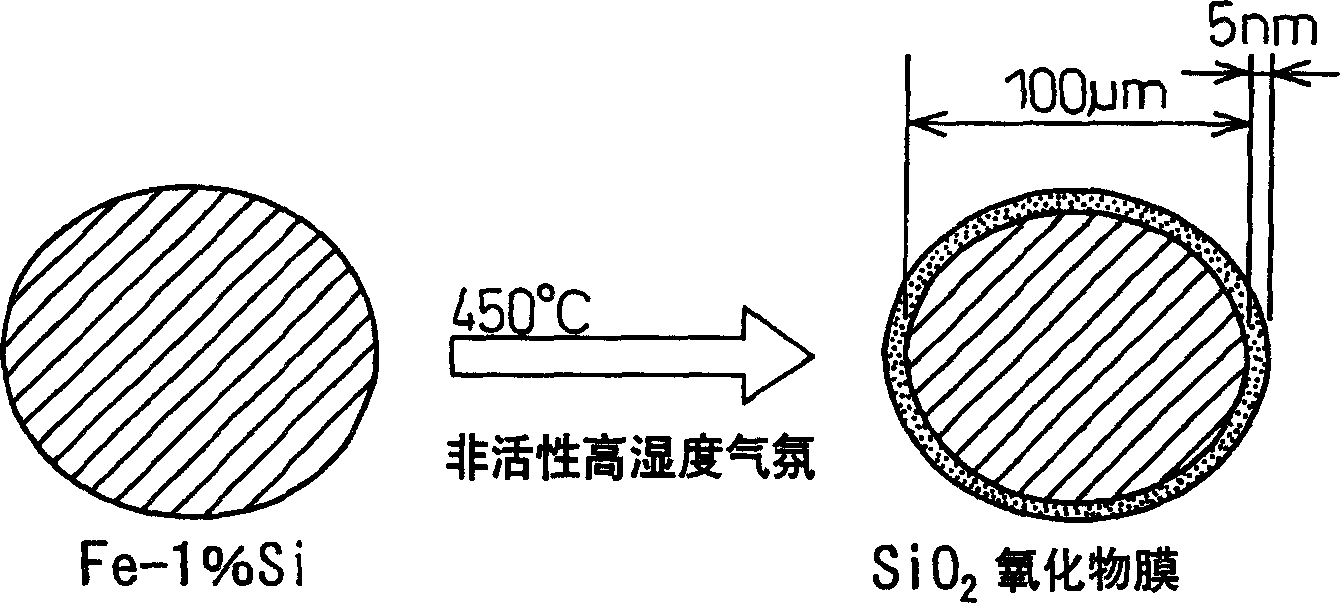

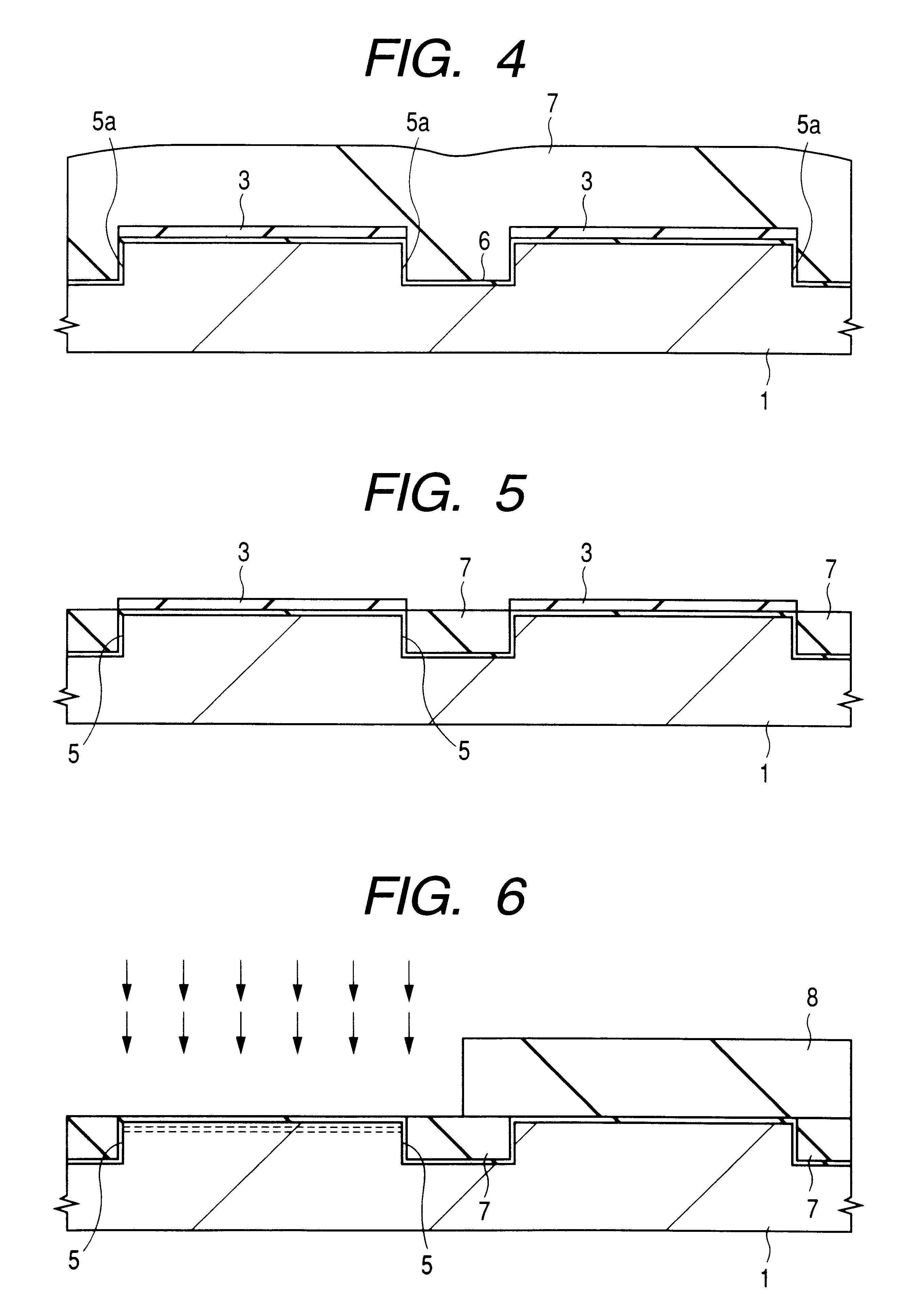

Method for manufacturing soft magnetic material

The invention provides a method for manufacturing a soft magnetic material, wherein an Fe-Si alloy powder is heated in a weakly oxidizing atmosphere to form a SiO2 oxide film on the surface, and the powder is then press-molded and fired in a weakly oxidizing atmosphere to obtain a sintered product. By performing the surface oxidizing step in a weakly oxidizing atmosphere such as water vapor, Si is selectively oxidized to form a thin oxide film with high electrical resistance. Furthermore, by firing the molded product in a weakly oxidizing atmosphere, the sintering can be performed while the oxide film, in which cracks and the like are generated at the press-molding, is repaired.

Owner:DENSO CORP

Dense finFET SRAM

Owner:GLOBALFOUNDRIES U S INC

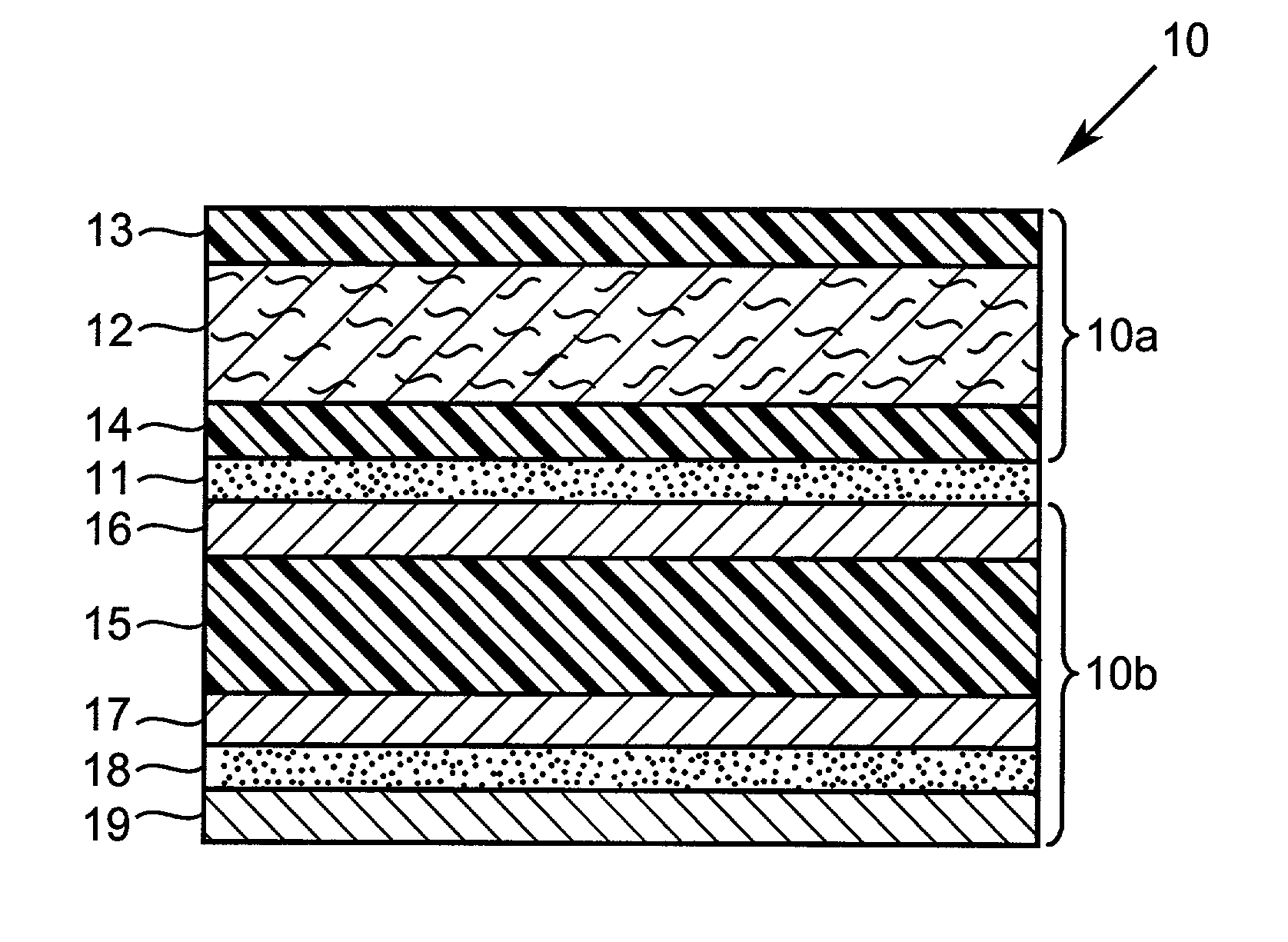

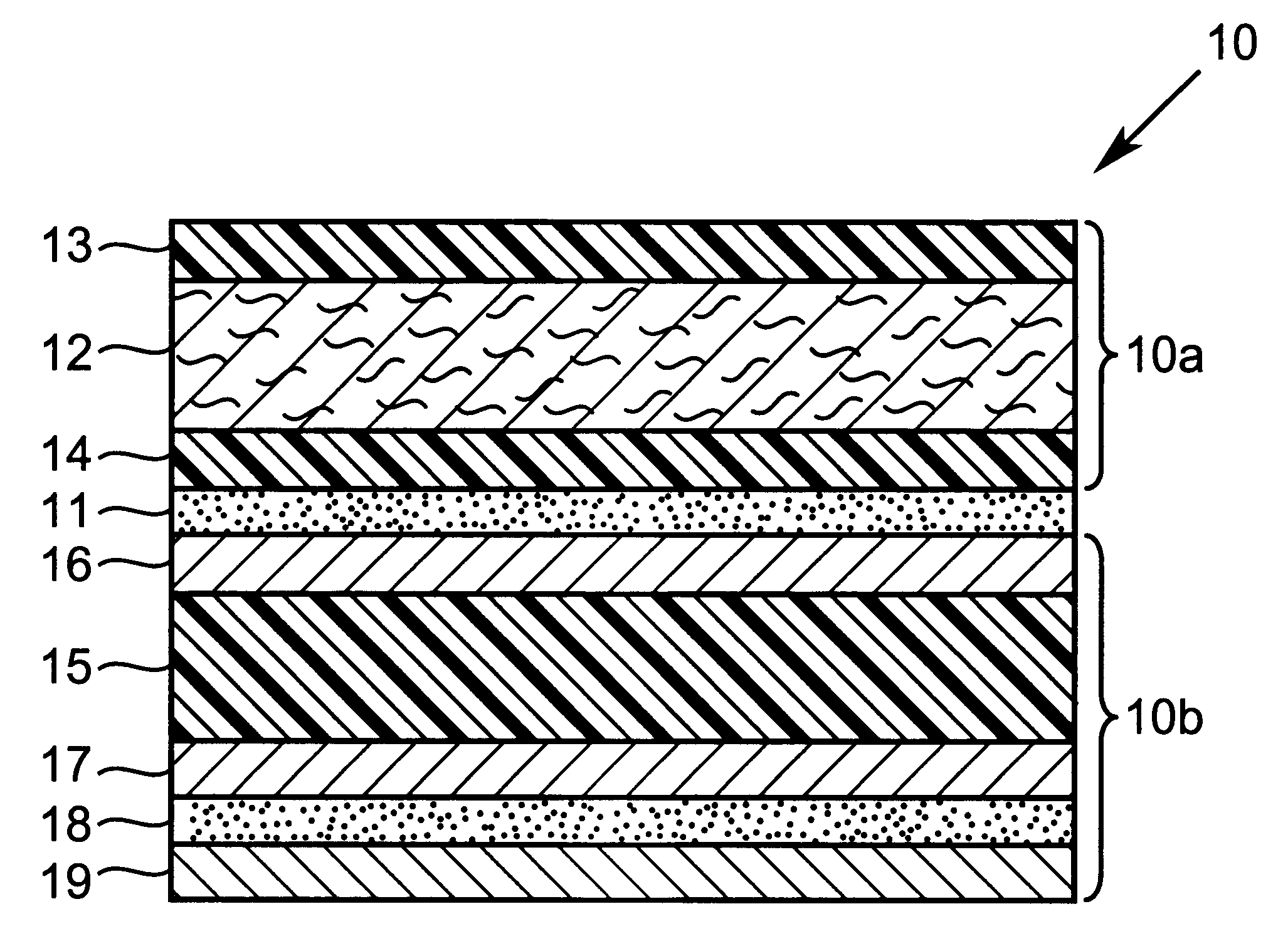

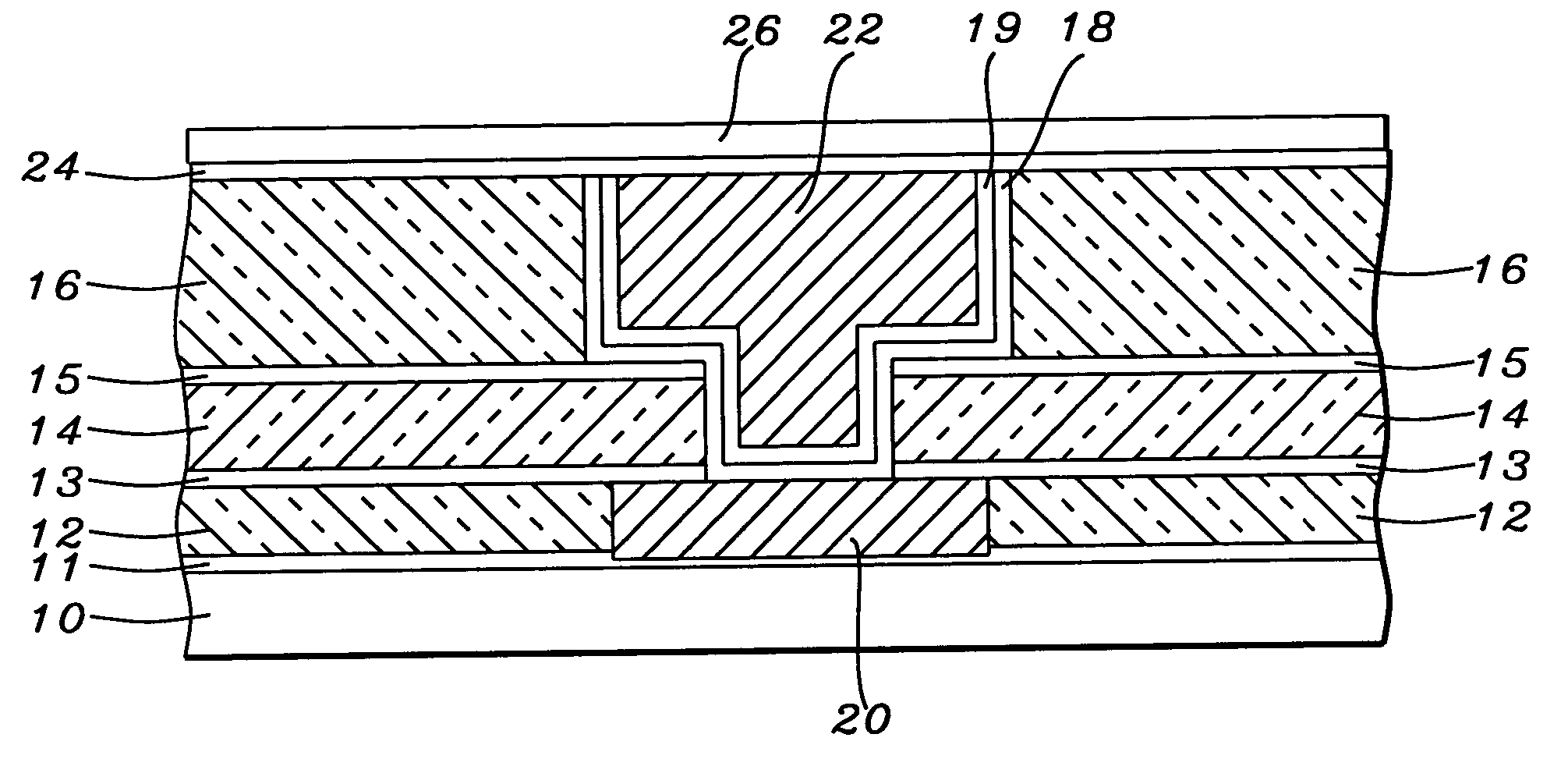

Packaging laminate with gas and aroma barrier properties

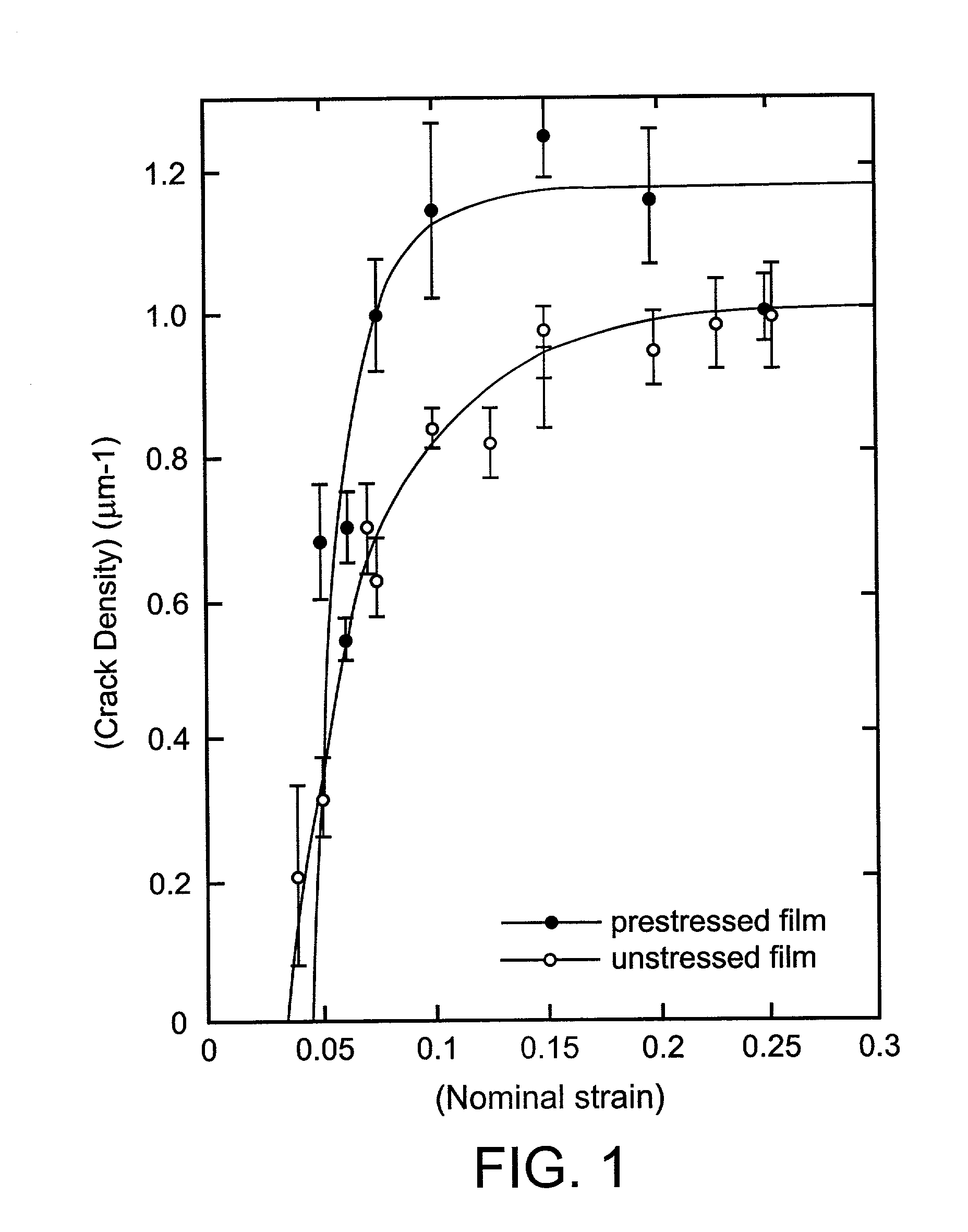

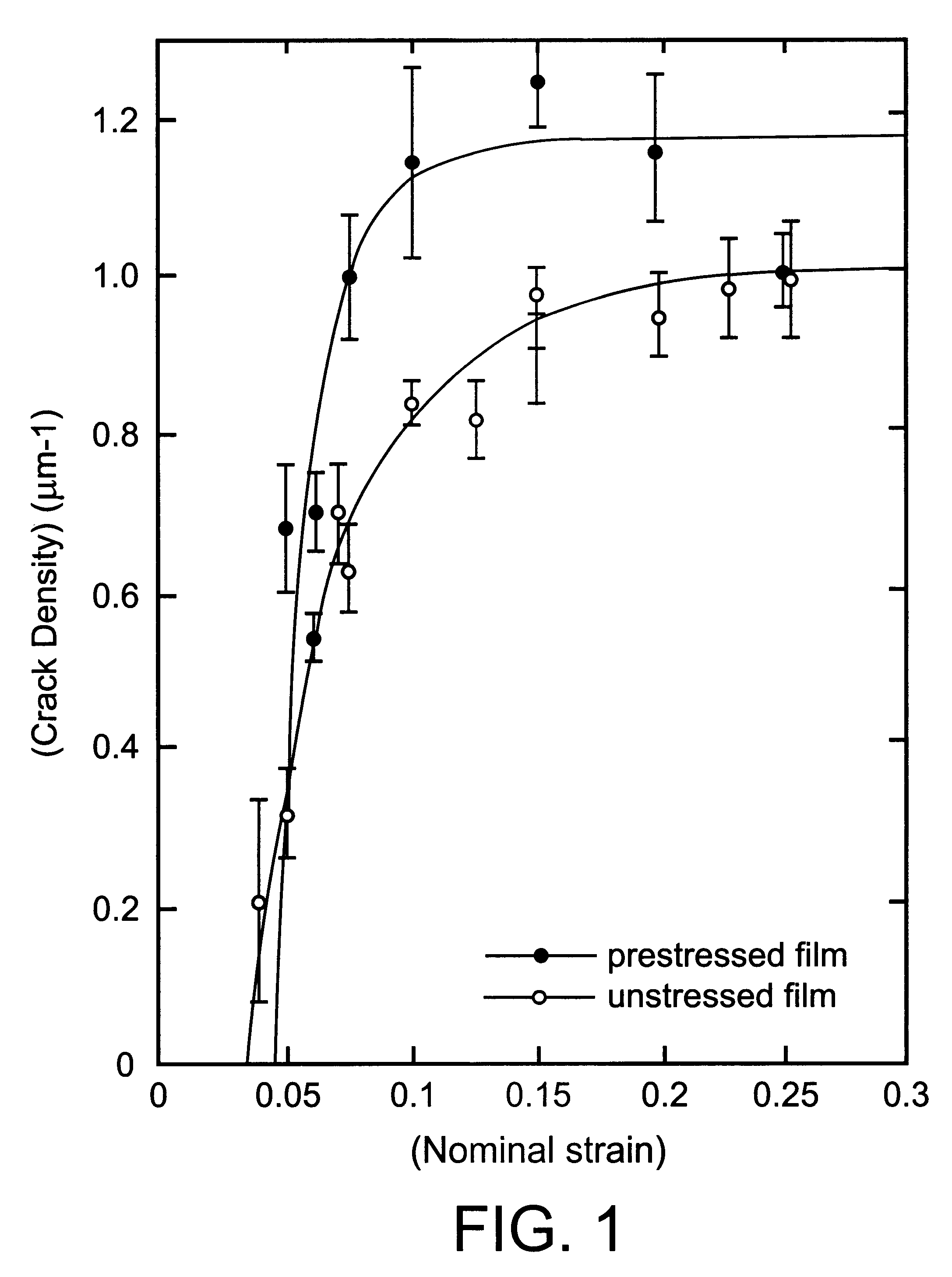

InactiveUS20020028336A1Improved barrier and durability propertyCapable being formedLiquid surface applicatorsFlexible coversThin oxidePaperboard

A packaging laminate (10) including a substrate film (15) coated with a carbon containing silicon oxide layer (16, 17) on both surfaces is disclosed herein. A method for producing the laminate (10), and blanks and packages fabricated from the laminate are also disclosed herein. The PECVD process of the present invention strains the substrate film (15) during deposition thereby creating a very thin oxide layer with superior durability, oxygen and aroma barrier properties. The carbon-containing silicon oxide coating (16, 17) has a stoichiometry of SiOxCy in which x is within the range of 1.5-2.2 and y is within the range of 0.15-0.80. The substrate film (15) may include a core layer (12) of a material selected from the group consisting of paper, paperboard, a foamed core, polyethylene terephtalate, polyamide, polyethylene and polypropylene.

Owner:JACCOUD BERTRAND

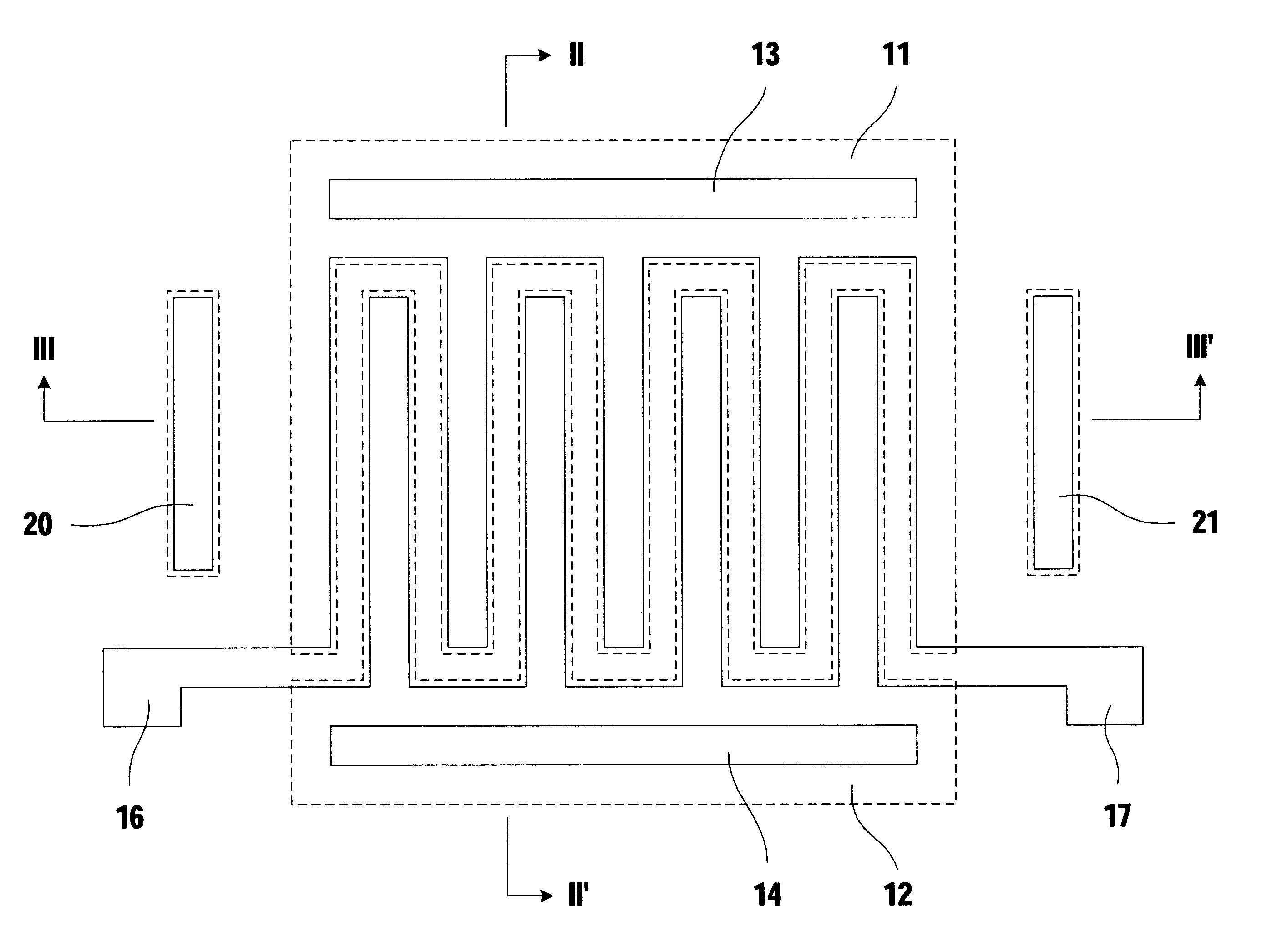

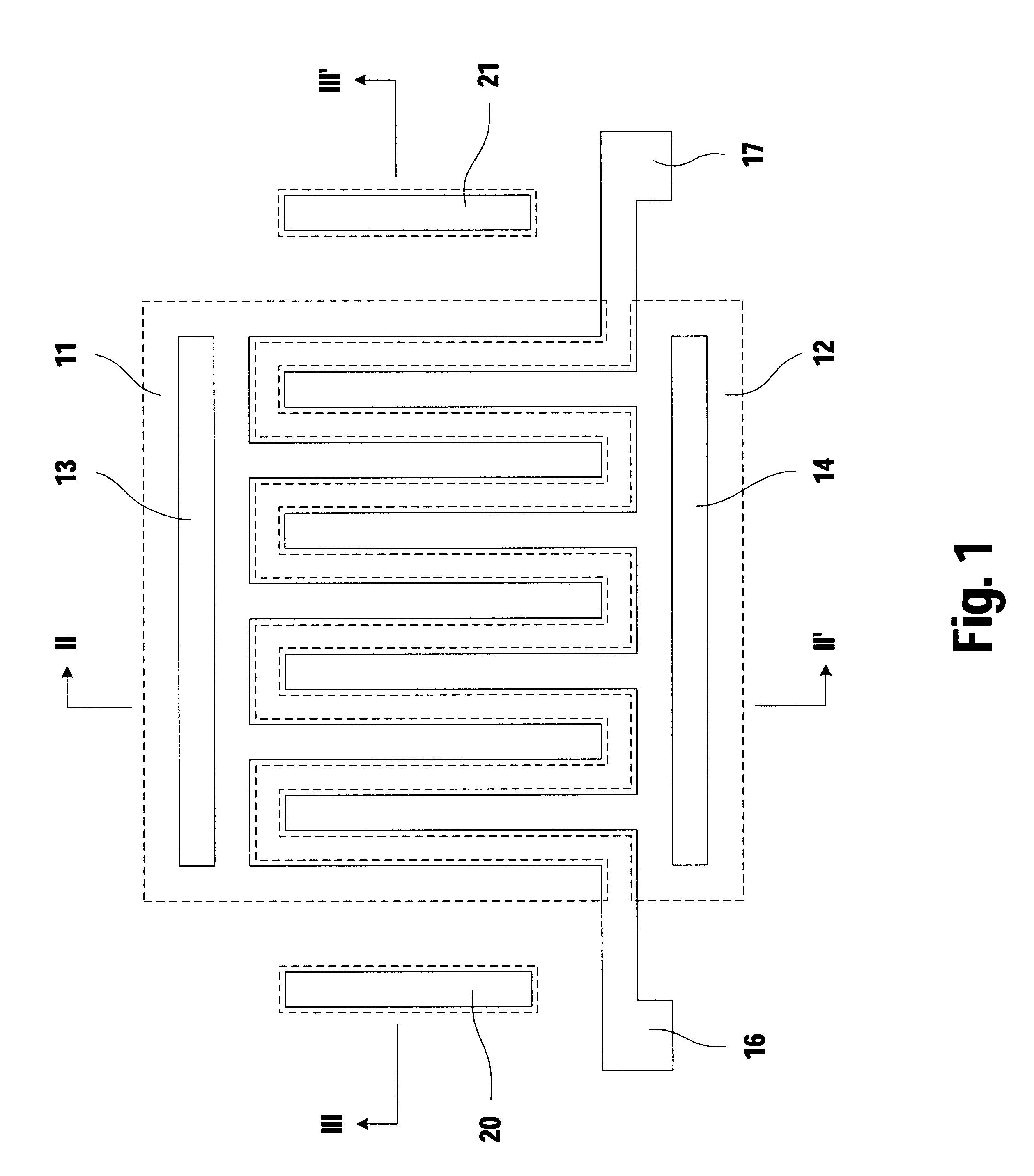

Circuit and system of using junction diode as program selector for one-time programmable devices with heat sink

ActiveUS9070437B2Low costSmall sizeTransistorSemiconductor/solid-state device detailsHigh resistanceElectrical conductor

Junction diodes fabricated in standard CMOS logic processes can be used as program selectors with at least one heat sink or heater to assist programming for One-Time Programmable (OTP) devices, such as electrical fuse, contact / via fuse, contact / via anti-fuse, or gate-oxide breakdown anti-fuse, etc. The heat sink can be at least one thin oxide area, extended OTP element area, or other conductors coupled to the OTP element to assist programming. A heater can be at least one high resistance area such as an unsilicided polysilicon, unsilicided active region, contact, via, or combined in serial, or interconnect to generate heat to assist programming. The OTP device has at least one OTP element coupled to at least one diode in a memory cell. The diode can be constructed by P+ and N+ active regions in a CMOS N well, or on an isolated active region as the P and N terminals of the diode. The isolation between P+ and the N+ active regions of the diode in a cell or between cells can be provided by dummy MOS gate, SBL, or STI / LOCOS isolations. The OTP element can be polysilicon, silicided polysilicon, silicide, polymetal, metal, metal alloy, local interconnect, metal-0, thermally isolated active region, CMOS gate, or combination thereof.

Owner:ATTOPSEMI TECH CO LTD

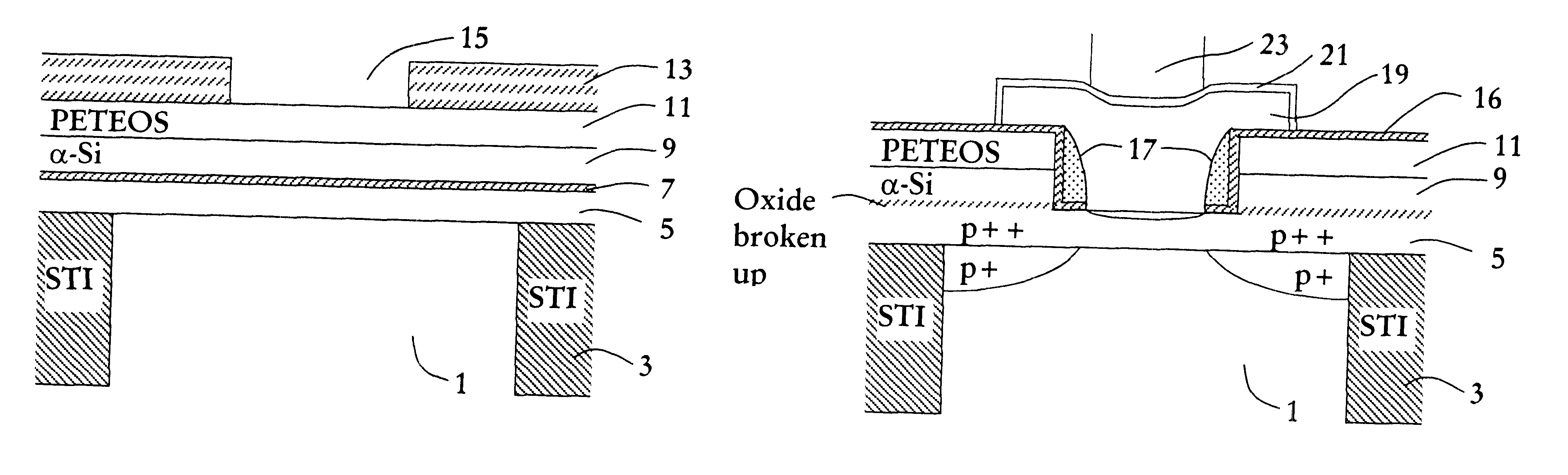

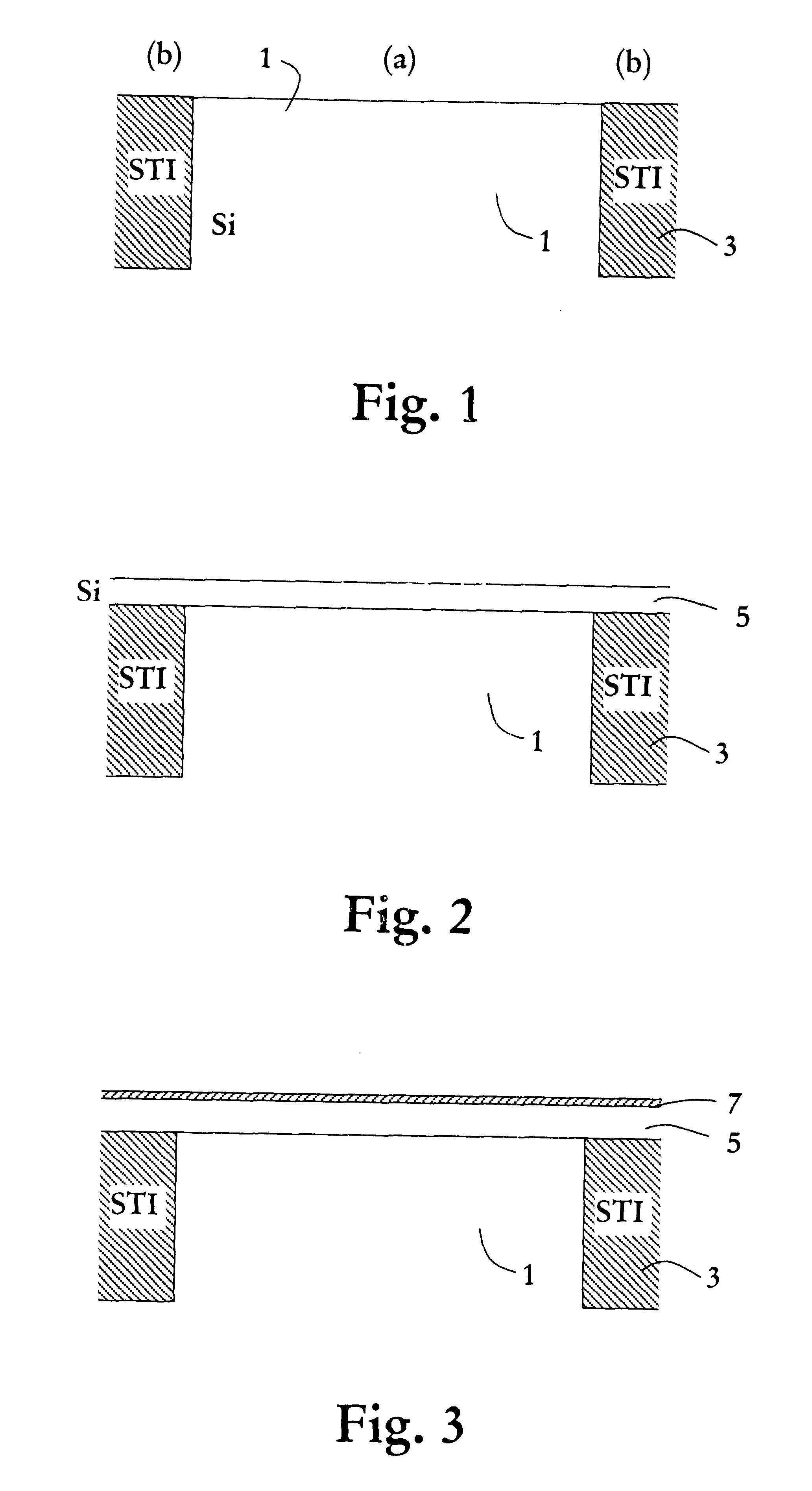

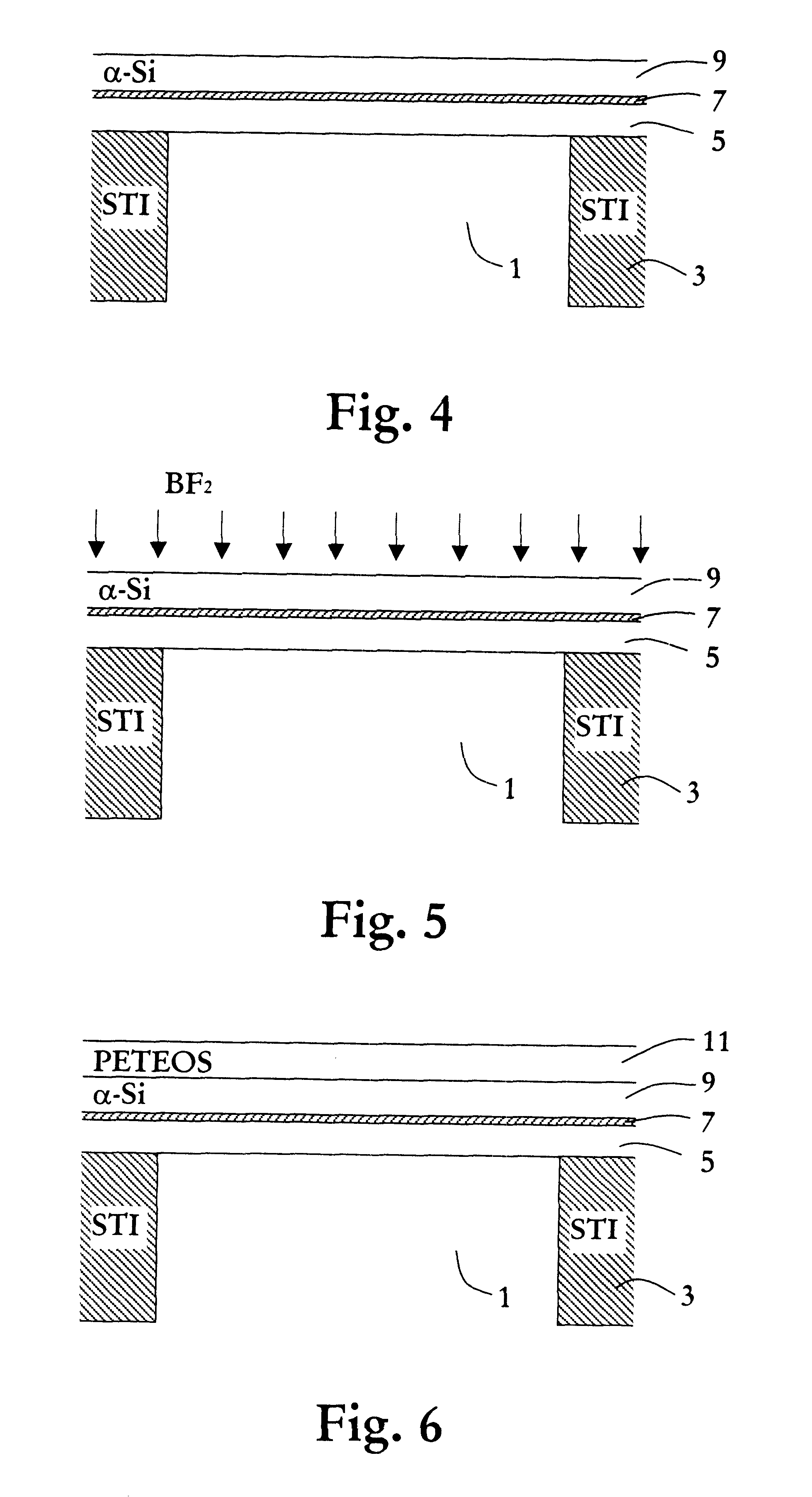

Method in the fabrication of a silicon bipolar transistor

InactiveUS6440810B1Reduce riskImproved profileSemiconductor/solid-state device manufacturingSemiconductor devicesThin oxideDielectric

In the fabrication of a silicon bipolar transistor, a method for forming base regions and for opening an emitter window is provided. A silicon substrate is provided with suitable device isolation. A first base region is formed in or on top of the substrate. A thin layer of oxide is formed on the first base region. A layer of silicon is formed on top of the thin oxide layer, the silicon layer is to be a second base region. The silicon layer is ion implanted. A layer of a dielectric is formed on top of the silicon layer, the dielectric is to isolate base and emitter regions of the transistor. The obtained structure is patterned in order to define the emitter window. The structure inside the defined emitter window area is etched and through the dielectric and silicon layers, wherein the thin oxide layer is used as etch stop, thus forming the emitter window. The structure is subsequently heat treated and thus break up the oxide such that the first and second base regions will contact each other.

Owner:INFINEON TECH AG

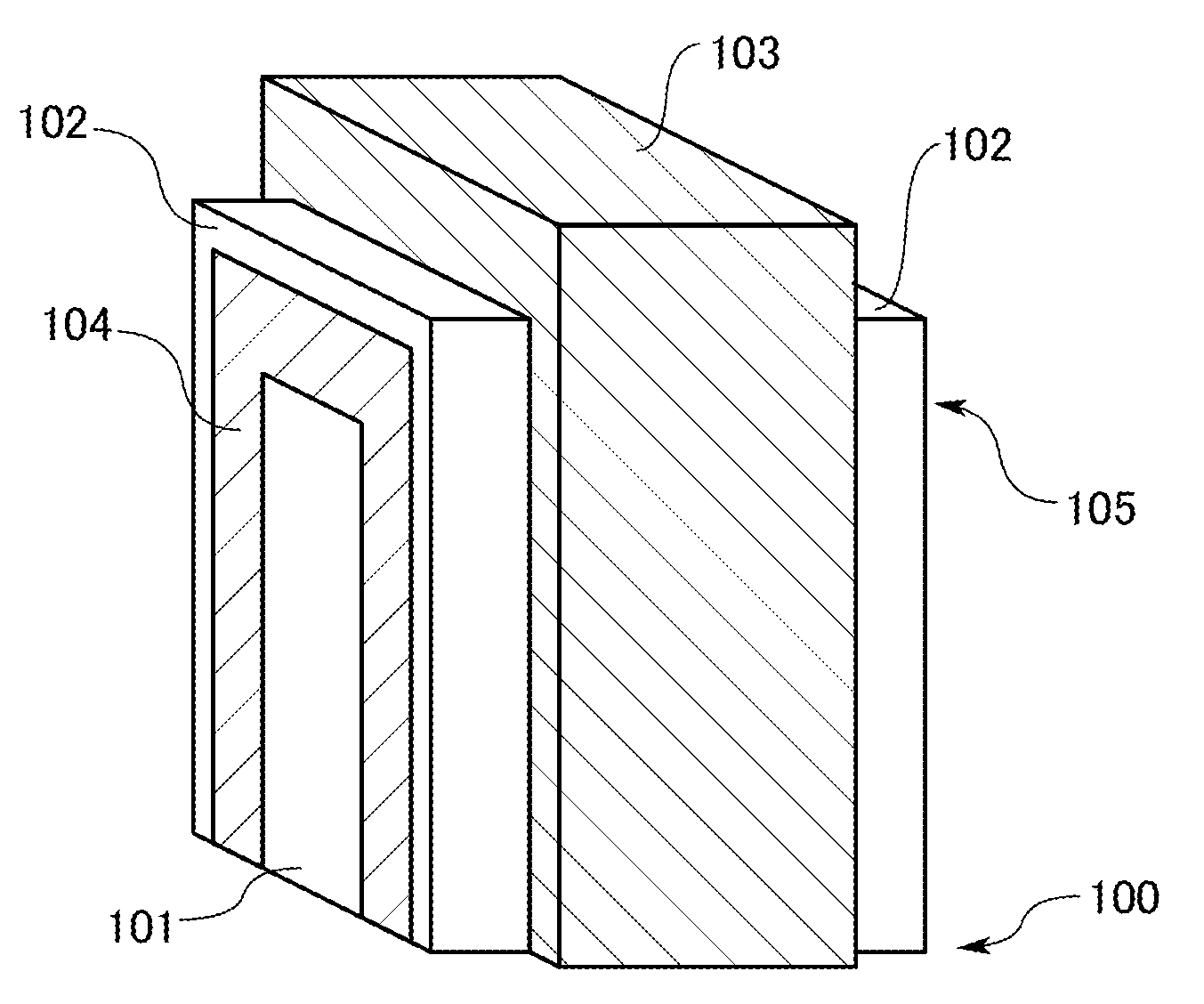

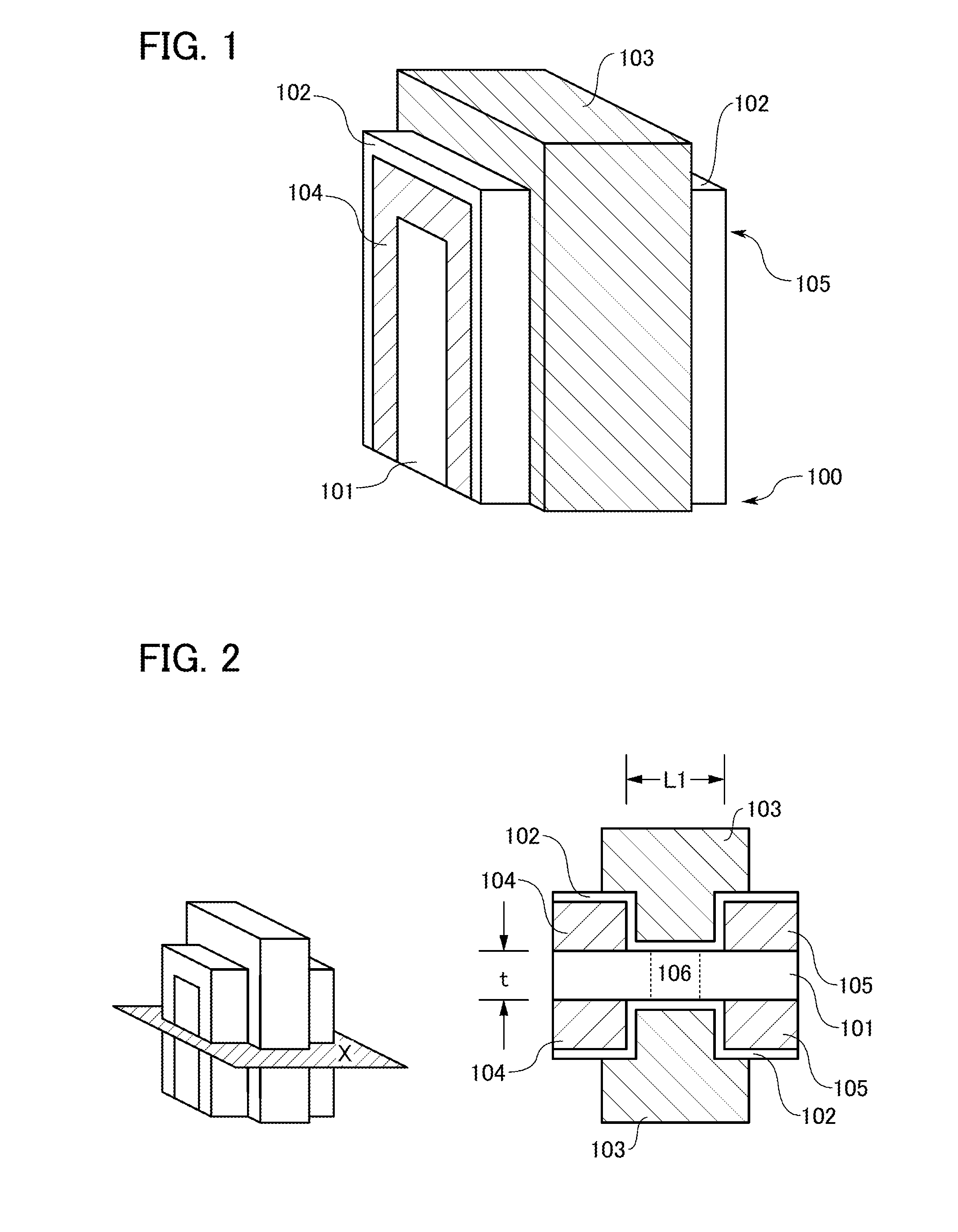

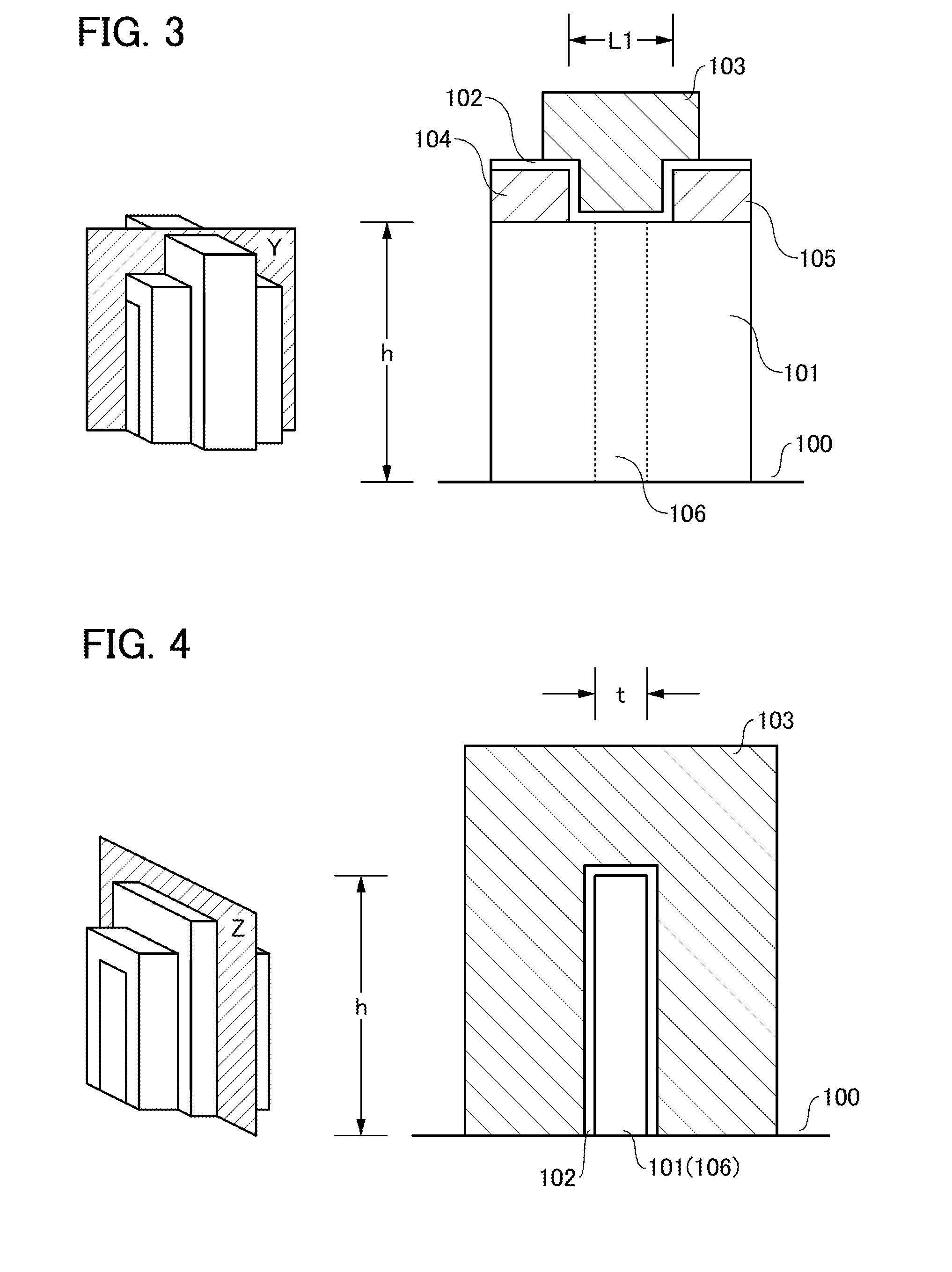

Field-effect transistor, and memory and semiconductor circuit including the same

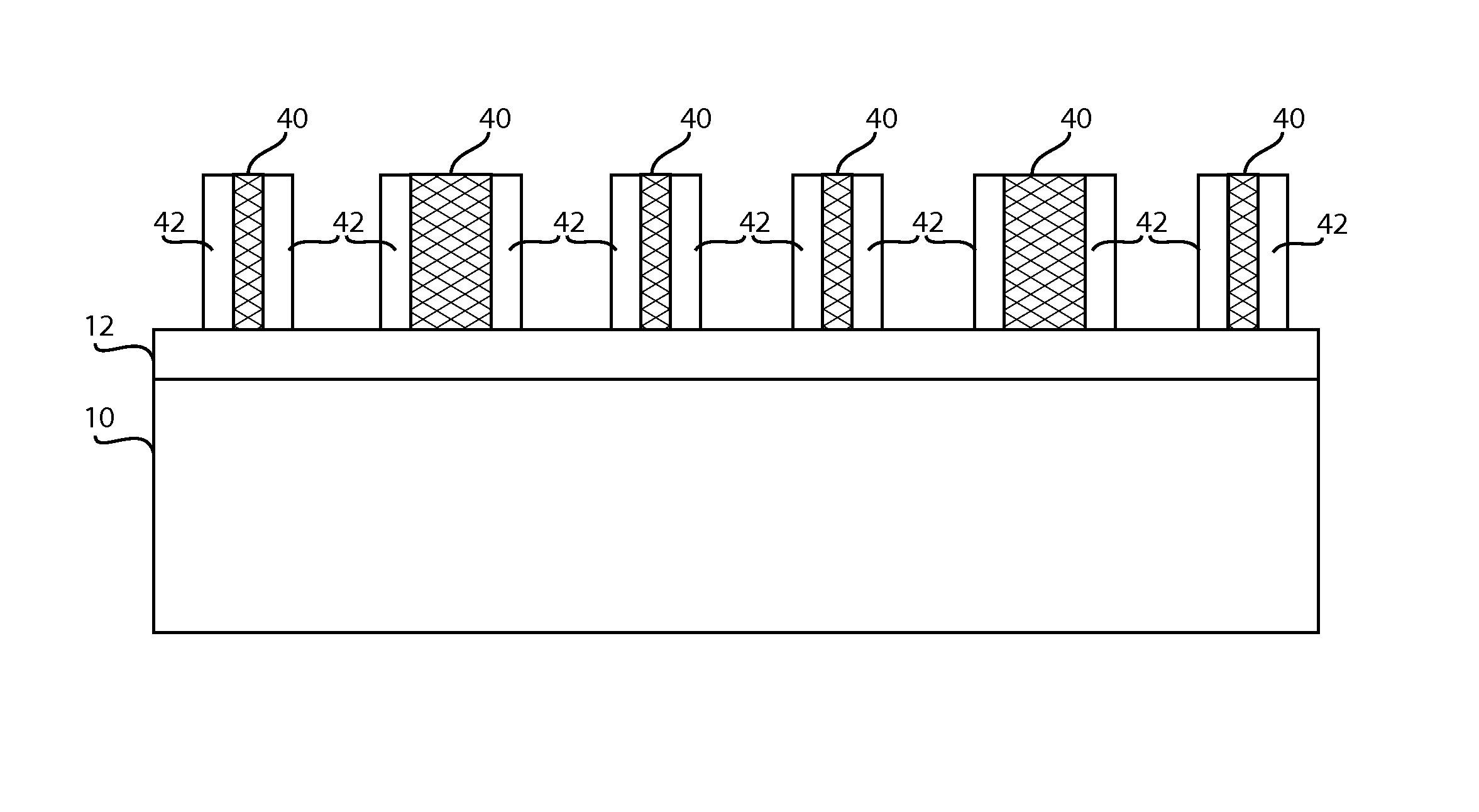

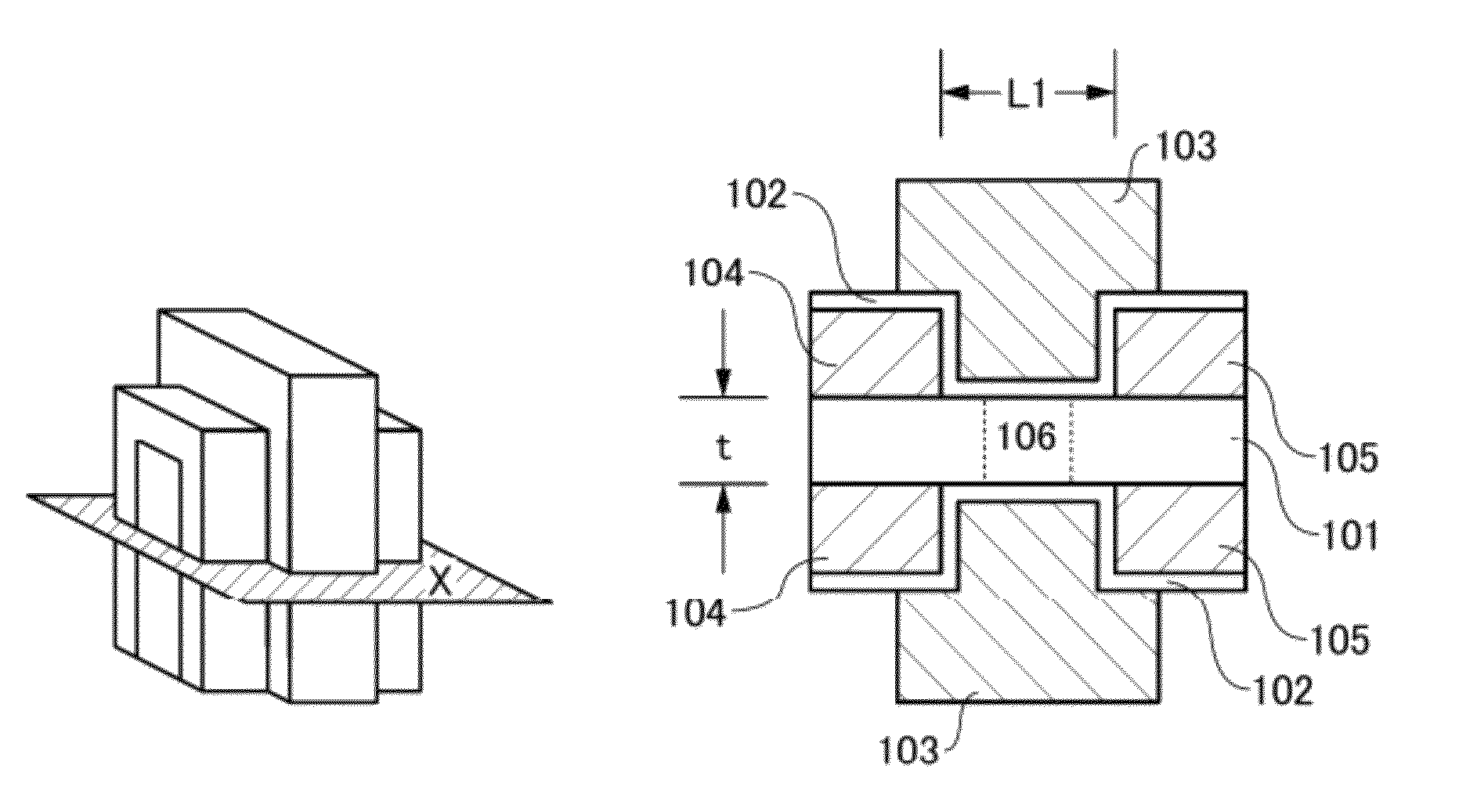

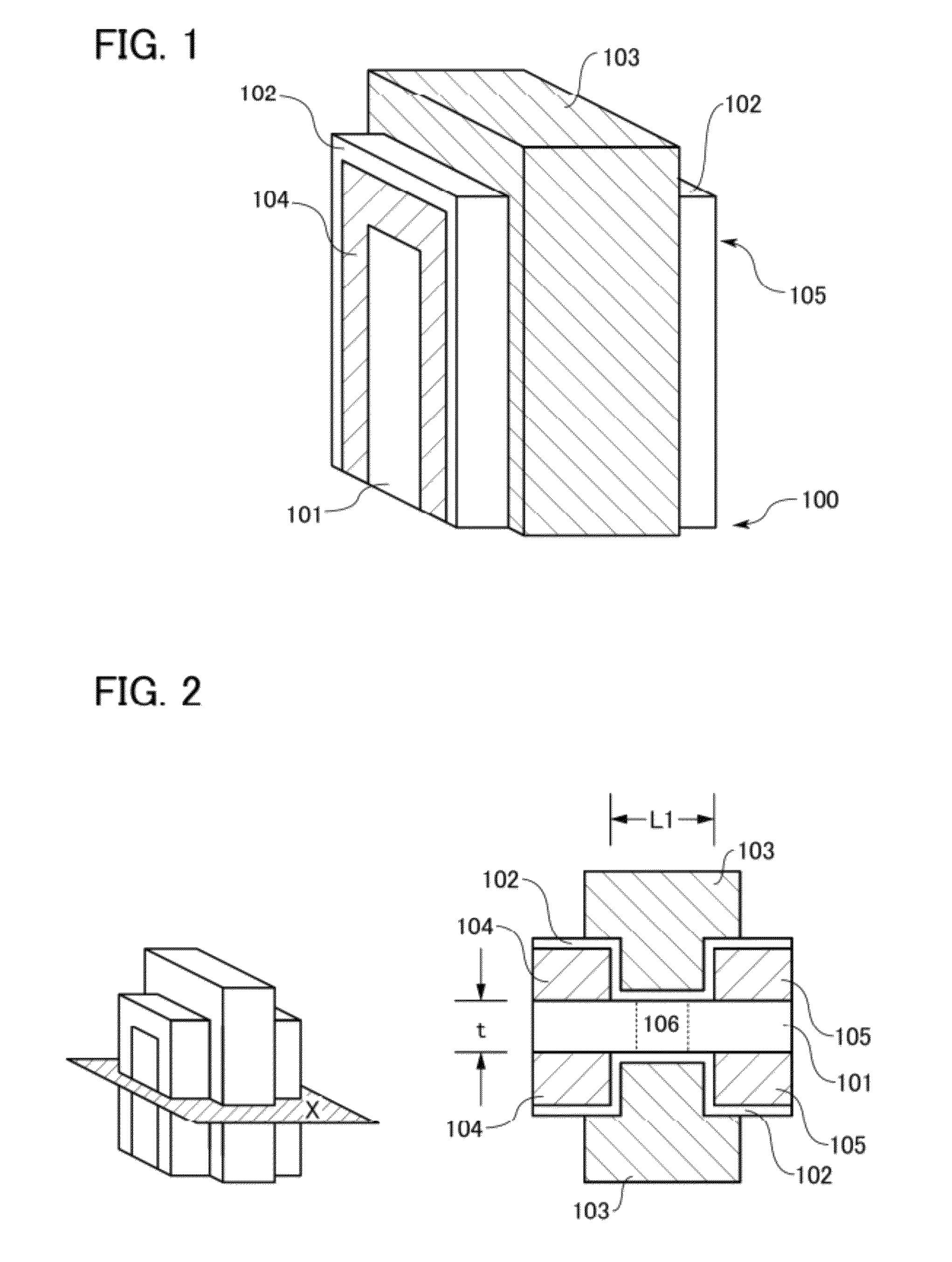

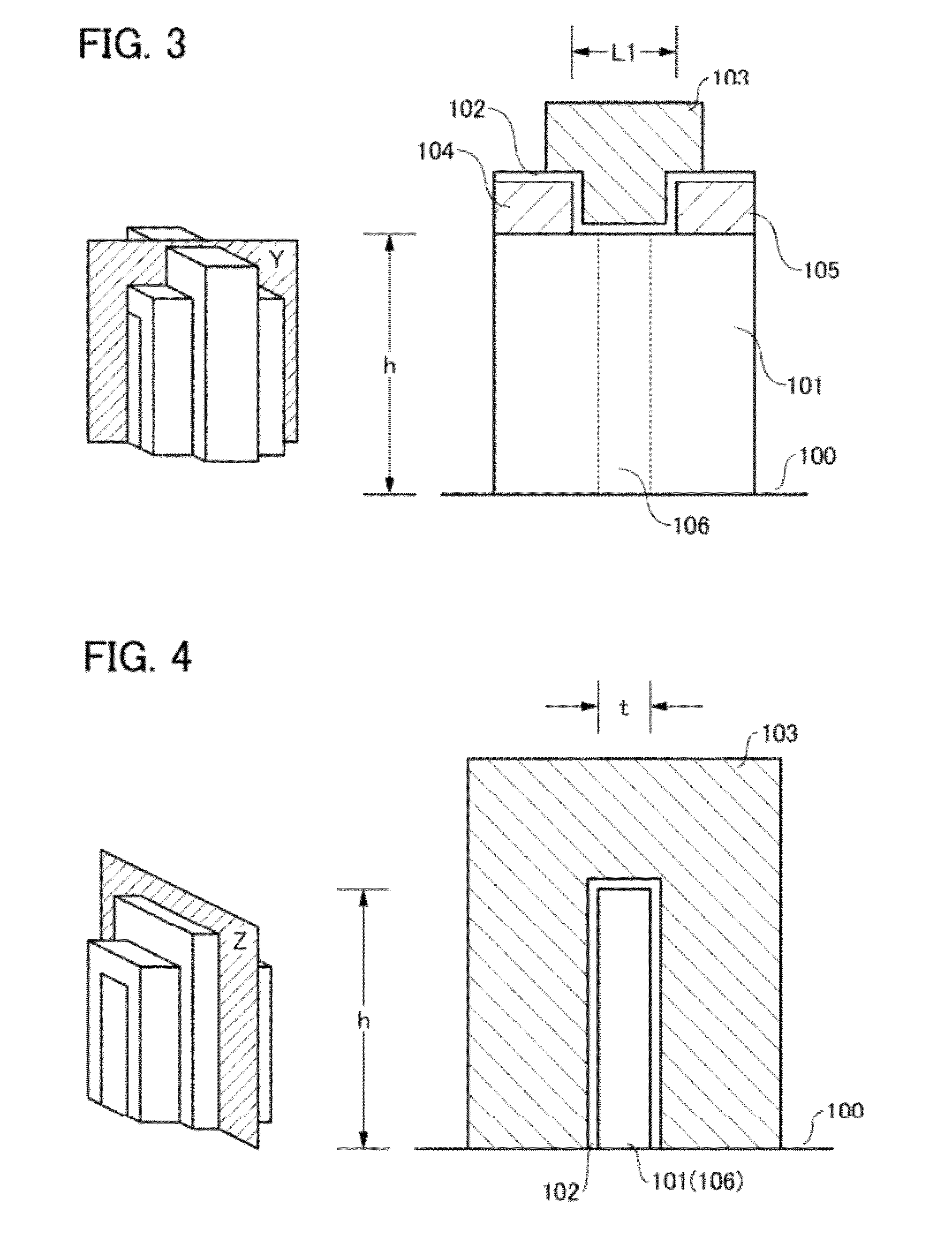

InactiveUS20120241739A1Reduction in off-state currentEfficient removalTransistorSolid-state devicesThin oxideMiniaturization

Provided is a field-effect transistor (FET) having small off-state current, which is used in a miniaturized semiconductor integrated circuit. The field-effect transistor includes a thin oxide semiconductor which is formed substantially perpendicular to an insulating surface and has a thickness of greater than or equal to 1 nm and less than or equal to 30 nm, a gate insulating film formed to cover the oxide semiconductor, and a strip-like gate which is formed to cover the gate insulating film and has a width of greater than or equal to 10 nm and less than or equal to 100 nm. In this structure, three surfaces of the thin oxide semiconductor are covered with the gate, so that electrons injected from a source or a drain can be effectively removed, and most of the space between the source and the drain can be a depletion region; thus, off-state current can be reduced.

Owner:SEMICON ENERGY LAB CO LTD

Packaging laminate with gas and aroma barrier properties

InactiveUS6338870B1Improved barrier and durability propertyWrappersMolten spray coatingThin oxidePaperboard

A packaging laminate (10) including a substrate film (15) coated with a carbon containing silicon oxide layer (16, 17) on both surfaces is disclosed herein. A method for producing the laminate (10), and blanks and packages fabricated from the laminate are also disclosed herein. The PECVD process of the present invention strains the substrate film (15) during deposition thereby creating a very thin oxide layer with superior durability, oxygen and aroma barrier properties. The carbon-containing silicon oxide coating (16, 17) has a stoichiometry of SiOxCy in which x is witin the range of 1.5-2.2 and y is within the range of 0.15-0.80. The substrate film (15) may include a core layer (12) of a material selected from the group consisting of paper, paperboard, a foamed core, polyethylene terephtalate, polyamide, polyethylene and polypropylene.

Owner:TETRA LAVAL HLDG & FINANCE SA

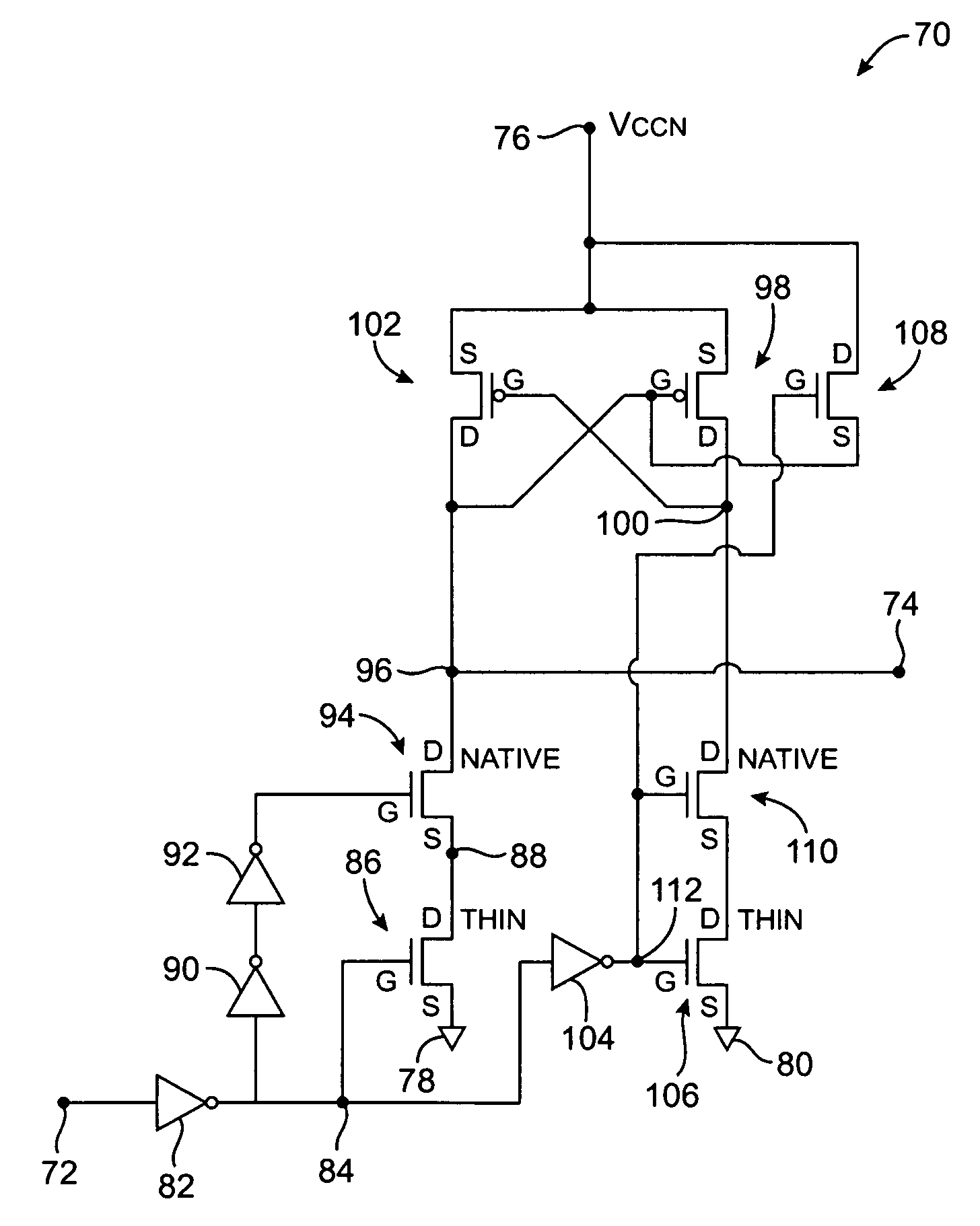

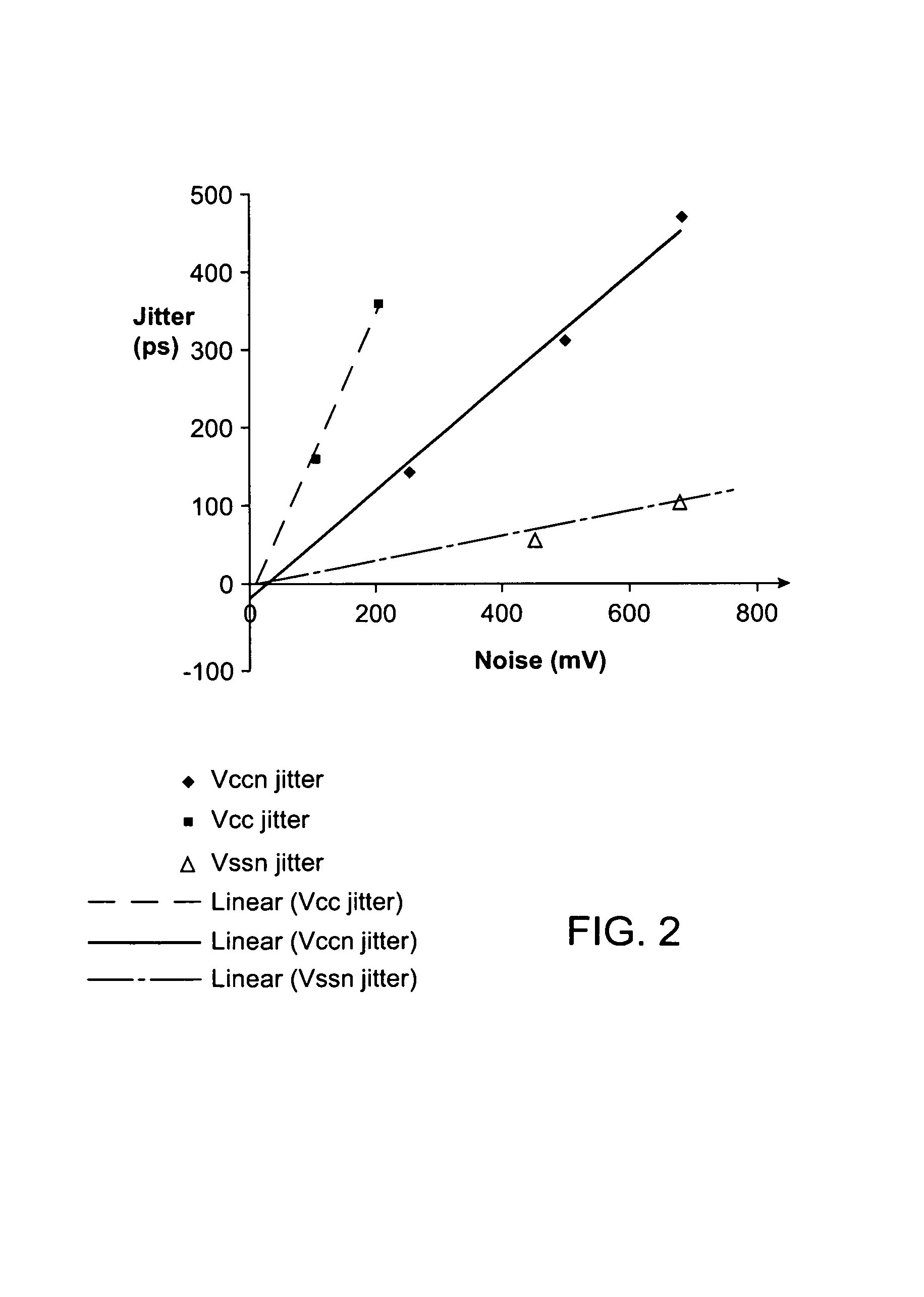

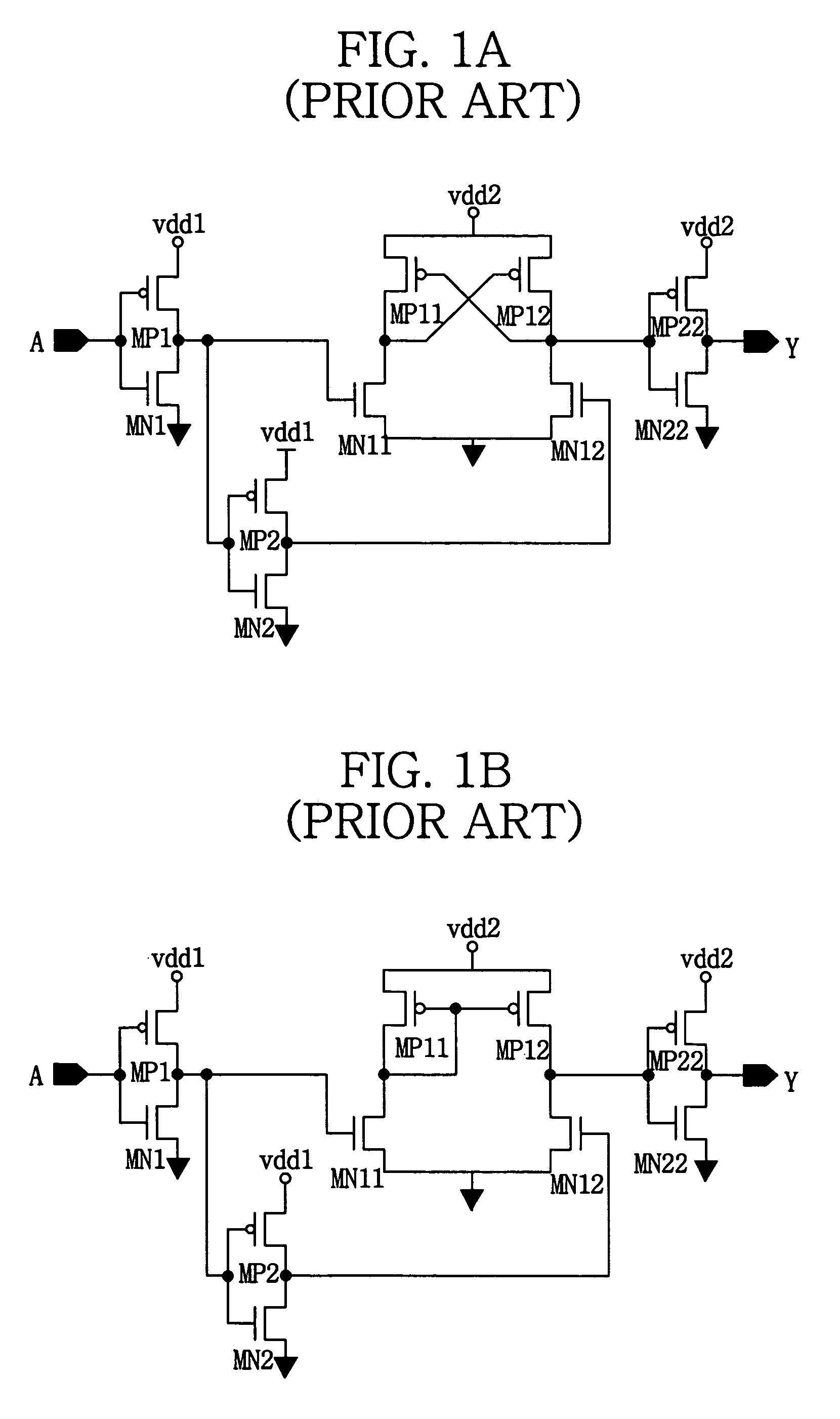

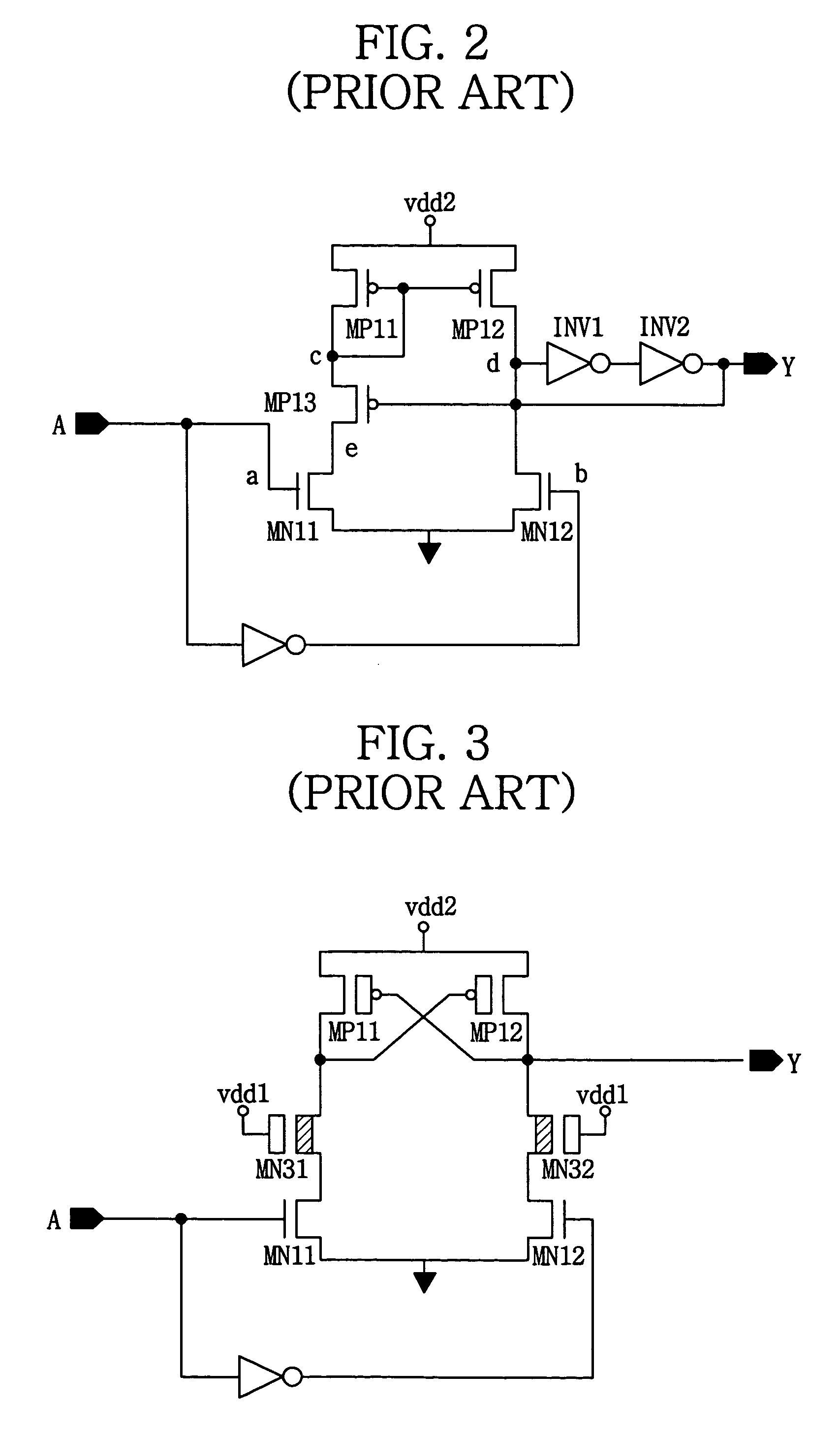

Low-jitter adjustable level shifter with native devices and kicker

InactiveUS7180329B1Reduce jitterFast switching speedElectric pulse generatorLogic circuit coupling/interface arrangementsData terminalThin oxide

An adjustable level shifter with native and kicker transistors is provided. The level shifter provides high switching speeds, adjustable output voltage levels, and low jitter. The level shifter has first and second thick-oxide p-channel metal-oxide-semiconductor (PMOS) transistors, first and second thick-oxide native n-channel metal-oxide-semiconductor (NMOS) transistors, and first and second thin-oxide NMOS transistors. The first PMOS transistor, first native transistor, and first NMOS transistor are connected in series and the second PMOS transistor, second native transistor, and second NMOS transistor are connected in series. An input data signal and an inverted version of the input data signal drive the gates of the thin-oxide NMOS transistors. A node located between the first PMOS transistor and first native transistor is connected to an output data terminal. The kicker transistor is connected in parallel with the first PMOS transistor.

Owner:ALTERA CORP

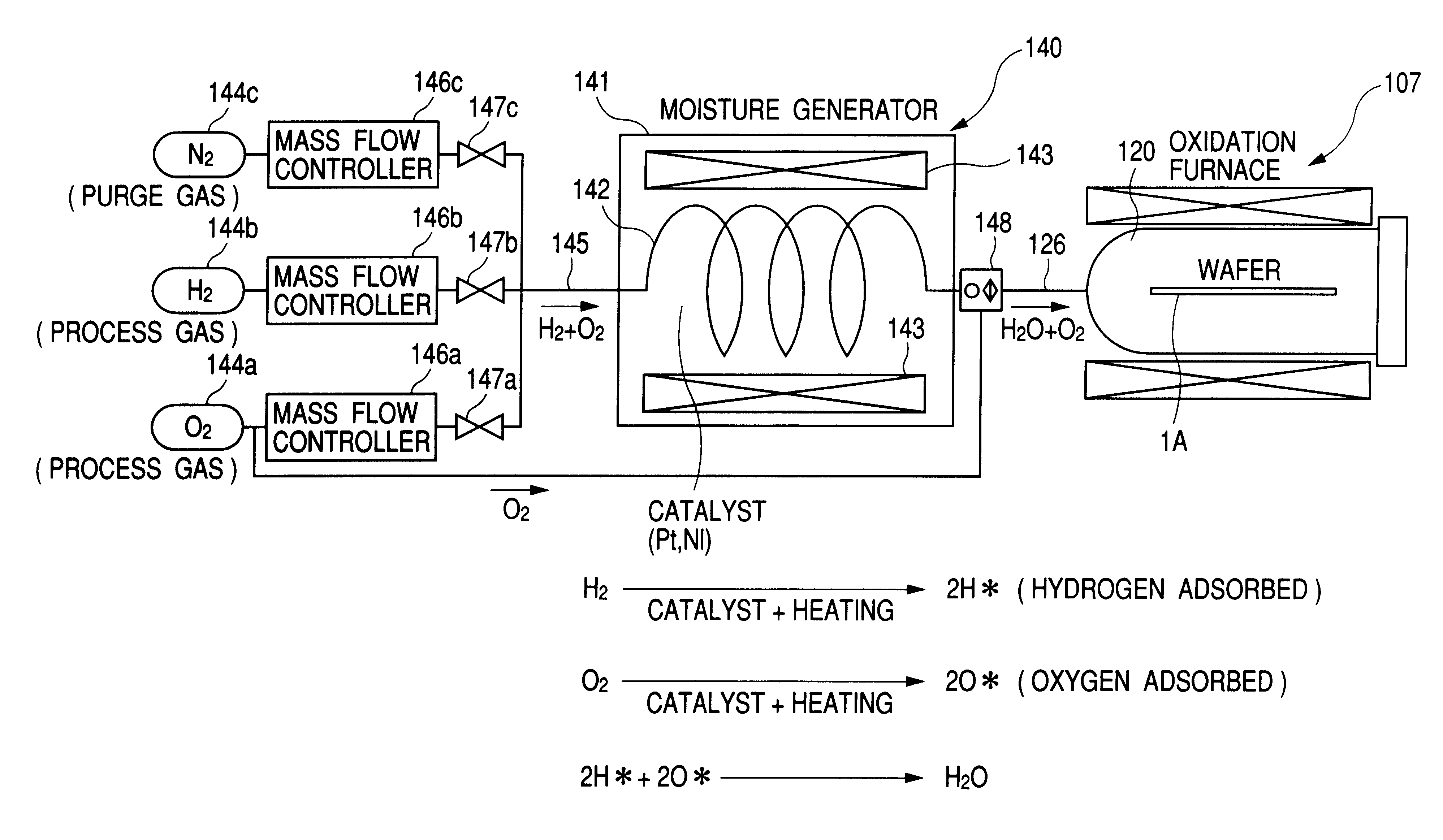

Method for fabricating semiconductor integrated circuit device

InactiveUS6239041B1Semiconductor/solid-state device manufacturingSemiconductor devicesThin oxideHydrogen

A method for fabricating a semiconductor integrated circuit device of the invention comprises feeding oxidation species containing a low concentration of water, which is generated from hydrogen and oxygen by the catalytic action, to the main surface of or in the vicinity of a semiconductor wafer, and forming a thin oxide film serving as a gate insulating film of an MOS transistor and having a thickness of 5 nm or below on the main surface of the semiconductor wafer at an oxide film-growing rate sufficient to ensure fidelity in formation of an oxide film and uniformity in thickness of the oxide film.

Owner:RENESAS ELECTRONICS CORP

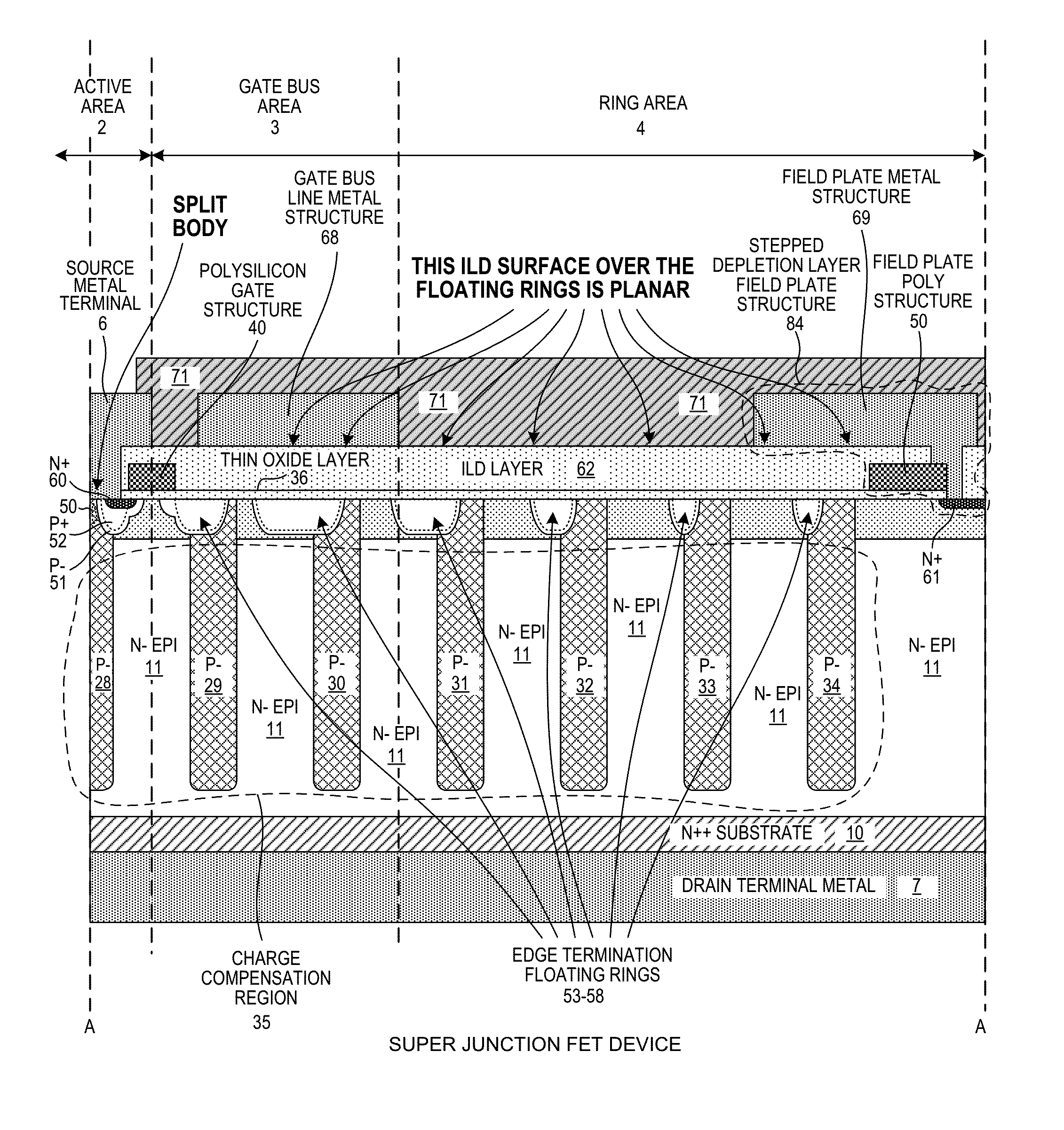

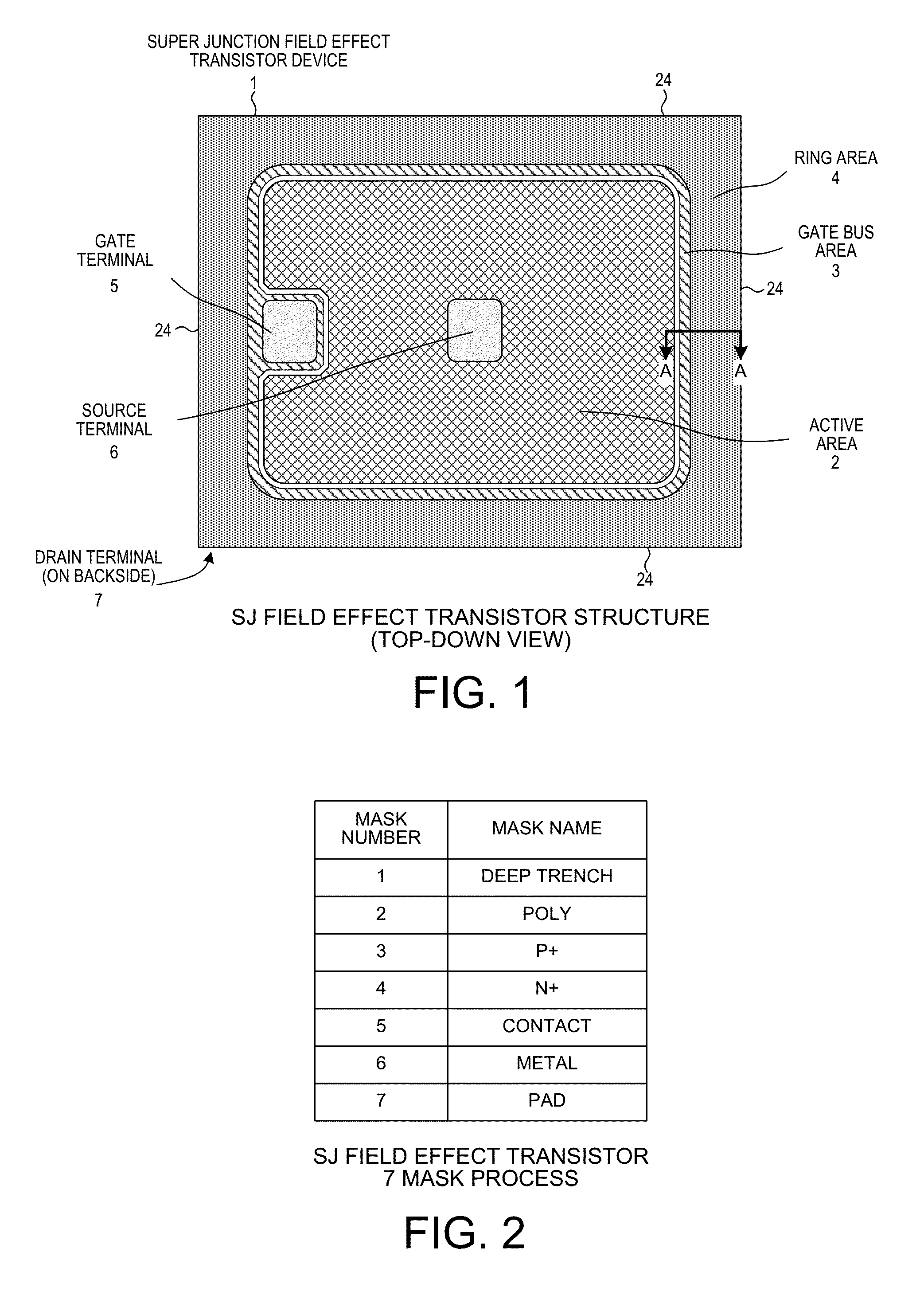

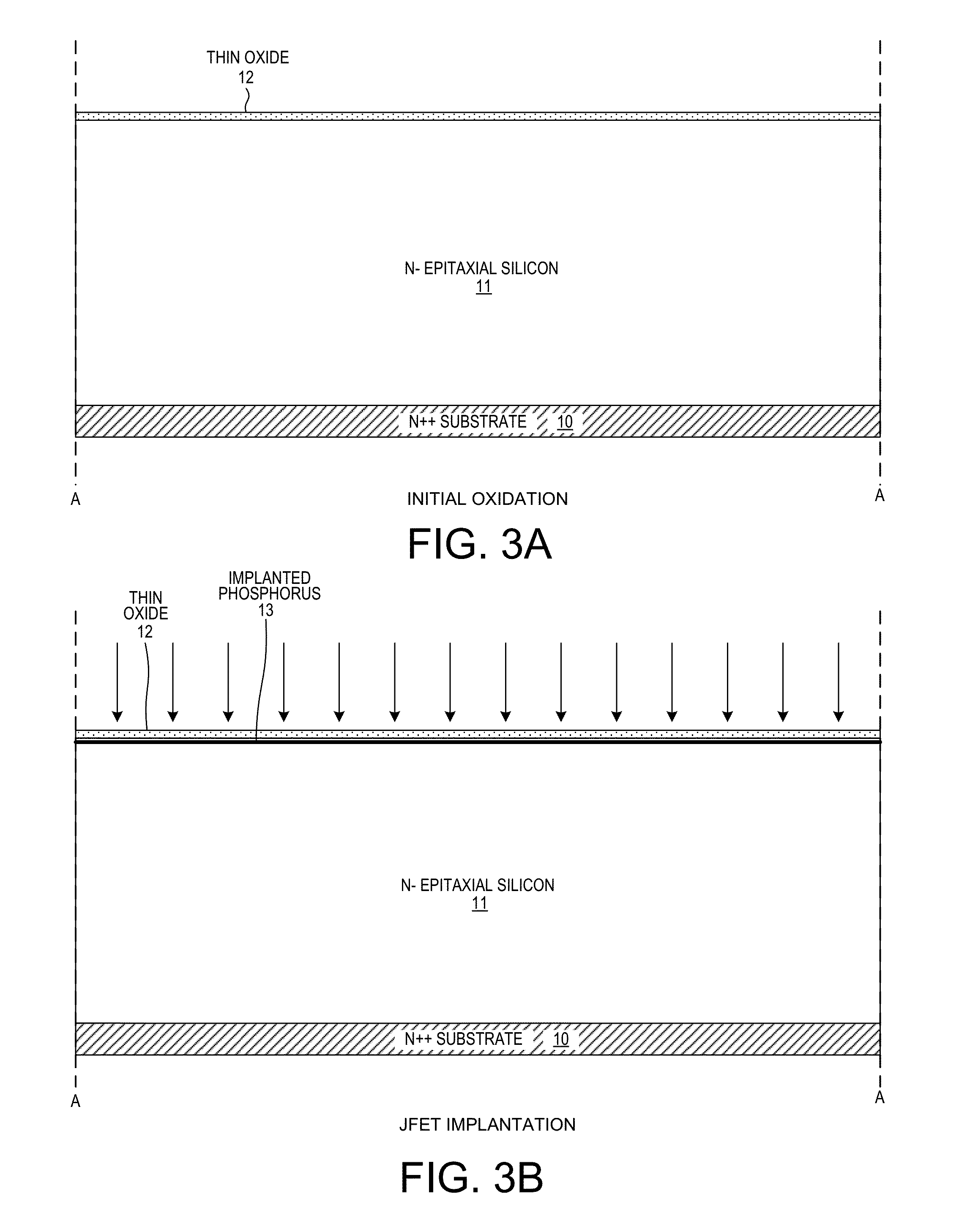

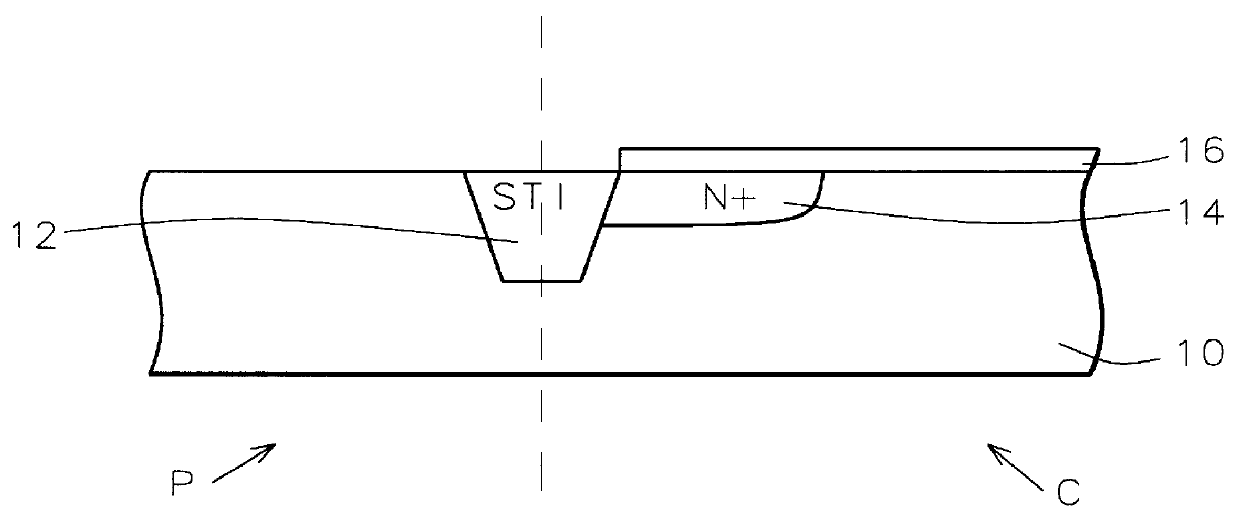

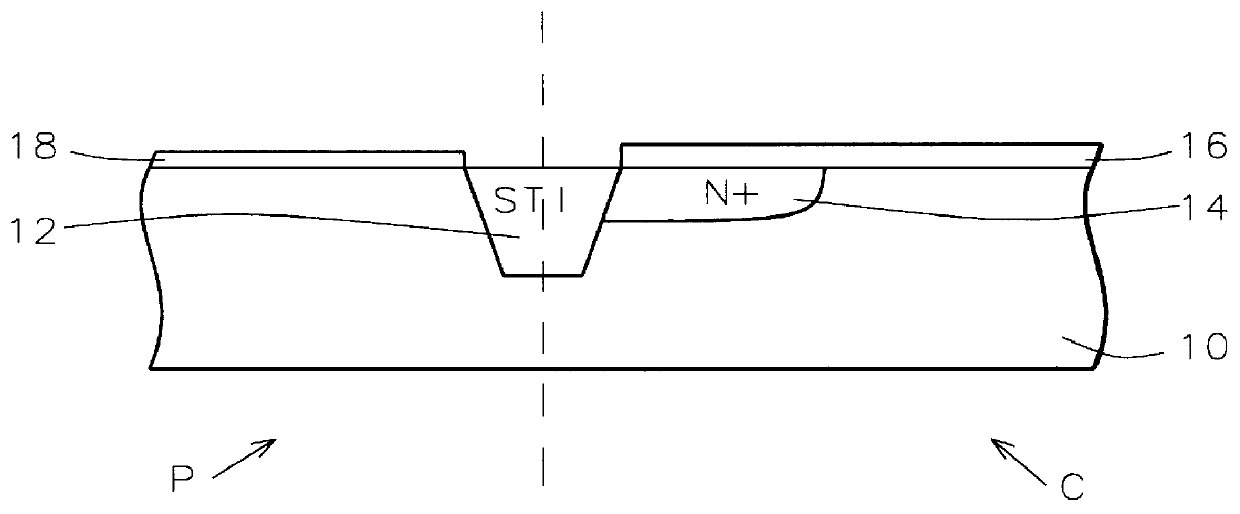

Super junction field effect transistor

ActiveUS9082845B1Semiconductor/solid-state device manufacturingSemiconductor devicesThin oxidePolycrystalline silicon

A split-body Super Junction FET is made using only seven masks. Thin oxide is disposed on an upper semiconductor surface of a super junction charge compensation region. A polysilicon gate is disposed on the thin oxide. An ILD (InterLayer Dielectric) layer is disposed on the upper surface of the thin oxide so that the ILD layer covers the polysilicon gate. A gate bus line metal structure and a field plate metal structure are disposed on the upper surface of the ILD. A portion of the upper surface of the ILD extends from the gate bus line metal, laterally over floating rings, and to the field plate metal. This portion of the upper surface of the ILD layer is substantially planar where the ILD layer passes over the floating rings. The field plate metal structure, a polysilicon feature, and a diffusion region together form a stepped depletion layer field plate structure.

Owner:LITTELFUSE INC

Using NO or N2O treatment to generate different oxide thicknesses in one oxidation step for single poly non-volatile memory

InactiveUS6110780APrevent photoresist damageSemiconductor/solid-state device manufacturingSemiconductor devicesThin oxideEngineering

A new method of using a NO or N2O treatment on a first area on a wafer in order to form a thinner oxide film in the first area and a thicker oxide film in a second area on a wafer using a single oxidation step is achieved. A semiconductor substrate of a silicon wafer is provided wherein a first area is separated from a second area by an isolation region. The silicon substrate in the second area is treated with NO or N2O whereby a high-nitrogen silicon oxide layer is formed on the surface of semiconductor substrate in the second area. A tunnel window is defined in the first area and the oxide layer within the tunnel window is removed. The silicon wafer is oxidized whereby a tunnel oxide layer forms within the tunnel window and whereby a gate oxide layer is formed overlying the high-nitrogen silicon oxide layer in the second area. The tunnel oxide layer has a greater thickness than the combined thickness of the gate oxide layer and the high-nitrogen silicon oxide layer. A conducting layer is deposited and patterned overlying the tunnel oxide layer and the gate oxide layer and fabrication of the integrated circuit device is completed.

Owner:TAIWAN SEMICON MFG CO LTD

Field-effect transistor, and memory and semiconductor circuit including the same

Provided is a field-effect transistor (FET) having small off-state current, which is used in a miniaturized semiconductor integrated circuit. The field-effect transistor includes a thin oxide semiconductor which is formed substantially perpendicular to an insulating surface and has a thickness of greater than or equal to 1 nm and less than or equal to 30 nm, a gate insulating film formed to cover the oxide semiconductor, and a strip-like gate which is formed to cover the gate insulating film and has a width of greater than or equal to 10 nm and less than or equal to 100 nm. In this structure, three surfaces of the thin oxide semiconductor are covered with the gate, so that electrons injected from a source or a drain can be effectively removed, and most of the space between the source and the drain can be a depletion region; thus, off-state current can be reduced.

Owner:SEMICON ENERGY LAB CO LTD

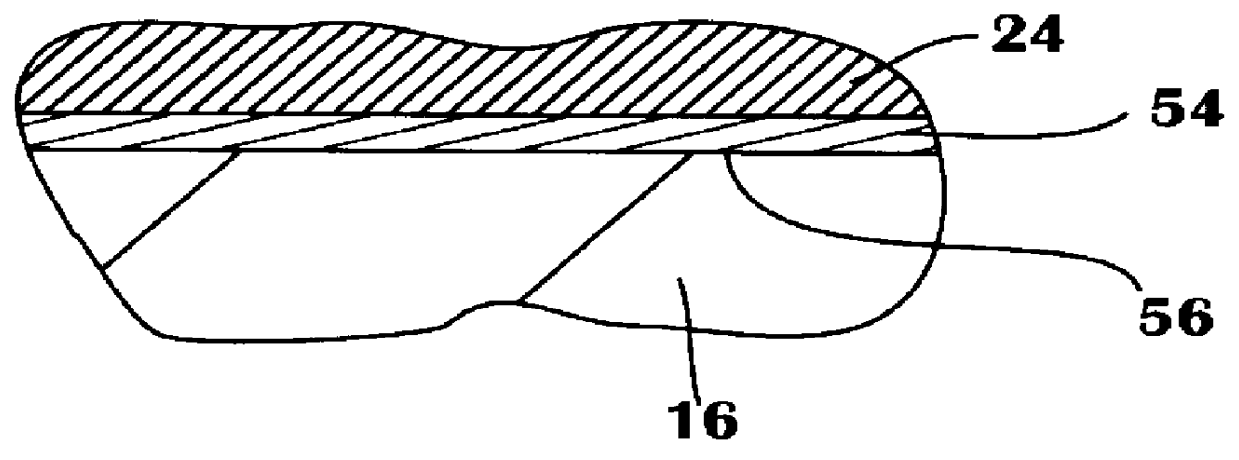

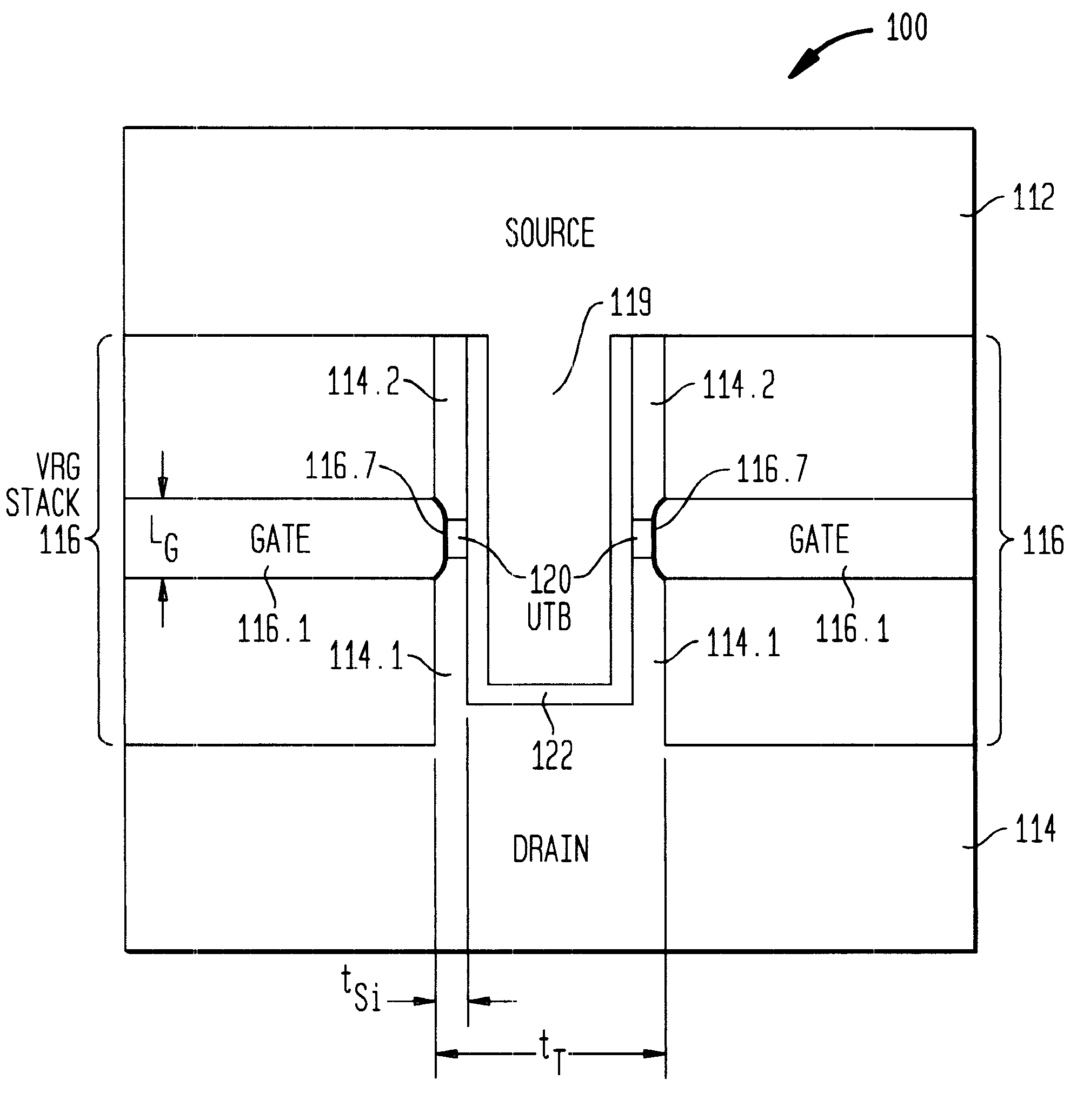

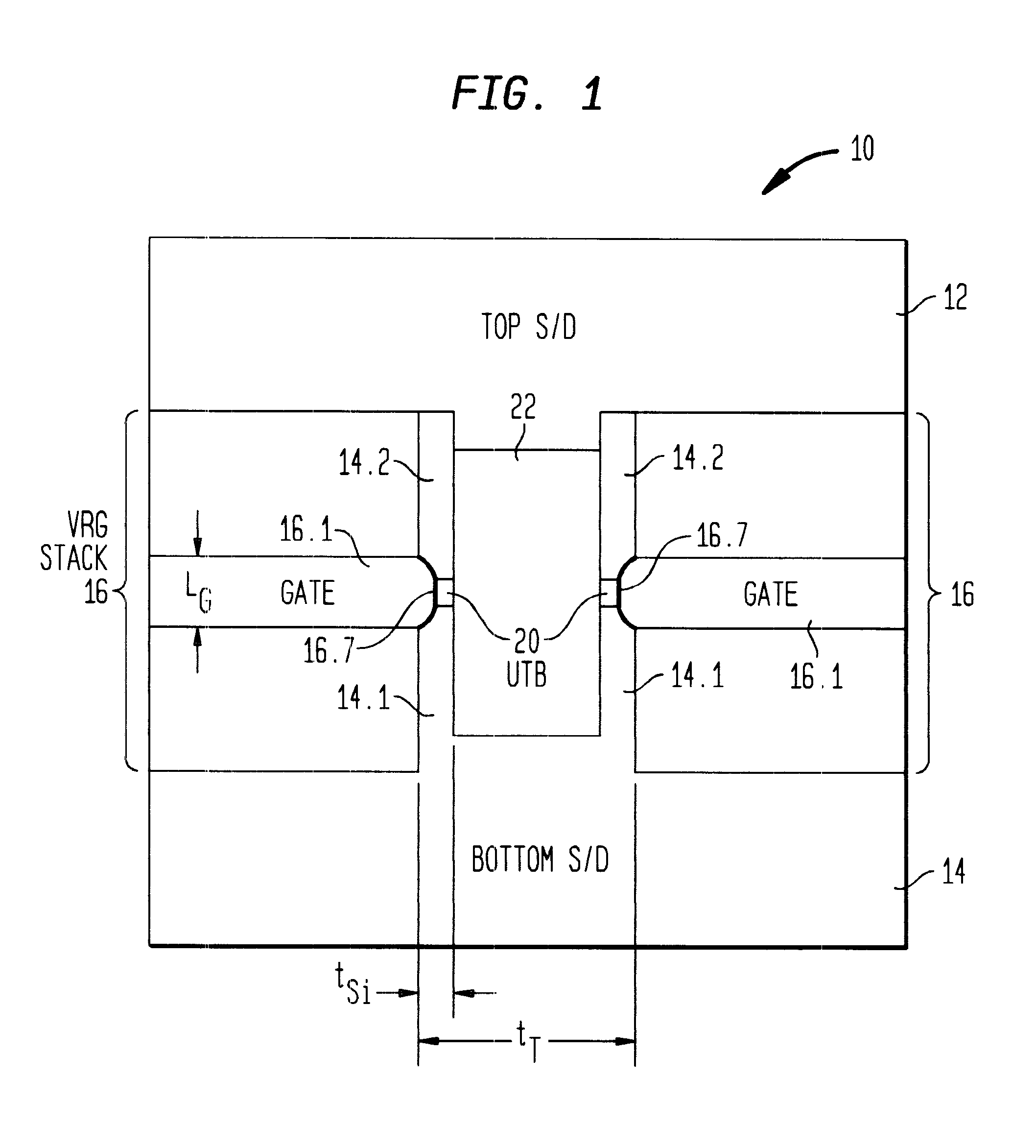

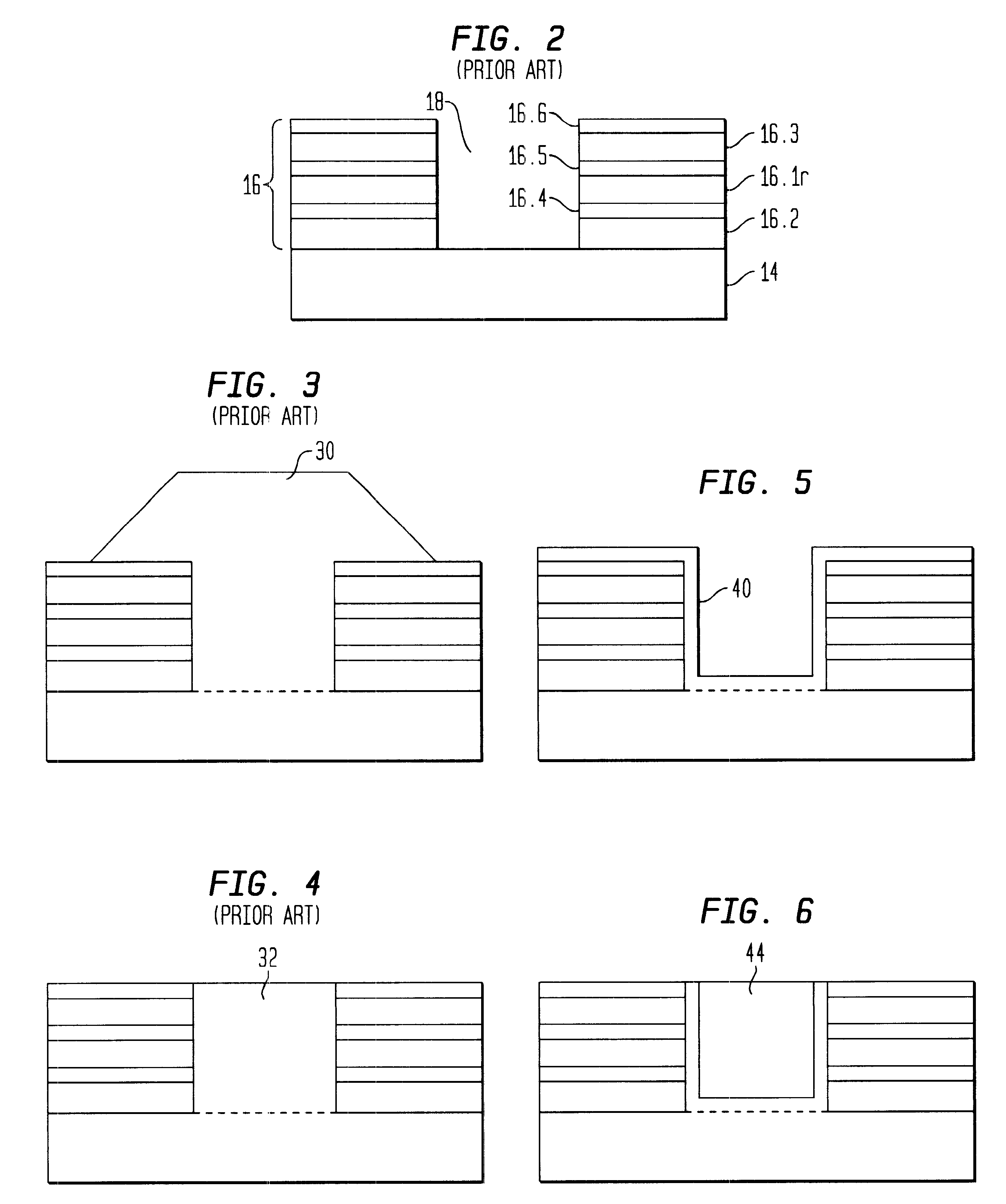

Ultra thin body vertical replacement gate MOSFET

InactiveUS6635924B1Semiconductor/solid-state device manufacturingSemiconductor devicesThin oxideThin layer

A method of fabricating a VRG MOSFET includes the steps of: (a) forming a VRG multilayer stack; (b) forming a trench in the stack; (c) depositing an ultra thin, amorphous semiconductor (alpha-semic) layer on the sidewalls of the trench (portions of the ultra thin layer on the sidewalls of the trench will ultimately form the channel or ultra thin body (UTB) of the MOSFET); (d) forming a thicker, alpha-semic sacrificial layer on the ultra thin layer; (e) annealing the alpha-semic layers to recrystallize them into single crystal layers; (f) selectively removing the recrystallized sacrificial layer; and (g) performing additional steps to complete the VRG MOSFET. In general, the sacrificial layer should facilitate the recrystallization of the ultra thin layer into single crystal material. In addition, the etch rate of the sacrificial layer should be sufficiently higher than that the ultra thin layer so that the sacrificial layer can be selectively removed in the presence of the ultra thin layer after recrystallization. The latter condition is illustratively satisfied by doping the sacrificial layer and by not (intentionally) doping the ultra thin layer. In accordance with one embodiment of our invention, step (g) includes filling the trench with oxide to form a thick back oxide region. In accordance with another embodiment of our invention, step (g) includes depositing a thin oxide layer (the back oxide) in the trench and then filling the remainder of the trench with a polycrystalline region (the back gate). VRG MOSFETs fabricated in accordance with our invention are expected to be electrostatically scalable with precise dimensional control. In addition, they can be fully depleted. Novel UTB device designs are also described.

Owner:BELL SEMICON LLC

Programmable eraseless memory

InactiveUS20050035429A1Easy to manufactureSemiconductor/solid-state device detailsSolid-state devicesThin oxideLow voltage

An electrically programmable non-volatile memory cell comprises a first electrode, a second electrode and an inter-electrode layer, such as ultra-thin oxide, between the first and second electrodes which is characterized by progressive change in resistance in response to program stress of relatively low voltages. A programmable resistance representing stored data is established by stressing the inter-electrode layer between the electrodes. Embodiments of the memory cell are adapted to store multiple bits of data per cell and / or adapted for programming more than one time without an erase process.

Owner:MACRONIX INT CO LTD

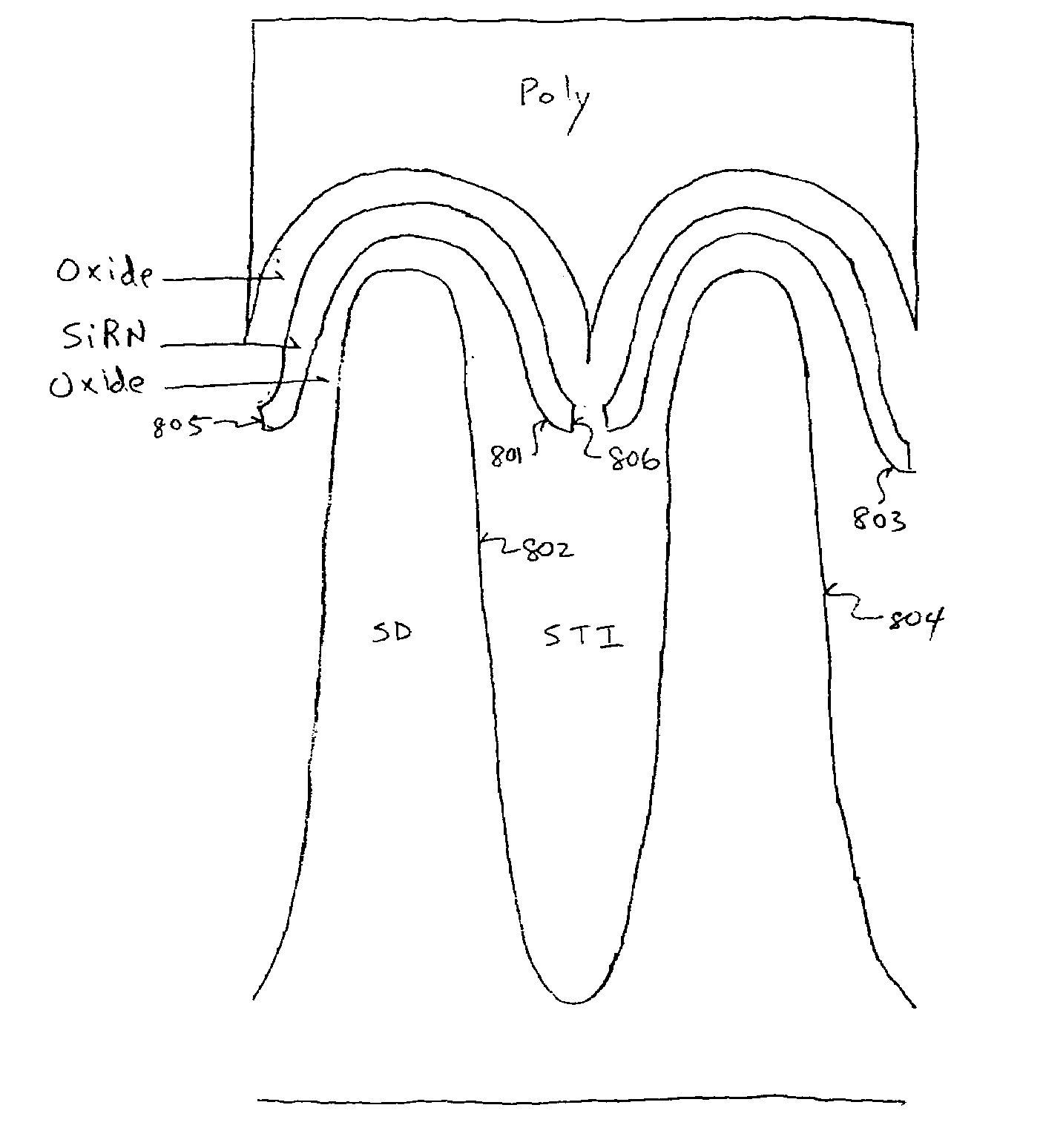

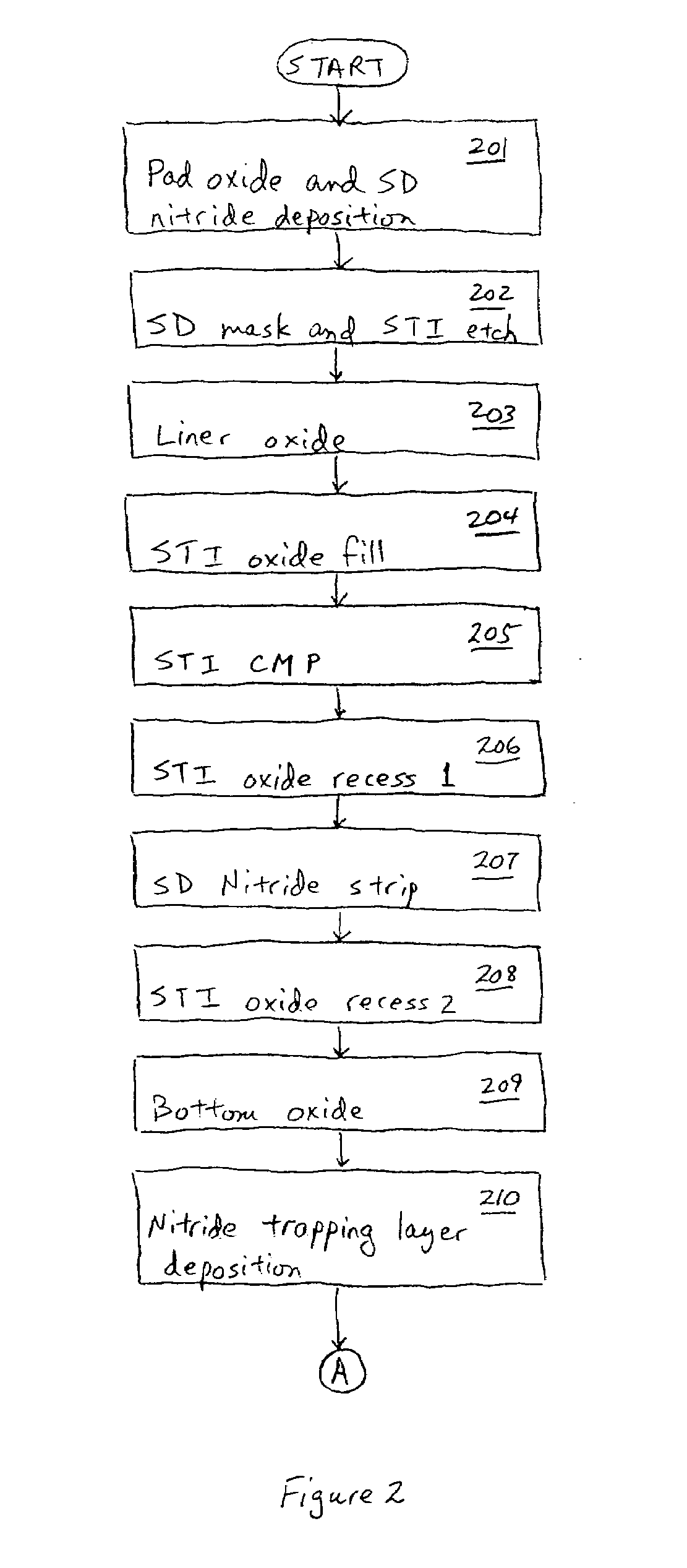

Self-aligned patterning method by using non-conformal film and etch back for flash memory and other semiconductor applications

A method for fabricating a memory device with a self-aligned trap layer which is optimized for scaling is disclosed. In the present invention, a non-conformal oxide is deposited over the charge trapping layer to form a thick oxide on top of the core source / drain region and a pinch off and a void at the top of the STI trench. An etch is performed on the pinch-off oxide and the thin oxide on the trapping layer on the STI oxide. The trapping layer is then partially etched between the core cells. A dip-off of the oxide on the trapping layer is performed. And a top oxide is formed. The top oxide converts the remaining trap layer to oxide and thus isolate the trap layer.

Owner:MONTEREY RES LLC

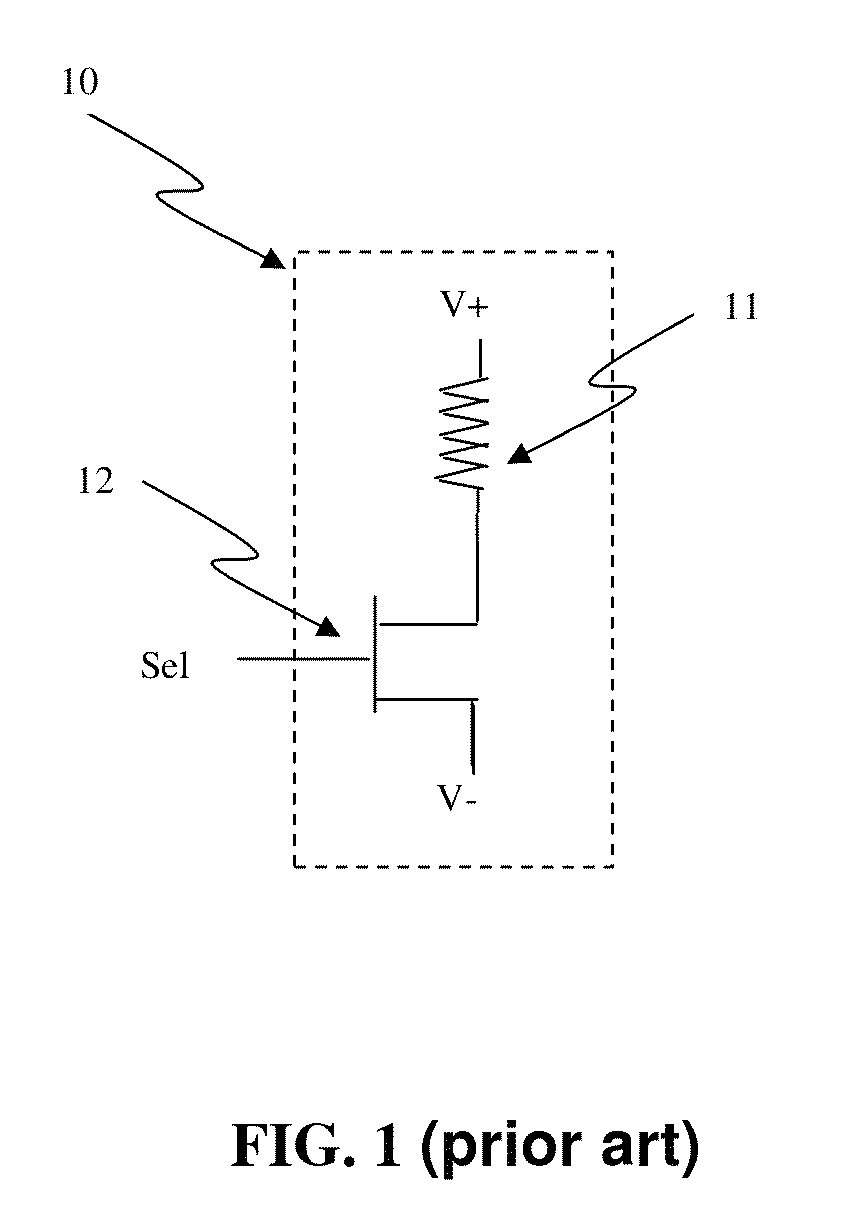

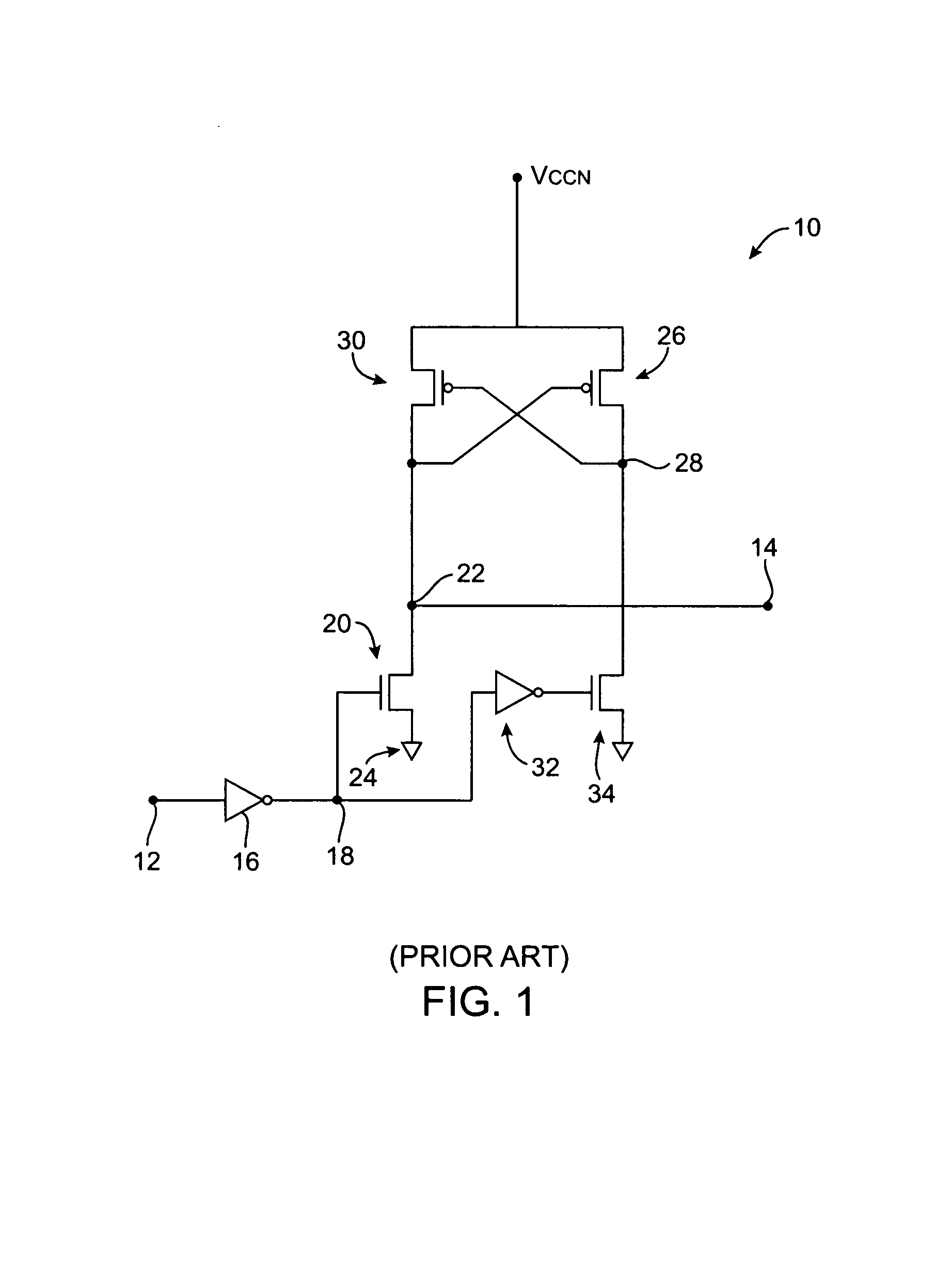

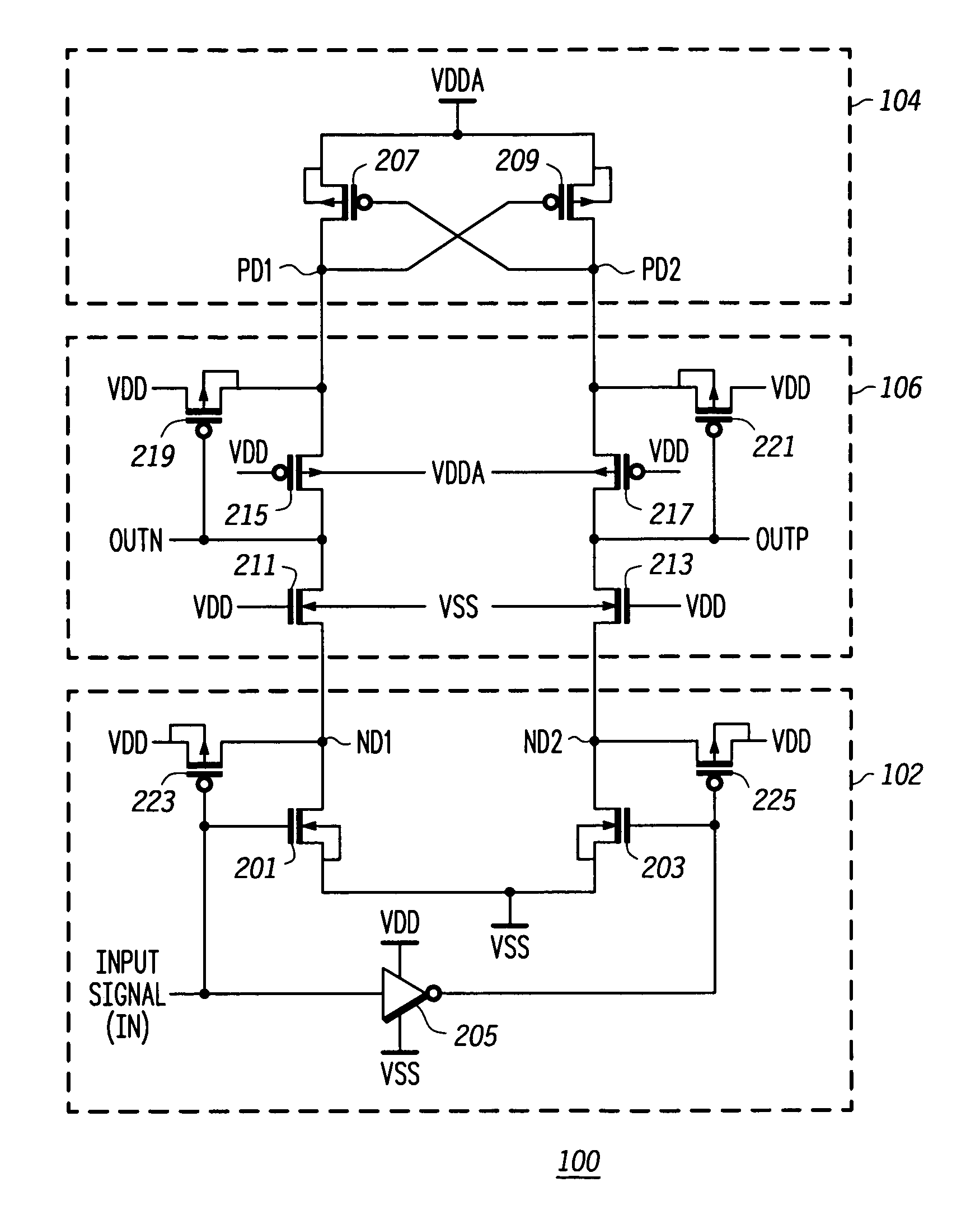

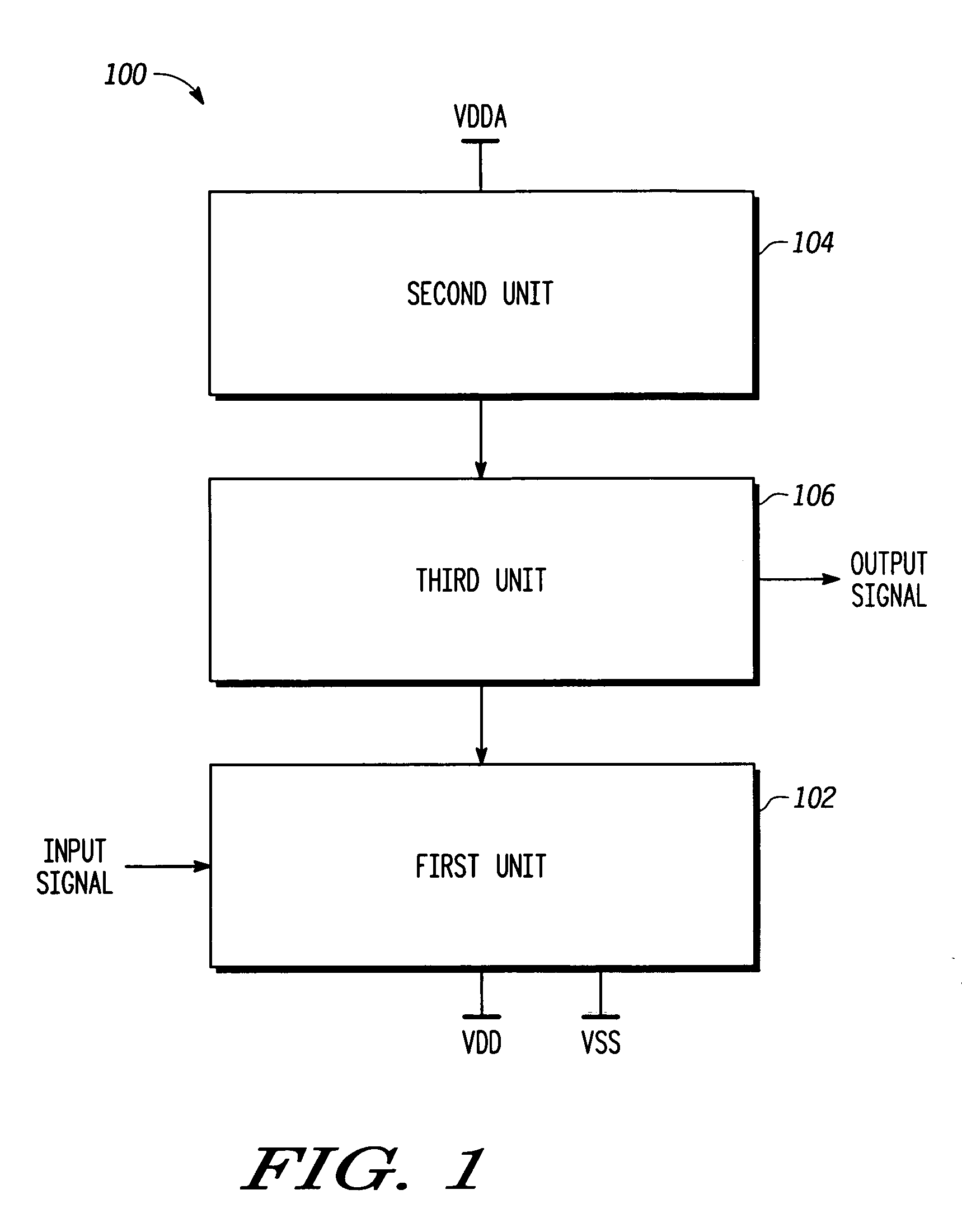

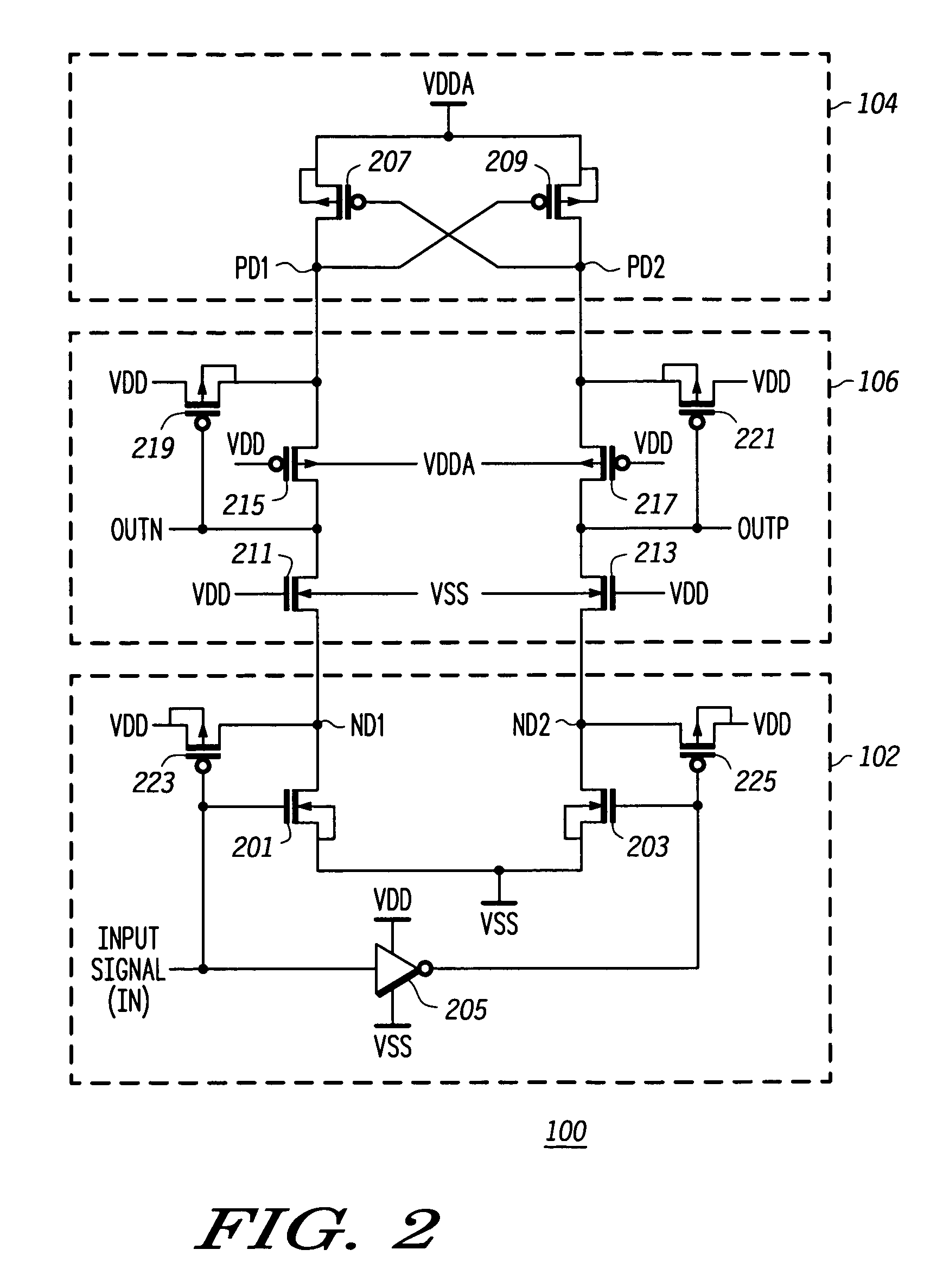

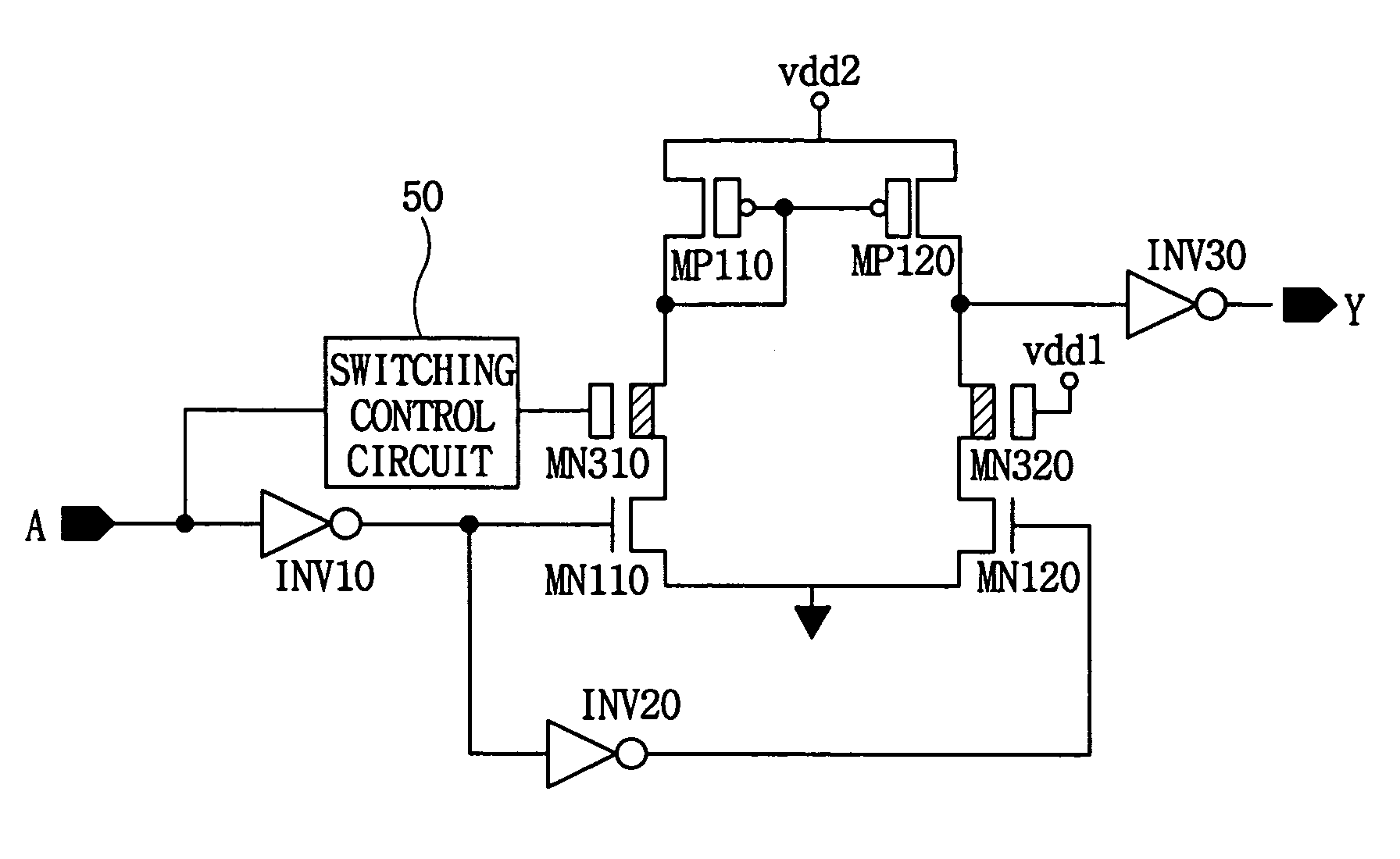

High voltage level converter using low voltage devices

A circuit for converting an input signal at a first voltage level to an output signal at a second voltage level uses only thin oxide transistors. The circuit includes a first unit operating at a first power supply voltage and receiving the input signal, a second unit operating at a second power supply voltage, and a third unit coupling the first unit to the second unit. The third unit enables generation of the output signal. Use of an extra fabrication mask for thick oxide transistors is avoided by using only thin oxide transistors.

Owner:NORTH STAR INNOVATIONS

Adhesion of copper and etch stop layer for copper alloy

InactiveUS20050006776A1Improve adhesionImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesCopper interconnectThin layer

A new method and structure is provided for the creation of a copper dual damascene interconnect. A dual damascene structure is created in the layer of dielectric, optionally a metal barrier layer is deposited over exposed surfaces of the dual damascene structure. A copper seed layer is deposited, the dual damascene structure is filled with copper. An anneal is applied to the created copper interconnect after which excess copper is removed from the dielectric. Of critical importance to the invention, a thin layer of oxide is then deposited as a cap layer over the copper dual damascene interconnect, an etch stop layer is then deposited over the thin layer of oxide for continued upper-level metallization.

Owner:TAIWAN SEMICON MFG CO LTD

Level shifter utilizing input controlled zero threshold blocking transistors

ActiveUS7053656B2Logic circuits coupling/interface using field-effect transistorsElectric variable regulationThin oxideInput control

Owner:SAMSUNG ELECTRONICS CO LTD

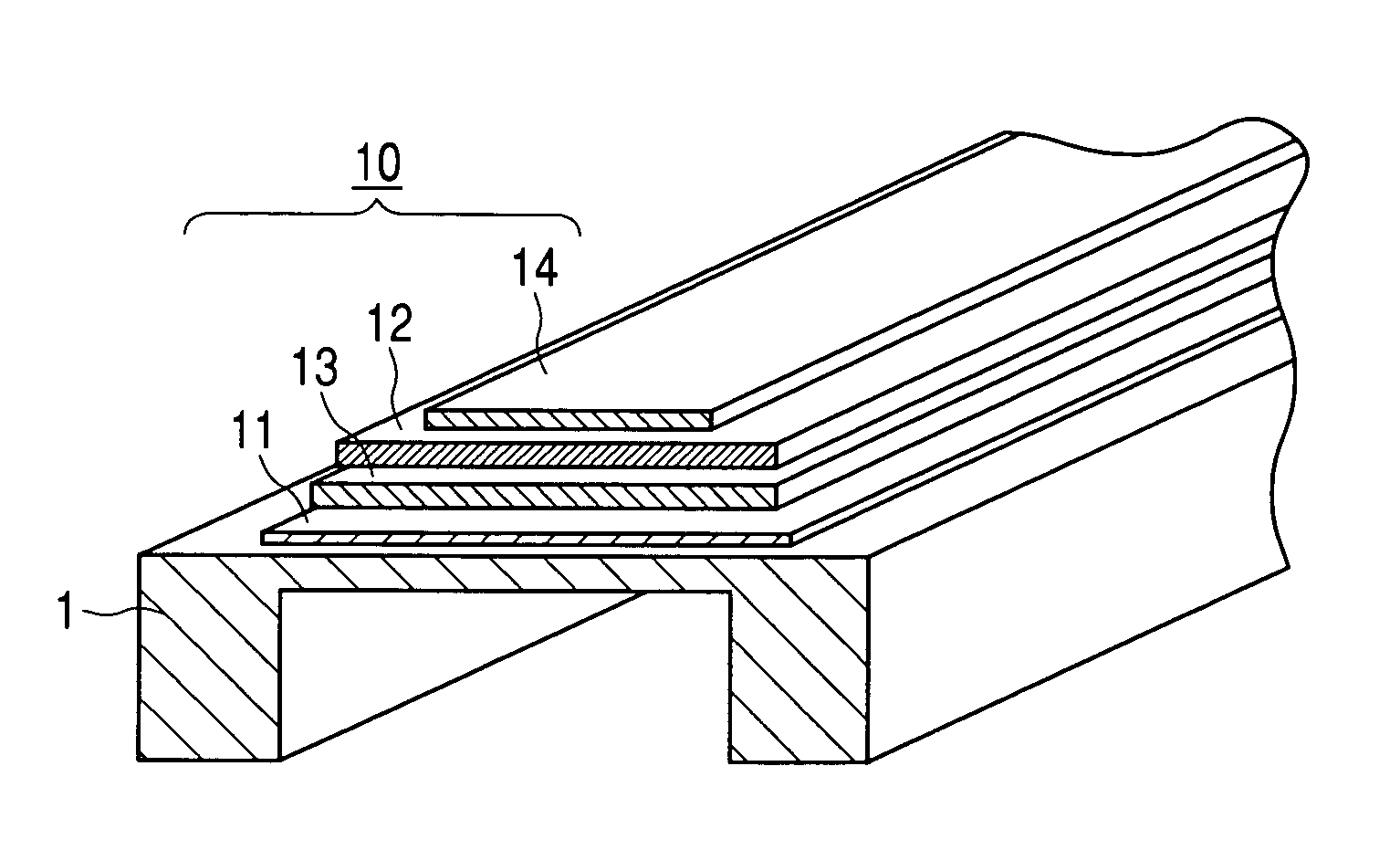

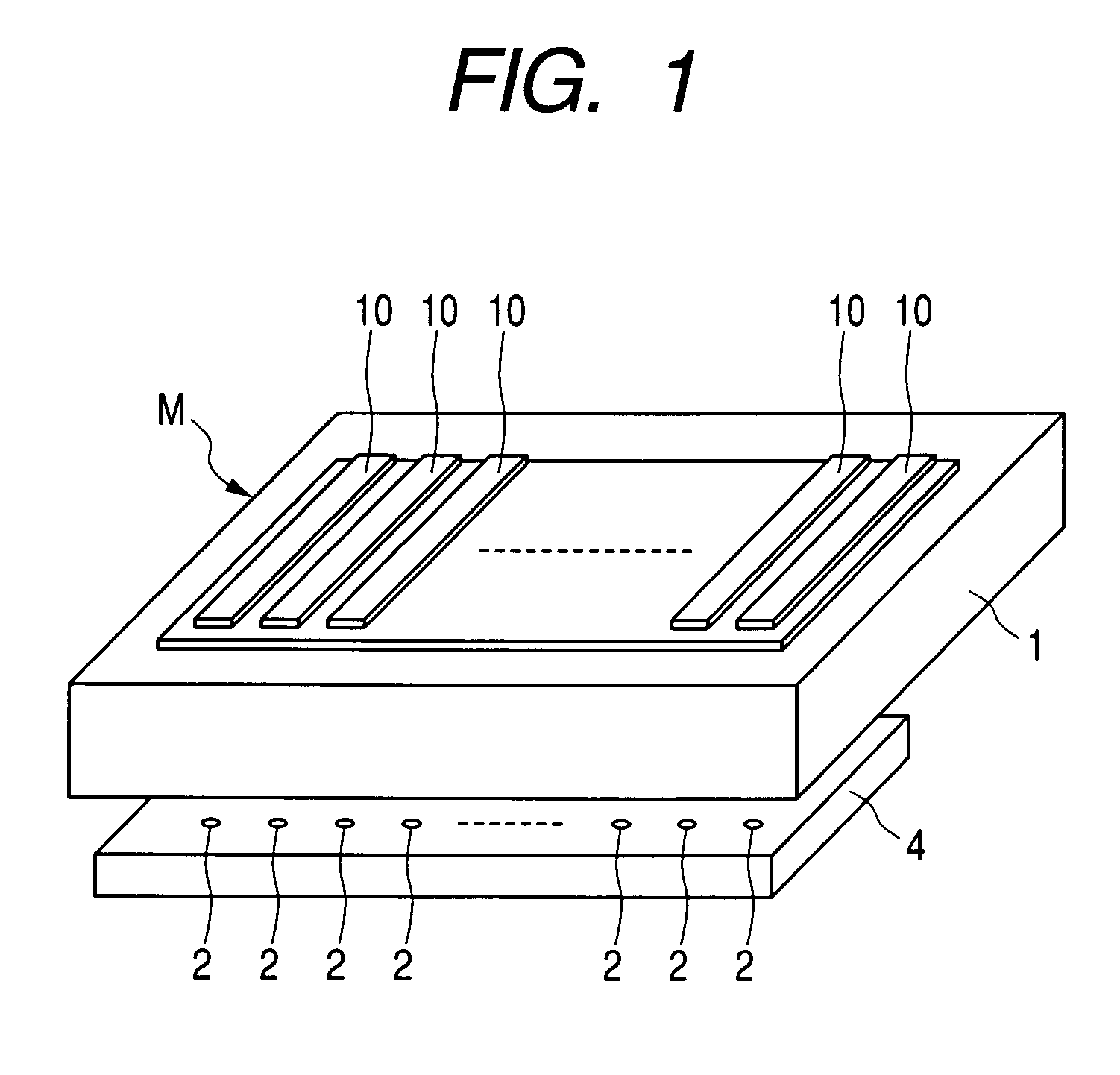

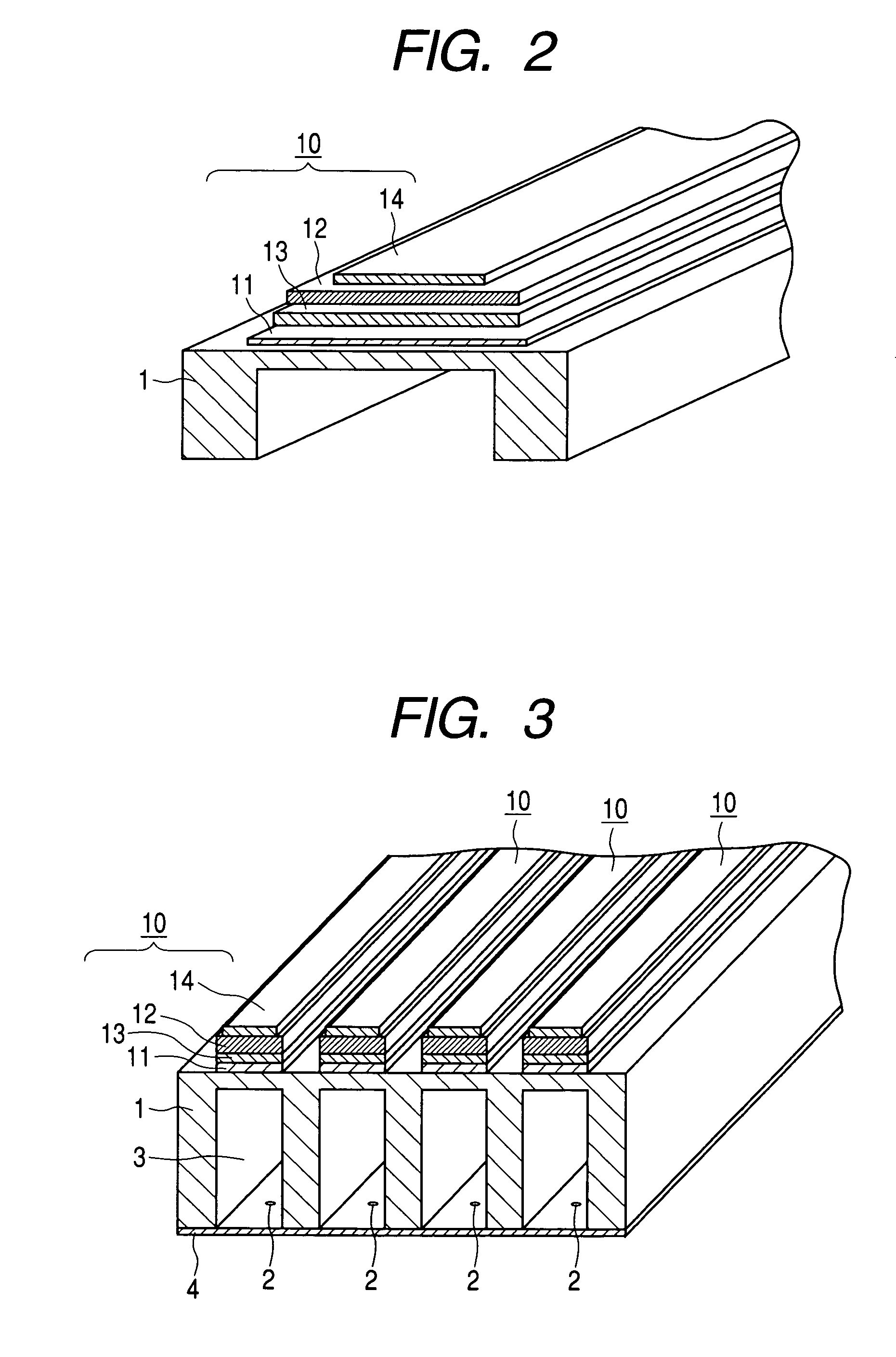

Actuator and liquid discharge head, and method for manufacturing liquid discharge head

InactiveUS7045935B2Improve reliabilityGood reproducibilityPiezoelectric/electrostrictive device manufacture/assemblyInking apparatusThin oxideEngineering

An actuator comprises a laminated structure having a vibration plate, a lower electrode, a piezoelectric element, and an upper electrode laminated sequentially on a basic element, and then, at least the lower electrode of the two electrodes is a thin oxide film doped with La of single orientated crystal or monocrystal that contains Sr and Ti. Thus, it is made possible to materialize the micro miniaturized actuator having a strong structure of lamination with high adhesion, which is capable of obtaining large displacement with sufficient durability without spoiling the piezo-electrostrictive property thereof even with the small thickness of the piezoelectric element. With the micro miniaturized actuator thus structured, it is made possible to make a liquid discharge head more precisely.

Owner:CANON KK

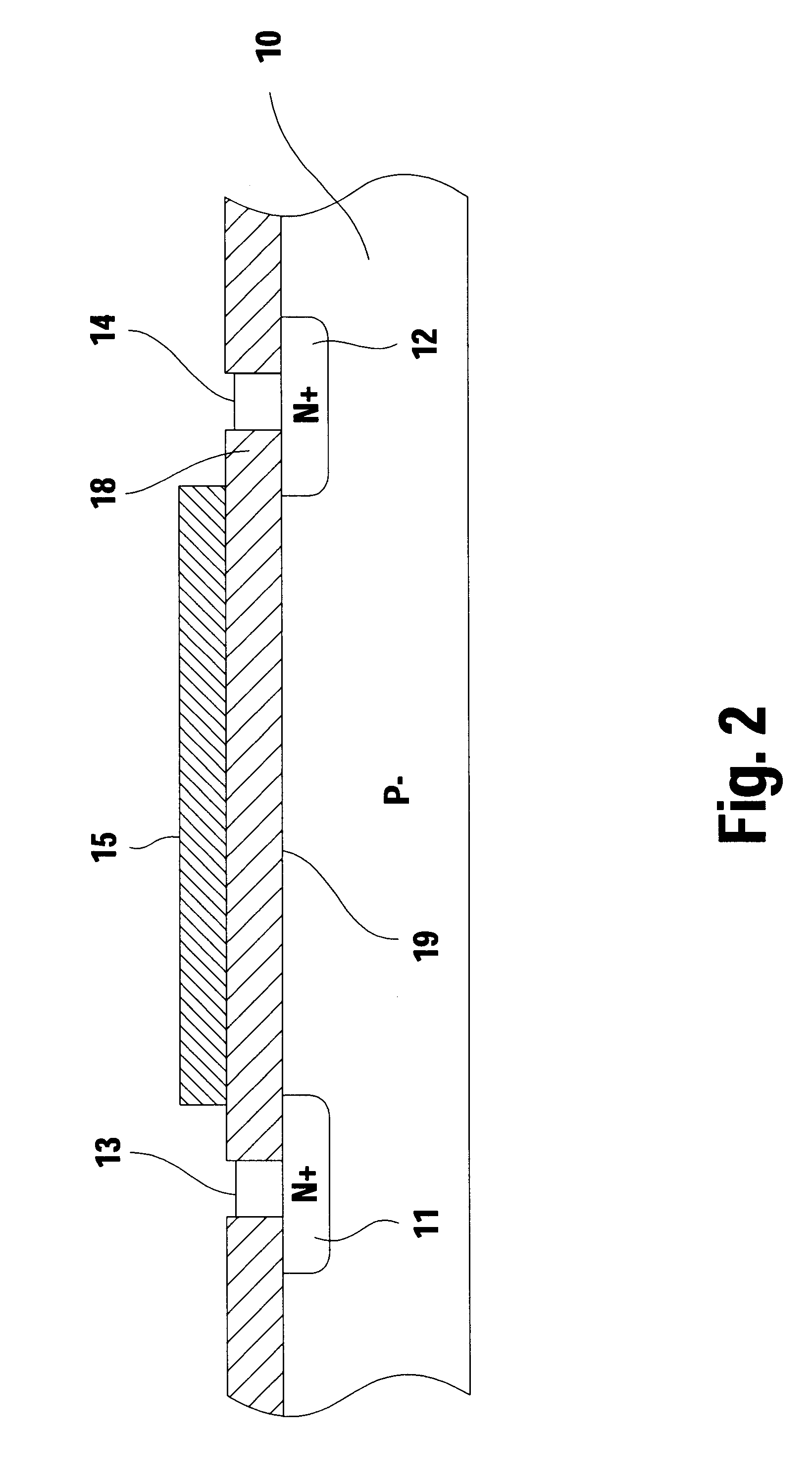

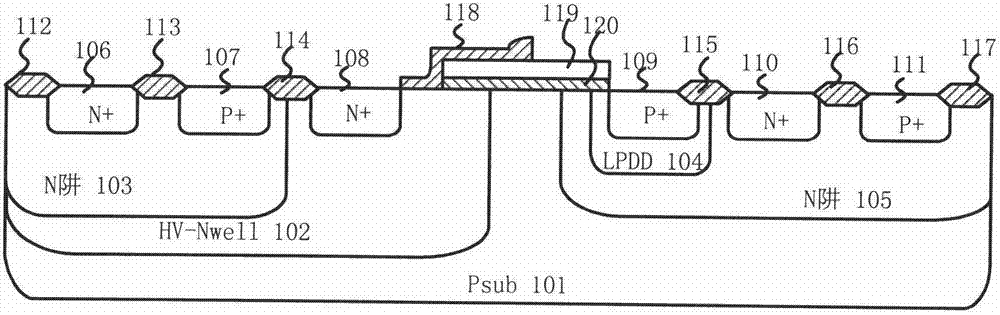

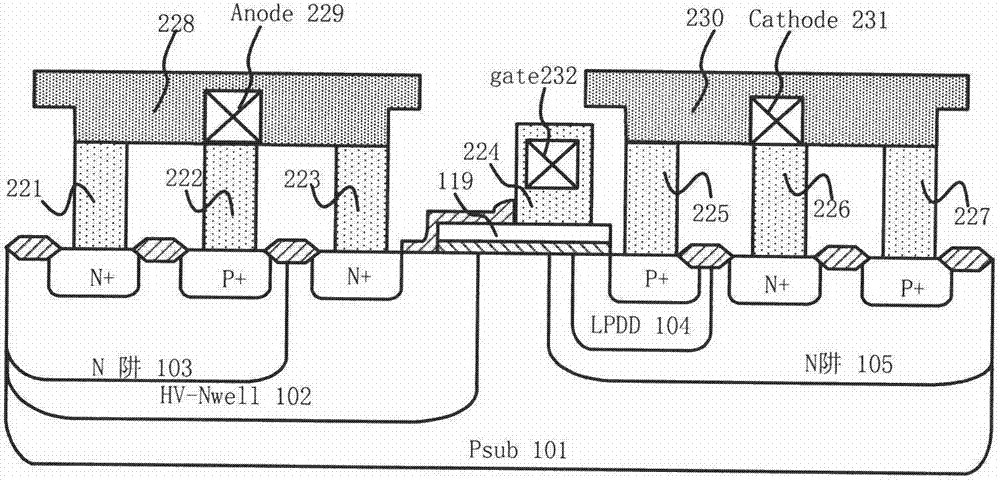

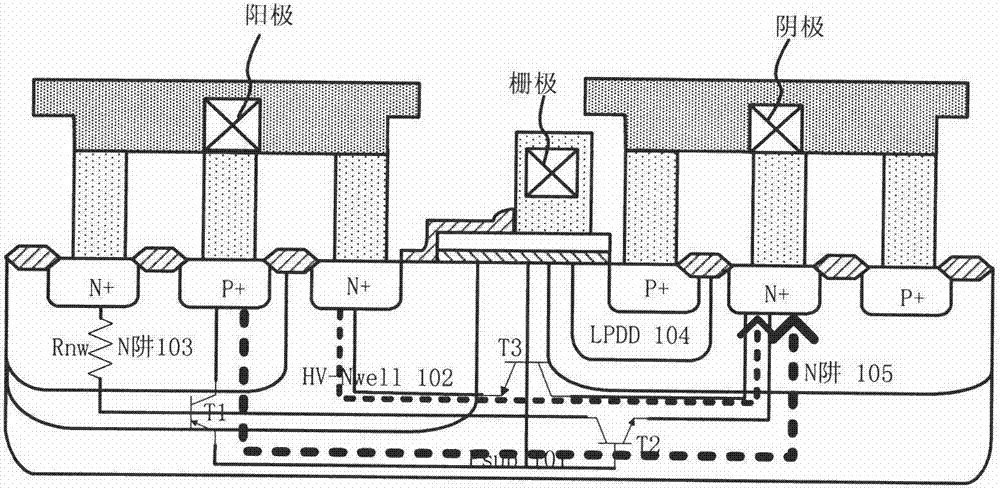

High-voltage ESD (electro-static discharge) protective device triggered by bidirectional substrate

ActiveCN102969312AOpen fastLarge secondary breakdown currentSolid-state devicesSemiconductor devicesSilicon-controlled rectifierThin oxide

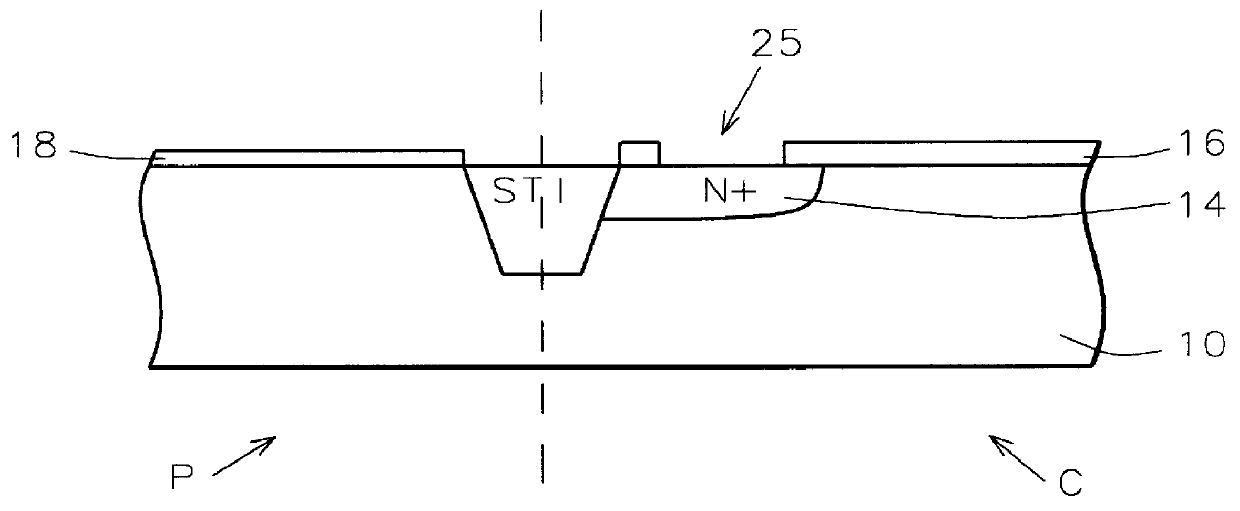

The invention discloses a high-voltage ESD (electro-static discharge) protective device triggered by a bidirectional substrate. The high-voltage ESD protective device triggered by the bidirectional substrate can be used for an on-chip IC (integrated circuit) ESD protective circuit and mainly comprises a substrate Psub, a high-voltage deep N trap, a lightly doped p-type drift region, a first highly doped N+ injection region, a first P+ injection region, a second N+ injection region, a second P+ injection region, a third N+ injection region, a third P+ injection region, a polycrystalline silicon grid, a grid thin oxide layer and a plurality of field oxide isolation regions. Reverse PN nodes at the interface part of the high-voltage N well or the N well and the substrate can be triggered and conducted through the forward and reverse ESD high-voltage pulse effect, two structures of internal SCR (silicon controlled rectifier) and LDMOS (laterally diffused metal oxide semiconductor) operate at the same time so as to form an ESD current discharge path to improve the secondary breakdown current of the device and lower the conducted resistance. The maintaining voltage of the device is improved through hoisting the channel length of the LDMOS device, the internal structure design as well as optimization of layout hierarchy, and the high-performance ESD protection is realized.

Owner:铜陵汇泽科技信息咨询有限公司