Patents

Literature

51 results about "Ultra thin body" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

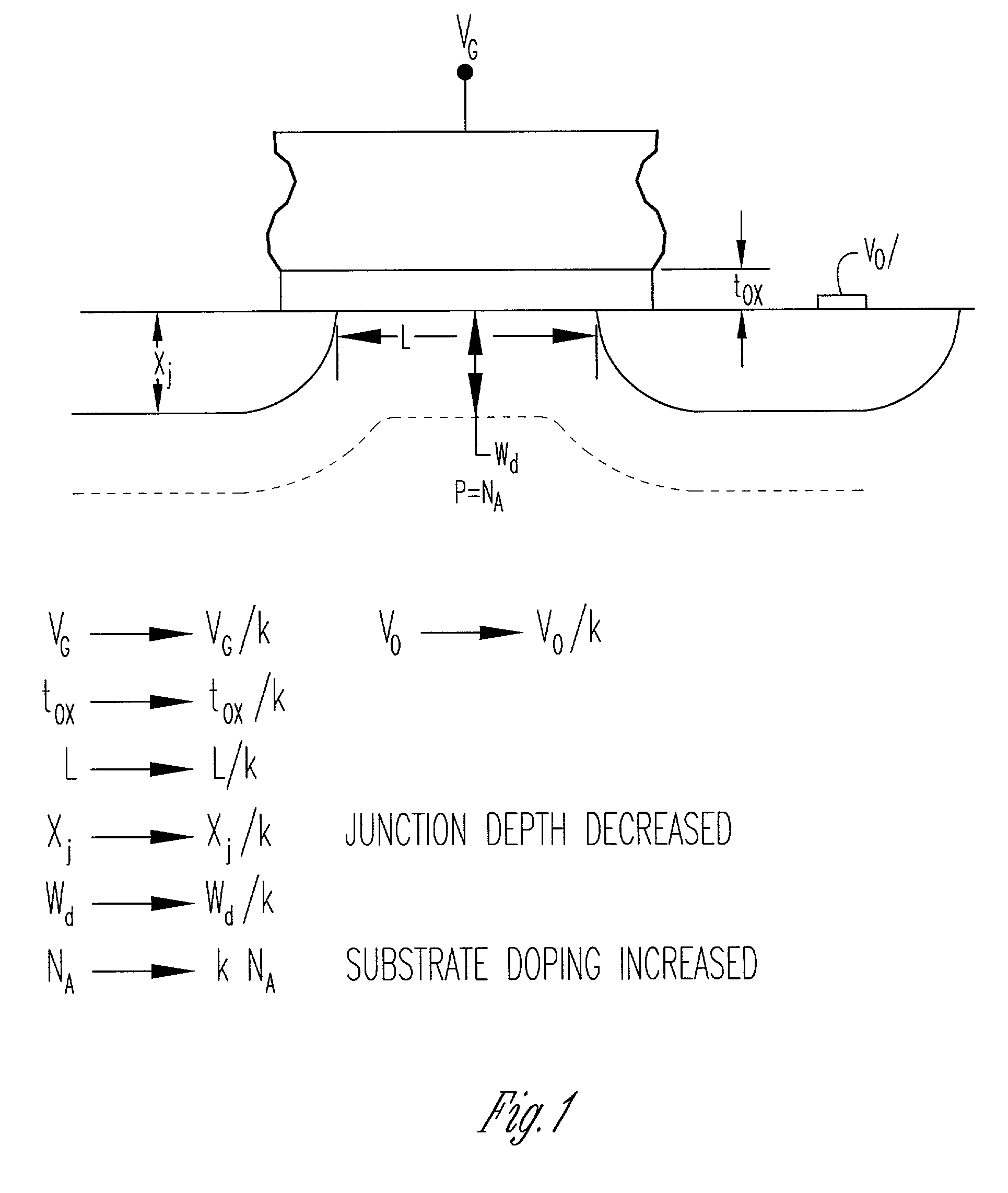

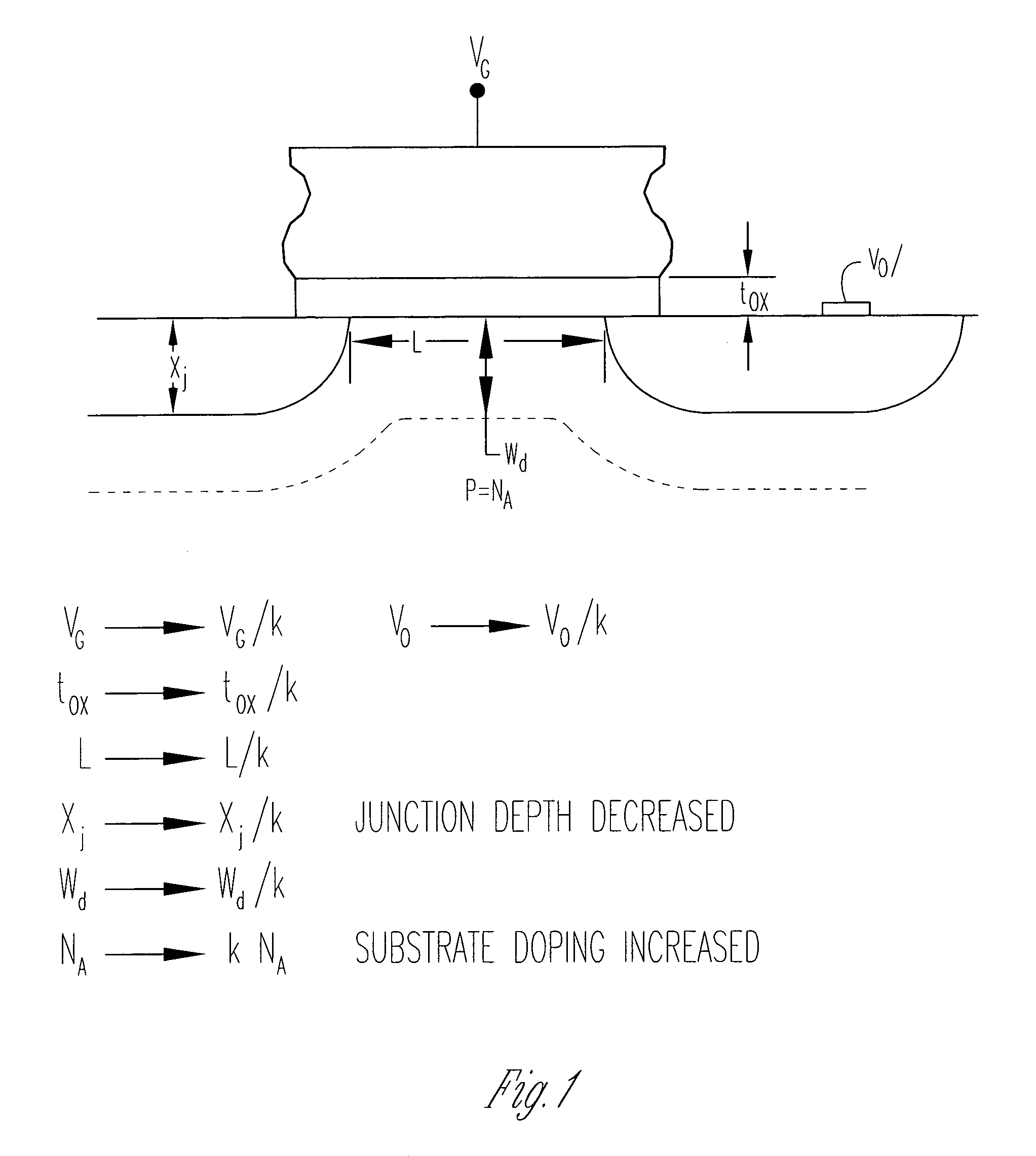

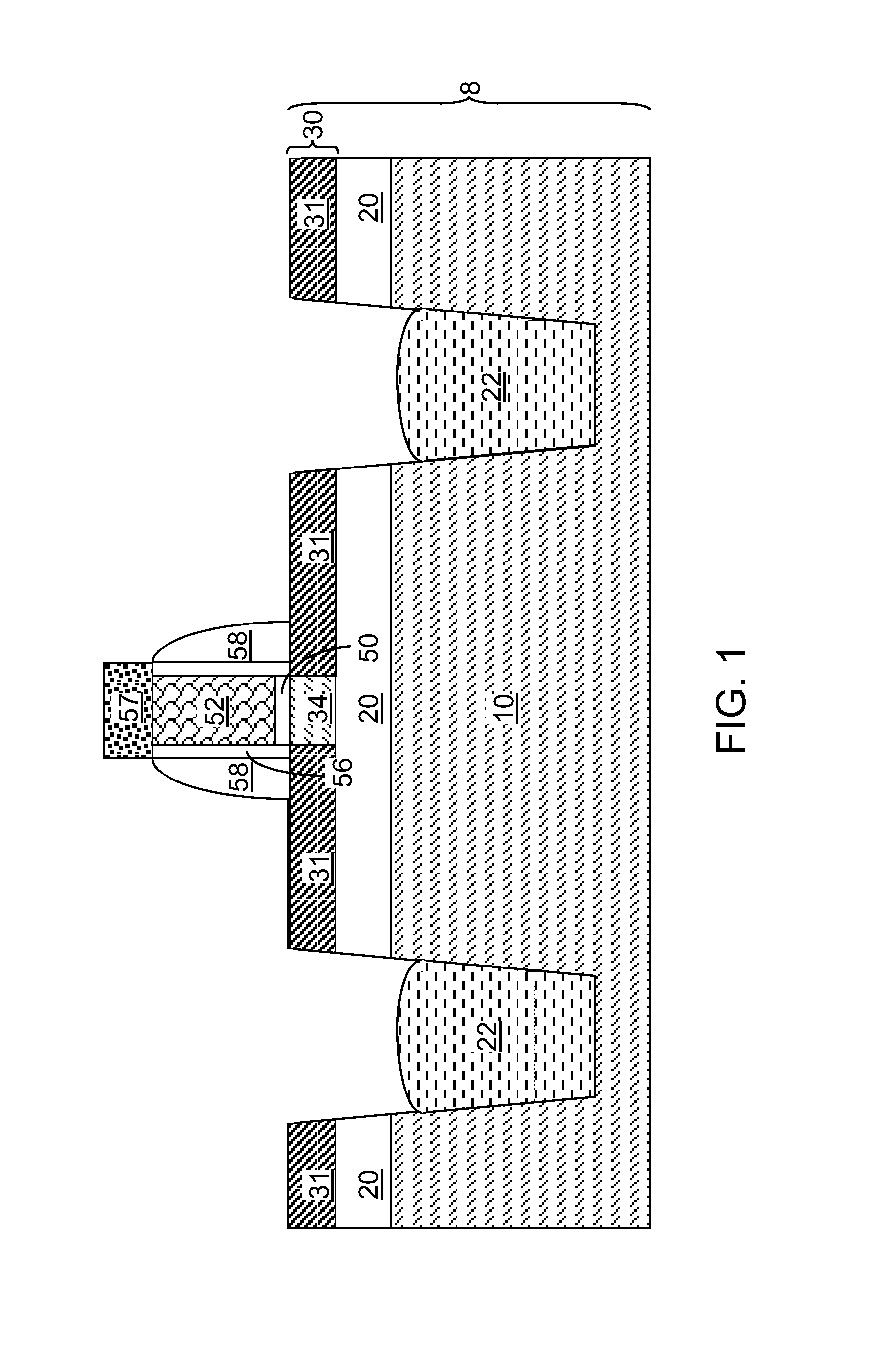

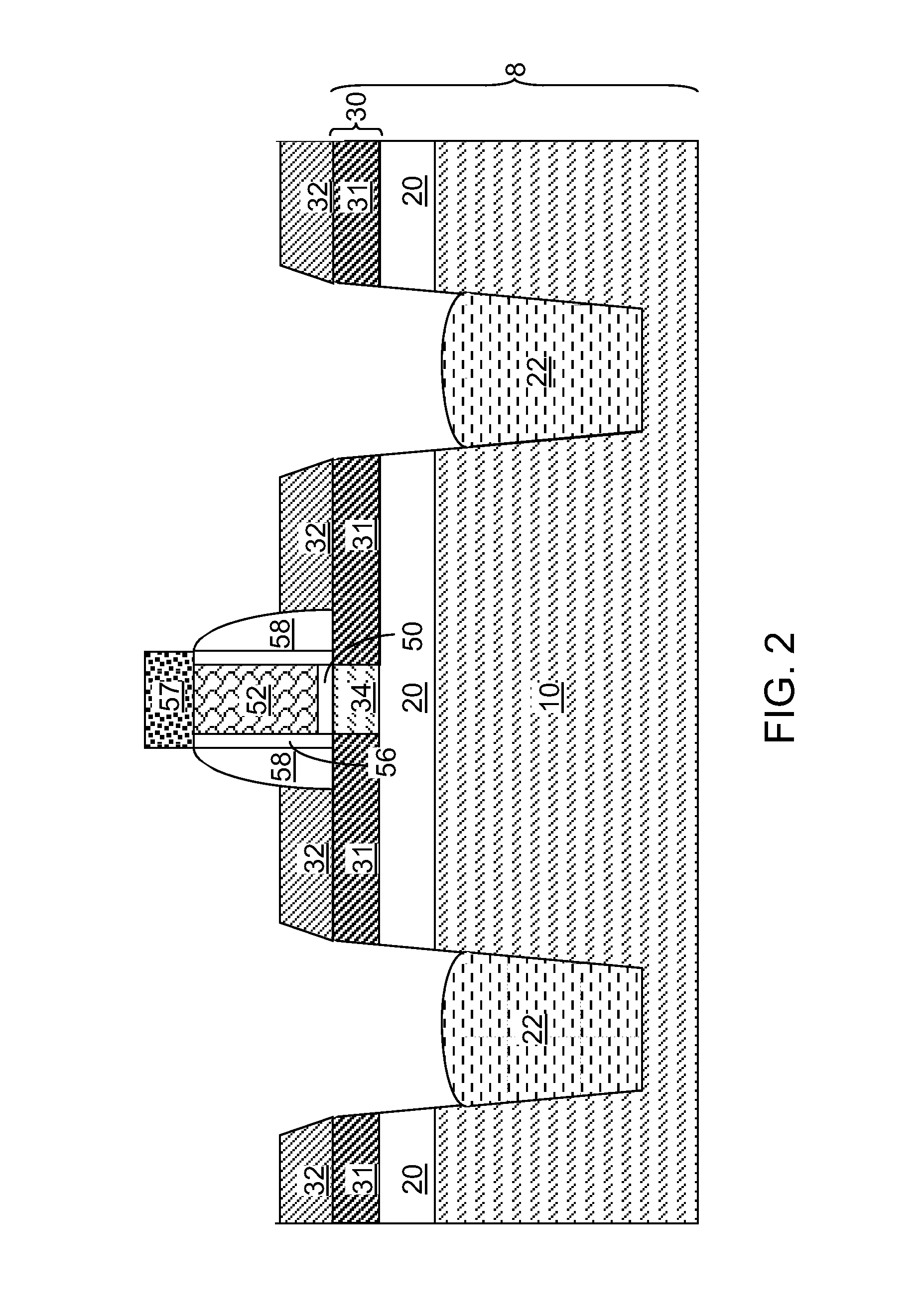

Ultra-thin body super-steep retrograde well (SSRW) FET devices

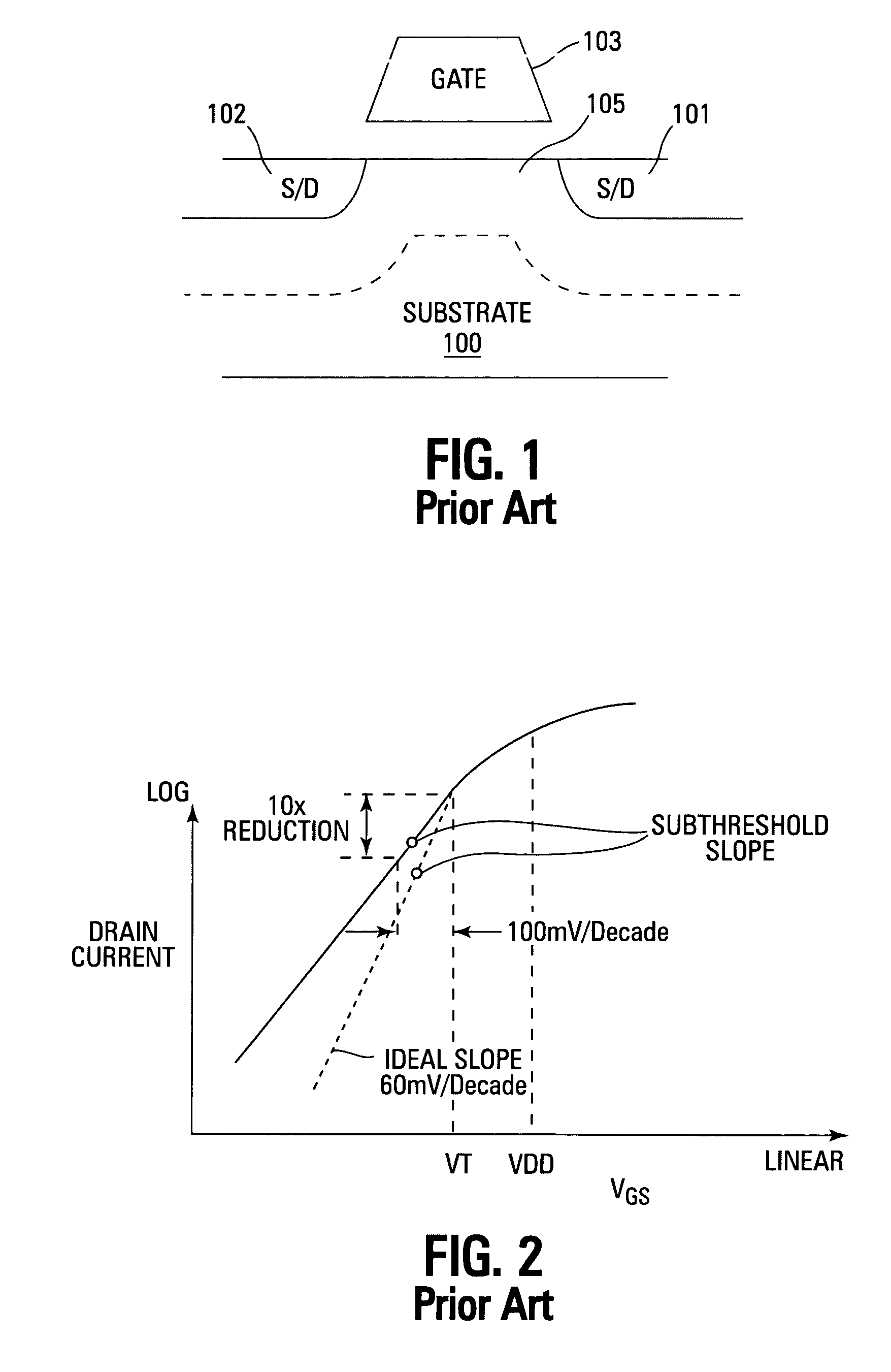

ActiveUS20060022270A1Minimize space-charge related fluctuationReduce capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingDopantGround plane

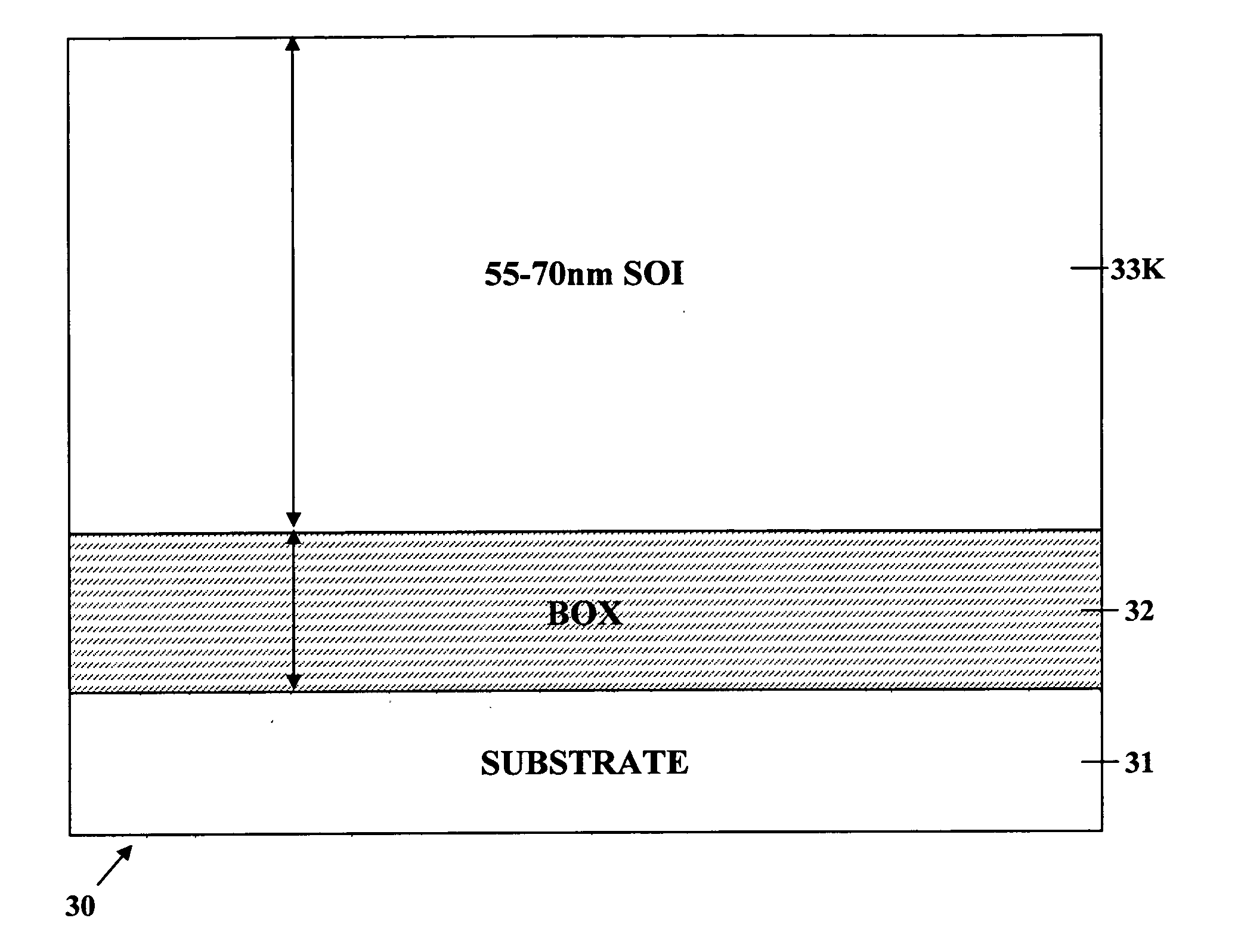

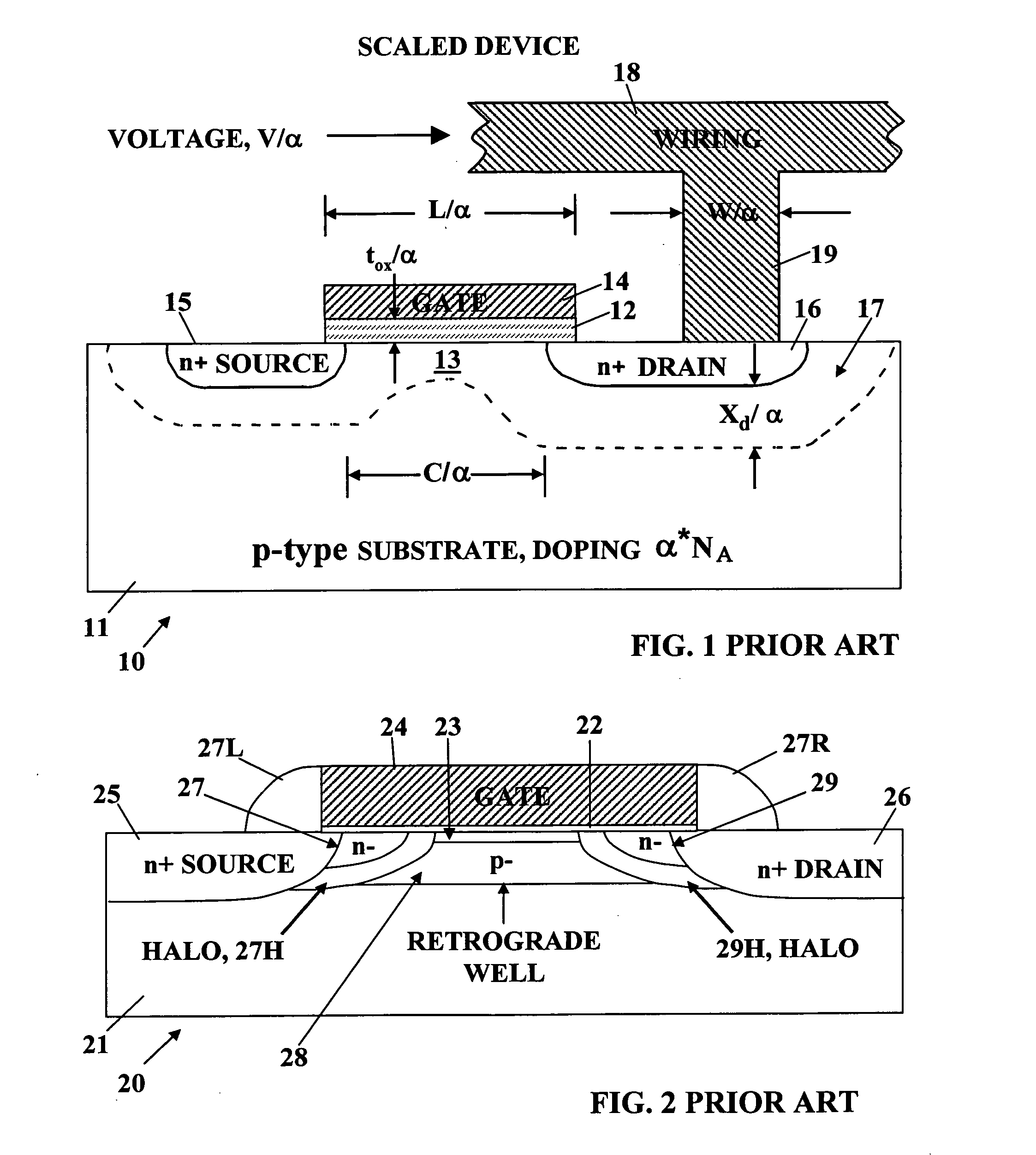

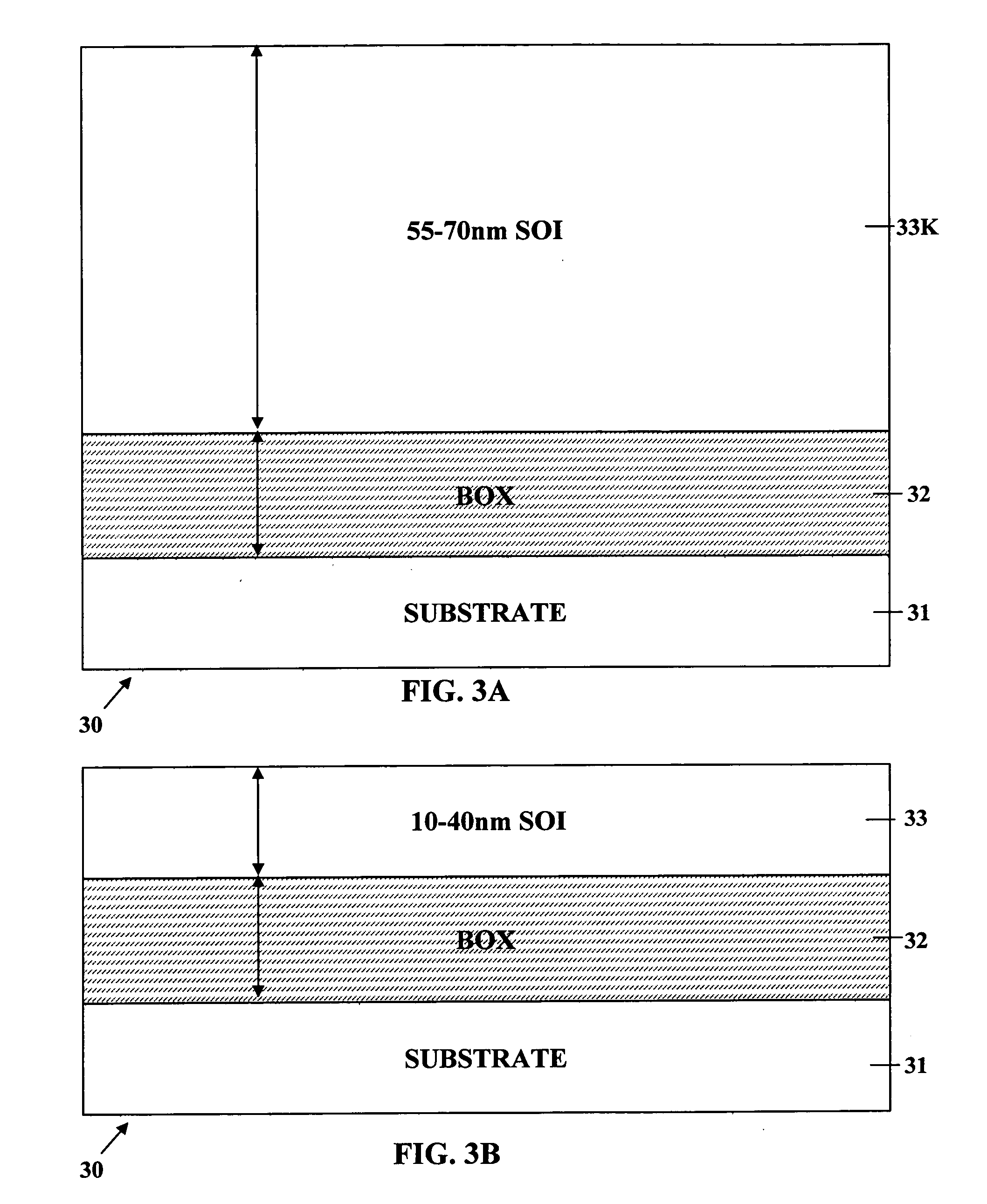

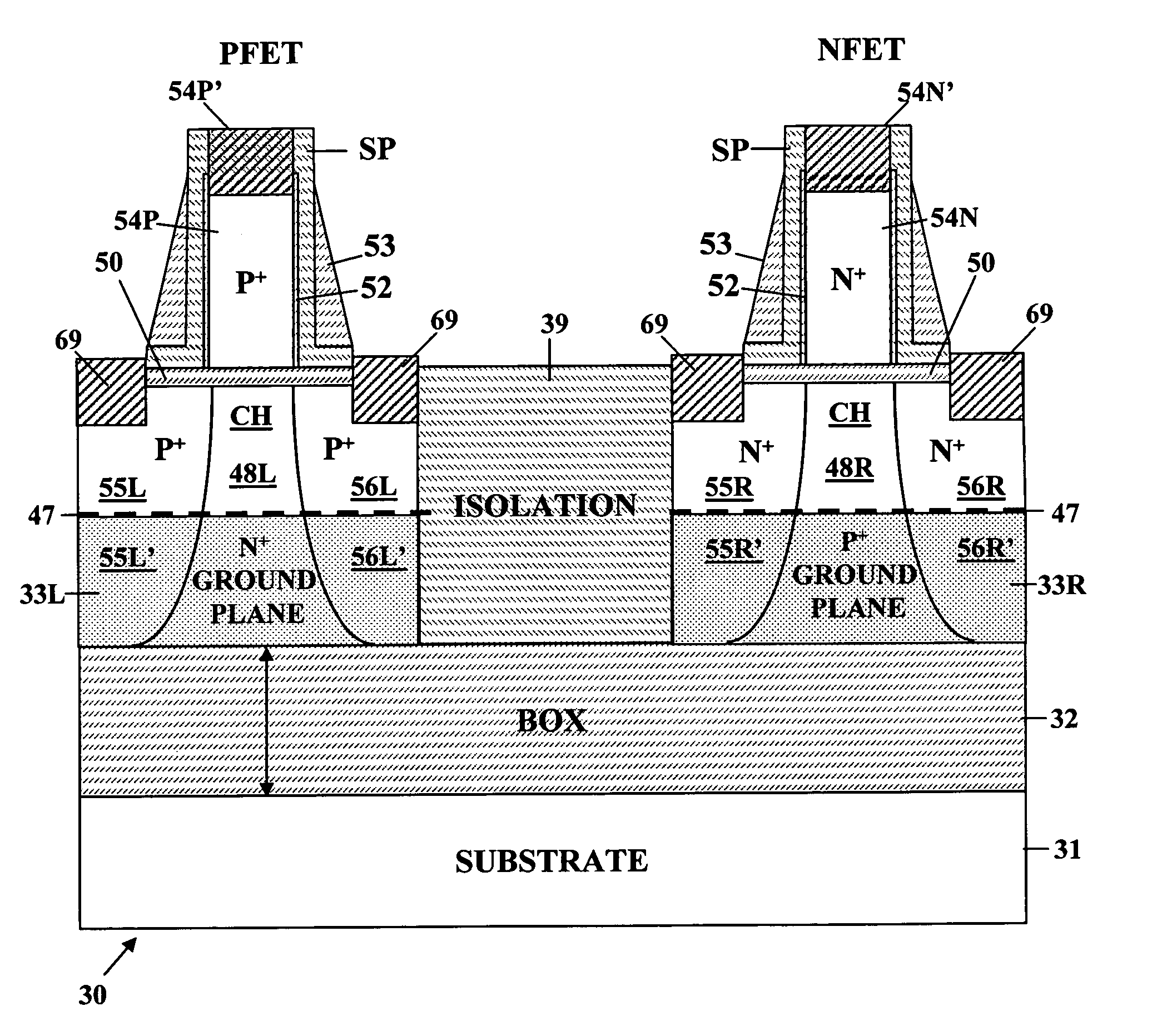

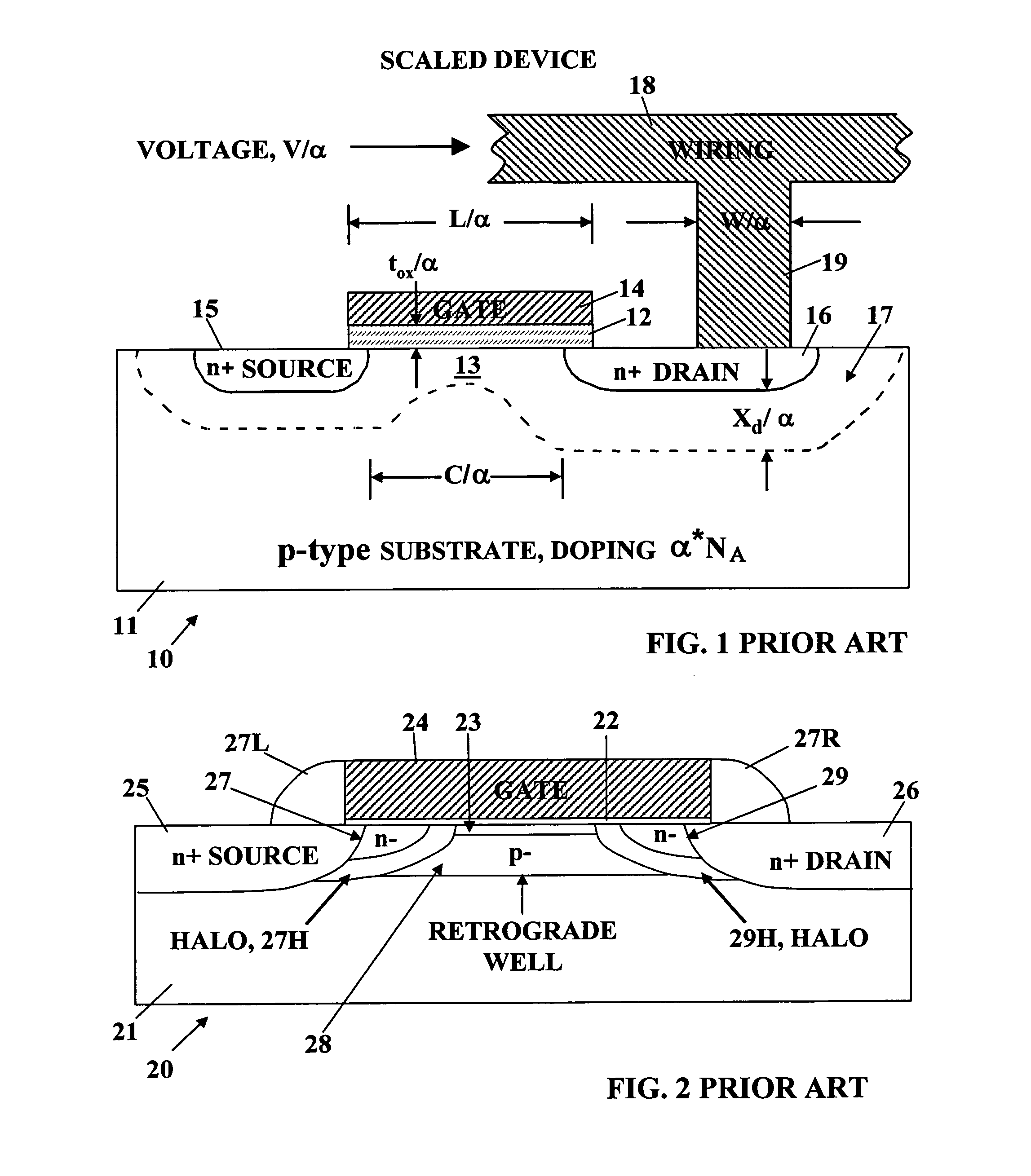

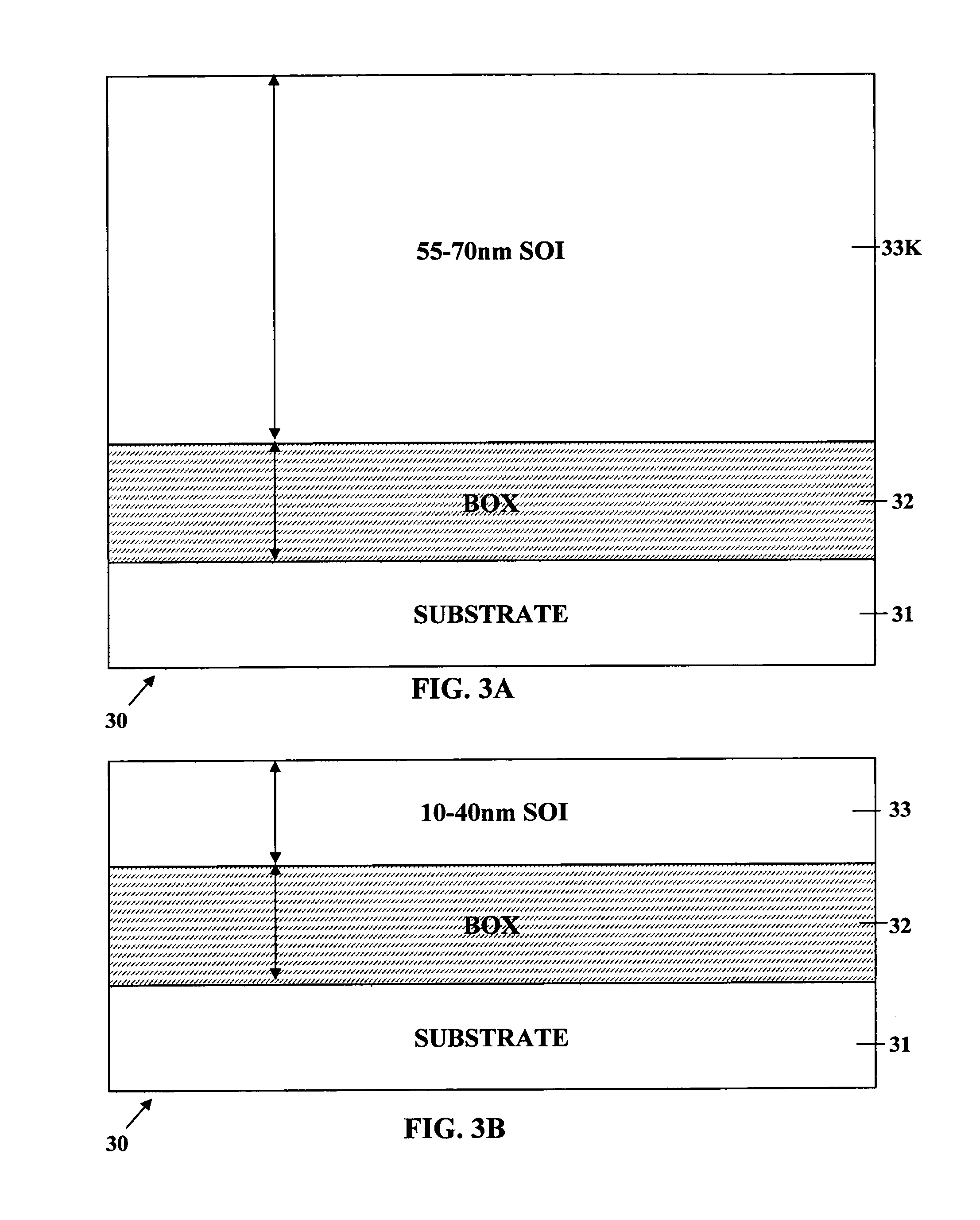

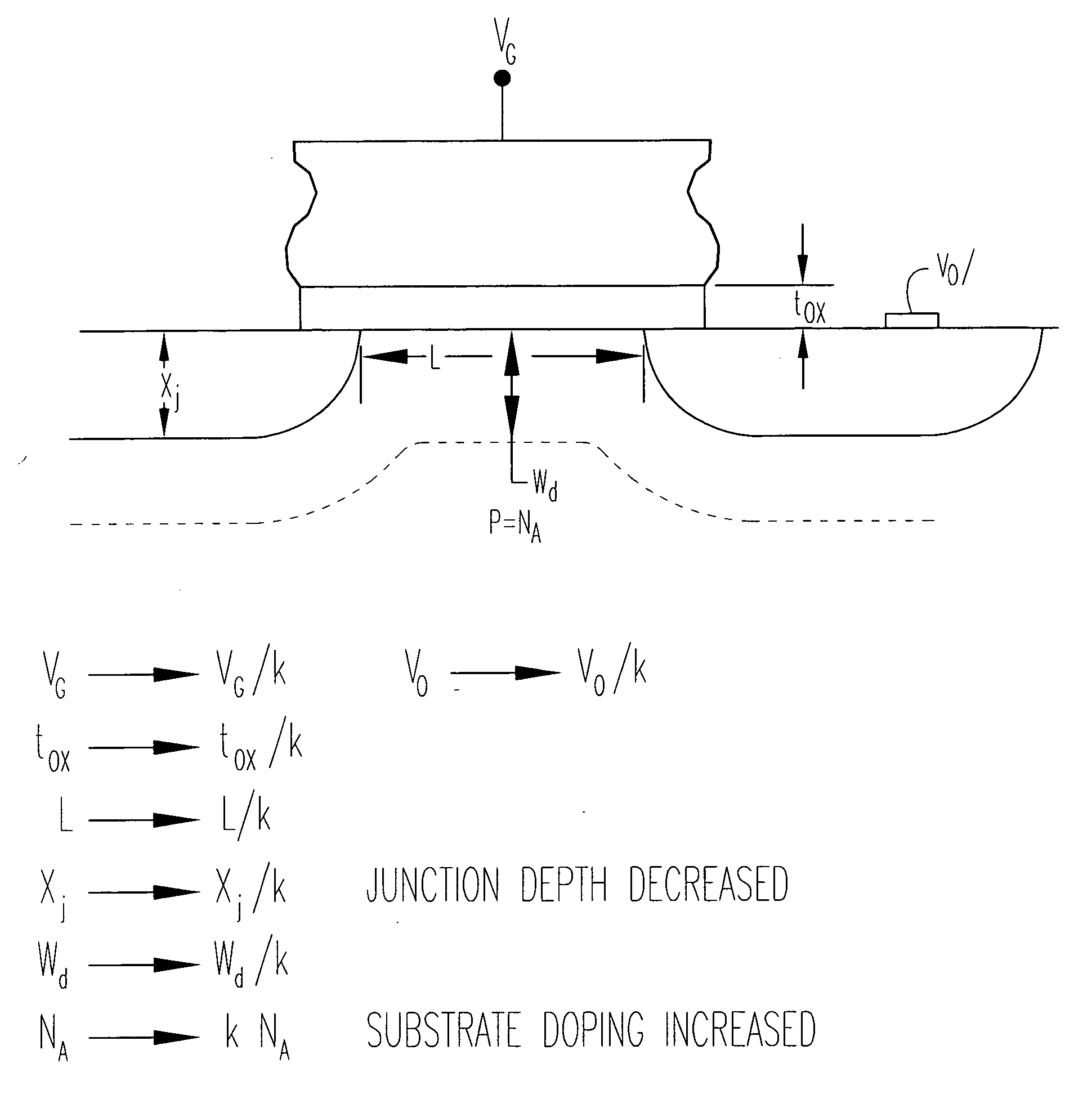

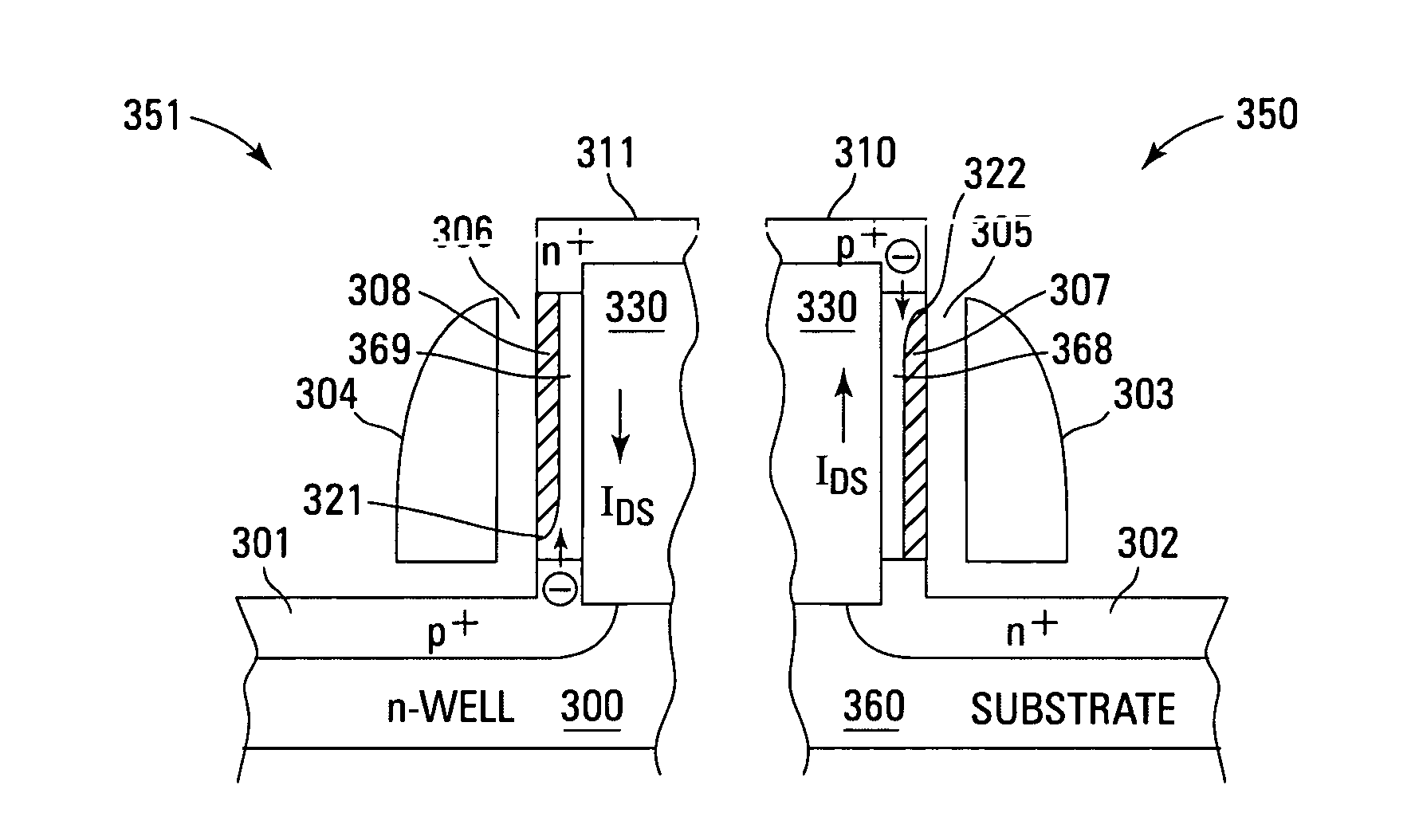

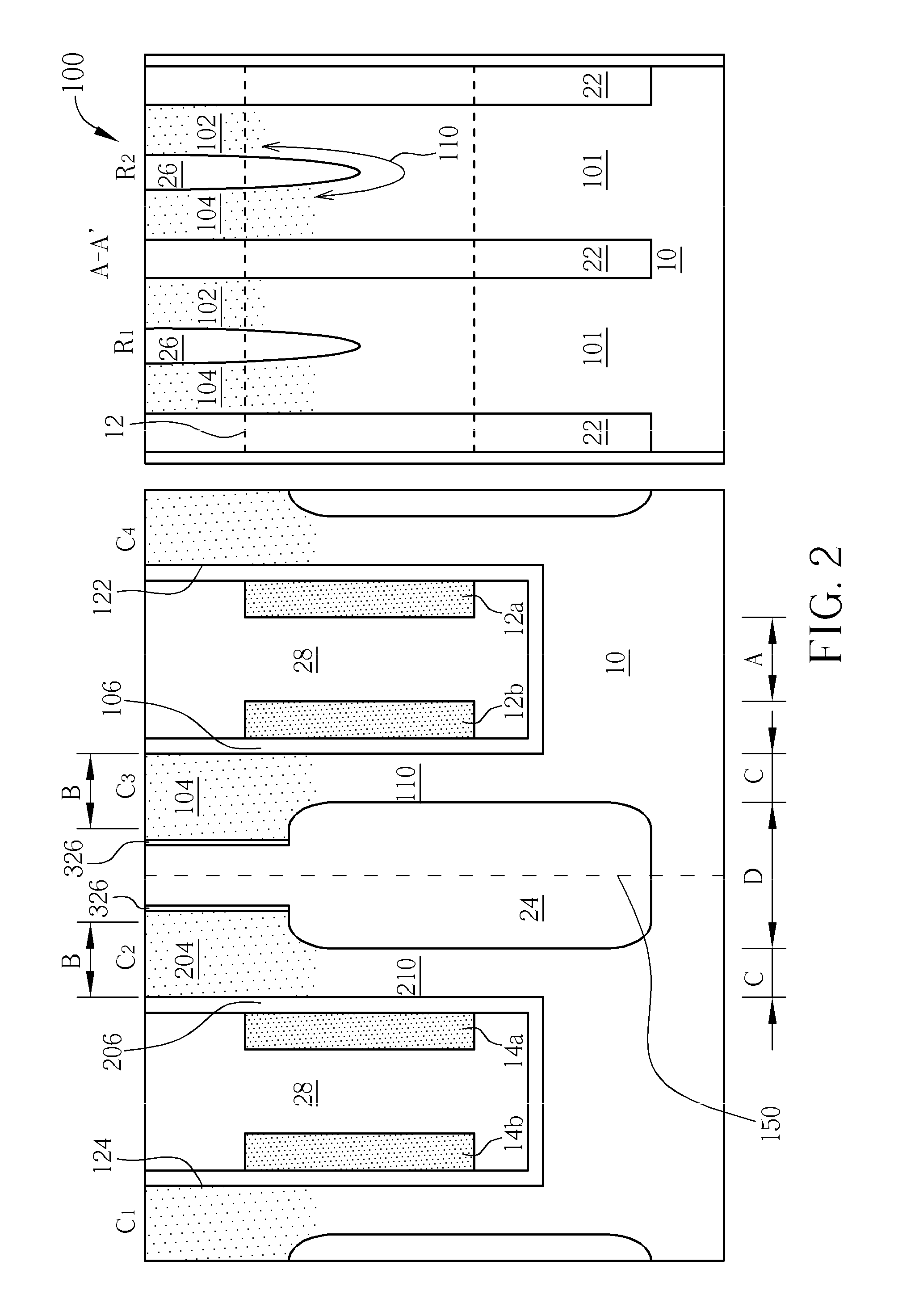

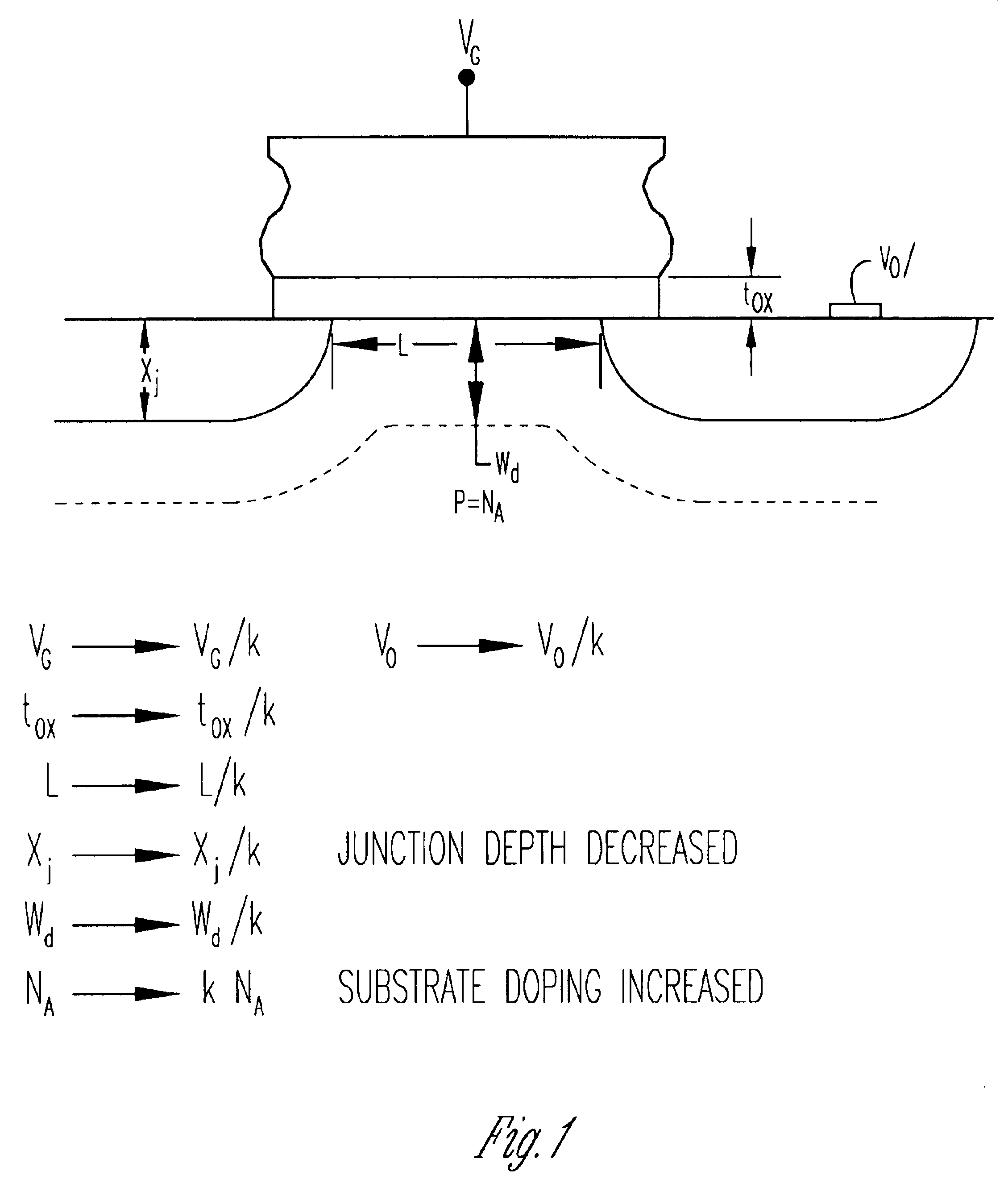

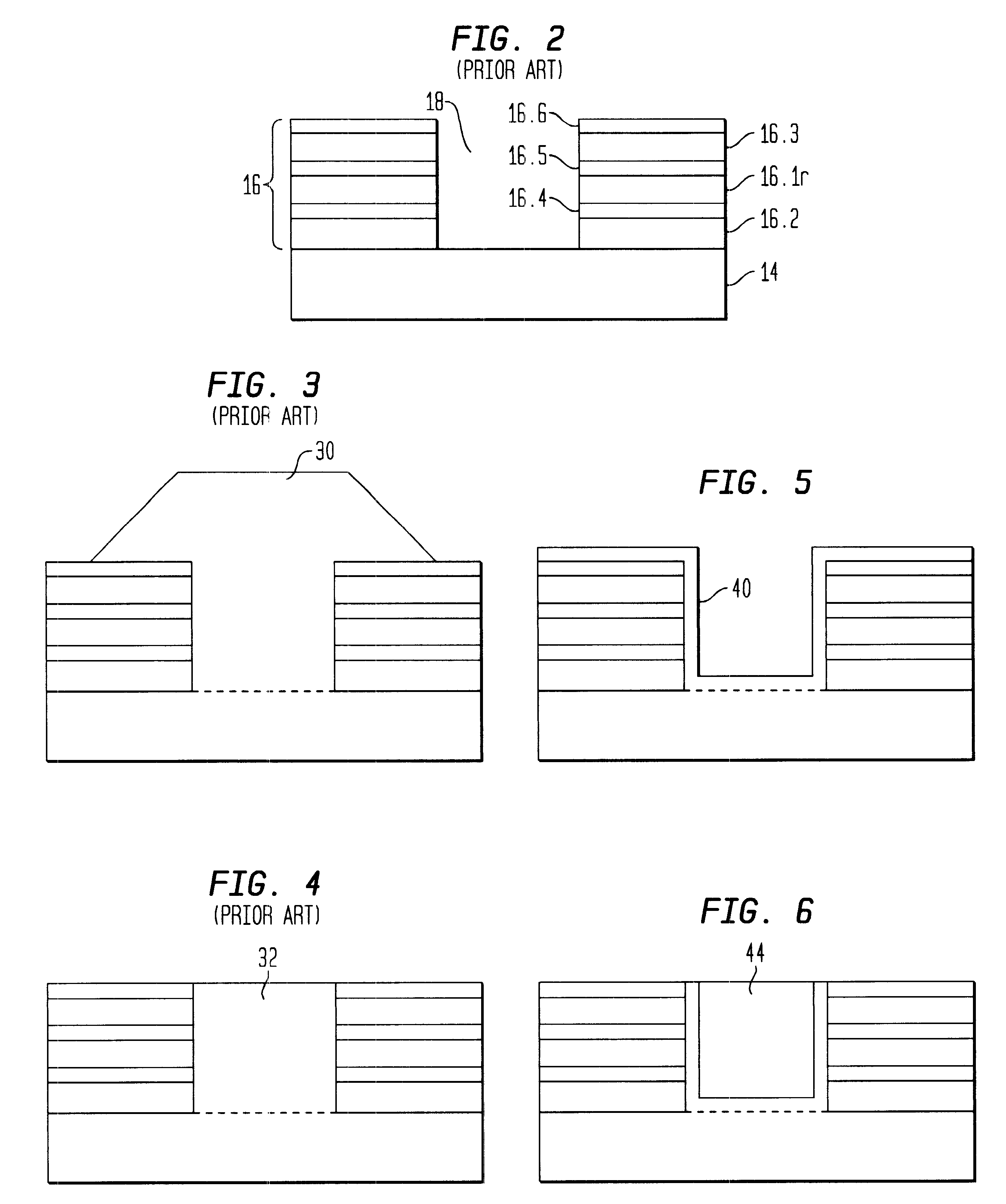

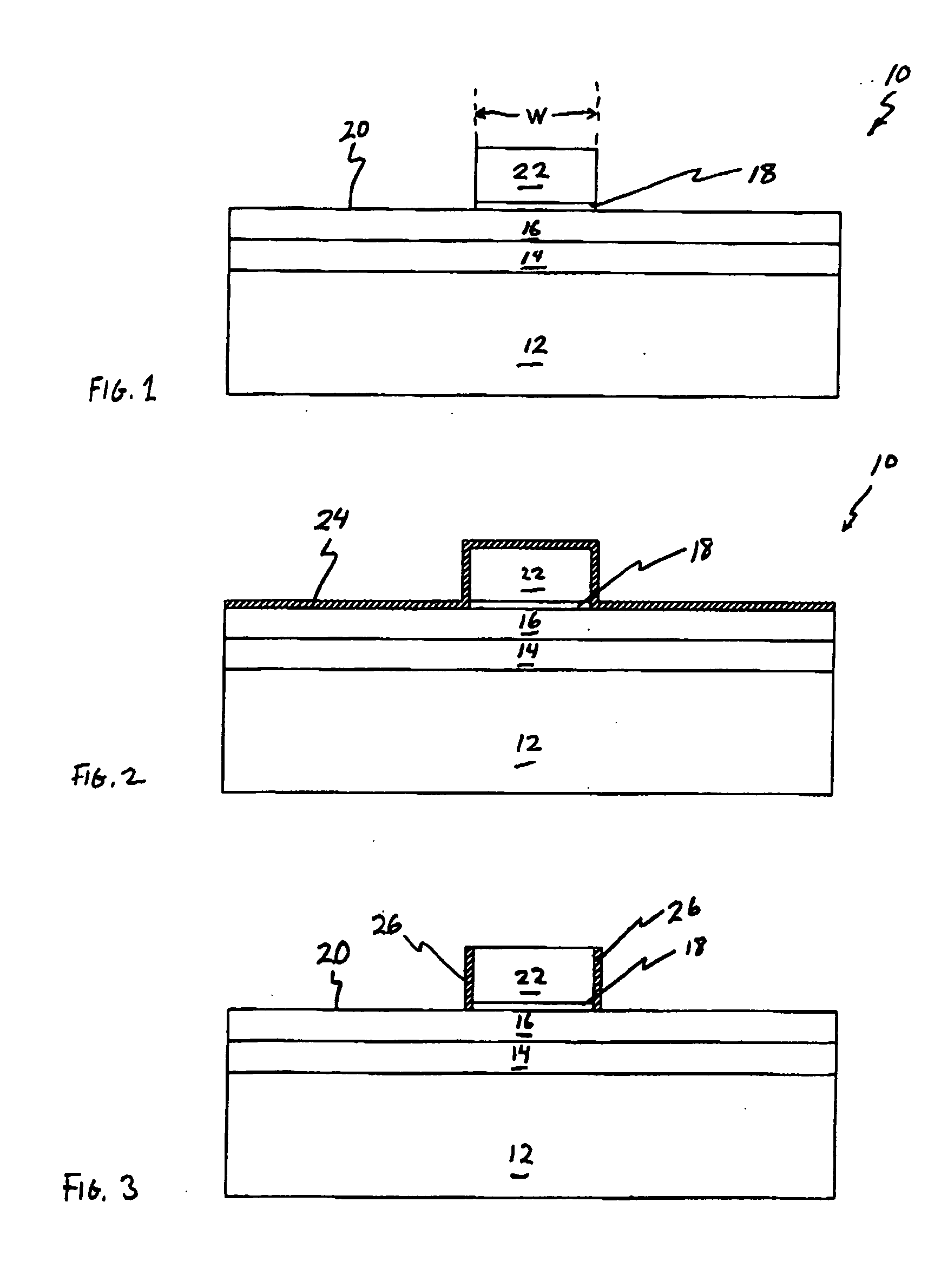

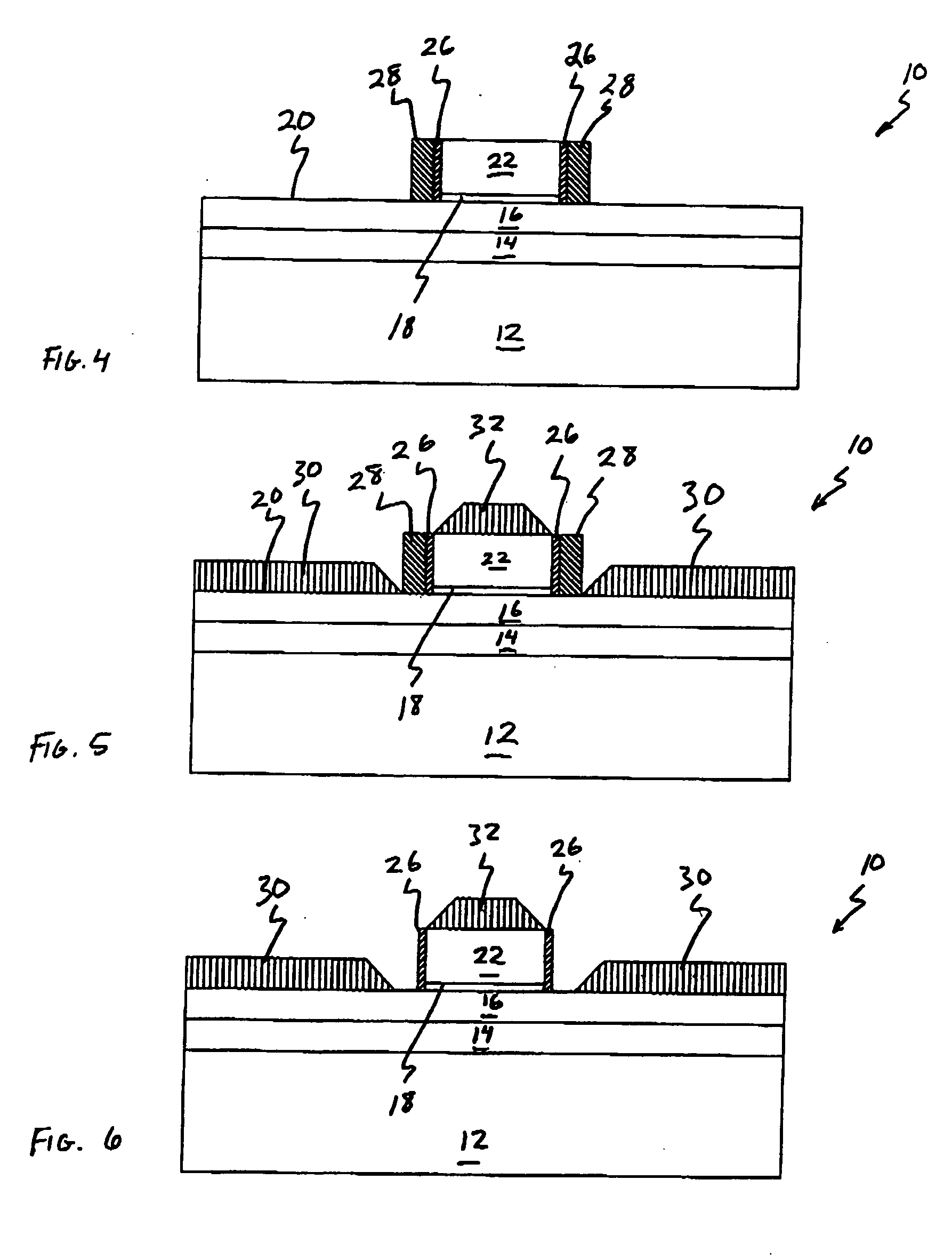

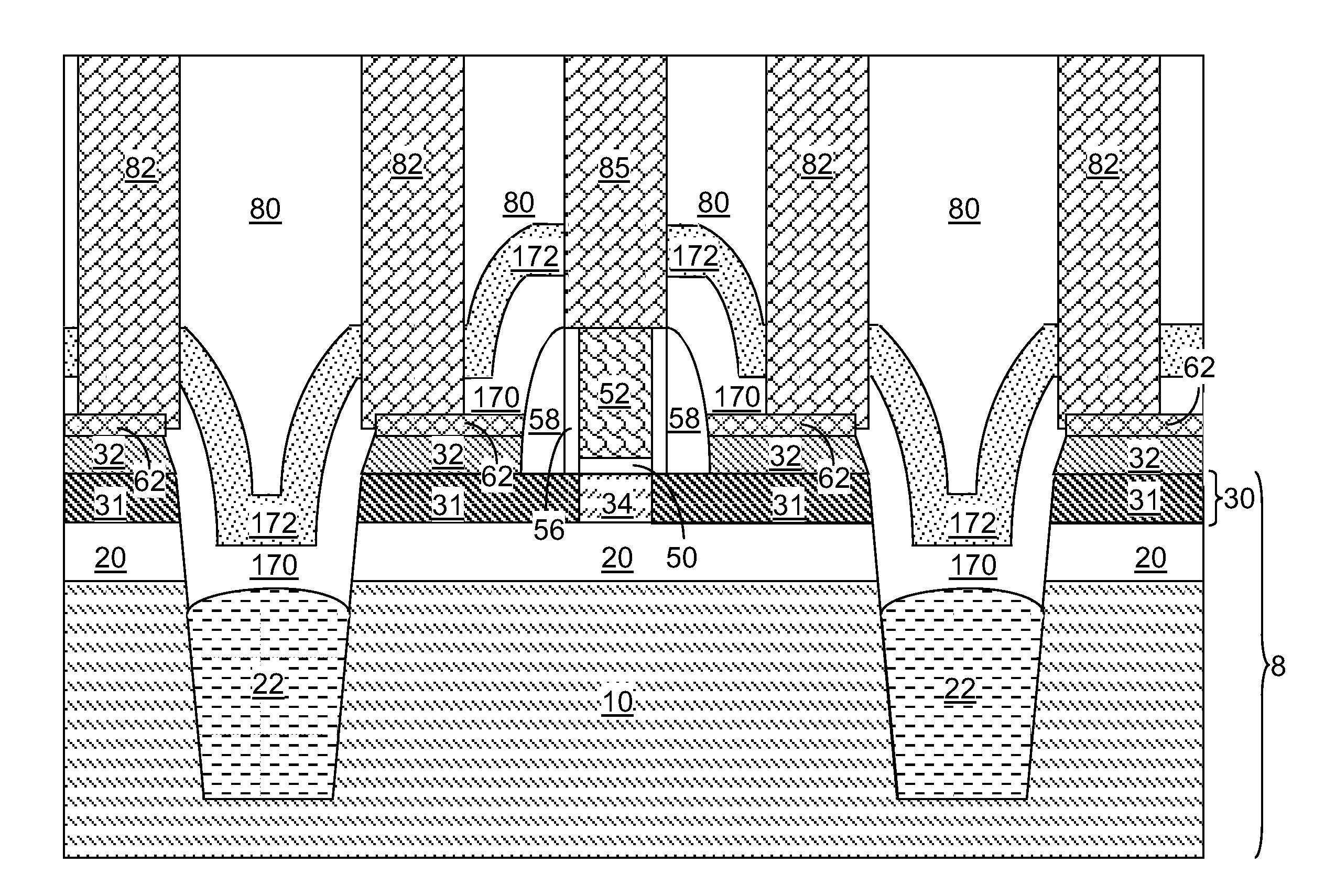

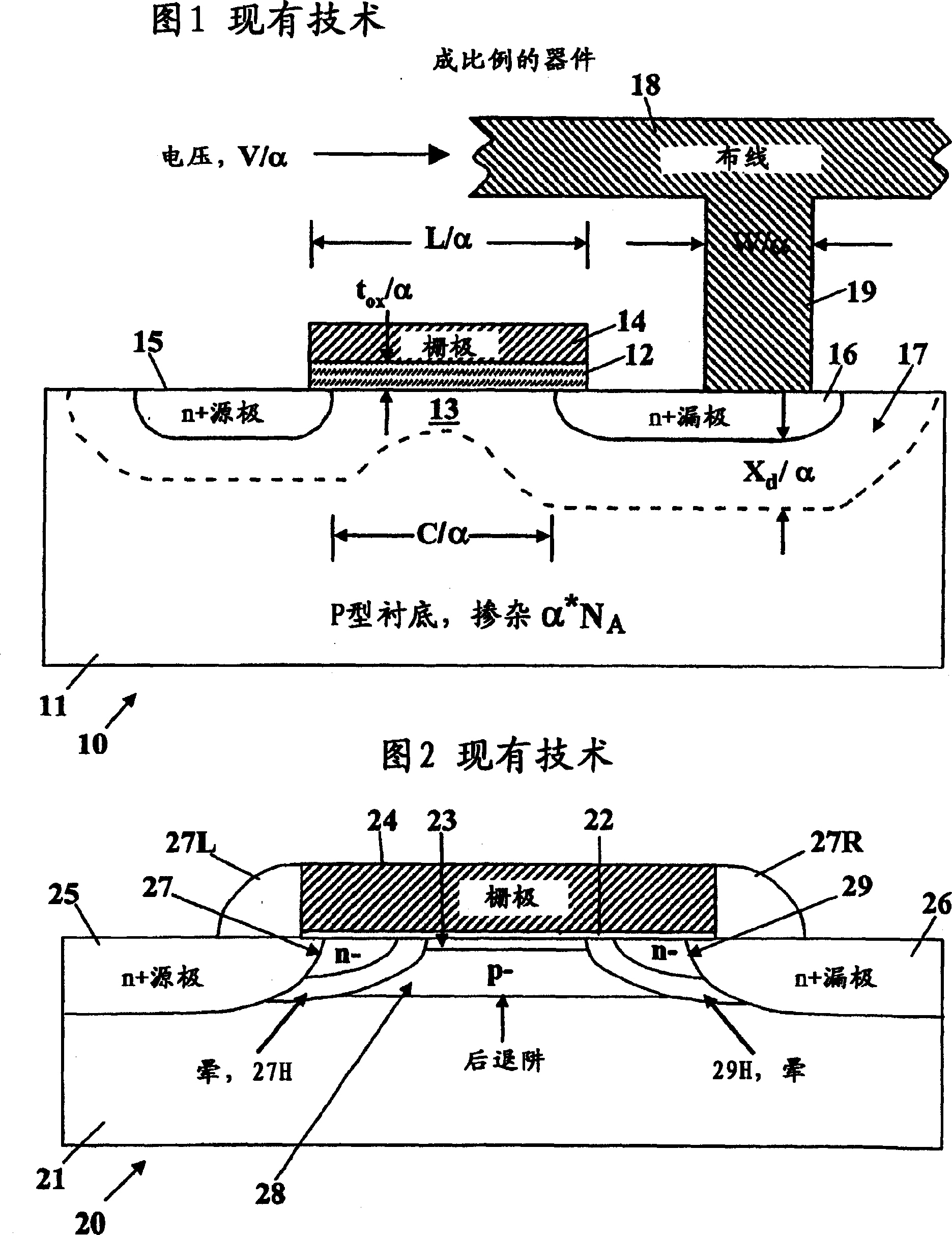

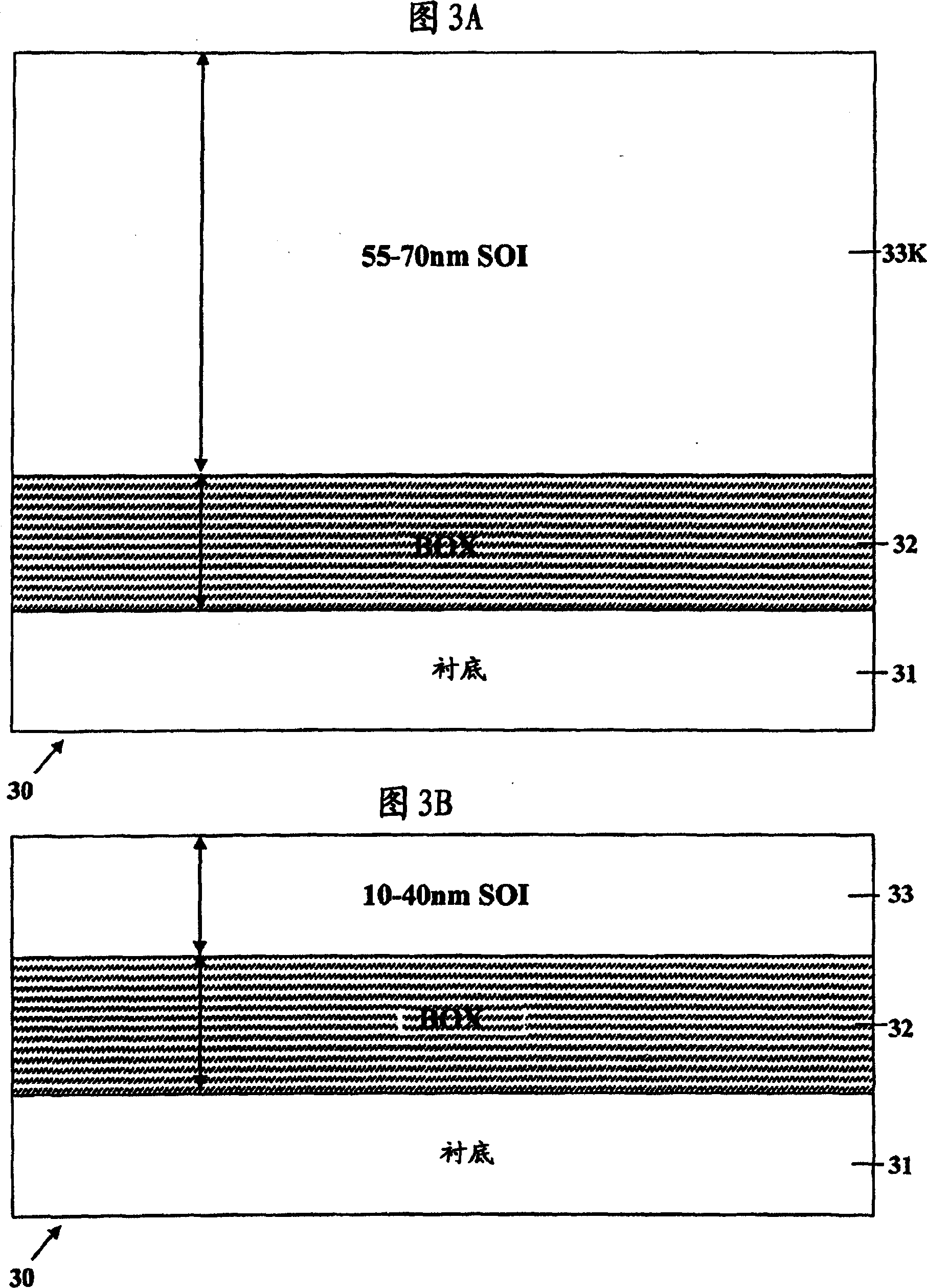

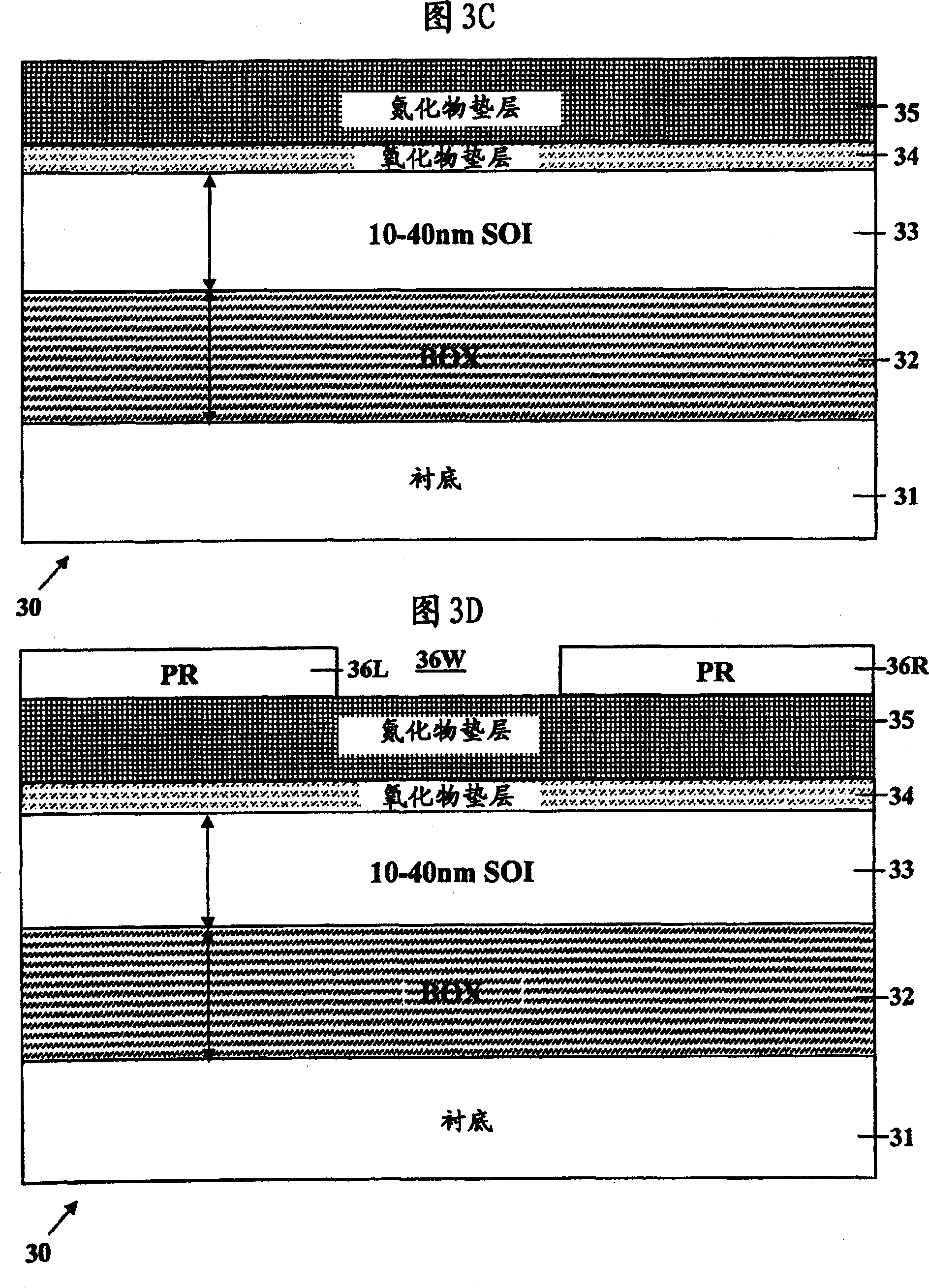

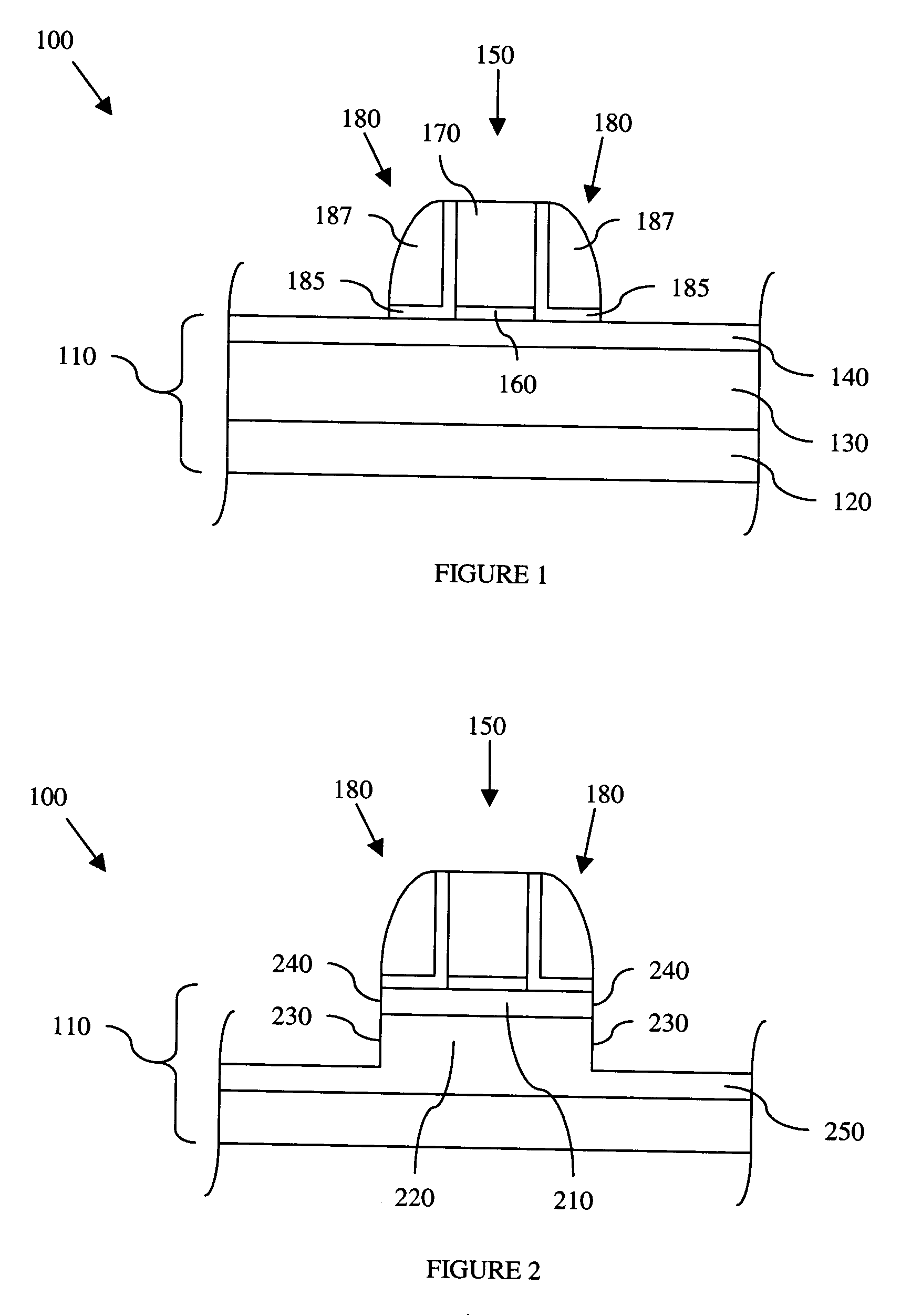

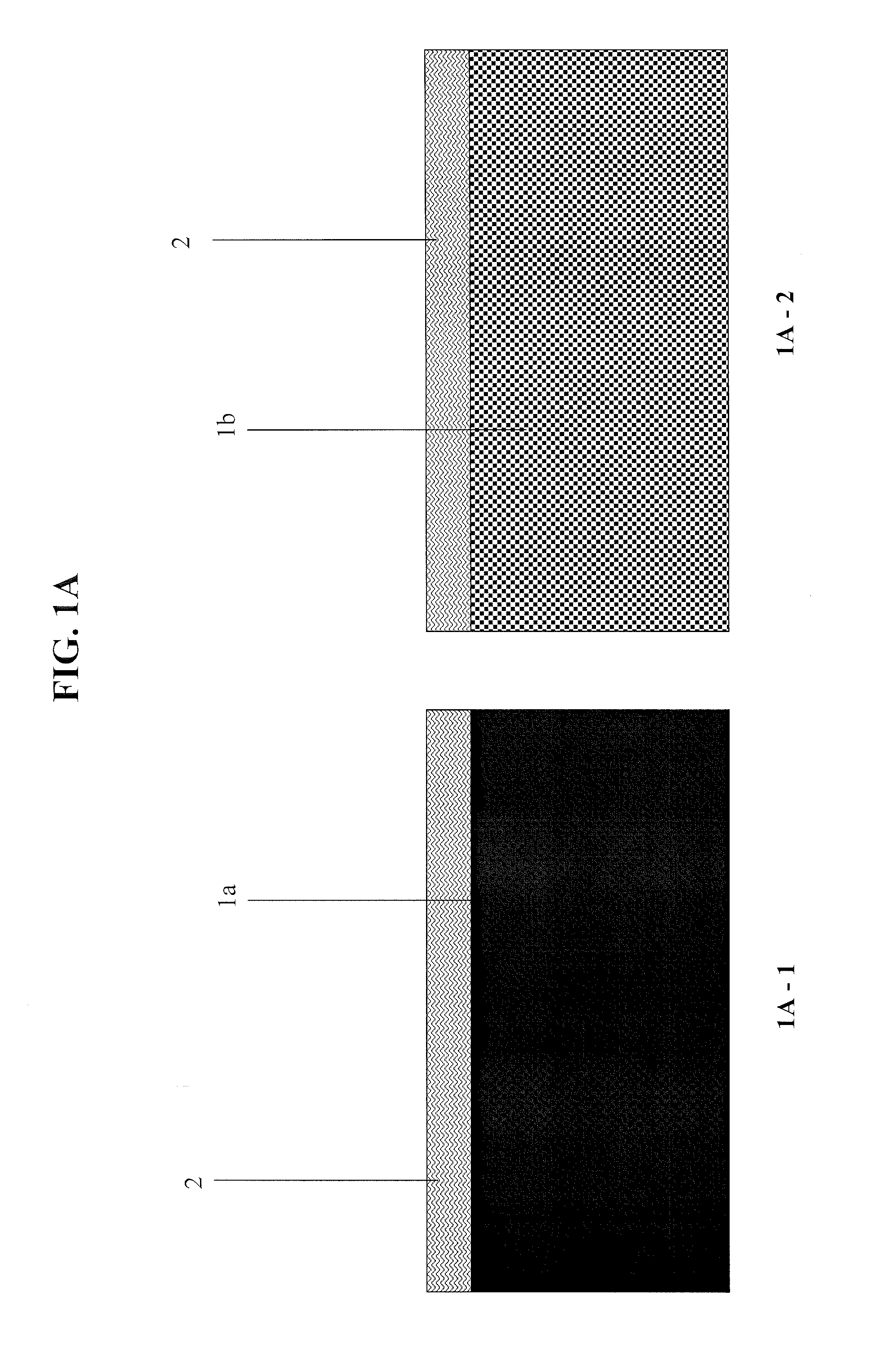

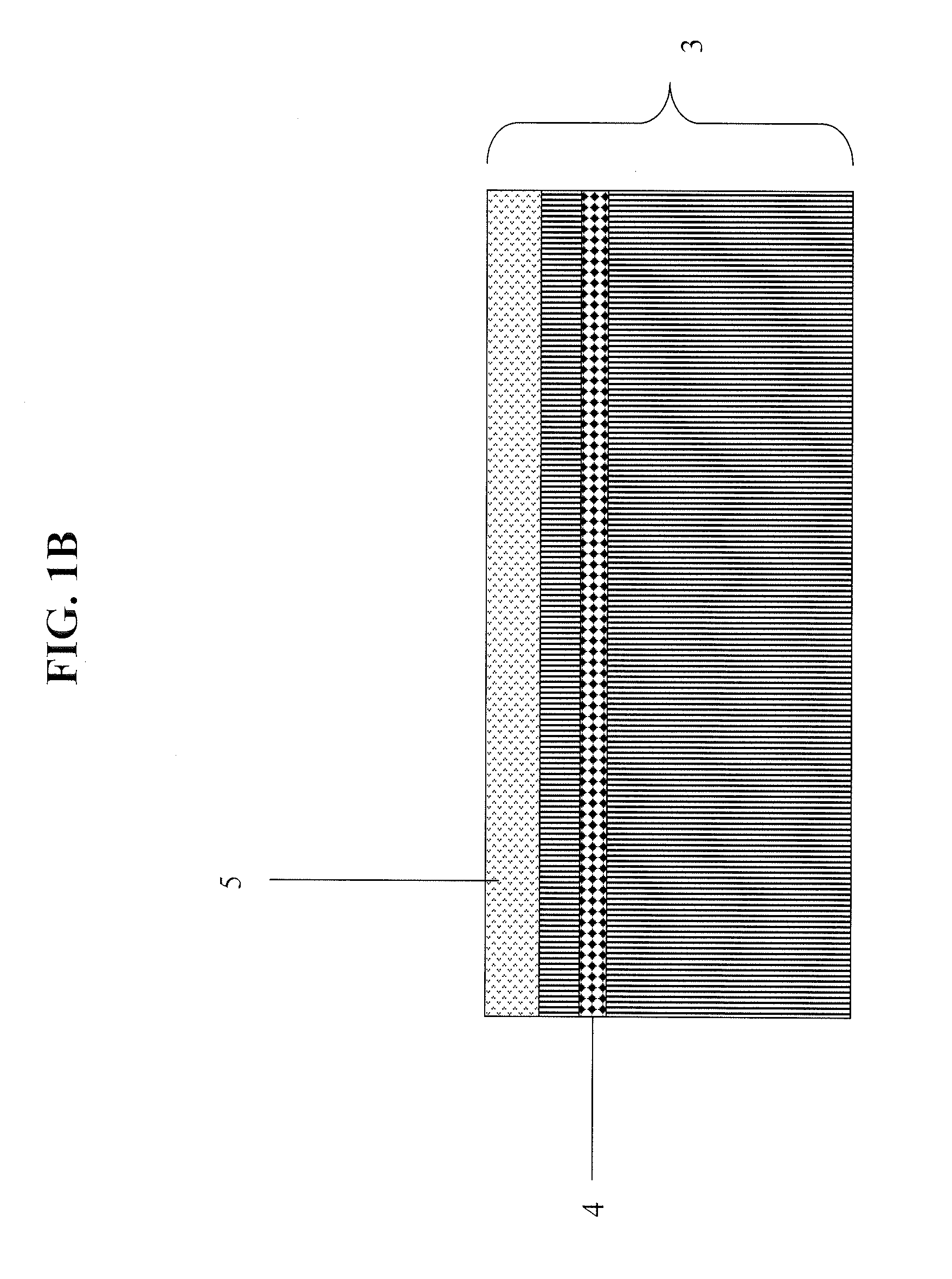

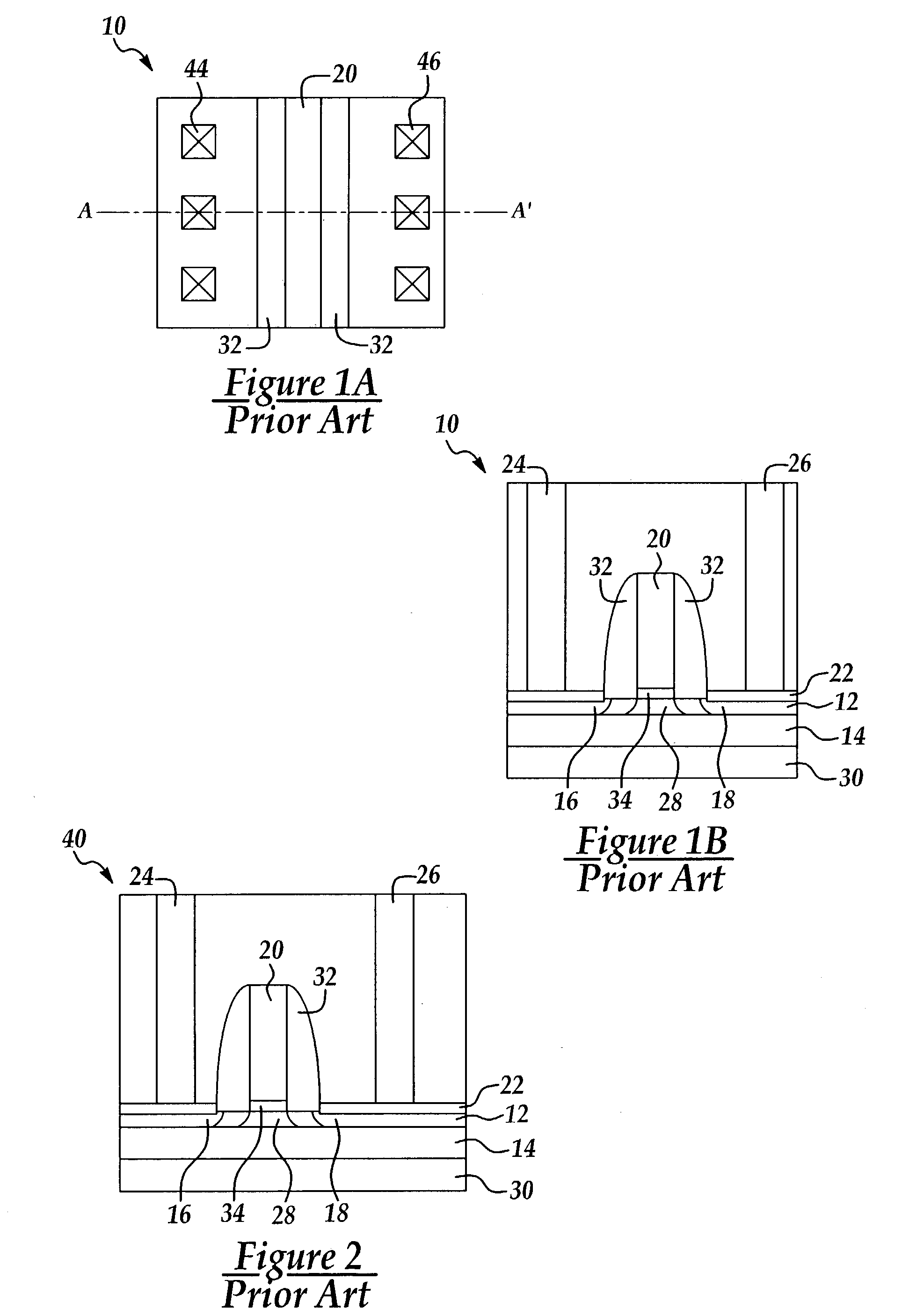

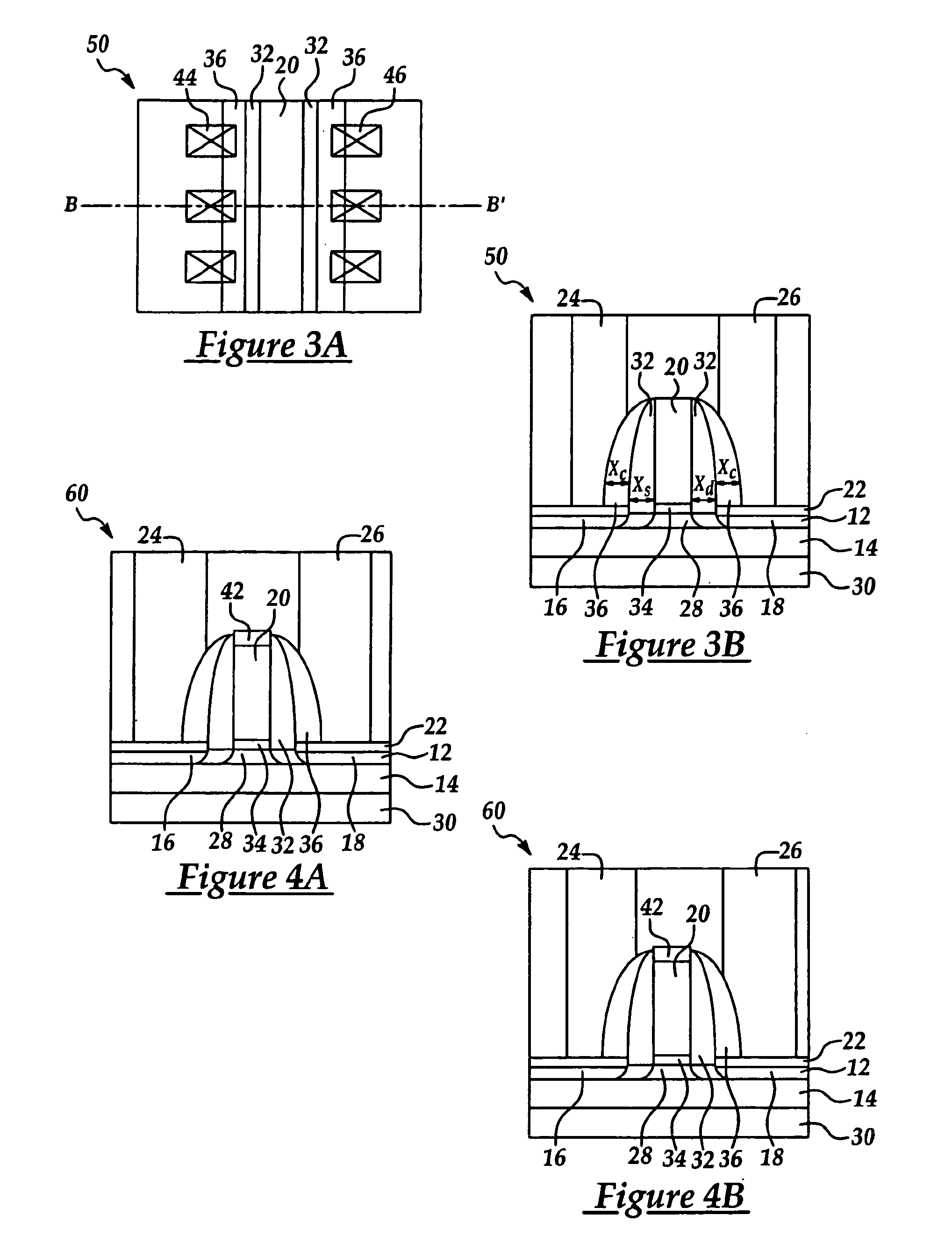

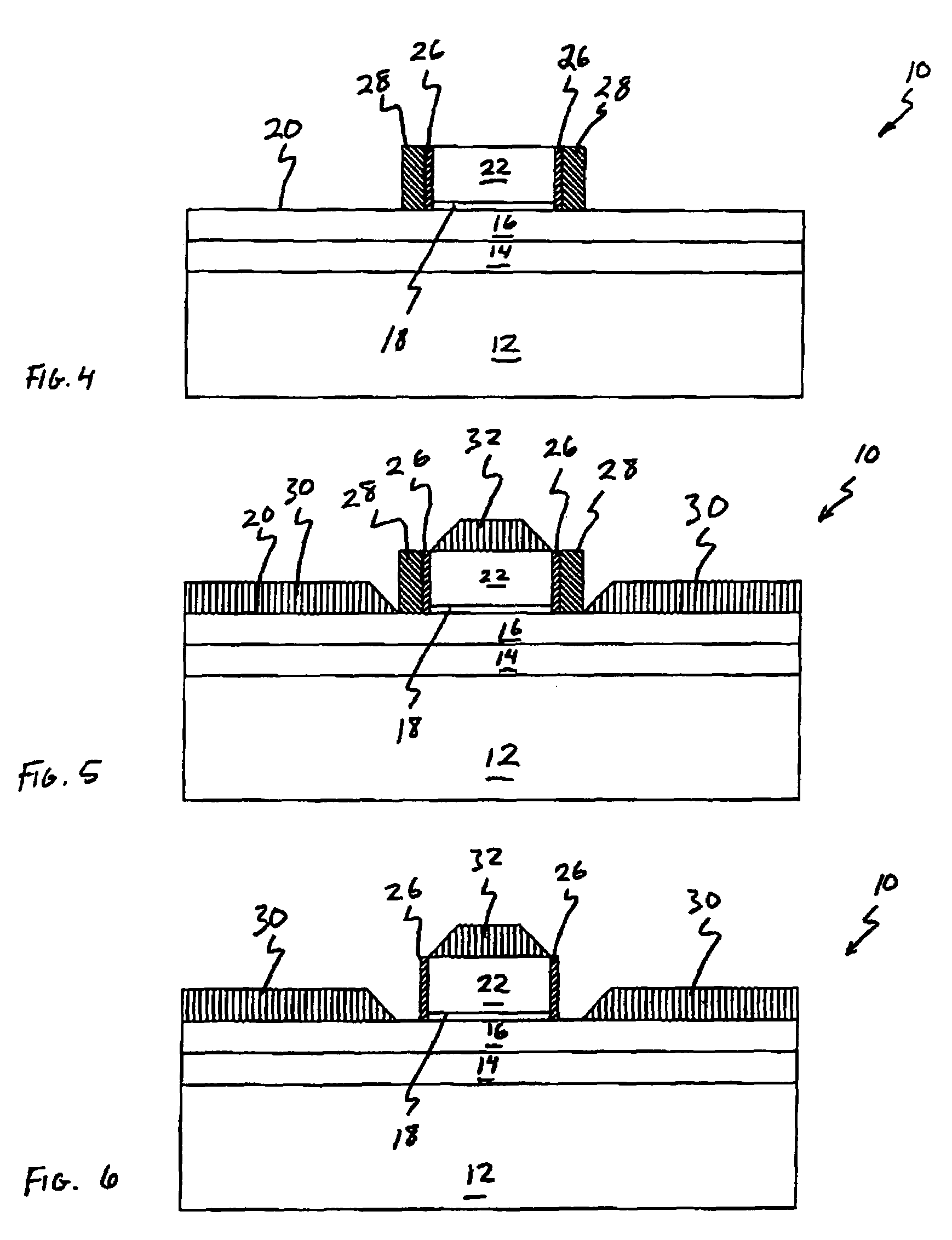

A method of manufacture of a Super Steep Retrograde Well Field Effect Transistor device starts with an SOI layer formed on a substrate, e.g. a buried oxide layer. Thin the SOI layer to form an ultra-thin SOI layer. Form an isolation trench separating the SOI layer into N and P ground plane regions. Dope the N and P ground plane regions formed from the SOI layer with high levels of N-type and P-type dopant. Form semiconductor channel regions above the N and P ground plane regions. Form FET source and drain regions and gate electrode stacks above the channel regions. Optionally form a diffusion retarding layer between the SOI ground plane regions and the channel regions.

Owner:GLOBALFOUNDRIES US INC

Ultra-thin body super-steep retrograde well (SSRW) FET devices

ActiveUS7002214B1Reduce capacitanceReduce junctionSolid-state devicesSemiconductor/solid-state device manufacturingDopantGround plane

A method of manufacture of a Super Steep Retrograde Well Field Effect Transistor device starts with an SOI layer formed on a substrate, e.g. a buried oxide layer. Thin the SOI layer to form an ultra-thin SOI layer. Form an isolation trench separating the SOI layer into N and P ground plane regions. Dope the N and P ground plane regions formed from the SOI layer with high levels of N-type and P-type dopant. Form semiconductor channel regions above the N and P ground plane regions. Form FET source and drain regions and gate electrode stacks above the channel regions. Optionally form a diffusion retarding layer between the SOI ground plane regions and the channel regions.

Owner:GLOBALFOUNDRIES US INC

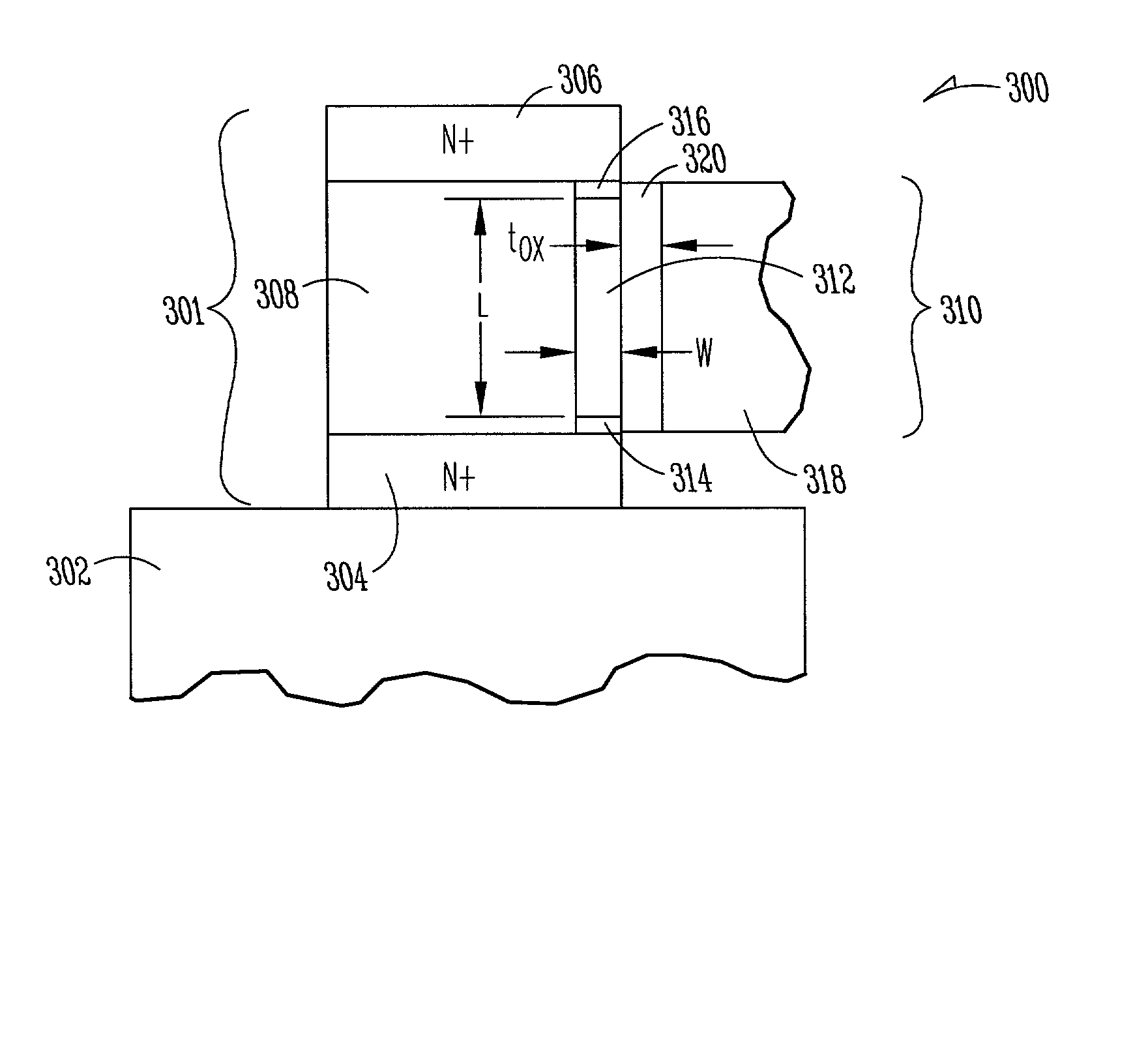

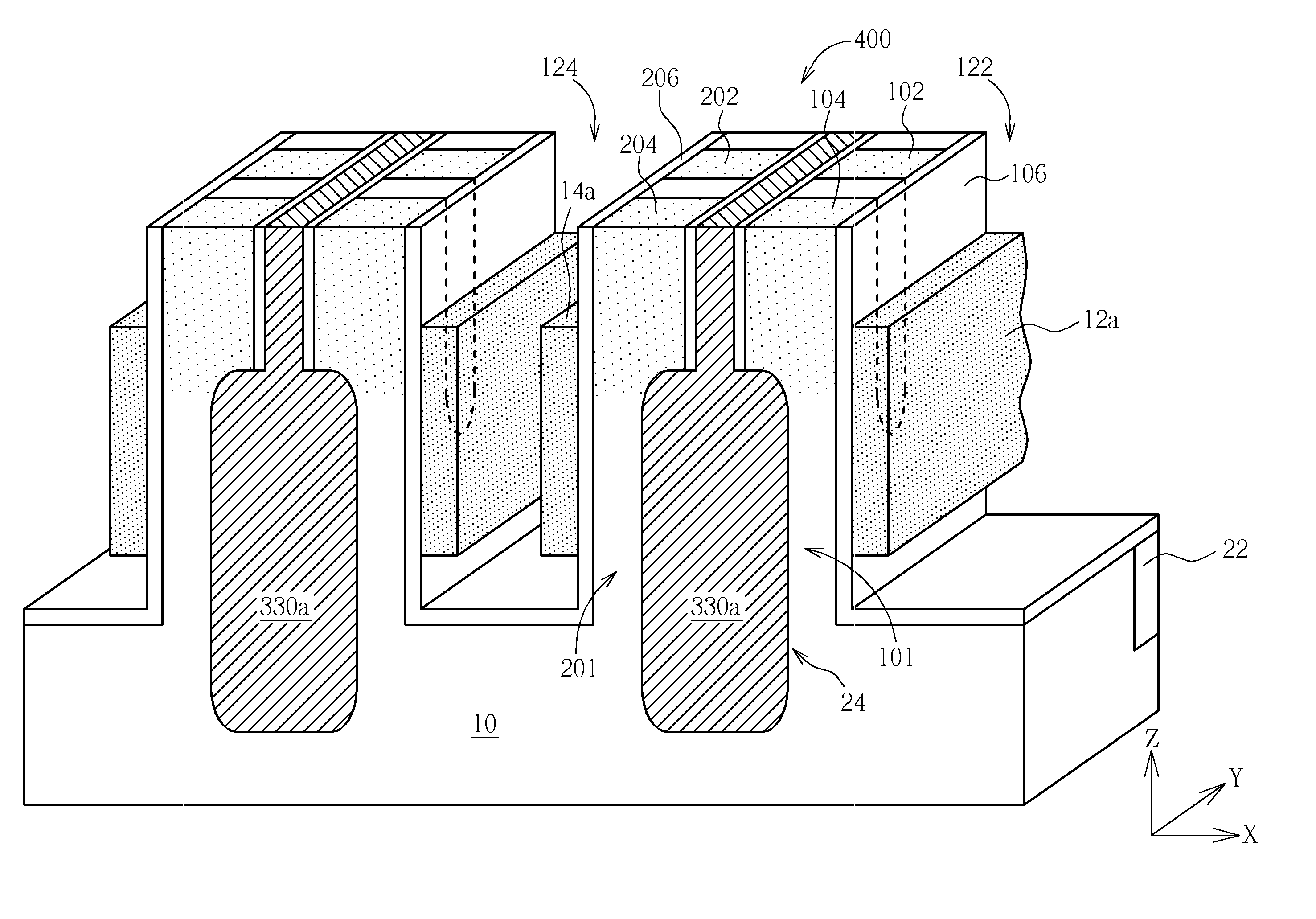

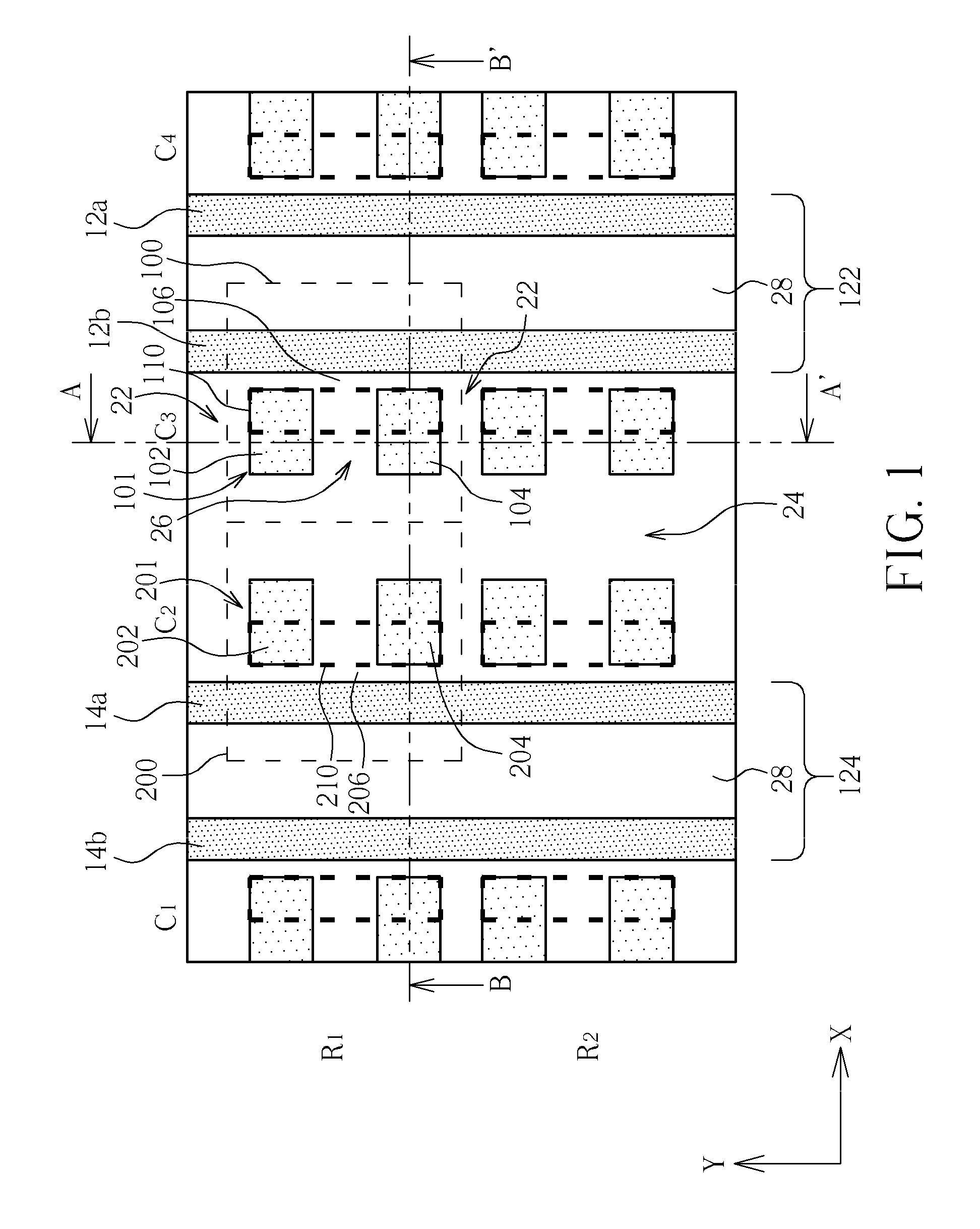

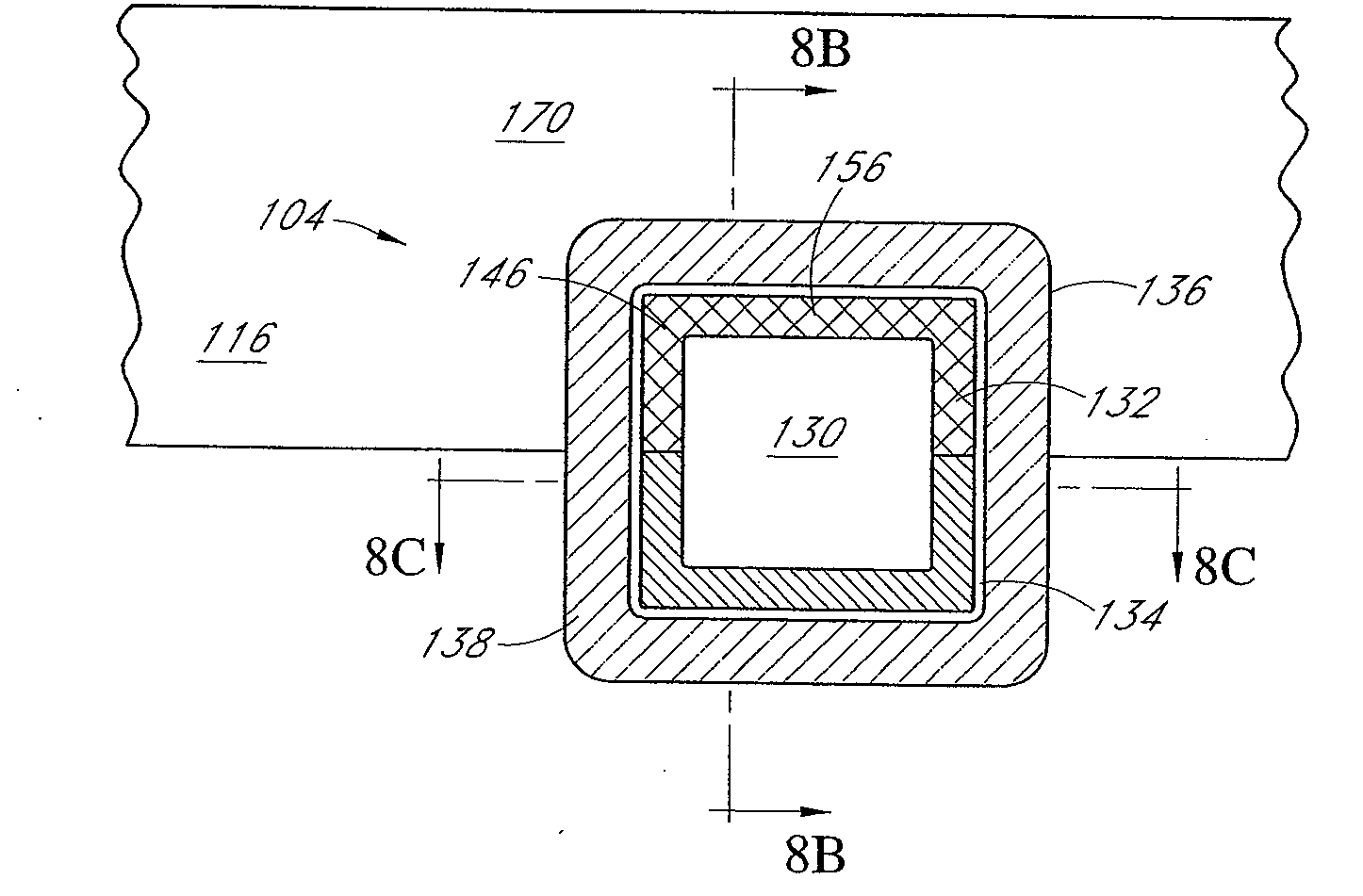

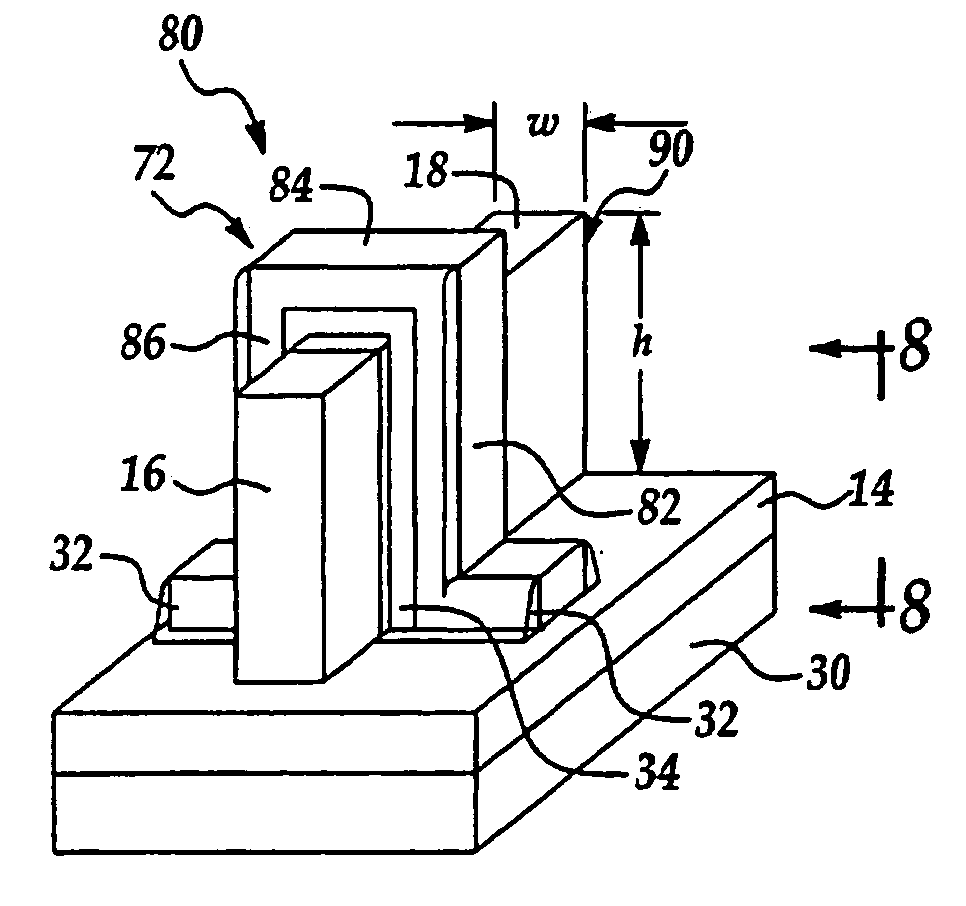

Surround gate access transistors with grown ultra-thin bodies

ActiveUS20070018206A1Satisfies needGood conductivitySolid-state devicesSemiconductor devicesLateral asymmetryBit line

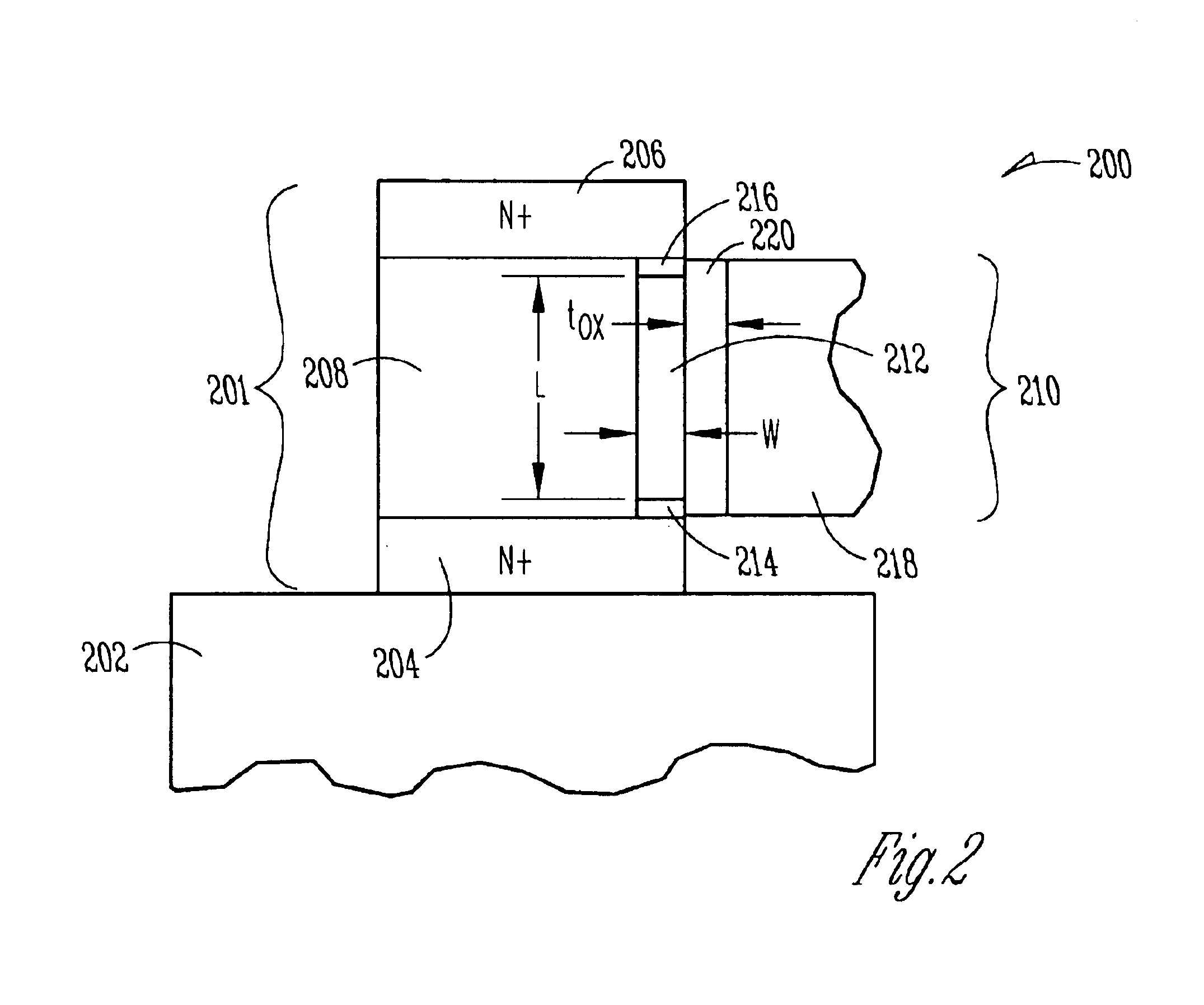

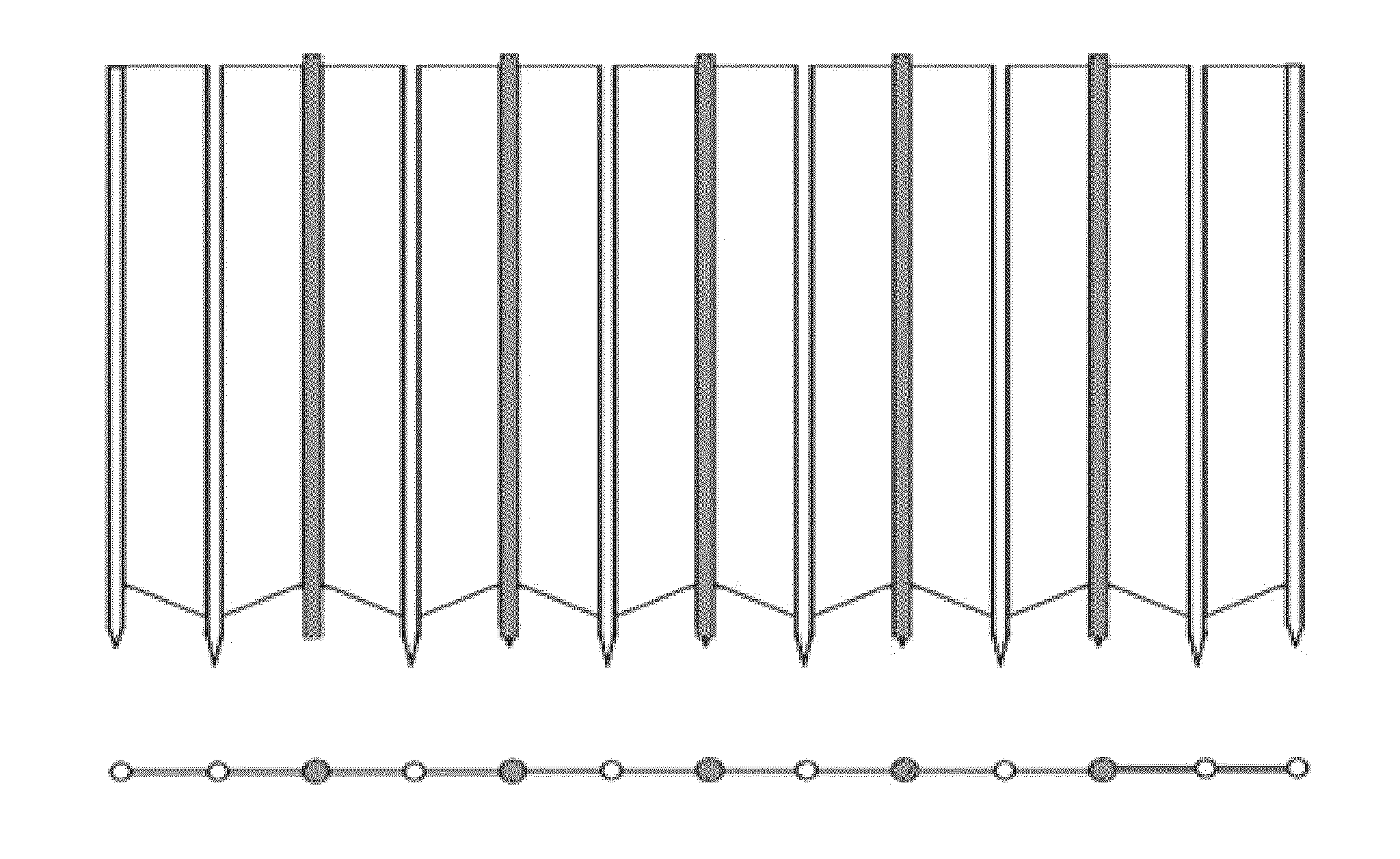

A vertical transistor having an annular transistor body surrounding a vertical pillar, which can be made from oxide. The transistor body can be grown by a solid phase epitaxial growth process to avoid difficulties with forming sub-lithographic structures via etching processes. The body has ultra-thin dimensions and provides controlled short channel effects with reduced need for high doping levels. Buried data / bit lines are formed in an upper surface of a substrate from which the transistors extend. The transistor can be formed asymmetrically or offset with respect to the data / bit lines. The offset provides laterally asymmetric source regions of the transistors. Continuous conductive paths are provided in the data / bit lines which extend adjacent the source regions to provide better conductive characteristics of the data / bit lines, particularly for aggressively scaled processes.

Owner:MICRON TECH INC

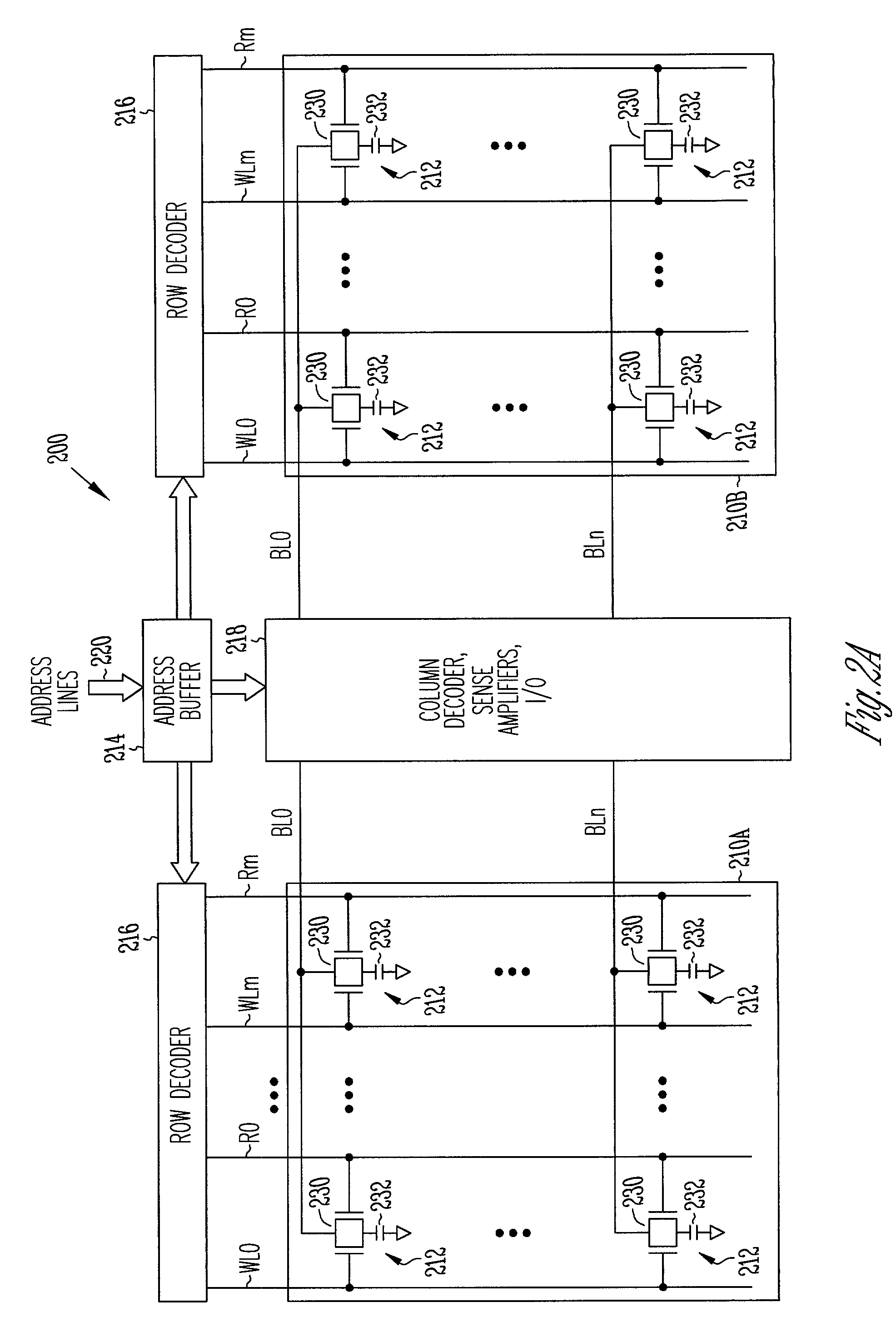

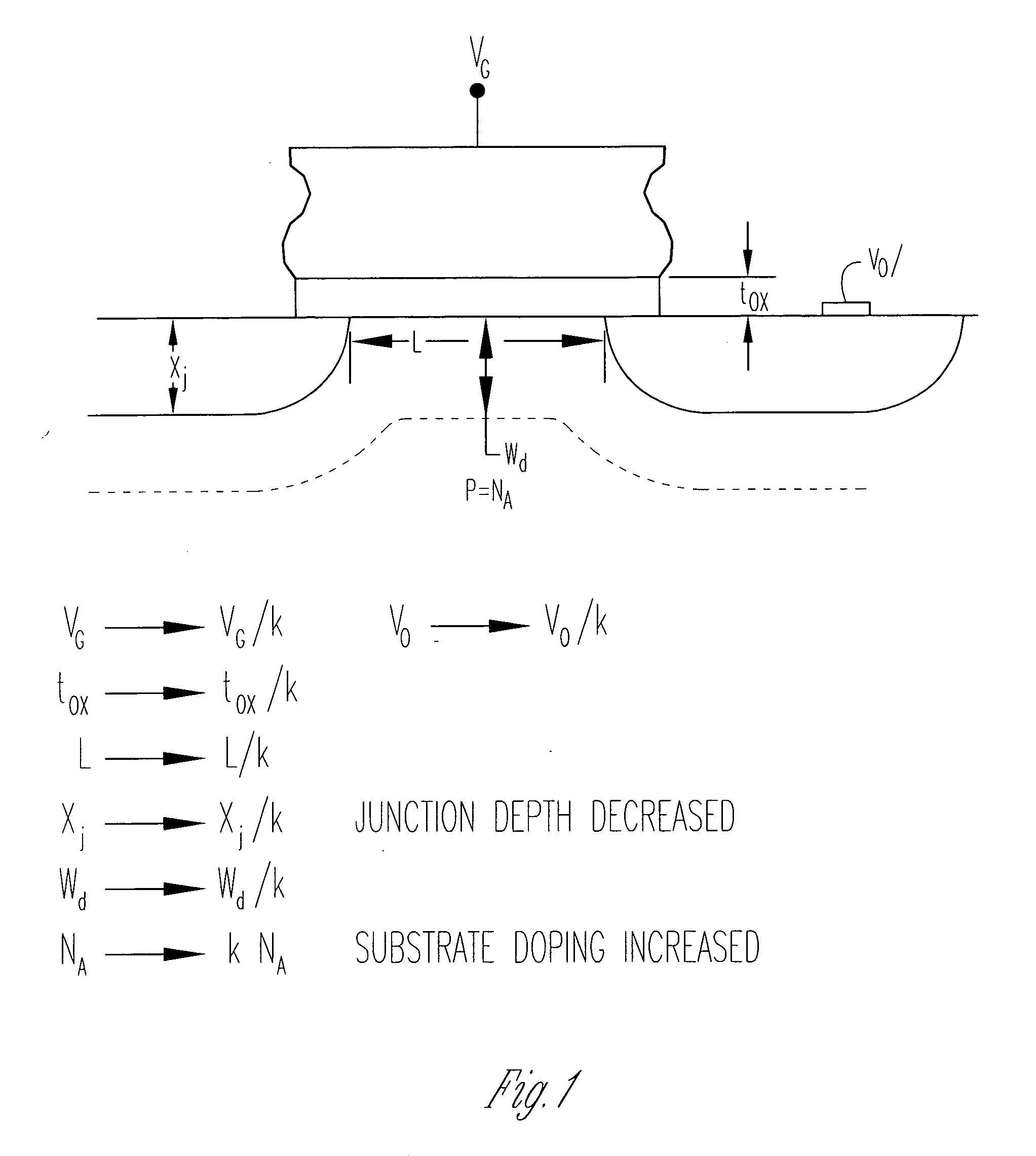

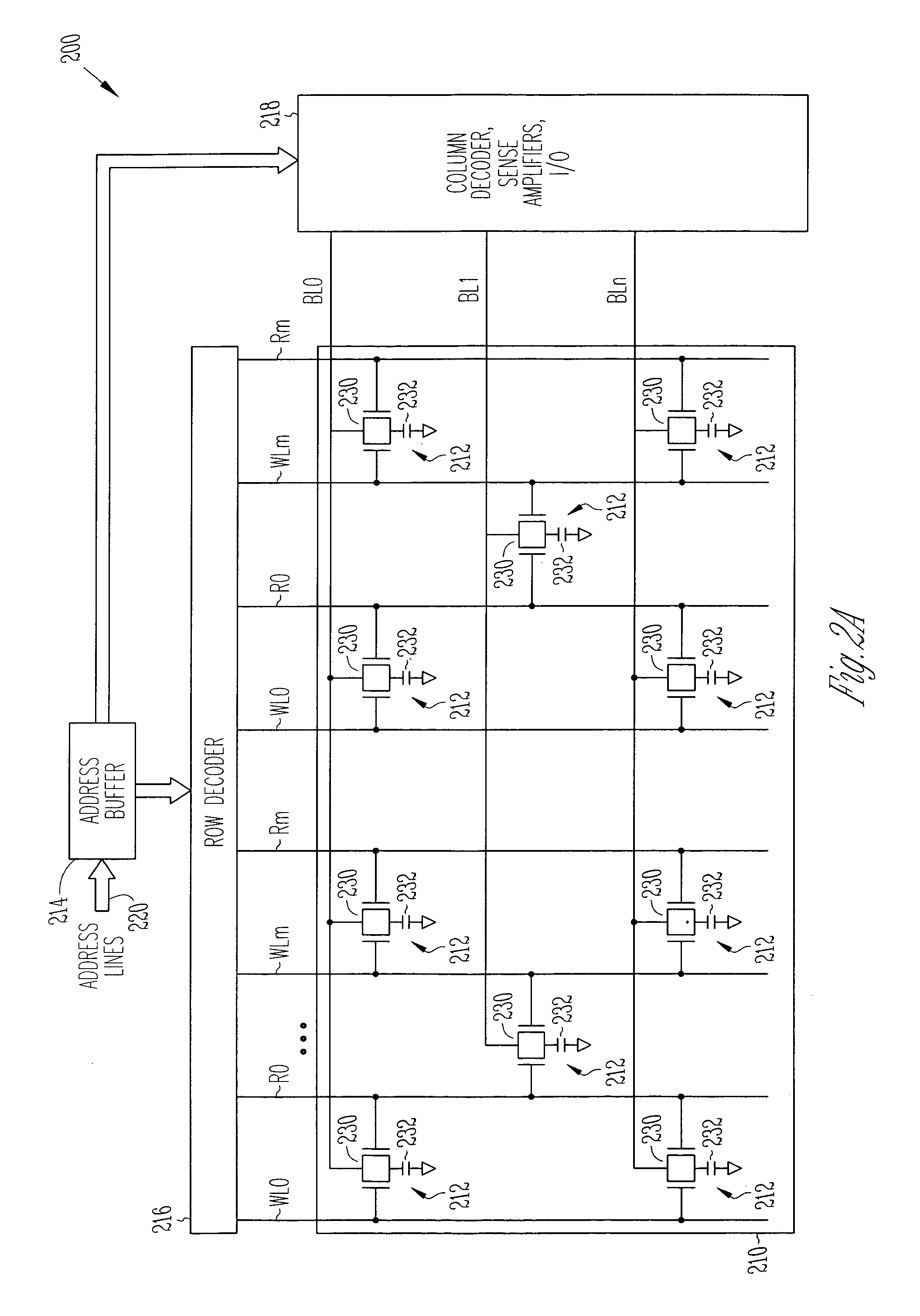

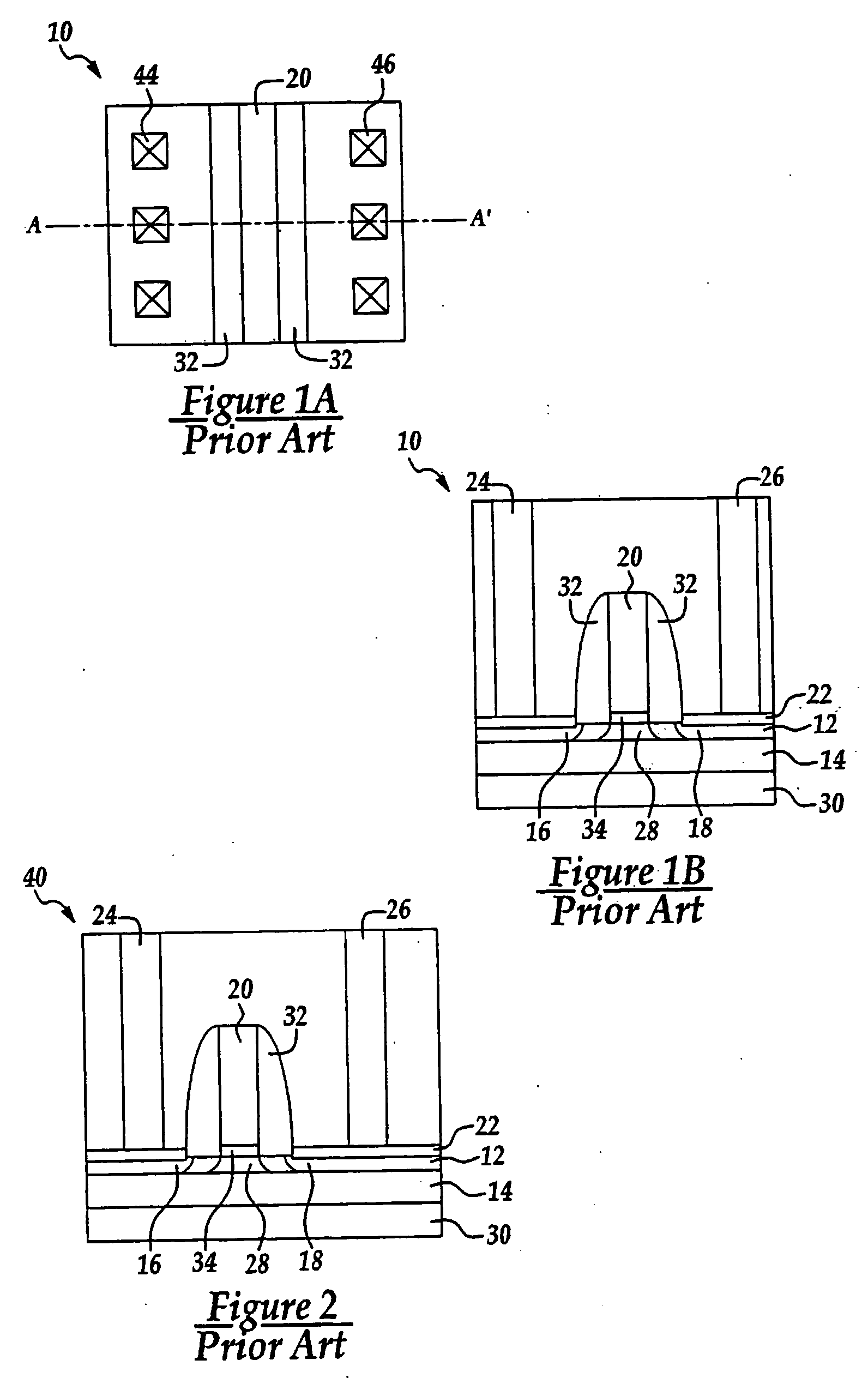

Open bit line dram with ultra thin body transistors

InactiveUS20020109176A1High and high density requirementMaintain performance advantageTransistorSolid-state devicesBit lineSingle crystal

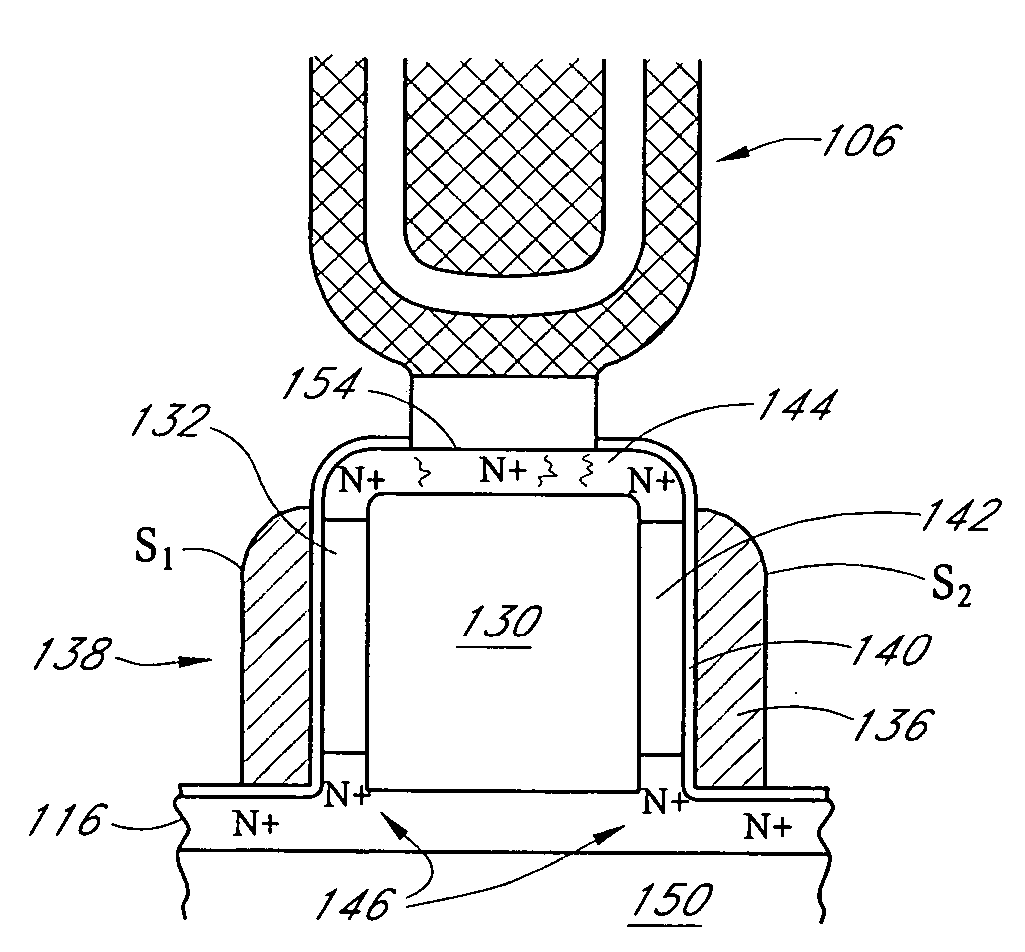

Structures and method for an open bit line DRAM device are provided. The open bit line DRAM device includes an array of memory cells. Each memory cell in the array of memory cells includes a pillar extending outwardly from a semiconductor substrate. The pillar includes a single crystalline first contact layer and a single crystalline second contact layer separated by an oxide layer. In each memory cell a single crystalline vertical transistor is formed along side of the pillar. The single crystalline vertical transistor includes an ultra thin single crystalline vertical first source / drain region coupled to the first contact layer, an ultra thin single crystalline vertical second source / drain region coupled to the second contact layer, an ultra thin single crystalline vertical body region which opposes the oxide layer and couples the first and the second source / drain regions, and a gate opposing the vertical body region and separated therefrom by a gate oxide. A plurality of buried bit lines are formed of single crystalline semiconductor material and disposed below the pillars in the array memory cells for interconnecting with the first contact layer of column adjacent pillars in the array of memory cells. Also, a plurality of word lines are included. Each word line is disposed orthogonally to the plurality of buried bit lines in a trench between rows of the pillars for addressing gates of the single crystalline vertical transistors that are adjacent to the trench.

Owner:MICRON TECH INC

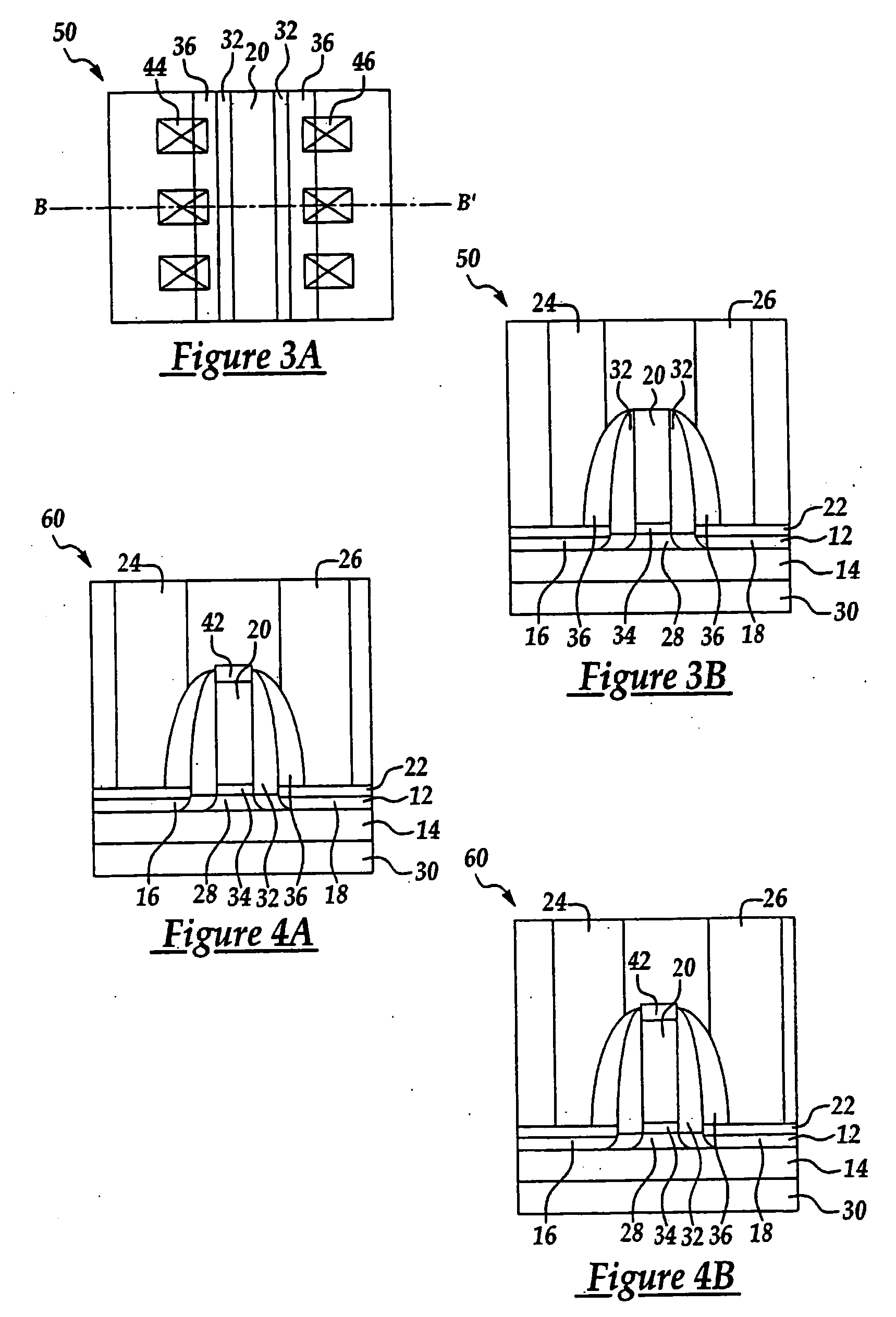

Folded bit line DRAM with vertical ultra thin body transistors

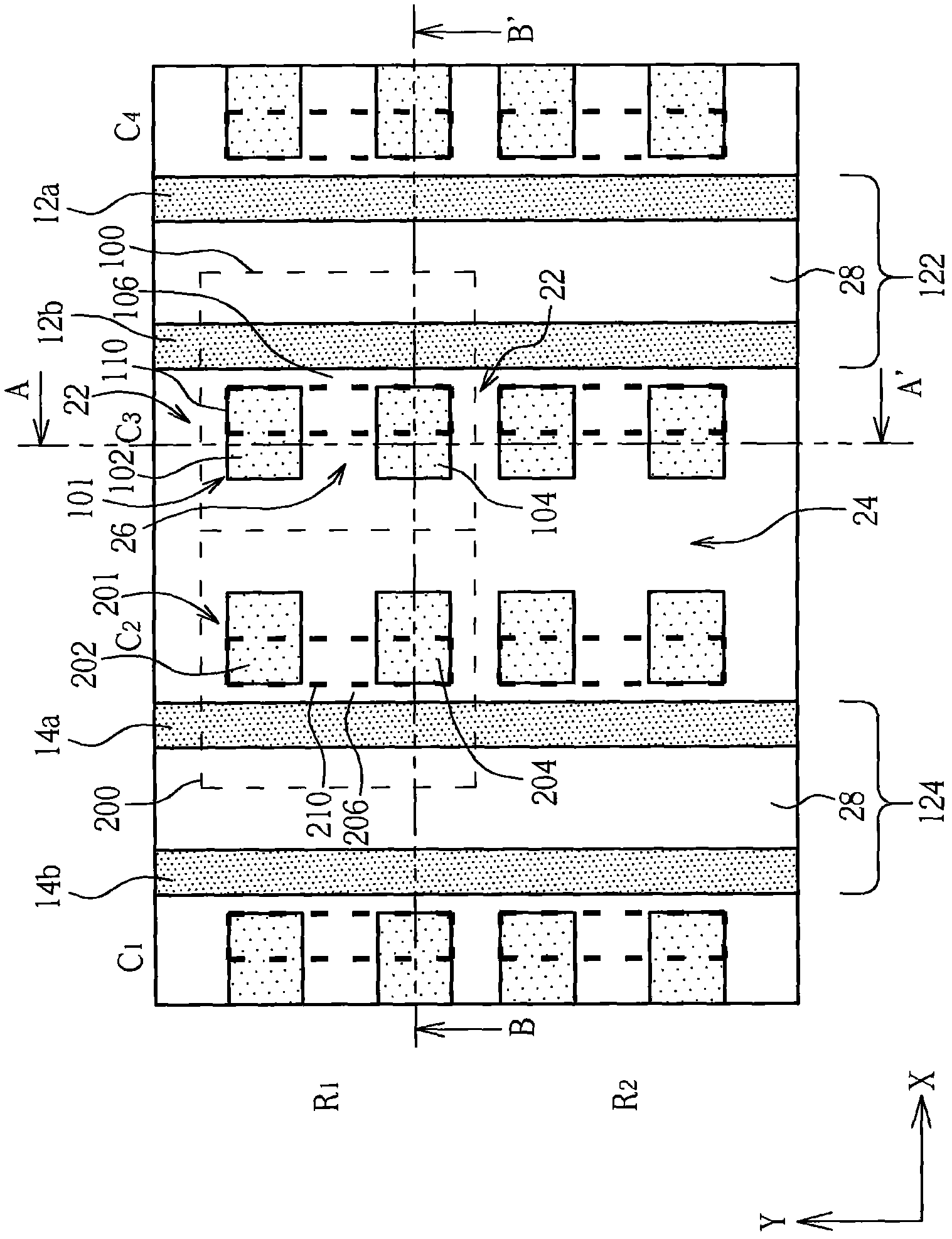

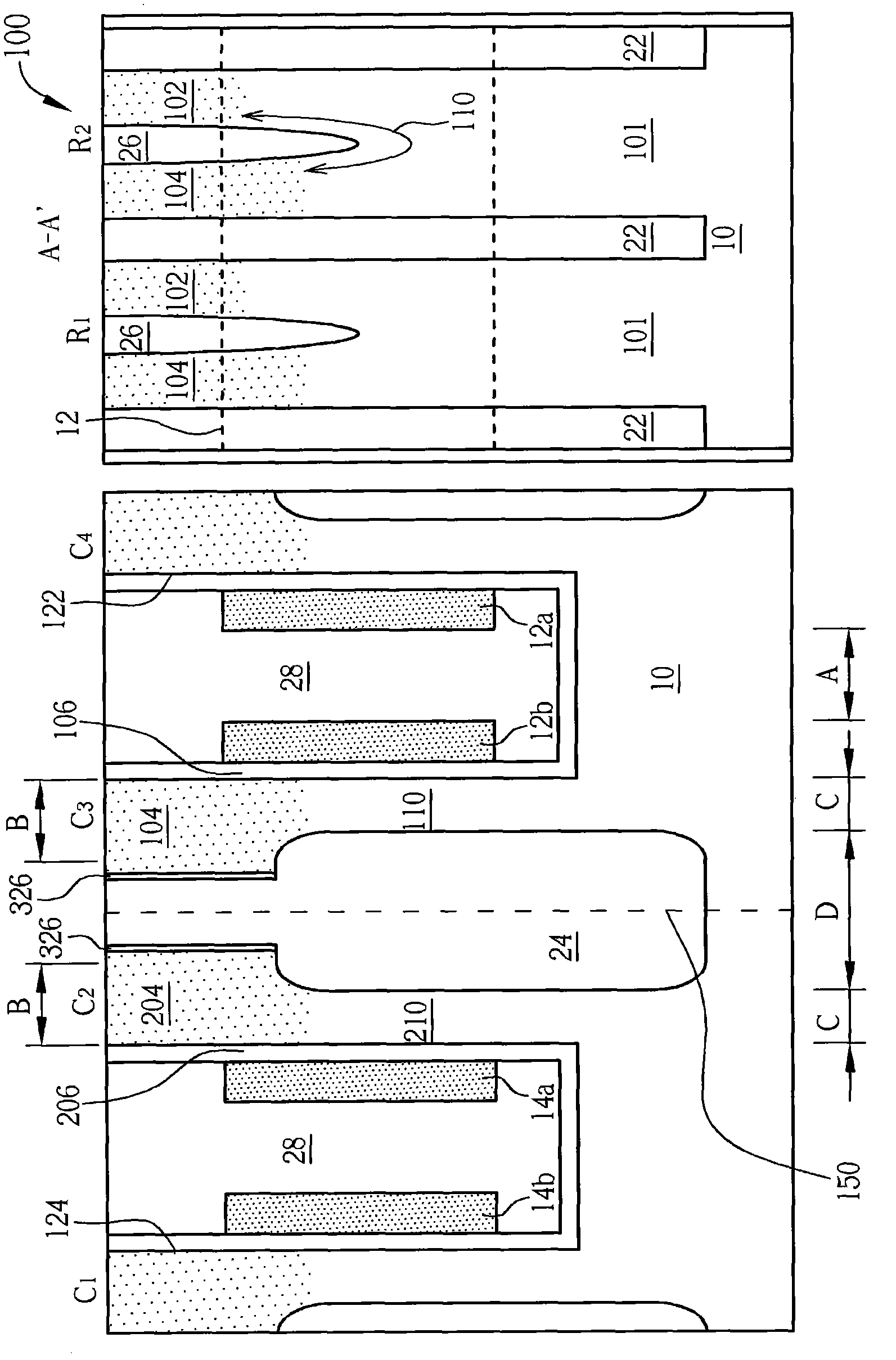

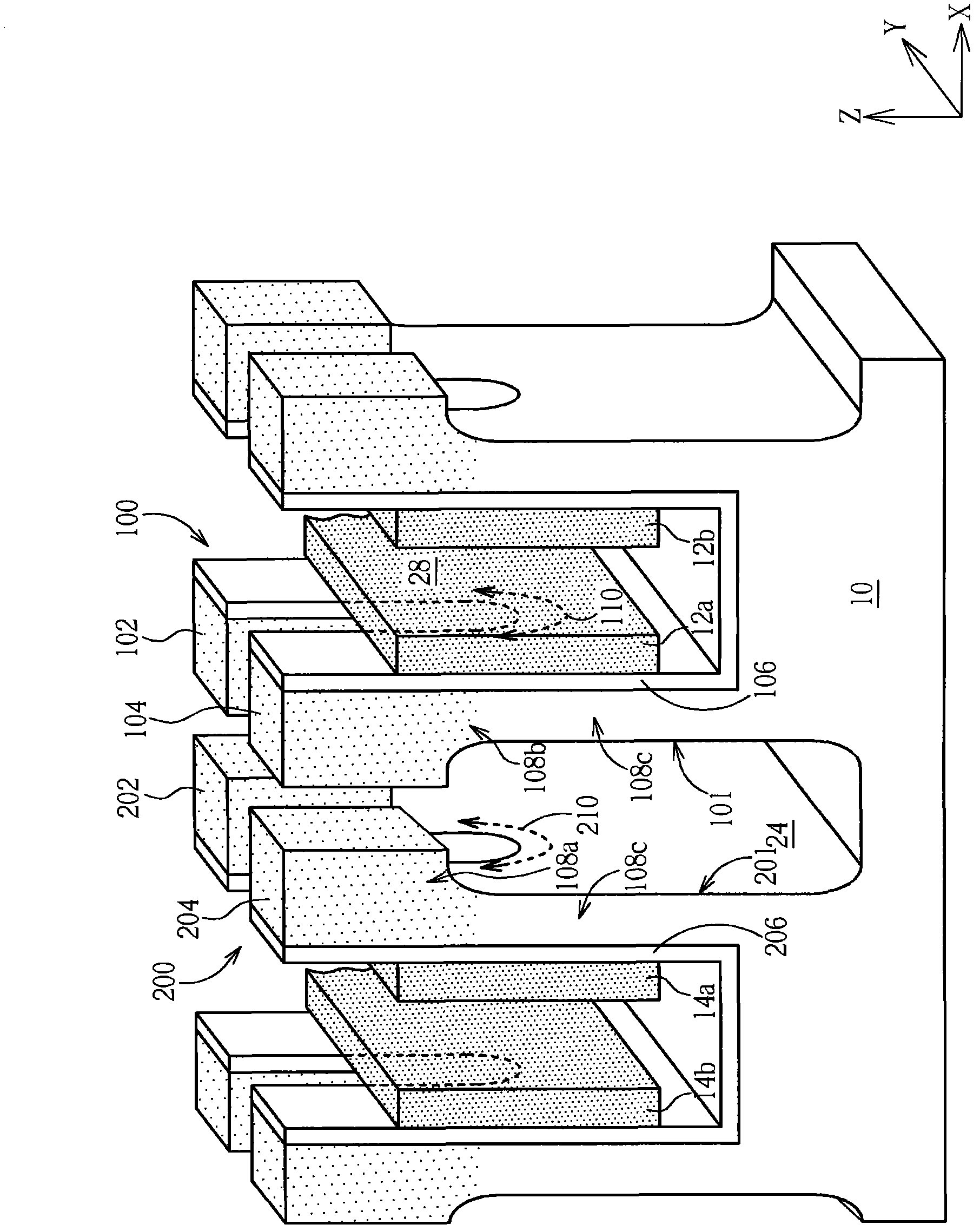

A folded bit line DRAM device is provided. The folded bit line DRAM device includes an array of memory cells. Each memory cell in the array of memory cells includes a pillar extending outwardly from a semiconductor substrate. Each pillar includes a single crystalline first contact layer and a single crystalline second contact layer separated by an oxide layer. A single crystalline vertical transistor is formed along alternating sides of the pillar within a row of pillars. The single crystalline vertical transistor includes an ultra thin single crystalline vertical first source / drain region coupled to the first contact layer, an ultra thin single crystalline vertical second source / drain region coupled to the second contact layer, and an ultra thin single crystalline vertical body region which opposes the oxide layer and couples the first and the second source / drain regions. A plurality of buried bit lines are formed of single crystalline semiconductor material and disposed below the pillars in the array memory cells for interconnecting with the first contact layer of column adjacent pillars in the array of memory cells. Further, a plurality of word lines are included. Each word line is disposed orthogonally to the plurality of buried bit lines in a trench between rows of the pillars for addressing alternating body regions of the single crystalline vertical transistors that are adjacent to the trench.

Owner:MICRON TECH INC

DRAM tunneling access transistor

Owner:MICRON TECH INC

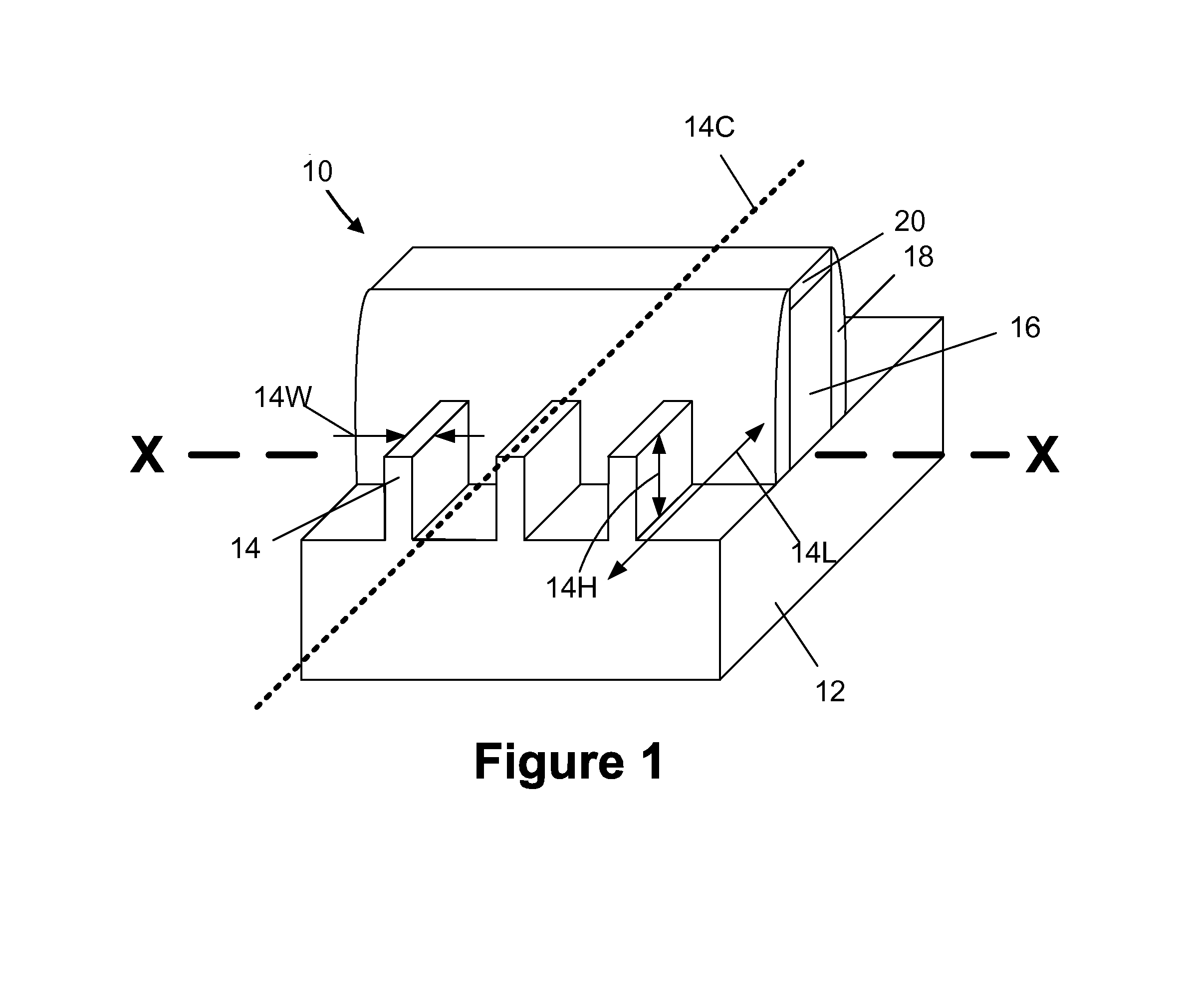

Single-gate finfet and fabrication method thereof

InactiveUS20110298041A1Resolving and eliminating coupling effectSolid-state devicesSemiconductor devicesUltra thin bodyEngineering

A single-gate FinFET structure includes an active fin structure having two enlarged head portions and two respective tapered neck portions that connect the enlarged head portions with an underlying ultra-thin body. Two source / drain regions are doped in the two enlarged head portions respectively. An insulation region is interposed between the two source / drain regions. A trench isolation structure is disposed at one side of the tuning fork-shaped fin structure. A single-sided sidewall gate electrode is disposed on a vertical sidewall of the active fin structure opposite to the trench isolation structure.

Owner:NAN YA TECH

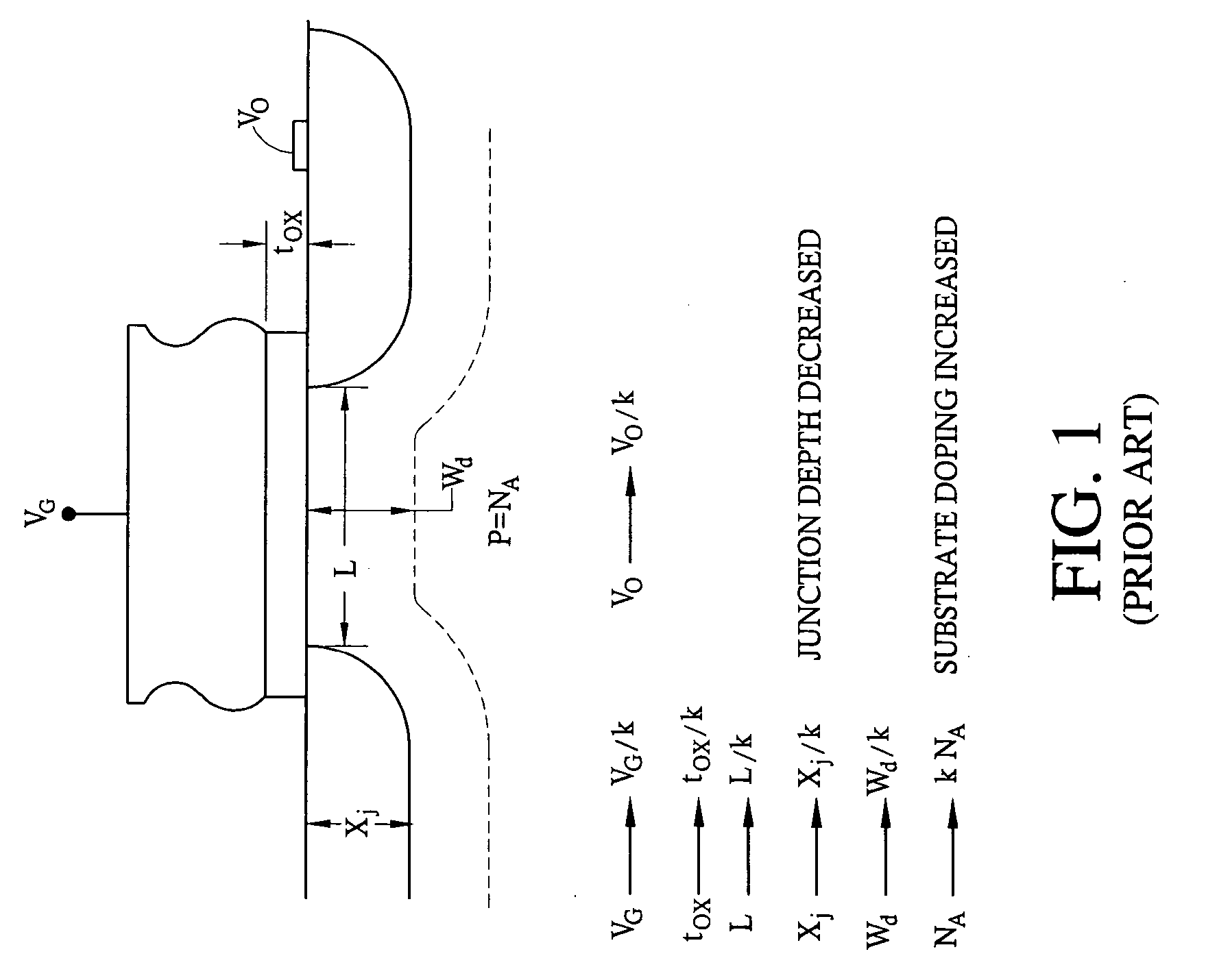

Ultra thin body fully-depleted SOI MOSFETs

InactiveUS7091069B2Easy to controlMinimizing threshold voltage variationSolid-state devicesSemiconductor/solid-state device manufacturingLength variationNitrogen

A method of creating ultra tin body fully-depleted SOI MOSFETs in which the SOI thickness changes with gate-length variations thereby minimizing the threshold voltage variations that are typically caused by SOI thickness and gate-length variations is provided. The method of present invention uses a replacement gate process in which nitrogen is implanted to selectively retard oxidation during formation of a recessed channel. A self-limited chemical oxide removal (COR) processing step can be used to improve the control in the recessed channel step. If the channel is doped, the inventive method is designed such that the thickness of the SOI layer is increased with shorter channel length. If the channel is undoped or counter-doped, the inventive method is designed such that the thickness of the SOI layer is decreased with shorter channel length.

Owner:GLOBALFOUNDRIES INC

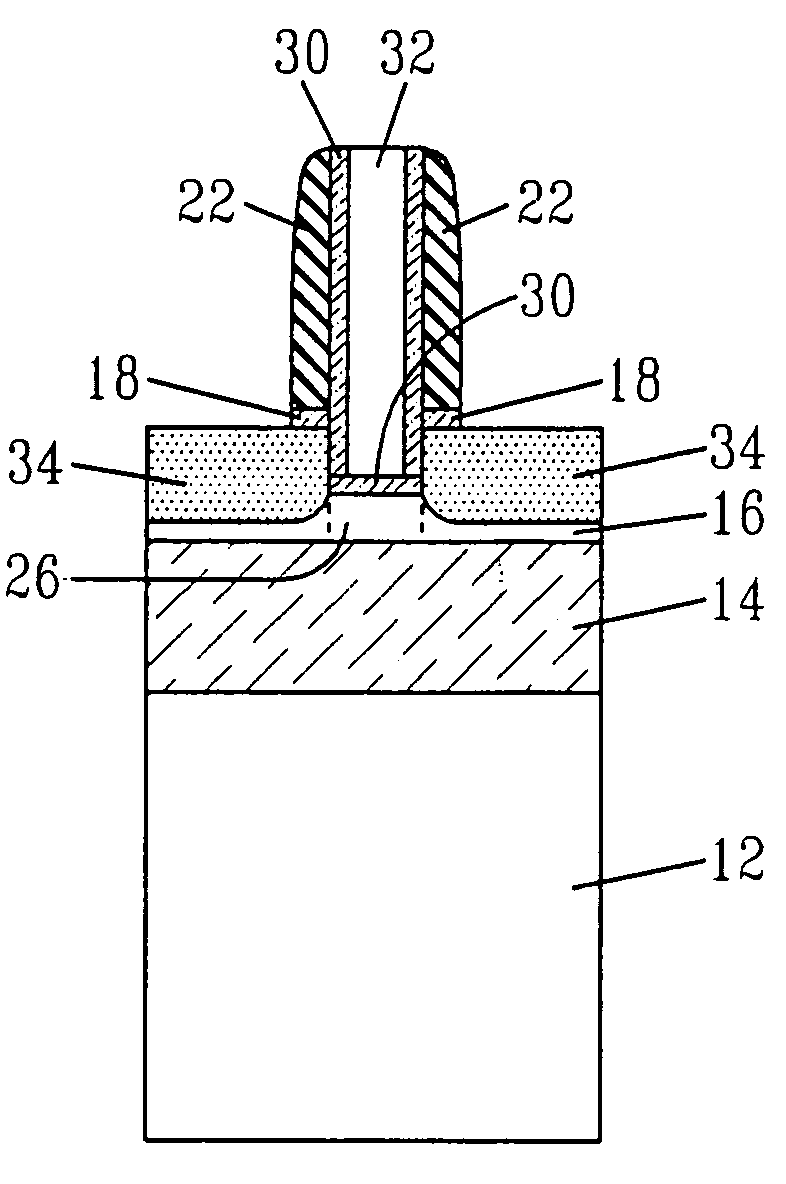

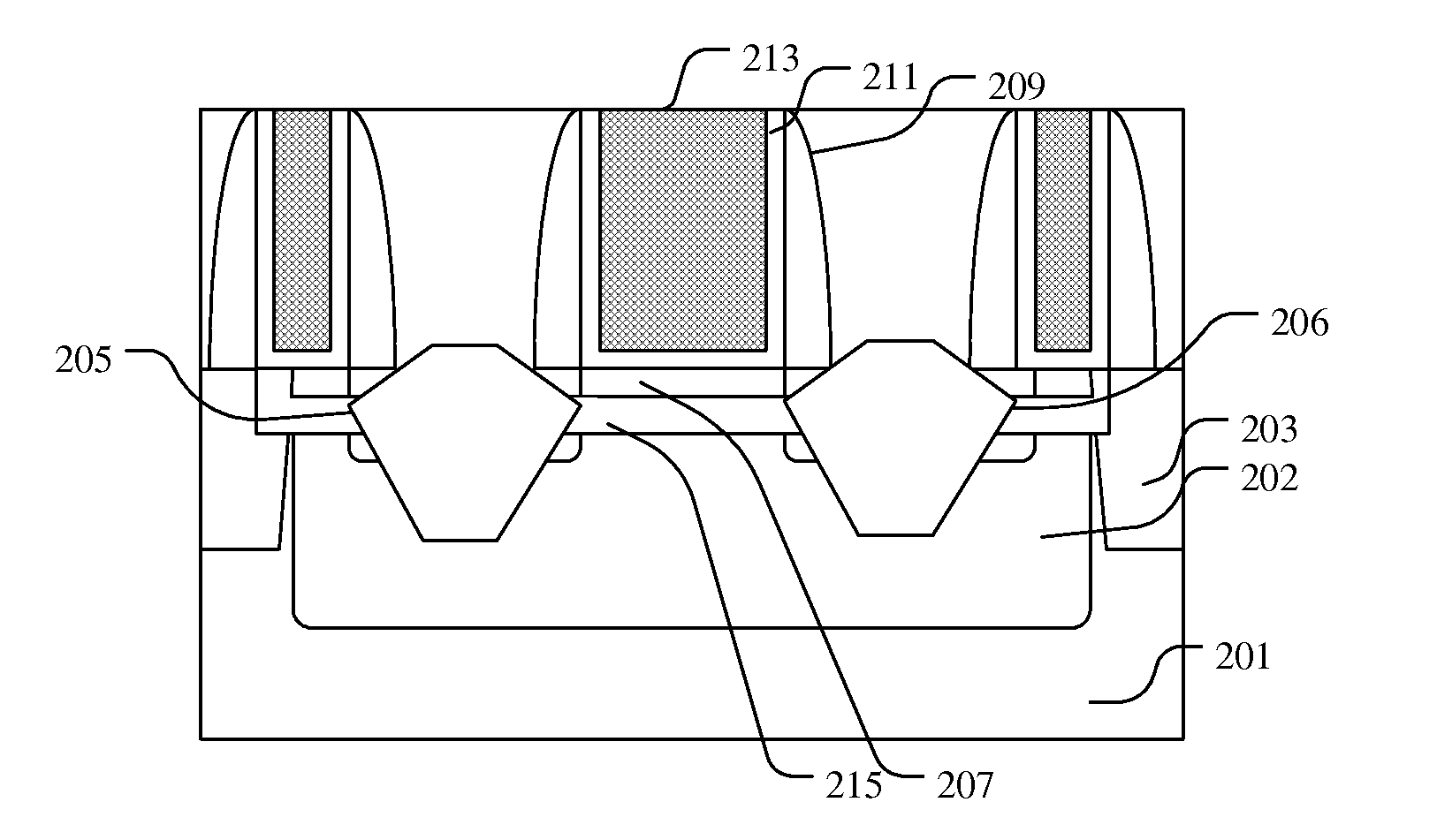

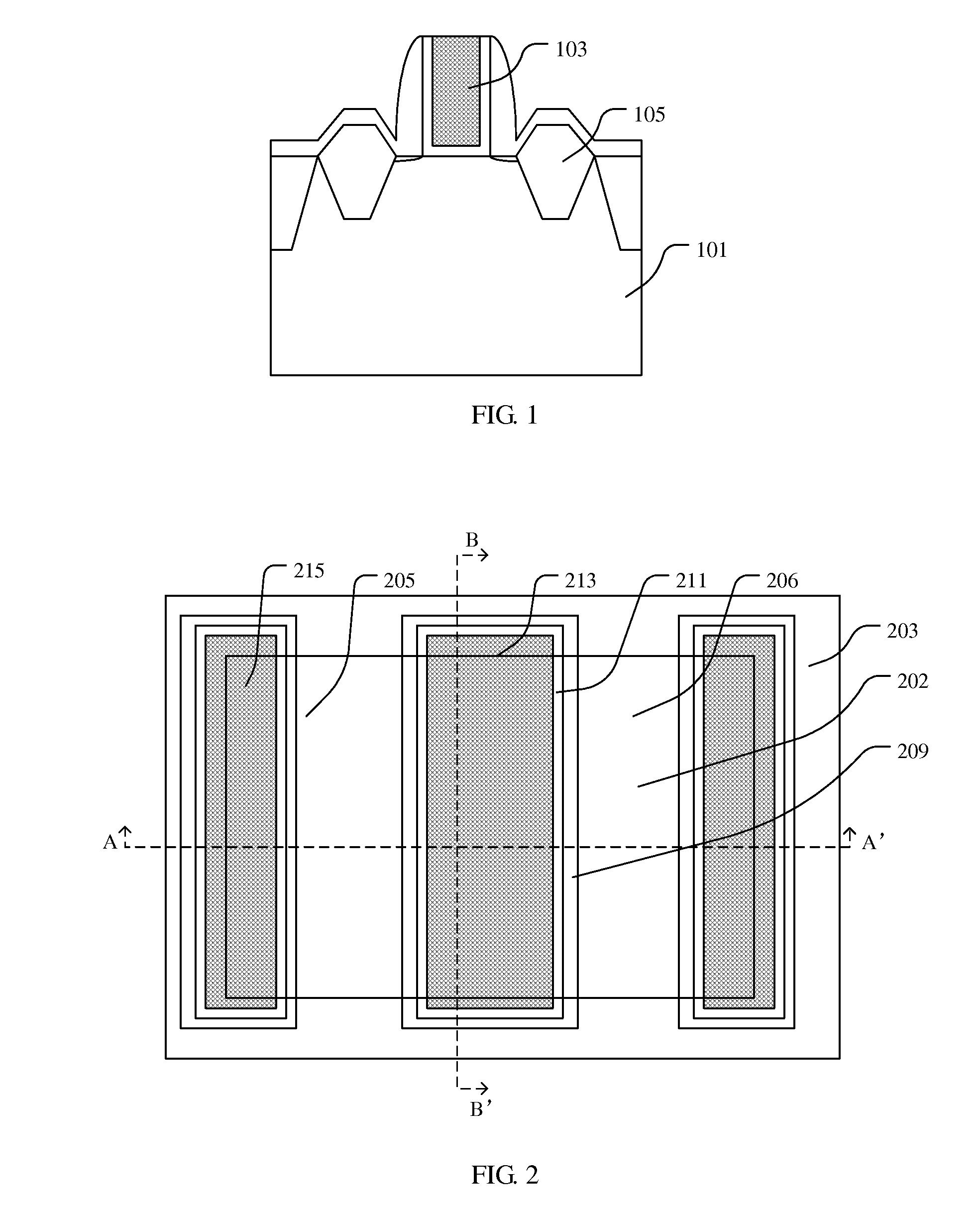

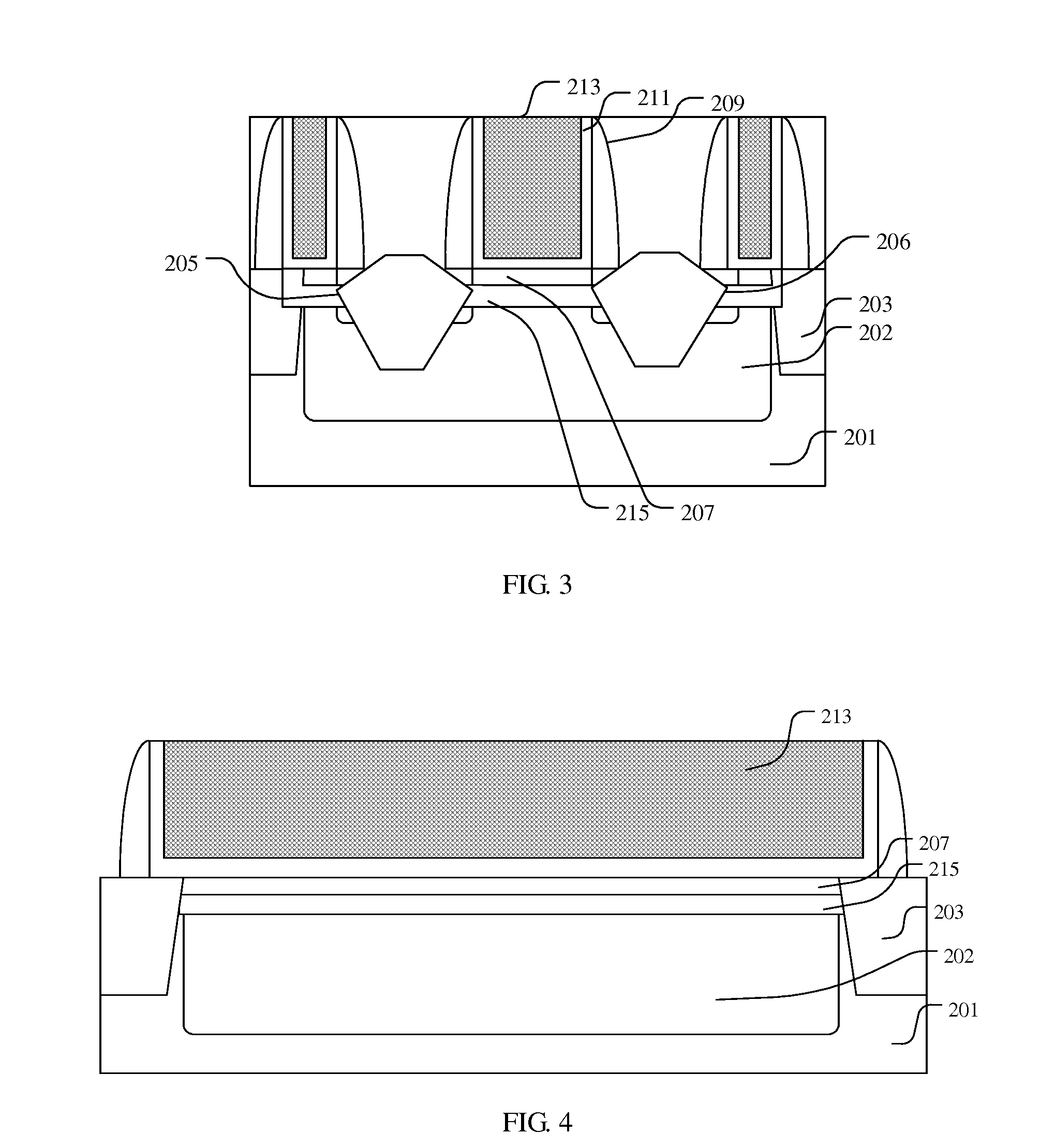

Ultra-thin body transistor and method for manufcturing the same

InactiveUS20120043624A1Decreases effect to effective lengthRegion of becomes thinSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricUltra thin body

An ultra-thin body transistor and a method for manufacturing an ultra-thin body transistor are disclosed. The ultra-thin body transistor comprises: a semiconductor substrate; a gate structure on the semiconductor substrate; and a source region and a drain region in the semiconductor substrate and on either side of the gate structure; in which the gate structure comprises a gate dielectric layer, a gate embedded in the gate dielectric layer, and a spacer on both sides of the gate; the ultra-thin body transistor further comprises: a body region and a buried insulated region located sequentially under the gate structure and in a well region; two ends of the body region and the buried insulated region are connected with the source region and the drain region respectively; and the body region is isolated from other regions in the well region by the buried insulated region under the body region. The ultra-thin body transistor has a thinner body region, which decreases the short channel effect. In the method for manufacturing an ultra-thin body transistor together with the replacement-gate process, the forming of the buried insulated region is self-aligned with the gate, which reduces the parasitic resistance under the spacer.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Programmable logic arrays with ultra thin body transistors

Structures and methods for programmable logic arrays are provided. In one embodiment, the programmable logic array includes a first logic plane and a second logic plane. The first logic plane receives a number of input signals. The first logic plane has a plurality of logic cells arranged in rows and columns that are interconnected to provide a number of logical outputs. The second logic plane has a number of logic cells arranged in rows and columns that receive the outputs of the first logic plane and that are interconnected to produce a number of logical outputs such that the programmable logic array implements a logical function. Each of the logic cells includes a vertical pillar extending outwardly from a semiconductor substrate. Each pillar includes a single crystalline first contact layer and a second contact layer separated by an oxide layer. Each logic cell further includes at least one single crystalline ultra thin vertical transistor that is selectively disposed adjacent the vertical pillar. The single crystalline vertical transistors have an ultra thin single crystalline vertical first source / drain region coupled to the first contact layer, an ultra thin single crystalline vertical second source / drain region coupled to the second contact layer; and an ultra thin single crystalline vertical body region which opposes the oxide layer and couples the first and the second source / drain regions.

Owner:MICRON TECH INC

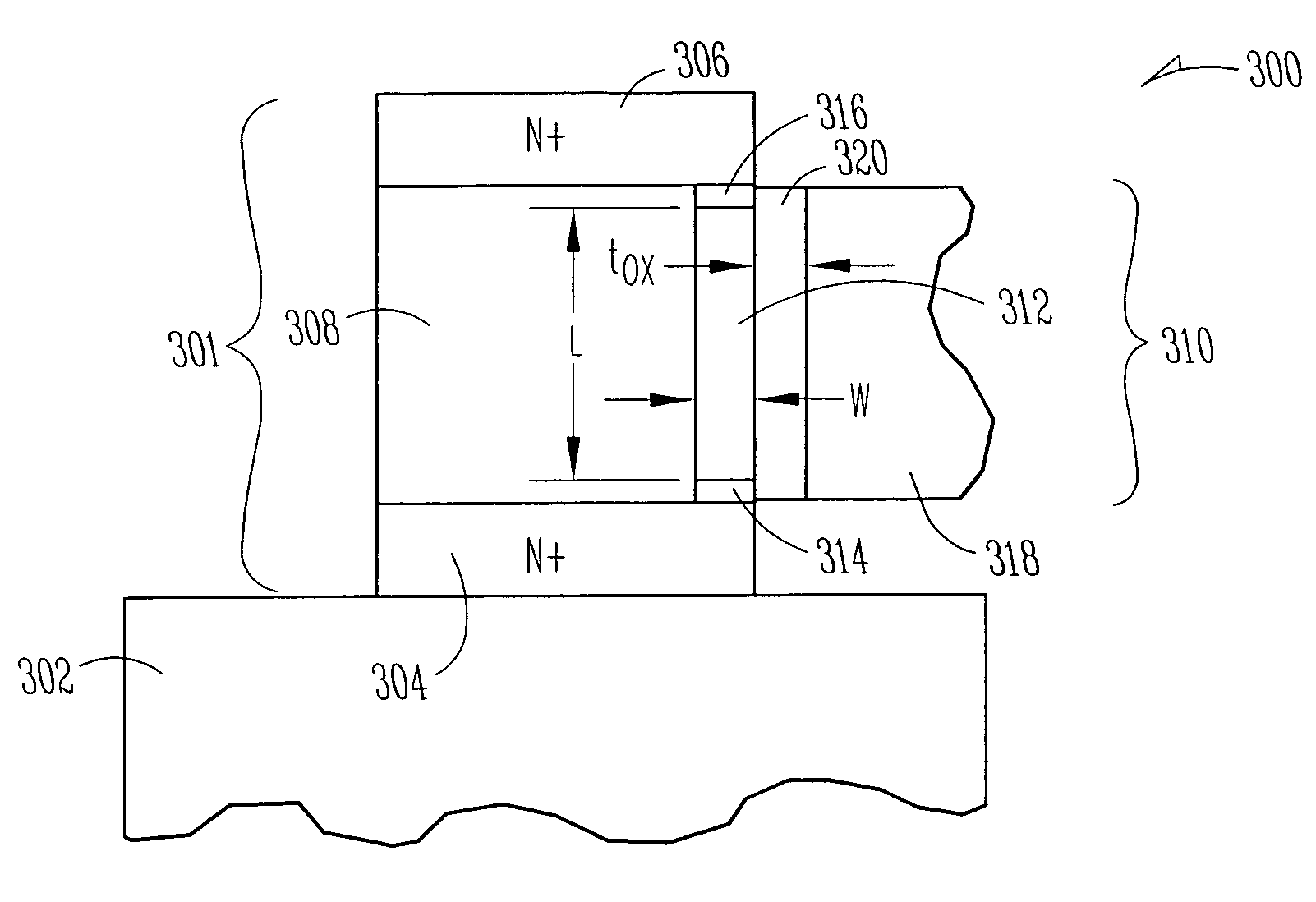

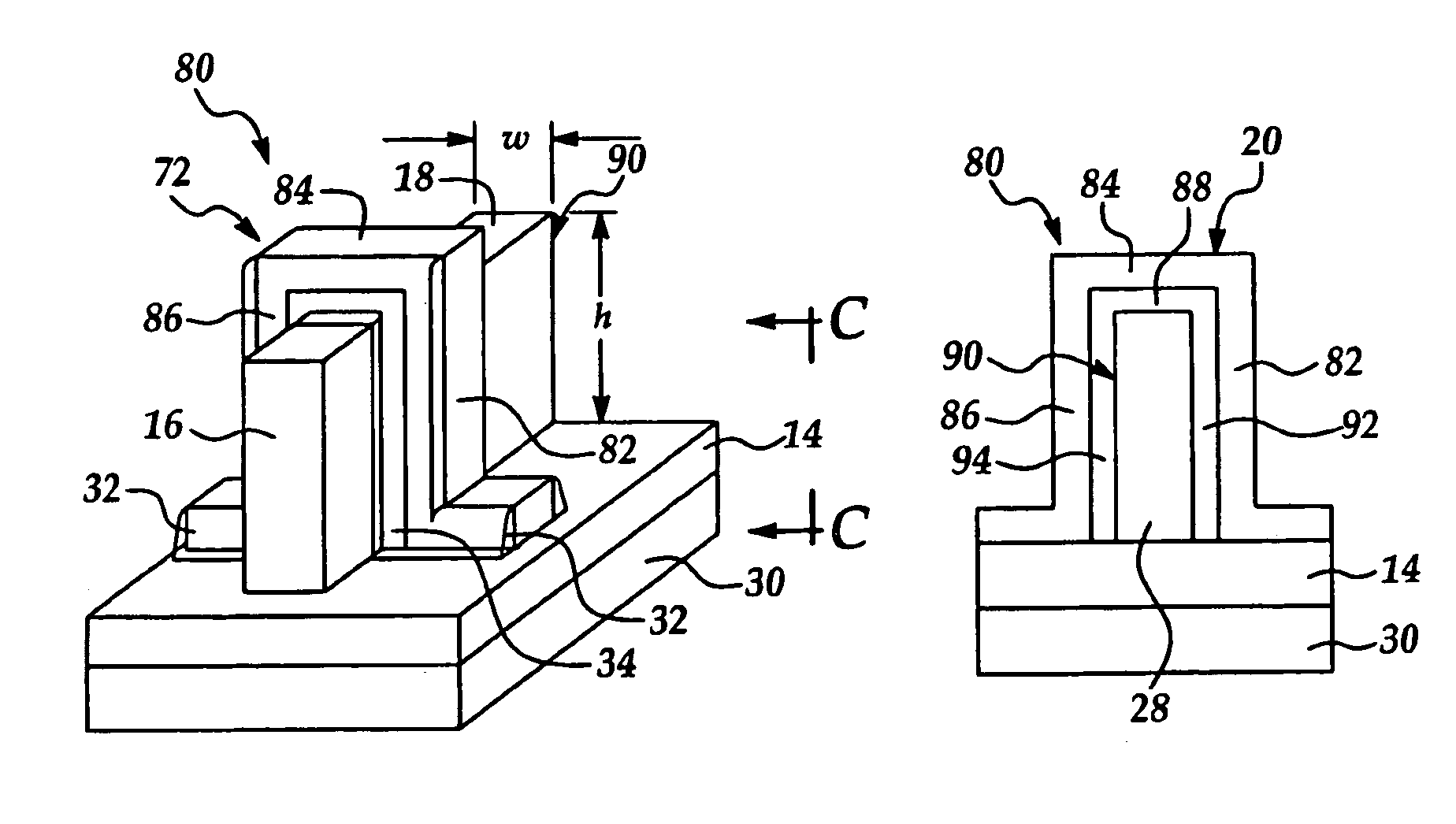

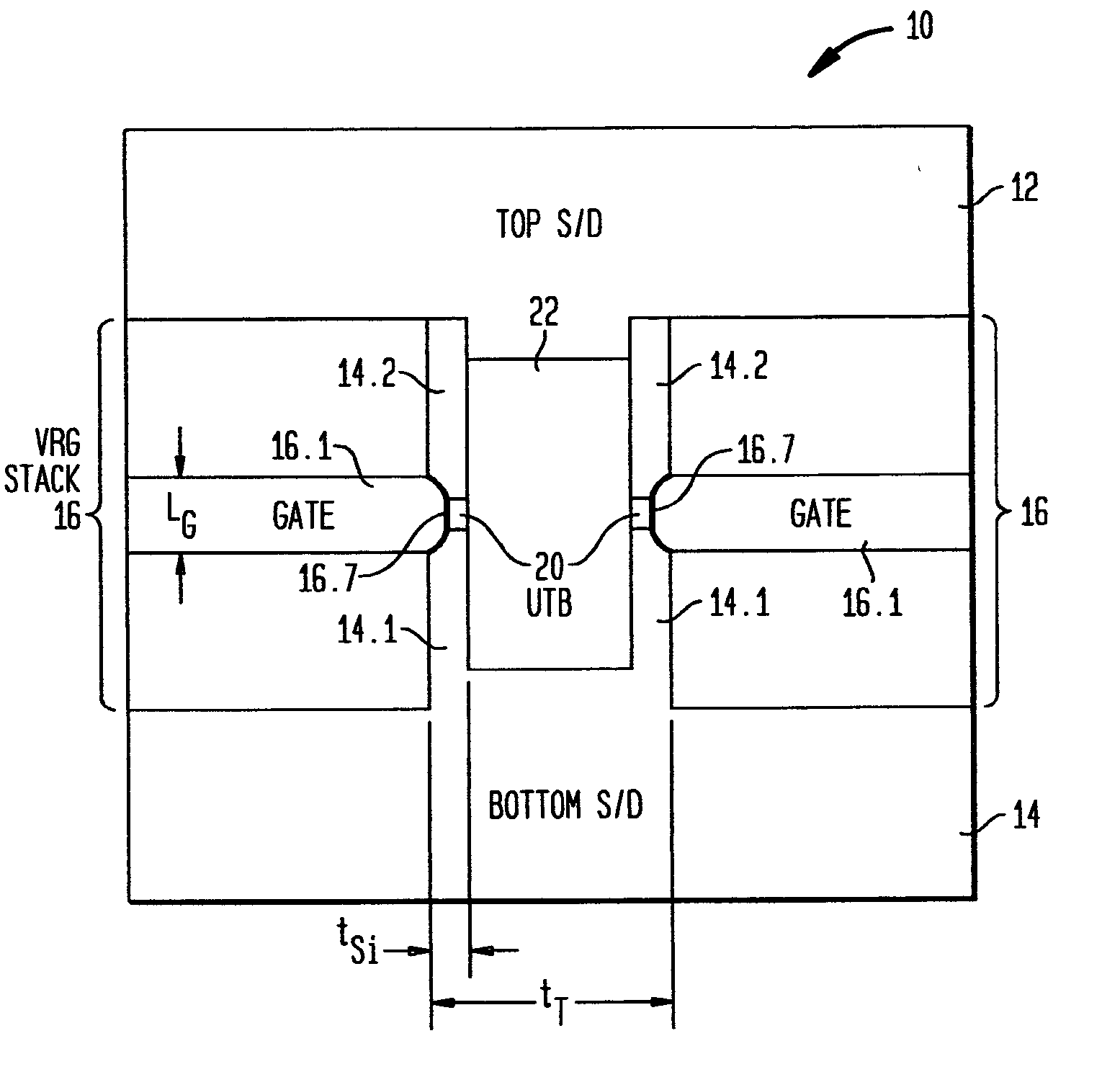

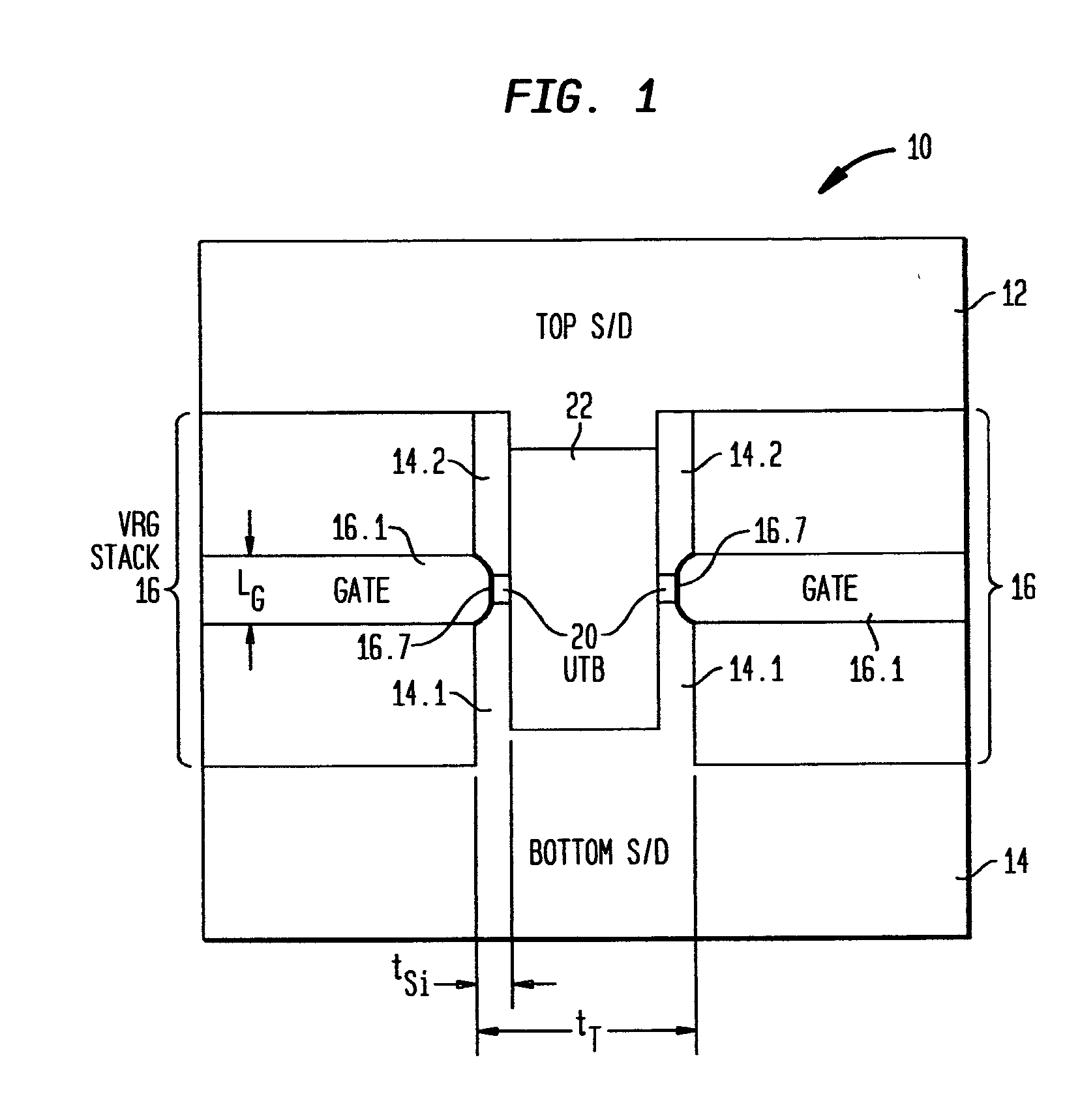

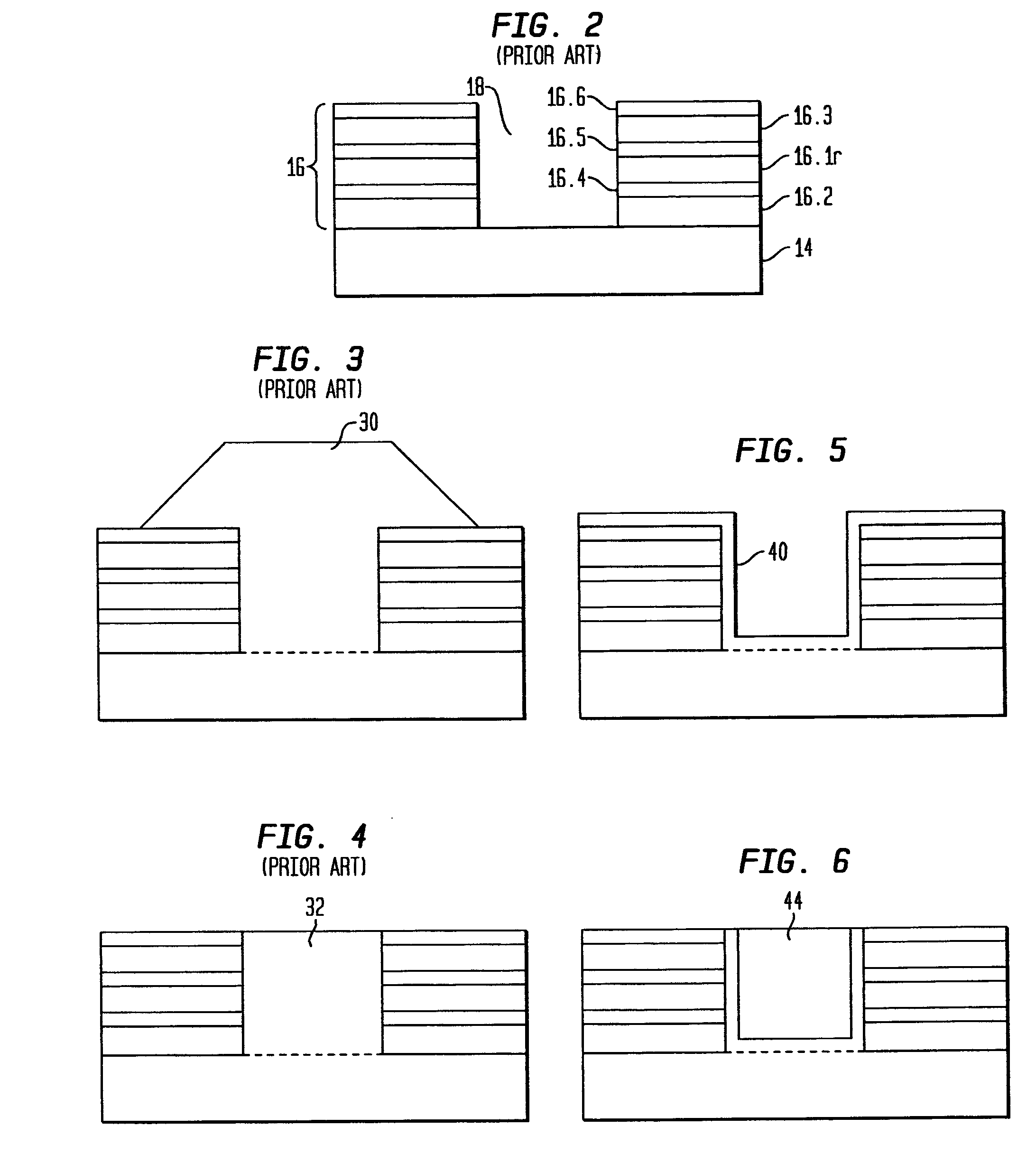

Ultra thin body vertical replacement gate MOSFET

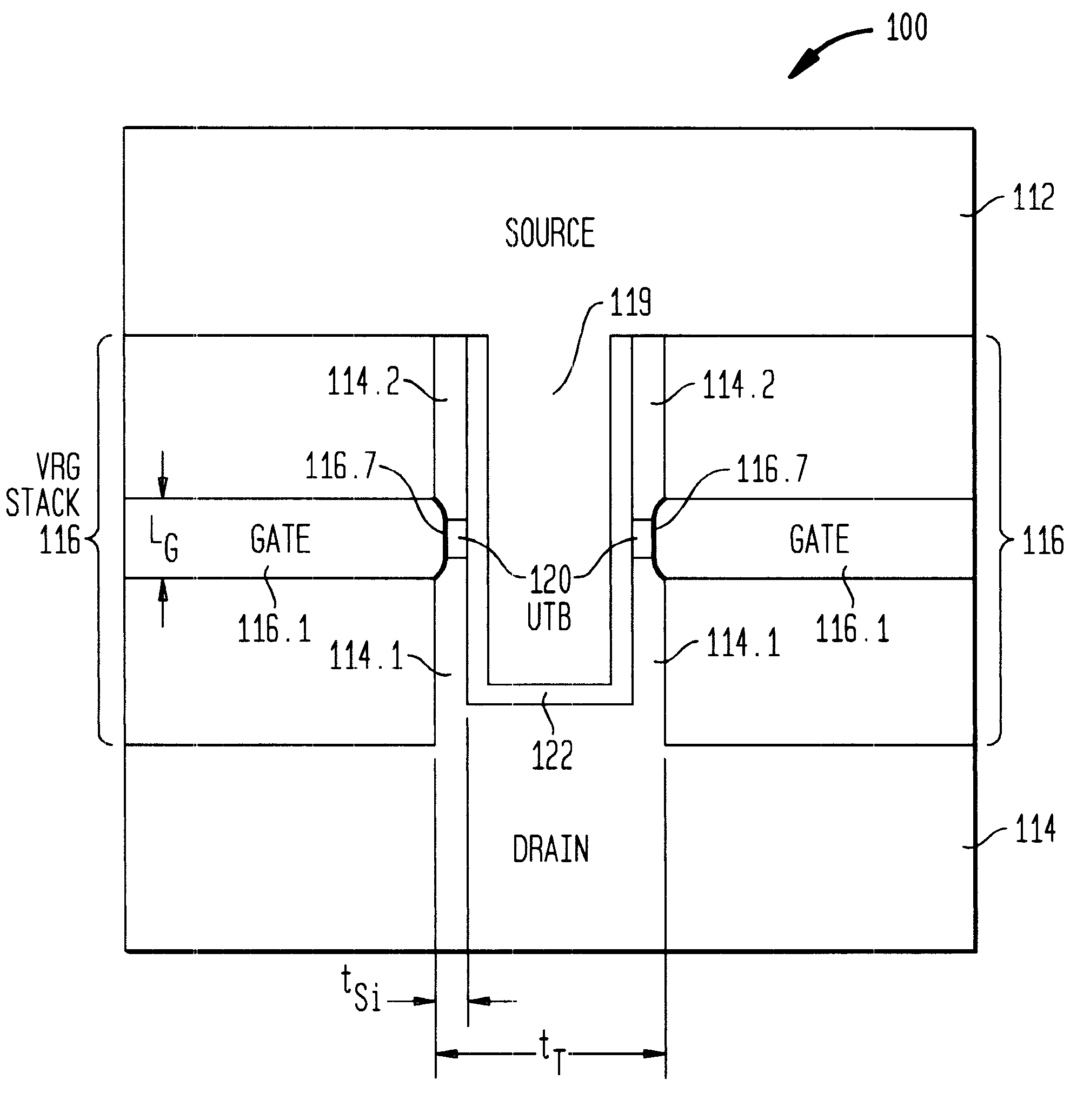

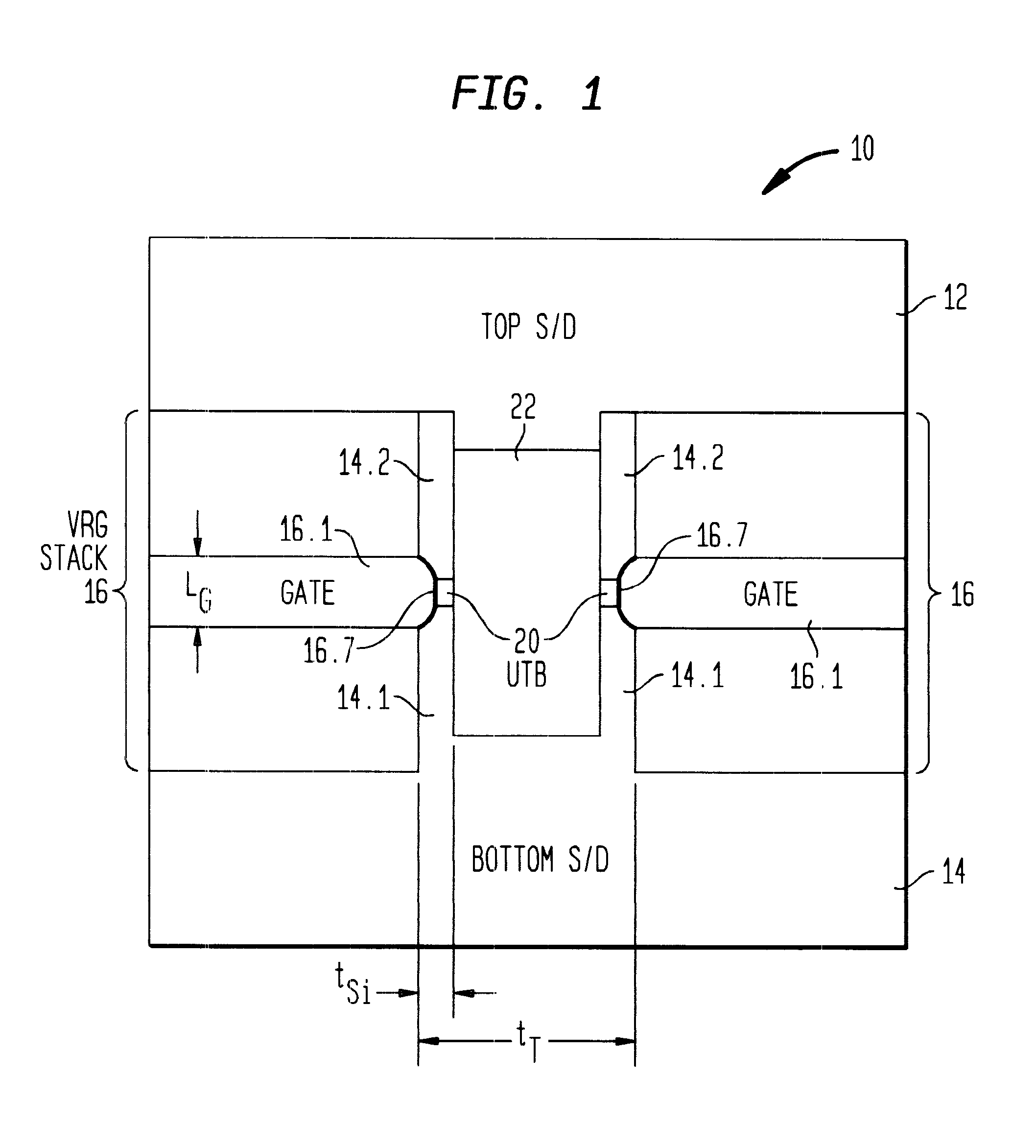

InactiveUS6635924B1Semiconductor/solid-state device manufacturingSemiconductor devicesThin oxideThin layer

A method of fabricating a VRG MOSFET includes the steps of: (a) forming a VRG multilayer stack; (b) forming a trench in the stack; (c) depositing an ultra thin, amorphous semiconductor (alpha-semic) layer on the sidewalls of the trench (portions of the ultra thin layer on the sidewalls of the trench will ultimately form the channel or ultra thin body (UTB) of the MOSFET); (d) forming a thicker, alpha-semic sacrificial layer on the ultra thin layer; (e) annealing the alpha-semic layers to recrystallize them into single crystal layers; (f) selectively removing the recrystallized sacrificial layer; and (g) performing additional steps to complete the VRG MOSFET. In general, the sacrificial layer should facilitate the recrystallization of the ultra thin layer into single crystal material. In addition, the etch rate of the sacrificial layer should be sufficiently higher than that the ultra thin layer so that the sacrificial layer can be selectively removed in the presence of the ultra thin layer after recrystallization. The latter condition is illustratively satisfied by doping the sacrificial layer and by not (intentionally) doping the ultra thin layer. In accordance with one embodiment of our invention, step (g) includes filling the trench with oxide to form a thick back oxide region. In accordance with another embodiment of our invention, step (g) includes depositing a thin oxide layer (the back oxide) in the trench and then filling the remainder of the trench with a polycrystalline region (the back gate). VRG MOSFETs fabricated in accordance with our invention are expected to be electrostatically scalable with precise dimensional control. In addition, they can be fully depleted. Novel UTB device designs are also described.

Owner:BELL SEMICON LLC

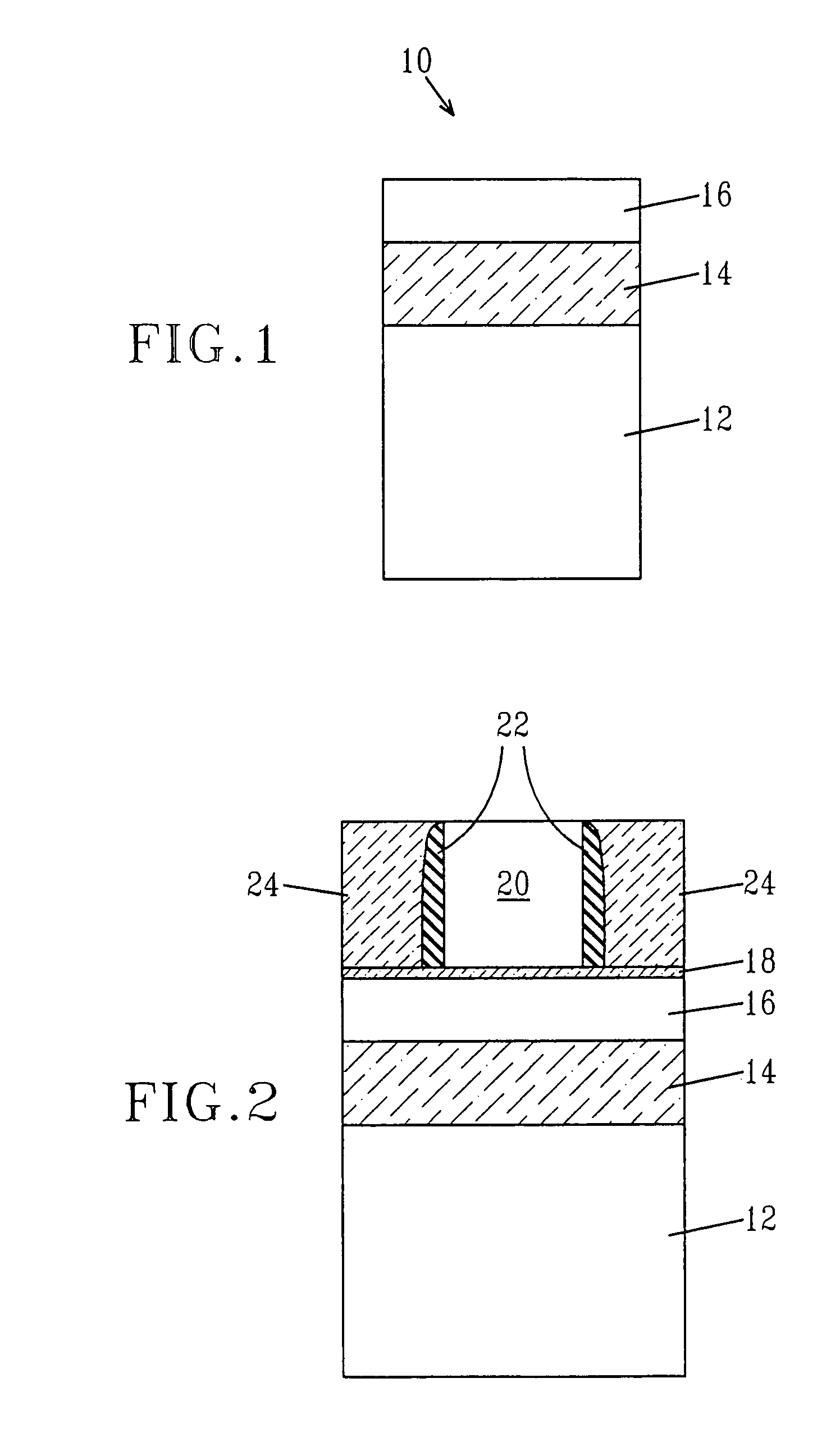

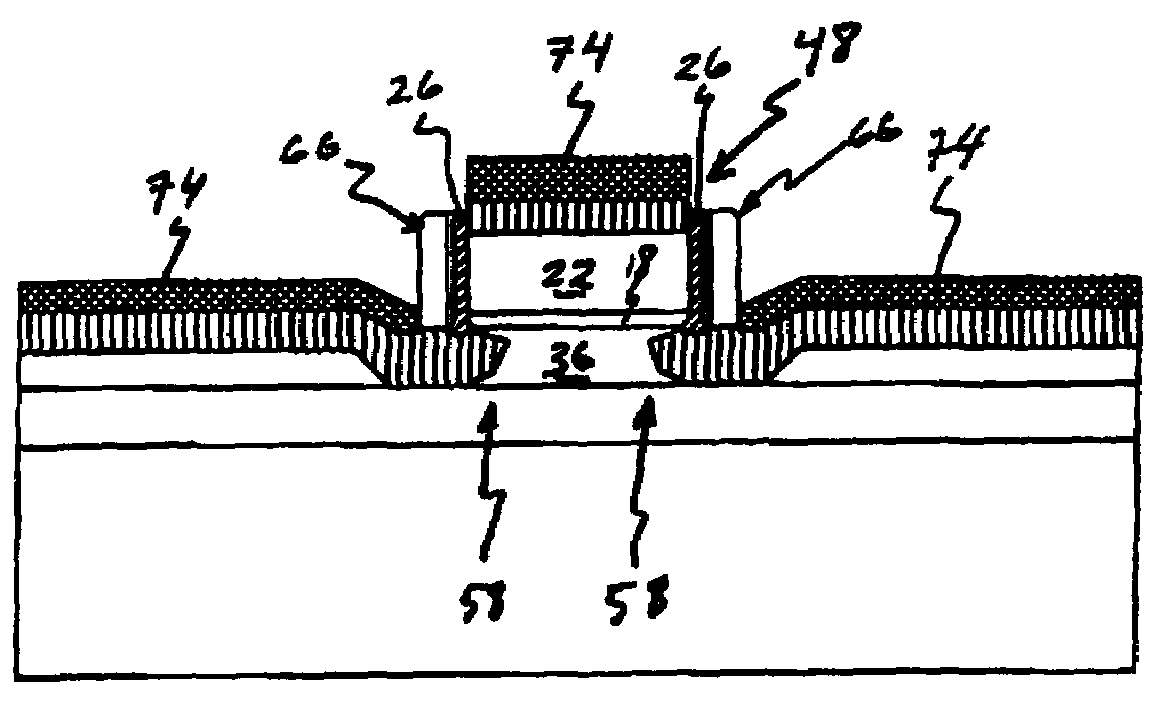

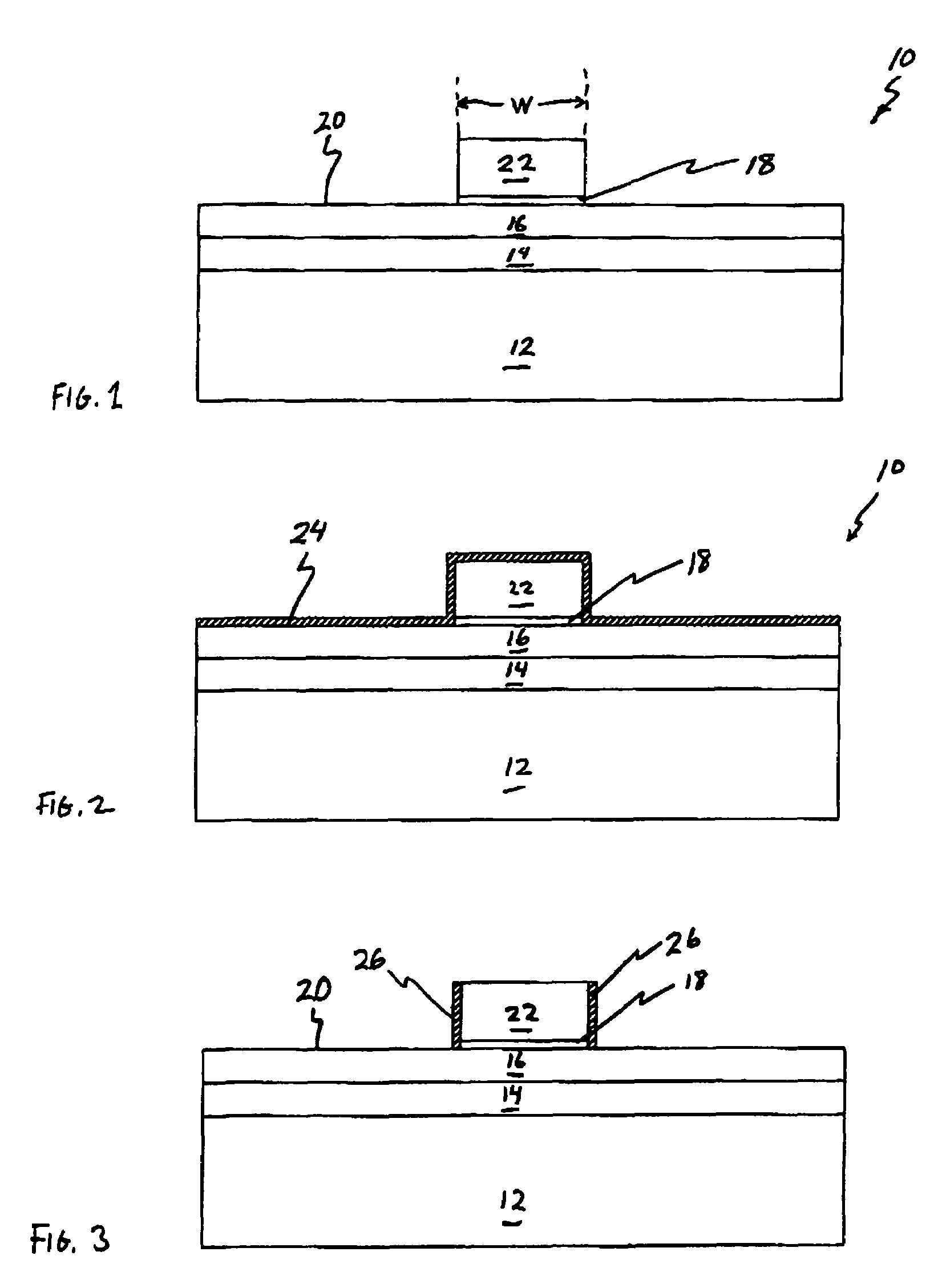

Process for ultra-thin body SOI devices that incorporate EPI silicon tips and article made thereby

InactiveUS20050272187A1Small sizeTransistorSemiconductor/solid-state device manufacturingGate stackUltra thin body

The invention relates to a transistor that includes an ultra-thin body epitaxial layer that forms an embedded junction with a channel that has a length dictated by an undercut under the gate stack for the transistor. The invention also relates to a process of forming the transistor and to a system that incorporates the transistor.

Owner:INTEL CORP

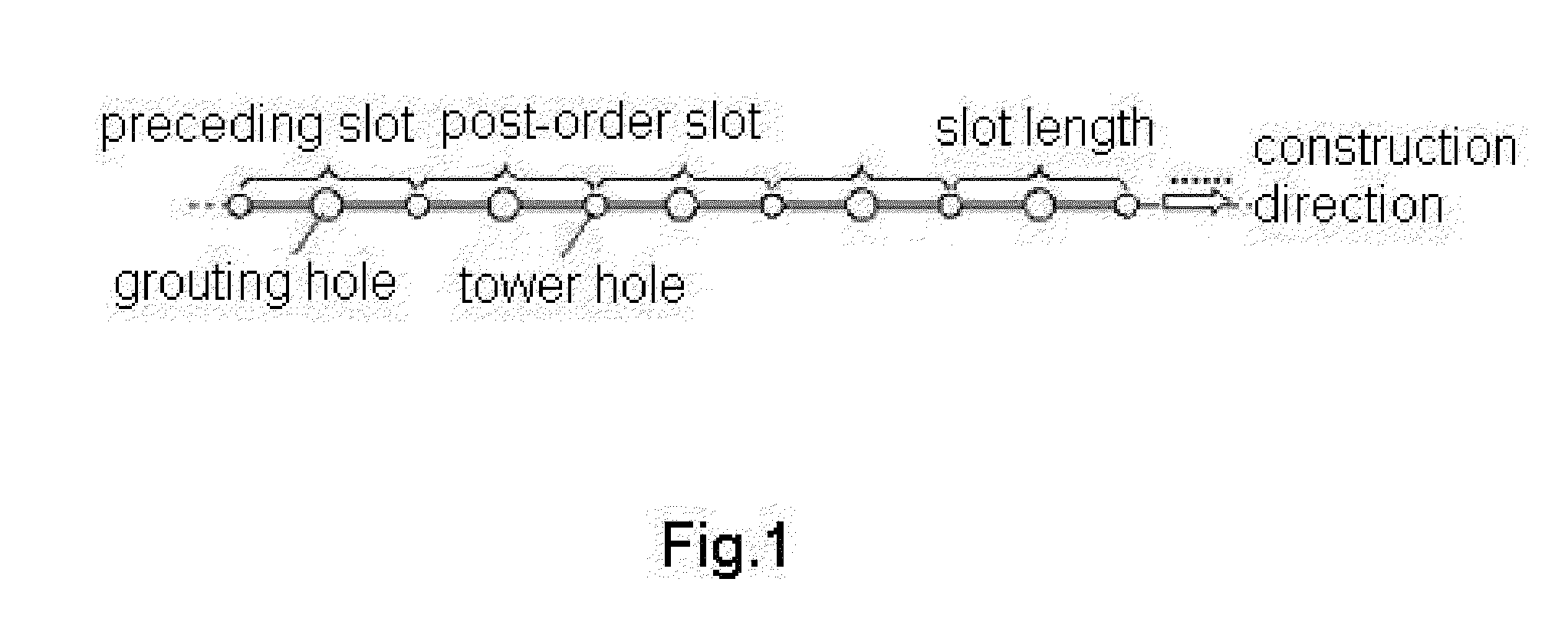

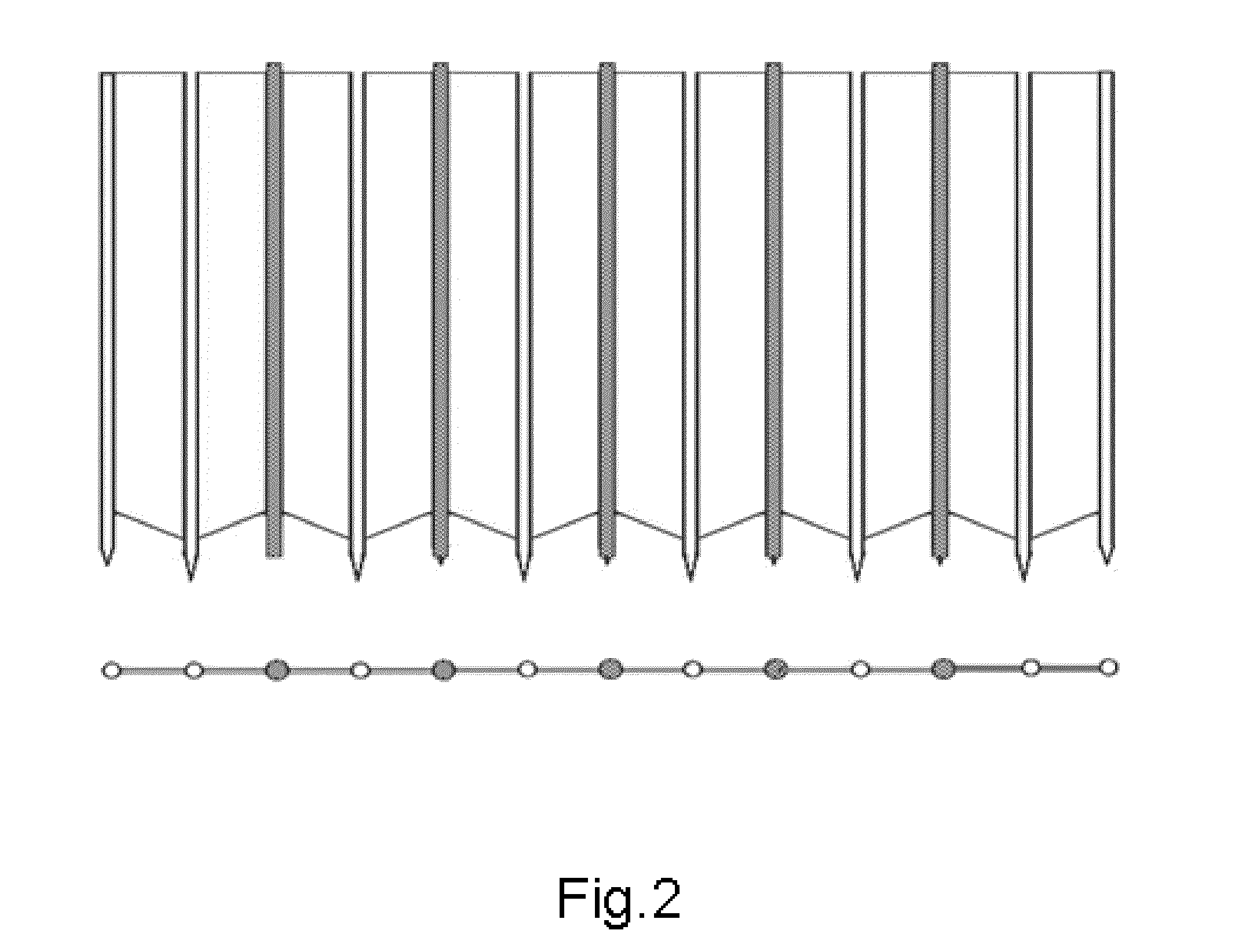

Polymer grouting method for constructing ultra-thin anti-seepage wall

ActiveUS20140314498A1Improve performanceAdvanced and efficient and economicalOrganic fertilisersSoil preservationUltra thin bodyPolymer

A polymer grouting method for constructing an ultra-thin anti-seepage wall meeting requirements of anti-seepage designs of dams, includes the following steps of: forming continuous slots on a body of the dam and the foundation which need seepage-proofing and reinforcing; and injecting two-component expansive polymer grouting materials to the slots through grouting pipes, a volume rapidly expands after the polymer grouting materials reacts and the slots are filled to form a polymer ultra-thin body, the polymer ultra-thin bodies which are adjacent are cemented together to form a continuous, uniform, and regular cementing ultra-thin polymer anti-seepage wall; this invention is different from the conventional anti-seepage wall technology whatever through the material, the mechanism or the construction methods, which has the advantages such as speediness, ultra-thinness, minimally invasive, lightness, high toughness, economy, and durability, applied in reinforcement projects of a number of the dams and dikes.

Owner:WANG FUMING

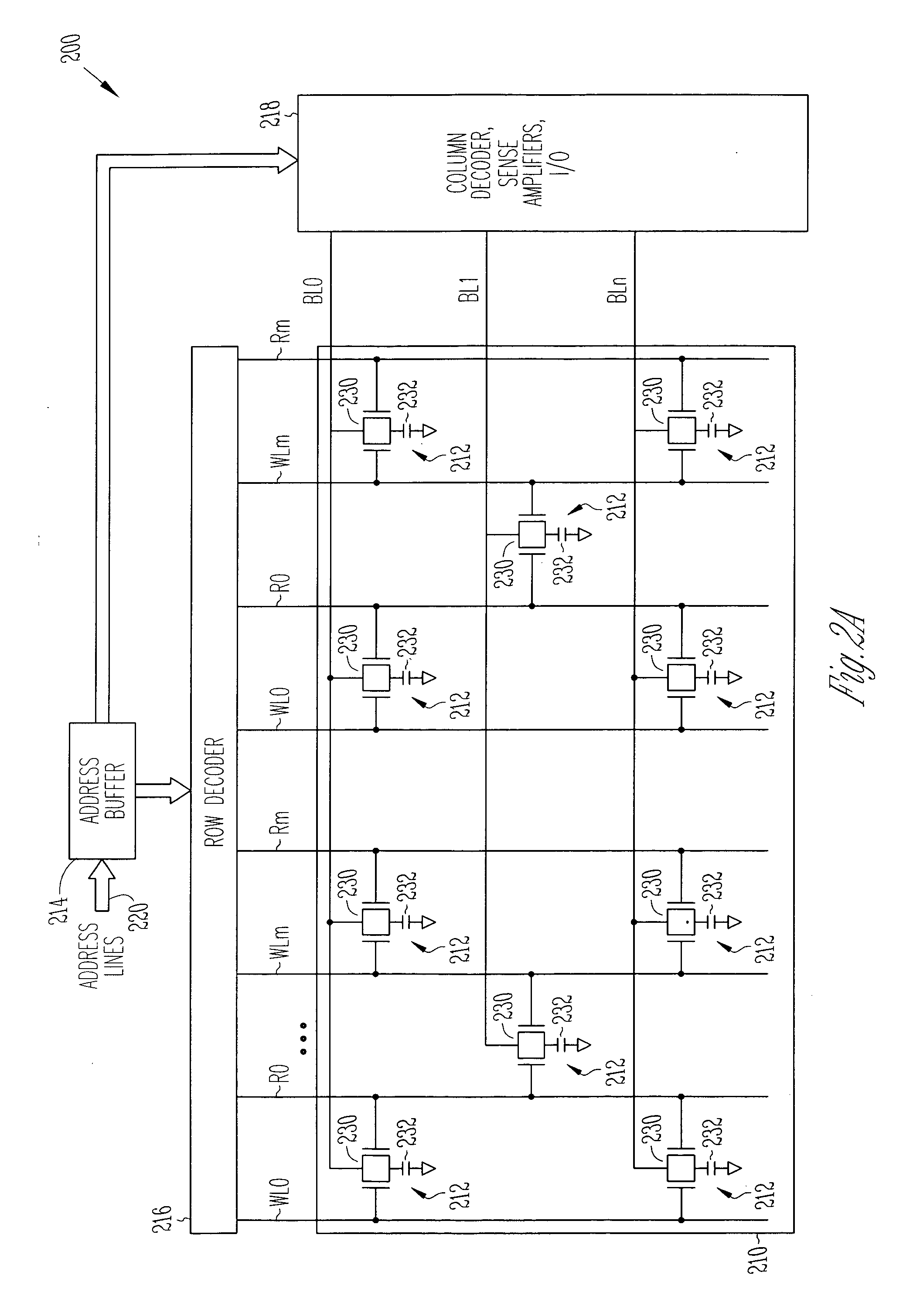

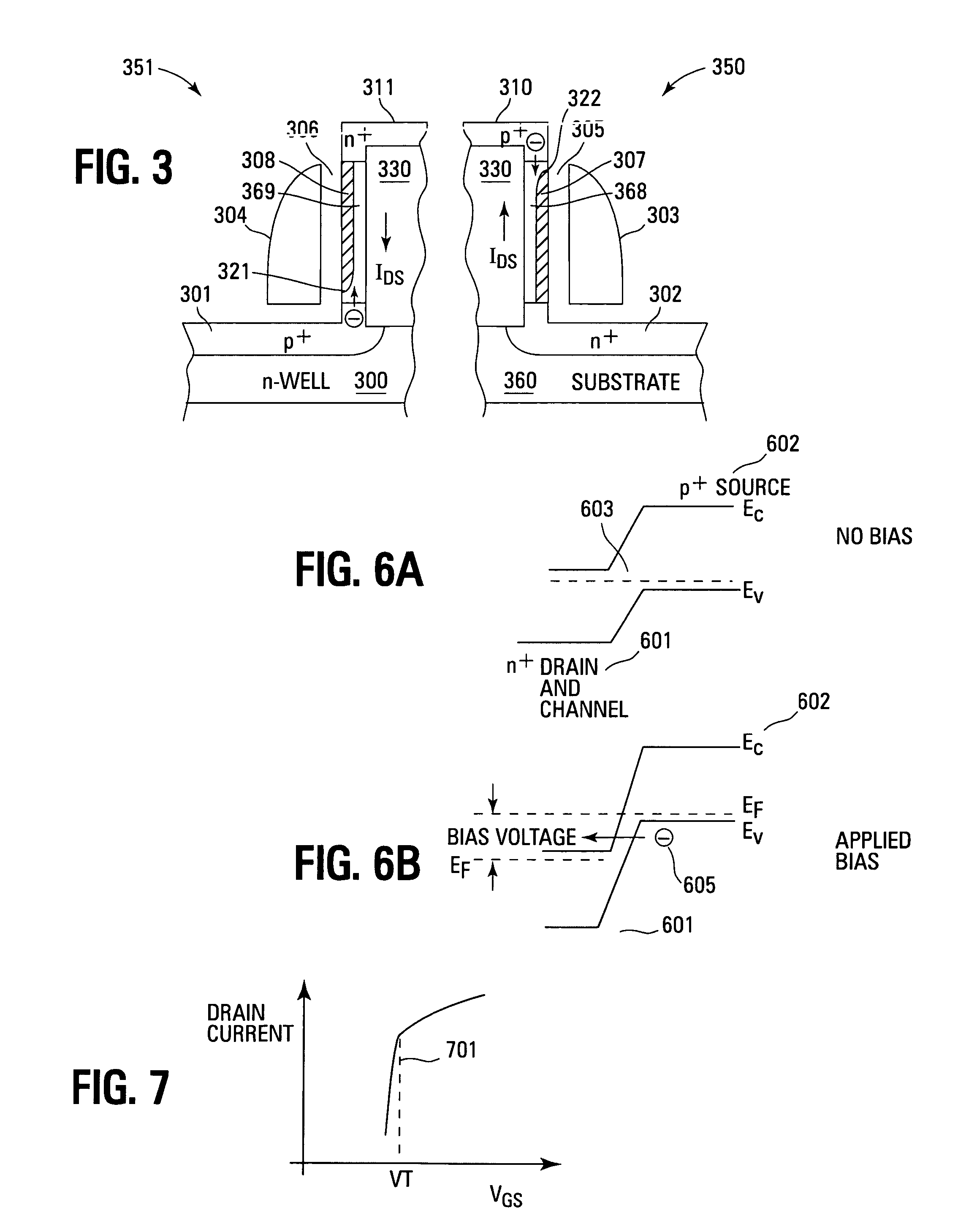

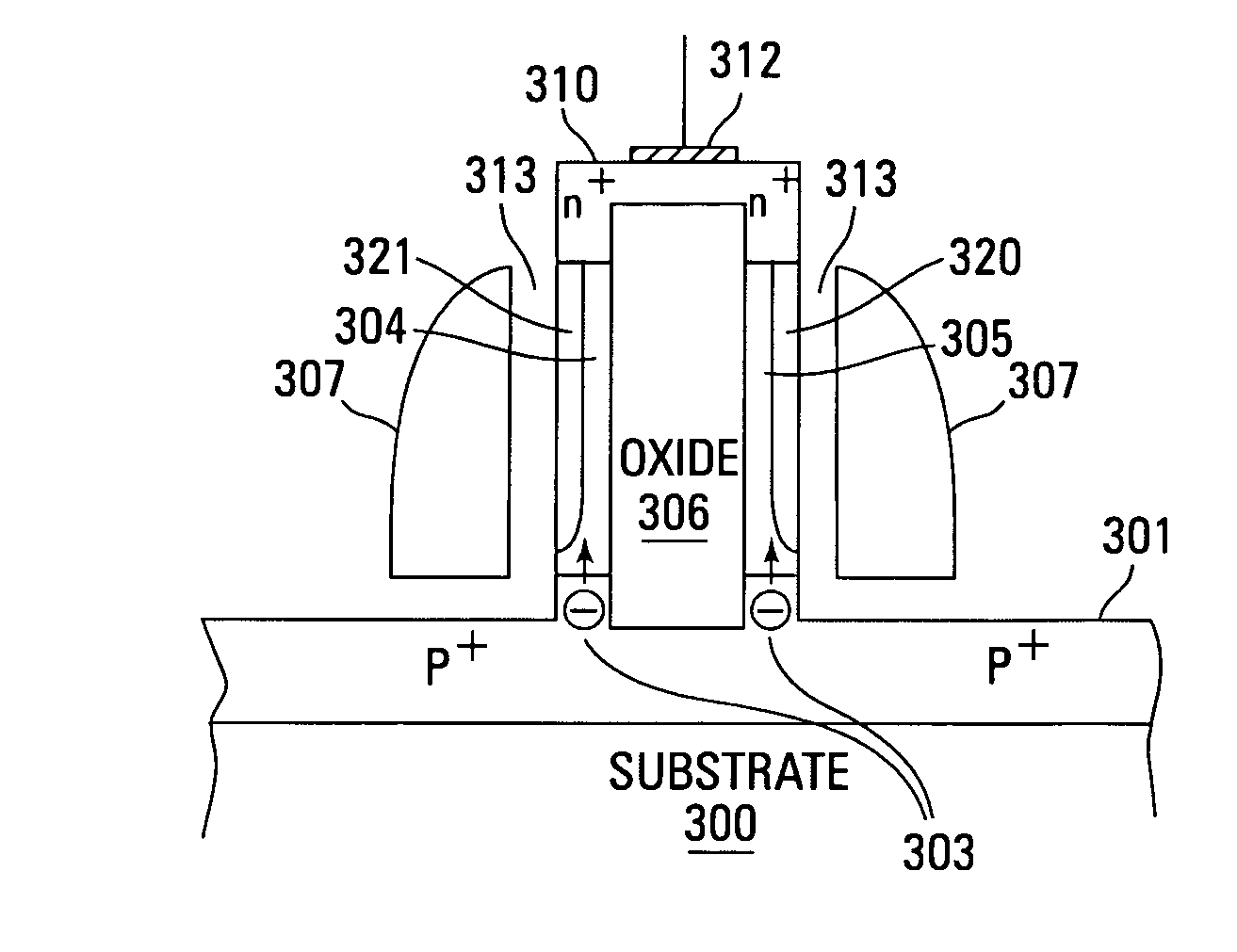

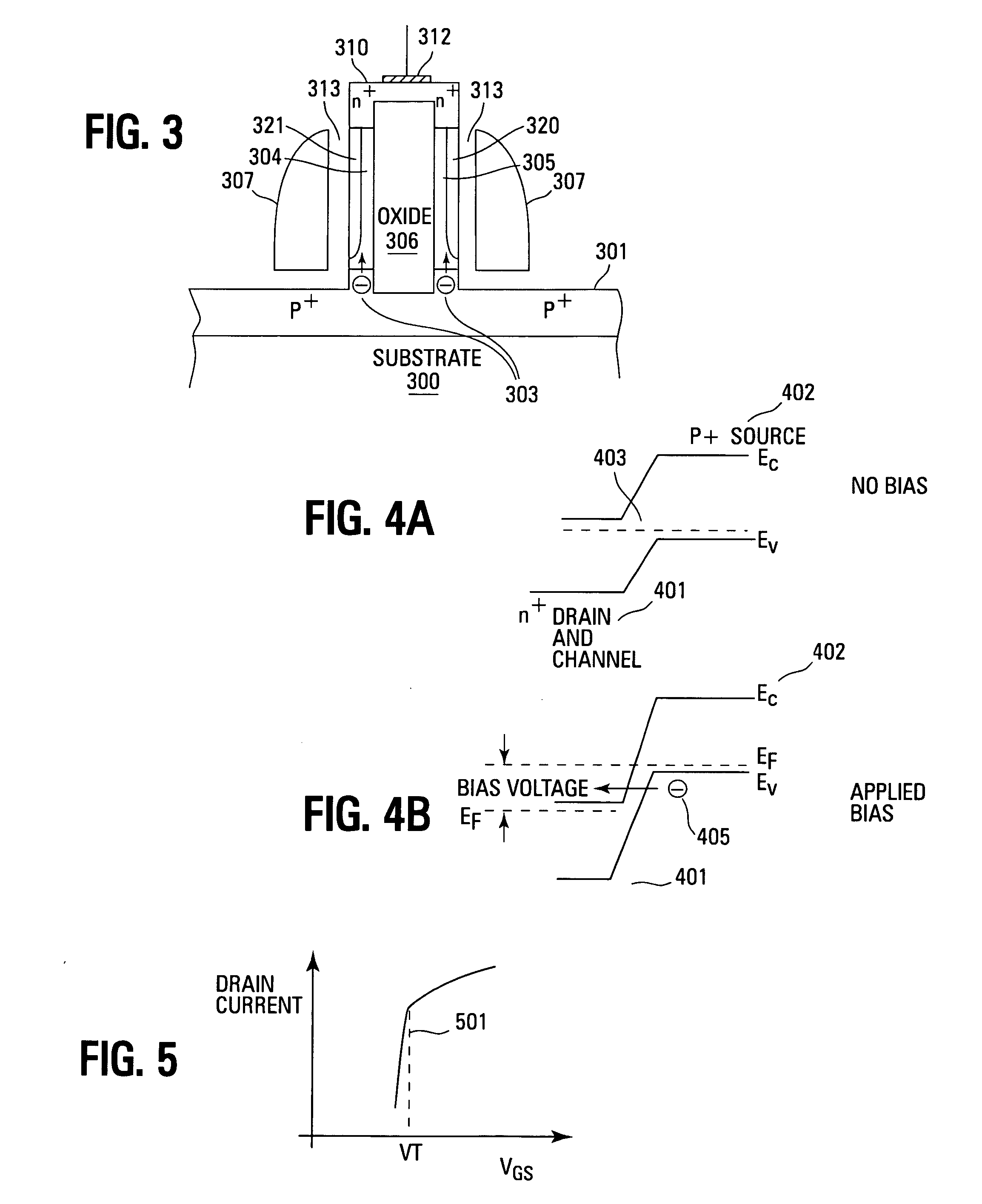

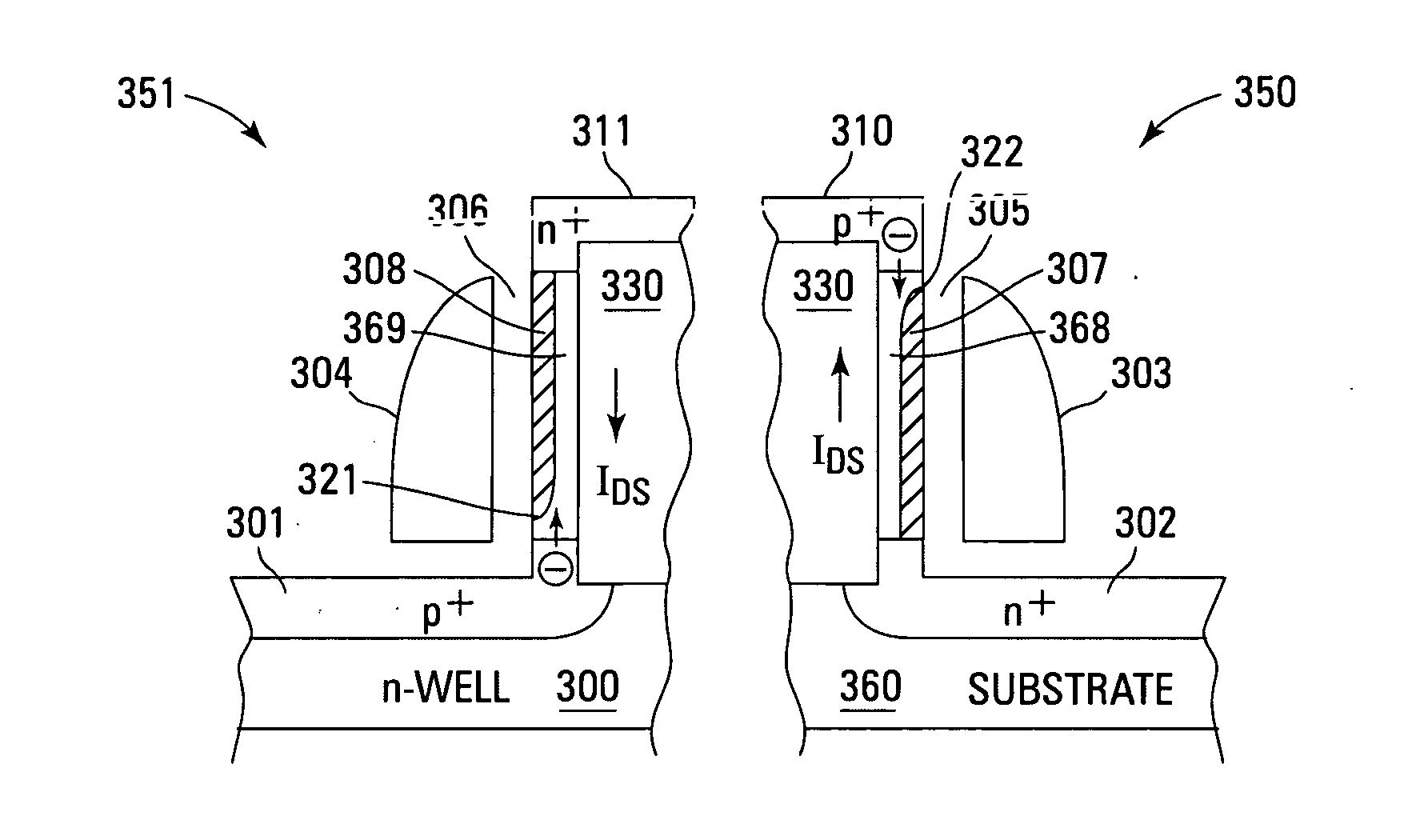

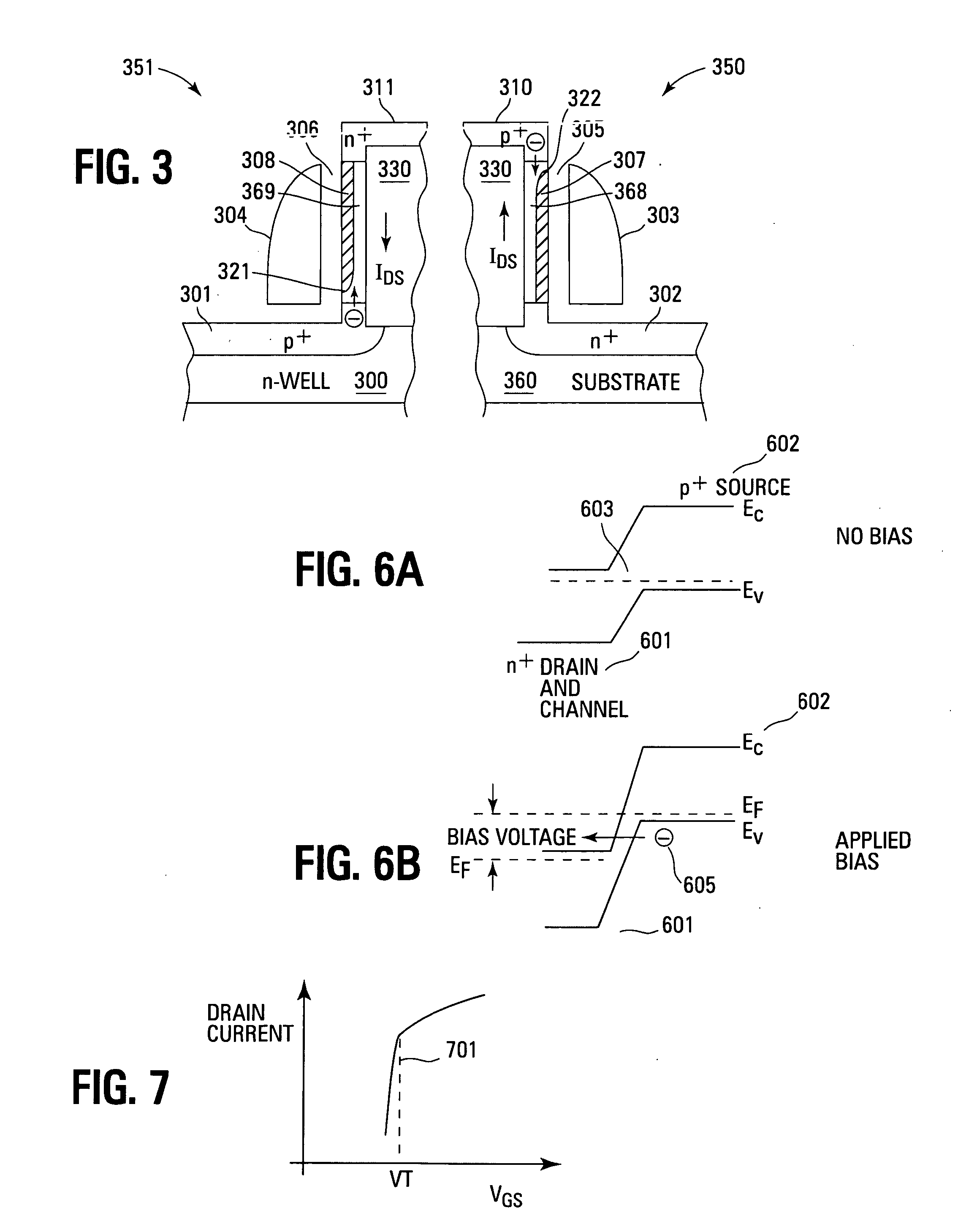

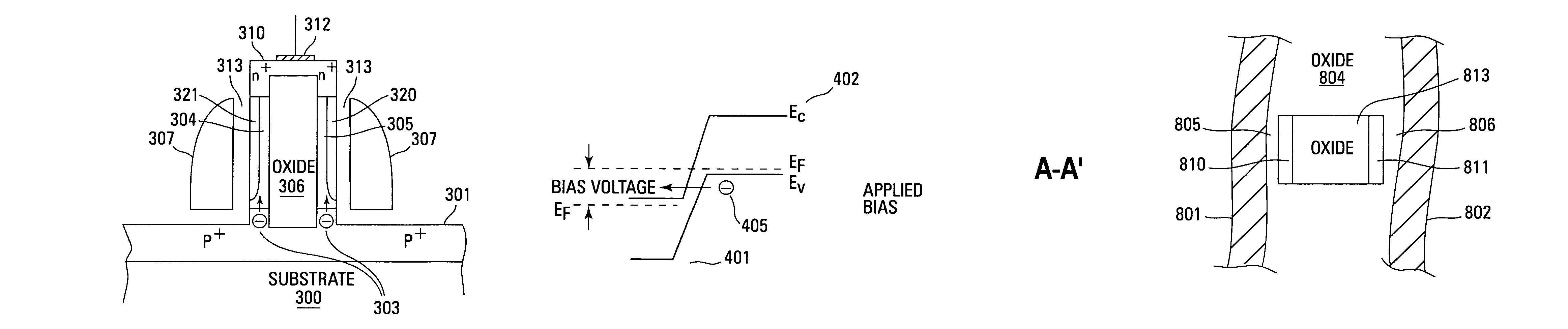

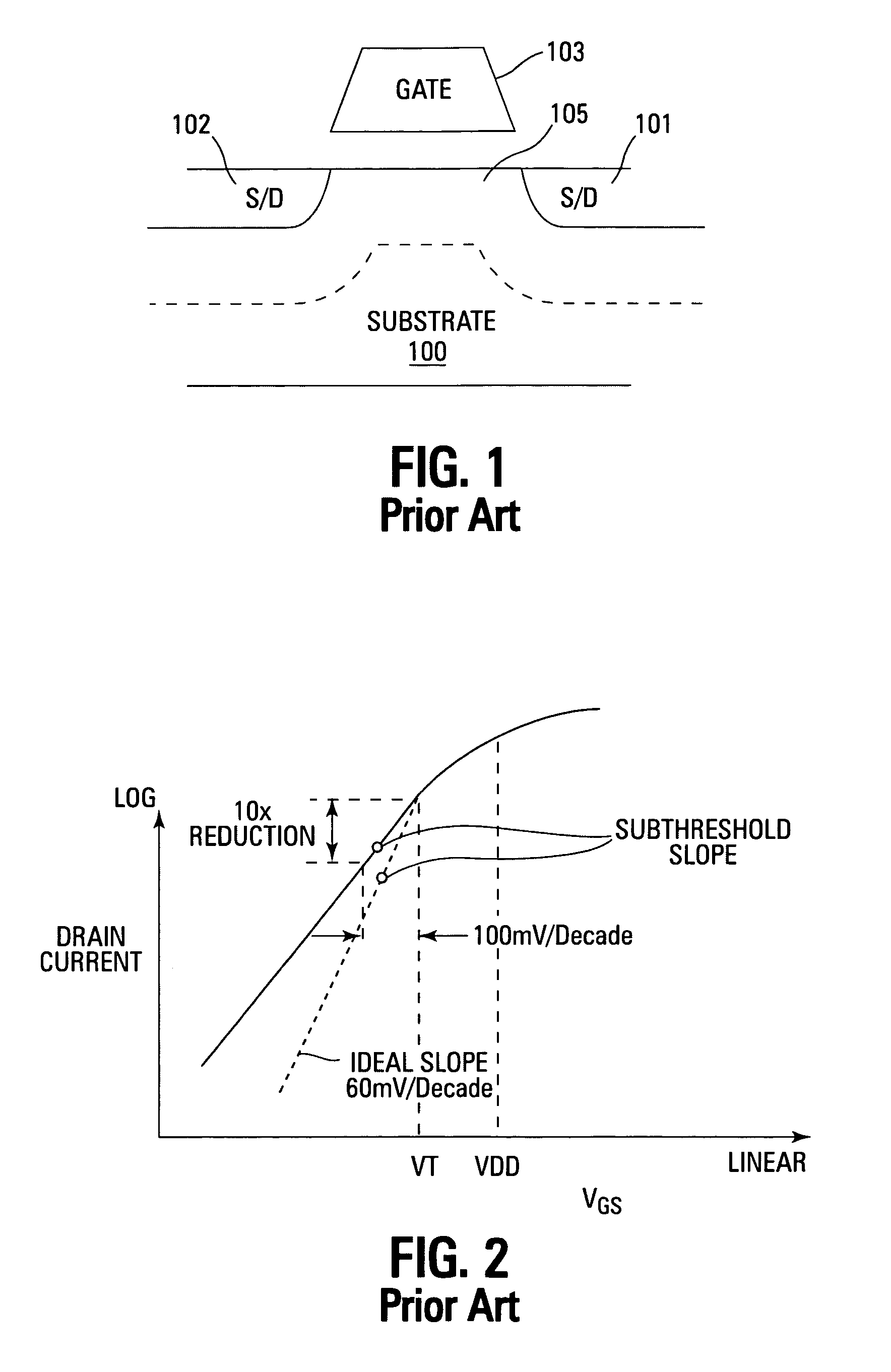

Ultra-thin body vertical tunneling transistor

A vertical tunneling, ultra-thin body transistor is formed on a substrate out of a vertical oxide pillar having active regions of opposing conductivity on opposite ends of the pillar. In one embodiment, the source region is a p+ region in the substrate under the pillar and the drain region is an n+ region at the top of the pillar. A gate structure is formed along the pillar sidewalls and over the body layers. The transistor operates by electron tunneling from the source valence band to the gate bias-induced n-type channels, along the ultra-thin silicon bodies, thus resulting in a drain current.

Owner:MICRON TECH INC

Folded bit line DRAM with vertical ultra thin body transistors

A folded bit line DRAM device is provided. The folded bit line DRAM device includes an array of memory cells. Each memory cell in the array of memory cells includes a pillar extending outwardly from a semiconductor substrate. Each pillar includes a single crystalline first contact layer and a single crystalline second contact layer separated by an oxide layer. A single crystalline vertical transistor is formed along alternating sides of the pillar within a row of pillars. The single crystalline vertical transistor includes an ultra thin single crystalline vertical first source / drain region coupled to the first contact layer, an ultra thin single crystalline vertical second source / drain region coupled to the second contact layer, and an ultra thin single crystalline vertical body region which opposes the oxide layer and couples the first and the second source / drain regions. A plurality of buried bit lines are formed of single crystalline semiconductor material and disposed below the pillars in the array memory cells for interconnecting with the first contact layer of column adjacent pillars in the array of memory cells. Further, a plurality of word lines are included. Each word line is disposed orthogonally to the plurality of buried bit lines in a trench between rows of the pillars for addressing alternating body regions of the single crystalline vertical transistors that are adjacent to the trench.

Owner:MICRON TECH INC

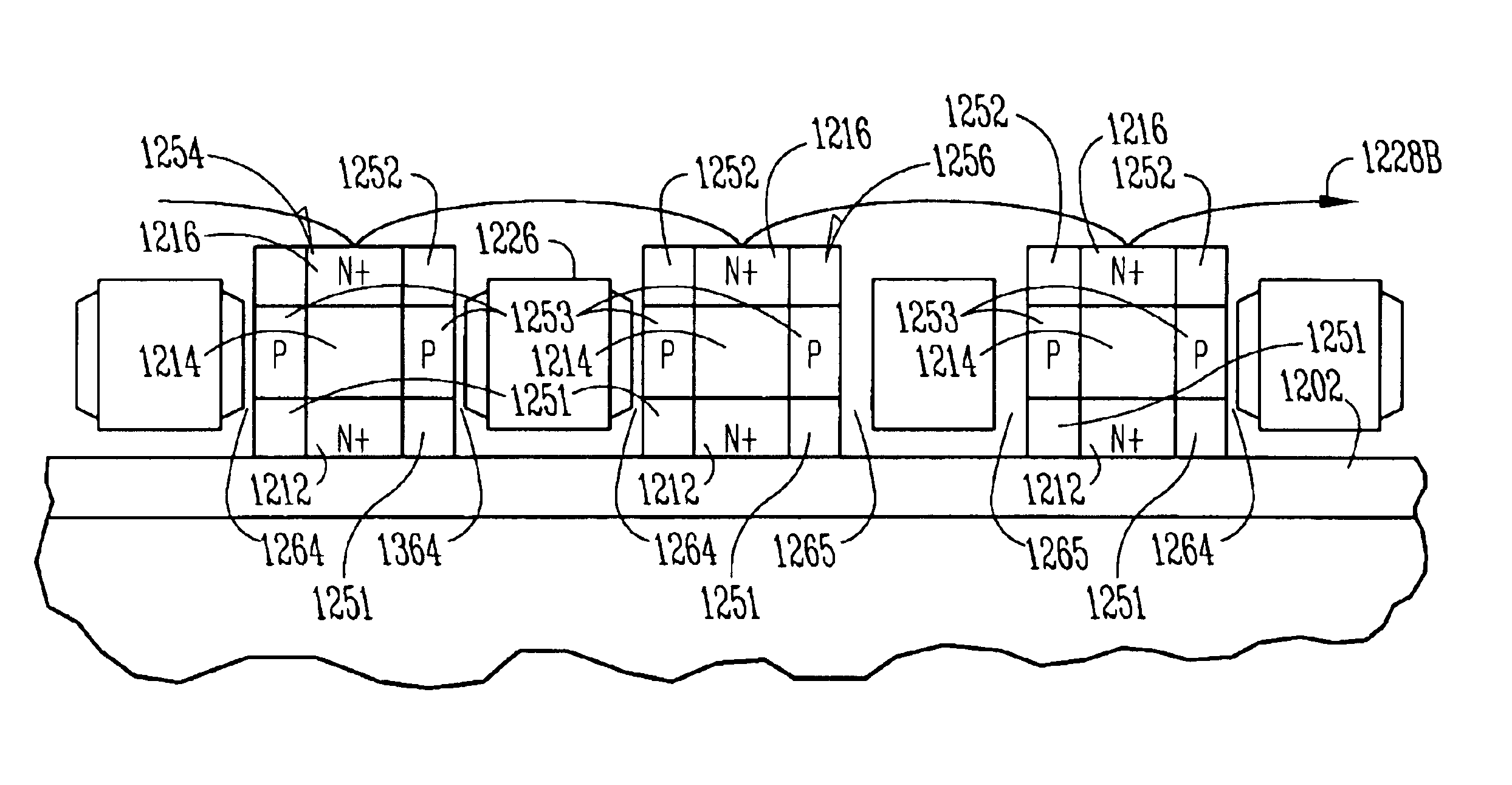

DRAM tunneling access transistor

In one embodiment, a first transistor is comprised of a first p+ source region doped in an n-well in the substrate and a first n+ drain region doped on one side at the top of the pillar. A second transistor is comprised of a second p+ source region doped into the second side of the top of the pillar and serially coupled to the top drain region for the first transistor. A second n+ drain region is doped into the substrate adjacent the pillar. Ultra-thin body layer run along each pillar sidewall between their respective active regions. A gate structure is formed along the pillar sidewalls and over the body layers. The transistors operate by electron tunneling from the source valence band to the gate bias-induced n-type channels, along the ultra-thin silicon bodies, thus resulting in a drain current.

Owner:MICRON TECH INC

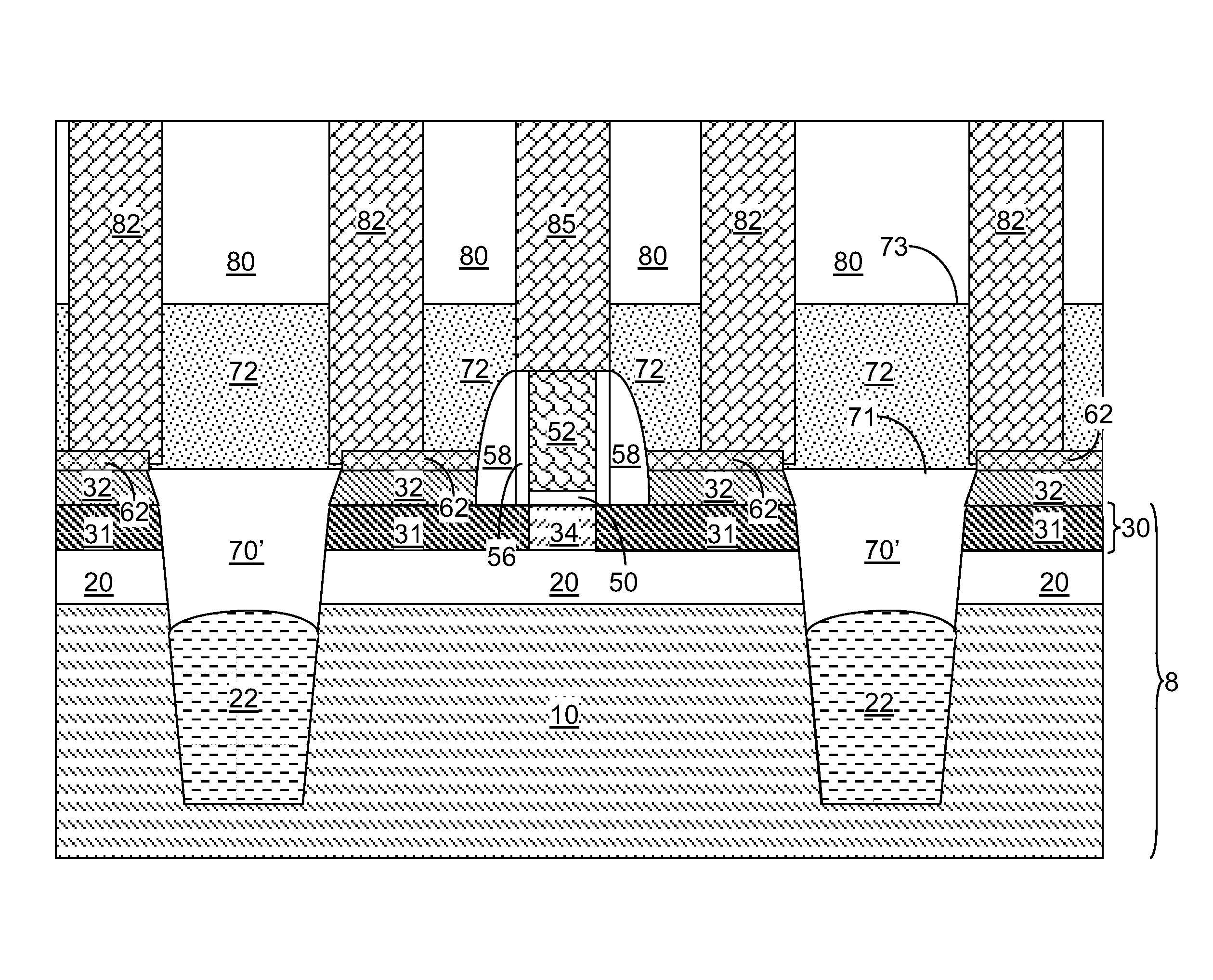

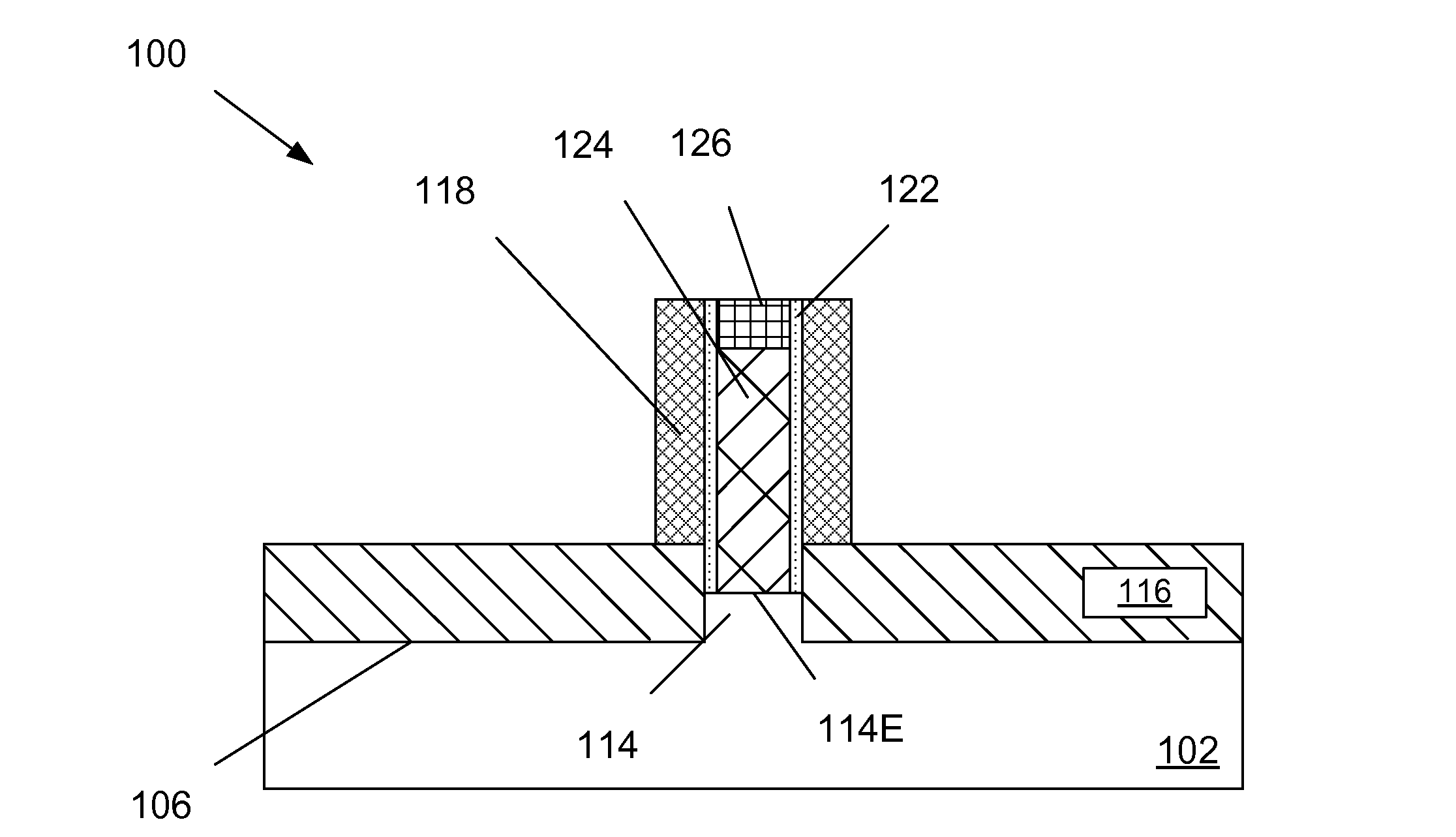

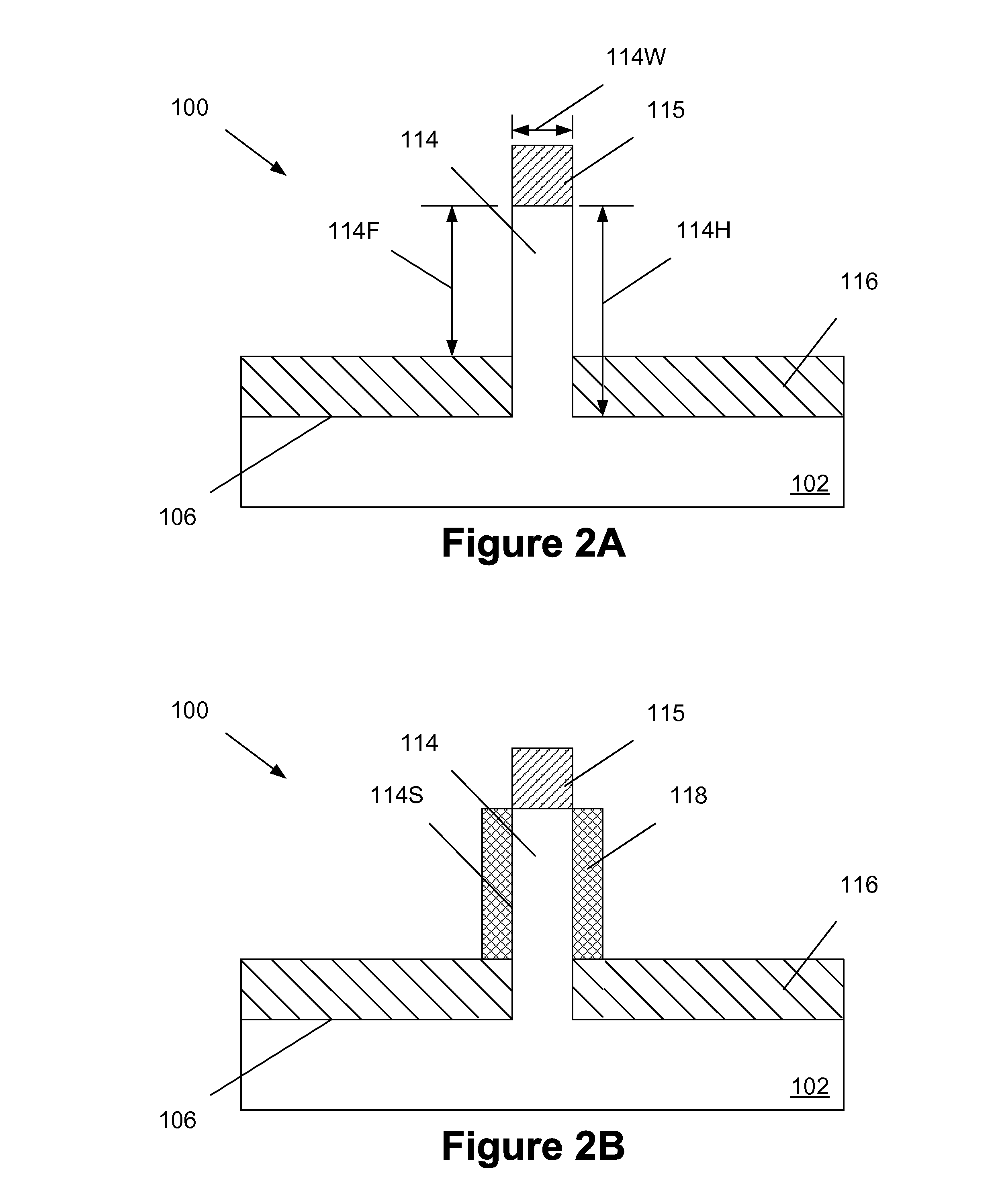

Borderless contact for ultra-thin body devices

ActiveUS20130026570A1Semiconductor/solid-state device detailsSolid-state devicesDevice materialUltra thin body

After formation of a semiconductor device on a semiconductor-on-insulator (SOI) layer, a first dielectric layer is formed over a recessed top surface of a shallow trench isolation structure. A second dielectric layer that can be etched selective to the first dielectric layer is deposited over the first dielectric layer. A contact via hole for a device component located in or on a top semiconductor layer is formed by an etch. During the etch, the second dielectric layer is removed selective to the first dielectric layer, thereby limiting overetch into the first dielectric layer. Due to the etch selectivity, a sufficient amount of the first dielectric layer is present between the bottom of the contact via hole and a bottom semiconductor layer, thus providing electrical isolation for the ETSOI device from the bottom semiconductor layer.

Owner:GLOBALFOUNDRIES US INC

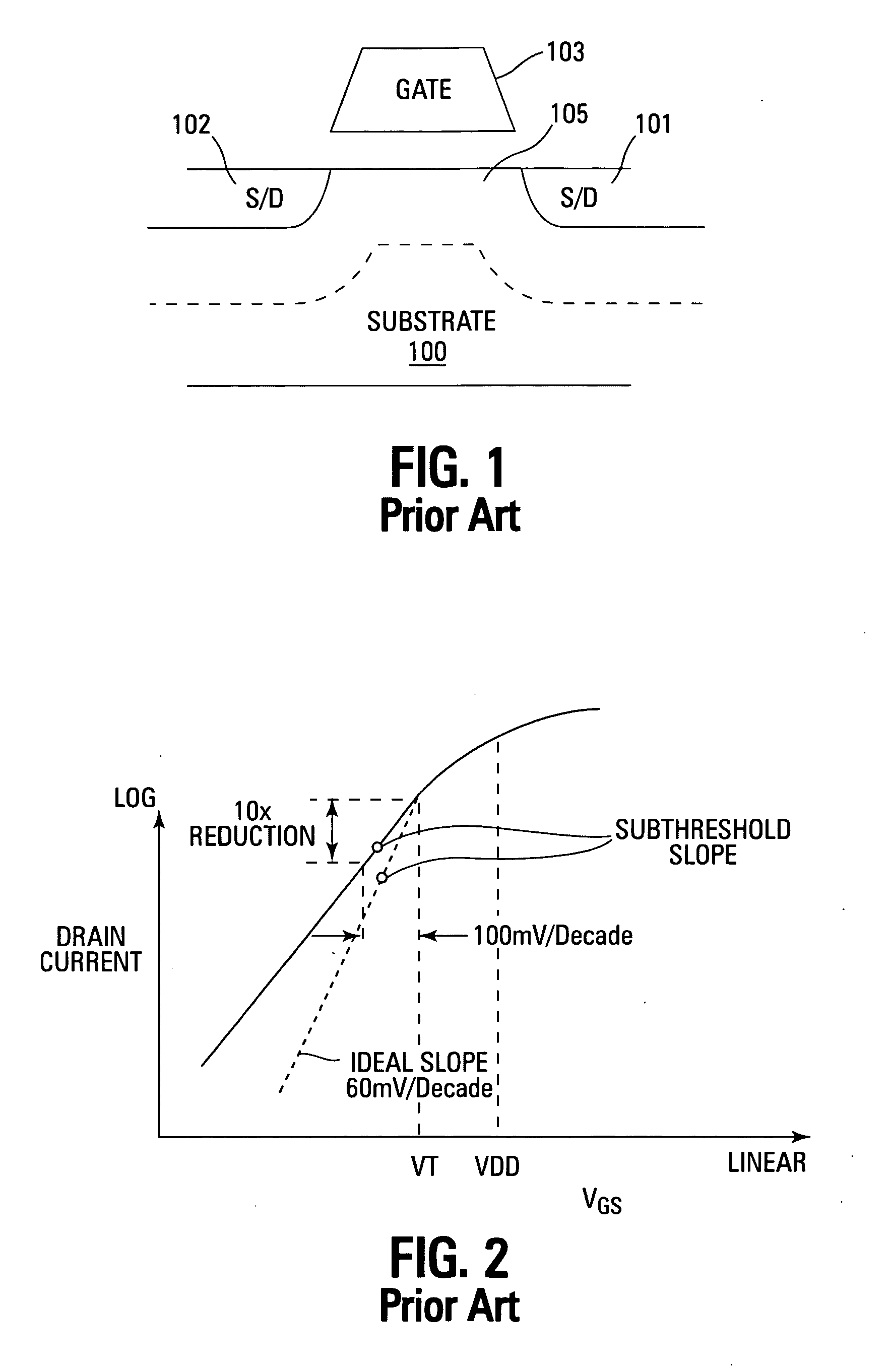

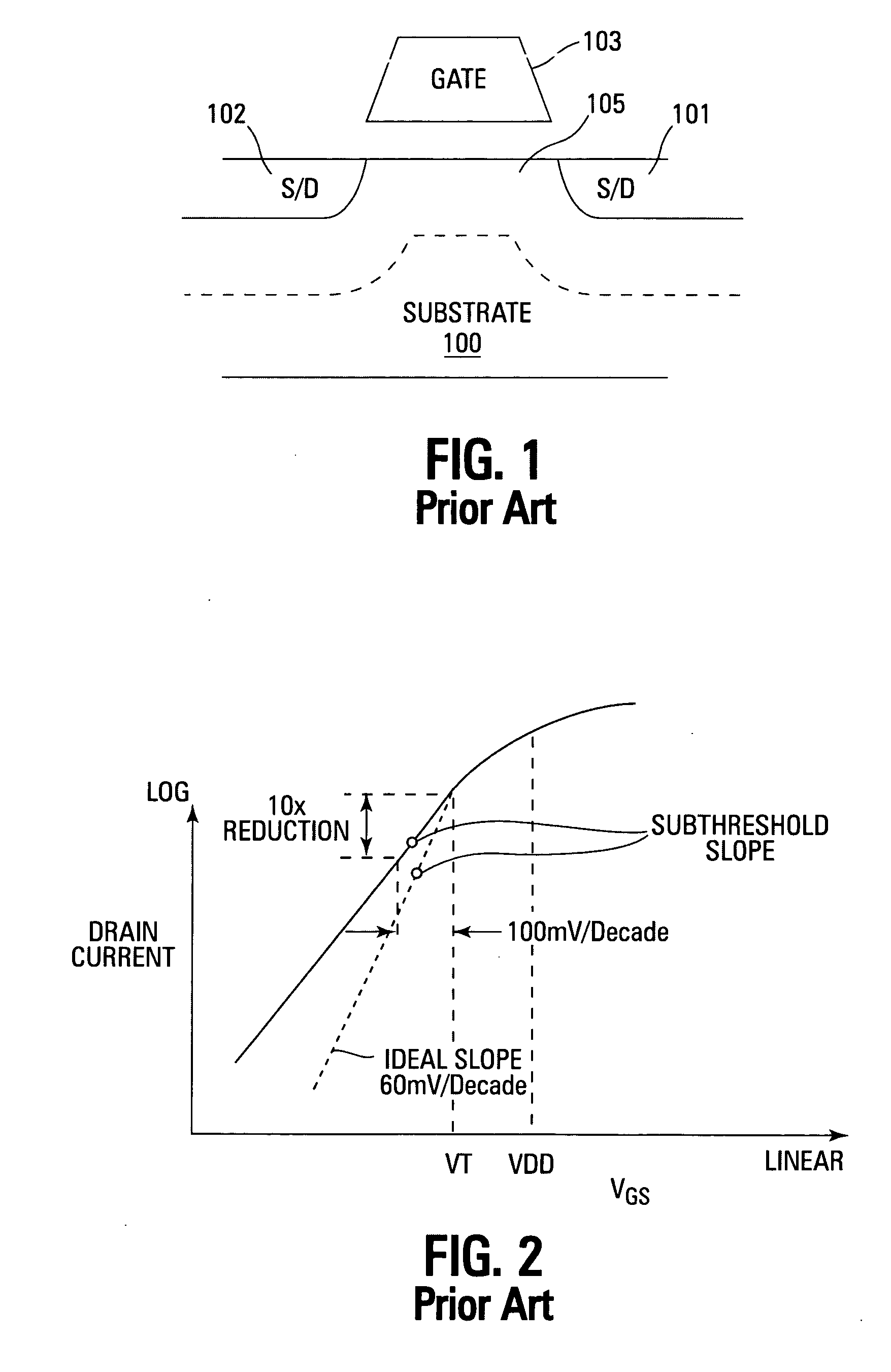

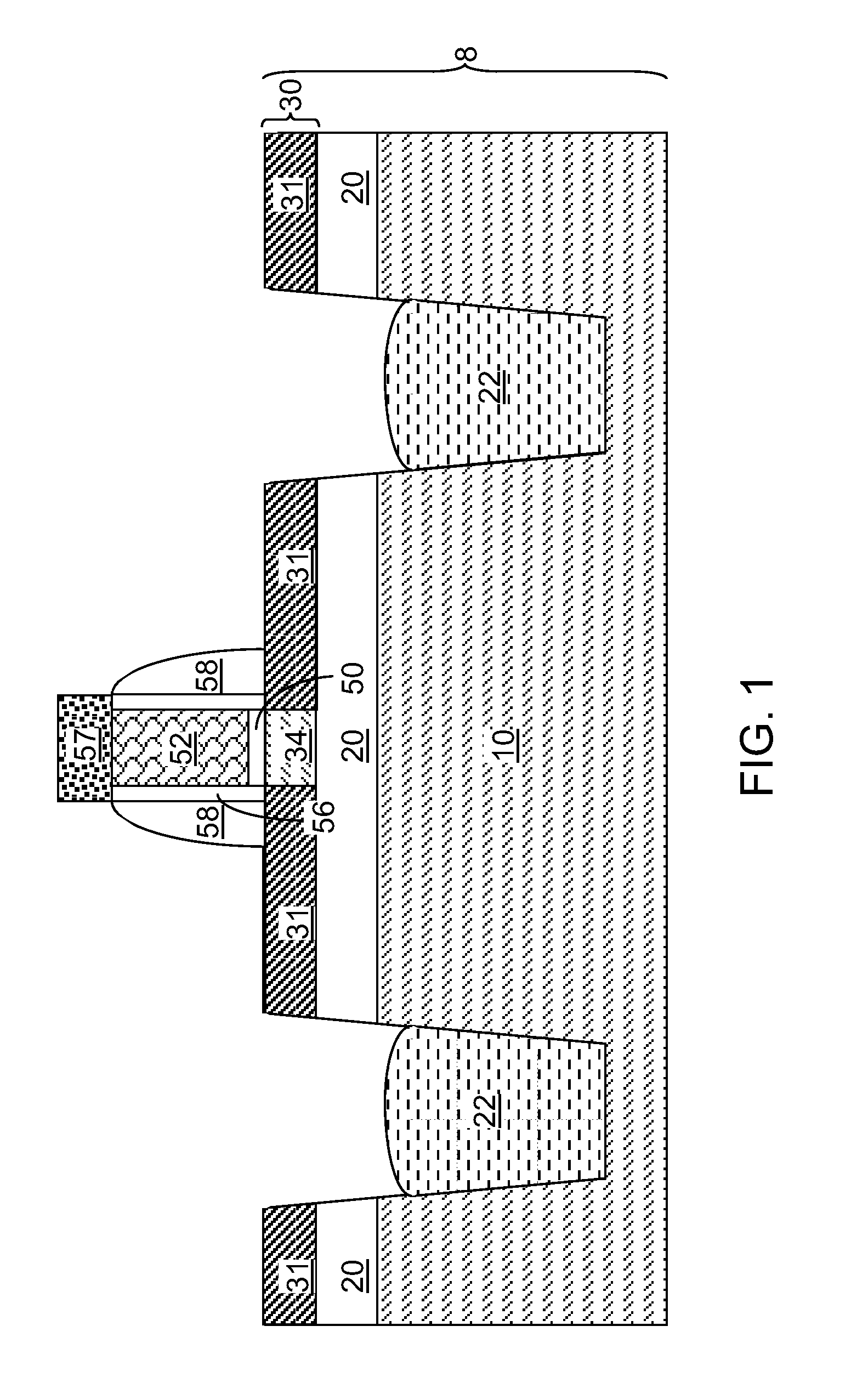

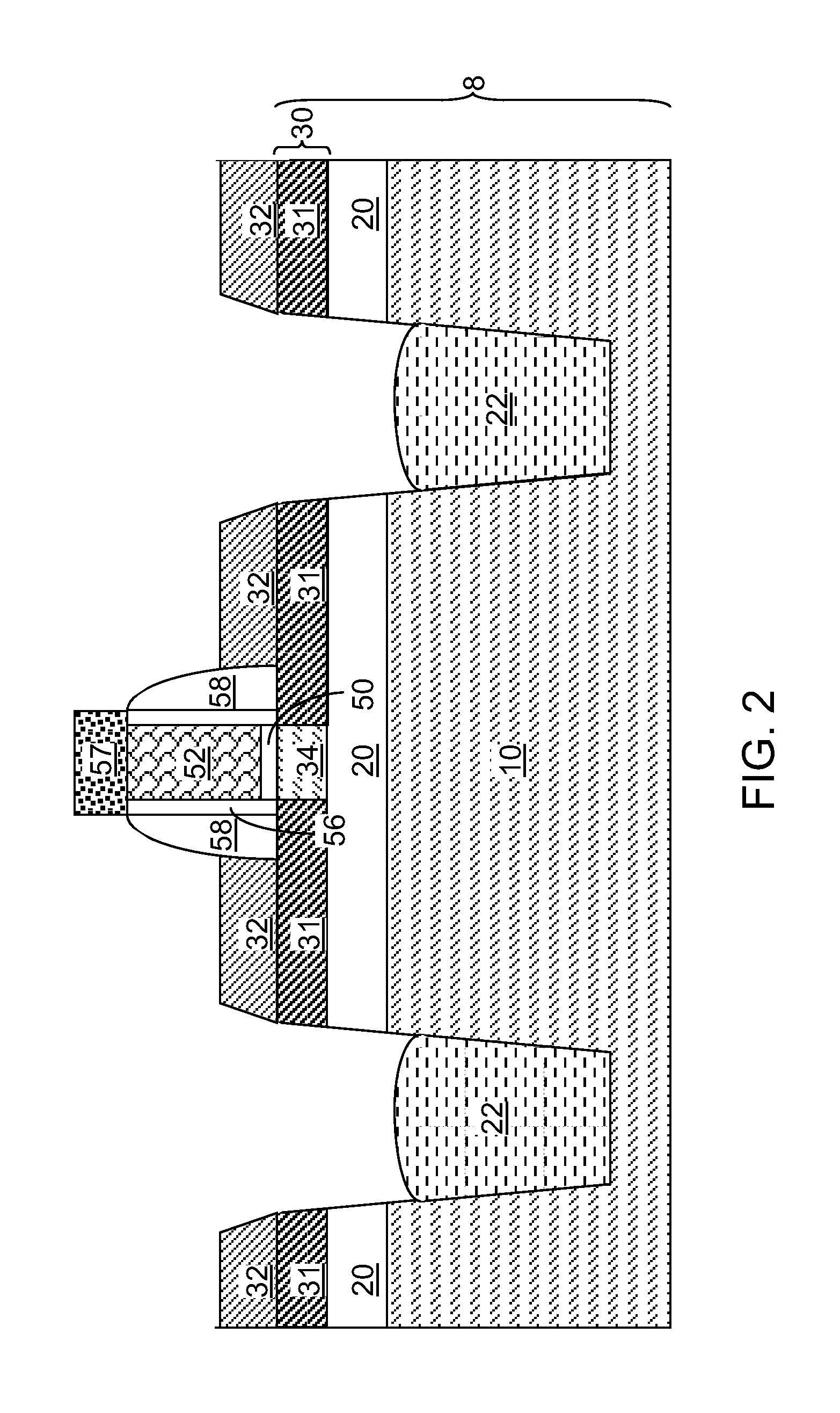

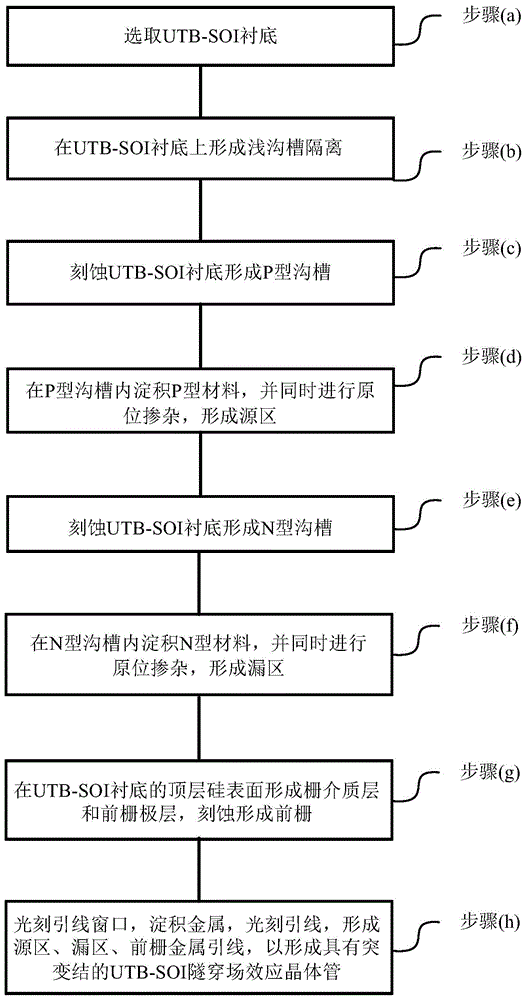

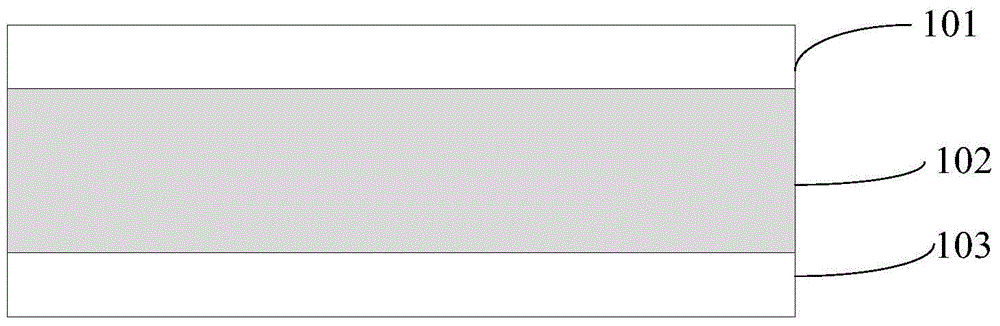

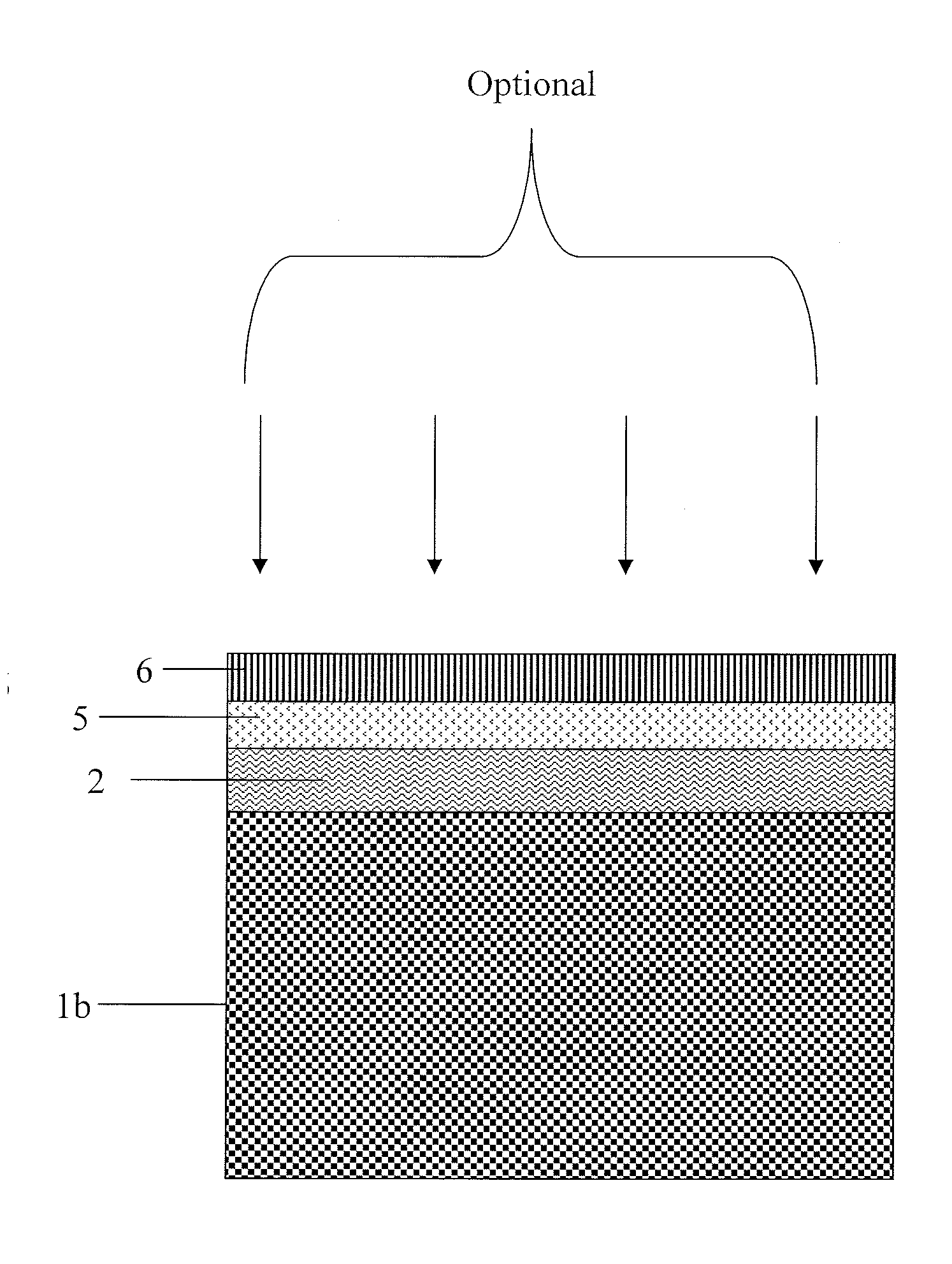

UTB-SOI tunneling field-effect transistor with abrupt junction and preparation method thereof

InactiveCN105118781AIncrease drive currentImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricConcentration gradient

The invention relates to an ultra-thin-body-silicon-on-insulator (UTB-SOI) tunneling field-effect transistor with an abrupt junction and a preparation method thereof. The preparation method comprises: selecting a UTB-SOI substrate; forming a shallow trench isolation unit; carrying out etching to form a P type / N type trench; carrying out silicon material deposition in the P type / N type trench and carrying out in-situ doping to form a P type / N type highly-doped source region; carrying out etching to form an N type / P type trench; carrying out silicon material deposition in the N type / P type trench and carrying out in-situ doping to form a low doped N type / P type drain region; forming a gate dielectric layer and a front gate layer on the top layer silicon surface of the substrate and carrying out etching to form a front gate; and carrying out lead window photoetching, metal deposition, and lead photoetching to form source region, drain region, and front gate metal leads. According to the invention, with the technique and preparation of trench etching and selective epitaxy deposition and filling at the source and drain regions, the tunnel junction area can be limited precisely; and on the basis of in-situ doping, the tunnel junction with the steep doping concentration gradient and the source and drain regions with uniform doping can be formed well and the driving current of the device can be effectively improved and the sub-threshold slope can be reduced.

Owner:XIAN UNIV OF SCI & TECH

Ultra-thin body super-steep retrograde well (ssrw) fet devices

ActiveCN1728402AGuaranteed normal transmissionEasy to controlTransistorSolid-state devicesDopantGround plane

The present invention provides a method of manufacture of a Super Steep Retrograde Well Field Effect Transistor device starts with an SOI layer formed on a substrate, e.g. a buried oxide layer. Thin the SOI layer to form an ultra-thin SOI layer. Form an isolation trench separating the SOI layer into N and P ground plane regions. Dope the N and P ground plane regions formed from the SOI layer with high levels of N-type and P-type dopant. Form semiconductor channel regions above the N and P ground plane regions. Form FET source and drain regions and gate electrode stacks above the channel regions. Optionally form a diffusion retarding layer between the SOI ground plane regions and the channel regions.

Owner:GLOBALFOUNDRIES INC

Ultra-thin body vertical tunneling transistor

A vertical tunneling, ultra-thin body transistor is formed on a substrate out of a vertical oxide pillar having active regions of opposing conductivity on opposite ends of the pillar. In one embodiment, the source region is a p+ region in the substrate under the pillar and the drain region is an n+ region at the top of the pillar. A gate structure is formed along the pillar sidewalls and over the body layers. The transistor operates by electron tunneling from the source valence band to the gate bias-induced n-type channels, along the ultra-thin silicon bodies, thus resulting in a drain current.

Owner:MICRON TECH INC

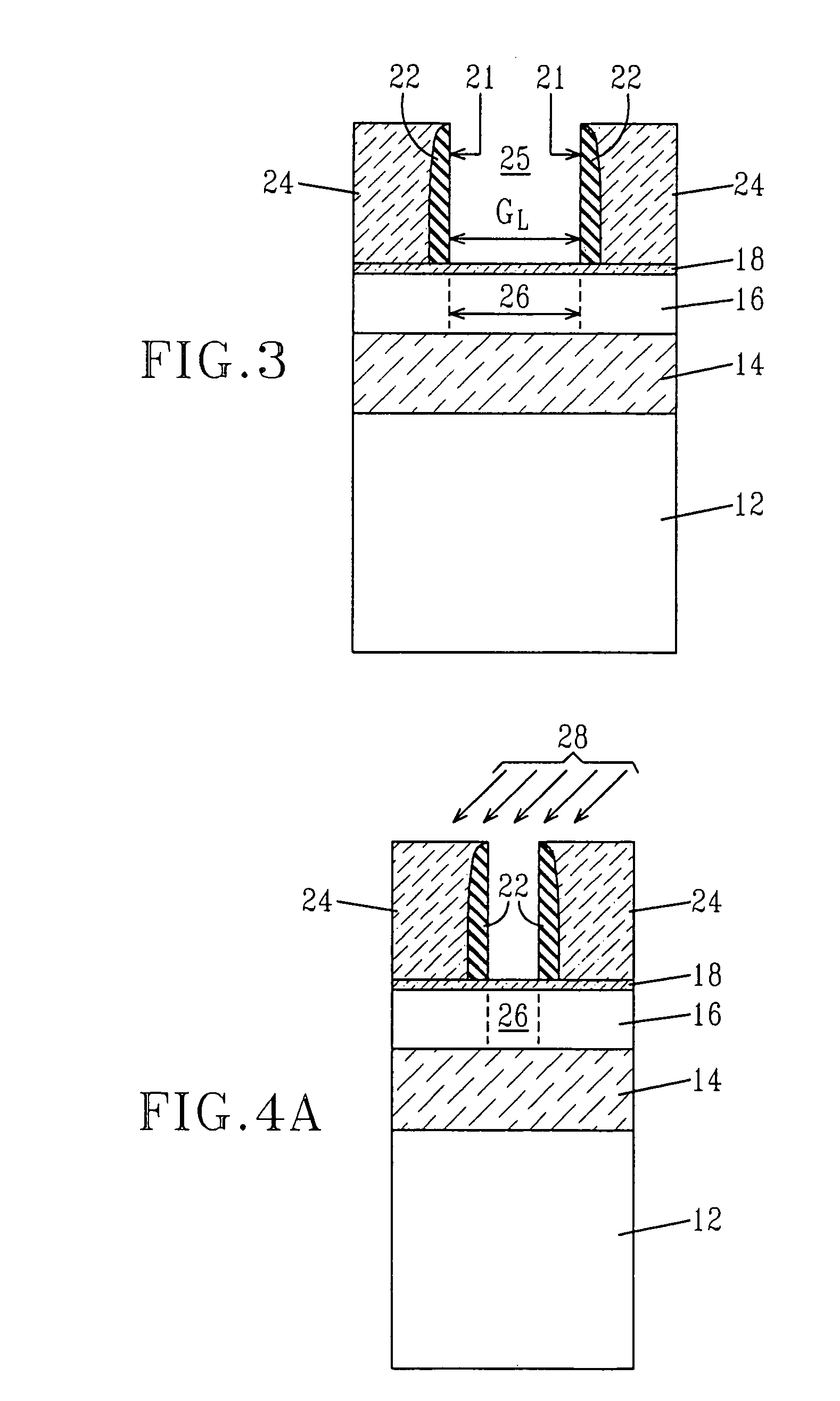

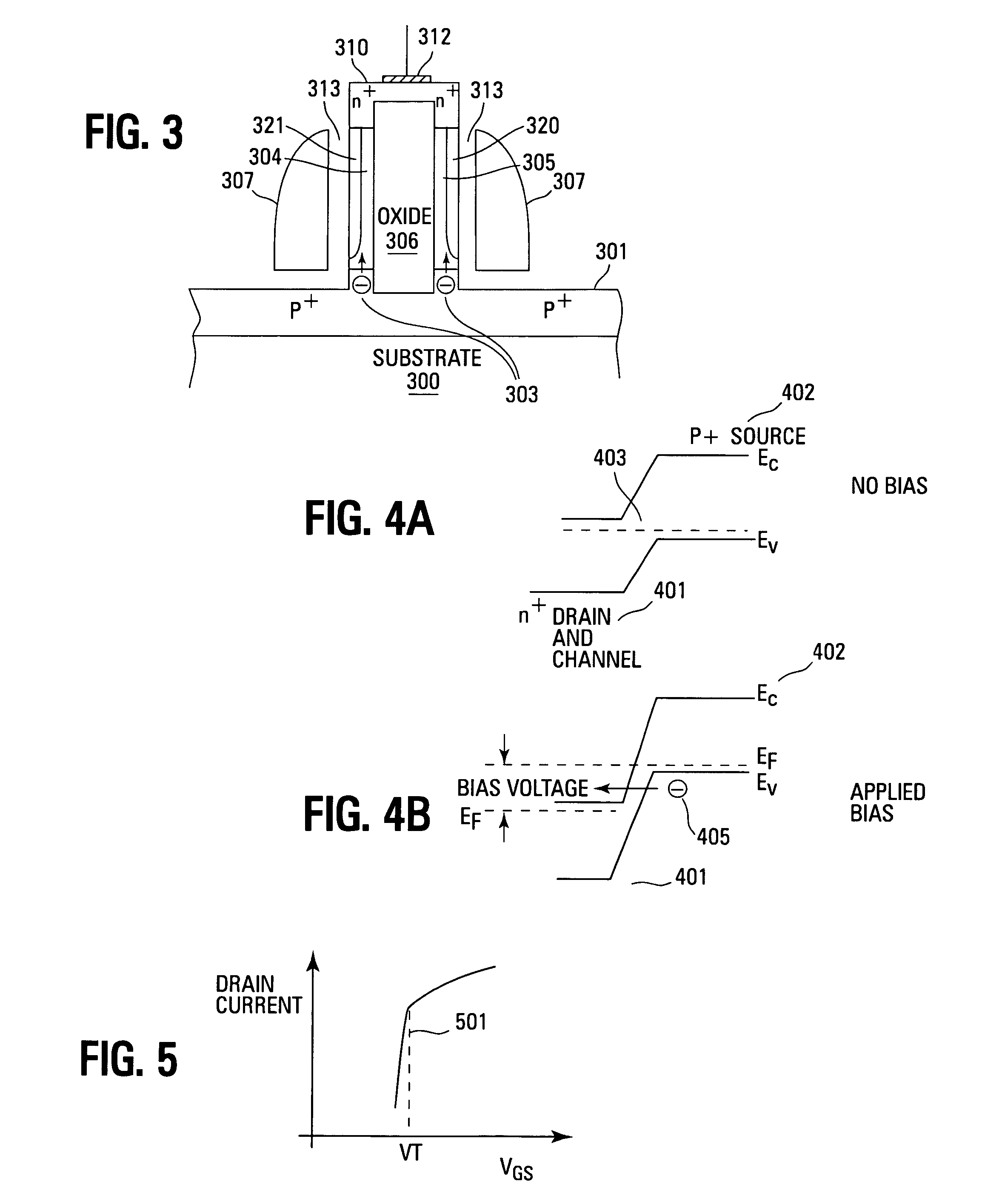

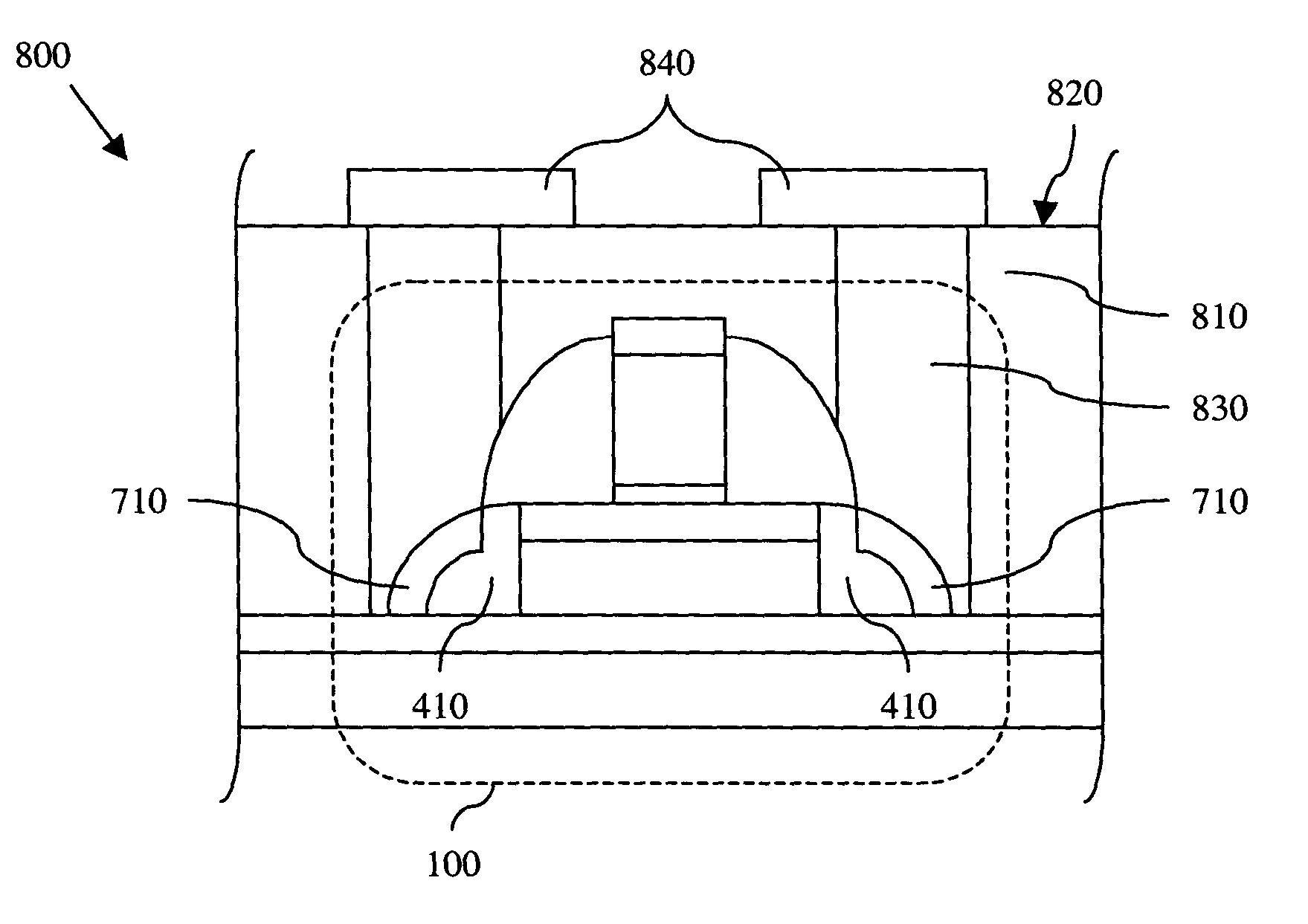

Ultra-thin body transistor with recessed silicide contacts

InactiveUS20050045949A1Avoid insufficient thicknessIncreasing the thicknessTransistorSolid-state devicesDielectricDevice material

A semiconductor device (100), including a dielectric pedestal (220) located above and integral to a substrate (110) and having first sidewalls (230), a channel region (210) located above the dielectric pedestal (220) and having second sidewalls (240), and source and drain regions (410) opposing the channel region (210) and each substantially spanning one of the second sidewalls (240). An integrated circuit (800) incorporating the semiconductor device (100) is also disclosed, as well as a method of manufacturing the semiconductor device (100).

Owner:TAIWAN SEMICON MFG CO LTD

Surround gate access transistors with grown ultra-thin bodies

ActiveUS20070066019A1Good conductivityAvoid difficultySolid-state devicesSemiconductor/solid-state device manufacturingLateral asymmetryBit line

Owner:MICRON TECH INC

Borderless contact for ultra-thin body devices

ActiveUS8383490B2Solid-state devicesSemiconductor/solid-state device manufacturingUltra thin bodyDielectric layer

After formation of a semiconductor device on a semiconductor-on-insulator (SOI) layer, a first dielectric layer is formed over a recessed top surface of a shallow trench isolation structure. A second dielectric layer that can be etched selective to the first dielectric layer is deposited over the first dielectric layer. A contact via hole for a device component located in or on a top semiconductor layer is formed by an etch. During the etch, the second dielectric layer is removed selective to the first dielectric layer, thereby limiting overetch into the first dielectric layer. Due to the etch selectivity, a sufficient amount of the first dielectric layer is present between the bottom of the contact via hole and a bottom semiconductor layer, thus providing electrical isolation for the ETSOI device from the bottom semiconductor layer.

Owner:GLOBALFOUNDRIES U S INC

Method to reduce ground-plane poisoning of extremely-thin soi (ETSOI) layer with thin buried oxide

ActiveUS20120112207A1Reduce rateLow and no defectSolid-state devicesSemiconductor/solid-state device manufacturingDopantUltra thin body

Owner:GLOBALFOUNDRIES US INC

Methods of forming a non-planar ultra-thin body device

InactiveUS20150255555A1Well formedTransistorSolid-state devicesInsulation layerSemiconductor materials

One illustrative method disclosed herein involves, among other things, forming a first epi semiconductor material on the exposed opposite sidewalls of a fin to thereby define a semiconductor body, performing at least one etching process to remove at least a portion of the substrate portion of the fin positioned between the first epi semiconductor materials positioned on the opposite sidewalls of the fin and to thereby define a back-gate cavity, forming a back-gate insulating material within the back-gate cavity and on the first epi semiconductor materials, forming a back-gate electrode on the back-gate insulation material within the back-gate cavity and forming a gate structure comprised of a gate insulation layer and a gate electrode around the semiconductor bodies.

Owner:GLOBALFOUNDRIES INC

Self-aligned contact for silicon-on-insulator devices

A method for forming a self-aligned contact to an ultra-thin body transistor first providing an ultra-thin body transistor with source and drain regions operated by a gate stack; forming a contact spacer on the gate stack; forming a passivation layer overlying the transistor; forming a contact hole in the passivation layer exposing the contact spacer and the source / drain regions; filling the contact hole with an electrically conductive material; and establishing electrical communication with the source / drain region.

Owner:TAIWAN SEMICON MFG CO LTD

Self-aligned contact for silicon-on-insulator devices

A method for forming a self-aligned contact to an ultra-thin body transistor first providing an ultra-thin body transistor with source and drain regions operated by a gate stack; forming a contact spacer on the gate stack; forming a passivation layer overlying the transistor; forming a contact hole in the passivation layer exposing the contact spacer and the source / drain regions; filling the contact hole with an electrically conductive material; and establishing electrical communication with the source / drain region.

Owner:TAIWAN SEMICON MFG CO LTD

Method of making ultra thin body vertical replacement gate MOSFET

InactiveUS20040152269A1Semiconductor/solid-state device manufacturingSemiconductor devicesThin oxideThin layer

Owner:BELL SEMICON LLC

Process for ultra-thin body SOI devices that incorporate EPI silicon tips and article made thereby

InactiveUS7422971B2Small sizeTransistorSemiconductor/solid-state device manufacturingGate stackUltra thin body

The invention relates to a transistor that includes an ultra-thin body epitaxial layer that forms an embedded junction with a channel that has a length dictated by an undercut under the gate stack for the transistor. The invention also relates to a process of forming the transistor and to a system that incorporates the transistor.

Owner:INTEL CORP

Single-side gate fin field effect transistor and manufacturing method thereof

InactiveCN102270661ASolve the problem of electrical couplingTransistorSolid-state devicesEngineeringUltra thin body

A single-gate FinFET structure includes an active fin structure having two enlarged head portions and a tapered neck portion that connects the enlarged head portions with an underlying ultra-thin body. Two source / drain regions are doped in the two enlarged head portions respectively. An insulation region is interposed between the two source / drain regions. A trench isolation structure is disposed at one side of the tuning fork-shaped fin structure. A single-sided sidewall gate electrode is disposed on a vertical sidewall of the active fin structure opposite to the trench isolation structure.

Owner:NAN YA TECH