Single-side gate fin field effect transistor and manufacturing method thereof

A field-effect transistor and fin-shaped technology, applied in the field of single-side gate fin-shaped field-effect transistors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

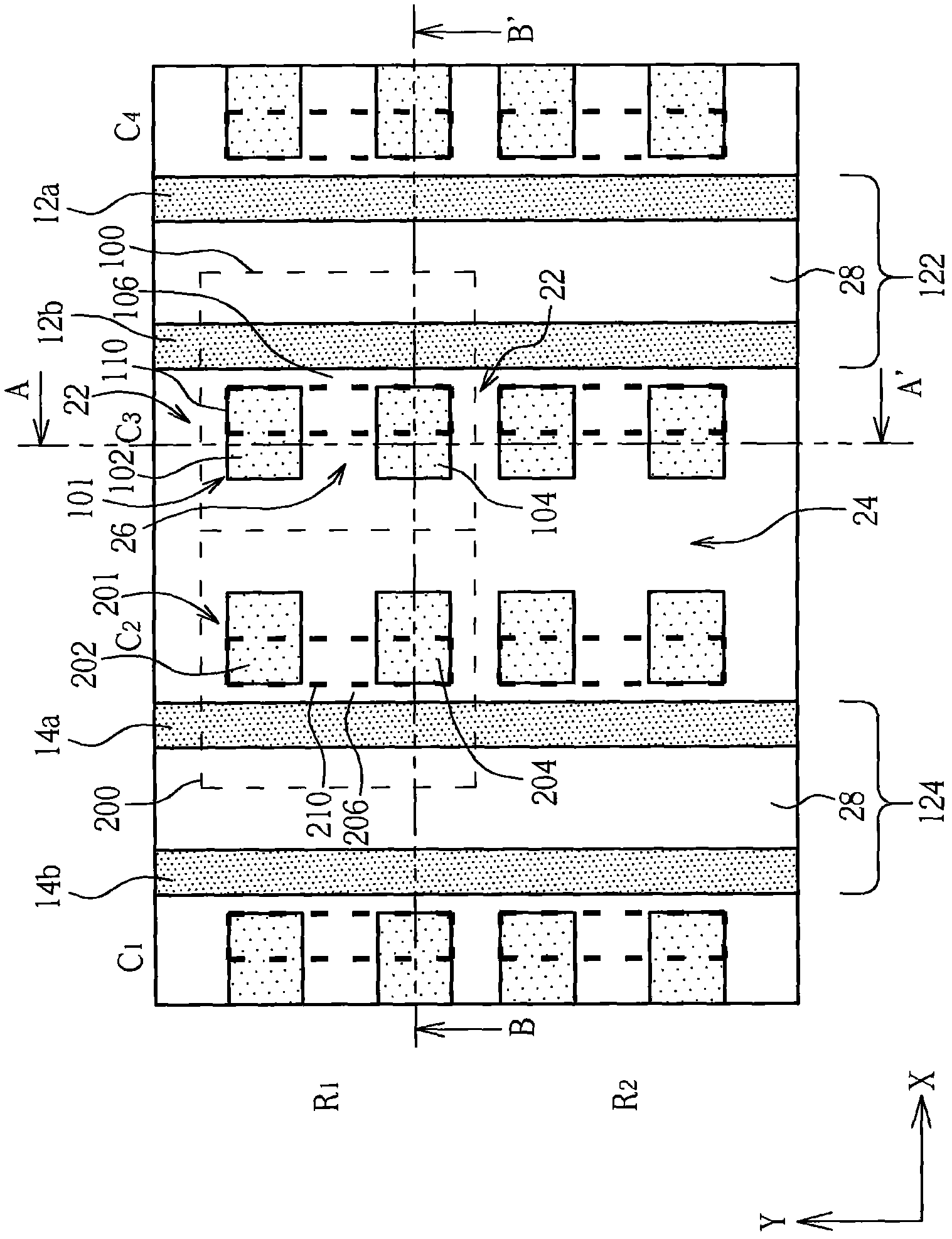

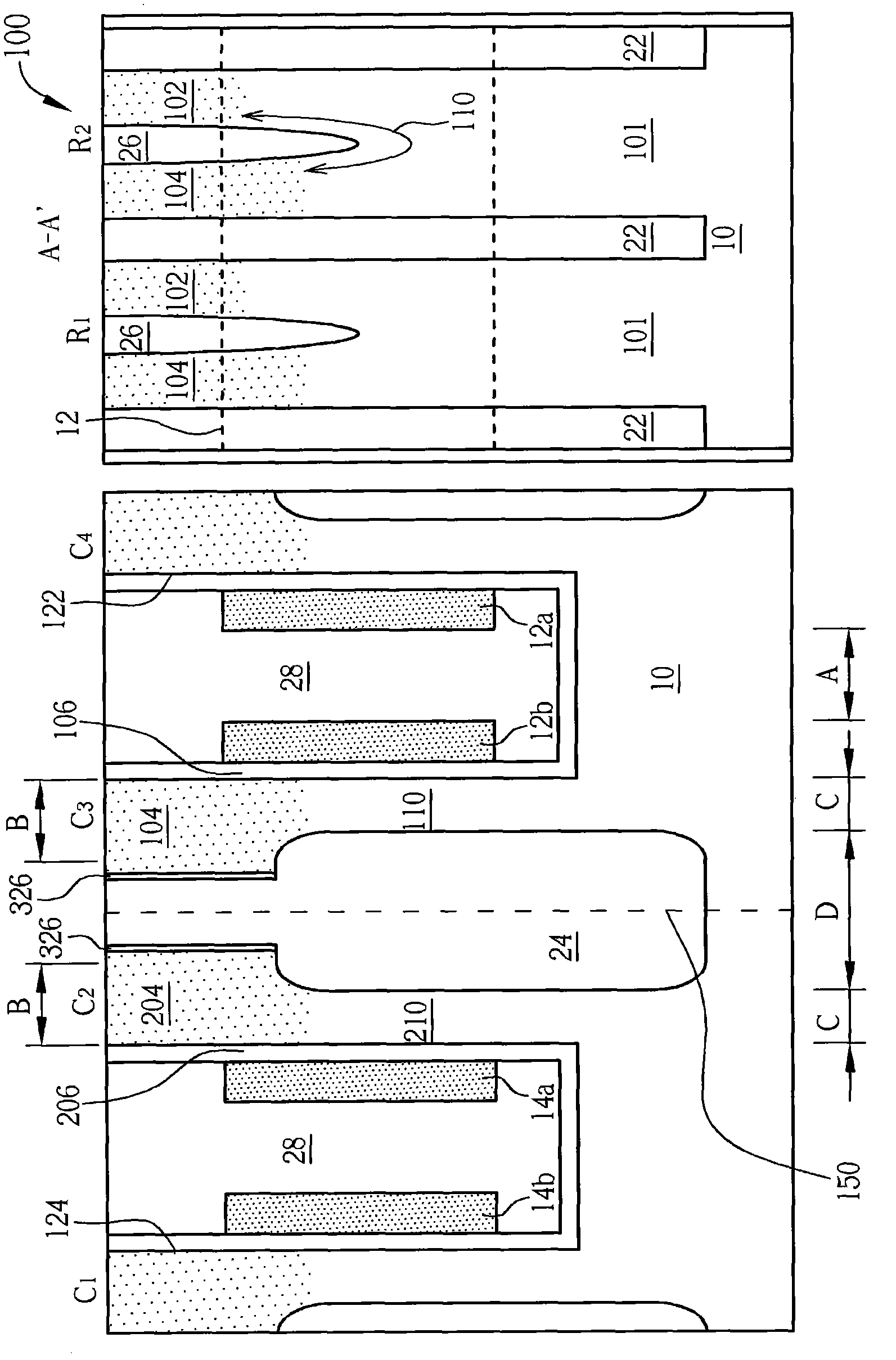

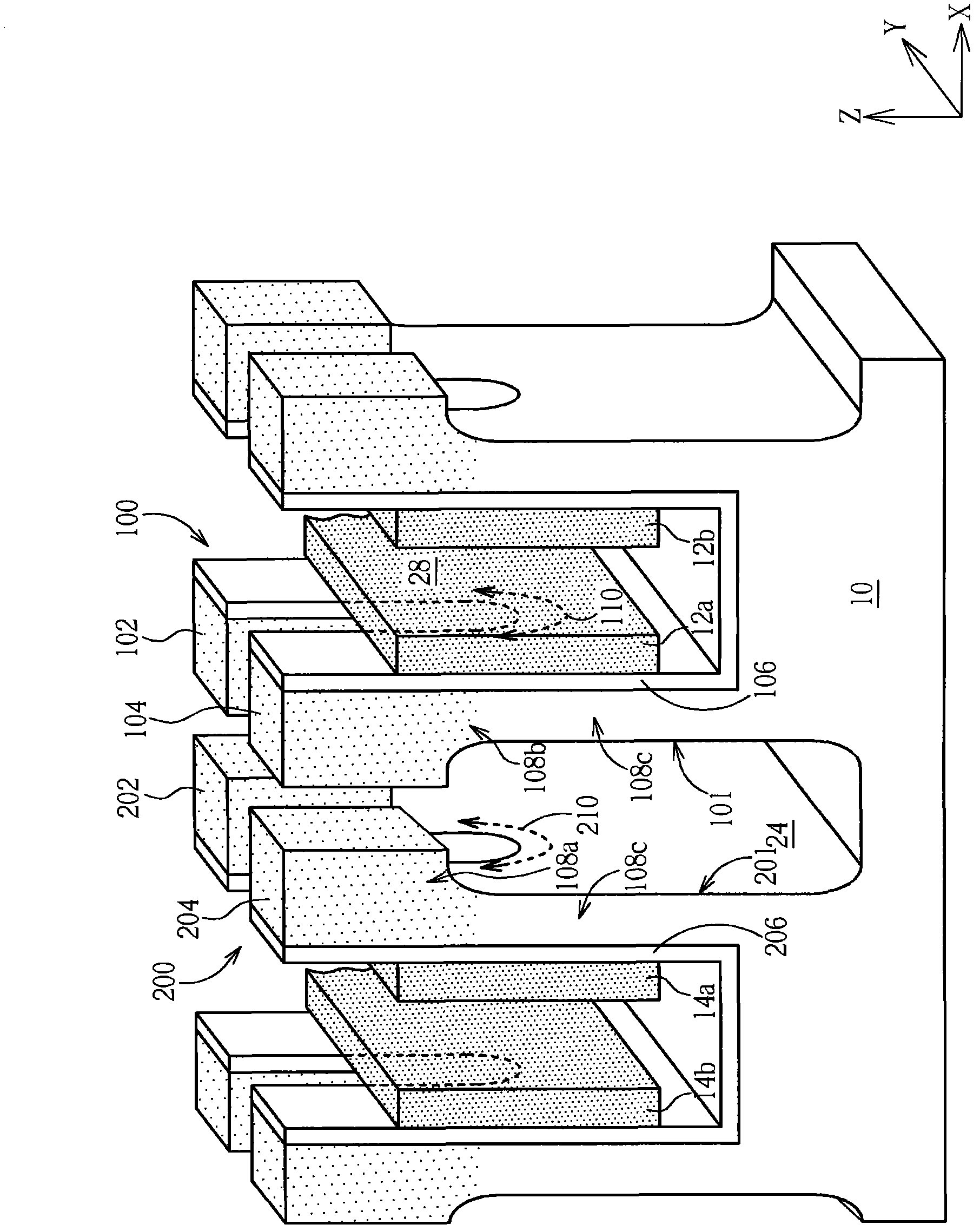

[0019] Although the present invention is disclosed as follows with examples, it is not intended to limit the present invention. Any person skilled in the art may make some changes and modifications without departing from the spirit and scope of the present invention. Therefore, the protection of the present invention The scope should be defined by the claims, and in order not to obscure the spirit of the present invention, details of some well-known structures and process steps will not be disclosed herein.

[0020] Likewise, the figures shown are schematic diagrams of the devices in the embodiments but are not intended to limit the size of the devices. In particular, in order to make the present invention more clearly presented, the sizes of some components may be enlarged in the figures. Furthermore, the same components disclosed in multiple embodiments will be marked with the same or similar symbols to make the description easier and clearer.

[0021] "Horizontal" referred ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More