Patents

Literature

381results about How to "Accurate spacing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

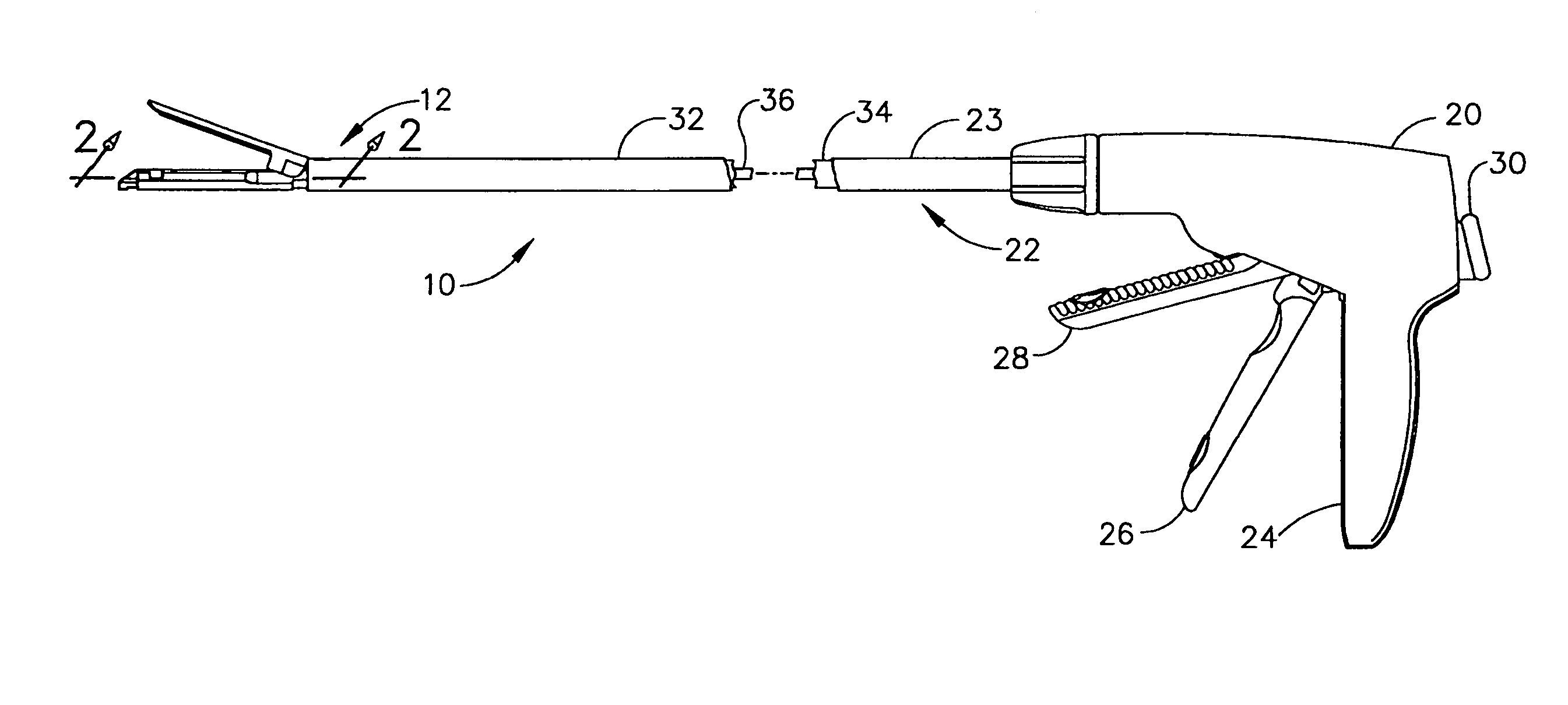

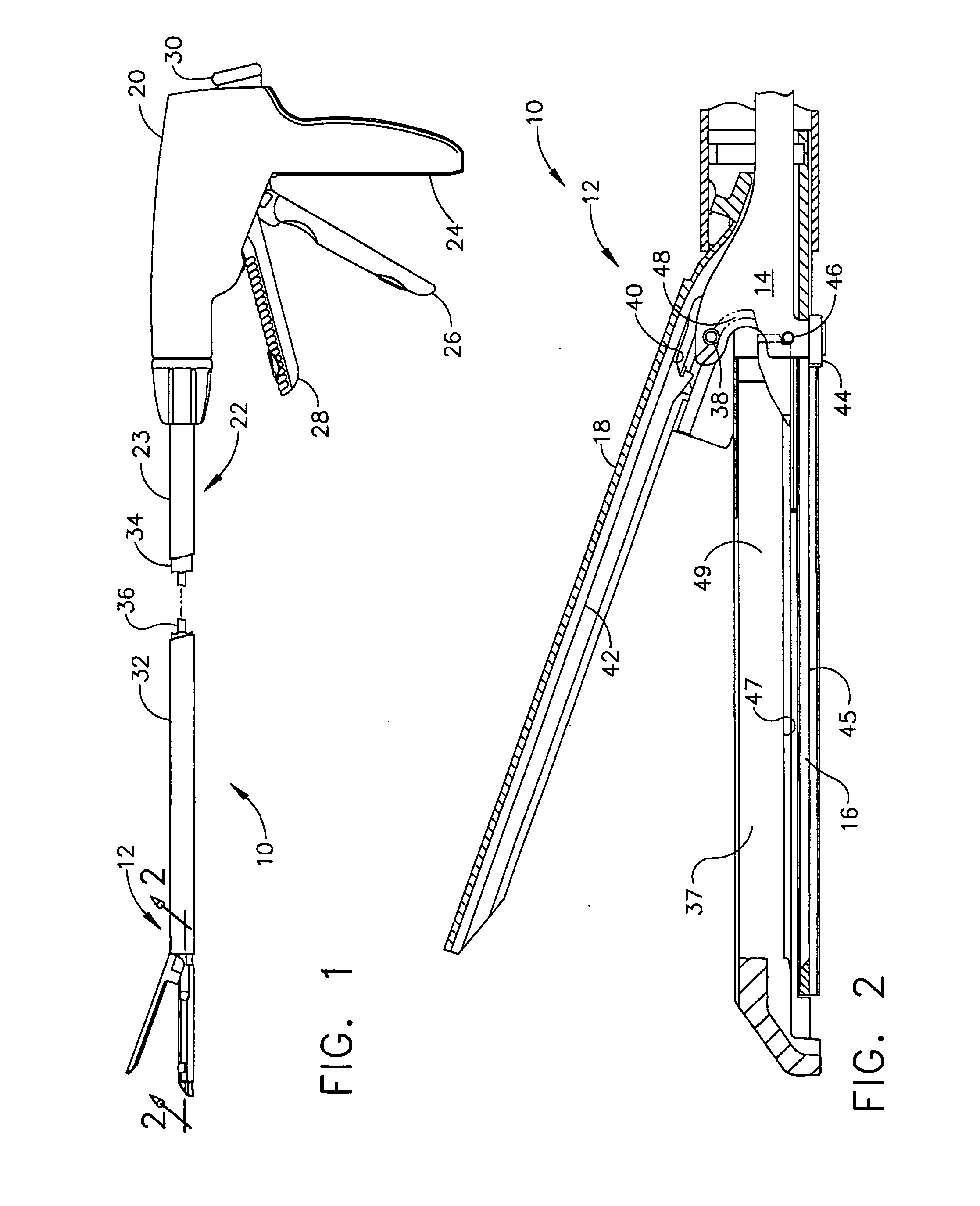

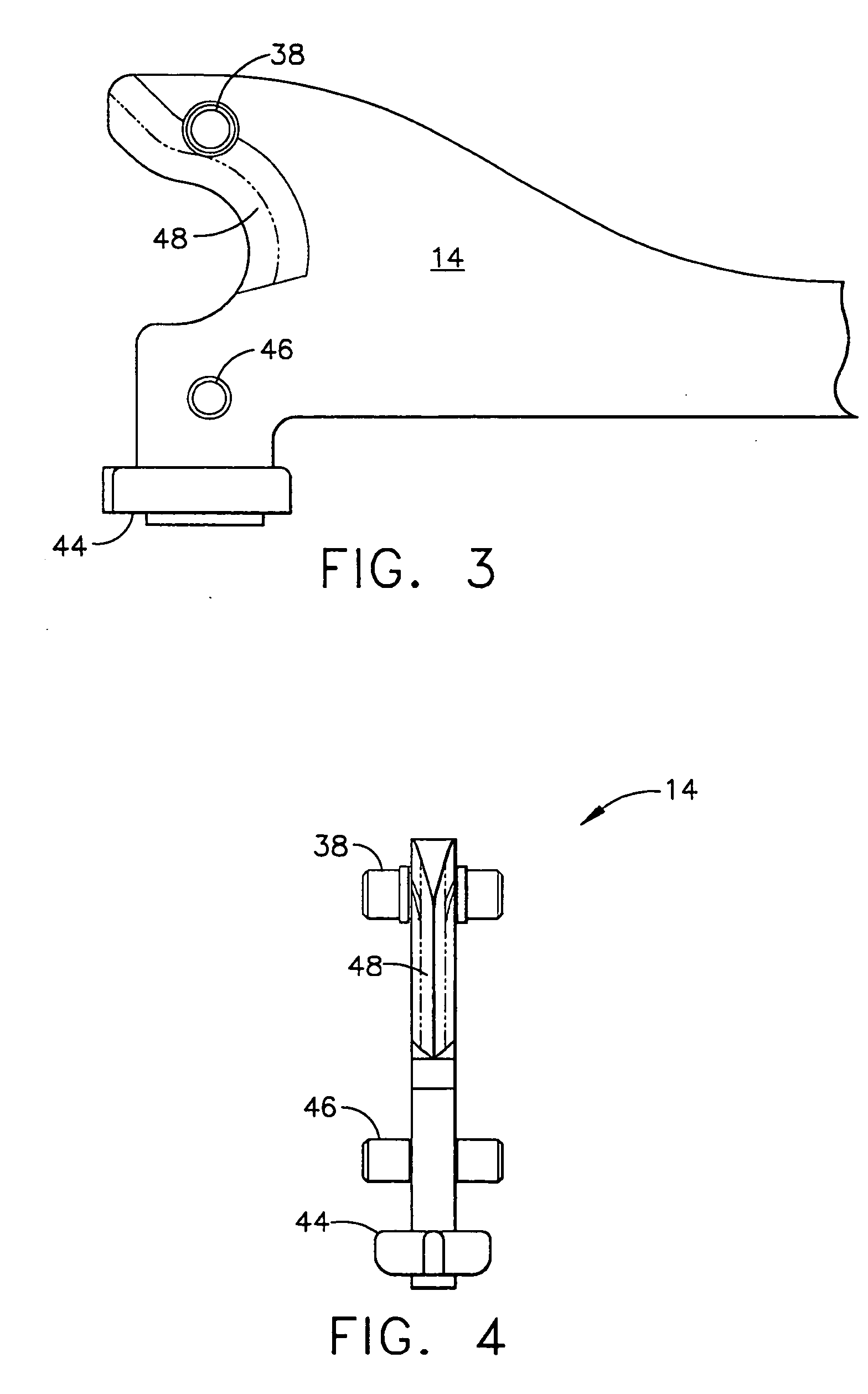

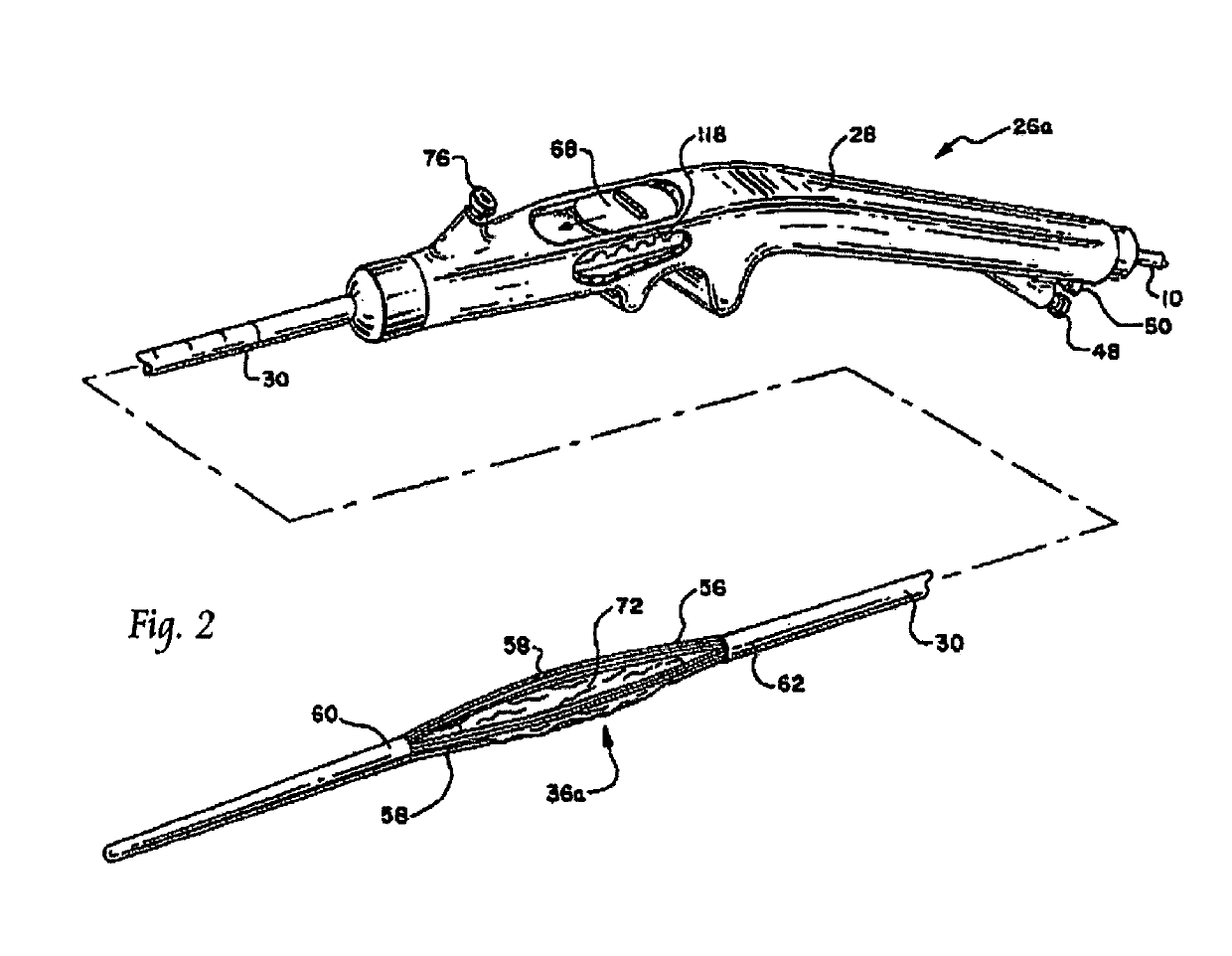

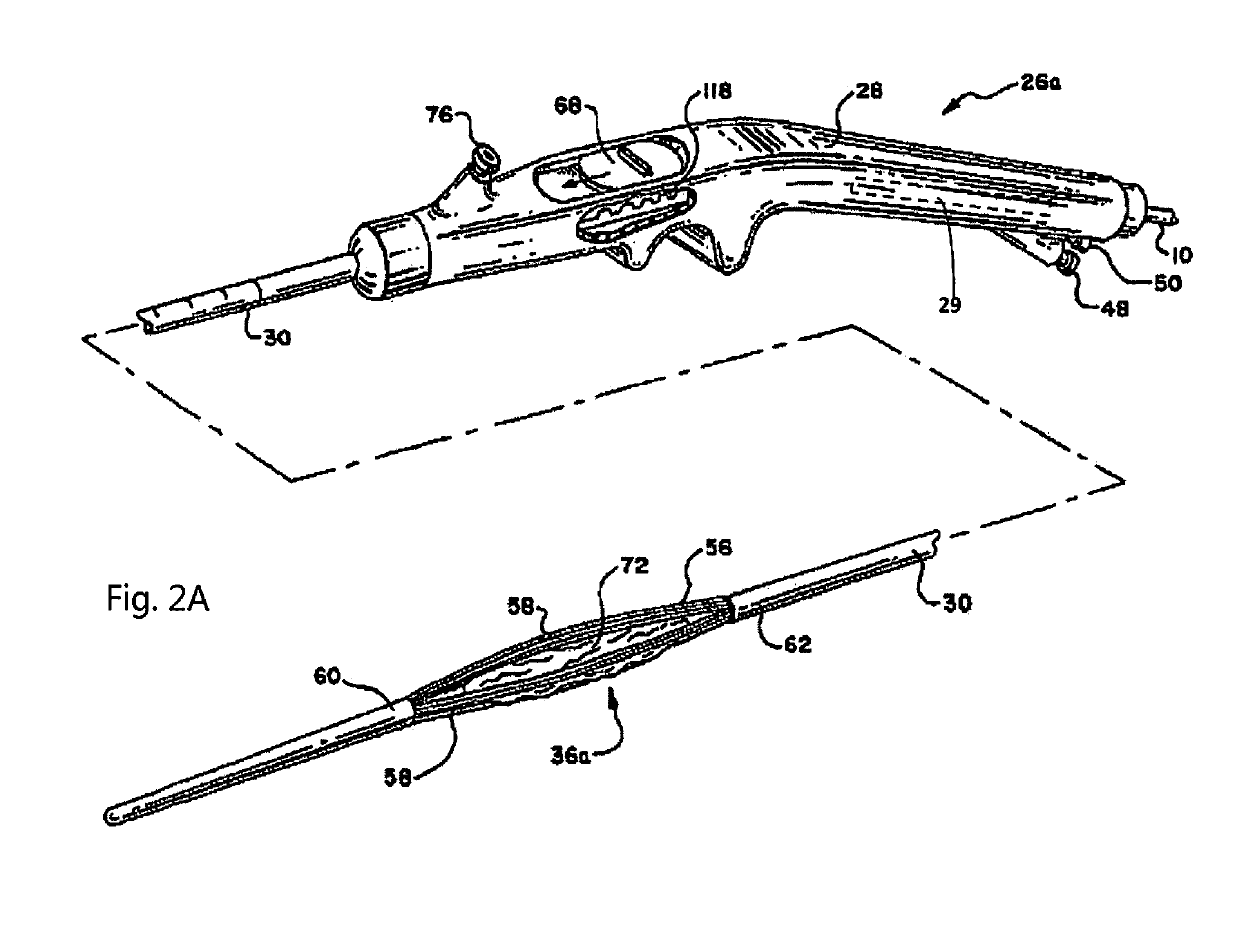

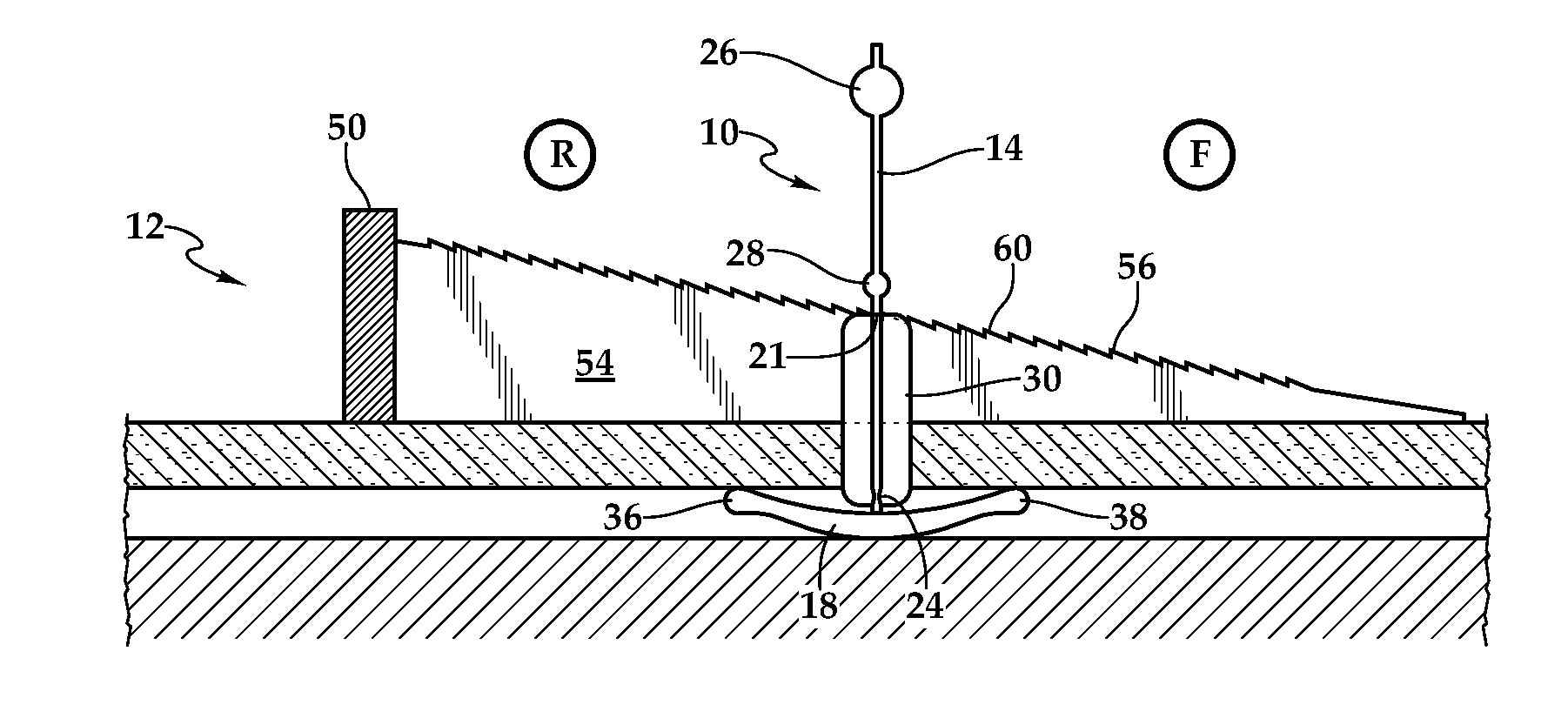

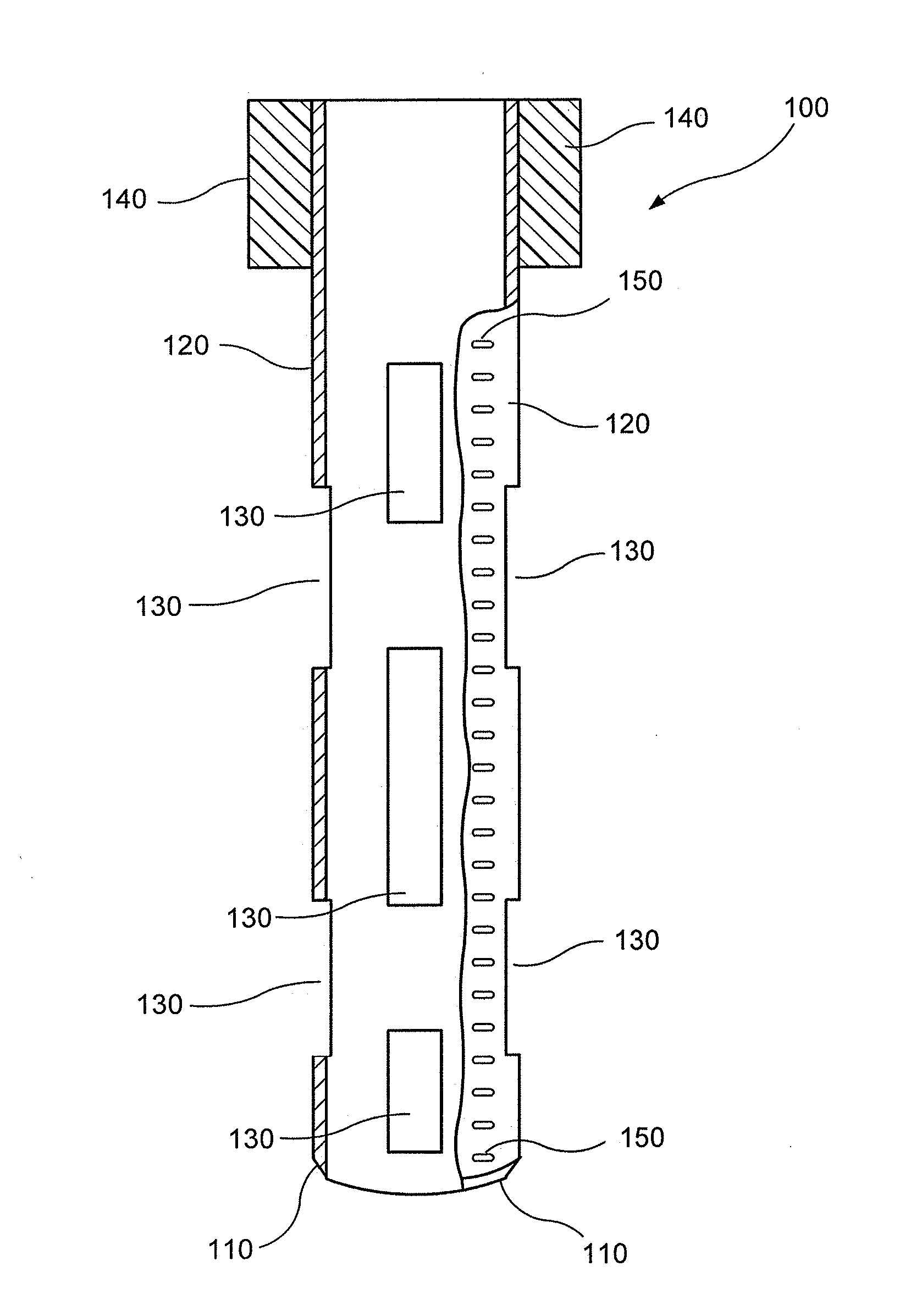

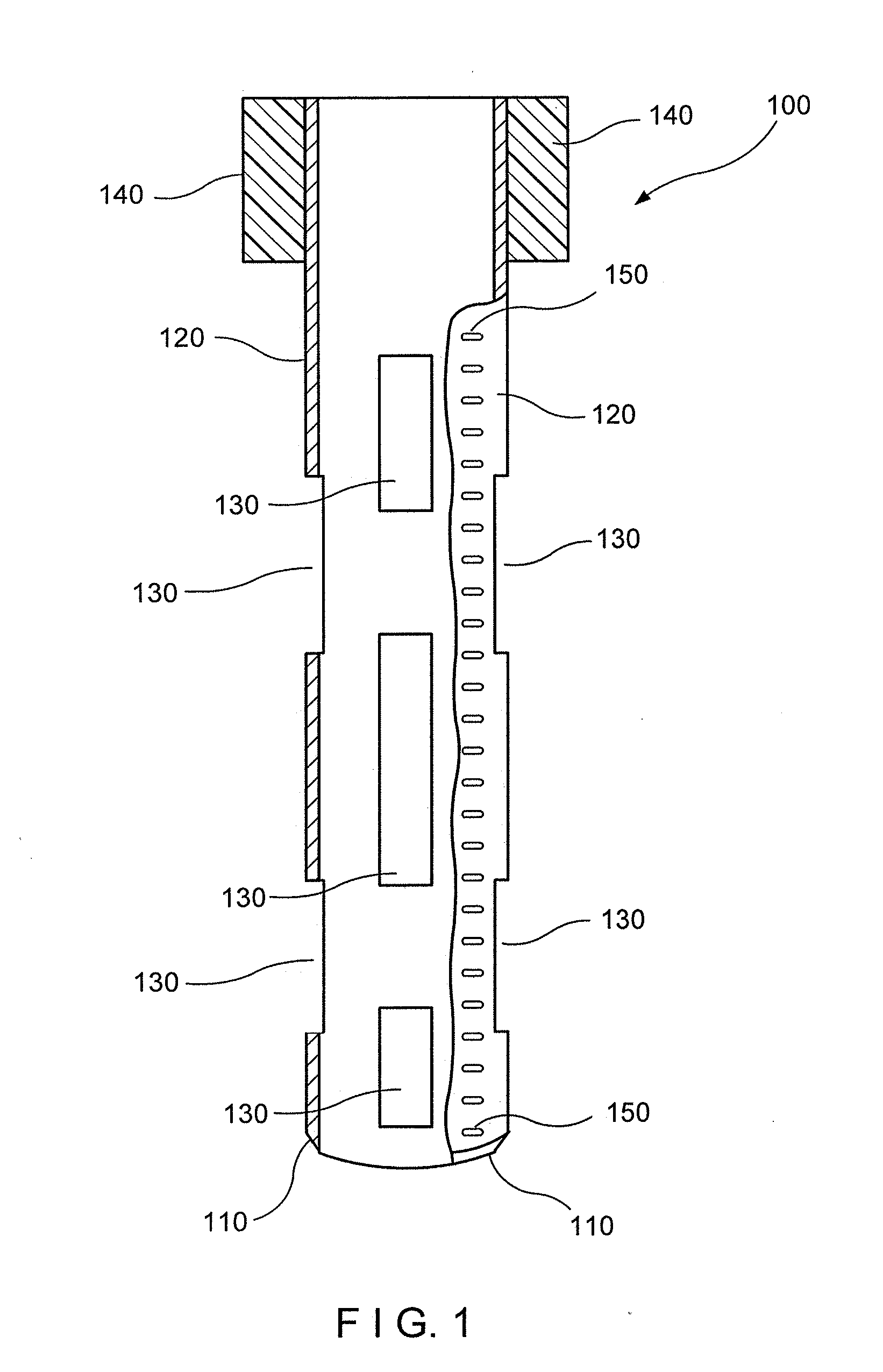

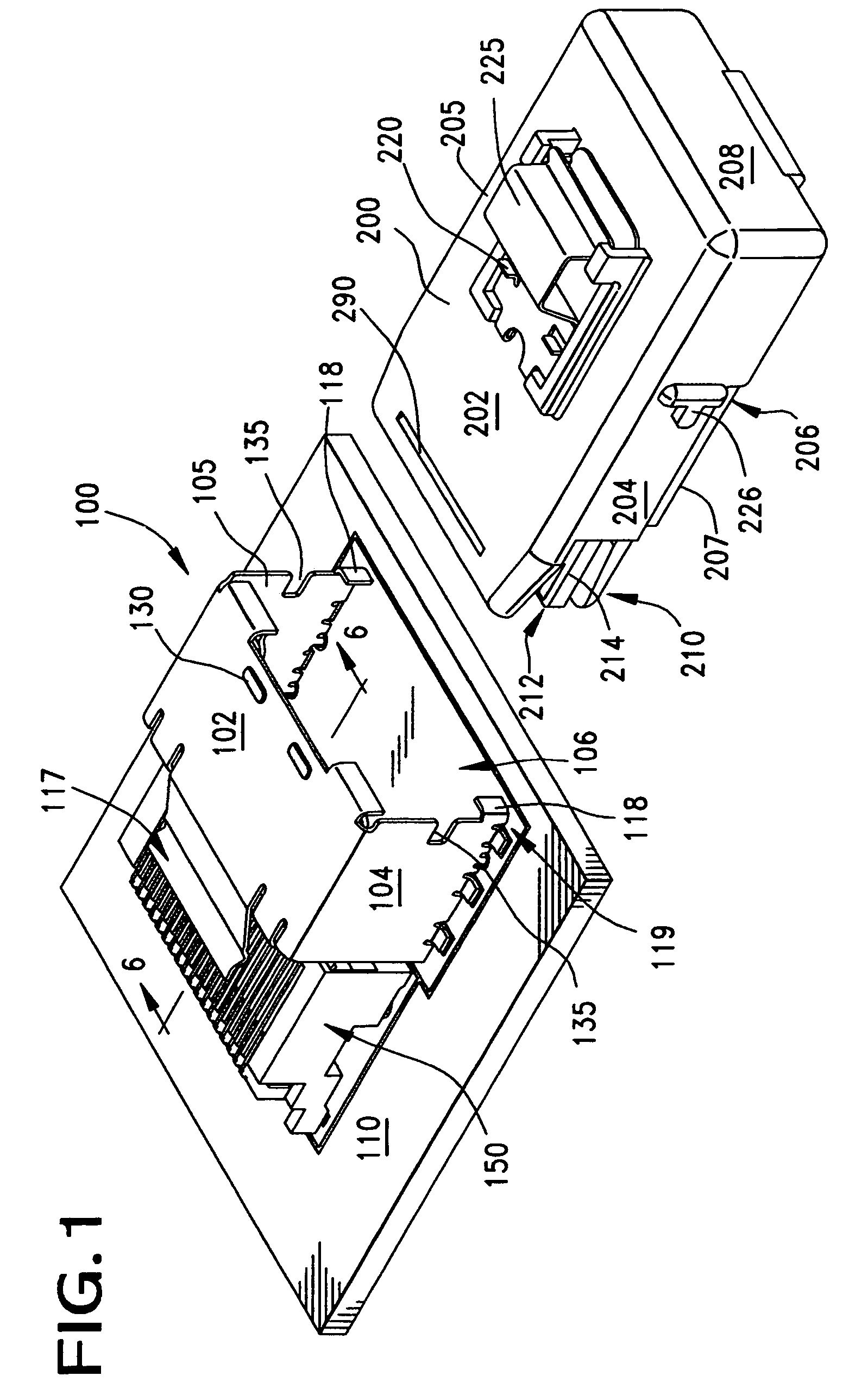

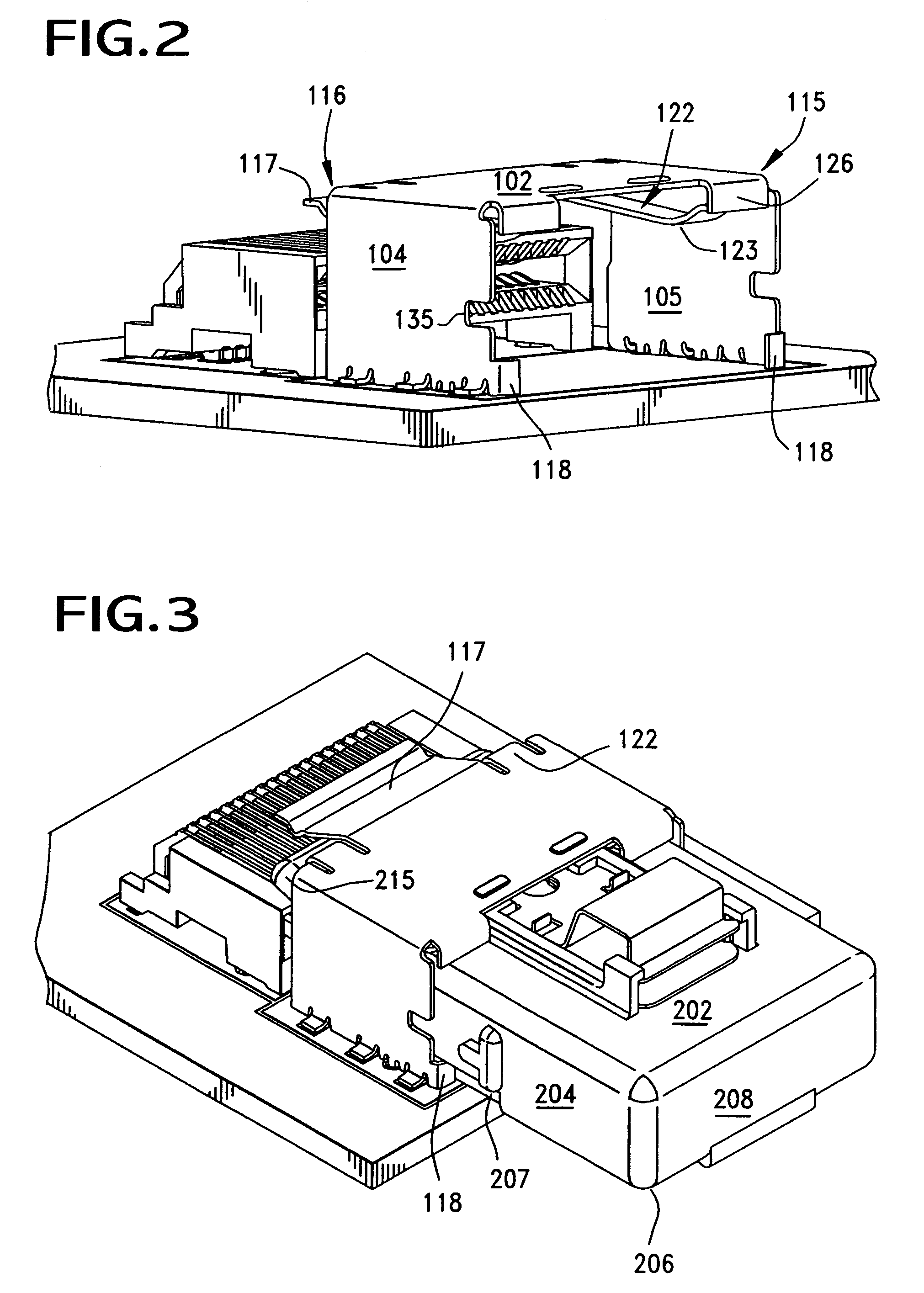

Surgical stapling instrument having a firing lockout for an unclosed anvil

InactiveUS20070010838A1Accurate spacingExpand selectionDiagnosticsSurgical staplesSurgical staplePERITONEOSCOPE

A surgical instrument for laparoscopic and endoscopic clinical procedures simultaneously severs and staples tissue clamped in an end effector comprising an elongate channel, which holds a staple cartridge, and a pivotally attached anvil. An E-beam firing bar engages the channel and selectively engages the anvil during distal firing movements, wherein the tissue is severed and stapled driven upward from the staple cartridge to form against the anvil. In particular an upper pin of the firing bar is disengaged from the anvil before firing. A ramped transition from an anvil to an anvil slot avoids misfiring when the end effector has clamped too much tissue, yet assists in successfully clamping a slightly excess amount of tissue.

Owner:CILAG GMBH INT

Systems and methods for treating tissue with radiofrequency energy

ActiveUS10386990B2Reduce morbidityAccurate CalibrationPhysical therapies and activitiesDiagnosticsThermal treatmentRadio frequency

A system for controlling operation of a radiofrequency treatment device to apply radiofrequency energy to tissue to heat tissue to create lesions without ablating the tissue. The system includes a first treatment device having at least one electrode for applying radiofrequency energy to tissue, a controller including a connector to which a first treatment device is coupled for use, and a generator for applying radiofrequency energy to the electrodes. The controller controls application of energy so that the tissue is thermally treated to create lesions but preventing thermal treatment beyond a threshold which would ablate the tissue.

Owner:MEDERI RF LLC

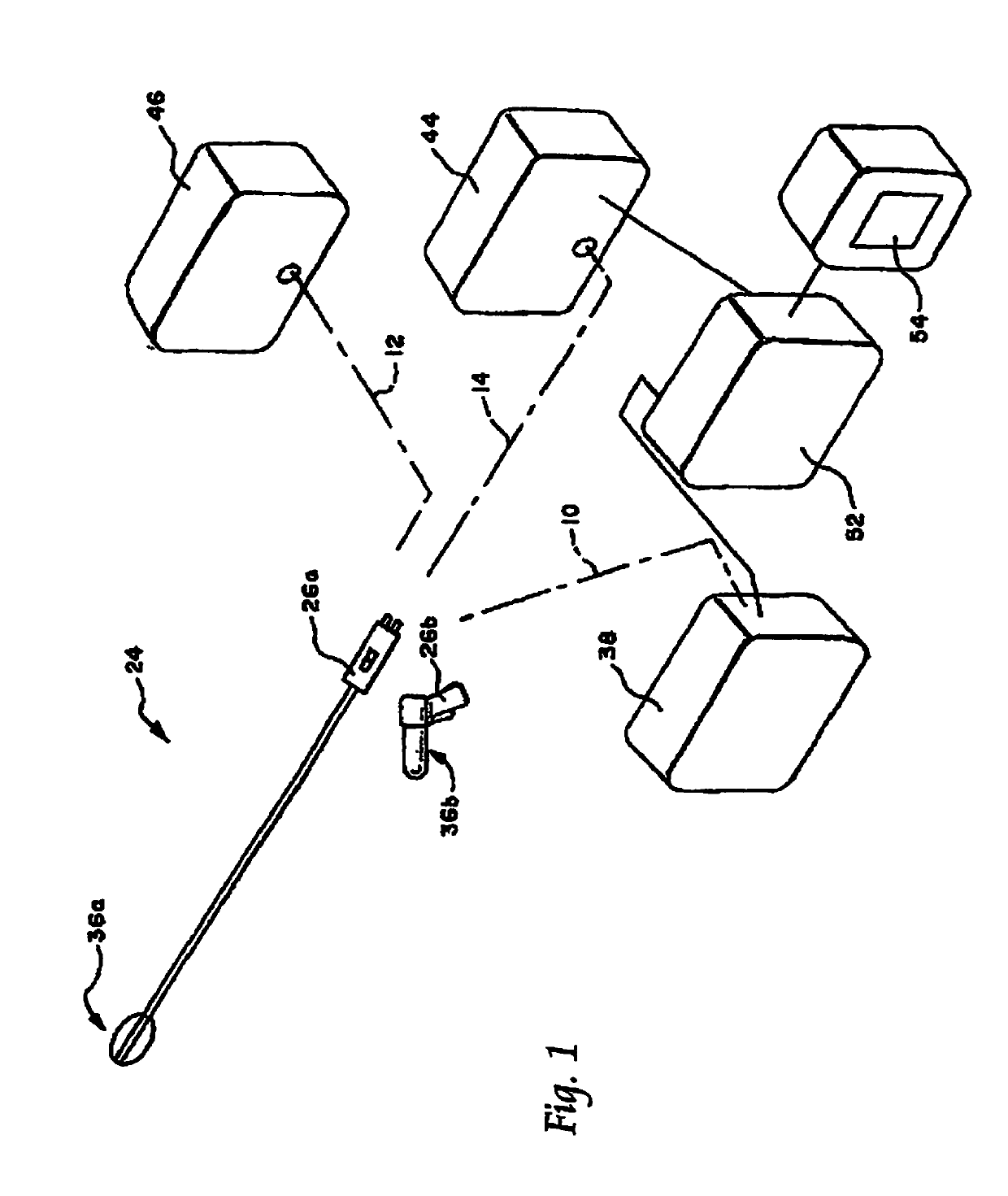

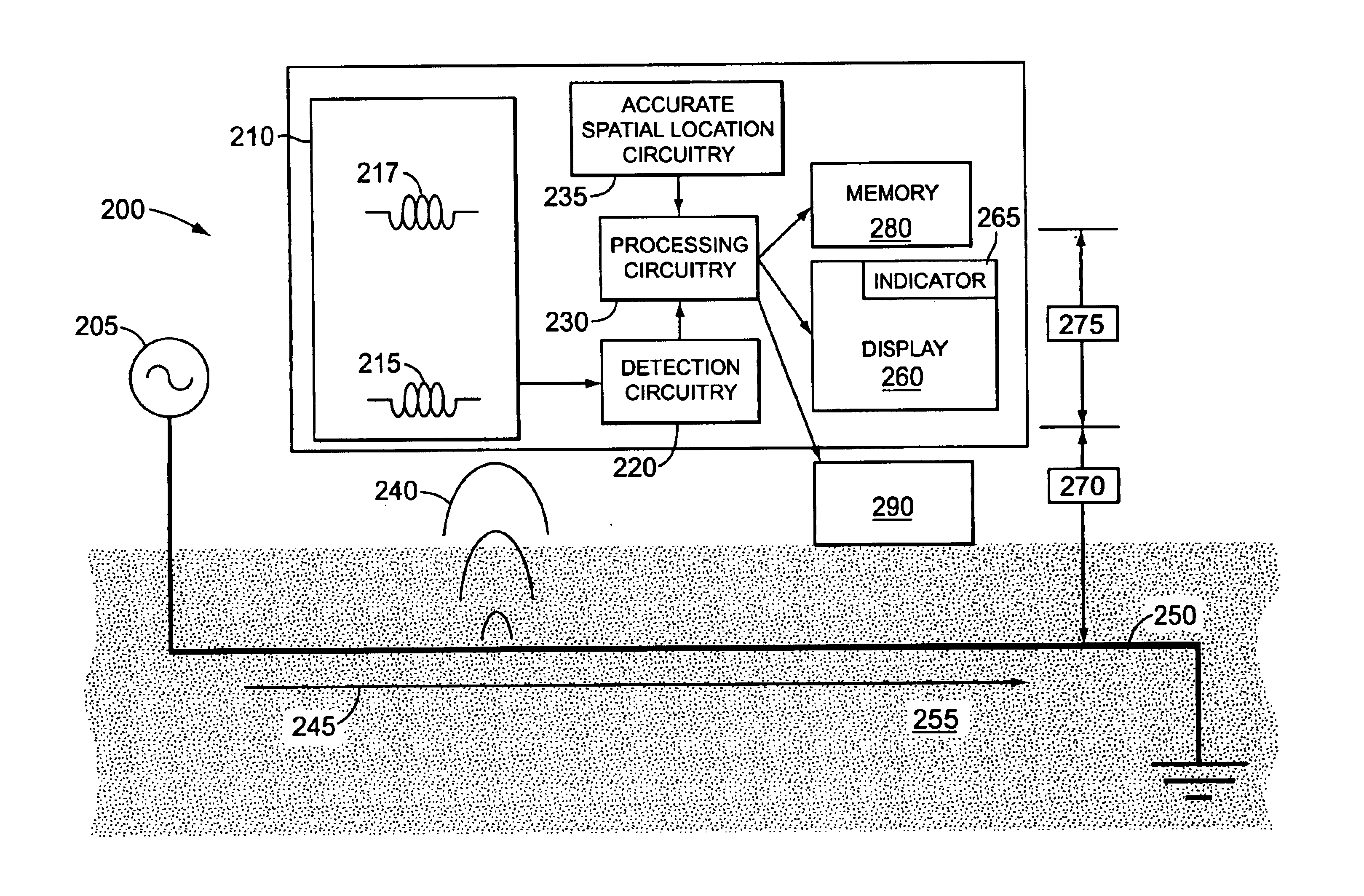

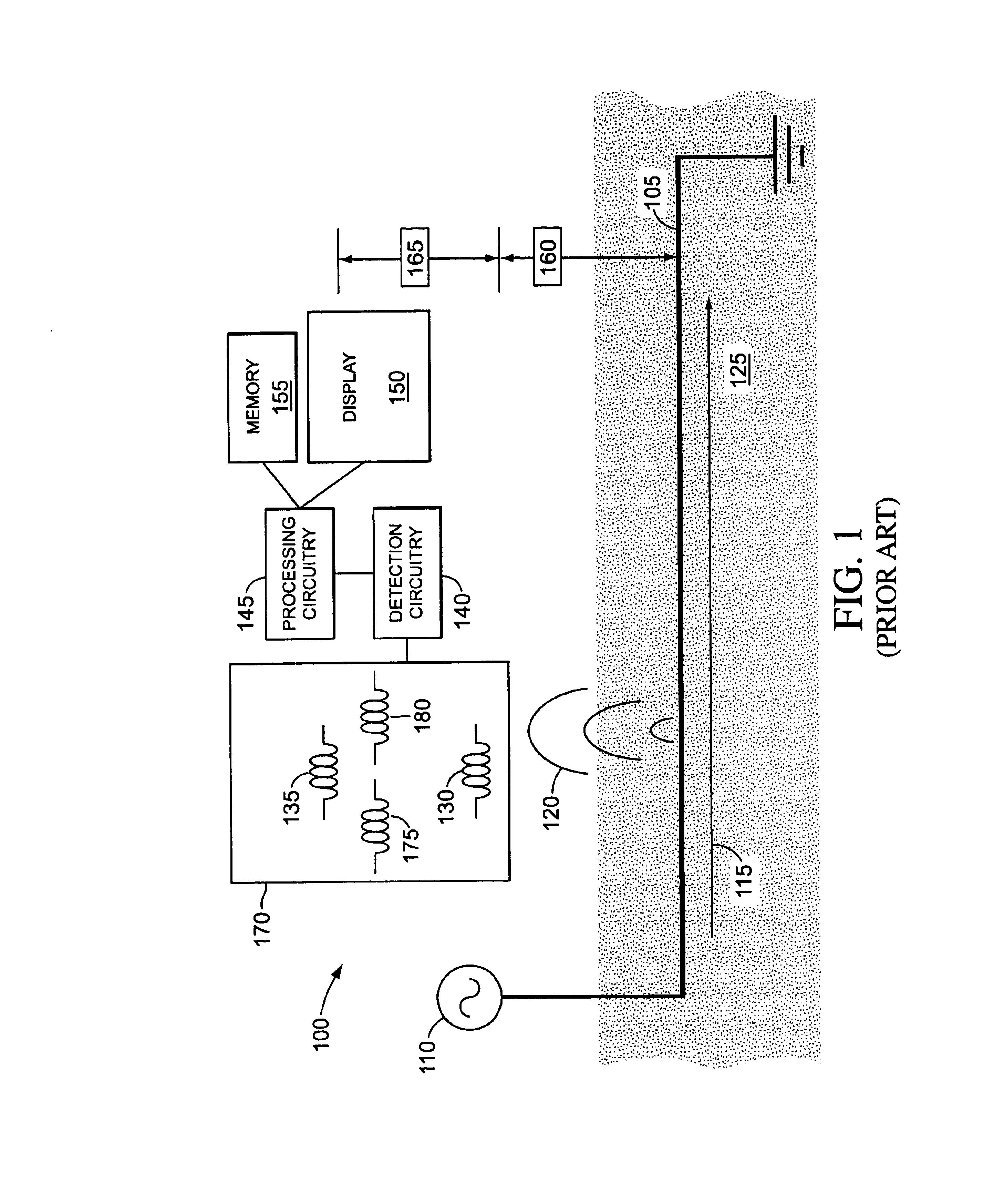

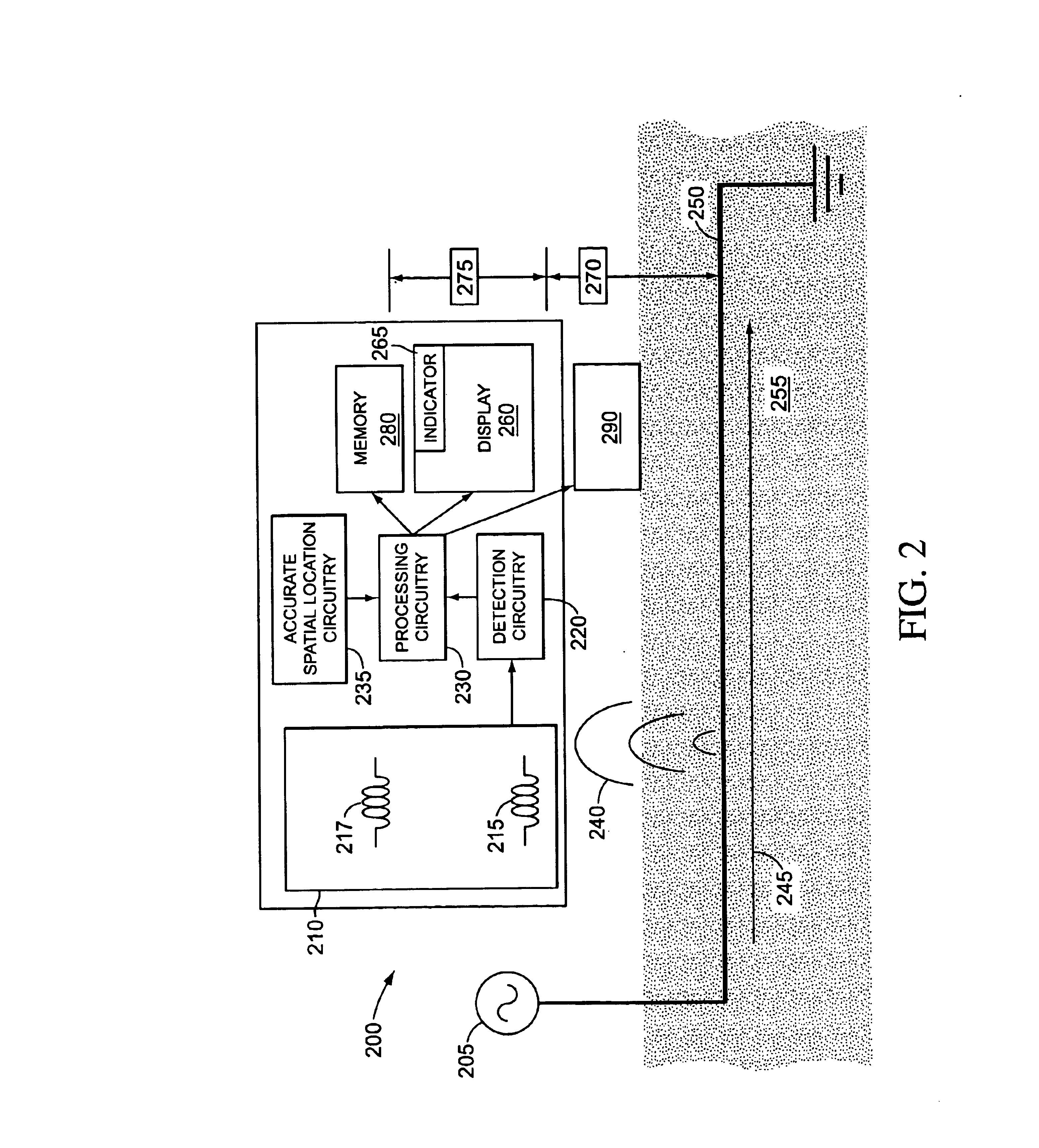

Buried line locator with integral position sensing

ActiveUS7120564B2Accurate spacingProvide accuratelyAmplifier modifications to reduce noise influenceDigital computer detailsField strengthDistortion

A device for detecting and compensating field distortion in underground line locators by means of mapping the field-strength of the field generated by electrical currents within the buried line. Signals from the underground structure can be mapped with respect to the position of the device. From the map, distortions from the expected signals can be determined, indicating interference from other structures or errors in detected location of the structure.

Owner:BUSAN TRANSPORTATION CORPORATION

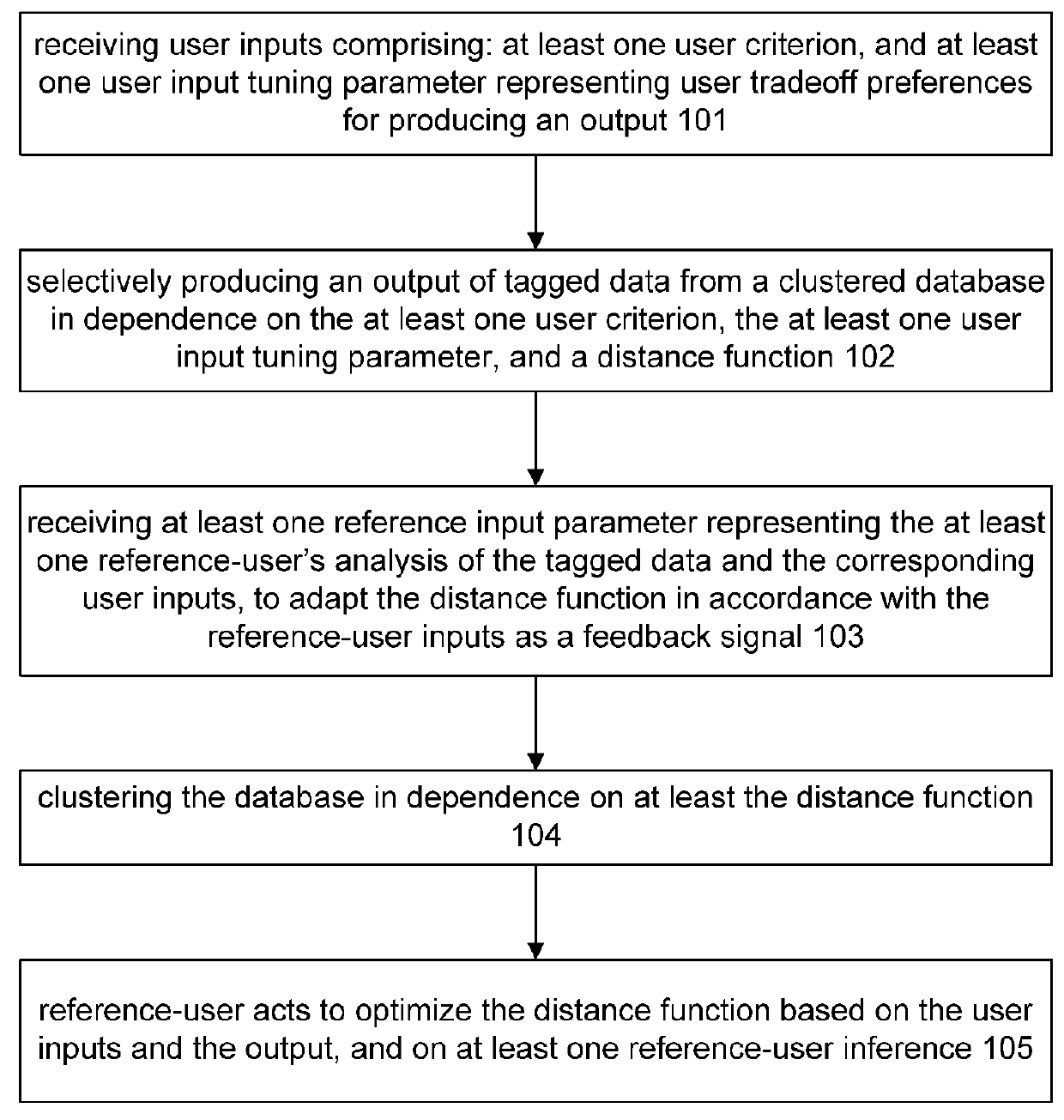

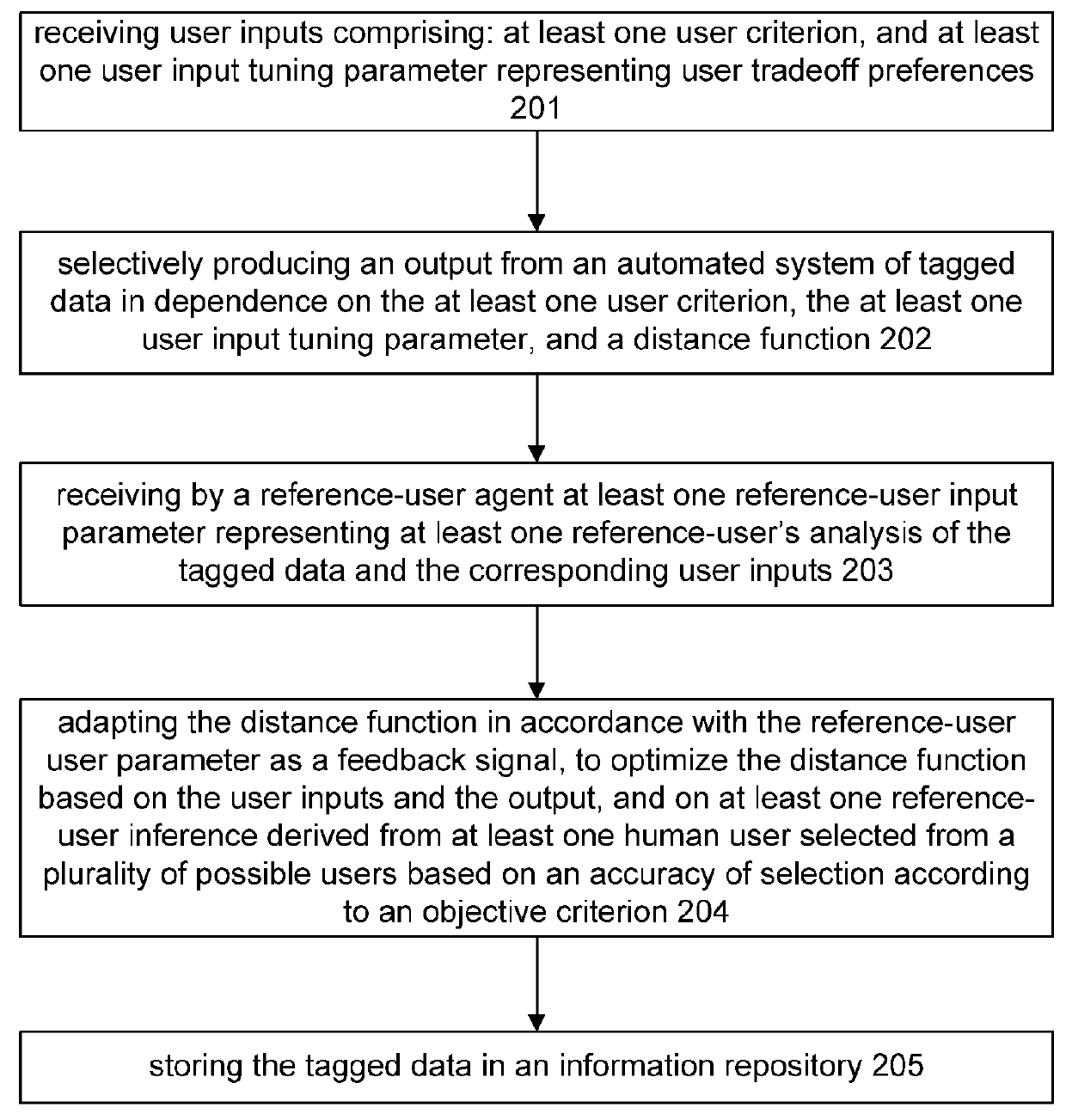

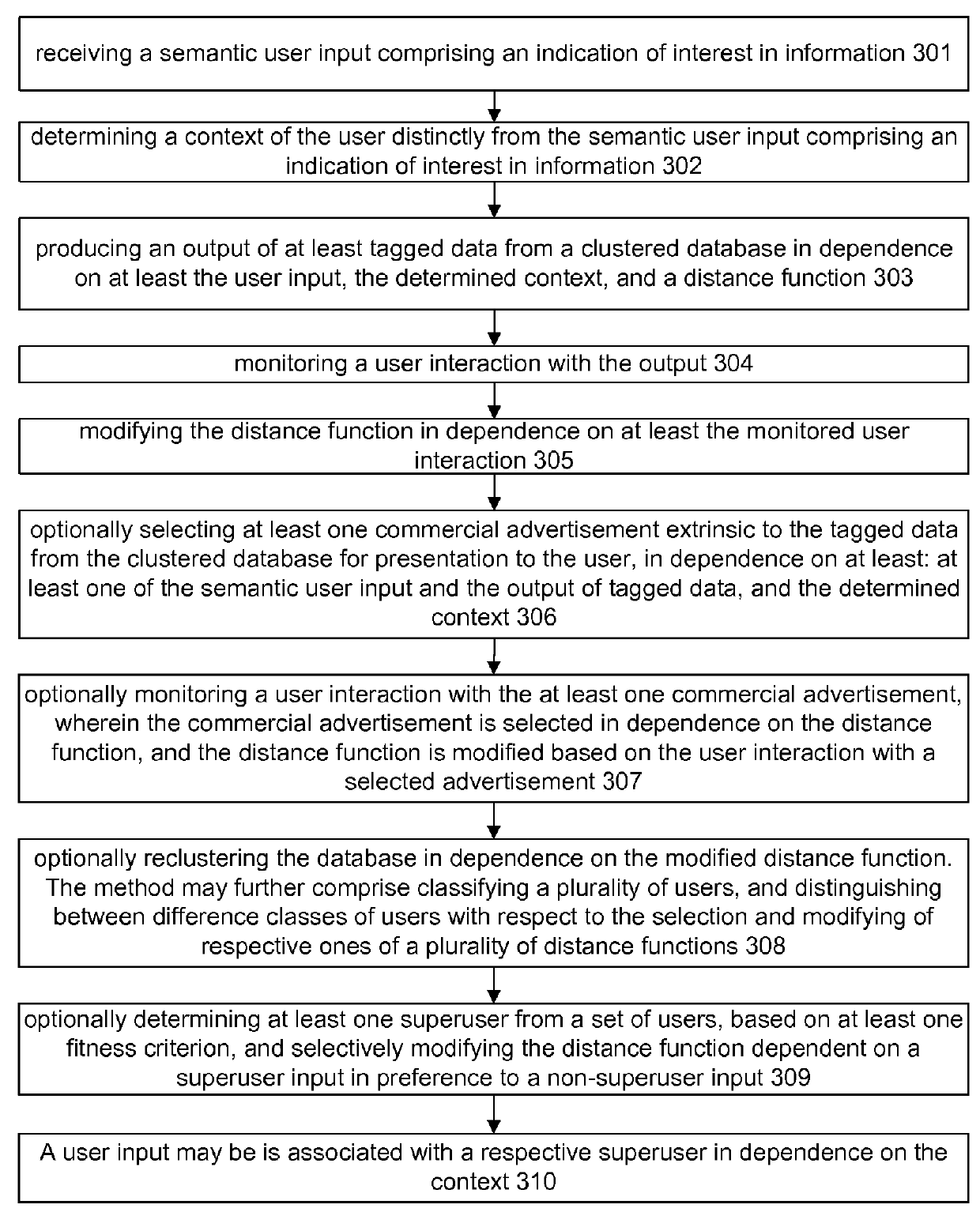

Insight and algorithmic clustering for automated synthesis

ActiveUS9336302B1Accurate assessmentImprove liquidityRelational databasesBiostatisticsUser inputLabeled data

A decision support system and method, which receives user inputs comprising: at least one user criterion, and at least one user input tuning parameter representing user tradeoff preferences for producing an output; and selectively produces an output of tagged data from a clustered database in dependence on the at least one user criterion, the at least one user input tuning parameter, and a distance function; receives at least one reference-user input parameter representing the at least one reference-user's analysis of the tagged data and the corresponding user inputs, to adapt the distance function in accordance with the reference-user inputs as a feedback signal; and clusters the database in dependence on at least the distance function, wherein the reference-user acts to optimize the distance function based on the user inputs and the output, and on at least one reference-user inference.

Owner:OOL LLC

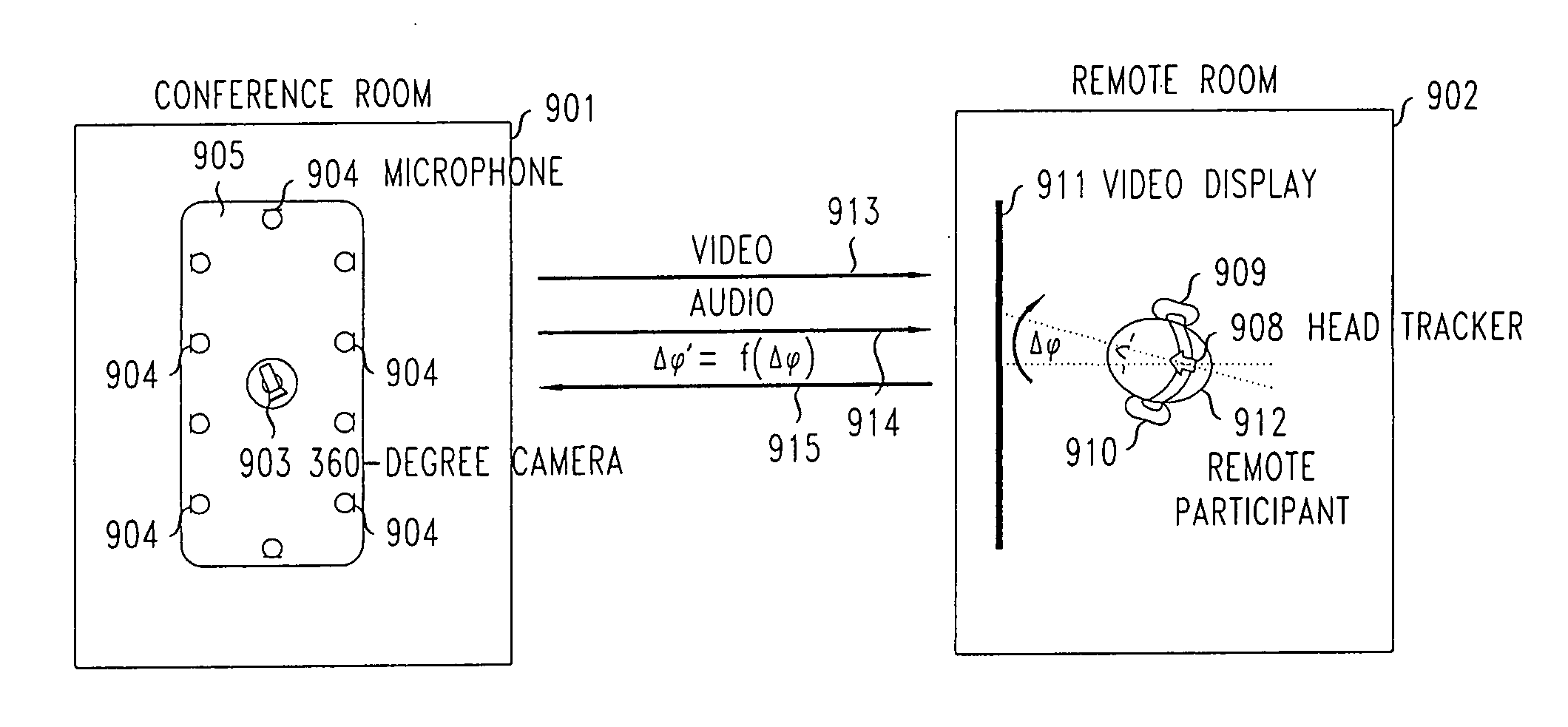

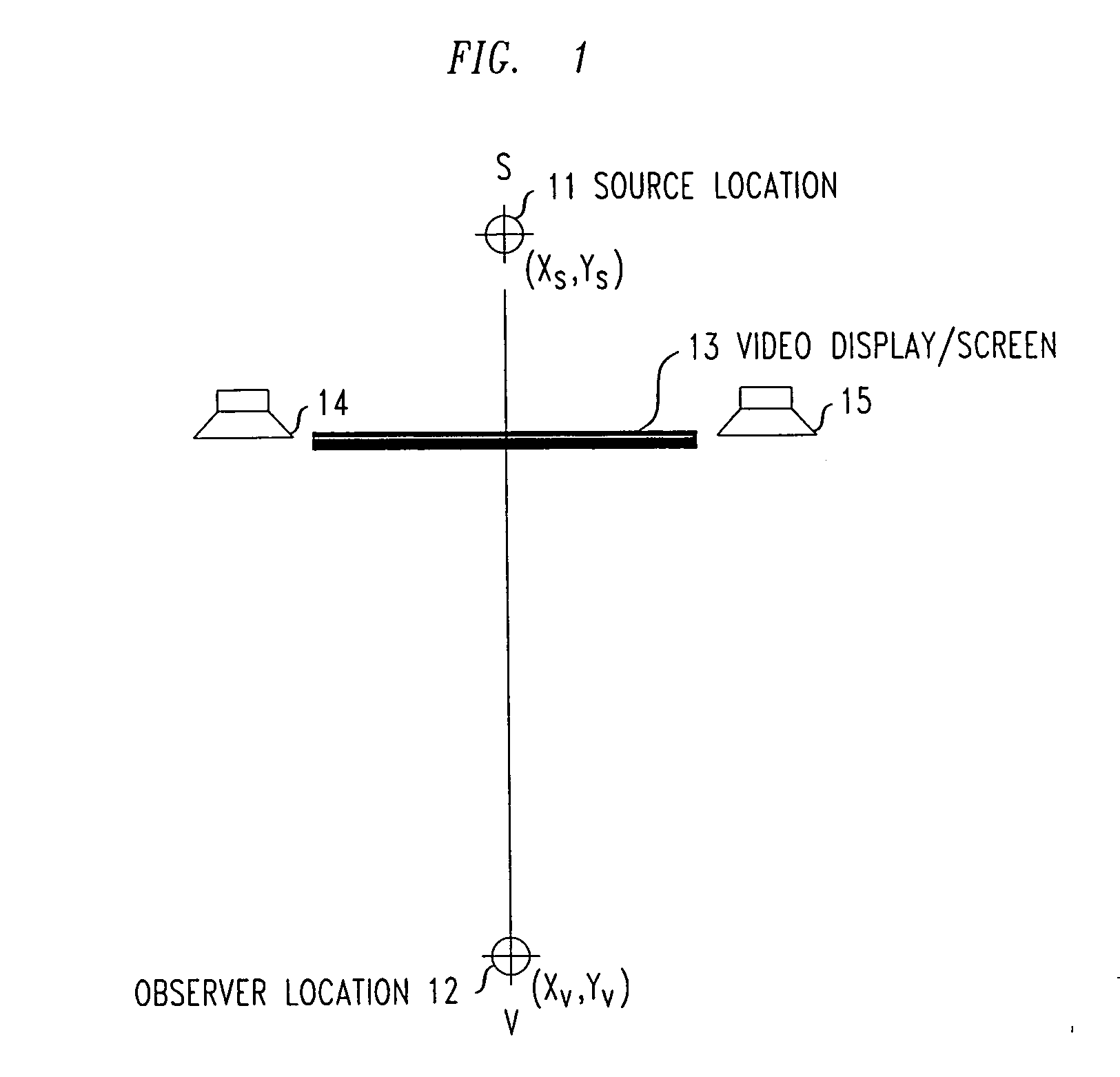

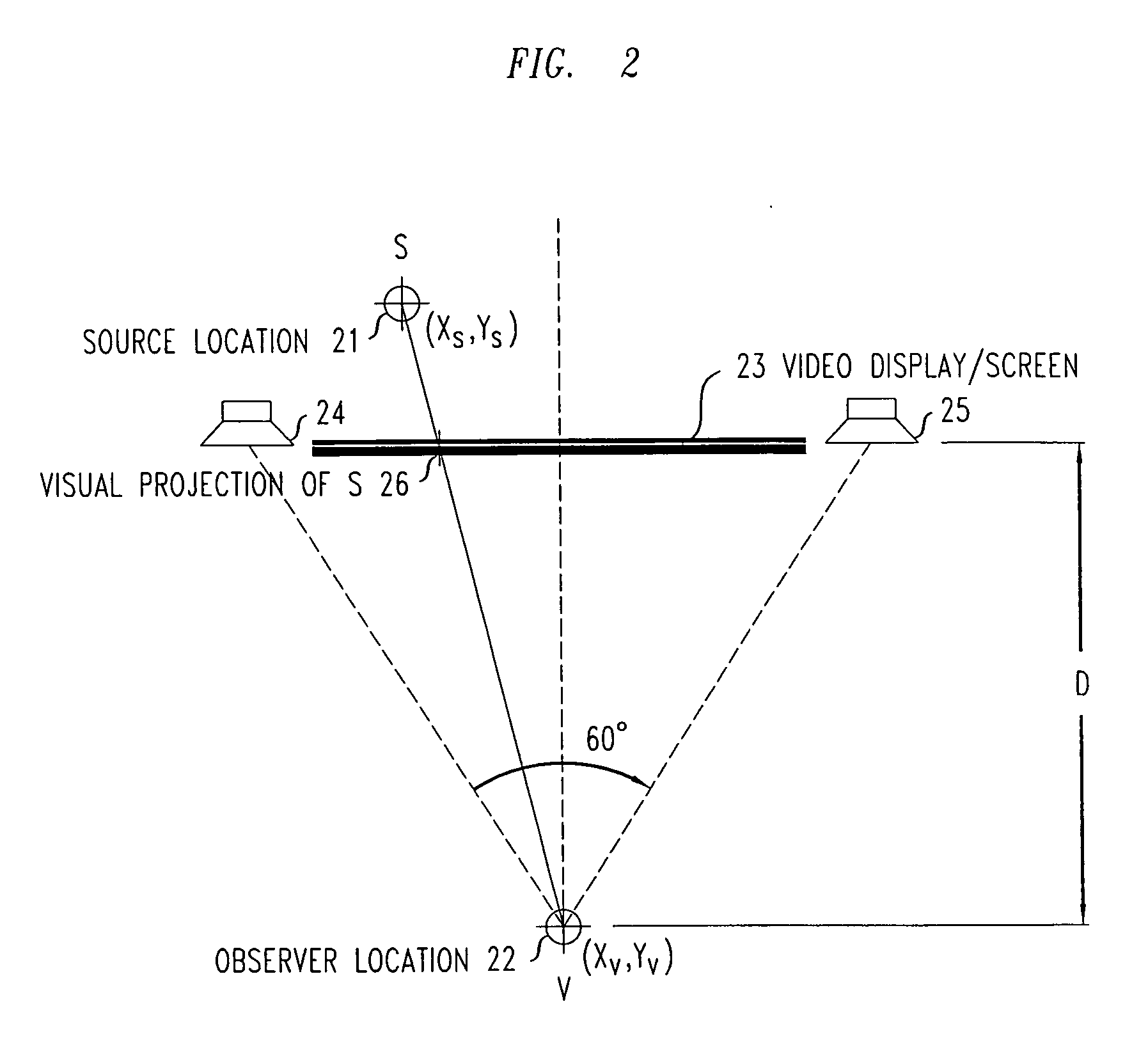

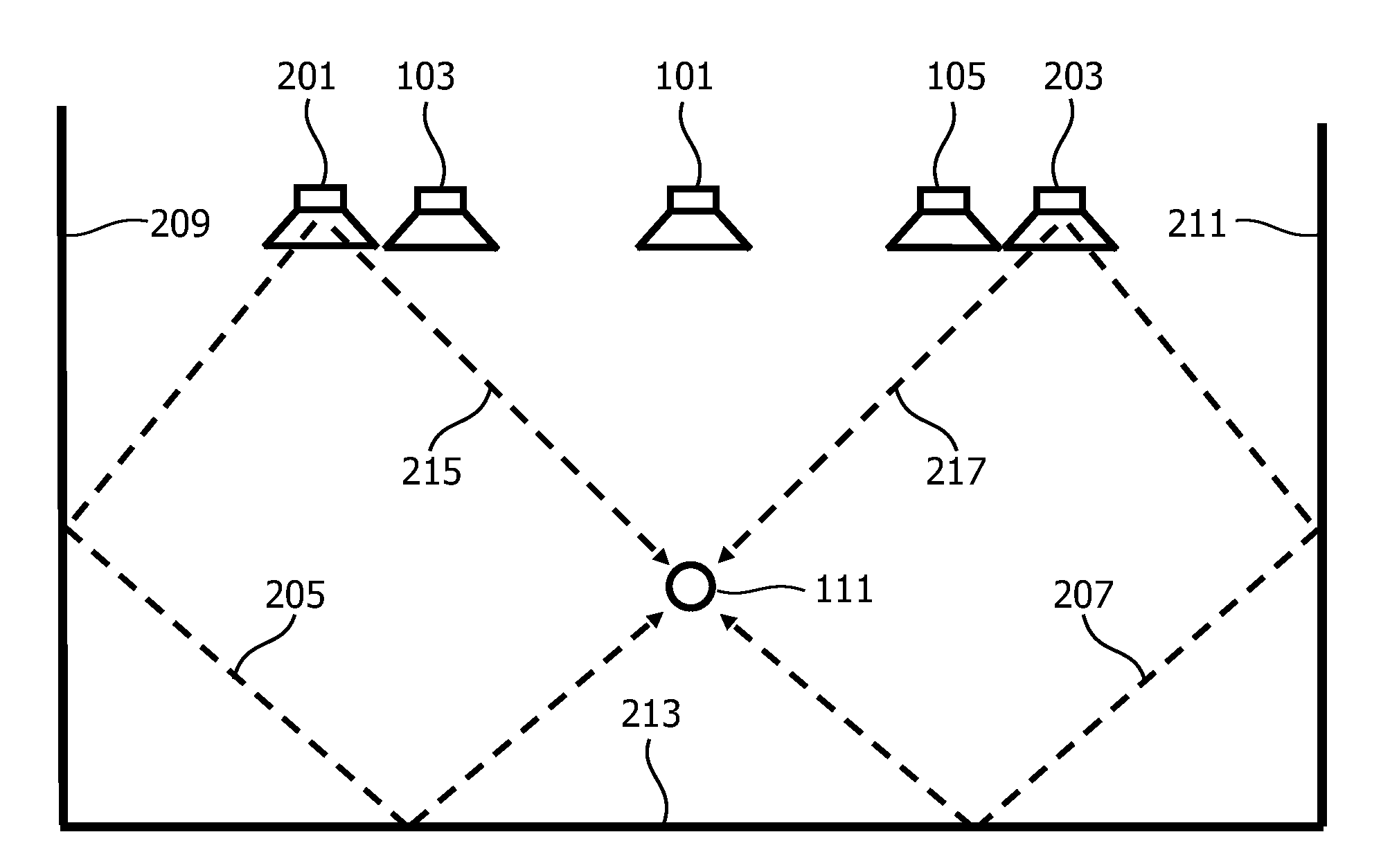

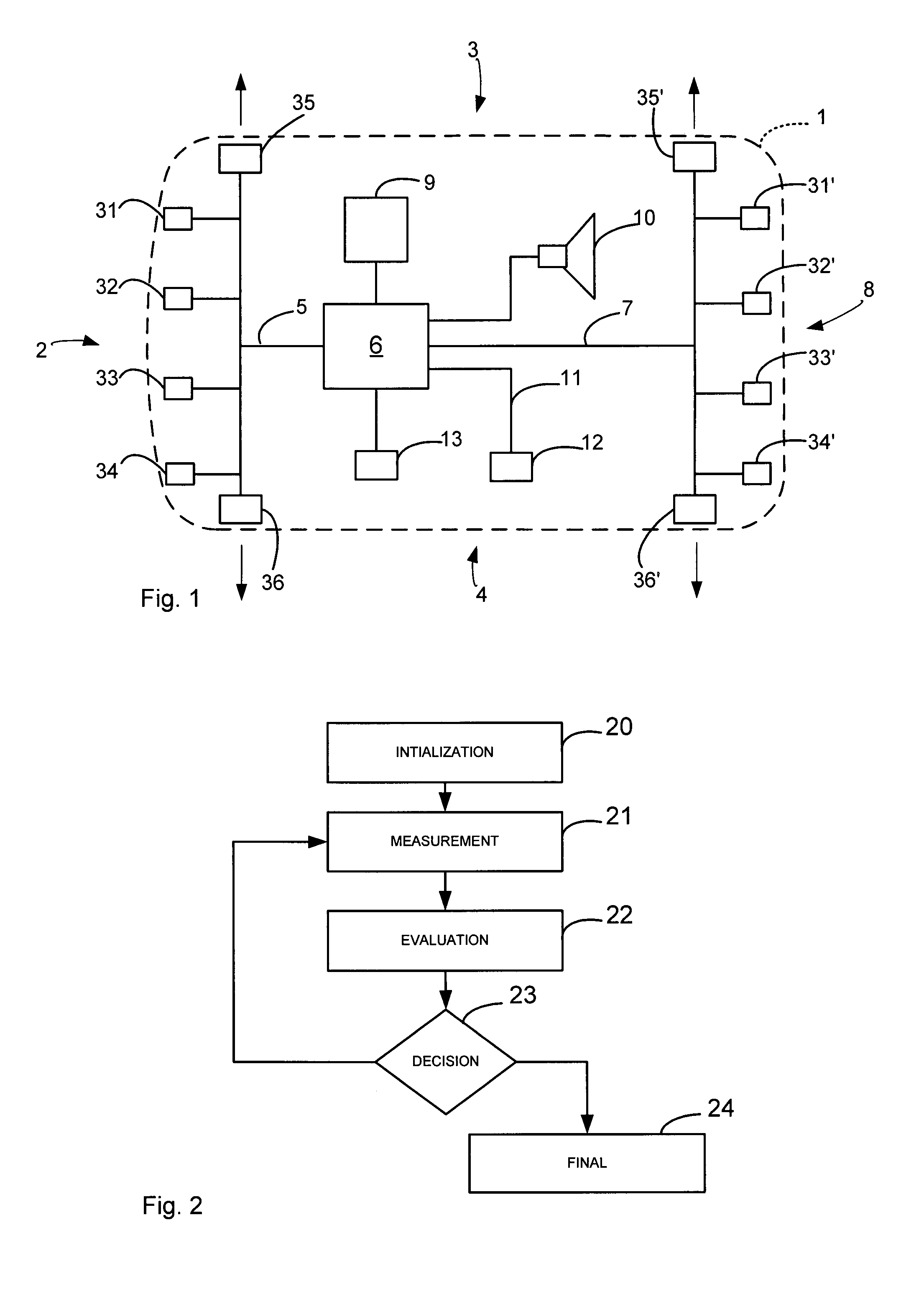

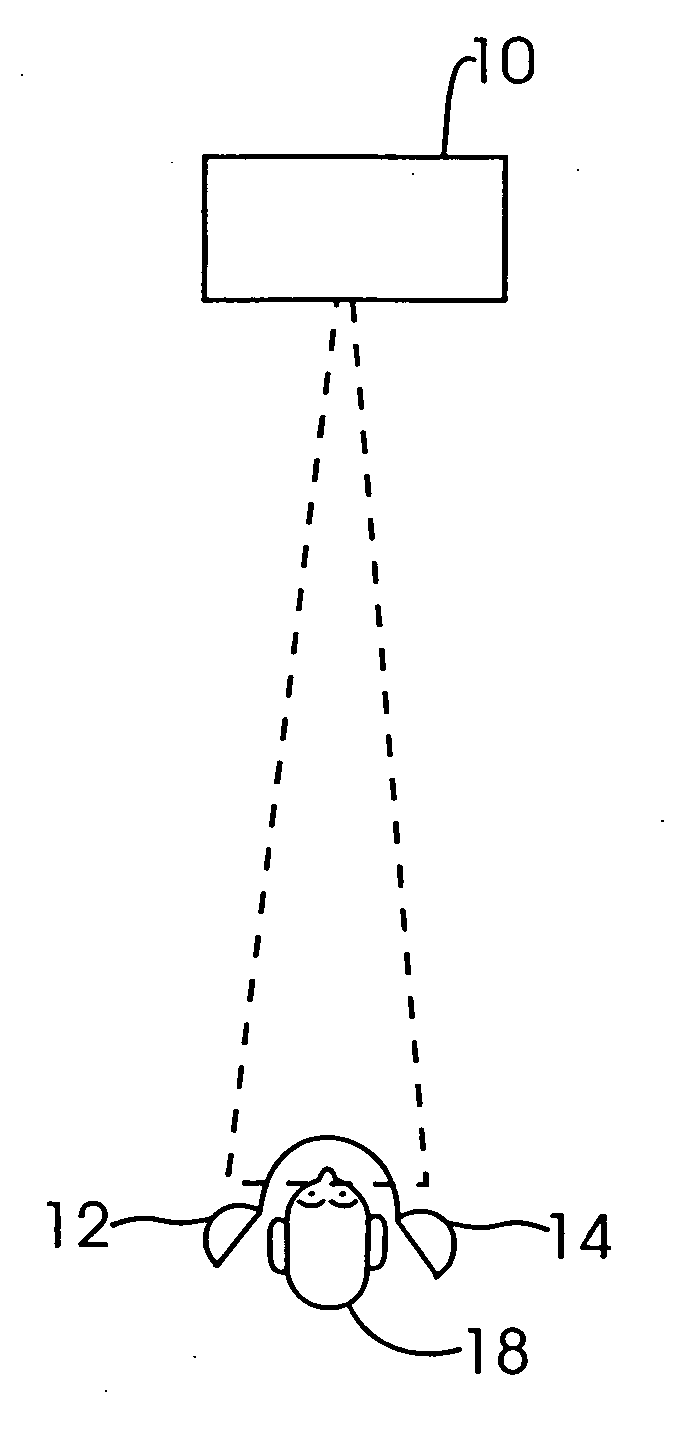

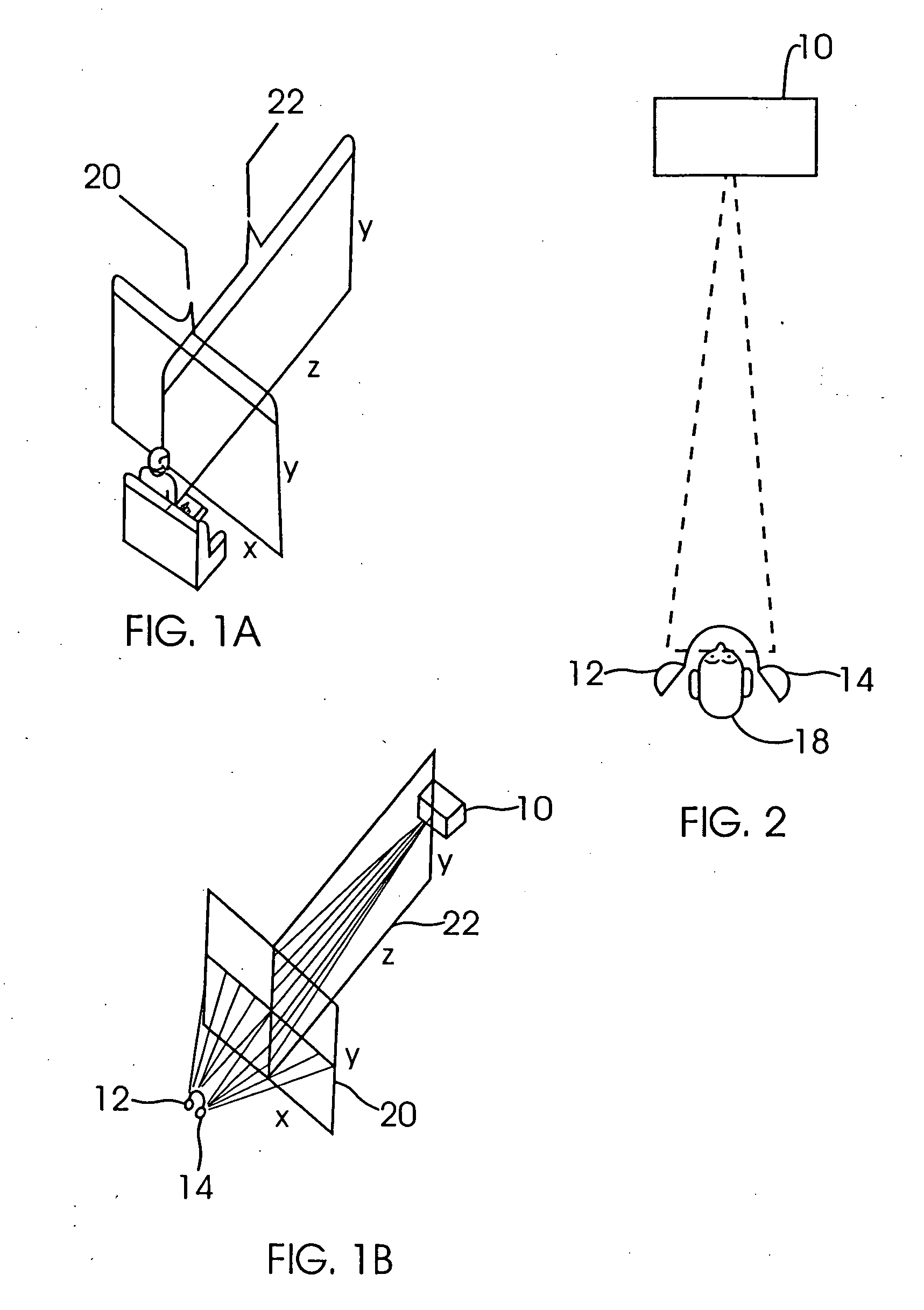

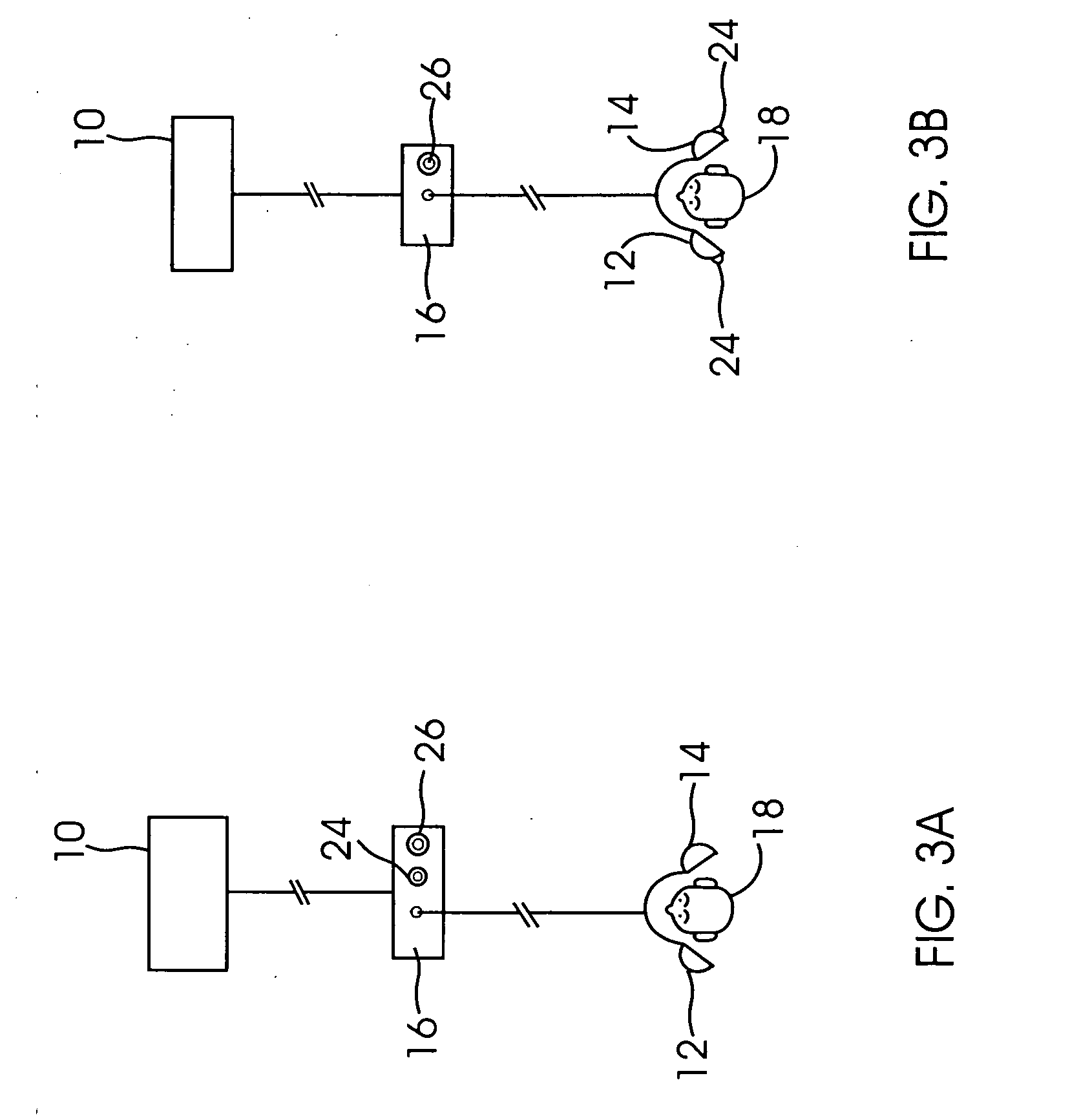

Method and apparatus for improved matching of auditory space to visual space in video viewing applications

InactiveUS20100328419A1Good matchAccurate spacingTelevision system detailsColor television detailsComputer visionHead position

A method and apparatus for enabling an improved experience by better matching of the auditory space to the visual space in video viewing applications such as those that may be used in video teleconferencing systems and in the viewing of videos with associated audio (e.g., movies). In one embodiment, a viewer's location and head position relative to a video display screen is determined, one or more desired sound source locations (which may, for example, be related to a projection on the video display) are determined, and binaural stereo audio signals which accurately locate the sound sources at the desired sound source locations are advantageously generated.

Owner:ALCATEL LUCENT SAS

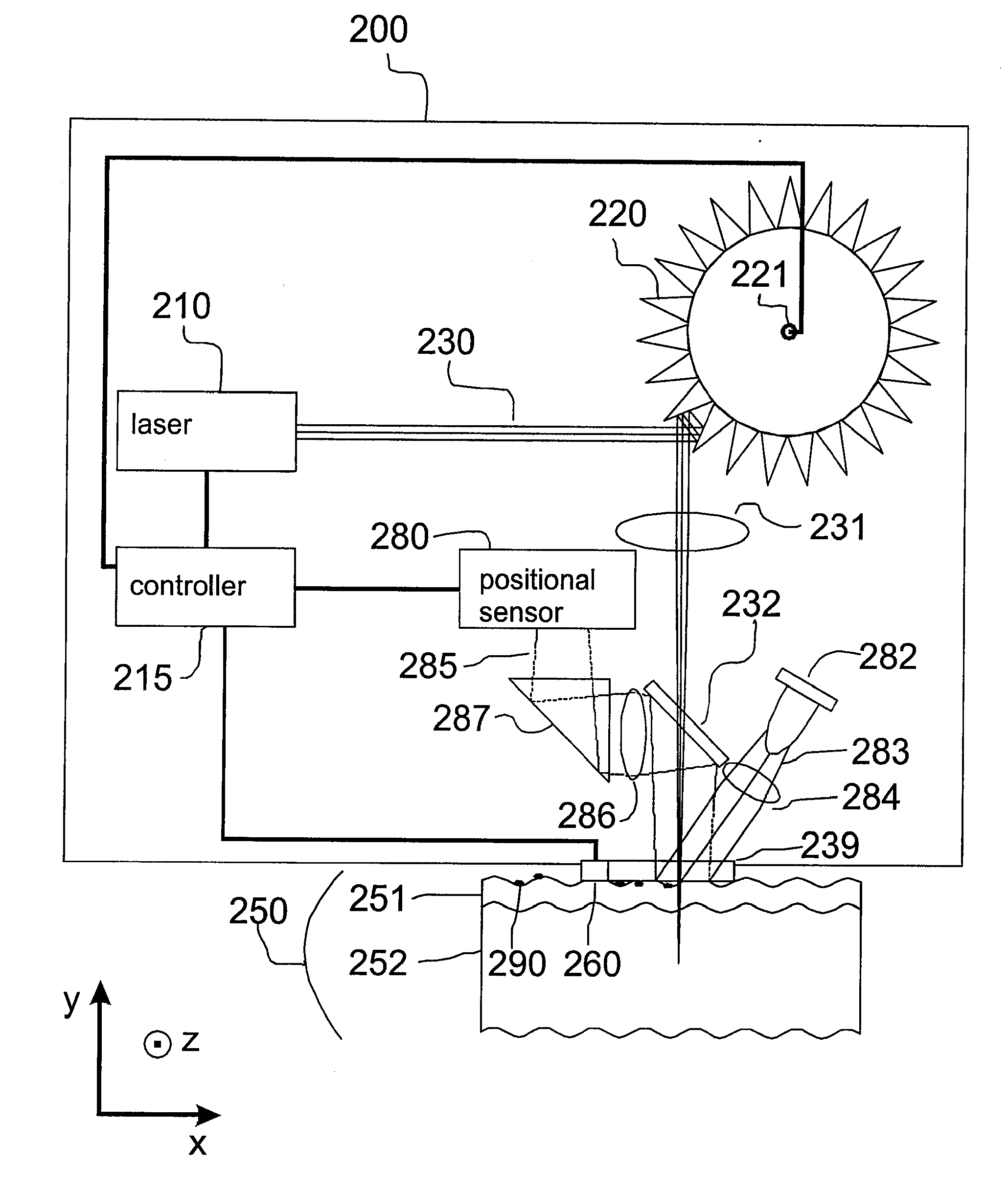

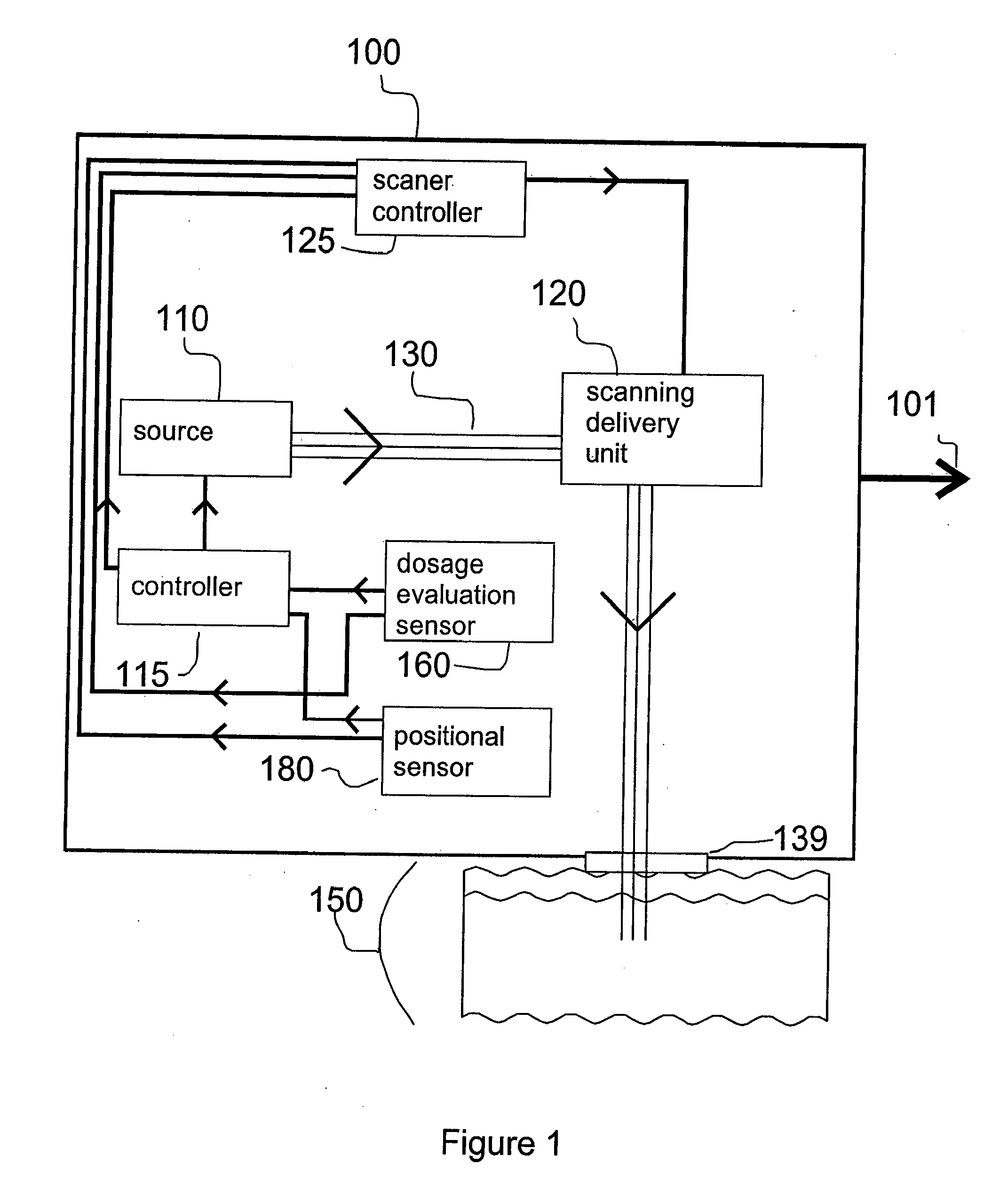

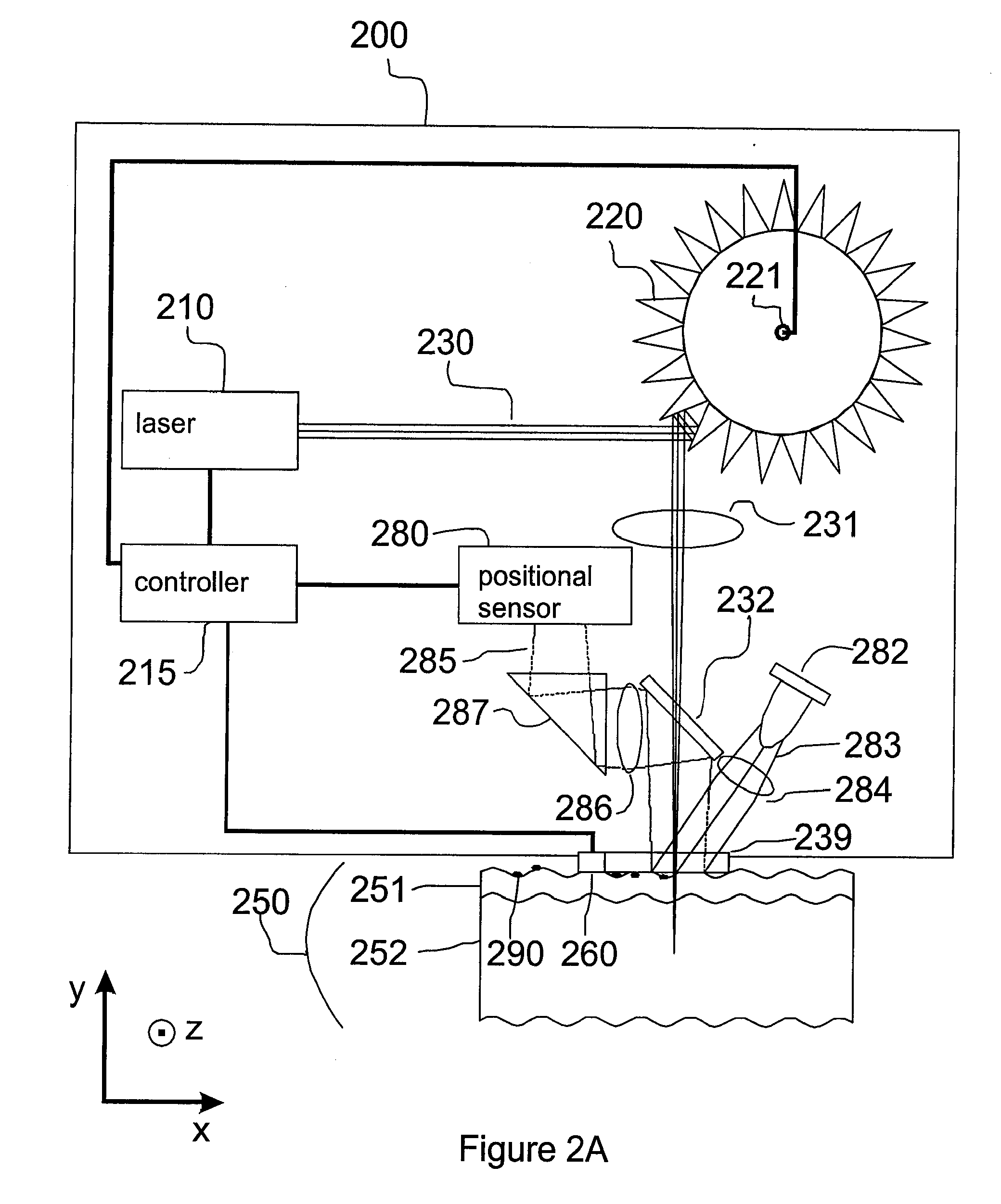

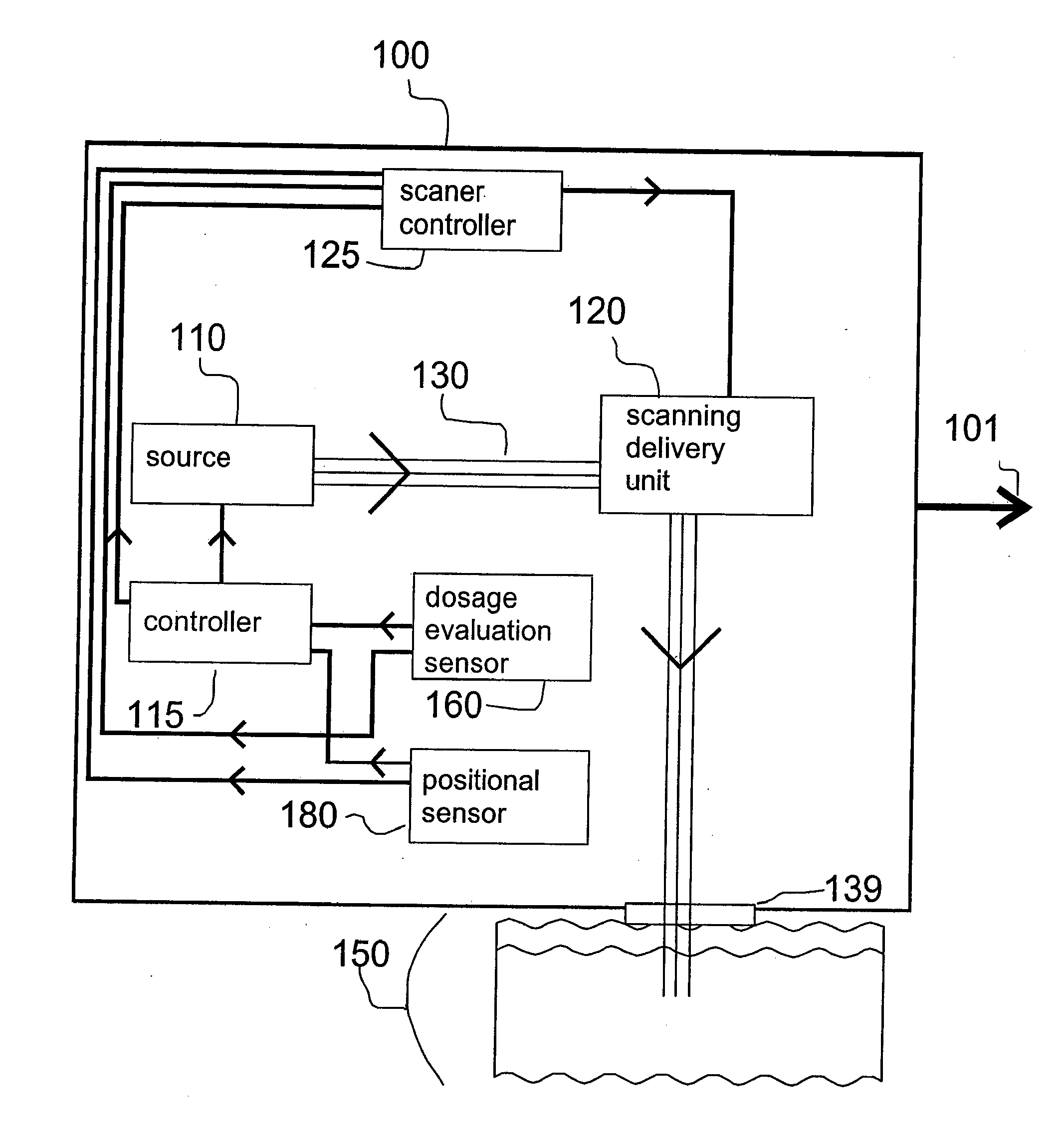

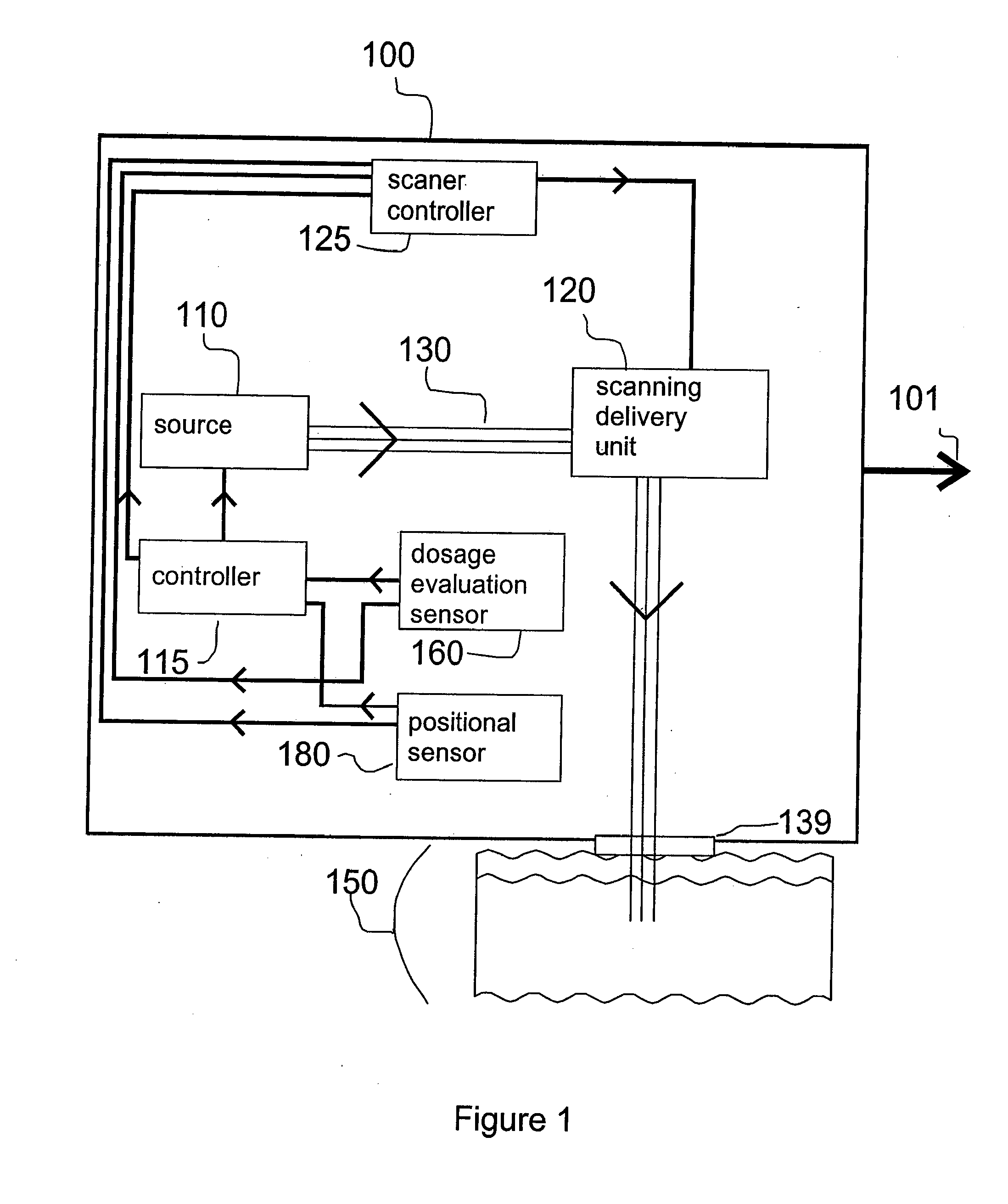

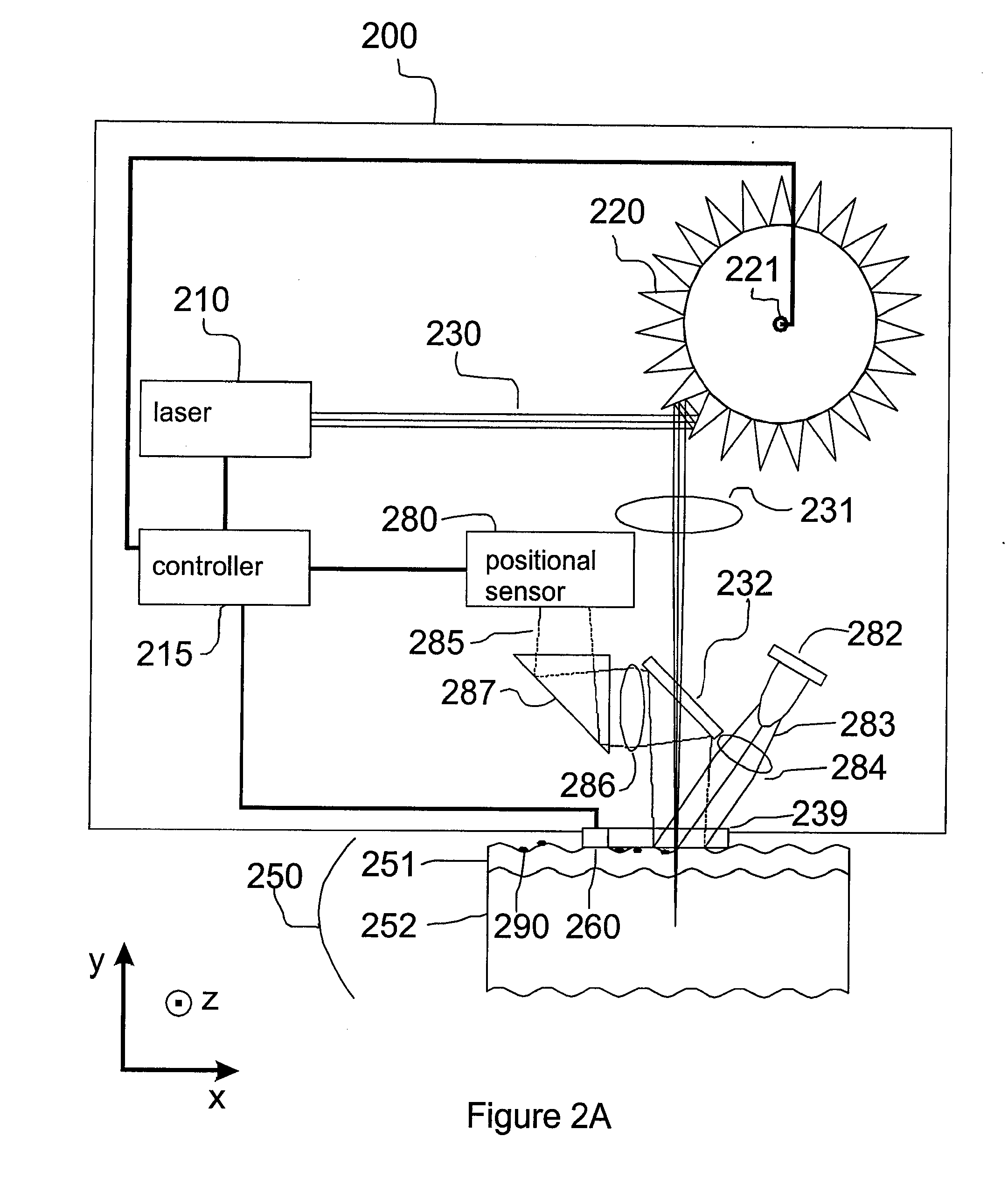

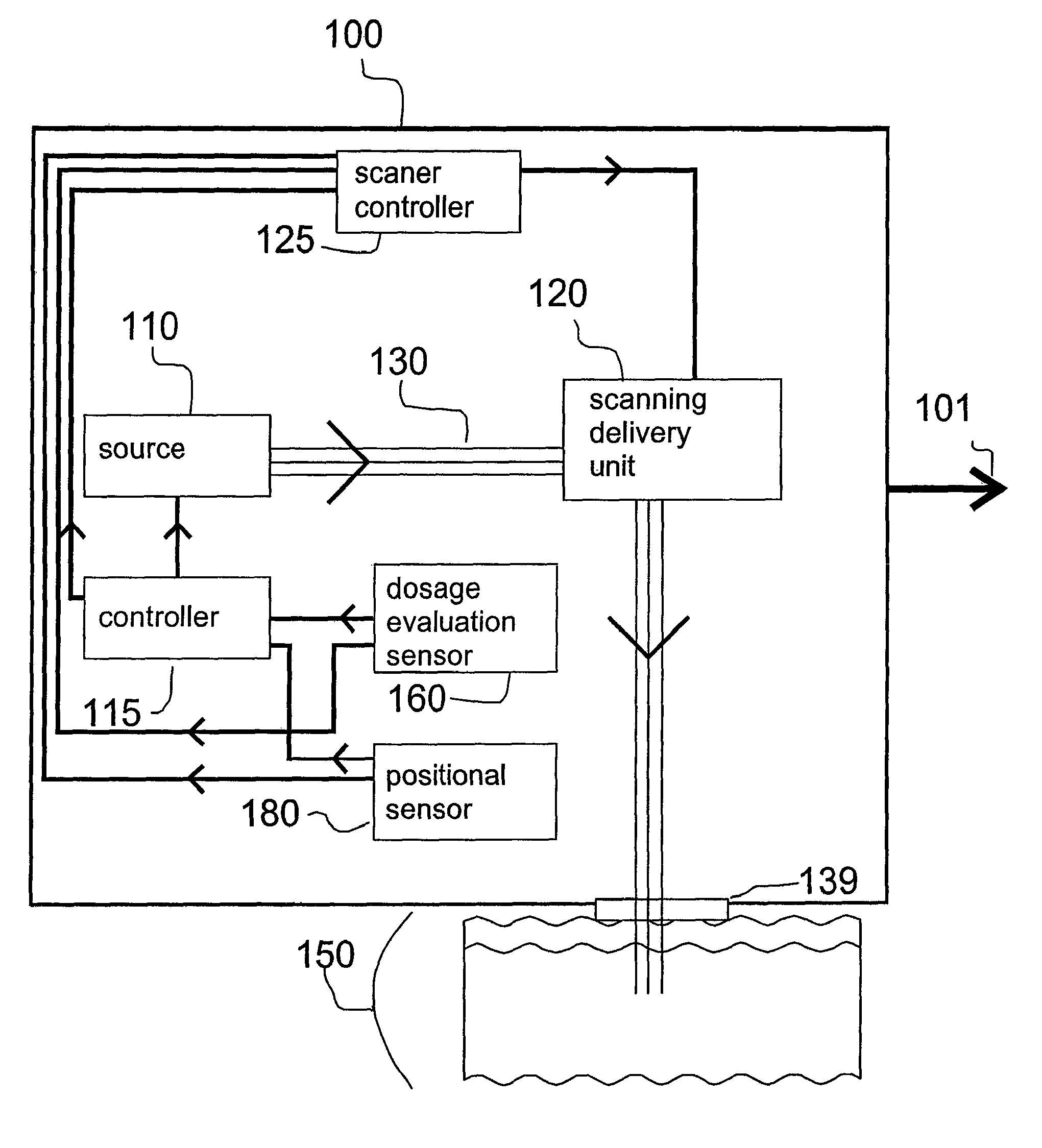

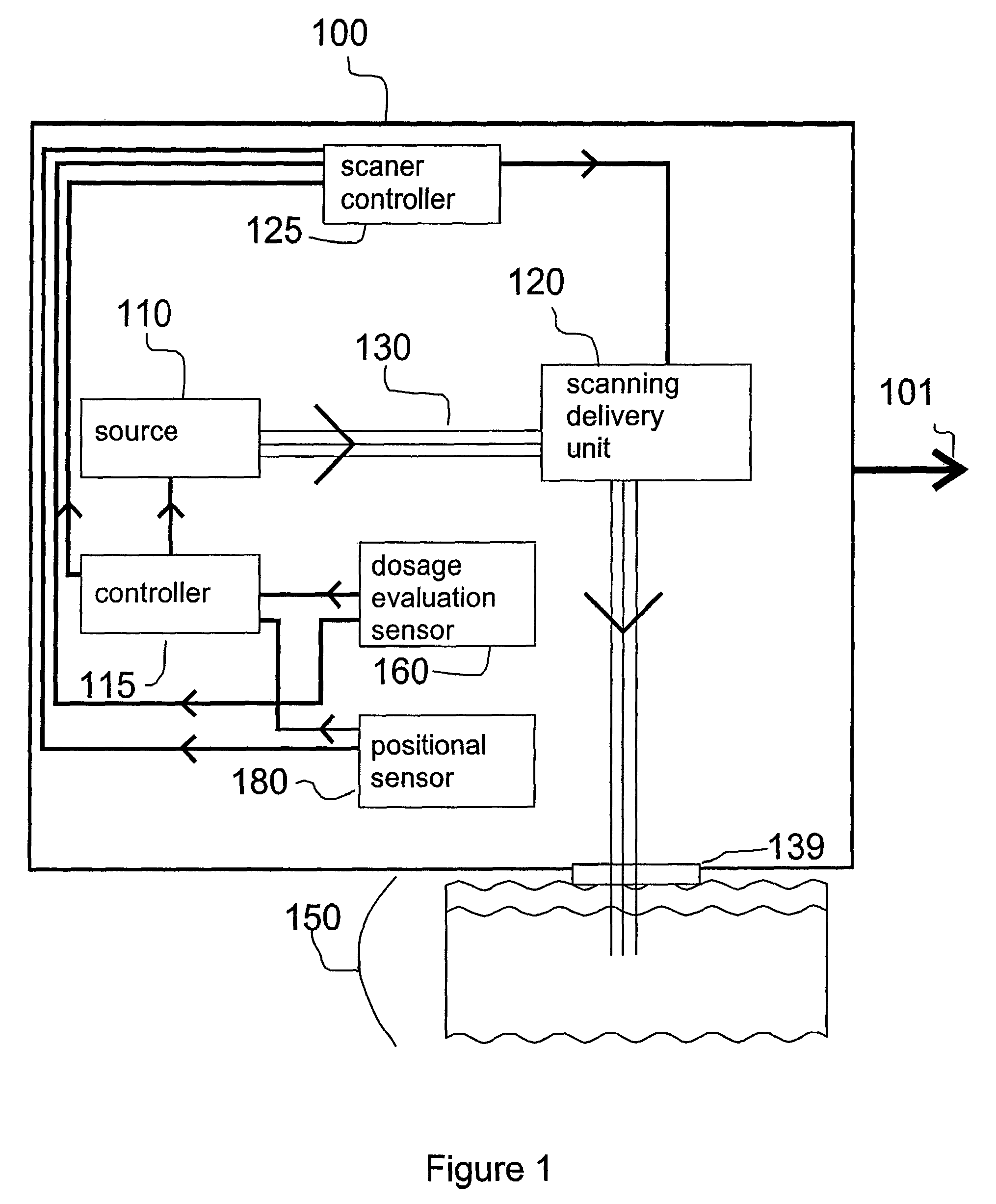

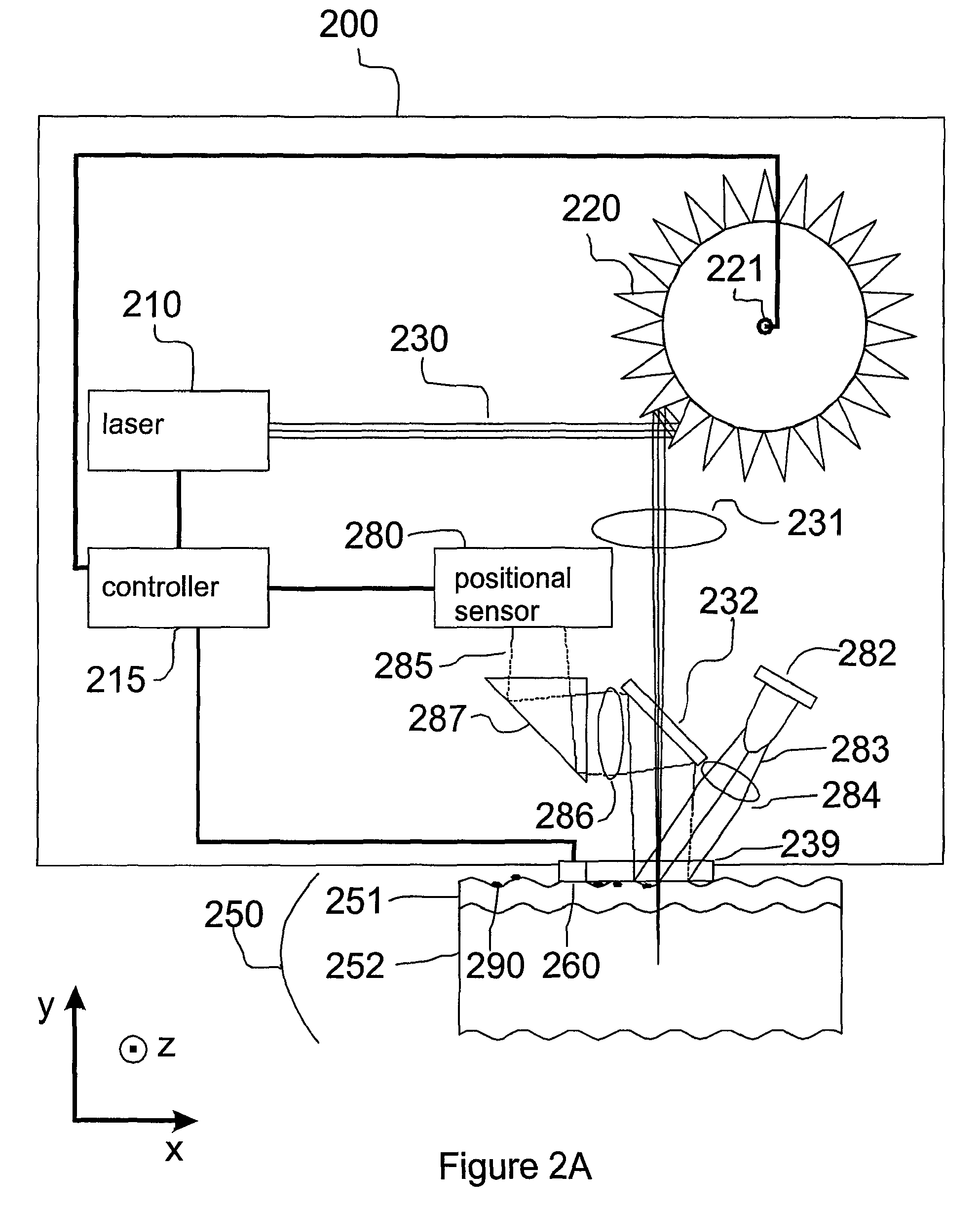

Method and Apparatus for Monitoring and Controlling Thermally Induced Tissue Treatment

InactiveUS20070093798A1Reduce treatment intensityIncrease in sizeElectrotherapyDiagnosticsRadio frequencyTissue skin

A method and apparatus for thermal treatment of tissue by irradiating the skin with electromagnetic energy is disclosed. Sources of electromagnetic energy include radio frequency (RF) generators, lasers, and flashlamps. The apparatus includes either a positional sensor or a dosage evaluation sensor, or both types of sensors. These sensors provide feedback to a controller. The controller may control the electromagnetic source parameters, the electromagnetic source activation, and / or the sensor measurement parameters. An additional scanning delivery unit may be operably coupled to the controller or to the sensors to provide a controlled distribution of electromagnetic energy to the target region of the skin. The use of positional measurement sensors and dosage evaluation sensors permits the controller to automatically determine the proper electromagnetic source parameters including, for example, pulse timing and pulse frequency.

Owner:RELIANT TECH INC

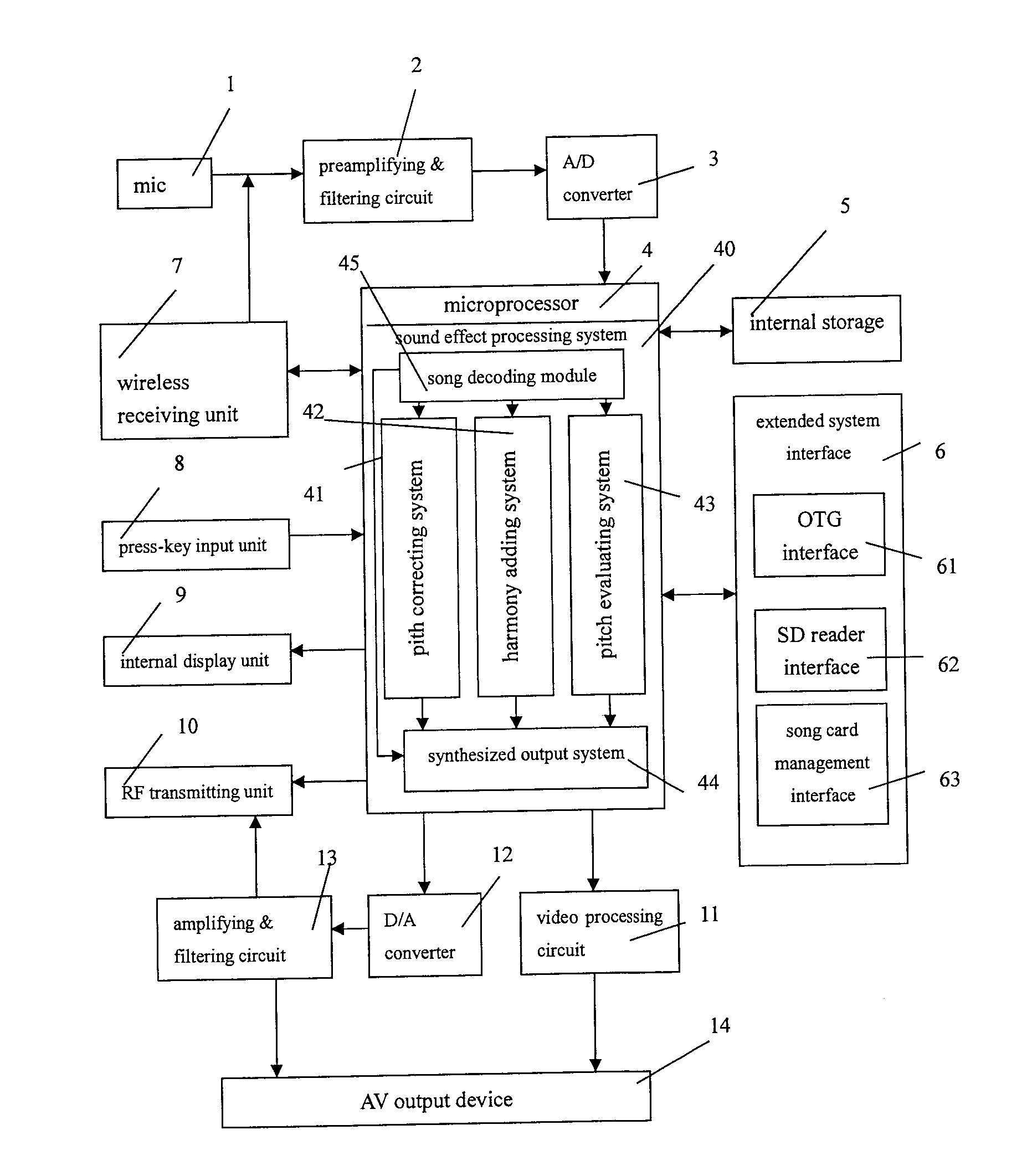

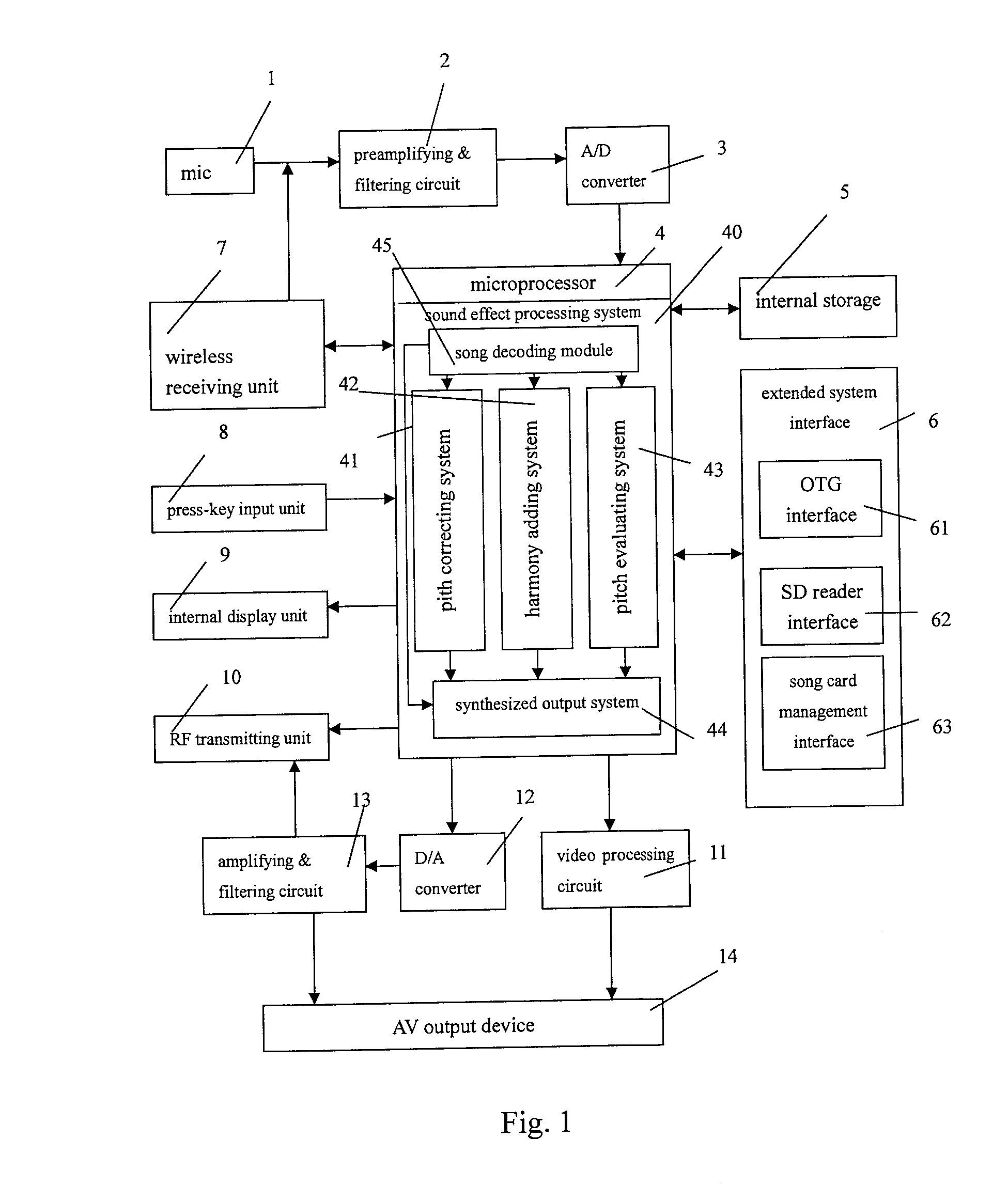

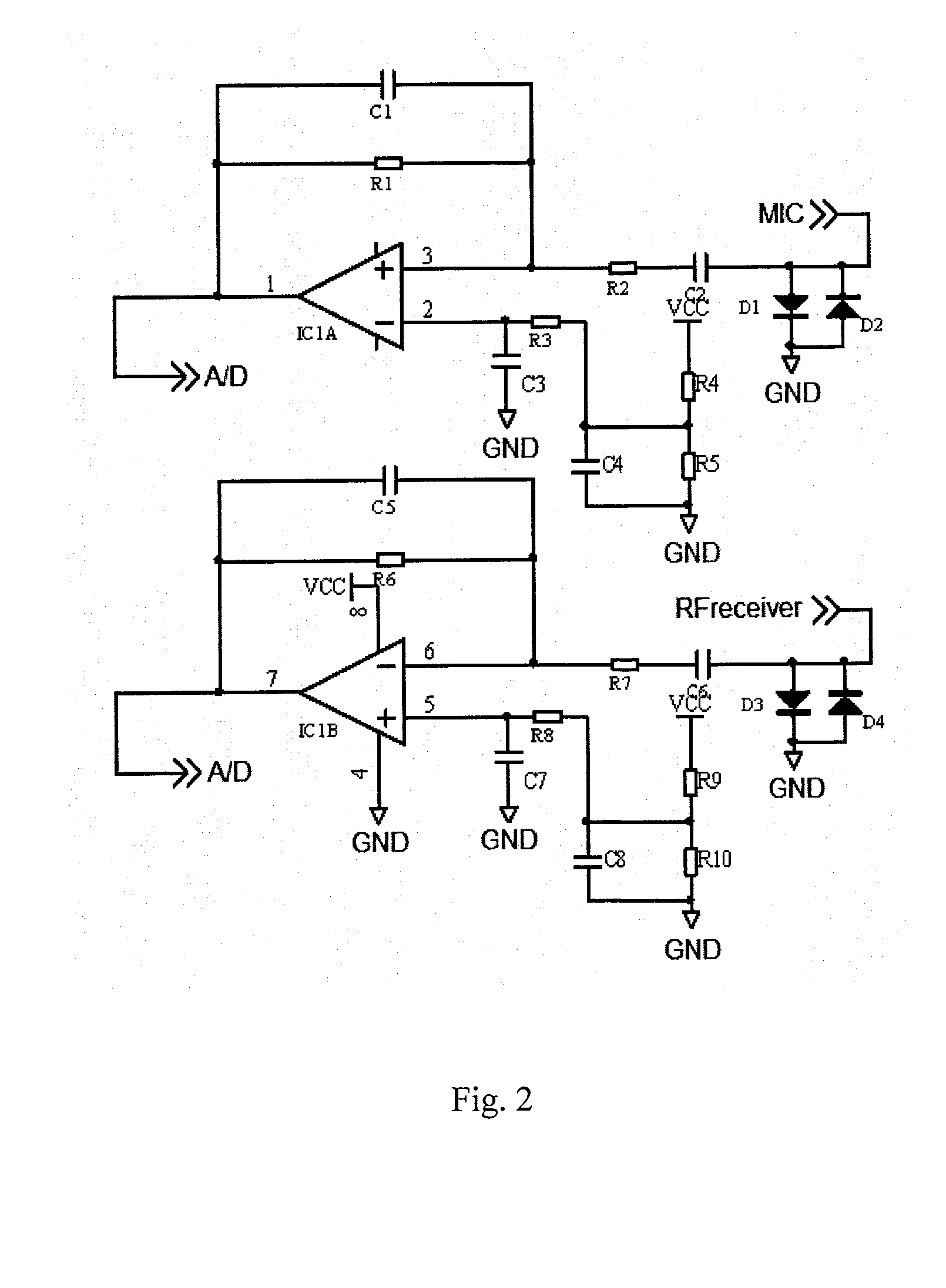

Karaoke apparatus

InactiveUS20100192753A1Accurate spacingIncrease entertainmentElectrophonic musical instrumentsInternal memoryExternal storage

A karaoke apparatus includes a sound effect processing system provided in a microprocessor. The system decodes standard song data from an internal storage or an external storage connected to an extended system interface by a song decoding module; corrects pitches of sing voices by a pitch correcting system, so the pitches of the singing voices are corrected to the pitches of the standard song or close to the pitches of the standard song. The singing voices are processed with harmony adding, tonal modification and speed-changing by a harmony adding system to produce an effect of chorus being composed of three voice parts. A pitch evaluating system is used for comparing the pitch sequence of the singing voices with the pitch sequence of the standard song to draw a voice graph so as to visually show a difference between the pitches of the singing voices and the pitches of the standard song, while providing score and comment of the singing voices. Therefore, a singer can be aware of the effect of his / her performance to immediately so as to increase the amusement in a karaoke singing.

Owner:MULTAK TECH DEV

Method and Apparatus for Monitoring and Controlling Thermally Induced Tissue Treatment

InactiveUS20070093797A1Reduce treatment intensityIncrease in sizeElectrotherapyDiagnosticsEngineeringBiological activation

A method and apparatus for thermal treatment of tissue by irradiating the skin with electromagnetic energy is disclosed. Sources of electromagnetic energy include radio frequency (RF) generators, lasers, and flashlamps. The apparatus includes either a positional sensor or a dosage evaluation sensor, or both types of sensors. These sensors provide feedback to a controller. The controller may control the electromagnetic source parameters, the electromagnetic source activation, and / or the sensor measurement parameters. An additional scanning delivery unit may be operably coupled to the controller or to the sensors to provide a controlled distribution of electromagnetic energy to the target region of the skin. The use of positional measurement sensors and dosage evaluation sensors permits the controller to automatically determine the proper electromagnetic source parameters including, for example, pulse timing and pulse frequency.

Owner:RELIANT TECH INC

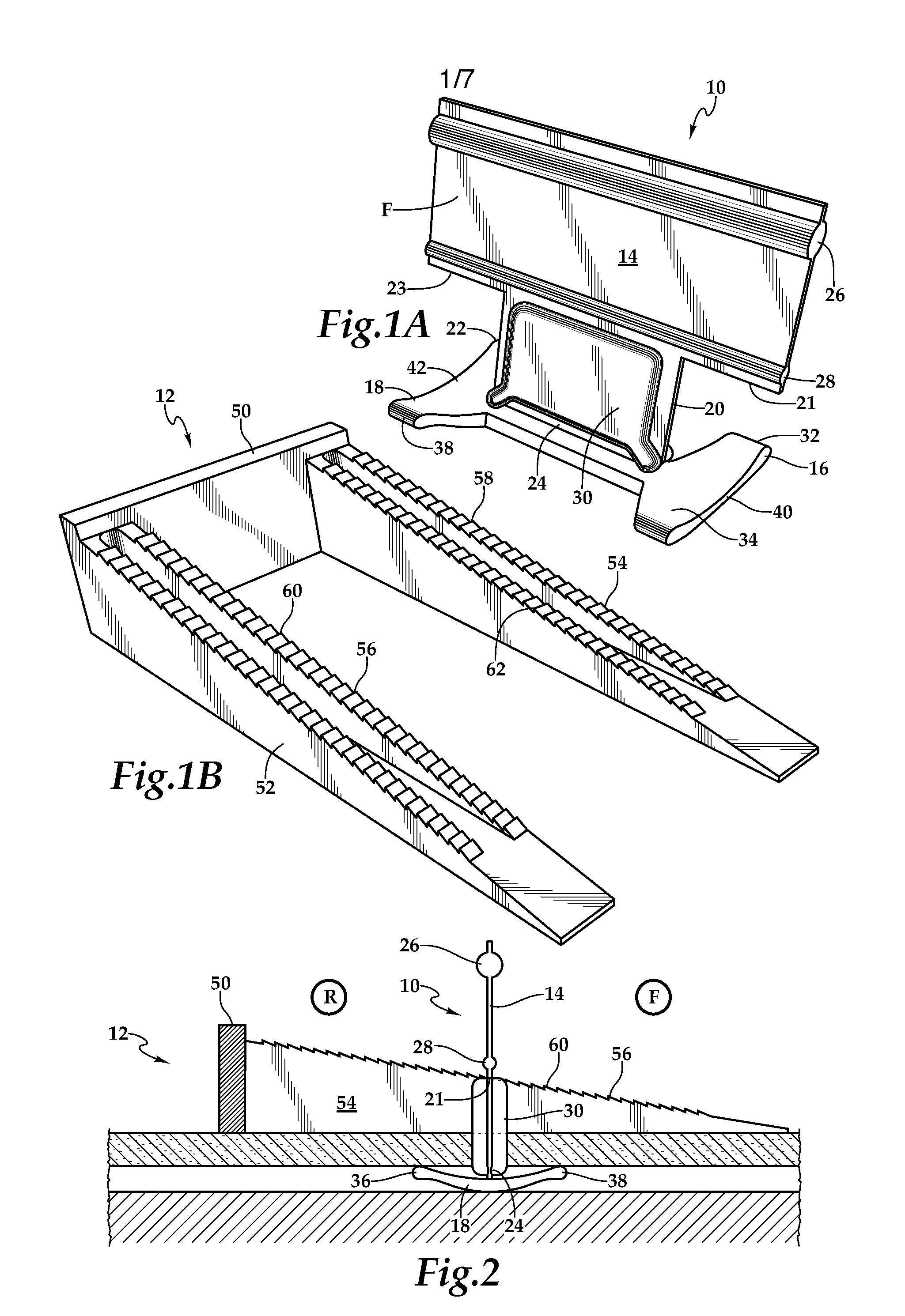

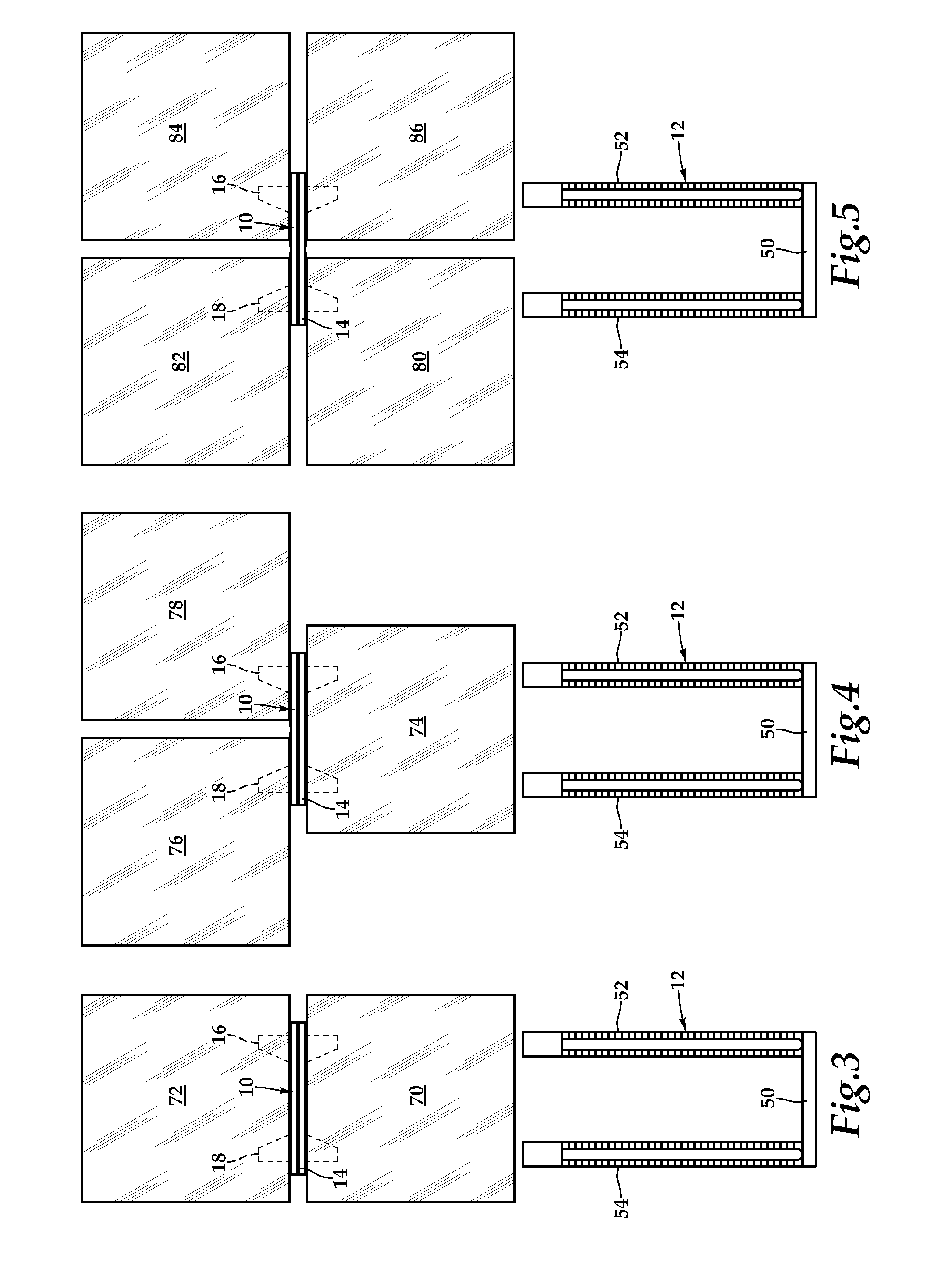

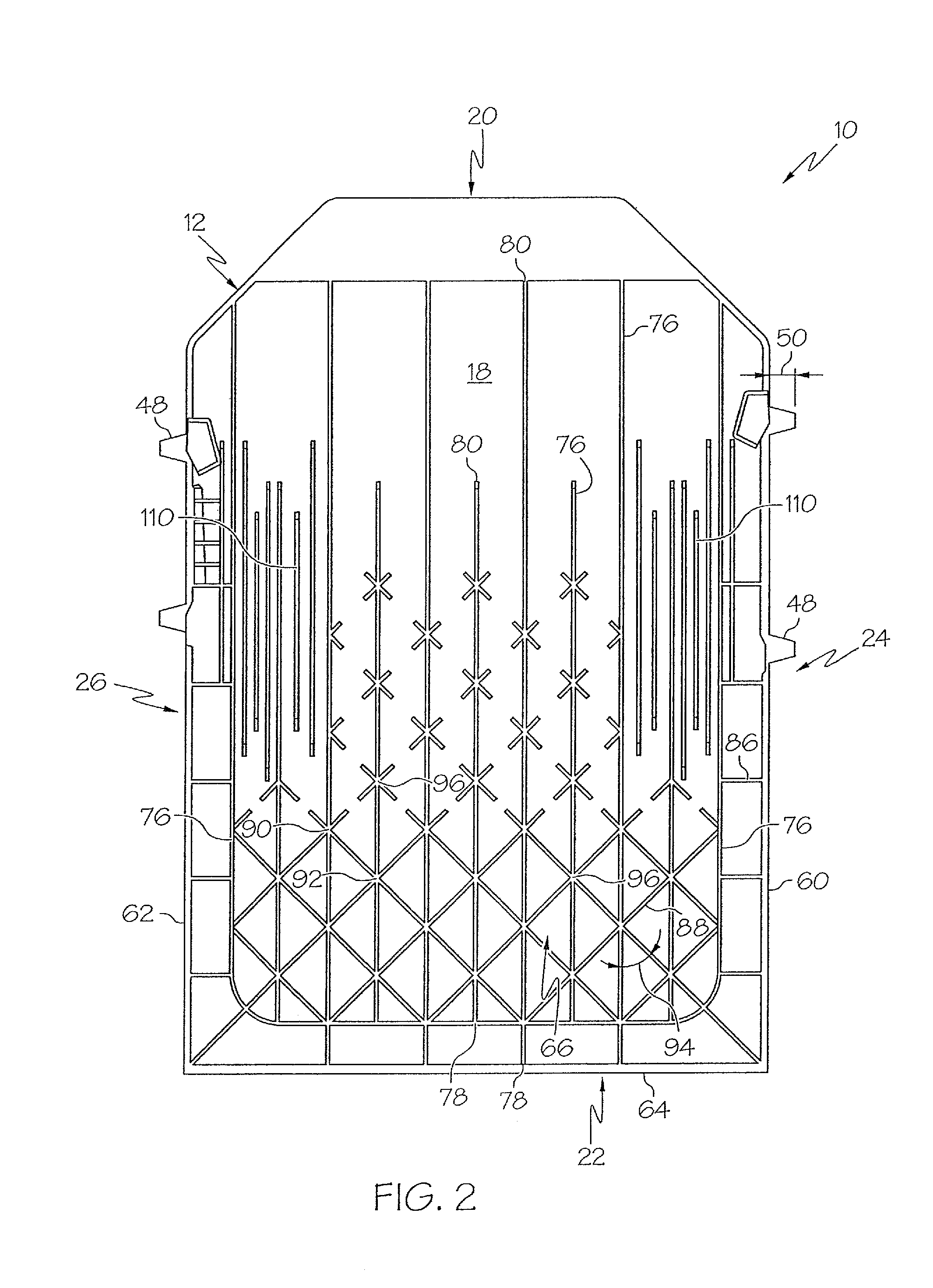

Grating connector and spacer apparatus, system, and methods of using the same

ActiveUS9731730B2Length of may varyAccurate spacingAngles/taper measurementsWagons/vansGratingEngineering

The present invention relates to an apparatus, system, and method of using the same for connecting and spacing grating and the like. Specifically, the present invention relates to connecting and spacing wire gratings, for example wire gratings used as vehicle tire support material or for mounting wheel chocks thereon in the transportation of automobiles. Even more specifically, the present invention may be used to connect a plurality of wire gratings together and to space in a first direction the plurality of gratings apart from each other at multiple selectable distances in one configuration. In a second configuration, the present invention may be used to space in a second direction the plurality of gratings from other objects, such as a wall or guard rail. The second configuration may be used in multiple orientations in order to provide multiple different spacing distances.

Owner:HOLLAND CO

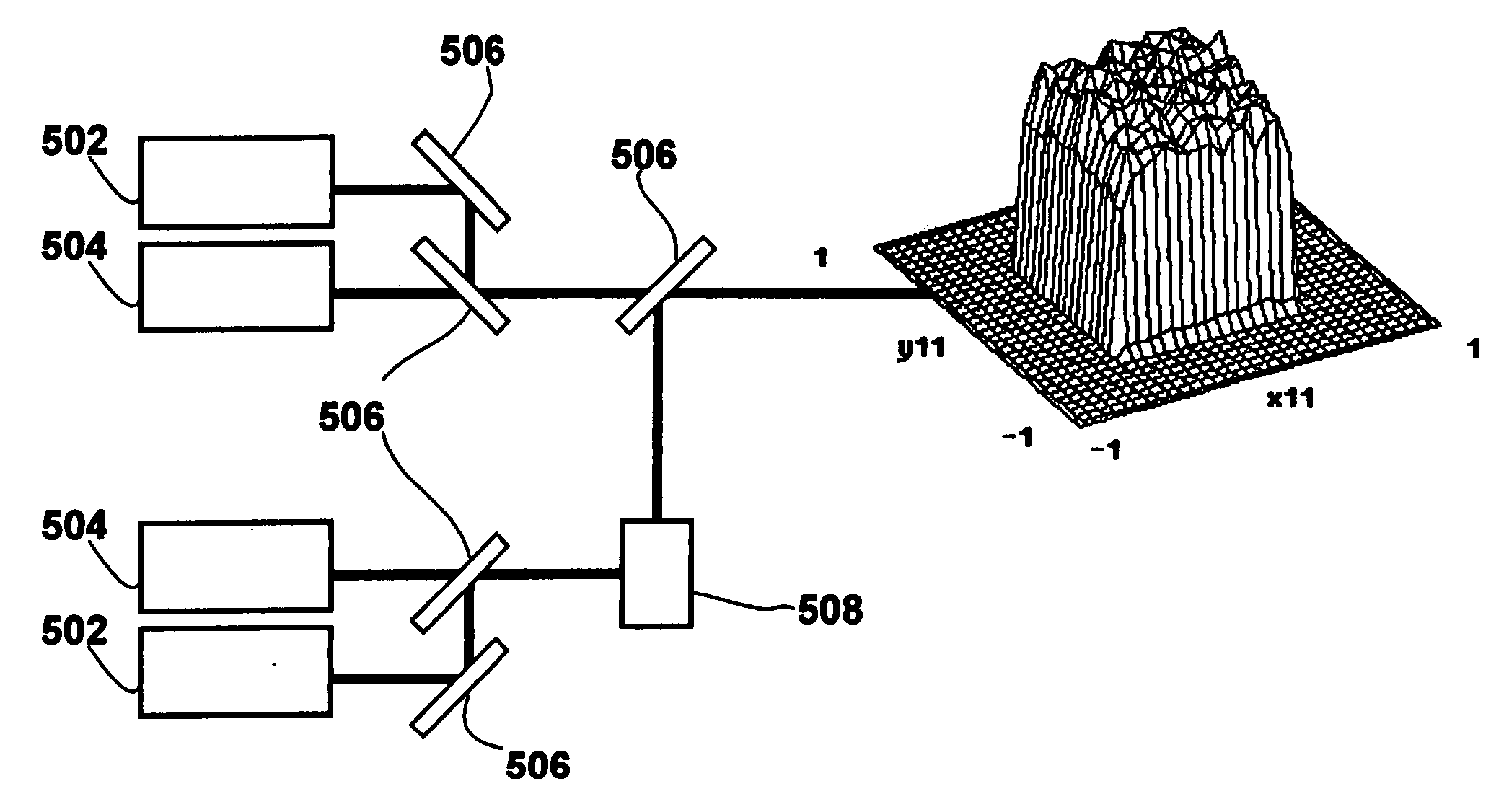

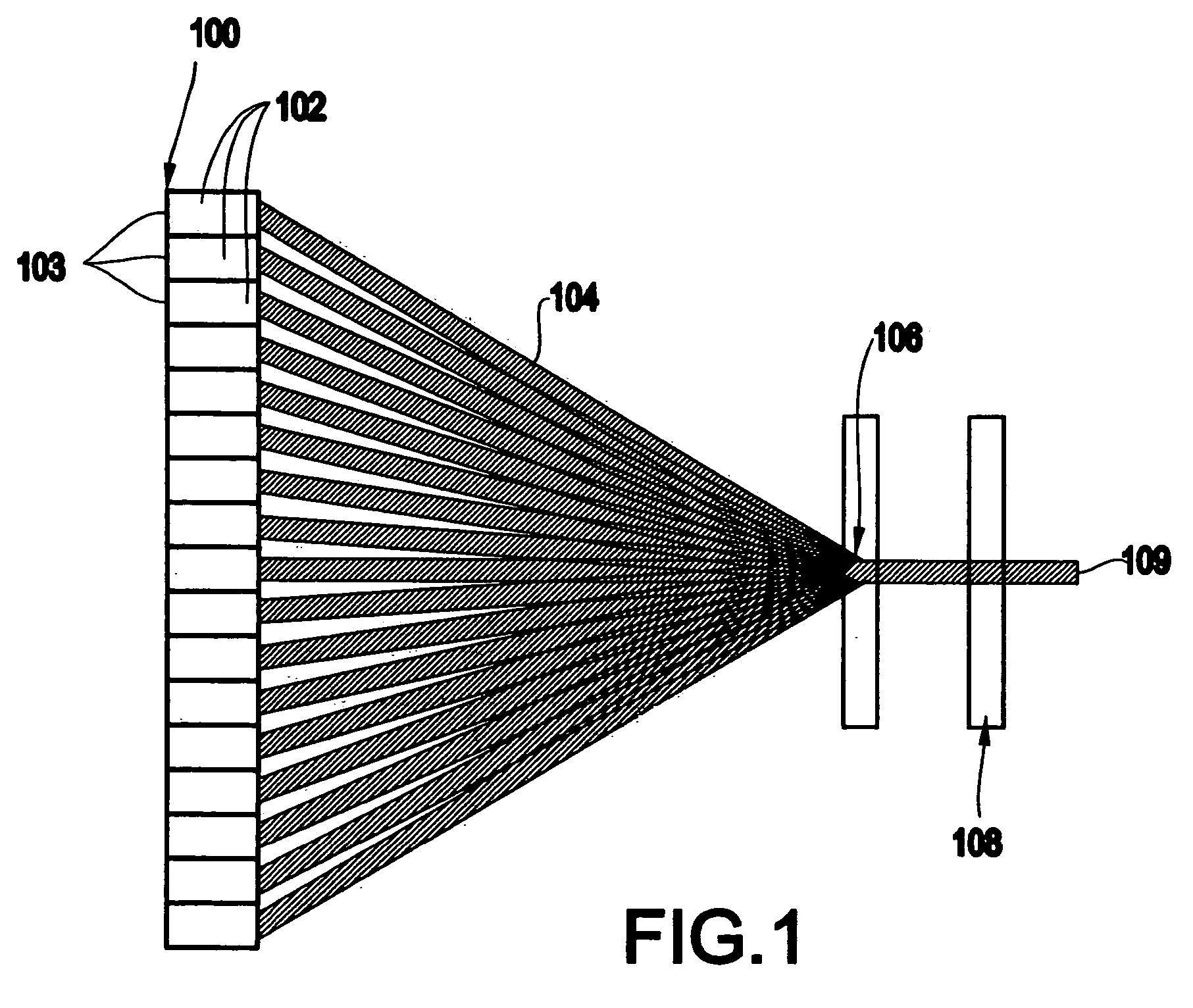

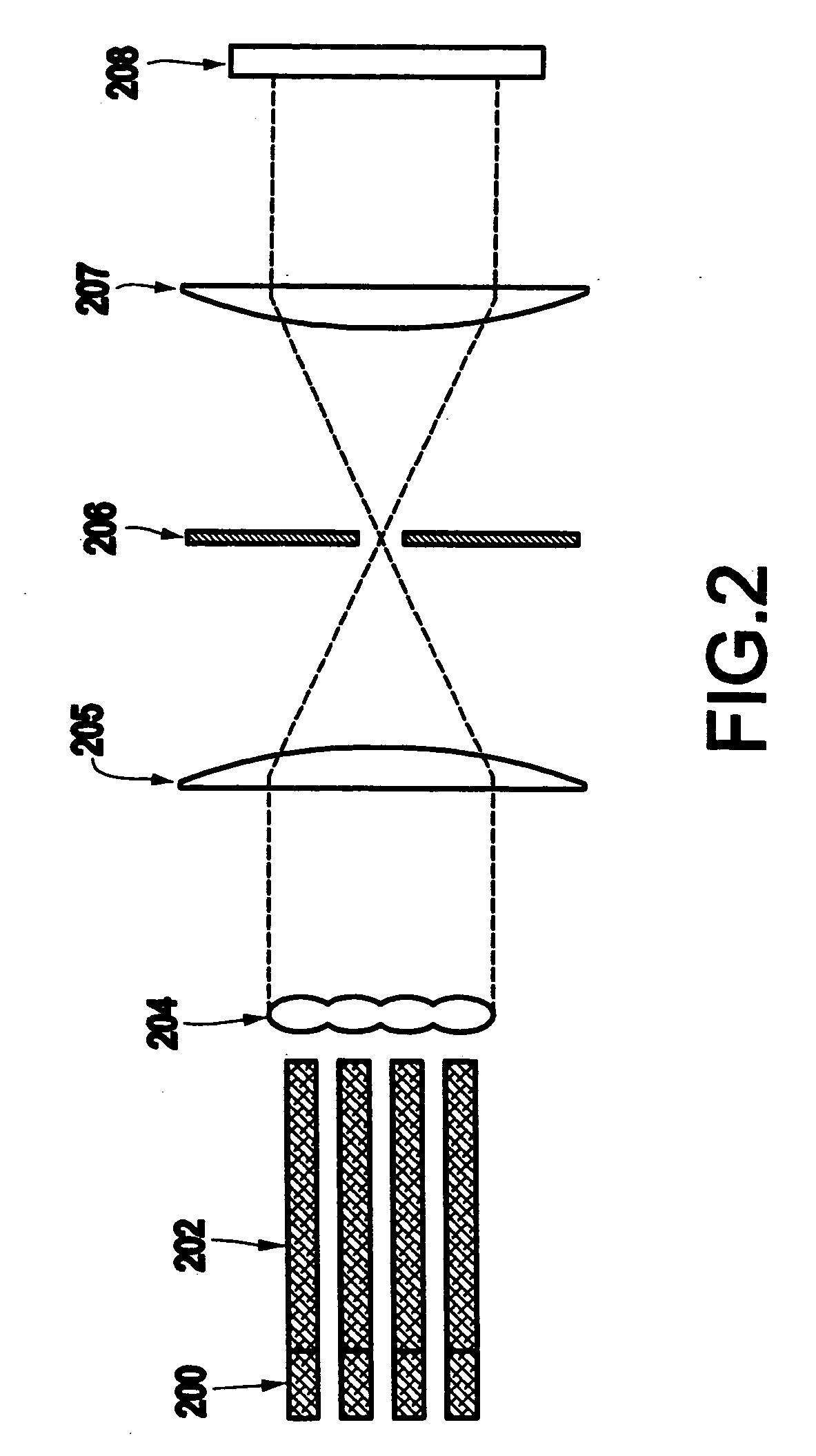

External cavity laser diode system and method thereof

InactiveUS20070002925A1Accurate spacingEasy to combineOptical resonator shape and constructionSemiconductor lasersExternal cavity laserOptoelectronics

A method (and system) of coherently combining a plurality of diodes in an external cavity laser diode system includes adjusting the phase of the plurality of diodes to correct phase errors, wherein the adjusting the phase includes intercavity phase adjustment. The laser diode external cavity system includes an adjuster for intercavity phase adjustment.

Owner:COHERENT INC

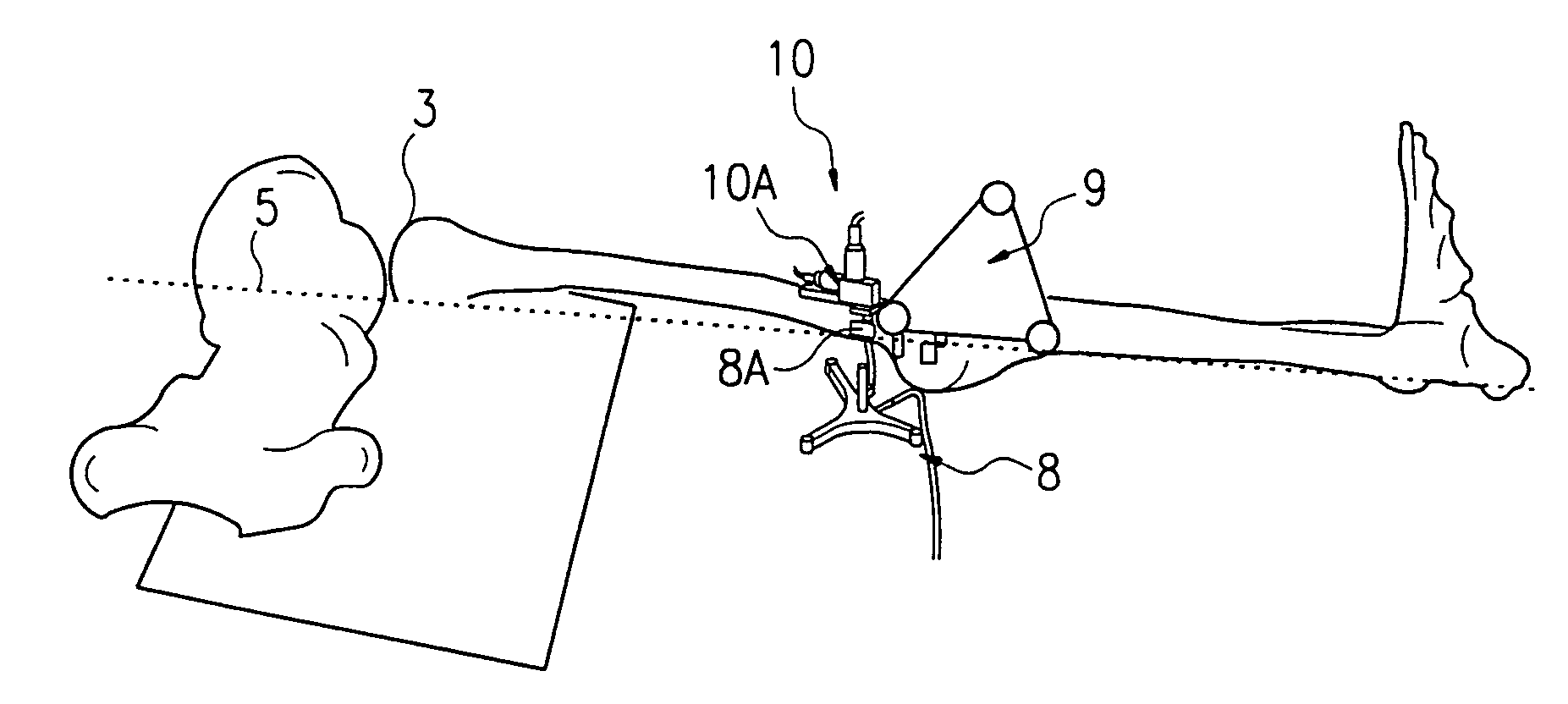

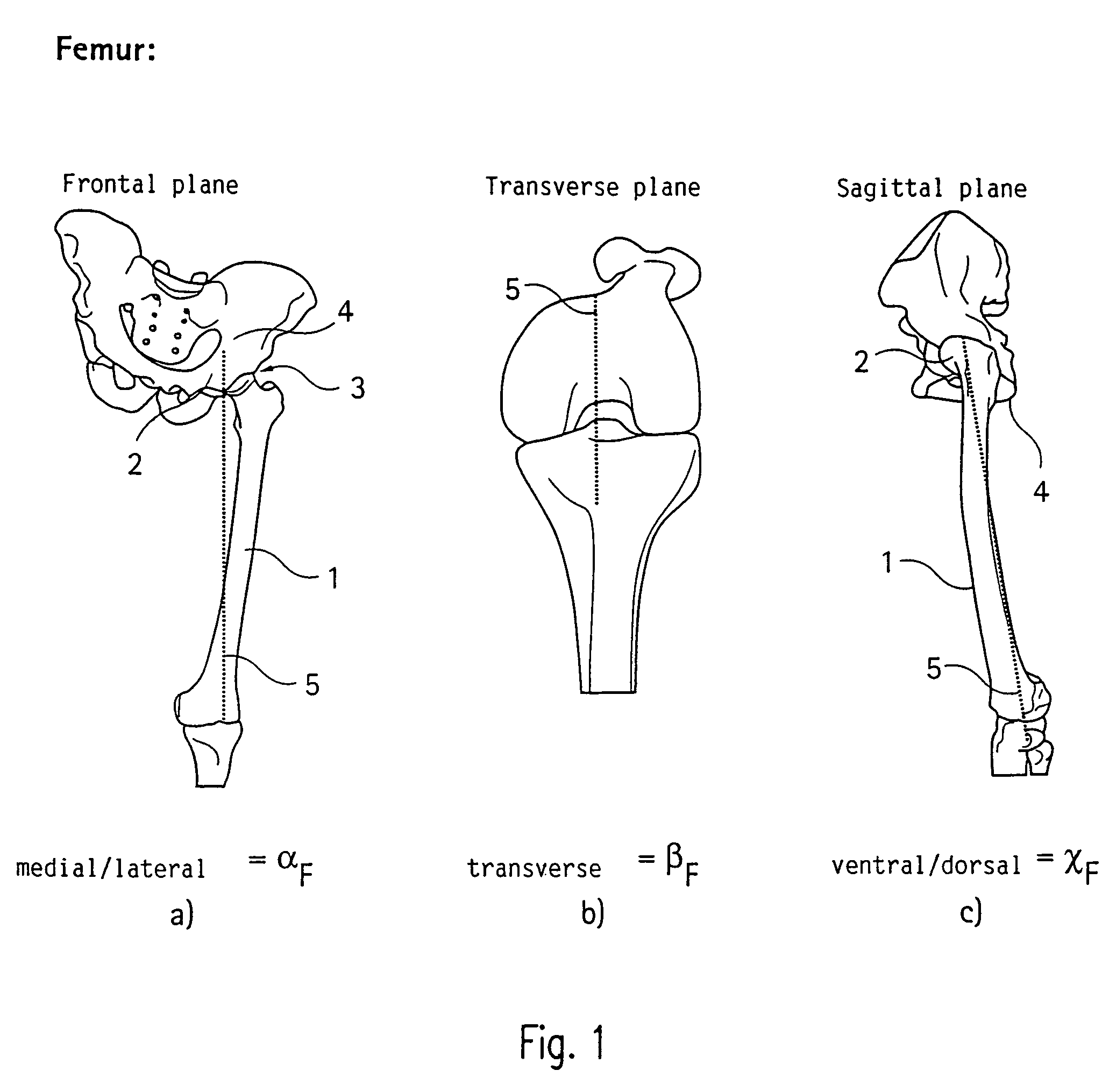

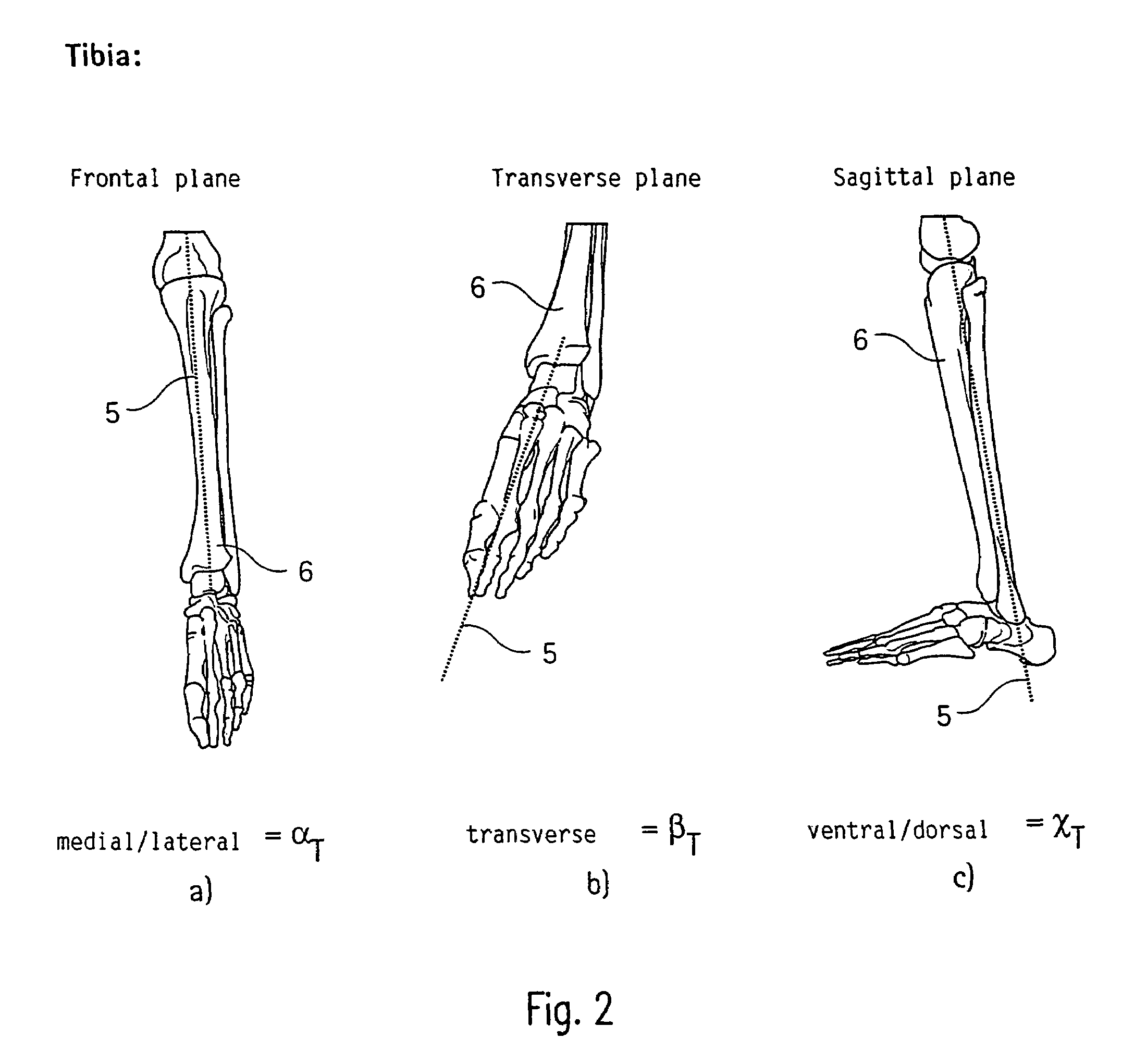

Method and apparatus for finding the position of a mechanical axis of a limb

InactiveUS7611520B2Rapidly and easily to locateDetermination of its position would be fairly trivialSurgical navigation systemsPerson identificationMeasurement deviceMeasurement point

A method of finding the position of a mechanical axis running in the longitudinal direction through a limb that is rotatably supported by its first end in a center of rotation that is not fixed and is not accessible for the mechanical determination of coordinates, by means of an optical coordinate-measurement device with an indicator to detect measurement-point coordinates in one rotational position of the limb such that, for each rotational position, a multi-point indicator rigidly attached near the second end of the limb signals several measurement-point coordinates, and, from the sets of measurement-point coordinates detected in a plurality of rotational positions, at least one group is selected that can be assigned to the same site of the center of rotation, and the measurement-point-coordinate sets assigned to this site of the center of rotation are used to calculate the mechanical axis.

Owner:SMITH & NEPHEW ORTHOPAEDICS

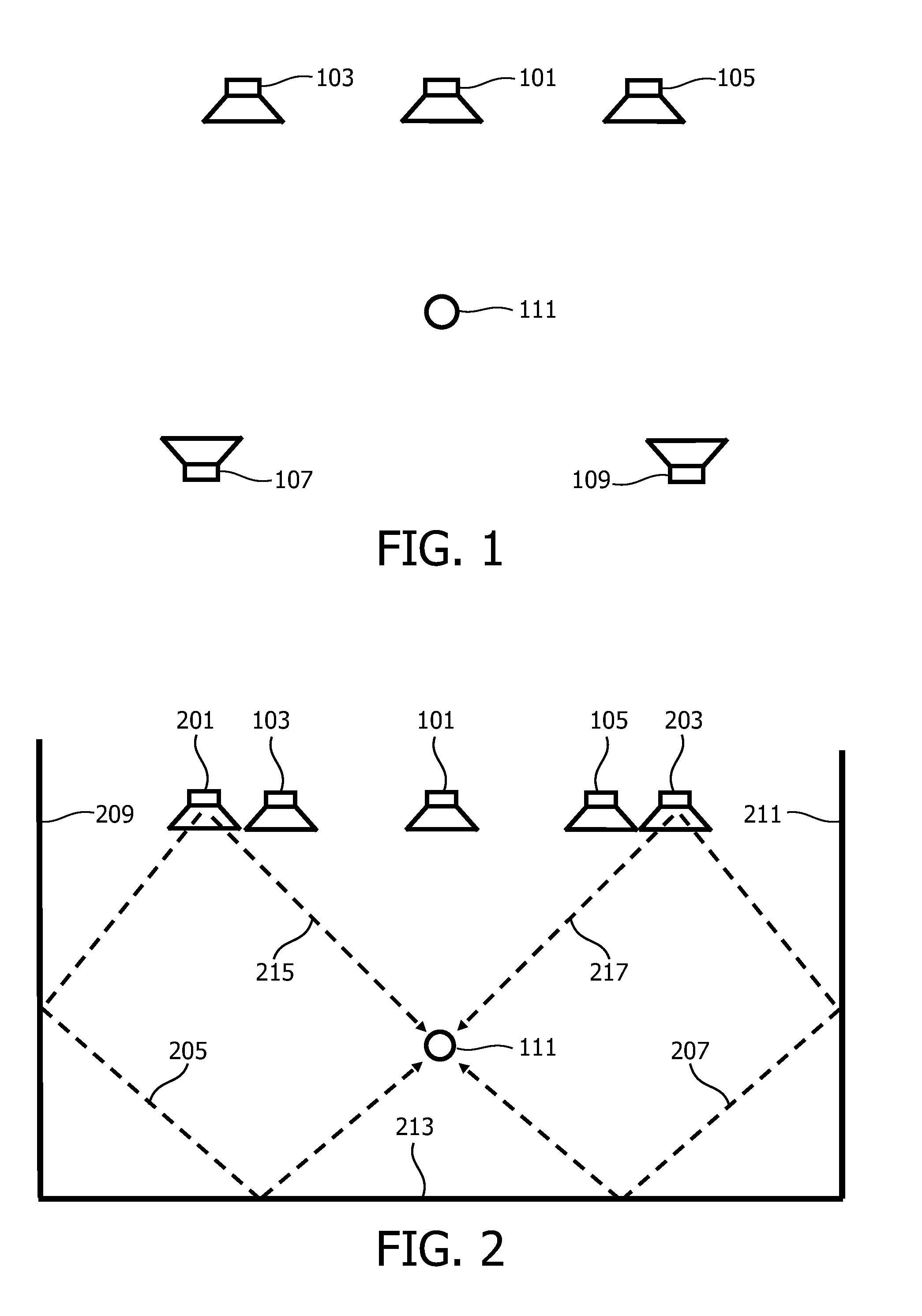

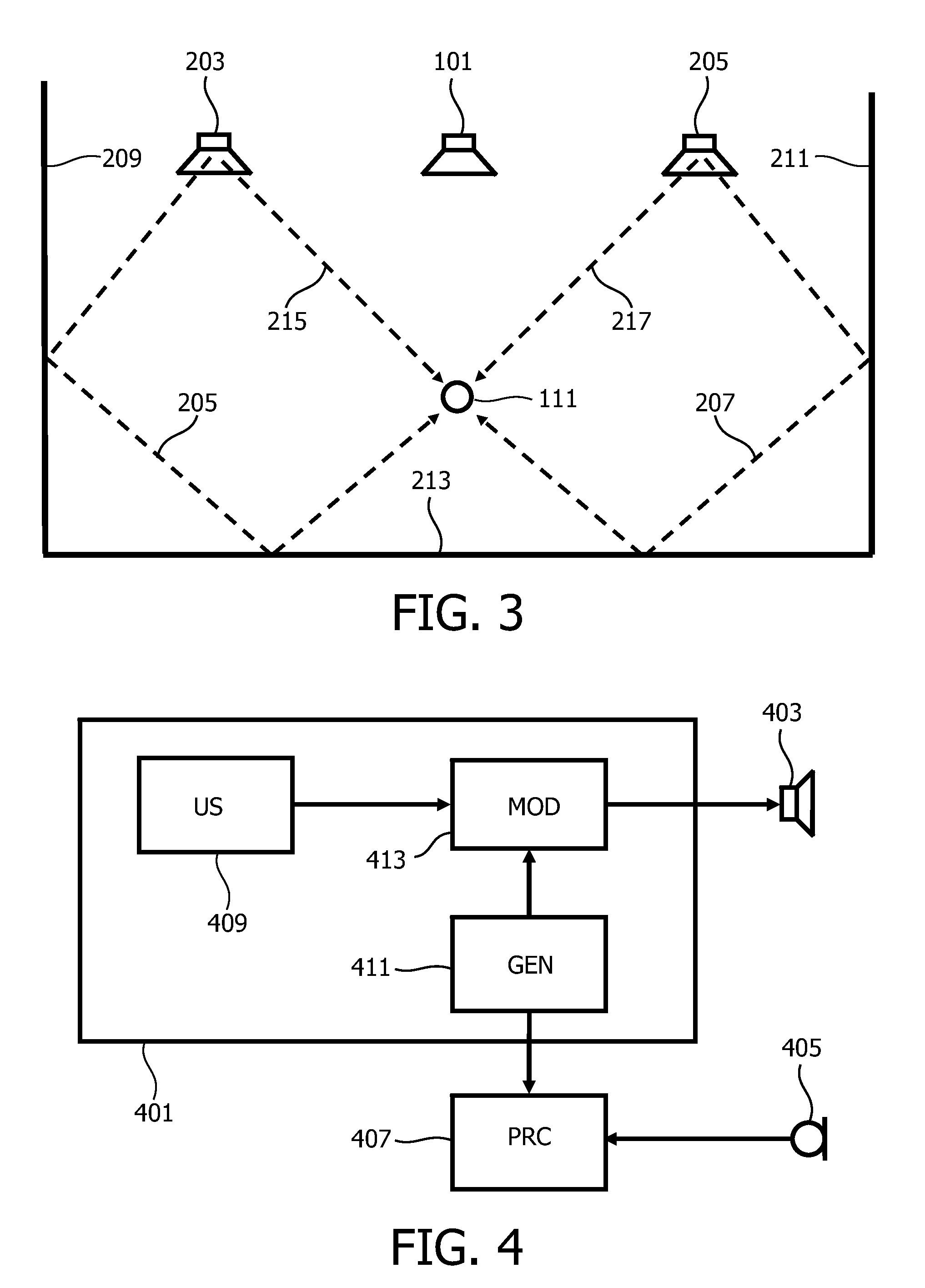

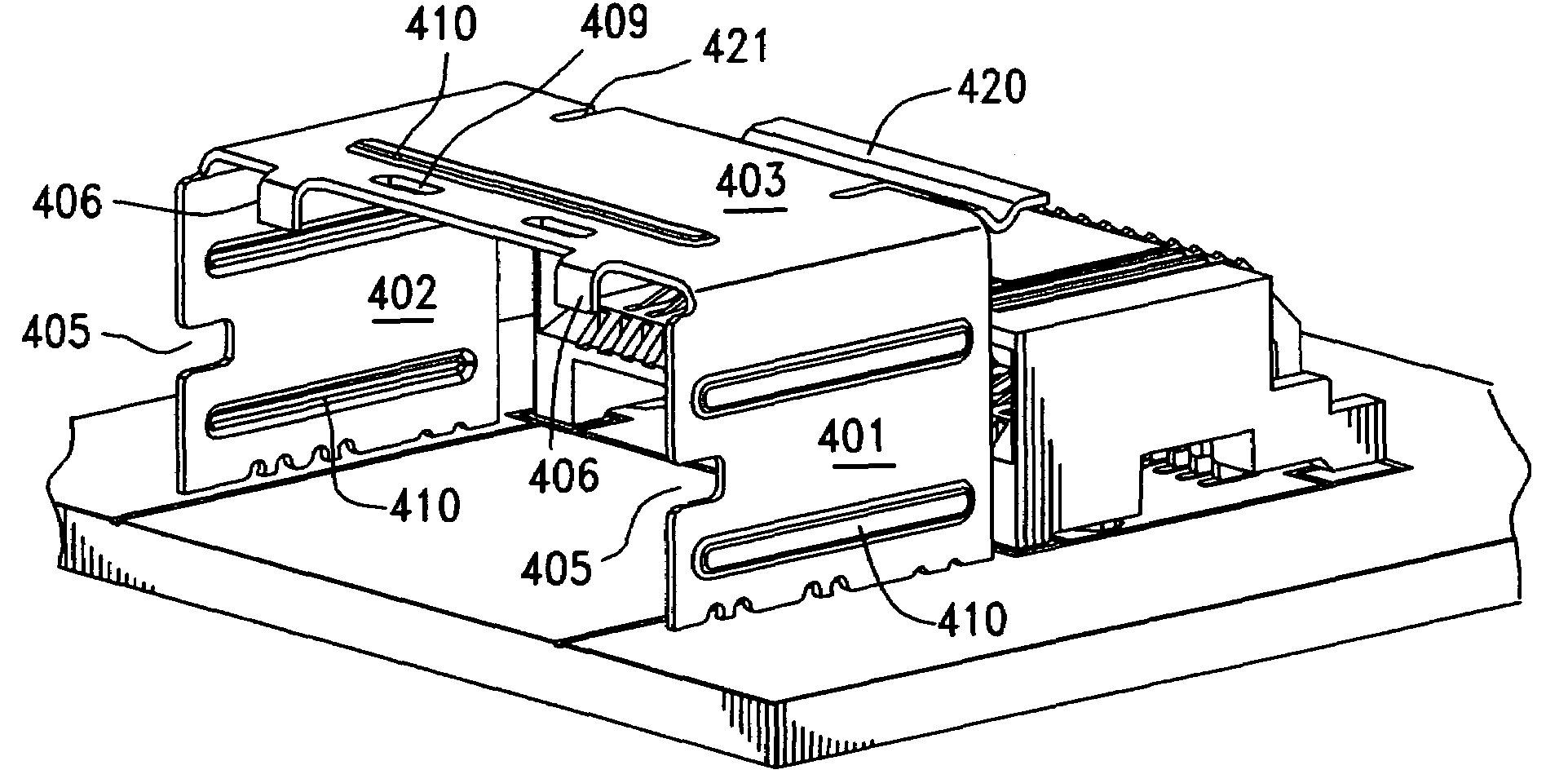

Distance estimation using sound signals

ActiveUS20130064042A1Improve sound reproductionAccurate measurementMicrophonesLoudspeakersPath lengthSonification

An apparatus comprises a test signal generator (401) which generates an ultrasonic test signal by modulating an audio band test signal on an ultrasonic signal. The ultrasonic test signal is radiated from a parametric loudspeaker (403) and is demodulated by non-linearities in the air. A reflected audio signal may arise from reflections of an object, such as a wall. An audio band sensor (405) generates an audio band captured signal which comprises the demodulated reflected audio band signal. A distance circuit (407) then generates a distance estimate for the distance from the parametric loudspeaker (403) to the object in response to a comparison of the audio band captured signal and the audio band test signal. Specifically two signals may be correlated to determine a delay corresponding to the full path length. Based on the distance estimates an audio environment may be estimated and a sound system may be adapted accordingly.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

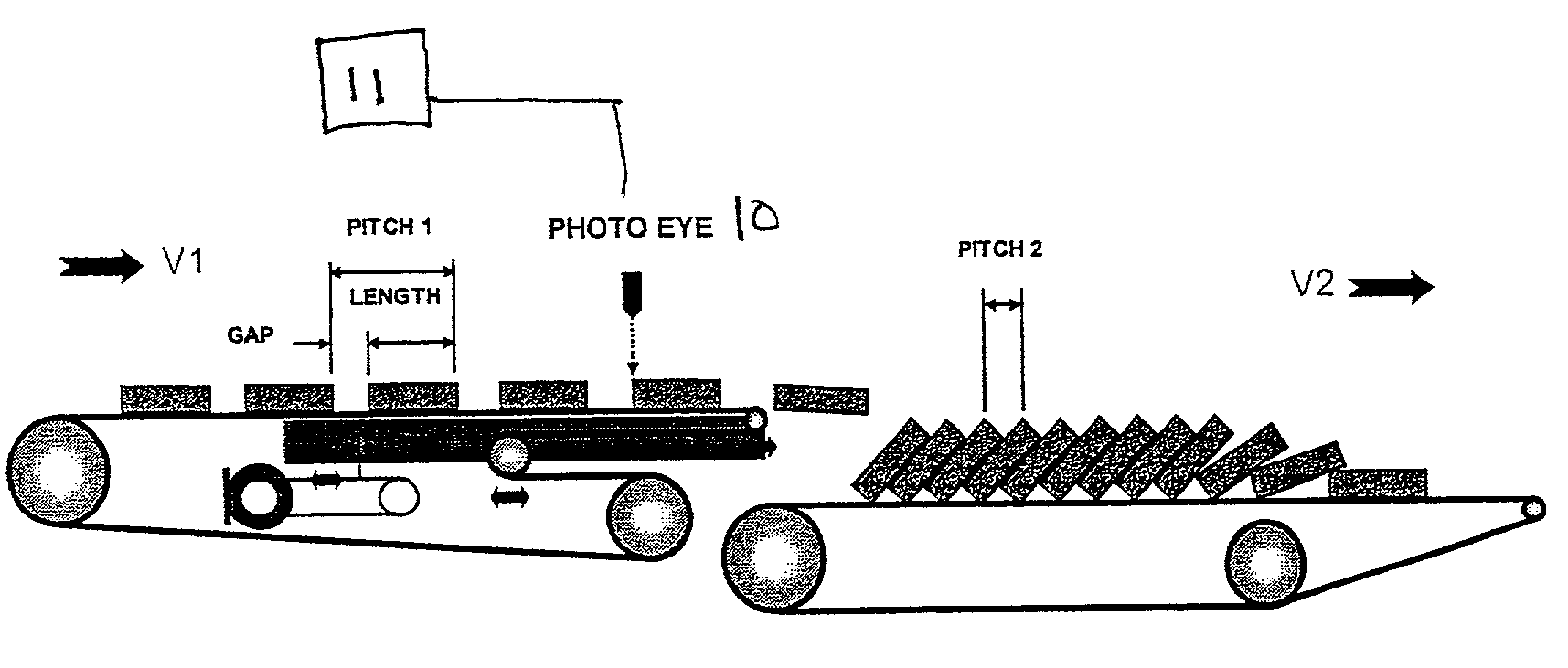

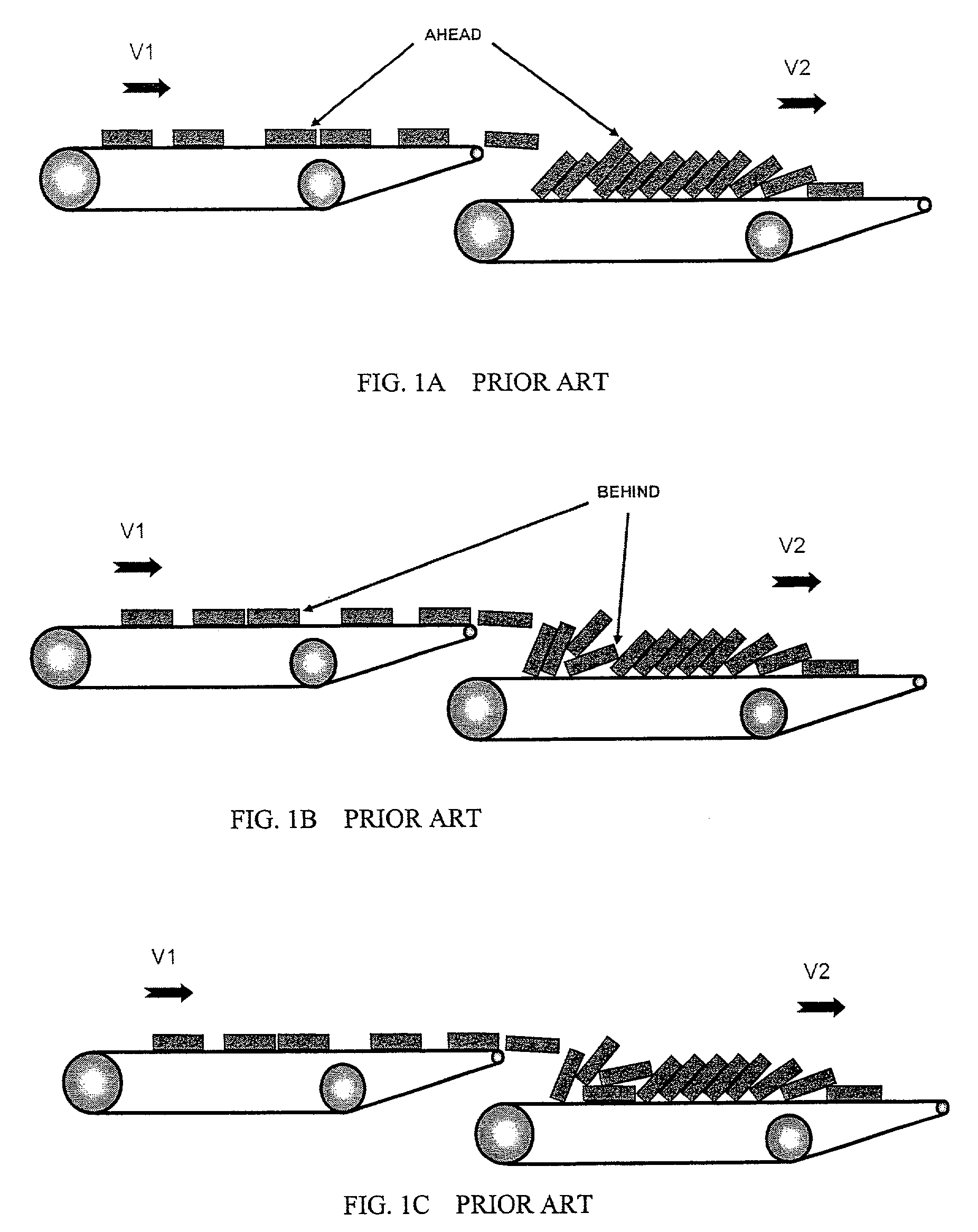

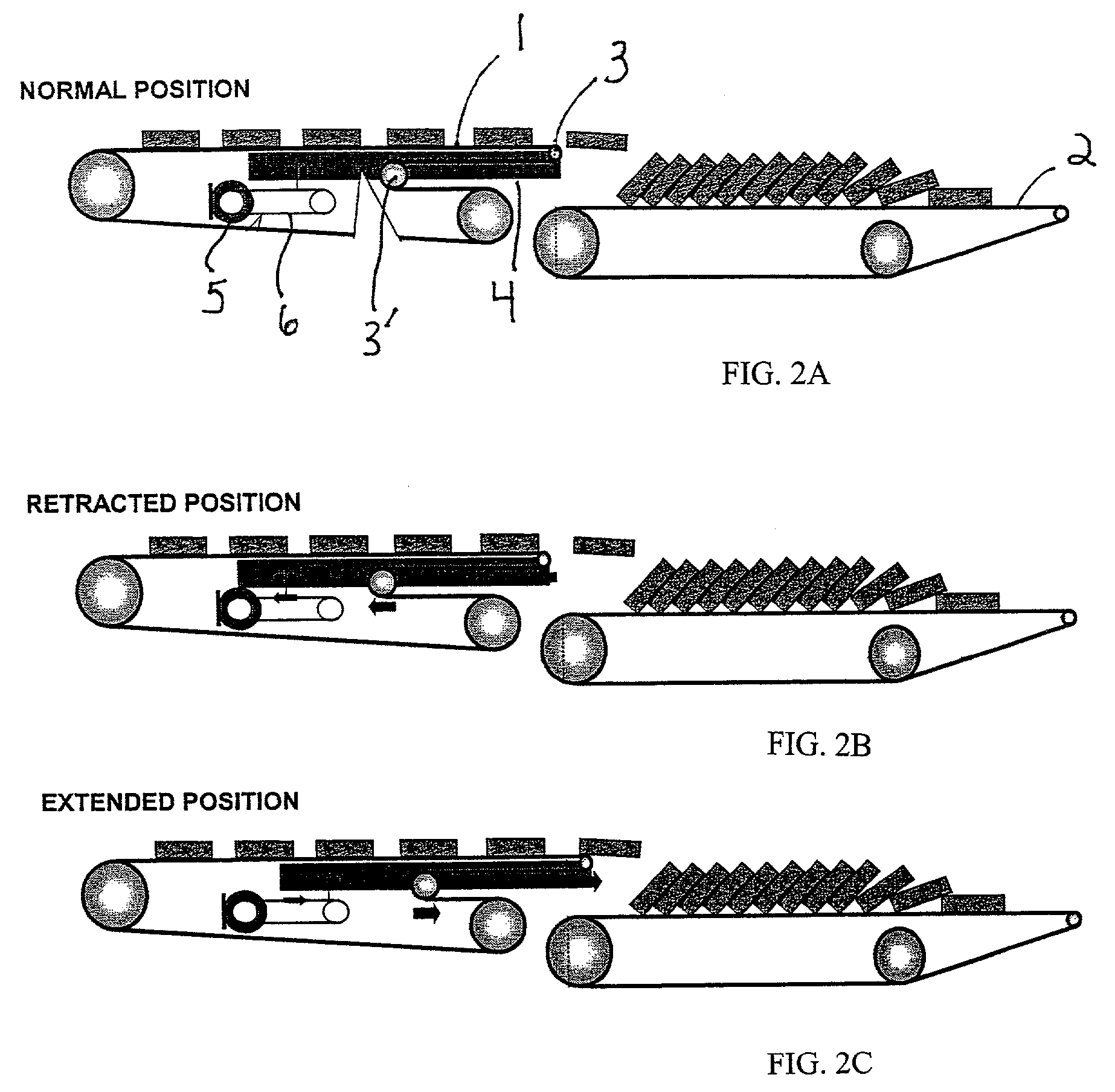

Device and method to correct uneven spacing of successive articles

InactiveUS7021450B2Accurate spacingConveyorsControl devices for conveyorsEngineeringMechanical engineering

Owner:INTERCONTINENTAL GREAT BRANDS LLC

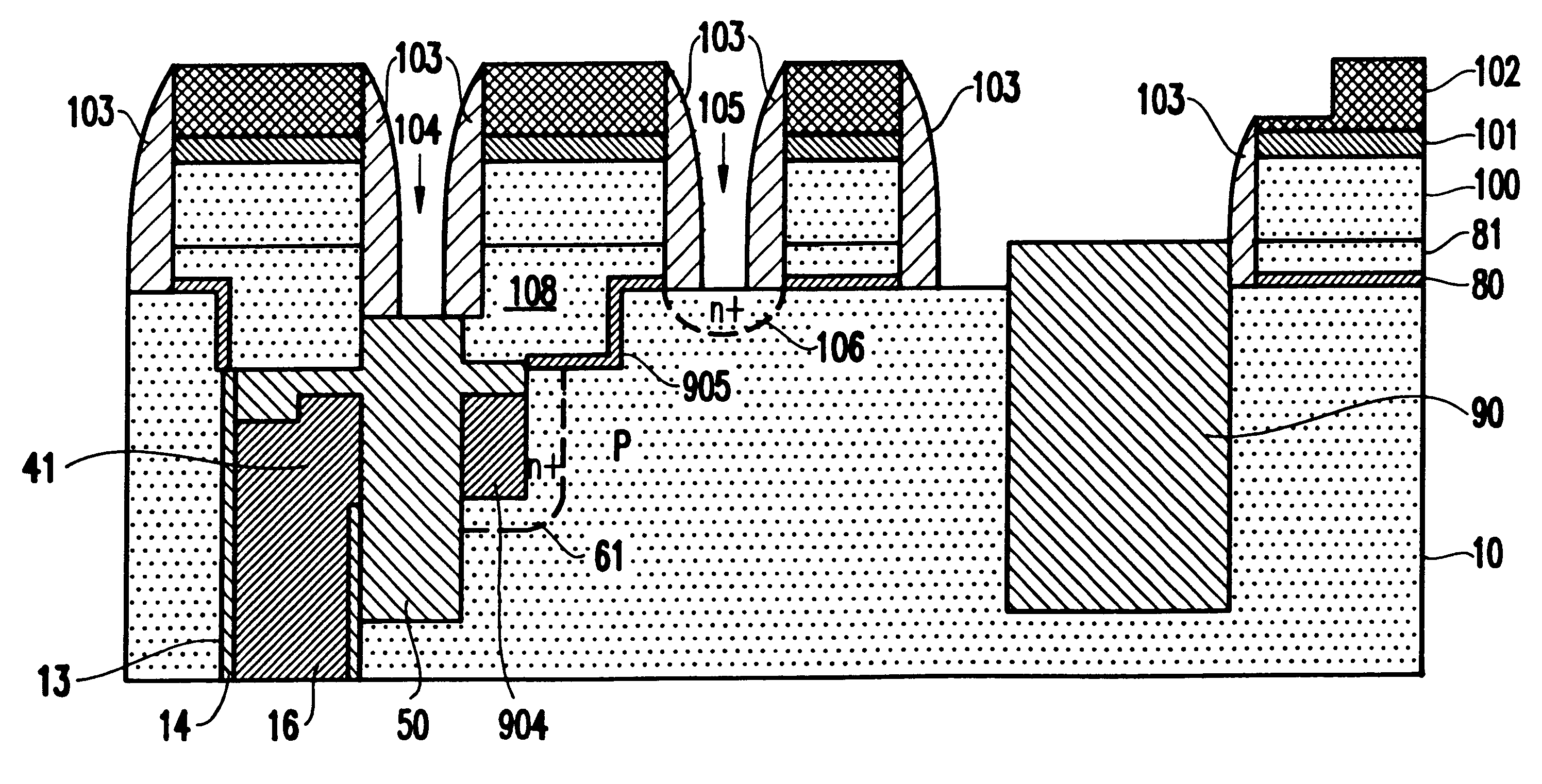

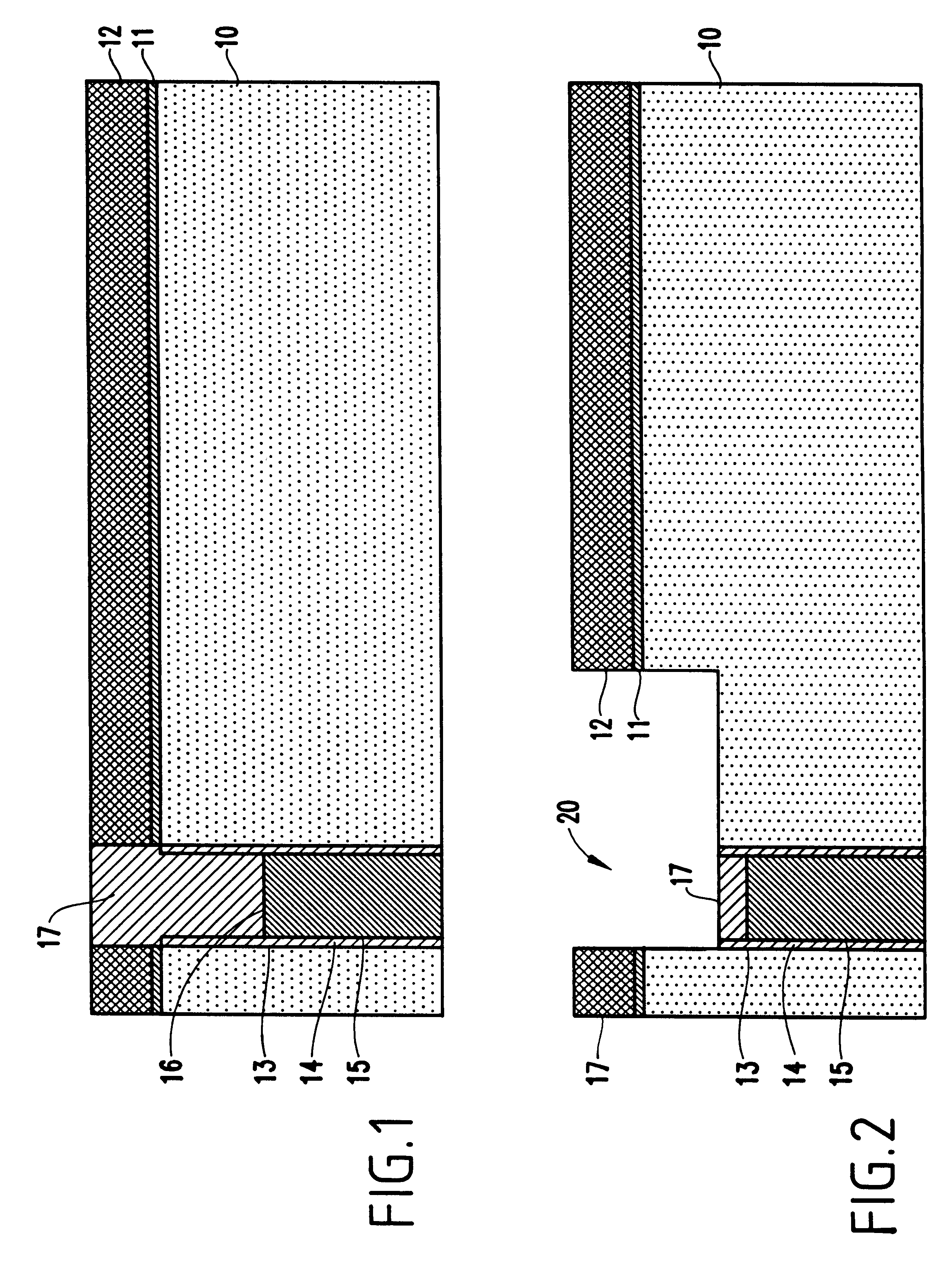

Formation of 5F2 cell with partially vertical transistor and gate conductor aligned buried strap with raised shallow trench isolation region

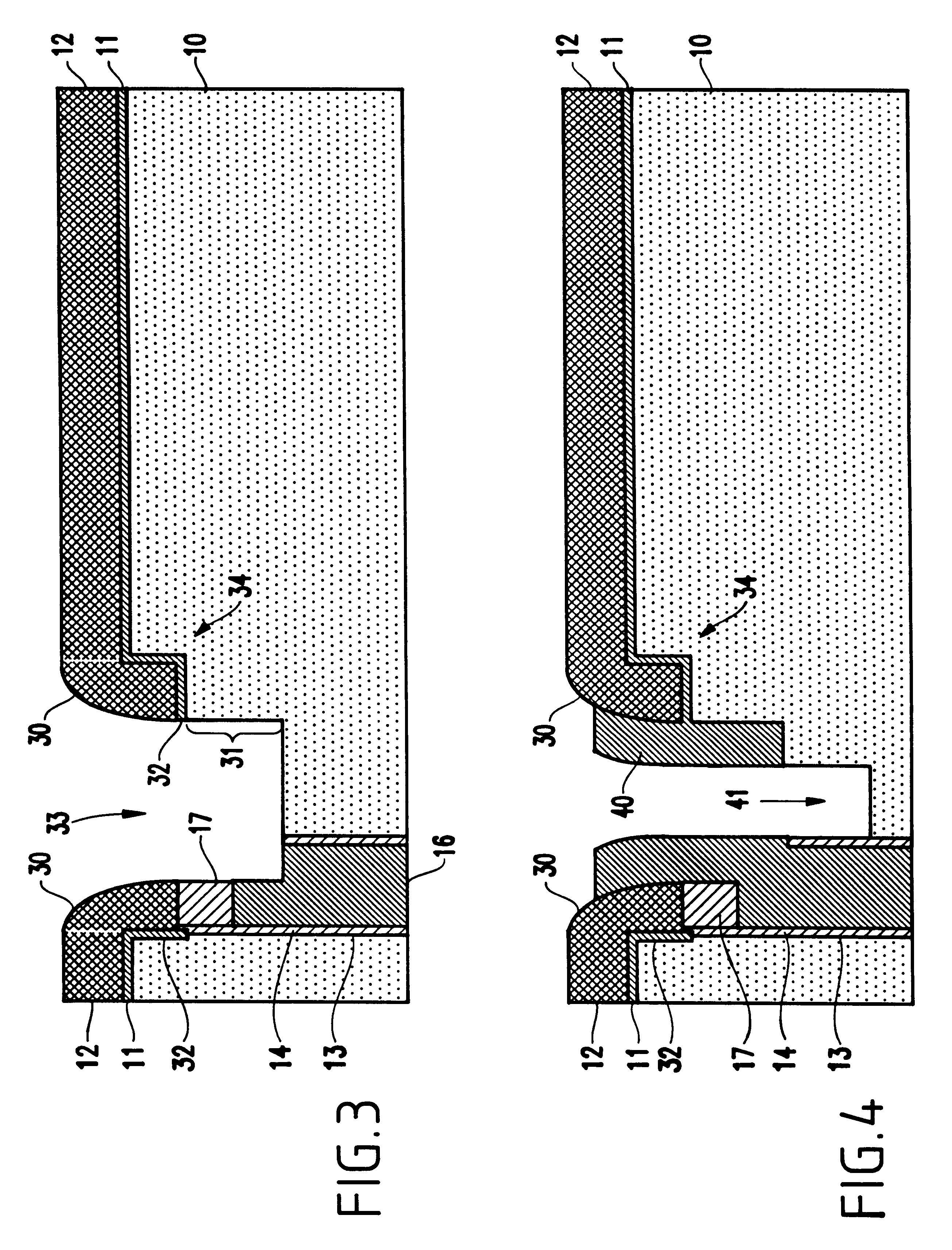

InactiveUS6190971B1Reduce the amount requiredReduce in quantityTransistorSolid-state devicesElectrical conductorGate insulator

A method and structure for manufacturing an integrated circuit device includes forming a storage device in a substrate, lithographically forming a gate opening in the substrate over the storage device, forming first spacers in the gate opening, forming a strap opening in the substrate using the first spacers to align the strap opening, forming second spacers in the strap opening, forming an isolation opening in the substrate using the second spacers to align the isolation opening, filling the isolation opening with an isolation material, removing the first spacers and a portion of the second spacers to form a step in the gate opening, (wherein the second spacers comprise at least one conductive strap electrically connected to the storage device) forming a first diffusion region in the substrate adjacent the conductive strap, forming a gate insulator layer over the substrate and the step, forming a gate conductor over a portion of the gate insulator layer above the step, forming a second diffusion region in the substrate adjacent the gate conductor and forming a contact over the diffusion region and isolated from the gate conductor, wherein a voltage in the gate conductor forms a conductive region in the substrate adjacent the step and the conductive region electrically connects the strap and the contact.

Owner:INFINEON TECH AG +1

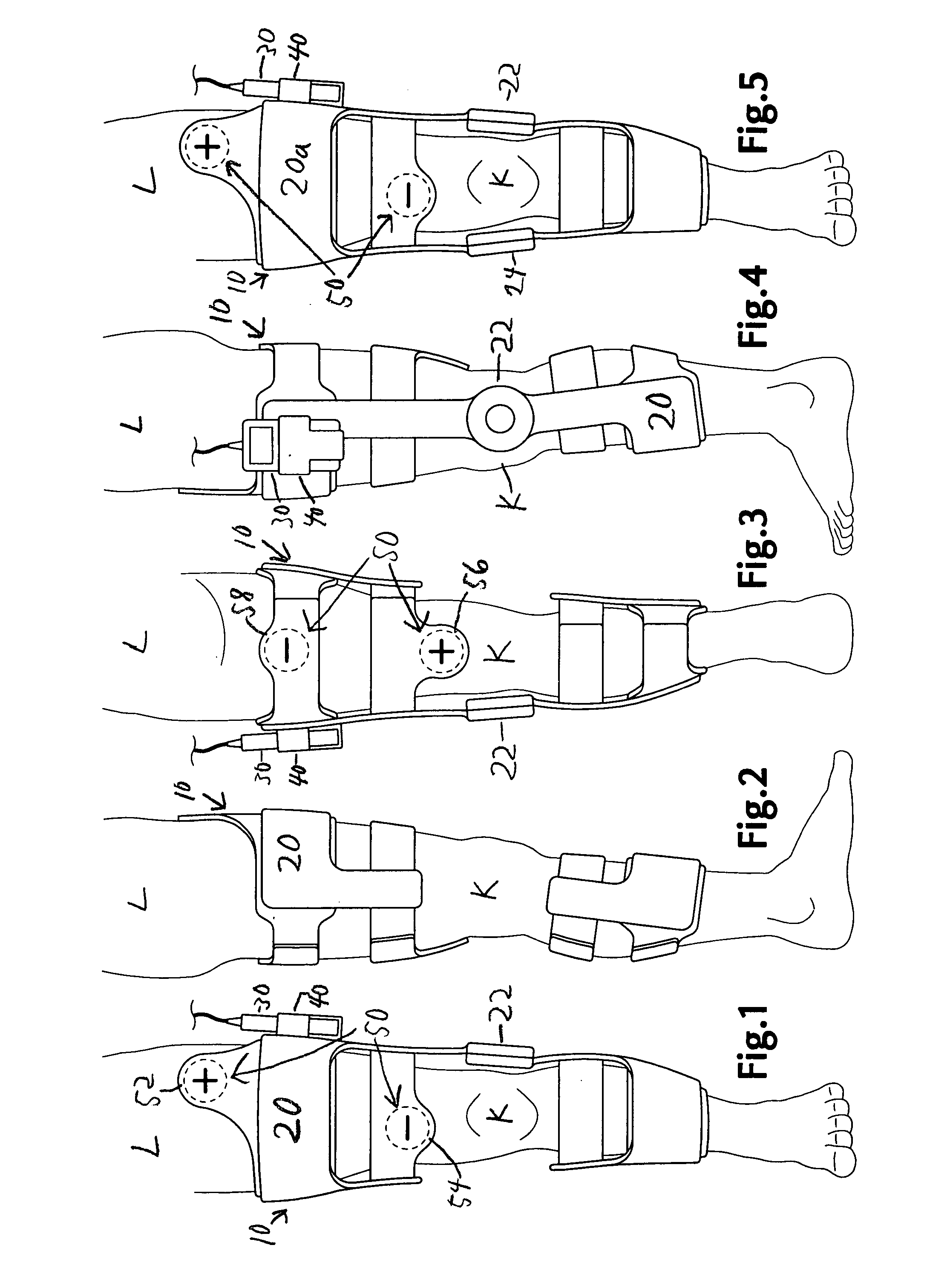

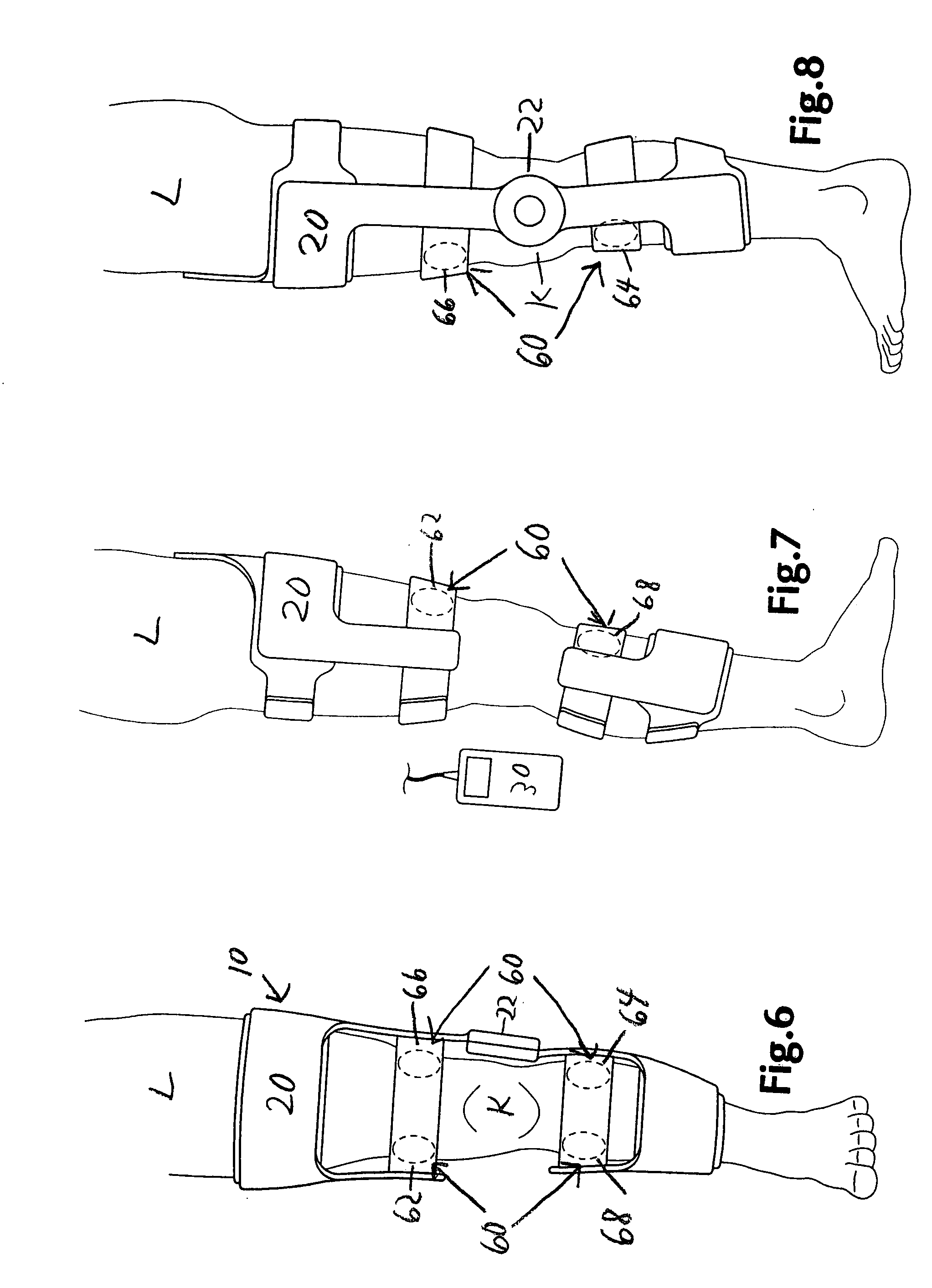

Apparatus for surface electrical stimulation and stabilization to treat disorders of the joints

Owner:INT REHABILITATIVE SCI

Method for parking a vehicle

InactiveUS7248153B2Reduce in quantityFacilitates effective parkingDetection of traffic movementIndication of parksing free spacesParking spaceEngineering

Owner:ROBERT BOSCH GMBH

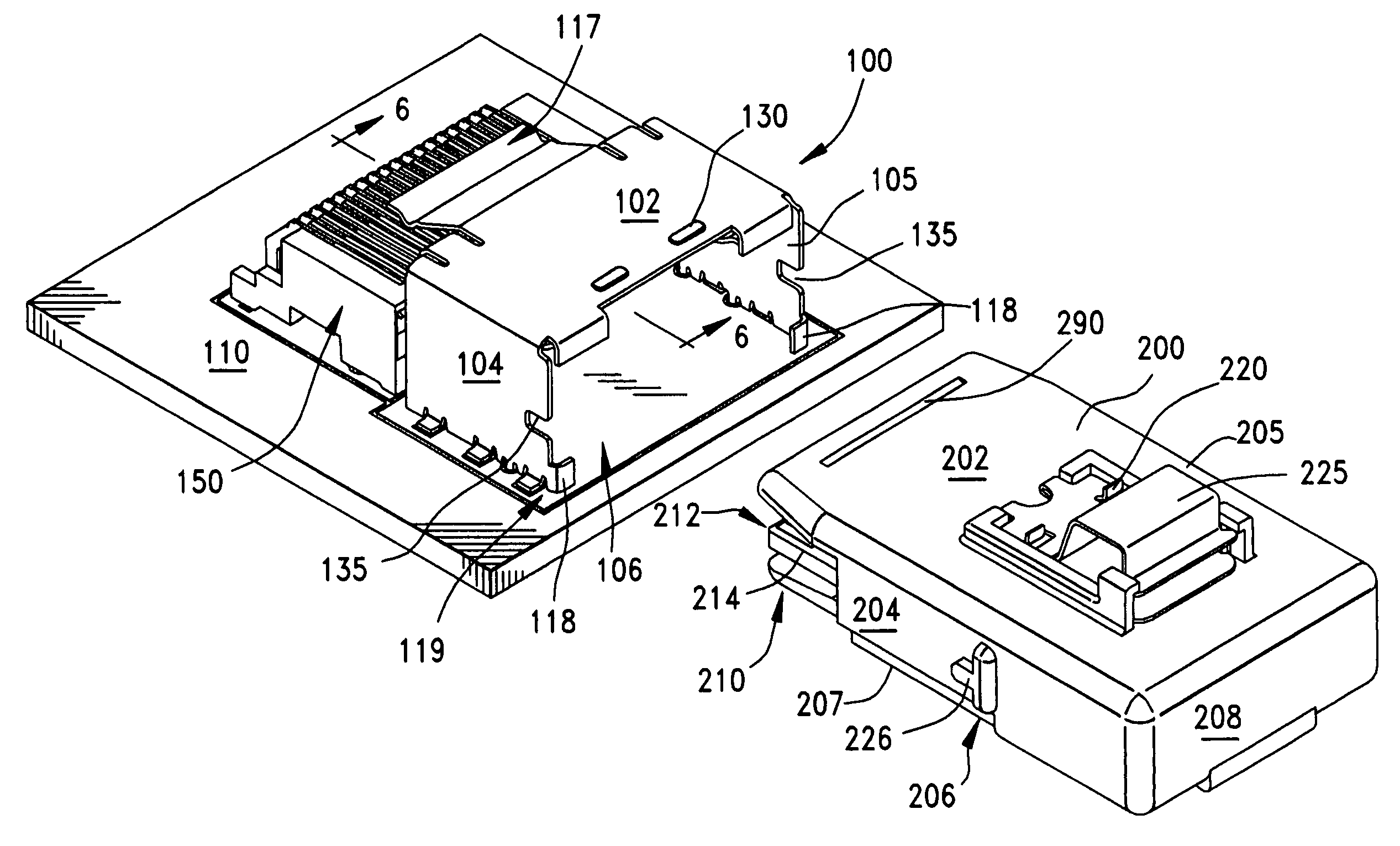

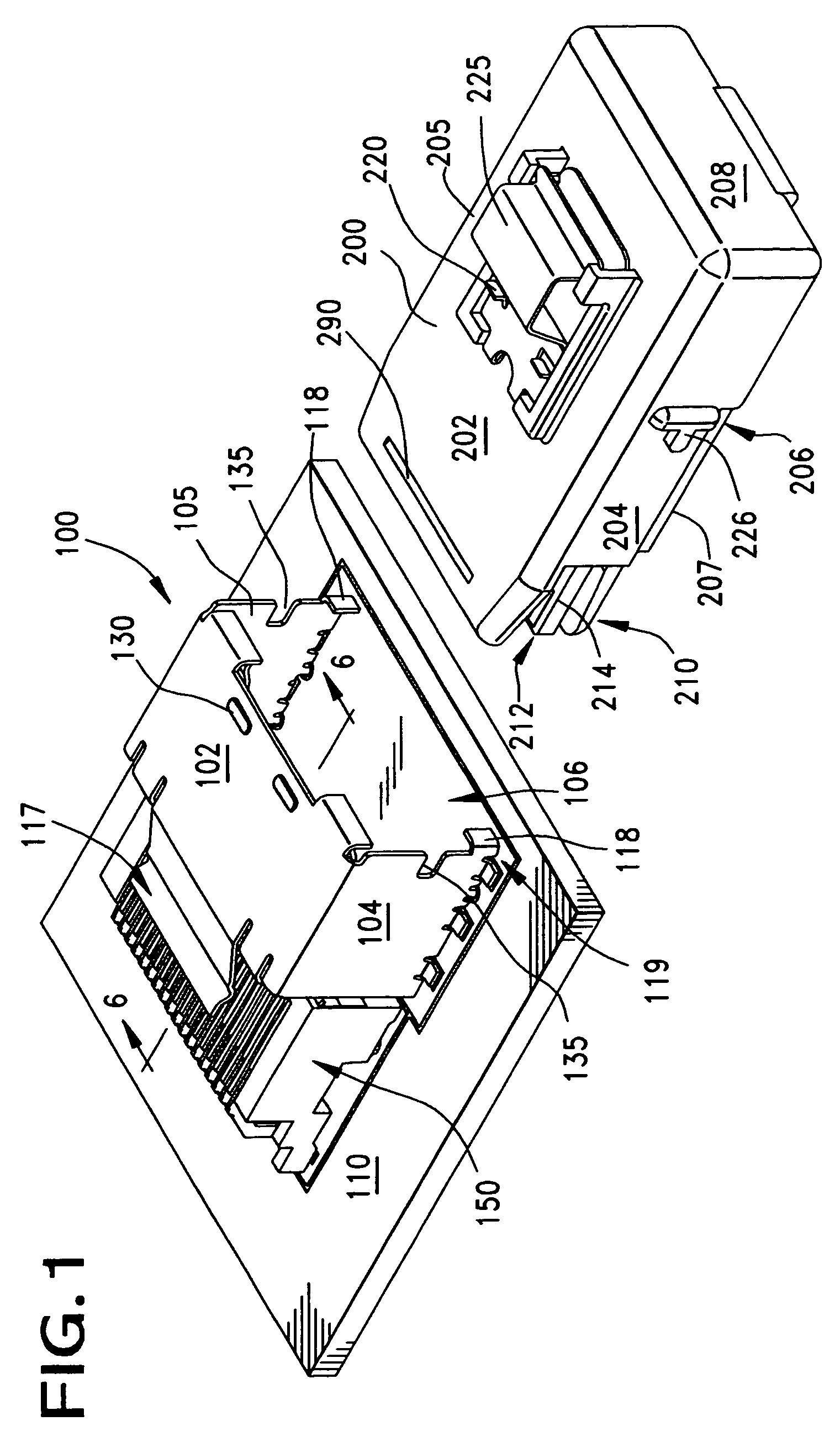

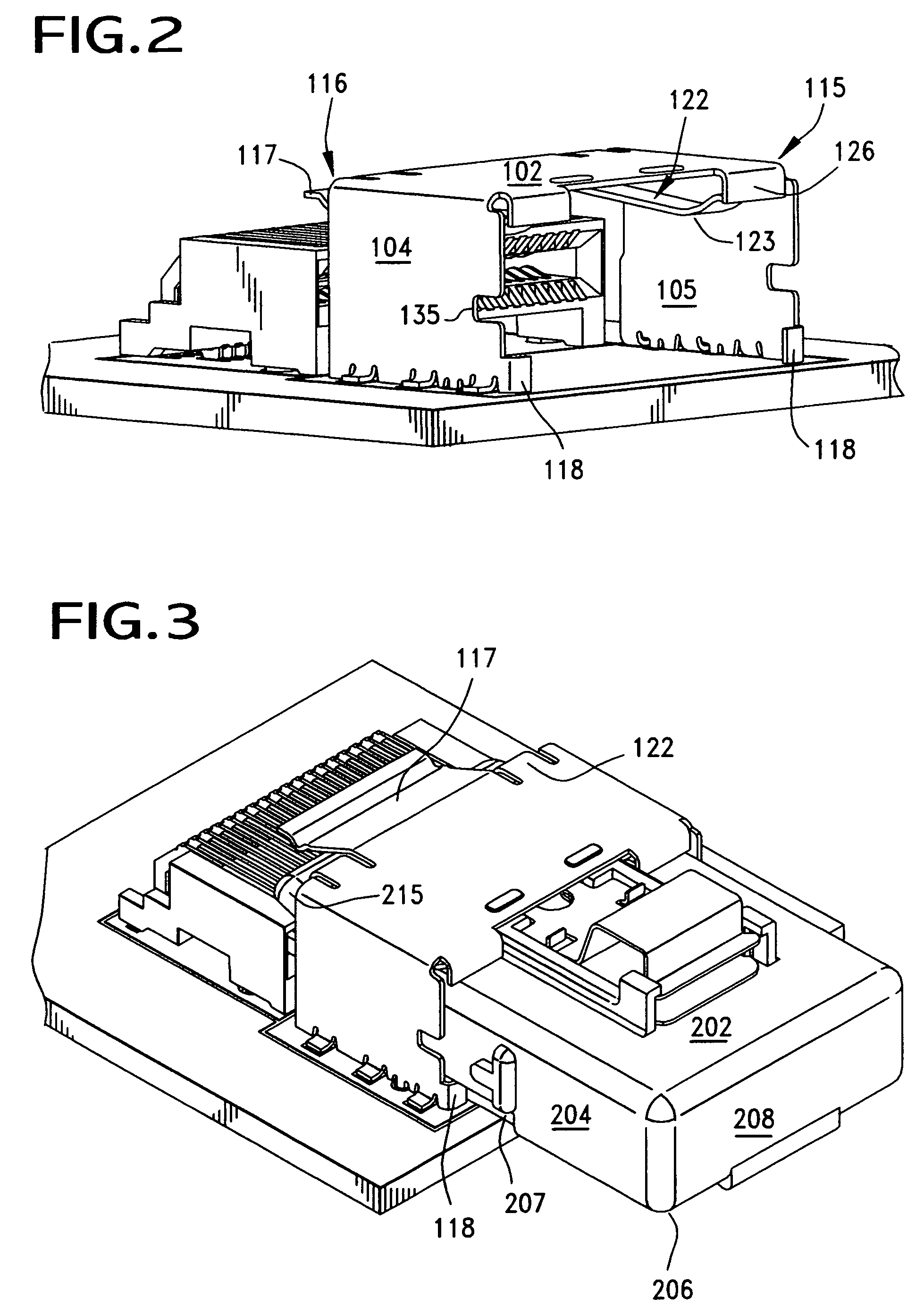

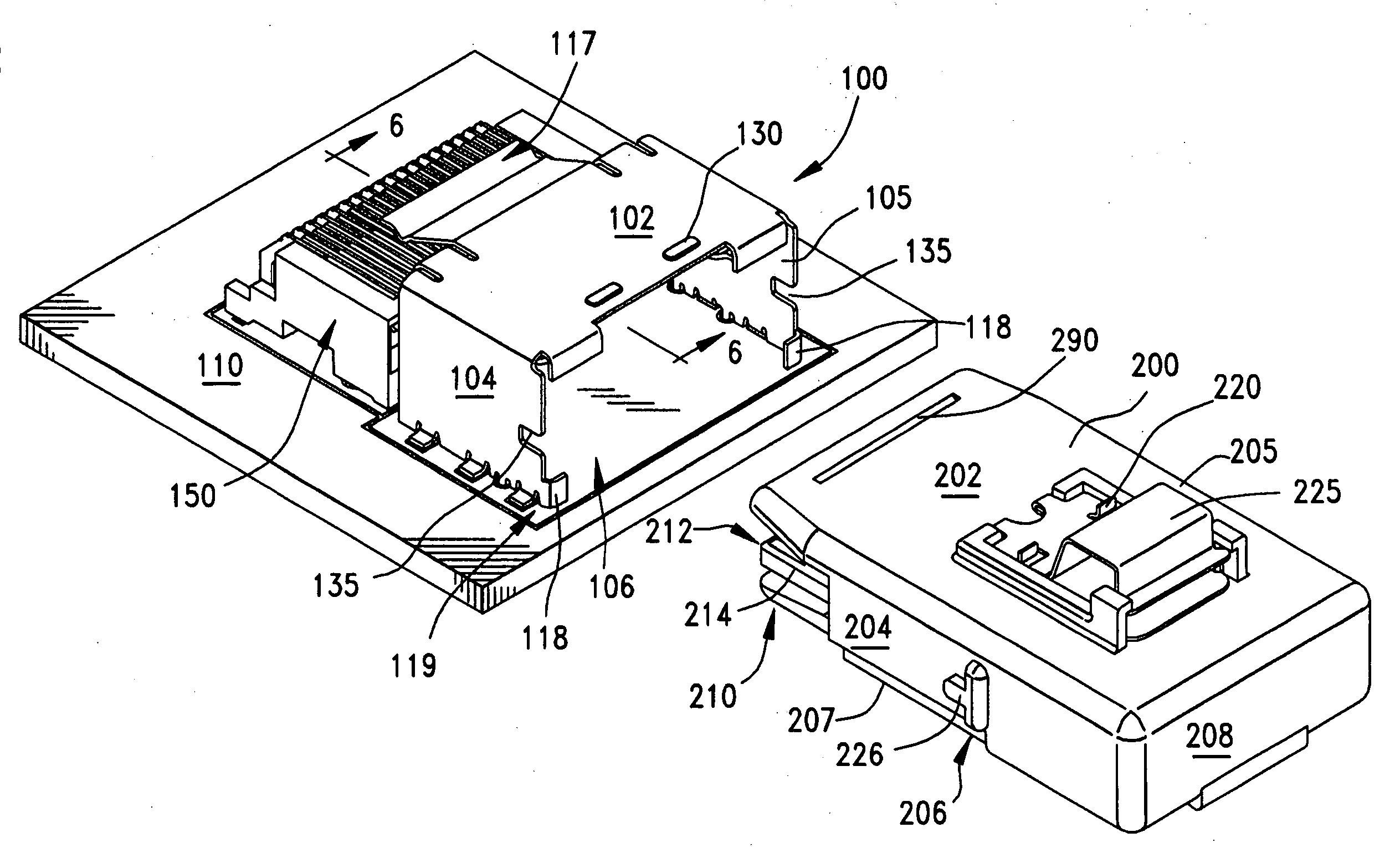

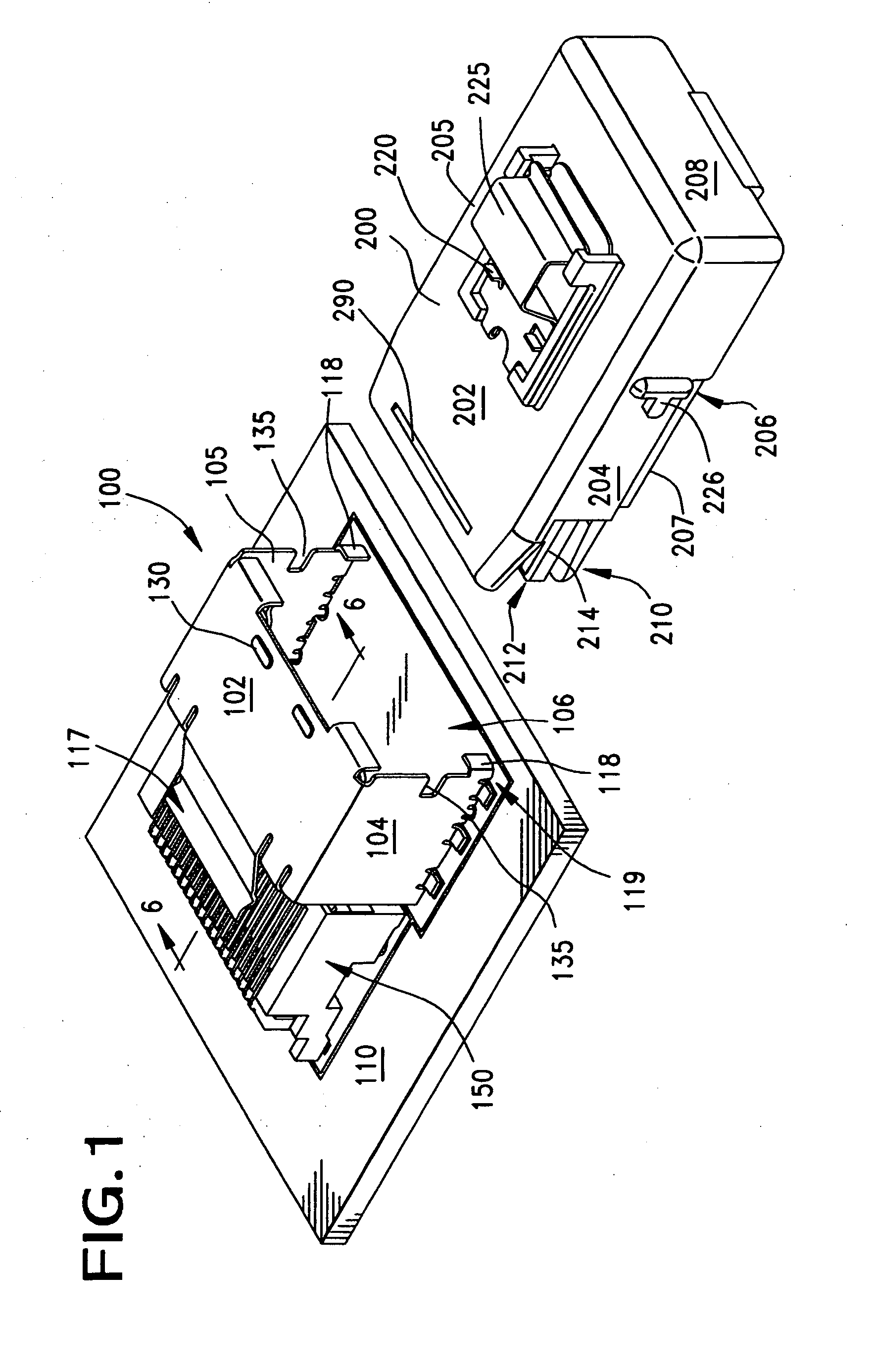

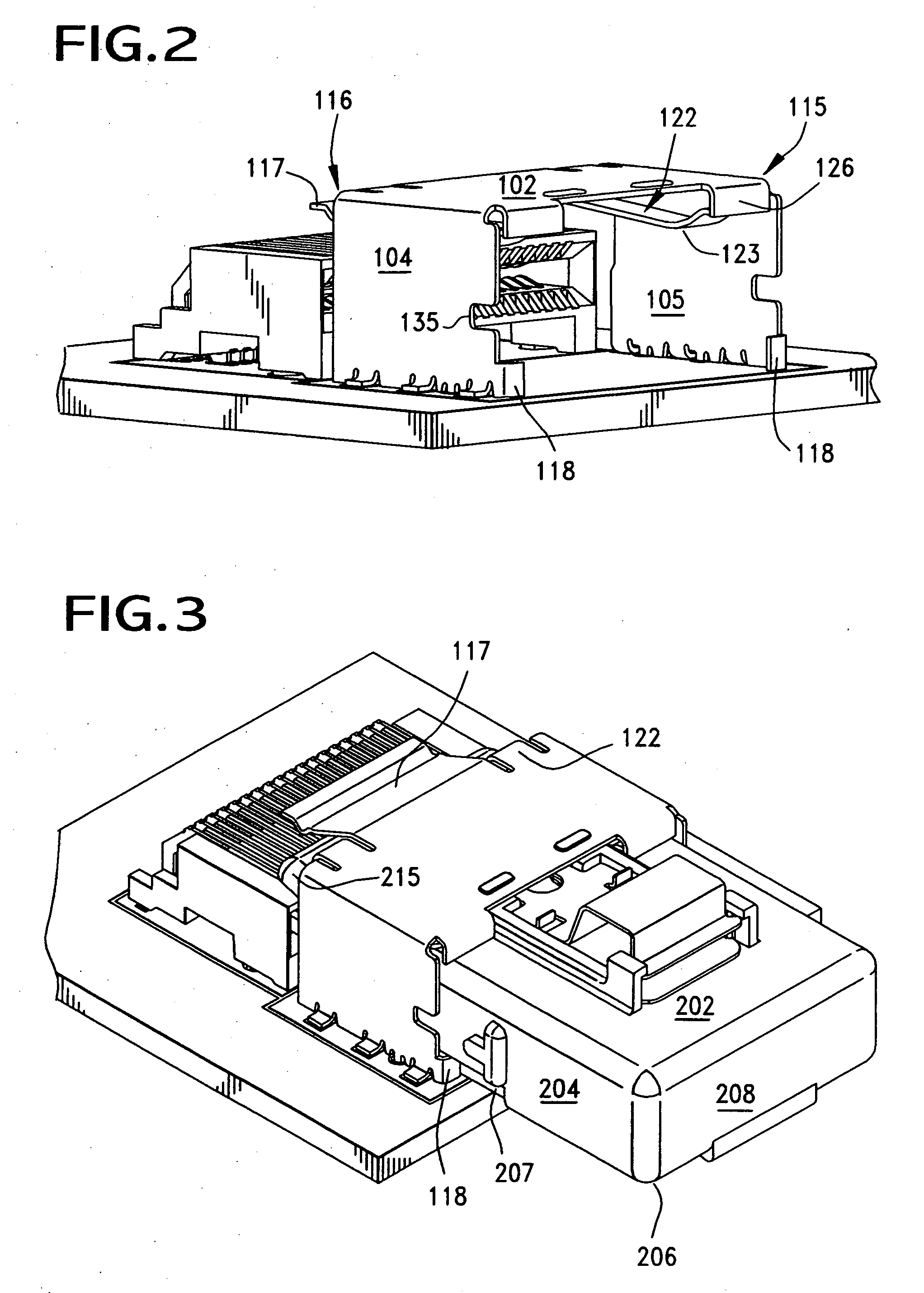

Connector and guide placement member

ActiveUS7226314B2Easy to installAccurate spacingCoupling protective earth/shielding arrangementsEngineeringMechanical engineering

A shroud that forms a guide channel for a receptacle connector is disclosed and it has the shape of an inverted U-shape, with a press tab for engaging a mating connector. The shroud has notches and tabs formed on it that serve to orient the mating connector for entry into the shroud. A placement member is described that holds the connector and the shroud together as a single unit for robotic placement of the shroud and connector in preselected positions on the circuit board.

Owner:MOLEX INC

Method and apparatus for producing a phantom three-dimensional sound space with recorded sound

InactiveUS20060050890A1Reduced effectivenessAccurate spacingHeadphones for stereophonic communicationLoudspeaker enclosure positioningSound sourcesPattern perception

A central speaker and personal headset speakers are used to create a three-dimensional phantom sound space for each listener. The speakers of the headset are located in close proximity to, but do not isolate, the ears of the listener such that external sounds are allowed to impinge upon the pinna of the ears. The headset speakers form an isosceles triangle with the distant central speaker as the apex. This speaker configuration with personal controls can achieve a state of sound equilibrium for a phantom three-dimensional sound space. The sound signal may be synchronized with a video signal, and the sound pressure level of the left and right speakers can be adjusted to control the listener's perception of the virtual movement of phantom sound source image within the sound space according to changes in the point of view represented in a displayed video image.

Owner:TSUHAKO PARKER

Method and apparatus for monitoring and controlling thermally induced tissue treatment

InactiveUS7824395B2Improve signal-to-noise ratioEnhanced signalElectrotherapyDiagnosticsEngineeringBiological activation

A method and apparatus for thermal treatment of tissue by irradiating the skin with electromagnetic energy is disclosed. Sources of electromagnetic energy include radio frequency (RF) generators, lasers, and flashlamps. The apparatus includes either a positional sensor or a dosage evaluation sensor, or both types of sensors. These sensors provide feedback to a controller. The controller may control the electromagnetic source parameters, the electromagnetic source activation, and / or the sensor measurement parameters. An additional scanning delivery unit may be operably coupled to the controller or to the sensors to provide a controlled distribution of electromagnetic energy to the target region of the skin. The use of positional measurement sensors and dosage evaluation sensors permits the controller to automatically determine the proper electromagnetic source parameters including, for example, pulse timing and pulse frequency.

Owner:RELIANT TECH INC

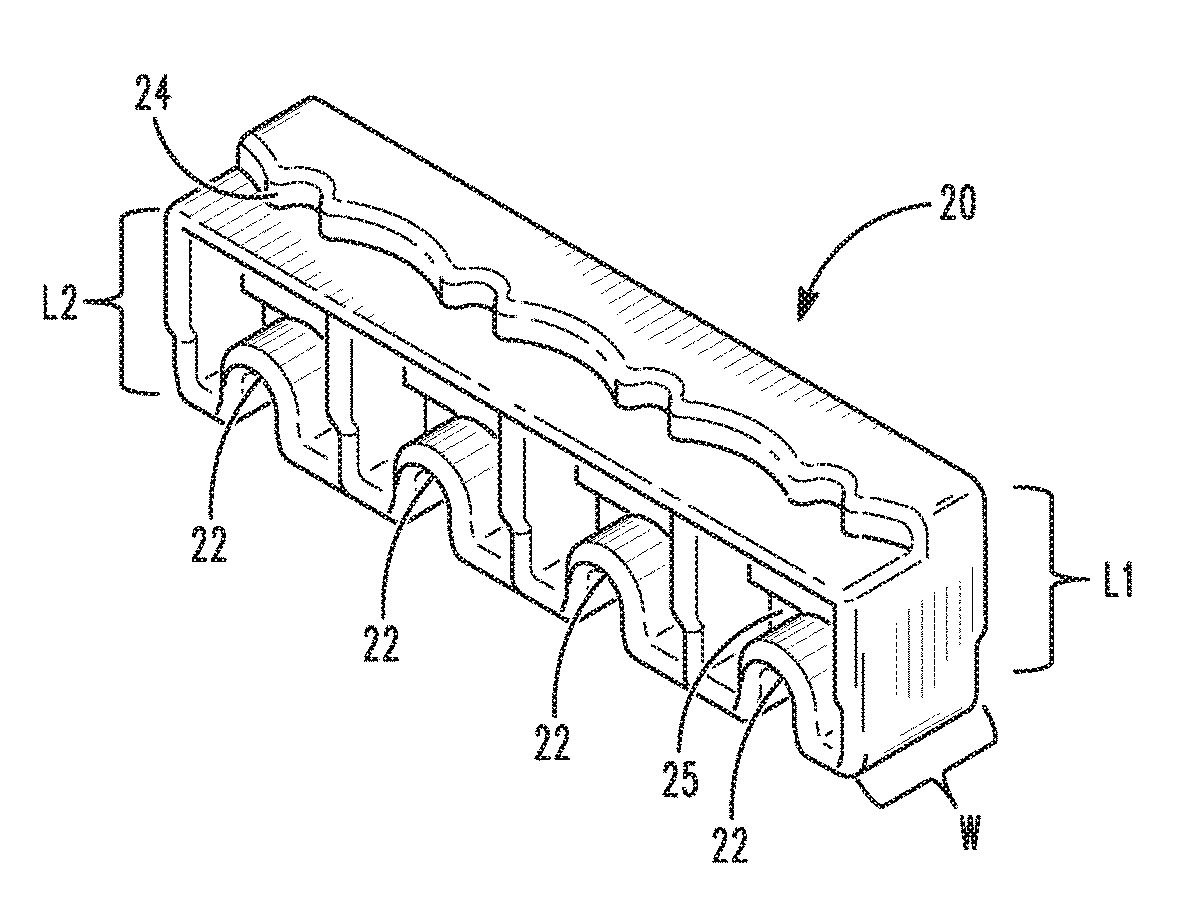

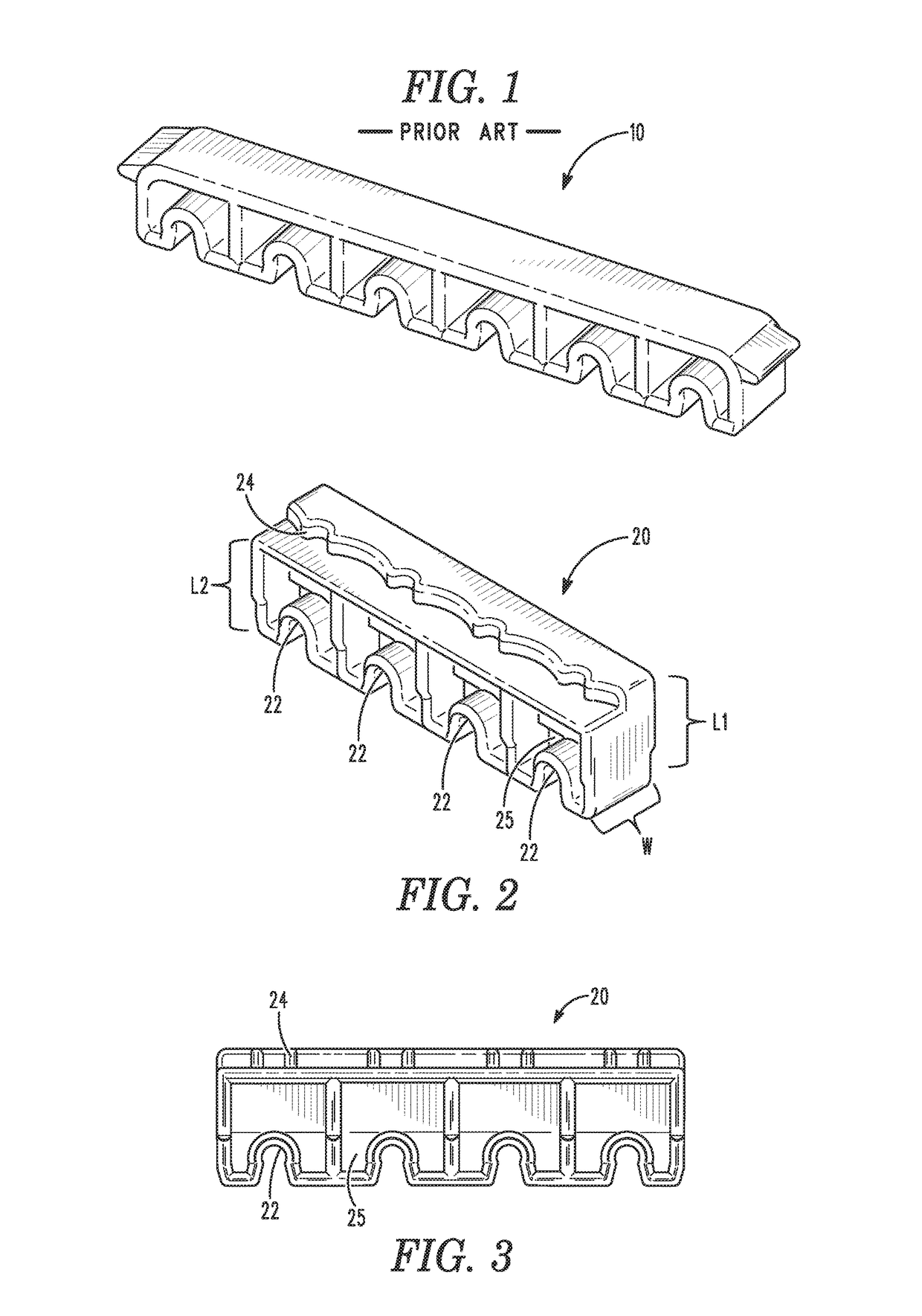

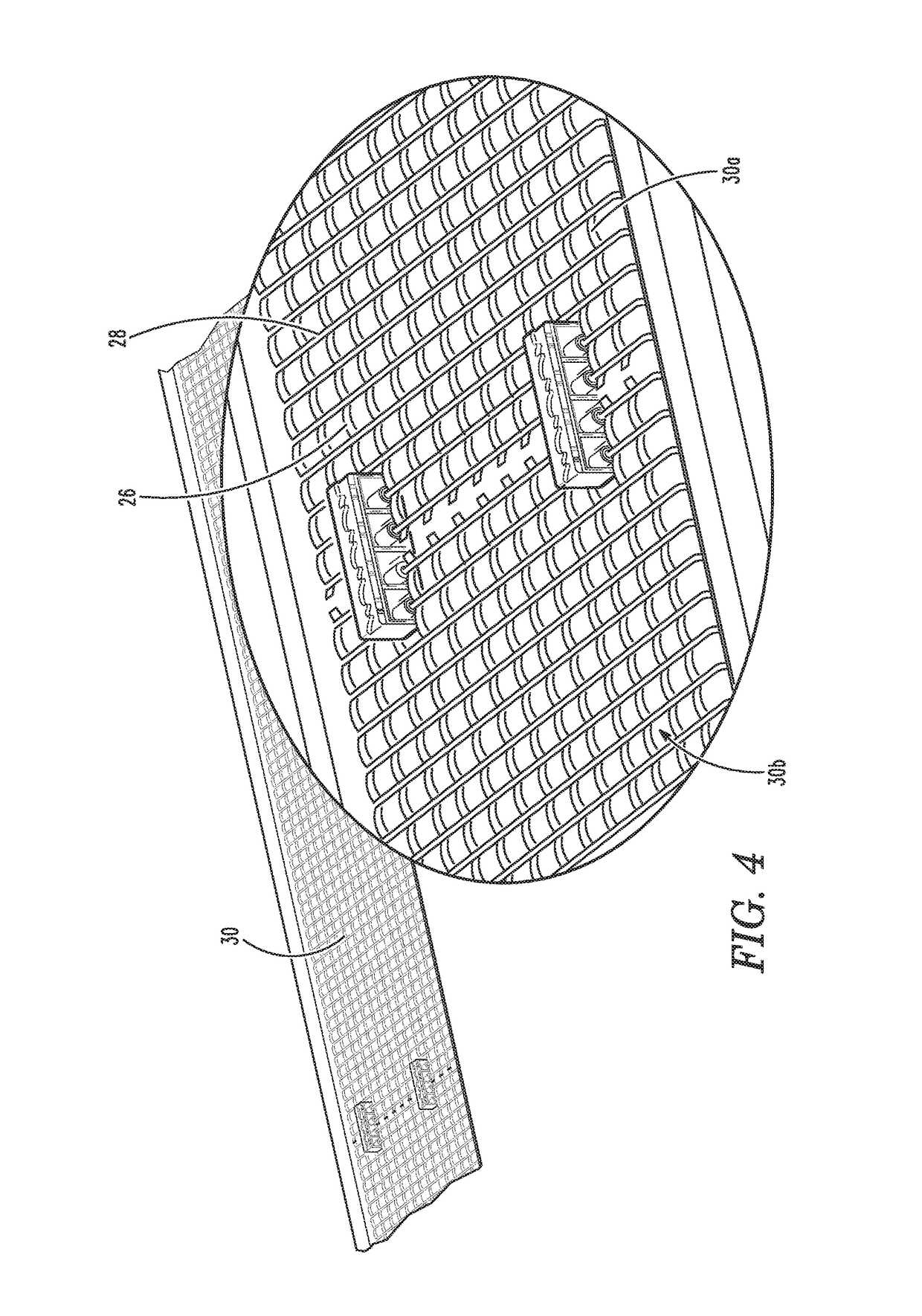

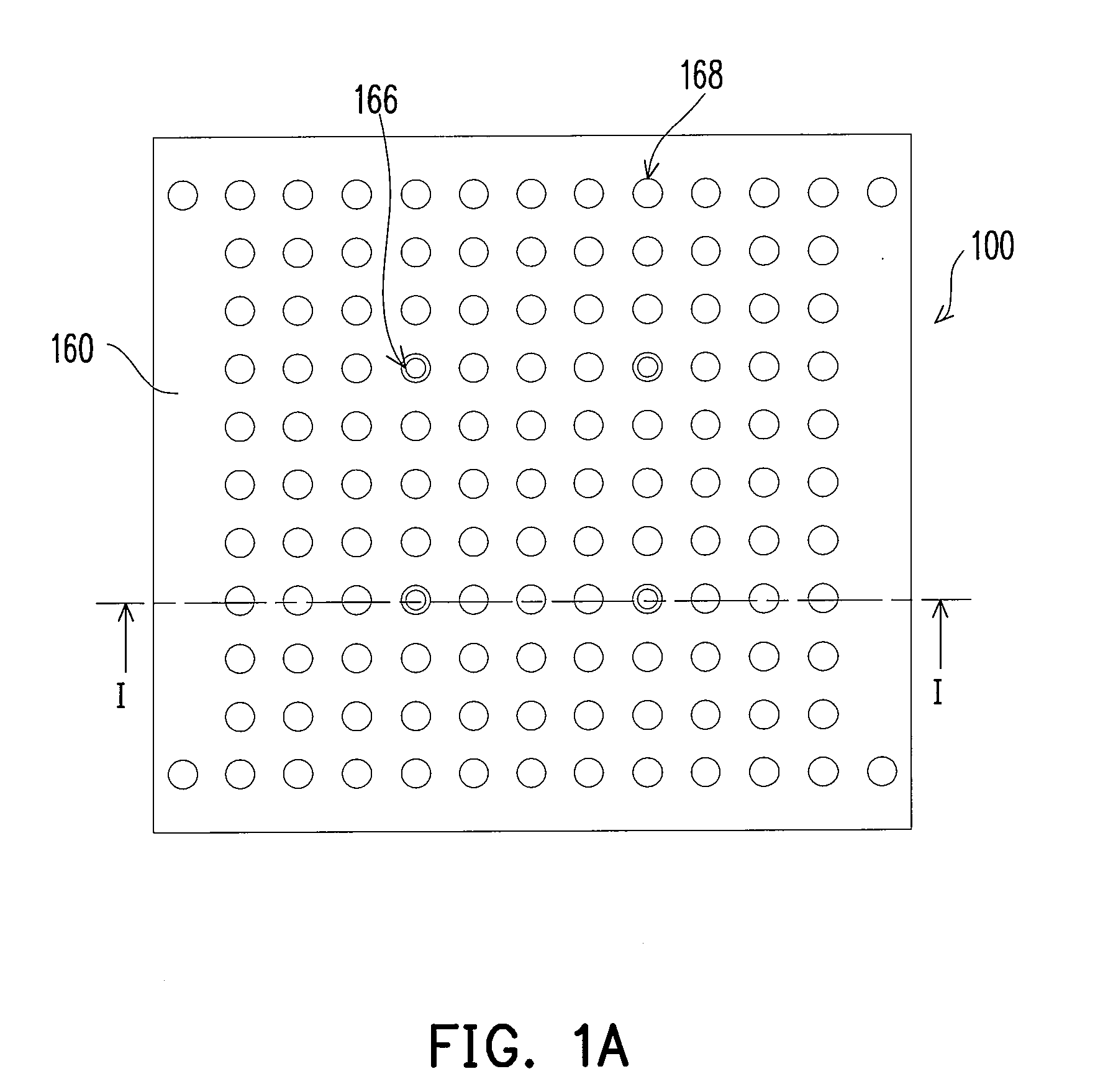

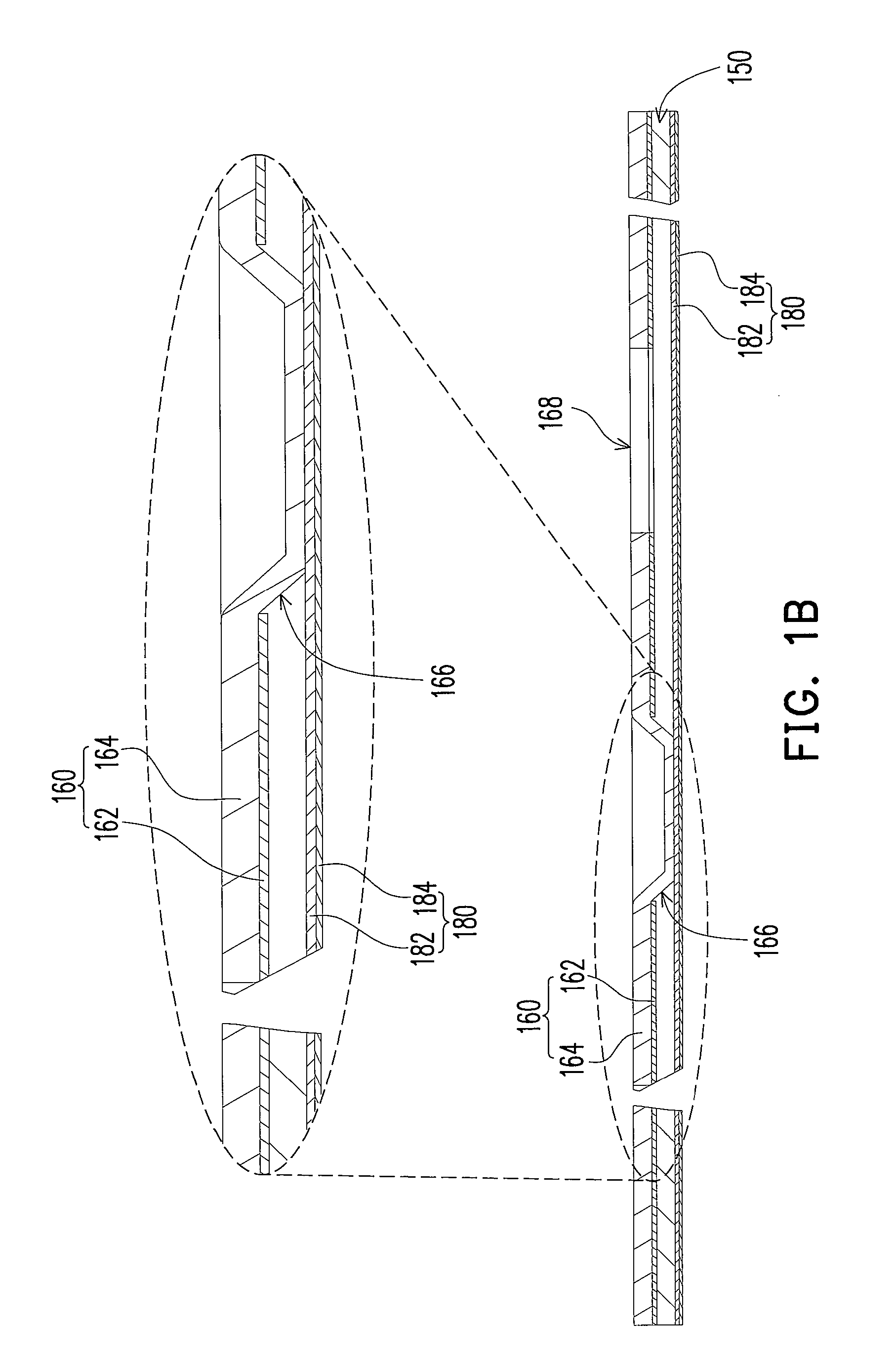

Flexible electret transducer assembly, speaker, and method for fabricating flexible electret transducer assembly

ActiveUS20090304212A1Precise processImprove audio qualityElectrets selectrostatic transducerSemiconductor/solid-state device manufacturingTransducerEngineering

A flexible electret transducer assembly including an electrical backplate and a membrane made of an electret material is disclosed. A plurality of spacers is formed on a surface of the electrical backplate in a longitudinal or latitudinal direction, and the spacers are used for supporting a vibrating room of the membrane. A working area of the membrane is formed between adjacent spacers, and in each of the working area, the space between the electrical backplate and the membrane is smaller than that in a conventional electrostatic speaker. The spacers between the electrical backplate and the membrane are mass produced through a stamping process. Thereby, an accurate space between the electrical backplate and the membrane can be maintained and accordingly the audio quality can be improved. In addition, a speaker including the flexible electret transducer assembly and a method for fabricating the flexible electret transducer assembly are also disclosed.

Owner:IND TECH RES INST

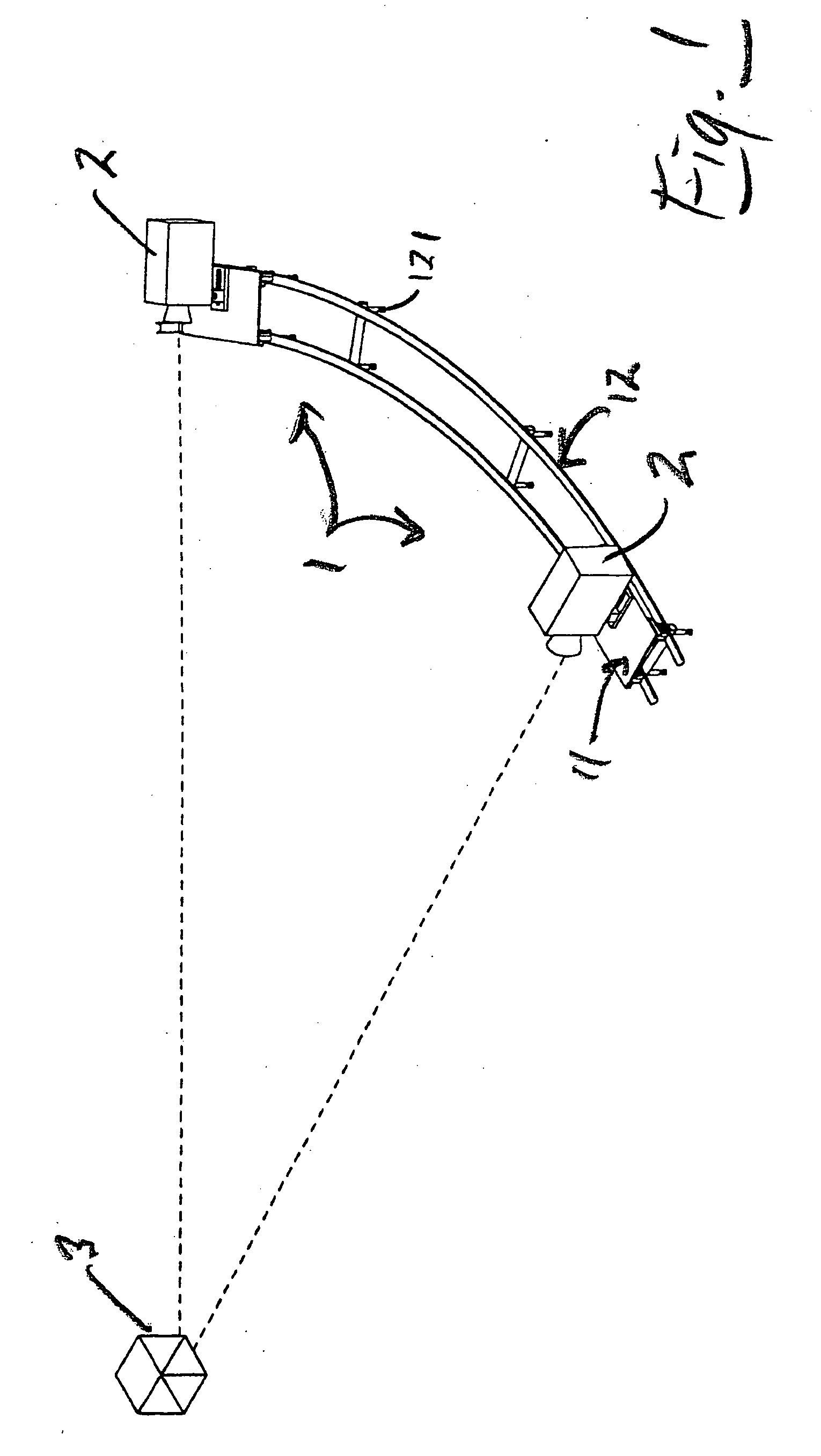

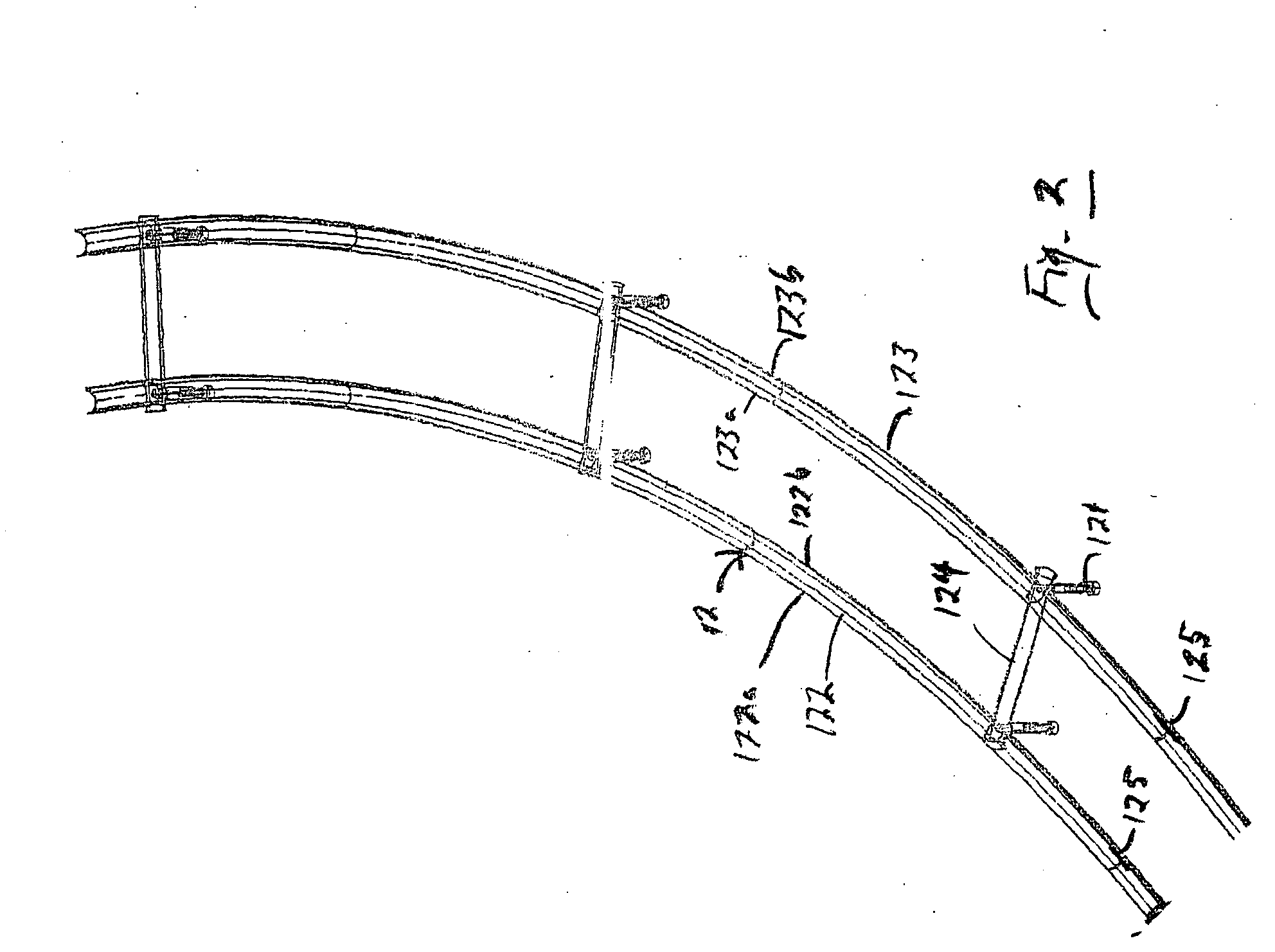

Economical camera-support-and-movement track-and-dolly system providing high stability and precision to camera movement

InactiveUS20050231689A1Cheap constructionEasy to useProjectorsStands/trestlesEngineeringAngular orientation

A system for moving a camera in space has a track with two spaced-parallel rails, each rail having two upward-extending spaced-parallel lips, and a dolly holding the camera and riding upon both rails of the track. The track is preferably segmented with each elongate rail segment preferably in the cross-section of half of a tube, while the dolly has wheels that contact only, and that ride upon, the upward-extending spaced-parallel lips of each half-tubular rail. The camera is mounted close upon the support platform of the generally rectangular wheeled dolly, which is itself squat and low to the track's two spaced-parallel rails. According to the geometries of construction, the camera is relatively insensitive in space and in angular orientation to such irregularities in track and moving dolly as are in any case minor by design, and the camera can be moved along complex paths with great precision for purposes of motion pictures and movies.

Owner:LONGLEY BRIAN

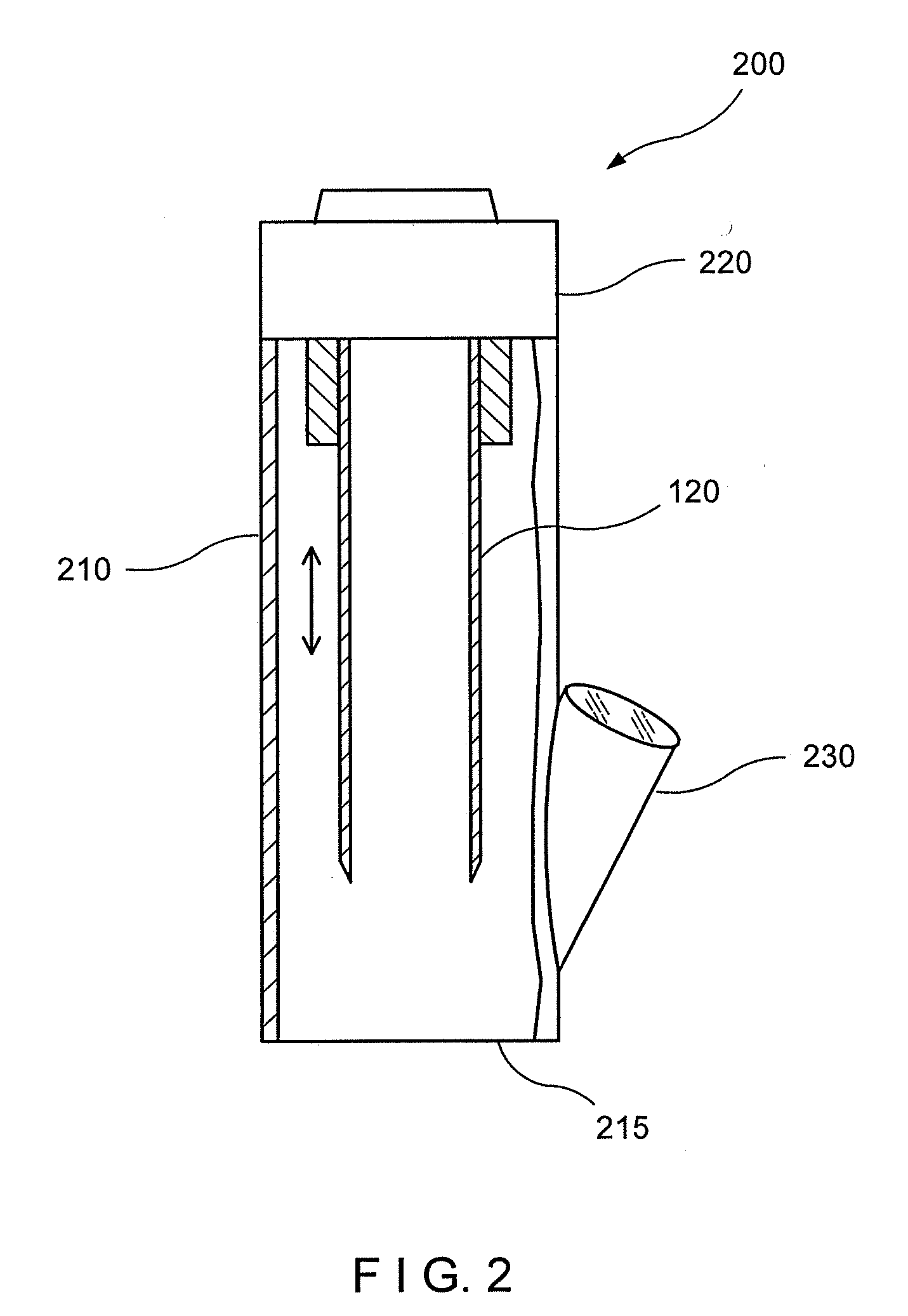

Apparatus and method for tissue biopsy

ActiveUS20140200484A1Easy accessConvenient distanceSurgical needlesVaccination/ovulation diagnosticsTissue biopsyActuator

Exemplary embodiments of an apparatus can be provided for obtaining portions or samples of tissue from a target region of a biological tissue. One or more needles can be provided that have a small internal diameter, e.g., about 1 mm or less, and the needles can be configured to extract the tissue portions when the needles are inserted into and withdrawn from the tissue. Windows and / or markings can be provided on the wall of the needles to facilitate access to the sample. The needles can be provided in an enclosure, and an actuator can be provided to direct the needles into the tissue and / or withdraw them. A plurality of tissue portions having known relative locations in the target region can be obtained, and extraction of the tissue portions can be well-tolerated by the tissue as compared with conventional punch biopsies or the like.

Owner:THE GENERAL HOSPITAL CORP

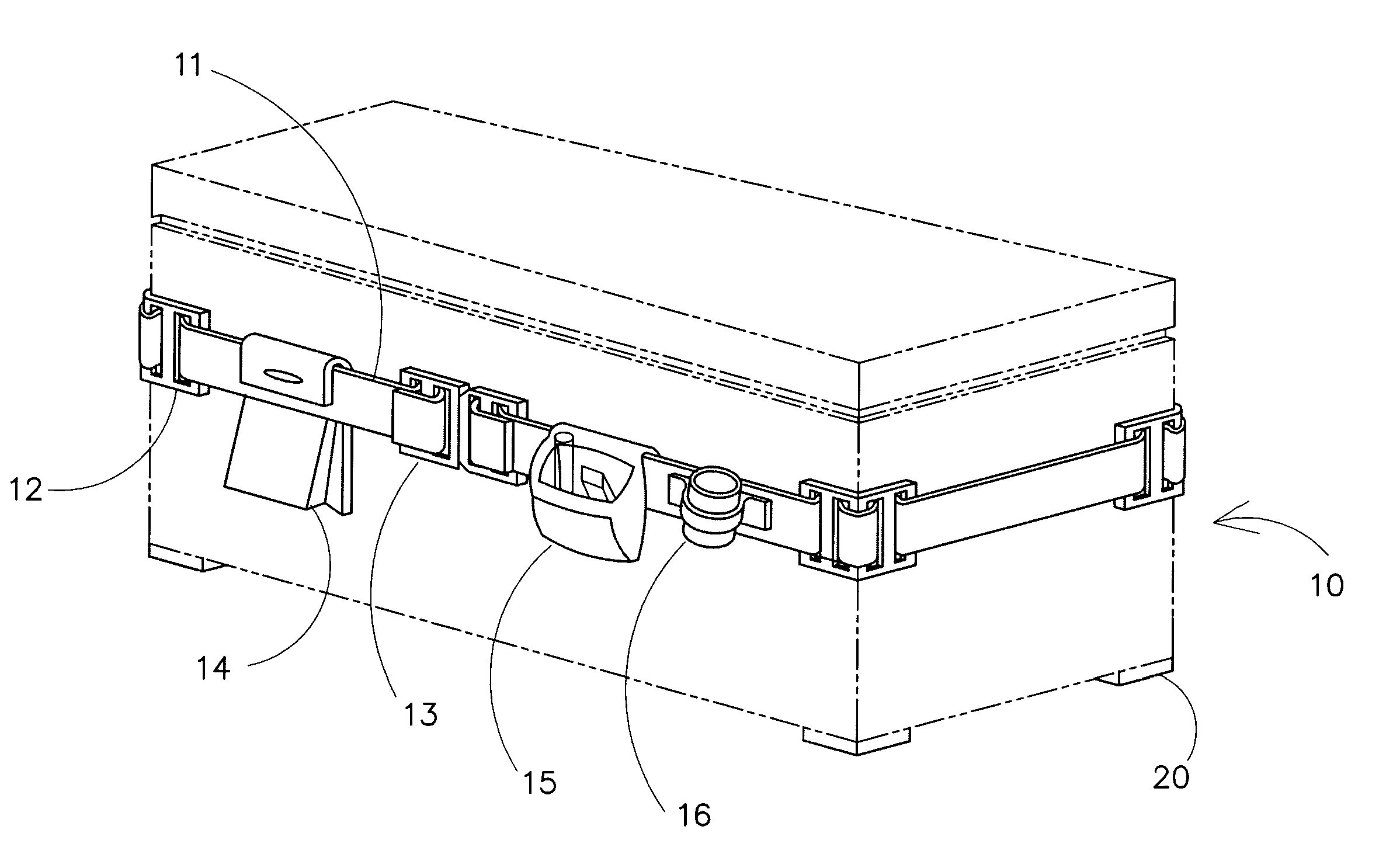

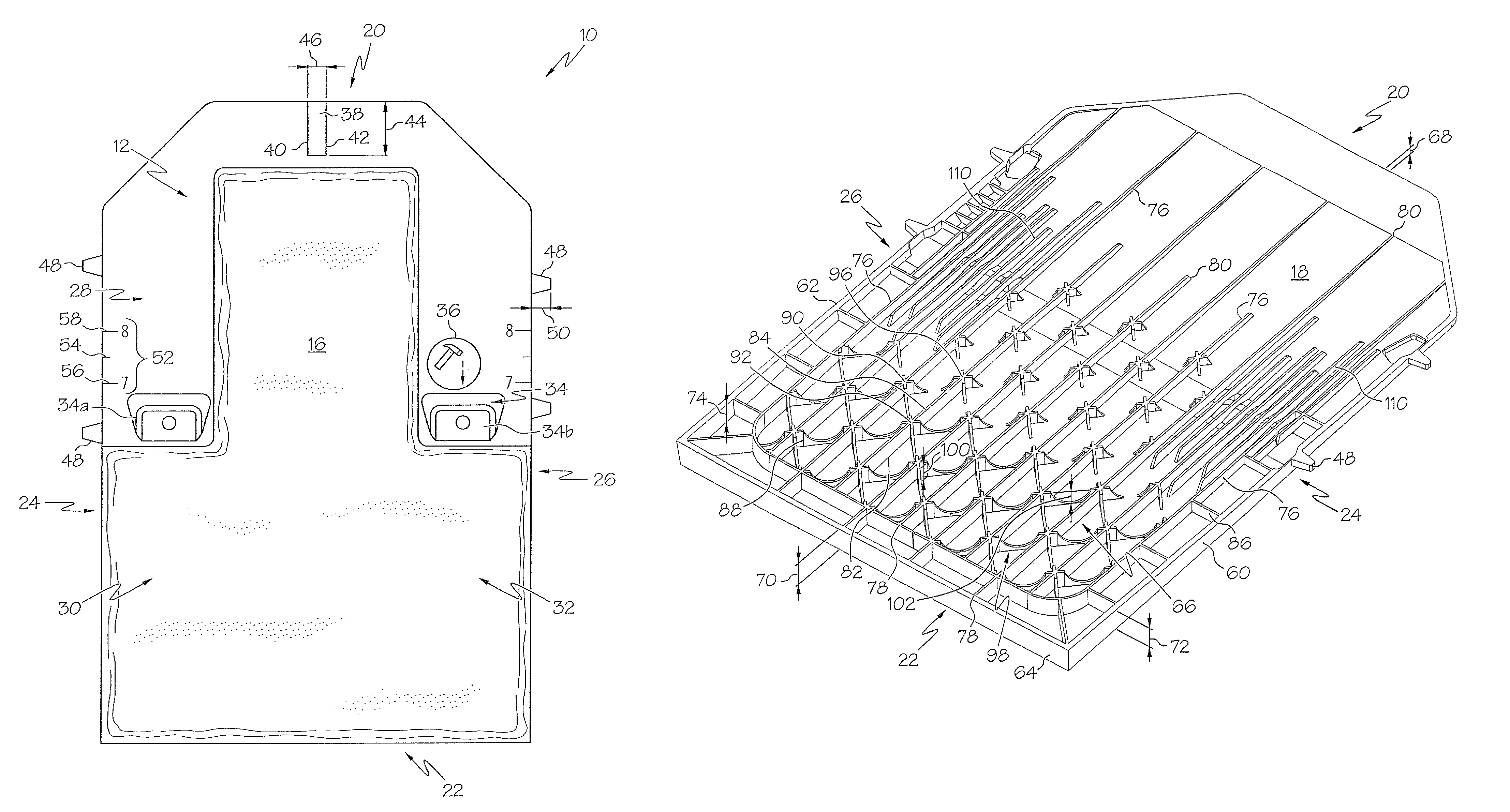

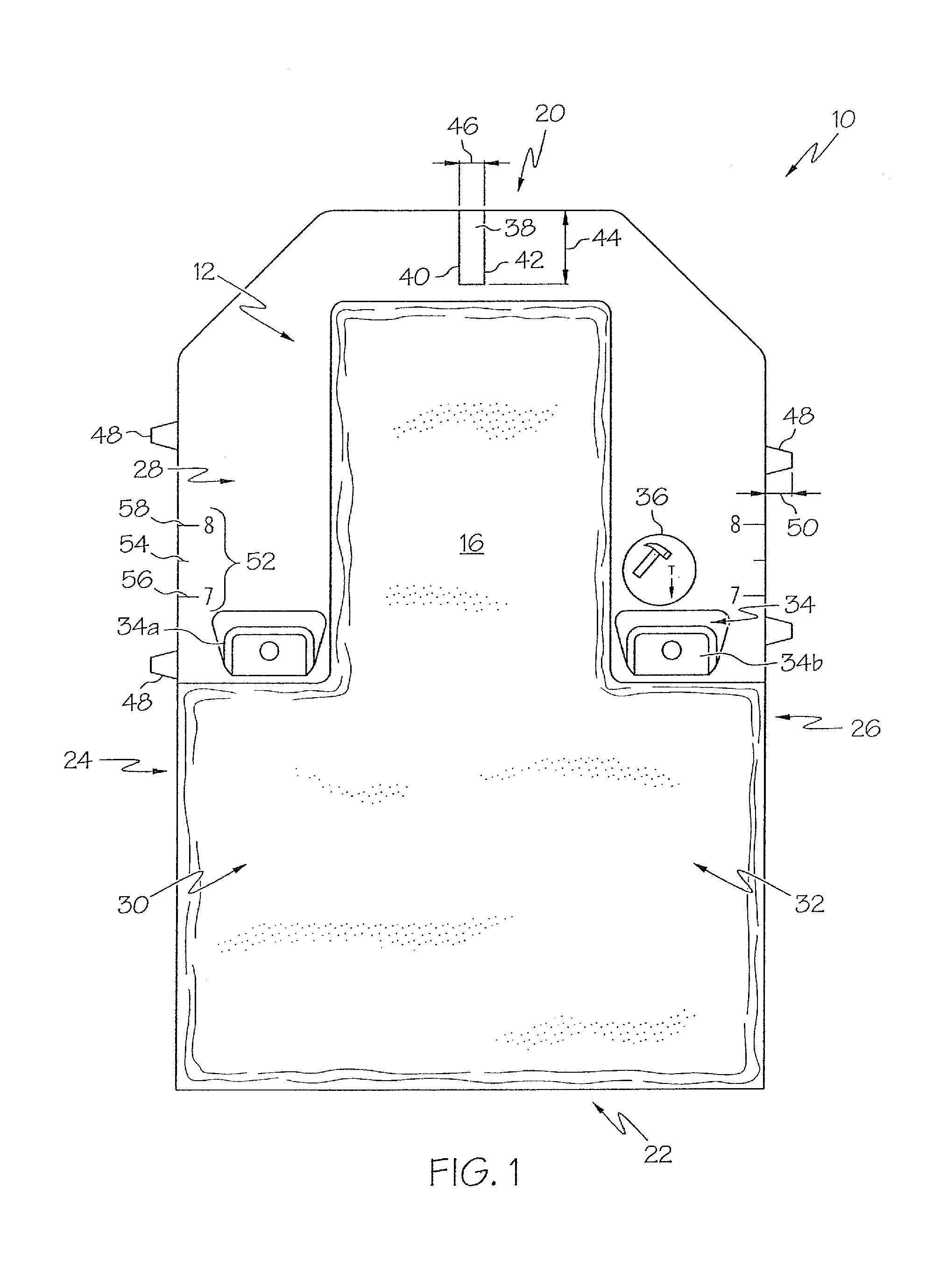

Composite shingle

InactiveUS8136322B2Reduce material usageSmall depthRoof covering using tiles/slatesBuilding repairsEngineeringBuilding construction

A composite shingle having unitary construction is presented that includes a body shell, a plurality of longitudinal ribs, and a plurality of rib stiffeners. The present composite shingle may also include transverse ribs, a depressed nailing zone, nailing zone ribs, and / or at least one alignment aid. The plurality of rib stiffeners may include a material saving profile. Further, the dimensions of the composite shingle more closely resemble true slate and shake shingles and at least a portion of the outside face of composite shingle may be textured to resemble slate or wood shake shingles.A plurality of assembled composite shingles of the present invention is also claimed as part of this invention. Finally, a method of applying multiple courses of shingles on a roof including the composite shingle of the present invention is presented.

Owner:TAMKO BUILDING PRODS

Connector guide member

ActiveUS7344409B2Easy to installAccurate spacingEngagement/disengagement of coupling partsIncorrect coupling preventionMating connectionEngineering

A shroud that forms a guide channel for a connector is disclosed and it has the shape of an inverted U-shape, with a press tab for engaging a mating connector. The shroud has notches and tabs formed on it that serve to orient the mating connector for entry into the shroud. A placement member is also described and it serves to hold the connector and the shroud together as a single unit for robotic placement of the shroud and connector in preselected positions on the circuit board.

Owner:MOLEX INC

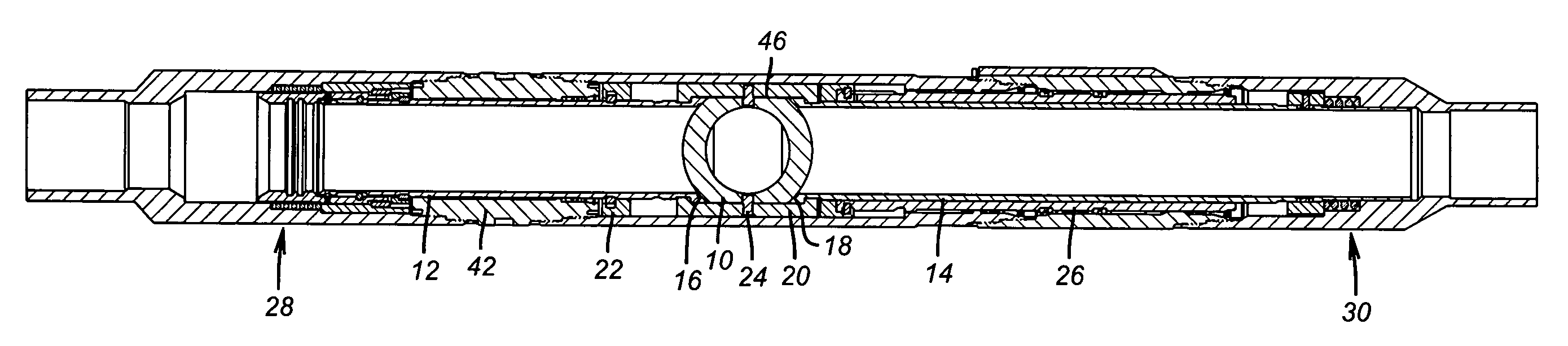

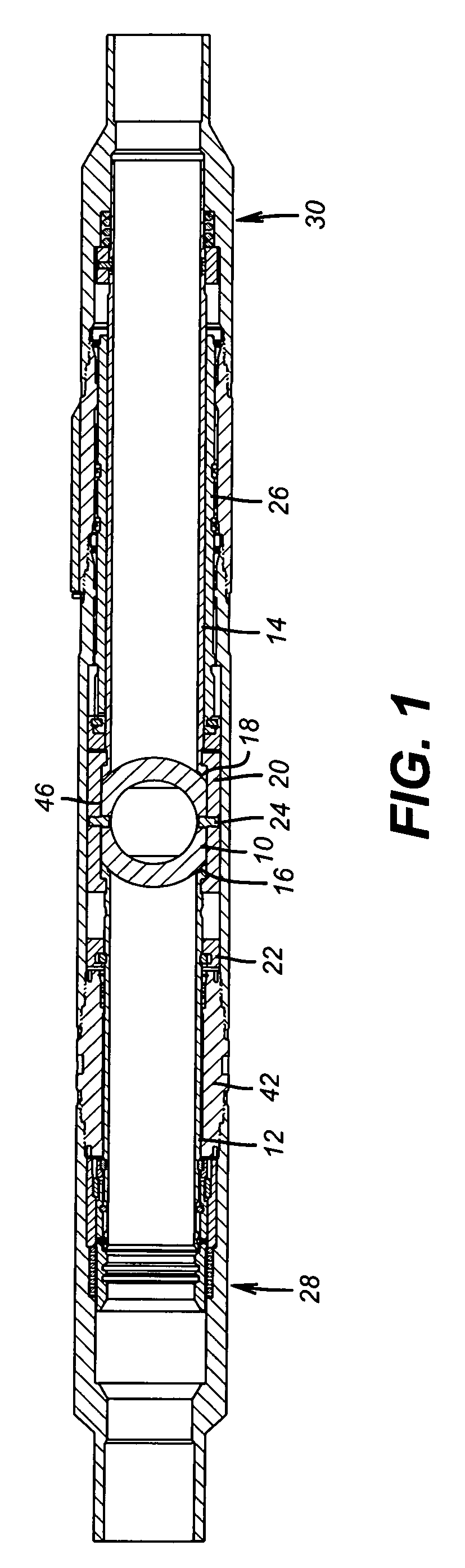

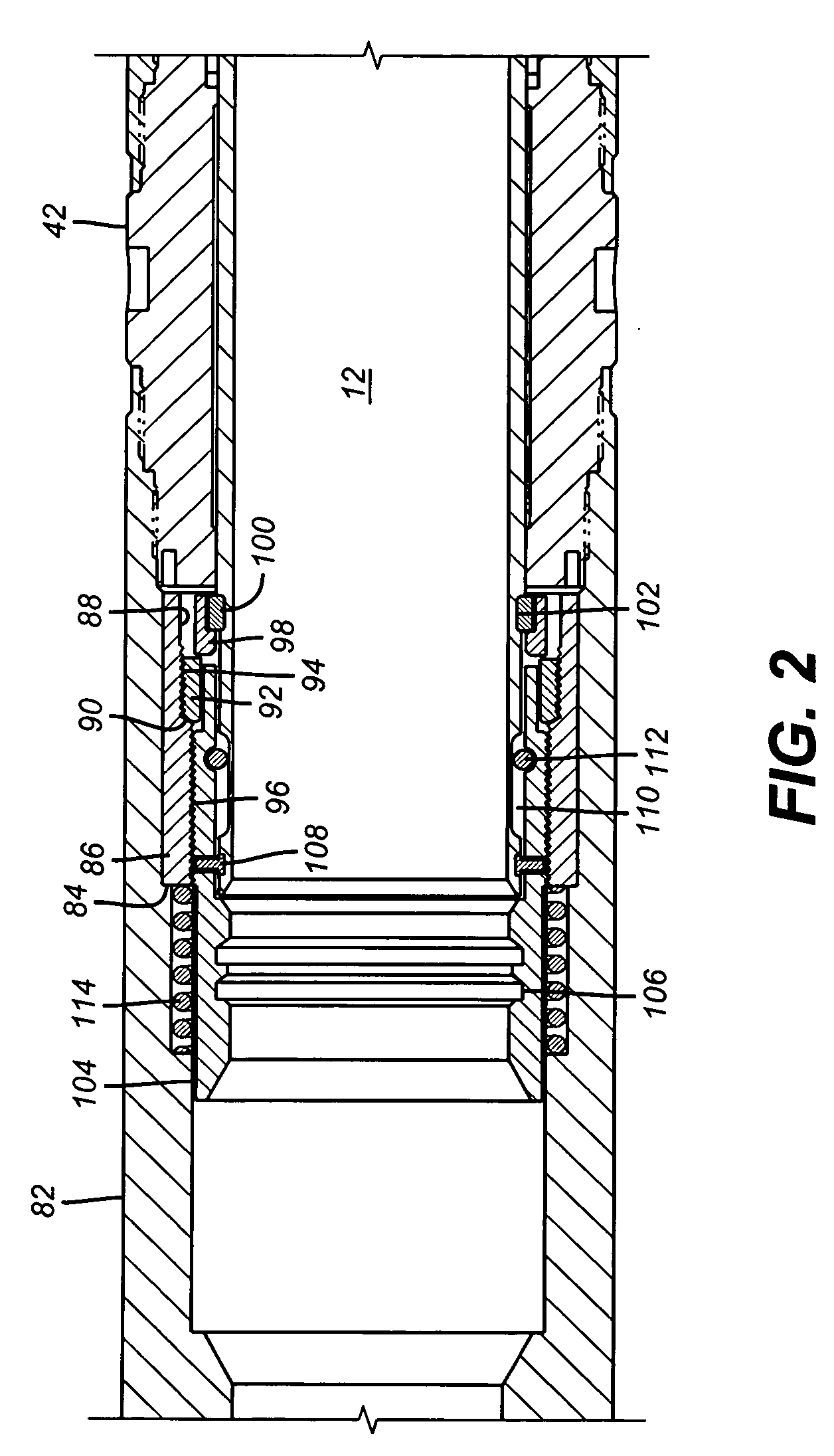

Downhole Barrier Valve

ActiveUS20080223581A1Prevent leakageAccurate spacingConstructionsFluid removalLine tubingDifferential pressure

A ball type downhole barrier valve capable of bidirectional sealing features a ball rotating on its axis to open or close with control line pressure to an actuating rod piston assembly. The ball is also shiftable to a locked open position. A cage surrounds the ball and retains opposed seats to it. The cage is made from one piece and tangential holes are drilled and tapped before the piece is longitudinally split with a wire EDM cutting technique. Fasteners to rejoin the cut halves properly space them to the original one piece internal dimension. Auxiliary tools allow determination of spacing of internal components so that a desired spring preload on the seats against the ball can be achieved. Seals on the sleeves that form ball seats help prevent leakage due to ball distortion at high differential pressures when the valve is closed.

Owner:BAKER HUGHES INC

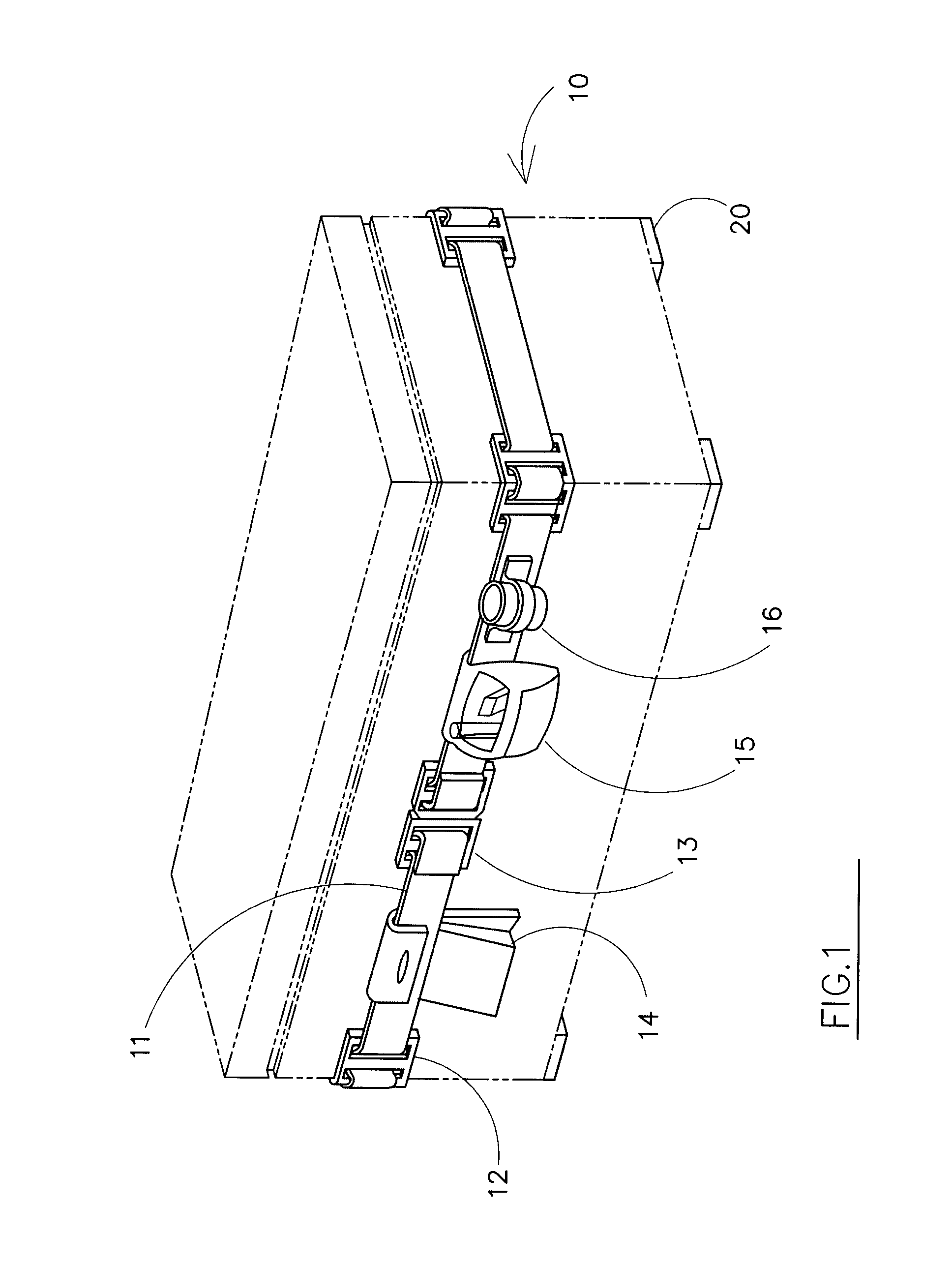

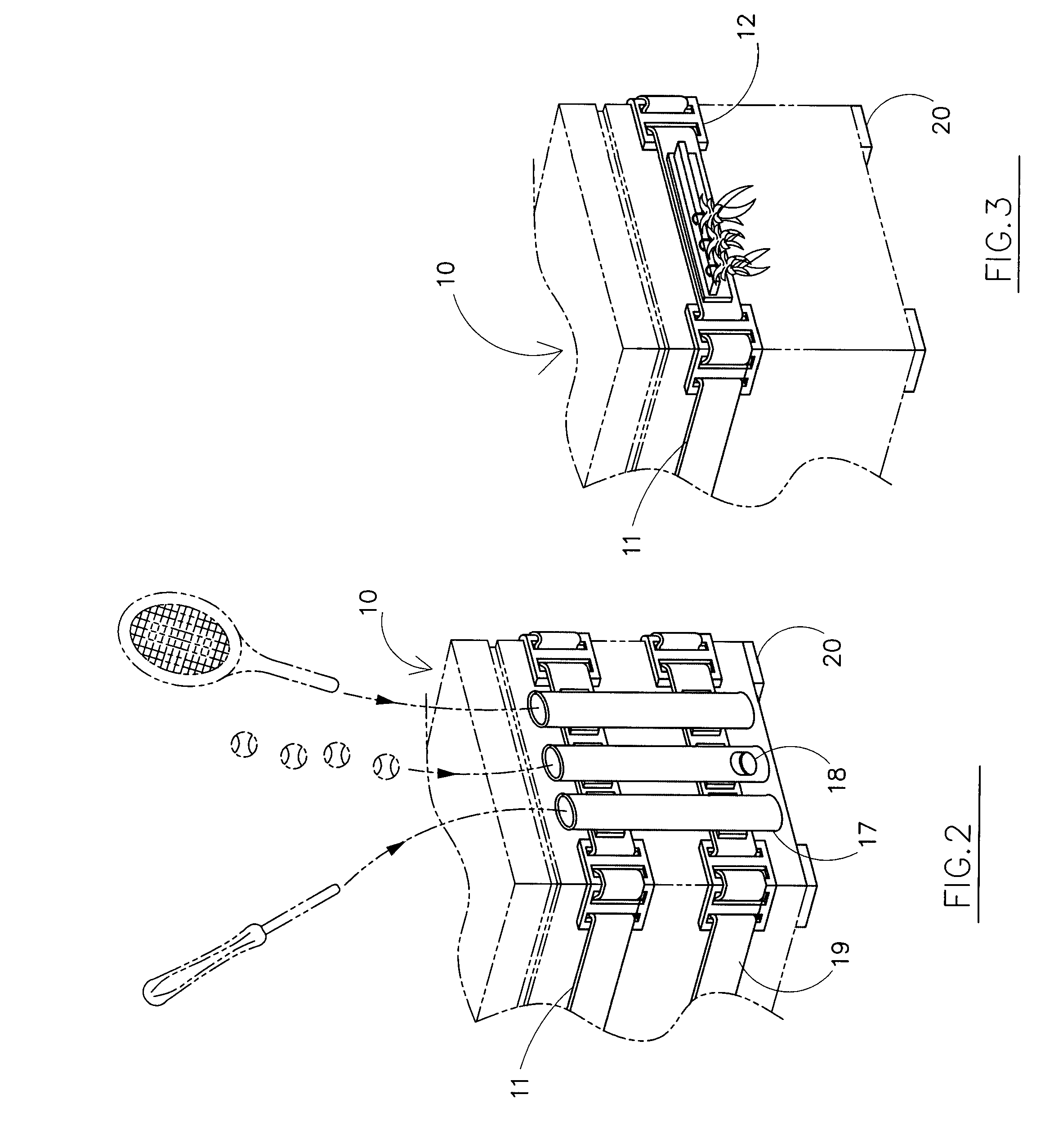

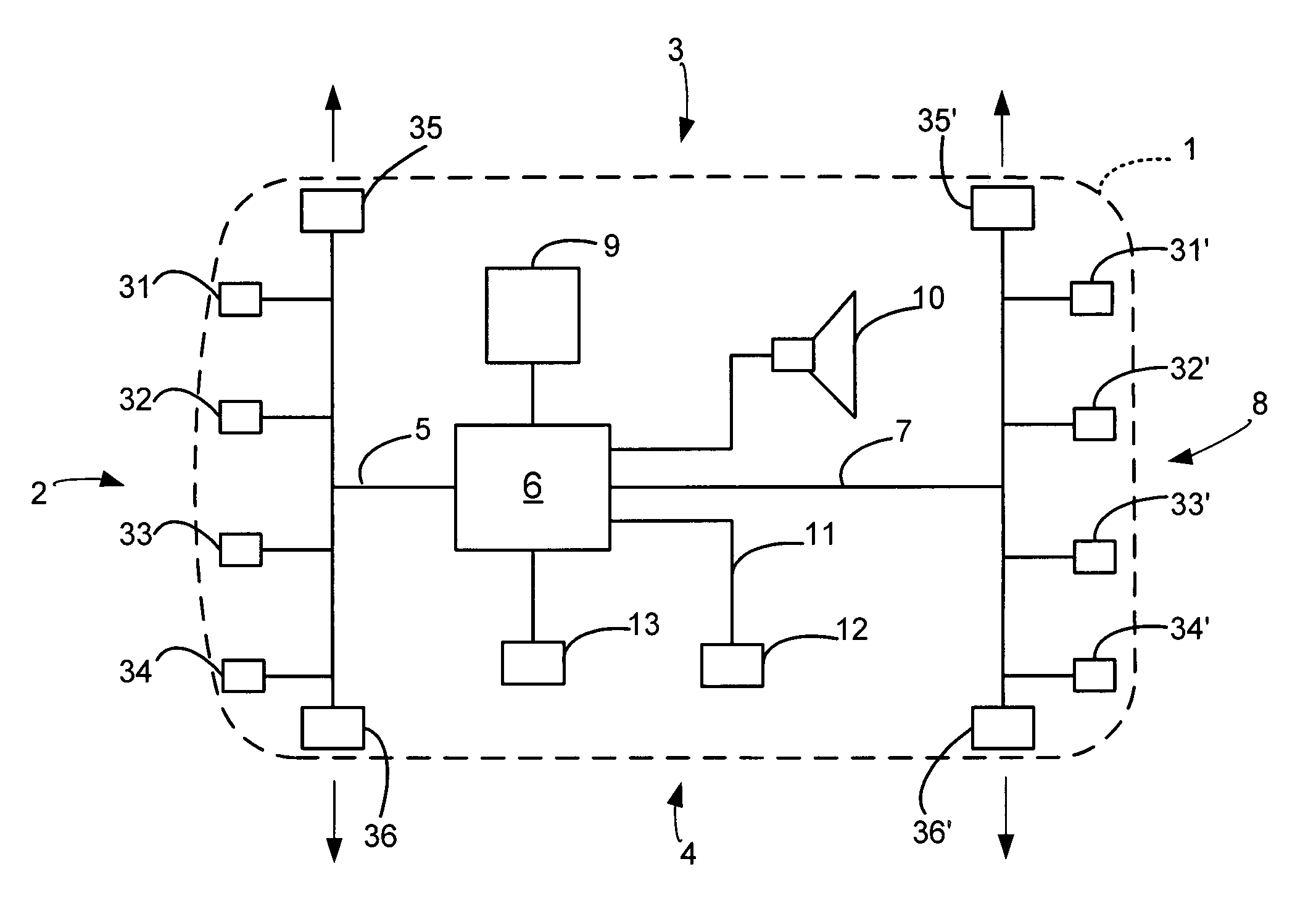

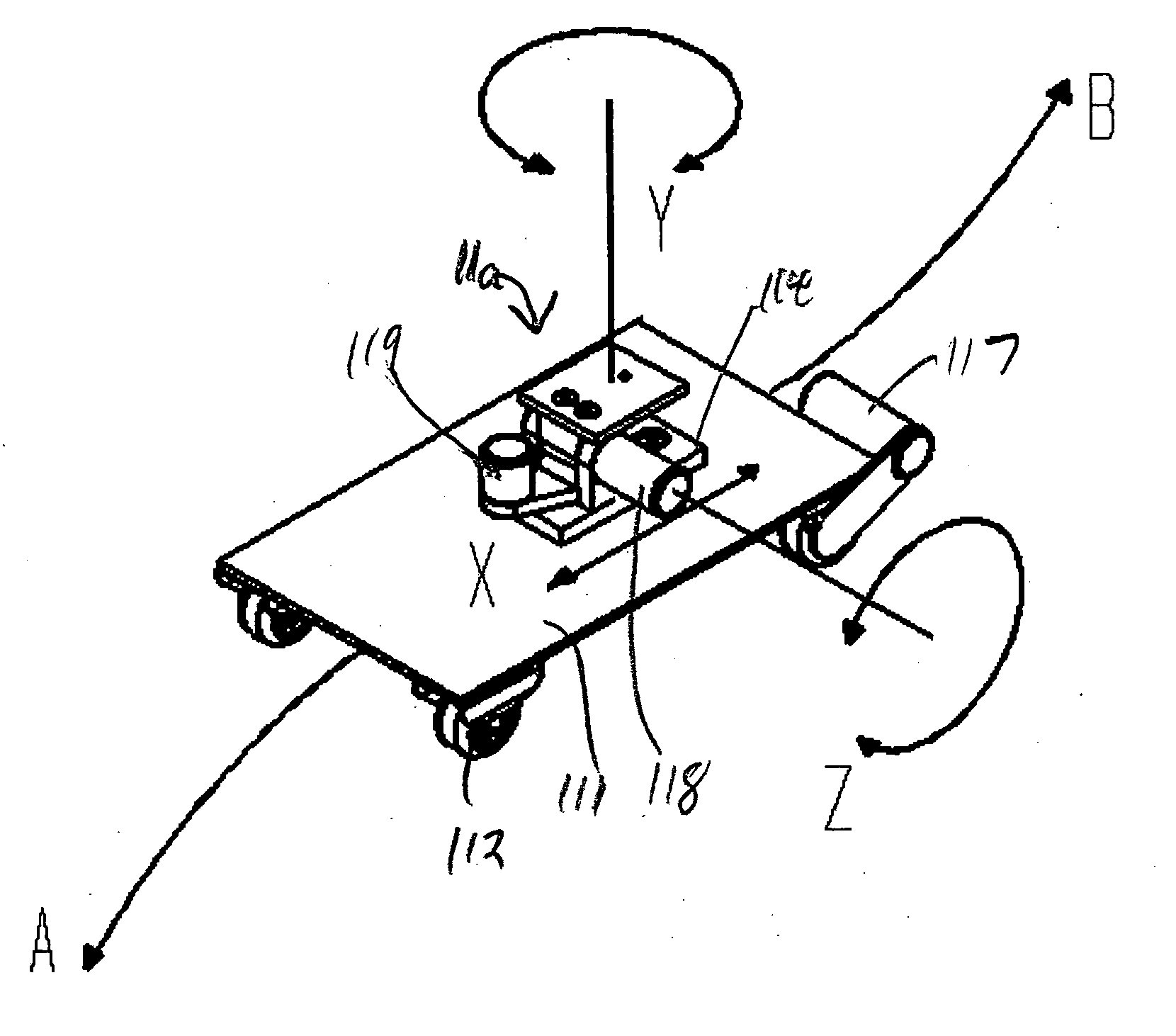

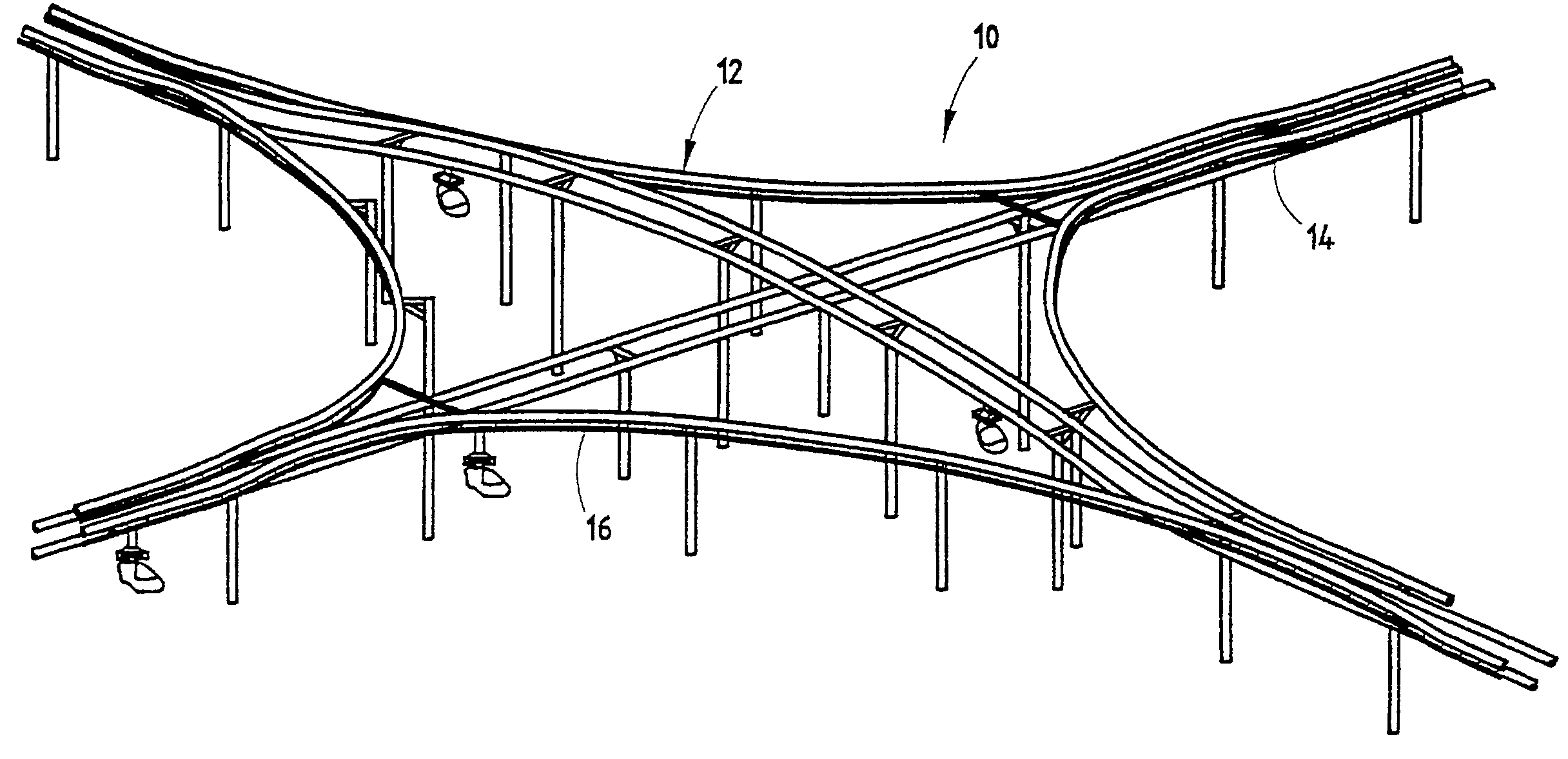

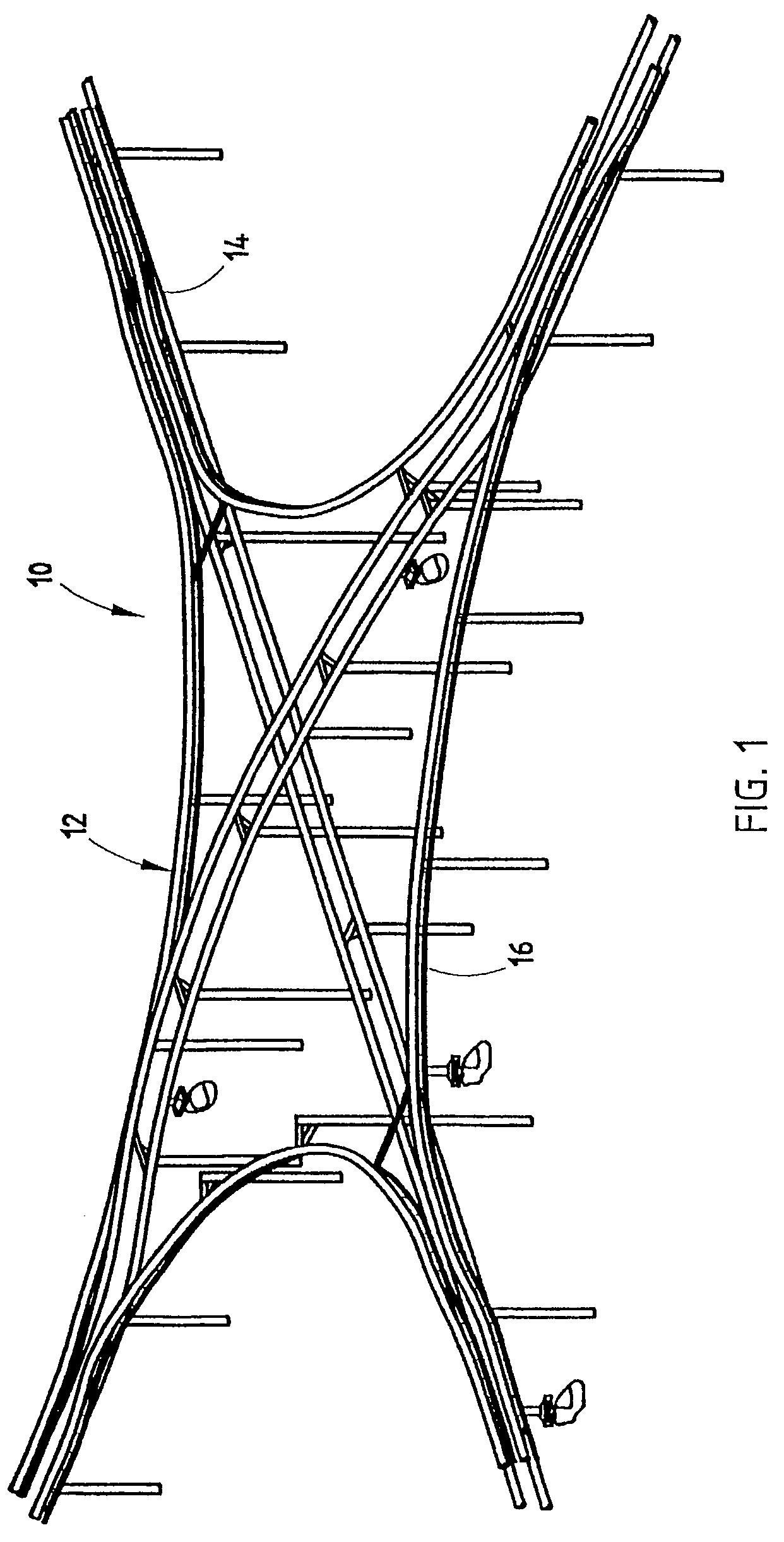

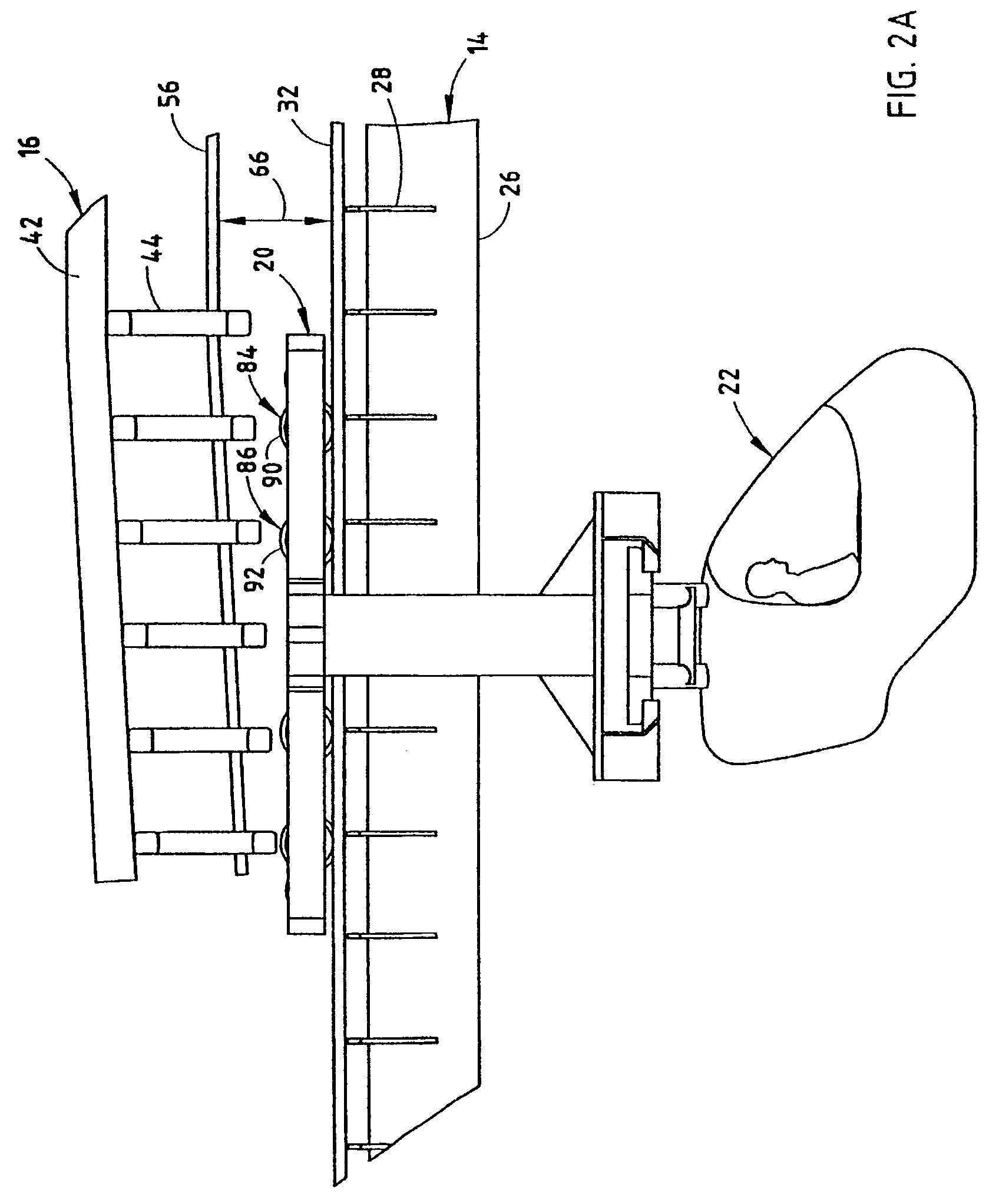

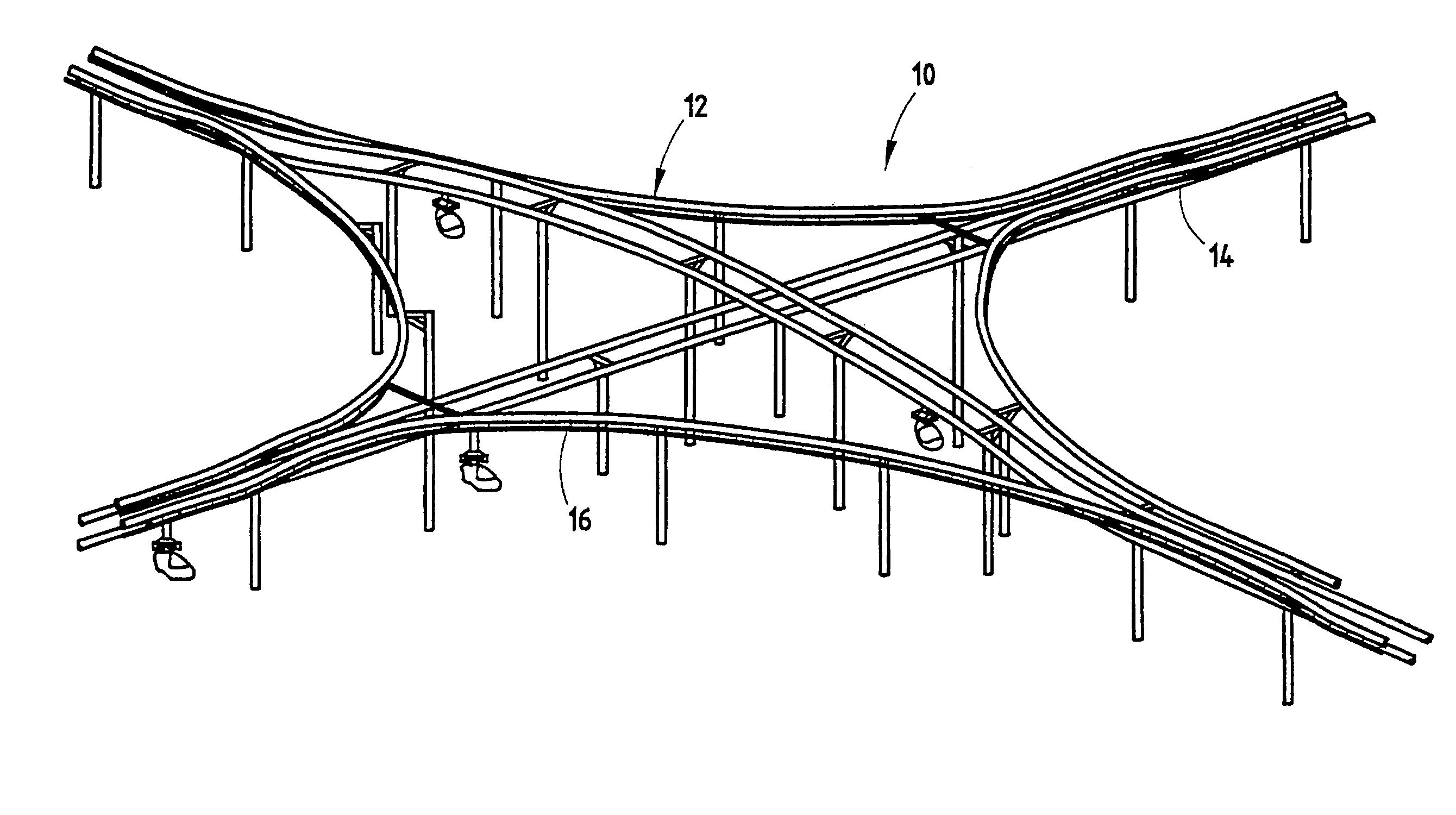

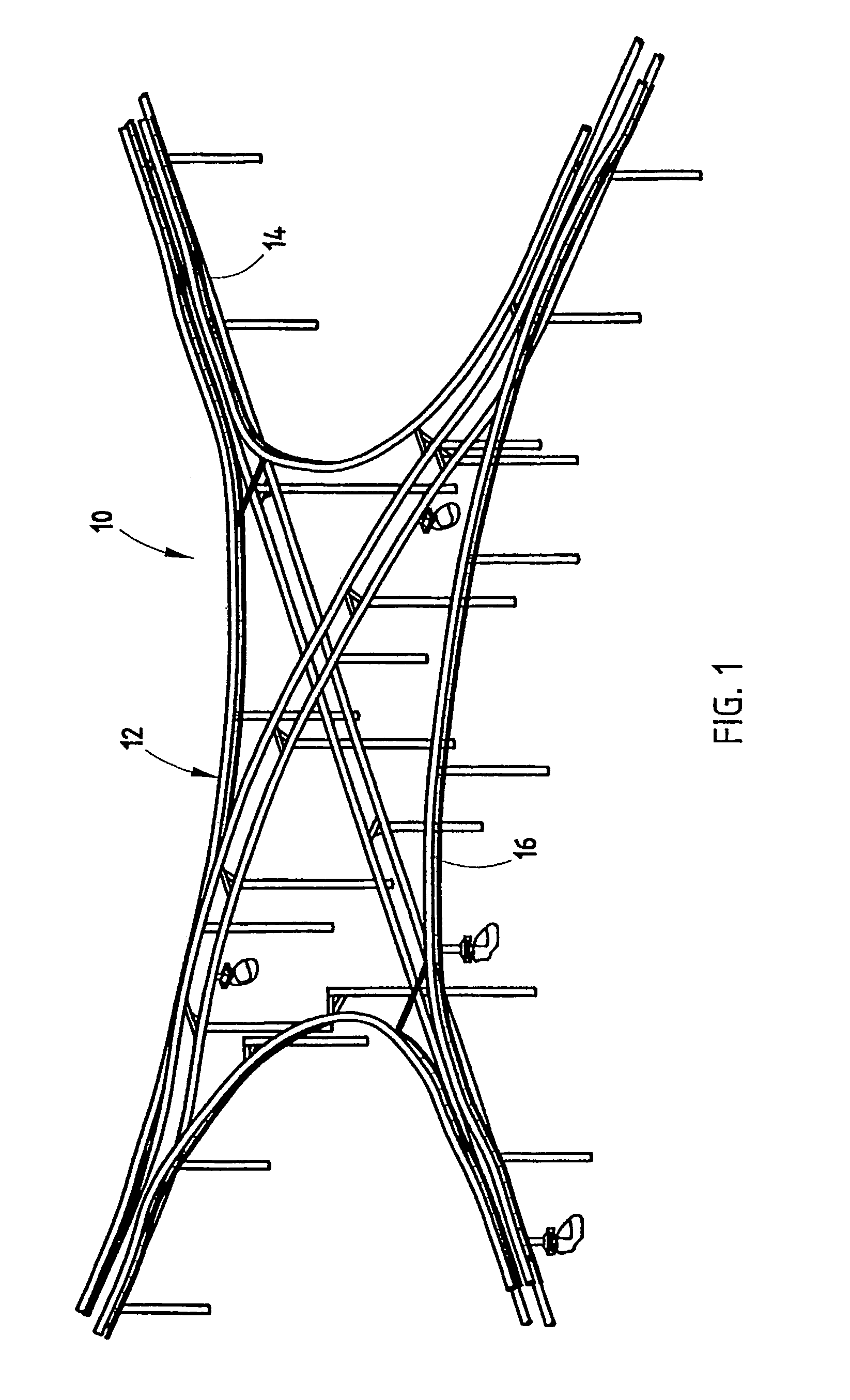

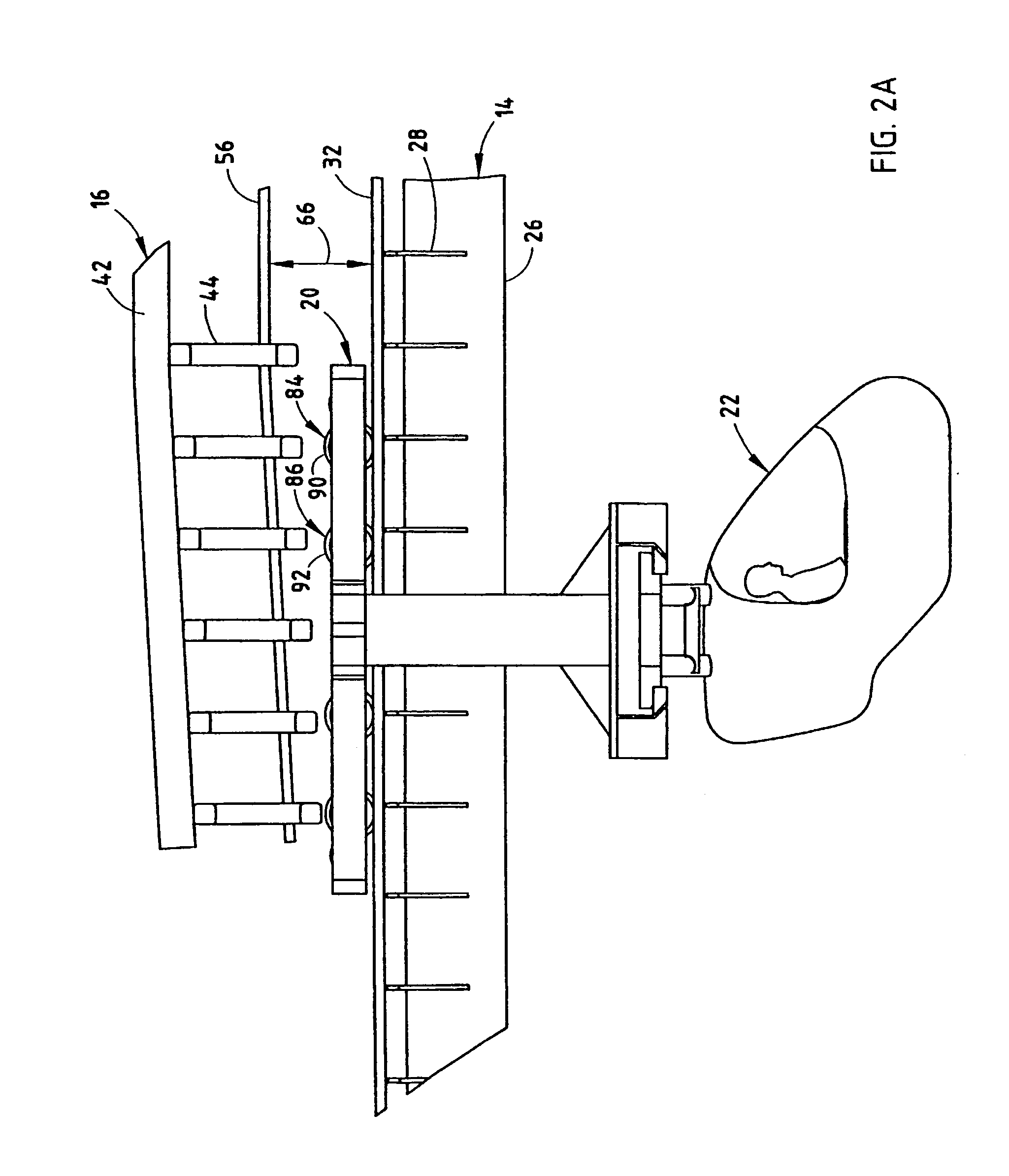

Individual transport control and communication system

InactiveUS7561948B2Maximize throughputAccurate spacingVehicle fittingsDigital data processing detailsCommunications systemTransit system

An automated transportation system includes a plurality of vehicles adapted to travel along a pathway, and a monitoring system located within each vehicle and adapted to monitor a location and a speed between an associated vehicle and the pathway. The automated transportation system also includes a transmitter located within each vehicle and adapted to transmit a signal that includes data on the location and the speed monitored, and a receiver located within each vehicle and adapted to receive the signal from each of the other vehicles. The automated transportation system further includes a controller located within each vehicle and adapted to interpret the signal received by the receiver and control the associated vehicle to provide proper spacing between the remaining vehicles to avoid collisions therebetween and maximize throughput of the vehicles along the pathway.

Owner:CASCADE ENG

Individual transport control and communication system

InactiveUS7286934B2Maximize throughputAccurate spacingVehicle fittingsDigital data processing detailsCommunications systemMonitoring system

An automated transportation (10) system includes a plurality of vehicles (22) adapted to travel along a pathway, and a monitoring system (70) located within each vehicle and adapted to monitor a location and a speed between an associated vehicle and the pathway. The automated transportation system (10) also includes a transmitter (72) located within each vehicle (22) and adapted to transmit a signal that includes data on the location and the speed monitored, and a receiver (76) located within each vehicle and adapted to receive the signal from each of the other vehicles. The automated transportation system (10) further includes a controller (78) located within each vehicle and adapted to interpret the signal received by the receiver and control the associated vehicle to provide proper spacing between the remaining vehicles to avoid collisions therebetween and maximize throughput of the vehicles along the pathway.

Owner:CASCADE ENG

Connector guide member

ActiveUS20060189199A1Easy to installAccurate spacingEngagement/disengagement of coupling partsIncorrect coupling preventionMating connectionEngineering

A shroud that forms a guide channel for a connector is disclosed and it has the shape of an inverted U-shape, with a press tab for engaging a mating connector. The shroud has notches and tabs formed on it that serve to orient the mating connector for entry into the shroud. A placement member is also described and it serves to hold the connector and the shroud together as a single unit for robotic placement of the shroud and connector in preselected positions on the circuit board.

Owner:MOLEX INC