Ultra-thin body super-steep retrograde well (ssrw) fet devices

一种场效应晶体管、超陡后退阱的技术,应用在超薄型本体FET器件领域,能够解决不能实现严格的掺杂分布等问题,达到减小结电容和、减小结泄漏的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

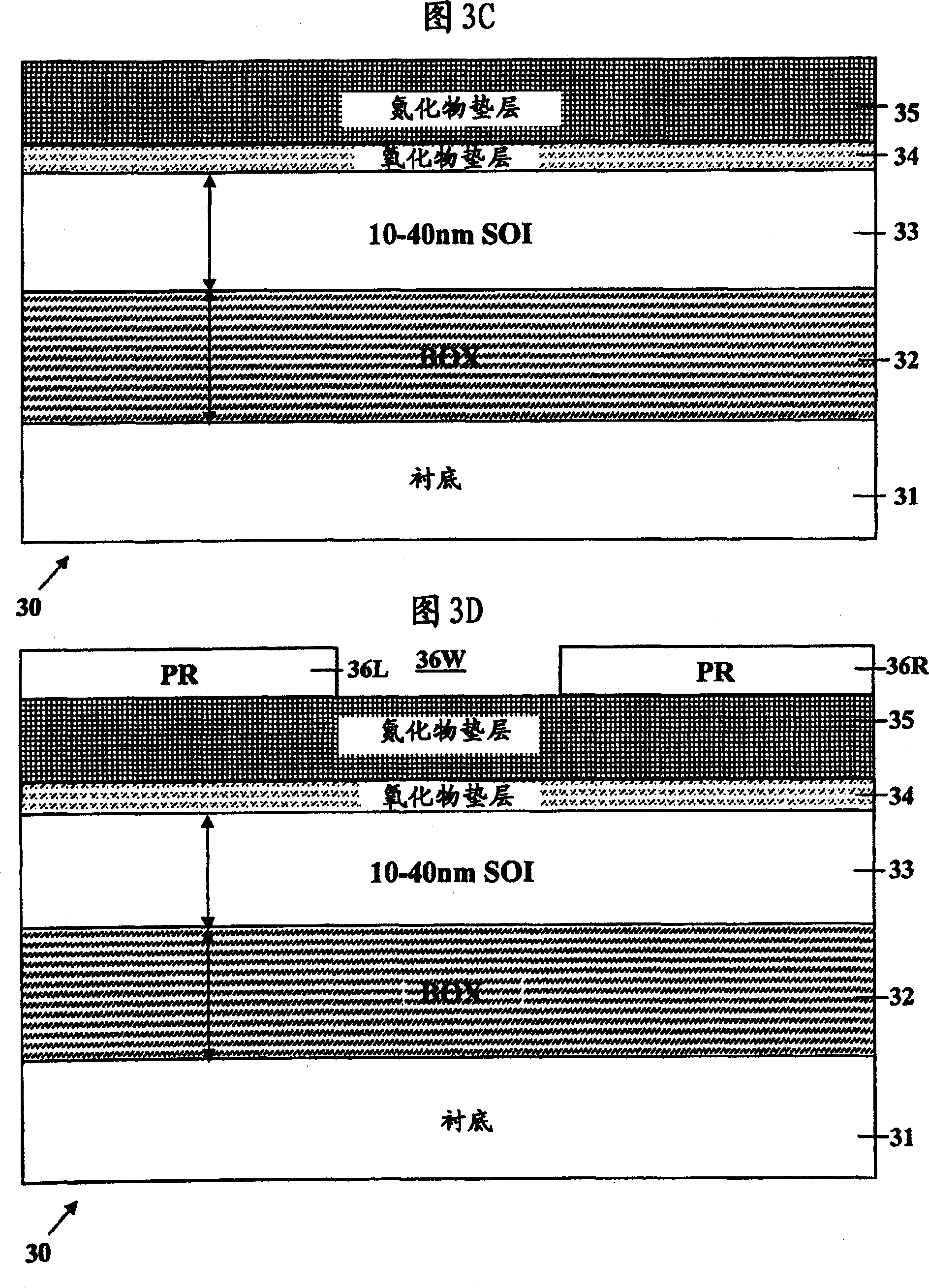

[0065] Figure 4 A flow chart of a first embodiment of the method of the invention is shown. Figure 4 The illustrated process begins (Start) 70 and proceeds to step 71 in which device 30 is processed. The SOI layer 33K initially having a thickness of 55 nm or more on the BOX substrate 31 in FIG. 3A is thinned to an ultra-thin thickness of about 10 nm to 40 nm by the oxidation and lift-off process described above with reference to FIG. 3B.

[0066] At the end of step 71, the desired thickness of the SOI layer 33 has been obtained.

[0067] In step 72 , an oxide pad layer 34 and a nitride pad layer 35 are formed on the thinned SOI layer 33 as shown in FIG. 3C . Next, as shown in FIG. 3D , an isolation image mask 36L / 36R having a central isolation window 36W therein is formed on the nitride pad layer 35 (over the SOI layer 33 ).

[0068]In step 73, isolation trench 37 is formed by etching from the top of device 30 down through isolation window 36W, wherein trench 37 goes dow...

no. 2 example

[0080] Figure 5 A flow chart of a second embodiment of the method of the invention is shown. Figure 5 The illustrated process starts at 90 and proceeds to step 91 in which device 30 is processed. The SOI layer 33K initially having a thickness of 55 nm or more on the BOX substrate 31 in FIG. 3A is thinned to an ultra-thin thickness of about 10 nm to 40 nm by the oxidation and lift-off process described above with reference to FIG. 3B.

[0081] At the end of step 91, the desired thickness of the SOI layer 33 has been obtained.

[0082] In step 92 , an oxide pad layer 34 and a nitride pad layer 35 are formed on the thinned SOI layer 33 as shown in FIG. 3C . Next, as shown in FIG. 3D , an isolation image mask 36L / 36R having a central isolation window 36W therein is formed on the nitride pad layer 35 (over the SOI layer 33 ).

[0083] In step 93, an isolation trench 37 is formed by etching from the top of the device 30 down through the isolation window 36W, wherein the trench...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More