Patents

Literature

4783 results about "Gate oxide" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The gate oxide is the dielectric layer that separates the gate terminal of a MOSFET (metal-oxide-semiconductor field-effect transistor) from the underlying source and drain terminals as well as the conductive channel that connects source and drain when the transistor is turned on. Gate oxide is formed by thermal oxidation of the silicon of the channel to form a thin (5 - 200 nm) insulating layer of silicon dioxide. The insulating silicon dioxide layer is formed through a process of self-limiting oxidation, which is described by the Deal Grove model. A conductive gate material is subsequently deposited over the gate oxide to form the transistor. The gate oxide serves as the dielectric layer so that the gate can sustain as high as 1 to 5 MV/cm transverse electric field in order to strongly modulate the conductance of the channel.

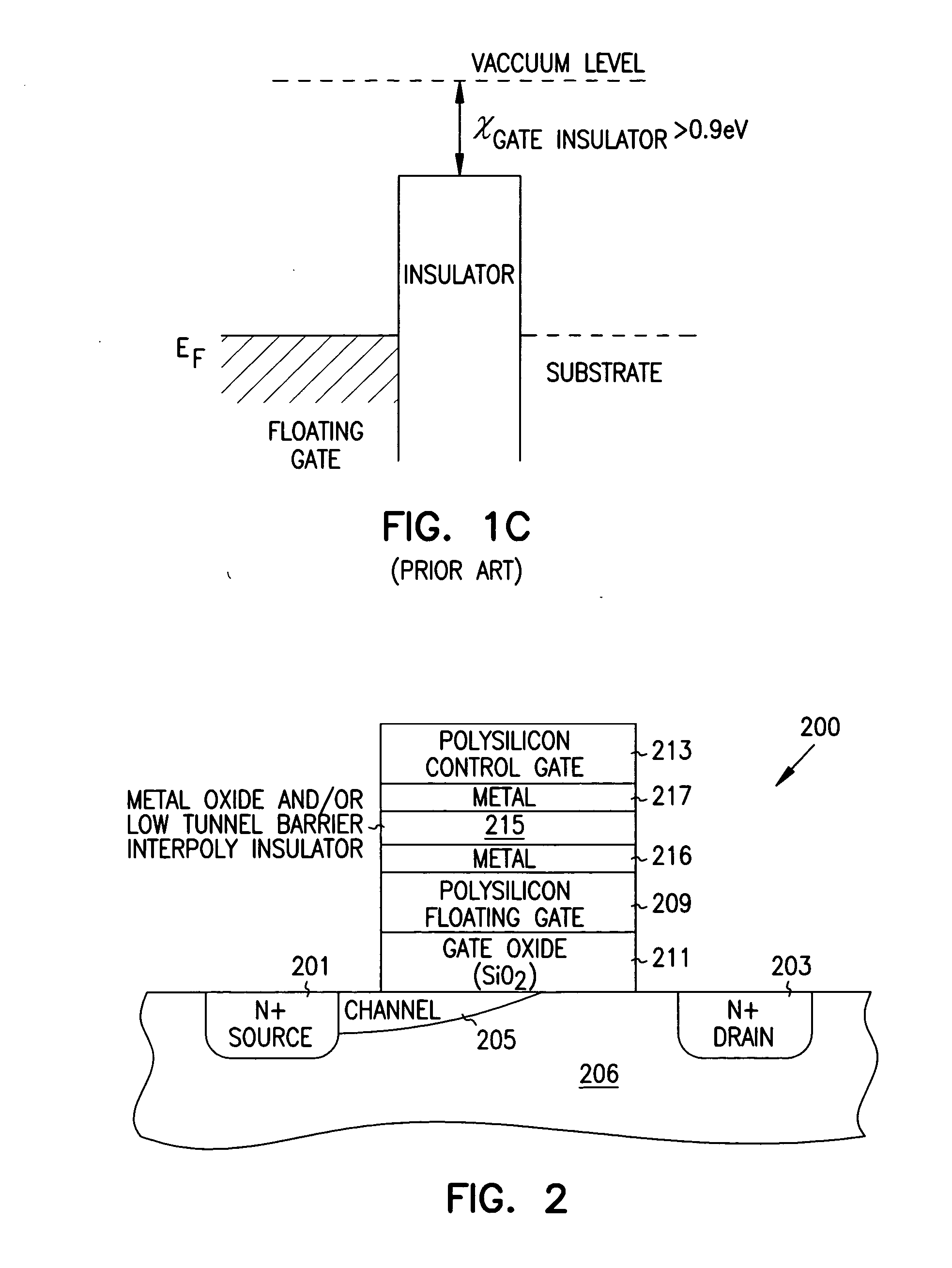

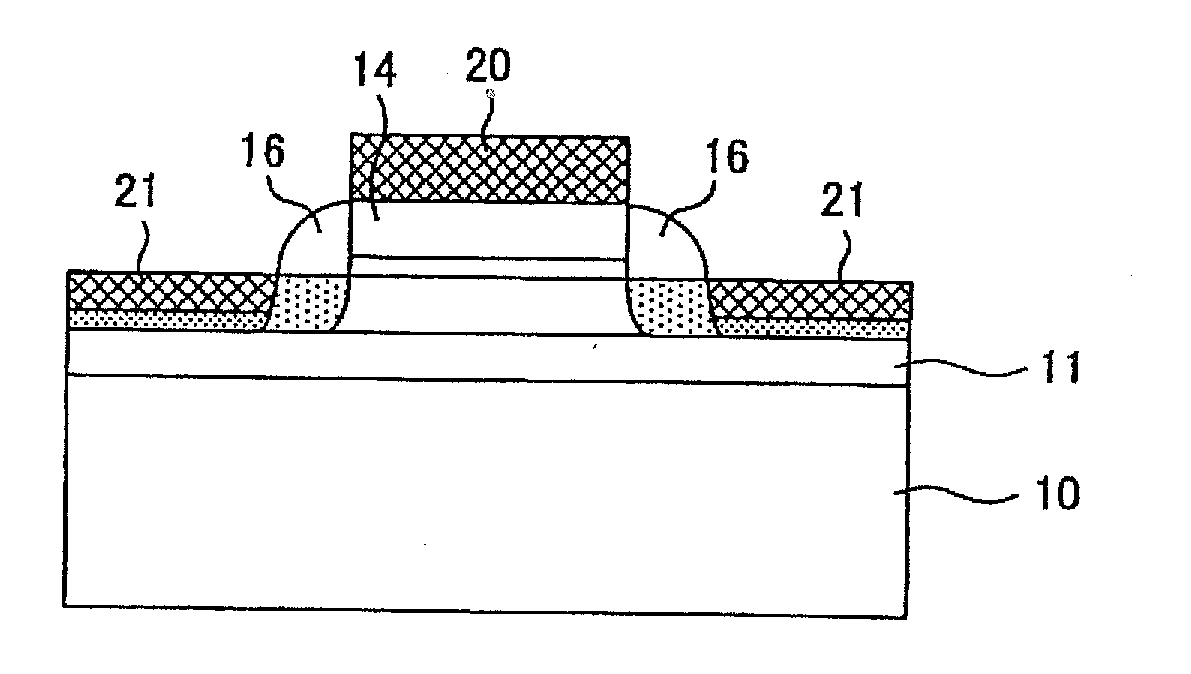

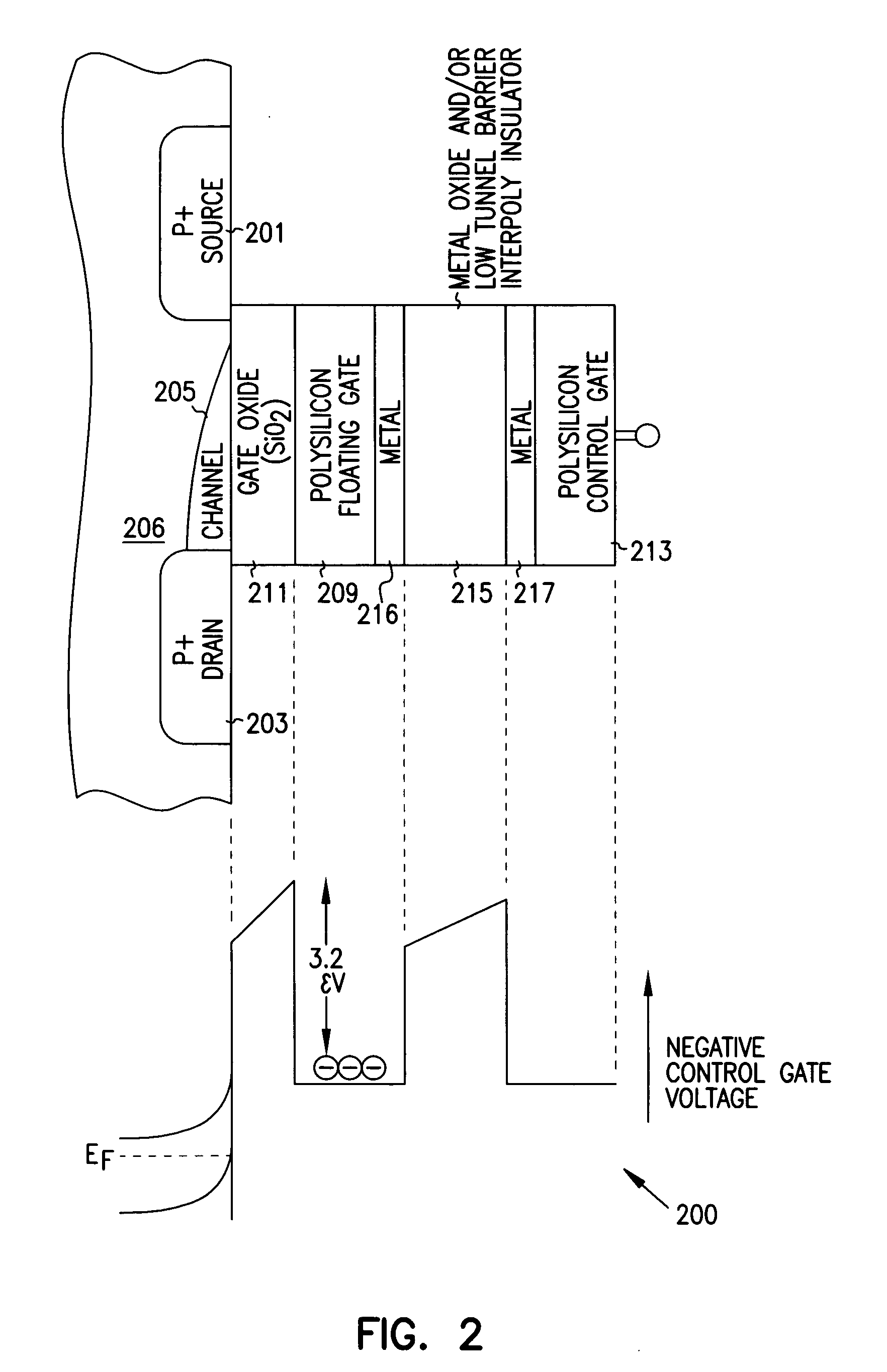

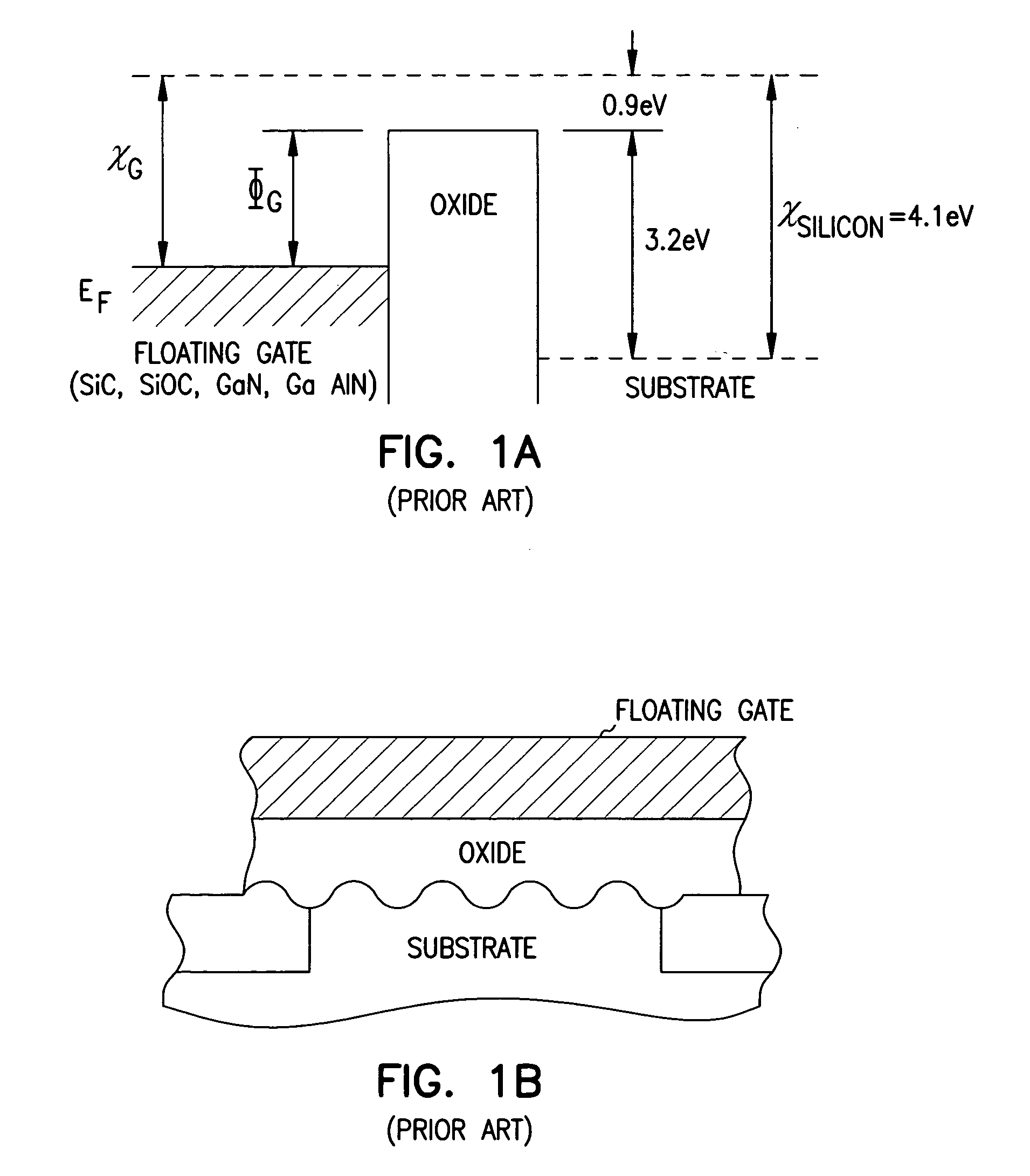

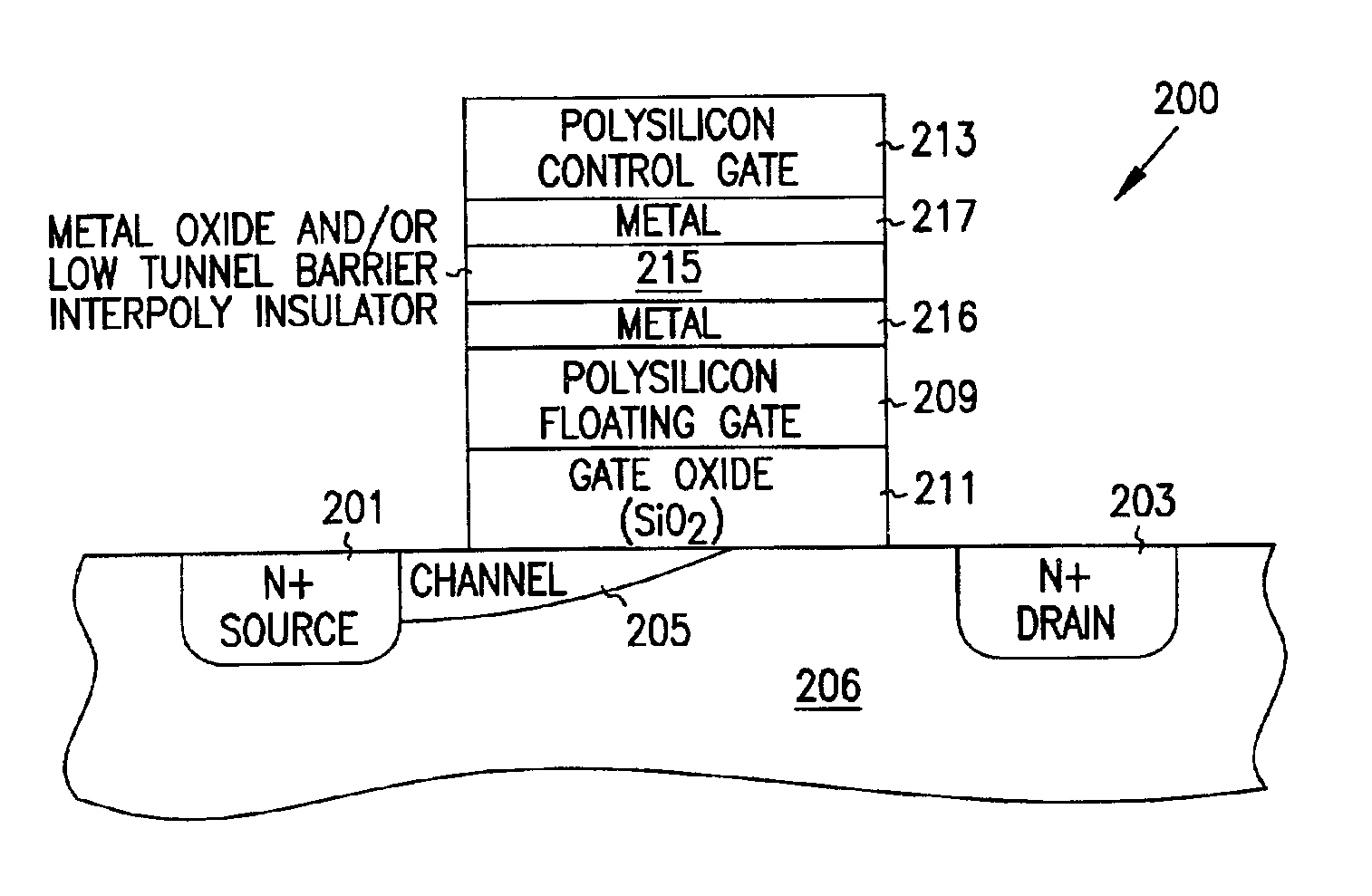

Atomic layer deposition of metal oxide and/or low asymmetrical tunnel barrier interpoly insulators

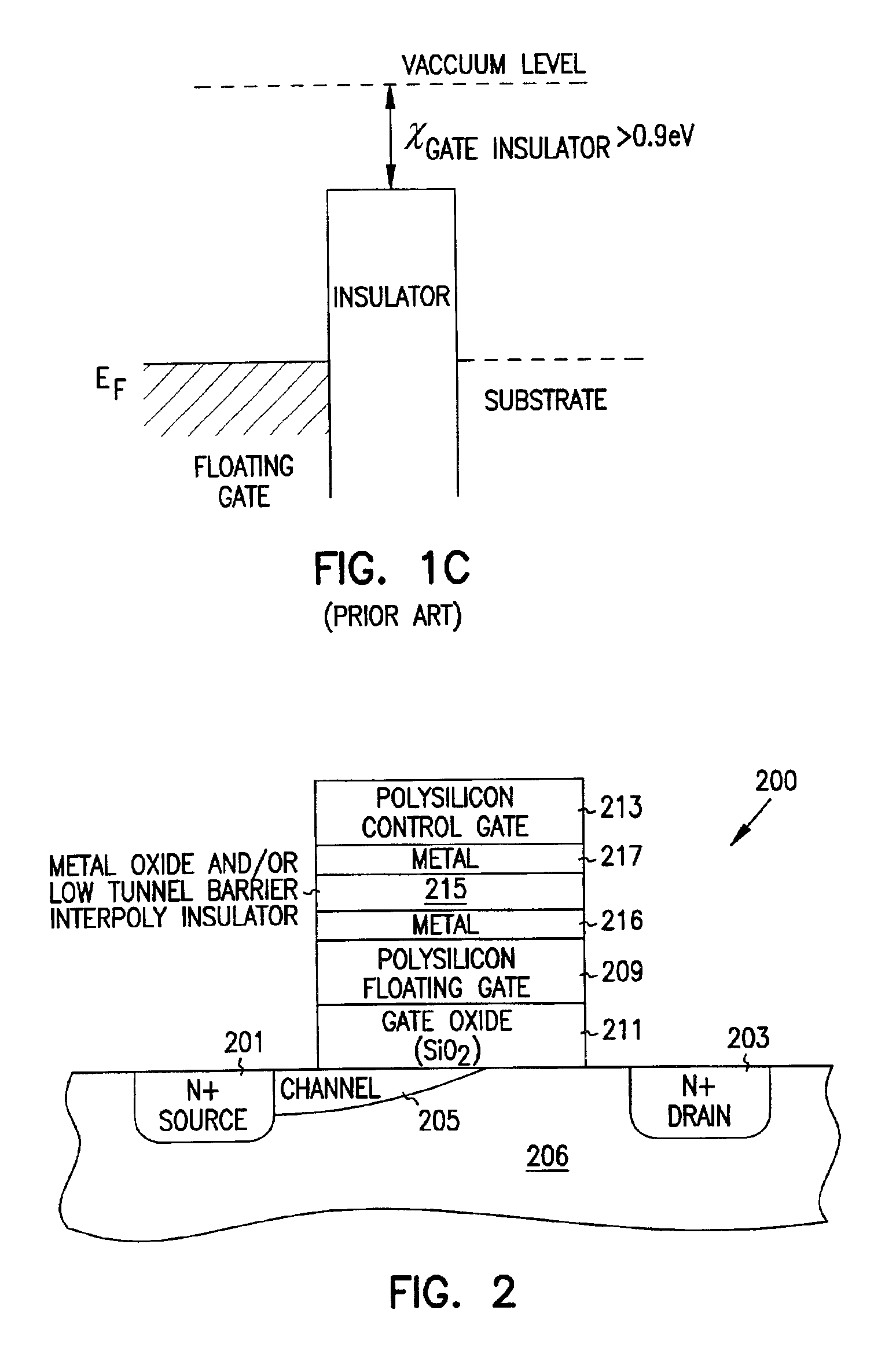

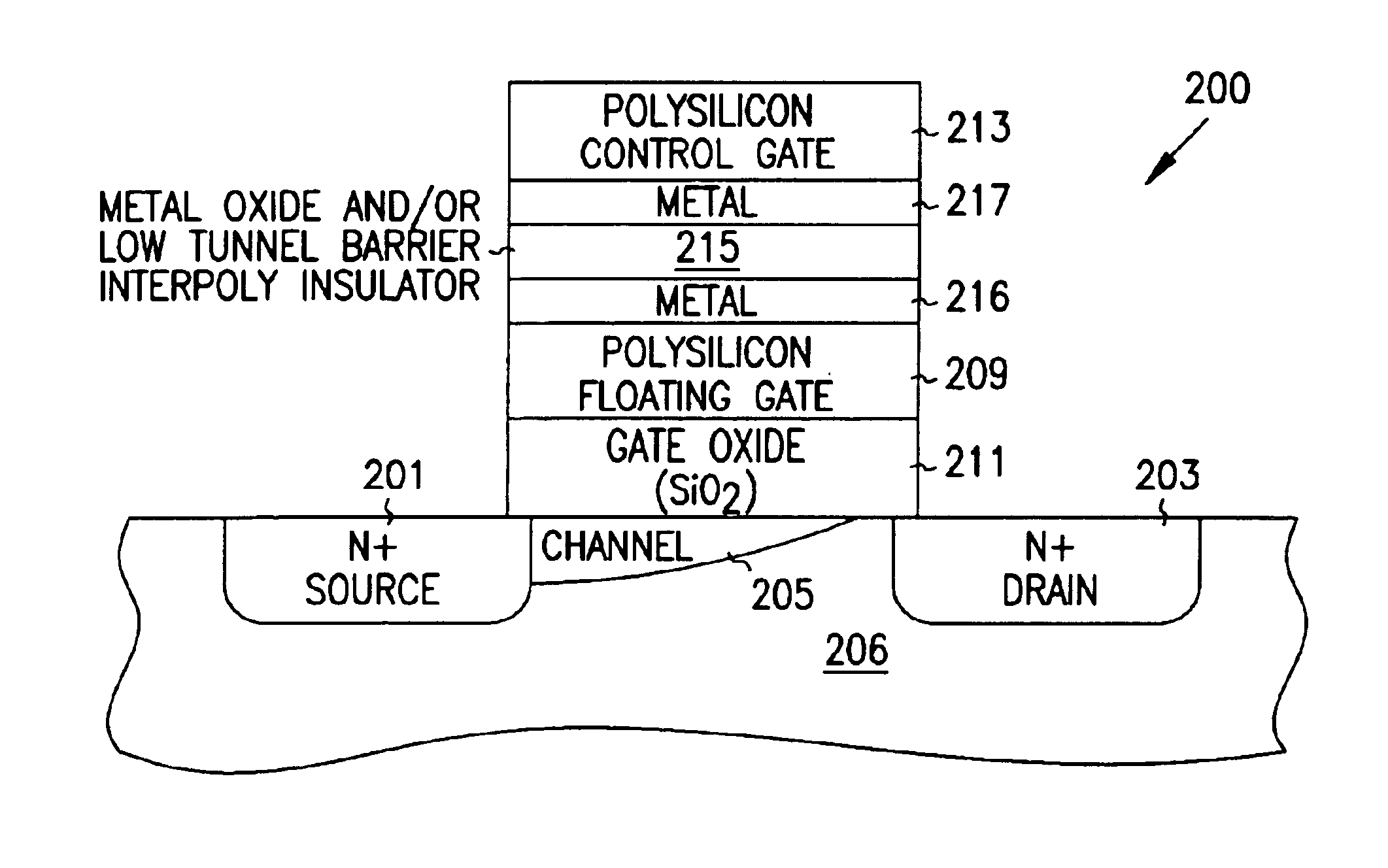

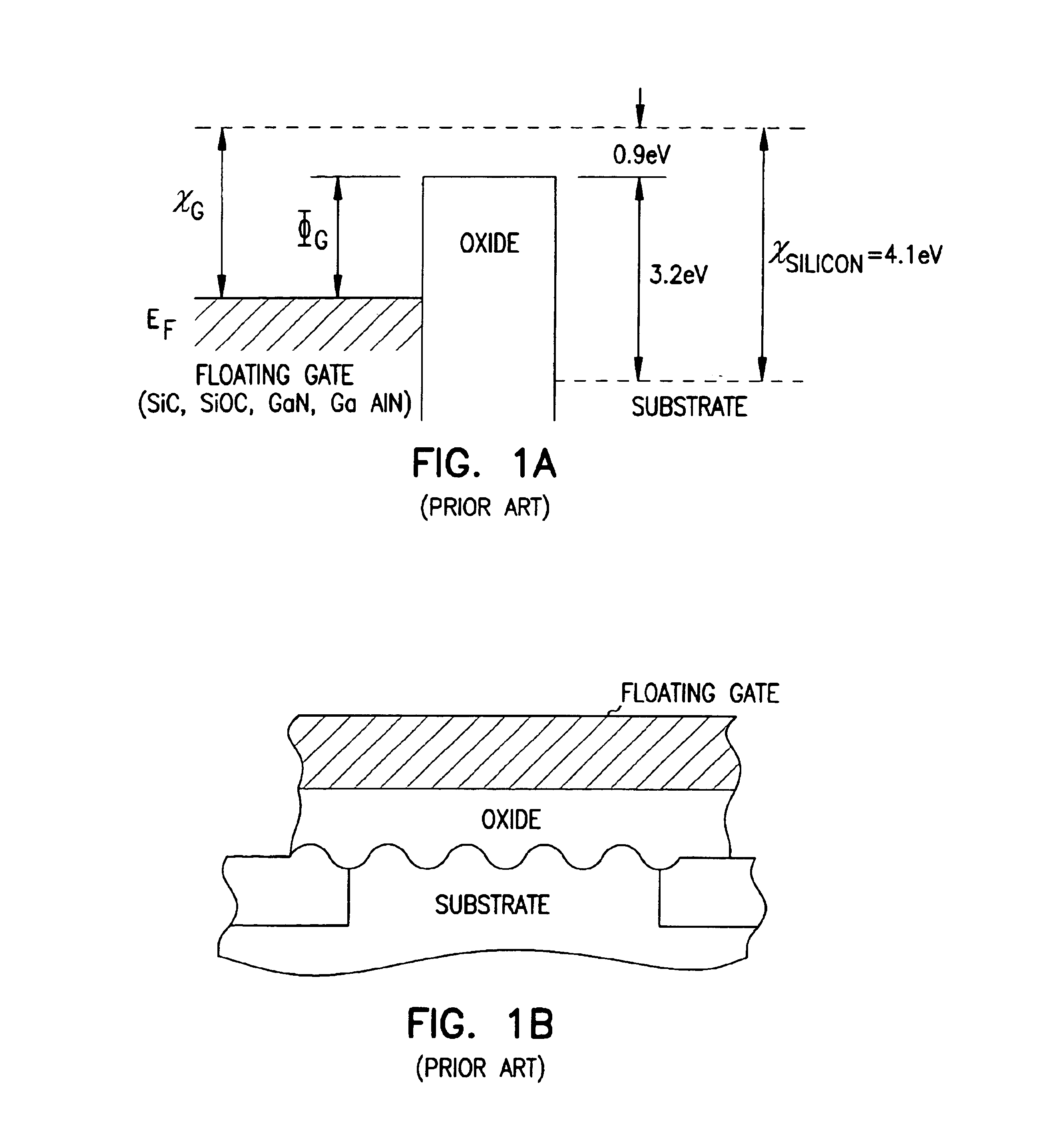

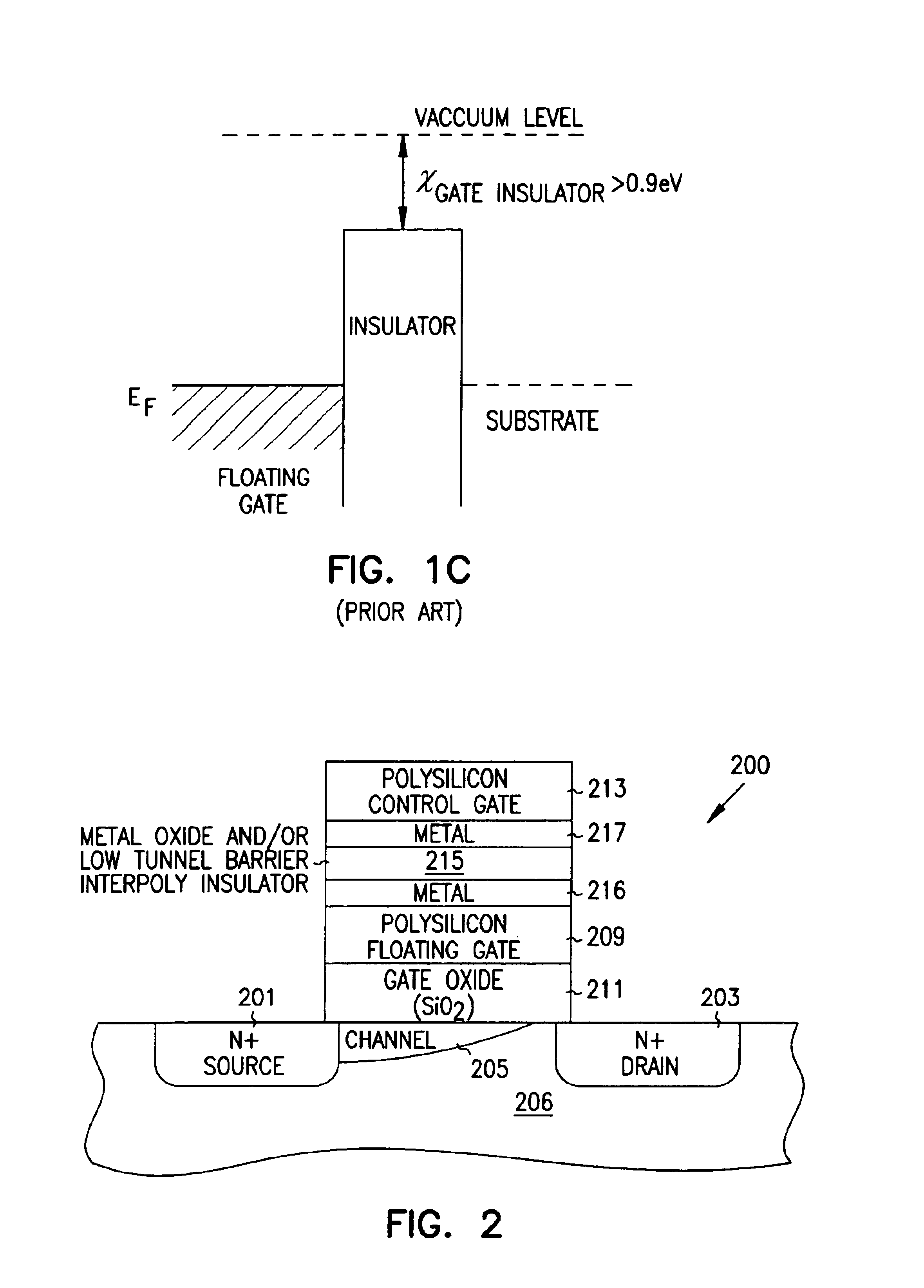

Structures and methods for programmable array type logic and / or memory devices with asymmetrical low tunnel barrier intergate insulators are provided. The programmable array type logic and / or memory devices include non-volatile memory which has a first source / drain region and a second source / drain region separated by a channel region in a substrate. A floating gate opposing the channel region and is separated therefrom by a gate oxide. A control gate opposes the floating gate. The control gate is separated from the floating gate by an asymmetrical low tunnel barrier intergate insulator formed by atomic layer deposition. The asymmetrical low tunnel barrier intergate insulator includes a metal oxide insulator selected from the group consisting of Al2O3, Ta2O5, TiO2, ZrO2, Nb2O5, SrBi2Ta2O3, SrTiO3, PbTiO3, and PbZrO3.

Owner:MICRON TECH INC

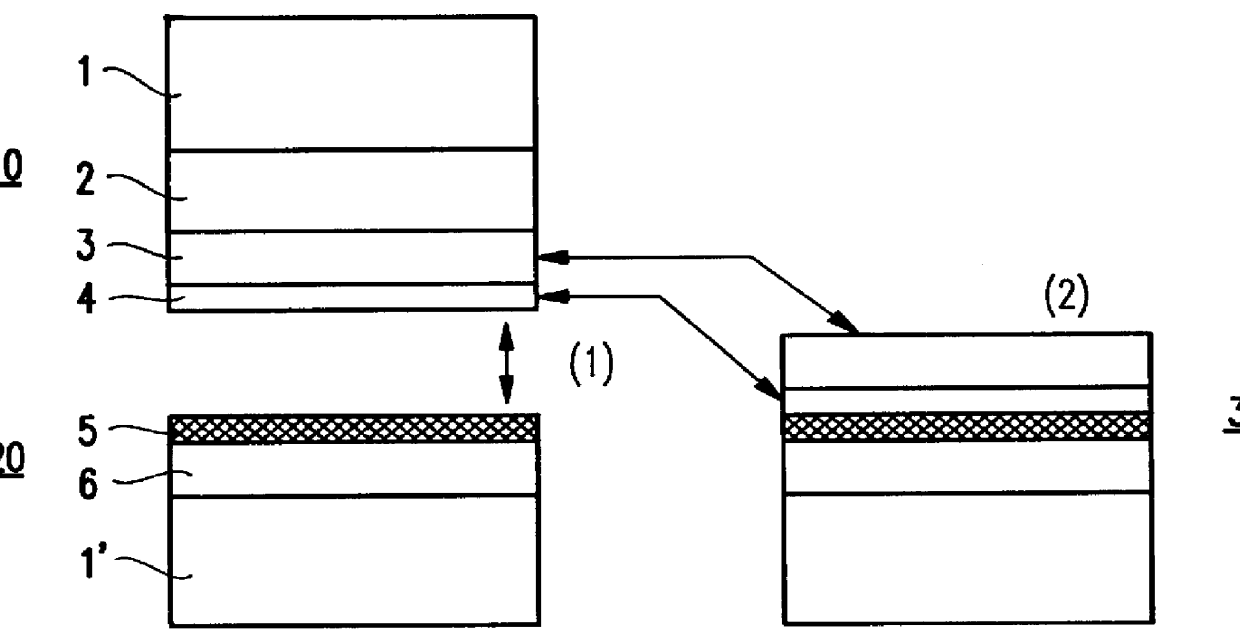

Method for making bonded metal back-plane substrates

InactiveUS6057212AMaintain its interface acuityHigh-temperature bondingSemiconductor/solid-state device manufacturingSemiconductor structureEngineering

A method of forming a semiconductor structure, includes steps of growing an oxide layer on a substrate to form a first wafer, separately forming a metal film on an oxidized substrate to form a second wafer, attaching the first and second wafers, performing a heat cycle for the first and second wafers to form a bond between the first and second wafers, and detaching a portion of the first wafer from the second wafer. Thus, a device, such as a back-plane for a semiconductor device, formed by the method includes an oxidized substrate, a metal film formed on the oxidized substrate forming a back-gate, a back-gate oxide formed on the back-gate, and a silicon layer formed on the back-gate oxide.

Owner:IBM CORP

Multiple-gate device with floating back gate

Disclosed is a multiple-gate transistor that includes a channel region and source and drain regions at ends of the channel region. A gate oxide is positioned between a logic gate and the channel region and a first insulator is formed between a floating gate and the channel region. The first insulator is thicker than the gate oxide. The floating gate is electrically insulated from other structures. Also, a second insulator is positioned between a programming gate and the floating gate. Voltage in the logic gate causes the transistor to switch on and off, while stored charge in the floating gate adjusts the threshold voltage of the transistor. The transistor can comprise a fin-type field effect transistor (FinFET), where the channel region comprises the middle portion of a fin structure and the source and drain regions comprise end portions of the fin structure.

Owner:GLOBALFOUNDRIES U S INC

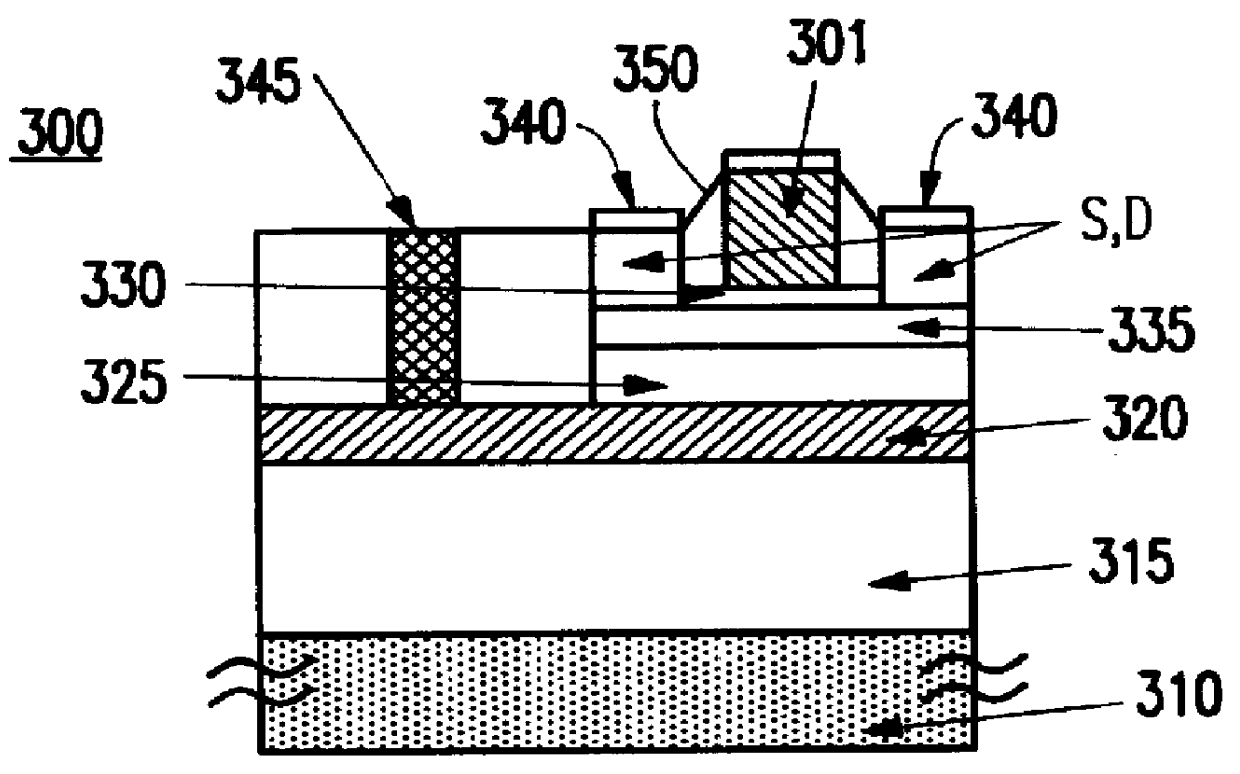

Structures and methods for making strained mosfets

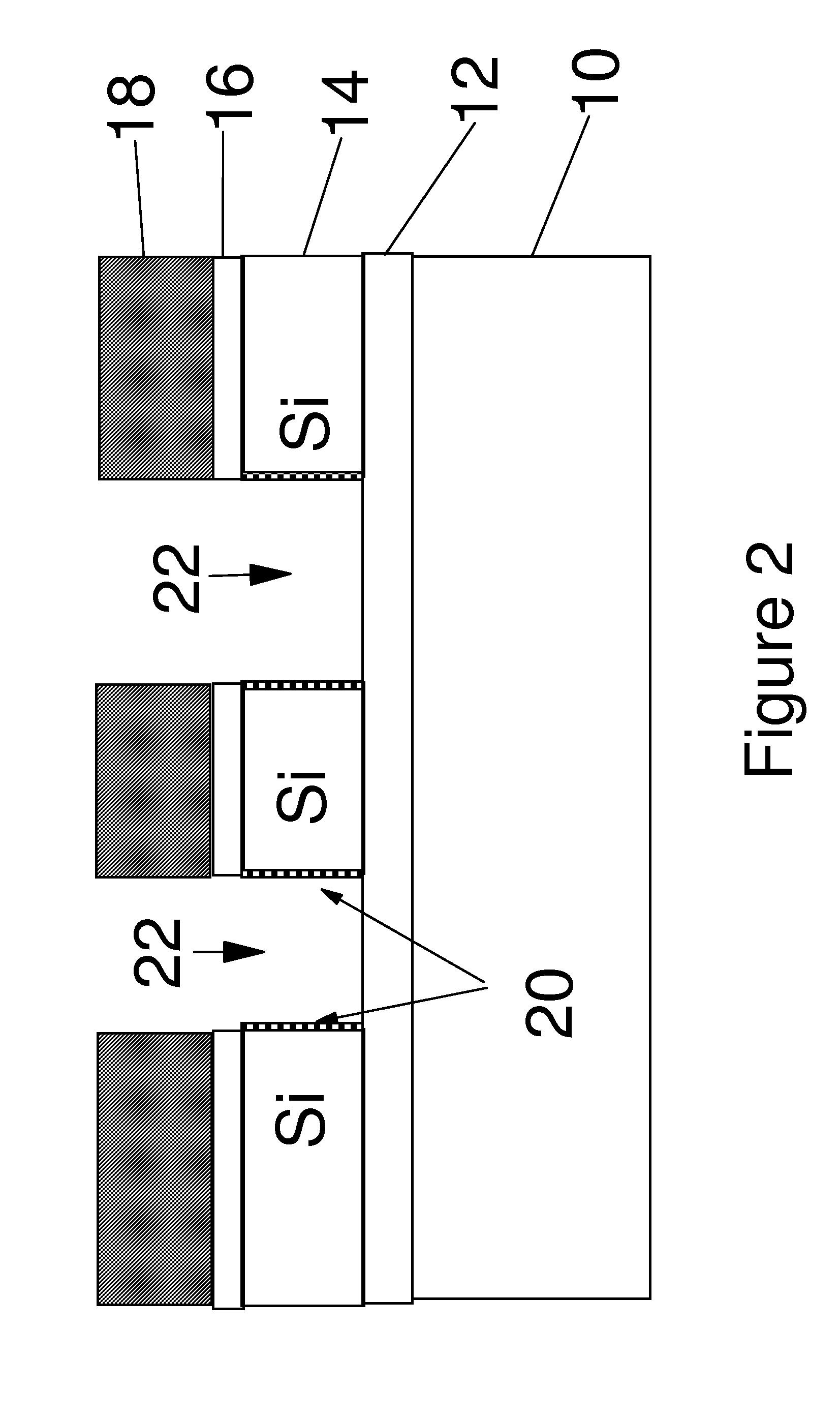

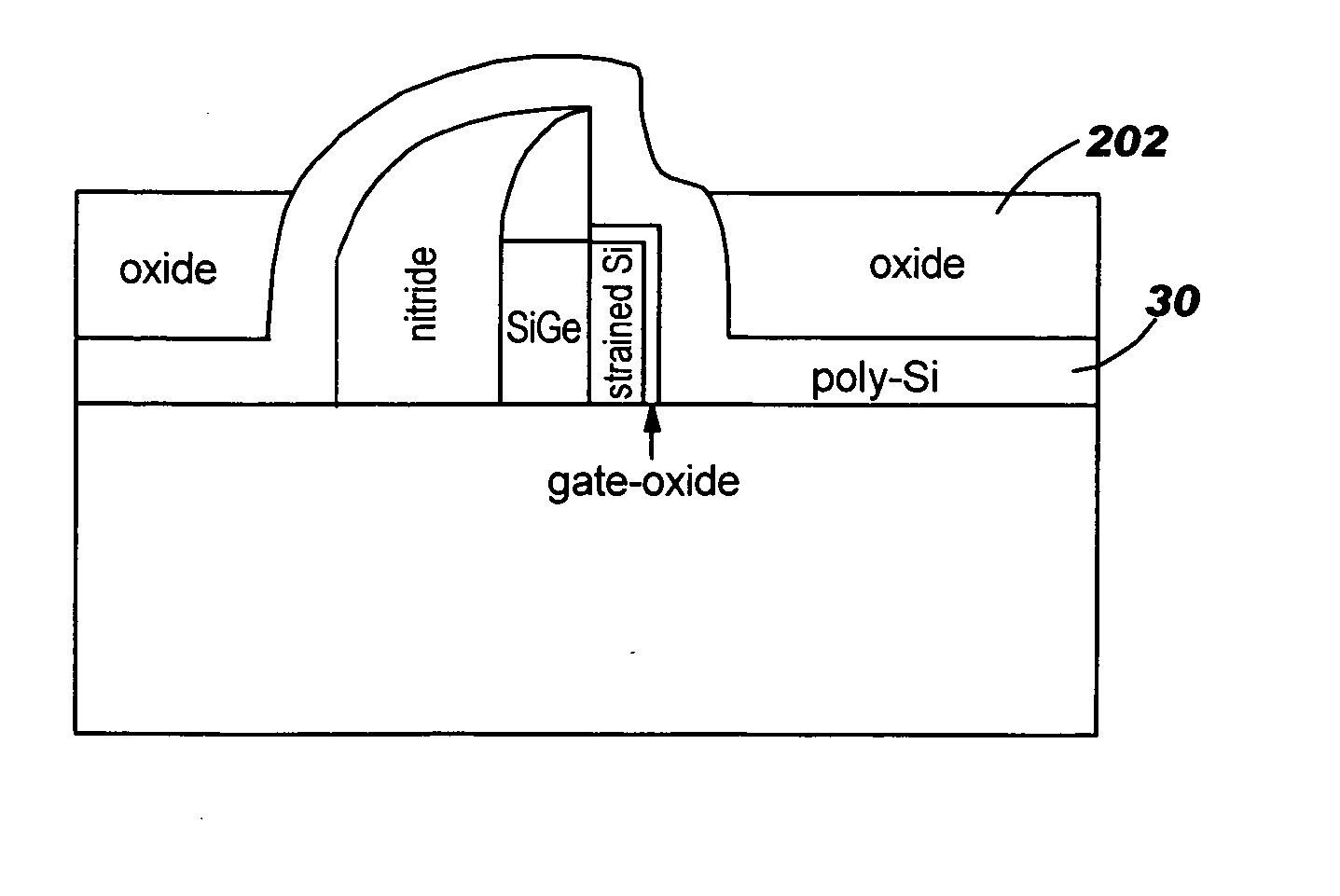

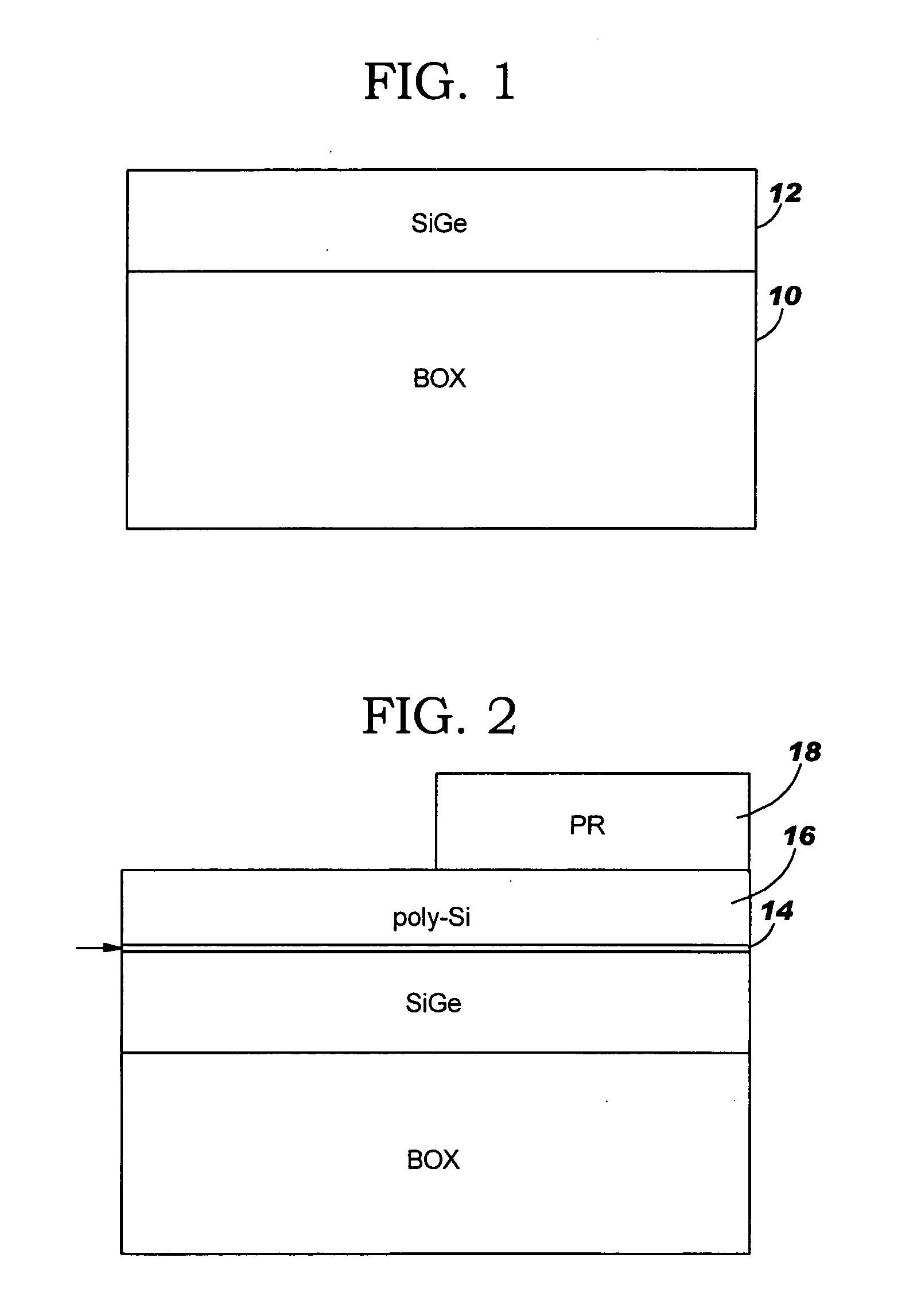

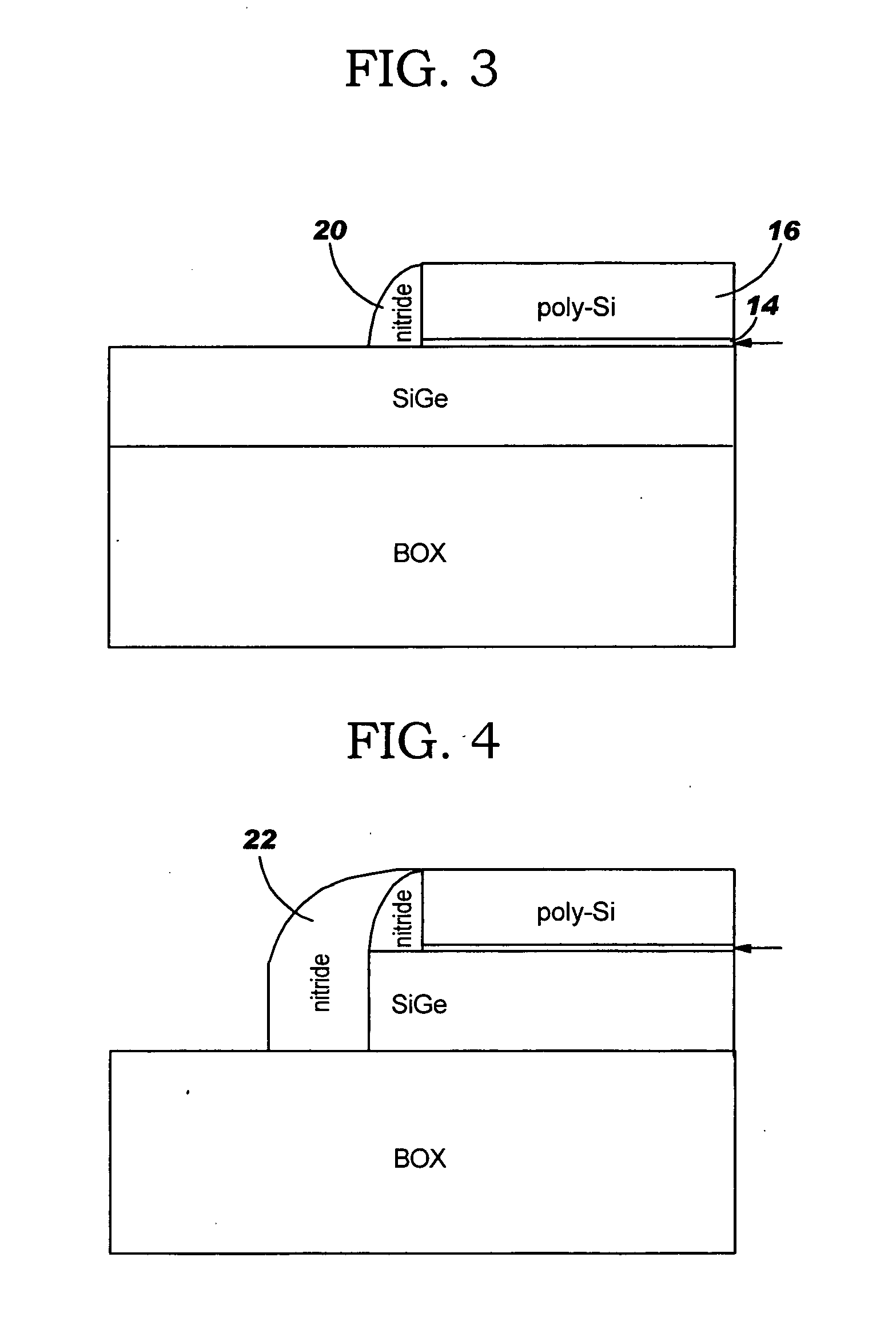

A method and device providing a strained Si film with reduced defects is provided, where the strained Si film forms a fin vertically oriented on a surface of a non-conductive substrate. The strained Si film or fin may form a semiconductor channel having relatively small dimensions while also having few defects. The strained Si fin is formed by growing Si on the side of a relaxed SiGe block. A dielectric gate, such as, for example, an oxide, a high “k” material, or a combination of the two, may be formed on a surface of the strained Si film. Additionally, without substantially affecting the stress in the strained Si film, the relaxed SiGe block may be removed to allow a second gate oxide to be formed on the surface previously occupied by the relaxed SiGe block. Accordingly, a semiconductor device having a strained Si fin vertically oriented on a non-conductive substrate may be formed where the strained Si film is oriented such that it may form a channel of small dimensions allowing access to both sides and top in order to from single gate, double gate, or more gate MOSFETs and finFETs with a channel having a reduced number of defects and / or reduced dimensions.

Owner:GLOBALFOUNDRIES US INC

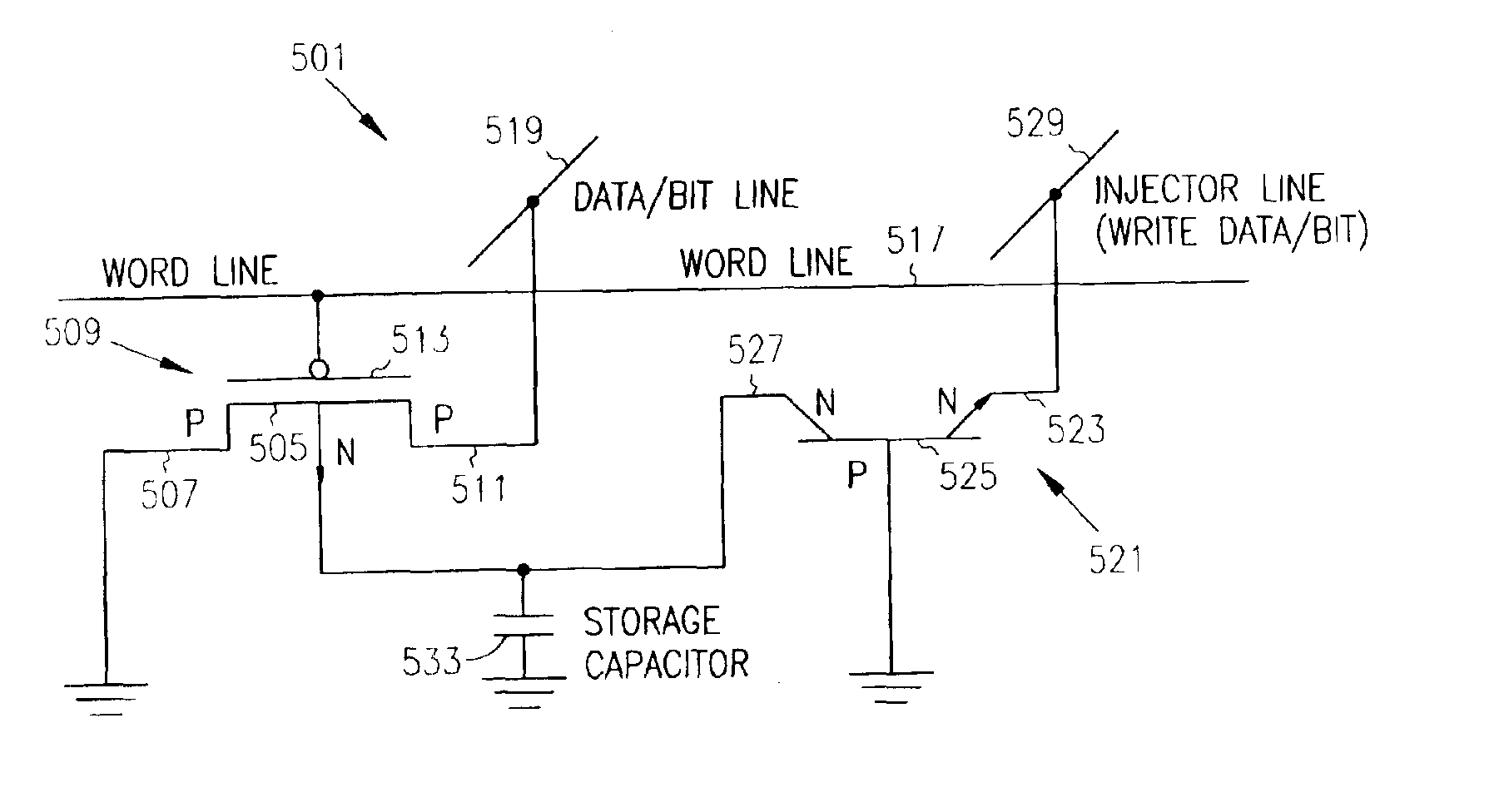

Embedded DRAM gain memory cell having MOS transistor body provided with a bi-polar transistor charge injecting means

A high density horizontal merged MOS-bipolar gain memory cell is realized for DRAM operation. The gain cell includes a horizontal MOS transistor having a source region, a drain region, and a floating body region therebetween. The gain cell includes a horizontal bi-polar transistor having an emitter region, a base region and a collector region. The collector region for the horizontal bi-polar transistor serves as the floating body region for the horizontal MOS transistor. A gate opposes the floating body region and is separated therefrom by a gate oxide. The emitter region for the horizontal bi-polar transistor is coupled to a write data line.

Owner:MICRON TECH INC

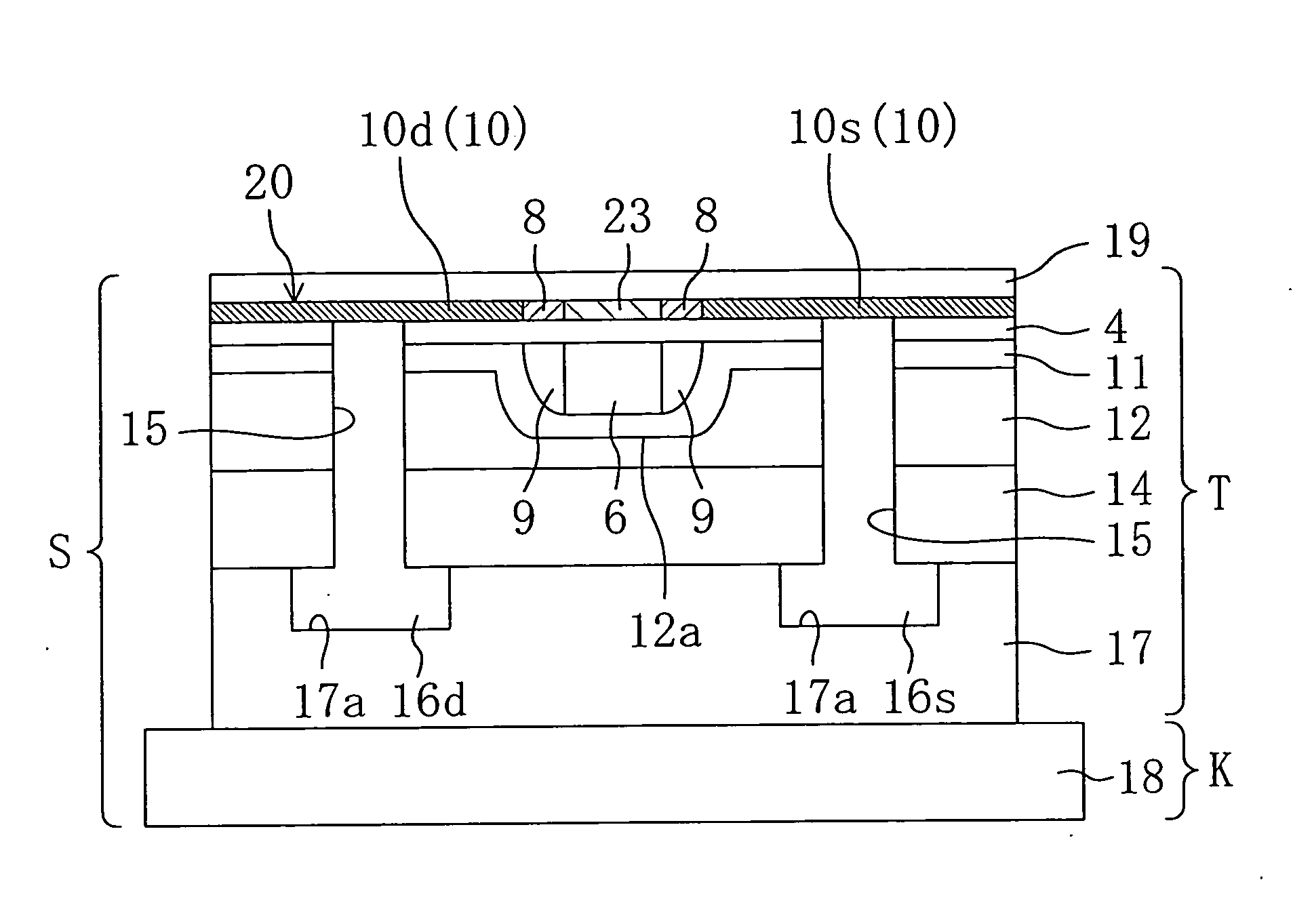

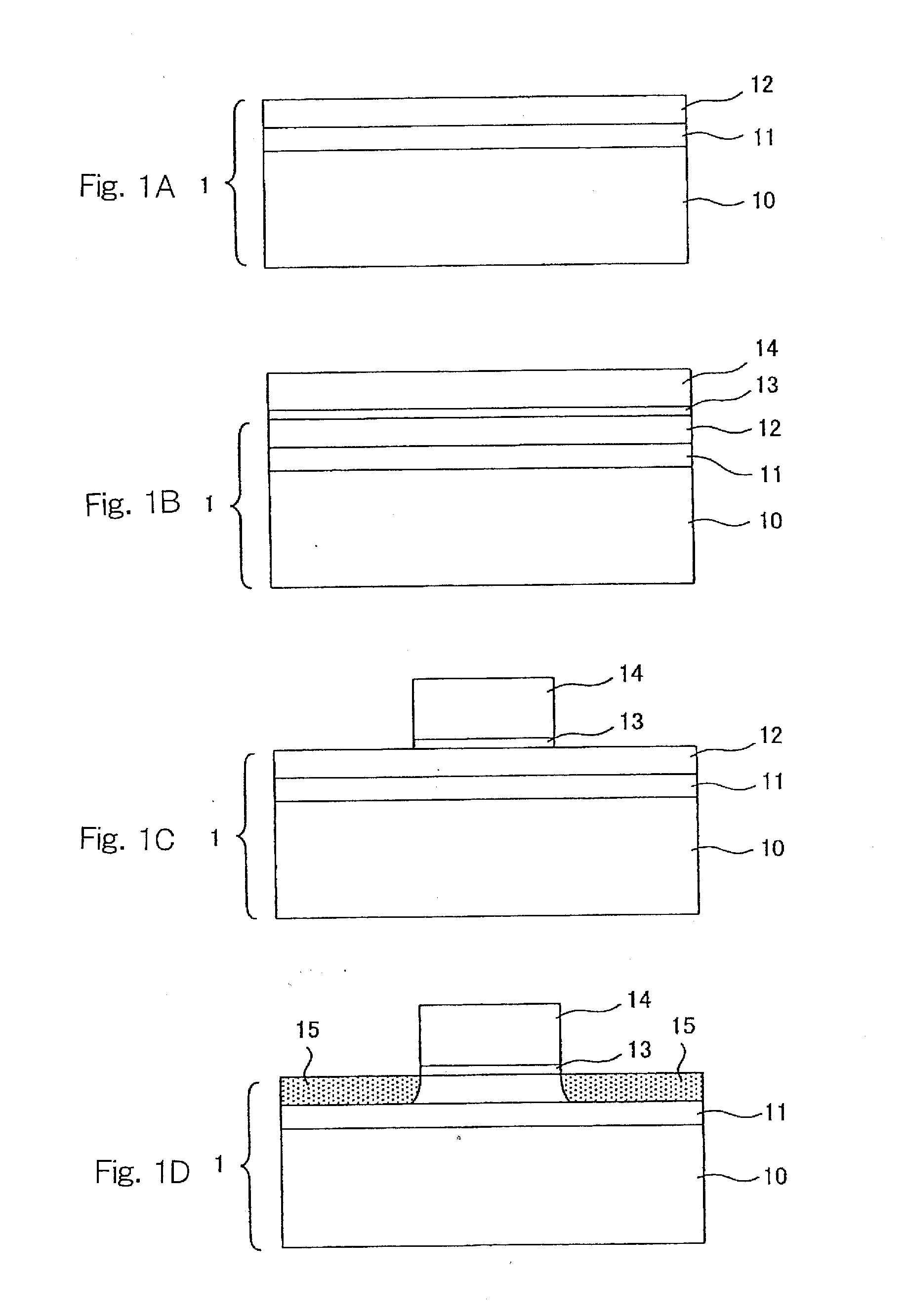

Method for manufacturing semiconductor substrate and semiconductor substrate

InactiveUS20050282019A1Reduce adverse effectsInhibit migrationSolid-state devicesSemiconductor/solid-state device manufacturingHydrogenGate oxide

A method for manufacturing a semiconductor substrate comprises the steps of: forming a gate oxide film as an insulating layer on the surface of a semiconductor substrate; implanting boron ions for inhibiting the migration of a peeling substance in the semiconductor substrate to form an anti-diffusion layer in the semiconductor substrate; activating boron in the anti-diffusion layer by heat treatment; implanting hydrogen ions into the semiconductor substrate to form a peel layer in part of the semiconductor substrate at a side of the anti-diffusion layer opposite to the gate oxide film; bonding a glass substrate to the surface of the semiconductor substrate where the gate oxide film has been formed; and heat-treating the semiconductor substrate to separate part of the semiconductor substrate along the peel layer.

Owner:SHARP KK

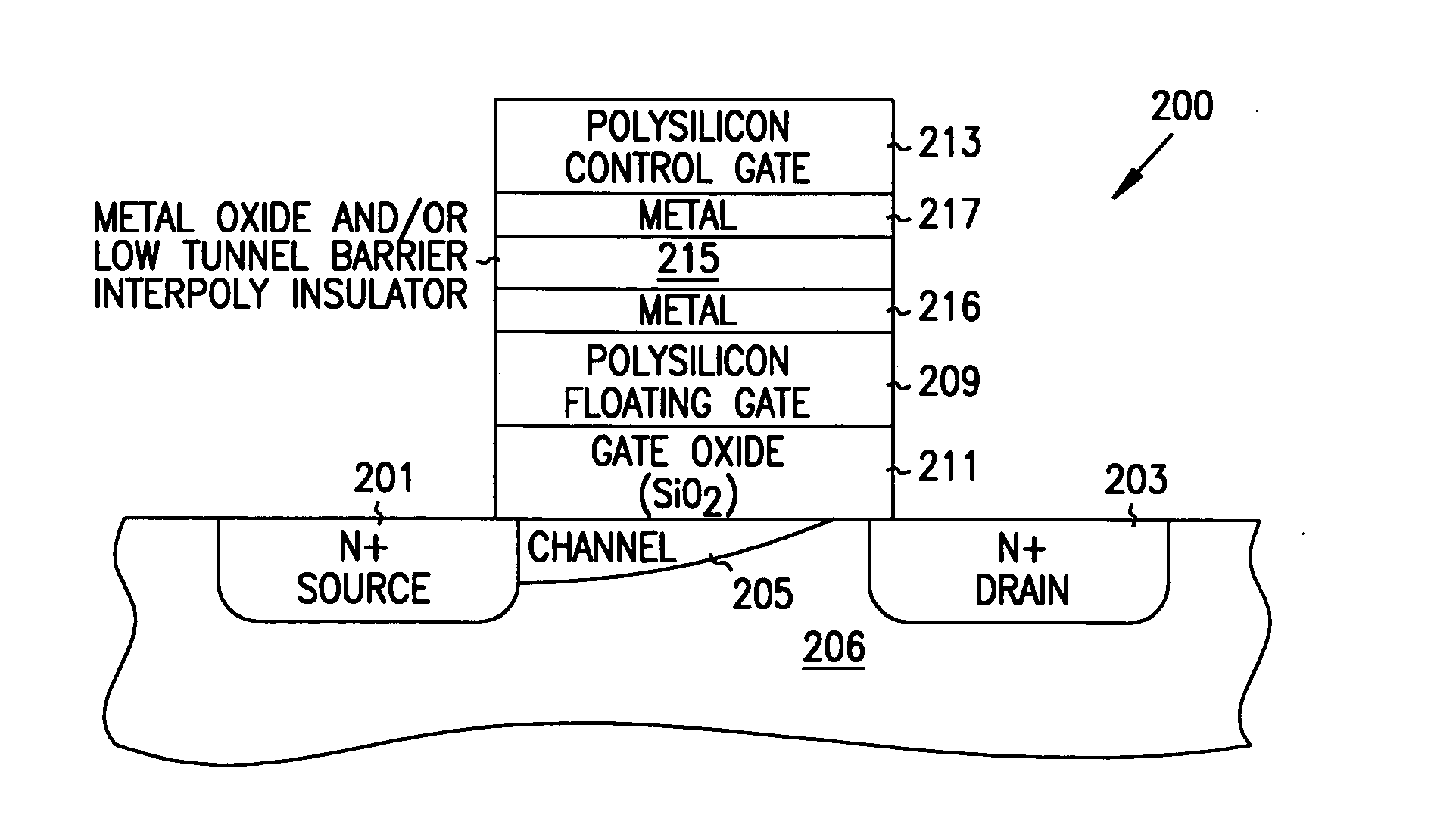

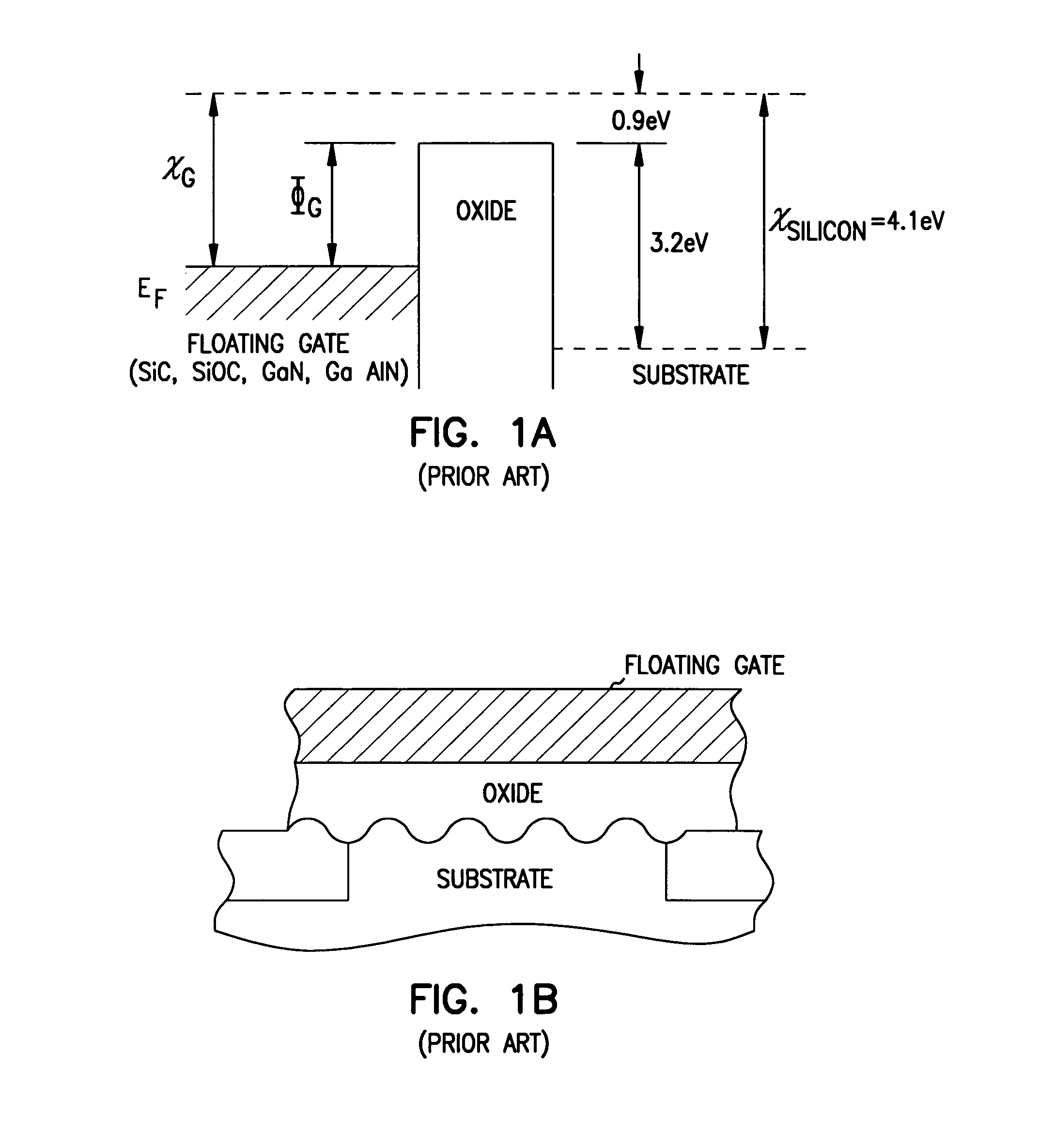

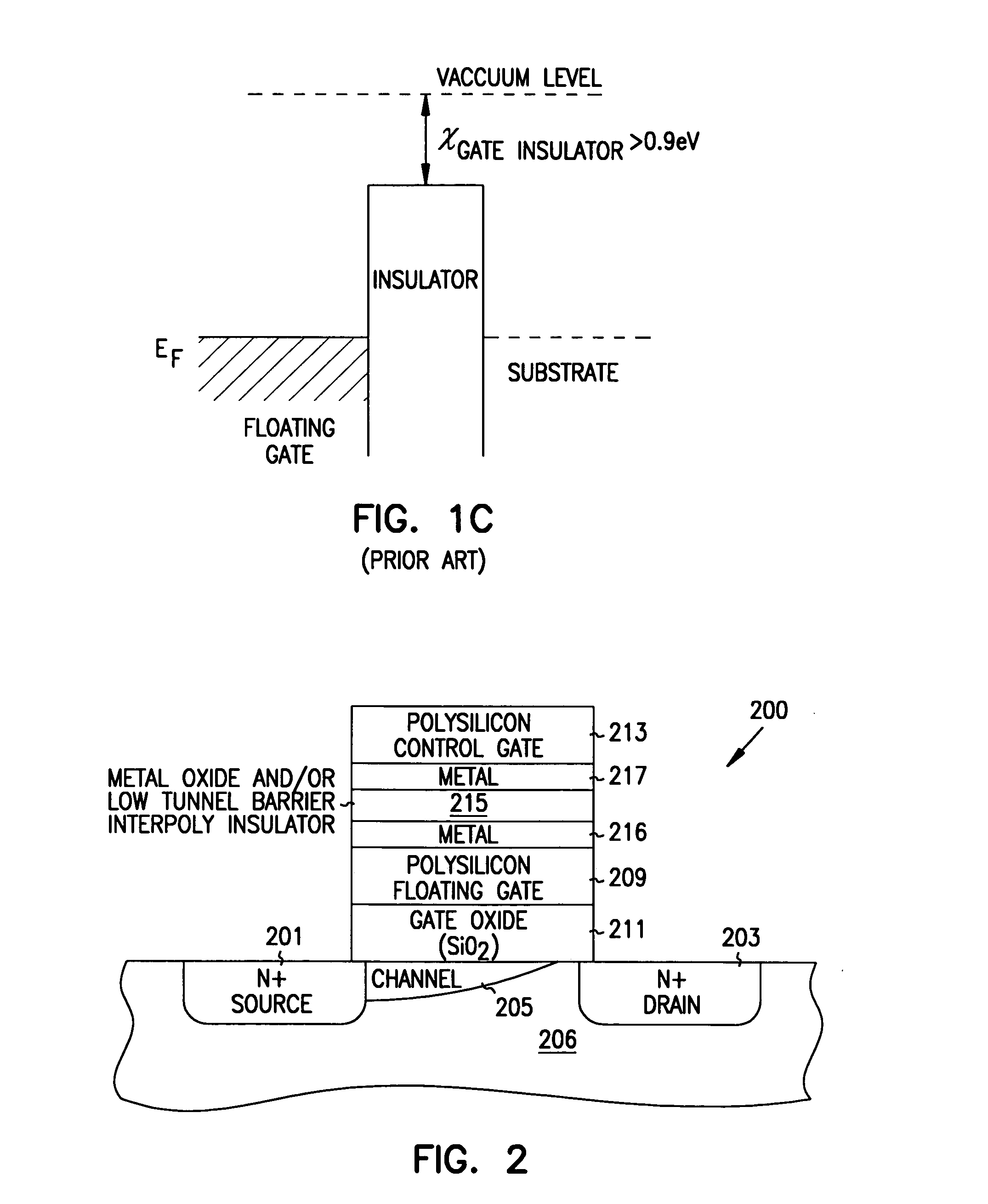

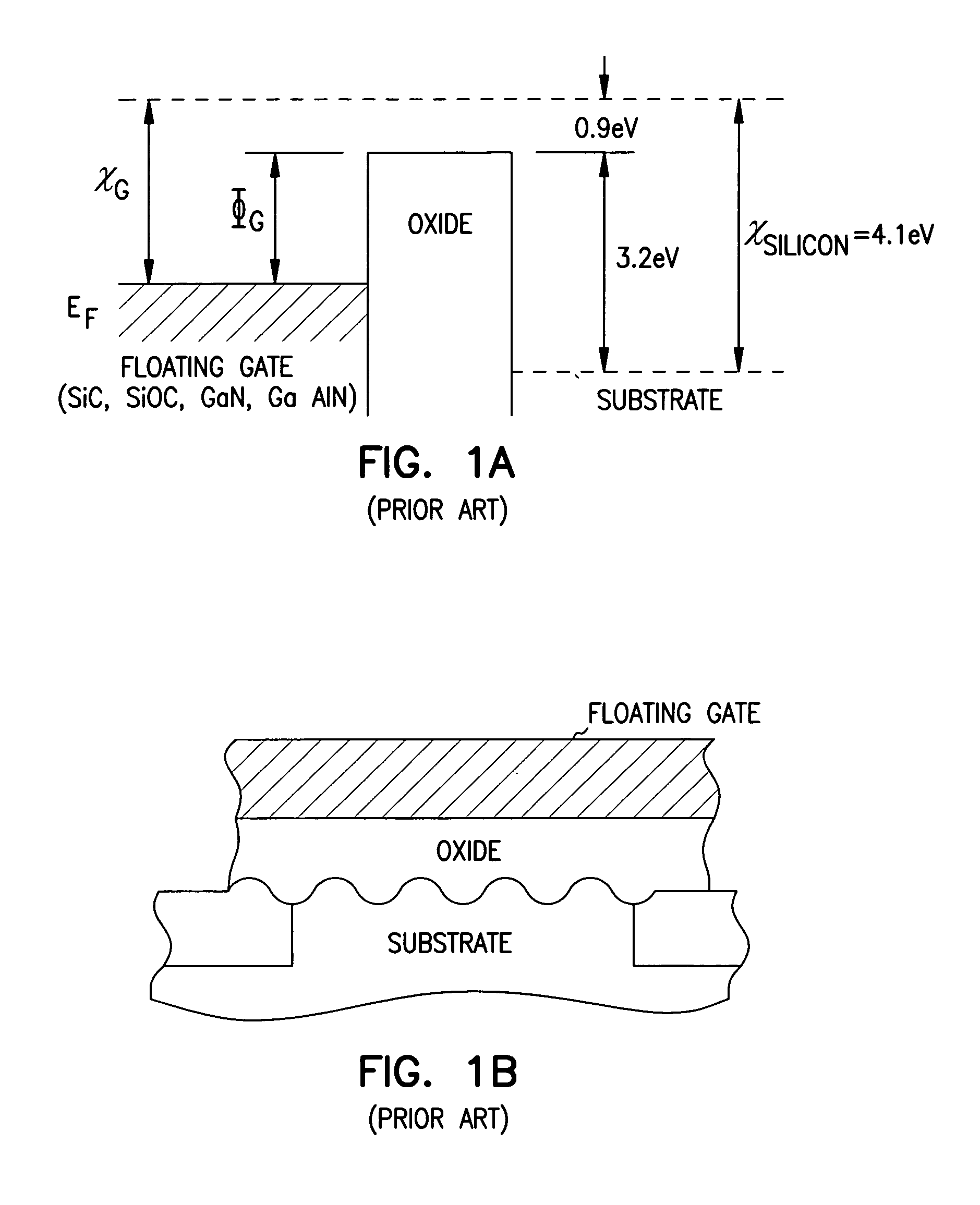

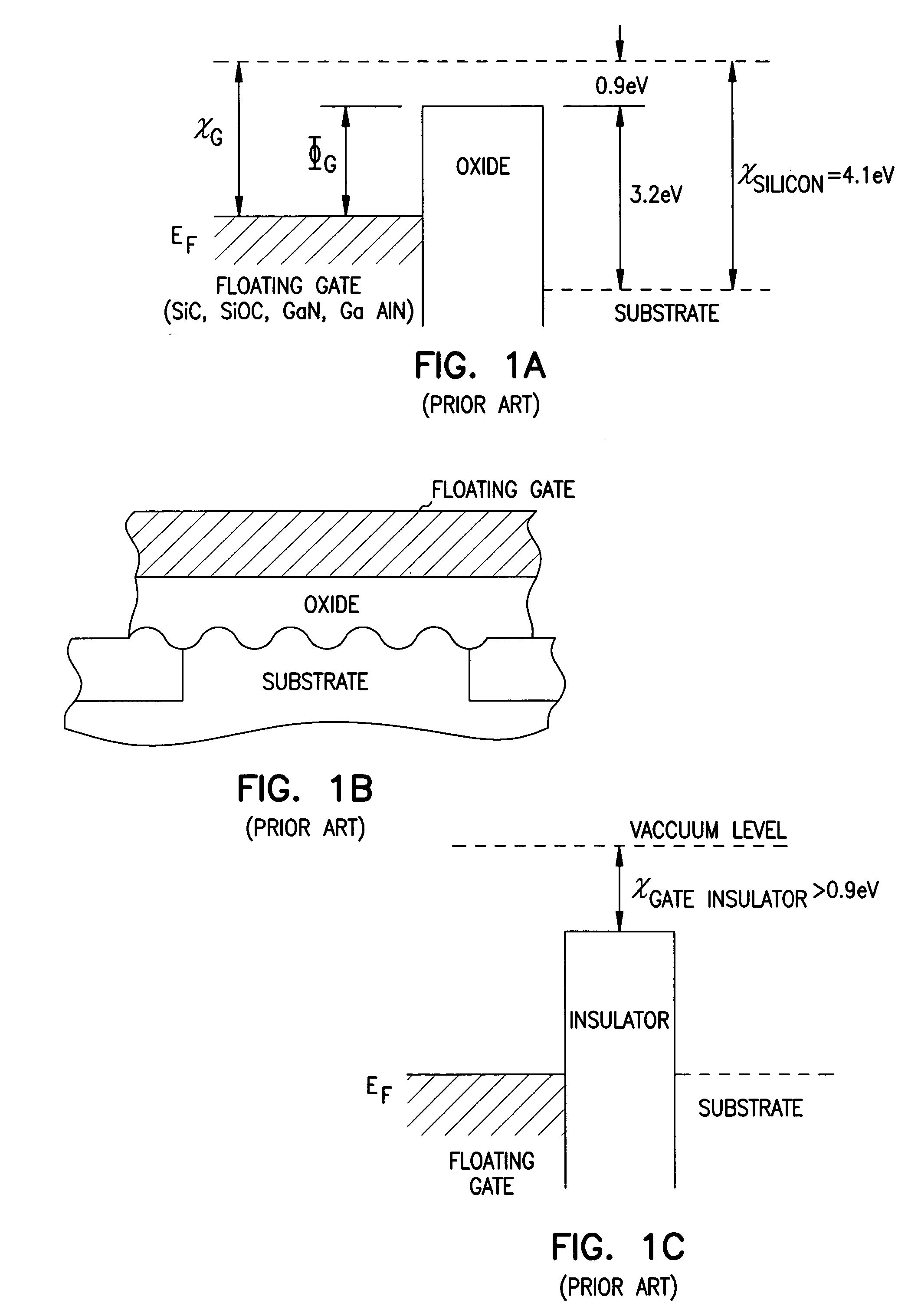

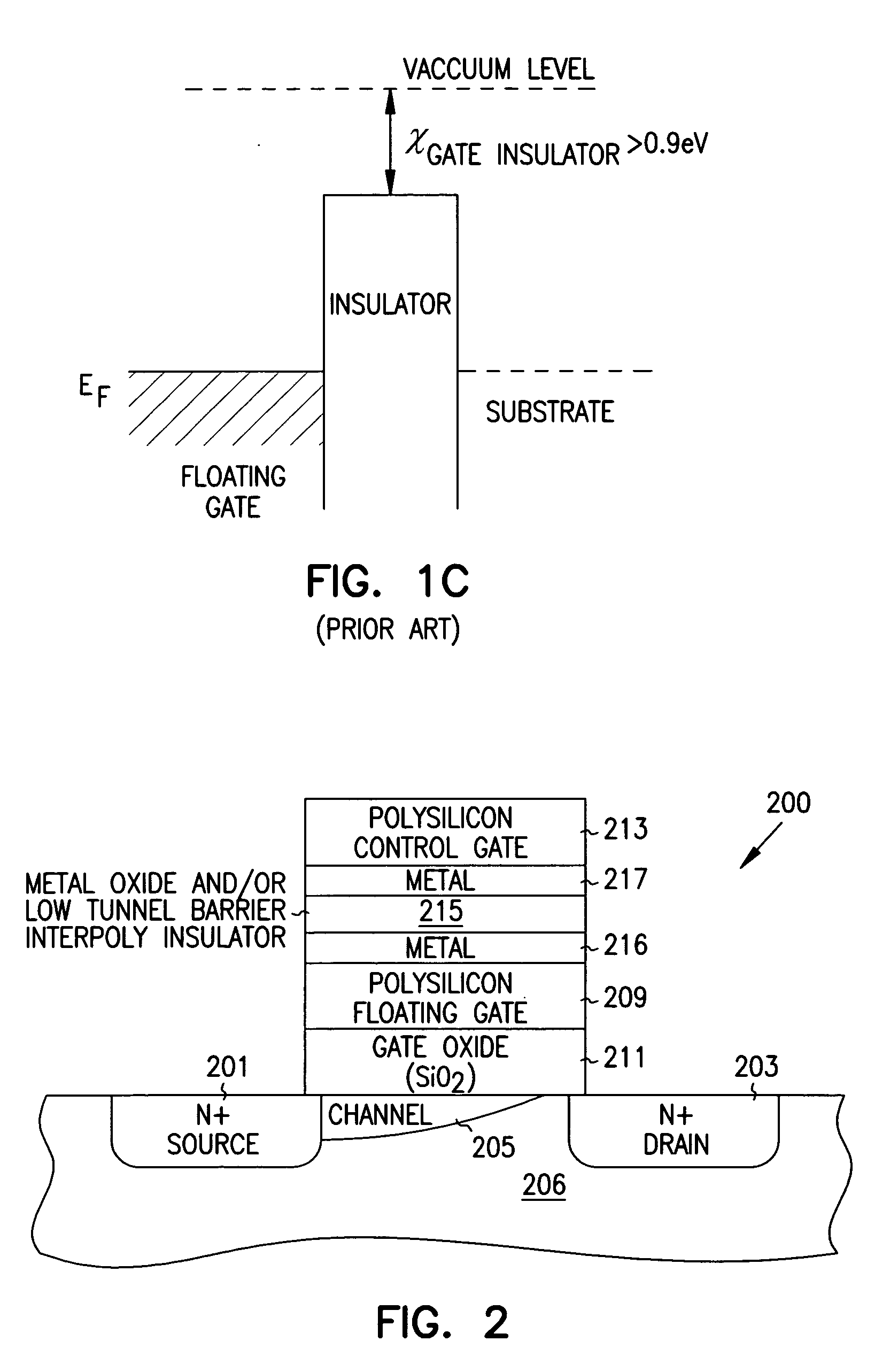

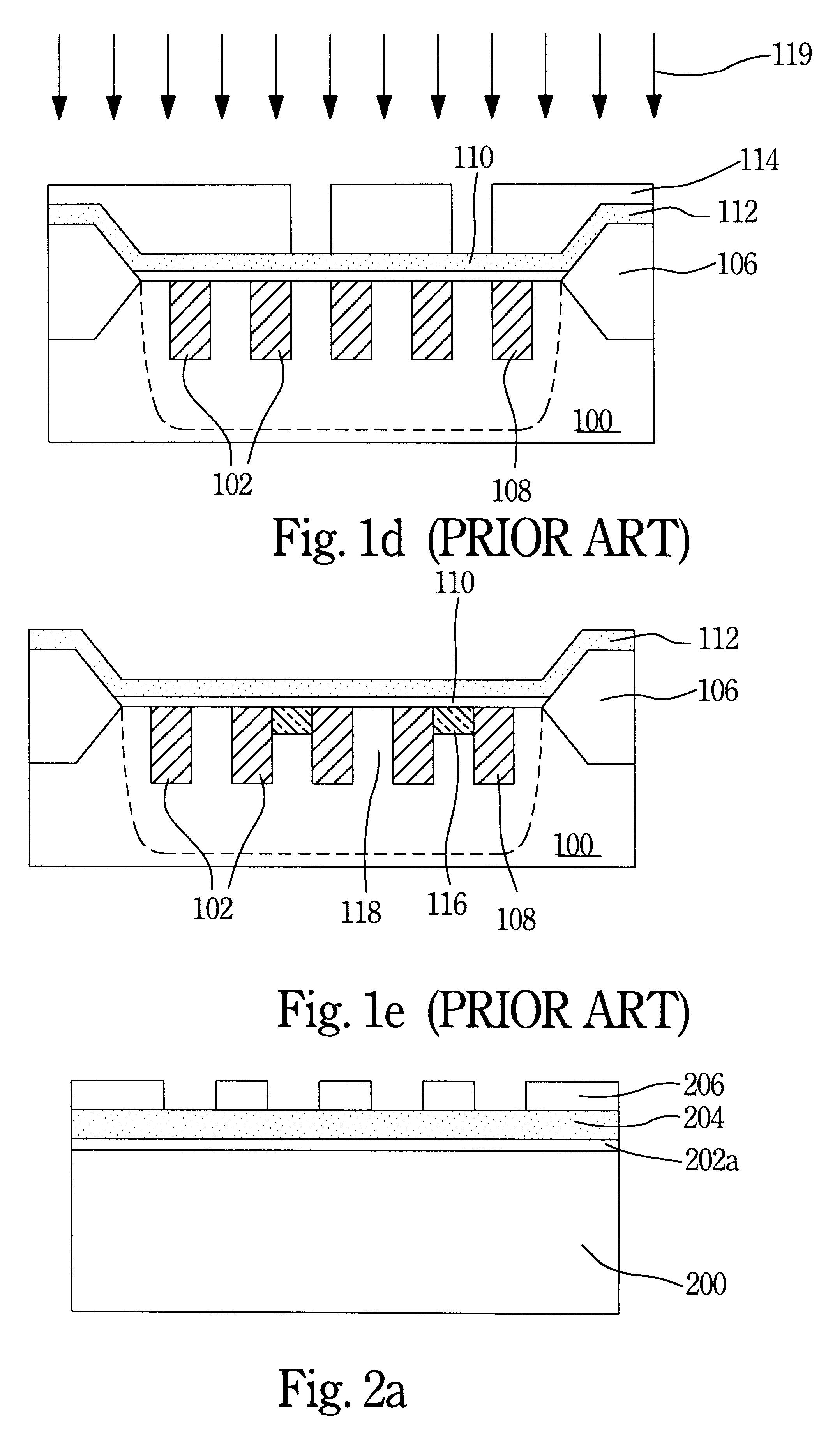

Flash memory with low tunnel barrier interpoly insulators

Structures and methods for Flash memory with low tunnel barrier intergate insulators are provided. The non-volatile memory includes a first source / drain region and a second source / drain region separated by a channel region in a substrate. A floating gate opposing the channel region and is separated therefrom by a gate oxide. A control gate opposes the floating gate. The control gate is separated from the floating gate by a low tunnel barrier intergate insulator. The low tunnel barrier intergate insulator includes a metal oxide insulator selected from the group consisting of PbO, Al2O3, Ta2O5, TiO2, ZrO2, and Nb2O5. The floating gate includes a polysilicon floating gate having a metal layer formed thereon in contact with the low tunnel barrier intergate insulator. And, the control gate includes a polysilicon control gate having a metal layer formed thereon in contact with the low tunnel barrier intergate insulator.

Owner:MICRON TECH INC

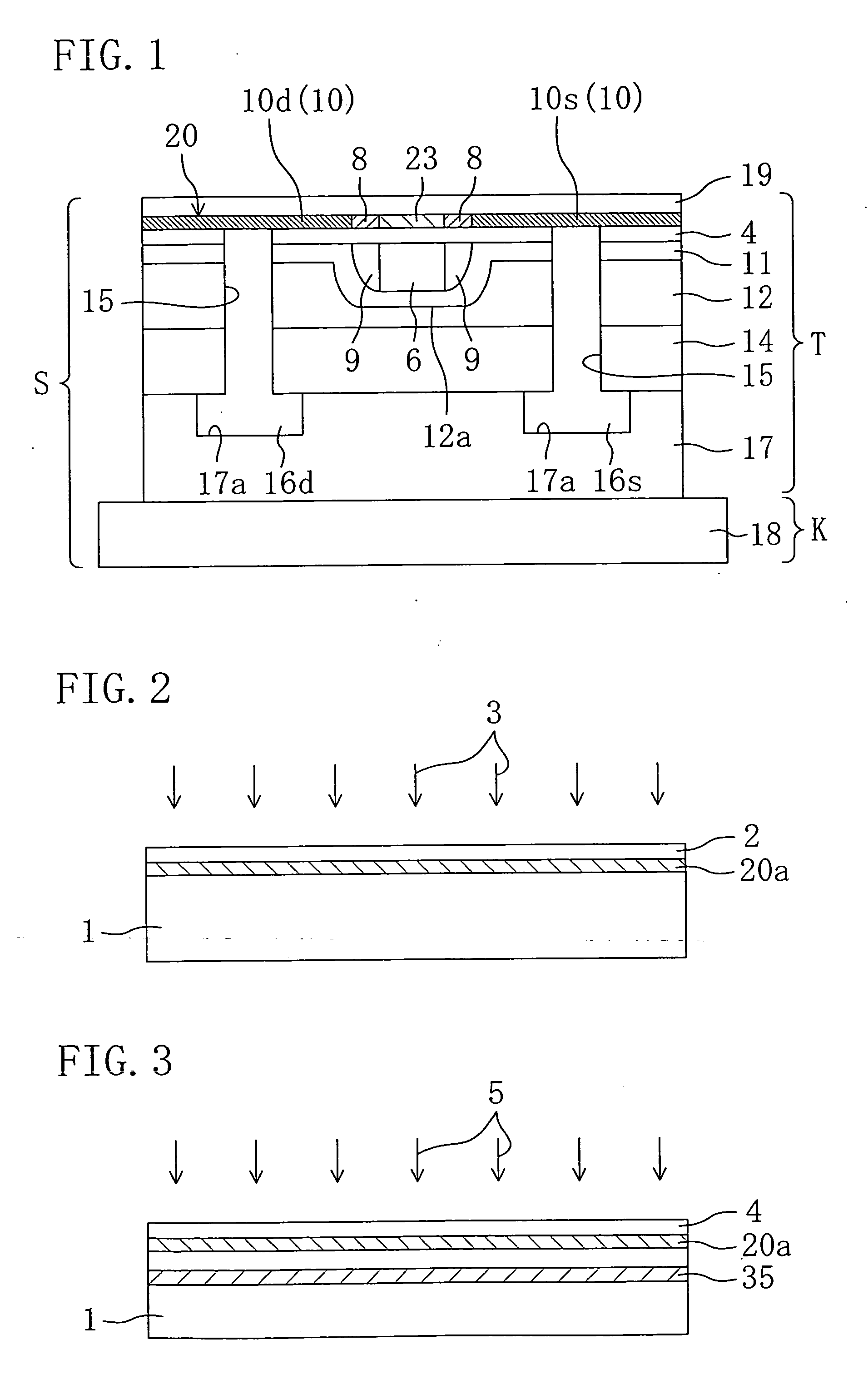

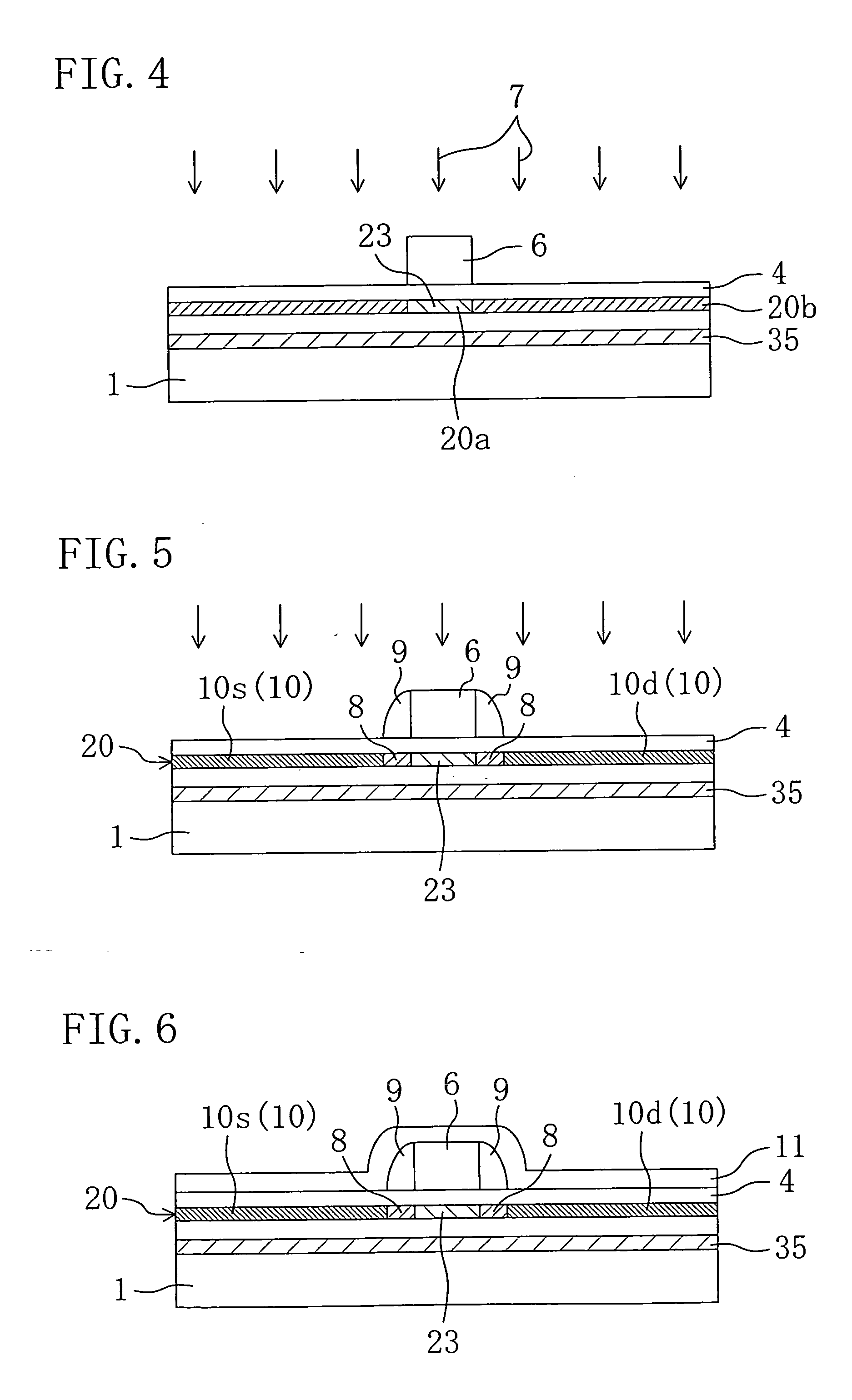

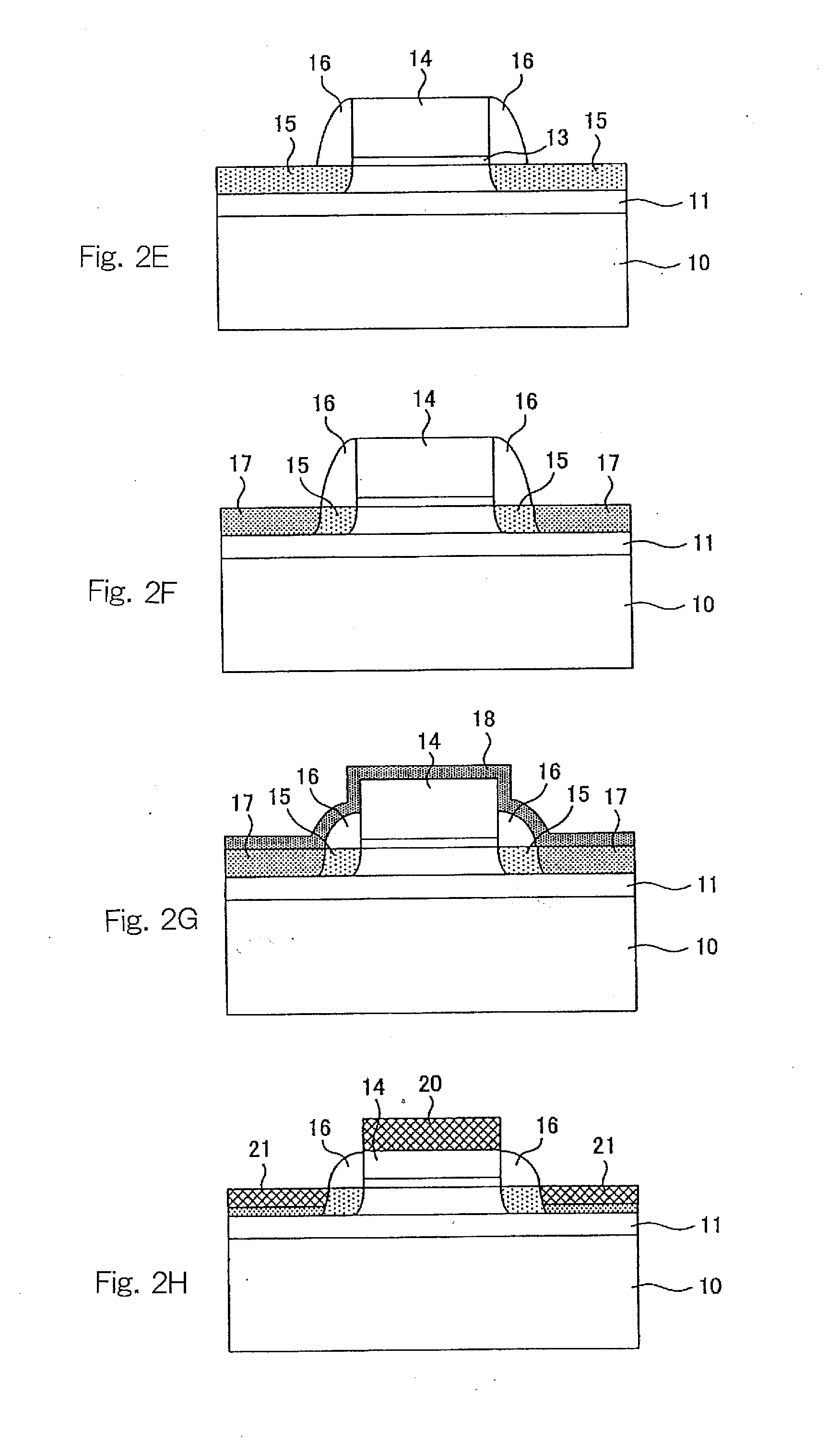

Method of manufacturing semiconductor device

InactiveUS20090317950A1Reduce parasitic resistanceImprove leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor packageSoi substrate

A semiconductor device manufacturing method which sequentially forms a gate oxide film and gate electrode material over a semiconductor layer of an SOI substrate and patterns the material into gate electrodes. The method further comprises the steps of forming sidewalls made of an insulator to cover side surfaces of the gate electrode; ion-implanting into the semiconductor layer on both sides of the gate electrode to form drain / source regions; partially etching the sidewalls to expose upper parts of the side surfaces of the gate electrode; depositing a metal film to cover the tops of the drain / source regions and of the gate electrode and the exposed upper parts of the side surfaces of the gate electrode; and performing heat treatment on the SOI substrate to form silicide layers respectively in the surfaces of the gate electrode and of the drain / source regions.

Owner:LAPIS SEMICON CO LTD

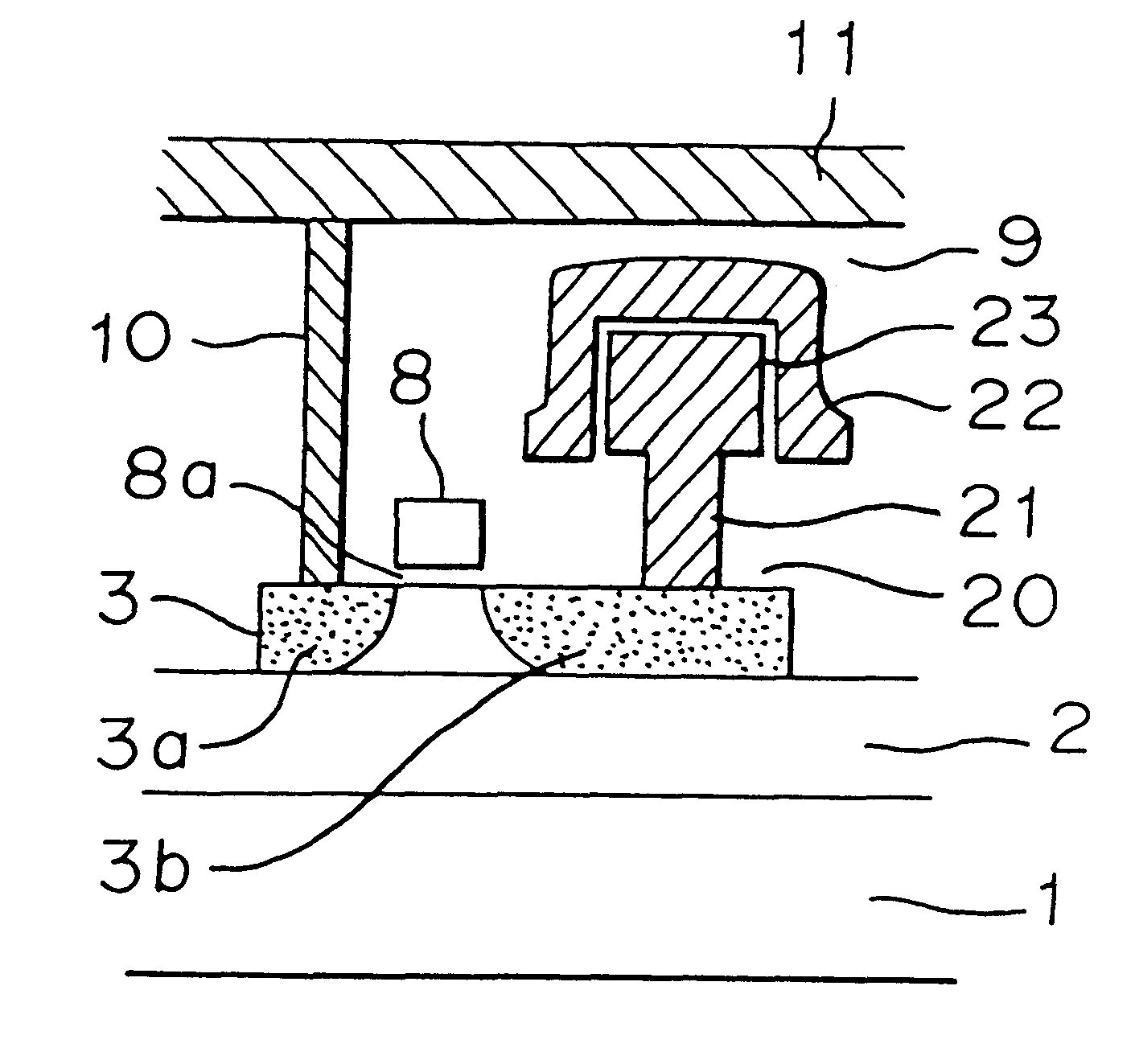

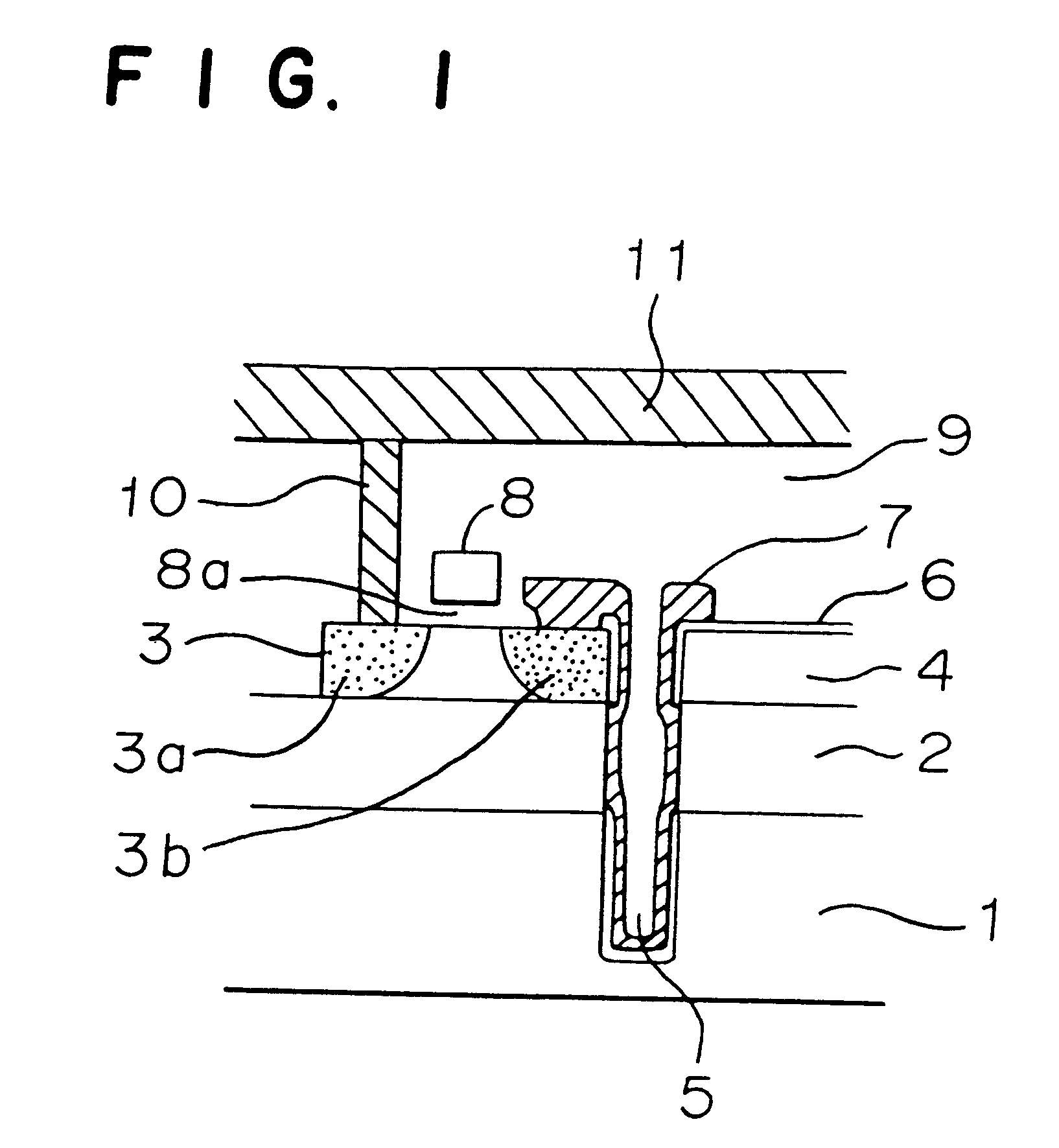

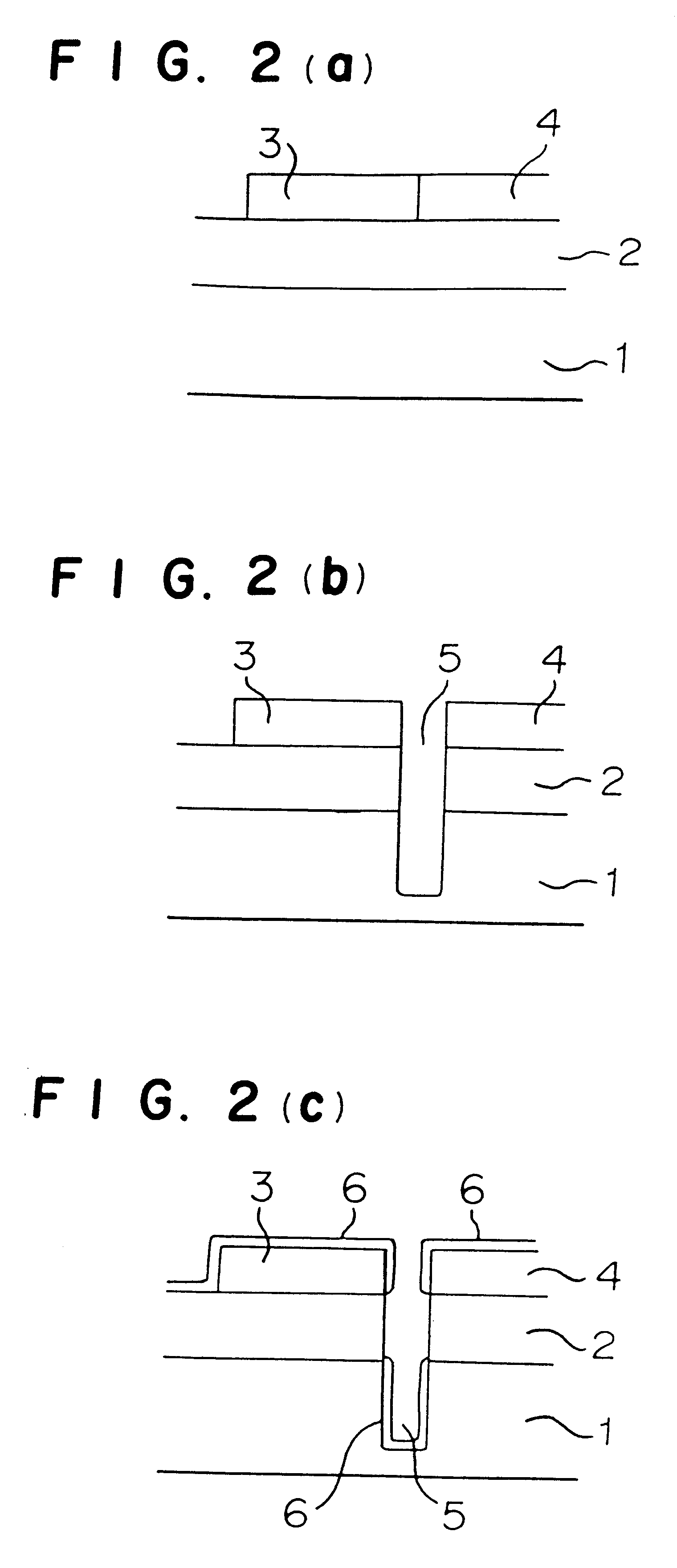

Method of manufacturing a semiconductor memory device

A method of manufacturing a semiconductor memory device comprising: a step of forming a storage node in which a conductive layer 7 to be the storage node is formed in the vicinity of single crystalline silicon 3 formed on an insulator 2, a gettering step for conducting heat treatment to the single crystalline silicon 3 after the step of forming the storage node and gettering contaminants contained in the single crystalline silicon 3 by the conductive layer 7 connected to the single crystalline silicon, and a step of forming a gate oxide film 8a on the single crystalline silicon 3 after the step of gettering is provided to thereby obtain a sufficient gettering effect even though the width of an element and / or the thickness of the element is reduced in accordance with microminiaturization of the element.

Owner:MITSUBISHI ELECTRIC CORP

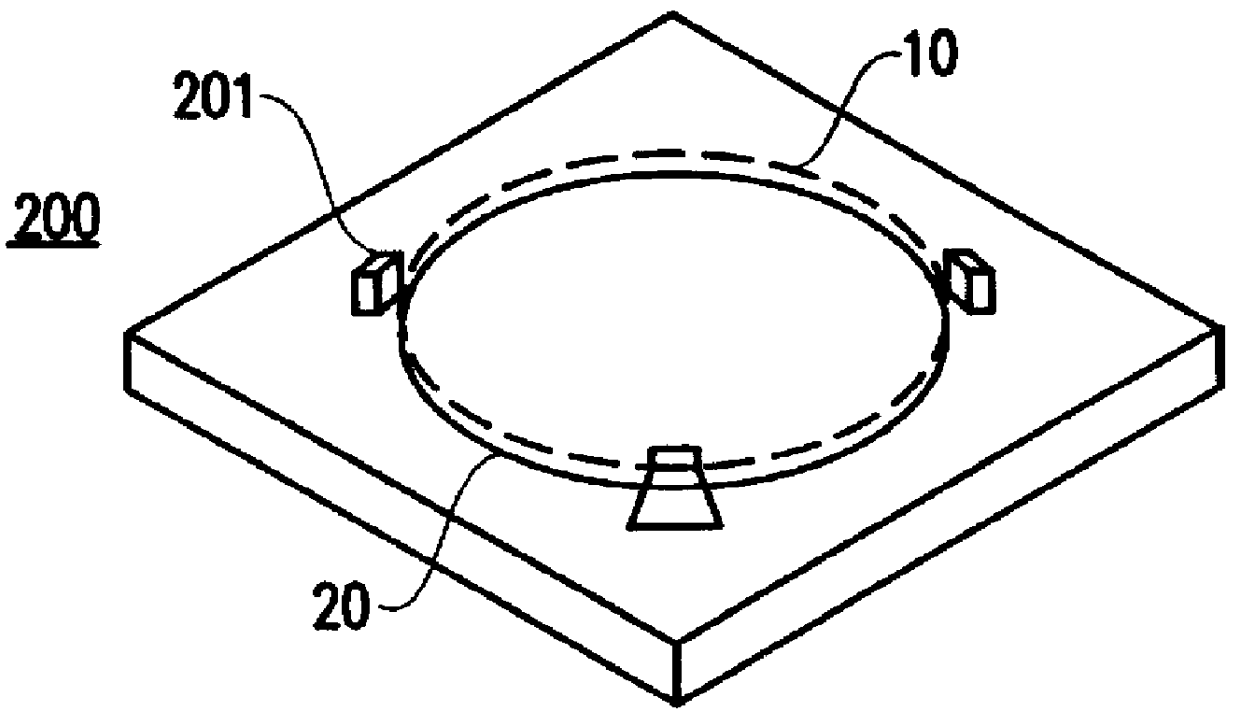

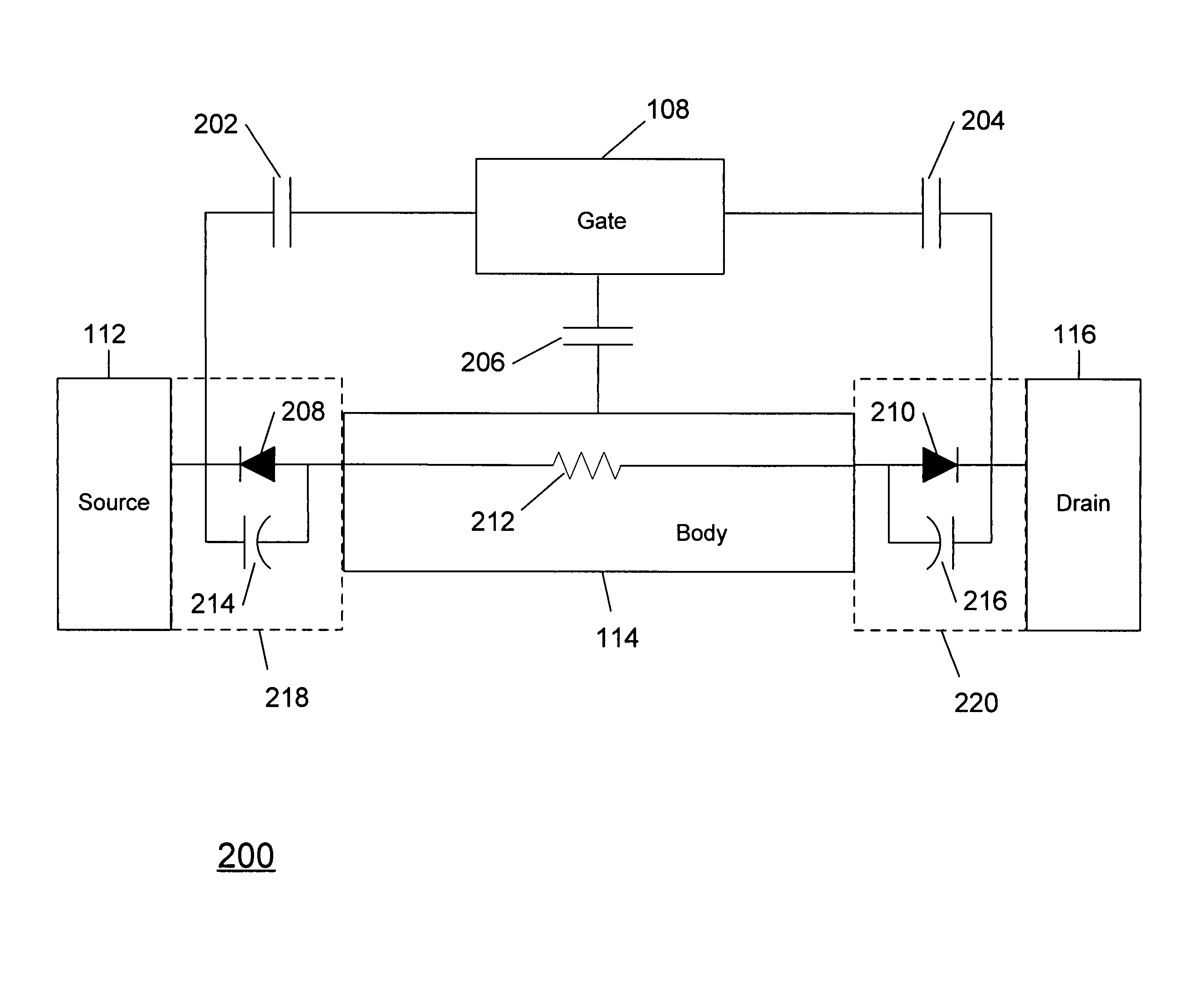

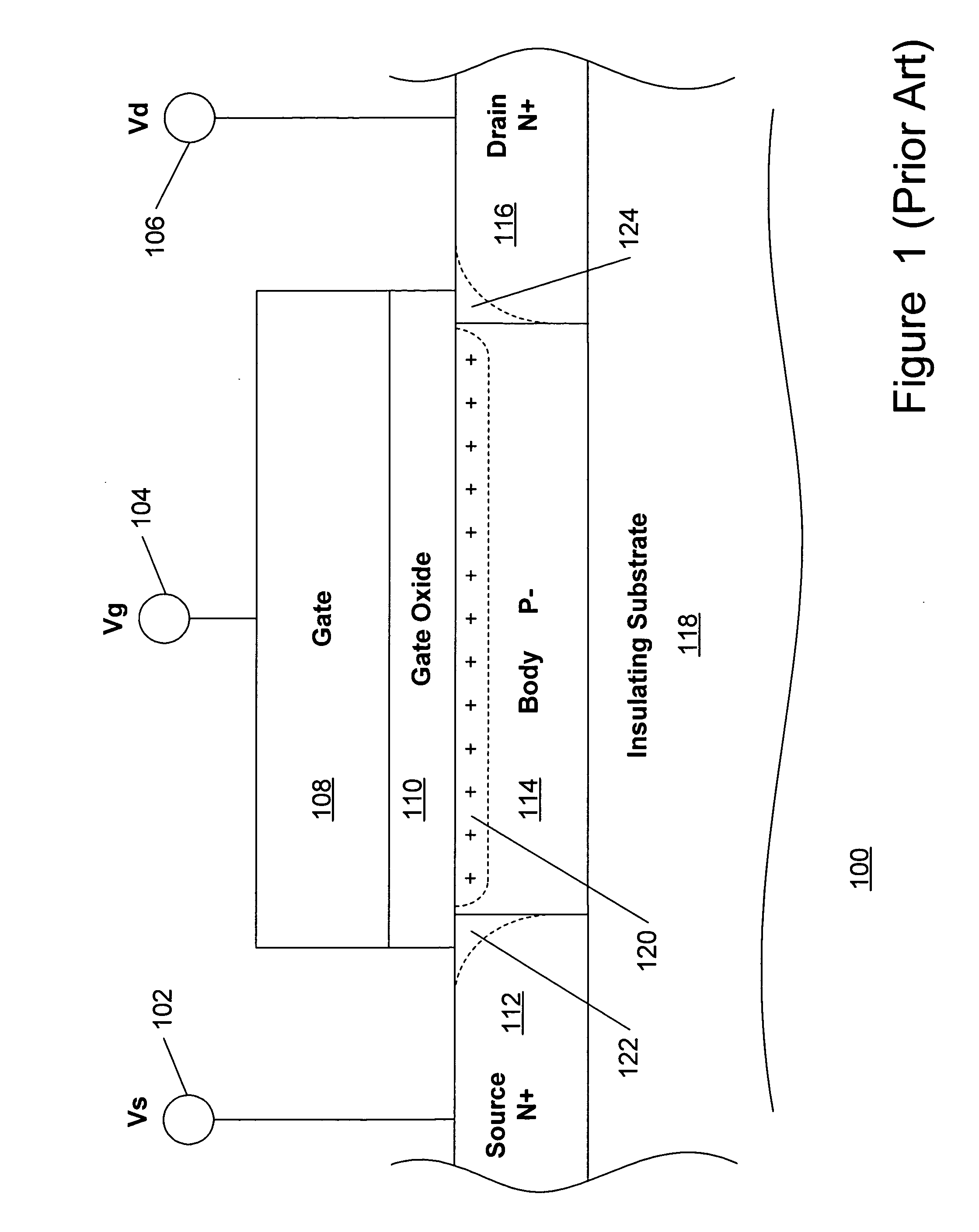

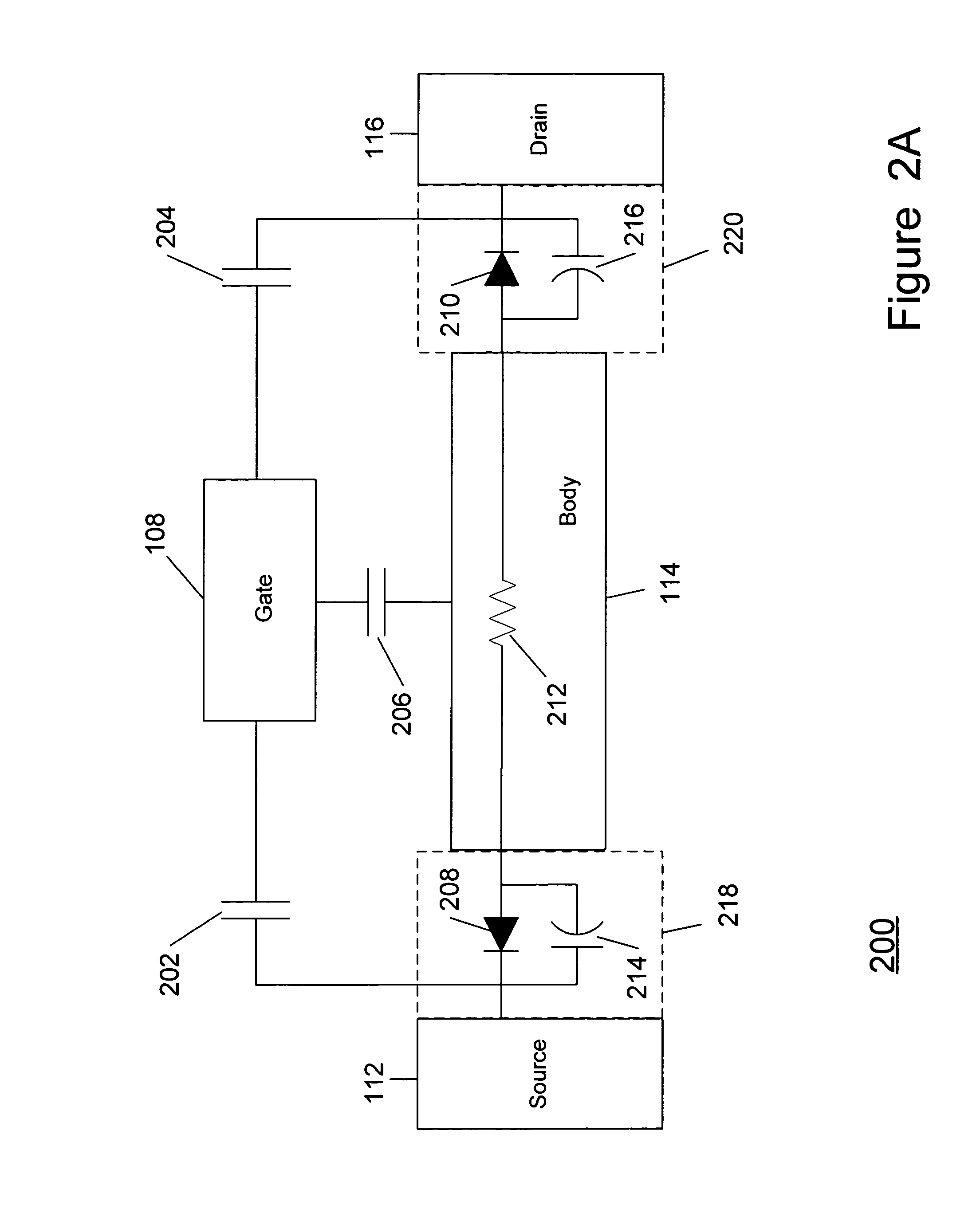

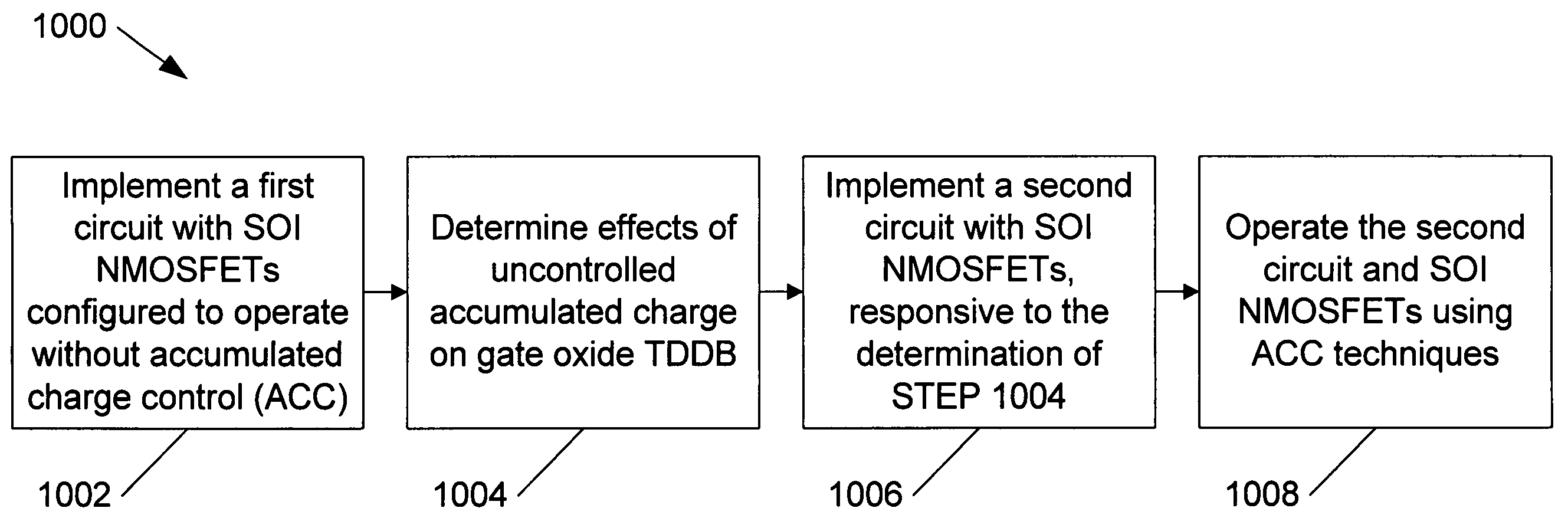

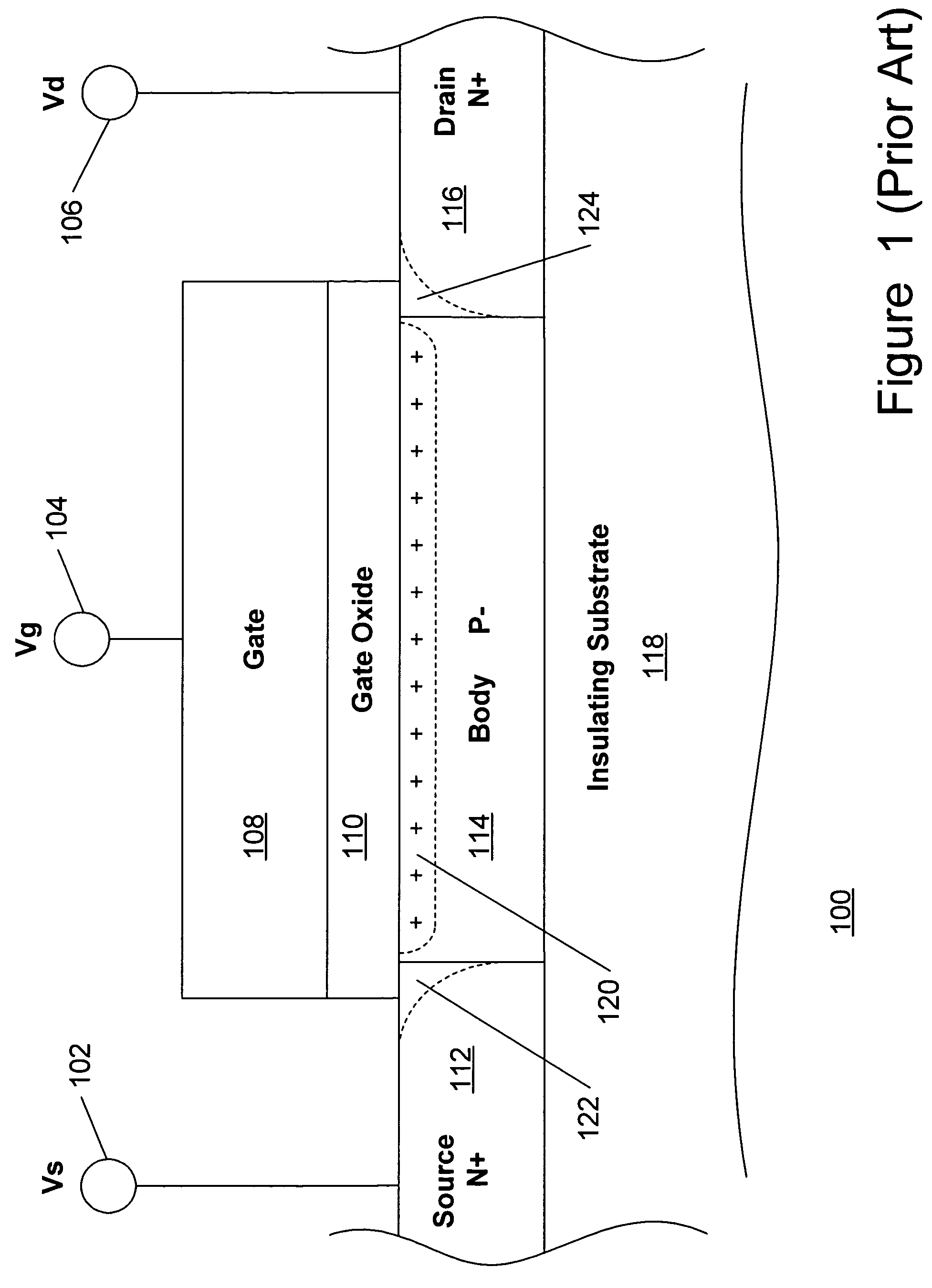

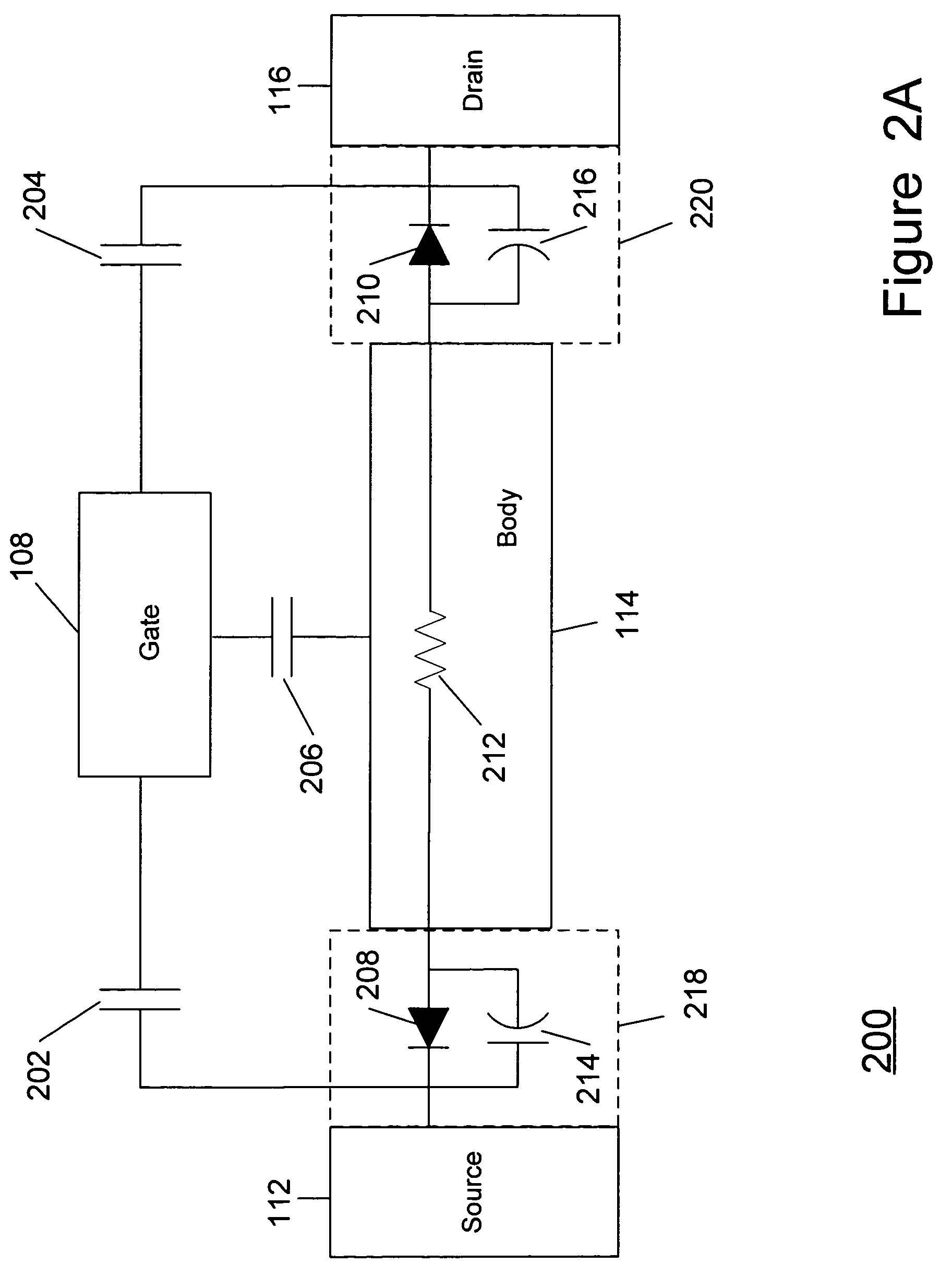

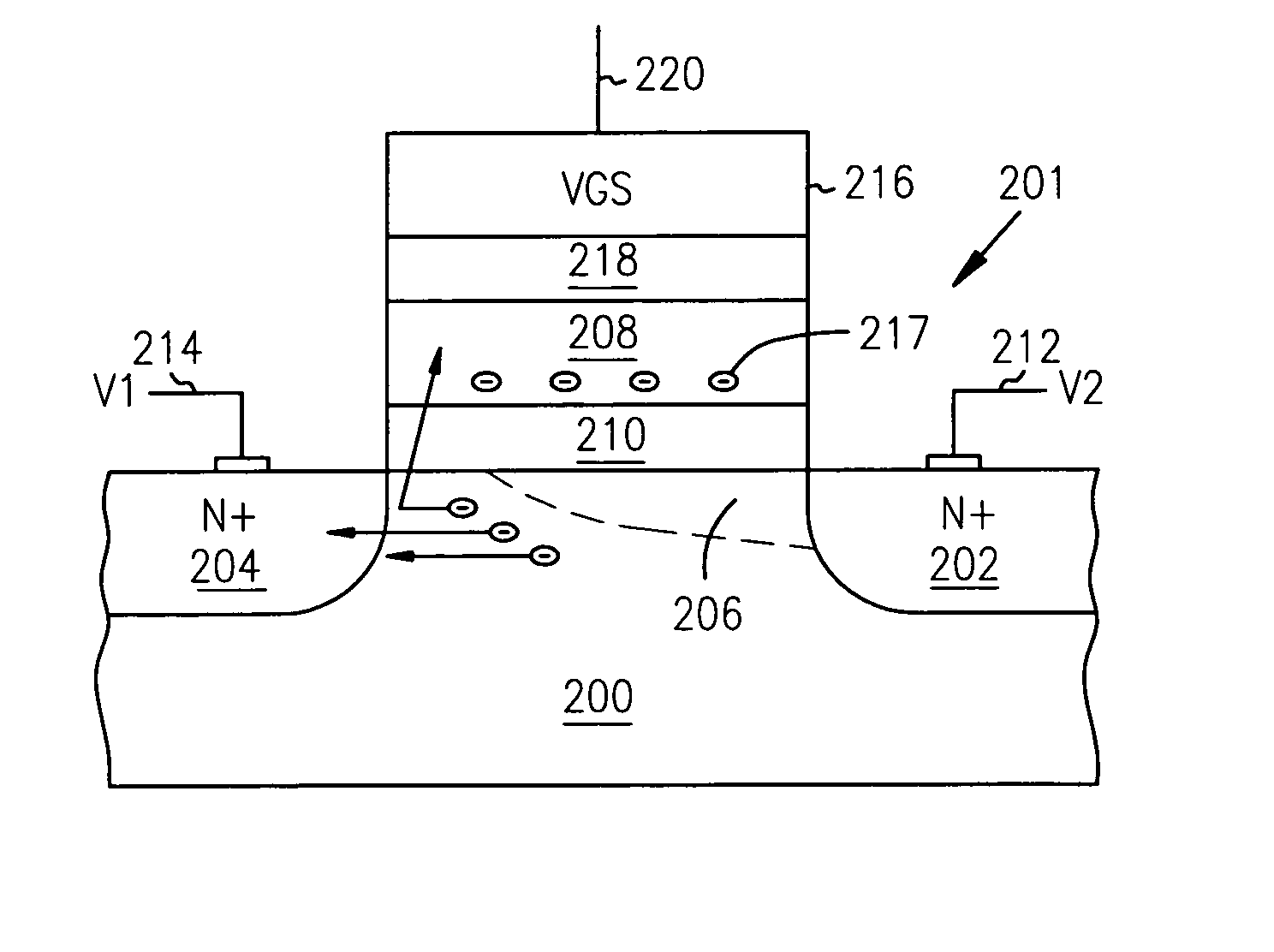

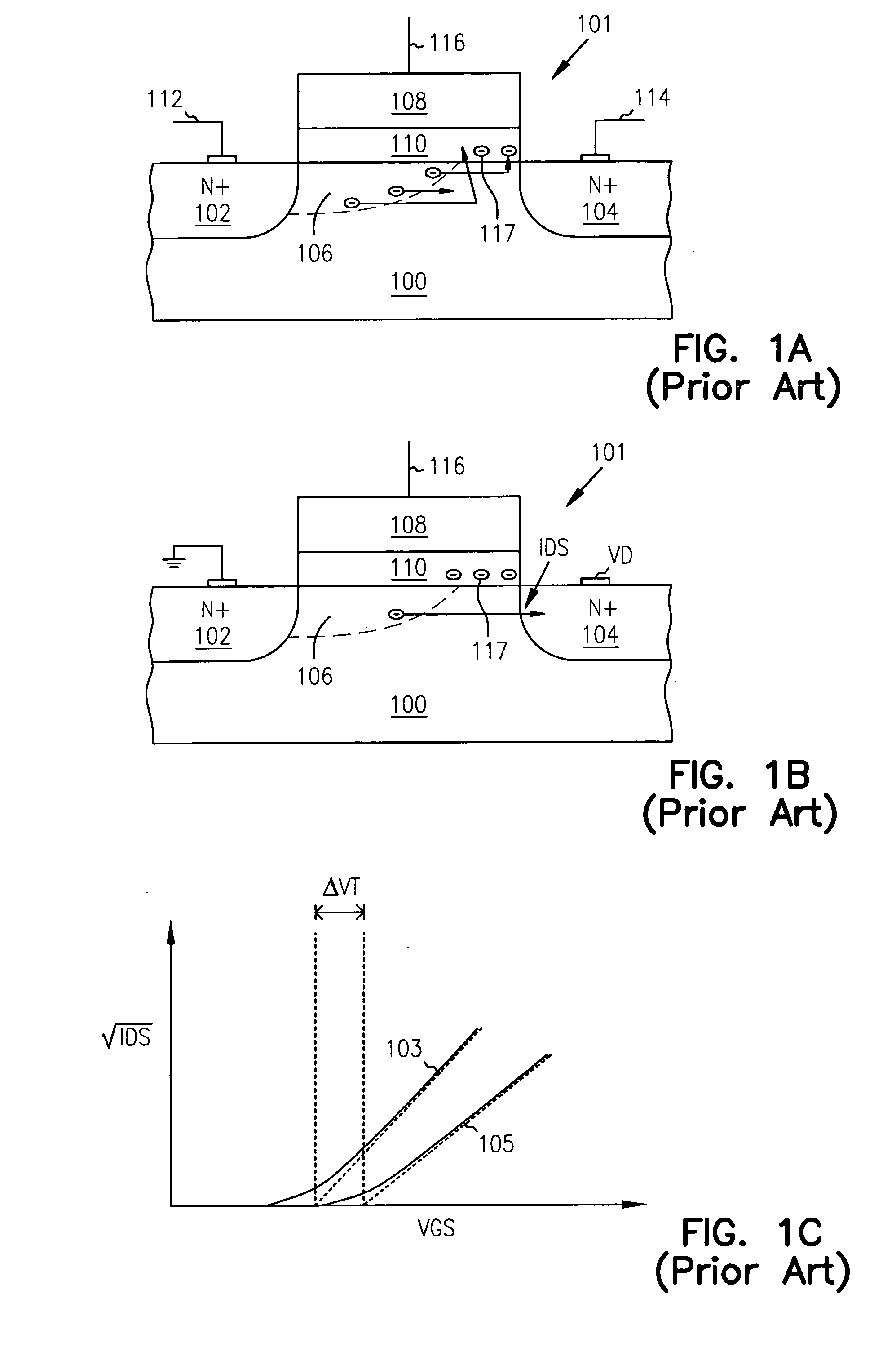

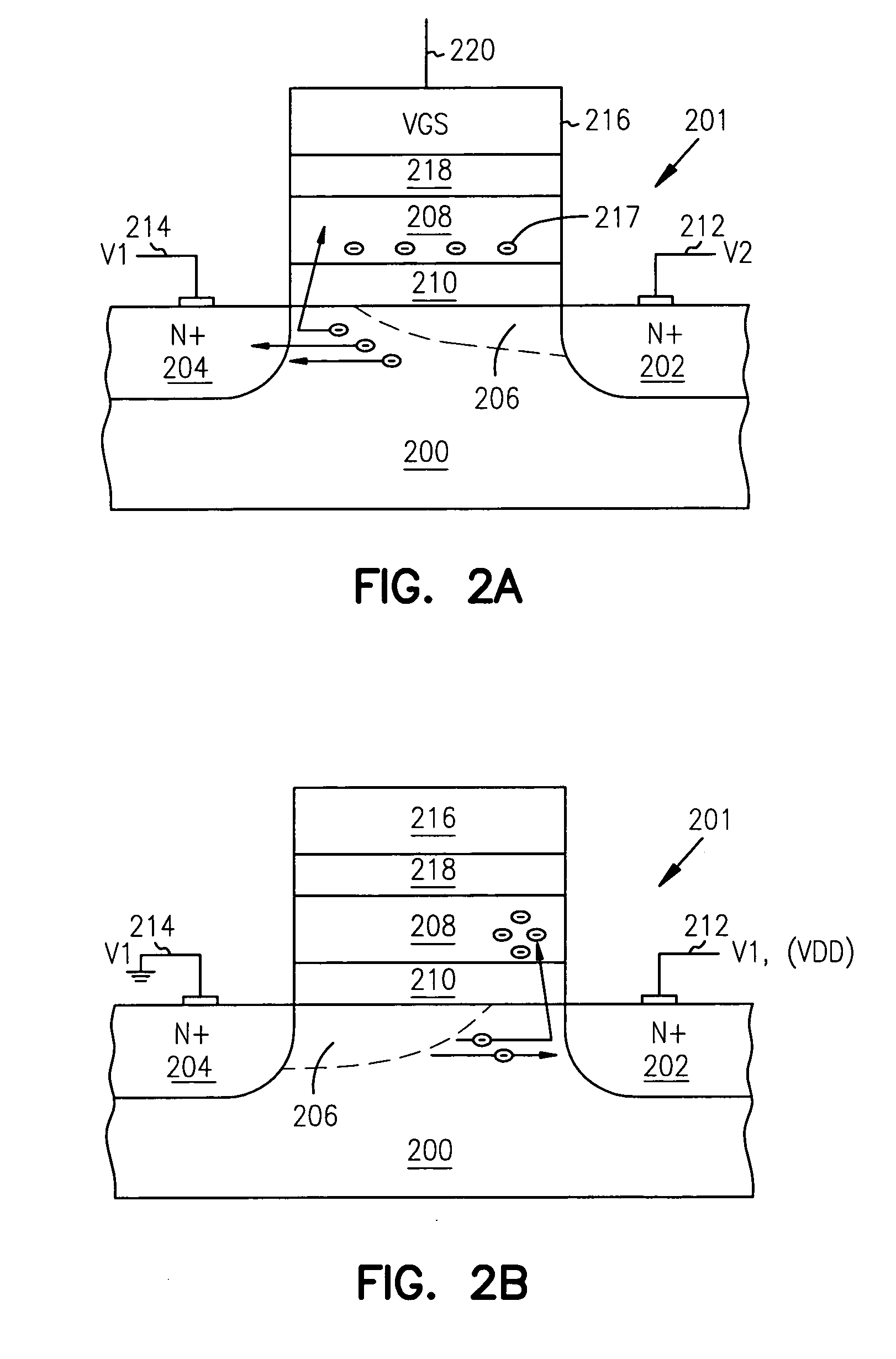

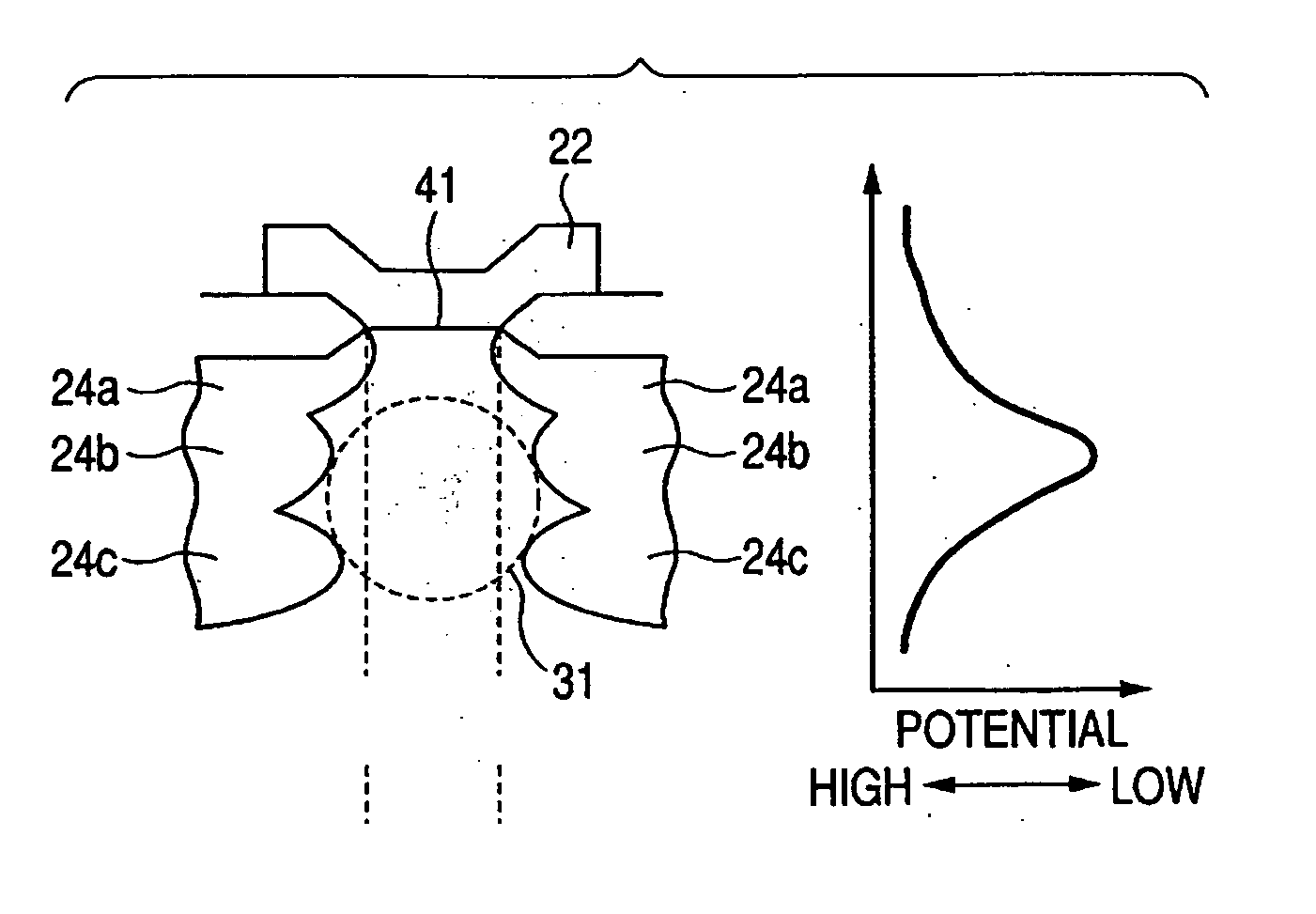

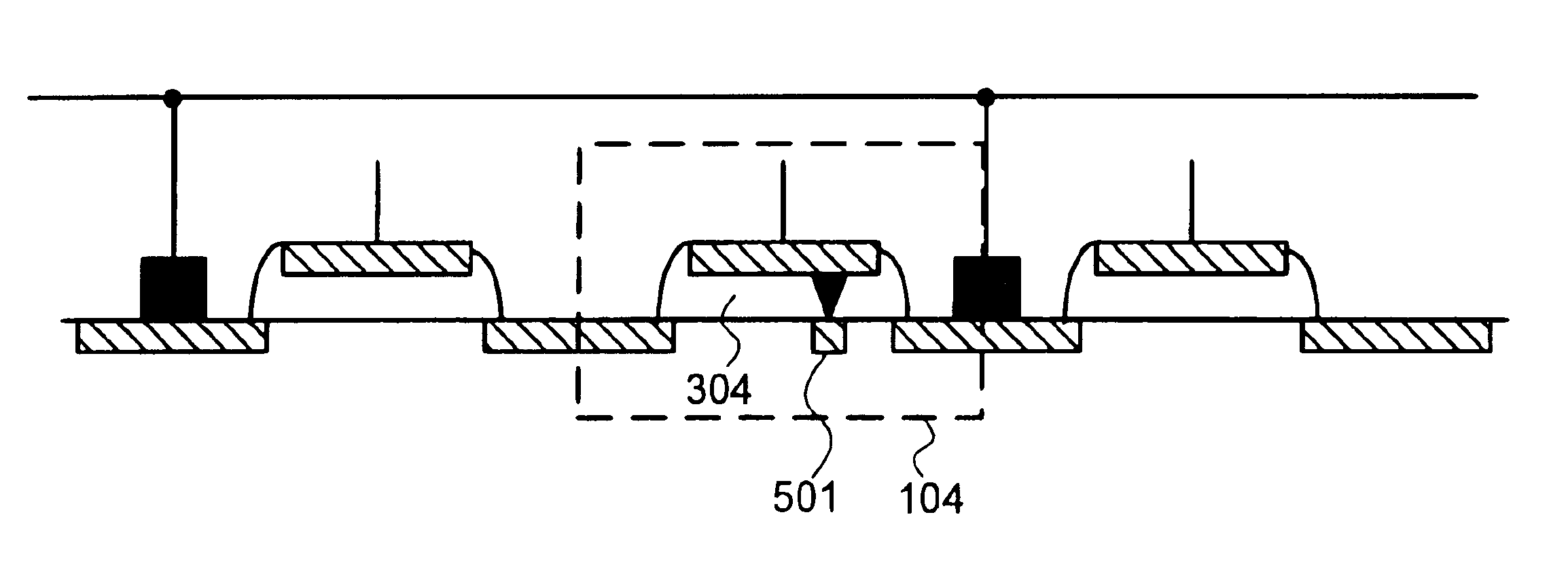

Method and apparatus improving gate oxide reliability by controlling accumulated charge

ActiveUS20070069291A1Improving nonlinear responses and harmonic and intermodulaton distortion effectsReduce non-linearitySolid-state devicesElectronic switchingMOSFETDielectric

A method and apparatus are disclosed for use in improving the gate oxide reliability of semiconductor-on-insulator (SOI) metal-oxide-silicon field effect transistor (MOSFET) devices using accumulated charge control (ACC) techniques. The method and apparatus are adapted to remove, reduce, or otherwise control accumulated charge in SOI MOSFETs, thereby yielding improvements in FET performance characteristics. In one embodiment, a circuit comprises a MOSFET, operating in an accumulated charge regime, and means for controlling the accumulated charge, operatively coupled to the SOI MOSFET. A first determination is made of the effects of an uncontrolled accumulated charge on time dependent dielectric breakdown (TDDB) of the gate oxide of the SOI MOSFET. A second determination is made of the effects of a controlled accumulated charge on TDDB of the gate oxide of the SOI MOSFET. The SOI MOSFET is adapted to have a selected average time-to-breakdown, responsive to the first and second determinations, and the circuit is operated using techniques for accumulated charge control operatively coupled to the SOI MOSFET. In one embodiment, the accumulated charge control techniques include using an accumulated charge sink operatively coupled to the SOI MOSFET body.

Owner:PSEMI CORP

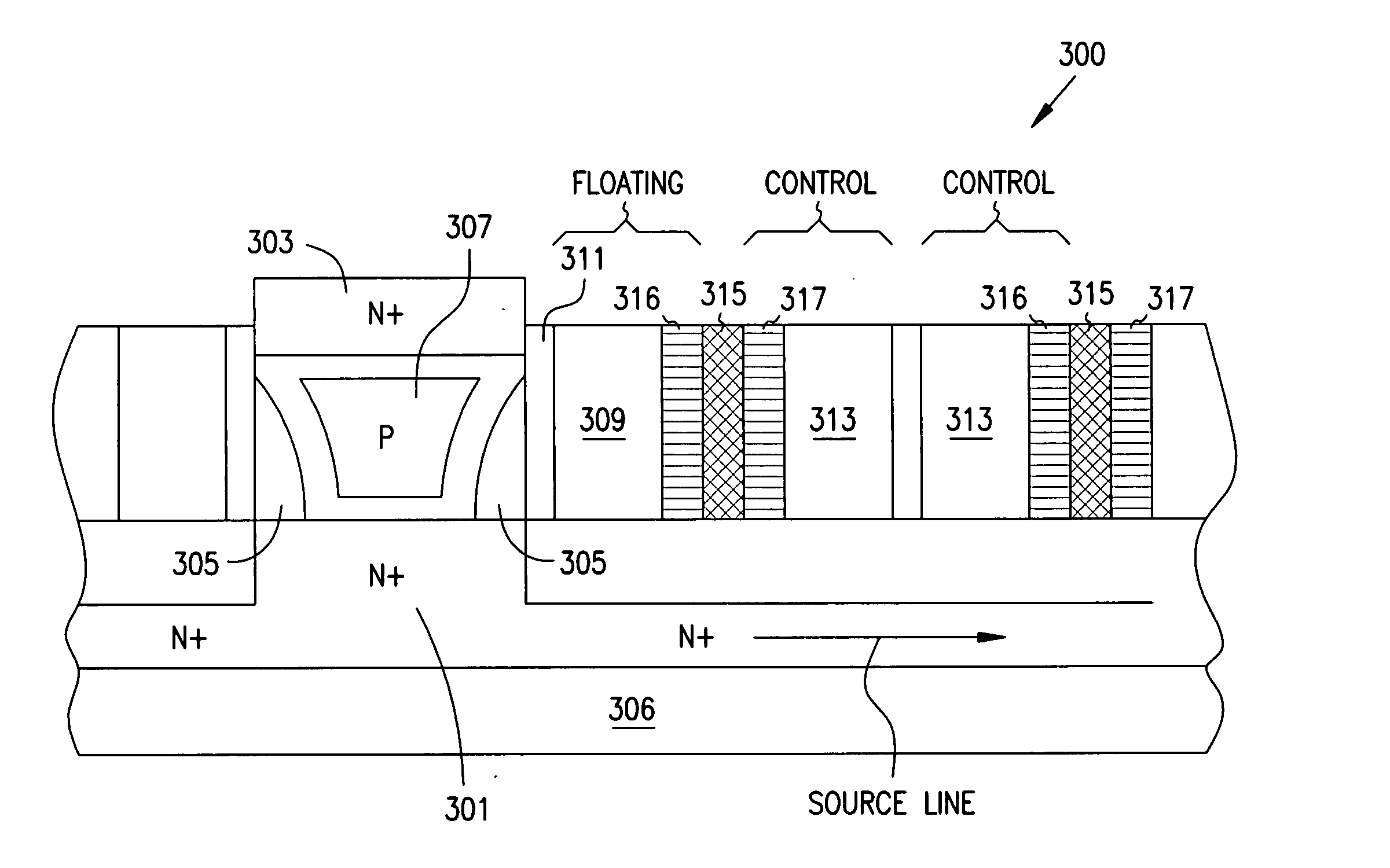

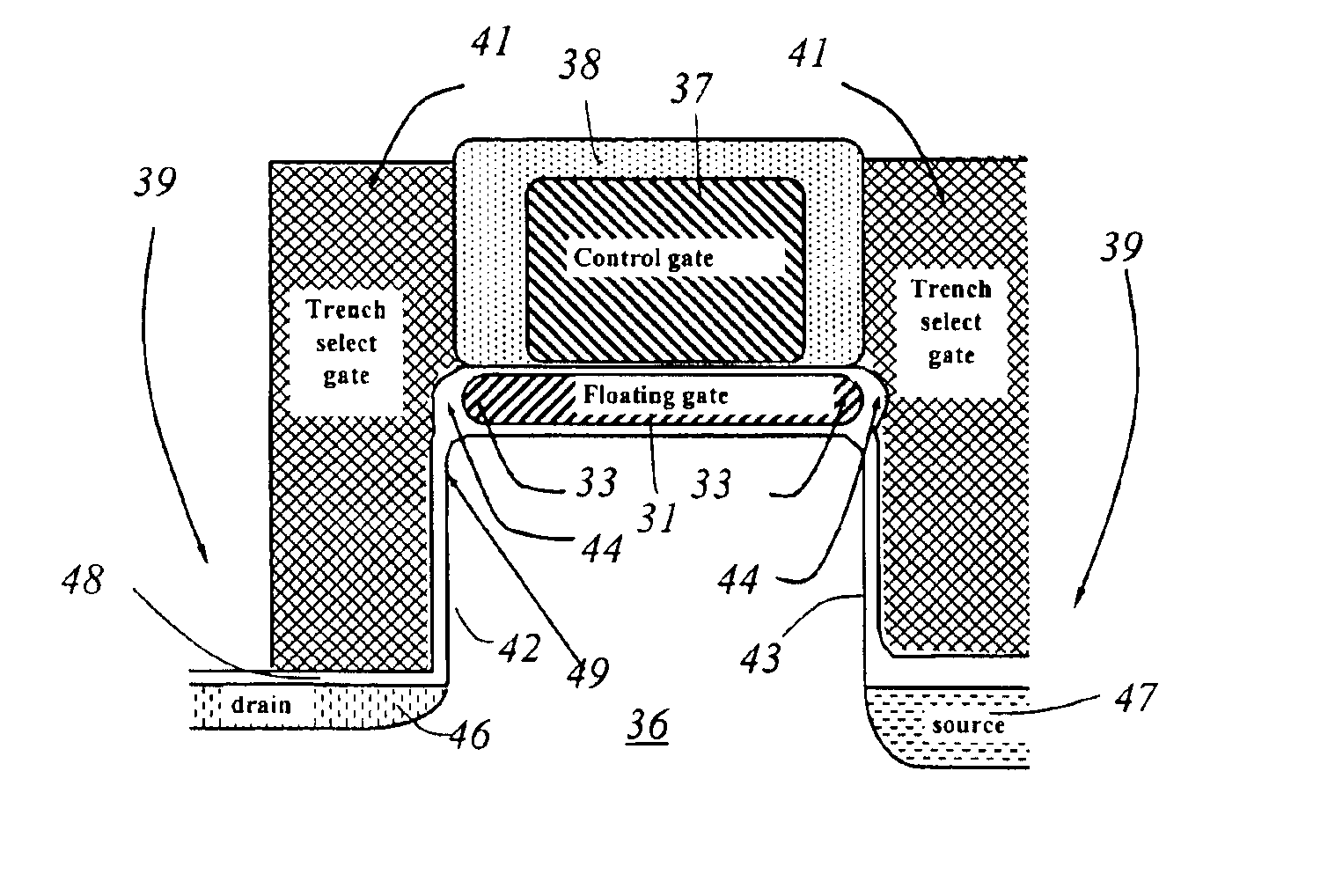

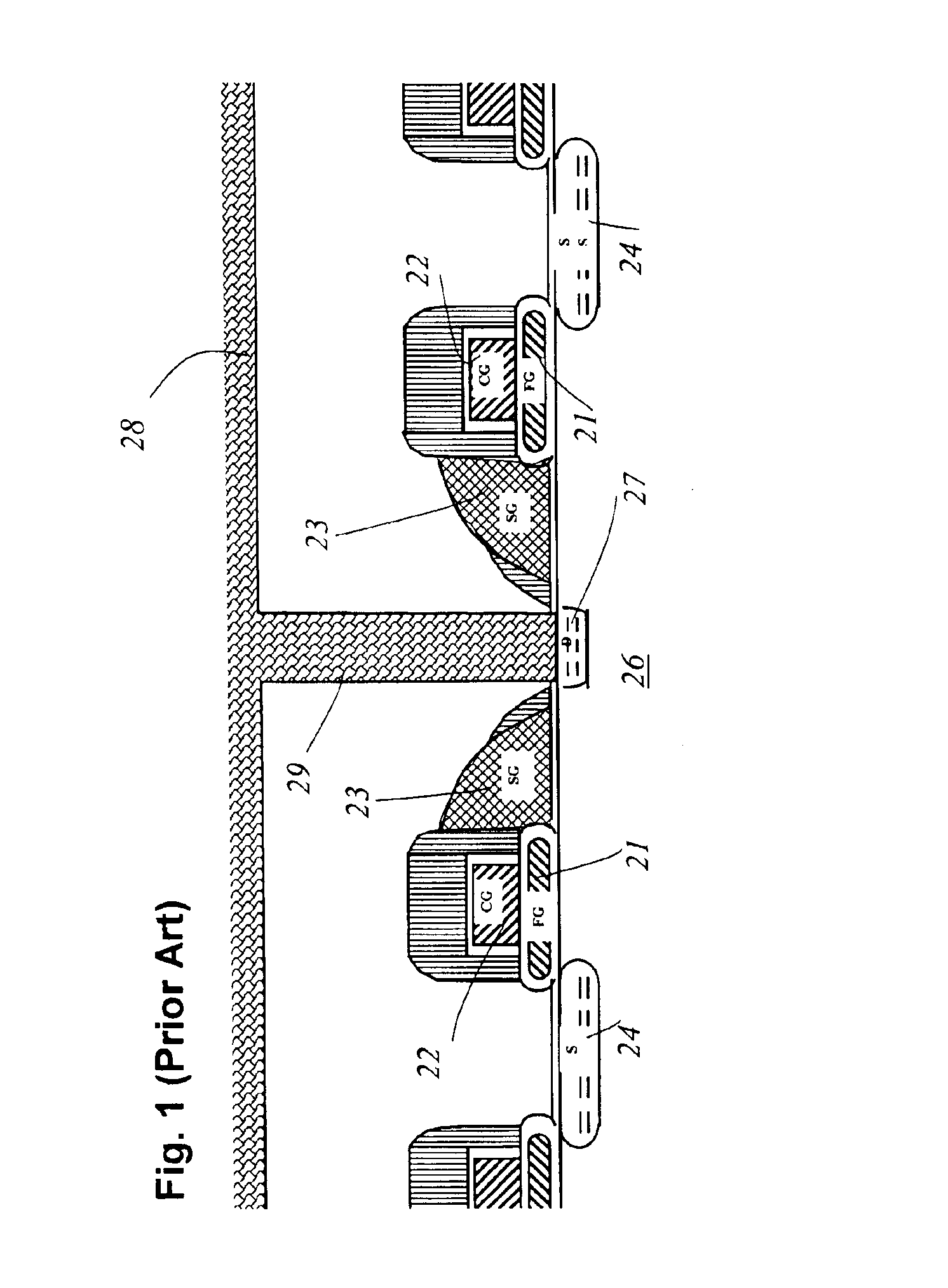

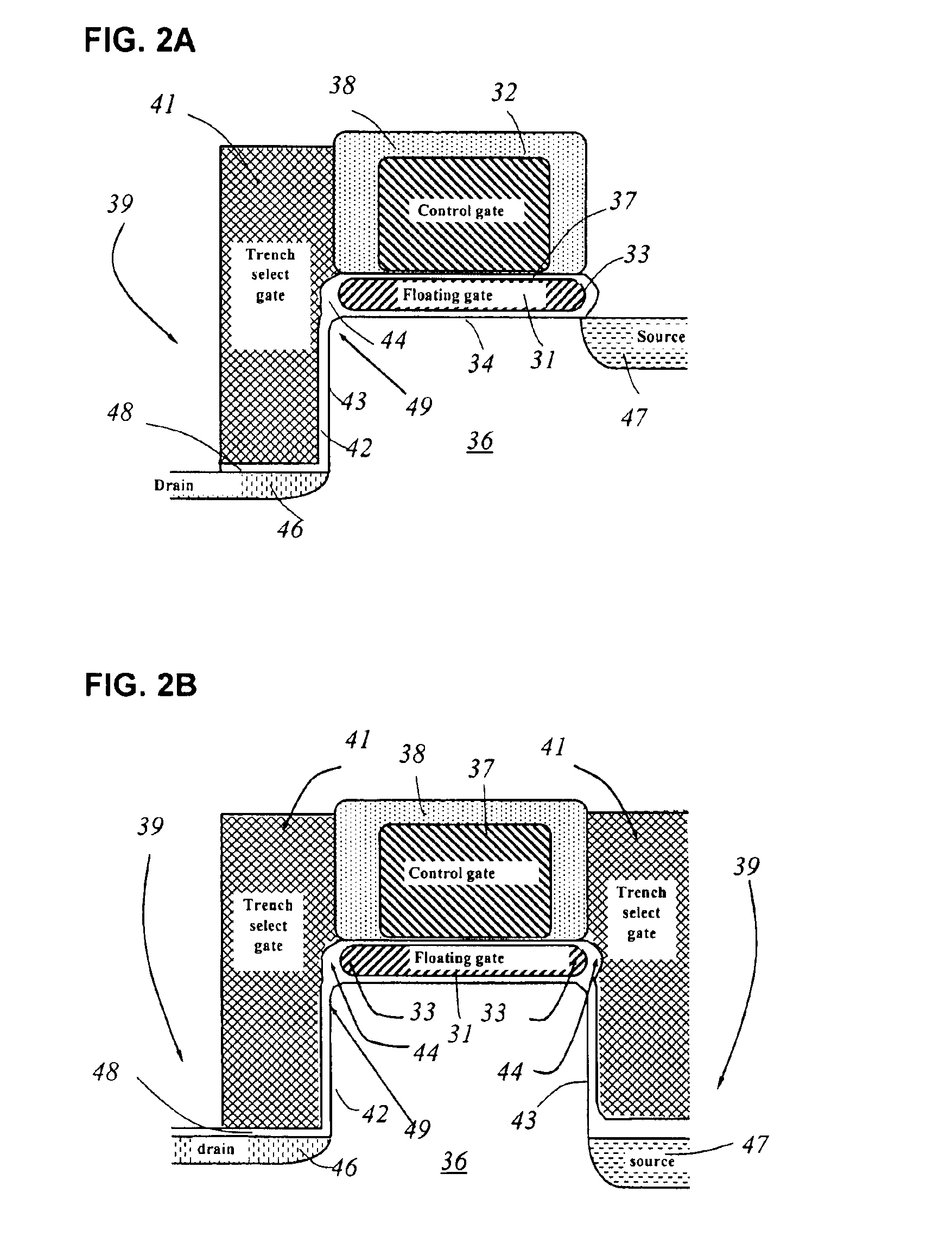

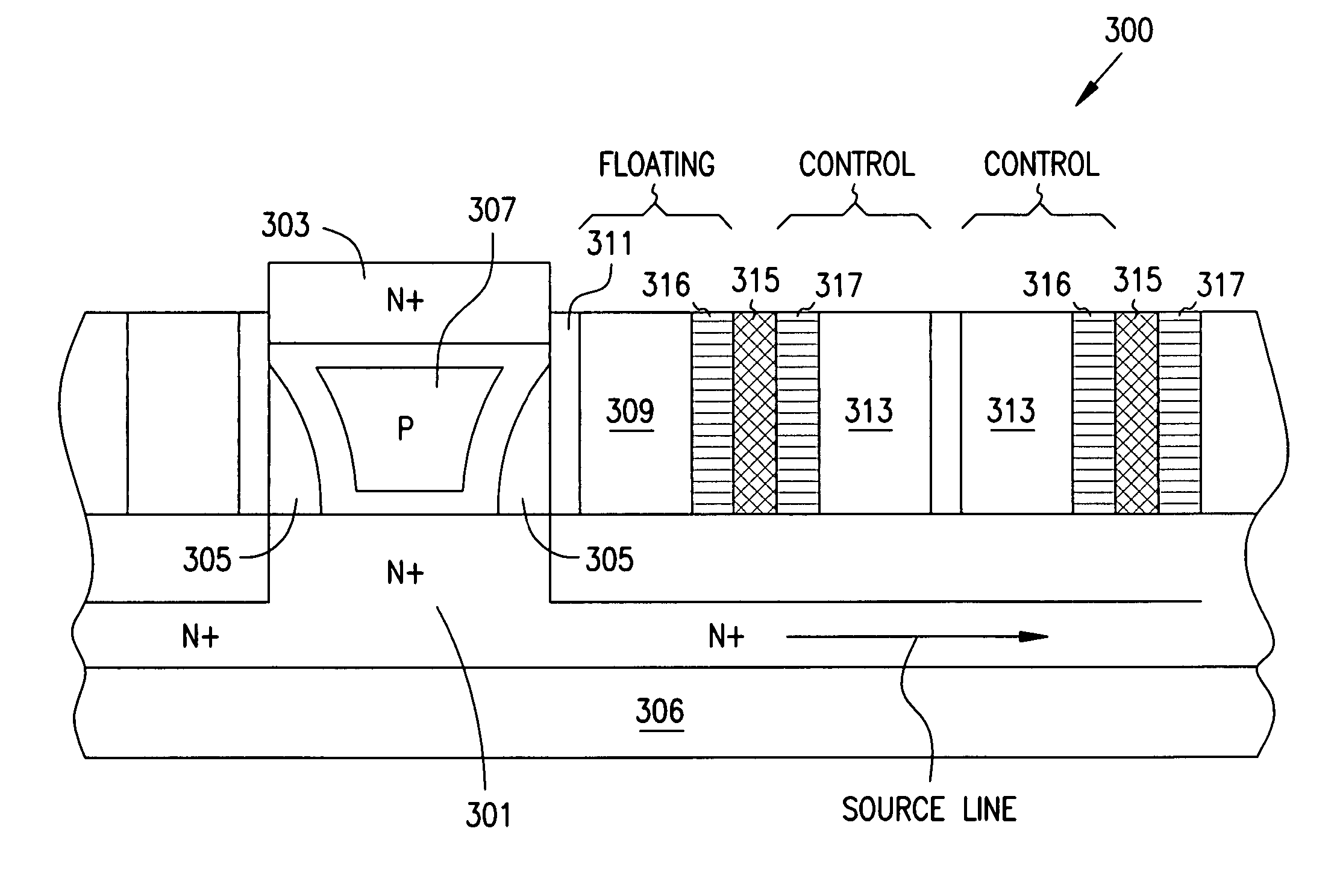

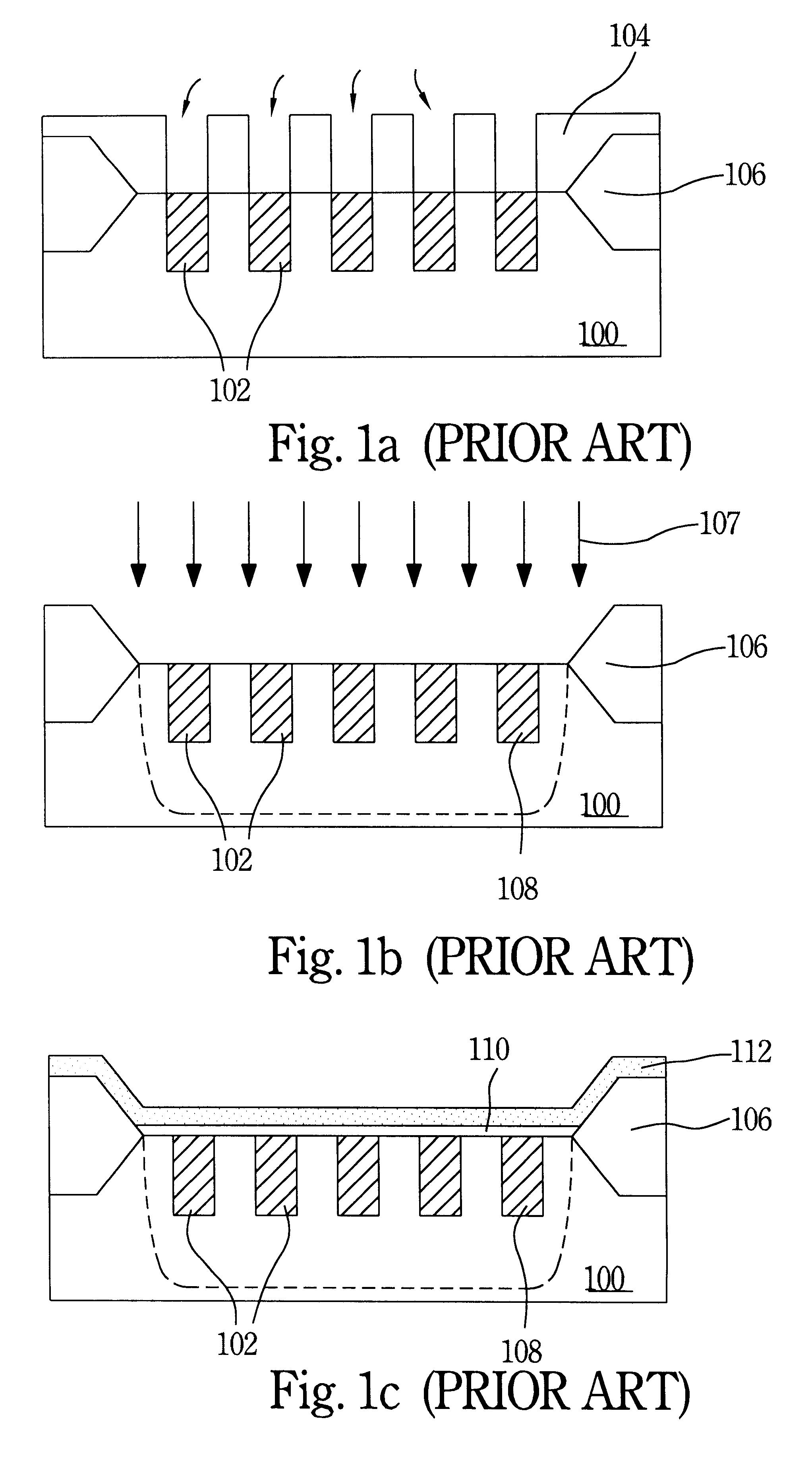

Flash memory with trench select gate and fabrication process

Flash memory and process of fabrication in which memory cells are formed with select gates in trenches between stacked, self-aligned floating and control gates, with buried source and drain regions which are gated by the select gates. Erase paths are formed between projecting rounded edges of the floating gates and the select gates, and programming paths extend from the mid-channel regions between the select gates and floating gates through the gate oxide to the edges of the floating gates. Trenched select gates can be provided on one or both sides of the floating and control gates, depending upon array architecture, and the stacked gates and dielectric covering them are used as a self-aligned mask in etching the substrate and other materials to form the trenches.

Owner:SILICON STORAGE TECHNOLOGY

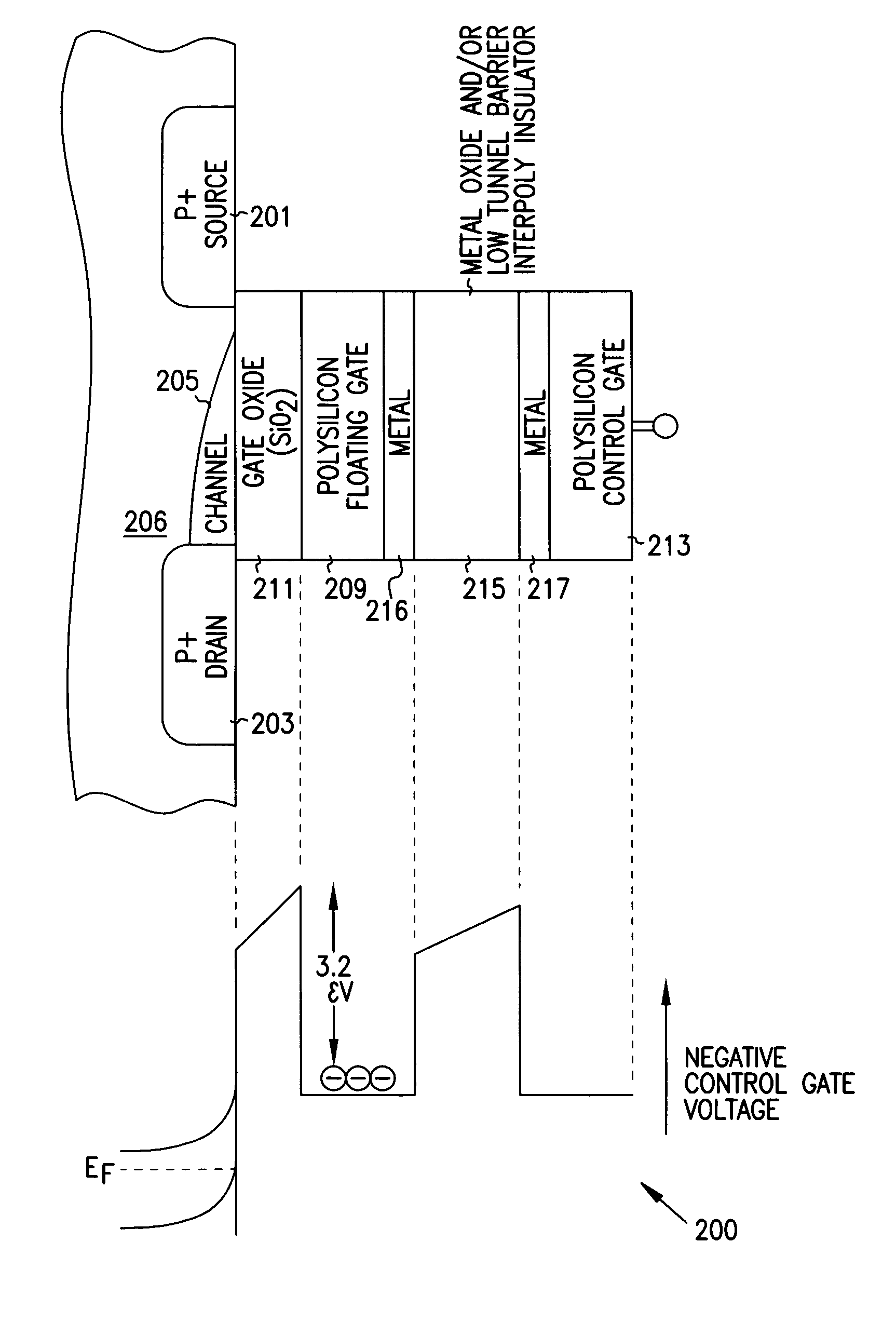

Programmable array logic or memory with p-channel devices and asymmetrical tunnel barriers

Structures and methods for programmable array type logic and / or memory with p-channel devices and asymmetrical low tunnel barrier intergate insulators are provided. The programmable array type logic and / or memory devices include p-channel non-volatile memory which has a first source / drain region and a second source / drain region separated by a p-type channel region in an n-type substrate. A floating gate opposing the p-type channel region and is separated therefrom by a gate oxide. A control gate opposes the floating gate. The control gate is separated from the floating gate by an asymmetrical low tunnel barrier intergate insulator. The asymmetrical low tunnel barrier intergate insulator includes a metal oxide insulator selected from the group consisting of Al2O3, Ta2O5, TiO2, ZrO2, Nb2O5, SrBi2Ta2O3, SrTiO3, PbTiO3, and PbZrO3. The floating gate includes a polysilicon floating gate having a metal layer formed thereon in contact with the low tunnel barrier intergate insulator. And, the control gate includes a polysilicon control gate having a metal layer, having a different work function from the metal layer formed on the floating gate, formed thereon in contact with the low tunnel barrier intergate insulator.

Owner:MICRON TECH INC

Programmable array logic or memory devices with asymmetrical tunnel barriers

Structures and methods for programmable array type logic and / or memory devices with asymmetrical low tunnel barrier intergate insulators are provided. The programmable array type logic and / or memory devices include non-volatile memory which has a first source / drain region and a second source / drain region separated by a channel region in a substrate. A floating gate opposing the channel region and is separated therefrom by a gate oxide. A control gate opposes the floating gate. The control gate is separated from the floating gate by an asymmetrical low tunnel barrier intergate insulator. The asymmetrical low tunnel barrier intergate insulator includes a metal oxide insulator selected from the group consisting of Al2O3, Ta2O5, TiO2, ZrO2, Nb2O5, SrBi2Ta2O3, SrTiO3, PbTiO3, and PbZrO3. The floating gate includes a polysilicon floating gate having a metal layer formed thereon in contact with the low tunnel barrier intergate insulator. And, the control gate includes a polysilicon control gate having a metal layer, having a different work function from the metal layer formed on the floating gate, formed thereon in contact with the low tunnel barrier intergate insulator.

Owner:MICRON TECH INC

Method for fabricating a type of trench mask ROM cell

A method for fabricating a type of Trench Mask ROM cell comprises steps including: providing a substrate doped lightly with p-type dopant, sequentially forming a pad oxide layer and a nitride layer on the substrate; etching back the pad oxide layer, the nitride layer and the substrate to form plural trenches; a gate oxide layer being formed on surfaces of each trench; then, implanting n+-type ions into the substrate beneath the pad oxide layer and between each two adjacent trenches; and, forming a polysilicon layer on the gate oxide and pad oxide; finally, implanting n+-type ions into the substrate beneath the gate oxide layer on bottoms of selected trenches. And, it is appreciated that the sequence of the formation of plural trenches and implanting n+-type ions into substrate between each trench can be reversed in the embodiment without affecting subsequent steps.

Owner:PROMOS TECH INC

Flash memory with low tunnel barrier interpoly insulators

Structures and methods for Flash memory with low tunnel barrier intergate insulators are provided. The non-volatile memory includes a first source / drain region and a second source / drain region separated by a channel region in a substrate. A floating gate opposing the channel region and is separated therefrom by a gate oxide. A control gate opposes the floating gate. The control gate is separated from the floating gate by a low tunnel barrier intergate insulator. The low tunnel barrier intergate insulator includes a metal oxide insulator selected from the group consisting of PbO, Al2O3, Ta2O5, TiO2, ZrO2, and Nb2O5. The floating gate includes a polysilicon floating gate having a metal layer formed thereon in contact with the low tunnel barrier intergate insulator. And, the control gate includes a polysilicon control gate having a metal layer formed thereon in contact with the low tunnel barrier intergate insulator.

Owner:MICRON TECH INC

Programmable array logic or memory devices with asymmetrical tunnel barriers

Structures and methods for programmable array type logic and / or memory devices with asymmetrical low tunnel barrier intergate insulators are provided. The programmable array type logic and / or memory devices include non-volatile memory which has a first source / drain region and a second source / drain region separated by a channel region in a substrate. A floating gate opposing the channel region and is separated therefrom by a gate oxide. A control gate opposes the floating gate. The control gate is separated from the floating gate by an asymmetrical low tunnel barrier intergate insulator. The asymmetrical low tunnel barrier intergate insulator includes a metal oxide insulator selected from the group consisting of Al2O3, Ta2O5, TiO2, Zro2, Nb2O5, SrBi2Ta2O3, SrTiO3, PbTiO3, and PbZrO3. The floating gate includes a polysilicon floating gate having a metal layer formed thereon in contact with the low tunnel barrier intergate insulator. And, the control gate includes a polysilicon control gate having a metal layer, having a different work function from the metal layer formed on the floating gate, formed thereon in contact with the low tunnel barrier intergate insulator.

Owner:MICRON TECH INC

Method and apparatus improving gate oxide reliability by controlling accumulated charge

ActiveUS7890891B2Improving nonlinear responses and harmonic and intermodulaton distortion effectsReduce non-linearitySolid-state devicesElectronic switchingMOSFETDielectric

A method and apparatus are disclosed for use in improving the gate oxide reliability of semiconductor-on-insulator (SOI) metal-oxide-silicon field effect transistor (MOSFET) devices using accumulated charge control (ACC) techniques. The method and apparatus are adapted to remove, reduce, or otherwise control accumulated charge in SOI MOSFETs, thereby yielding improvements in FET performance characteristics. In one embodiment, a circuit comprises a MOSFET, operating in an accumulated charge regime, and means for controlling the accumulated charge, operatively coupled to the SOI MOSFET. A first determination is made of the effects of an uncontrolled accumulated charge on time dependent dielectric breakdown (TDDB) of the gate oxide of the SOI MOSFET. A second determination is made of the effects of a controlled accumulated charge on TDDB of the gate oxide of the SOI MOSFET. The SOI MOSFET is adapted to have a selected average time-to-breakdown, responsive to the first and second determinations, and the circuit is operated using techniques for accumulated charge control operatively coupled to the SOI MOSFET. In one embodiment, the accumulated charge control techniques include using an accumulated charge sink operatively coupled to the SOI MOSFET body.

Owner:PSEMI CORP

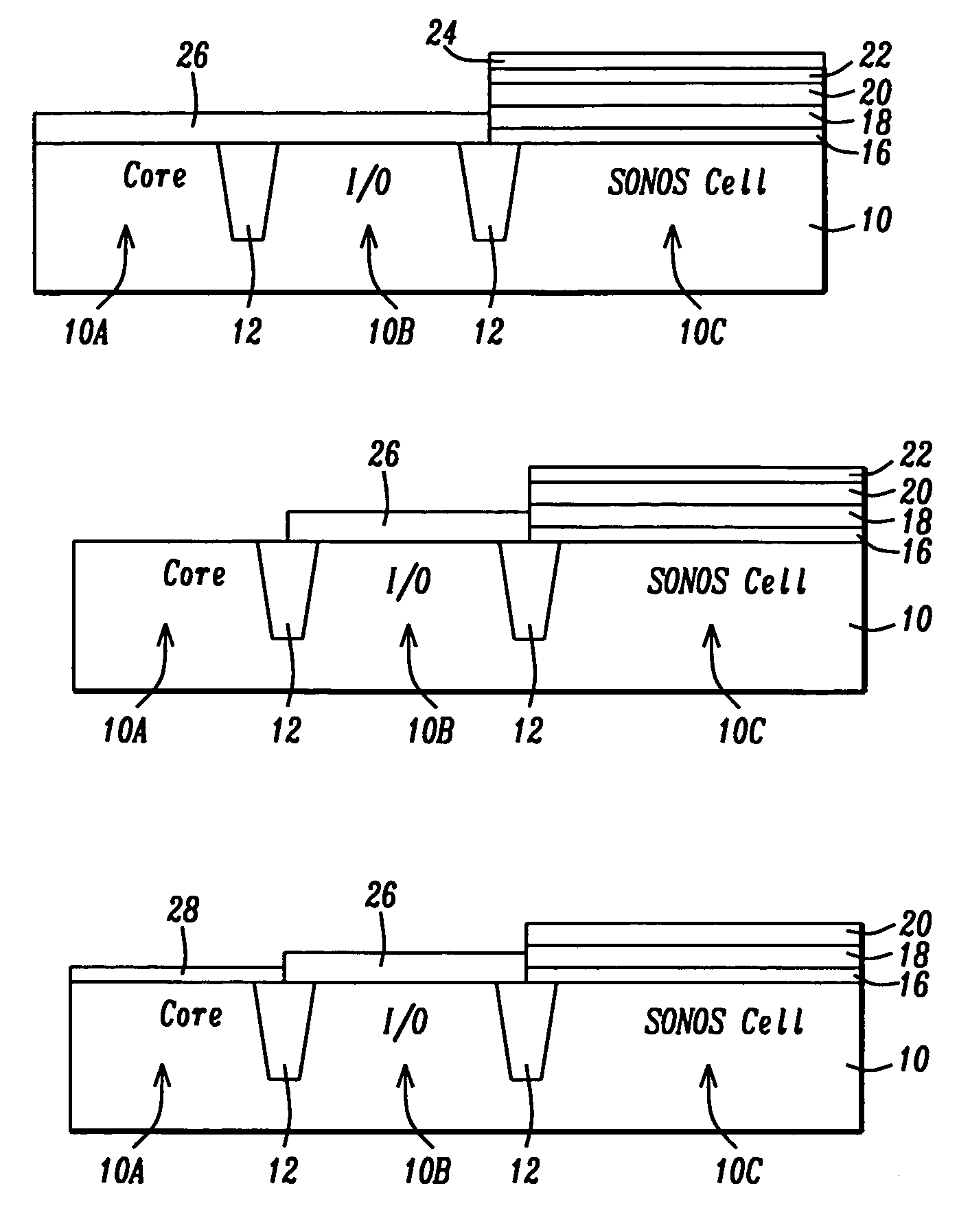

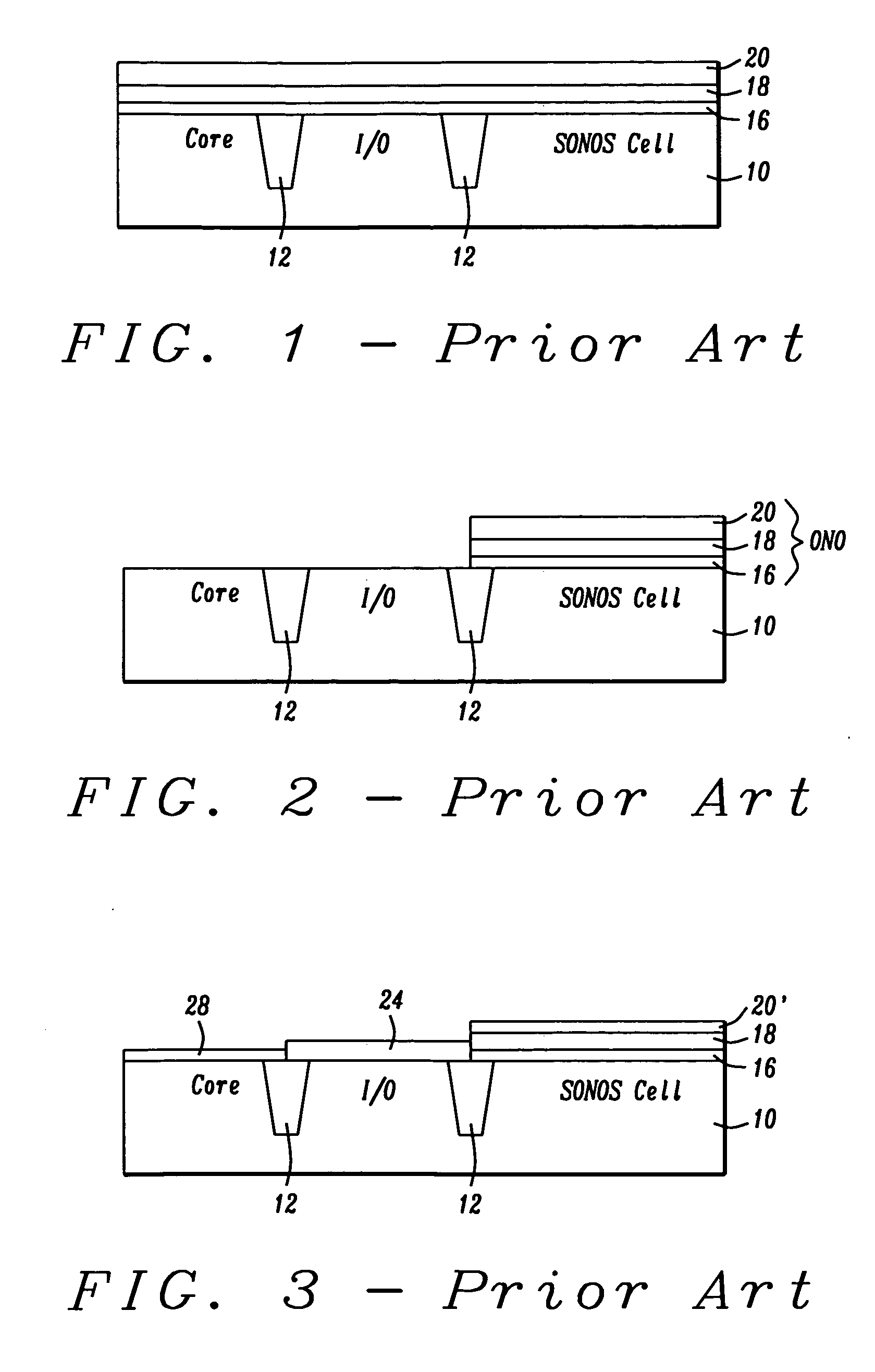

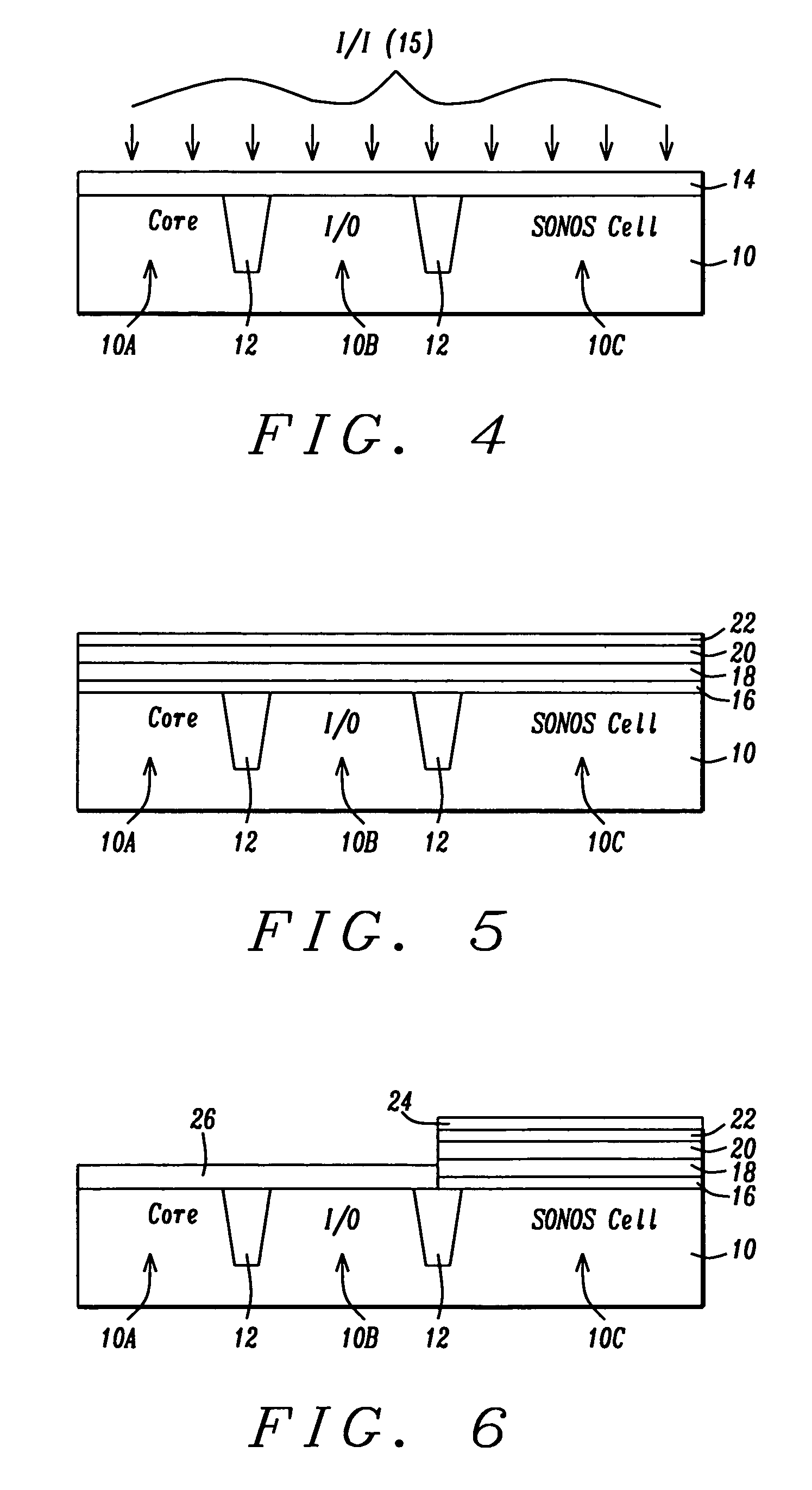

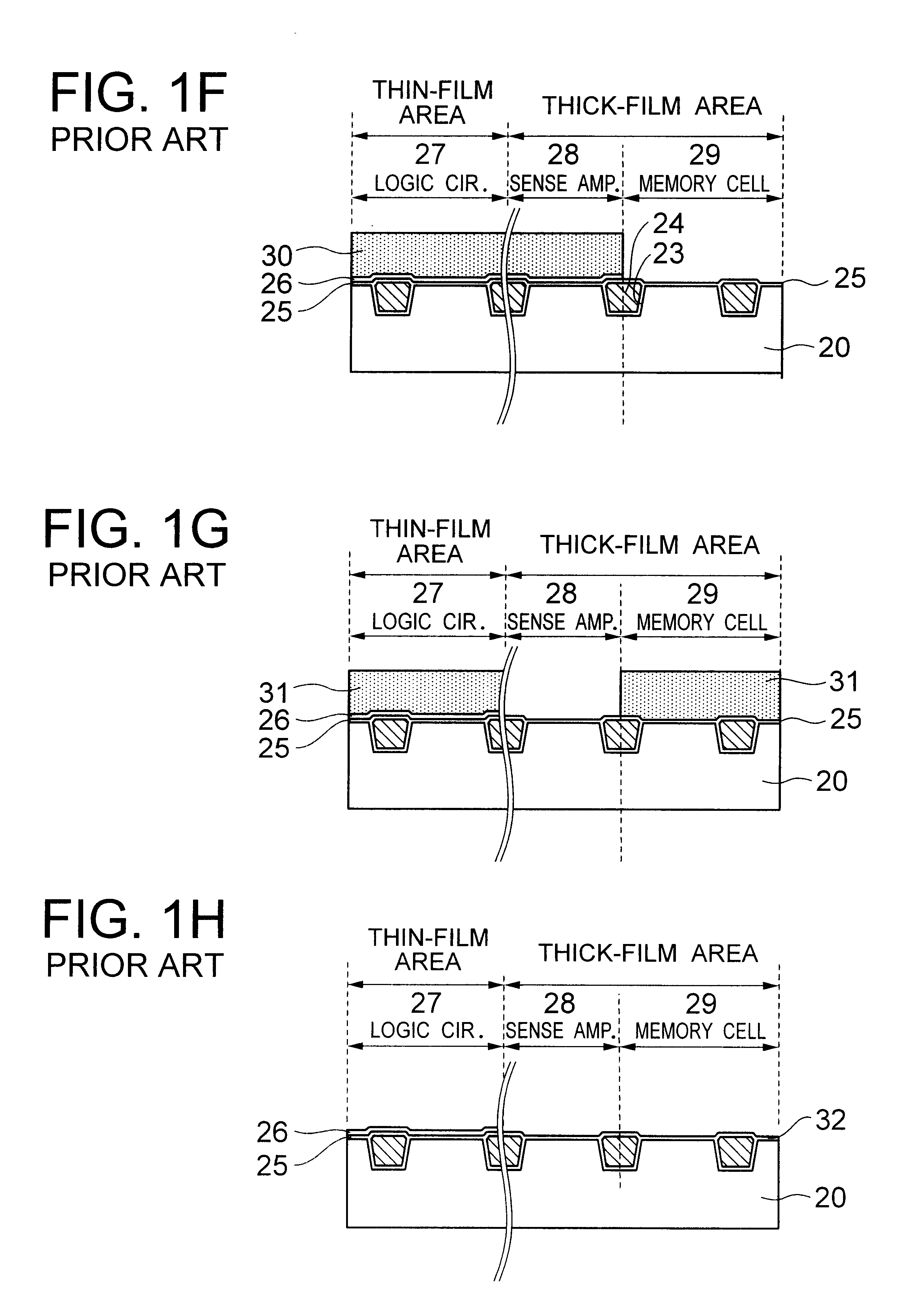

Method for integrating a SONOS gate oxide transistor into a logic/analog integrated circuit having several gate oxide thicknesses

ActiveUS6946349B1Simple manufacturing processMore cost-effectivelySolid-state devicesSemiconductor/solid-state device manufacturingEngineeringGate oxide

A method for integrating a SONOS device with an improved top oxide with SiO2 gate oxides of different thickness is described. In a first embodiment during ISSG oxidation to form the SiO2 gate oxides, a thin sacrificial silicon nitride layer is used over the top oxide of the ONO to minimize loss and to control the top oxide thickness. In a second embodiment the top oxide layer for the SONOS device is formed by depositing an NO stack. During ISSG oxidation to form the SiO2 gate oxides a portion of the Si3N4 in the NO stack is converted to SiO2 to form the top oxide with improved thickness control.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

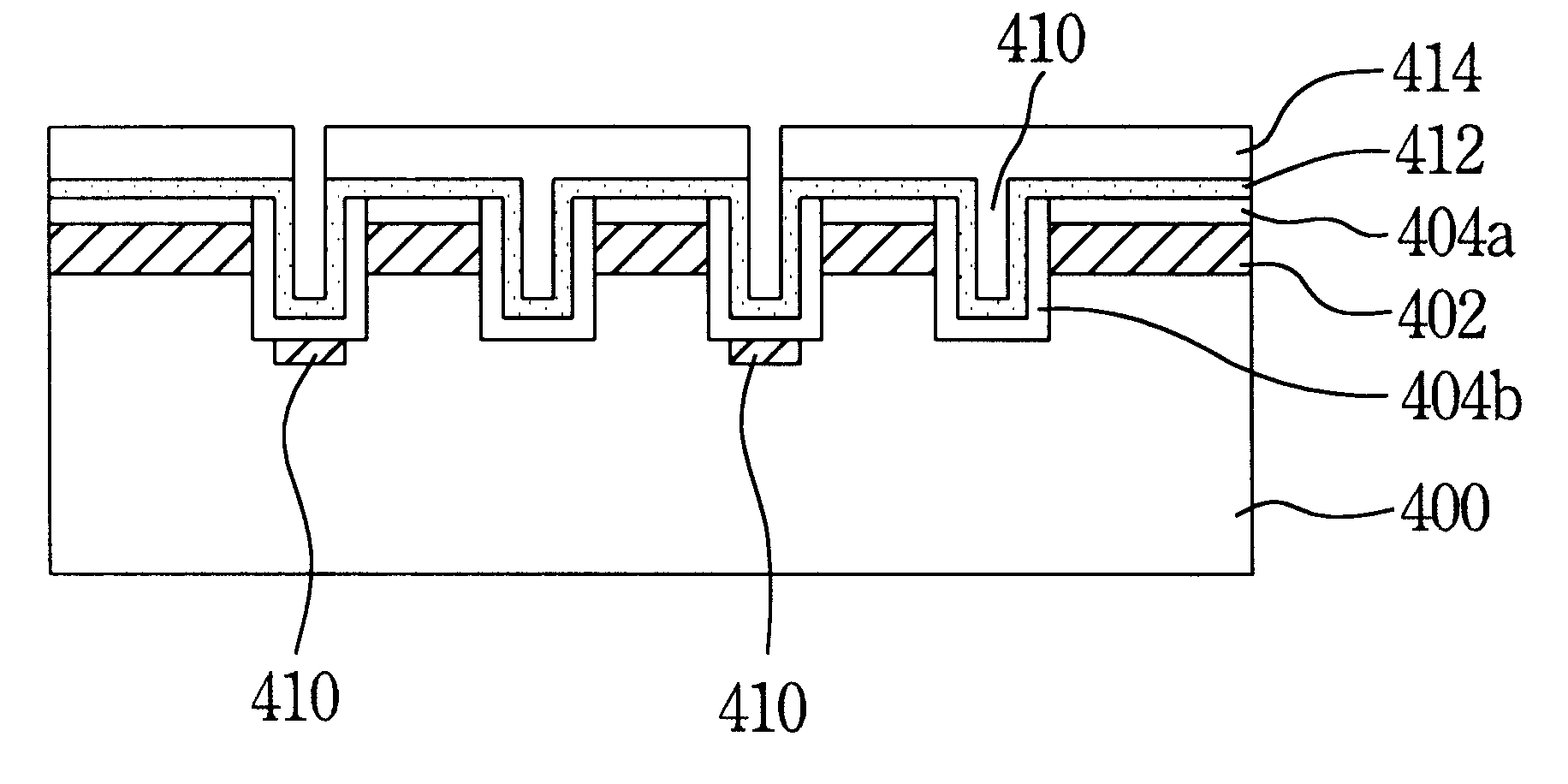

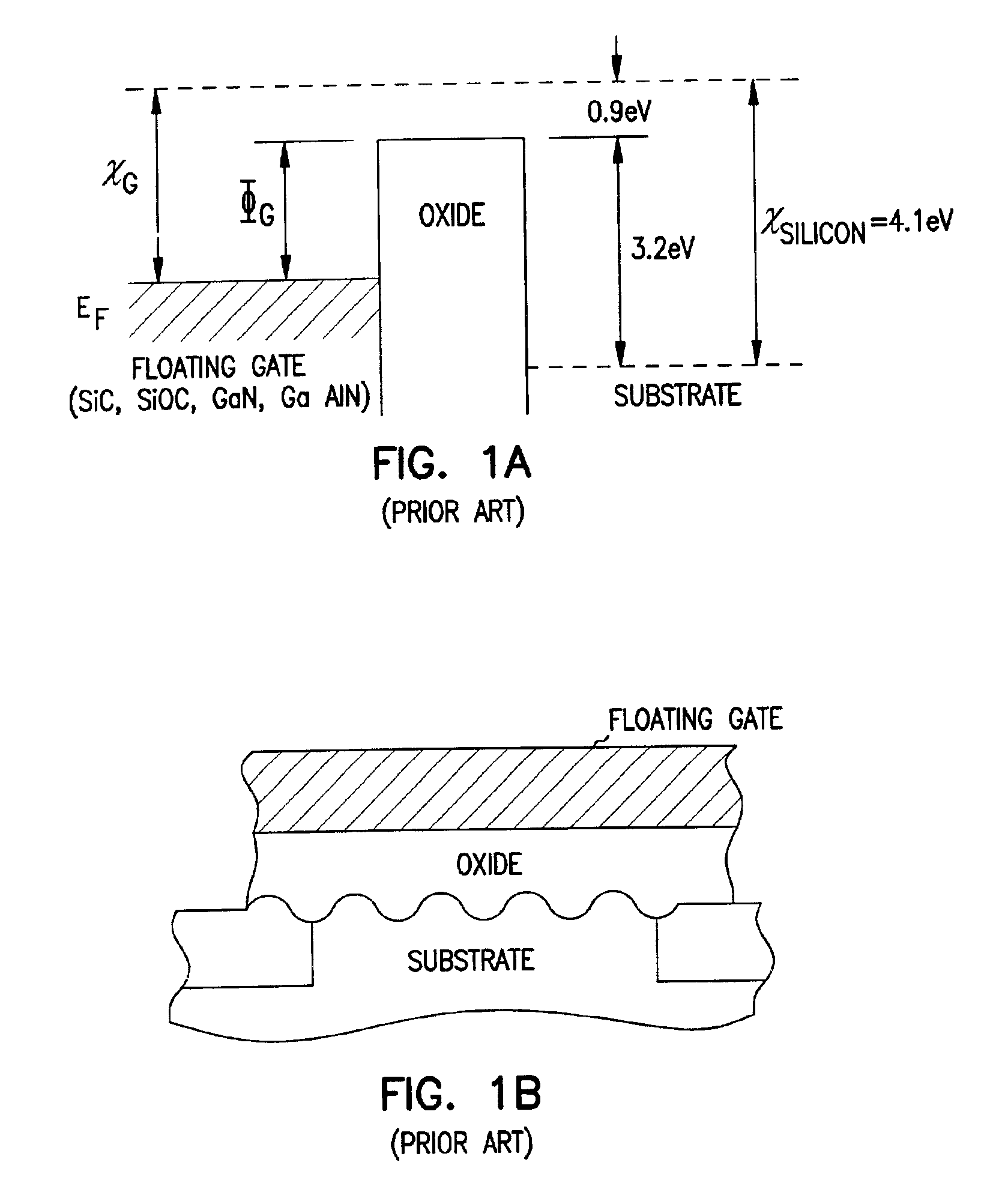

Memory utilizing oxide-conductor nanolaminates

Structures, systems and methods for floating gate transistors utilizing oxide-conductor nanolaminates are provided. One floating gate transistor embodiment includes a first source / drain region, a second source / drain region, and a channel region therebetween. A floating gate is separated from the channel region by a first gate oxide. The floating gate includes oxide-conductor nanolaminate layers to trap charge in potential wells formed by different electron affinities of the oxide-conductor nanolaminate layers.

Owner:MICRON TECH INC

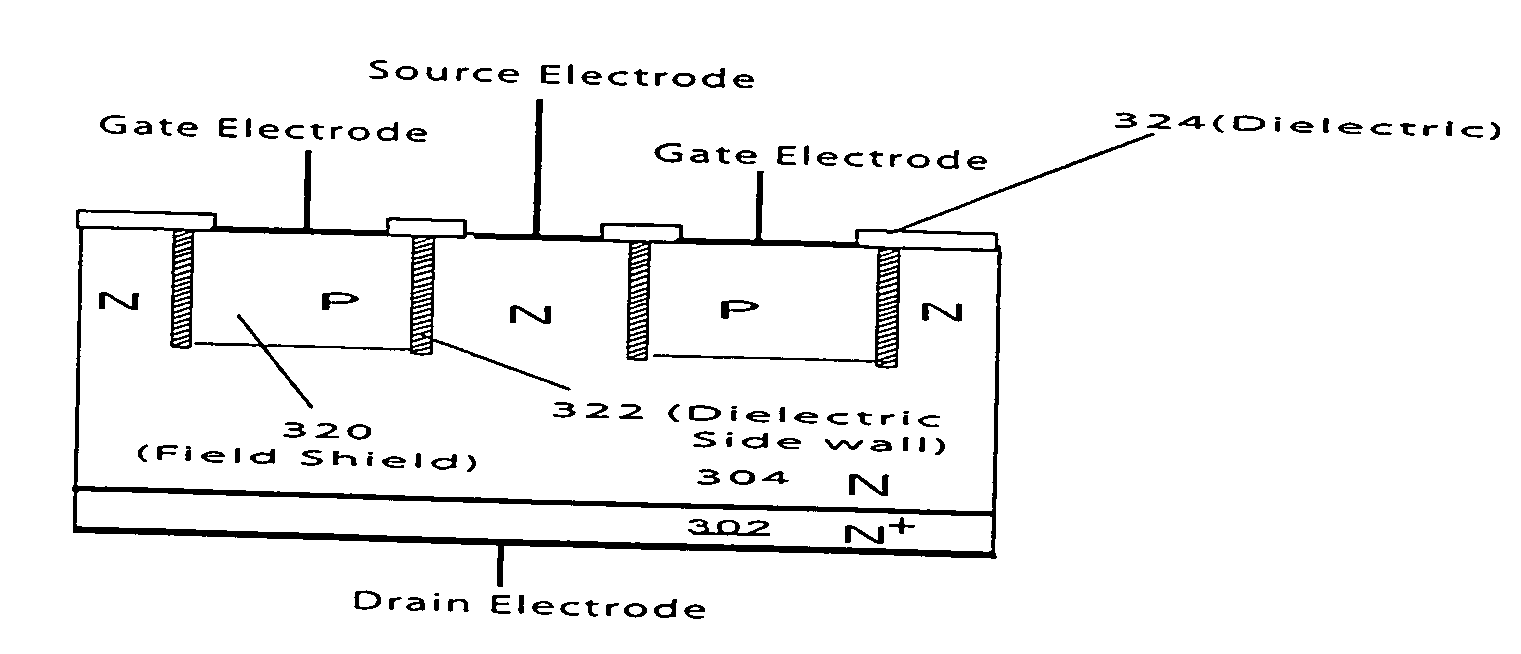

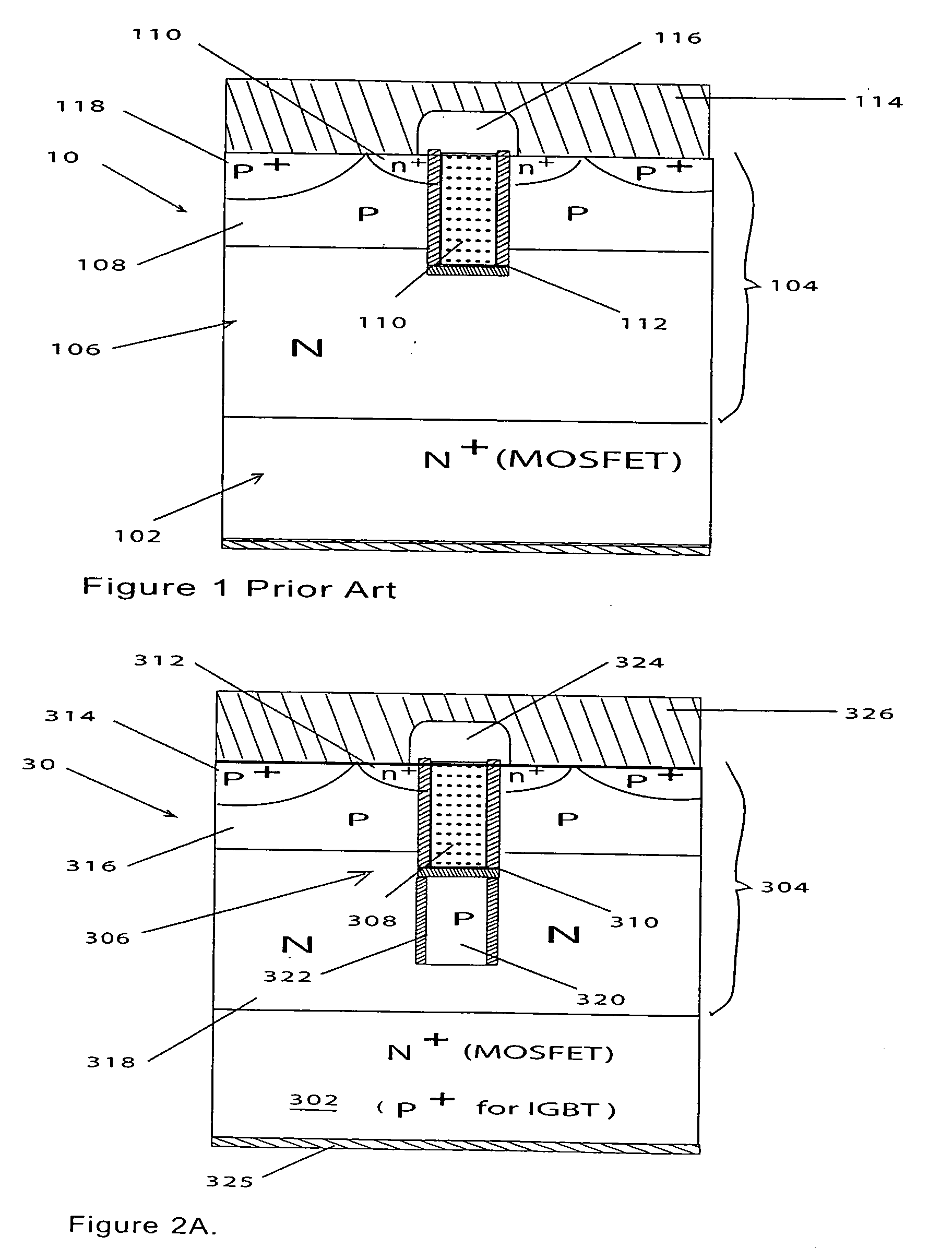

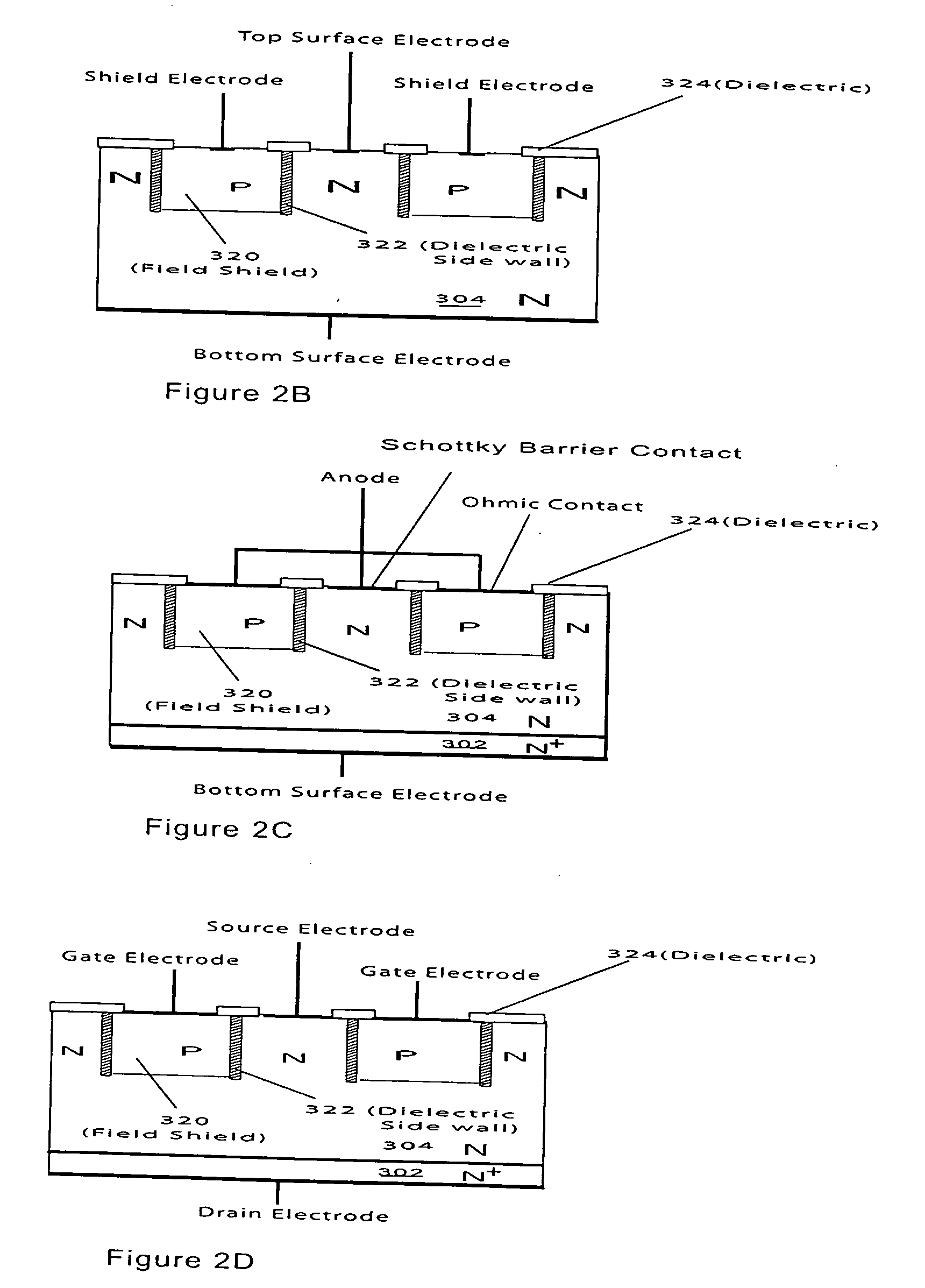

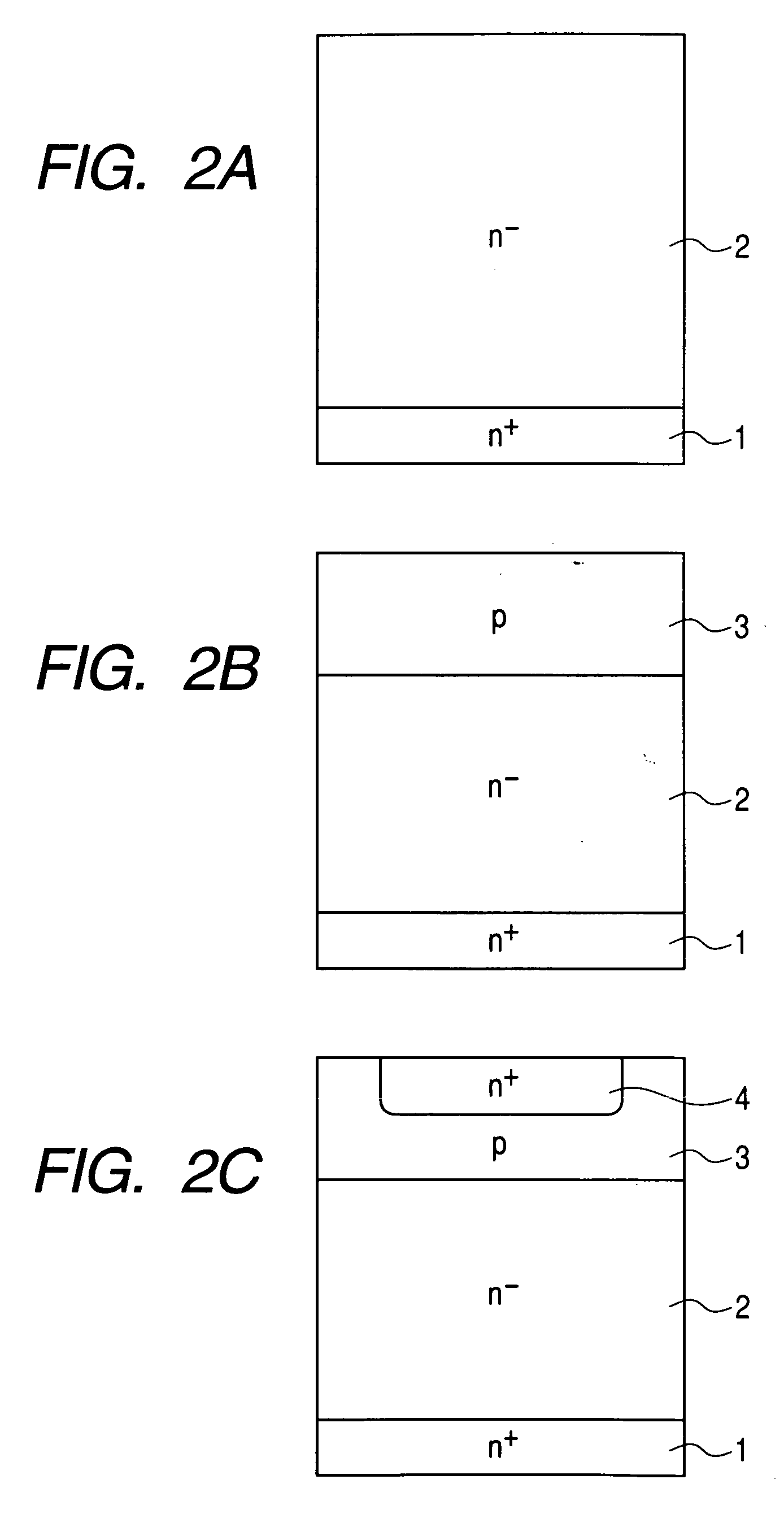

Semiconductor device containing dielectrically isolated pn junction for enhanced breakdown characteristics

InactiveUS20050167695A1Increased avalanche breakdown voltageLower on-resistanceThyristorSemiconductor/solid-state device manufacturingDevice materialPower MOSFET

A semiconductor device includes a field shield region that is doped opposite to the conductivity of the substrate and is bounded laterally by dielectric sidewall spacers and from below by a PN junction. For example, in a trench-gated MOSFET the field shield region may be located beneath the trench and may be electrically connected to the source region. When the MOSFET is reverse-biased, depletion regions extend from the dielectric sidewall spacers into the “drift” region, shielding the gate oxide from high electric fields and increasing the avalanche breakdown voltage of the device. This permits the drift region to be more heavily doped and reduces the on-resistance of the device. It also allows the use of a thin, 20 Å gate oxide for a power MOSFET that is to be switched with a 1V signal applied to its gate while being able to block over 30V applied across its drain and source electrodes, for example.

Owner:ALPHA & OMEGA SEMICON INC

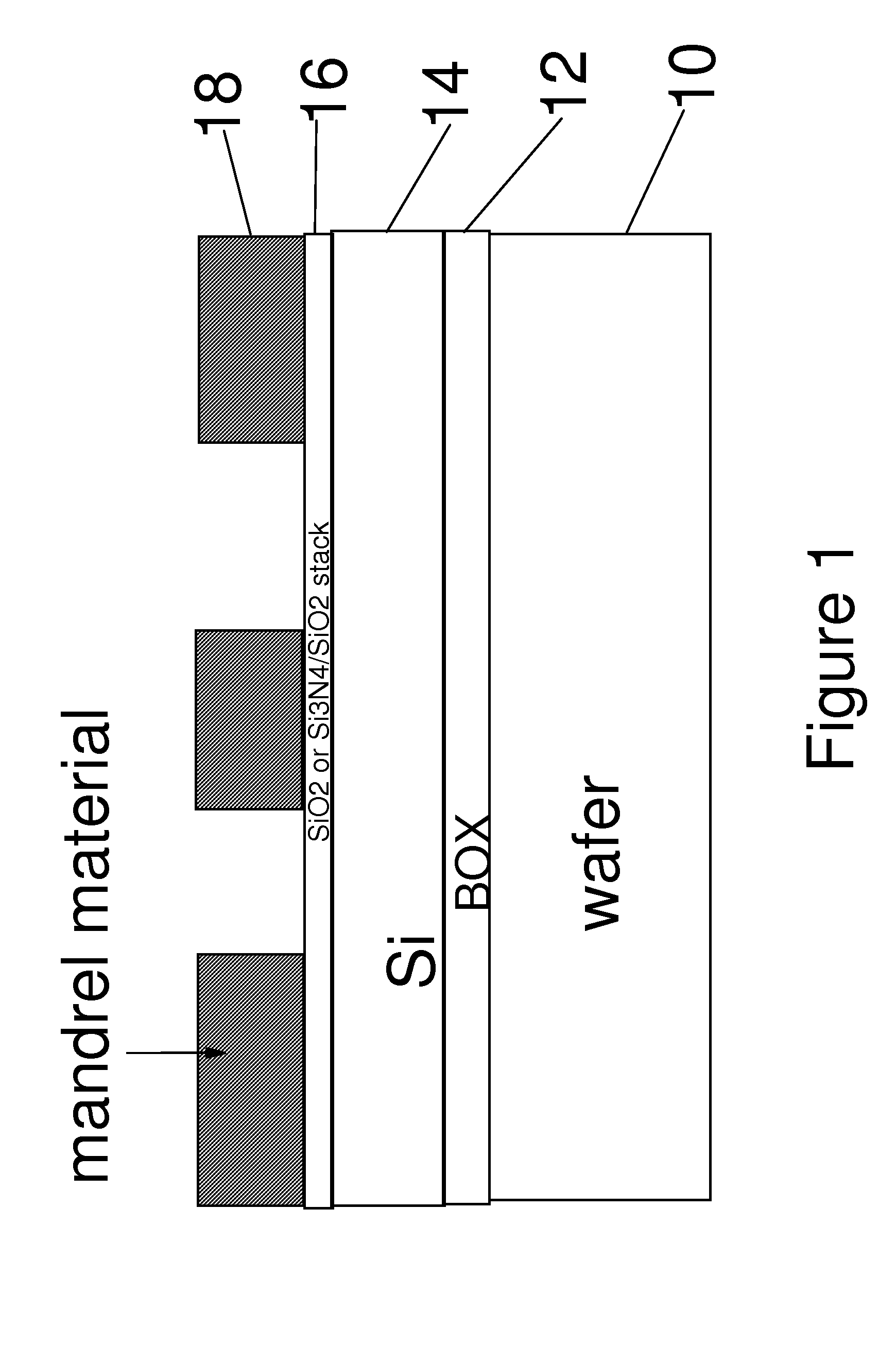

Method for fabricating graphene transistors on a silicon or soi substrate

ActiveUS20090181502A1Well formedSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricSoi substrate

A method of fabricating graphene transistors, comprising providing an SOI substrate, performing an optional threshold implant on the SOI substrate, forming an upper silicon layer mesa island, carbonizing the silicon layer into SiC utilizing a gaseous source, converting the SiC into graphene, forming source / drain regions on opposite longitudinal ends of the graphene, forming gate oxide between the source / drain regions on the graphene, forming gate material over the gate oxide, creating a transistor edge, depositing dielectric onto the transistor edge and performing back end processing.

Owner:TEXAS INSTR INC

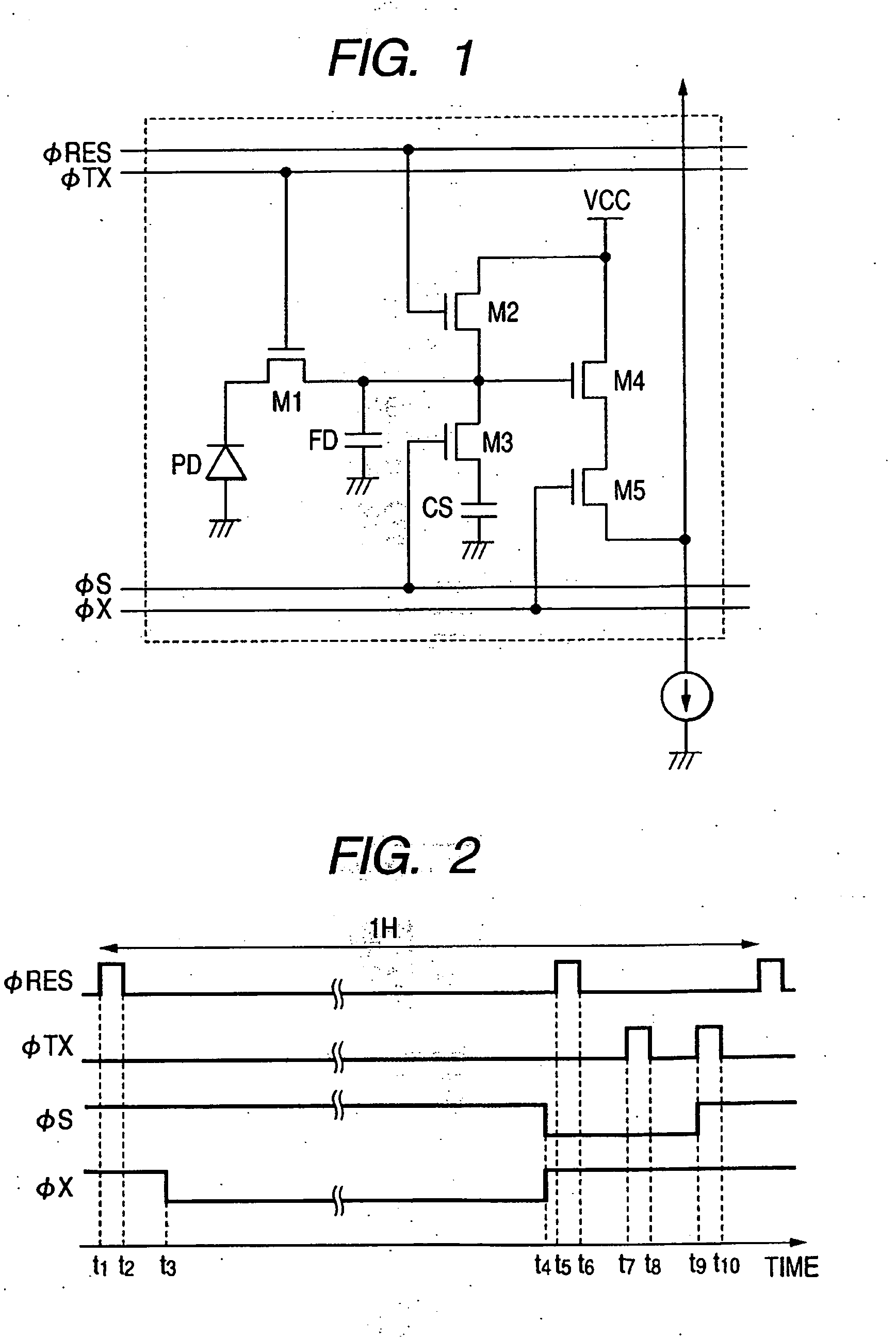

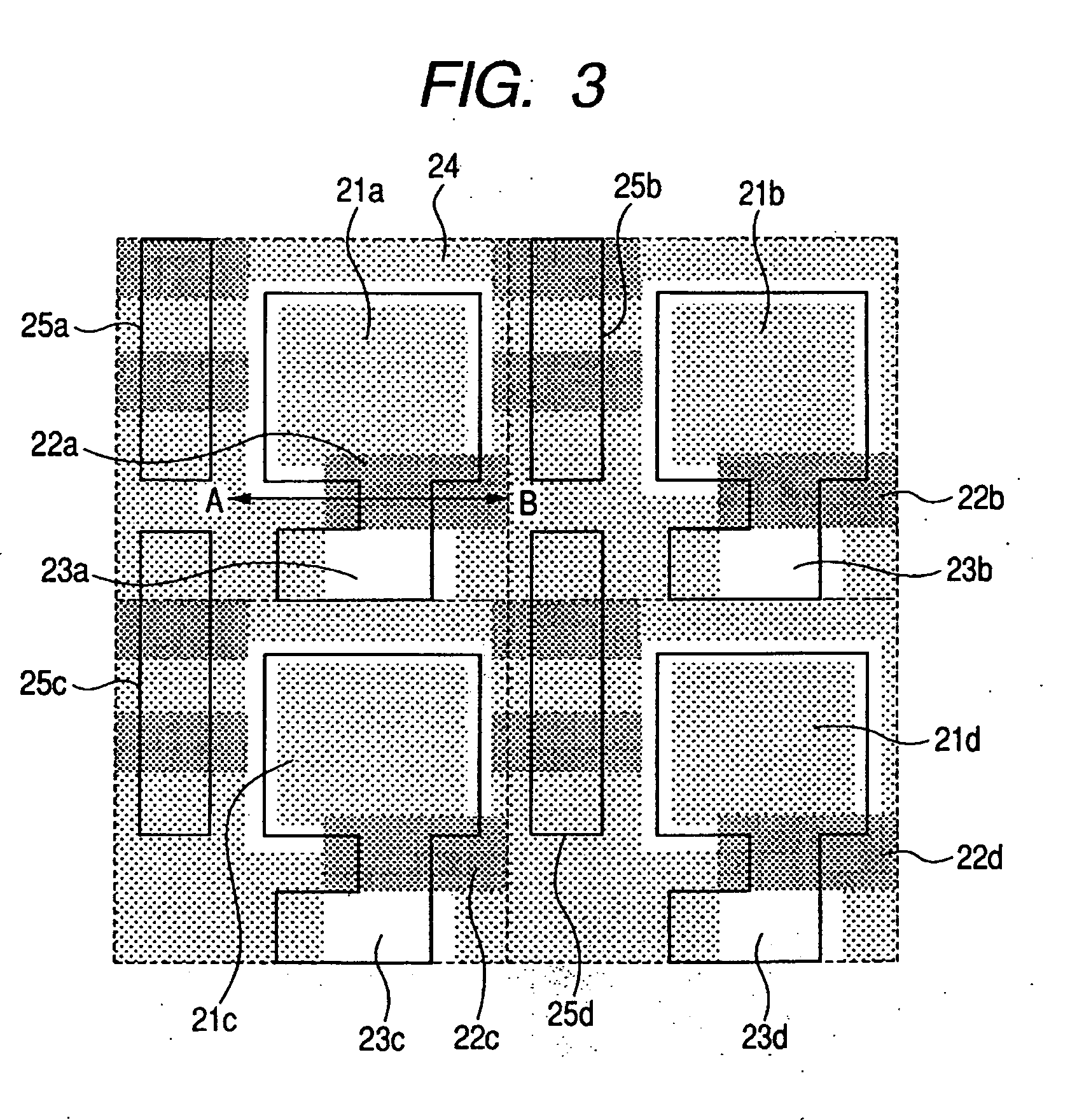

Image pickup device and camera with expanded dynamic range

The image pickup device of the invention has a path deeper in a semiconductor substrate, than a region wherein a channel is formed, upon turning on a first MOS transistor, under a gate thereof. The path is arranged by forming a P-type layer for forming a potential barrier, within a P-type well excluding a region below the gate of the first MOS transistor. Thus, even when the first transfer MOS transistor is securely turned off at accumulation, carriers overflowing from a photodiode can flow into the path, thereby enabling to accumulate the carriers, overflowing from the photodiode, in a carrier accumulation region. Such structure allows to suppress a dark current generation from an interface of a gate oxide film of the first transfer MOS transistor, and also to expand the dynamic range of the image pickup device by the carriers overflowing from the photodiode and flowing through the path into the carrier accumulation region.

Owner:CANON KK

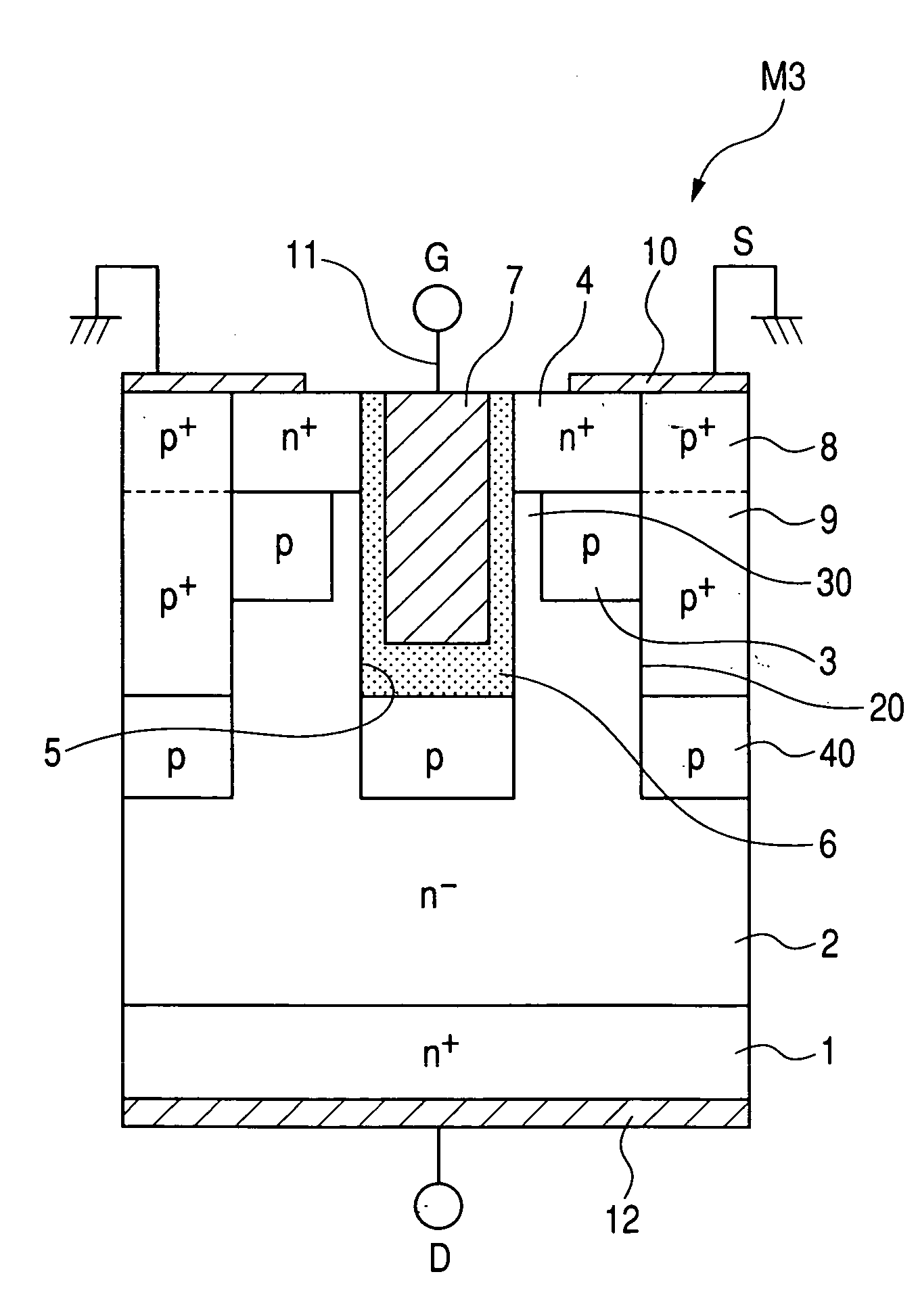

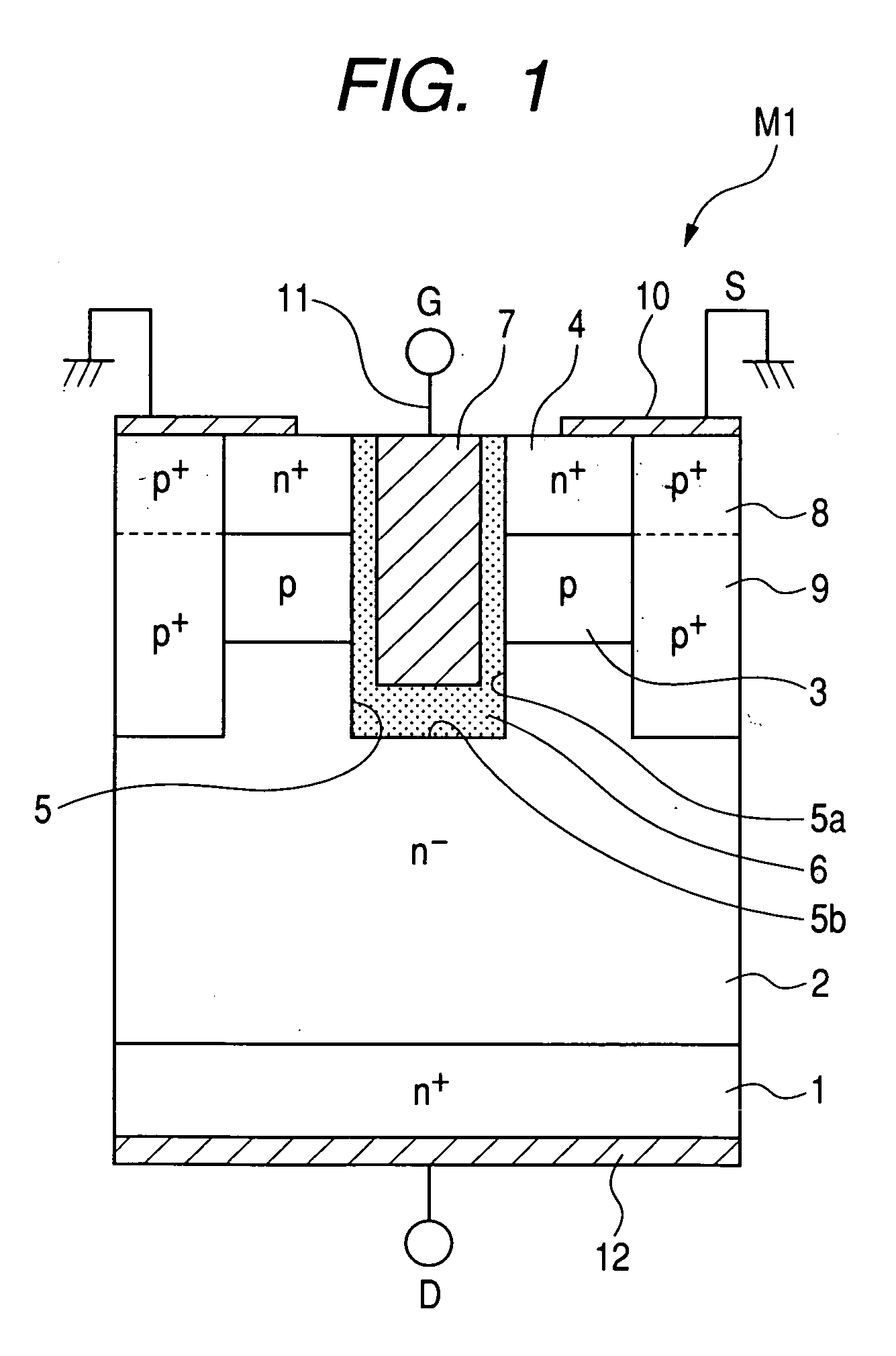

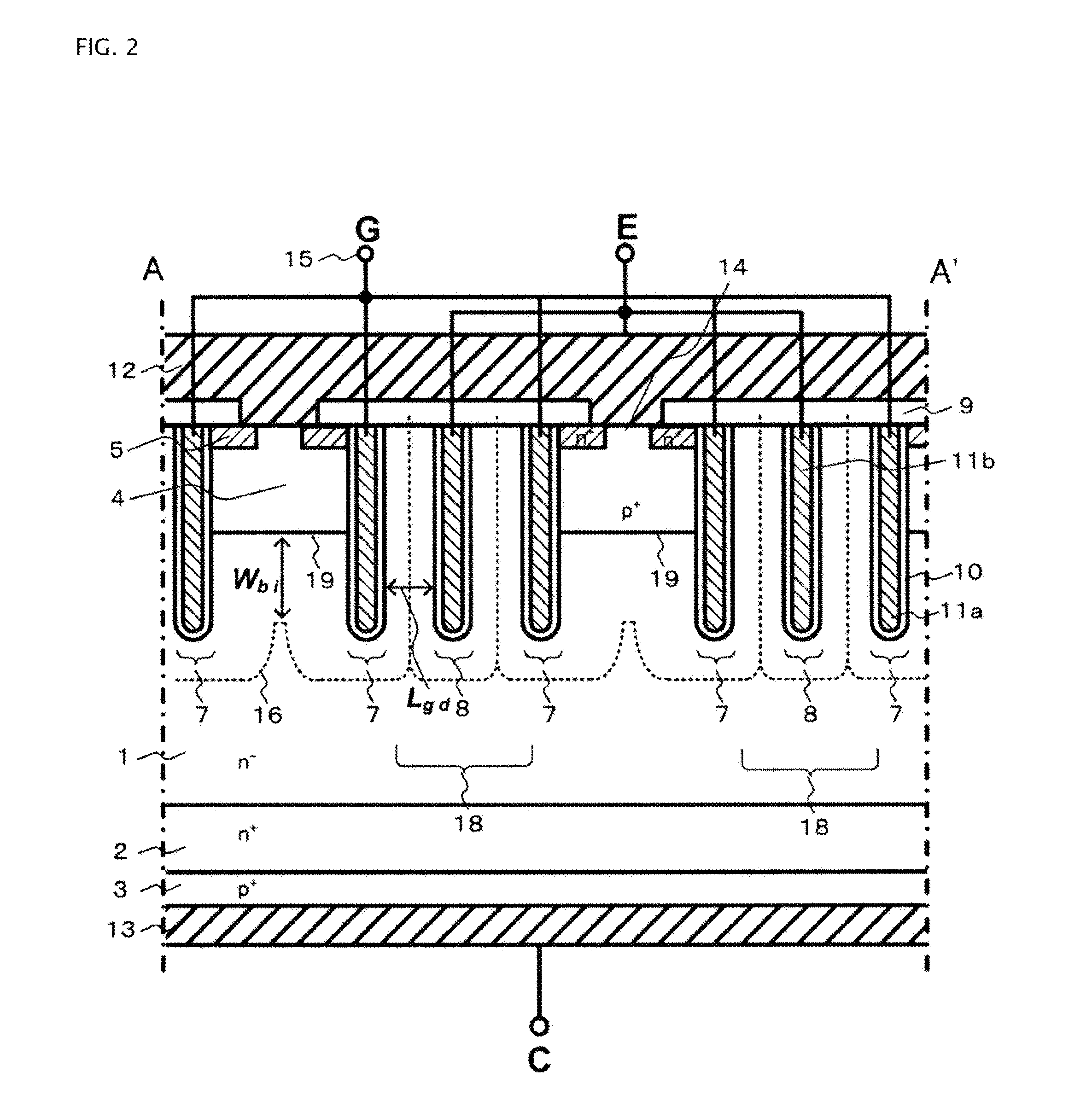

Silicon carbide semiconductor device and related manufacturing method

ActiveUS20090114969A1Increase concentrationReduce concentrationTransistorSolid-state devicesP–n junctionGate oxide

An SiC semiconductor device and a related manufacturing method are disclosed having a structure provided with a p+-type deep layer formed in a depth equal to or greater than that of a trench to cause a depletion layer between at a PN junction between the p+-type deep layer and an n−-type drift layer to extend into the n−-type drift layer in a remarkable length, making it difficult for a high voltage, resulting from an adverse affect arising from a drain voltage, to enter a gate oxide film. This results in a capability of minimizing an electric field concentration in the gate oxide film, i.e., an electric field concentration occurring at the gate oxide film at a bottom wall of the trench.

Owner:DENSO CORP

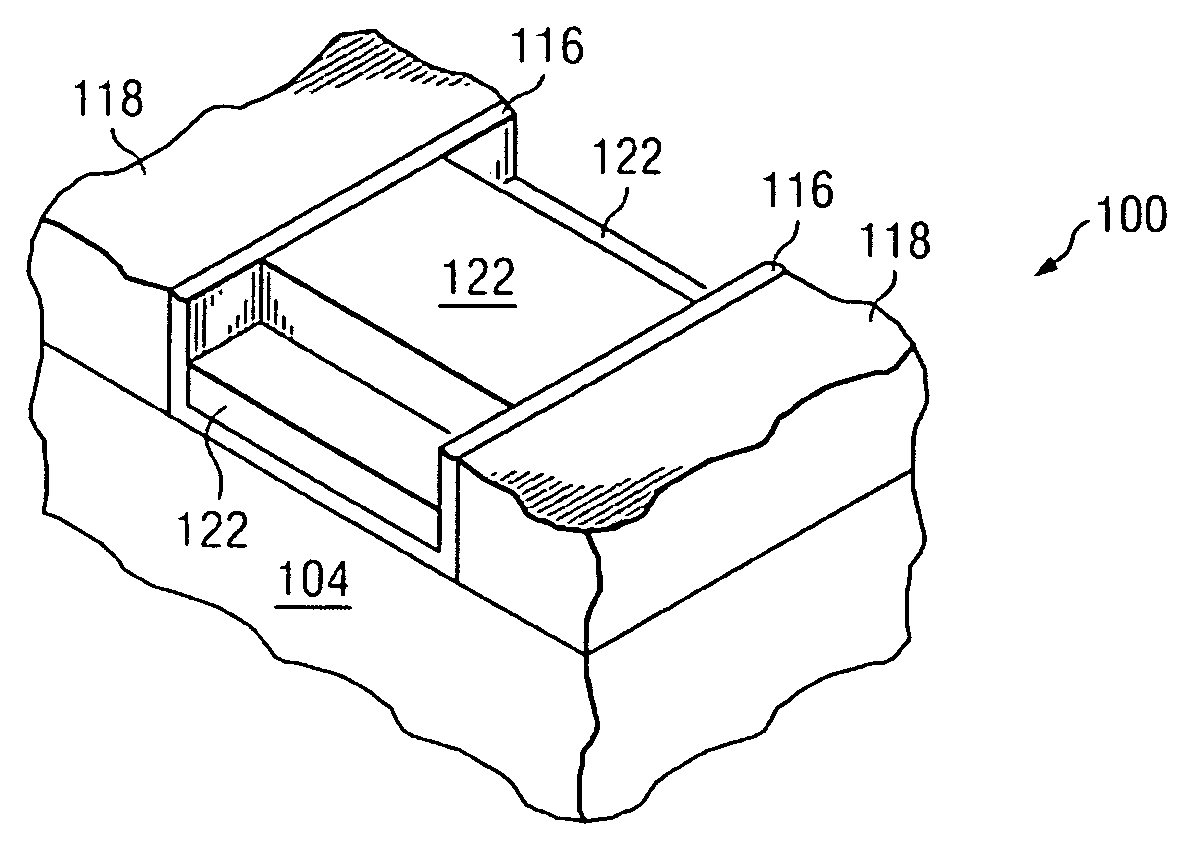

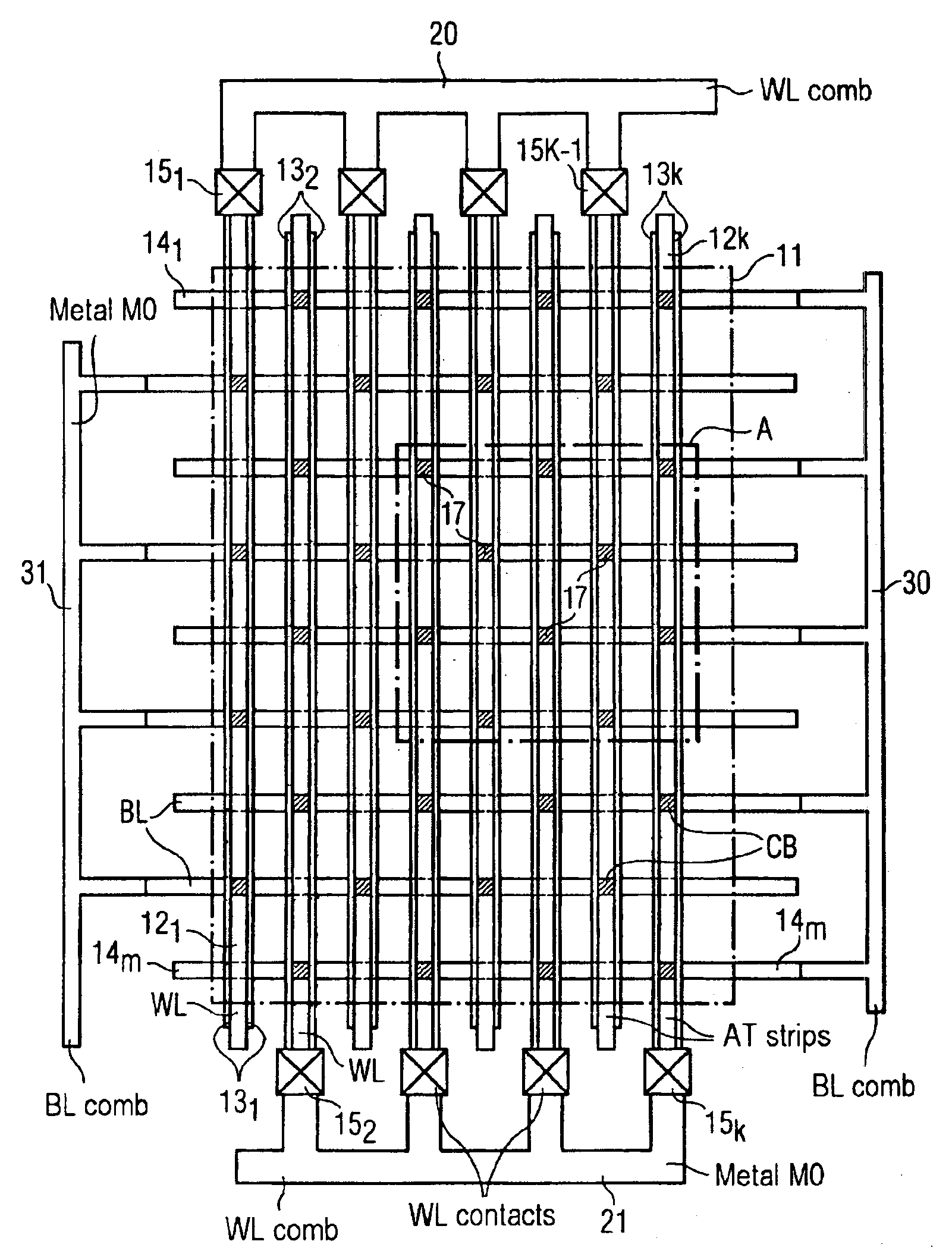

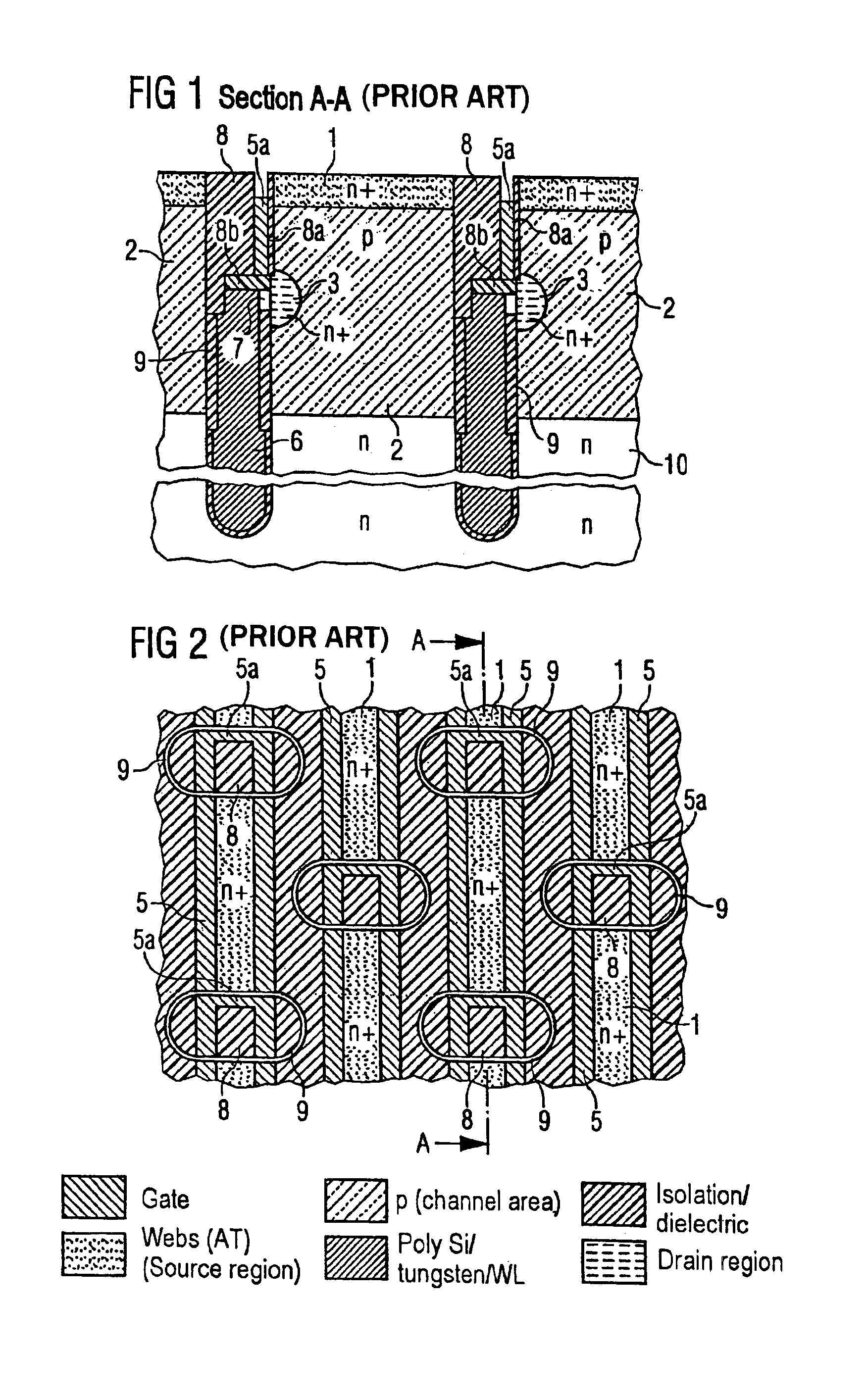

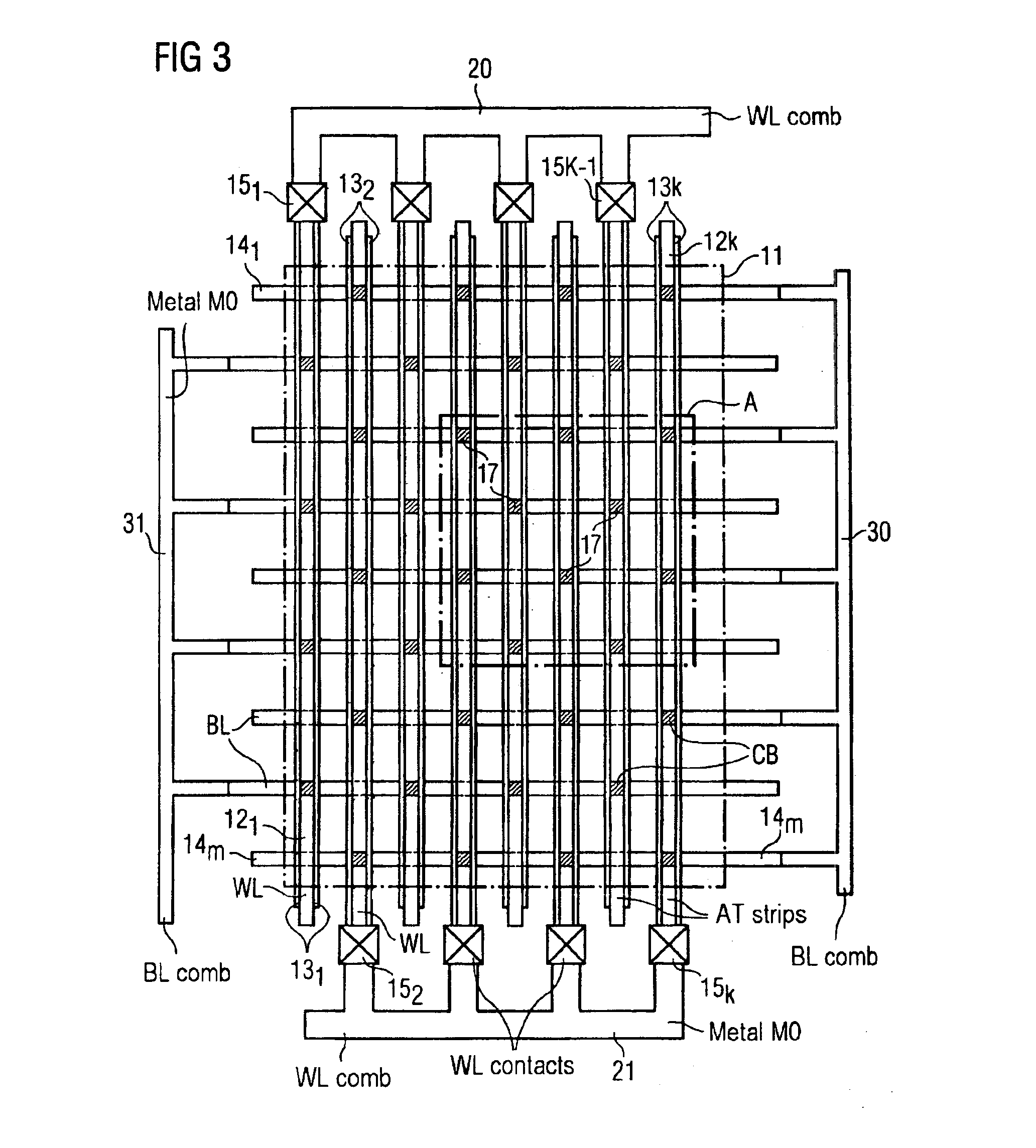

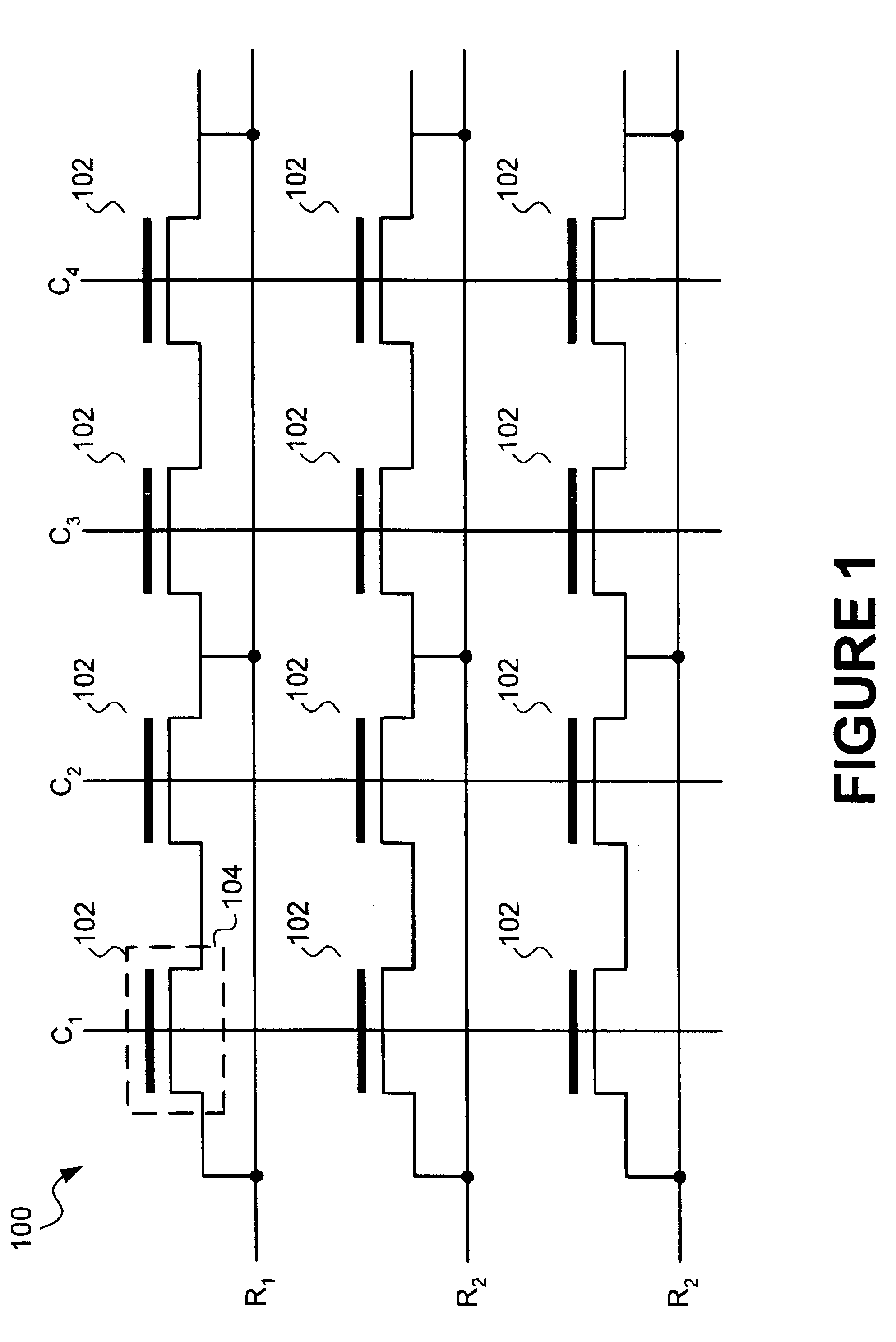

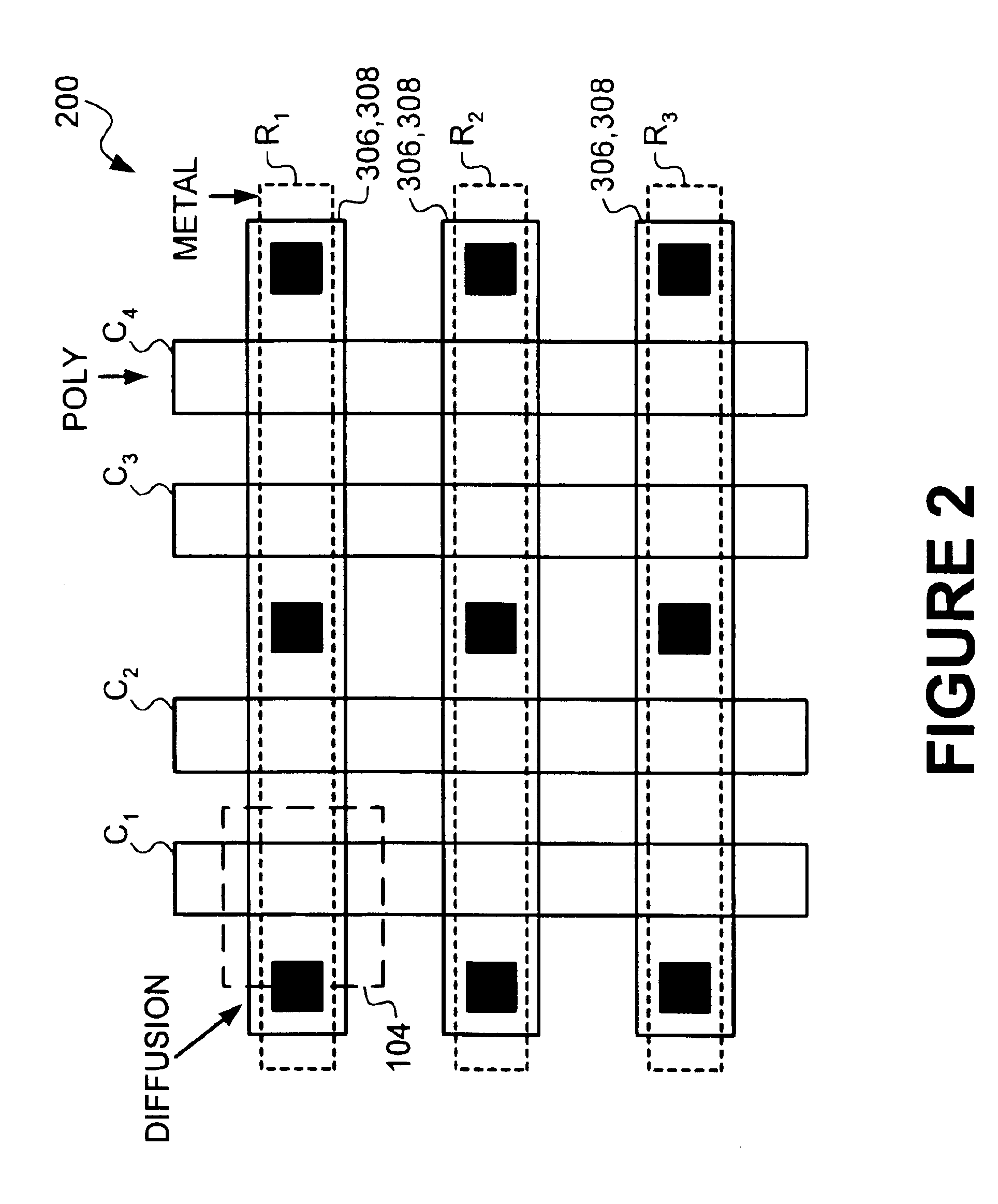

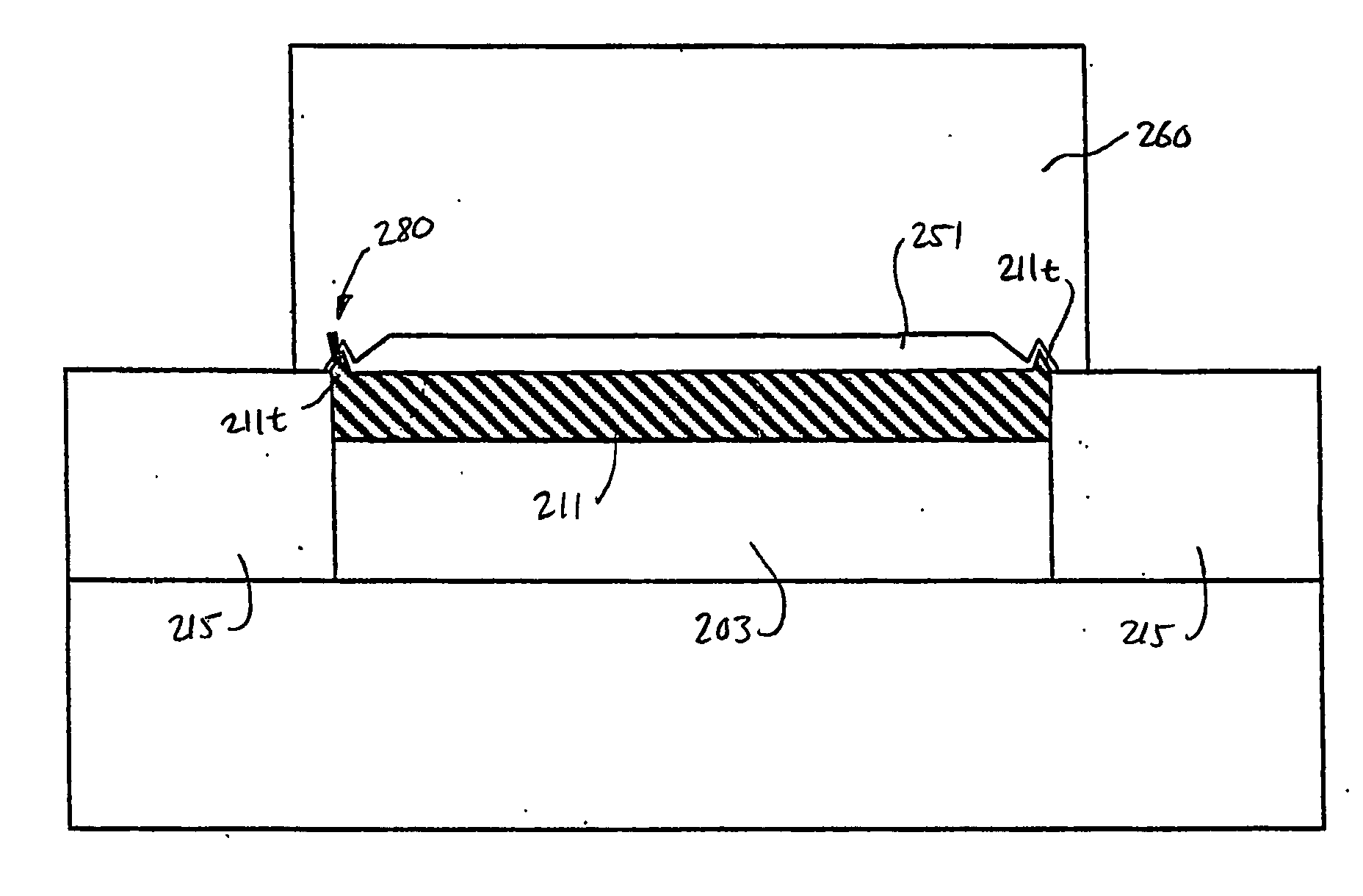

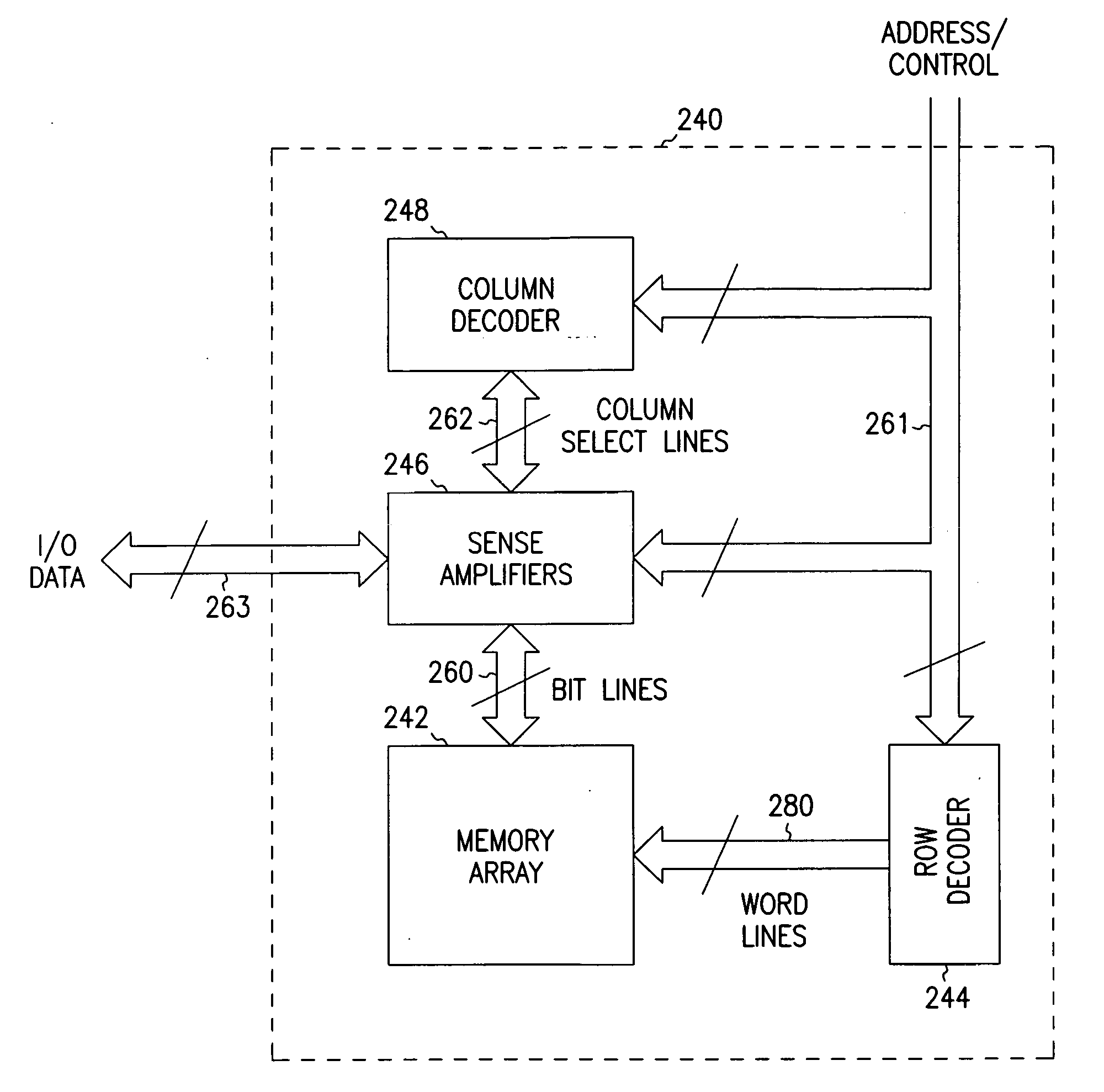

Device architecture and process for improved vertical memory arrays

InactiveUS6930324B2TransistorSemiconductor/solid-state device testing/measurementTransistor arrayDielectric

An array process diagnosis test structure for an integrated circuit including a transistor array composed of vertical FET memory cell access transistors, which are formed into the depth of a substrate in the form of active webs which run parallel in the lateral direction of the circuit is disclosed. Memory cell storage capacitors in the array test structure are formed in deep trenches on the end faces of those sections of the active webs which form the vertical FET transistors. Word lines are arranged along the webs and along parallel intersecting bit lines of the array, outside of which, and on two mutually opposite edges, are located a first and second word line comb. The wordline combs are offset and connected alternately to different word lines. In addition, a first and a second bit line comb are formed on the two other opposing edges of the transistor array mutually offset and each connected to different bit lines. The test structure provides a convenient means to carry out reliability investigations on the gate oxide of the vertical FET transistors and on the capacitor dielectric in the deep trenches, capacitance measurements between the word lines, and between the word lines and other circuit layers, as well as capacitance measurements between the bit lines and between the bit lines and other circuit layers, and thus facilitates diagnosis of possible fault sources arising during the production process.

Owner:POLARIS INNOVATIONS

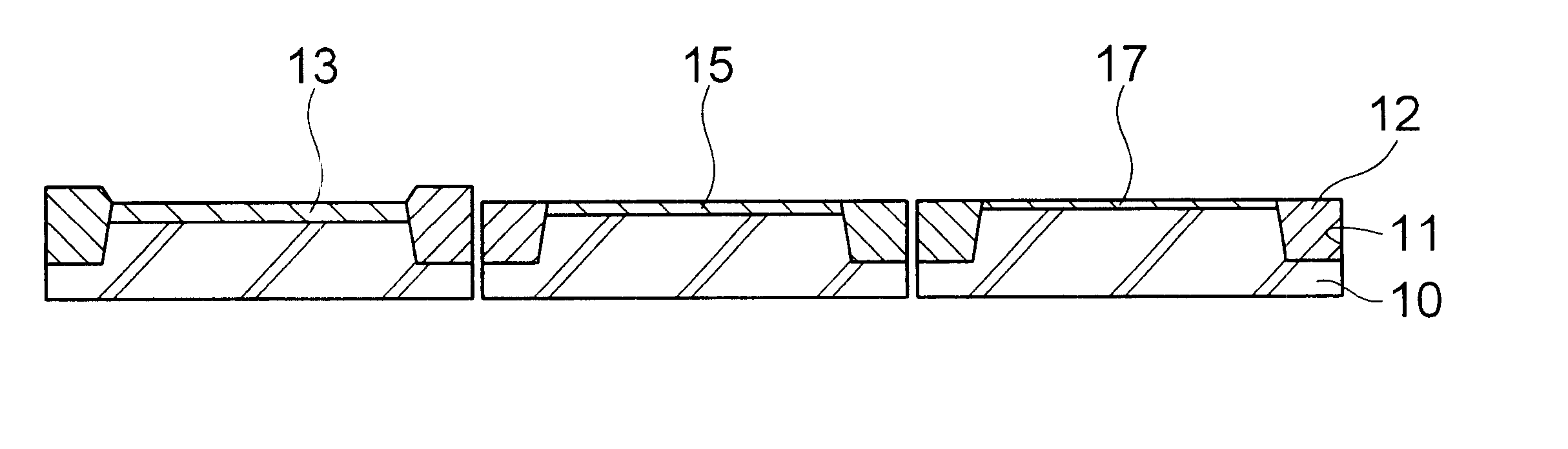

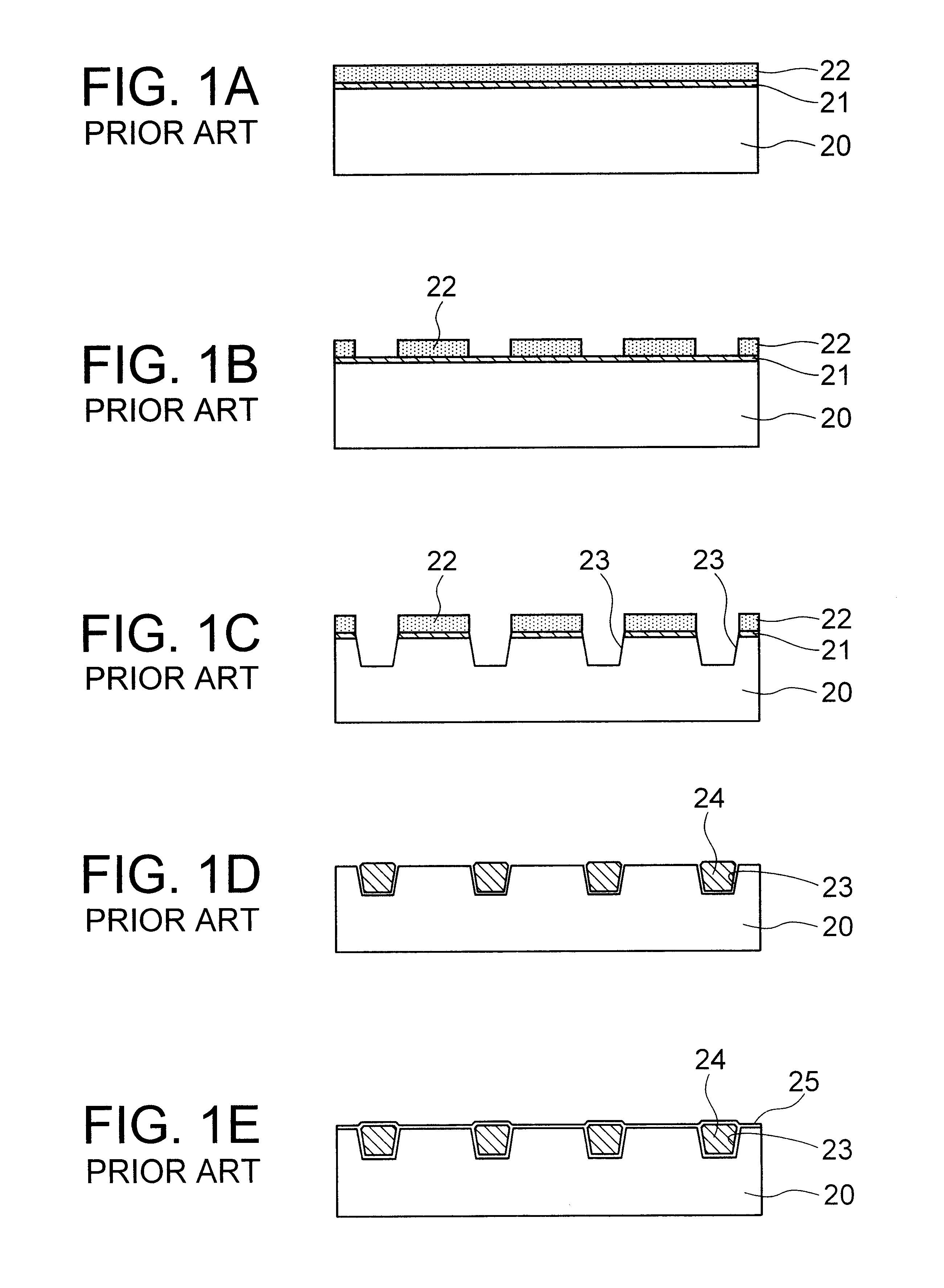

Semiconductor device including gate insulation films having different thicknesses

A method for forming three gate oxide films having different thicknesses in first through third circuit areas, respectively. The method includes the consecutive steps of forming a first gate oxide film having a largest thickness in all the areas, removing the first gate oxide film and forming a second gate oxide film having a second largest thickness in the second circuit area, and removing the first gate oxide and forming a third gate oxide film having a smallest thickness in the third circuit area. The resultant gate oxide films have accurate thicknesses.

Owner:RENESAS ELECTRONICS CORP

High density semiconductor memory cell and memory array using a single transistor and having variable gate oxide breakdown

A programmable memory cell comprised of a transistor located at the crosspoint of a column bitline and a row wordline is disclosed. The transistor has its gate formed from the column bitline and its source connected to the row wordline. The memory cell is programmed by applying a voltage potential between the column bitline and the row wordline to produce a programmed n+ region in the substrate underlying the gate of the transistor. Further, a gate dielectric of the transistor has a higher breakdown voltage near the source connected to the row wordline than its drain.

Owner:SYNOPSYS INC

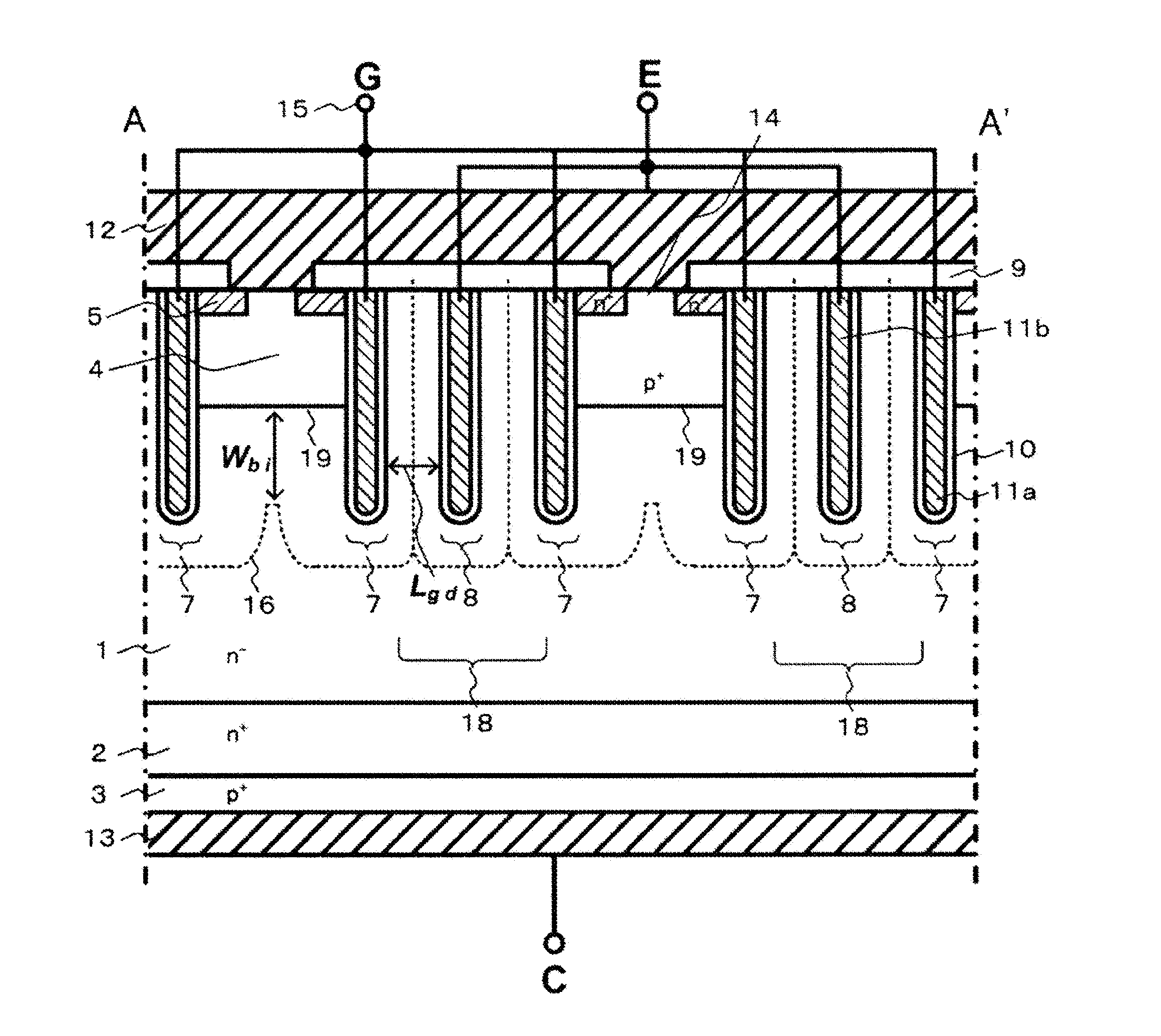

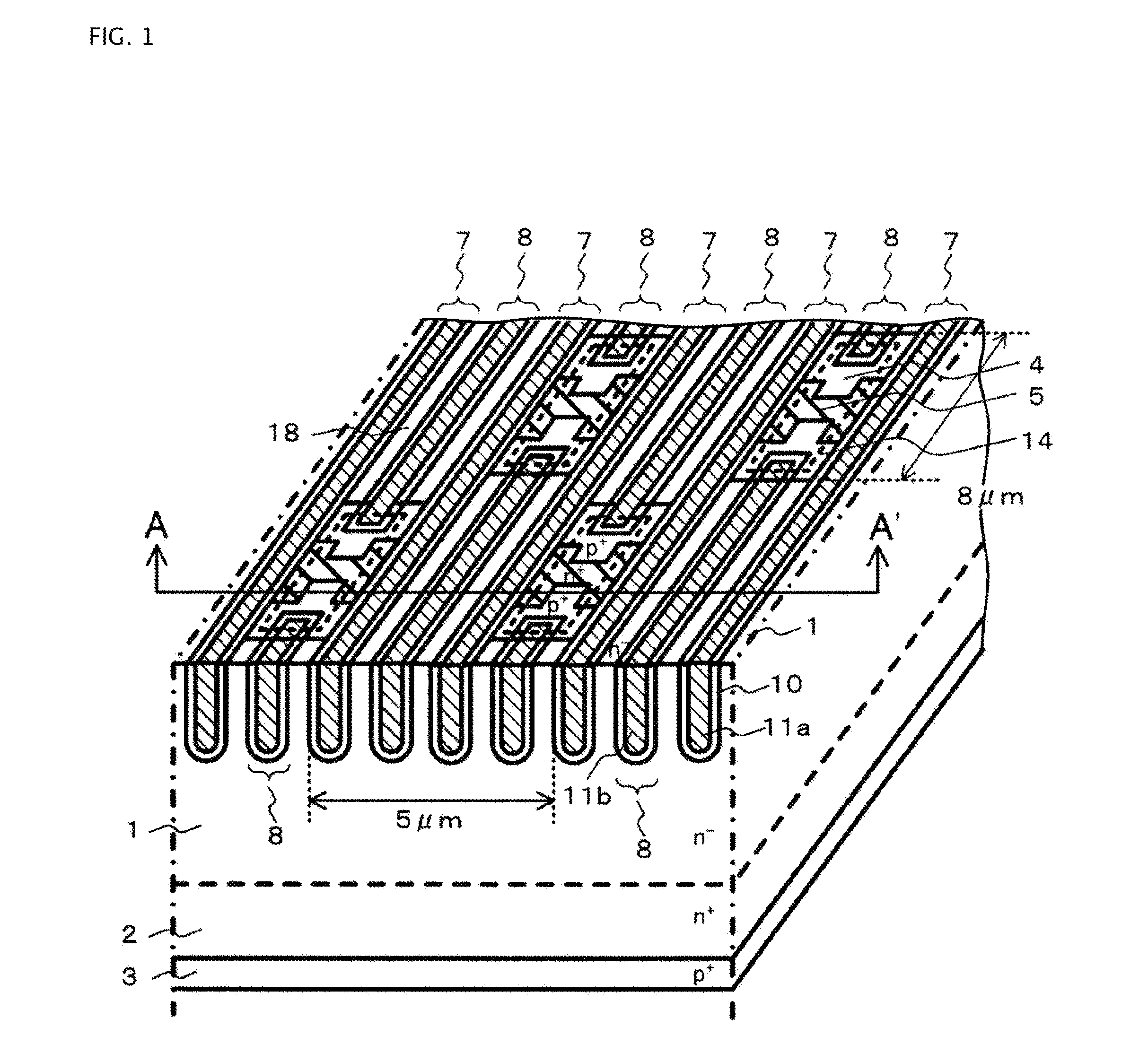

Semiconductor device

ActiveUS20130037853A1Miller capacitance is smallSolve the large switching lossSemiconductor devicesPower semiconductor deviceGate oxide

A semiconductor device includes a stripe-shaped gate trench formed in one major surface of n-type drift layer, a gate trench including gate polysilicon formed therein, and a gate polysilicon connected to a gate electrode. A p-type base layer is formed selectively in mesa region between adjacent gate trenches and a p-type base layer including an n-type emitter layer and connected to emitter electrode. One or more dummy trenches are formed between p-type base layers adjoining to each other in the extending direction of gate trenches. An electrically conductive dummy polysilicon is formed on an inner side wall of dummy trench with a gate oxide film interposed between the dummy polysilicon and dummy trench. The dummy polysilicon is spaced apart from the gate polysilicon and may be connected to the emitter electrode.

Owner:FUJI ELECTRIC CO LTD

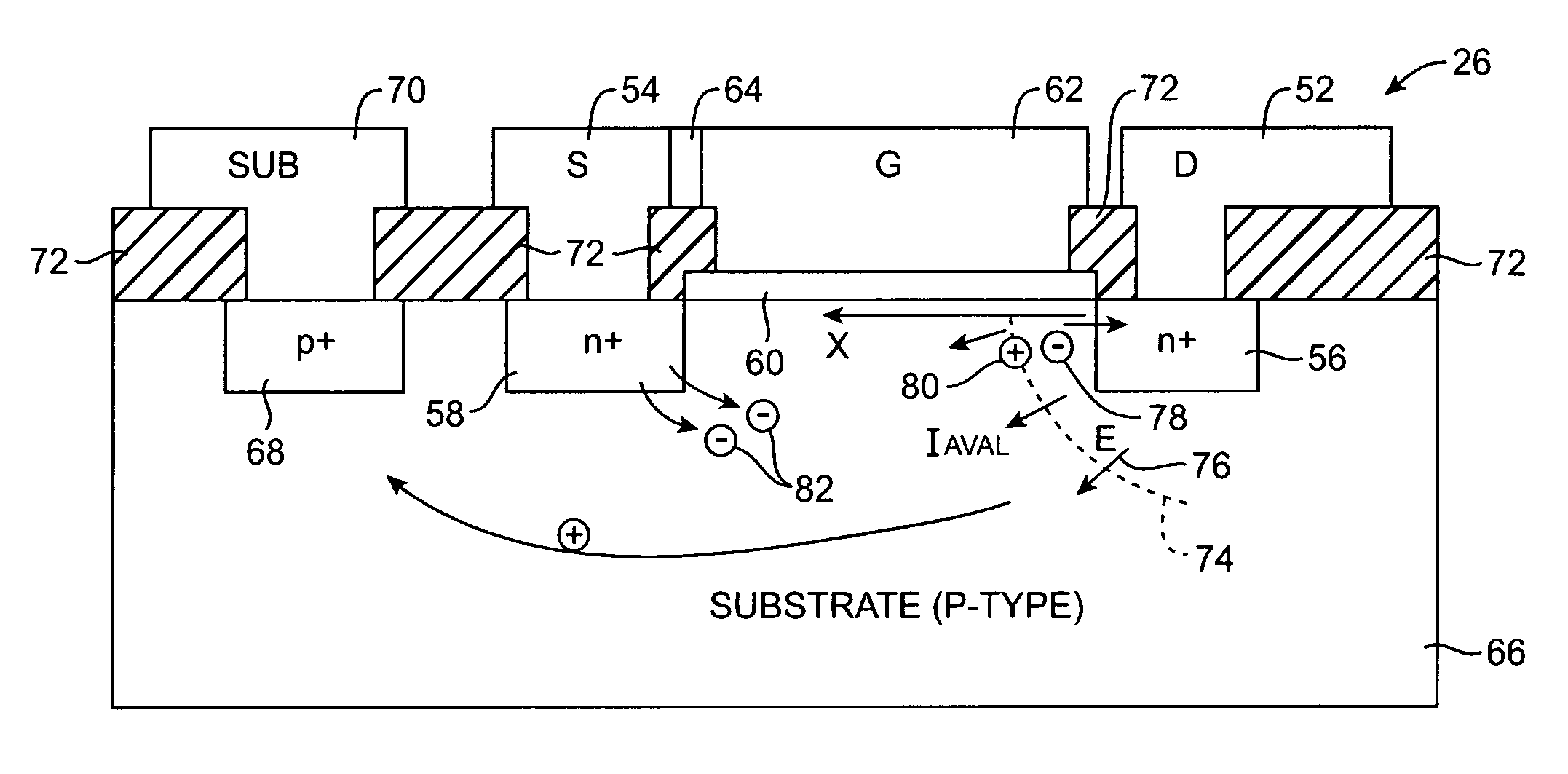

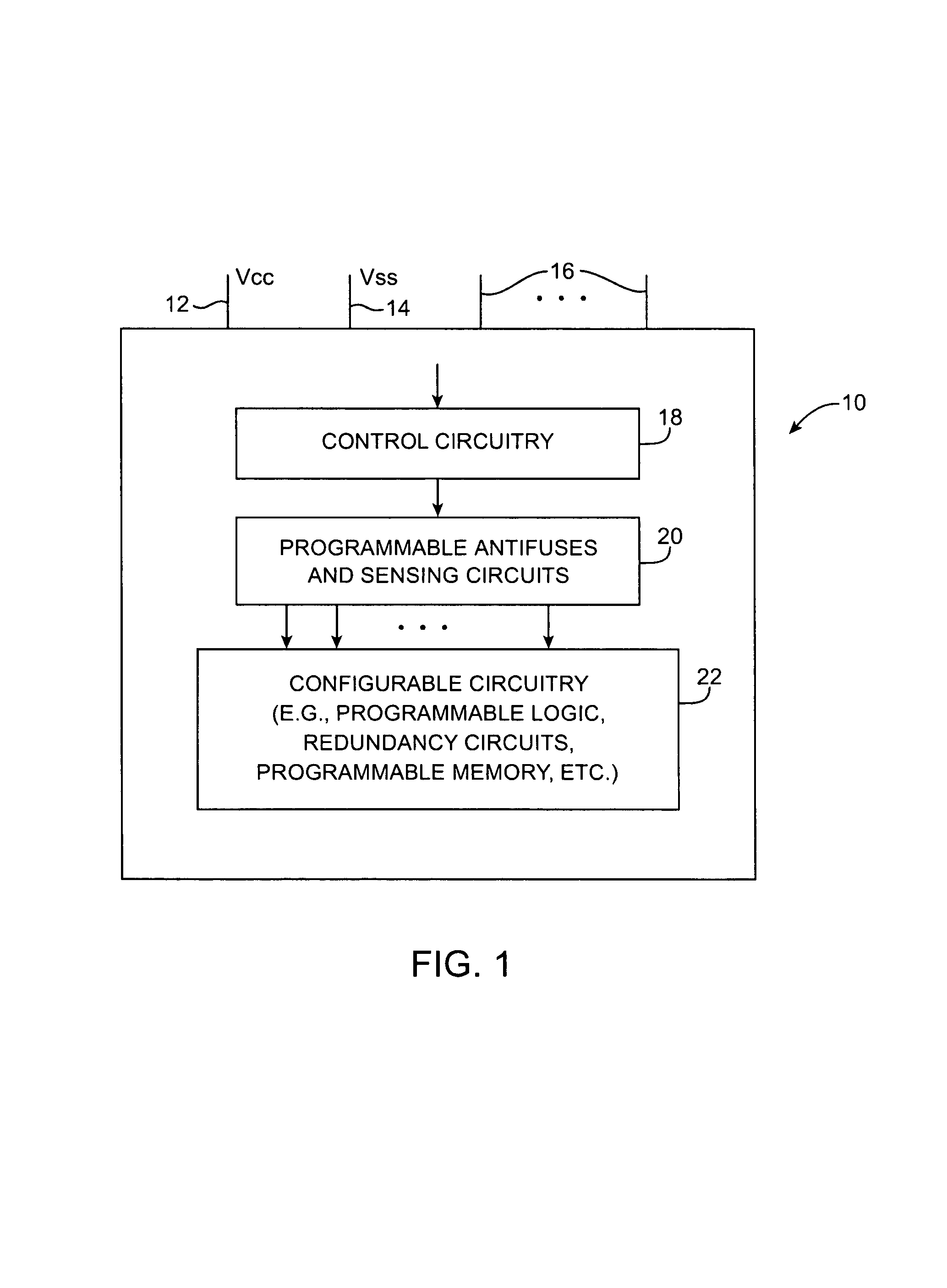

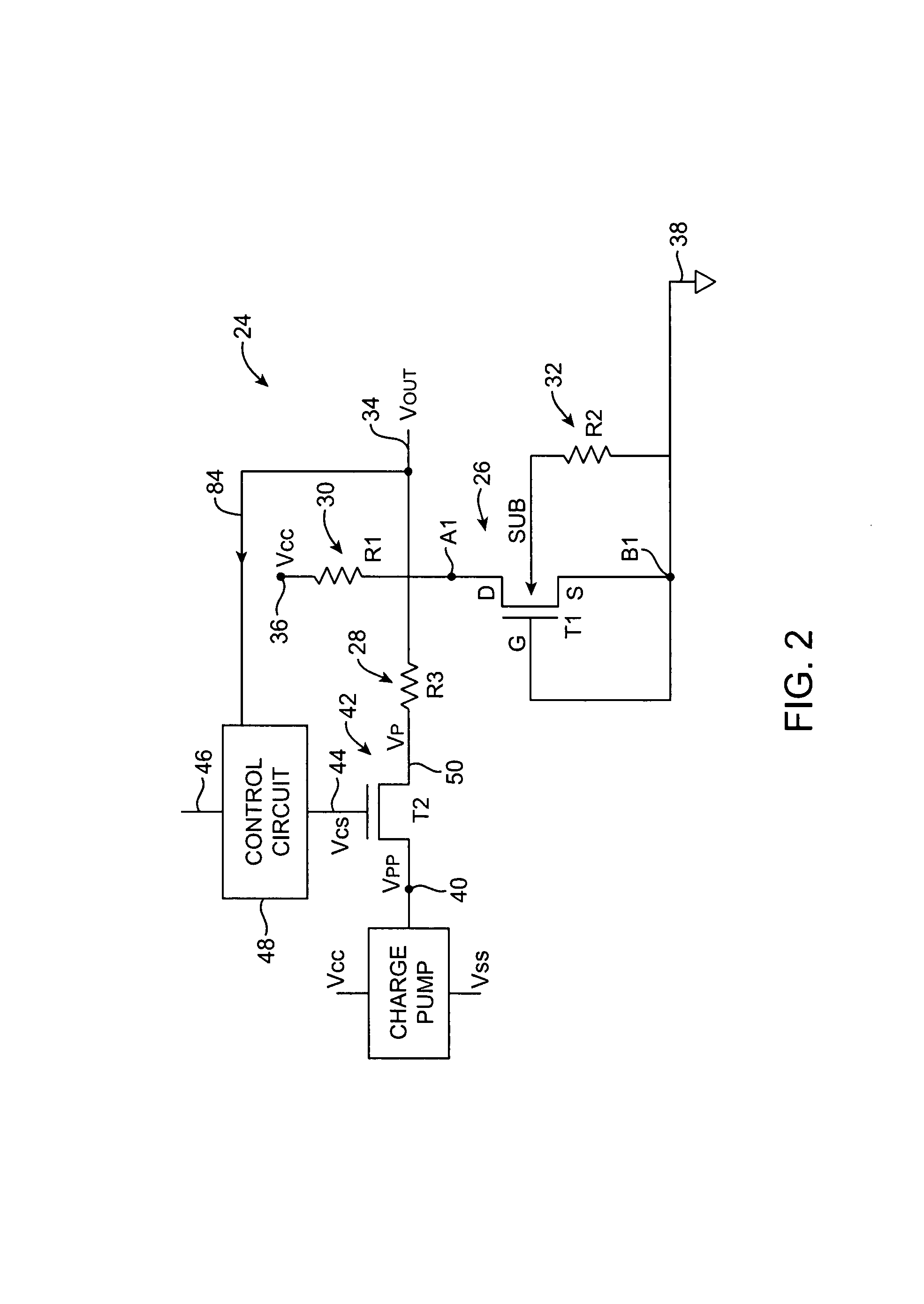

Electrically-programmable transistor antifuses

InactiveUS7157782B1Minimize powerMinimize timeTransistorSemiconductor/solid-state device detailsHigh resistanceEngineering

Integrated circuit antifuse circuitry is provided. A metal-oxide-semiconductor (MOS) transistor serves as an electrically-programmable antifuse. The antifuse transistor has source, drain, gate, and substrate terminals. The gate has an associated gate oxide. In its unprogrammed state, the gate oxide is intact and the antifuse has a relatively high resistance. During programming, the gate oxide breaks down, so in its programmed state the antifuse transistor has a relatively low resistance. The antifuse transistor can be programmed by injecting hot carriers into the substrate of the device in the vicinity of the drain. Because there are more hot carriers at the drain than at the substrate, the gate oxide is stressed asymmetrically, which enhances programming efficiency. Feedback can be used to assist in turning the antifuse transistor on to inject the hot carriers.

Owner:ALTERA CORP

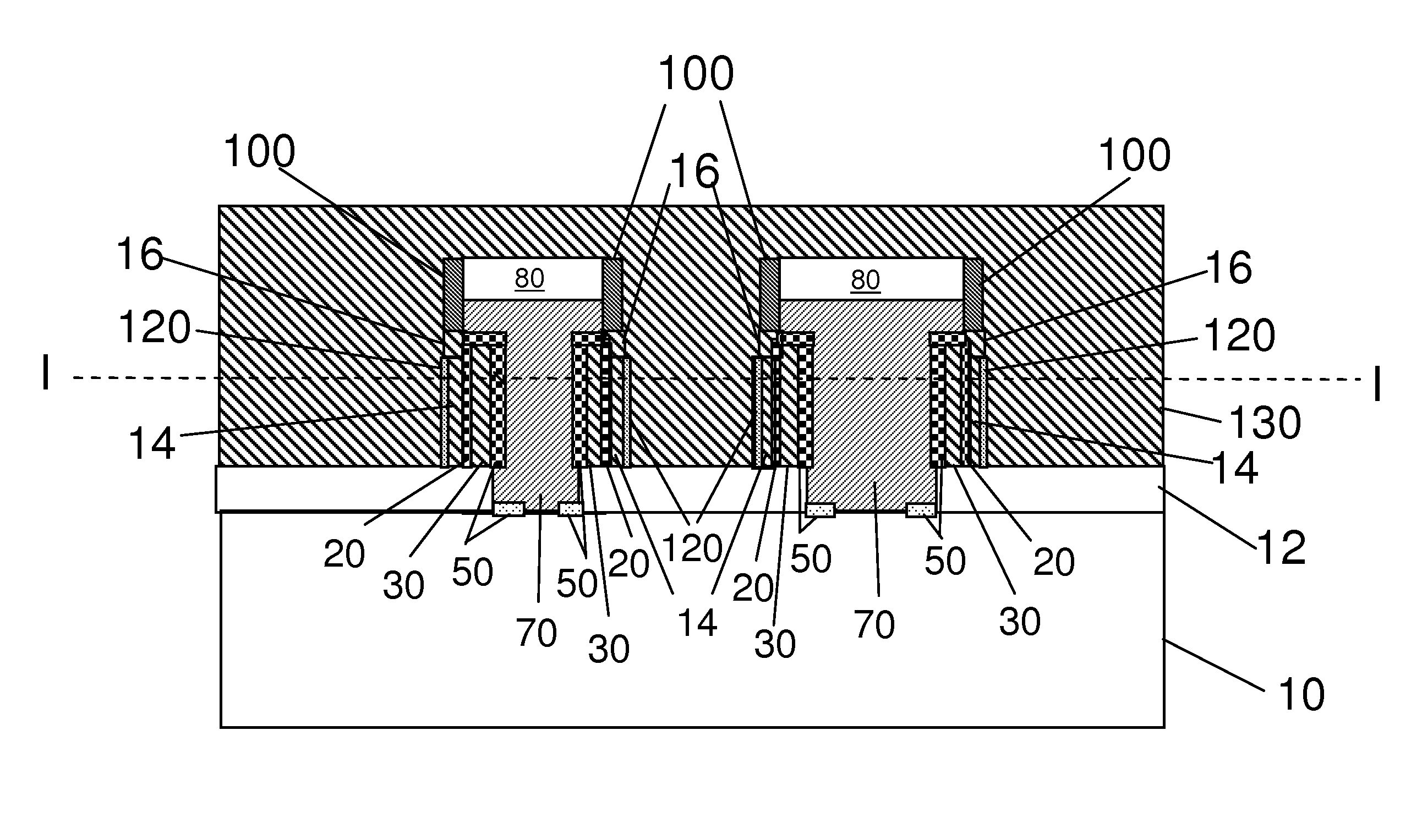

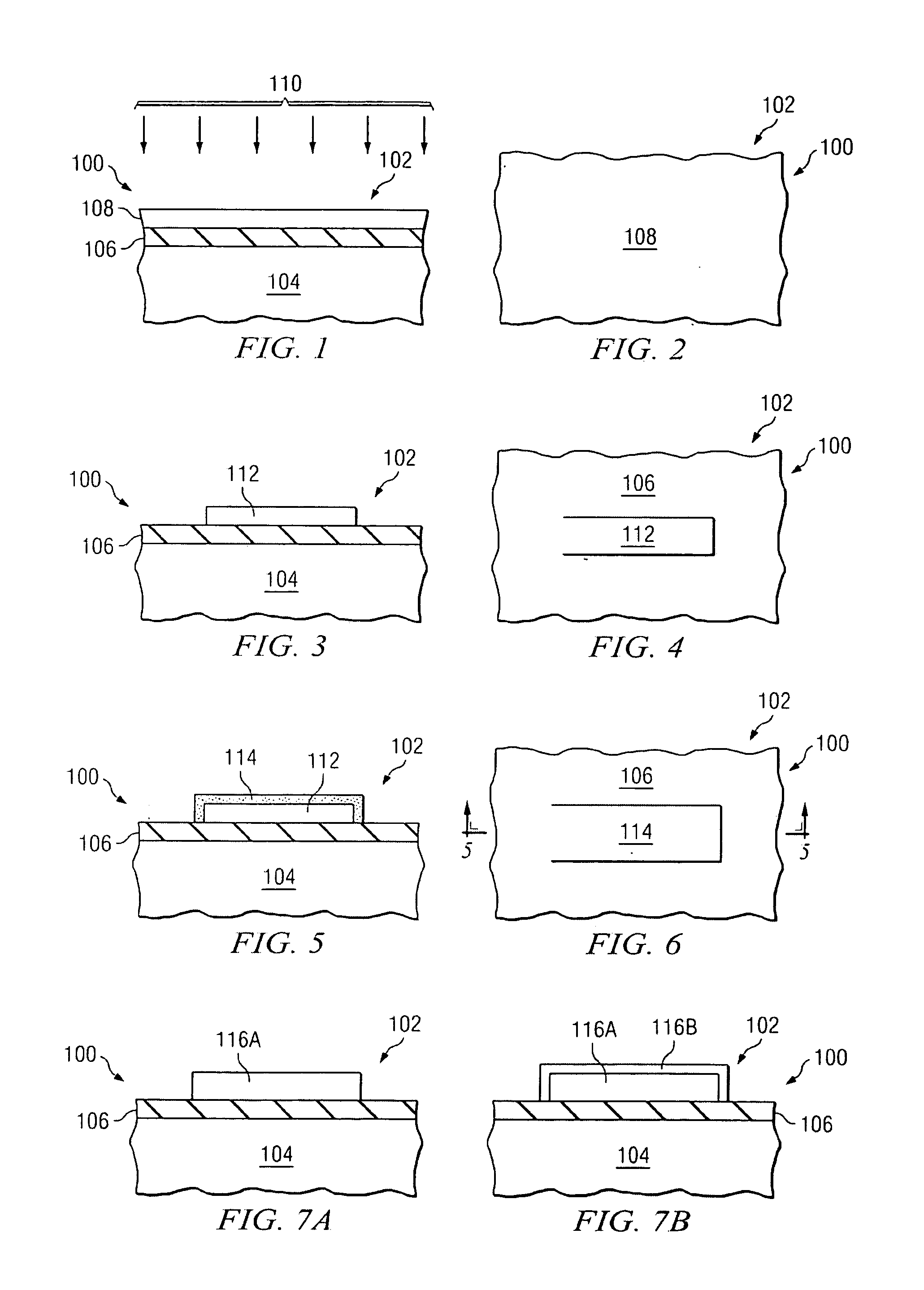

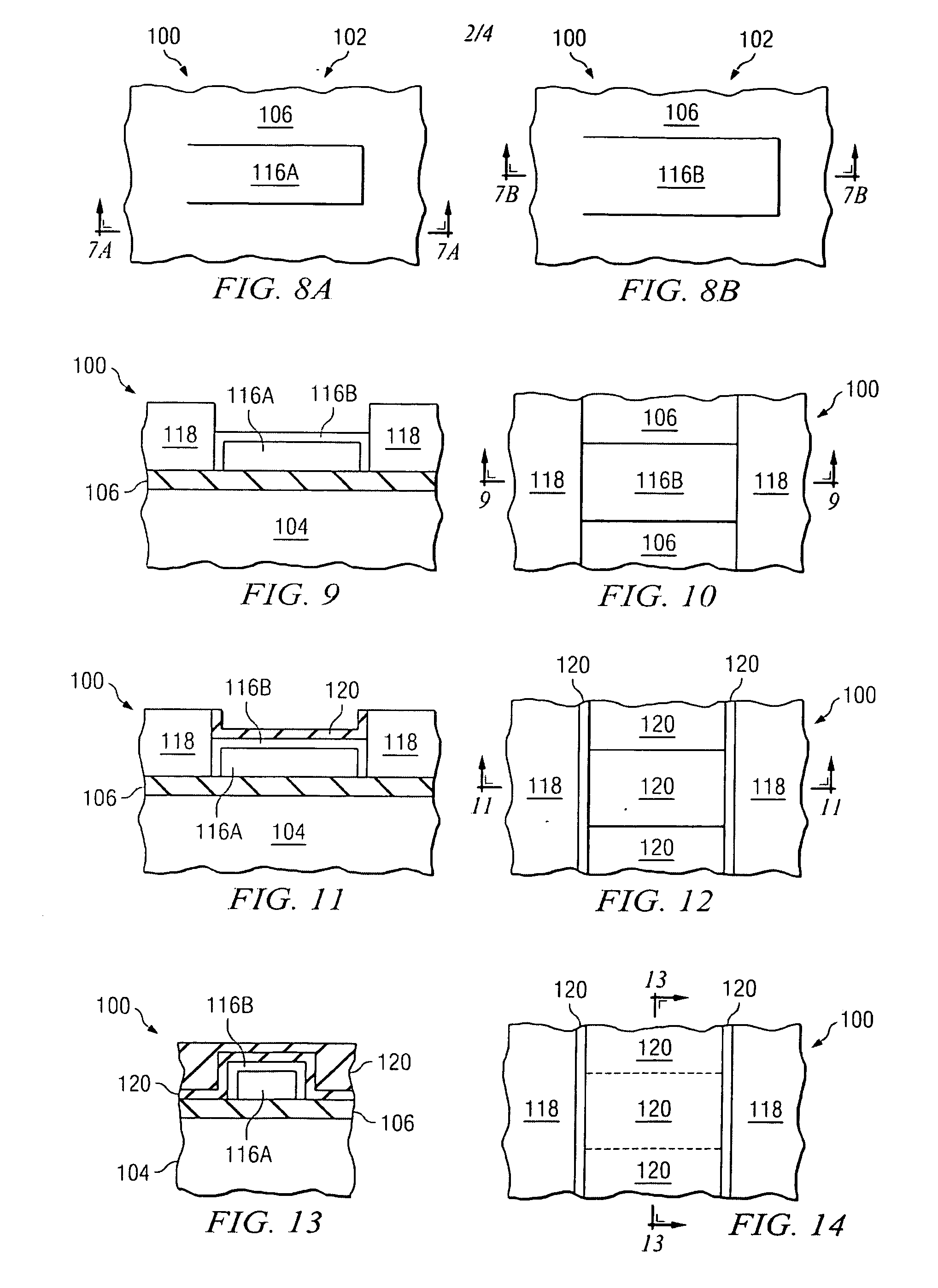

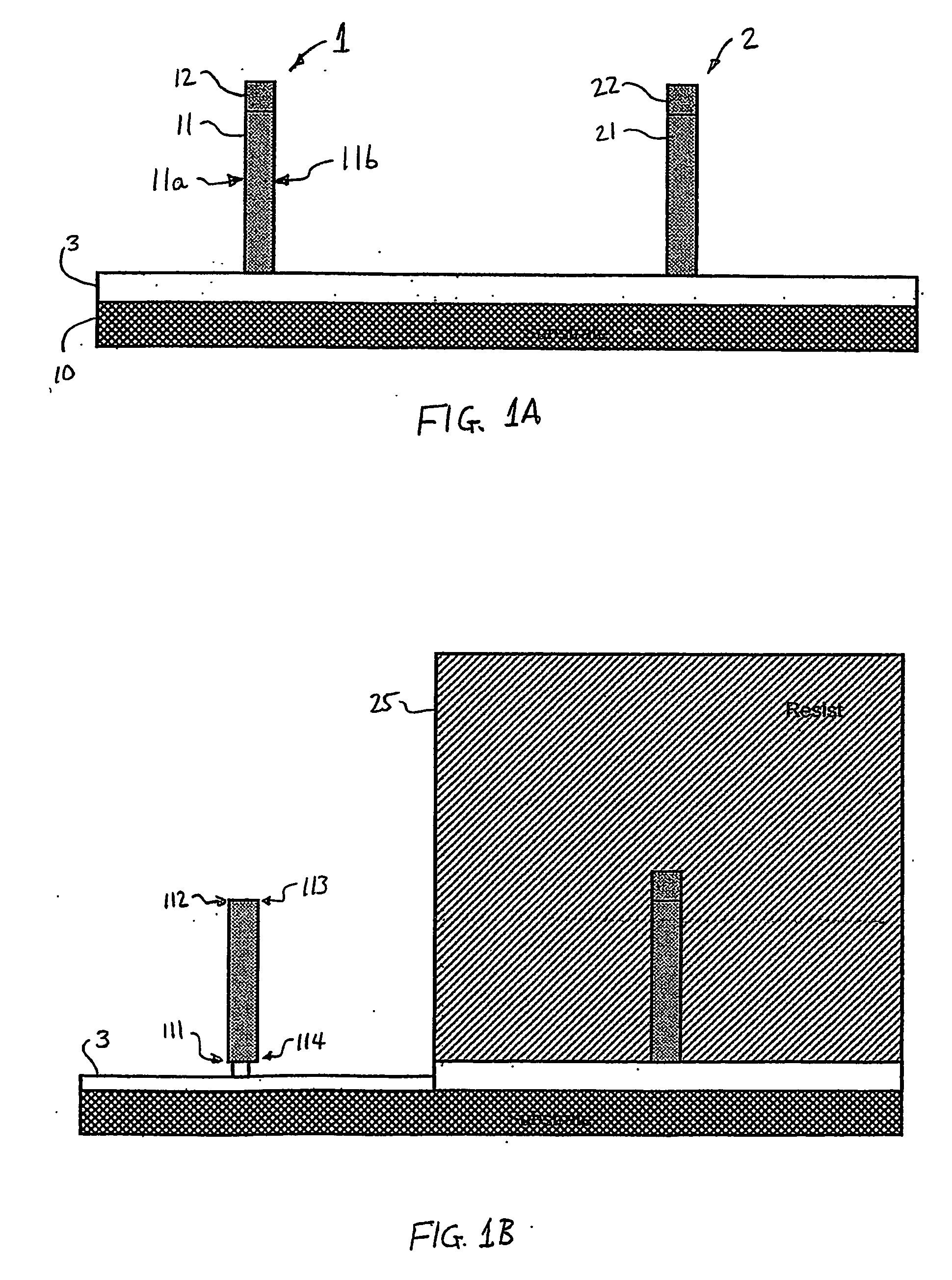

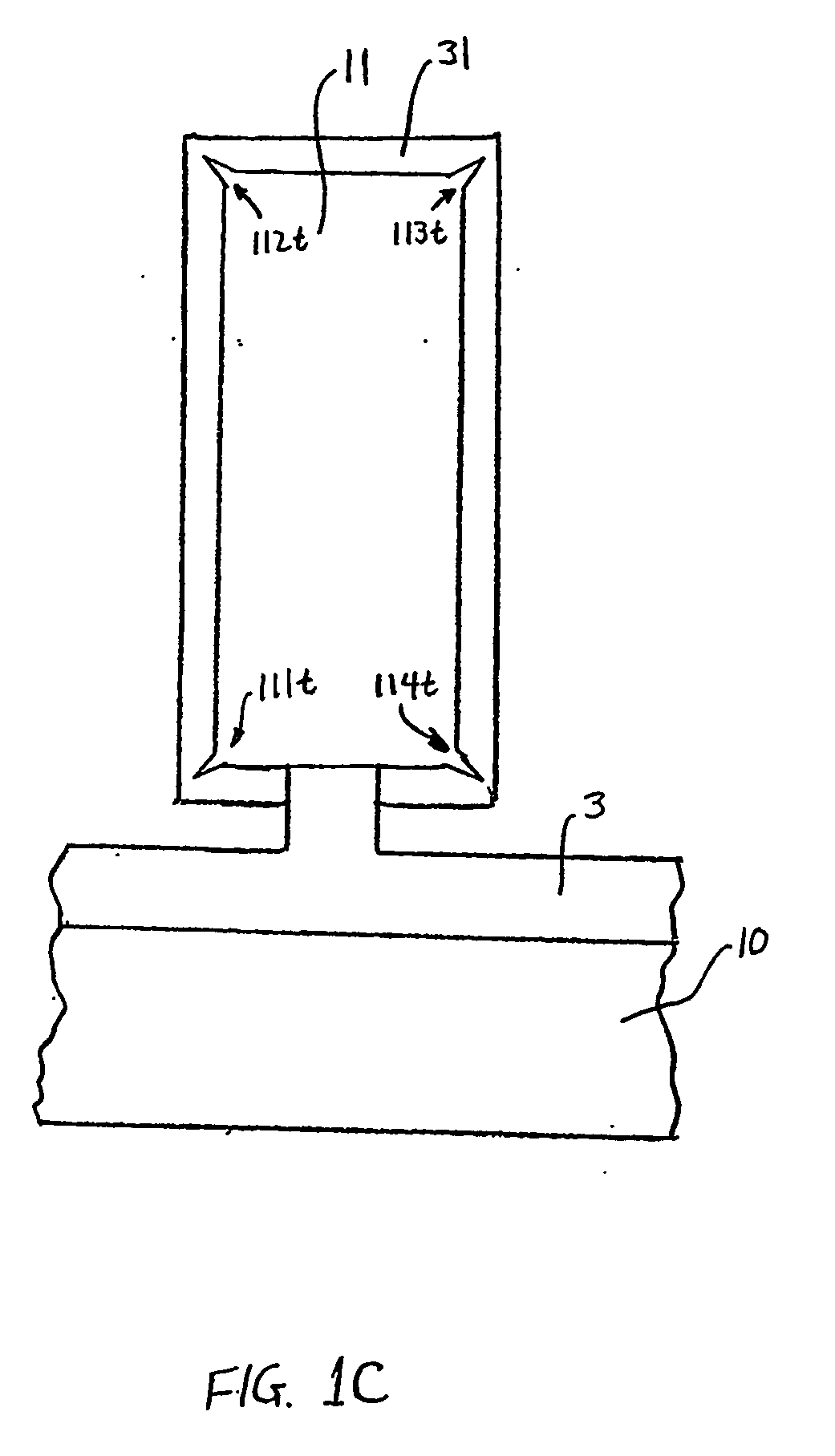

Integrated antifuse structure for finfet and cmos devices

InactiveUS20060128071A1Solid-state devicesSemiconductor/solid-state device manufacturingCMOSSemiconductor materials

A method is described for fabricating and antifuse structure (100) integrated with a semiconductor device such as a FINFET or planar CMOS devise. A region of semiconducting material (11) is provided overlying an insulator (3) disposed on a substrate (10); an etching process exposes a plurality of corners (111-114) in the semiconducting material. The exposed corners are oxidized to form elongated tips (111t-114t) at the corners; the oxide (31) overlying the tips is removed. An oxide layer (51), such as a gate oxide, is then formed on the semiconducting material and overlying the corners; this layer has a reduced thickness at the corners. A layer of conducting material (60) is formed in contact with the oxide layer (51) at the corners, thereby forming a plurality of possible breakdown paths between the semiconducting material and the layer of conducting material through the oxide layer. Applying a voltage, such as a burn-in voltage, to the structure converts at least one of the breakdown paths to a conducting path (103, 280).

Owner:GLOBALFOUNDRIES US INC

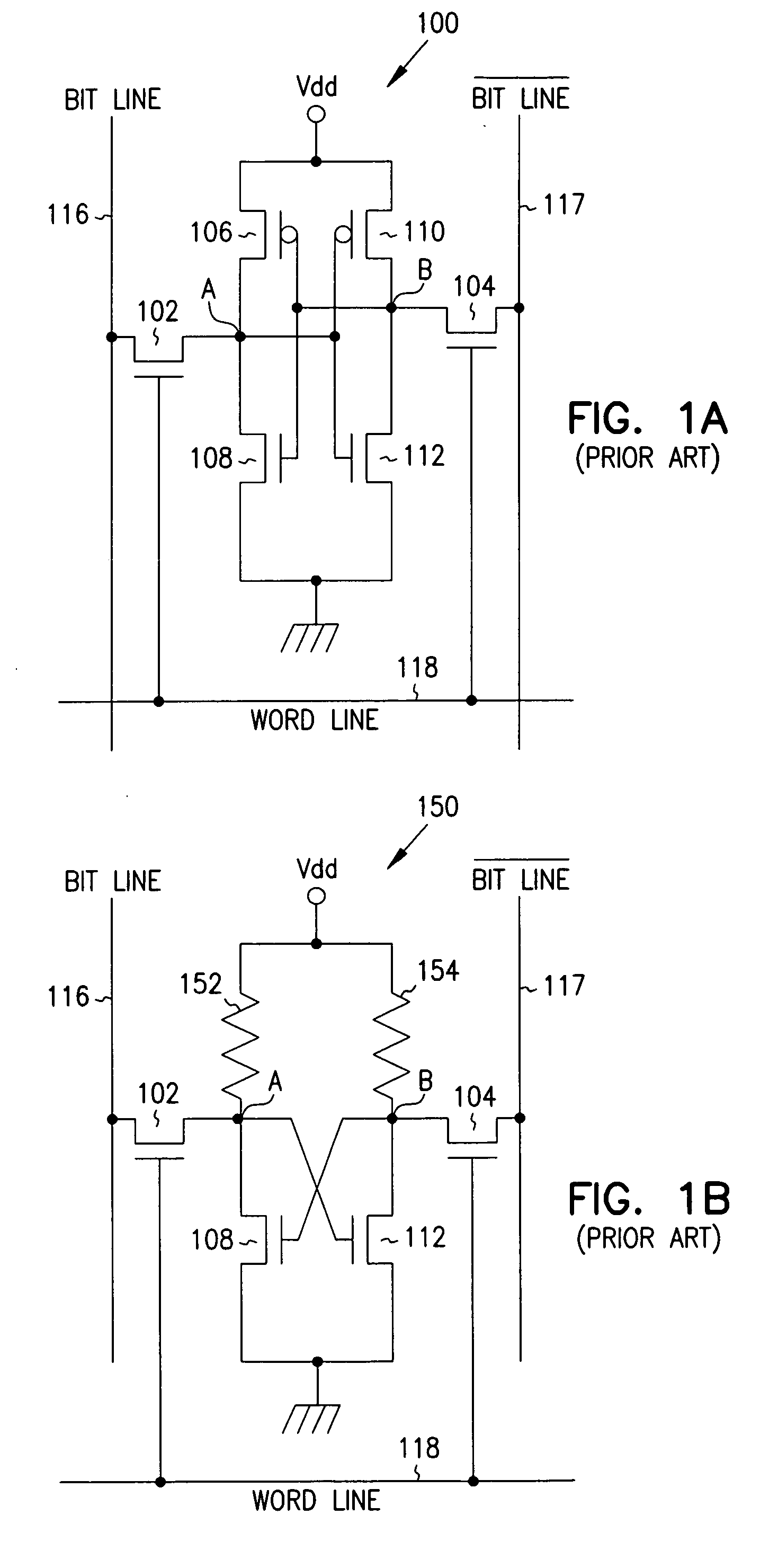

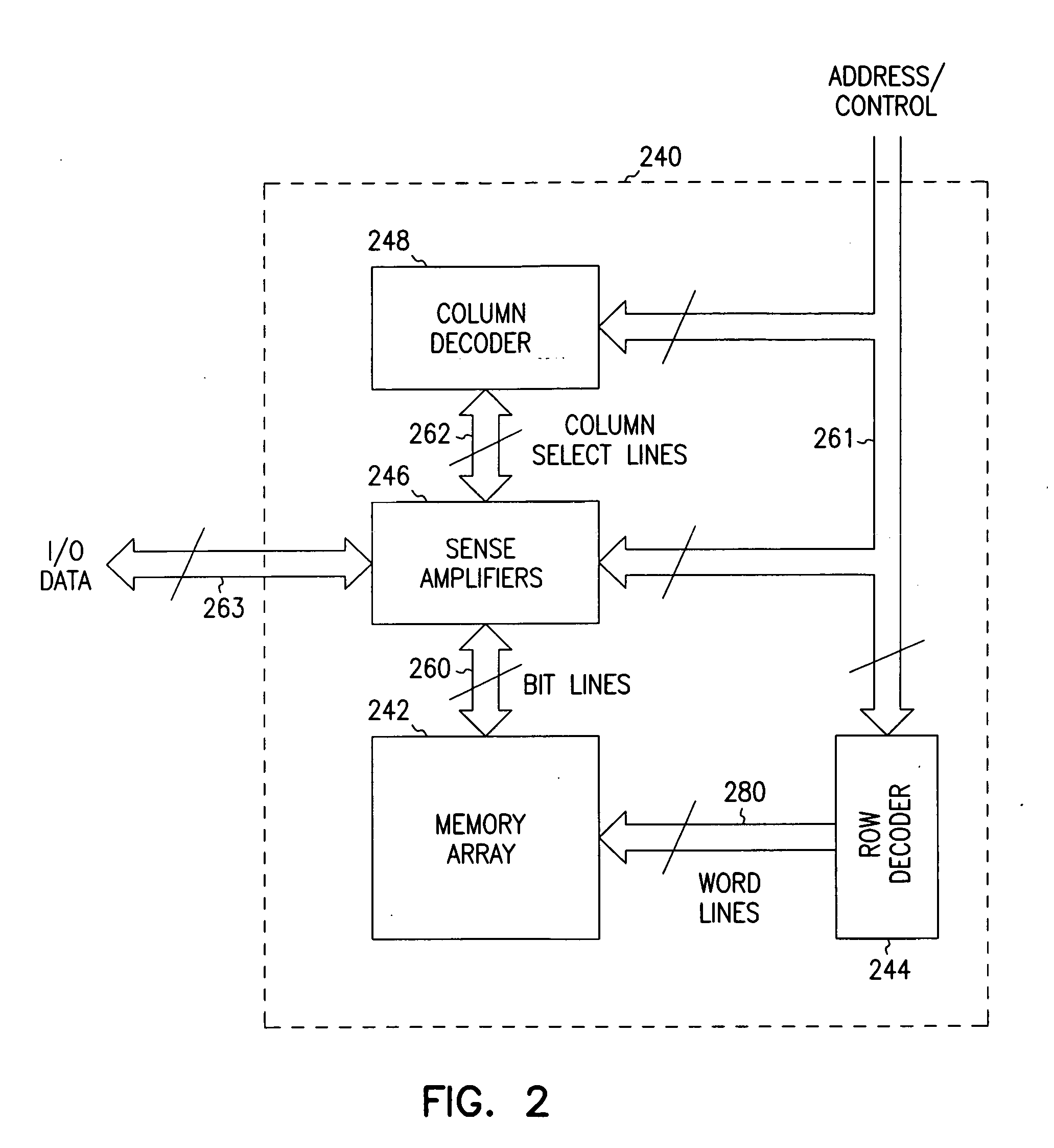

SRAM cells with repressed floating gate memory, low tunnel barrier interpoly insulators

InactiveUS20050169054A1Solid-state devicesSemiconductor/solid-state device manufacturingGate oxideSram cell

Structures and methods are provided for SRAM cells having a novel, non-volatile floating gate transistor, e.g. a non-volatile memory component, within the cell which can be programmed to provide the SRAM cell with a definitive asymmetry so that the cell always starts in a particular state. The SRAM cells include a pair of cross coupled transistors. At least one of the cross coupled transistors includes a first source / drain region and a second source / drain region separated by a channel region in a substrate. A floating gate opposes the channel region and separated therefrom by a gate oxide. A control gate opposes the floating gate. The control gate is separated from the floating gate by a low tunnel barrier intergate insulator.

Owner:MICRON TECH INC