Patents

Literature

473results about How to "More cost-effectively" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

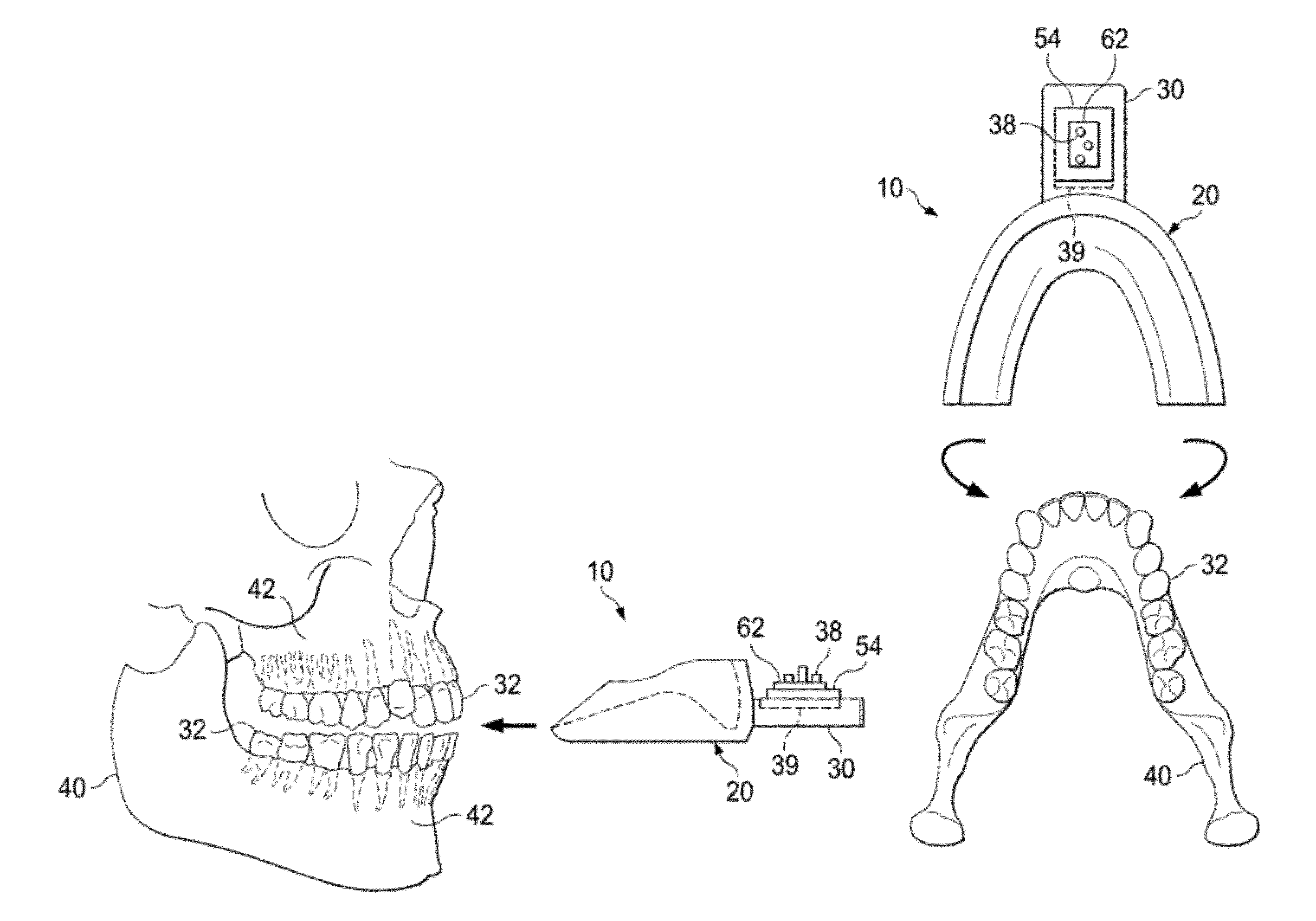

Surgical templates

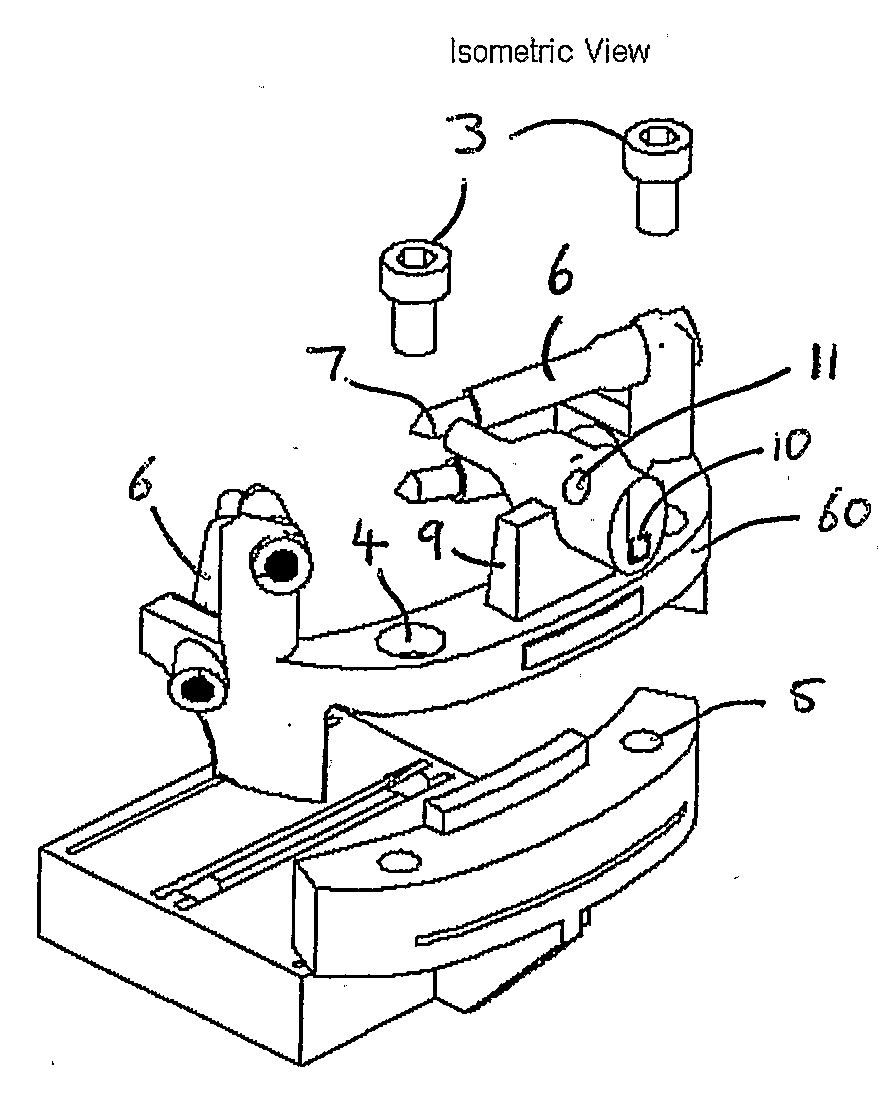

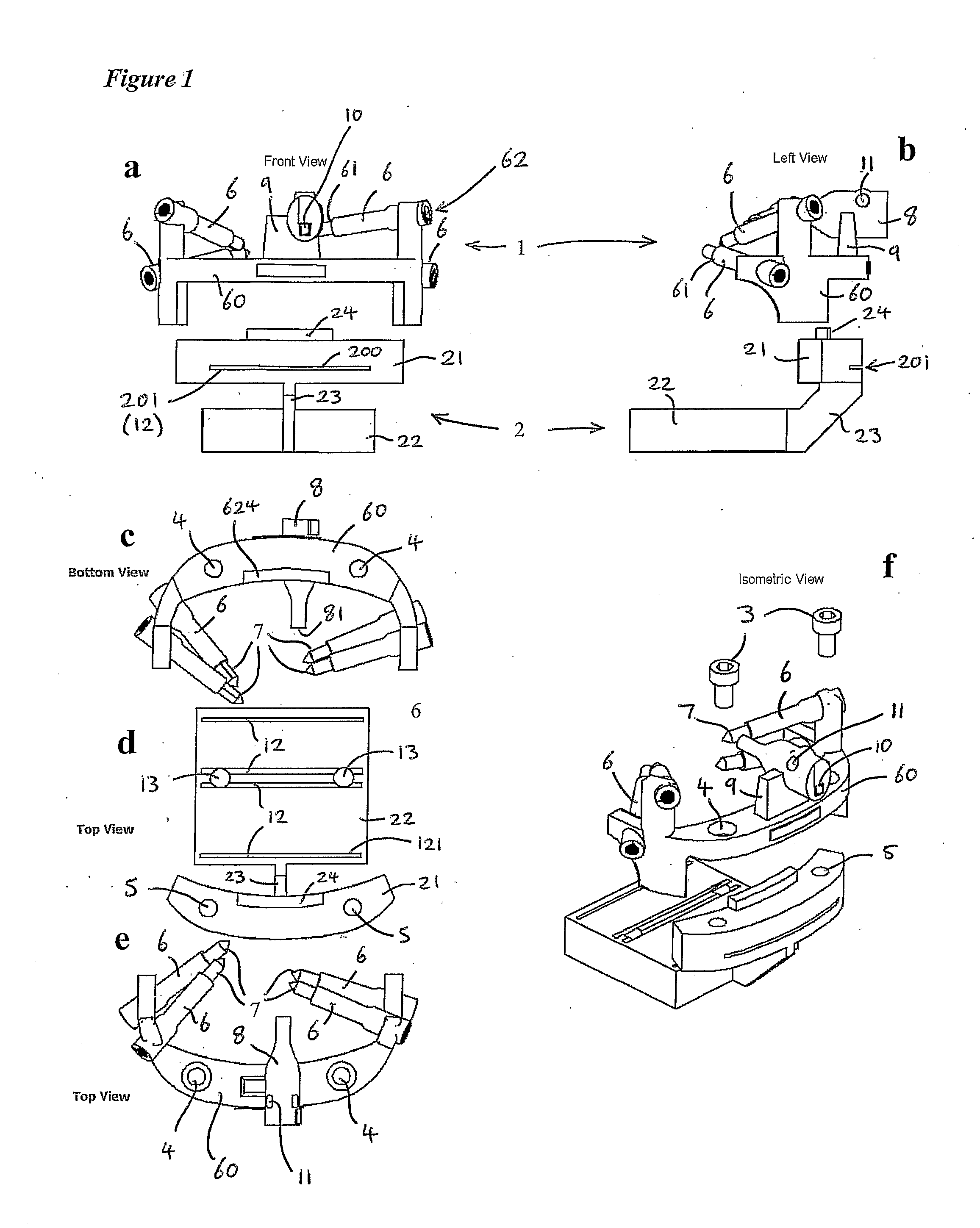

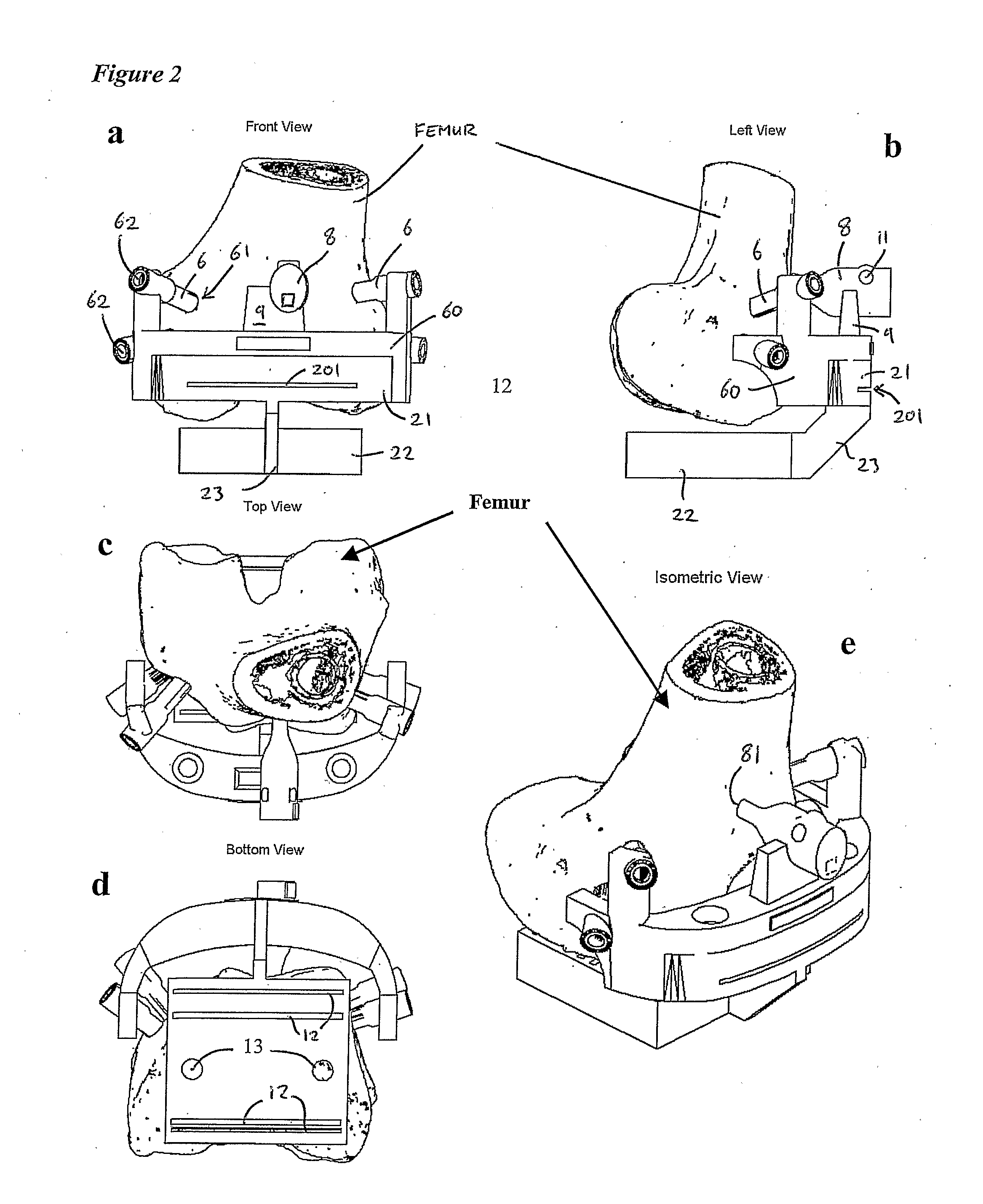

ActiveUS20100191244A1Quick checkShort timeAdditive manufacturing apparatusDiagnosticsProsthesisSurgical template

A surgical template system for use in working on a bone comprises: a tool guide block comprising at least one guide aperture for receiving and guiding a tool to work on a bone; locating means comprising a plurality of locating members, each member having a respective end surface for positioning against a surface of the bone; and attachment means for non-adjustably attaching the tool guide block to the locating means such that, when attached, the member end surfaces are secured in fixed position with, respect to each other, for engaging different respective portions of the surface of the bone, and the at least one guide aperture is secured in a fixed position with respect to the end surfaces. Corresponding methods of manufacturing a surgical template system, methods of manufacturing locating means for a surgical template system, methods of fitting a prosthesis to a bone, surgical methods, and surgical apparatus are described.

Owner:XIROS

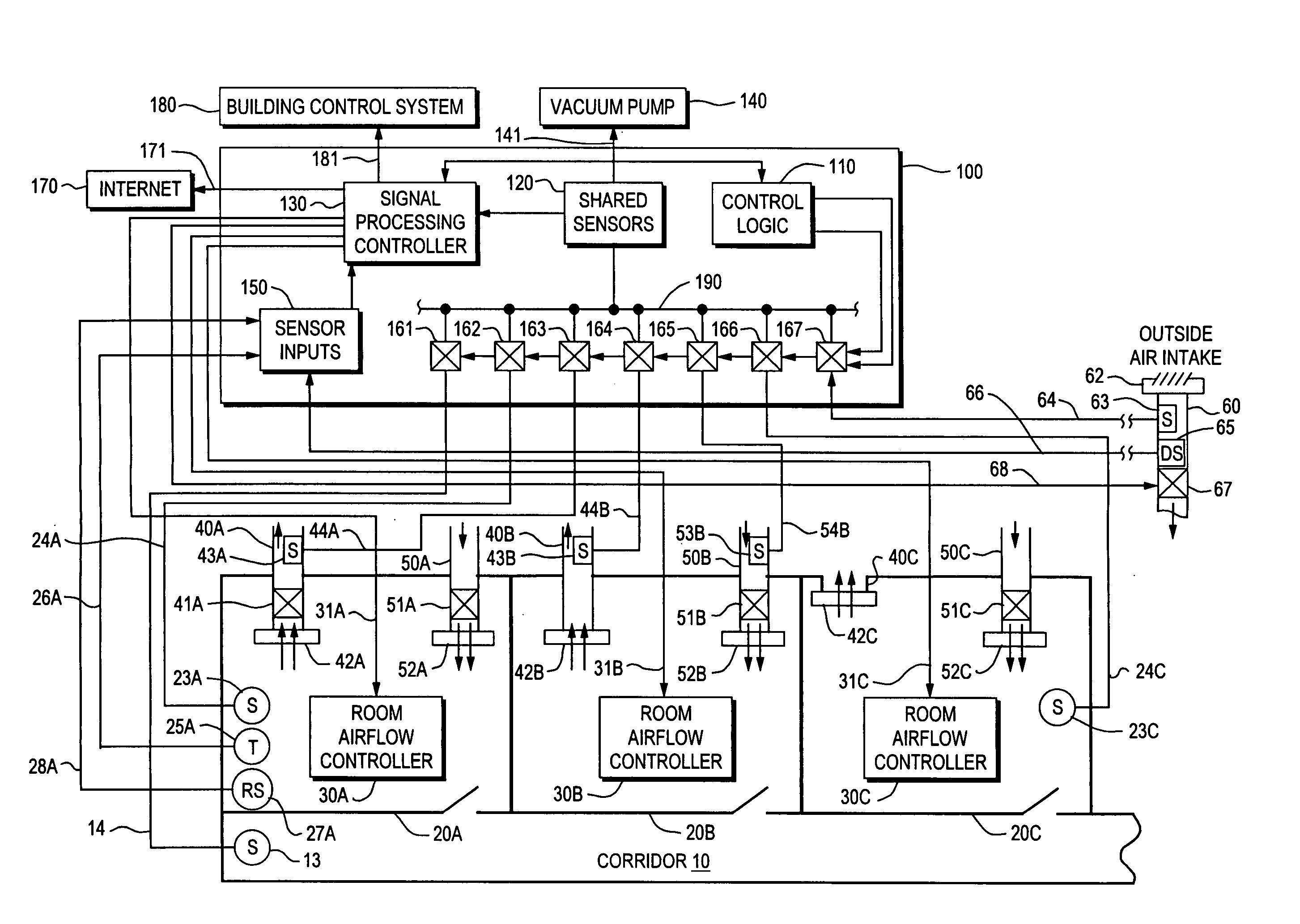

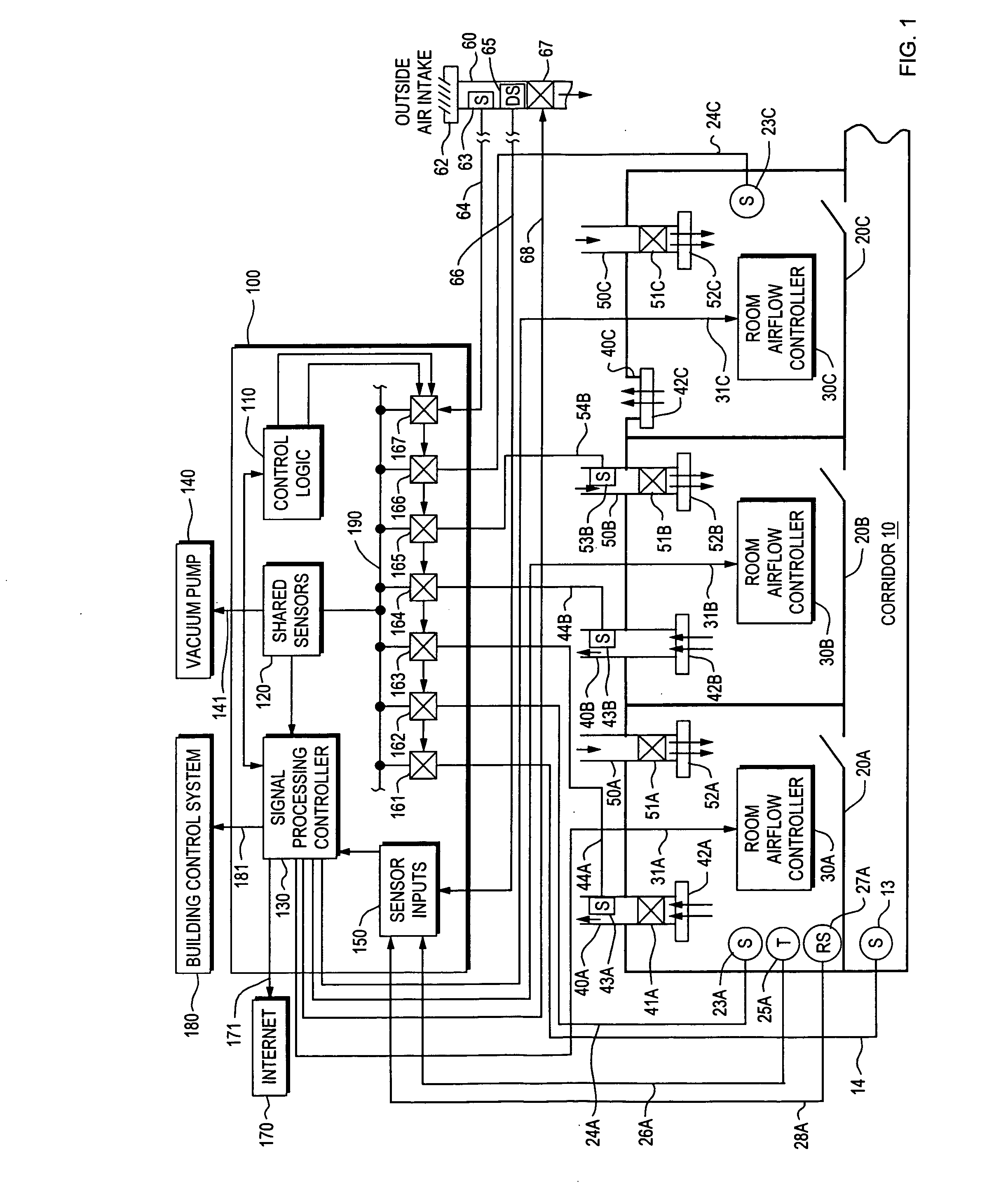

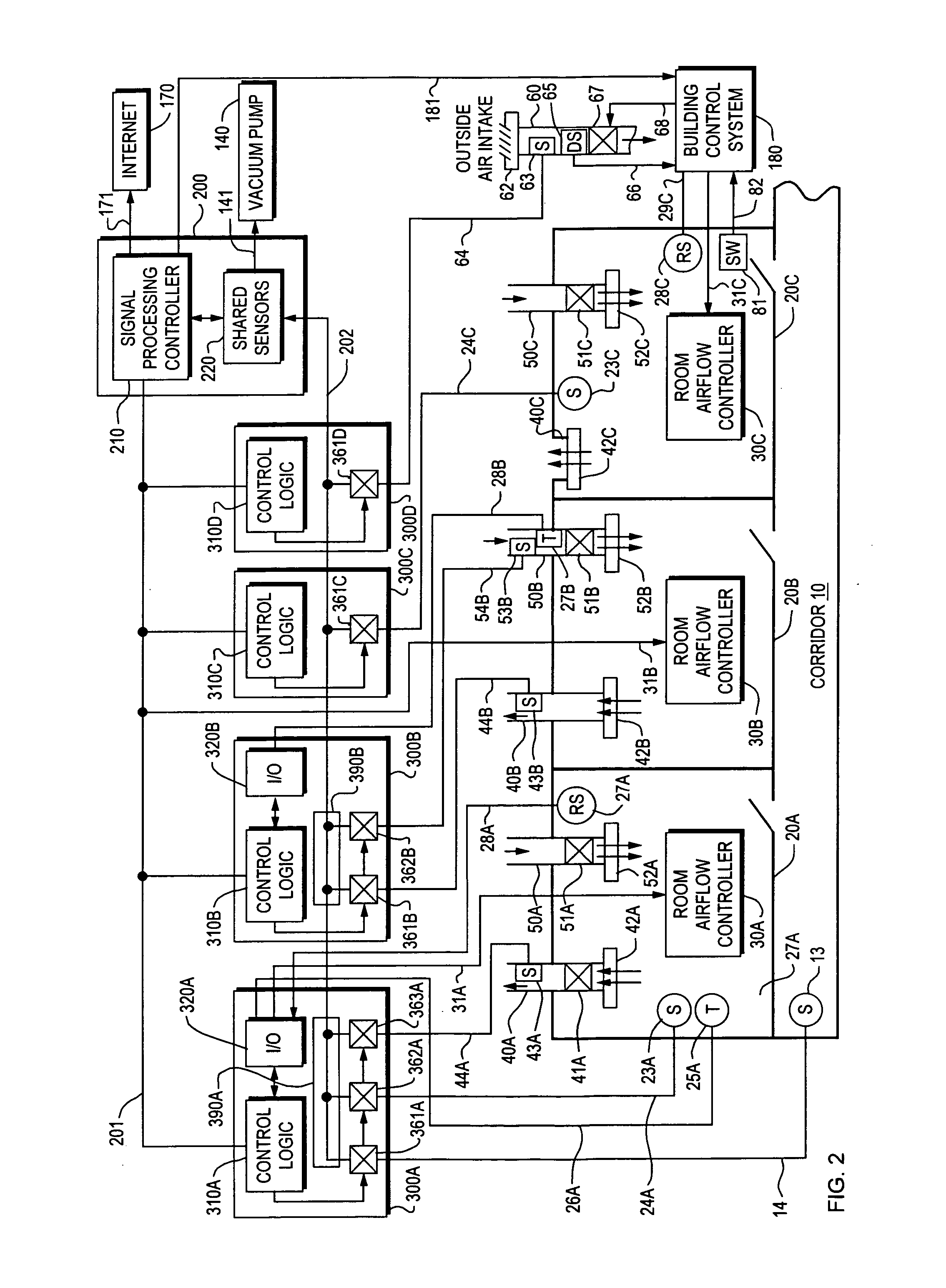

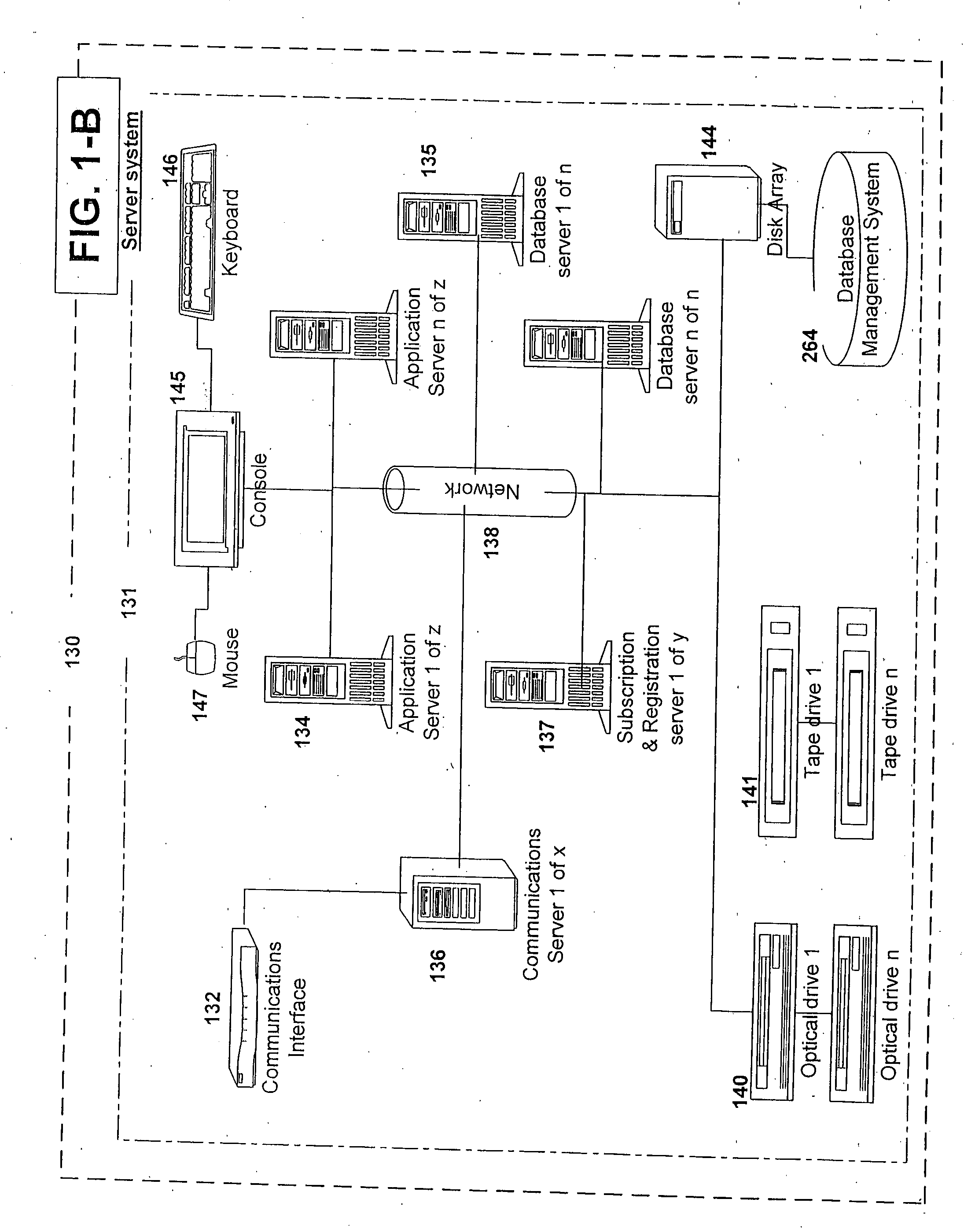

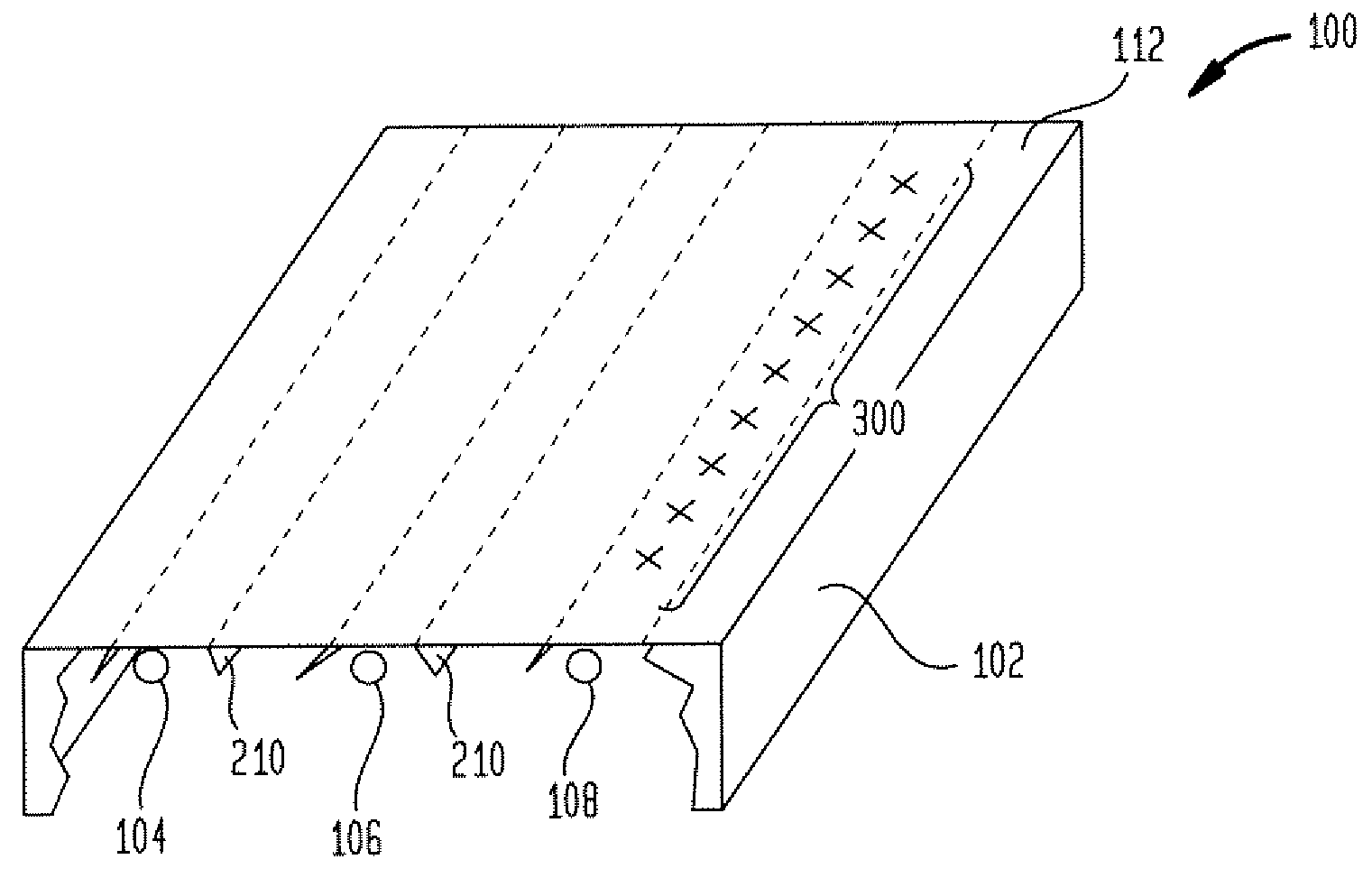

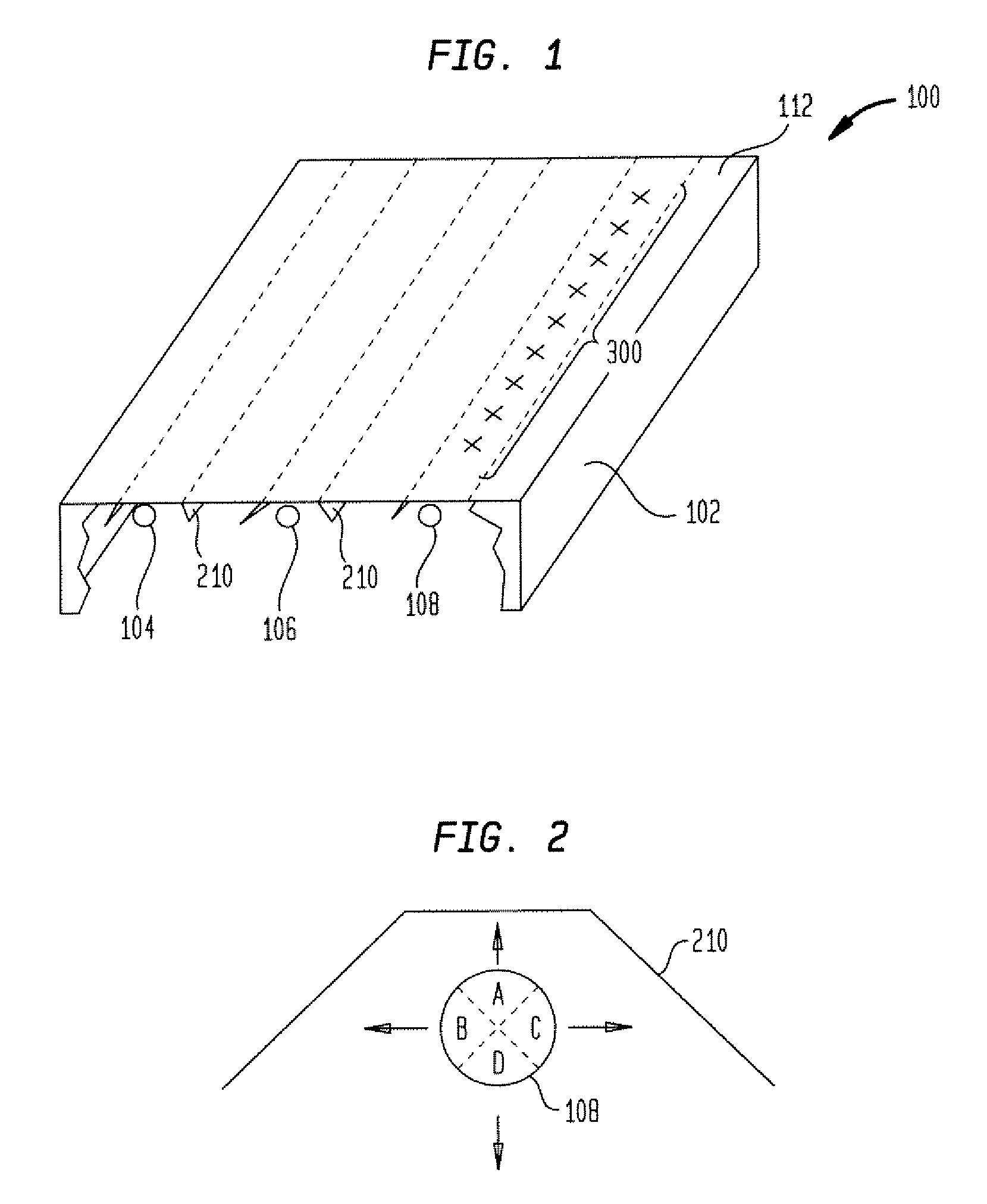

Multipoint air sampling system having common sensors to provide blended air quality parameter information for monitoring and building control

ActiveUS20060234621A1Improve accuracyMore accuratelySampled-variable control systemsSpace heating and ventilationAir monitoringQuality data

A system for monitoring air quality conditions, comprising, a multi-point air monitoring system comprising, a plurality of sensors for collecting air quality data from a plurality of at least partially enclosed areas; one or more data processing units for processing one or more air quality parameters based on the collected air quality data; and one or more communication devices for communicating the data from the sensor to the processing unit; and a signal processing controller that generates one or more blended air quality parameter signals via the multi-point air monitoring system based at least in part on one or more of the processed air quality parameters representative of data from a plurality of the sensors.

Owner:AIRCUITY

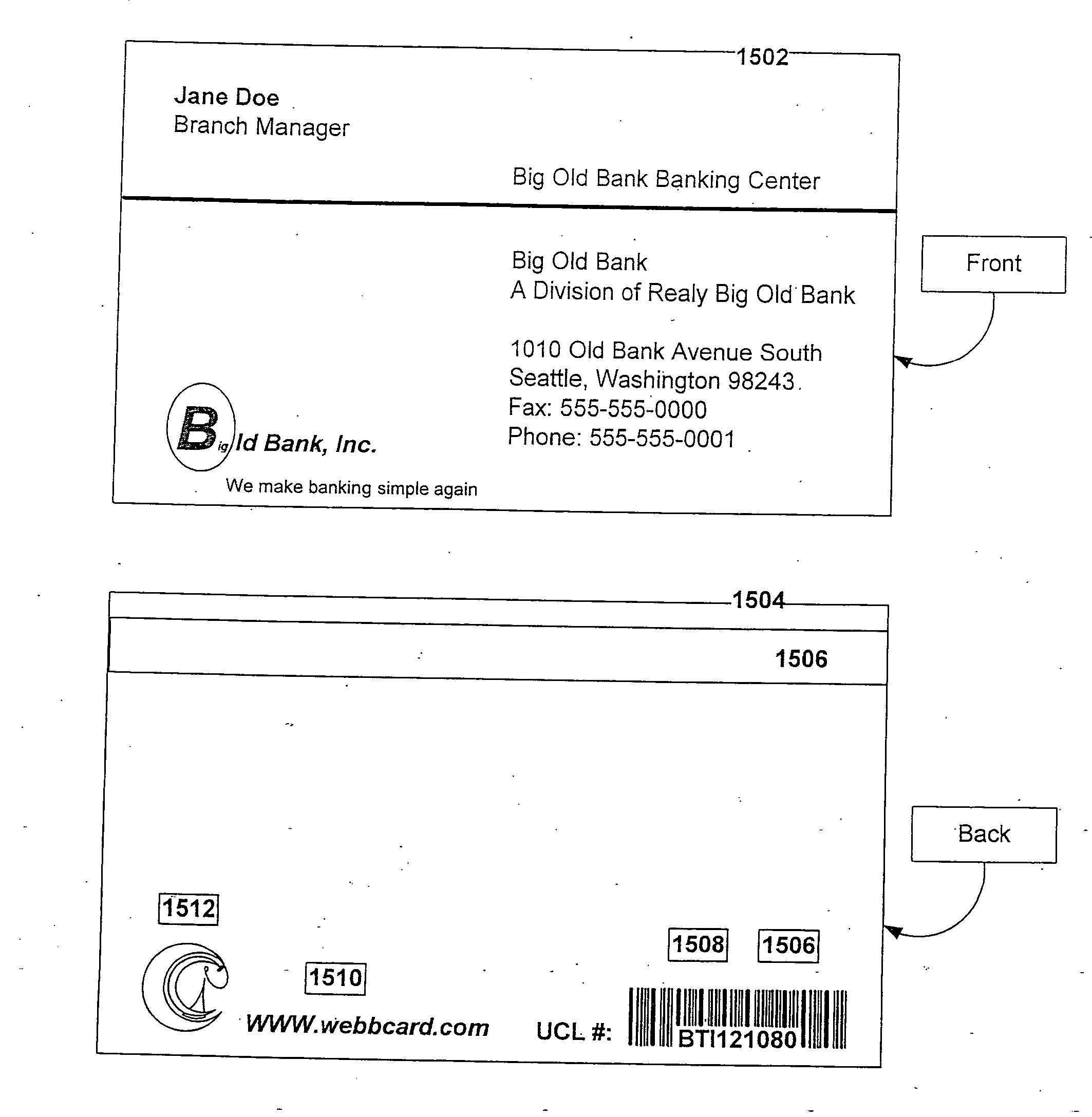

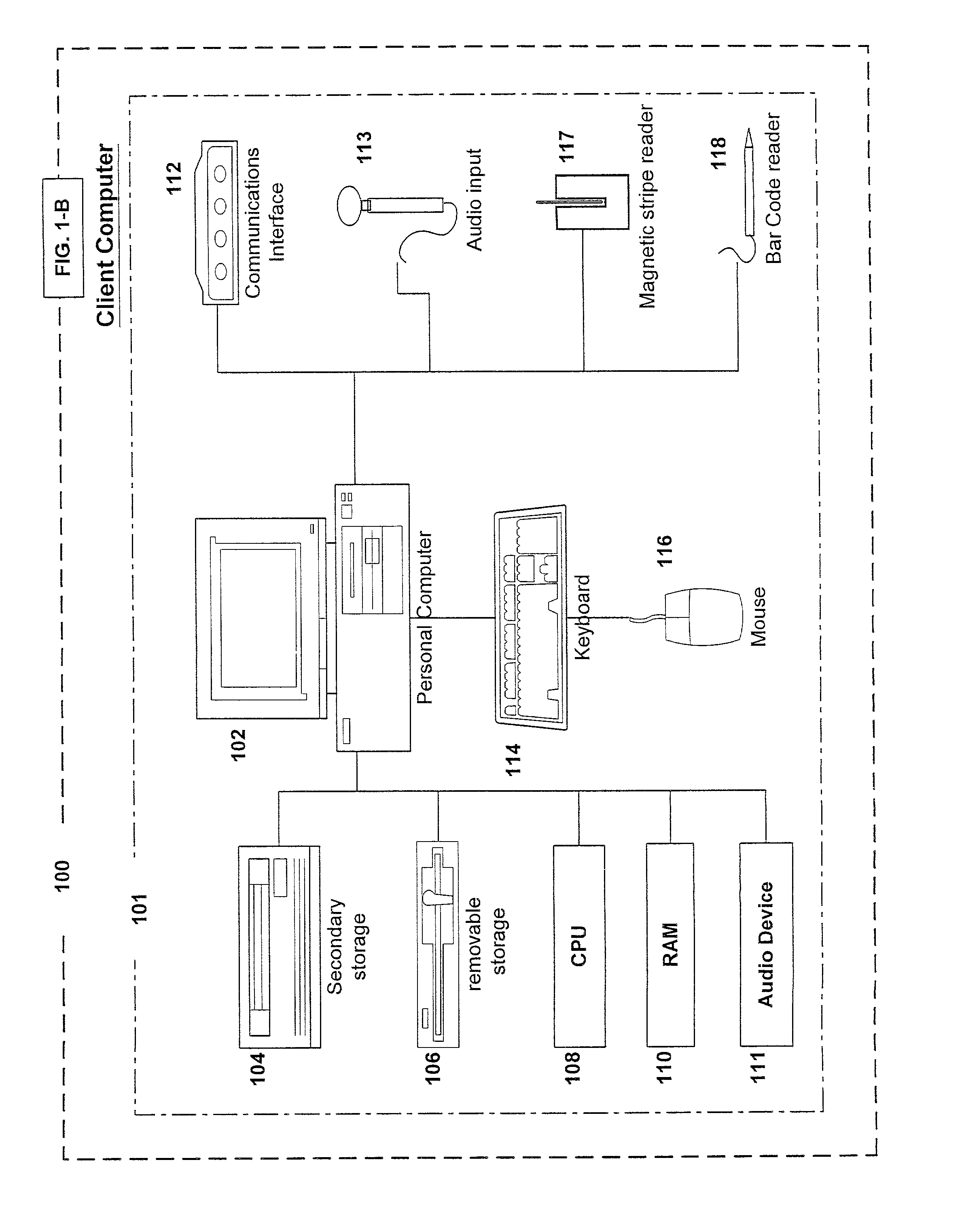

Business card and contact management system

InactiveUS20050251448A1More cost-effectivelyMore accurateAdvertisementsOffice automationWeb browserBusiness card

Owner:MICROSOFT TECH LICENSING LLC

Method and Apparatus For a Variable User Interface

ActiveUS20080194987A1Economy of scaleGrow with diabeticCatheterSensorsAnalyteGraphical user interface

An analyte monitoring system is provided. The system may include a housing (200) and a visual display (206) on the housing (200), the visual display (206) having at lease one visual indicator position next to a corresponding marking (208, 210, 212, 214 and 216) on the housing (200). The system may include a processor (60) driving the visual display (206), wherein the processor (60) runs software that is modifiable to provide a variable user interface on the visual display (206). The system may include a wireless communication to allow applets or programs to be down-loaded by the processor (60).

Owner:SANOFI AVENTIS DEUT GMBH

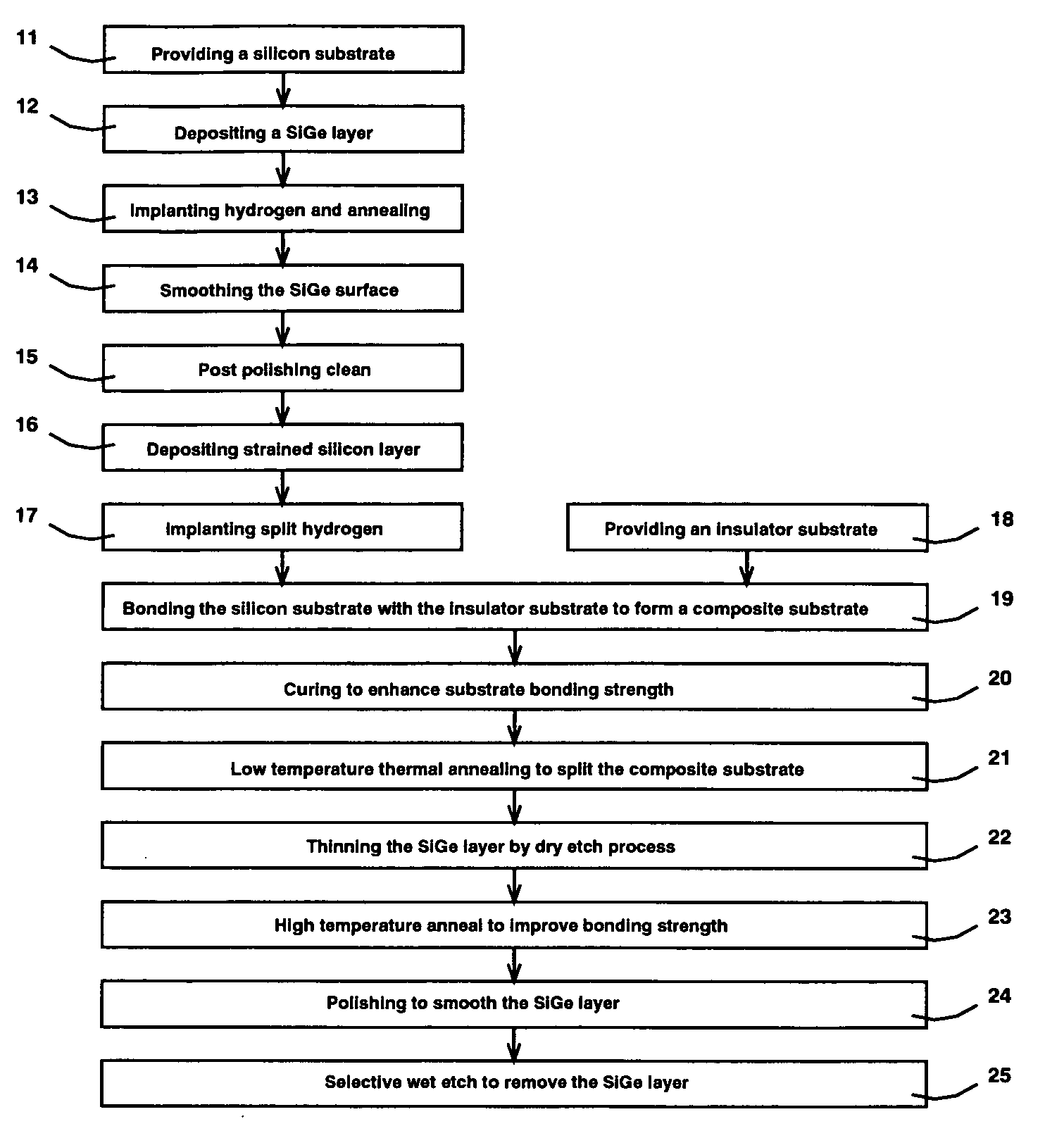

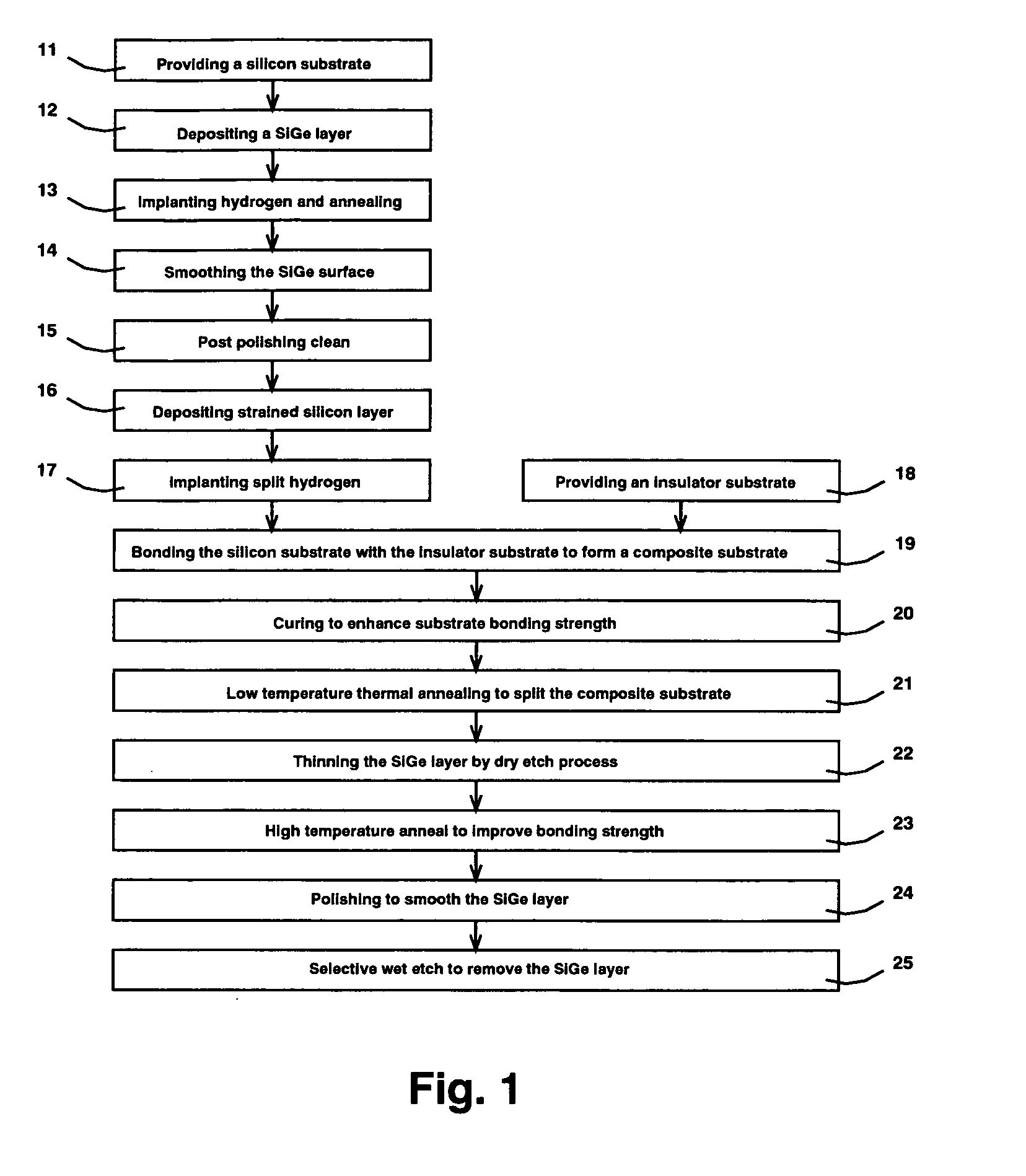

Strained silicon on insulator from film transfer and relaxation by hydrogen implantation

ActiveUS20050153524A1Easy to relaxEasy to integrateSolid-state devicesSemiconductor/solid-state device manufacturingThreading dislocationsHydrogen

Transistors fabricated on SSOI (Strained Silicon On Insulator) substrate, which comprises a strained silicon layer disposed directly on an insulator layer, have enhanced device performance due to the strain-induced band modification of the strained silicon device channel and the limited silicon volume because of the insulator layer. The present invention discloses a SSOI substrate fabrication process comprising various novel approaches. One is the use of a thin relaxed SiGe layer as the strain-induced seed layer to facilitate integration and reduce processing cost. Another is the formation of split implant microcracks deep in the silicon substrate to reduce the number of threading dislocations reaching the strained silicon layer. And lastly is the two step annealing / thinning process for the strained silicon / SiGe multilayer film transfer without blister or flaking formation.

Owner:SHARP KK

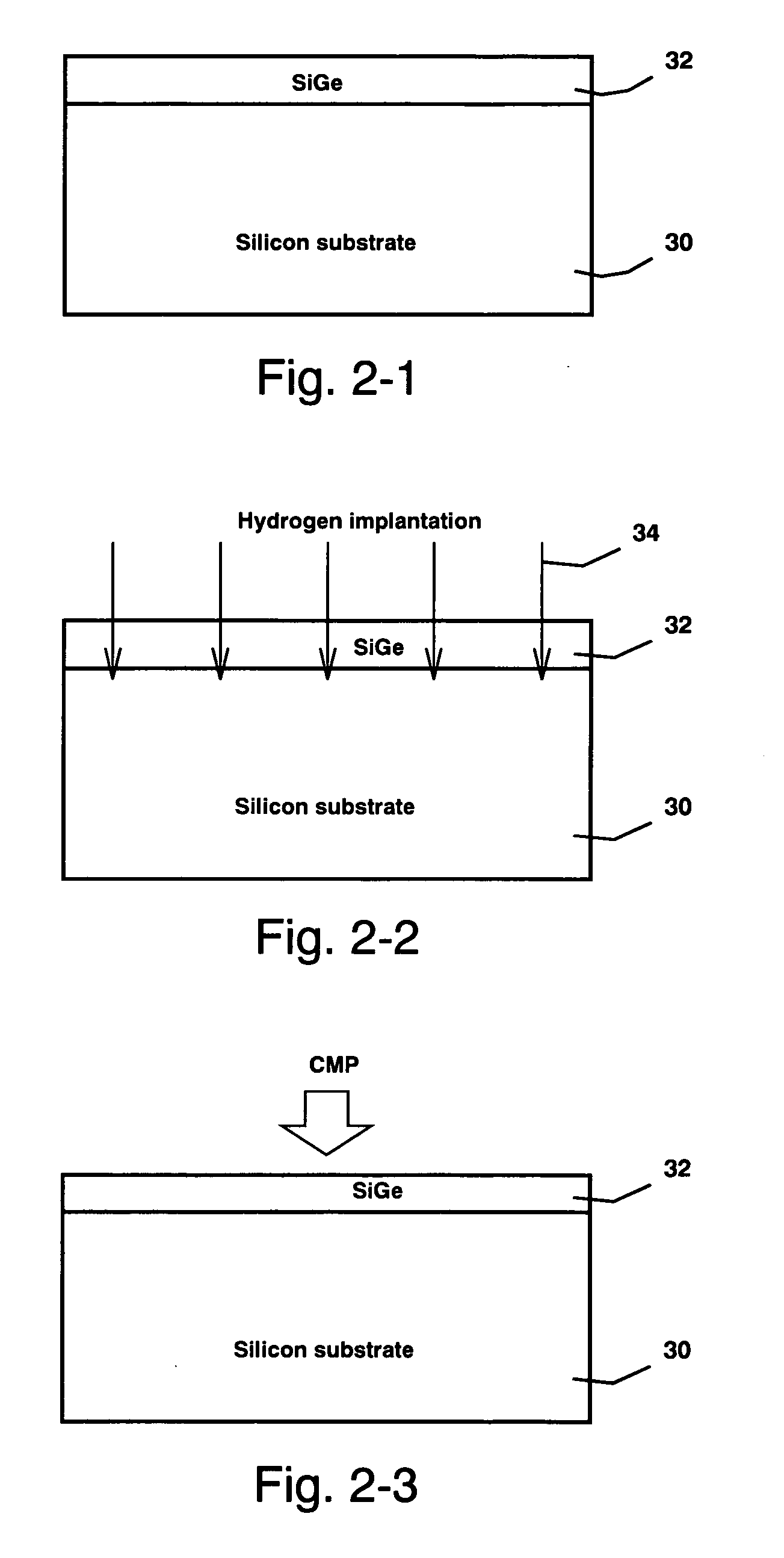

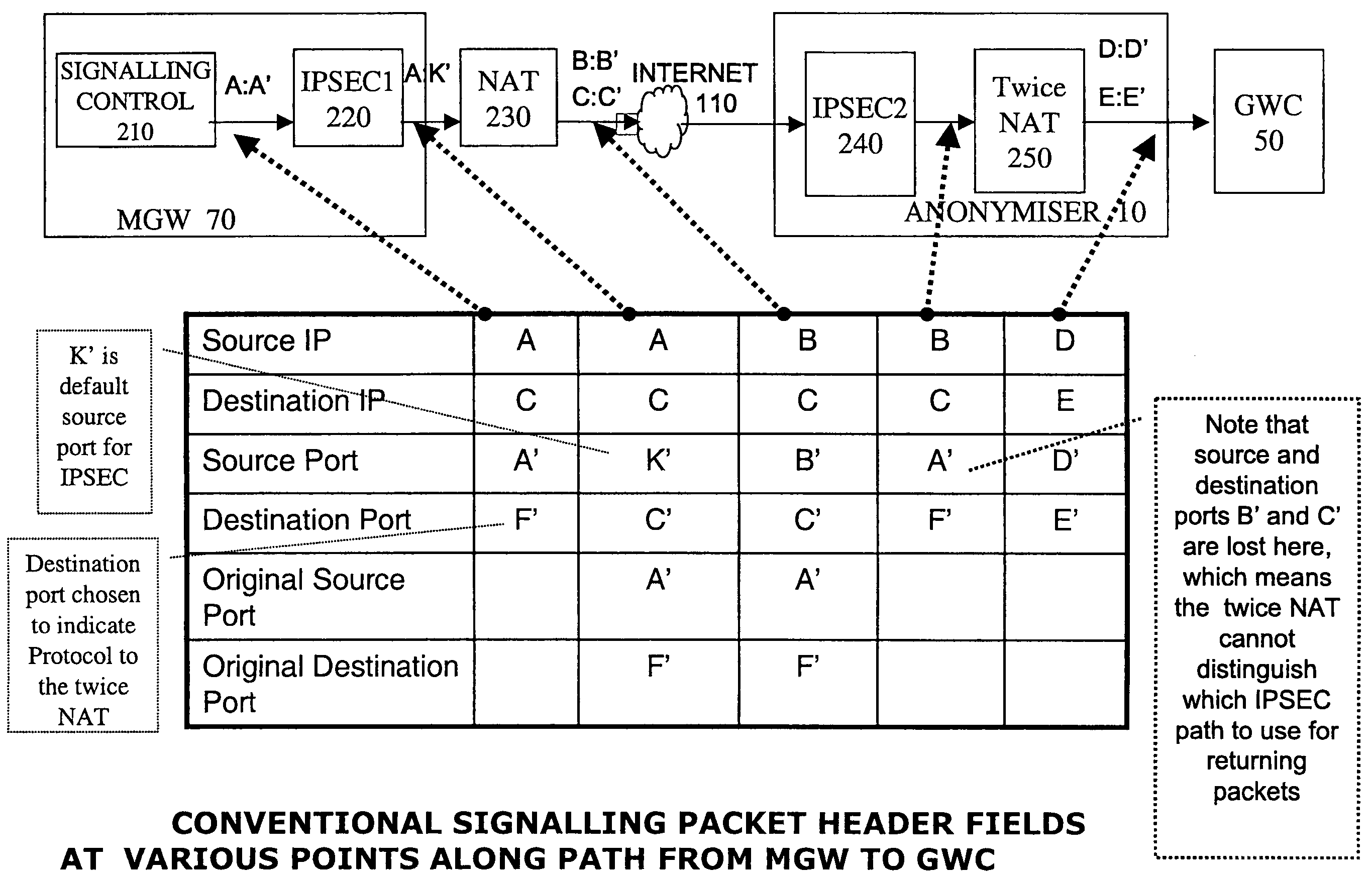

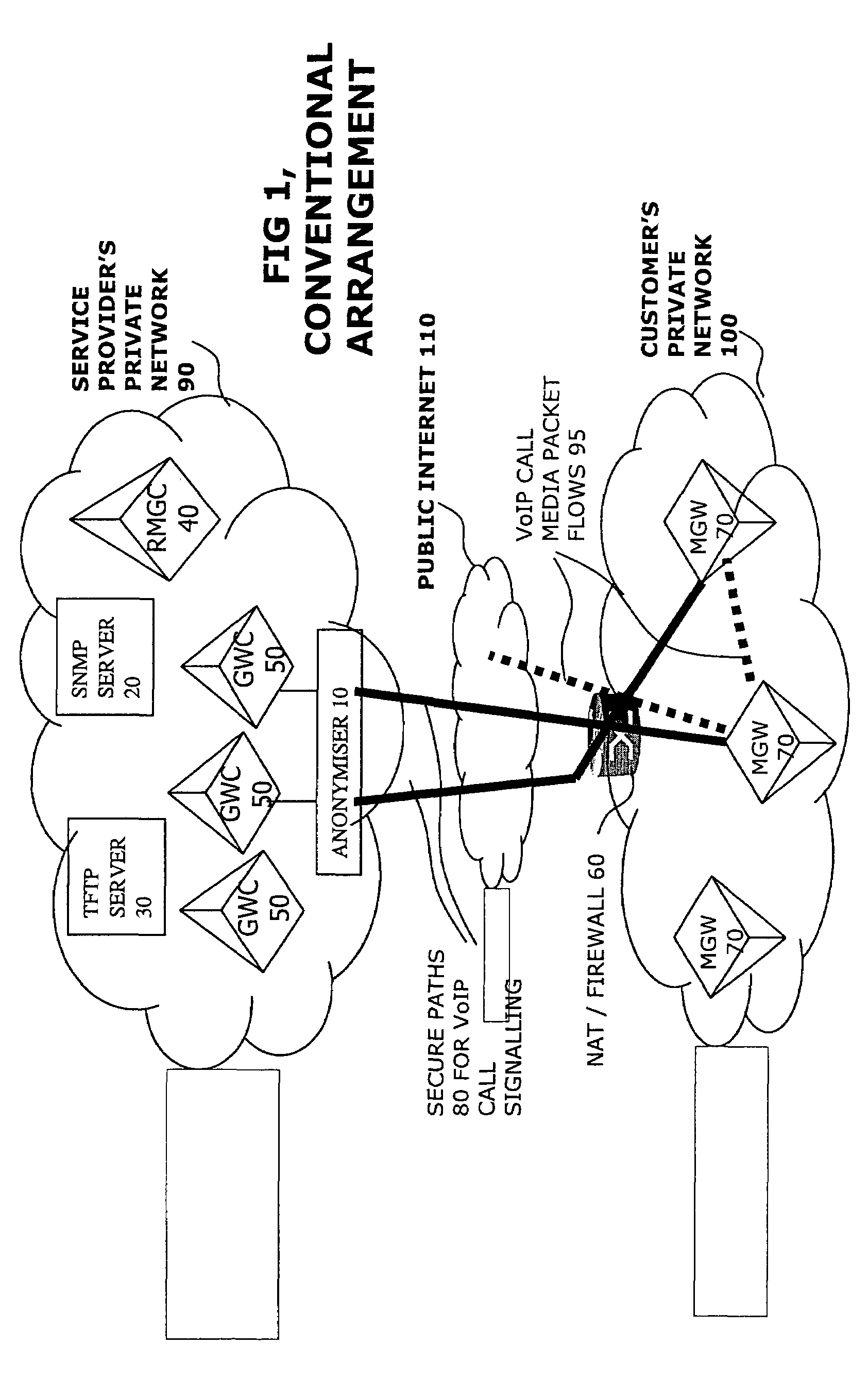

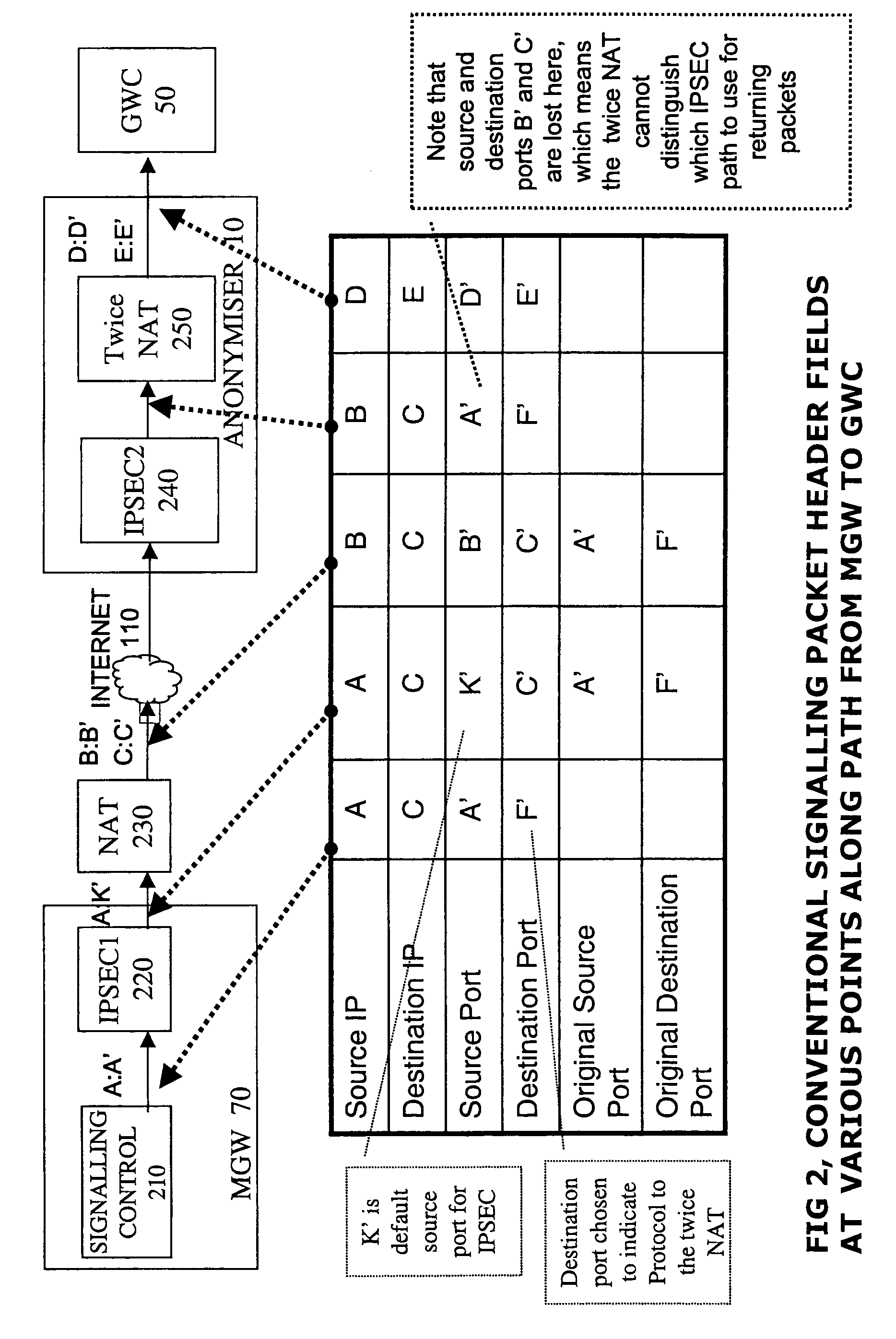

Network address translator and secure transfer device for interfacing networks

ActiveUS7283542B2Avoid less flexibilityReduce in quantityData switching by path configurationMultiple digital computer combinationsPrivate IPSecure transmission

An interface for a private IP network interfaces flows of packets between gateway controllers and external media gateways. It has a network address translator and an IPsec device for maintaining secure paths to the external devices. A path identifier records which of the packet flows corresponds to which path. It is incorporated in the packet header, and means that the same interface can be used to couple many different external gateways, and interface them with many of the gateway controllers. Widespread deployment of such interfaces in anonymisers to achieve hiding of device addresses and network topology, as well as the reduction in use of expensive registered addresses is facilitated. By sending the path identifier in the packet, the IPsec device and the address translator can be loosely coupled devices, so standard readily available devices can be used.

Owner:GENBAND US LLC

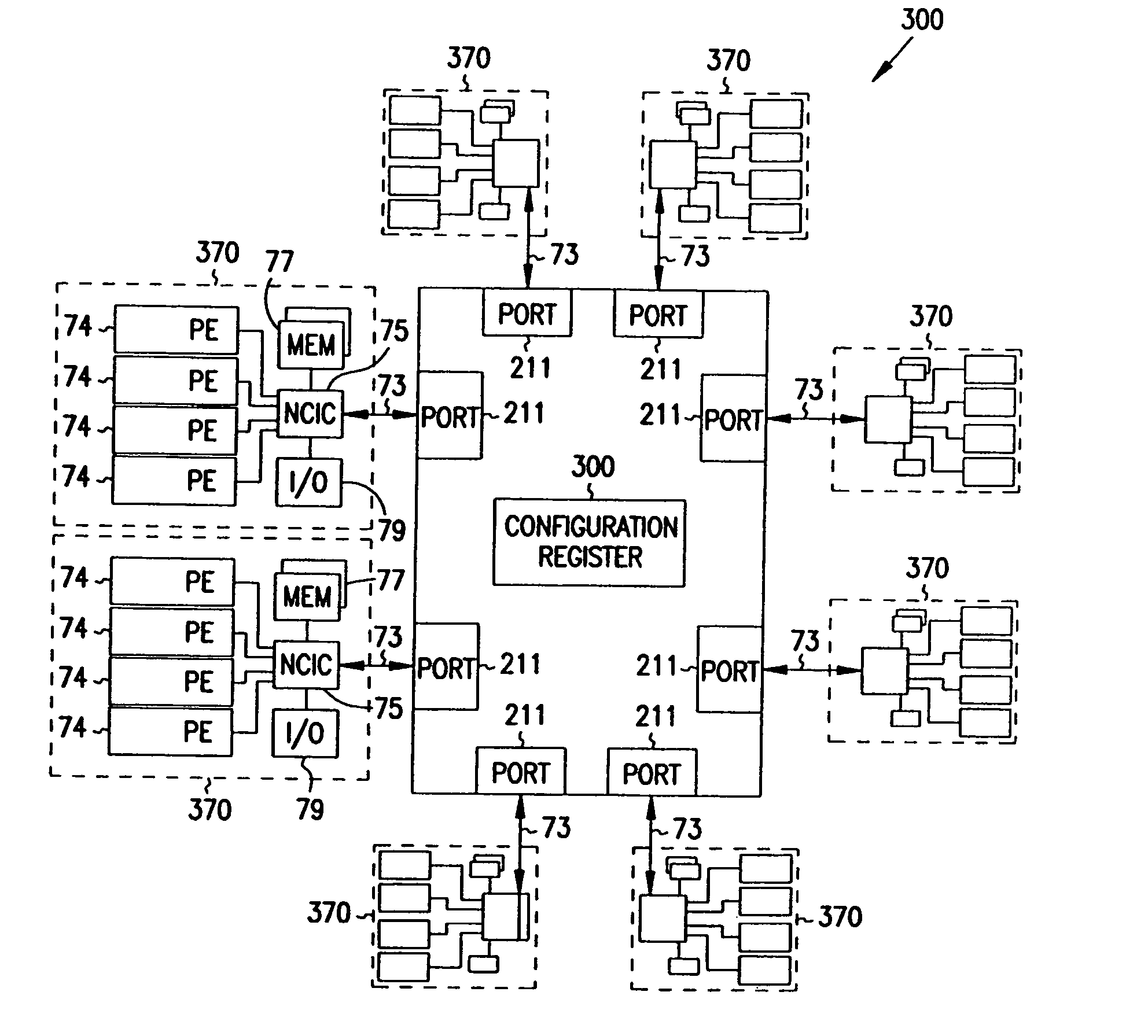

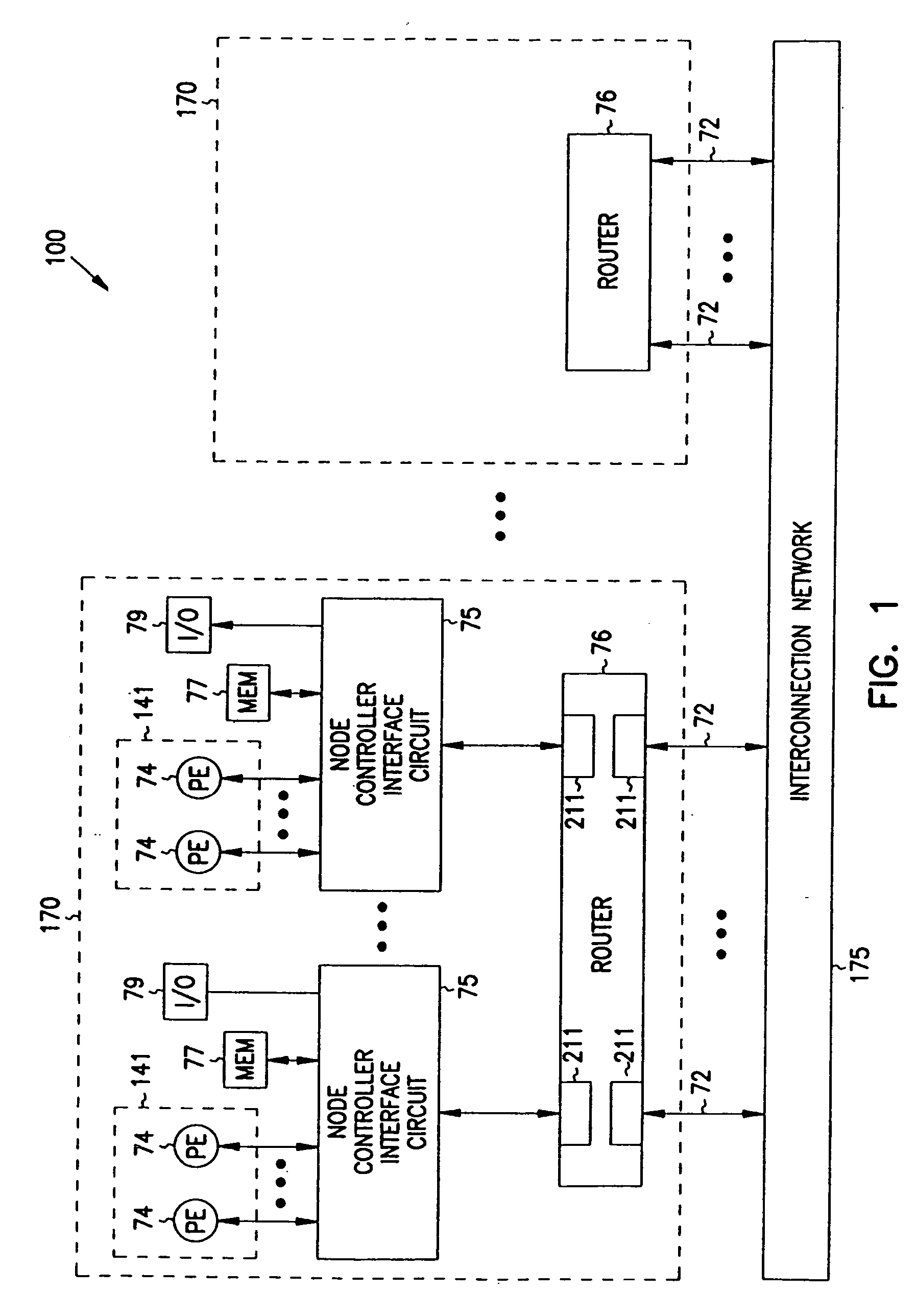

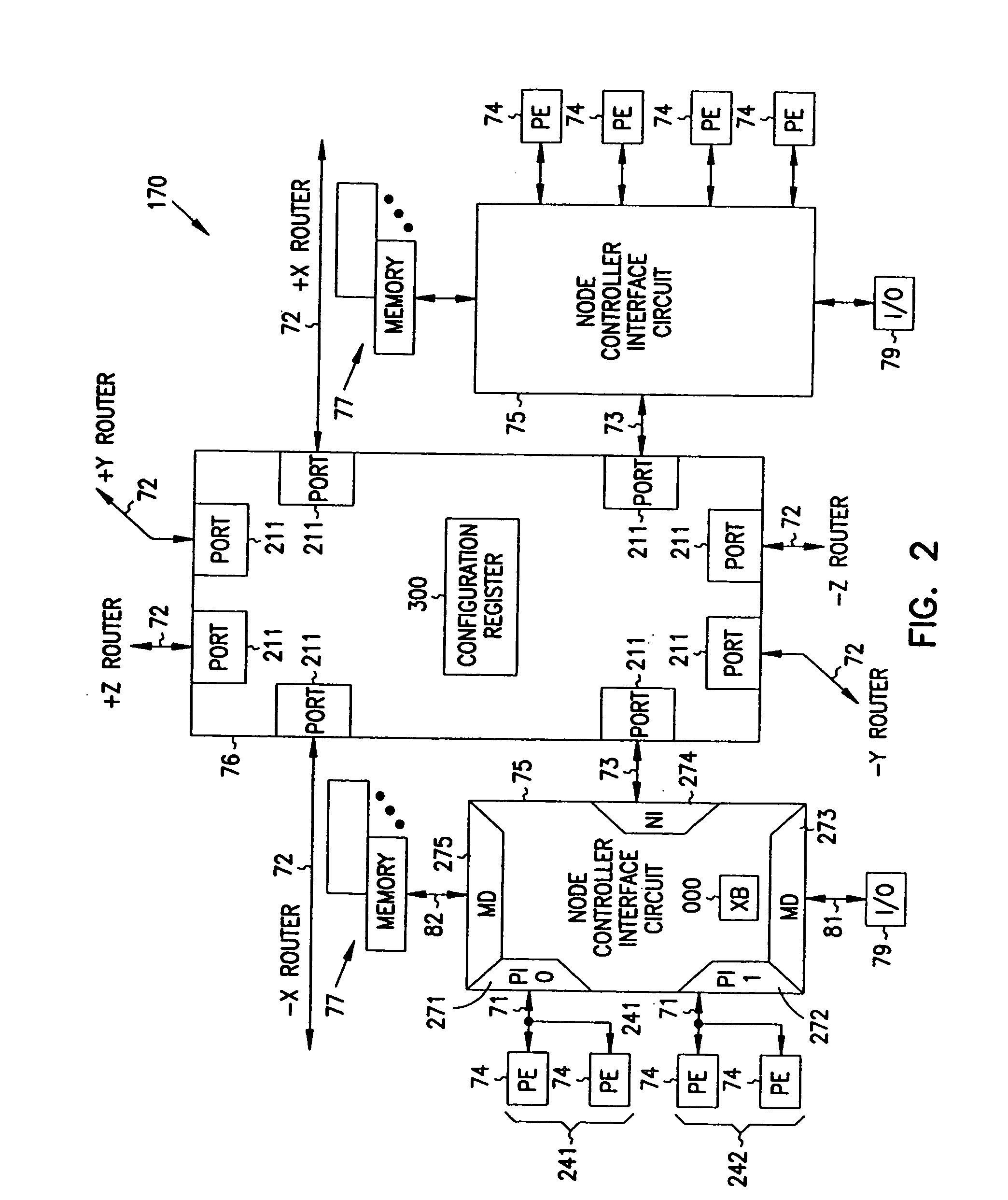

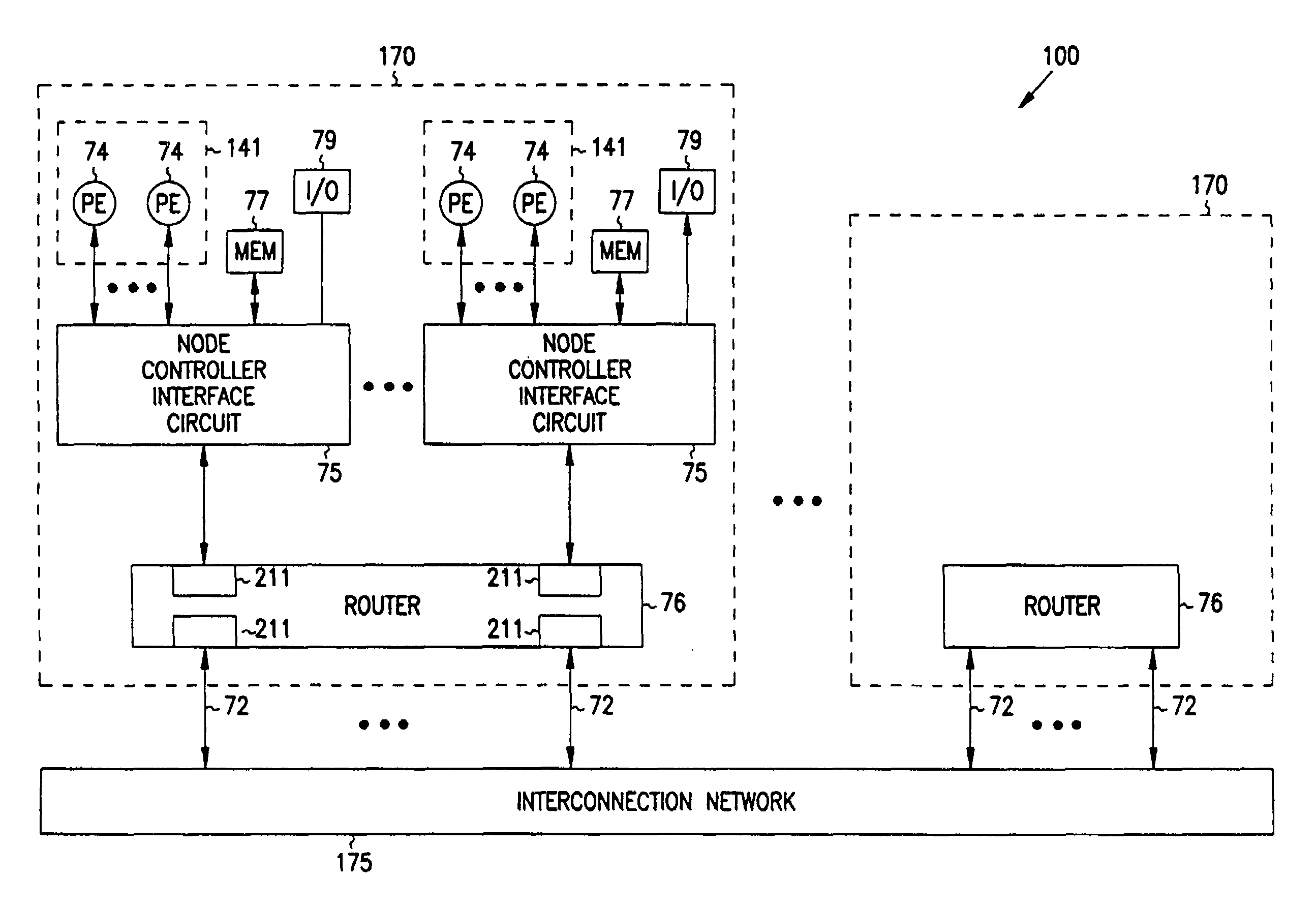

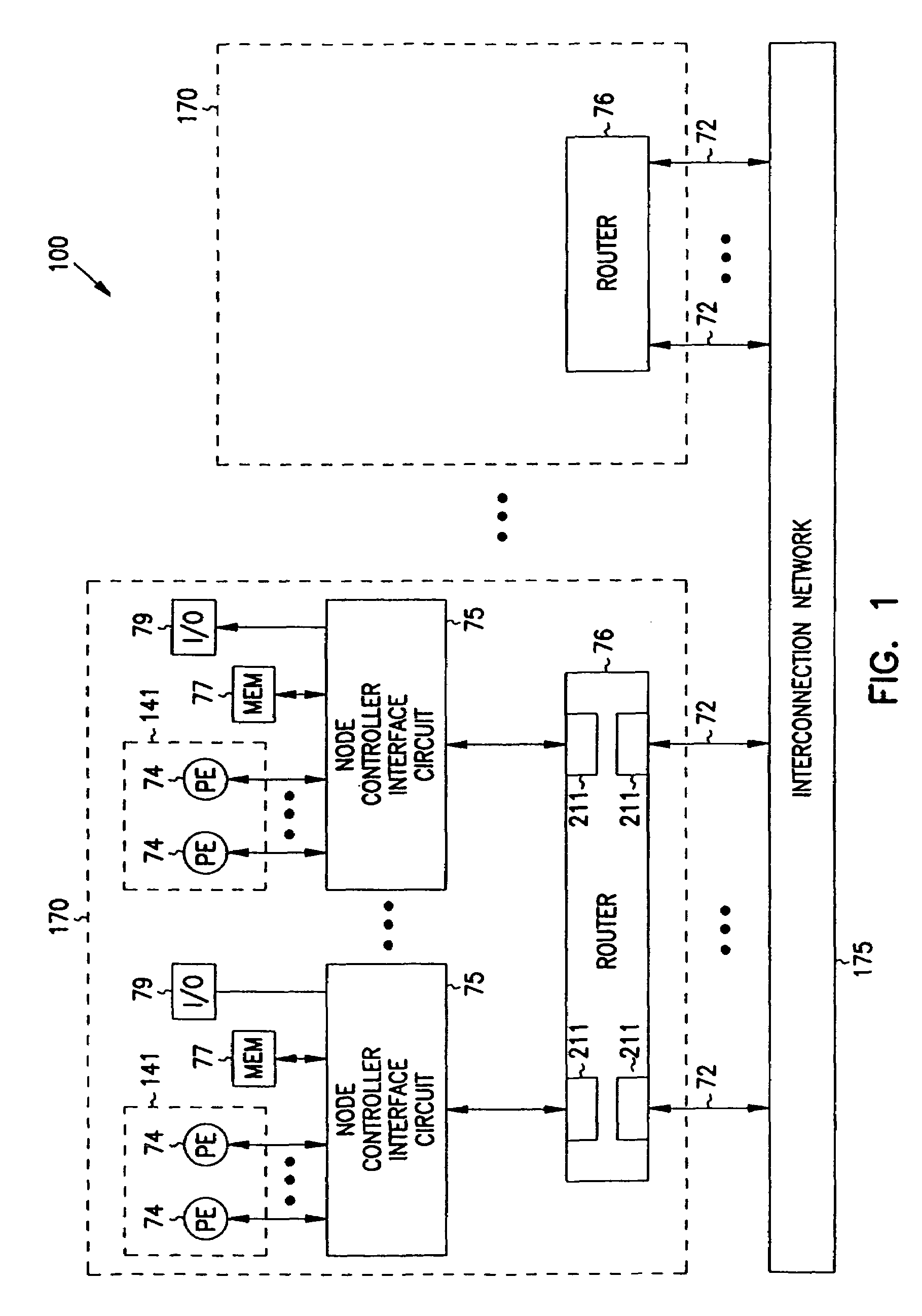

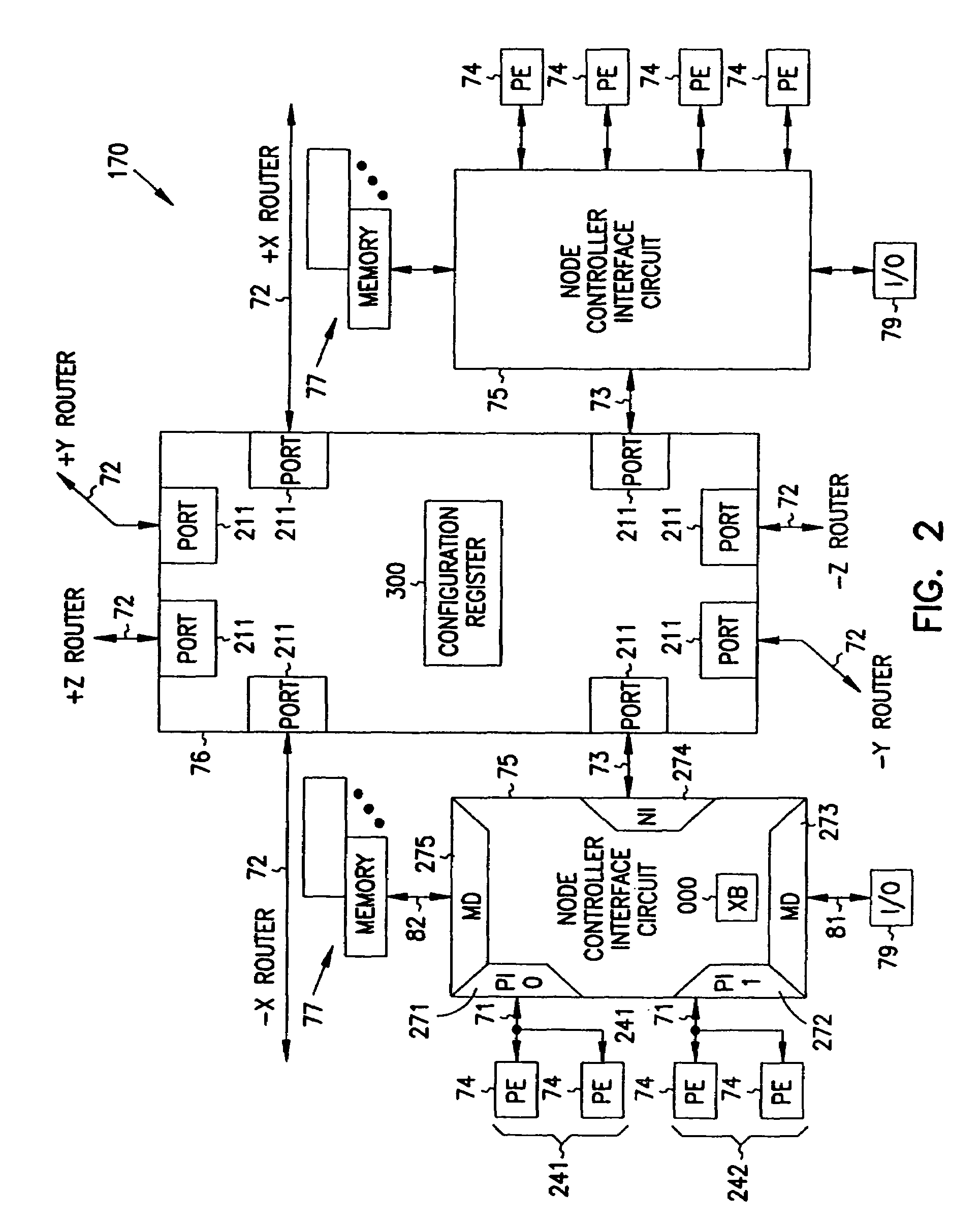

Multiprocessor node controller circuit and method

InactiveUS20050053057A1Ease of parallel processingImprove welfareMultiplex system selection arrangementsMemory adressing/allocation/relocationMemory addressCrossbar switch

Improved method and apparatus for parallel processing. One embodiment provides a multiprocessor computer system that includes a first and second node controller, a number of processors being connected to each node controller, a memory connected to each controller, a first input / output system connected to the first node controller, and a communications network connected between the node controllers. The first node controller includes: a crossbar unit to which are connected a memory port, an input / output port, a network port, and a plurality of independent processor ports. A first and a second processor port connected between the crossbar unit and a first subset and a second subset, respectively, of the processors. In some embodiments of the system, the first node controller is fabricated onto a single integrated-circuit chip. Optionally, the memory is packaged on plugable memory / directory cards wherein each card includes a plurality of memory chips including a first subset dedicated to holding memory data and a second subset dedicated to holding directory data. Further, the memory port includes a memory data port including a memory data bus and a memory address bus coupled to the first subset of memory chips, and a directory data port including a directory data bus and a directory address bus coupled to the second subset of memory chips. In some such embodiments, the ratio of (memory data space) to (directory data space) on each card is set to a value that is based on a size of the multiprocessor computer system.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP +1

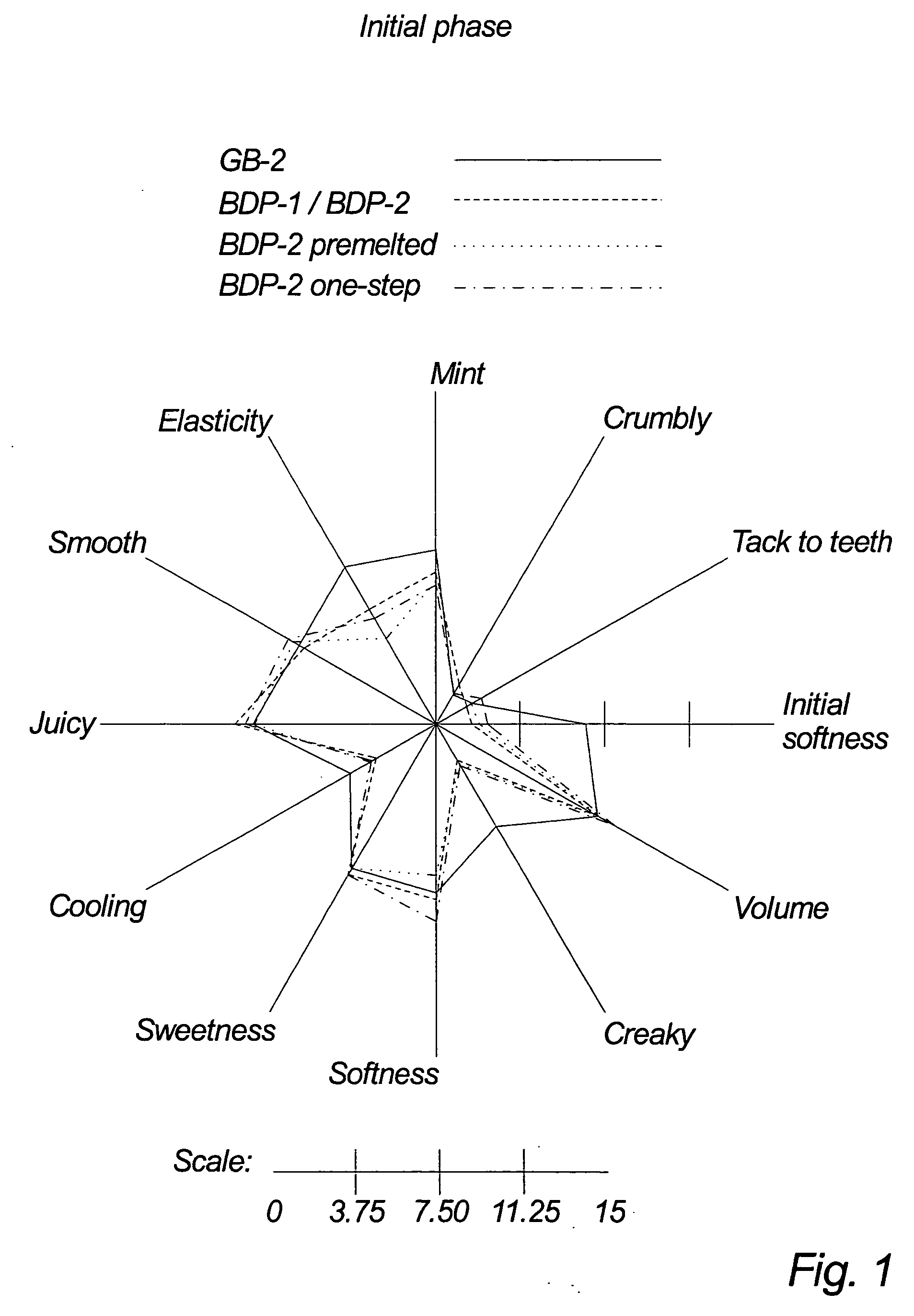

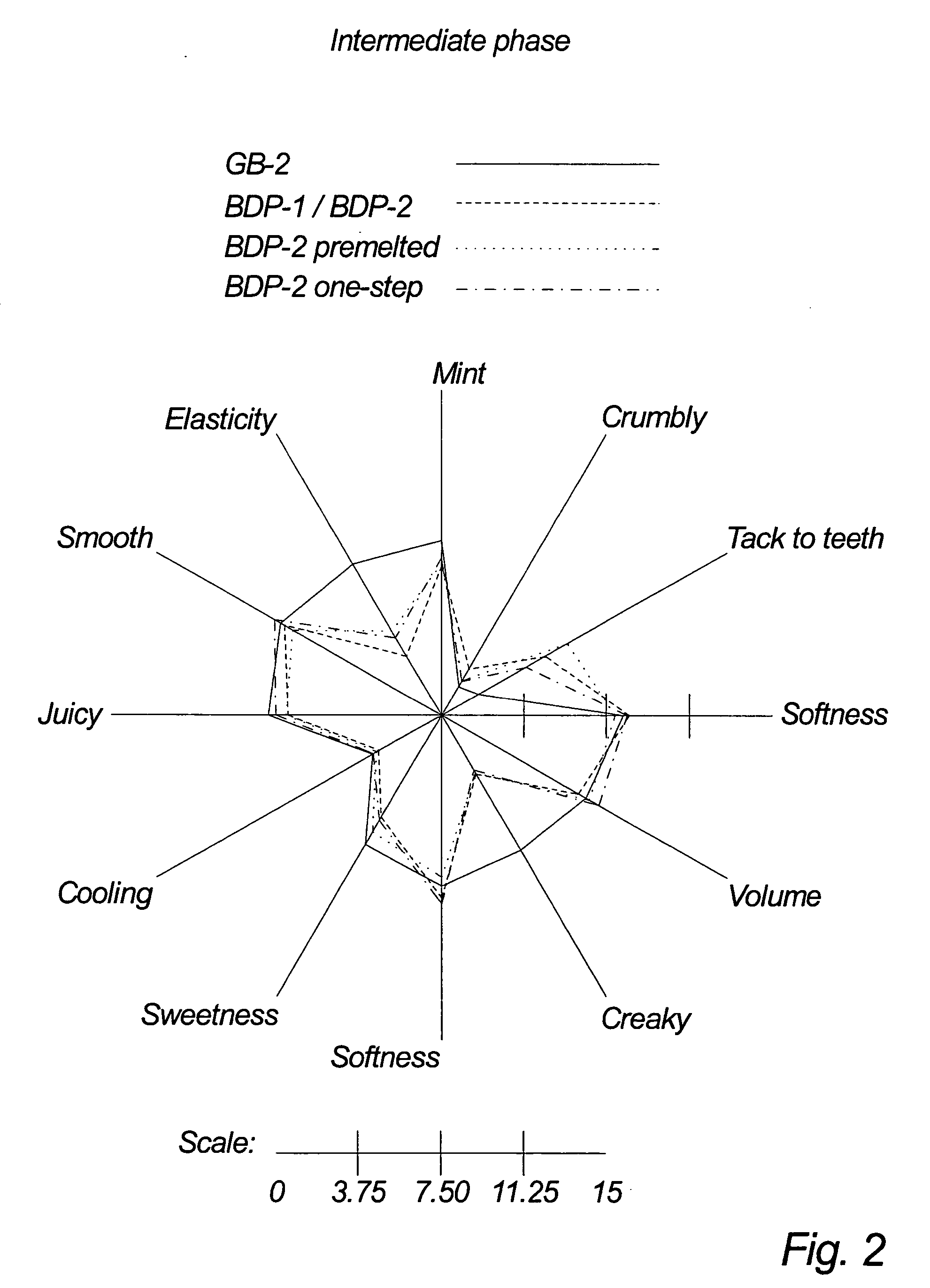

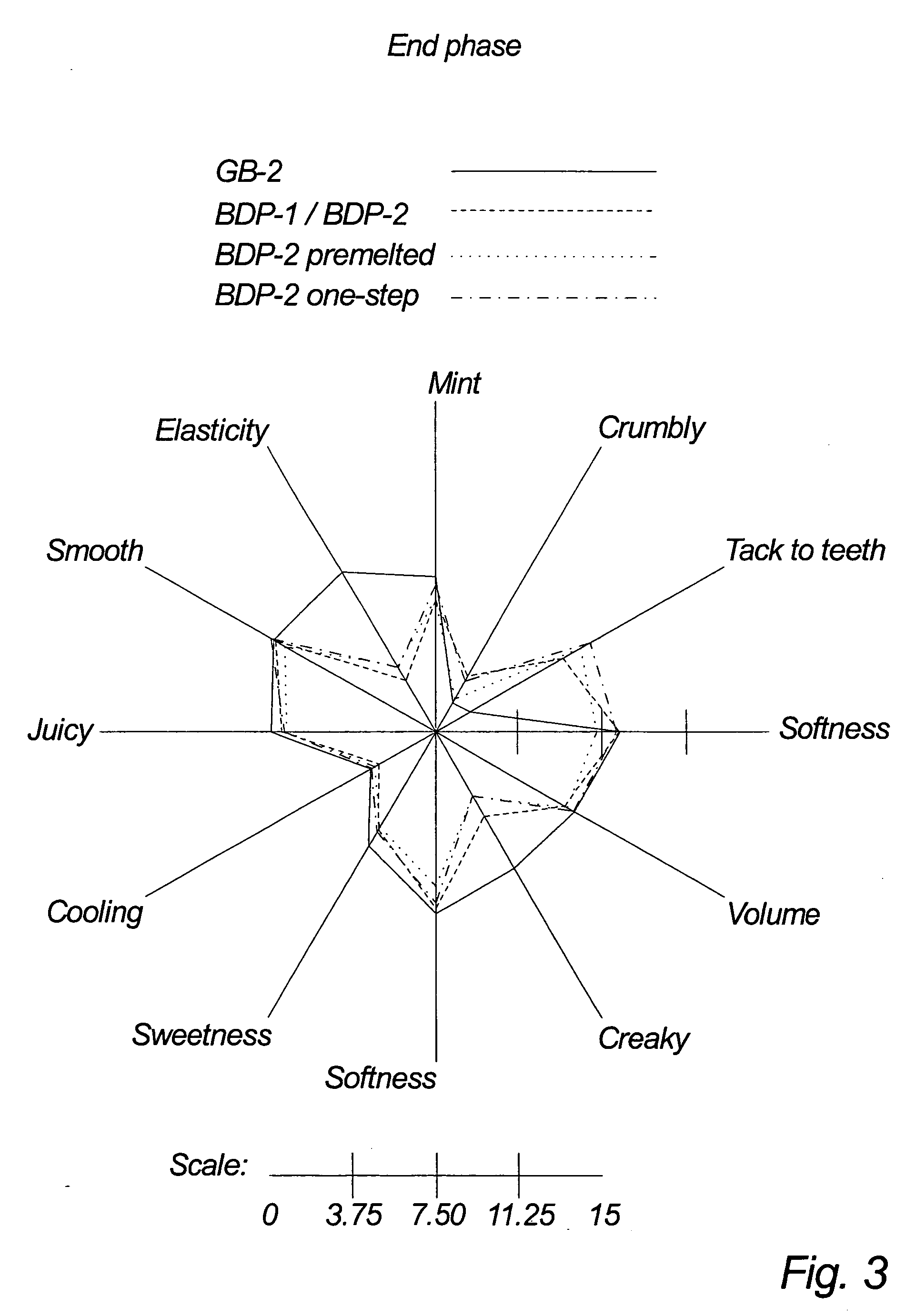

One-step process for preparing chewing gum

InactiveUS20040115305A1More cost-effectivelyLess process equipmentOrganic active ingredientsNervous disorderPolyesterPolymer science

A process for preparing a chewing gum wherein all of the gum base components and all of the chewing gum additives are charged, in any appropriate order, into a mixing apparatus and the apparatus operated at atmospheric pressure to obtain the chewing gum, subject to the limitation that the gum base does not contain a vinyl polyester as the sole polymer. In certain embodiments, the gum base comprises at least one environmentally or biodegradable polymer such as a polyester, a polycarbonates, a polyester amide, a polypeptide and a protein.

Owner:GUMLINK AS

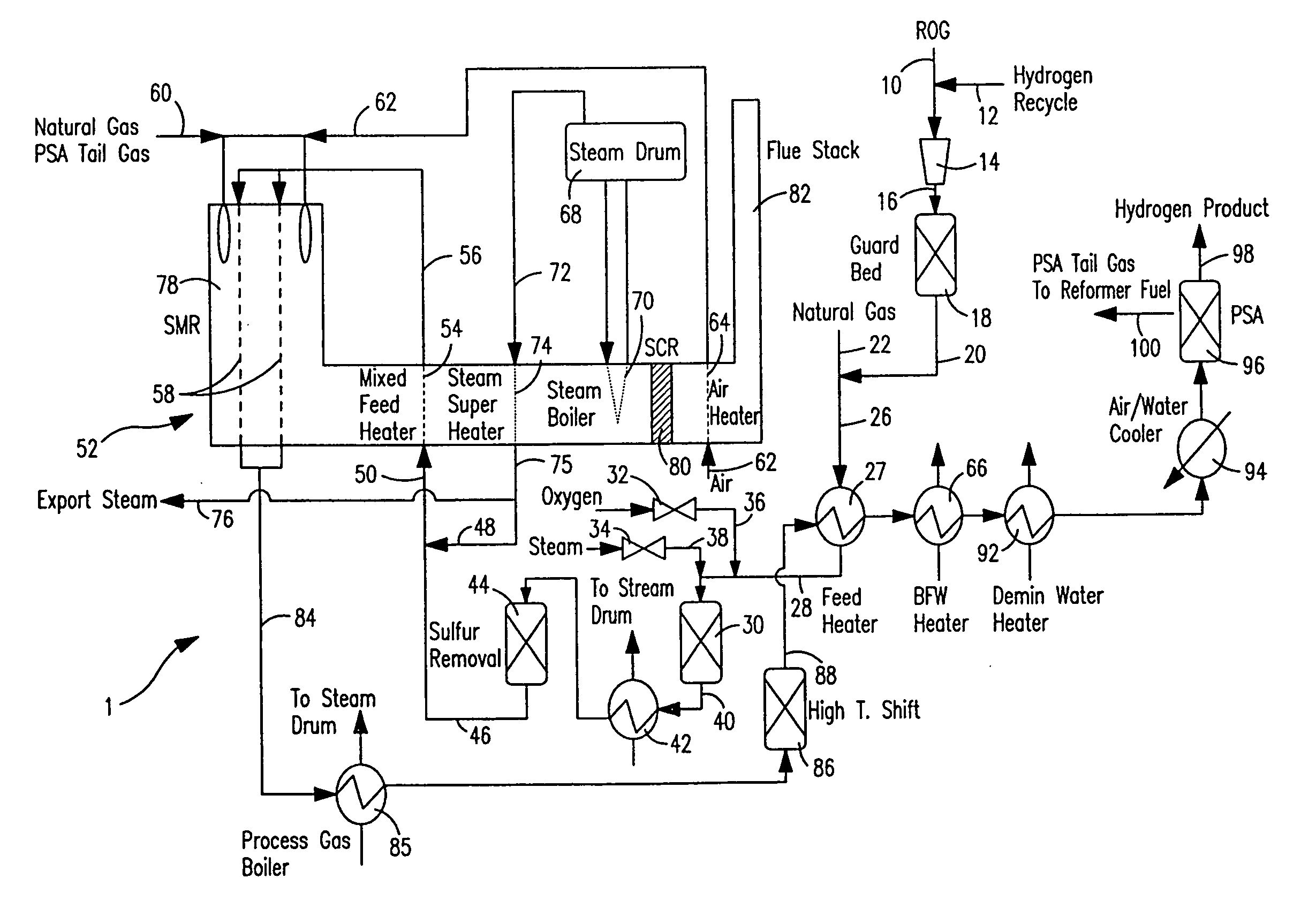

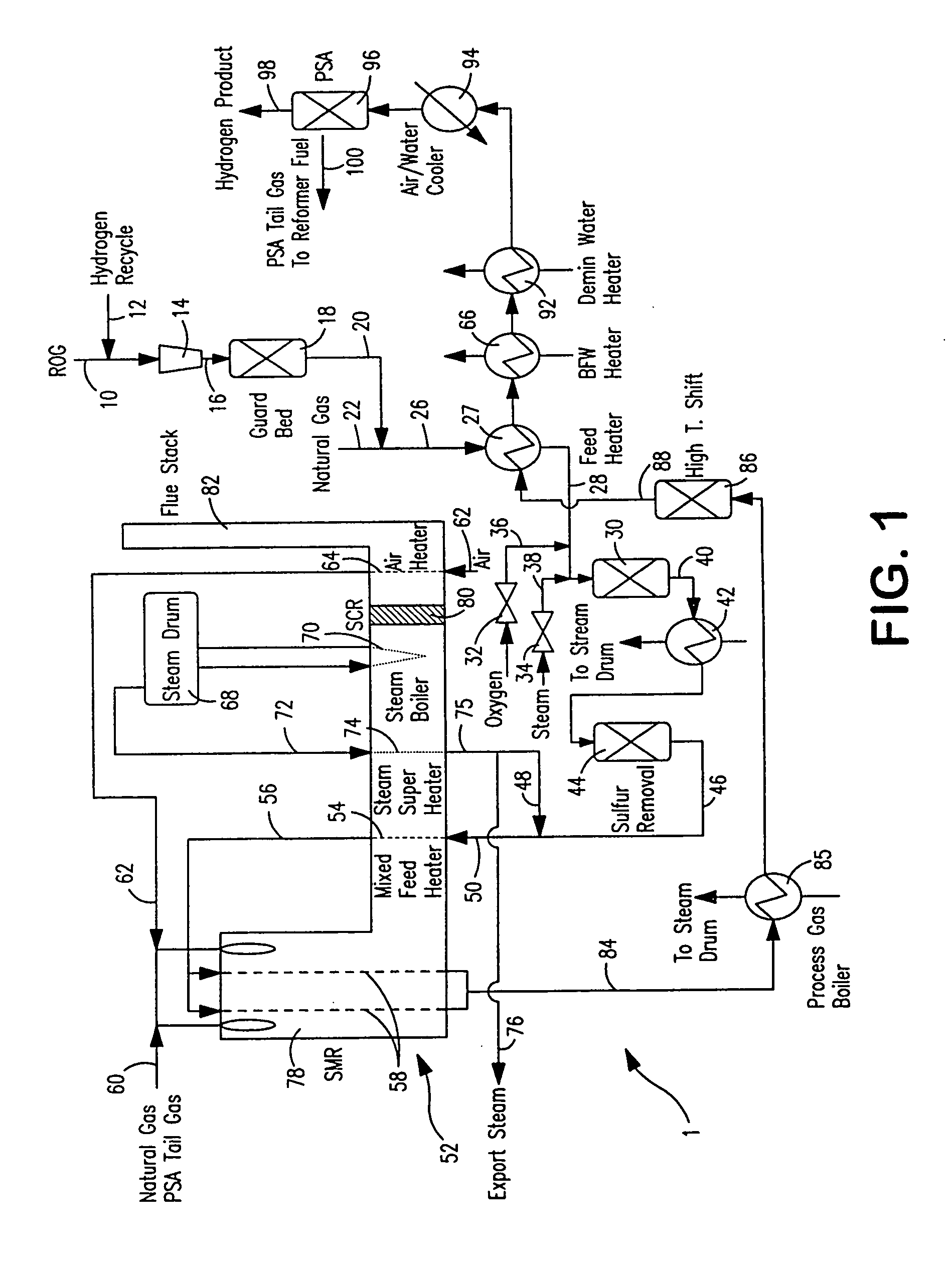

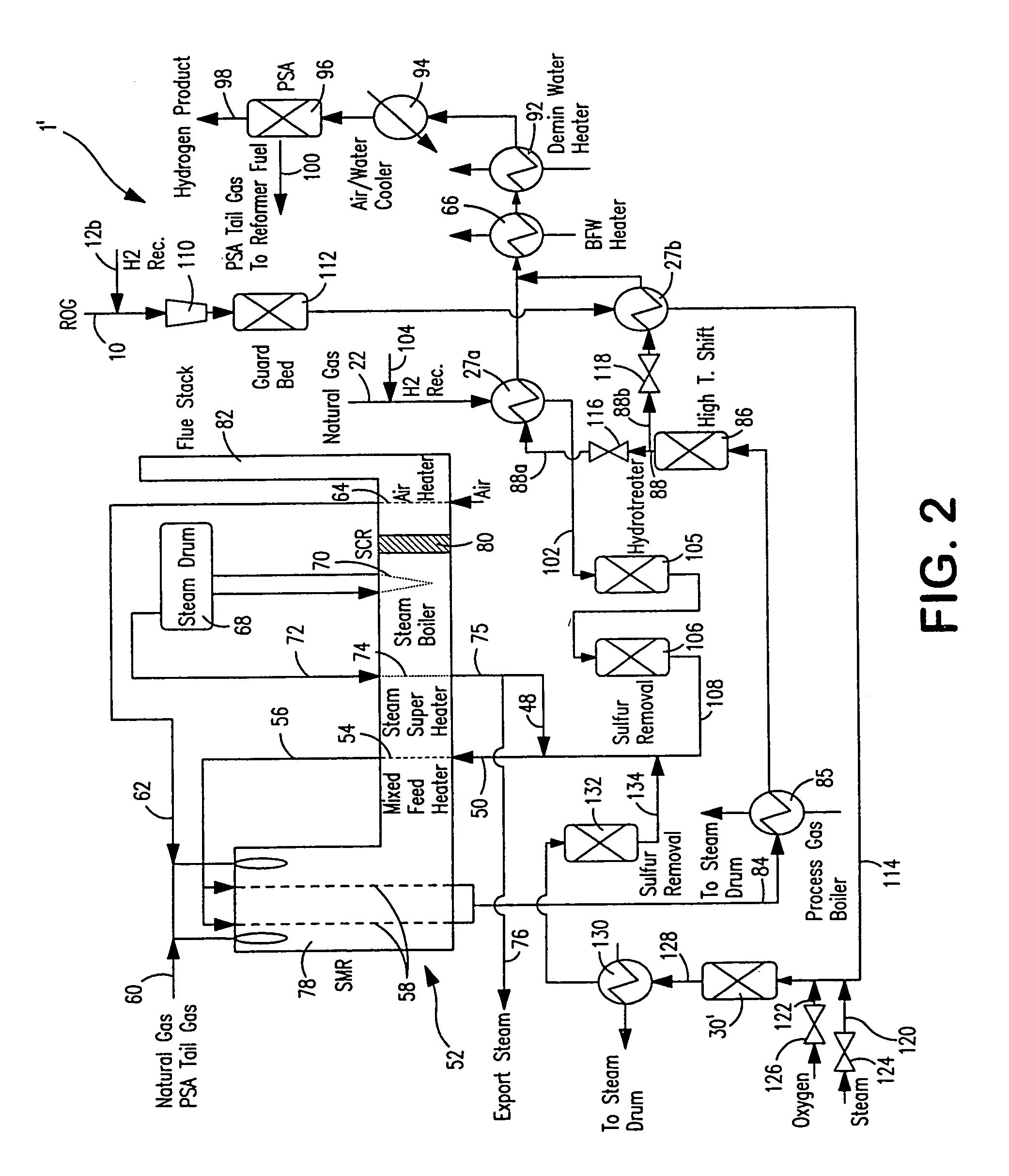

Steam methane reforming method

ActiveUS7037485B1Reduce fuel usageReduce firing rateHydrocarbon from carbon oxidesHydrogen separation using solid contactMethane reformerAlkane

A steam methane reforming method in which a feed stream is treated in a reactor containing a catalyst that is capable of promoting both hydrogenation and partial oxidation reactions. The reactor is either operated in a catalytic hydrogenation mode to convert olefins into saturated hydrocarbons and / or to chemically reduce sulfur species to hydrogen sulfide or a catalytic oxidative mode utilizing oxygen and steam to prereform the feed and thus, increase the hydrogen content of a synthesis gas produced by a steam methane reformer. The method is applicable to the treatment of feed streams containing at least 15% by volume of hydrocarbons with two or more carbon atoms and / or 3% by volume of olefins, such as a refinery off-gas. In such case, the catalytic oxidative mode is conducted with a steam to carbon ratio of less than 0.5, an oxygen to carbon ratio of less than 0.25 and a reaction temperature of between about 500° C. and about 860° C. to limit the feed to the steam methane reformer to volumetric dry concentrations of less than about 0.5% for the olefins and less than about 10% for alkanes with two or more carbon atoms.

Owner:PRAXAIR TECH INC

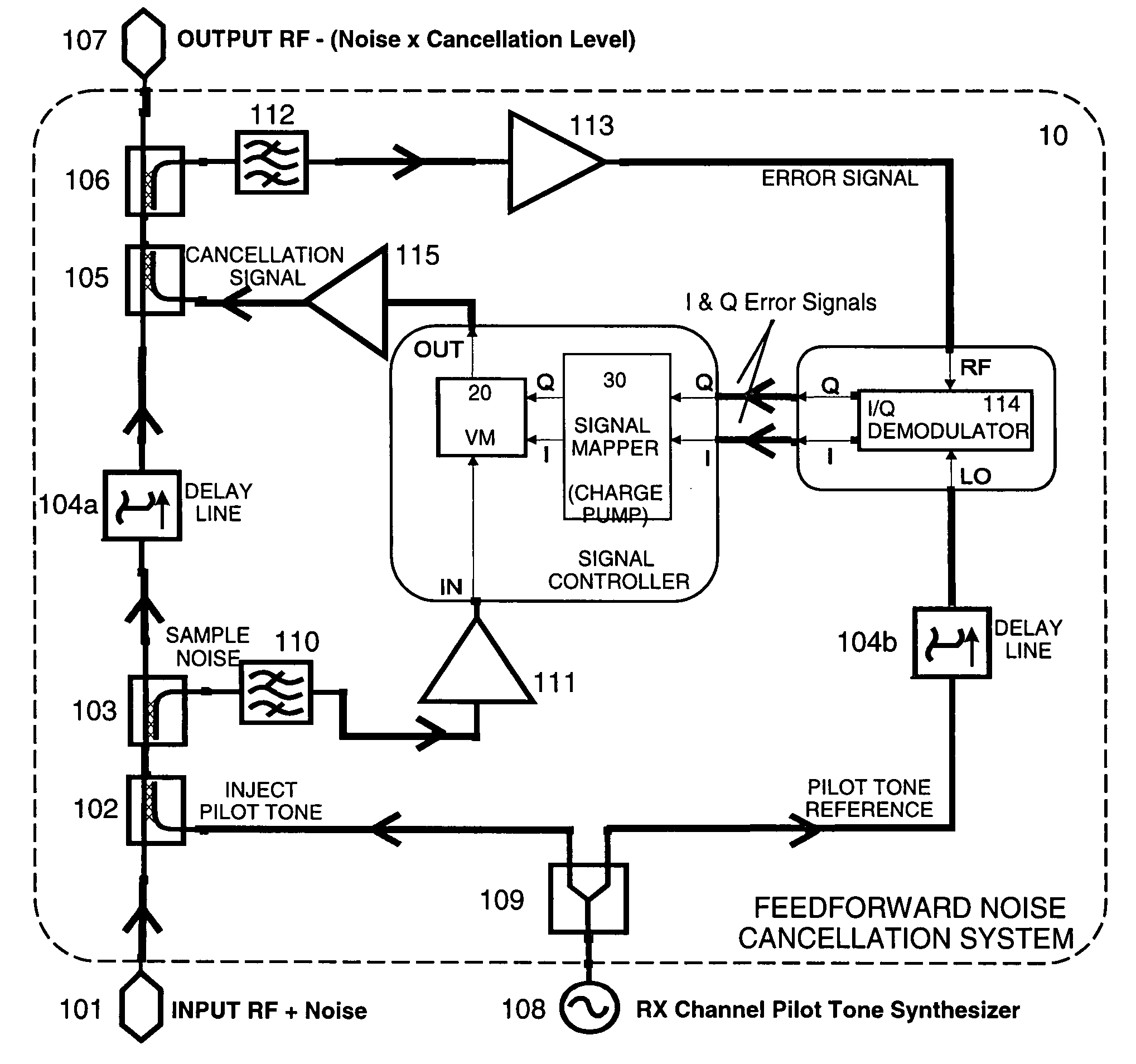

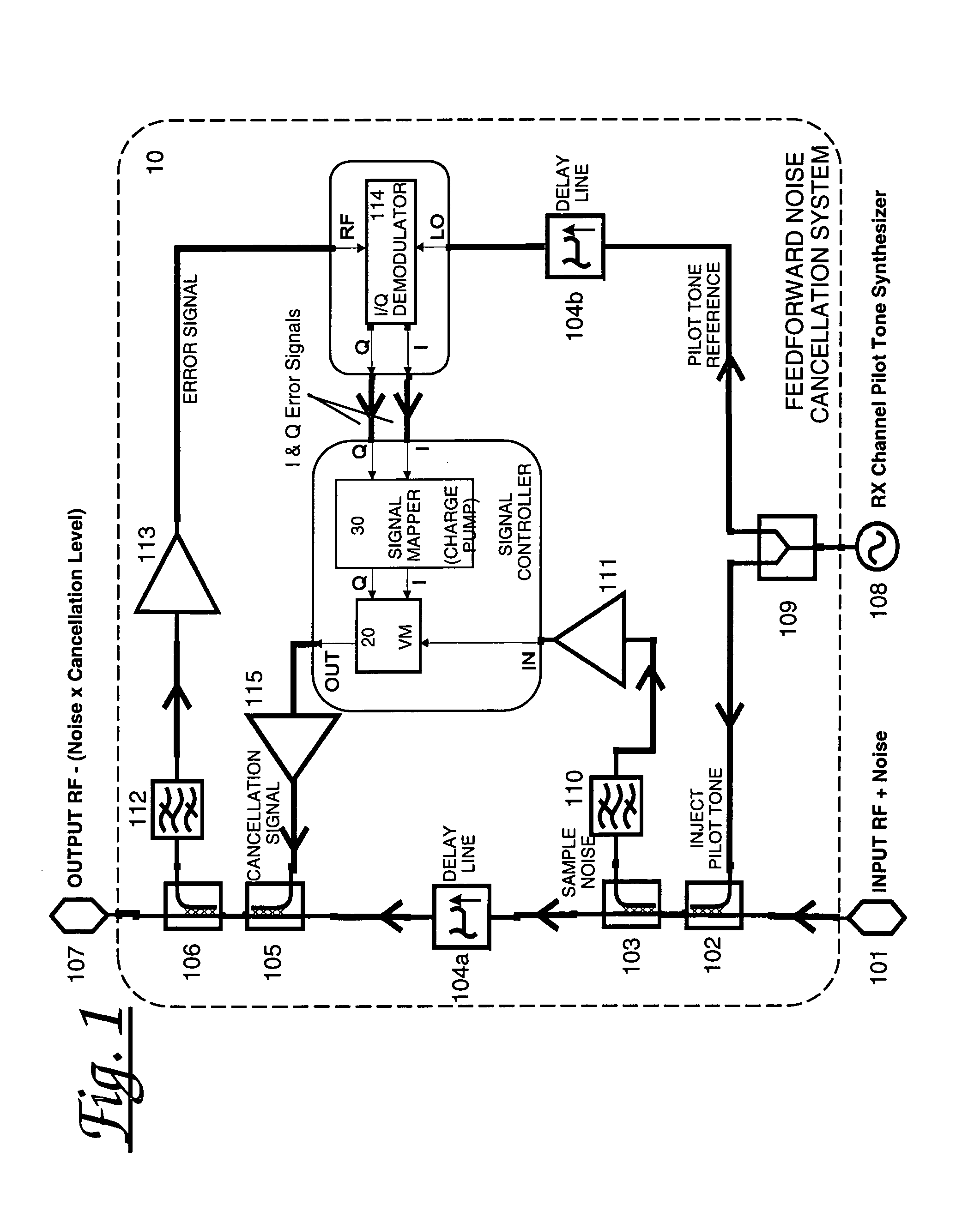

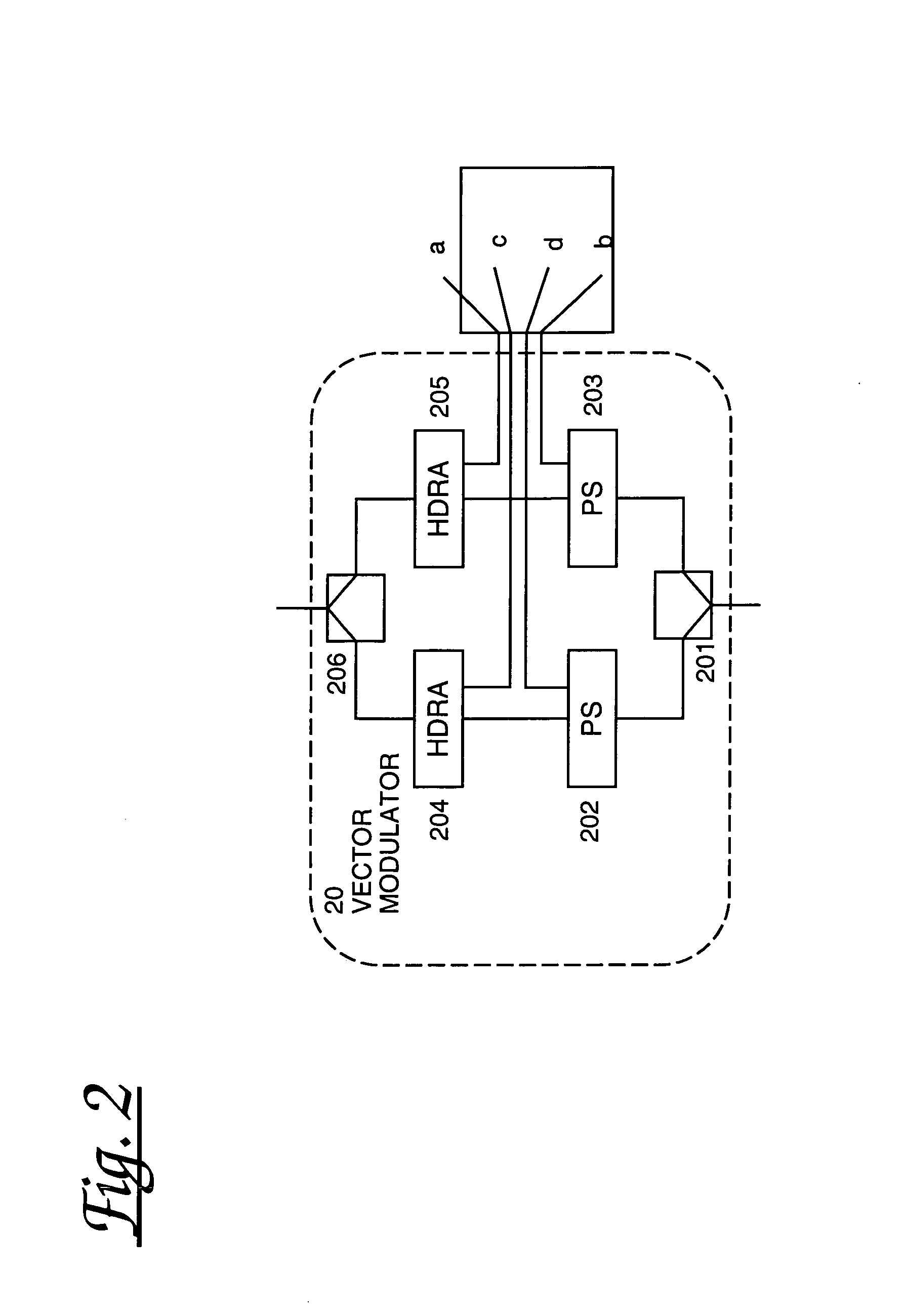

Adaptive feedforward noise cancellation circuit

InactiveUS7058368B2AdaptableBandwidth be controlledTwo-way loud-speaking telephone systemsError preventionCommunications systemEngineering

Owner:MICROSOFT TECH LICENSING LLC

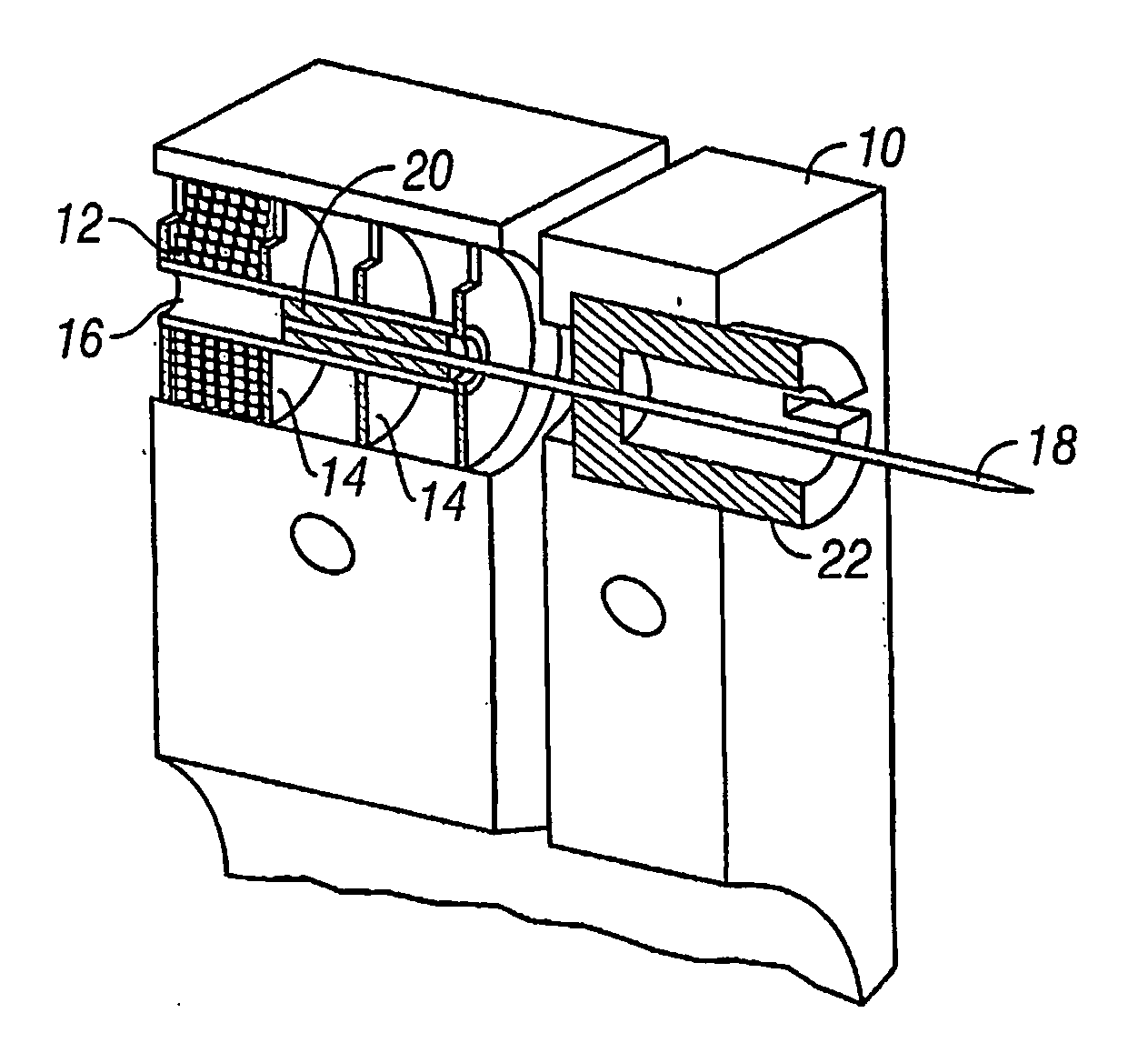

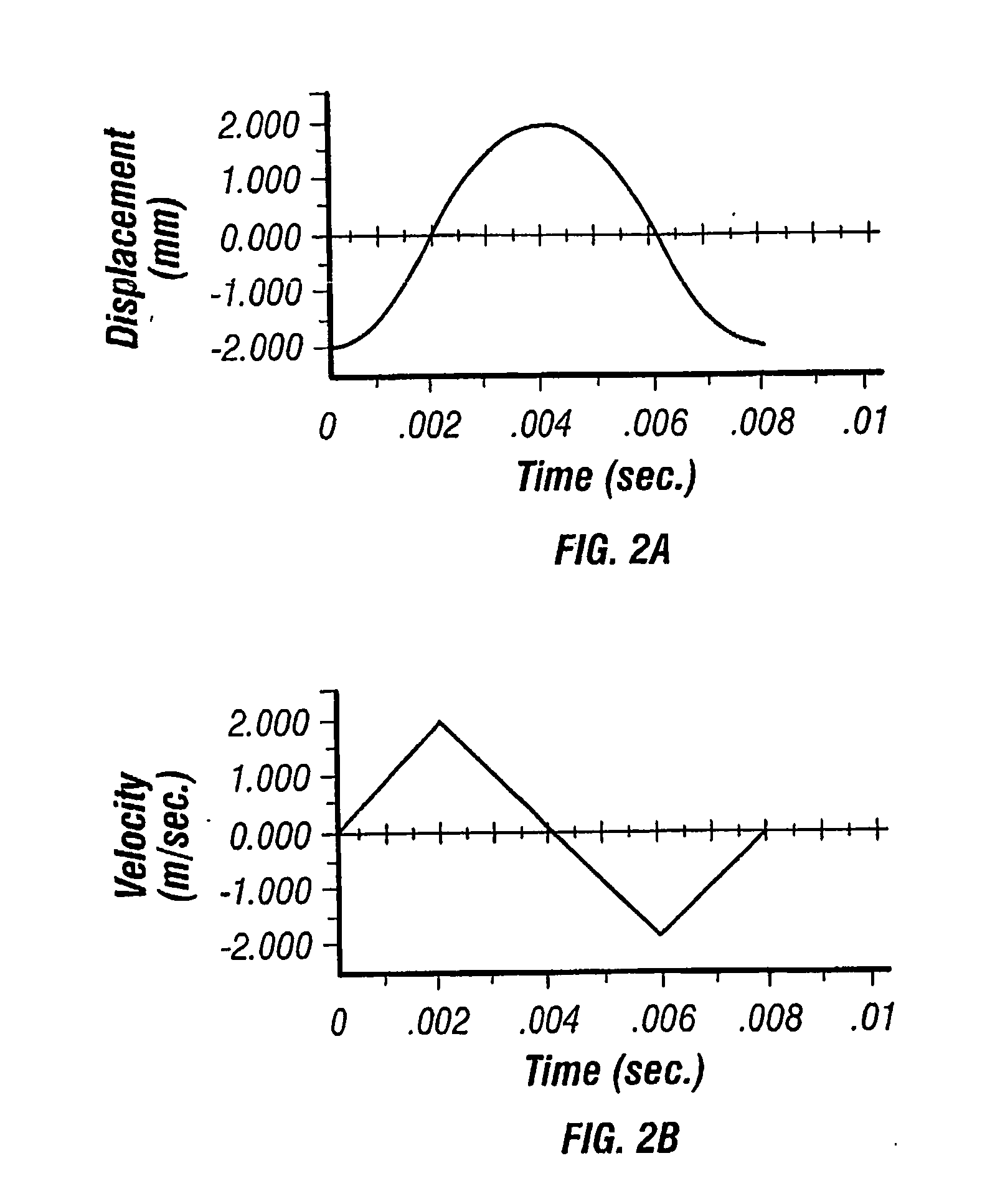

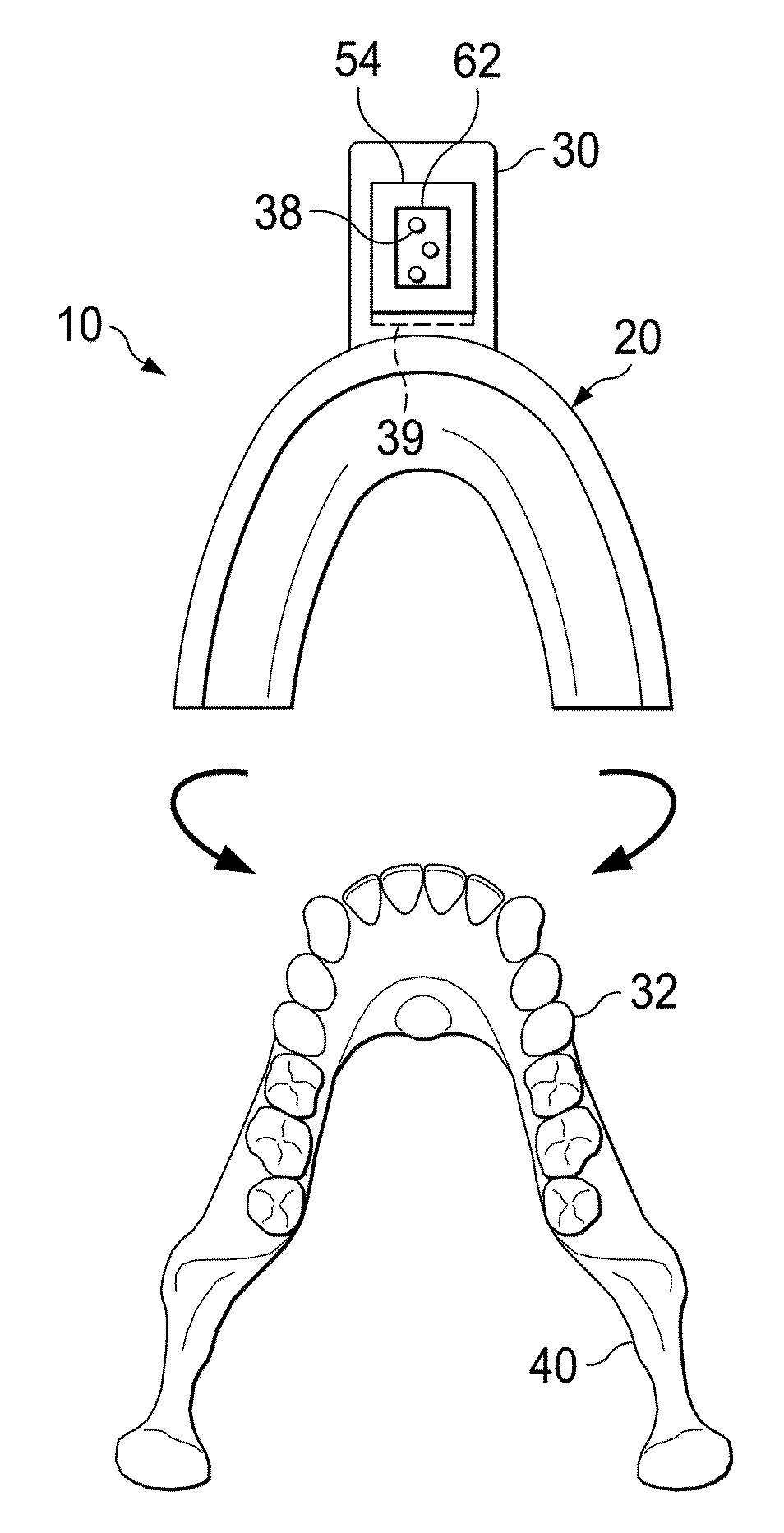

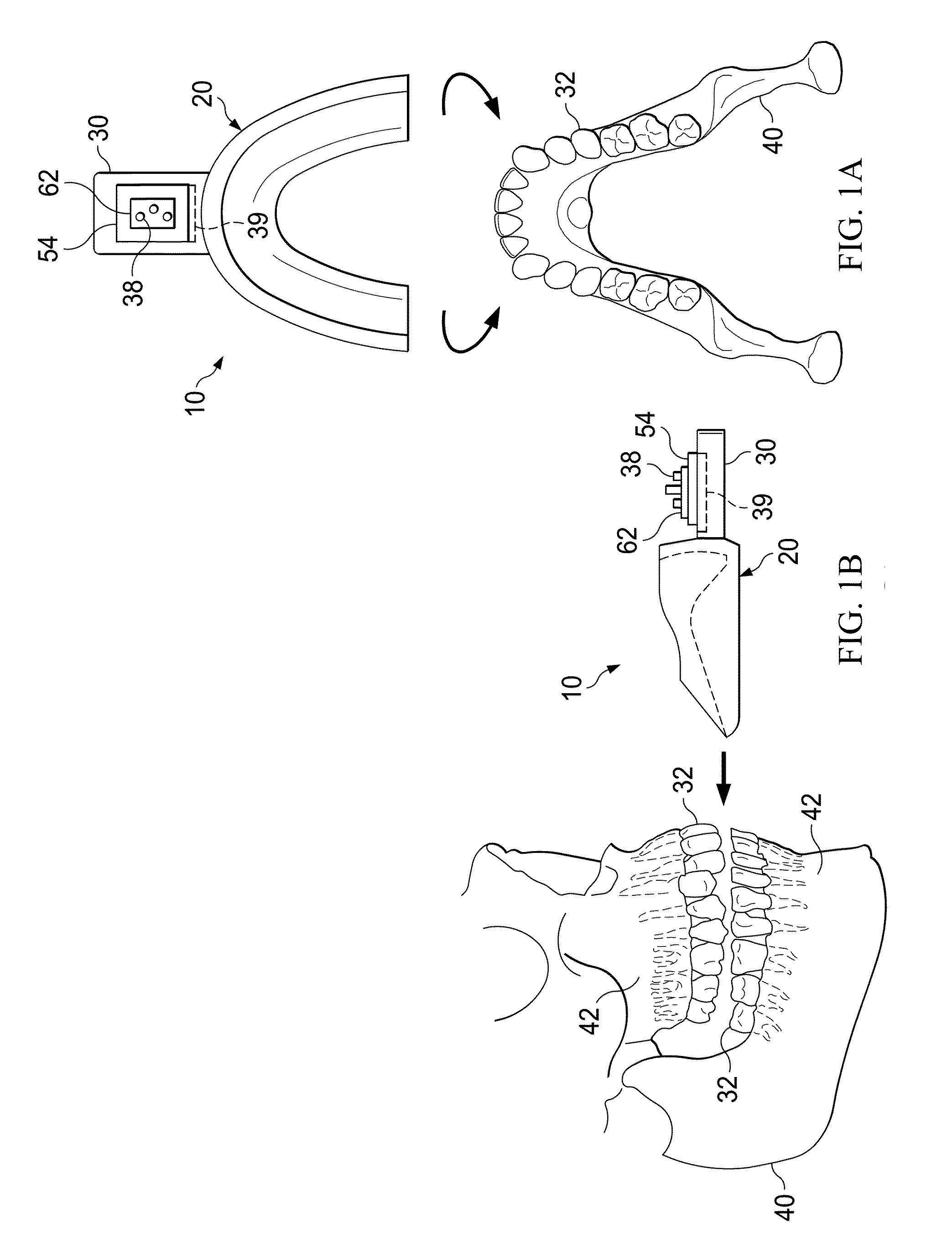

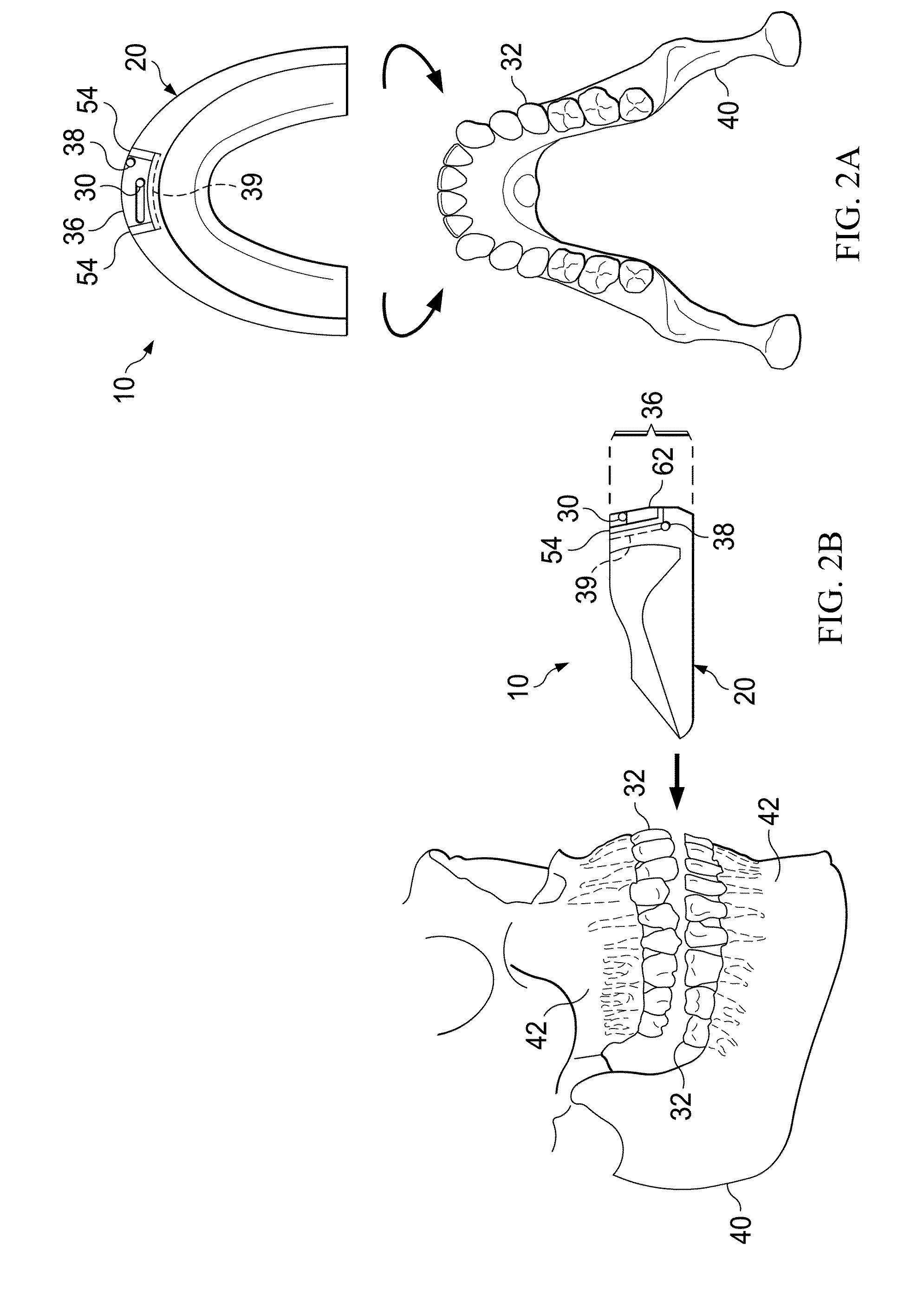

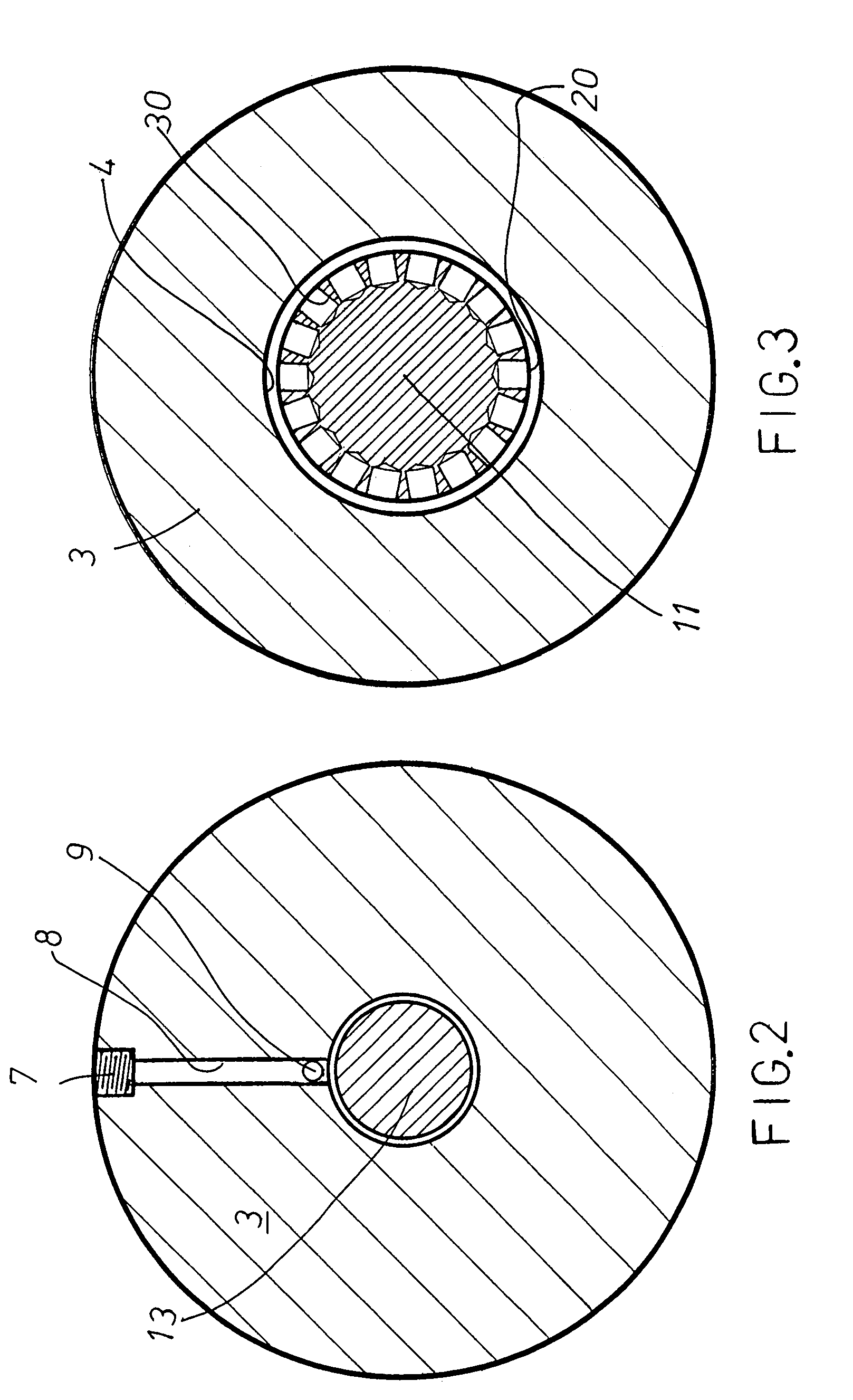

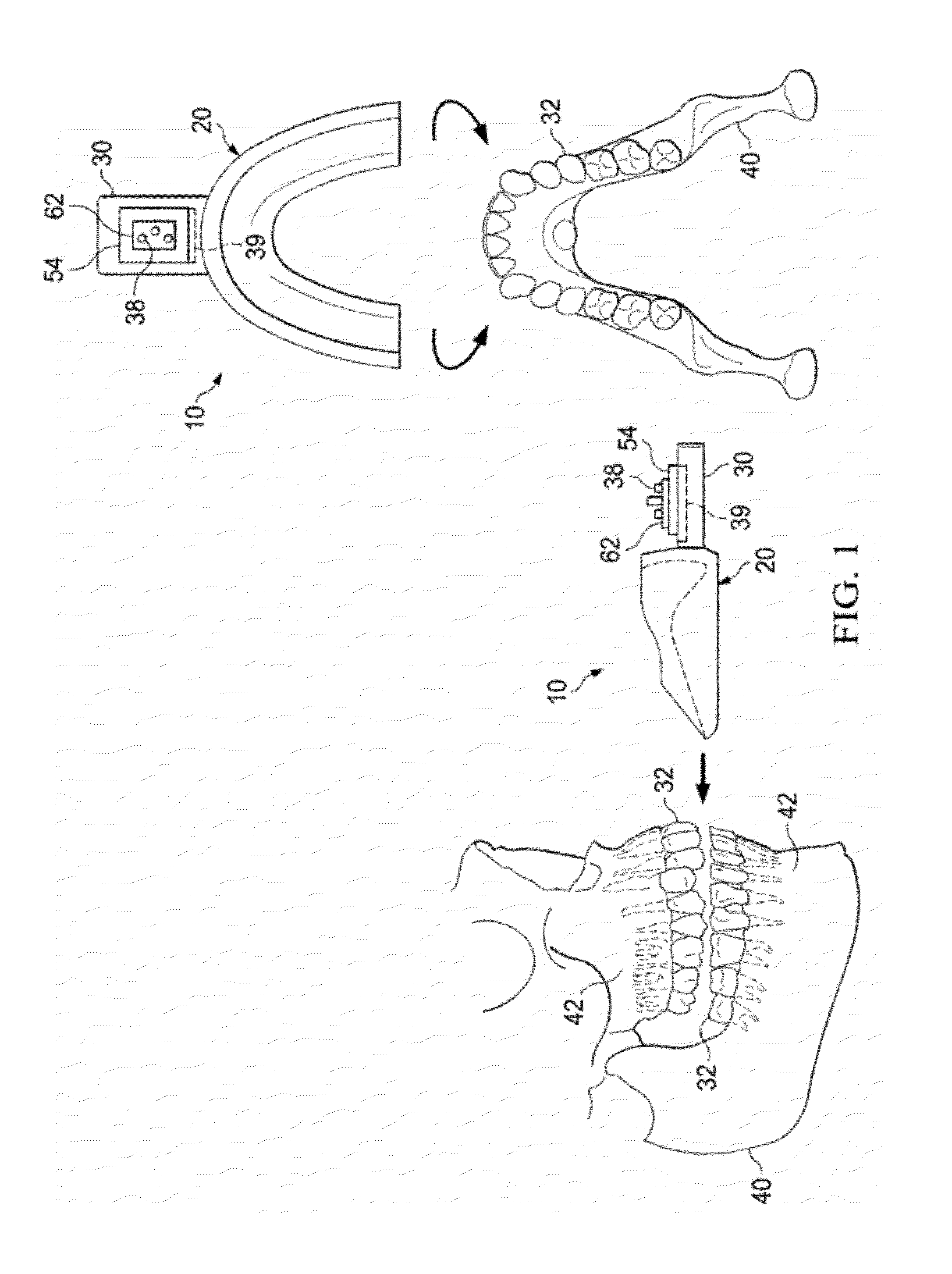

Pulsatile orthodontic device and methods

InactiveUS20160184054A1Faster rate of movementMethod be fastBracketsDental toolsBite platesBite registration

Orthodontic remodeling devices having an extraoral housing containing a power source operably coupled to an actuator operably coupled to a processor that controls said actuator; the extraoral housing operably connected to an intraoral U-shaped bite plate; the bite plate having upper and lower vertical edges on a facial edge thereof and upper and lower vertical edges on a lingual edge thereof. During usage the orthodontic remodeling device is held in place only by teeth clamping on the bite plate and vibrates at a selected frequency between 0.1 and 400 Hz. Methods of using same for faster orthodontic remodeling and pain reduction are also provided.

Owner:ADVANCED ORTHODONTICS & EDUCATION ASSOC LLC

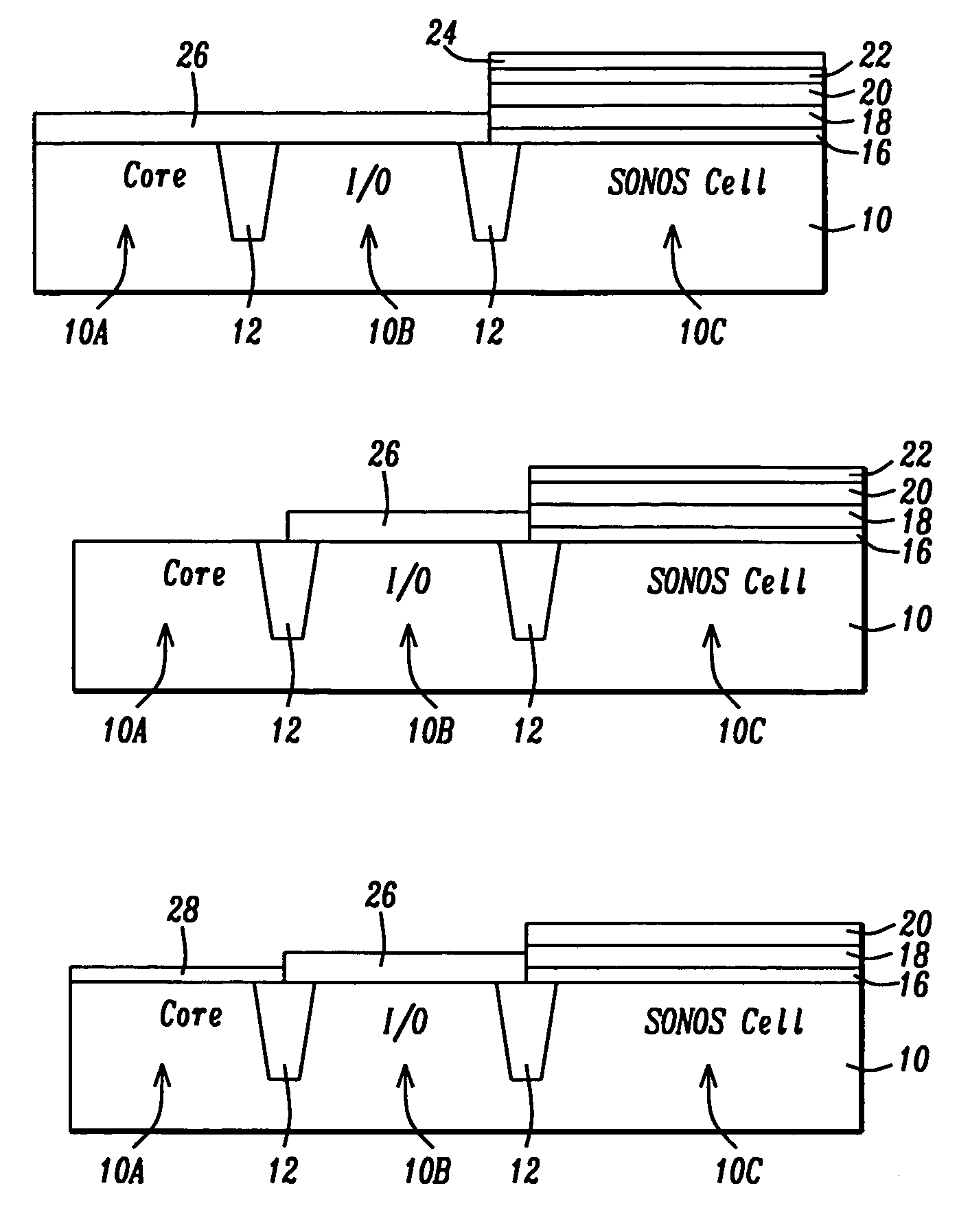

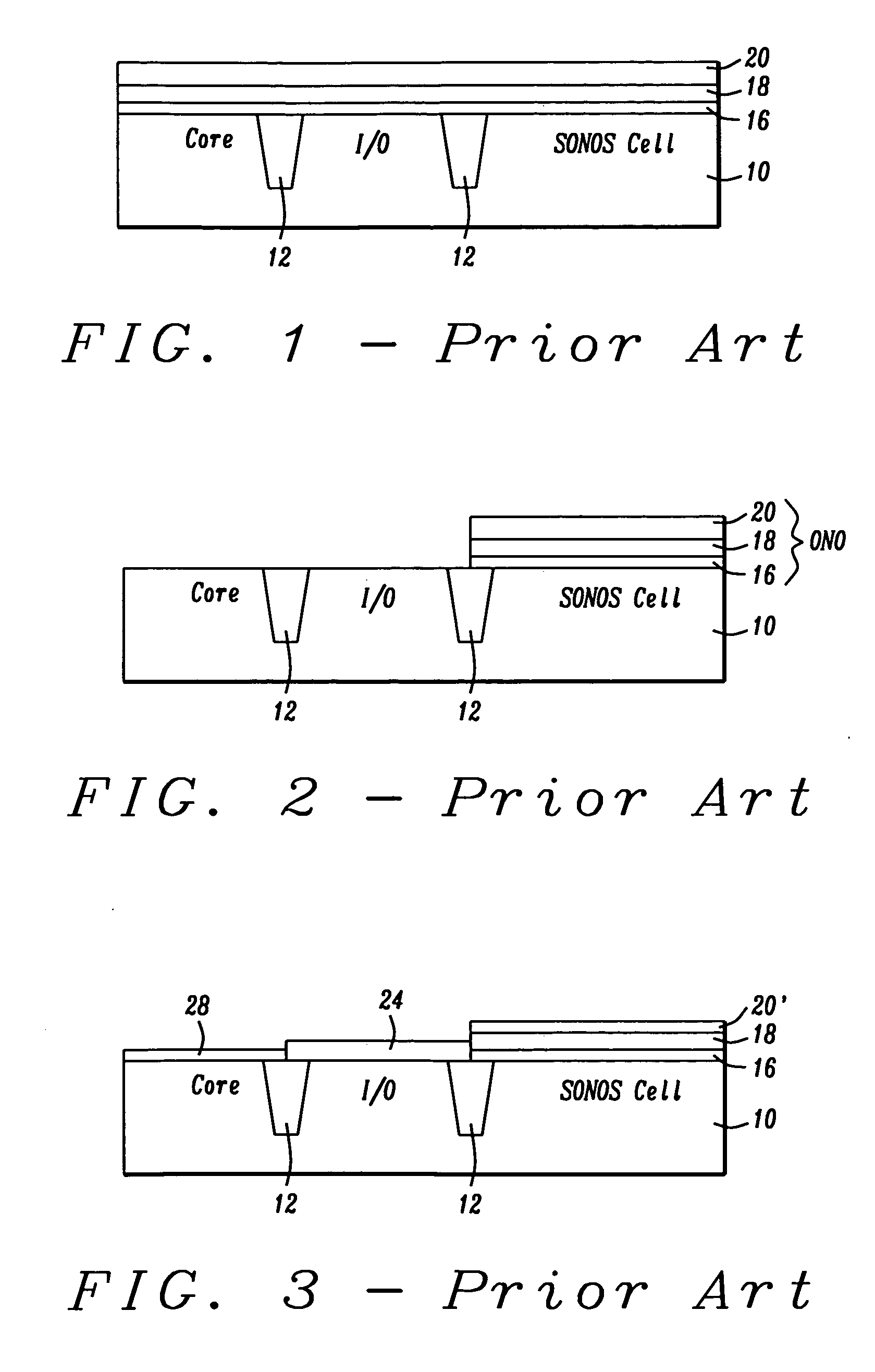

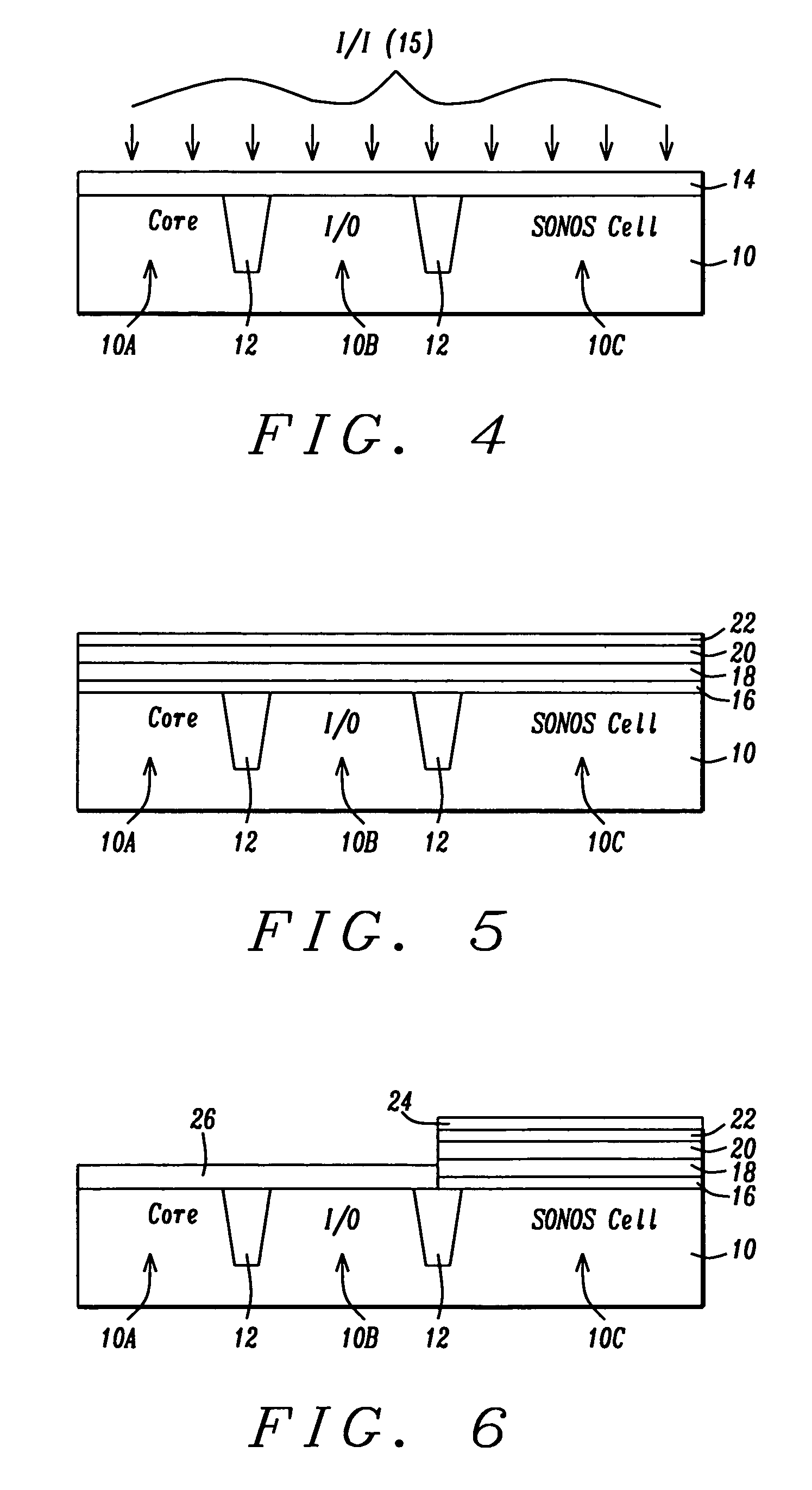

Method for integrating a SONOS gate oxide transistor into a logic/analog integrated circuit having several gate oxide thicknesses

ActiveUS6946349B1Simple manufacturing processMore cost-effectivelySolid-state devicesSemiconductor/solid-state device manufacturingEngineeringGate oxide

A method for integrating a SONOS device with an improved top oxide with SiO2 gate oxides of different thickness is described. In a first embodiment during ISSG oxidation to form the SiO2 gate oxides, a thin sacrificial silicon nitride layer is used over the top oxide of the ONO to minimize loss and to control the top oxide thickness. In a second embodiment the top oxide layer for the SONOS device is formed by depositing an NO stack. During ISSG oxidation to form the SiO2 gate oxides a portion of the Si3N4 in the NO stack is converted to SiO2 to form the top oxide with improved thickness control.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

Methods and Apparatus for Improved Heat Spreading in Solid State Lighting Systems

ActiveUS20080089069A1Reduce weightEfficient transferLighting support devicesPoint-like light sourceEngineeringLED lamp

A solid state lighting subassembly or fixture includes an anisotropic heat spreading material. A heat spreading layer may be placed between a light emitting diode (LED) and luminaire or reflector and serves to spread heat laterally away from the LED. Low profile, low weight heat spreading may be utilized both to retrofit existing light fixtures with. LEDs or to replace existing incandescent and fluorescent fixtures with LED based fixtures.

Owner:IDEAL IND LIGHTING LLC

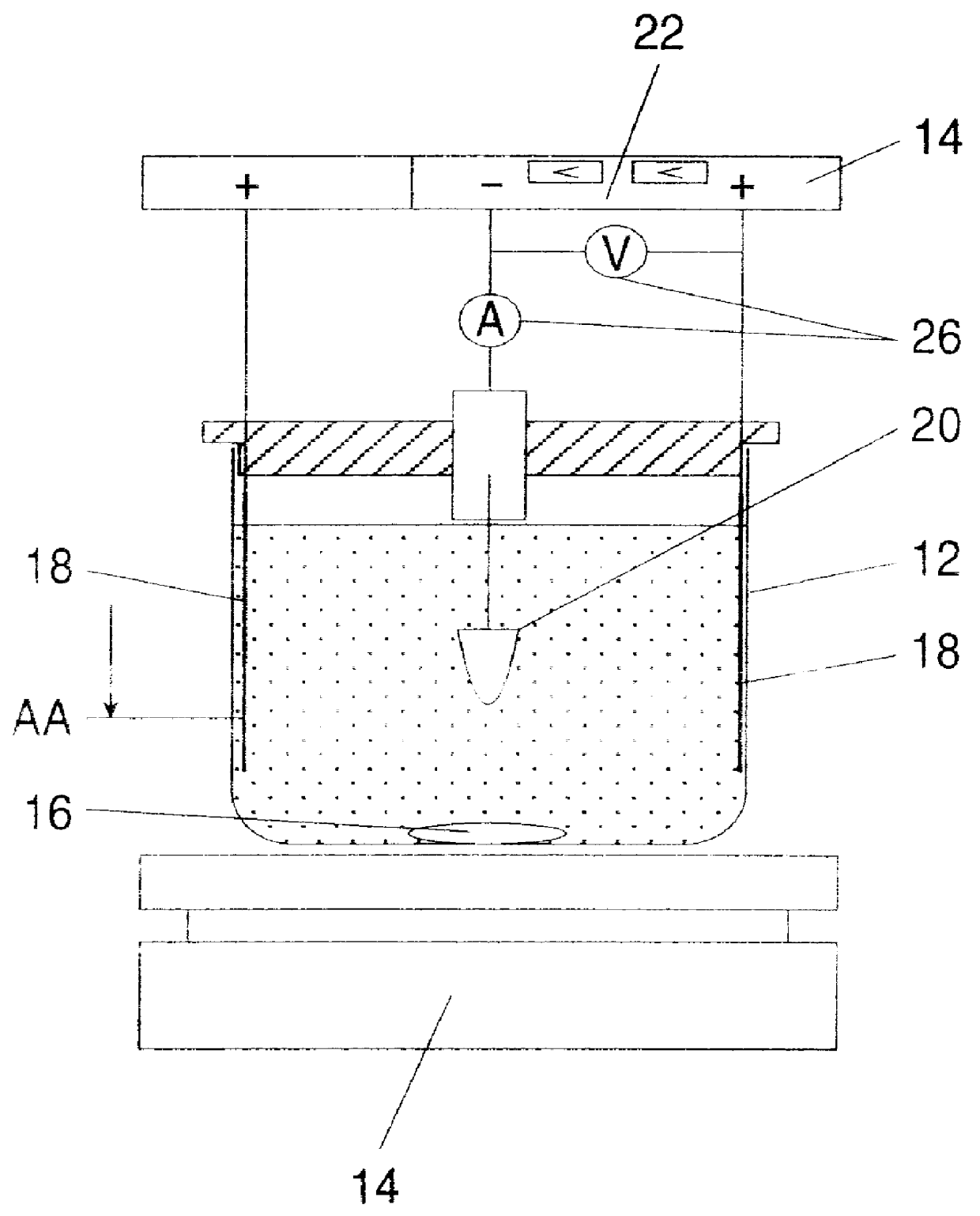

Method of electrophoretic deposition of ceramic bodies for use in manufacturing dental appliances

InactiveUS6059949AHigh strengthImprove toughnessElectrolysis componentsTeeth fillingMetallurgyElectrophoresis

A method for electrophoretic deposition of ceramic particles as a green body shaped as a dental appliance, the method comprising the steps of (a) forming a suspension of the ceramic particles in a first polar solvent, the ceramic particles constituting at least about 5% of the first suspension by weight; (b) passing a direct electrical current through the first suspension, using a deposition electrode shaped as the dental appliance to form a green body; (c) coating the green body with glass particles; and (d) sintering the resultant coated body for obtaining a glass coated all-ceramic dental appliance.

Owner:CEREL CERAMIC TECH

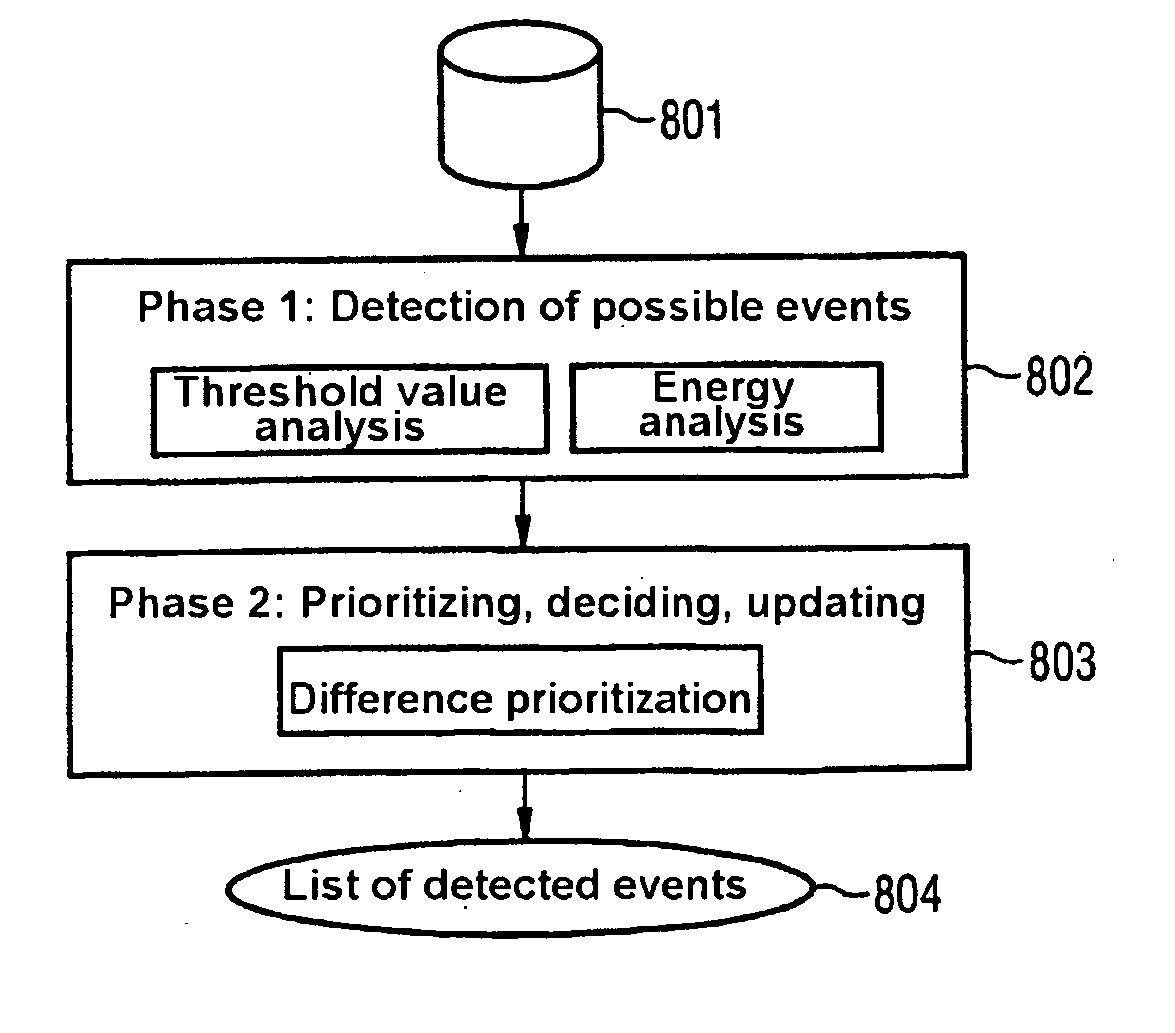

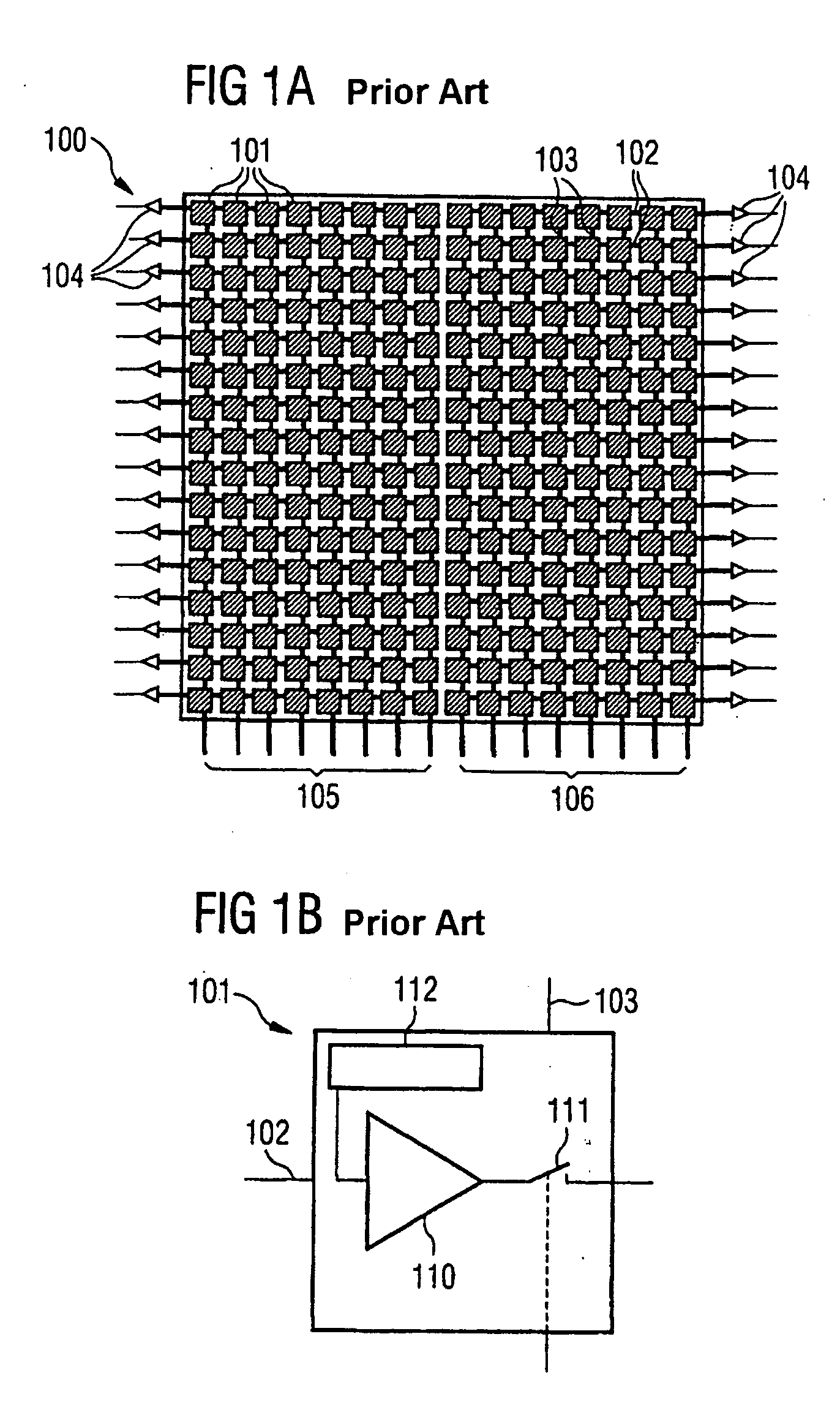

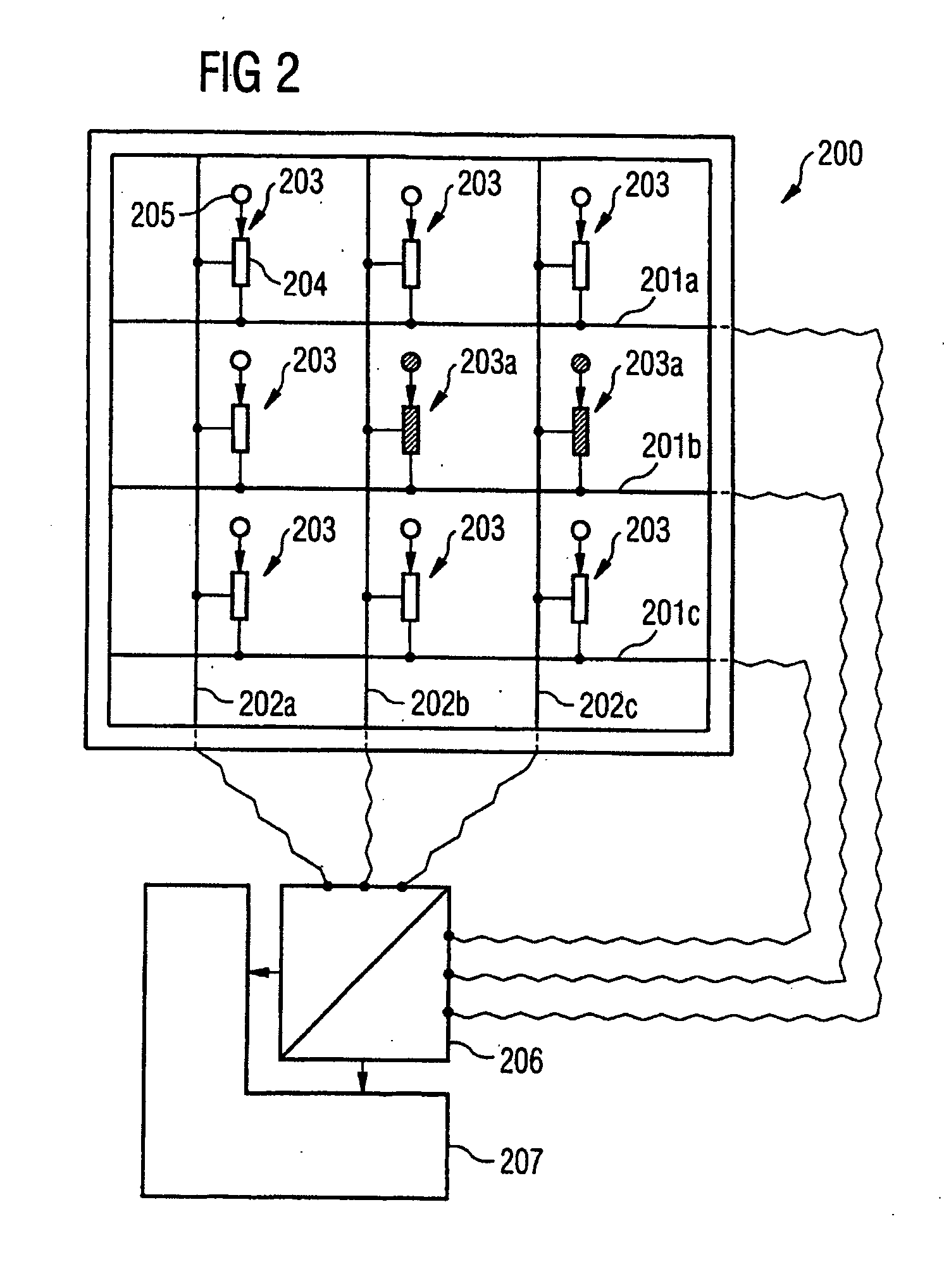

Sensor arrangement with improved spatial and temporal resolution

InactiveUS20050202582A1Quick fixMore cost-effectivelySemiconductor/solid-state device manufacturingMaterial electrochemical variablesSensor arrayTemporal resolution

Sensor arrangement having sensor arrays arranged in crossover regions of row and column lines, each of the sensor arrays having a coupler and a sensor element, which influences current flow between a row and column line through the coupler, an accumulative current flow detector that detects accumulative current flow from individual electric current flows provided by the sensor arrays, and a decoder that determines a sensor element at which a sensor signal is present from the accumulative electric current flows. Accumulative current flows which satisfy a predetermined first criterion can be determined from the detected accumulative current flows, and from the accumulative current flows determined an accumulative current flow can be selected as an accumulative current flow which represents a sensor signal and which satisfies a predetermined second criterion, and the sensor element at which a sensor signal is present can be determined from the selected accumulative current flow.

Owner:INFINEON TECH AG

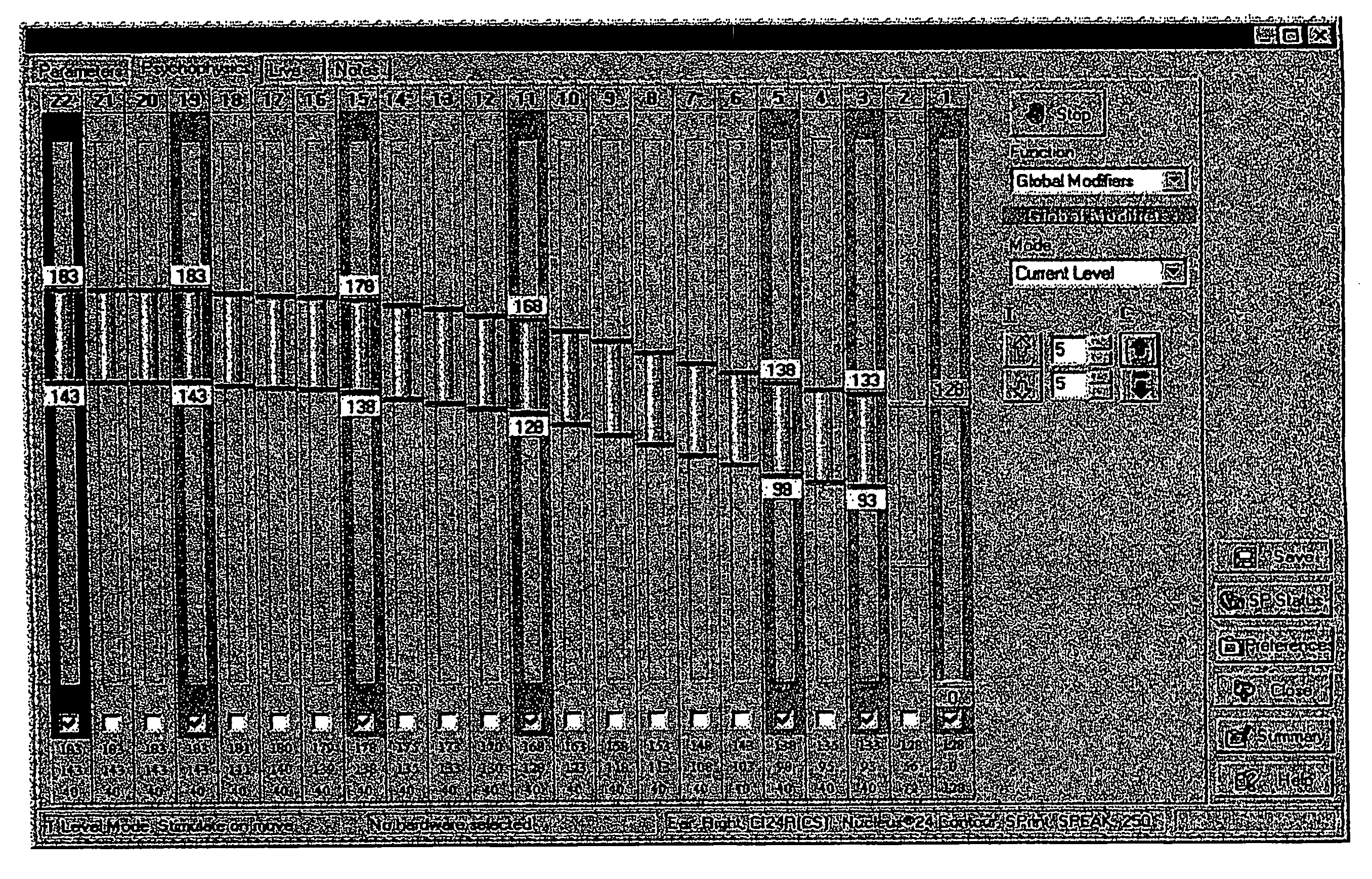

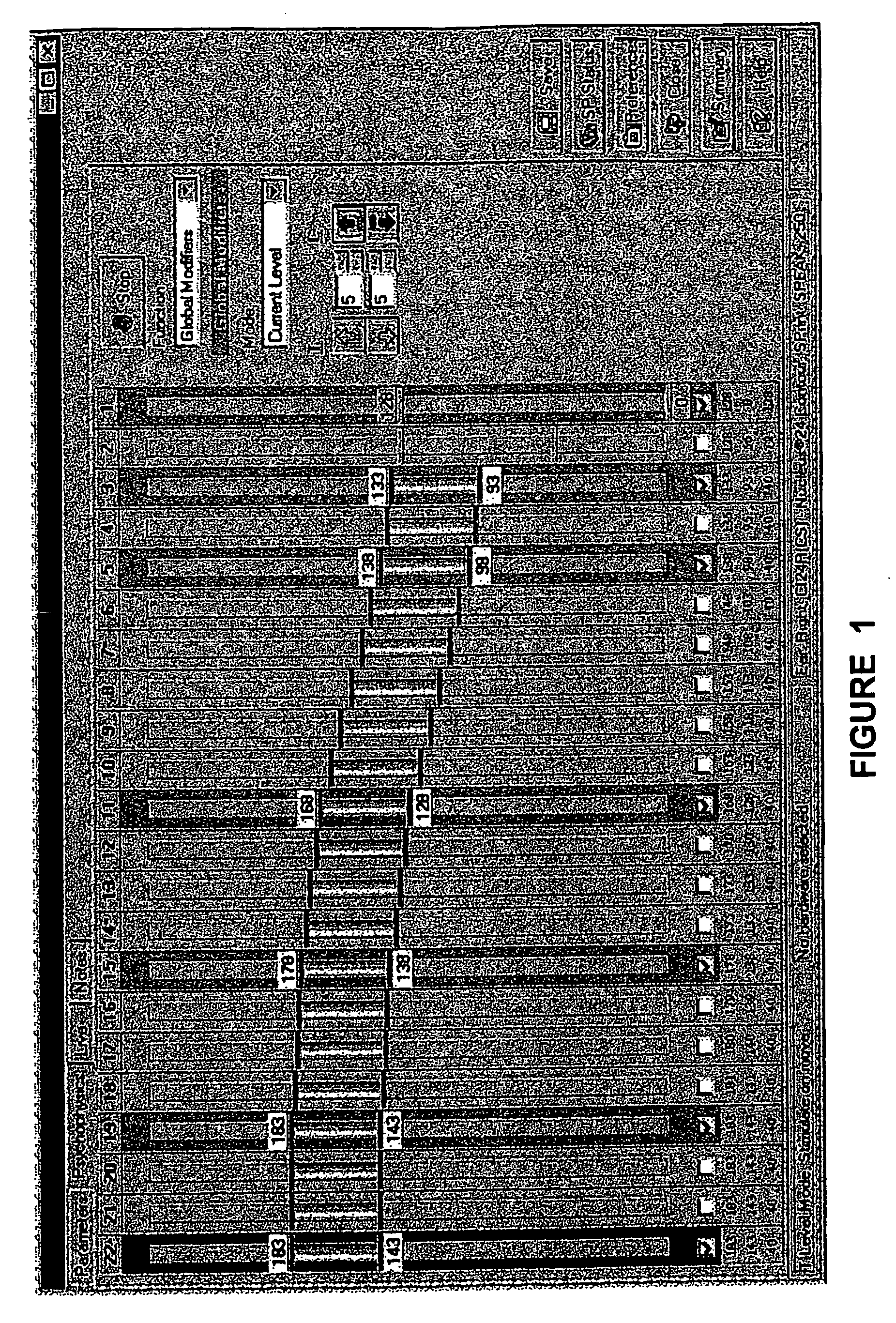

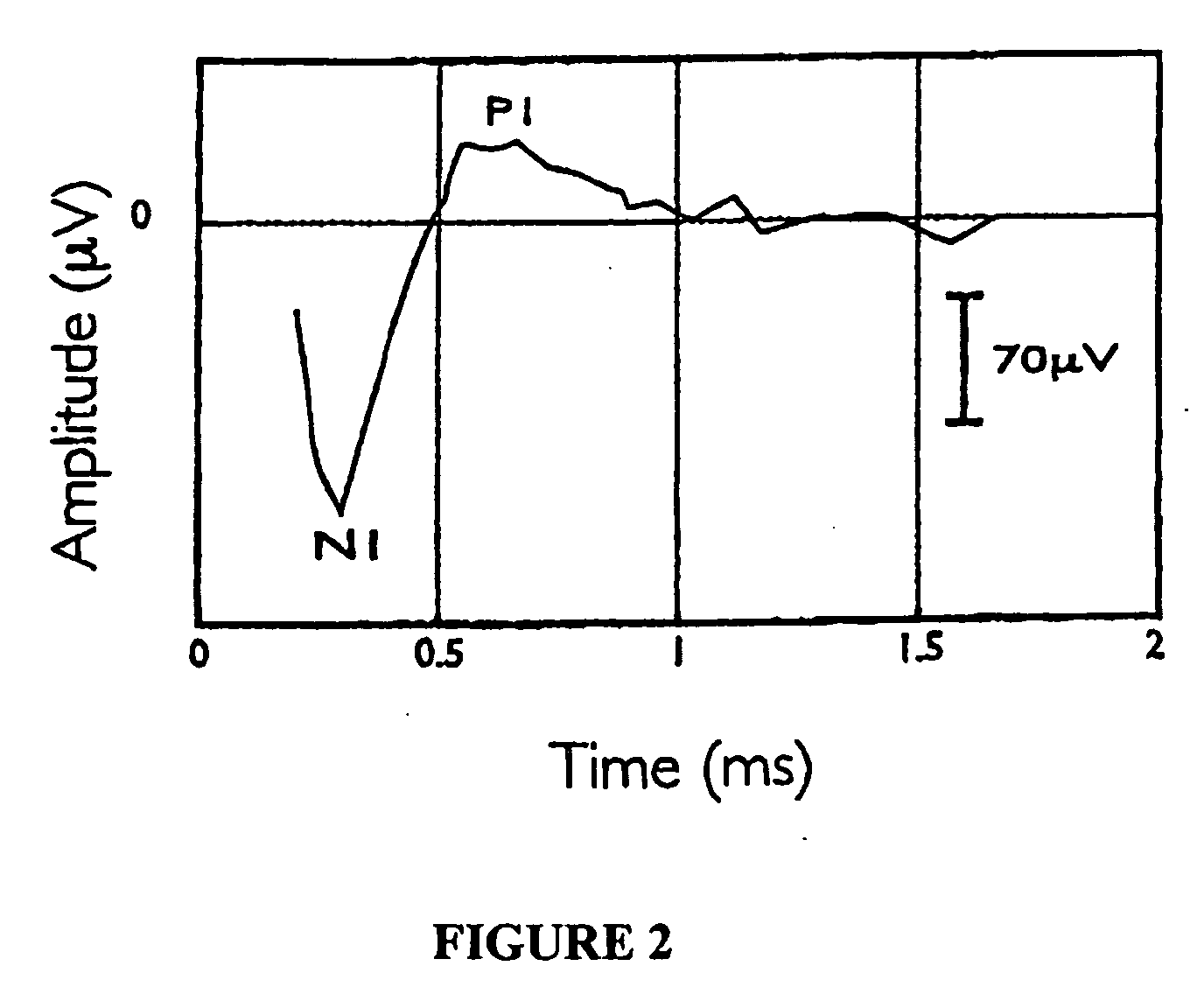

Parametric fitting of a cochlear implant

ActiveUS20060235332A1Reduce the amount requiredMore recipient friendlyElectrotherapyDiagnostic recording/measuringPower flowEngineering

A method of fitting an auditory stimulation system to a recipient the system having a plurality of channels, and the method including the steps of establishing an initial current level profile representative of a current level setting spanning across at least some of the plurality of channels and adjusting parameters of the initial current level profile in the presence of a stimulation signal. There is further included a programming apparatus adapted to be interfaced with the auditory stimulation system to allow manipulation of threshold (T) and comfort (C) levels of the system. The apparatus includes a graphical display means adapted to display a graphical representation of the current profile of the channel array and means for adjusting a current level setting of the current pmfile of the array.

Owner:COCHLEAR LIMITED

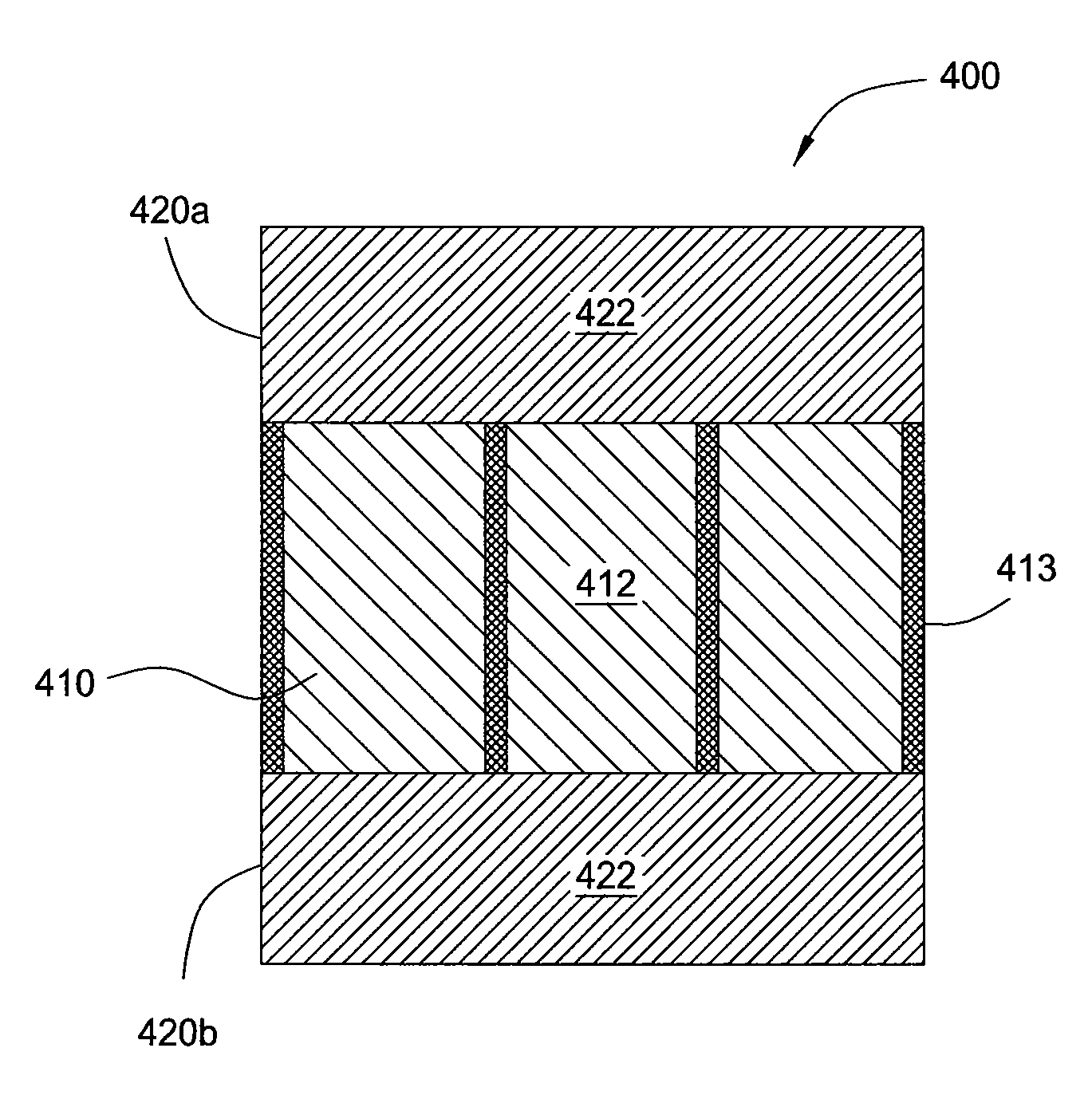

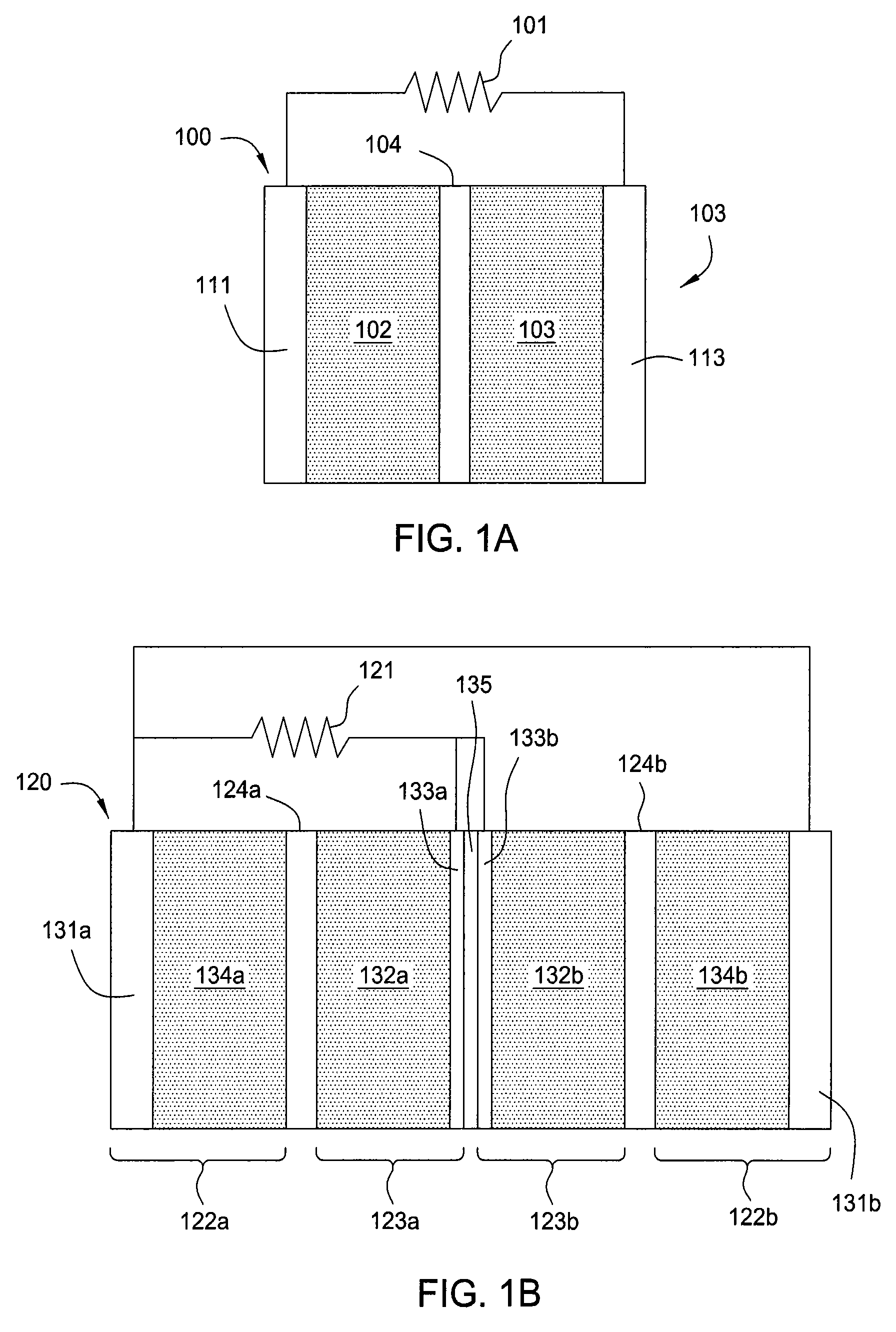

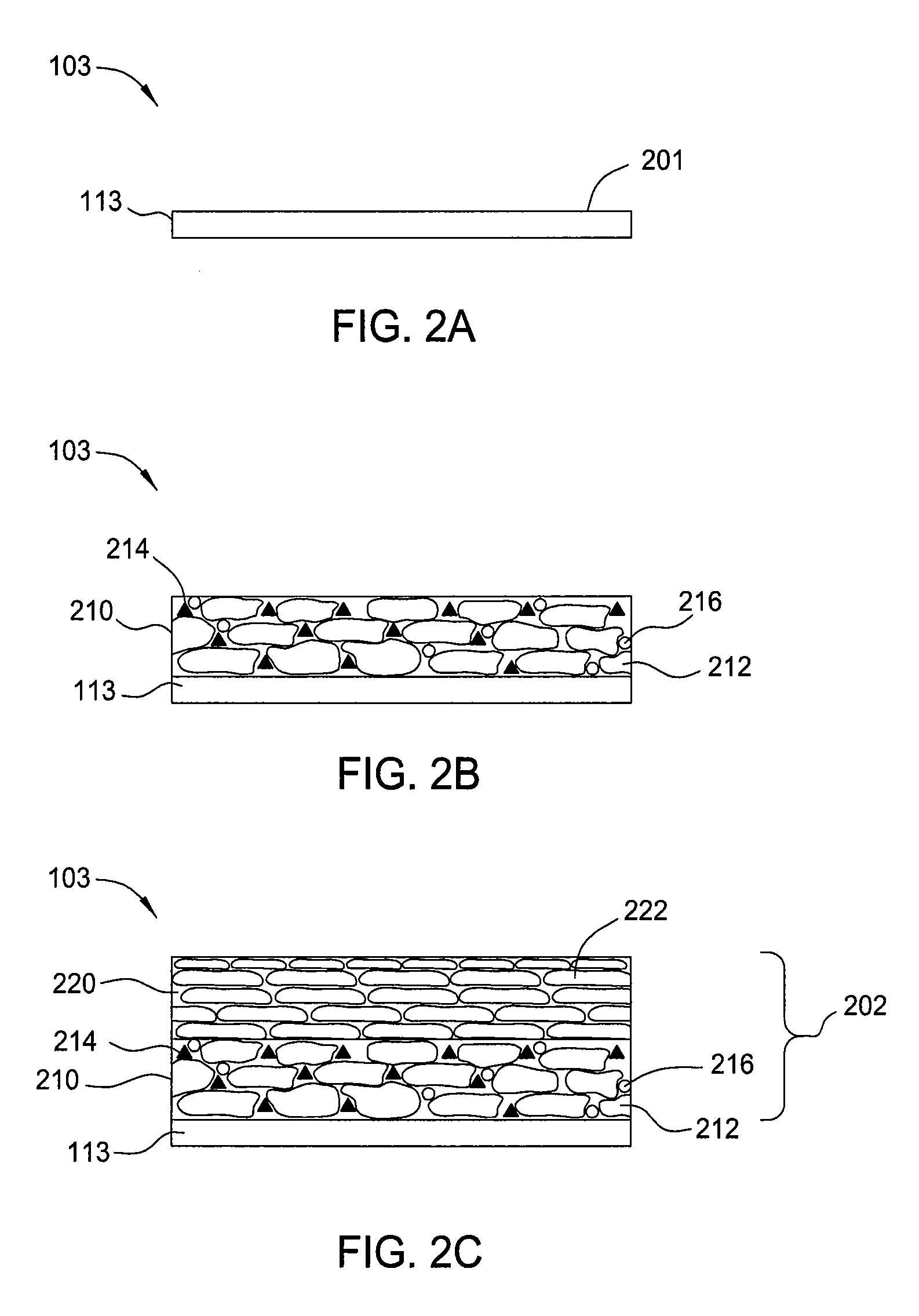

Graded electrode technologies for high energy lithium-ion batteries

InactiveUS20110168550A1Reduce separator material costEasy to manufactureMachining electrodesElectrode carriers/collectorsProduction rateElectrical battery

Embodiments described herein provide methods and systems for manufacturing faster charging, higher capacity energy storage devices that are smaller, lighter, and can be more cost effectively manufactured at a higher production rate. In one embodiment, a graded cathode structure is provided. The graded cathode structure comprises a conductive substrate, a first porous layer comprising a first cathodically active material having a first porosity formed on the conductive substrate, and a second porous layer comprising a second cathodically active material having a second porosity formed on the first porous layer. In certain embodiments, the first porosity is greater than the second porosity. In certain embodiments, the first porosity is less than the second porosity.

Owner:APPLIED MATERIALS INC

Rumen by-pass delivery system

InactiveUS20020127259A1Prevent oxidationEffective absorptionBiocideAnimal feeding stuffBiotechnologyNutrition

The present invention relates to a composition for the delivery of active agents that are protected from environmental oxidation and are resistant to ruminal fermentation degradation but not intestinal digestion and adsorption. The composition may contain biologically active ingredients such as for example, vitamins, minerals, proteins, amino acids, fatty acids, nutritional supplements, and pharmaceuticals together with natural and / or synthetic lecithin phospholipids.

Owner:ORTHOEFER FRAND T

Method of producing micropulp and micropulp made therefrom

InactiveUS20030114641A1More cost-effectivelySmall sizeCellulose coatingsPaper/cardboardFiberSolid component

The present invention is directed to a process for producing micropulp. The process includes contacting organic fibers with a medium comprising a liquid component and a solid component, agitating the medium and the organic fibers to transform the organic fibers into the micropulp dispersed in the medium. If desired, the slurry of the micropulp in the liquid component can be used or the micropulp can be separated from the medium. The micropulp can be readily incorporated into coating compositions such as those used in automotive OEM or refinish applications. The micropulp can also be incorporated into powder coating applications or as a thixotrope or reinforcement in polymer formulations.

Owner:EI DU PONT DE NEMOURS & CO

Pathogen inactivating compositions for disinfecting biological fluids

InactiveUS6106773AAvoid bulk processingAvoid capital intensive equipmentBiocideSolvent extractionBlood componentAqueous solution

The present invention is directed to pathogen inactivating compositions that can be used to disinfect various biological fluids, such as blood, blood fractions, and the like. The compositions are suitable for disinfecting biological fluids containing valuable, but labile, components such as proteins without destroying the desired properties of such components. The pathogen inactivating compositions of the present invention are produced by contacting water or an aqueous solution with iodinated matrix material. The compositions can be pre-formulated and stored for subsequent use in disinfecting a wide range of biological fluids.

Owner:AMERICAN NAT RED CROSS

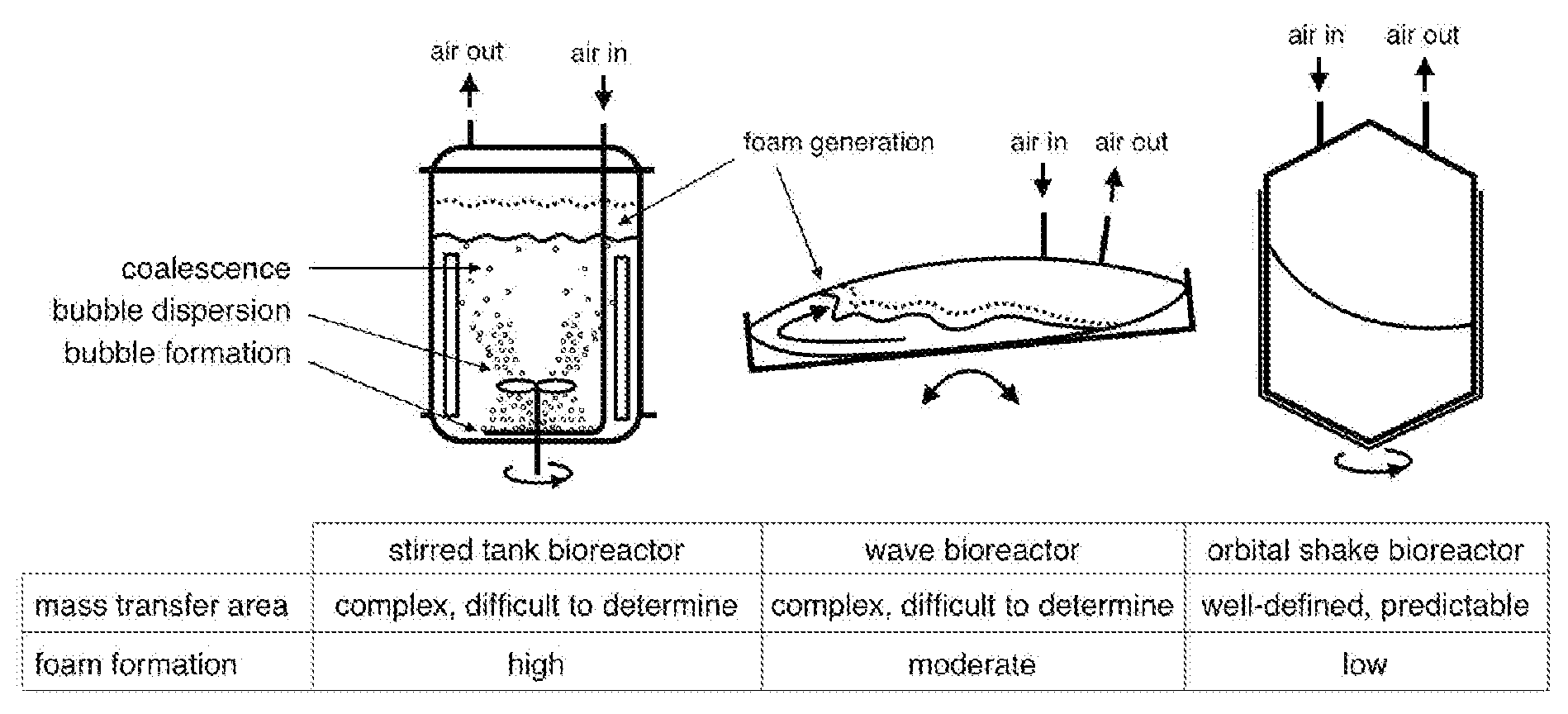

Cell cultivation and production of recombinant proteins by means of an orbital shake bioreactor system with disposable bags at the 1,500 liter scale

InactiveUS20090233334A1High degreeEasy to handleMicroorganismsBiochemistry apparatusCulture cellBiology

The present invention provides a novel method for culturing cells as well as a novel method for producing a recombinant protein by culturing cells at large scale (up to 1,500 L nominal volume and 750 L working volume), whereby an inflated bag provides a sterile, disposable cultivation chamber. The inflated bag is partially filled with liquid cultivation media and cells, and placed into a containment vessel. The containment vessel is positioned onto an orbitally shaken platform. The orbital shaking moves the containment vessel and thus the bag and induces thereby motion to the liquid contained therein (“shake mixing”). This motion (caused by orbital shaking) induces a dynamic force field that ensures cell suspension, bulk mixing, and oxygen transfer from the liquid surface to the respiring cells without damaging shear or foam generation.

Owner:EXCELLGENE SA

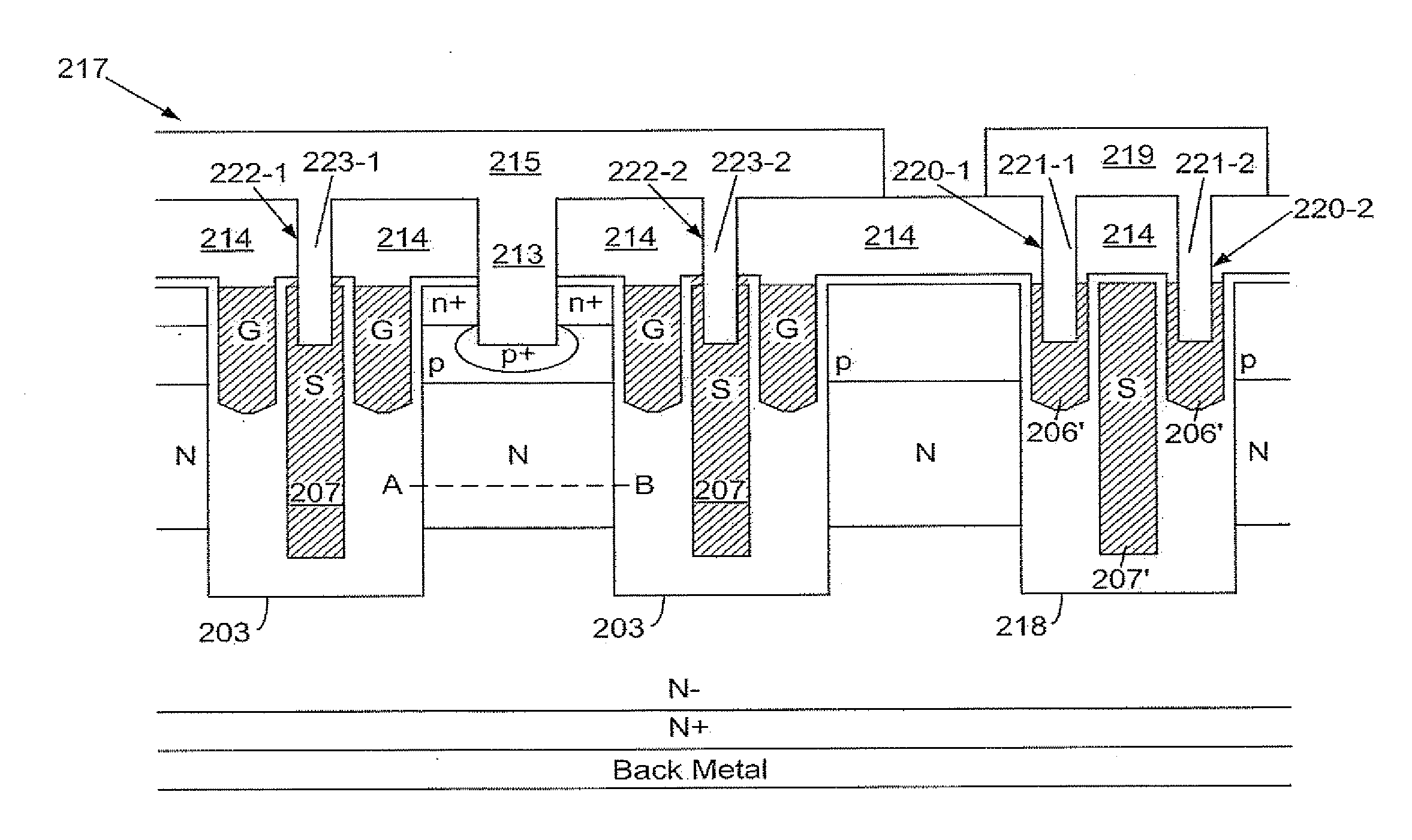

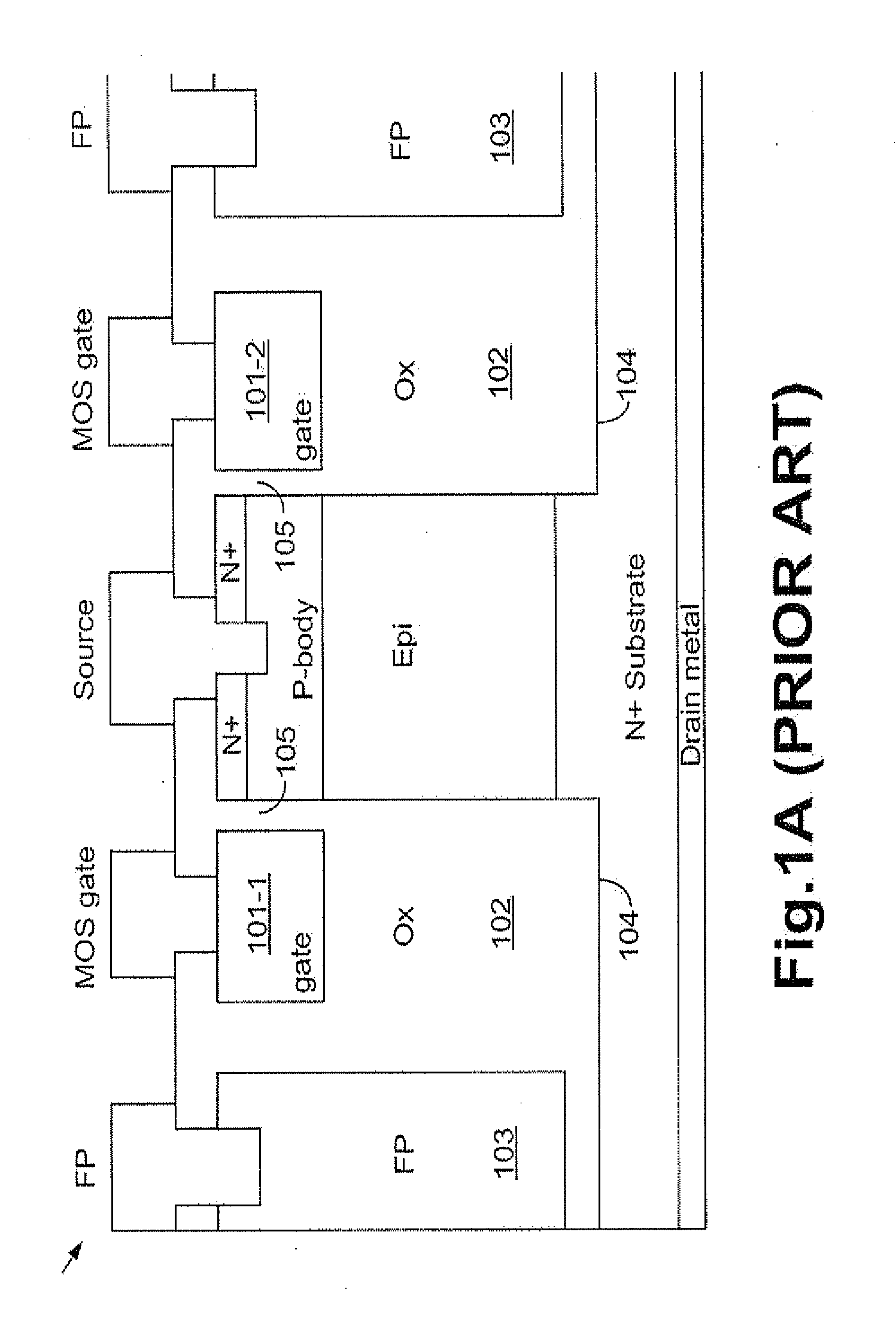

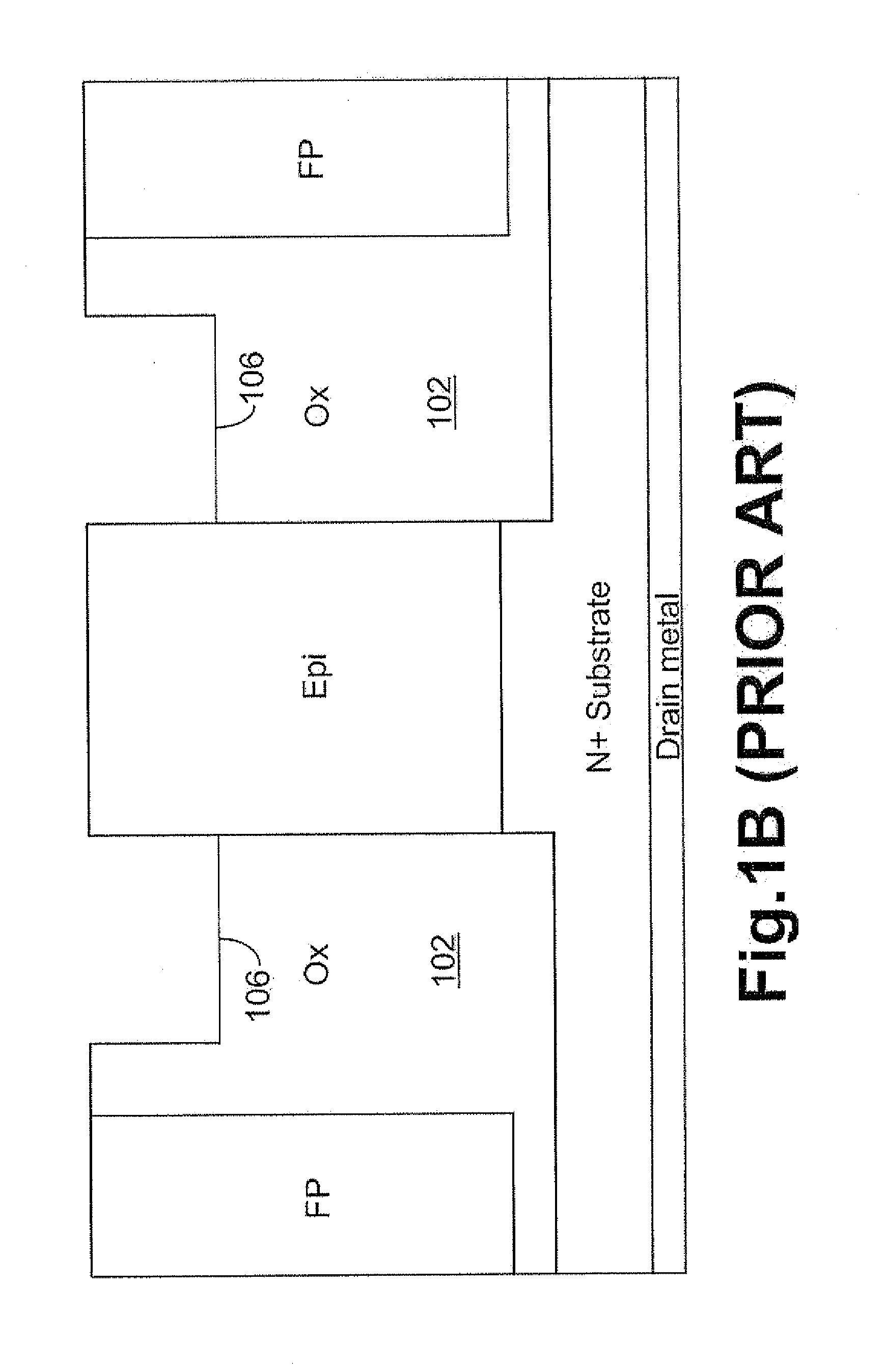

Trench mosfet with resurf stepped oxide and diffused drift region

ActiveUS20130168760A1Super cost-effectiveEasy to controlSemiconductor/solid-state device manufacturingSemiconductor devicesTrench mosfetEngineering

A trench MOSFET with split gates and diffused drift region for on-resistance reduction is disclosed. Each of the split gates is symmetrically disposed in the middle of the source electrode and adjacent trench sidewall of a deep trench. The inventive structure can save a mask for definition of the location of the split gate electrodes. Furthermore, the fabrication method can be implemented more reliably with lower cost.

Owner:FORCE MOS TECH CO LTD

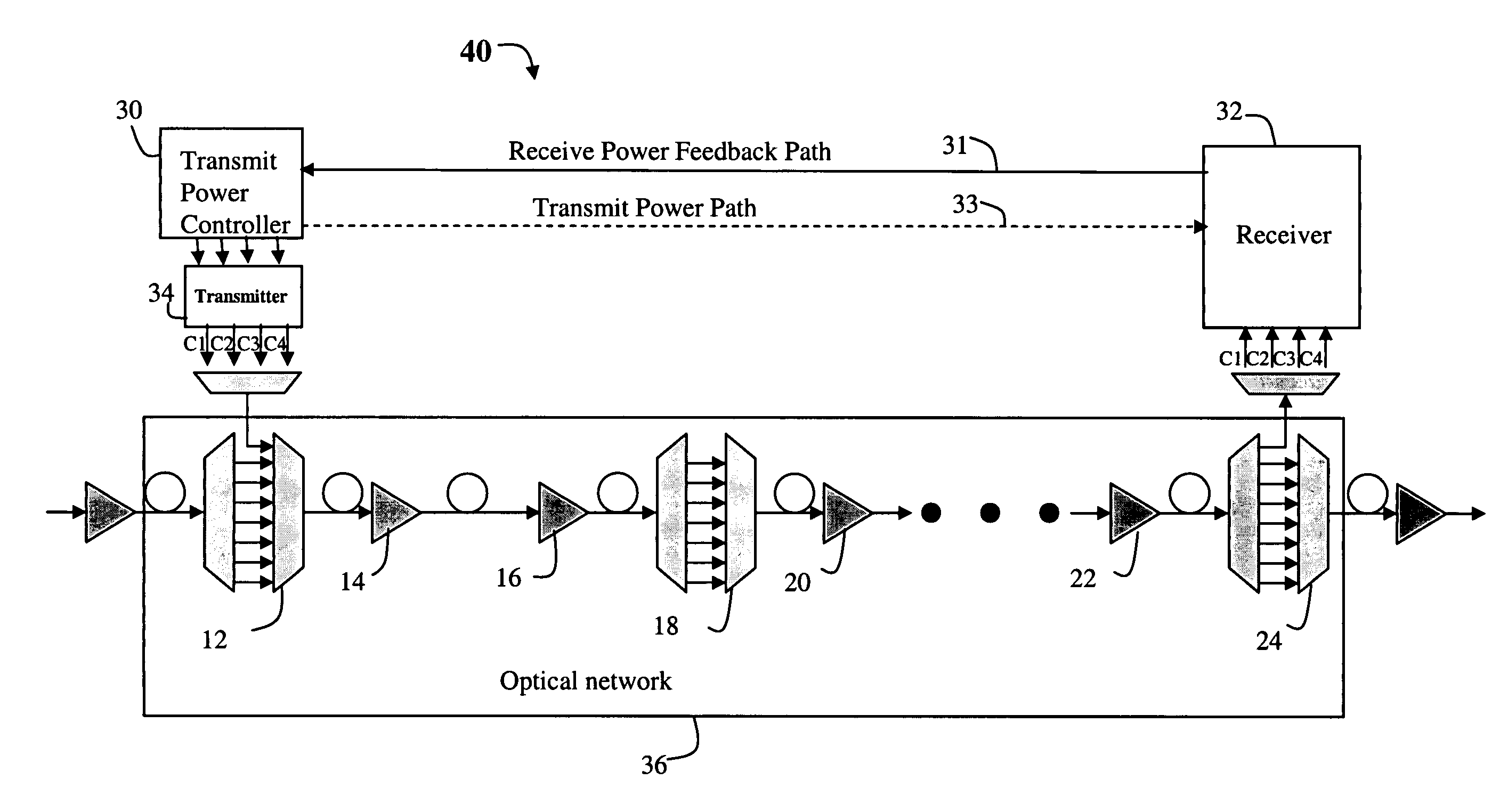

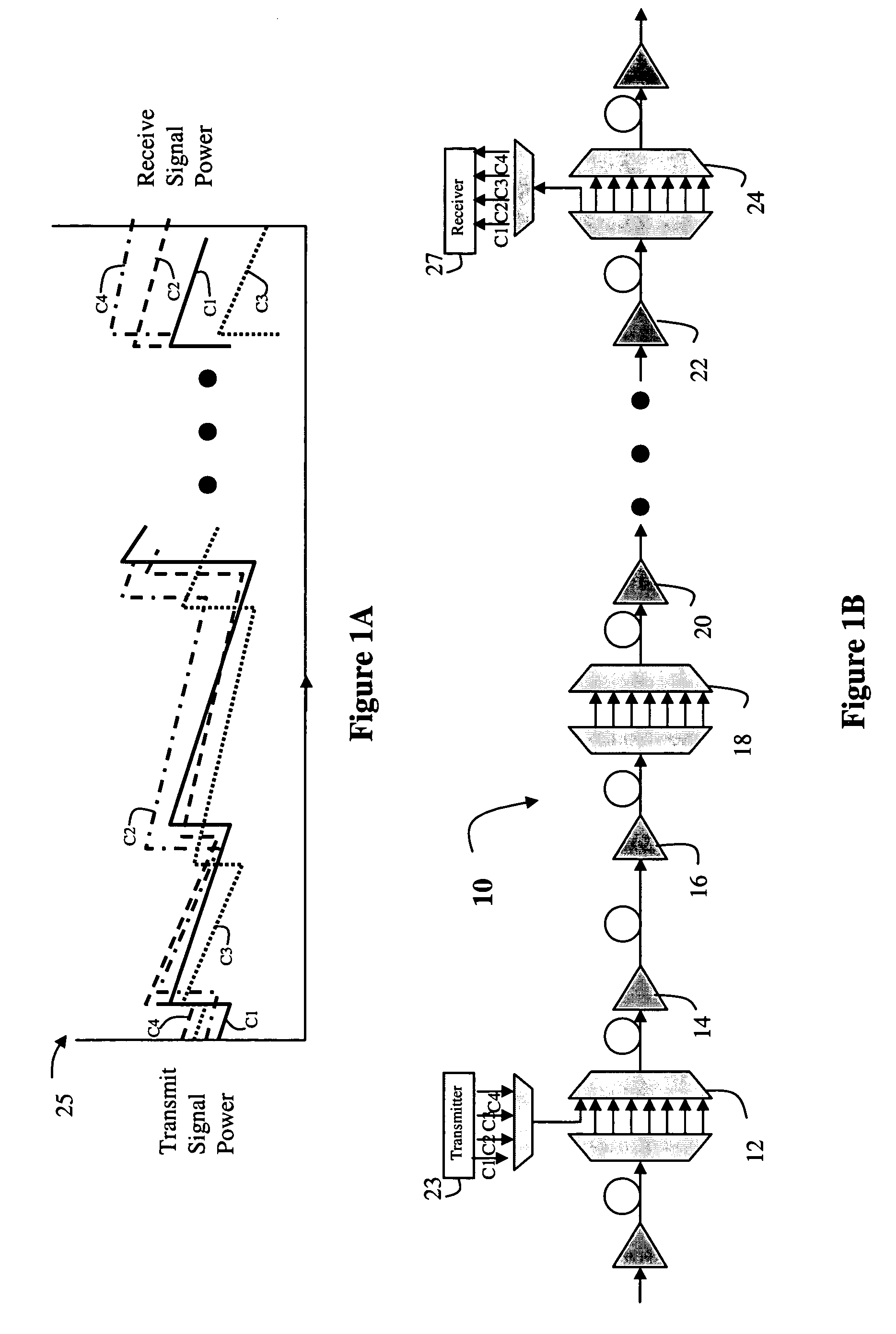

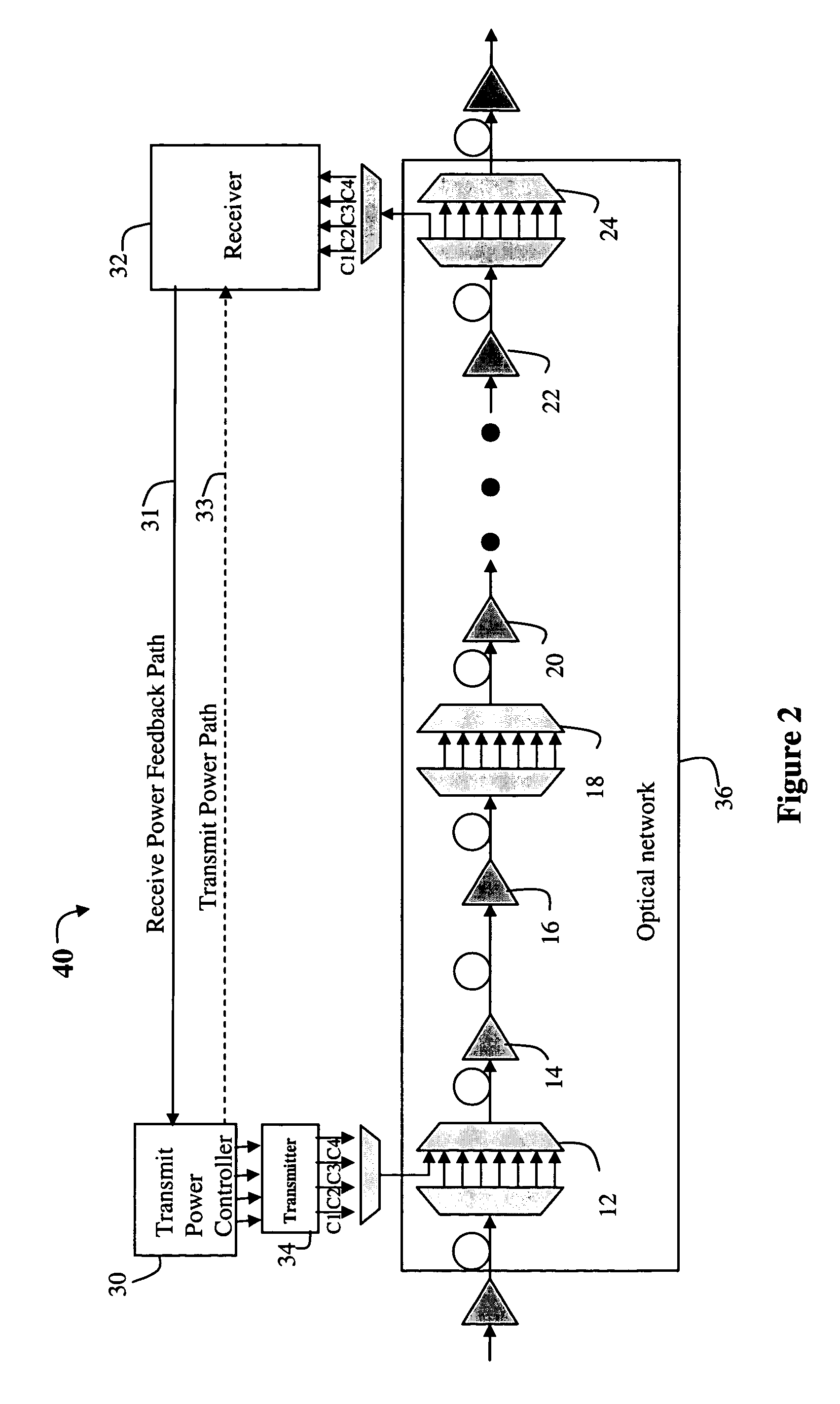

Transmission power optimization apparatus and method

ActiveUS7522846B1Low costReduce power deviationOptical multiplexElectromagnetic transmittersEngineeringTransmission point

A method and system is provided that is capable of controlling transmit power to achieve a desired OSNR at a receive endpoint. The system utilizes the fact that the aggregate power for a plurality of channels is controllable between a transmission point and a receive point in the network, and uses this characteristic to coarsely adjust transmission powers in the network to achieve desired OSNR results.

Owner:CIENA

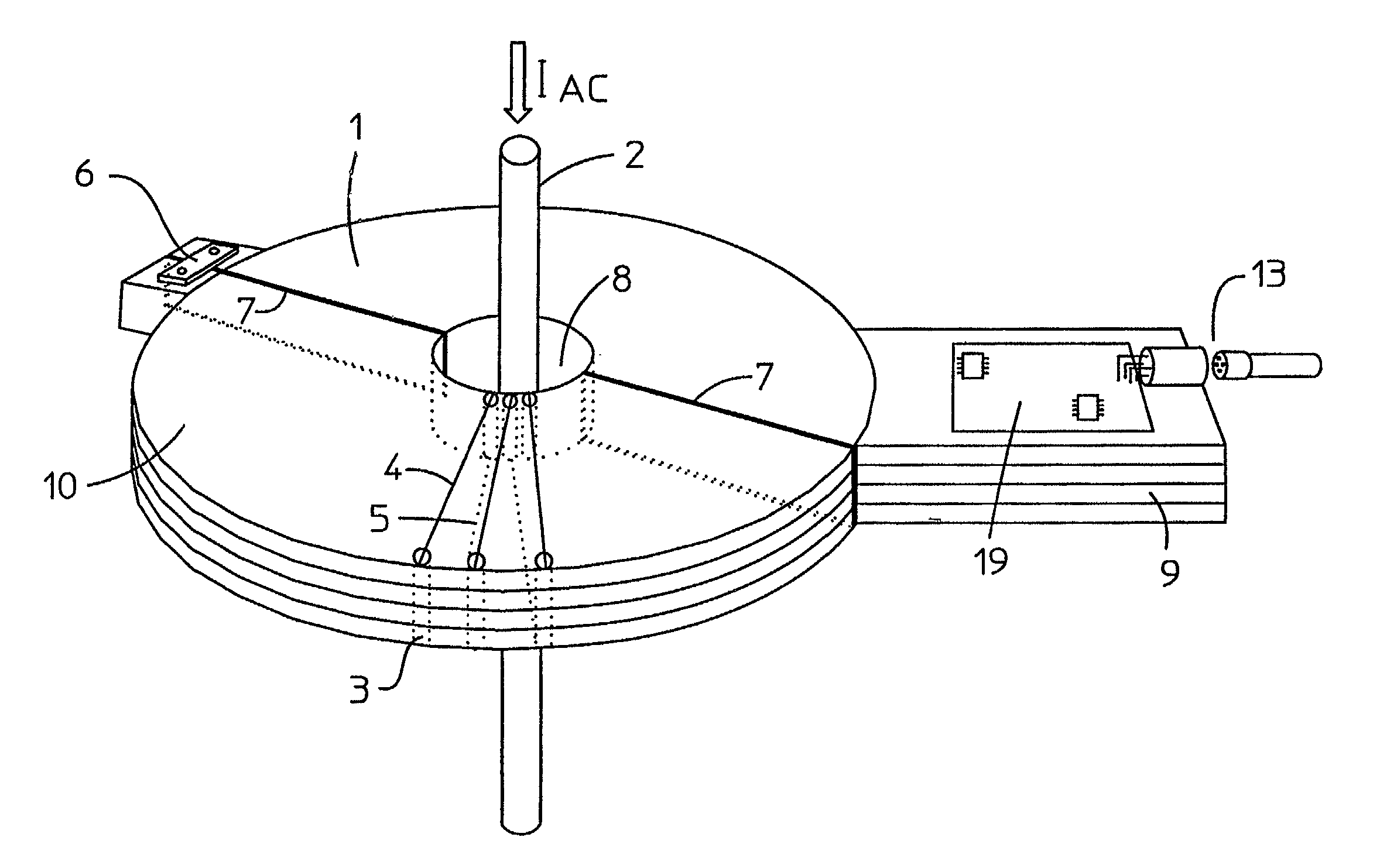

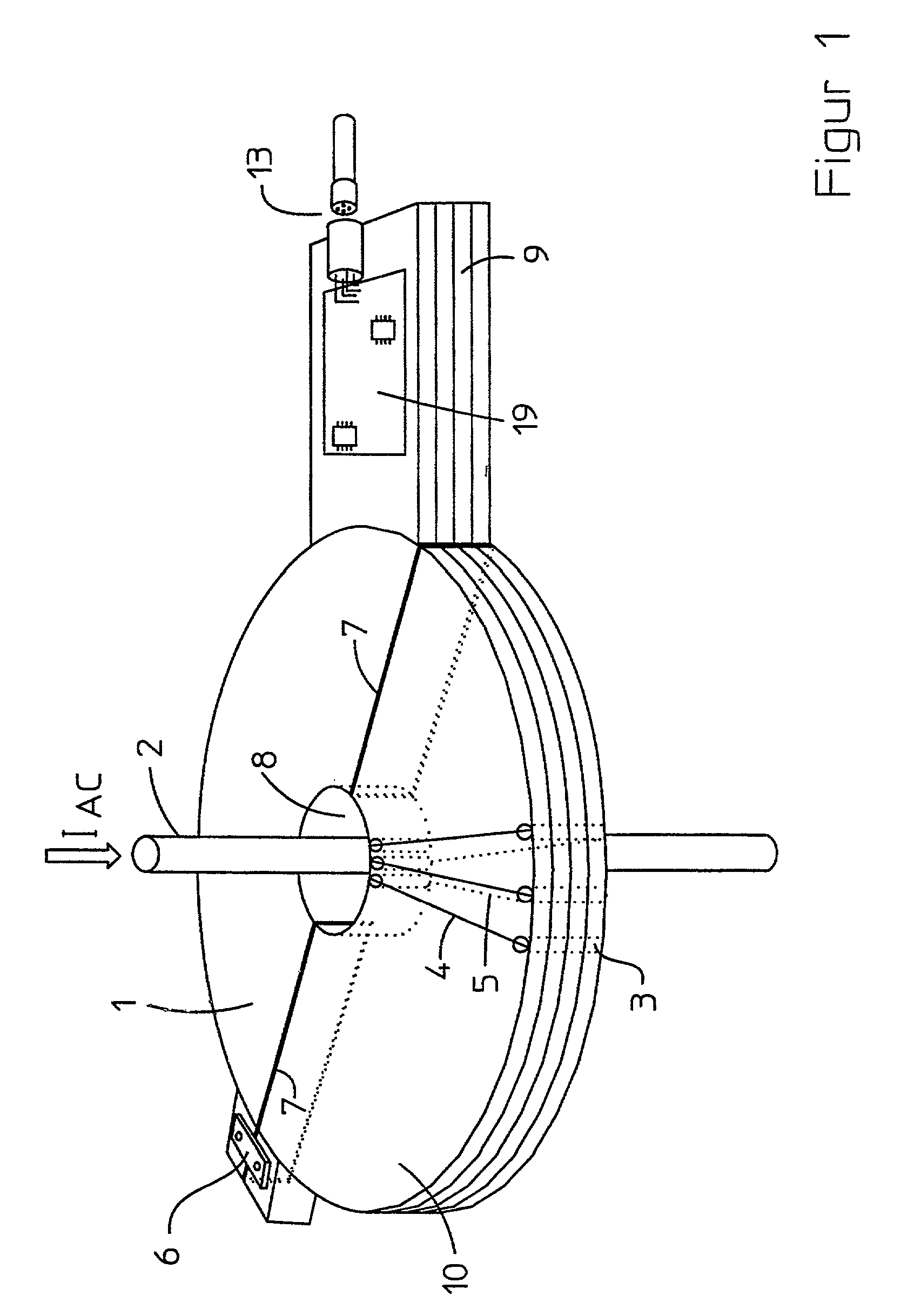

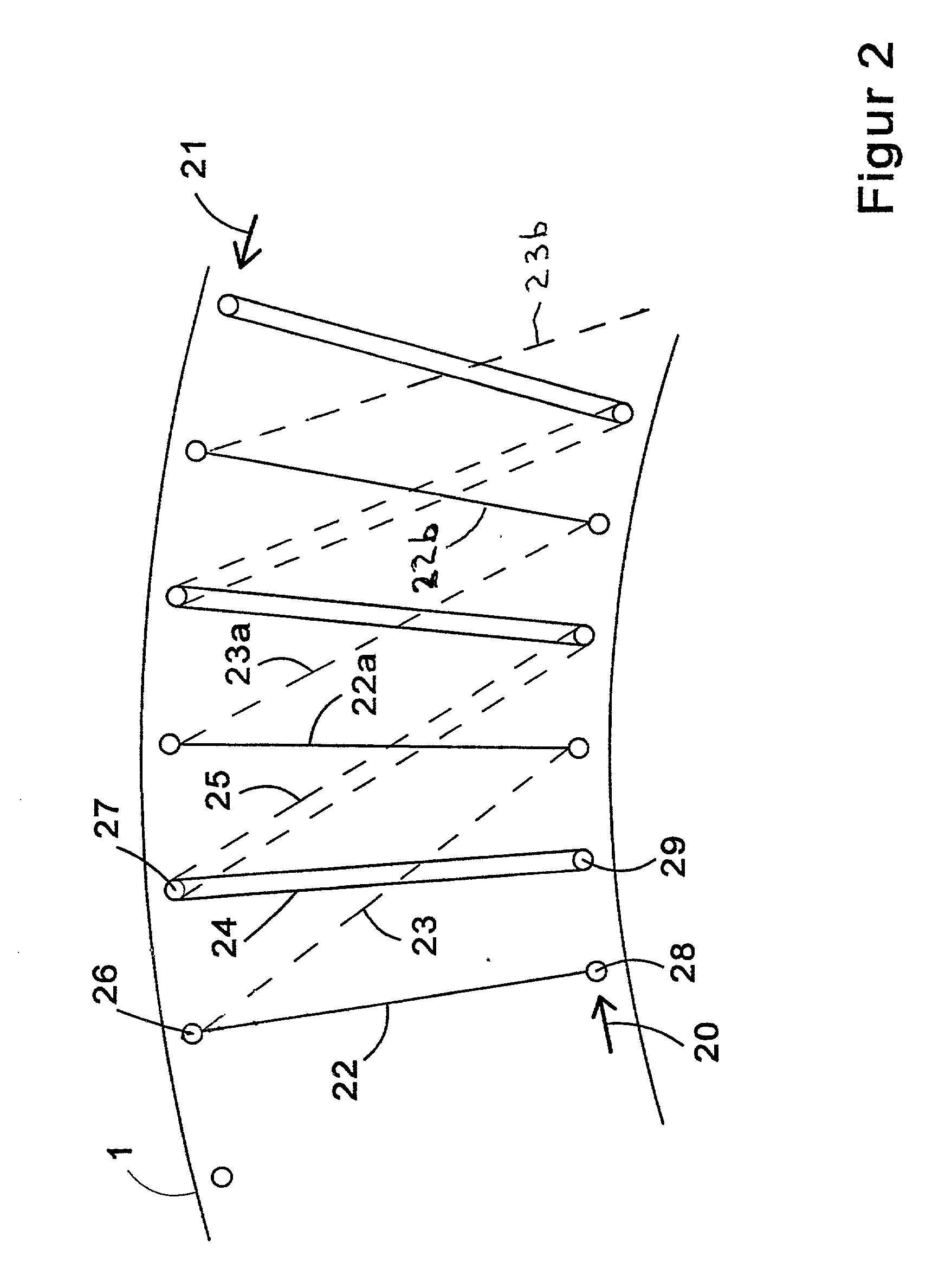

Printed circuit board-based current sensor

InactiveUS20030137388A1Small scaleMore cost-effectivelyTransformers/inductances coils/windings/connectionsVoltage/current isolationElectrical conductorCurrent sensor

The object of the invention is to provide a slotted current acquisition coil according to the Rogowski principle in which the printed circuit board base of the measuring coil can be opened to insert an electrical conductor to be measured without having to interrupt the latter. To this end, the two printed circuit board segments linked together by a hinge are opened. Twisting a single-piece printed circuit board also opens the arrangement for inserting the conductor to be measured.

Owner:PHOENIX CONTACT GMBH & CO KG

Multiprocessor node controller circuit and method

InactiveUS7406086B2Ease of parallel processingImprove welfareMultiplex system selection arrangementsMemory adressing/allocation/relocationMemory addressMemory chip

Improved method and apparatus for parallel processing. One embodiment provides a multiprocessor computer system that includes a first and second node controller, a number of processors being connected to each node controller, a memory connected to each controller, a first input / output system connected to the first node controller, and a communications network connected between the node controllers. The first node controller includes: a crossbar unit to which are connected a memory port, an input / output port, a network port, and a plurality of independent processor ports. A first and a second processor port connected between the crossbar unit and a first subset and a second subset, respectively, of the processors. In some embodiments of the system, the first node controller is fabricated onto a single integrated-circuit chip. Optionally, the memory is packaged on plugable memory / directory cards wherein each card includes a plurality of memory chips including a first subset dedicated to holding memory data and a second subset dedicated to holding directory data. Further, the memory port includes a memory data port including a memory data bus and a memory address bus coupled to the first subset of memory chips, and a directory data port including a directory data bus and a directory address bus coupled to the second subset of memory chips. In some such embodiments, the ratio of (memory data space) to (directory data space) on each card is set to a value that is based on a size of the multiprocessor computer system.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP +1

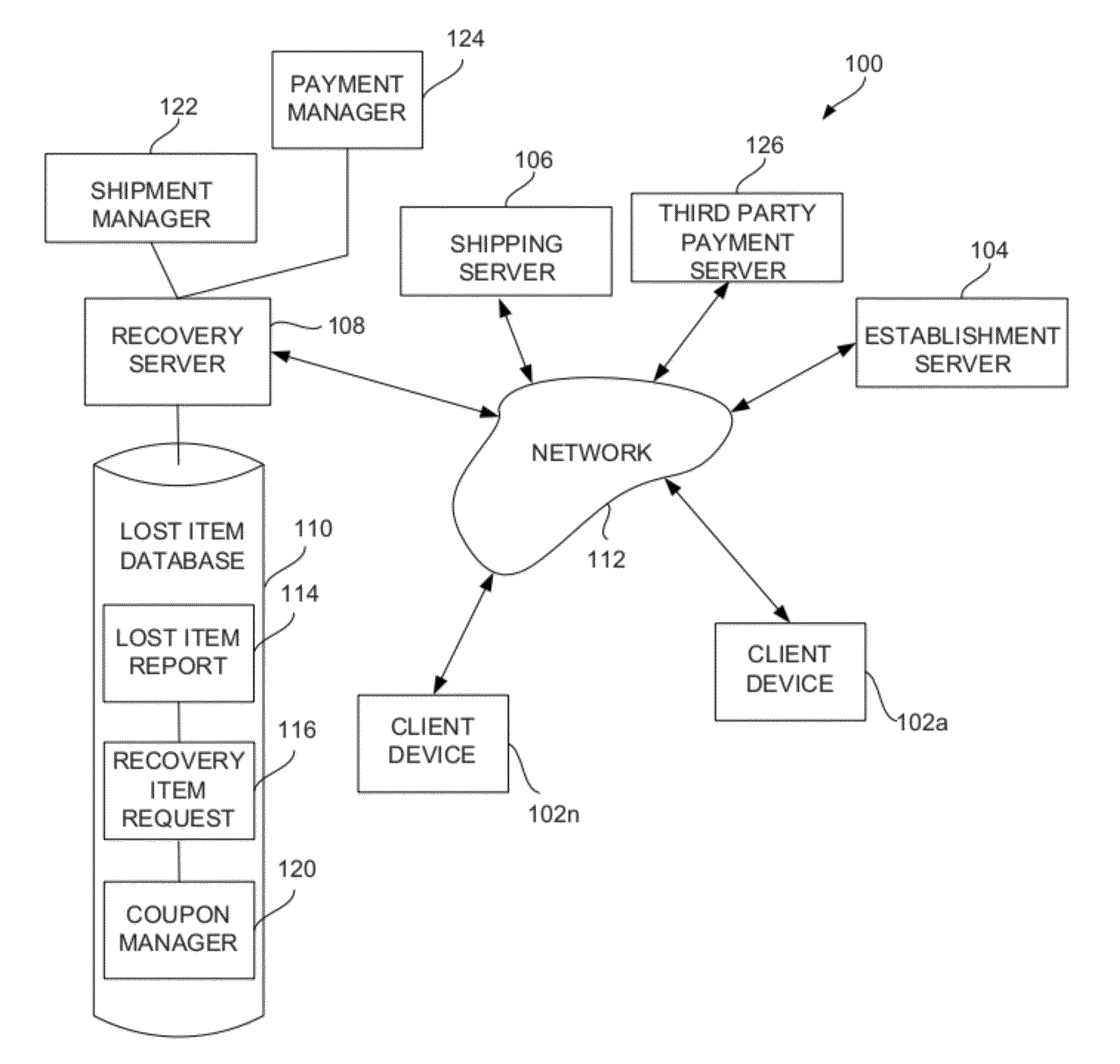

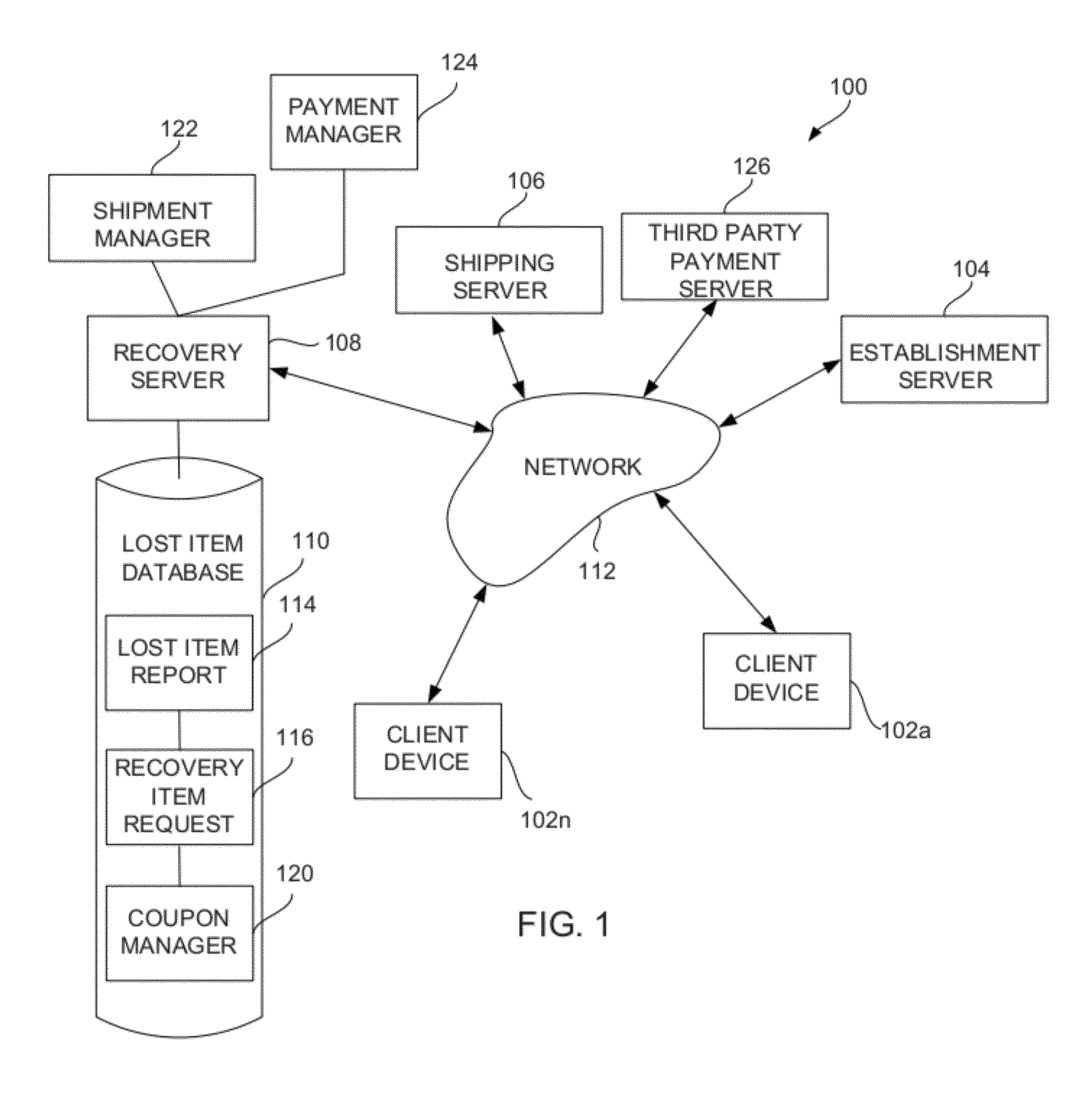

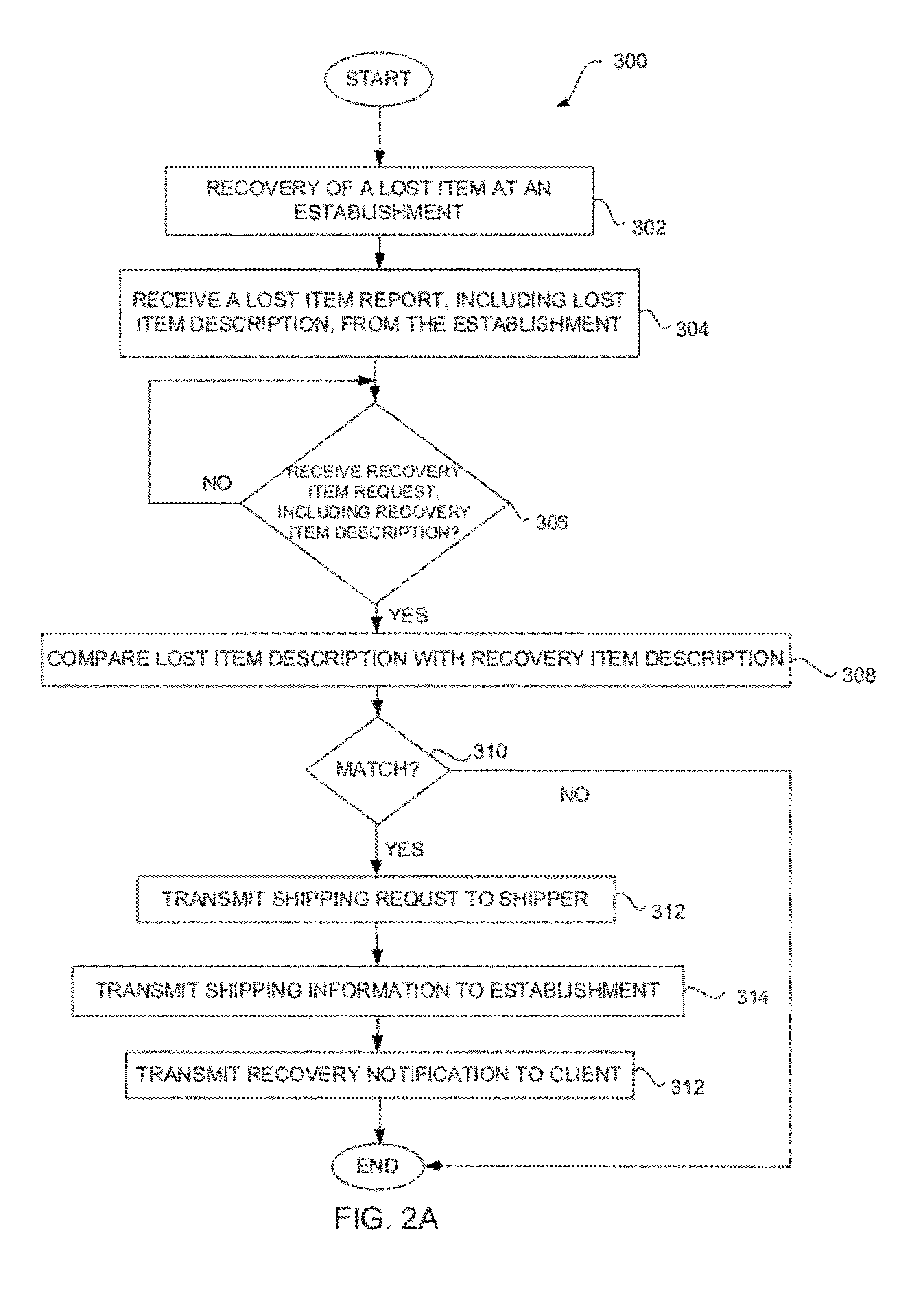

System and method for inventory and return of lost items

PendingUS20120059693A1Cost-effectiveLower costDiscounts/incentivesDigital data processing detailsDatabaseEngineering

In one embodiment, a system and method for monitoring lost items includes a lost item database including a first memory operable to store lost item information and a second memory operable to store recovery item information and a processor operable to (i) receive the lost item information and the recovery item information; (ii) associate a status indicator with the lost item associated with the lost item information and the forgotten item with the recovery item information; (iii) browse or search the lost item database to compare the lost item information and the recovery item information; (iv) determine whether there is a match between the lost item information and the recovery item information; (v) facilitating transmission of an electronic recovery notification to a patron device of an establishment if there is a match; and (vi) automatically update the status indicator to indicate the lost item and the forgotten item have been recovered.

Owner:CHARGERBACK

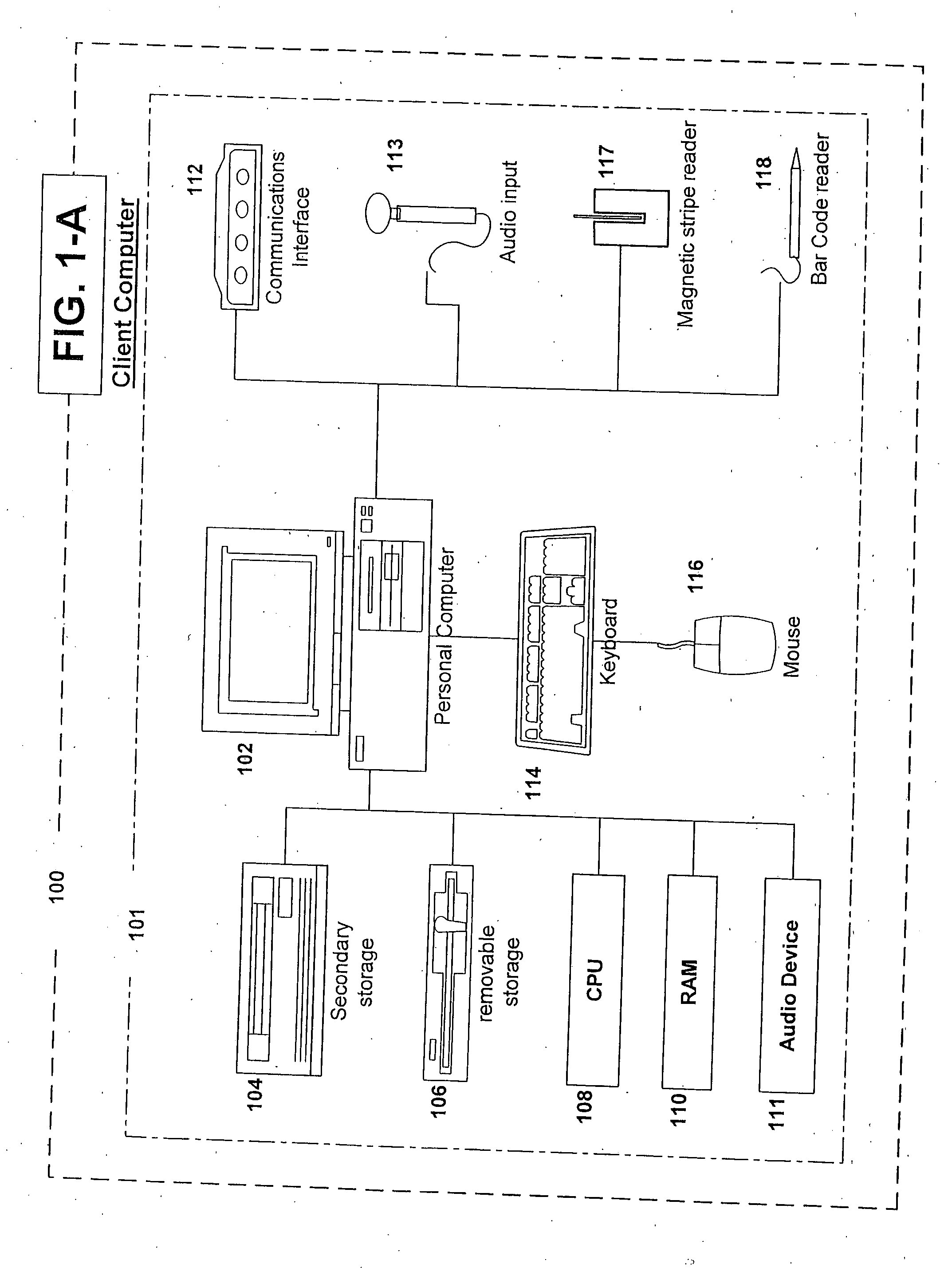

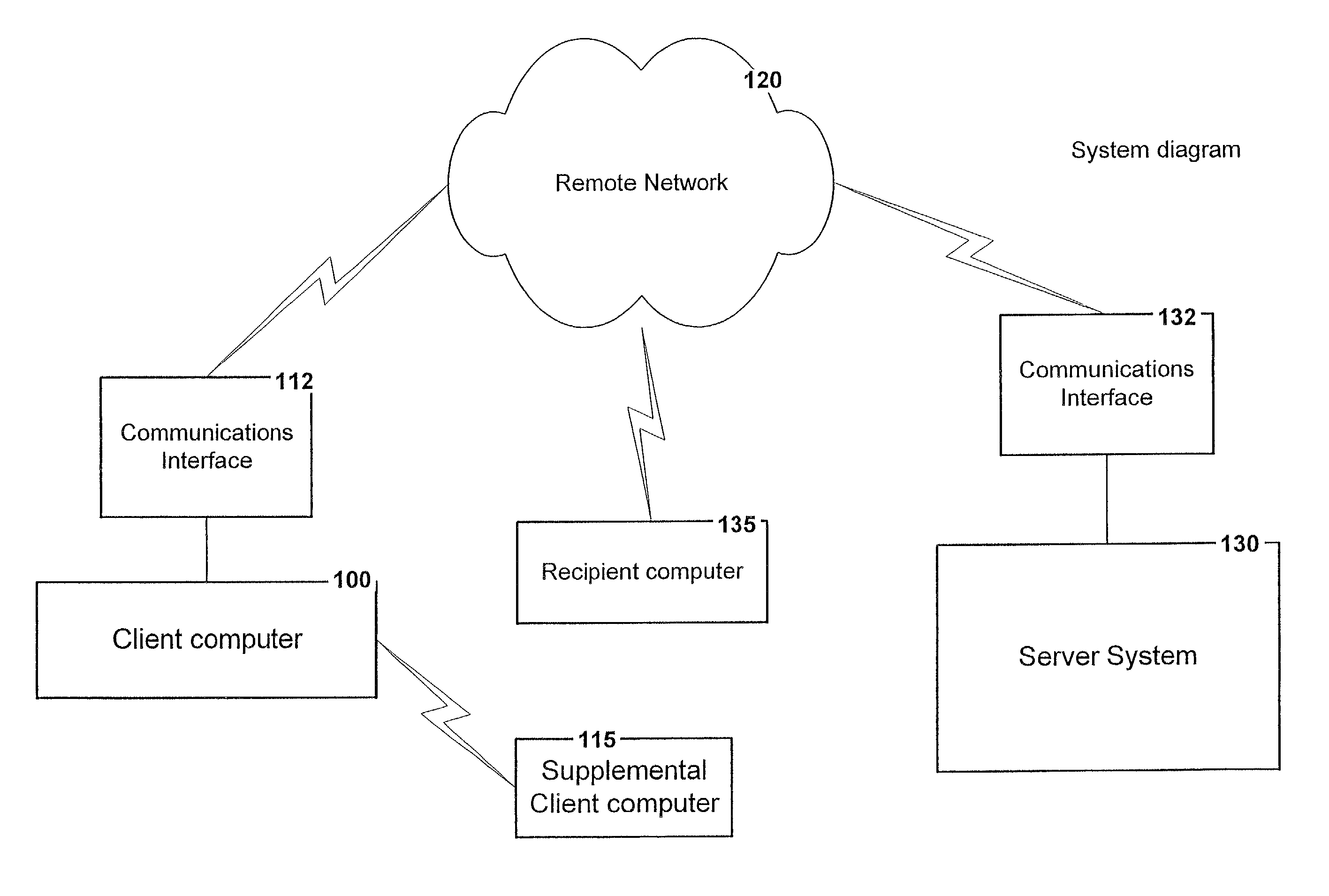

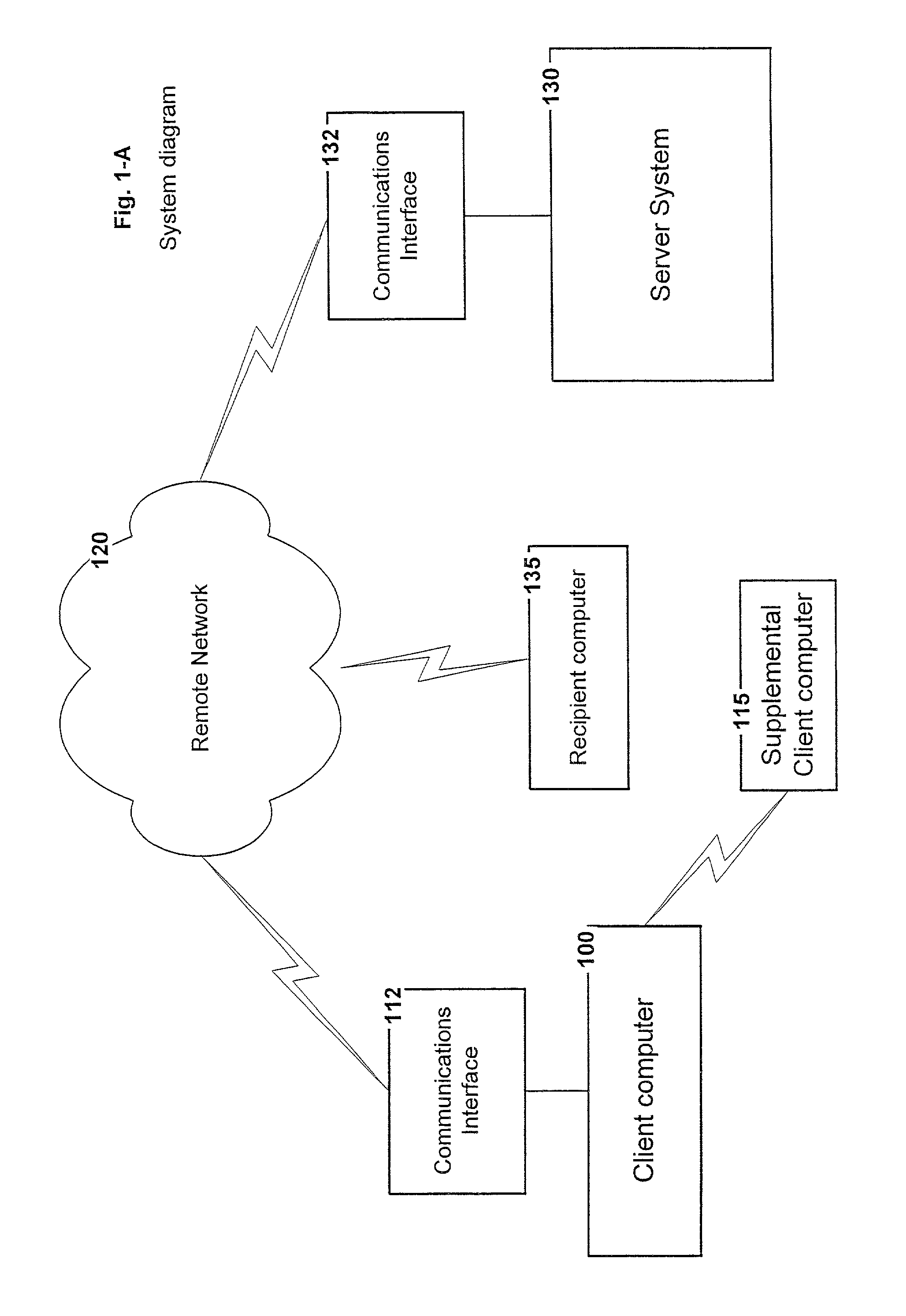

Auto update utility for digital address books

InactiveUS7505974B2More cost-effectivelyMore efficientDigital data processing detailsMarketingAddress bookRelevant information

An Internet-based system capable of automatically maintaining contact-related information in any computer software application or digital device which stores or manages contact-related information. More particularly, the system allows users to automatically enter and maintain contact-related information in a digital address book or similar application or device (such as a wireless phone or PDA) with minimal or no manual entry of the contact-related information by the user. The system also allows contacts of the user (i.e. people who's contact information or partial contact information is present in the user's address book application) to make corrections to their contact-related information contained in the user's address book, request reciprocal contact information from the user, deny the user access to additional or corrected contact-related information and take other actions relative to managing the contact-related information which others (users) have about them.

Owner:MICROSOFT TECH LICENSING LLC

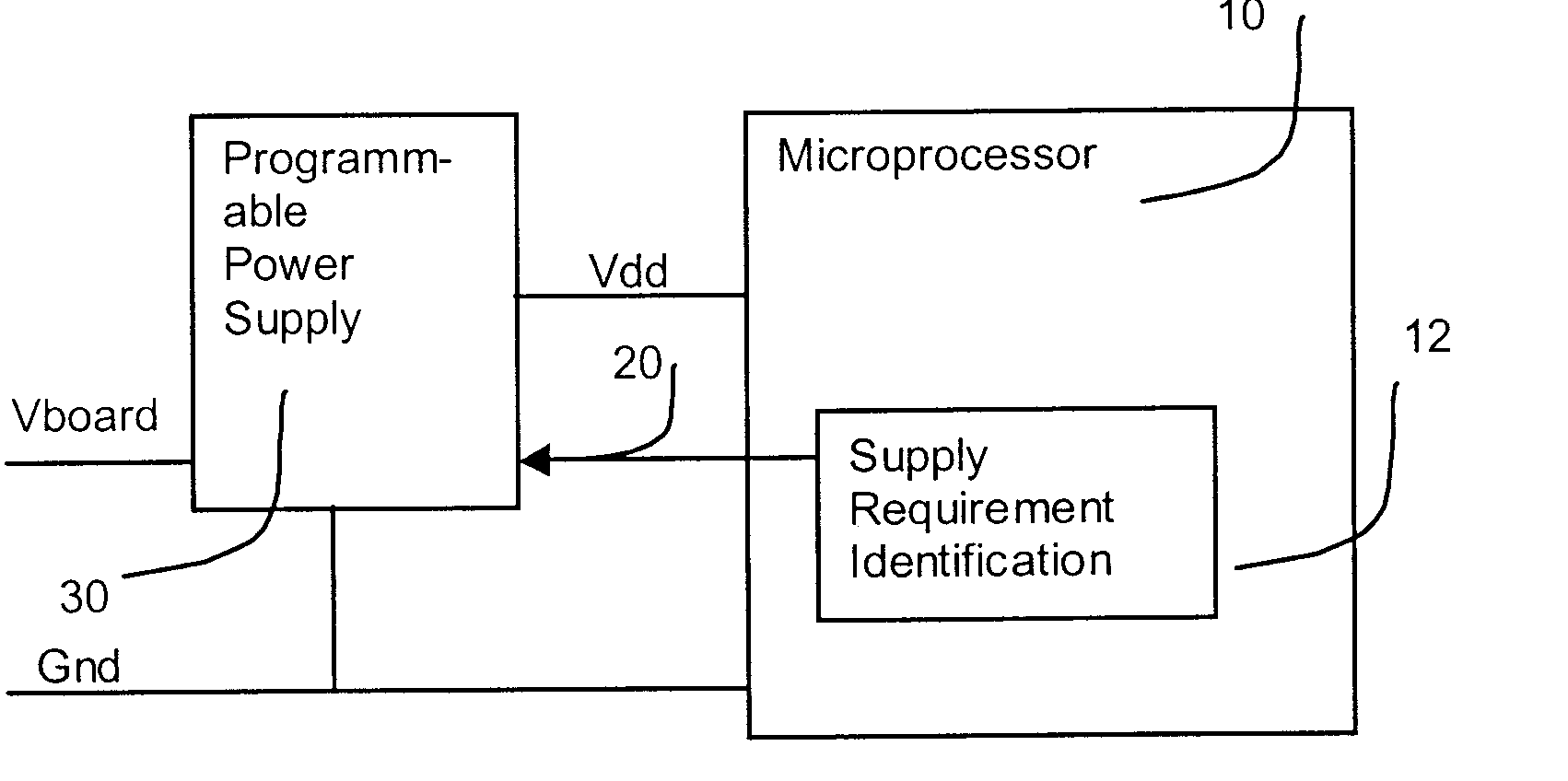

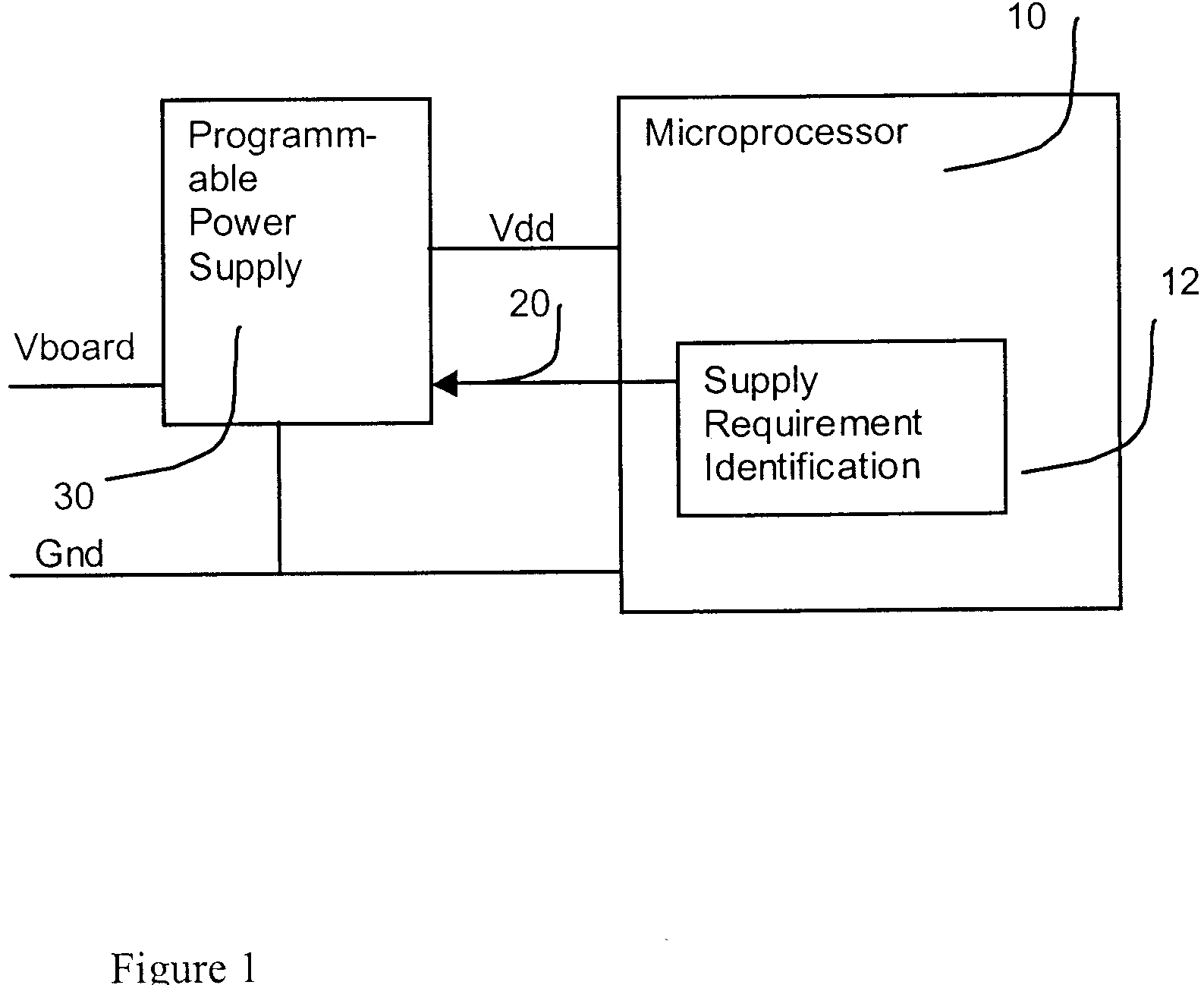

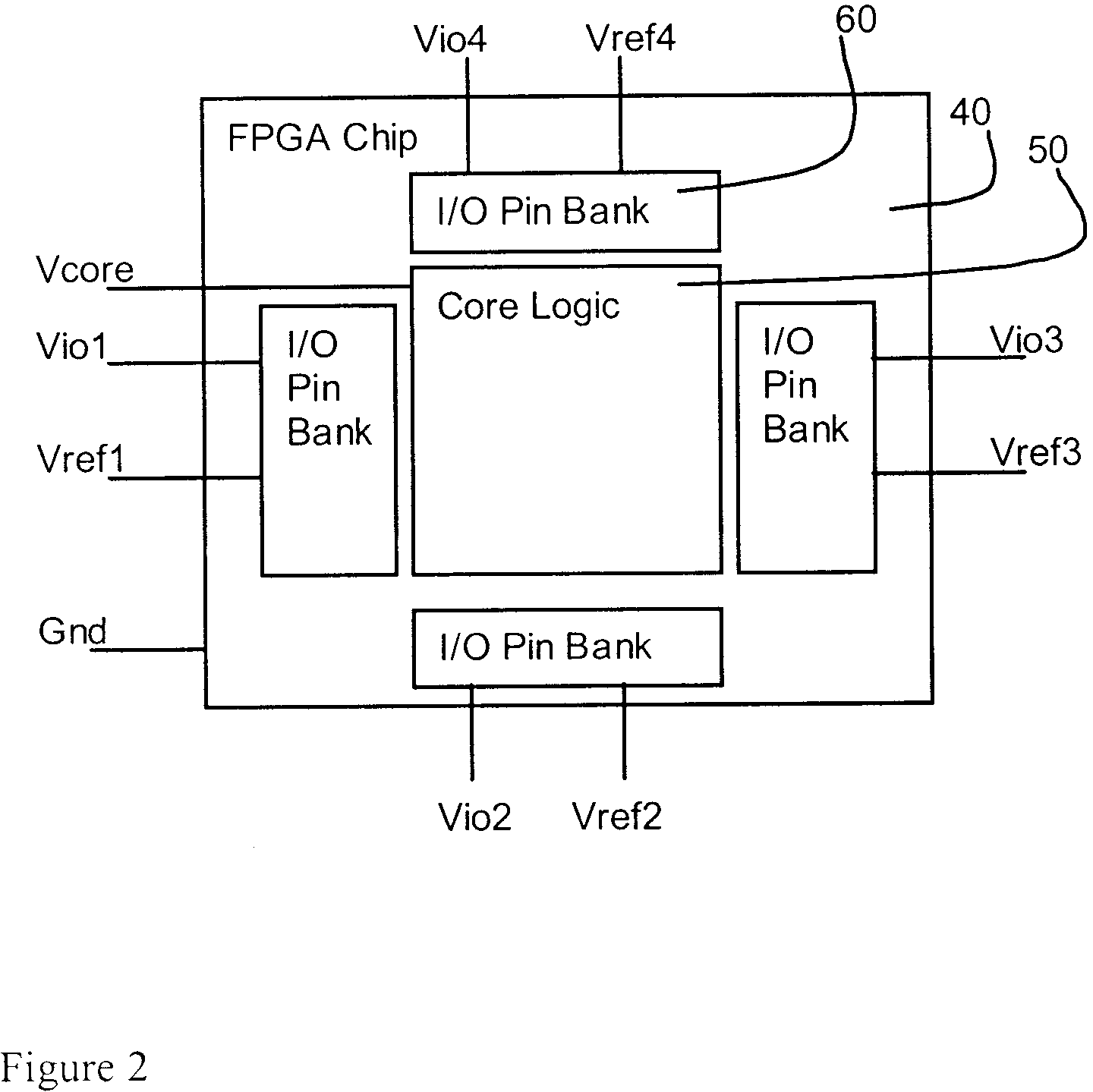

Programmable power supply system

InactiveUS20050088201A1Low costHigh densityVolume/mass flow measurementSolid-state devicesBaseboardModularity

A module standard for integrated circuit such as FPGAs is provided in which power supply voltages for daughtercards are not fixed in advance. Instead programmable power supplies are provided and a method is provided in which each daughtercard can specify the required power supply voltage. Thus, unlike prior-art systems, this modular system is backward and forward compatible with chips, such as FPGAs, from many process generations allowing easy upgrading as new FPGA families become available. A motherboard or baseboard for use with this invention includes a plurality of module connectors into which compatible modules or “daughtercards” can be plugged and a plurality of programmable power supplies. In a preferred embodiment there are four sets of module connectors and sixteen programmable power supplies. This allows each module to have four independently specifiable power supply voltages. A module may also connect several power supplies together in order to obtain higher current at a single voltage. Various schemes are described to ensure that the programmable power supplies will never deliver too high a voltage to the components on the modules.

Owner:NALLATECH

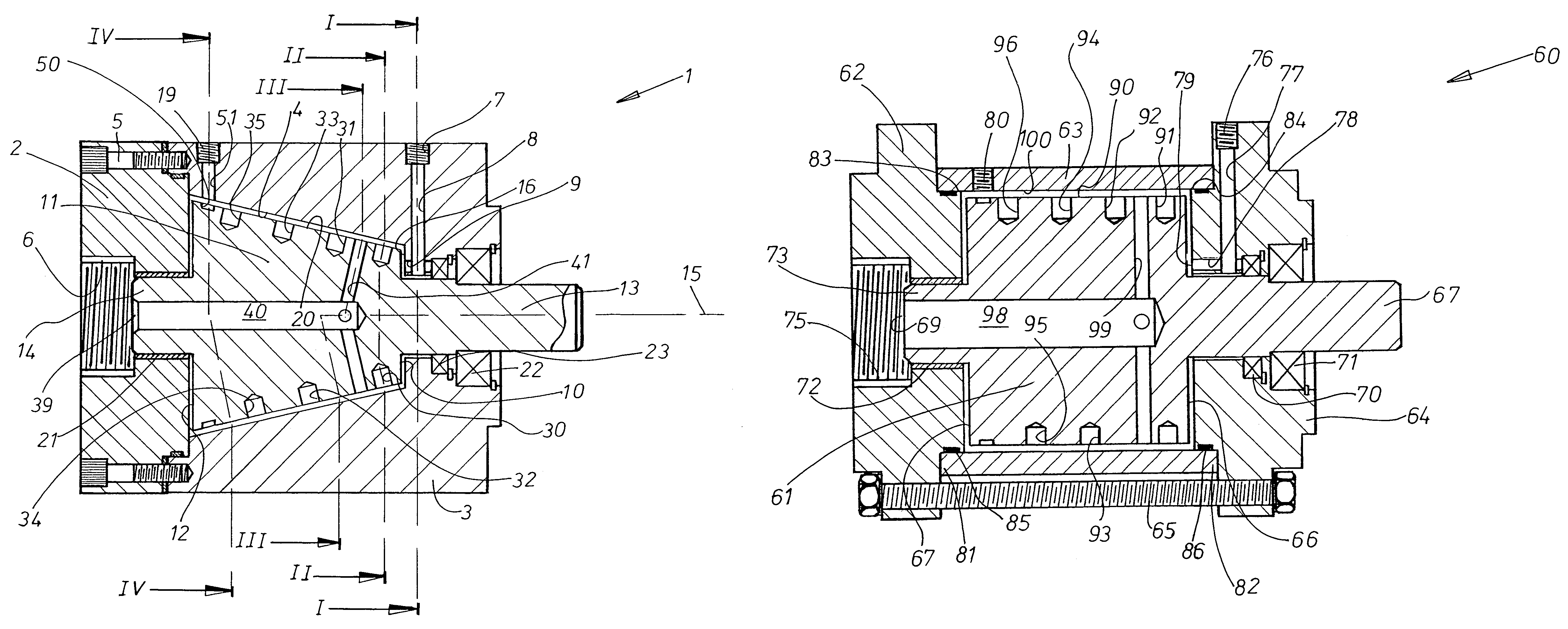

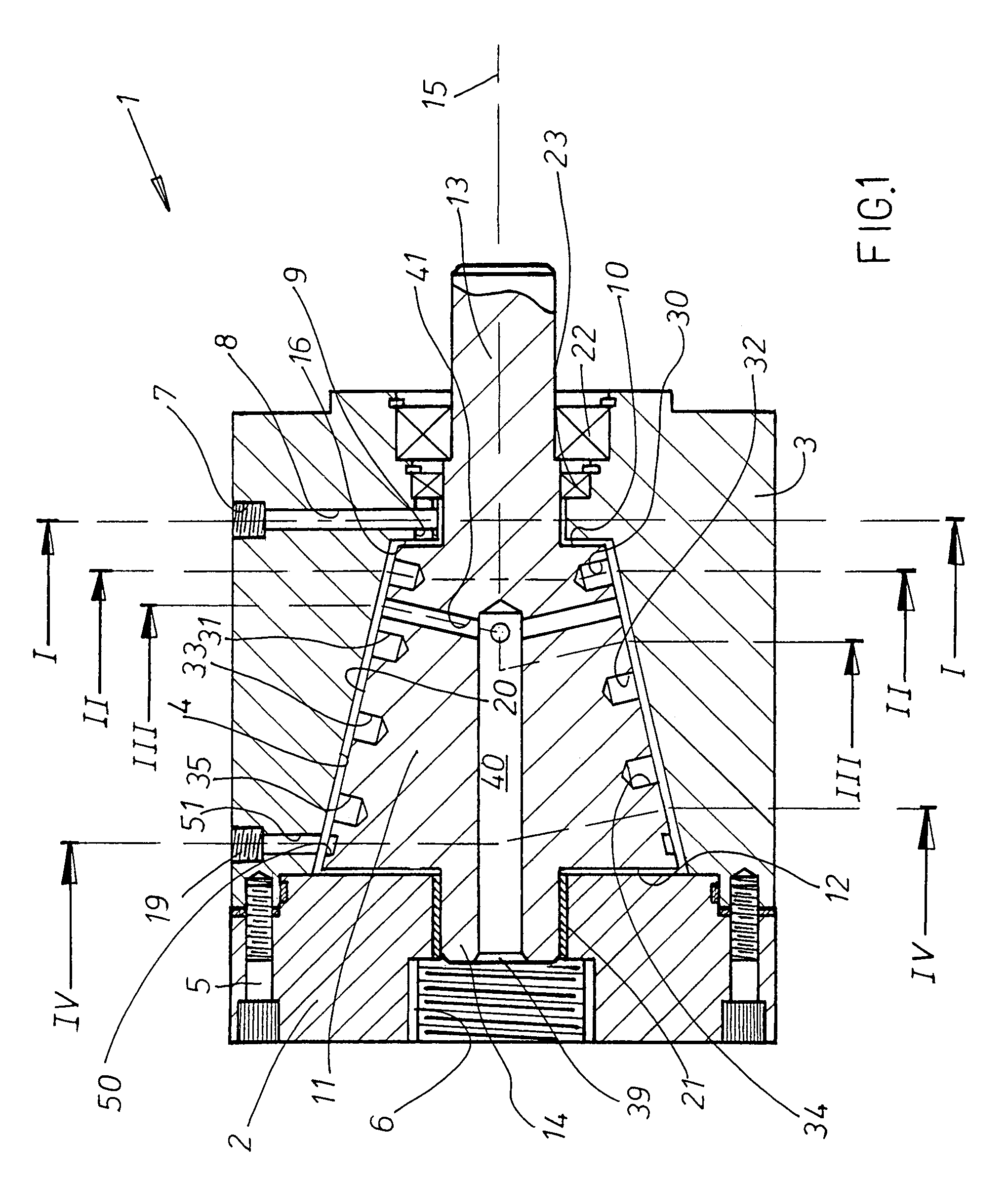

Apparatus and method for mixing dissimilar fluids

InactiveUS7316501B2Well mixedEnhance stirringTransportation and packagingMixing methodsBiomedical engineeringFluid input

An apparatus and method for fluid mixing comprising a housing having an internal chamber and a rotatable unit disposed in the chamber. Sufficient clearance is provided between the rotatable unit and the housing to create space for the mixing of the two or more dissimilar fluids. As one example, one fluid input arrives in the mixing chamber by suitable ducting in the housing and the other fluid input arrives in the mixing chamber via a passage in the rotatable unit, the fluids collide and mix and where preferably at least one array of surface irregularities are disposed on an exterior face of the rotatable unit. The refined fluid mixture leaves the apparatus from a exit in the housing preferably poritioned radially outwardly of the rotatable unit.

Owner:THOMA CHRISTIAN

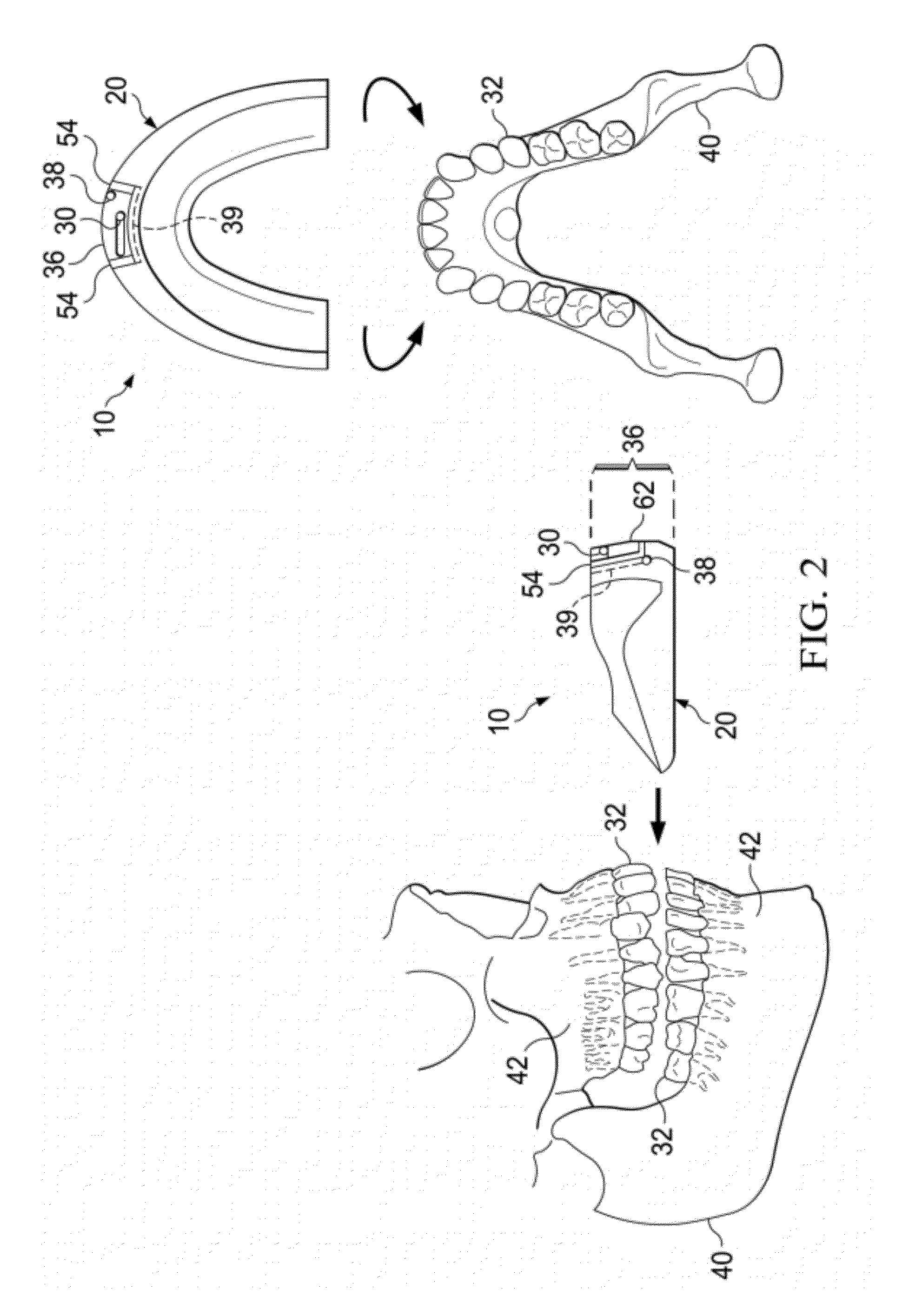

Vibrating orthodontic remodelling device

ActiveUS20120322018A1Increase bone formationIncrease bone formation rateOthrodonticsDental toolsBite platesMandibular tooth

A bite plate allowing for contact with occlusal and facial and / or lingual maxillary and mandibular teeth is coupled to an extraoral housing containing a rechargeable battery coupled to a vibrator coupled to a processor coupled to data and charging port or ports. The housing is at least water resistant, and a hatch allows access to the data and charging port or ports only. The device is fitted with a very smooth and quiet vibrator, with minimal variance on operating specifications.

Owner:ADVANCED ORTHODONTICS & EDUCATION ASSOC LLC