Patents

Literature

3765 results about "Thinning" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Thinning is a term used in agricultural sciences to mean the removal of some plants, or parts of plants, to make room for the growth of others but does not involve the cutting of the whole tree. Selective removal of parts of a plant such as branches, buds, or roots is typically known as pruning.

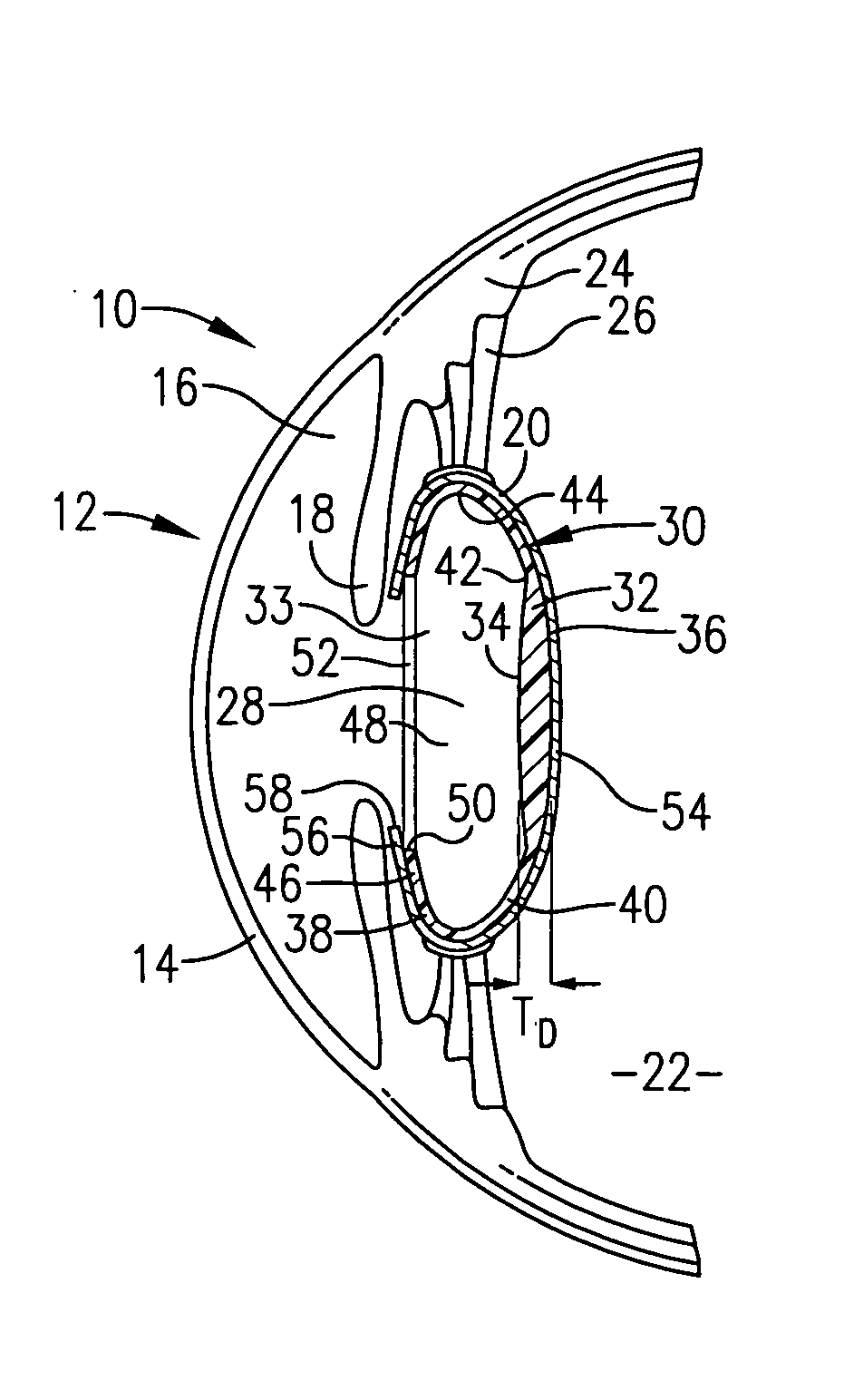

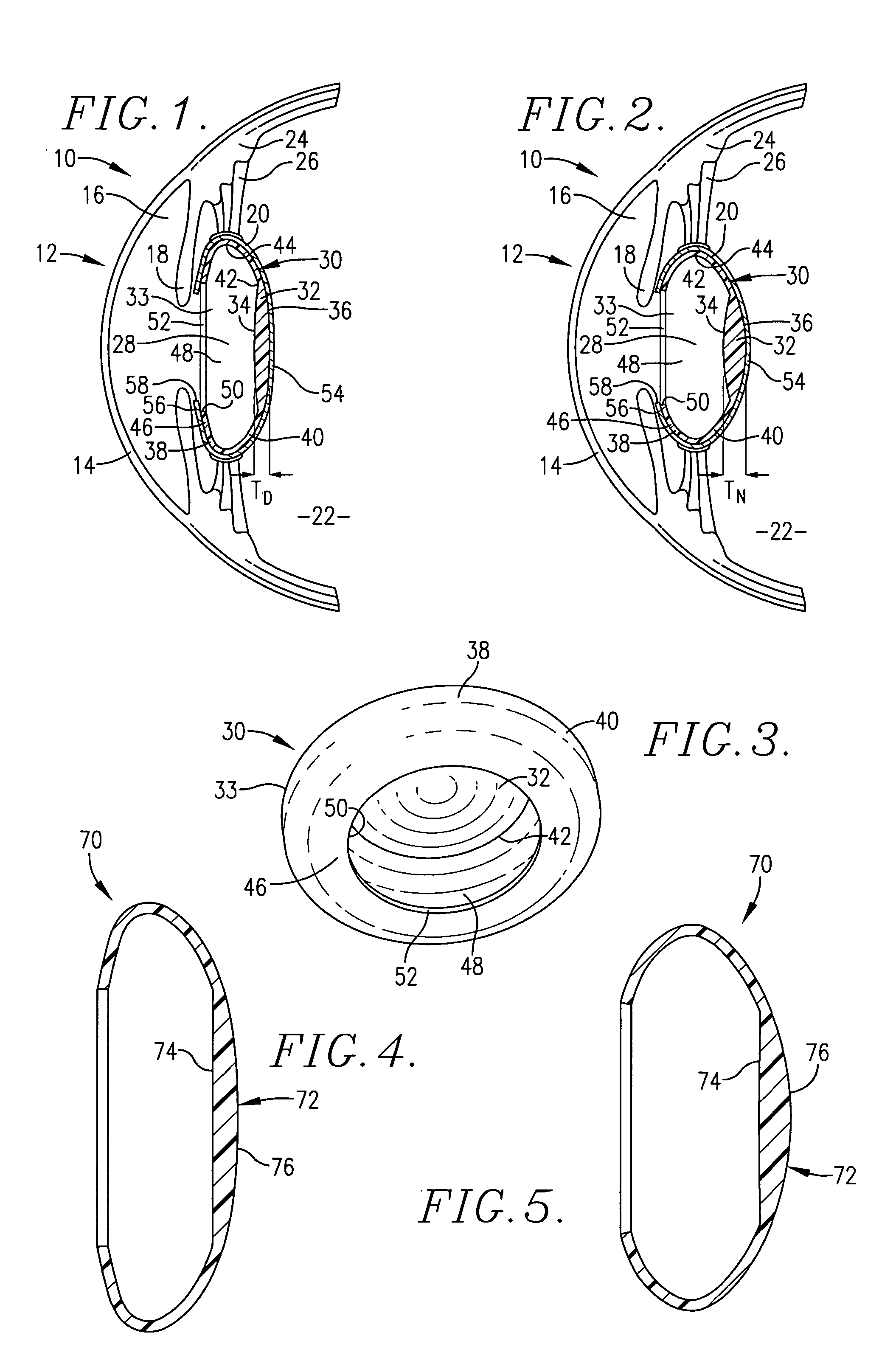

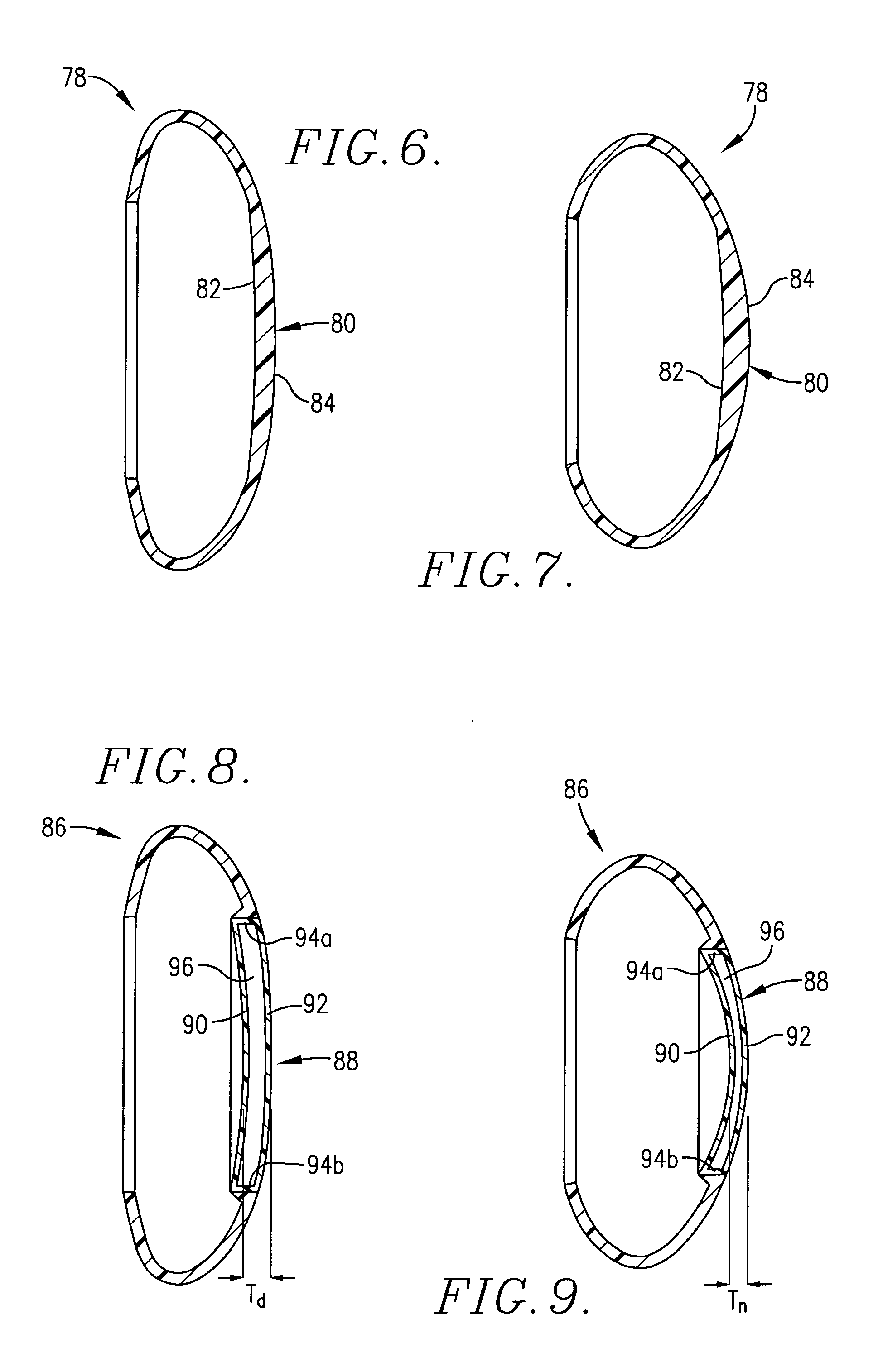

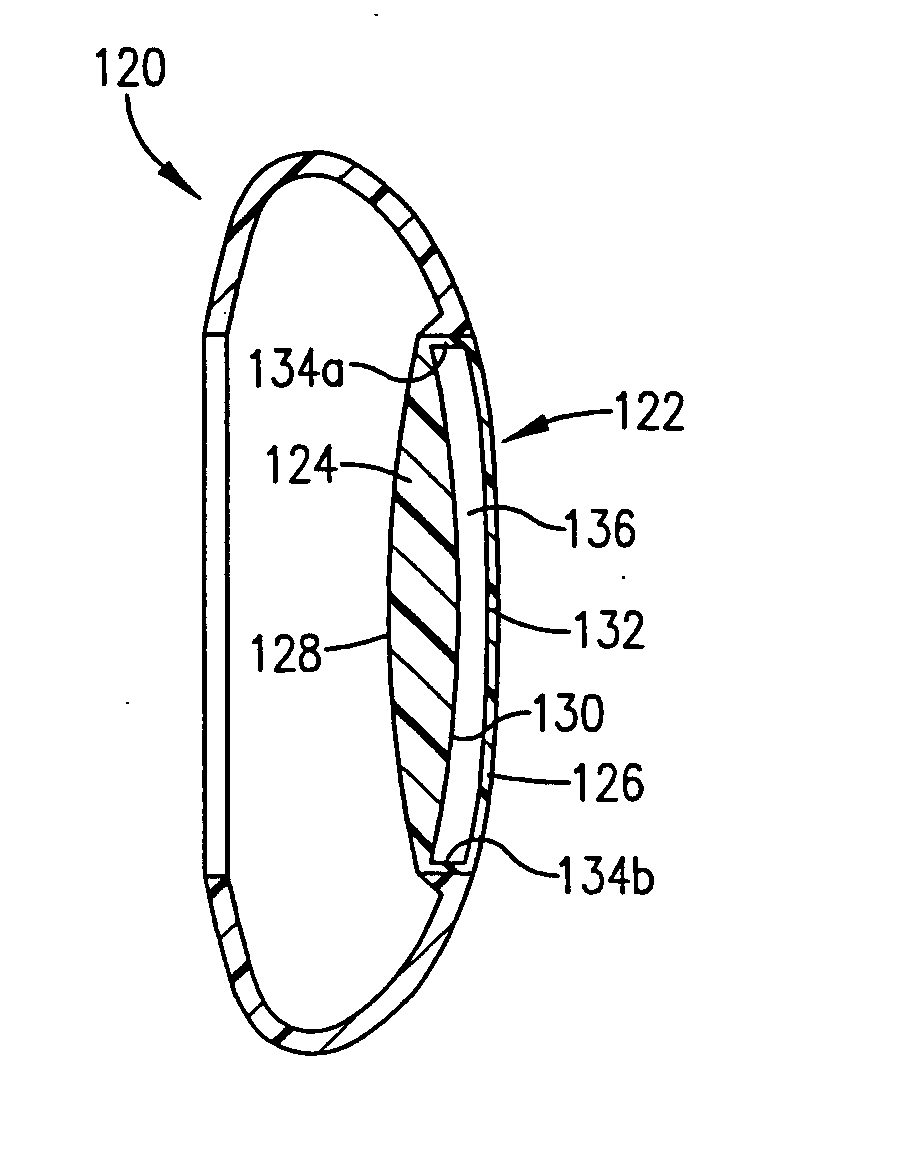

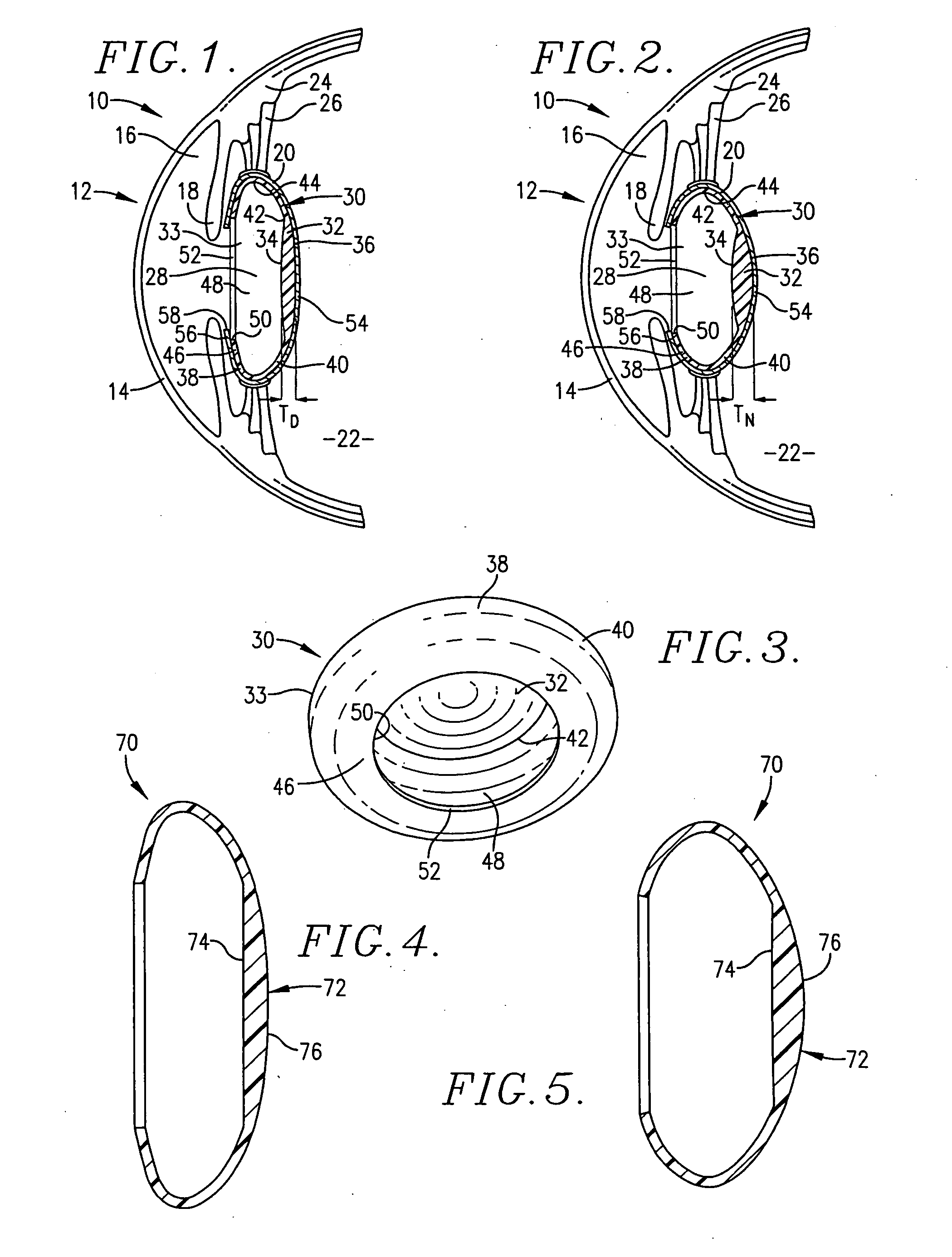

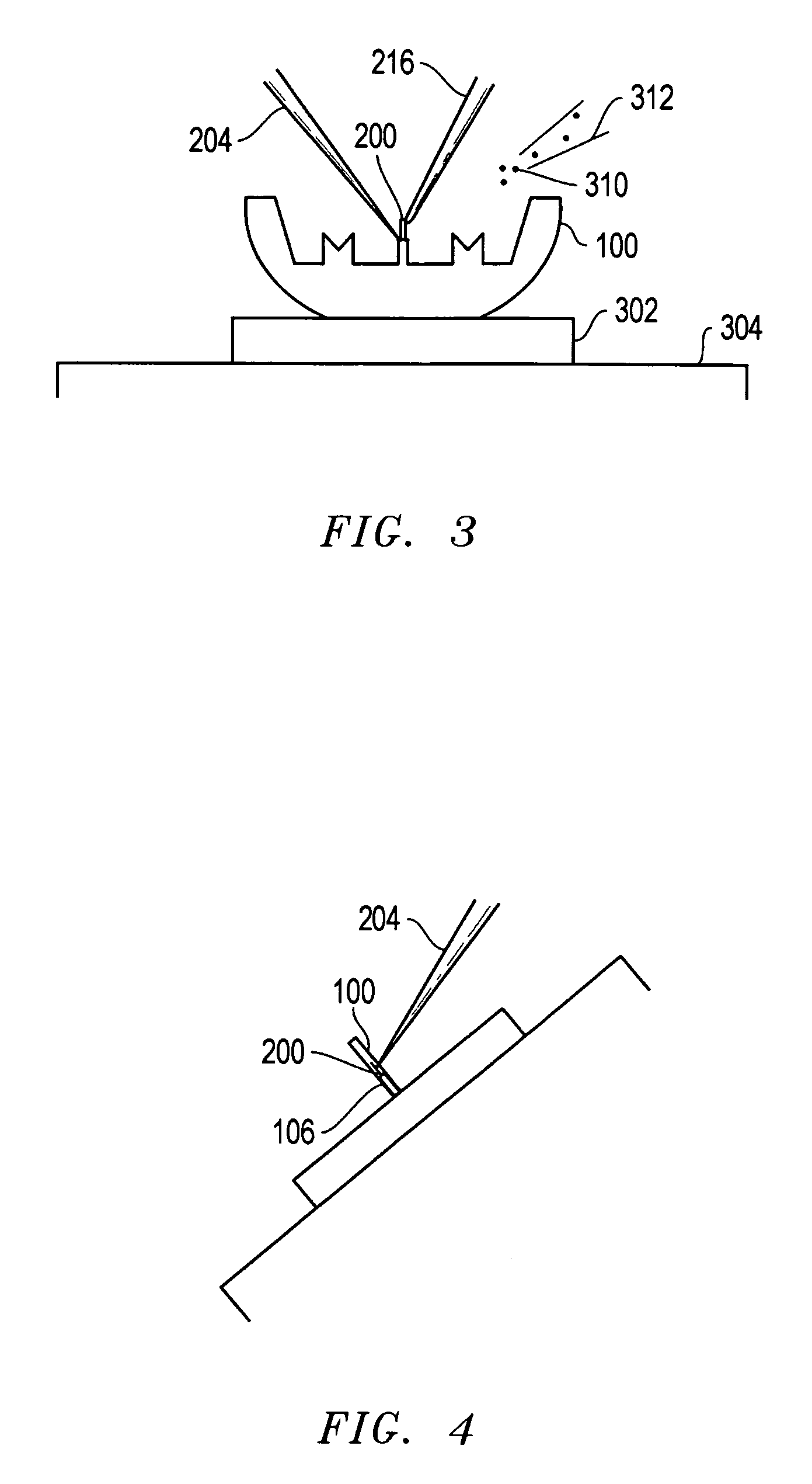

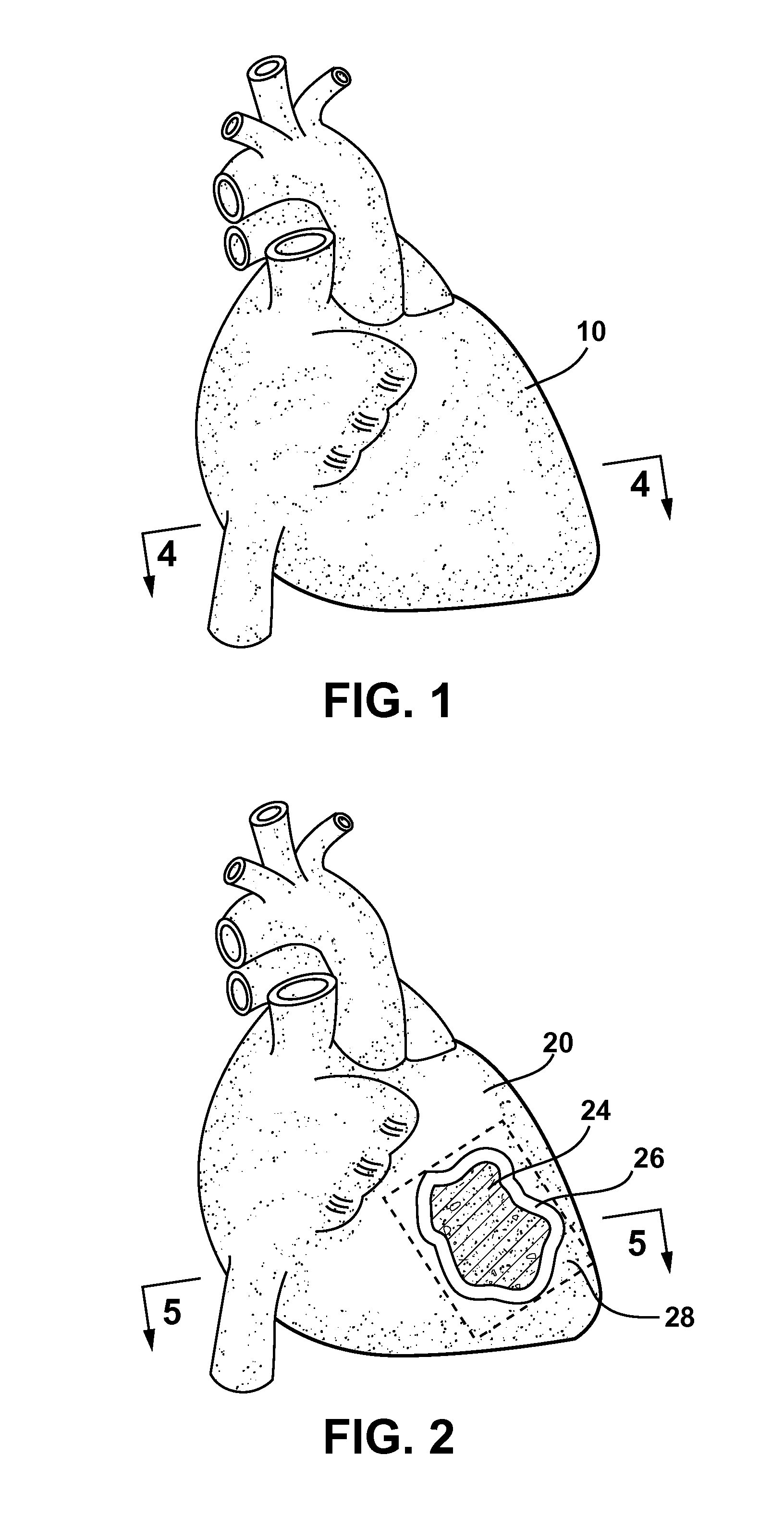

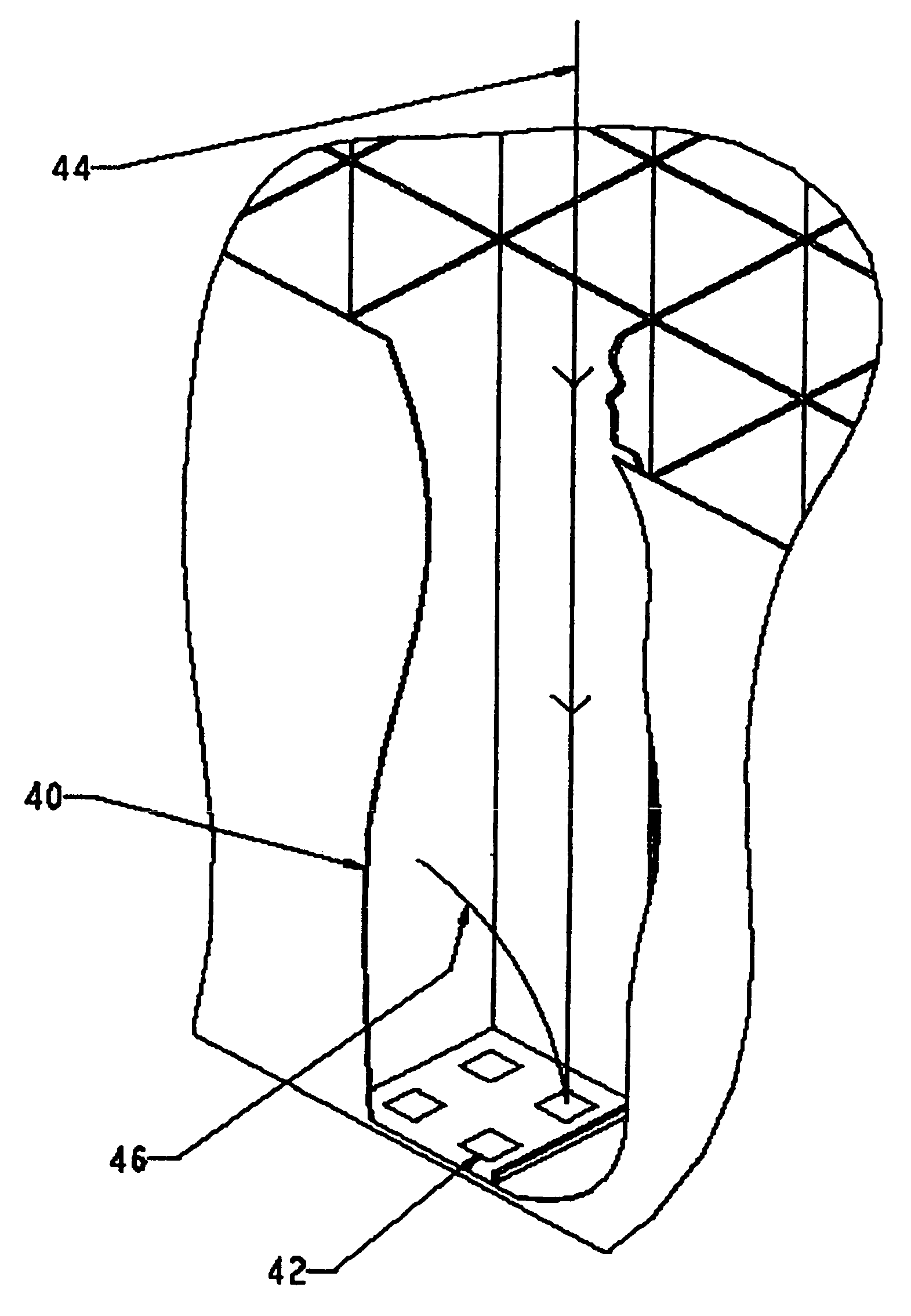

Intraocular lens implant having posterior bendable optic

InactiveUS20050131535A1Safe for long-term use in eyeReduce lightIntraocular lensCiliary epitheliumThinning

An intraocular lens (30) having focusing capabilities permitting focusing movement of the lens (30) in response to normal ciliary body (24) movement incident to changes in the distance between the eye and an object under observation is provided. The lens (30) is designed for surgical implantation within the capsule (20) of an eye (10) and includes an optic (32) and an optic positioning element (33) which cooperate to form the lens (30). Accommodation is achieved by relying upon the thickening and thinning of the optic (32) as a result of the normal retracting and contracting of the ciliary body (24) in response to the distance of an object from the viewer.

Owner:ABBOTT MEDICAL OPTICS INC

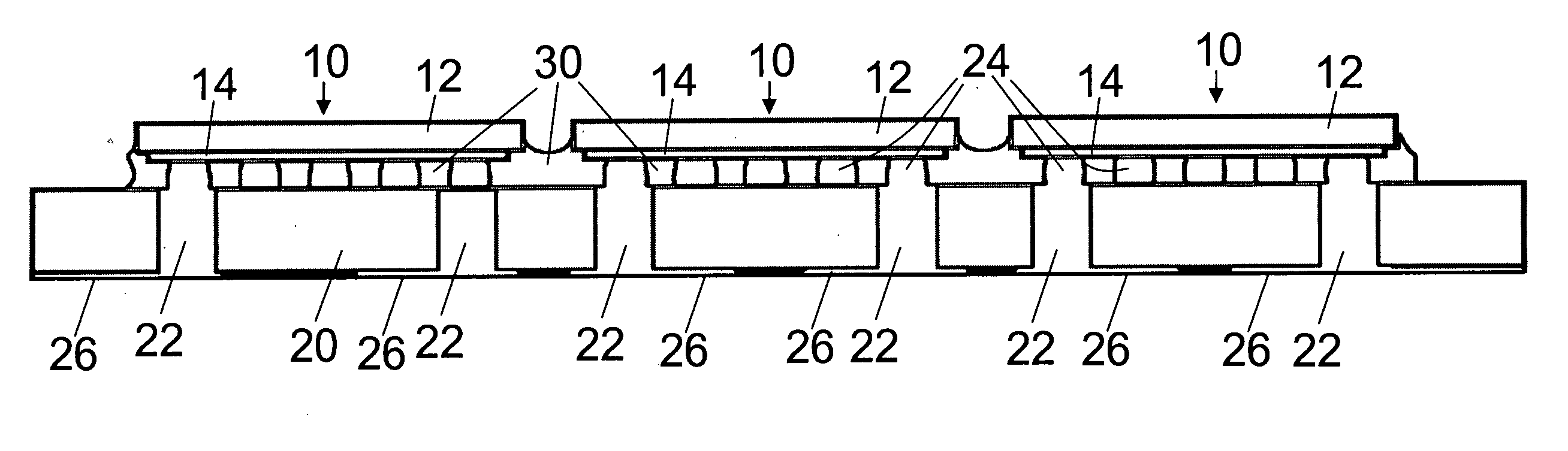

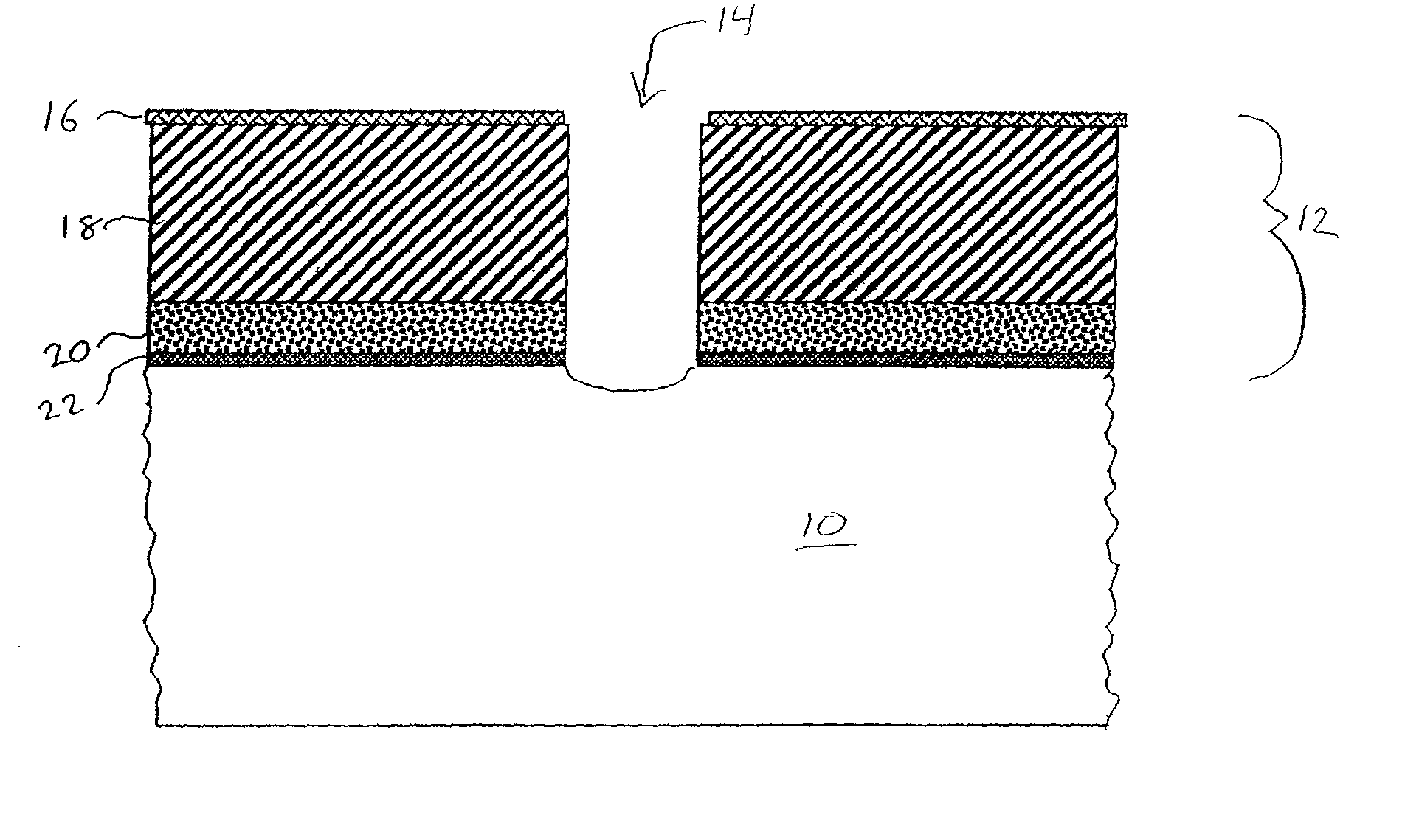

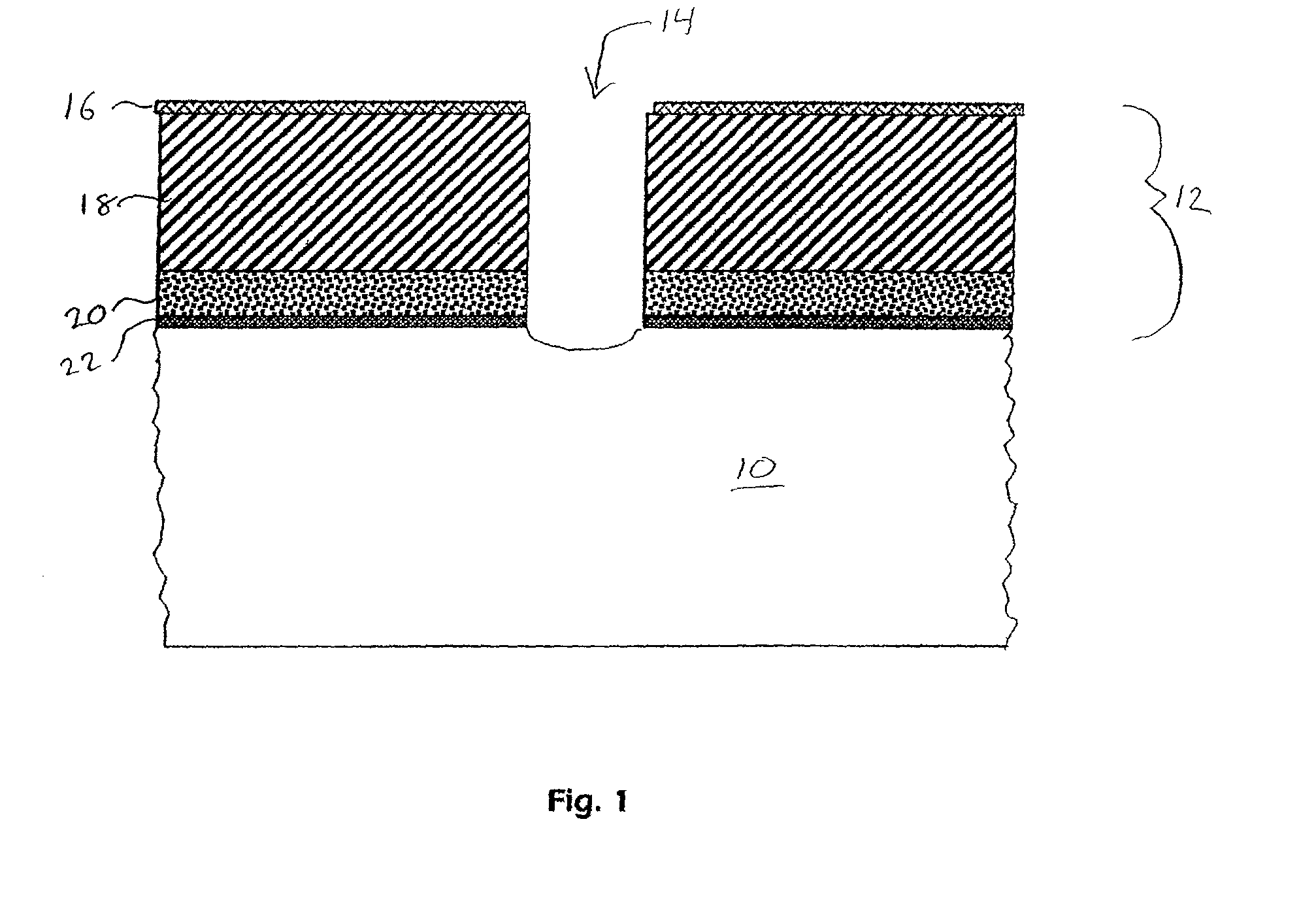

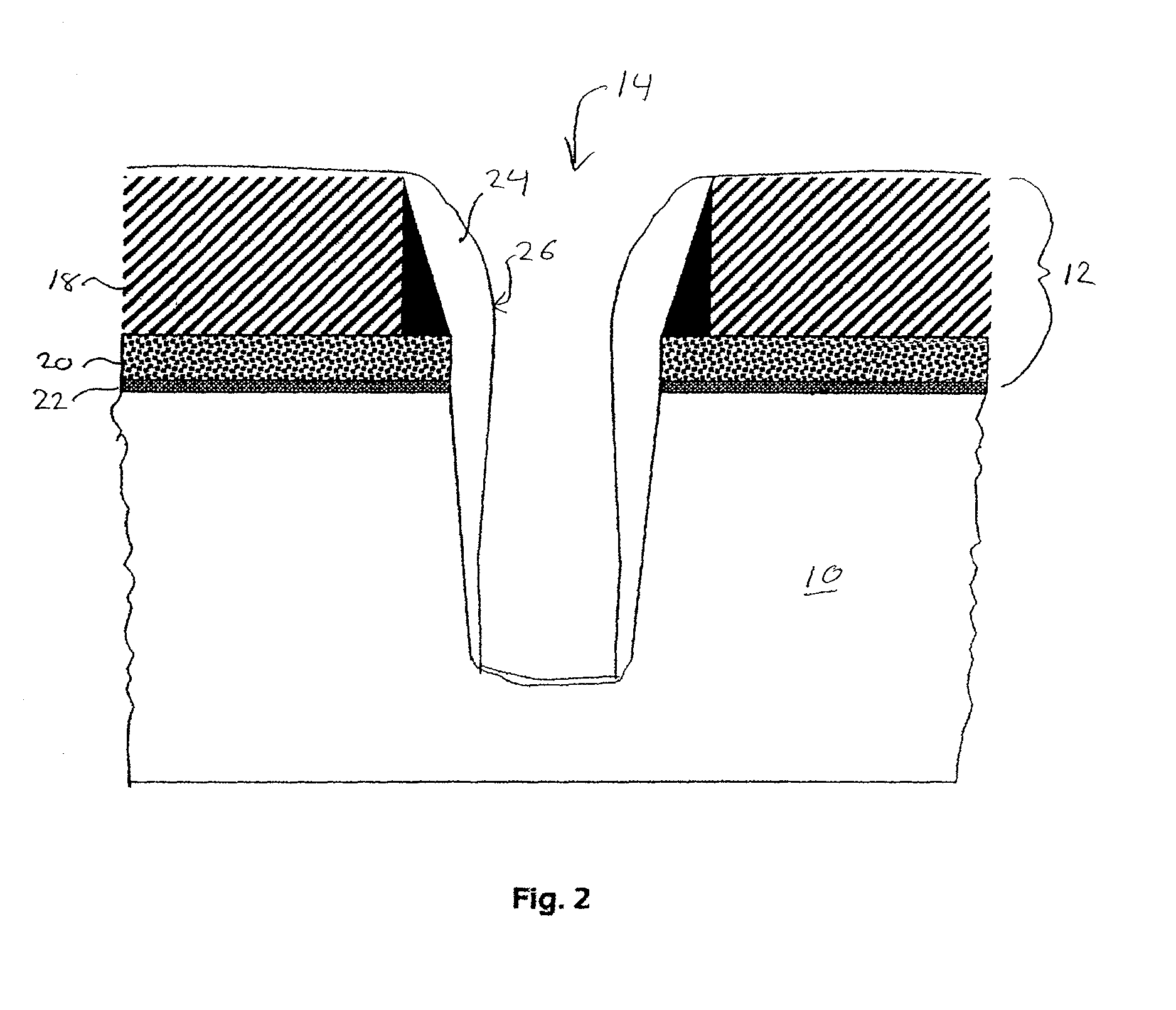

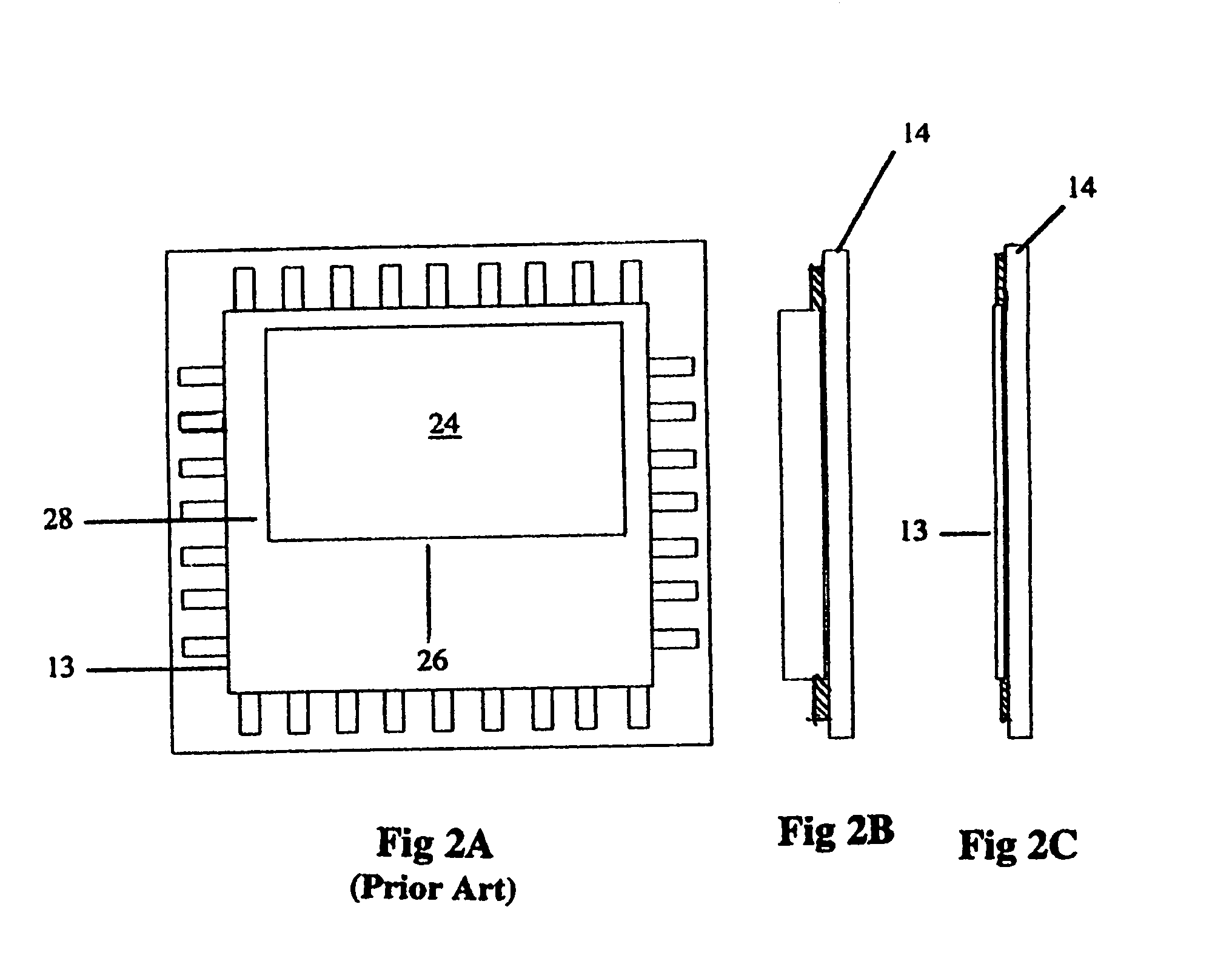

Lock and Key Through-Via Method for Wafer Level 3 D Integration and Structures Produced

InactiveUS20100078770A1High yieldFirmly connectedSemiconductor/solid-state device detailsSolid-state devicesThinningActive devices

A three dimensional device stack structure comprises two or more active device and interconnect layers further connected together using through substrate vias. Methods of forming the three dimensional device stack structure comprise alignment, bonding by lamination, thinning and post thinning processing. The via features enable the retention of alignment through the lamination process and any subsequent process steps thus achieving a mechanically more robust stack structure compared to the prior art.

Owner:GLOBALFOUNDRIES US INC

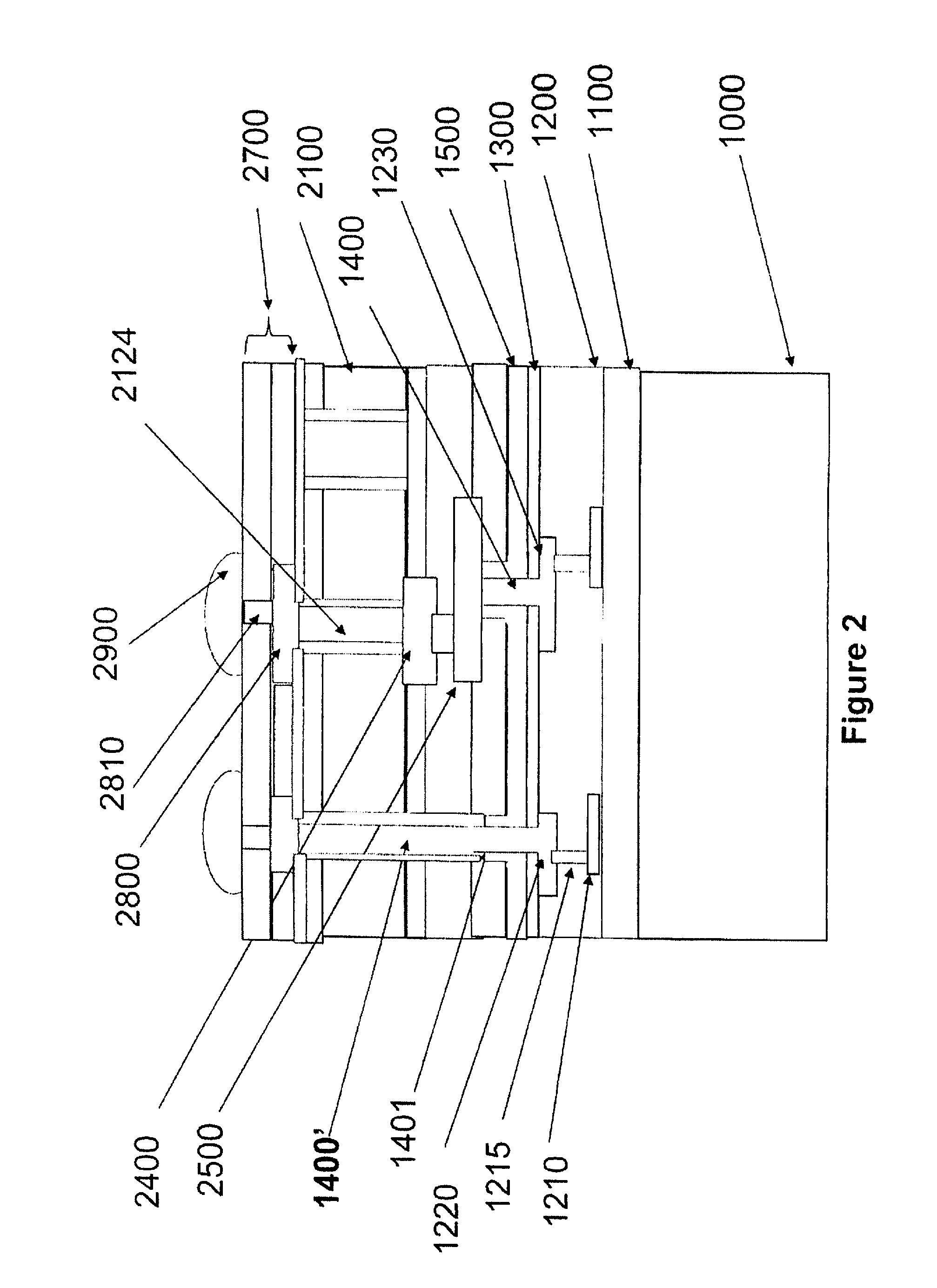

Lock and Key Through-Via Method for Wafer Level 3D Integration and Structures Produced Thereby

ActiveUS20110111560A1High yieldFirmly connectedSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringThinning

A three dimensional device stack structure comprises two or more active device and interconnect layers further connected together using through substrate vias. Methods of forming the three dimensional device stack structure comprise alignment, bonding by lamination, thinning and post thinning processing. The via features enable the retention of alignment through the lamination process and any subsequent process steps thus achieving a mechanically more robust stack structure compared to the prior art.

Owner:GLOBALFOUNDRIES US INC

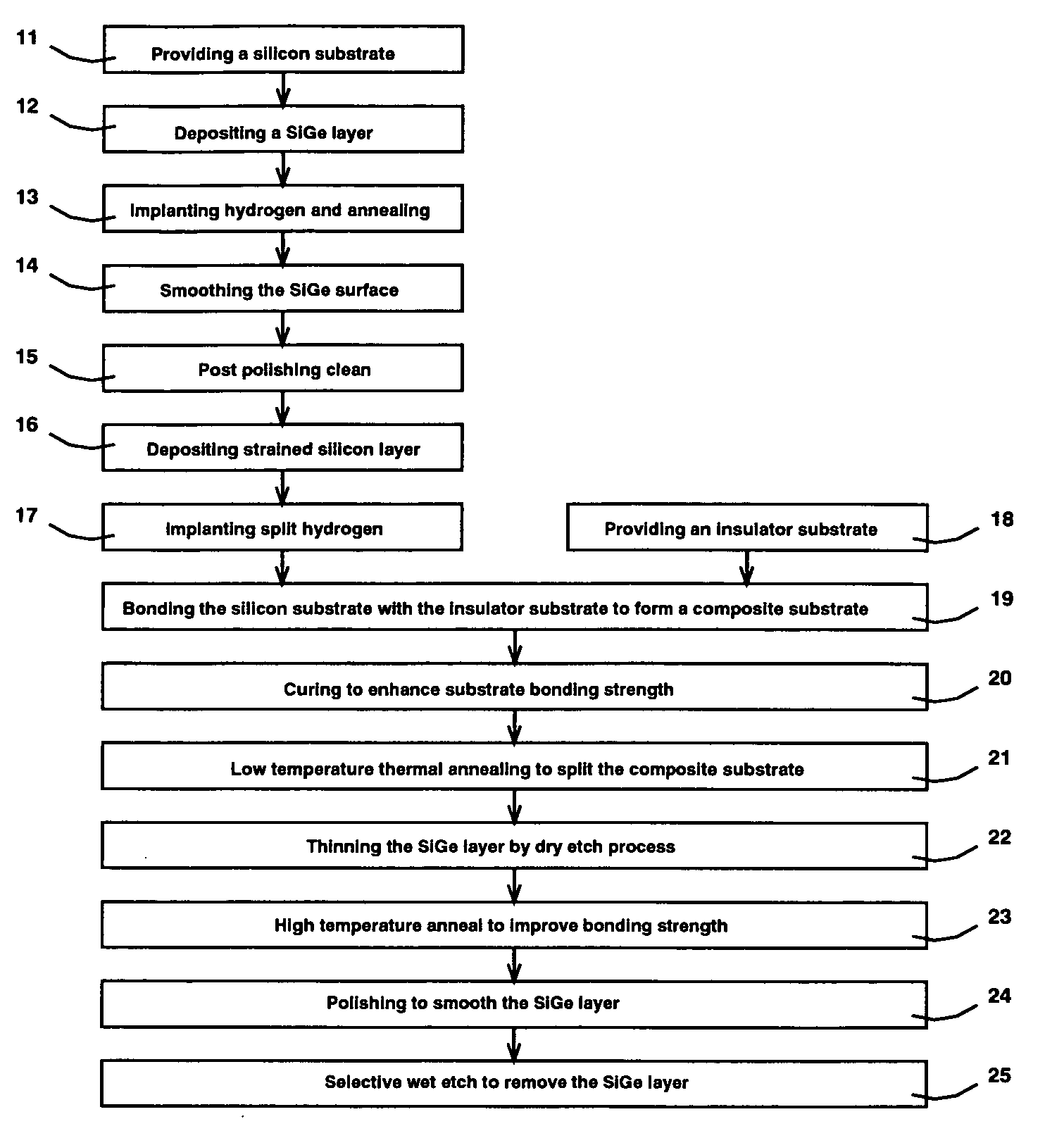

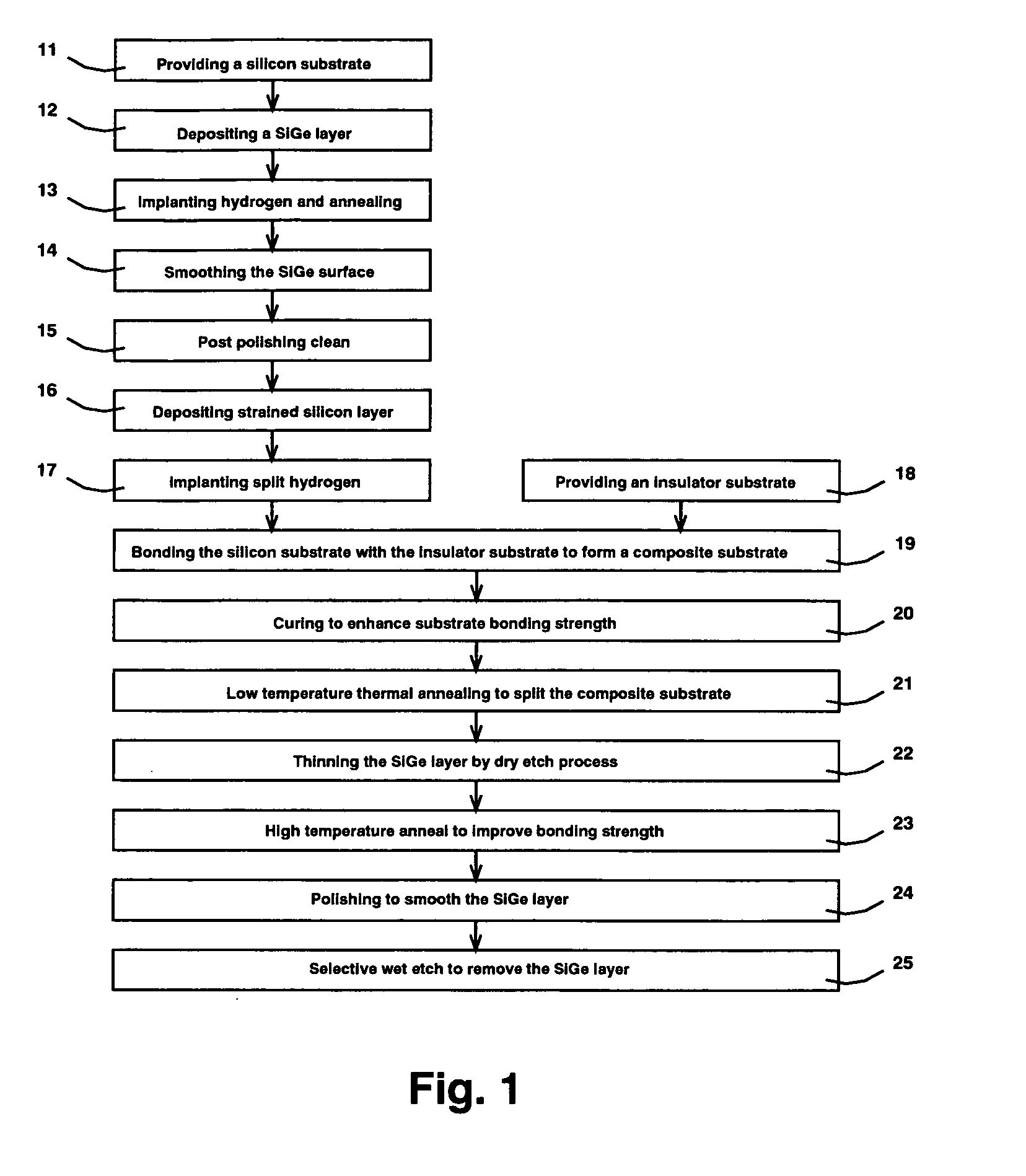

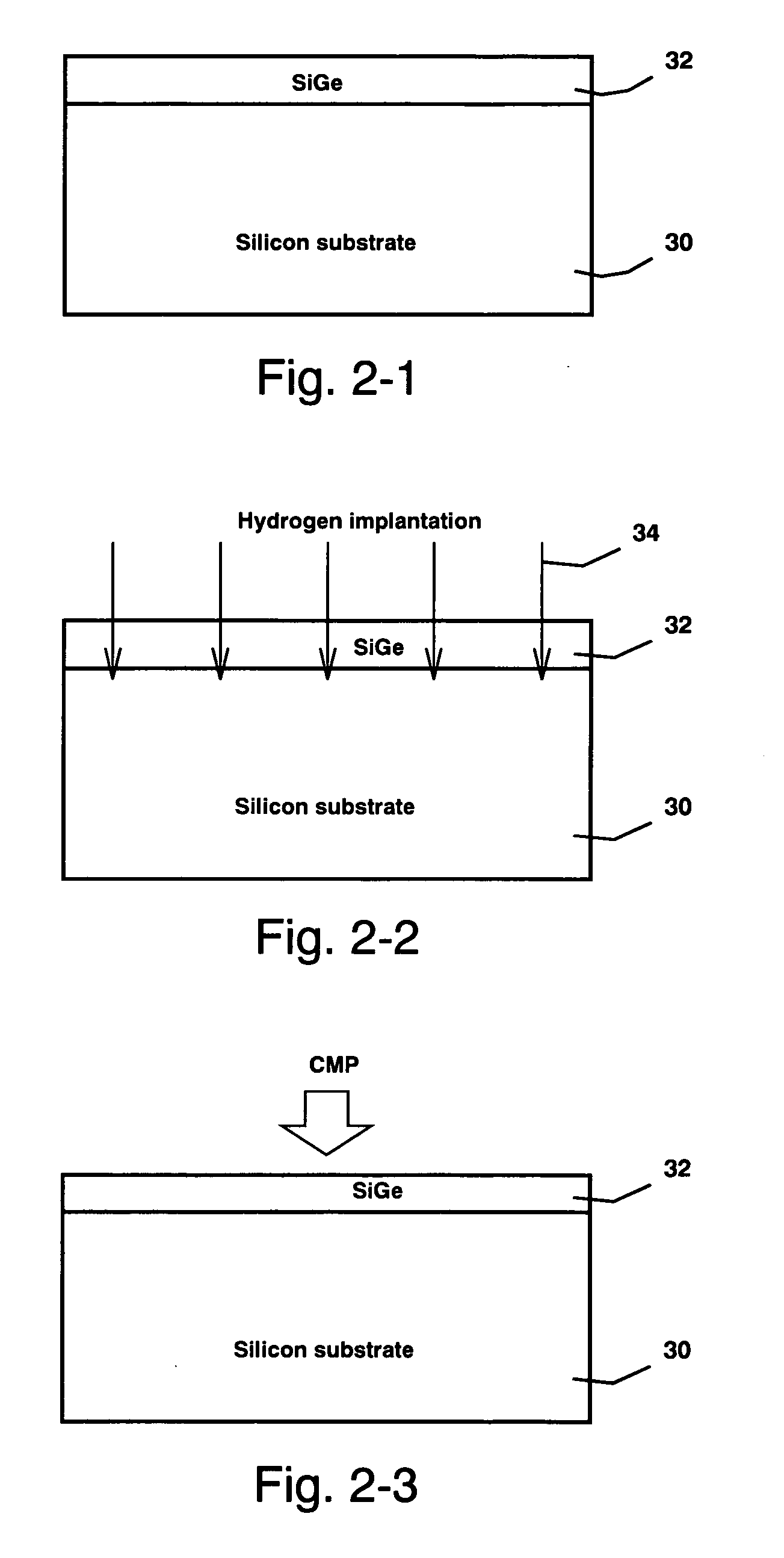

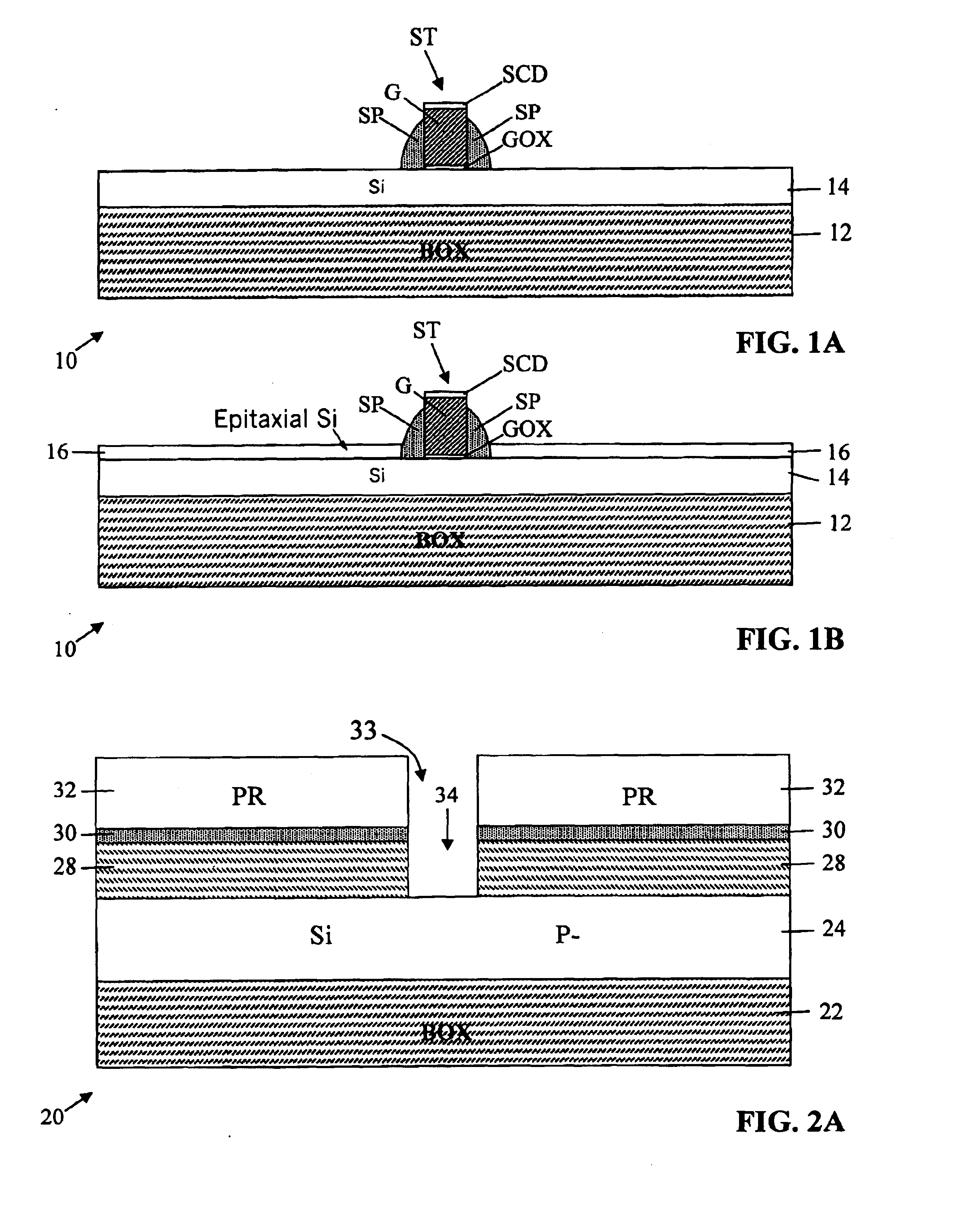

Strained silicon on insulator from film transfer and relaxation by hydrogen implantation

ActiveUS20050153524A1Easy to relaxEasy to integrateSolid-state devicesSemiconductor/solid-state device manufacturingThreading dislocationsHydrogen

Transistors fabricated on SSOI (Strained Silicon On Insulator) substrate, which comprises a strained silicon layer disposed directly on an insulator layer, have enhanced device performance due to the strain-induced band modification of the strained silicon device channel and the limited silicon volume because of the insulator layer. The present invention discloses a SSOI substrate fabrication process comprising various novel approaches. One is the use of a thin relaxed SiGe layer as the strain-induced seed layer to facilitate integration and reduce processing cost. Another is the formation of split implant microcracks deep in the silicon substrate to reduce the number of threading dislocations reaching the strained silicon layer. And lastly is the two step annealing / thinning process for the strained silicon / SiGe multilayer film transfer without blister or flaking formation.

Owner:SHARP KK

Intraocular lens implant having posterior bendable optic

ActiveUS20060253196A1Safe for long-term use in eyeReduce lightIntraocular lensCiliary epitheliumThinning

An intraocular lens (30) having focusing capabilities permitting focusing movement of the lens (30) in response to normal ciliary body (24) movement incident to changes in the distance between the eye and an object under observation is provided. The lens (30) is designed for surgical implantation within the capsule (20) of an eye (10) and includes an optic (32) and an optic positioning element (33) which cooperate to form the lens (30). Accommodation is achieved by relying upon the thickening and thinning of the optic (32) as a result of the normal retracting and contracting of the ciliary body (24) in response to the distance of an object from the viewer.

Owner:JOHNSON & JOHNSON SURGICAL VISION INC

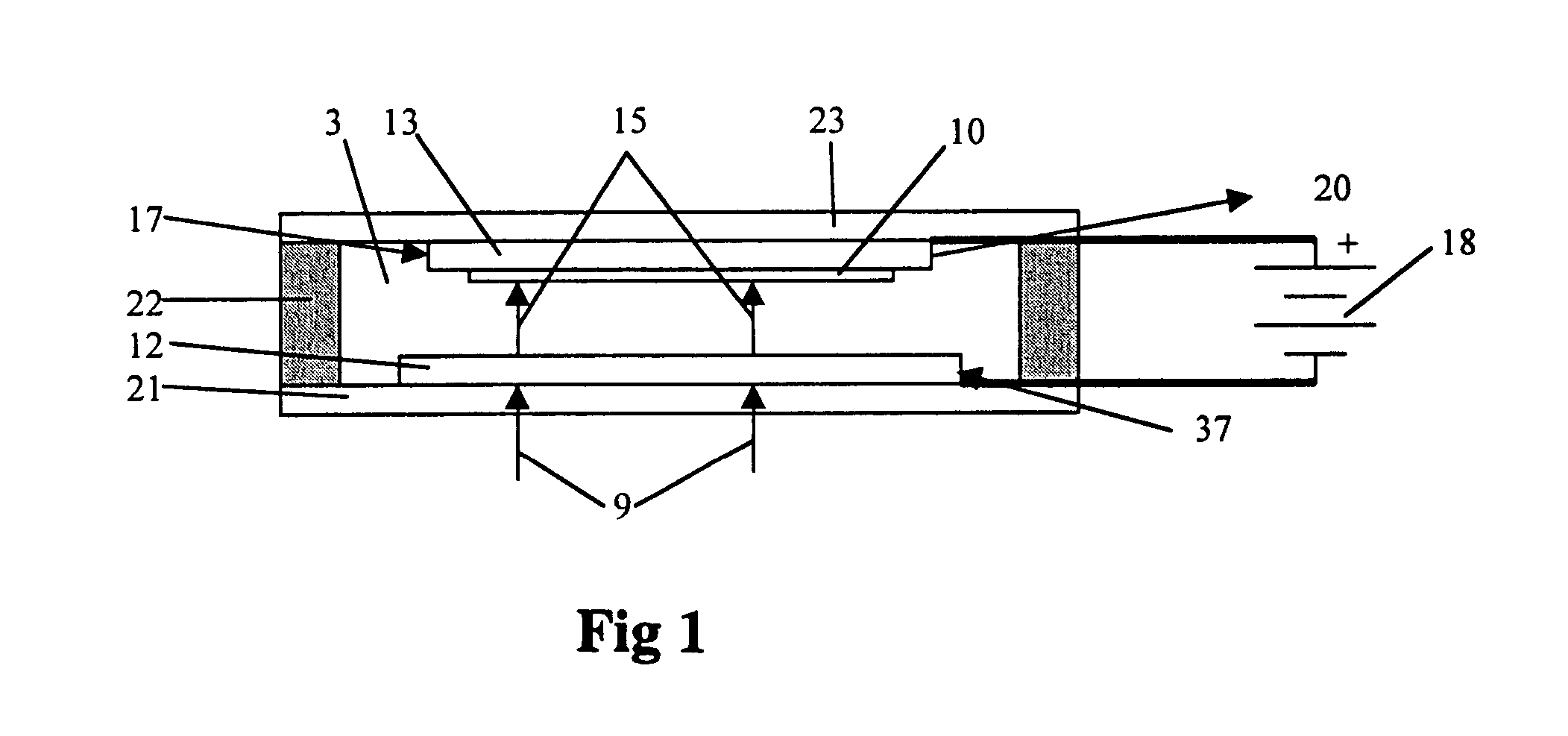

Wafer level package for very small footprint and low profile white LED devices

ActiveUS20070202623A1Low costEmission of light is minimalSolid-state devicesSemiconductor/solid-state device manufacturingSurface mountingPhosphor

A surface mount LED package having a tight footprint and small vertical image size is fabricated by a method comprising: forming light emitting diode chips each having a substrate and a plurality of layers configured to emit electroluminescence responsive to electrical energizing; forming electrical vias in a sub mount, the electrical vias passing from a front side of the sub-mount to a back-side of the sub-mount; flip chip bonding the light emitting diode chips on the front-side of the sub mount such that each light emitting diode chip electrically contacts selected electrical vias; thinning or removing the substrates of the flip-chip bonded light emitting diode chips; and after the thinning, disposing a phosphor over the flip chip bonded light emitting diode chips.

Owner:GE LIGHTING SOLUTIONS LLC

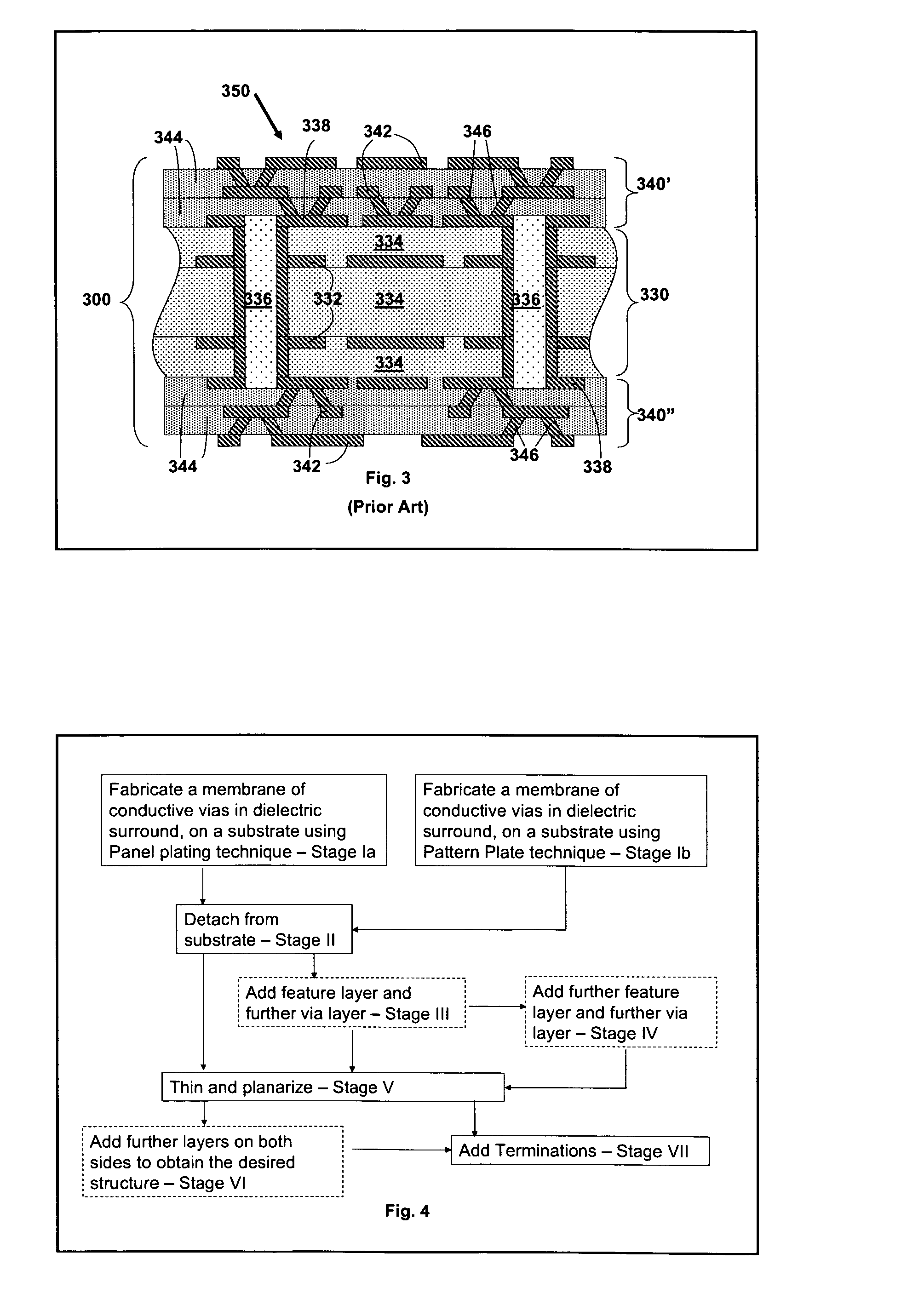

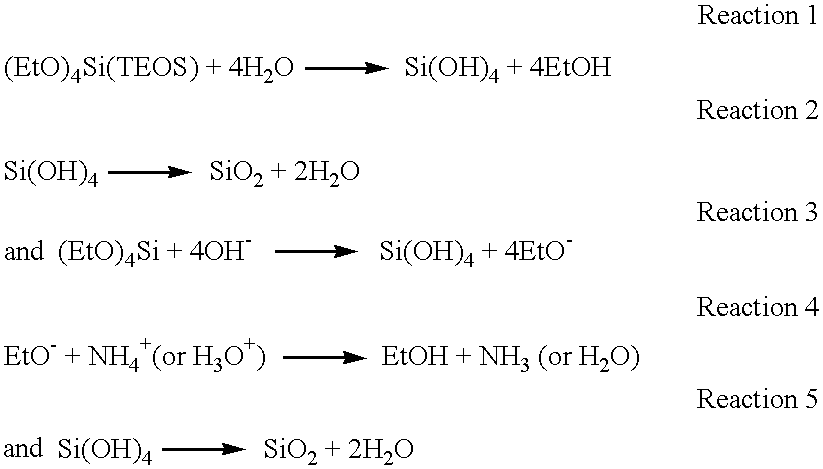

Advanced Multilayered Coreless Support Structures and their Fabrication

ActiveUS20070281471A1Suitable for mass productionHigh yieldSemiconductor/solid-state device detailsPrinted circuit aspectsDielectricEngineering

A method of fabricating a free standing membrane comprising a via array in a dielectric for use as a precursor in the construction of superior electronic support structures, comprising the stages:I—Fabricating a membrane comprising conductive vias in a dielectric surround on a sacrificial carrier, andII—Detaching the membrane from the sacrificial carrier to form a free standing laminated array, and a method of fabricating an electronic substrate based on such a membrane comprising at least the stages of:(I) Fabricating a membrane comprising conductive vias in a dielectric surround on a sacrificial carrier;(II) Detaching the membrane from the sacrificial carrier to form a free standing laminated array;(V) Thinning and planarizing, and(VII) Terminating.

Owner:ZHUHAI ADVANCED CHIP CARRIERS & ELECTRONICS SUBSTRATE SOLUTIONS TECH

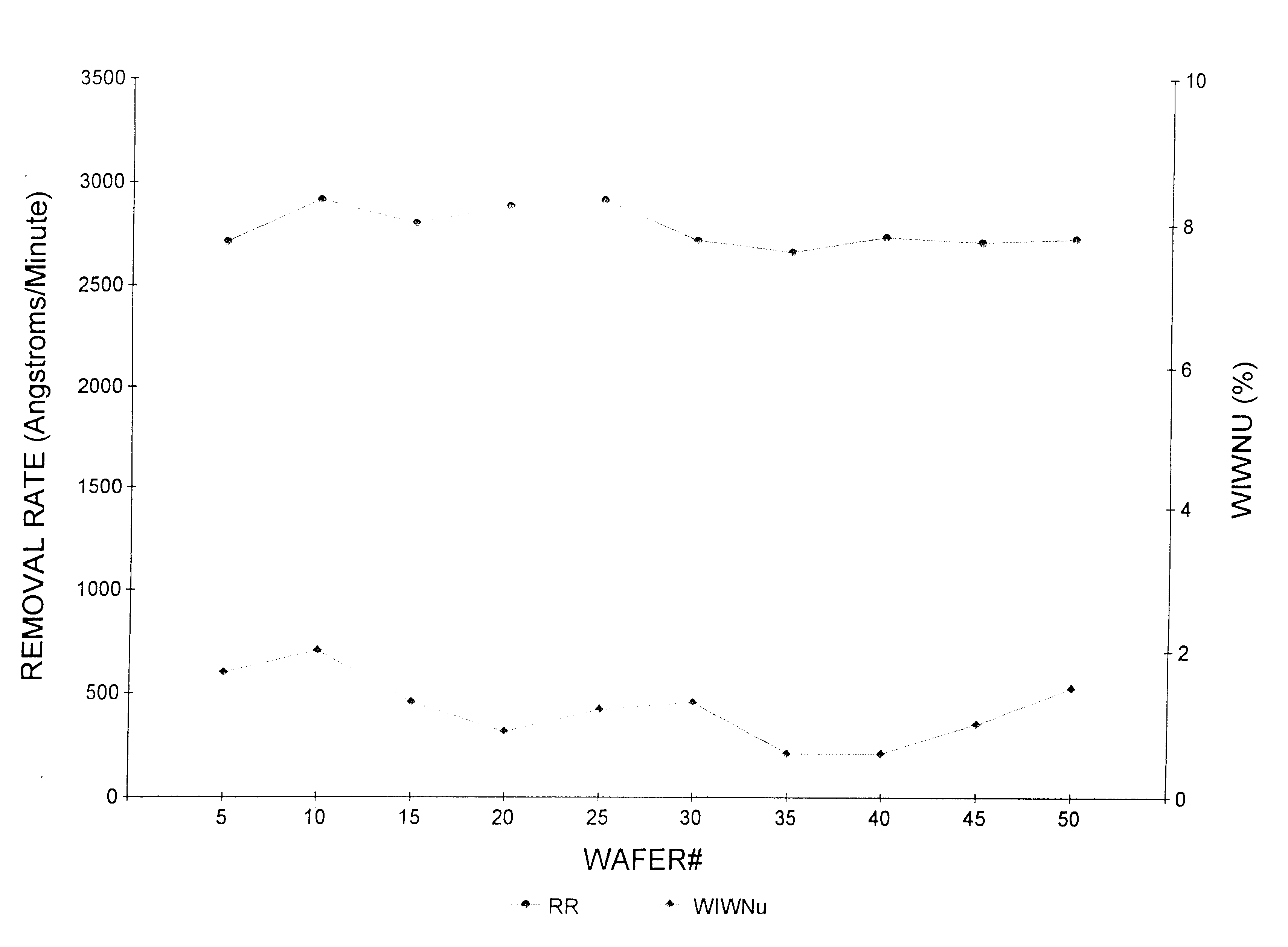

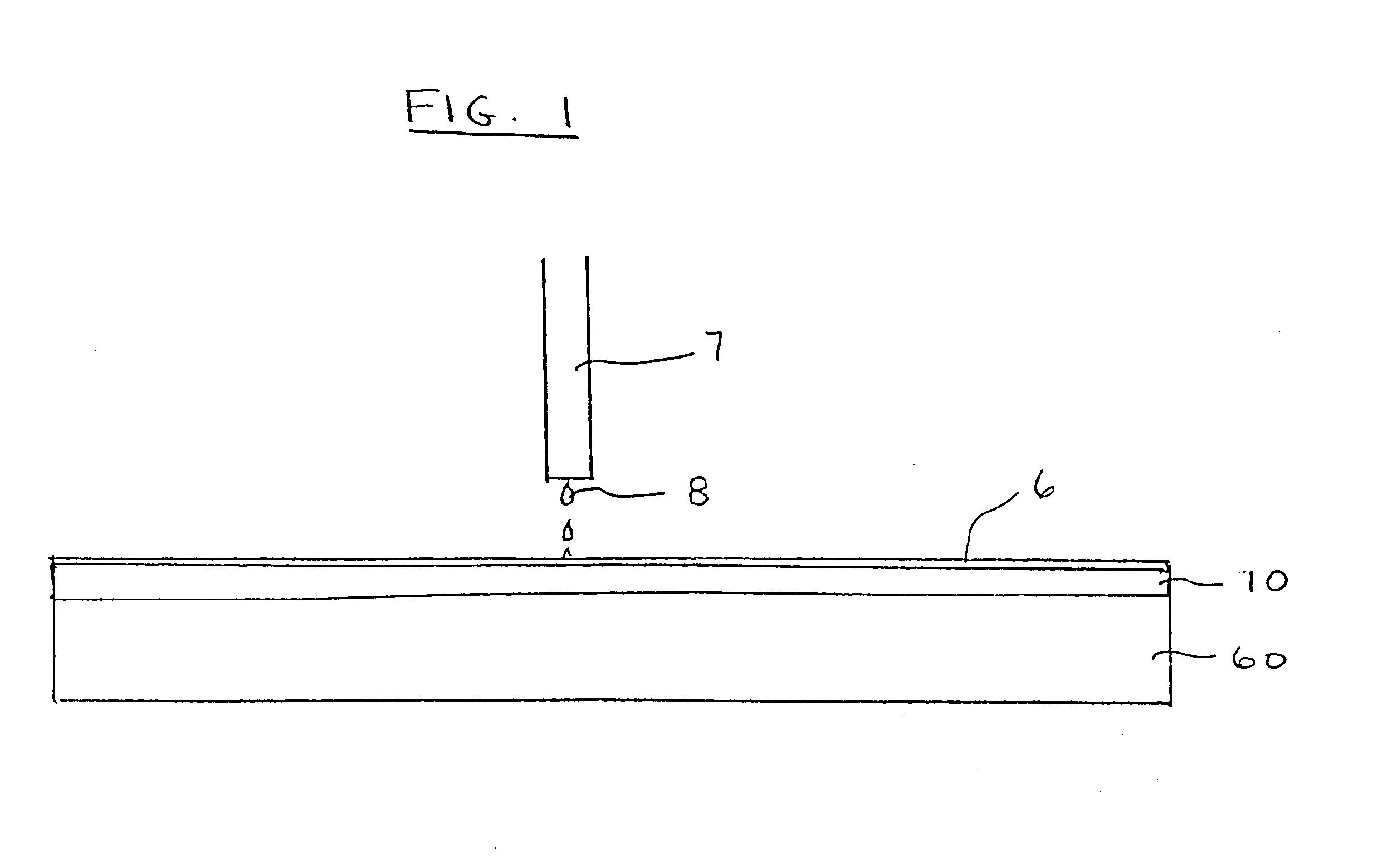

Planarization compositions and methods for removing interlayer dielectric films

InactiveUS6322600B1Improve planarization qualityQuality improvementPigmenting treatmentOther chemical processesThinningDielectric thin films

A planarization composition is set forth for chemical mechanical planarization of dielectric layers for semiconductor manufacture. The composition comprises spherical silica particles having an average diameter of from 30 nm to about 400 nm, and a narrow range of particle sizes, wherein about 90% of the particles is within 20% of the average particle diameter. The composition includes a liquid carrier comprising up to about 9% alcohol and an amine hydroxide in the amount of about 0.2 to about 9% by weight. The pH of the composition is in the range of about 9 to about 11.5, and the remainder of the solution is water. The composition has low amounts of metal ions, and the composition is used for thinning, polishing and planarizing interlayer dielectric thin films, shallow trench isolation structures, and isolation of gate structures. The invention also comprises methods for using the planarization composition in the manufacture of semiconductor devices.

Owner:ADVANCED TECH MATERIALS INC

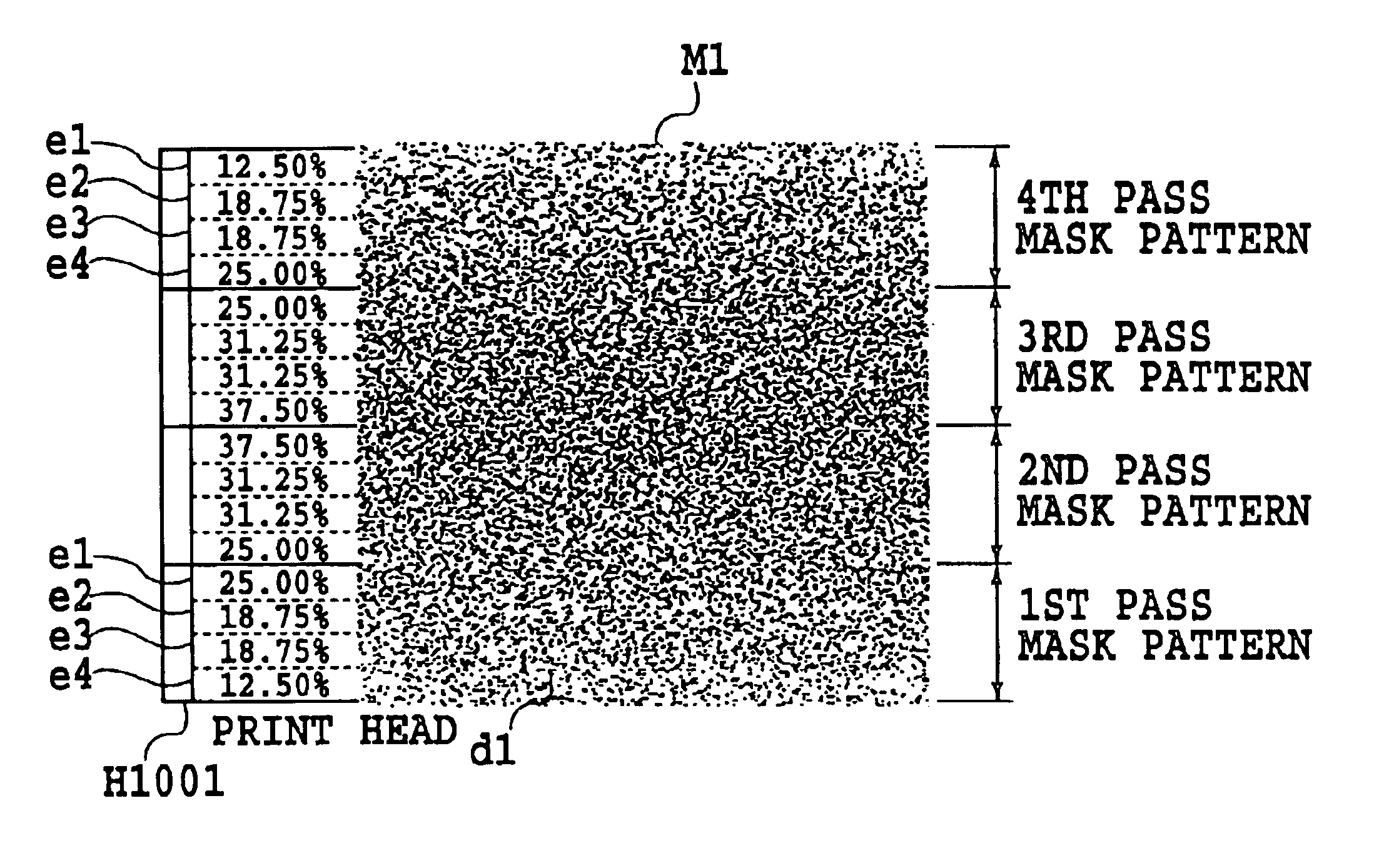

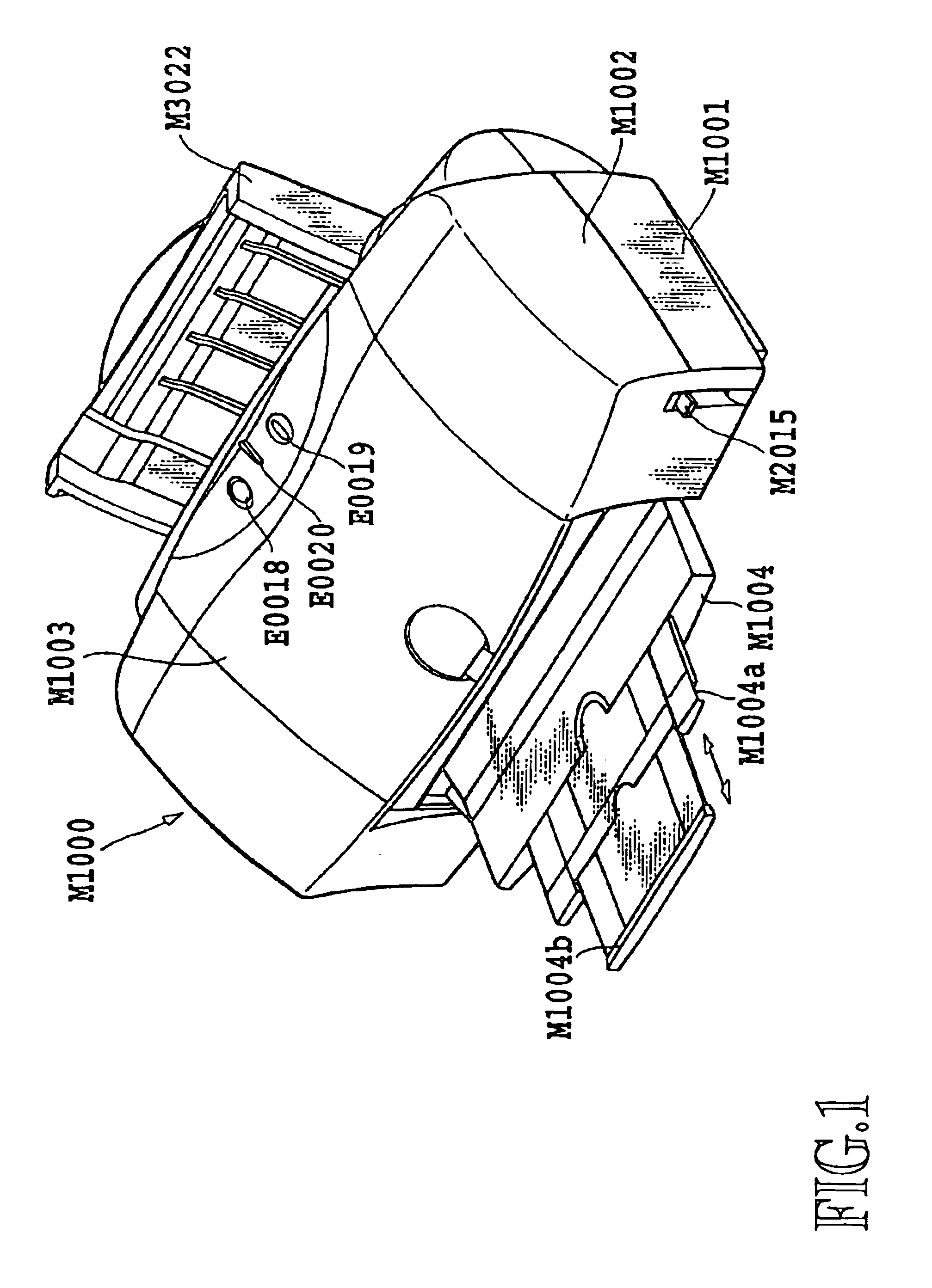

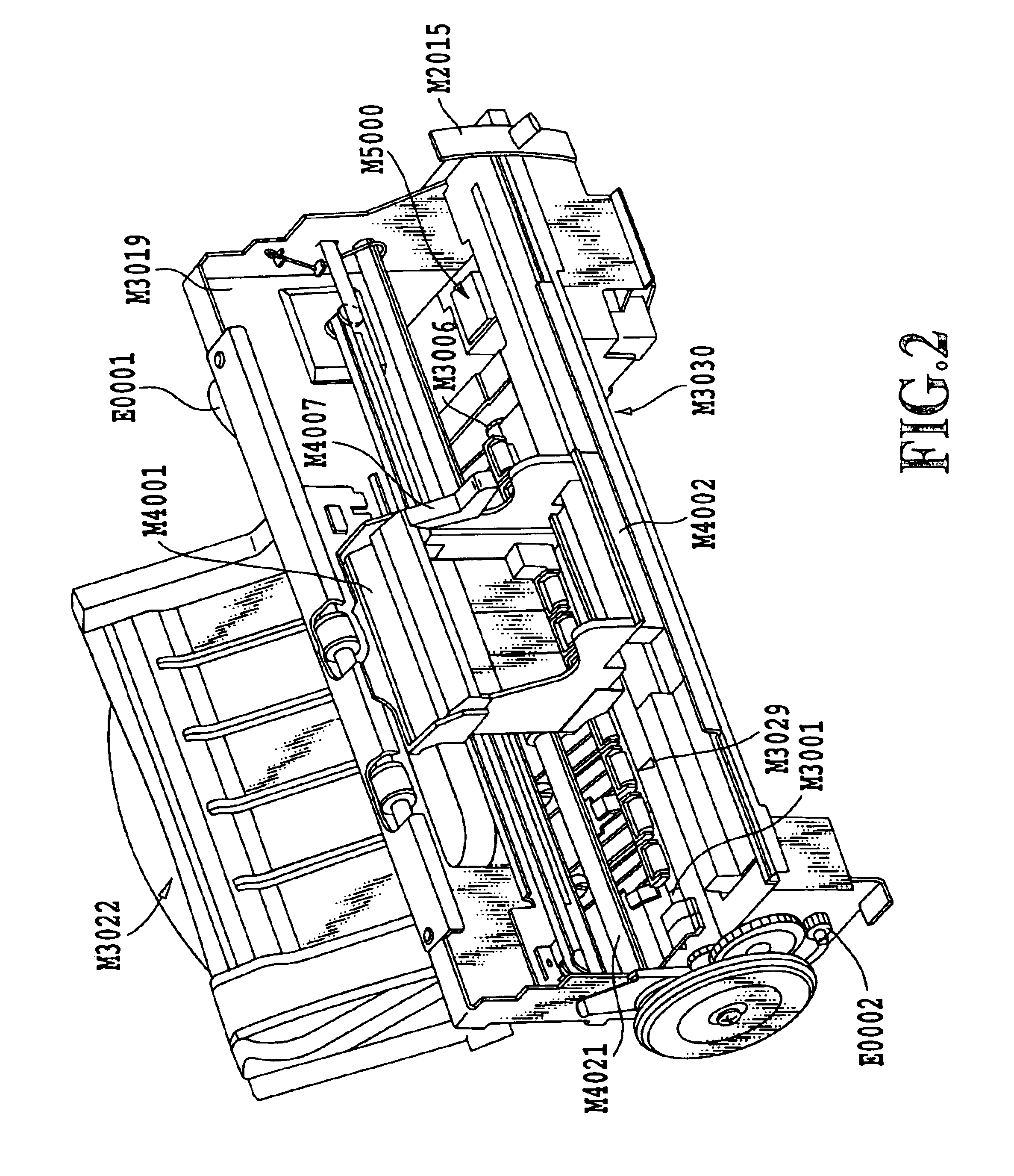

Ink jet printing apparatus and ink jet printing method for forming an image on a print medium

InactiveUS6874864B1Preventing Image Quality DeteriorationIncrease speedVisual representation by matrix printersOther printing apparatusImaging qualityVolumetric Mass Density

An apparatus and method are provided to enable high speed printing of an image with high resolution while suppressing degradation of image quality due to white stripes and density variations. In an ink jet printing apparatus using a multi-pass printing system, the same scan print area is divided at a predetermined pitch and the printing duties of the divided areas determined by the thinning out mask pattern are set to different values. In regard to the same scan print area formed by a plurality of the main scans, the divided areas corresponding to the ends of the print head have their printing duties set smaller than those of the divided areas on the inner side of the ends of the print head.

Owner:CANON KK

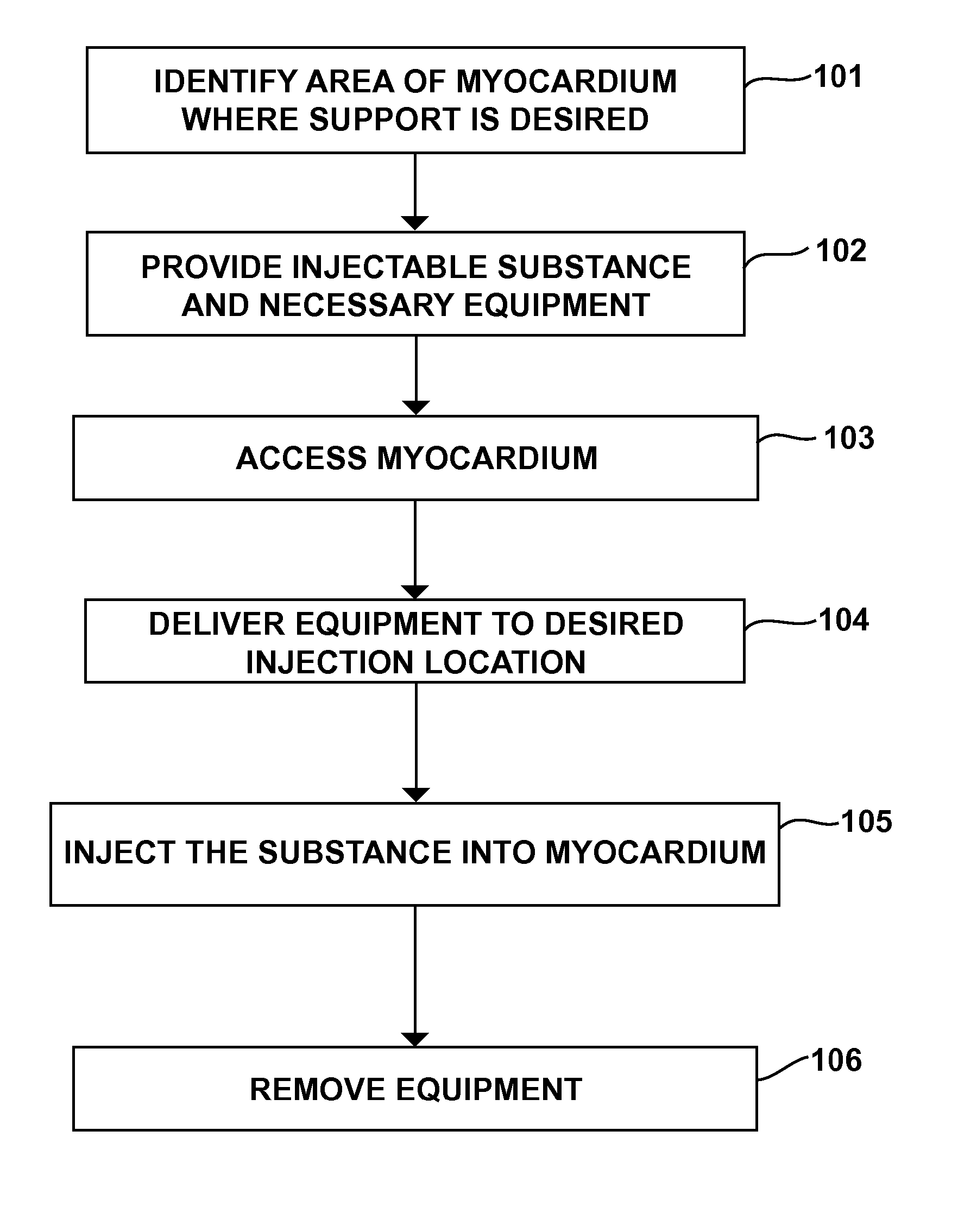

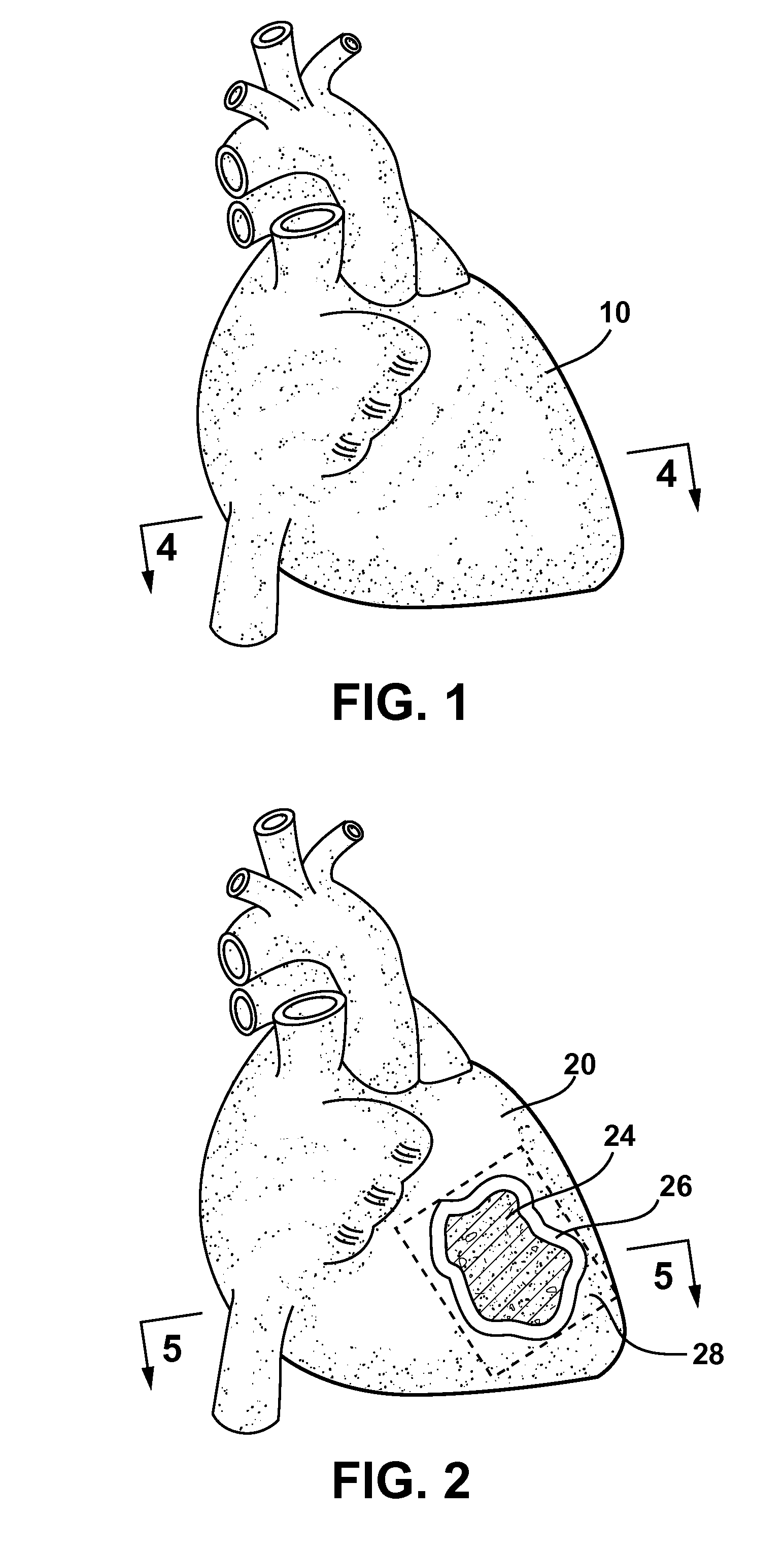

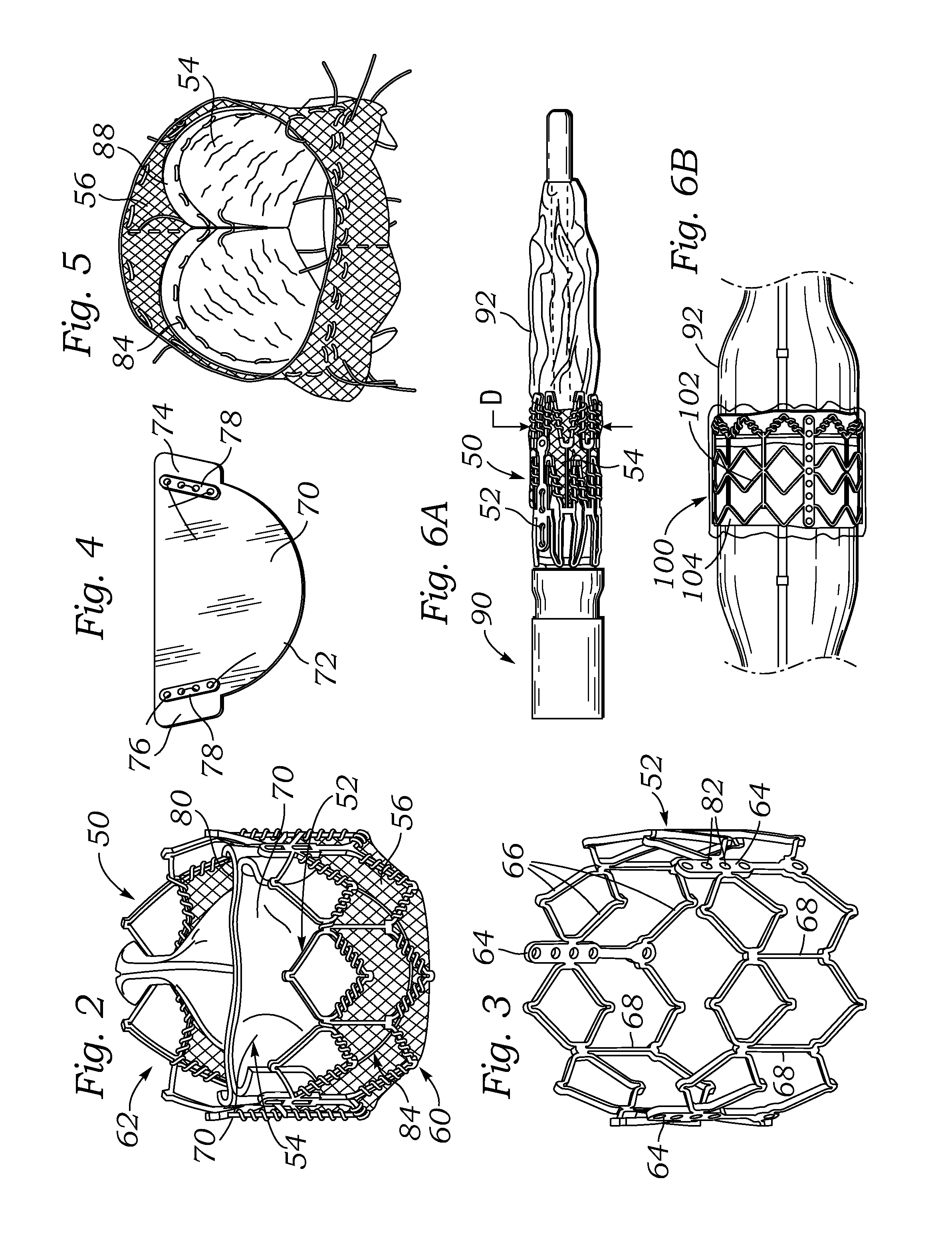

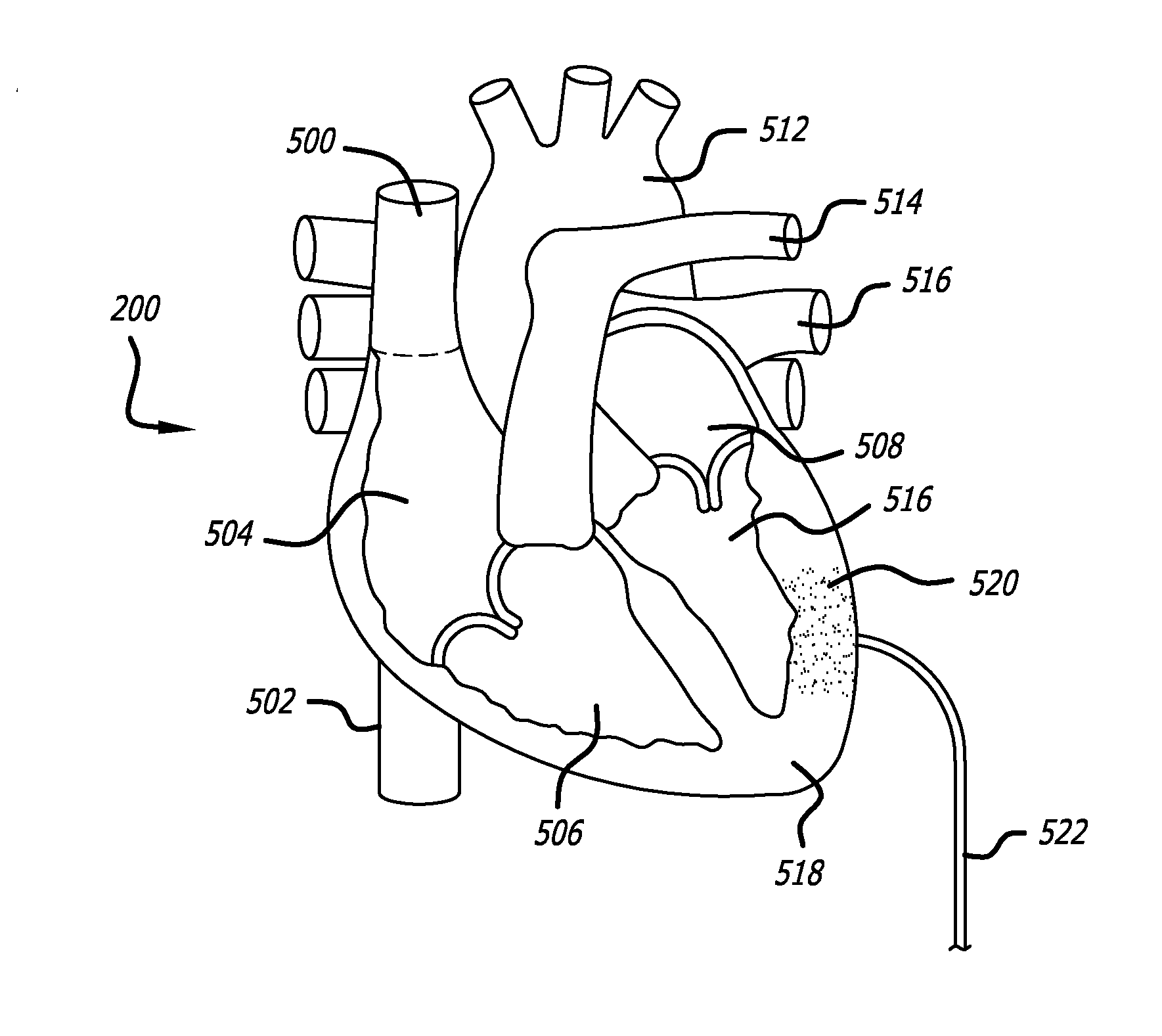

Methods and Systems for Treating Injured Cardiac Tissue

InactiveUS20070014784A1Simple processReduce riskDiagnosticsInfusion syringesAutologous plateletThinning

Methods and systems are disclosed for treating injury to cardiac tissue by delivering a composition which provides structural support to the cardiac tissue. The composition helps to prevent chamber remodeling by providing structural reinforcement of the tissue or structural reinforcement of the tissue combined with biological therapy. The structurally reinforcing composition can thicken the wall of a heart, or act to prevent further thinning and thereby provide resistance against further remodeling. A number of compositions are disclosed, including multi-component substances such as autologous platelet gel, and other substances. The compositions disclosed can contain additives to augment / enhance the desired effects of the injection.

Owner:MEDTRONIC VASCULAR INC

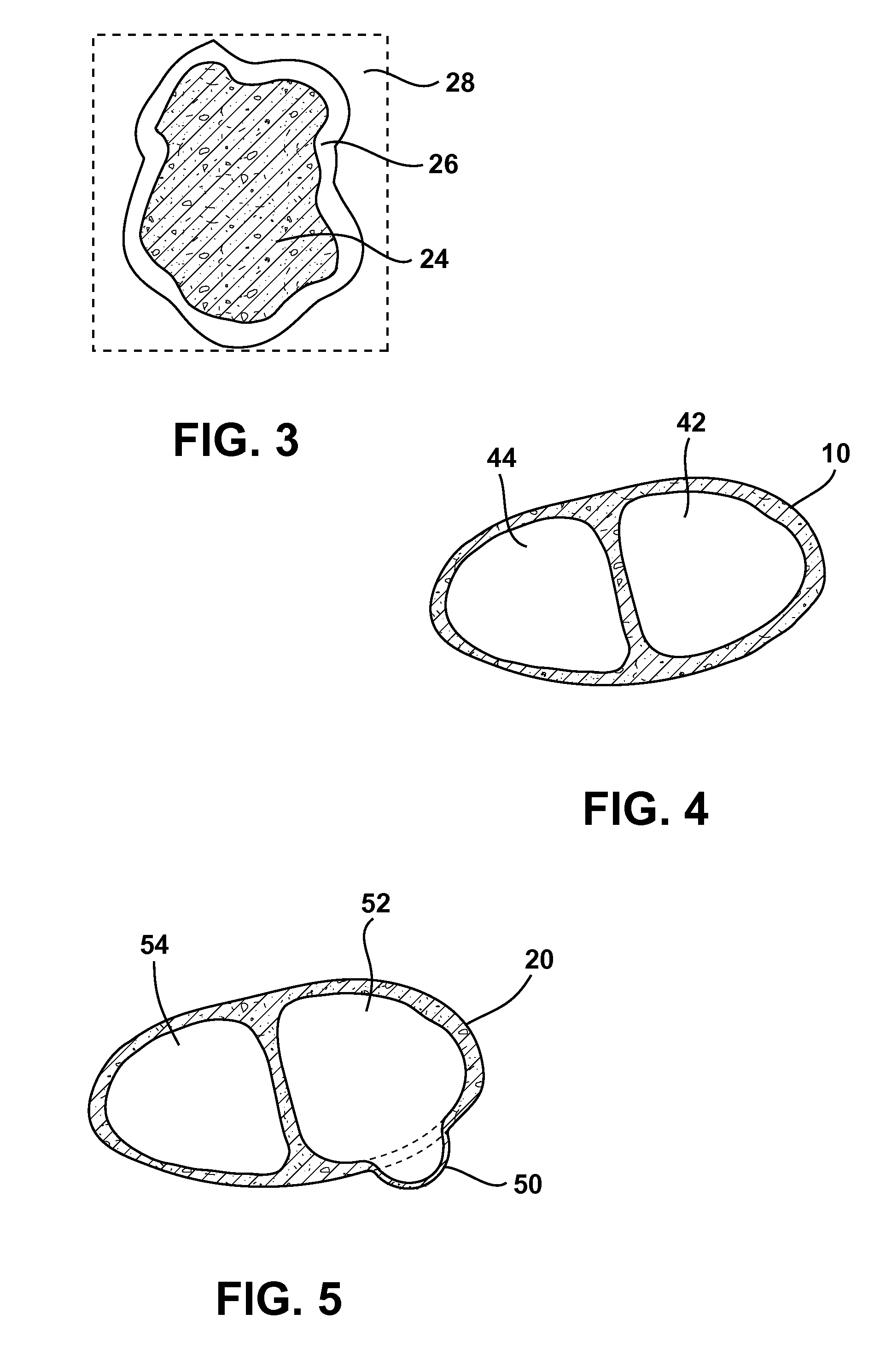

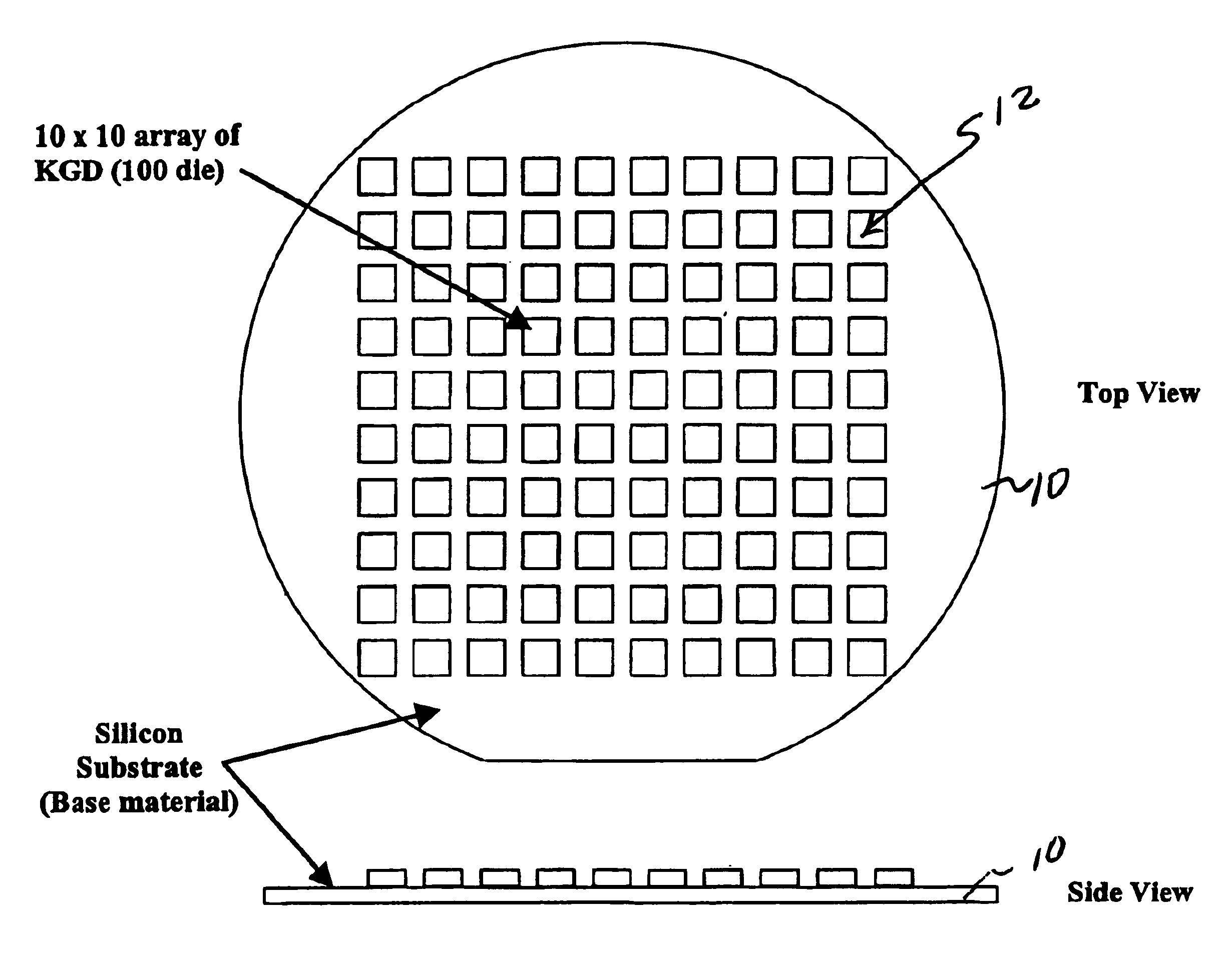

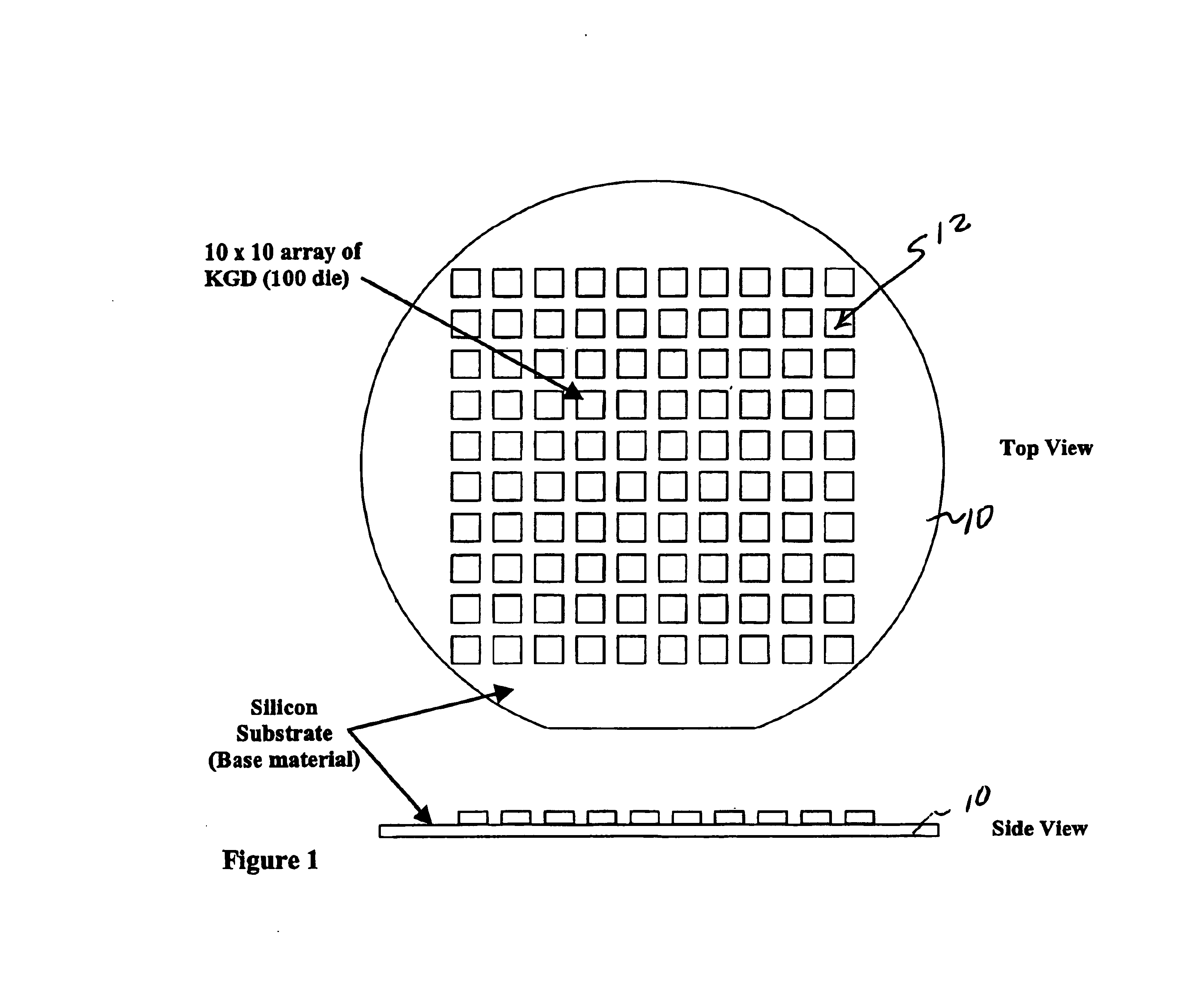

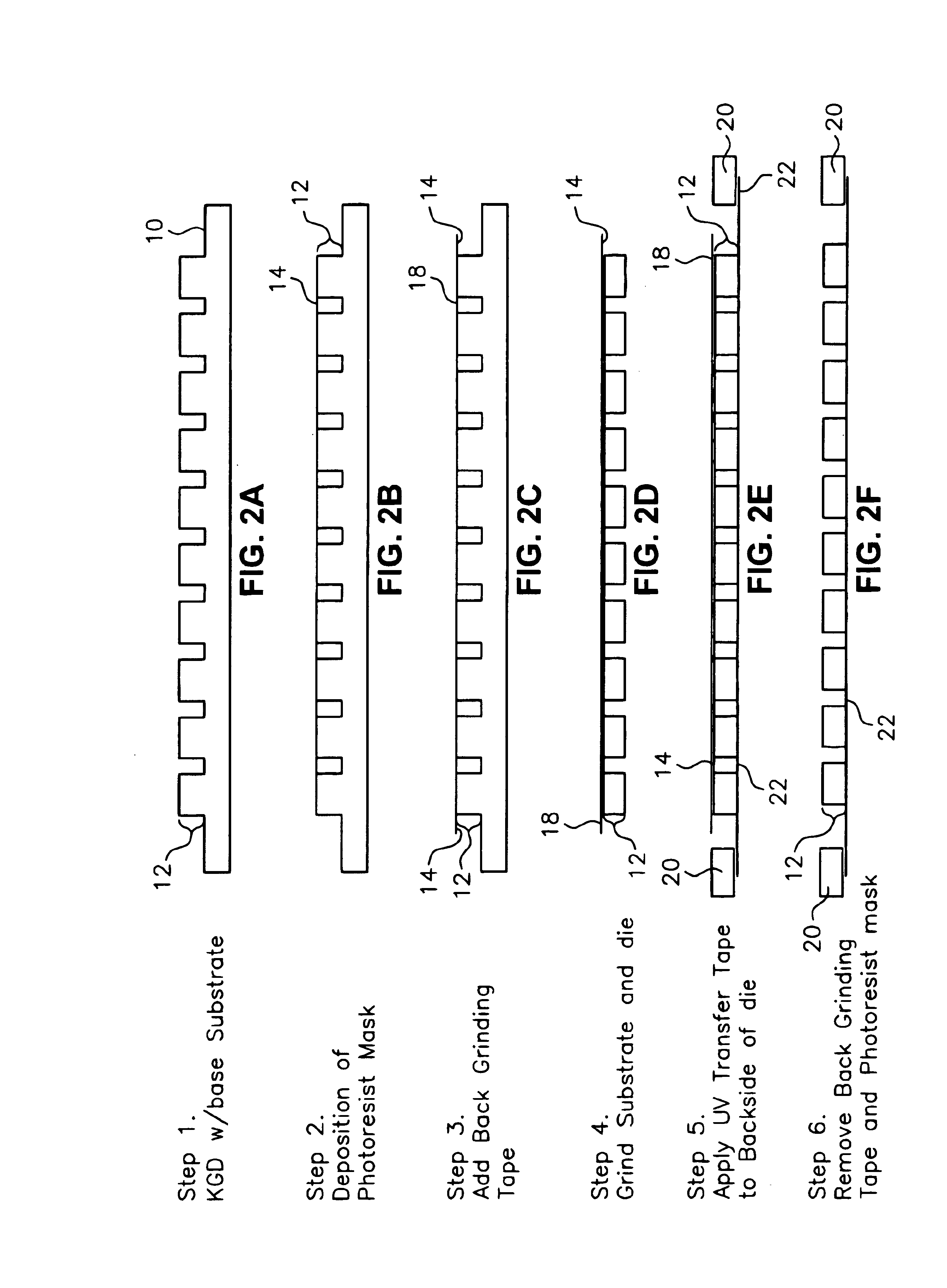

Die thinning methods

InactiveUS6861336B1Securing pluralityReduce thicknessSemiconductor/solid-state device manufacturingResistEngineering

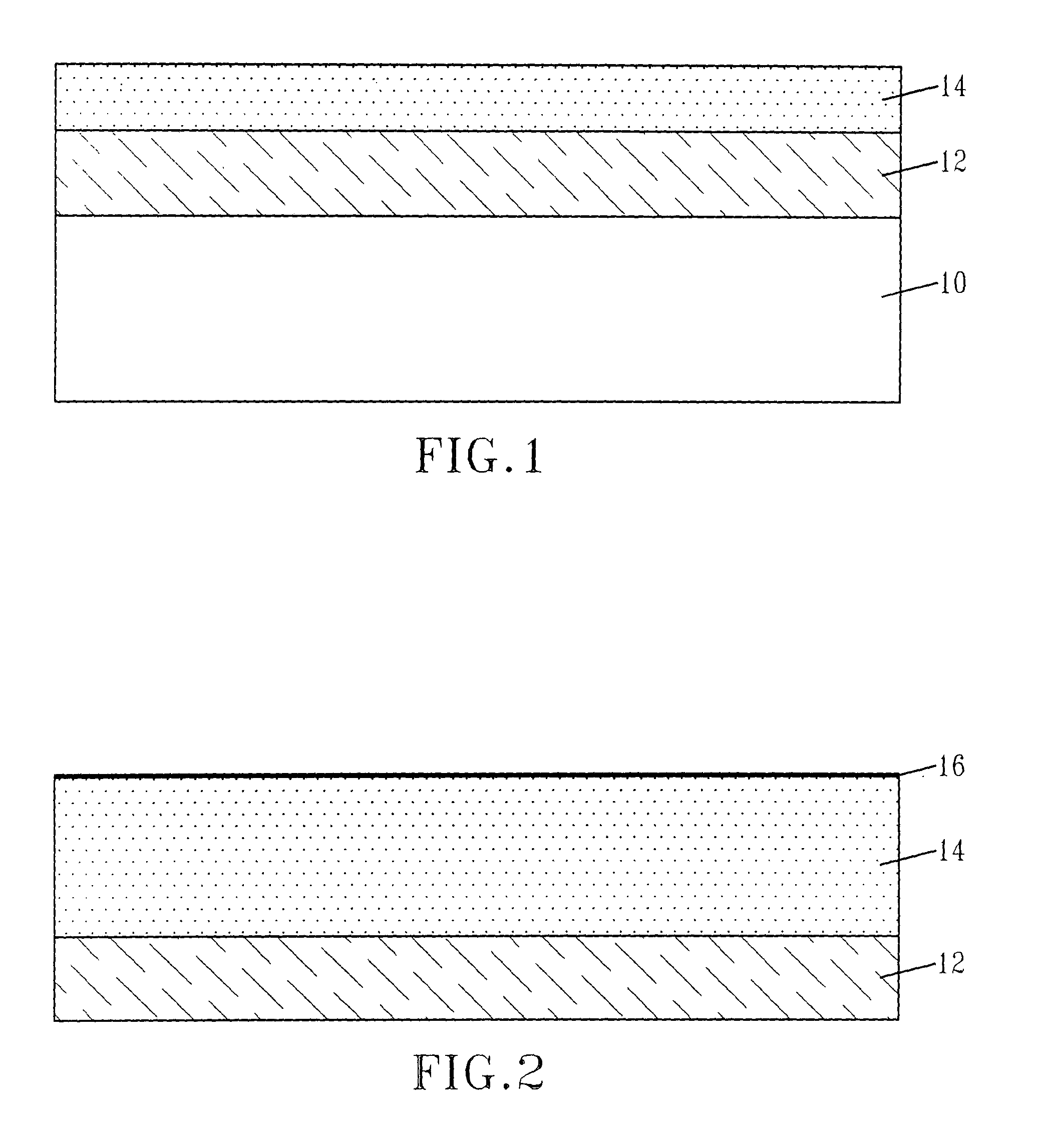

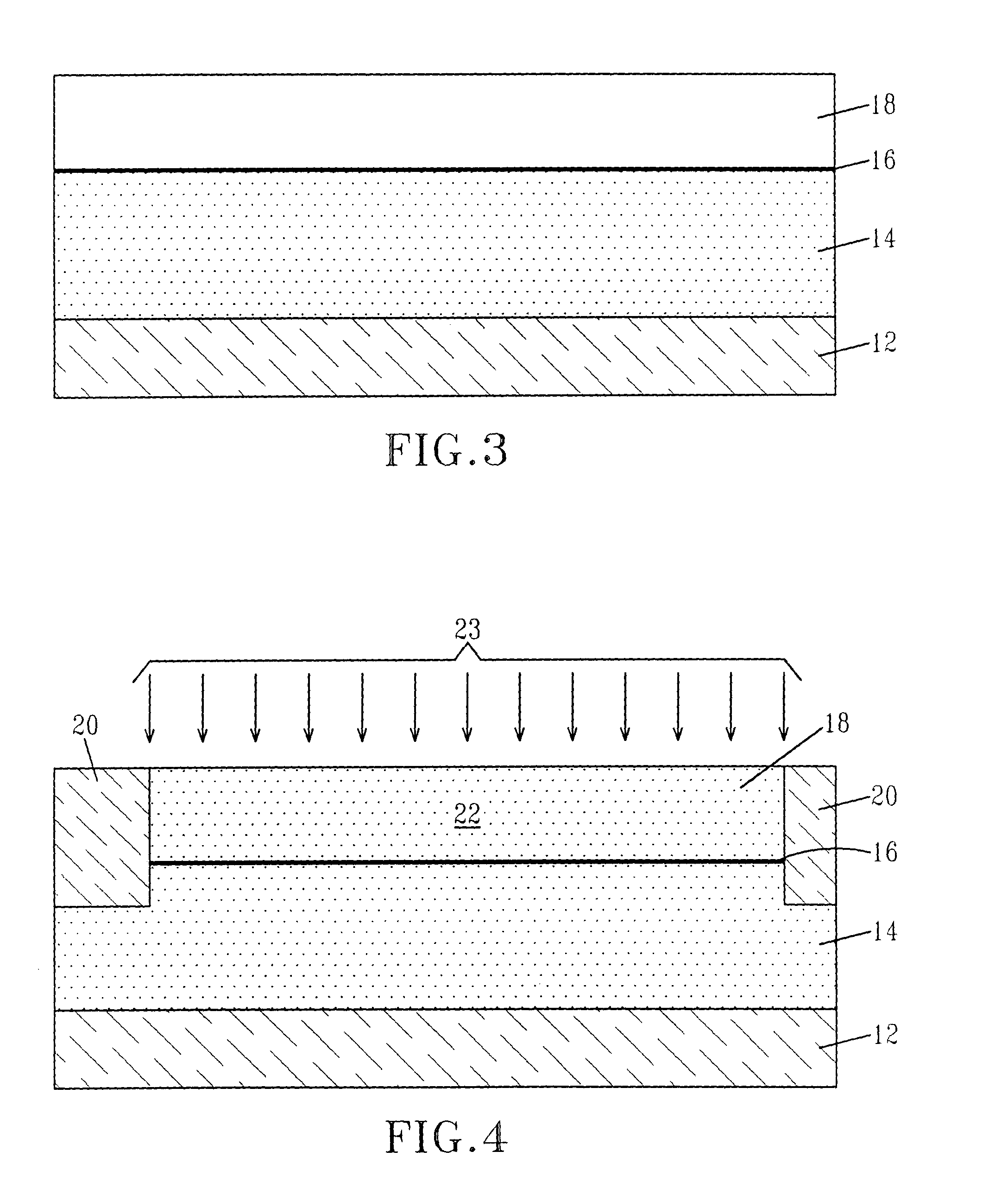

A die thinning method includes providing a wafer (10) and depositing a substrate bonding material on the wafer. The die thinning method places a plurality of die (12) on the wafer (10), cures the substrate bonding material to secure the individual ICs to the base wafer (10), and covers the substrate (10) and the die (12) with a mask material. The substrate bonding material is BCB. The mask material is a photoresist (14). The method further back grinds the wafer to remove the wafer and to reduce the original die thickness from 26 mils to 5 mils. A UV transfer tape (22) is applied to the die (12) on a film frame (20). The mask material and back grinding tape (18) are then removed. The plurality of die (12), UV transfer tape (22), and film frame (20) are placed face down in a UV cure station. The UV transfer tape (22) is UV irradiated and the plurality of die (12) are removed from the UV transfer tape (22).

Owner:UNION SEMICON TECH

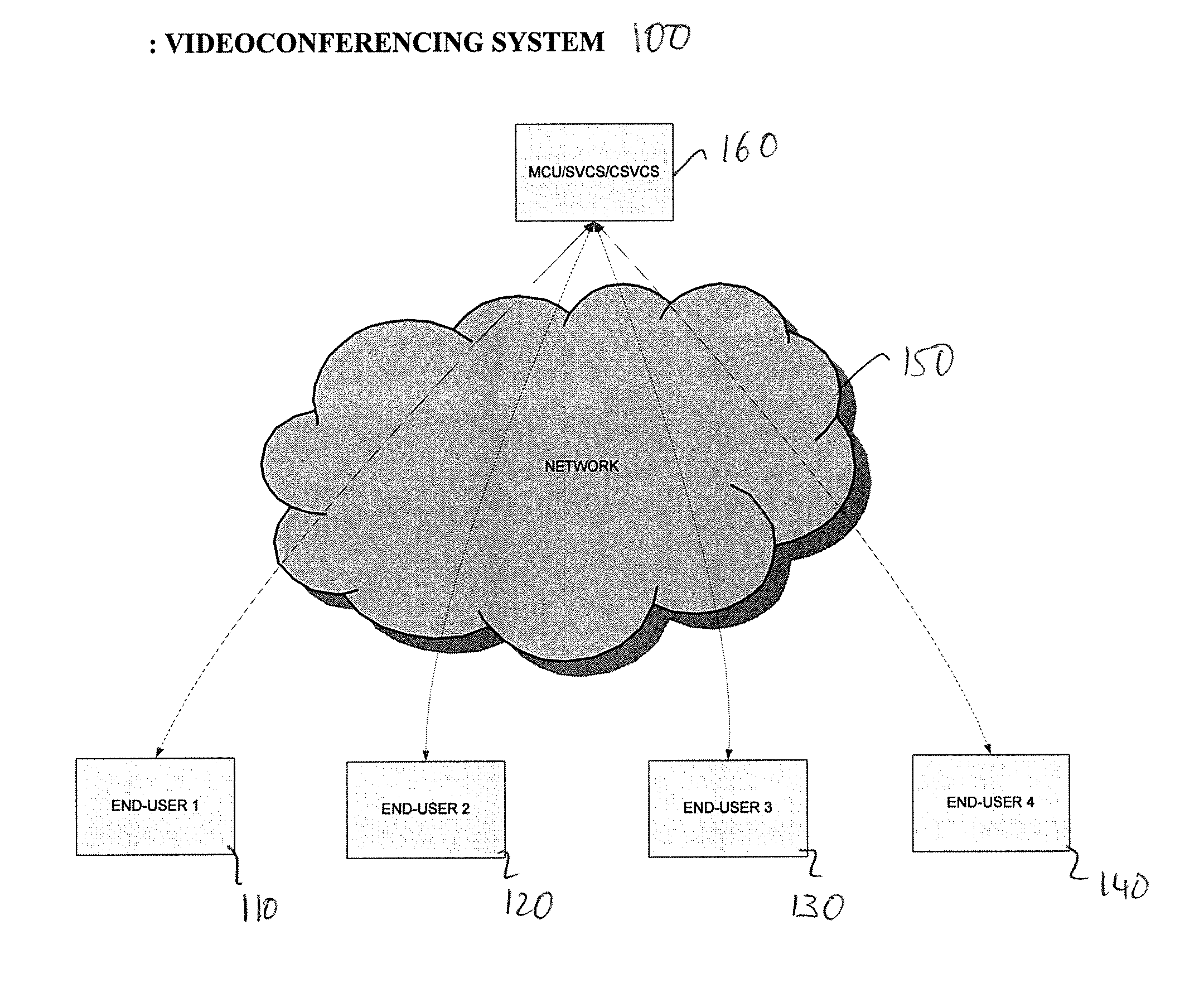

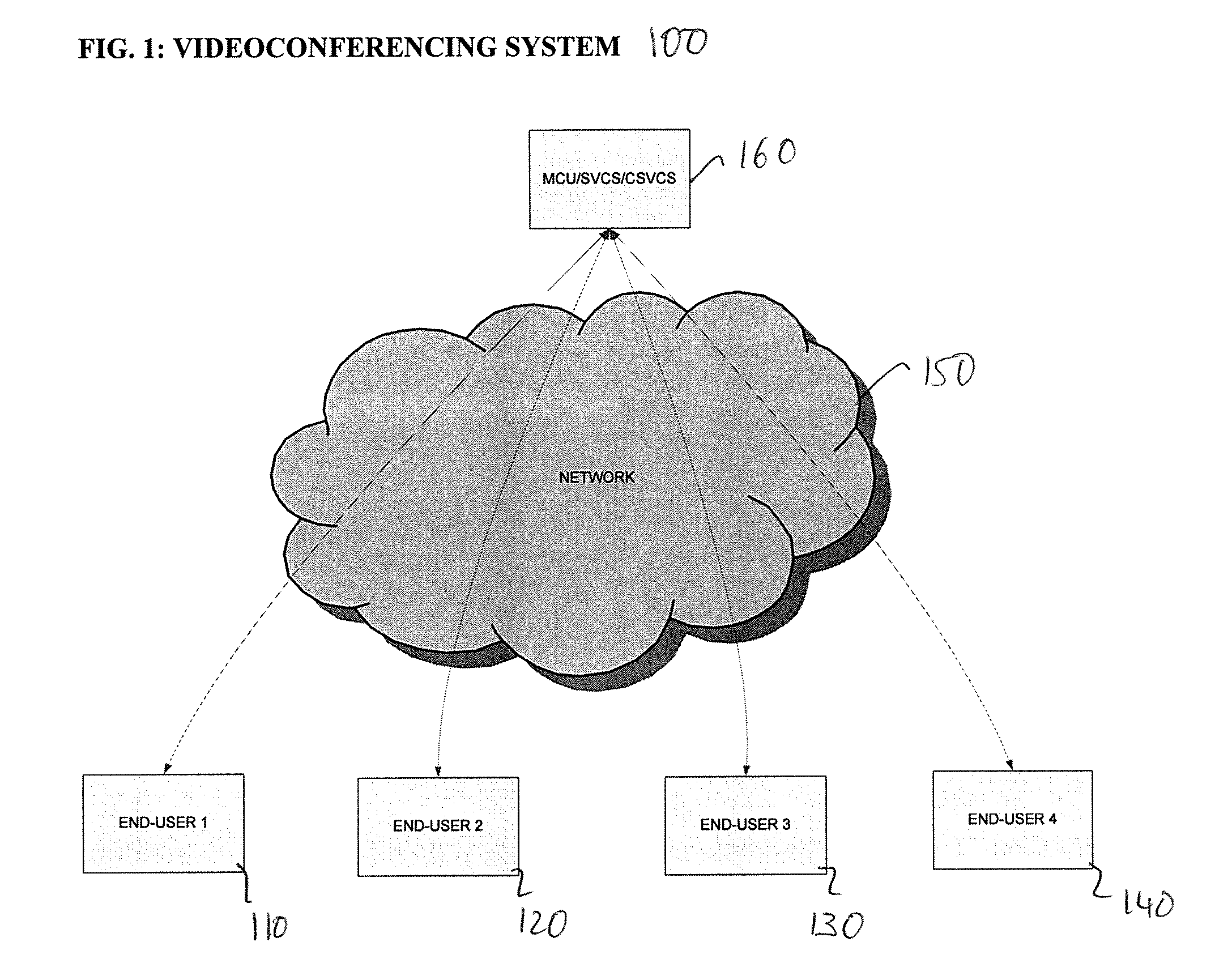

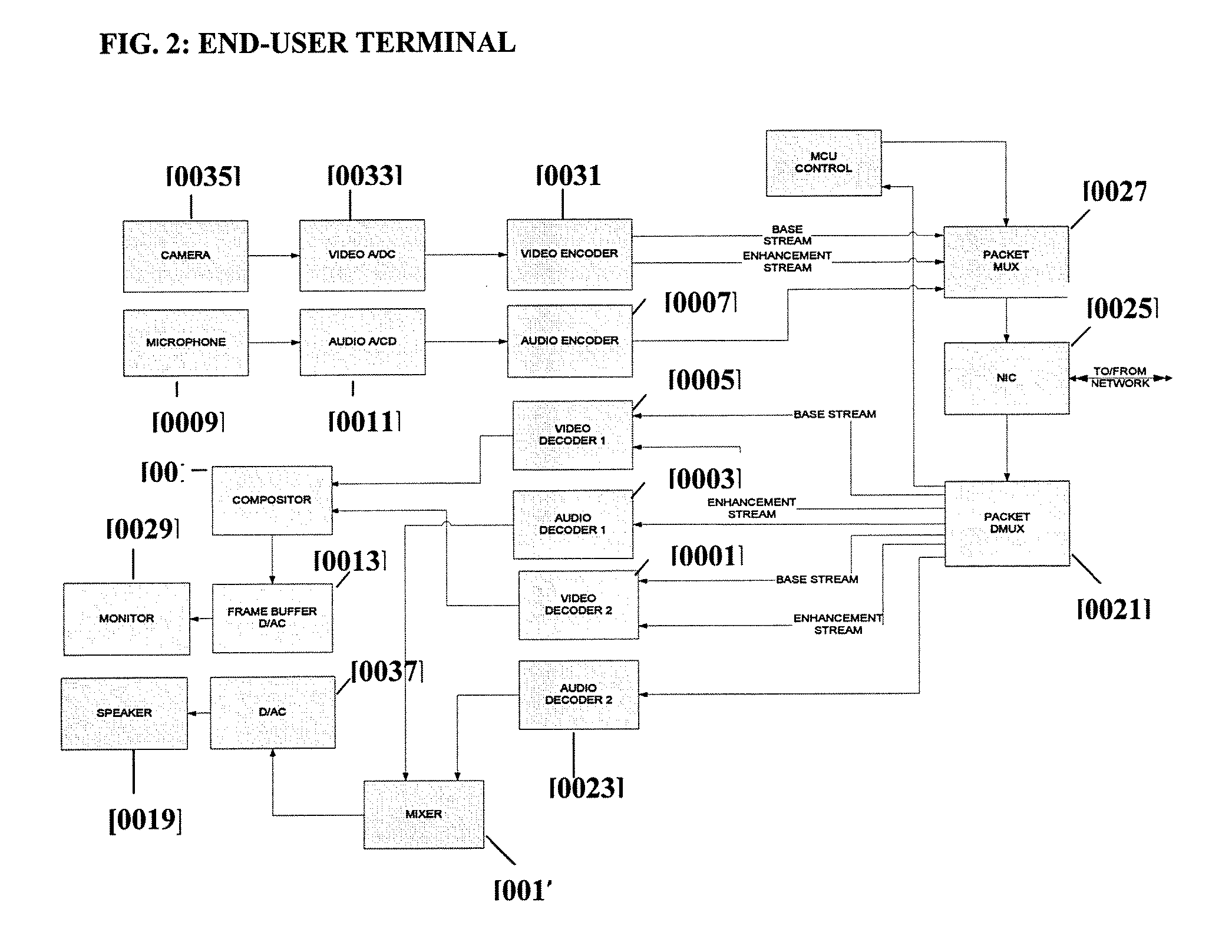

System And Method For Thinning Of Scalable Video Coding Bit-Streams

InactiveUS20070263087A1Flexibility in processingImprove coding efficiencyColor television with pulse code modulationColor television with bandwidth reductionExtensibilityComputer architecture

A system for videoconferencing that offers, among other features, extremely low end-to-end delay as well as very high scalability. The system accommodates heterogeneous receivers and networks, as well as the best-effort nature of networks such as those based on the Internet Protocol. The system relies on scalable video coding to provide a coded representation of a source video signal at multiple temporal, quality, and spatial resolutions. These resolutions are represented by distinct bitstream components that are created at each end-user encoder. System architecture and processes called SVC Thinning allow the separation of data into data used for prediction in other pictures and data not used for prediction in other pictures. SVC Thinning processes, which can be performed at video conferencing endpoints or at MCUs, can selectively remove or replace with fewer bits the data not used for prediction in other pictures from transmitted bit streams. This separation and selective removal or replacement of data for transmission allows a trade-off between scalability support (i.e. number of decodable video resolutions), error resiliency and coding efficiency.

Owner:VIDYO

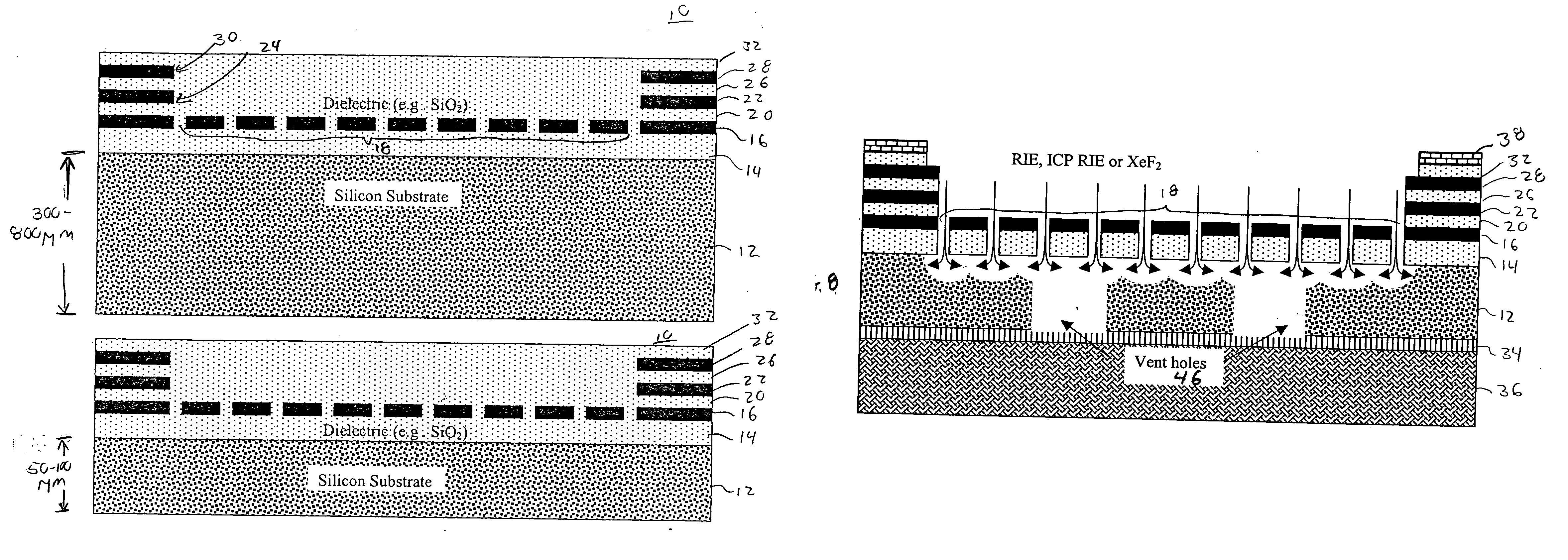

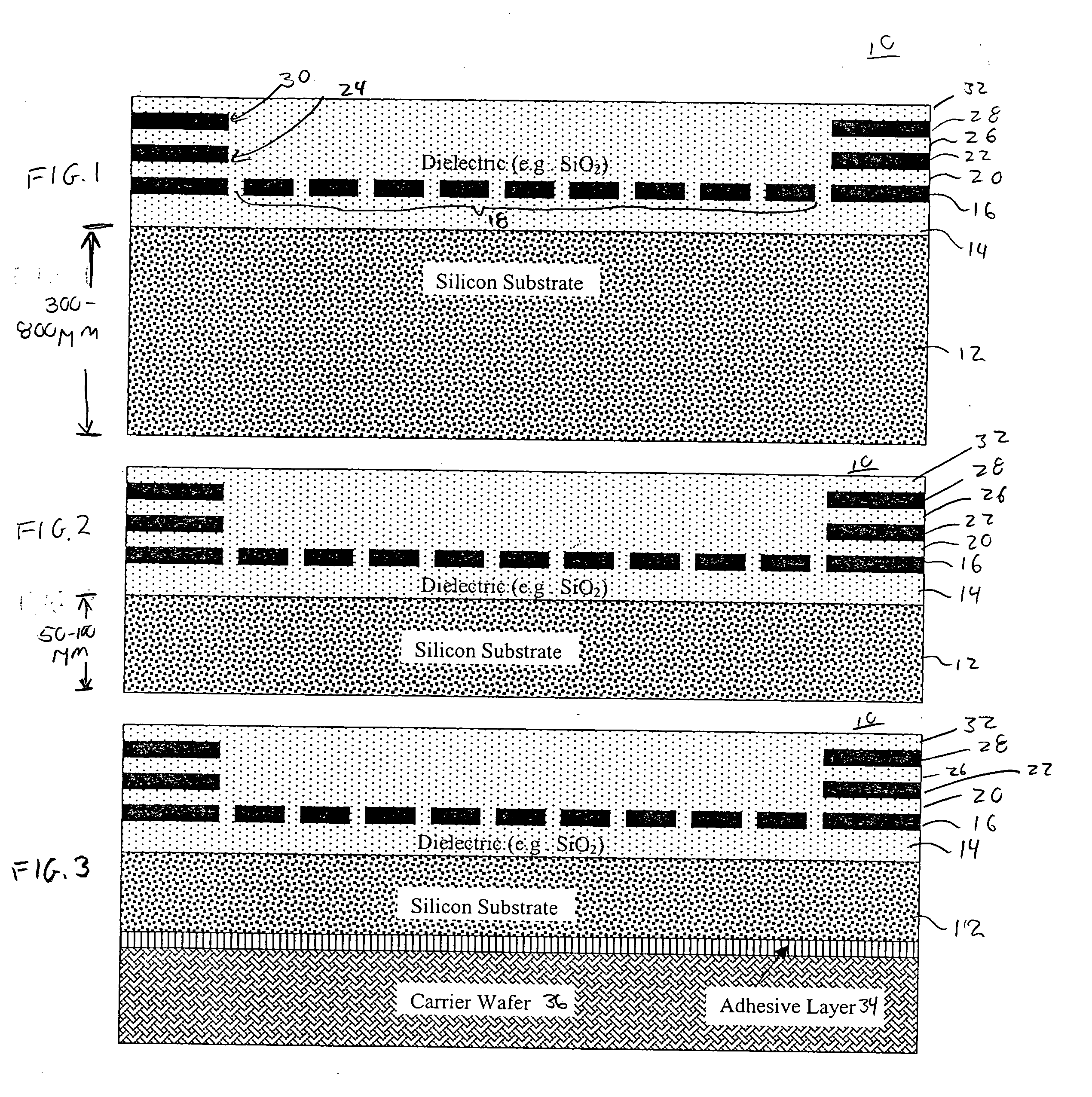

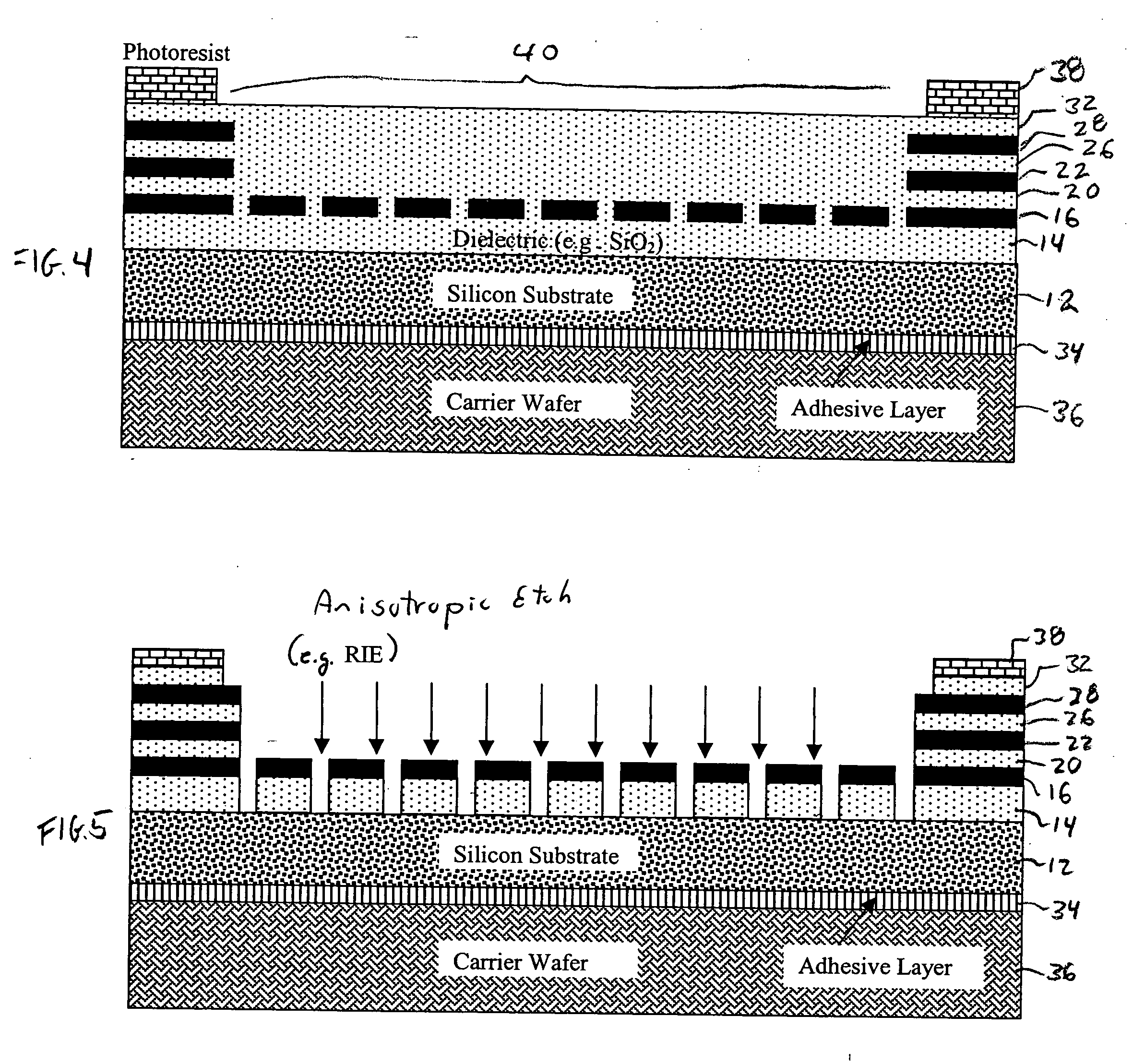

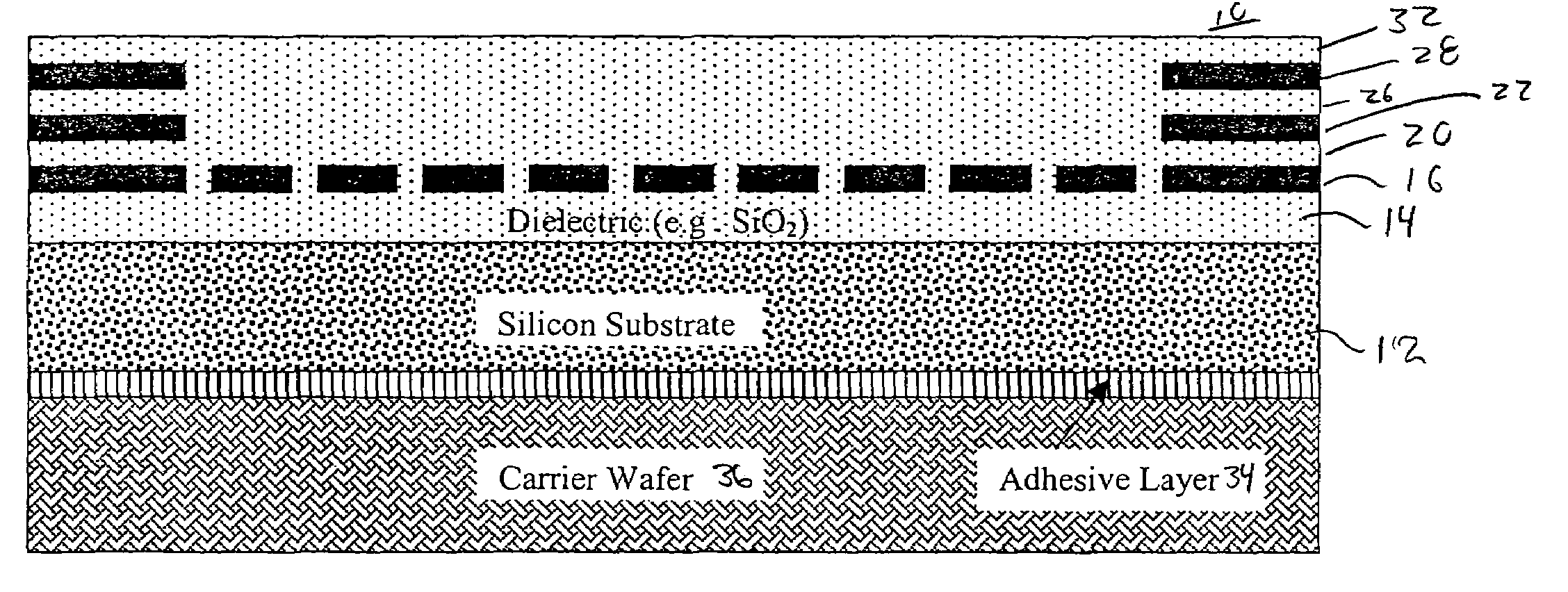

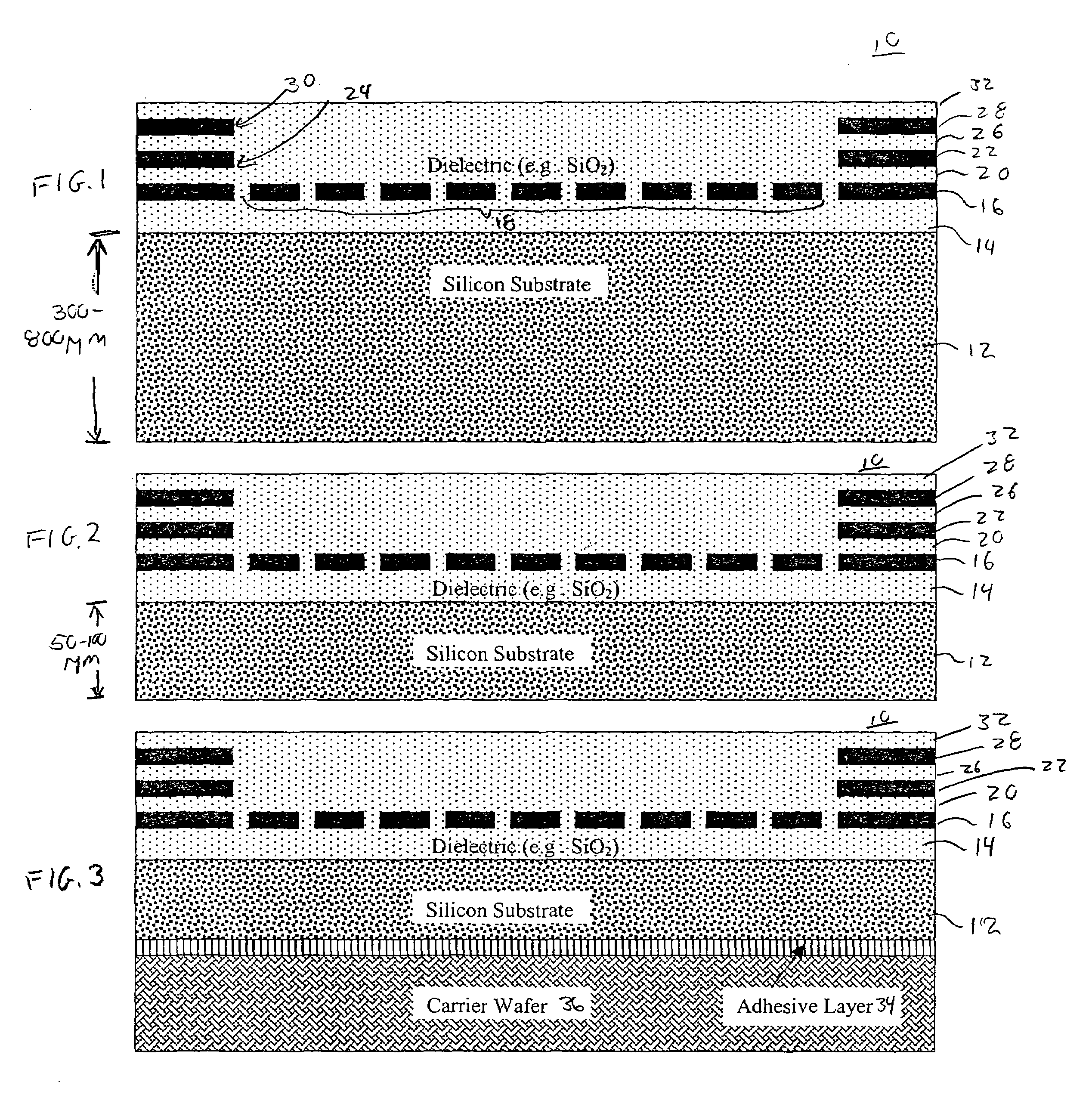

Ultrathin form factor MEMS microphones and microspeakers

ActiveUS20050095813A1Reduce thicknessSemiconductor electrostatic transducersSemiconductor/solid-state device manufacturingThinningLoudspeaker

A process comprises reducing the thickness of a substrate carrying a plurality of devices, with at least certain of the devices having a micro-machined mesh. A carrier wafer is attached to the back side of the substrate and the fabrication of the devices is completed from the top side of the substrate. Thereafter the plurality of devices is singulated. Various alternative embodiments are disclosed which demonstrate that the thinning of the wafer may occur at different times during the process of fabricating the MEMS devices such as before the mesh is formed or after the mesh is formed. Additionally, the use of carrier wafers to support the thinned wafer enables process steps to be carried out on the side opposite from the side having the carrier wafer. The various alternative embodiments demonstrate that the side carrying the carrier wafer can be varied throughout the process.

Owner:AKUSTICA

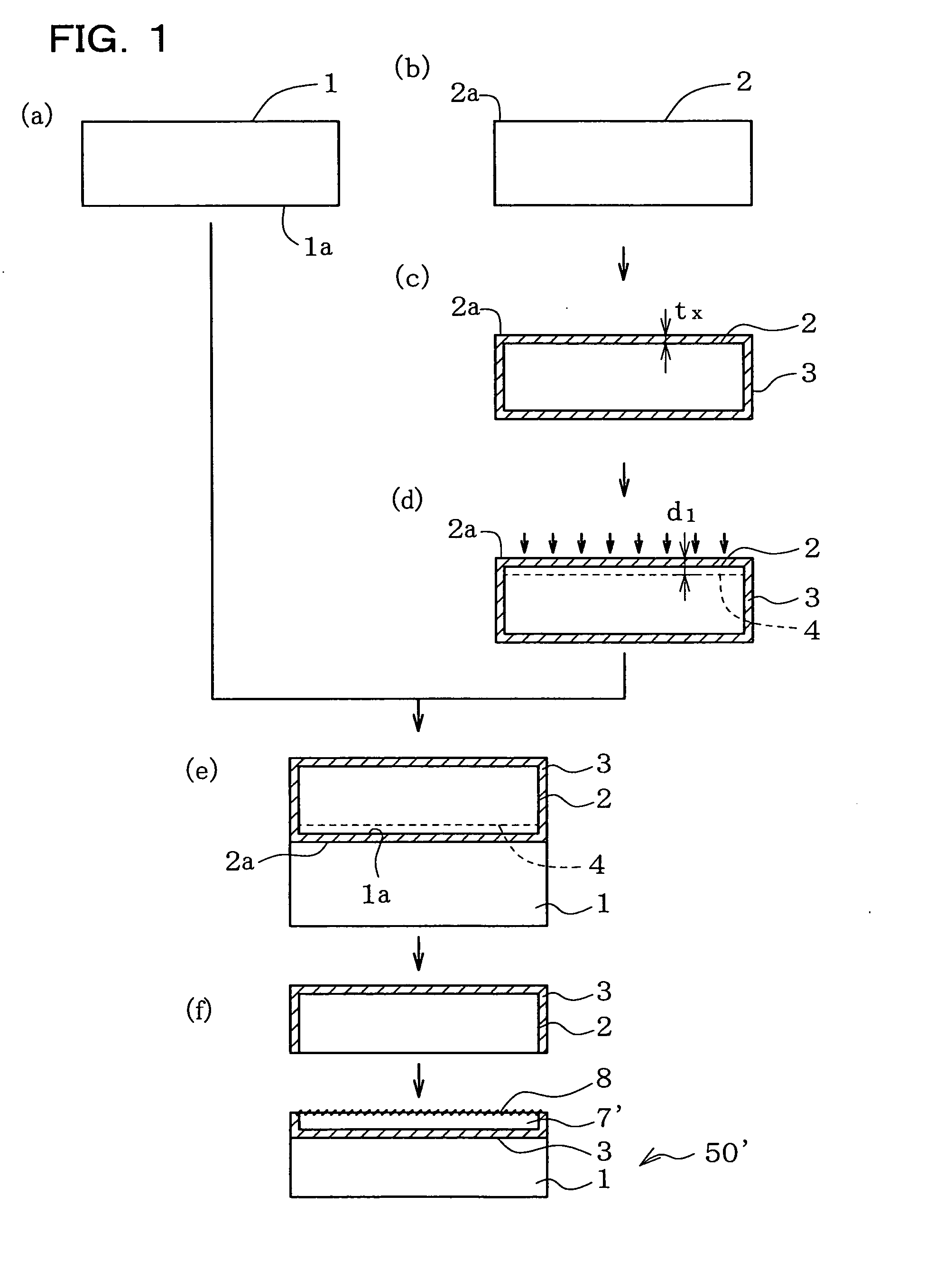

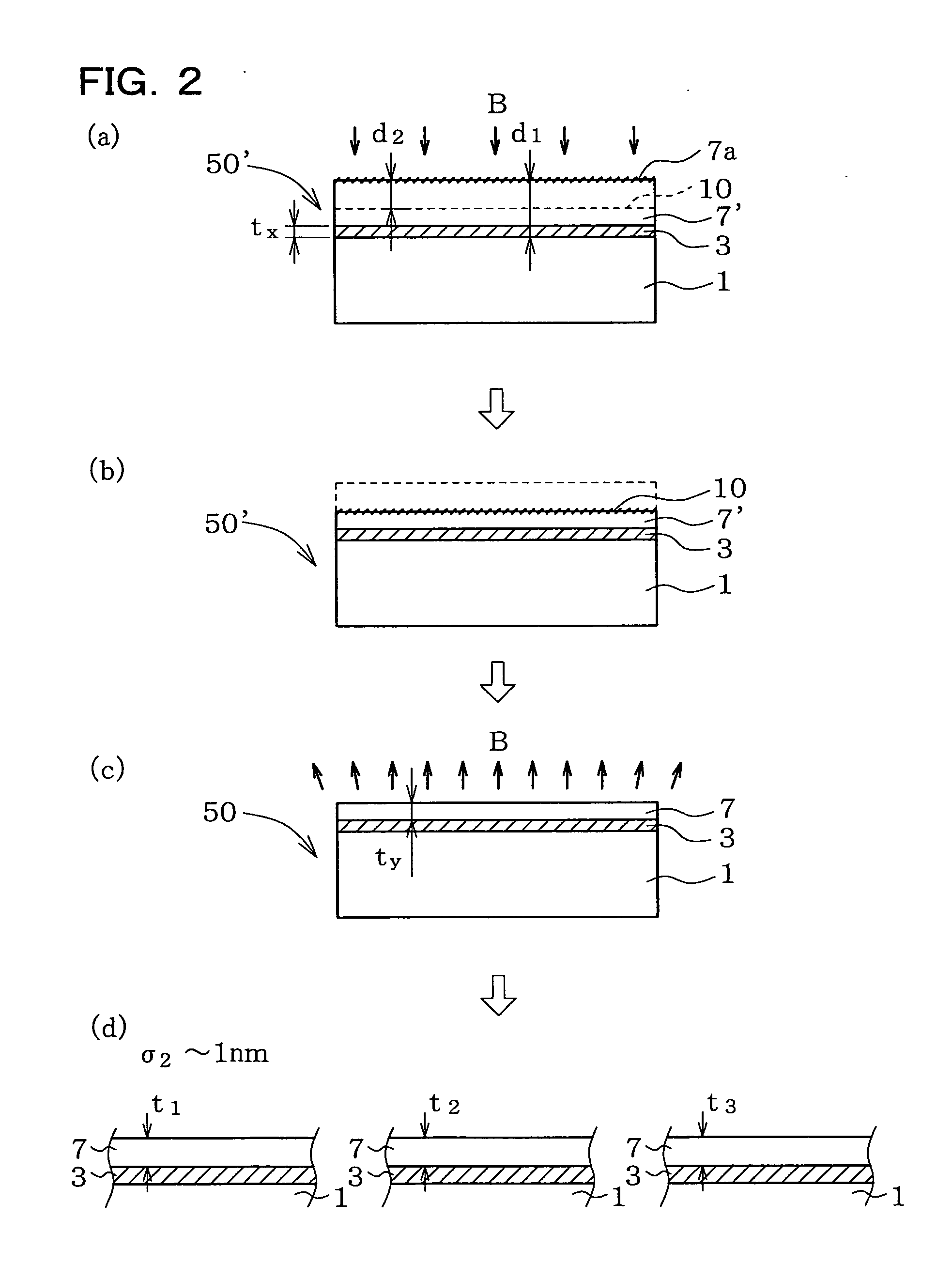

Production method for soi wafer

InactiveUS20050014346A1Improving film thickness distributionReduce surface defectsSolid-state devicesSemiconductor/solid-state device manufacturingEtchingThinning

After completion of annealing for bonding of the base wafer 1 and bond wafer 2, the bond wafer 2 is thinned to a first thickness suitable for ion implantation, and boron is ion-implanted to thereby form a high-boron-concentration layer 10. A second thinning step based on selective etching is then carried out while using the high-boron-concentration layer 10 as an etch stop layer. This is successful in providing a method of fabricating an SOI wafer which is suppressed both in intra-wafer uniformity of the firm thickness and in inter-wafer uniformity of the film thickness even when a required level for the thickness of the SOI layer is extremely small.

Owner:SHIN-ETSU HANDOTAI CO LTD

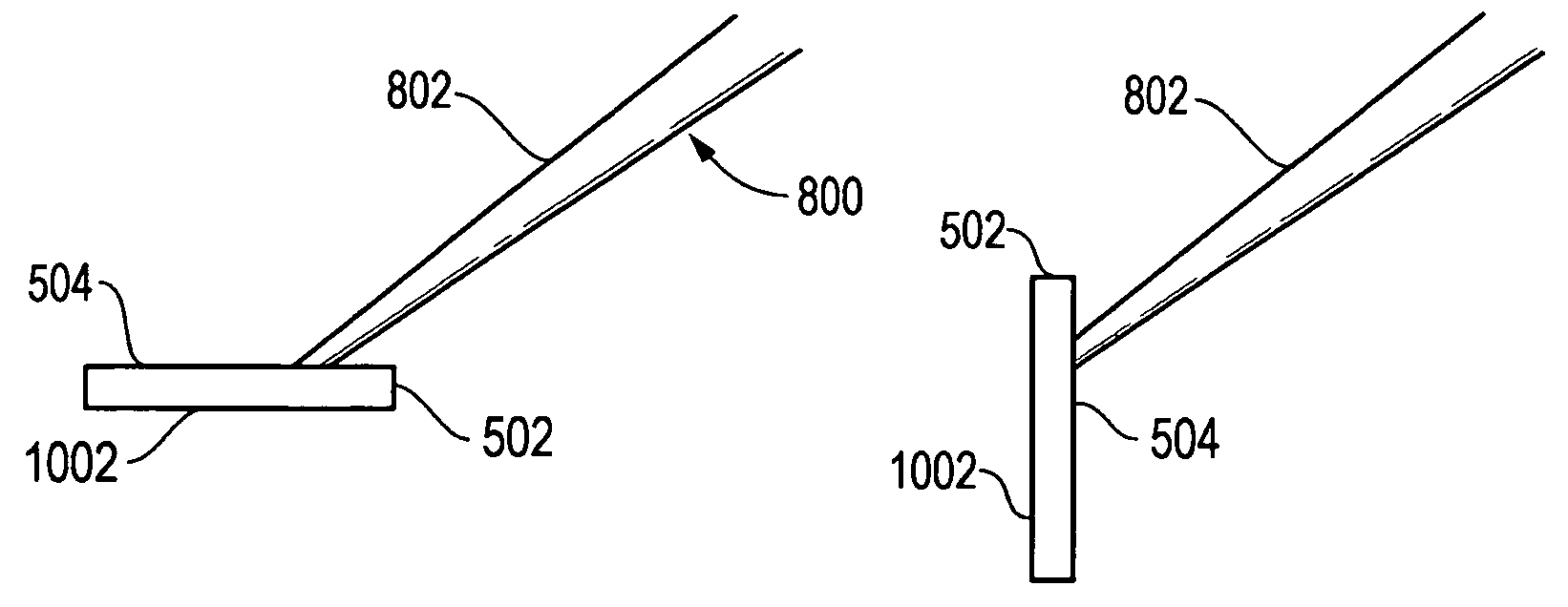

Planar view sample preparation

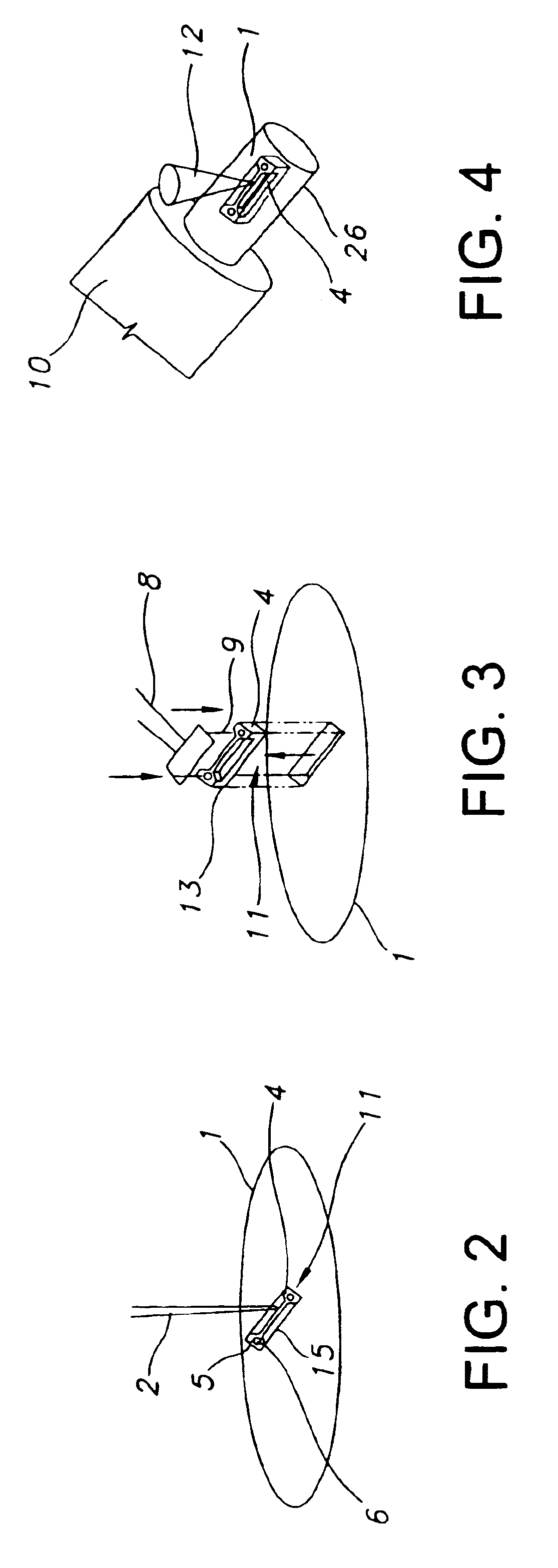

ActiveUS7423263B2Easy to changeFacilitate subjectingMaterial analysis using wave/particle radiationElectric discharge tubesIon beamThinning

A method and apparatus is described for orienting samples for charged particle beam operations. A sample is attached to a probe with a major surface of the sample at a non-normal angle to the probe shaft, and the probe shaft is rotated to reorient the sample. The invention is particularly useful for preparing planar view TEM samples. The invention allows for a sample to be mounted to a TEM grid and thinning by an ion beam without removing the grid from the vacuum chamber for reorienting. In one embodiment, a probe oriented at an angle, such as 45 degrees, to the sample stage has a probe tip with a flat area oriented parallel at 45 degrees to the probe axis, that is, the flat area is parallel to the sample stage. The flat area of the probe tip is attached to the sample, and when the probe is rotated 180 degrees, the orientation of the sample changes by 90 degrees, from horizontal to vertical. The sample can then be attached to a vertically oriented TEM grid on a sample stage. The sample stage is rotated and tilted to present the backside of the sample to the ion beam for thinning.

Owner:FEI CO

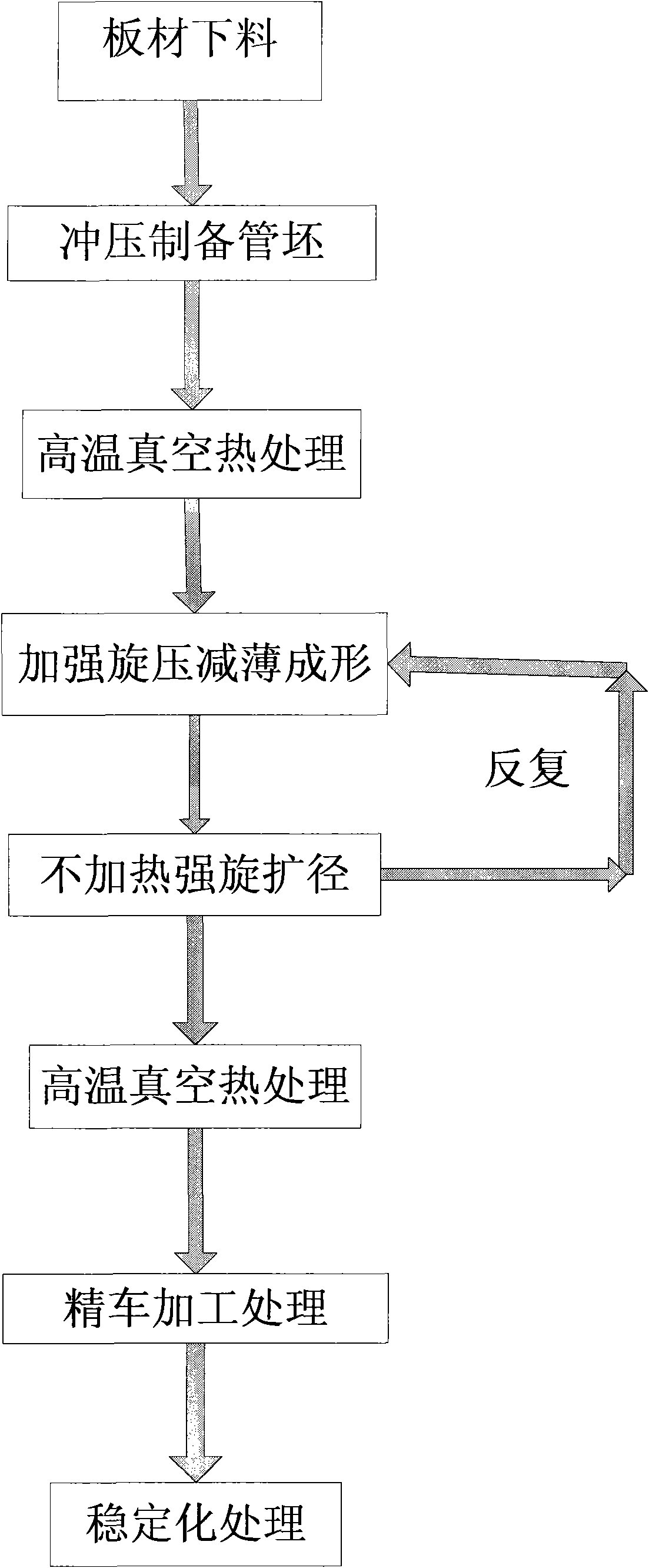

Integral forming method of large size thin-walled titanium alloy cylindrical part without welding line

ActiveCN101579804ASolve UtilizationSolving with longitudinal weldsFurnace typesHeat treatment furnacesThinningLarge size

The invention provides an integral forming method of a large size thin-walled titanium alloy cylindrical part without a welding line. The integral forming method comprises the following steps of: (1) tube blank preparation by stamping; (2) high-temperature vacuum heat treatment; (3) heating power spinning thinning; (4) unheating power spinning diameter expanding; (5) repetitive and alternate conduction of steps (3) and (4) for 2-3 times; (6) high-temperature vacuum heat treatment; (7) finish turning treatment; and (8) stabilizing treatment. The integral forming method prepares the large size thin-walled titanium alloy cylindrical part without the welding line (wall thickness is 1-7mm) which has high precision and high performance by utilizing titanium alloy plates and adopting a composite technique combining a stamping method, a spinning method and a stabilizing treatment method, and solves the problems of low material utilization ratio, having longitudinal welding lines, low precision of tube performance and the like in the forging and roll bending welding forming of the large size titanium alloy thin-walled tubes.

Owner:AEROSPACE RES INST OF MATERIAL & PROCESSING TECH

Method of etching high aspect ratio openings

InactiveUS20020179570A1High aspect ratioIncrease the wall areaDecorative surface effectsSemiconductor/solid-state device manufacturingSilanesThinning

A method of etching a deep, high aspect ratio opening in a silicon substrate includes etching the substrate with a first plasma formed using a first gaseous mixture including a bromine containing gas, an oxygen containing gas and a first fluorine containing gas. The etching process with the first gaseous mixture produces a sidewall passivating deposit, which builds up near the opening entrance. To reduce this buildup, and to increase the average etching rate, the sidewall passivating deposit is periodically thinned by forming a second plasma using a mixture containing silane and a second fluorine containing gas. The substrate remains in the same plasma reactor chamber during the entire process and the plasma is continuously maintained during the thinning step. Holes of a depth greater than 40 times the width may be produced using repeated cycles of etching and thinning.

Owner:INFINEON TECH AG +1

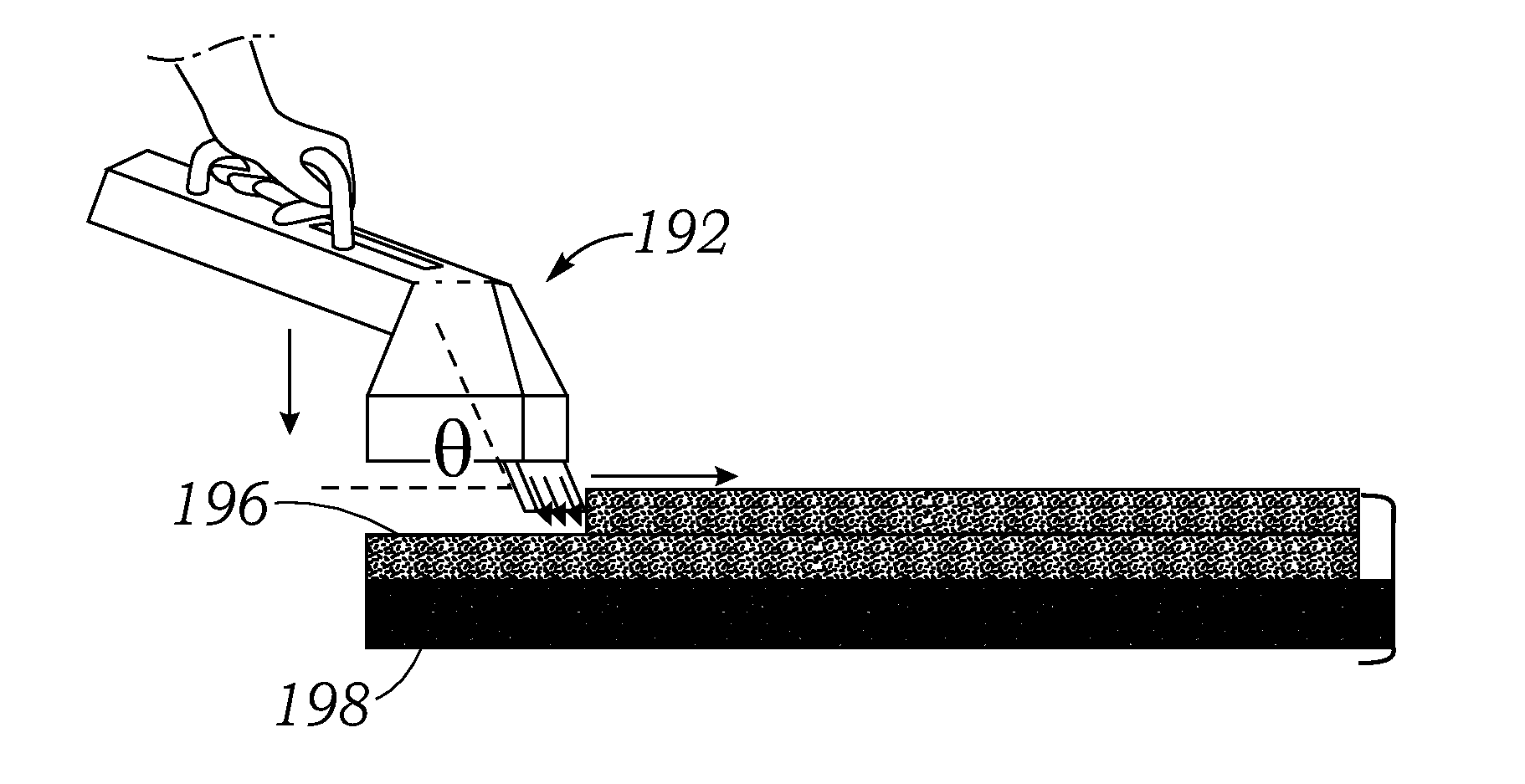

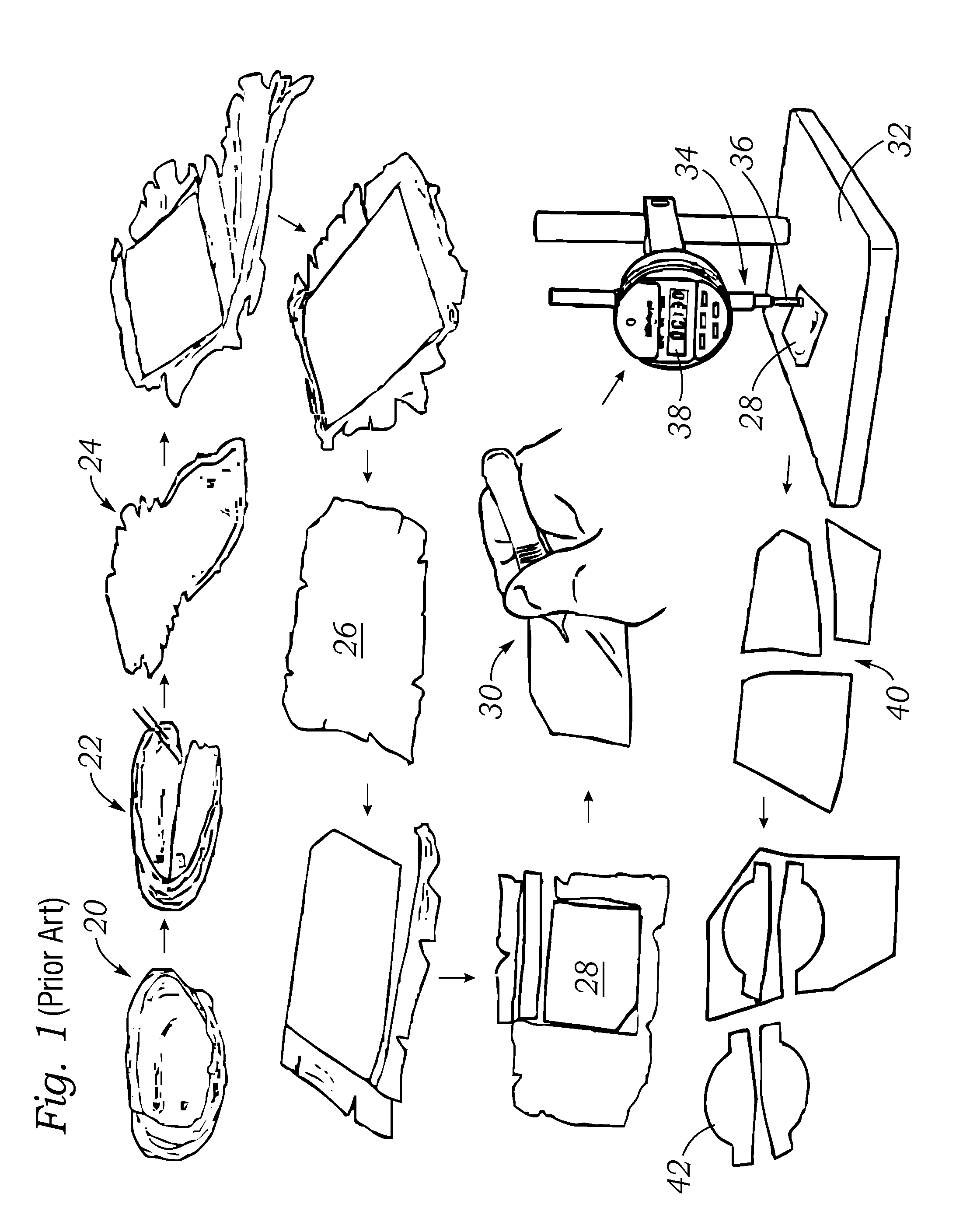

Methods of conditioning sheet bioprosthetic tissue

Methods for the conditioning of bioprosthetic material employ bovine pericardial membrane. A laser directed at the fibrous surface of the membrane and moved relative thereto reduces the thickness of the membrane to a specific uniform thickness and smoothes the surface. The wavelength, power and pulse rate of the laser are selected which will smooth the fibrous surface as well as ablate the surface to the appropriate thickness. Alternatively, a dermatome is used to remove a layer of material from the fibrous surface of the membrane. Thinning may also employ compression. Stepwise compression with cross-linking to stabilize the membrane is used to avoid damaging the membrane through inelastic compression. Rather, the membrane is bound in the elastic compressed state through addition cross-linking. The foregoing several thinning techniques may be employed together to achieve strong thin membranes. The finally thinned membrane may then be treated by capping of calcification nucleation sites and borohydride reduction. The leaflets may be formed to have more than one region of uniform thickness, such as a thicker peripheral sewing region.

Owner:EDWARDS LIFESCIENCES CORP

Methods and Systems for Treating Injured Cardiac Tissue

InactiveUS20070042016A1Simple processReduce riskInfusion syringesSurgical needlesAutologous plateletThinning

Methods and systems are disclosed for treating injury to cardiac tissue by delivering a composition which provides structural support to the cardiac tissue. The composition helps to prevent chamber remodeling by providing structural reinforcement of the tissue or structural reinforcement of the tissue combined with biological therapy. The structurally reinforcing composition can thicken the wall of a heart, or act to prevent further thinning and thereby provide resistance against further remodeling. A number of compositions are disclosed, including multi-component substances such as autologous platelet gel, and other substances. The compositions disclosed can contain additives to augment / enhance the desired effects of the injection.

Owner:MEDTRONIC VASCULAR INC

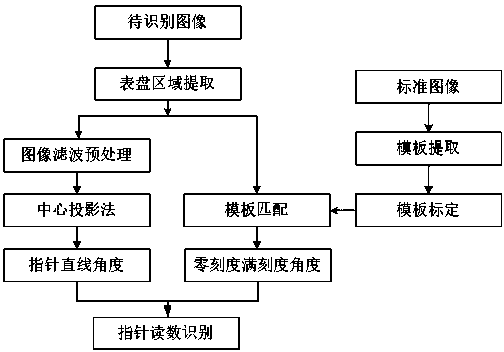

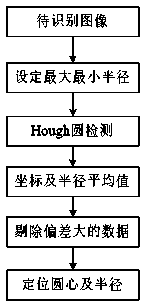

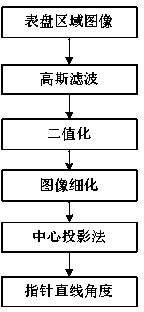

Image processing method for automatic pointer-type instrument reading recognition

ActiveCN104392206ASmall amount of calculationHigh positioning accuracyCharacter and pattern recognitionTemplate matchingImaging processing

The invention discloses an image processing method for automatic pointer-type instrument reading recognition. The method comprises the following steps: (1) Hough circle detection is carried out on the image, a weighted average method is used for positioning the circle center and the radius of a dial, and a dial region square image is extracted; (2) the image is pre-treated, and a binary thinning image of the instrument pointer is extracted; (3) a central projection method is used for determining a pointer angle; (4) a zero graduation line and full graduation line position templates are extracted, and a range starting point and ending point positions are calibrated; (5) by using template matching, zero graduation line and full graduation line angles are obtained; and (6) according to the pointer angle, the zero graduation line angle and the full graduation line angle, the pointer reading is obtained through calculation. Thus, the problem that the instrument dial position on the acquired image is not fixed as the relative position between a camera and the pointer-type instrument is not fixed can be solved, subjective errors as the reading of the instrument is read manually can be eliminated, the efficiency and the precision can be improved, safety of people is ensured, the application range is wide, and robustness is strong.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

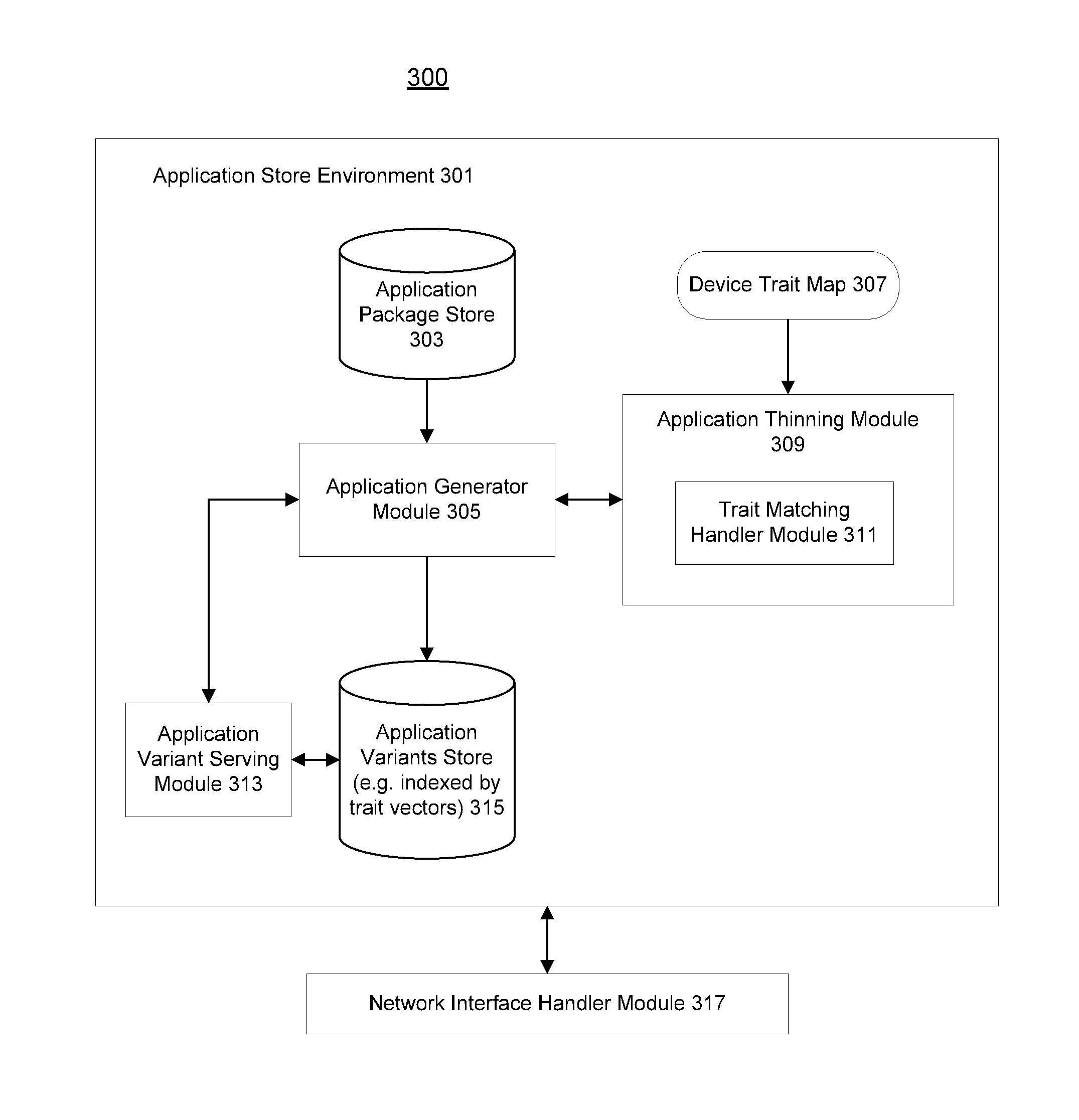

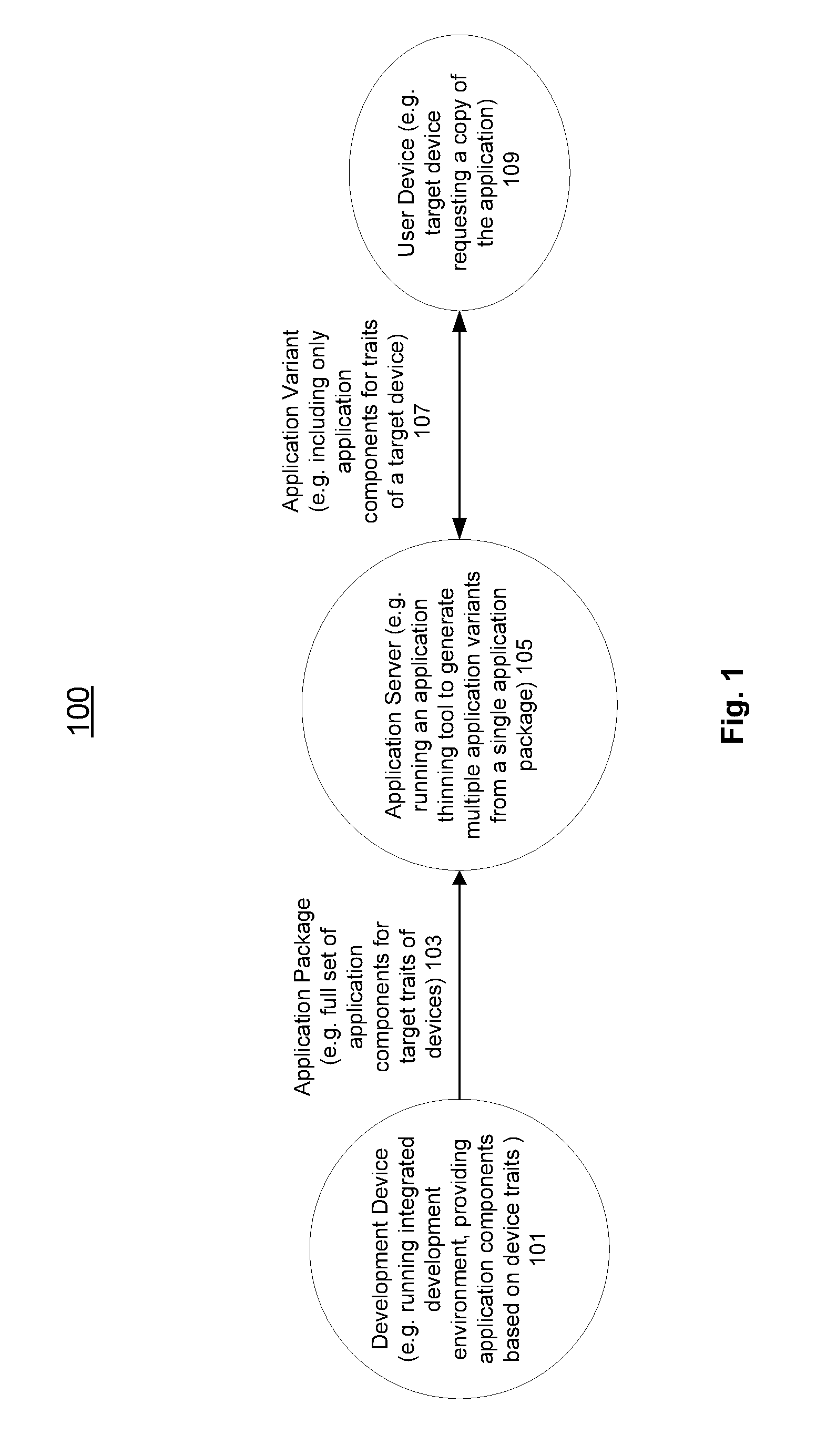

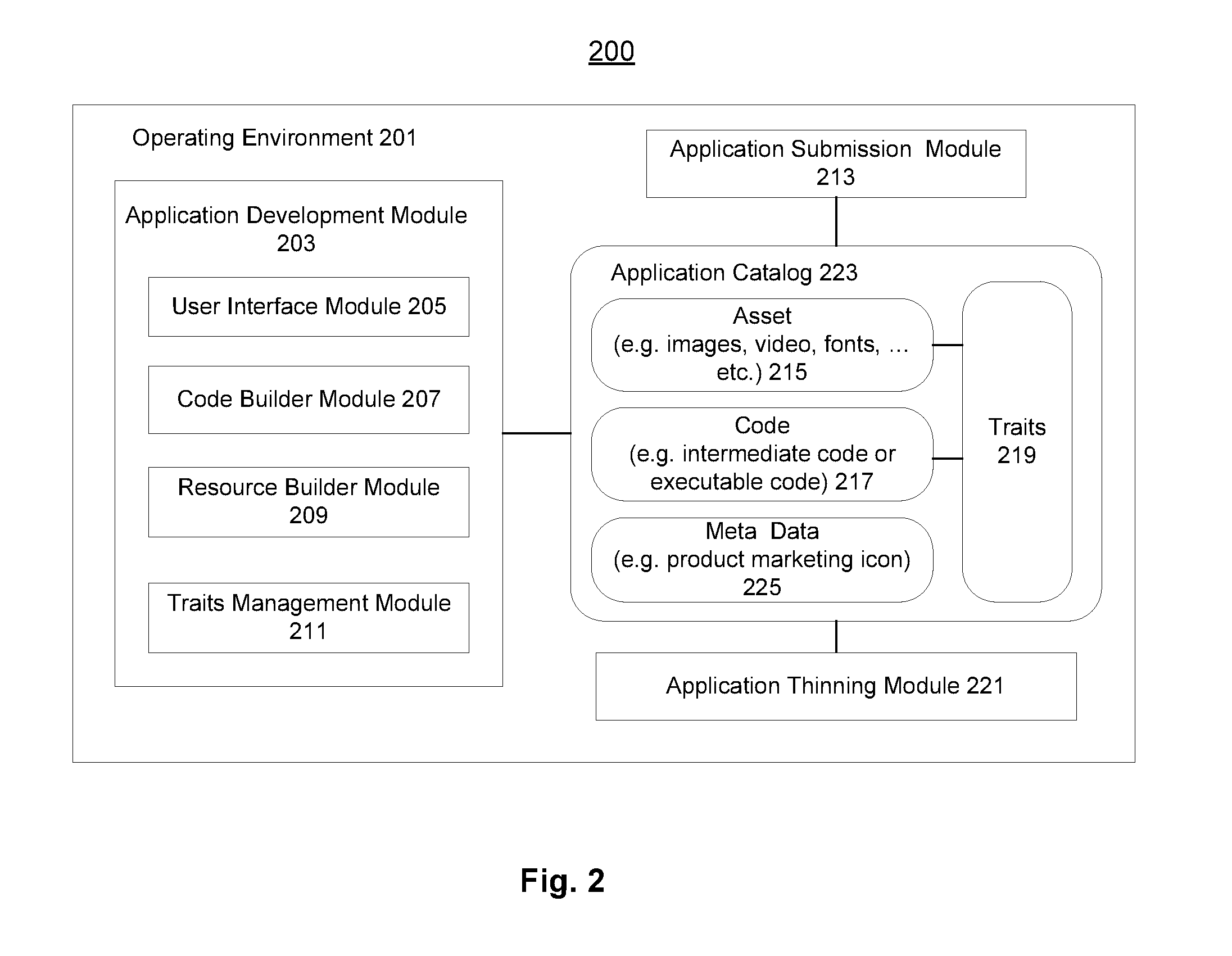

Capability attributes based application packaging

A method and an apparatus for an application thinning mechanism are described. The thinning mechanism can select a subset of components from a universal application to assemble an application variant to be distributed and installed to a specific type of devices. The universal application may include every component, such as asset, resource or executable, built / developed for targeted device attributes to install one common application to multiple devices. For example, the thinning mechanism can use a trait vector associated with a type of devices to iterate through the components and identify assets to be included or packaged into in each target device specific application or application variant.

Owner:APPLE INC

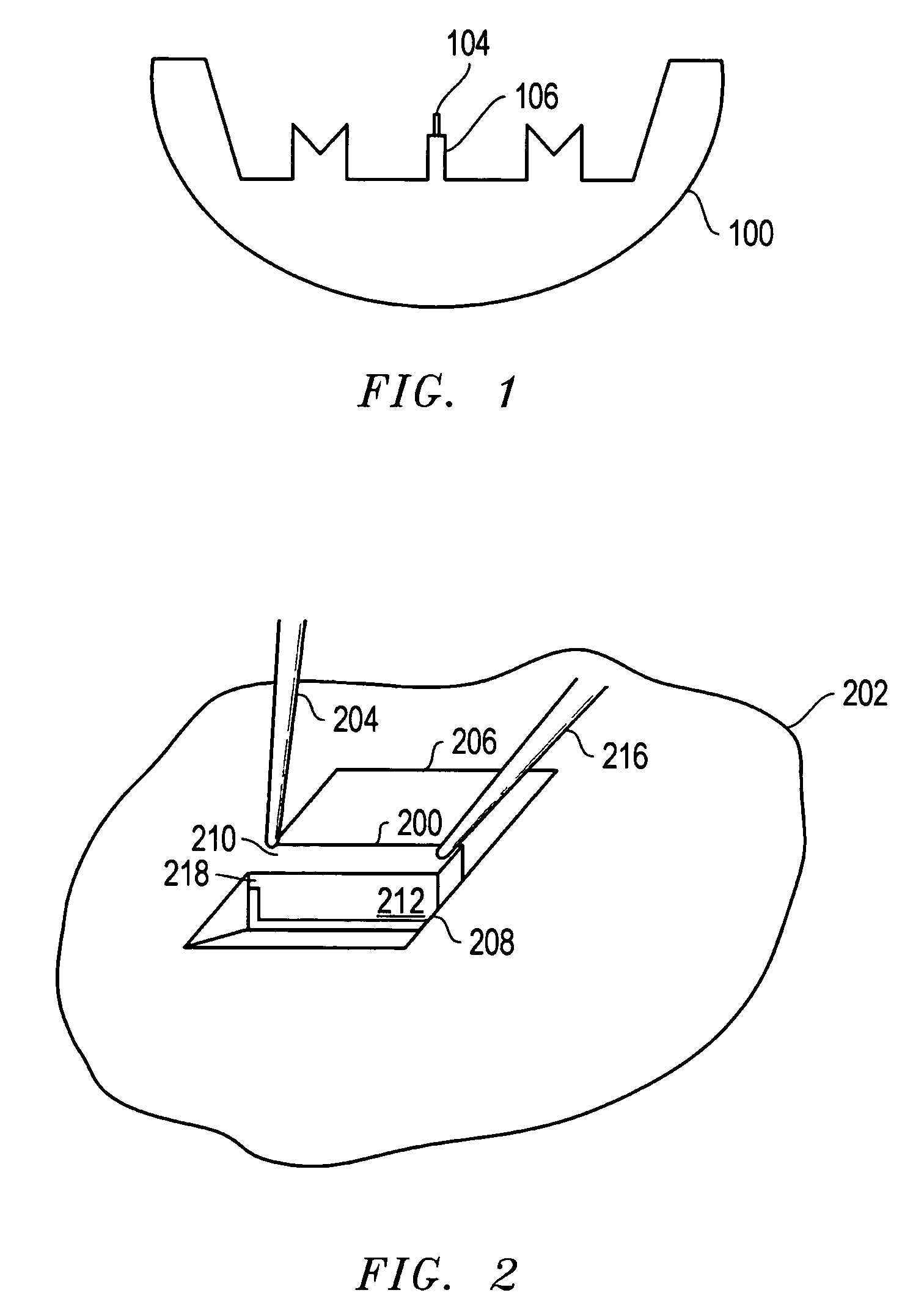

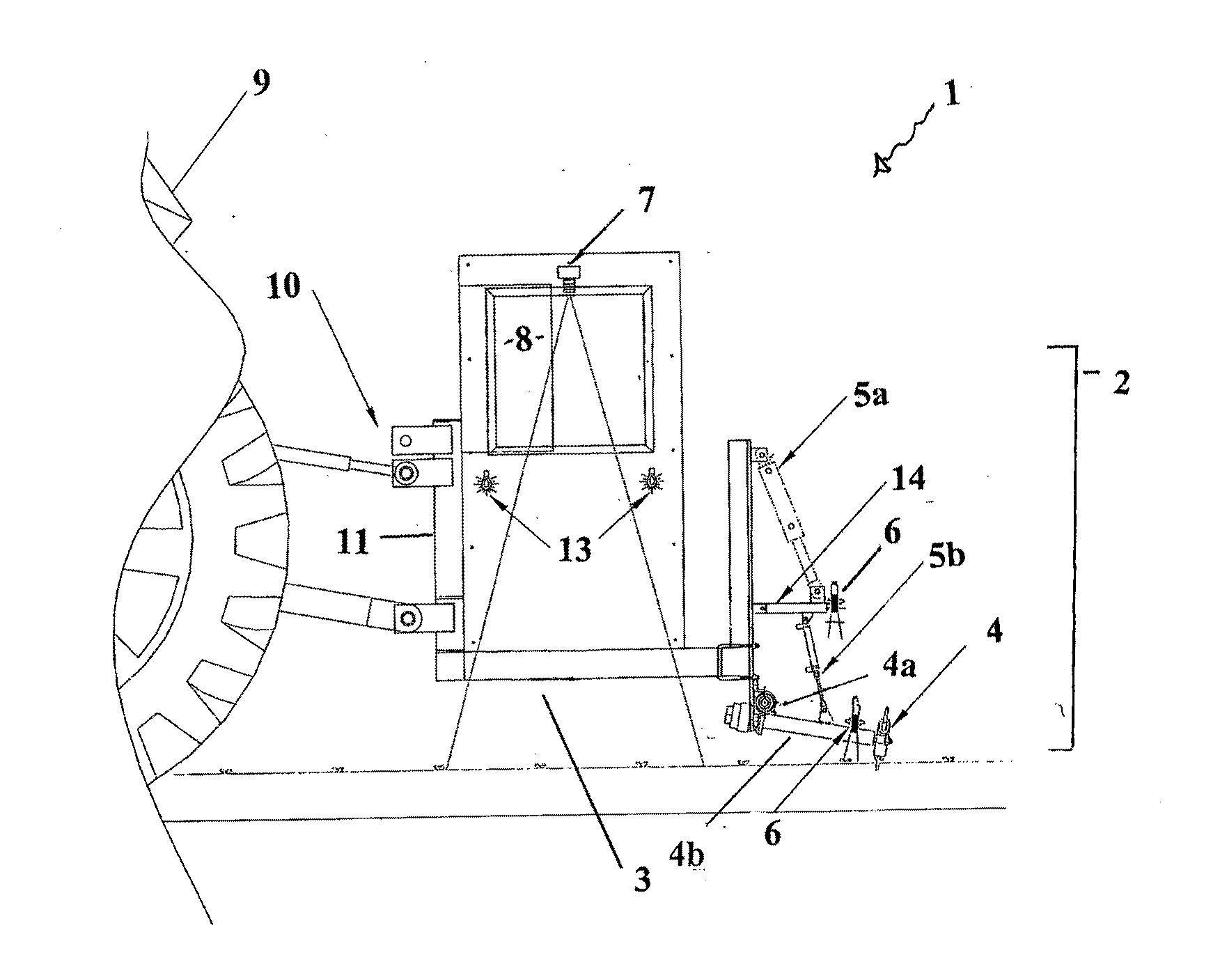

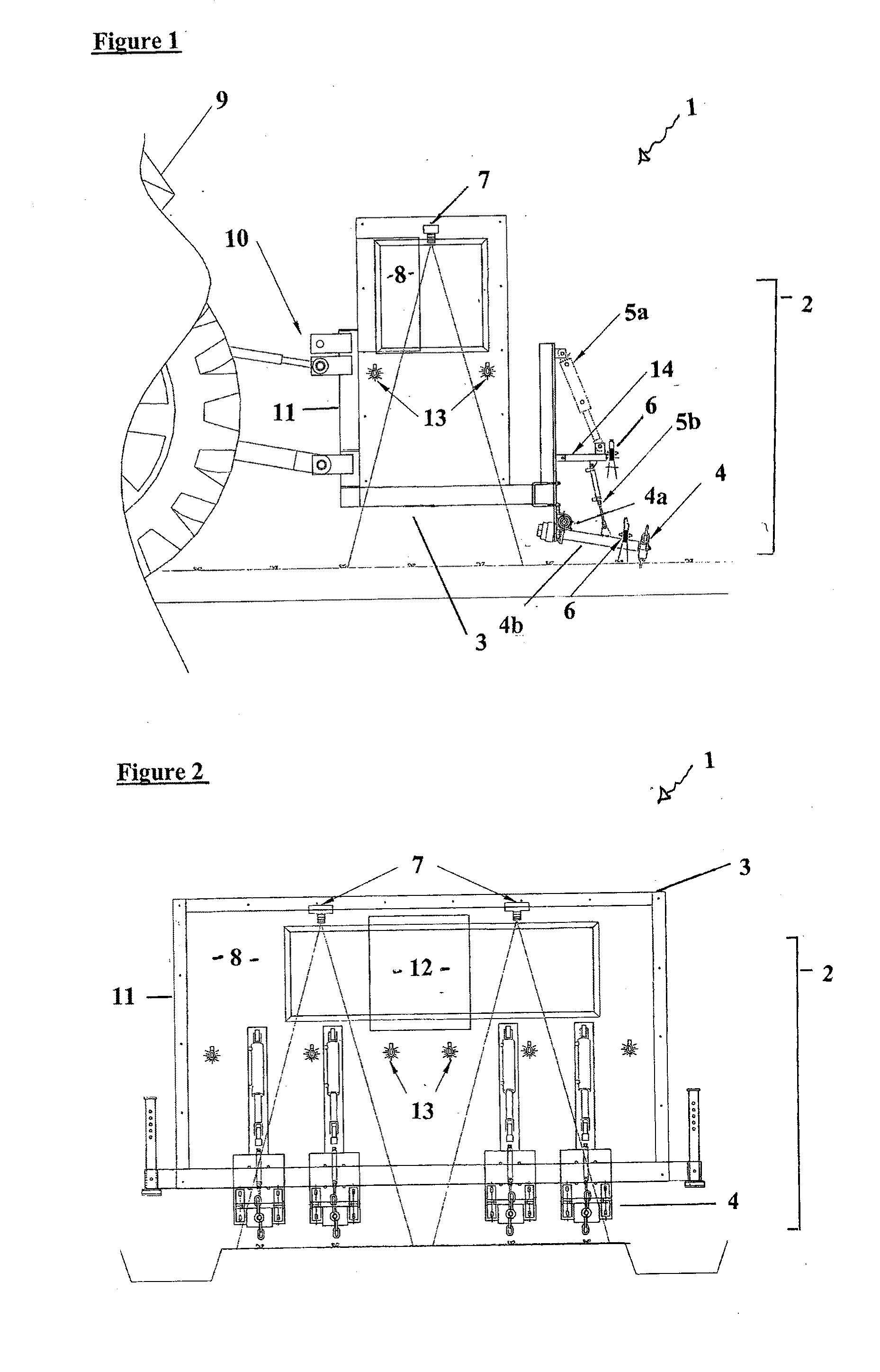

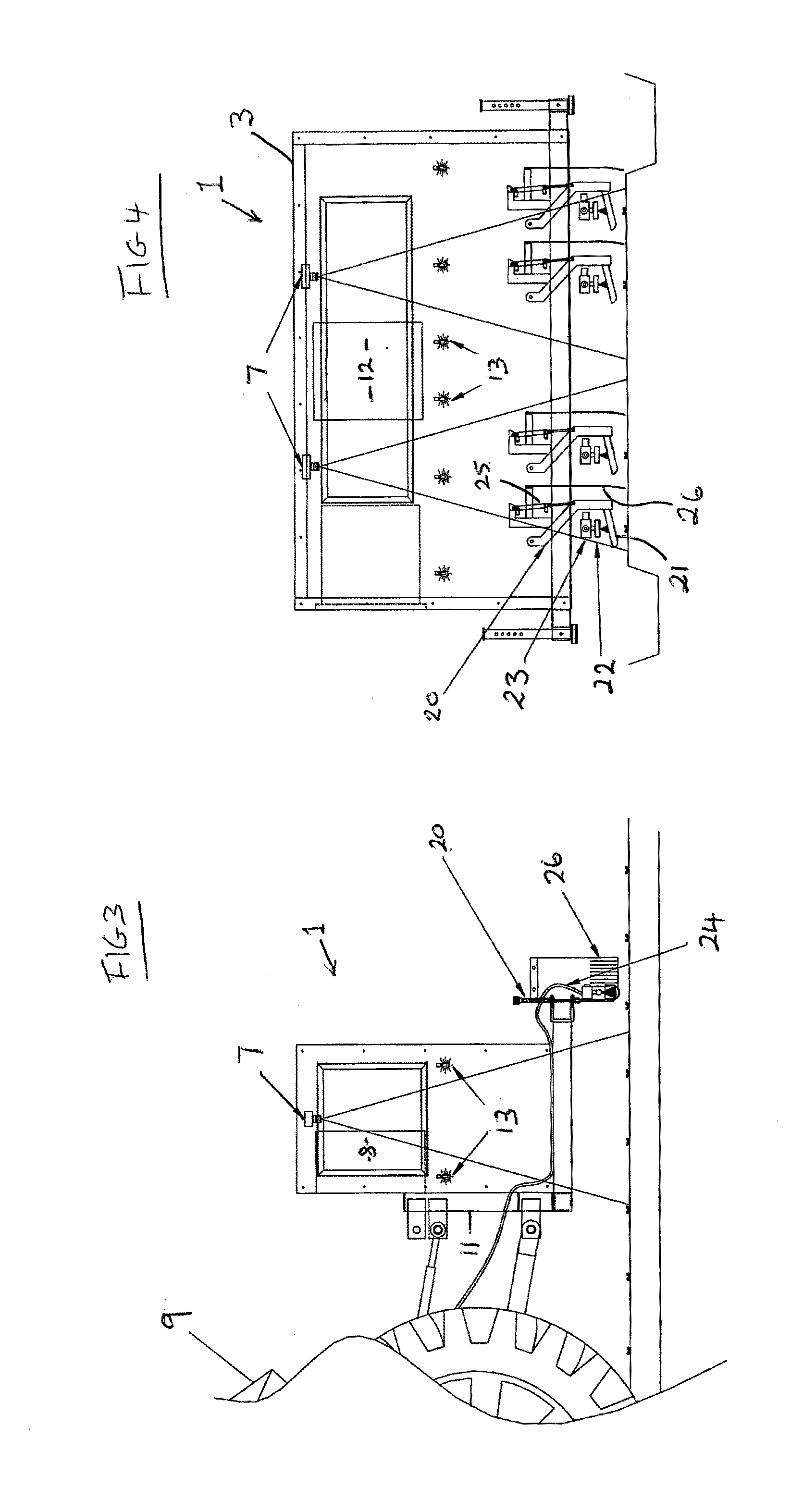

Crop thinning systems

InactiveUS20110211733A1Achieve the thinning or weeding of crops more economicallyImage enhancementImage analysisImaging processingThinning

A thinning or weeding apparatus includes an image processing apparatus. The image processing apparatus includes an automated visual detection system which includes a visual sensor system and an image processing system capable of receiving an image from the visual sensor system. The image processing apparatus then processes the image in the image processing system to determine where plants are located and to determine which plants will be thinned or weeded and which will not.

Owner:FOOTHILL PACKING

Ultrathin form factor MEMS microphones and microspeakers

InactiveUS6936524B2Semiconductor electrostatic transducersSemiconductor/solid-state device manufacturingThinningLoudspeaker

A process comprises reducing the thickness of a substrate carrying a plurality of devices, with at least certain of the devices having a micro-machined mesh. A carrier wafer is attached to the back side of the substrate and the fabrication of the devices is completed from the top side of the substrate. Thereafter the plurality of devices is singulated. Various alternative embodiments are disclosed which demonstrate that the thinning of the wafer may occur at different times during the process of fabricating the MEMS devices such as before the mesh is formed or after the mesh is formed. Additionally, the use of carrier wafers to support the thinned wafer enables process steps to be carried out on the side opposite from the side having the carrier wafer. The various alternative embodiments demonstrate that the side carrying the carrier wafer can be varied throughout the process.

Owner:AKUSTICA

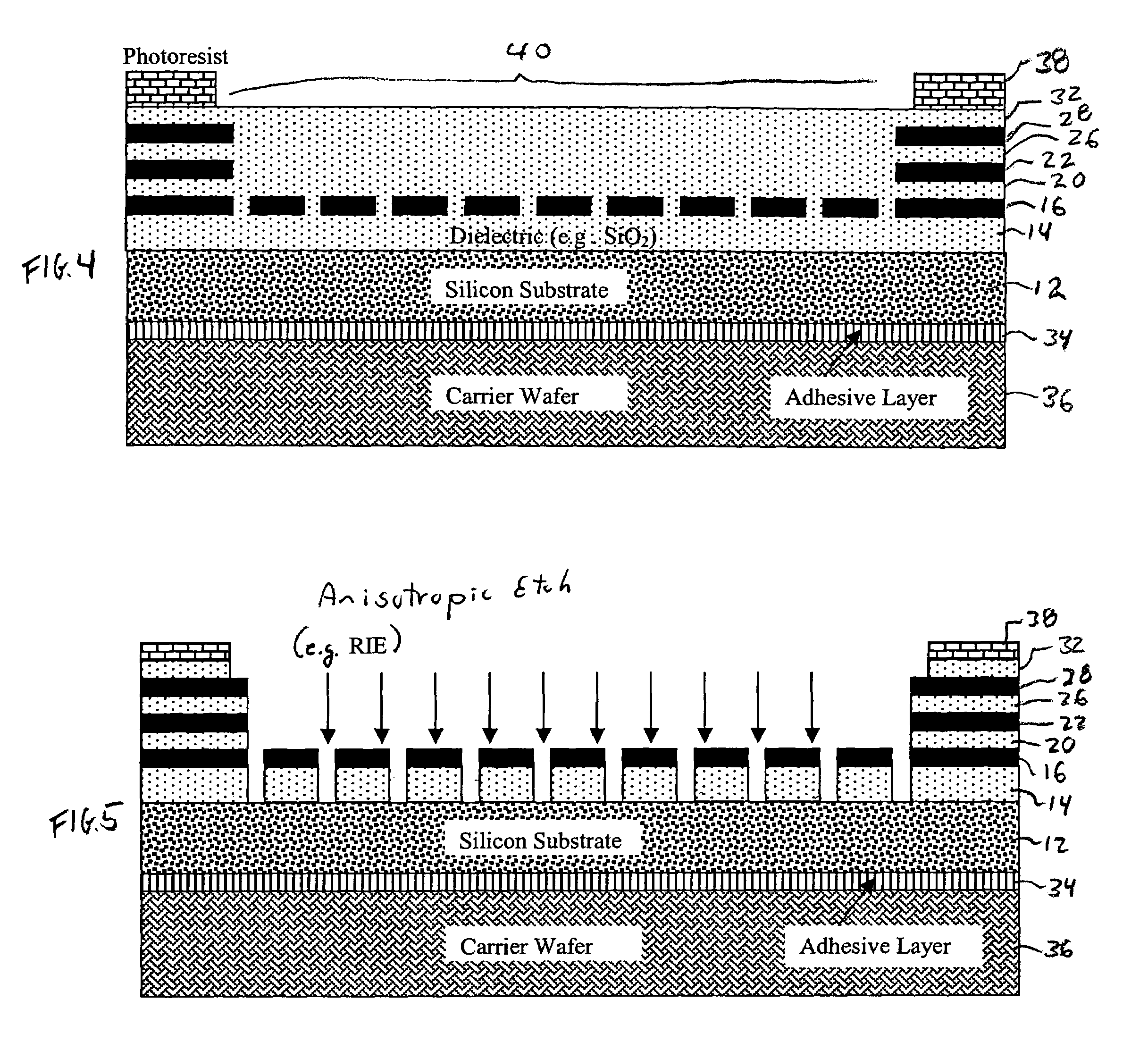

Transmission electron microscope sample preparation

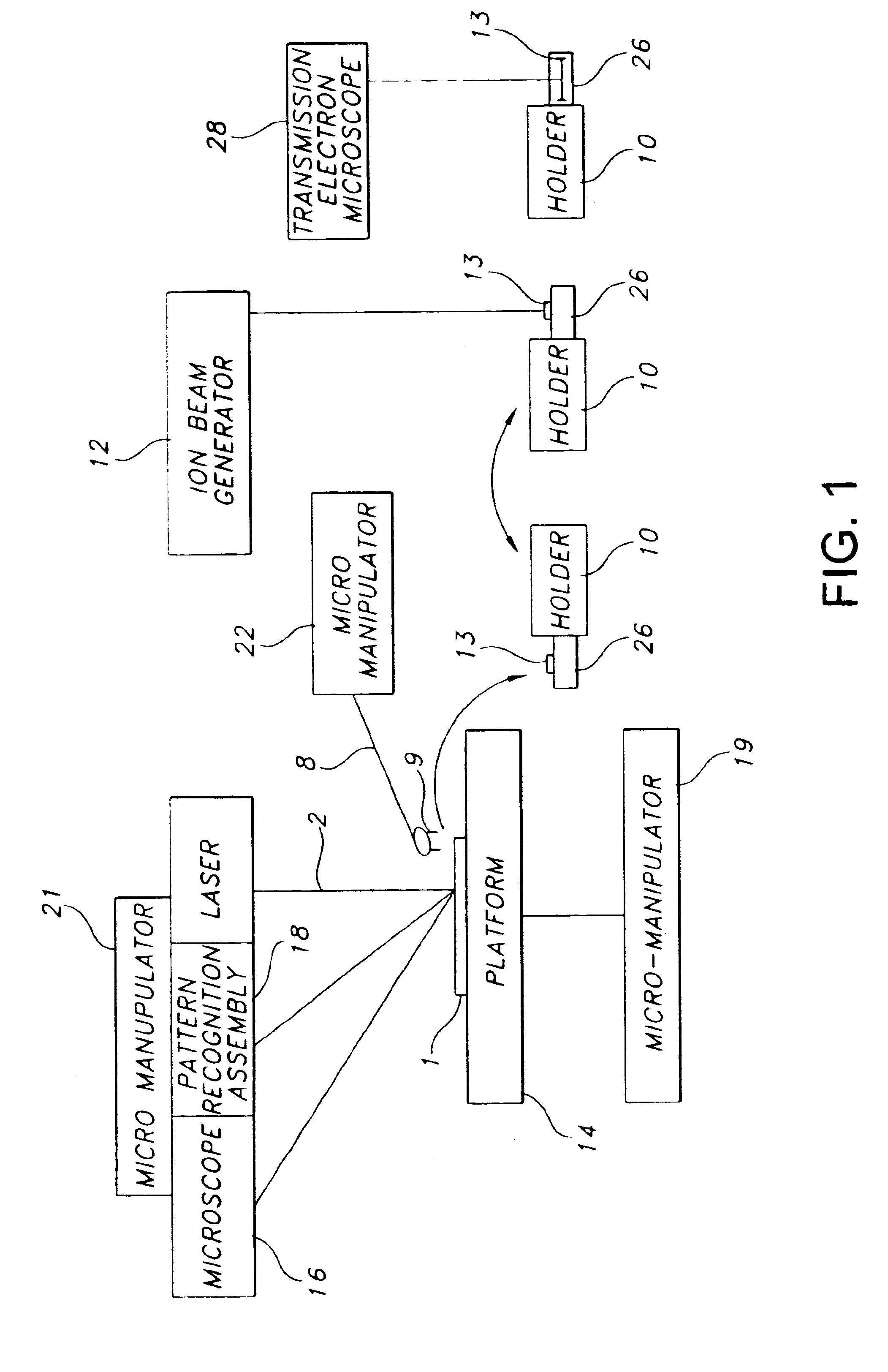

InactiveUS6841788B1Easy to useProvide protectionElectric discharge tubesPreparing sample for investigationElectron microscopeThinning

Sample preparation apparatus and method includes a wafer stage platform with an optical microscope and integrated pattern recognition to automatically address specific locations on the wafer sample of interest. A laser attaches to the optical microscope to mill a set pattern around the area of interest. A precision micro-manipulator engages the sample support structure, extracts the structure, and places the structure in a TEM holder or holder tip. The holder or holder tip can then be placed inside a FIB for final thinning, followed by direct transfer into the TEM.

Owner:OXFORD INSTR AMERICA

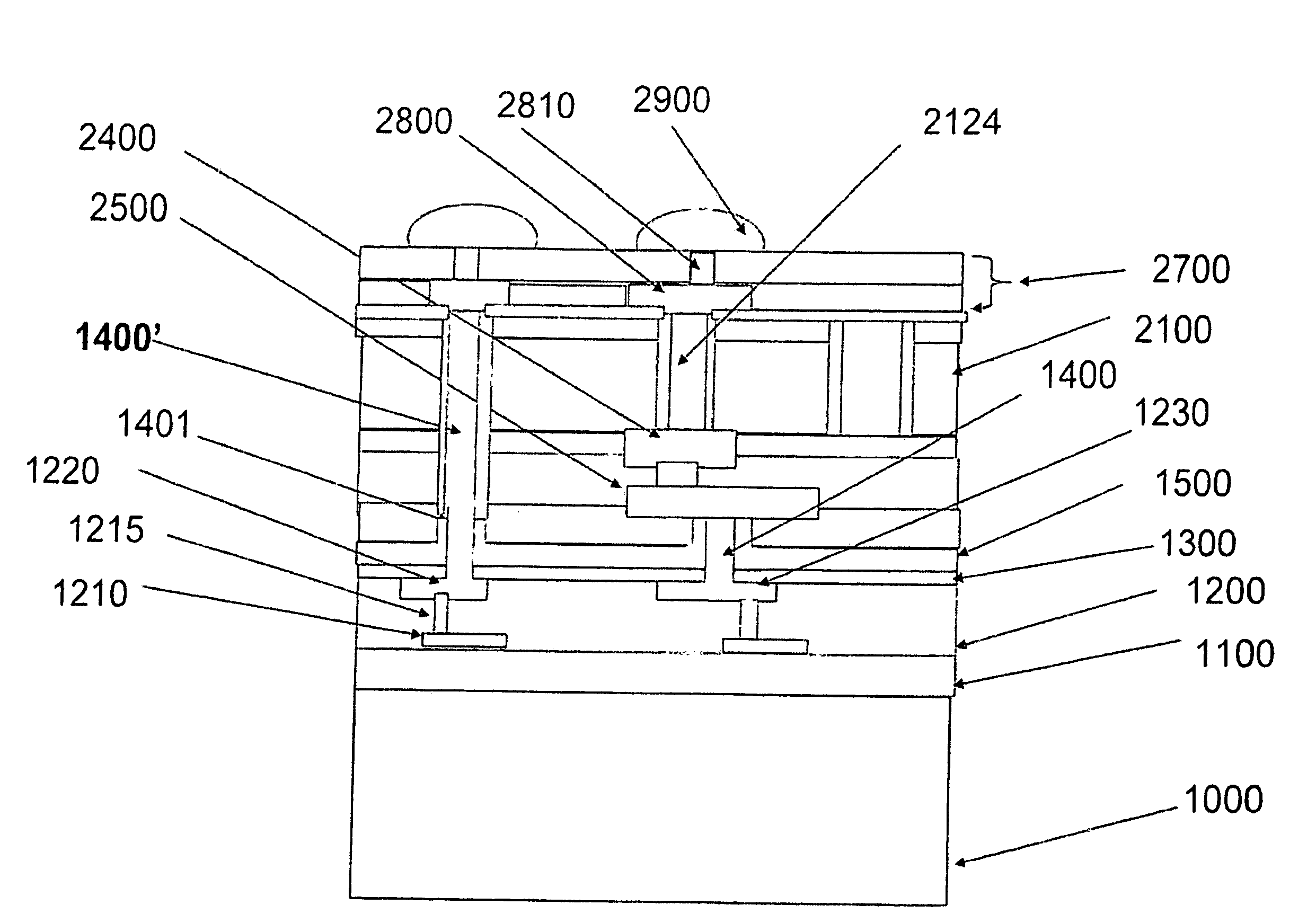

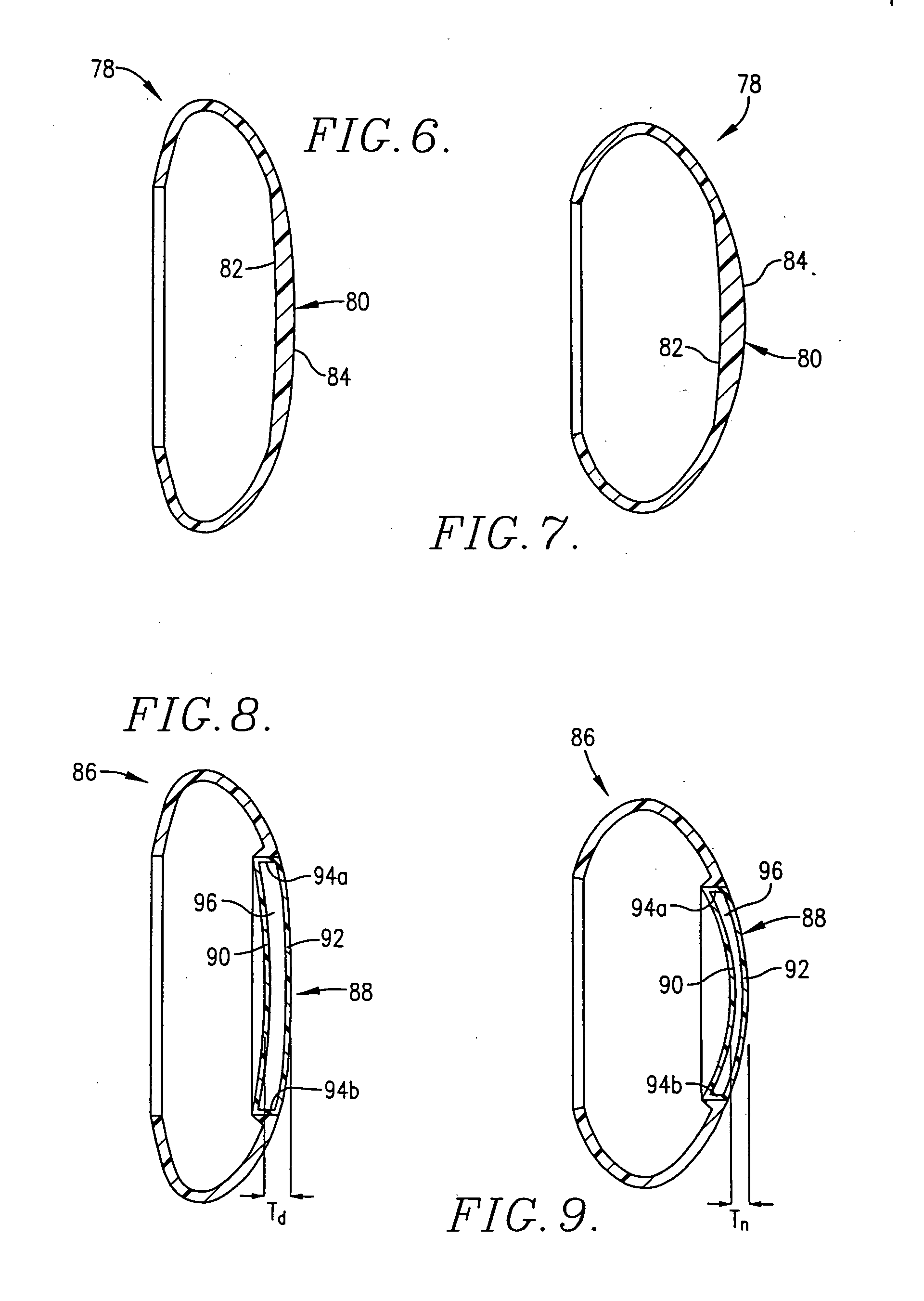

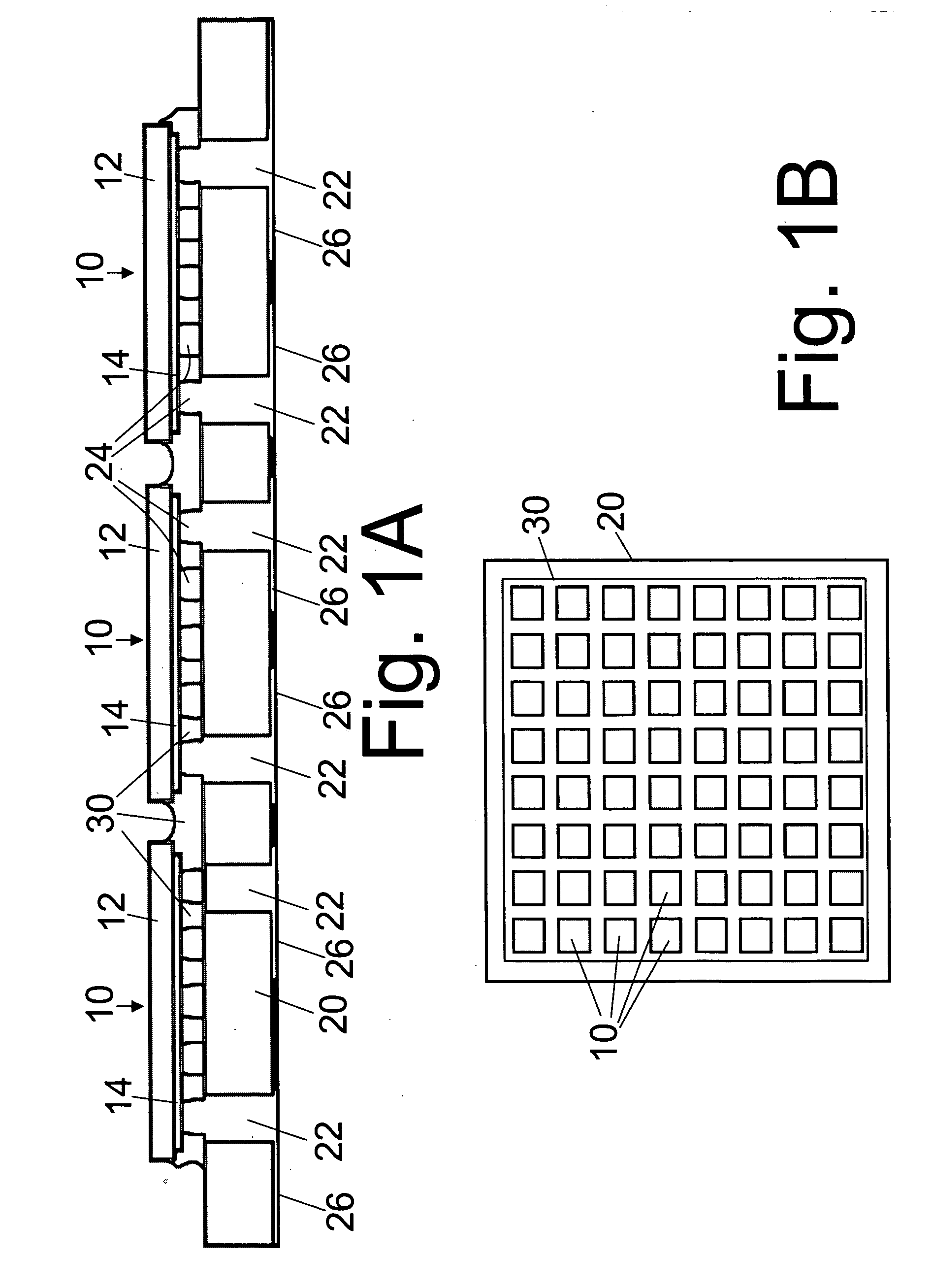

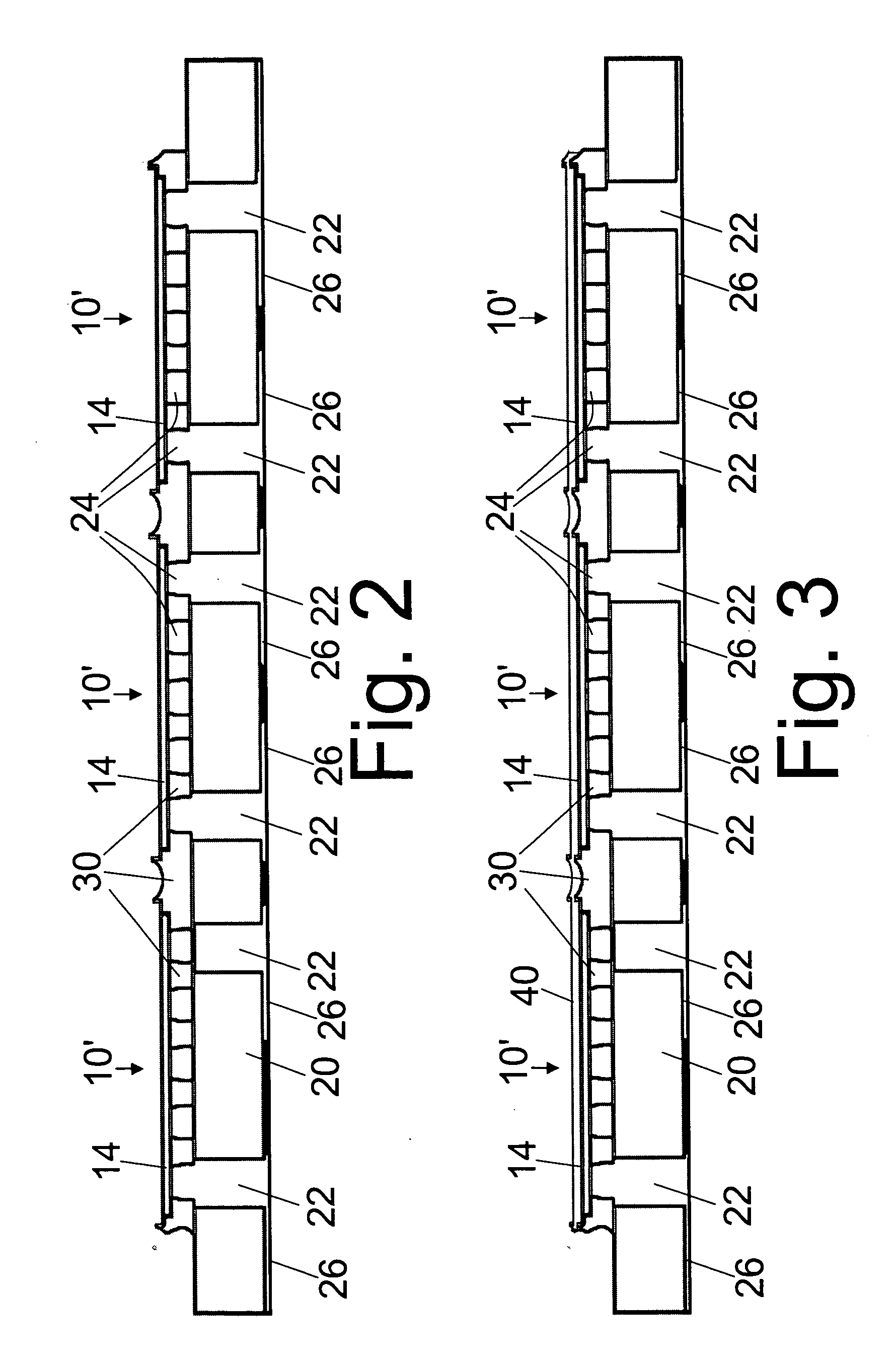

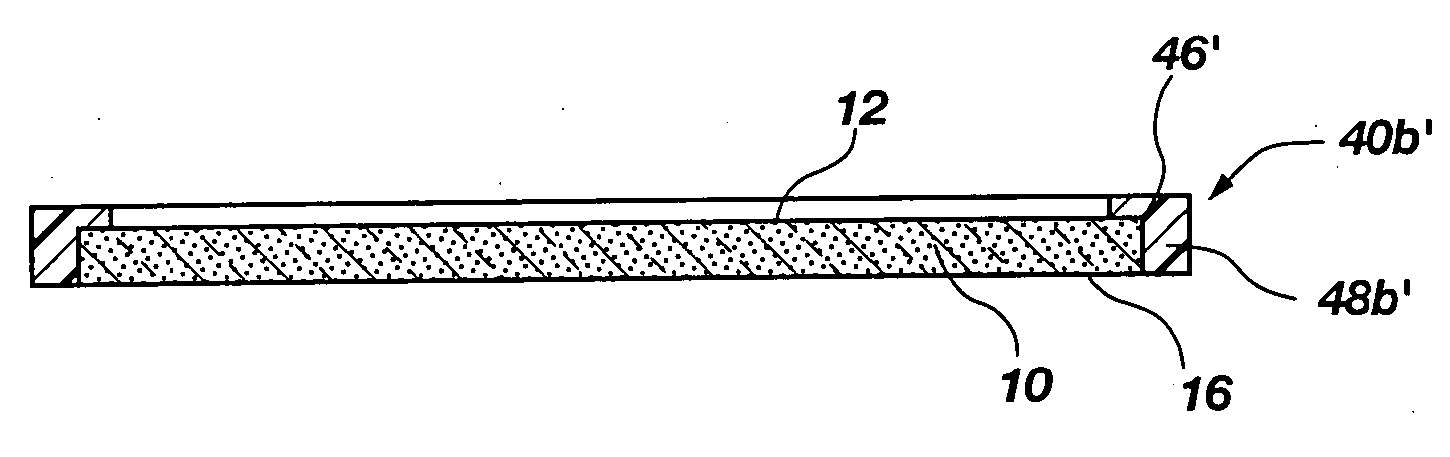

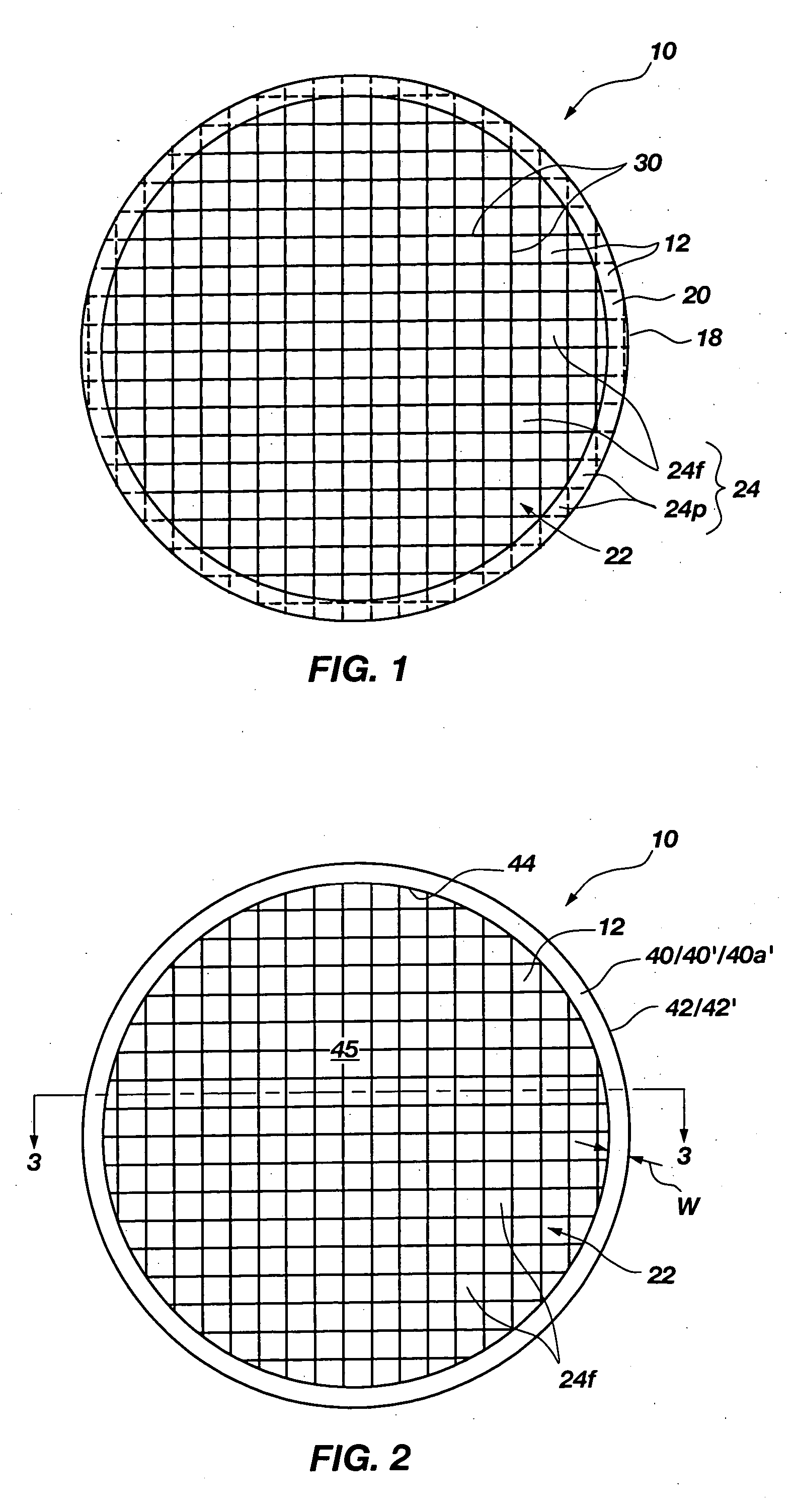

Support structure for thinning semiconductor substrates and thinning methods employing the support structure

ActiveUS20050064681A1Additive manufacturing apparatusSemiconductor/solid-state device manufacturingEngineeringThinning

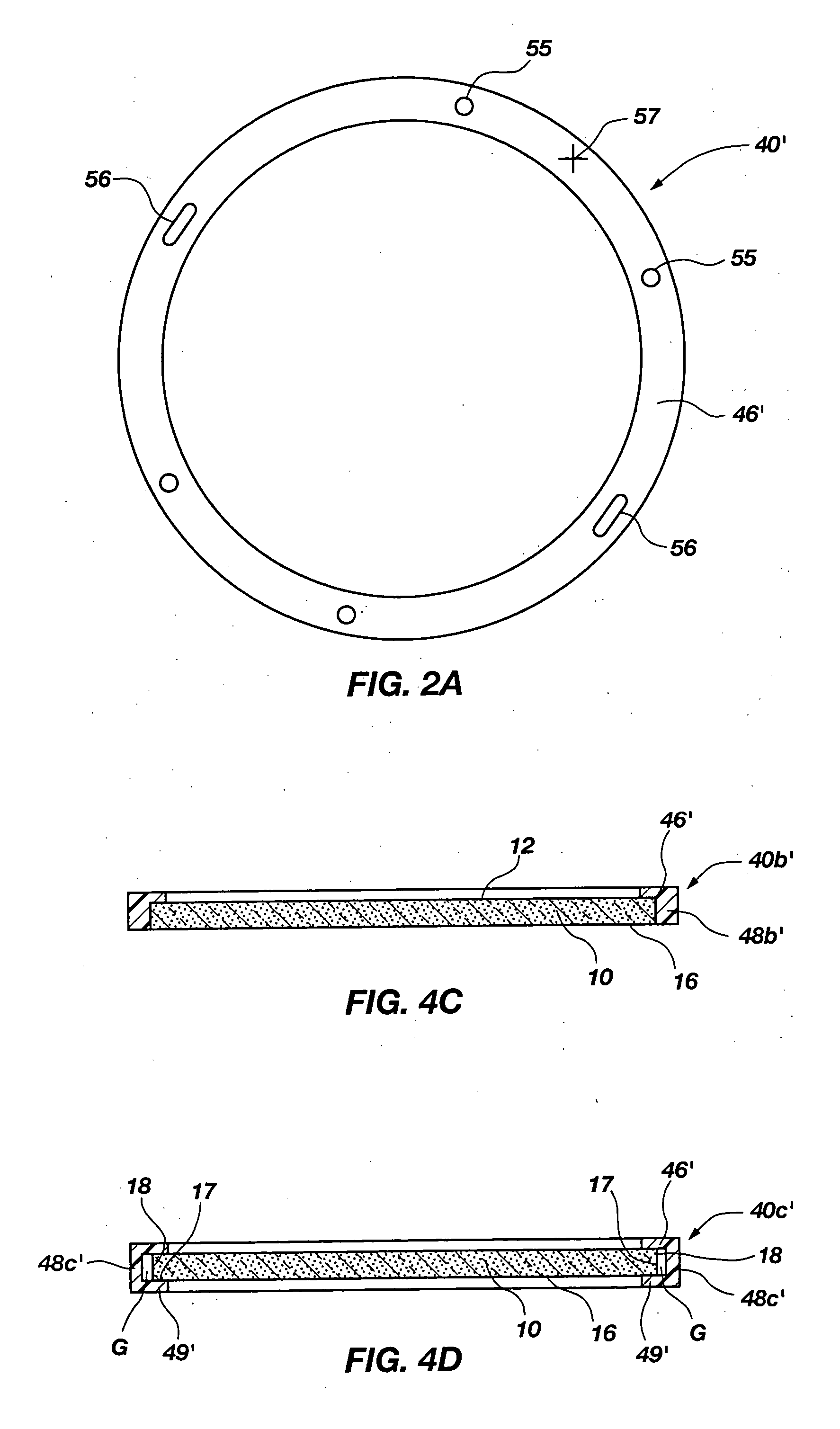

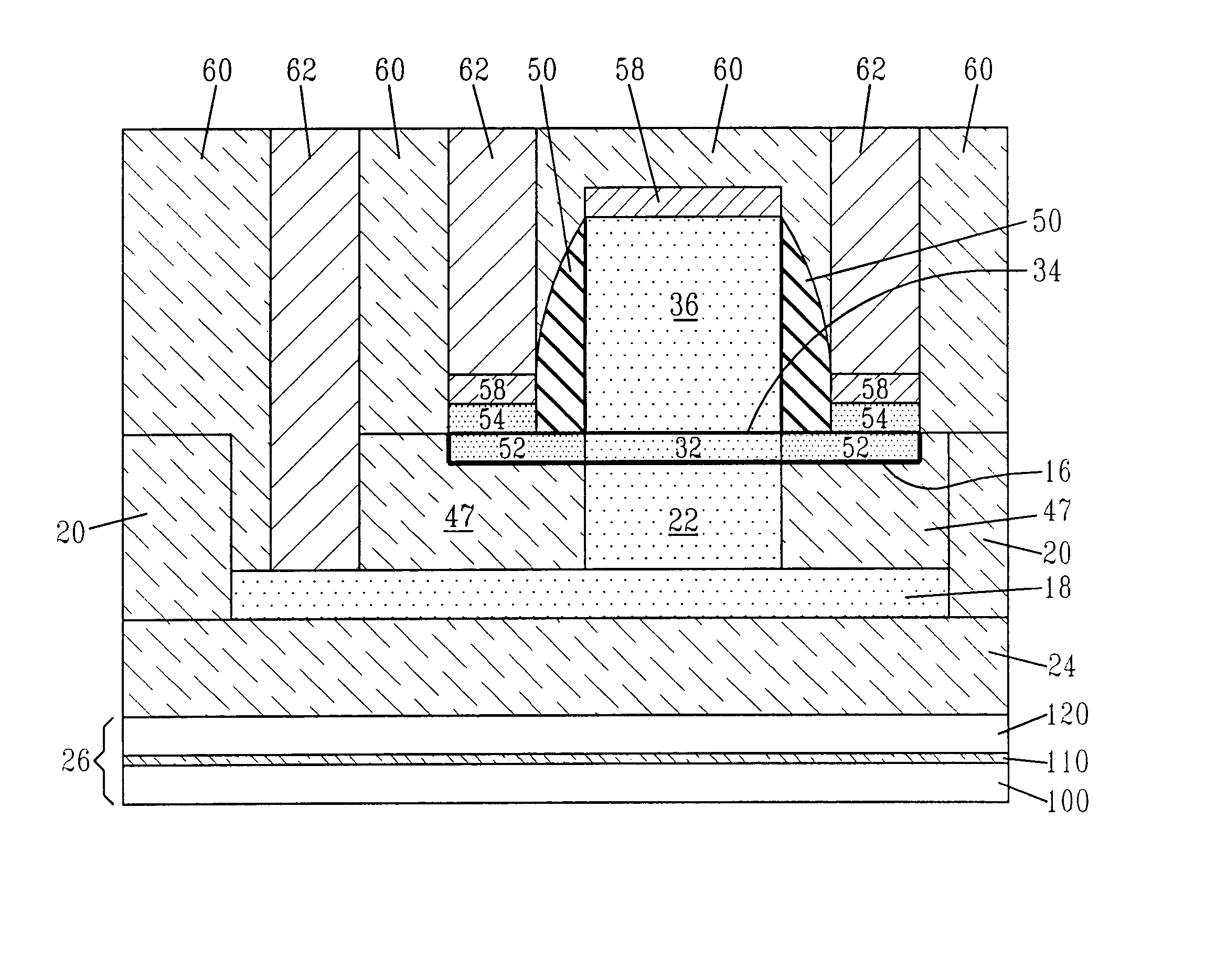

A support structure for use with a semiconductor substrate in thinning, or backgrinding, thereof, as well as during post-thinning processing of the semiconductor substrate includes a portion which extends substantially along and around an outer periphery of the semiconductor substrate to impart the thinned semiconductor substrate with rigidity. The support structure may be configured as a ring or as a member which substantially covers an active surface of the semiconductor substrate and forms a protective structure over each semiconductor device carried by the active surface. Assemblies that include the support structure and a semiconductor substrate are also within the scope of the present invention, as are methods for forming the support structures and thinning and post-thinning processes that include use of the support structures.

Owner:MICRON TECH INC

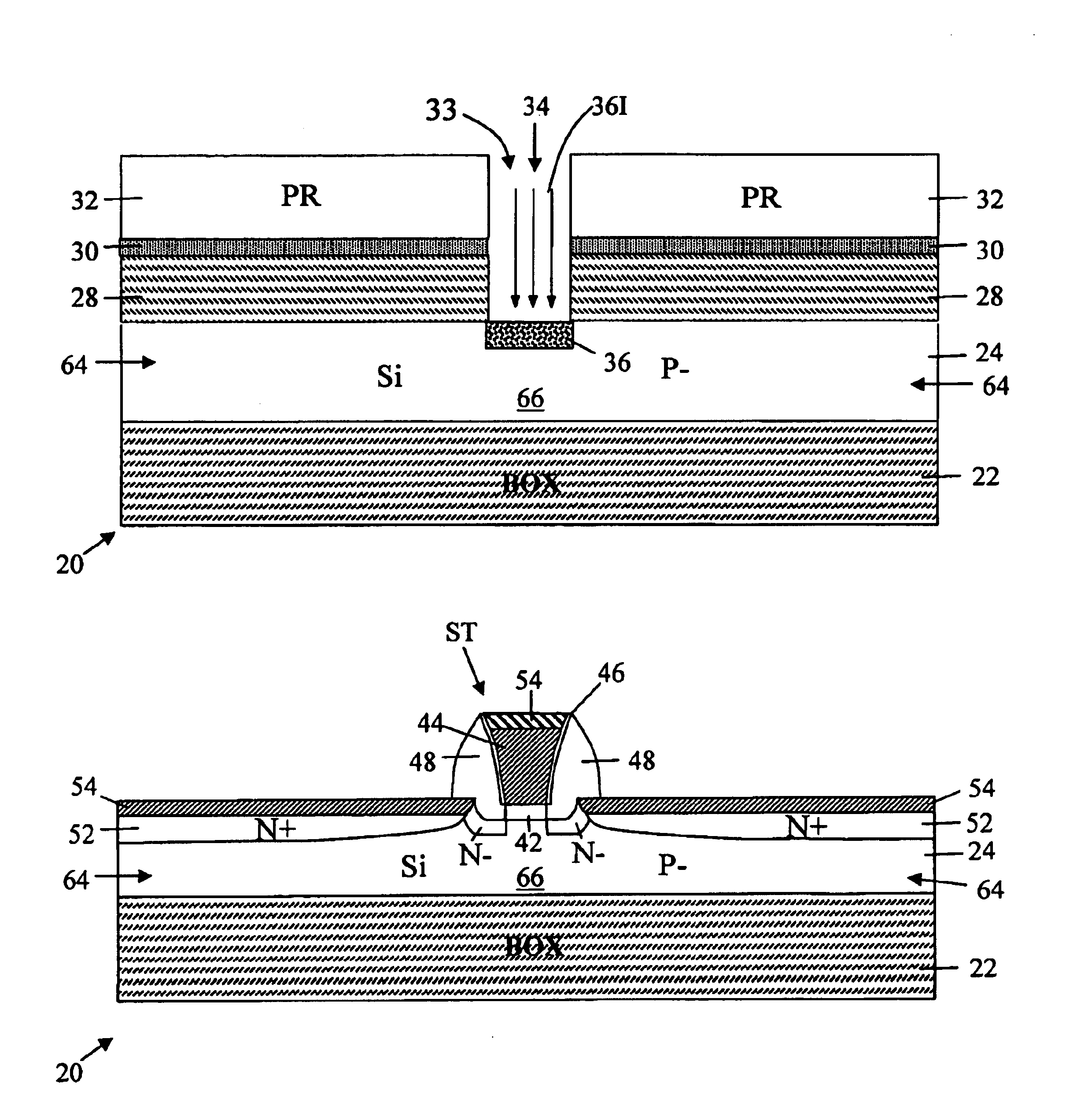

Device threshold control of front-gate silicon-on-insulator mosfet using a self-aligned back-gate

InactiveUS20050037582A1Minimize capacitanceImprove circuit performanceTransistorSemiconductor/solid-state device manufacturingCapacitanceMOSFET

The present invention provides SOI CMOS technology whereby a polysilicon back-gate is used to control the threshold voltage of the front-gate device, and the nMOS and pMOS back-gates are switched independently of each other and the front gates. Specifically, the present invention provides a method of fabricating a back-gated fully depleted CMOS device in which the device's back-gate is self-aligned to the device's front-gate as well as the source / drain extension. Such a structure minimizes the capacitance, while enhancing the device and circuit performance. The back-gated fully depleted CMOS device of the present invention is fabricated using existing SIMOX (separation by ion implantation of oxygen) or bonded SOI wafers, wafer bonding and thinning, polySi etching, low-pressure chemical vapor deposition and chemical-mechanical polishing.

Owner:GLOBALFOUNDRIES INC

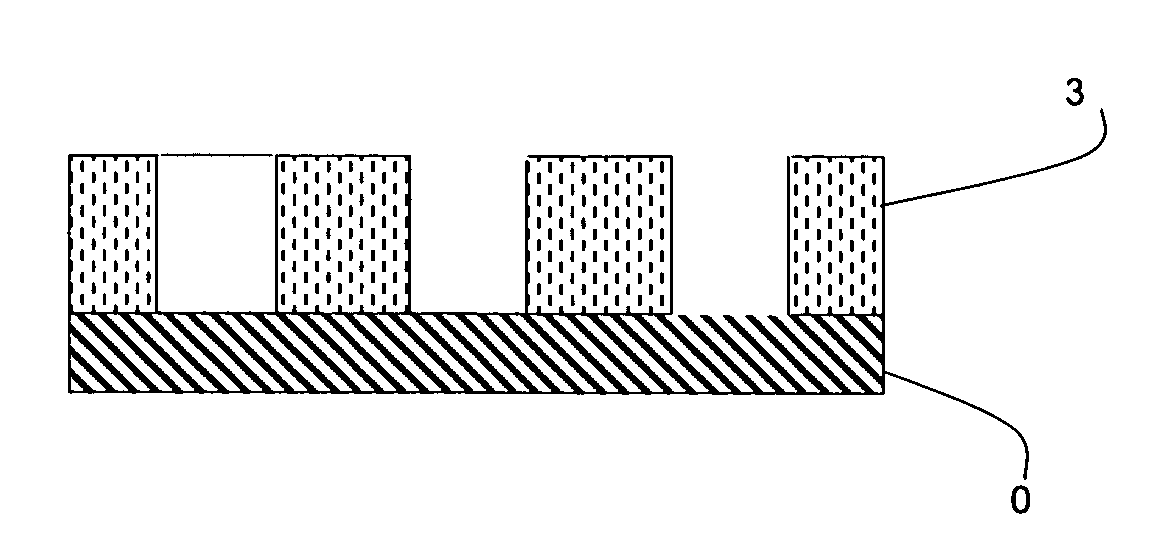

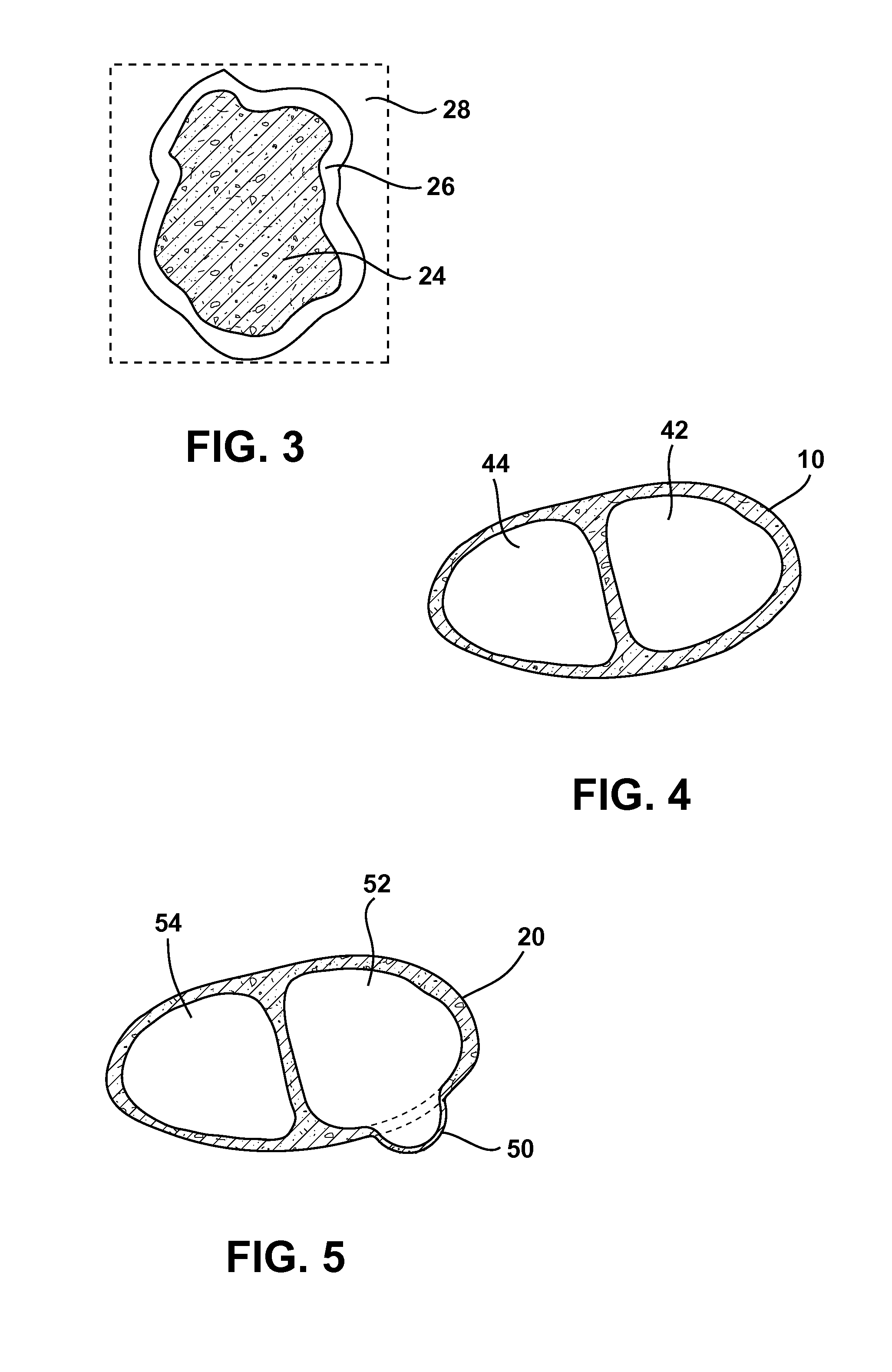

Backside thinning of image array devices

InactiveUS7005637B2Improve imaging effectImprove device yieldSolid-state devicesSemiconductor/solid-state device manufacturingImage resolutionImage contrast

Backthinning in an area selective manner is applied to imaging sensors 12 for use in electron bombarded devices. A further arrangement results in an array of collimators 51 aligned with pixels 42 or groups of pixels providing improved image contrast of such image sensor. Provision of a thin P-doped layer 52 on the illuminated rear surface provides both a diffusion barrier resulting in improved resolution and a functional shield for reference pixels. A gradient in concentration of P-doped layer 52 optimizes electron collection at the pixel array.

Owner:EOTECH LLC

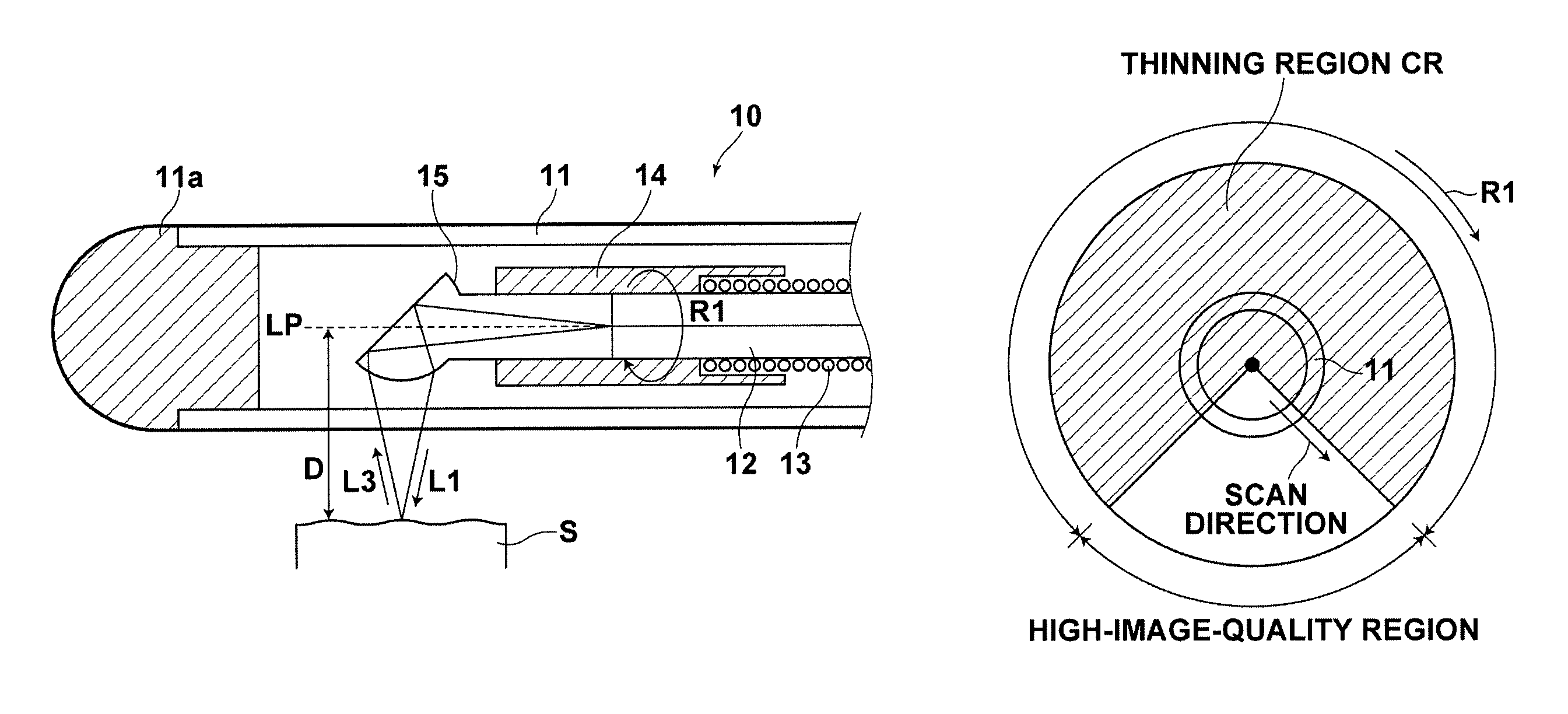

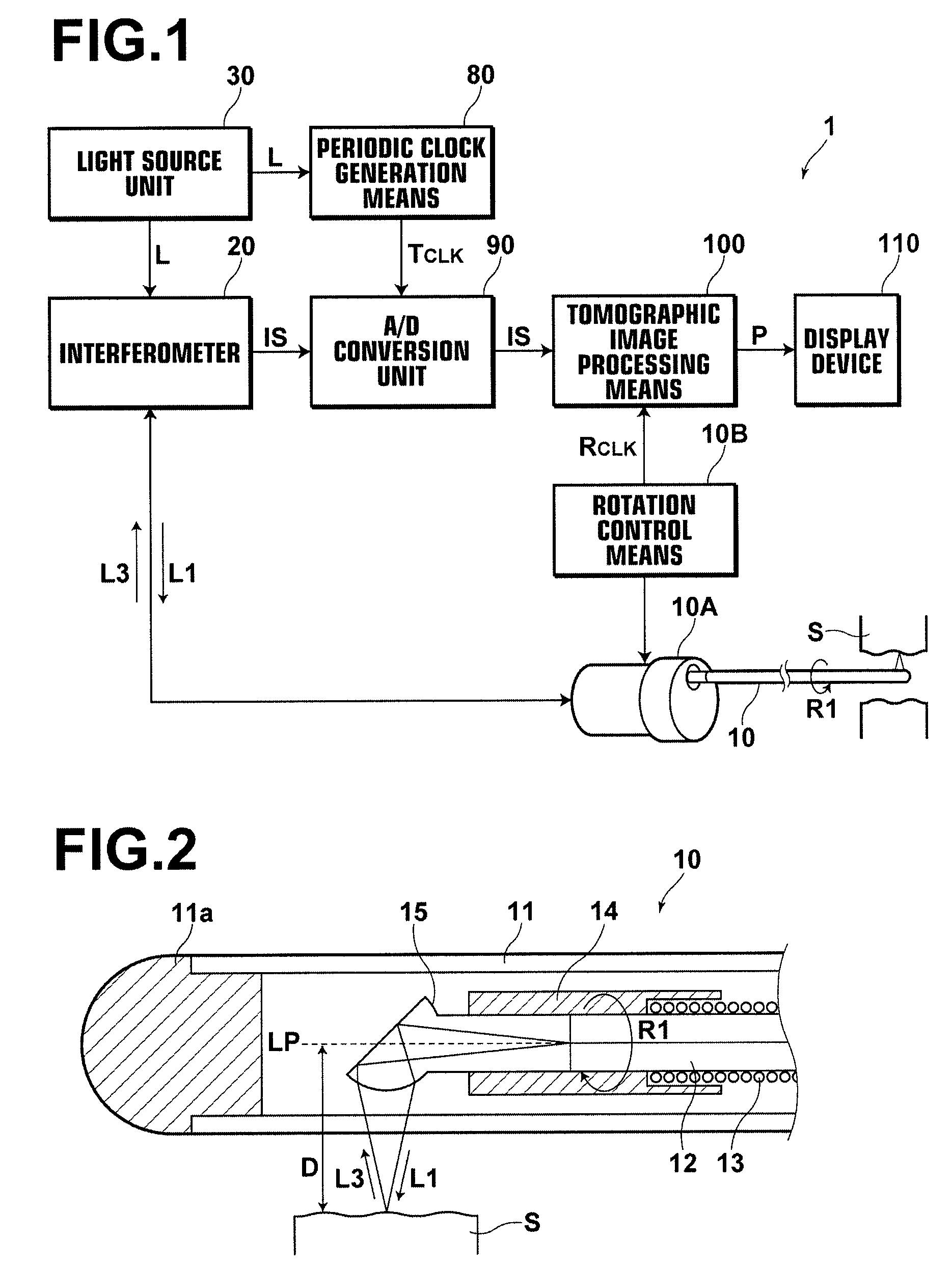

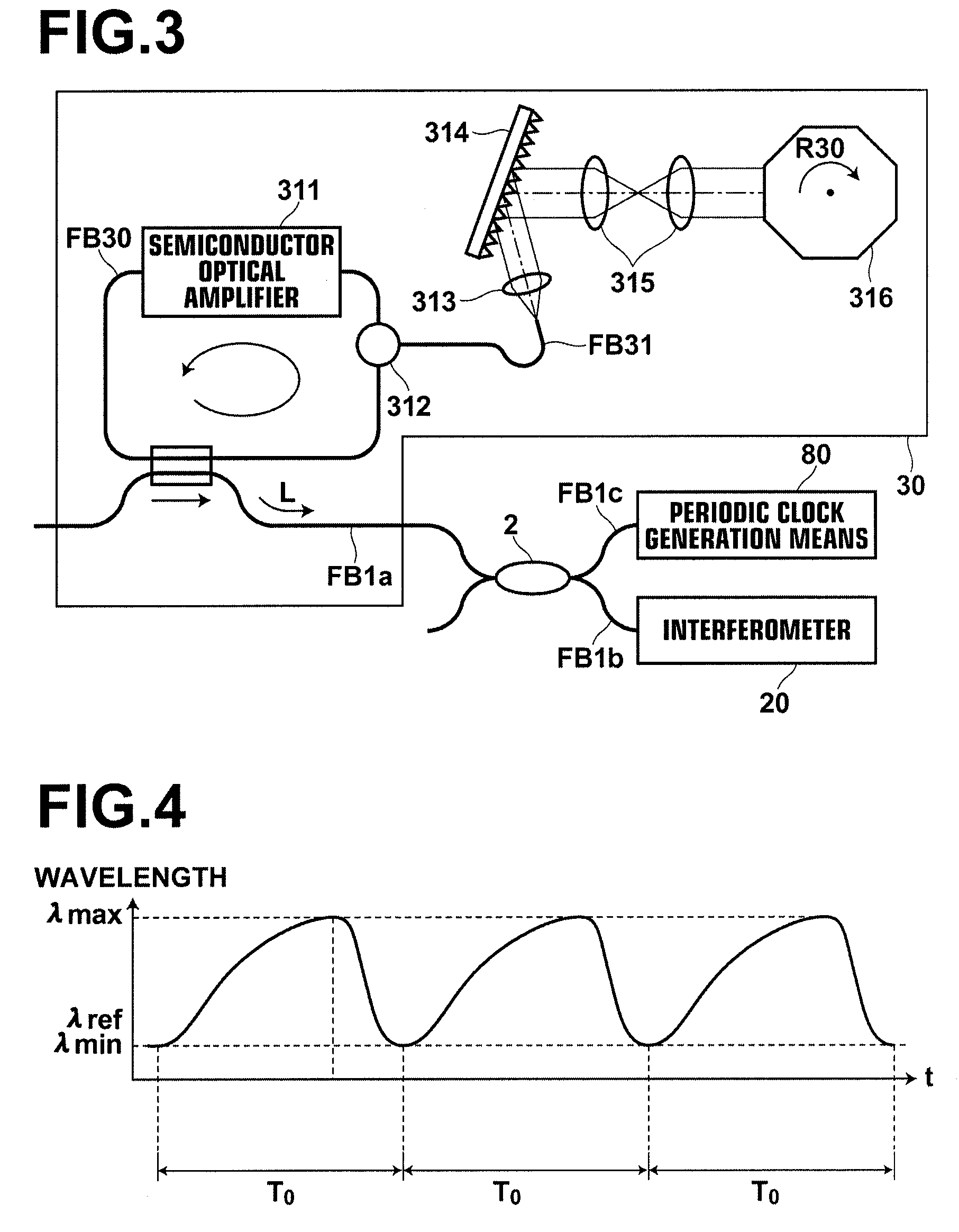

Method and system for producing tomographic image by optical tomography with processing of interference light signals

ActiveUS7944568B2High motion-image response characteristicLow cost processingInterferometersUsing optical meansOptical tomographyLength wave

When reflection light, reflected from a measurement target that has been irradiated with measurement light in such a manner to scan the measurement target, and reference light are combined in each wavelength sweep, interference light is detected as interference signals. When a thinning region in which the interference signals obtained by detecting the interference light in each wavelength sweep are thinned so that the interference signals that are used to produce the tomographic image remain is set, thinning is performed on the plurality of interference signals in the thinning region. Light intensity information about the measurement target in the thinning region is obtained, based on the interference signals for the respective wavelength sweeps, the interference signals remaining after thinning. The tomographic image in the thinning region is produced based on the obtained light intensity information.

Owner:KK TOPCON

Ultraviolet-cured hard coating and application thereof

ActiveCN102236113AImprove wear resistanceImprove antifouling performanceLayered productsPolyurea/polyurethane coatingsUltravioletPliability

The invention discloses an ultraviolet-cured hard coating and an application thereof. The ultraviolet-cured hard coating comprises a transparent supporting body and a scratch-proof coating coated on the transparent supporting body; the scratch-proof coating comprises the following components in part by weight: 5 to 90 parts of light-cured prepolymer, 5 to 90 parts of thinning agent, 1 to 10 parts of photoinitiator, 0 to 80 parts of active thinning agent, 0 to 20 parts of inorganic nanopadding and 0 to 18 parts of aid. By the invention, the defects that the conventional hard coating is not hard enough, the scratch resistance and the wear resistance are limited, the flexibility is relatively low and the like are overcome; and the ultraviolet-cured hard coating has relatively low surface energy, relatively good antifouling effect, high strength, relatively good scratch resistance and wear resistance, and excellent adhesion, flexibility and transparence.

Owner:中国航天科技集团公司第四研究院第四十二所

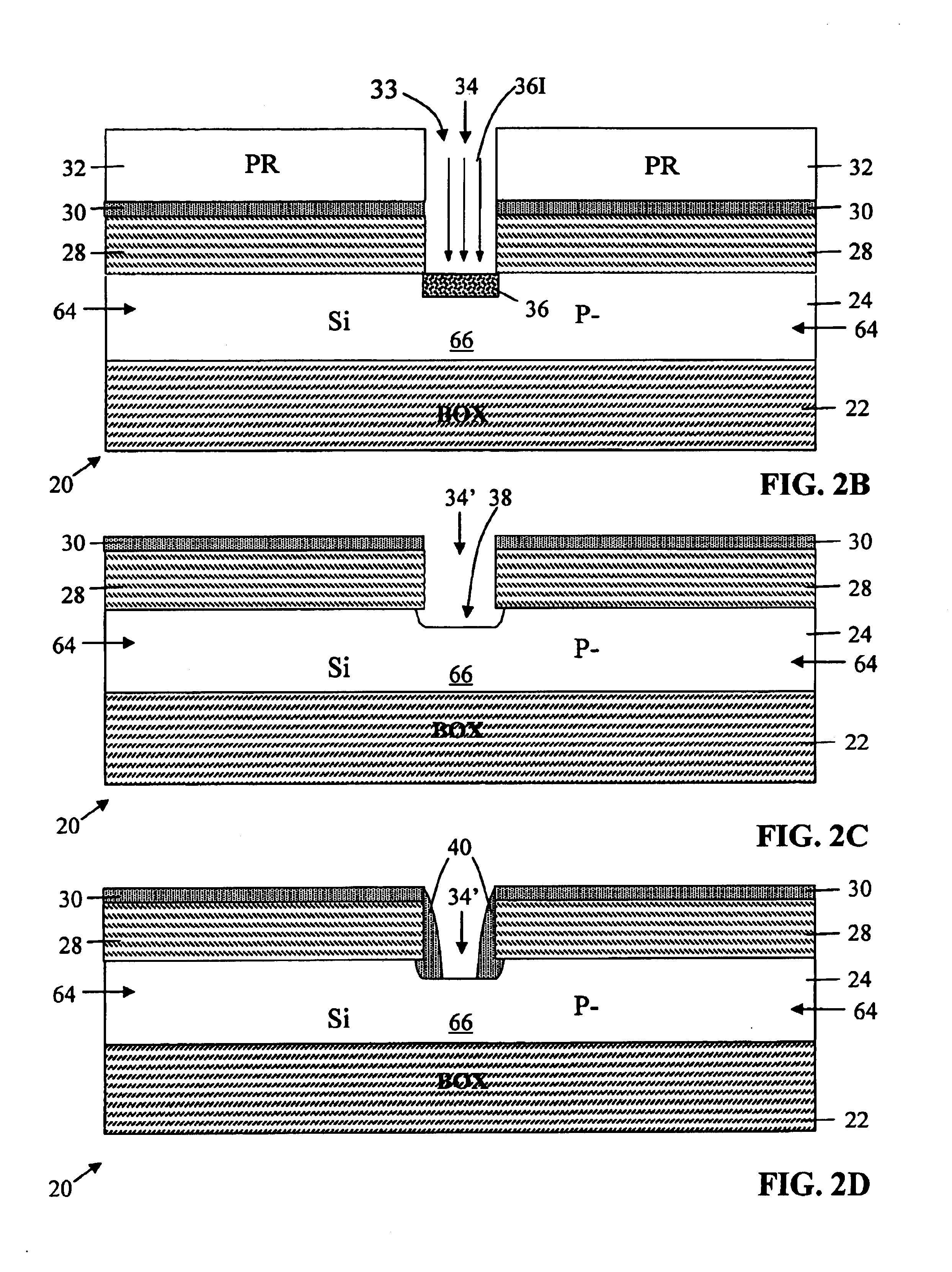

Method of forming an electronic device on a recess in the surface of a thin film of silicon etched to a precise thickness

InactiveUS6930030B2Semiconductor/solid-state device manufacturingSemiconductor devicesMOSFETSalicide

A method for precise thinning to form a recess to a precise depth in a crystalline silicon layer, which can be used to form various devices, such as MOSFET devices, includes the following steps. Form a patterning mask with a window therethrough over the top surface of the silicon layer. Form an amorphized region in the top surface of the silicon layer below the window. Selectively etch away the amorphized region of the silicon layer to form a recess in the surface of the silicon layer, and remove the patterning mask. In the case of an MOSFET device form a hard mask below the patterning mask with the window extending therethrough. Then create sidewall spacers in the window through the hard mask and form a gate electrode stack in the window. Then remove the hard mask and form the source / drain extensions, halos and regions plus silicide and complete the MOSFET device.

Owner:INTELLECTUAL DISCOVERY INC