Patents

Literature

95 results about "Soi cmos" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

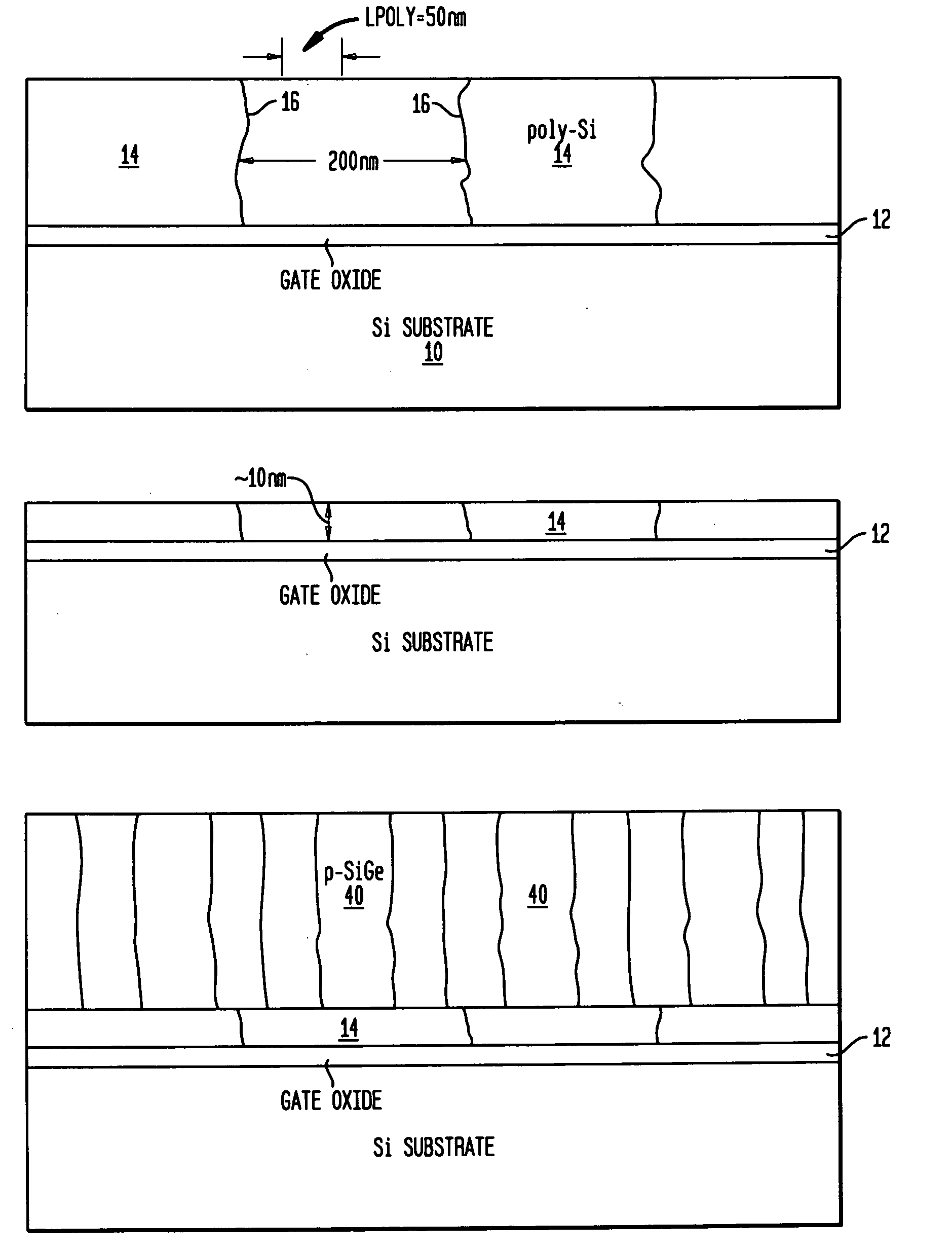

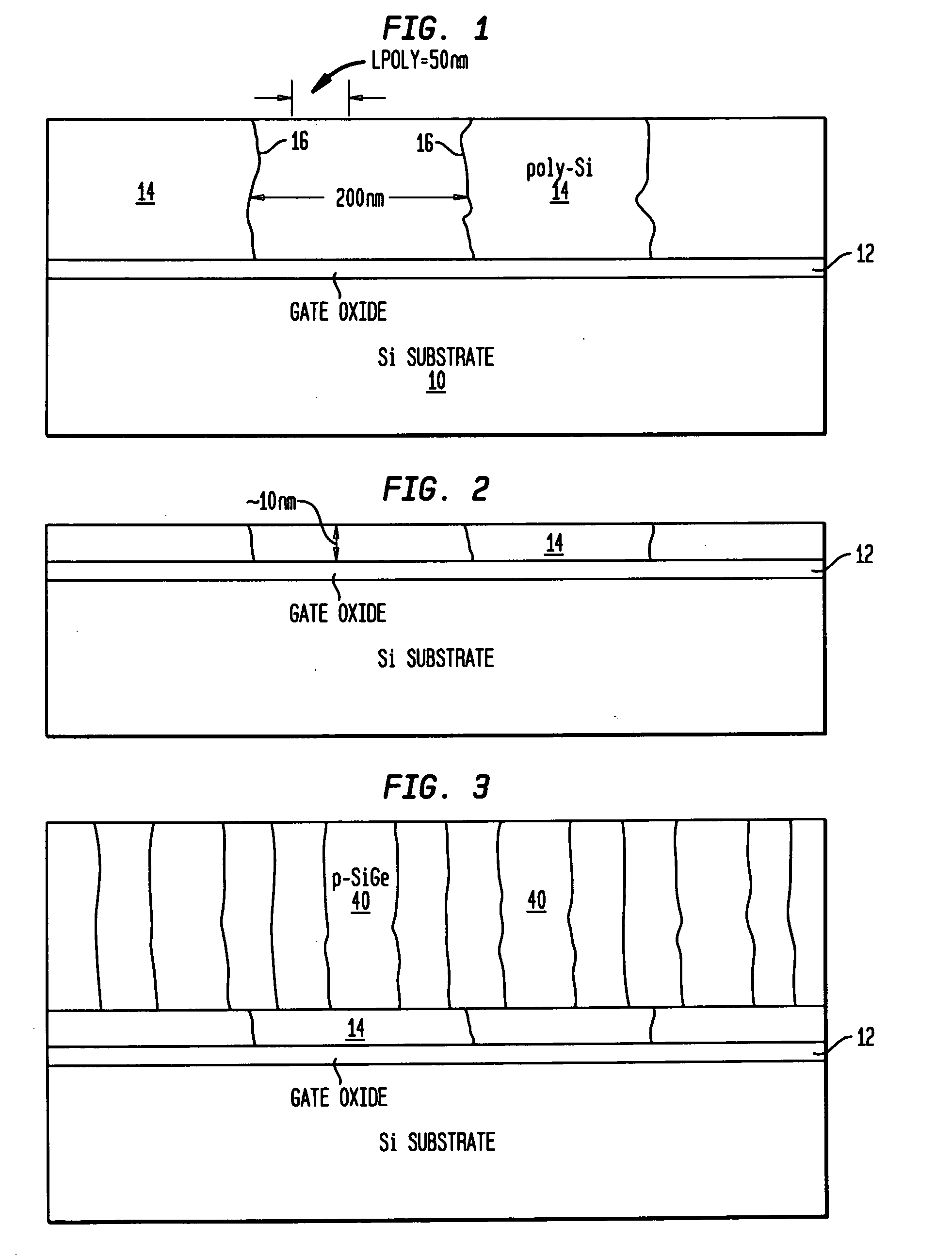

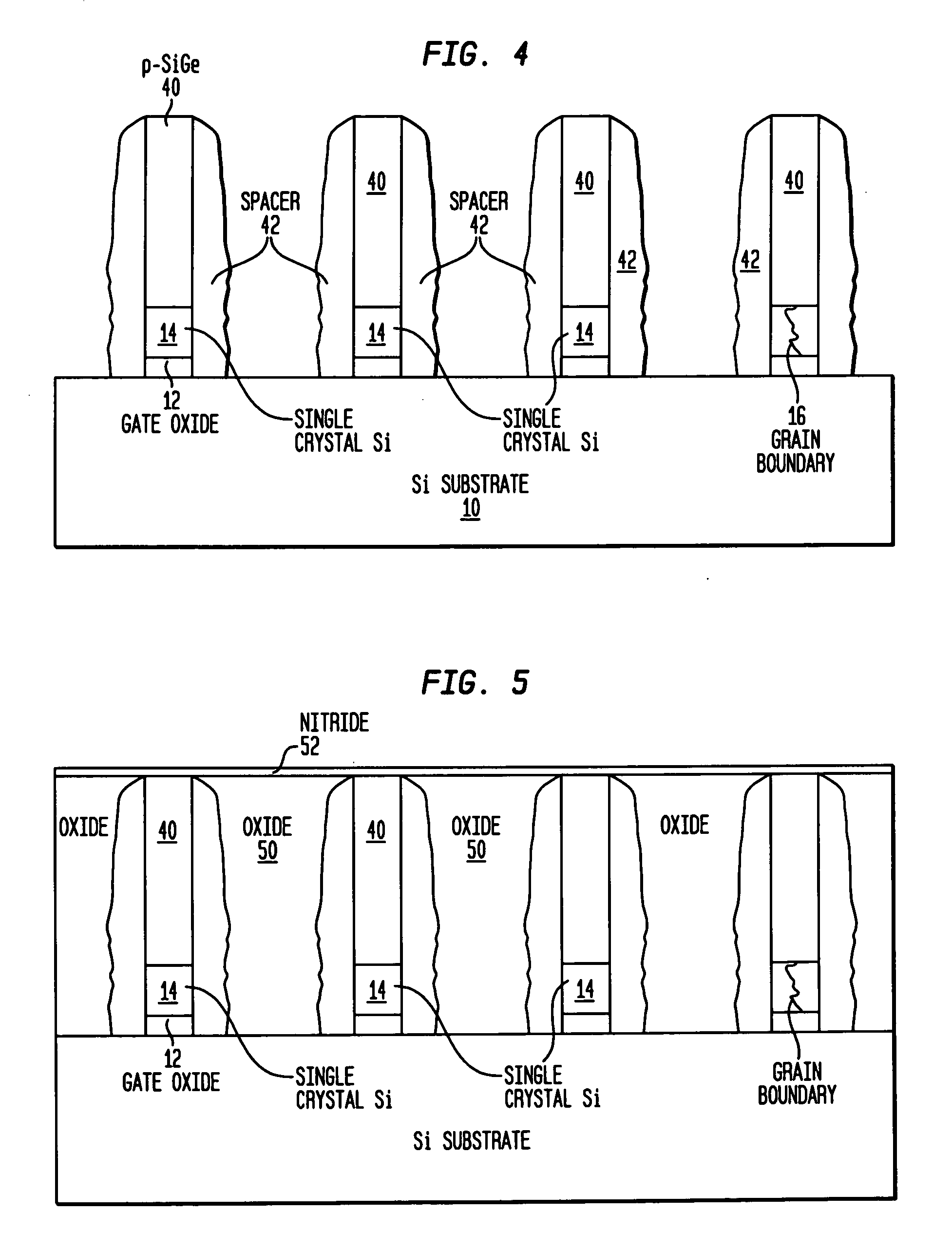

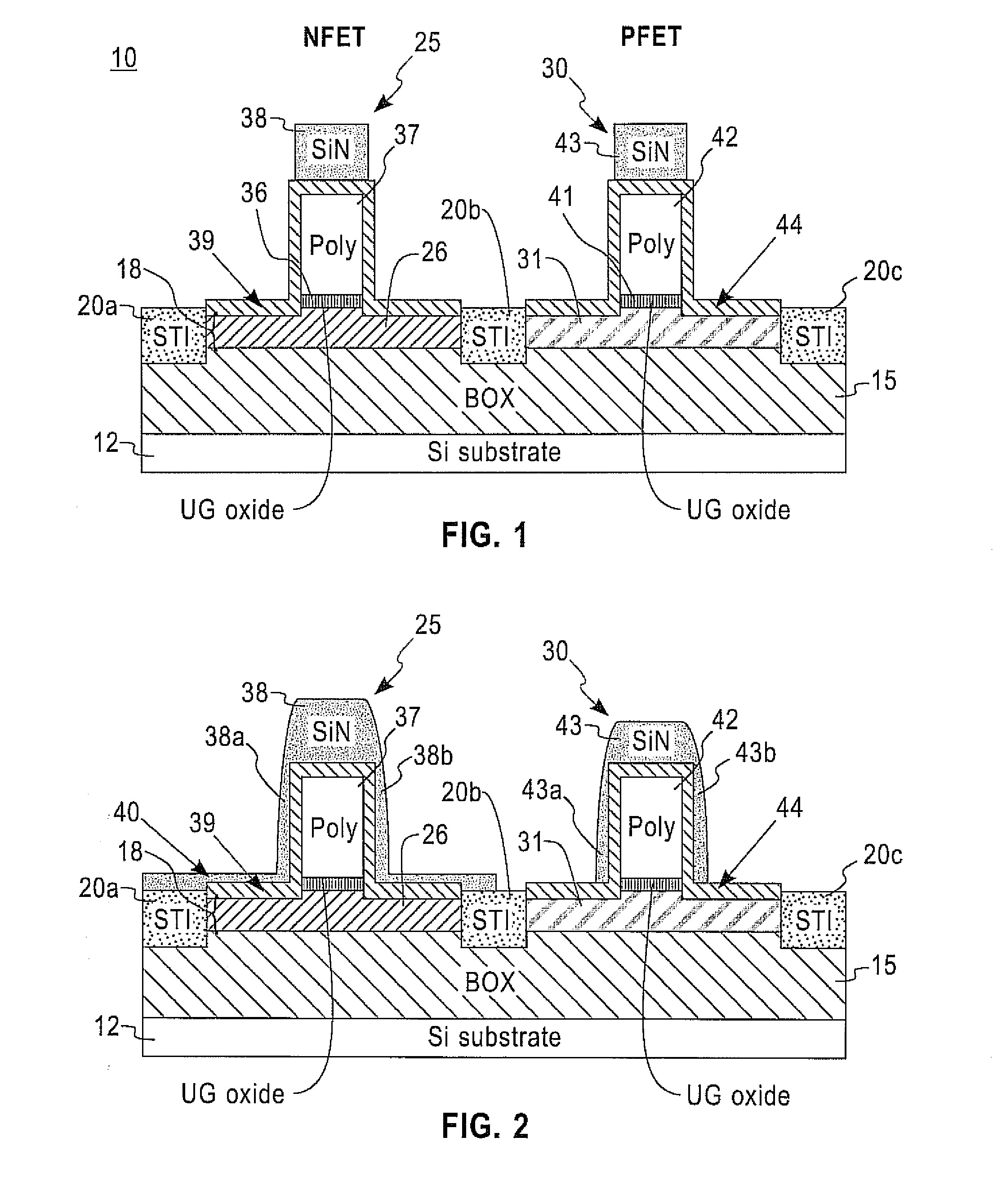

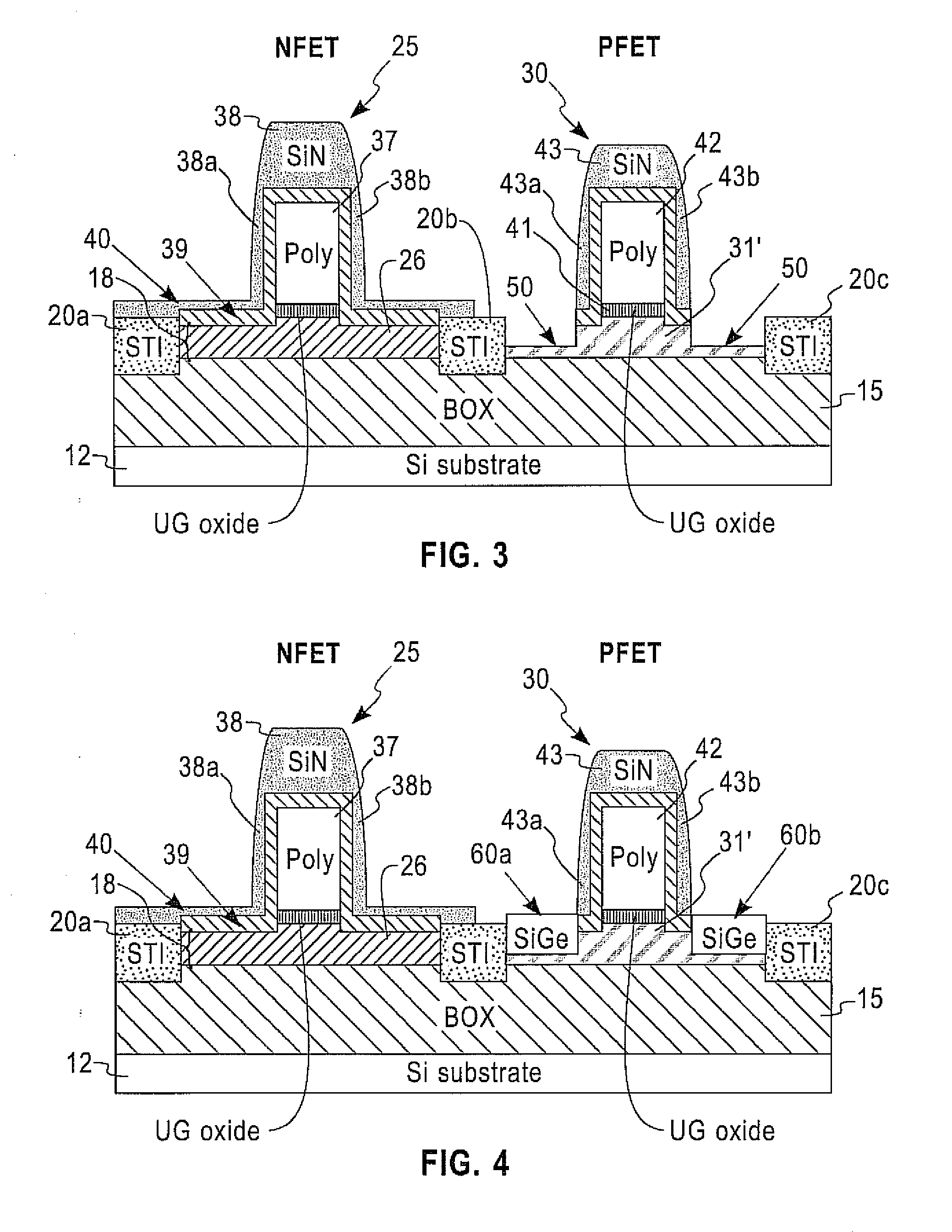

STRUCTURES AND METHODS FOR MANUFACTURING OF DISLOCATION FREE STRESSED CHANNELS IN BULK SILICON AND SOI CMOS DEVICES BY GATE STRESS ENGINEERING WITH SiGe AND/OR Si:C

ActiveUS20050236668A1Avoid misalignmentReduce generationTransistorSemiconductor/solid-state device detailsSoi cmosCMOS

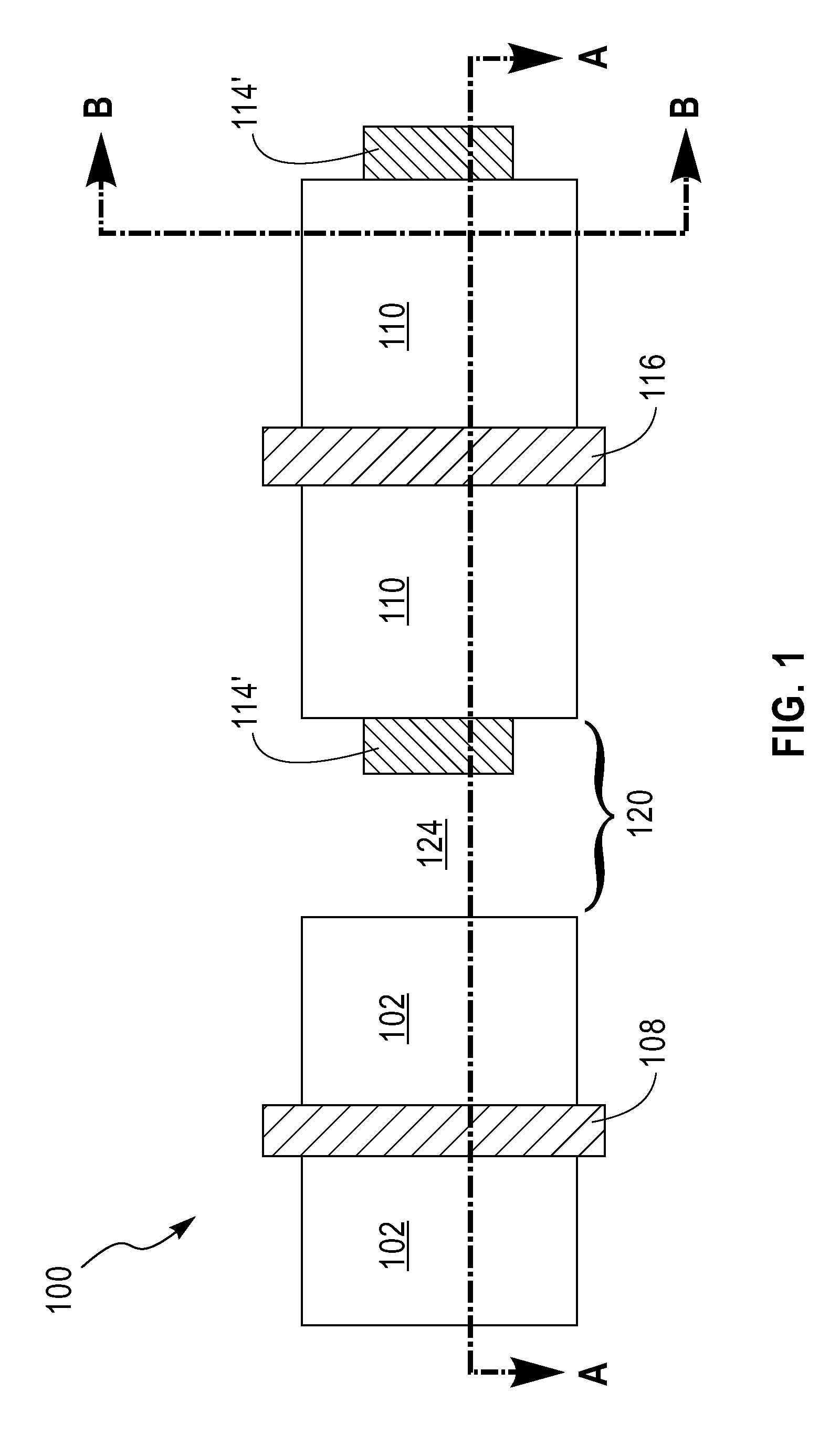

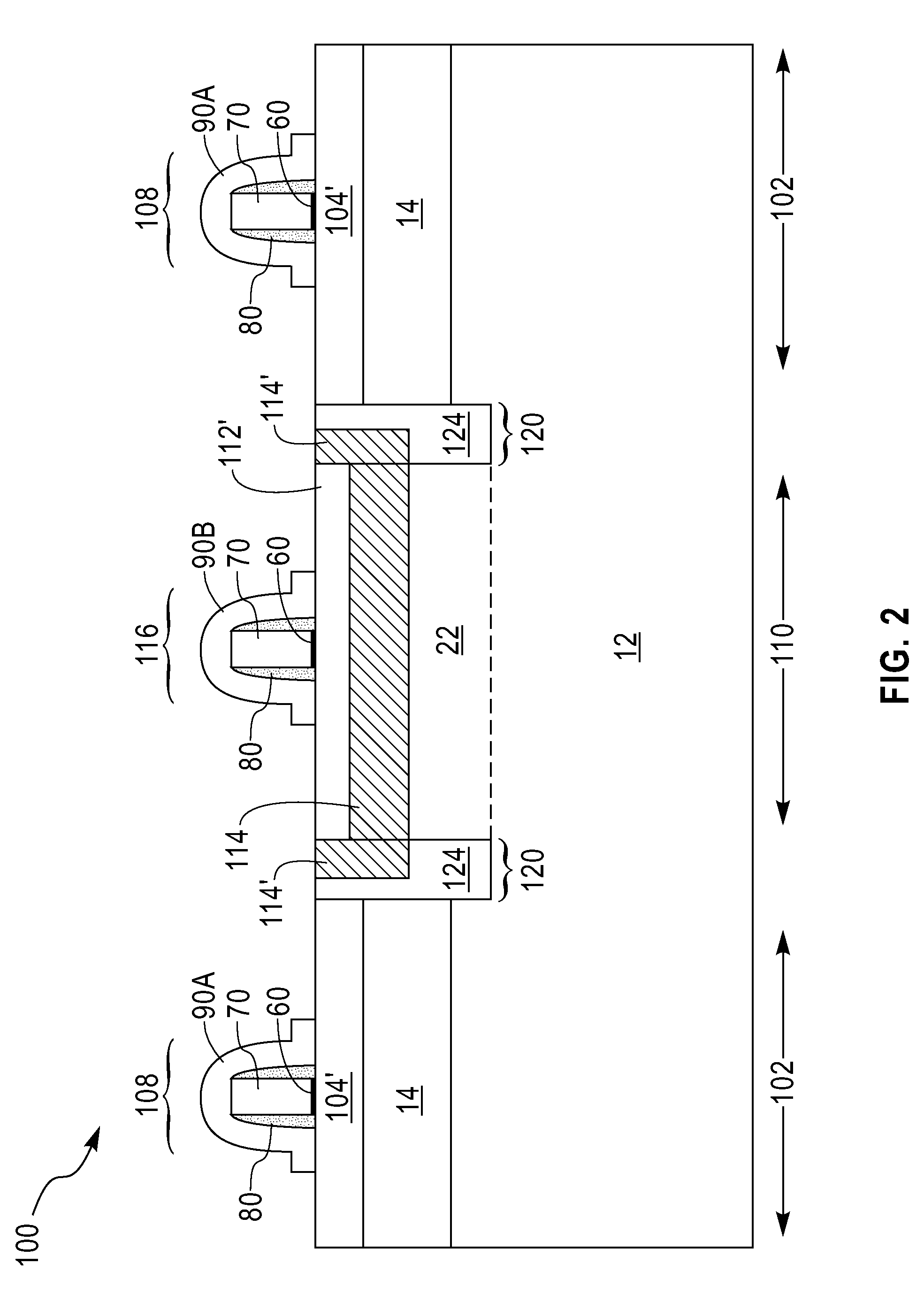

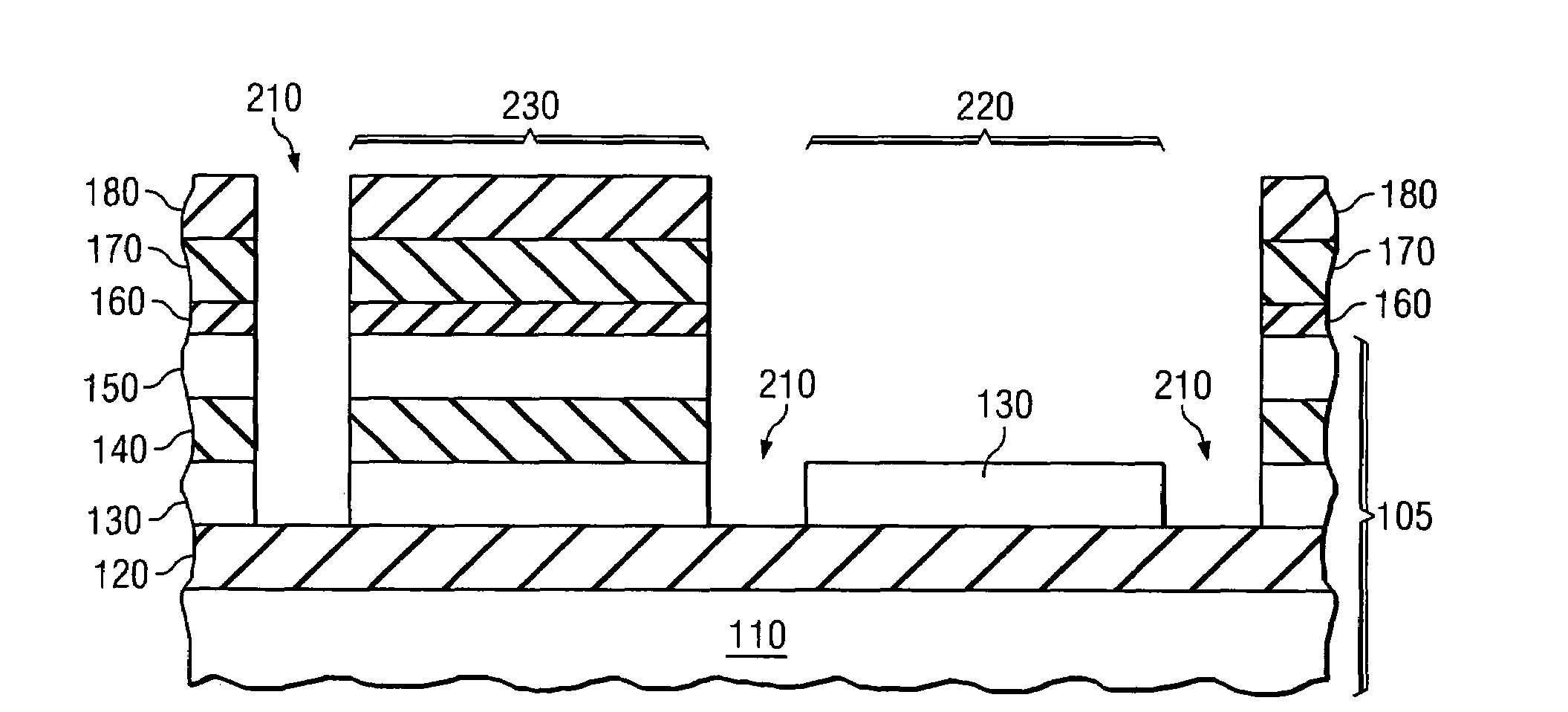

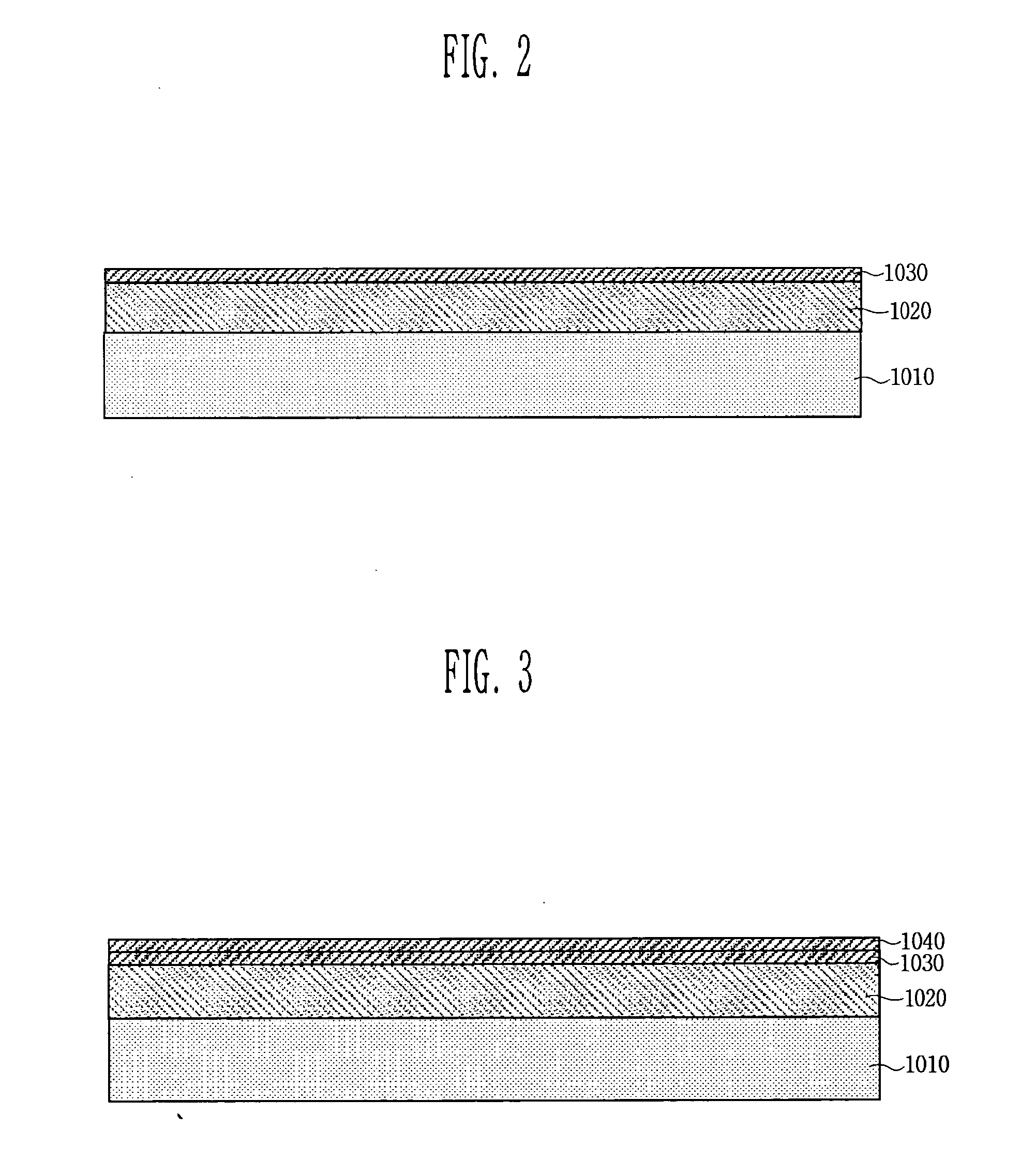

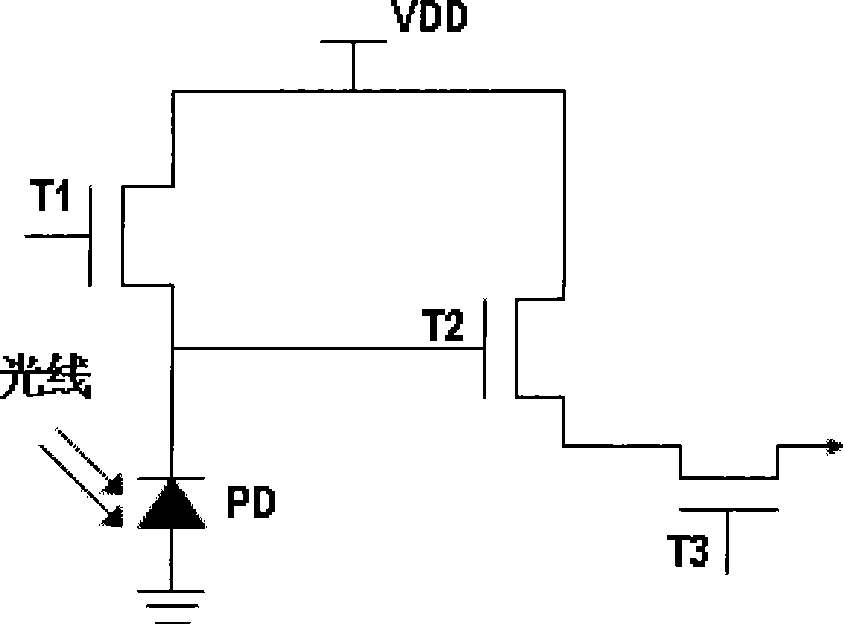

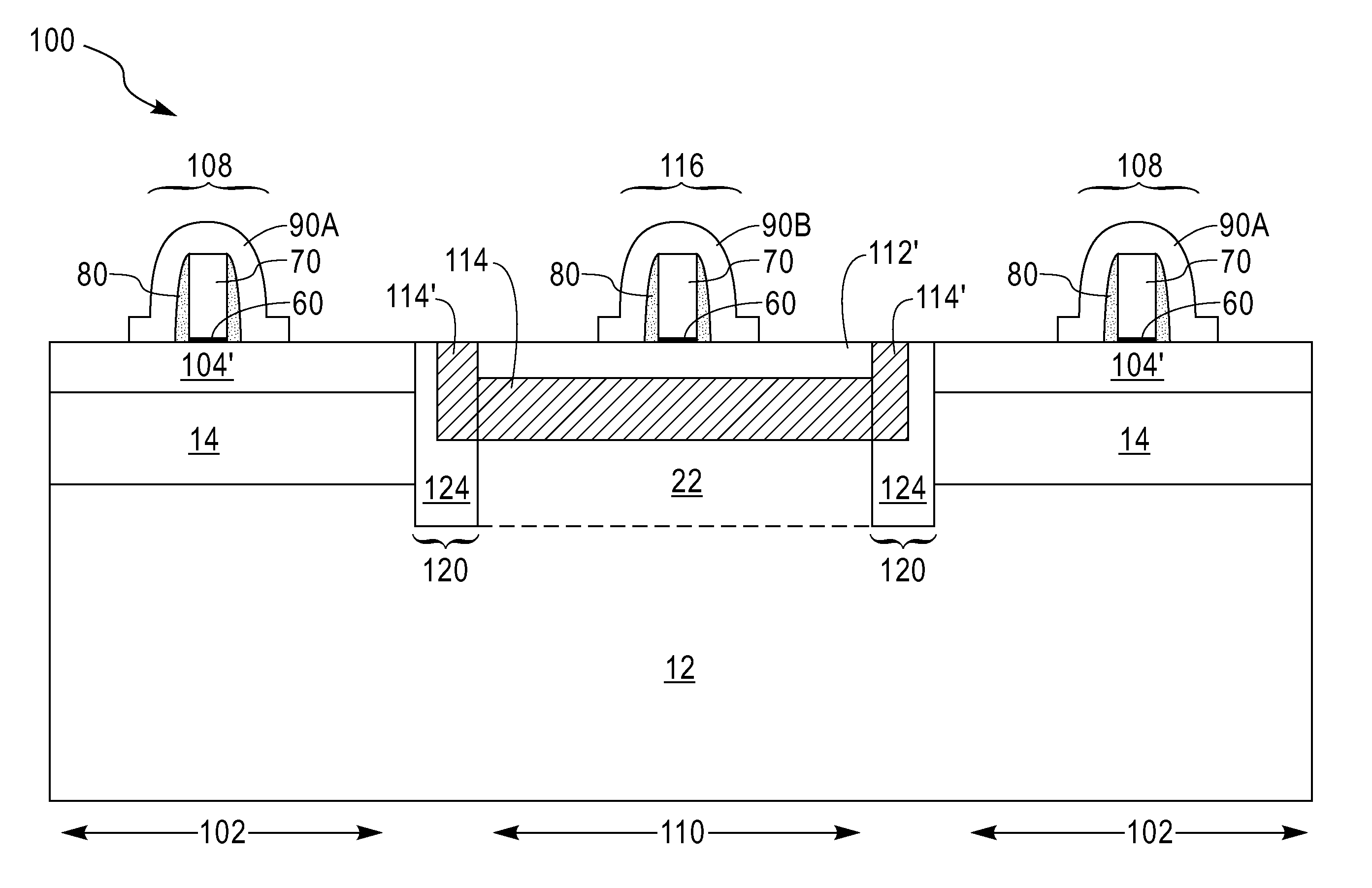

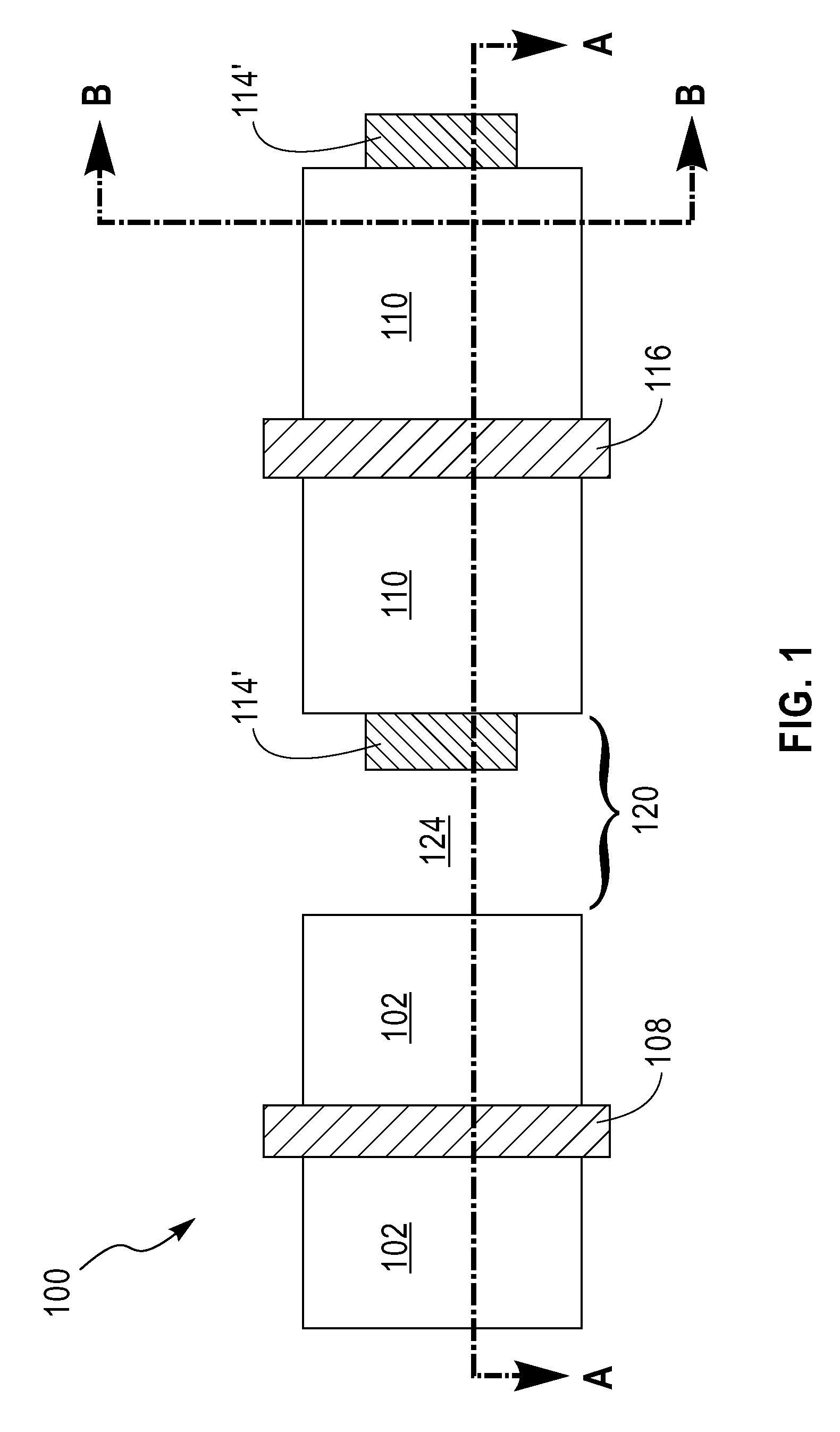

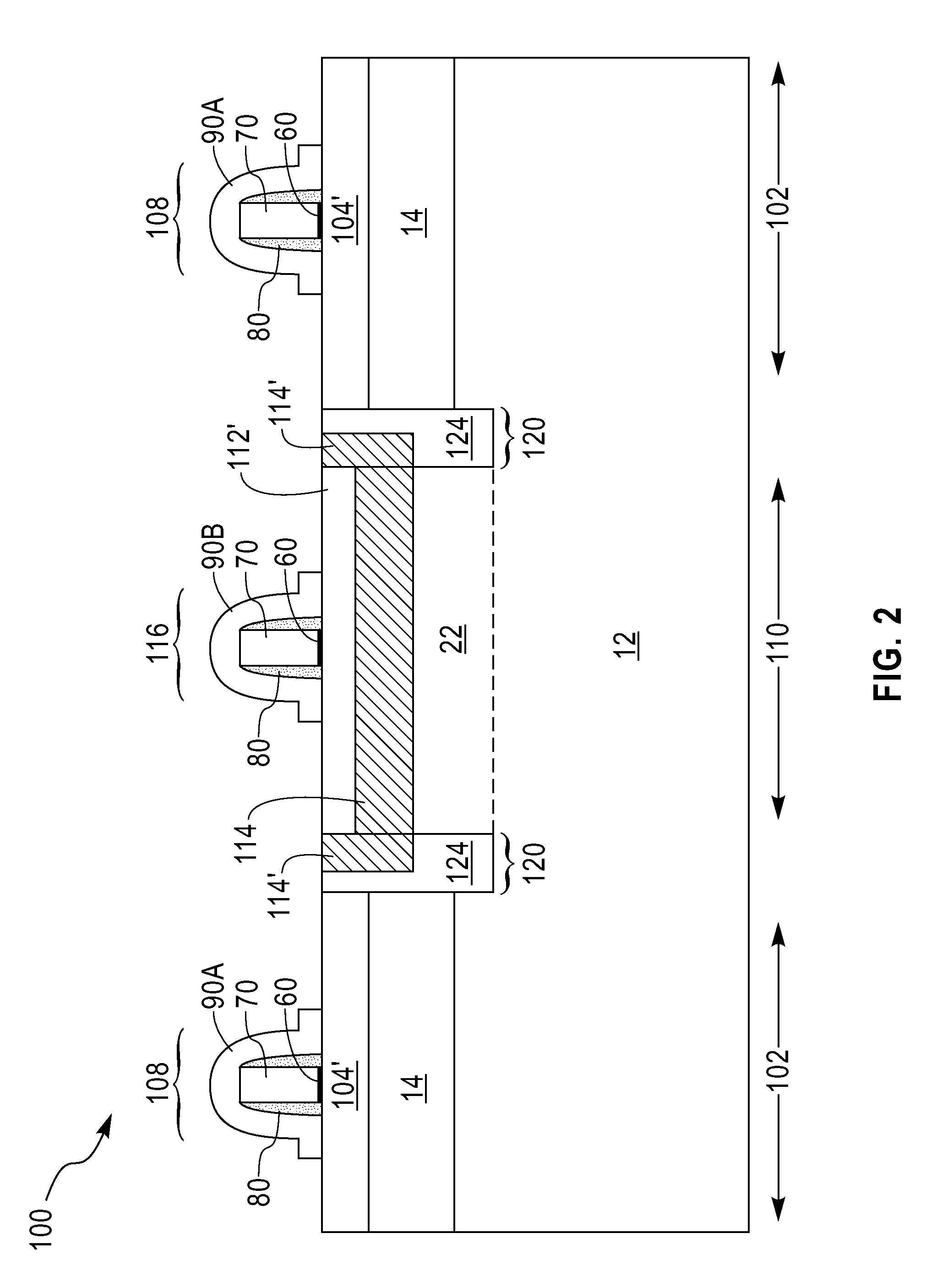

Structures and methods of manufacturing are disclosed of dislocation free stressed channels in bulk silicon and SOI (silicon on insulator) CMOS (complementary metal oxide semiconductor) devices by gate stress engineering with SiGe and / or Si:C. A CMOS device comprises a substrate of either bulk Si or SOI, a gate dielectric layer over the substrate, and a stacked gate structure of SiGe and / or Si:C having stresses produced at the interfaces of SSi(strained Si) / SiGe or SSi / Si:C in the stacked gate structure. The stacked gate structure has a first stressed film layer of large grain size Si or SiGe over the gate dielectric layer, a second stressed film layer of strained SiGe or strained Si:C over the first stressed film layer, and a semiconductor or conductor such as p(poly)-Si over the second stressed film layer.

Owner:GLOBALFOUNDRIES US INC

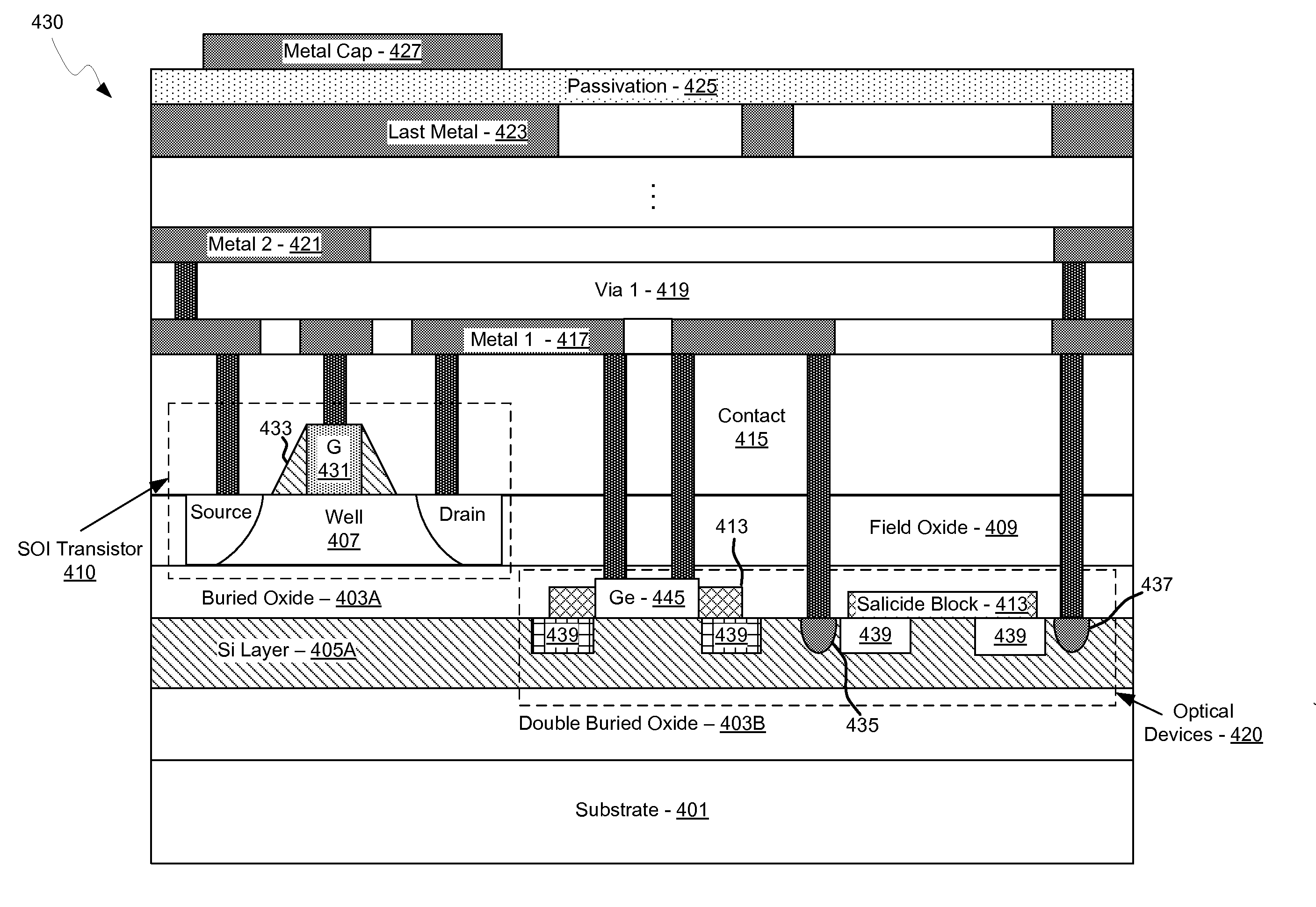

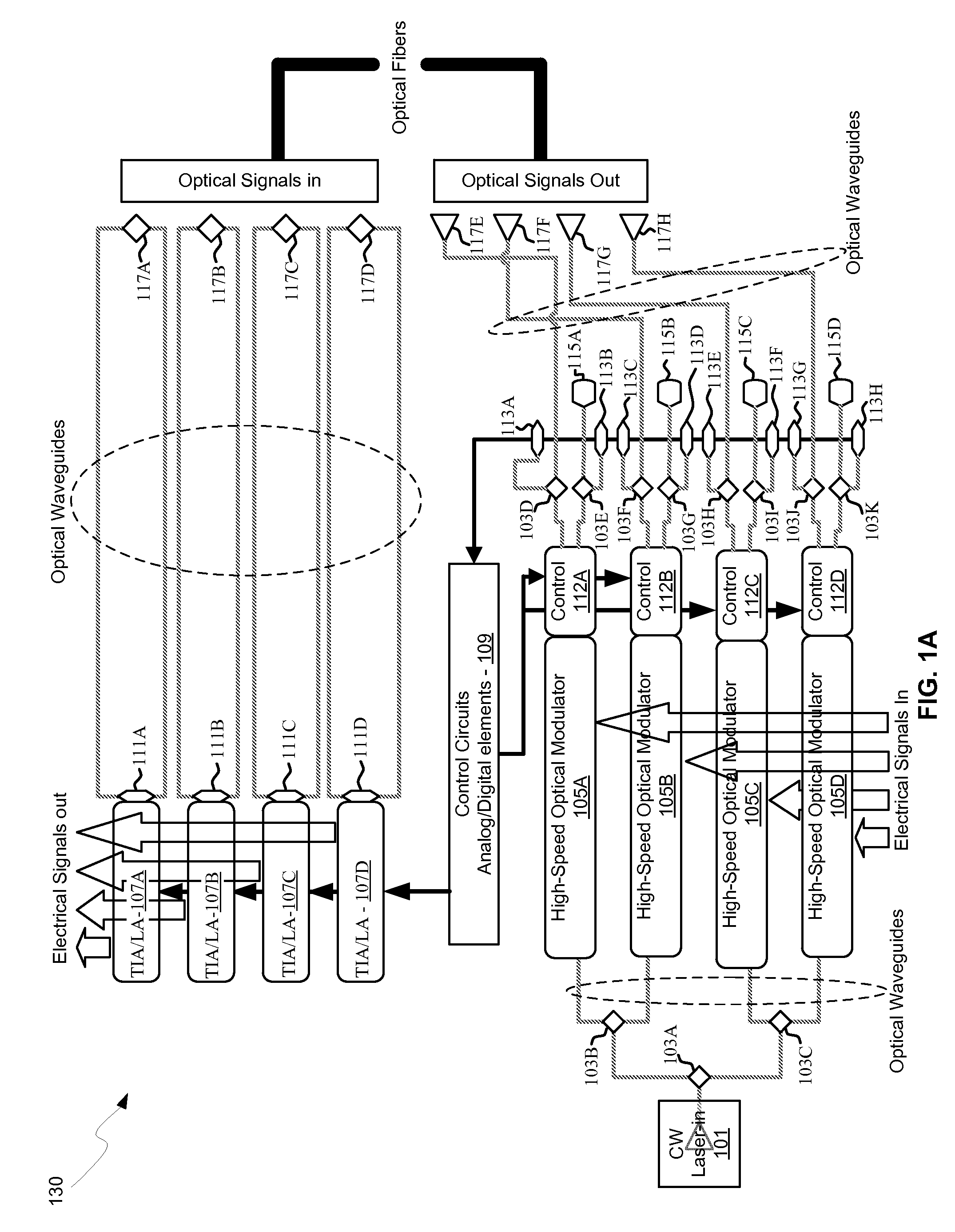

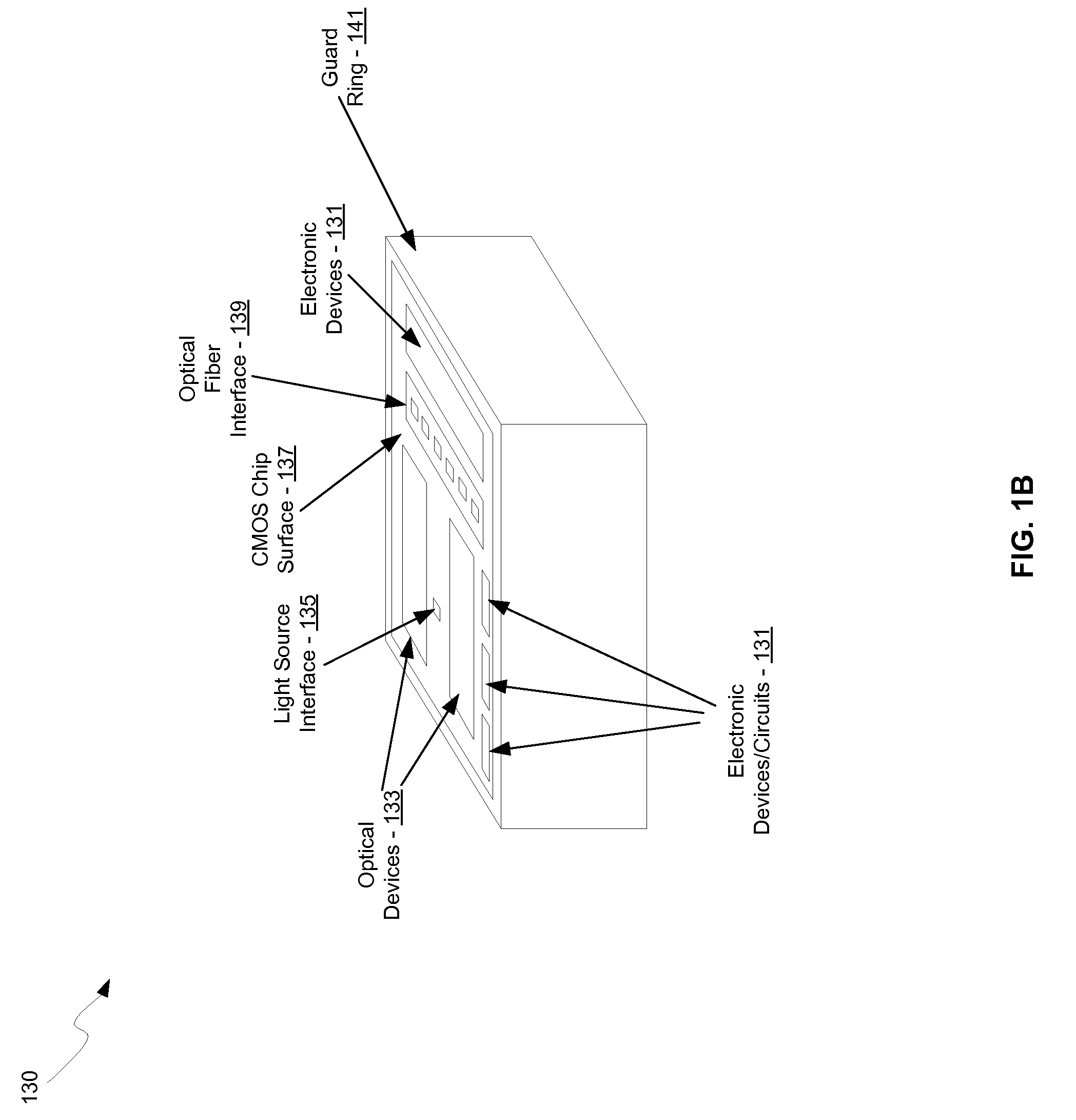

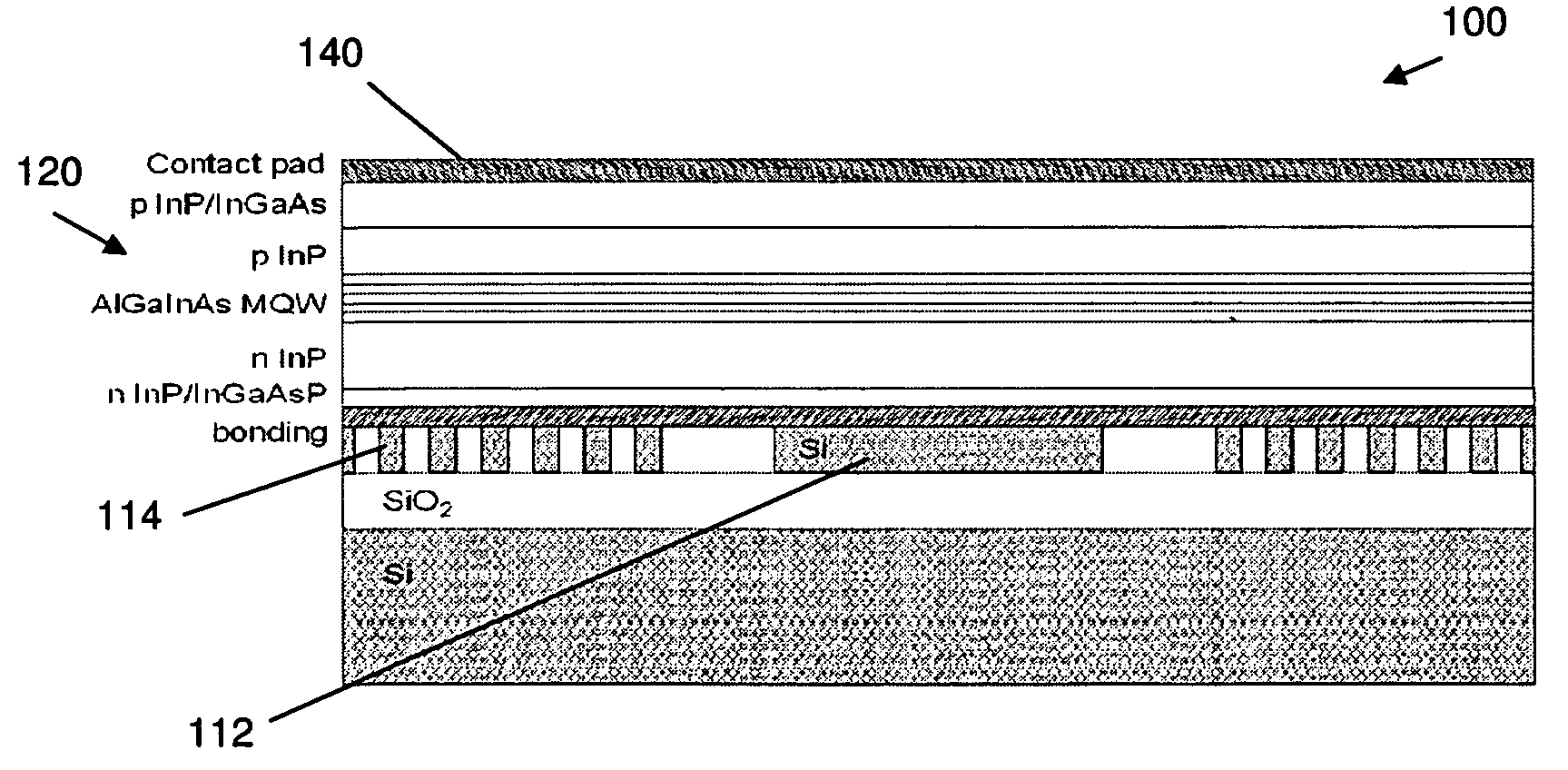

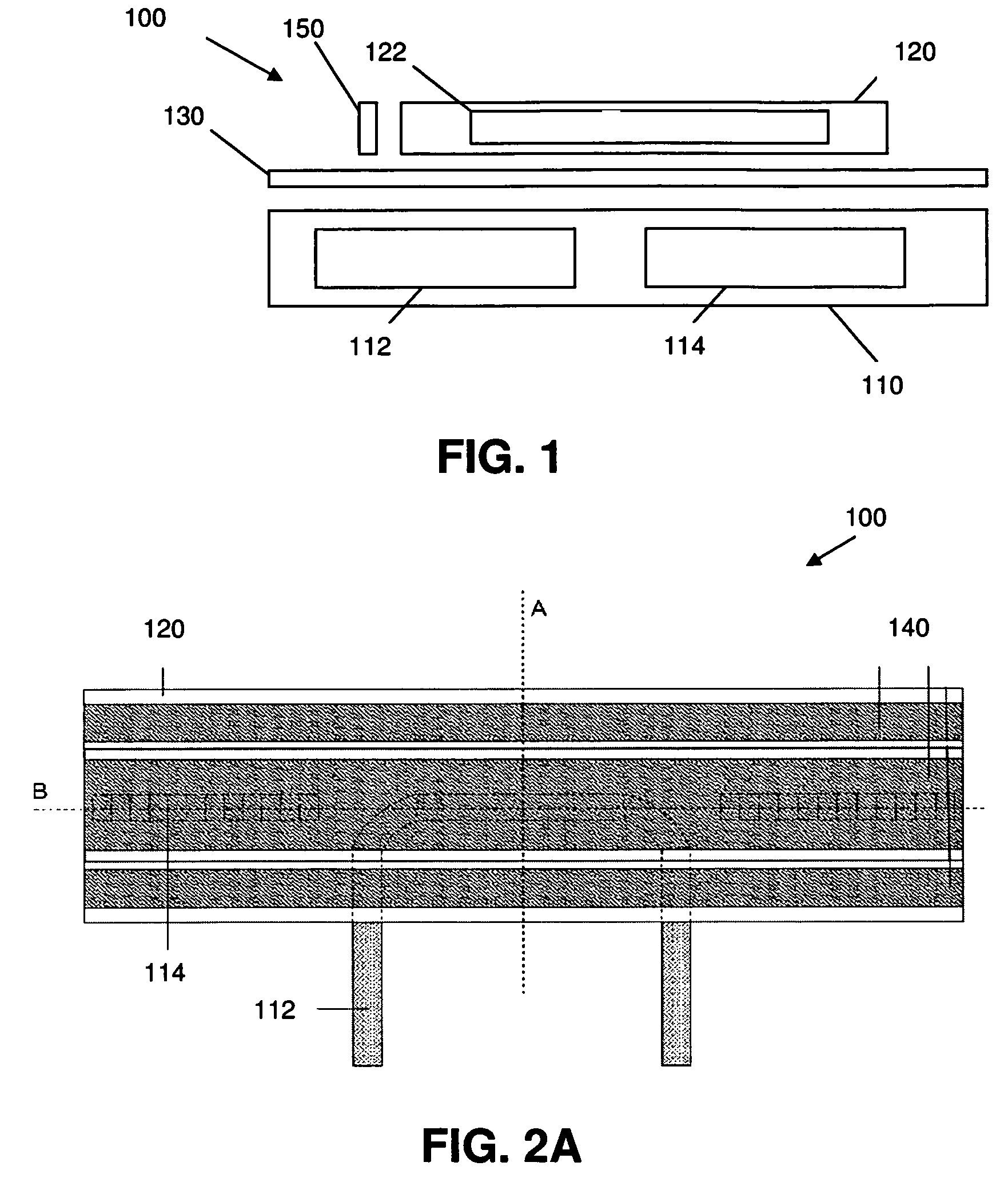

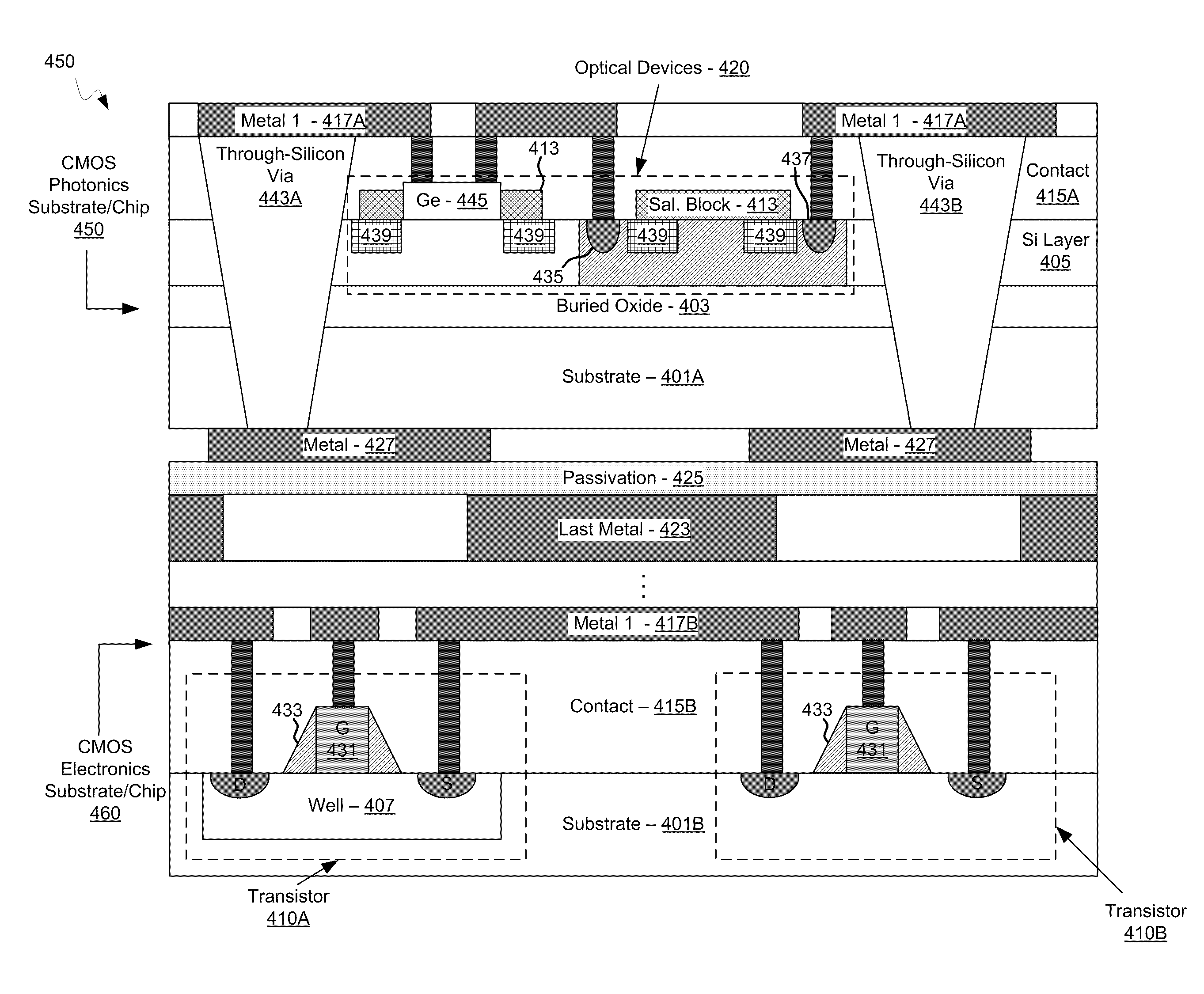

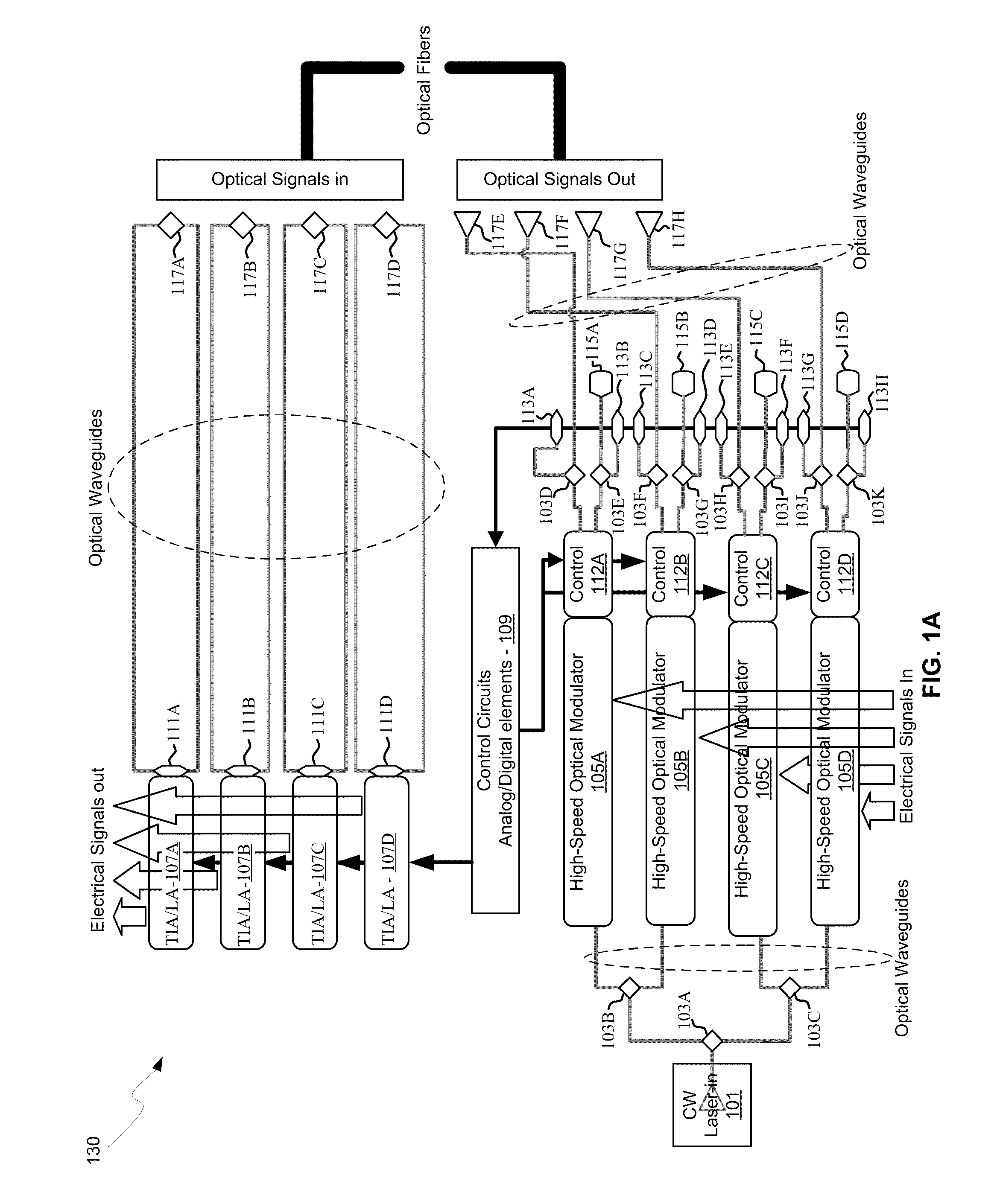

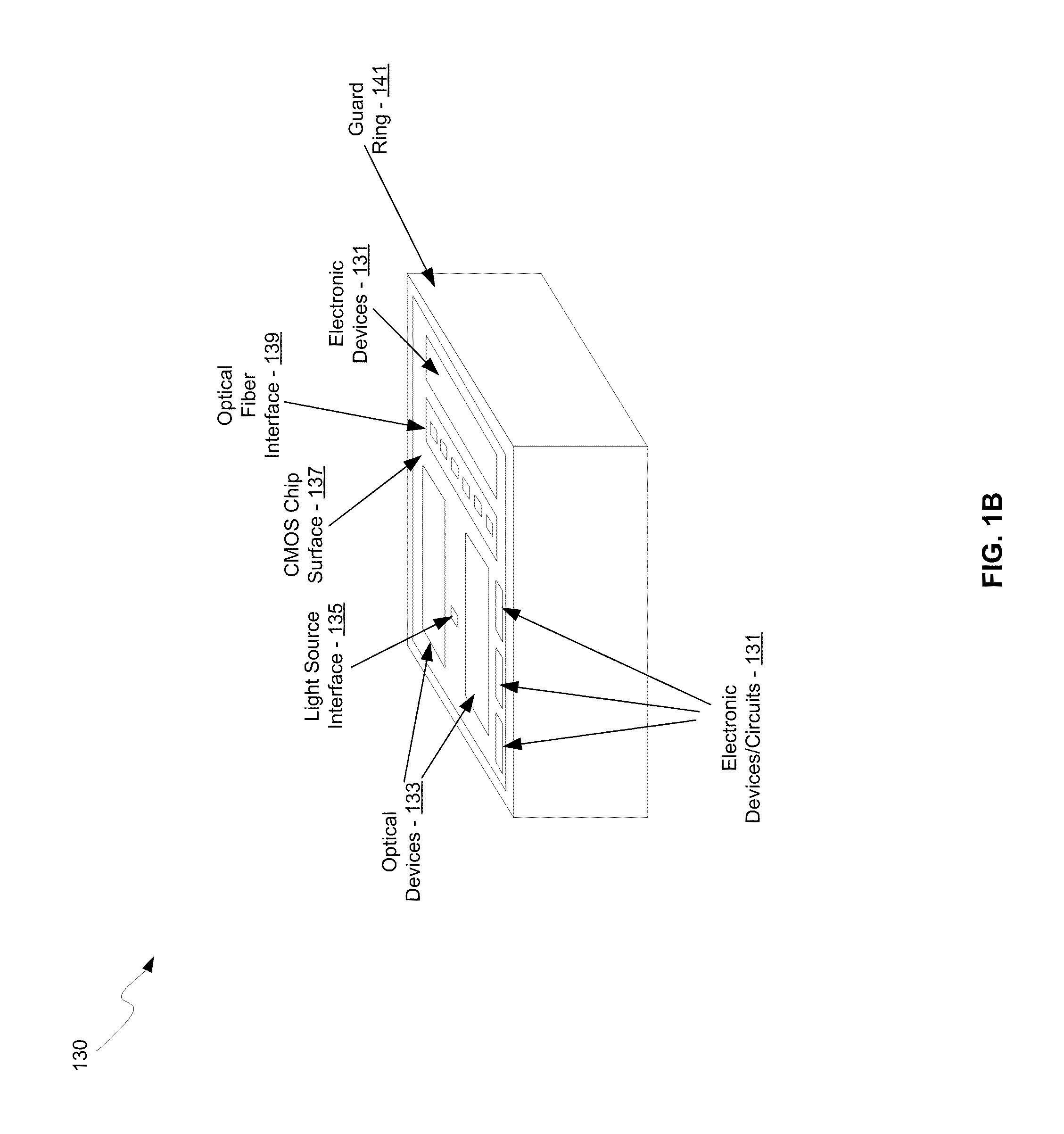

Method and system for monolithic integration of photonics and electronics in CMOS processes

ActiveUS20100059822A1Solid-state devicesSemiconductor/solid-state device manufacturingSoi cmosEtching

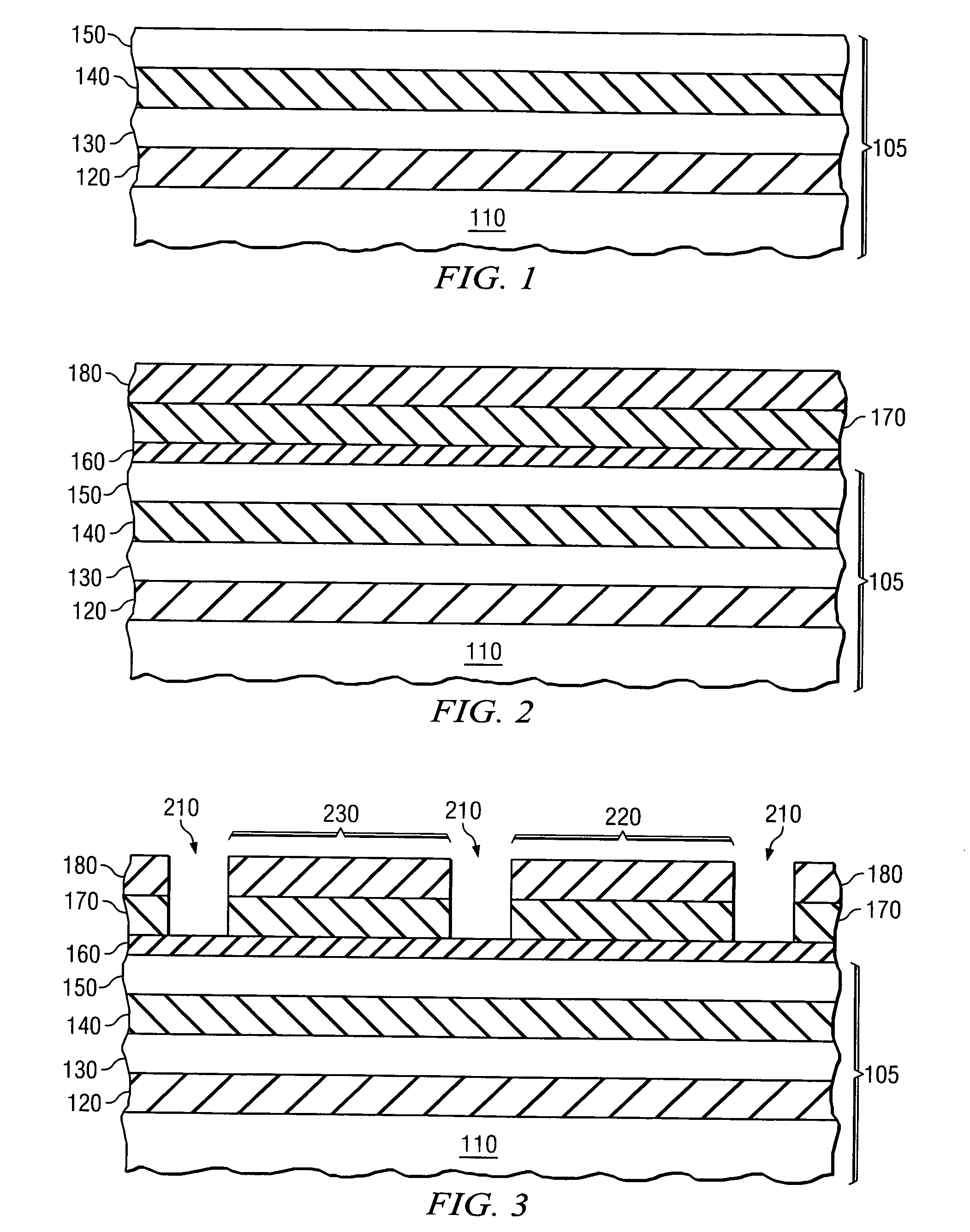

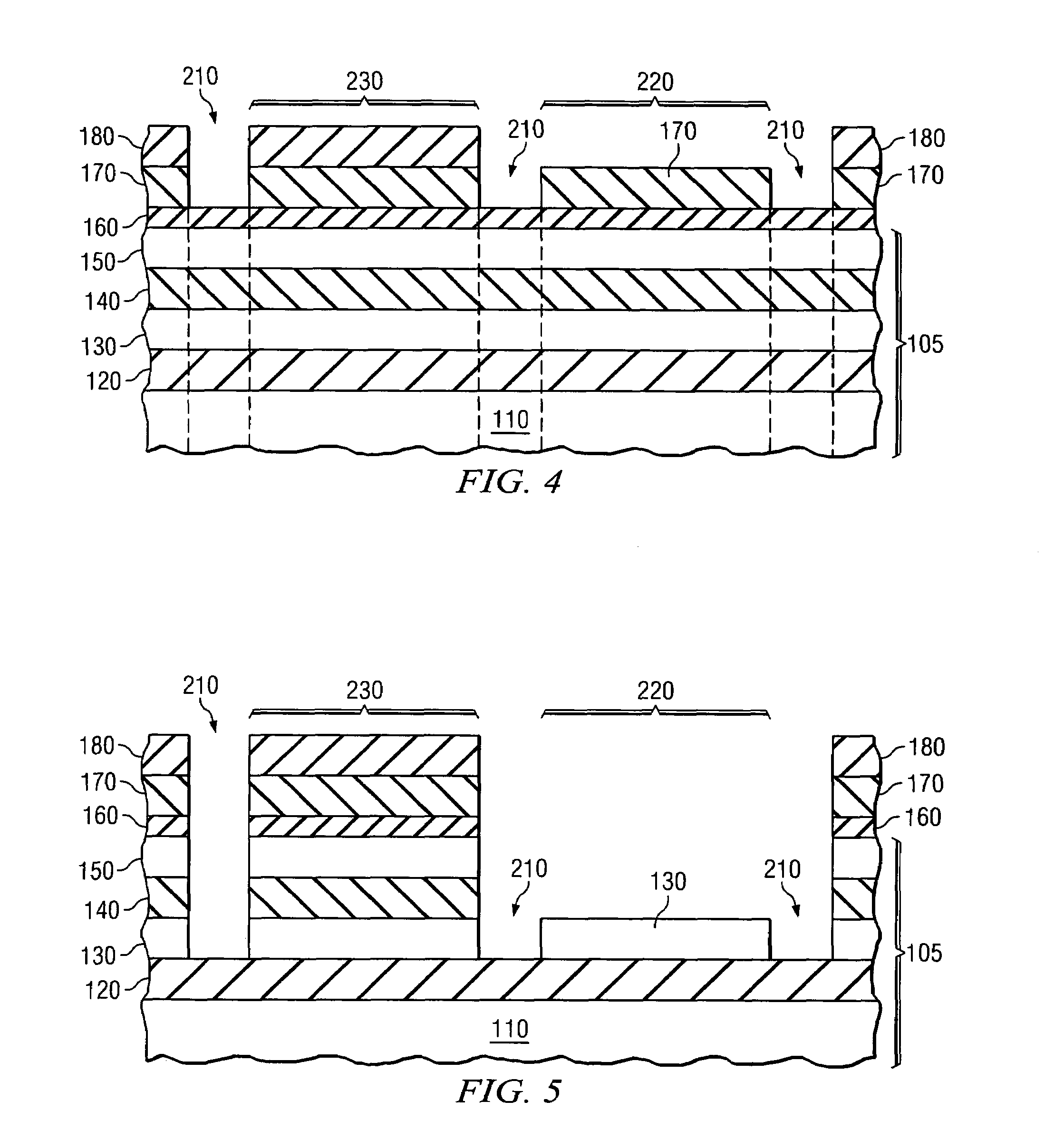

Methods and systems for monolithic integration of photonics and electronics in CMOS processes are disclosed and may include fabricating photonic and electronic devices on a single CMOS wafer with different silicon layer thicknesses. The devices may be fabricated on a semiconductor-on-insulator (SOI) wafer utilizing a bulk CMOS process and / or on a SOI wafer utilizing a SOI CMOS process. The different thicknesses may be fabricated utilizing a double SOI process and / or a selective area growth process. Cladding layers may be fabricated utilizing one or more oxygen implants and / or utilizing CMOS trench oxide on the CMOS wafer. Silicon may be deposited on the CMOS trench oxide utilizing epitaxial lateral overgrowth. Cladding layers may be fabricated utilizing selective backside etching. Reflective surfaces may be fabricated by depositing metal on the selectively etched regions. Silicon dioxide or silicon germanium integrated in the CMOS wafer may be utilized as an etch stop layer.

Owner:CISCO TECH INC

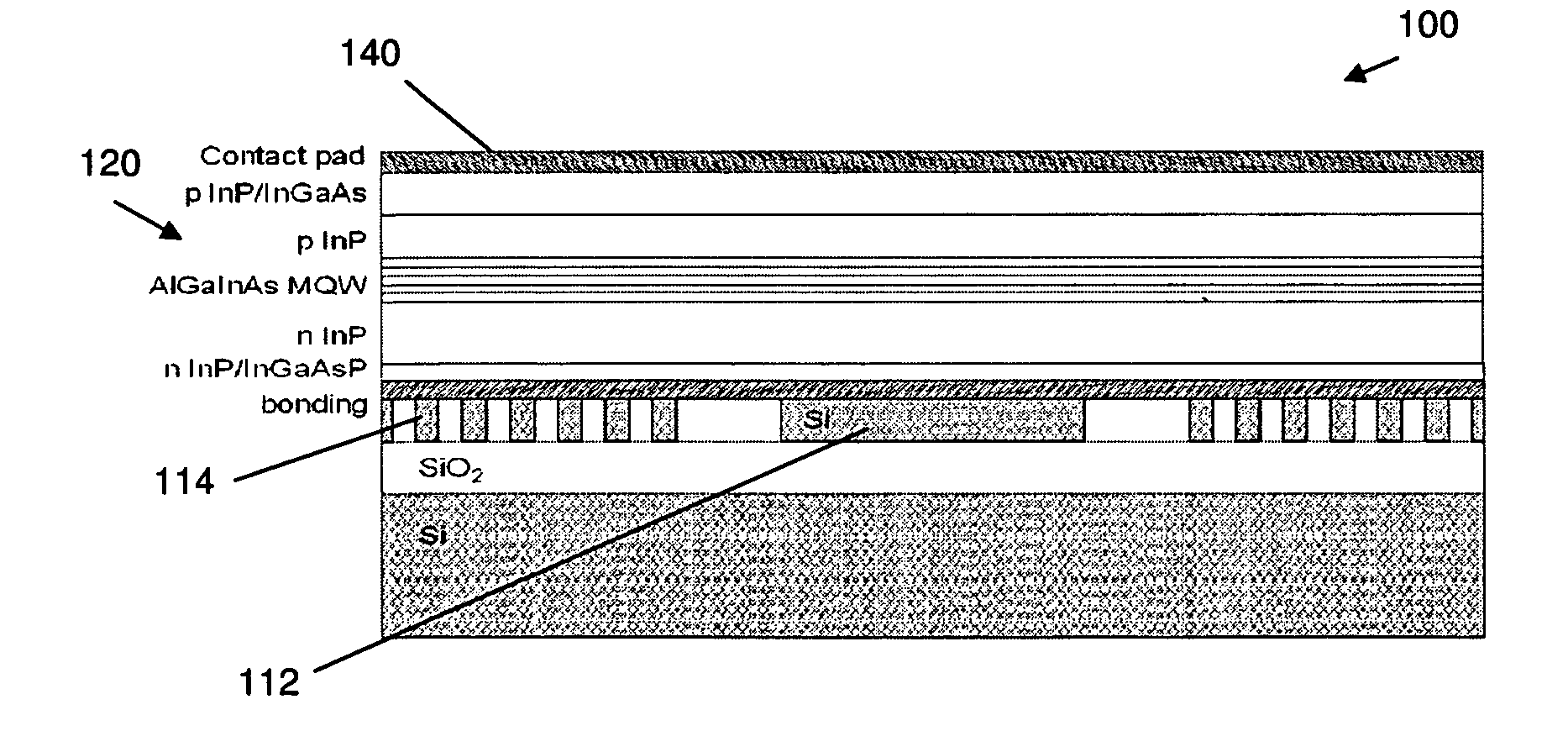

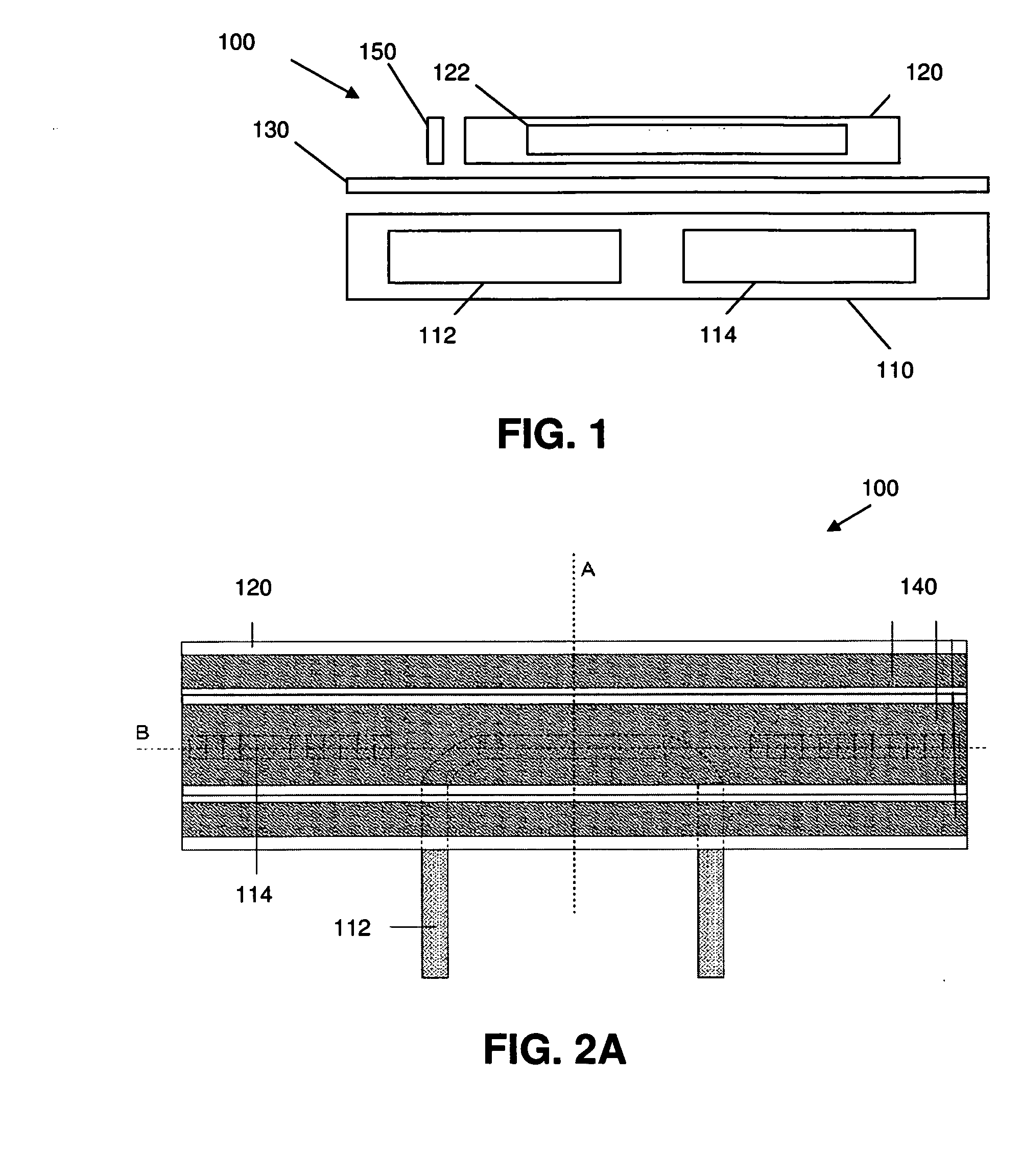

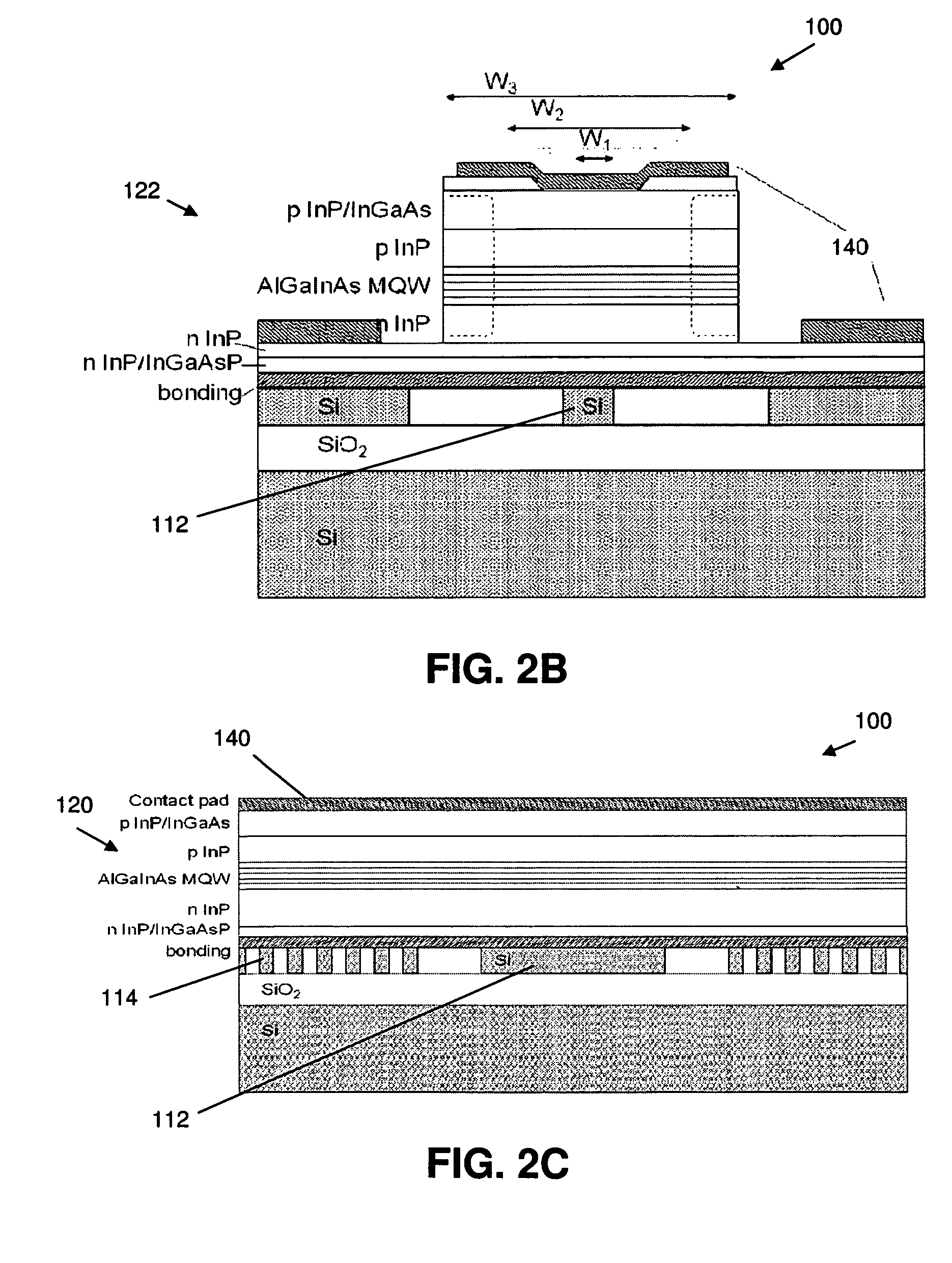

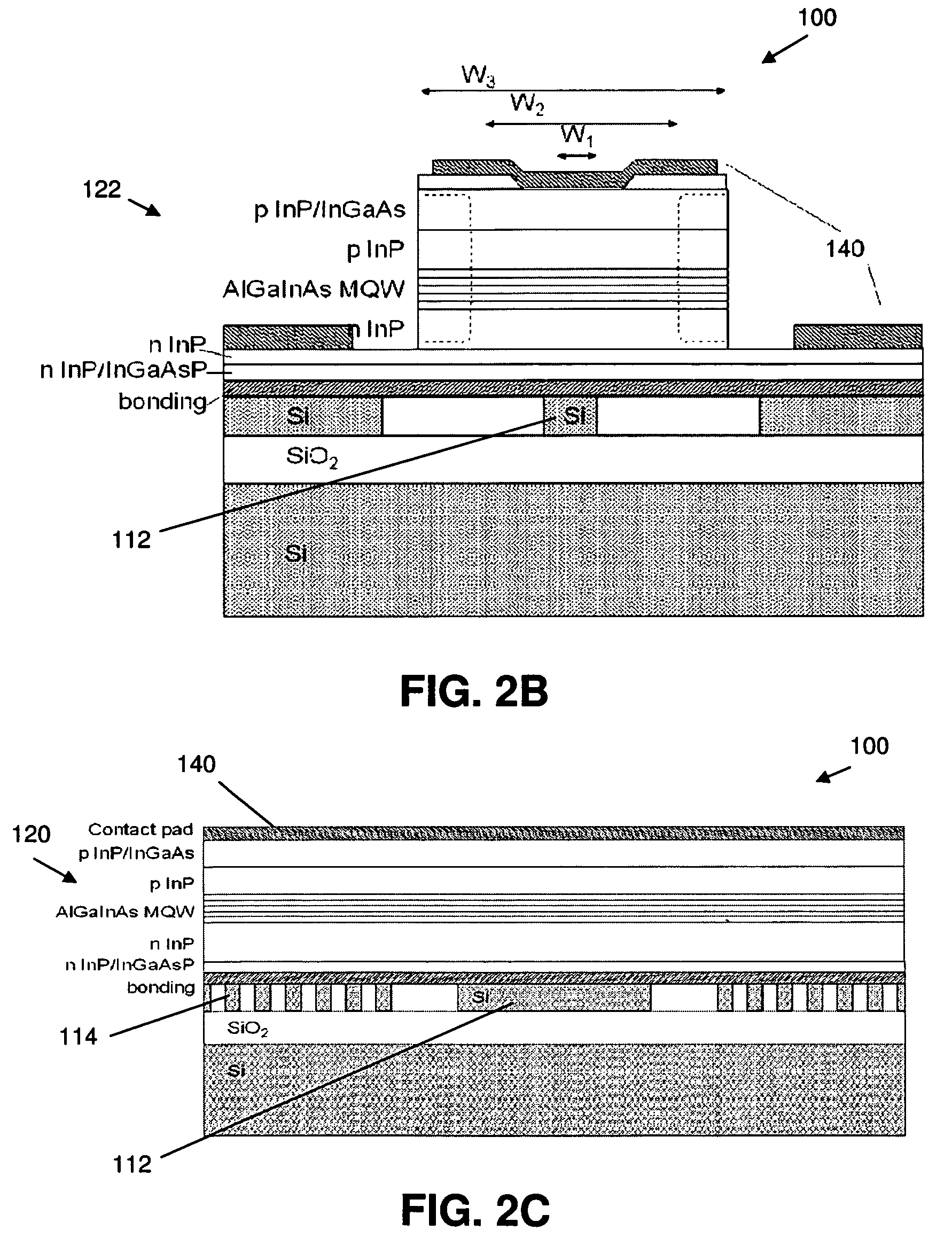

Laser light coupling into soi CMOS photonic integrated circuit

ActiveUS20120320939A1Less complexSmall sizeLaser detailsSemiconductor laser structural detailsSoi cmosCoupling

A hybrid laser for generating radiation includes an optical passive material and an optical active material. The laser includes a first optical waveguide and optical laser components with reflectors in the optical passive material. The first optical waveguide is adapted for coupling out radiation from the hybrid laser. The laser also includes a second optical waveguide defined in the optical active material. The optical laser components include reflectors defining a cavity and furthermore are adapted for providing laser cavity confinement in the first optical waveguide and the second optical waveguide. The second optical waveguide thereby is positioned at least partly over the first optical waveguide so that an evanescent coupling interface is defined between the second optical waveguide and the first optical waveguide and the evanescent coupling interface is positioned within the laser cavity.

Owner:UNIV GENT +1

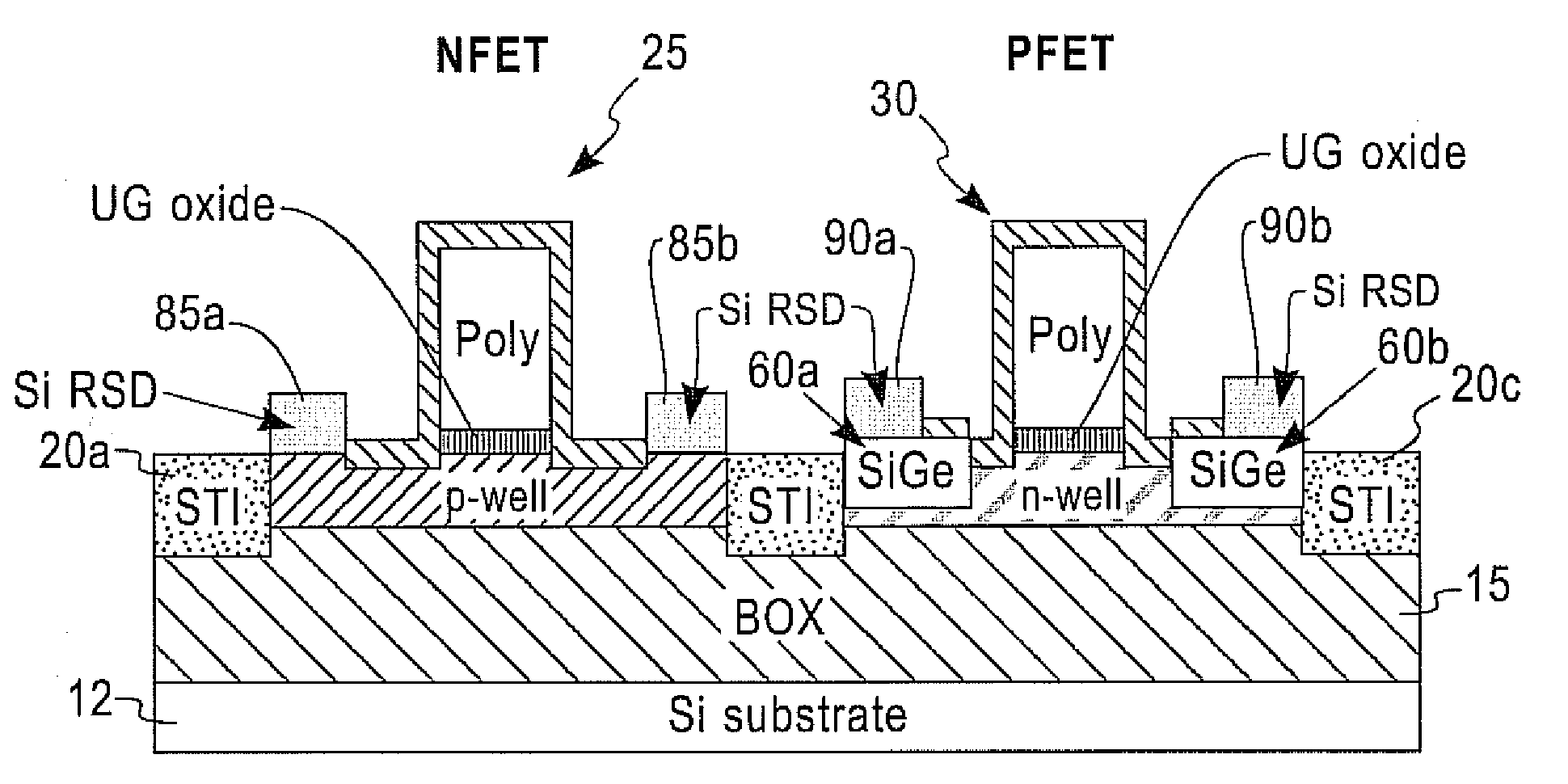

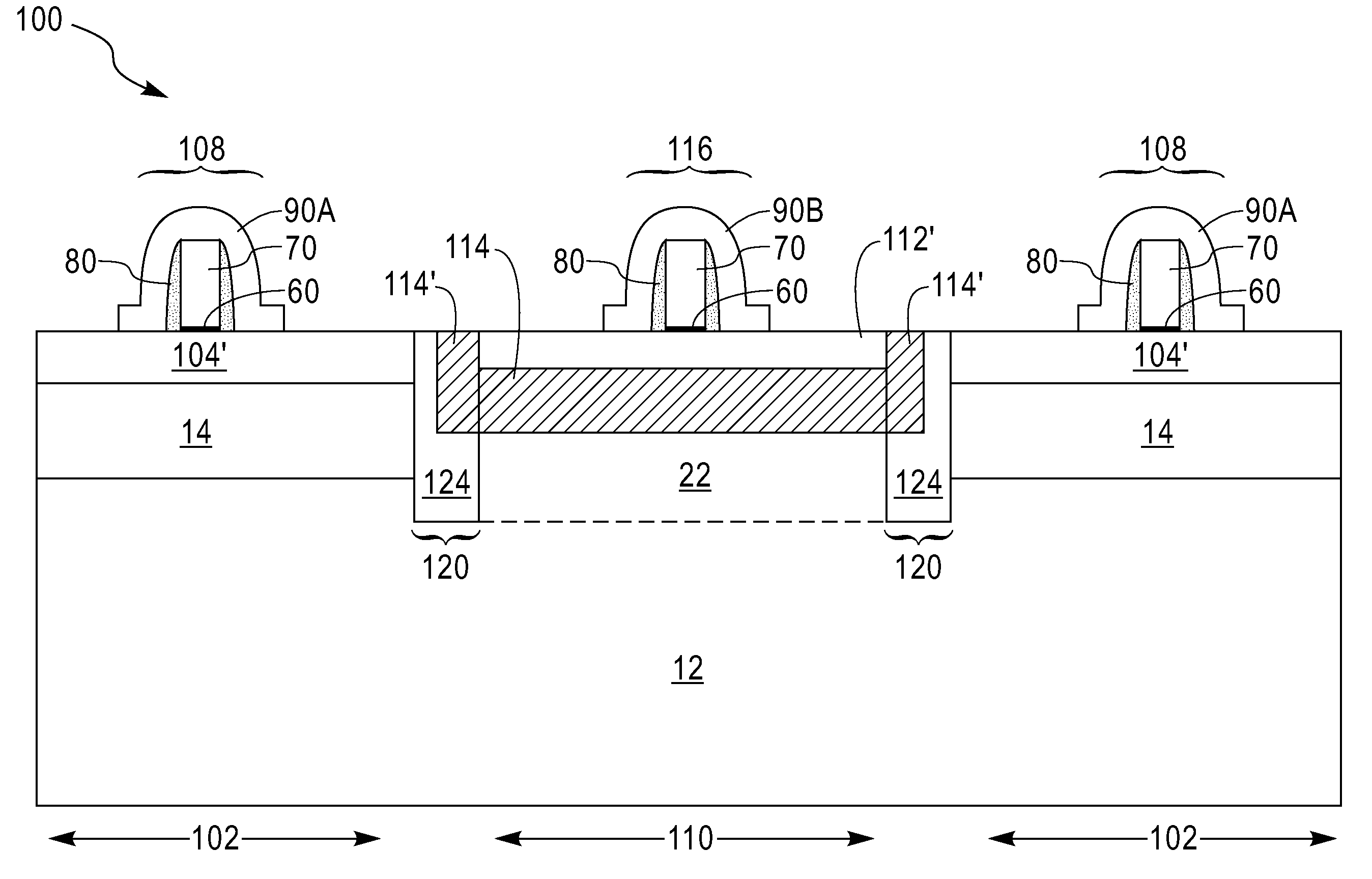

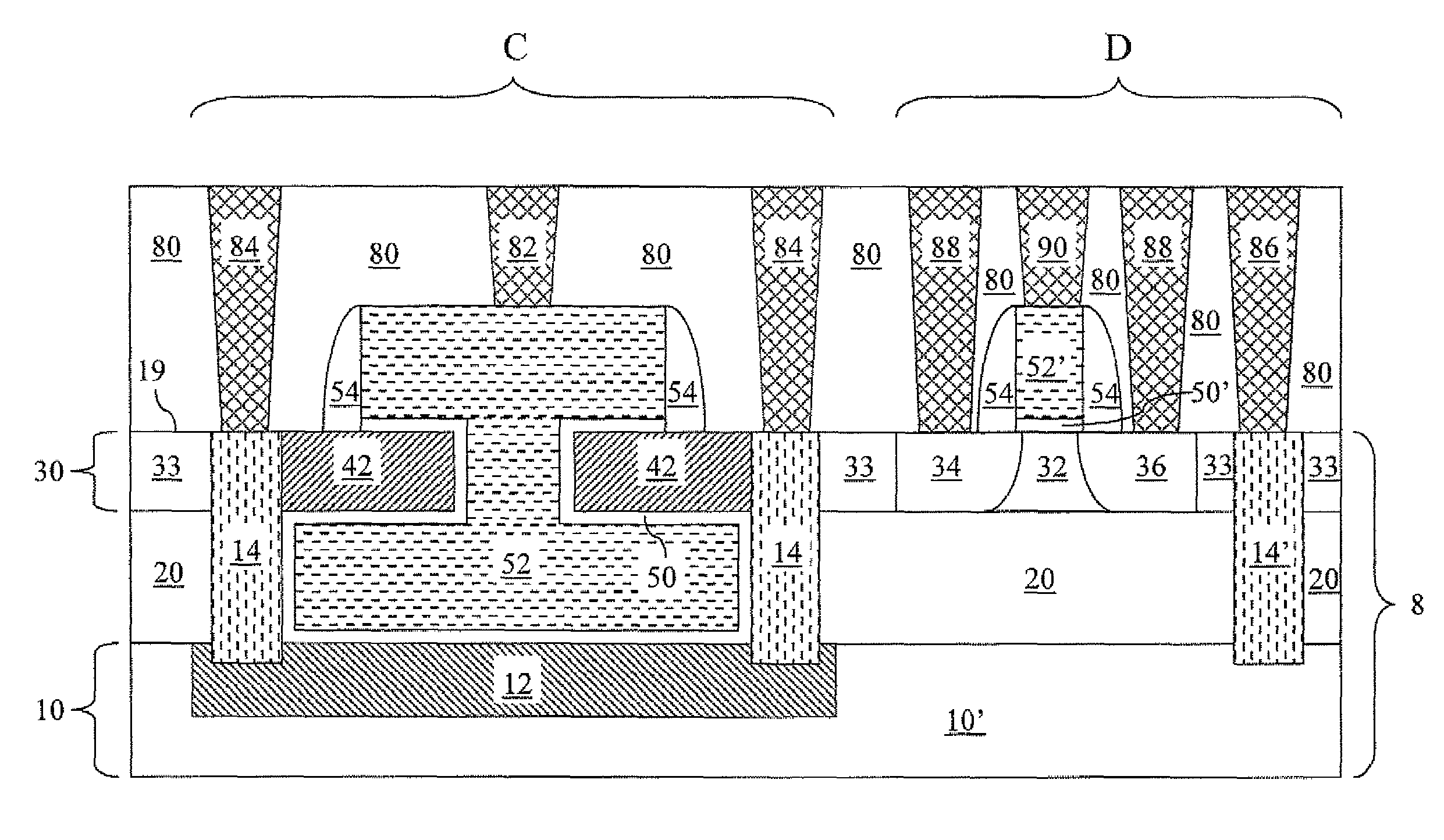

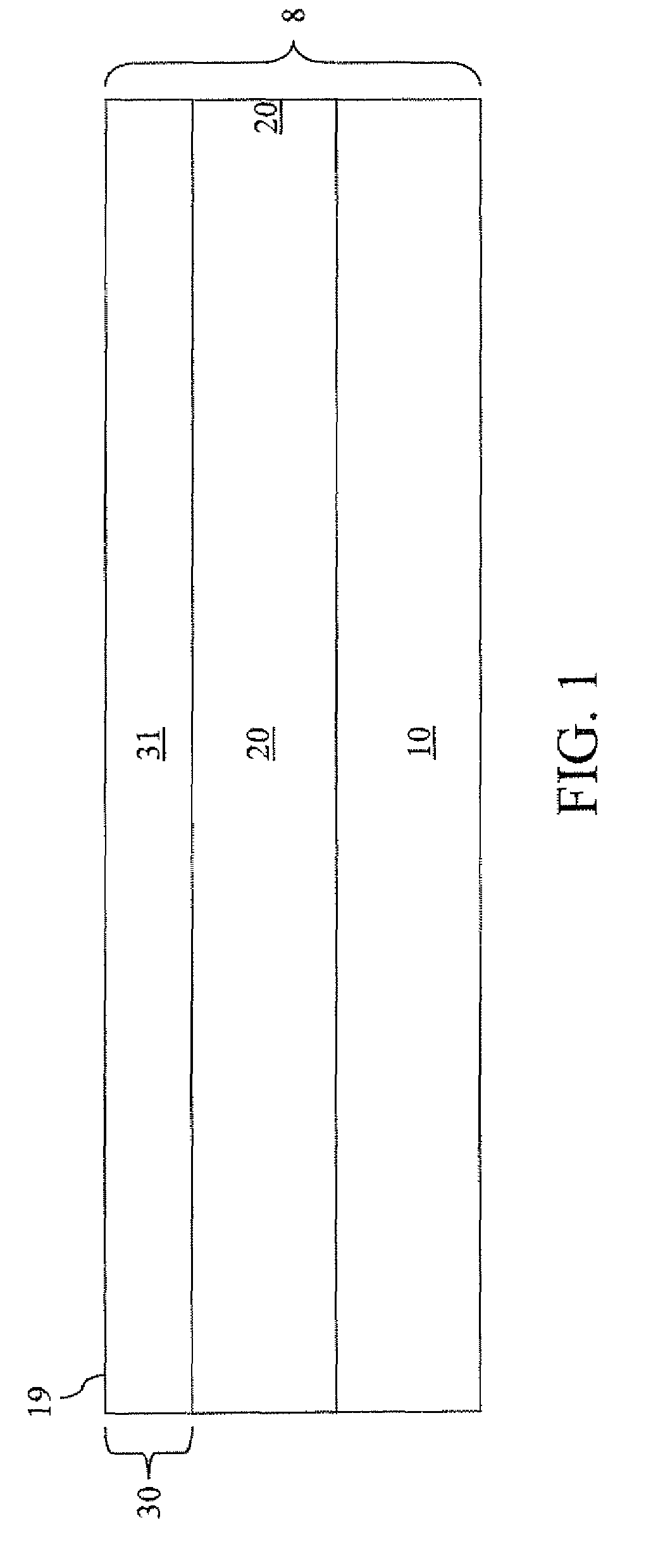

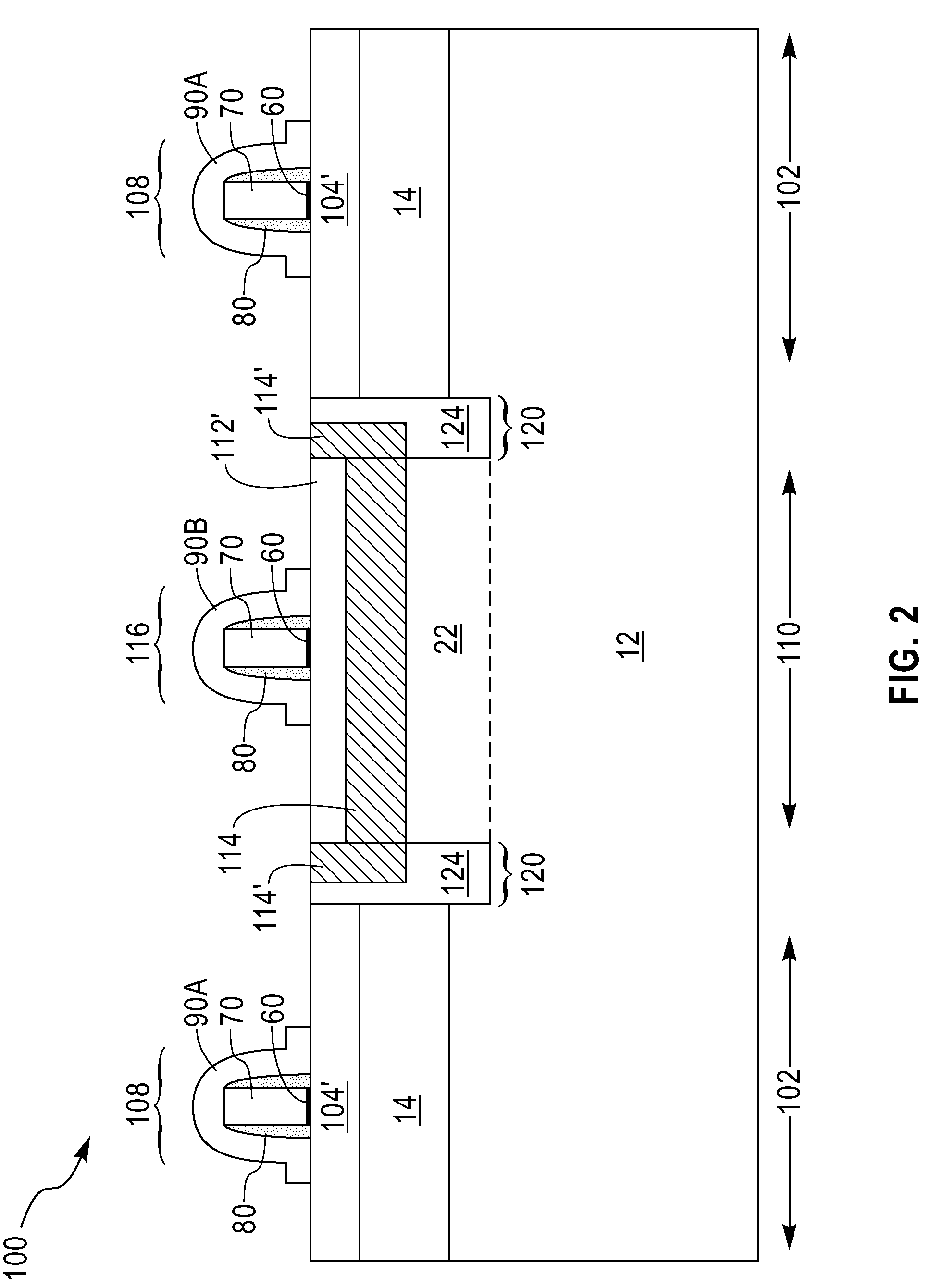

Ultra-thin soi CMOS with raised epitaxial source and drain and embedded sige pfet extension

InactiveUS20080217686A1Reduce contact resistanceReduce source/drain resistanceSolid-state devicesSemiconductor/solid-state device manufacturingSoi cmosCMOS

A method for improving channel carrier mobility in ultra-thin Silicon-on-oxide (UTSOI) FET devices by integrating an embedded pFET SiGe extension with raised source / drain regions. The method includes selectively growing embedded SiGe (eSiGe) extensions in pFET regions and forming strain-free raised Si or SiGe source / drain (RSD) regions on CMOS. The eSiGe extension regions enhance hole mobility in the pFET channels and reduce resistance in the pFET extensions. The strain-free raised source / drain regions reduce contact resistance in both UTSOI pFETs and nFETs.

Owner:IBM CORP +1

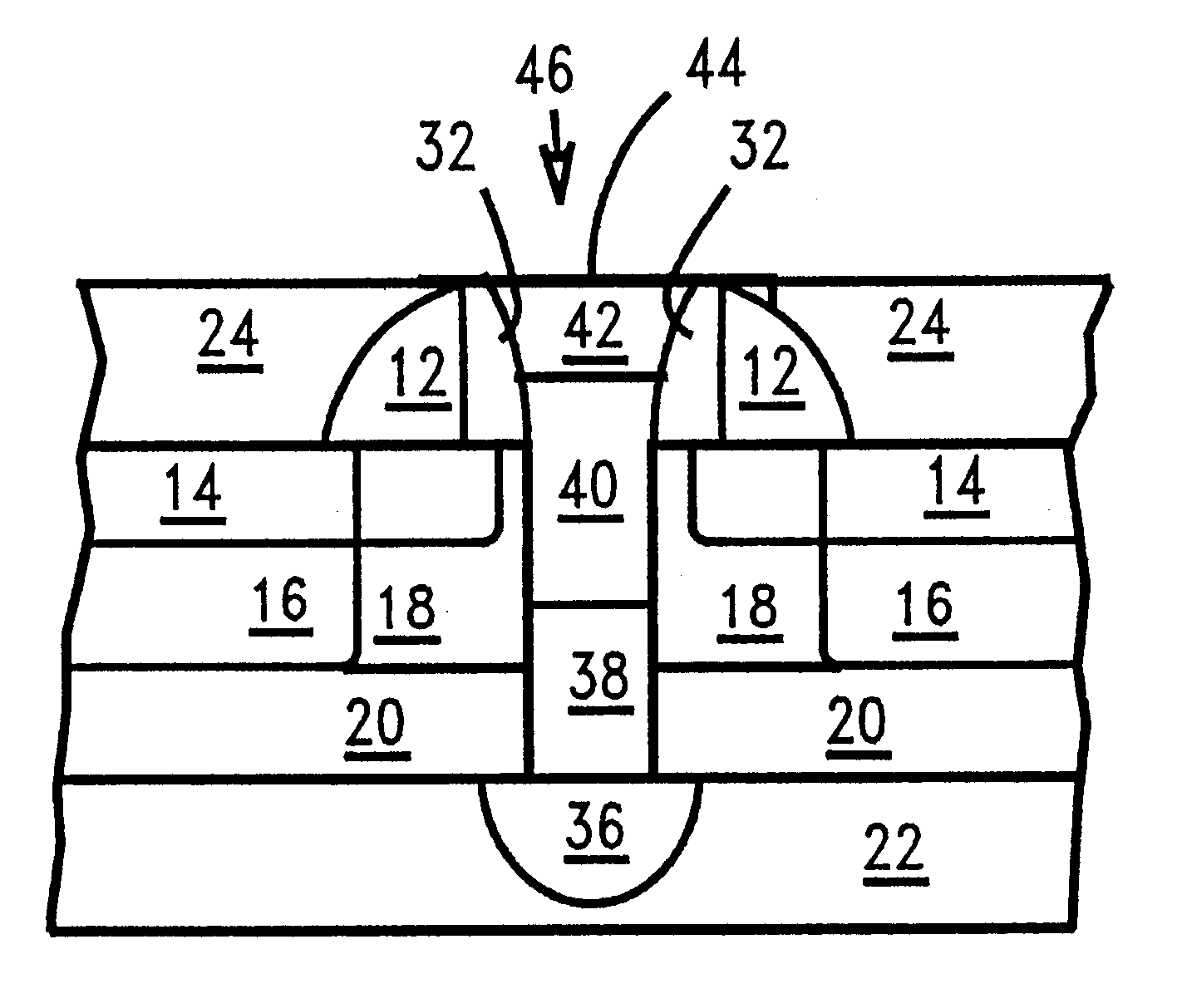

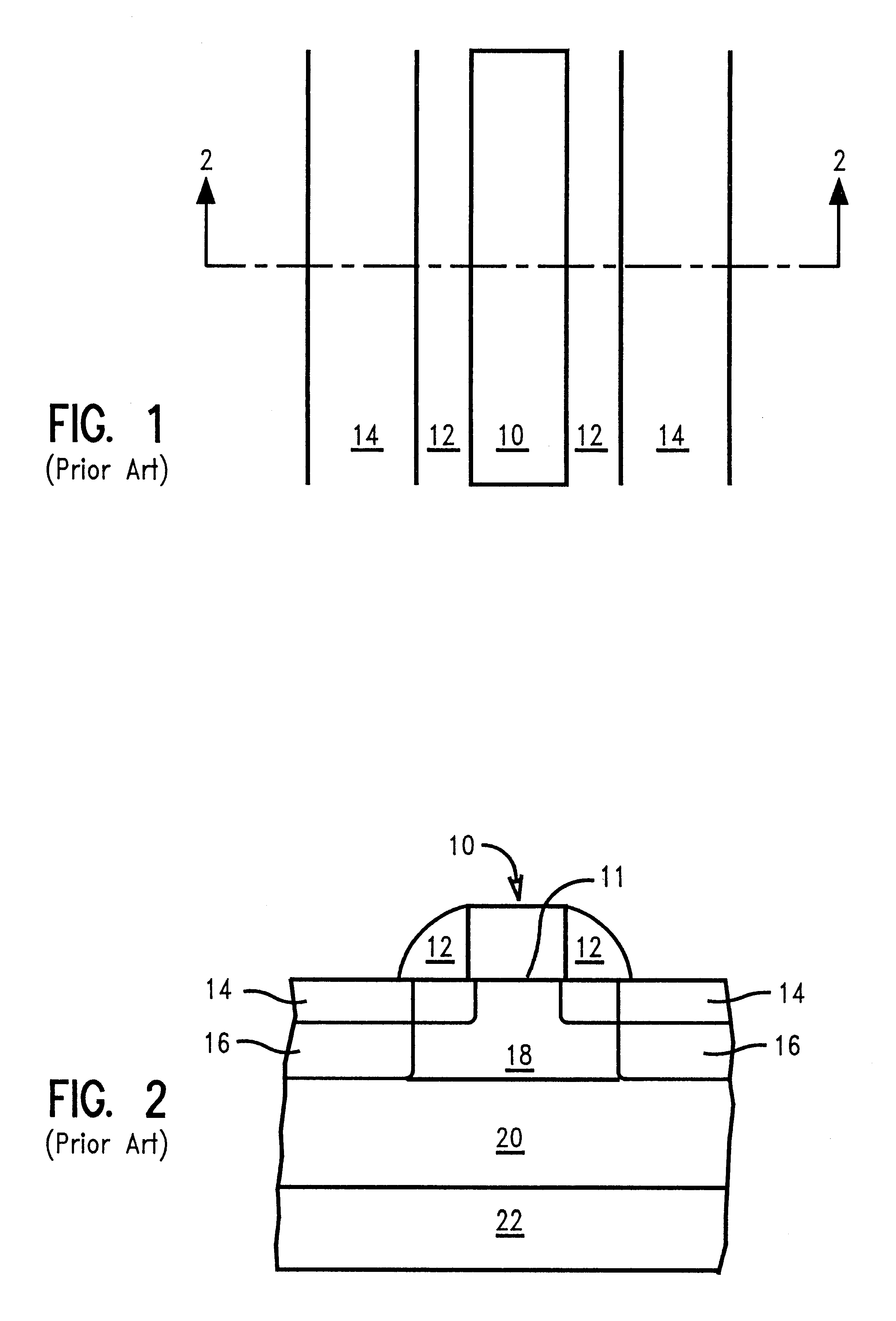

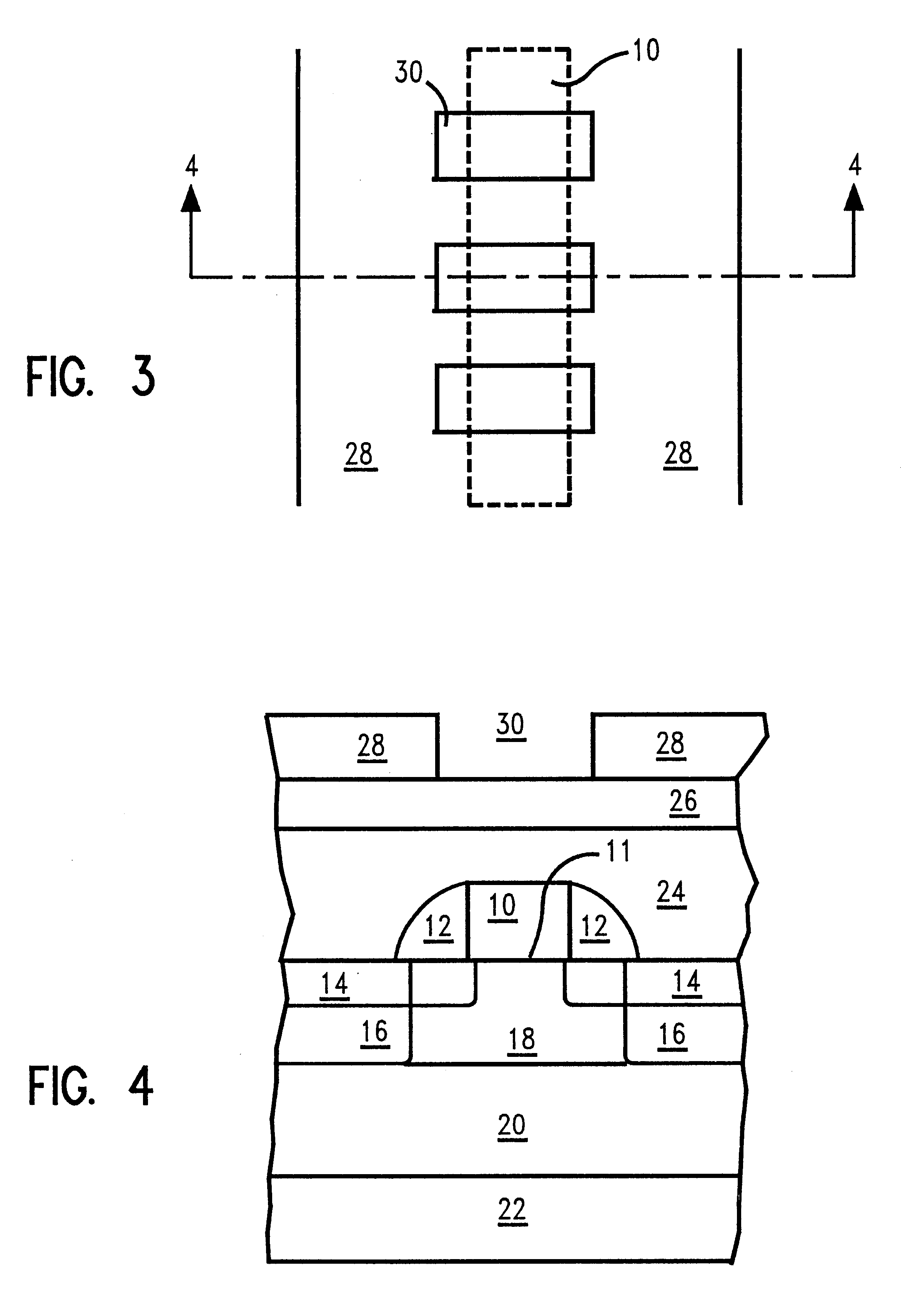

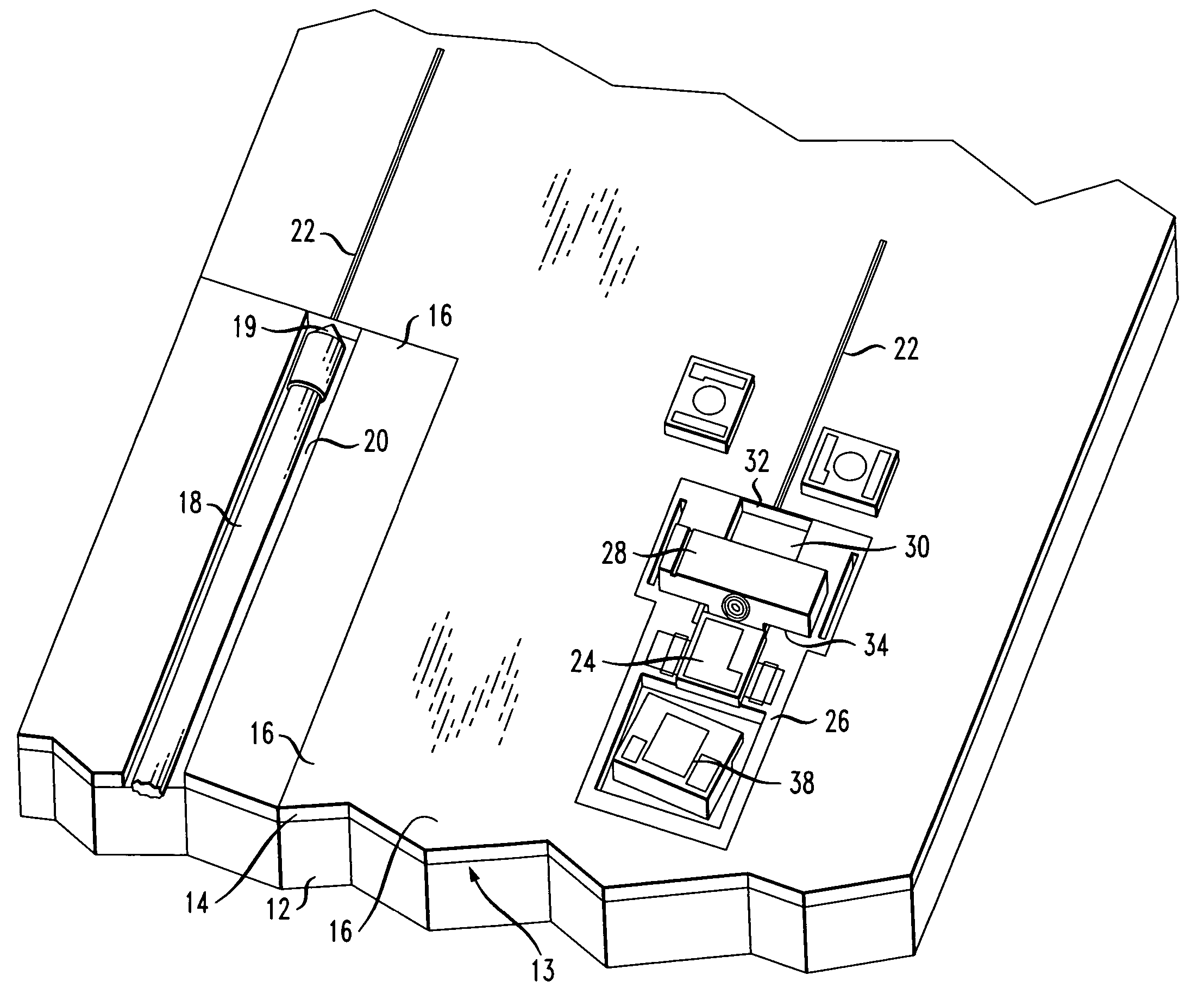

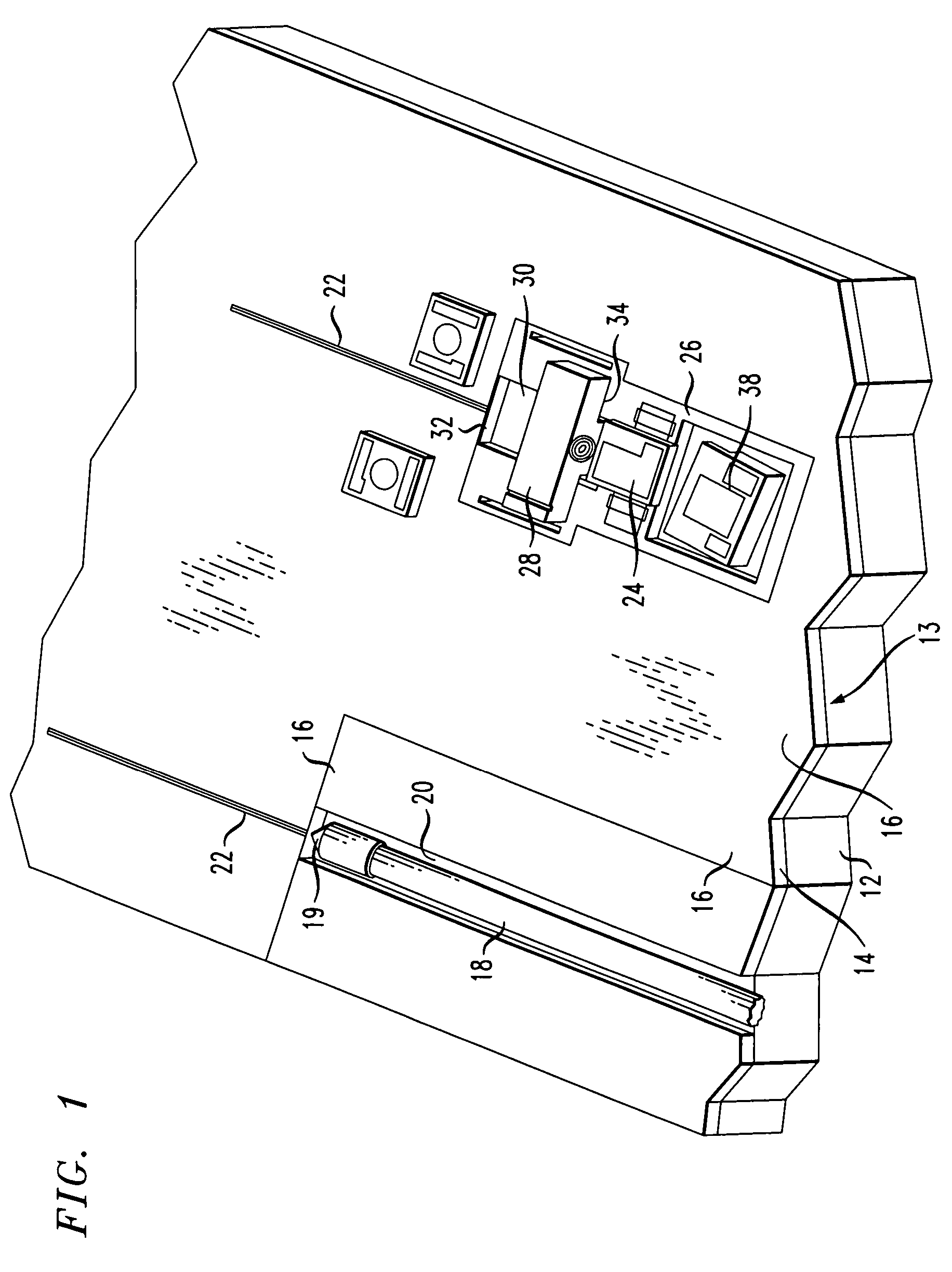

SOI CMOS body contact through gate, self-aligned to source- drain diffusions

A structure and process for making a semiconductor device with SOI body contacts under the gate conductor. The gate conductor is partitioned into segments and provides a body contact under each gate conductor segment over the width of the device. A plurality of body contacts may be distributed across the length of the gate conductor. This results in a relatively short path for holes leaving the body to traverse and allows accumulated charge to be removed from the body region under the gate. The structure provides for stable and efficient body-contact operation for SOI MOSFETS of any width operating at high speeds.

Owner:GLOBALFOUNDRIES INC

Super hybrid soi CMOS devices

InactiveUS20080303090A1Improve mobilityLower the pressure valueSolid-state devicesSemiconductor/solid-state device manufacturingSoi cmosSurface layer

The present invention provides semiconductor structures comprised of stressed channels on hybrid oriented. In particular, the semiconductor structures include a first active area having a first stressed semiconductor surface layer of a first crystallographic orientation located on a surface of a buried insulating material and a second active area having a second stressed semiconductor surface layer of a second crystallographic orientation located on a surface of a dielectric material. A trench isolation region is located between the first and second active area, and the trench isolation region is partially filled with a trench dielectric material and the dielectric material that is present underneath said second stressed semiconductor surface layer. The dielectric material within the trench isolation region has lower stress compared to that is used in conventional STI process and it is laterally abuts at least the second stressed semiconductor surface layer and extends to an upper surface of the trench isolation region.

Owner:IBM CORP

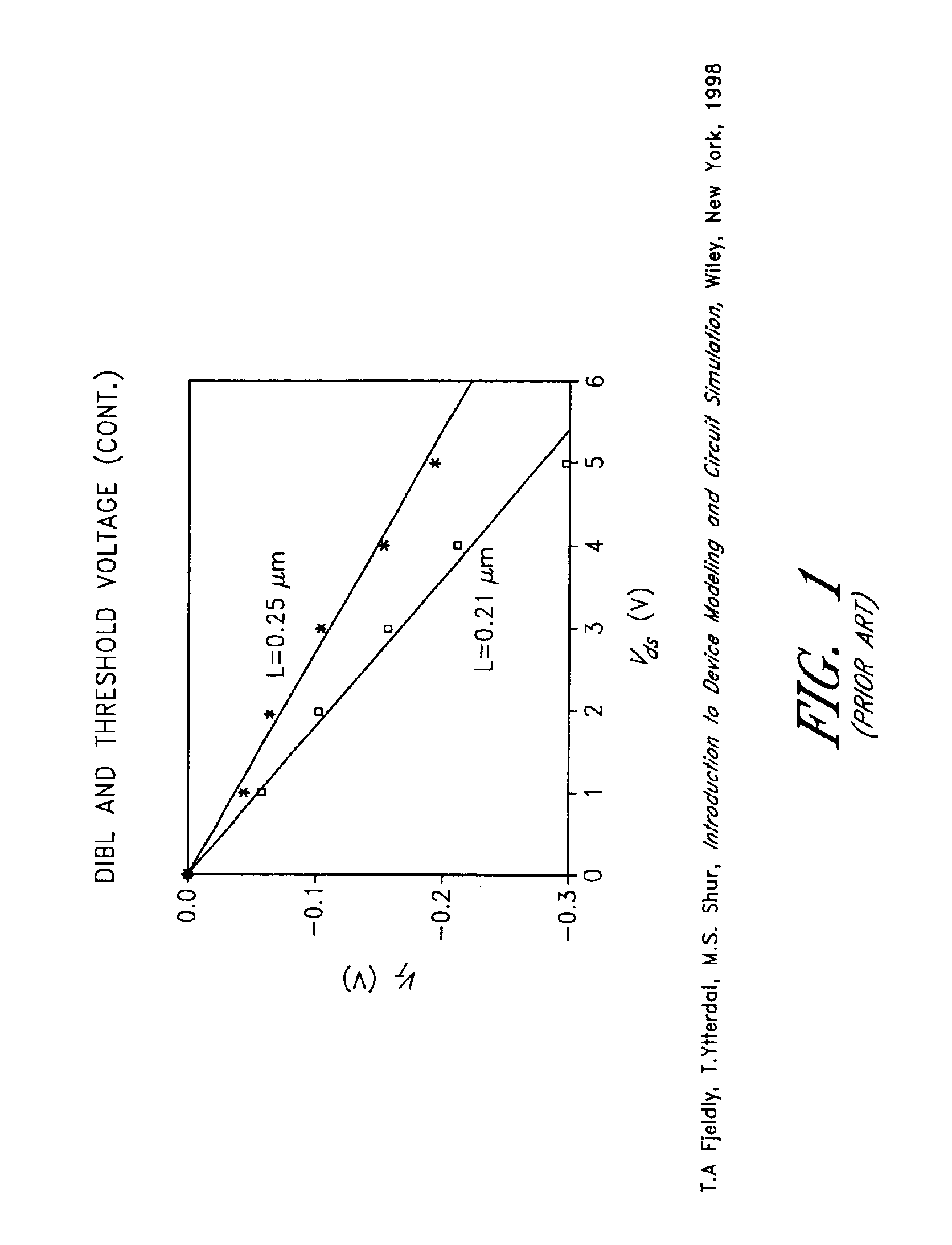

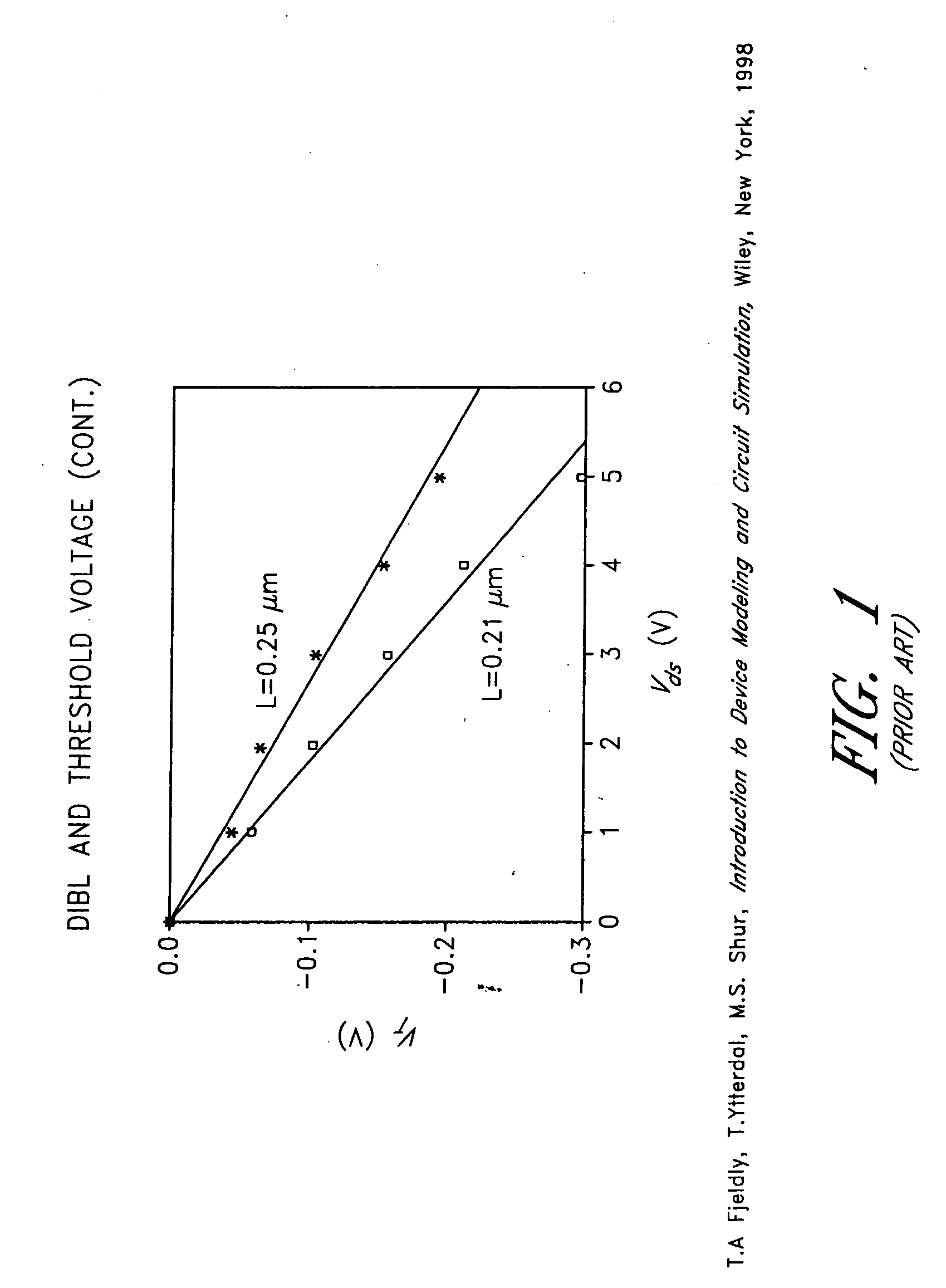

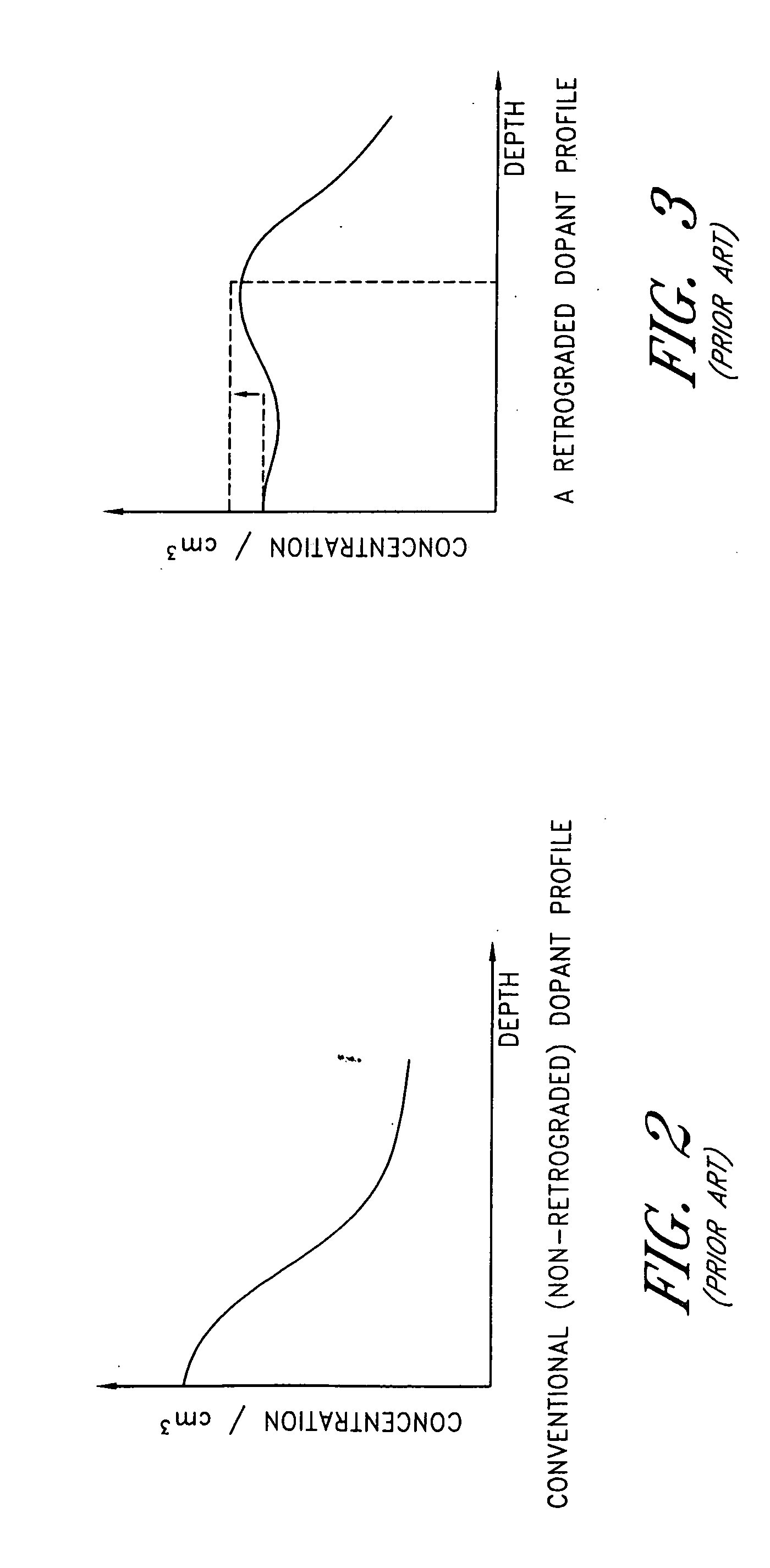

SOI CMOS device with reduced DIBL

ActiveUS6872640B1Prevent penetrationSolid-state devicesSemiconductor/solid-state device manufacturingSoi cmosDopant

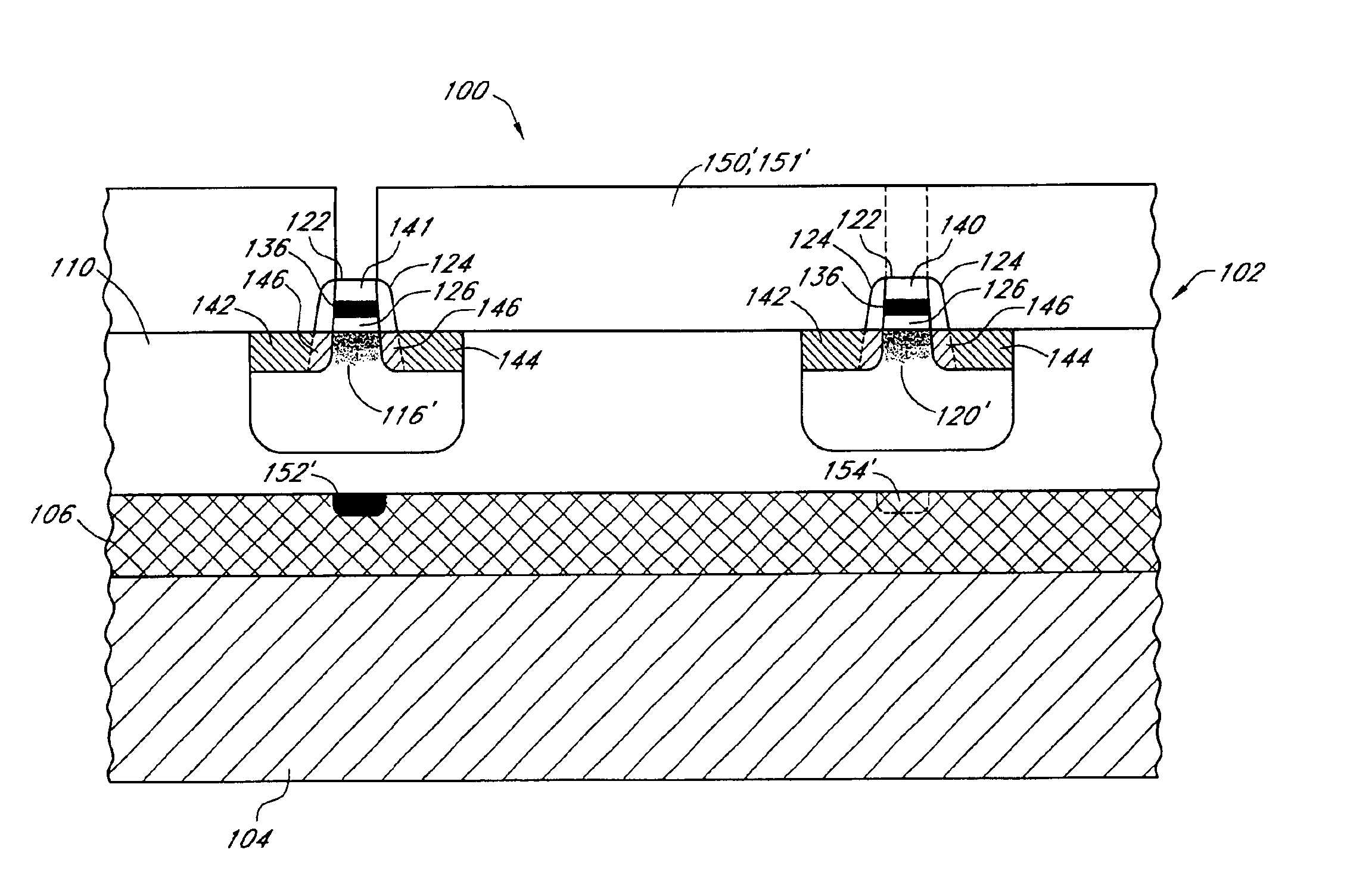

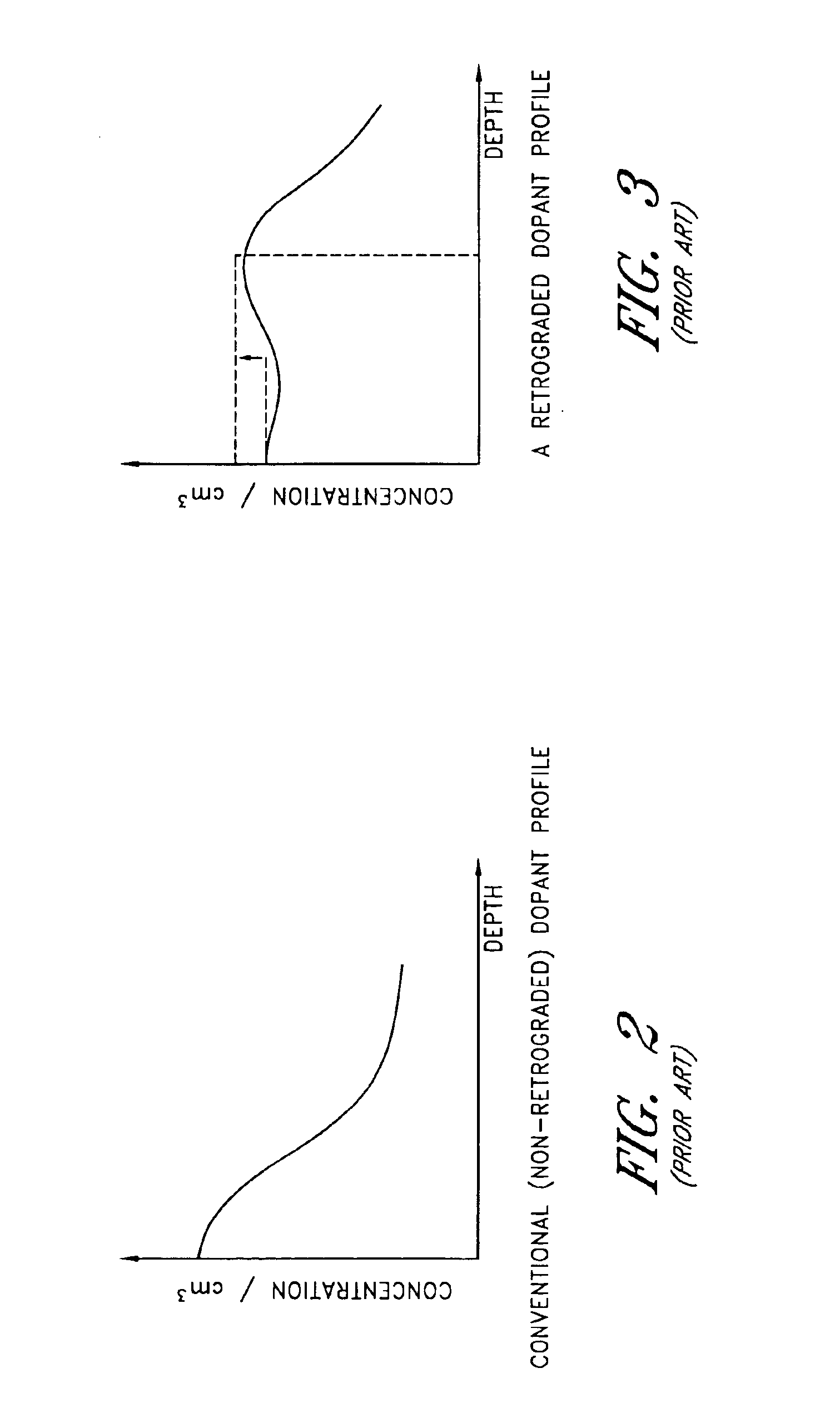

CMOS devices formed with a Silicon On Insulator (SOI) technology with reduced Drain Induced Barrier Lowering (DIBL) characteristics and a method for producing the same. The method involves a high energy, high dose implant through openings in a masking layer and through channel regions of the p- and n-wells, into the insulator layer, thereby creating a borophosphosilicate glass (BPSG) diffusion source within the insulation layer underlying the gate regions of the SOI wafer substantially between the source and drain. Backend high temperature processing steps induce diffusion of the dopants contained in the diffusion source into the p- and n-wells, thereby forming asymmetric retrograde dopant profiles in the channel under the gate. The method can be selectively applied to selected portions of a wafer to tailor device characteristics, such as for memory cells.

Owner:APTINA IMAGING CORP

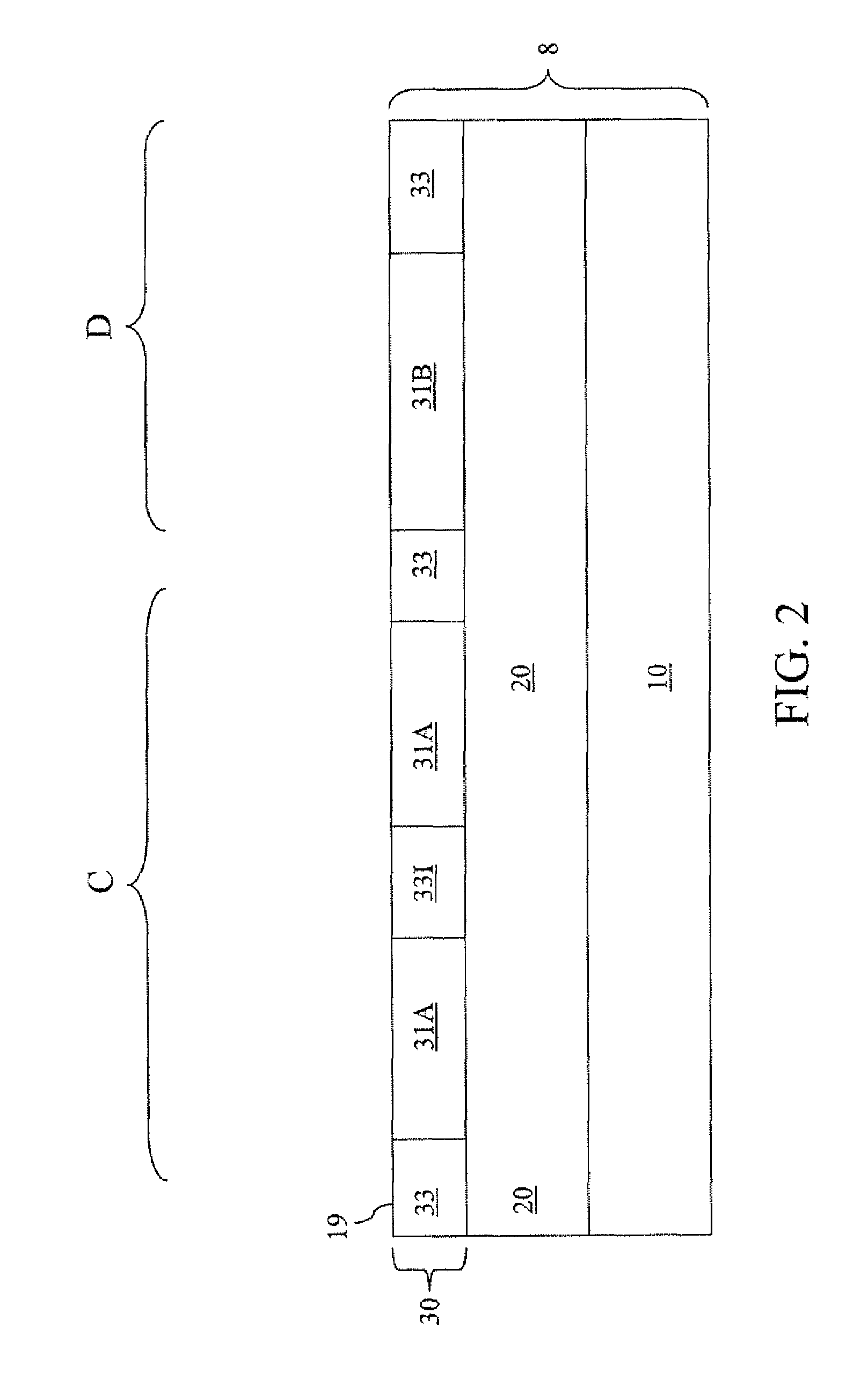

CMOS on SOI substrates with hybrid crystal orientations

Methods and structures for CMOS devices with hybrid crystal orientations using double SOI substrates is provided. In accordance with preferred embodiments, a manufacturing sequence includes the steps of forming an SOI silicon epitaxy layer after the step of forming shallow trench isolation regions. The preferred sequence allows hybrid SOI CMOS fabrication without encountering problems caused by forming STI regions after epitaxy. A preferred device includes an NFET on a {100} crystal orientation and a PFET on a {110} crystal orientation. An NMOS channel may be oriented along the <100> direction, which is the direction of maximum electron mobility for a {100} substrate. A PMOS channel may be oriented along the <110> direction, which is the direction where hole mobility is maximum for a {110} substrate.

Owner:TAIWAN SEMICON MFG CO LTD

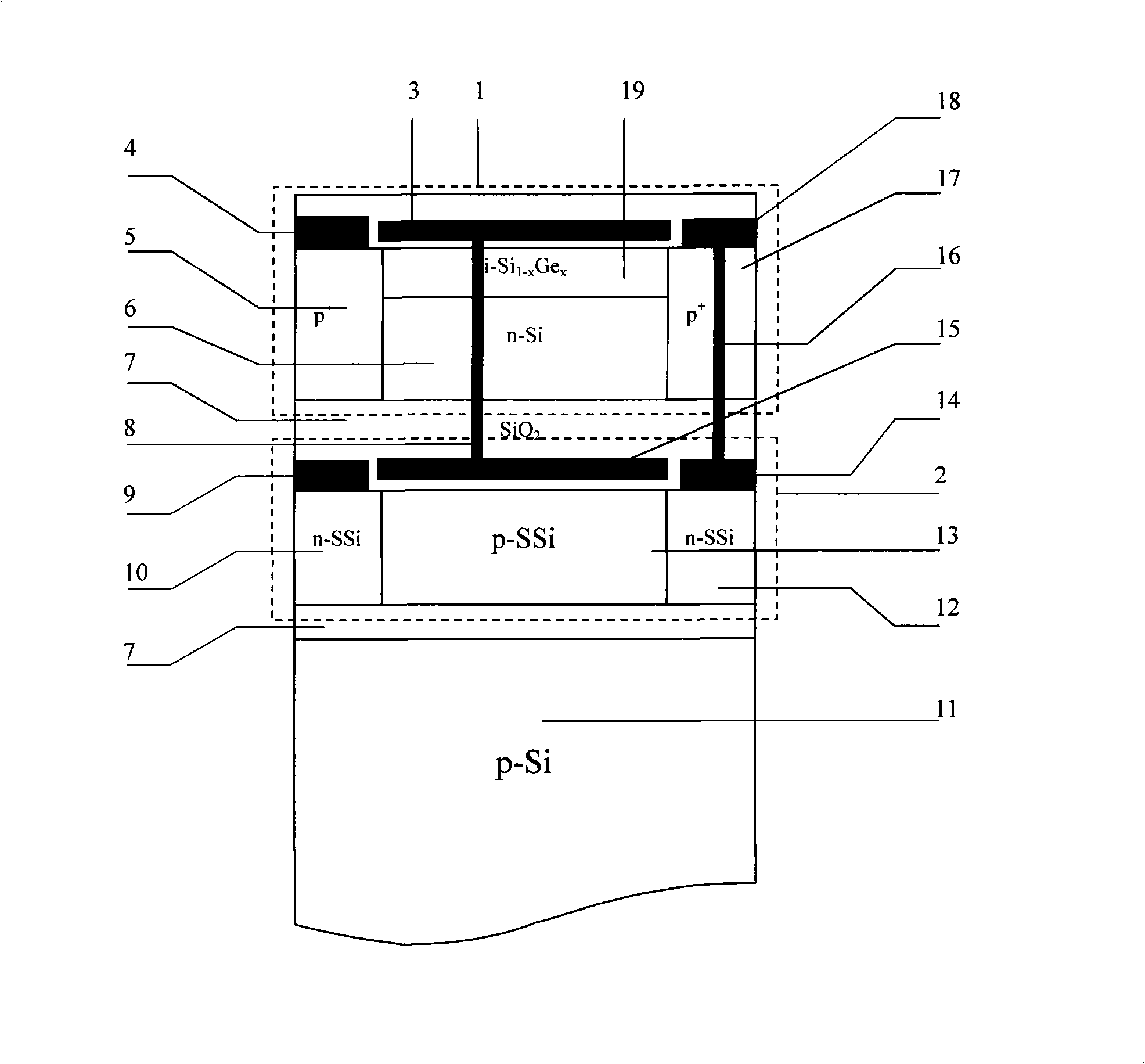

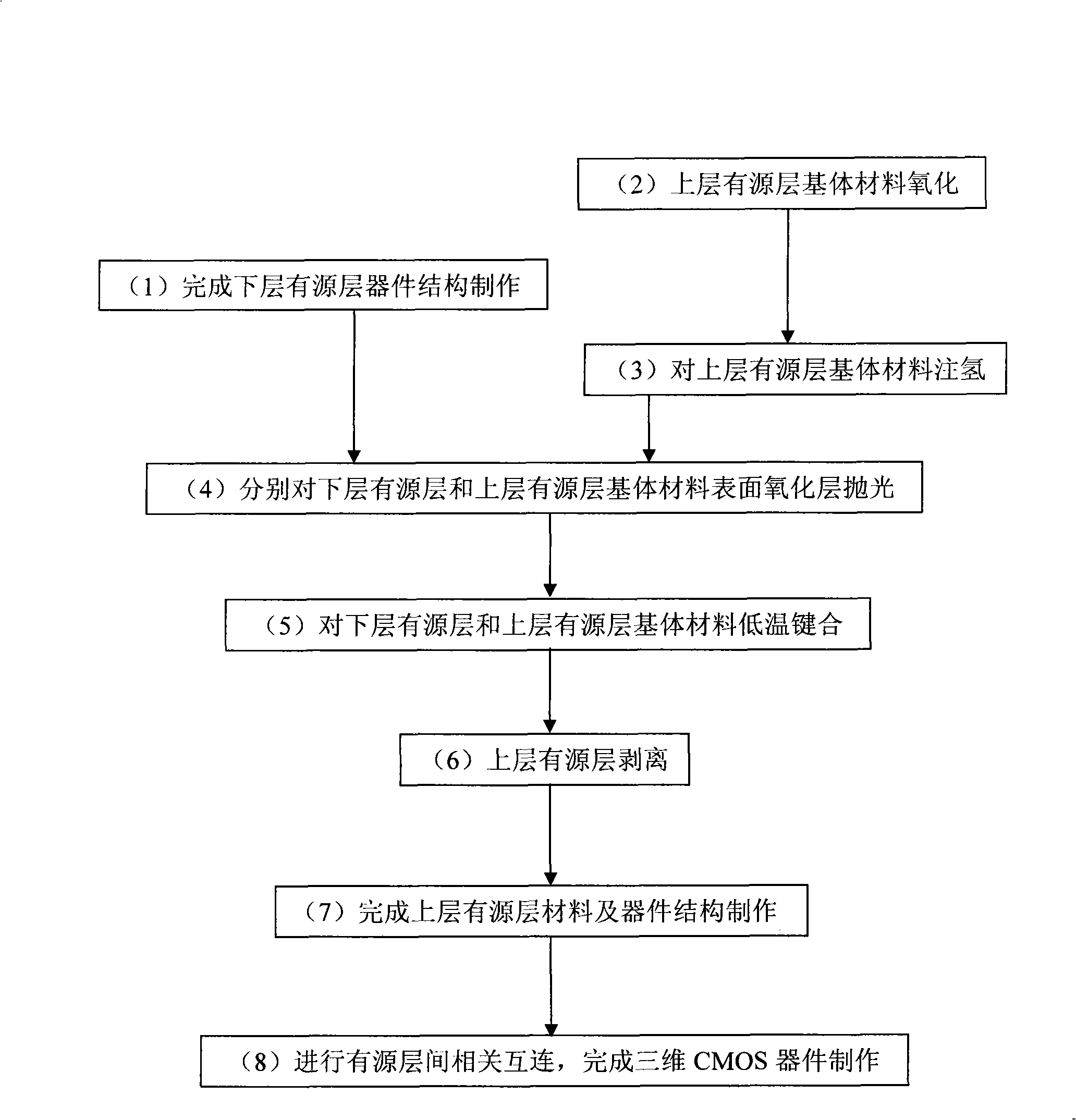

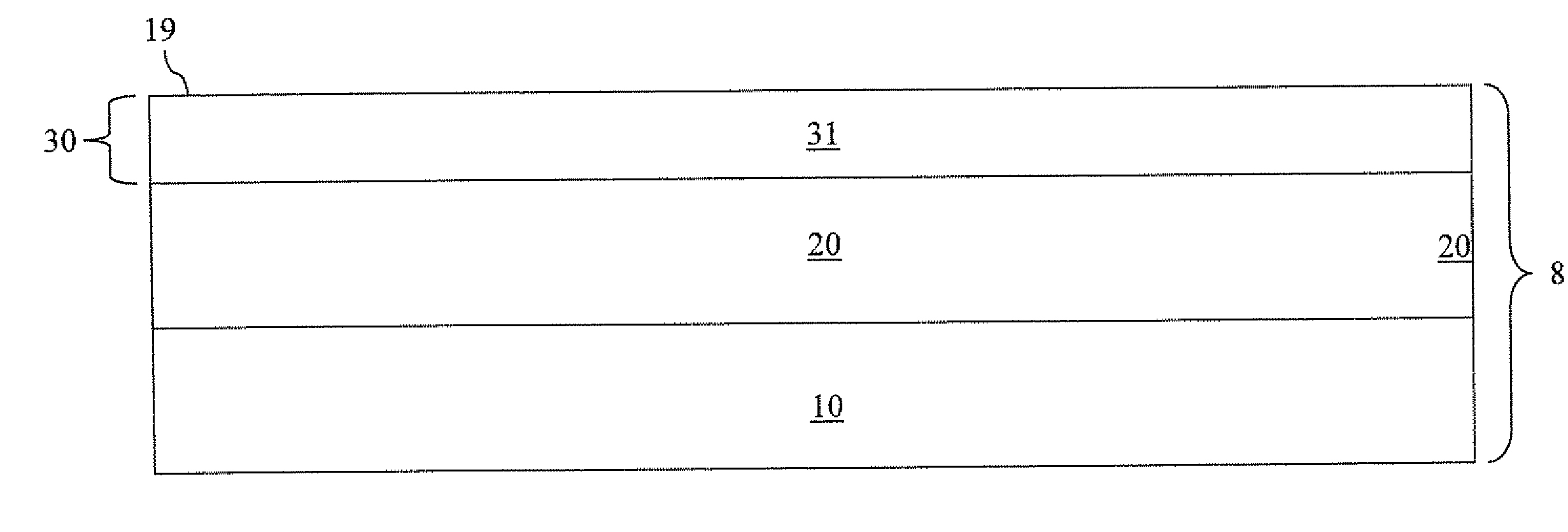

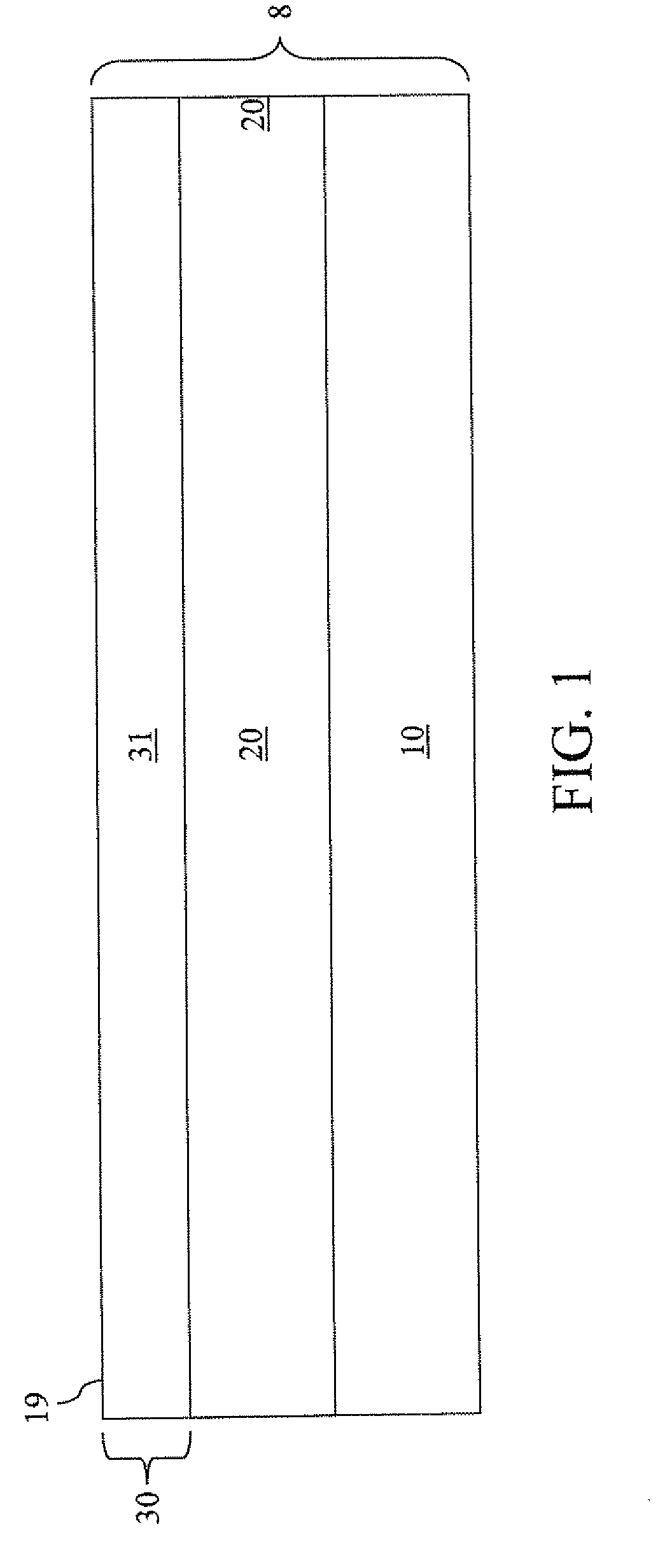

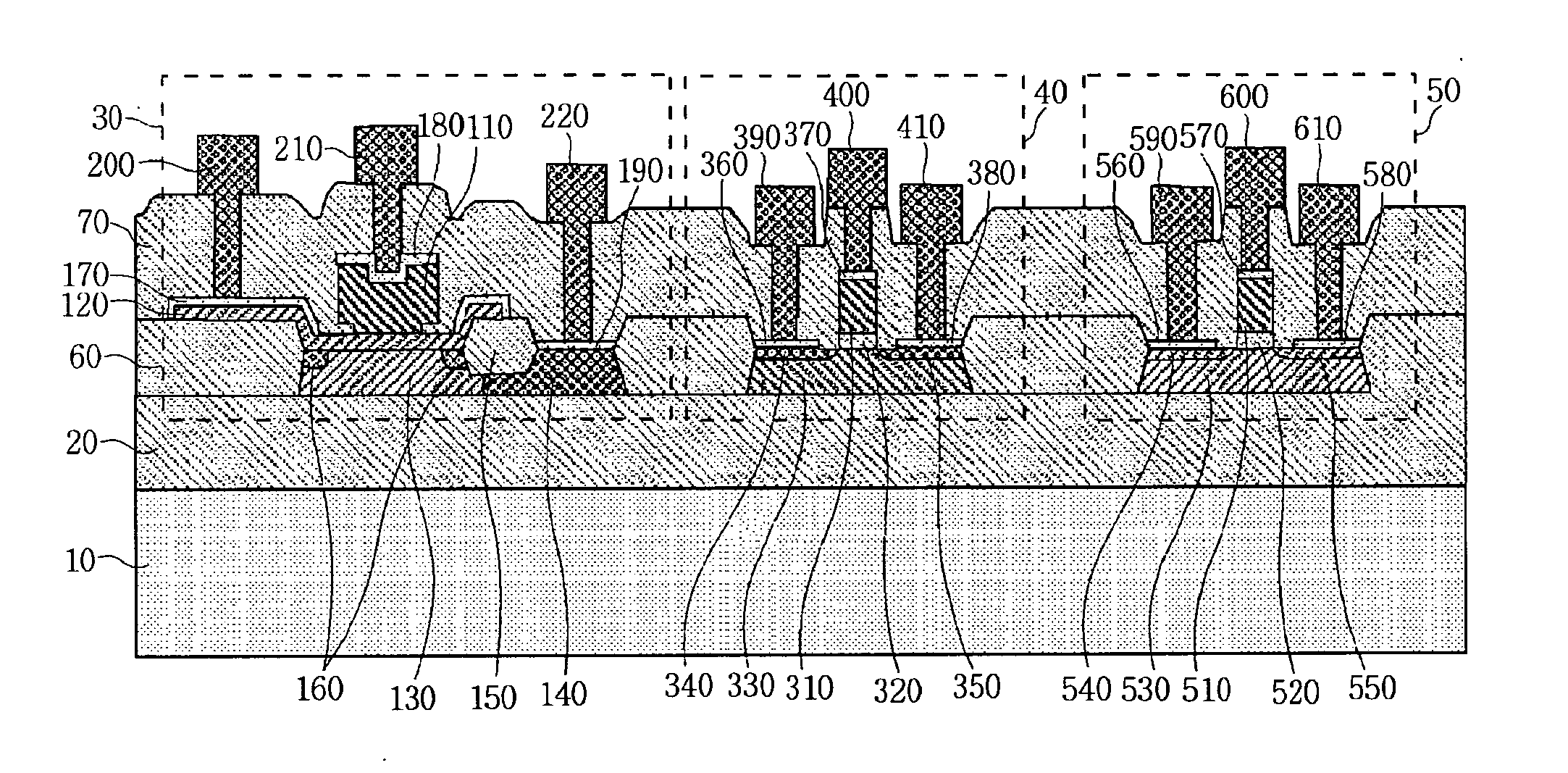

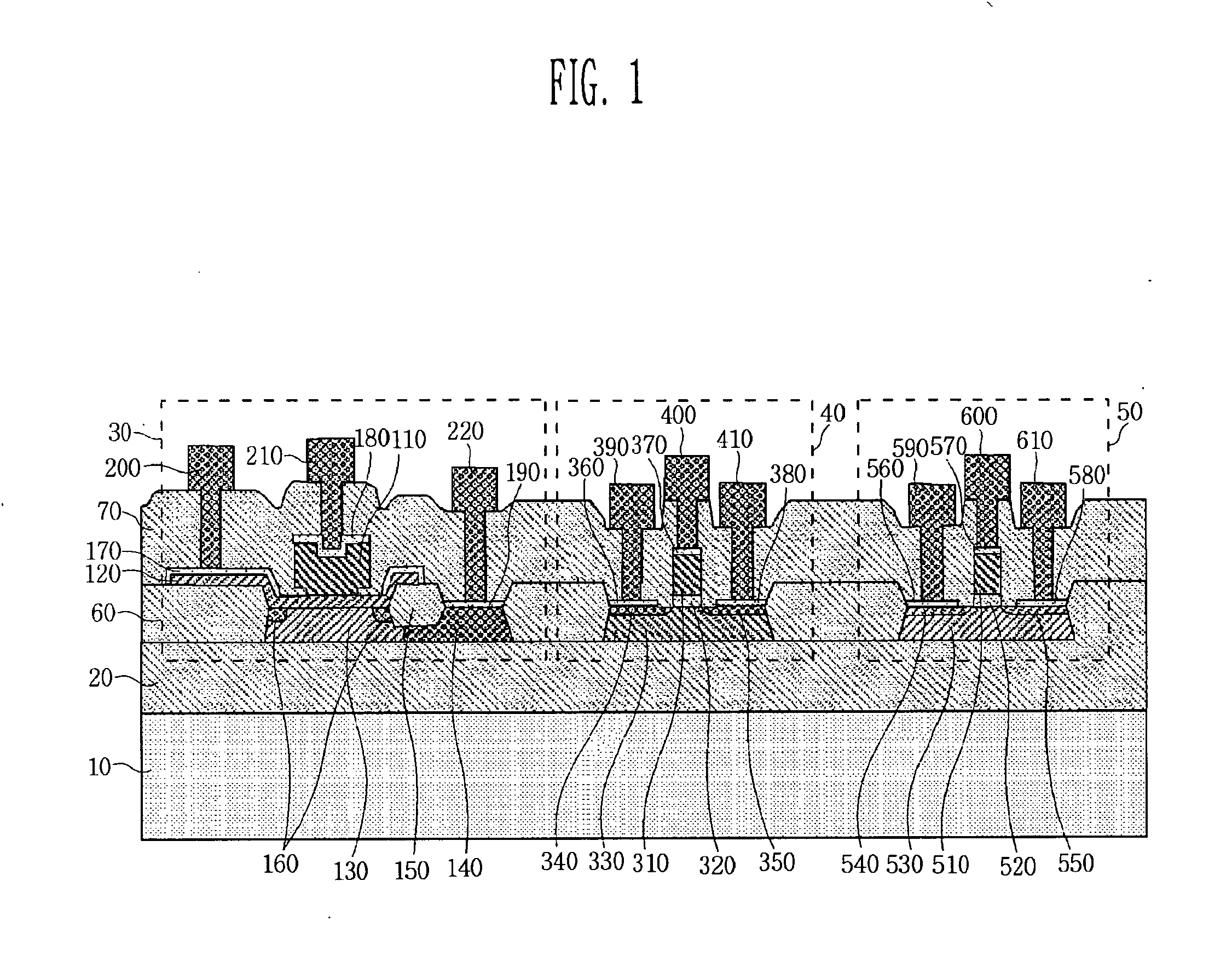

SOI three-dimensional CMOS integrated component and preparation method thereof

InactiveCN101409292AHigh hole mobilityImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingSoi cmosLow speed

The invention discloses a 3D SOI CMOS integrated device and a manufacturing method thereof, relates to the technical field of microelectronics, and mainly solves the problem of low speed of the existing 3D integrated circuits. The proposal is that an SSOI substrate and an SSGOI substrate are employed to construct two active layers of a new 3D CMOS integrated device; wherein, the lower active layer is the SSOI substrate and is made into a strained Si nMOSFET device by utilizing the characteristic of high electron mobility of a strained Si material in the SSOI substrate; the upper active layer is the SSGOI substrate and is made into a strained SiGe surface channel pMOSFET device by utilizing the characteristic of high hole mobility of the strained Si material in the SSGOI substrate; the upper active layer and the lower active layer form a 3D active layer structure by a bonding process, and are connected by an interconnection line to form the 3D CMOS integrated device with a conducting channel of 65nm to 130nm. Compared with the existing 3D integrated devices, the 3D SOI CMOS integrated device manufactured by the manufacturing method has the advantages of high speed and good performance, and can be applied to manufacturing large-scale and high-speed 3D CMOS integrated circuits.

Owner:XIDIAN UNIV

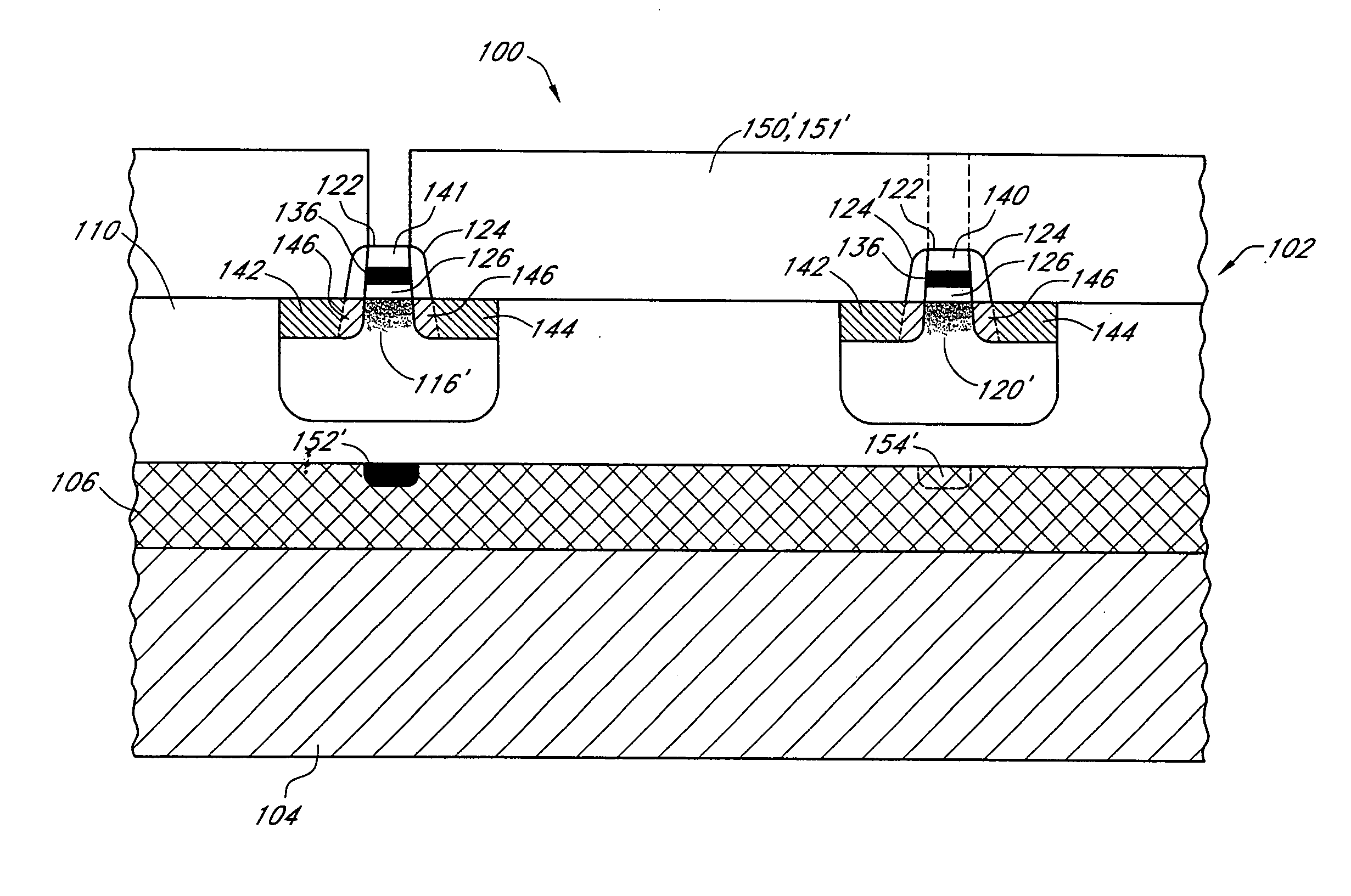

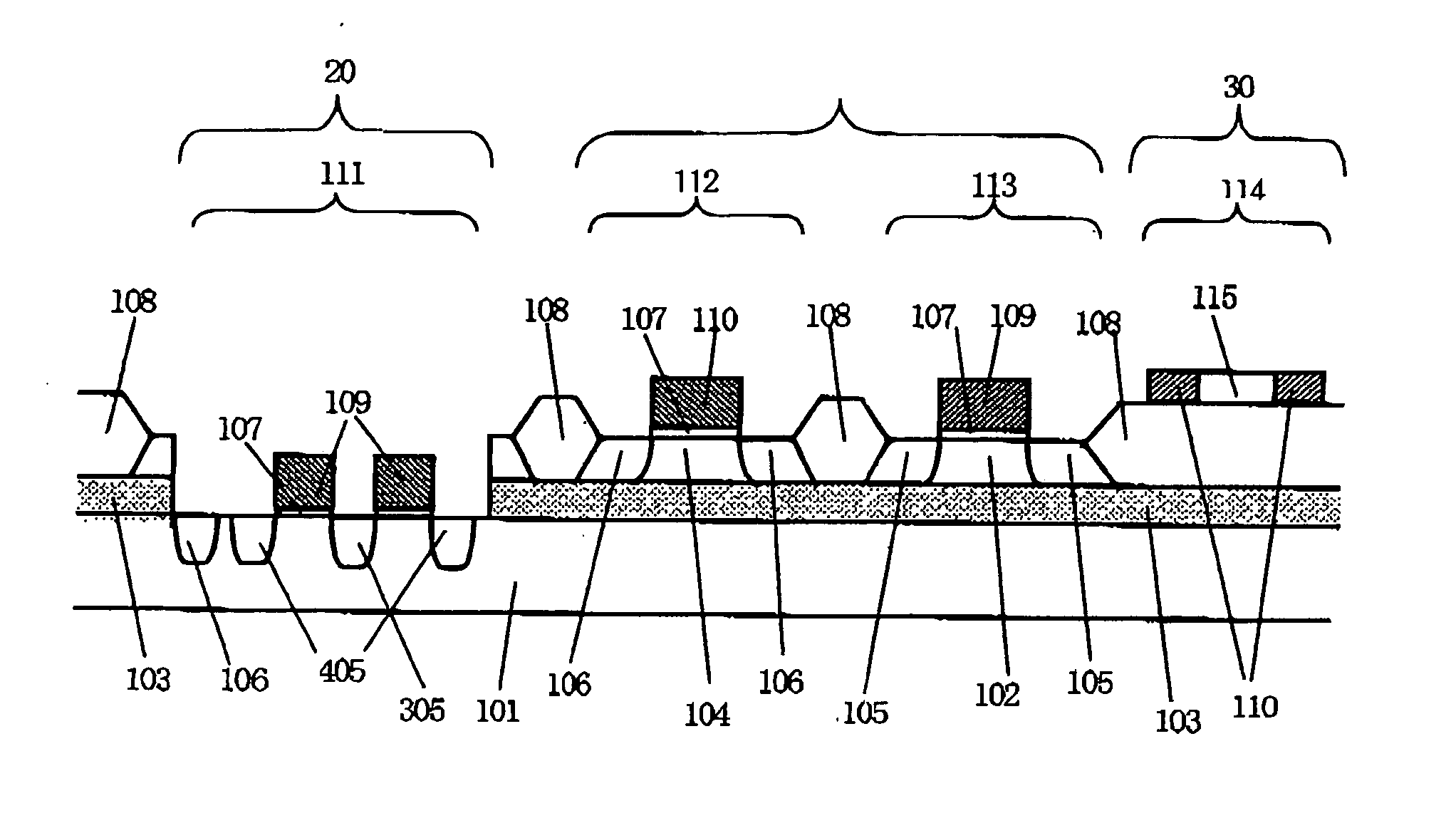

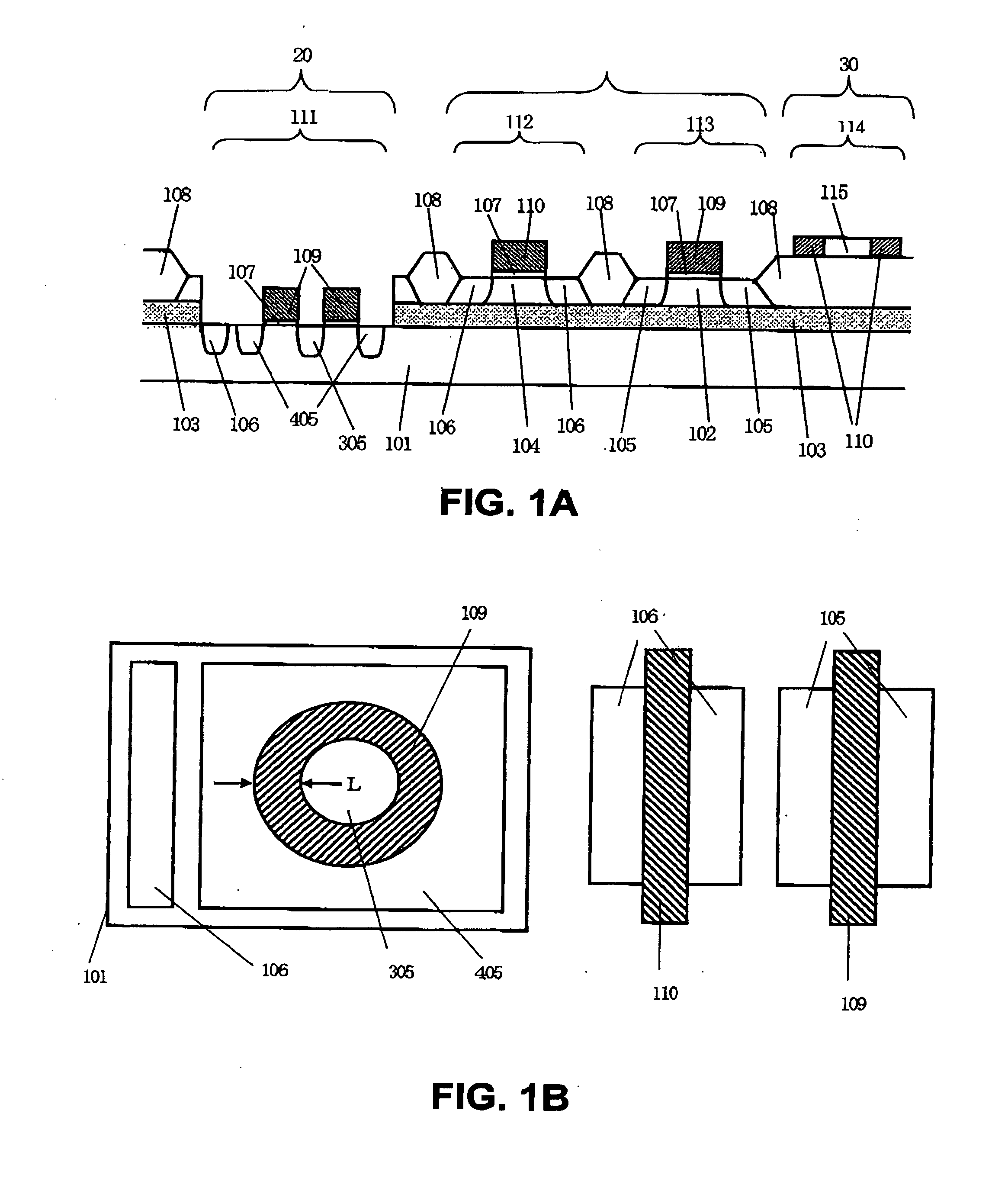

Soi CMOS compatible multiplanar capacitor

An isolated shallow trench isolation portion is formed in a top semiconductor portion of a semiconductor-on-insulator substrate along with a shallow trench isolation structure. A trench in the shape of a ring is formed around a doped top semiconductor portion and filled with a conductive material such as doped polysilicon. The isolated shallow trench isolation portion and the portion of a buried insulator layer bounded by a ring of the conductive material are etched to form a cavity. A capacitor dielectric is formed on exposed semiconductor surfaces within the cavity and above the doped top semiconductor portion. A conductive material portion formed in the trench and above the doped top semiconductor portion constitutes an inner electrode of a capacitor, while the ring of the conductive material, the doped top semiconductor portion, and a portion of a handle substrate abutting the capacitor dielectric constitute a second electrode.

Owner:TWITTER INC

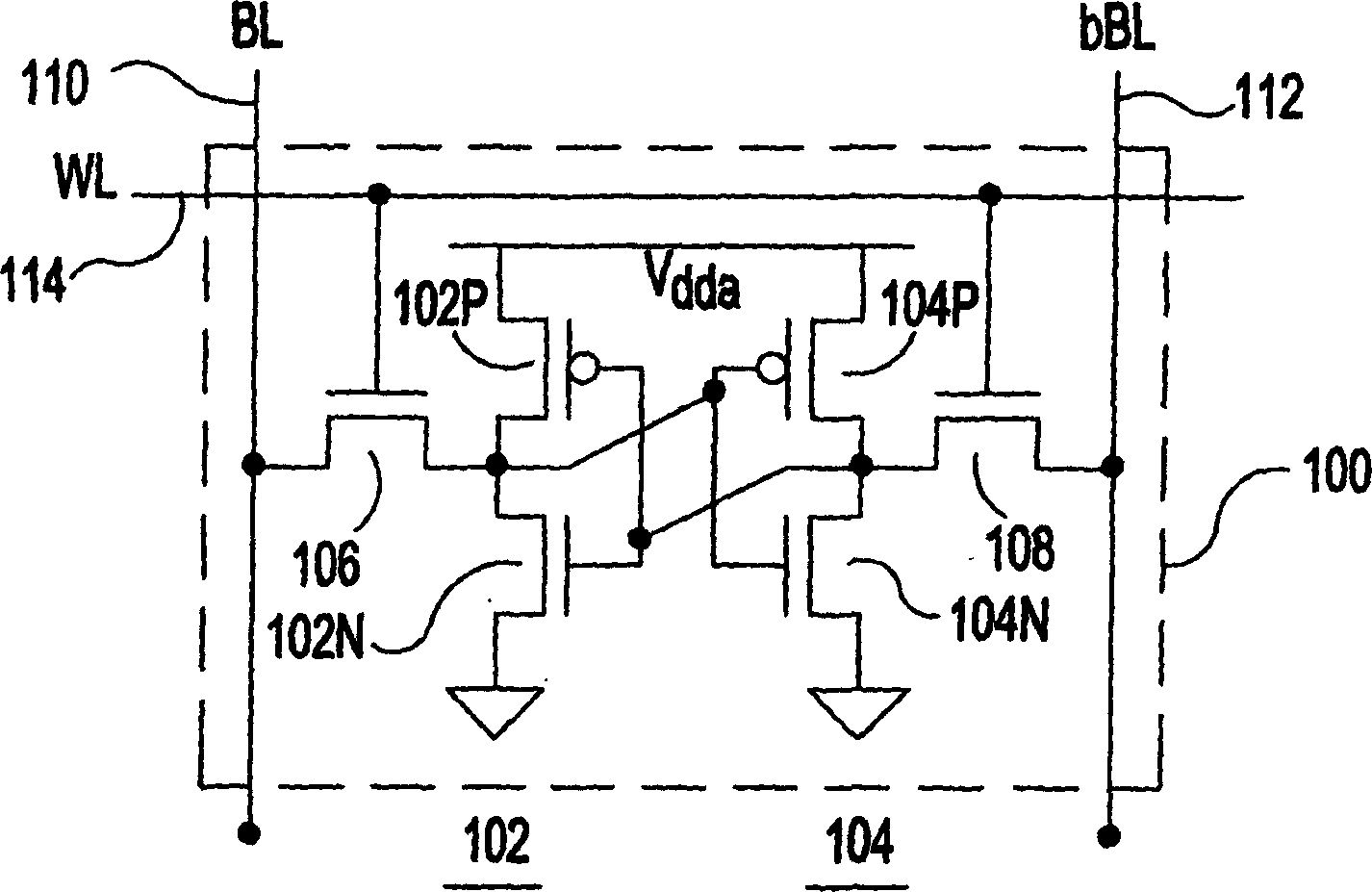

Coupled body contacts for SOI differential circuits

A silicon on insulator (SOI) CMOS circuit, macro and integrated circuit (IC) chip. The chip or macro may include be an SRAM in partially depleted (PD) SOI CMOS. Most field effect transistors (FETs) do not have body contacts. FETs otherwise exhibiting a sensitivity to history effects have body contacts. The body contact for each such FET is connected to at least one other body contact. A back bias voltage may be provided to selected FETs.

Owner:GLOBALFOUNDRIES US INC

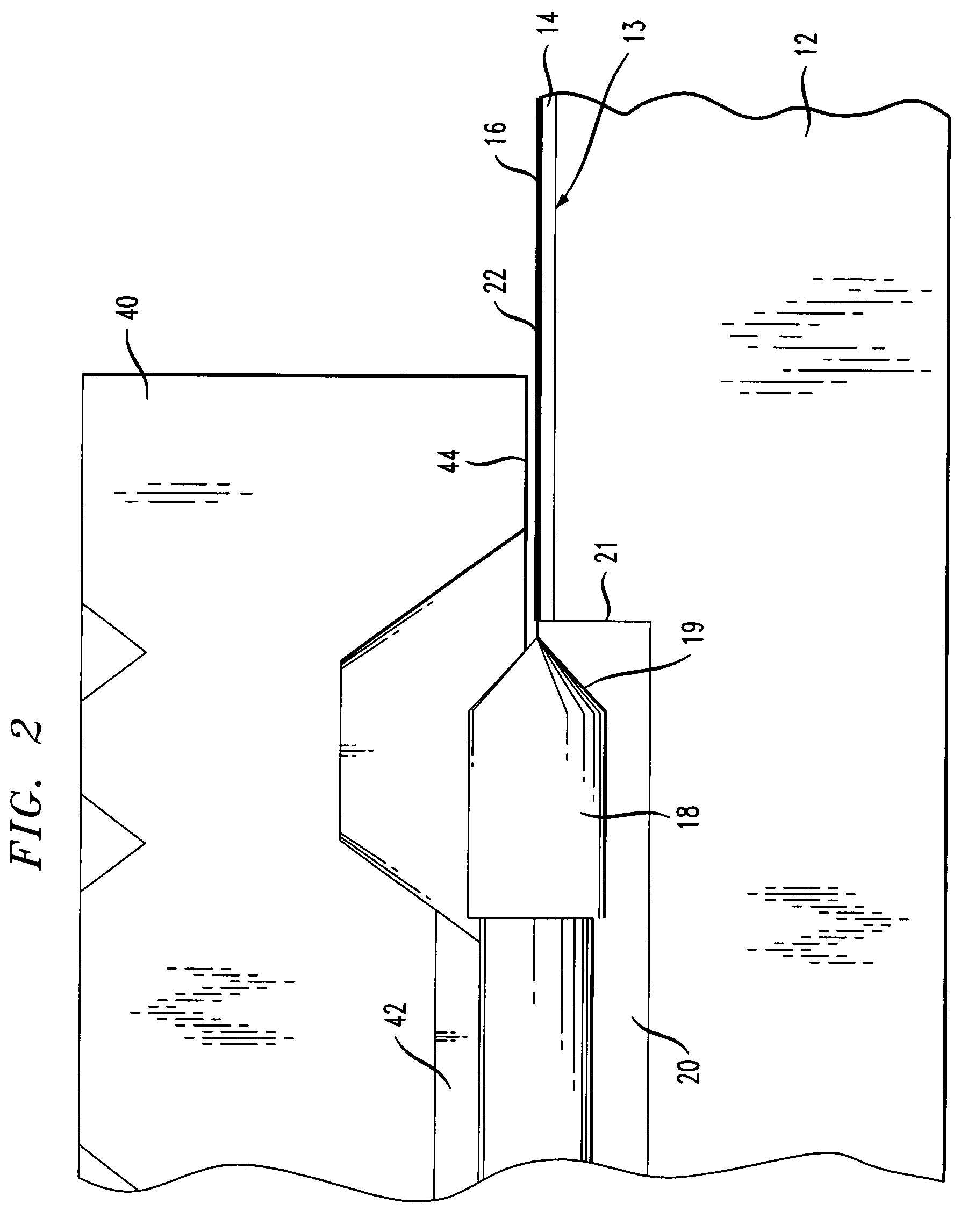

Wideband optical coupling into thin SOI CMOS photonic integrated circuit

An arrangement for providing optical coupling into and out of a relatively thin silicon waveguide formed in the SOI layer of an SOI structure includes a lensing element and a defined reference surface within the SOI structure for providing optical coupling in an efficient manner. The input to the waveguide may come from an optical fiber or an optical transmitting device (laser). A similar coupling arrangement may be used between a thin silicon waveguide and an output fiber (either single mode fiber or multimode fiber).

Owner:CISCO TECH INC

Laser light coupling into SOI CMOS photonic integrated circuit

ActiveUS8787417B2Small sizeReduce power consumptionSemiconductor/solid-state device manufacturingOptical resonator shape and constructionSoi cmosCoupling

A hybrid laser for generating radiation includes an optical passive material and an optical active material. The laser includes a first optical waveguide and optical laser components with reflectors in the optical passive material. The first optical waveguide is adapted for coupling out radiation from the hybrid laser. The laser also includes a second optical waveguide defined in the optical active material. The optical laser components include reflectors defining a cavity and furthermore are adapted for providing laser cavity confinement in the first optical waveguide and the second optical waveguide. The second optical waveguide thereby is positioned at least partly over the first optical waveguide so that an evanescent coupling interface is defined between the second optical waveguide and the first optical waveguide and the evanescent coupling interface is positioned within the laser cavity.

Owner:UNIV GENT +1

Bipolar transistor, BiCMOS device, and method for fabricating thereof

InactiveUS20050104127A1Reduce the numberReduce in quantitySolid-state devicesSemiconductor/solid-state device manufacturingSoi cmosHigh density

Provided are bipolar transistor, BiCMOS device and method of fabricating thereof, in which an existing sub-collector disposed beneath a collector of a SiGe HBT is removed and a collector plug disposed at a lateral side of the collector is approached to a base when fabricating a Si-based very high-speed device, whereby it is possible to fabricate the SiGe HBT and an SOI CMOS on a single substrate, reduce the size of the device and the number of masks to be used, and implement the device of high density, low power consumption, and wideband performance.

Owner:ELECTRONICS & TELECOMM RES INST

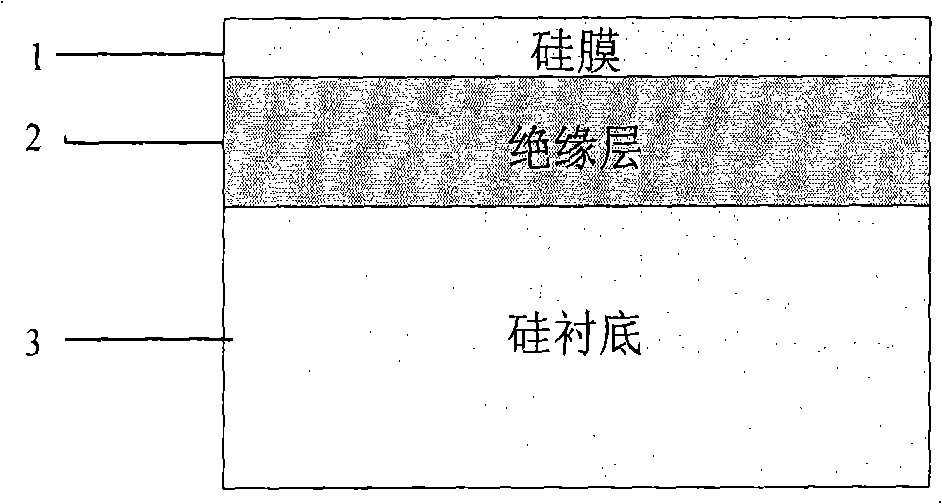

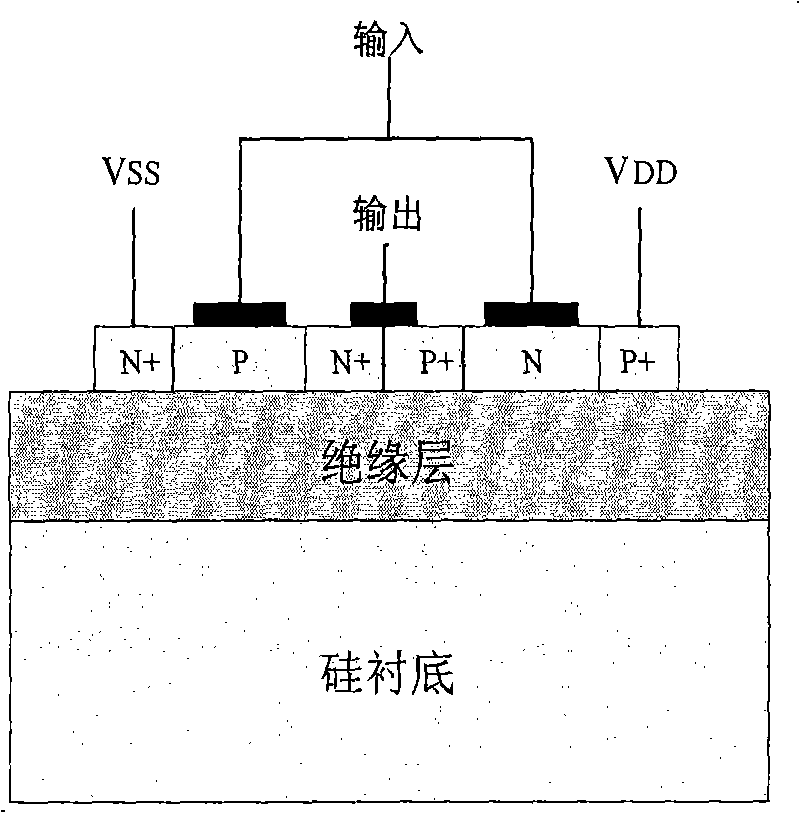

SOI CMOS image sensor structure and manufacturing method thereof

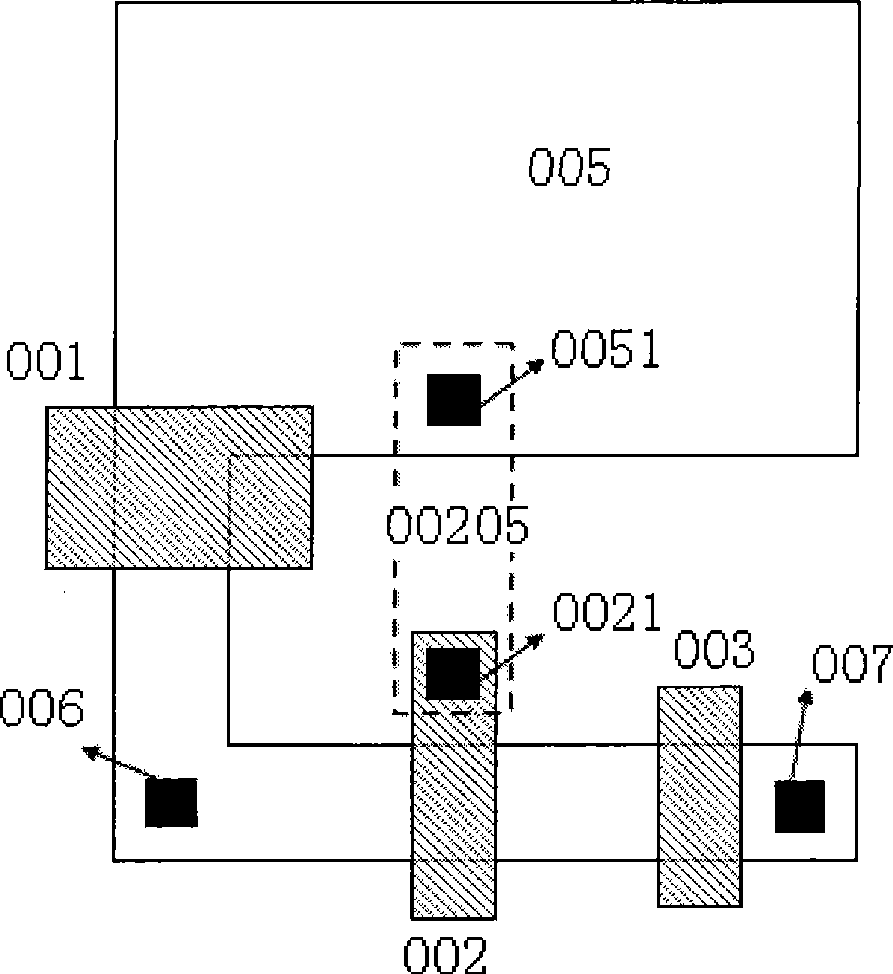

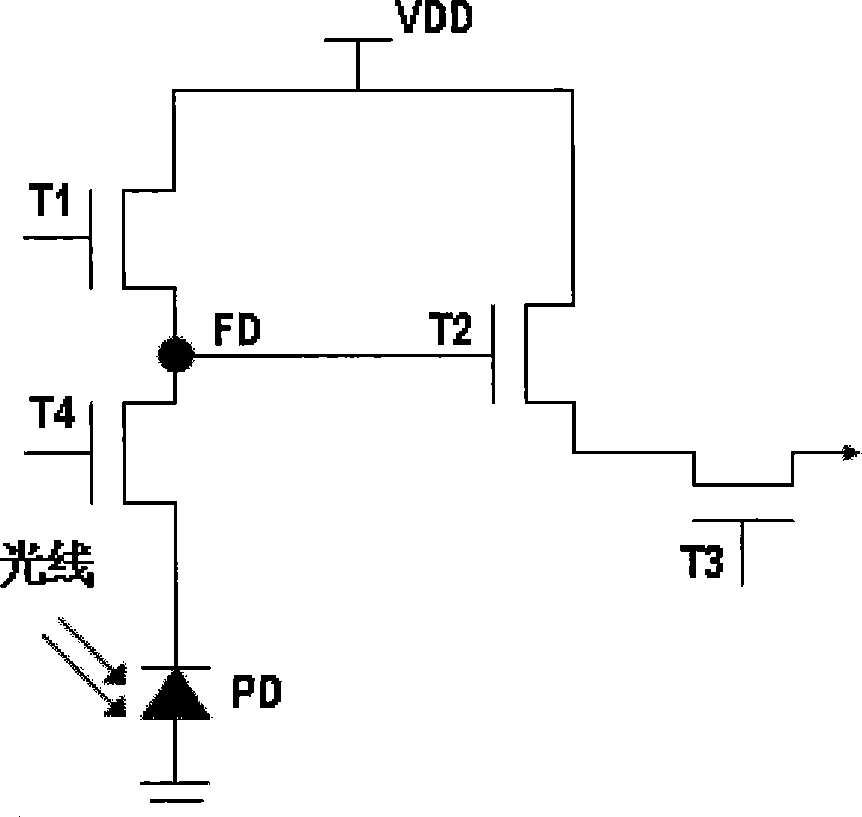

InactiveCN101546777AReduce power consumptionLow resistance to latch-upSemiconductor/solid-state device manufacturingRadiation controlled devicesSoi cmosCMOS sensor

The invention discloses an SOI CMOS image sensor structure and a manufacturing method thereof. The manufacturing method comprises that: a CMOS image sensor is manufactured on an SOI material, and a photosensitive diode of the CMOS image sensor is manufactured in a silicon base of the SOI material; other devices of a CMOS circuit are manufactured on a silicon film; and the N pole and the P pole of the photosensitive diode are respectively led out by a metal plug and then connected with the CMOS circuit. The structure and the method not only has the advantages of high speed, low power consumption, lockout resistance and low probability of soft errors, but also make the light absorption efficiency of the photosensitive diode approximate to that of the bulk silicon CMOS sensor.

Owner:BEIJING SUPERPIX MICRO TECHNOLOGY CO LTD

Dual port gain cell with side and top gated read transistor

Owner:GLOBALFOUNDRIES US INC

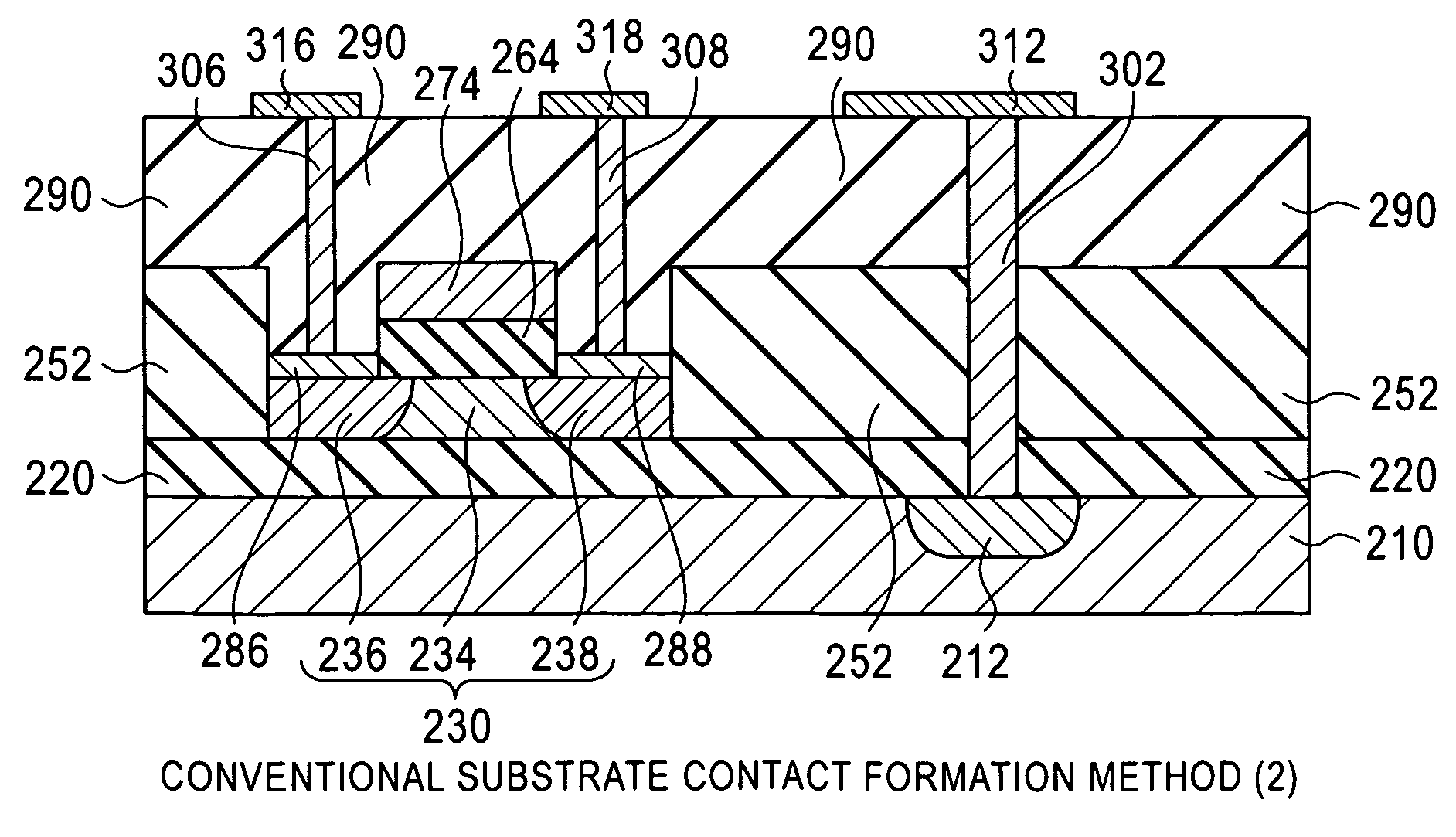

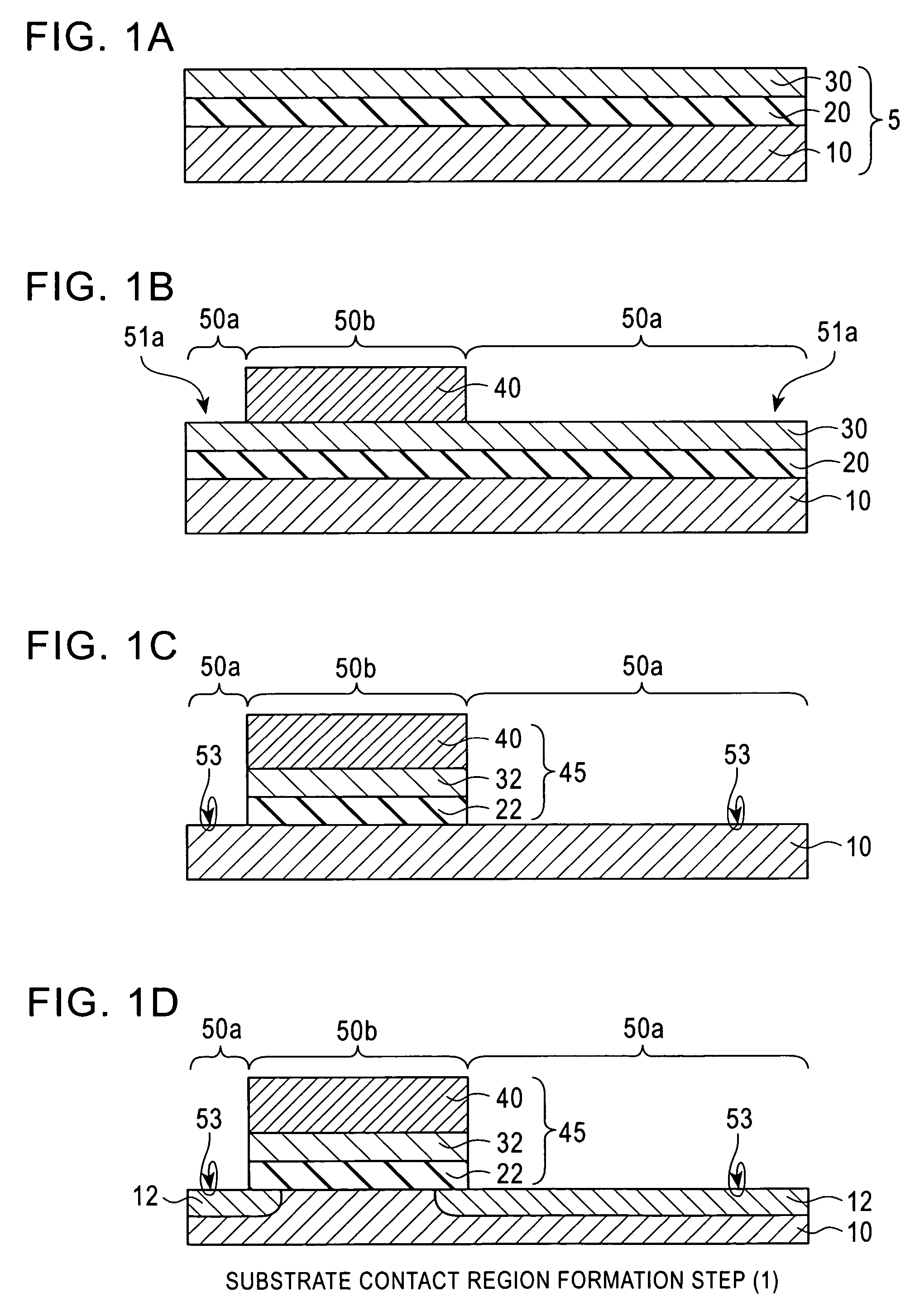

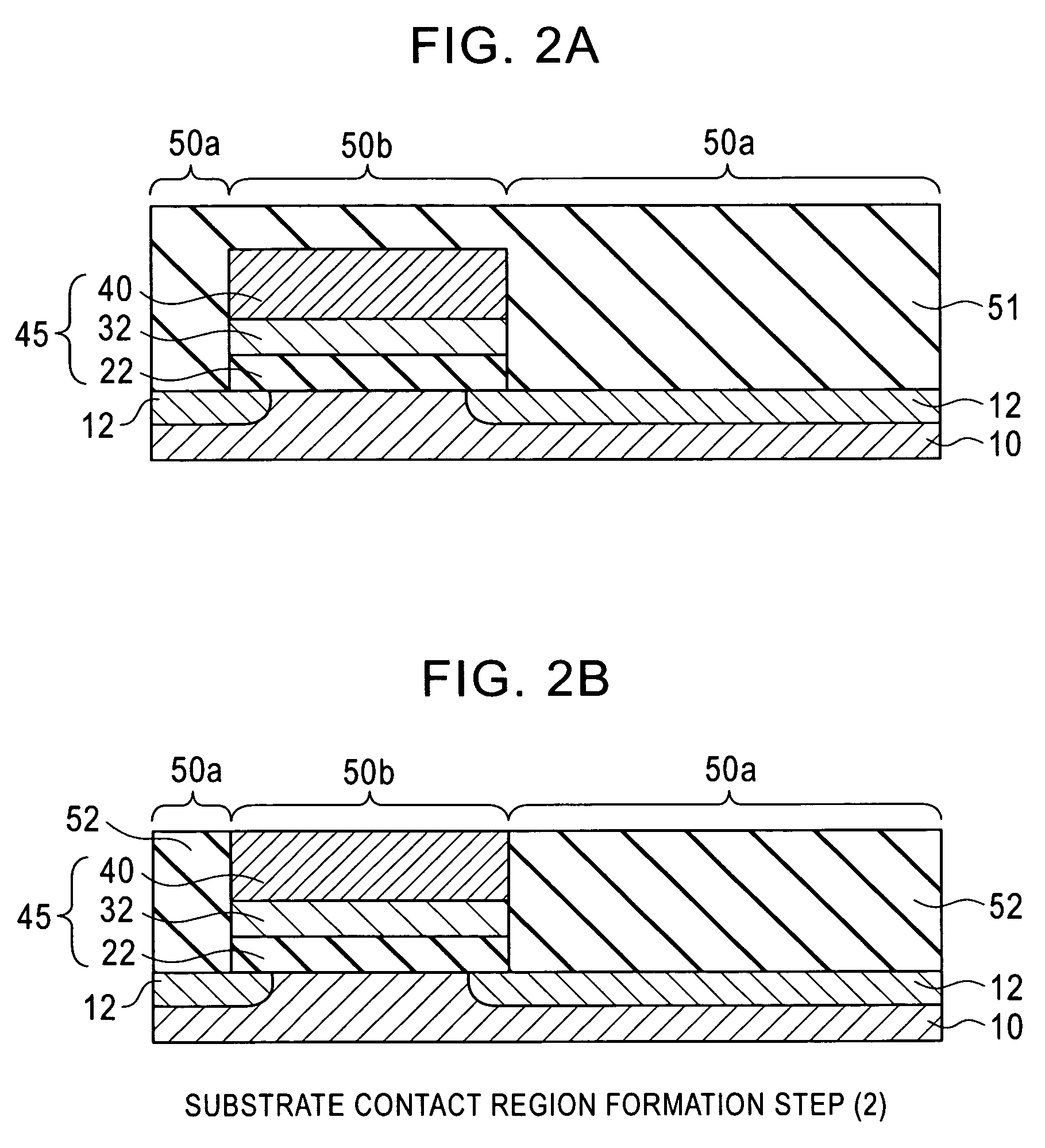

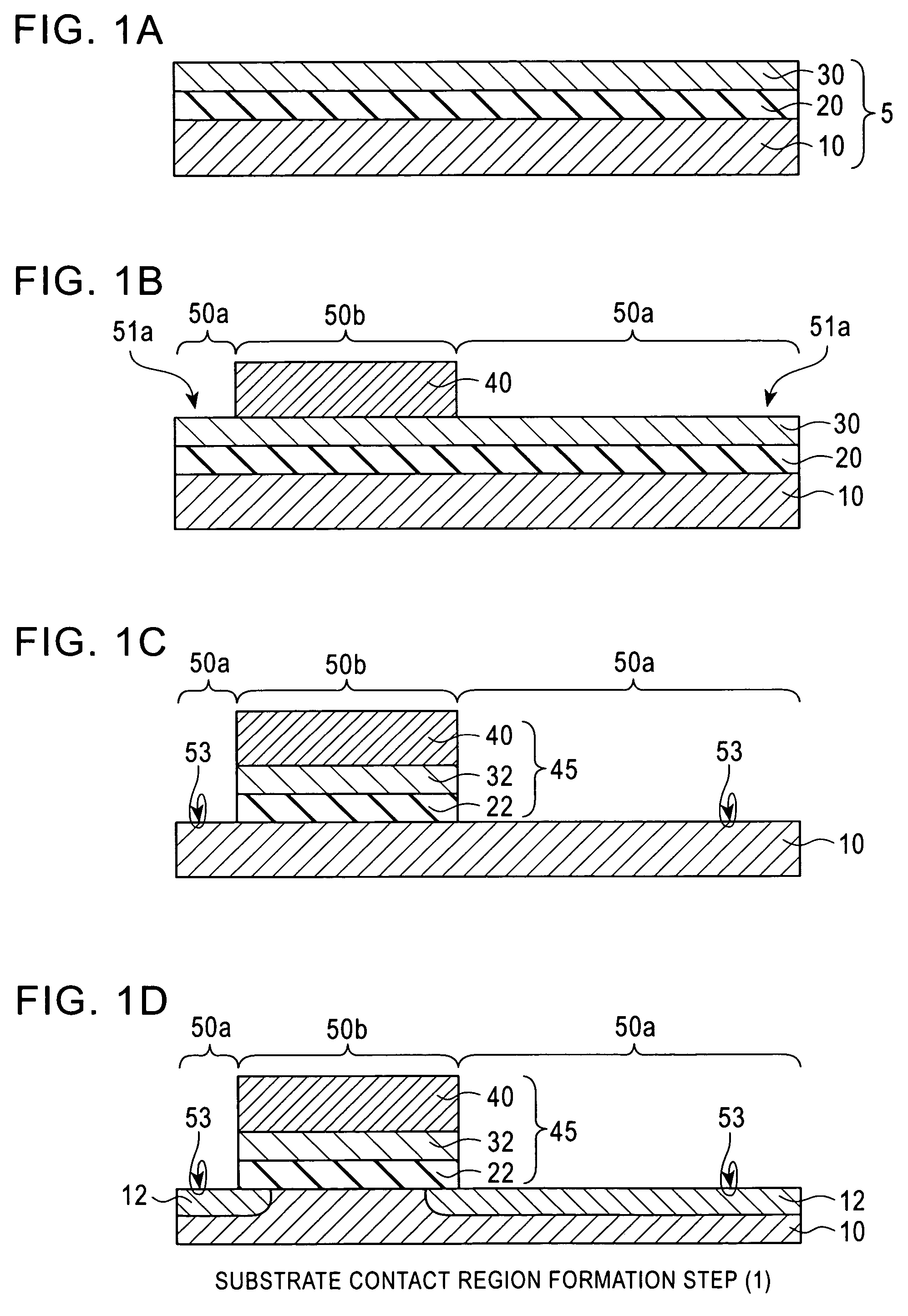

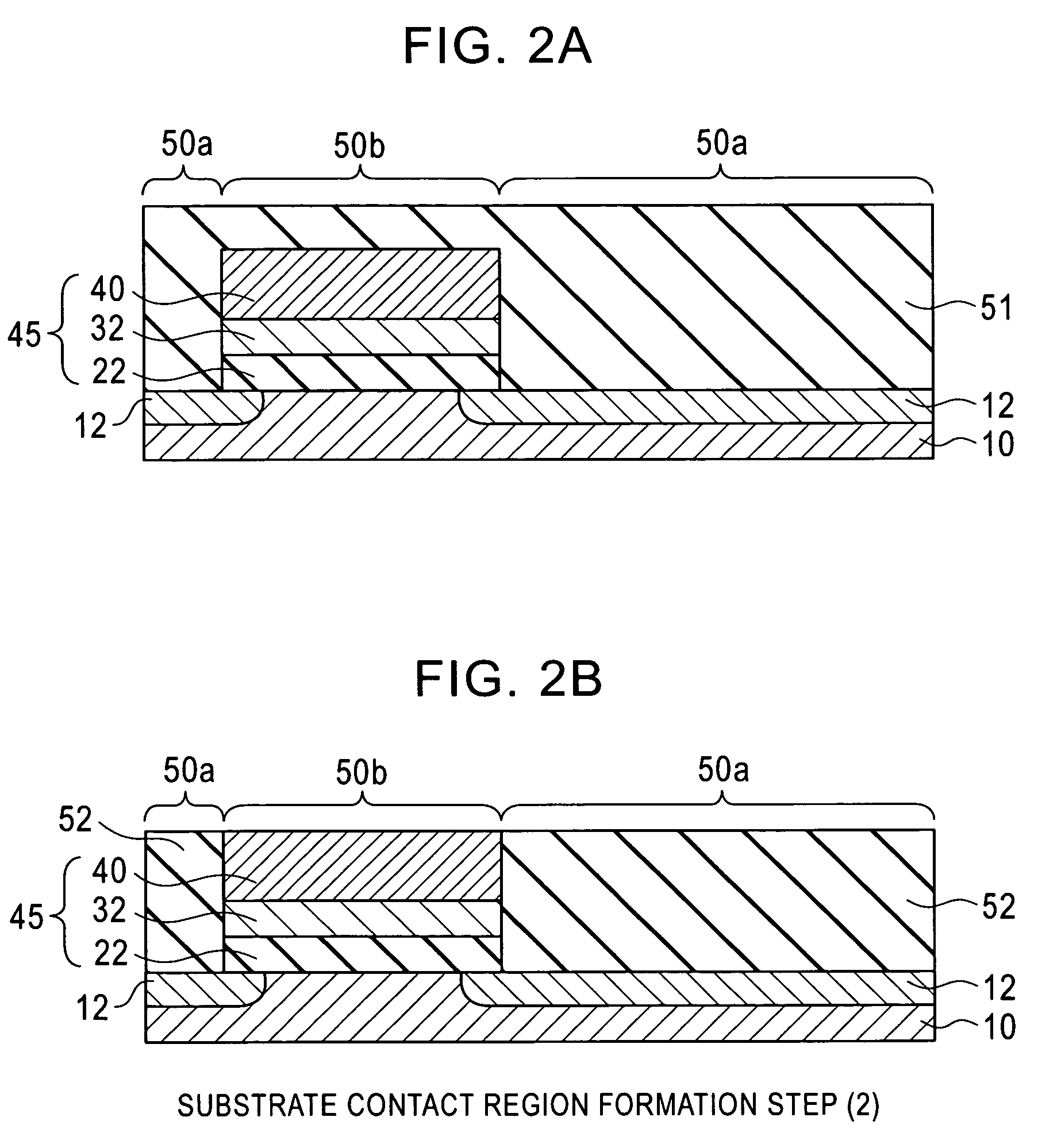

Semiconductor device fabrication method

The present invention adequately activates a substrate contact region of a support substrate without substantially changing the conventional SOI-CMOS device formation process. An exposed face of the support substrate is formed in an element isolation region of a layered substrate, which includes a support substrate having a first semiconductor layer, an insulating layer provided on the support substrate, and a second semiconductor layer provided on the insulating layer, by etching away the insulating layer and the second semiconductor layer. A substrate contact region is then formed in the support substrate by performing ion implantation from the side of the exposed face of the support substrate. Thereafter, an element isolation insulation layer is formed on the exposed face of the support substrate and a gate oxide film and a gate electrode are formed on the remaining second semiconductor layer. In addition, drain and source regions are formed by performing the ion implantation to the remaining second semiconductor layer with the gate electrode serving as a mask. Annealing to activate the substrate contact region, the drain region and the source region is then performed. Thereafter, a metal layer with a high melting point is formed on the drain and source regions and the metal layer is silicided through heat treatment.

Owner:LAPIS SEMICON CO LTD

Method and system for monolithic integration of photonics and electronics in CMOS processes

Methods and systems for monolithic integration of photonics and electronics in CMOS processes are disclosed and may include fabricating photonic and electronic devices on a single CMOS wafer with different silicon layer thicknesses. The devices may be fabricated on a semiconductor-on-insulator (SOI) wafer utilizing a bulk CMOS process and / or on a SOI wafer utilizing a SOI CMOS process. The different thicknesses may be fabricated utilizing a double SOI process and / or a selective area growth process. Cladding layers may be fabricated utilizing one or more oxygen implants and / or utilizing CMOS trench oxide on the CMOS wafer. Silicon may be deposited on the CMOS trench oxide utilizing epitaxial lateral overgrowth. Cladding layers may be fabricated utilizing selective backside etching. Reflective surfaces may be fabricated by depositing metal on the selectively etched regions. Silicon dioxide or silicon germanium integrated in the CMOS wafer may be utilized as an etch stop layer.

Owner:CISCO TECH INC

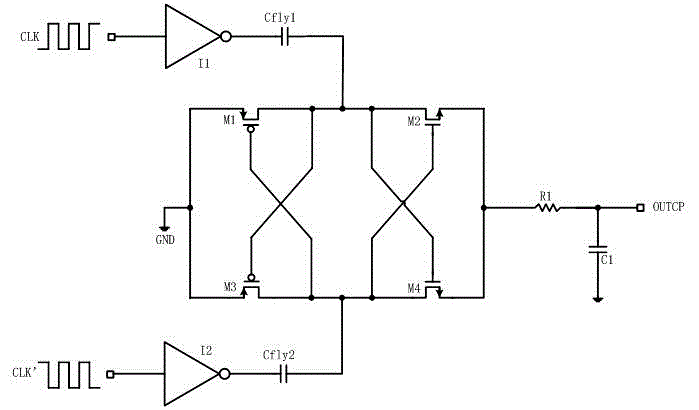

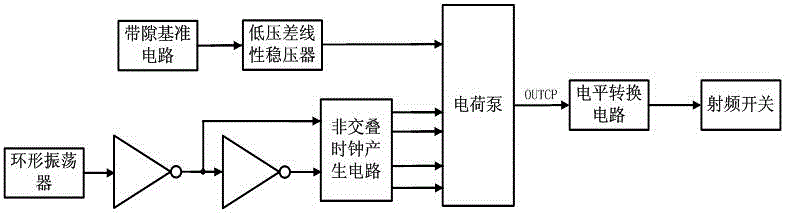

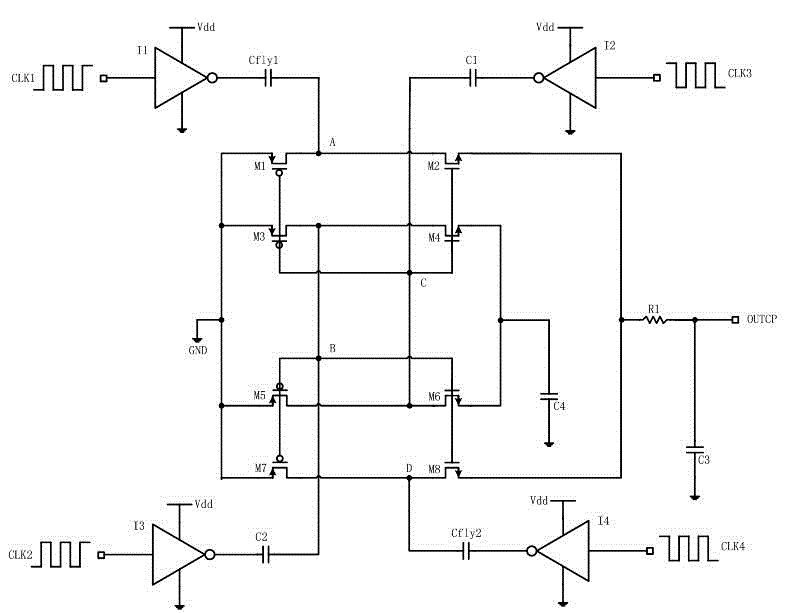

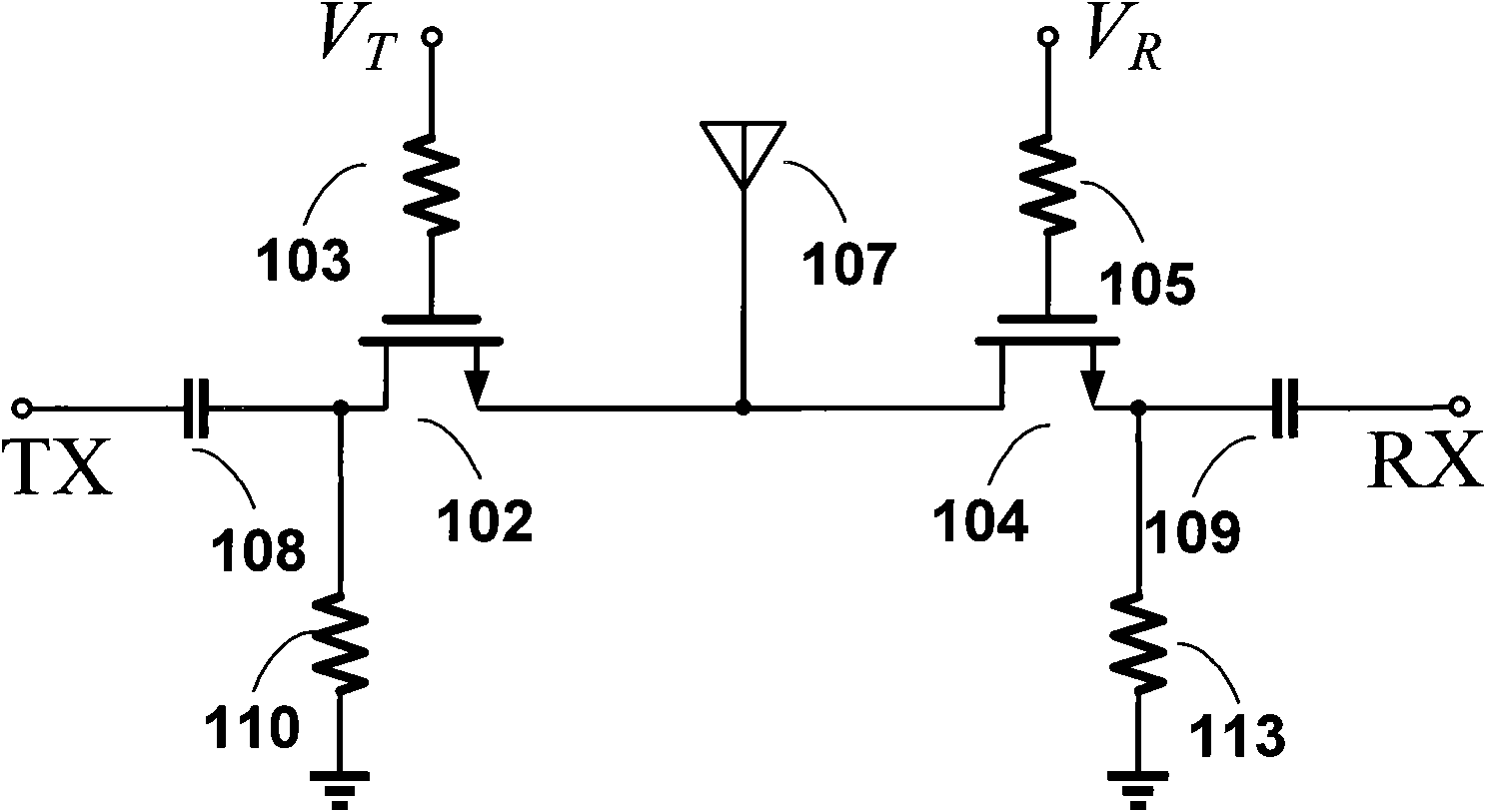

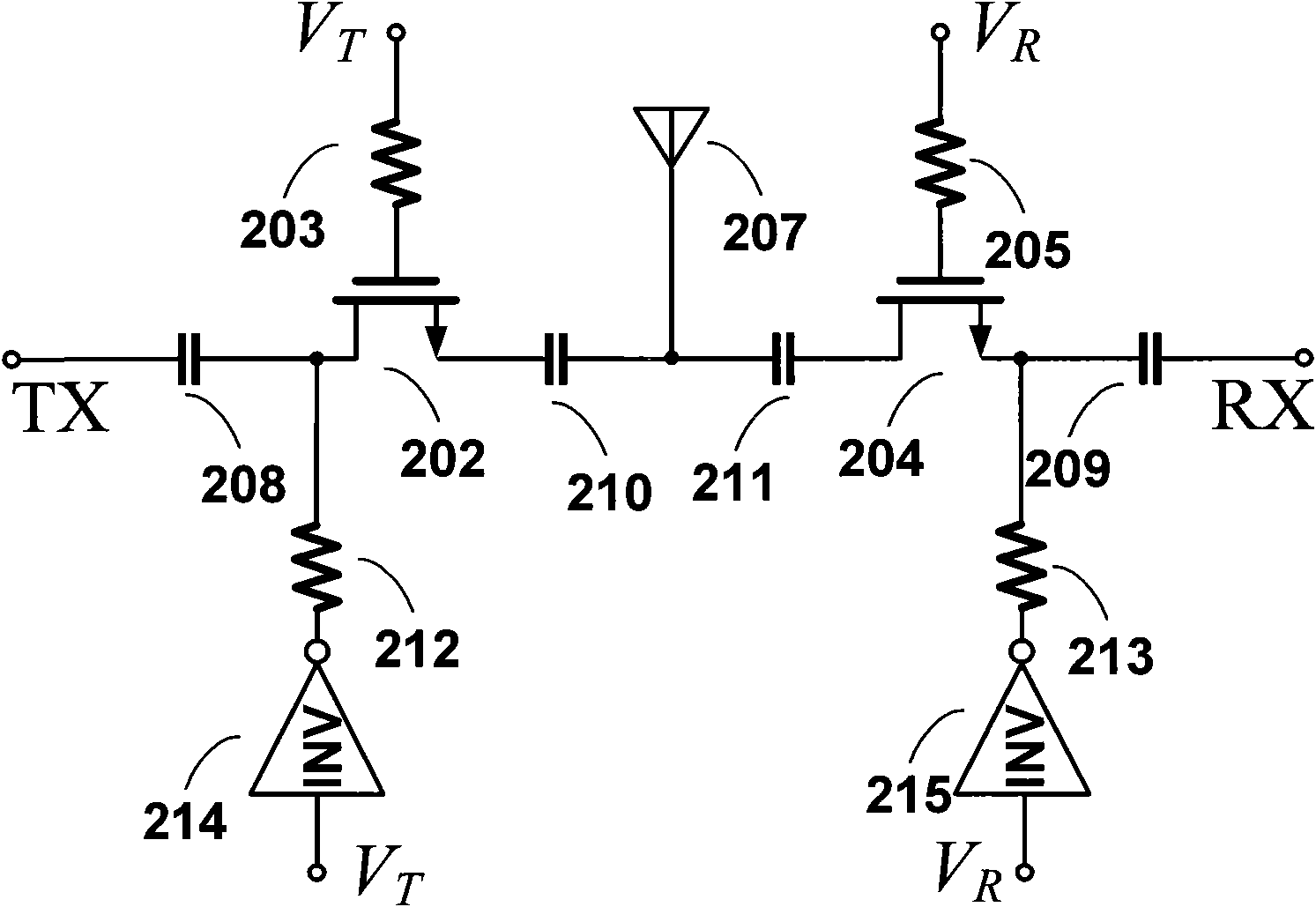

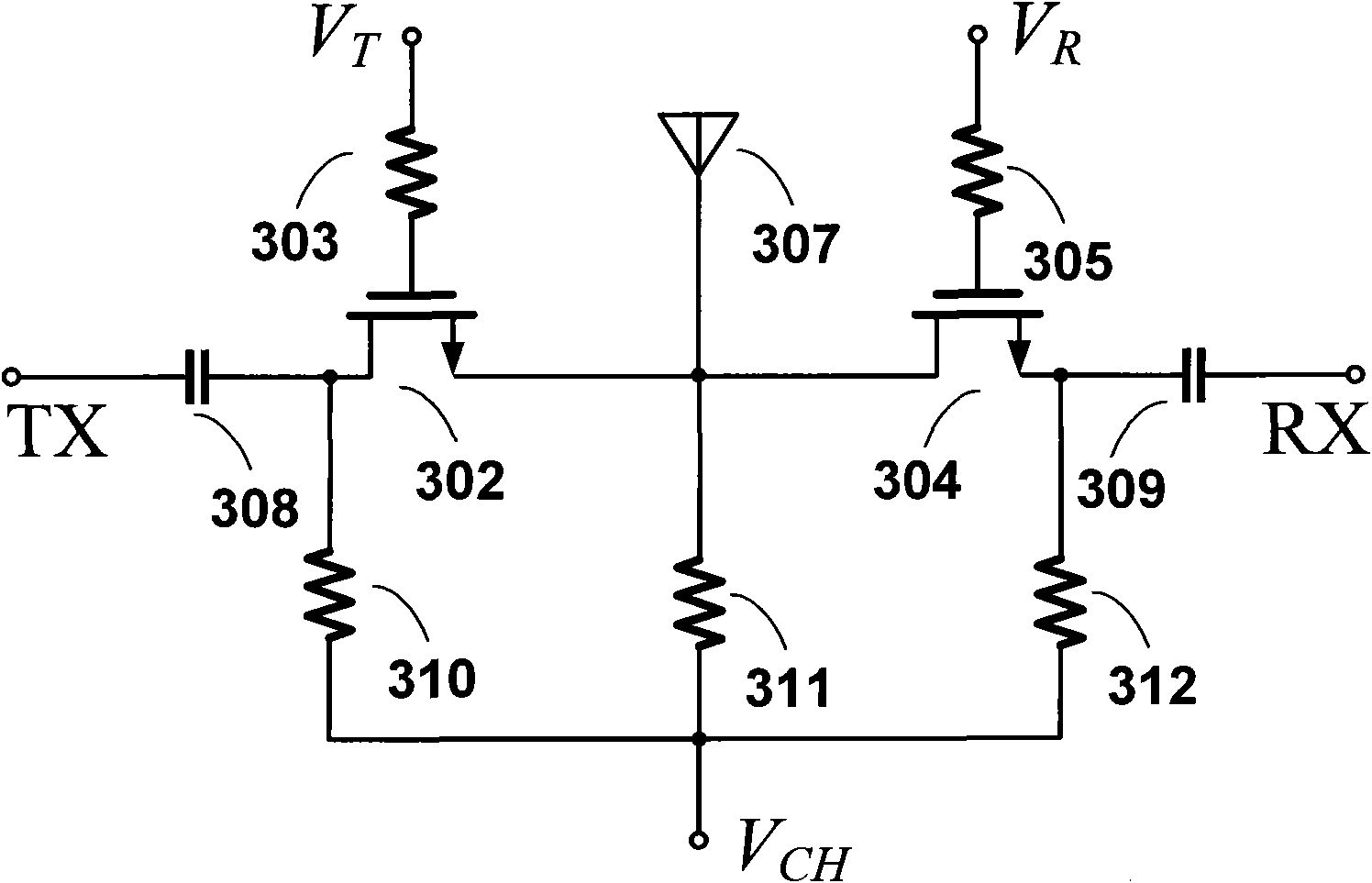

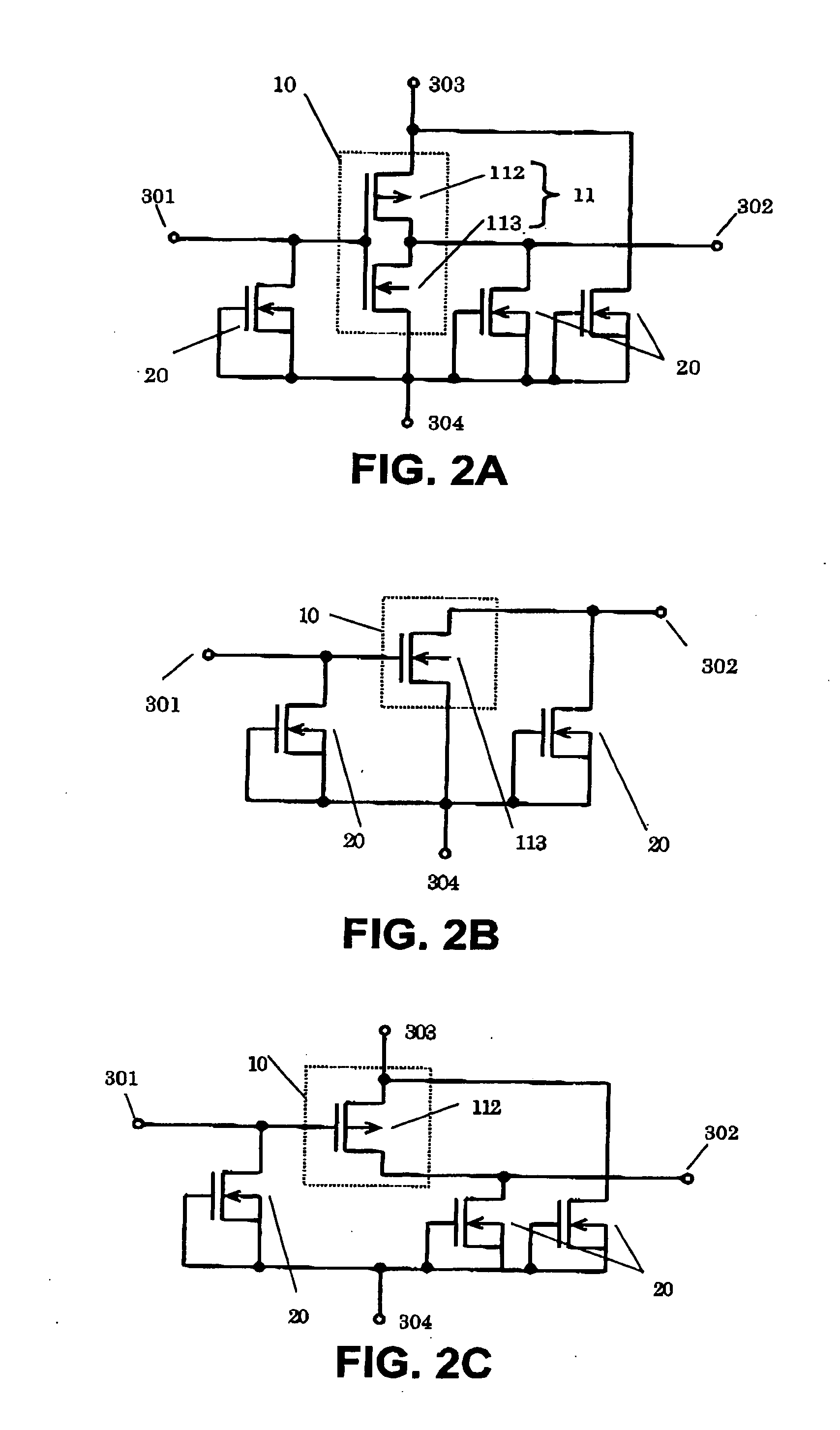

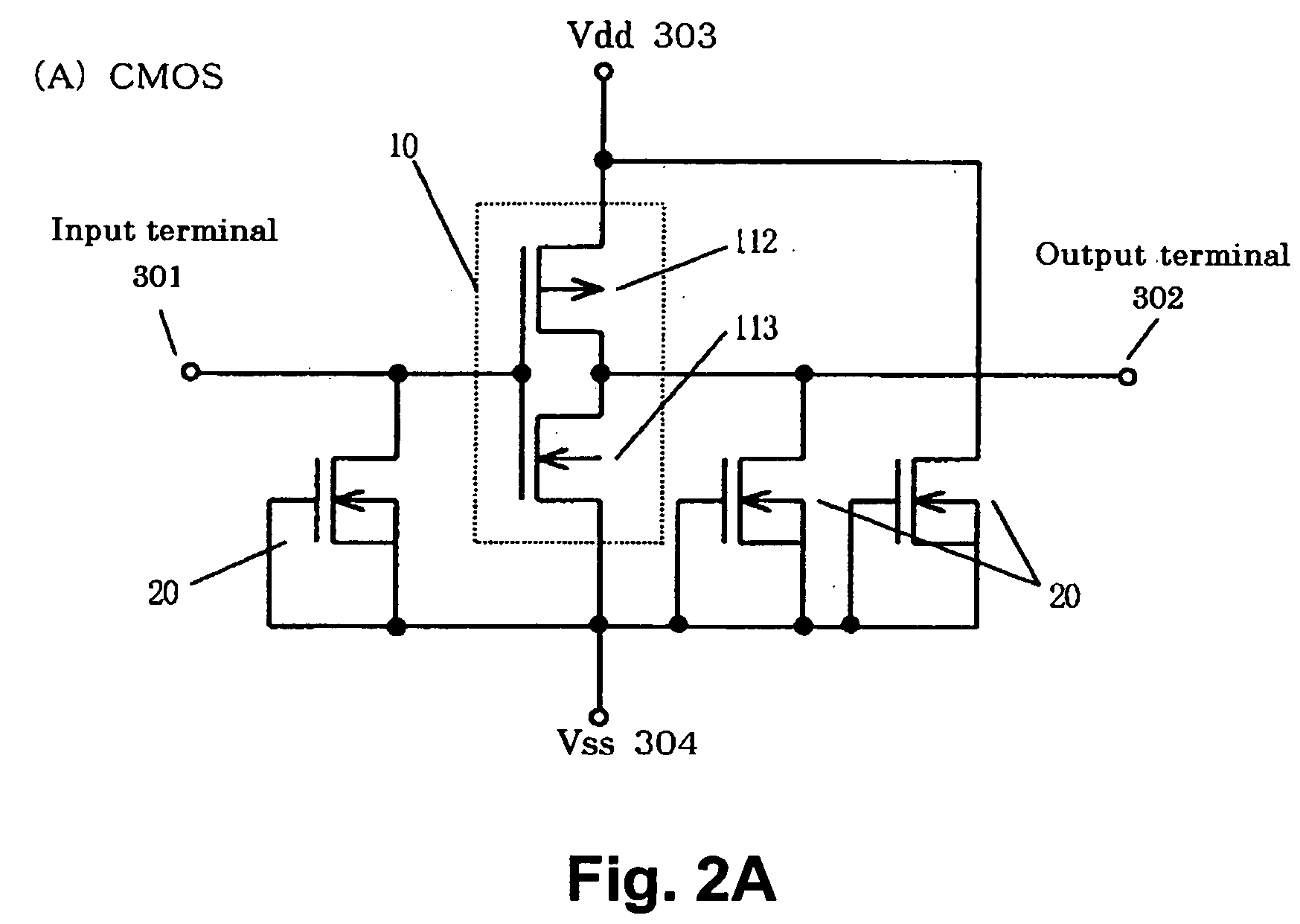

Control circuit applied to SOI (silicon on insulator) CMOS (complementary metal oxide semiconductor) radiofrequency switches

The invention discloses a control circuit applied to SOI (silicon on insulator) CMOS (complementary metal oxide semiconductor) radiofrequency switches. The control circuit comprises a band-gap reference circuit, a low-dropout linear voltage regulator, an annular oscillator, voltage inverters, a non-overlapping clock circuit, a charge pump and a level switching circuit. A core unit of the control circuit is a charge pump circuit capable of generating negative voltages. The band-gap reference circuit is connected with the low-dropout linear voltage regulator, an output end of the low-dropout linear voltage regulator is connected with the charge pump, an output end of the annular oscillator is connected with an input end of the inverter I2 by the inverter I1, an output end of the inverter I1 and an output end of the inverter I2 are connected with an input end of the non-overlapping clock generating circuit, four output ends of the non-overlapping clock generating circuit is connected with an input end of the charge pump, and the SOI CMOS radiofrequency switches can be controlled by an output end OUTPUT of the charge pump via the level switching circuit. The control circuit has the advantages that the charge pump capable of generating the negative voltages can be quickly started and has low steady-state currents, accordingly, radiofrequency switch tubes can be assuredly in excellent closed states under the conditions of high radiofrequency signals, and the linearity and the isolation of the radiofrequency switches can be improved.

Owner:广东拓思软件科学园有限公司

SOI (Silicon on Insulator) CMOS (Complementary Metal Oxide Semiconductor) RF (Radio Frequency) switch and RF transmitter front-end module comprising same

The invention relates to an SOI (Silicon On Insulator) CMOS (Complementary Metal Oxide Semiconductor) RF (Radio Frequency) switch and an RF transmitter front-end module comprising the same. The SOI CMOS RF switch comprises a plurality of DC-blocking capacitors, a plurality of resistors and a plurality of switching tubes, wherein the switching tubes are SOI CMOS switching tubes, the drain electrode of each switching tube is connected to a channel control voltage through a resistor, the source electrode of each switching tube is connected to the channel control voltage through another resistor and connected with an antenna, and the channel control voltage is larger than 0 V and smaller than the difference of a high level and a threshold voltage of the switching tube. At the same moment, only one switching tube has a control signal at a high-level voltage, and the other switching tubes have control signals at the voltage of 0 V. The technical scheme provided by the invention simplifies the structure of the RF switch; and the RF switch can work under a signal power supply to ensure that the control signal voltage in a switching transistor in each SOI CMOS RF switch can be higher than the safe voltage of the transistor, thus the reliability of the RF switch is improved.

Owner:RDA MICROELECTRONICS BEIJING

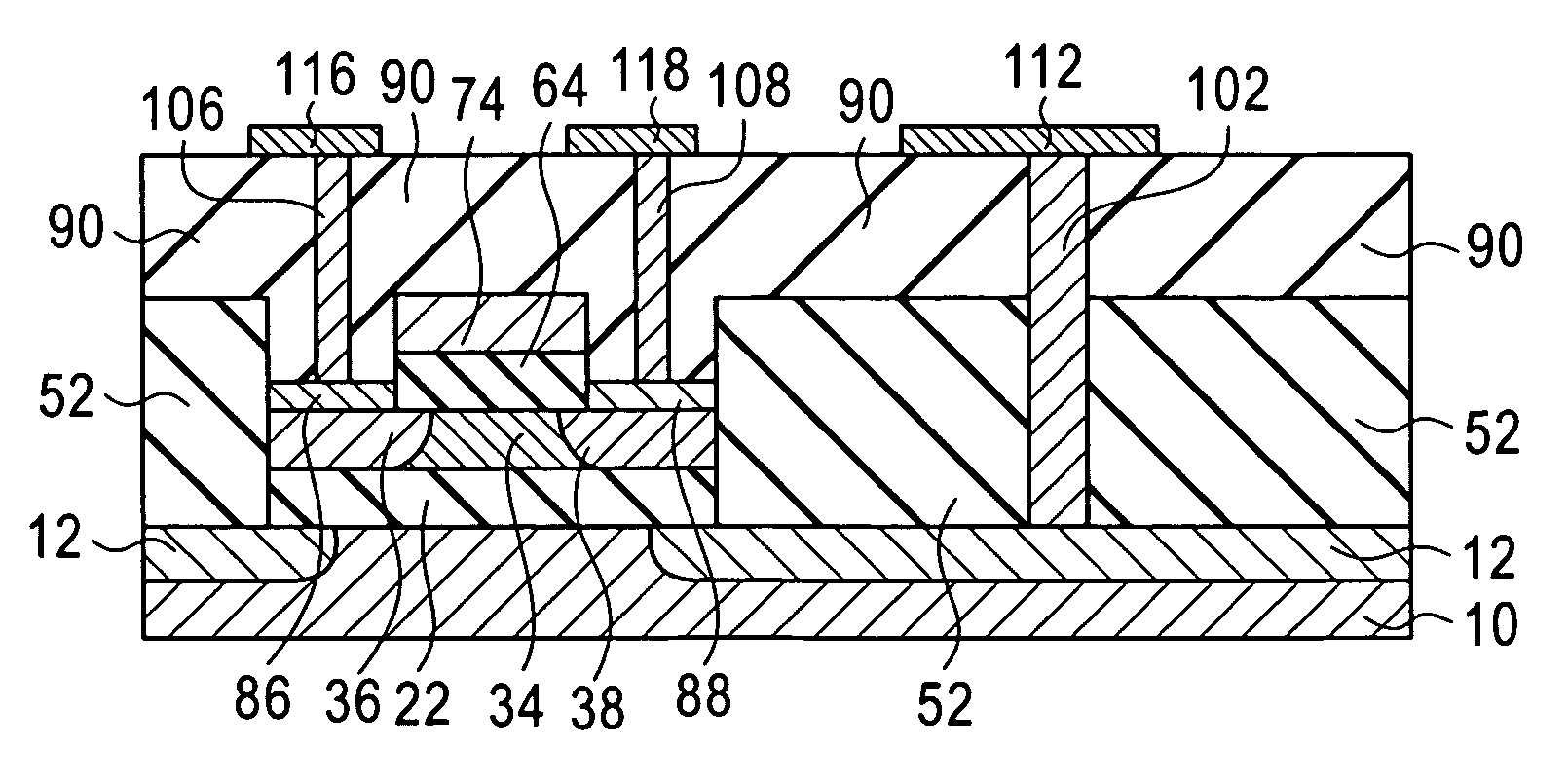

Semiconductor device fabrication method

InactiveUS7205190B2Sufficient formHigh melting pointTransistorSemiconductor/solid-state device detailsSoi cmosInsulation layer

The present invention adequately activates a substrate contact region of a support substrate without substantially changing the conventional SOI-CMOS device formation process. An exposed face of the support substrate is formed in an element isolation region of a layered substrate, which includes a support substrate having a first semiconductor layer, an insulating layer provided on the support substrate, and a second semiconductor layer provided on the insulating layer, by etching away the insulating layer and the second semiconductor layer. A substrate contact region is then formed in the support substrate by performing ion implantation from the side of the exposed face of the support substrate. Thereafter, an element isolation insulation layer is formed on the exposed face of the support substrate and a gate oxide film and a gate electrode are formed on the remaining second semiconductor layer. In addition, drain and source regions are formed by performing the ion implantation to the remaining second semiconductor layer with the gate electrode serving as a mask. Annealing to activate the substrate contact region, the drain region and the source region is then performed. Thereafter, a metal layer with a high melting point is formed on the drain and source regions and the metal layer is silicided through heat treatment.

Owner:LAPIS SEMICON CO LTD

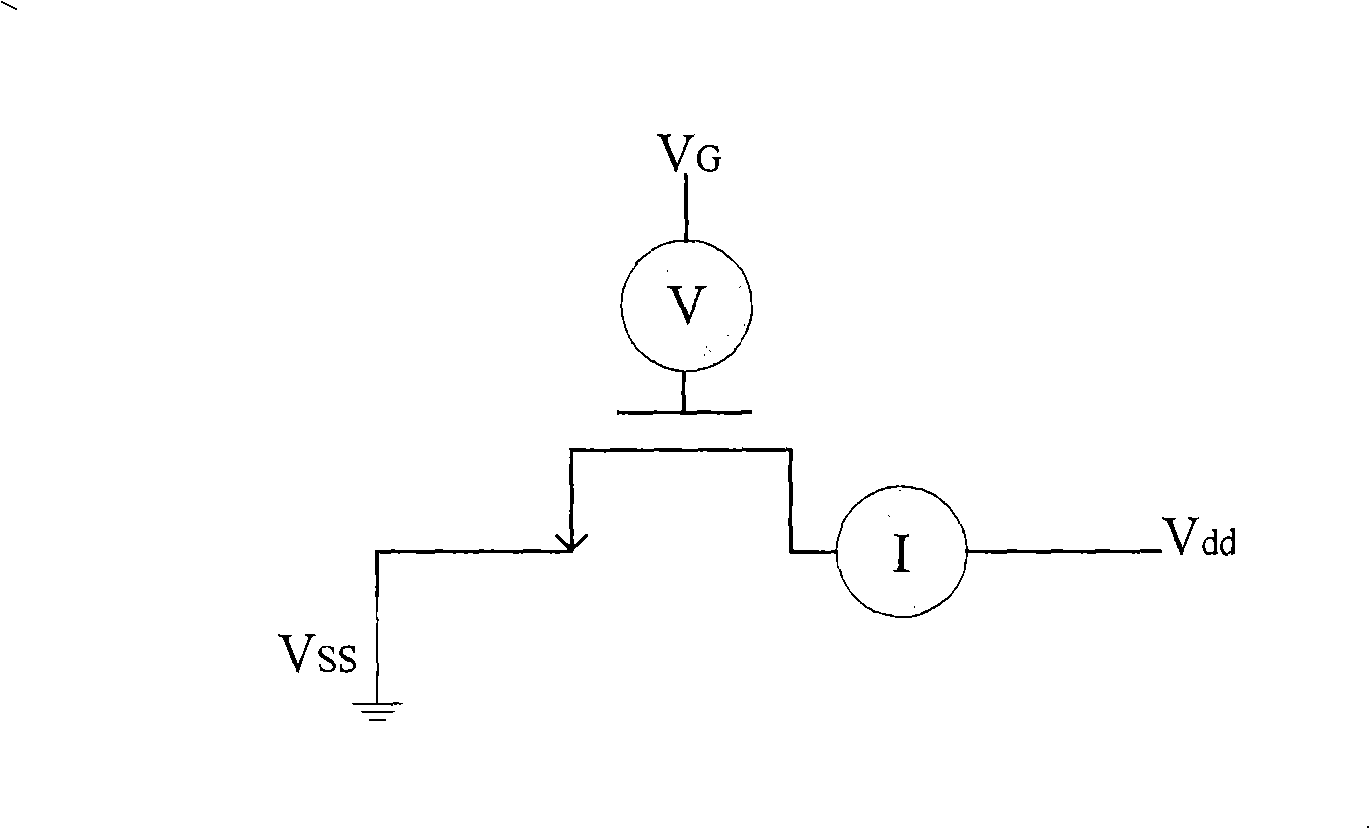

Test method of metal oxide semiconductor field-effect transistor threshold voltage

InactiveCN101275983AGuaranteed to workSemiconductor/solid-state device testing/measurementElectronic circuit testingSoi cmosField-effect transistor

The present invention provides a method for testing a threshold voltage of a field effect transistor of the metal oxide semiconductor. The back substrate of the SOI-CMOS circuit is connected with an earth potential or an electric power potential, wherein, when the threshold voltage of the NMOS is tested, the back substrate is connected with the earth potential; and when the threshold voltage of the PMOS is tested, the back substrate is connected with the negative electric power potential. When the threshold voltage of the NMOS is tested, the back substrate is connected to the electric power potential; and when the threshold voltage of PMOS is tested, the back substrate is connected to the earth potential. The invention fixes the back substrate of SOI-CMOS circuit on a certain potential, and the operations of N, PMOS devices in SOI circuit are in back grid biases which are totally indifferent. Therefore, the condition for singly characterize the threshold voltage of N, PMOS should be altered correspondingly, and in this way the threshold voltage can be correctly recognized and controlled in order to guarantee the normal operation of SOI circuit.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

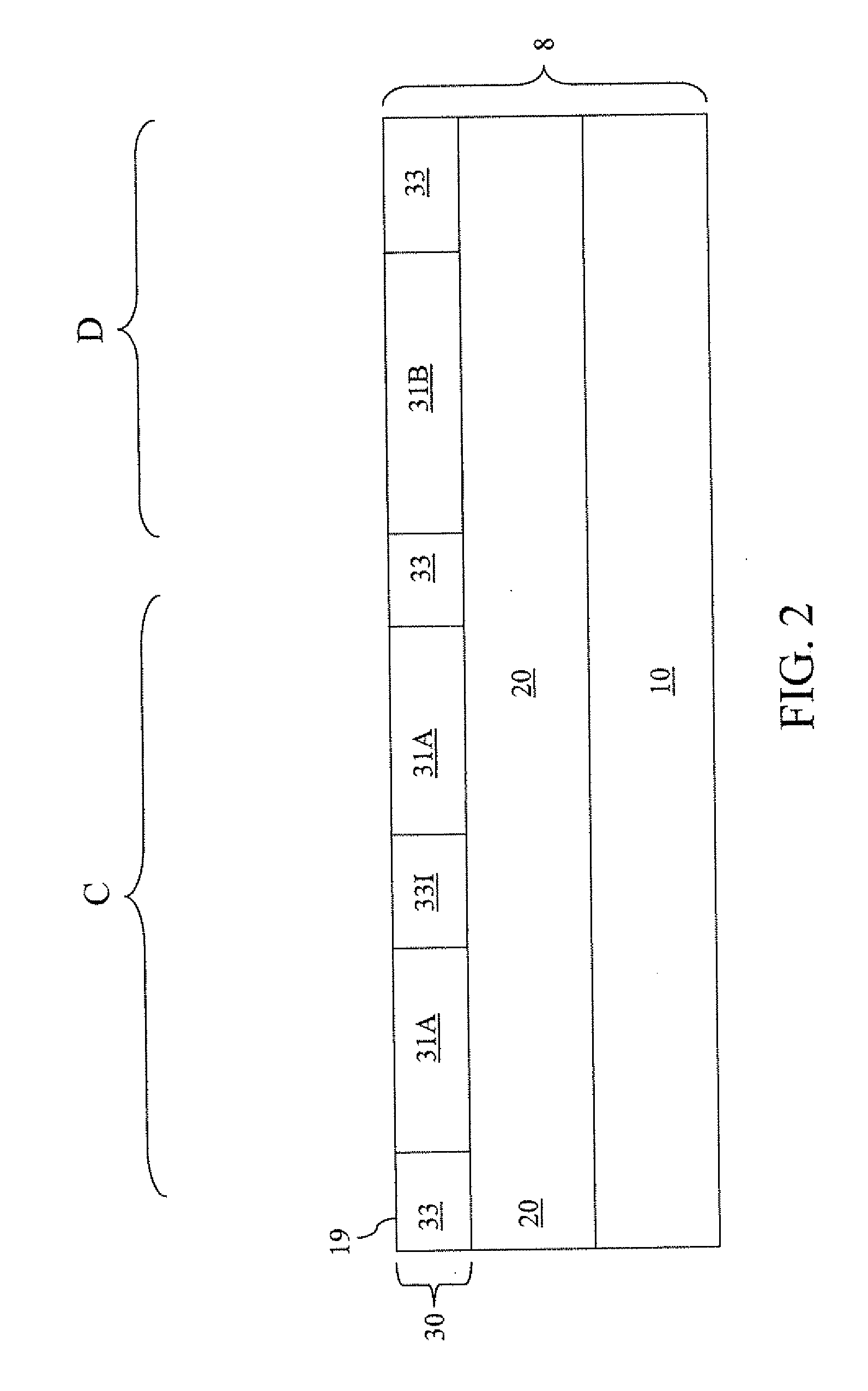

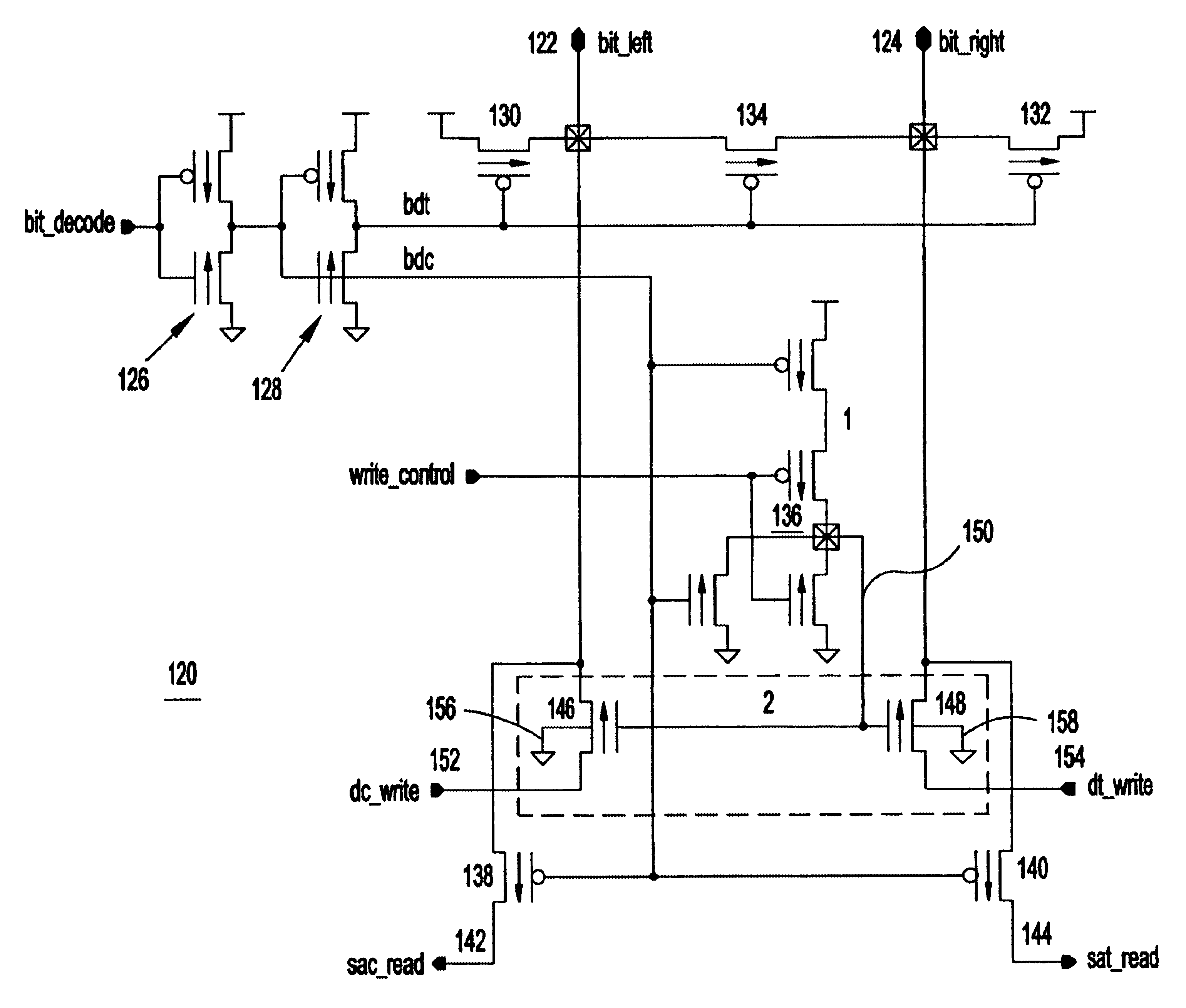

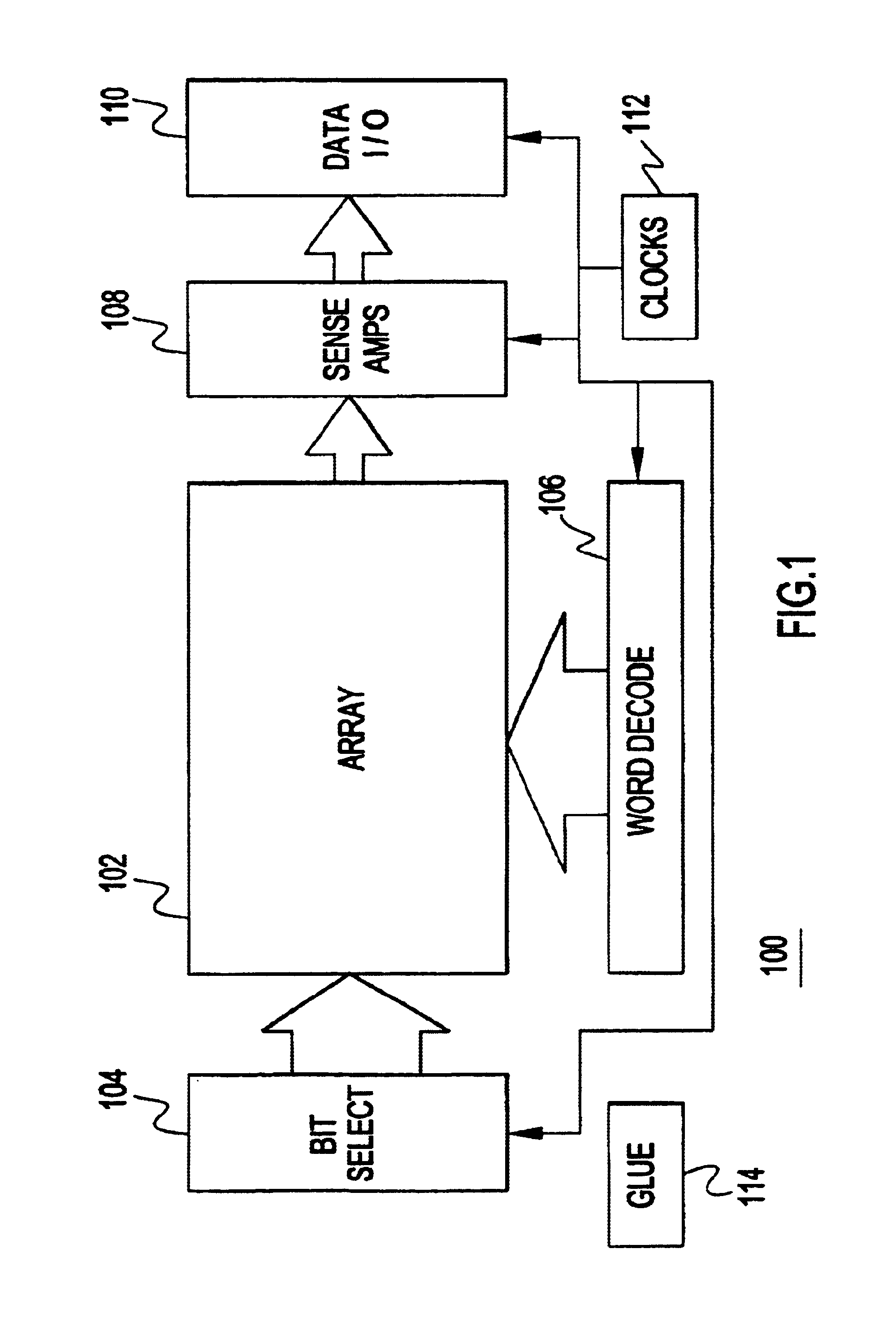

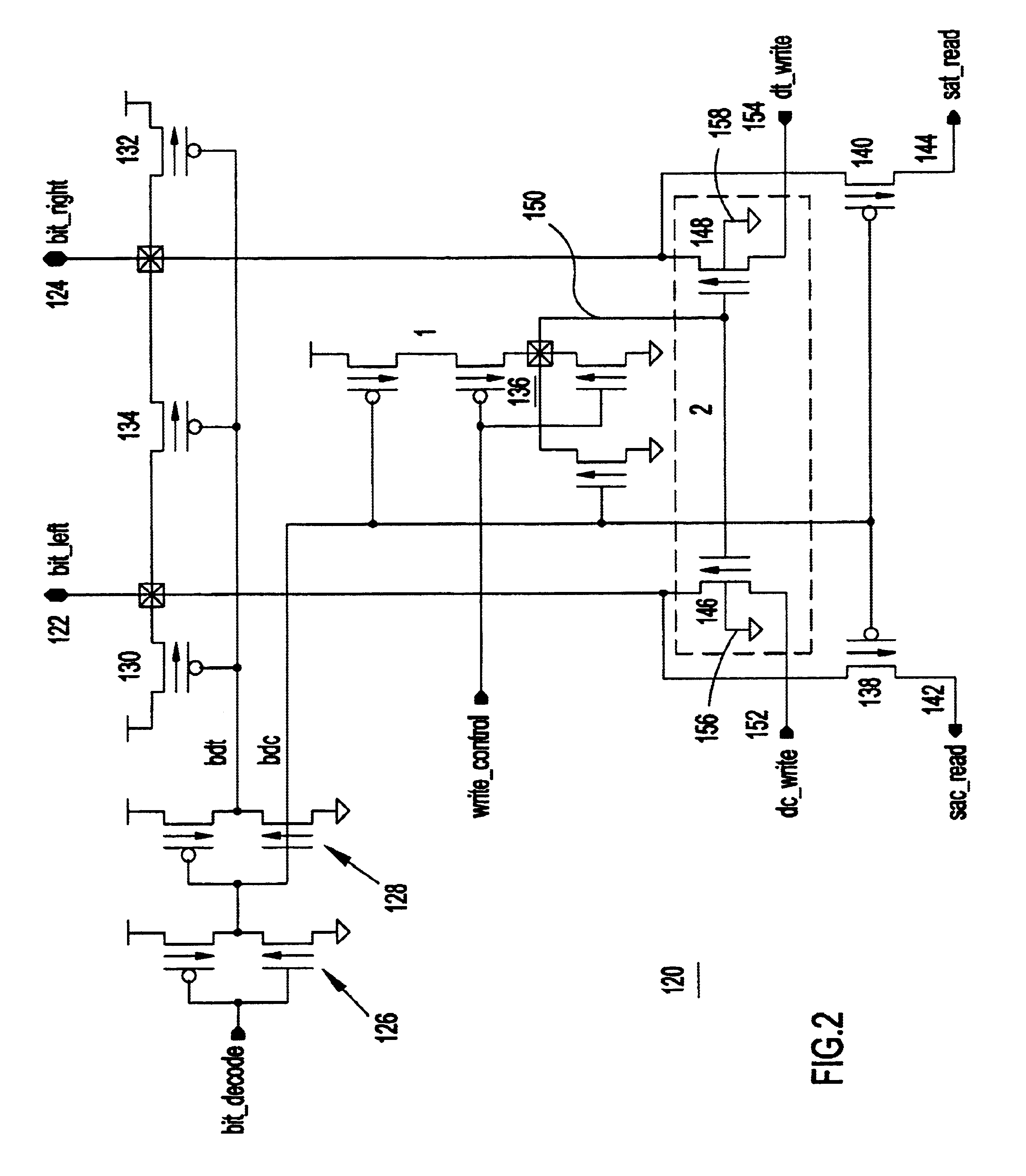

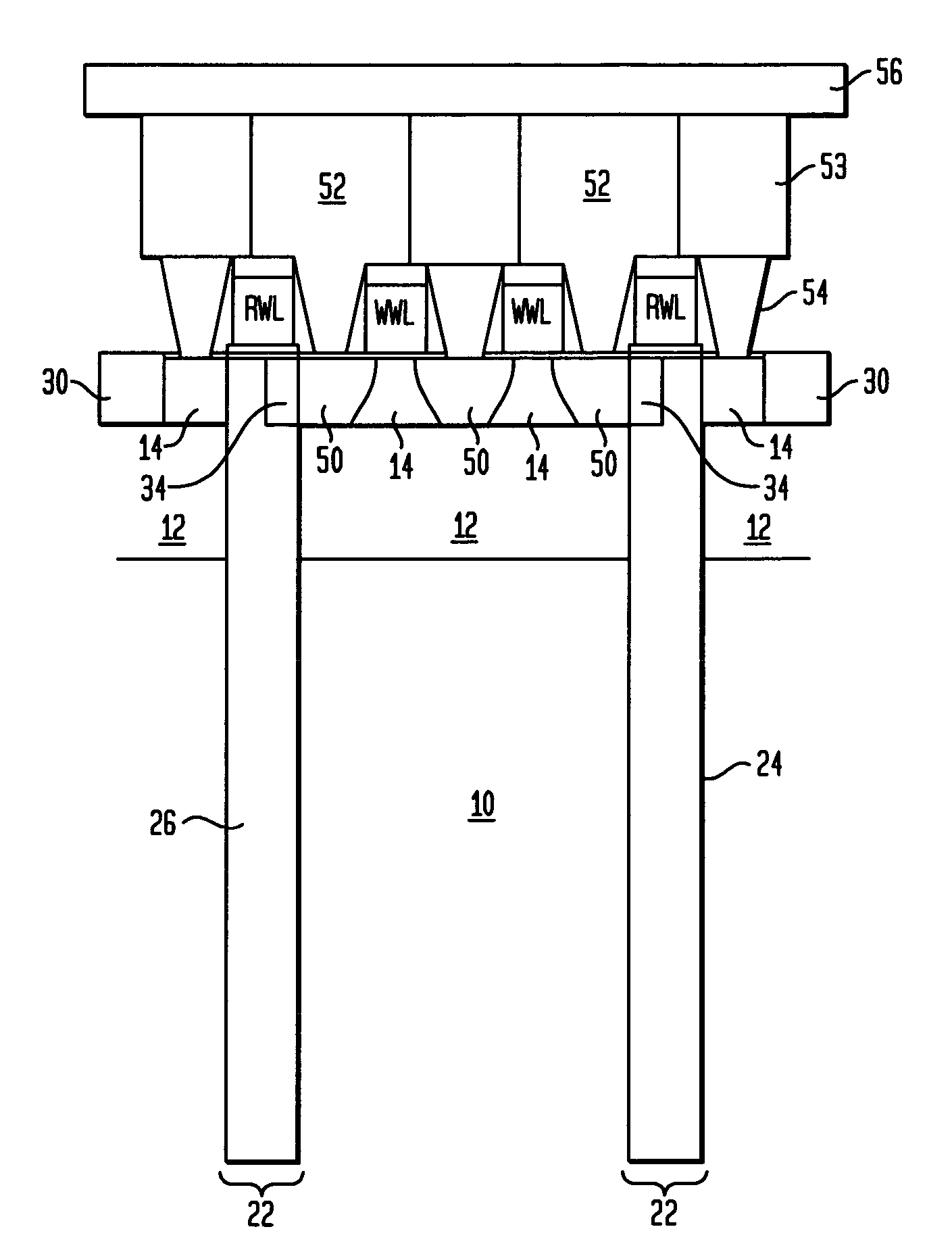

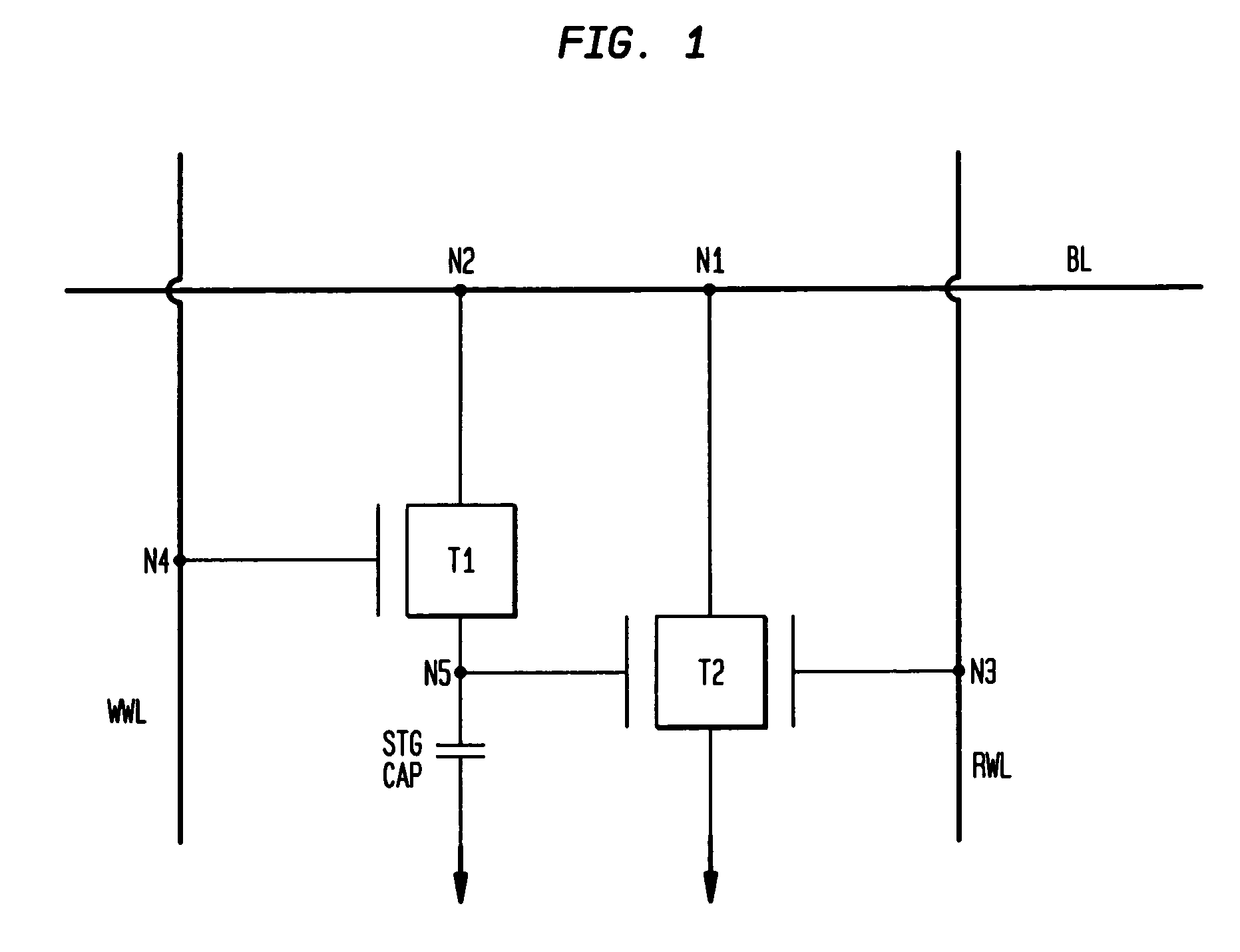

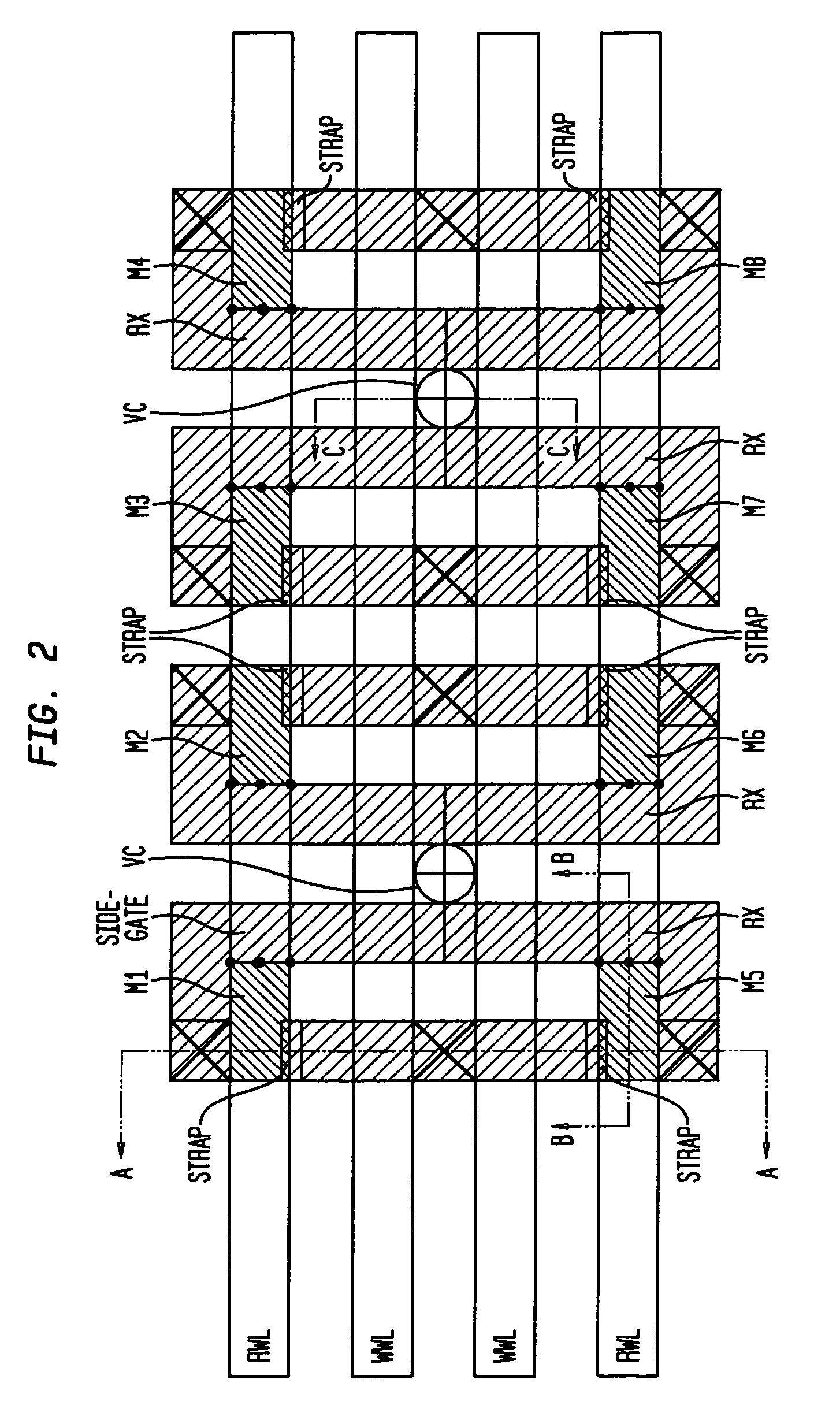

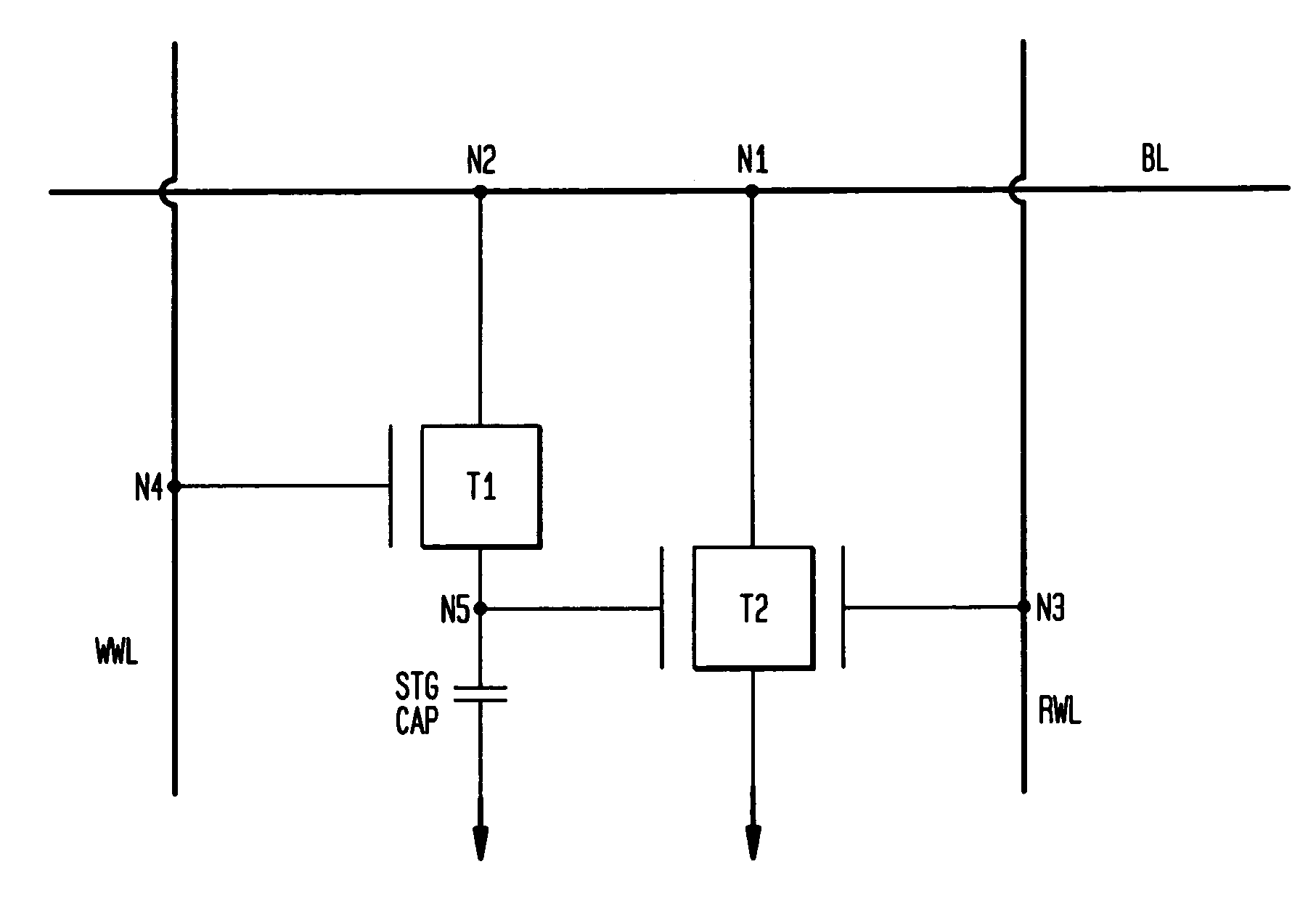

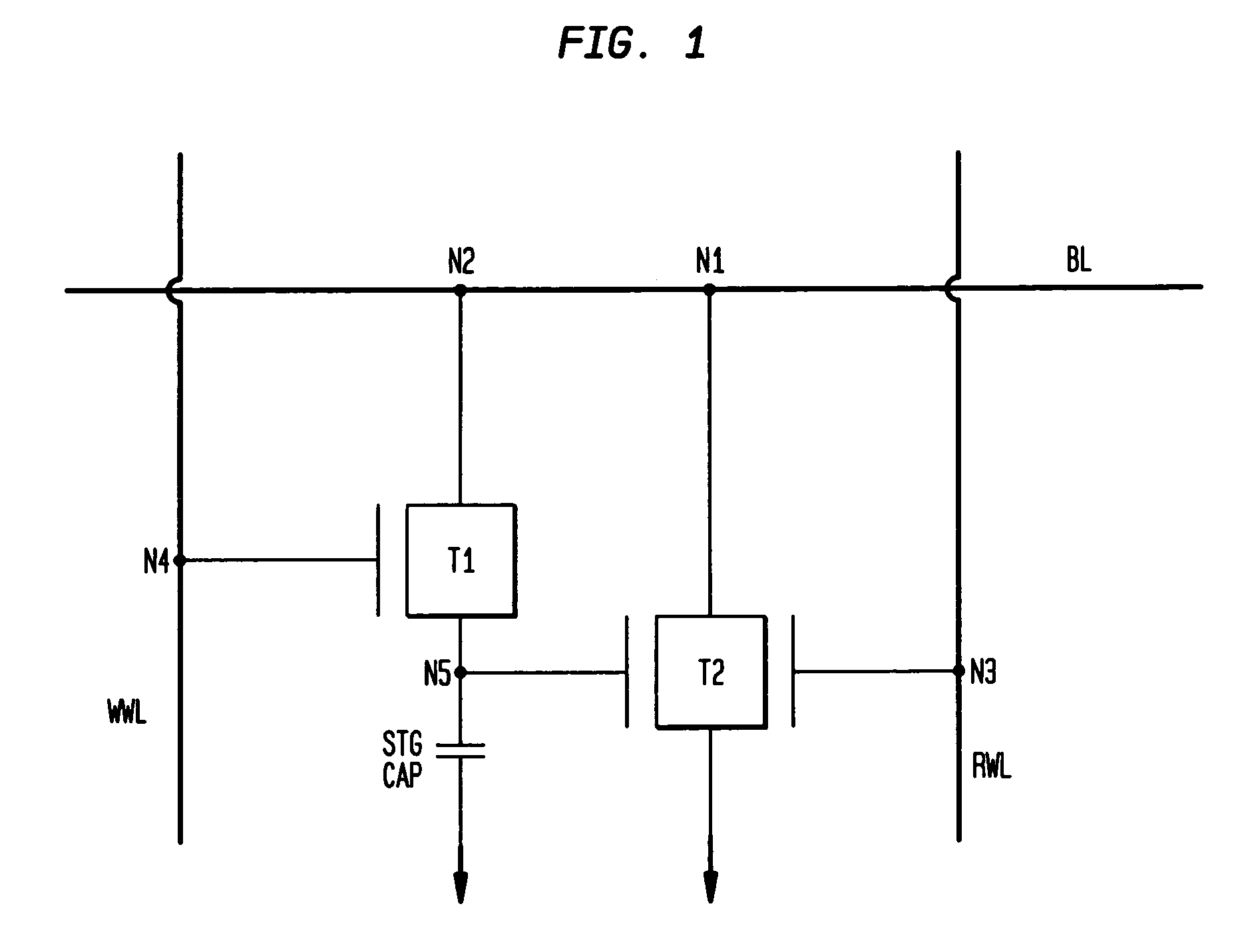

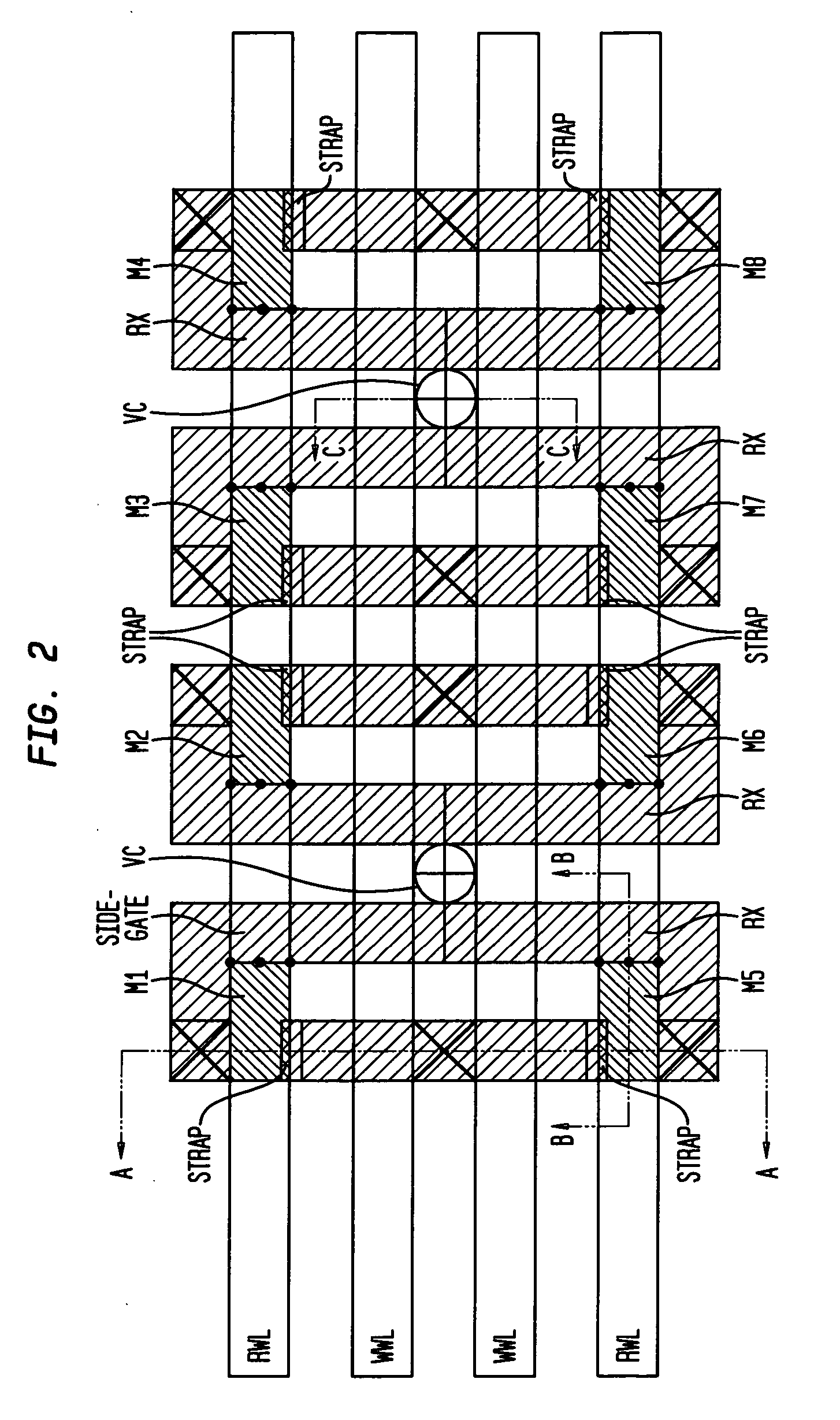

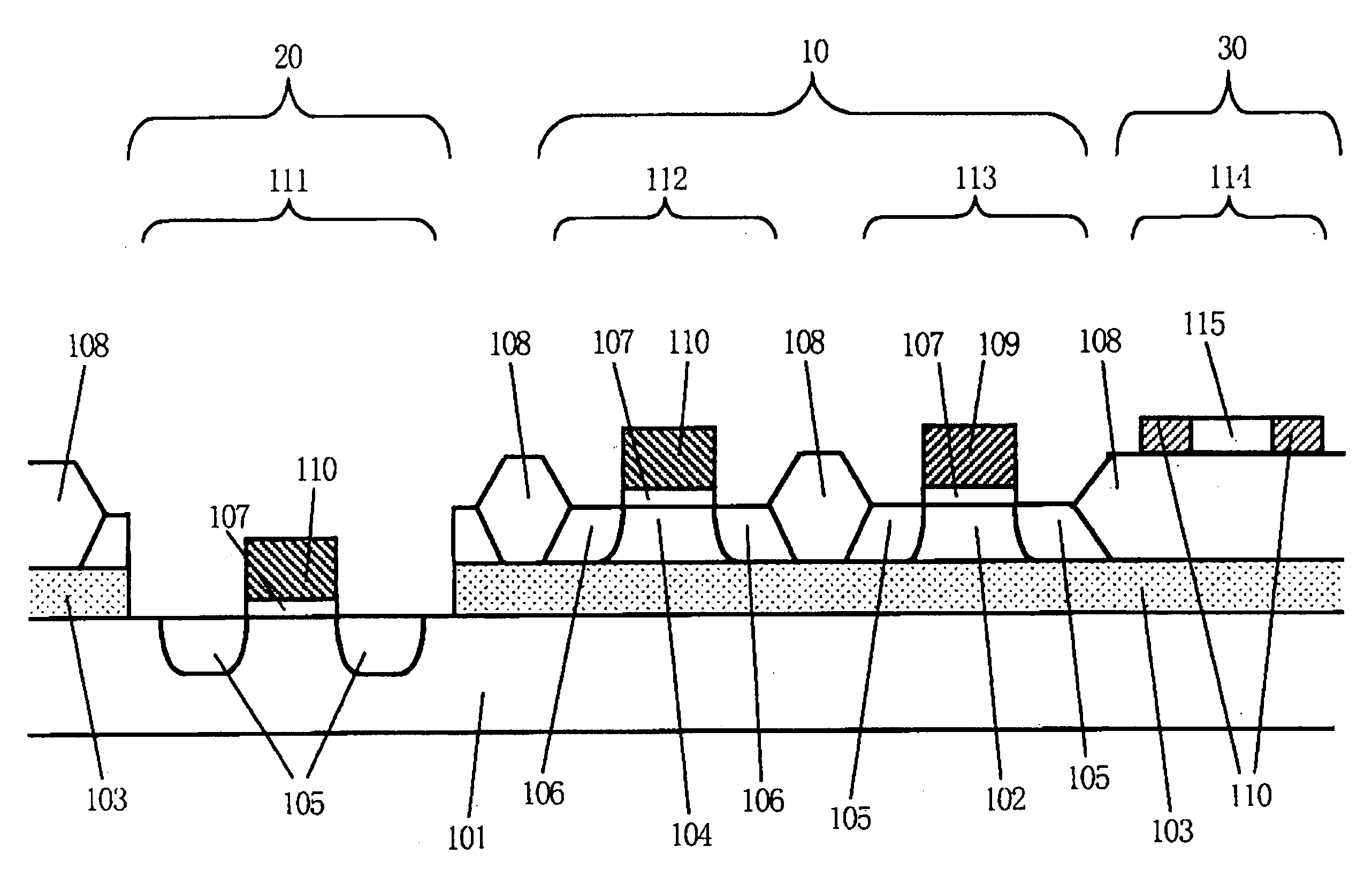

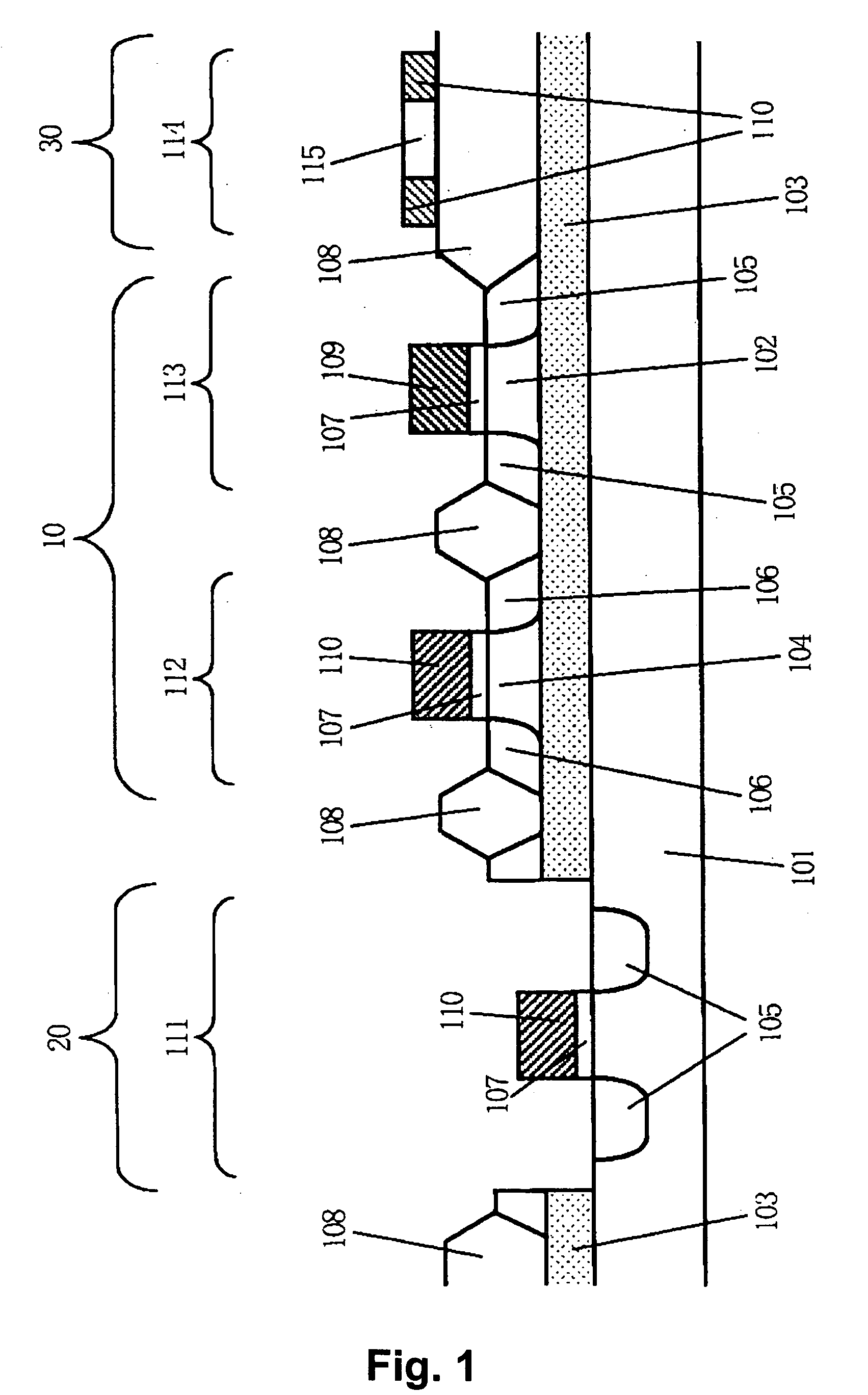

Dual port gain cell with side and top gated read transistor

ActiveUS20070047293A1Good conditionVt of the read transistor is highTransistorSolid-state devicesSoi cmosCMOS

A DRAM memory cell and process sequence for fabricating a dense (20 or 18 square) layout is fabricated with silicon-on-insulator (SOI) CMOS technology. Specifically, the present invention provides a dense, high-performance SRAM cell replacement that is compatible with existing SOI CMOS technologies. Various gain cell layouts are known in the art. The present invention improves on the state of the art by providing a dense layout that is fabricated with SOI CMOS. In general terms, the memory cell includes a first transistor provided with a gate, a source, and a drain respectively; a second transistor having a first gate, a second gate, a source, and a drain respectively; and a capacitor having a first terminal, wherein the first terminal of said capacitor and the second gate of said second transistor comprise a single entity.

Owner:GLOBALFOUNDRIES US INC

Super hybrid soi CMOS devices

InactiveUS20090212329A1Lower the pressure valueSolid-state devicesSemiconductor/solid-state device manufacturingSoi cmosSurface layer

The present invention provides semiconductor structures comprised of stressed channels on hybrid oriented. In particular, the semiconductor structures include a first active area having a first stressed semiconductor surface layer of a first crystallographic orientation located on a surface of a buried insulating material and a second active area having a second stressed semiconductor surface layer of a second crystallographic orientation located on a surface of a dielectric material. A trench isolation region is located between the first and second active area, and the trench isolation region is partially filled with a trench dielectric material and the dielectric material that is present underneath said second stressed semiconductor surface layer. The dielectric material within the trench isolation region has lower stress compared to that is used in conventional STI process and it is laterally abuts at least the second stressed semiconductor surface layer and extends to an upper surface of the trench isolation region.

Owner:INT BUSINESS MASCH CORP

SOI CMOS device with reduced DIBL

InactiveUS20050205931A1Solid-state devicesSemiconductor/solid-state device manufacturingSoi cmosDopant

CMOS devices formed with a Silicon On Insulator (SOI) technology with reduced Drain Induced Barrier Lowering (DIBL) characteristics and a method for producing the same. The method involves a high energy, high dose implant through openings in a masking layer and through channel regions of the p- and n-wells, into the insulator layer, thereby creating a borophosphosilicate glass (BPSG) diffusion source within the insulation layer underlying the gate regions of the SOI wafer substantially between the source and drain. Backend, high temperature processing steps induce diffusion of the dopants contained in the diffusion source into the p- and n-wells, thereby forming asymmetric retrograde dopant profiles in the channel under the gate. The method can be selectively applied to selected portions of a wafer to tailor device characteristics, such as for memory cells.

Owner:SEMICON COMPONENTS IND LLC

Semiconductor integrated circuit device

InactiveUS20070138558A1High ESD breakdown strengthEasy to controlTransistorSemiconductor/solid-state device detailsBreakdown strengthSoi cmos

In a protection NMOS transistor serving as an ESD input / output protection element formed on a semiconductor support substrate, a drain region of the N-type protection transistor is formed so as to surround the source region, and a minimum distance between the source and the drain is kept constant, which makes it possible to ensure a sufficient ESD breakdown strength and to realize a structure capable of protecting input / output terminal, particularly an output terminal, of the fully depleted SOI CMOS device vulnerable to ESD noise.

Owner:ABLIC INC

Semiconductor integrated circuit device

InactiveUS20060022274A1Reduce leakage currentReduction of gate lengthTransistorSemiconductor/solid-state device detailsCMOSBreakdown strength

Provided is a structure in which a gate electrode of an MMOS transistor of a fully depleted SOT CMOS circuit formed on a semiconductor thin film has an N-type conductivity, while a gate electrode of an protection NMOS transistor as an ESD input / output protection element formed on a semiconductor support substrate has a P-type conductivity, making it possible to protect input / output terminals, especially, an output terminal of a fully depleted SOI CMOS device, which is weak against ESD noise, while ensuring a sufficient ESD breakdown strength.

Owner:SEIKO INSTR INC

SOI CMOS compatible multiplanar capacitor

An isolated shallow trench isolation portion is formed in a top semiconductor portion of a semiconductor-on-insulator substrate along with a shallow trench isolation structure. A trench in the shape of a ring is formed around a doped top semiconductor portion and filled with a conductive material such as doped polysilicon. The isolated shallow trench isolation portion and the portion of a buried insulator layer bounded by a ring of the conductive material are etched to form a cavity. A capacitor dielectric is formed on exposed semiconductor surfaces within the cavity and above the doped top semiconductor portion. A conductive material portion formed in the trench and above the doped top semiconductor portion constitutes an inner electrode of a capacitor, while the ring of the conductive material, the doped top semiconductor portion, and a portion of a handle substrate abutting the capacitor dielectric constitute a second electrode.

Owner:TWITTER INC

Reduced integrated circuit chip leakage and method of reducing leakage

An integrated circuit that may include an array such as a static random access memory (SRAM) with high threshold device array devices and in selected other devices to reduce leakage. Devices with high threshold have a thicker gate oxide or a high k dielectric gate oxide that is selected based on threshold voltage (VT) variations with gate oxide dielectric type or gate oxide thickness for the particular technology, e.g., PD SOI CMOS. High threshold devices may be used in non-critical path margin identified. A thicker device threshold is selected for non-critical path FETs based on the non-critical path margin. Non-critical path delays are re-checked. FETs are formed with the selected thicker gate oxide for any non-critical paths passing the re-check and in array FETs with non-selected FETs being formed with normal gate oxide thickness.

Owner:IBM CORP