Ultra-thin soi CMOS with raised epitaxial source and drain and embedded sige pfet extension

a technology of embedded pfet extension and epitaxial source, which is applied in the field of forming ultrathin soi (utsoi) field effect transistors, can solve the problems of incorporating stress into utsoi fets, and none of this prior art addresses the integration of embedded pfet sige extension with raised source/drain regions, so as to improve pfet device extension and channel region conductivity, reduce contact and source/

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038]The present invention is directed to a method for forming ultra-thin SOI (UTSOI) field effect transistors with stressed channel regions that provide increased carrier mobility.

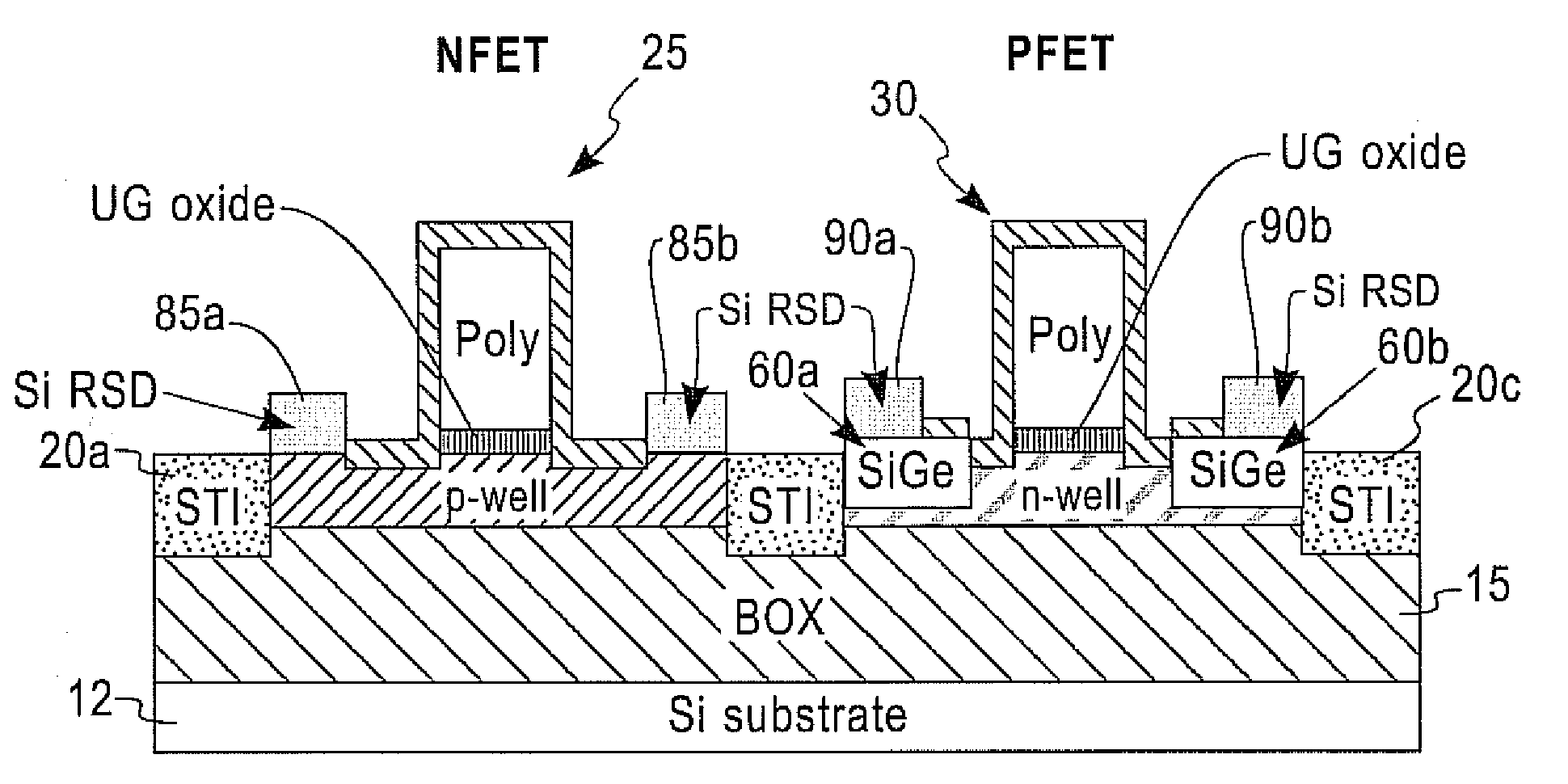

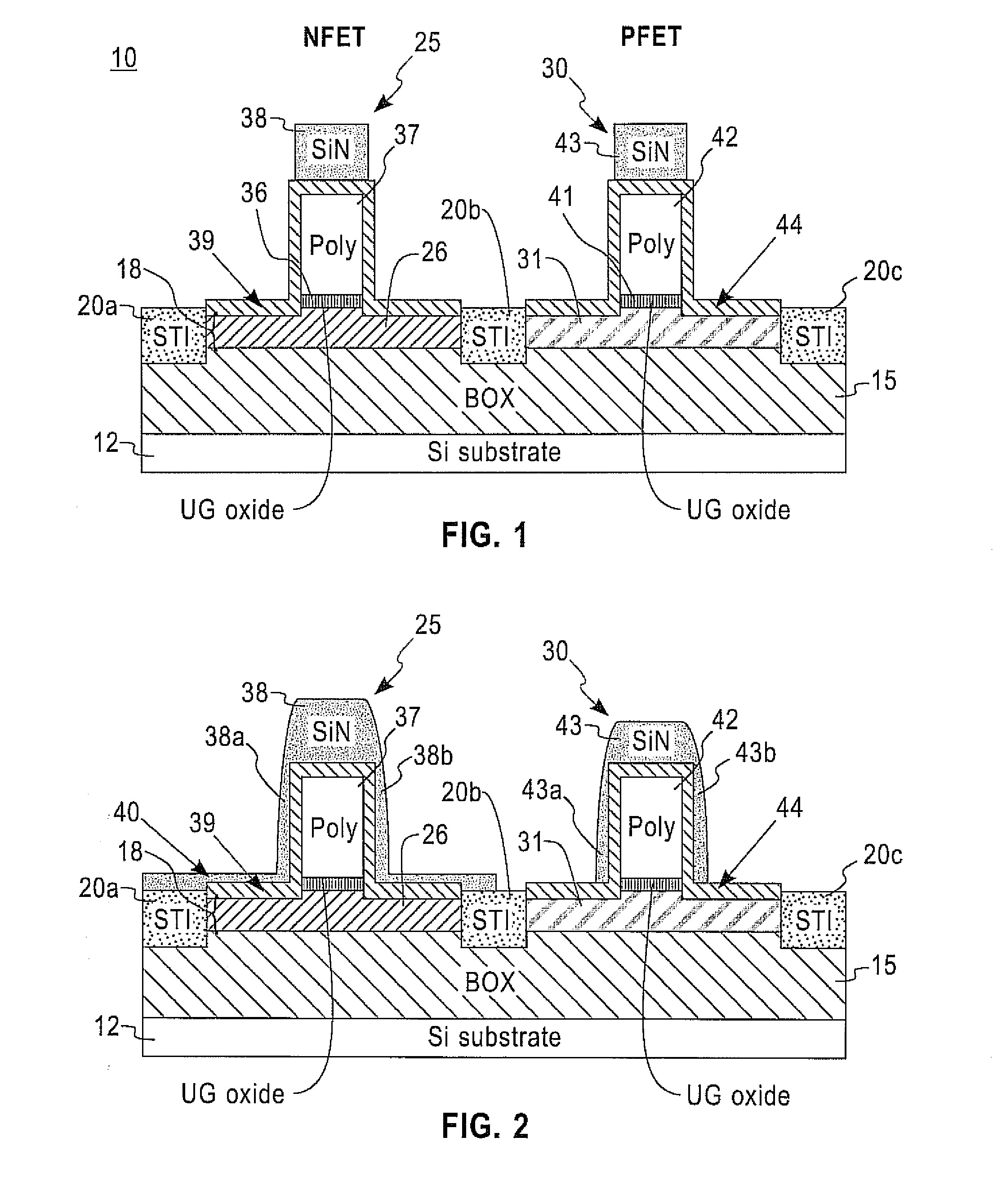

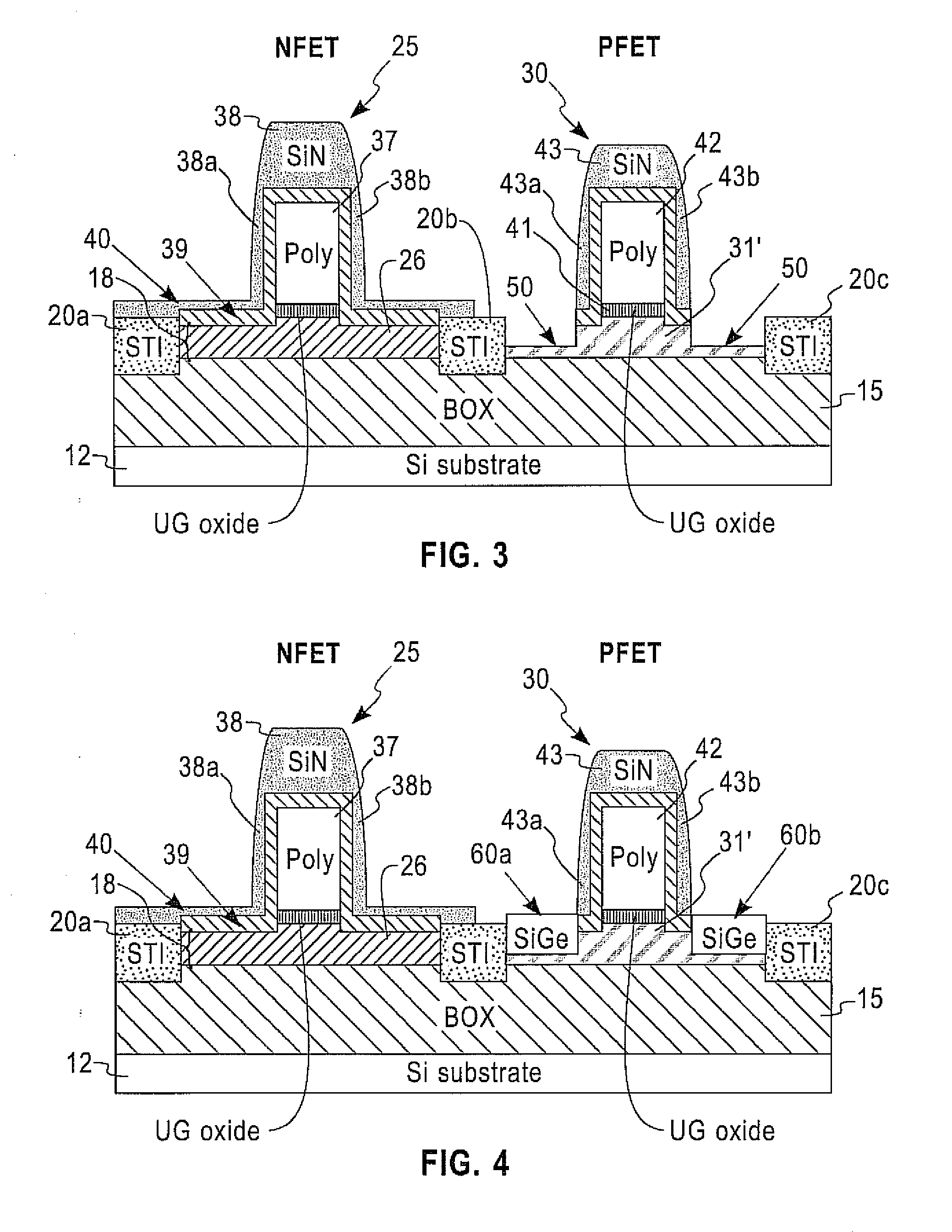

[0039]FIG. 1 shows, through cross-sectional view, a semiconductor structure 10 resulting from conventional UTSOI processing. As shown, in FIG. 1, there is first fabricated an SOI structure including a buried oxide (BOX) region 15 (e.g., an oxide, nitride, oxynitride or any combination thereof, with an oxide such as SiO2 being most typical) that is located between a top Si-containing layer 18 and a bottom Si-containing layer 12. Preferably, the BOX region 15 is continuous. The thickness of the BOX region 15 formed in the present invention may vary depending upon the exact embodiments and conditions used in fabricating the same. Typically, however, the BOX region has a thickness from about 200 to about 1800 Å, with a BOX thickness from about 1300 to about 1600 Å being more typical.

[0040]Insofar as the top ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More