Test method of metal oxide semiconductor field-effect transistor threshold voltage

An oxide semiconductor and field effect transistor technology is applied in the field of testing and characterization of the threshold voltage of N-type or P-type metal oxide semiconductor field effect transistors, and can solve the problem of inaccurate device threshold voltage, large circuit power consumption, and device subthreshold leakage. and other problems to ensure the effect of normal work

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] In order to further illustrate the technical content of the present invention, the following detailed description is as follows in conjunction with the embodiments and accompanying drawings.

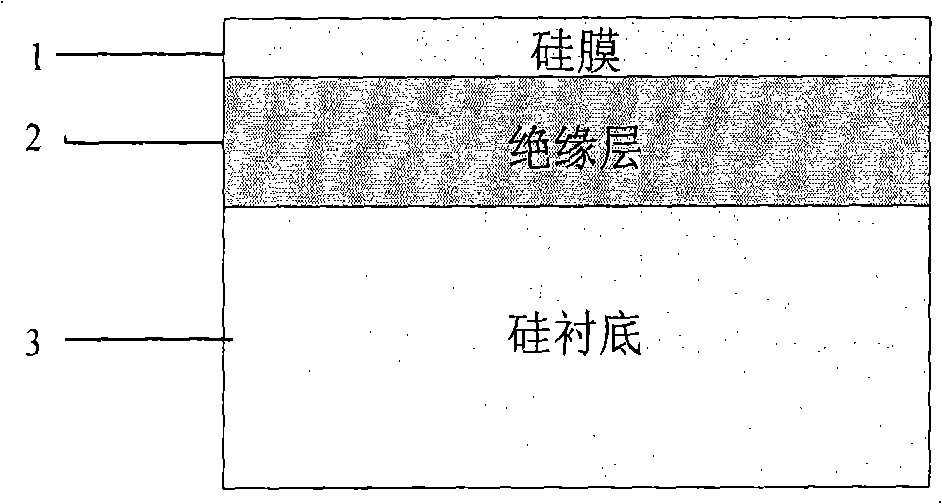

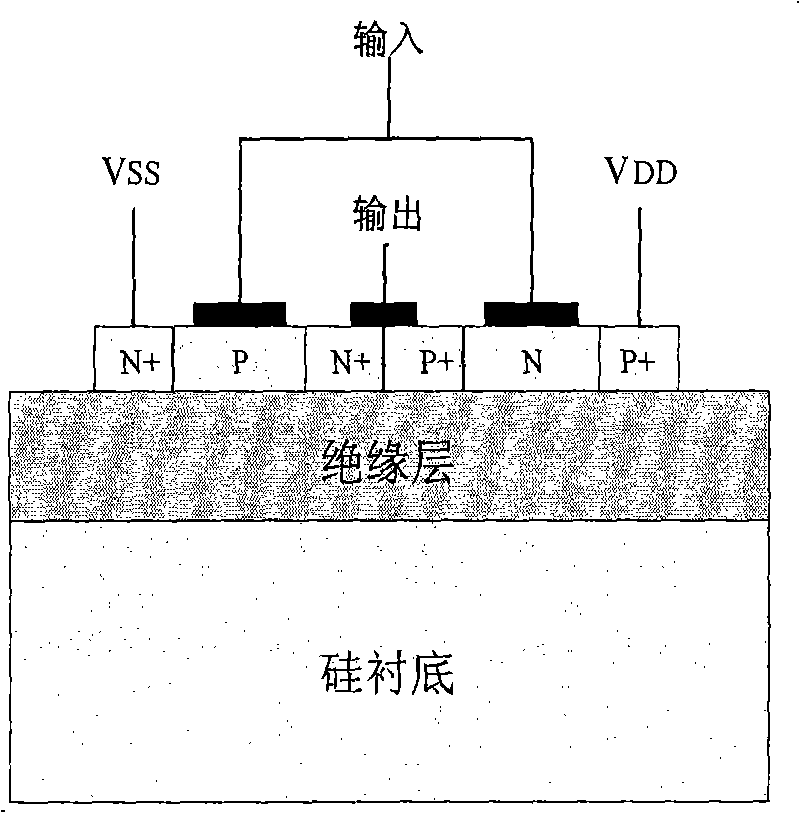

[0022] Figure 1 illustrates a starting SOI silicon wafer that can be used in the present invention. SOI silicon wafer It consists of top silicon film (1), insulating oxide layer (2) and silicon substrate (3). An SOICMOS circuit and N and PMOS devices for monitoring are prepared on the top silicon film (1). The SOI material is a commercial conventional oxygen ion implantation isolation (SIMOX) sheet, and other thermal bonding and smart-cut (Smart-Cut) sheets can also be used. For SOI CMOS circuits, the positive power supply voltage is applied to the source of the PMOS, and the ground potential (Vss) is applied to the source of the NMOS short.

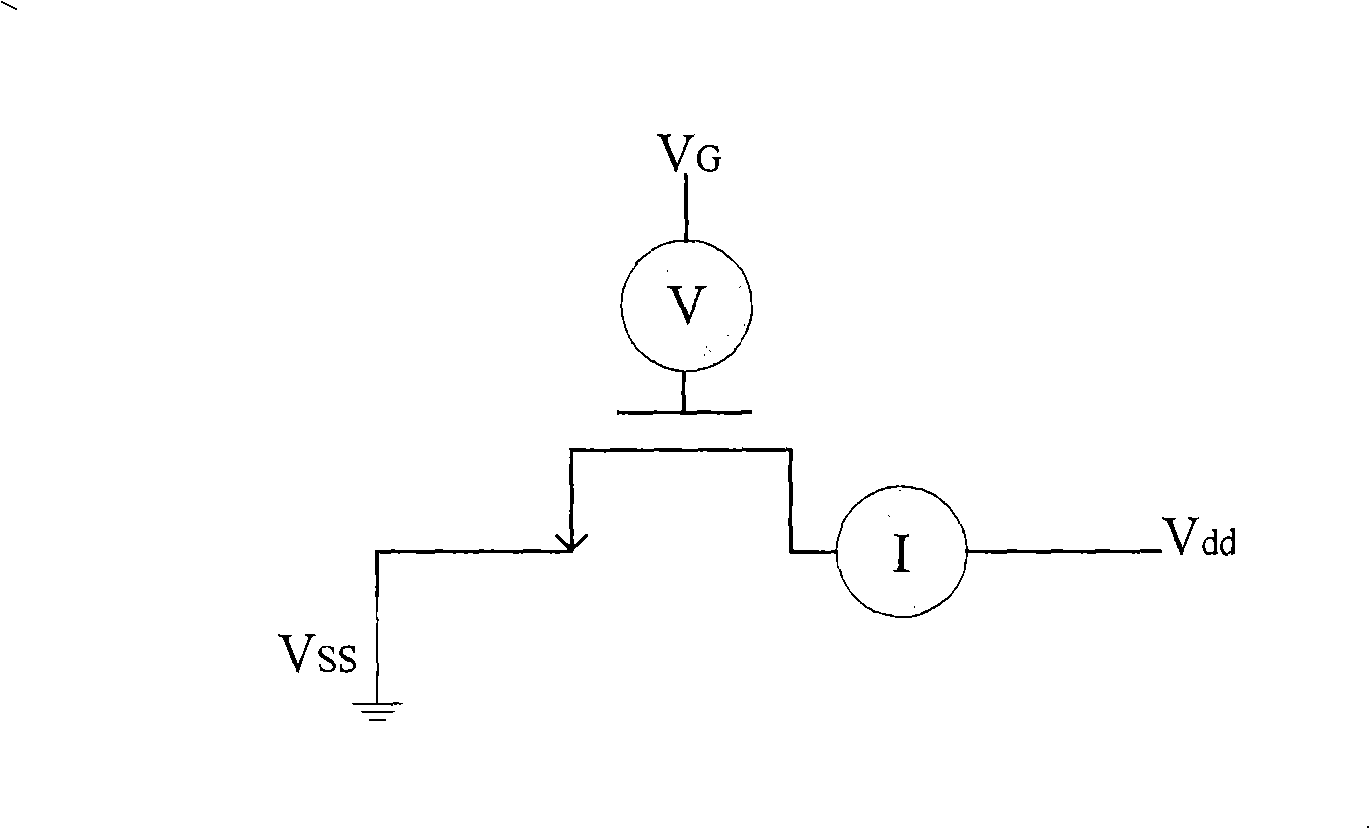

[0023] The invention relates to the bias of the back substrate of the SOI-CMOS integrated circuit, and provides the condition for charact...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More