Patents

Literature

944 results about "Junction area" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

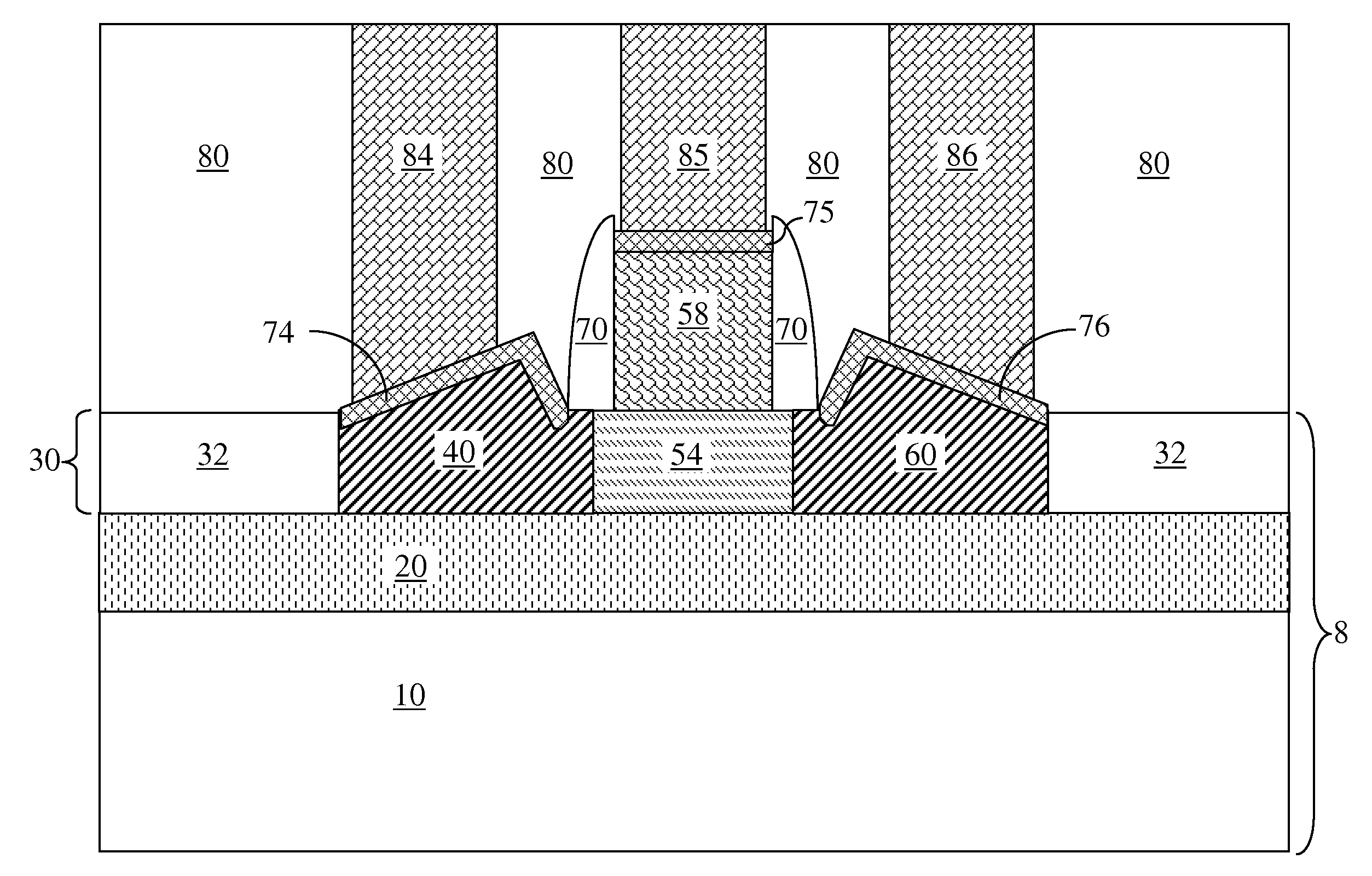

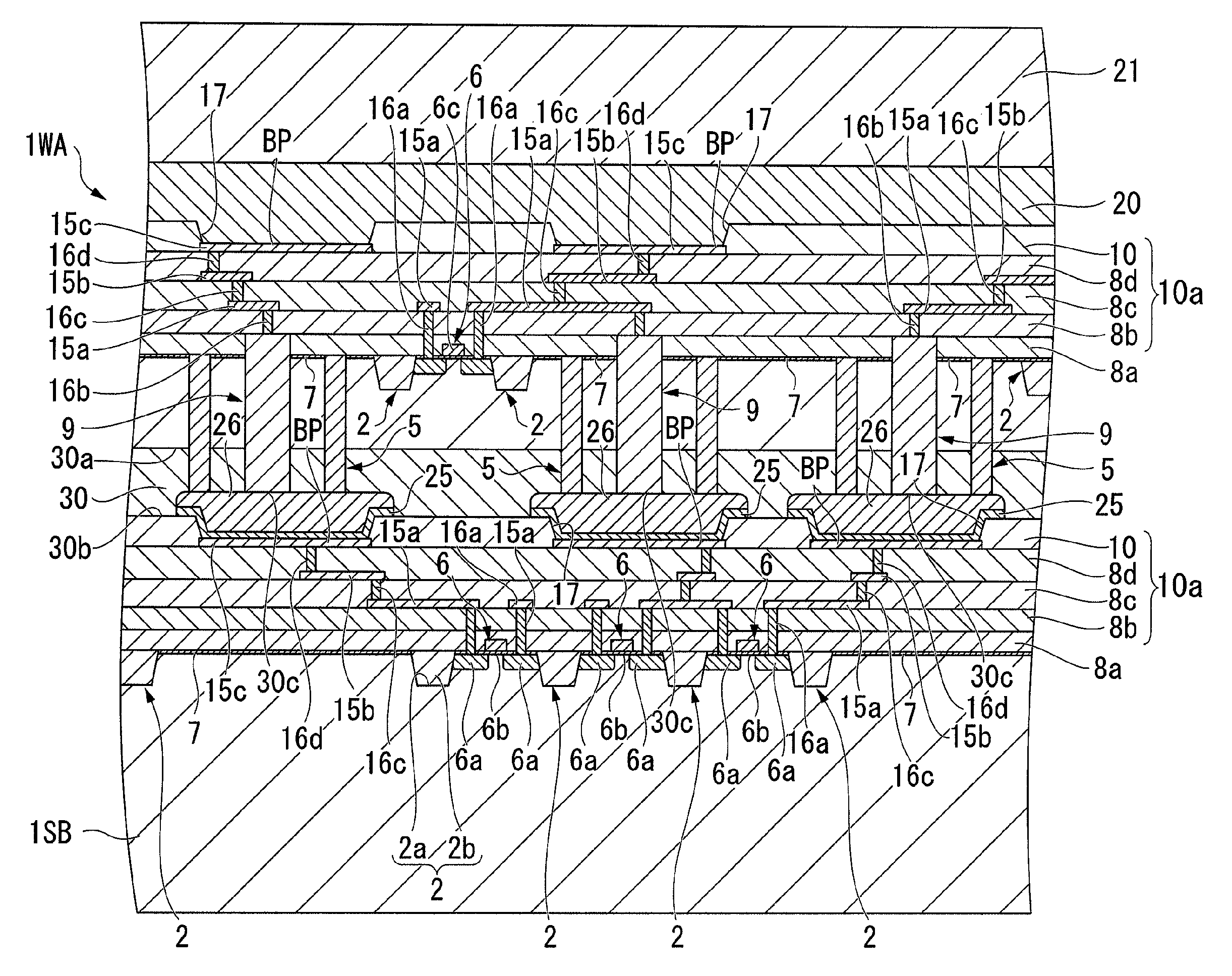

SOI SiGe-Base Lateral Bipolar Junction Transistor

ActiveUS20120139009A1Great current densityNoise minimizationSolid-state devicesSemiconductor/solid-state device manufacturingCarrier scatteringParasitic capacitance

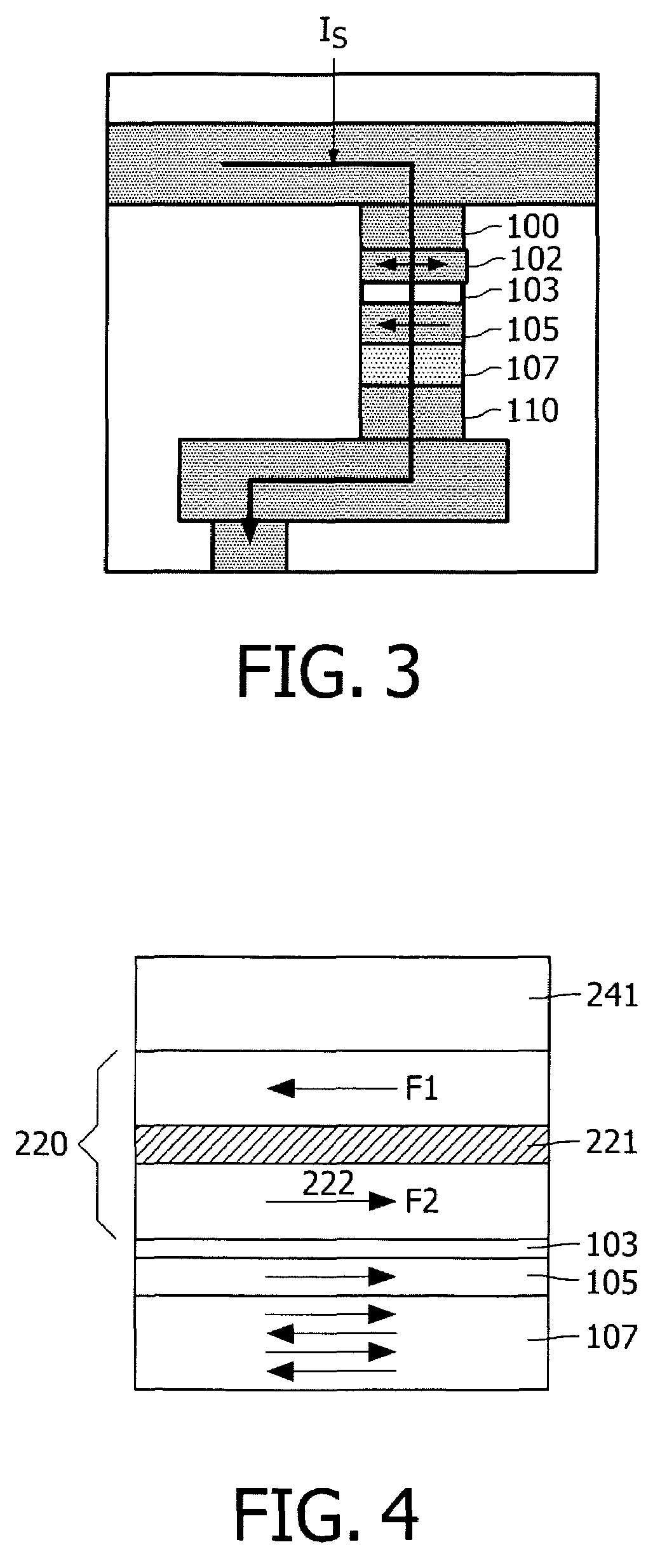

A lateral heterojunction bipolar transistor (HBT) is formed on a semiconductor-on-insulator substrate. The HBT includes a base including a doped silicon-germanium alloy base region, an emitter including doped silicon and laterally contacting the base, and a collector including doped silicon and laterally contacting the base. Because the collector current is channeled through the doped silicon-germanium base region, the HBT can accommodate a greater current density than a comparable bipolar transistor employing a silicon channel. The base may also include an upper silicon base region and / or a lower silicon base region. In this case, the collector current is concentrated in the doped silicon-germanium base region, thereby minimizing noise introduced to carrier scattering at the periphery of the base. Further, parasitic capacitance is minimized because the emitter-base junction area is the same as the collector-base junction area.

Owner:IBM CORP

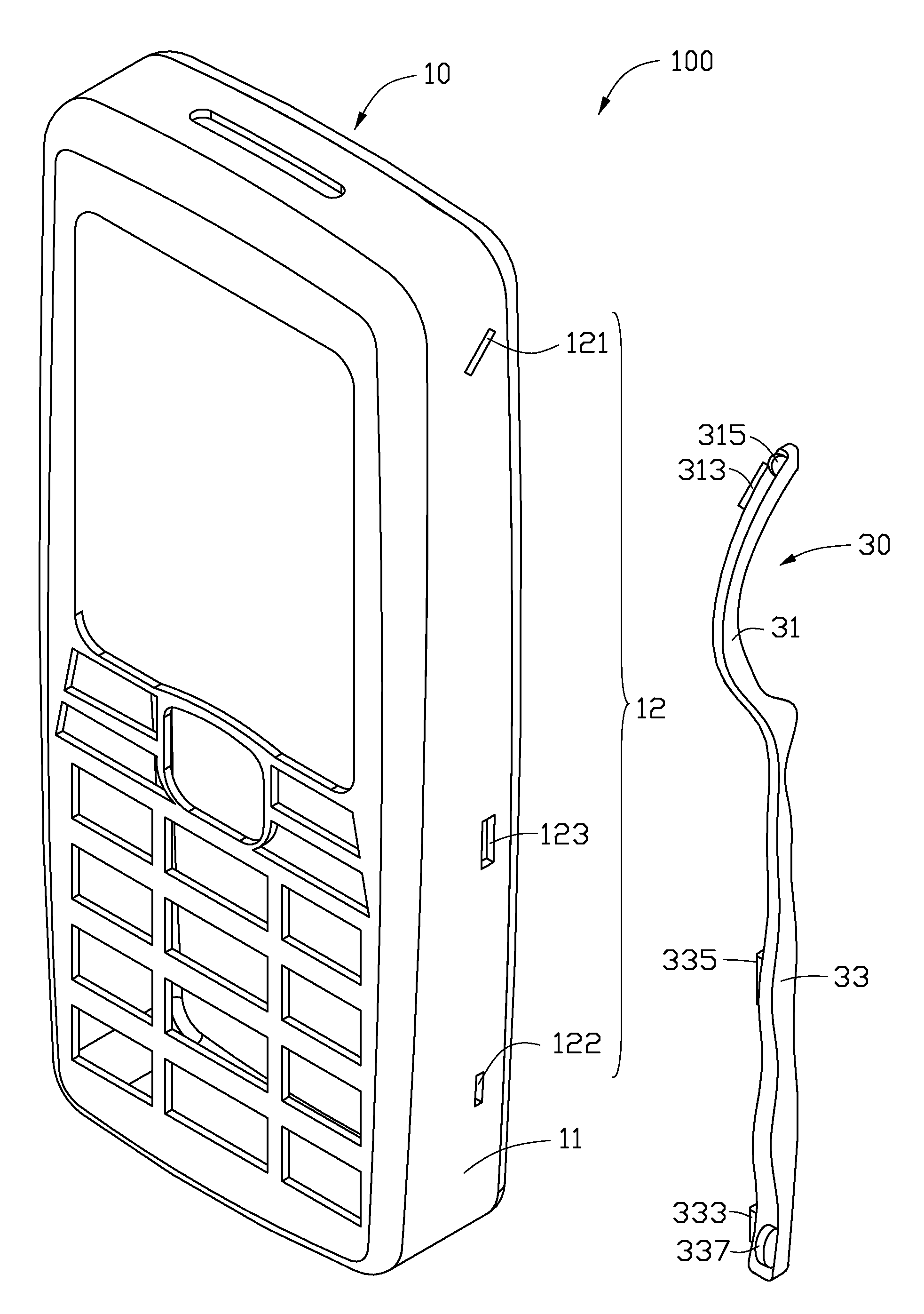

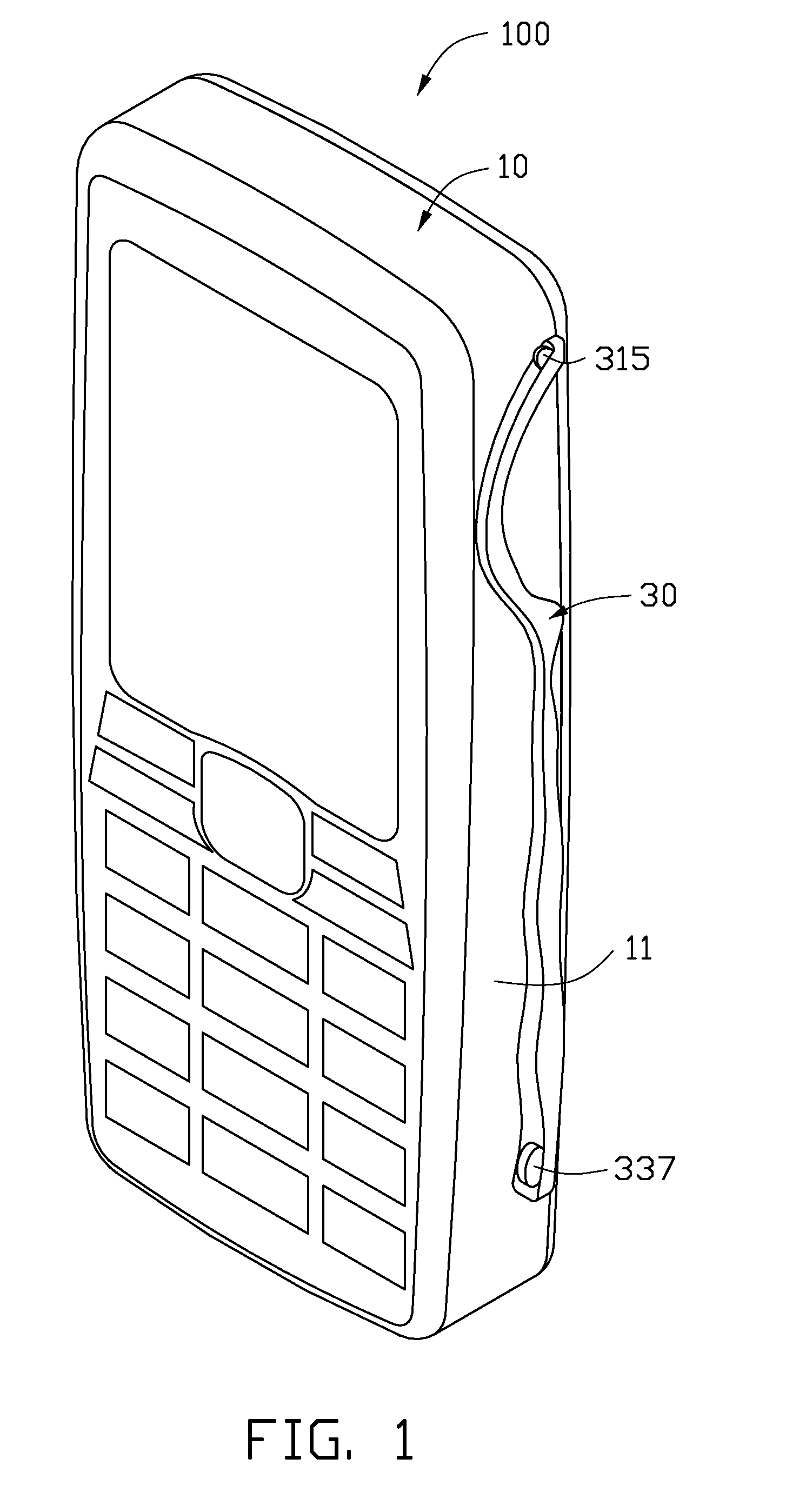

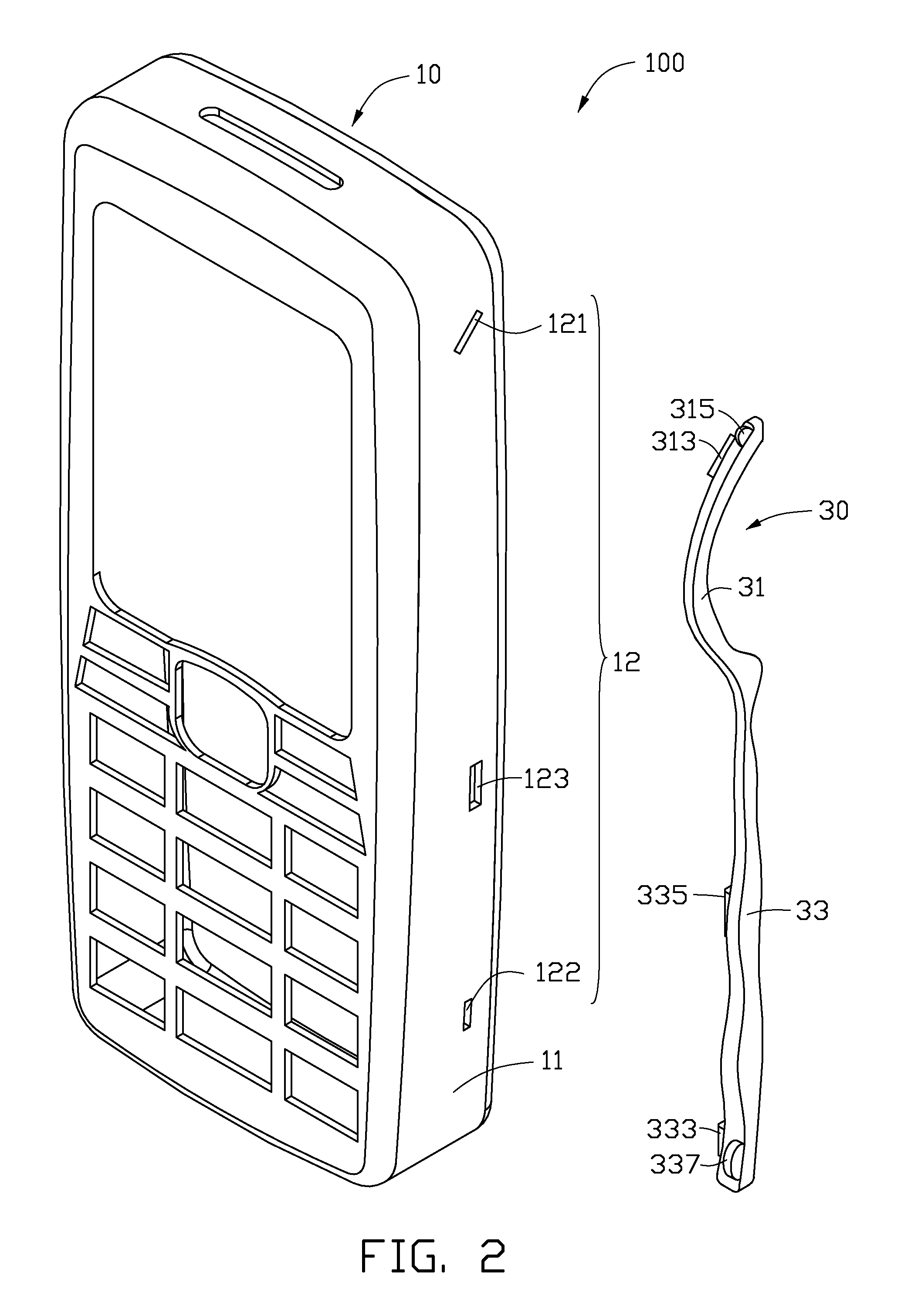

Wireless earphone and portable electronic device using the same

A wireless earphone includes an earphone, a microphone, a hanging portion and an adjusting portion fixed with the hanging portion. The answering portion is mounted on the junction area of the hanging portion and the adjusting portion. The microphone is mounted on the other end of the adjusting portion. The wireless earphone is made of flexible, elastic material. The bluetooth has at least one block protruding thereon, to make the wireless earphone be disassembly mounted on a portable electronic device. The invention also includes a portable electronic device using the wireless earphone.

Owner:SHENZHEN FUTAIHONG PRECISION IND CO LTD +1

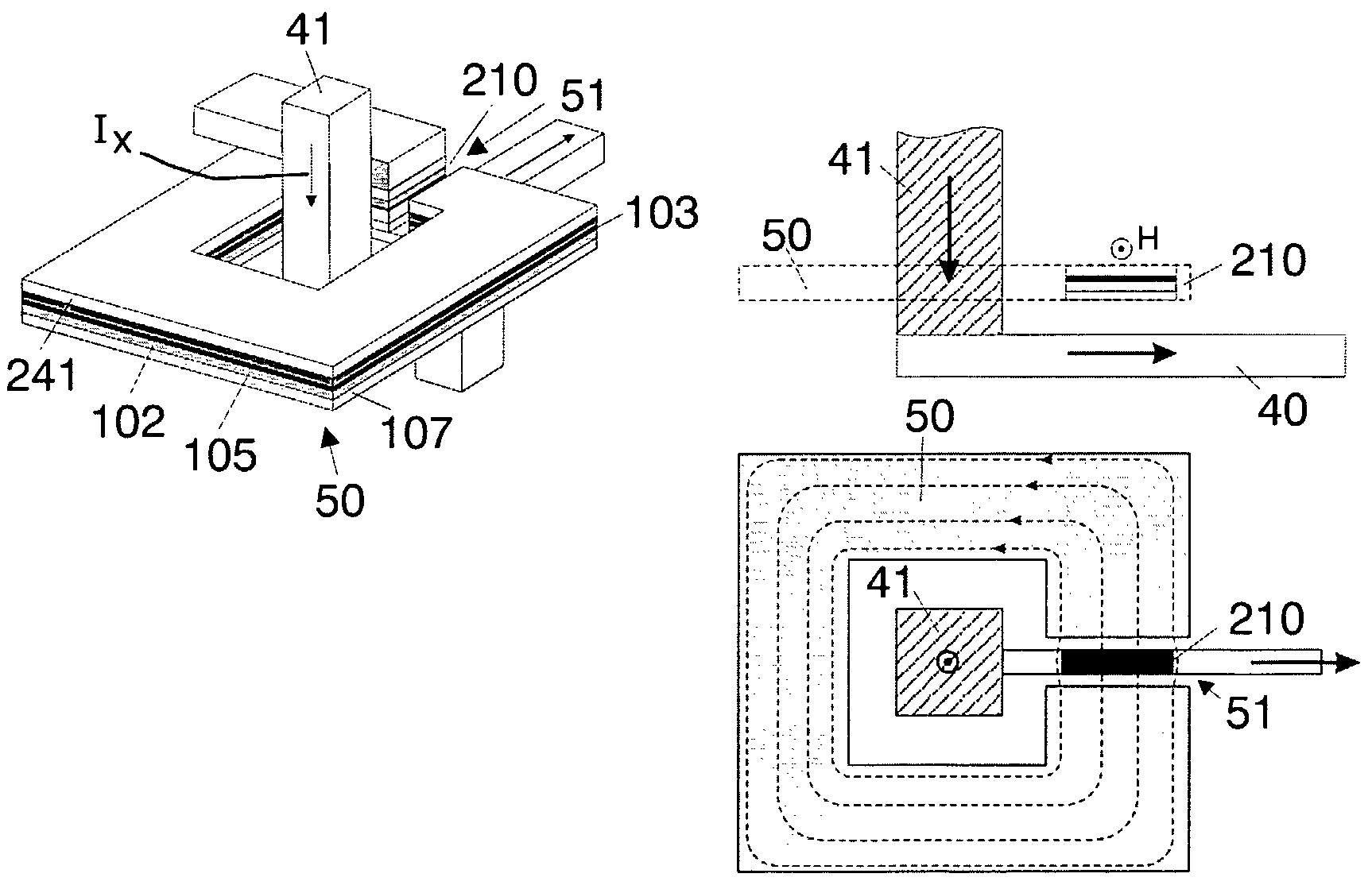

High sensitivity magnetic built-in current sensor

InactiveUS7619431B2Improve sensor sensitivityHigh sensitivityMagnetic measurementsDigital storageElectrical conductorEngineering

A sensor for contactlessly detecting currents, has a sensor element having a magnetic tunnel junction (MTJ), and detection circuitry, the sensor element having a resistance which varies with the magnetic field, and the detection circuitry is arranged to detect a tunnel current flowing through the tunnel junction. The sensor element may share an MTJ stack with memory elements. Also it can provide easy integration with next generation CMOS processes, including MRAM technology, be more compact, and use less power. Solutions for increasing sensitivity of the sensor, such as providing a flux concentrator, and for generating higher magnetic fields with a same current, such as forming L-shaped conductor elements, are given. The greater sensitivity enables less post processing to be used, to save power for applications such as mobile devices. Applications include current sensors, built-in current sensors, and IDDQ and IDDT testing, even for next generation CMOS processes.

Owner:ELIPOSKI REMOTE

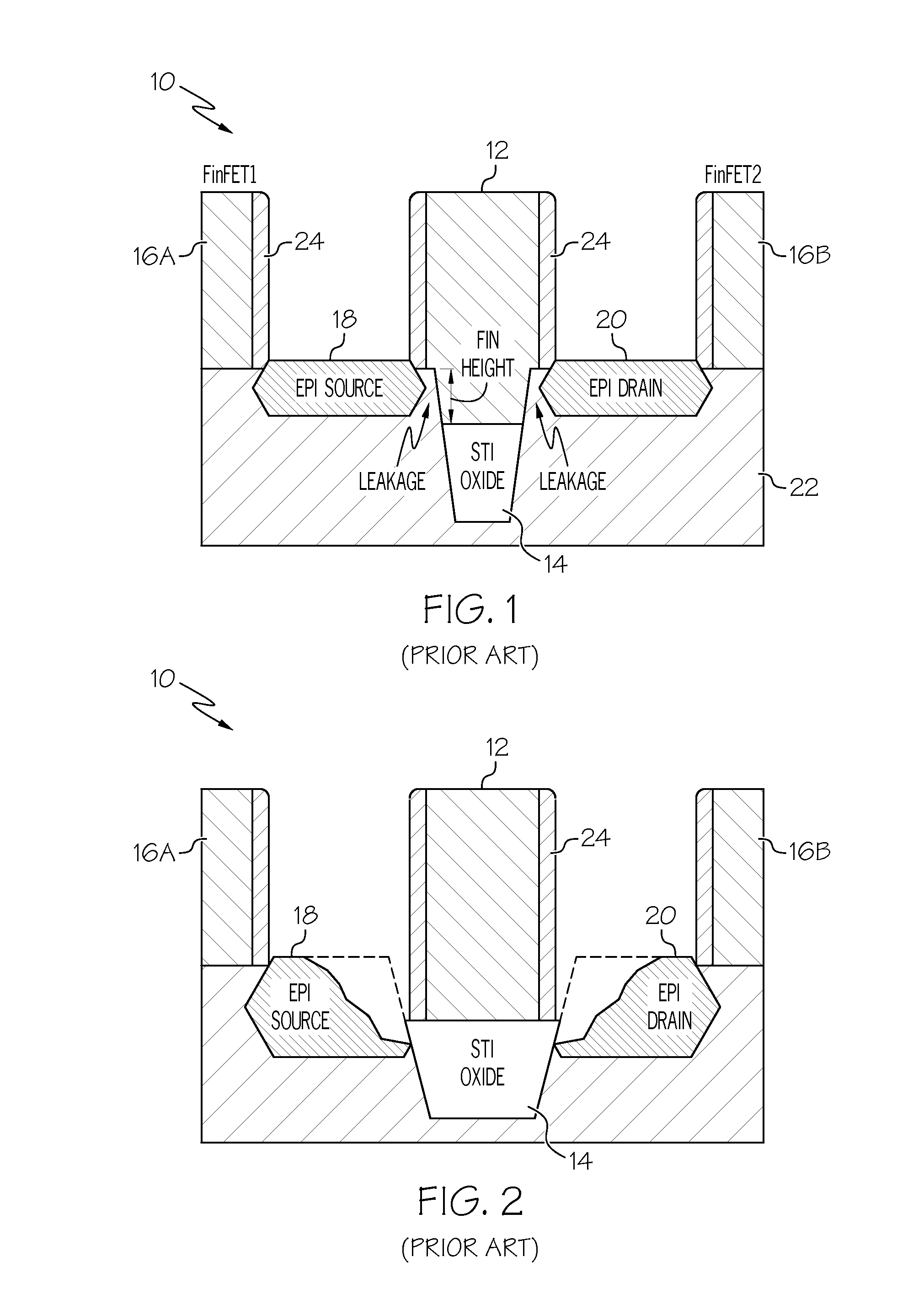

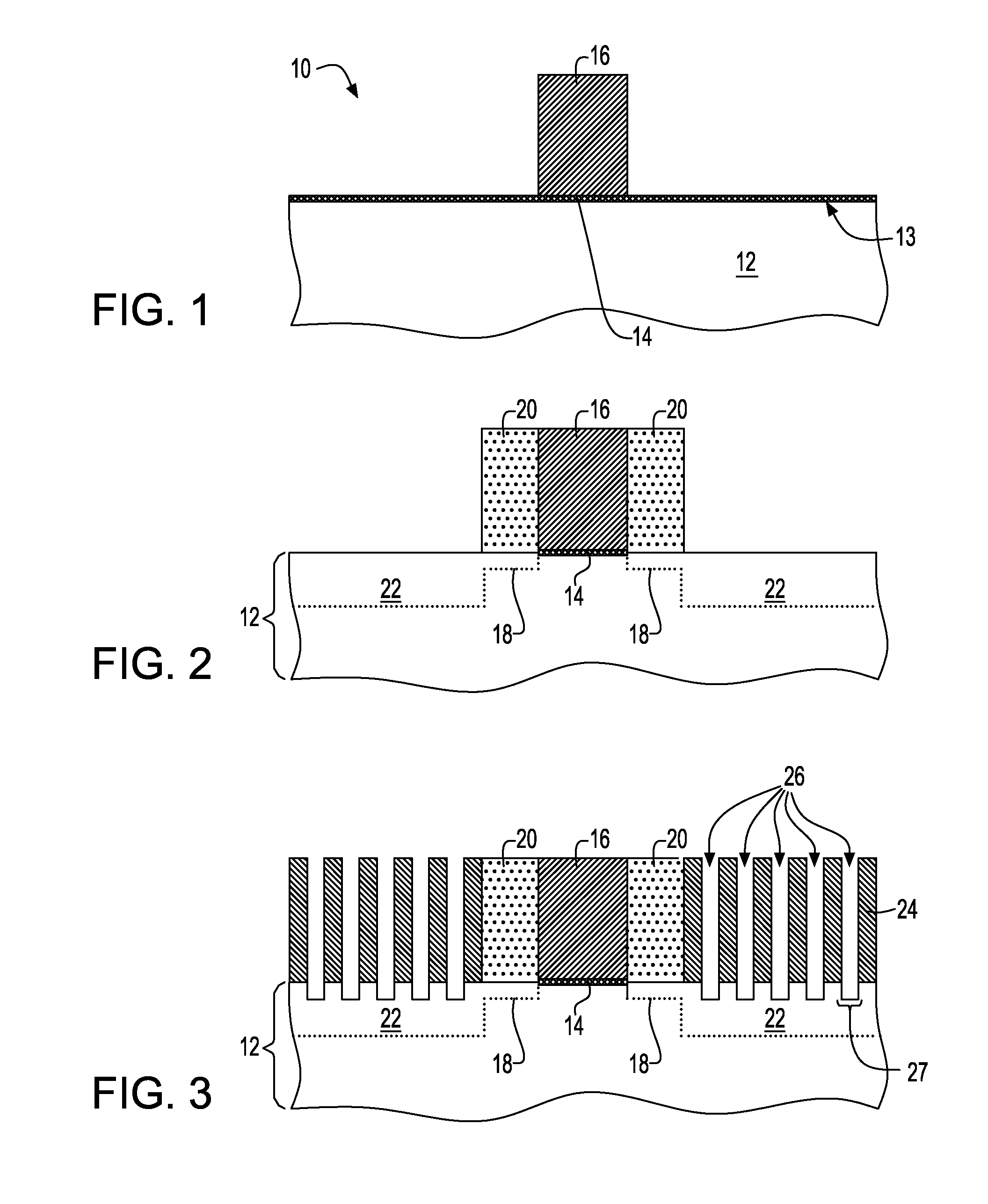

Forming a diffusion break during a RMG process

ActiveUS8846491B1Solid-state devicesSemiconductor/solid-state device manufacturingSemiconductorMetal

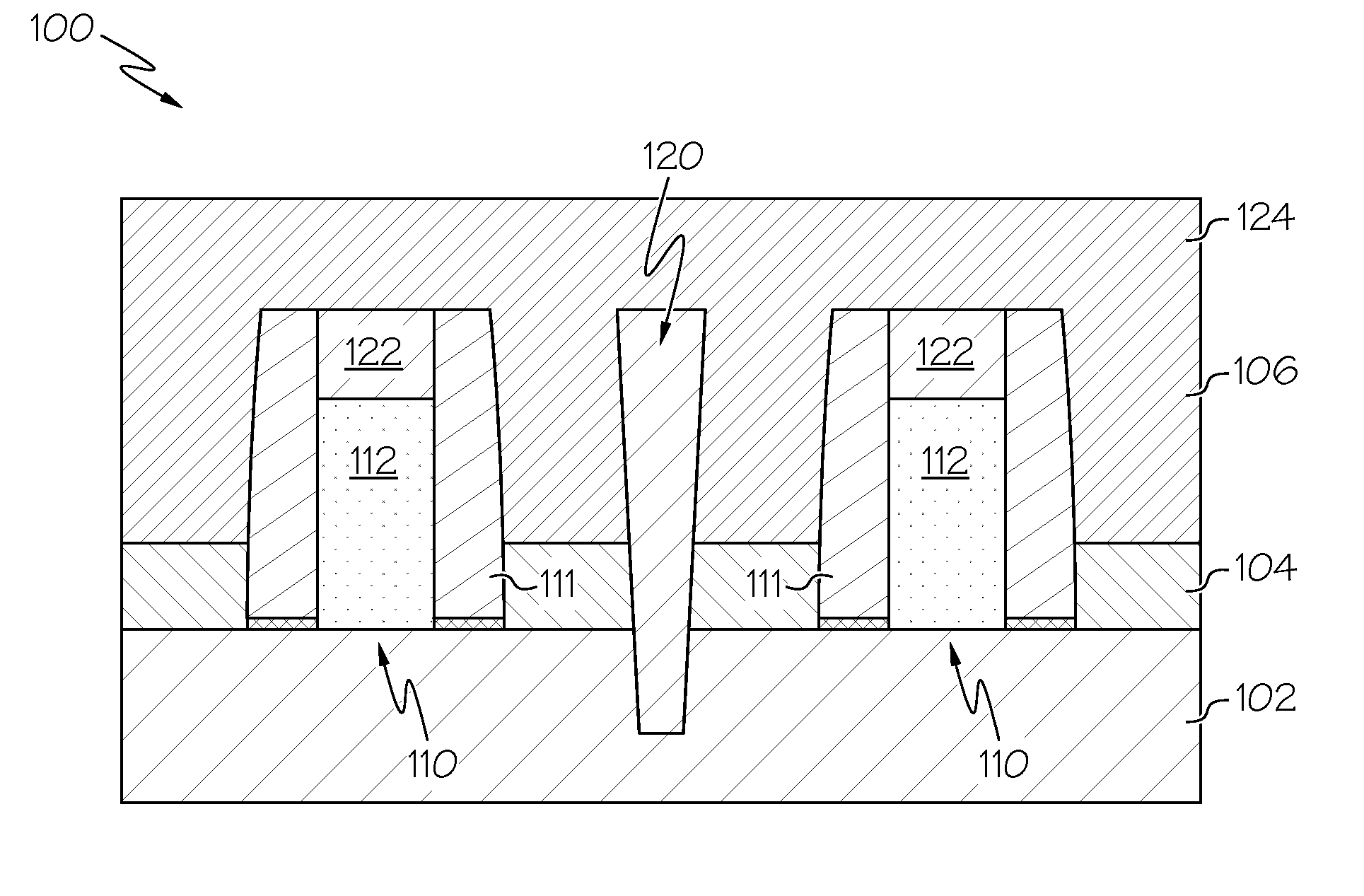

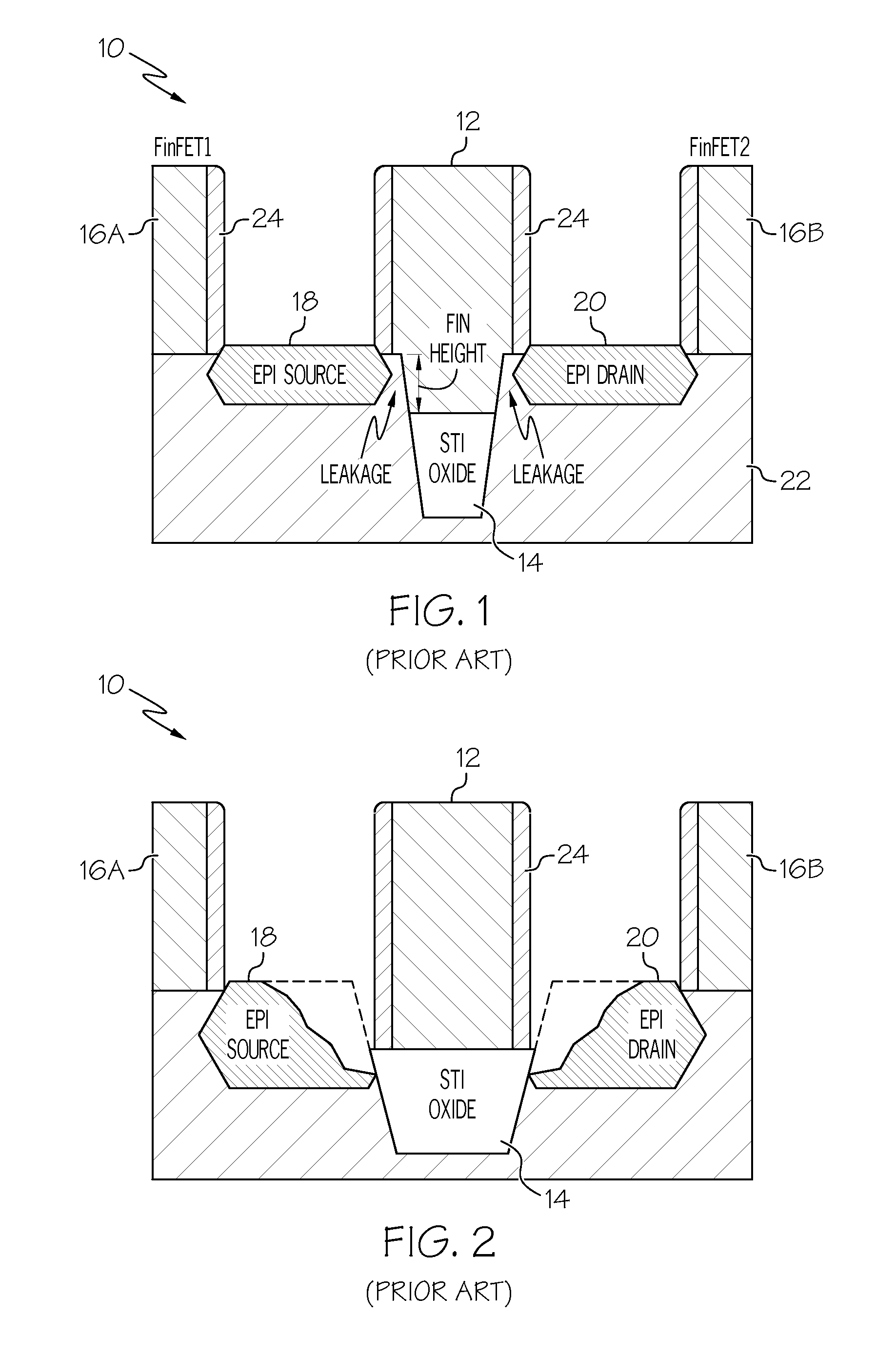

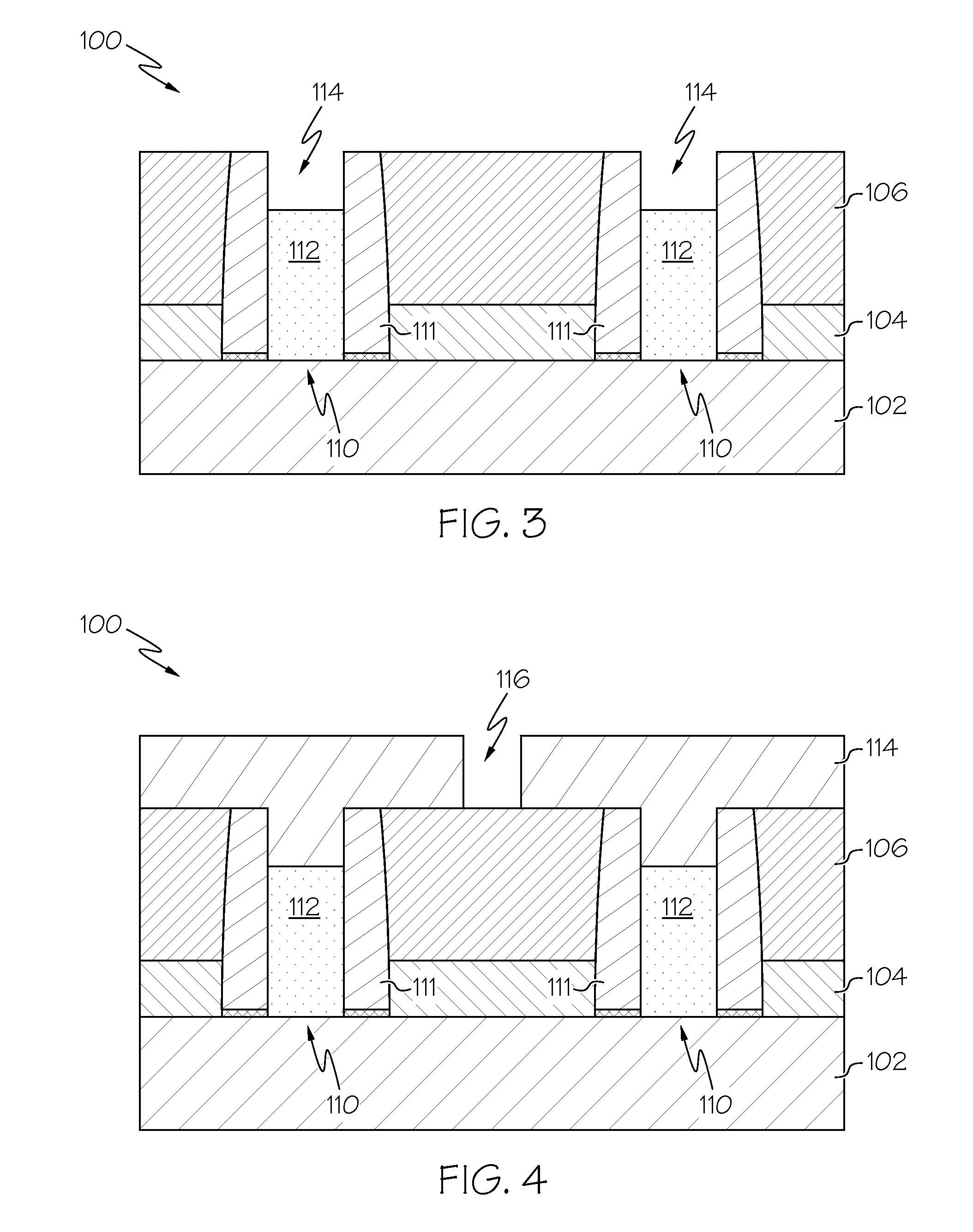

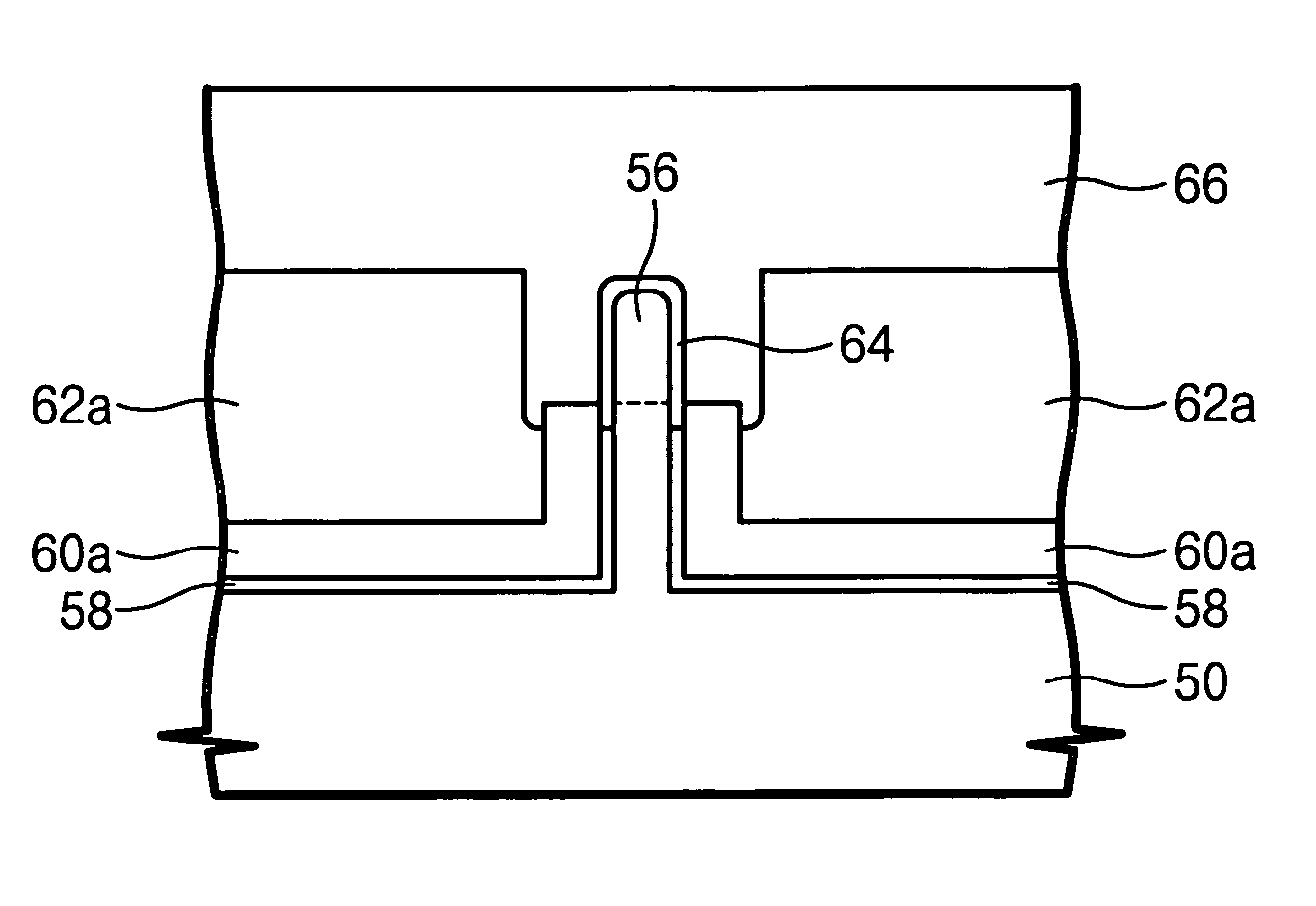

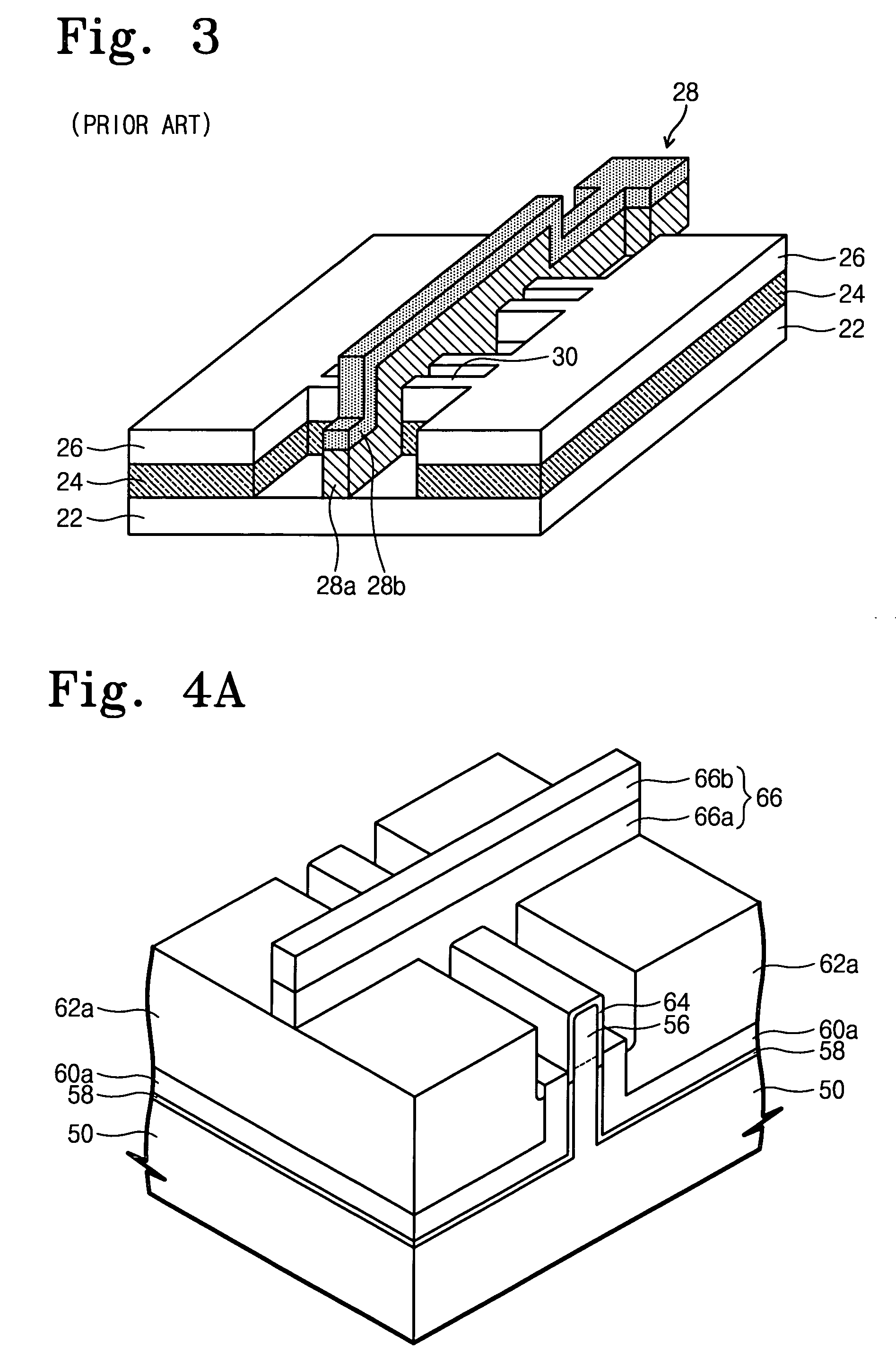

Embodiments herein provide approaches for forming a diffusion break during a replacement metal gate process. Specifically, a semiconductor device is provided with a set of replacement metal gate (RMG) structures over a set of fins patterned from a substrate; a dielectric material over an epitaxial junction area; an opening formed between the set of RMG structures and through the set of fins, wherein the opening extends through the dielectric material, the expitaxial junction area, and into the substrate; and silicon nitride (SiN) deposited within the opening to form the diffusion break.

Owner:GLOBALFOUNDRIES US INC

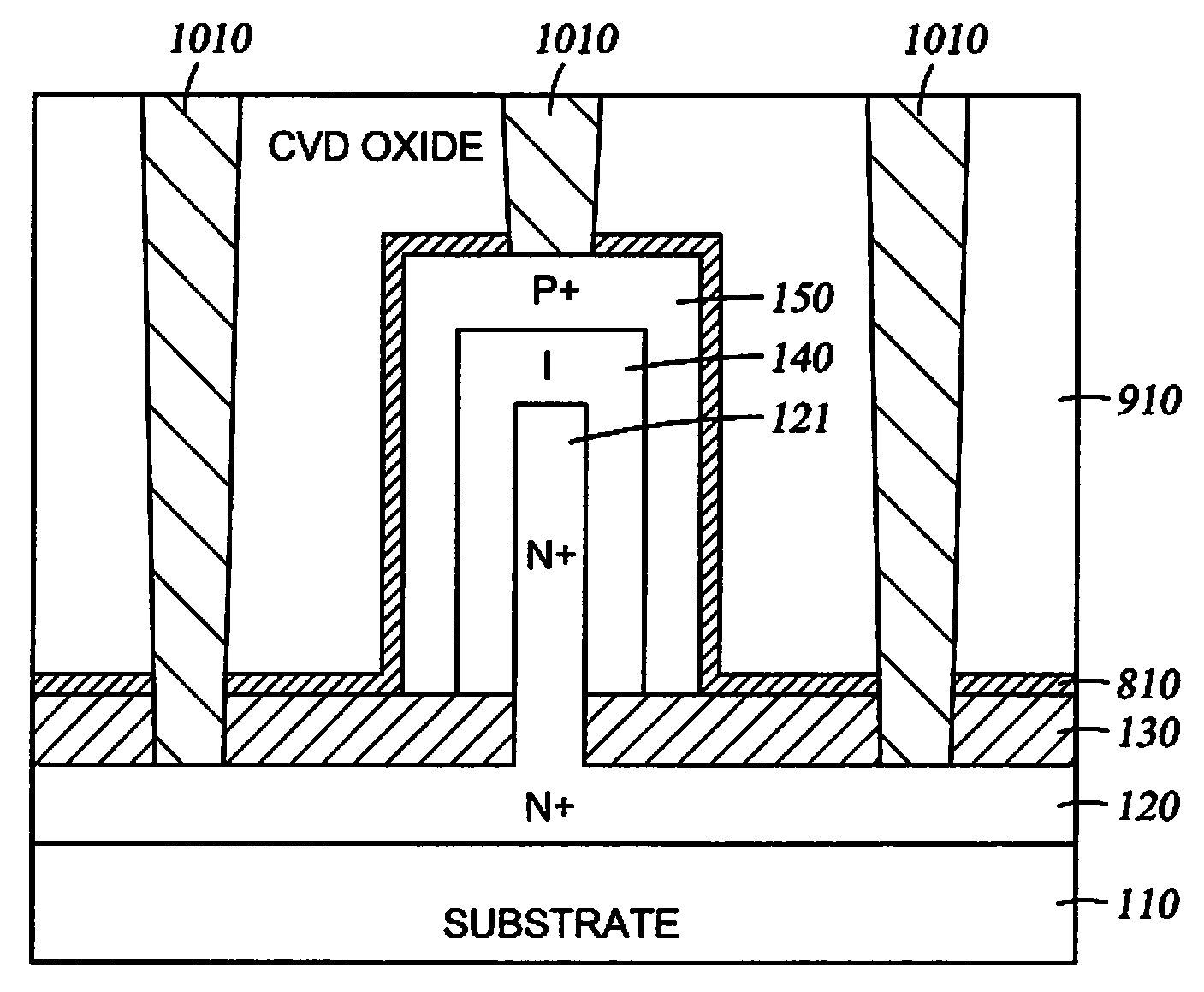

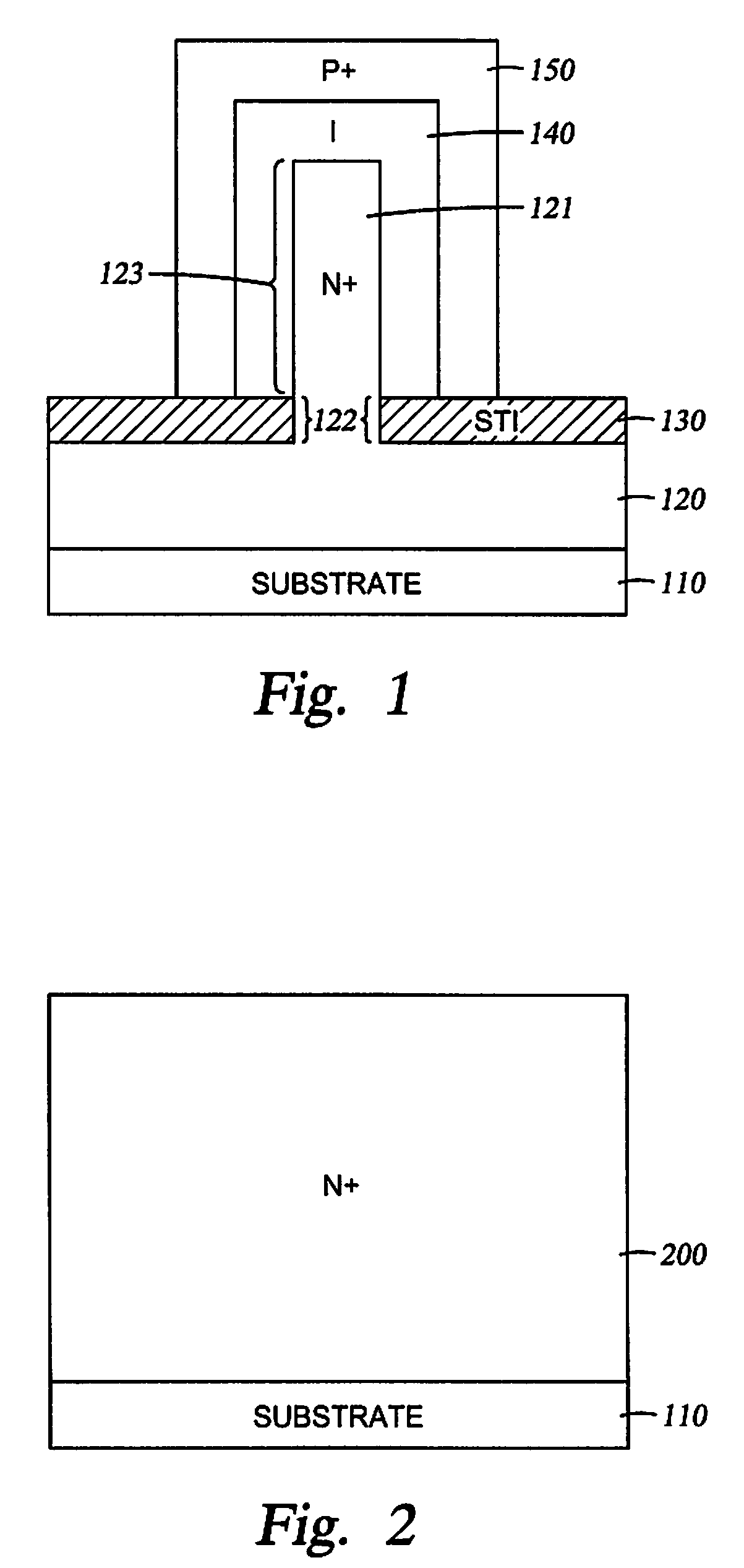

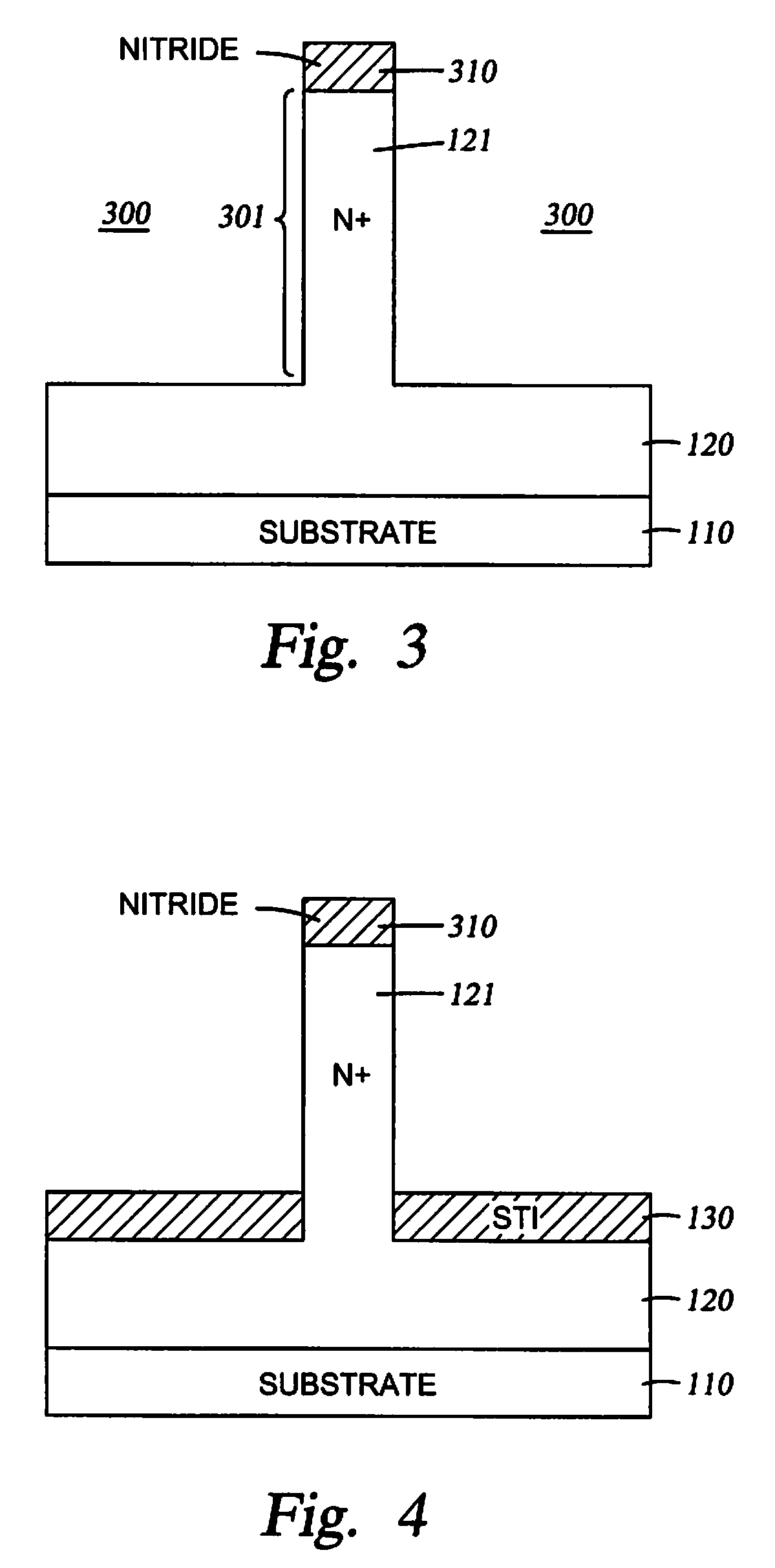

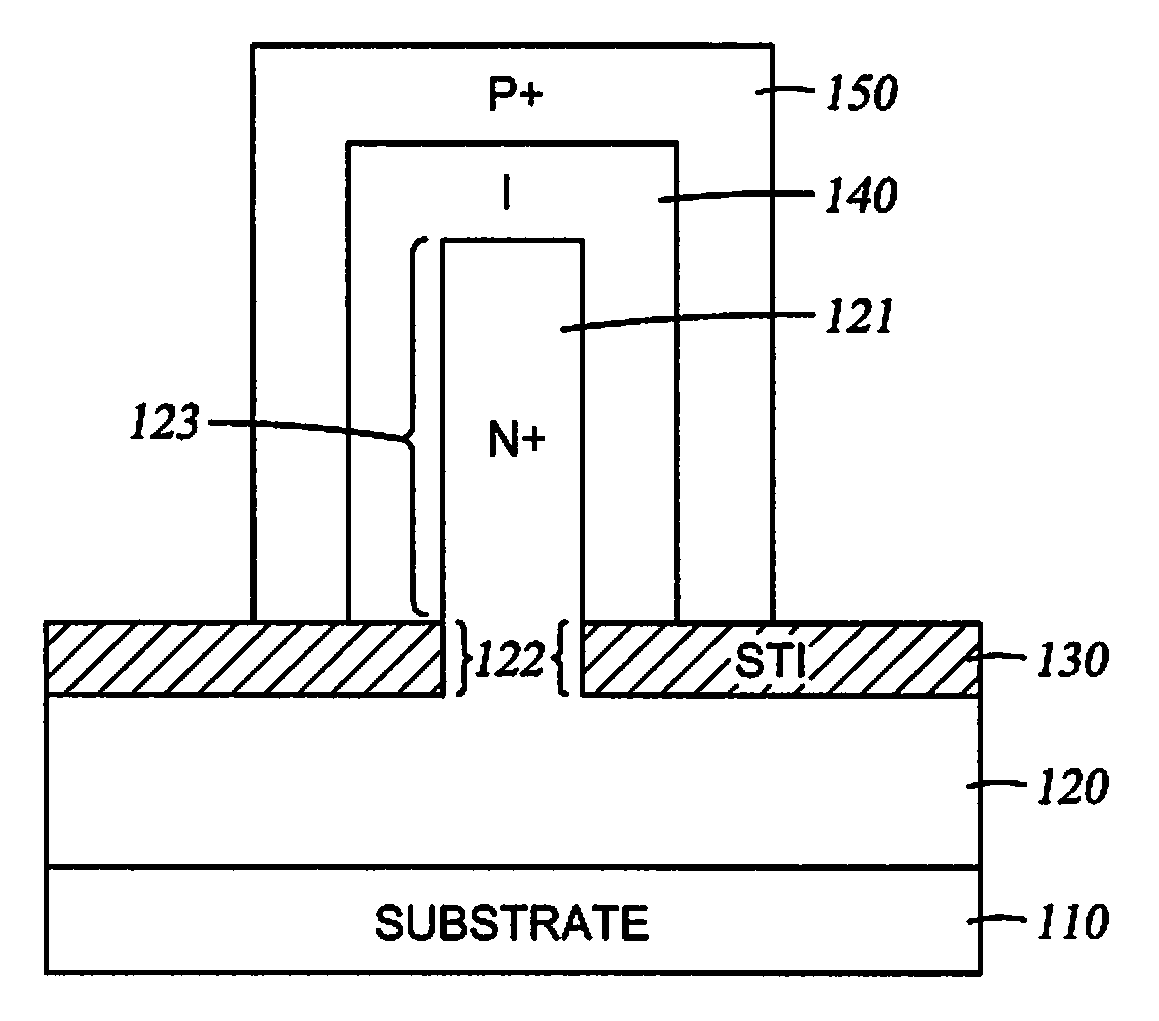

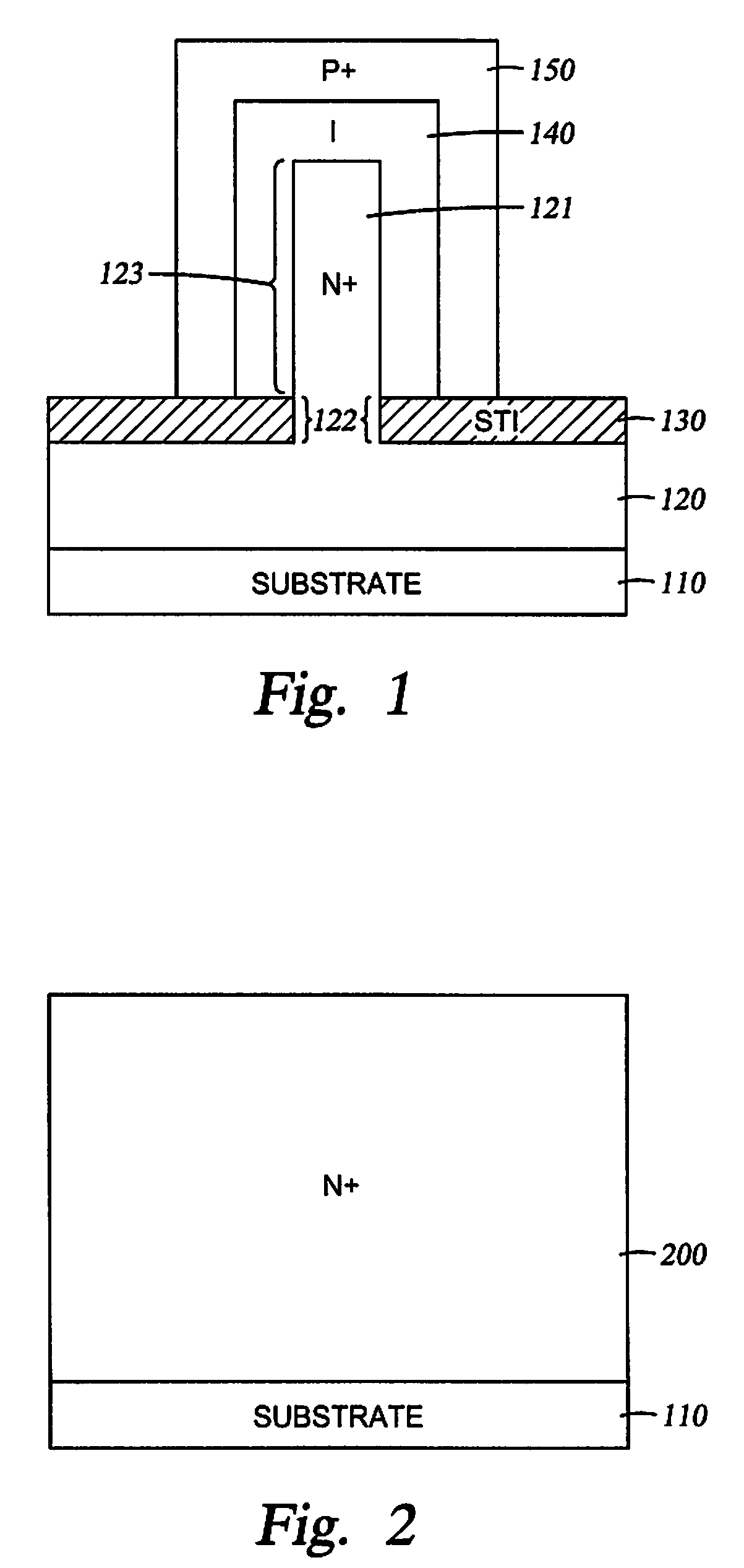

Fin PIN diode

Embodiments of the invention generally relate to the field of semiconductor devices, and more specifically to fin-based junction diodes. A portion of a doped semiconductor fin may protrude through a first doped layer. An intrinsic layer may be disposed on the protruding semiconductor fin. A second semiconductor layer may be disposed on the intrinsic layer, thereby forming a PIN diode compatible with FinFET technology and having increased junction area.

Owner:INT BUSINESS MASCH CORP

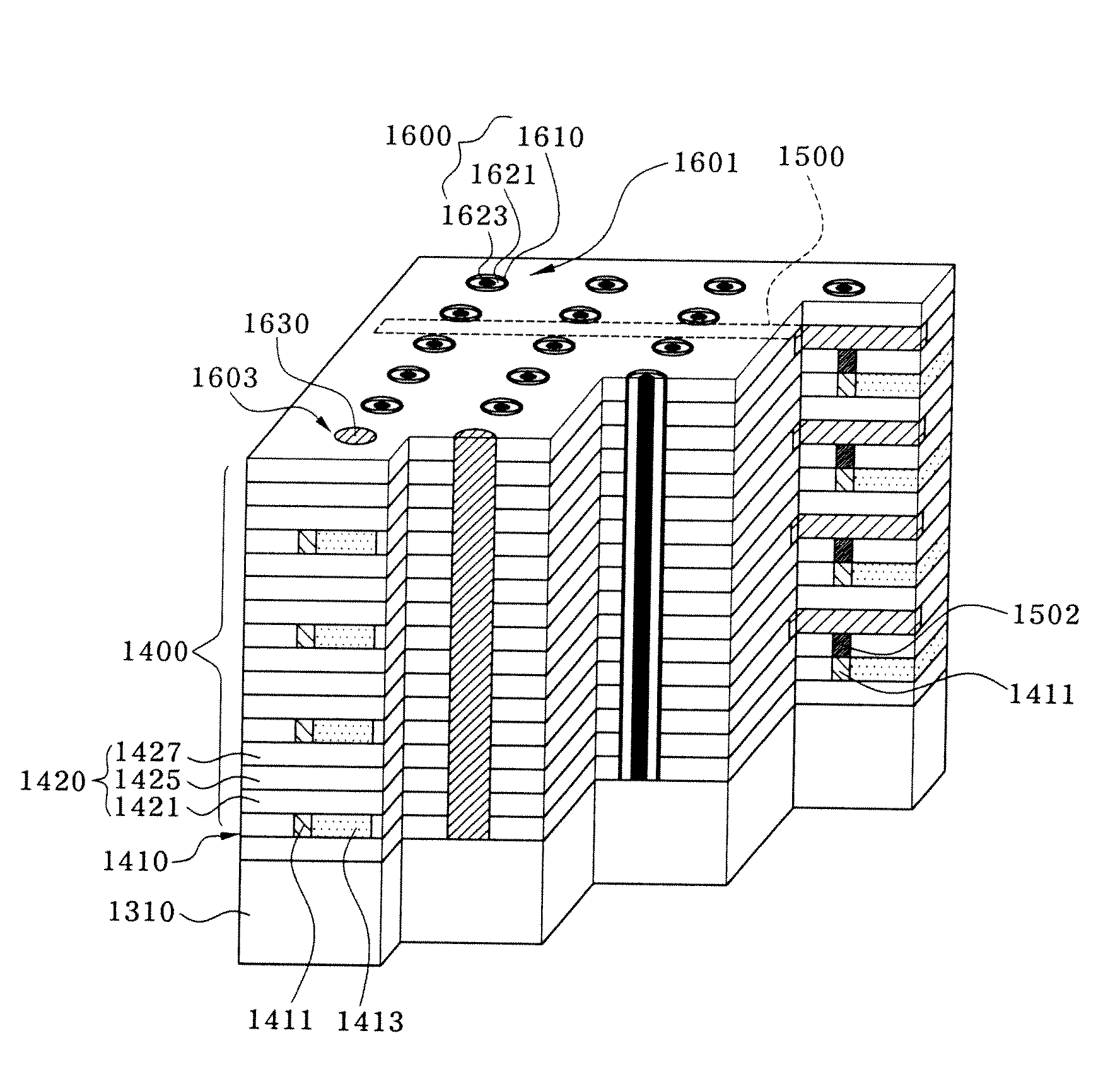

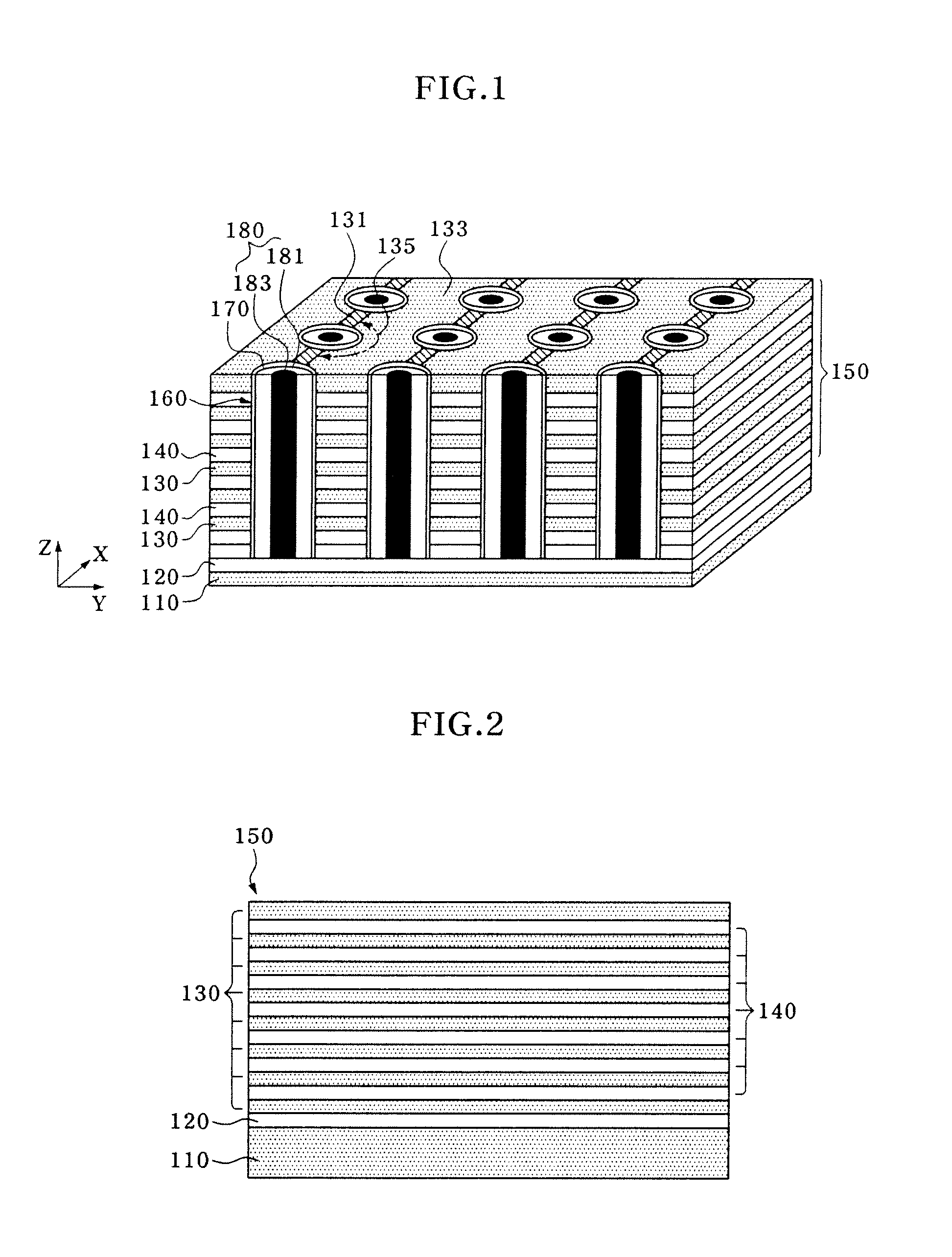

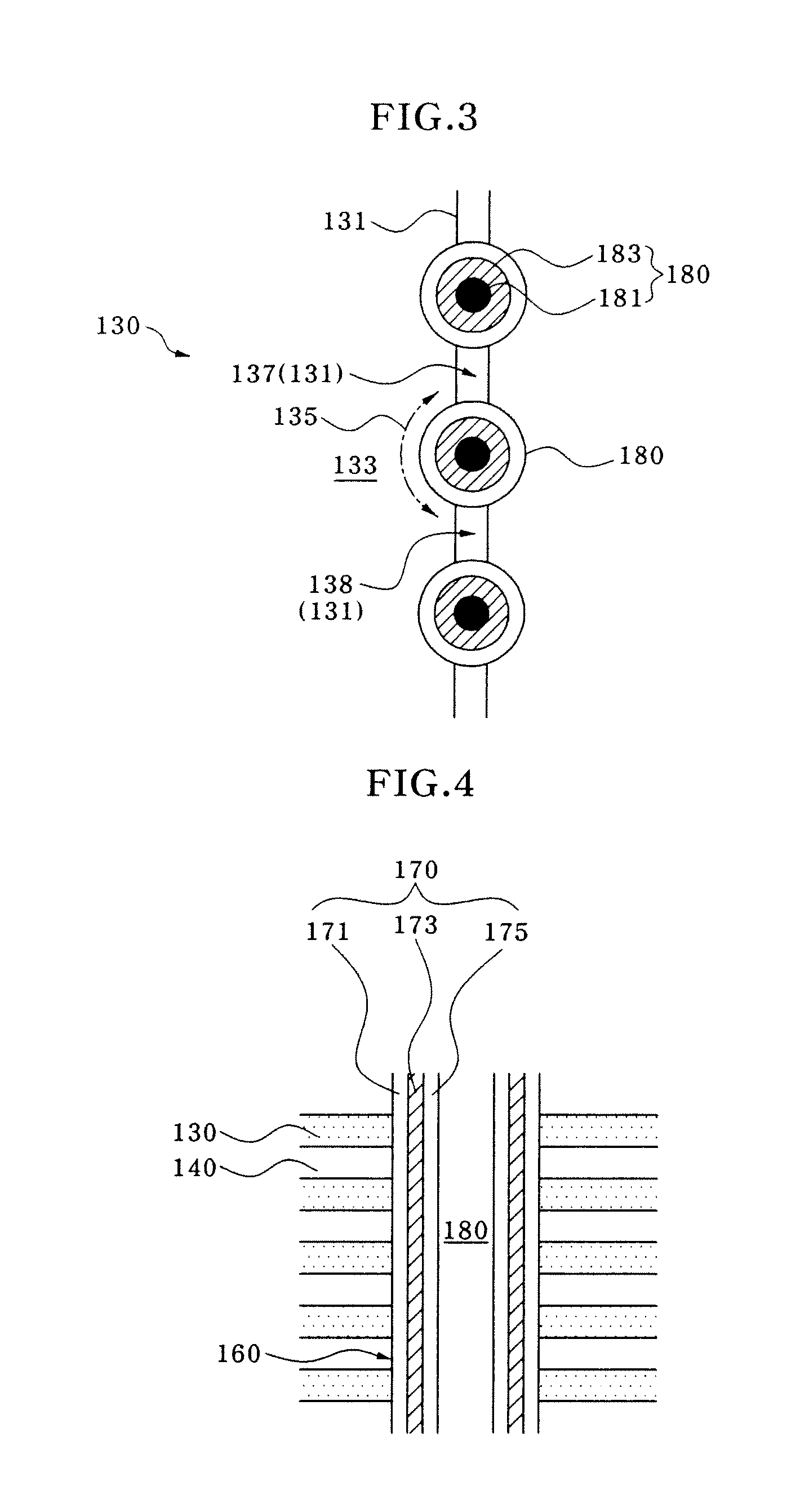

Flash Memory Device and Method for Manufacturing the Same

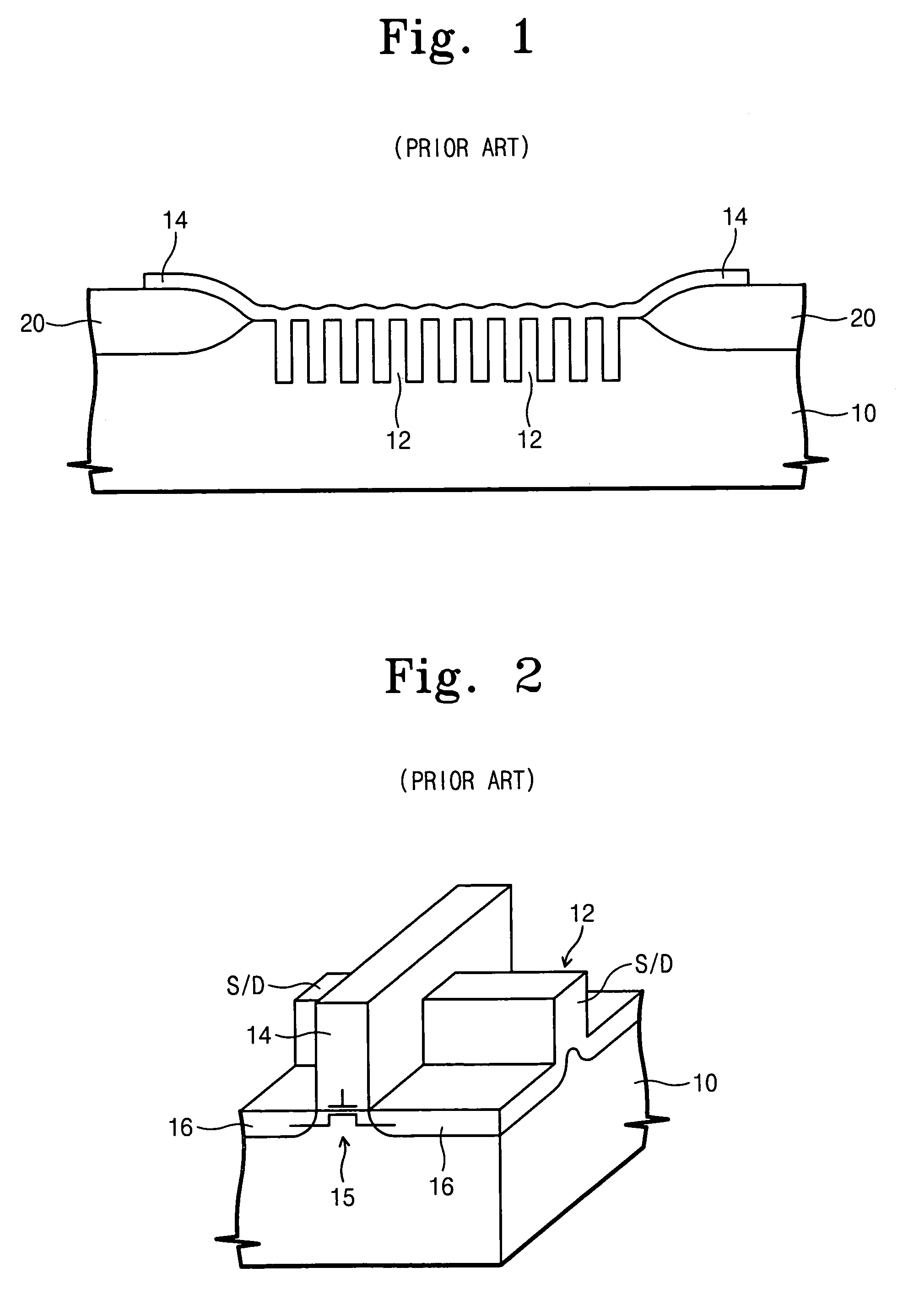

A flash memory device includes a substrate, a cell stack having a semiconductor layer, in which junction areas for setting areas therebetween to channel areas are formed in a shape of a stripe, and an interlayer isolation layer for insulating the semiconductor layer, wherein the semiconductor layer and the interlayer isolation layer are repeatedly stacked. The flash memory device further includes an array of gate columns penetrating through the cell stack, perpendicular to the substrate and cutting through the junction areas to dispose the junction areas at both sides thereof, and a trap layered stack introduced into an interface between the gate column and the cell stack to store charge.

Owner:SK HYNIX INC

Fin Pin Diode

Embodiments of the invention generally relate to the field of semiconductor devices, and more specifically to fin-based junction diodes. A portion of a doped semiconductor fin may protrude through a first doped layer. An intrinsic layer may be disposed on the protruding semiconductor fin. A second semiconductor layer may be disposed on the intrinsic layer, thereby forming a PIN diode compatible with FinFET technology and having increased junction area.

Owner:IBM CORP

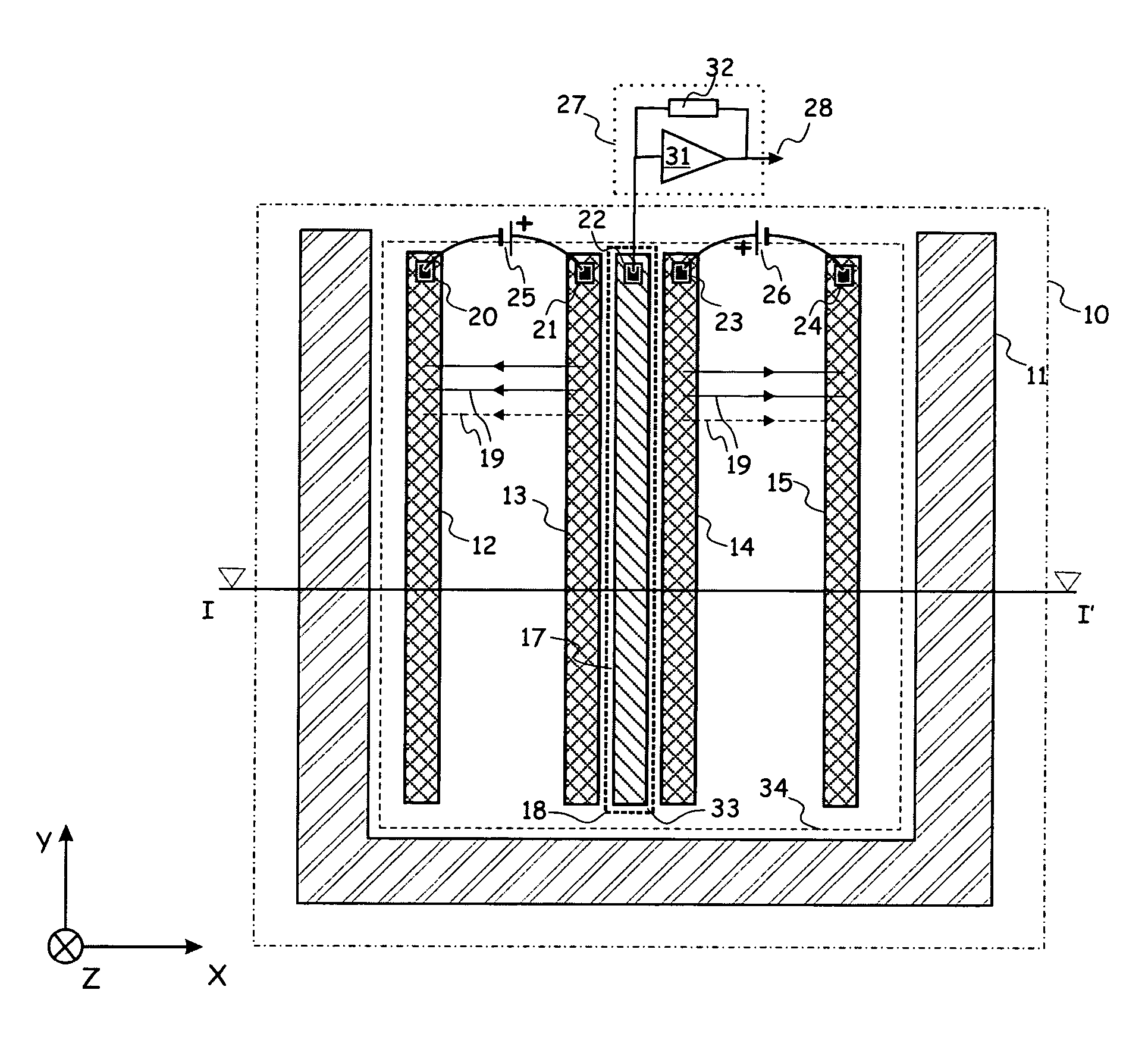

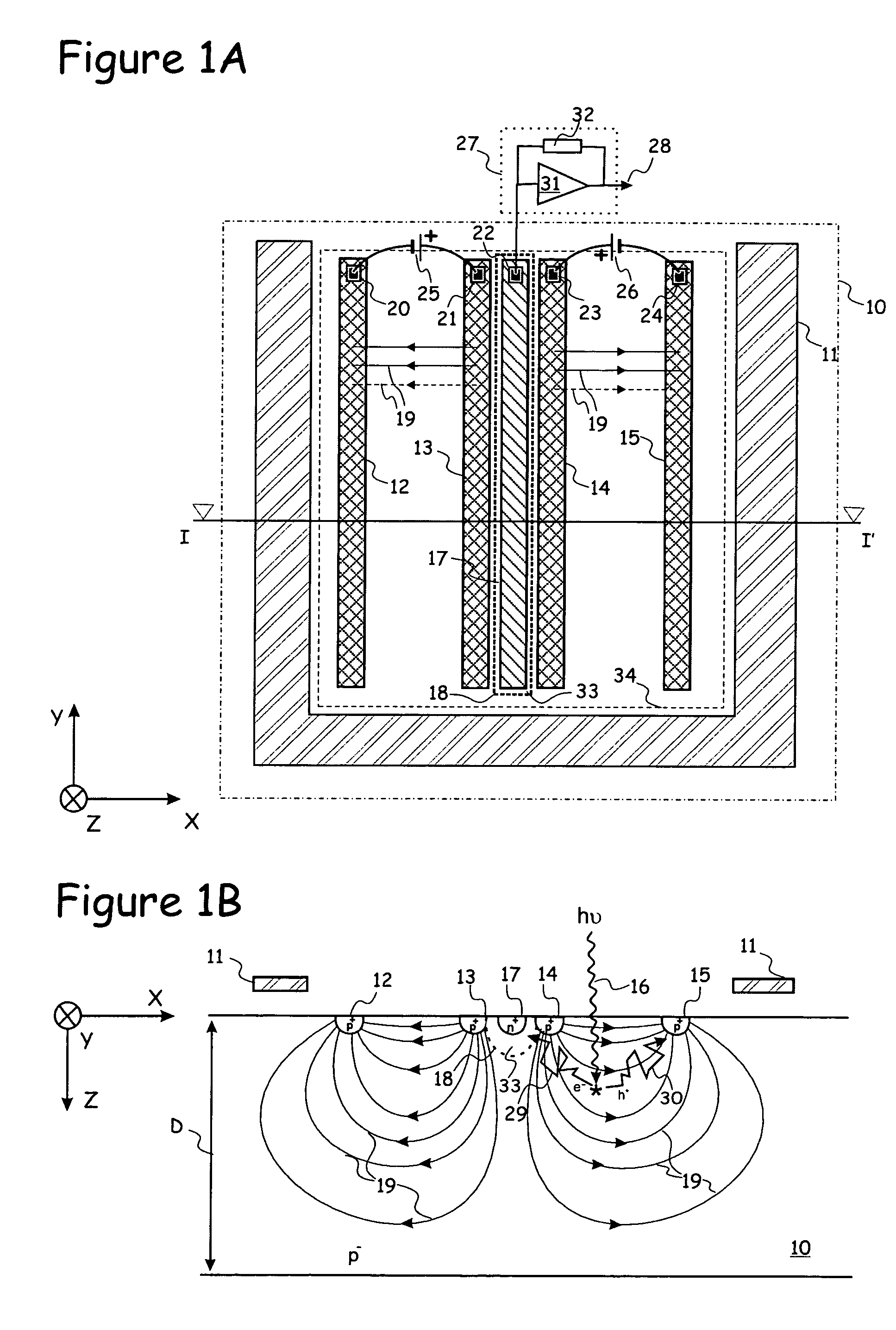

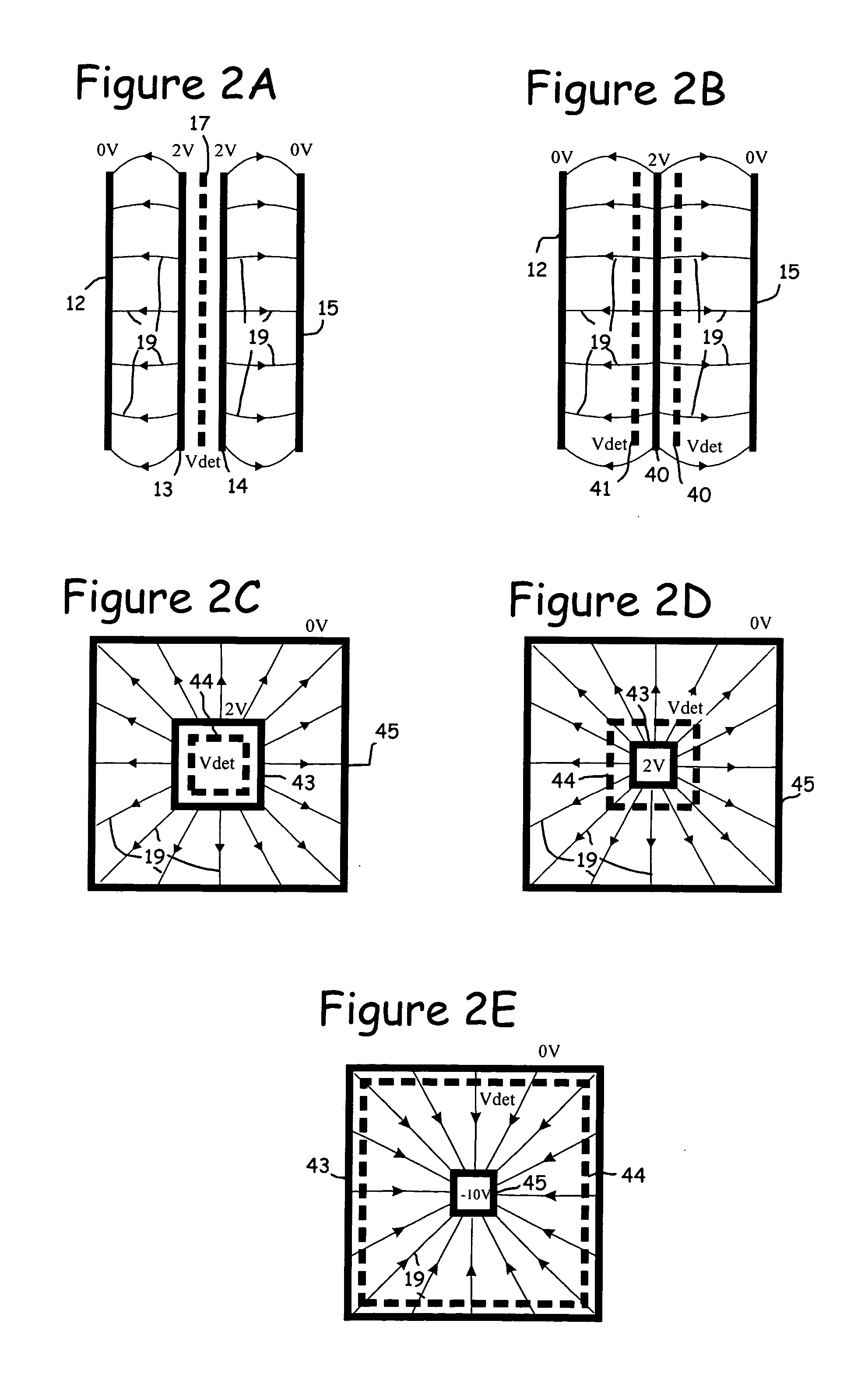

Photonic mixer and use thereof

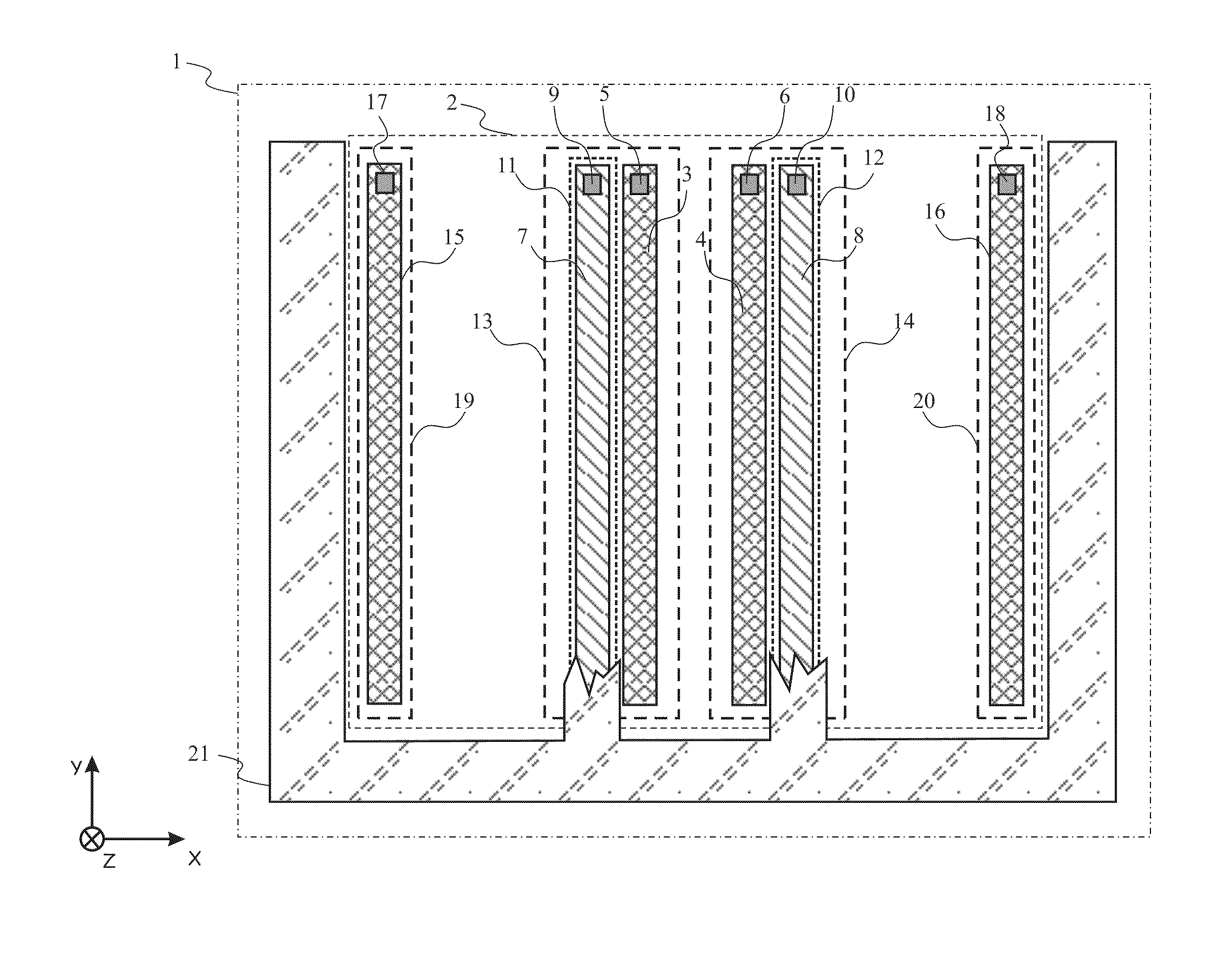

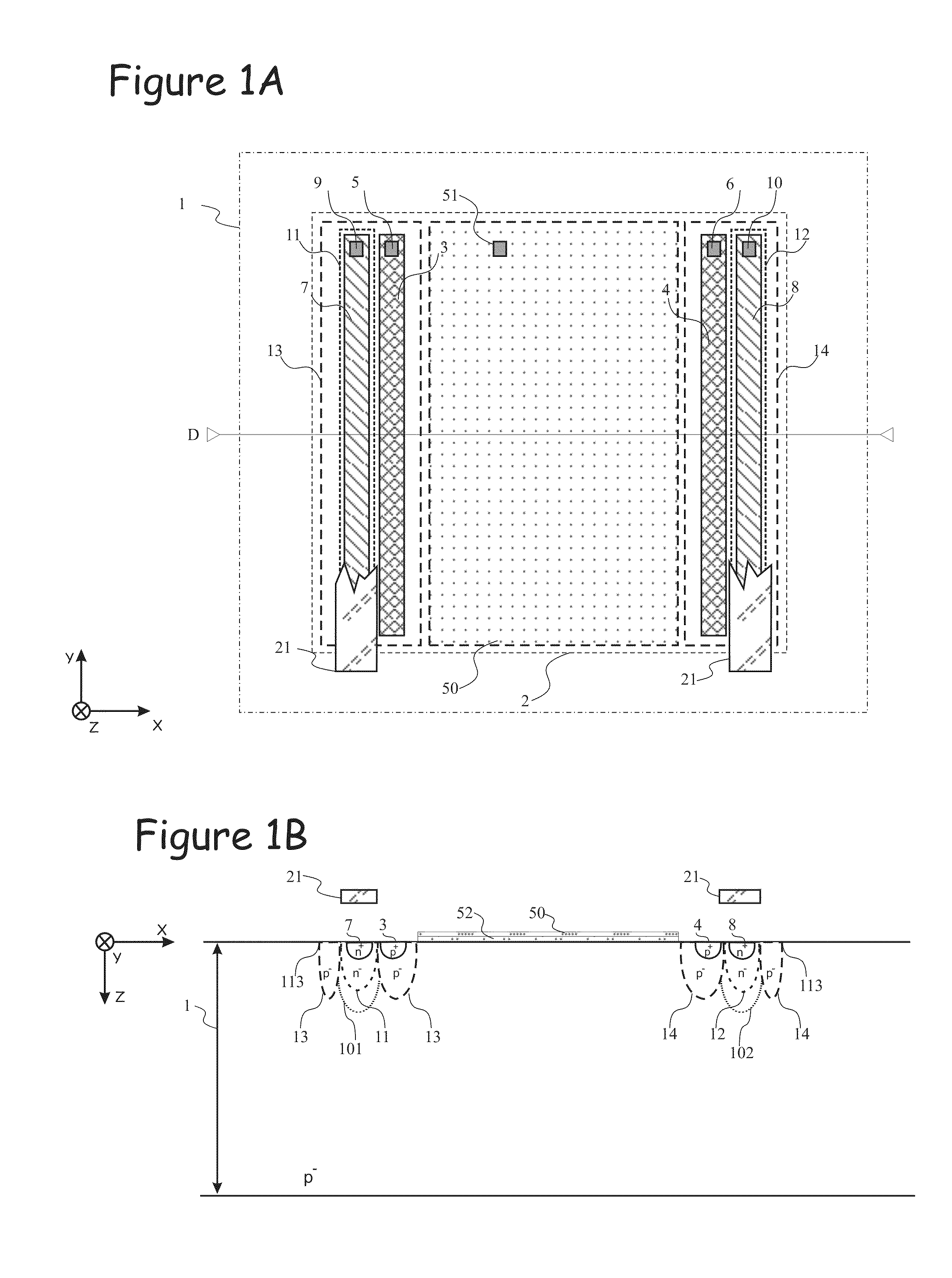

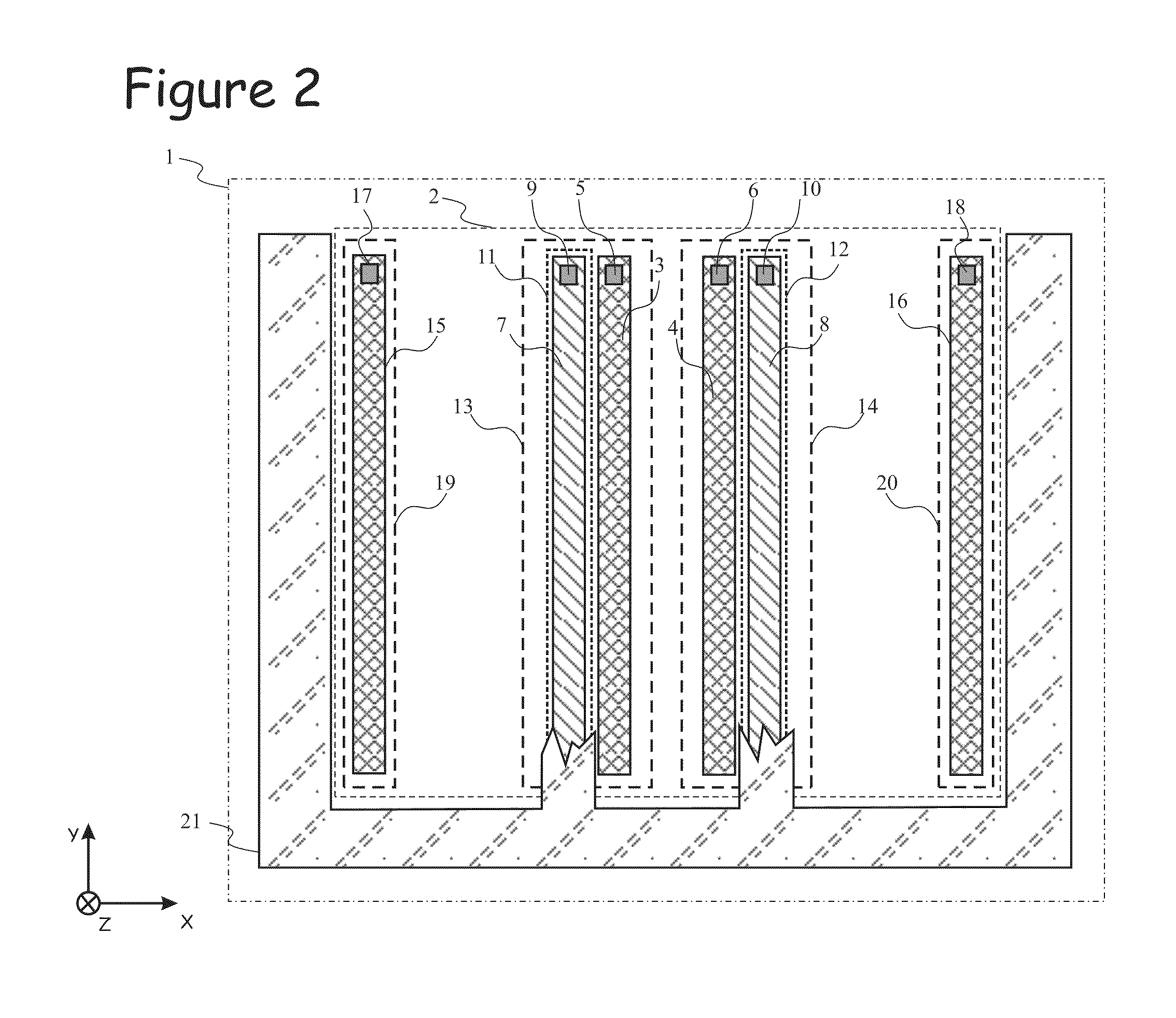

ActiveUS20110255071A1High resolutionSmall sizeOptical rangefindersSolid-state devicesDopantPhotonics

The photonic mixer comprises a couple of an injecting contact region (3,4) for injecting the majority carrier current into the semiconductor substrate (1) and a detector region (7,8) for collecting the photocurrent. The injecting contact region (3,4) is doped with a dopant of the first conductivity type (p+) at a higher dopant concentration than the semiconductor substrate (1). The detector region (7,8) is doped with a dopant of a second conductivity type (n+) opposite the first conductivity type and has a junction (11,12) with the semiconductor substrate (1), a zone of the semiconductor substrate (1) around said junction (11,12) being a depleted substrate zone (101, 102). The couple further comprises a field shaping zone (13, 14) of the first conductivity type (p−) defining a lateral edge of the couple and having a dopant concentration higher than the dopant concentration of the semiconductor substrate (1), for example between the dopant concentrations of the semiconductor substrate (1) and the injecting contact region (3,4), which field shaping zone (13, 14) is designed to limit said depleted substrate zone (101, 102) laterally.

Owner:SOFTKINETIC SENSORS +1

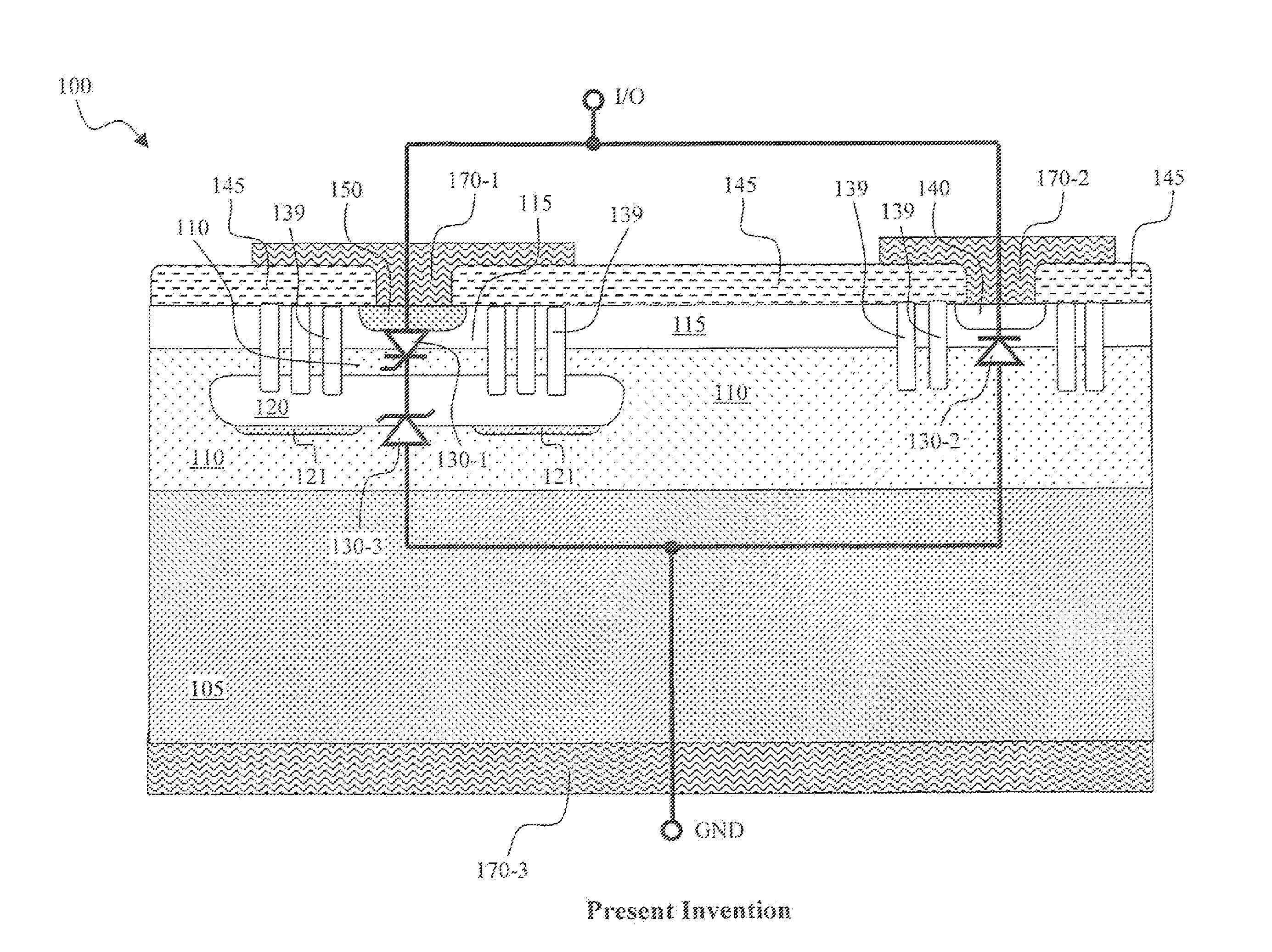

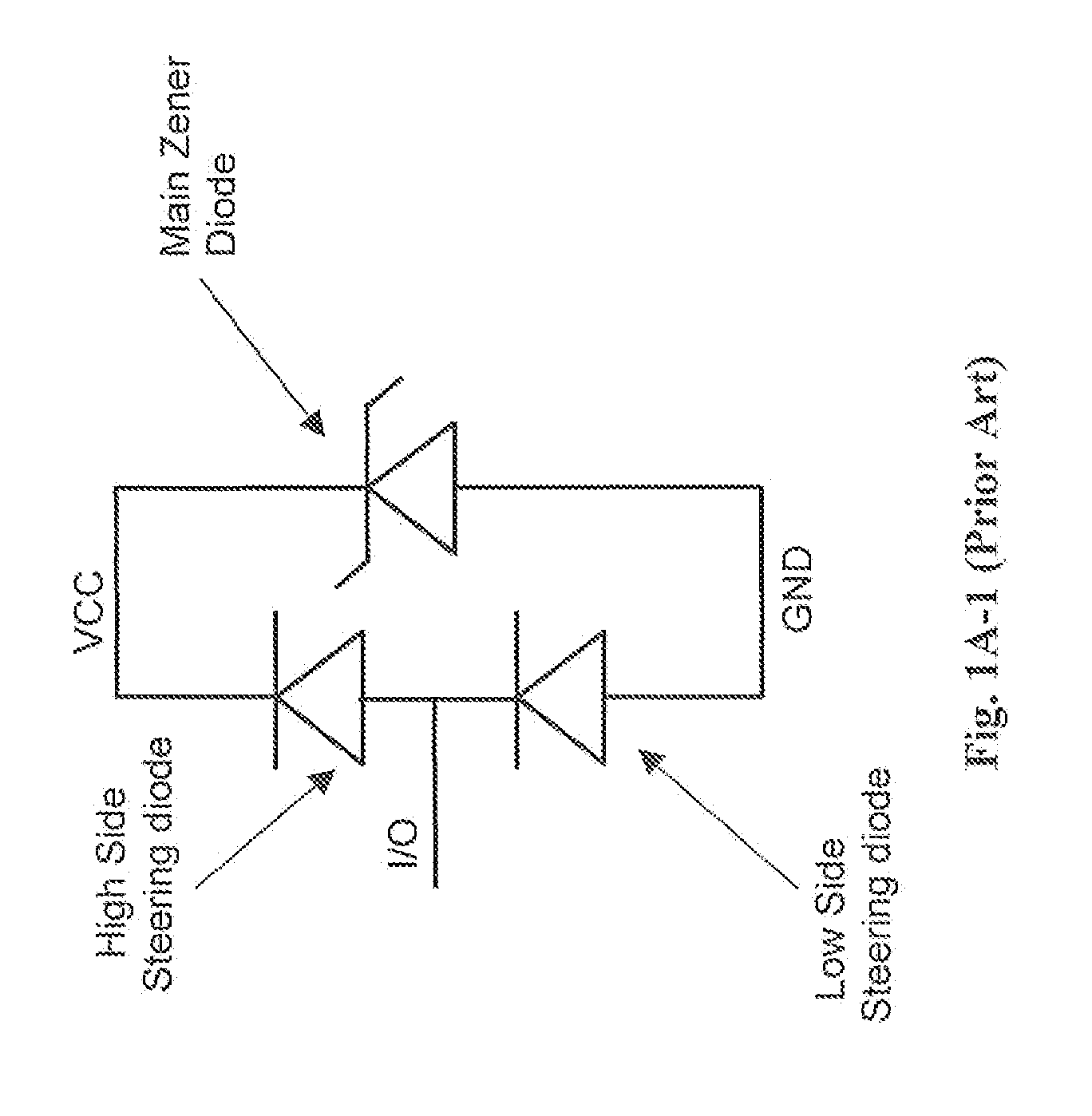

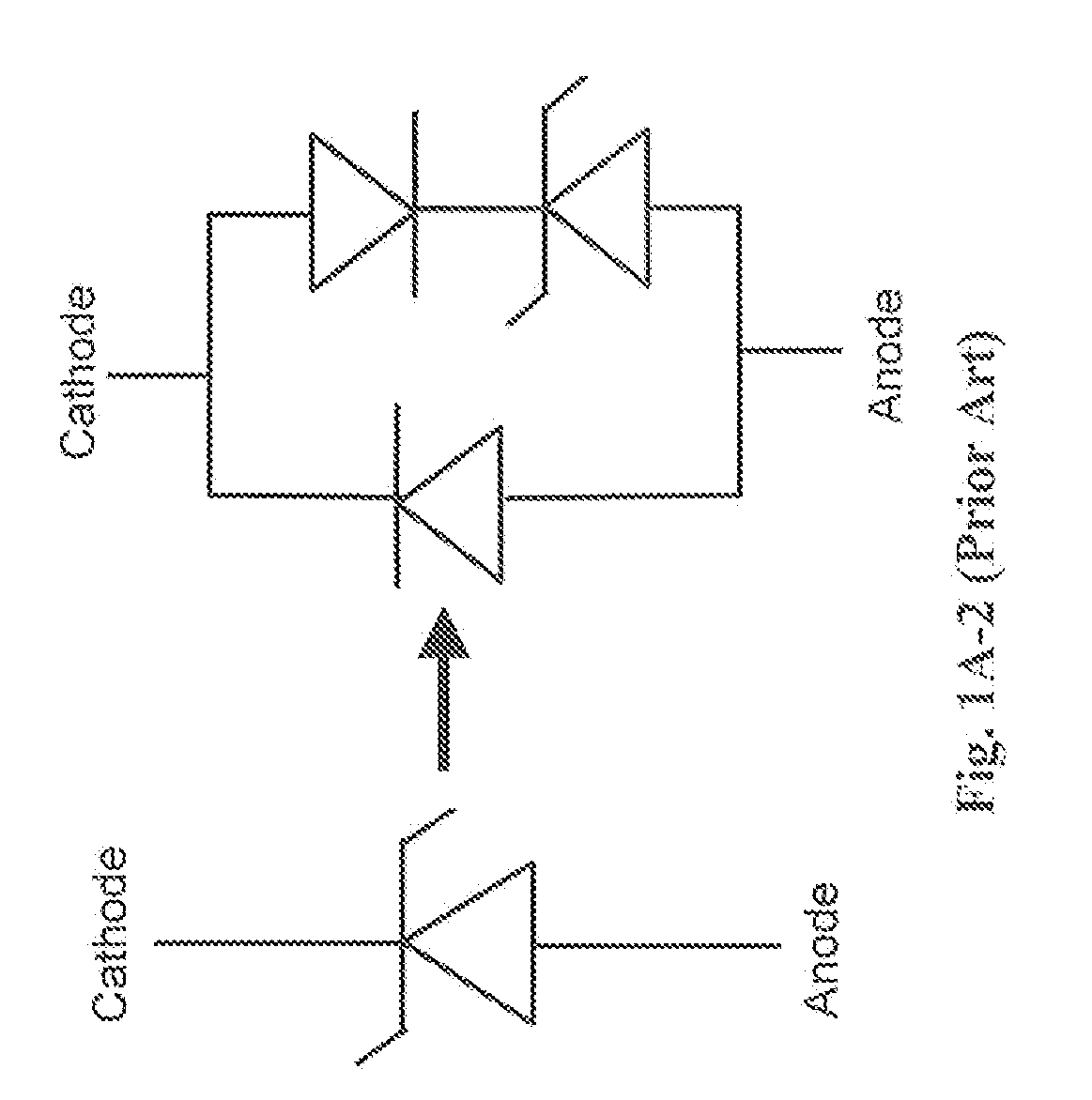

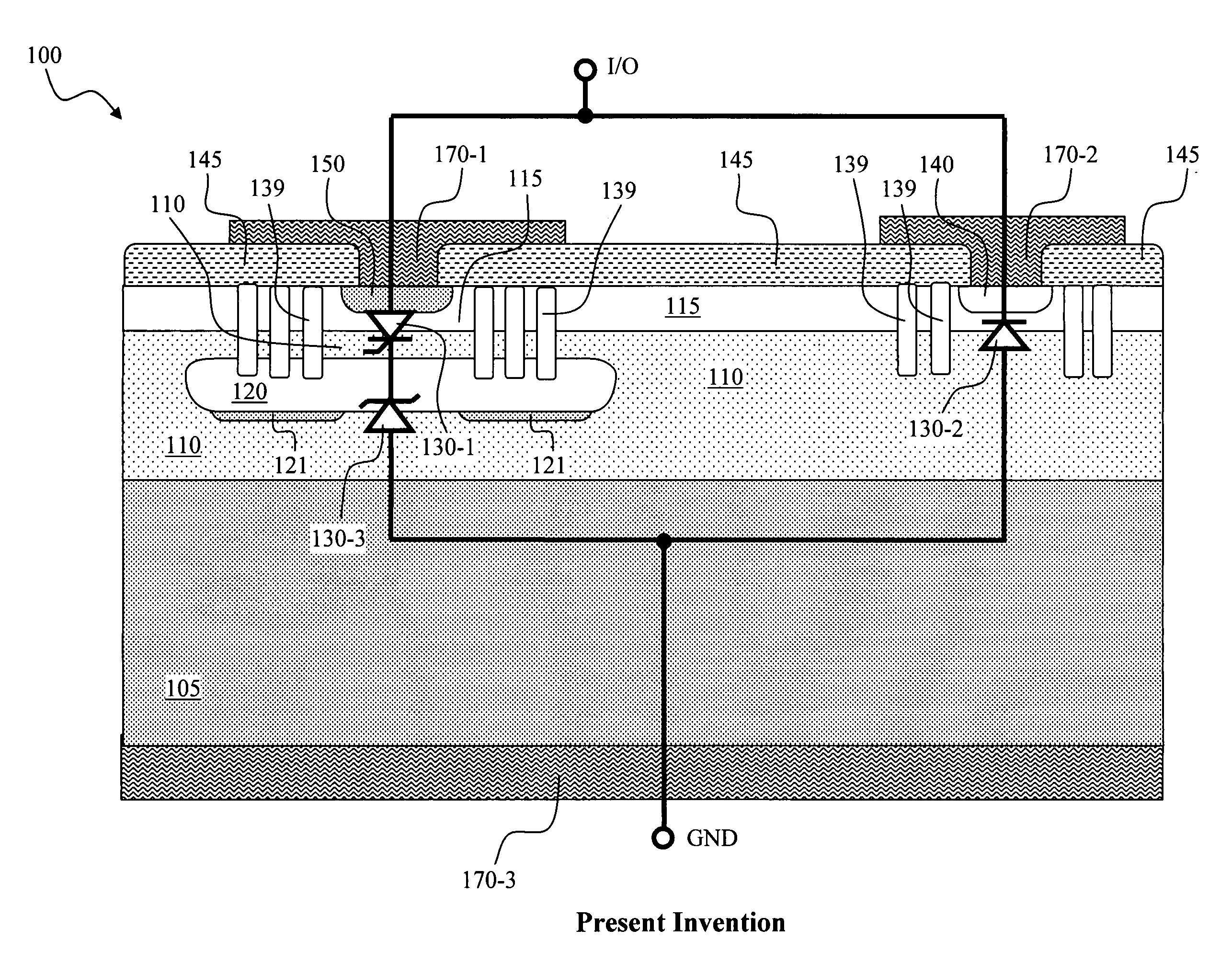

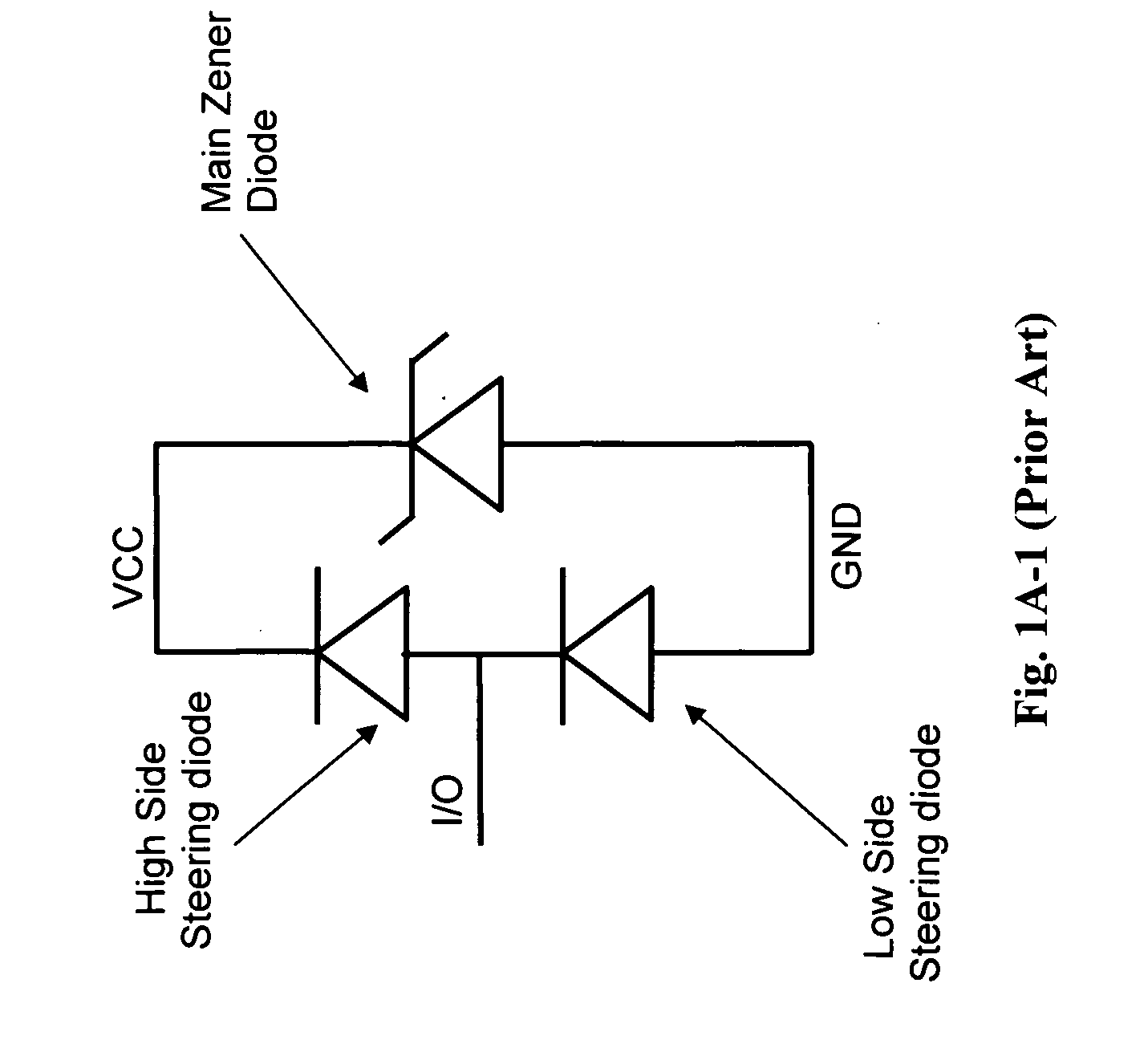

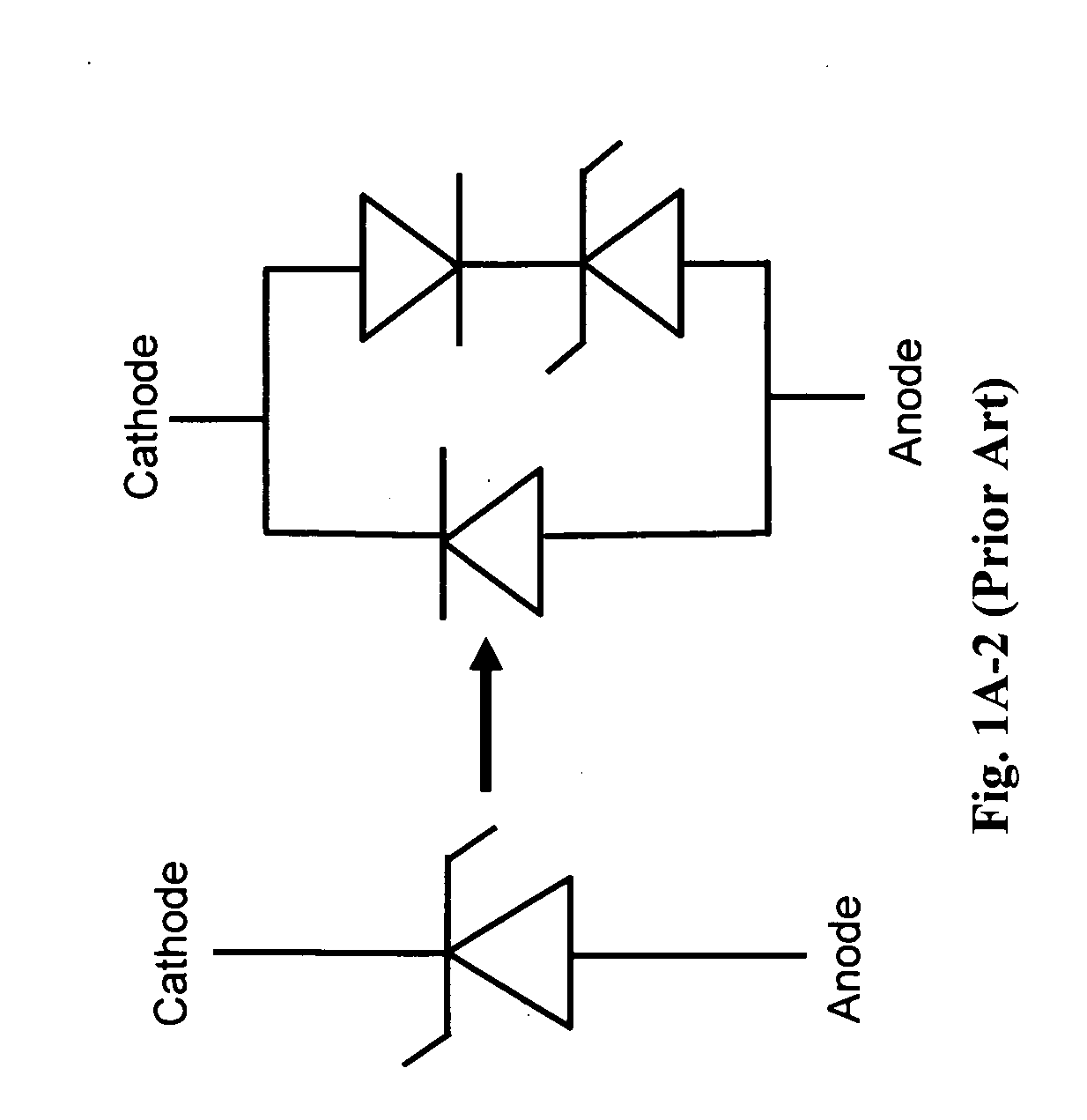

Tvs with low capacitance & forward voltage drop with depleted scr as steering diode

A transient-voltage suppressing (TVS) device disposed on a semiconductor substrate of a first conductivity type. The TVS includes a buried dopant region of a second conductivity type disposed and encompassed in an epitaxial layer of the first conductivity type wherein the buried dopant region extends laterally and has an extended bottom junction area interfacing with the underlying portion of the epitaxial layer thus constituting a Zener diode for the TVS device. The TVS device further includes a region above the buried dopant region further comprising a top dopant layer of a second conductivity type and a top contact region of a second conductivity type which act in combination with the epitaxial layer and the buried dopant region to form a plurality of interfacing PN junctions constituting a SCR acting as a steering diode to function with the Zener diode for suppressing a transient voltage.

Owner:ALPHA & OMEGA SEMICON INC

TVS with low capacitance & Forward voltage drop with depleted SCR as steering diode

A transient-voltage suppressing (TVS) device disposed on a semiconductor substrate of a first conductivity type. The TVS includes a buried dopant region of a second conductivity type disposed and encompassed in an epitaxial layer of the first conductivity type wherein the buried dopant region extends laterally and has an extended bottom junction area interfacing with the underlying portion of the epitaxial layer thus constituting a Zener diode for the TVS device. The TVS device further includes a region above the buried dopant region further comprising a top dopant layer of a second conductivity type and a top contact region of a second conductivity type which act in combination with the epitaxial layer and the buried dopant region to form a plurality of interfacing PN junctions constituting a SCR acting as a steering diode to function with the Zener diode for suppressing a transient voltage.

Owner:ALPHA & OMEGA SEMICON INC

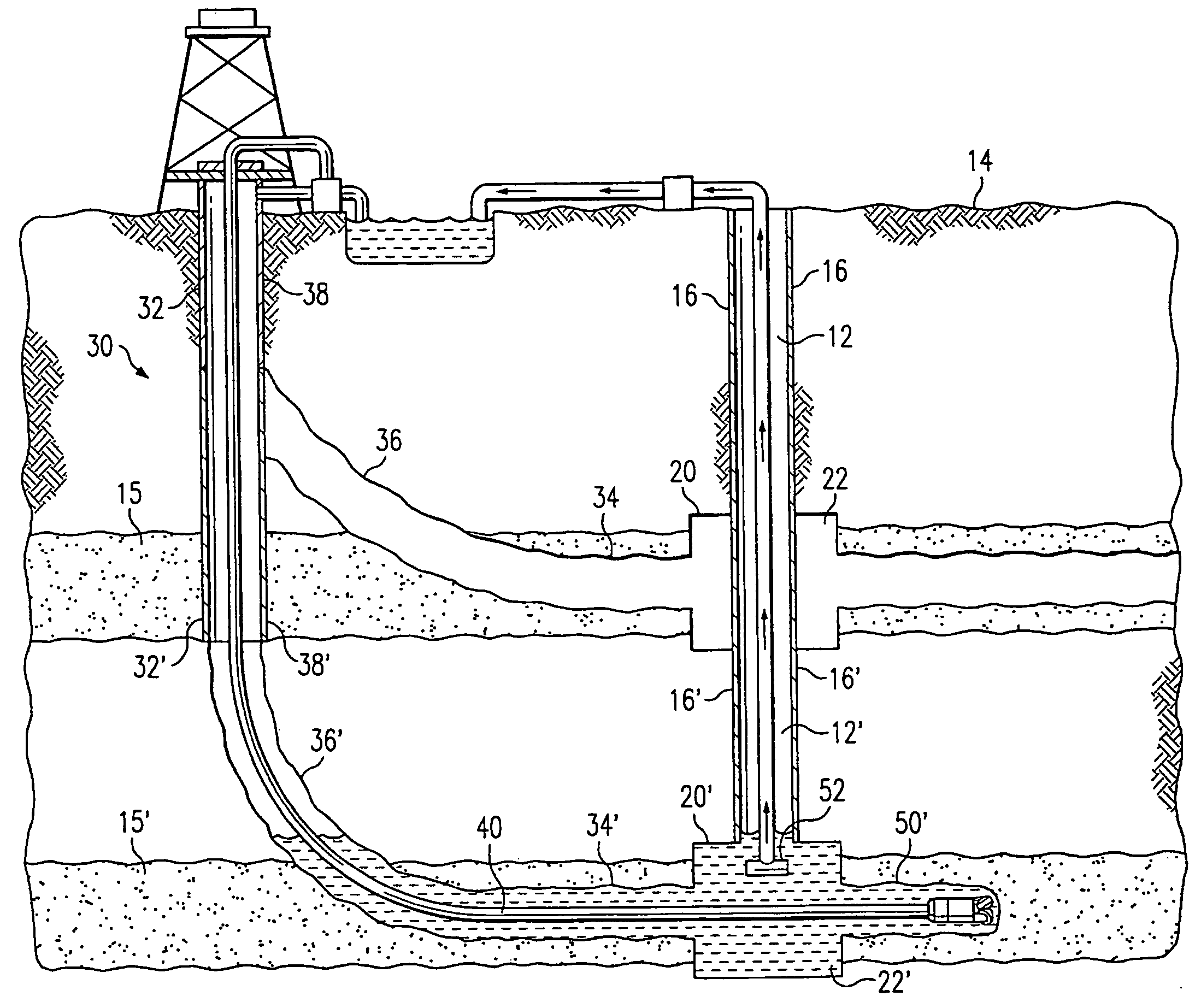

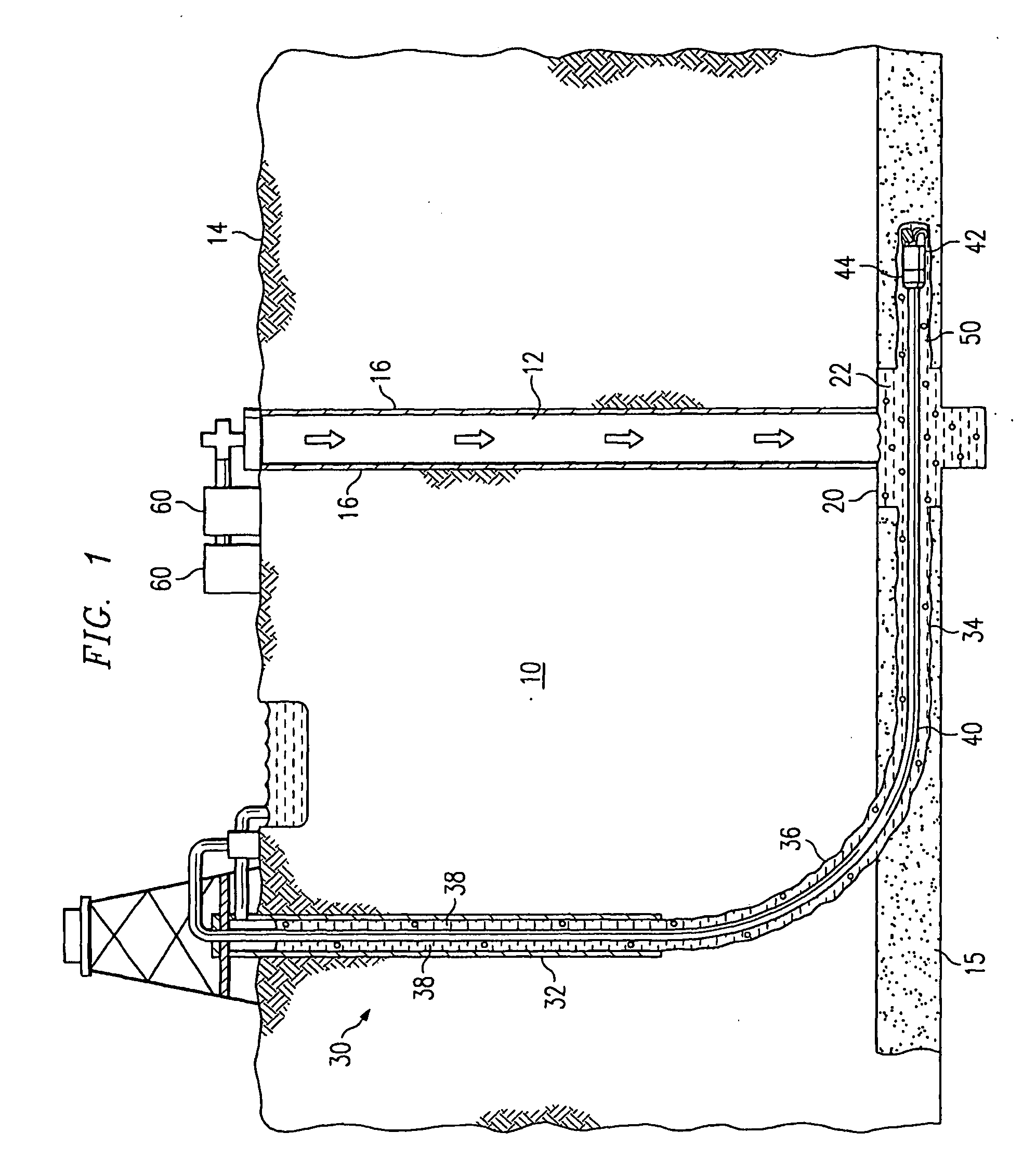

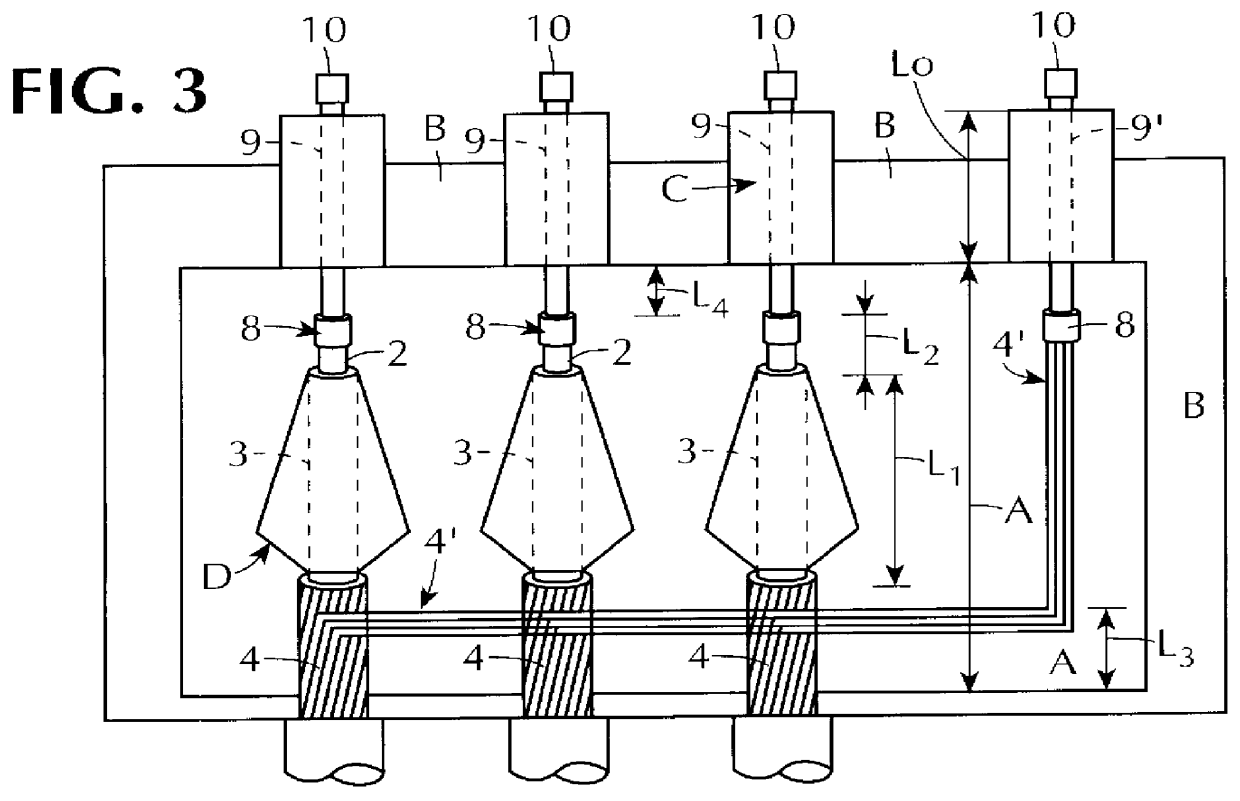

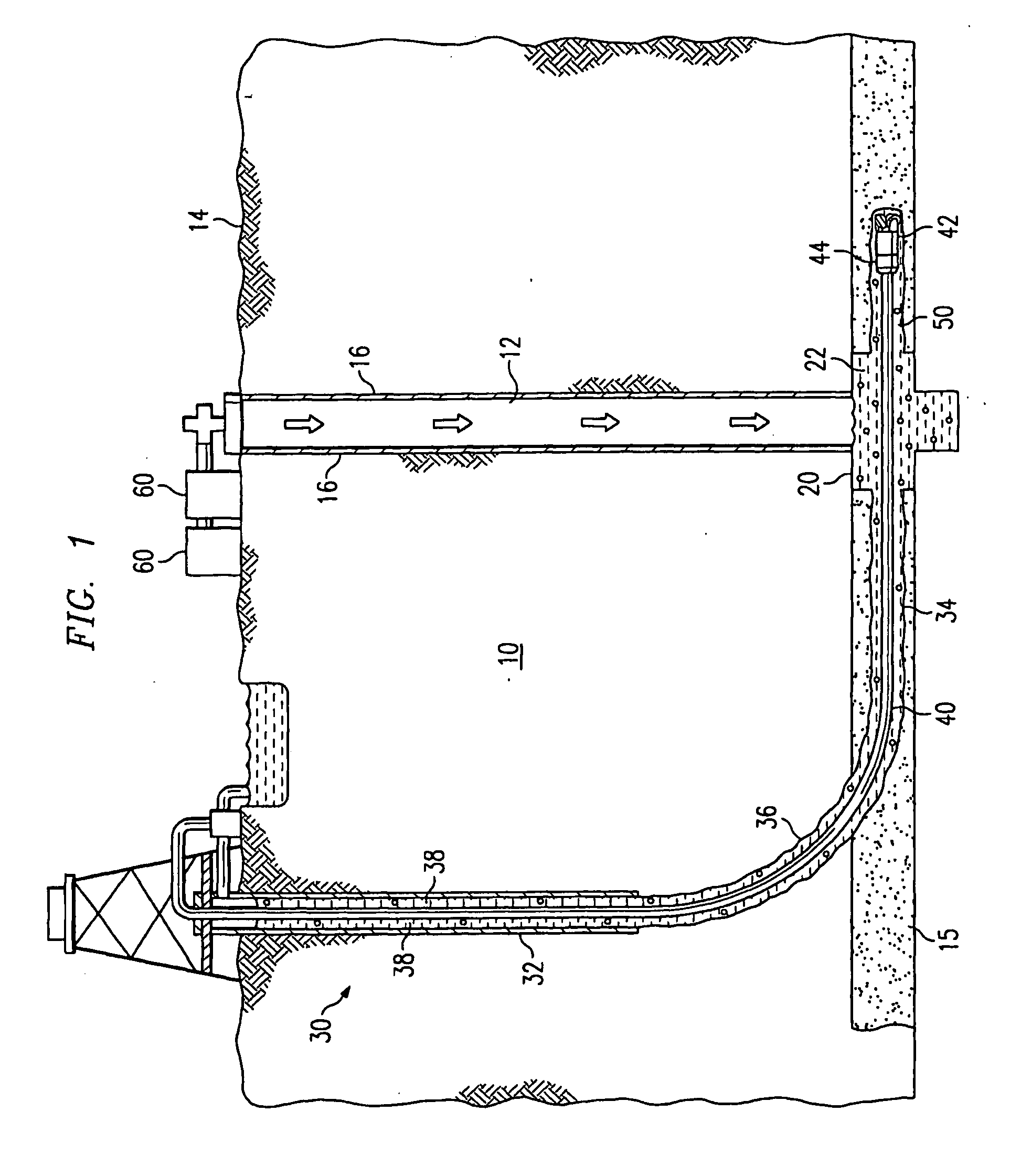

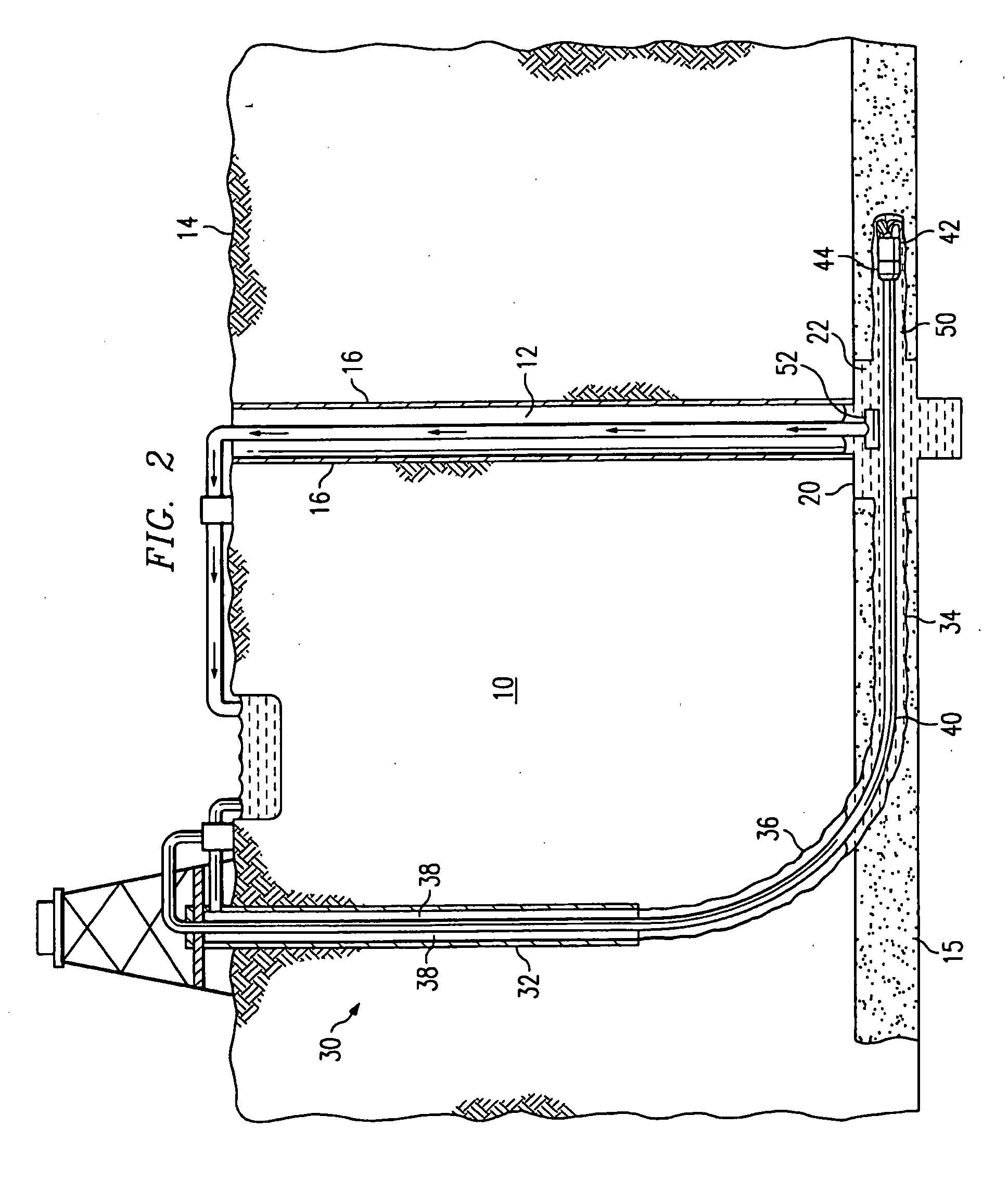

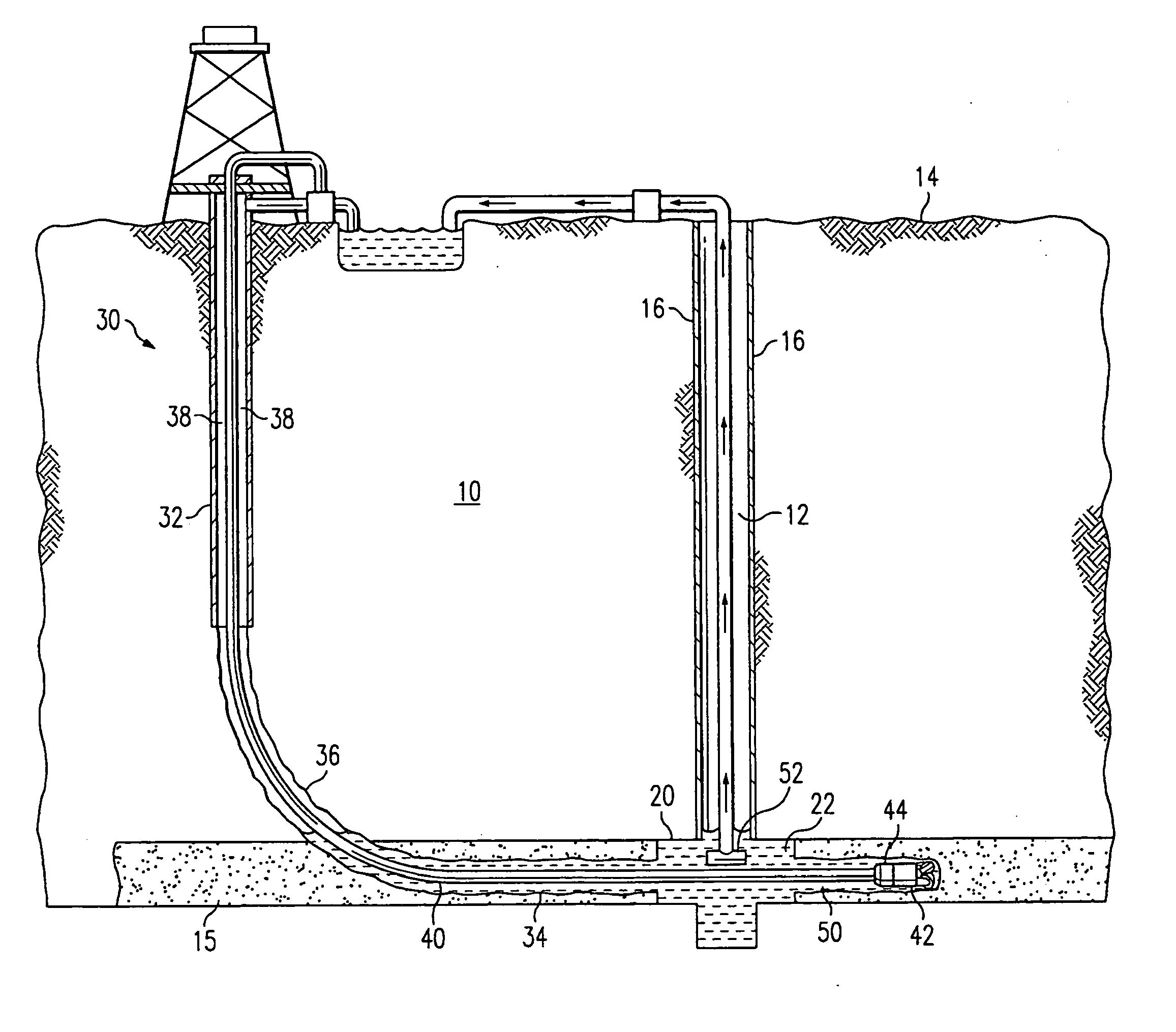

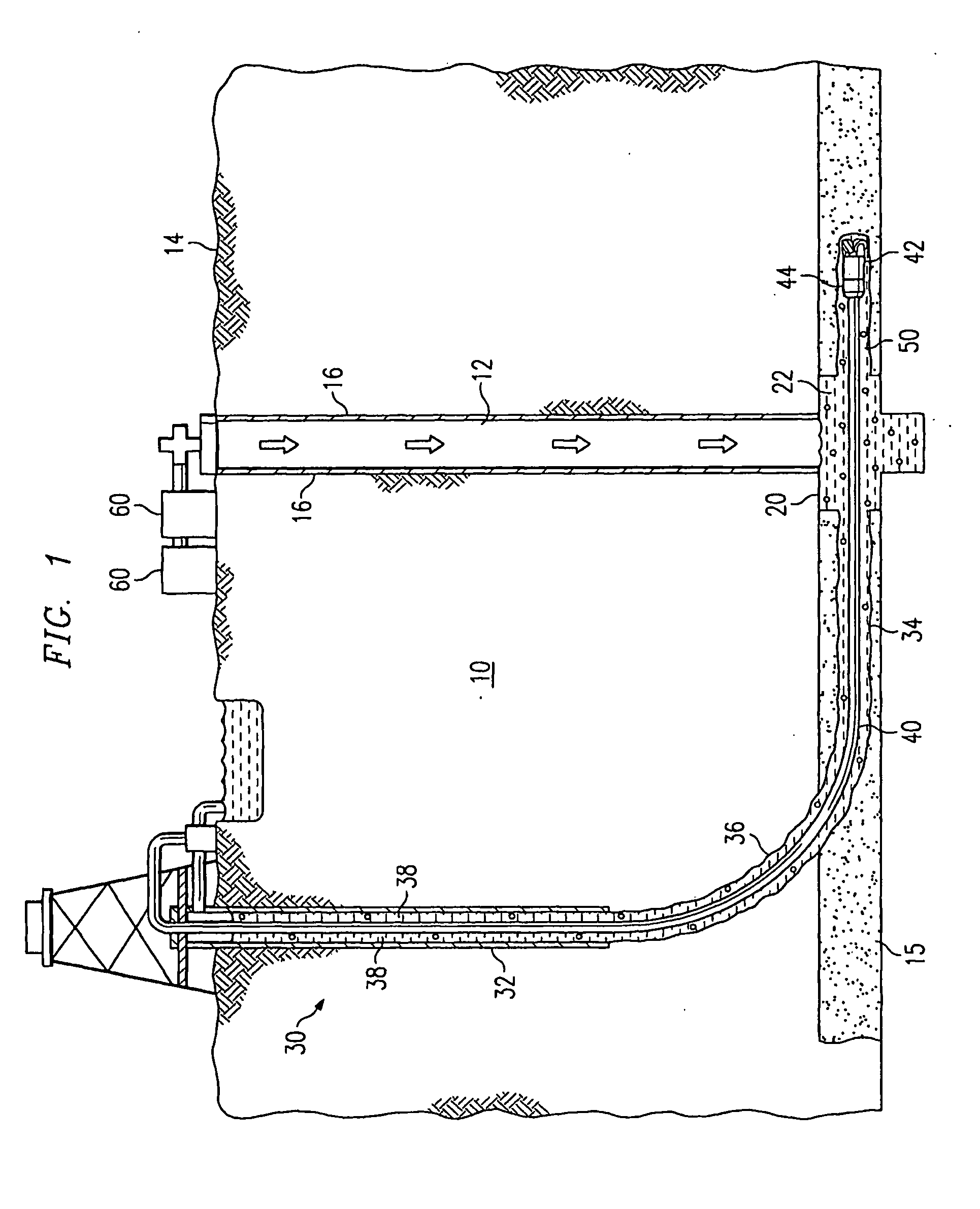

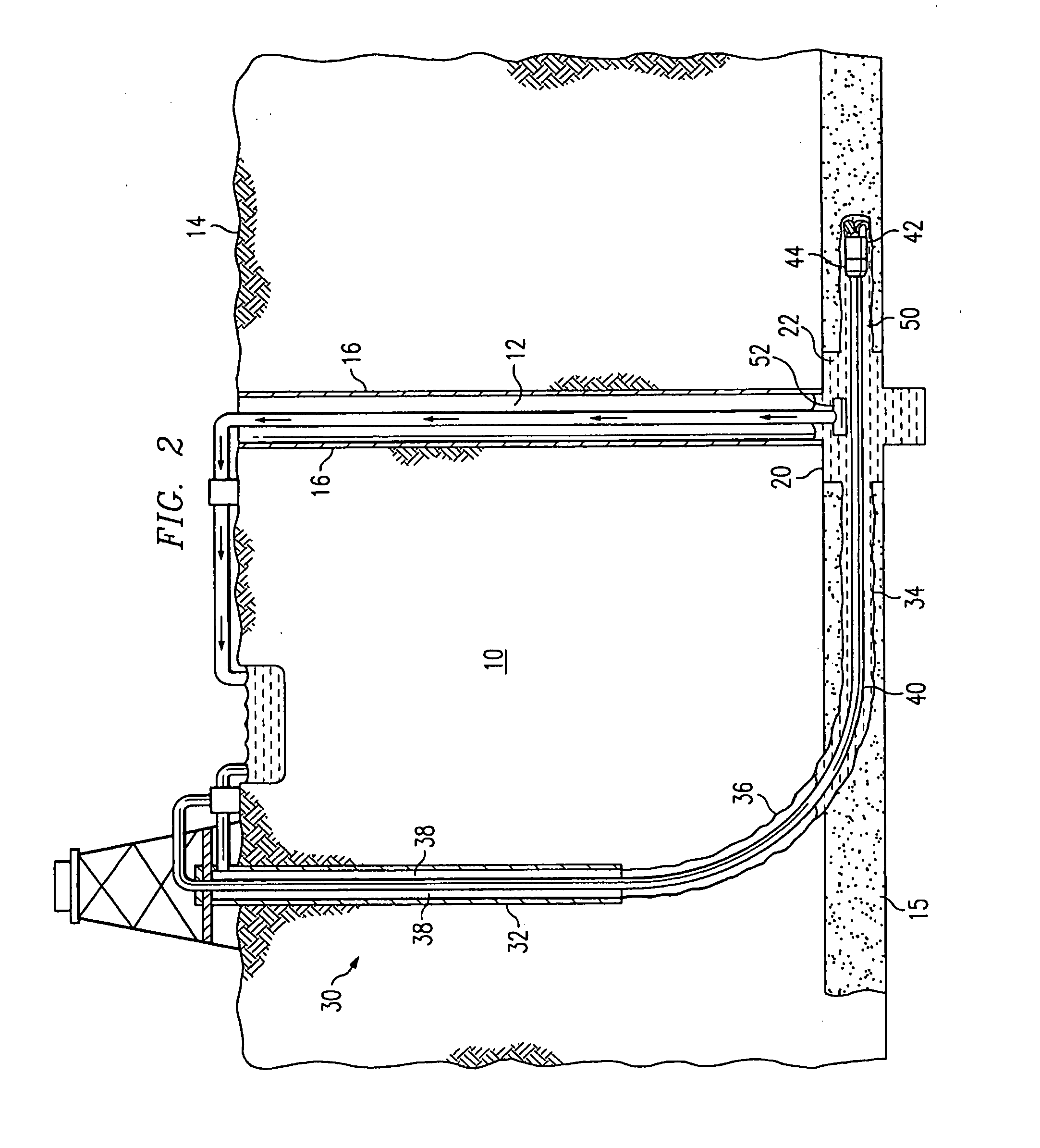

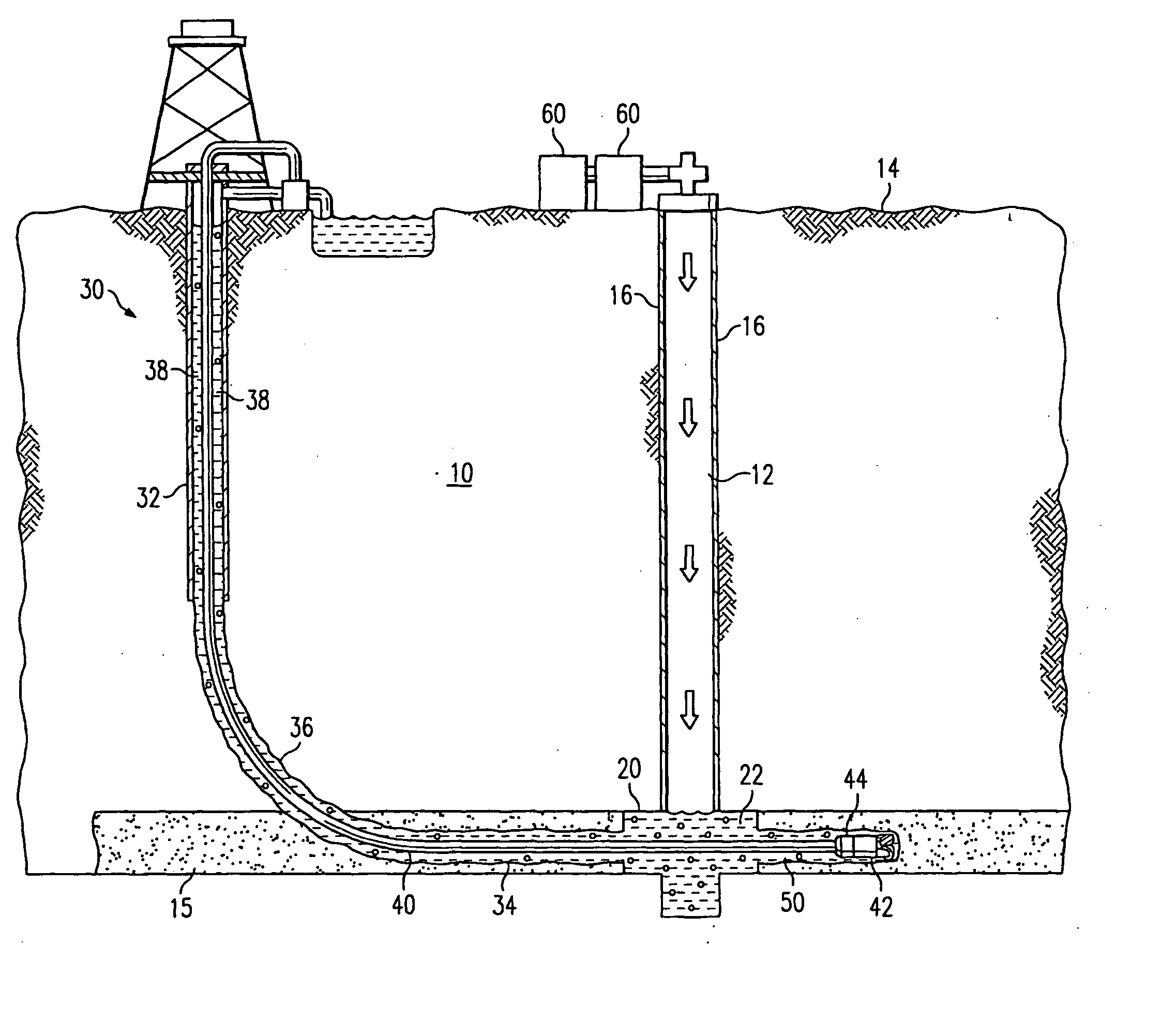

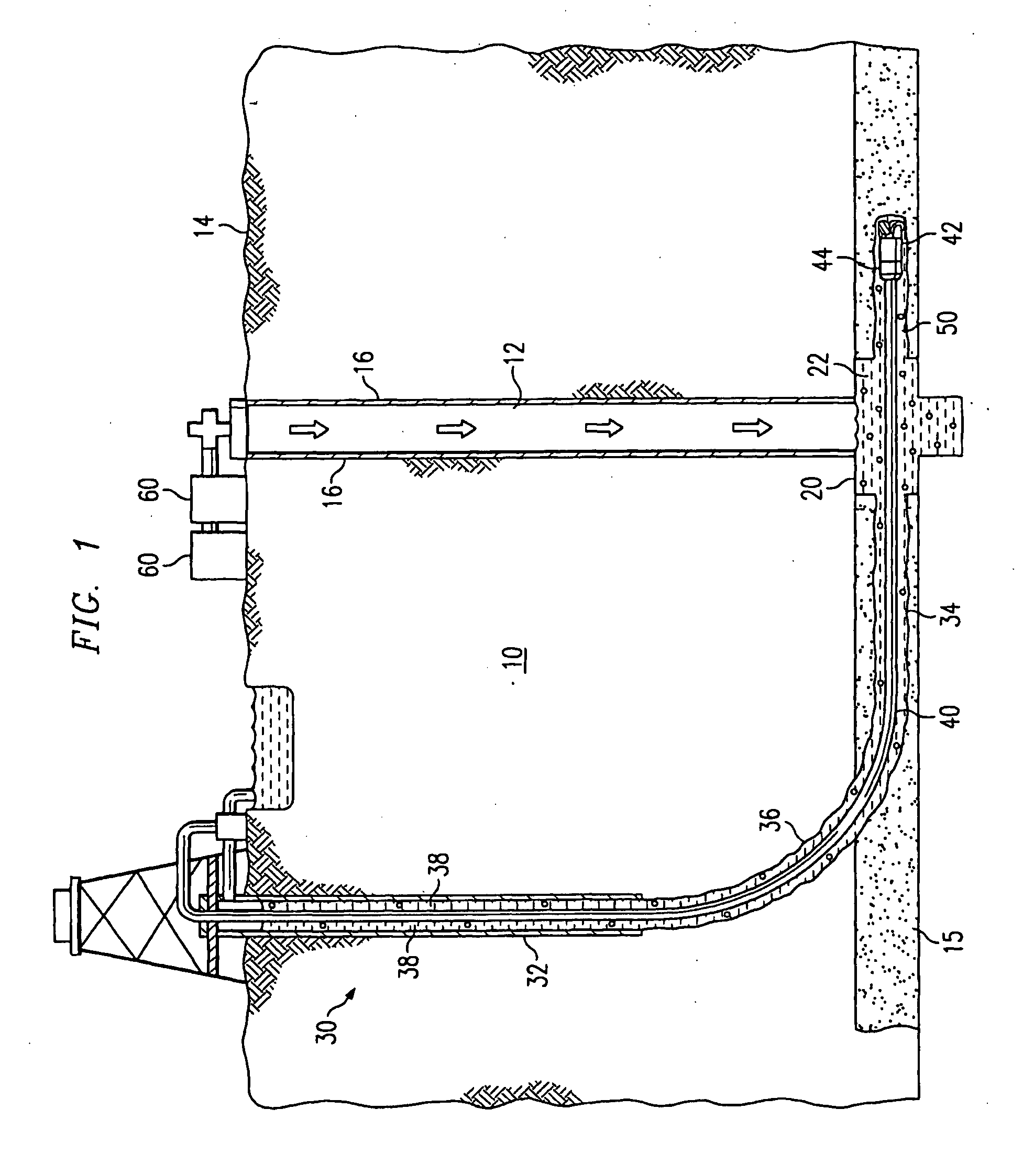

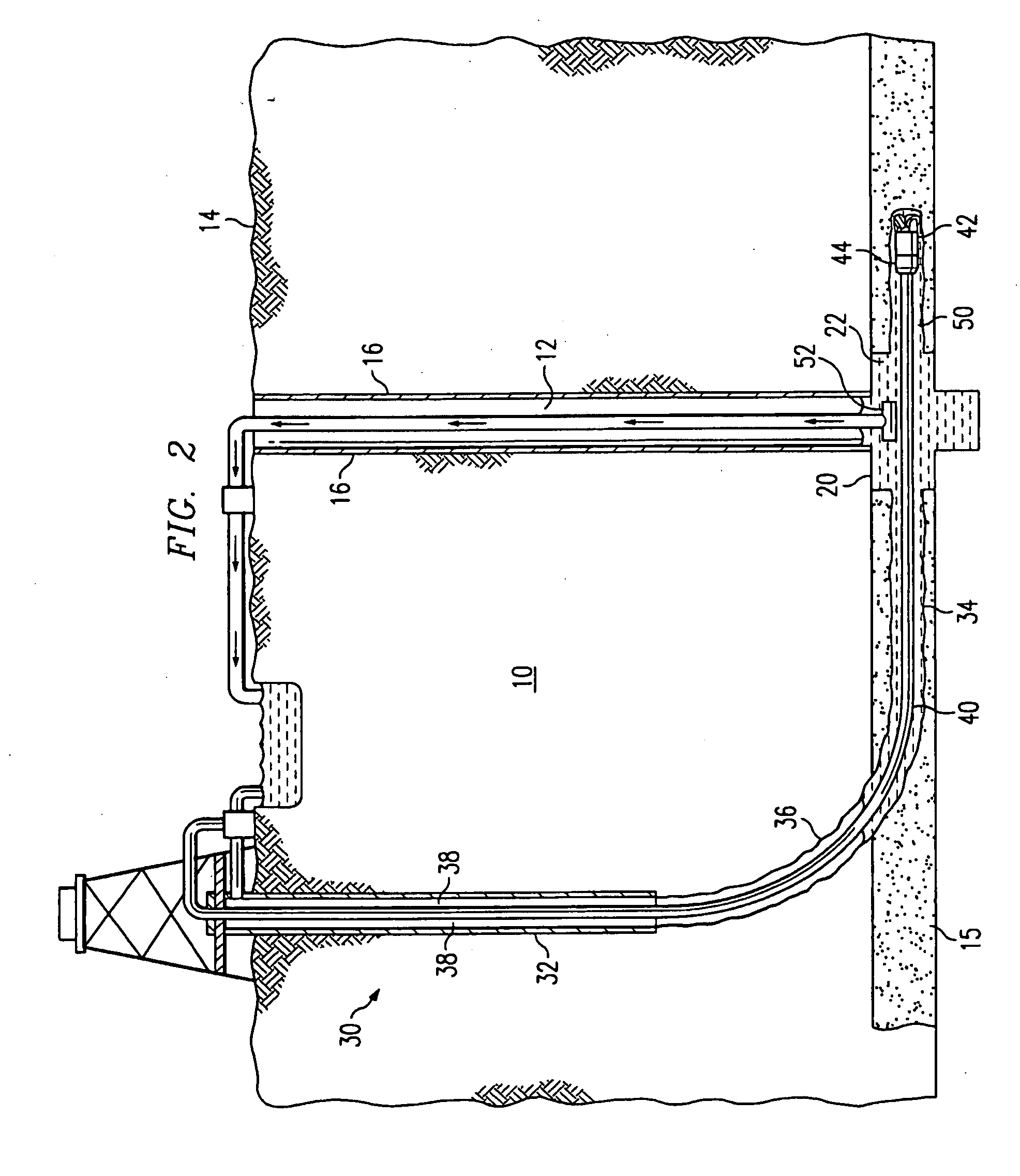

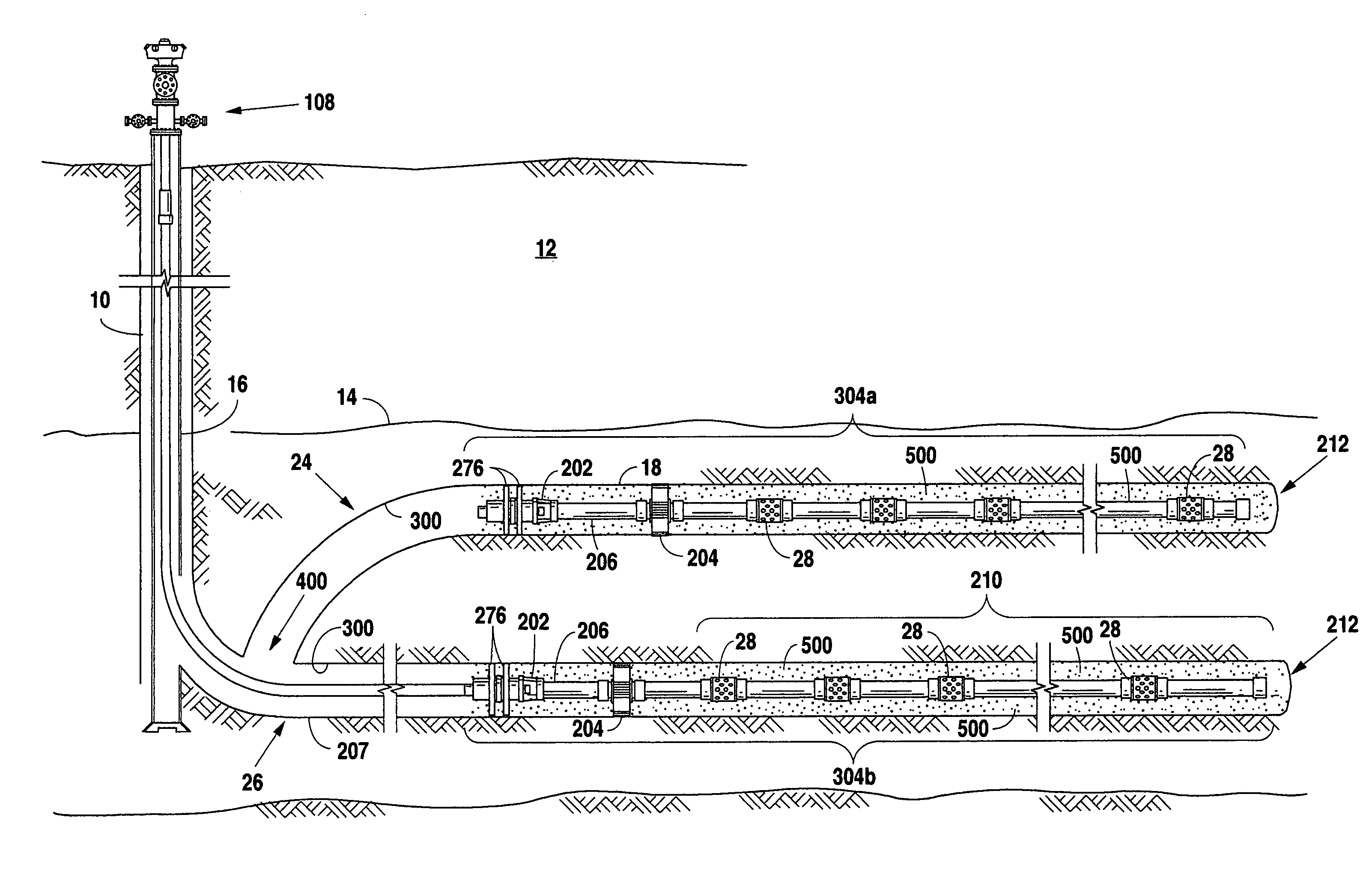

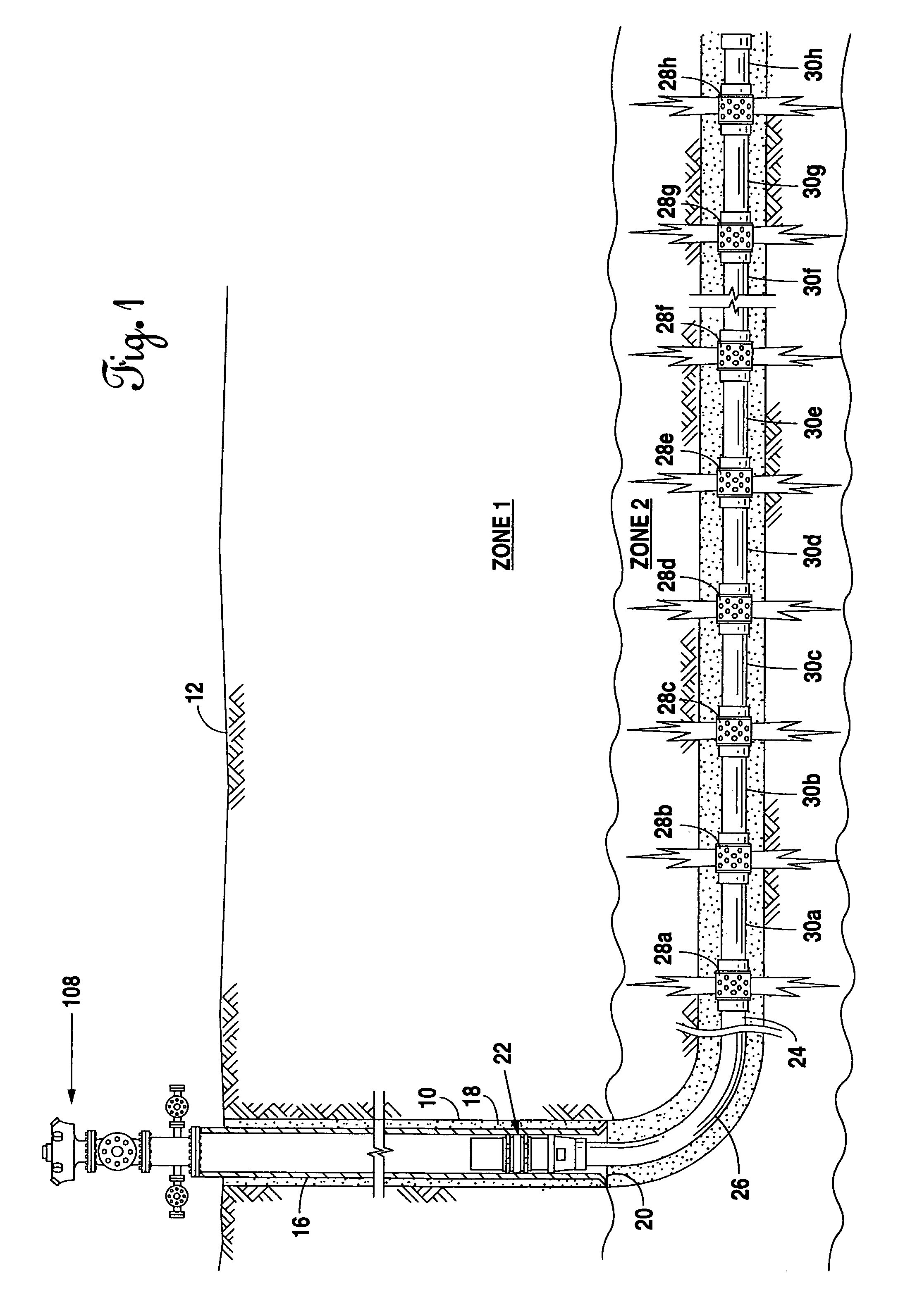

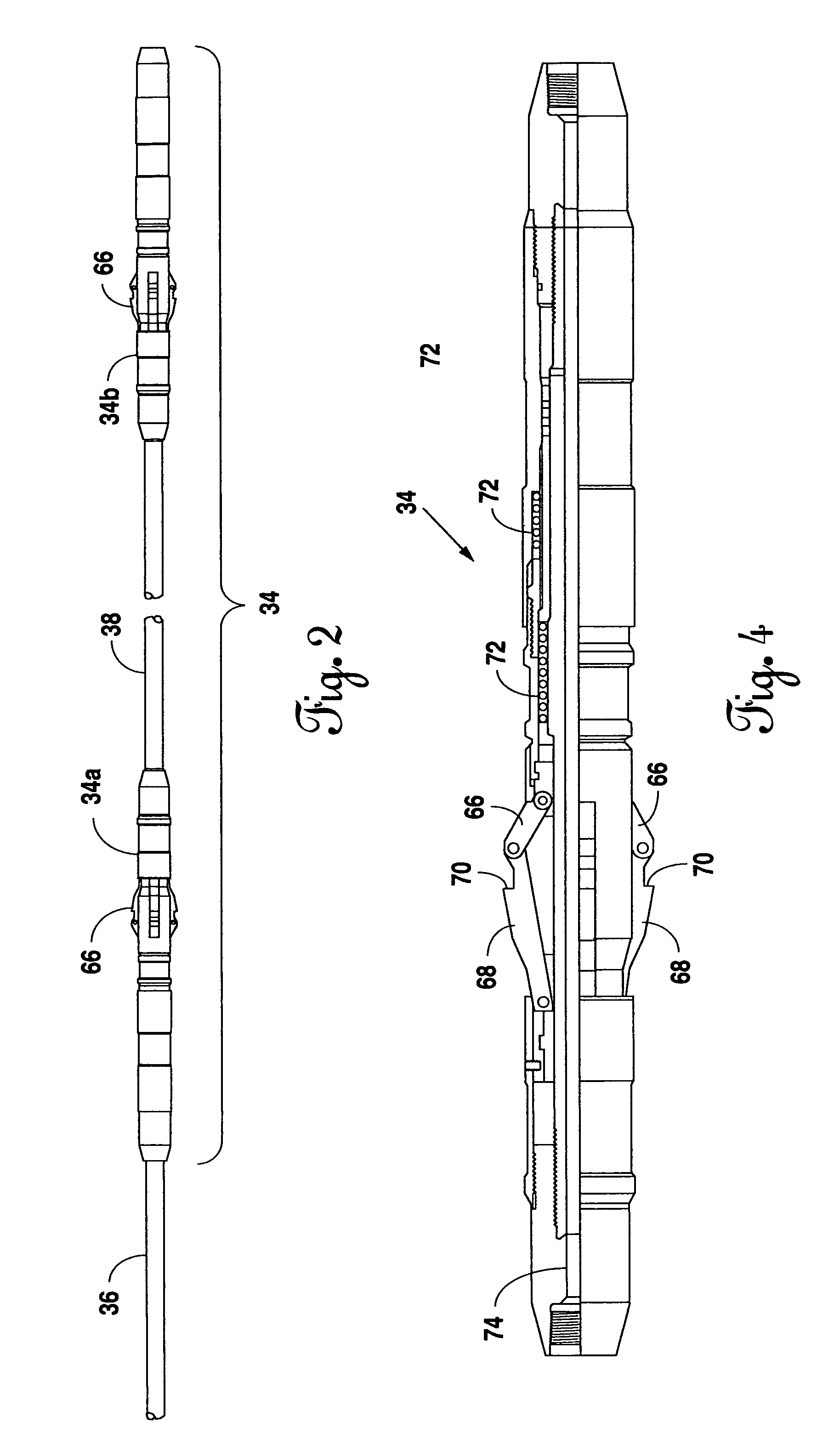

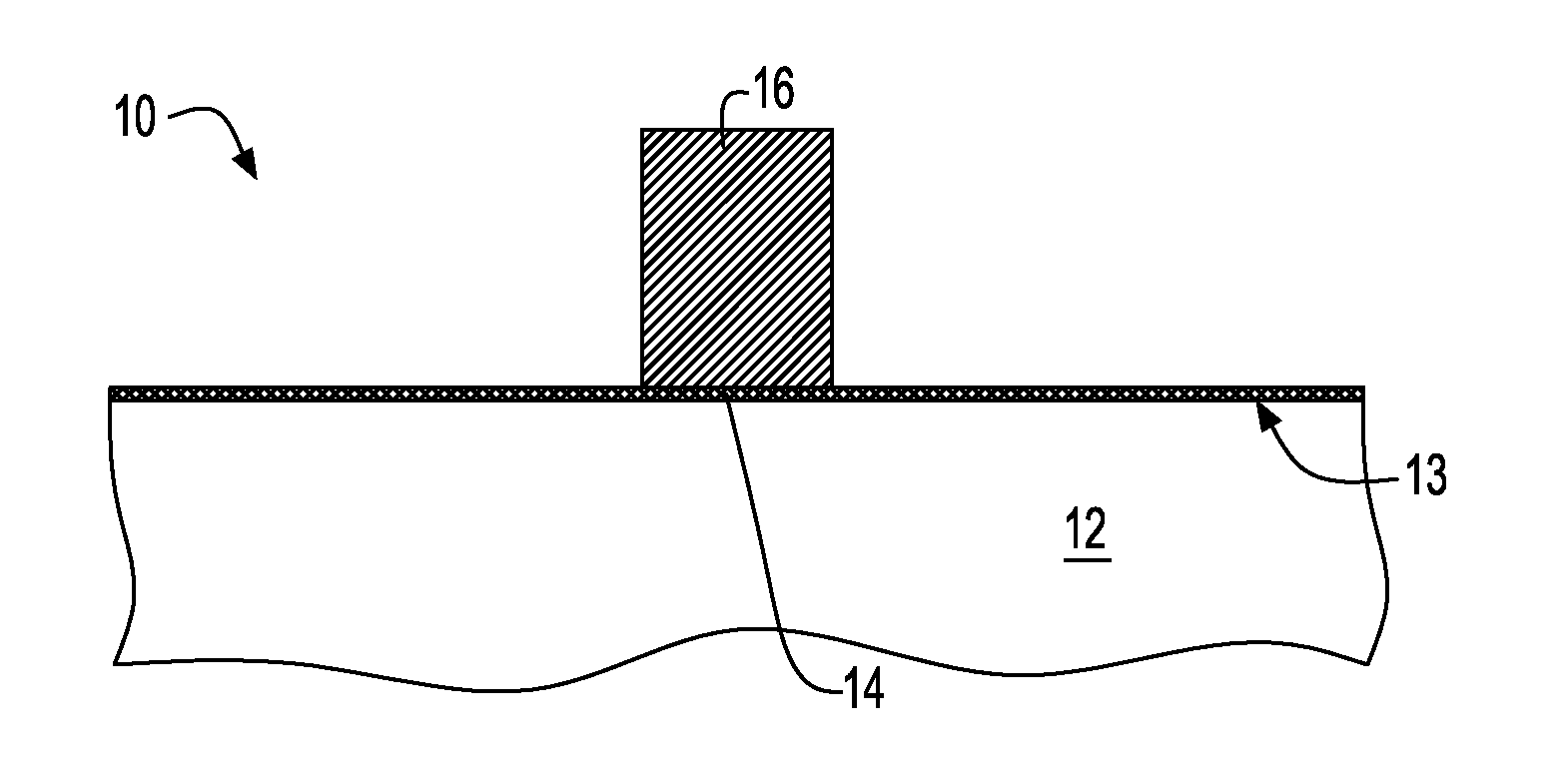

Method and system for accessing subterranean deposits from the surface and tools therefor

Owner:EFFECTIVE EXPLORATION

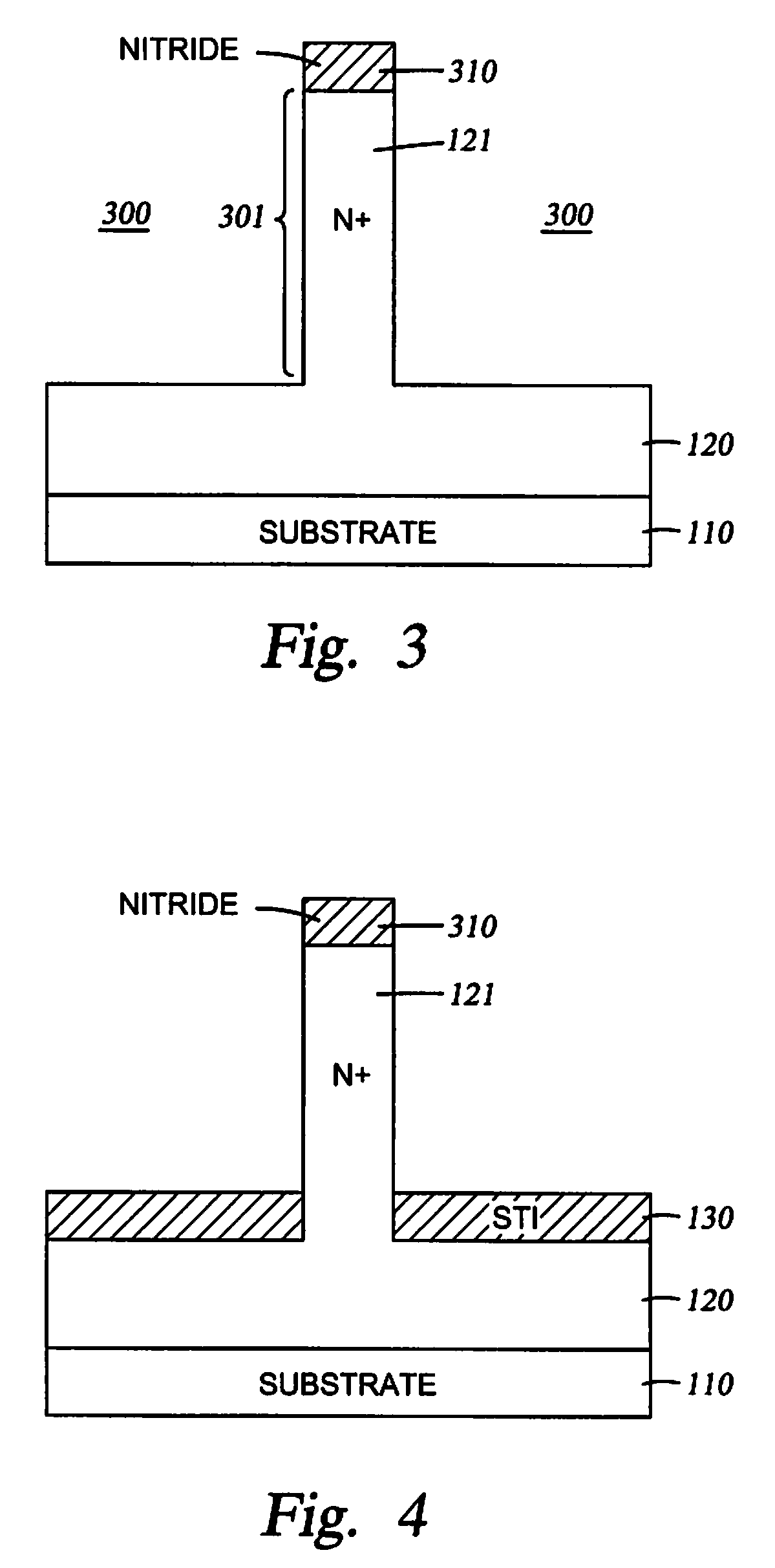

Vertical channel field effect transistors having insulating layers thereon

A field effect transistor can include a vertical channel protruding from a substrate including a source / drain region junction between the vertical channel and the substrate, and an insulating layer extending on a side wall of the vertical channel toward the substrate to beyond the source / drain region junction. The transistor can also include a nitride layer extending on the side wall away from the substrate to beyond the insulating layer, a second insulating layer extending on the side wall that is separated from the channel by the nitride layer, and a gate electrode extending on the side wall toward the substrate to beyond the source / drain region junction. Related methods are also disclosed.

Owner:HONDA MOTOR CO LTD +1

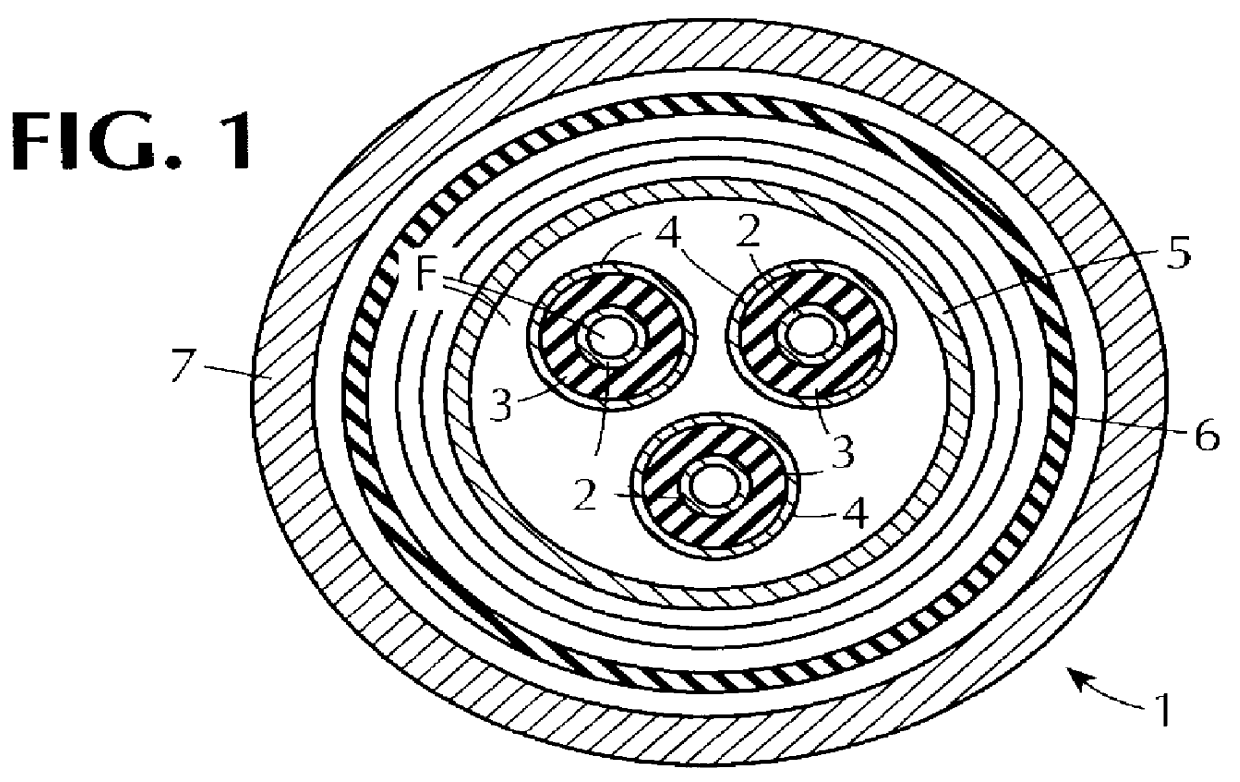

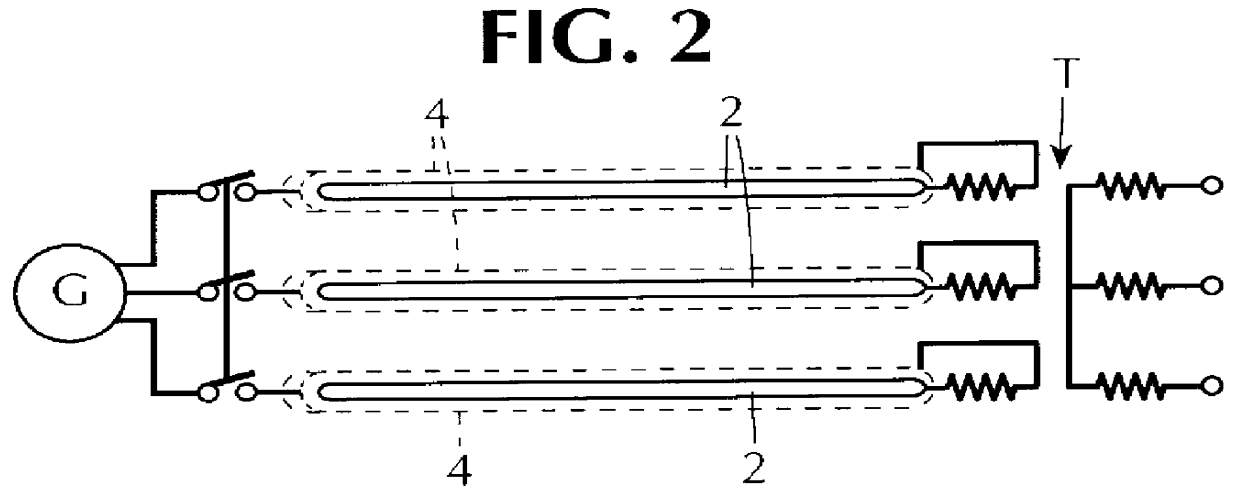

Terminal for connecting a superconducting multiphase cable to a room temperature electrical equipment

InactiveUS6049036ALine/current collector detailsSuperconductors/hyperconductorsElectrical conductorRoom temperature

A terminal for connecting a superconducting multiphase cable, a superconducting three-phase cable for example, to a room temperature electrical equipment is described. The terminal includes a casing with cooling fluid, inside which the three cable superconductors are each connected with a resistive conductor the end of which is connected to the room temperature equipment phases at the outside of the casing. The terminal includes superconducting connectors between the three neutral superconductors and a single resistive conductor the end of which is externally associated with the room temperature equipment. The neutral superconducting connectors and the junction area of the connector of the single conductor are disposed inside the cold area of the casing.

Owner:PRYSMIAN CAVI E SISTEMI ENERGIA

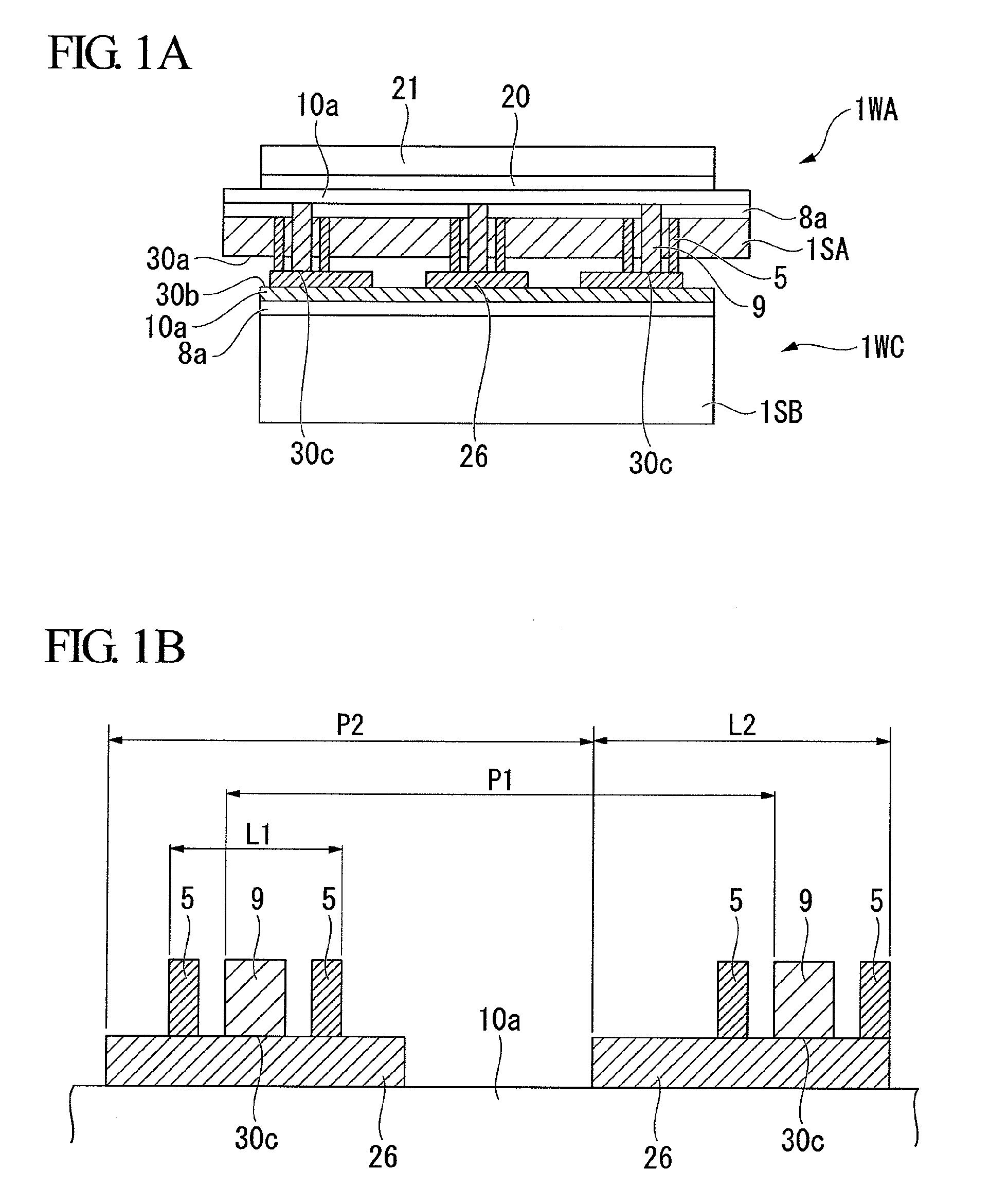

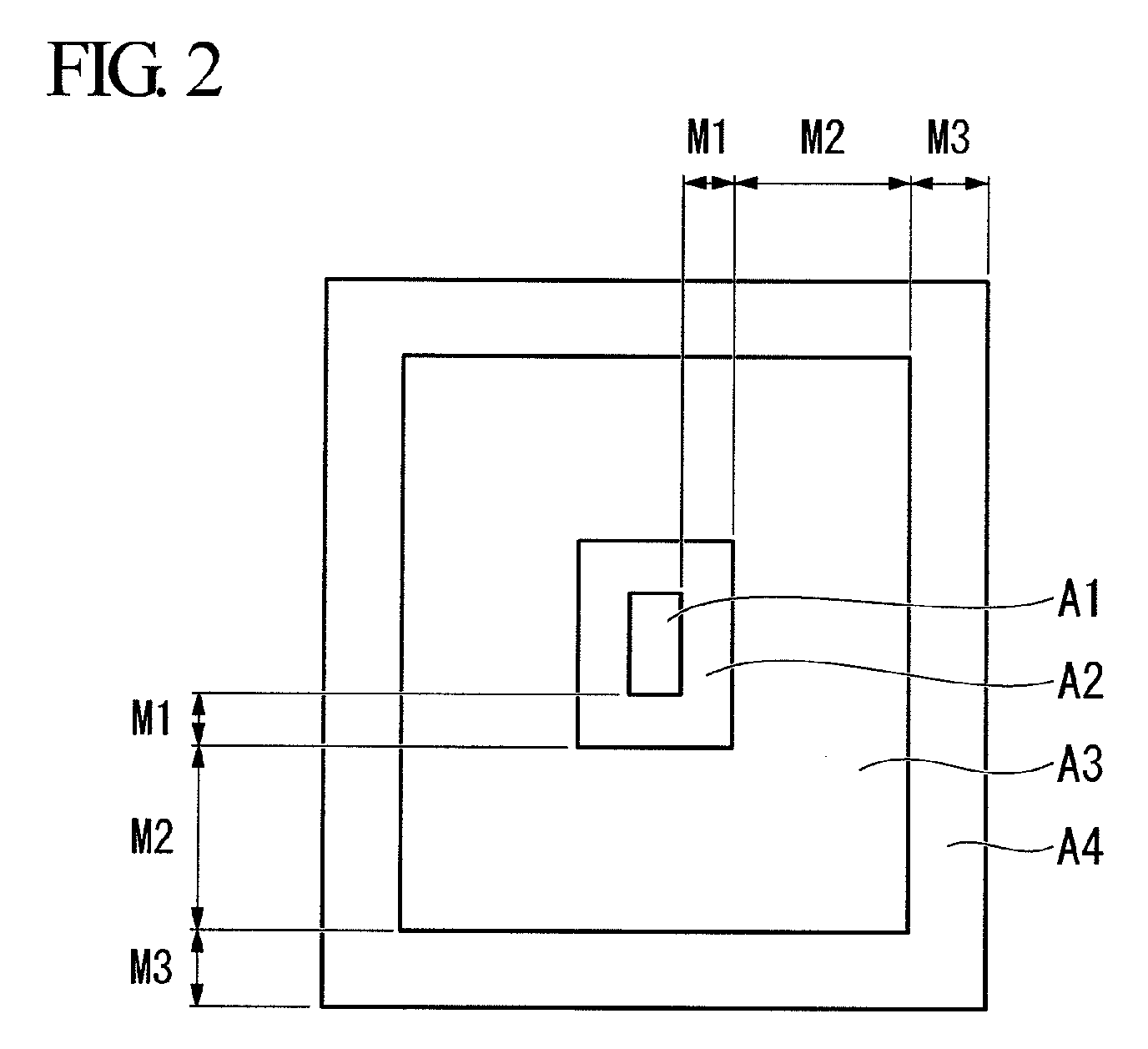

Semiconductor device

InactiveUS20090057890A1High reliability in electrical connectionIncrease the areaSemiconductor/solid-state device detailsSolid-state devicesEngineeringFace shape

In this semiconductor device, connection parts between wafers are electrically insulated from each other, and a junction face shape of second electrical signal connection parts is larger than the shape of a positioning margin face that is formed by an outer shape when the periphery of a minimum junction face, which has half the area of a junction area of the first electrical signal connection part, is enclosed by a same width dimension as a positioning margin dimension between the first wafer and the second wafer.

Owner:HONDA MOTOR CO LTD

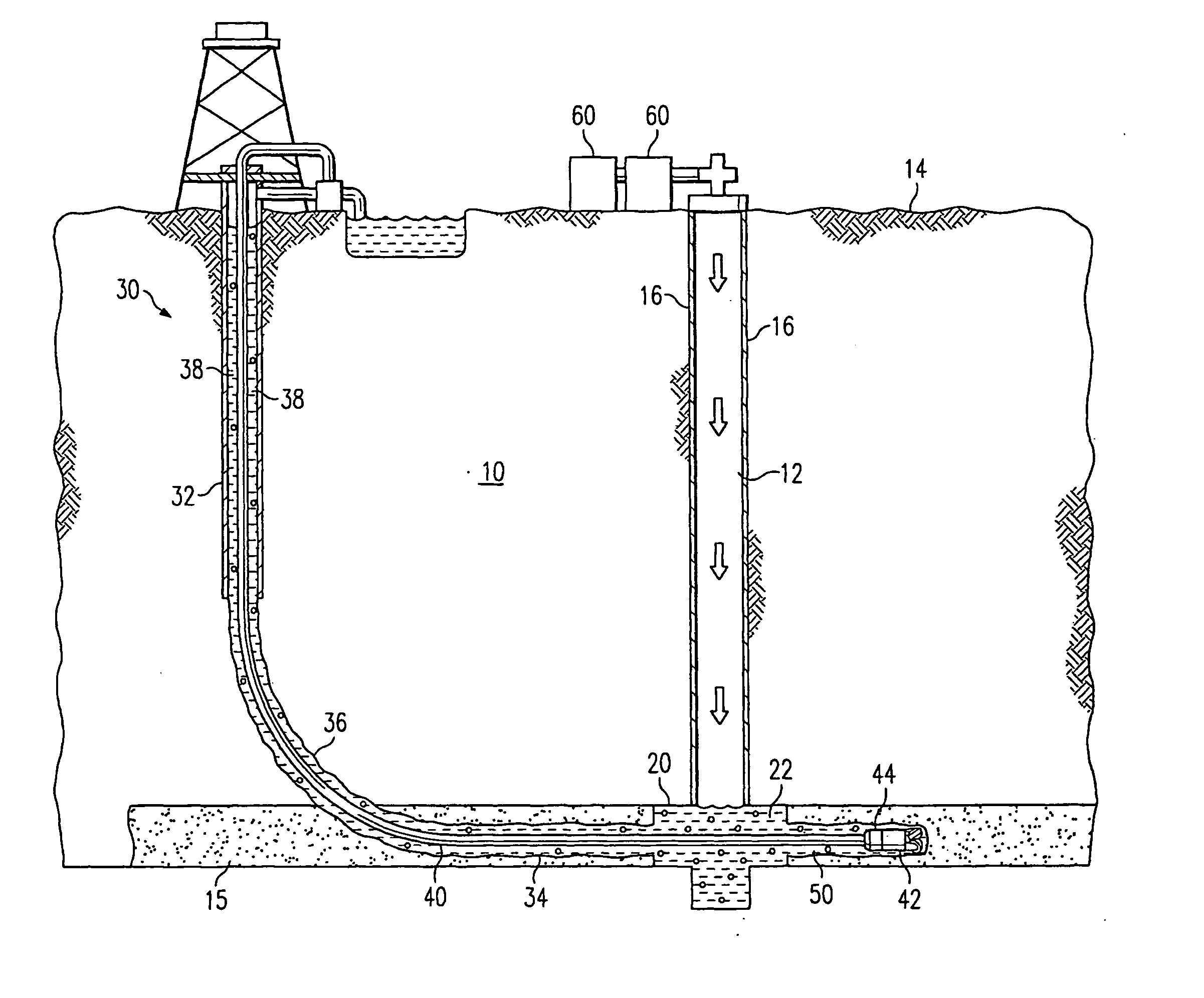

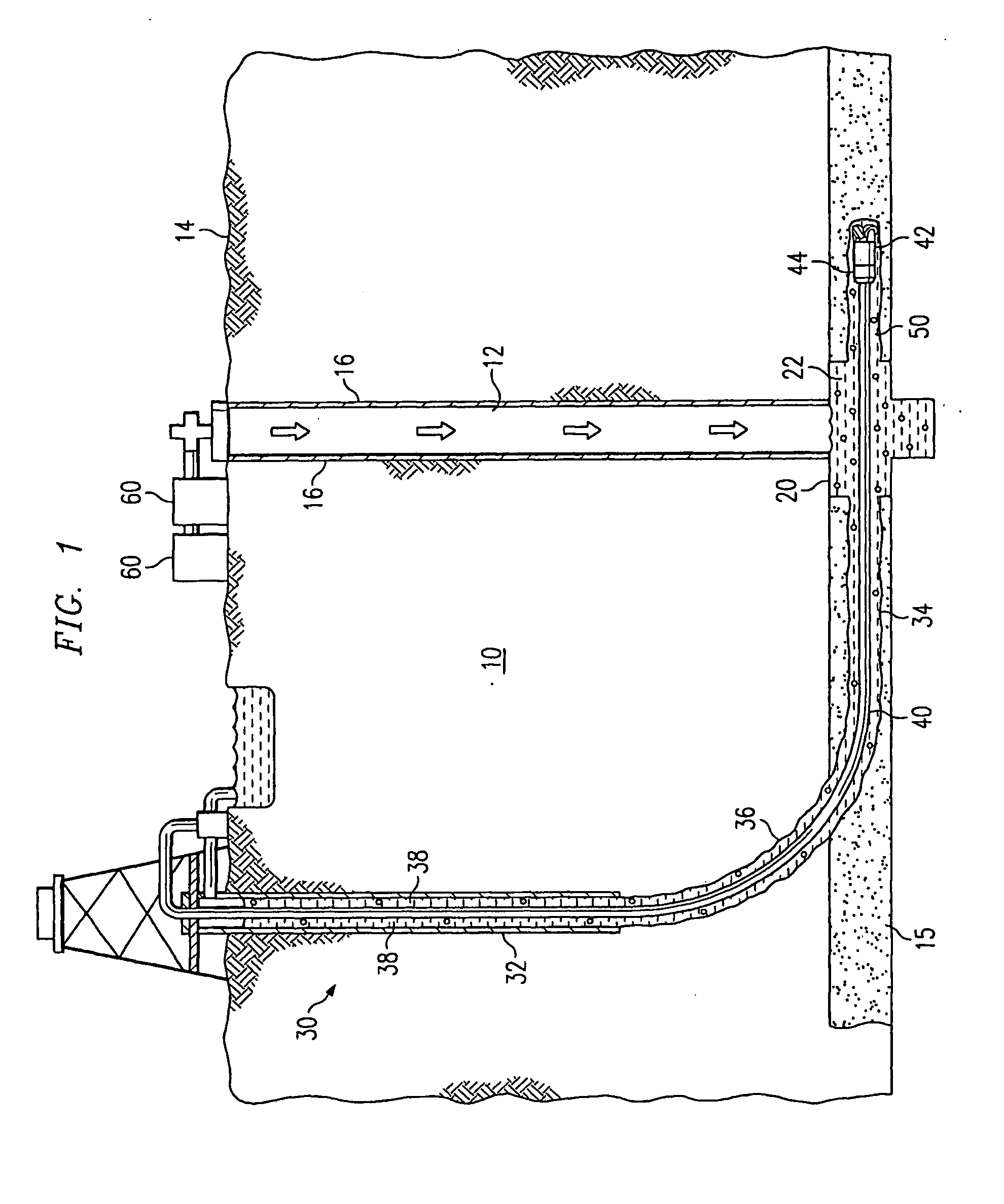

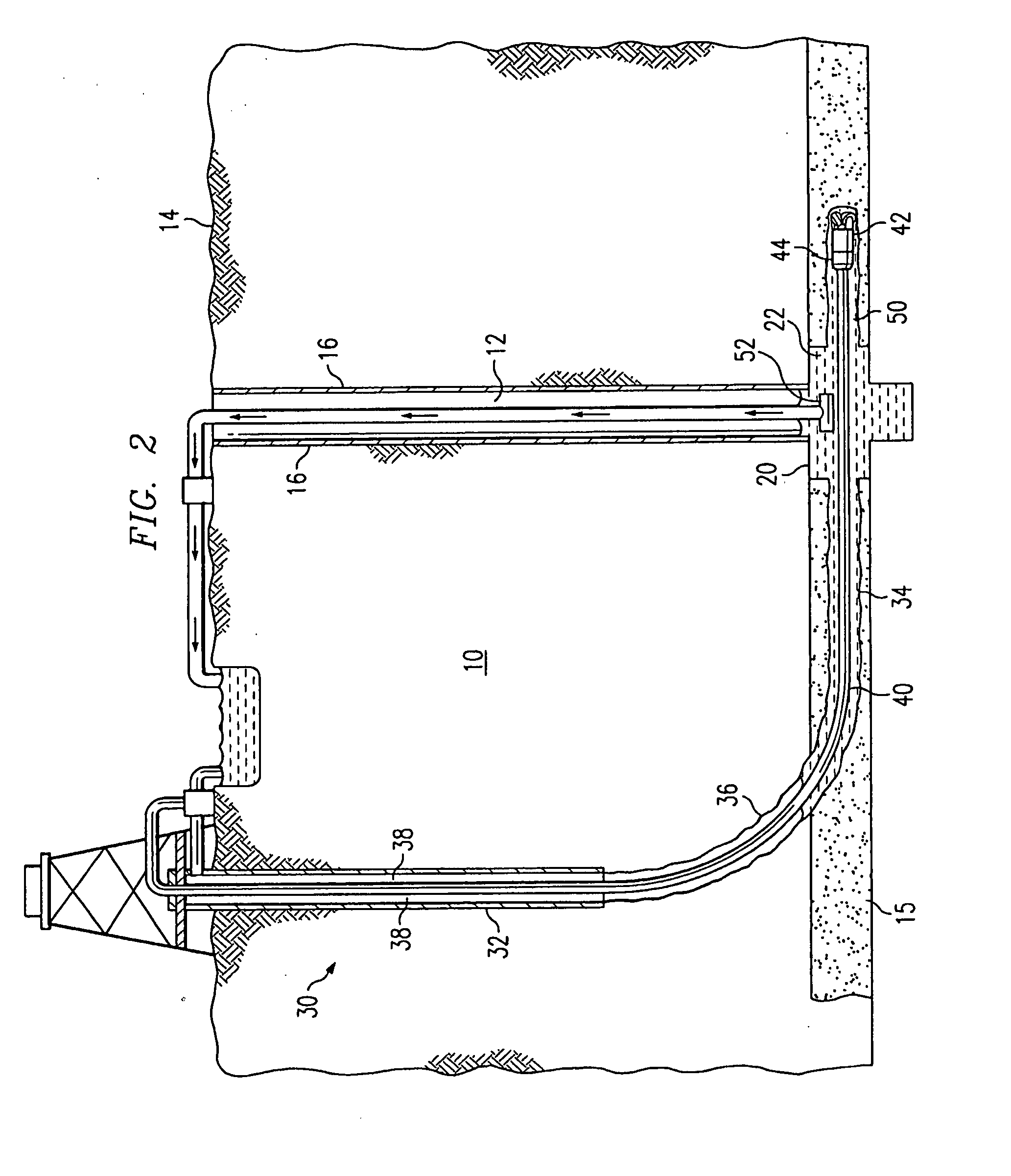

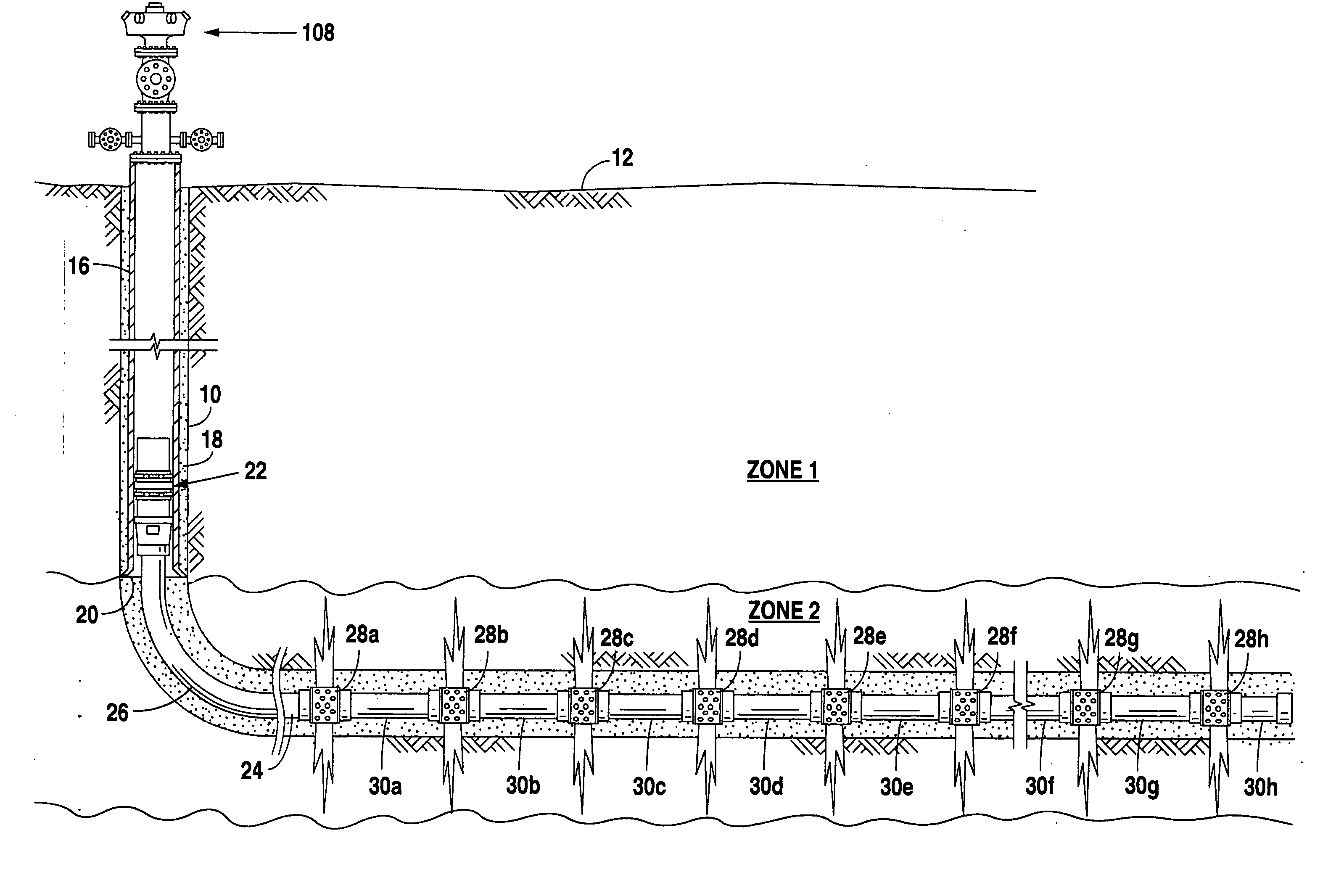

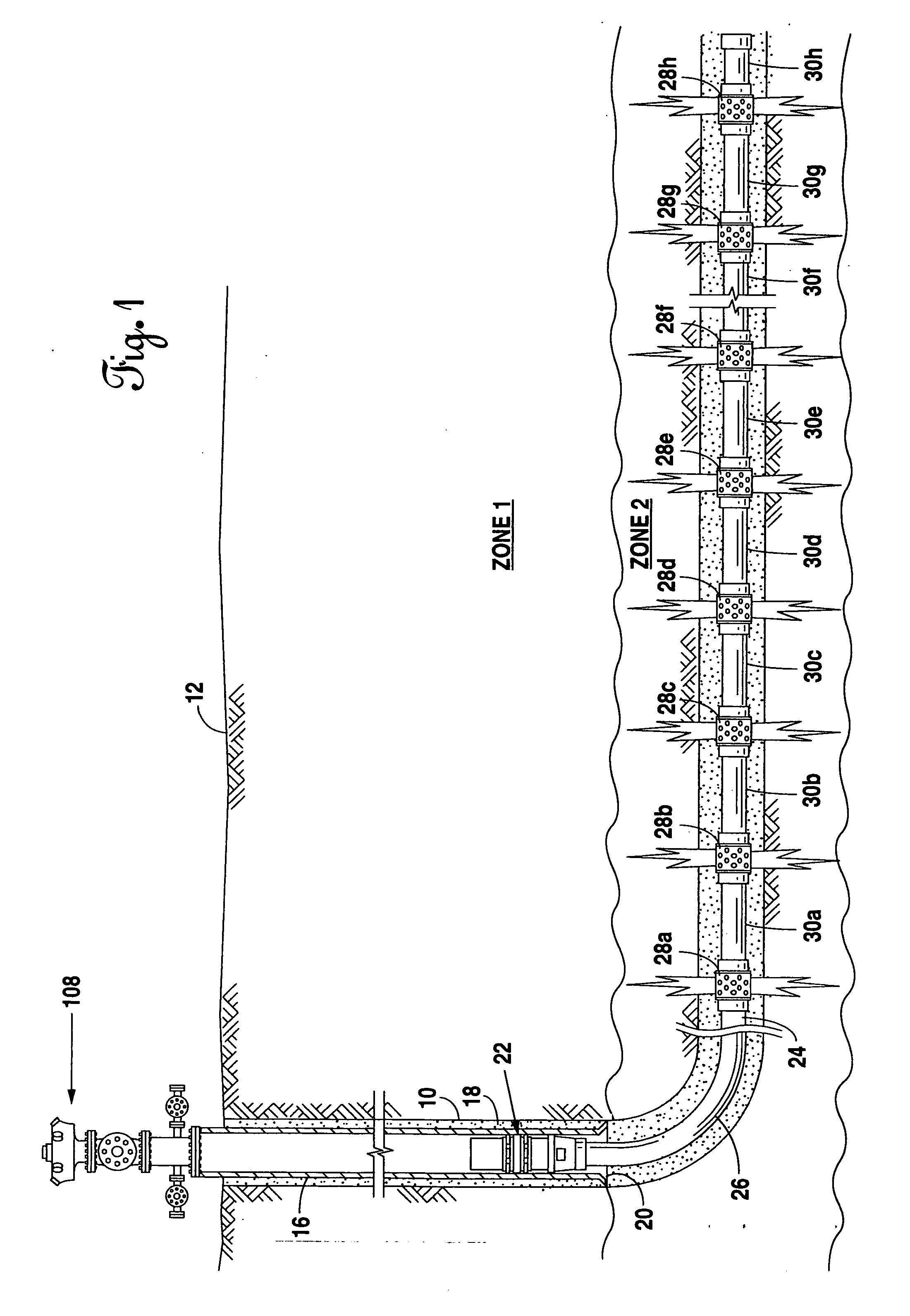

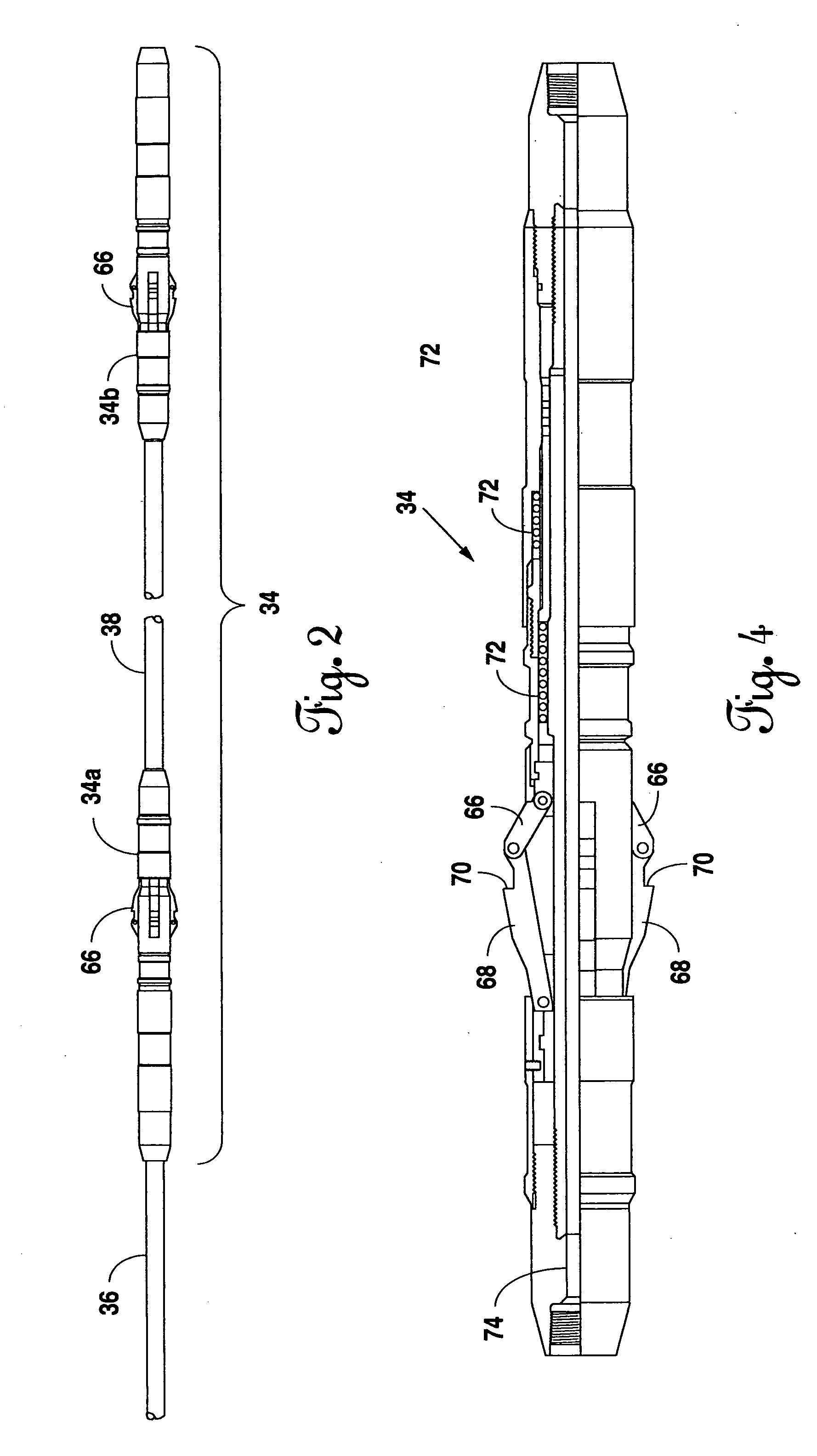

Method and system for accessing subterranean deposits from the surface and tools therefor

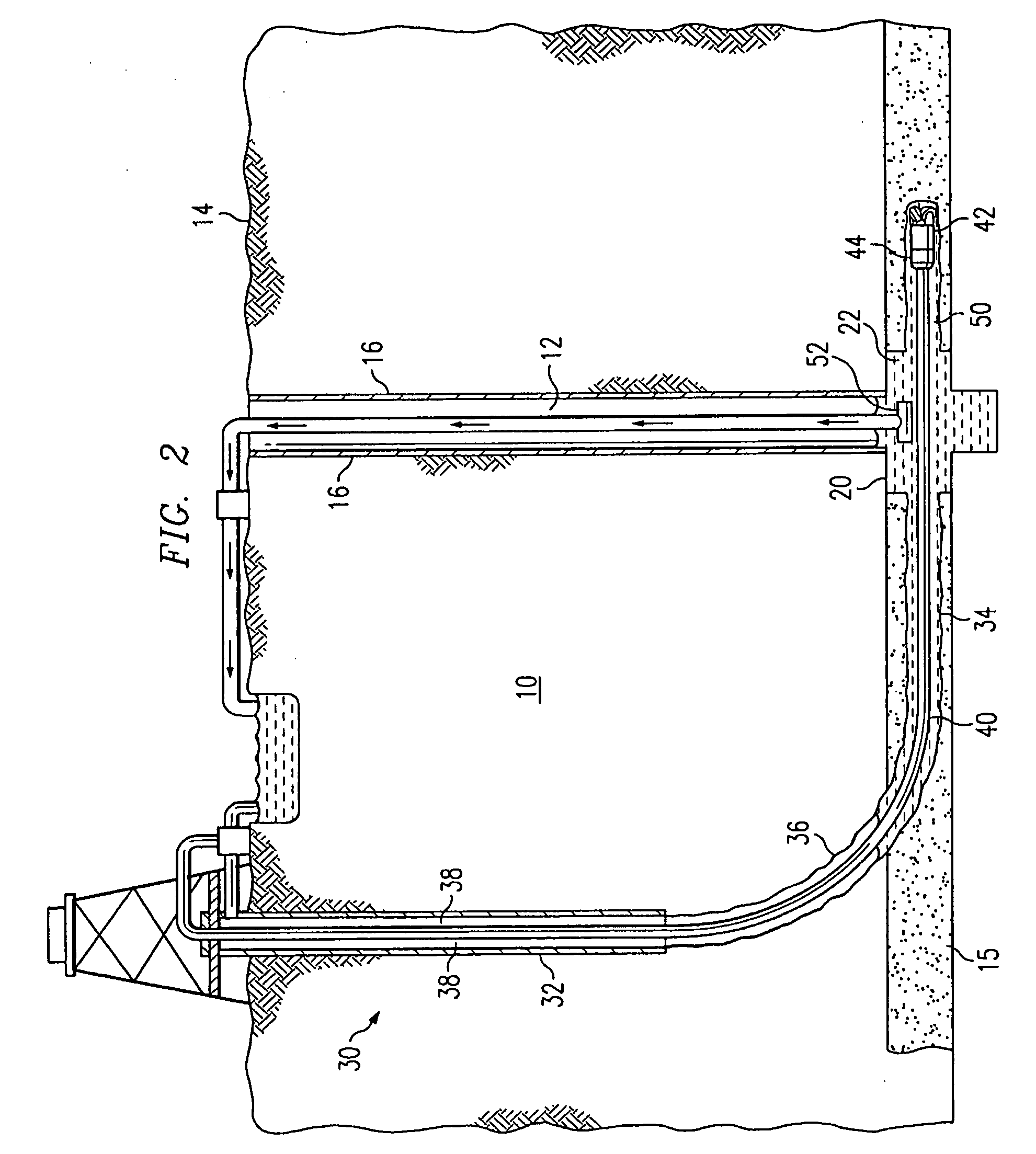

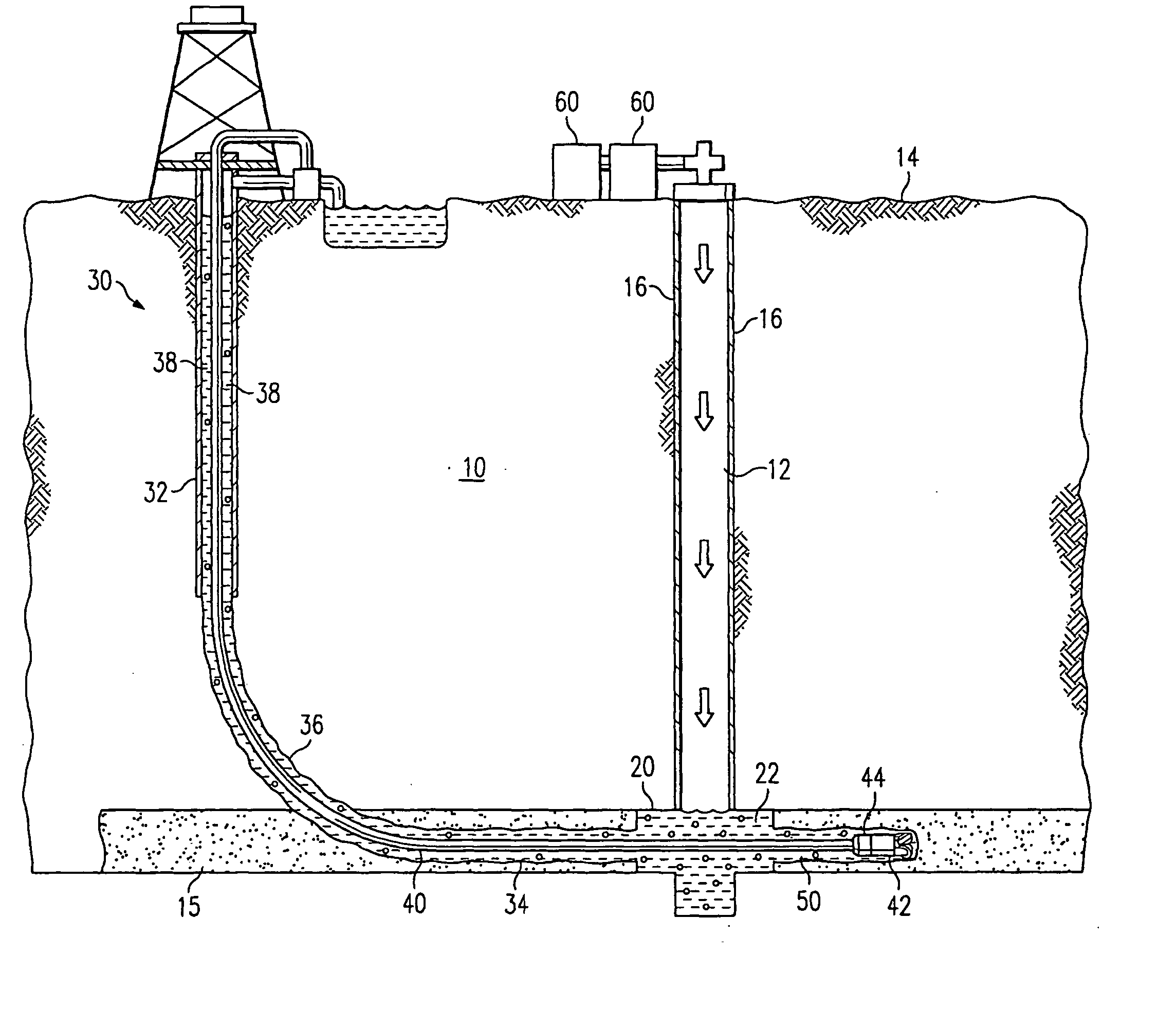

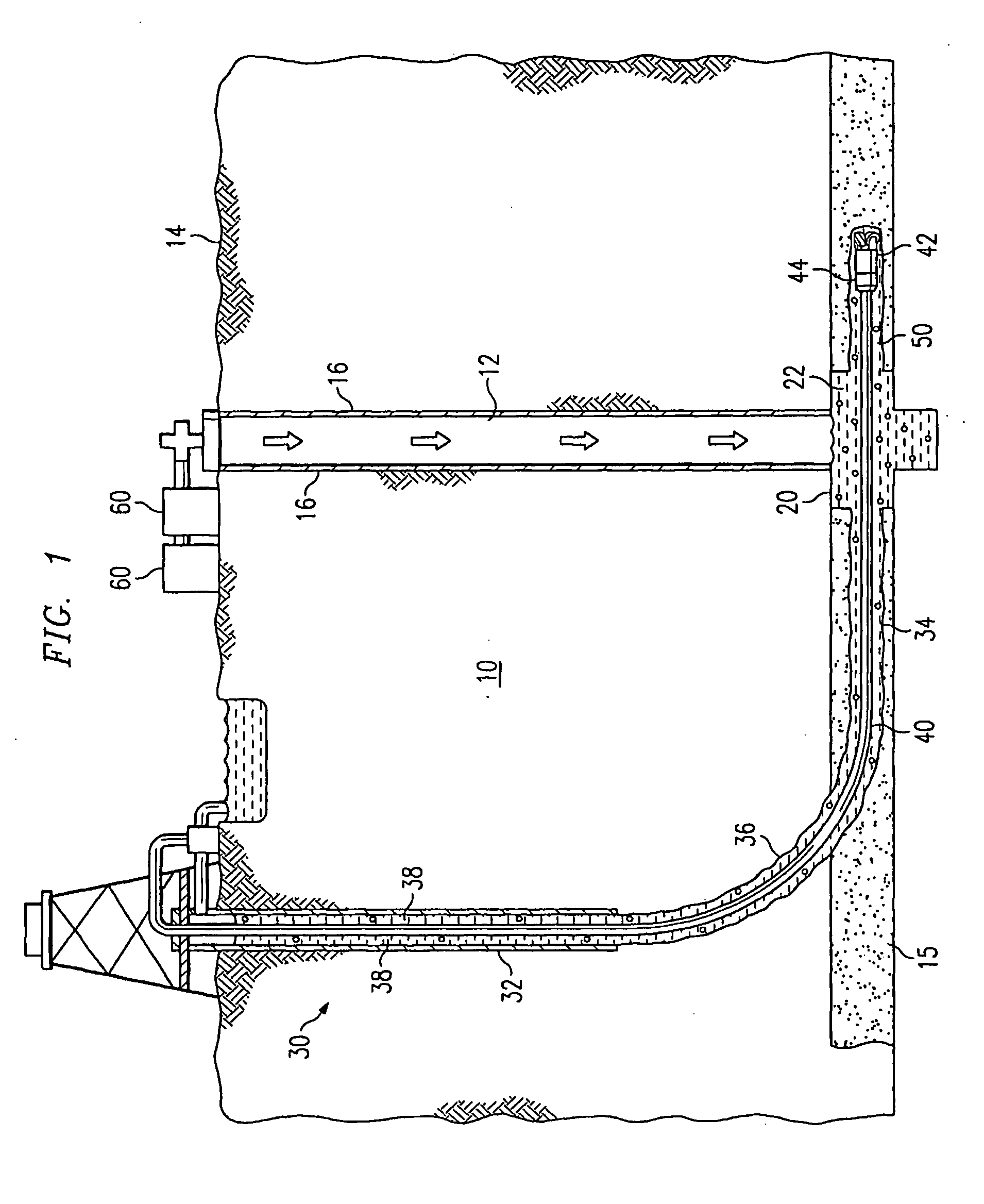

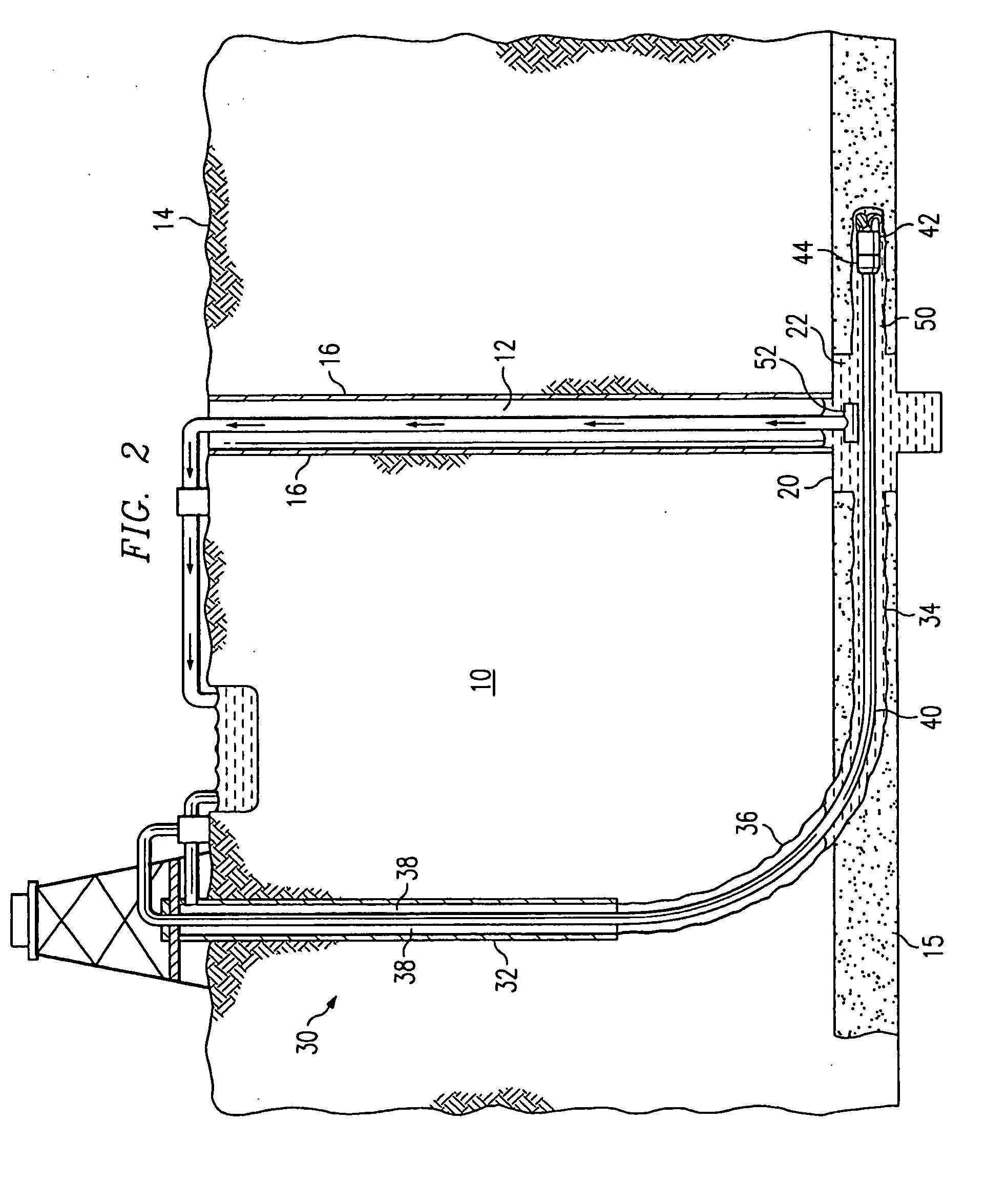

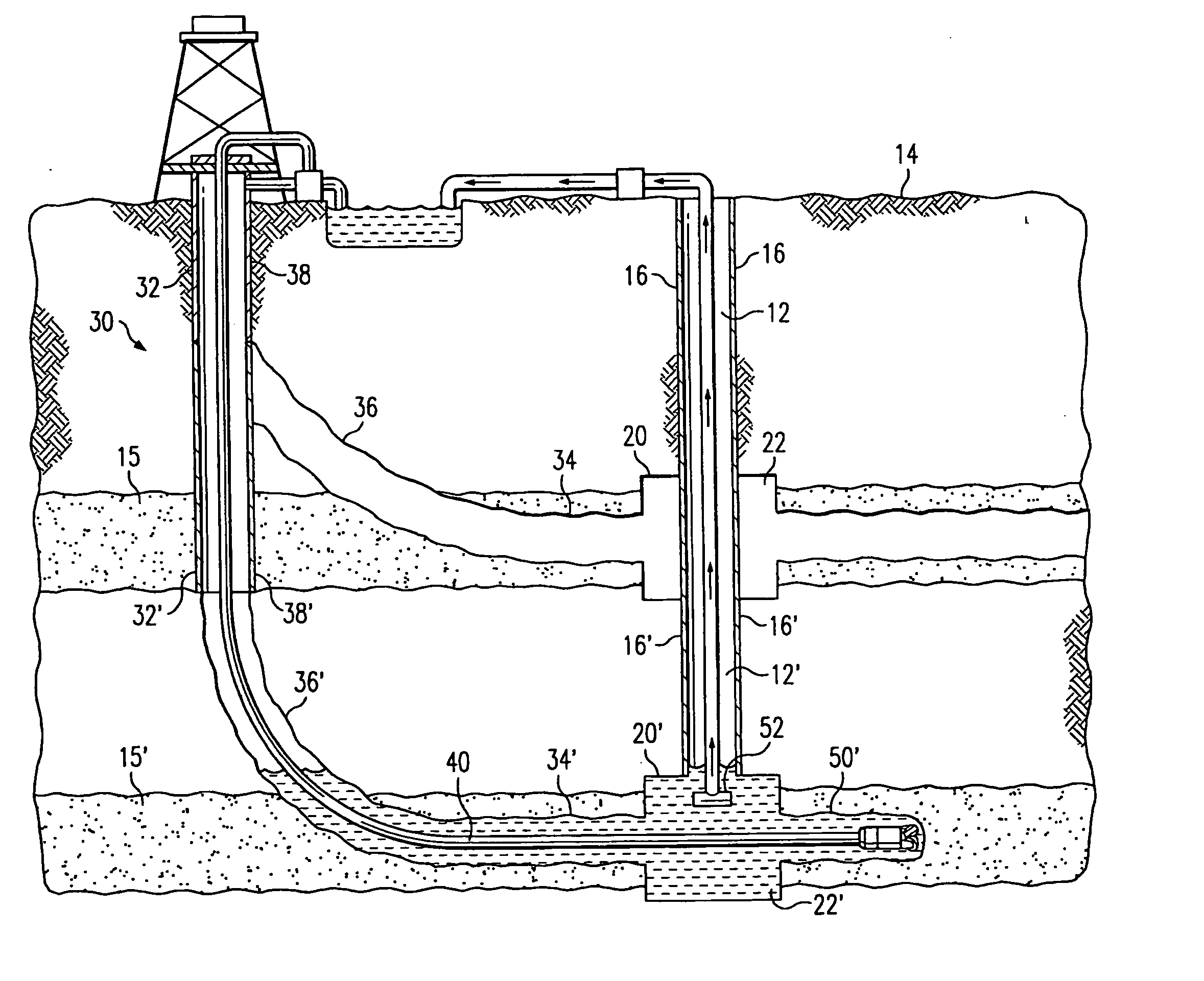

According to one embodiment, a system for accessing a subterranean zone from the surface includes a well bore extending from the surface to the subterranean zone, and a well bore pattern connected to the junction and operable to drain fluid from a region of the subterranean zone to the junction.

Owner:EFFECTIVE EXPLORATION

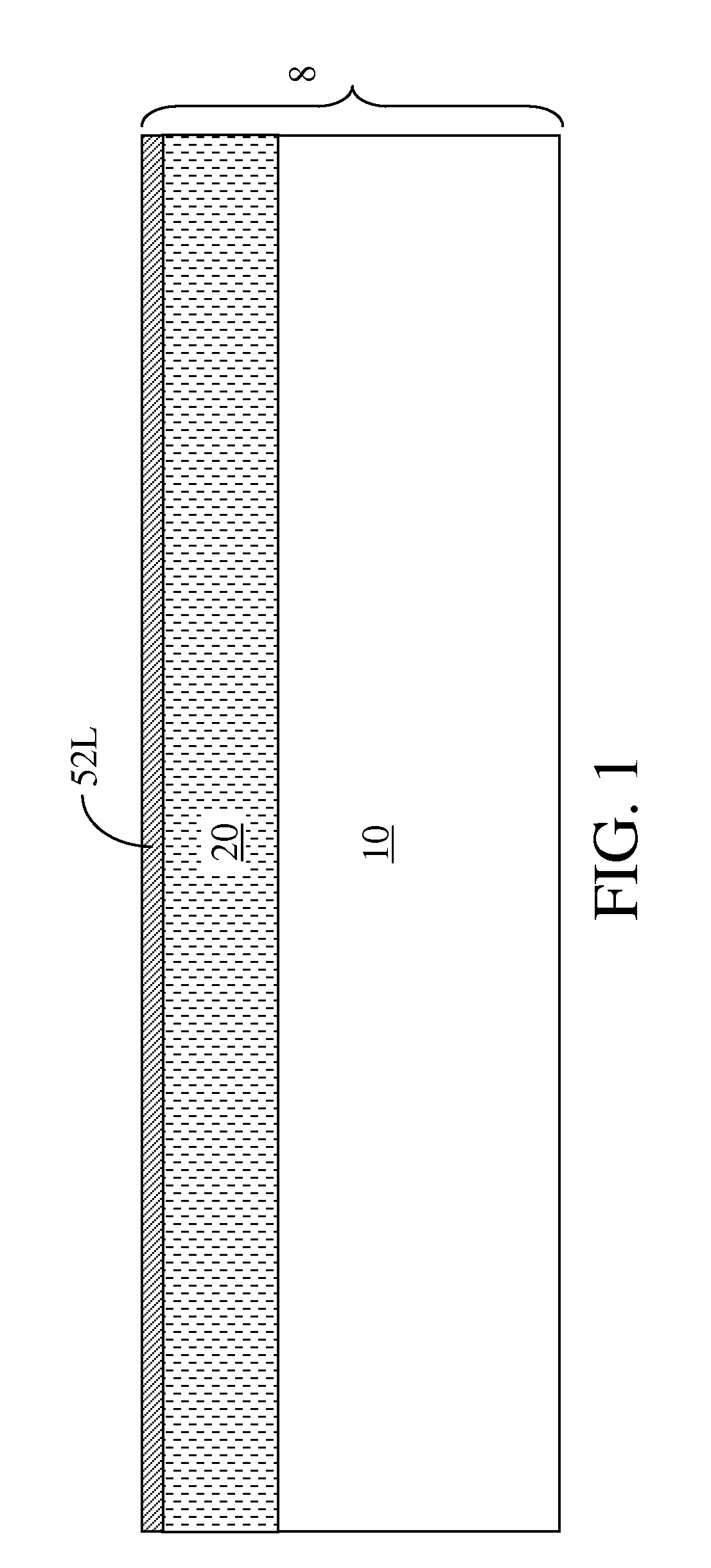

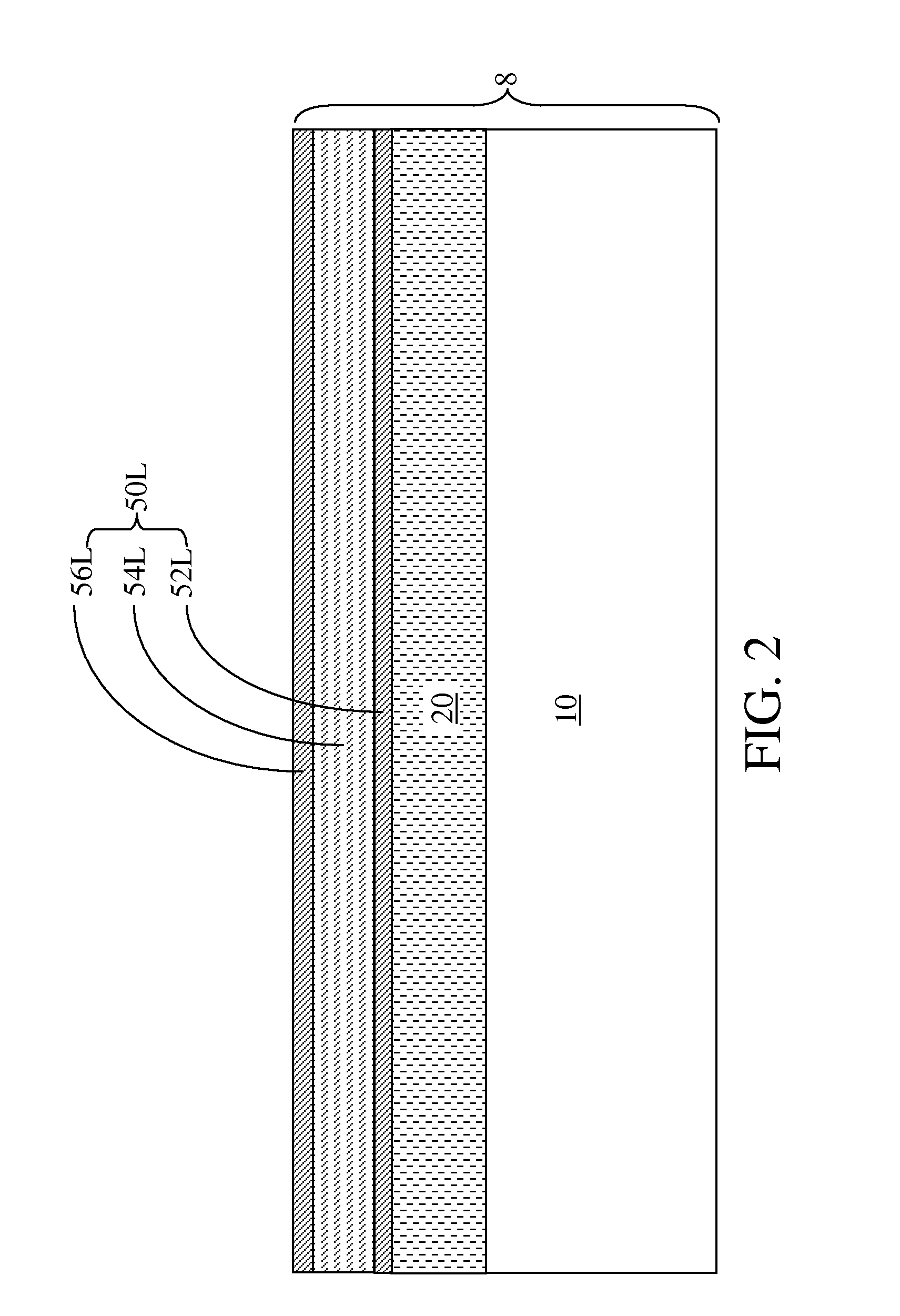

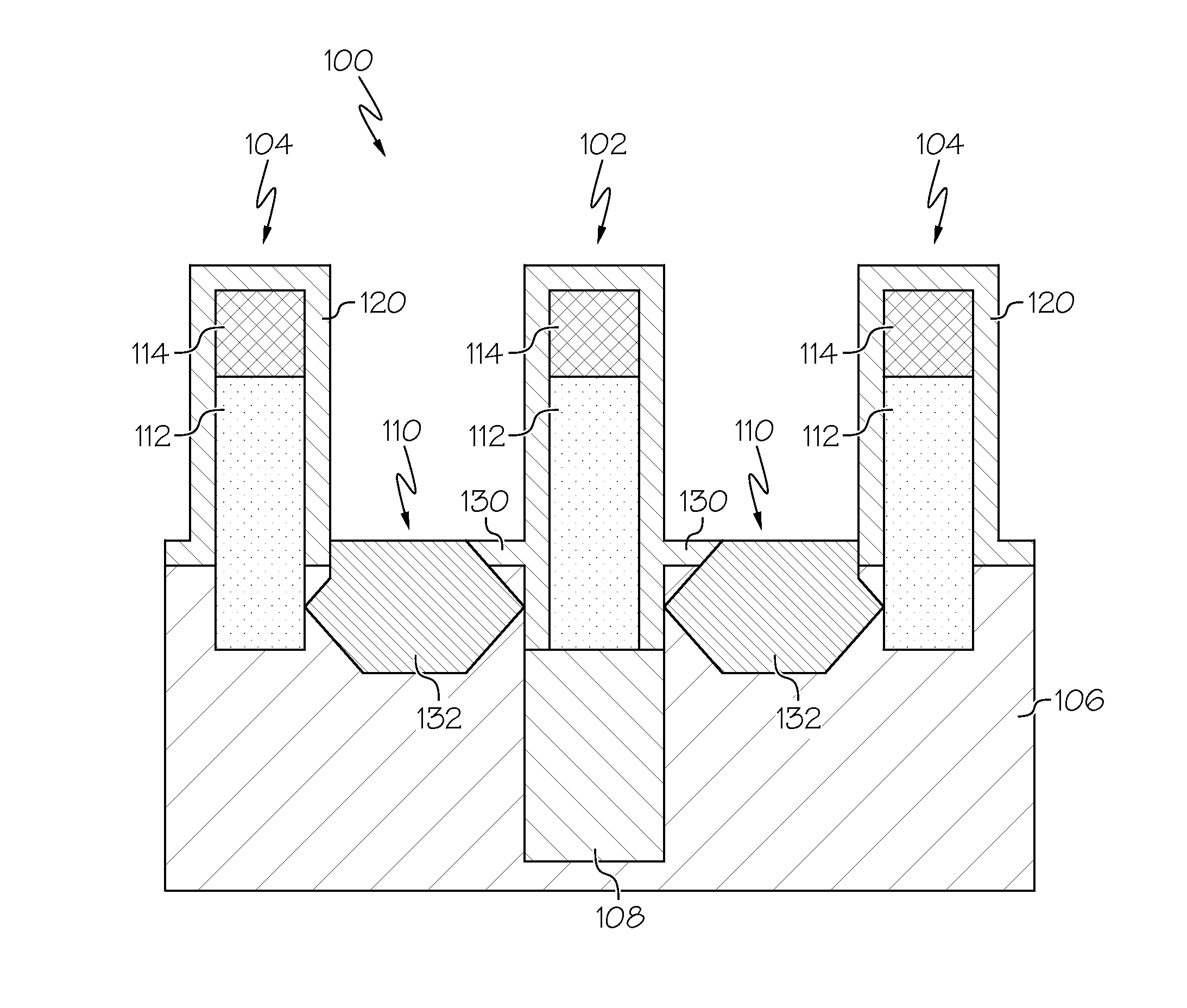

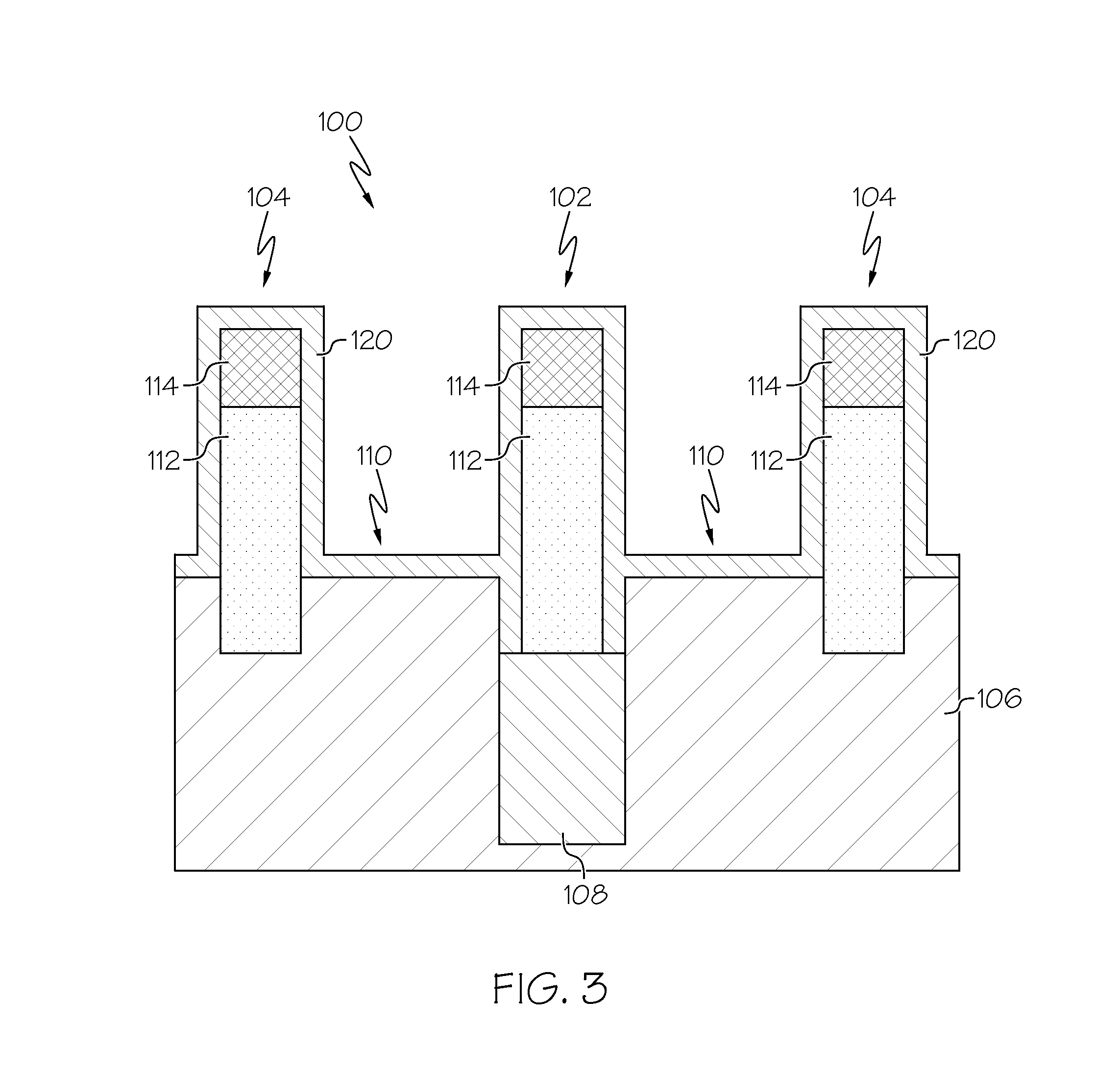

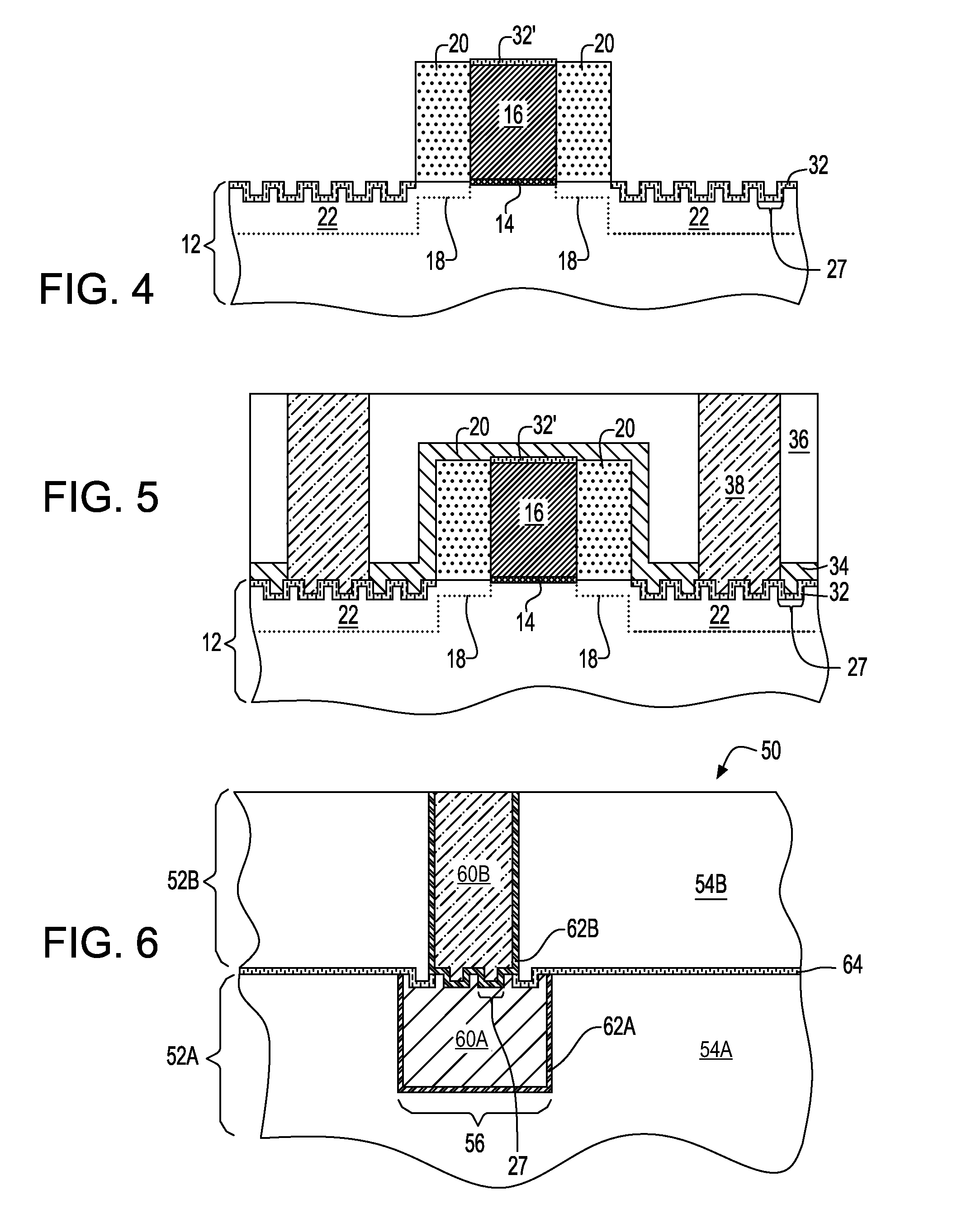

Epitaxial block layer for a fin field effect transistor device

ActiveUS20150021695A1Uniform growthSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialEpitaxial material

Approaches for enabling uniform epitaxial (epi) growth in an epi junction area of a semiconductor device (e.g., a fin field effect transistor device) are provided. Specifically, a semiconductor device is provided including a dummy gate and a set of fin field effect transistors (FinFETs) formed over a substrate; a spacer layer formed over the dummy gate and each of the set of FinFETs; and an epi material formed within a set of recesses in the substrate, the set of recesses formed prior to removal of an epi block layer over the dummy gate.

Owner:GLOBALFOUNDRIES US INC

Method and system for accessing subterranean deposits from the surface and tools therefor

According to one embodiment, a system for accessing a subterranean zone from the surface includes a well bore extending from the surface to the subterranean zone, and a well bore pattern connected to the junction and operable to drain fluid from a region of the subterranean zone to the junction.

Owner:EFFECTIVE EXPLORATION

Method and system for accessing subterranean deposits from the surface and tools therefor

According to one embodiment, a system for accessing a subterranean zone from the surface includes a well bore extending from the surface to the subterranean zone, and a well bore pattern connected to the junction and operable to drain fluid from a region of the subterranean zone to the junction.

Owner:EFFECTIVE EXPLORATION

Method and system for accessing subterranean deposits from the surface and tools therefor

According to one embodiment, a system for accessing a subterranean zone from the surface includes a well bore extending from the surface to the subterranean zone, and a well bore pattern connected to the junction and operable to drain fluid from a region of the subterranean zone to the junction.

Owner:EFFECTIVE EXPLORATION

Detector for electromagnetic radiation assisted by majority current

ActiveUS20050051730A1Reduce capacitanceFast and sensitiveSolid-state devicesMaterial analysis by optical meansCapacitancePhotonics

The present invention relates to a novel photo-detector structure and method whereby light is detected in a semiconductor substrate. Through the use of a small current of majority carriers an electrical field is created that directs photo-generated minority carriers towards a detection region. In this way, a large sensitive area 34 for a detector can be designed with a detection region having low junction area and low associated detector capacitance, thus enhancing output signal to noise ratio and / or speed of attached readout circuits. Simultaneously, the assistant majority current can sweep the minority carriers from deep within the substrate towards the detection region, thus improving the overall detector sensitivity. By making the majority current reconfigurable, a photonic mixer structure with two or more detection regions can be conceived, whereby the direction of the applied current will determine in an efficient way to which detection region the photo-generated minority carriers will be directed. In this way, incident modulated light can get demodulated, such that phase and amplitude of the modulated light can be measured for a.o. range-finding applications.

Owner:SOFTKINETIC SENSORS

Method and system for accessing subterranean deposits from the surface and tools therefor

According to one embodiment, a system for accessing a subterranean zone from the surface includes a well bore extending from the surface to the subterranean zone, and a well bore pattern connected to the junction and operable to drain fluid from a region of the subterranean zone to the junction.

Owner:EFFECTIVE EXPLORATION

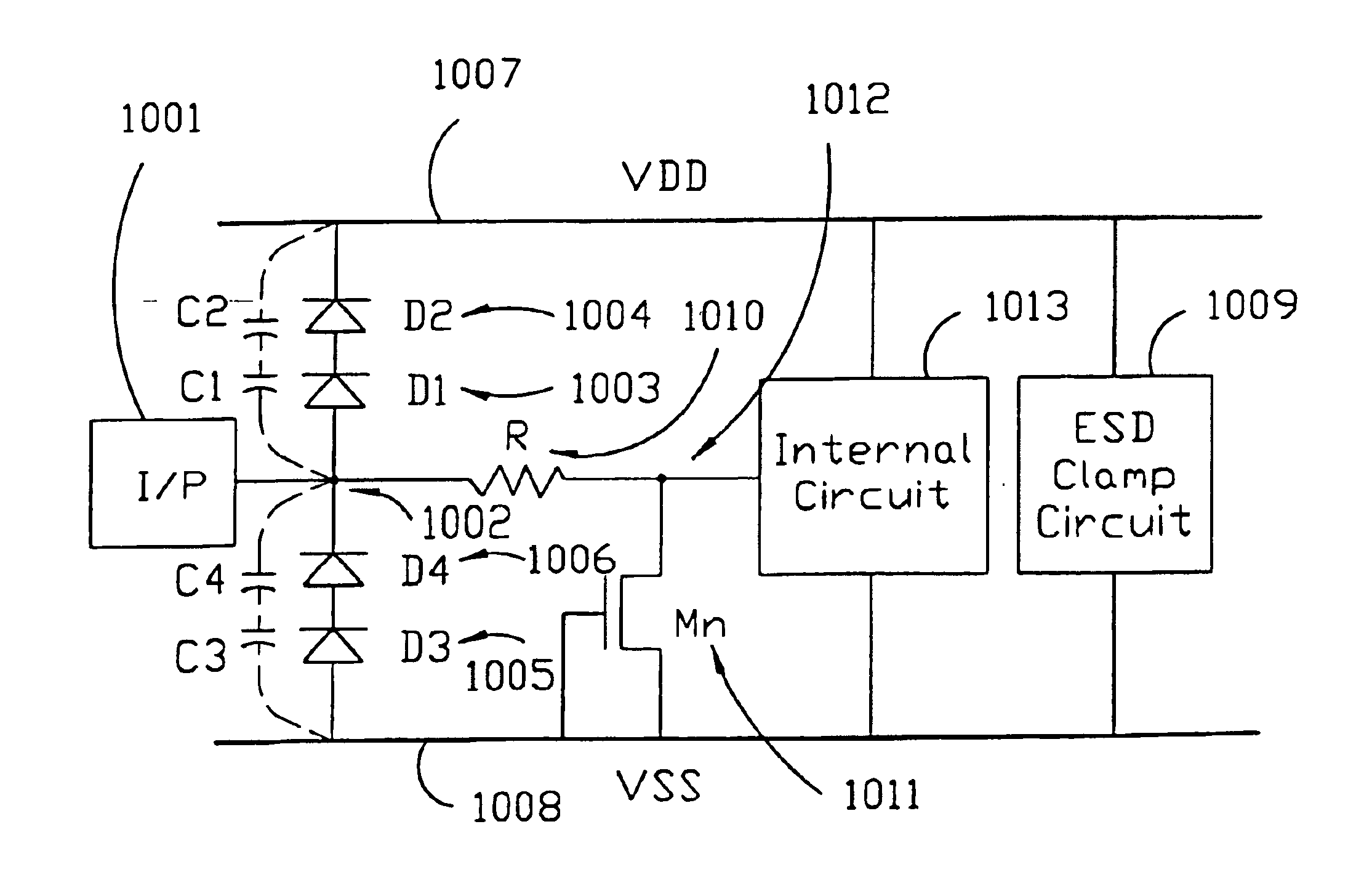

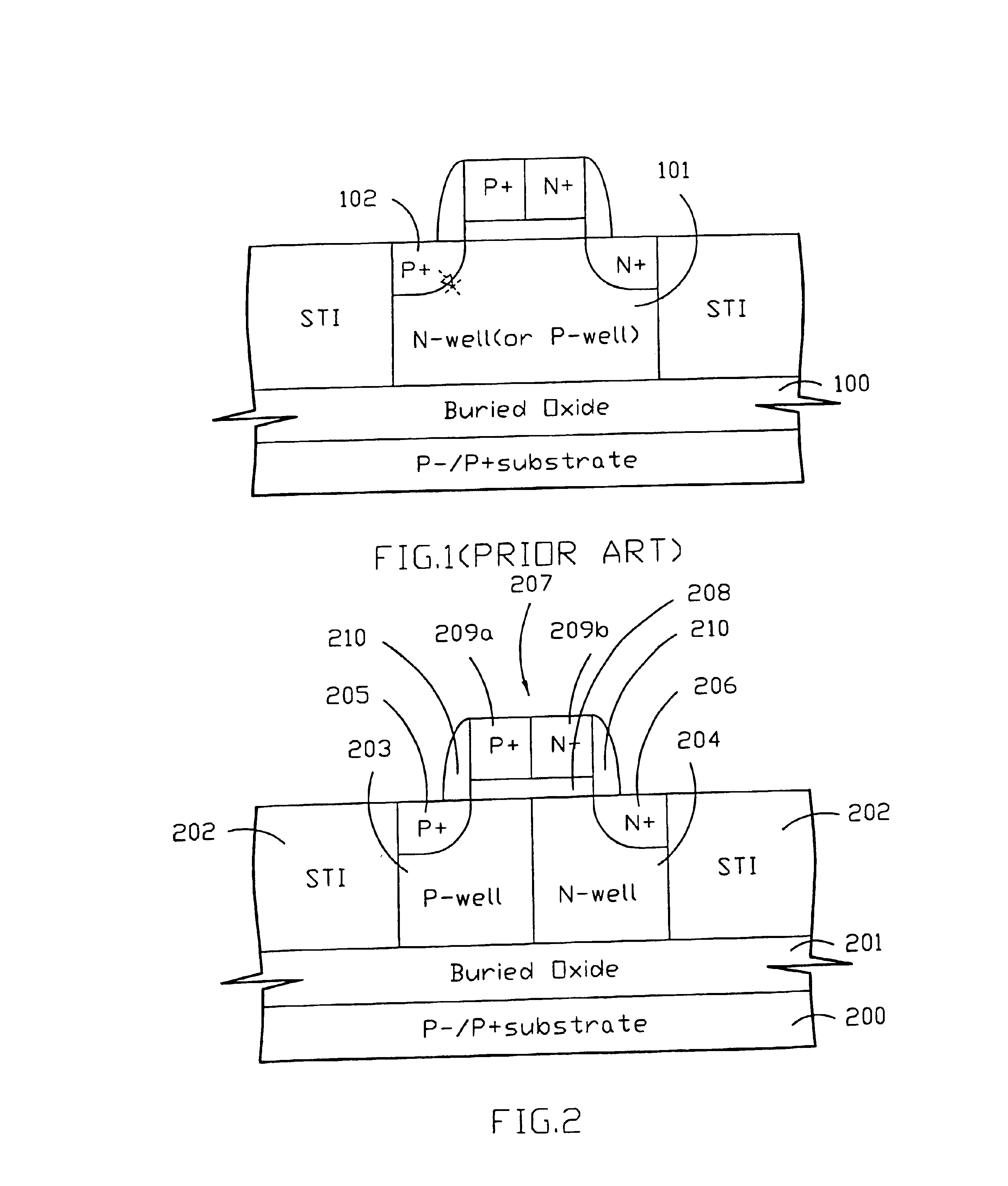

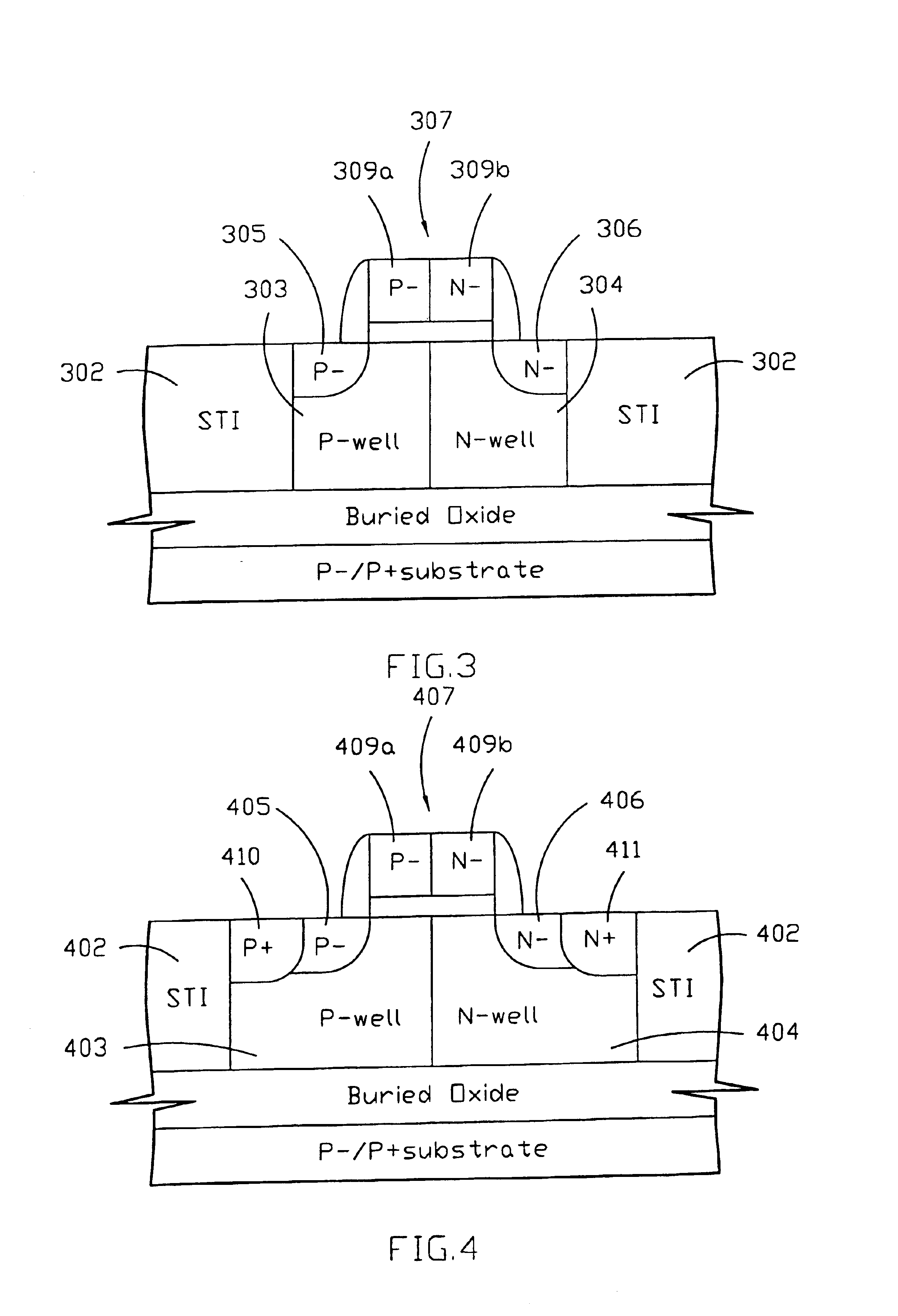

Silicon-on-insulator diodes and ESD protection circuits

InactiveUS6861680B2Reduce power densityHigh protection levelTransistorSolid-state devicesCapacitanceSilicon on insulator

A silicon-on-insulator (SOI) gated diode and non-gated junction diode are provided. The SOI gated diode has a PN junction at the middle region under the gate, which has more junction area than a normal diode. The SOI non-gated junction diode has a PN junction at the middle region thereof, and also has more junction area than a normal diode. The SOI diodes of the present invention improve the protection level offered for electrical overstress (EOS) / electrostatic discharge (ESD) due to the low power density and heating for providing more junction area than normal ones. The I / O ESD protection circuits, which comprise primary diodes, a first plurality of diodes, and a second plurality of diodes, all of which are formed of the present SOI diodes, could effectively discharge the current when there is an ESD event. And the ESD protection circuits, which comprise more primary diodes, could effectively reduce the parasitic input capacitance, so that they can be used in the RF circuits or HF circuits. The proposed gated diode and non-gated diode can be fully process-compatiable to general partially-depleted or fully-depleted silicon-on-insulator CMOS processes.

Owner:UNITED MICROELECTRONICS CORP

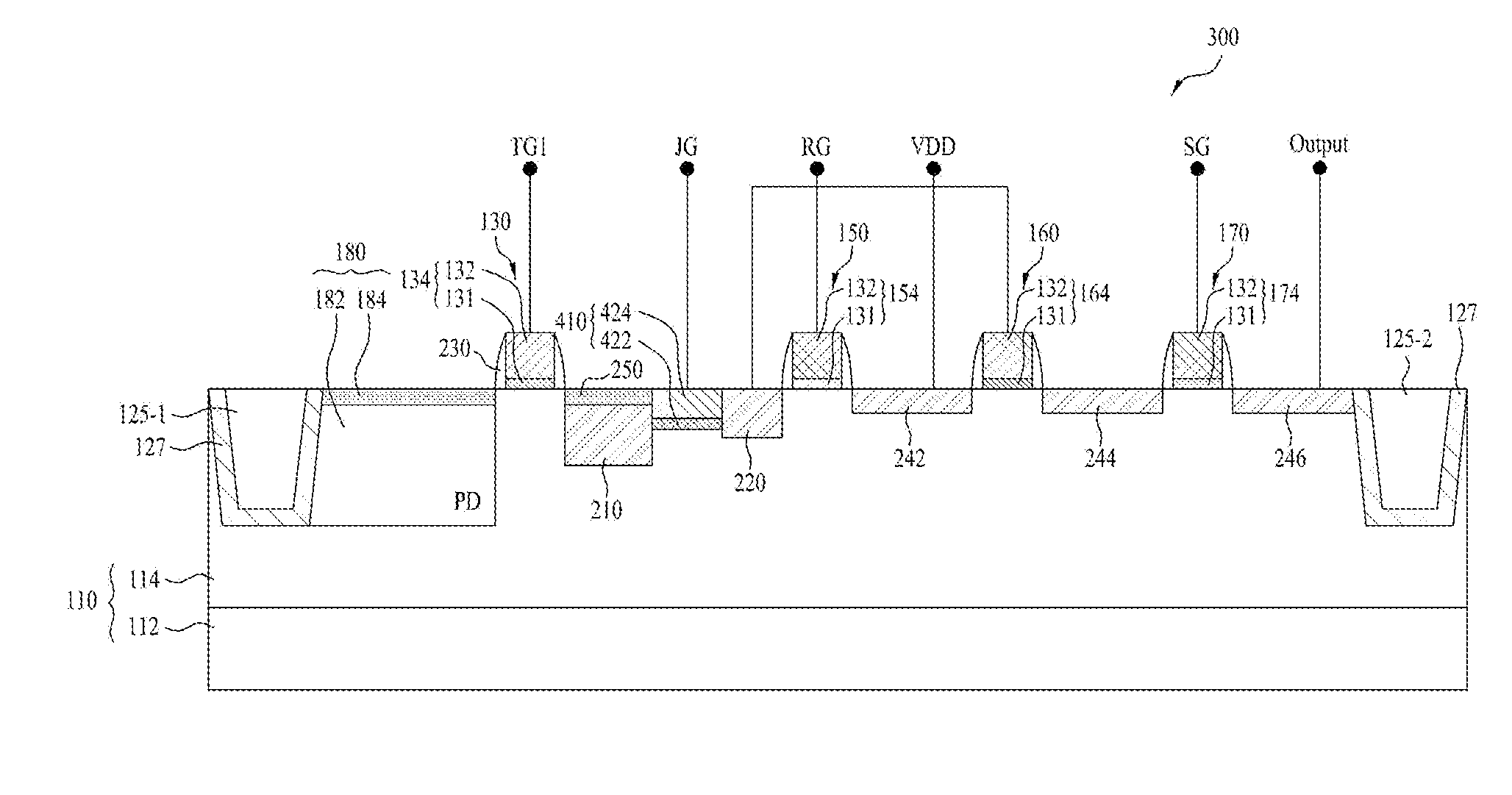

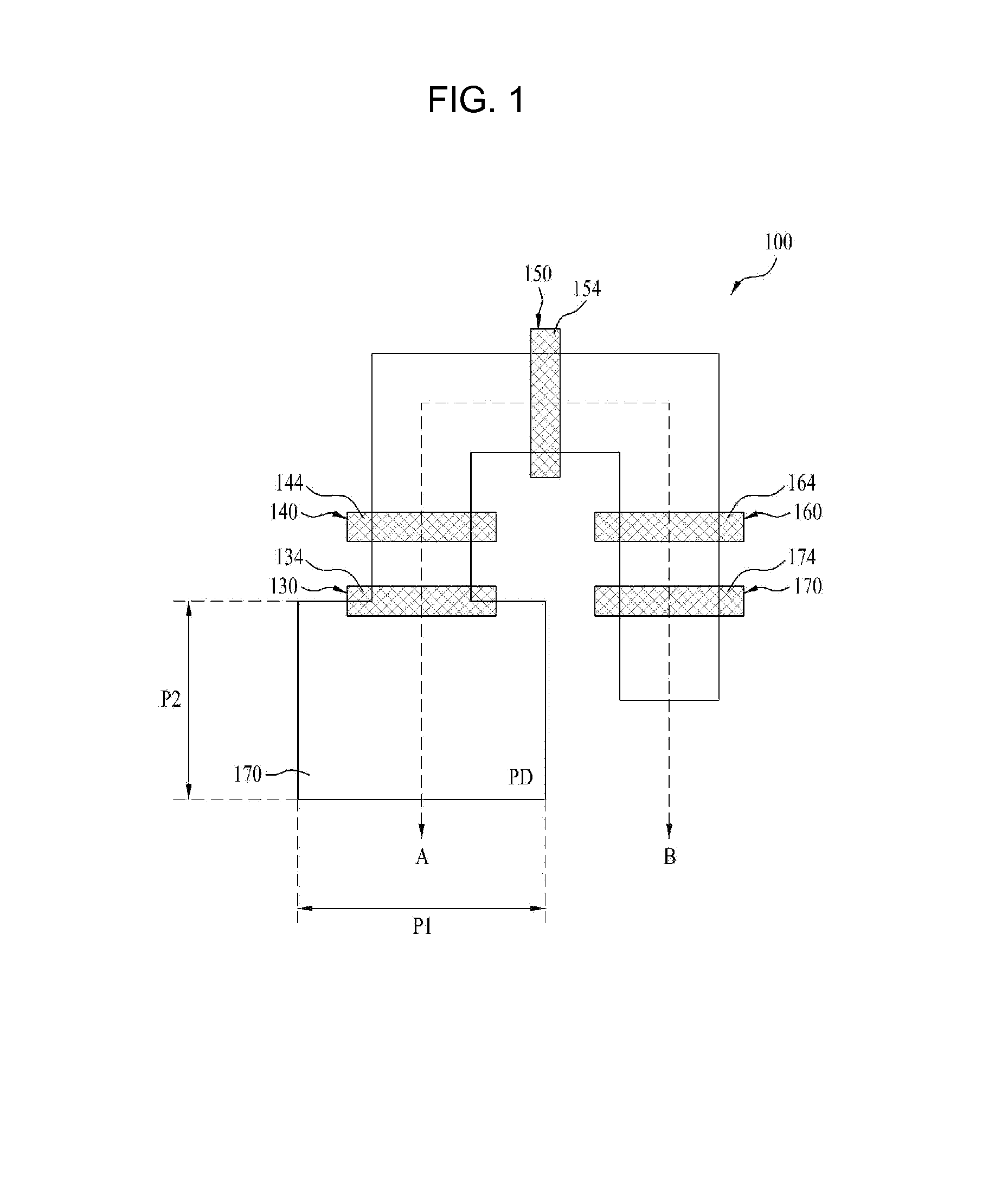

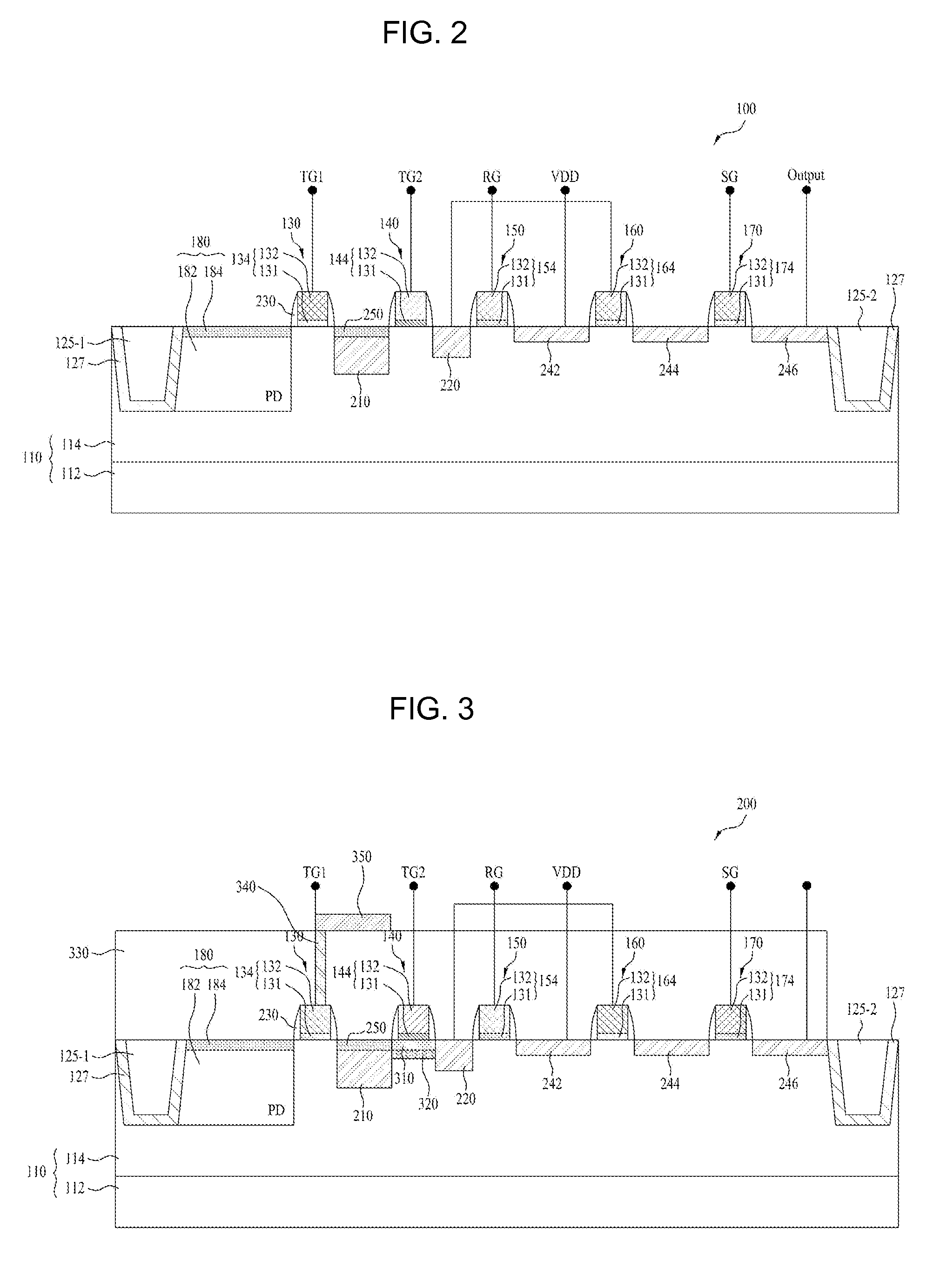

Image Sensor

InactiveUS20140117428A1Reduce generationReduce brightnessSolid-state devicesDiodeFloating diffusionPhotodiode

Disclosed is an image sensor including a photodiode region on a first conductive type semiconductor substrate; a first floating diffusion region having a second conductive type, separate from the photodiode region; a second floating diffusion region having the second conductive type, separate from the first floating diffusion region; a first gate on the semiconductor substrate between the photodiode region and the first floating diffusion region; and a second gate on the semiconductor substrate between the first floating diffusion region and the second floating diffusion region, wherein the semiconductor substrate and the first floating diffusion region forms a junction area that is larger than that of the semiconductor substrate and the second floating diffusion region.

Owner:DONGBU HITEK CO LTD

Method and apparatus for cementing production tubing in a multilateral borehole

A hydraulically actuated anchor and a mechanically actuated packer are used in combination to secure a production tubing system in a lateral prior to injection of a cement to line the lateral borehole in which the production tubing is positioned. The packer is expanded to prevent fluid cement material from flowing past the packer into a junction area of the lateral with other laterals and aid the removal of superfluous cement material after hardening of the injected cement material around the production tubing system.

Owner:PEAK COMPLETIONS TECH INC

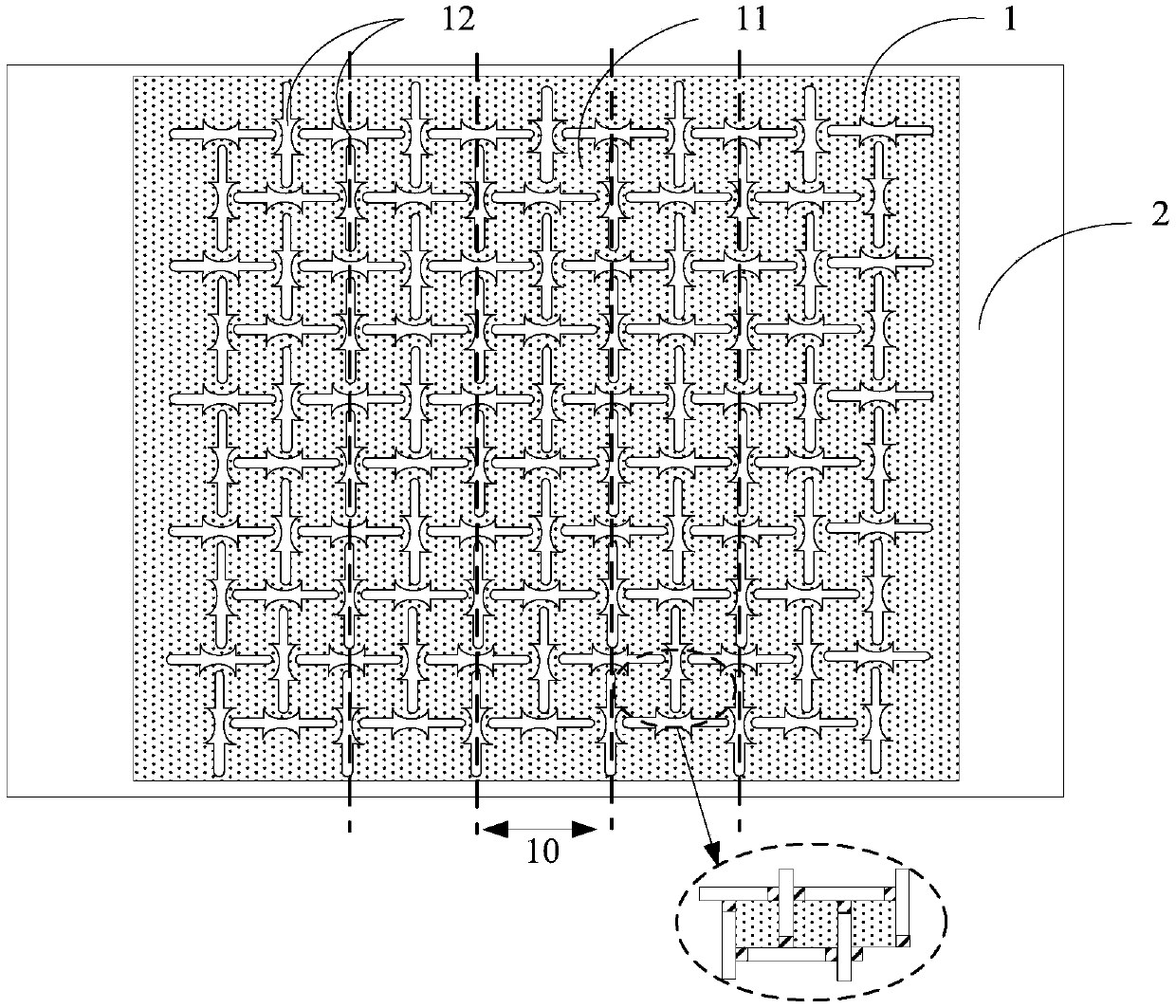

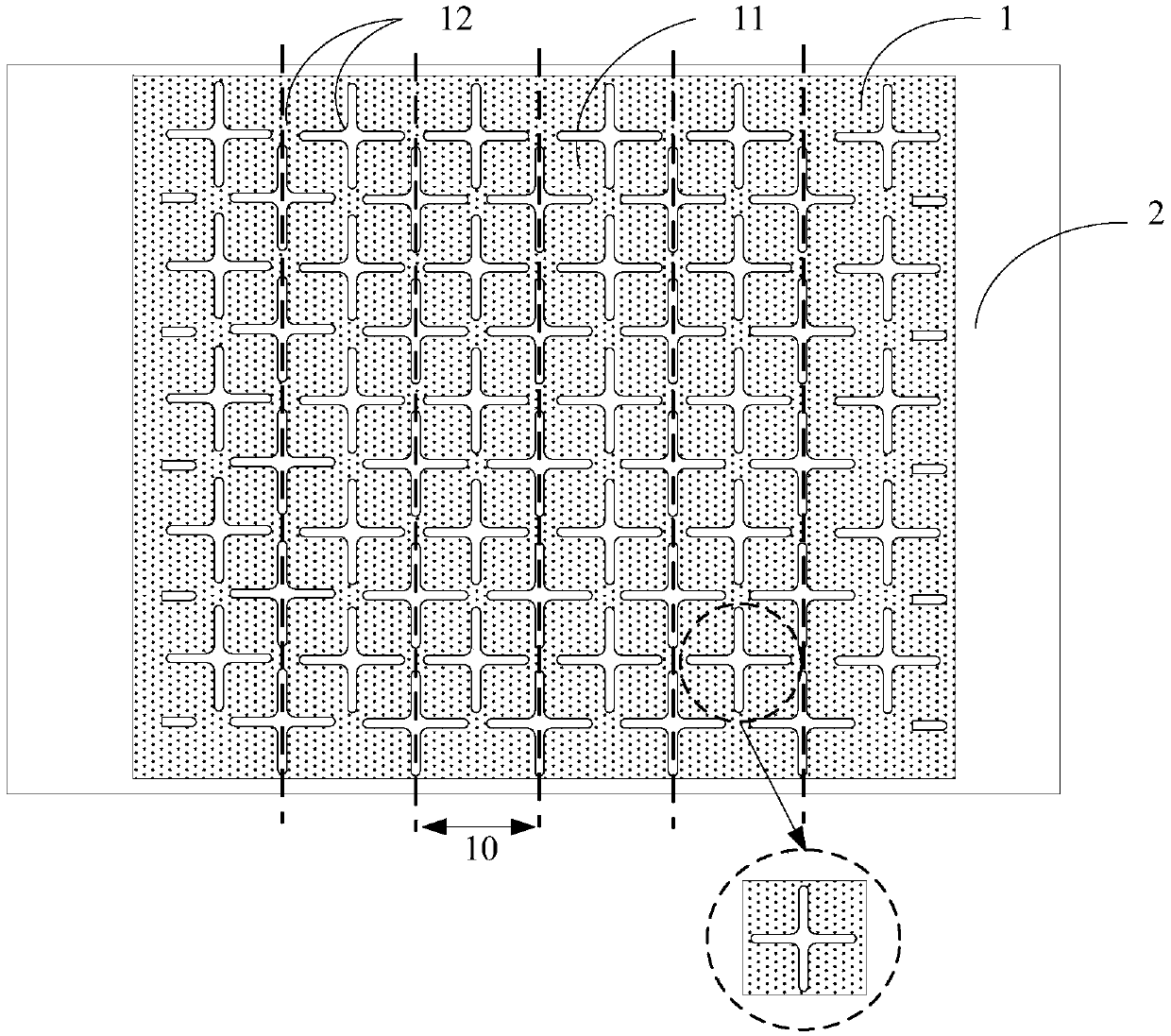

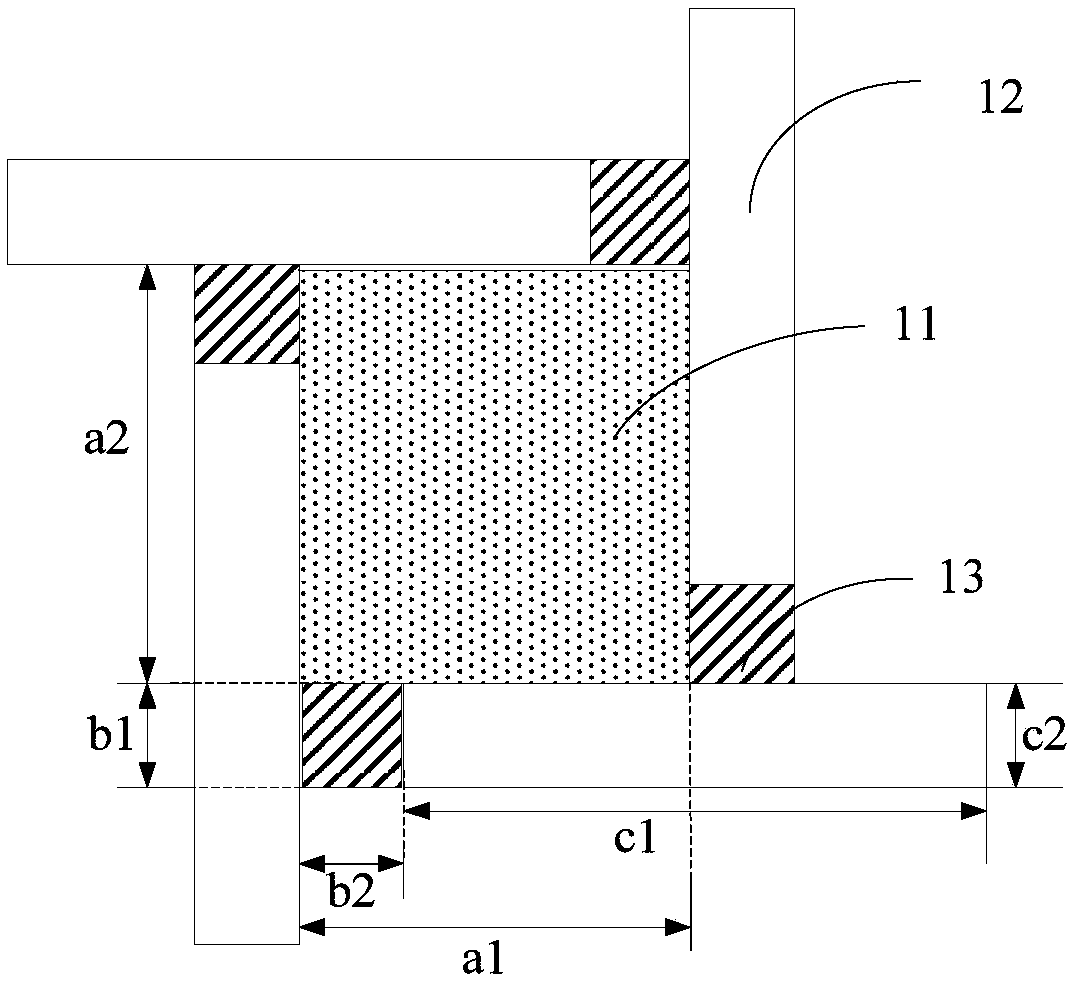

Display substrate and display device

ActiveCN109599402AAvoid stress concentrationThe modulus of elasticity decreases uniformlySolid-state devicesPhotovoltaic energy generationStress concentrationDisplay device

Owner:BOE TECH GRP CO LTD

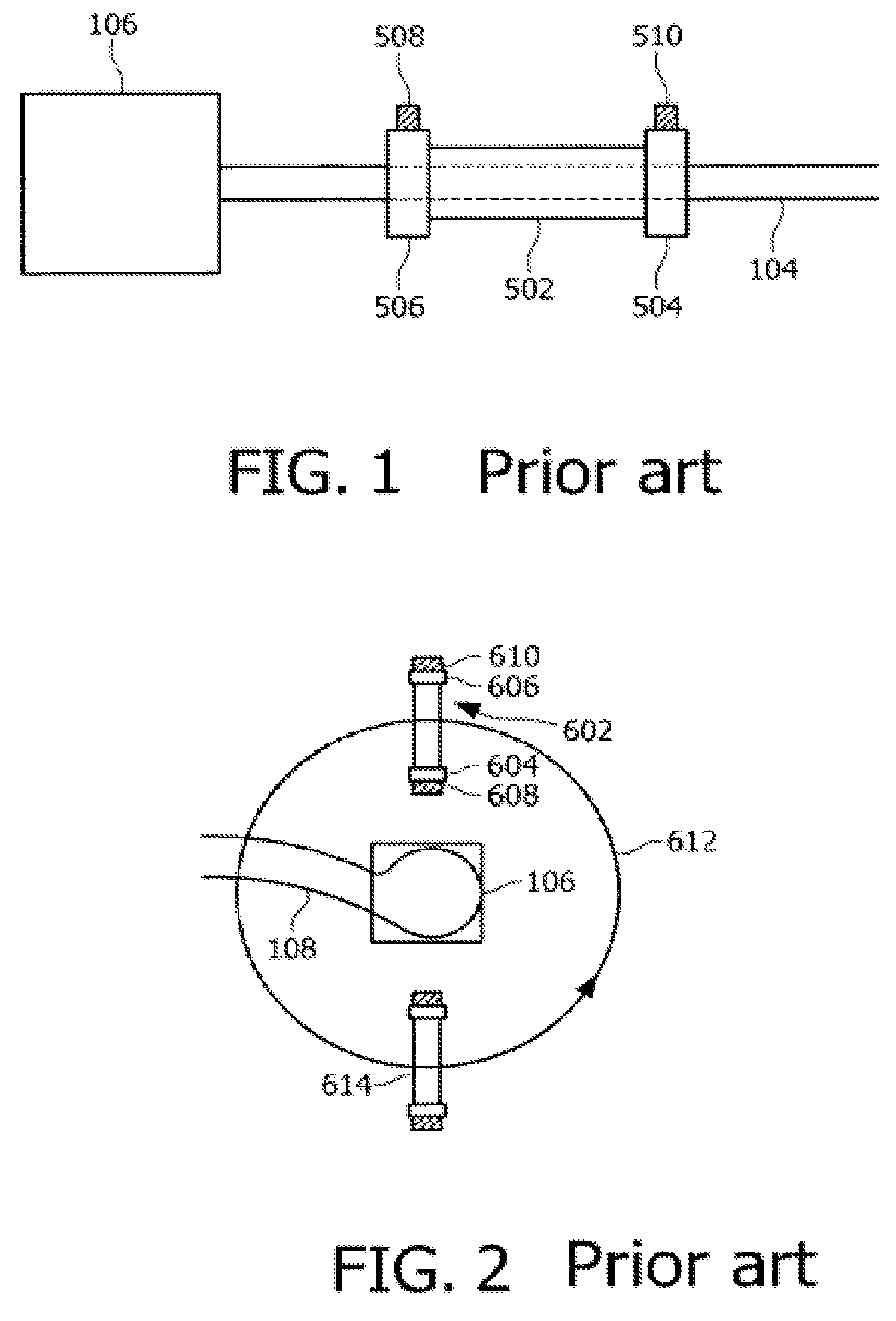

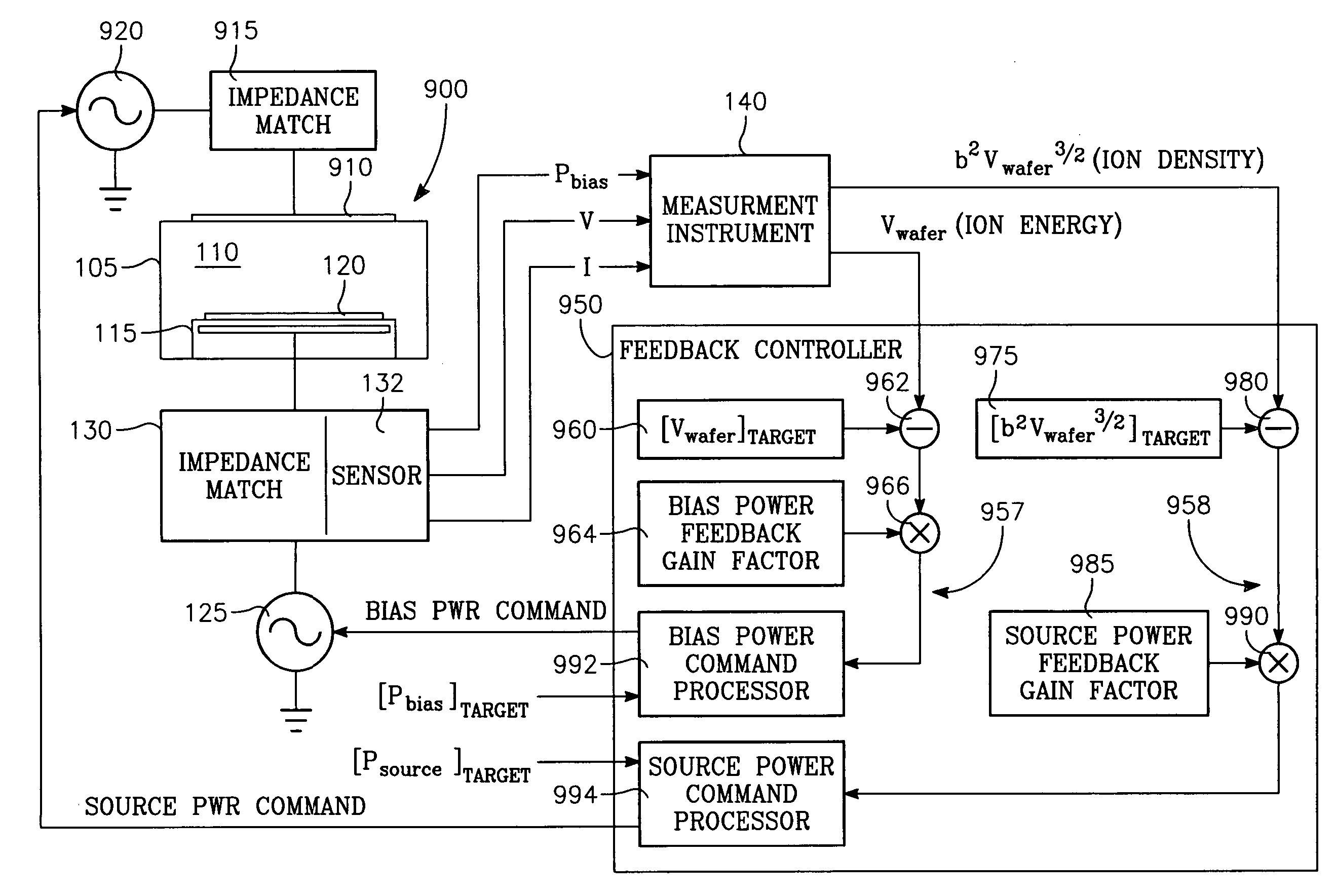

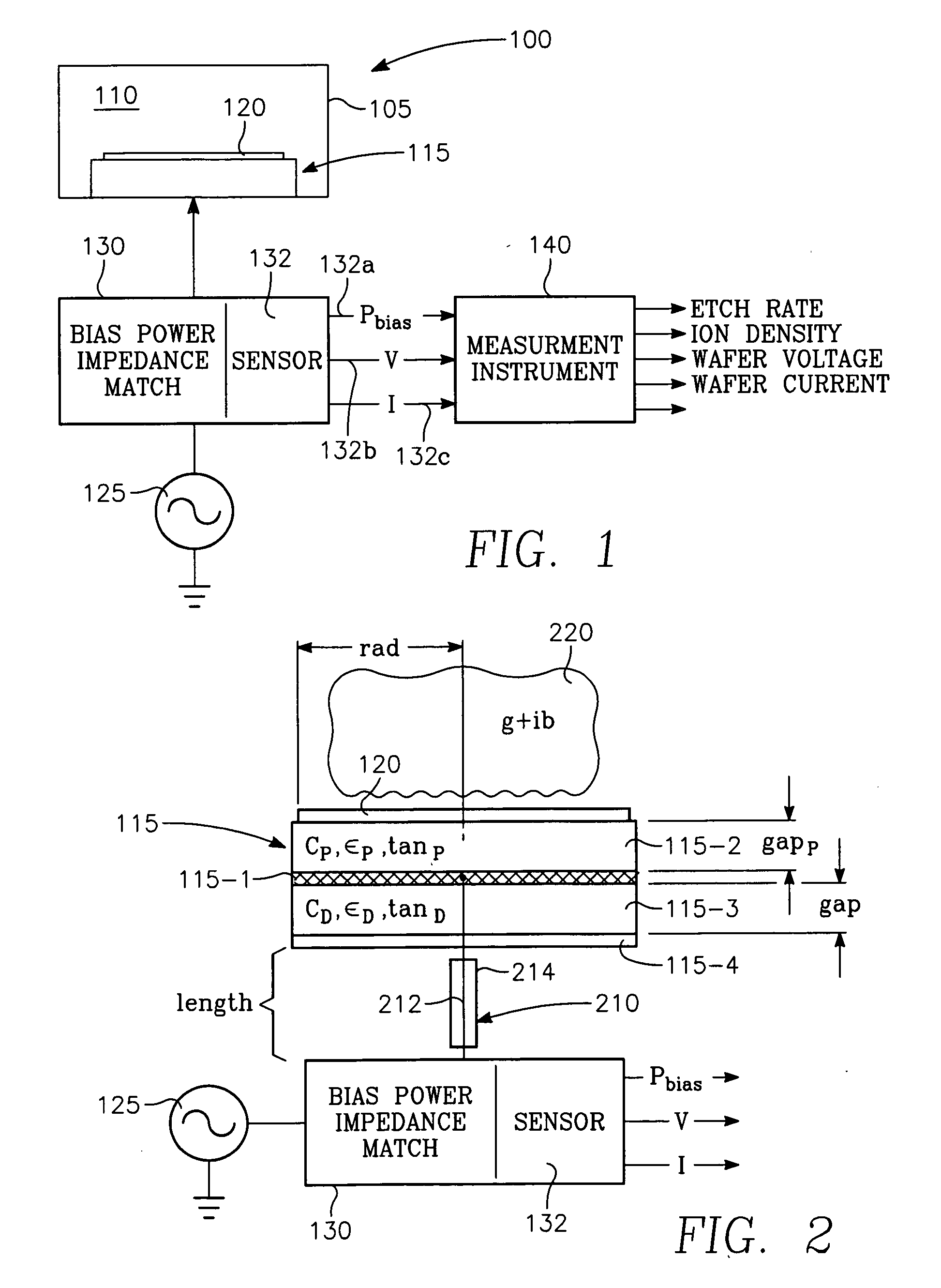

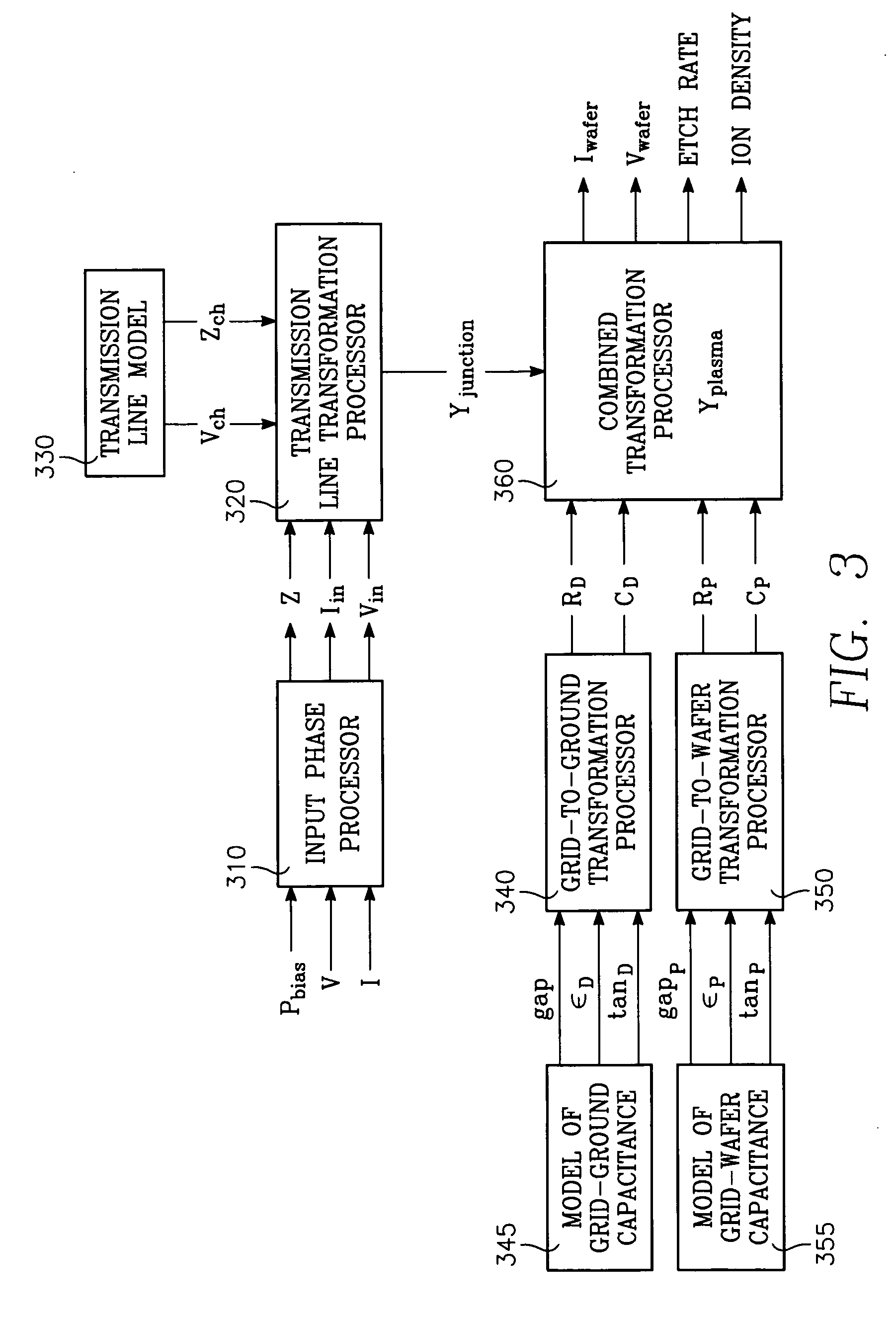

Method of determining plasma ion density, wafer voltage, etch rate and wafer current from applied bias voltage and current

ActiveUS20060278608A1Semiconductor/solid-state device testing/measurementElectric discharge tubesImpedance matchingShunt capacitance

Plasma parameters such as plasma ion density, wafer voltage, etch rate and wafer current in the chamber are determined from external measurements on the applied RF bias electrical parameters such as voltage and current. The method includes sensing RF parameters corresponding to an input impedance, an input current and an input voltage at the input of the impedance match element to a transmission line coupled between the bias generator and the wafer pedestal. The method continues by computing a junction admittance of a junction between the transmission line and the electrode within the wafer pedestal from the input impedance, input current and input voltage and from parameters of the transmission line. The method further includes providing shunt electrical quantities of a shunt capacitance between the electrode and a ground plane, and providing load electrical quantities of a load capacitance between the electrode and a wafer on the pedestal. The method further includes computing at least one of the plasma parameters from the junction admittance, the shunt electrical quantities, the load electrical quantities and a frequency of RF bias power applied to the electrode.

Owner:APPLIED MATERIALS INC

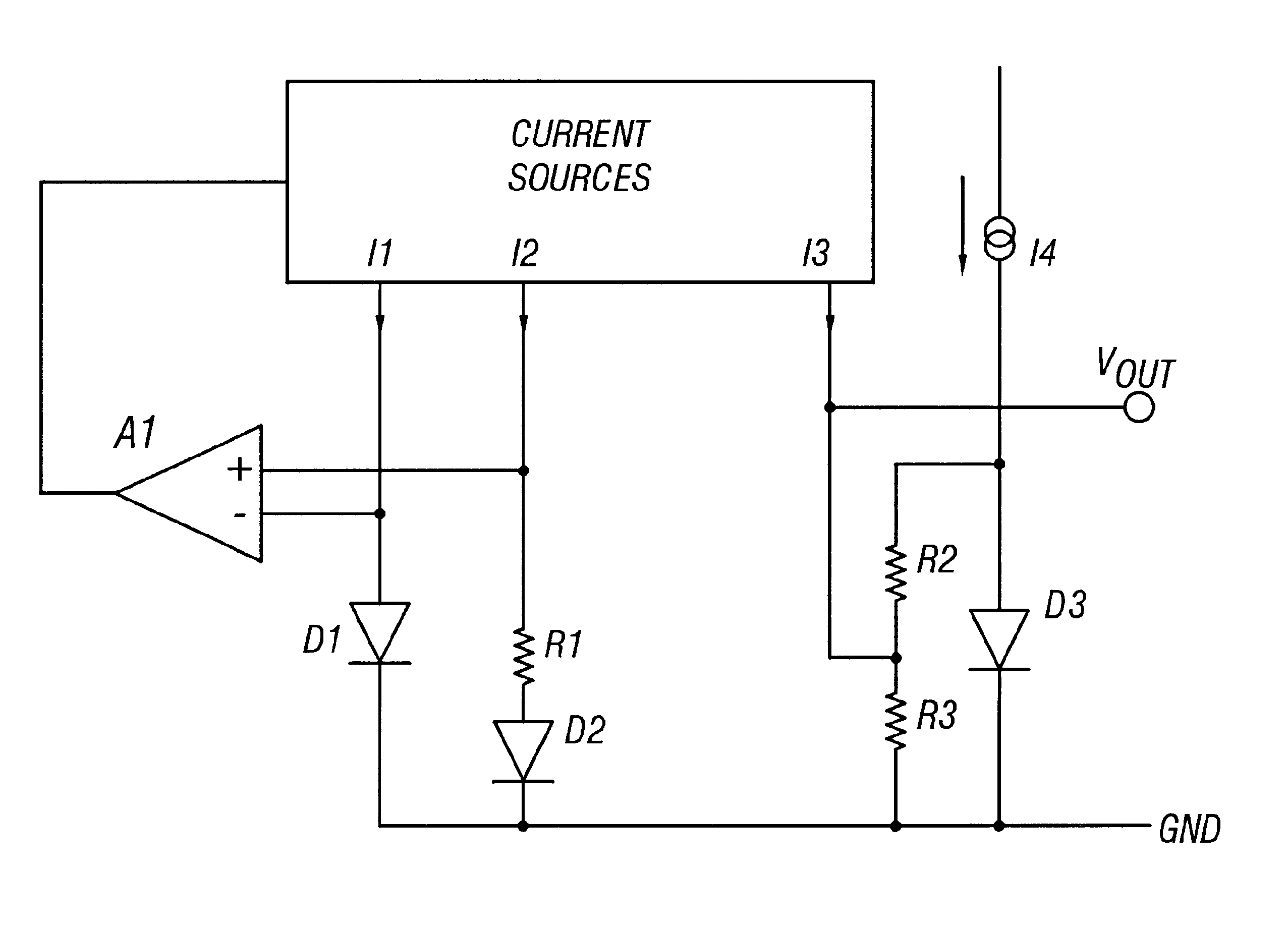

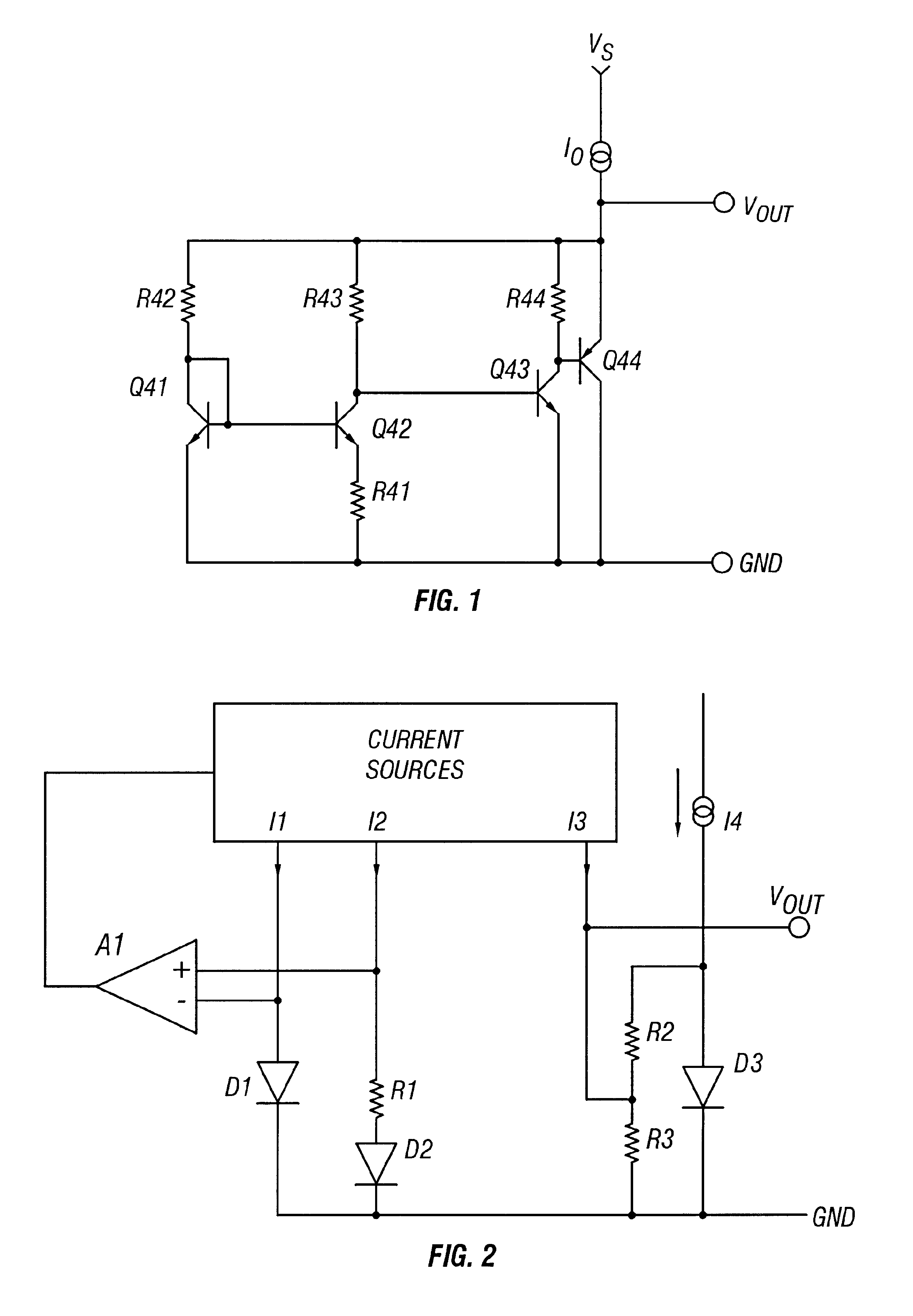

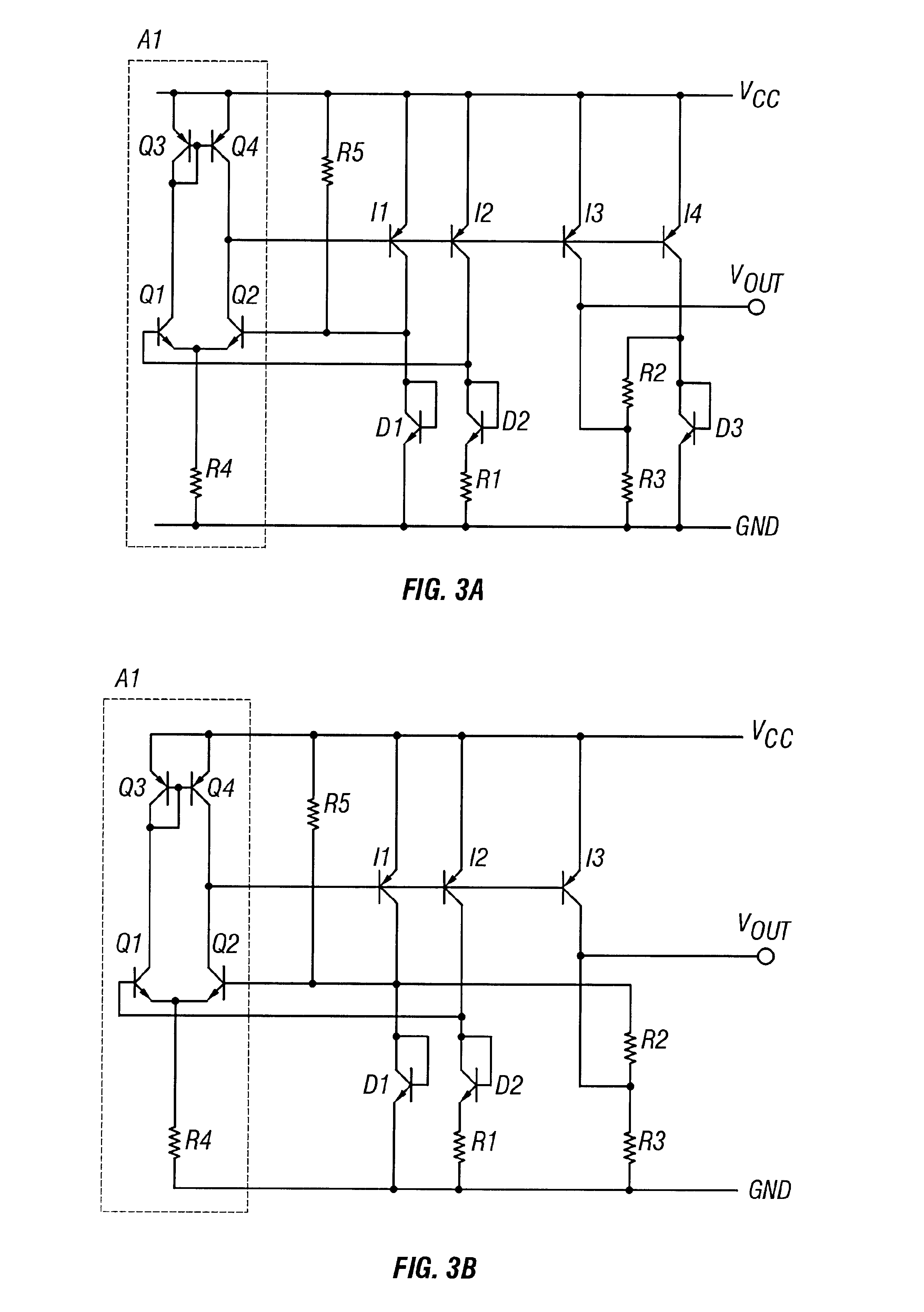

Regulated low-voltage generation circuit

A voltage reference generating circuit for providing voltage references substantially less than the typical 1300 mV, with a controllable thermal coefficient. By forcing equal-valued currents through two semiconductor junctions having disparate junction areas, a voltage differential is developed, as is a current proportional to the voltage differential. The voltage differential, and a current proportional to the voltage differential, have positive thermal coefficients. A third semiconductor junction is biased from a third current source and bridged by a resistor pair so as to synthesize a Thevenin-equivalent voltage equivalent series resistance. The equivalent voltage has a negative thermal coefficient. By forcing a current that is equal to the proportional current through the equivalent resistance, a reference voltage, equal to the sum of the Thevenin-equivalent voltage plus the voltage drop across the Thevenin-equivalent resistance, is created.

Owner:RENESAS ELECTRONICS AMERICA

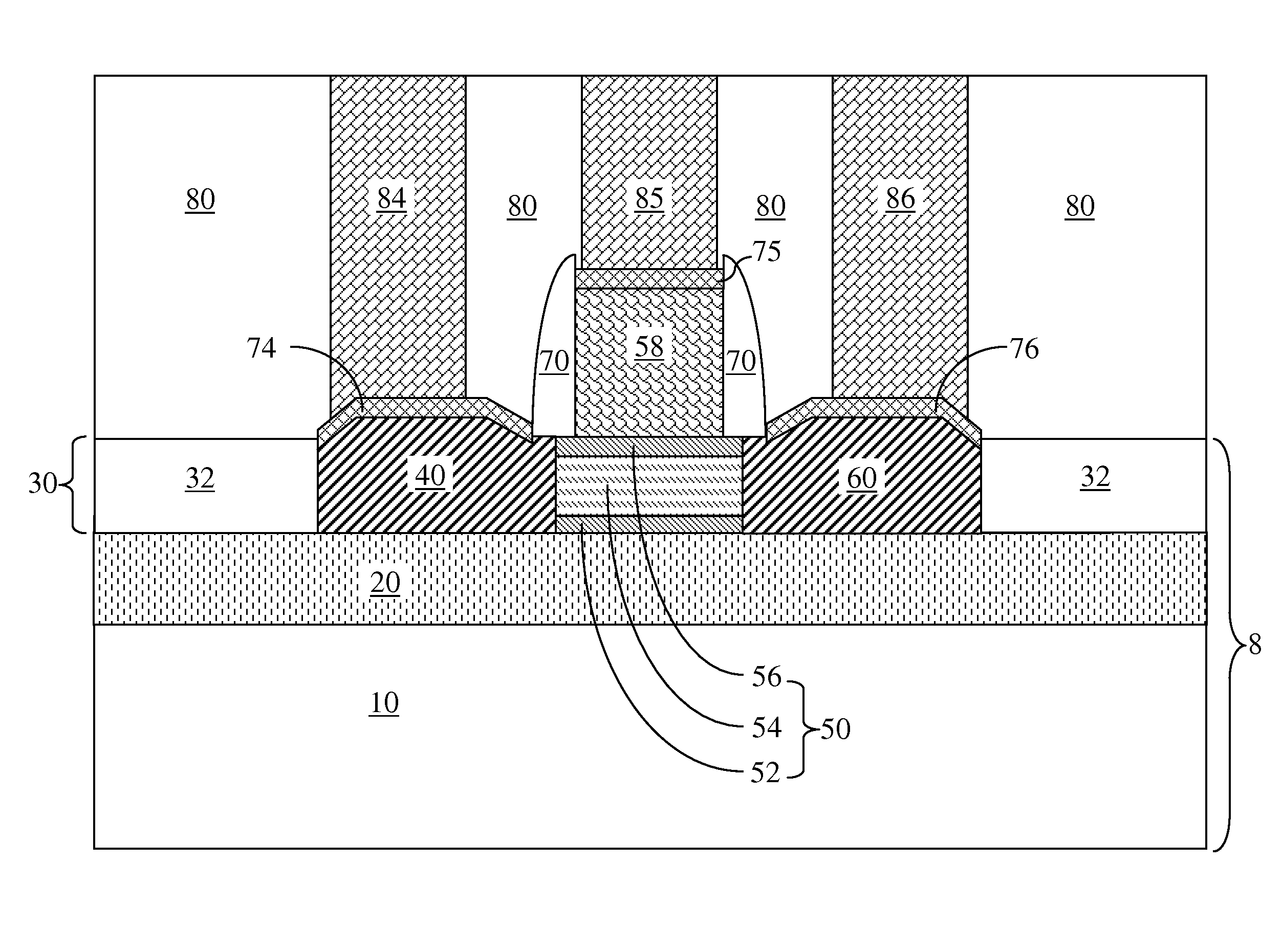

SOI SiGe-base lateral bipolar junction transistor

ActiveUS8288758B2Great current densityNoise minimizationSolid-state devicesSemiconductor/solid-state device manufacturingCarrier scatteringParasitic capacitance

A lateral heterojunction bipolar transistor (HBT) is formed on a semiconductor-on-insulator substrate. The HBT includes a base including a doped silicon-germanium alloy base region, an emitter including doped silicon and laterally contacting the base, and a collector including doped silicon and laterally contacting the base. Because the collector current is channeled through the doped silicon-germanium base region, the HBT can accommodate a greater current density than a comparable bipolar transistor employing a silicon channel. The base may also include an upper silicon base region and / or a lower silicon base region. In this case, the collector current is concentrated in the doped silicon-germanium base region, thereby minimizing noise introduced to carrier scattering at the periphery of the base. Further, parasitic capacitance is minimized because the emitter-base junction area is the same as the collector-base junction area.

Owner:IBM CORP

Method and apparatus for cementing production tubing in a multilateral borehole

A hydraulically actuated anchor and a mechanically actuated packer are used in combination to secure a production tubing system in a lateral prior to injection of a cement to line the lateral borehole in which the production tubing is positioned. The packer is expanded to prevent fluid cement material from flowing past the packer into a junction area of the lateral with other laterals and aid the removal of superfluous cement material after hardening of the injected cement material around the production tubing system.

Owner:PEAK COMPLETIONS TECH INC

Semiconductor structures having improved contact resistance

ActiveUS20120132966A1Increase the areaReduce contact resistanceSemiconductor/solid-state device detailsSolid-state devicesCapacitanceSemiconductor structure

Self-assembled polymer technology is used to form at least one ordered nanosized pattern within material that is present in a conductive contact region of a semiconductor structure. The material having the ordered, nanosized pattern is a conductive material of an interconnect structure or semiconductor source and drain diffusion regions of a field effect transistor. The presence of the ordered, nanosized pattern material within the contact region increases the overall area (i.e., interface area) for subsequent contact formation which, in turn, reduces the contact resistance of the structure. The reduction in contact resistance in turn improves the flow of current through the structure. In addition to the above, the inventive methods and structures do not affect the junction capacitance of the structure since the junction area remains unchanged.

Owner:GLOBALFOUNDRIES US INC