Patents

Literature

109 results about "Tunnel current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Thermally-assisted magnetic random access memory (MRAM)

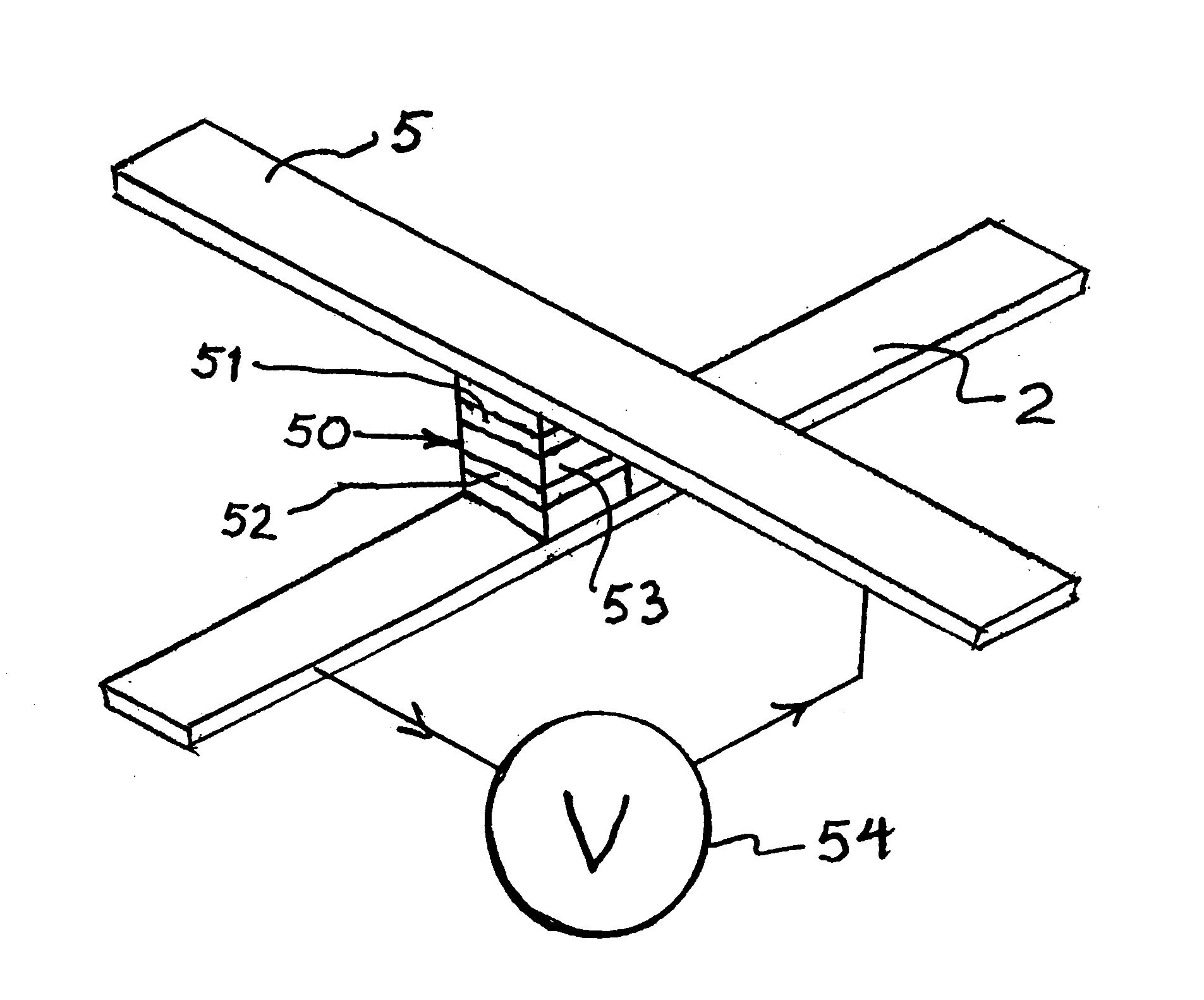

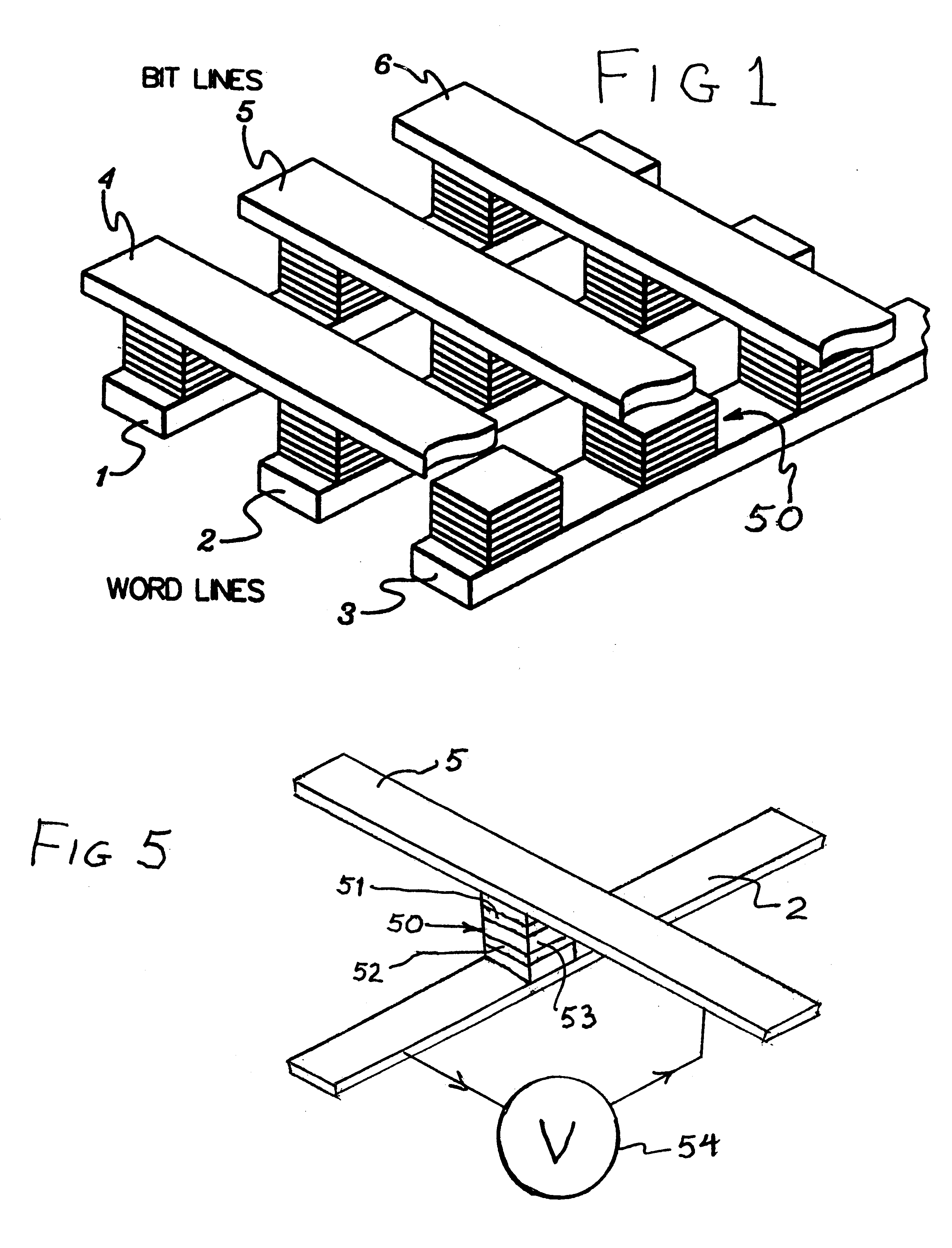

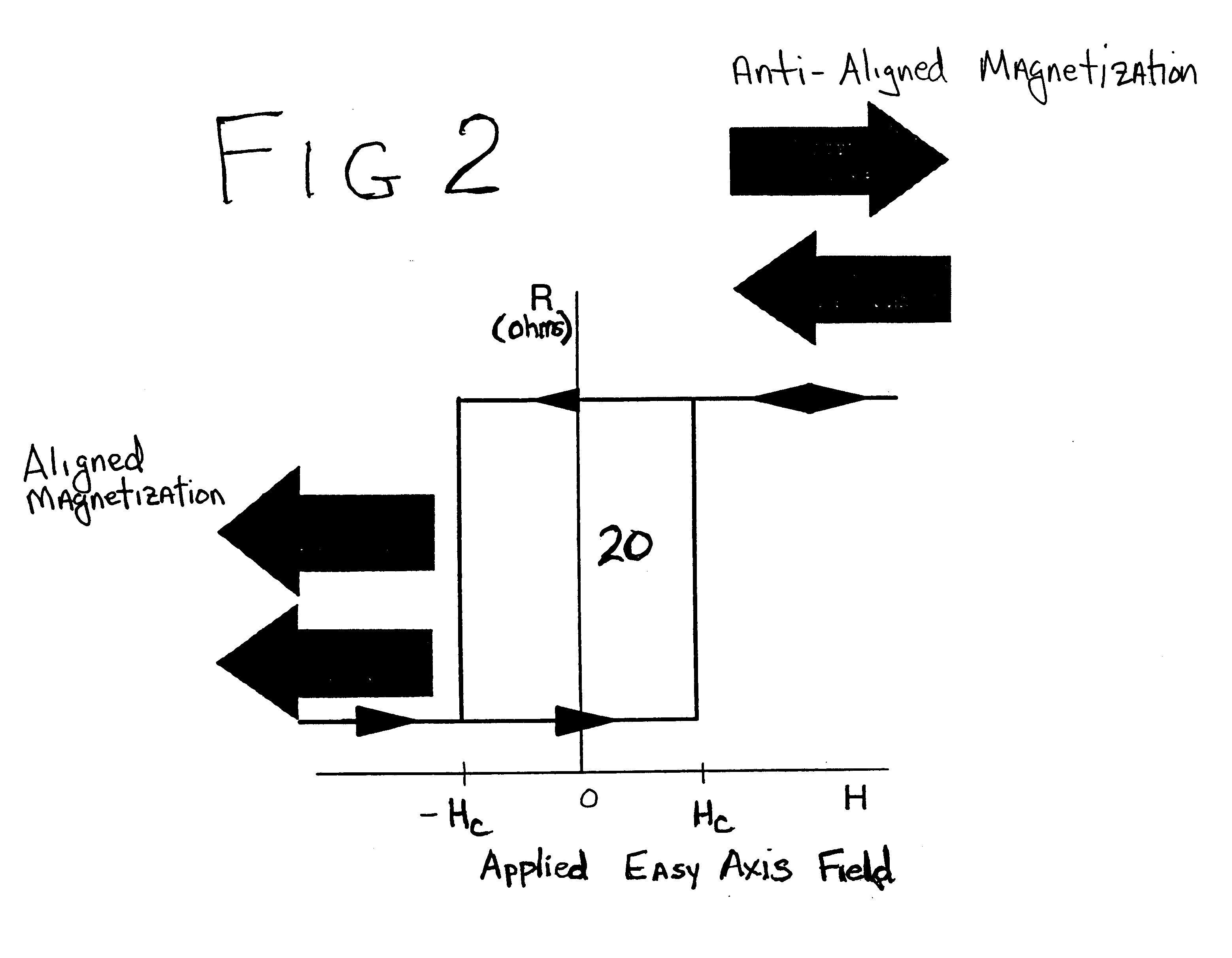

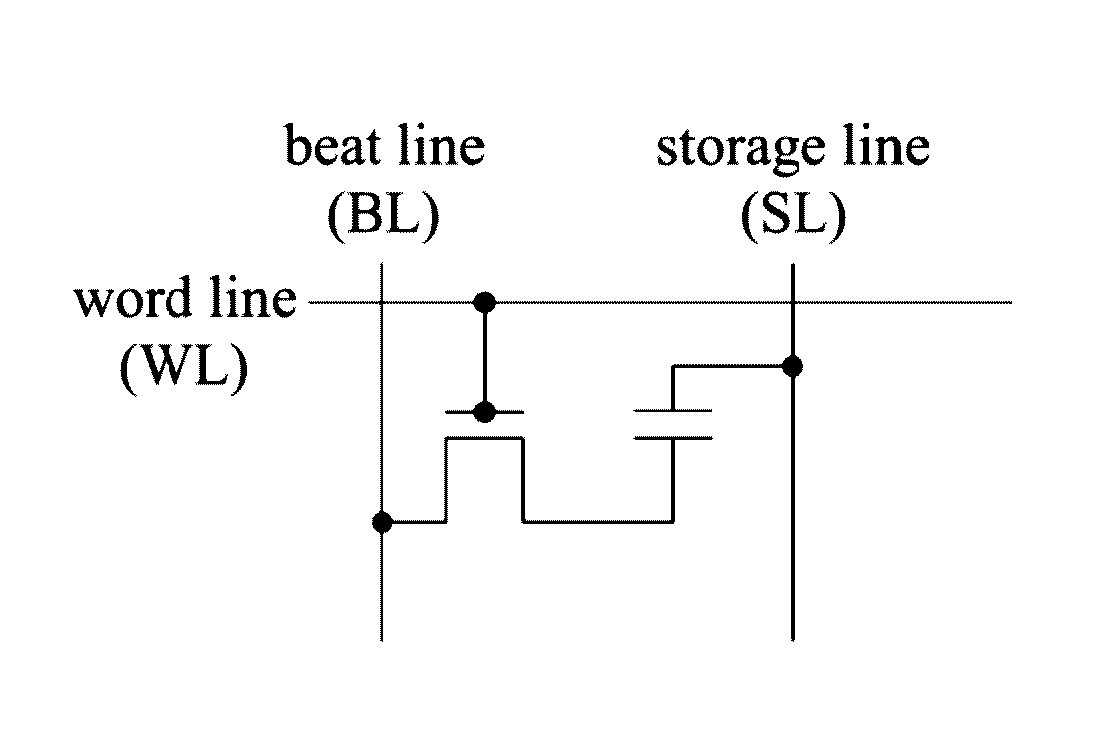

It is important to ensure good selectivity of a single magnetic tunnel junction storage cell within a memory array without affecting nearby storage cells. For this purpose, this memory array of storage cells preferably comprises a) an array of electrically conducting bit lines and electrically conducting word lines which form intersections therebetween, b) a storage cell disposed at each of said intersections, each storage cell comprising at least one reversible magnetic region or layer characterized by a magnetization state which can be reversed by applying thereto a selected external magnetic field, said reversible magnetic layer comprising a material whose magnetization state is more easily reversed upon a change in the temperature thereof, and c) a temperature change generator for changing the temperature of said reversible magnetic layer of only a selected one of said array of storage cells at any moment. To select a cell, it is preferable to select a cell by using a brief pulse of tunnelling current between the intersecting bit and word lines at that cell in order to provide sufficient Joule heating to facilitate a change in the magnetization state of its reversible magnetic layer, which preferably comprises a ferrimagnetic material.

Owner:IBM CORP

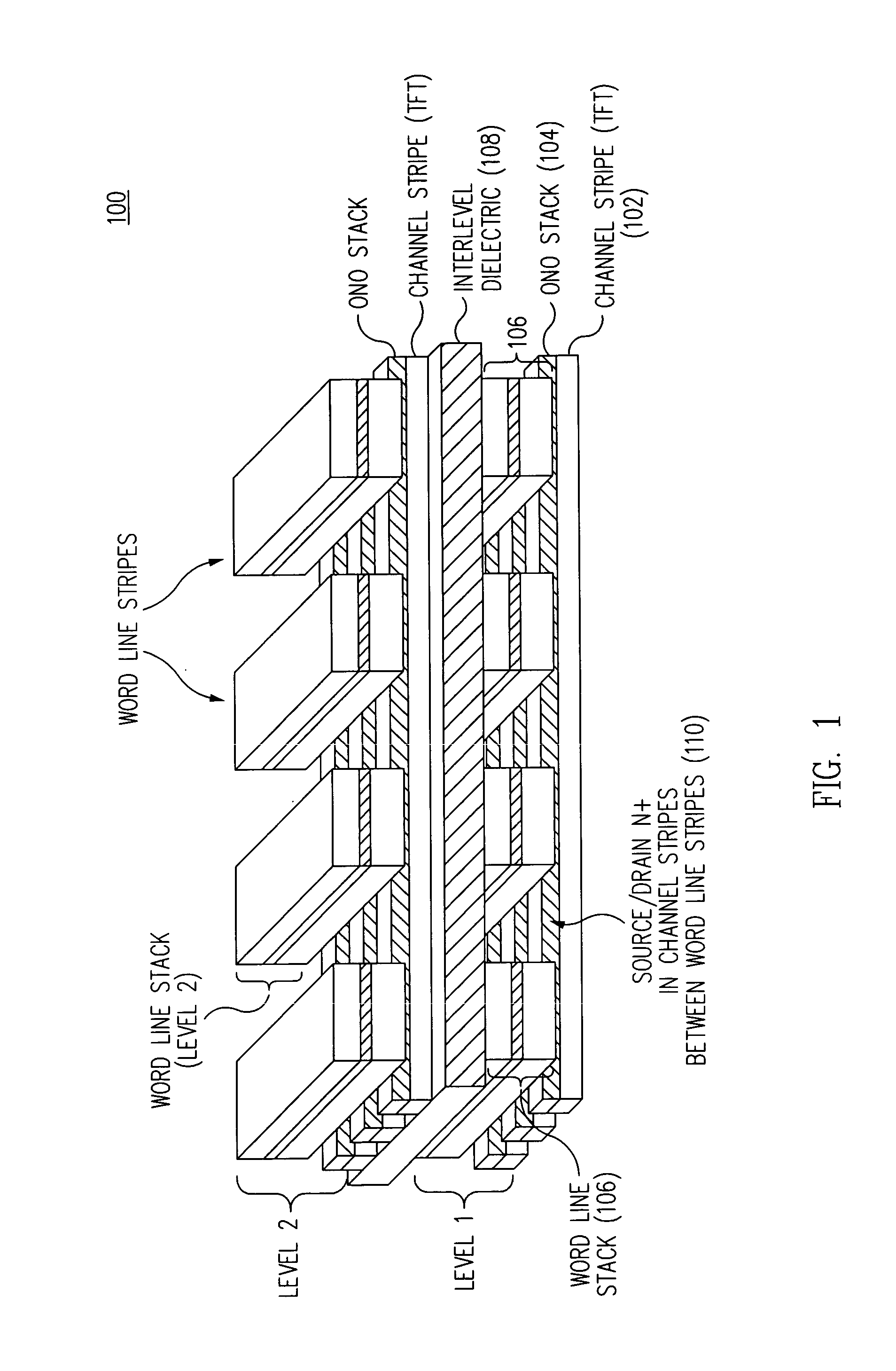

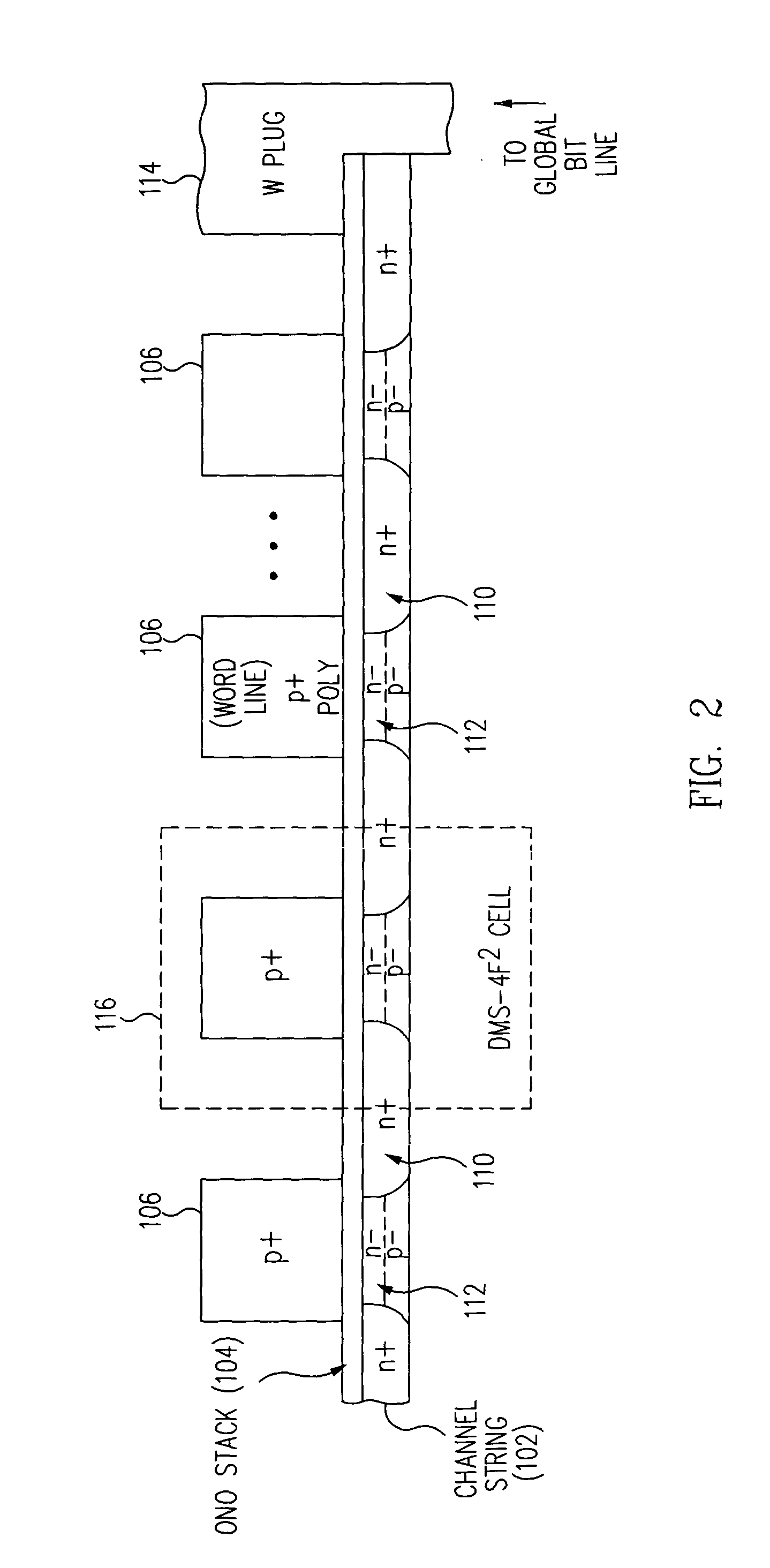

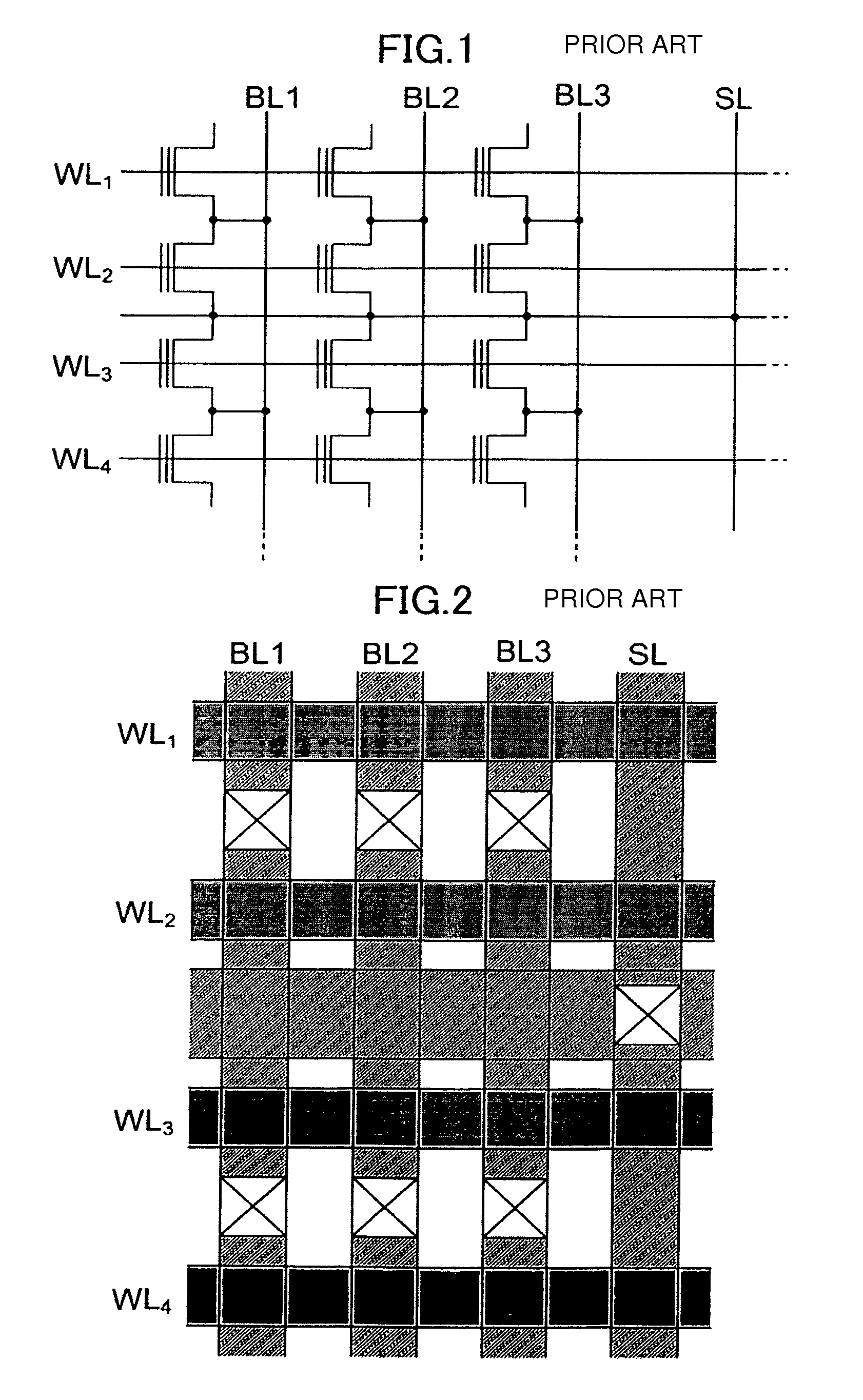

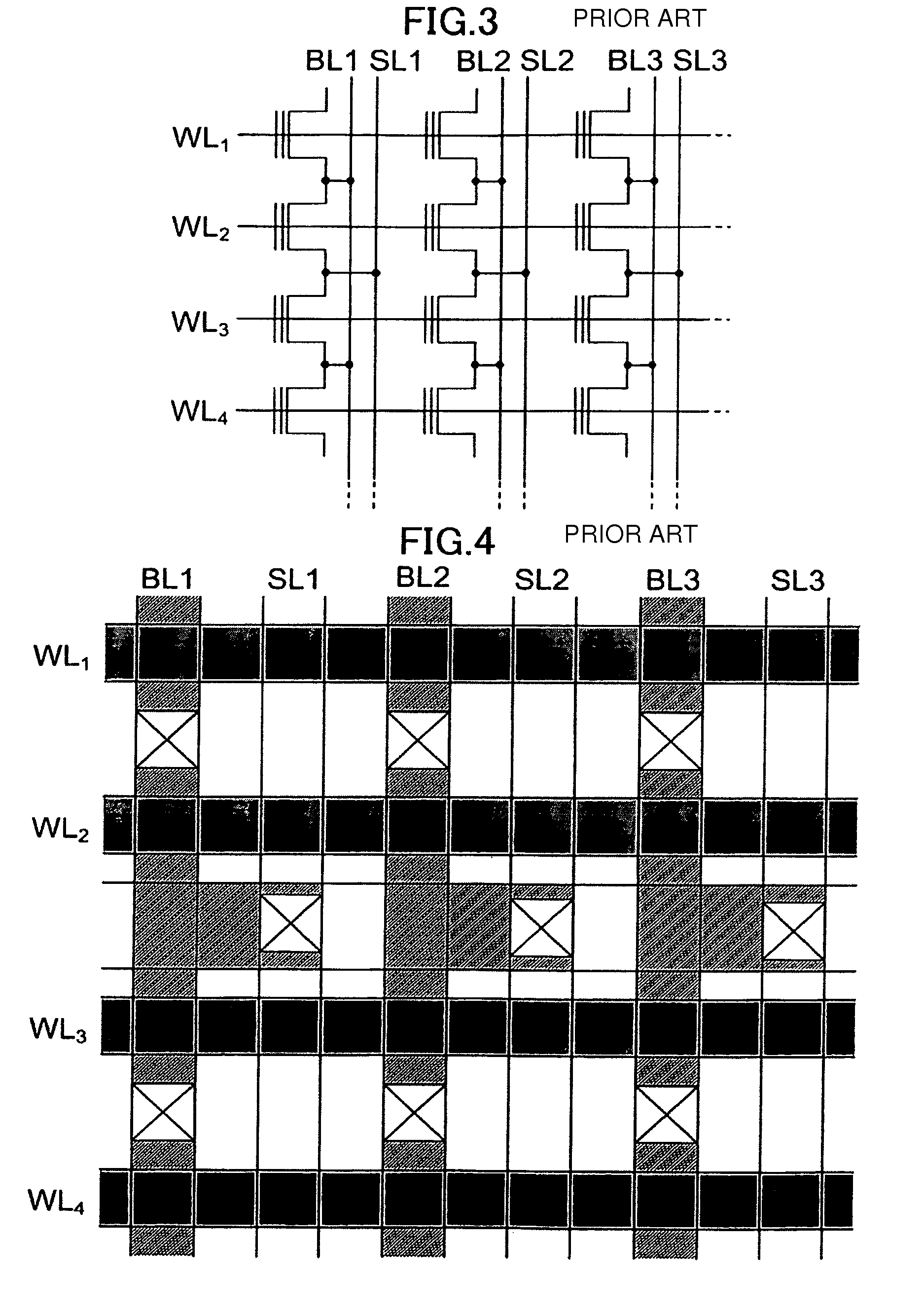

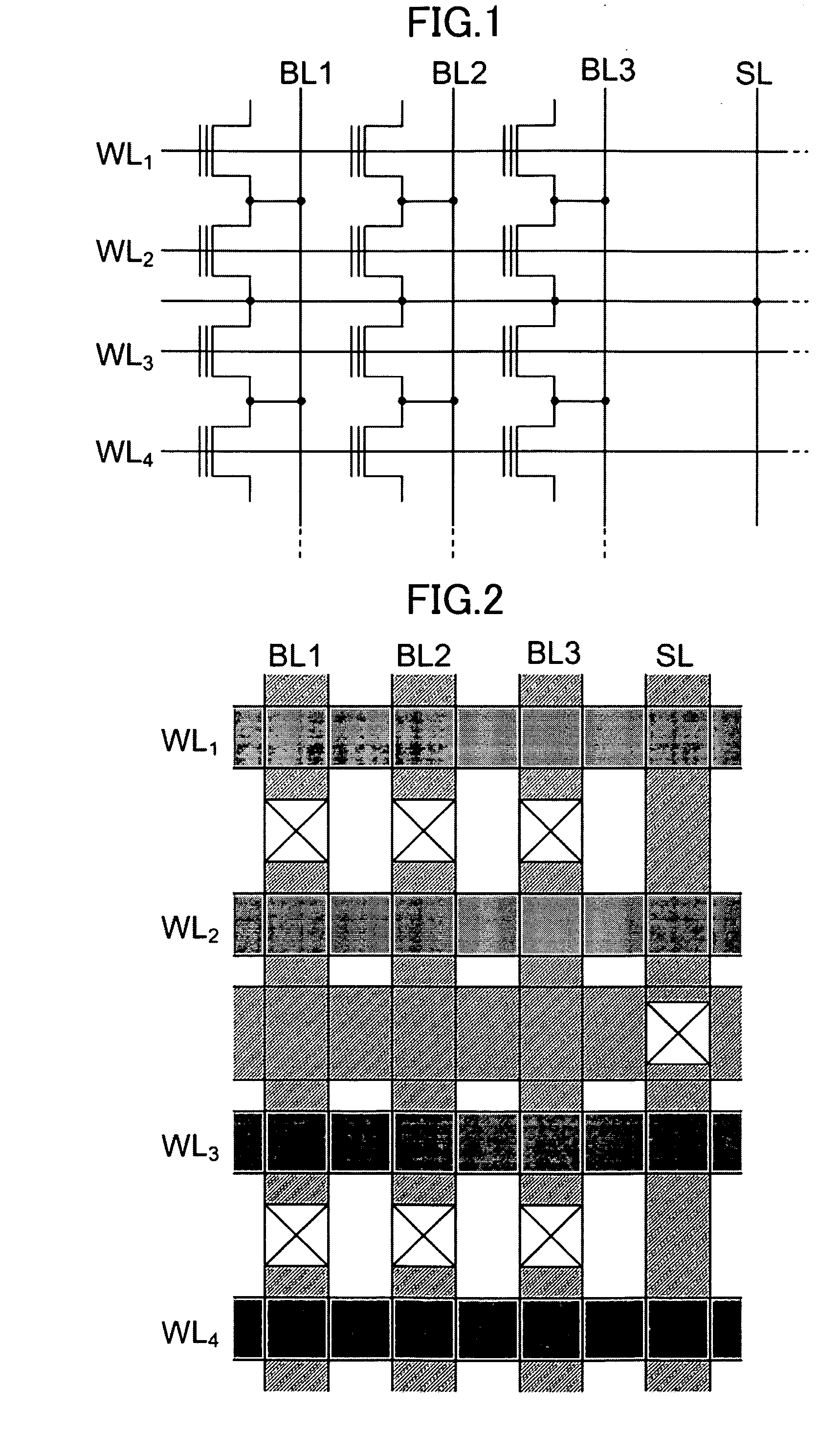

Programmable memory array structure incorporating series-connected transistor strings and methods for fabrication and operation of same

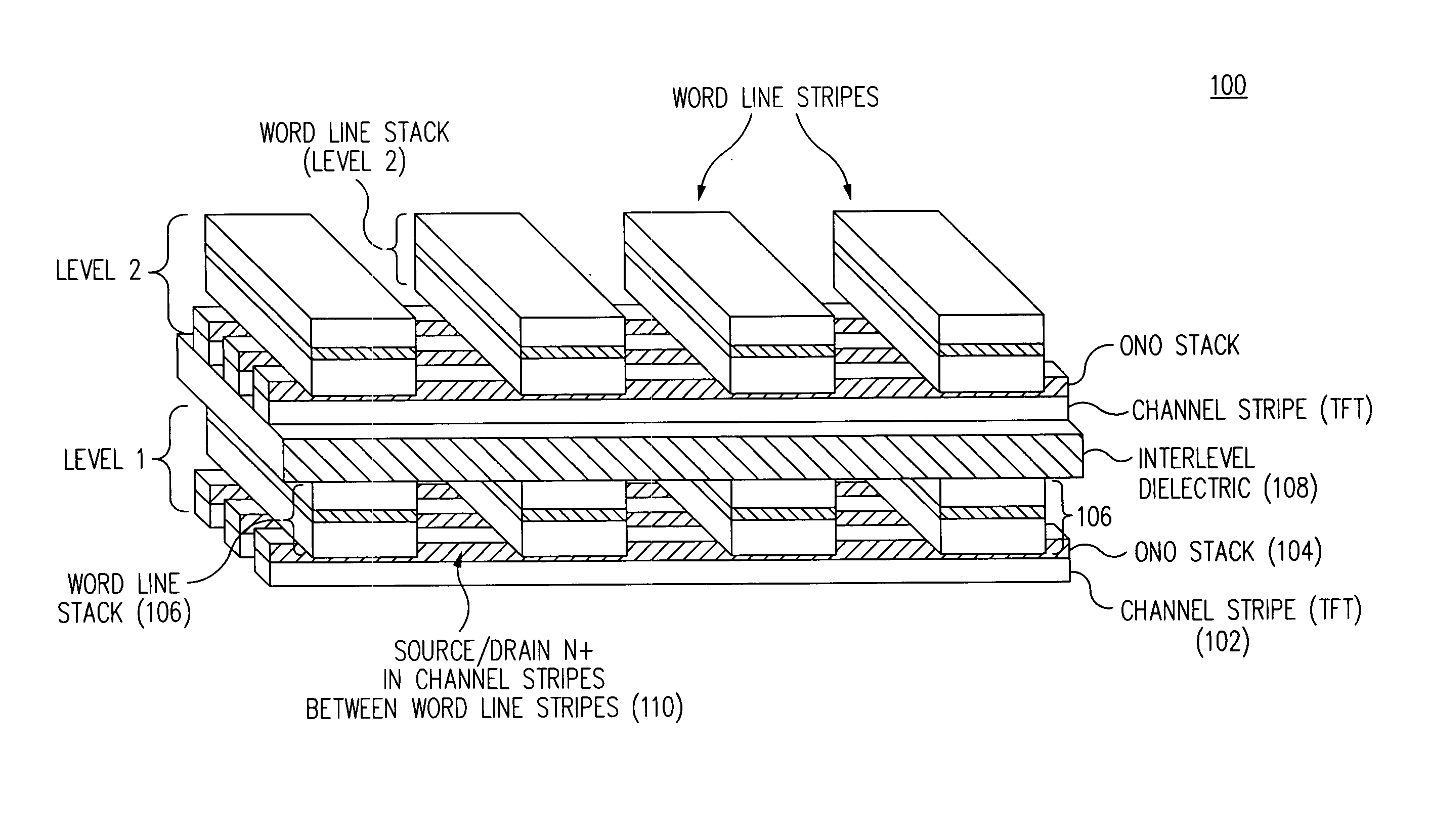

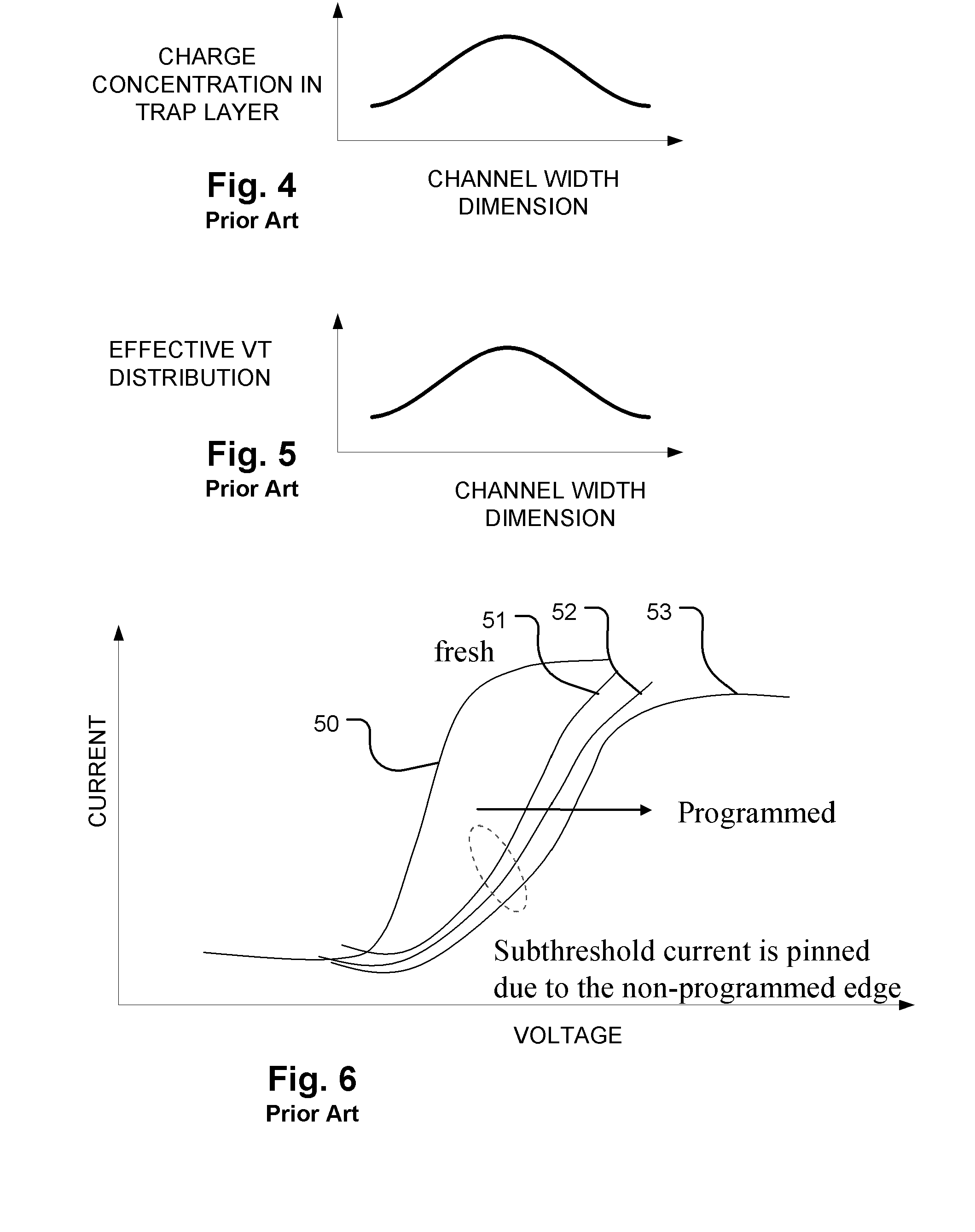

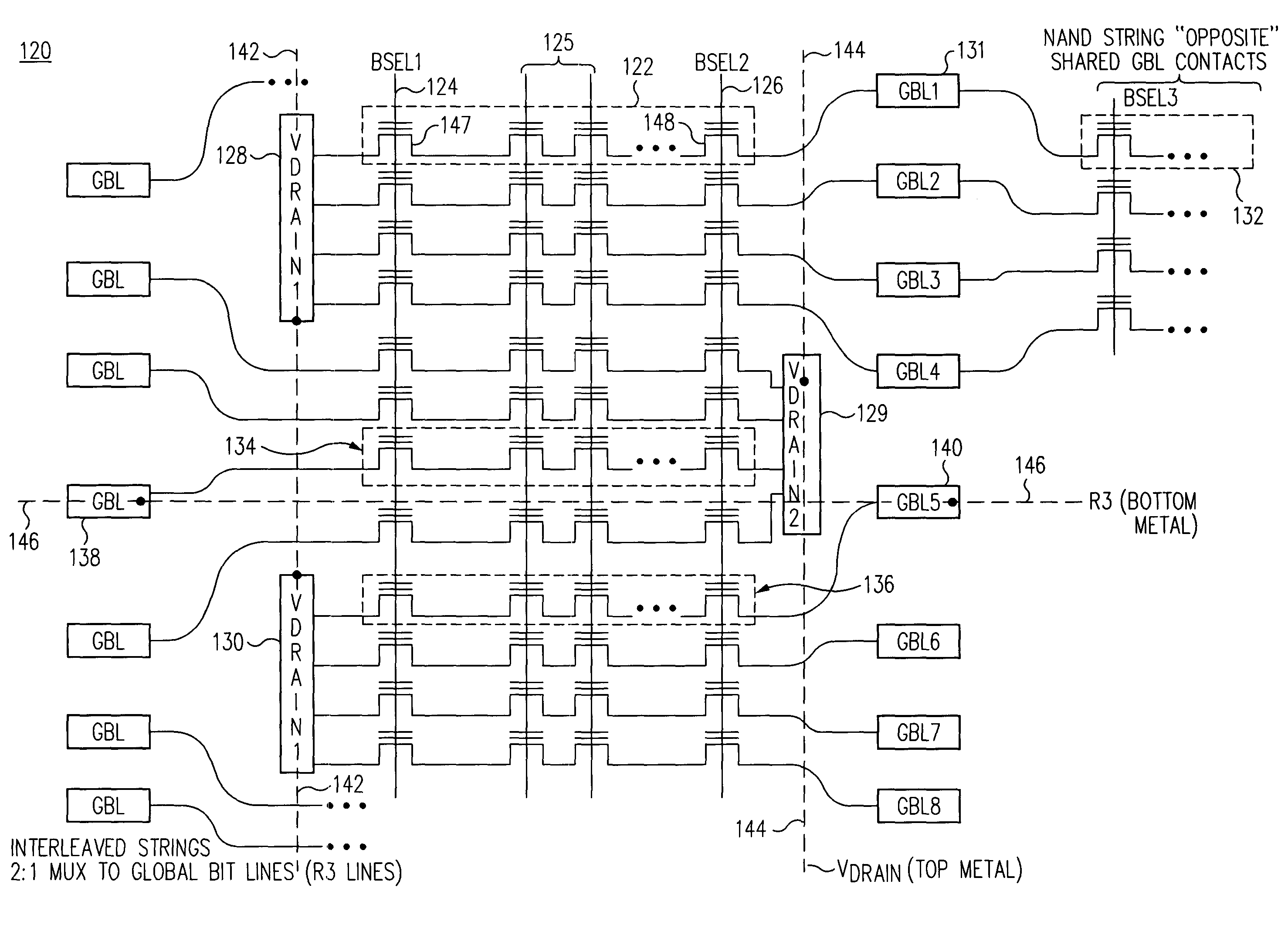

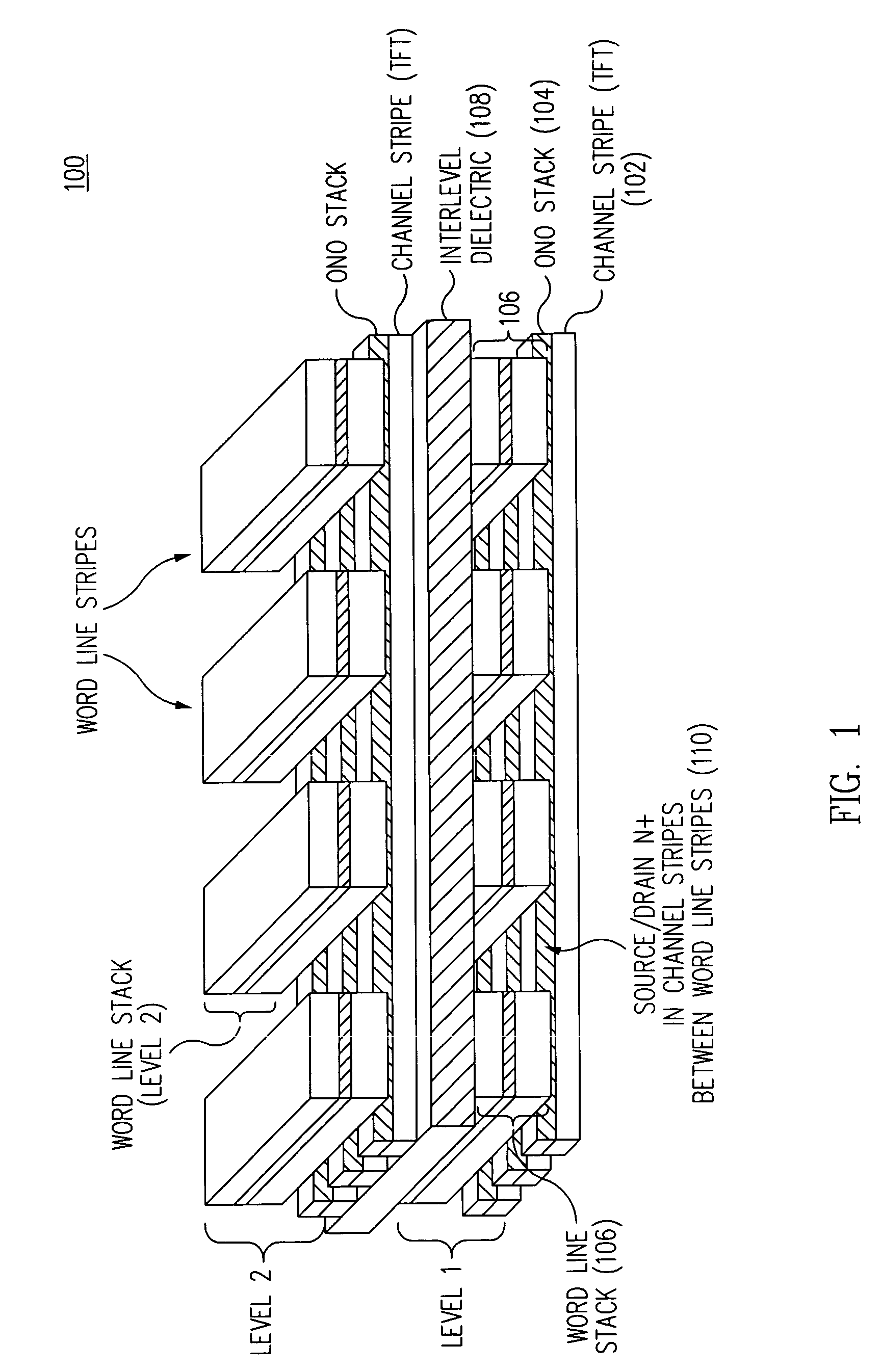

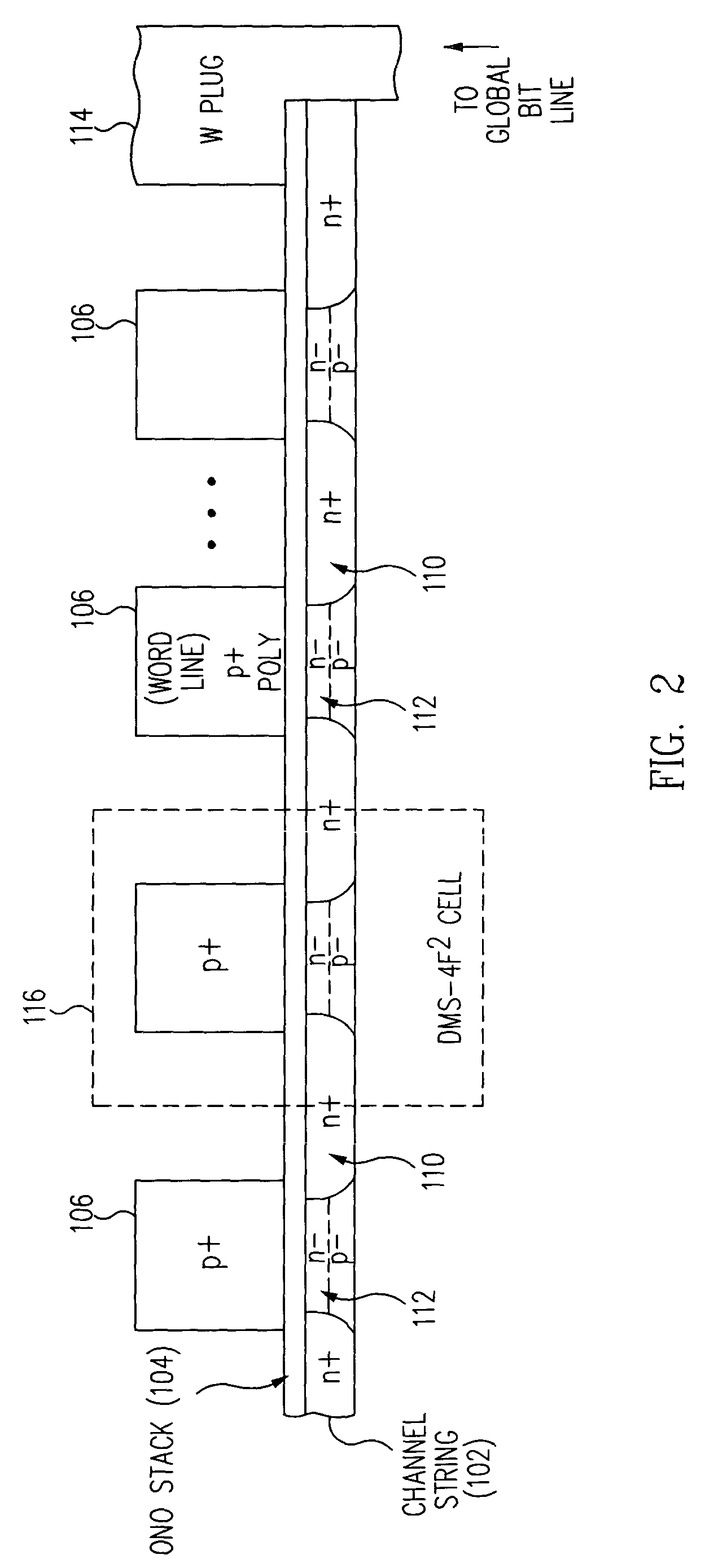

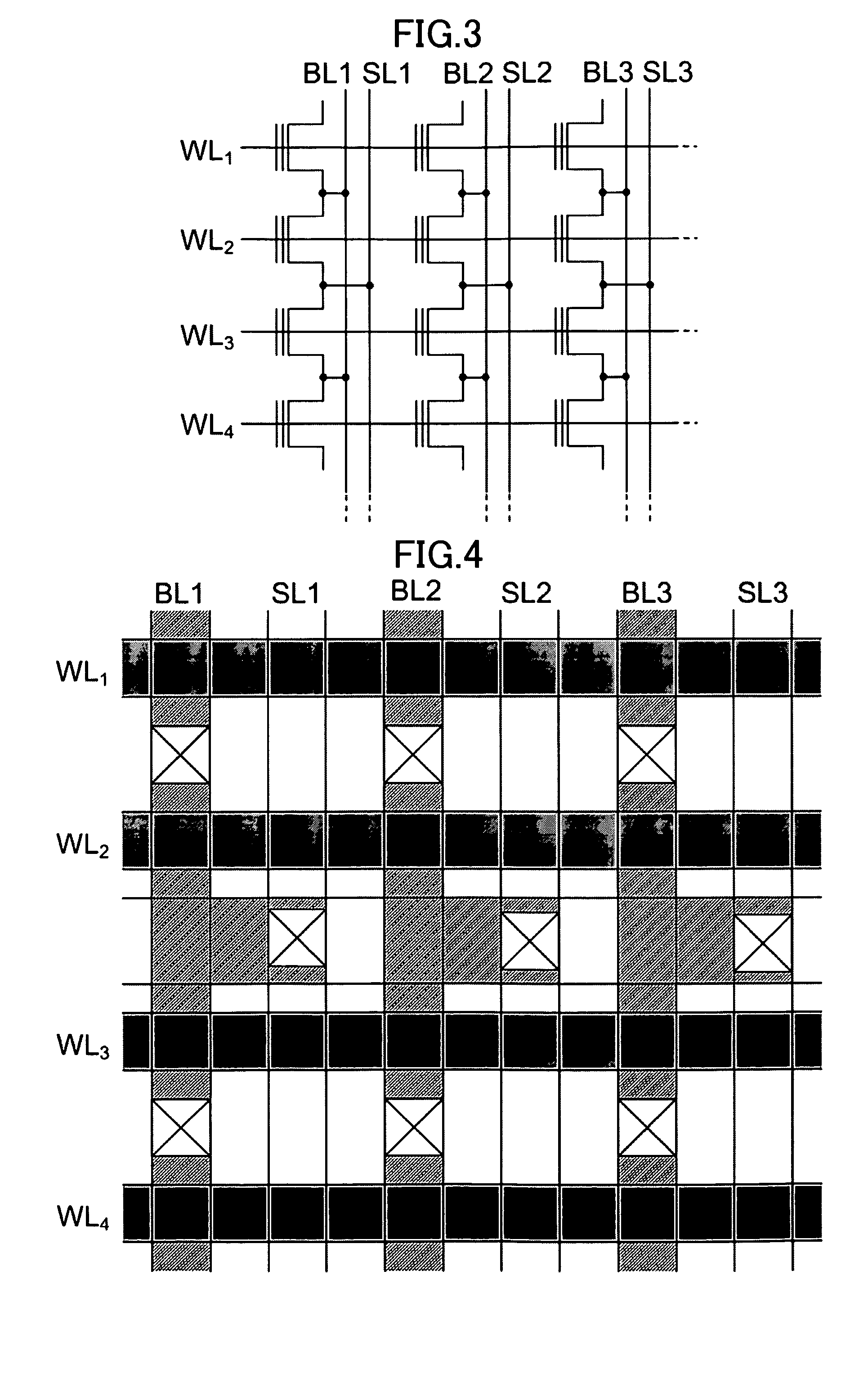

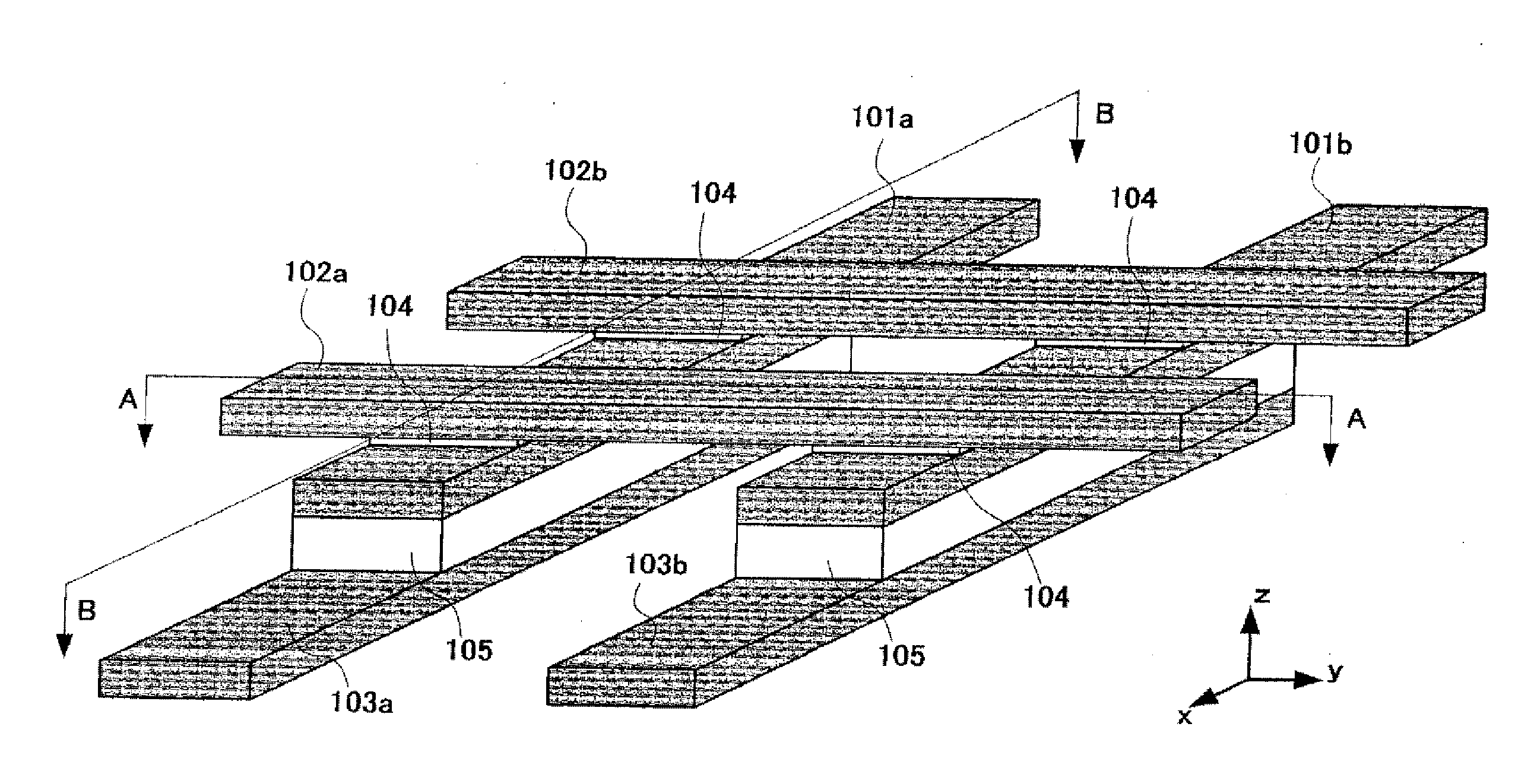

A three-dimensional flash memory array incorporates thin film transistors having a charge storage dielectric arranged in series-connected NAND strings to achieve a 4F<2 >memory cell layout. The memory array may be programmed and erased using only tunneling currents, and no leakage paths are formed through non-selected memory cells. Each NAND string includes two block select devices for respectively coupling one end of the NAND string to a global bit line, and the other end to a shared bias node. Pairs of NAND strings within a block share the same global bit line. The memory cells are preferably depletion mode SONOS devices, as are the block select devices. The memory cells may be programmed to a near depletion threshold voltage, and the block select devices are maintained in a programmed state having a near depletion mode threshold voltage. NAND strings on more than one layer may be connected to global bit lines on a single layer. By interleaving the NAND strings on each memory level and using two shared bias nodes per block, very little additional overhead is required for the switch devices at each end of the NAND strings. The NAND strings on different memory levels are preferably connected together by way of vertical stacked vias, each preferably connecting to more than one memory level. Each memory level may be produced with less than three masks per level.

Owner:SANDISK TECH LLC

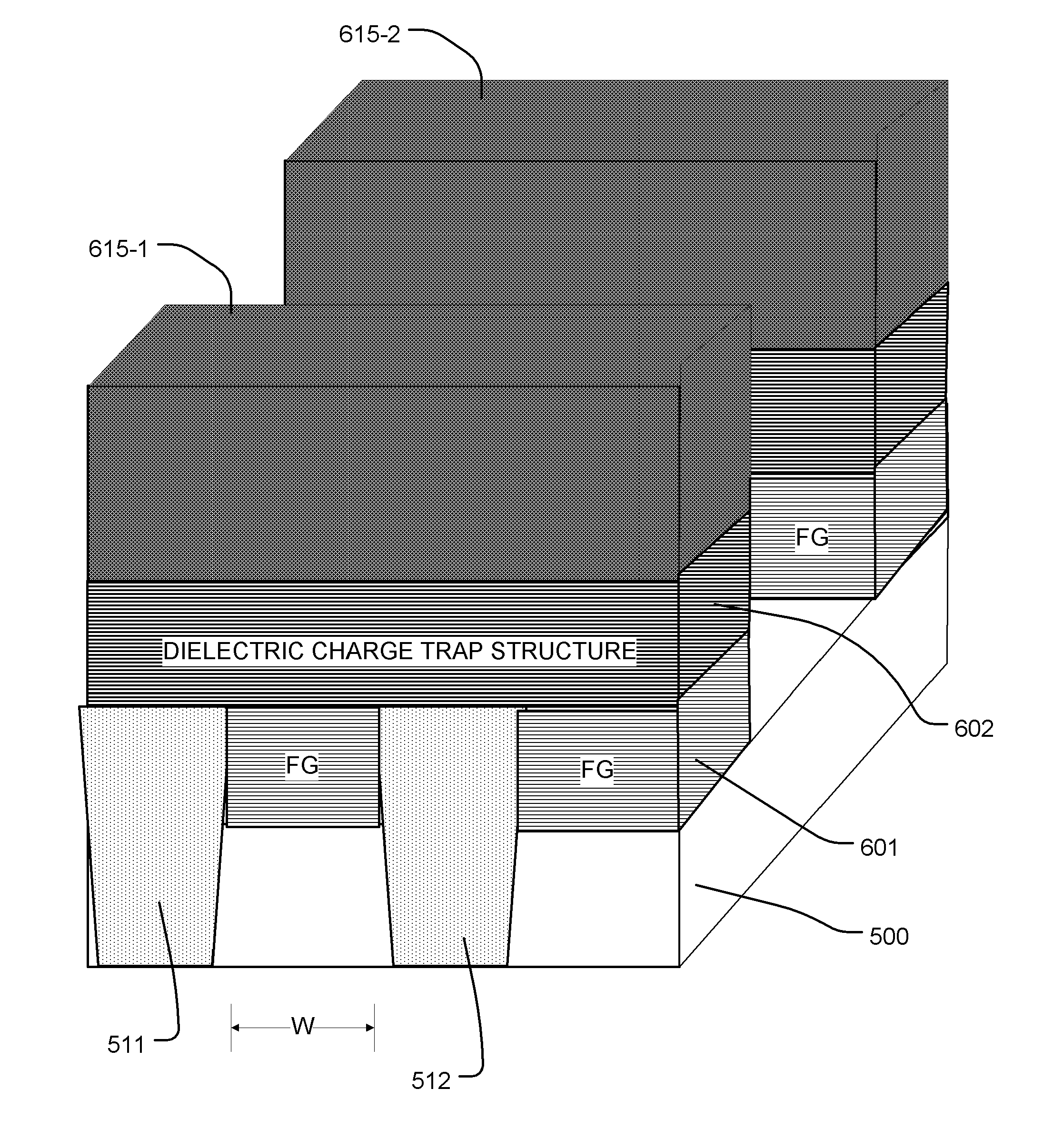

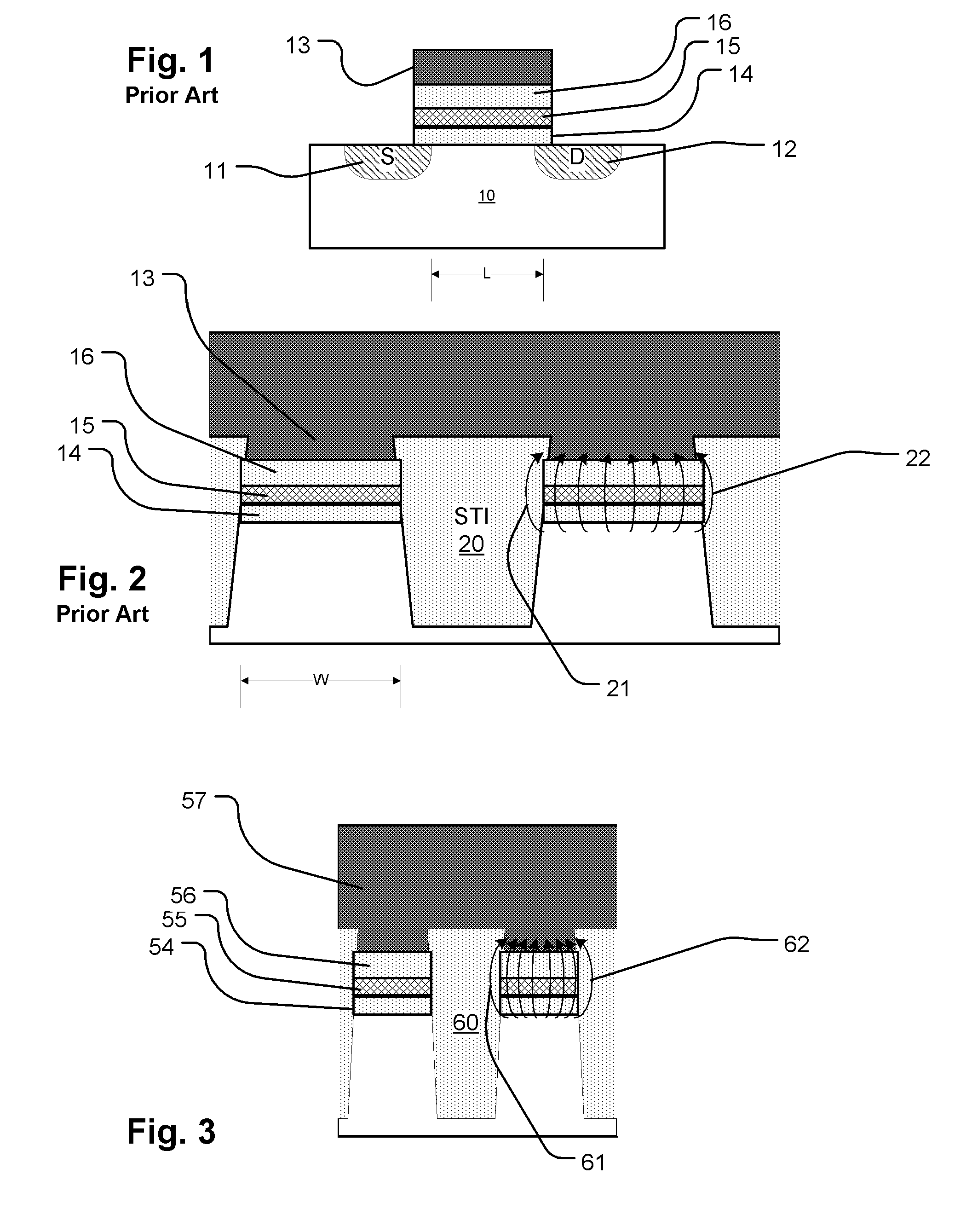

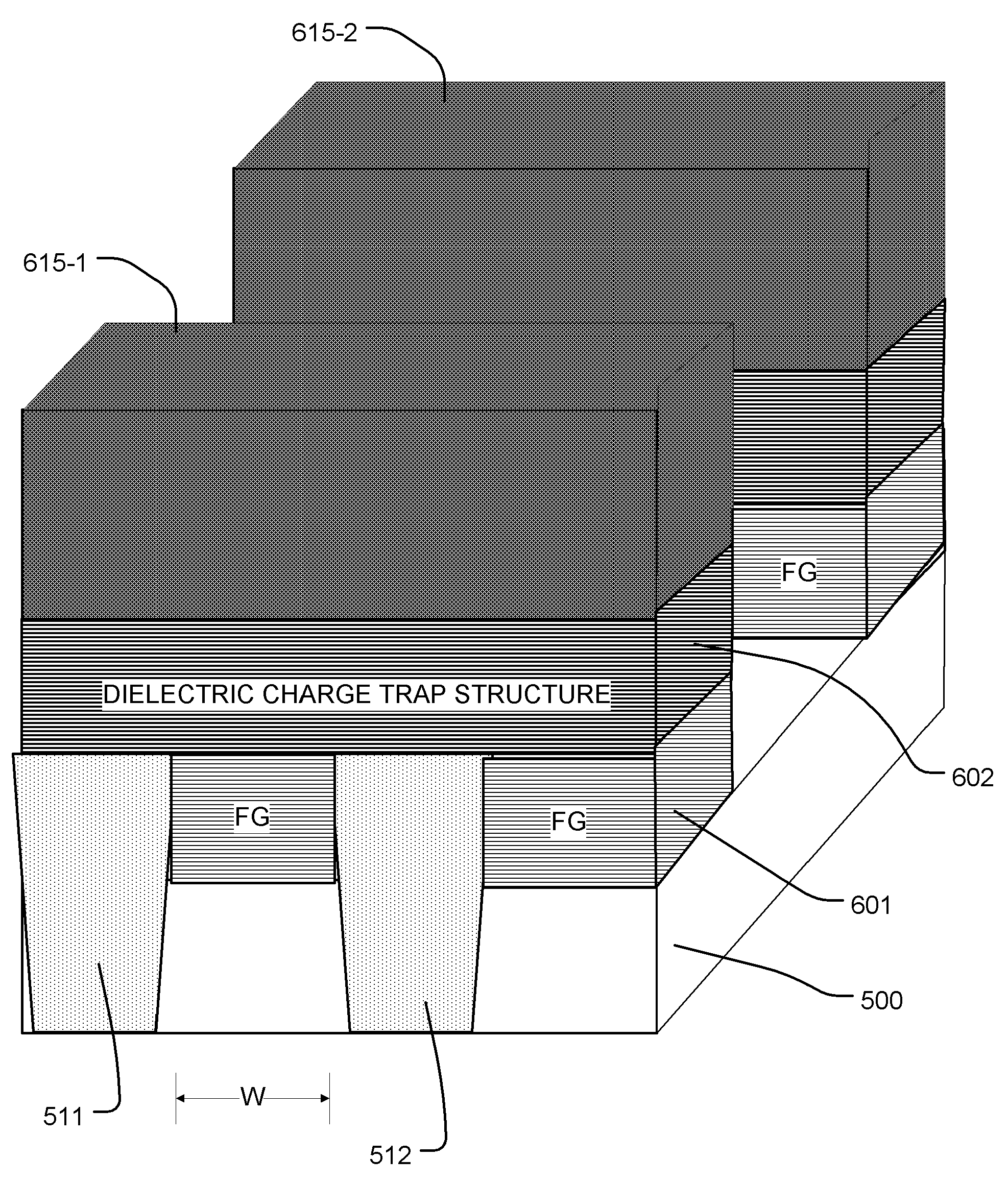

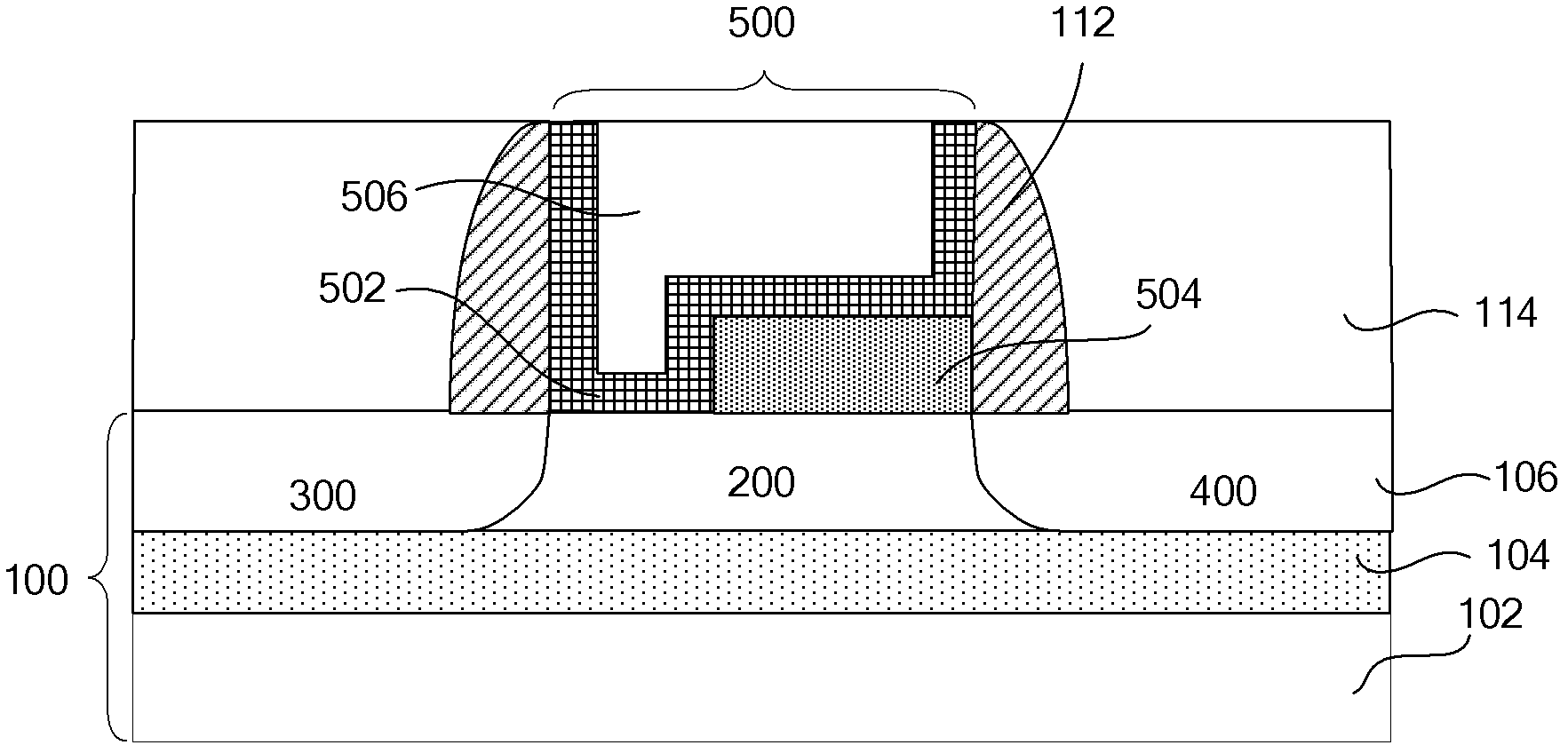

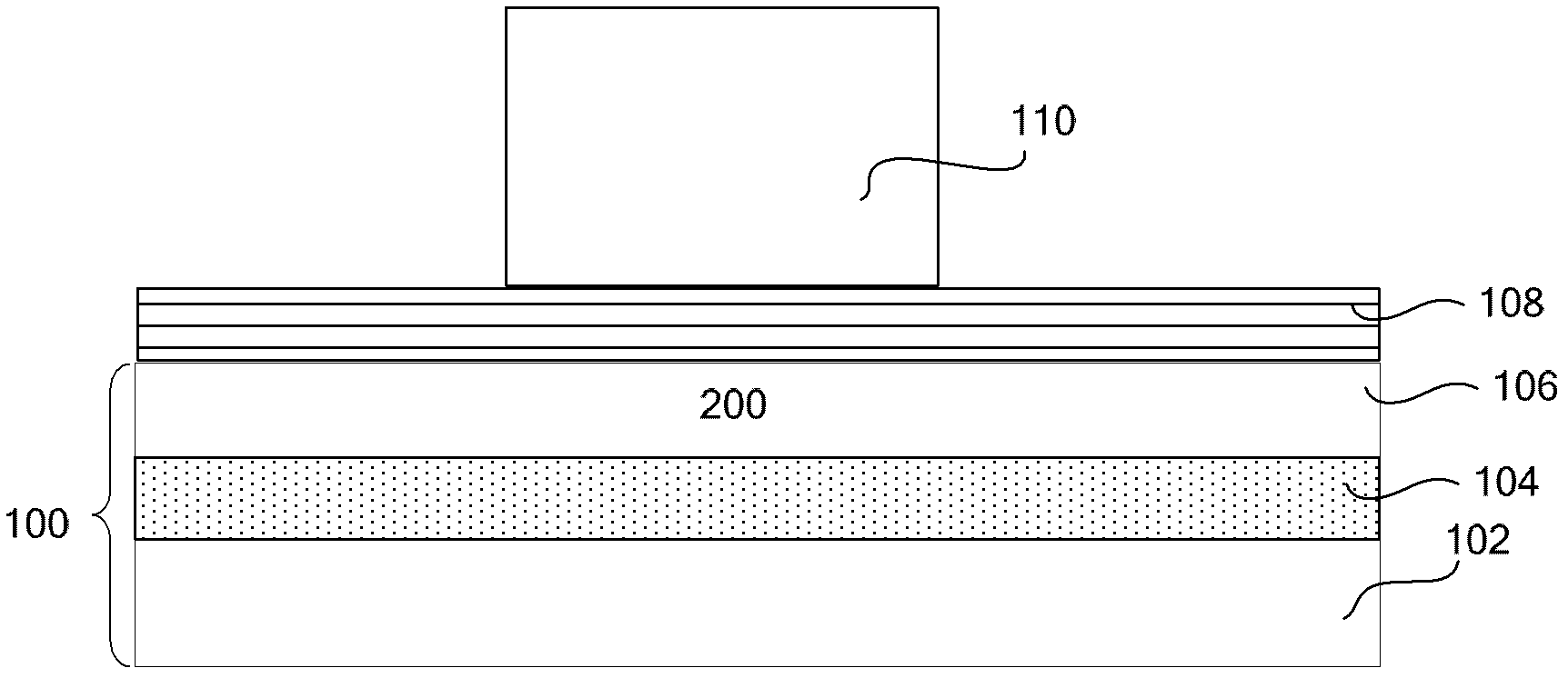

Floating gate memory device with interpoly charge trapping structure

ActiveUS20090262583A1Constant threshold voltageReduce distractionsTransistorSolid-state devicesElectrical conductorTrapping

A charge trapping floating gate is described with asymmetric tunneling barriers. The memory cell includes a source region and a drain region separated by a channel region. A first tunneling barrier structure is disposed above the channel region. A floating gate is disposed above the first tunneling barrier structure covering the channel region. A second tunneling barrier is disposed above the floating gate. A dielectric charge trapping structure disposed above the second tunneling barrier and a blocking dielectric structure is disposed above the charge trapping structure. A top conductive layer disposed above the top dielectric structure acts as a gate. The second tunneling barrier is a more efficient conductor of tunneling current, under bias conditions applied for programming and erasing the memory cell, than the first tunneling barrier structure.

Owner:MACRONIX INT CO LTD

Programmable memory array structure incorporating series-connected transistor strings and methods for fabrication and operation of same

InactiveUS7505321B2Reduce in quantityDense memory arraySolid-state devicesRead-only memoriesElectricityBit line

A three-dimensional flash memory array incorporates thin film transistors having a charge storage dielectric arranged in series-connected NAND strings to achieve a 4F2 memory cell layout. The memory array may be programmed and erased using only tunneling currents, and no leakage paths are formed through non-selected memory cells. Each NAND string includes two block select devices for respectively coupling one end of the NAND string to a global bit line, and the other end to a shared bias node. Pairs of NAND strings within a block share the same global bit line. The memory cells are preferably depletion mode SONOS devices, as are the block select devices. The memory cells may be programmed to a near depletion threshold voltage, and the block select devices are maintained in a programmed state having a near depletion mode threshold voltage. NAND strings on more than one layer may be connected to global bit lines on a single layer. By interleaving the NAND strings on each memory level and using two shared bias nodes per block, very little additional overhead is required for the switch devices at each end of the NAND strings. The NAND strings on different memory levels are preferably connected together by way of vertical stacked vias, each preferably connecting to more than one memory level. Each memory level may be produced with less than three masks per level.

Owner:SANDISK TECH LLC

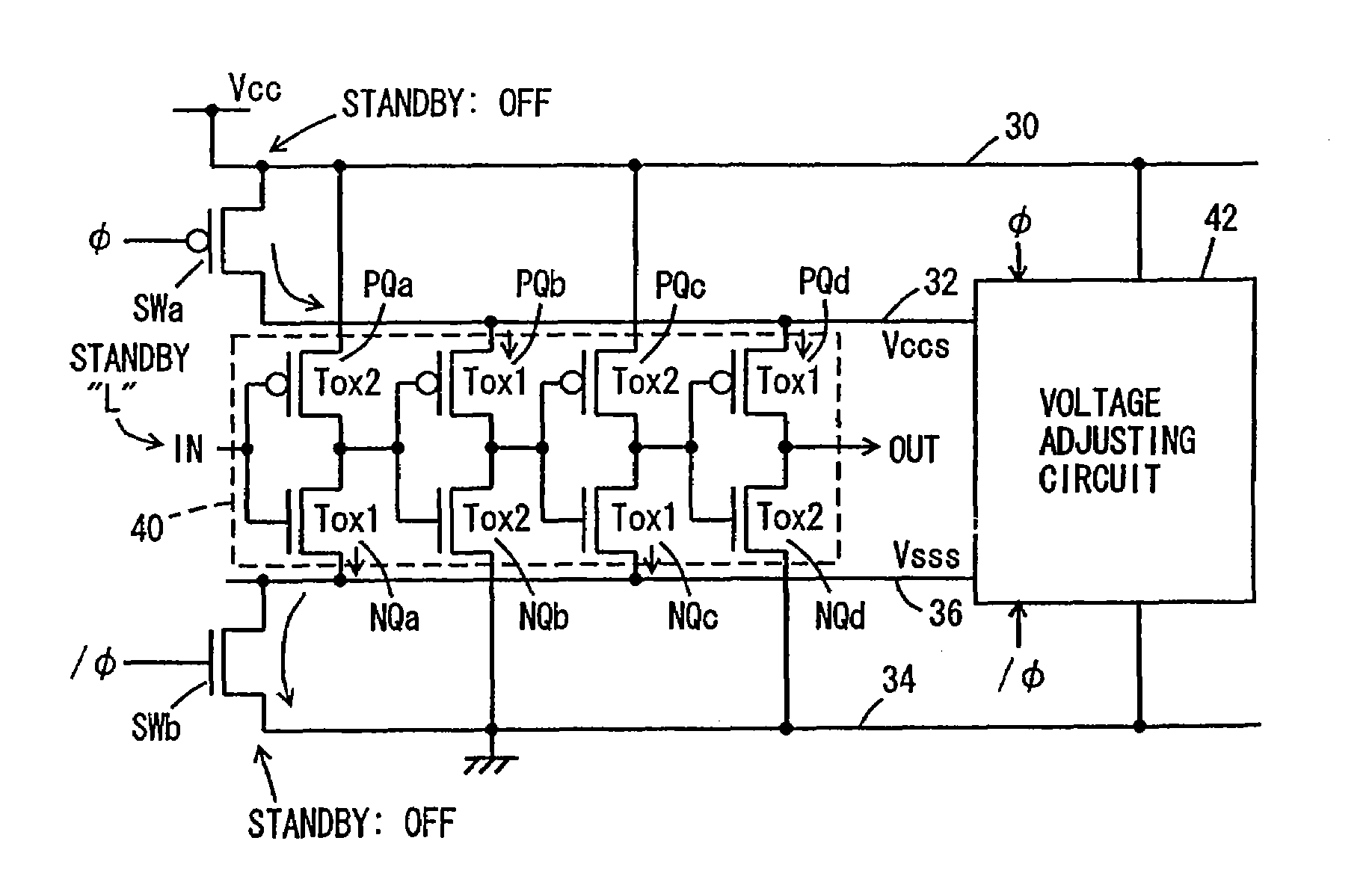

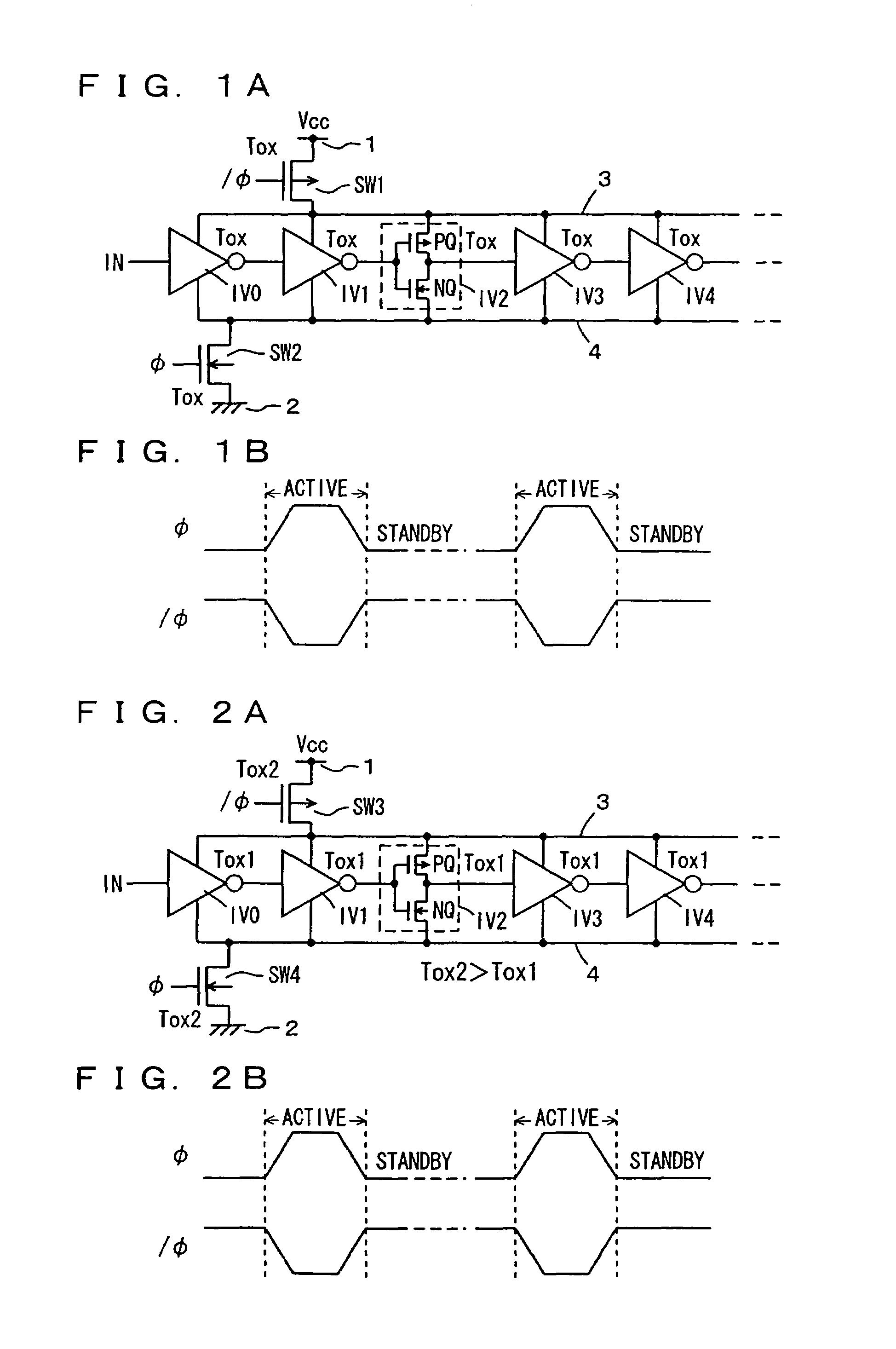

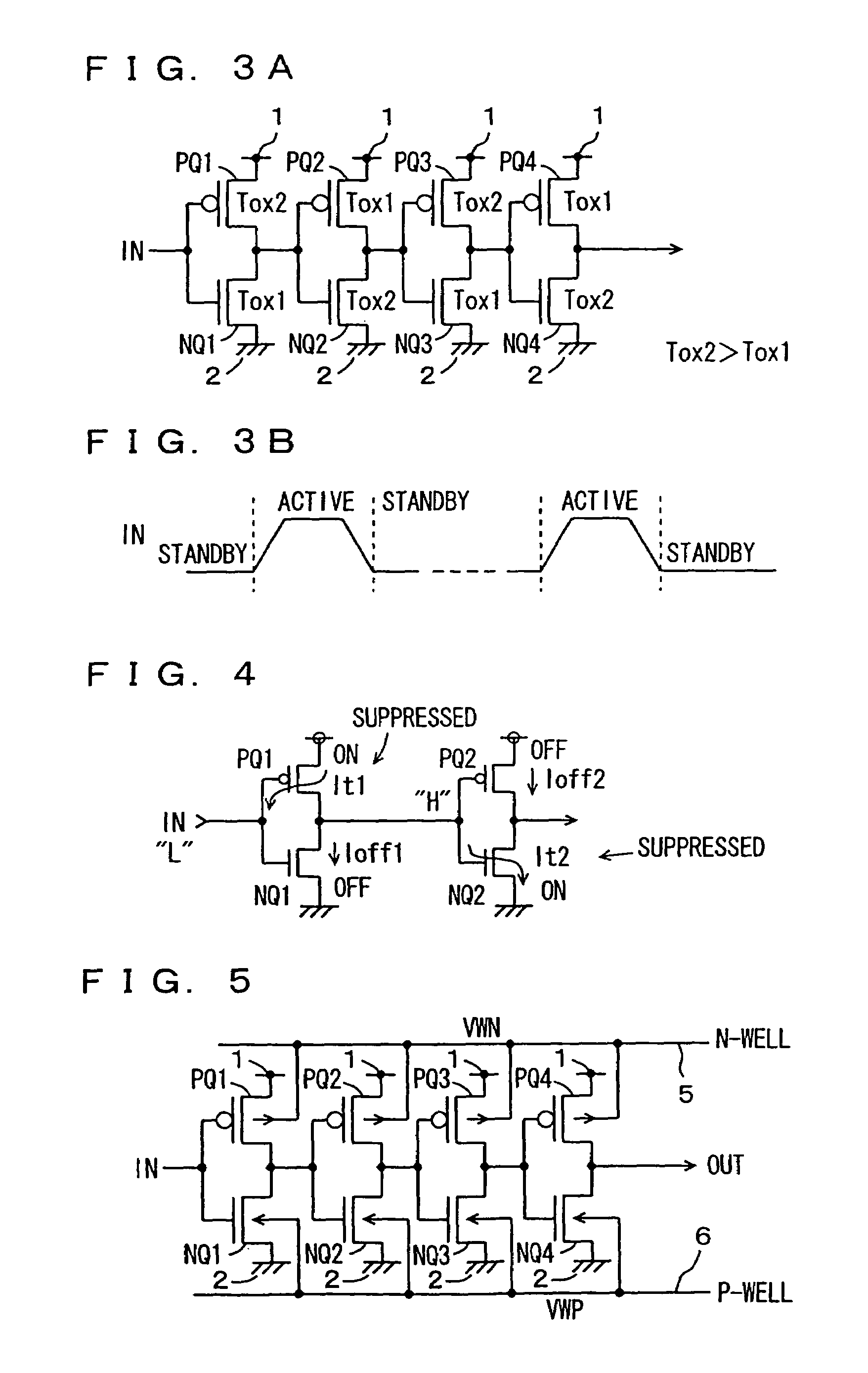

Semiconductor integrated circuit device operating with low power consumption

InactiveUS7521762B2Inhibit currentEasy to integrateTransistorReliability increasing modificationsActive stateGround line

Transistors having large gate tunnel barriers are used as transistors to be on in a standby state, MIS transistors having thin gate insulating films are used as transistors to be off in the standby state, and main and sub-power supply lines and main and sub-ground lines forming a hierarchical power supply structure are isolated from each other in the standby state so that a gate tunnel current is reduced in the standby state in which a low power consumption is required. In general, a gate tunnel current reducing mechanism is provided for any circuitry operating in a standby state and an active state, and is activated in the standby state to reduce the gate tunnel current in the circuitry in the standby state, to reduce power consumption in the standby state.

Owner:RENESAS ELECTRONICS CORP

Floating gate memory device with interpoly charge trapping structure

ActiveUS8068370B2Reduce distractionsImprove data retentionTransistorSolid-state devicesPower flowElectrical conductor

A charge trapping floating gate is described with asymmetric tunneling barriers. The memory cell includes a source region and a drain region separated by a channel region. A first tunneling barrier structure is disposed above the channel region. A floating gate is disposed above the first tunneling barrier structure covering the channel region. A second tunneling barrier is disposed above the floating gate. A dielectric charge trapping structure disposed above the second tunneling barrier and a blocking dielectric structure is disposed above the charge trapping structure. A top conductive layer disposed above the top dielectric structure acts as a gate. The second tunneling barrier is a more efficient conductor of tunneling current, under bias conditions applied for programming and erasing the memory cell, than the first tunneling barrier structure.

Owner:MACRONIX INT CO LTD

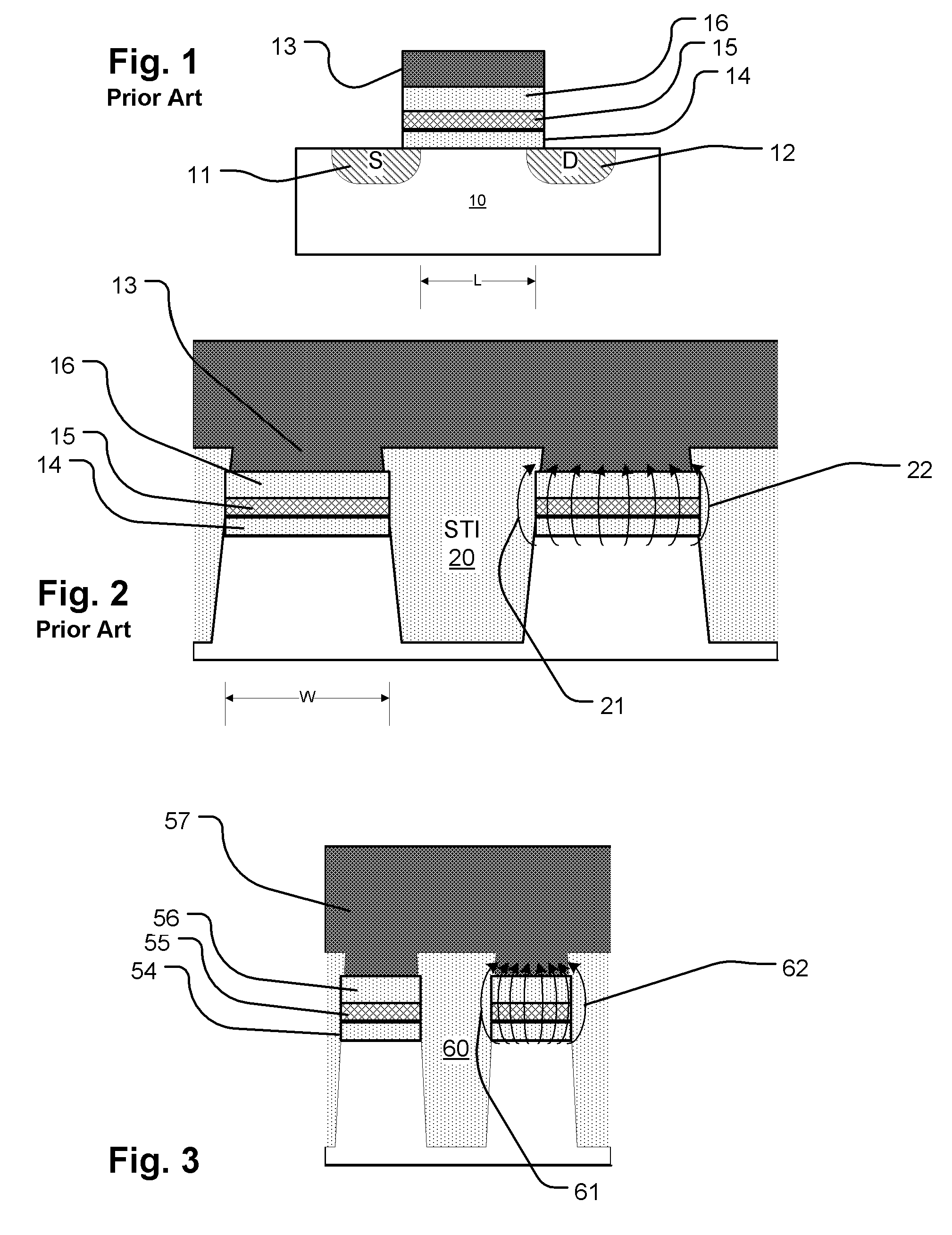

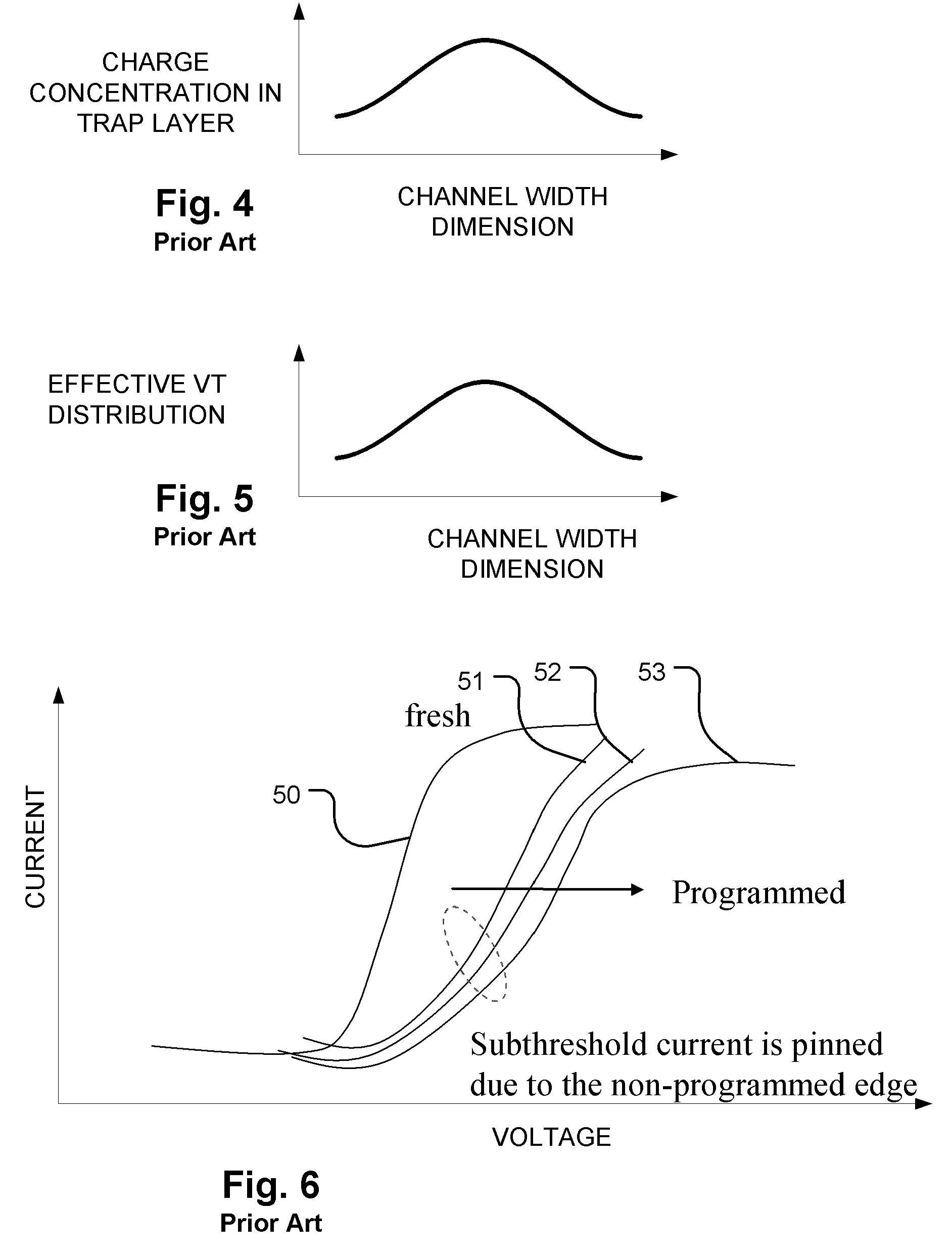

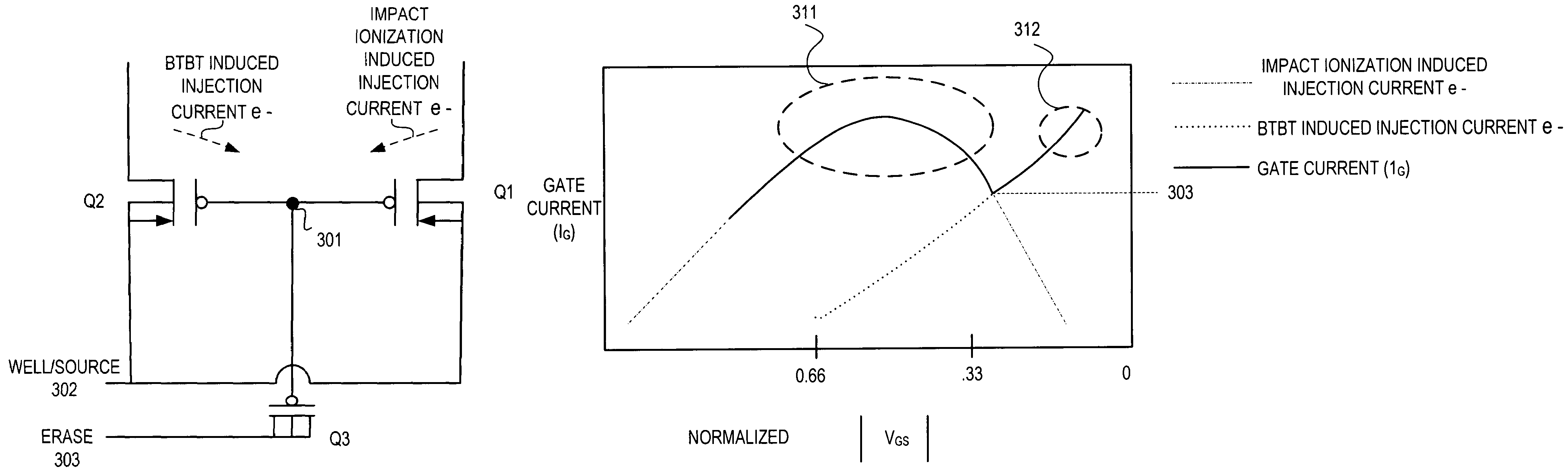

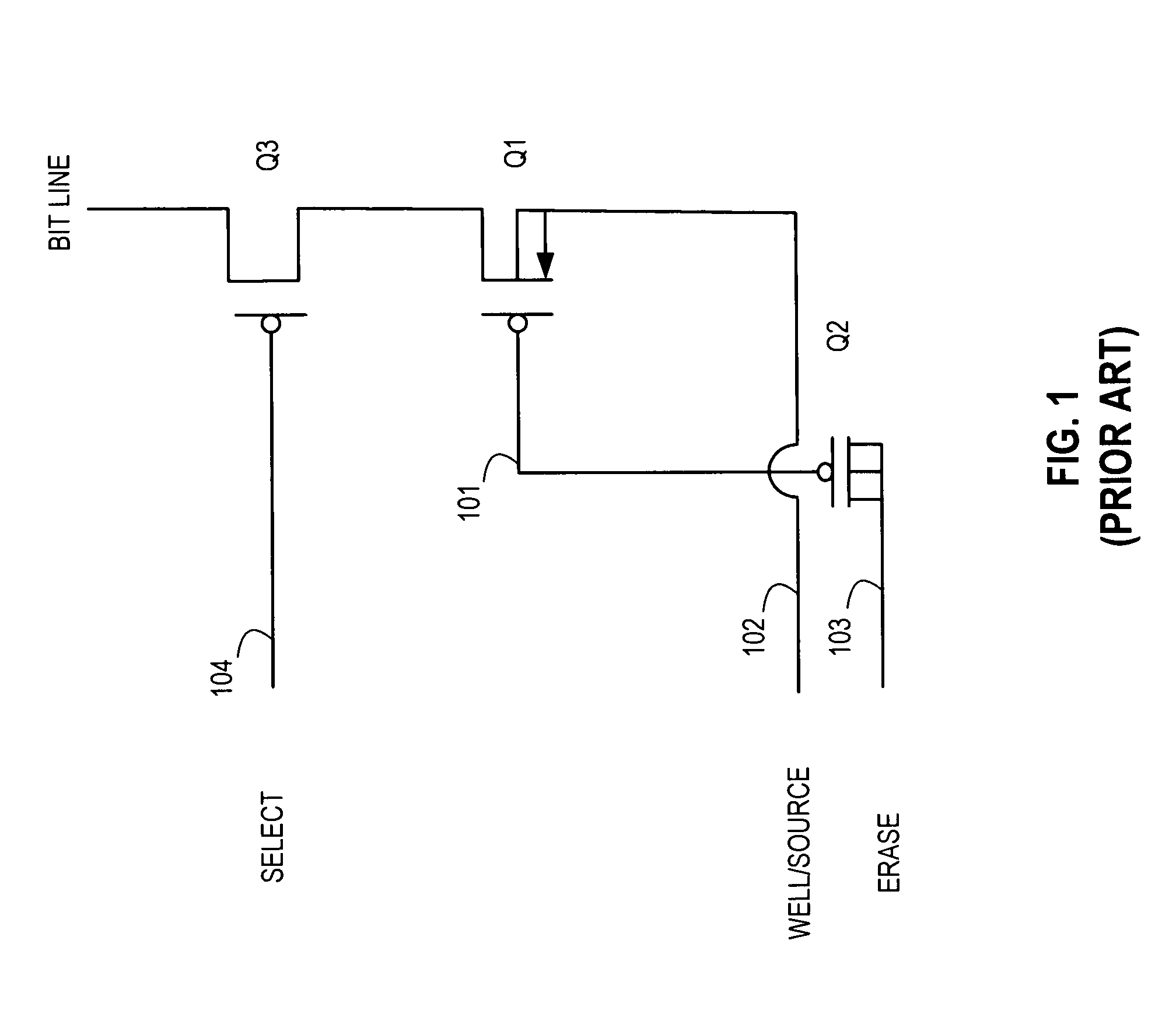

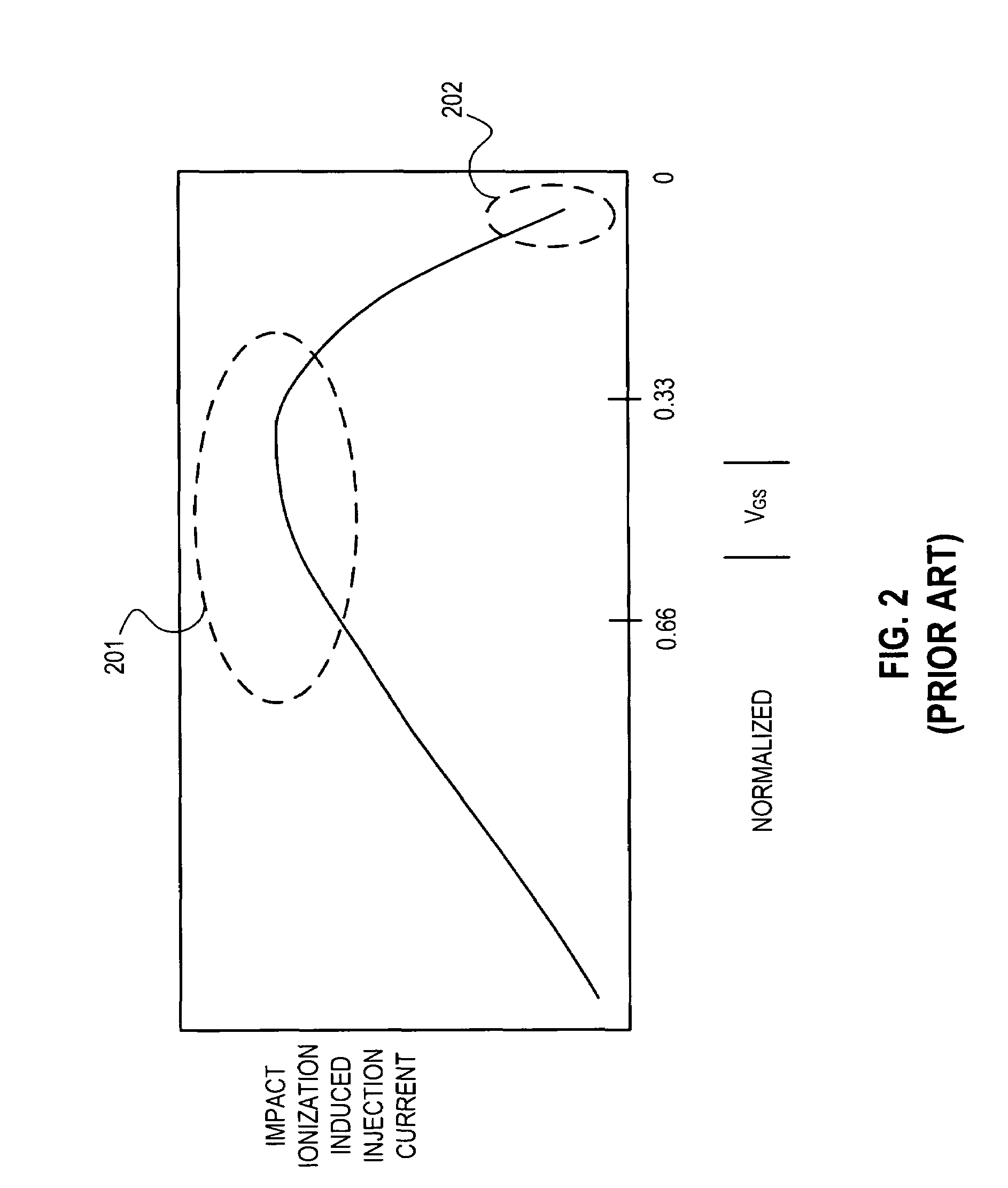

Non-volatile memory cell circuit with programming through band-to-band tunneling and impact ionization gate current

Electronic circuitry is described having a first transistor having a first gate dielectric located between an electrically floating gate and a semiconductor substrate. The first injection current flows through the first gate dielectric to establish a first amount of electrical charge on the gate electrode. The electronic circuitry also includes a second transistor having a second gate dielectric located between the gate electrode and the semiconductor substrate. A band-to-band tunneling current flows between valence and conduction bands of the second transistor to create a second injection current that flows through the second gate dielectric to establish the first amount of electrical charge on the gate electrode. Non volatile memory cell circuits having the above described circuitry are also described.

Owner:SYNOPSYS INC

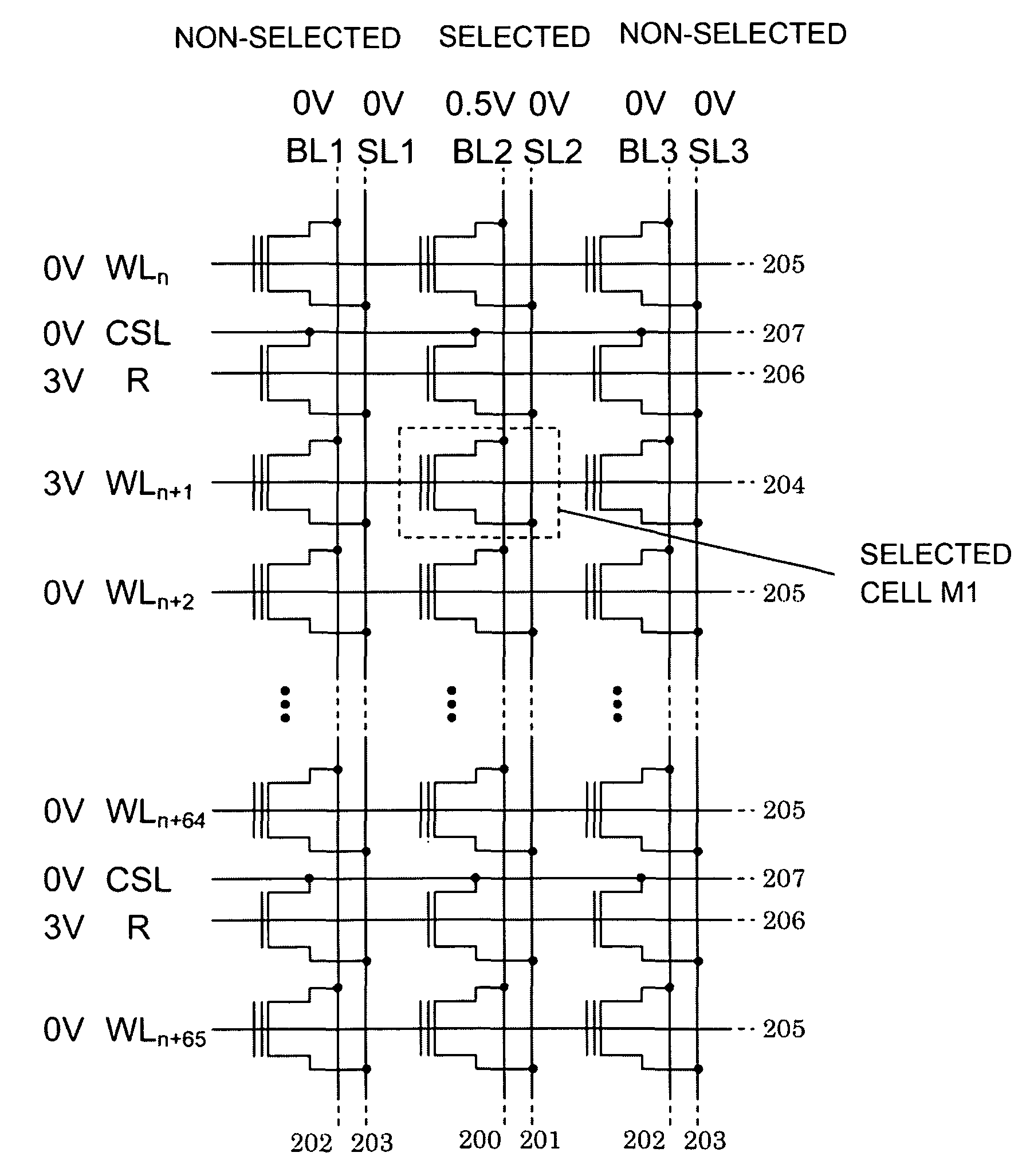

Nonvolatile semiconductor memory and method for driving the same

ActiveUS7940573B2Without compromising large scale integrationWithout increasing area of memory cellSolid-state devicesRead-only memoriesBit lineOptoelectronics

Owner:UNISANTIS ELECTRONICS SINGAPORE PTE LTD +1

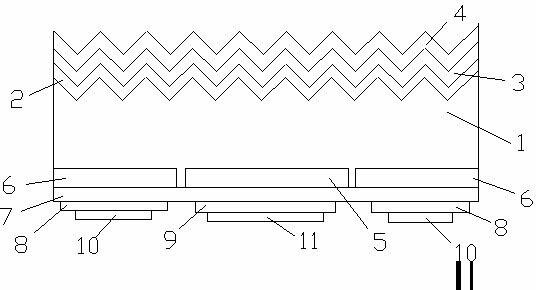

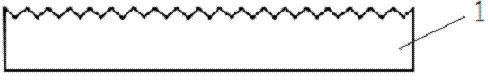

Back contact crystal silicon solar battery and manufacture process of back contact crystal silicon solar battery

InactiveCN102610686AImprove efficiencyReduce unforeseen damagePhotovoltaic energy generationSemiconductor devicesSilicon solar cellSlurry

The invention discloses a back contact silicon solar battery, which comprises an N type monocrystalline silicon piece subjected to surface texturing, wherein a first N type heavy doping layer is arranged at the front side of the N type monocrystalline silicon piece, a silicon dioxide (SiO2) passivation layer and a reflection reduction film layer are sequentially arranged at the outer side of the first N type heavy doping layer, a second N type heavy doping layer and a P type heavy doping layer are arranged at the back side of the N type monocrystalline silicon piece in a mutual separating way, second SiO2 passivation layers are arranged at the outer side of the second N type heavy doping layer and the P type heavy doping layer, a heavy doping AZO film layer and silver slurry are sequentially arranged outside the second SiO2 passivation layer arranged at the second N type heavy doping layer part, and a heavy doping CuAlO2 film layer and silver aluminum slurry are sequentially arranged outside the second SiO2 passivation layer arranged at the P type heavy doping layer part. The invention also discloses a manufacture process of the back contact silicon solar battery. The back contact silicon solar battery and the manufacture method solve the problems that in the prior art, the conversion rate of the solar battery is low, and the back contact battery generally adopts laser punching, so the manufacture cost is high. Through the technical improvement, heavy doping is realized on the contact surface, the heavy-doping low-resistance transparent conductive oxide (TCO) materials are attached to the contact surface so as to form tunnel current, and in addition, a low-temperature slurry sintering method is adopted, the manufacture cost is reduced on the premise that the battery efficiency is ensured.

Owner:XINGSHANG PHOTOVOLTAIC TECH SUZHOU

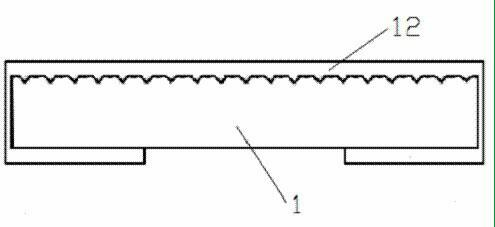

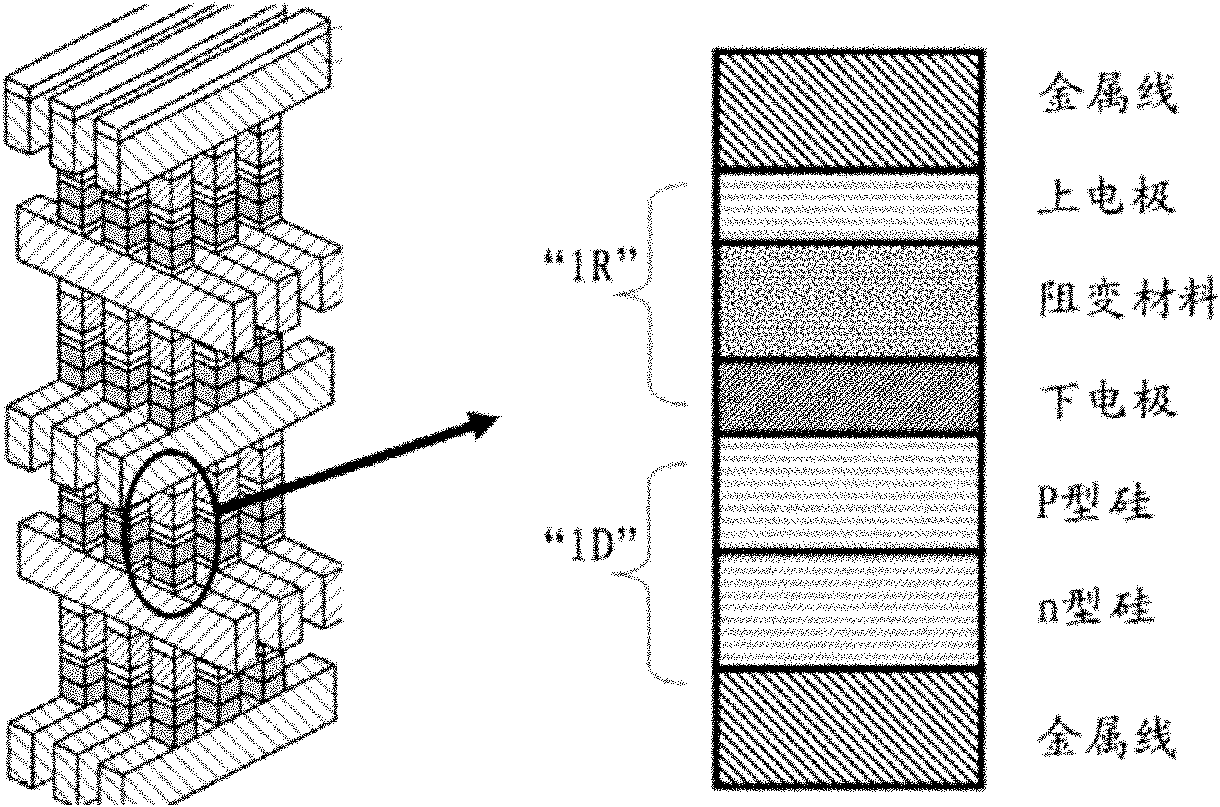

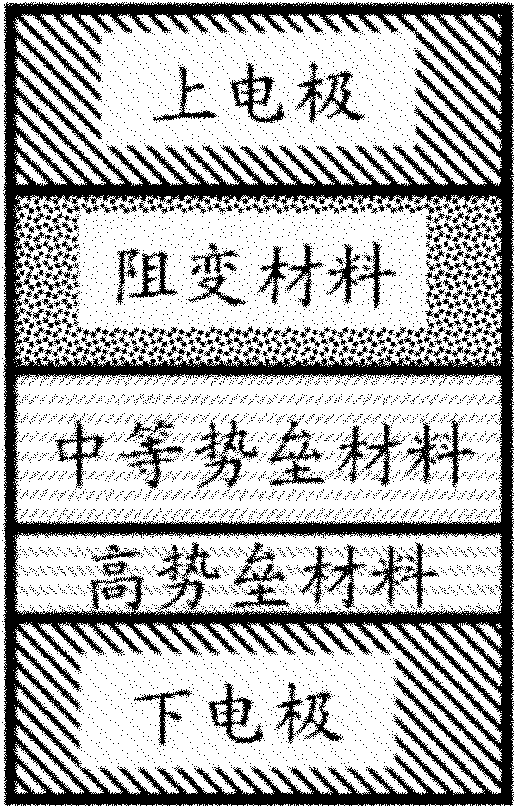

Nonvolatile memory unit and memory

ActiveCN102610748ALarge forward and reverse current differenceAchieve rectification characteristicsSolid-state devicesDigital storagePower flowReverse current

The invention discloses a nonvolatile memory unit and a memory. The memory unit comprises an upper electrode, an asymmetric tunneling potential barrier structure and a lower electrode from top to bottom in sequence, wherein the asymmetric tunneling potential barrier structure is used for commutating and modulating forward and reverse tunneling current tunneling through the nonvolatile memory unit. The nonvolatile memory unit uses the asymmetric tunneling potential barrier structure to apply voltages of different polarities on the two ends of the asymmetric tunneling potential barrier, abd the very large forward and reverse current difference on the tunneling current is obtained by adjusting the asymmetric barrier height and tunneling thickness, and therefore the commutation character is effectively realized.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

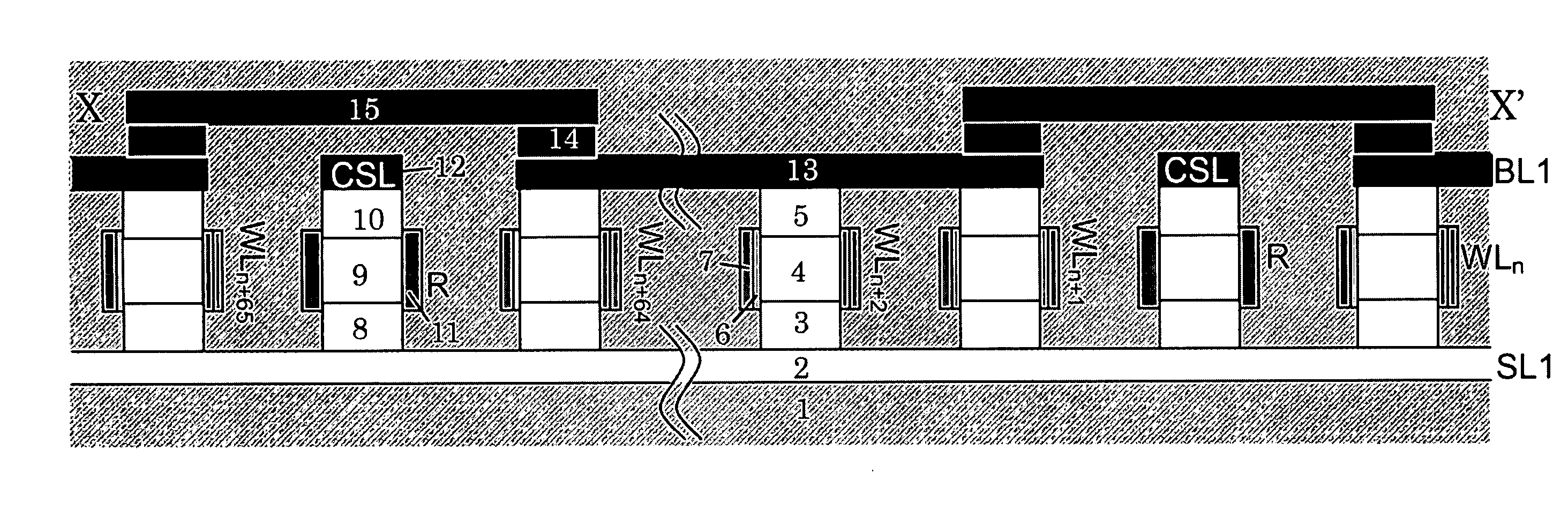

Nonvolatile semiconductor memory and method for driving the same

ActiveUS20090161441A1Without increasing area of memory cellReduce resistanceTransistorSolid-state devicesBit lineSemiconductor

To provide a NOR-type nonvolatile semiconductor memory that can inject electric charge into a charge accumulation layer through the use of an FN tunnel current without compromising an increase in the packing density of memory cells. The above problem is solved by a nonvolatile semiconductor memory in which nonvolatile semiconductor memory cells are arranged in a matrix, each nonvolatile semiconductor memory cell having an island semiconductor layer in which a drain diffusion layer formed in the upper part of the island semiconductor layer, a source diffusion layer formed in the lower part of the island semiconductor layer, a charge accumulation layer formed on a channel region of the side wall sandwiched between the drain diffusion layer and the source diffusion layer via a gate insulation film, and a control gate formed on the charge accumulation layer are formed. Further, bit lines connected to the drain diffusion layer are laid out in a column direction, control gate lines are laid out in a row direction, and source lines connected to the source diffusion layer are laid out in the column direction.

Owner:UNISANTIS ELECTRONICS SINGAPORE PTE LTD +1

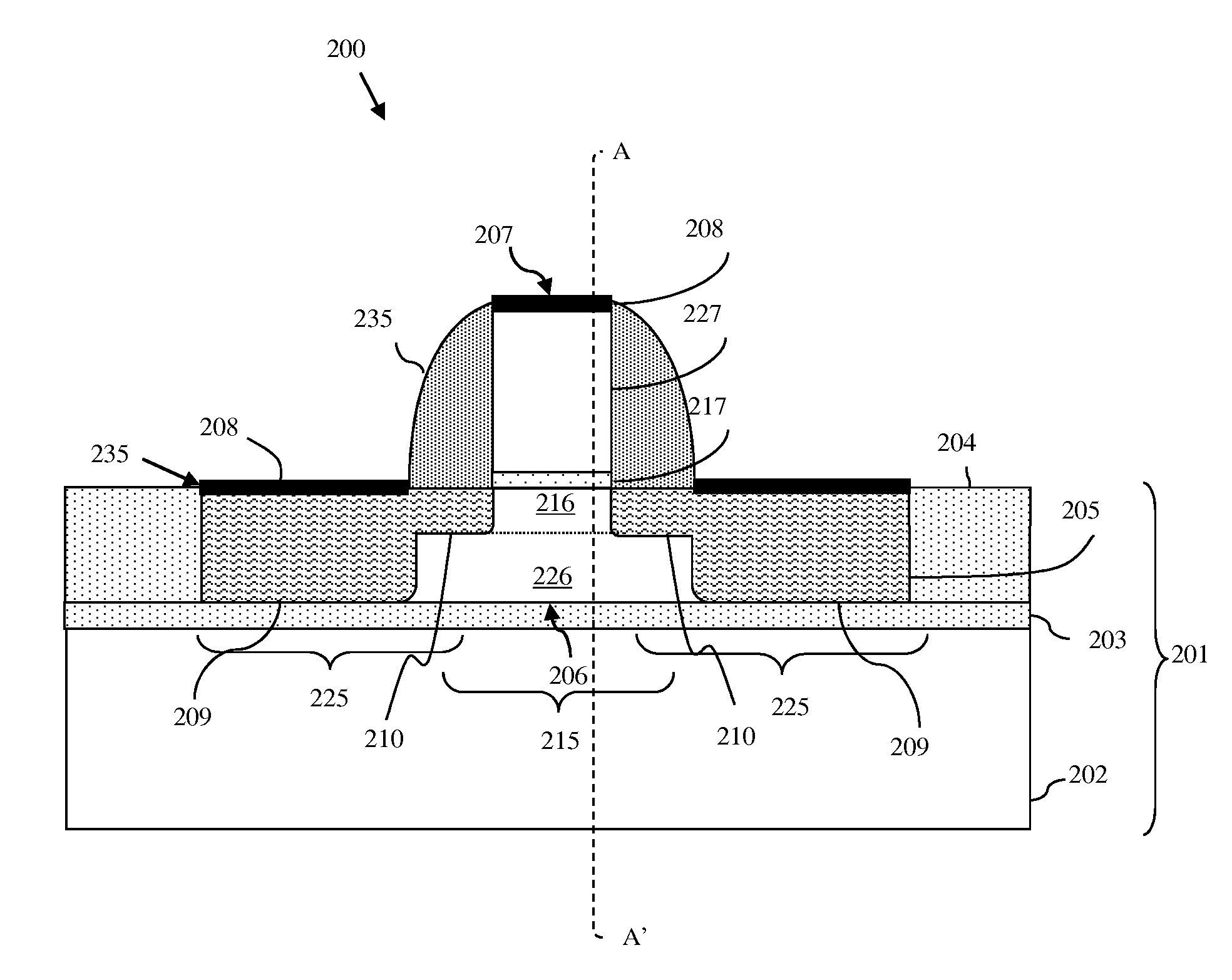

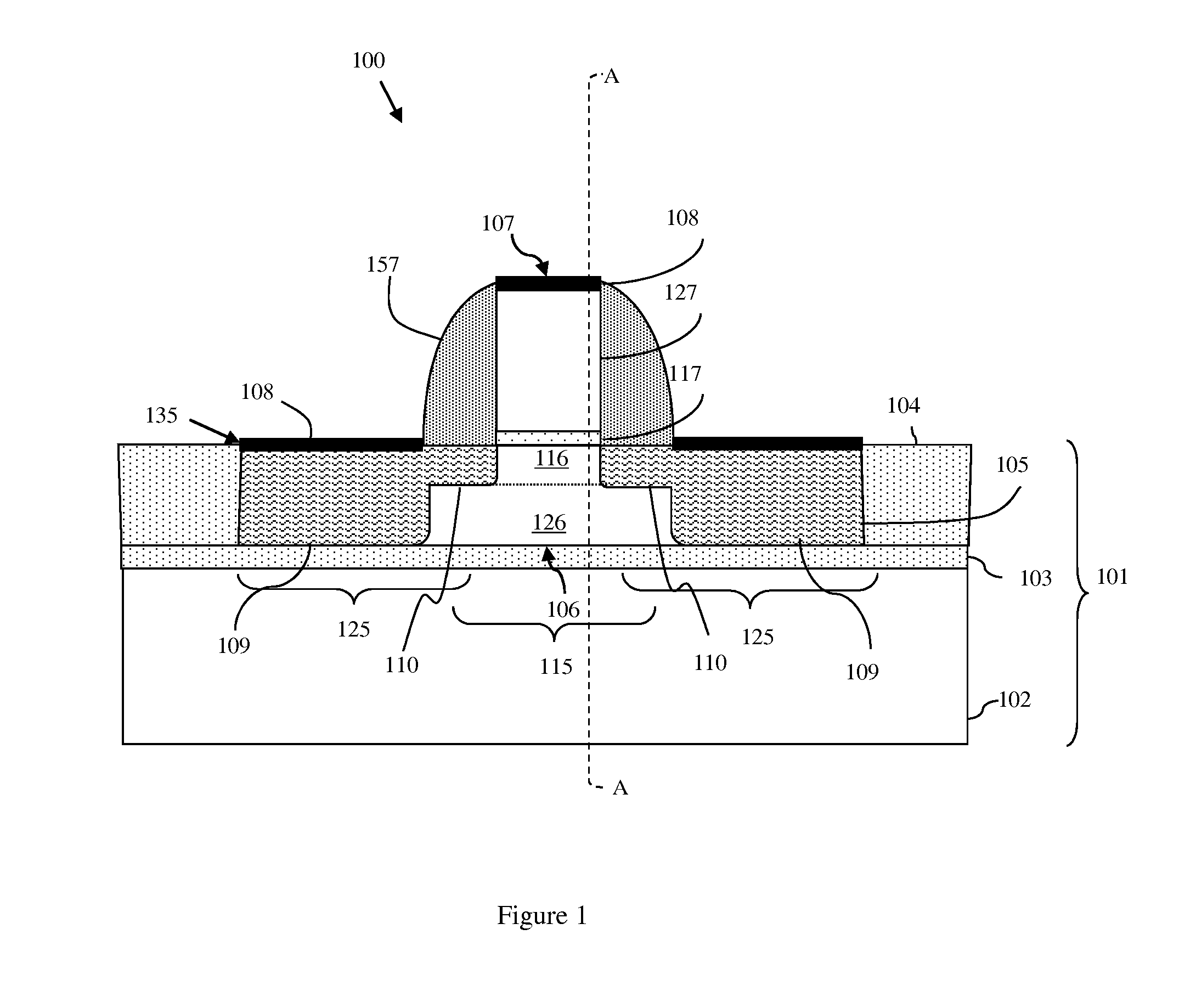

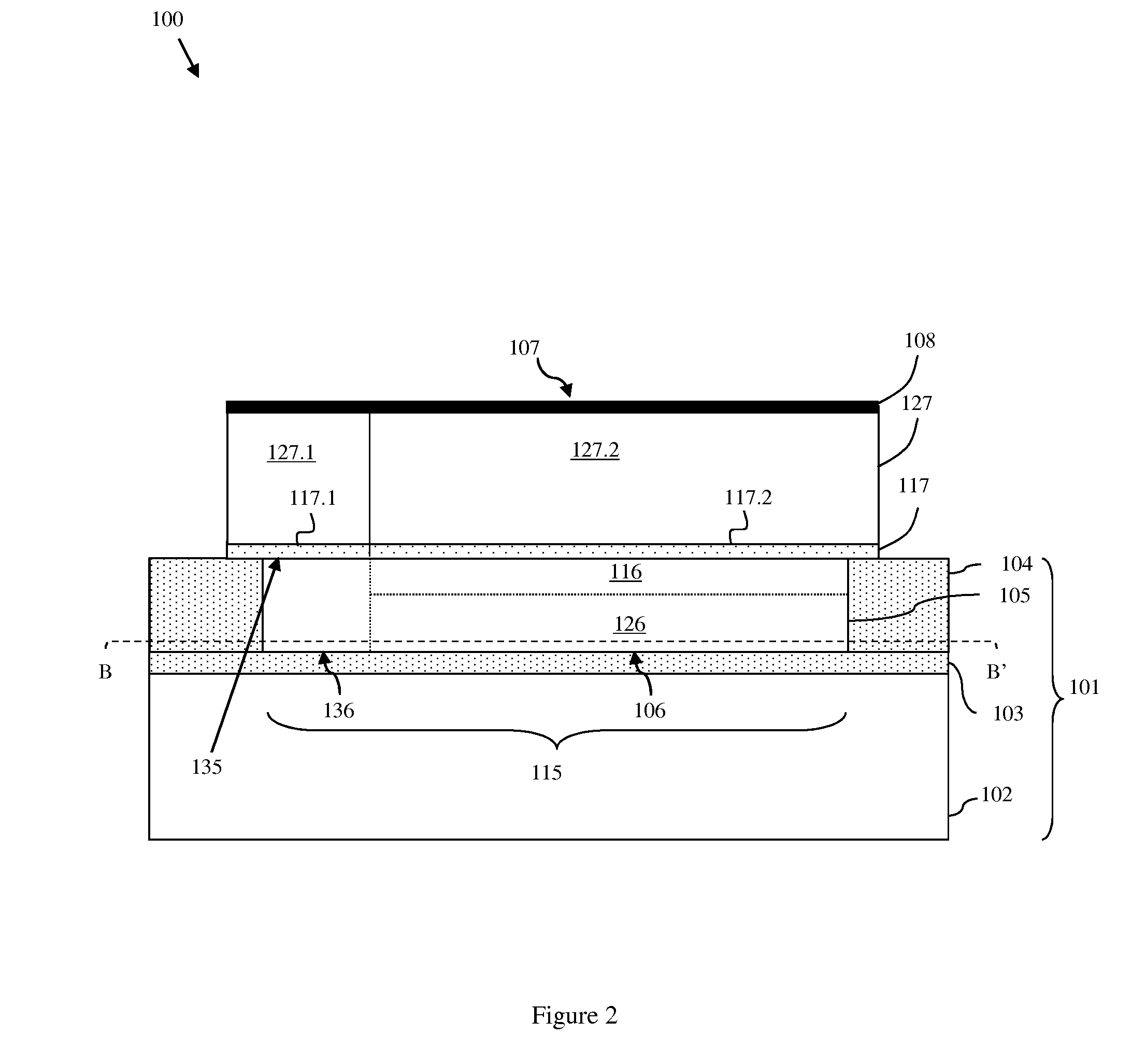

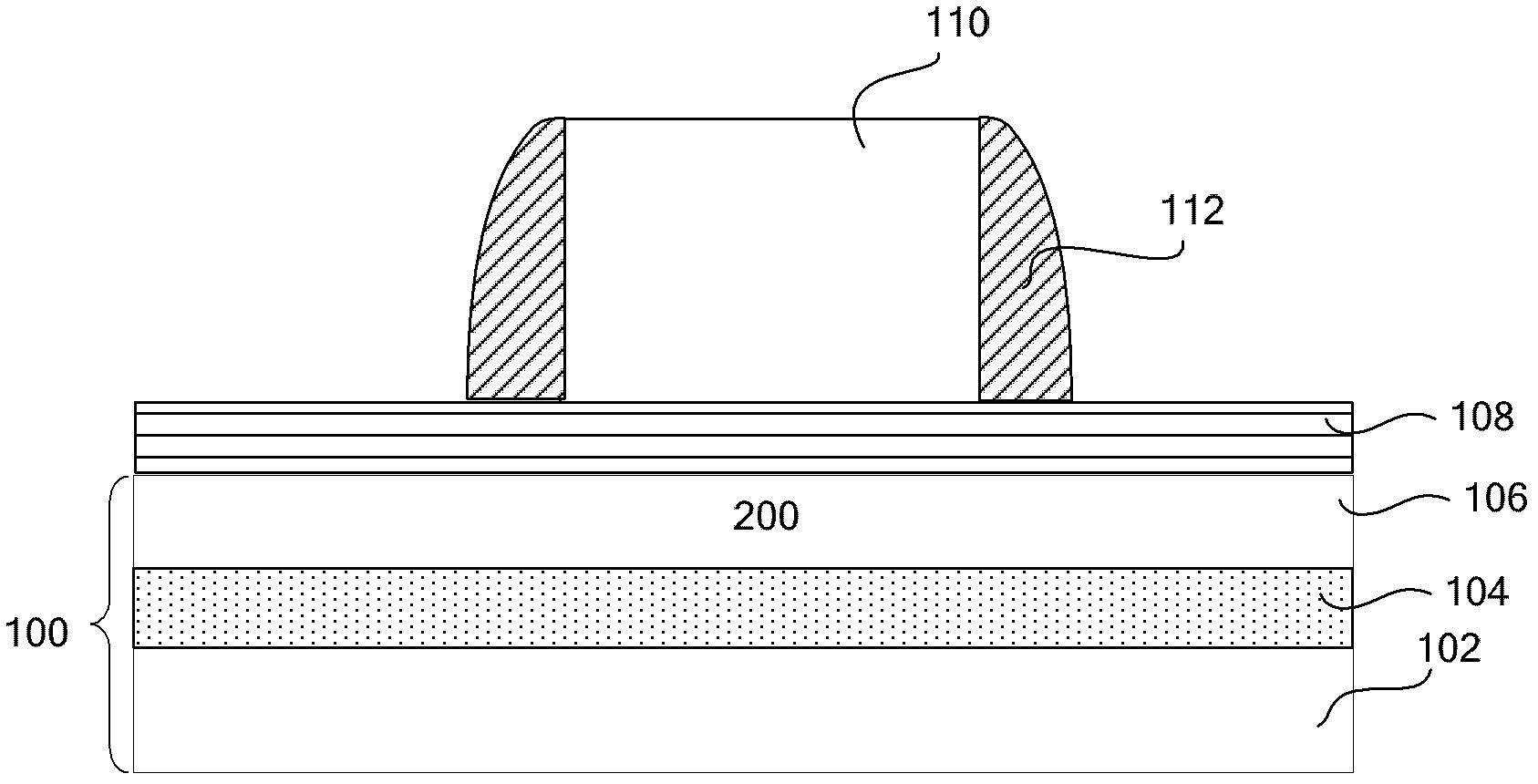

PARTIALLY DEPELETED (DP) SEMICONDUCTOR-ON-INSULATOR (SOI) FIELD EFFECT TRANSISTOR (FET) STRUCTURE WITH A GATE-TO-BODY TUNNEL CURRENT REGION FOR THRESHOLD VOLTAGE (Vt) LOWERING AND METHOD OF FORMING THE STRUCTURE

ActiveUS20120146146A1Enhanced generationEnhanced recombinationSolid-state devicesSemiconductor/solid-state device manufacturingHigh concentrationDopant

Disclosed are embodiments of a field effect transistor with a gate-to-body tunnel current region (GTBTCR) and a method. In one embodiment, a gate, having adjacent sections with different conductivity types, traverses the center portion of a semiconductor layer to create, within the center portion, a channel region and a GTBTCR below the adjacent sections having the different conductivity types, respectively. In another embodiment, a semiconductor layer has a center portion with a channel region and a GTBTCR. The GTBTCR comprises: a first implant region adjacent to and doped with a higher concentration of the same first conductivity type dopant as the channel region; a second implant region, having a second conductivity type, adjacent to the first implant region; and an enhanced generation and recombination region between the implant regions. A gate with the second conductivity type traverses the center portion.

Owner:TAIWAN SEMICON MFG CO LTD

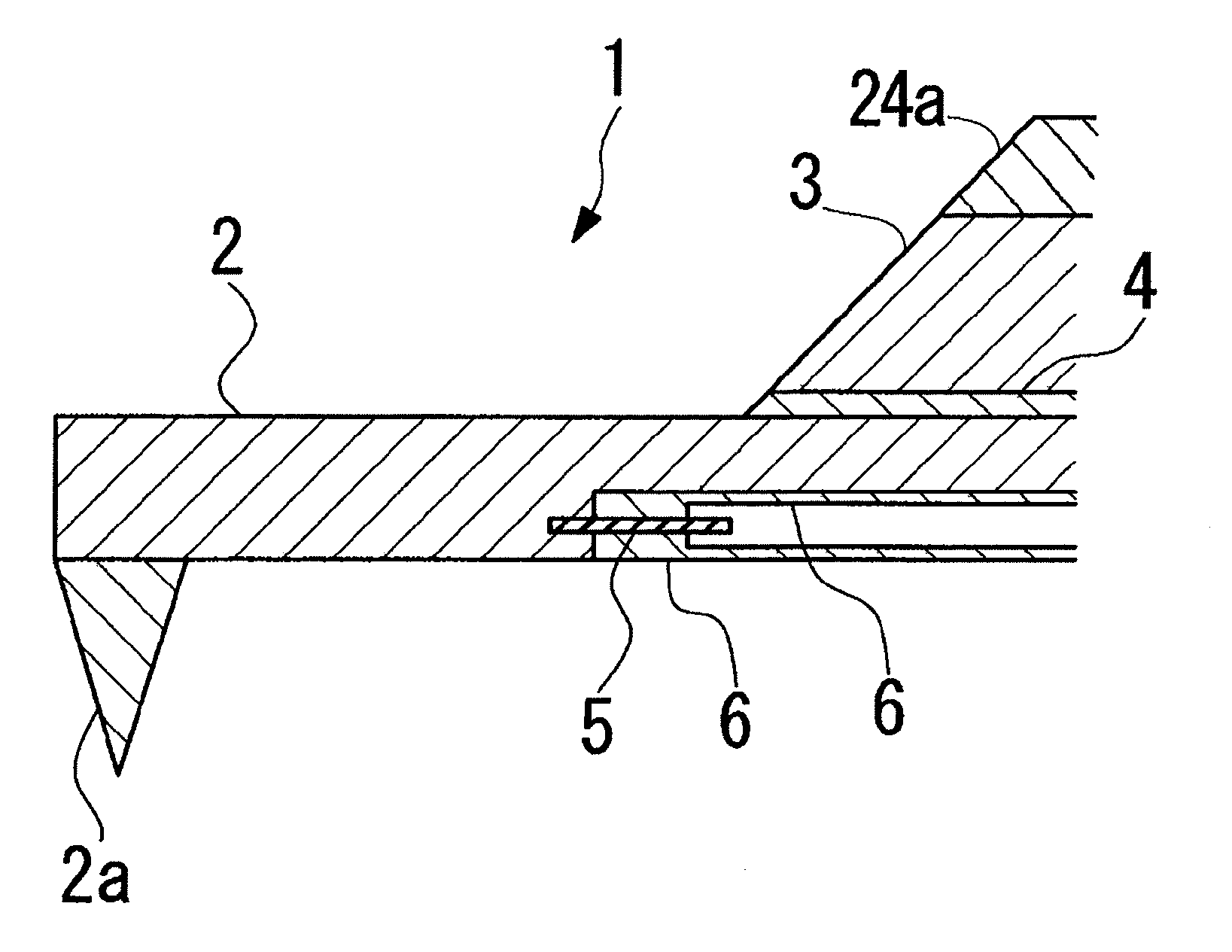

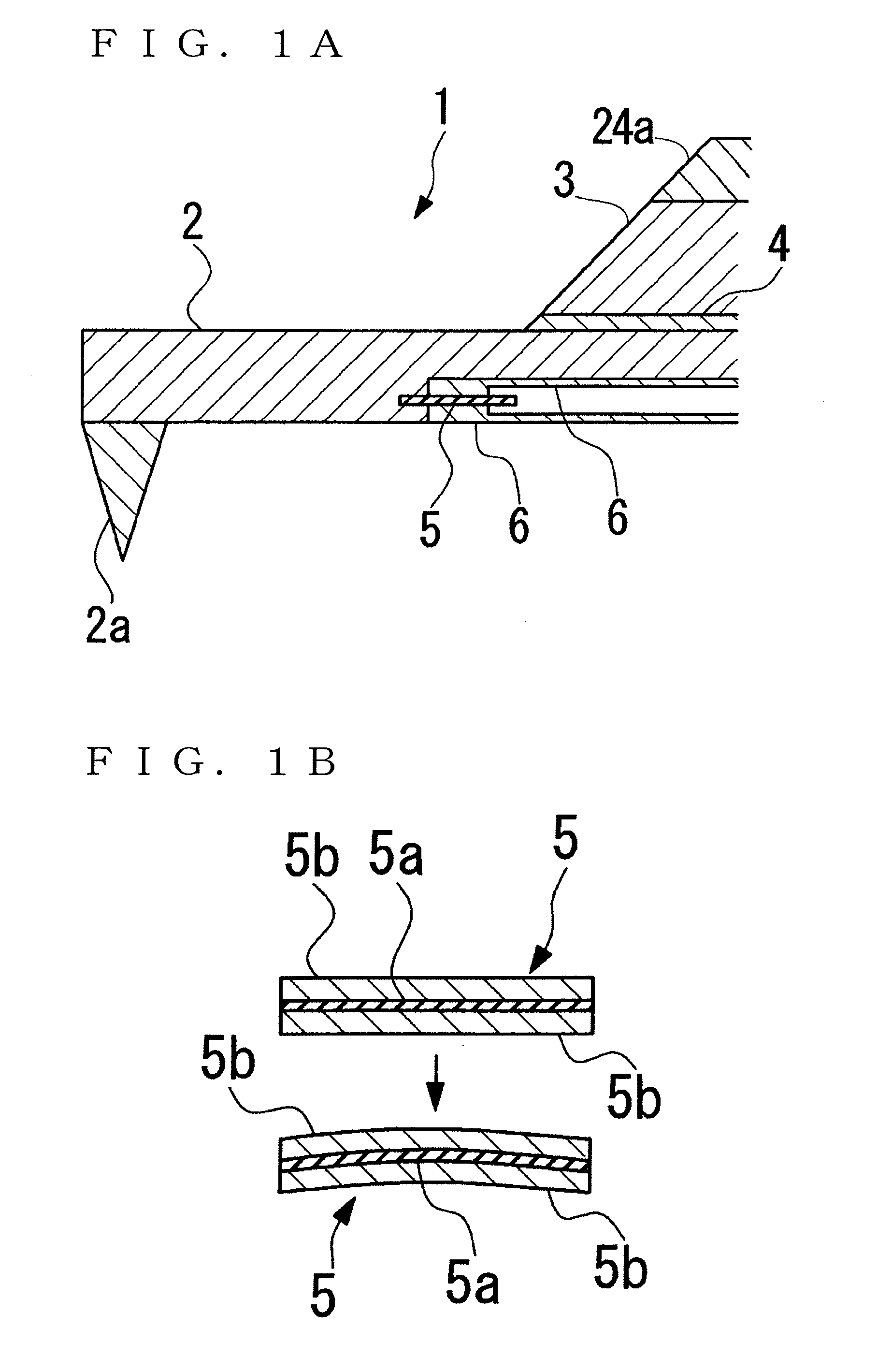

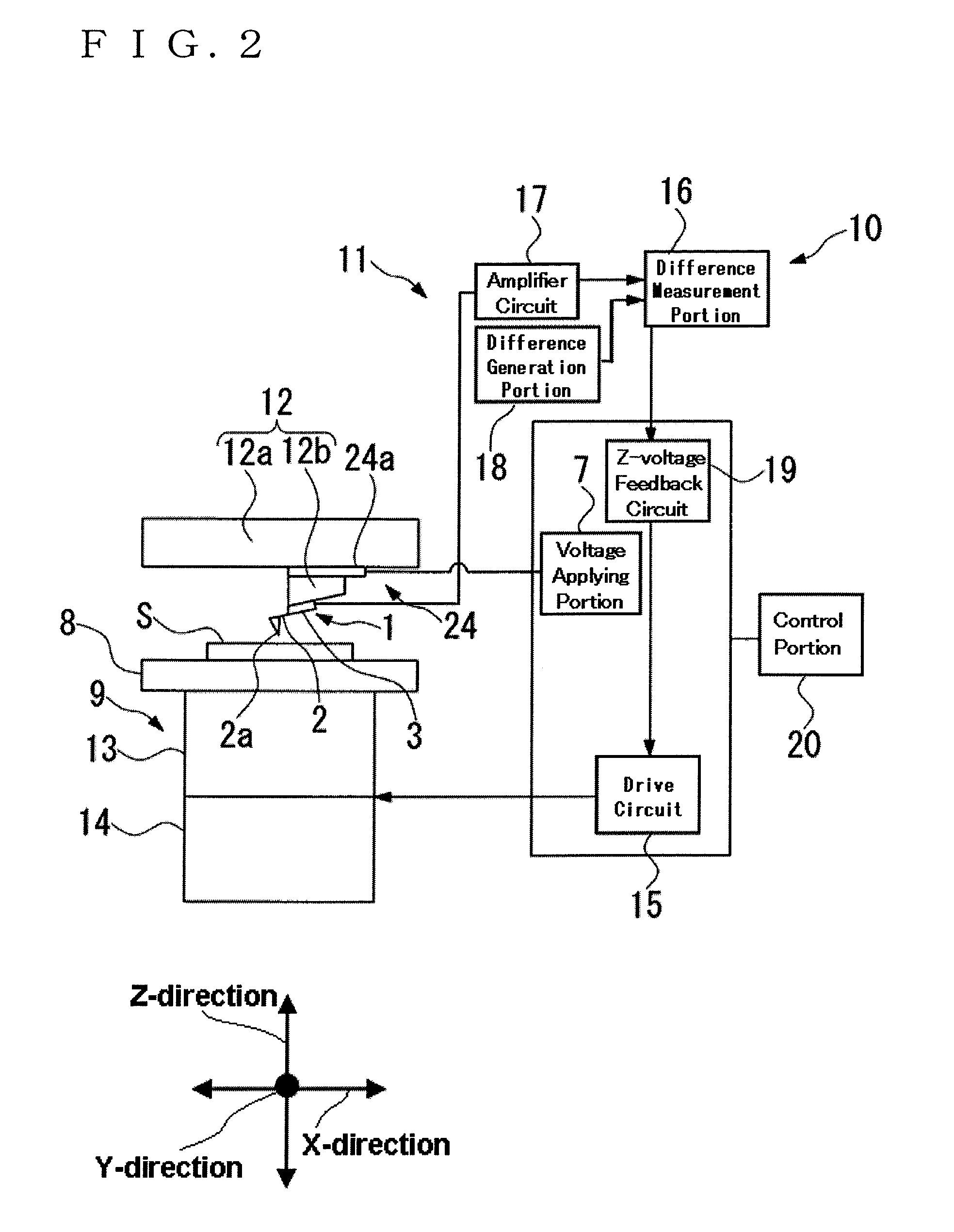

Cantilever, cantilever system, and probe microscope and adsorption mass sensor including the cantilever system

InactiveUS20100058499A1Simple structureSignificant changeSurface/boundary effectNanotechnologyPower flowElectrical conductor

A displacement detection portion is provided in a lever portion of a cantilever or between the lever portion and a main body portion. The displacement detection portion is provided by laminating two conductor electrodes to sandwich an insulating portion. A thickness of the insulating portion (electrode interval) is set to a value capable of detecting a variation in tunnel current due to a change in electrode interval which corresponds to a displacement of the lever portion while a predetermined voltage is applied. When the lever portion is slightly displaced, the interval between the conductor electrodes changes. Therefore, the displacement may be detected as the variation in tunnel current at high resolution with sensitivity of an exponential multiple of the change in interval.

Owner:HITACHI HIGH TECH SCI CORP

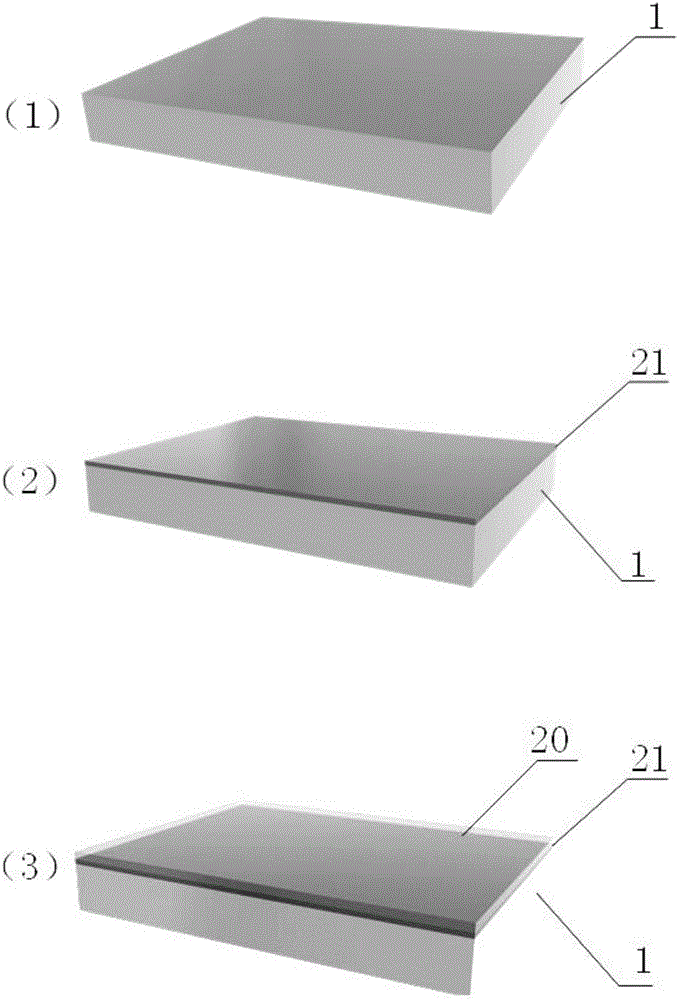

DNA sequencing device and manufacturing method

InactiveCN105838592AImprove signal-to-noise ratioImprove interferenceBioreactor/fermenter combinationsBiological substance pretreatmentsHexagonal boron nitrideGraphene nanoribbons

The invention provides a DNA sequencing device and a manufacturing method. The device mainly comprises a silicon dioxide thin film arranged on a double-side polished monocrystalline silicon piece. A silicon nitride thin film grows on the top of the silicon dioxide thin film. A bottom layer contact electrode is prepared on the silicon nitride thin film and covered with a bottom layer graphene micro-strip. The bottom layer graphene micro-strip is covered with a hexagonal boron nitride micro-strip. The hexagonal boron nitride micro-strip is covered with a top layer graphene micro-strip. A graphene-hexagonal boron nitride-graphene heterostructure is formed by the bottom layer graphene micro-strip, the hexagonal boron nitride micro-strip and the top layer graphene micro-strip. Graphene-hexagonal boron nitride-graphene nano-pores are etched. According to the device, the problem that a conventional solid-state nano-pore channel is too long, so that the sequencing resolution ratio does not reach single base is solved, and the problem that a tunneling electrode is difficult to manufacture in a tunneling current DNA sequencing method is solved. The advantages lay a foundation for achieving single base resolution ratio and direct nano-pore sequencing.

Owner:BEIJING JIAOTONG UNIV

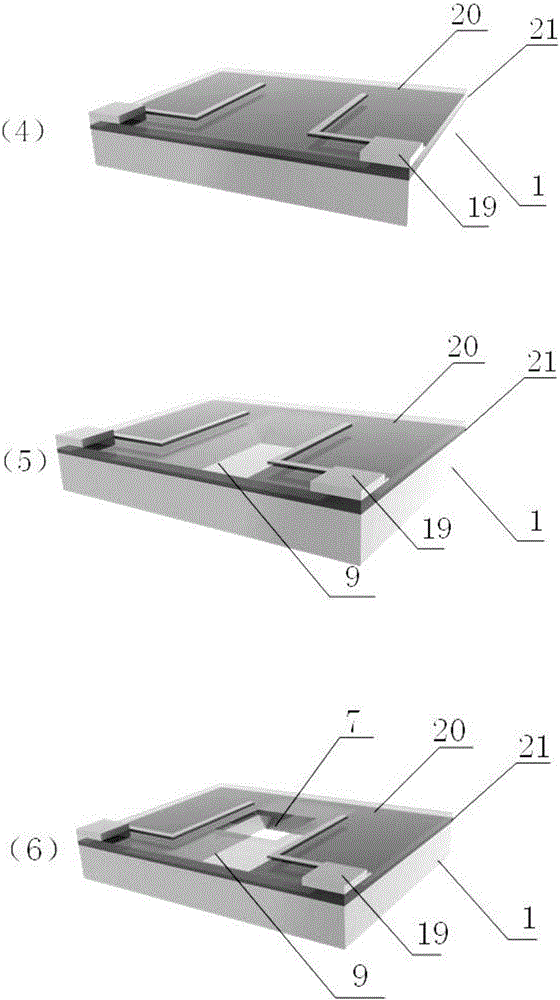

Tunneling transistor with hetero-material grid dielectrics and forming method of tunneling transistor

ActiveCN102610647AImprove driving abilityImprove gate control abilitySemiconductor/solid-state device manufacturingSemiconductor devicesPower flowEngineering

The invention provides a tunneling transistor with hetero-material grid dielectrics and a forming method of the tunneling transistor. The tunneling transistor comprises a substrate, a channel region, a source region, a drain region and a grid stack, wherein the channel region is formed in the substrate; the source region and the drain region are formed in the substrate and respectively at both sides of the channel region; the source region belongs to first type of heavy doping; the drain region belongs to second type of heavy doping; the grid stack is formed on the substrate; the grid stack comprises a grid dielectric layer and a grid electrode, wherein the grid dielectric layer is located on the channel region, and the grid electrode is located on the grid dielectric layer; the grid dielectric layer comprises a first section of grid dielectric near the source region and a second section of grid dielectric near the drain region; and the first section of grid dielectric and the second section of grid dielectric are different in material. Through introducing local stress into the channel region by the first section of grid dielectric near the source region, the tunneling effective mass is changed, and the tunneling current is increased, and through introducing the local stress into the channel region by the second section of grid dielectric near the drain region, the electronic mobility is increased.

Owner:TSINGHUA UNIV

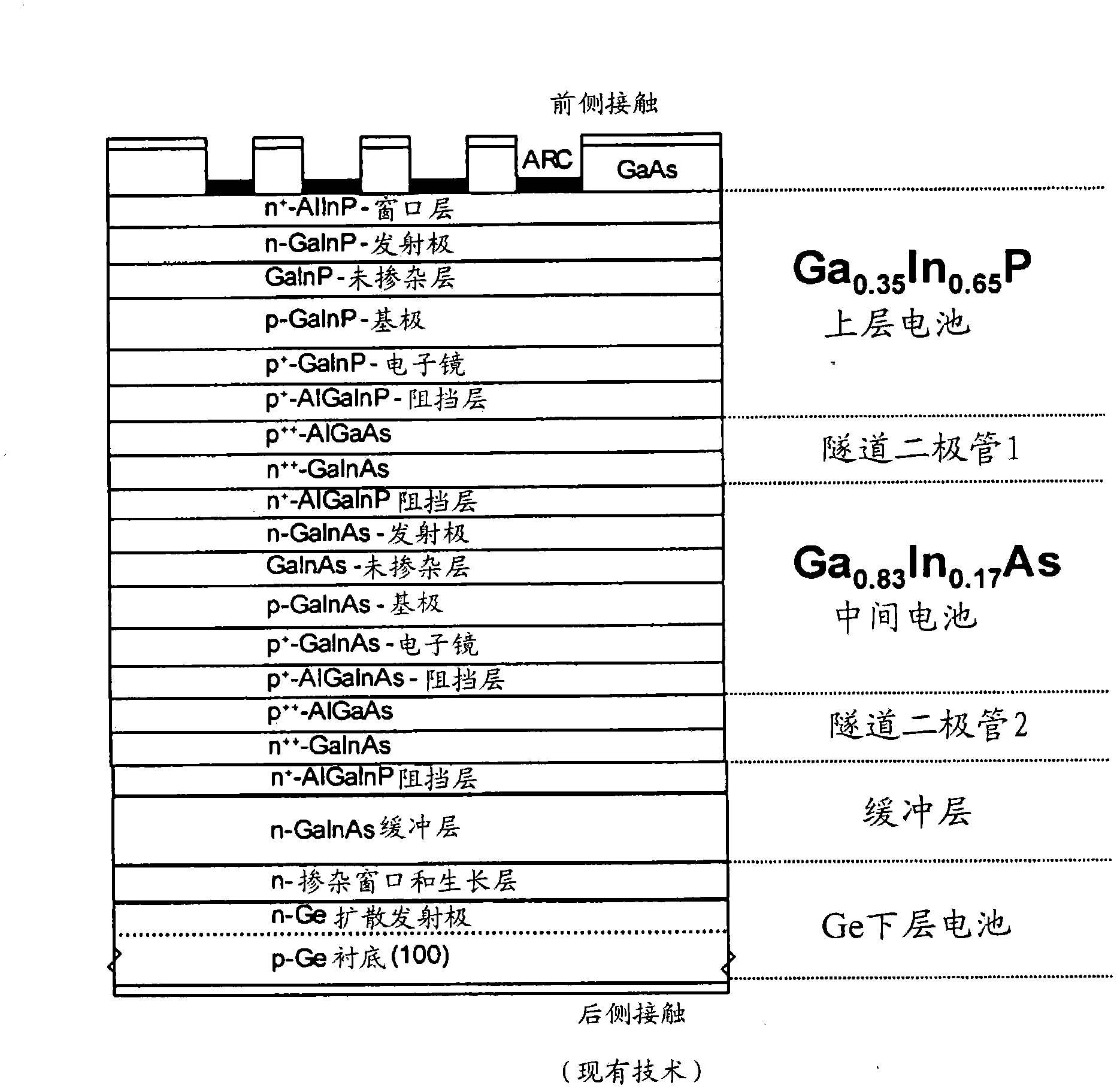

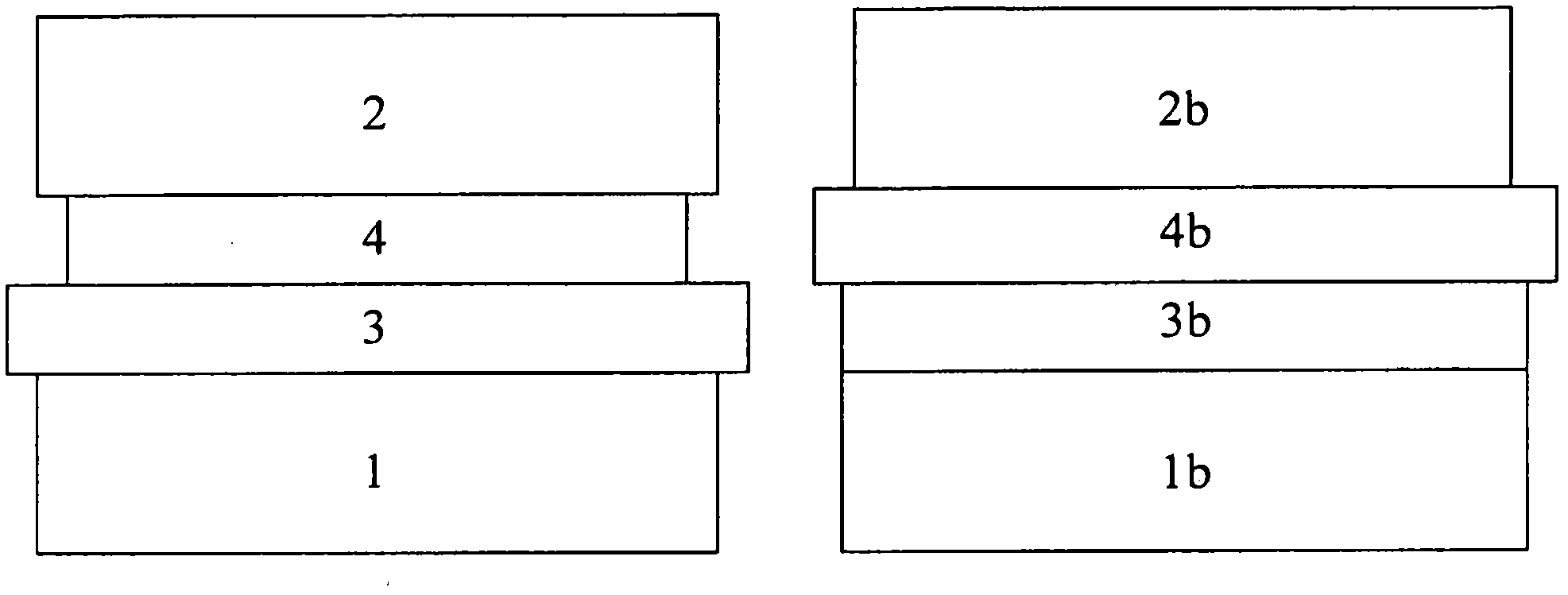

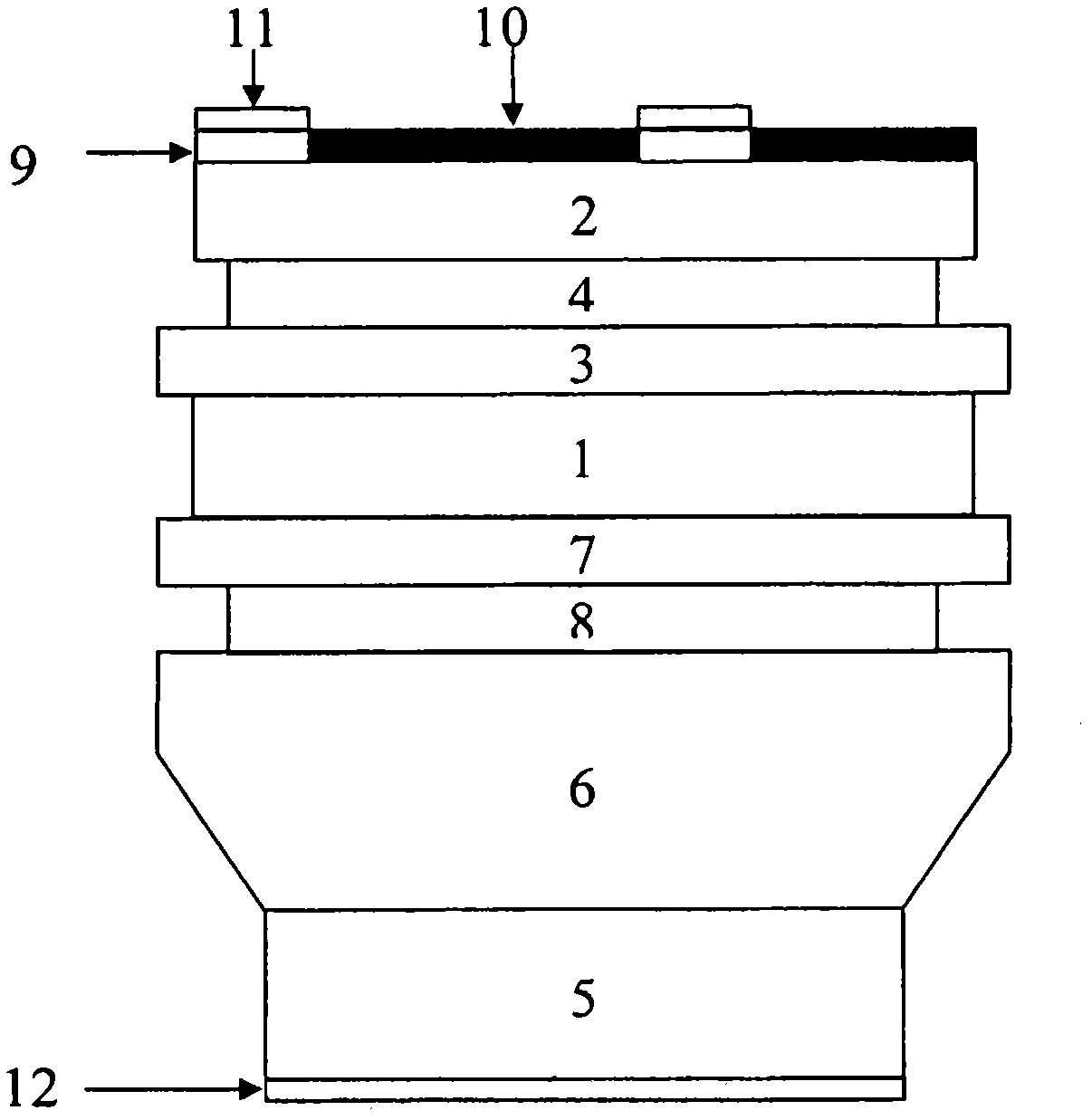

Tunnel diodes made of stress-compensated compound semiconductor layers

The invention relates to semiconductor components, particularly solar cells made of III-V compound semiconductors, as used in terrestrial PV concentrator systems or for the electrical power supply in satellites. It is also used in other optoelectronic components, such as laser and light emitting diodes, where either high tunnel current densities are required or special materials are used, and where stress of the overall structure is not desirable. The invention consists of forming tunnel diodes from semiconductor components made of stress-compensated semiconductor layers.

Owner:FRAUNHOFER GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG EV

A preparation method of nano-slit array of electron emission source of SED display

InactiveCN102262991AAddressing the source of strain required for fractureGuaranteed uniformityDecorative surface effectsChemical vapor deposition coatingStress concentrationTension stress

The invention relates to a preparation method of an electron emission source nano seam array of a surface conduction electron emitter display (SED). A layer of a laser photoexpansion polymer material is introduced between a transparent base material and an electron emission thin film material with a stress concentration opening, so that a sandwich structure of the transparent base material, the laser photoexpansion polymer material and the electron emission material is formed; laser irradiates the laser photoexpansion polymer material in a seam of a lead electrode on one side, which does not has an electron emission source pattern structure, of the transparent base material, so that the volume of the laser photoexpansion polymer material is expanded and a pulling stress is generated inside the electron emission thin film material on the surface of the laser photoexpansion polymer material; and when the pulling stress reaches a breakage limit of the thin film material, the electron emission thin film material is broken to form a nano crack structure. In the method, by introducing the laser photoexpansion polymer material, the problem of a stress source required by breakage of the electron emission thin film can be solved and the position of a crack can be controlled precisely; meanwhile, array mirror scanning is realized by an in-situ tunnel current control method, and the uniformity of electron emission characteristics of array nano seams can be guaranteed.

Owner:XI AN JIAOTONG UNIV

Pressure-sensitive type display screen touch unit, touch screen and manufacturing method of pressure-sensitive type display screen touch unit

ActiveCN104714672ASimple designHigh sensitivityInput/output processes for data processingCapacitanceEngineering

Disclosed are a pressure-sensitive display touch unit, a touch screen, and a manufacturing method thereof. The touch unit mainly comprises a drive electrode, a lower electrode, and a dielectric layer between the drive electrode and the lower electrode. When a pressure is applied between the drive electrode and the lower electrode, a tunnel current IT is formed, and a voltage VT exists between the drive electrode and the lower electrode. By using the touch unit of the present invention, an external pressure can be converted into a current signal, and the pressure becomes an information input manner. Further, by combining the touch unit of the present application with an existing capacitive touch screen or resistive touch screen, the touch unit not only can possess the existing multi-point touch function, but also can sensitively sense the change in pressure and enhance the function of the existing touch screen, providing more operational applications for the touch screen.

Owner:KUNSHAN NEW FLAT PANEL DISPLAY TECH CENT +1

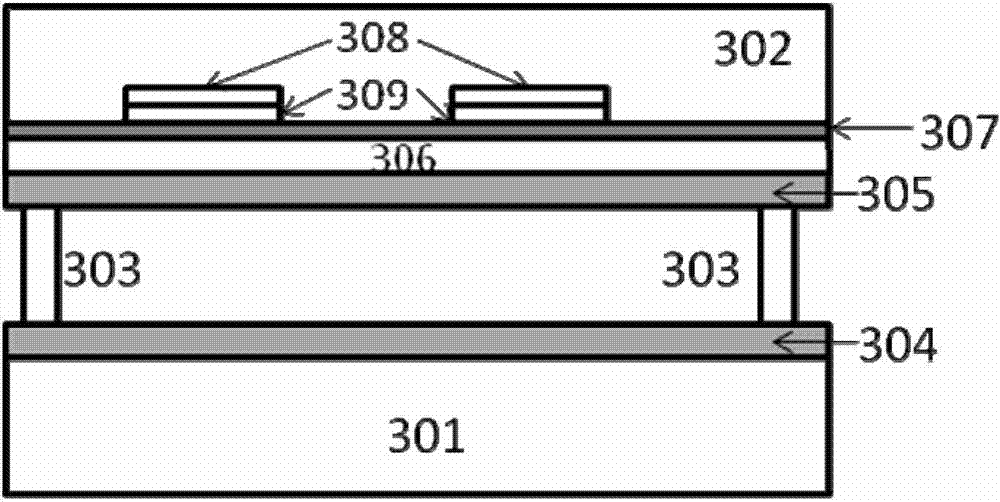

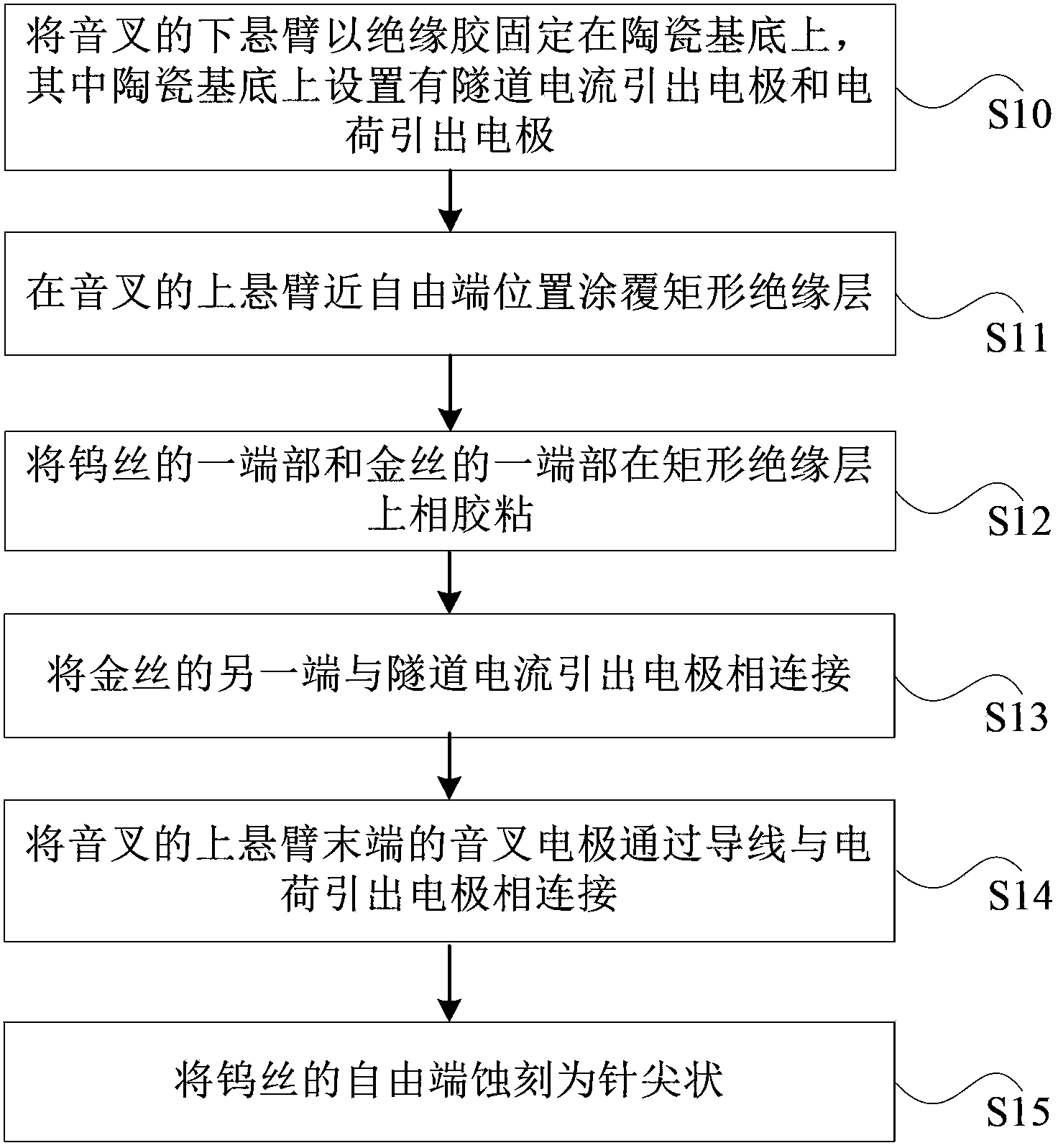

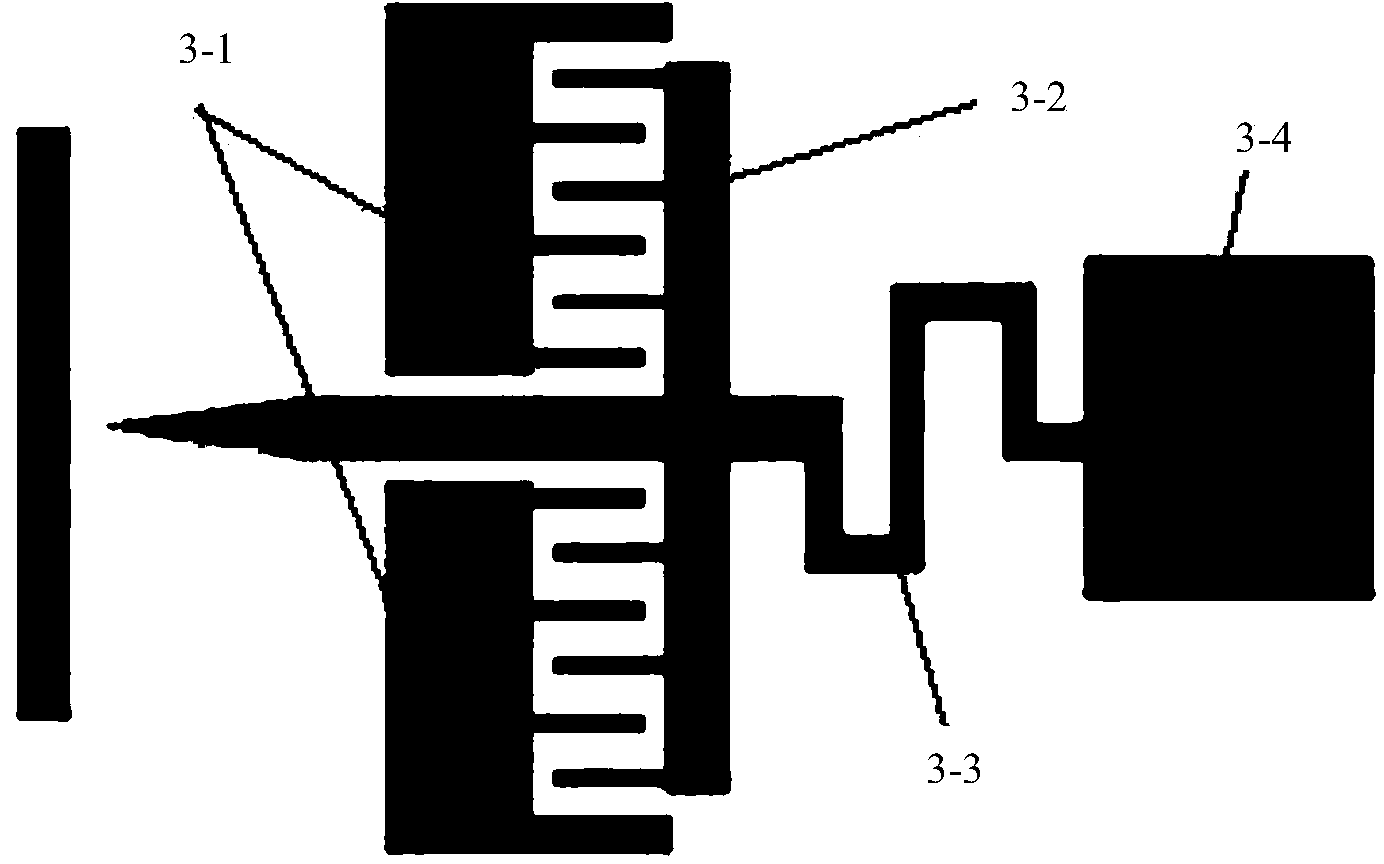

Manufacturing method for atomic power sensor, sensor, and atomic power sensor measuring apparatus and method thereof

InactiveCN103424572AHigh resolutionFast preparationScanning probe microscopyPower sensorImage resolution

The invention discloses a manufacturing method for an atomic power sensor, a sensor, and an atomic power sensor measuring apparatus and a method thereof. The manufacturing method comprises: a lower cantilever of a tuning fork is fixed at a ceramic substrate by an insulation paste, wherein the ceramic pedestal is provided with a tunnel current extraction electrode and a charge extraction electrode and tuning fork electrodes are respectively arranged at the tail end of the upper cantilever and the tail end of the lower cantilever of the tuning fork; a rectangular insulated layer is coated at a position, approaching a free end, of the upper cantilever of the tuning fork; one end portion of a tungsten filament and one end portion of a spun gold are pasted at the rectangular insulated layer, wherein the tungsten filament and the spun gold are respectively perpendicular to the upper cantilever of the tuning fork and the spun gold is in an approximate U shape; the other end of the spun gold is connected with the tunnel current extraction electrode; the tuning fork electrode of the tail end of the upper cantilever of the tuning fork is connected with the charge extraction electrode by a lead; and the free end of the tungsten filament is etched into a shape of a needle tip. According to the invention, a small-amplitude atomic power sensor with precisely controllable parameters can be manufactured rapidly; the proportion of a short-range force in a measuring signal is improved; and the resolution ratio of the sensor is enhanced.

Owner:THE NAT CENT FOR NANOSCI & TECH NCNST OF CHINA

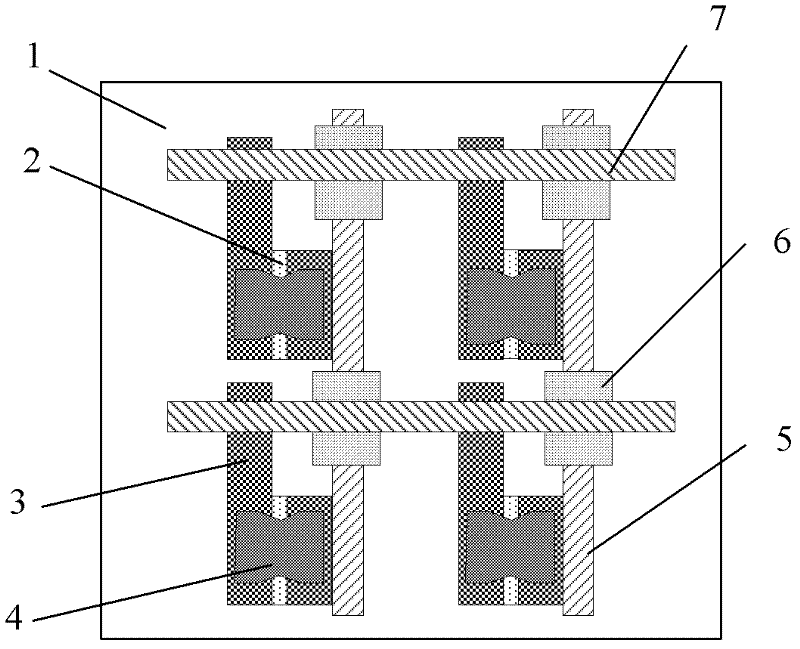

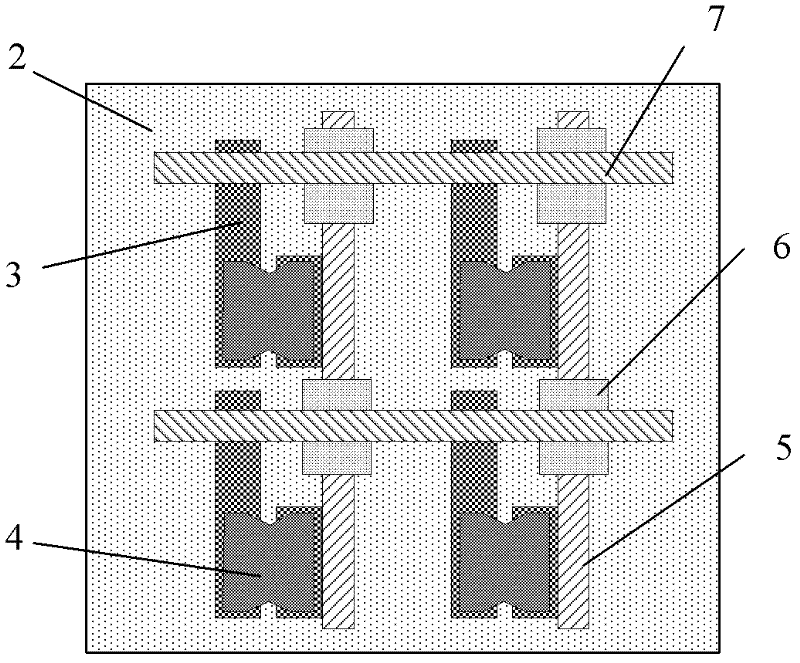

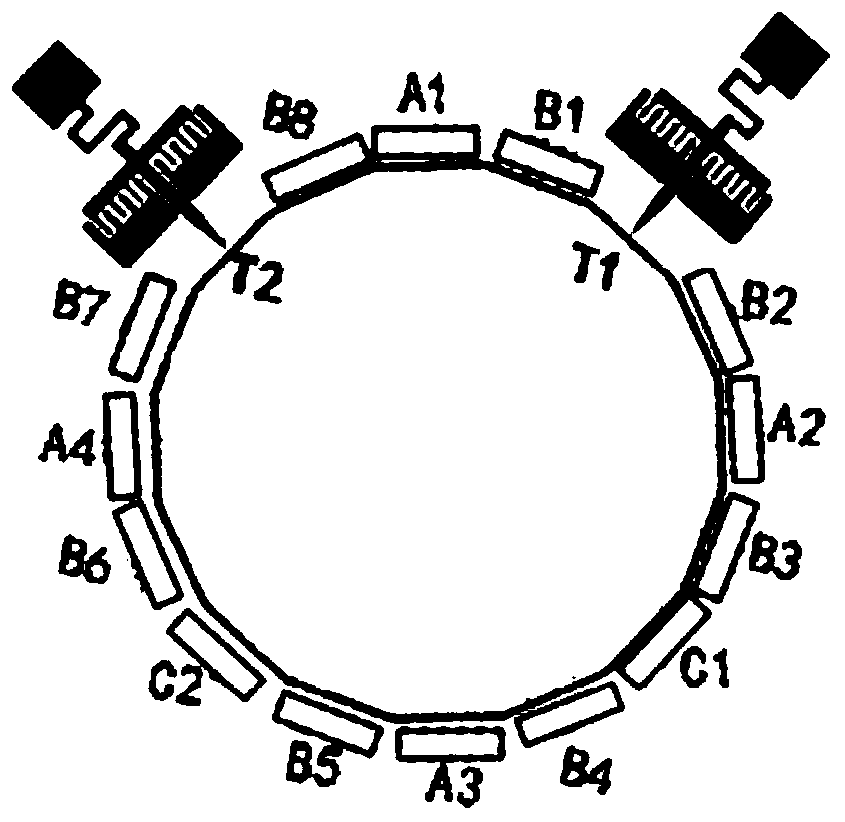

Tunnel type MEMS (Micro-electromechanical Systems) gyroscope

InactiveCN103913159AHigh sensitivityReduce driftTurn-sensitive devicesGyroscopeMicroelectromechanical systems

The invention discloses a tunnel type MEMS (Micro-electromechanical Systems) gyroscope and belongs to the technical field of micro-electromechanical systems. The tunnel type MEMS gyroscope provided by the invention comprises a thin plate with a normal hexadecagon shape; the thin plate is used as a sensitive mass block to be bonded on a glass substrate; each edge of the normal hexadecagon shape corresponds to one electrode; the sixteen electrodes are divided into four sets and are respectively used as driving electrodes, adjusting electrodes, feedback electrodes and wedged conical tip electrodes for generating tunneling current; the conical tip electrodes are arranged on a movable comb. The invention provides a brand-new structure and adopts the symmetrical polygonal mass block; the feedback electrodes and the adjusting electrodes are good for realizing the match of a driving modal frequency and a detection modal frequency, and the high sensitivity is realized; meanwhile, the movable comb is used for controlling the distance between the conical tip electrodes and the mass block; the two transverse conical tip electrodes are used for detecting the difference tunnel current so as to be good for reducing the drifting and further improve the detection sensitivity.

Owner:CHONGQING UNIV

Biomolecule sequencing devices, systems and methods

ActiveUS9644236B2Easy to distinguishImprove noiseMicrobiological testing/measurementSequence analysisPower flowElectrode pair

Devices, systems and methods for sequencing protein samples are provided. In some examples, currents generated when a monomer passes through between electrodes of a nanogap electrode pair are measured for each of several different distances, so that monomers are identified when compared to a reference physical quantity of a known monomer, which may be obtained from a current measured with a similar inter-electrode distance(s) at which each of plural kinds of monomers are identifiable and ordered with predetermined accuracy and based on a detected physical quantity obtained from a tunneling current, which may be further normalized by the use of one or more reference substances.

Owner:OSAKA UNIV

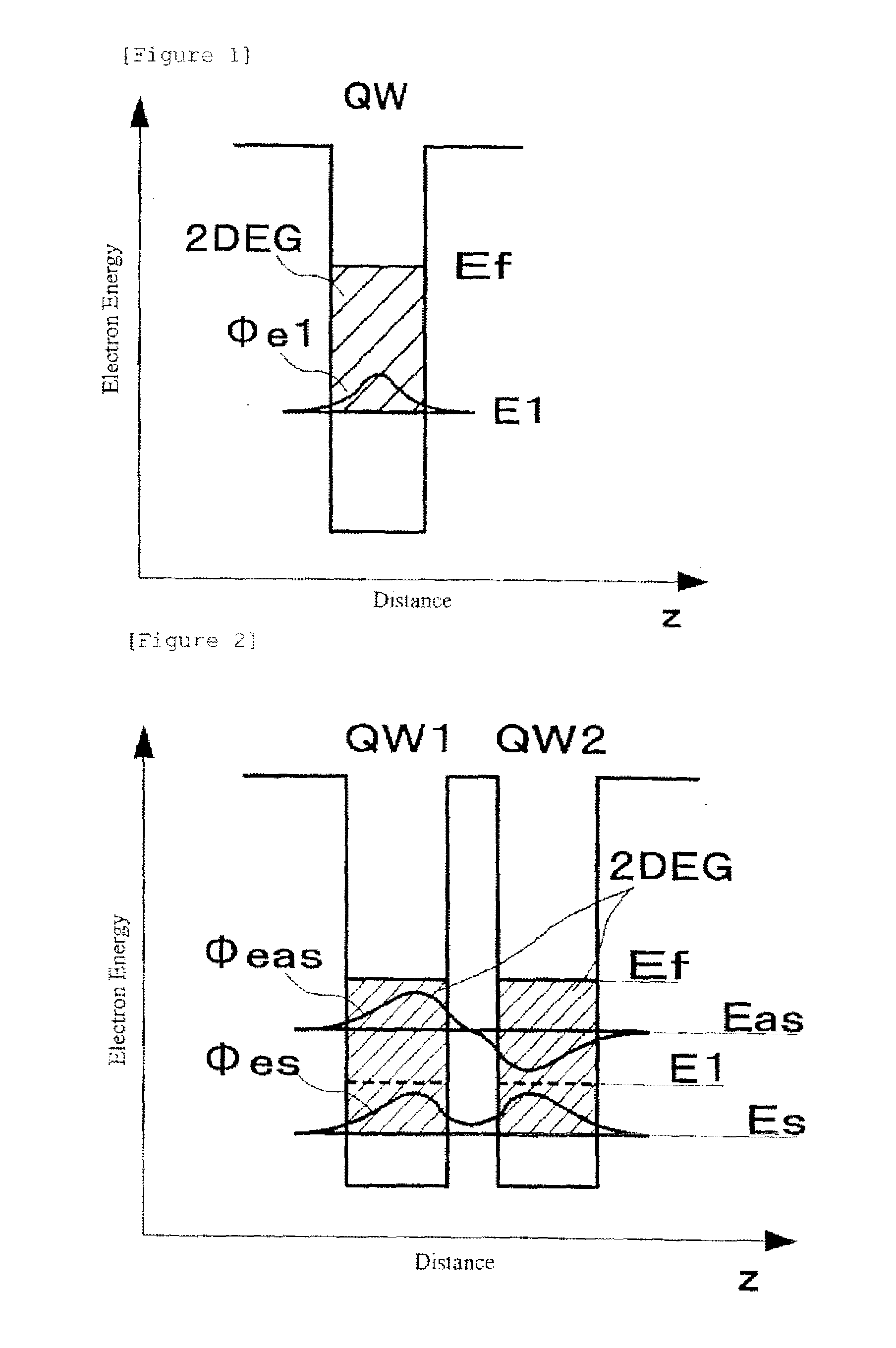

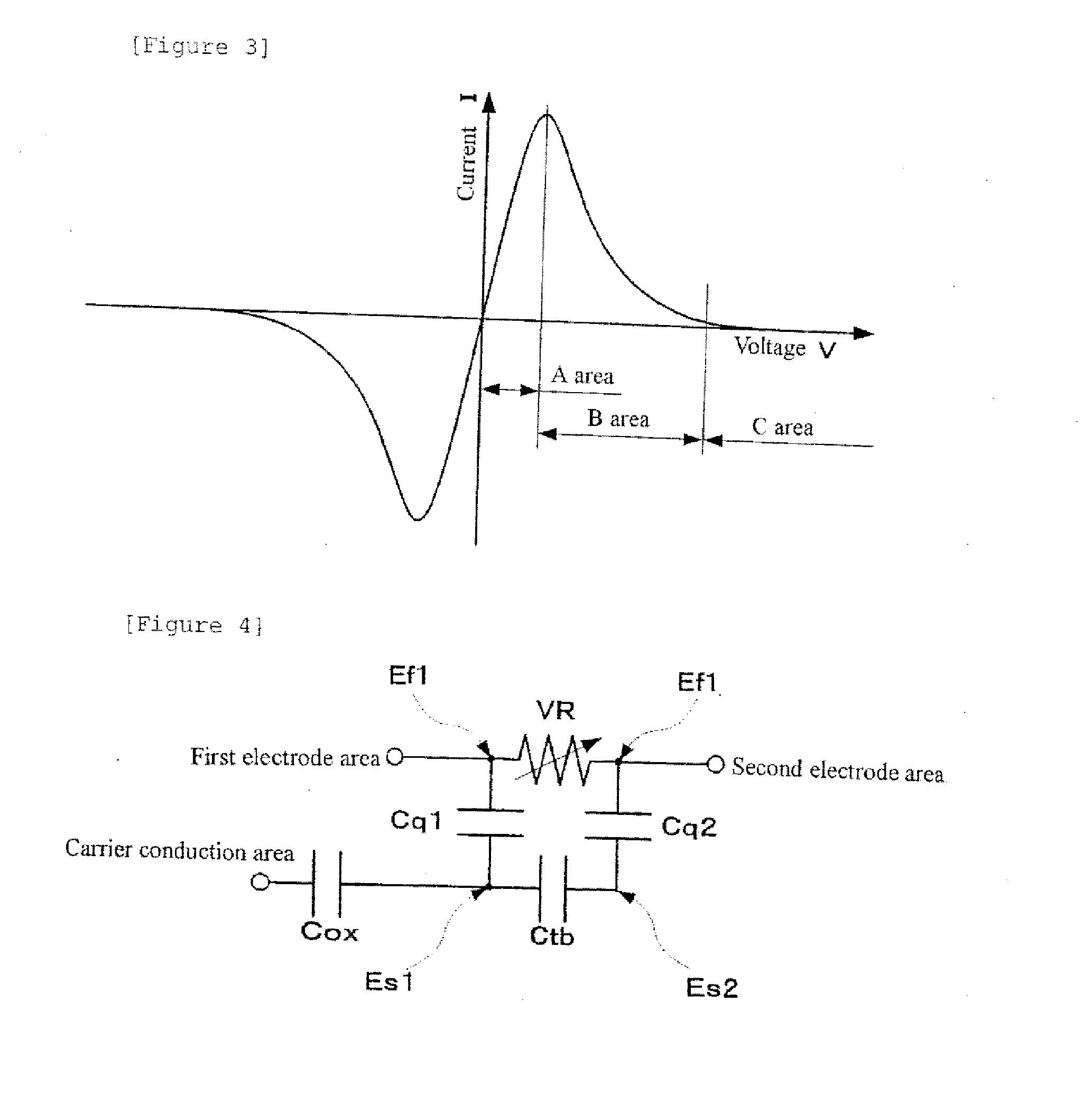

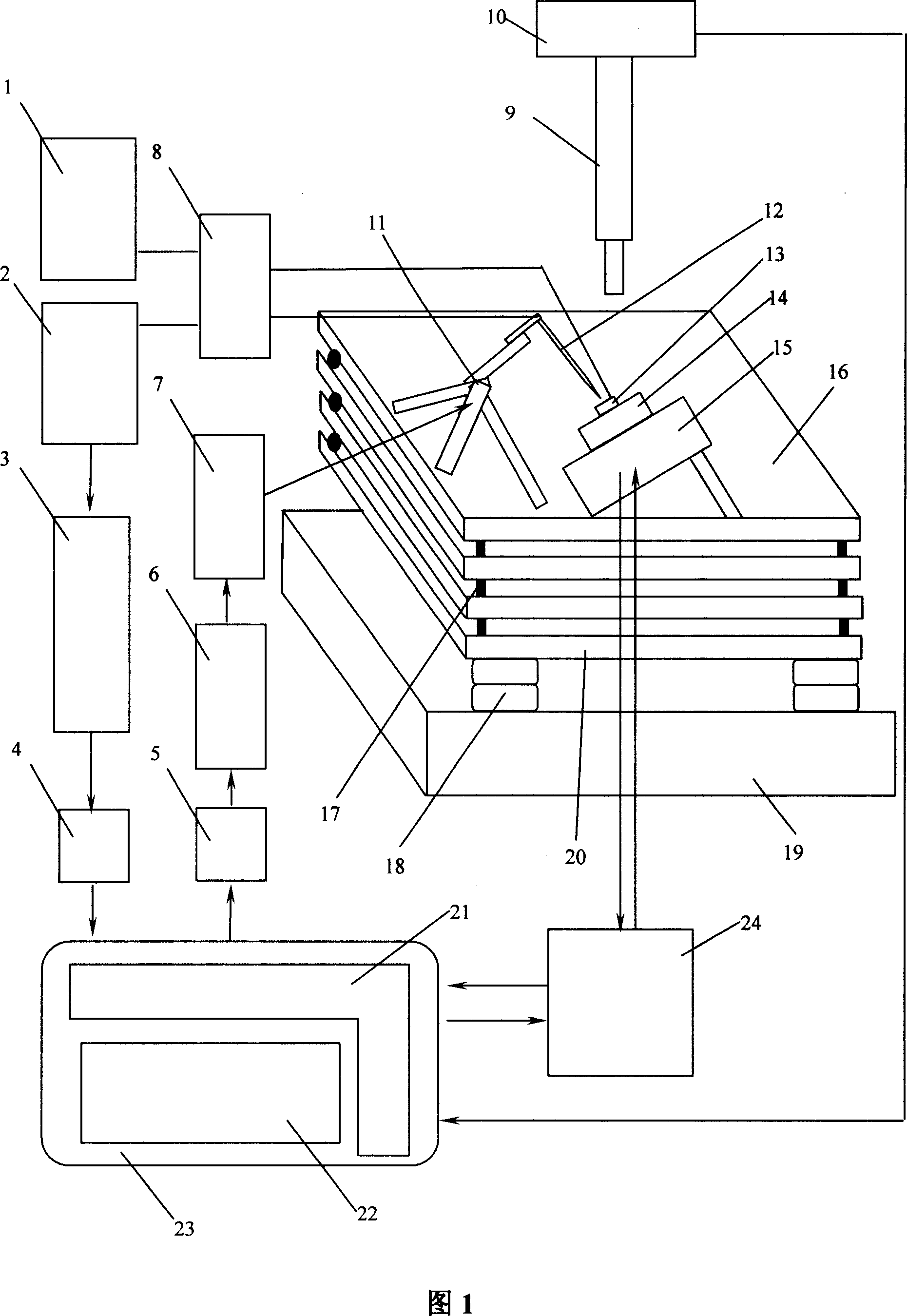

Complementary logic circuit

ActiveUS20090051384A1Improve performanceNanotechLogic circuits characterised by logic functionCharge carrierQuantum

A quantum device comprises first conductive members and second conductive members confining carriers in the z direction and having two dimensional electron gas on the xy plane. Third conductive members generating an electric field having an effect on the first conductive members. An insulating member easily passing a tunnel current between the first conductive members and the second conductive members. Another insulating member hardly passing a tunnel current between the first conductive members and the third conductive members. An electric field generated by a potential applied to the third conductive members has an effect on the sub-band of the first conductive members.

Owner:IBM CORP

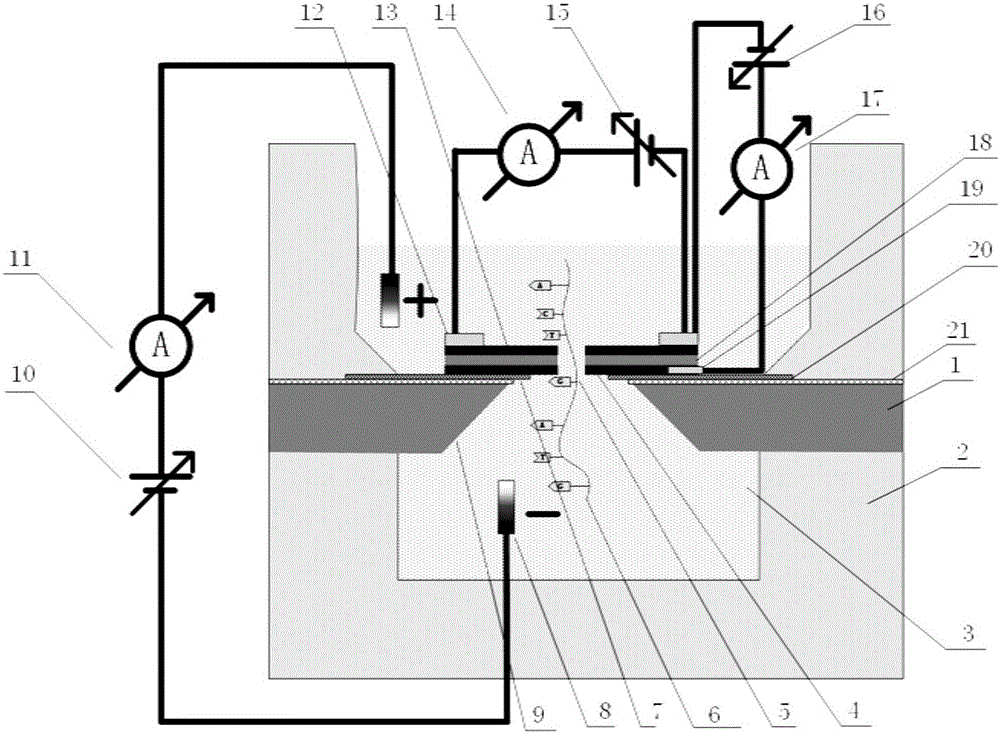

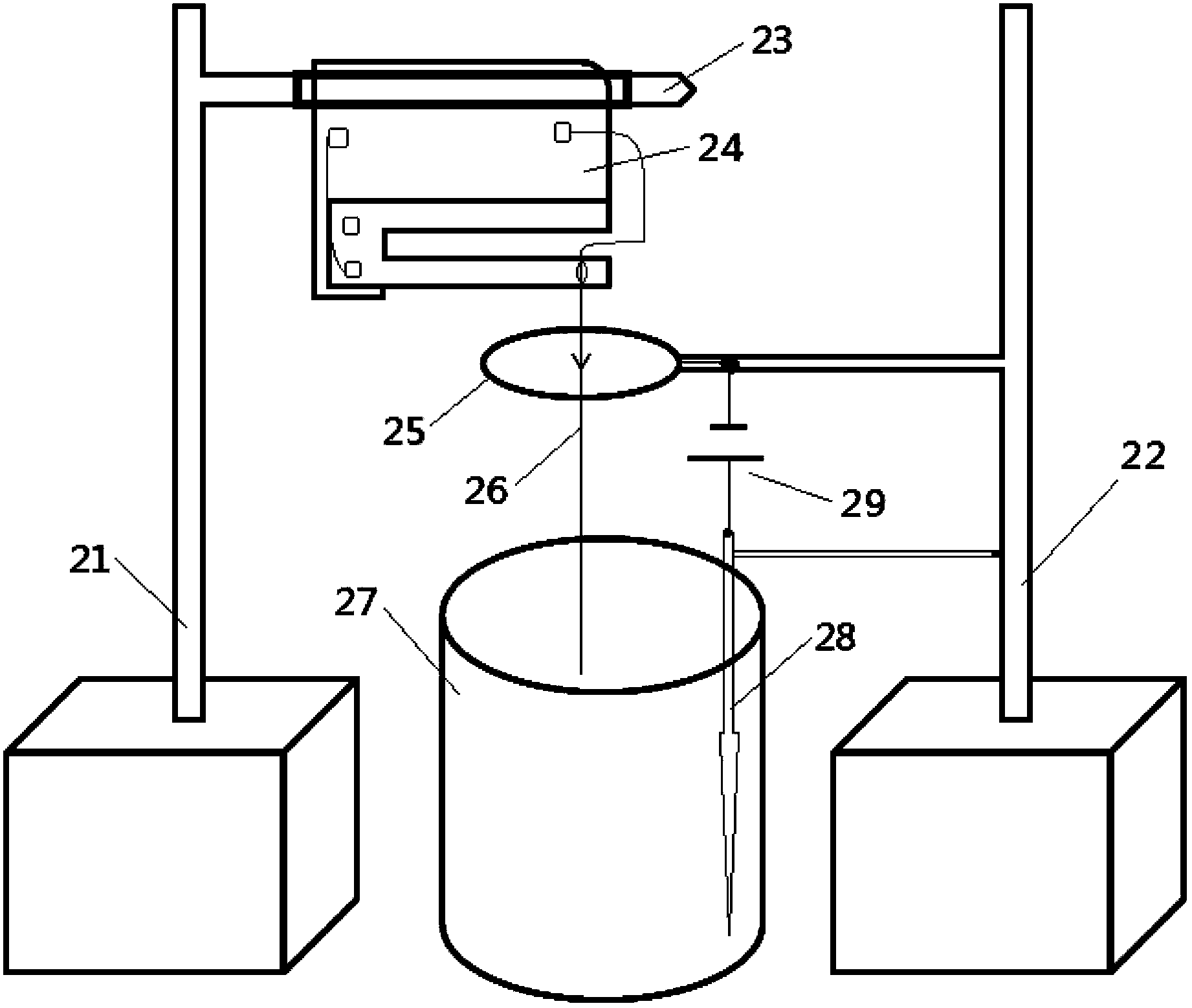

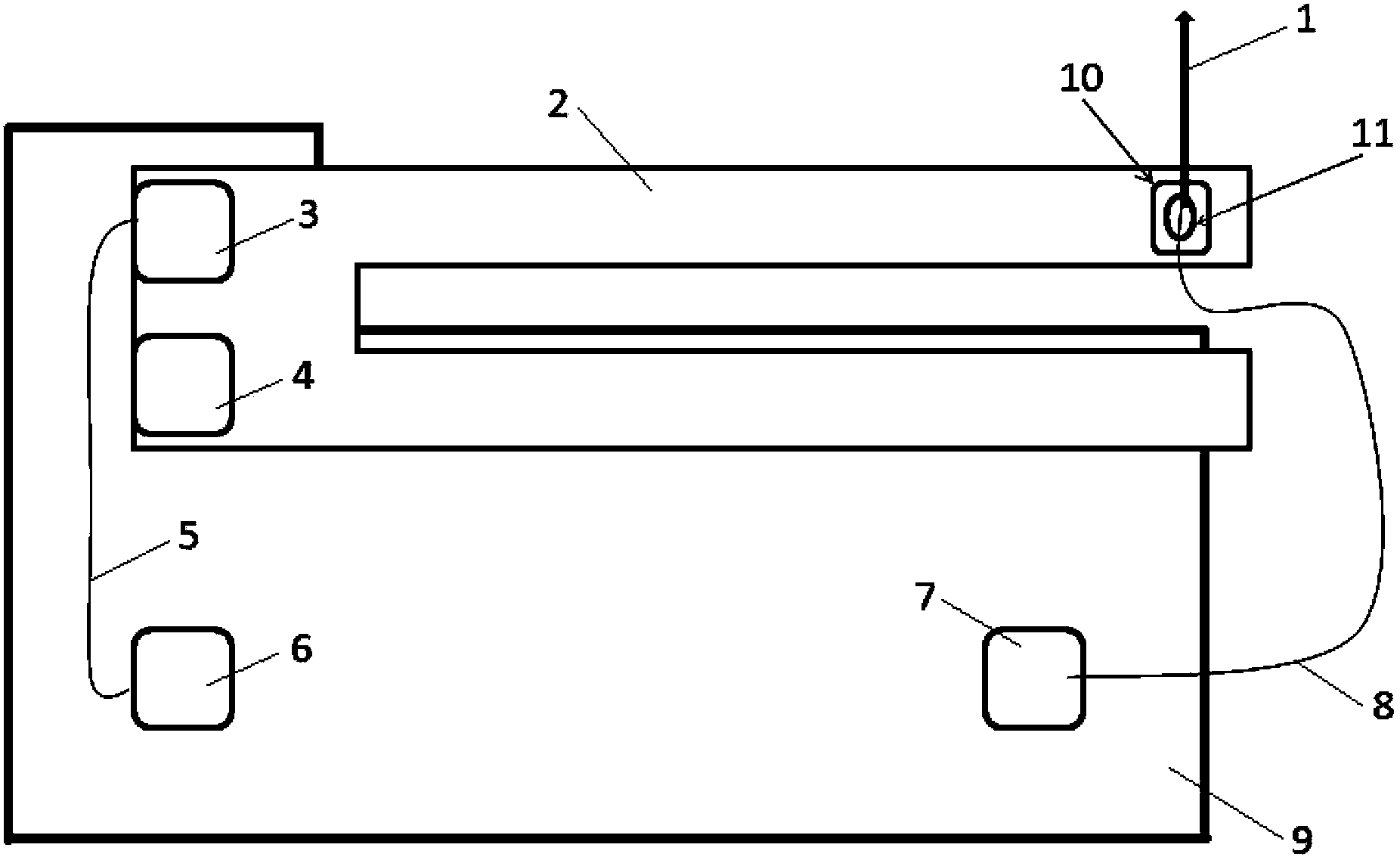

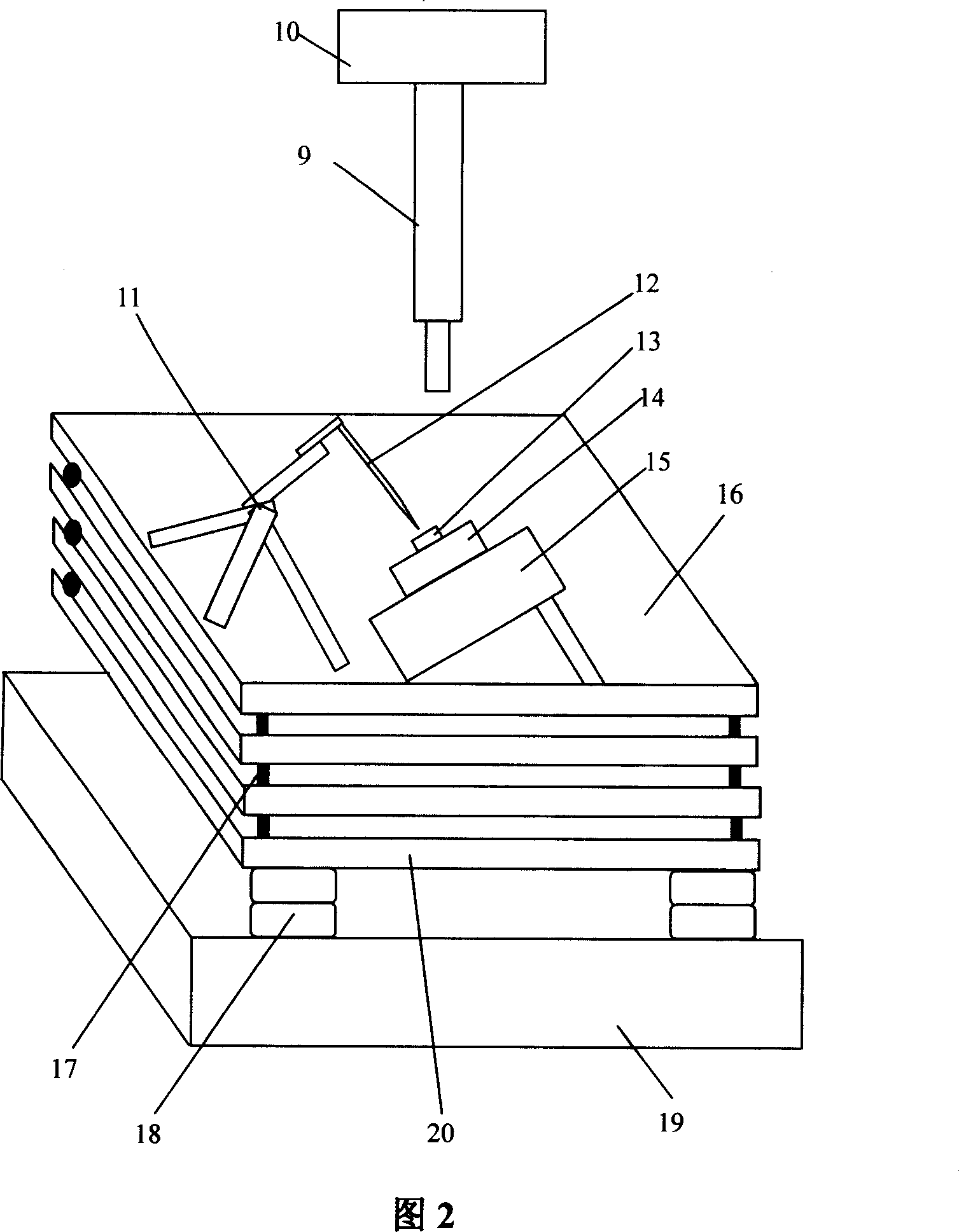

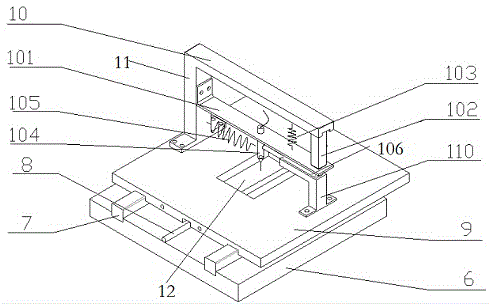

Novel micro nanometer electric spark and tunneling current composite processing device

InactiveCN101138799AEnabling Bulk MicromachiningSemi-permeable membranesNanostructure manufactureMicro nanoElectricity

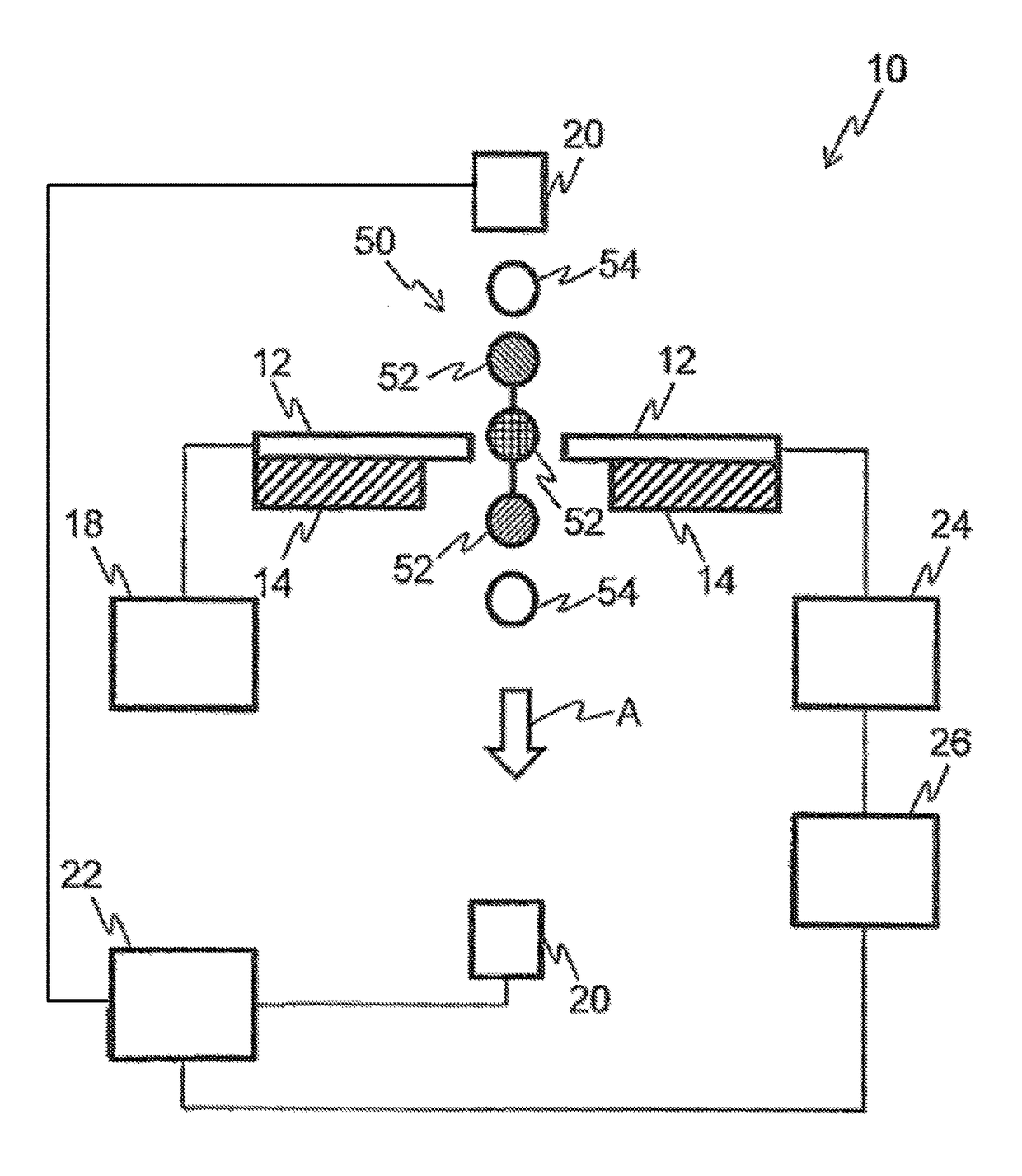

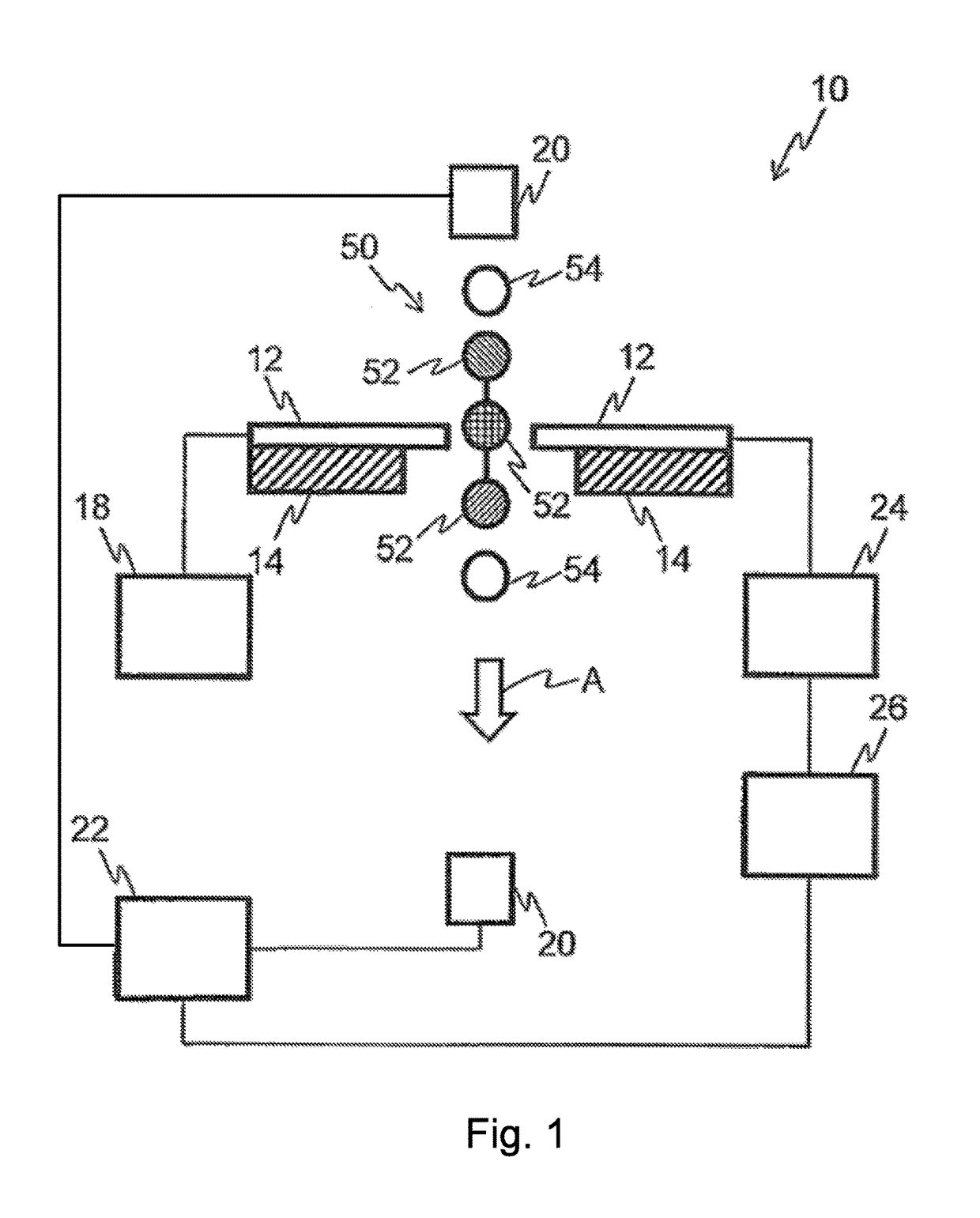

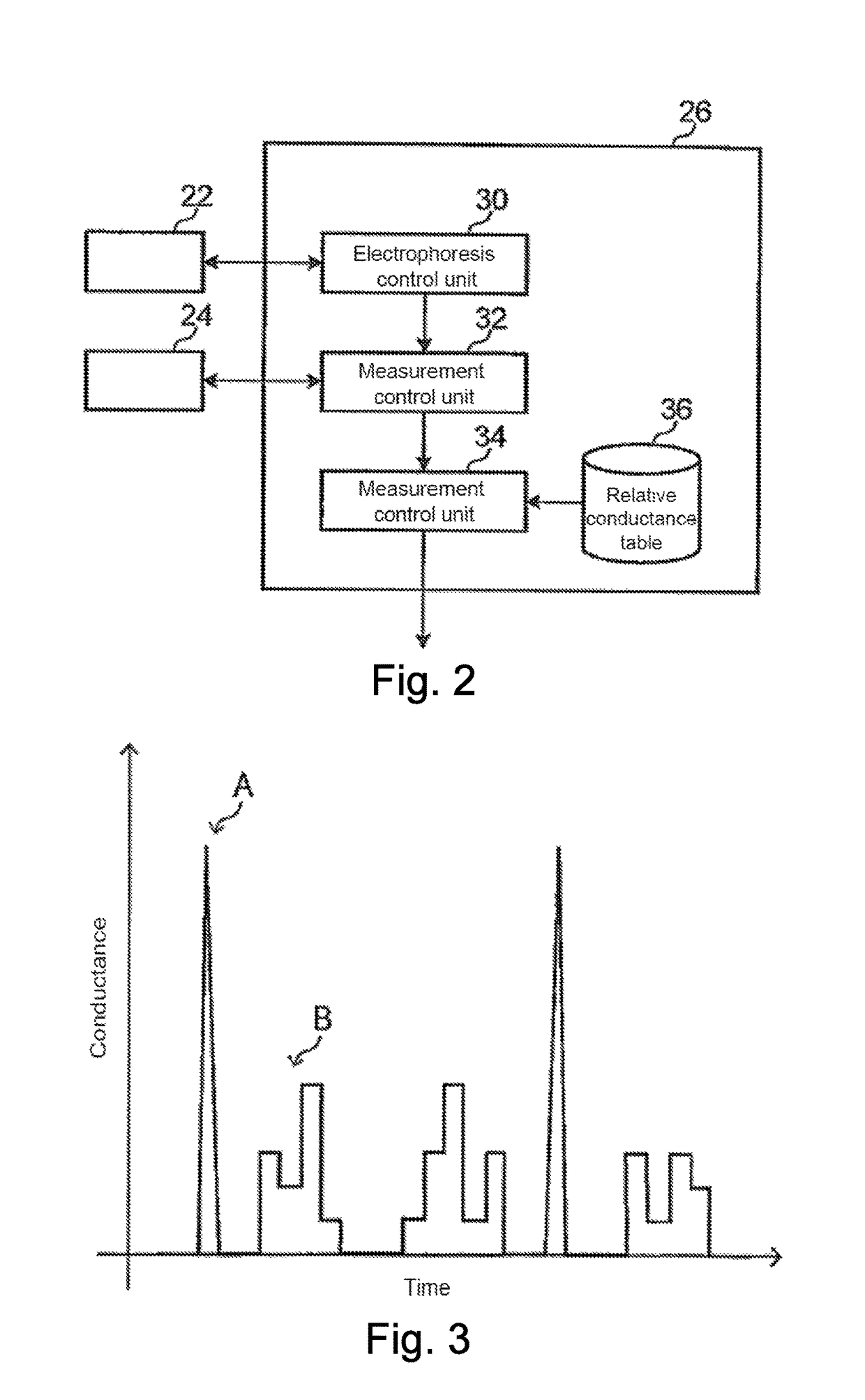

Operation procedures of a compound processing device of micro-nano electric spark machine and tunneling current scanning are: a computer 23 controls a power switch 8 to choose the micro-nano electric spark machine power supply 1 and processes of nano to hypo-nano for a workpiece 13 is performed, and then a switcher of power supply 8 chooses processing power supply 2 for the tunneling current scanning to make process of nano to hypo-nano performed for the workpiece 13. The whole processing is observed by a microscope system 9 and timely displayed on a screen of the computer 23 by CCD imaging system 10. During processing, position control data of the workpiece 13 is transferred to a coarse adjustment station of workpiece15 and a precise adjustment station of workpiece 14 by a motion servo of workpiece control of the computer 13 and a position feedback system 24. And position control for a probe 12 in the processing is performed by the computer 23 via D / A connector 6, a control circuit of piezoelectric ceramics 6, a fine adjustment controller for electrode position 7 and a fine adjustment mechanism of tri-electrode 11.

Owner:YANTAI UNIV

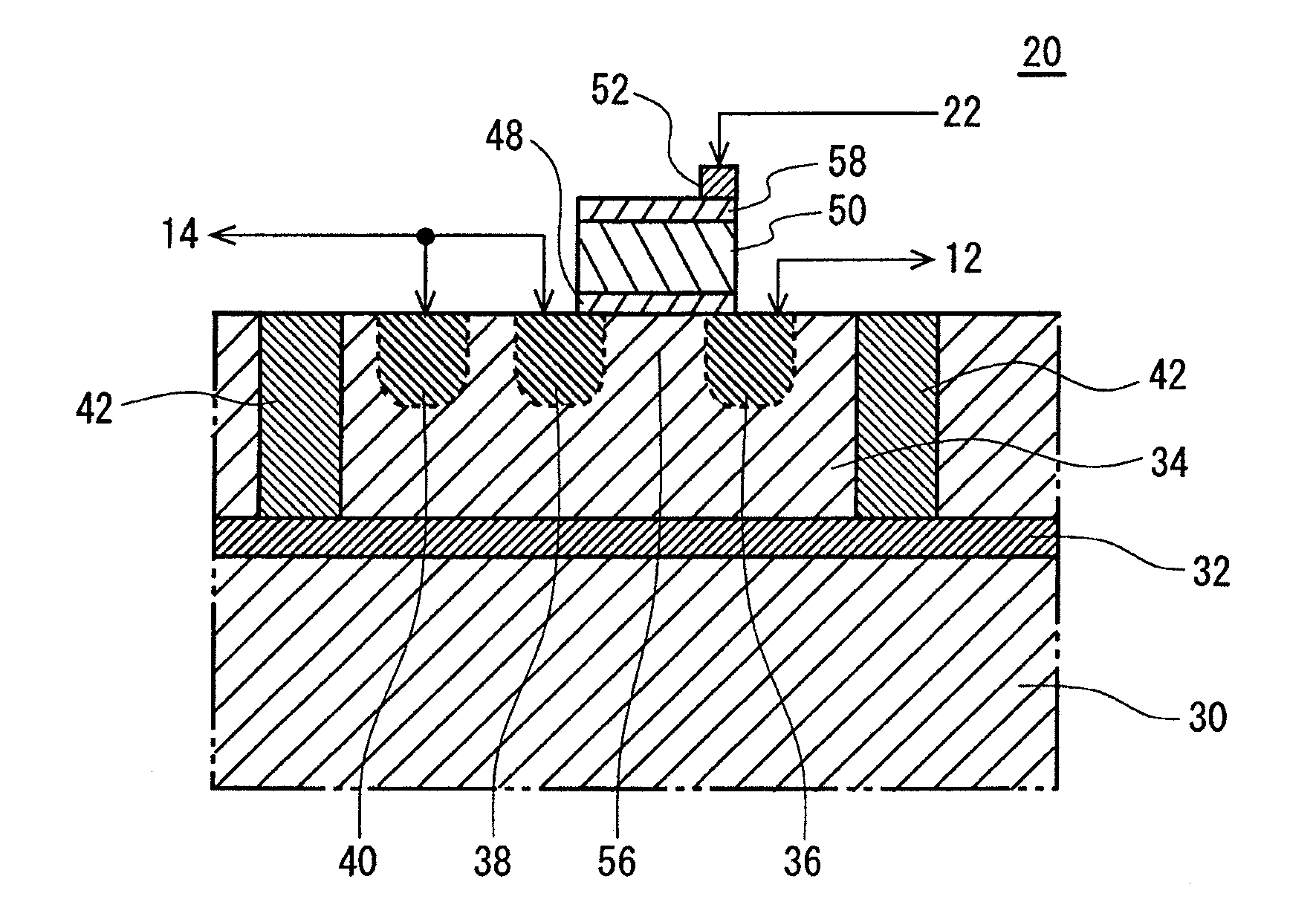

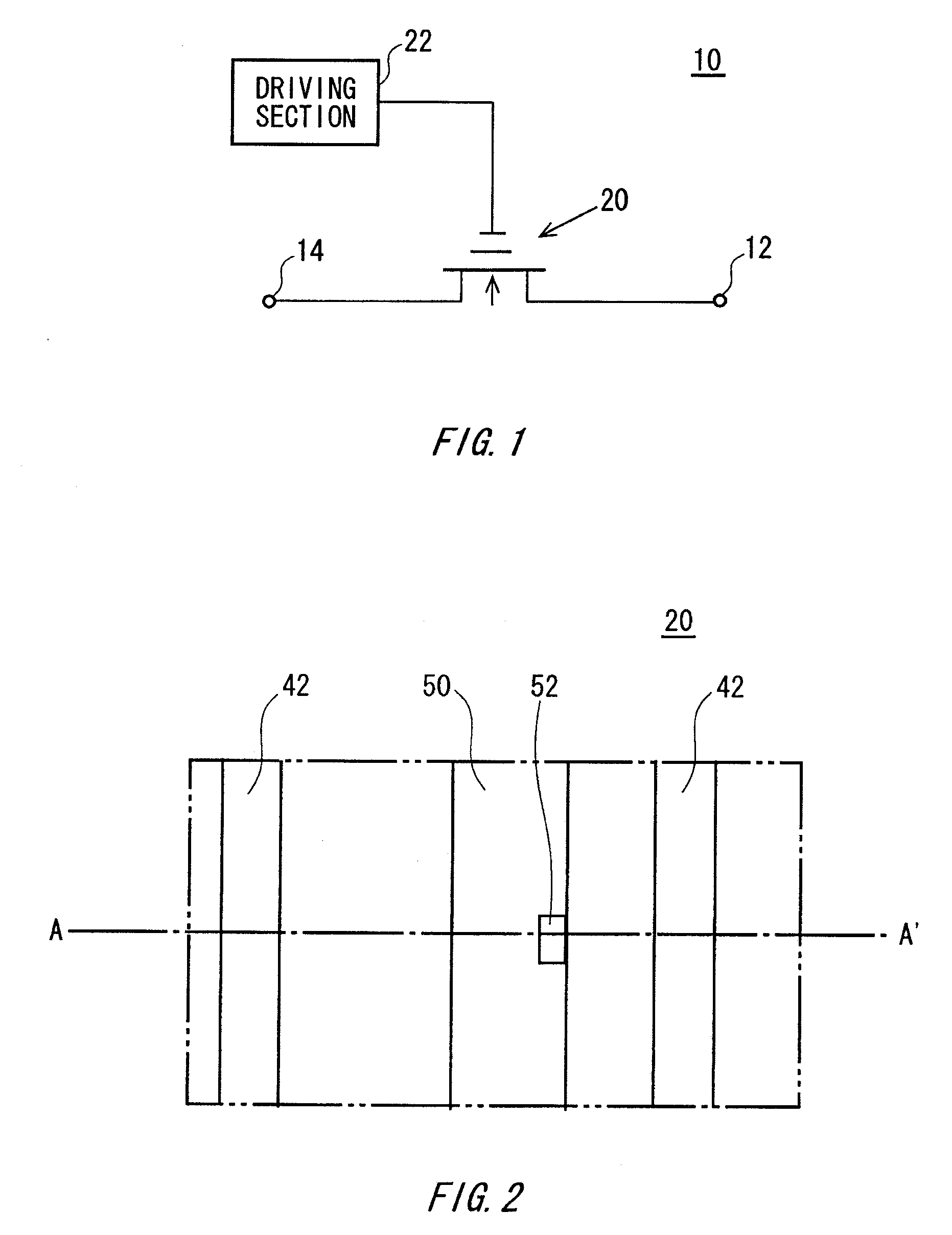

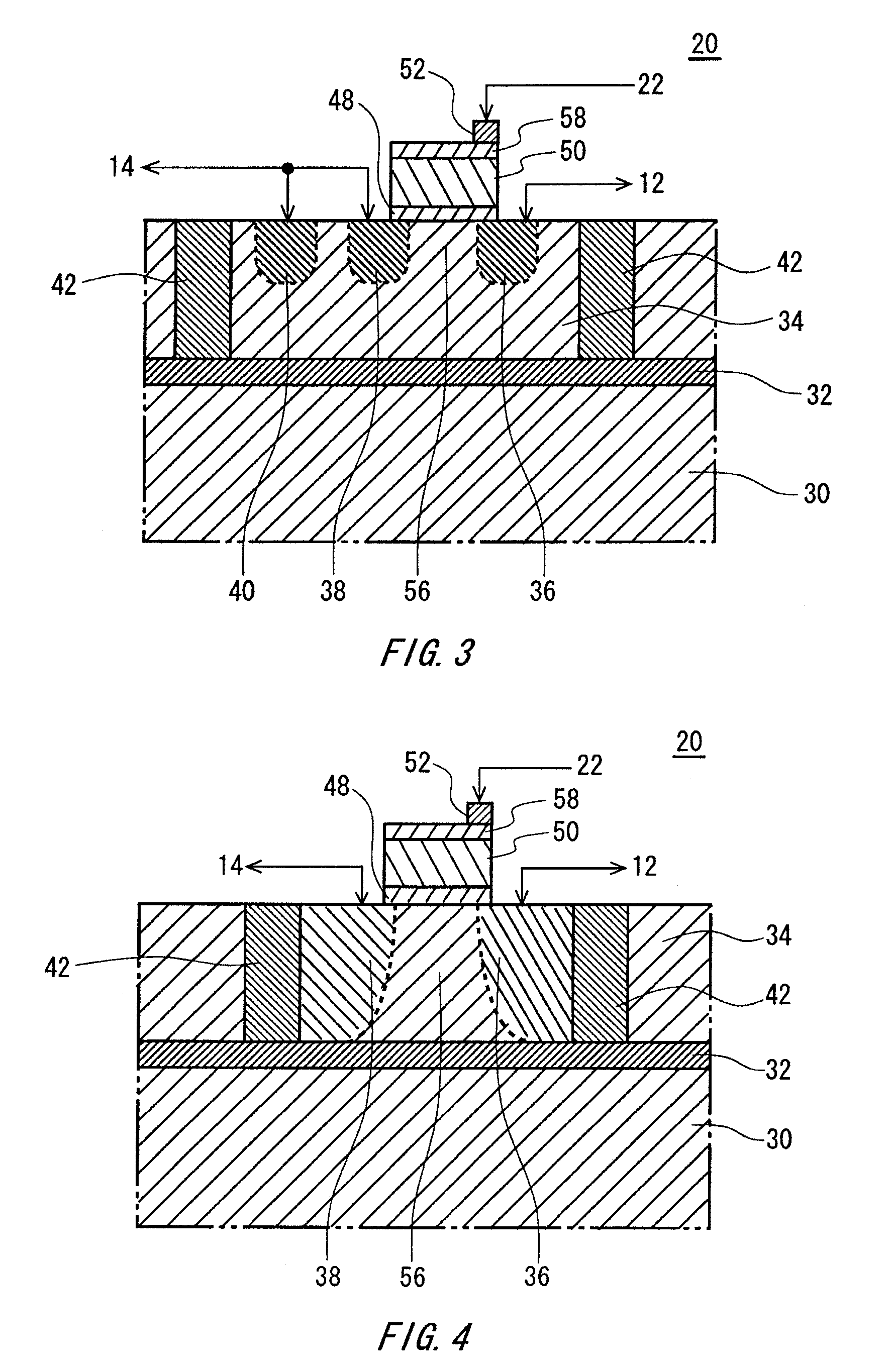

Switching device and testing apparatus

There is provided a switching device that electrically connects or disconnects a first terminal and a second terminal to / from each other. The switching device includes a semiconductor layer, a drain electrode that is formed in the semiconductor layer, where the drain electrode is connected to the first terminal, a source electrode that is formed in the semiconductor layer, where the source electrode is connected to the second terminal, a gate insulator that is formed on the semiconductor layer between the drain electrode and the source electrode, a floating gate that is formed on the gate insulator, where the floating gate retains a charge therein, and a tunnel gate that is formed on the floating gate, the tunnel gate supplying a tunnel current determined by a driving voltage applied thereto to charge or discharge the floating gate.

Owner:ADVANTEST CORP

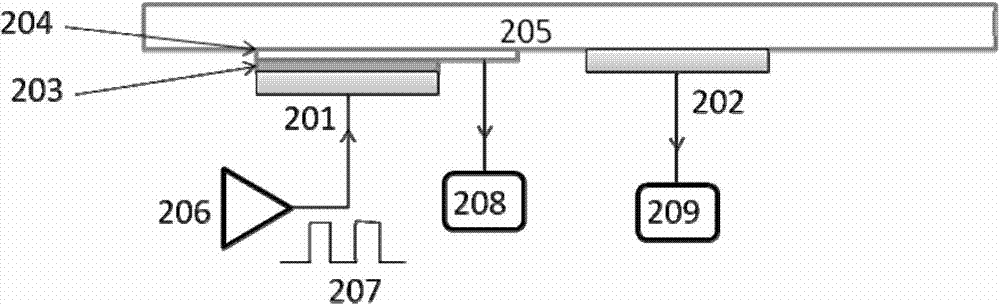

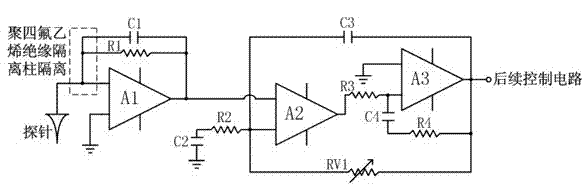

Low-noise, high-bandwidth tunnel current preamplifier circuit

InactiveCN102735879AHigh bandwidthGuaranteed accuracyScanning probe microscopyAmplifier modifications to extend bandwidthLow noiseCapacitance

The invention discloses a low-noise, high-bandwidth tunnel current preamplifier circuit. The low-noise, high-bandwidth tunnel current preamplifier circuit is connected between a probe and a subsequent control circuit, and comprises two stages of amplifier units; the first stage of amplifier unit is used for decreasing signal noise; the second stage of amplifier unit is used for increasing signal bandwidth; the first stage of amplifier unit is a transimpedance amplifier circuit, which comprises a first amplifier, a first resistor and a first capacitor; and the second stage of amplifier unit is a push-pull amplifier circuit, which comprises a second amplifier, a third amplifier, a second capacitor, a second resistor, a third capacitor, a third resistor, a fourth capacitor, a fourth resistor and an adjustable resistor. Since the low-noise, high-bandwidth tunnel current preamplifier circuit comprises the first stage of transimpedance amplifier circuit and the second stage of push-pull amplifier circuit, the introduction of the push-pull amplifier circuit greatly increases the bandwidth of tunnel current signal detection. Moreover, the joint end of the circuit and the probe is insulated by a teflon insulating column and suspended to be soldered, and therefore is not in contact with a circuit board, consequently, the noise of signal detection is greatly reduced, and while the bandwidth is increased, the precision of tunnel current signals is increased.

Owner:ZHEJIANG UNIV

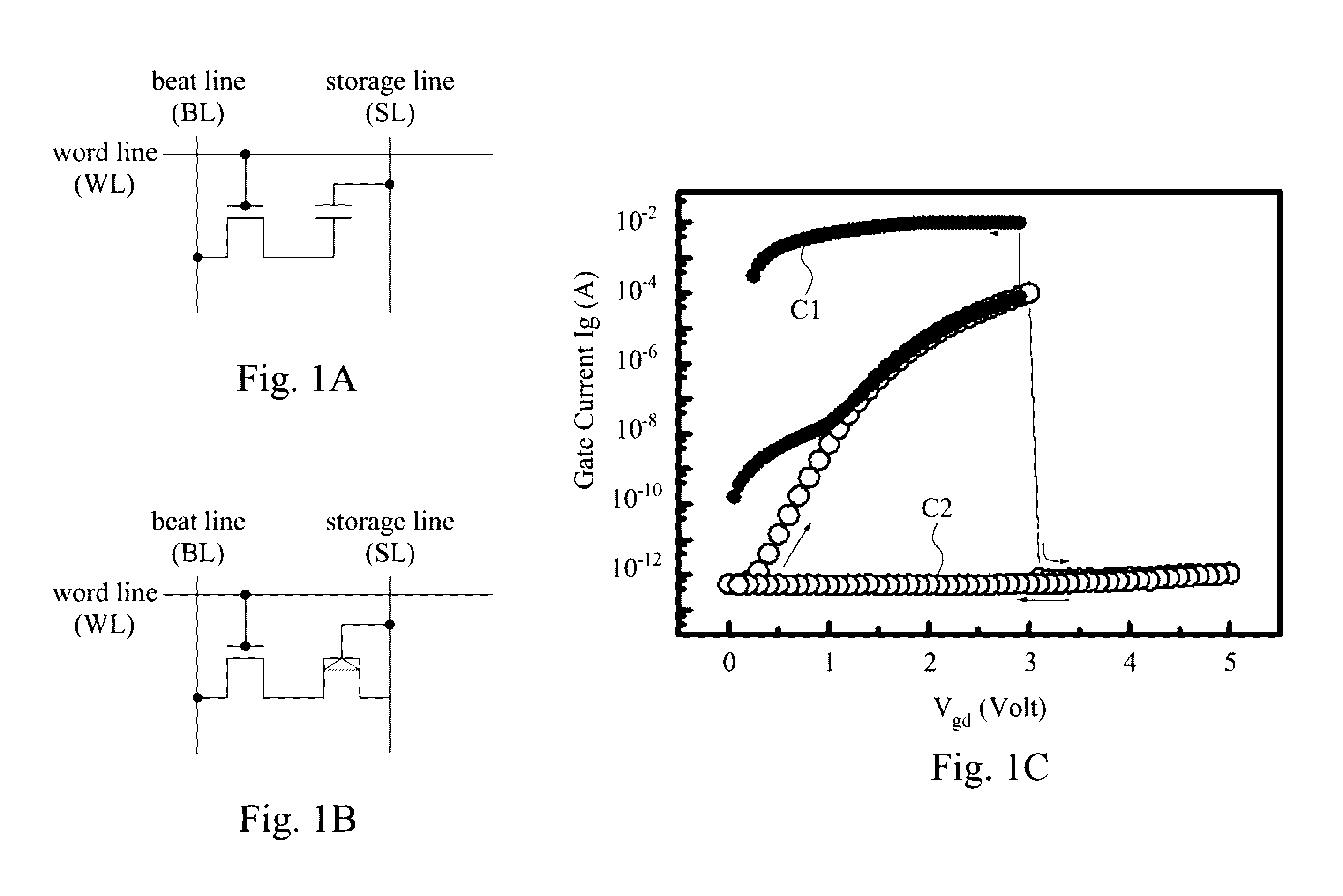

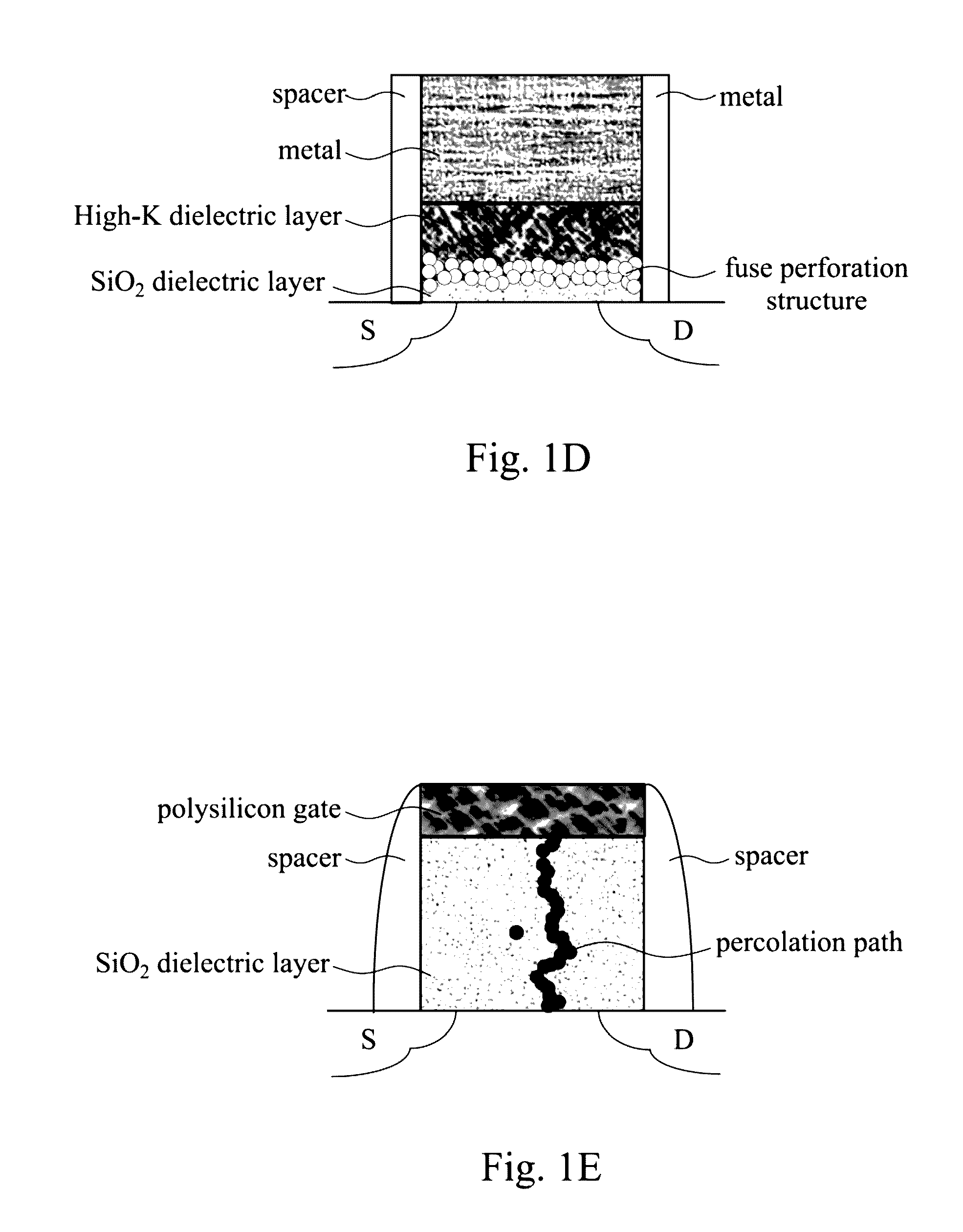

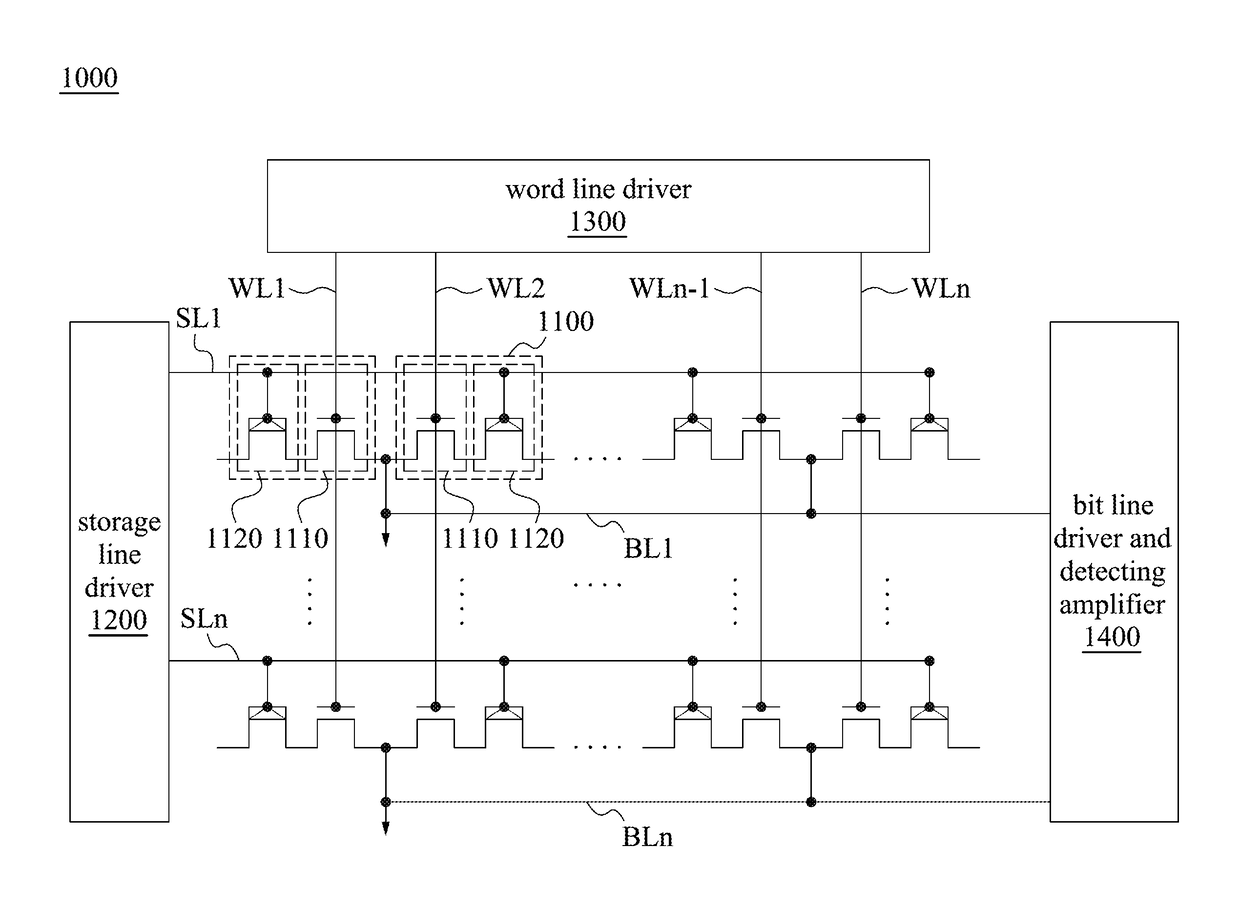

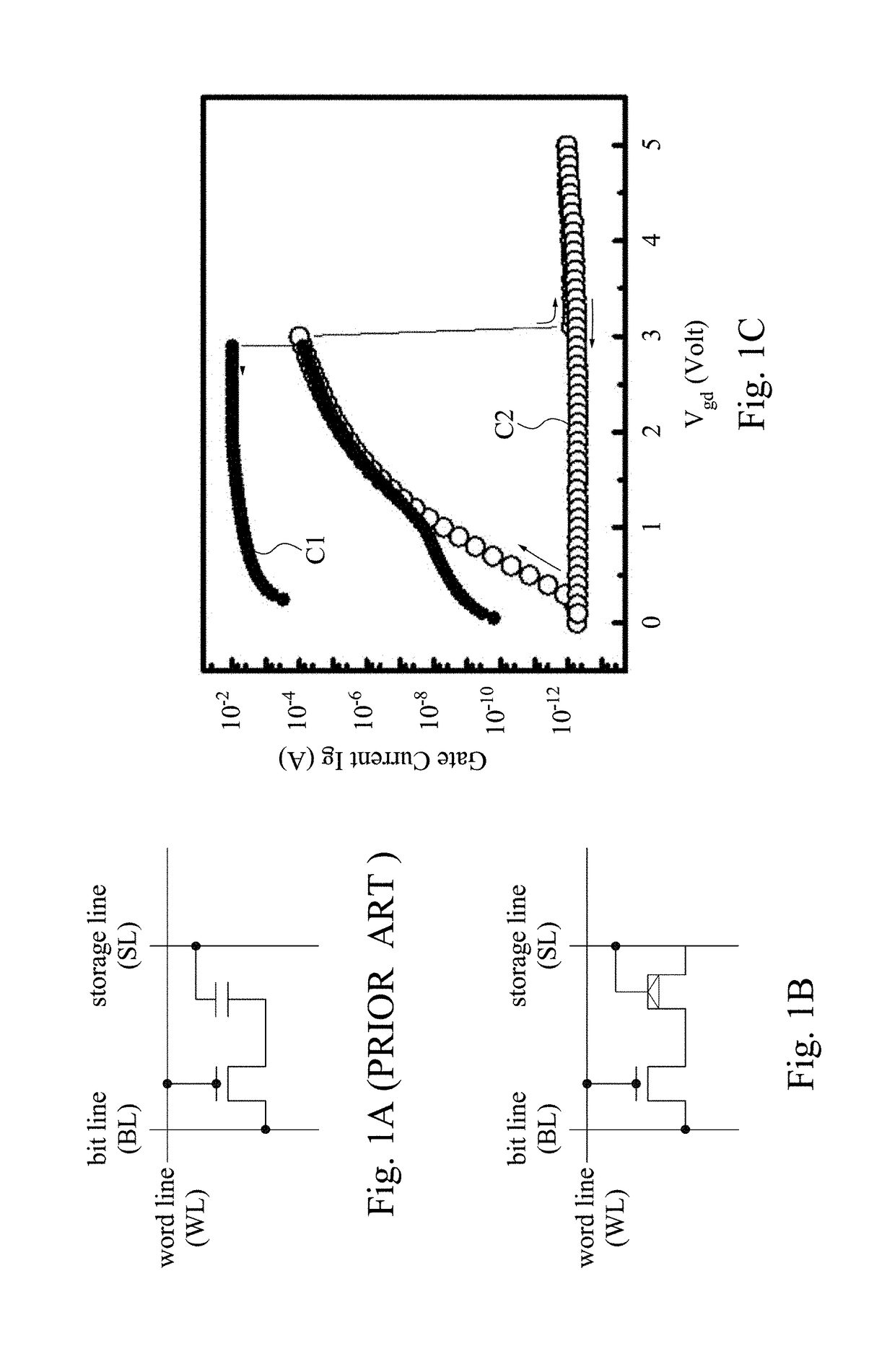

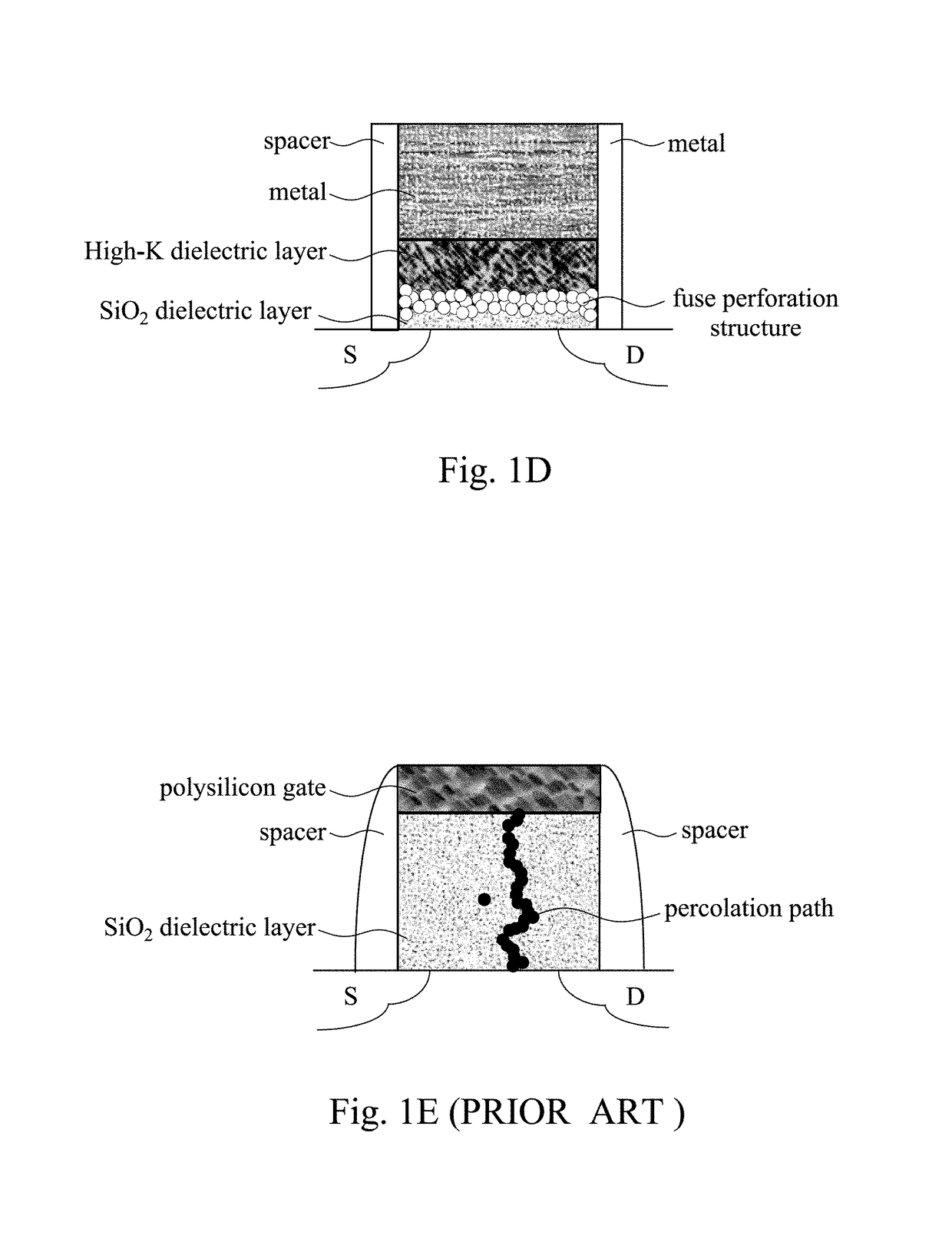

Dielectric fuse memory circuit and operation method thereof

ActiveUS20170032848A1TransistorSemiconductor/solid-state device detailsVery large scale integrated circuitsHemt circuits

This disclosure proposed one kind of one-time programming and repeatably random read integrated circuit memory. The storage device of this memory programs the information by using dielectric-fuse mechanism. The main characteristics of dielectric fuse mechanisms is that by applying an electric field on the dielectrics, the ions or atoms in the dielectrics are drifted-out, or the dielectrics are burned-out, that create damage of the dielectric structure in a form of porosity, and the conductivity (resistivity) of tunneling current through the dielectrics changes the state from high conductivity (resistivity) to low conductivity (resistivity). The dielectric fuse mechanism has been integrated in VLSI circuits, completed the validation, and implemented by the fabrication of CMOS process.

Owner:NAT CHIAO TUNG UNIV

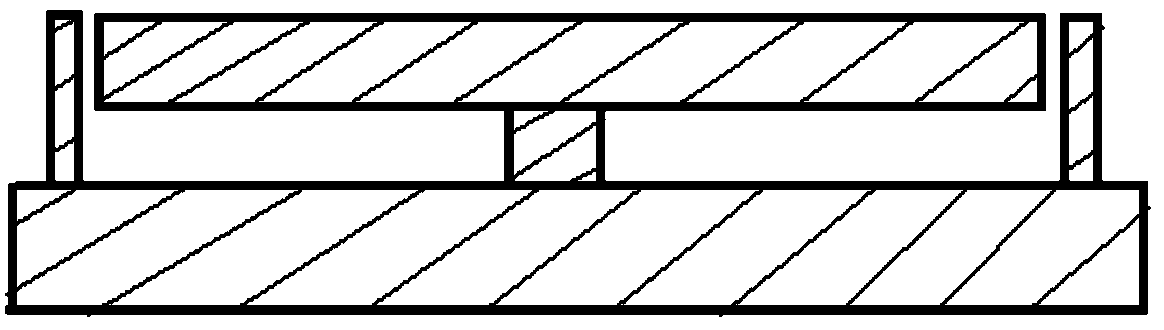

Micronano metal fiber surface topography measuring device, use method thereof and movement distance measuring method of drive in device

ActiveCN104931732AGuaranteed heightHeight unchangedScanning probe microscopyMeasurement deviceThree dimensional shape

The invention discloses a micronano metal fiber surface topography measuring device, a use method thereof and a movement distance measuring method of a drive in the device. A substrate is arranged on a base through a rail. A chute is arranged in the middle of the base. A template is placed in the chute. A visual window is arranged at the center of the base. One end of a cross beam is connected with the base. One end of a side beam is connected with a support leg, and the drive is arranged on the other end. One end of an electrode is arranged on the side beam. The other end points to the surface of the template through the visual window. The distance from one end, which points to the template, of the electrode to the surface of the template is 0.01 to 100nm. According to the invention, a produced tunnel current effect is used to scan the surface of a measured object, and the three-dimensional shape of the surface of the measured object is acquired through difference in current magnitude.

Owner:YANGZHOU UNIV

Dielectric fuse memory circuit and operation method thereof

One time programming and repeatably random read integrated circuit memory has a storage device that programs the information by using dielectric-fuse mechanism. The main characteristics of dielectric fuse mechanisms is that by applying an electric field on the dielectrics, the ions or atoms in the dielectrics are drifted-out, or the dielectrics are burned-out, that create damage of the dielectric structure in a form of porosity, and the conductivity (resistivity) of tunneling current through the dielectrics changes the state from high conductivity (resistivity) to low conductivity (resistivity). The dielectric fuse mechanism has been integrated in VLSI circuits, completed the validation, and implemented by the fabrication of CMOS process.

Owner:NAT CHIAO TUNG UNIV

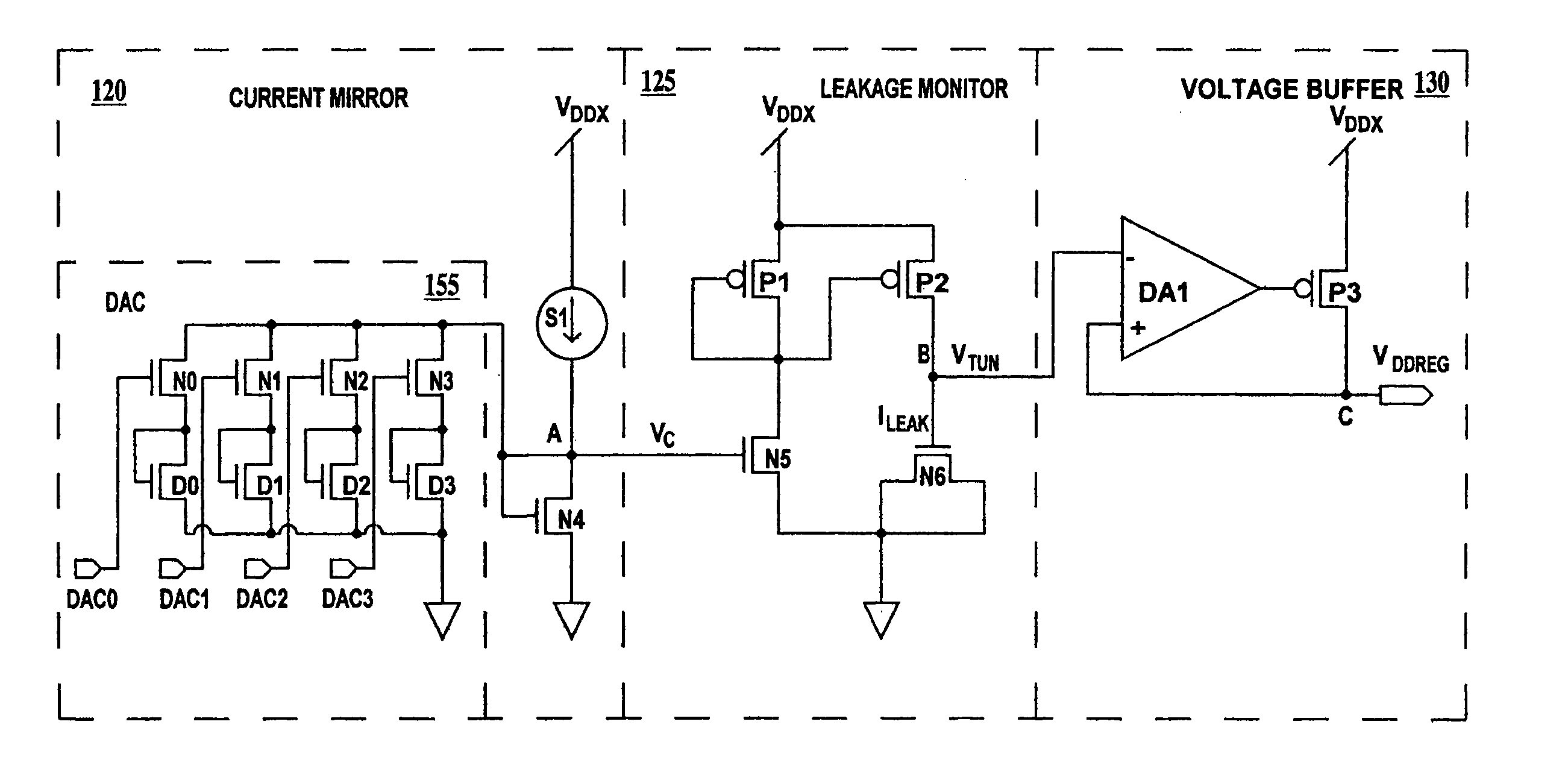

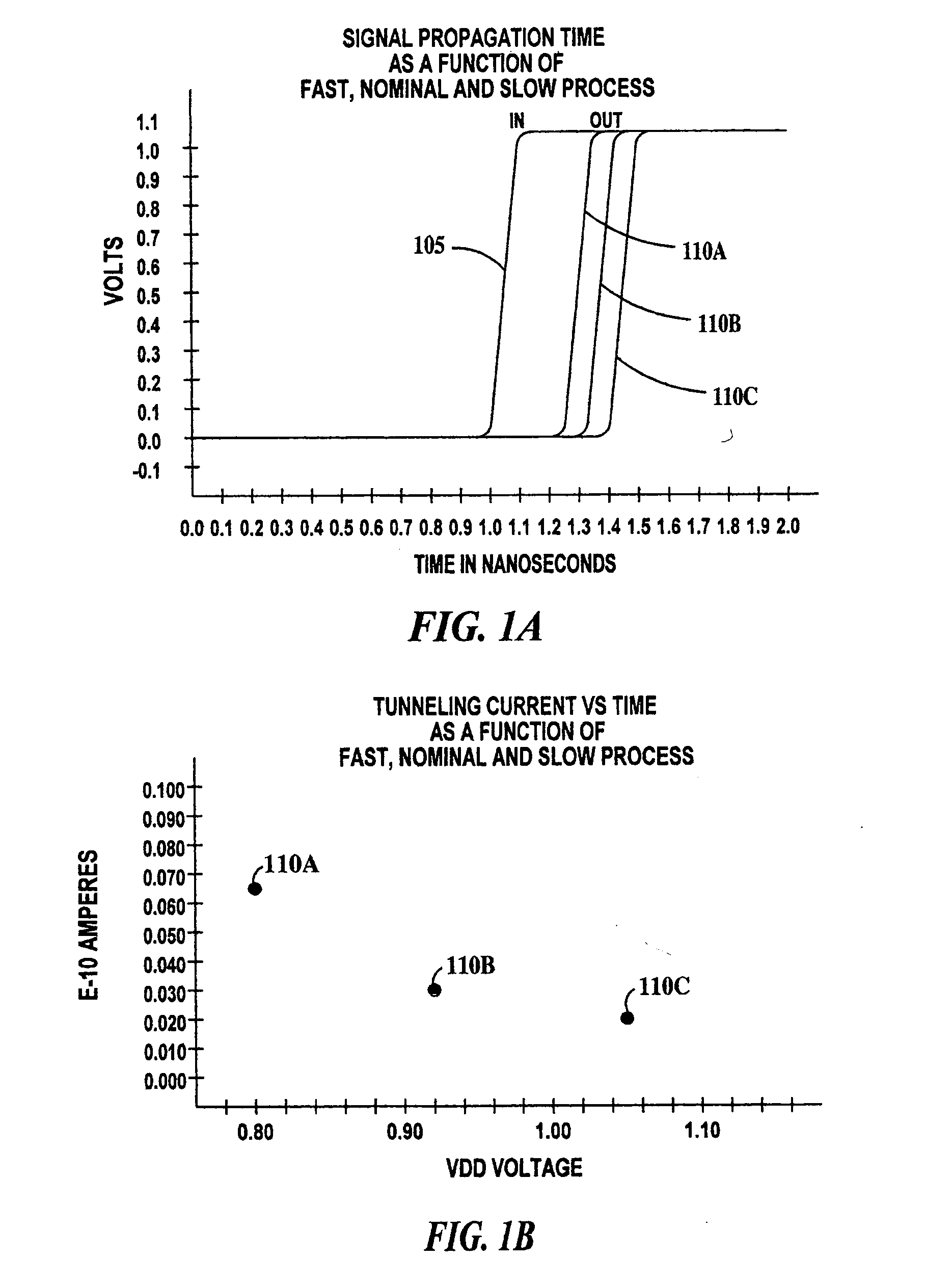

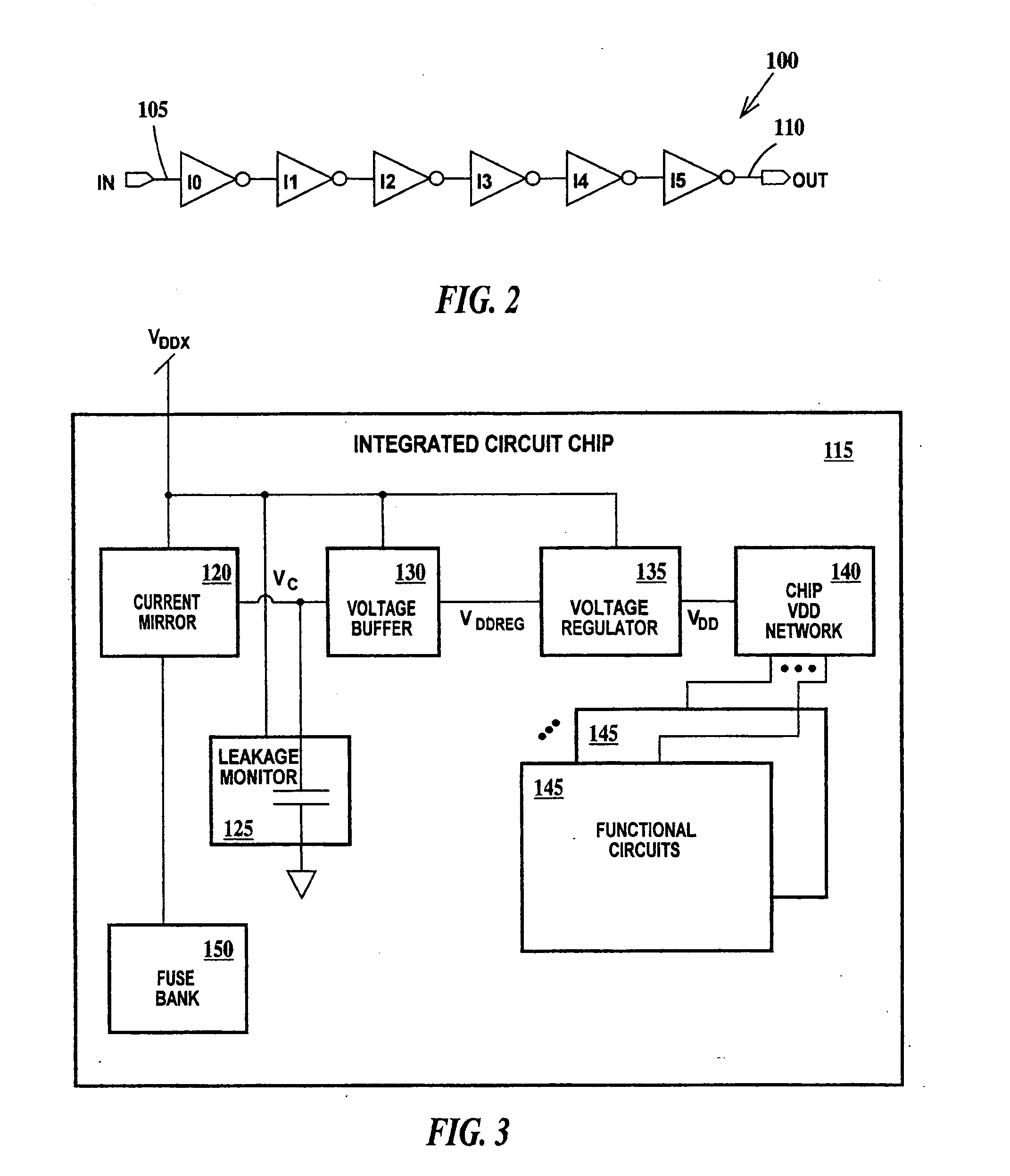

Method and circuit for compensating for tunneling current

A method and circuit for tunneling leakage current compensation, the method including: forcing a current of known value through a tunneling current leakage monitor device to provide a voltage signal; and regulating an on-chip power supply of the integrated circuit chip based on the voltage signal.

Owner:GLOBALFOUNDRIES INC

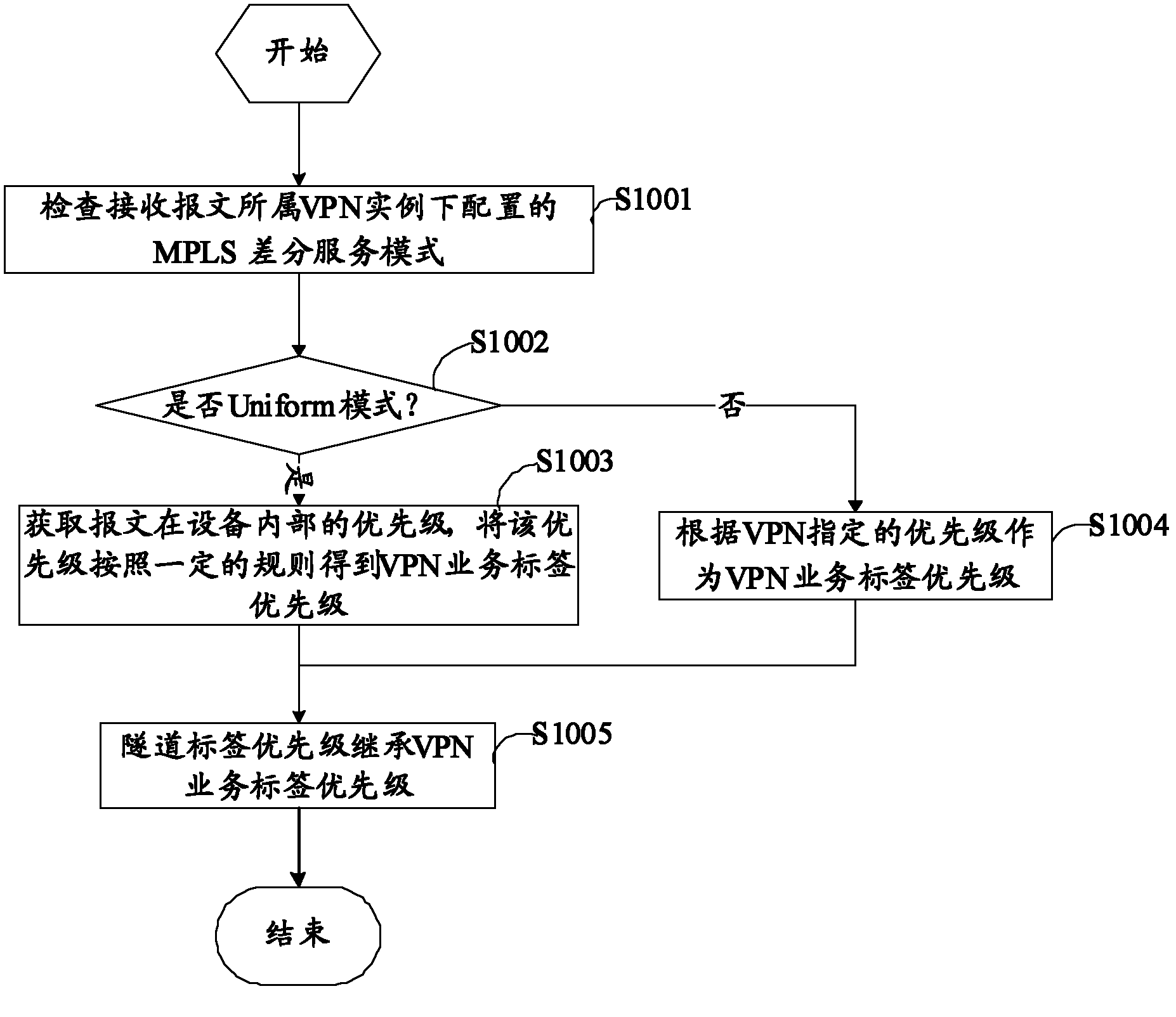

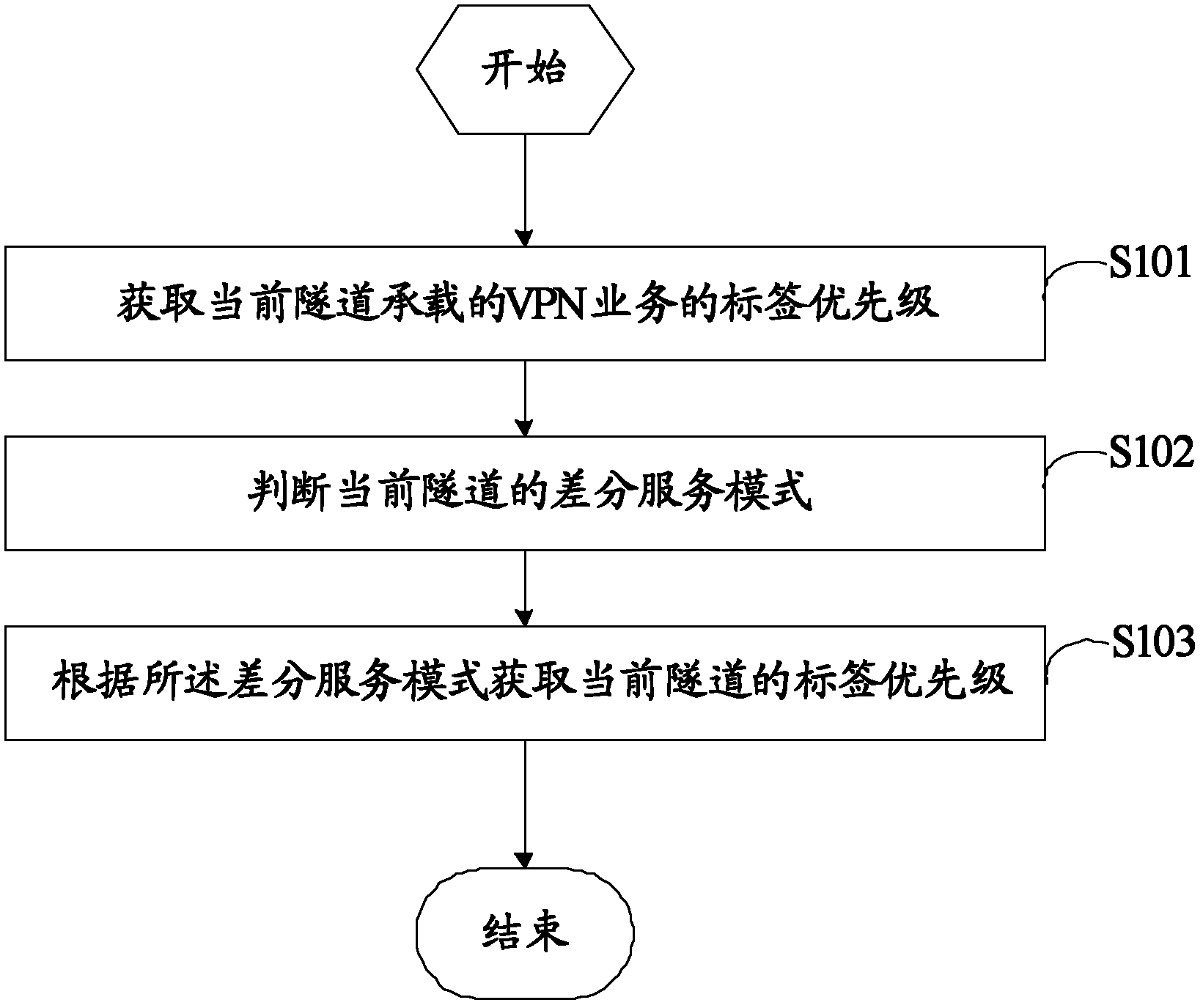

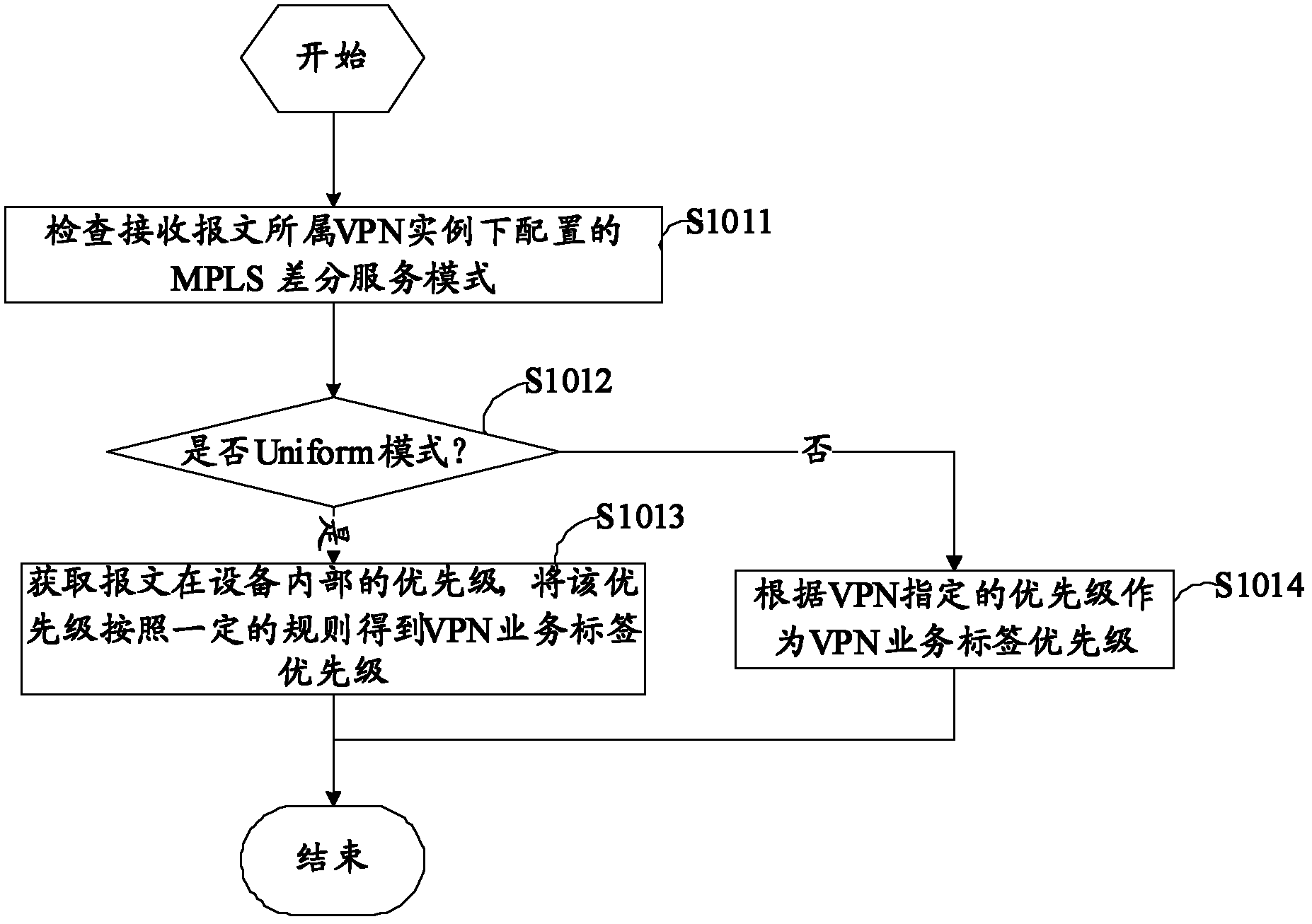

Implementation method and device of mpls network differential service carrying vpn service

ActiveCN102291297AFlexible QoS GuaranteeNetworks interconnectionDifferentiated servicesDifferentiated service

The invention discloses a method for realizing differential service of an MPLS network carrying VPN services, comprising: judging the differential service mode of the current tunnel; and obtaining the label priority of the current tunnel according to the differential service mode. The invention also provides a corresponding device. The invention provides a method and device for realizing differential service of an MPLS network carrying VPN services, so that the priority of the tunnel label can selectively define the service level of the current layer.

Owner:ZTE CORP