Patents

Literature

2509 results about "Cross point" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

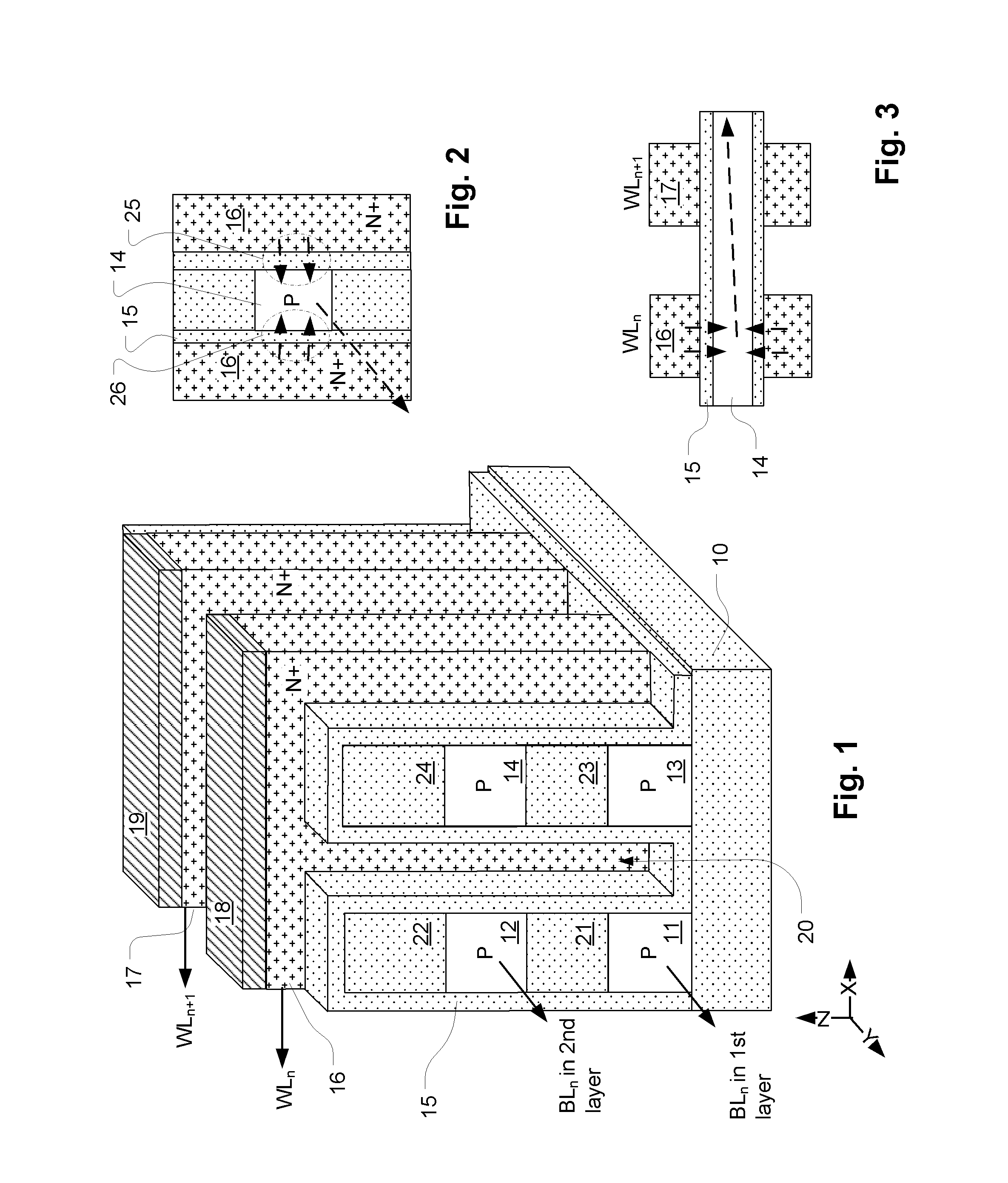

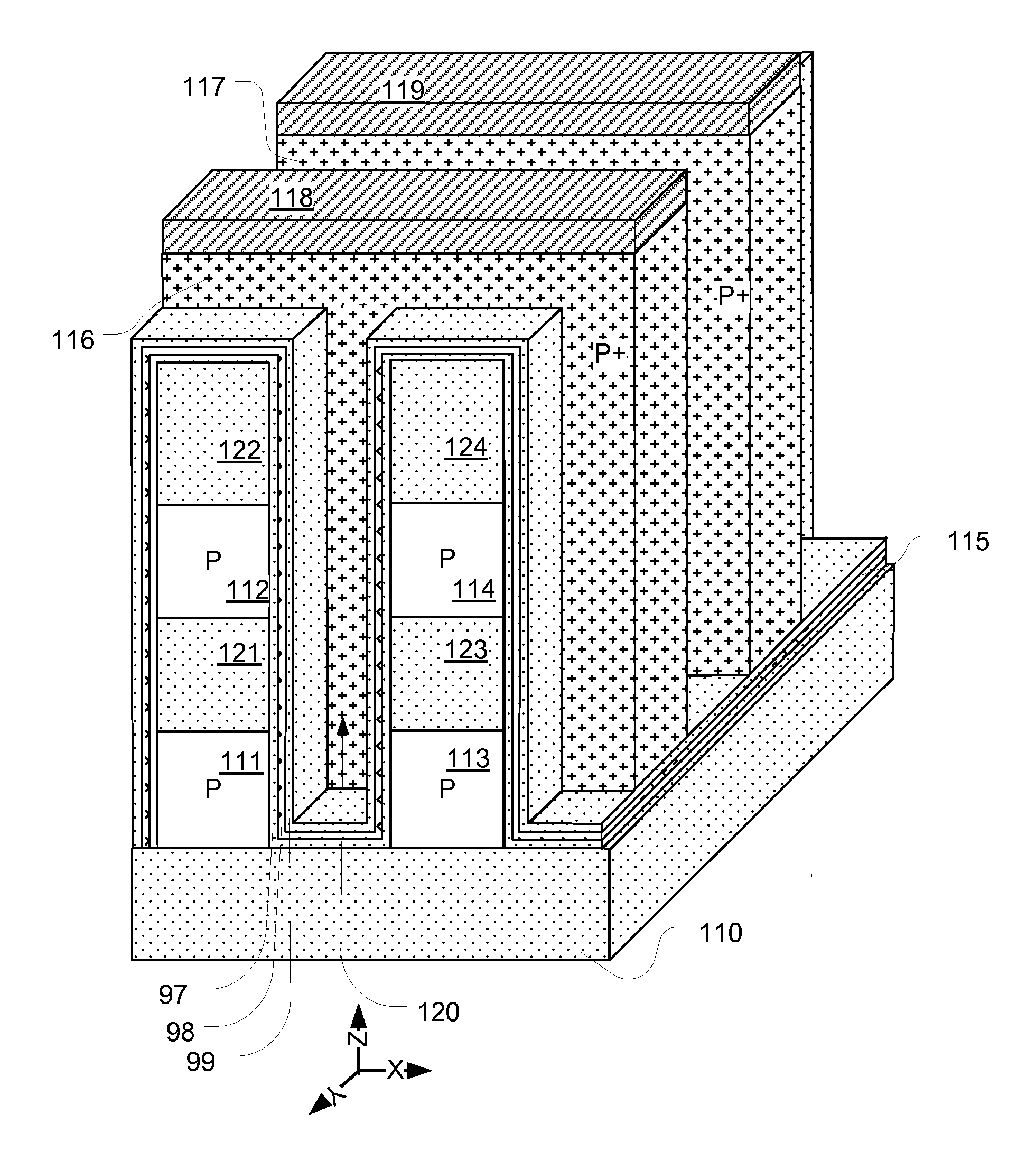

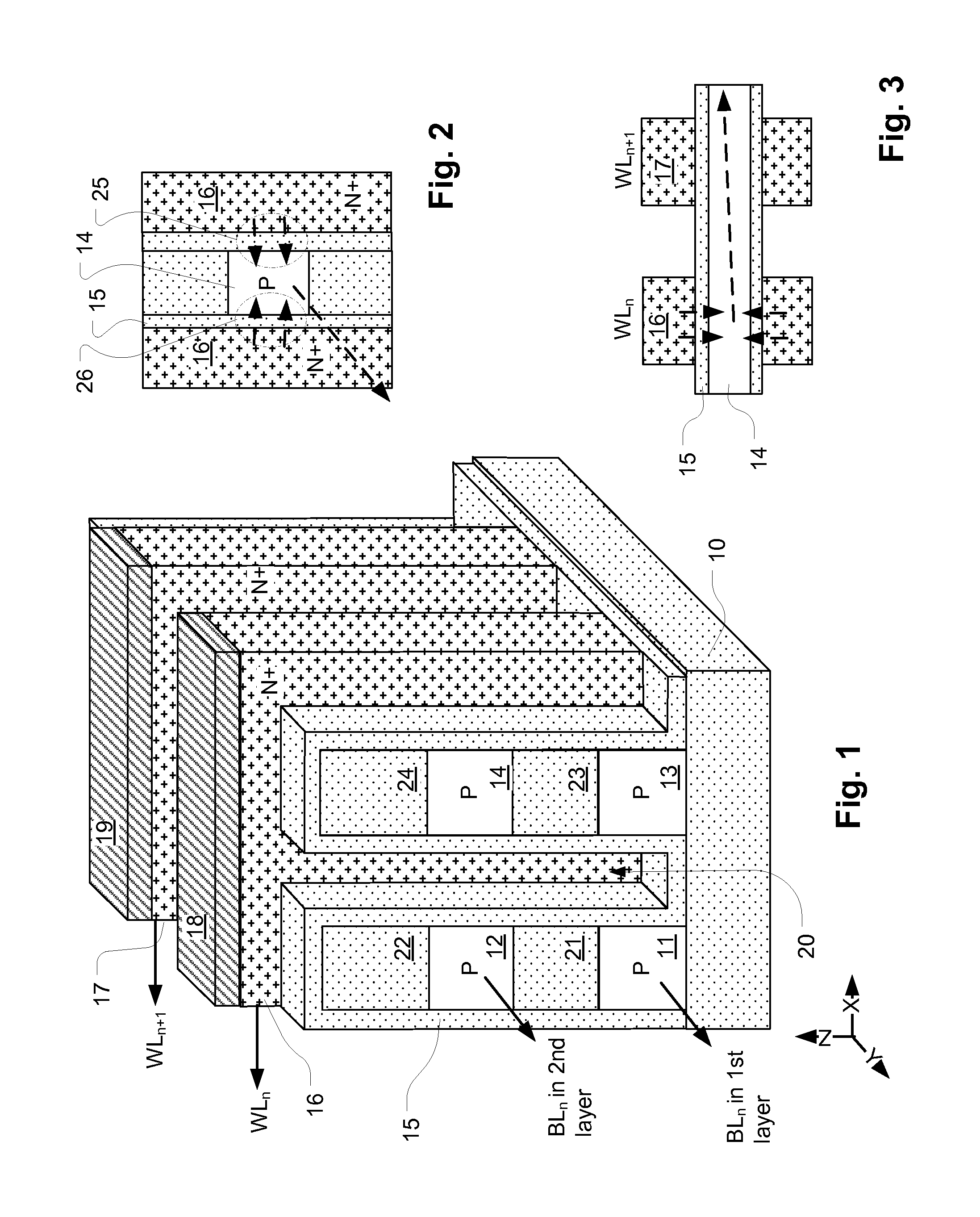

Unipolar resistance random access memory (RRAM) device and vertically stacked architecture

InactiveUS20070132049A1Improve performanceGalvano-magnetic devicesSolid-state devicesRandom access memoryEngineering

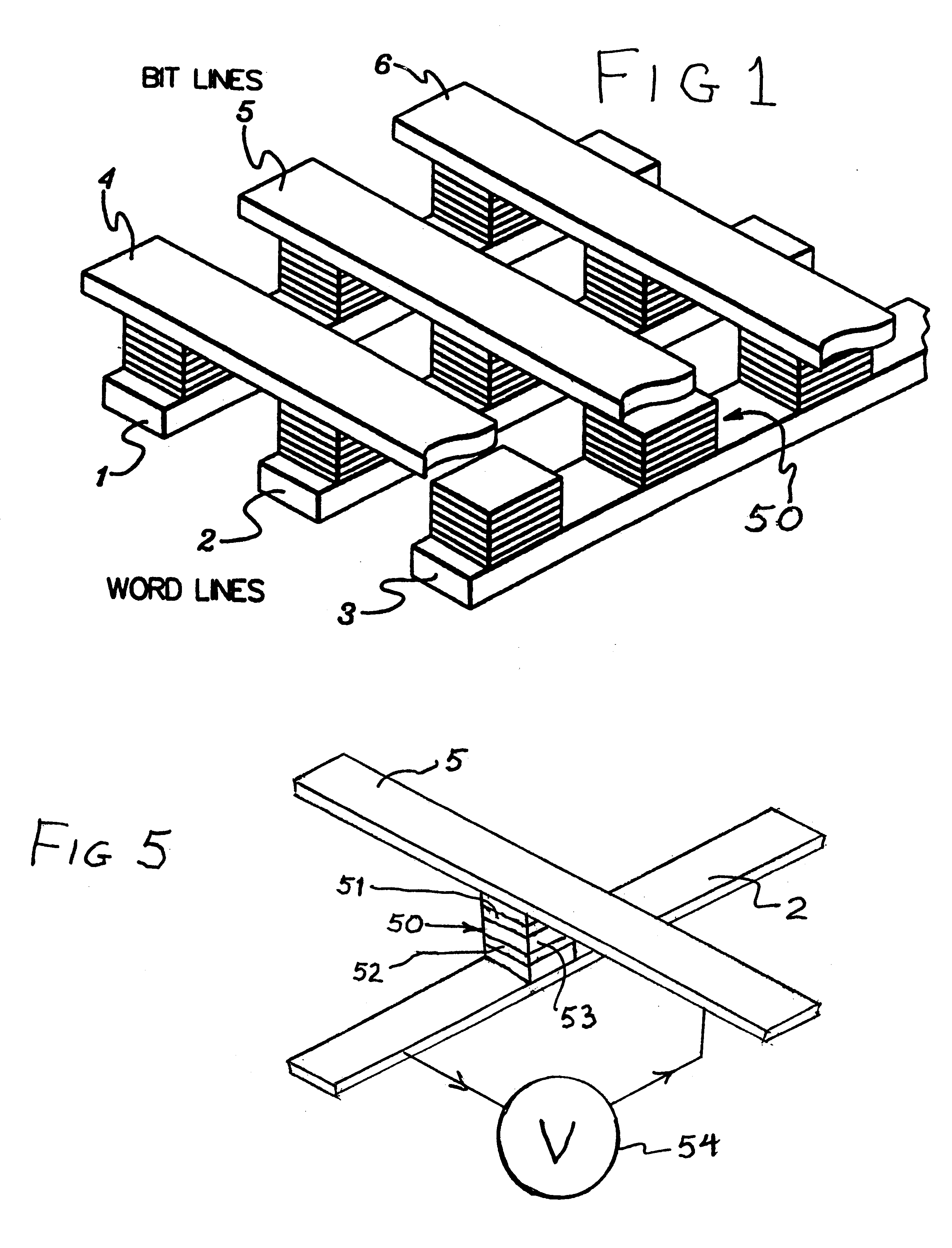

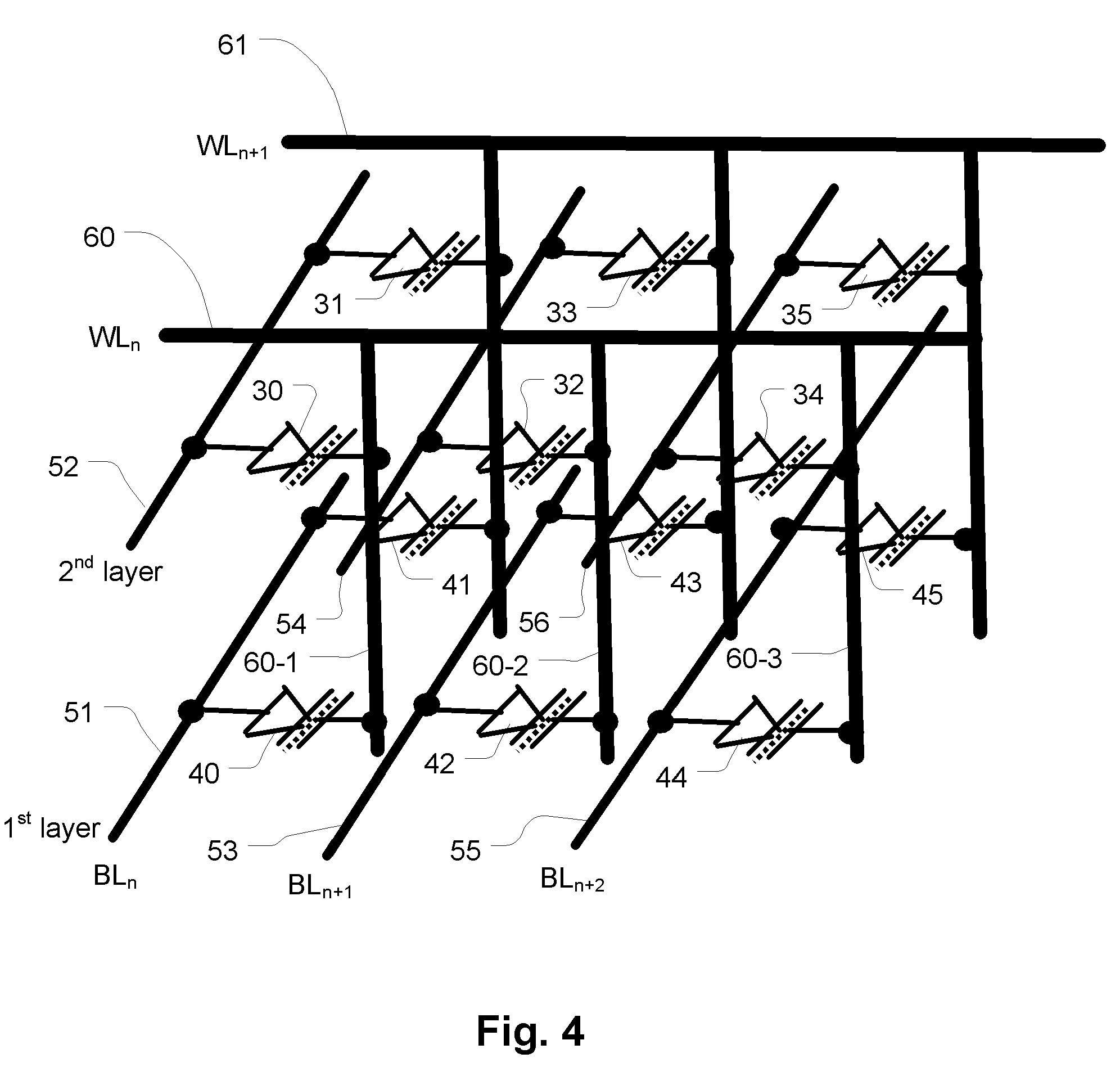

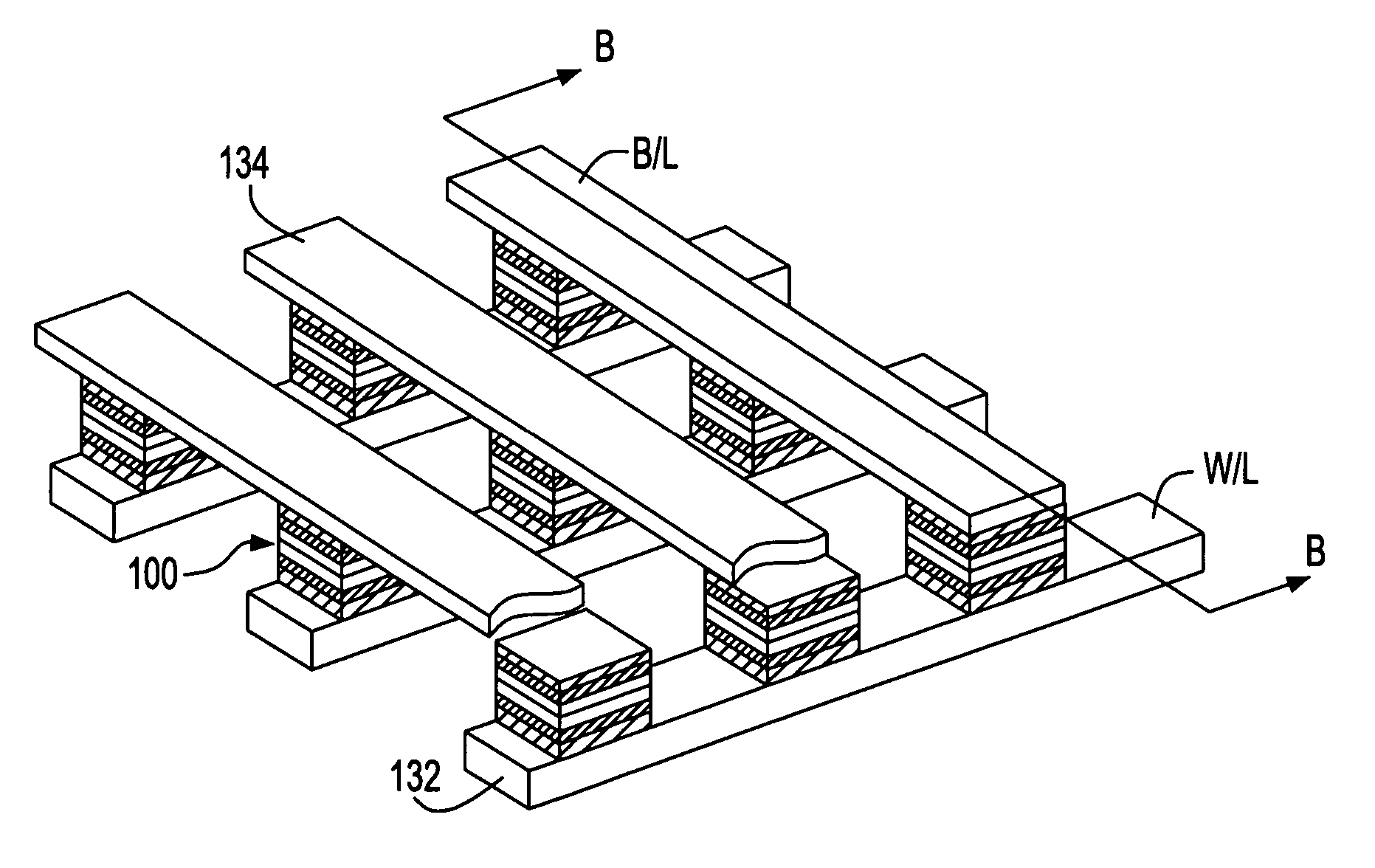

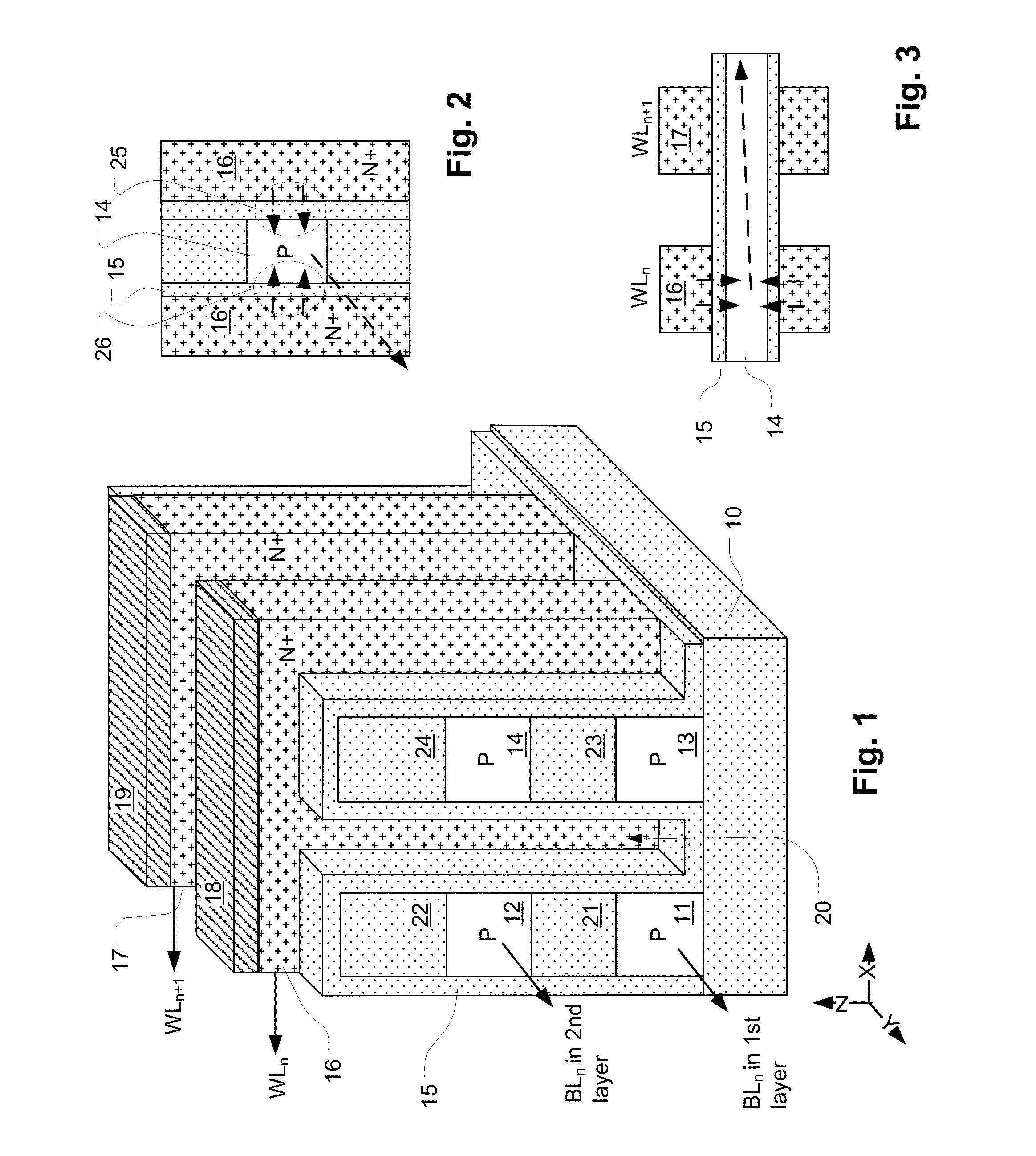

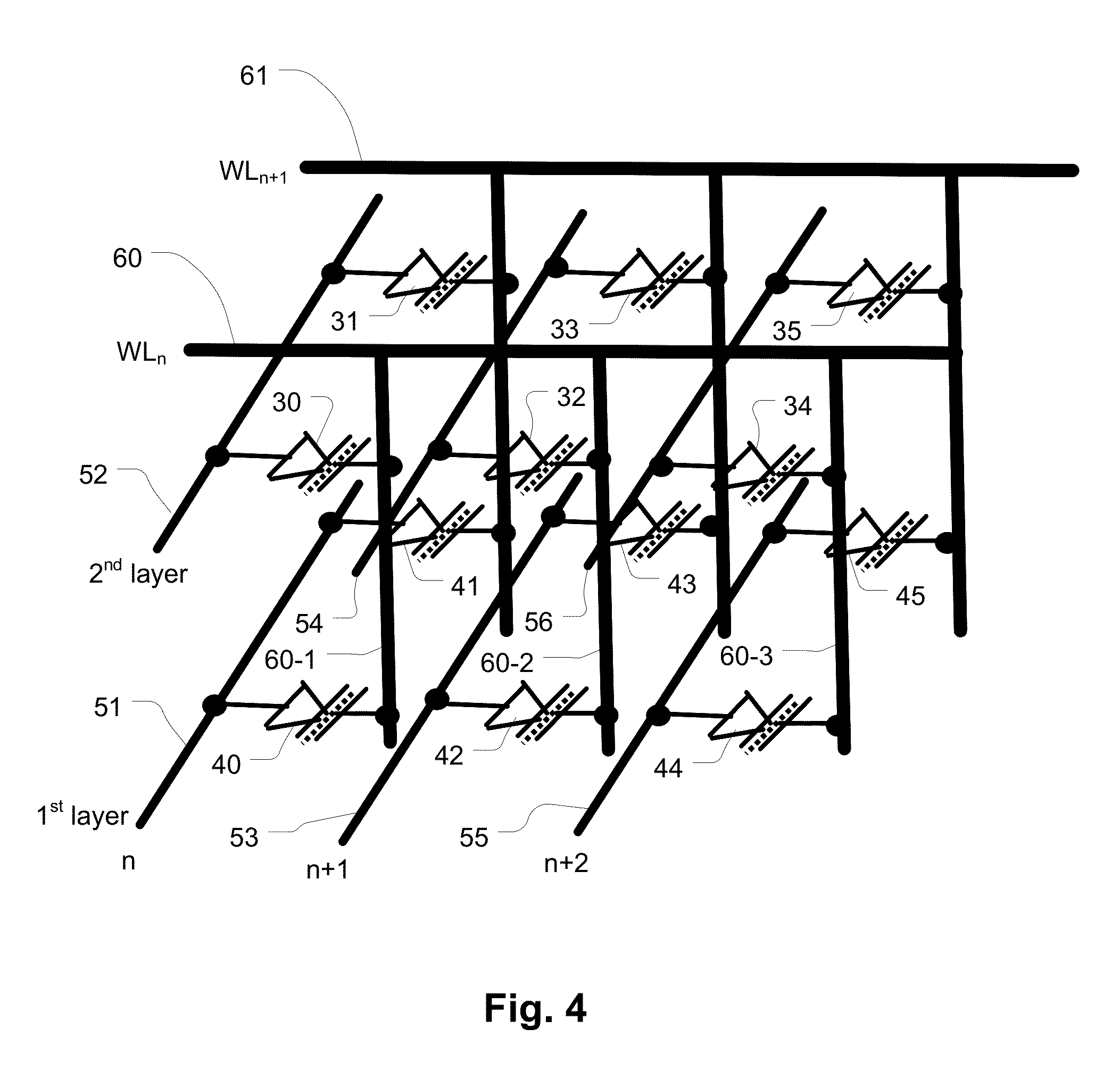

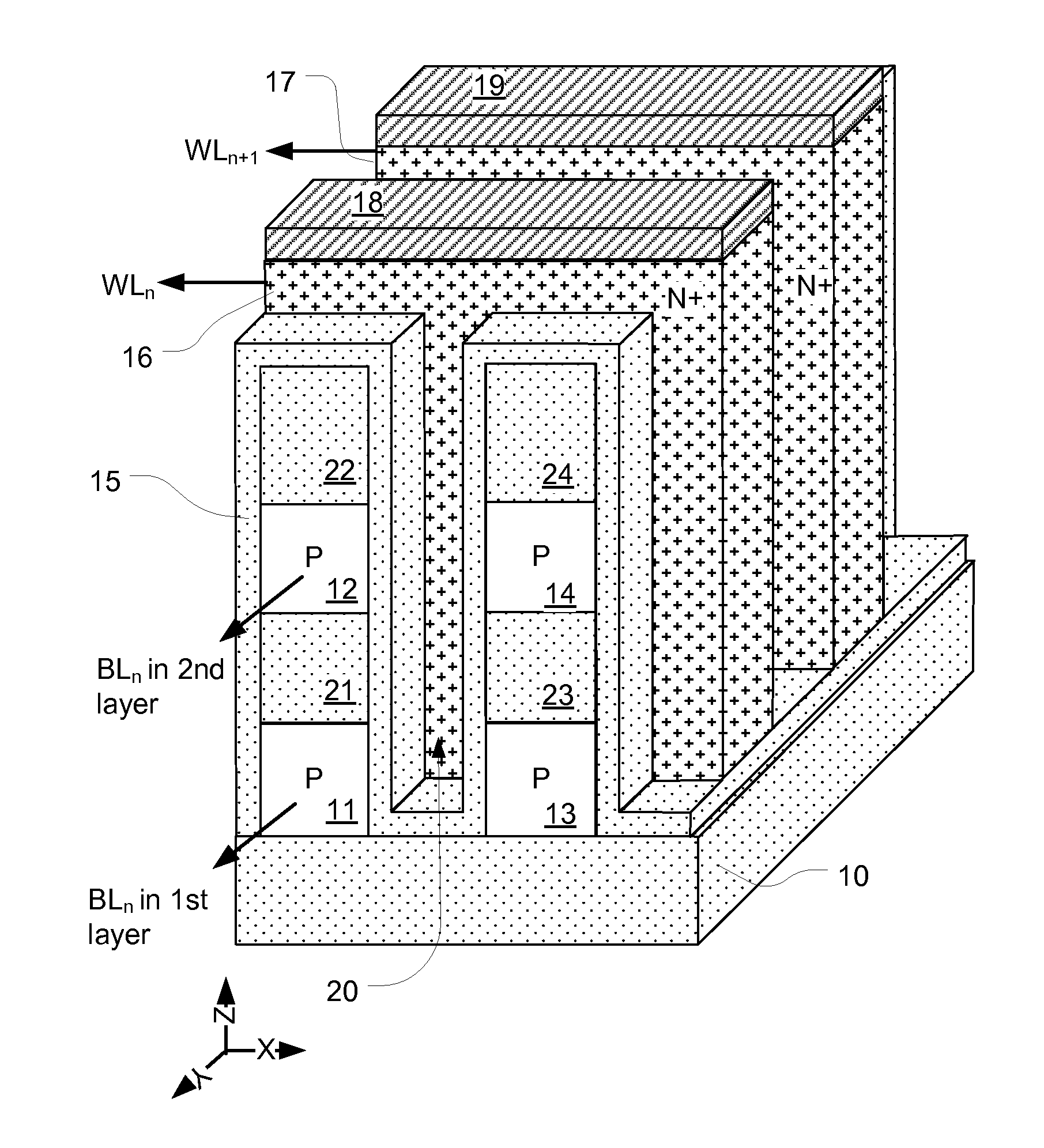

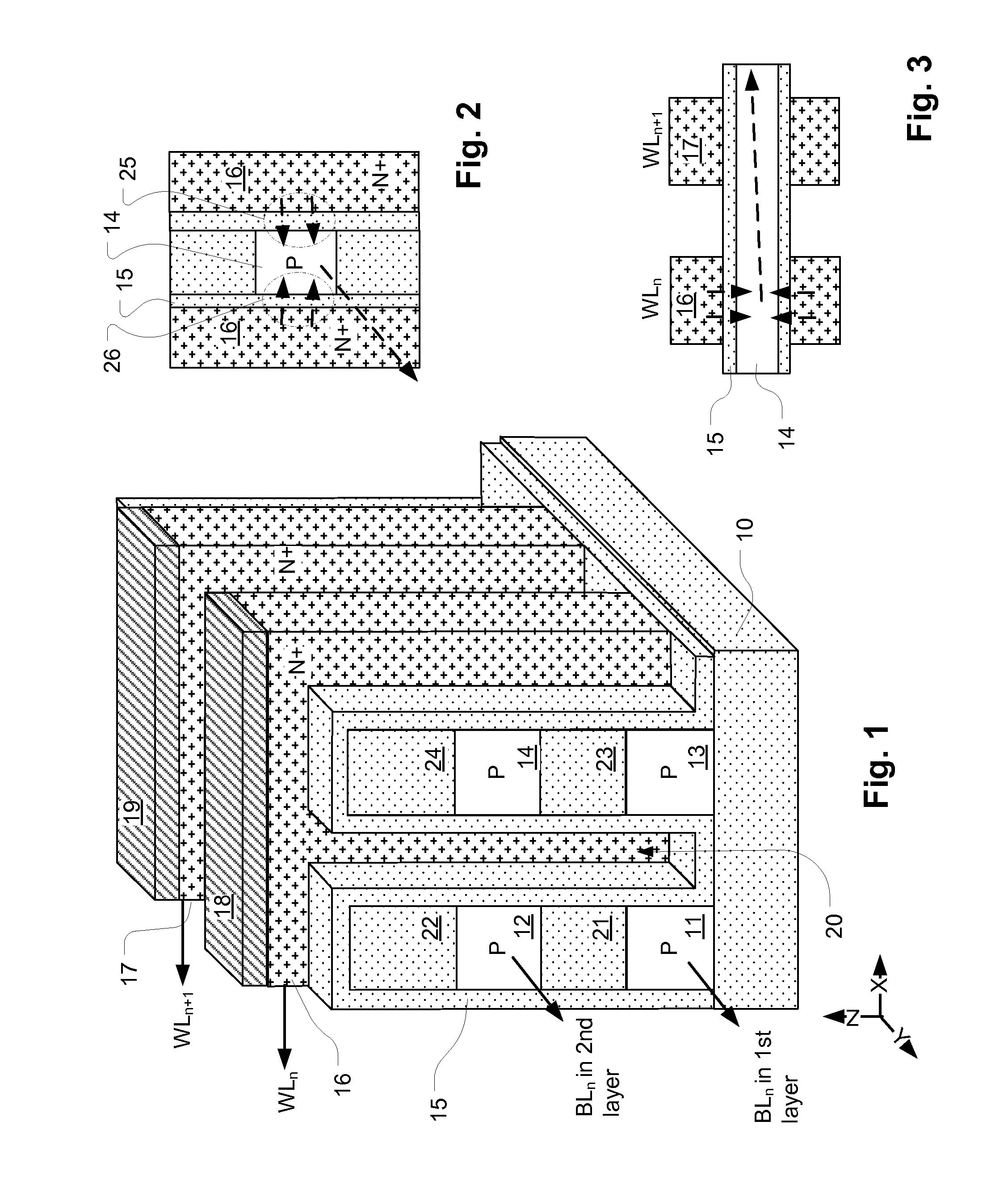

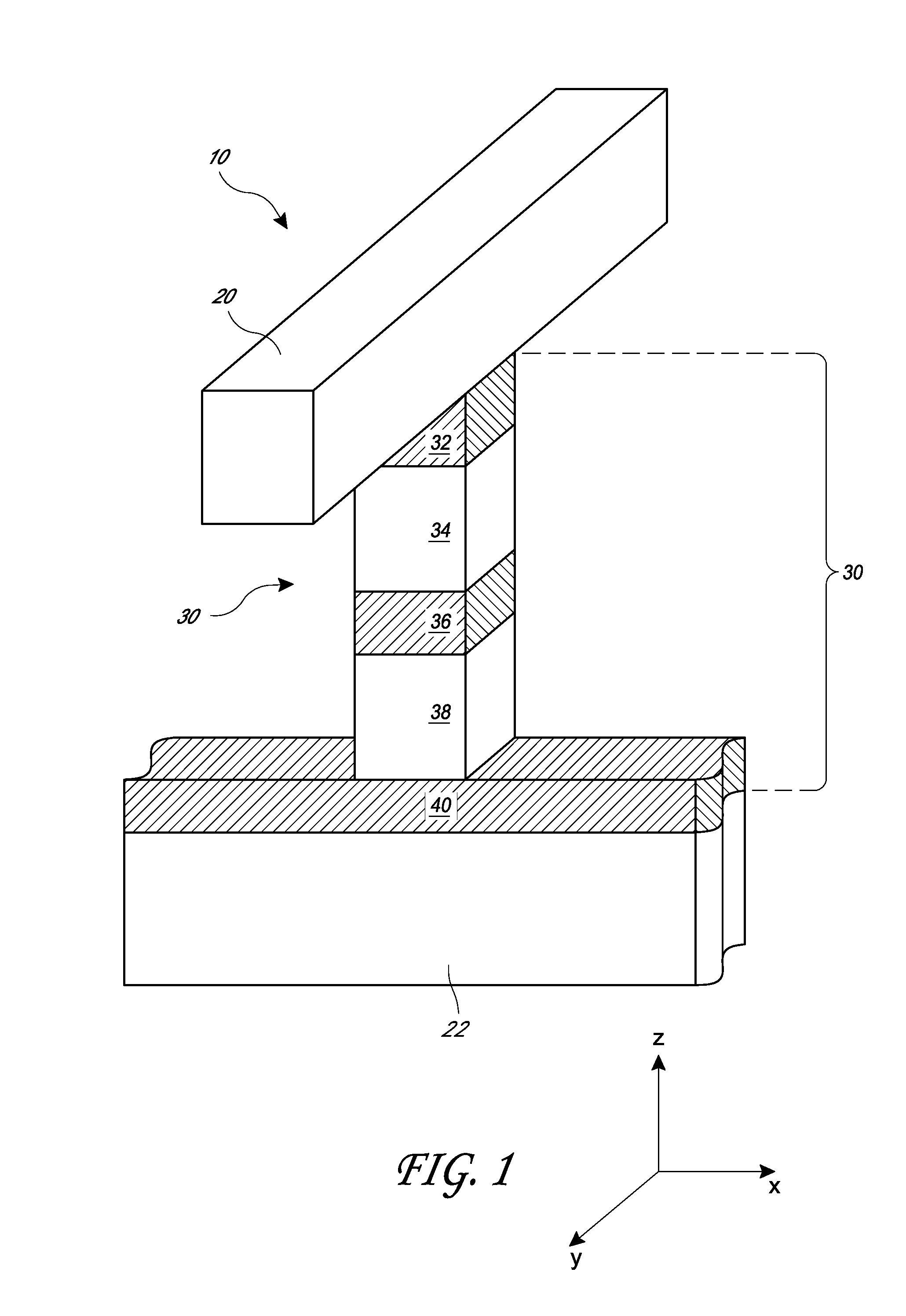

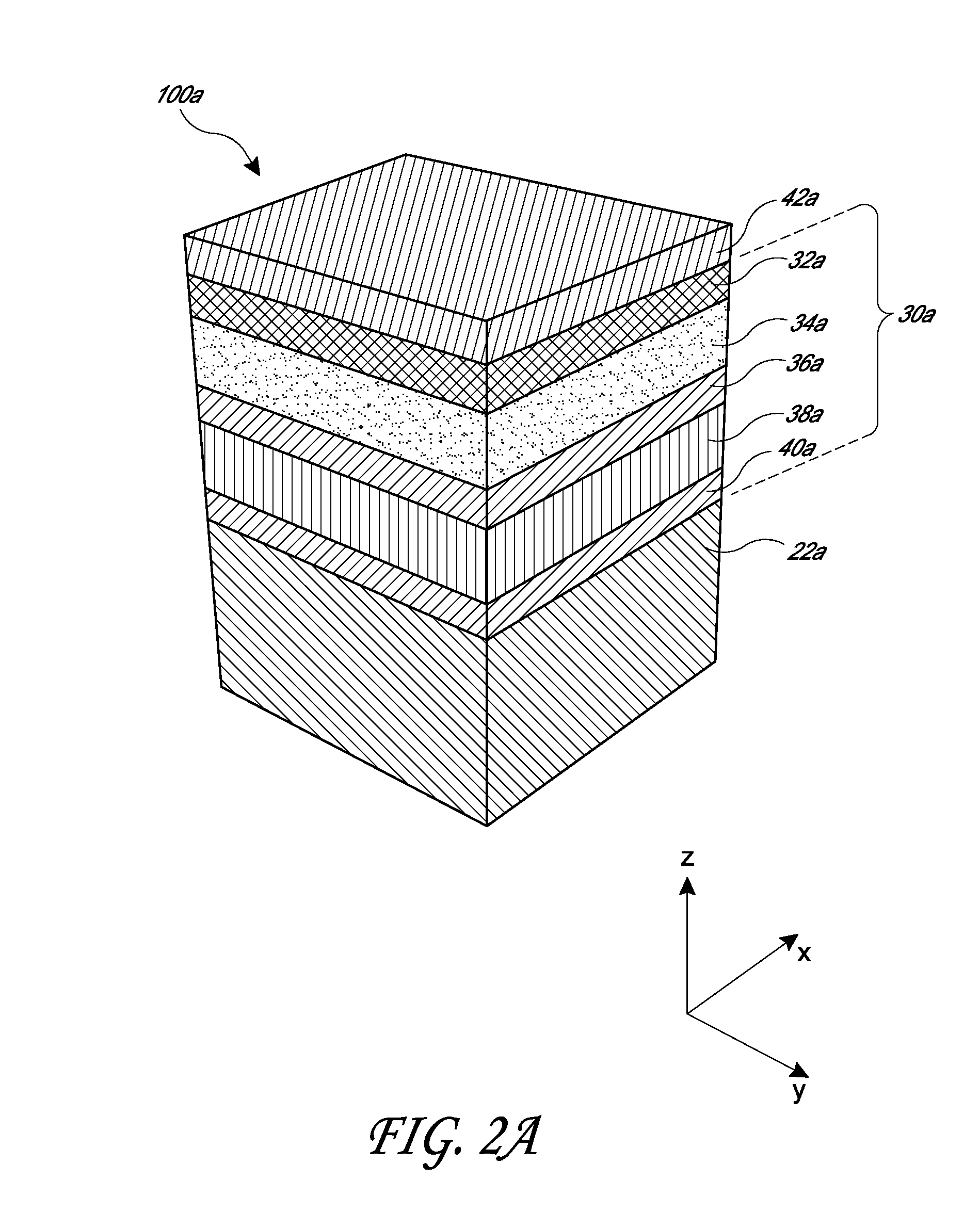

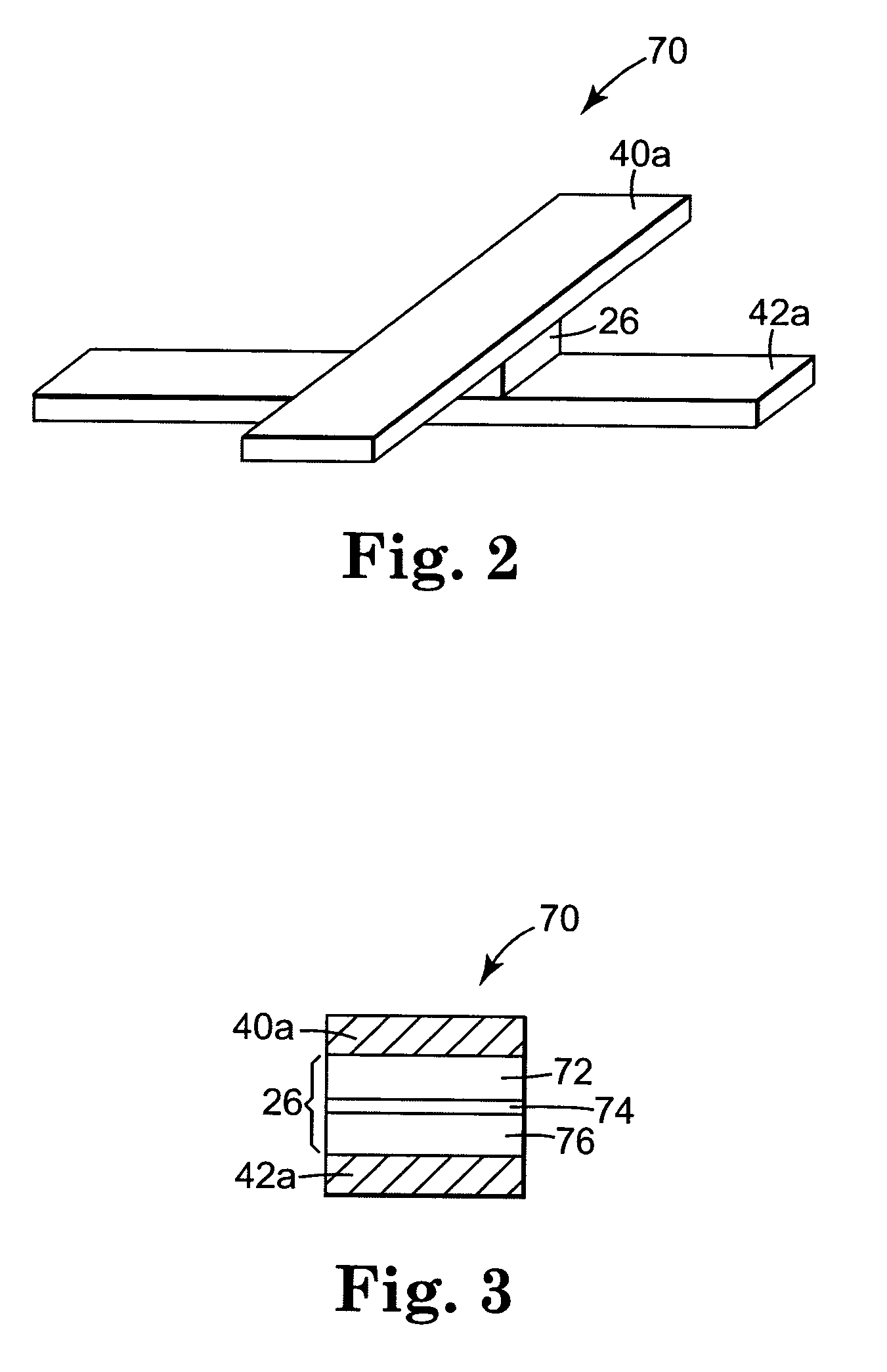

One embodiment of the present invention includes a low-cost unipolar rewritable variable-resistance memory device, made of cross-point arrays of memory cells, vertically stacked on top of one another and compatible with a polycrystalline silicon diode.

Owner:HITACHI GLOBAL STORAGE TECH NETHERLANDS BV

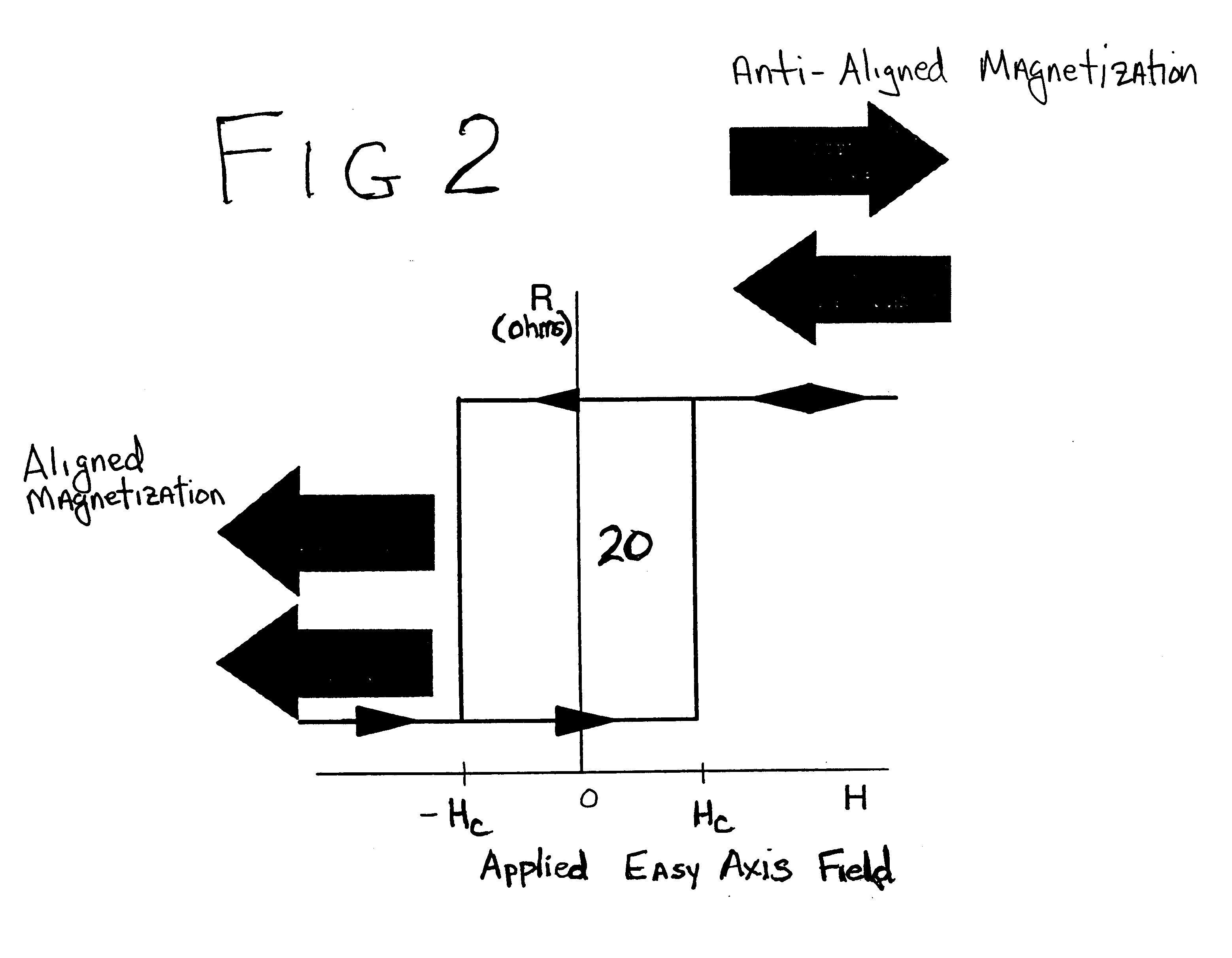

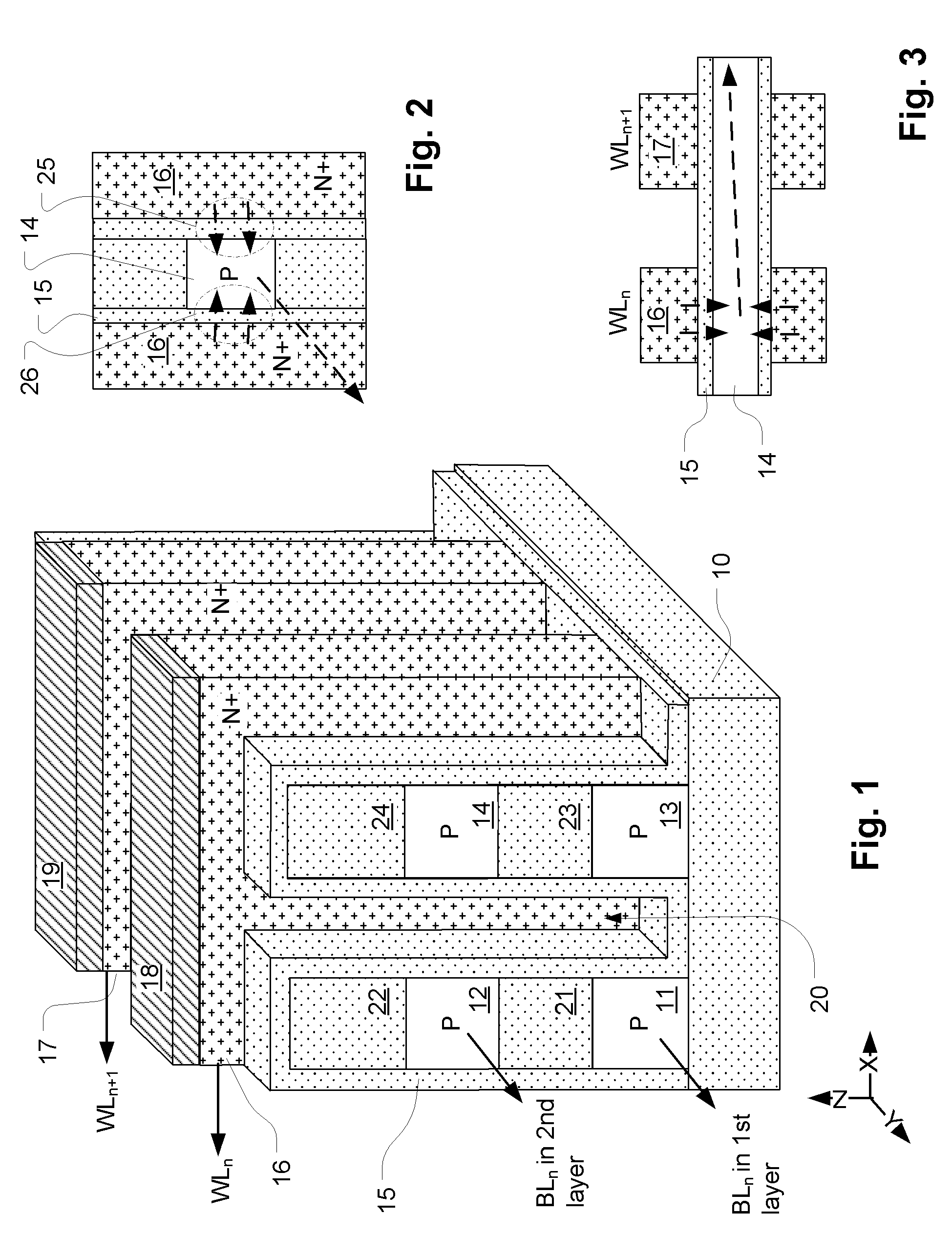

Thermally-assisted magnetic random access memory (MRAM)

It is important to ensure good selectivity of a single magnetic tunnel junction storage cell within a memory array without affecting nearby storage cells. For this purpose, this memory array of storage cells preferably comprises a) an array of electrically conducting bit lines and electrically conducting word lines which form intersections therebetween, b) a storage cell disposed at each of said intersections, each storage cell comprising at least one reversible magnetic region or layer characterized by a magnetization state which can be reversed by applying thereto a selected external magnetic field, said reversible magnetic layer comprising a material whose magnetization state is more easily reversed upon a change in the temperature thereof, and c) a temperature change generator for changing the temperature of said reversible magnetic layer of only a selected one of said array of storage cells at any moment. To select a cell, it is preferable to select a cell by using a brief pulse of tunnelling current between the intersecting bit and word lines at that cell in order to provide sufficient Joule heating to facilitate a change in the magnetization state of its reversible magnetic layer, which preferably comprises a ferrimagnetic material.

Owner:IBM CORP

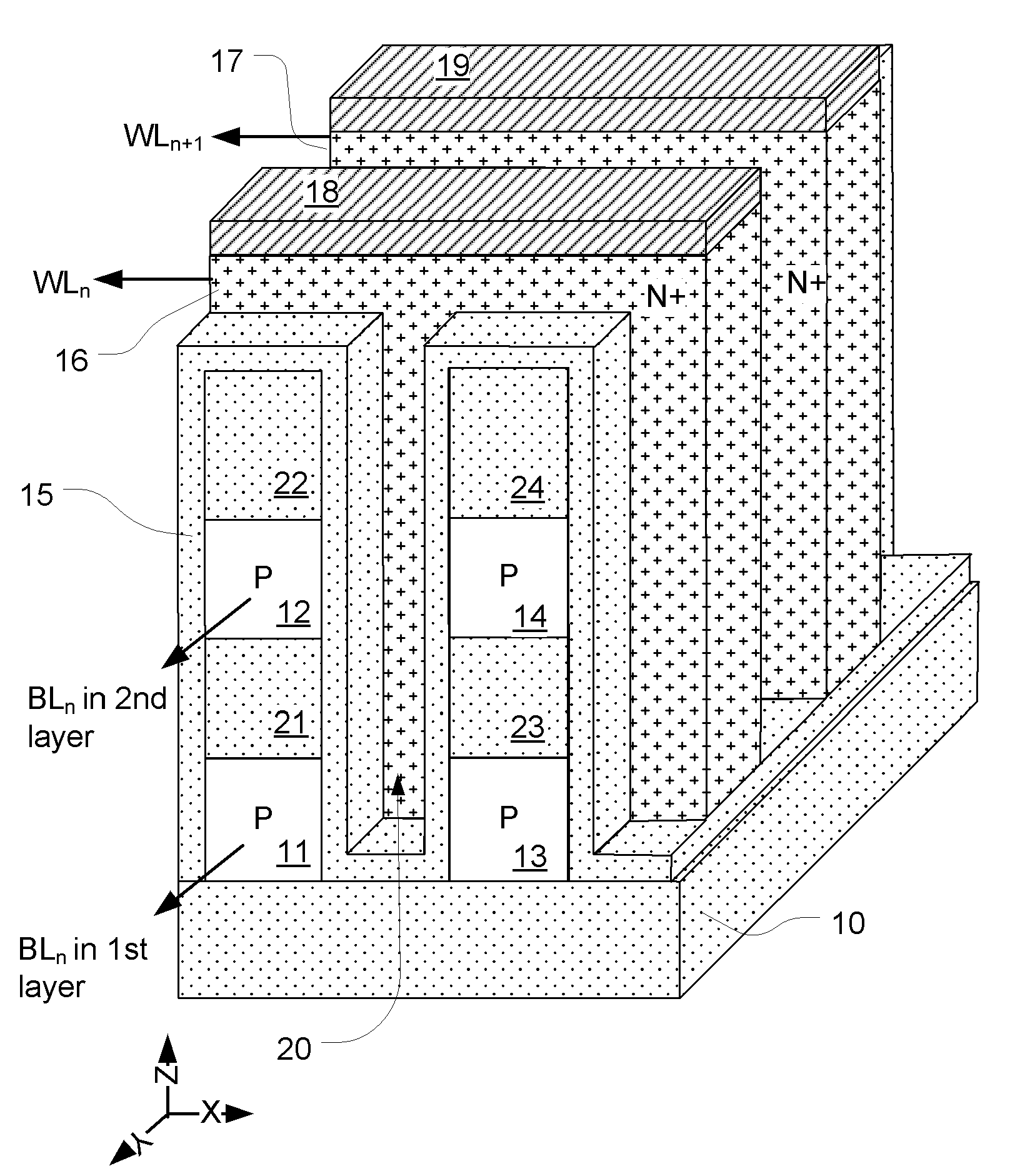

Integrated circuit self aligned 3D memory array and manufacturing method

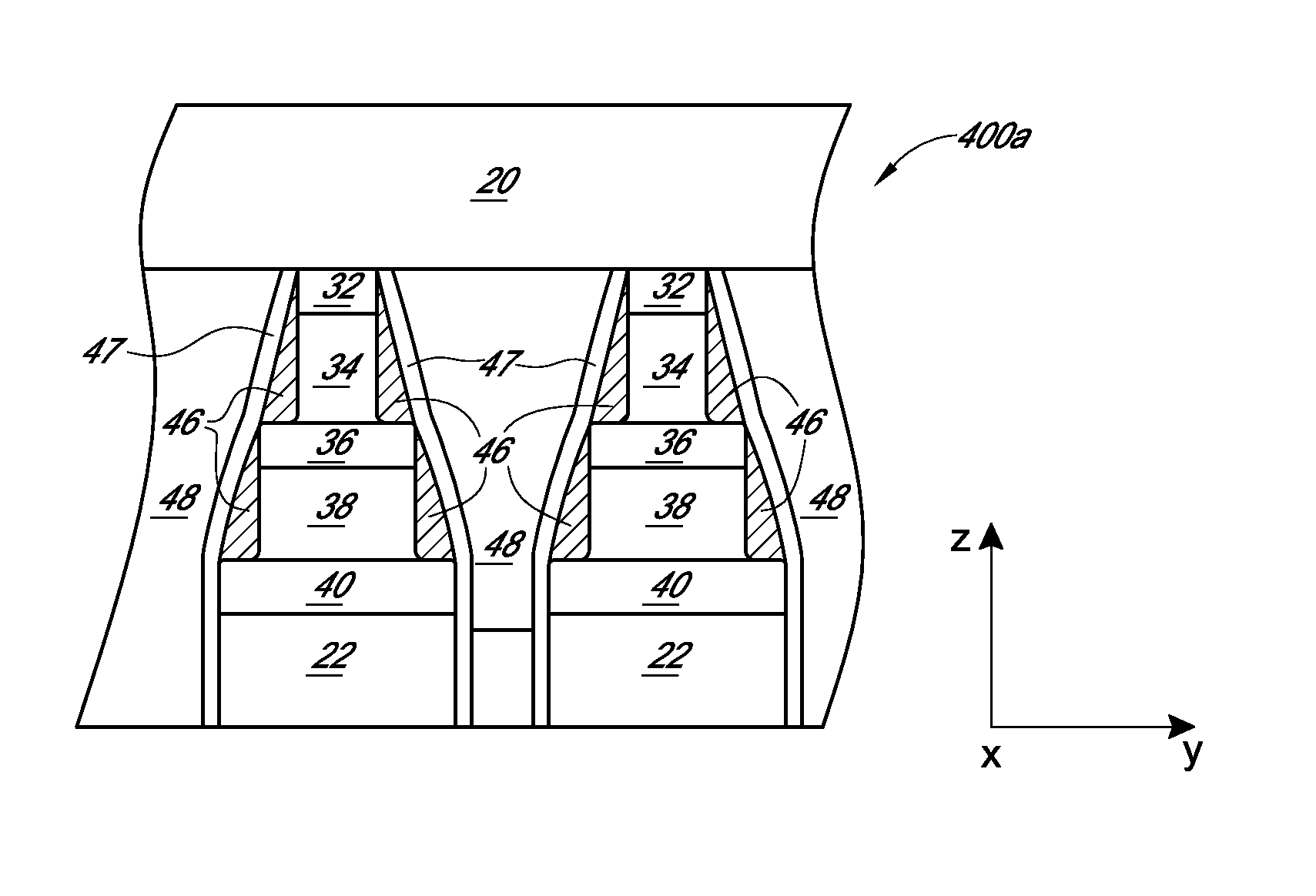

A 3D memory device includes a plurality of ridge-shaped stacks, in the form of multiple strips of conductive material separated by insulating material, arranged as bit lines which can be coupled through decoding circuits to sense amplifiers. The strips of conductive material have side surfaces on the sides of the ridge-shaped stacks. A plurality of conductive lines arranged as word lines which can be coupled to row decoders, extends orthogonally over the plurality of ridge-shaped stacks. The conductive lines conform to the surface of the stacks. Memory elements lie in a multi-layer array of interface regions at cross-points between side surfaces of the conductive strips on the stacks and the conductive lines. The memory elements are programmable, like the anti-fuses or charge trapping structures. The 3D memory is made using only two critical masks for multiple layers.

Owner:MACRONIX INT CO LTD

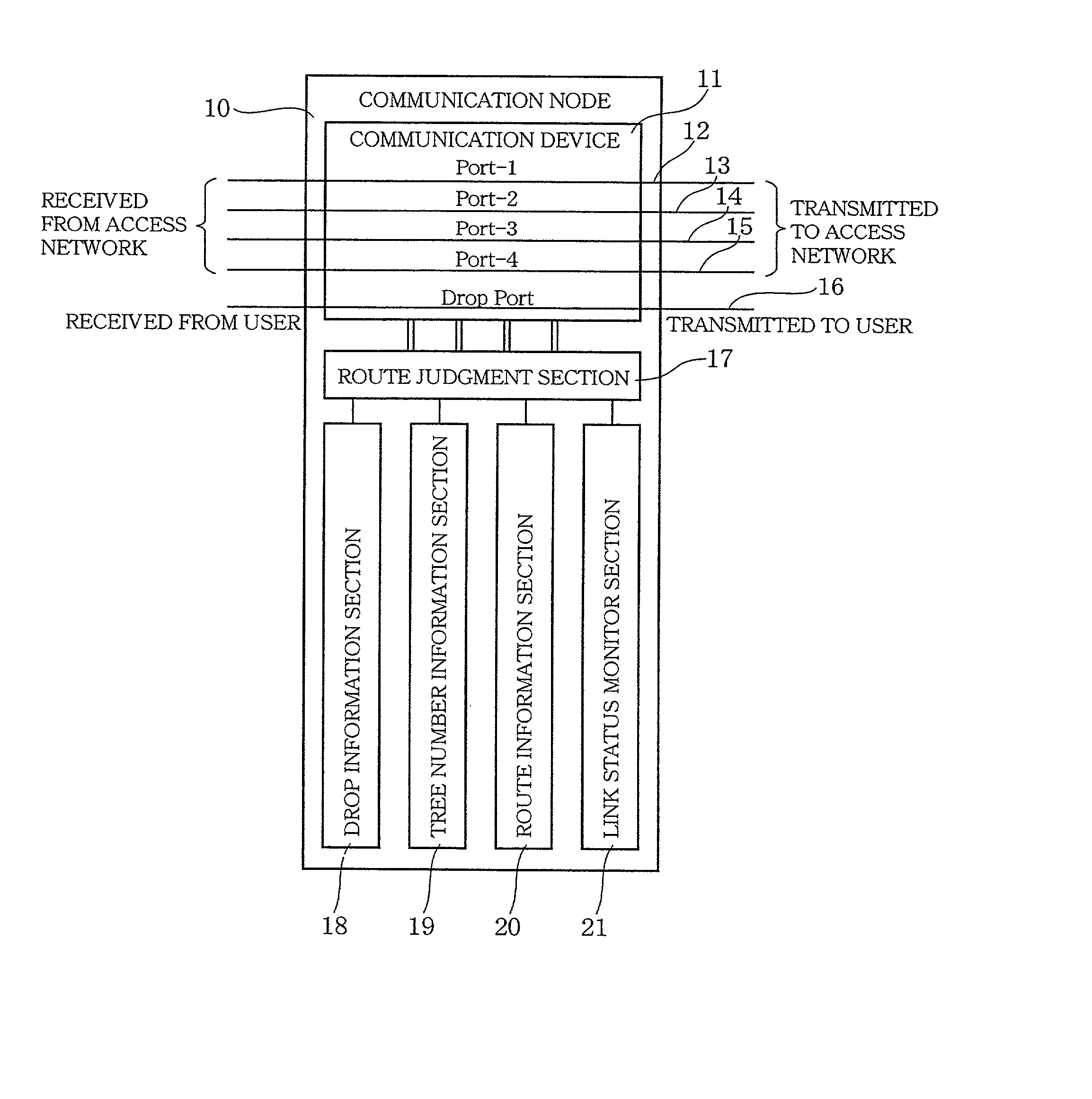

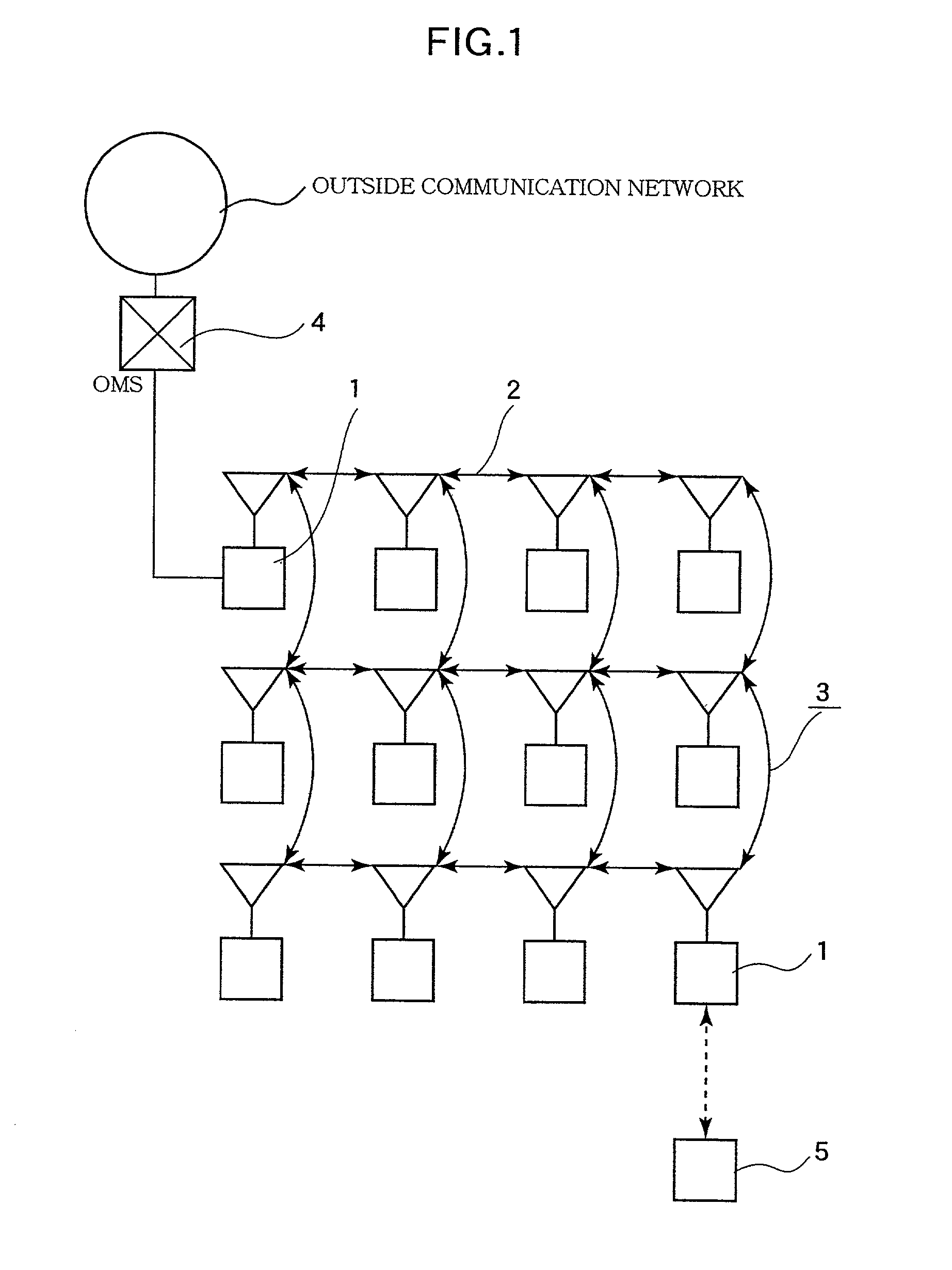

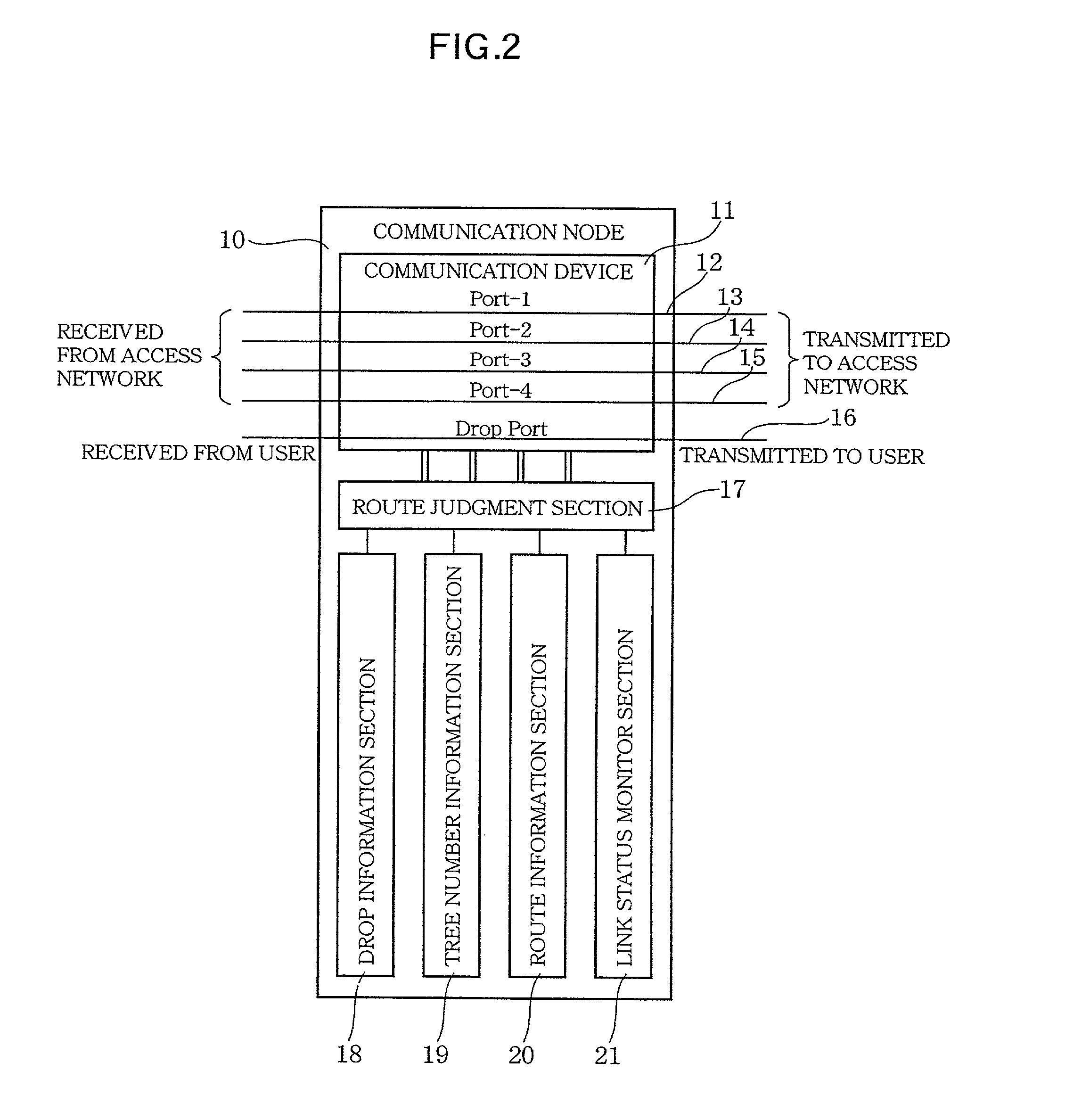

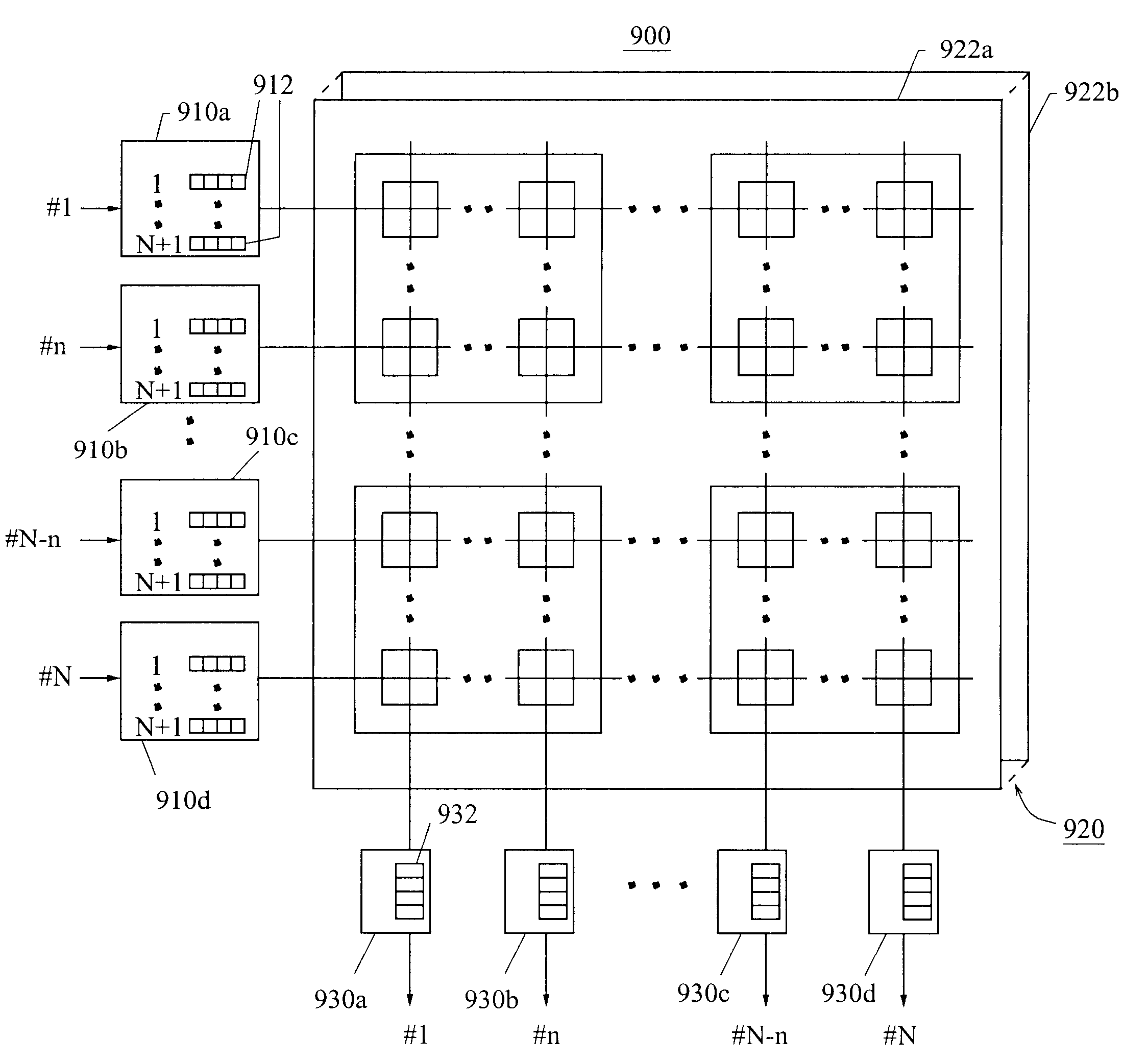

Access network system

InactiveUS20020054593A1Multiplex system selection arrangementsNetwork traffic/resource managementAccess networkRadio access network

In order to provide an access network system that has durability against transmission quality deterioration and fault and controls the causes of delay in the communication processing for data transmission, the base stations (communication nodes) are arranged in a plurality of cross-points, and the base stations have a function capable of transmitting and receiving the information of an optical wireless communication type and the like, and are mutually linked with each other by wireless and constitute an access network which is accessible cross-wise from each base station by a wireless communication link passage. This access network is wirelessly connected to other outside communication network by an access network terminating set.

Owner:KDDI CORP +1

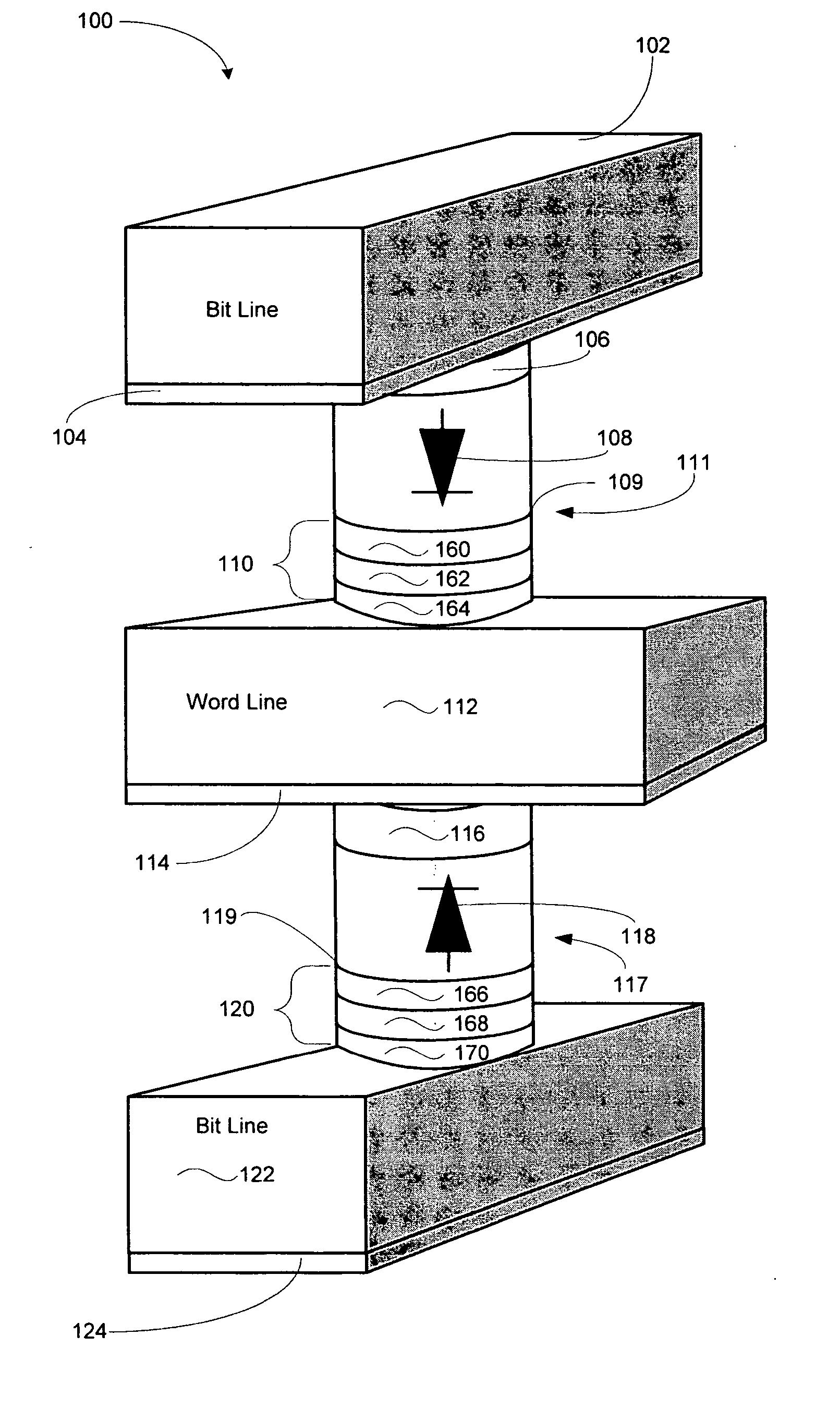

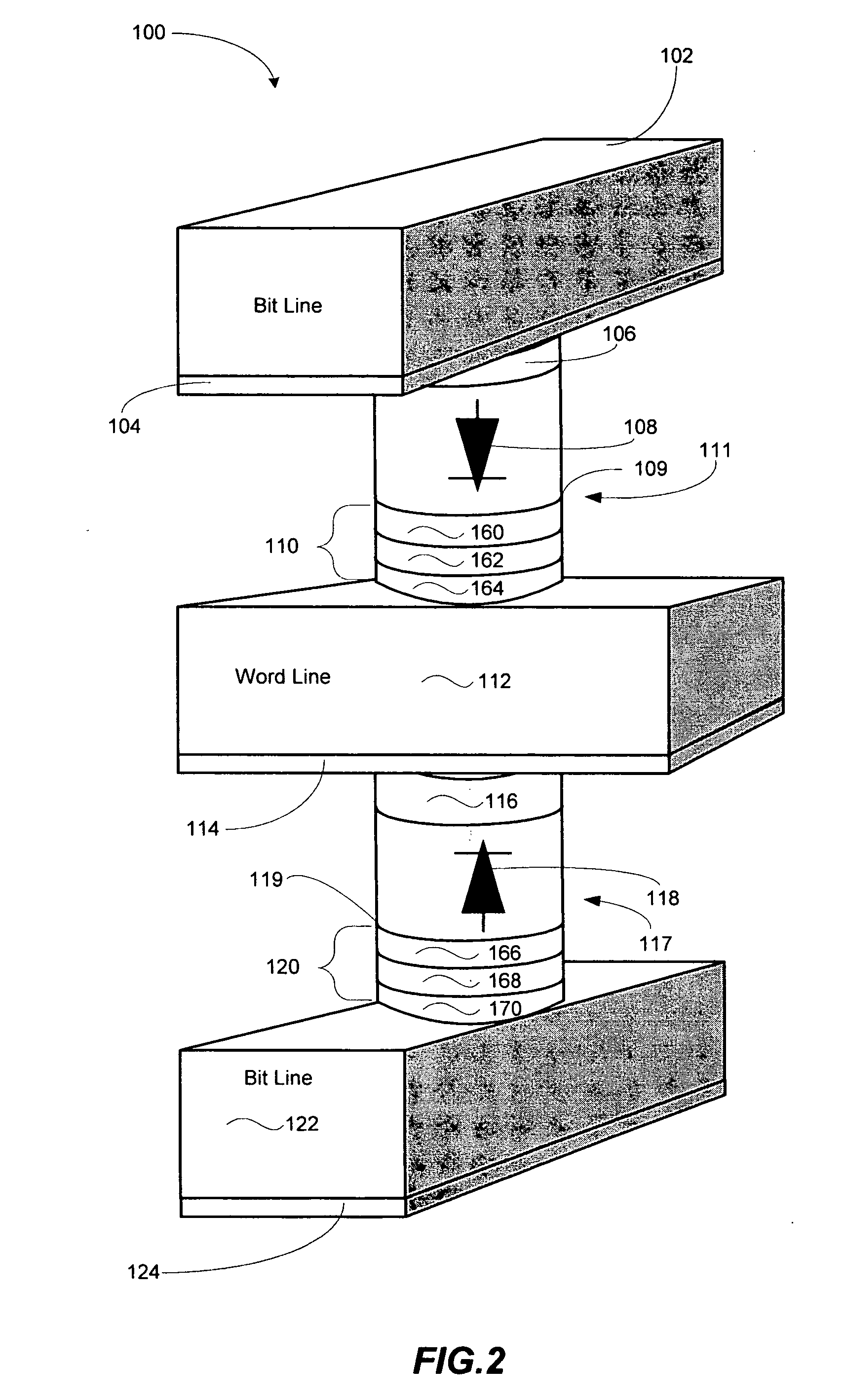

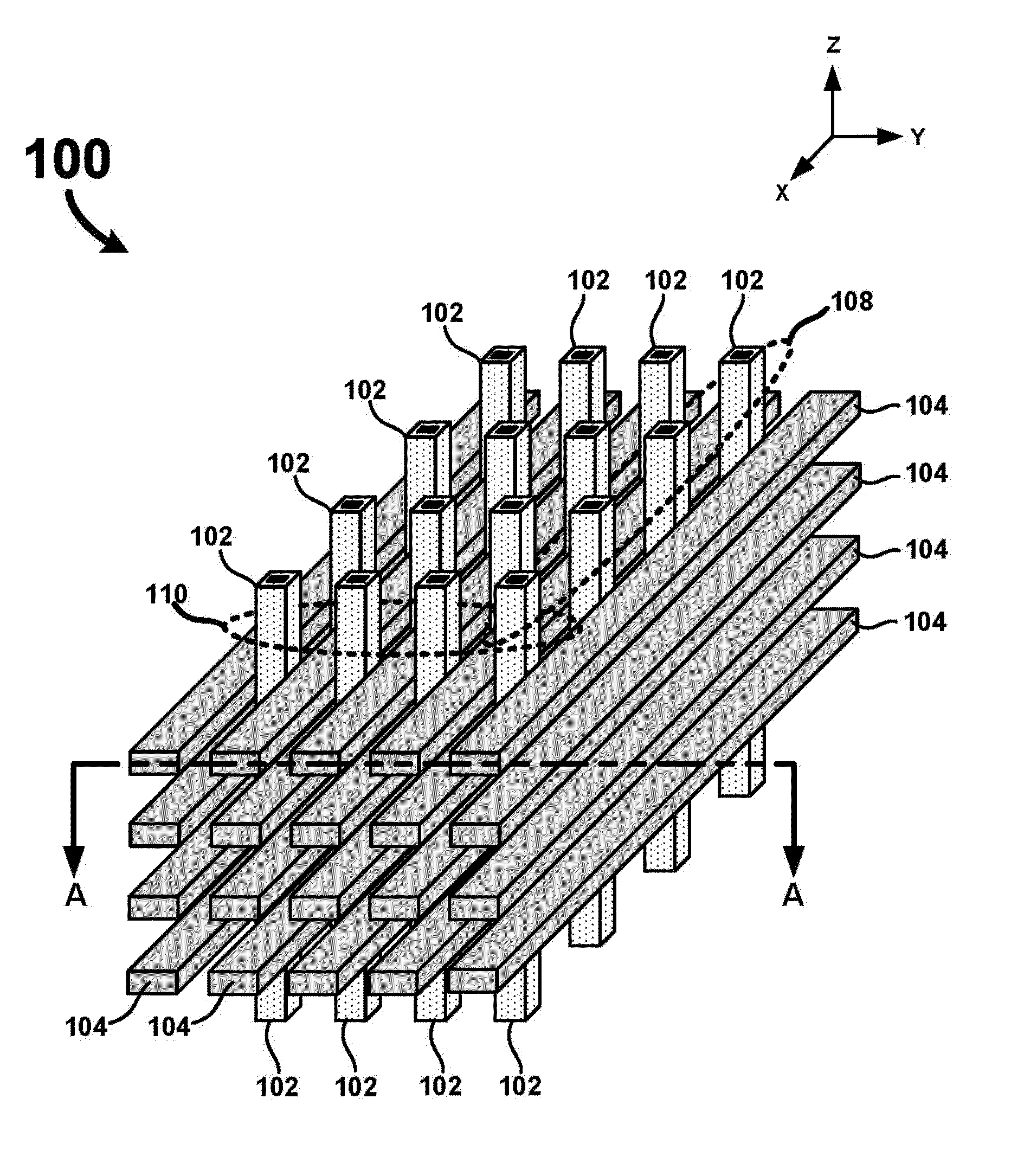

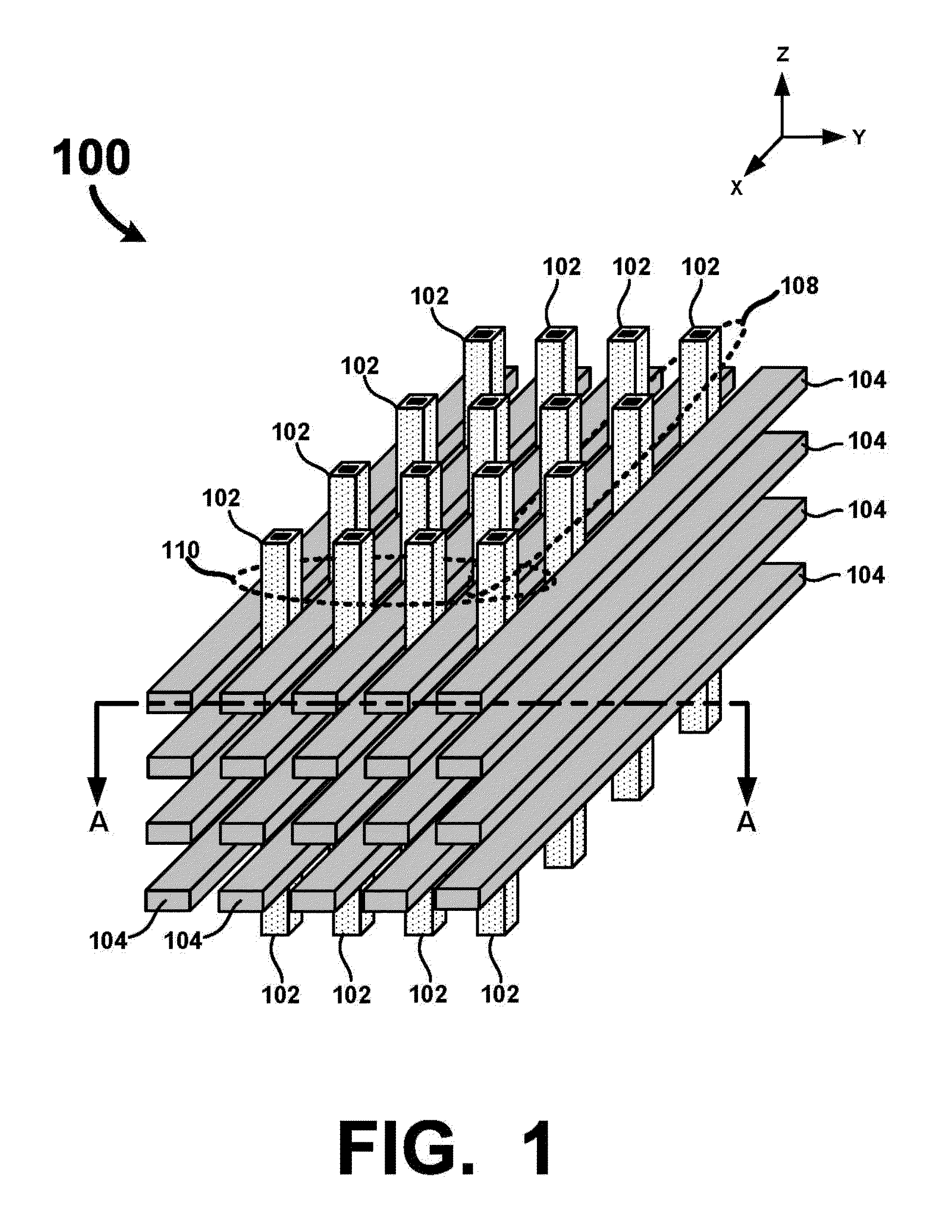

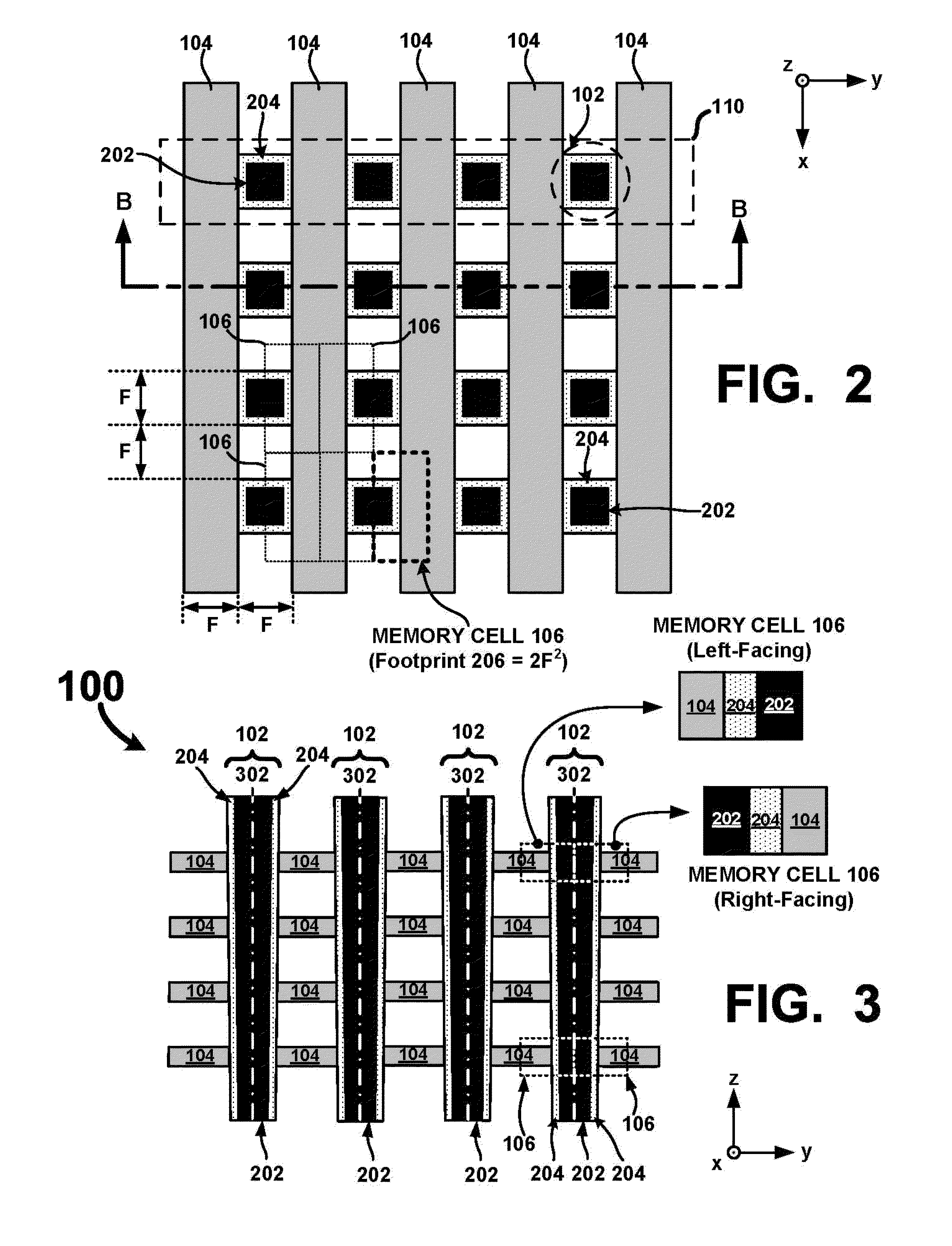

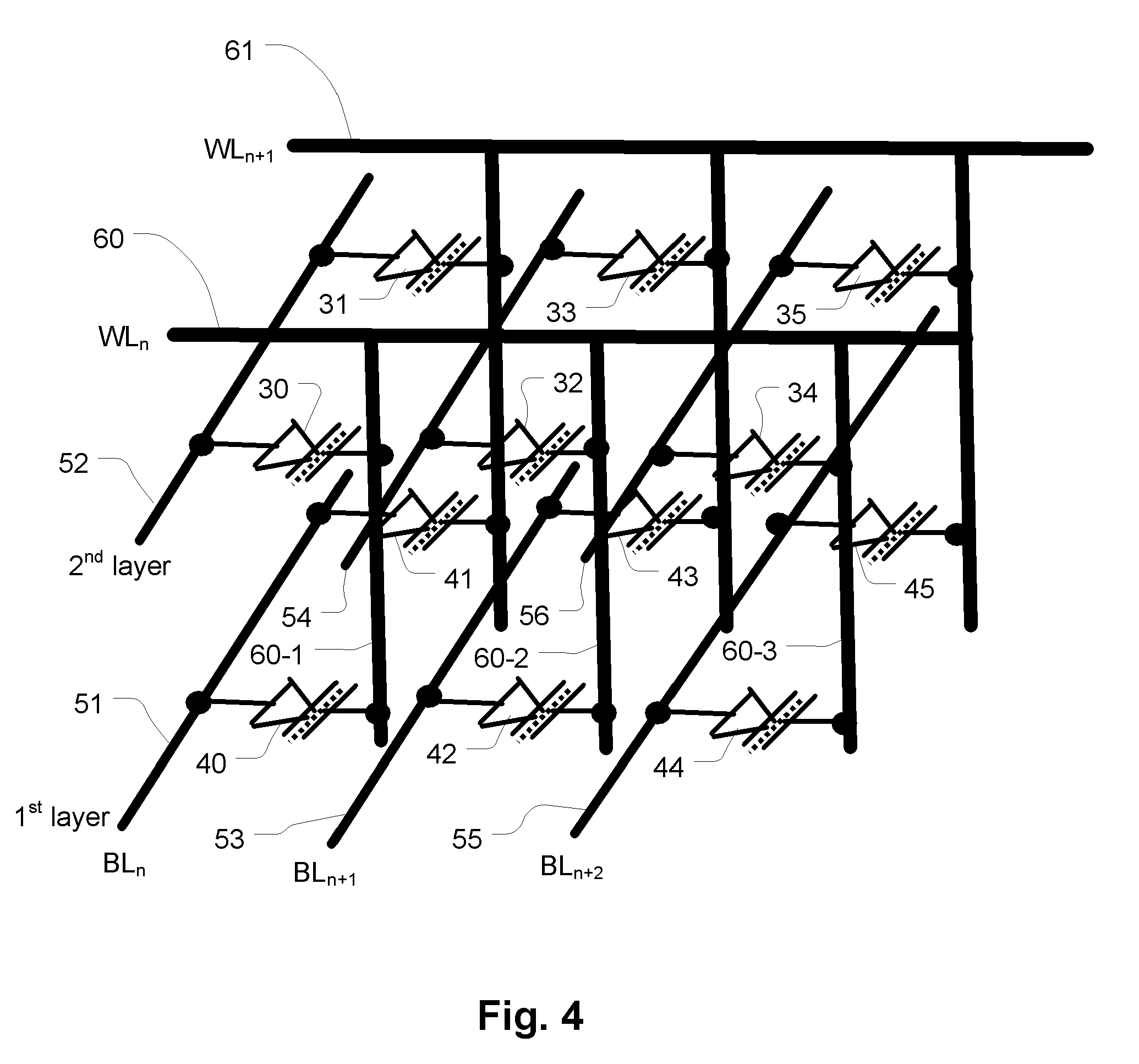

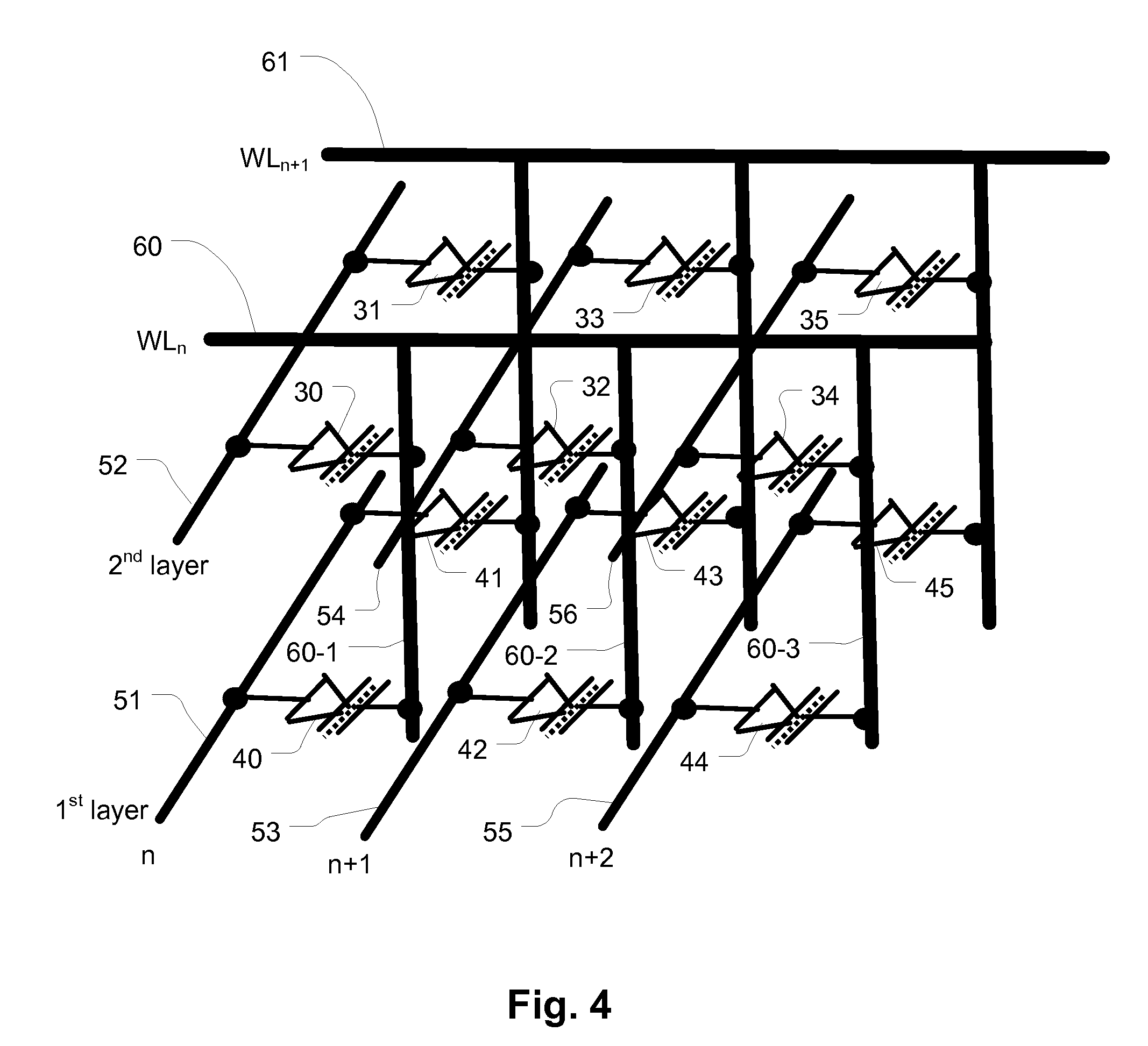

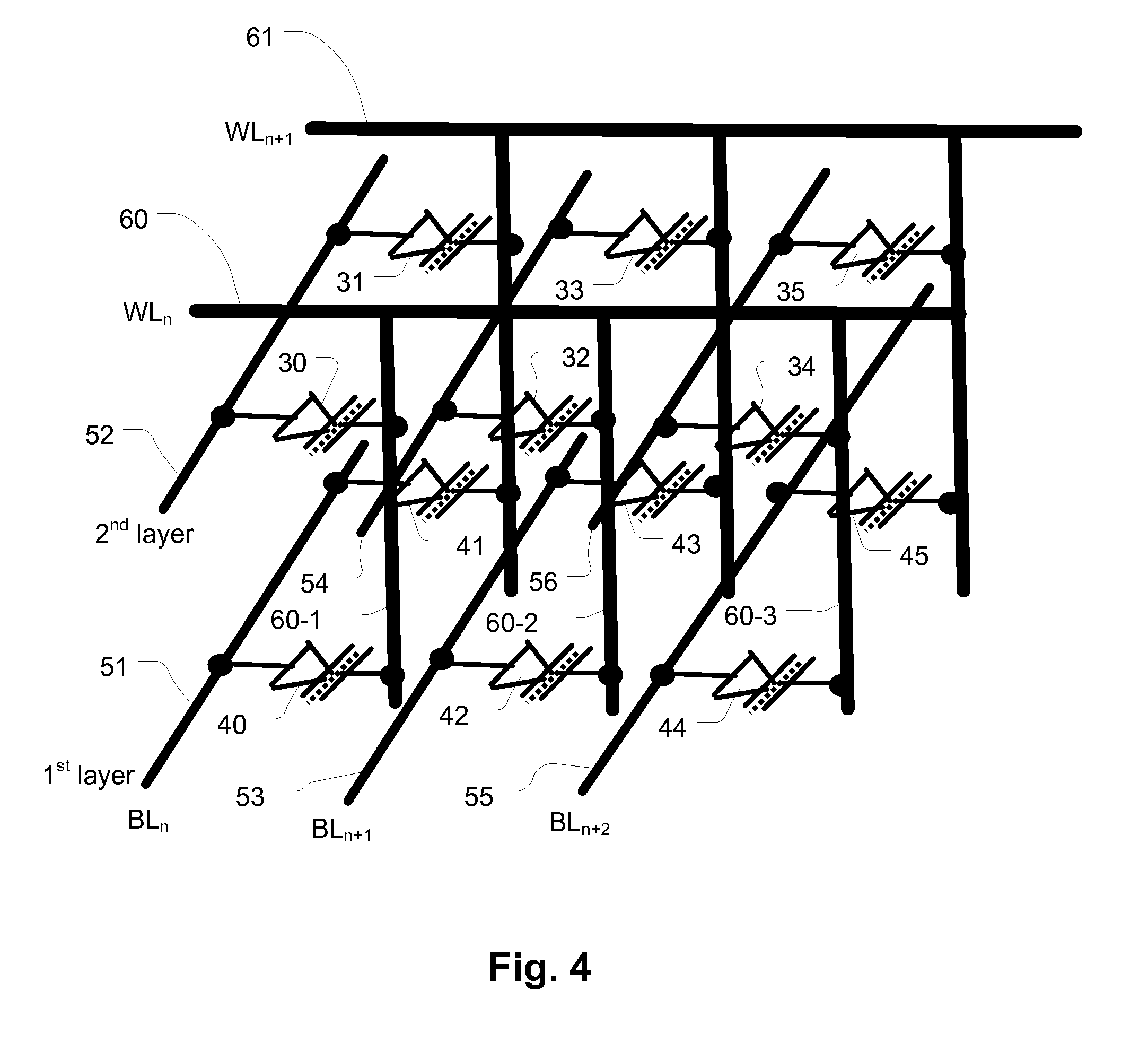

Vertical Cross Point Arrays For Ultra High Density Memory Applications

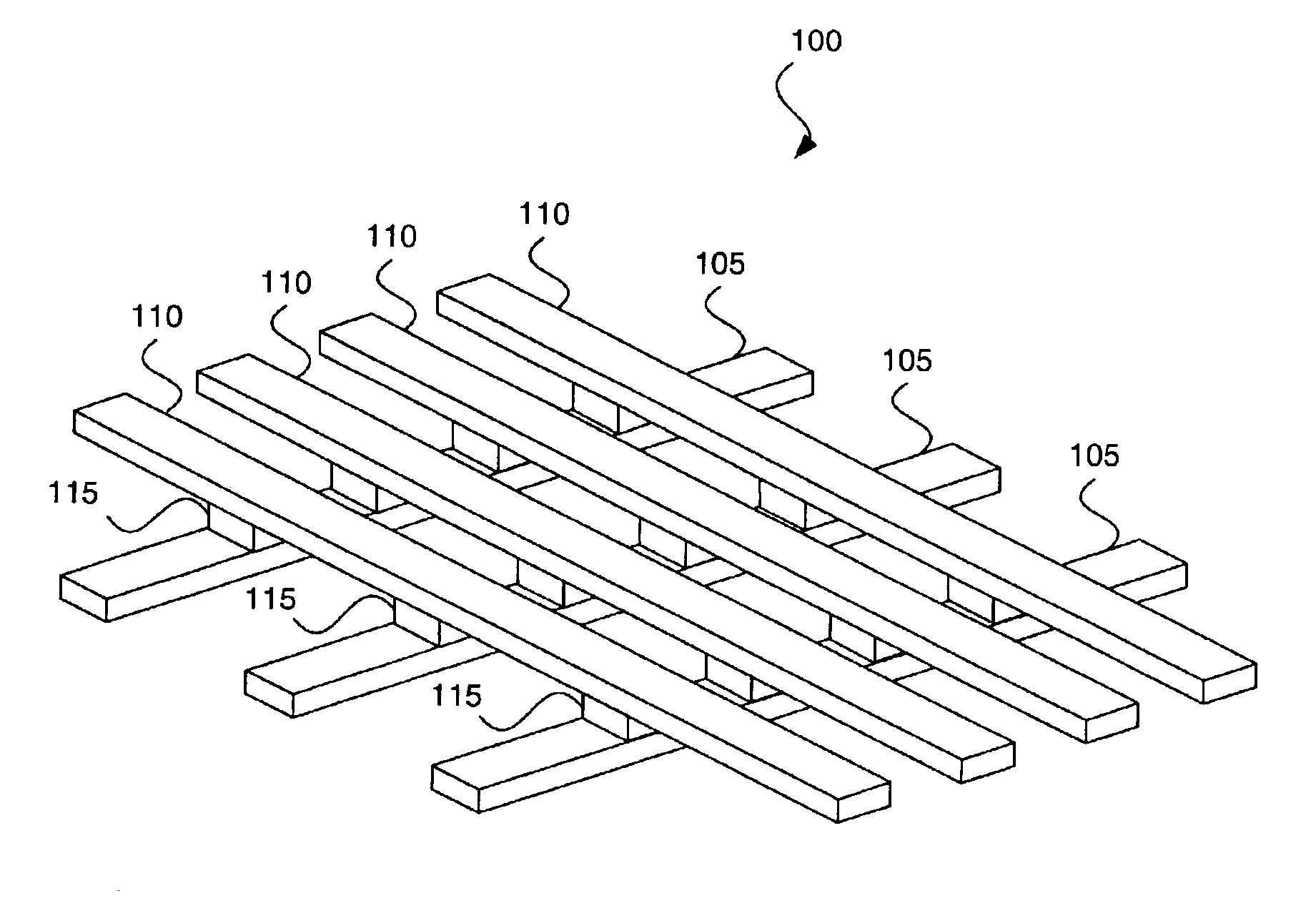

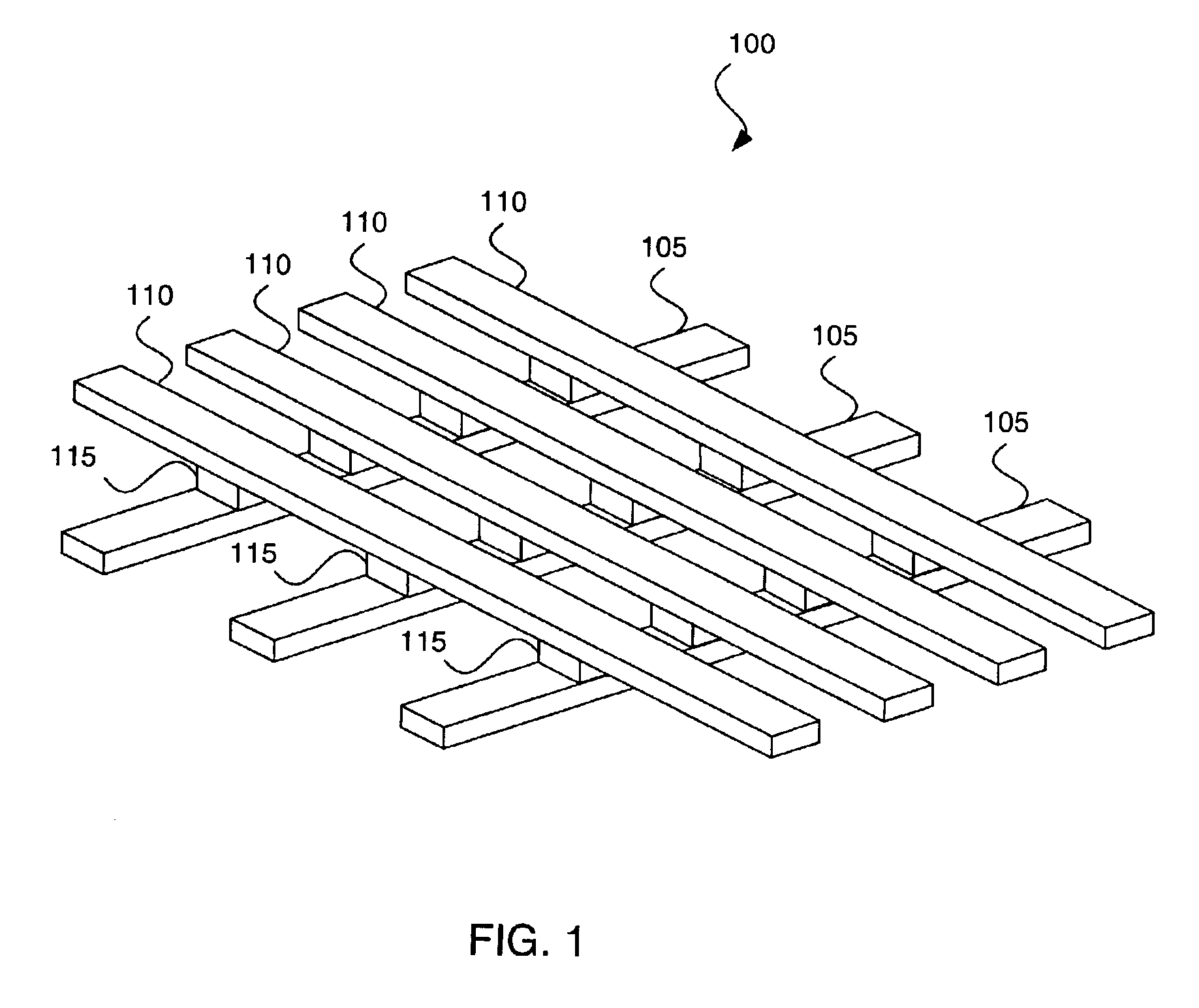

An ultra-high-density vertical cross-point array comprises a plurality of horizontal line layers having horizontal lines interleaved with a plurality of vertical lines arranged in rows and columns. The vertical lines are interleaved with the horizontal lines such that a row of vertical lines is positioned between each consecutive pair of horizontal lines in each horizontal line layer. Each vertical line comprises a center conductor surrounded by a single or multi-layered memory film. Accordingly, when interleaved with the horizontal lines, two-terminal memory cells are integrally formed between the center conductor of each vertical line and each crossing horizontal line. By configuring the vertical and horizontal lines so that a row of vertical lines is positioned between each consecutive pair of horizontal lines, a unit memory cell footprint of just 2F2 may be realized.

Owner:UNITY SEMICON

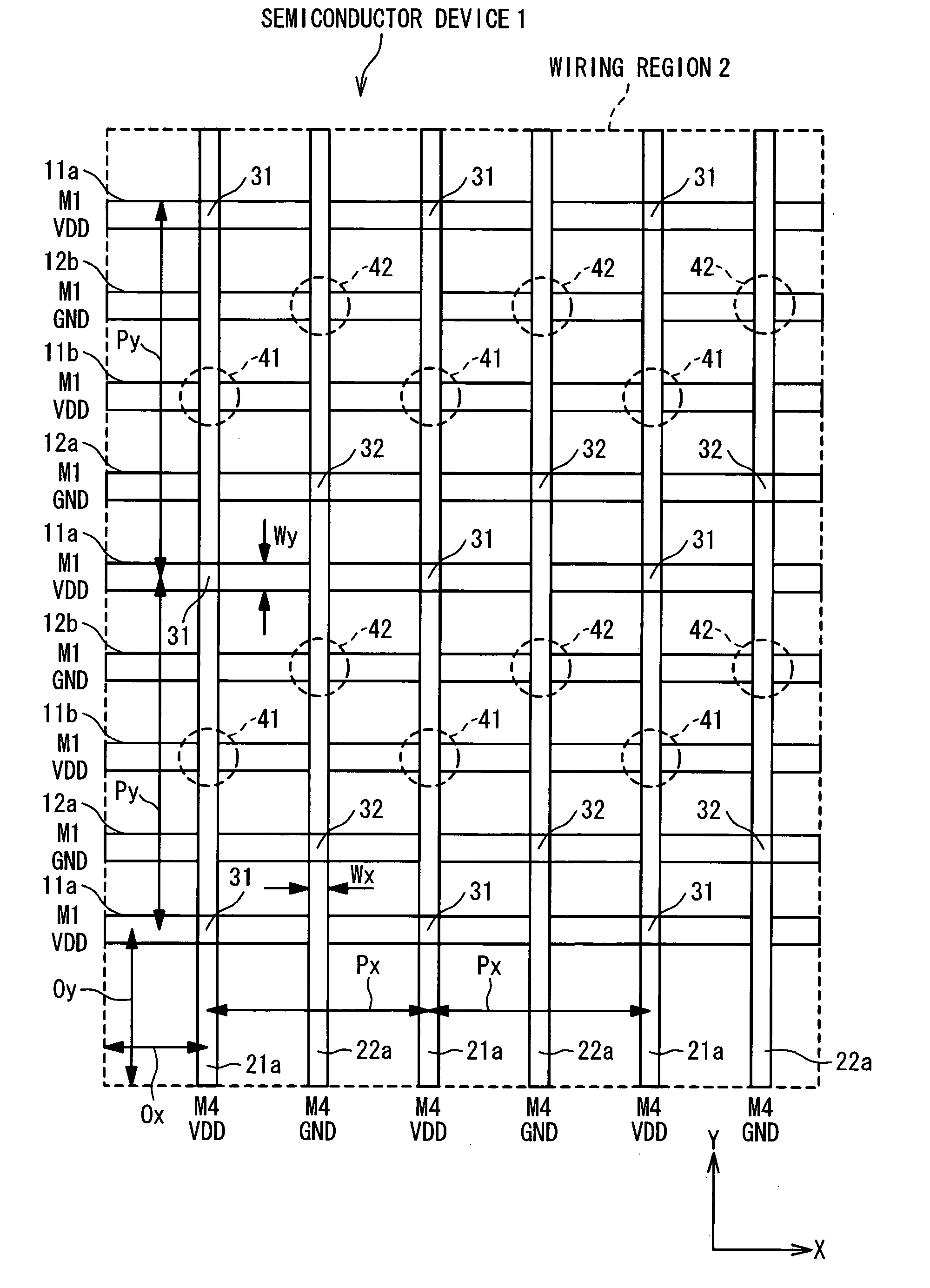

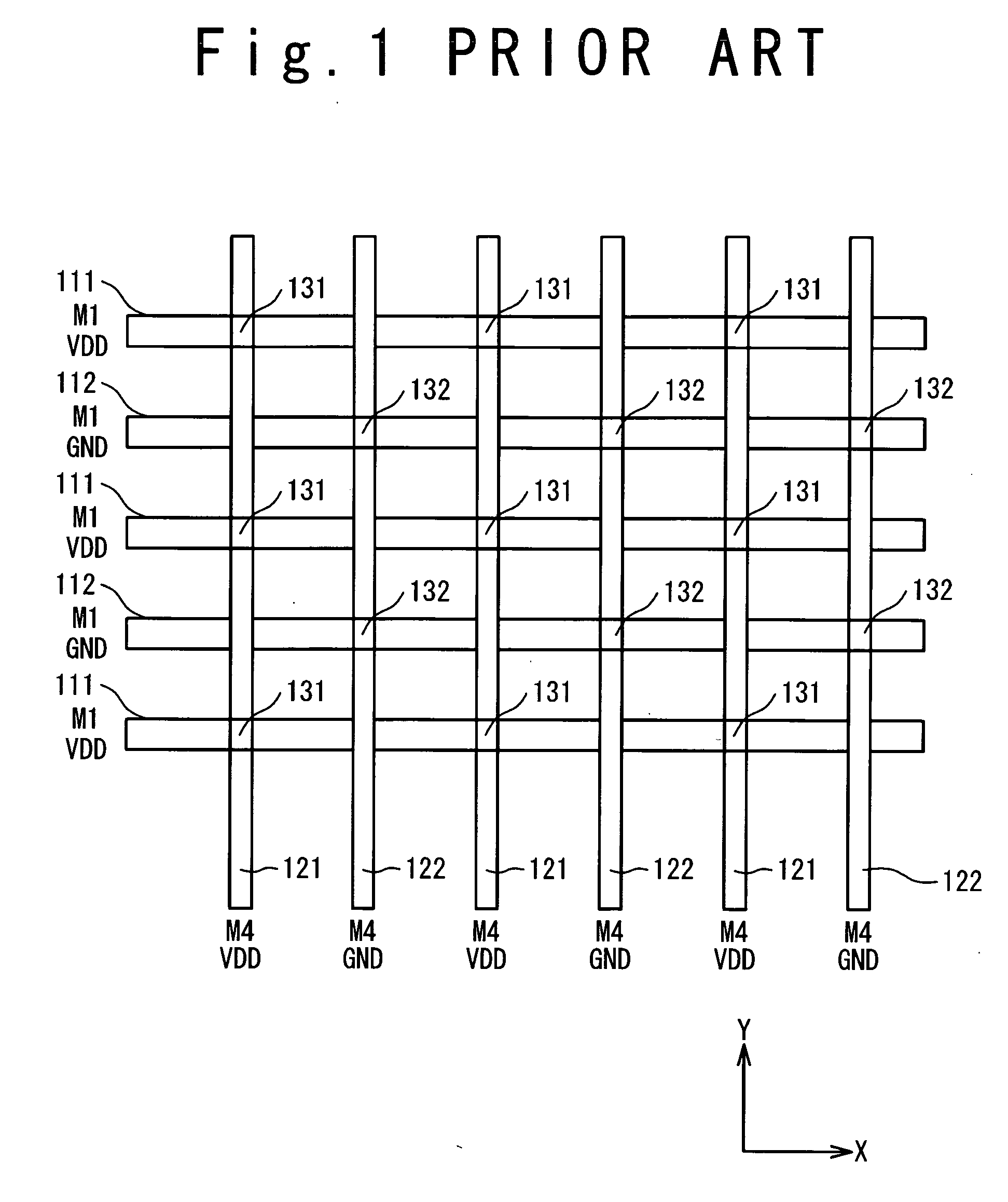

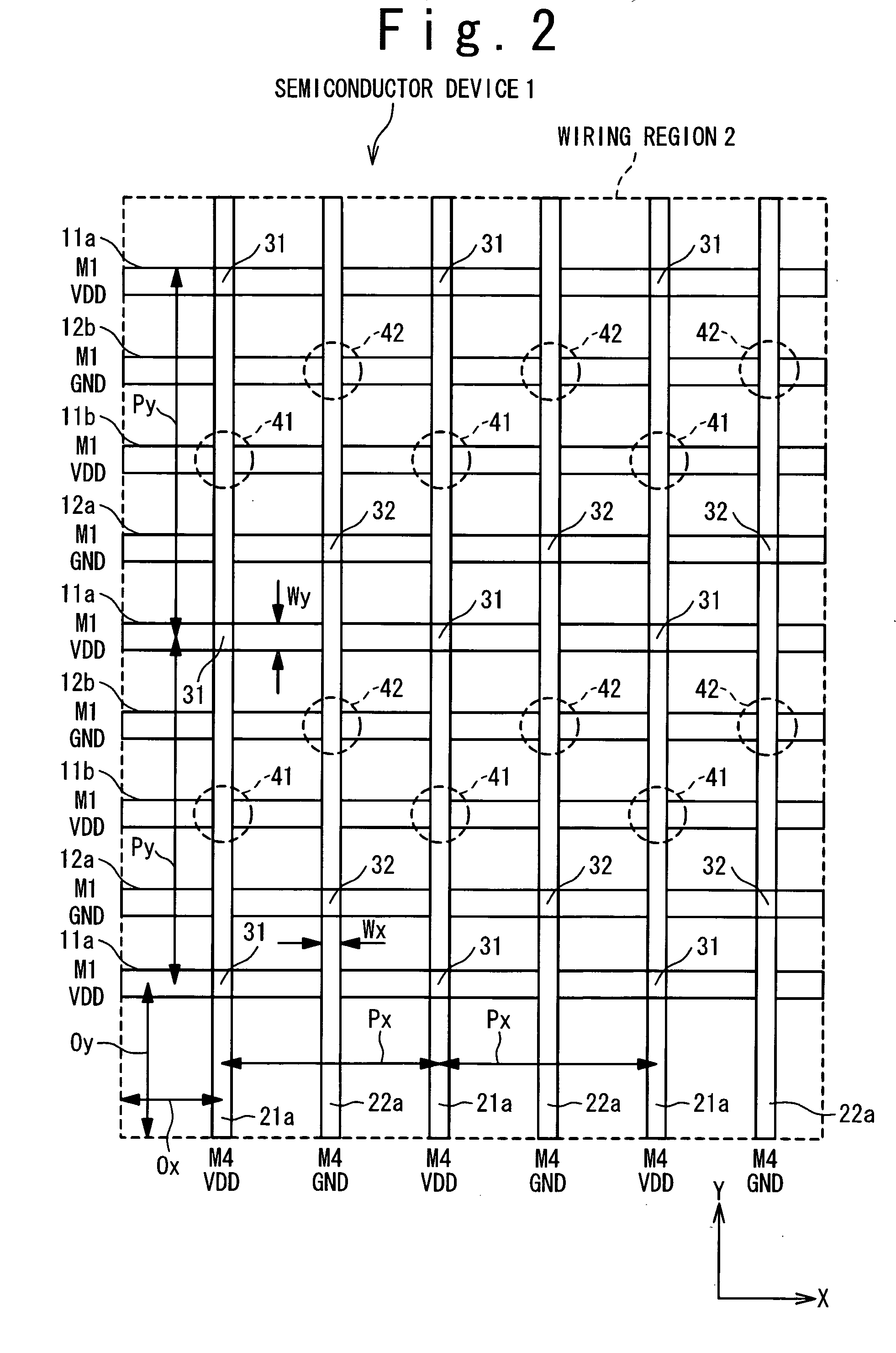

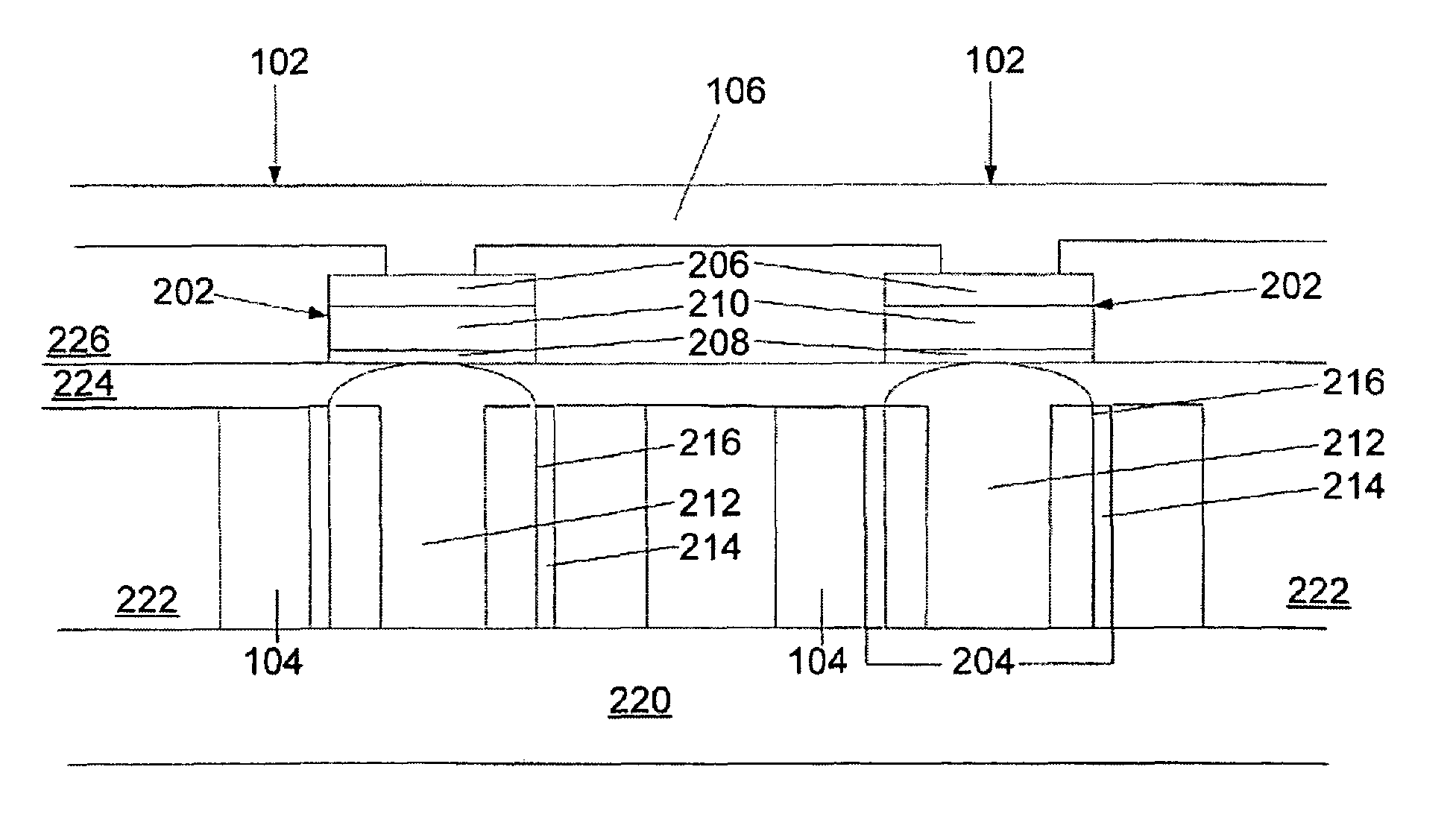

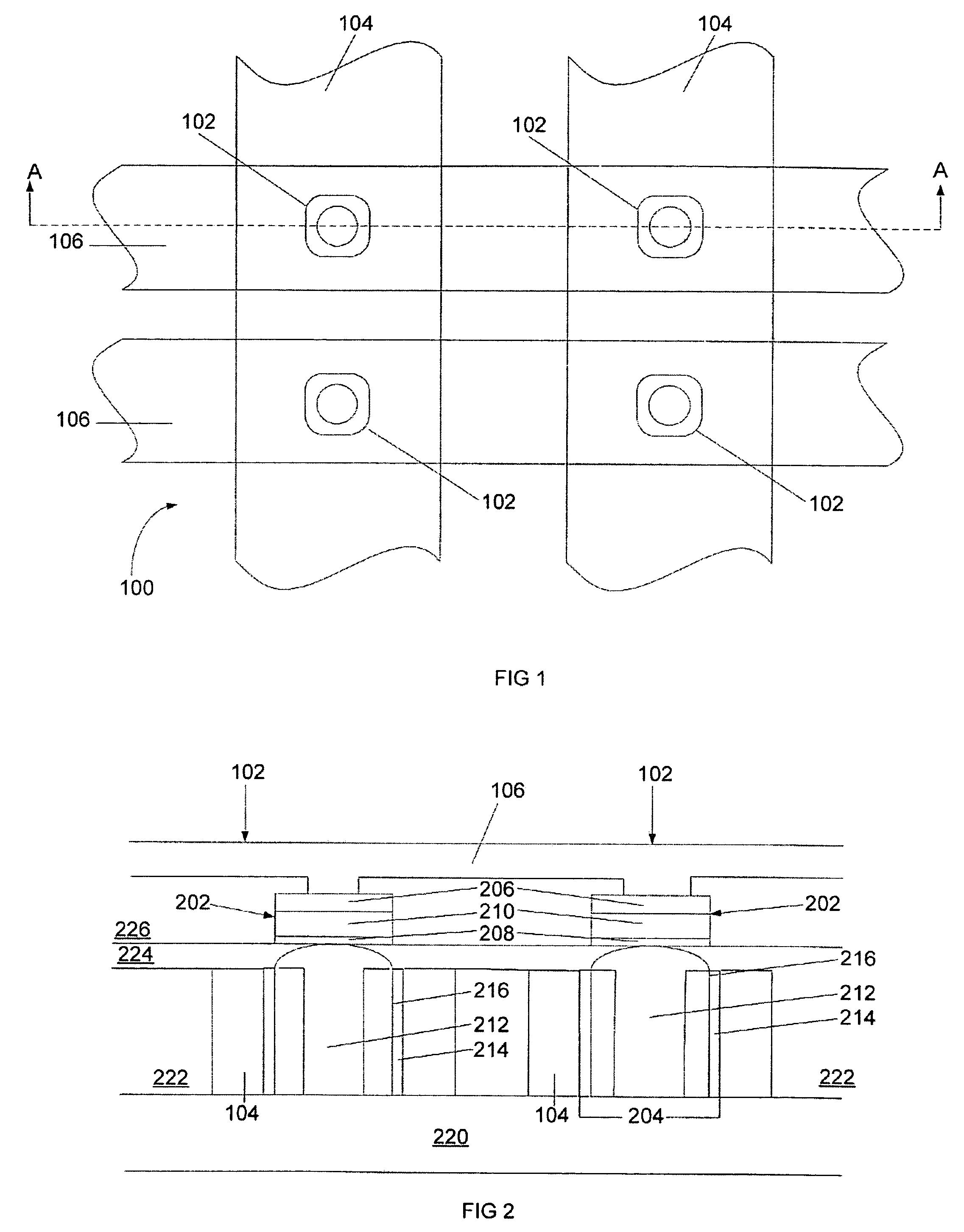

Semiconductor device and computer program product for designing the same

InactiveUS20060151810A1Reduce the amount requiredImprove performanceSemiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

A semiconductor device has: a plurality of first power supply wires formed in a first wiring layer; a plurality of second power supply wires formed in a second wiring layer; and a plurality of vias connecting between the first wiring layer and the second wiring layer. The plurality of second power supply wires overlap the plurality of first power supply wires at a plurality of intersections. The plurality of vias are arranged regularly at a part of the plurality of intersections.

Owner:NEC ELECTRONICS CORP

Integrated circuit self aligned 3D memory array and manufacturing method

ActiveUS20100226195A1Semiconductor/solid-state device detailsSolid-state devicesBit lineAudio power amplifier

A 3D memory device includes a plurality of ridge-shaped stacks, in the form of multiple strips of conductive material separated by insulating material, arranged as bit lines which can be coupled through decoding circuits to sense amplifiers. The strips of conductive material have side surfaces on the sides of the ridge-shaped stacks. A plurality of conductive lines arranged as word lines which can be coupled to row decoders, extends orthogonally over the plurality of ridge-shaped stacks. The conductive lines conform to the surface of the stacks. Memory elements lie in a multi-layer array of interface regions at cross-points between side surfaces of the conductive strips on the stacks and the conductive lines. The memory elements are programmable, like the anti-fuses or charge trapping structures. The 3D memory is made using only two critical masks for multiple layers.

Owner:MACRONIX INT CO LTD

Cross point switch

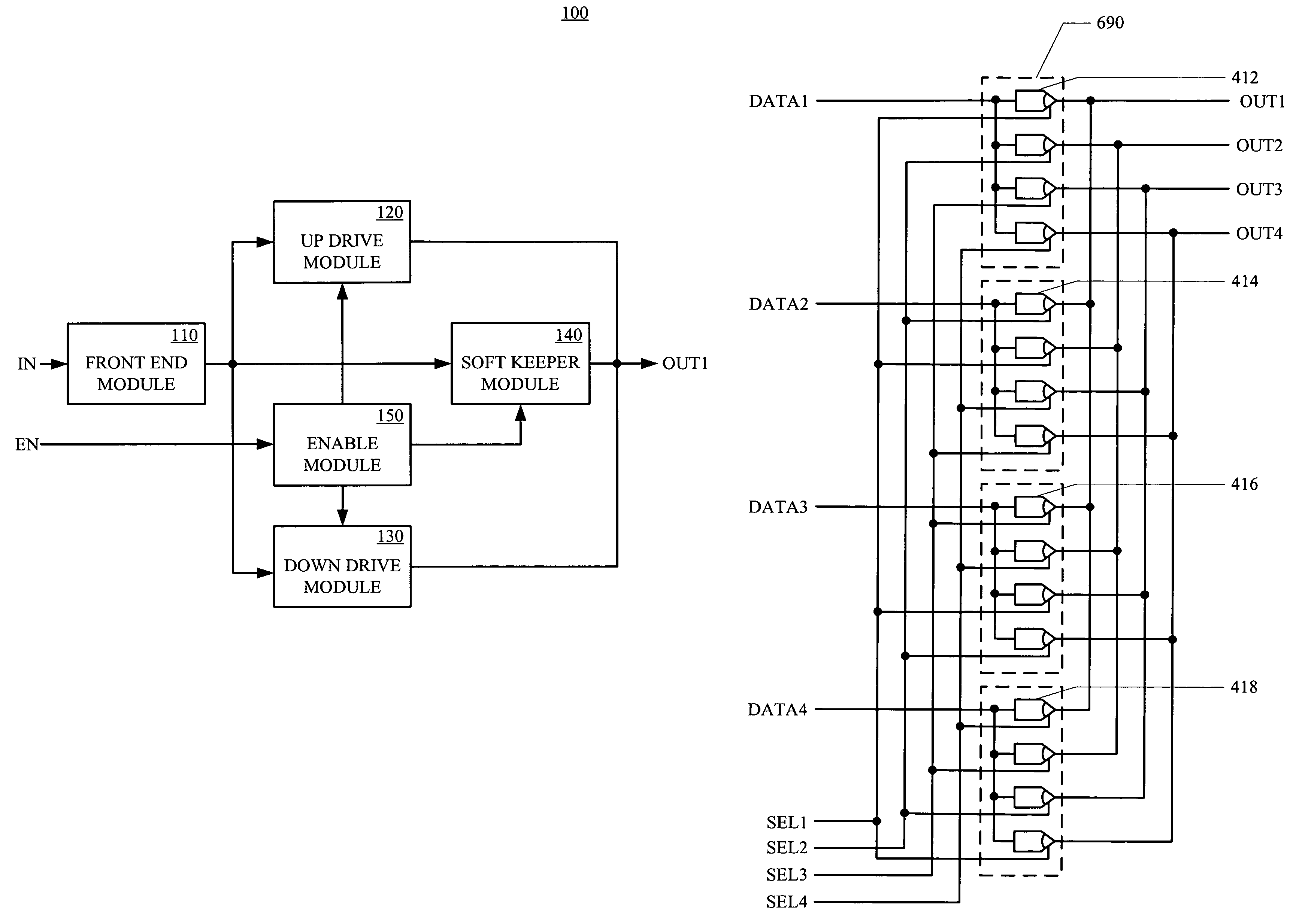

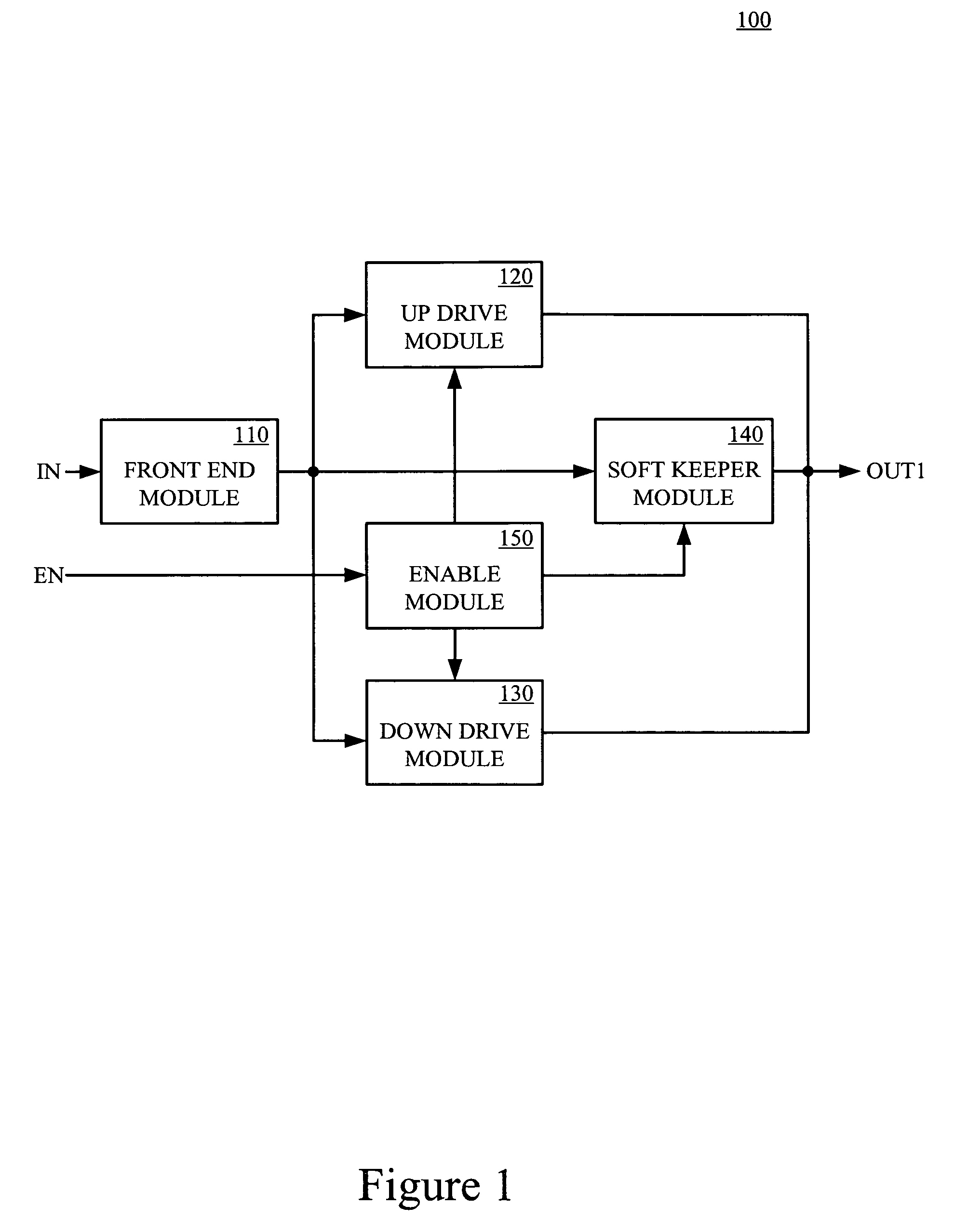

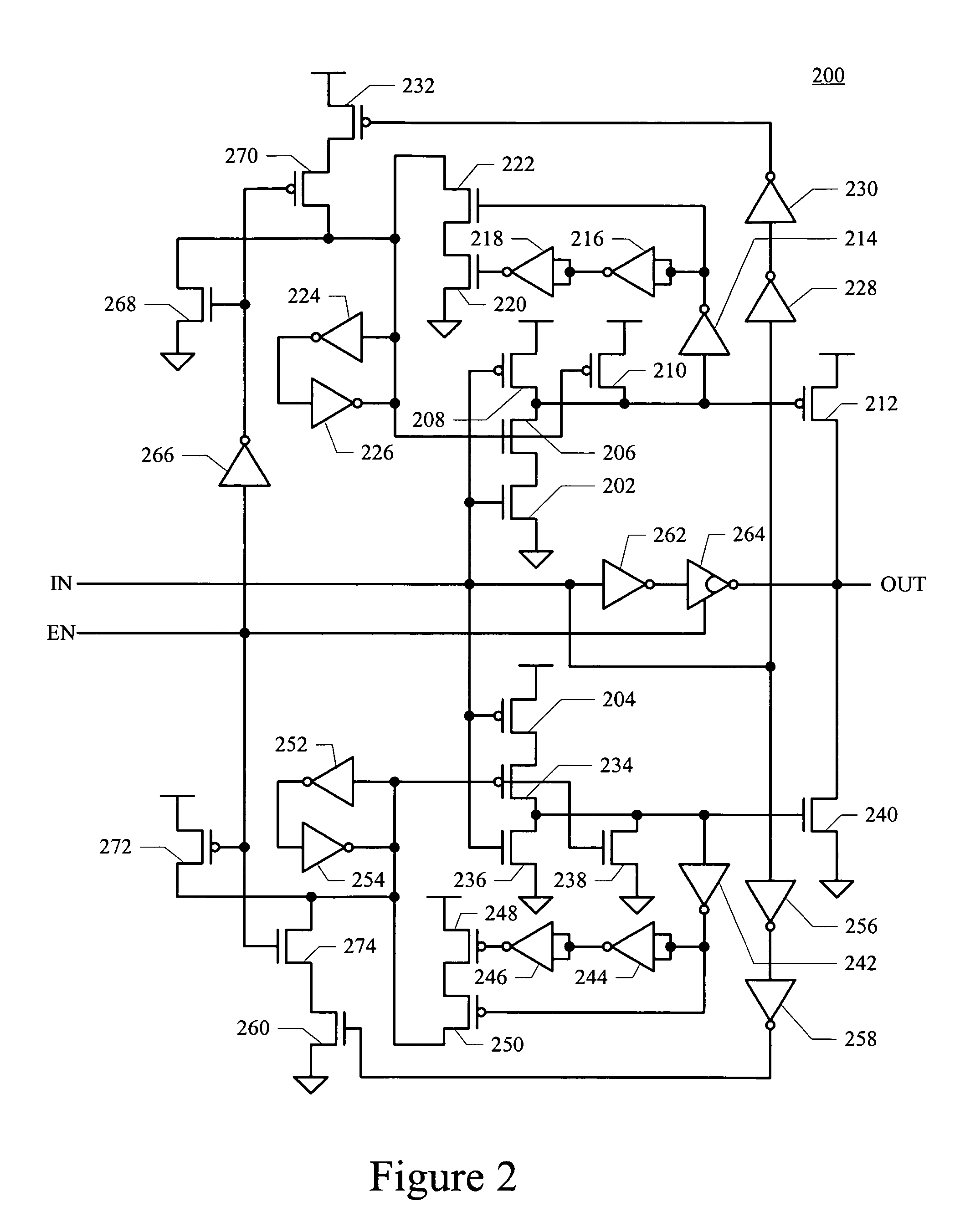

ActiveUS7710153B1Reduce delaysElectronic switchingLogic circuit coupling/interface arrangementsCapacitanceMultiplexer

A cross point switch, in accordance with one embodiment of the present invention, includes a plurality of tri-state repeaters coupled to form a plurality of multiplexers. Each set of corresponding tri-state repeaters in the plurality of multiplexers share a front end module such that delay through the cross point switch due to input capacitance is reduced as compared to conventional cross point switches.

Owner:INTELLECTUAL VENTURES HOLDING 81 LLC

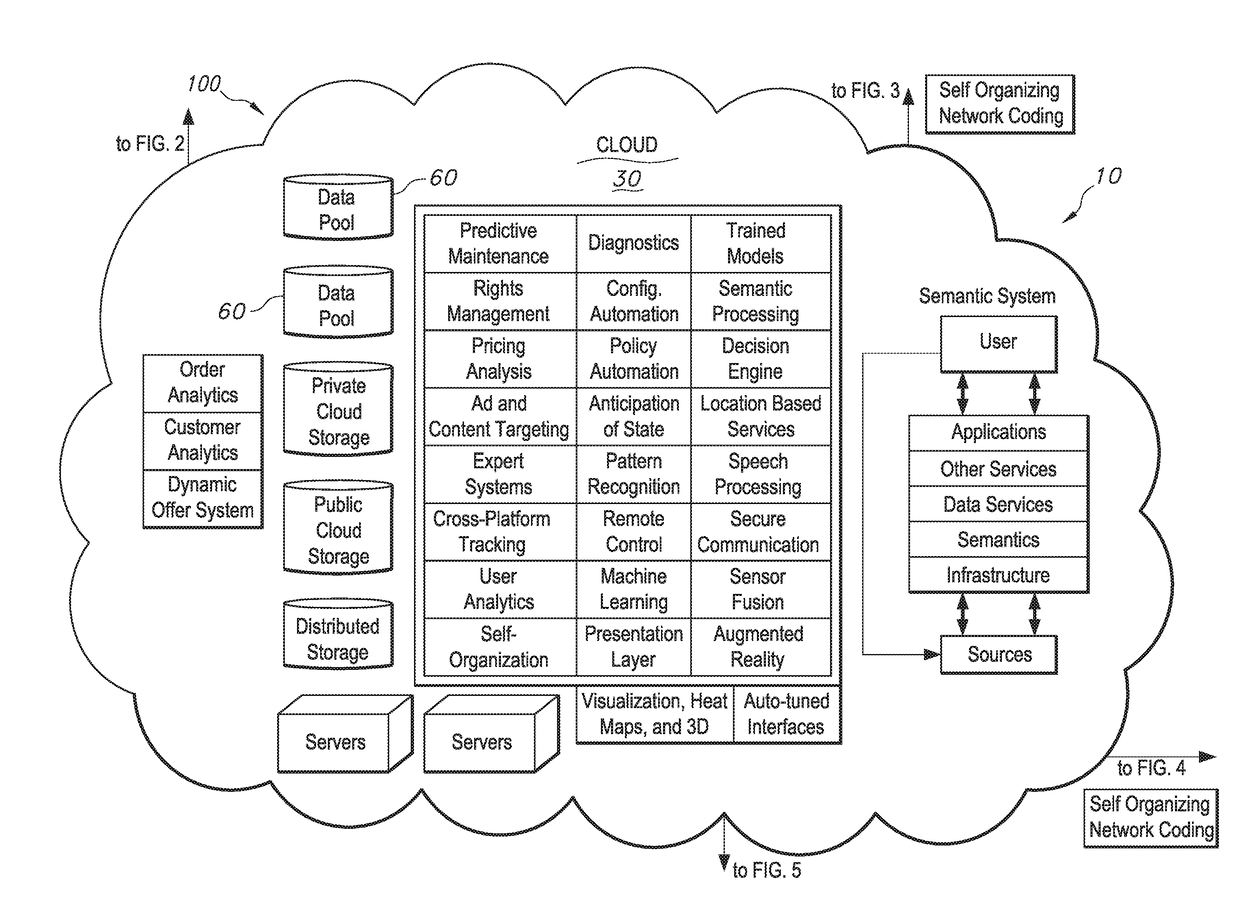

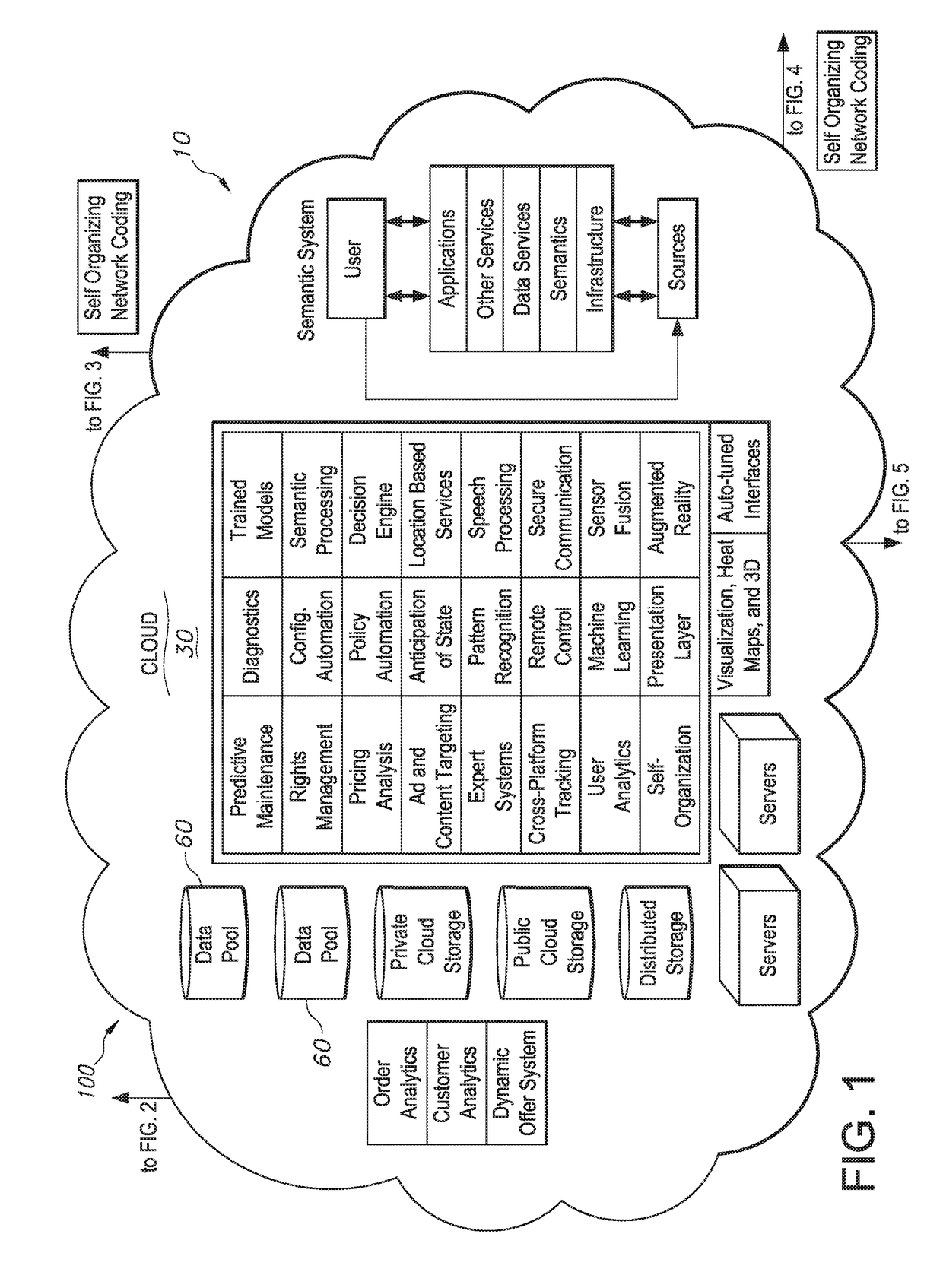

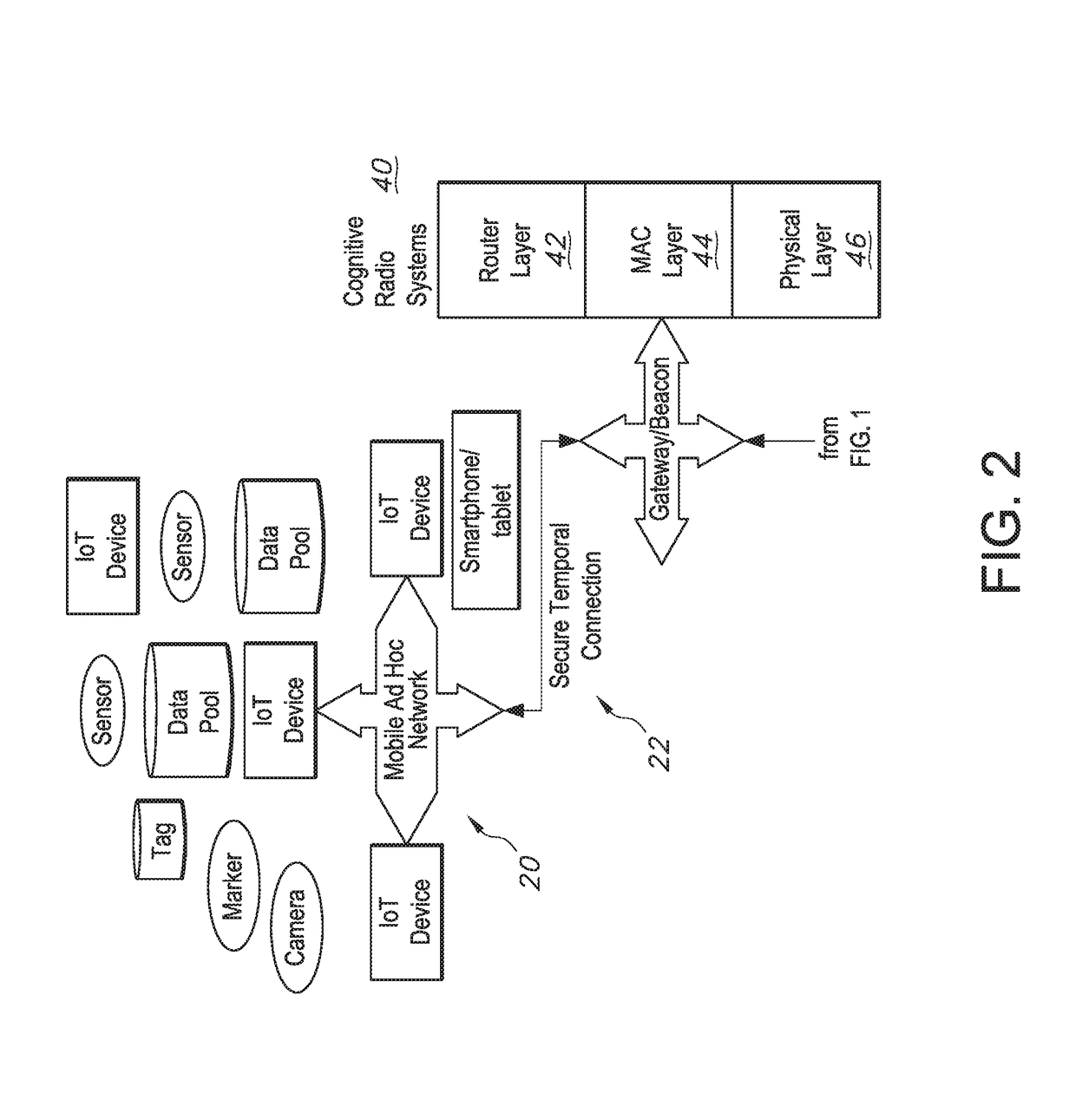

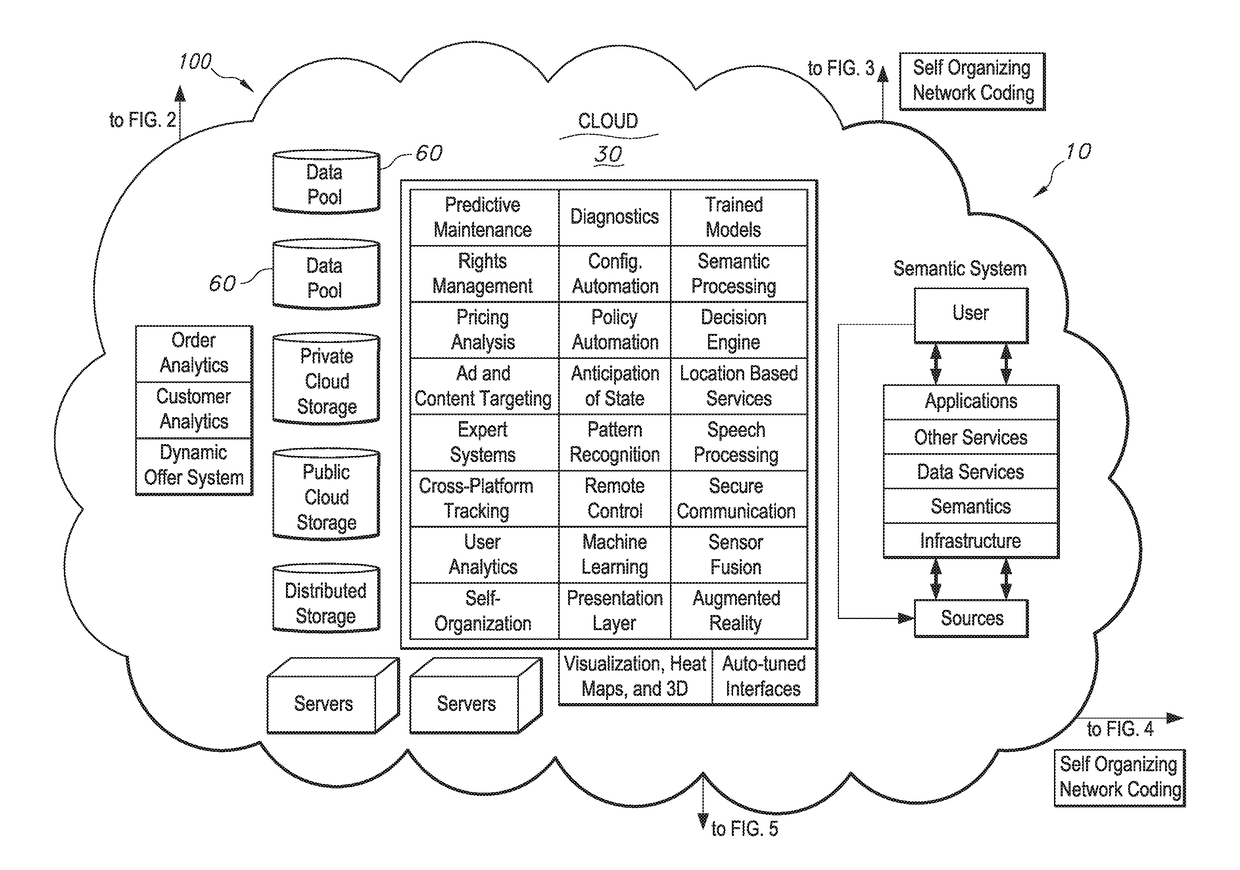

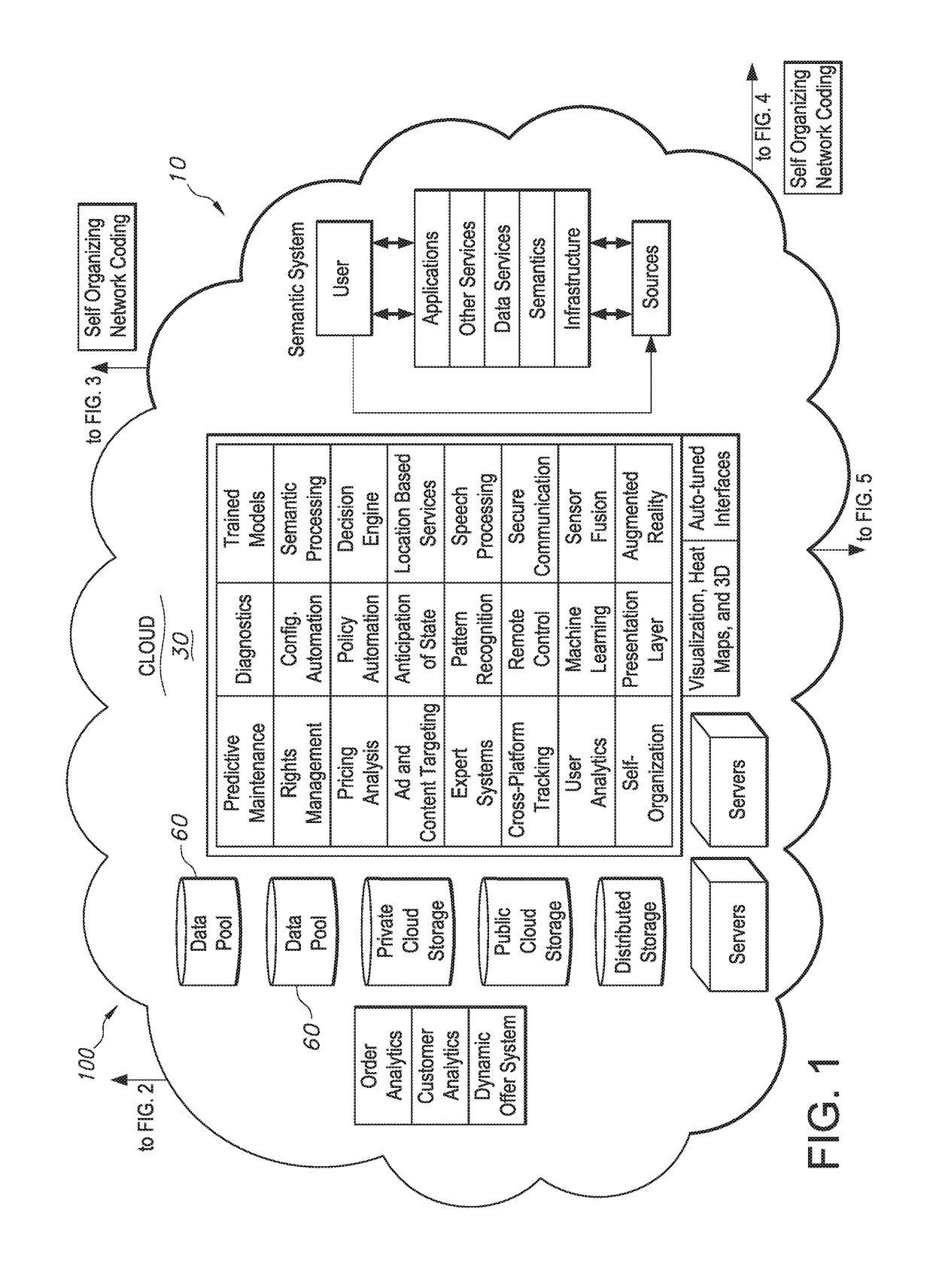

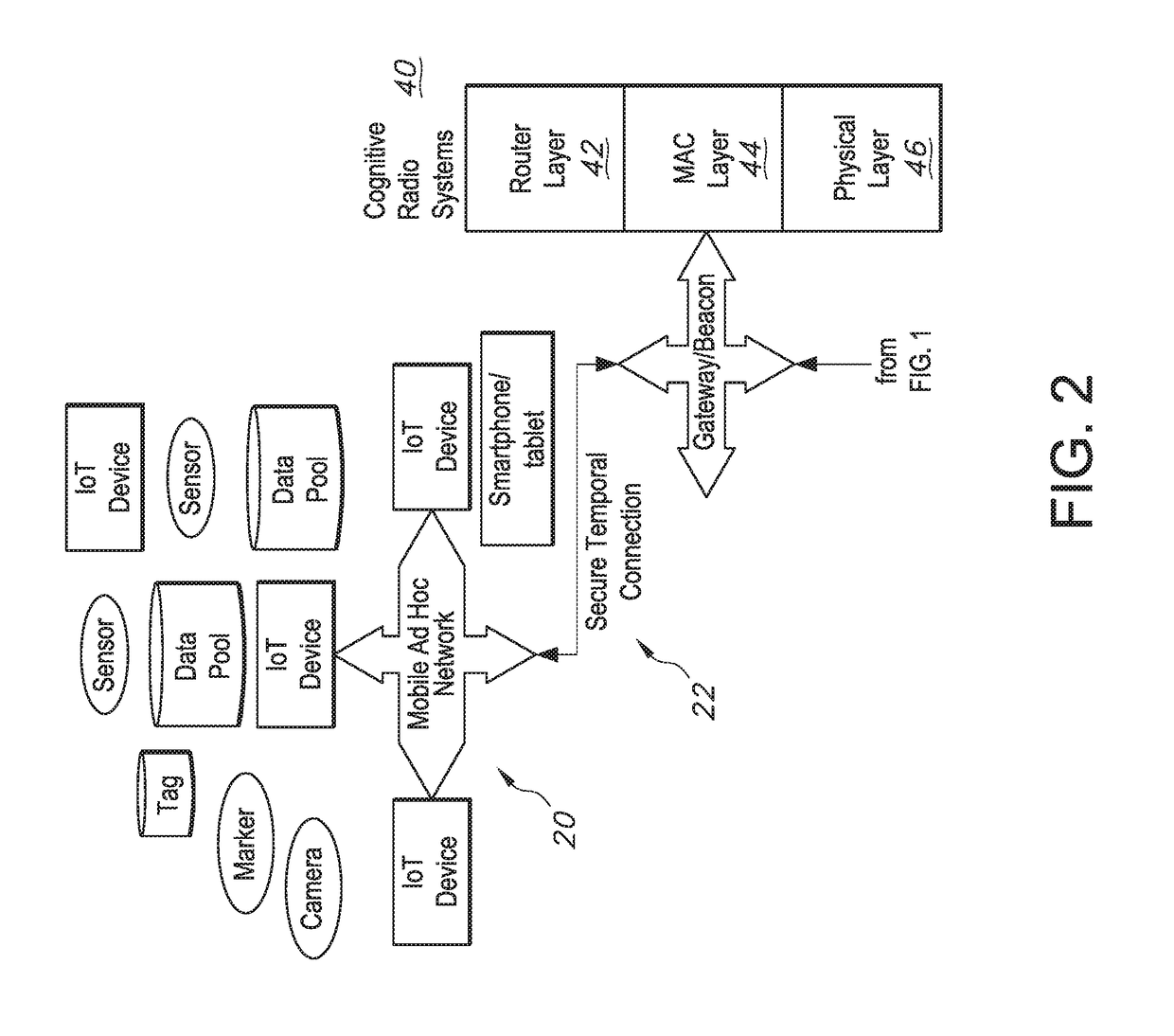

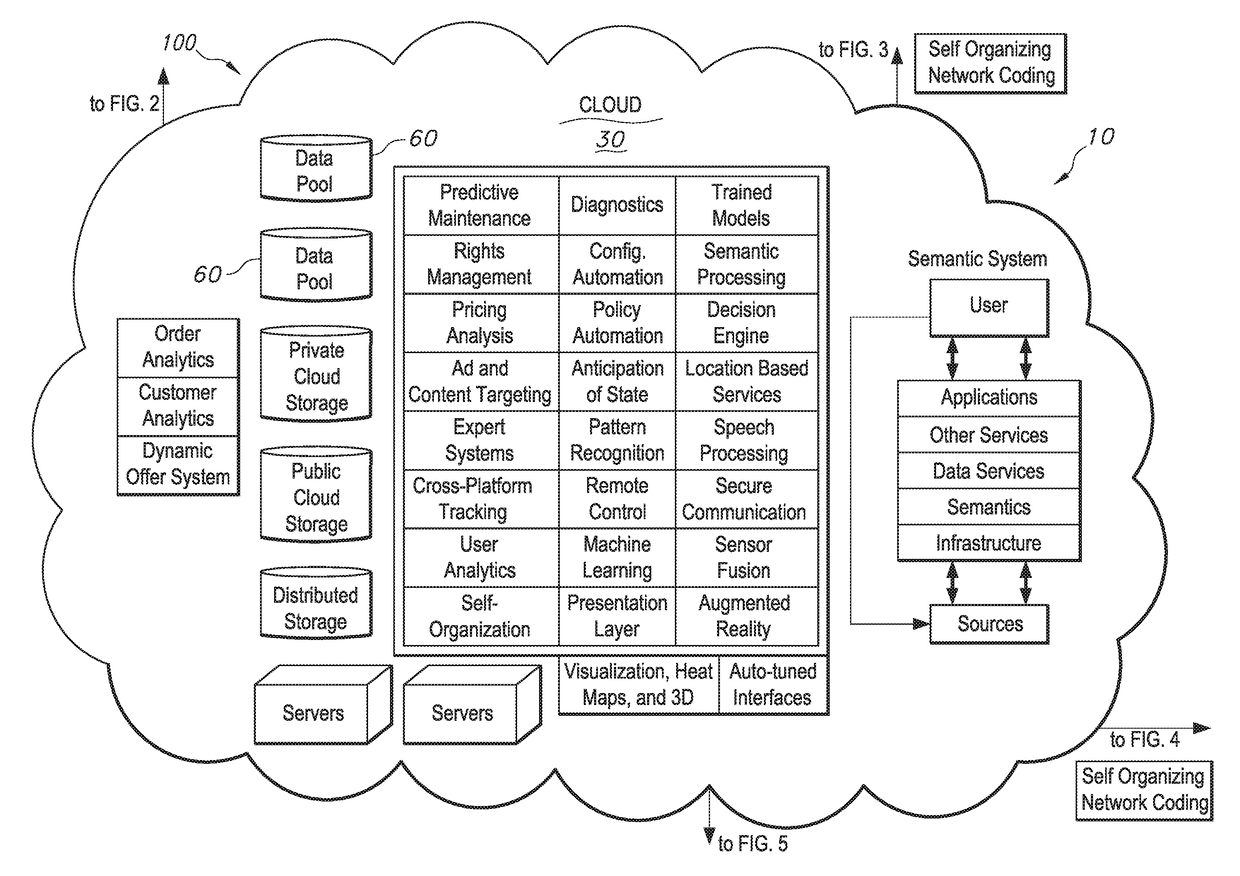

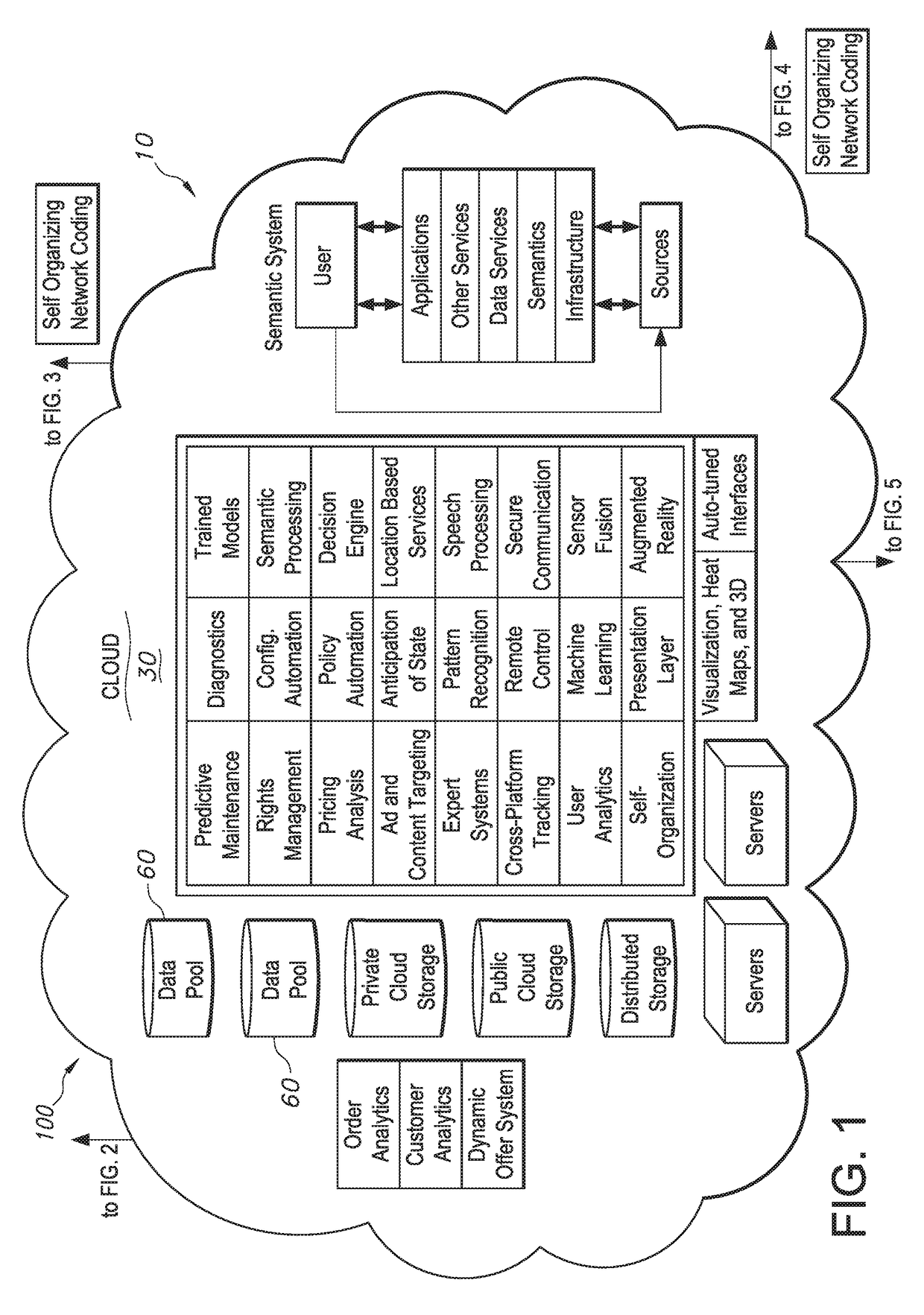

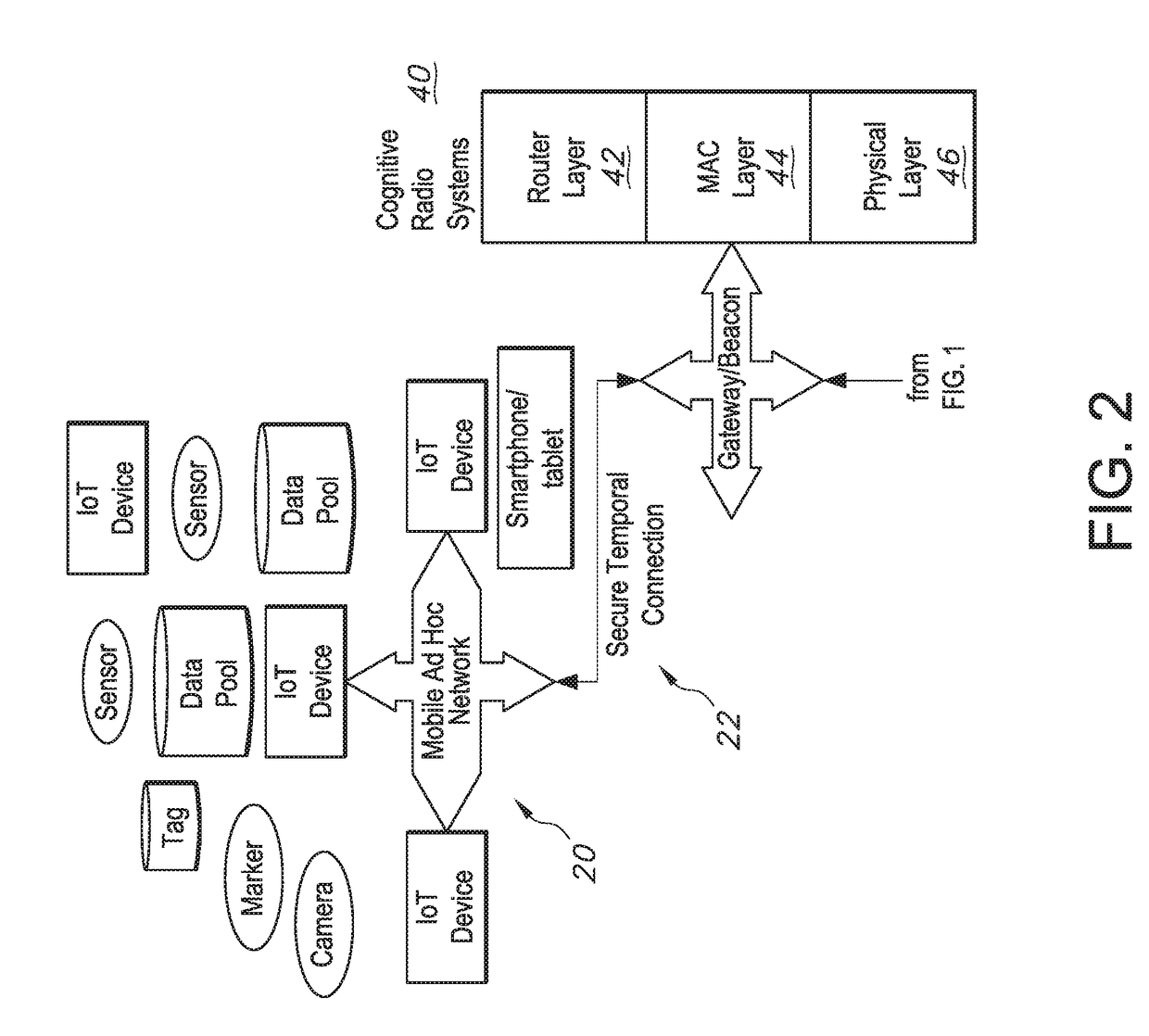

Methods and systems for the industrial internet of things

ActiveUS20180188704A1Improve signal-to-noise ratioLow sampling rateVibration measurement in solidsMachine part testingData streamData acquisition

The system generally includes a crosspoint switch in the local data collection system having multiple inputs and multiple outputs including a first input connected to the first sensor and a second input connected to the second sensor. The multiple outputs include a first output and a second output configured to be switchable between a condition in which the first output is configured to switch between delivery of the first sensor signal and the second sensor signal and a condition in which there is simultaneous delivery of the first sensor signal from the first output and the second sensor signal from the second output. Each of multiple inputs is configured to be individually assigned to any of the multiple outputs. Unassigned outputs are configured to be switched off producing a high-impedance state. The local data collection system includes multiple multiplexing units and multiple data acquisition units receiving multiple data streams from multiple machines in the industrial environment. The local data collection system includes distributed complex programmable hardware device (CPLD) chips each dedicated to a data bus for logic control of the multiple multiplexing units and the multiple data acquisition units that receive the multiple data streams from the multiple machines in the industrial environment. The local data collection system is configured to manage data collection bands.

Owner:STRONG FORCE IOT

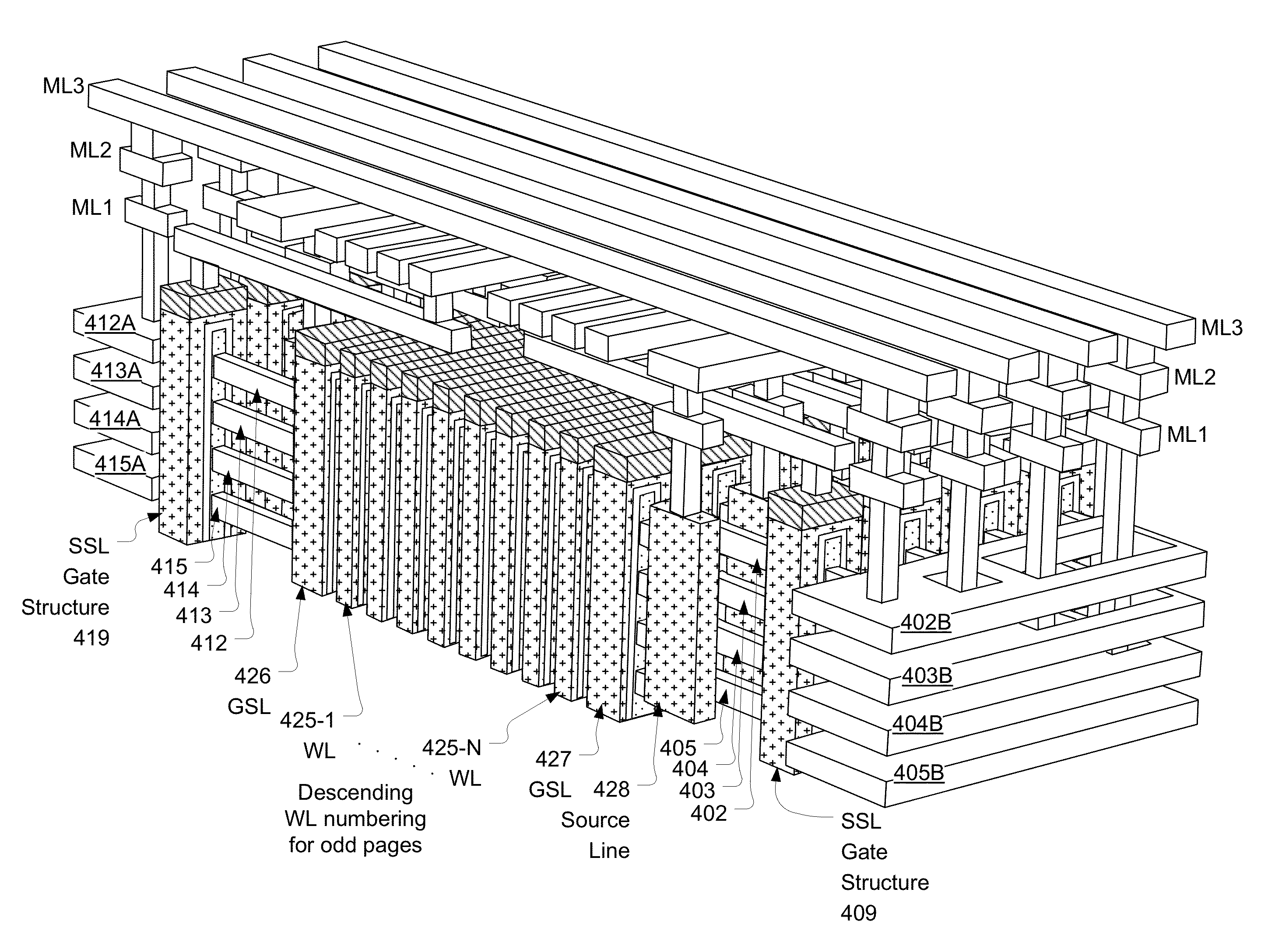

Memory Architecture of 3D Array With Alternating Memory String Orientation and String Select Structures

ActiveUS20120182806A1Increase pitchImproved gate structureSolid-state devicesRead-only memoriesArray data structureConductive materials

Owner:MACRONIX INT CO LTD

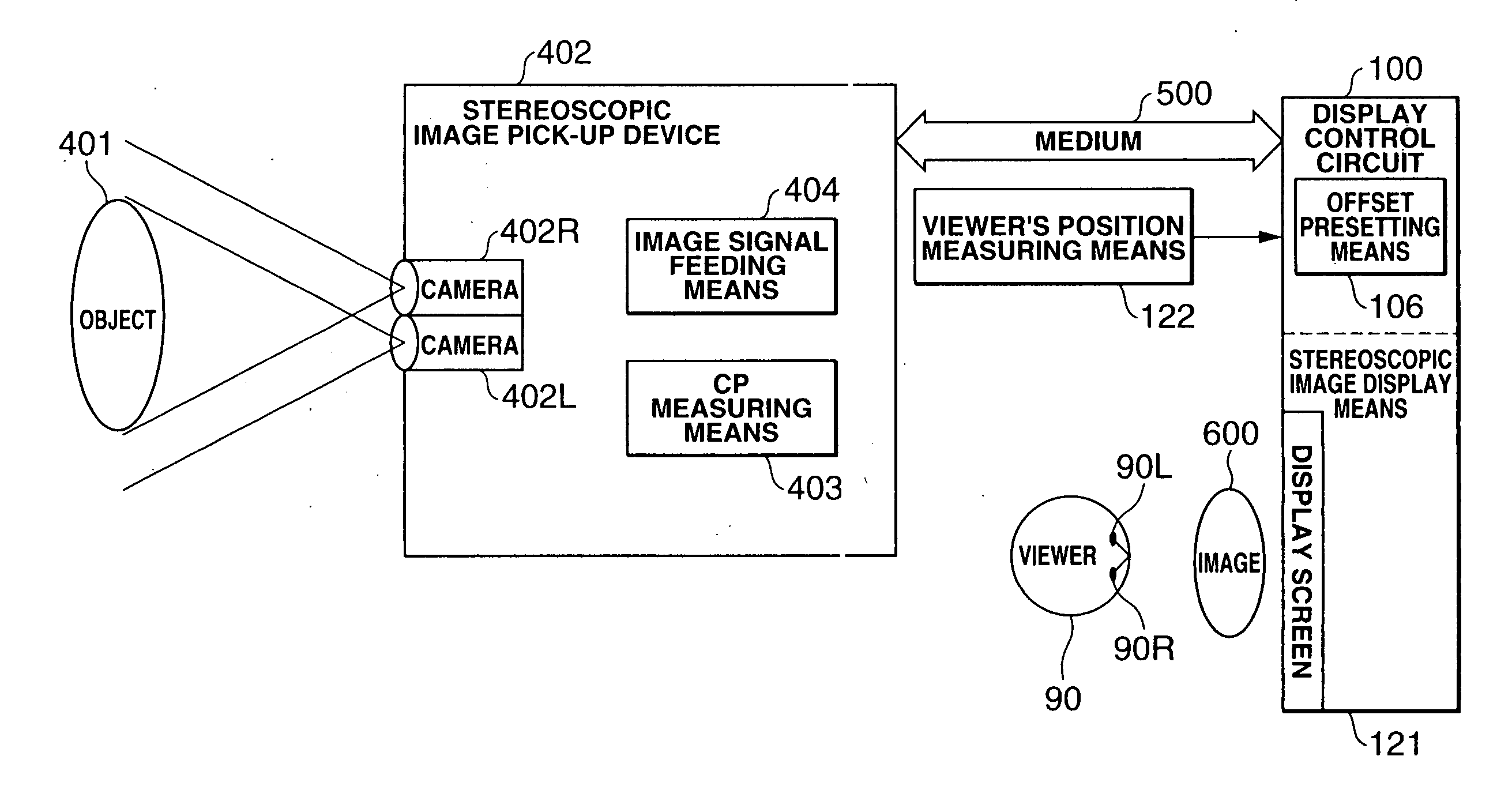

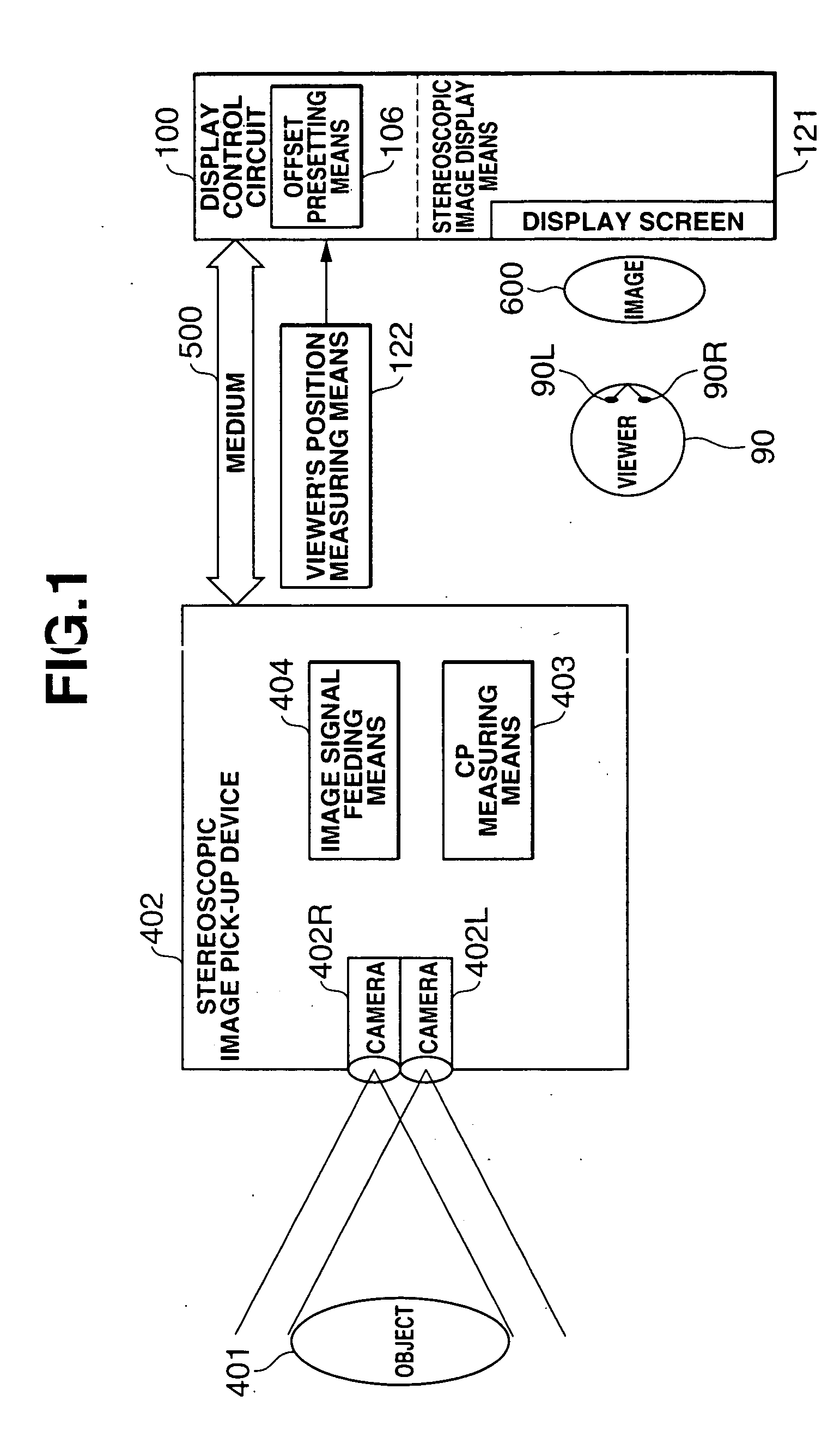

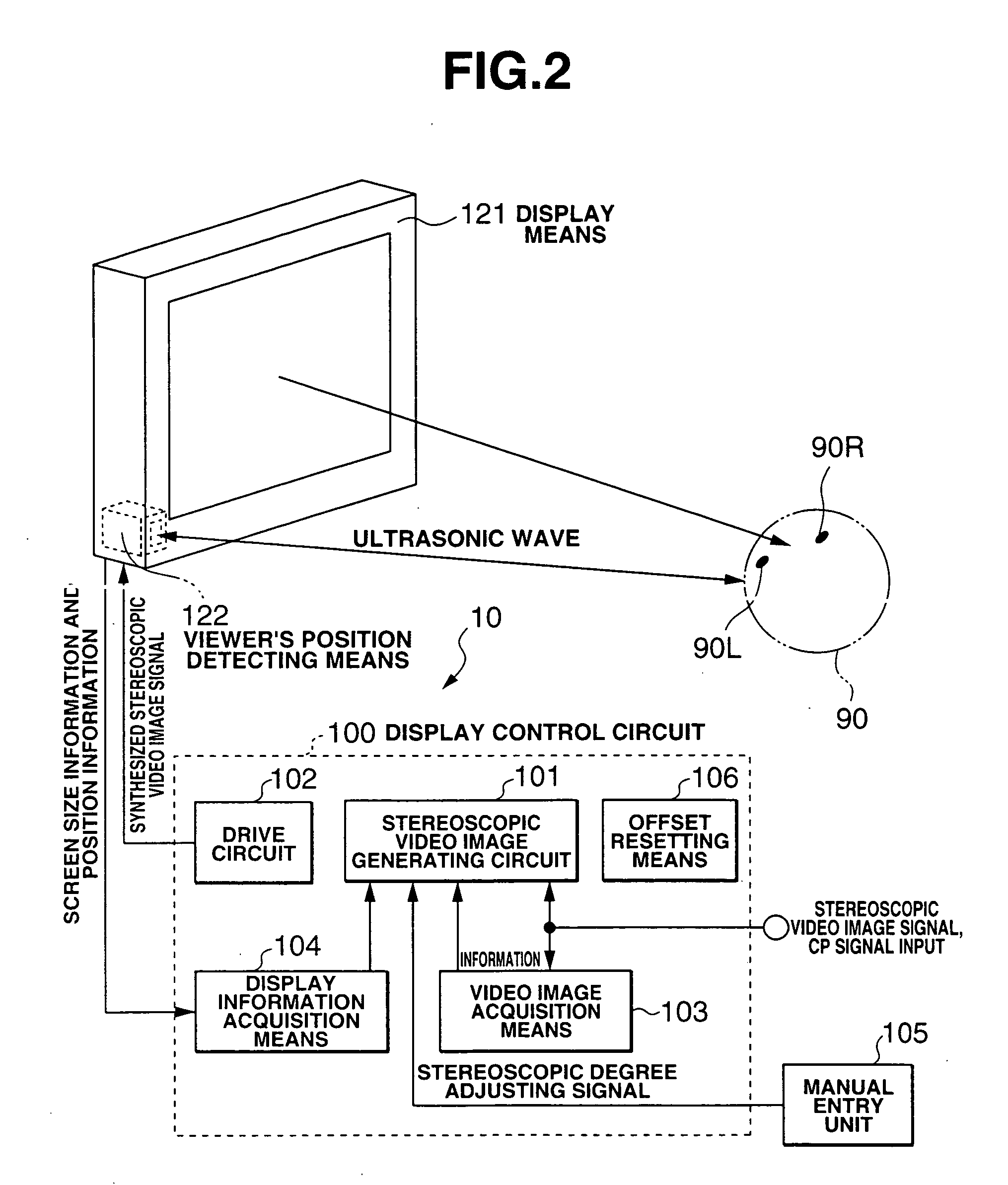

Stereoscopic image picking up and display system

InactiveUS20040233275A1Increase freedomSteroscopic systemsOptical elementsStereoscopic videoOptical axis

In a stereoscopic video image pick-up and display system comprising a stereoscopic video image pick-up device including two video image pick-up means (402R, L) for outputting video information from said pick-up means; a stereoscopic video image display device (400) for displaying different video images for the eyes of a viewer (60); and a medium (500) for transmitting said video image information from said stereoscopic video image pick-up device to said stereoscopic video image display device, said stereoscopic video image pick-up device includes cross-point measuring means (403) for measuring CP information on the cross-point (CP) of optical axes of said pick-up means and outputs information including the CP information and video image information to said medium, and said stereoscopic video image display device includes offset presetting means (106) for offsetting and displaying said different video images based upon said video image information, said cross-point information and information on the size of the image which is displayed by said stereoscopic video image display device.

Owner:TOMITA TECH INT

Methods and systems for the industrial internet of things

ActiveUS20180188714A1Reduce sampling rate outputMinimize anti-aliasing filter requirementVibration measurement in solidsMachine part testingIndustrial InternetMultiple input

The system generally includes a crosspoint switch in the local data collection system having multiple inputs and multiple outputs including a first input connected to the first sensor and a second input connected to the second sensor. The multiple outputs include a first output and a second output configured to be switchable between a condition in which the first output is configured to switch between delivery of the first sensor signal and the second sensor signal and a condition in which there is simultaneous delivery of the first sensor signal from the first output and the second sensor signal from the second output. Each of multiple inputs is configured to be individually assigned to any of the multiple outputs. Unassigned outputs are configured to be switched off producing a high-impedance state. The crosspoint switch includes a third input that is configured with a continuously monitored alarm having a pre-determined trigger condition when the third input is unassigned to any of the multiple outputs.

Owner:STRONG FORCE IOT

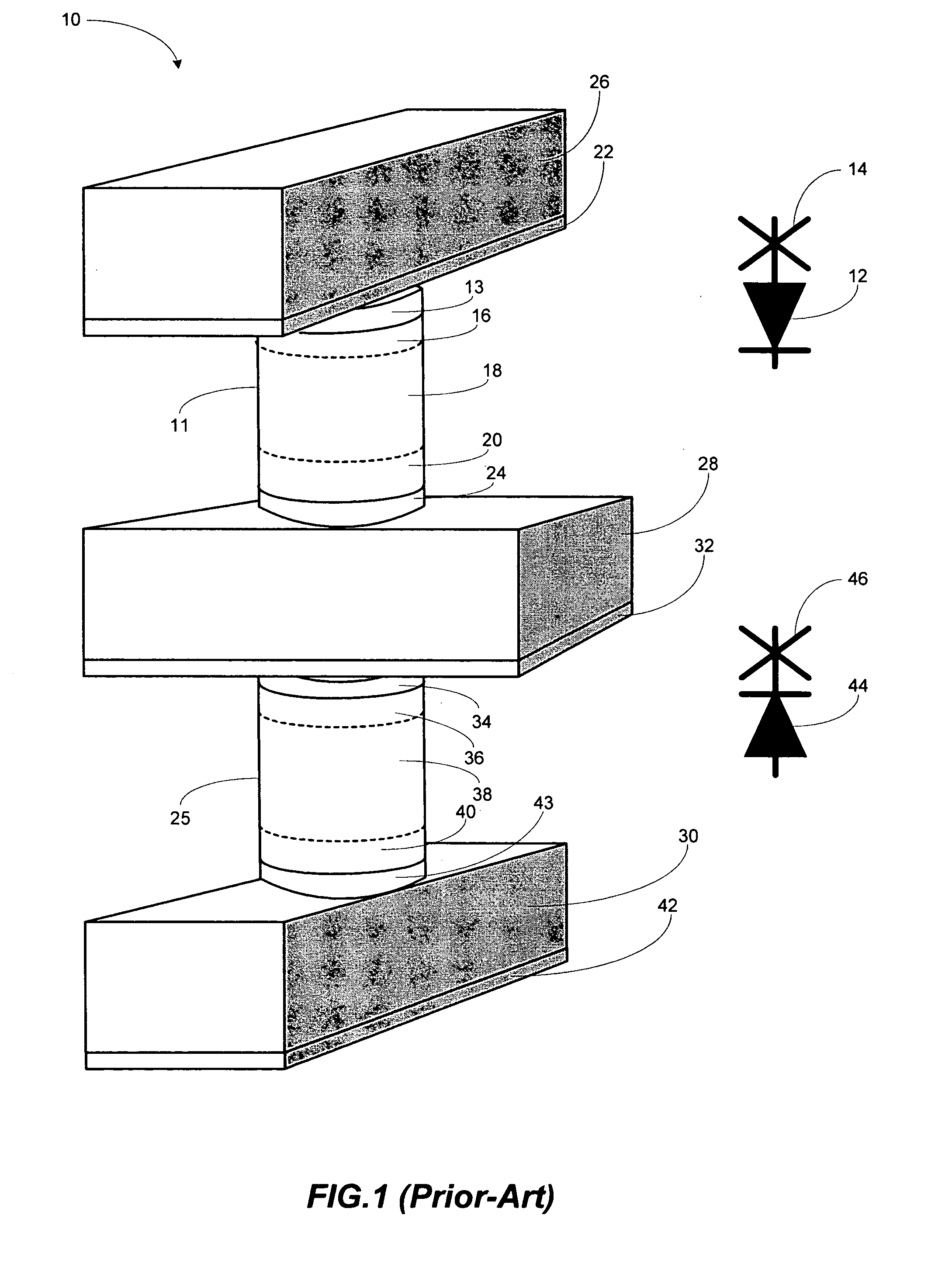

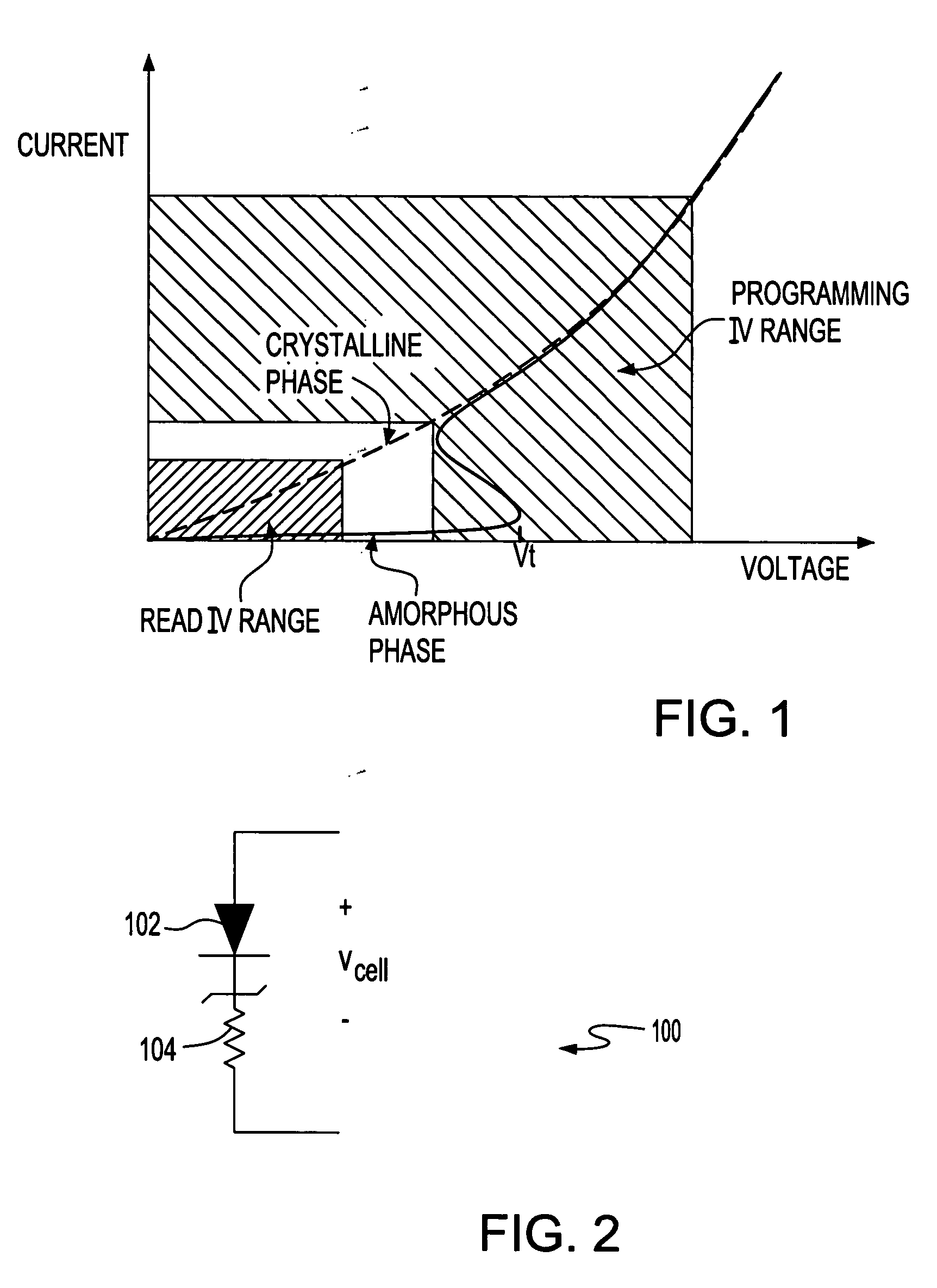

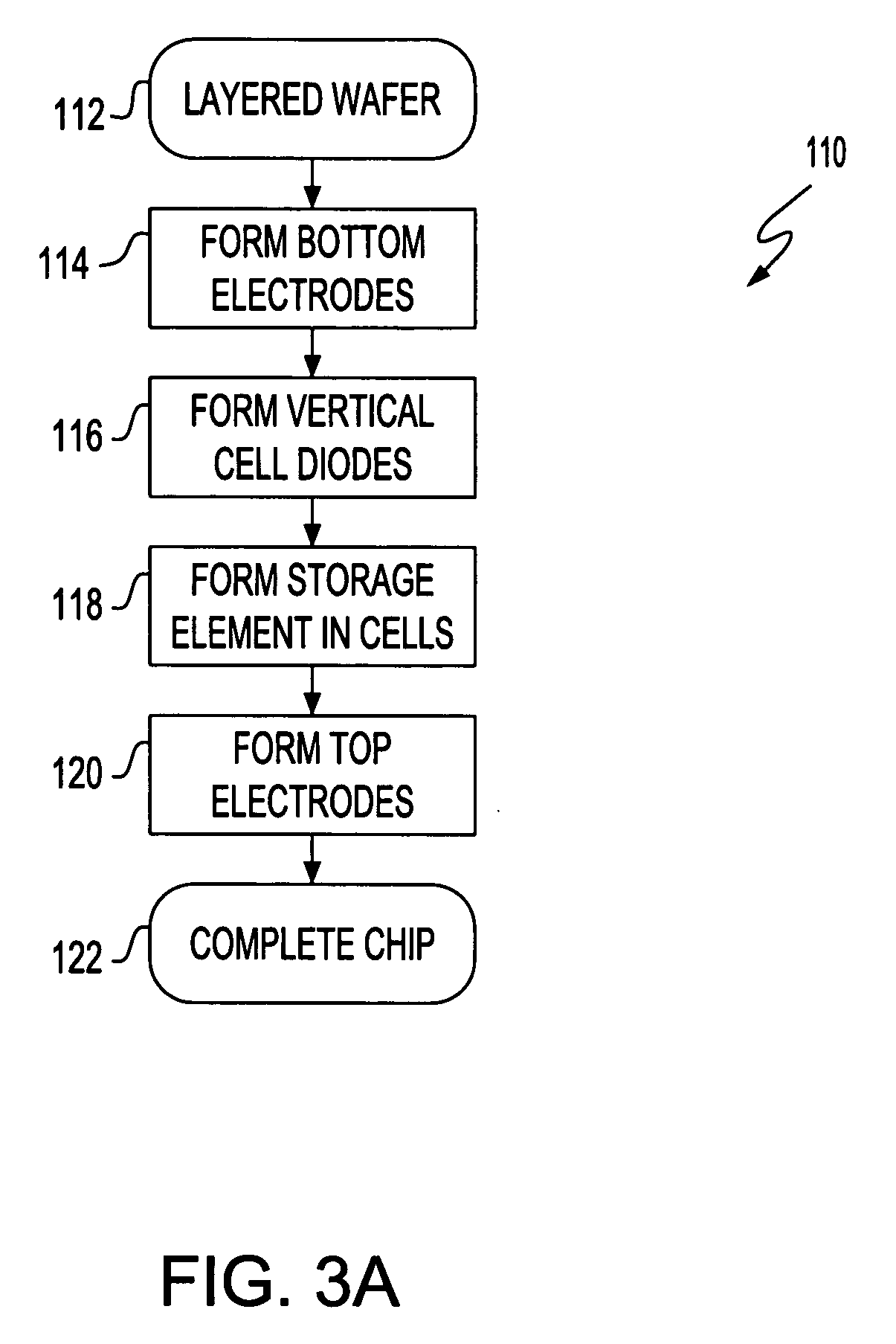

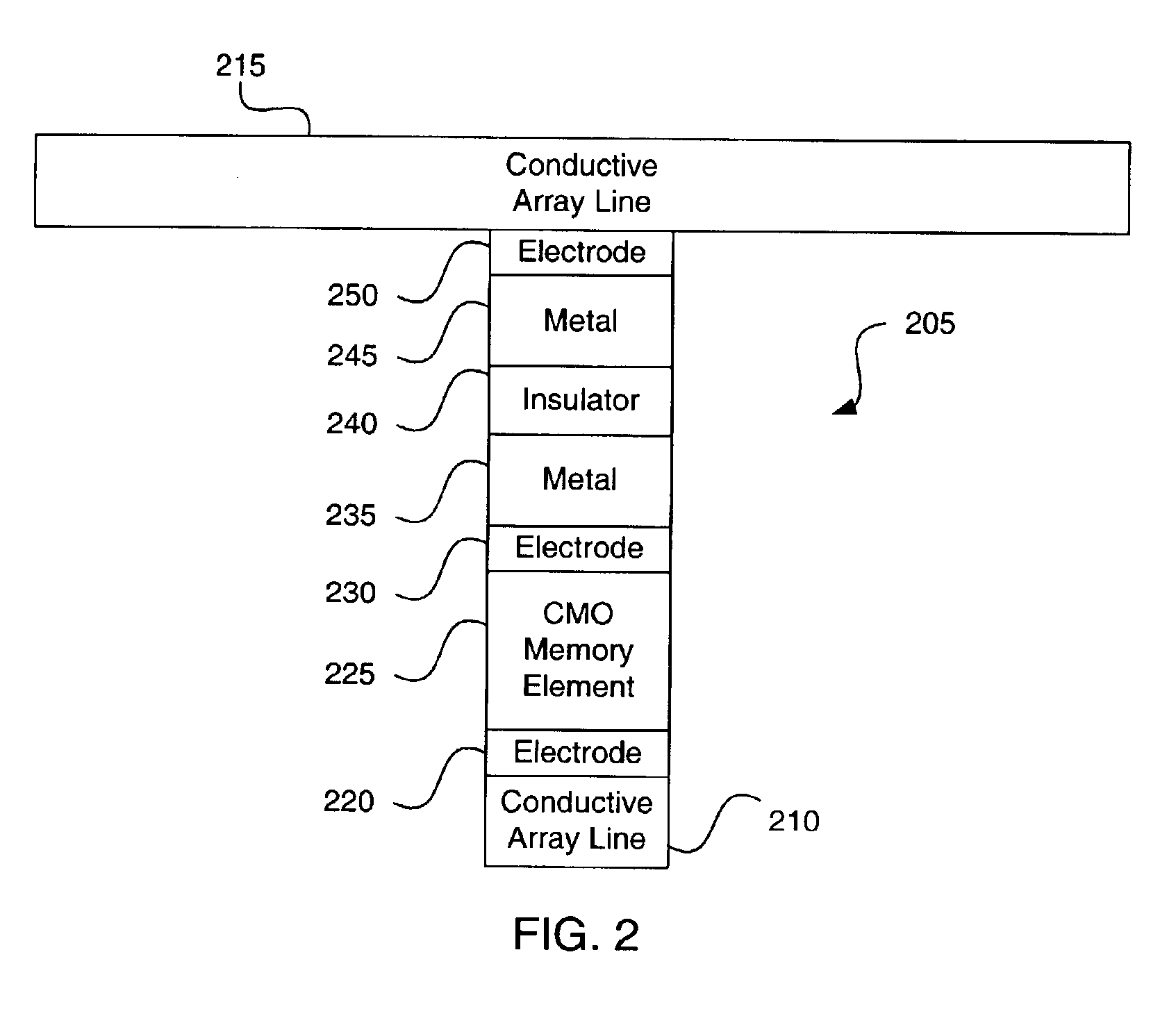

Cross point array cell with series connected semiconductor diode and phase change storage media

InactiveUS20060034116A1Reduce leakage phase change materialMaterial changeMaterial nanotechnologyNanoinformaticsNanowireEngineering

A storage cell that may be a memory cell, and an integrated circuit (IC) chip including an array of the memory cells and a method of forming the IC. Each storage cell includes a series connected diode and storage media formed between a top an bottom electrode. The diode is a vertical diode and may be formed in a semiconductor nanowire.

Owner:IBM CORP

Memory architecture of 3D array with alternating memory string orientation and string select structures

ActiveUS8503213B2Increase pitchPitch is improvedSolid-state devicesRead-only memoriesAudio power amplifierConductive materials

A 3D memory device includes a plurality of ridge-shaped stacks, in the form of multiple strips of conductive material separated by insulating material, arranged as bit lines which can be coupled through decoding circuits to sense amplifiers. Diodes are connected to the bit lines at either the string select of common source select ends of the strings. The strips of conductive material have side surfaces on the sides of the ridge-shaped stacks. A plurality of word lines, which can be coupled to row decoders, extends orthogonally over the plurality of ridge-shaped stacks. Memory elements lie in a multi-layer array of interface regions at cross-points between side surfaces of the semiconductor strips on the stacks and the word lines.

Owner:MACRONIX INT CO LTD

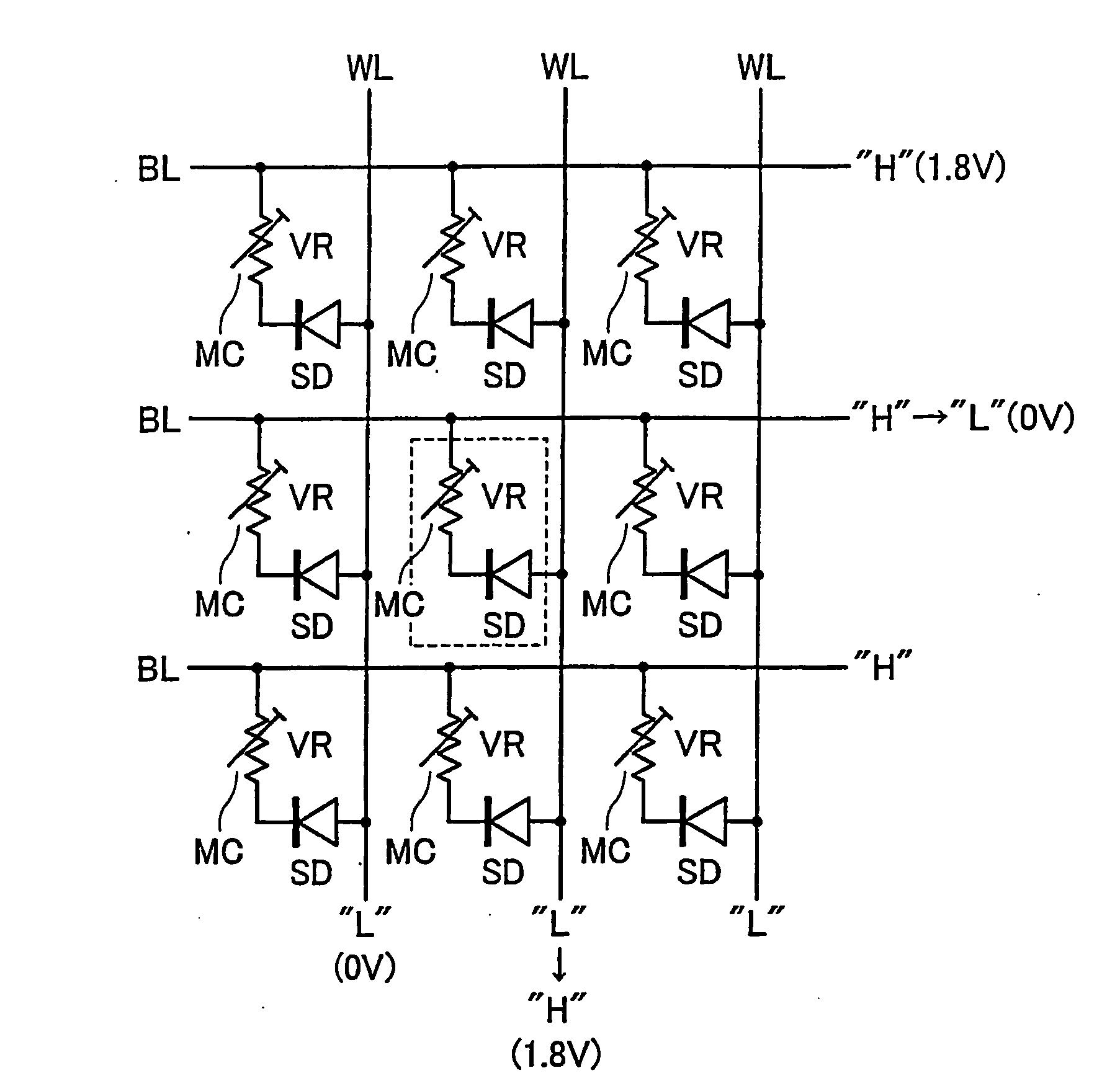

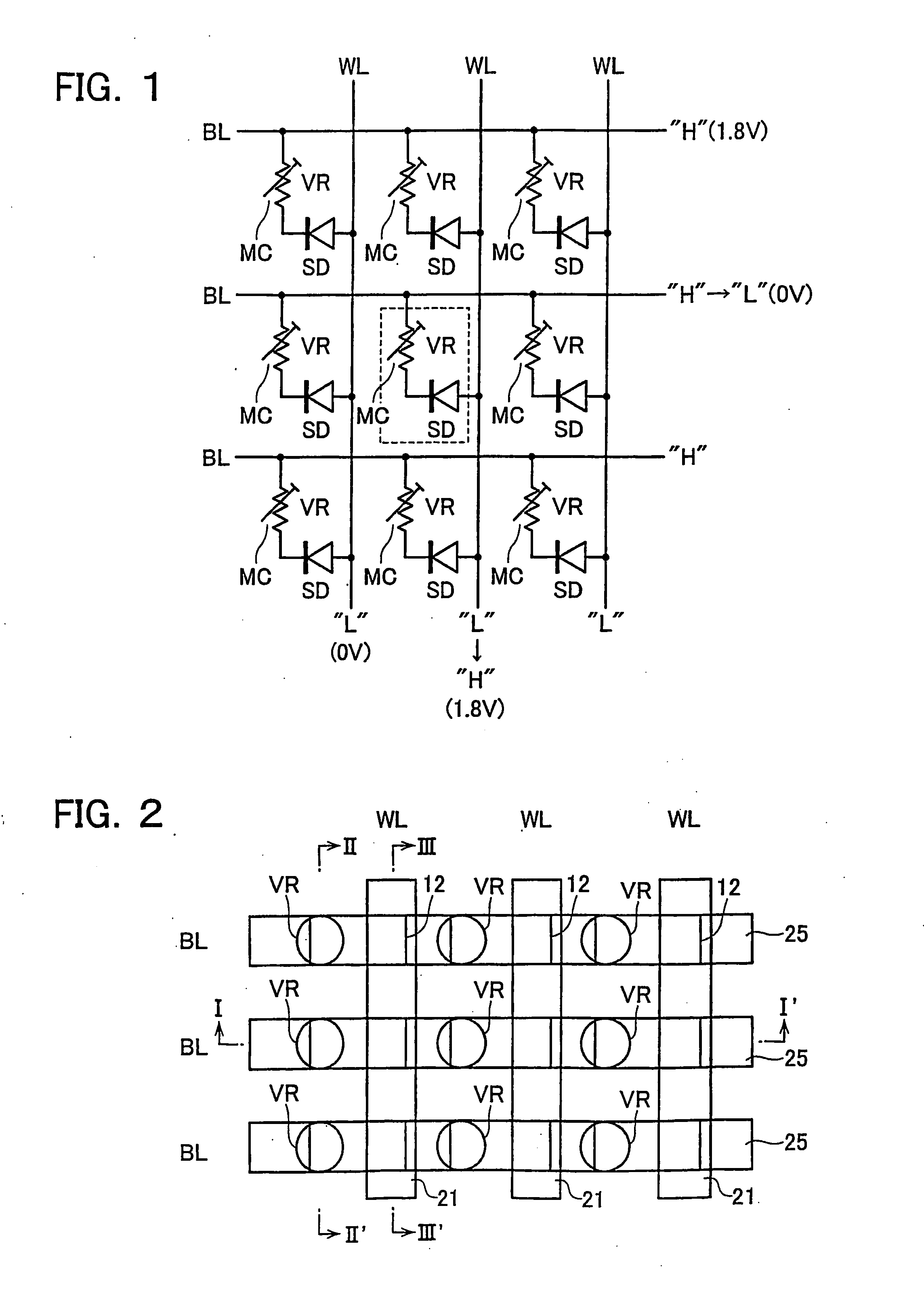

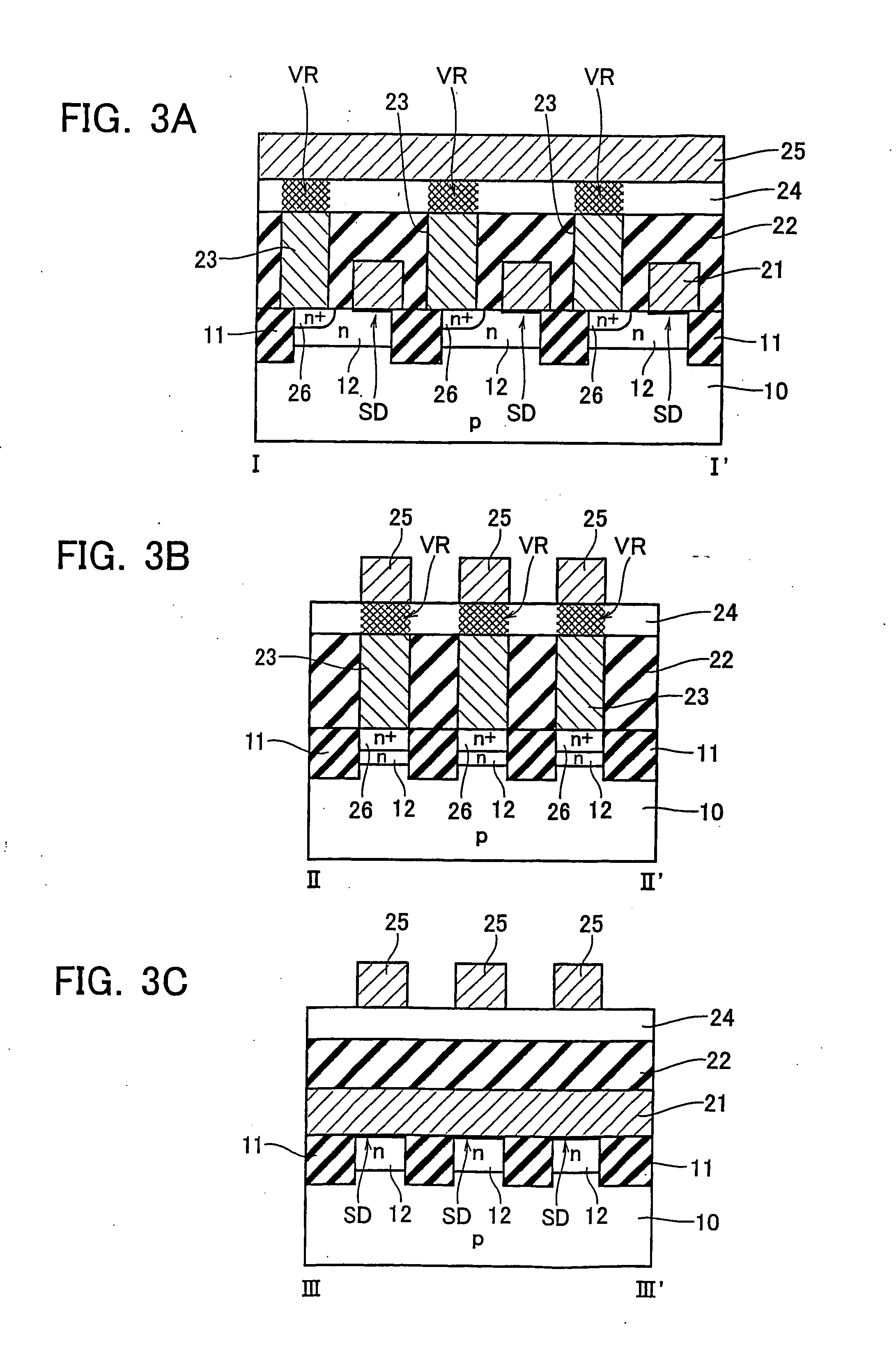

Phase-Change Memory Device

A phase-change memory device has a plurality of first wiring lines WL extending in parallel to each other, a plurality of second wiring lines BL which are disposed to cross the first wiring lines WL while being separated or isolated therefrom, and memory cells MC which are disposed at respective cross points of the first wiring lines WL and the second wiring lines BL and each of which has one end connected to a first wiring line WL and the other end connected to a second wiring line BL. The memory cell MC has a variable resistive element VR which stores as information a resistance value determined due to phase change between crystalline and amorphous states thereof, and a Schottky diode SD which is connected in series to the variable resistive element VR.

Owner:KK TOSHIBA

Methods and apparatus for providing a fast ring reservation arbitration

InactiveUS6449283B1Implementation reasonableReasonable timeTime-division multiplexLoop networksComputer scienceComputer network

Owner:POLYTECHNIC INST OF NEW YORK

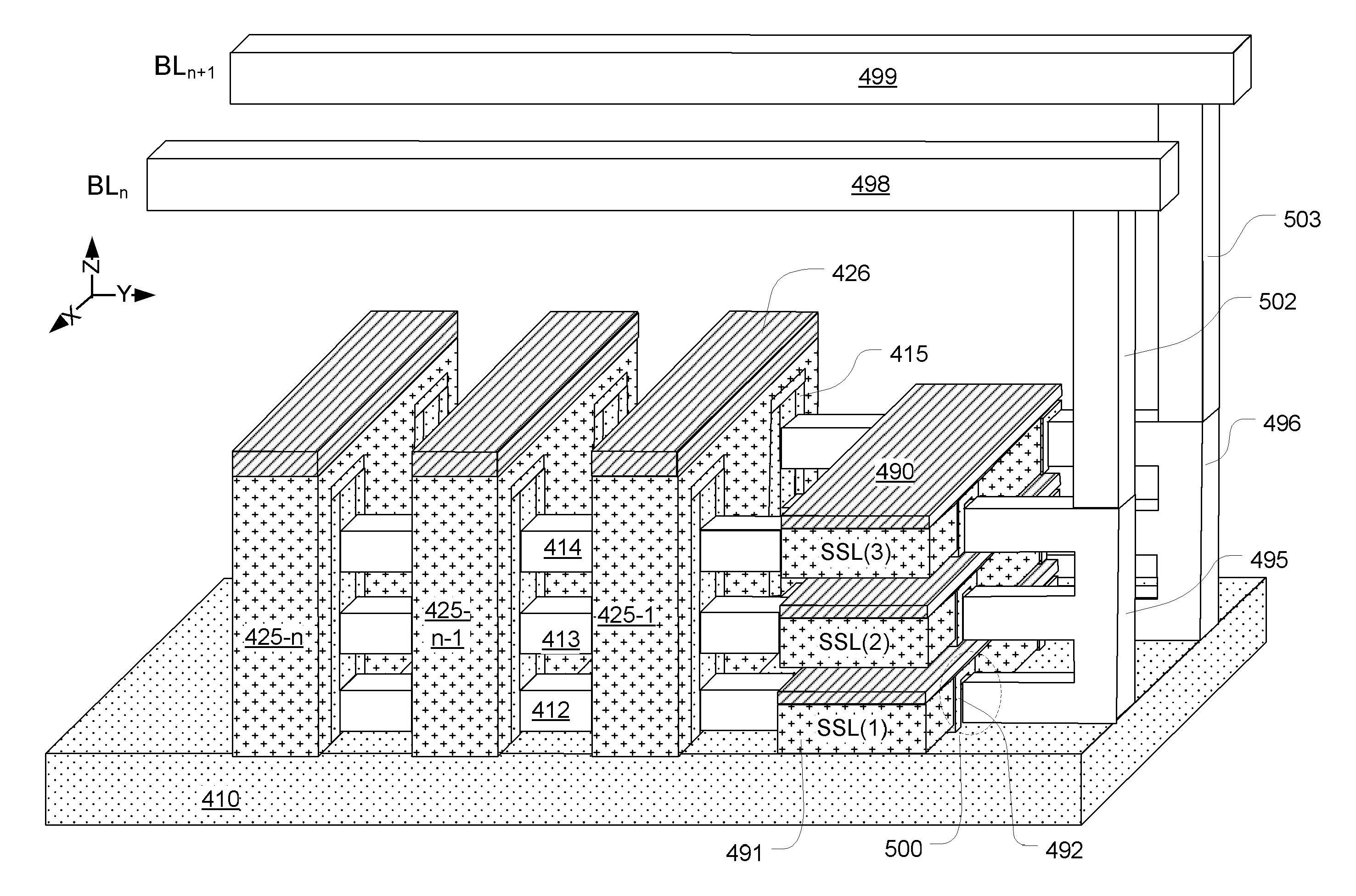

3D Memory Array With Improved SSL and BL Contact Layout

ActiveUS20120007167A1Semiconductor/solid-state device detailsSolid-state devicesAudio power amplifierSemiconductor materials

A 3D memory device includes a plurality of ridges, in some embodiments ridge-shaped, in the form of multiple strips of conductive material separated by insulating material, arranged as bit lines which can be coupled through decoding circuits to sense amplifiers. The strips of conductive material have side surfaces on the sides of the stacks. A plurality of conductive lines arranged as word lines which can be coupled to row decoders, extends orthogonally over the plurality of stacks. The conductive lines conform to the surface of the stacks. Memory elements lie in a multi-layer array of interface regions at cross-points between side surfaces of the semiconductor material strips on the stacks and the conductive lines. The memory elements are programmable, like the anti-fuses or charge trapping structures. In some embodiments, the 3D memory is made using only two critical masks for multiple layers. Some embodiments include a staircase-shaped structure positioned at ends of the semiconductor material strips. Some embodiments include SSL interconnects on a metal layer parallel to the semiconductor material strips, and further SSL interconnects on a higher metal layer, parallel to the word lines.

Owner:MACRONIX INT CO LTD

Cross-point memory and methods for fabrication of same

ActiveUS20150243708A1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringStorage material

The disclosed technology relates generally to integrated circuit devices, and in particular to cross-point memory arrays and methods for fabricating the same. In one aspect, a method of fabricating cross-point memory arrays comprises forming a memory cell material stack which includes a first active material and a second active material over the first active material, wherein one of the first and second active materials comprises a storage material and the other of the first and second active materials comprises a selector material. The method of fabricating cross-point arrays further comprises patterning the memory cell material stack, which includes etching through at least one of the first and second active materials of the memory cell material stack, forming protective liners on sidewalls of the at least one of the first and second active materials after etching through the one of the first and second active materials, and further etching the memory cell material stack after forming the protective liners on the sidewalls of the one of the first and second active materials.

Owner:MICRON TECH INC

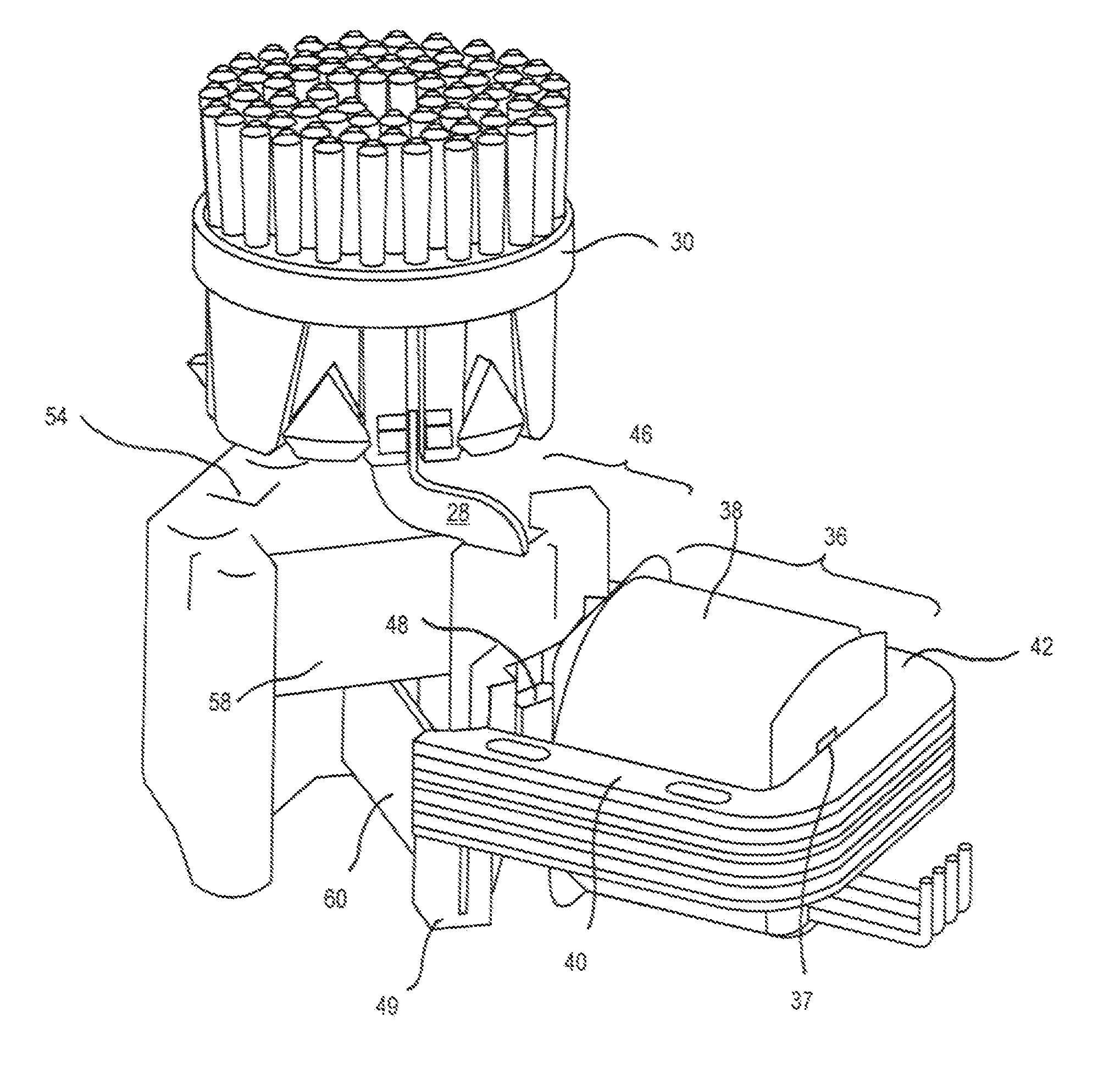

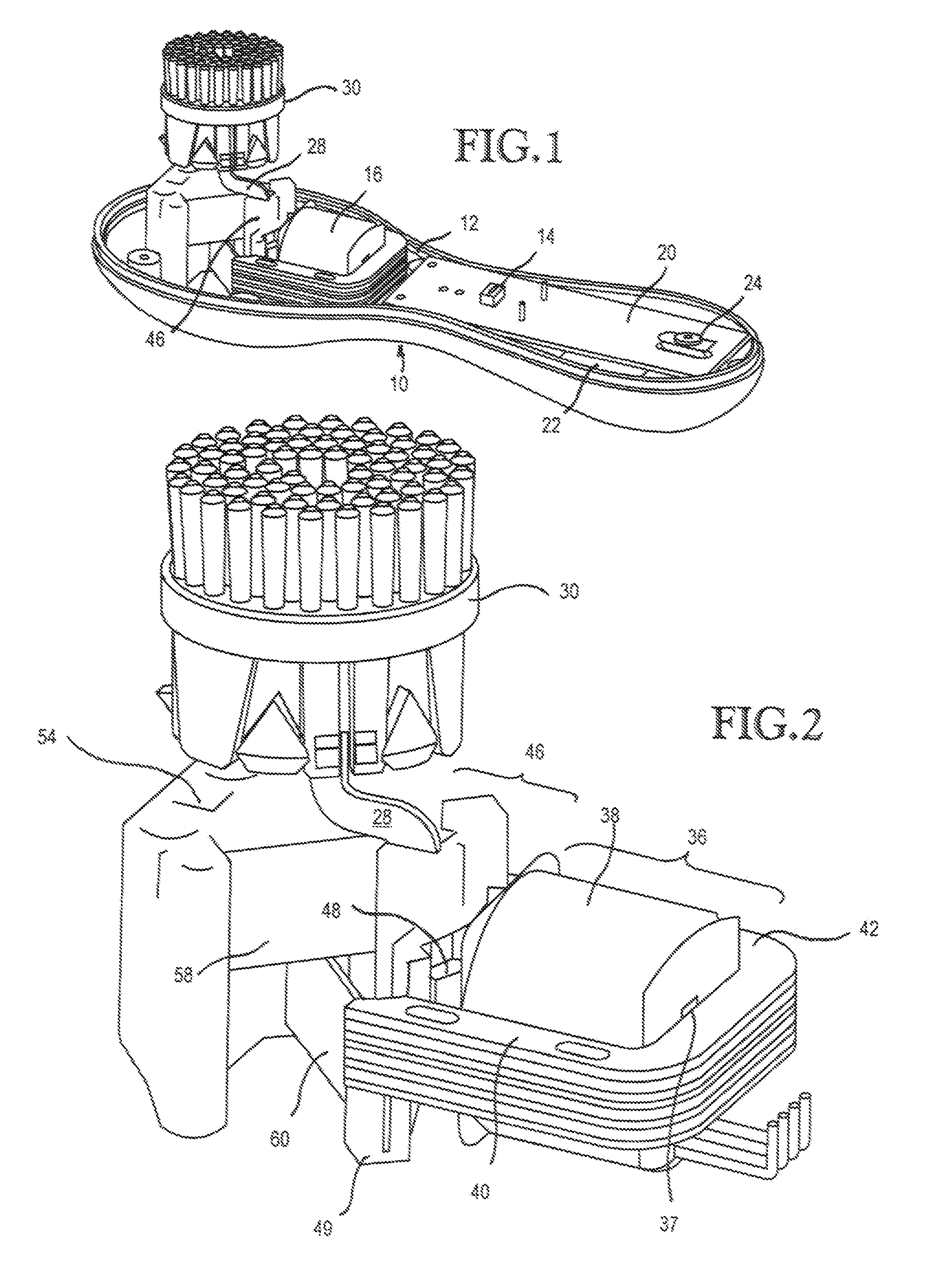

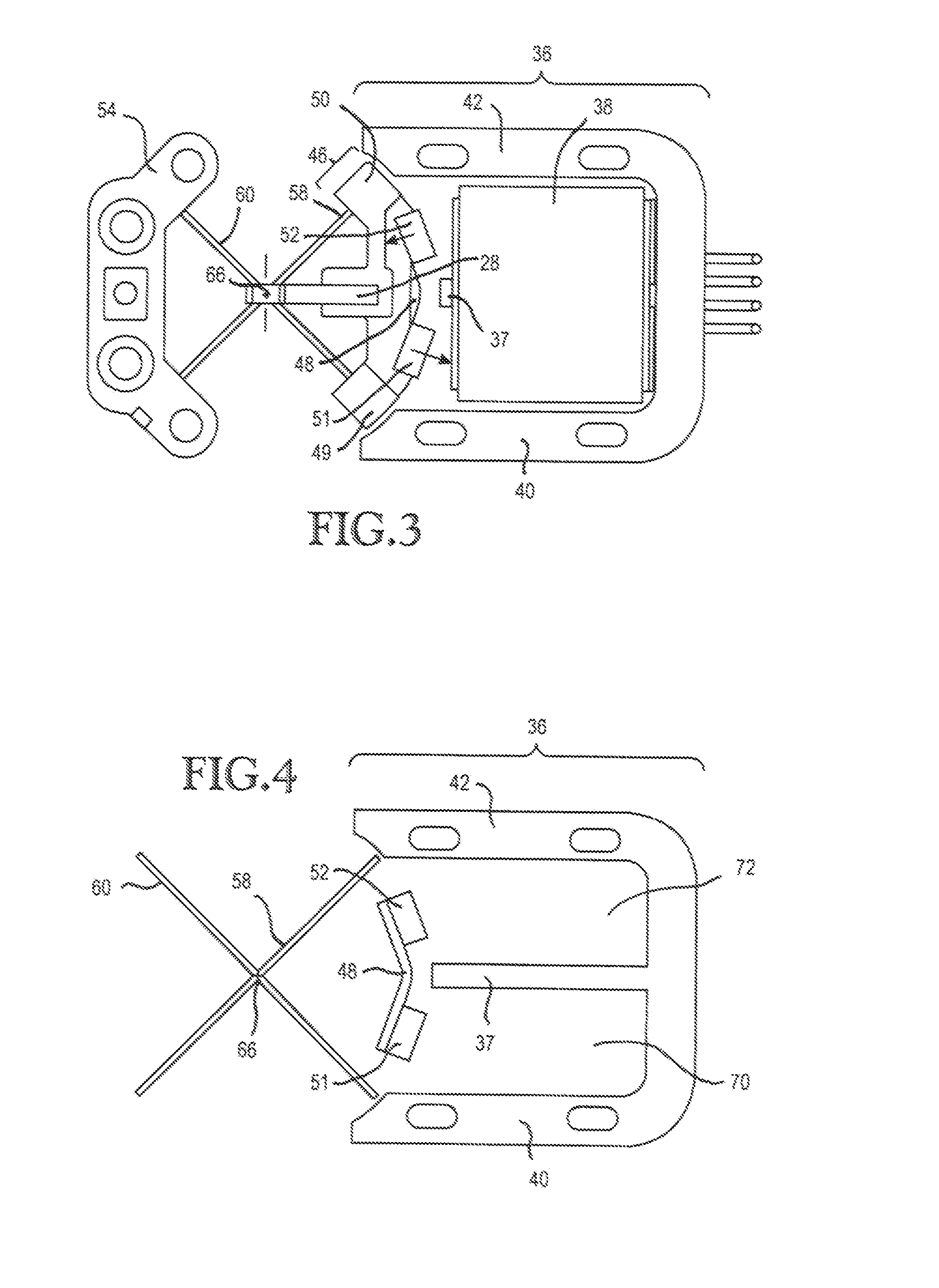

Oscillating motor for a personal care appliance

The motor includes an E-core stator assembly with a source of alternating current and an armature portion mounted to be responsive to the stator to oscillate back and forth through an arc portion of the personal care appliance and flexure elements are connected between the armature and the mounting member, the flexure elements crossing each other, wherein the crossing point defines a pivot point about which the armature rotates. A workpiece assembly, which includes a mounting arm, is configured so that a skin brush mounted on a free end of the mounting arm has an axis of rotation about the pivot point.

Owner:LOREAL SA

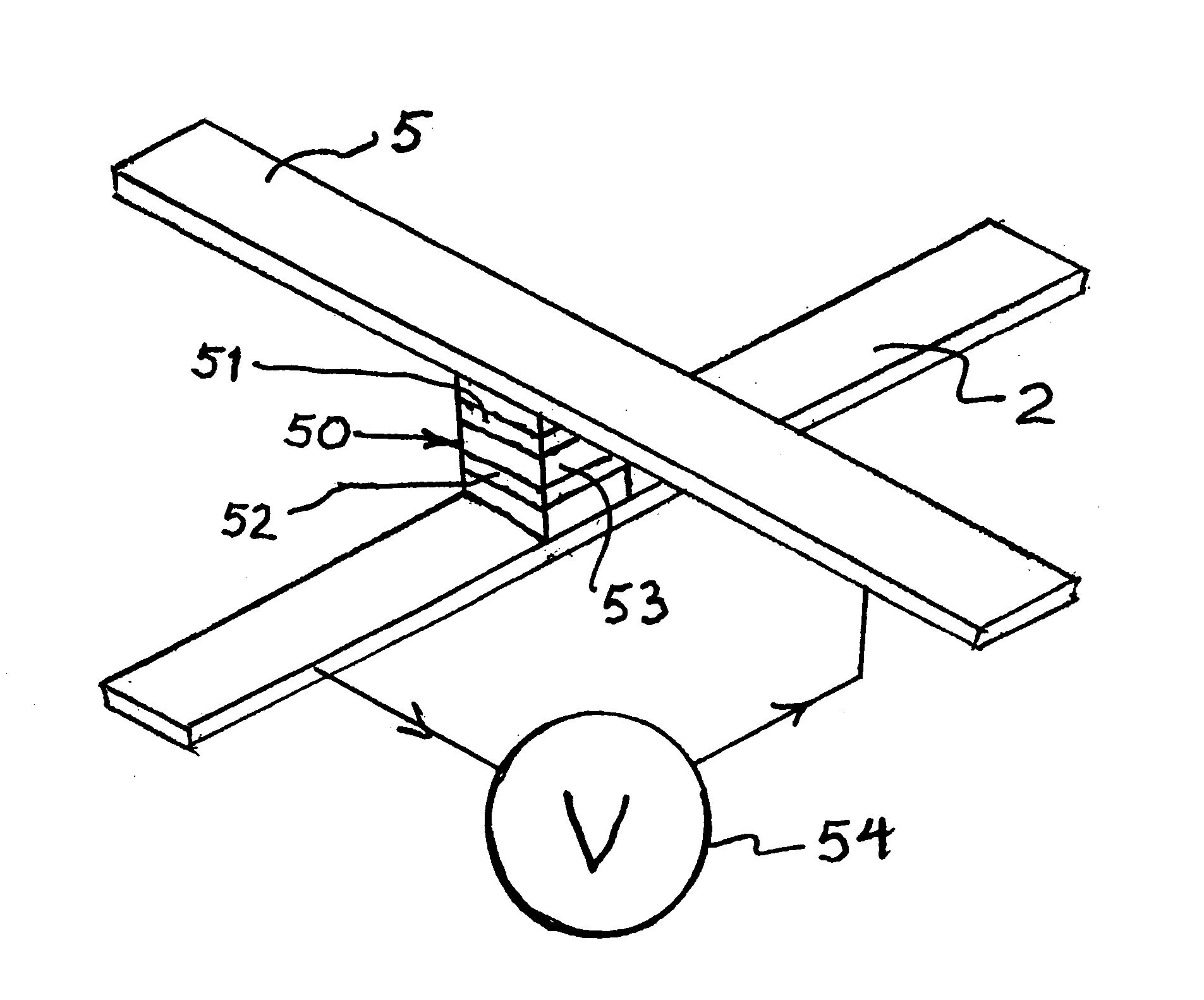

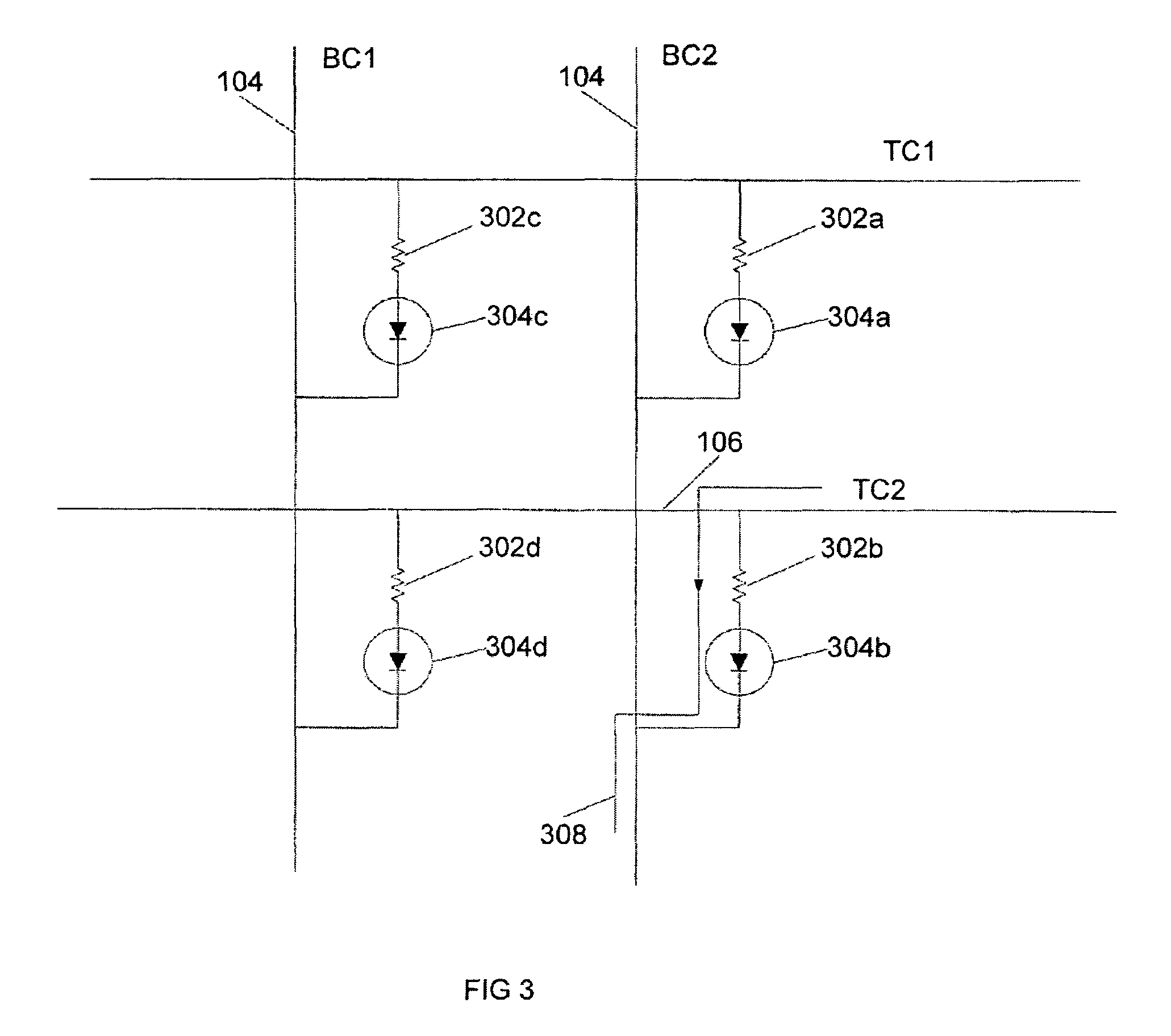

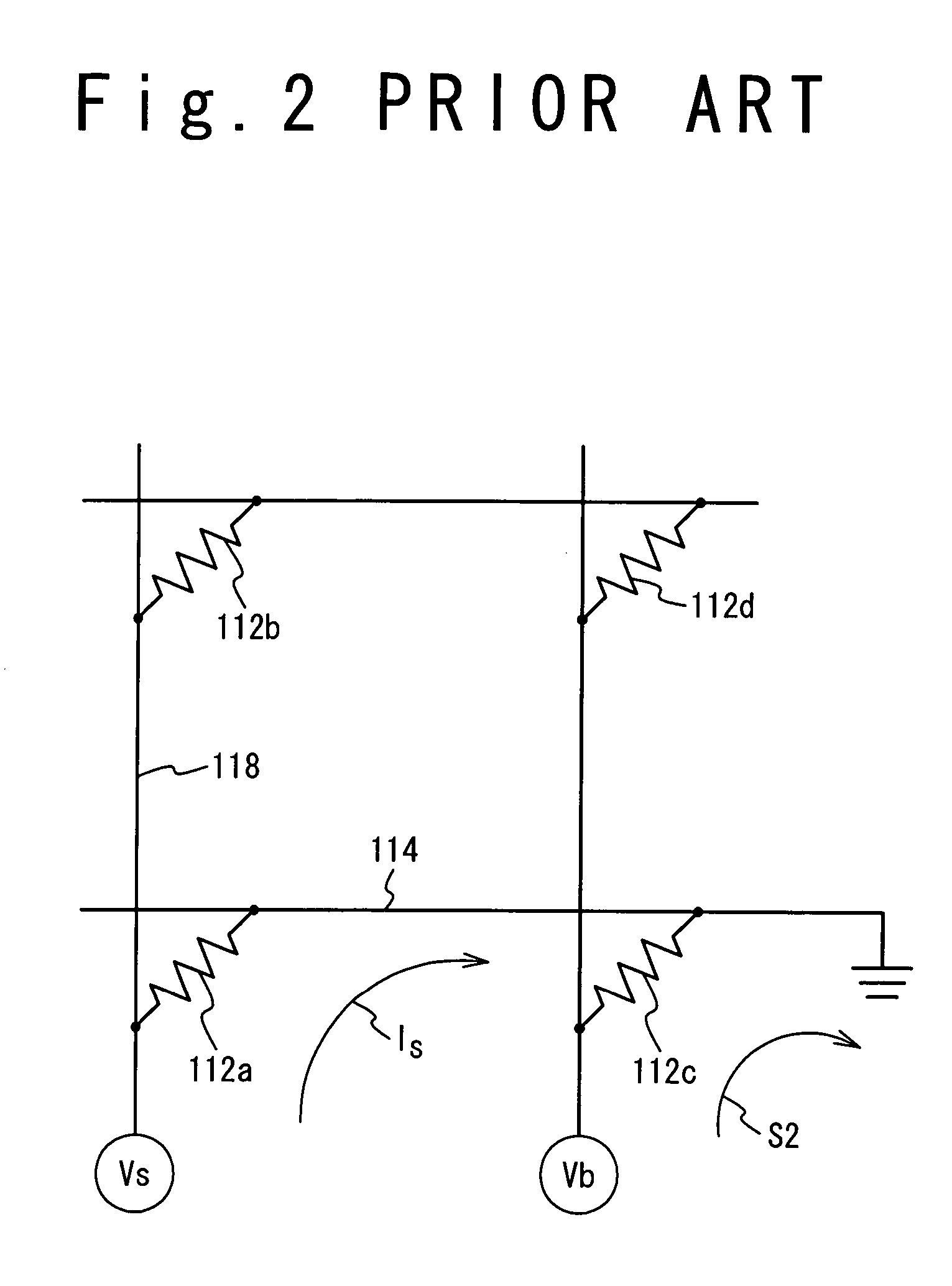

Cross point resistive memory array

A cross point resistive memory array has a first array of cells arranged generally in a plane. Each of the memory cells includes a memory storage element and is coupled to a diode. The diode junction extends transversely to the plane of the array of memory cells.

Owner:SAMSUNG ELECTRONICS CO LTD

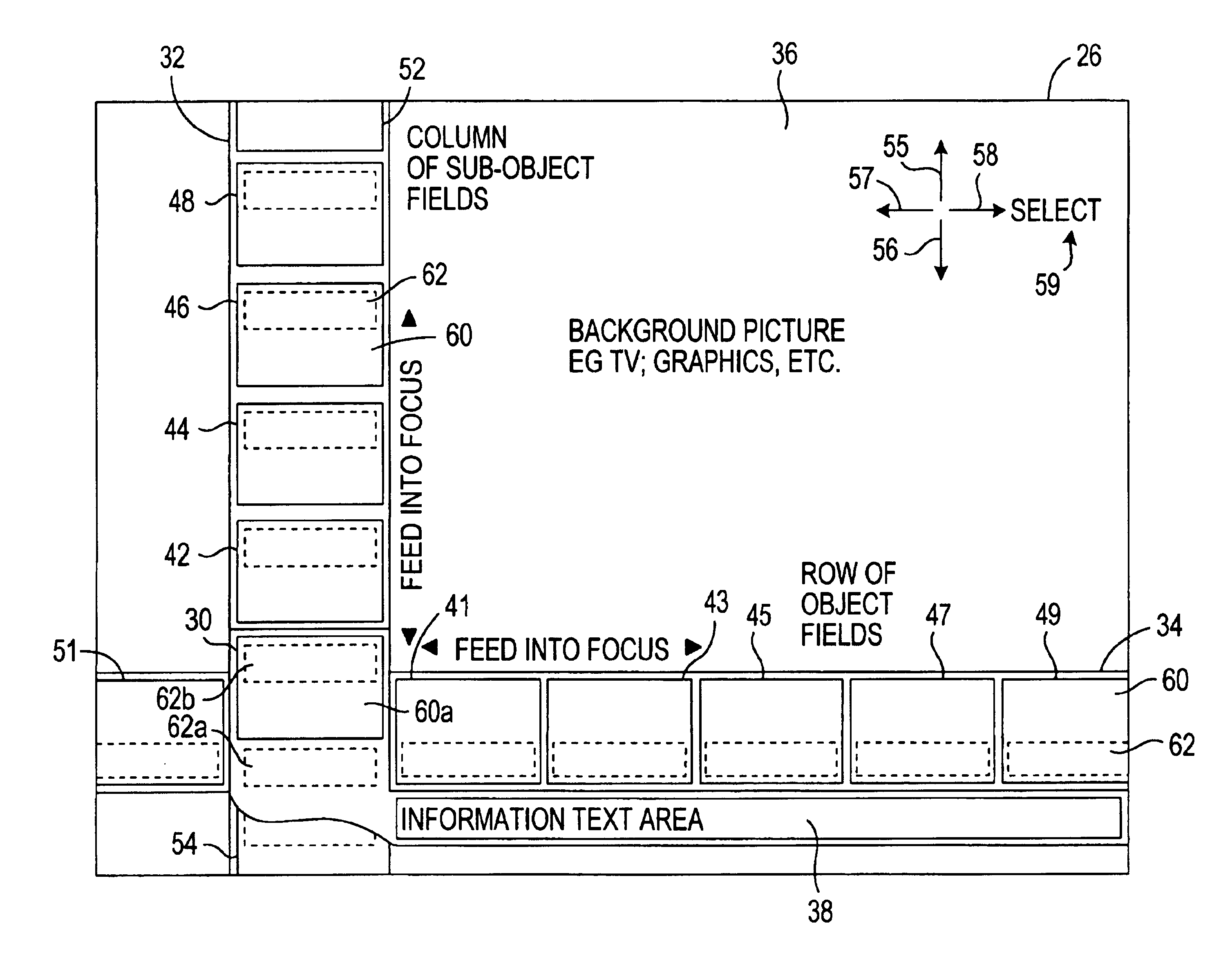

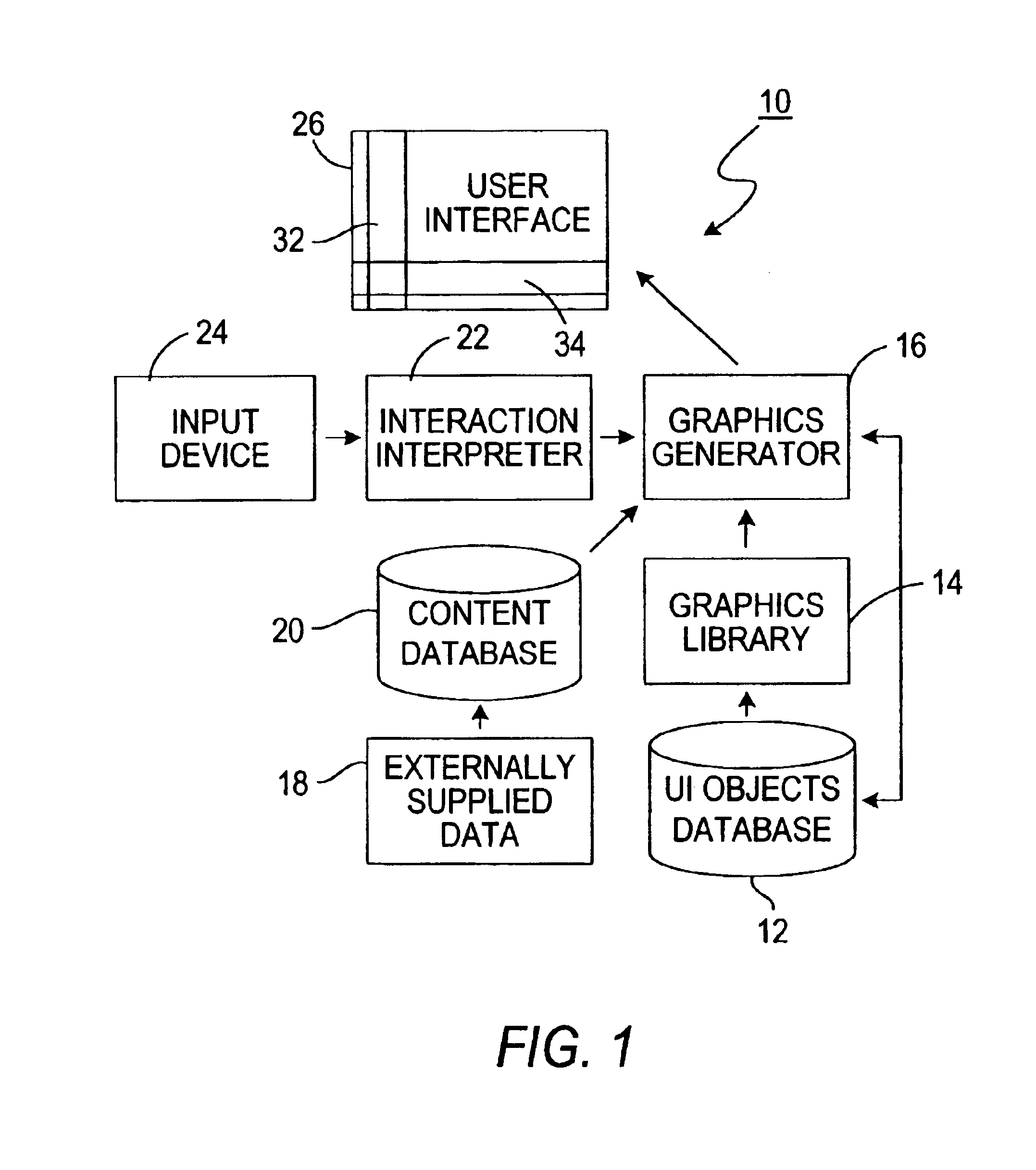

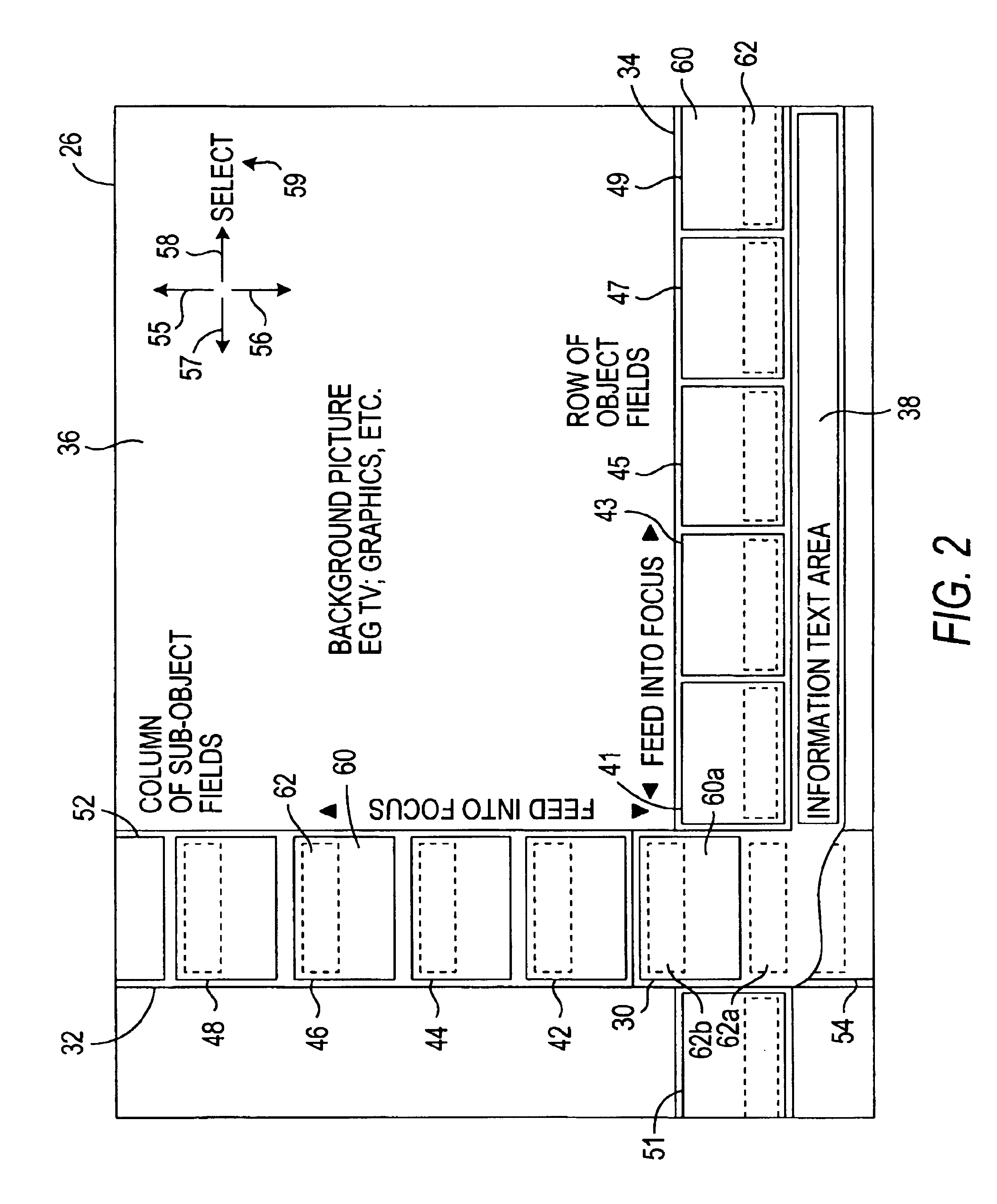

Method and apparatus for scrollable cross-point navigation in a calendar user interface

InactiveUS6966037B2Simplified navigationOffice automationInput/output processes for data processingComputer graphics (images)User interface

Owner:NOKIA CORP

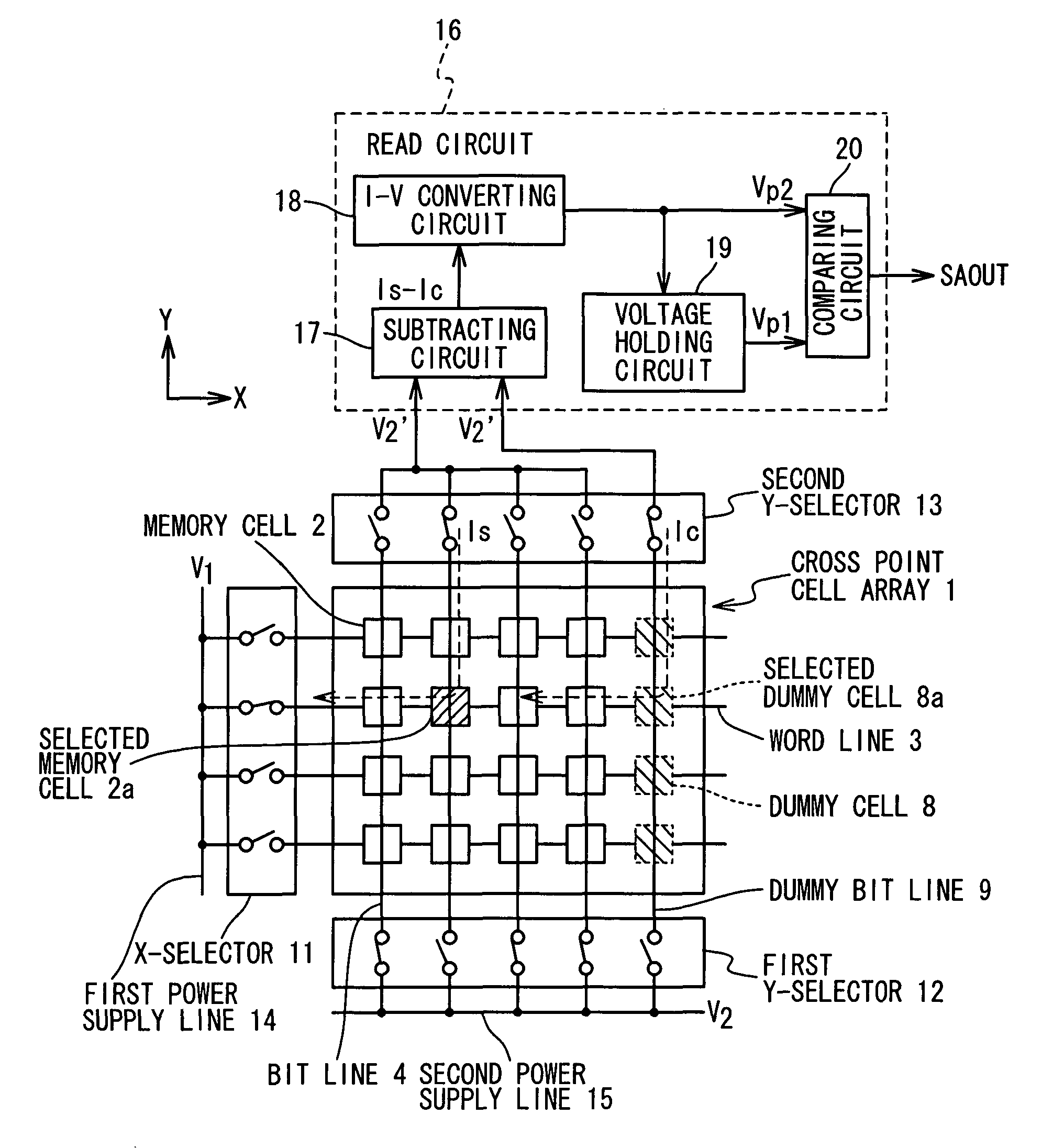

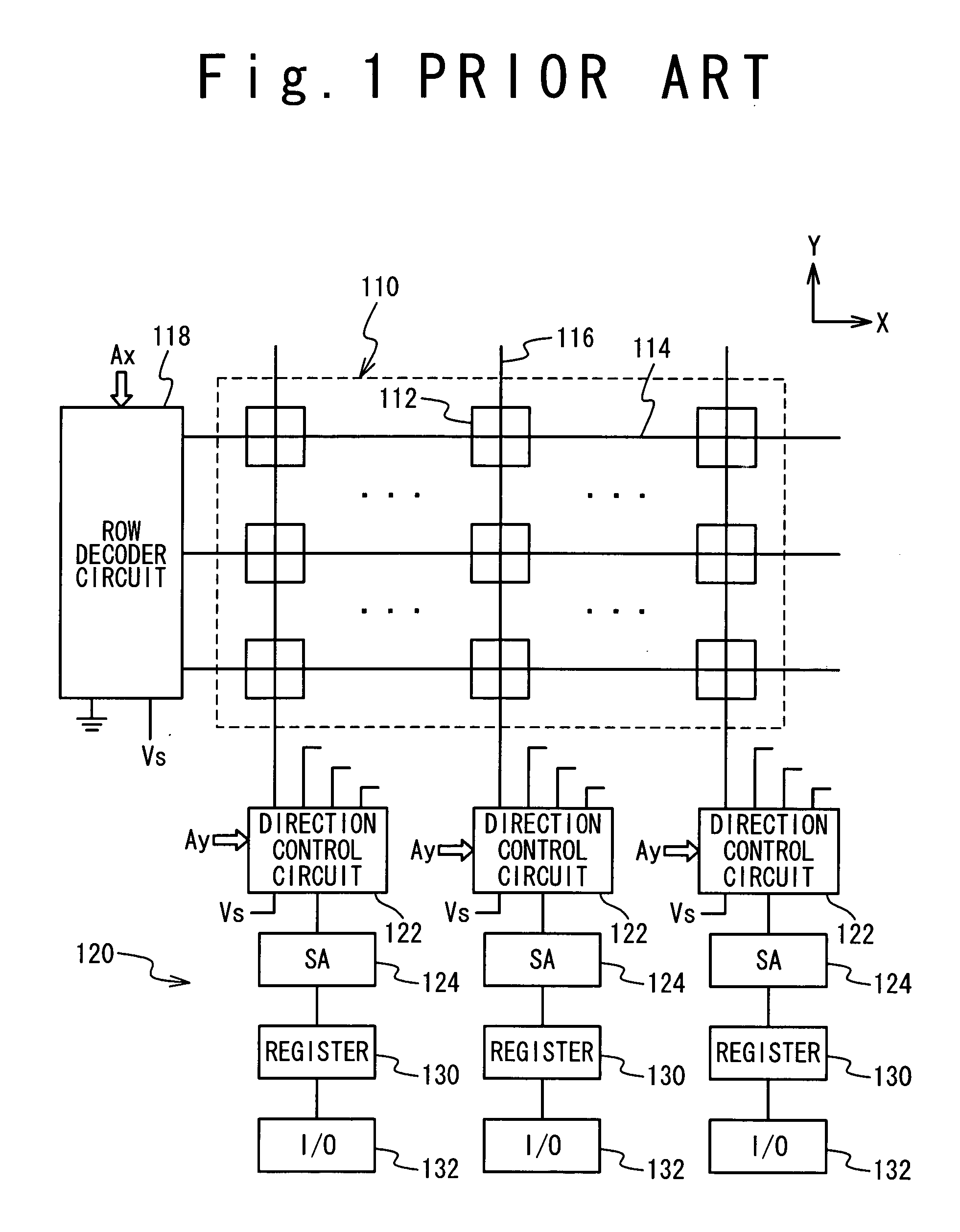

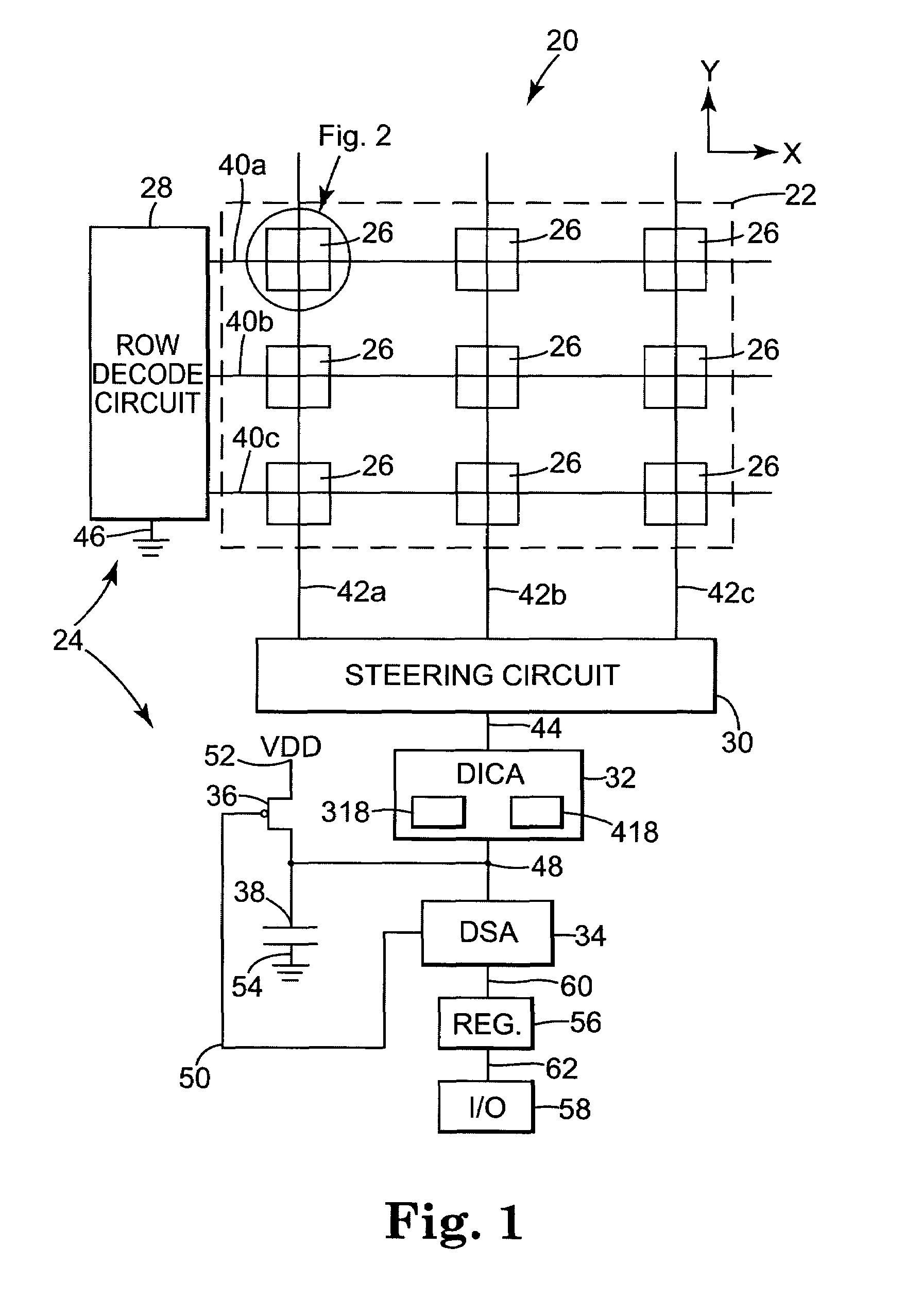

Magnetic random access memory

In a magnetic random access memory, a cross point cell array of memory cells is arranged in a matrix of columns and rows, and each of the memory cells has a magneto-resistance element. A column of dummy memory cells is provided, and each of the dummy memory cells has a magneto-resistance element. Word lines are provided for the rows of the memory cells and the dummy memory cells, respectively, and bit lines are provided for the columns of the memory cells, respectively. A dummy bit line is provided for the column of dummy memory cells. A read circuit is connected with the cross point cell array and the dummy bit line.

Owner:NEC CORP

Resistive cross point memory

InactiveUS7079436B2Magnetic-field-controlled resistorsSolid-state devicesComputer scienceCross point

Owner:SAMSUNG ELECTRONICS CO LTD

Providing a reference voltage to a cross point memory array

Providing a reference voltage to a cross point memory array. The invention is a cross point memory array and some peripheral circuitry that, when activated, provides a reference voltage to a cross point array in order to prevent unselected conductive array lines from floating to an undesired voltage. The peripheral circuitry can be activated before, after or during selection of a specific memory plug. If the peripheral circuitry is activated during selection, only the unselected conductive array lines should be brought to the reference voltage. Otherwise, all the conductive array lines can be brought to the reference voltage.

Owner:UNITY SEMICON

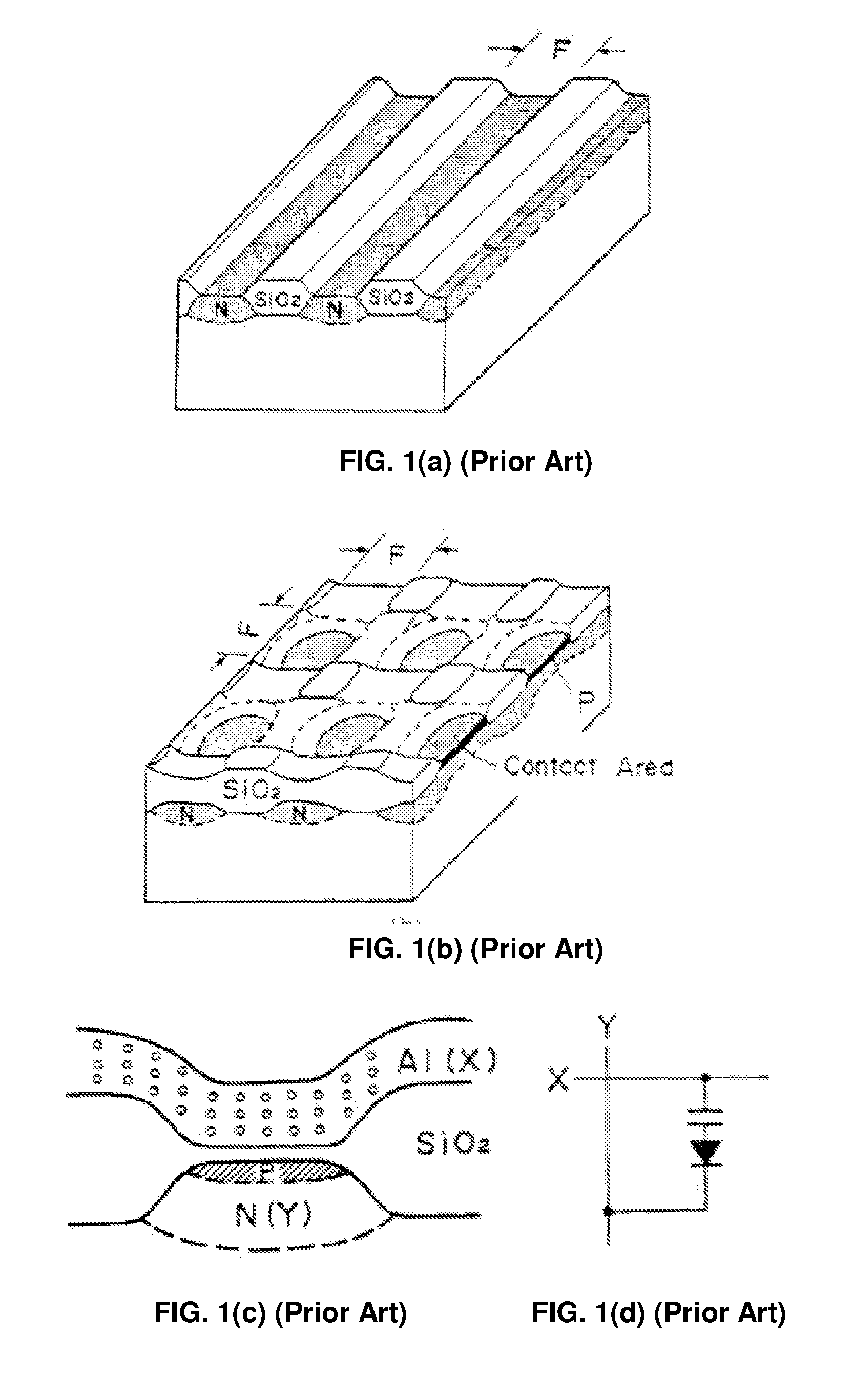

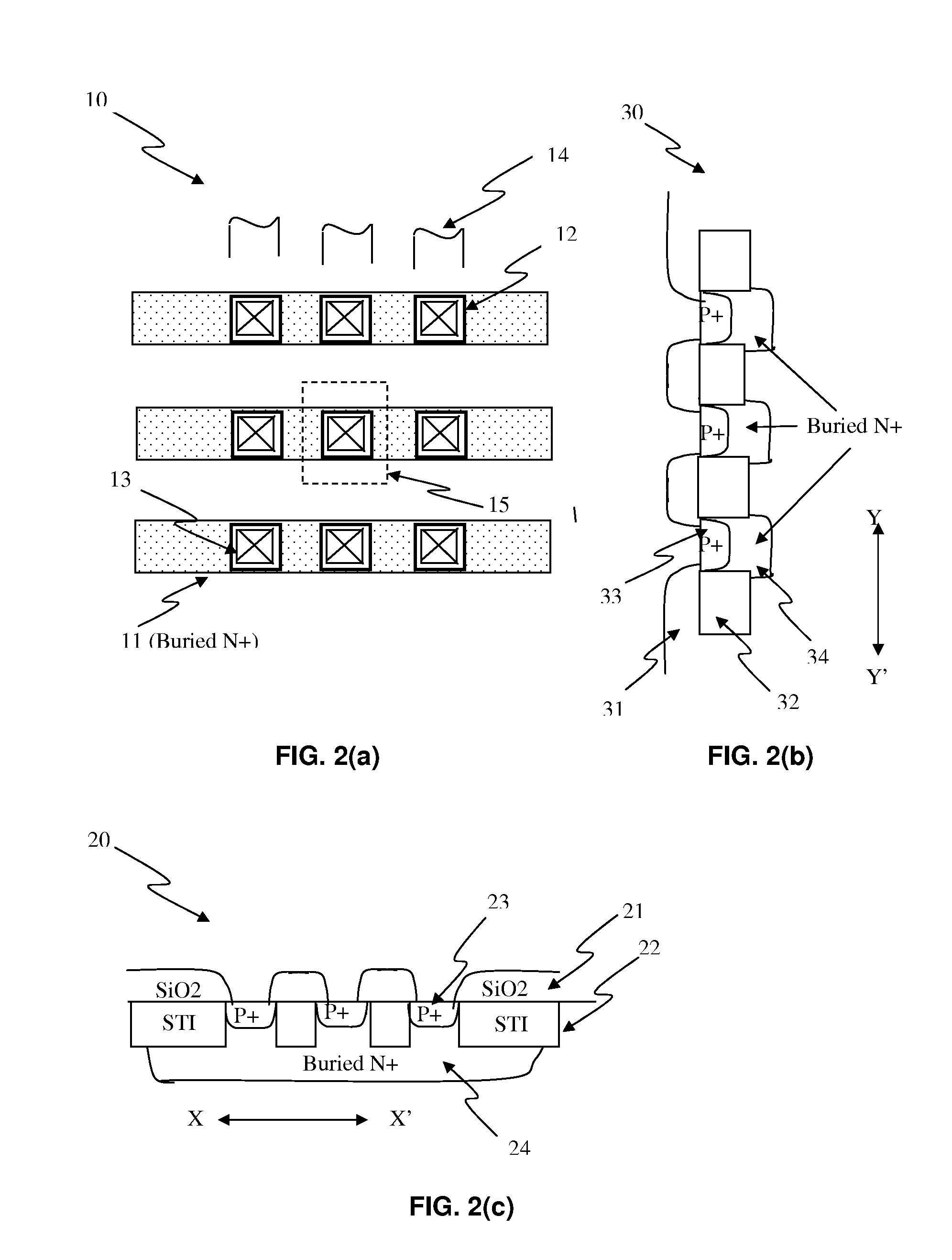

Circuit and system of a high density Anti-fuse

ActiveUS20120147653A1Eliminate needHigh voltageSemiconductor/solid-state device detailsSolid-state devicesThin oxideHigh density

A high density anti-fuse cell can be built at the cross points of two perpendicular interconnect lines, such as active region lines, active and polysilicon lines, active and metal lines, or polysilicon and metal lines. The cell size can be very small. At least one of the anti-fuse cells have a thin oxide fabricated before, after, or between a diode in at least one contact holes at the cross points of the interconnect lines. The thin oxide of the anti-fuse cells at the cross points can be selected for rupture by applying supply voltages in the two perpendicular lines. In some embodiments, a diode can be created after thin oxide is ruptured so that explicitly fabricating a diode or opening a contact hole at the cross-point may not be necessary.

Owner:ATTOPSEMI TECH CO LTD

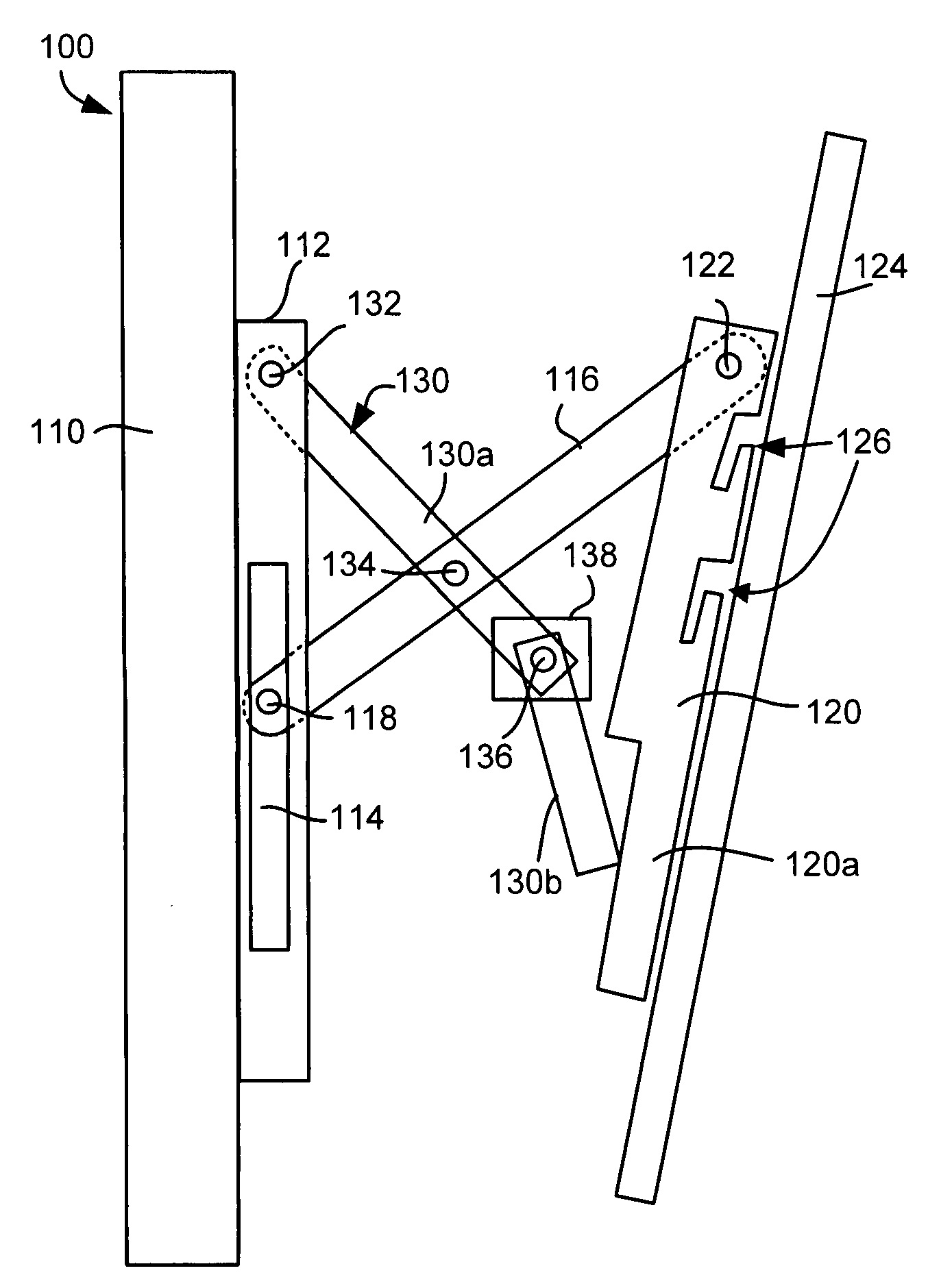

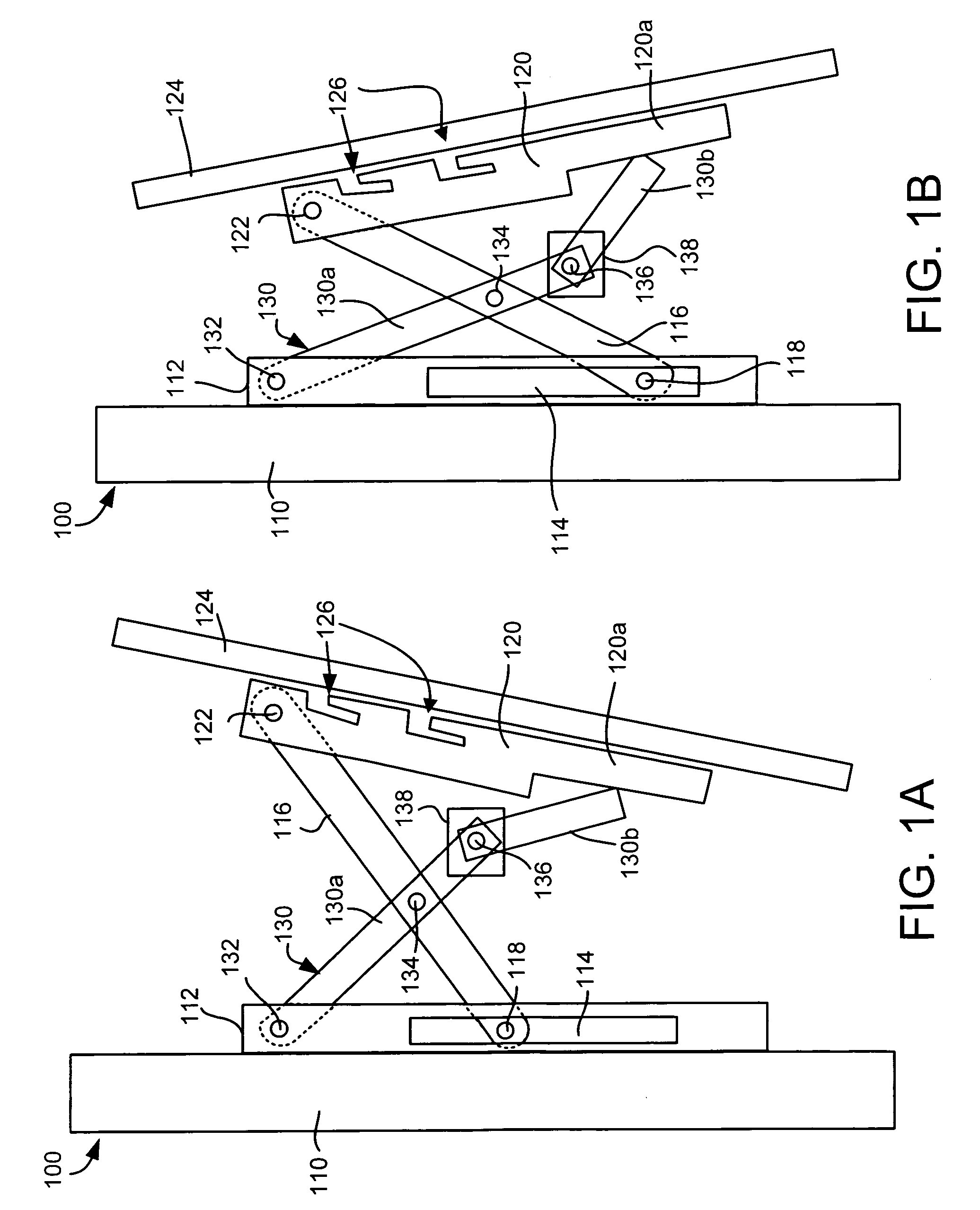

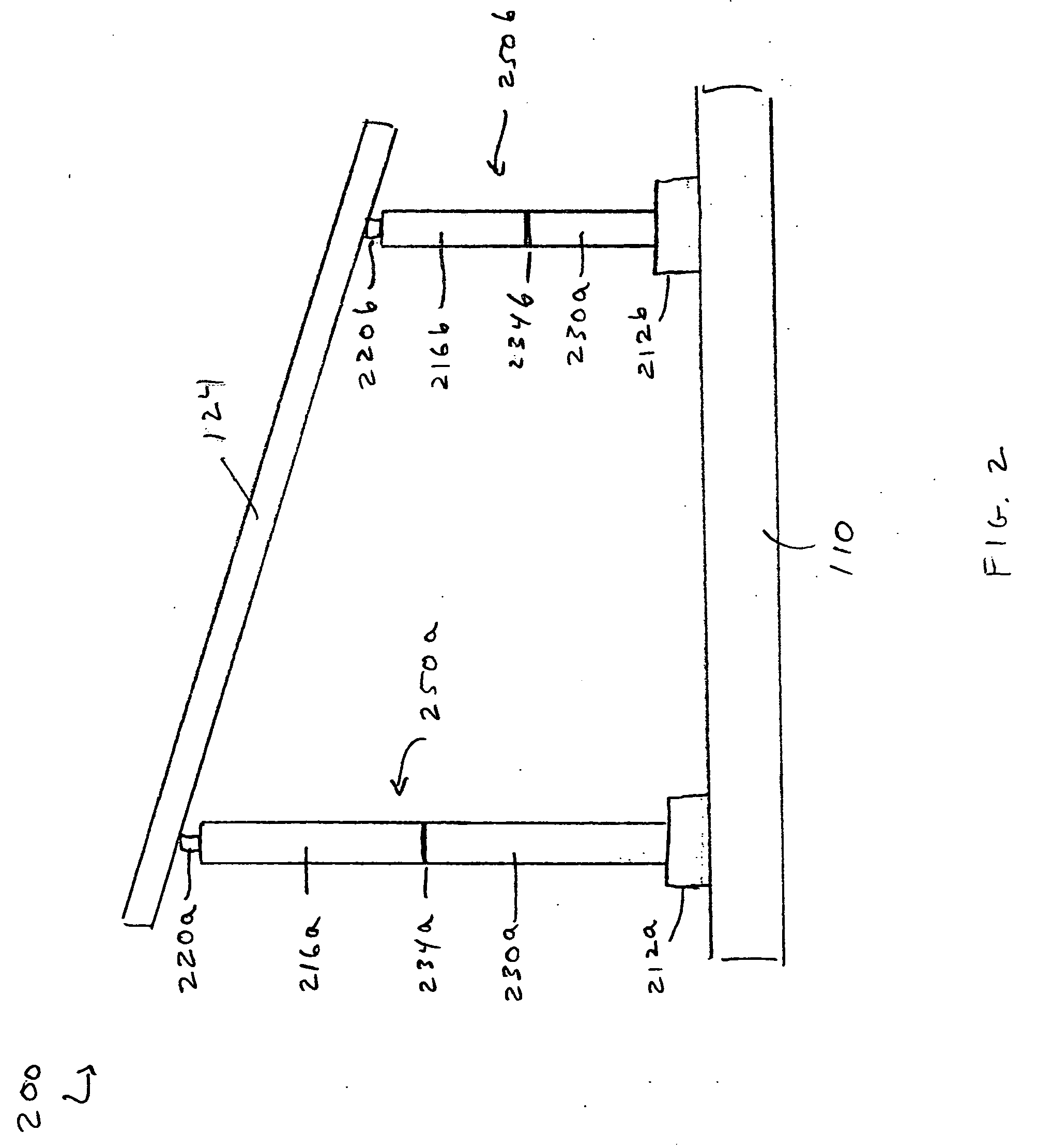

Adjustable display mount apparatus and system

InactiveUS20070023599A1Minimize complexityMinimizing problemDigital data processing detailsCathode-ray tube indicatorsDisplay deviceEngineering

An embodiment of an adjustable display mount apparatus and system comprises a mounting bracket for attachment to a mounting surface, a display attachment apparatus for attachment to the display, a first arm attached at one end to the mounting bracket and at the other end to the display attachment apparatus, and a second arm attached at one end to the mounting bracket in sliding engagement and at the other end to the display attachment apparatus. The arms cross each other at a pivotal cross point, enabling the arms to move relative to each other and the mounting surface, thus moving the display toward or away from the mounting surface. The first arm may articulate to enable tilting of the display.

Owner:FEDEWA DALE

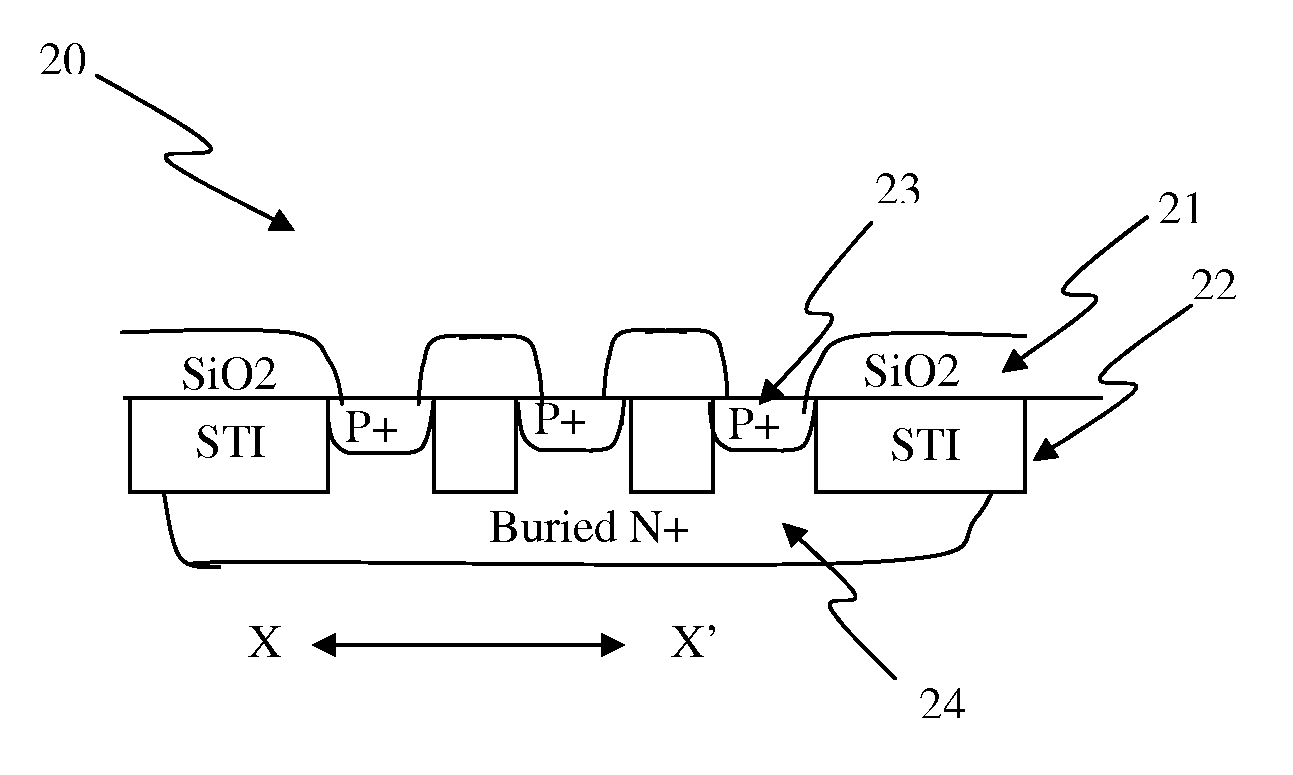

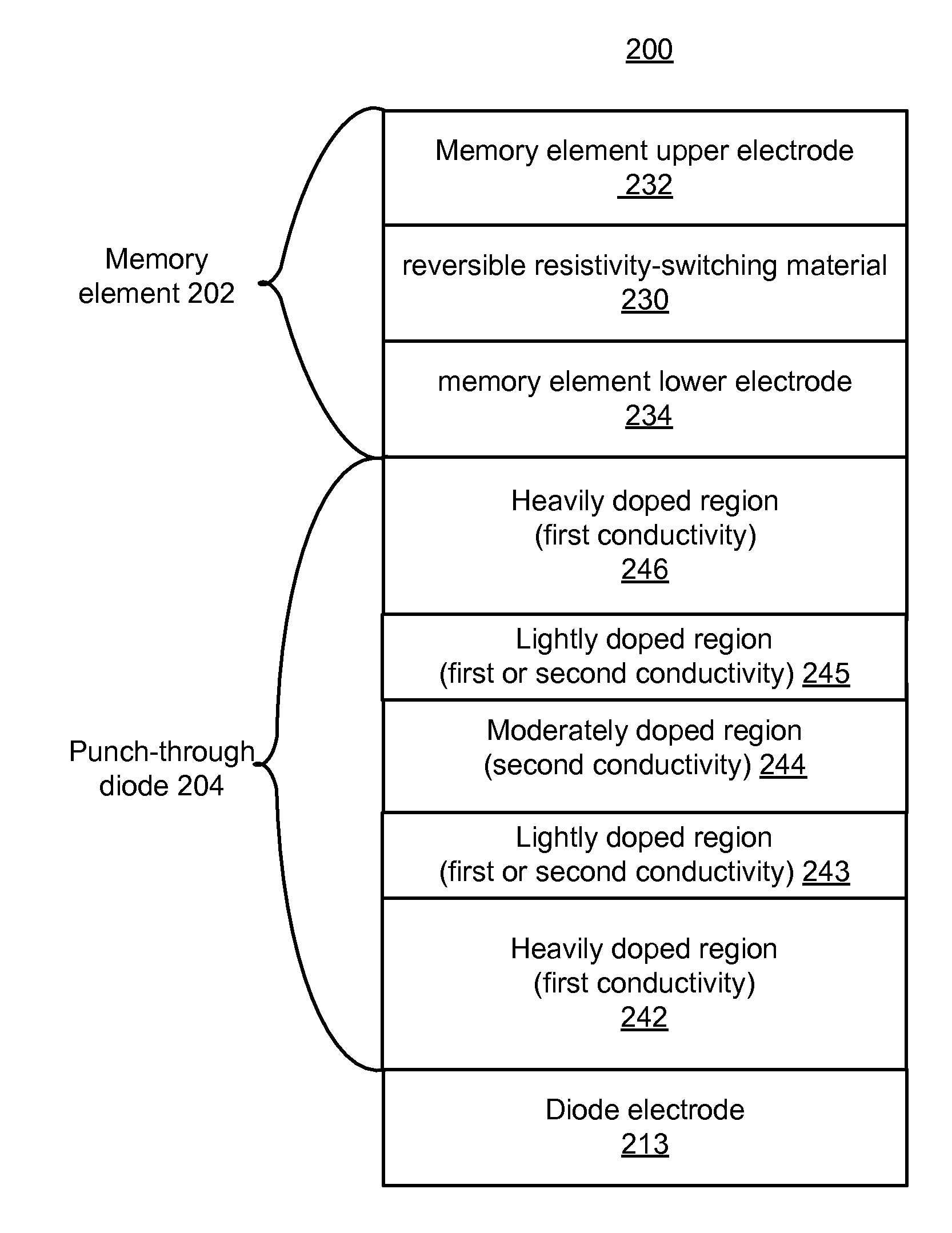

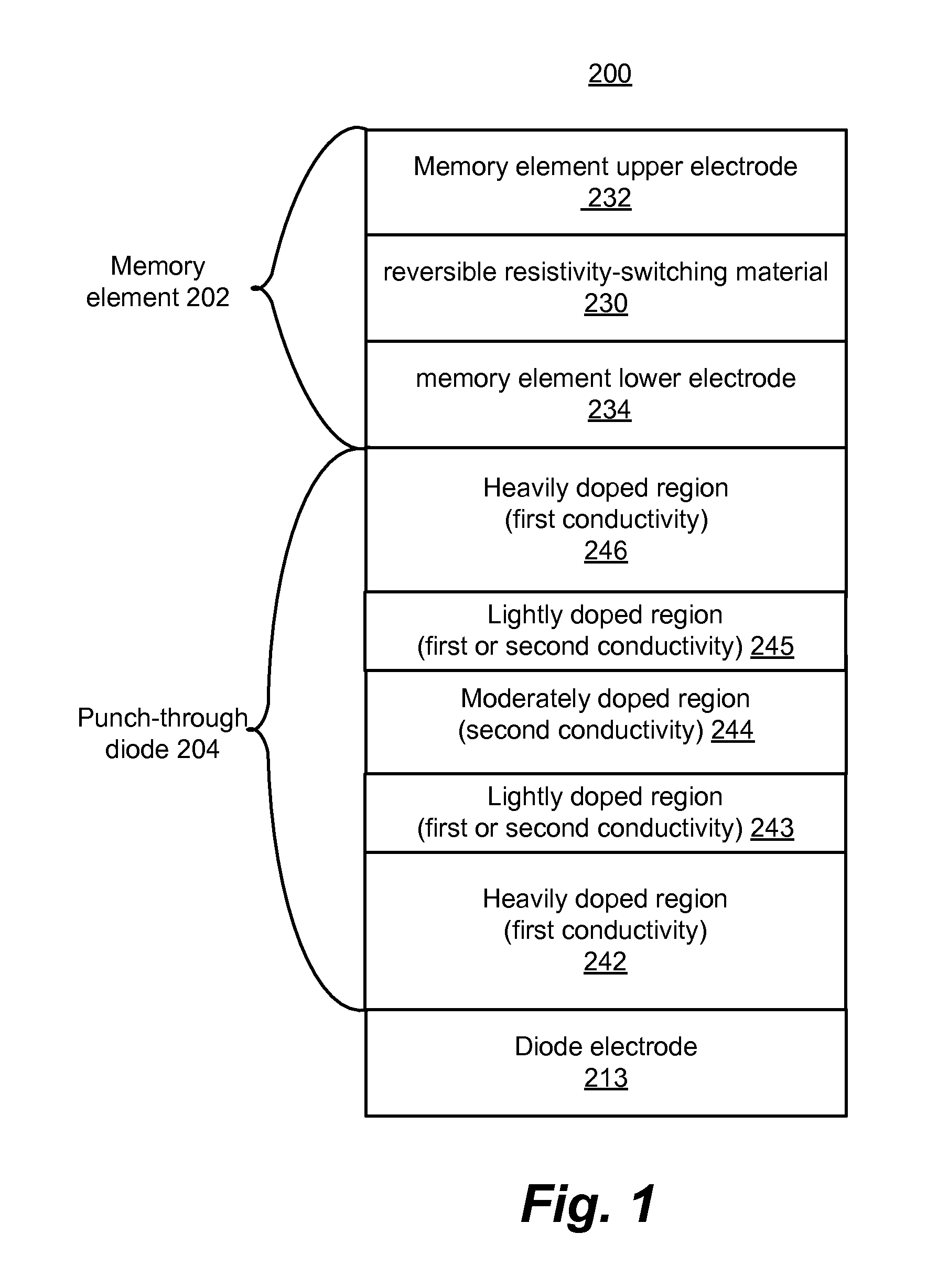

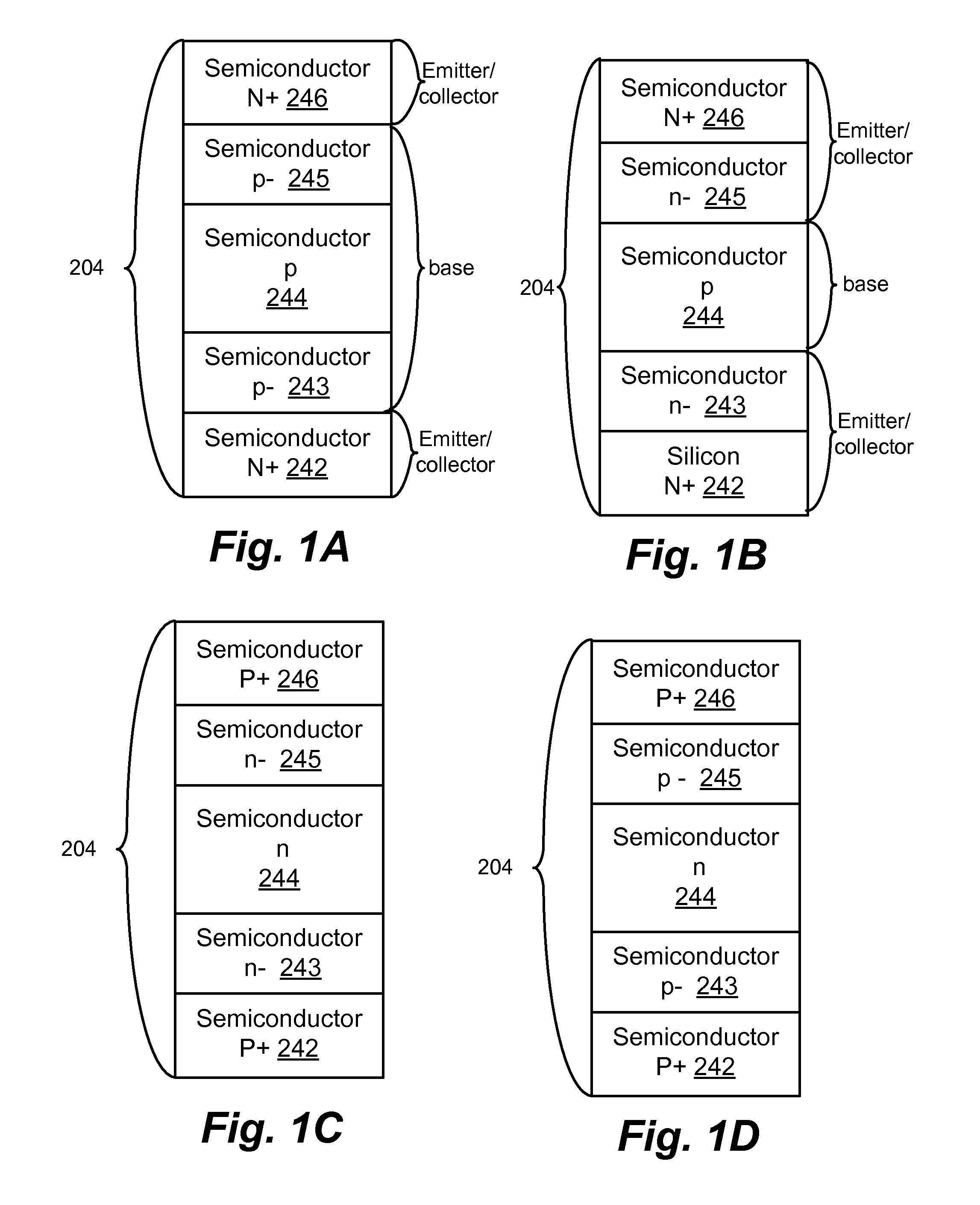

Punch-through diode

ActiveUS20120145984A1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringLow leakage

A punch-through diode and method of fabricating the same are disclosed herein. The punch-through diode may be used as a steering element in a memory device having a reversible resistivity-switching element. For example, a memory cell may include a reversible resistivity-switching element in series with a punch-through diode. The punch-through diode allows bipolar operation of a cross-point memory array. The punch-through diode may have a symmetrical non-linear current / voltage relationship. The punch-through diode has a high current at high bias for selected cells and a low leakage current at low bias for unselected cells. In other words, the ratio of Ion / Ioff is high. Therefore, the punch-through diode is compatible with bipolar switching in cross-point memory arrays having resistive switching elements.

Owner:SANDISK TECH LLC

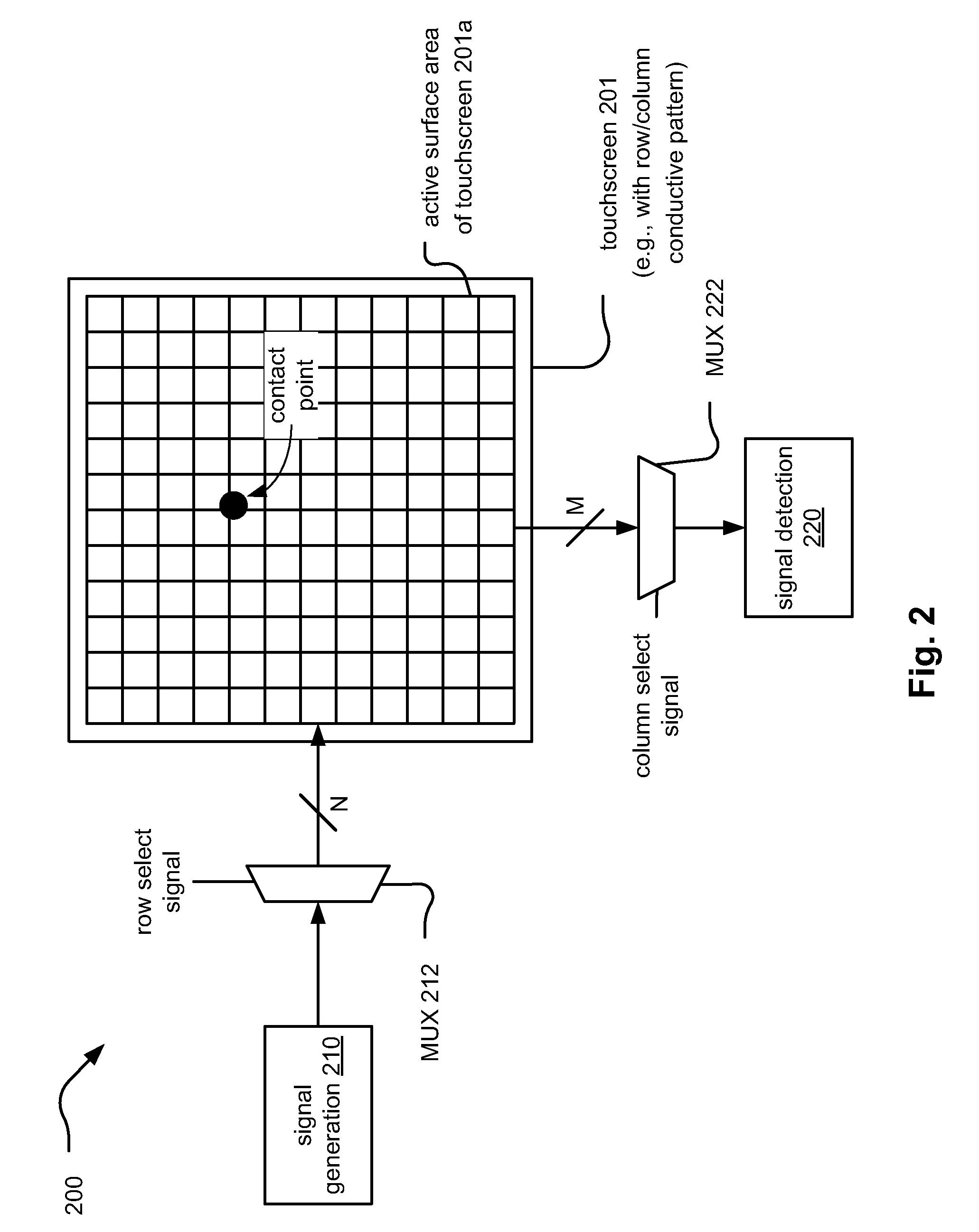

Meshed touchscreen pattern

Meshed touchscreen pattern. A conductive pattern implemented within a touchscreen (e.g., using indium tin oxide (ITO) such as may be deposited on a substrate composed of polyester or some other material) provides paths for signals traveling through the touchscreen. By monitoring these signal in accordance with some means (e.g., cross point detection, zone detection, etc.) an estimate may be made as to a location of user's interaction with the touchscreen (e.g., finger or stylus touching of the touchscreen). The conductive pattern includes a number of conductors aligned in various directions (e.g., row and column conductors) across the touchscreen, and they are separated by a dielectric layer (e.g., air, SiO2, or any other desirable dielectric layer). The conductors include a great deal of interlacing and meshing as achieved by spurs, extensions, and / or protrusions (e.g., of any desired shape) extending from one conductor into an adjacent conductor within the conductive pattern.

Owner:WACOM CO LTD

Method for determining diffusivity and molecular weight in a microfluidic device

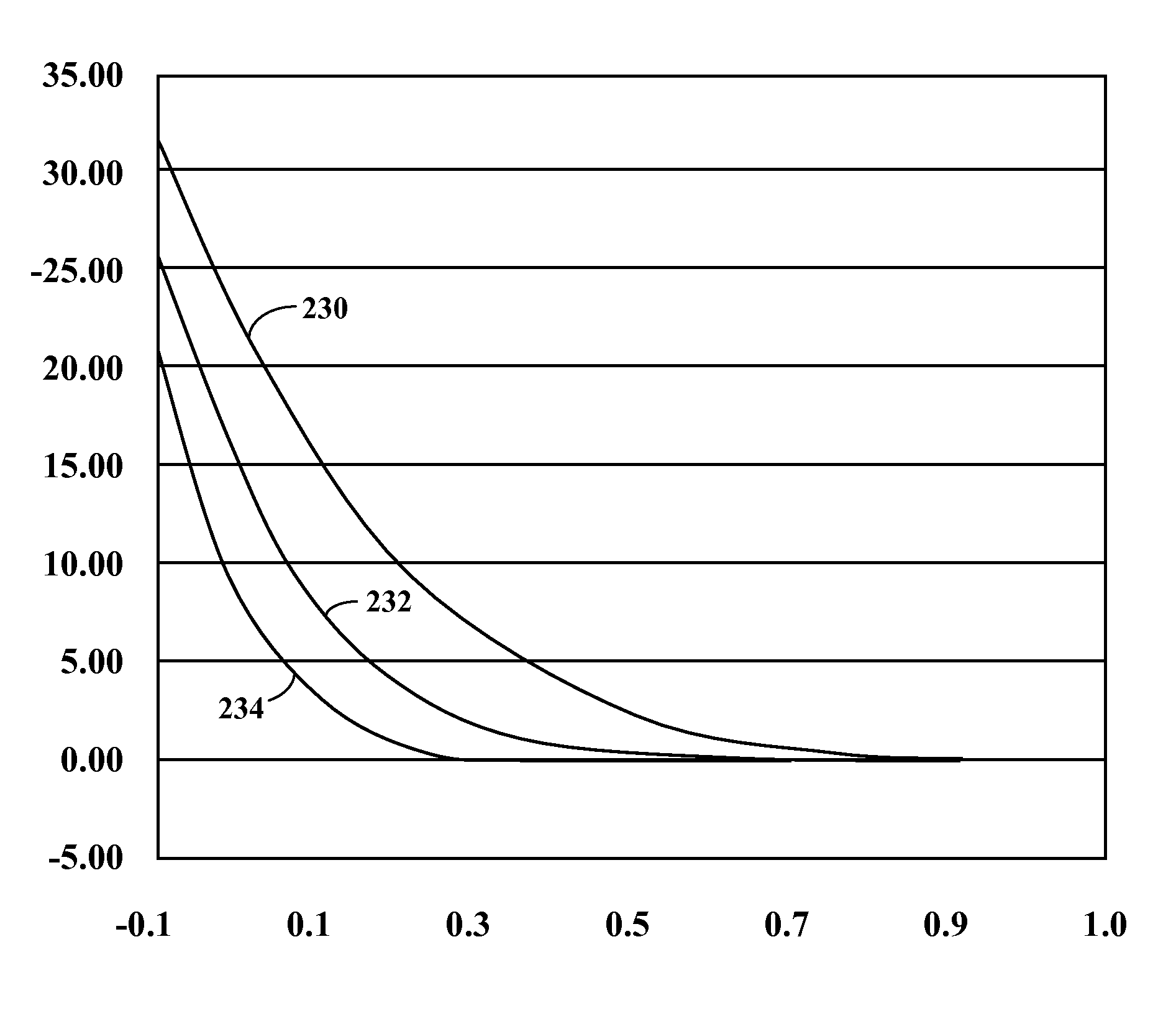

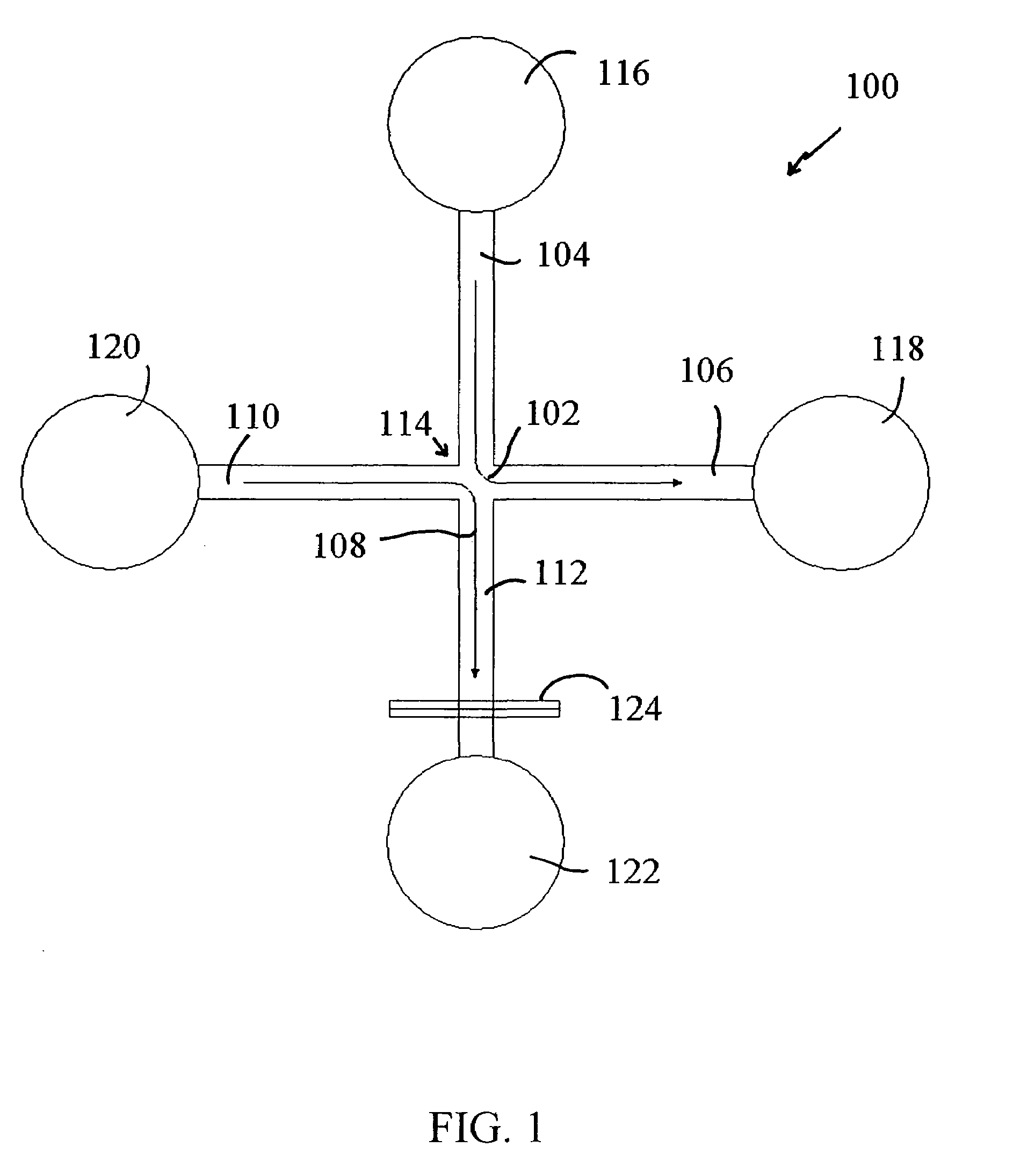

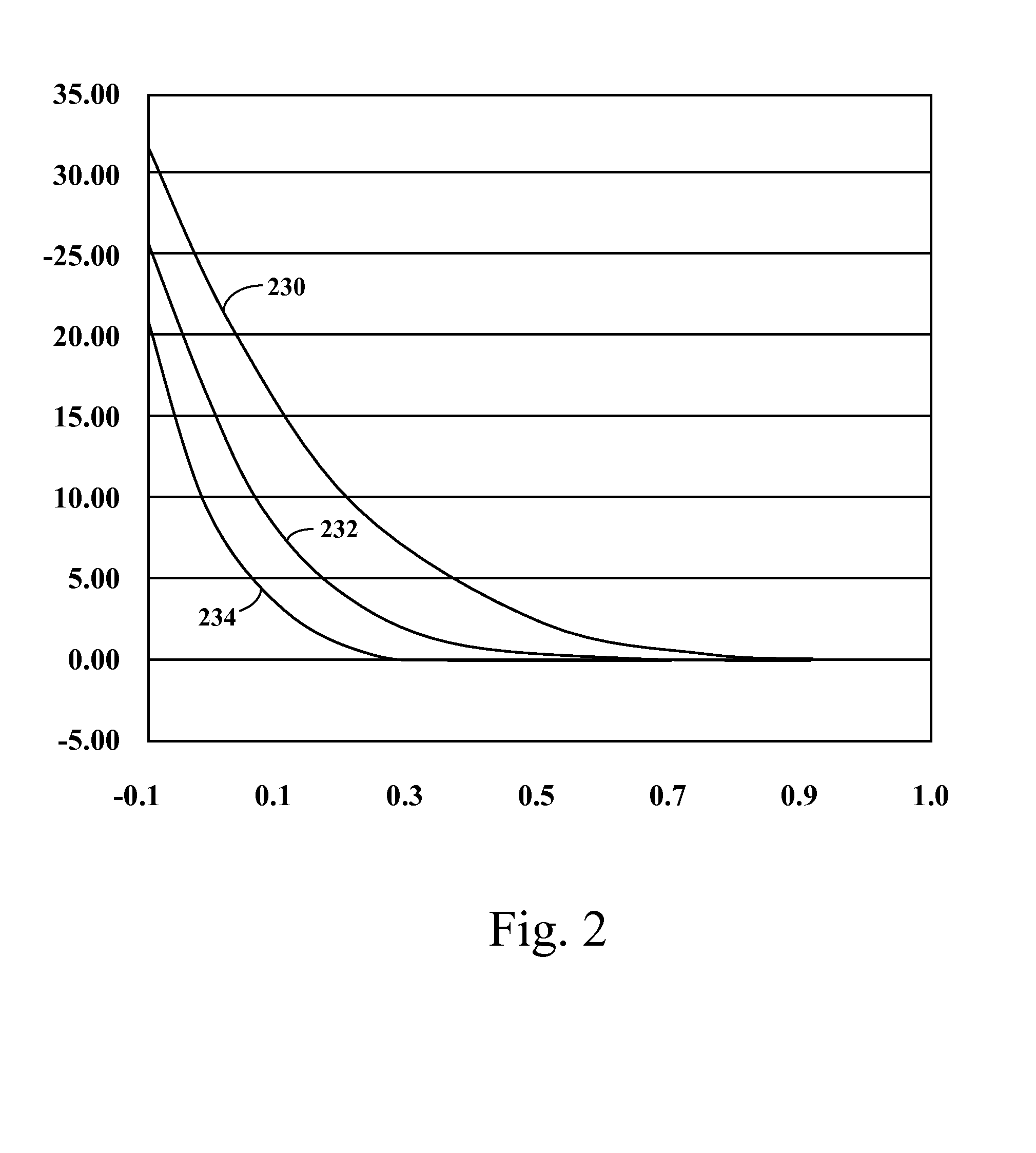

The present invention is directed to a method for determining the molecular weight and diffusivity of a sample solute by providing a plus shaped microchannel network on a microfluidic chip, having at least four microchannels intersecting at a cross point; flowing a sample stream comprising a sample solute of unknown diffusivity and a blank stream from separate microchannels through the cross point and out to separate microchannels; creating a sample curve measuring the concentration of the sample solute that diffuses from the sample stream to the blank stream at the cross point while altering the flowrate of one of the blank stream or the sample stream; and determining a diffusion coefficient of the sample solute by extrapolating data from similar curves of at least two solutes having known molecular weights and / or diffusion coefficients created under similar conditions as those generated by the sample solute.

Owner:CAPLIPER LIFE SCI INC

Methods and systems for the industrial internet of things

ActiveUS20180210425A1Improve signal-to-noise ratioLow sampling rateVibration measurement in solidsMachine part testingData acquisitionEngineering

The system generally includes a crosspoint switch in the local data collection system having multiple inputs and multiple outputs including a first input connected to the first sensor and a second input connected to the second sensor. The multiple outputs include a first output and a second output configured to be switchable between a condition in which the first output is configured to switch between delivery of the first sensor signal and the second sensor signal and a condition in which there is simultaneous delivery of the first sensor signal from the first output and the second sensor signal from the second output. Each of multiple inputs is configured to be individually assigned to any of the multiple outputs. Unassigned outputs are configured to be switched off producing a high-impedance state. The crosspoint switch includes a third input that is configured with a continuously monitored alarm having a pre-determined trigger condition when the third input is unassigned to any of the multiple outputs. The local data collection system is configured to manage data collection bands.

Owner:STRONG FORCE IOT