Patents

Literature

181 results about "Unit memory" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Memory unit is the amount of data that can be stored in the storage unit. This storage capacity is expressed in terms of Bytes. ... A computer word, like a byte, is a group of fixed number of bits processed as a unit, which varies from computer to computer but is fixed for each computer. The length of a computer word is called word-size or word length.

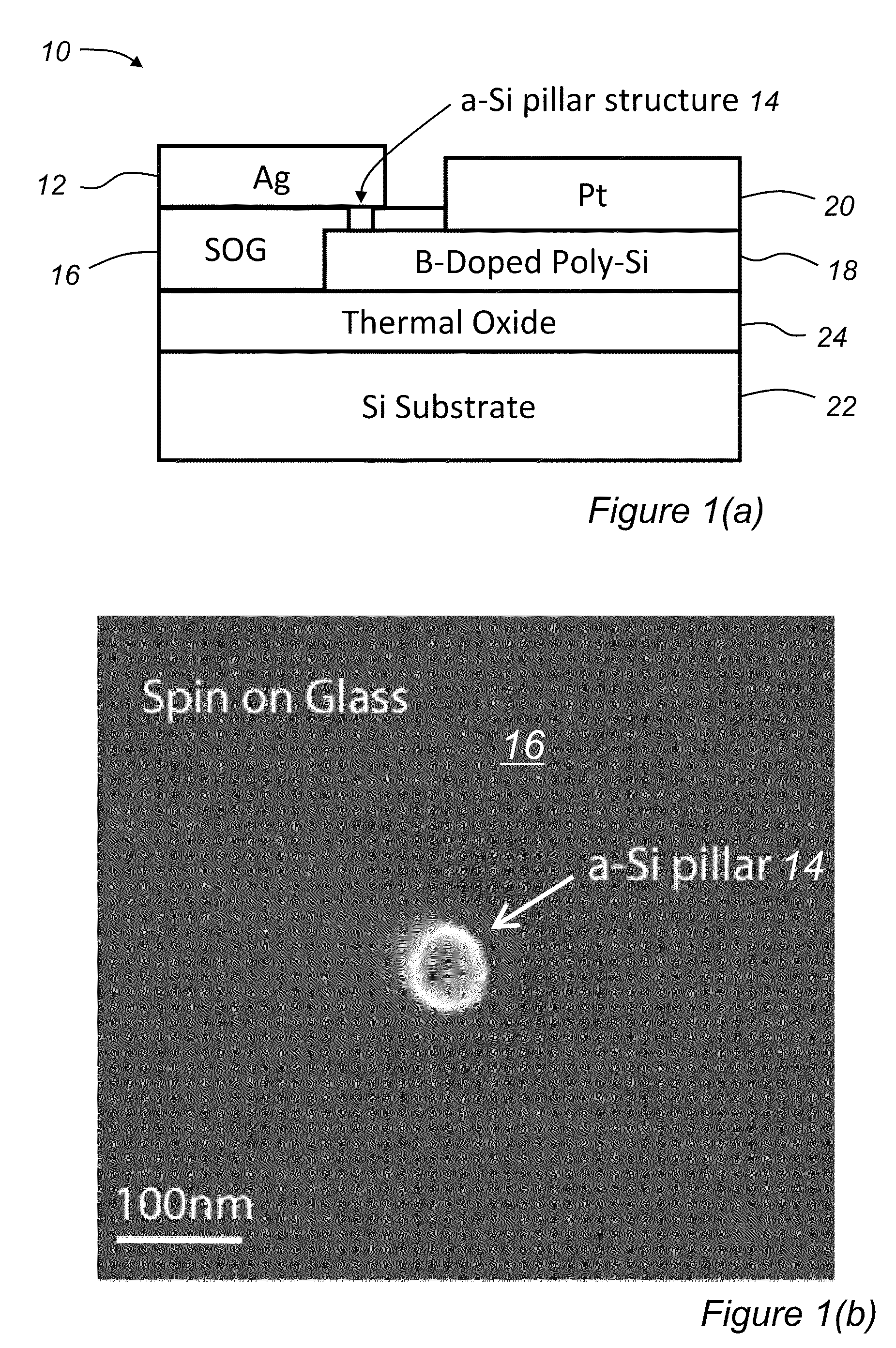

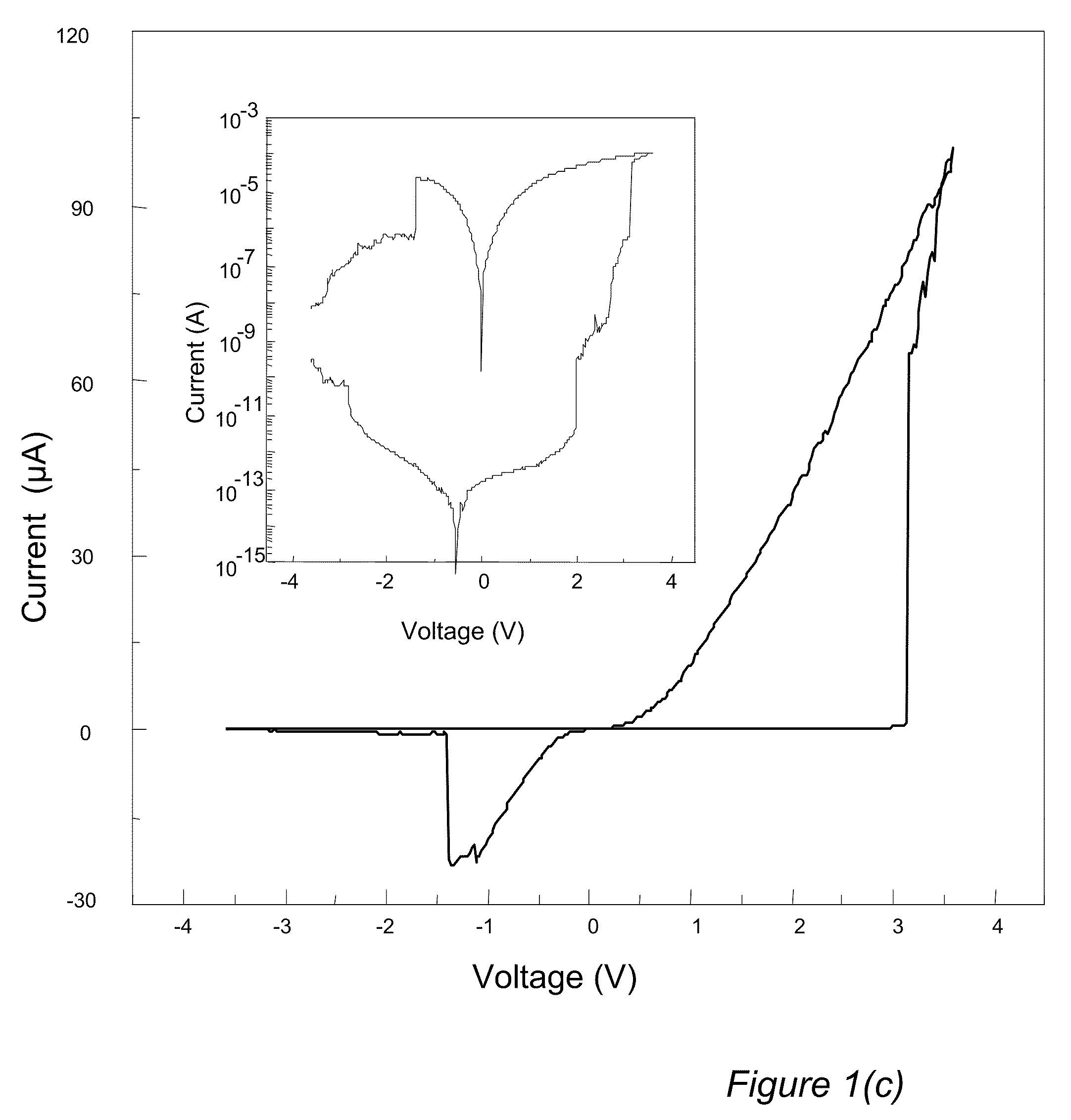

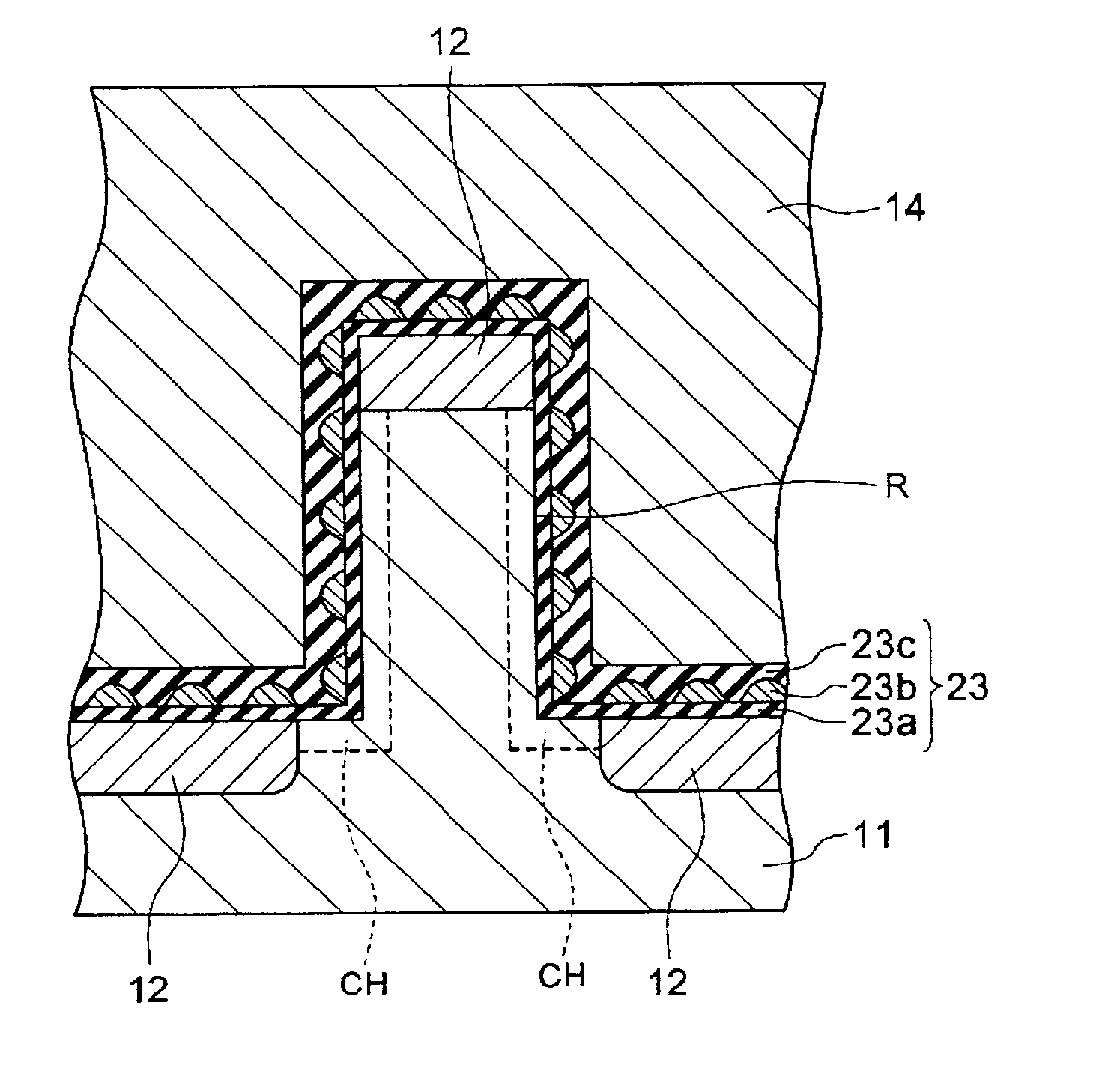

Silicon-based nanoscale resistive device with adjustable resistance

A non-volatile solid state resistive device that includes a first electrode, a p-type poly-silicon second electrode, and a non-crystalline silicon nanostructure electrically connected between the electrodes. The nanostructure has a resistance that is adjustable in response to a voltage being applied to the nanostructure via the electrodes. The nanostructure can be formed as a nanopillar embedded in an insulating layer located between the electrodes. The first electrode can be a silver or other electrically conductive metal electrode. A third (metal) electrode can be connected to the p-type poly-silicon second electrode at a location adjacent the nanostructure to permit connection of the two metal electrodes to other circuitry. The resistive device can be used as a unit memory cell of a digital non-volatile memory device to store one or more bits of digital data by varying its resistance between two or more values.

Owner:RGT UNIV OF MICHIGAN

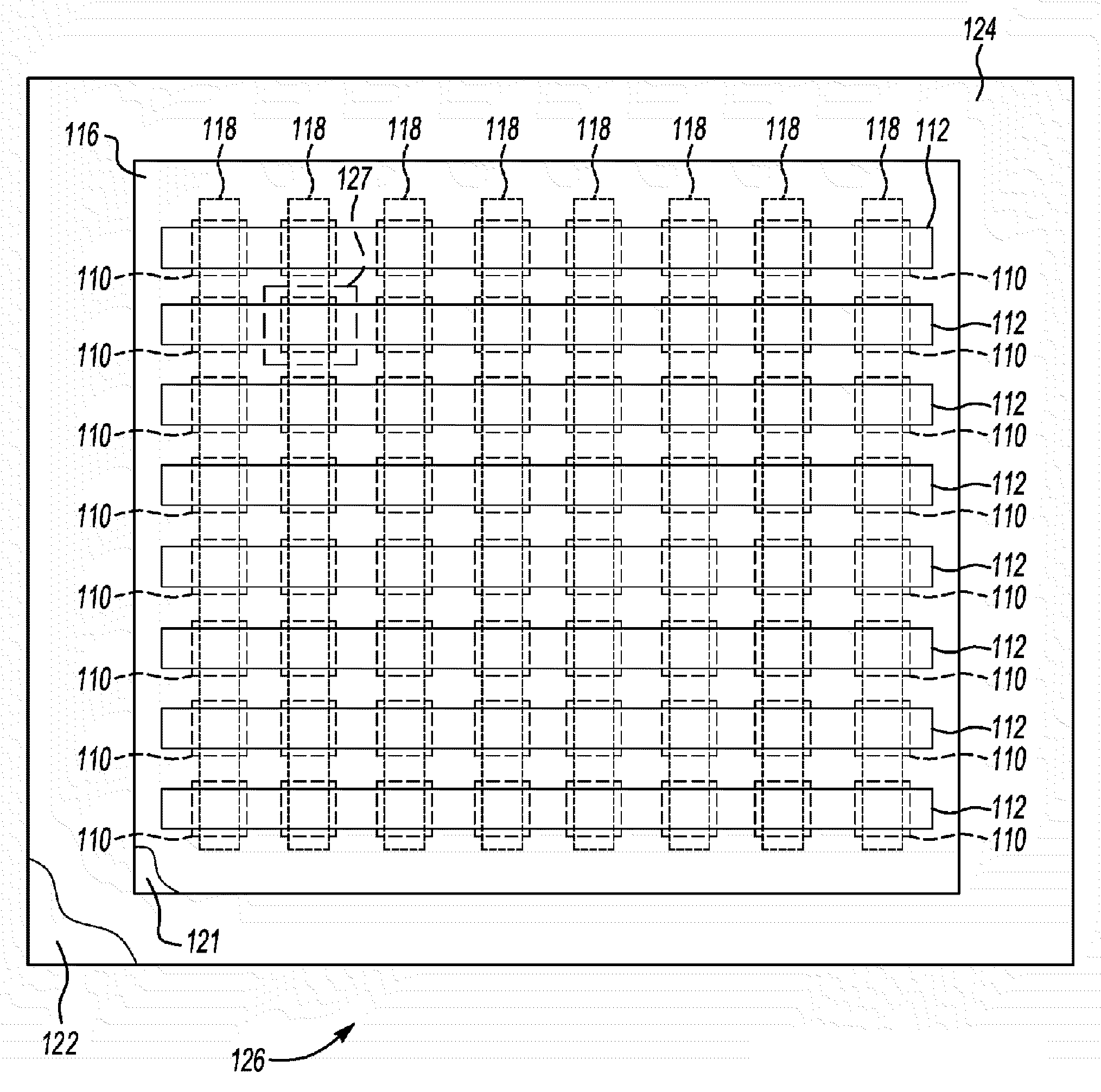

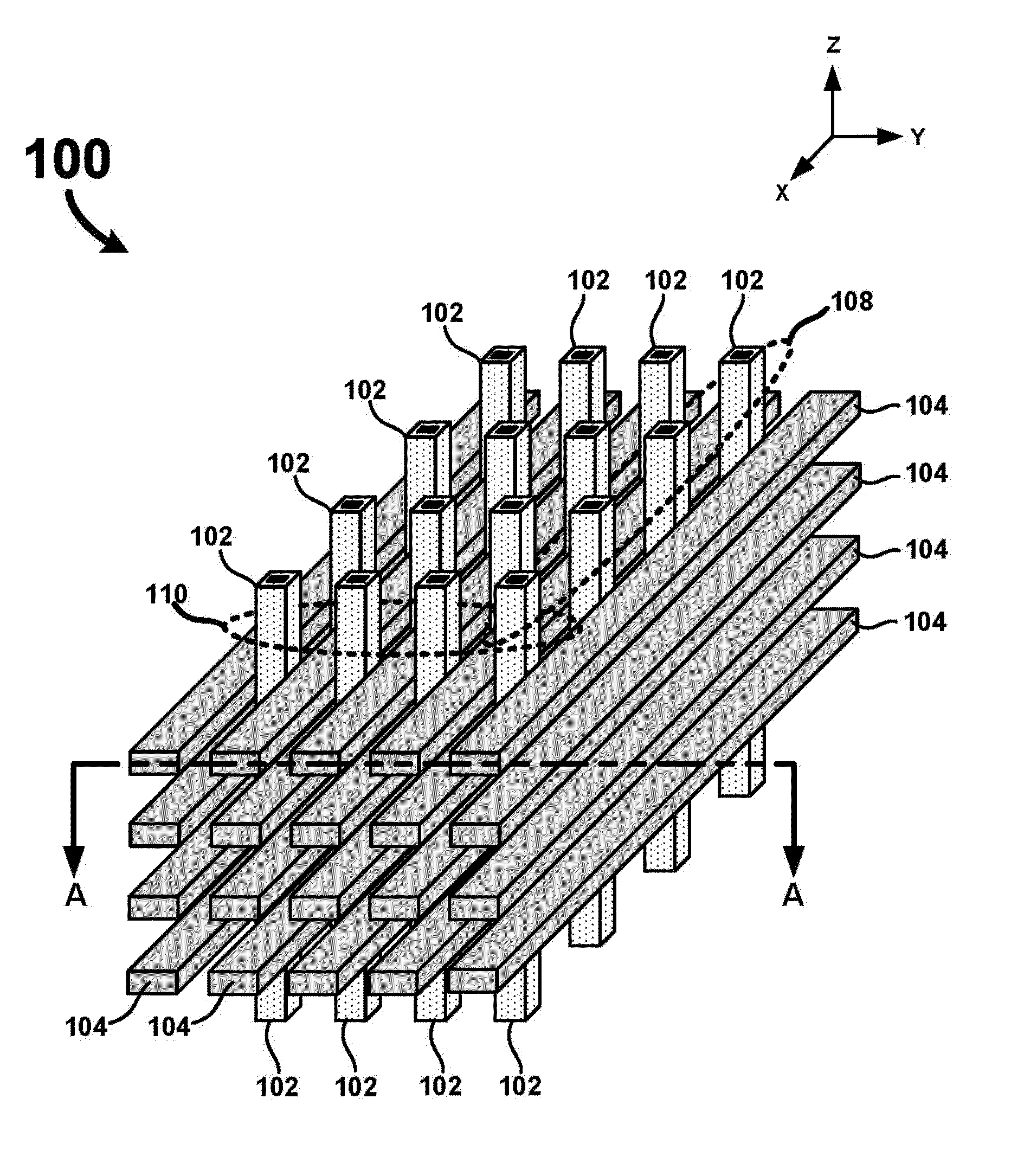

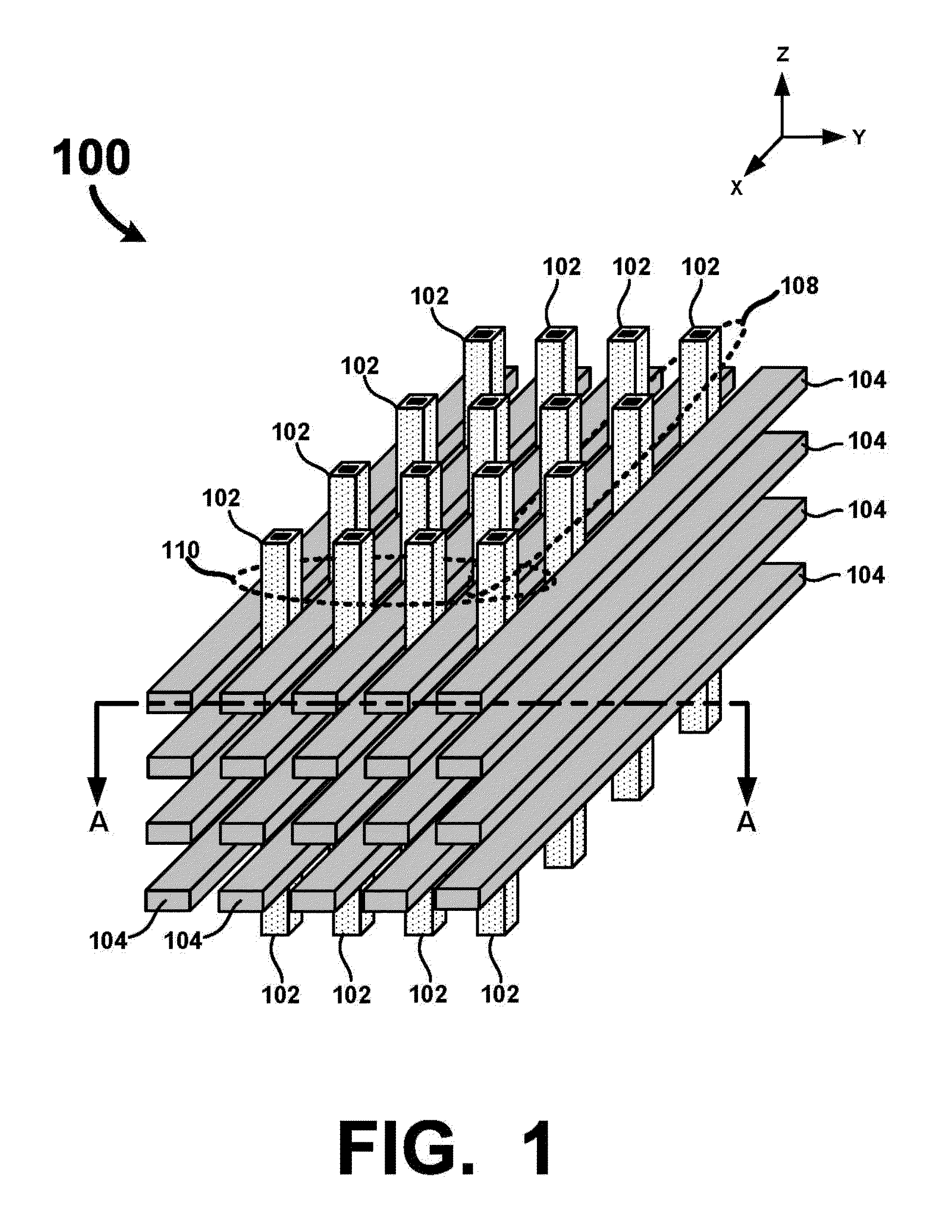

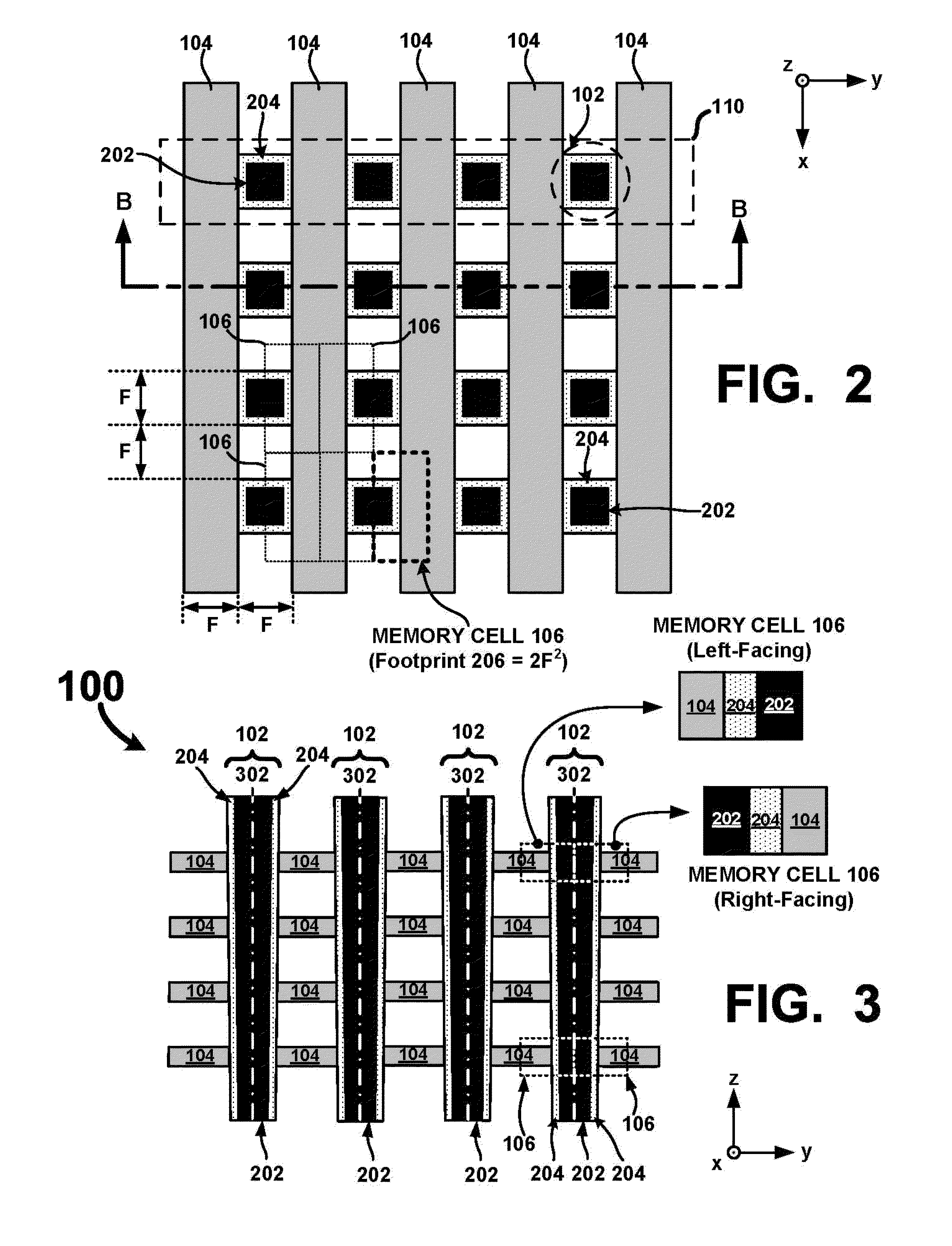

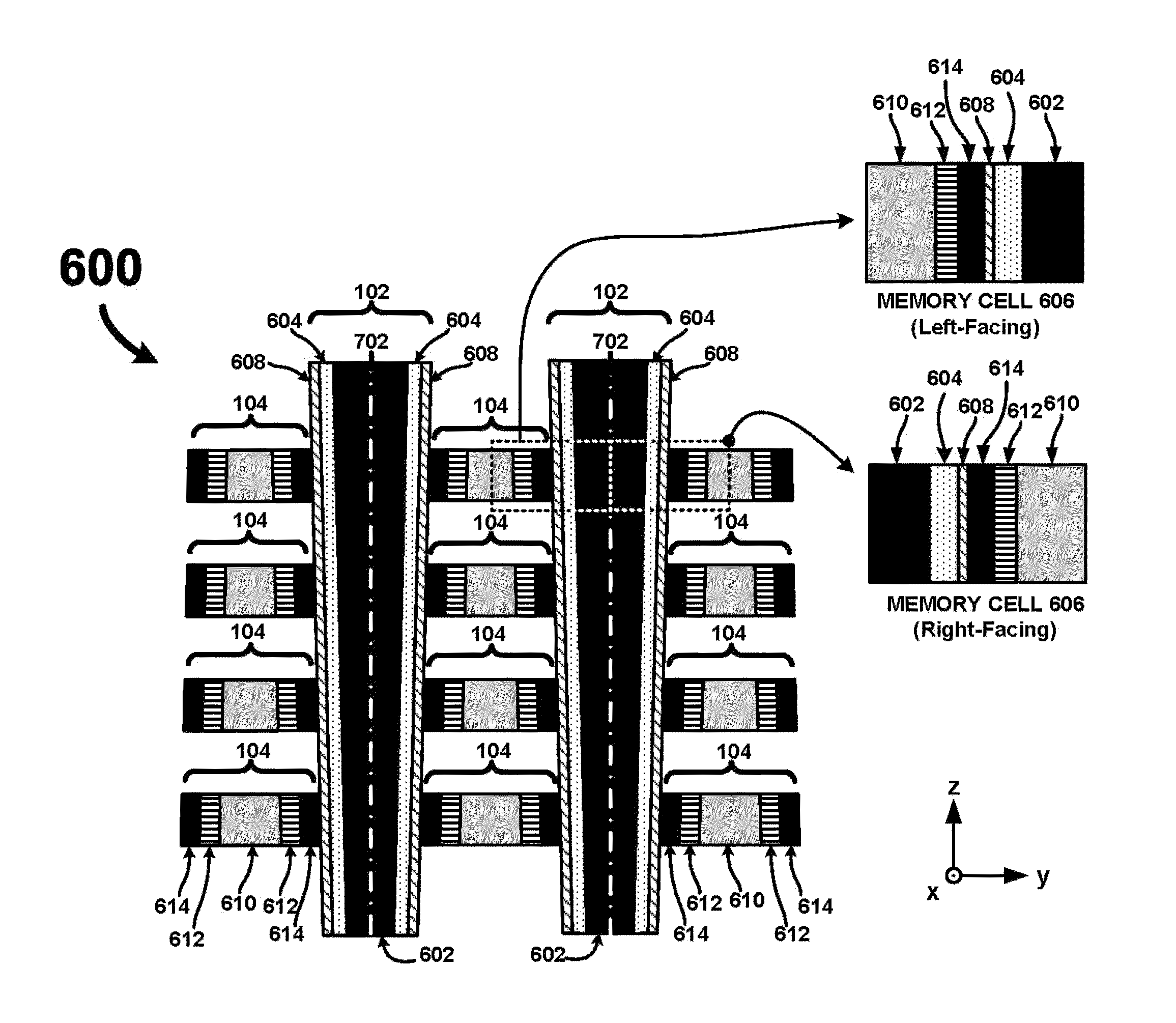

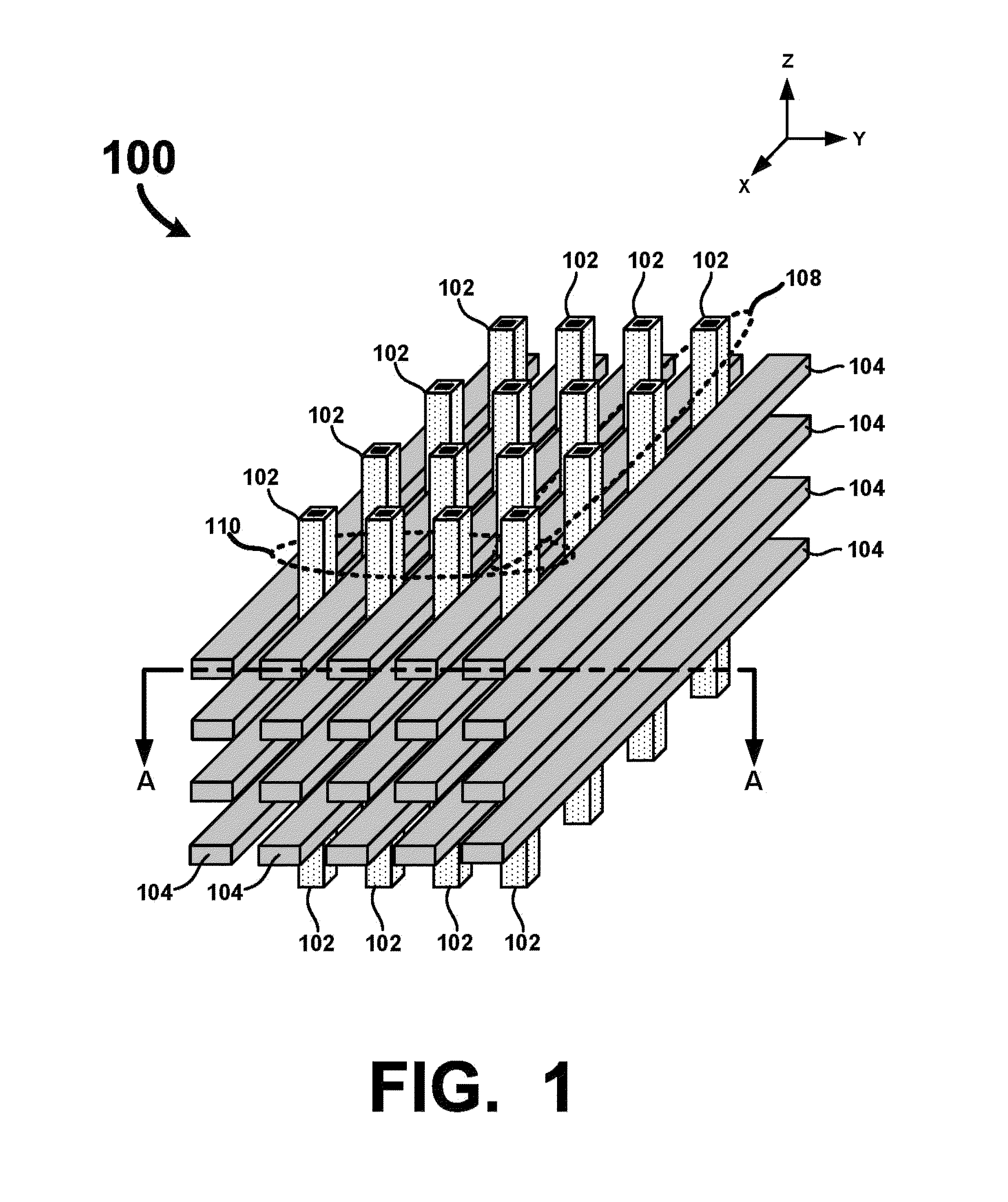

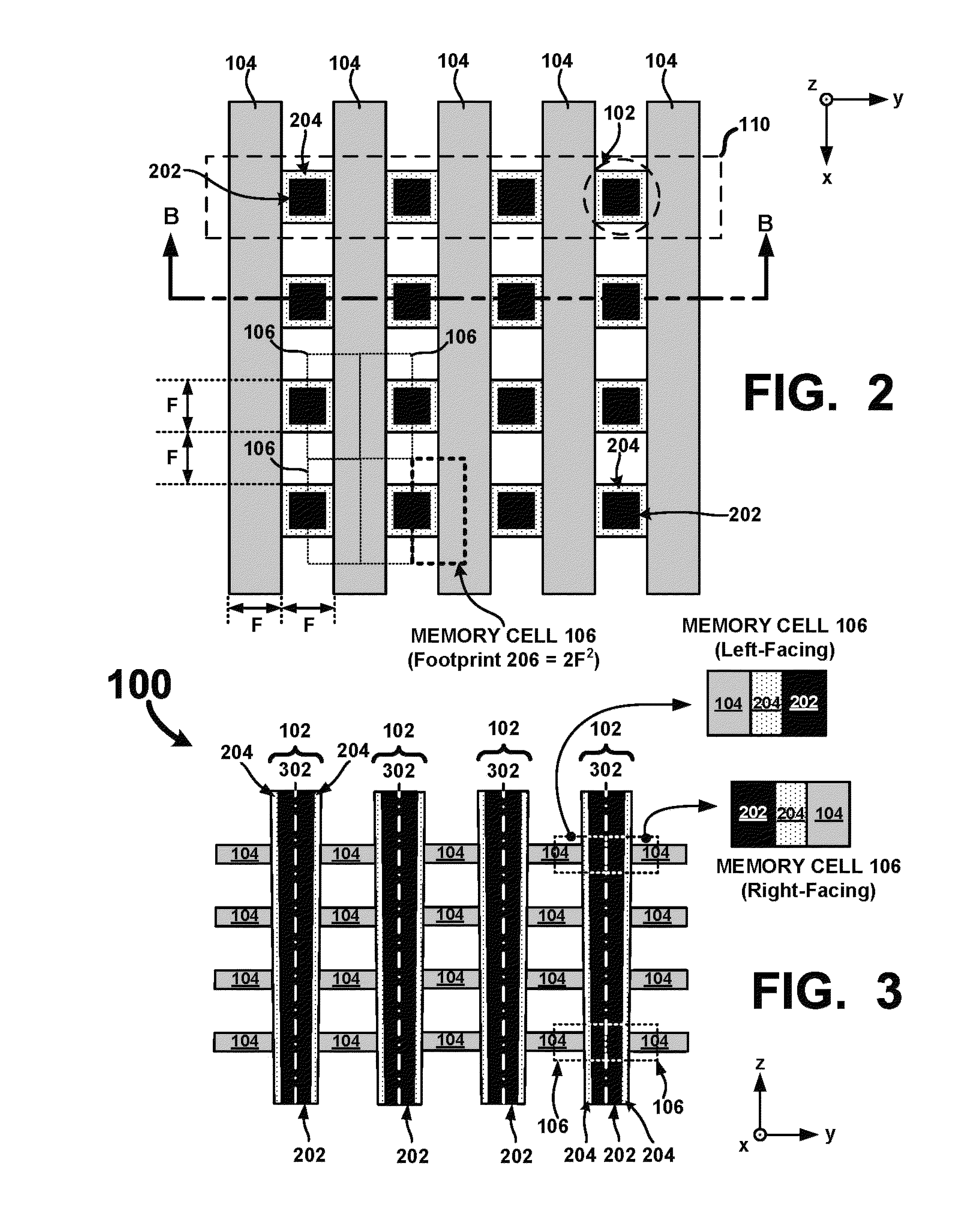

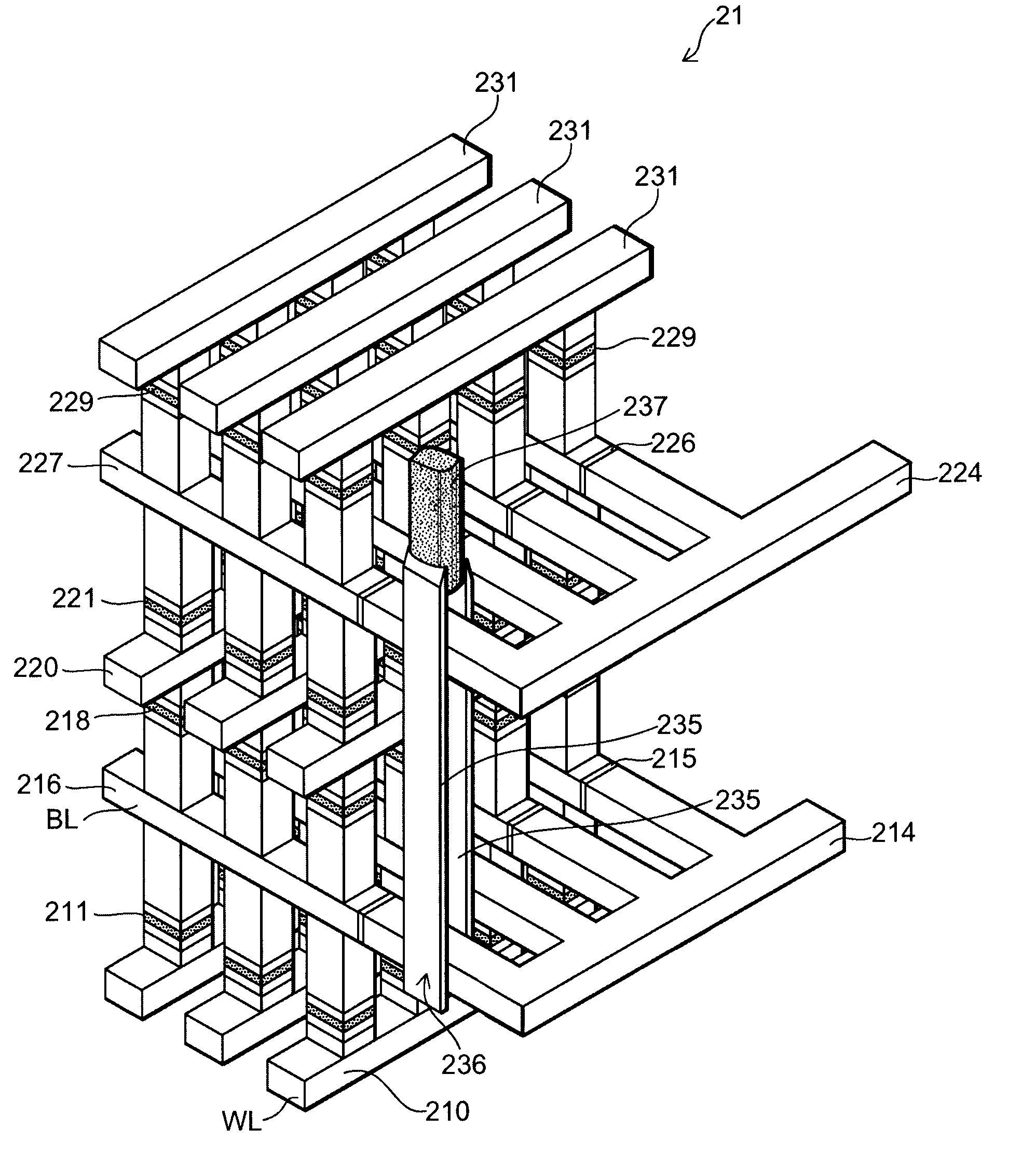

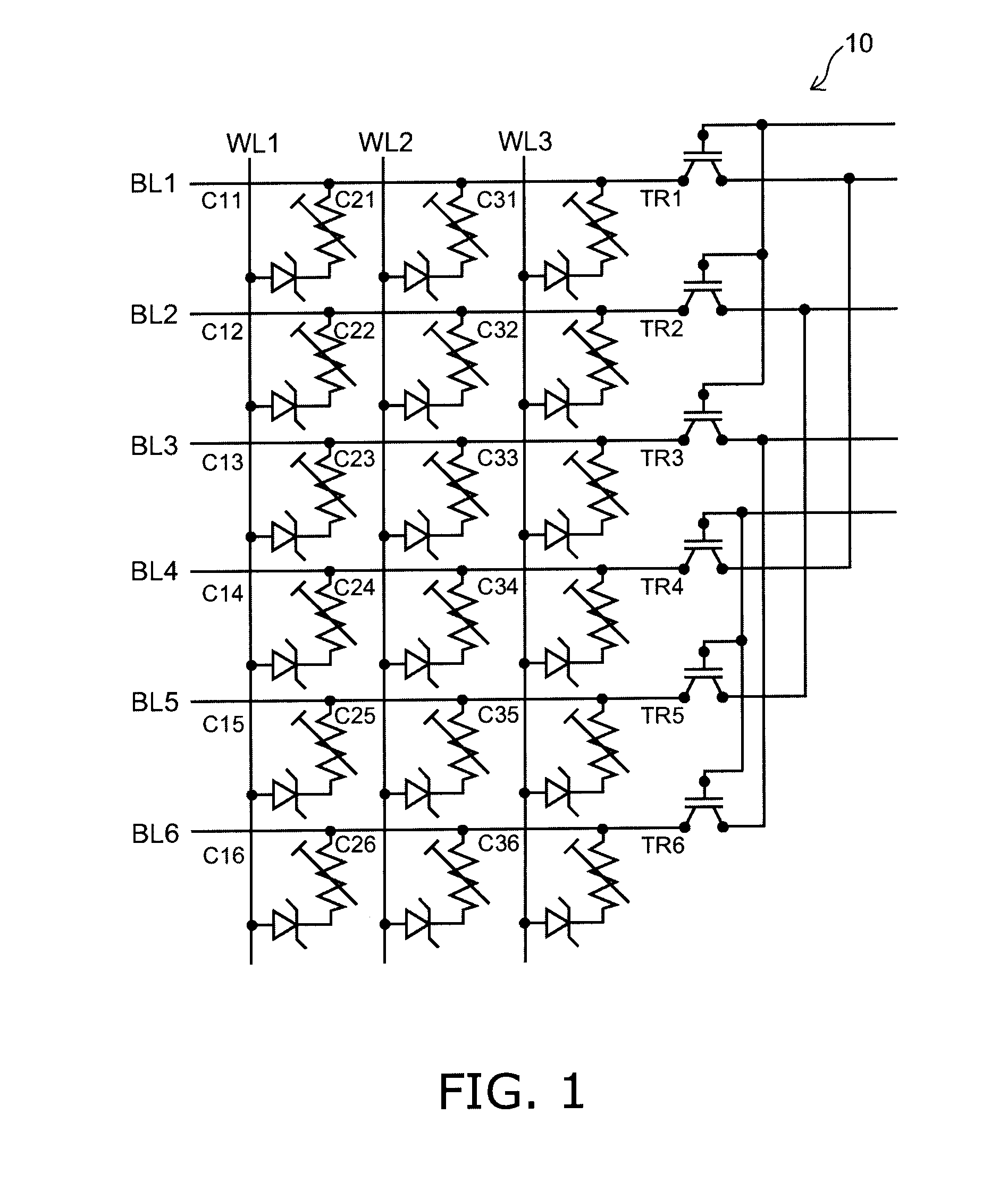

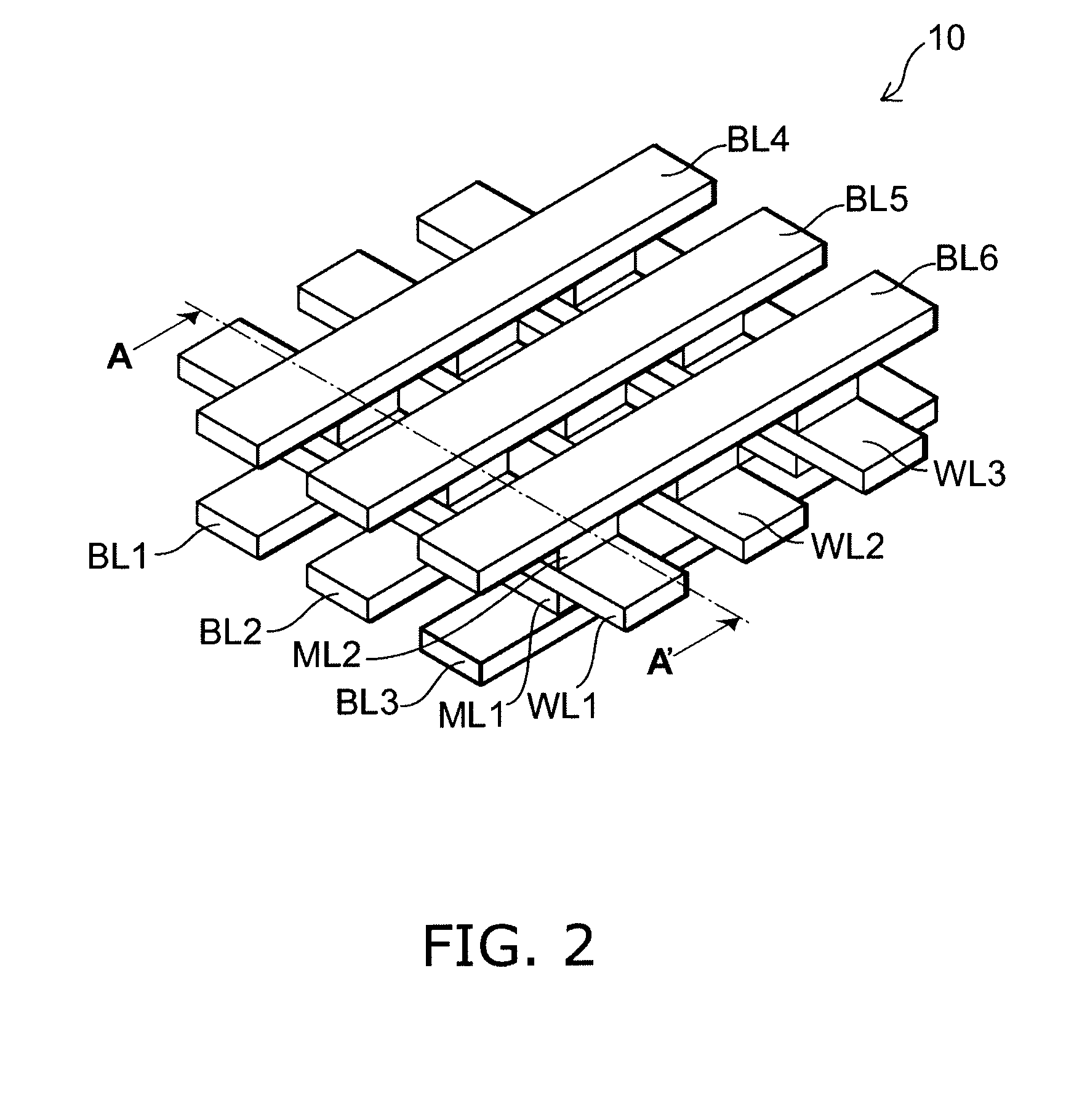

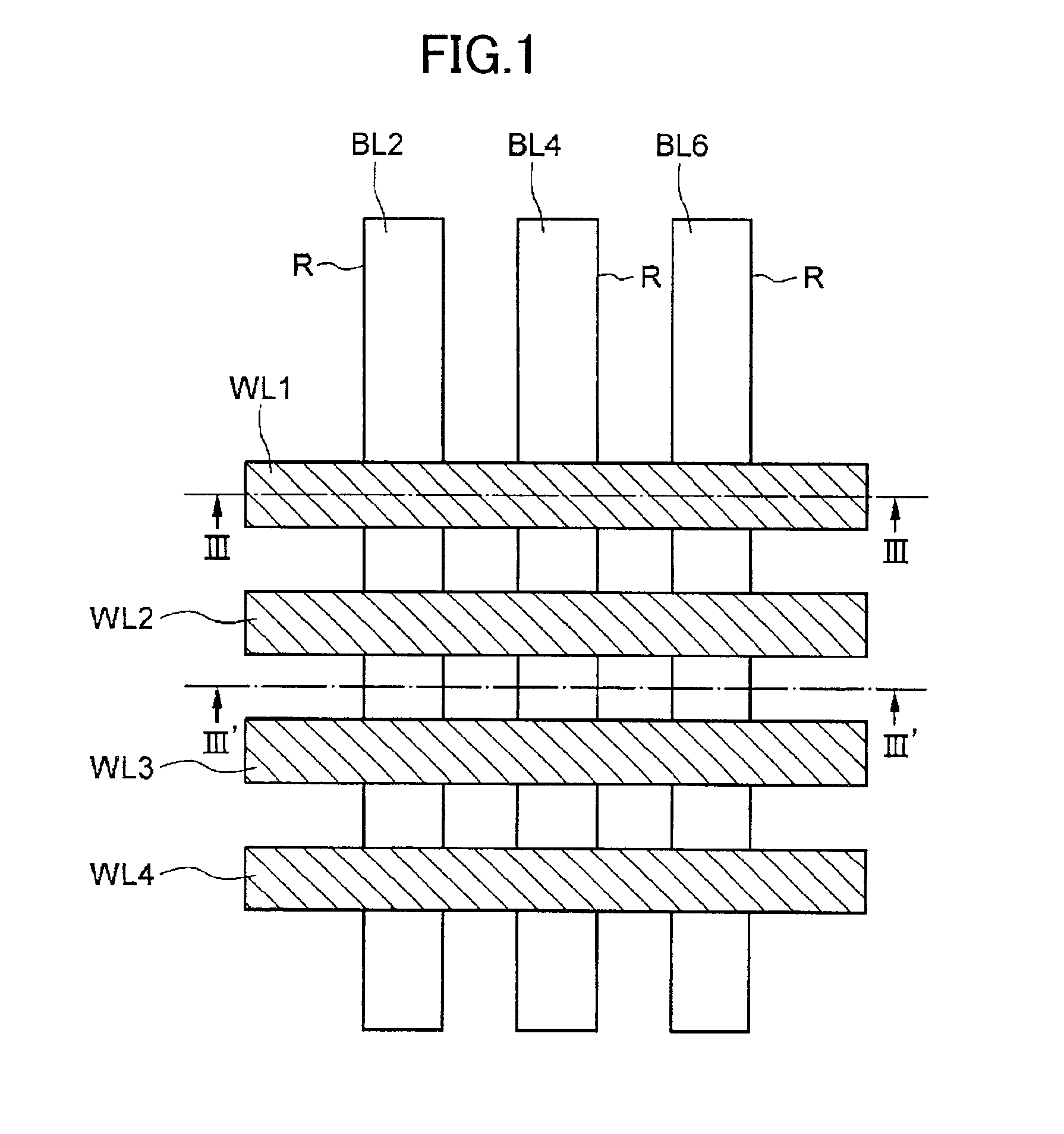

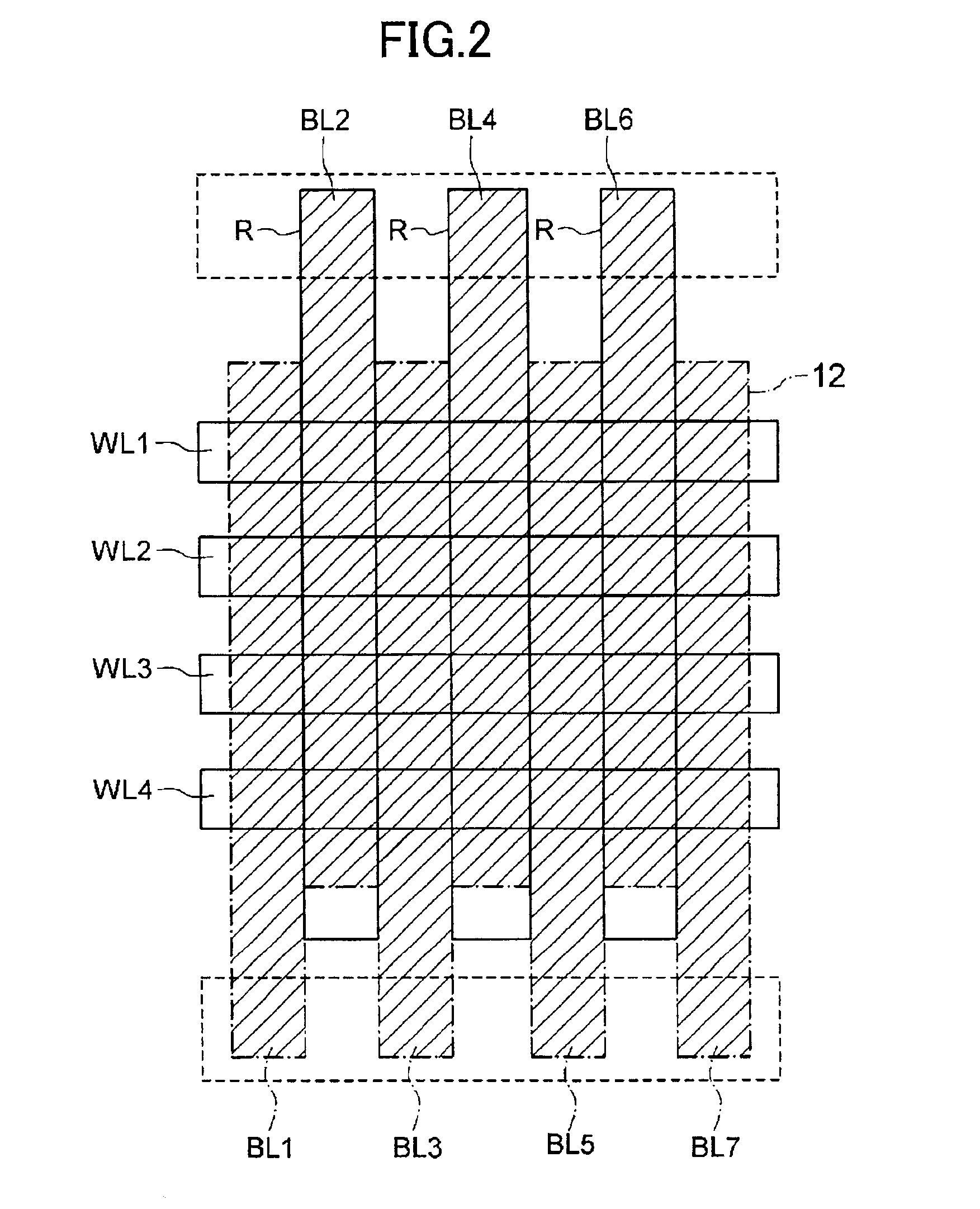

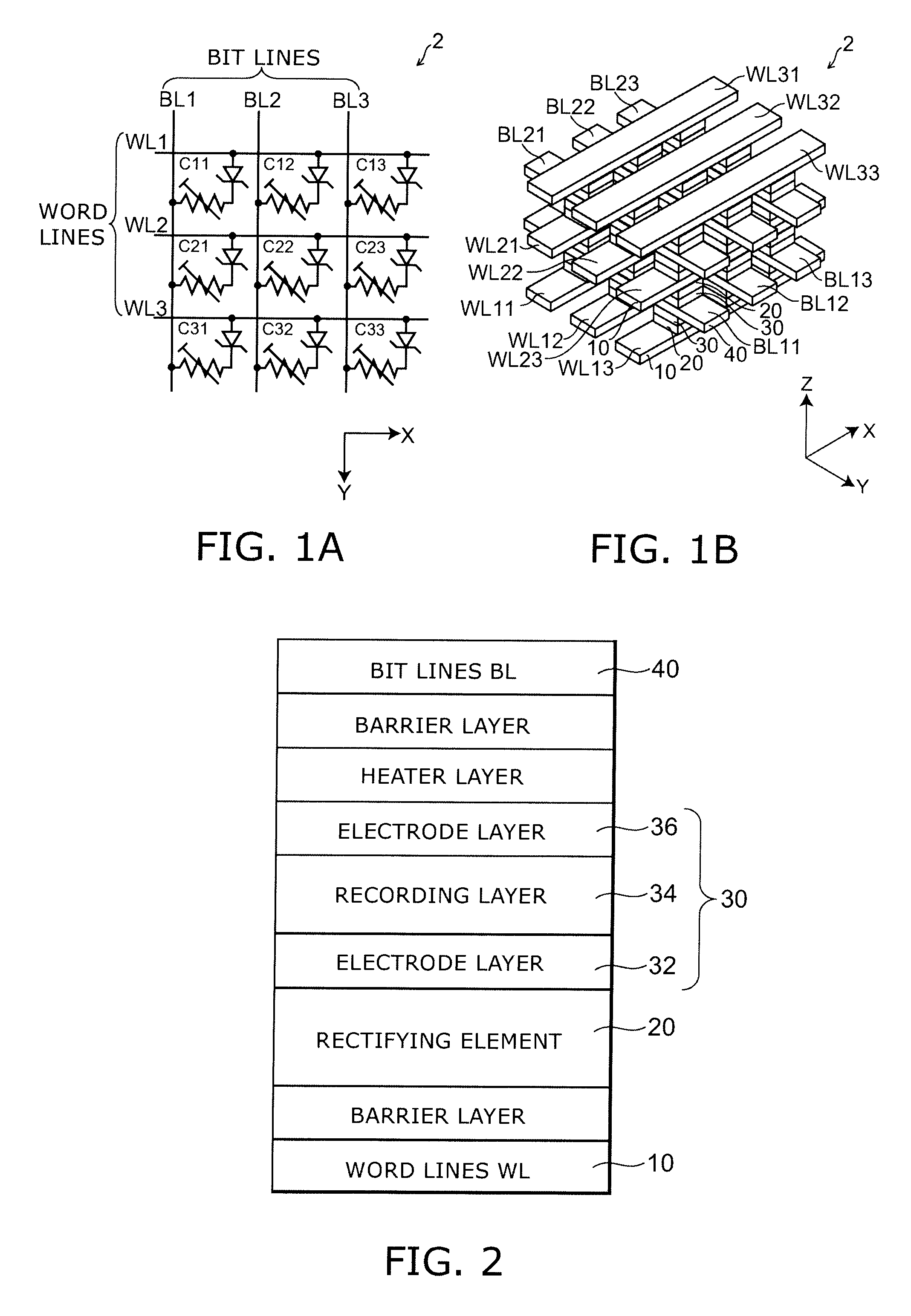

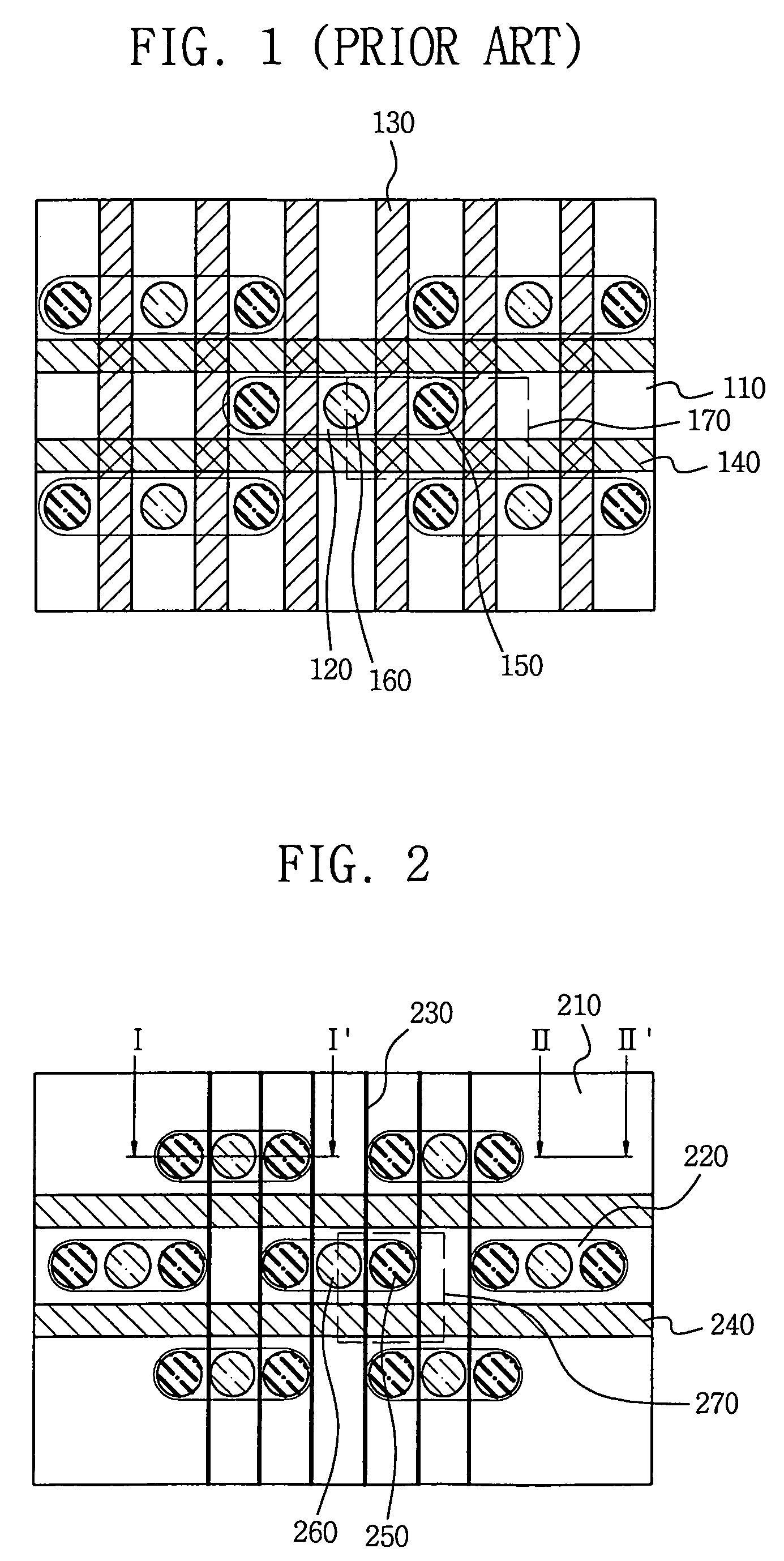

Vertical Cross Point Arrays For Ultra High Density Memory Applications

An ultra-high-density vertical cross-point array comprises a plurality of horizontal line layers having horizontal lines interleaved with a plurality of vertical lines arranged in rows and columns. The vertical lines are interleaved with the horizontal lines such that a row of vertical lines is positioned between each consecutive pair of horizontal lines in each horizontal line layer. Each vertical line comprises a center conductor surrounded by a single or multi-layered memory film. Accordingly, when interleaved with the horizontal lines, two-terminal memory cells are integrally formed between the center conductor of each vertical line and each crossing horizontal line. By configuring the vertical and horizontal lines so that a row of vertical lines is positioned between each consecutive pair of horizontal lines, a unit memory cell footprint of just 2F2 may be realized.

Owner:UNITY SEMICON

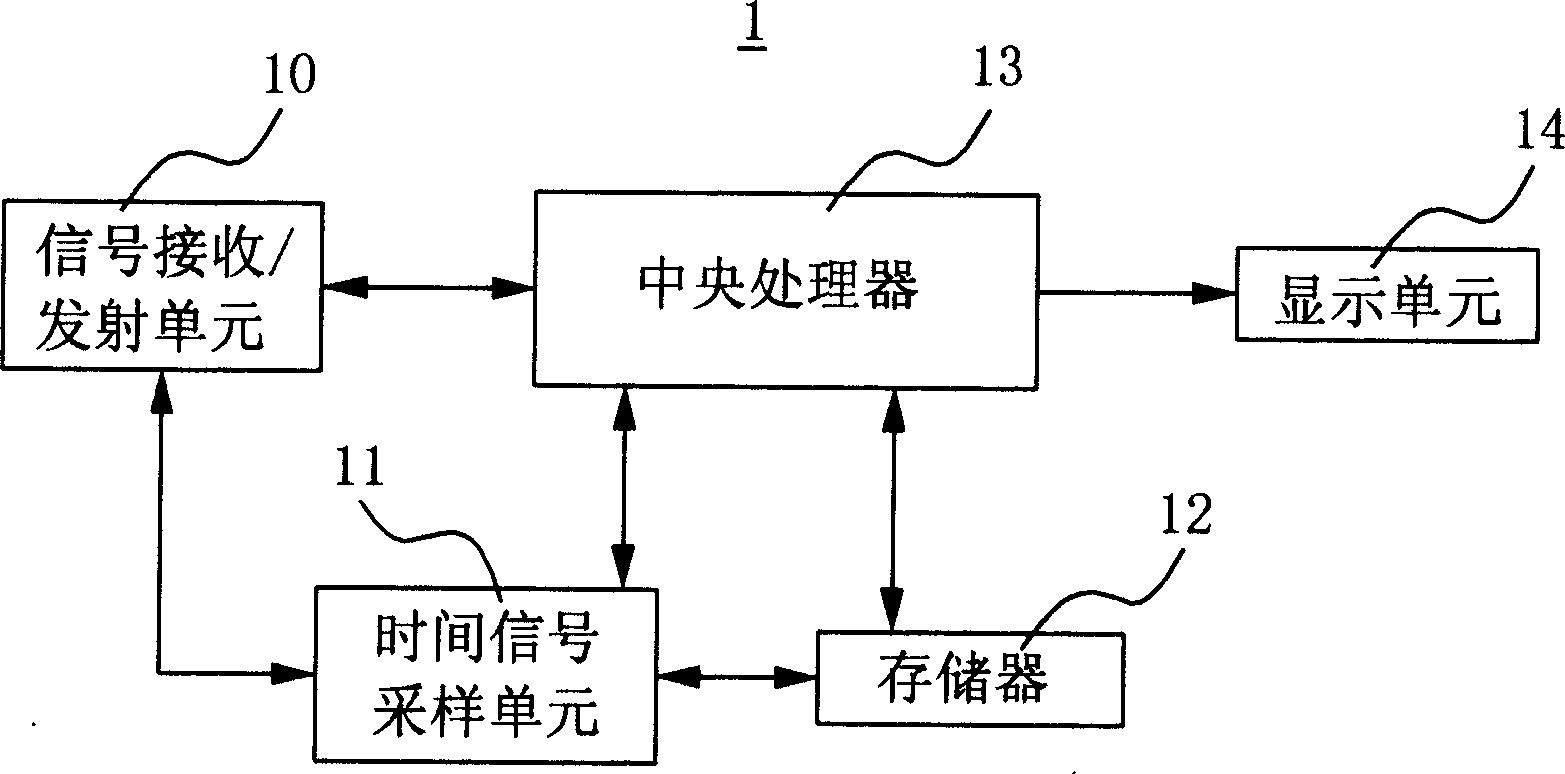

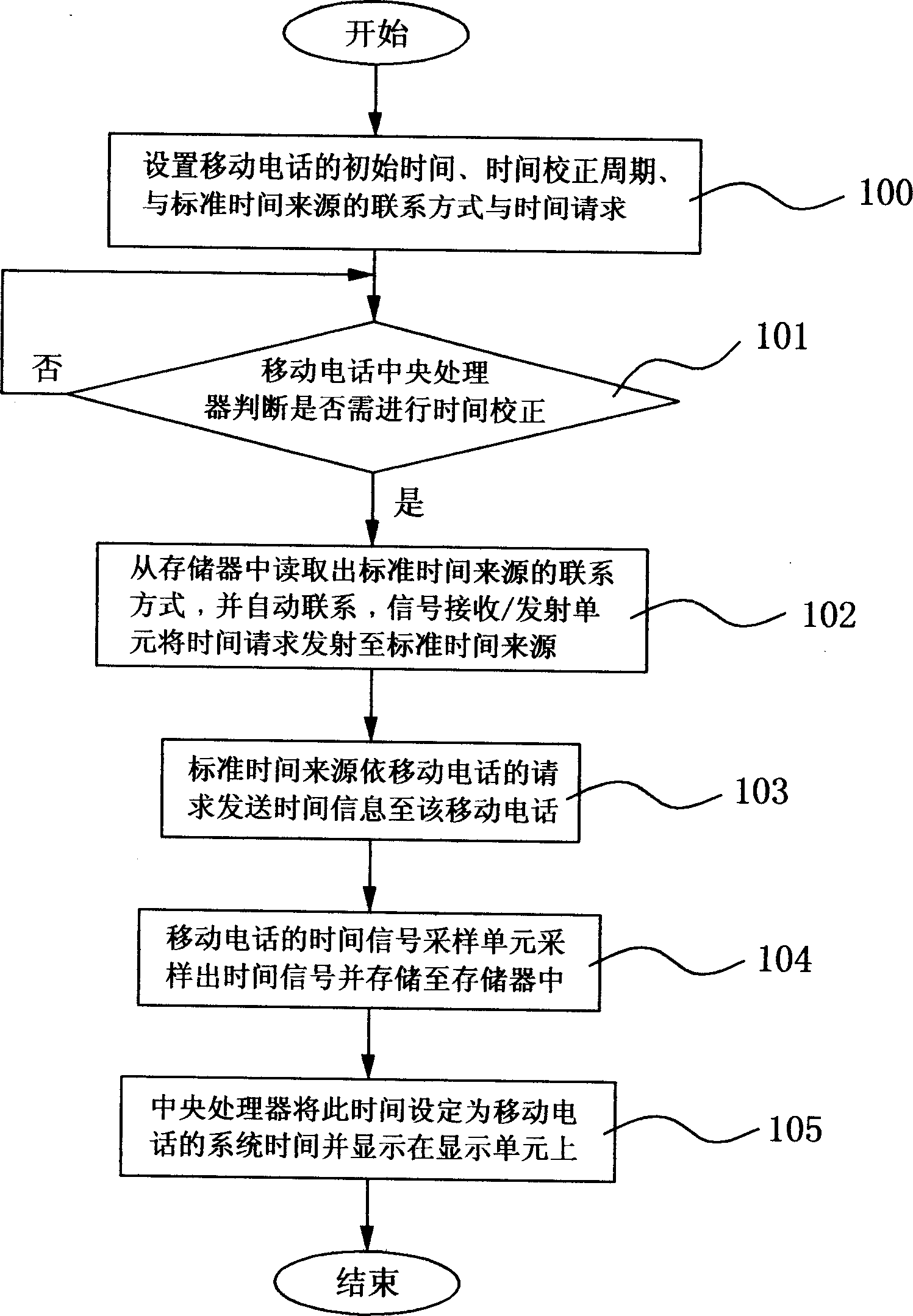

Mobile phone time automatic correction method

InactiveCN1801829ALow costMiniaturization hindranceSetting time indicationRadio-controlled time-piecesTemporal informationAutocorrection

Said invention provides a mobile telephone time autocorrection method. It contains signal reception / transmitting unit, time signal sampling unit memory unit, central processing unit and display unit, said method mainly setting mobile telephone initial time, time adjustment cycle, and standard time source connection mode and time request , when need proceeding time correction, said mobile telephone automatically transmitting time request to standard time source and taking standard time then configuring said standard time as system time of mobile telephone to reach higher time precision by using normal quartz oscillator.

Owner:KUNDA COMP TECHKUSN

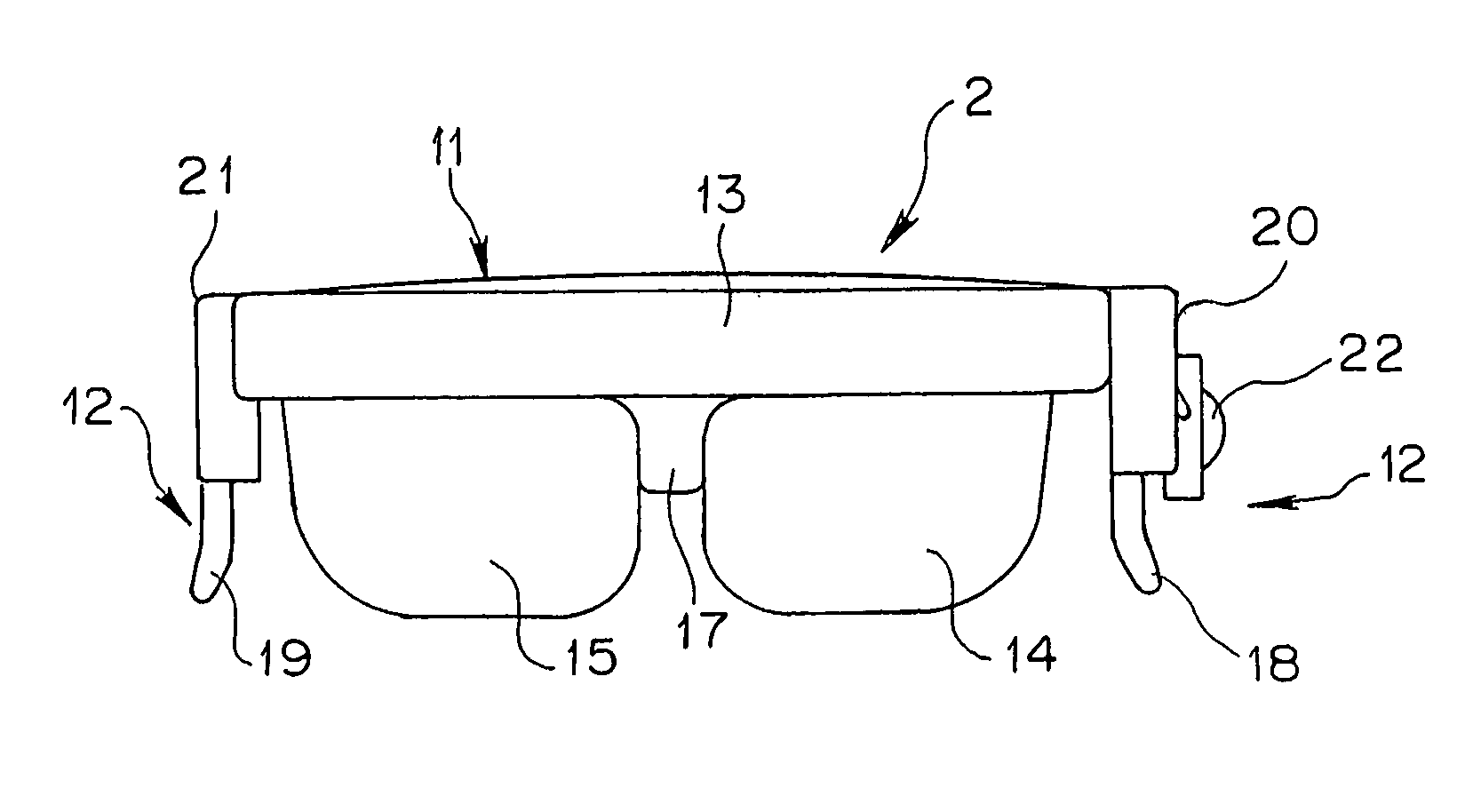

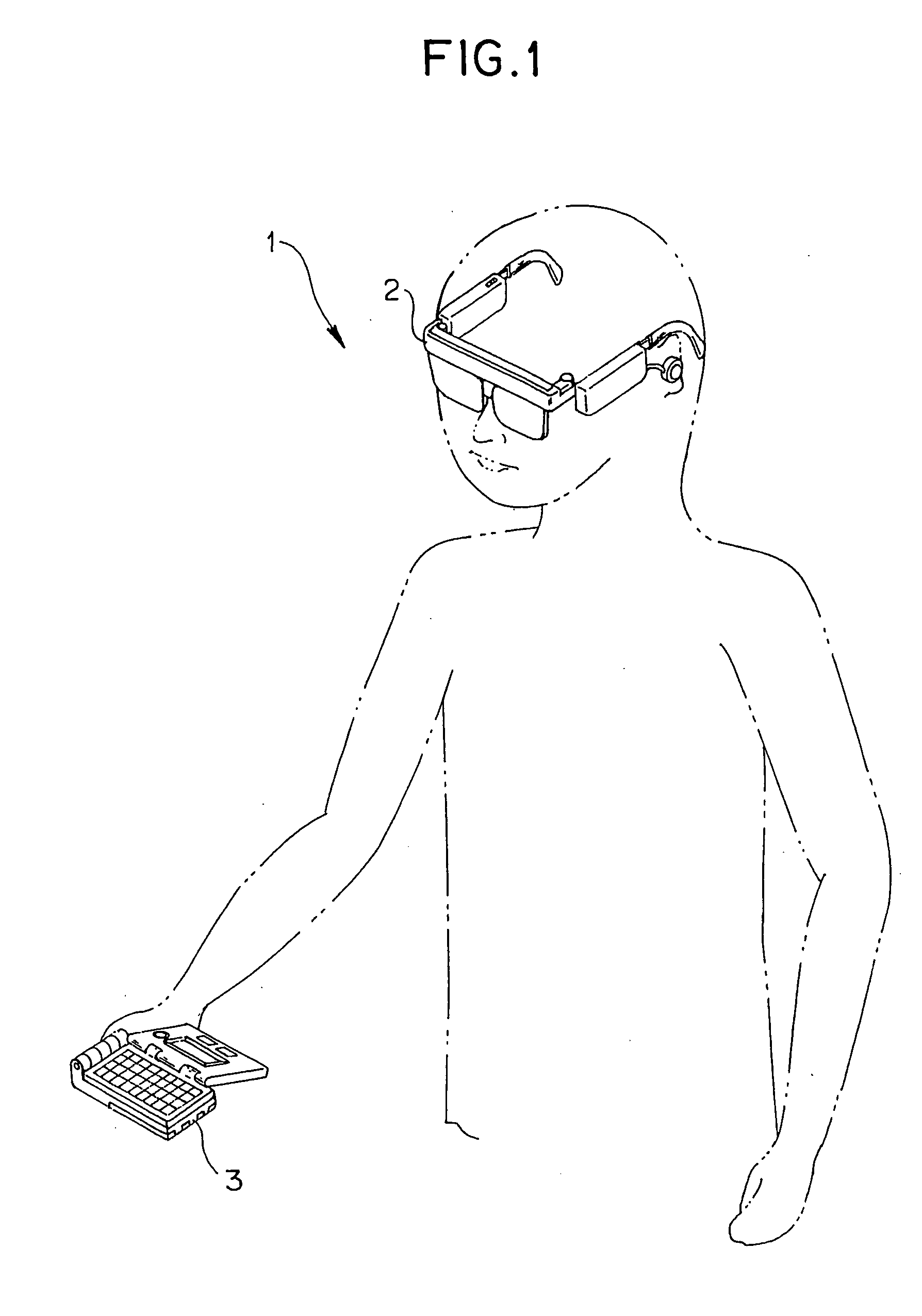

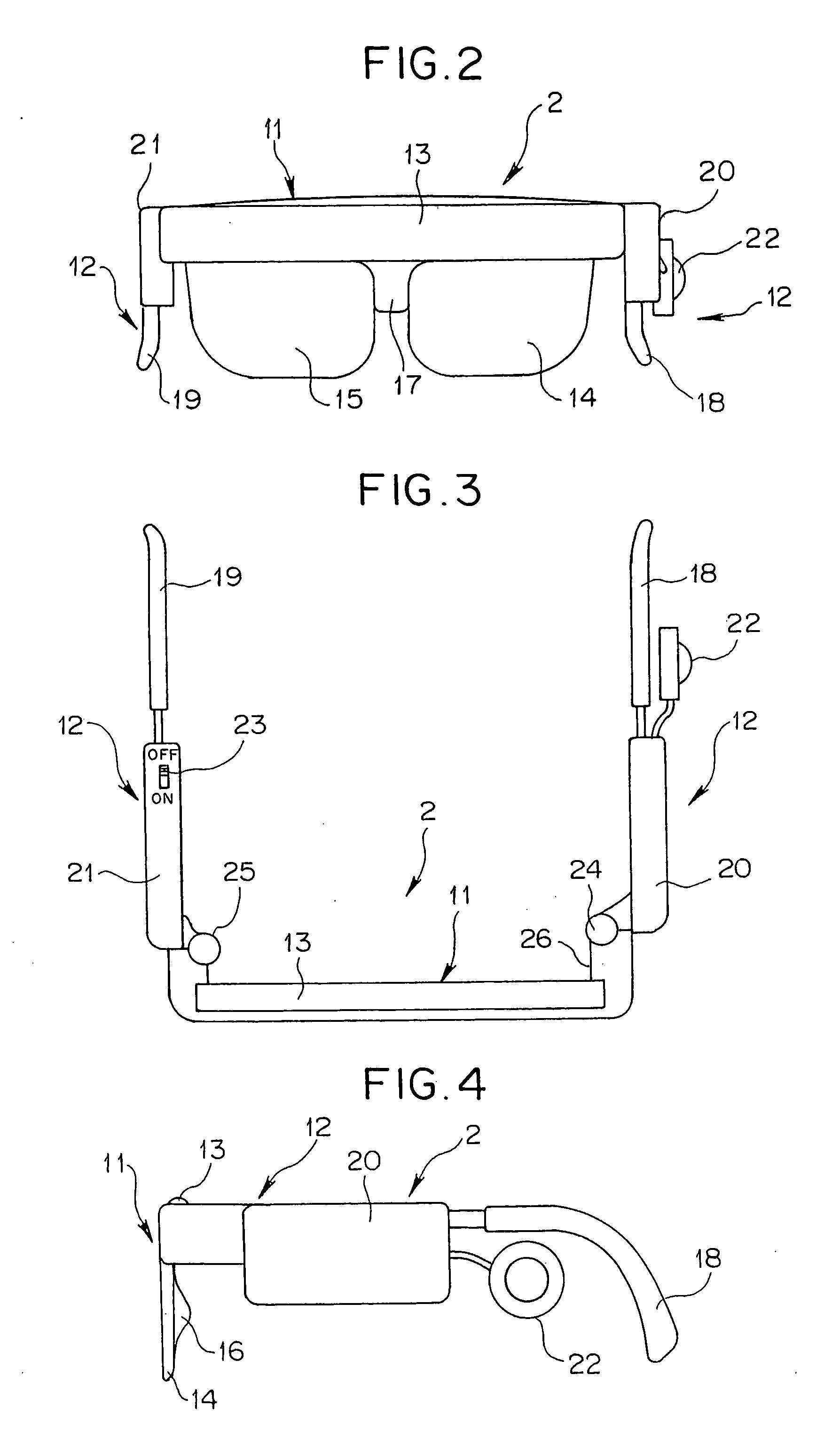

Information display system

InactiveUS20060017657A1Suppressing useless electric power consumptionCathode-ray tube indicatorsOptical elementsInformation display systemsUnit memory

An information display system according to the present invention includes a head-mounted unit for displaying images by projecting display data on eyes of an observer so that the images can be observed as virtual images and a main unit having a hard disk or a record memory for storing display original information, a main unit memory for temporarily storing the display data read out and converted from the display original information, an LCD for displaying images based on the display data, and a second operating switch including a display select switch for alternatively selecting any one of the displaying by the head-mounted unit and the displaying by the LCD.

Owner:OLYMPUS CORP

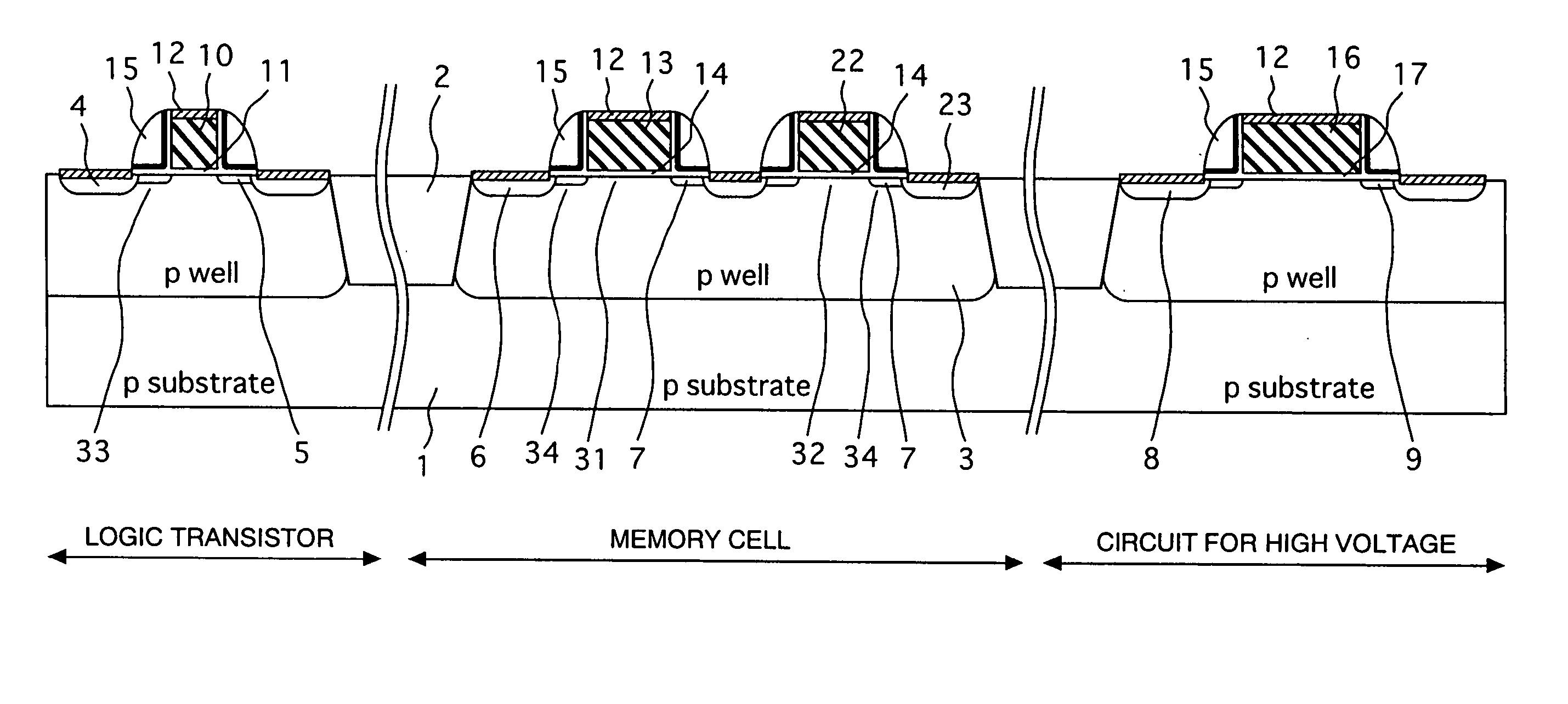

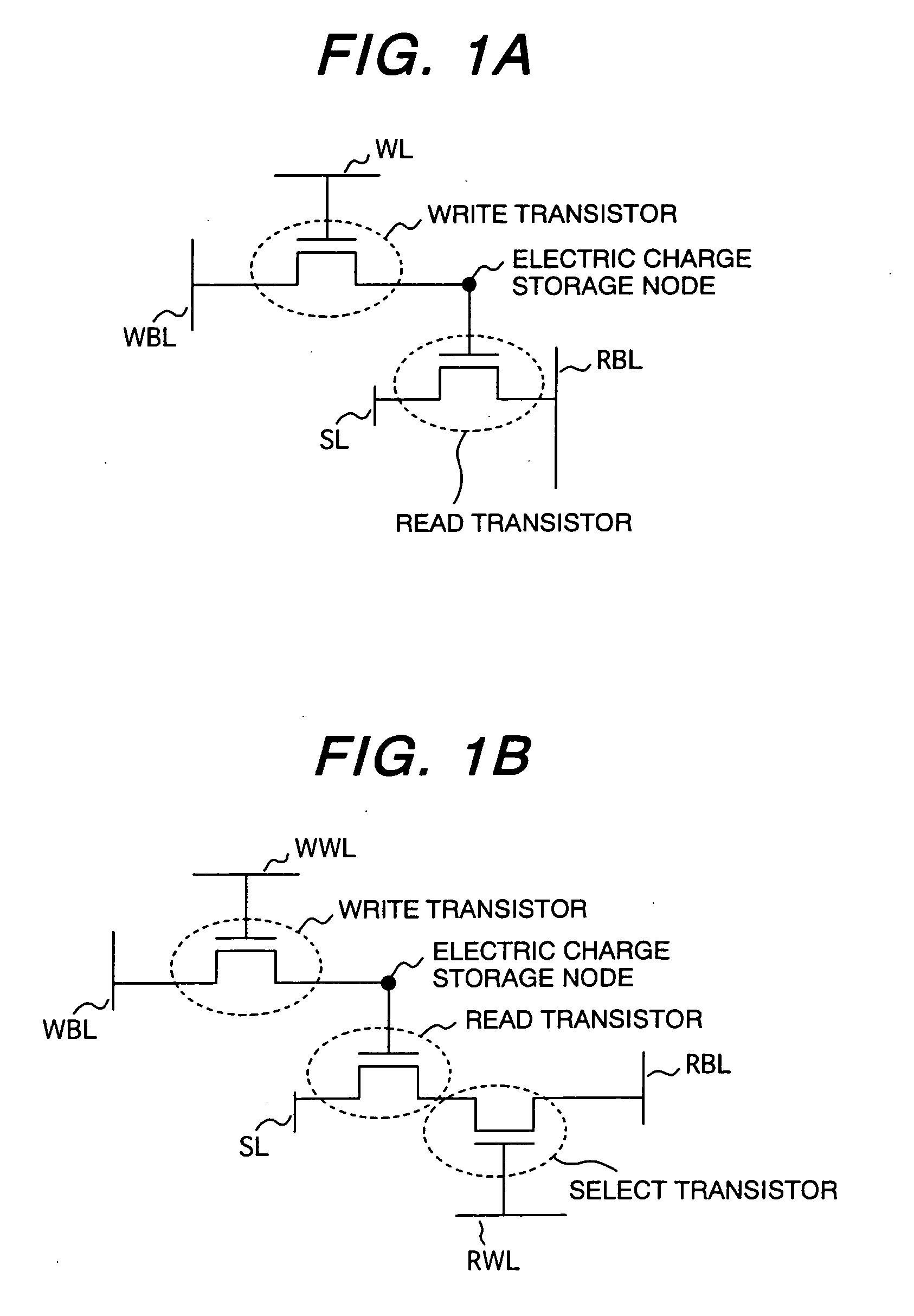

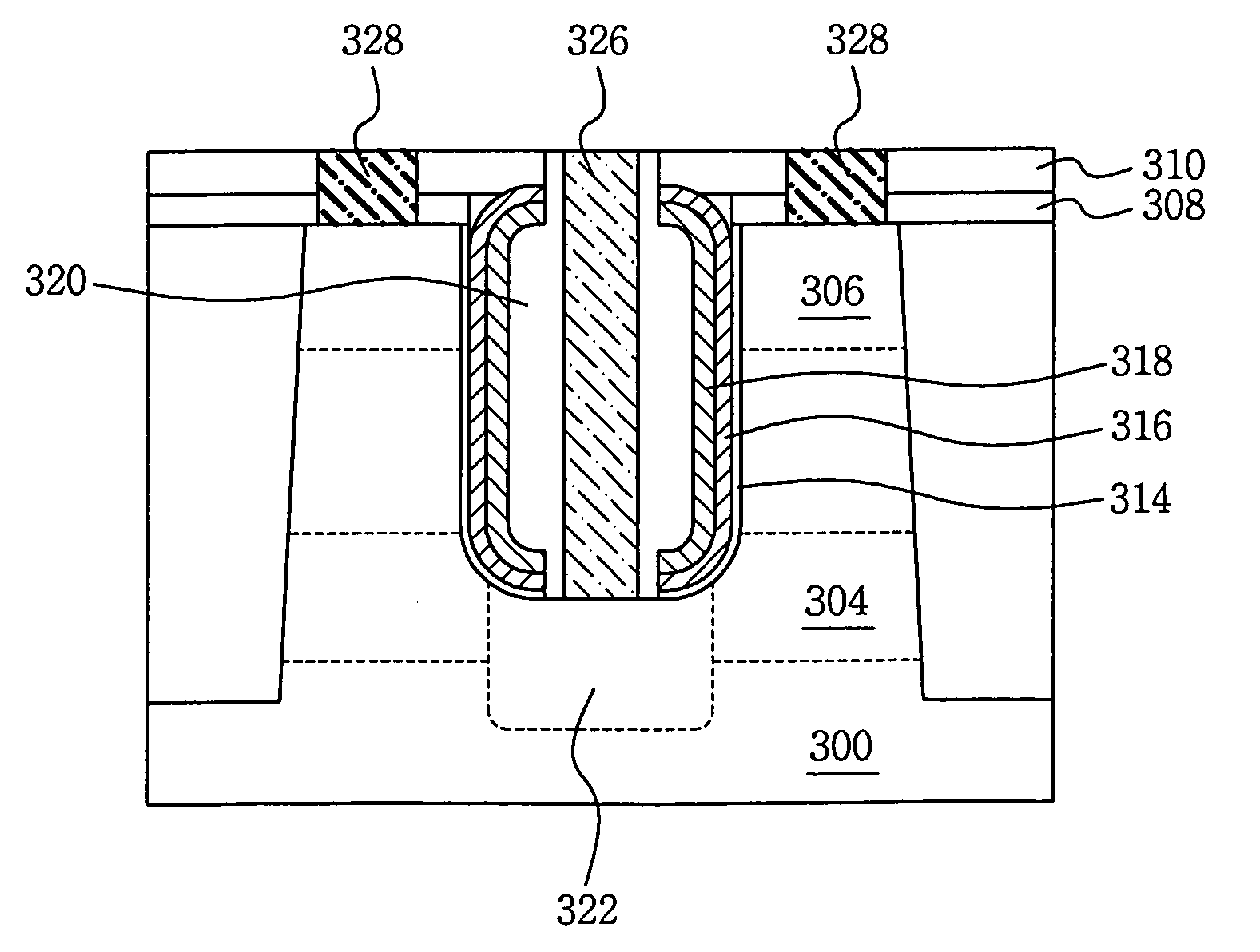

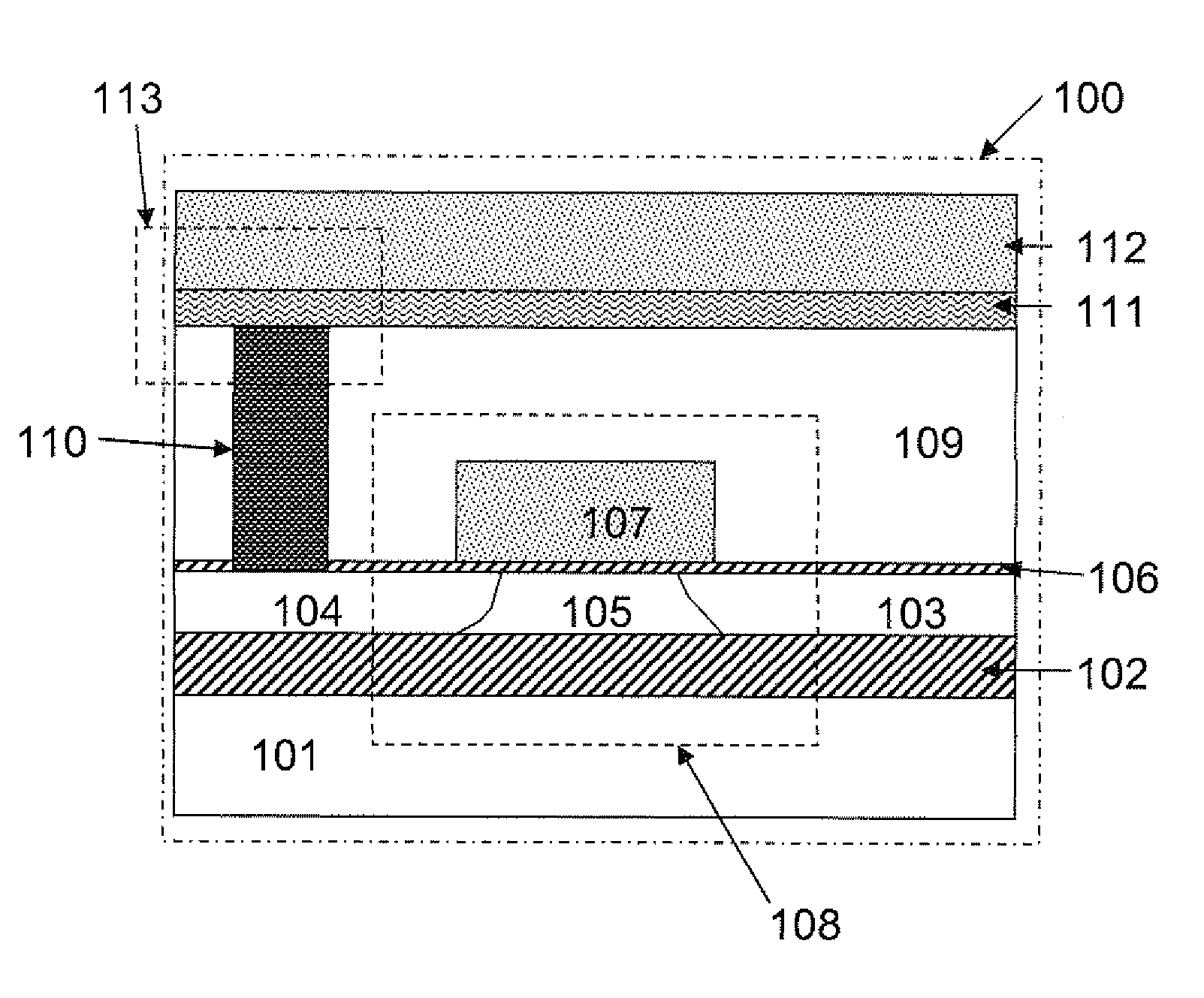

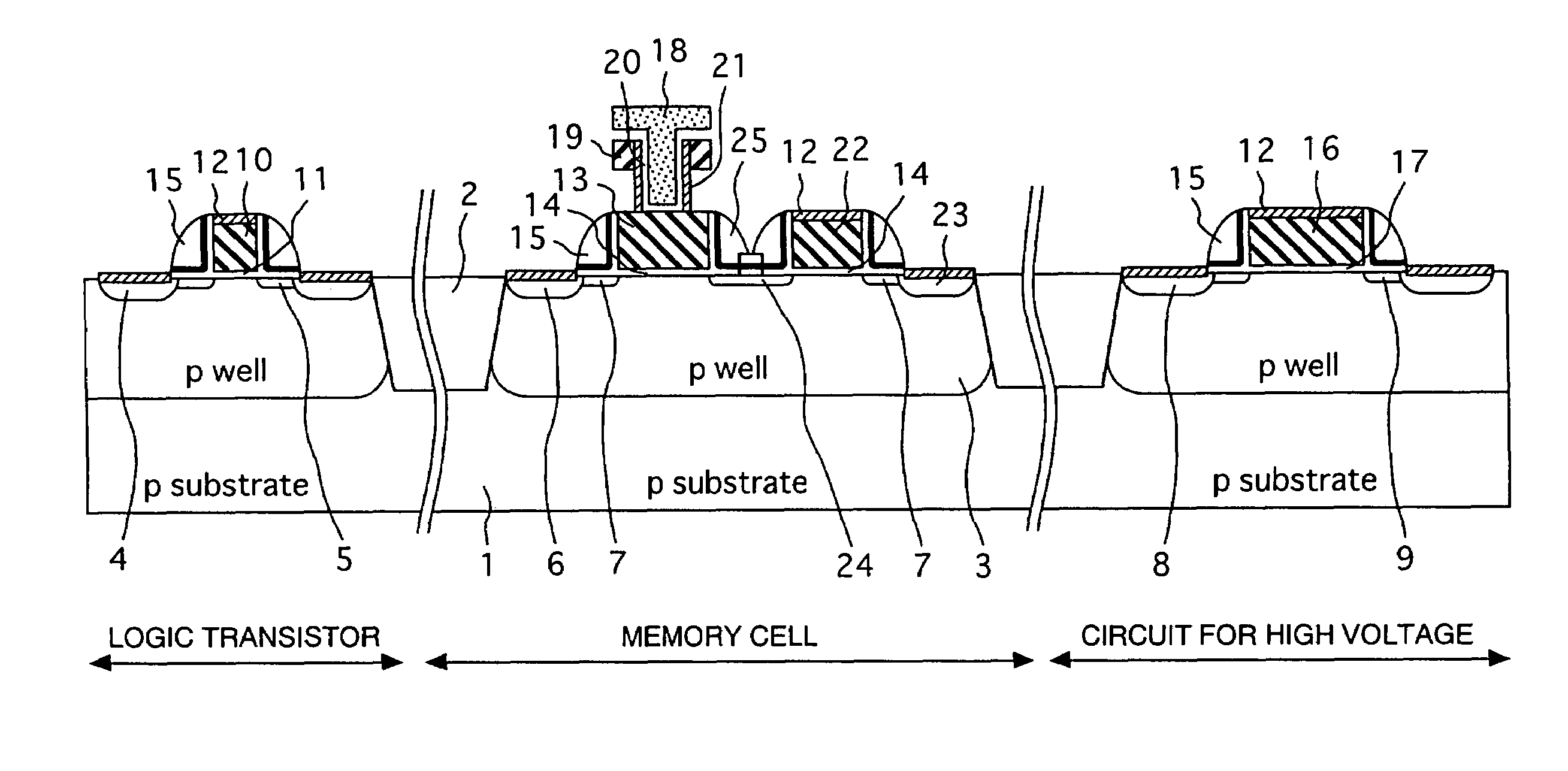

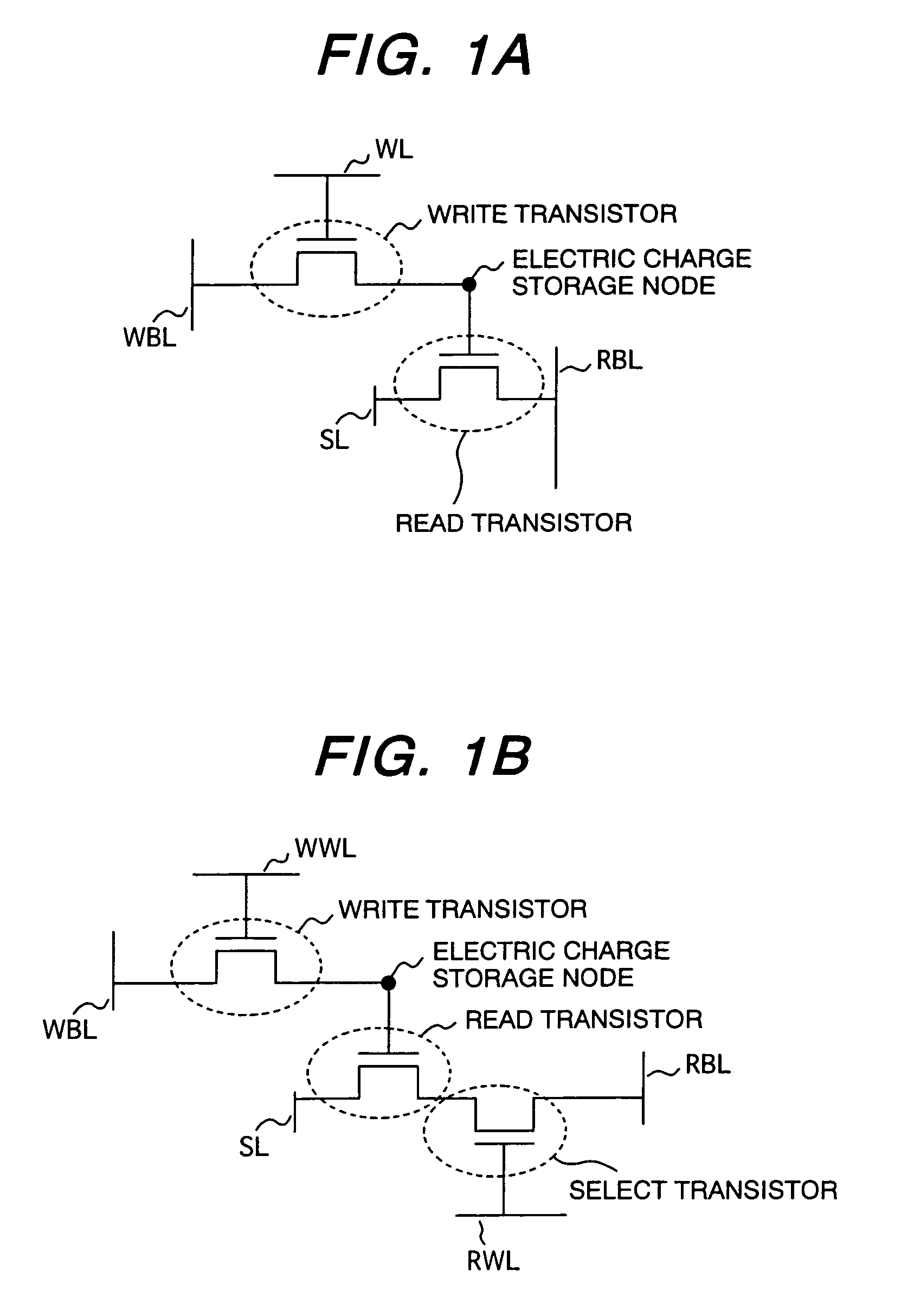

Semiconductor memory device

InactiveUS20050280000A1Low costSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringDiffusion layer

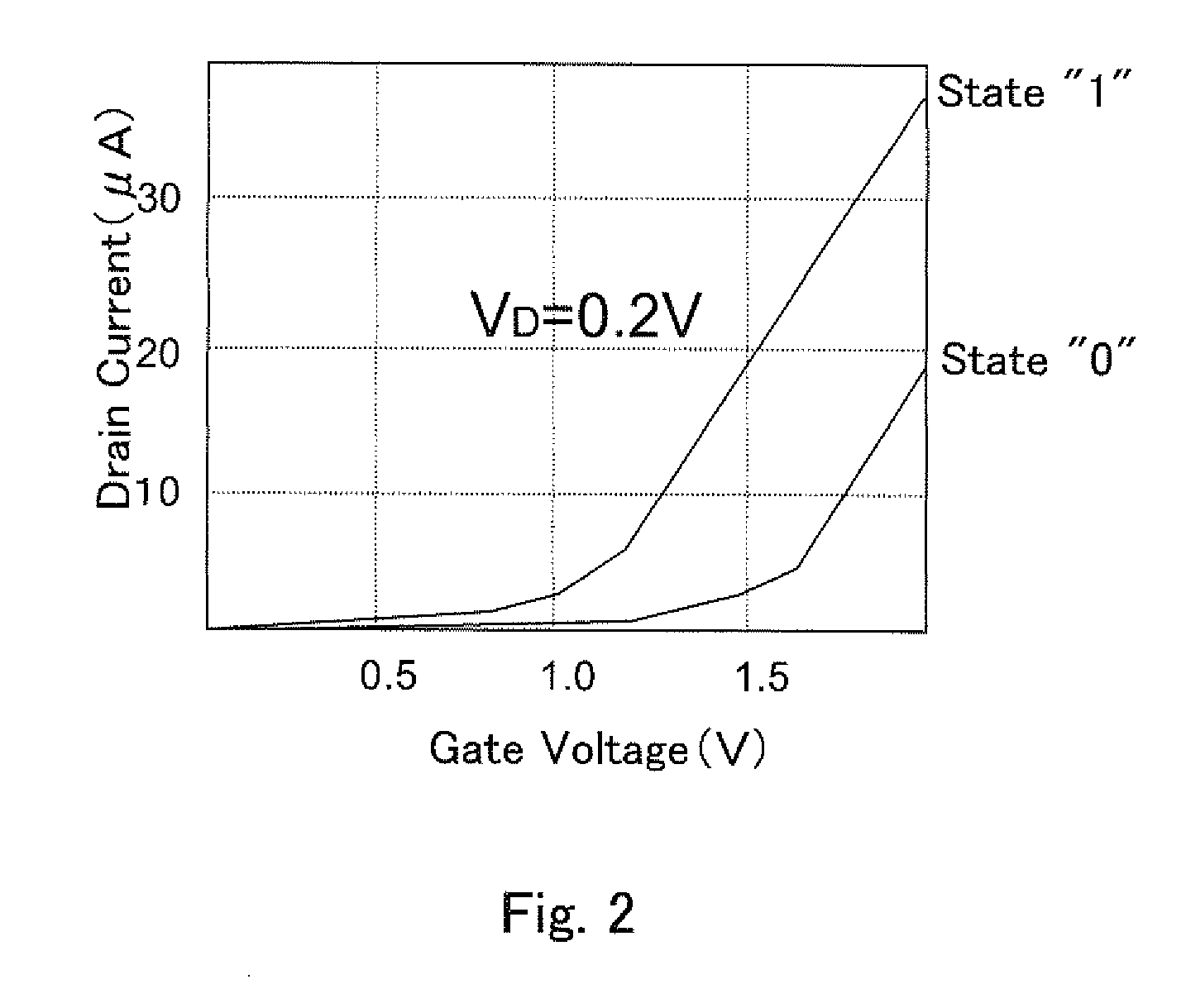

The present invention is a semiconductor memory device having a logic block and a memory block on the same chip. In the memory device, unit memory cells each include at least two transistors, one of which is a write transistor for storing an electric charge into and releasing it from an electric charge storage node, and the other is a read transistor whose conductance in a channel region provided between a source and drain of the read transistor is modulated dependently on the amount of electric charge stored into or released from the electric charge storage node by the write transistor. The read transistor has a gate-insulating film thicker than that of a transistor provided in the logic block, and uses the same diffusion layer structure as that of the logic block.

Owner:RENESAS ELECTRONICS CORP

Vertical cross point arrays for ultra high density memory applications

ActiveUS8937292B2Large capacitySolid-state devicesBulk negative resistance effect devicesElectrical conductorEngineering

An ultra-high-density vertical cross-point array comprises a plurality of horizontal line layers having horizontal lines interleaved with a plurality of vertical lines arranged in rows and columns. The vertical lines are interleaved with the horizontal lines such that a row of vertical lines is positioned between each consecutive pair of horizontal lines in each horizontal line layer. Each vertical line comprises a center conductor surrounded by a single or multi-layered memory film. Accordingly, when interleaved with the horizontal lines, two-terminal memory cells are integrally formed between the center conductor of each vertical line and each crossing horizontal line. By configuring the vertical and horizontal lines so that a row of vertical lines is positioned between each consecutive pair of horizontal lines, a unit memory cell footprint of just 2F2 may be realized.

Owner:UNITY SEMICON

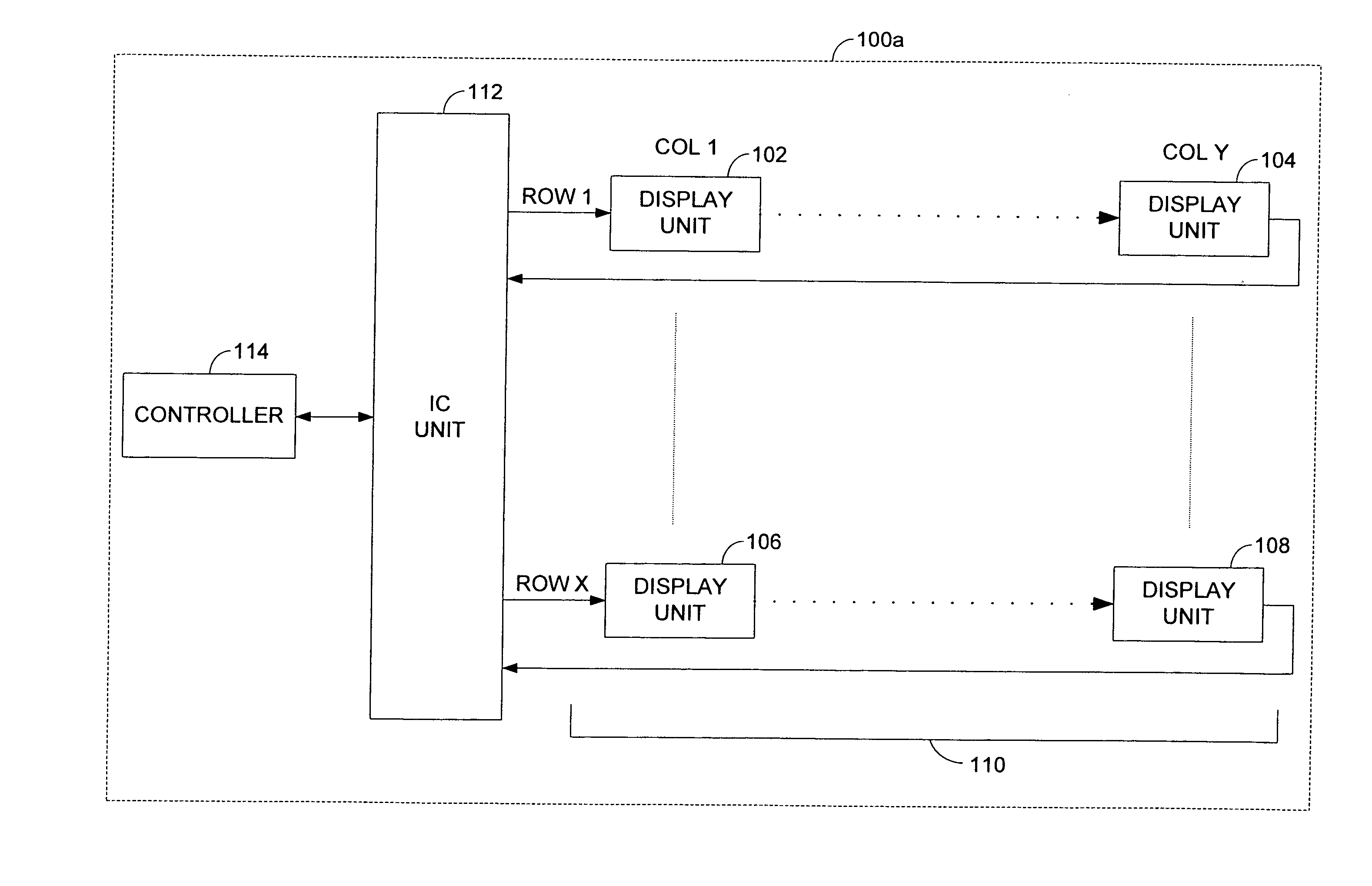

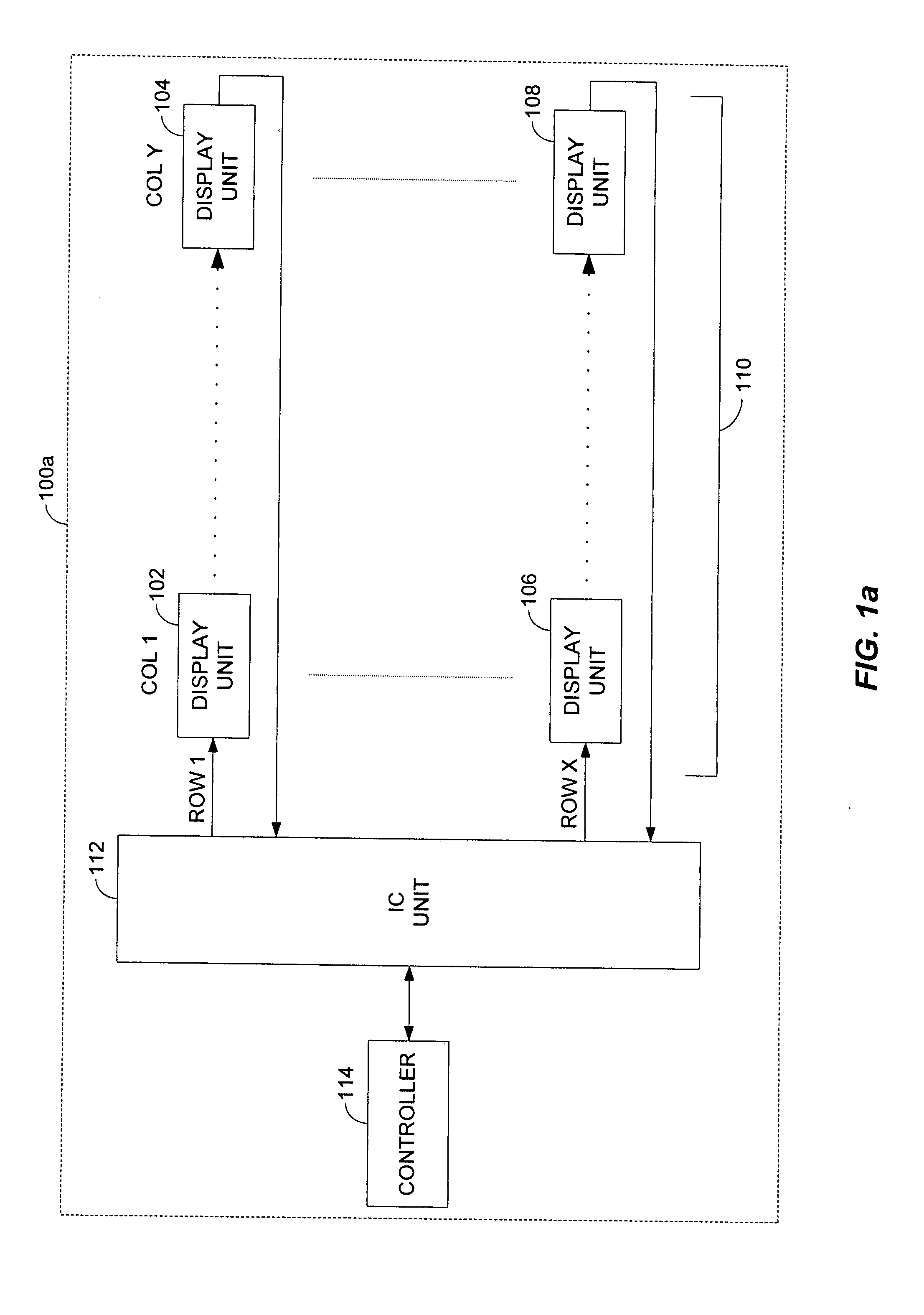

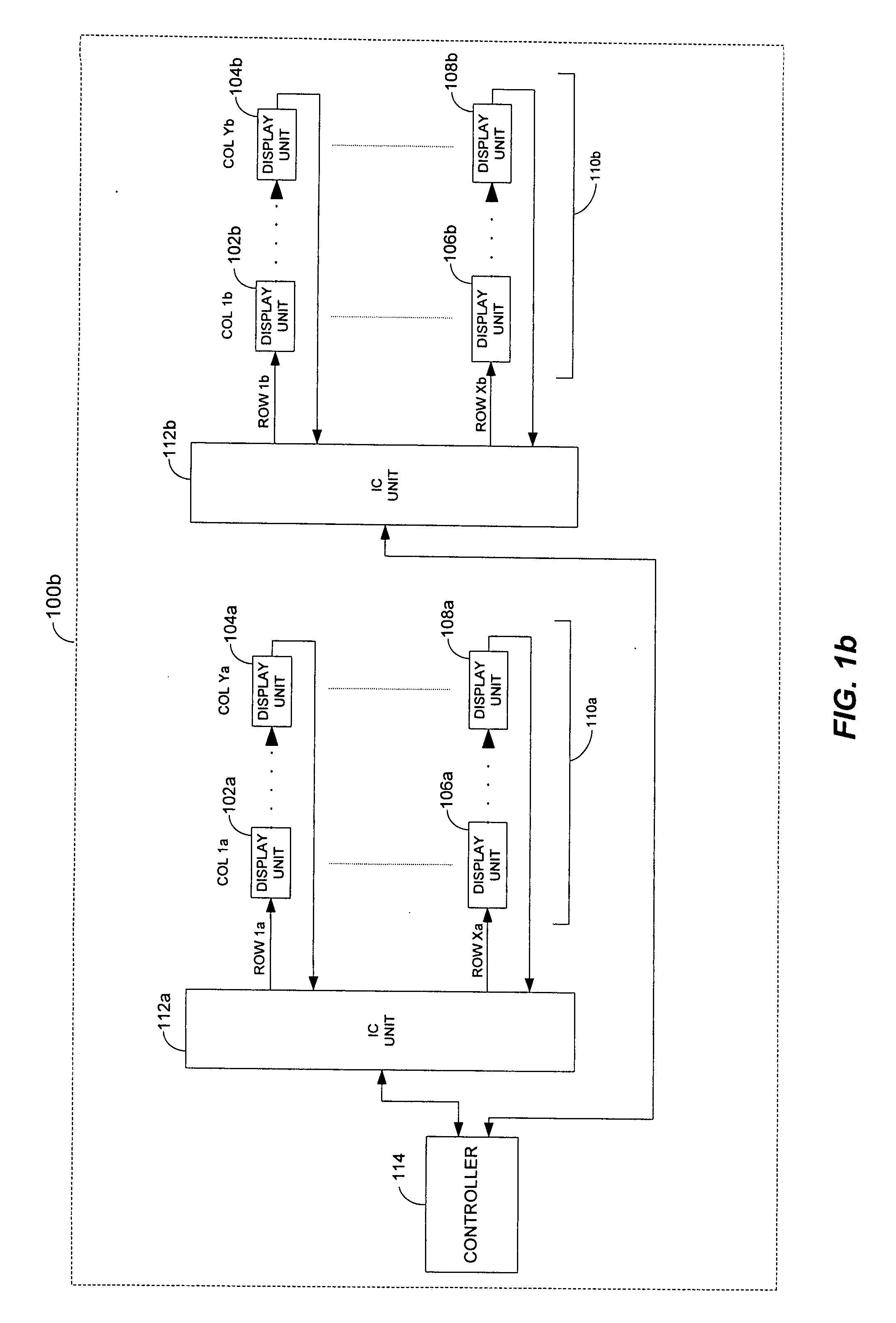

Dynamic message sign display panel error detection, correction, and notification

InactiveUS20070241988A1Cathode-ray tube indicatorsInput/output processes for data processingComputer scienceUnit memory

In accordance with the invention, the present disclosure is related to a sign display panel for displaying a sign display panel message. The sign display panel includes at least one set of display units. Each display unit of the at least one set of display units includes a plurality of display units. In addition, each of the plurality of display units includes a display unit central processing unit (CPU) configured to execute software instructions associated with the display of the sign display panel message, a display unit memory configured to store the software instructions for execution by the display unit CPU, and a plurality of display elements configured to respond to signals sent from the display unit CPU. The sign display panel also includes at least one interconnect (IC) unit. The at least one IC unit is coupled to a first display unit and a second display unit included in the at least one set of display units. In addition, the sign display panel includes a controller connected to the at least one IC unit.

Owner:ZERPHY BYRON L +1

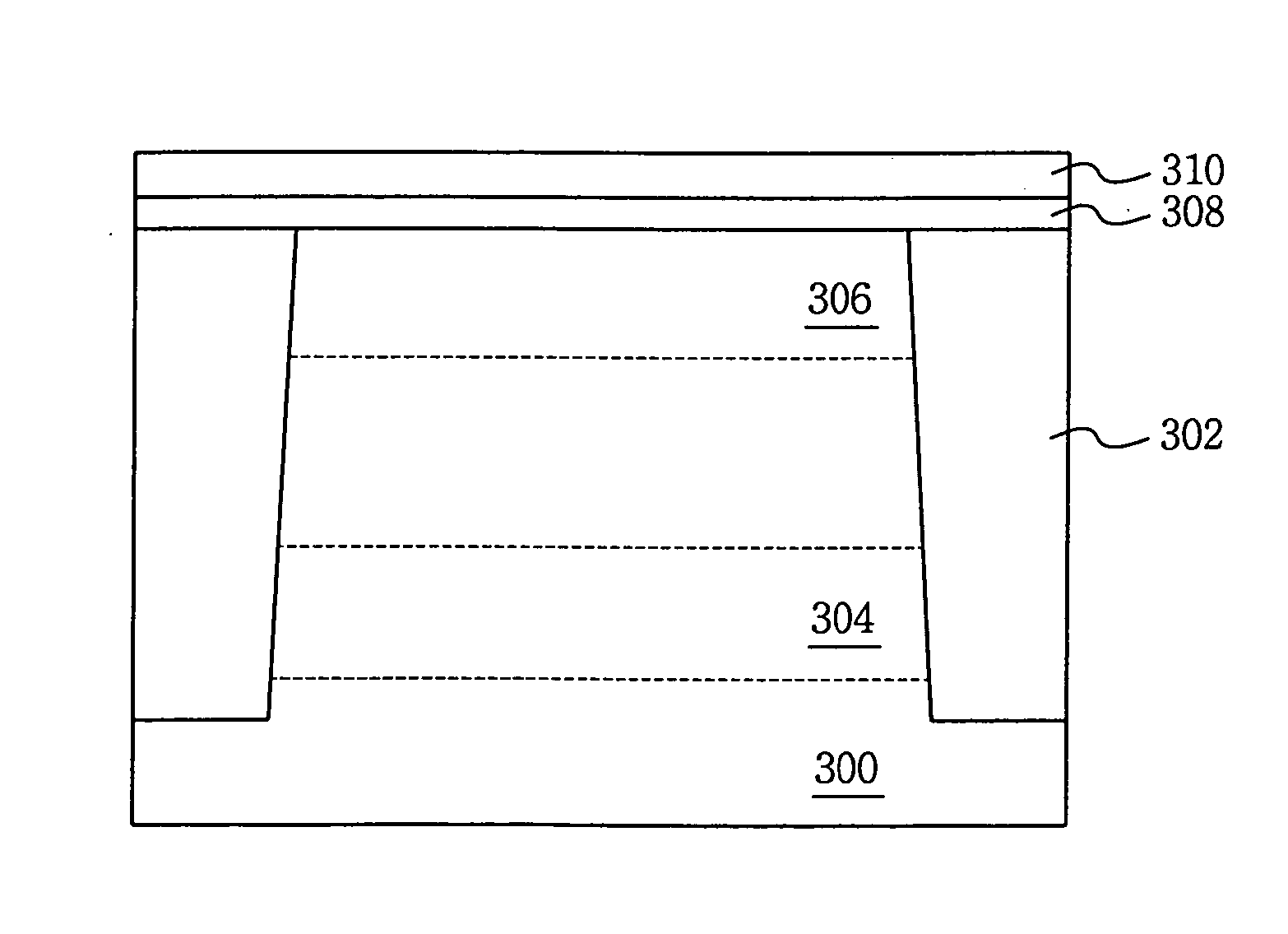

Nonvolatile storage device and method for manufacturing same

ActiveUS20090283737A1Solid-state devicesSemiconductor/solid-state device manufacturingComputer architectureRecording layer

A nonvolatile storage device having a plurality of unit memory layers, and a plurality of layer selection transistors is provided. The plurality of unit memory layers are laminated in a direction perpendicular to a layer surface of the unit memory layers. Each of the unit memory layers includes a plurality of first wirings, a plurality of second wirings provided non-parallel to the plurality of first wirings, and a recording layer provided between the plurality of first wirings and the plurality of second wirings. The plurality of layer selection transistors are connected to at least one of the plurality of first wirings and the plurality of second wirings of each of the unit memory layers, and collectively selects the at least one in the same plane.

Owner:KIOXIA CORP

Non-volatile semiconductor memory device and process for fabricating the same

InactiveUS6885060B2No deterioration in propertyPerform operationTransistorSolid-state devicesGate dielectricScale down

A non-volatile semiconductor memory device comprising a first conductive semiconductor having steps on a surface thereof, a second conductive semiconductor region formed on an upper portion and a bottom portion of each of the steps and being separated in a direction perpendicular to the main surface of the first conductive semiconductor to function as a source or a drain, a gate dielectric film containing therein charge storage means which is spatially discrete and being formed on the first conductive semiconductor so as to coat at least a sidewall of each of the steps, and a gate electrode formed on the gate dielectric film. Accordingly, there are provided a non-volatile semiconductor memory device which suffers almost no deterioration in the properties and can perform the operation of recording of 2 bits per unit memory device even when the size of the semiconductor memory device in the semiconductor substrate is scaled down, and a process for fabricating the non-volatile semiconductor memory device.

Owner:SONY CORP

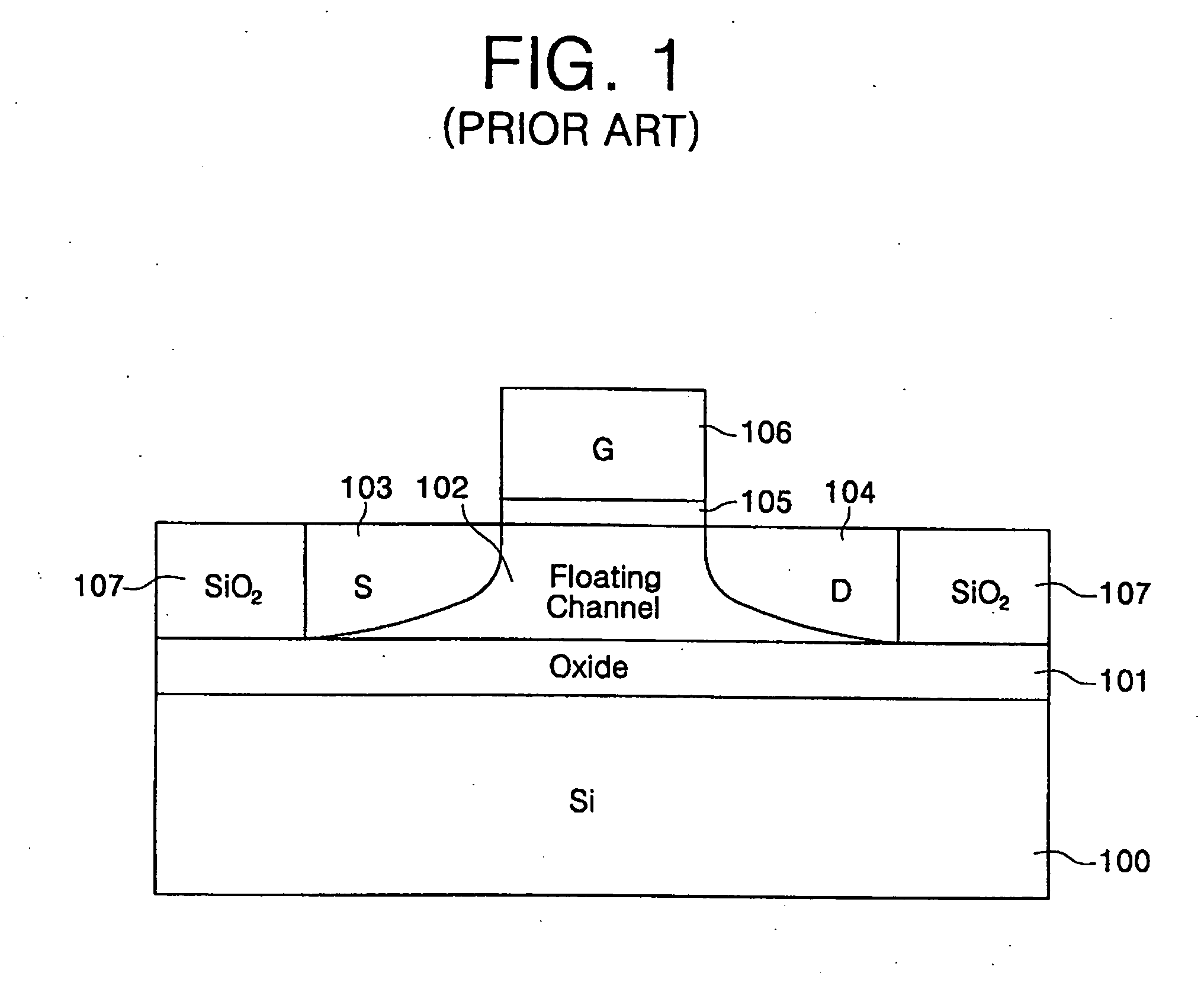

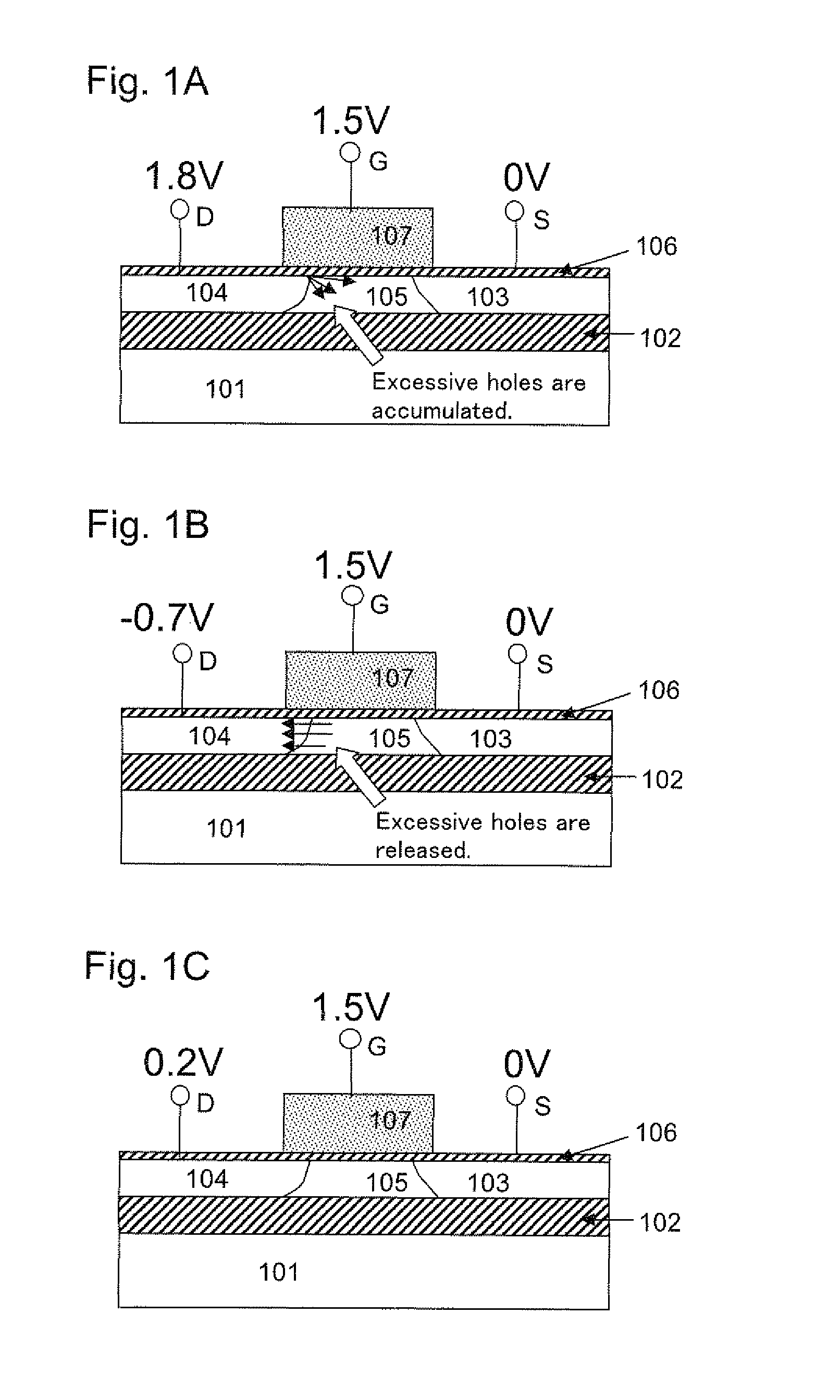

Memory devices including floating body transistor capacitorless memory cells and related methods

Owner:SAMSUNG ELECTRONICS CO LTD

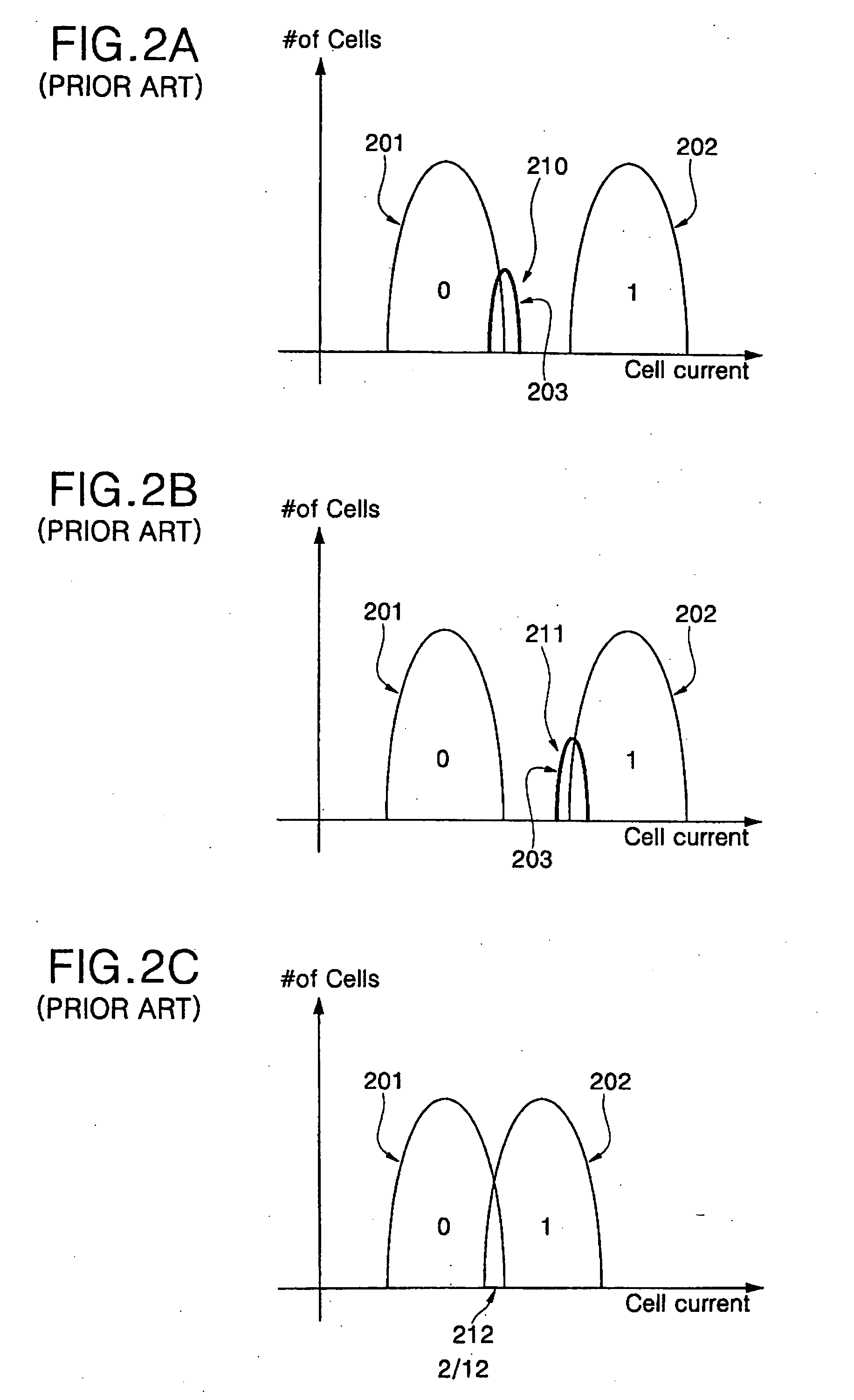

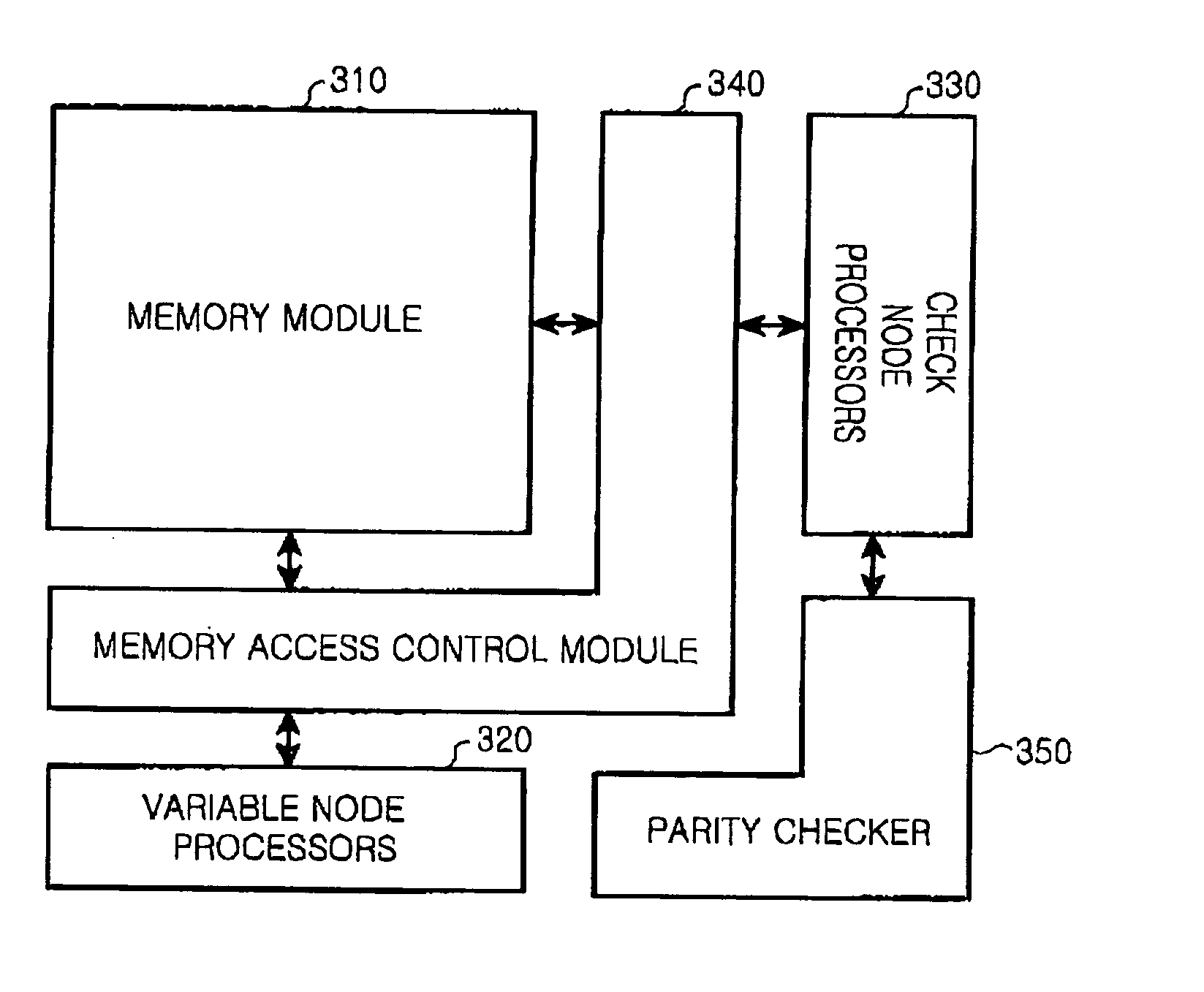

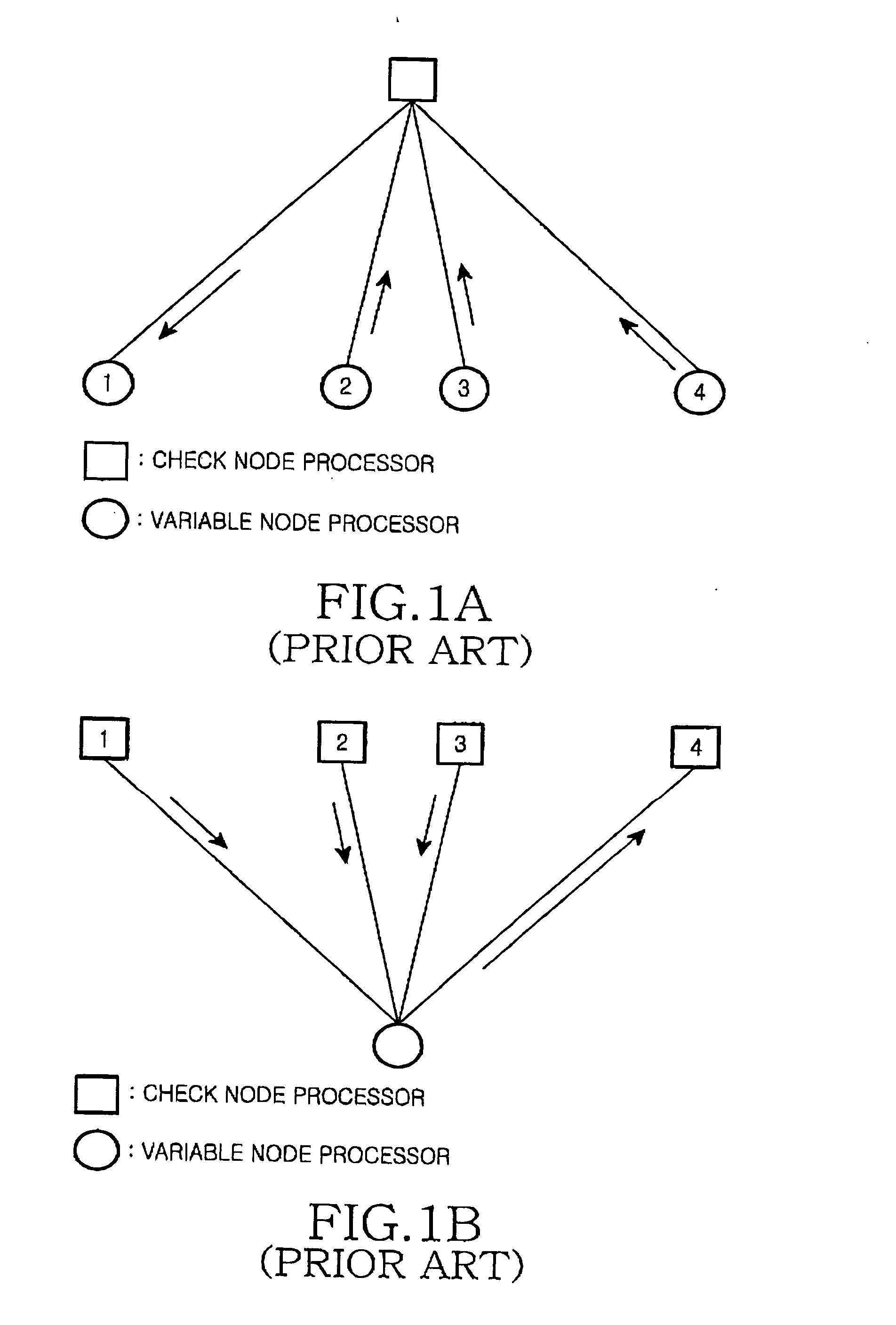

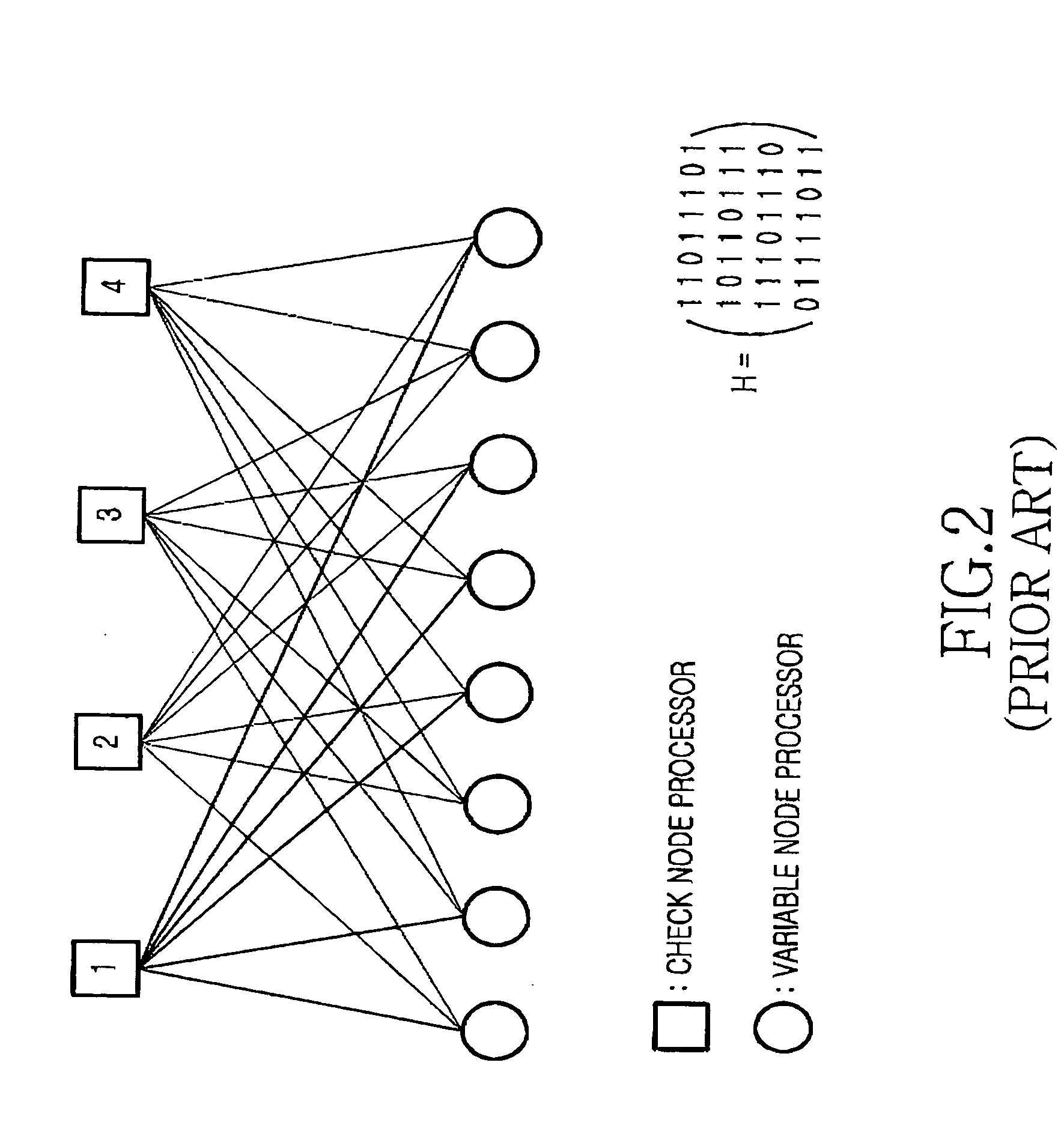

Apparatus and method for decoding low density parity check codes

ActiveUS20050262420A1Increased complexityIncrease ratingsError correction/detection using multiple parity bitsCode conversionLow-density parity-check codeLow density

An apparatus and method for decoding low density parity check (LDPC) codes are provided. A memory module configured by a plurality of unit memories stores a reliability value. Variable node processors perform a computation associated with a variable node, and update data of the memory module in a column direction, respectively. Check node processors perform a computation associated with a check node, and update data of the memory module in a row direction, respectively. A parity checker determines if all errors have been corrected such that an iterative decoding process is performed. A memory access control module selects a unit memory to be updated by a variable node processor or a check node processor.

Owner:SAMSUNG ELECTRONICS CO LTD

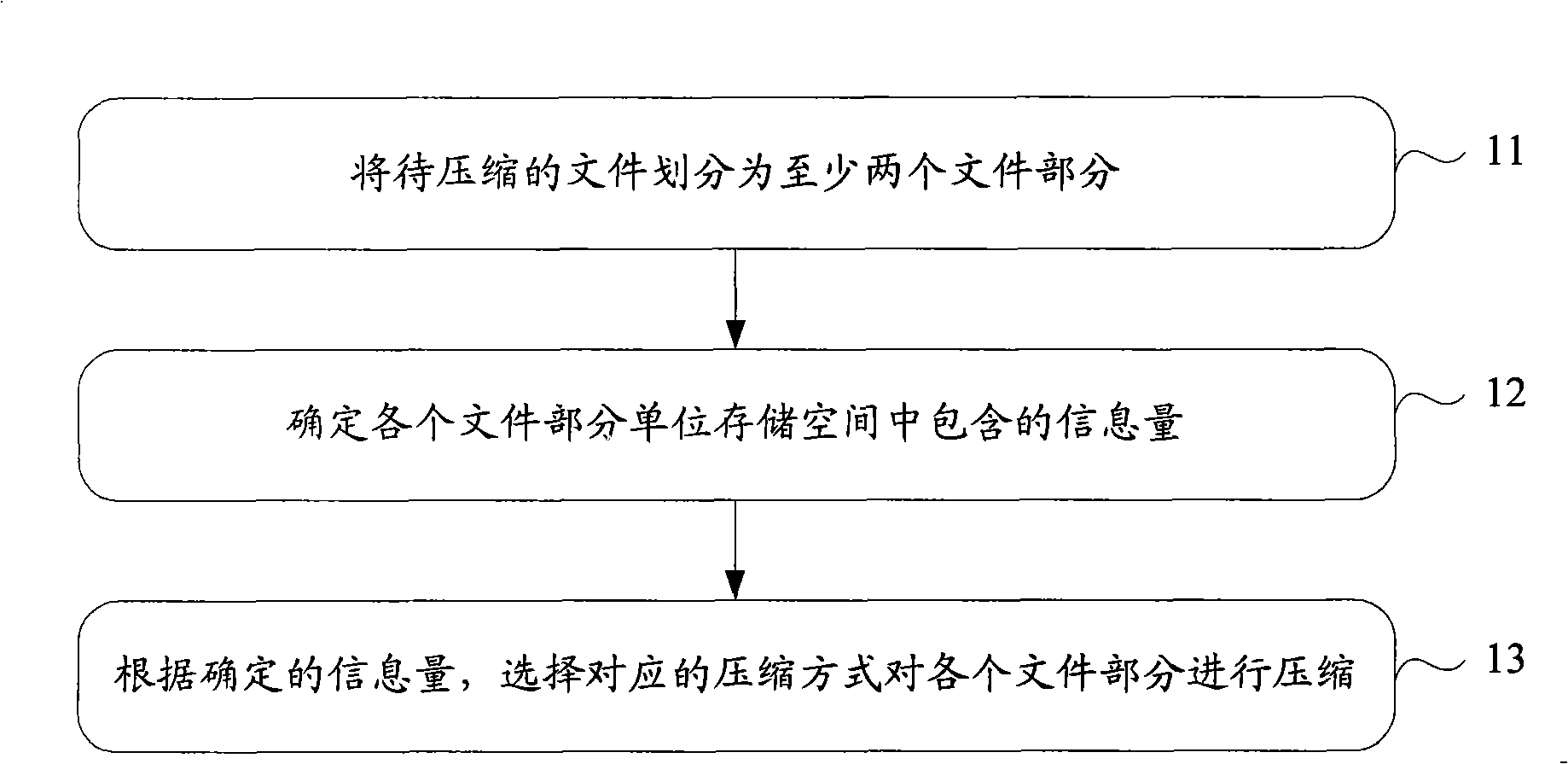

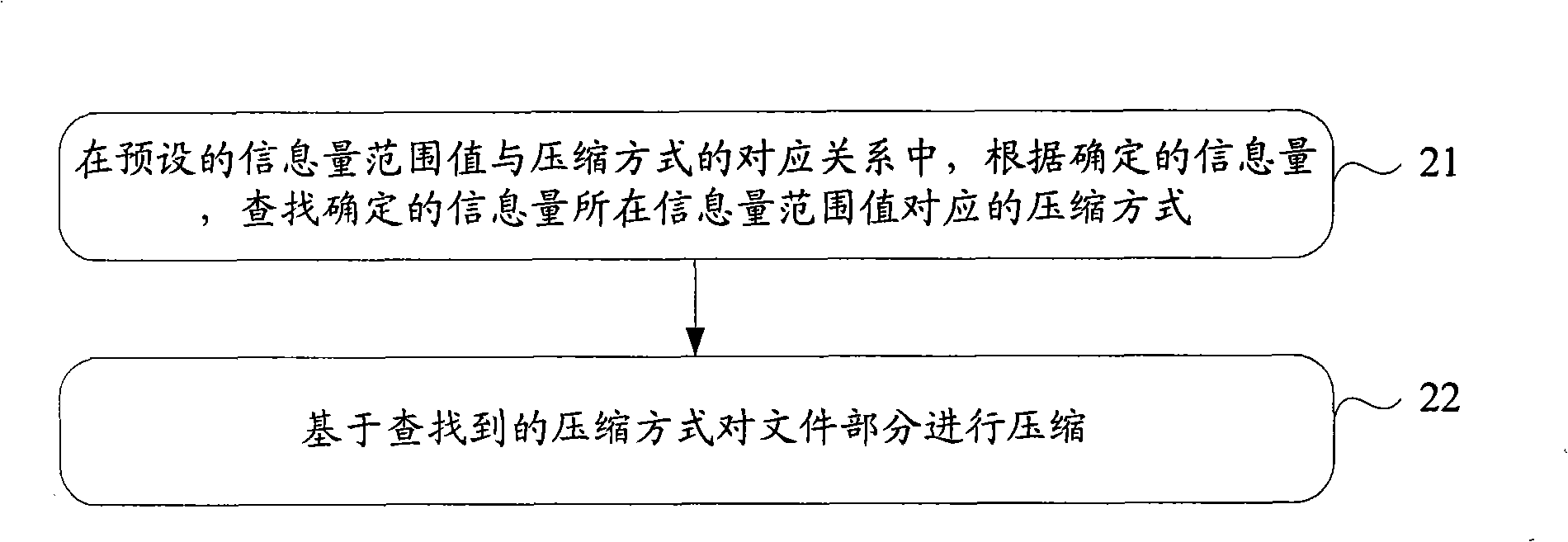

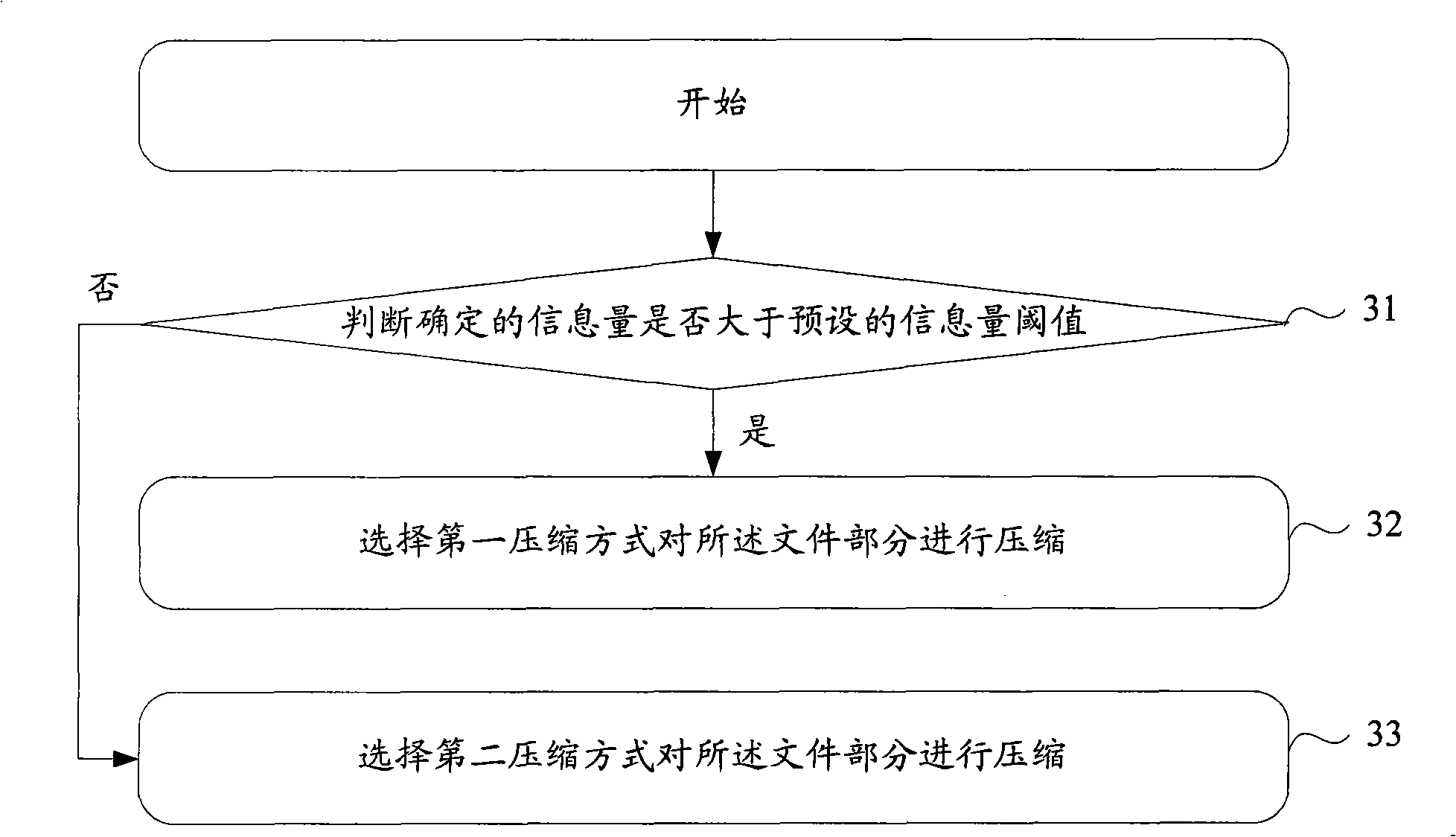

Method and apparatus for compressing and decompressing file

InactiveCN101355364ADecompression implementationPulse modulation television signal transmissionCode conversionState of artCompression method

The invention discloses a method for compressing files, comprising the following steps: files to be compressed is divided into at least two file parts; the obtained information content contained in the unit memory space of each divided file part is respectively determined and divided; according to the determined information content, and the file part is compressed respectively by selecting corresponding compression ways. The invention also discloses a device for file compression. The method and the device for file compression disclosed by the invention can solve the problem of the prior art that the contradiction between the compression ratio and the compression speed rate is not relieved well when single compression method is adopted to compress data in the whole file. Correspondingly, the invention also provides a method and a device for decompressing the files.

Owner:PEKING UNIV FOUNDER GRP CO LTD +1

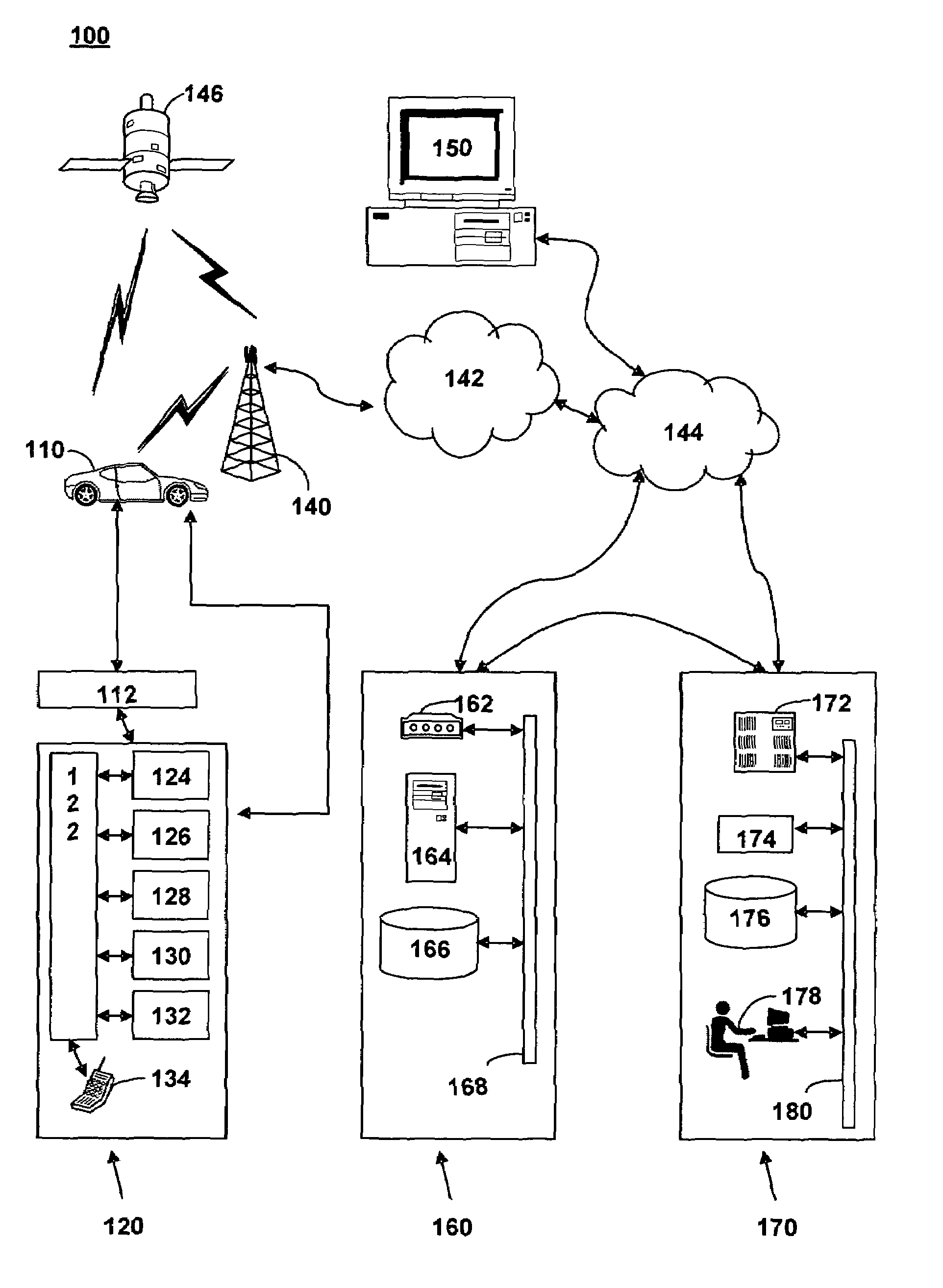

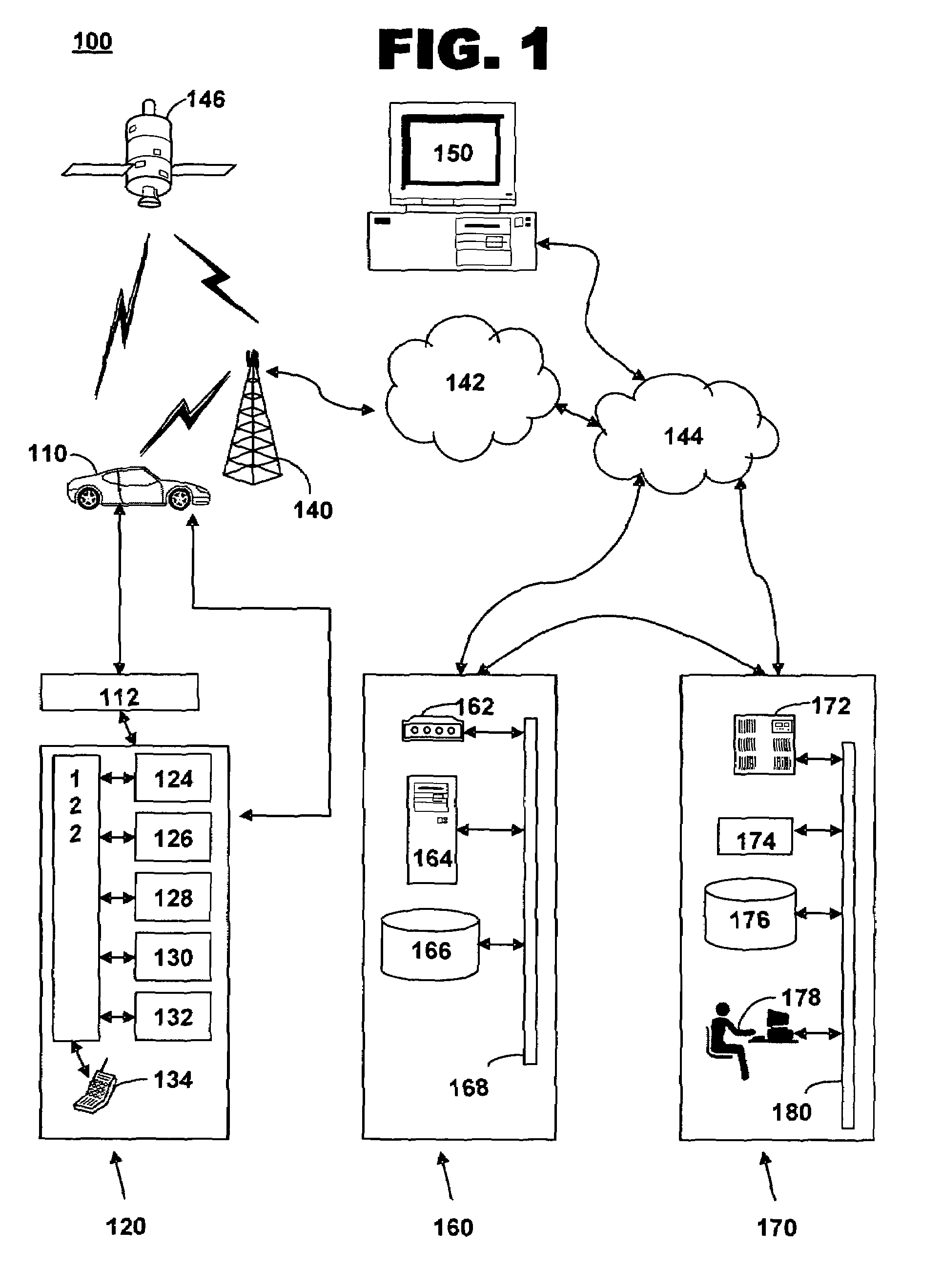

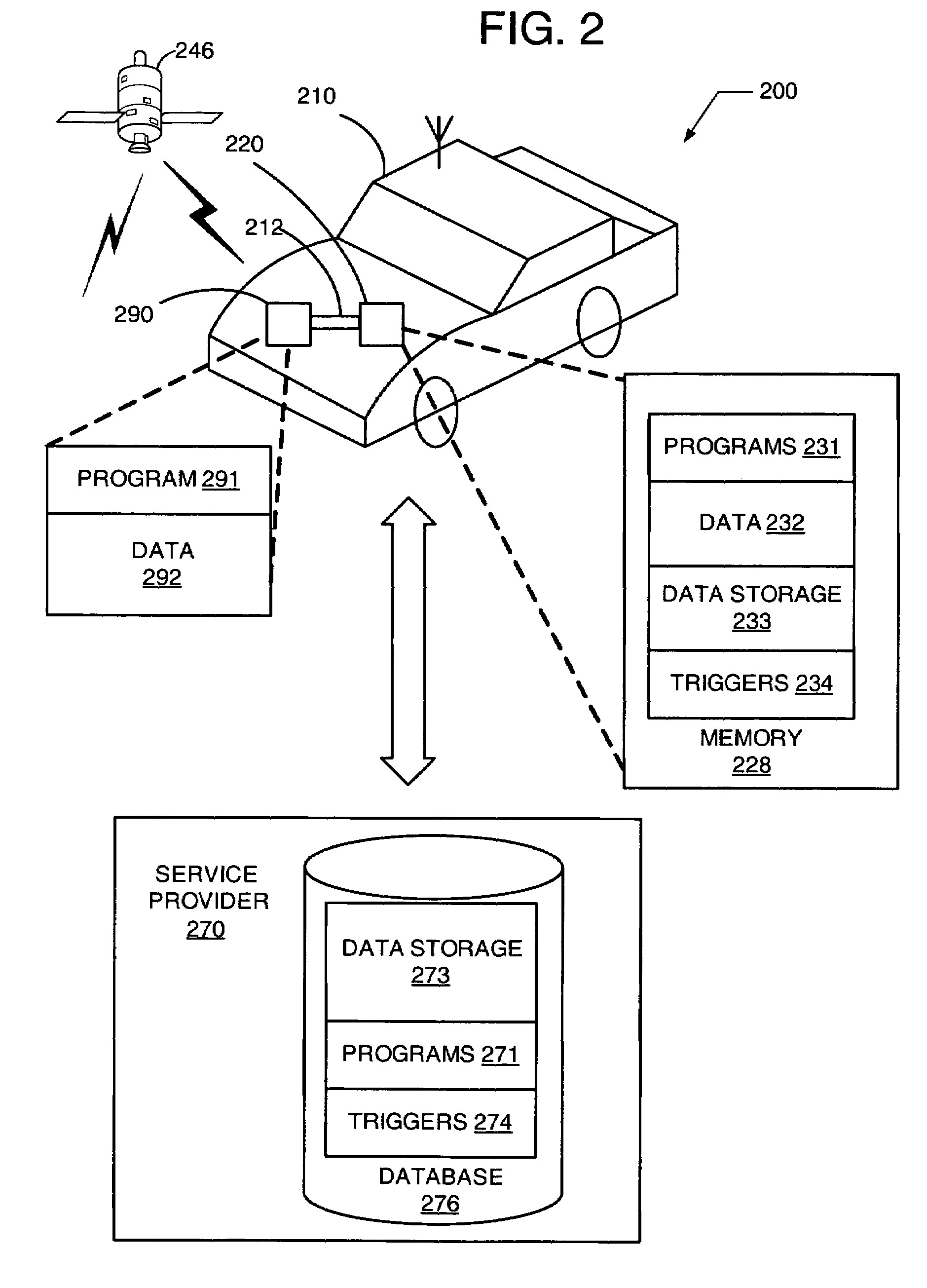

System and method for large route data handling within a telematics communication system

InactiveUS7657368B2Instruments for road network navigationRoad vehicles traffic controlMobile vehicleCommunications system

The present invention provides a method of operating a telematics enabled mobile vehicle communication system. The method includes receiving a navigation request at a service provider from a telematics unit. The navigation request includes current location information of the telematics unit, destination information, and telematics unit memory capacity information. The method further includes producing navigation instructions based on the received navigation request. The navigation instructions provide directions from the current location of the telematics unit to the destination. The navigation instructions include a plurality of data elements describing the navigation instructions. The amount of data elements included within the navigation instructions is associated with the received telematics unit memory capacity information. The method additionally includes communicating the produced navigation instructions to the telematics unit. The method may further include providing the produced navigation instructions to a user interface.

Owner:GENERA MOTORS LLC

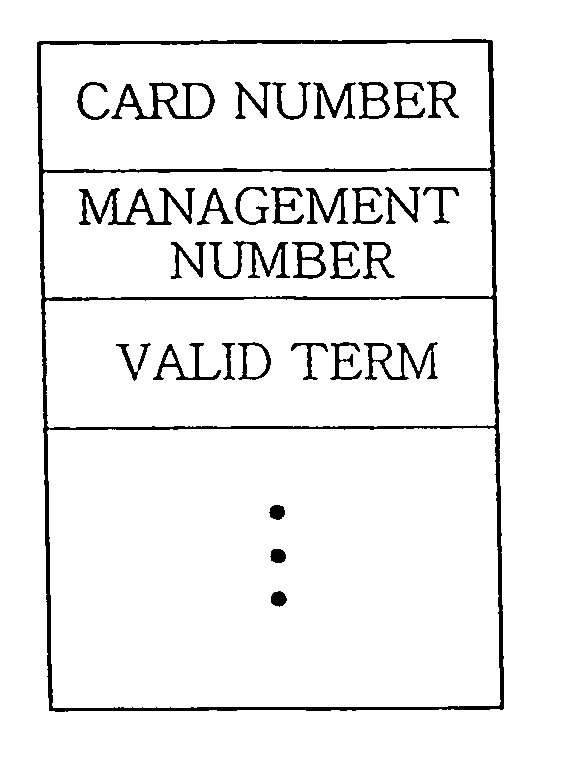

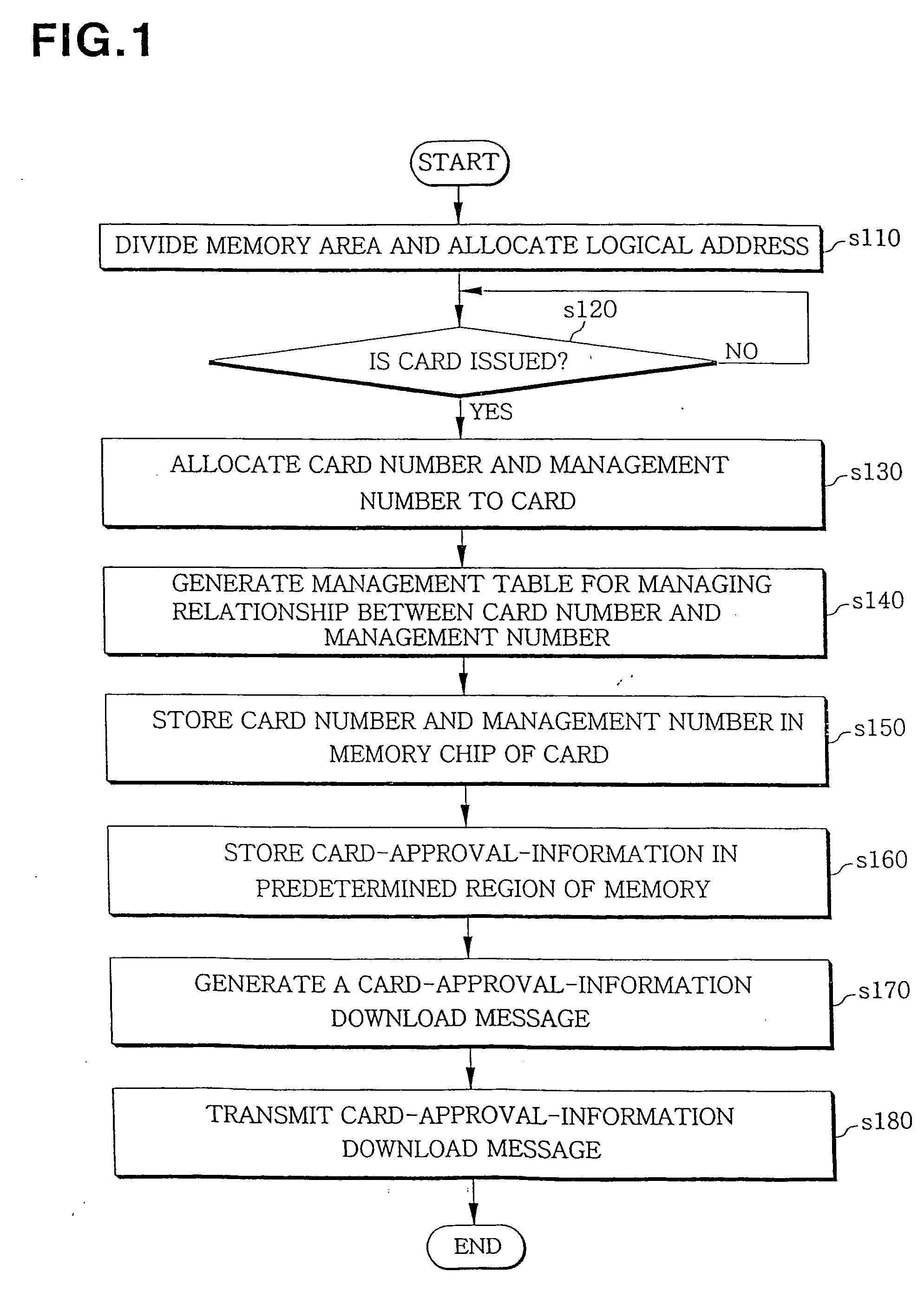

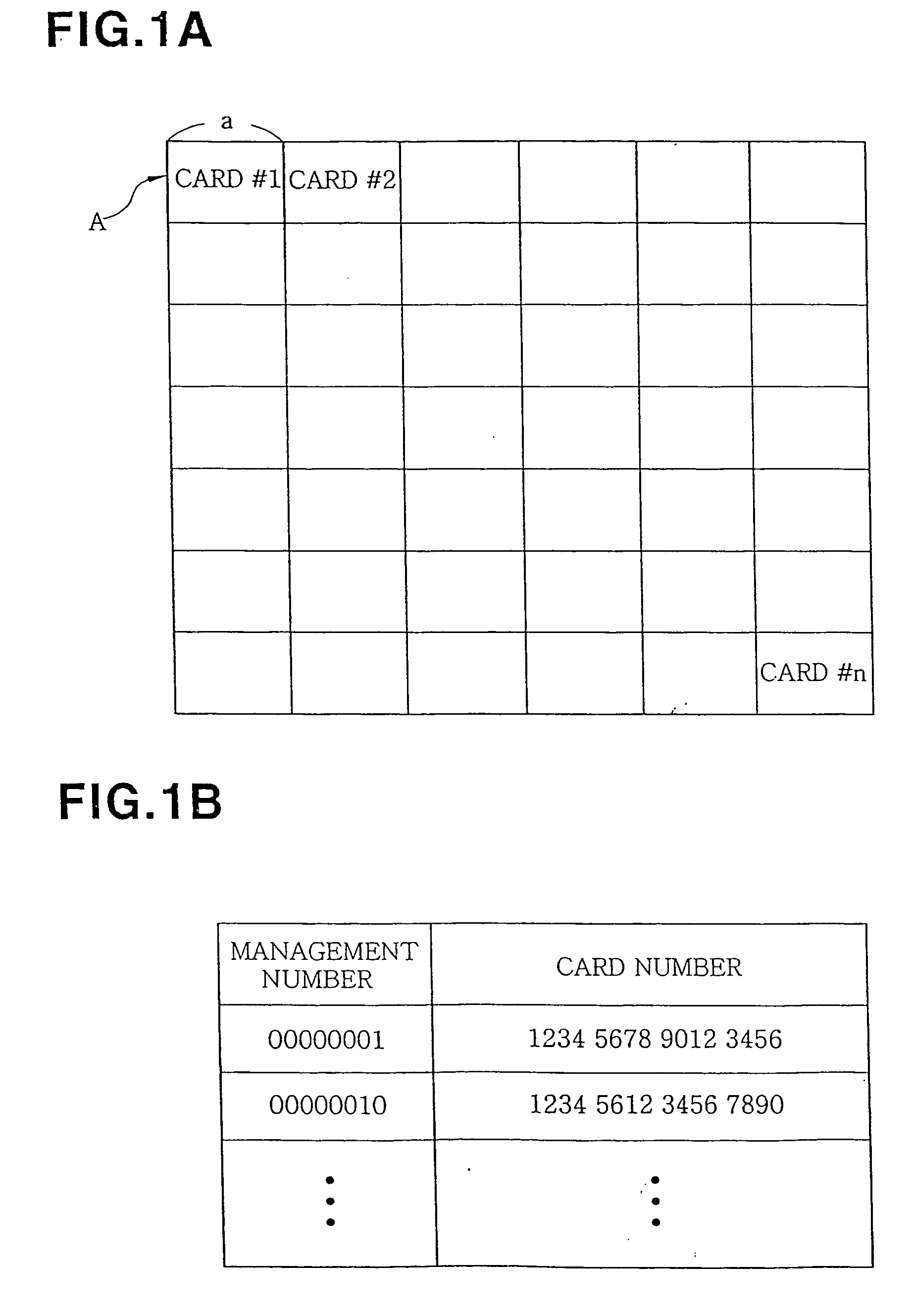

Method for managing card-approval-information using memory address and credit-card system using that

A method for managing card-approval-in-formation using a memory address and a credit-card system using the method are provided. The method includes dividing a memory area, which has a predetermined size and used for storing card-approval-information and user attribute information, into a plurality of unit memory sections having a predetermined size and allocating a logical address to each of the unit memory section; generating and allocating a unique card number to a card, selecting a logical address of each unit memory section in order, and allocating the selected logical address to the card as a management number, while initially issuing or reissuing the card; generating a management table for managing a relationship between the management number and the card number and storing the management number and the card number in a memory chip of the card; storing card-approval-information download attribute information of the card in a unit memory section corresponding to the management number of the card; and generating a card-approval-information download message including a start address of the memory area and data stored in the memory area and transmitting the card-approval-information download message to terminal apparatuses and a predetermined system, which require the card-approval-information.

Owner:SMART SYST CO

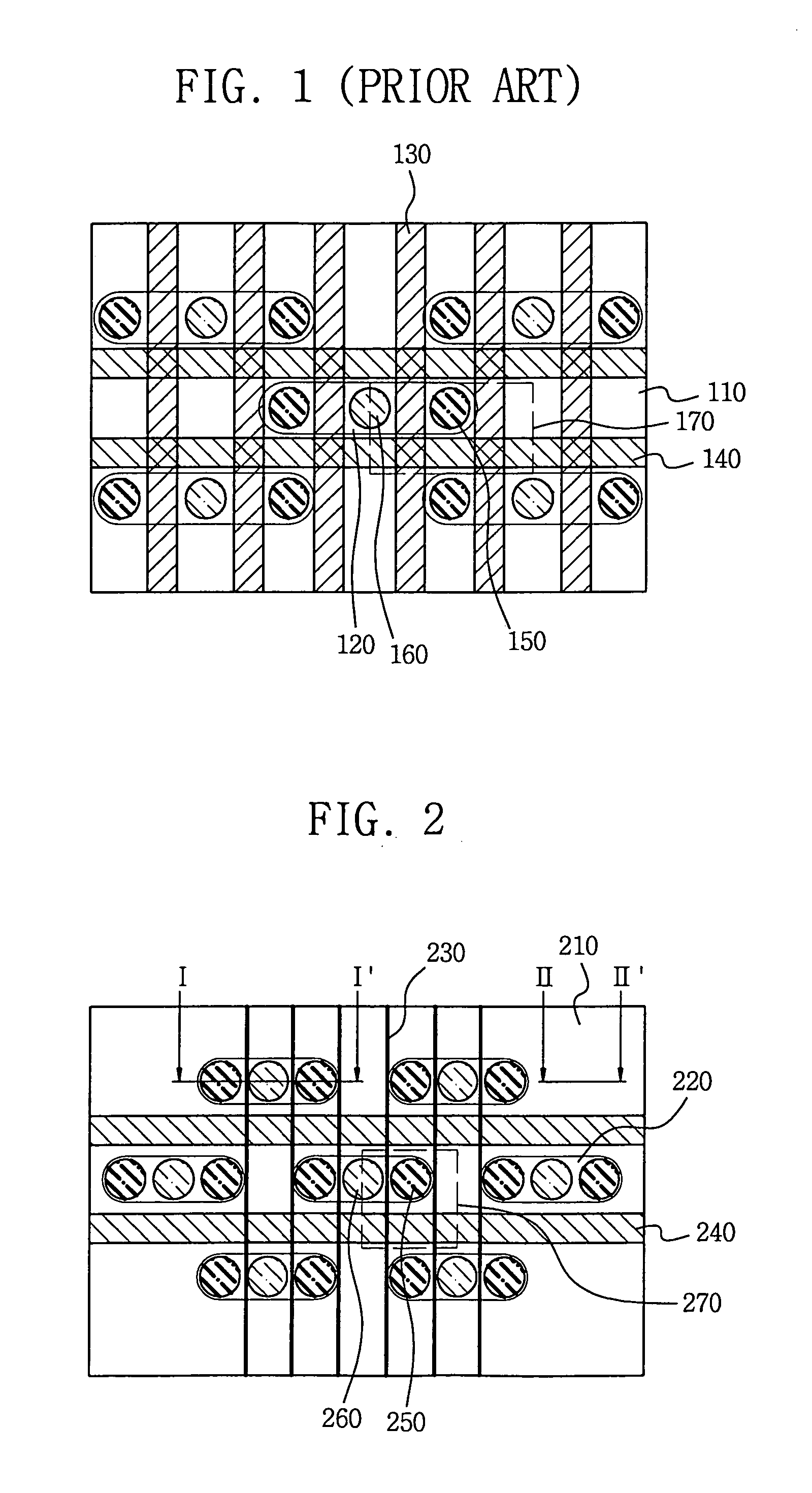

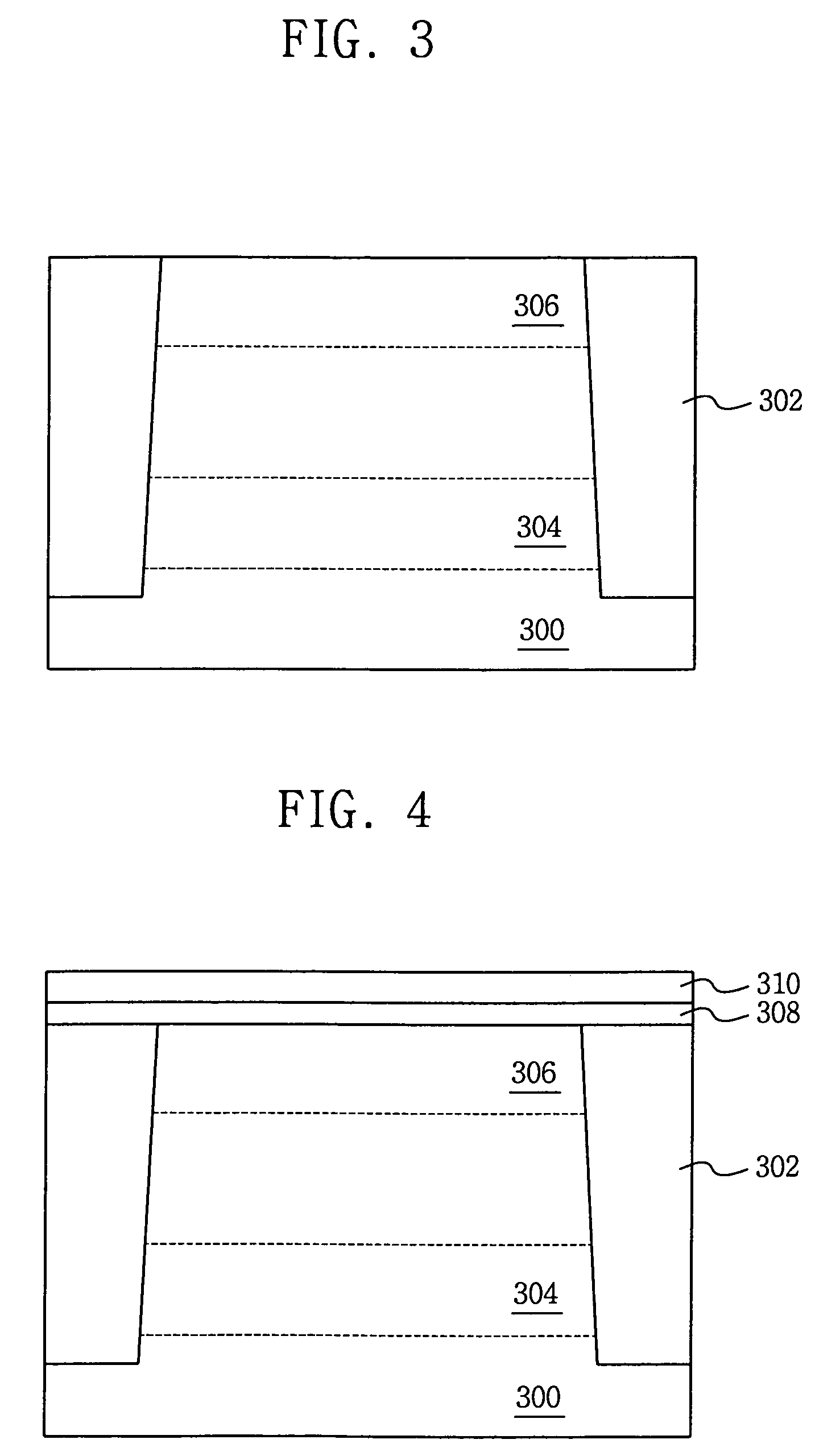

Vertical transistor structure for use in semiconductor device and method of forming the same

ActiveUS20050186740A1Small cell sizeEasy to integrateTransistorNon-mechanical controlsInsulation layerDevice material

According to some embodiments, a structure of vertical transistor includes gate electrodes distanced by a predetermined interval in an active region, formed in a vertical shape to have a predetermined depth from a top surface of a semiconductor substrate. A gate insulation layer is formed between one side wall of the gate electrode and the substrate. A gate spacer is formed in another sidewall of the gate electrode, covering the gate electrode. A contact plug is formed between the gate spacer. A plug impurity layer is formed in a lower part of the contact plug, and source and drain are formed opposite to the gate electrode within the active region. Thereby, an area occupied by a gate electrode is substantially reduced, so a unit memory cell has a 4F2 structure, reducing a memory cell size, by forming a vertical-type gate electrode within an active region.

Owner:SAMSUNG ELECTRONICS CO LTD

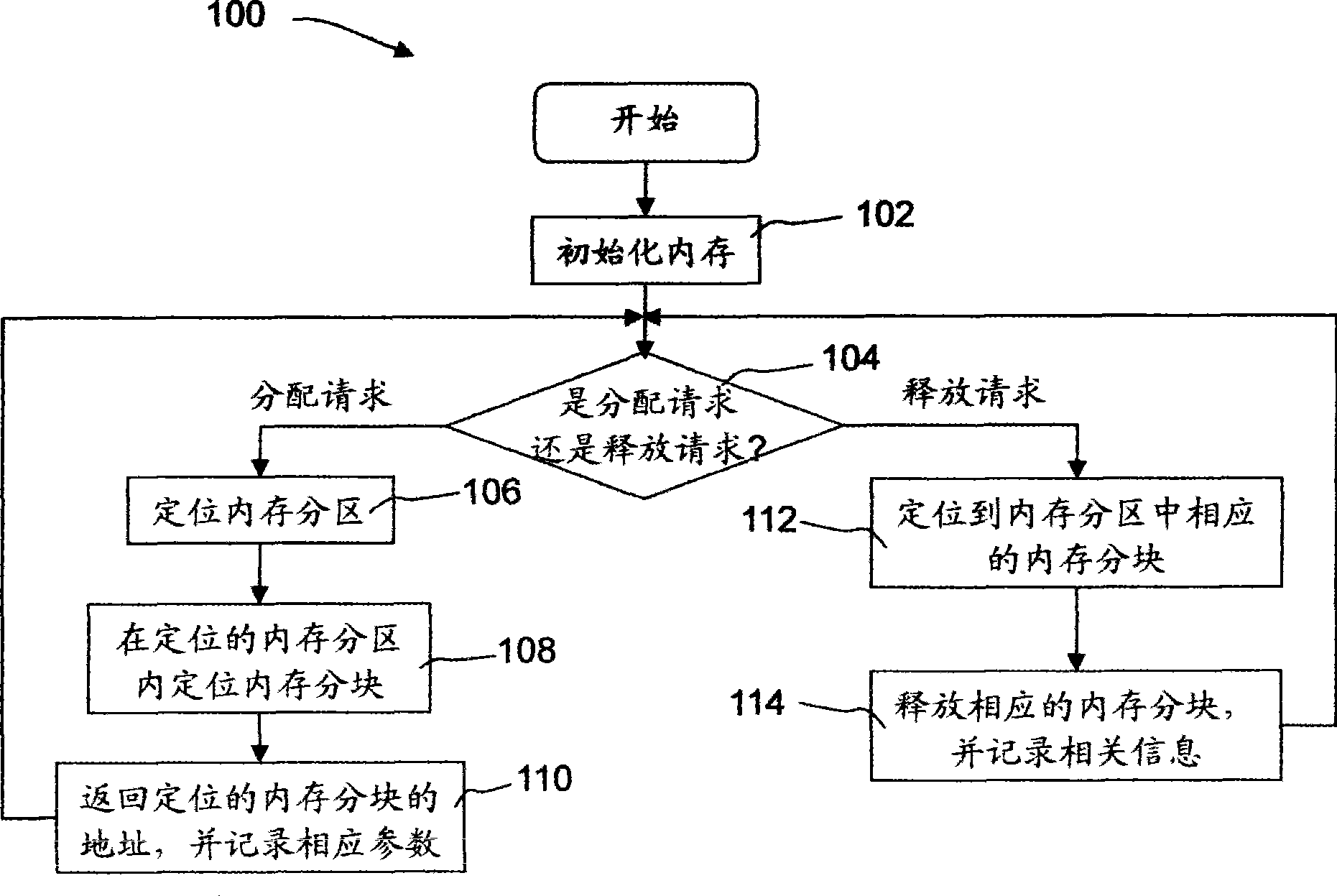

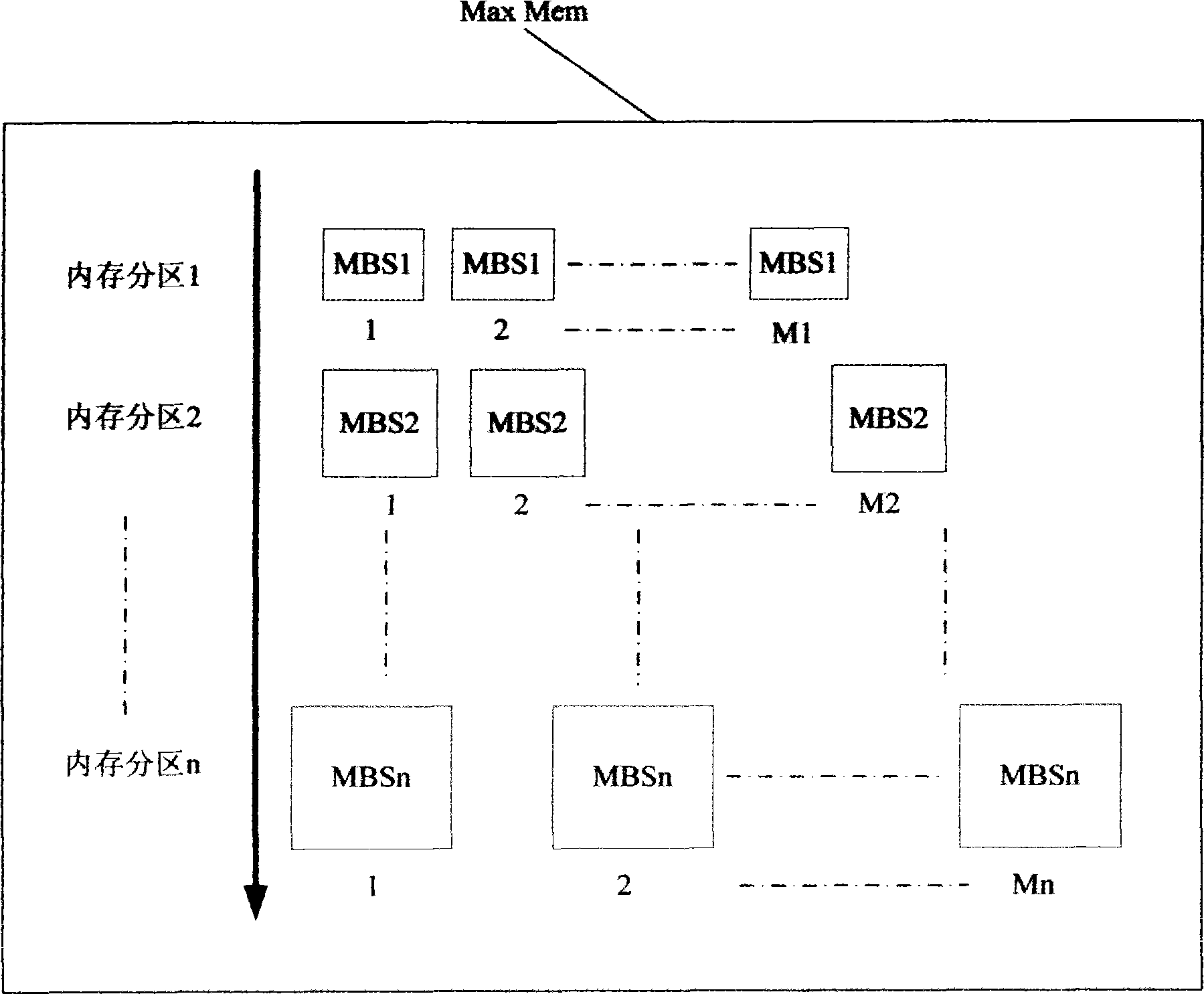

Internal memory management method

InactiveCN101499034AReal-timeAchieve reliabilityMemory adressing/allocation/relocationInternal memoryDistributed memory

The invention discloses a memory management method applicable for an embedded system, comprising steps of: providing a memory area with a certain volume; dividing a memory area into a plurality of memory branch areas and unit memory blocks; when it is necessary to provide memory, distributing the unit memory block greater than needed memory for use. The memory management method related to the invention uses a memory layout aiming at the embedded system, distributing memory via simple algorithm in a high effect manner and detecting whether memory error occurs.

Owner:VIMICRO CORP

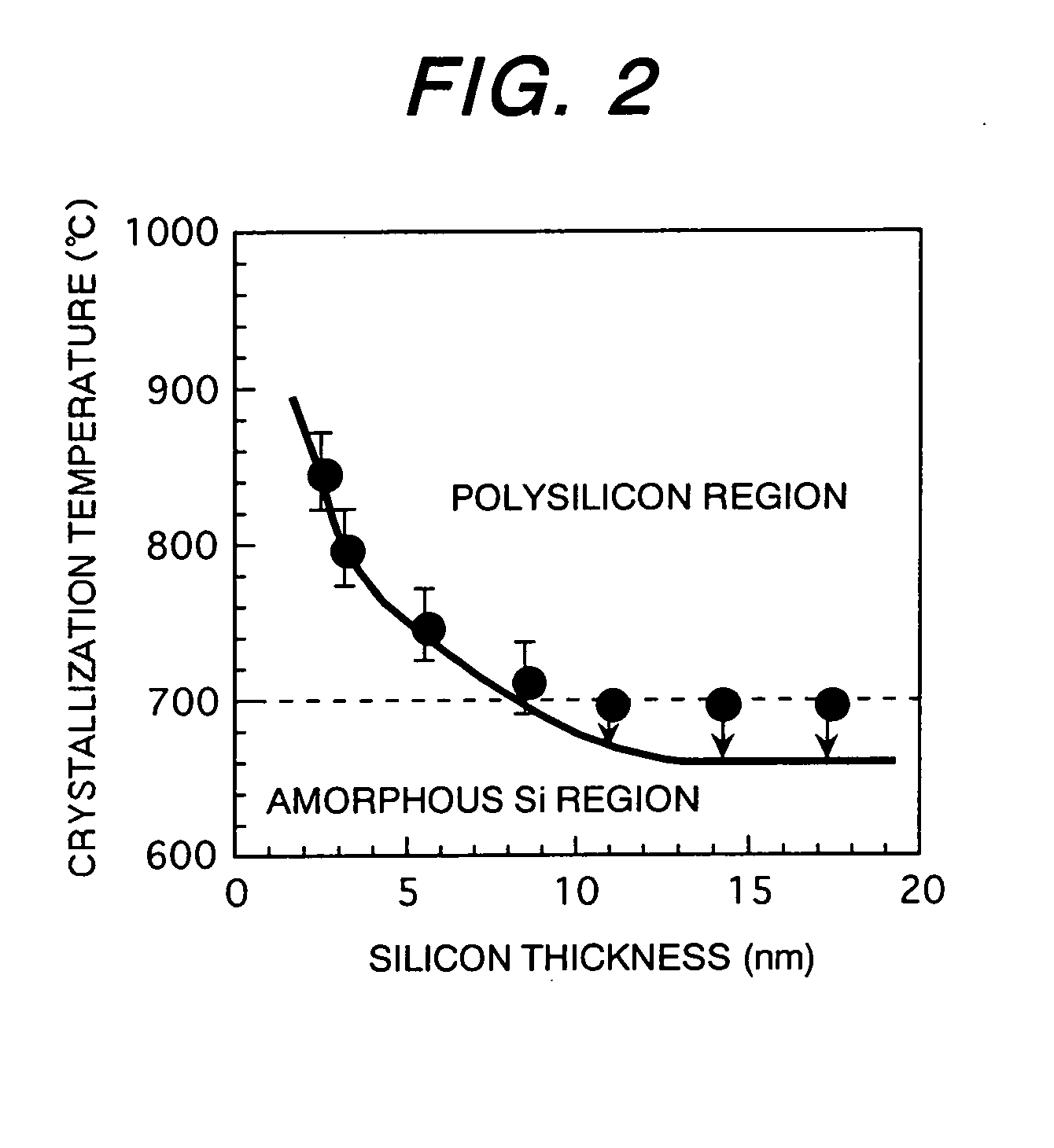

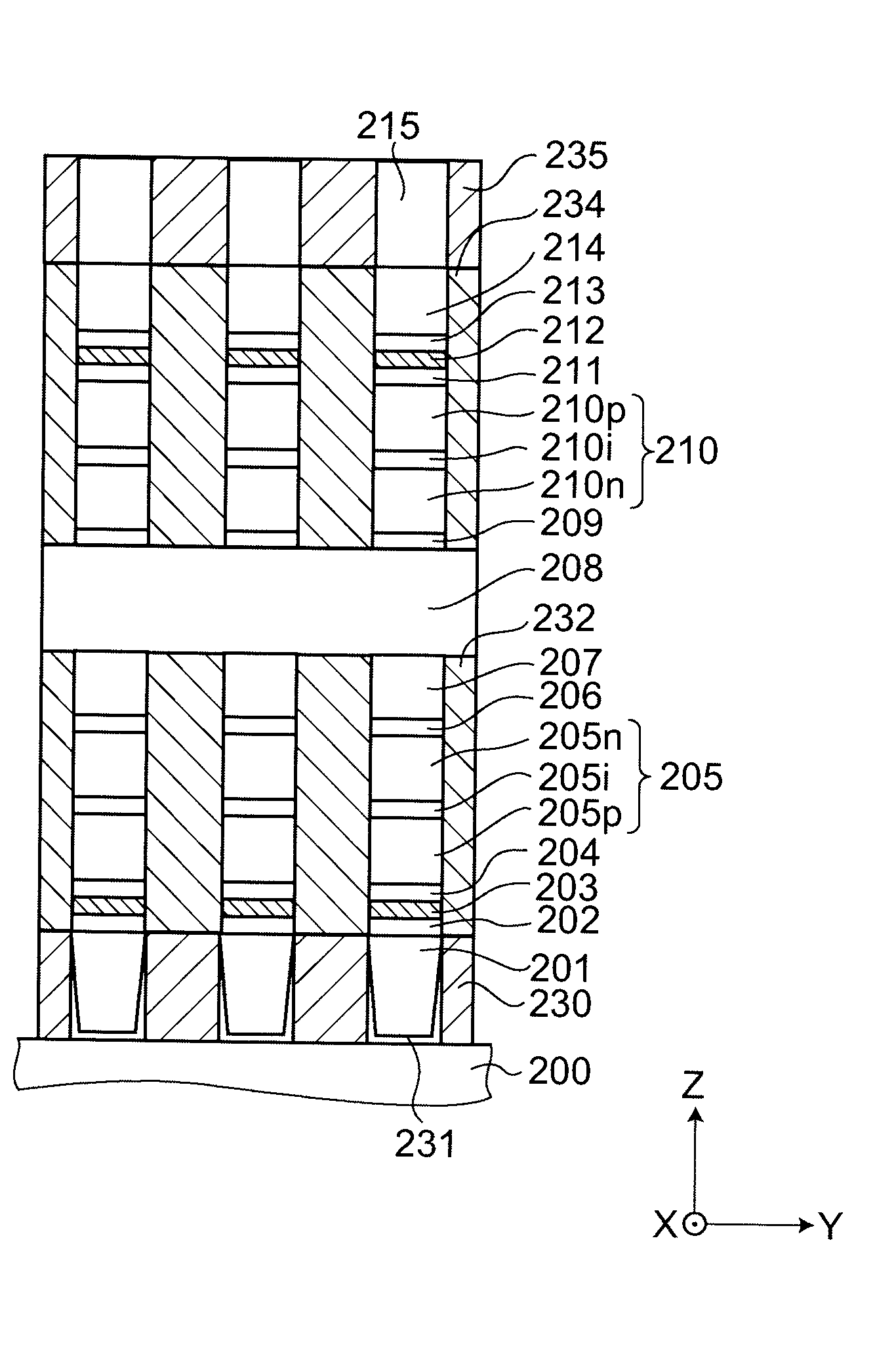

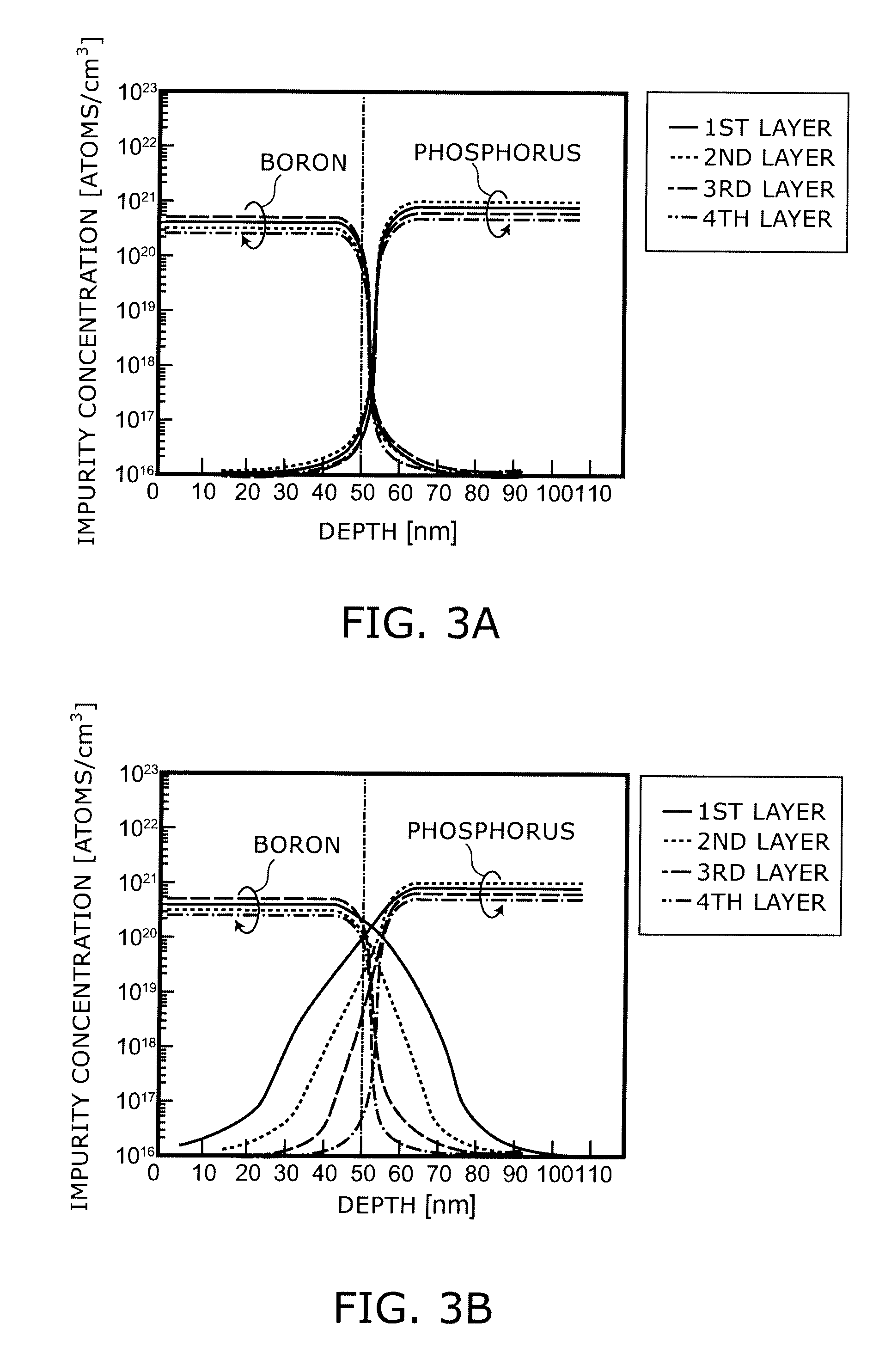

Nonvolatile storage device and method for manufacturing same

InactiveUS20090294751A1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringImpurity

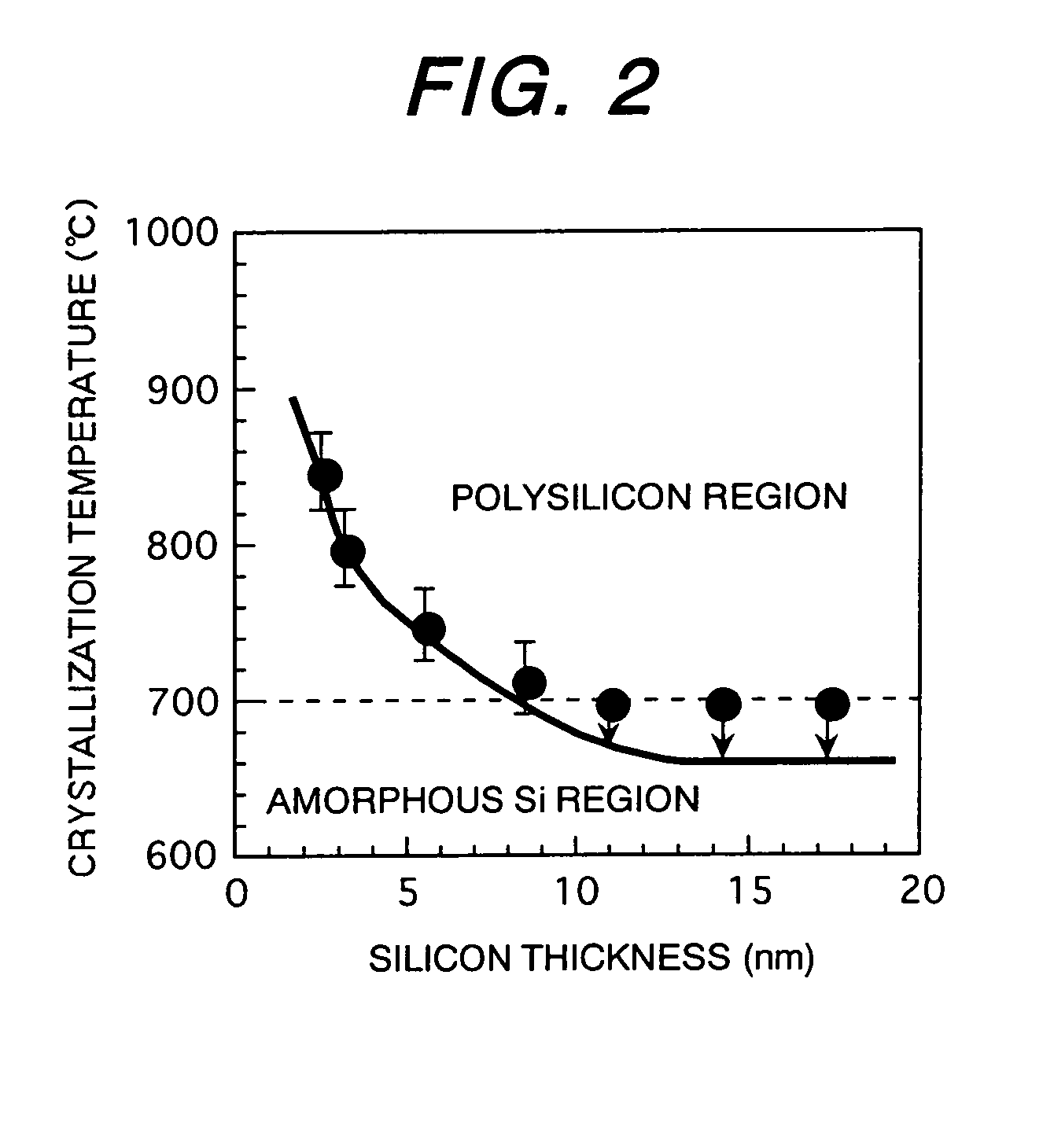

A method for manufacturing a nonvolatile storage device with a plurality of unit memory layers stacked therein is provided. Each of the unit memory layers includes: a first interconnect extending in a first direction; a second interconnect extending in a second direction; a recording unit sandwiched between the first and second interconnects and being capable of reversibly transitioning between a first state and a second state in response to a current supplied through the first and second interconnects; and a rectifying element sandwiched between the first interconnect and the recording unit and including at least one of p-type and n-type impurities. In the method, the first interconnect, the second interconnect, the recording unit, and a layer of an amorphous material including the at least one of p-type and n-type impurities used in the plurality of unit memory layers are formed at a temperature lower than a temperature at which the amorphous material is substantially crystallized. The amorphous material used in the plurality of unit memory layers is simultaneously crystallized and the impurities included in the amorphous material used in the plurality of unit memory layers are simultaneously activated.

Owner:KK TOSHIBA

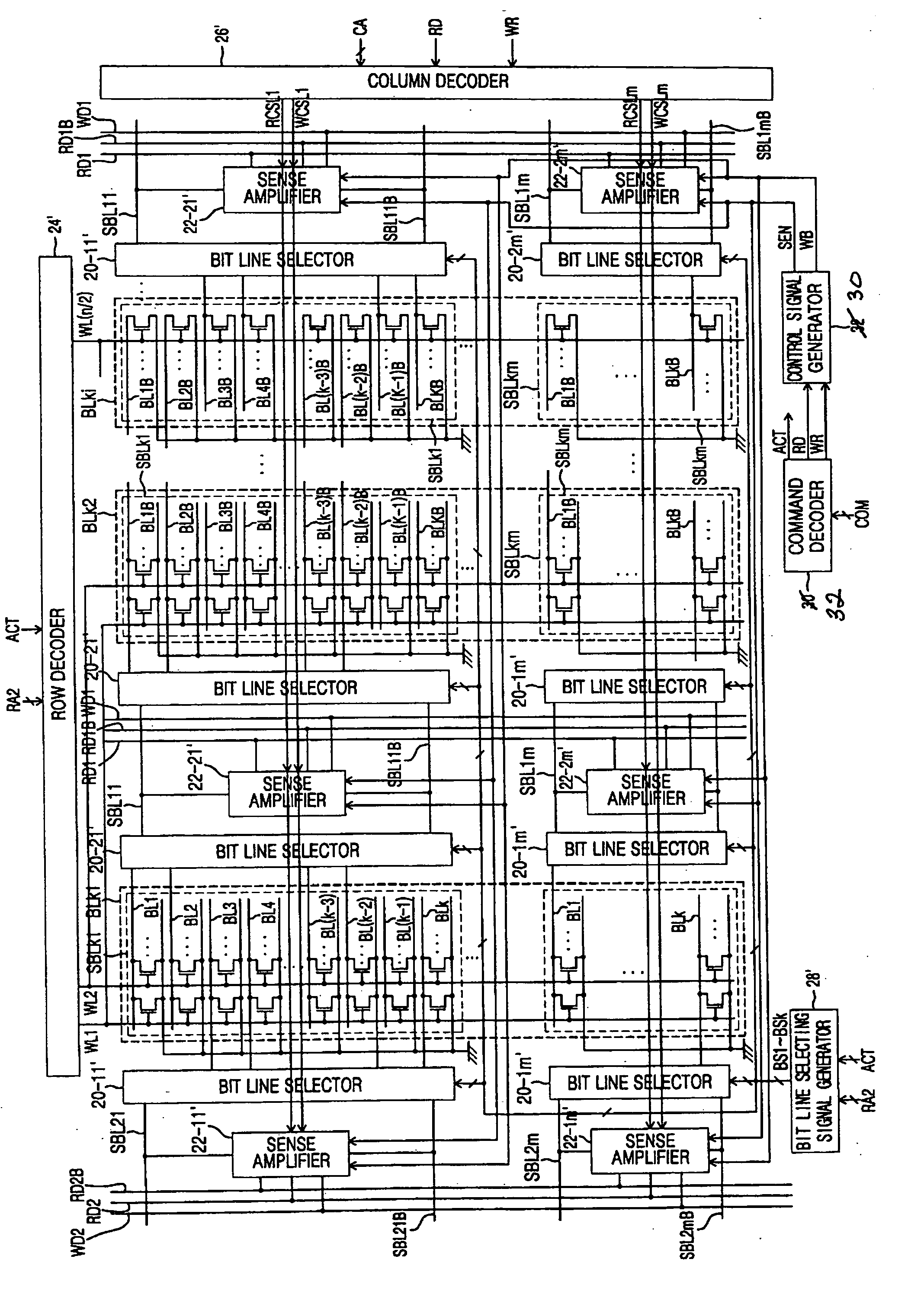

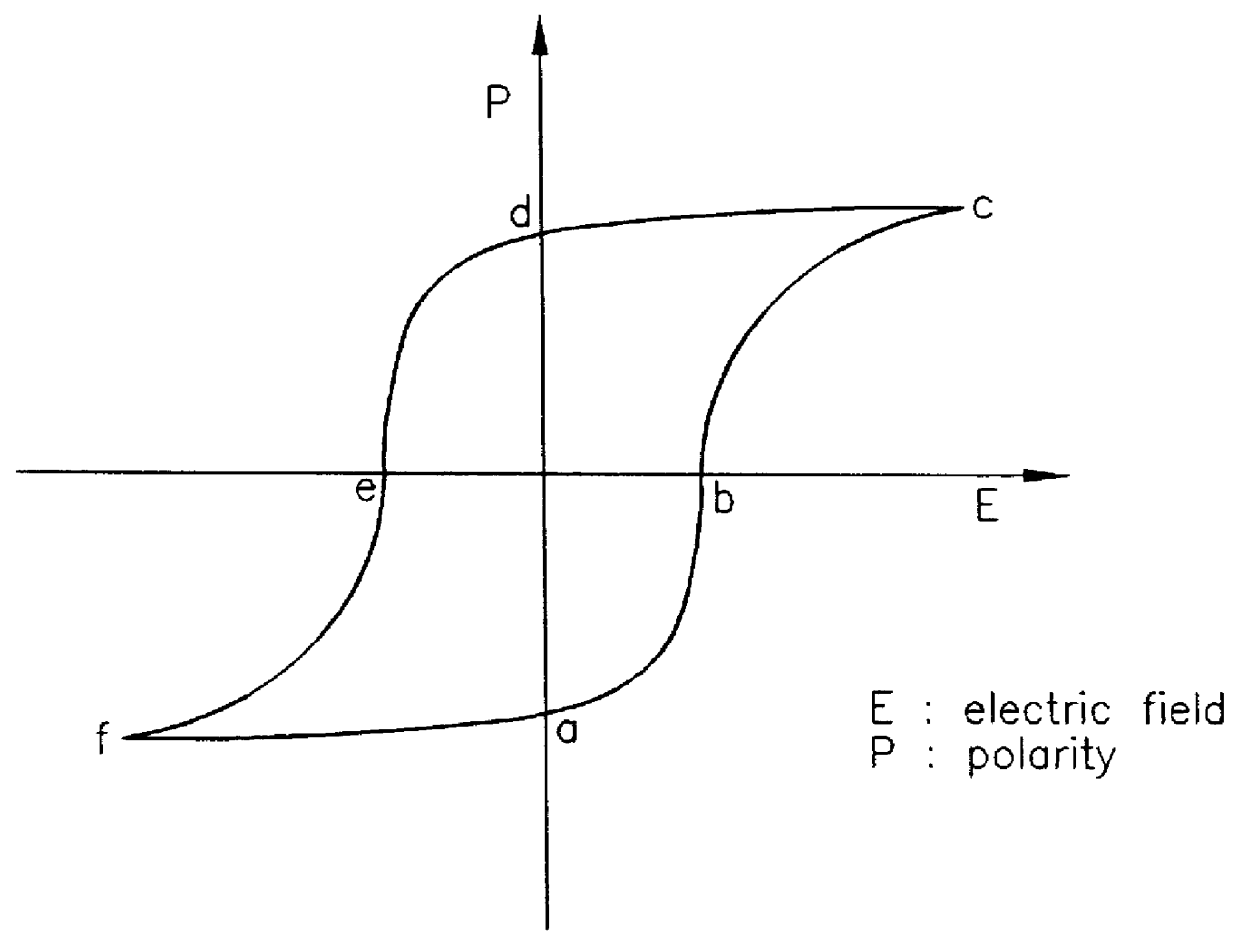

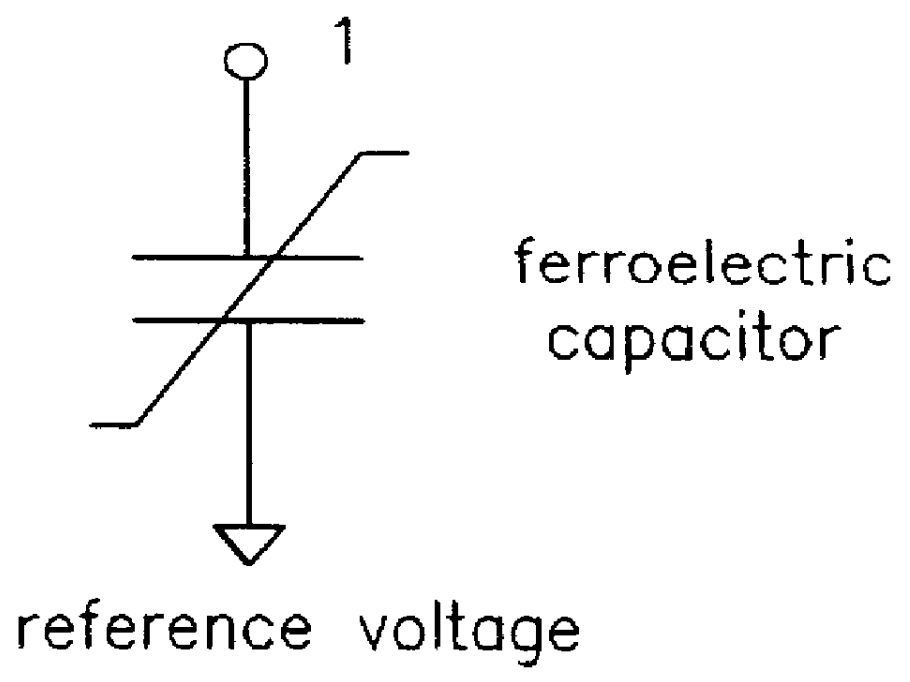

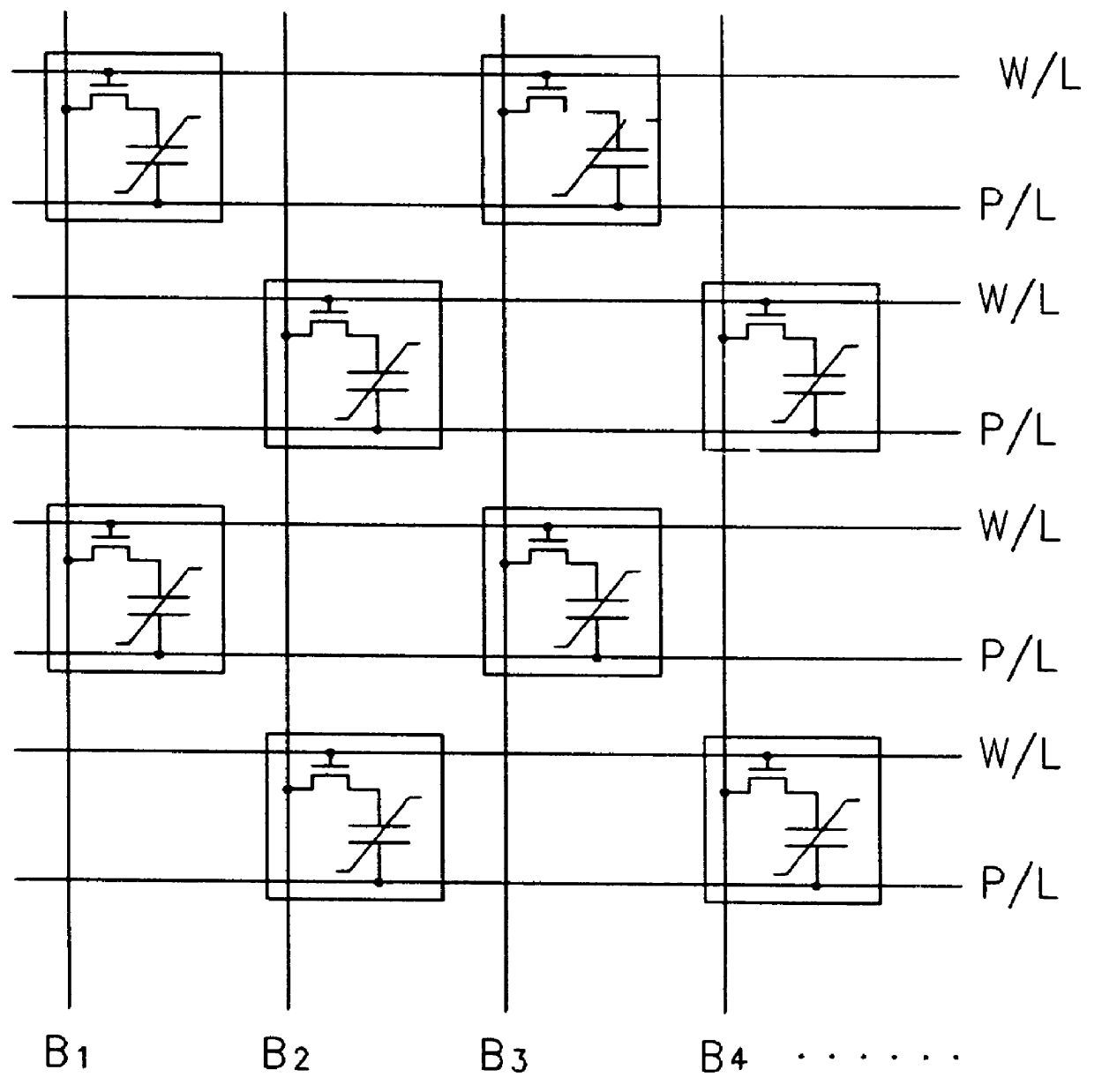

SWL ferroelectric memory and circuit for driving the same

A split wordline ferroelectric memory does not utilize plate lines and a circuit for driving the same is disclosed. The memory including unit cell arrays and each array has a plurality of split wordlines (SWLs) arranged in a first direction at fixed intervals, and a plurality of bitlines arranged in a second direction vertical to each of the SWLs at fixed intervals. A ferroelectric unit memory cell is arranged in each pair of adjacent two SWLs and adjacent two bitlines. The circuit includes a post X-decoder for receiving and decoding X and Z-addresses for controlling a cell array block operative, a global control pulse generator for providing a control pulse required for data write or read in response to a CSBpad signal received externally, a local control pulse generator for receiving the control pulse from the global control pulse generator and providing a control signal required for data write and read, an SWL cell array block for storage of data, an SWL driver for driving the SWL cell array block in response to control signals from the post X-decoder and the local control pulse generator, a Y-address decoder for decoding a Y-address signal received externally, a column controller for controlling columns in response to the control signal from the local control pulse generator and a decoded signal from the Y-address decoder, and a sense amplifier and I / O controller for sensing / recording a data from / to the SWL cell array block.

Owner:HYUNDAI ELECTRONICS IND CO LTD

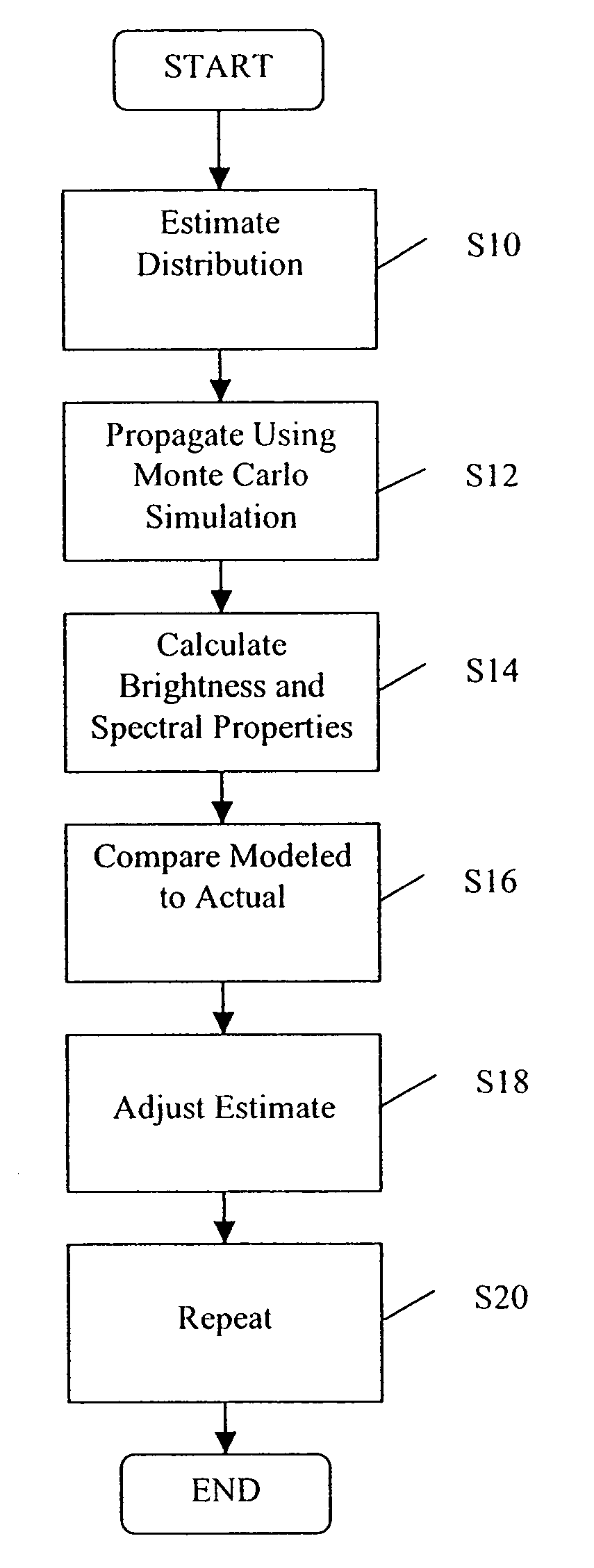

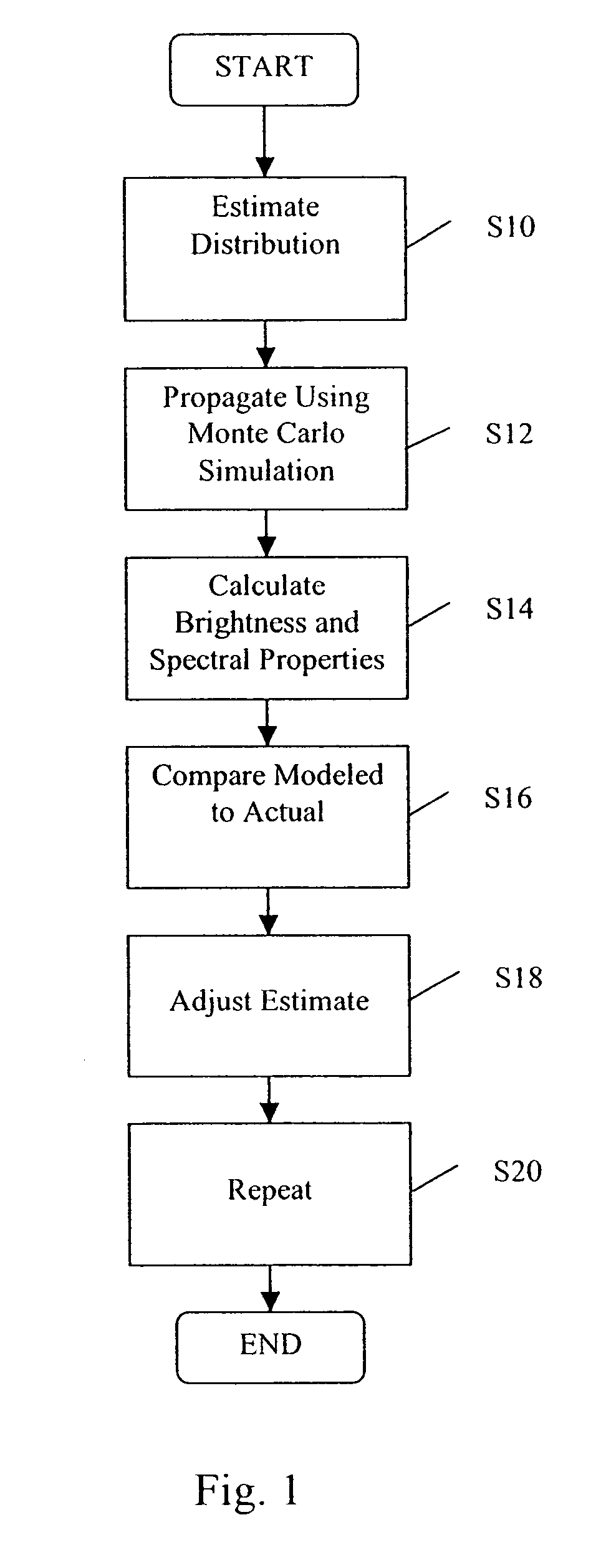

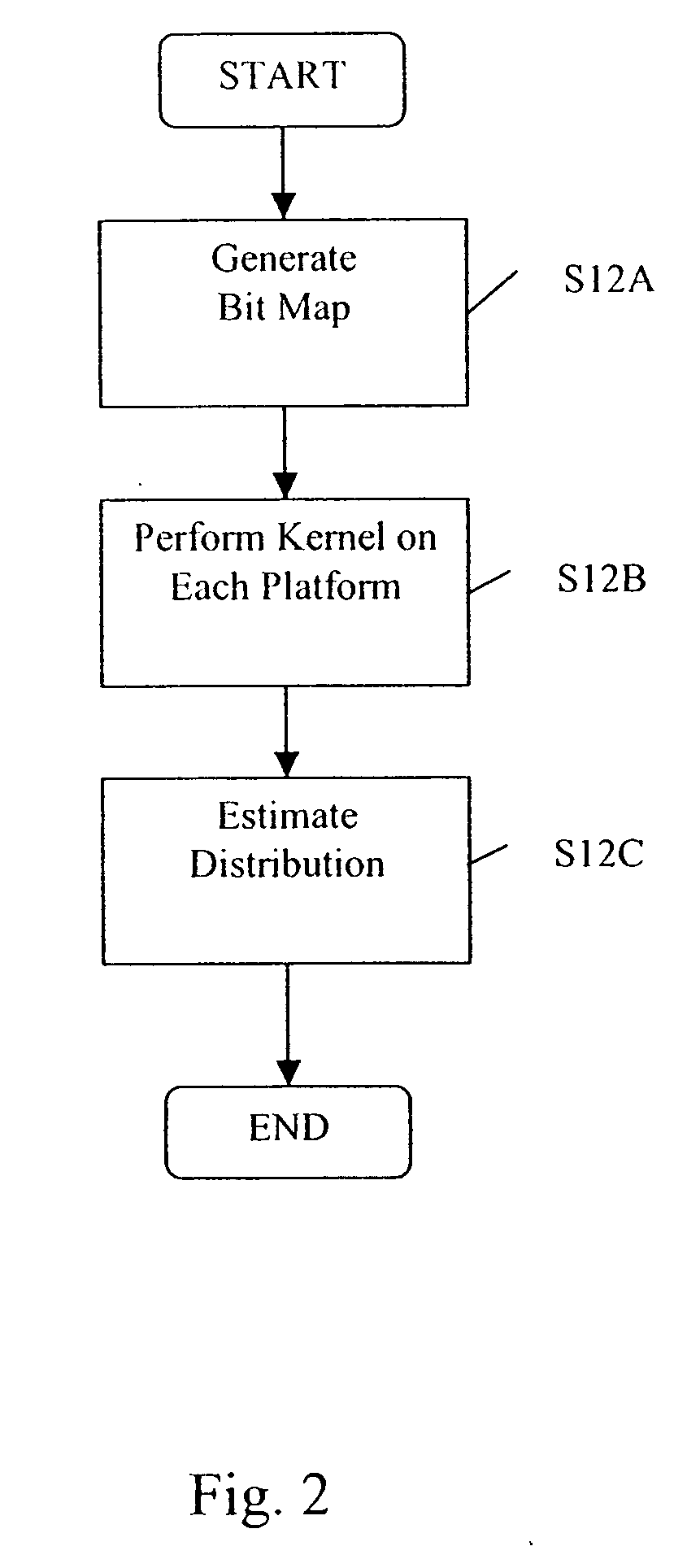

Monte Carlo simulation using GPU units on personal computers

ActiveUS20070282575A1Efficient use ofReduce computing timeComputation using non-denominational number representationDesign optimisation/simulationGraphicsData set

A method of performing a Monte Carlo analysis uses a graphical processor unit of a computer system, individual data sets to be analyzed are allocated to respective pixel locations in a graphical processor unit memory for Monte Carlo simulation and the outcome of the Monte Carlo simulation is calculated for each data set using stream processing in the graphical processor unit.

Owner:CAMBRIDGE RES & INSTR

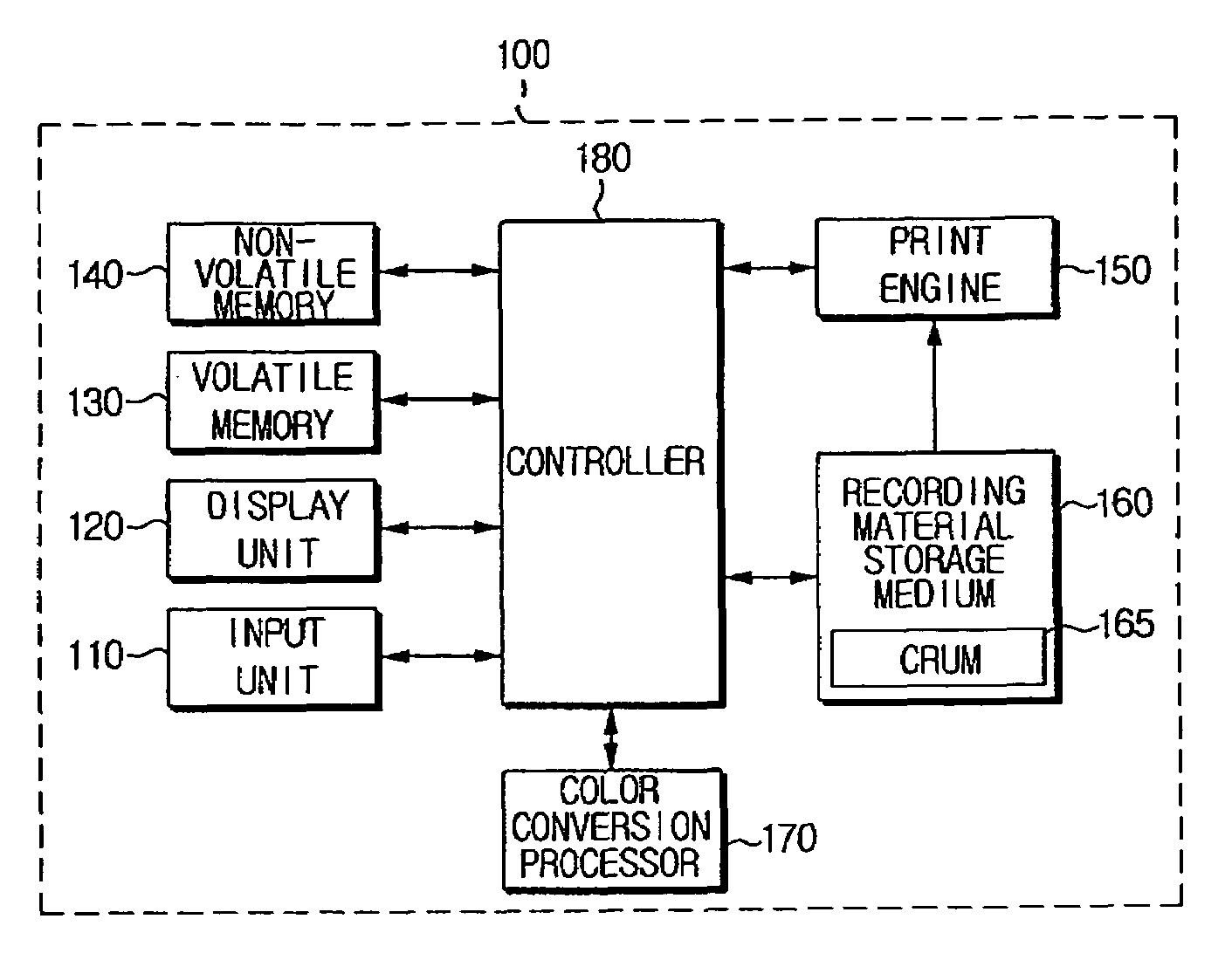

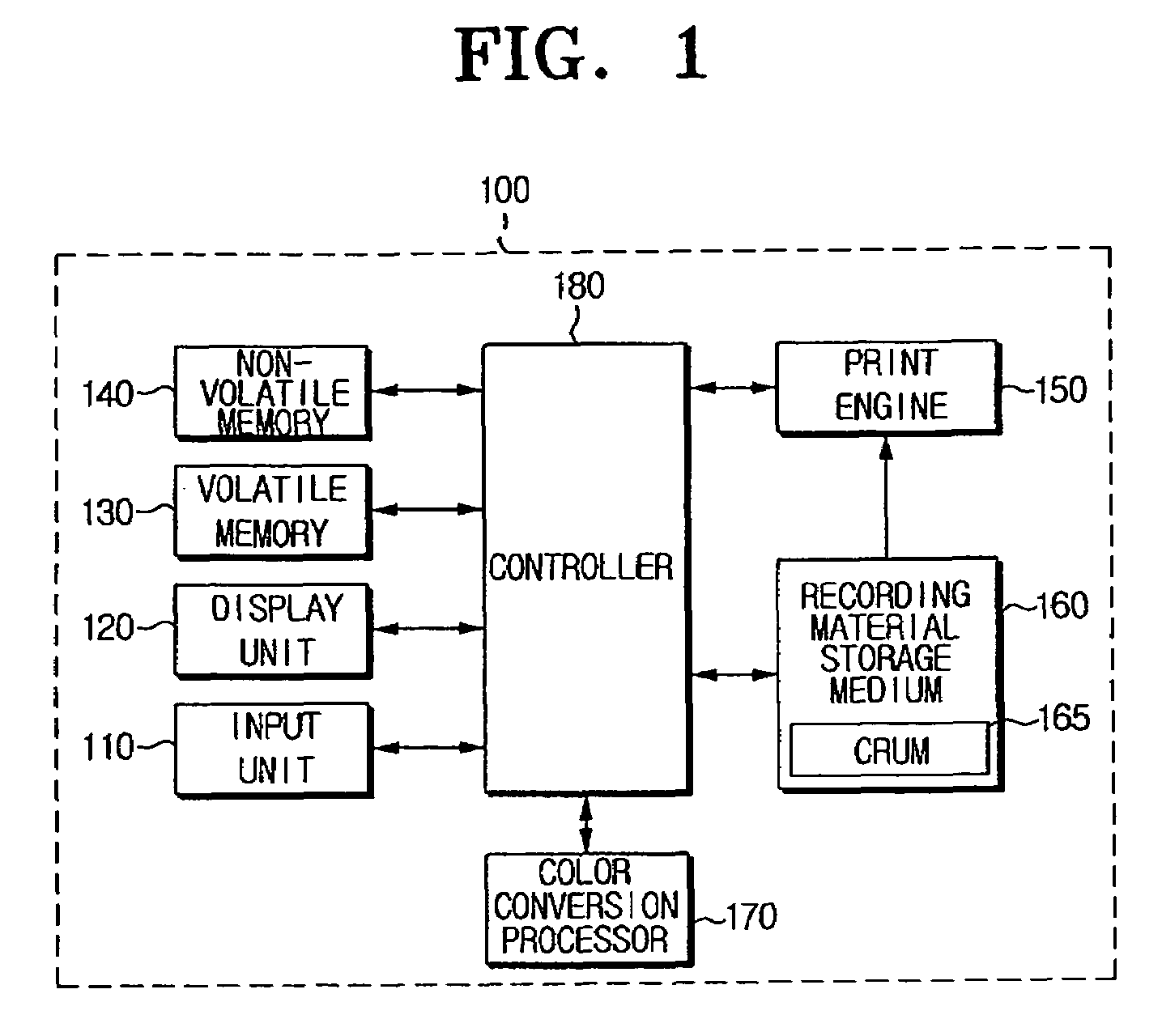

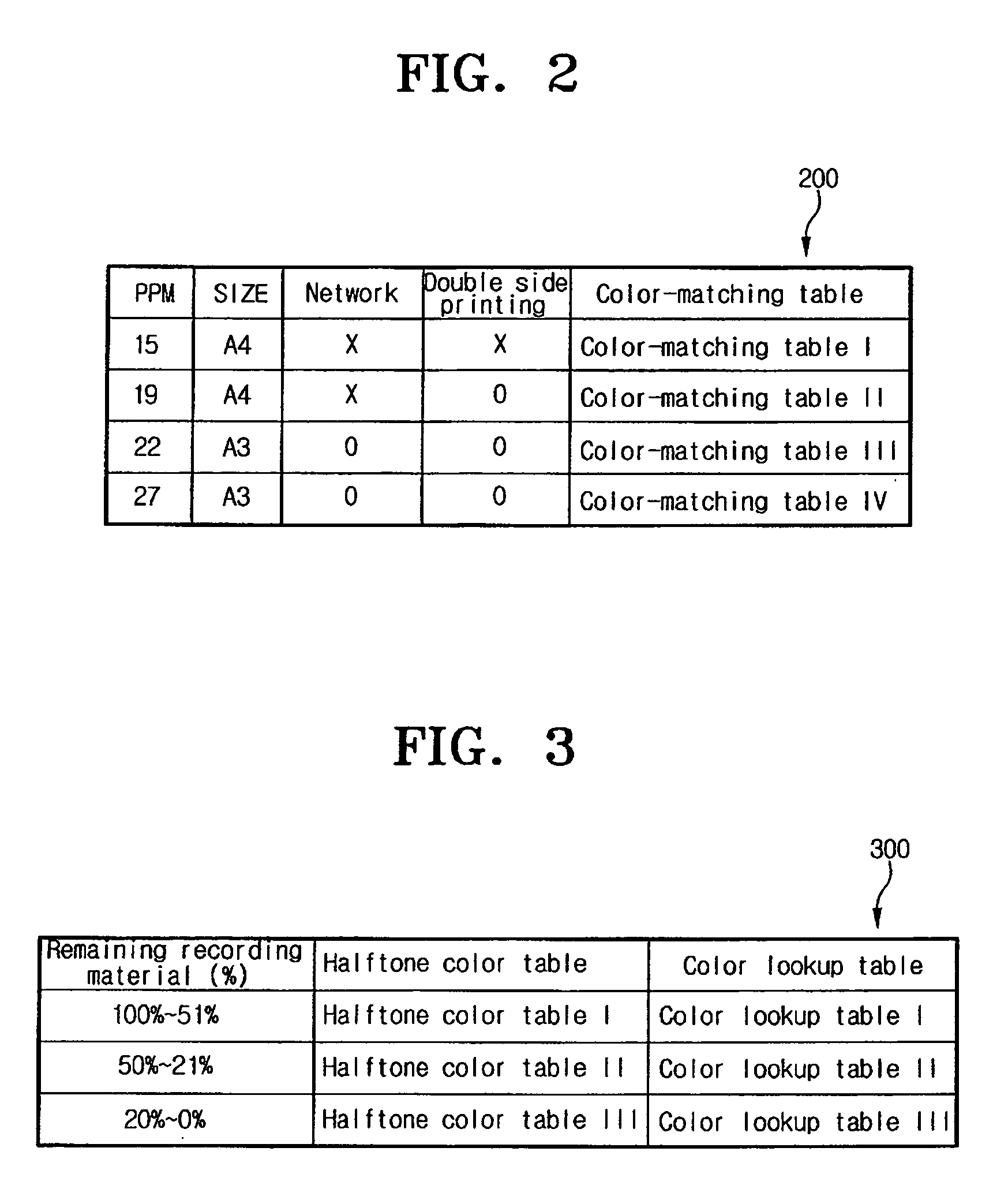

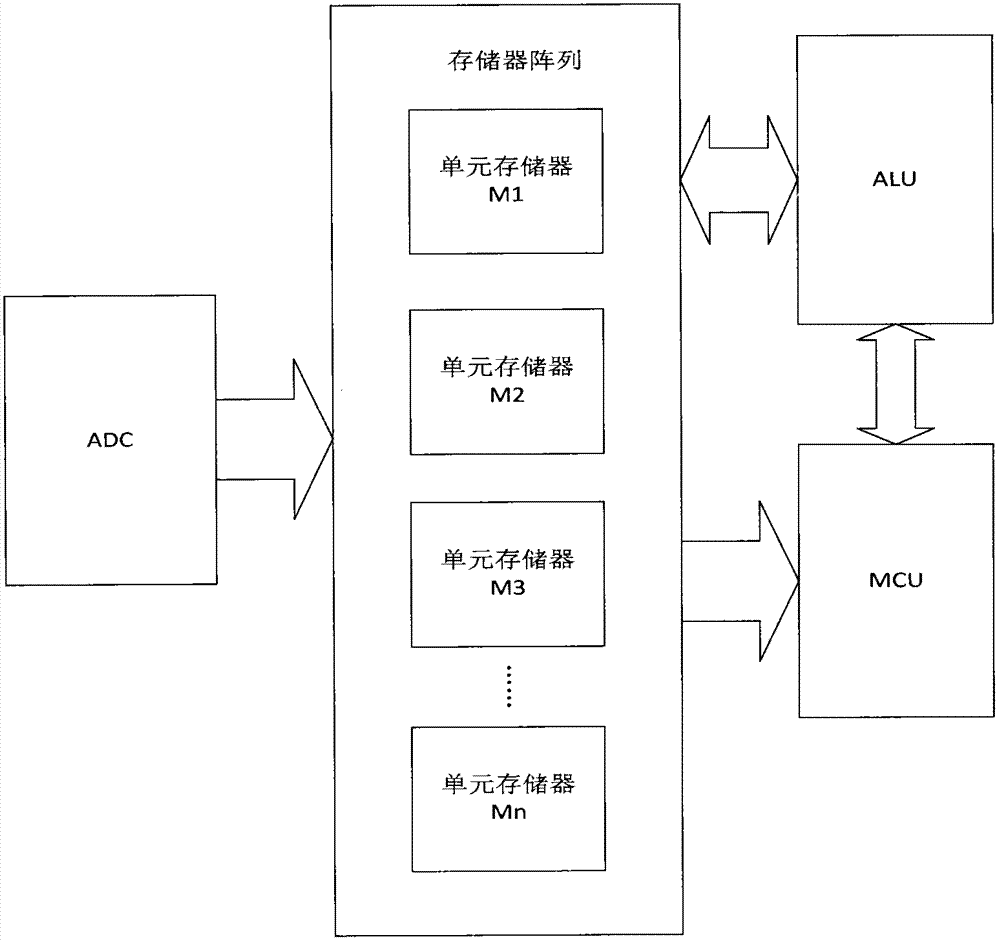

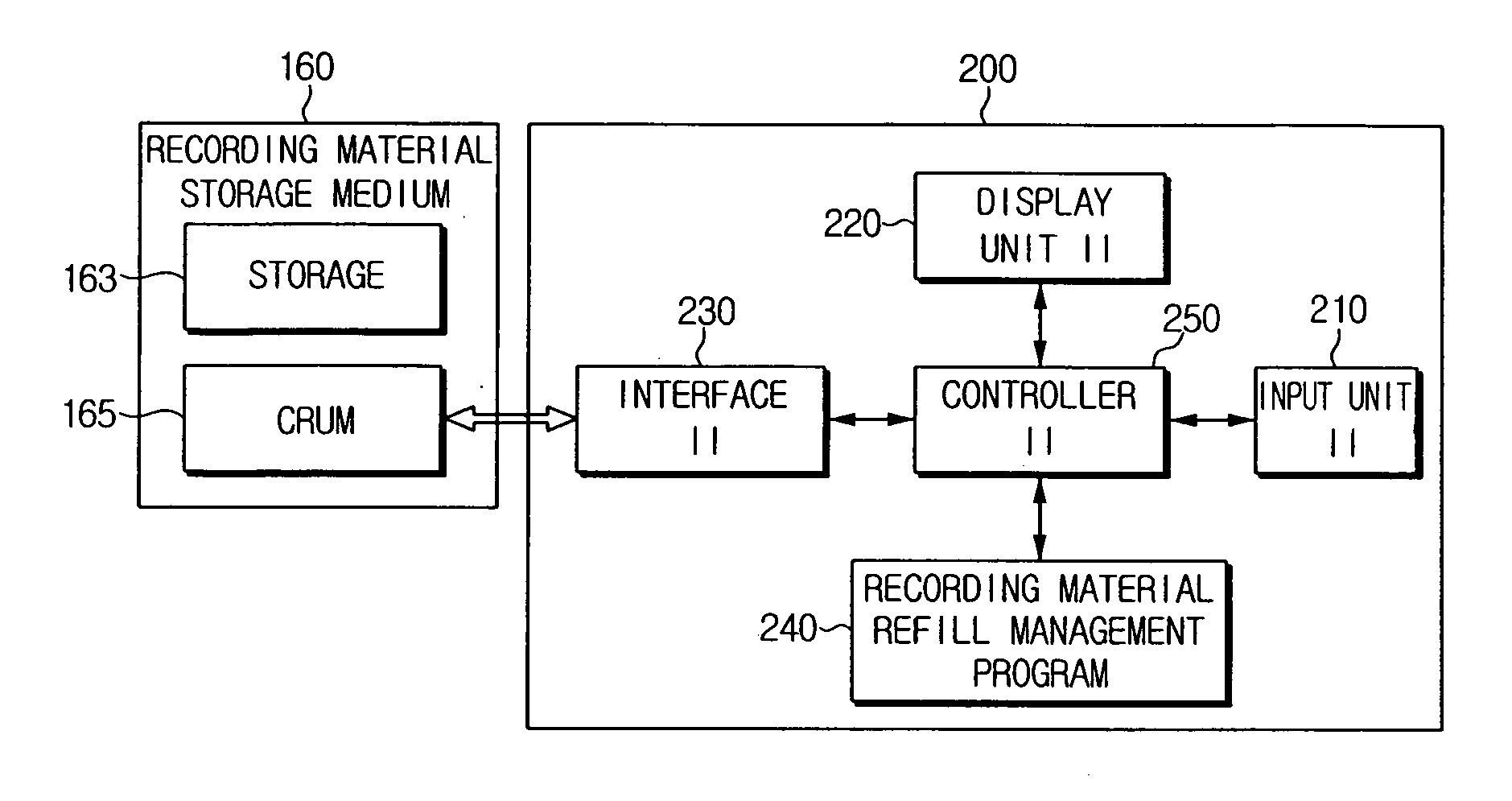

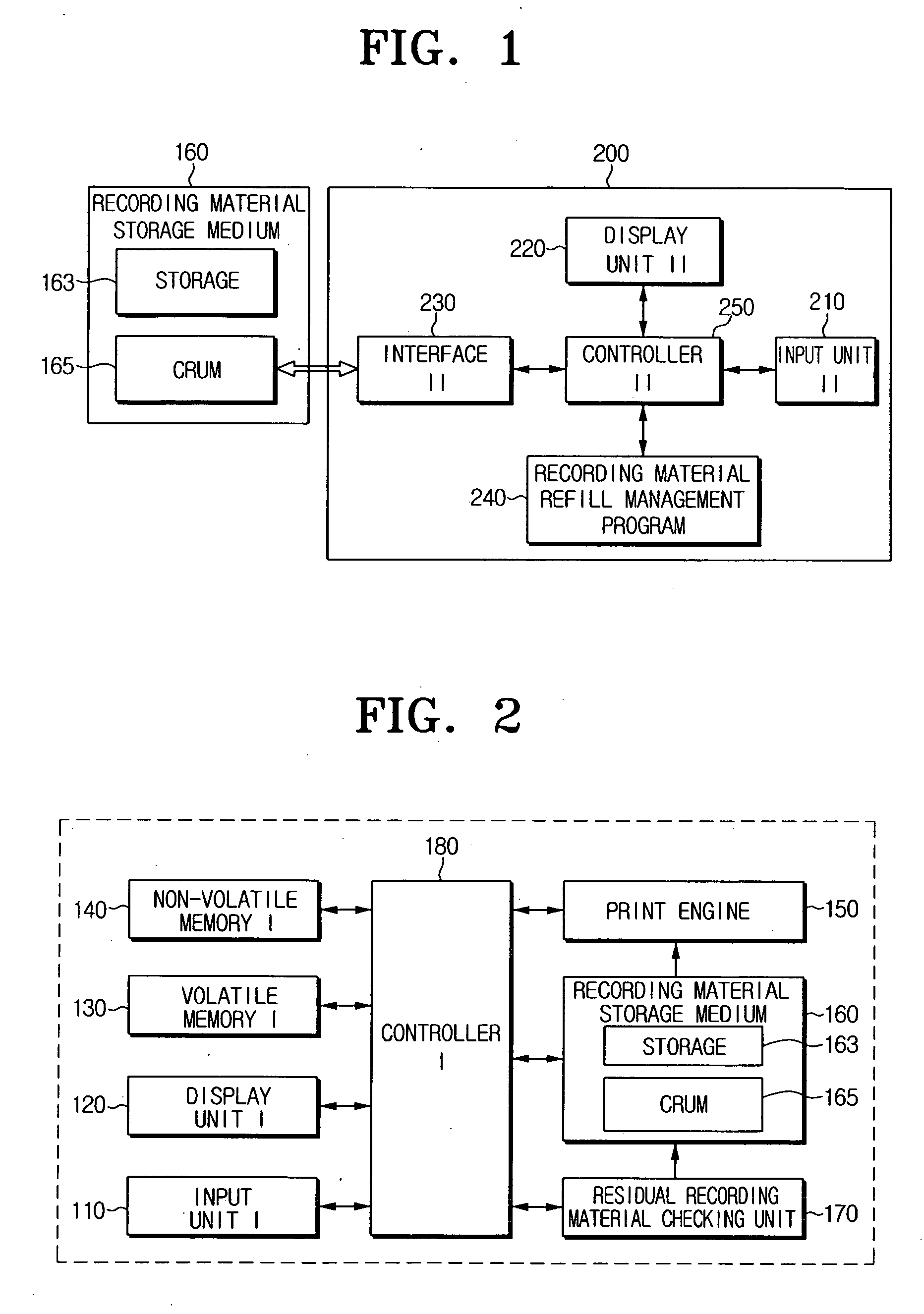

Image forming device and controlling method with recording material storage unit having replaceable memory storing color conversion tables selected based on image forming device status

ActiveUS7663781B2Improve printing qualityDigitally marking record carriersVisual presentation using printersImage formationDevice status

An image forming device and a controlling method thereof, in which the image forming device includes: a customer replaceable unit memory (CRUM) associated with a recording material storage medium to store a color conversion table group including a color conversion table that corresponds to status information of the image forming device, and a controller to determine current status information of the image forming device, to read a target color conversion table from among the color conversion table group according to the determined current status information, and to apply the target color conversion table to perform a printing operation on a document. Therefore, an optimum print quality can be guaranteed according to the determined current status of the image forming device.

Owner:HEWLETT PACKARD DEV CO LP

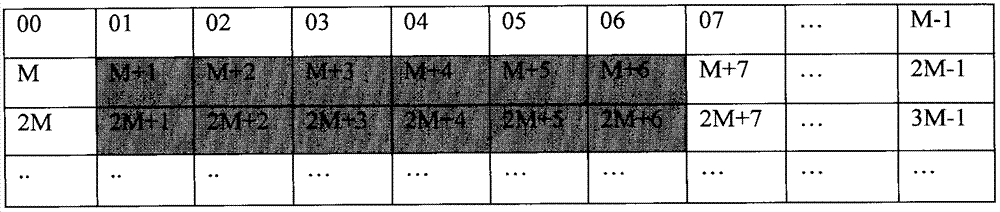

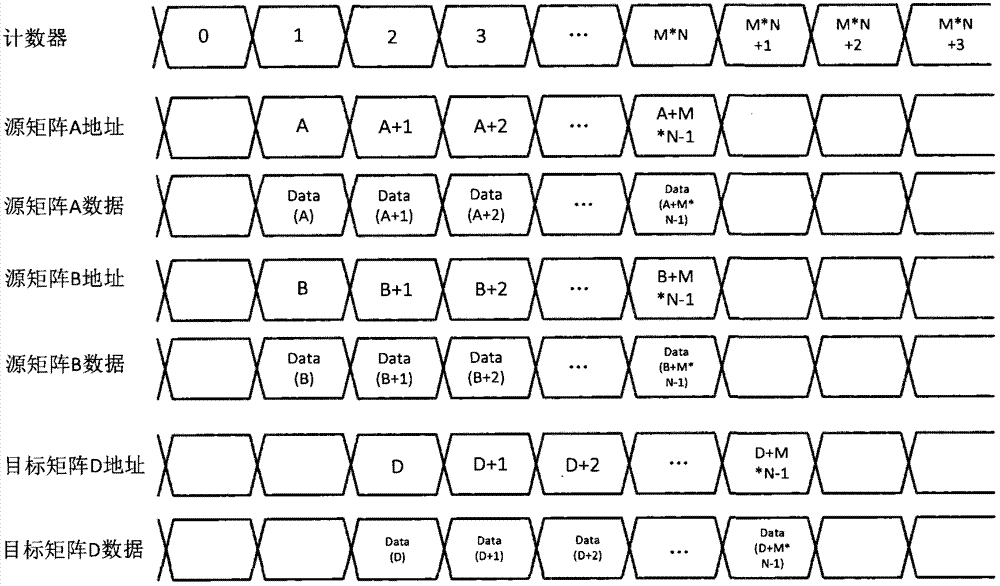

Touch screen data processing system, method and special arithmetic logic unit (ALU)

ActiveCN102880341AImprove computing efficiencyInput/output processes for data processingData processing systemArithmetic logic unit

The invention discloses a capacitive touch screen data processing system. The capacitive touch screen data processing system comprises a memory array, a micro control unit (MCU) and a special arithmetic logic unit (ALU), wherein the memory array is provided with a plurality of unit memories, and any unit memory is used for storing the complete or a part of original sampling capacitance data or data processing operation results of a touch screen; the MCU is used for performing flow control, and transmitting a special ALU command to the special ALU; and the ALU is used for performing operation on the data in the memory array according to the special ALU command transmitted by the MCU, and storing the results in the memory array, wherein the special ALU command has the command format so that the ALU can finish the batch processing of a plurality of storage data in a special ALU command. The special ALU command which can process batch data and the special ALU for processing the special ALU command are used in the capacitive touch screen data processing system, so that the workload of the MCU can be reduced, and the operation efficiency is greatly improved.

Owner:CHIPONE TECH BEIJINGCO LTD

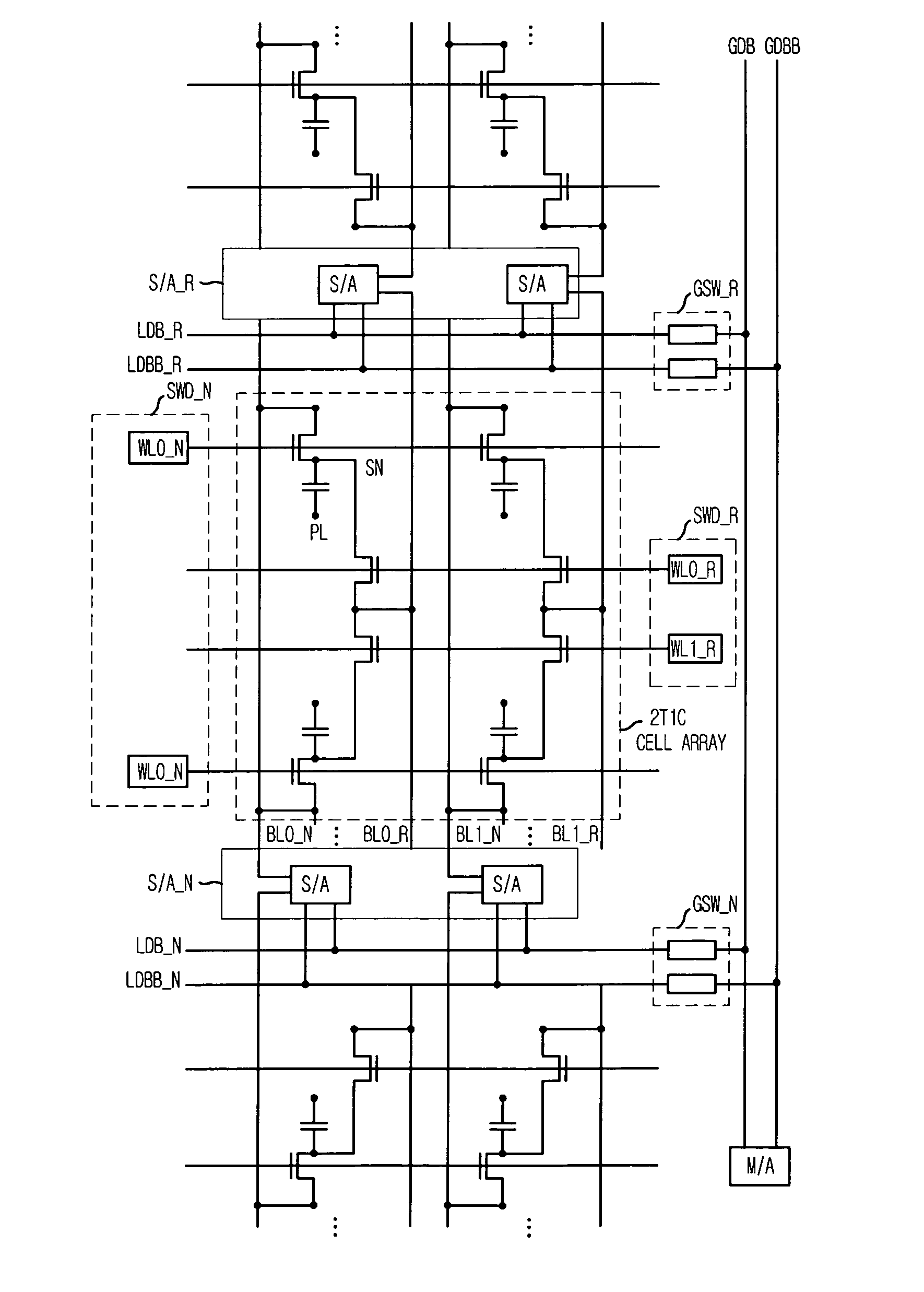

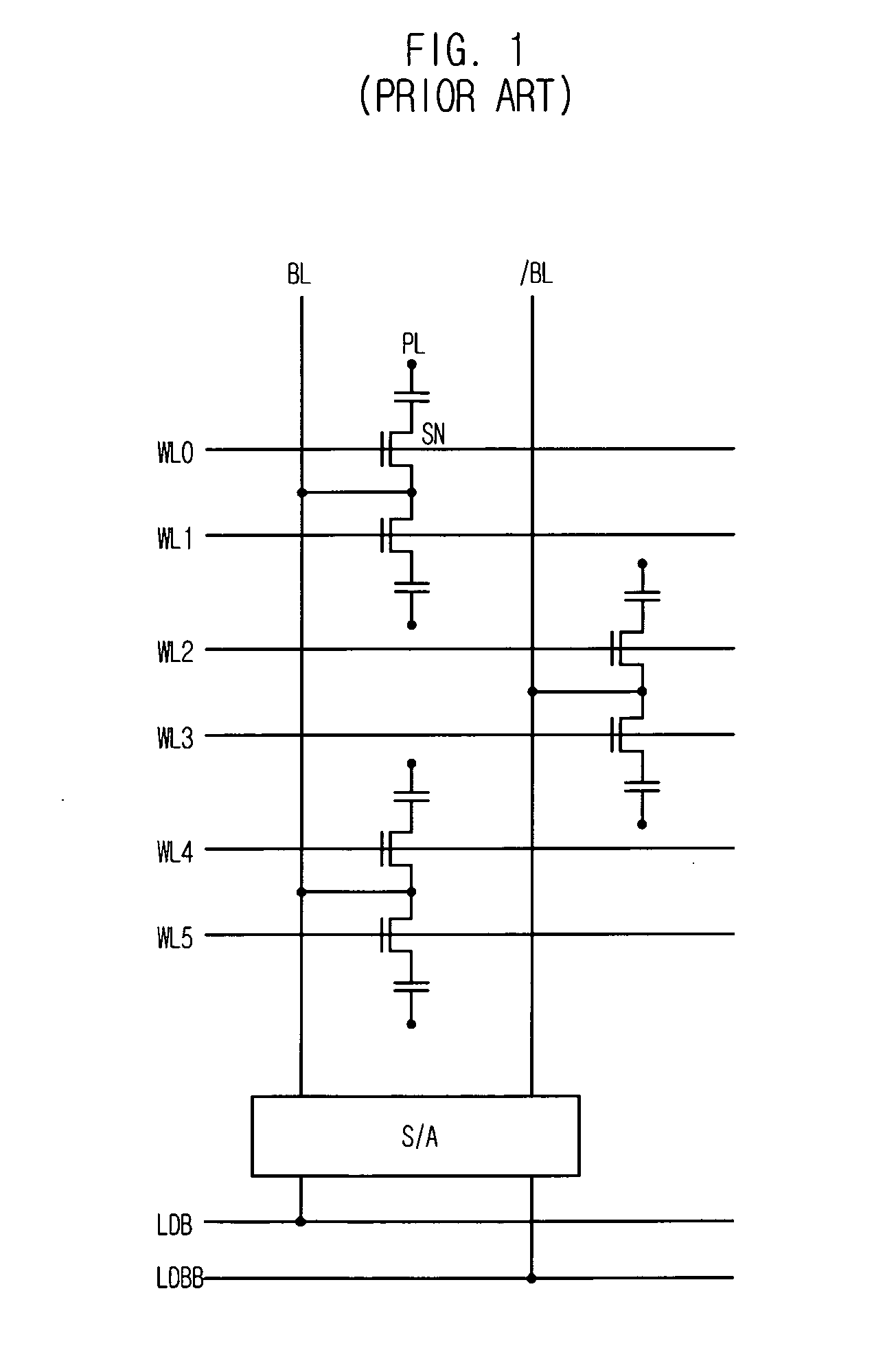

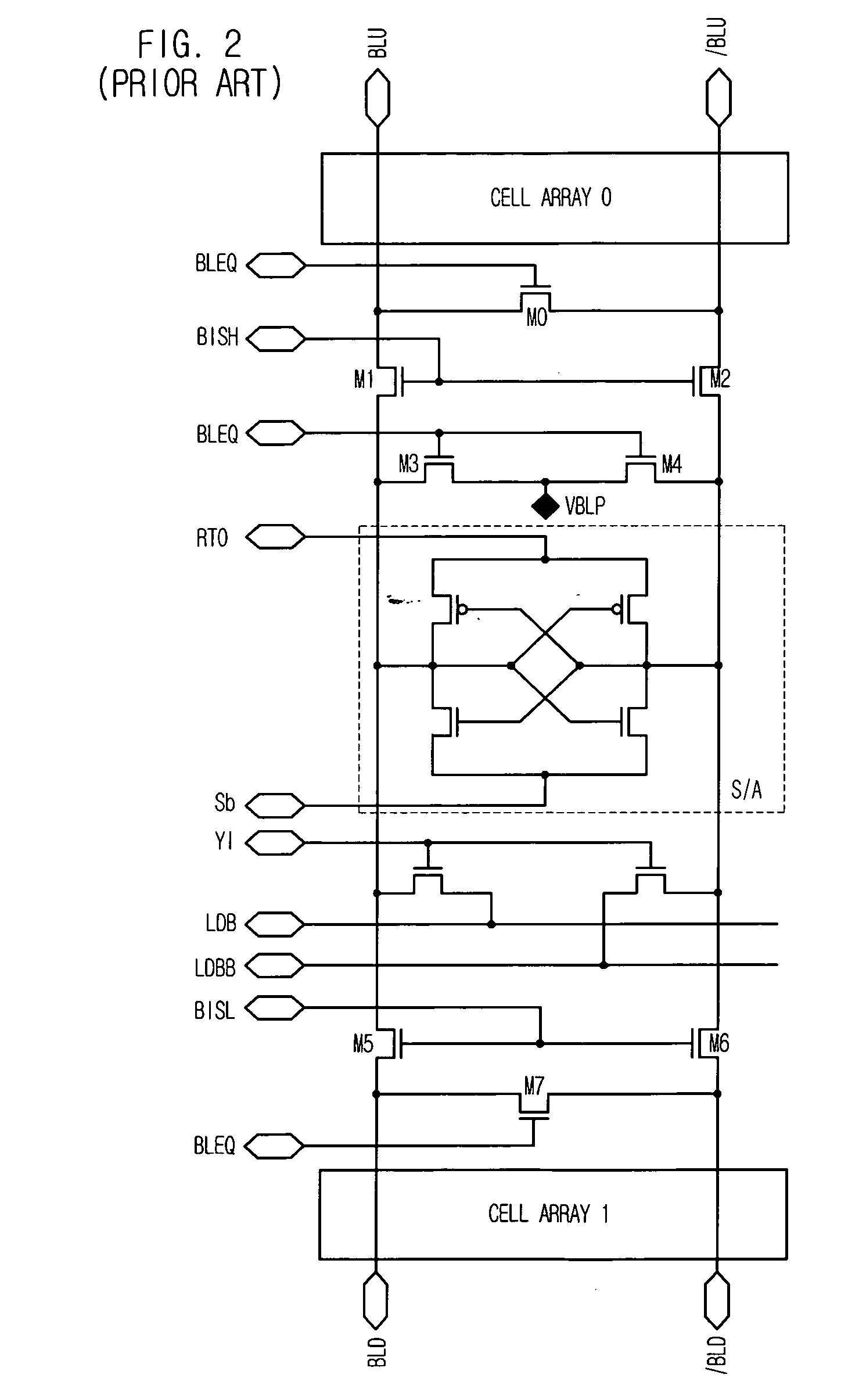

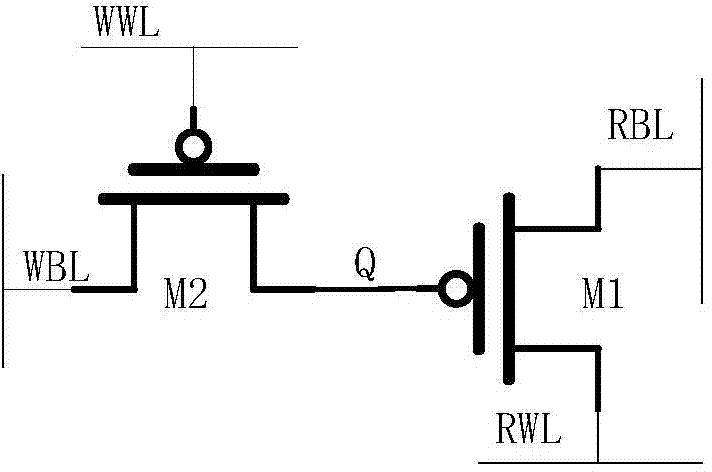

Pseudo SRAM

A unit memory cell for use in a pseudo static random access memory (SRAM) includes a cell capacitor; a normal accessing transistor whose gate, drain and source are respectively connected to a normal accessing word line, a normal accessing bit line and a storage node of the cell capacitor; and a refresh accessing transistor whose gate, drain and source are respectively connected to a refresh accessing word line, a refresh accessing bit line and the storage node of the cell capacitor.

Owner:SK HYNIX INC

Vertical transistor structure for use in semiconductor device and method of forming the same

ActiveUS7408224B2Small sizeHigh-integrated semiconductor devicesTransistorNon-mechanical controlsInsulation layerEngineering

According to some embodiments, a structure of vertical transistor includes gate electrodes distanced by a predetermined interval in an active region, formed in a vertical shape to have a predetermined depth from a top surface of a semiconductor substrate. A gate insulation layer is formed between one side wall of the gate electrode and the substrate. A gate spacer is formed in another sidewall of the gate electrode, covering the gate electrode. A contact plug is formed between the gate spacer. A plug impurity layer is formed in a lower part of the contact plug, and source and drain are formed opposite to the gate electrode within the active region. Thereby, an area occupied by a gate electrode is substantially reduced, so a unit memory cell has a 4F2 structure, reducing a memory cell size, by forming a vertical-type gate electrode within an active region.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor memory device

InactiveUS20100080038A1Improve performanceLow costSolid-state devicesDigital storageEngineeringSemiconductor

An inexpensive nonvolatile memory having high performance which makes random write and readout possible an unlimited number of times is provided. A unit memory cell is formed of a MISFET having a channel body that is electrically isolated from a semiconductor substrate and a resistance change element having a two-terminal structure with one end electrically connected to a drain of the MISFET. The MISFET functions as a volatile memory element, and the resistance change element functions as a nonvolatile memory element, so that information stored in the MISFET is copied to the resistance change element before the power is turned OFF and information stored in the resistance change element is transferred to the MISFET when the power is turned ON, and thus, the MISFET is used as a volatile memory which makes random write and readout possible.

Owner:SHARP KK

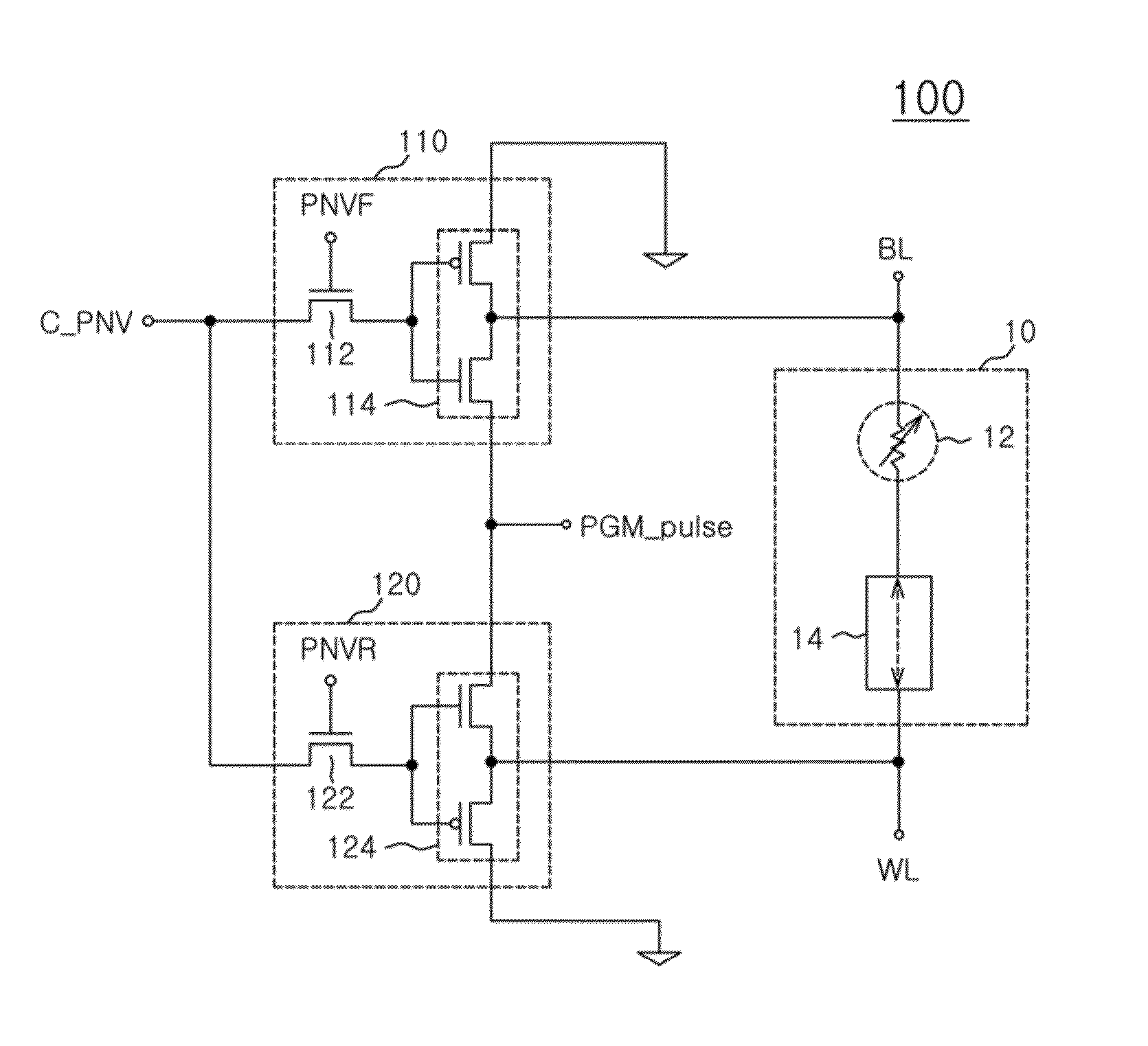

Resistive memory device and operation method thereof

A resistive memory device includes a memory cell array including a unit memory cell coupled between a word line and a bit line, wherein the unit memory cell includes a data storage material and a non-silicon-substrate-based type bidirectional access device coupled in series, a path setting circuit coupled between the bit line and the word line, suitable for providing a program pulse toward the bit line or the word line based on a path control signal, a forward write command, and a reverse write command, and a control unit suitable for providing a write path control signal, a forward program command, and a reverse program command based on an external command signal.

Owner:SK HYNIX INC

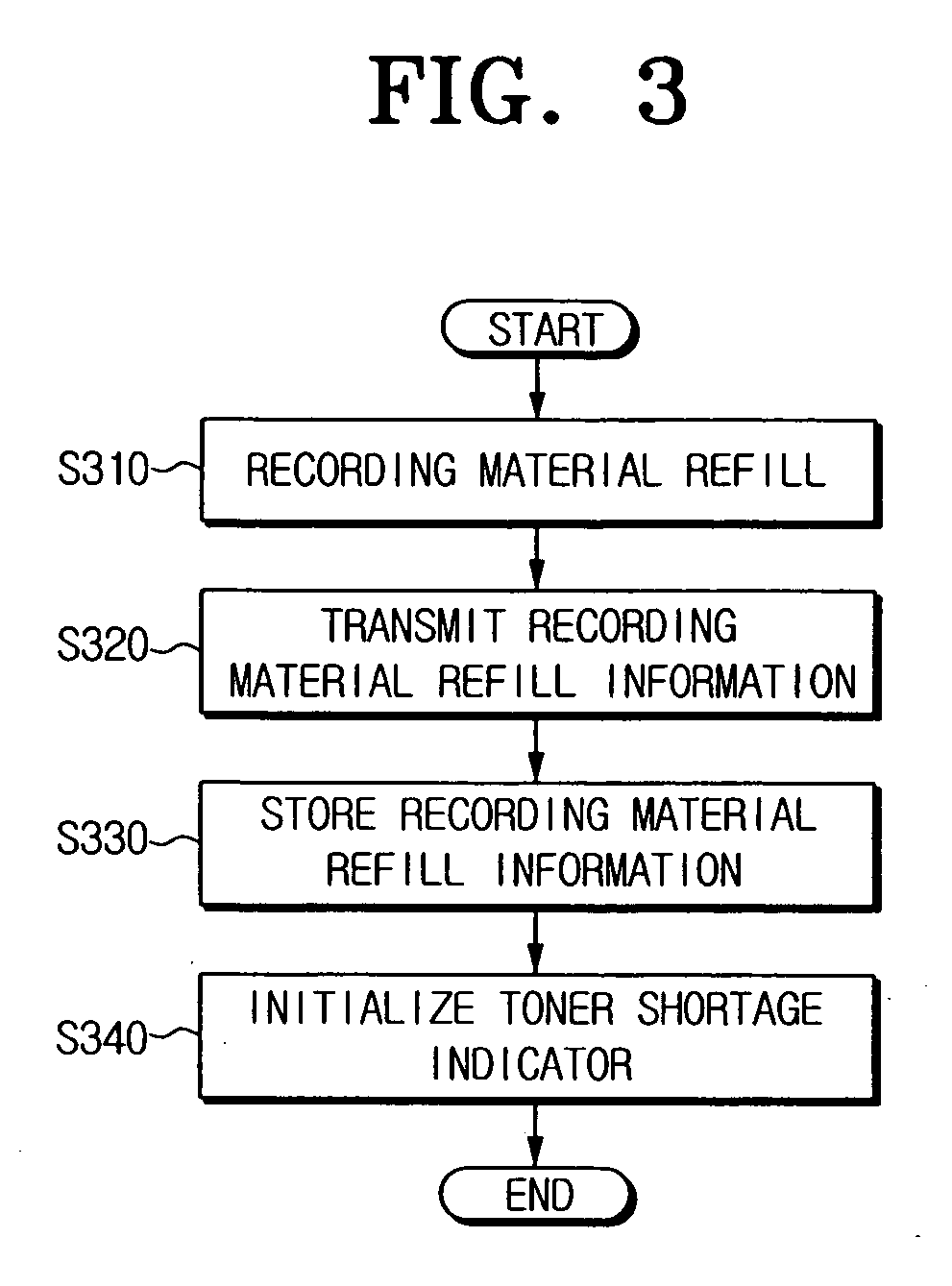

Image forming device, controlling method thereof, and recording material storage medium

InactiveUS20060114491A1Efficient managementElectrographic process apparatusVisual presentationImage formationEngineering

An image forming device, a controlling method thereof, and a recording material storage medium. The image forming device includes a customer replaceable unit memory (CRUM) provided to a recording material storage medium thereof to store a toner shortage indicator that is set to “Low” to indicate a recording material shortage if a remaining amount of the recording material in the recording material storage medium is not greater than a predetermined threshold, and a controller to determine that the recording material storage medium is refilled with the recording material by a non-authentic method if the remaining quantity of the recording material in the recording material storage medium is greater than the predetermined threshold and if the toner shortage indicator is set to “Low” to indicate the recording material shortage. Accordingly, a user can be encouraged to use an authentic recording material for refills.

Owner:SAMSUNG ELECTRONICS CO LTD

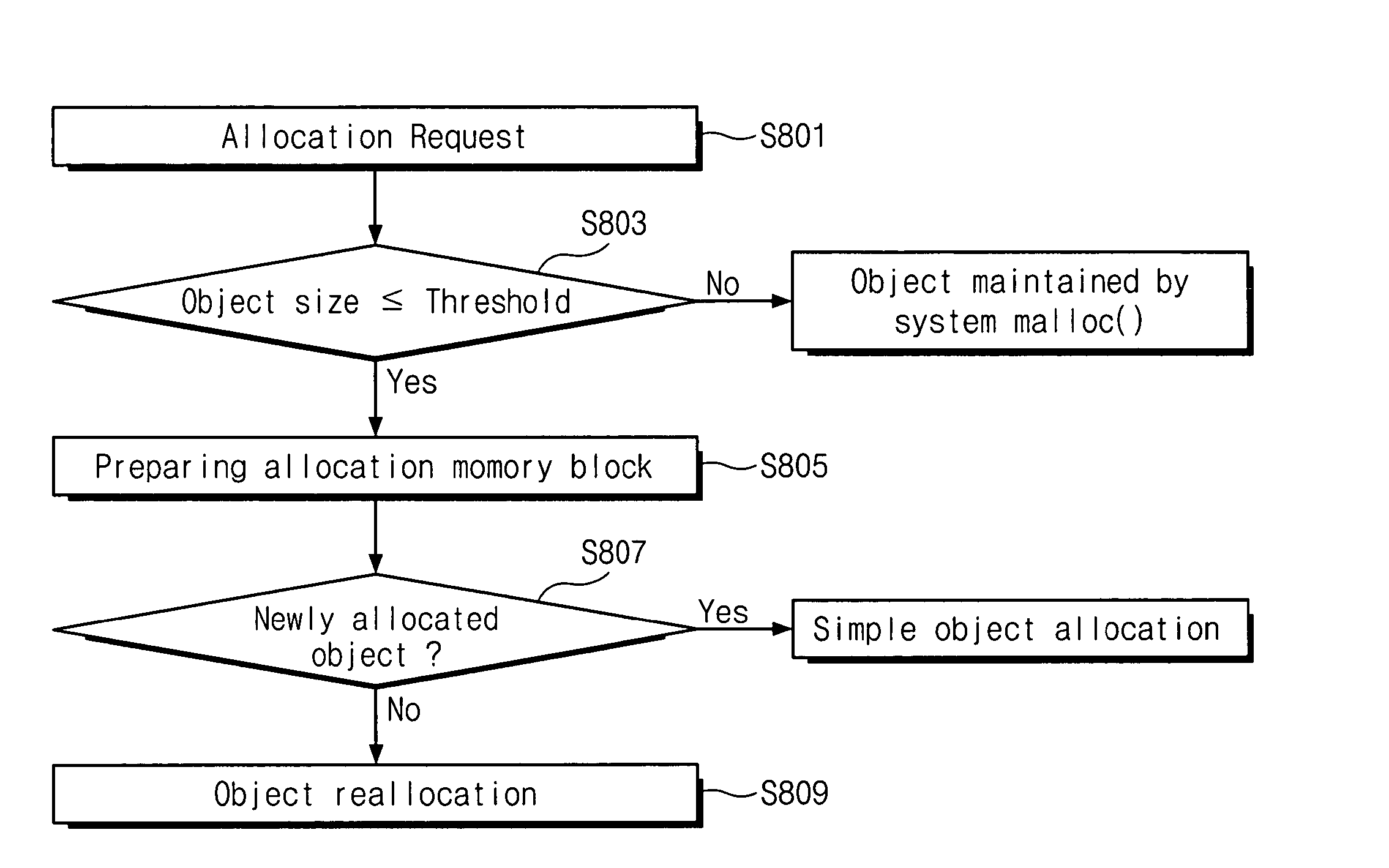

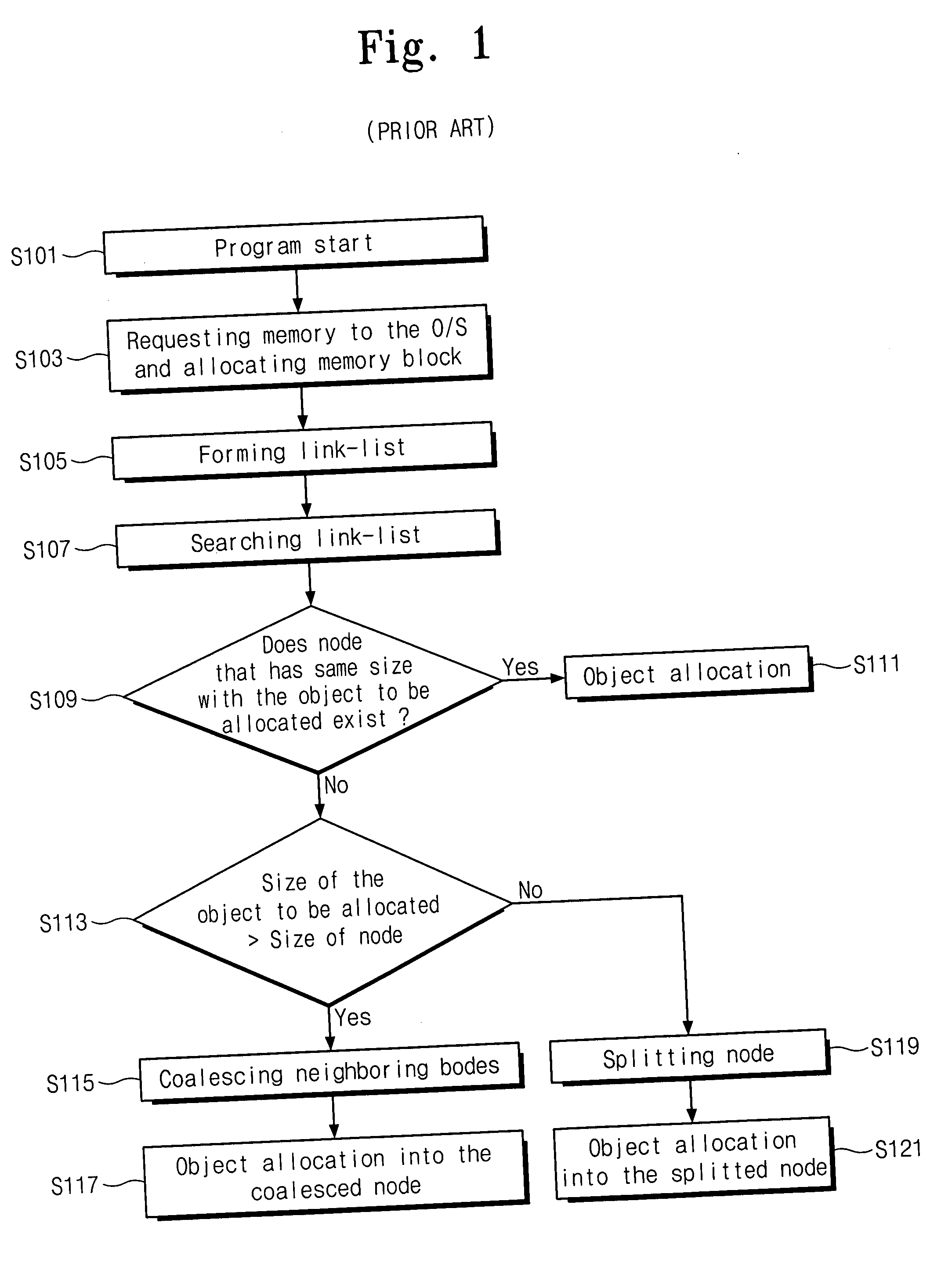

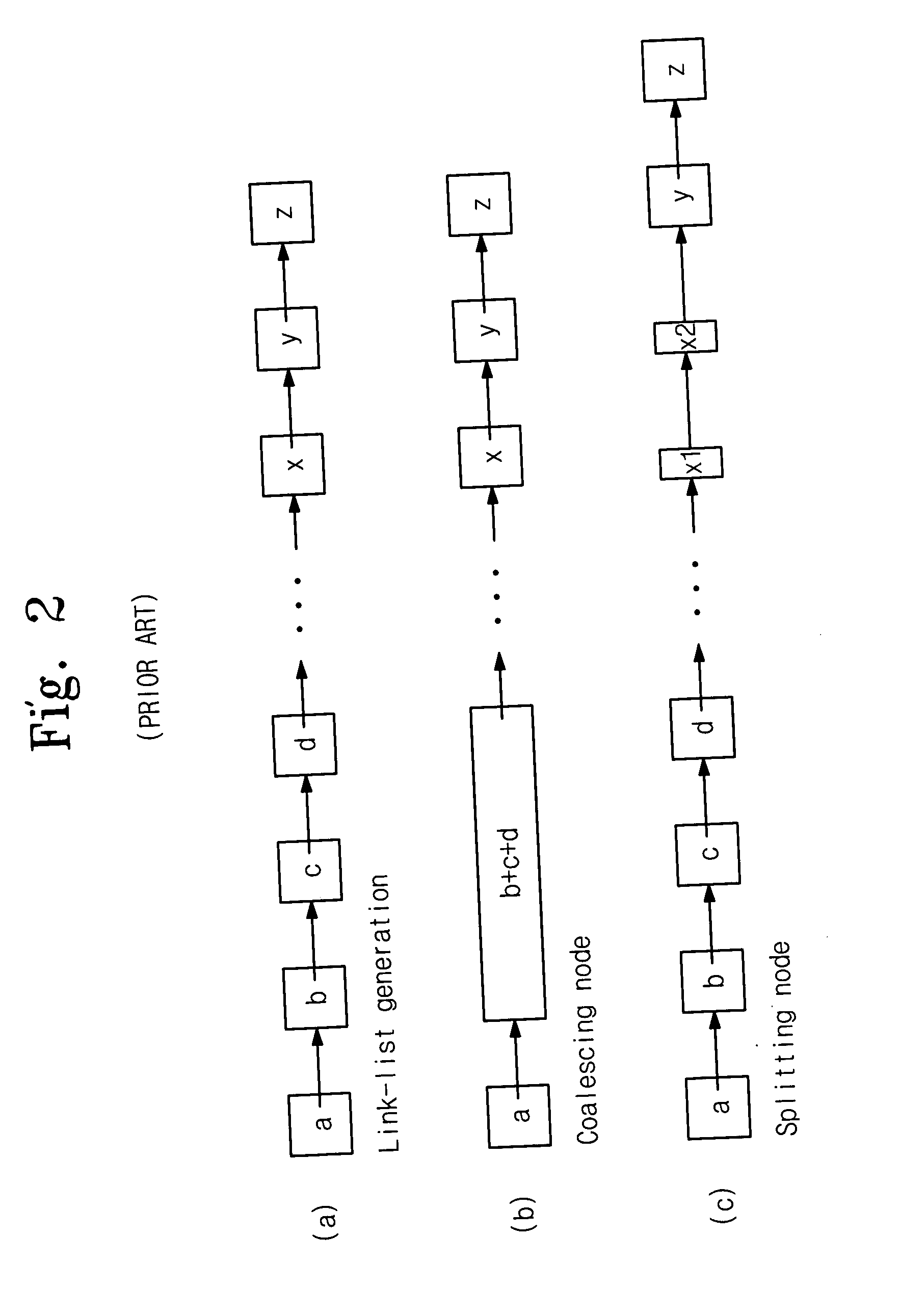

Method and apparatus for executing dynamic memory management with object-oriented program

ActiveUS20050071597A1Improve performanceShort operating timeData processing applicationsMemory adressing/allocation/relocationParallel computingUnit memory

The disclosure is a method and apparatus for operating dynamic memory management with an object-oriented program, by which objects with frequent creation and short life spans are allocated to a unit memory block in sequence. After released from the unit memory block, the objects are added on a free re-use list so as to be reused when there is an invocation of allocation for the same object size. It is advantageous to enhancing system performance.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor memory device

InactiveUS7375399B2Low costSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductorDiffusion layer

The present invention is a semiconductor memory device having a logic block and a memory block on the same chip. In the memory device, unit memory cells each include at least two transistors, one of which is a write transistor for storing an electric charge into and releasing it from an electric charge storage node, and the other is a read transistor whose conductance in a channel region provided between a source and drain of the read transistor is modulated dependently on the amount of electric charge stored into or released from the electric charge storage node by the write transistor. The read transistor has a gate-insulating film thicker than that of a transistor provided in the logic block, and uses the same diffusion layer structure as that of the logic block.

Owner:RENESAS ELECTRONICS CORP

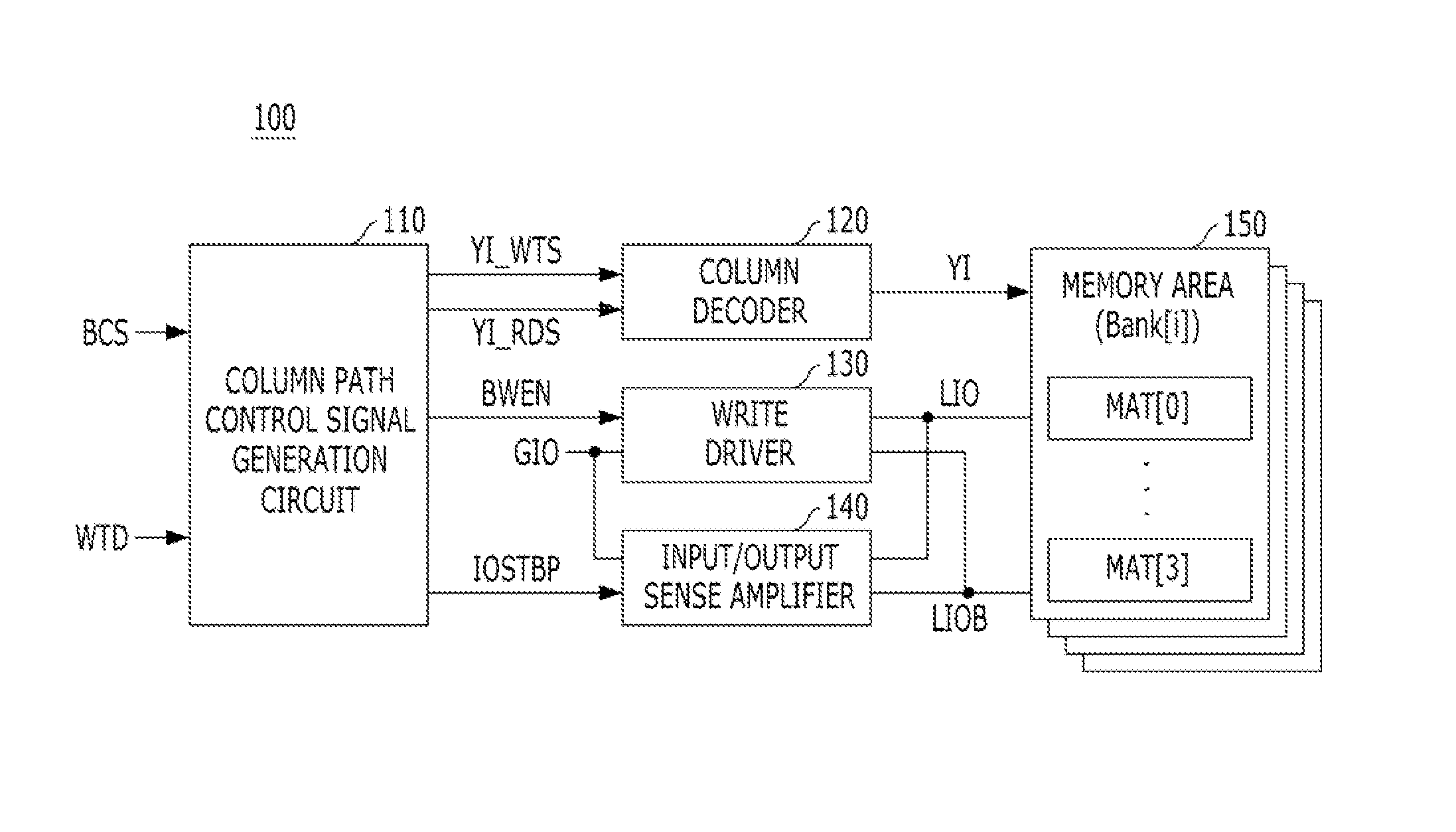

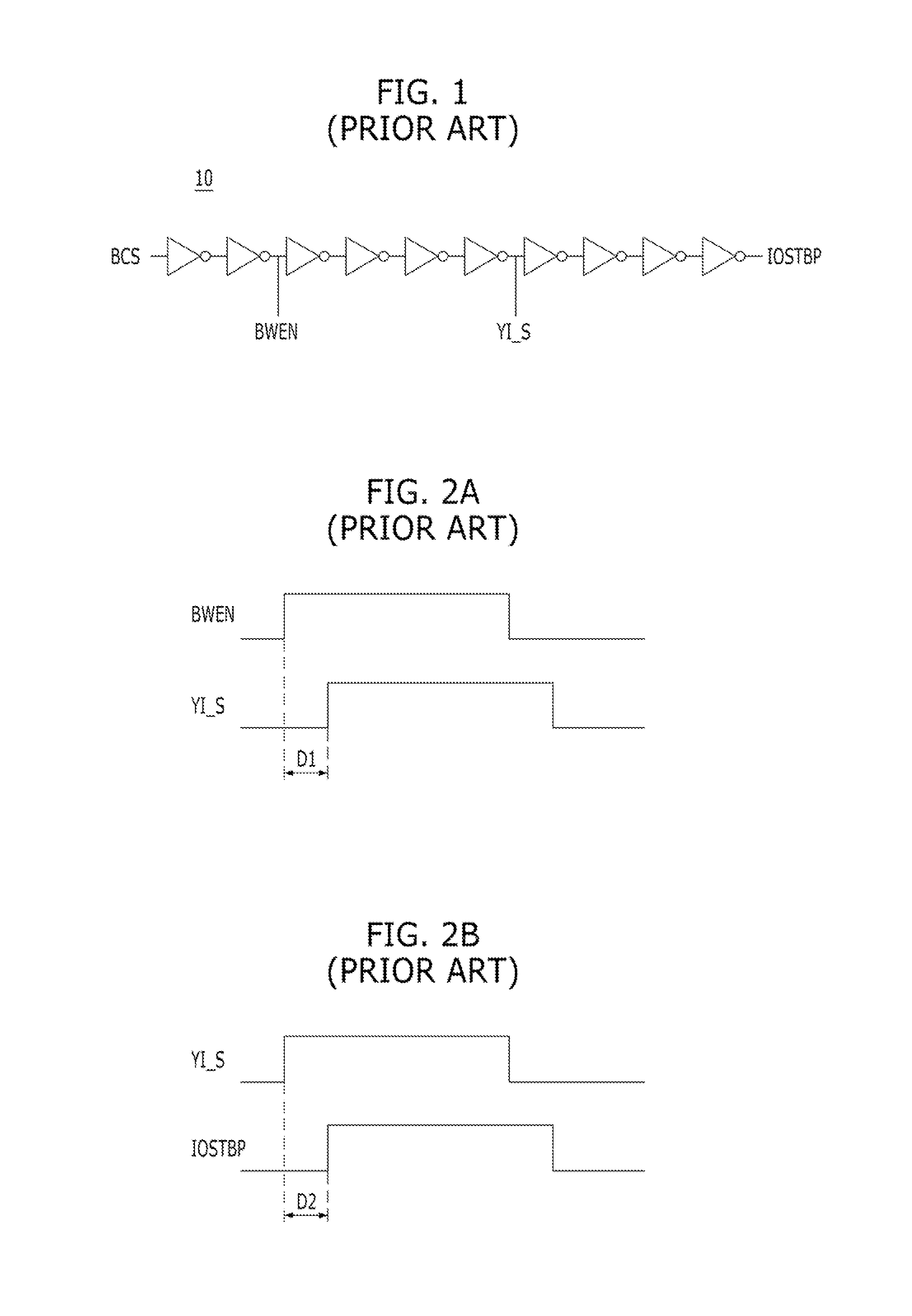

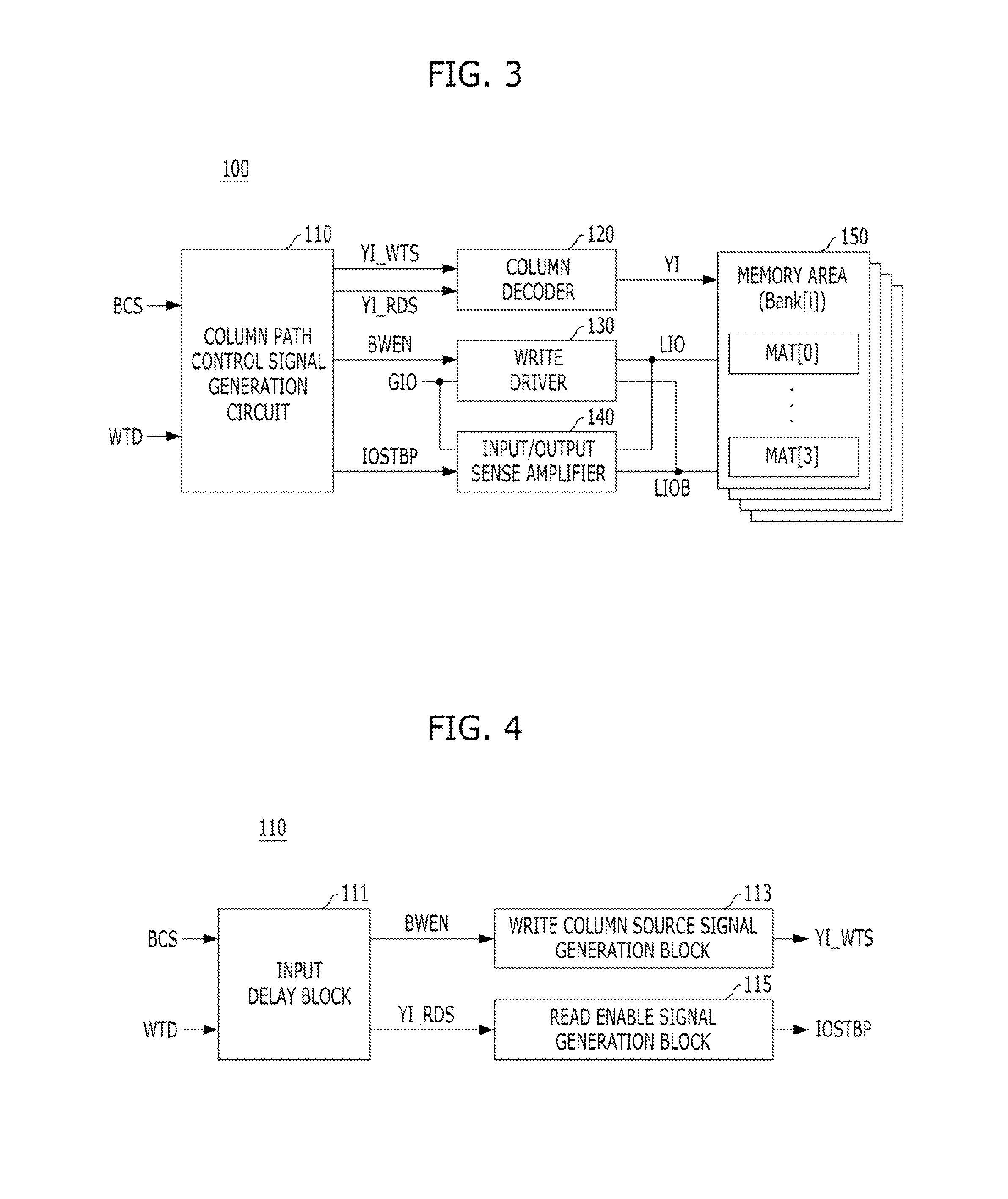

Semiconductor memory device

A semiconductor memory device includes a first signal generation unit configured to sequentially generate first and second delay signals in response to a first column control signal, the first and second delay signals having reflected a delay time and a multiplied delay time selected from a plurality of delay times in correspondence with an arrangement location of a unit memory region, through data is input / output, respectively, and a second signal generation unit configured to generate a second column control signal delayed by the selected delay time as compared with the first column control signal, to determine an activation time point of the second column control signal in response to the first delay signal, and to determine a deactivation time point of the second column control signal in response to the second delay signal.

Owner:SK HYNIX INC

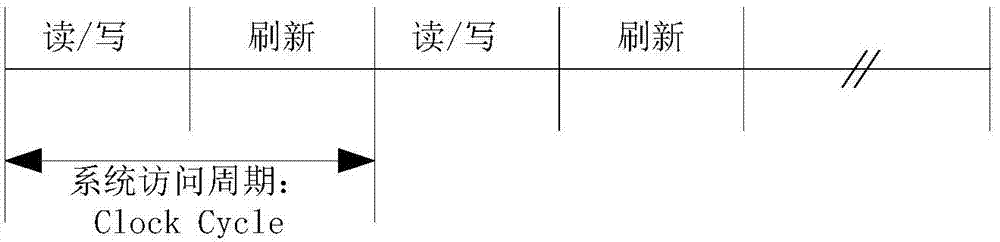

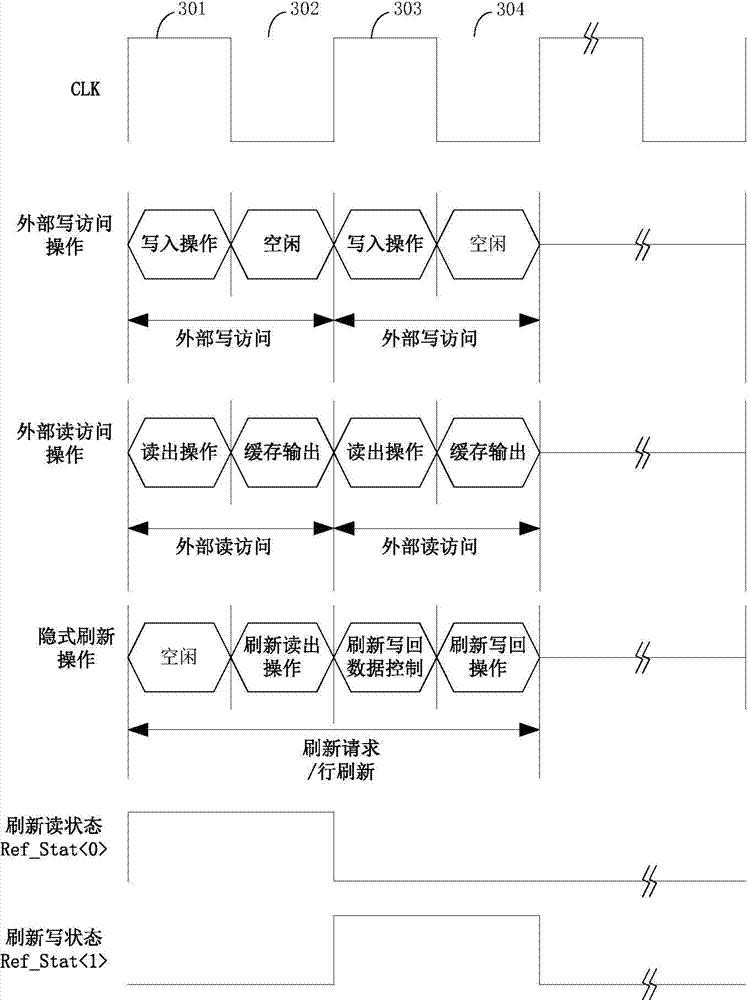

Dynamic memory refreshing method and refreshing controller

The invention discloses a dynamic memory refreshing method and a refreshing controller, and belongs to the technical field of semiconductor memories. According to the dynamic memory refreshing method, based on a grain unit memory, by using a manner than the grain memory unit has two groups of mutually independent word lines and bit lines, read / write operation of external access is completed within an upper-half period of a clock, and refreshing read / refreshing write operation is completed within a lower-half period of the clock. According to the dynamic memory refreshing method, a refreshing request signal and a refreshing state signal are generated according to a refreshing period of the gain unit, a line number of a memory Bank and a clock period; control signals of corresponding refreshing read and refreshing write operations are generated according to a refreshing state to control refreshing read and refreshing write operations and external read / external write operation to be performed in parallel. According to the dynamic memory refreshing method, the confliction between a refreshing operation and the external access is eliminated, so that the memory can be accessed completely randomly in real time.

Owner:HUAZHONG UNIV OF SCI & TECH