Patents

Literature

619 results about "Nanopillar" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

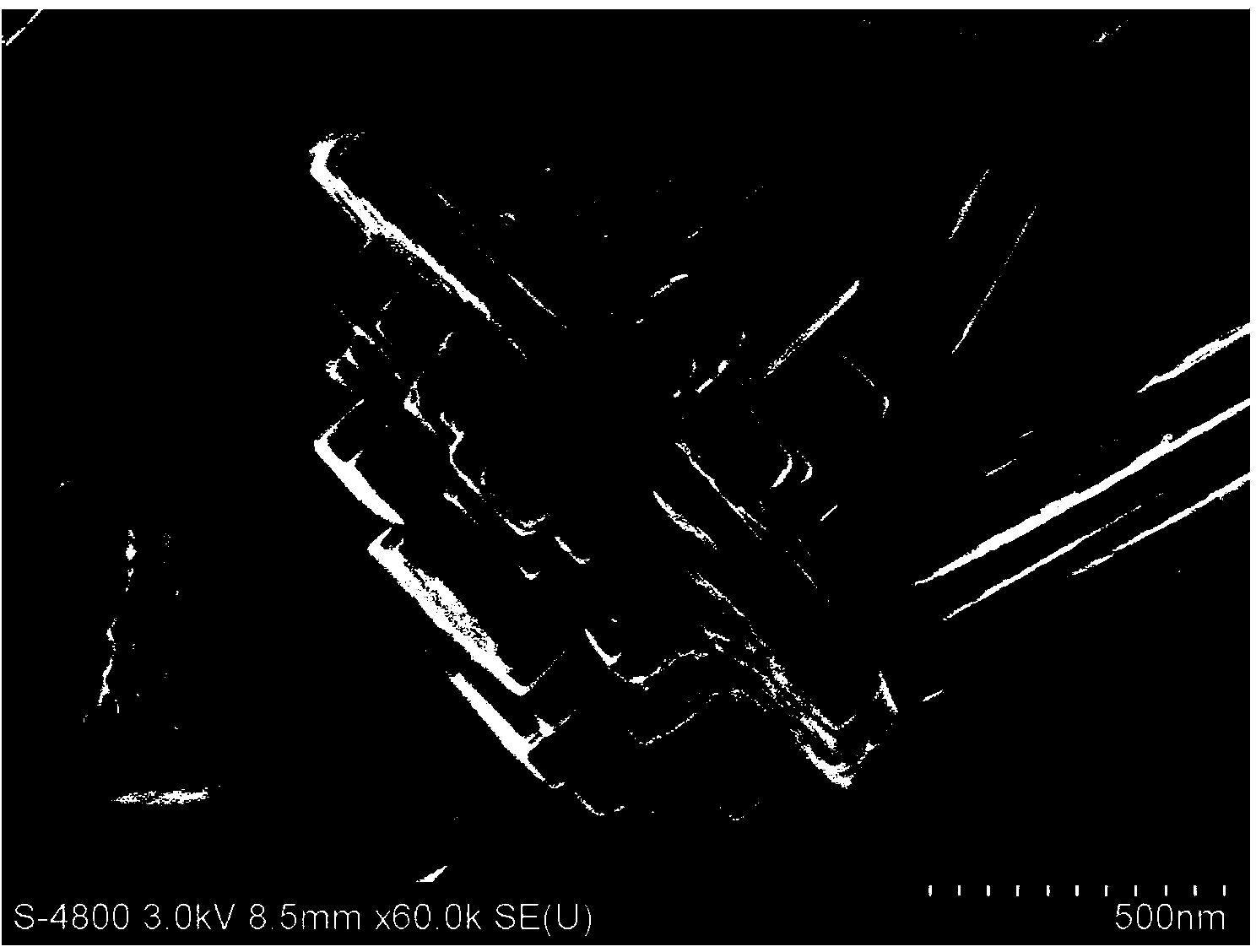

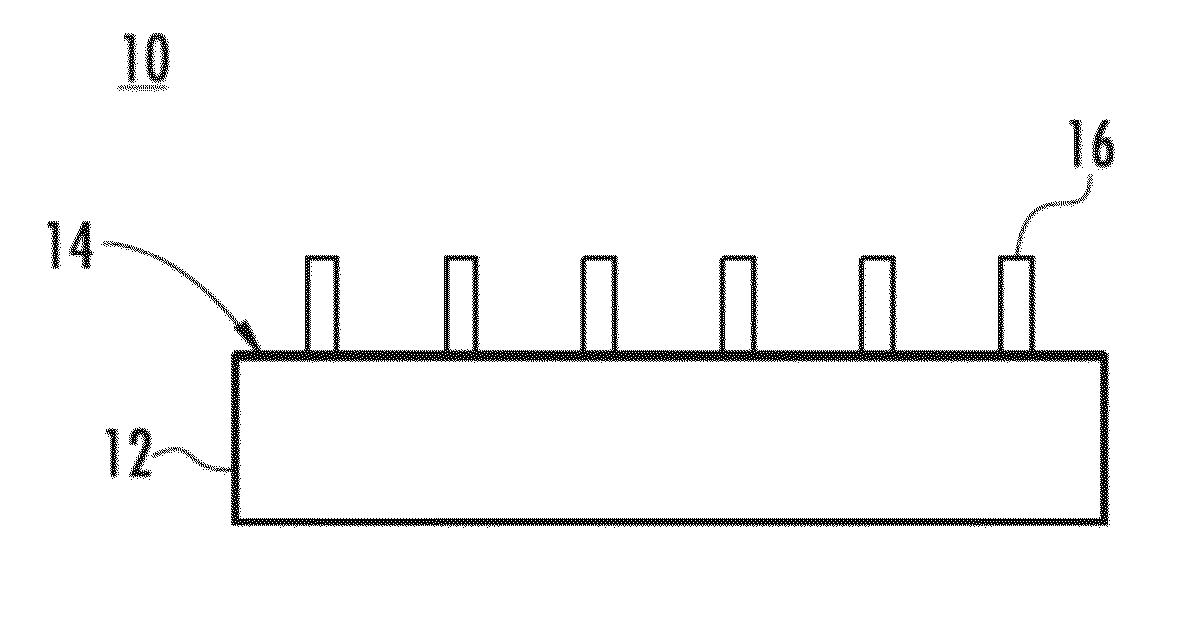

Nanopillars is an emerging technology within the field of nanostructures. Nanopillars are pillar shaped nanostructures approximately 10 nanometers in diameter that can be grouped together in lattice like arrays. They are a type of metamaterial, which means that nanopillars get their attributes from being grouped into artificially designed structures and not their natural properties. Nanopillars set themselves apart from other nanostructures due to their unique shape. Each nanopillar has a pillar shape at the bottom and a tapered pointy end on top. This shape in combination with nanopillars' ability to be grouped together exhibits many useful properties. Nanopillars have many applications including efficient solar panels, high resolution analysis, and antibacterial surfaces.

Silicon-based nanoscale resistive device with adjustable resistance

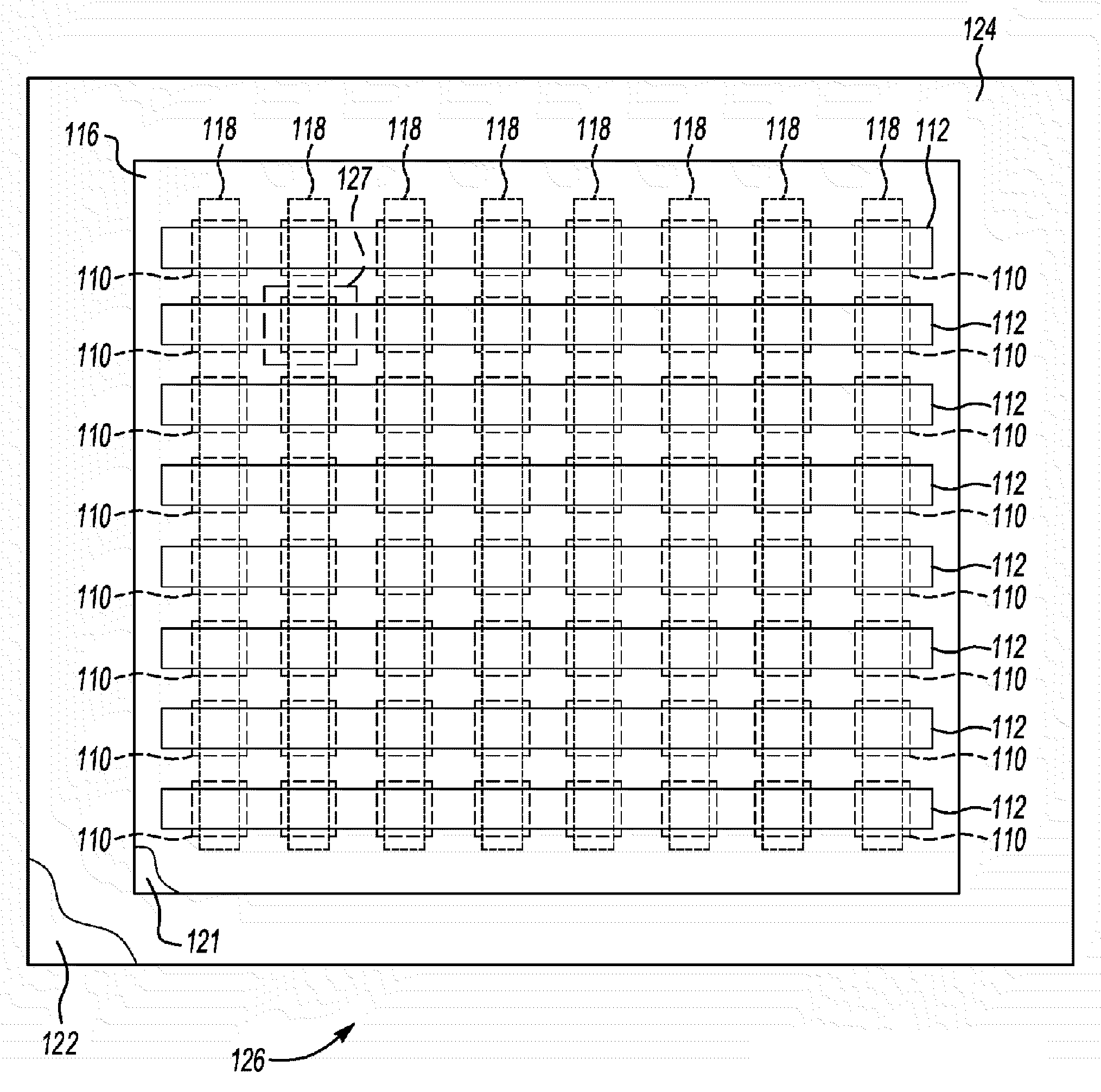

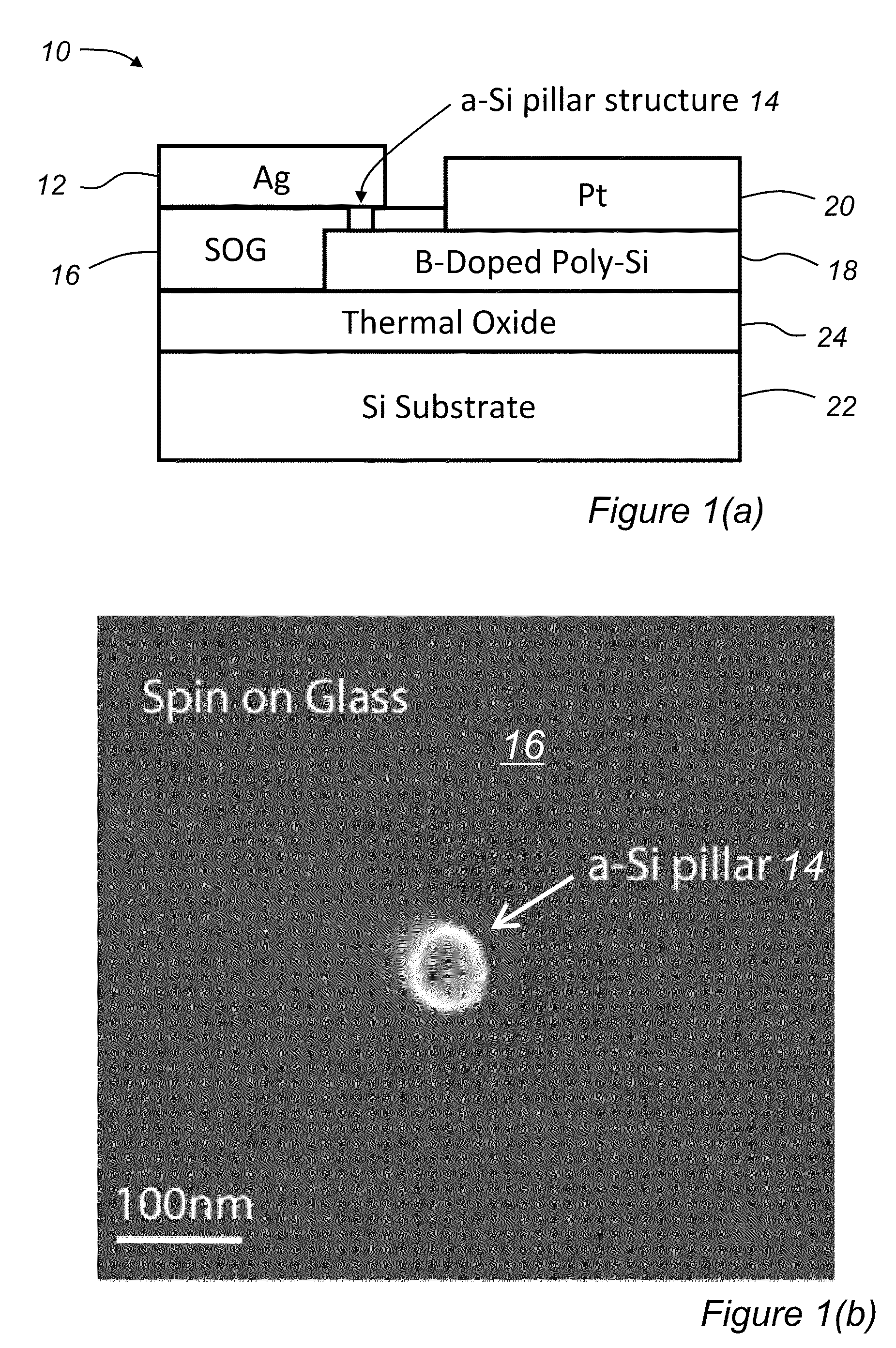

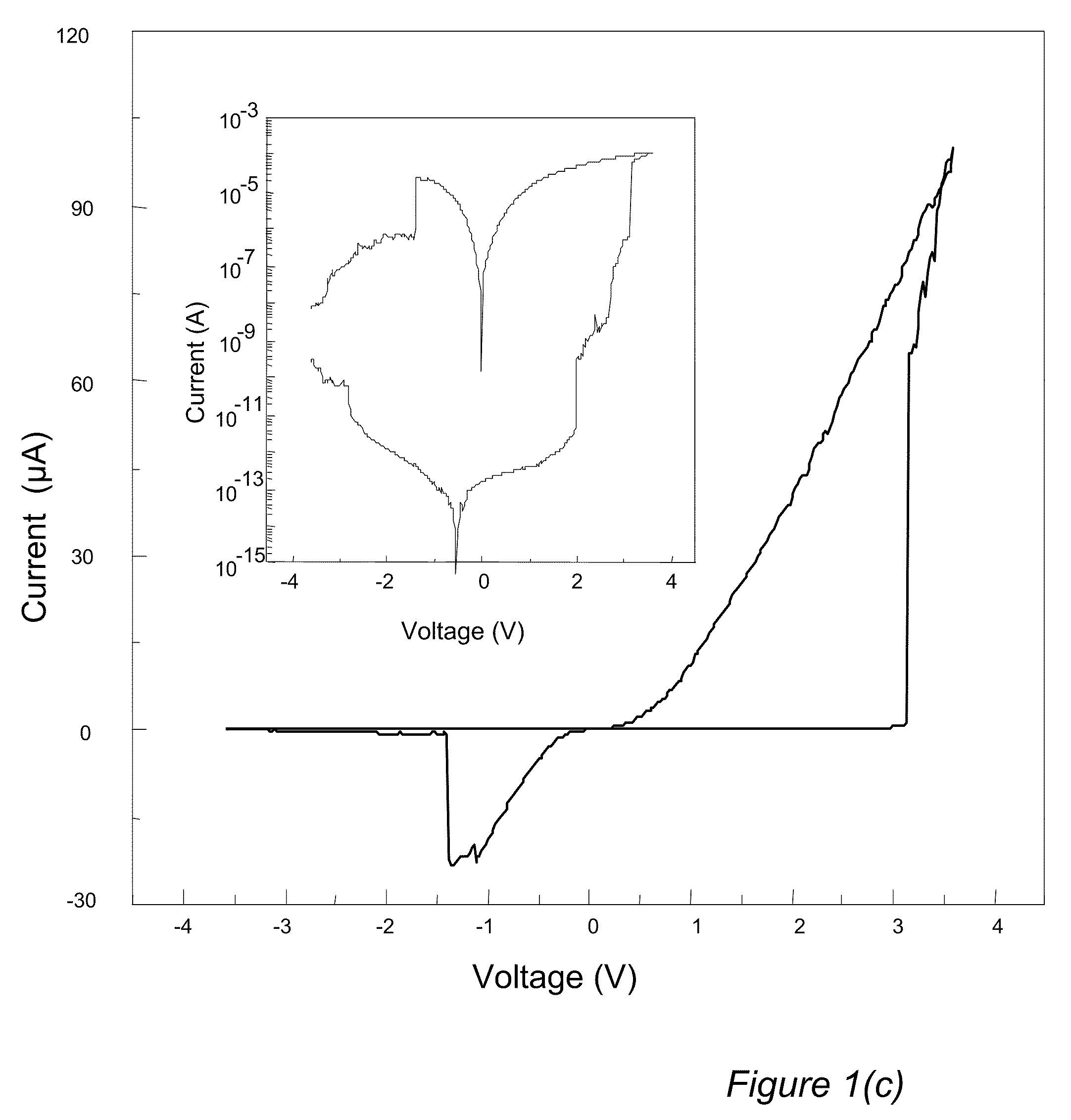

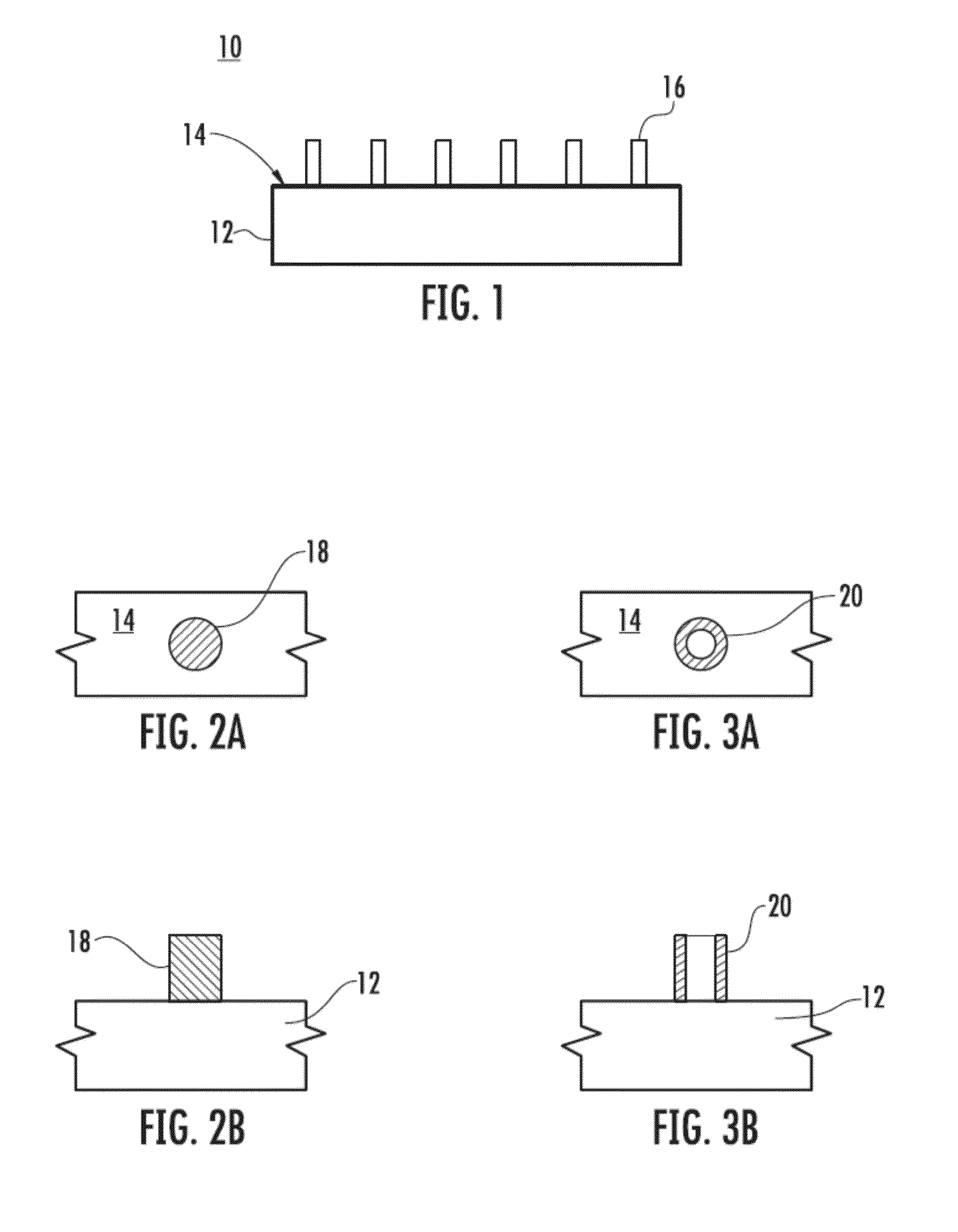

A non-volatile solid state resistive device that includes a first electrode, a p-type poly-silicon second electrode, and a non-crystalline silicon nanostructure electrically connected between the electrodes. The nanostructure has a resistance that is adjustable in response to a voltage being applied to the nanostructure via the electrodes. The nanostructure can be formed as a nanopillar embedded in an insulating layer located between the electrodes. The first electrode can be a silver or other electrically conductive metal electrode. A third (metal) electrode can be connected to the p-type poly-silicon second electrode at a location adjacent the nanostructure to permit connection of the two metal electrodes to other circuitry. The resistive device can be used as a unit memory cell of a digital non-volatile memory device to store one or more bits of digital data by varying its resistance between two or more values.

Owner:RGT UNIV OF MICHIGAN

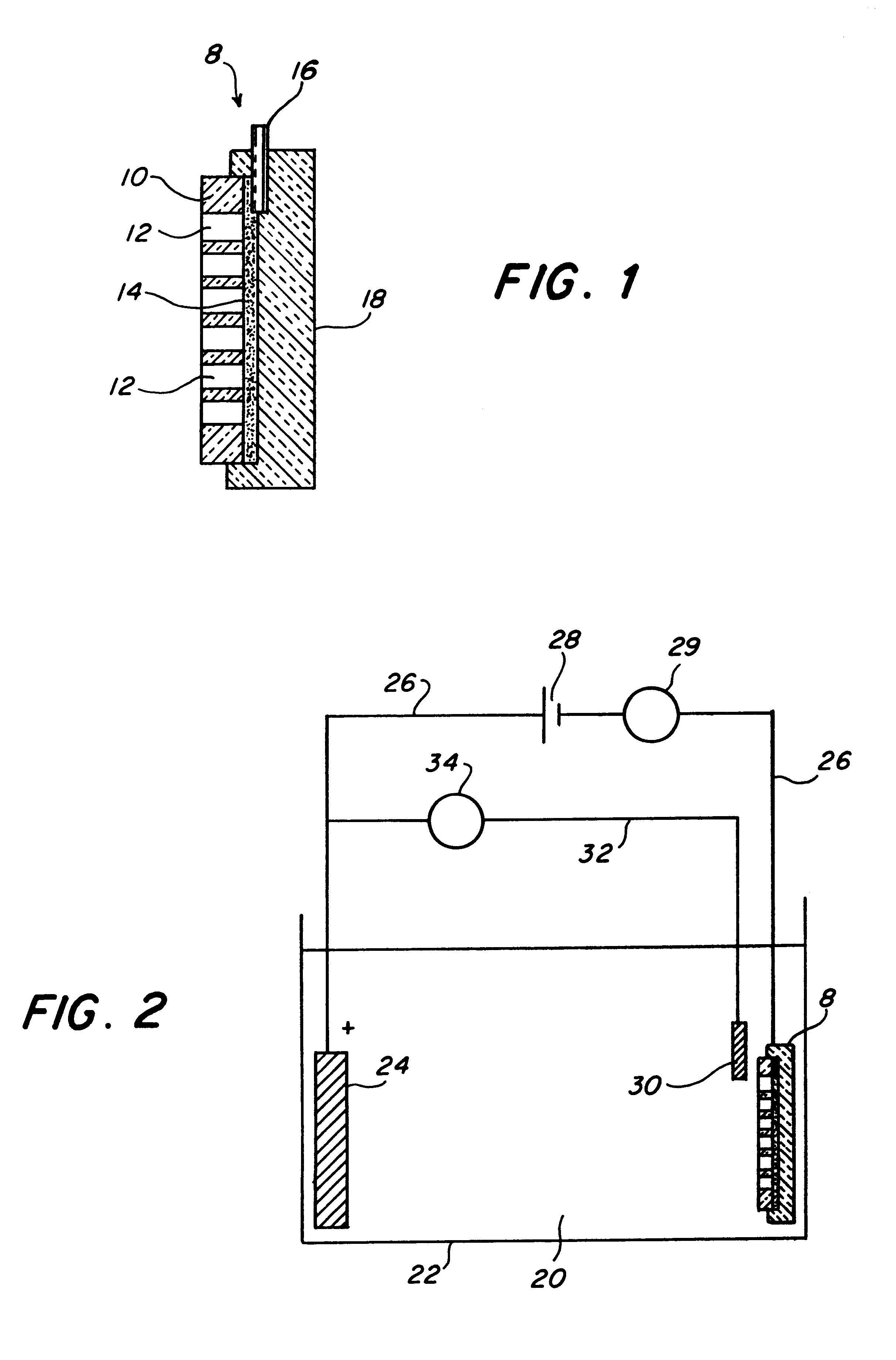

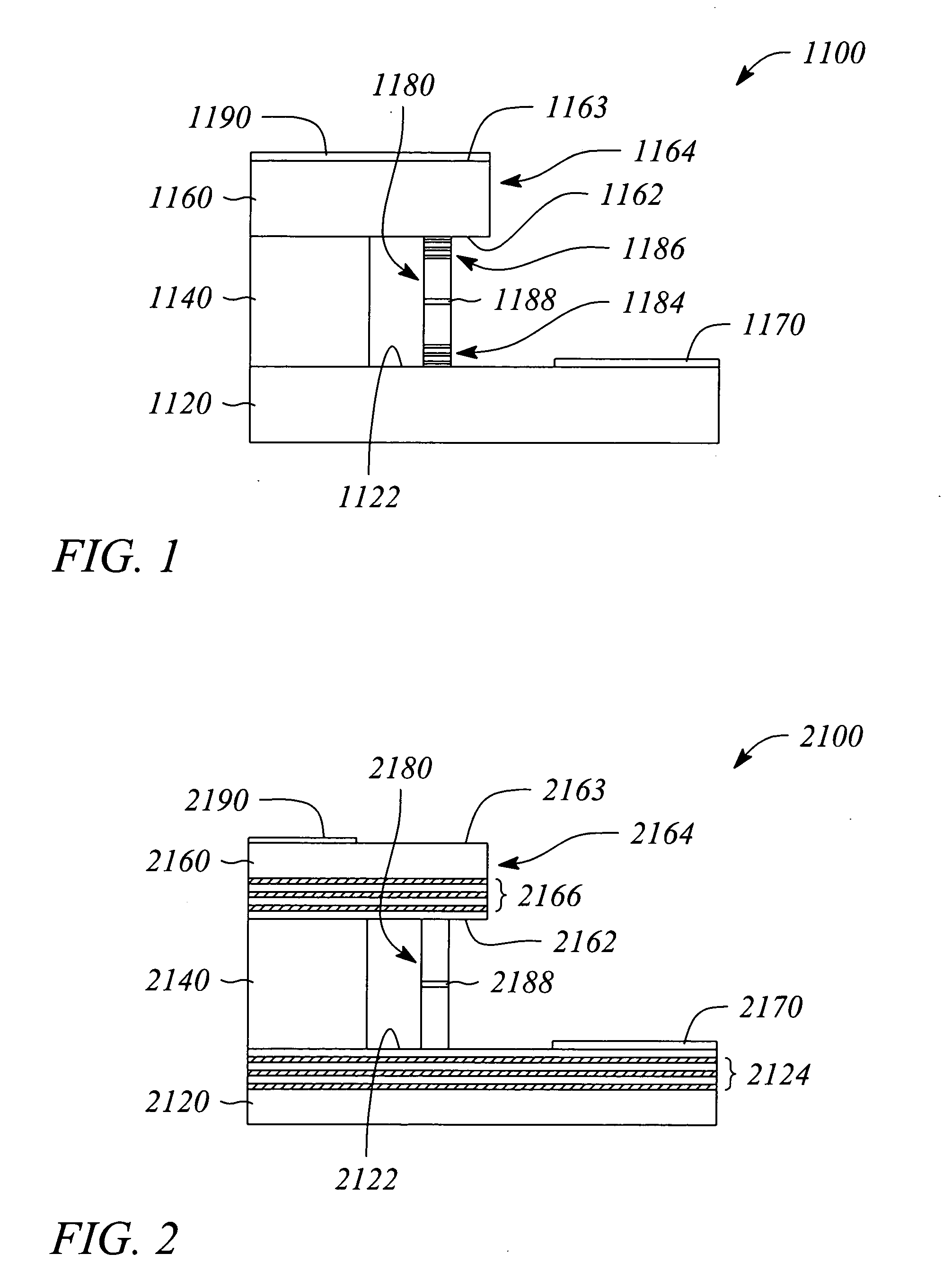

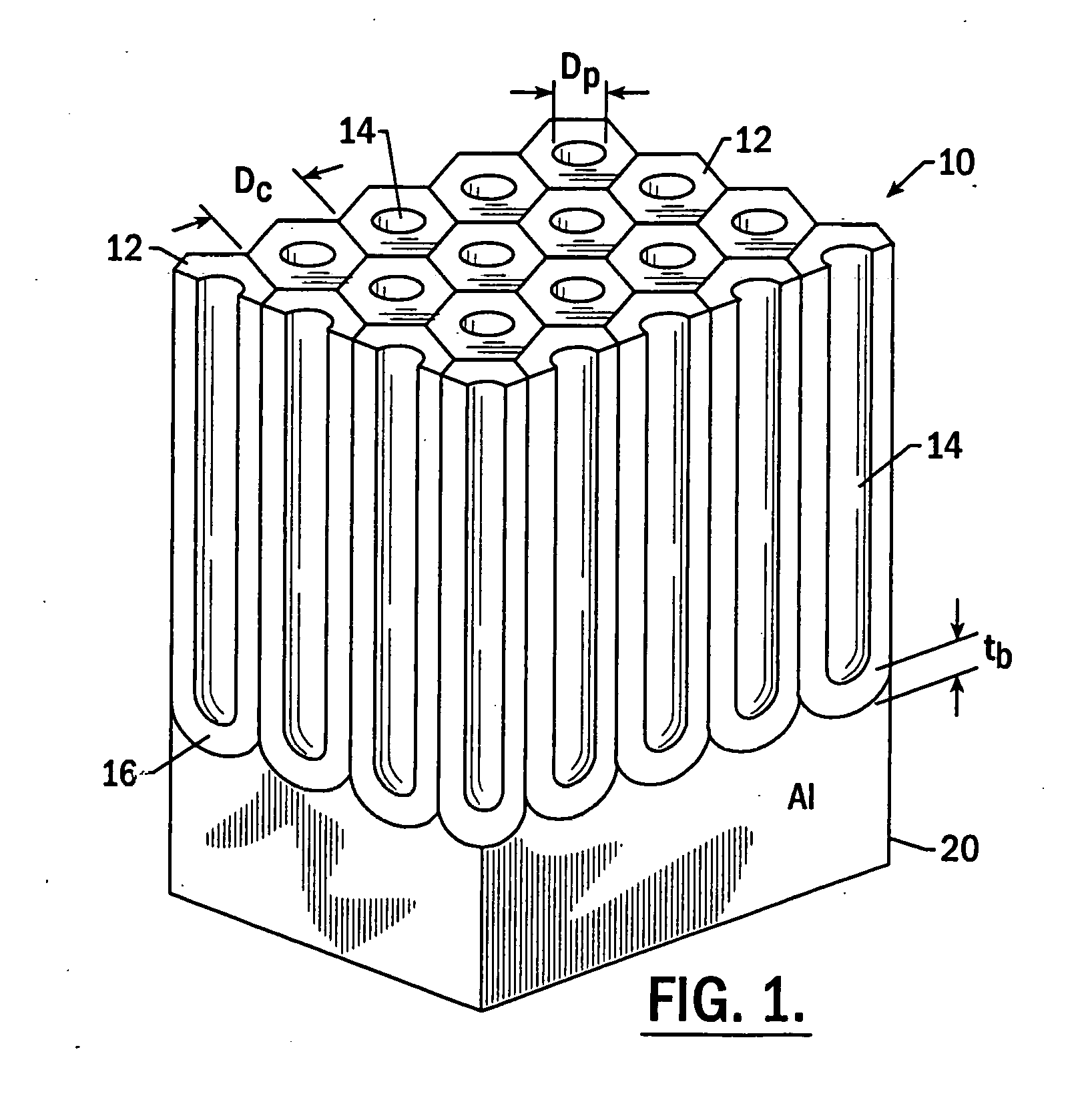

Nanopost arrays and process for making same

InactiveUS6185961B1Efficient depositionEfficiently magnetic materialNanostructure applicationNanomagnetismNanopillarEngineering

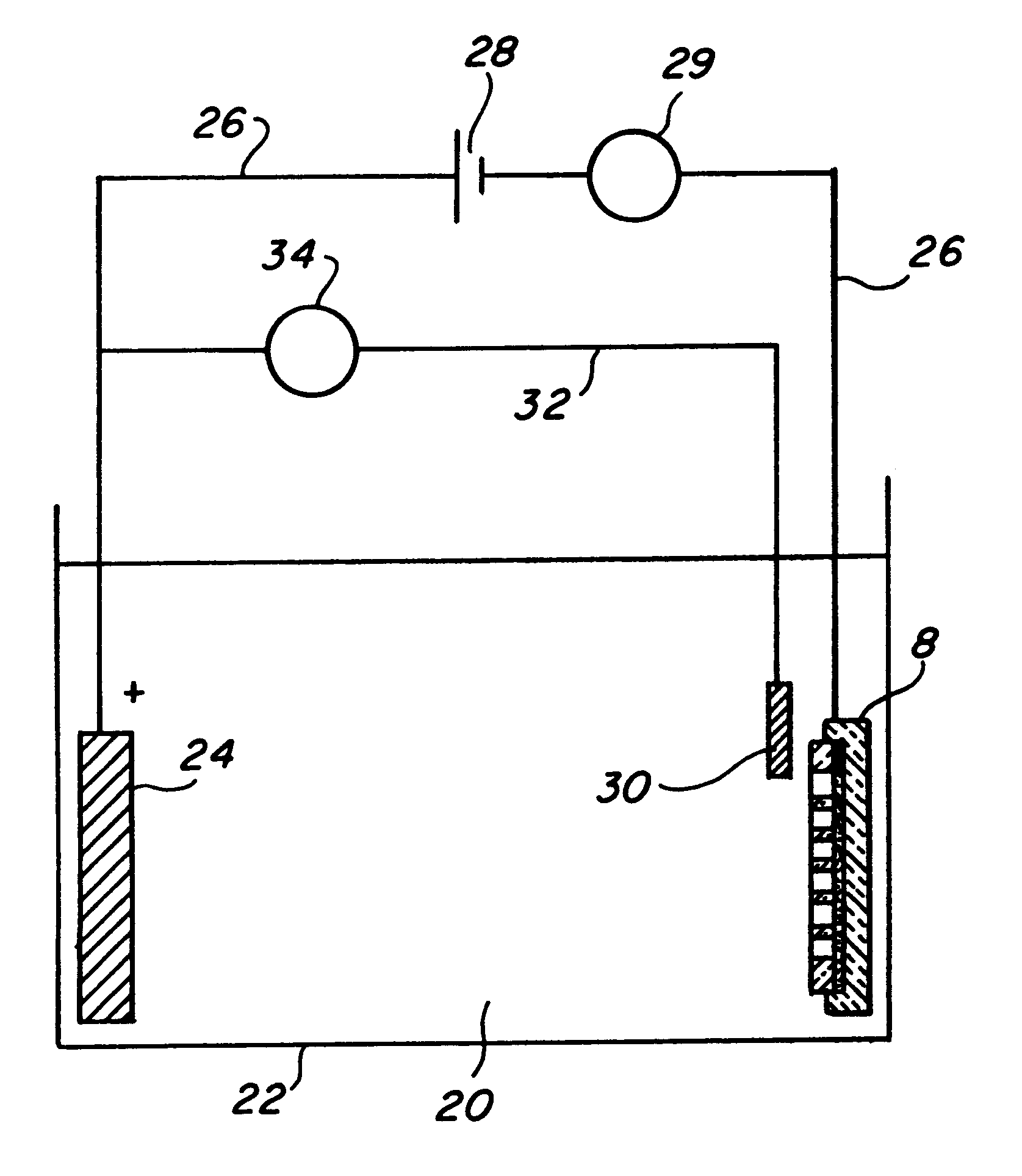

A nanopost glass array contains up to 1012 / cm2 of magnetizable nanoposts having diameter of 10-1000 nm that are straight and parallel to each other and are typically of a uniform diameter relative to each other and along the post length. The array is made using a reference electrode and a nanochannel glass template structure connected to each other electrically through an electrical source and both disposed in a plating solution. A magnetizable material is electroplated from the plating solution into the channels of the template structure.

Owner:THE UNITED STATES OF AMERICA AS REPRESENTED BY THE SECRETARY OF THE NAVY

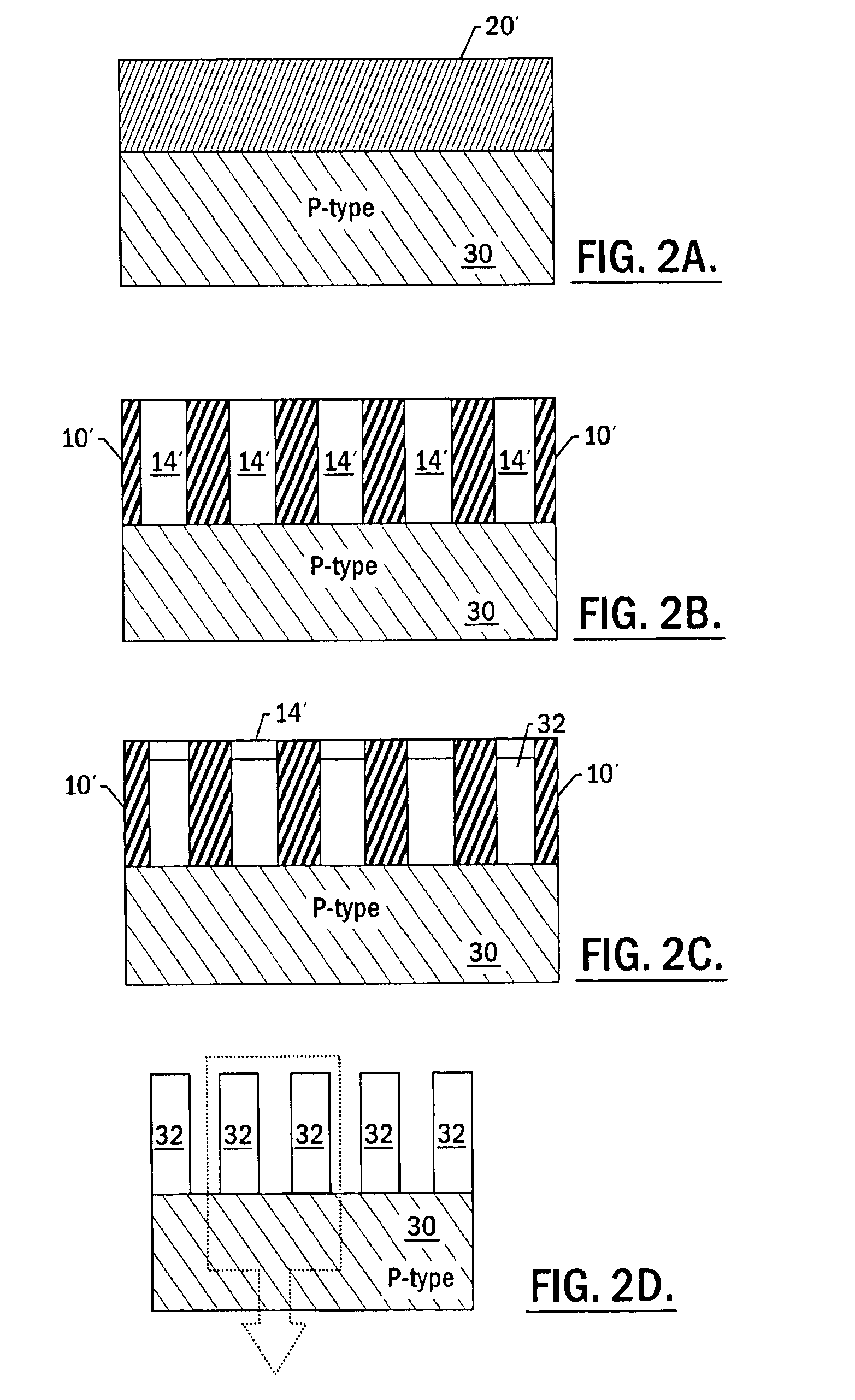

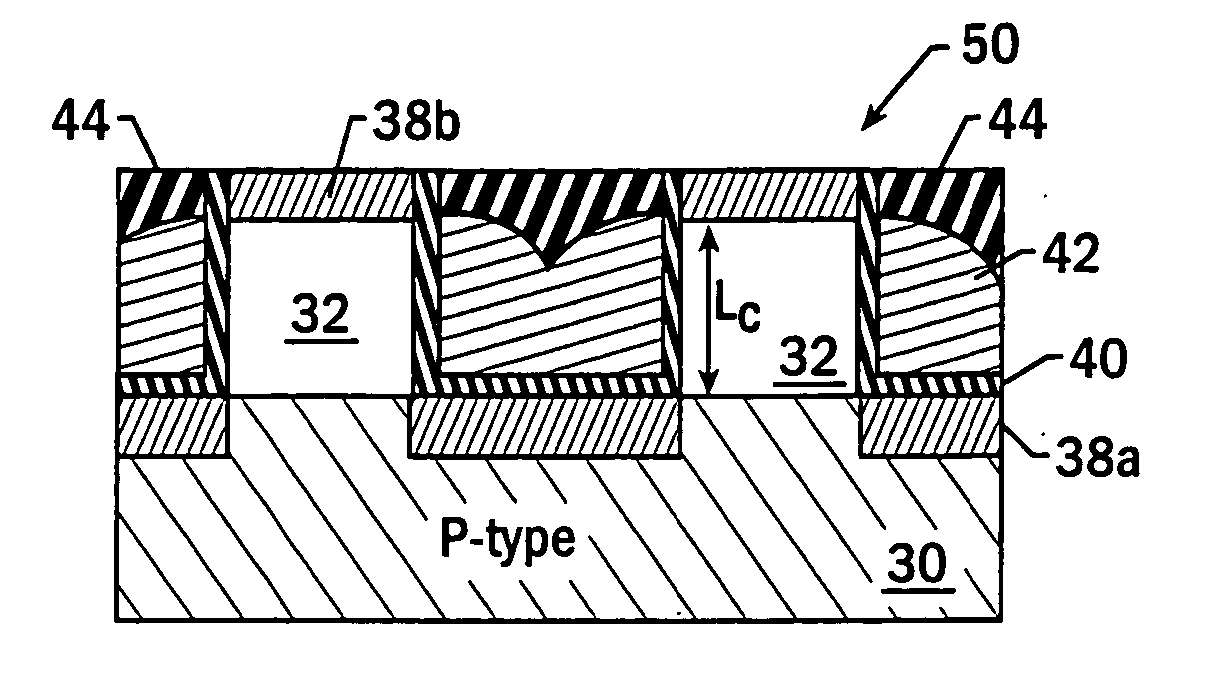

Optoelectronic devices having arrays of quantum-dot compound semiconductor superlattices therein

Methods of forming a nano-scale electronic and optoelectronic devices include forming a substrate having a semiconductor layer therein and a substrate insulating layer on the semiconductor layer. An etching template having a first array of non-photolithographically defined nano-channels extending therethrough, is formed on the substrate insulating layer. This etching template may comprise an anodized metal oxide, such as an anodized aluminum oxide (AAO) thin film. The substrate insulating layer is then selectively etched to define a second array of nano-channels therein. This selective etching step preferably uses the etching template as an etching mask to transfer the first array of nano-channels to the underlying substrate insulating layer, which may be thinner than the etching template. An array of semiconductor nano-pillars is then formed in the second array of nano-channels. The semiconductor nano-pillars in the array may have an average diameter in a range between about 8 nm and about 50 nm. The semiconductor nano-pillars are also preferably homoepitaxial or heteroepitaxial with the semiconductor layer.

Owner:NORTH CAROLINA STATE UNIV

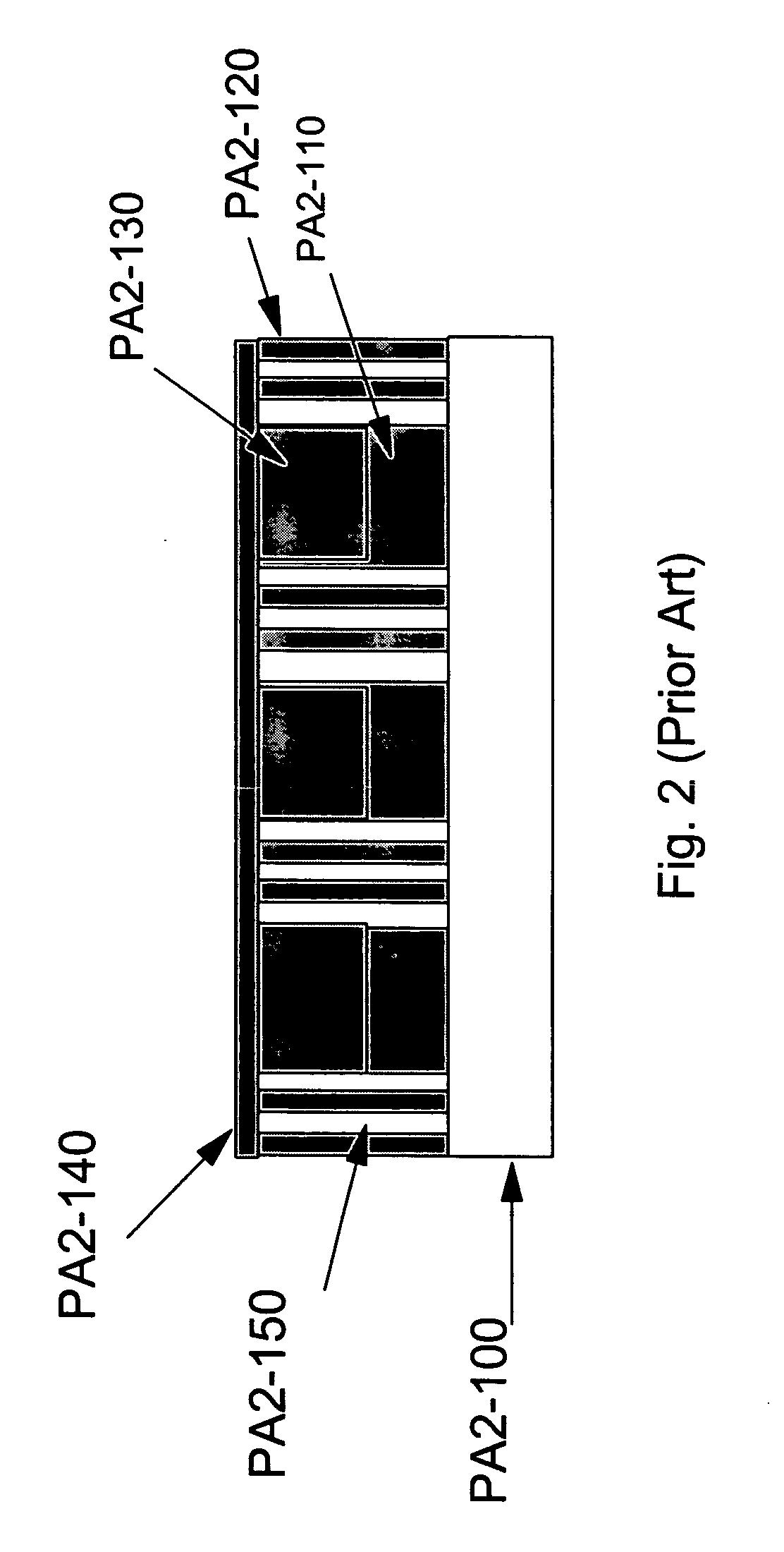

Nanostructured substrates for surface enhanced raman spectroscopy (SERS) and detection of biological and chemical analytes by electrical double layer (EDL) capacitance

InactiveUS20110053794A1Enhanced radiationMaterial nanotechnologySequential/parallel process reactionsCapacitanceNanopillar

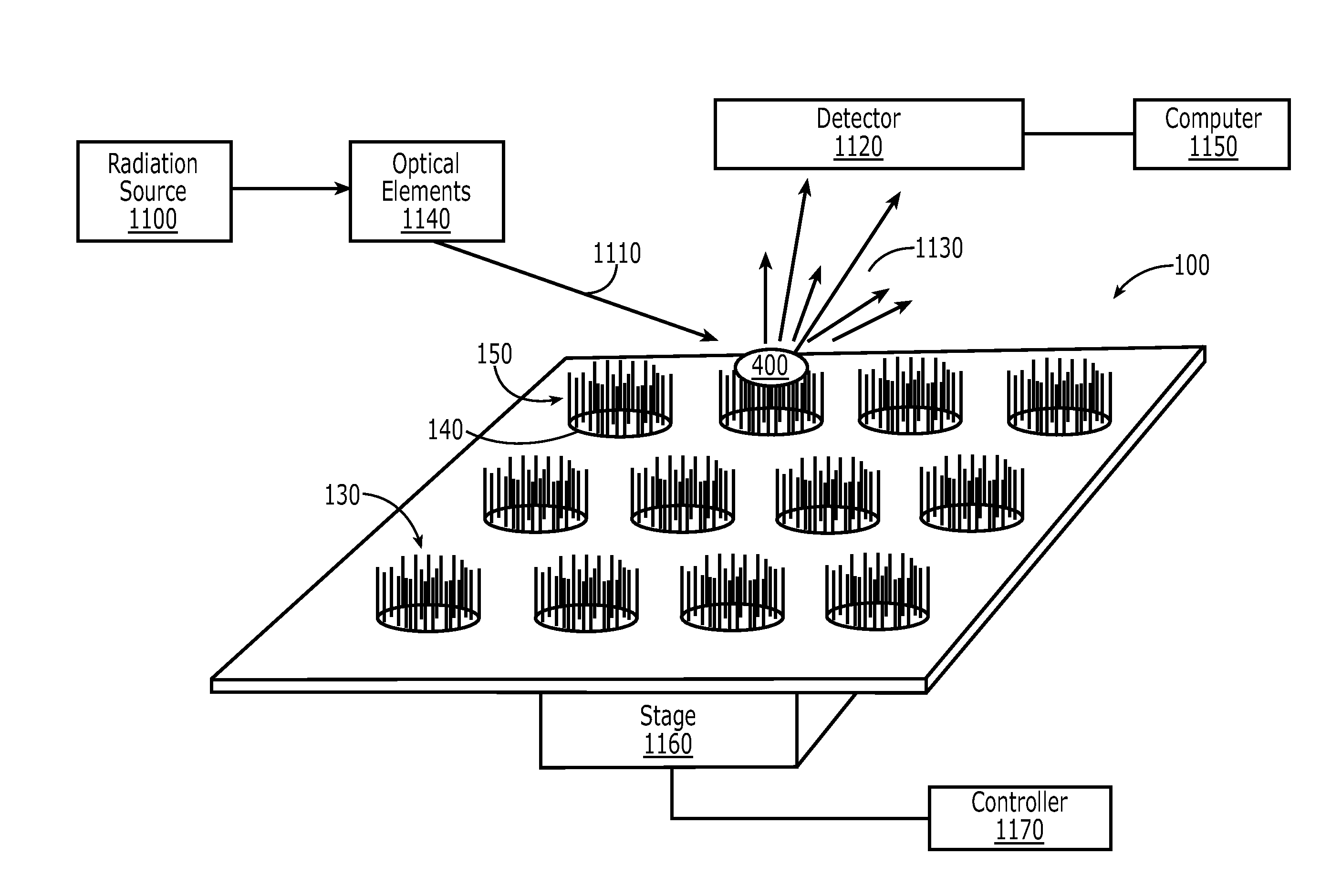

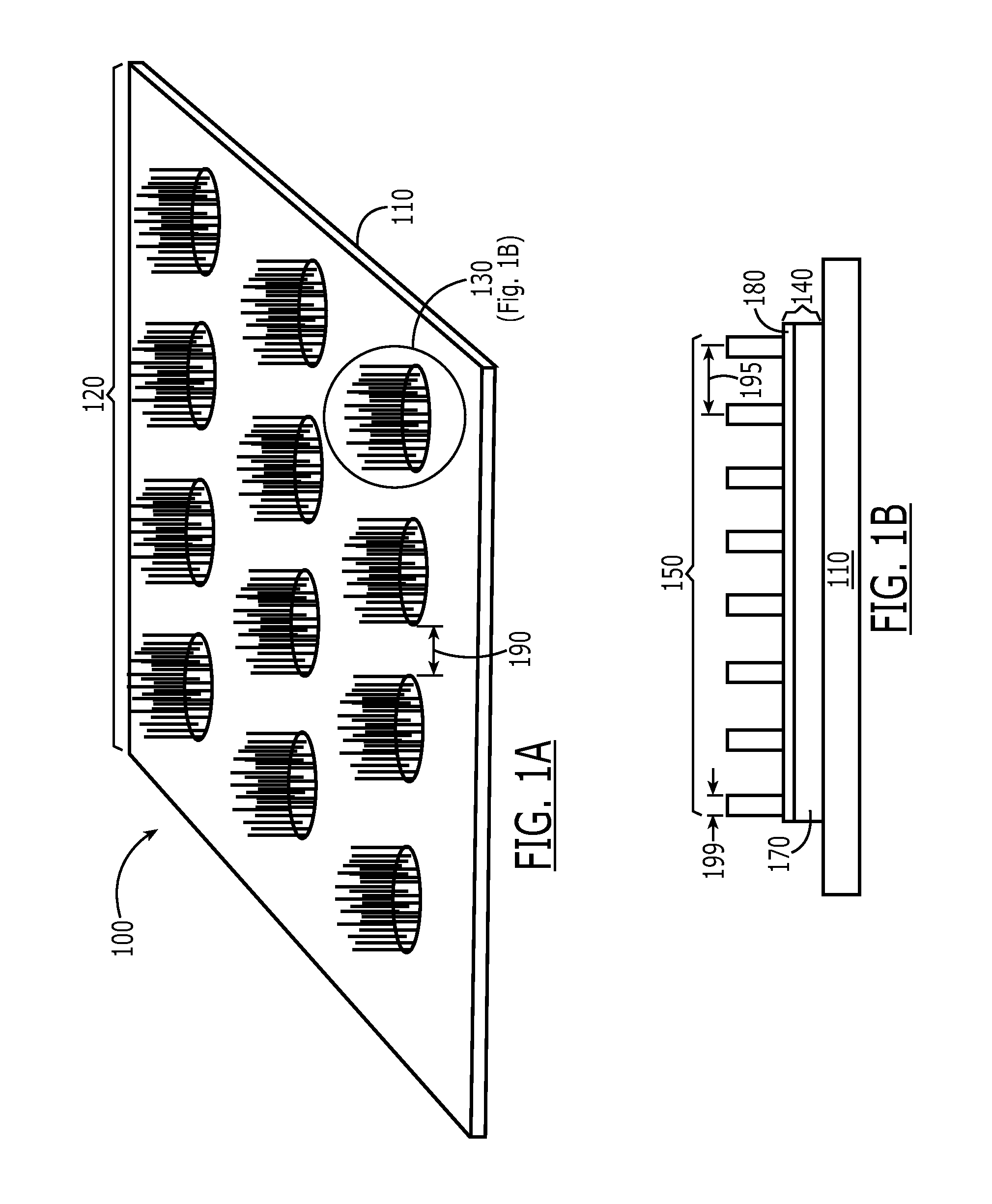

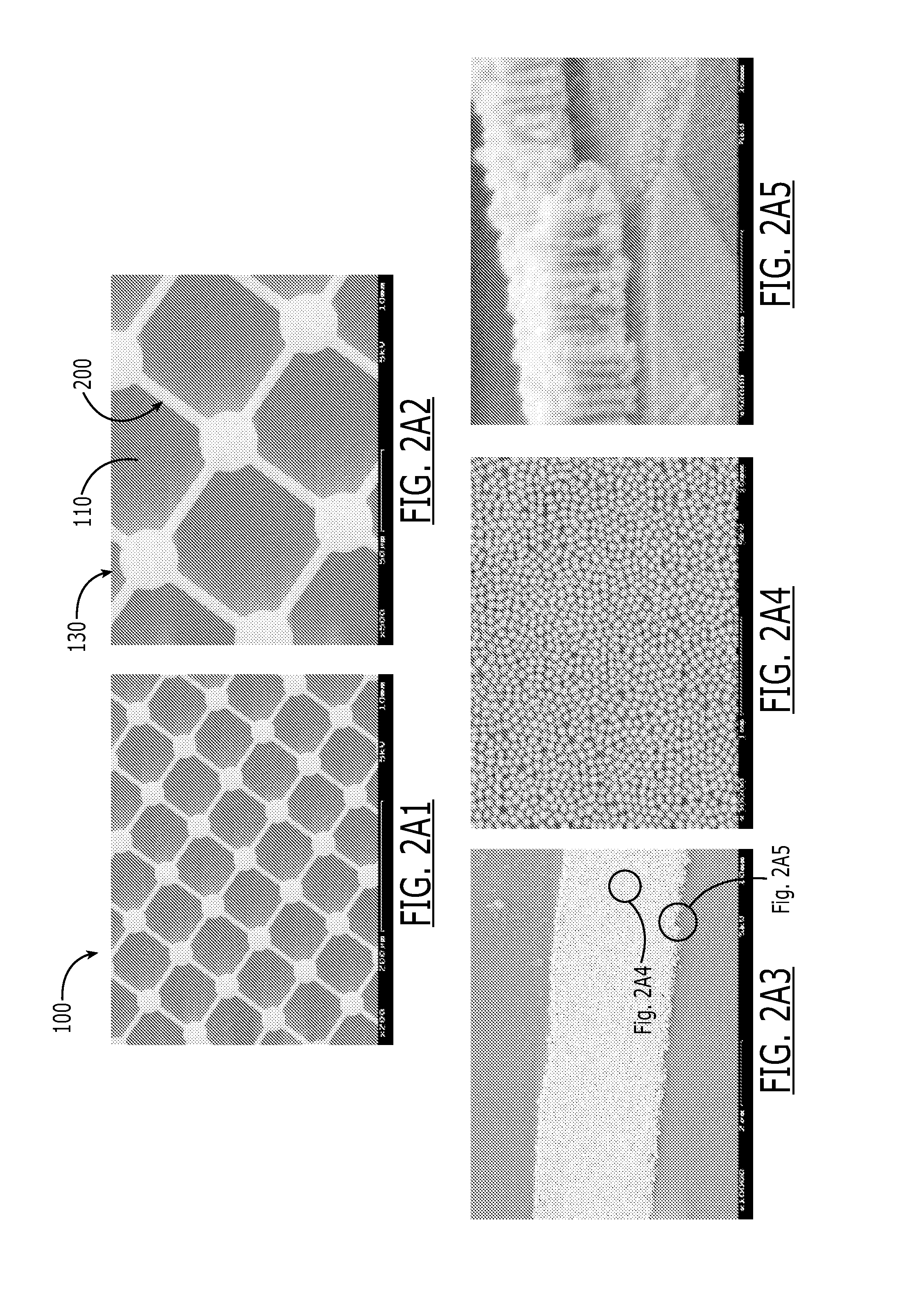

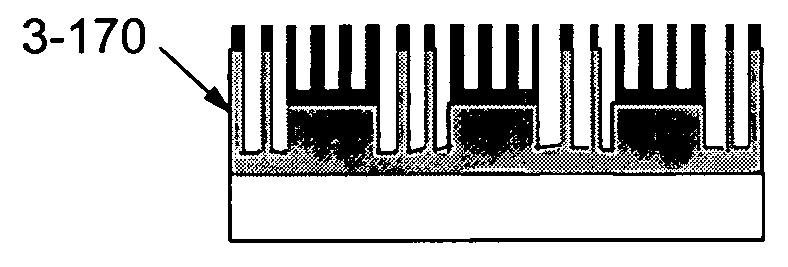

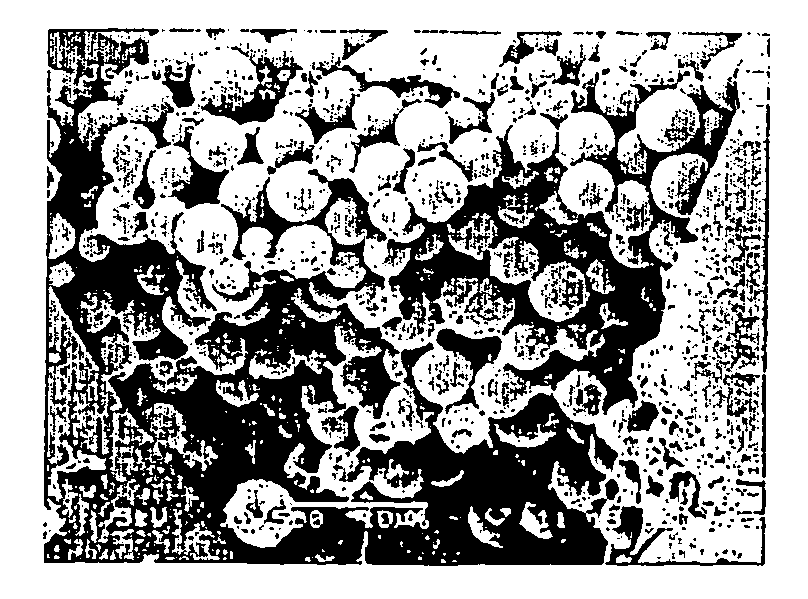

Provided according to embodiments of the invention are nanostructured surfaces that include a substrate; and an array of metallic nanopillar islands on the substrate, wherein each metallic nanopillar island includes a metal base layer on the substrate and a plurality of metallic nanopillars on the metal base layer, and wherein portions of the substrate between adjacent metallic nanopillar islands are free of the metal base layer. Also provided according to some embodiments of the invention are nanostructured surfaces that include a non-conductive substrate; and at least one nanoelectrode defined within the non-conductive substrate, wherein the at least one nanoelectrode is sized and / or shaped to immobilize an analyte or a probe molecule. Also provided are apparatuses and methods for SERS and detection of analytes or biological binding by EDL capacitance.

Owner:CLEMSON UNIV RES FOUND

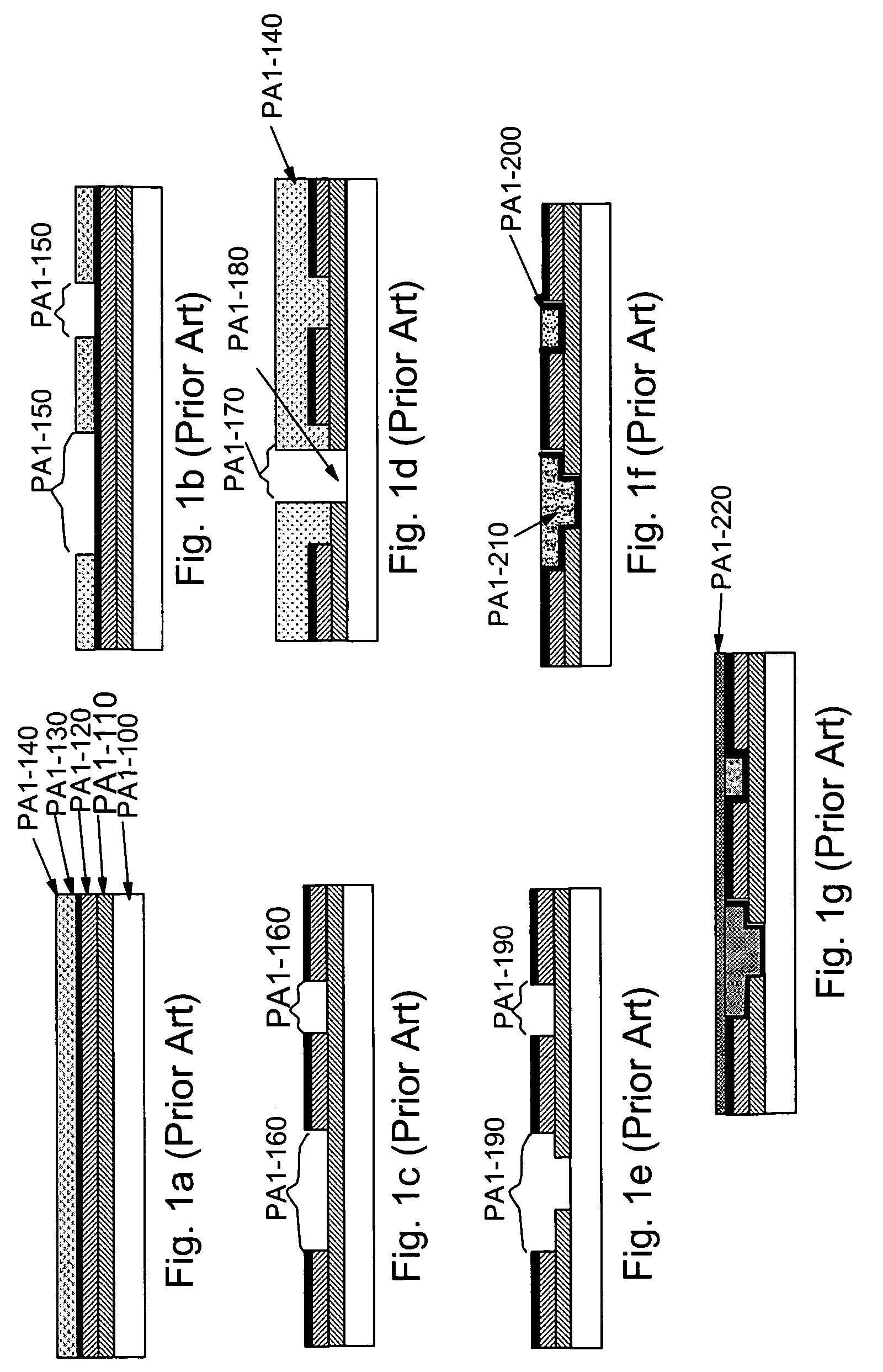

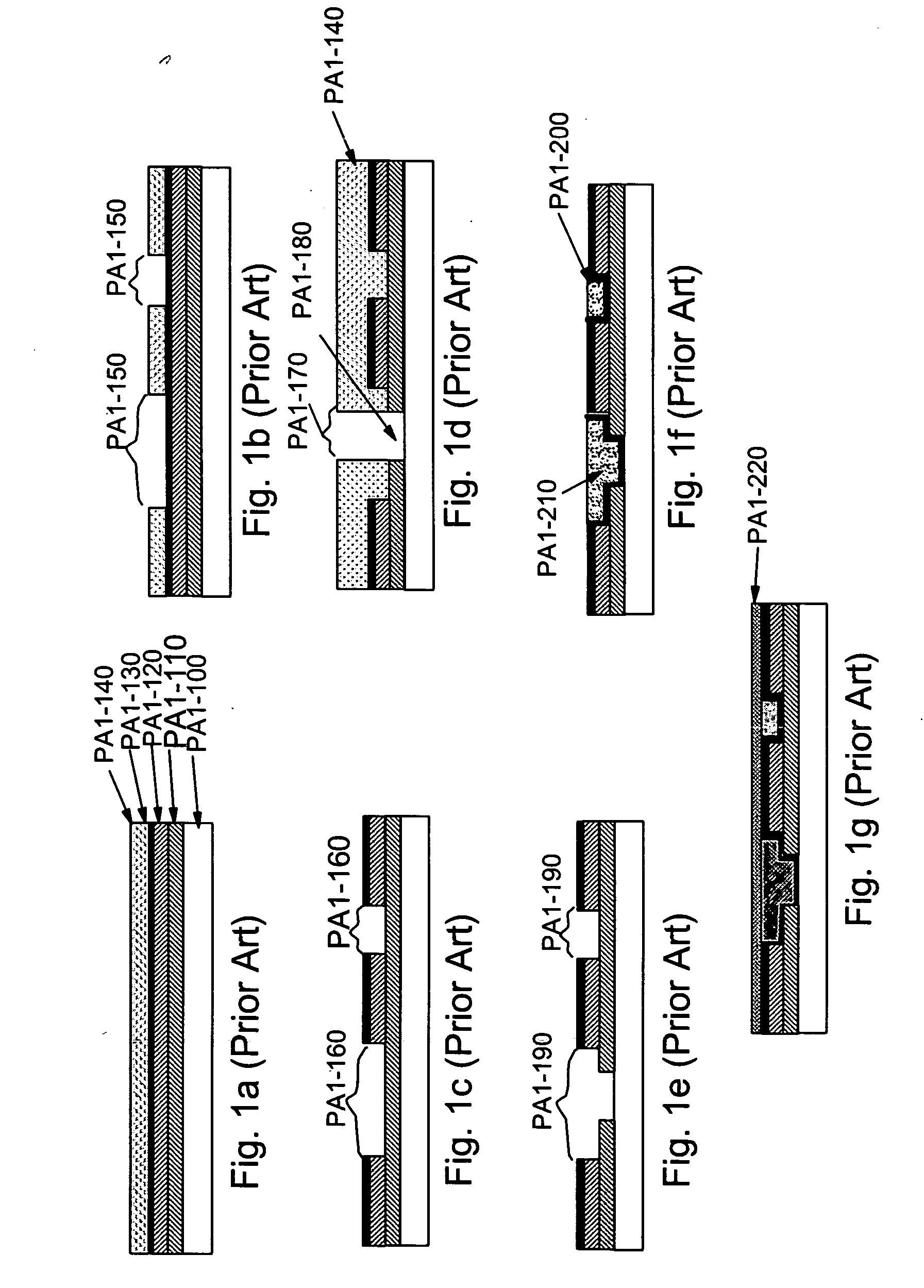

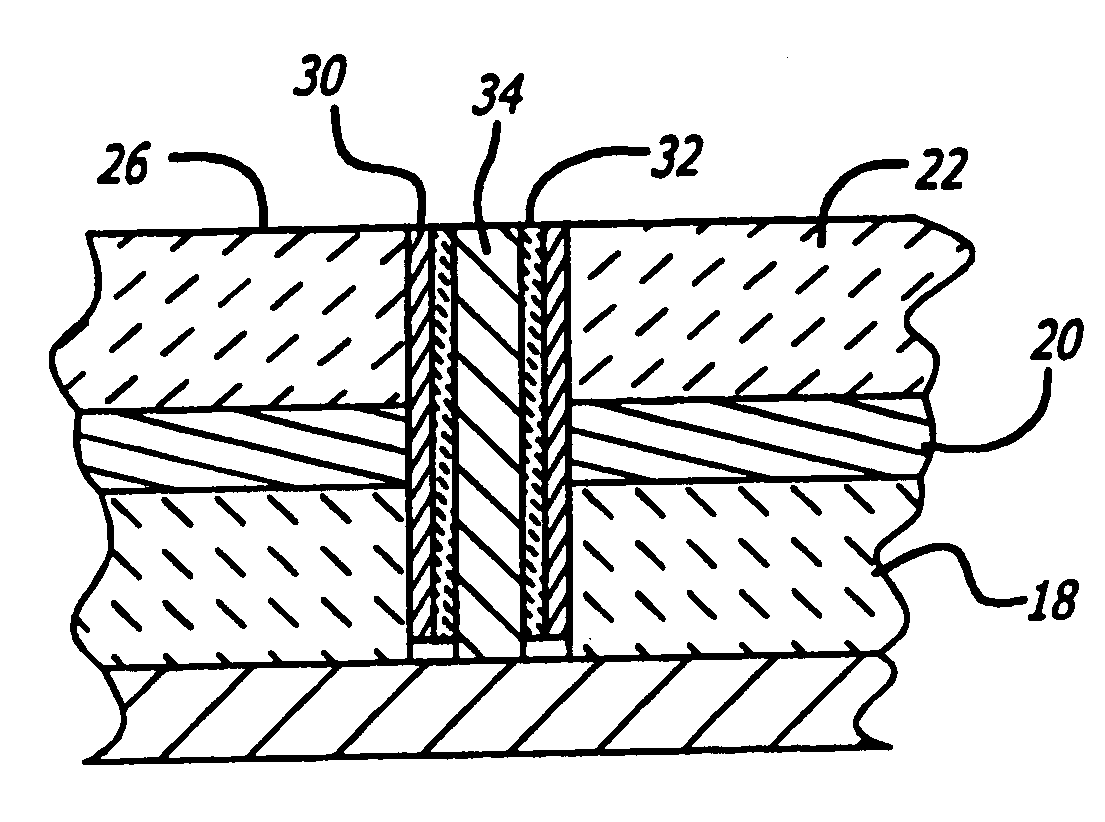

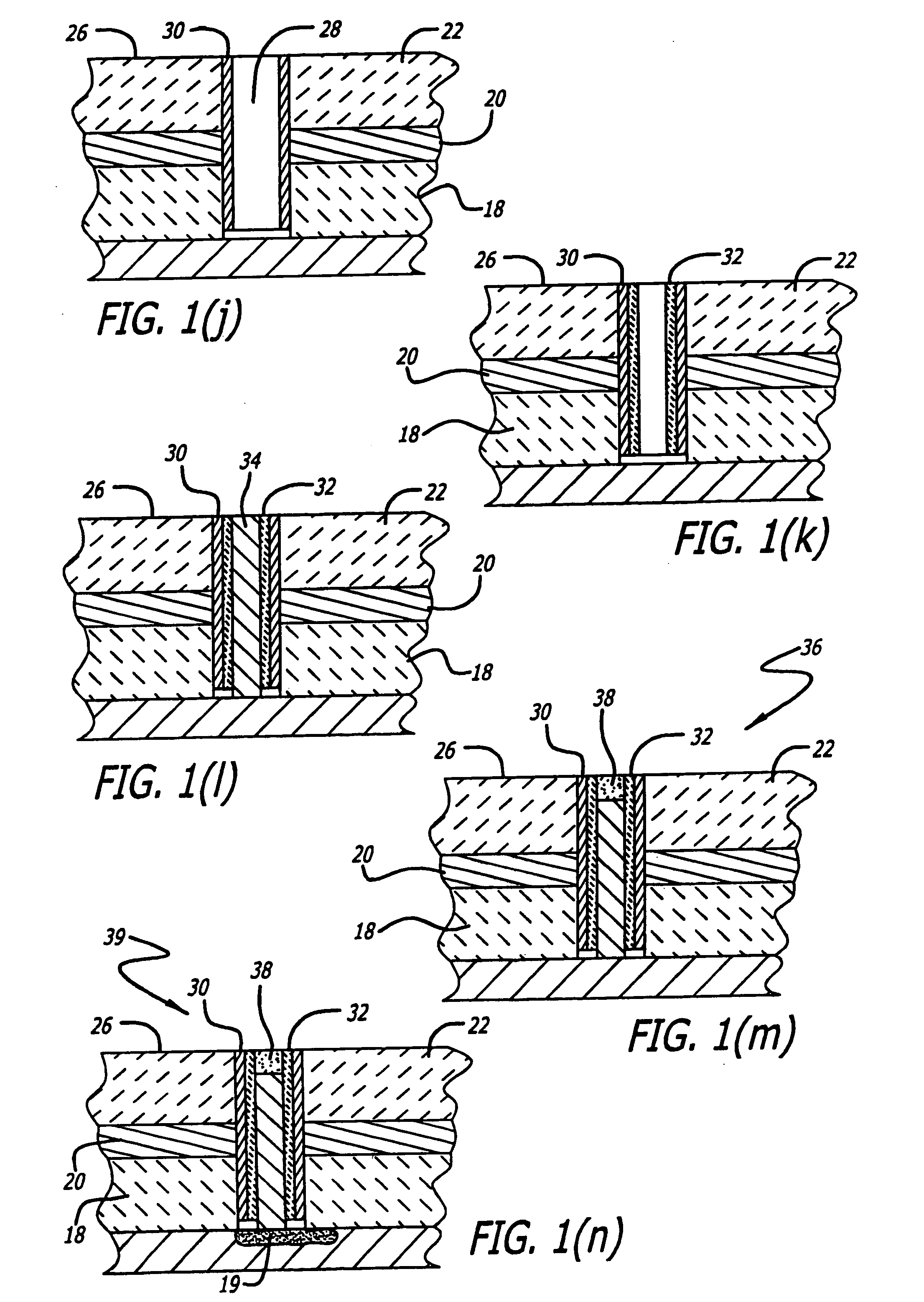

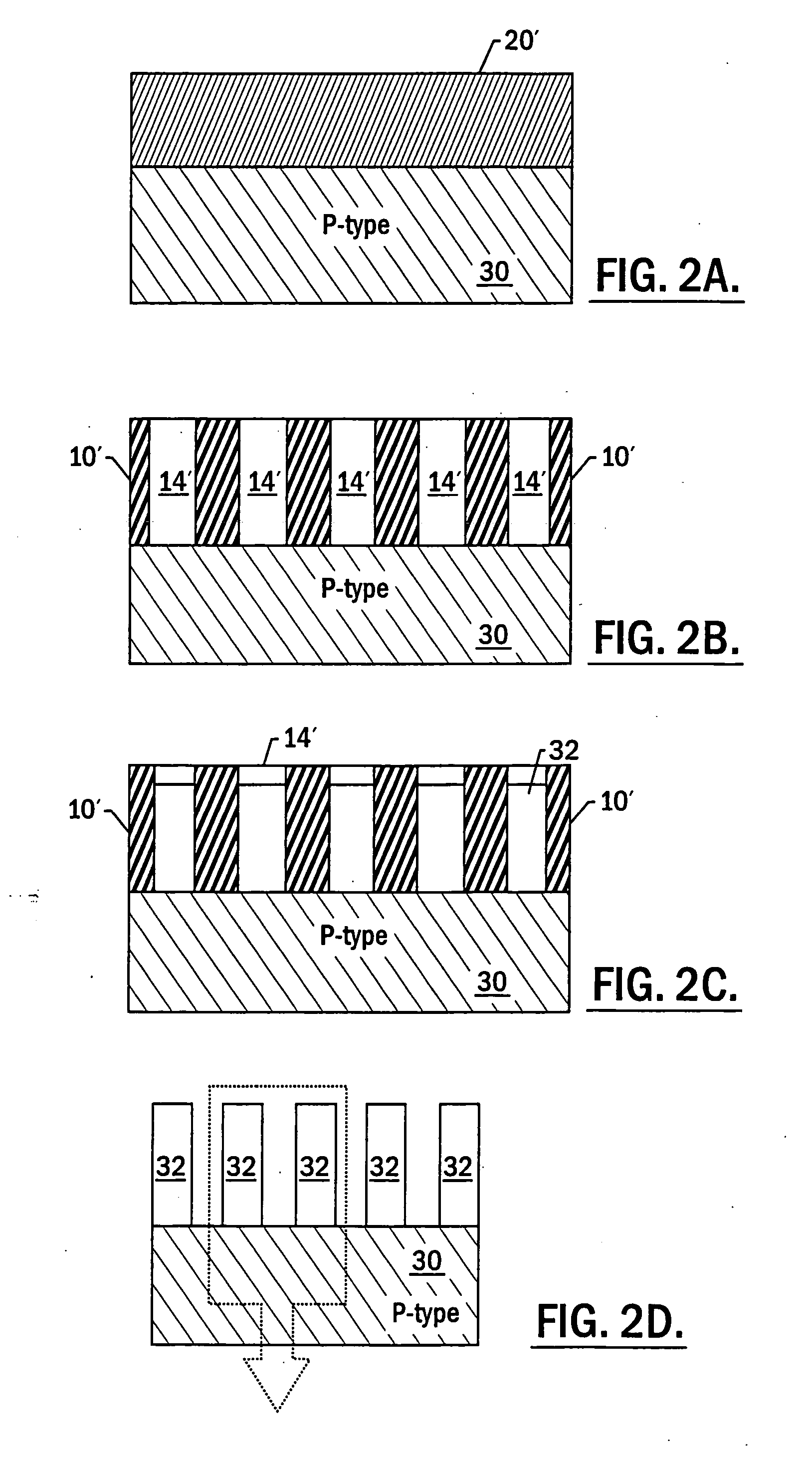

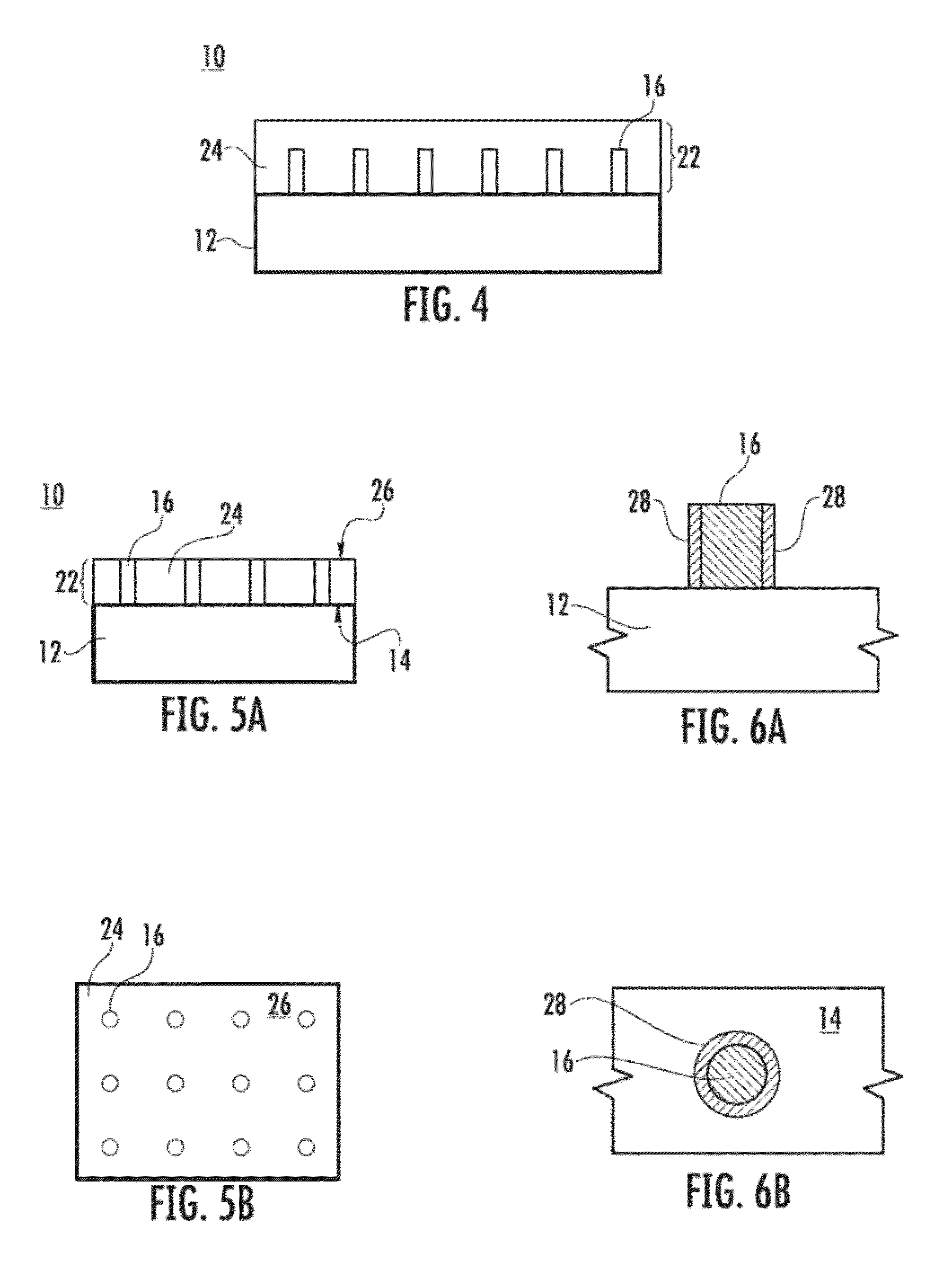

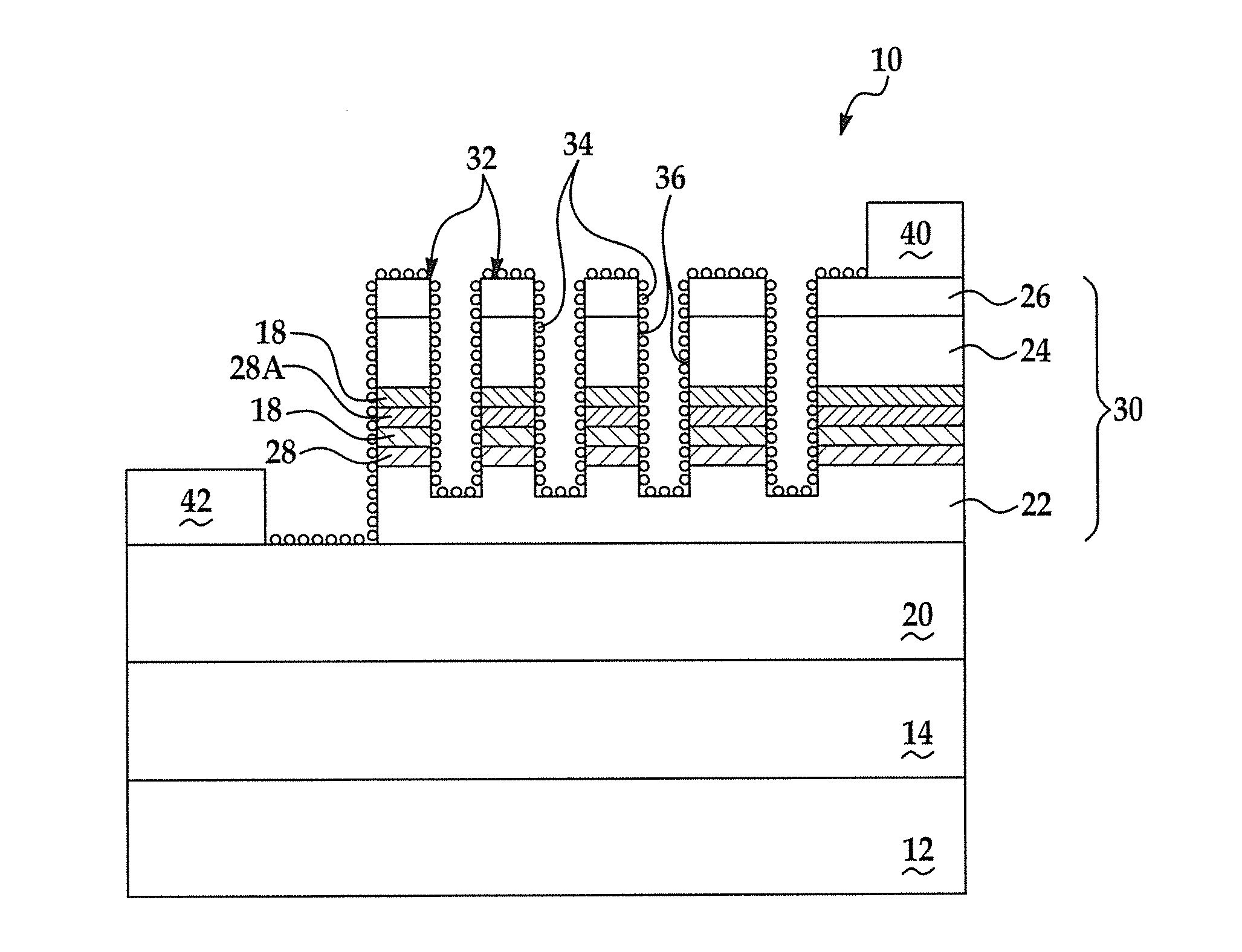

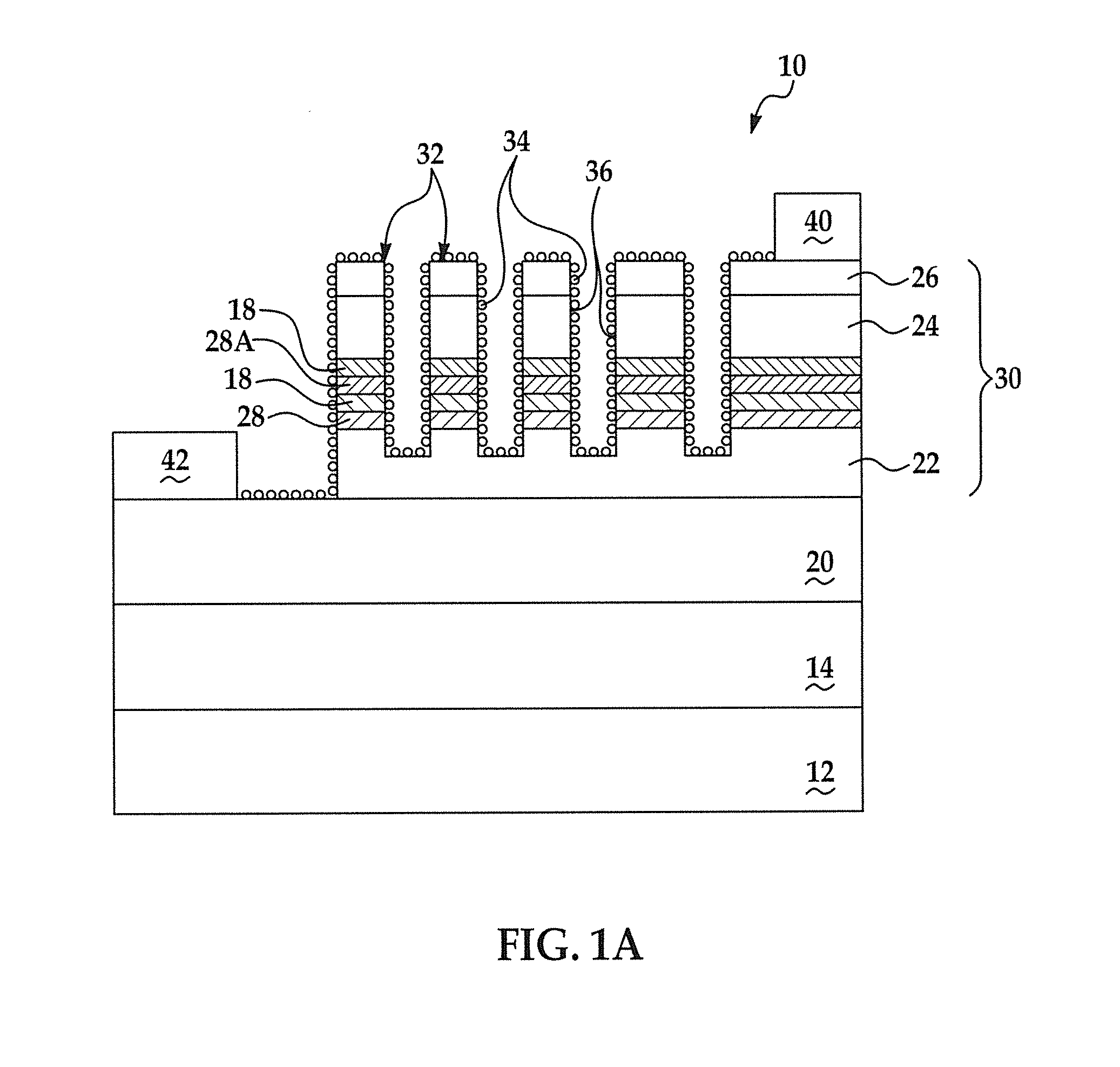

Method for fabricating a self-aligned nanocolumnar airbridge and structure produced thereby

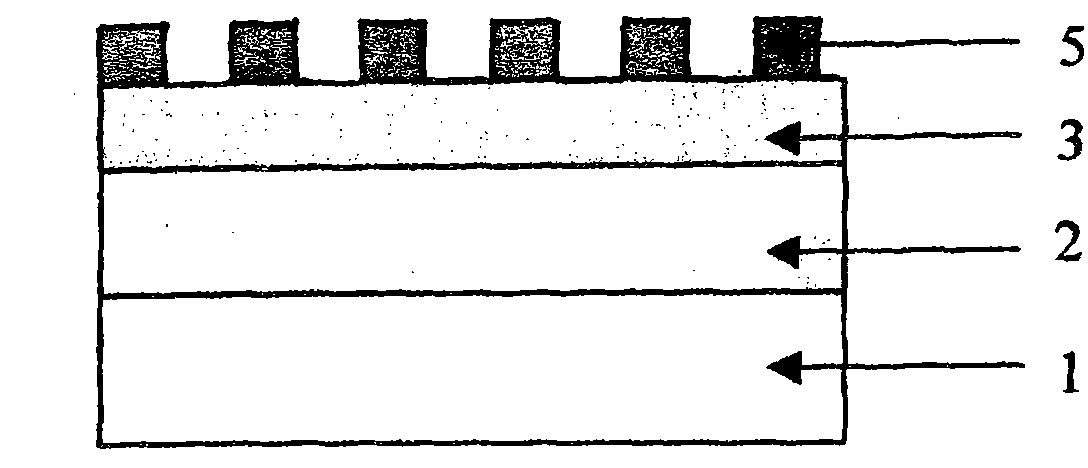

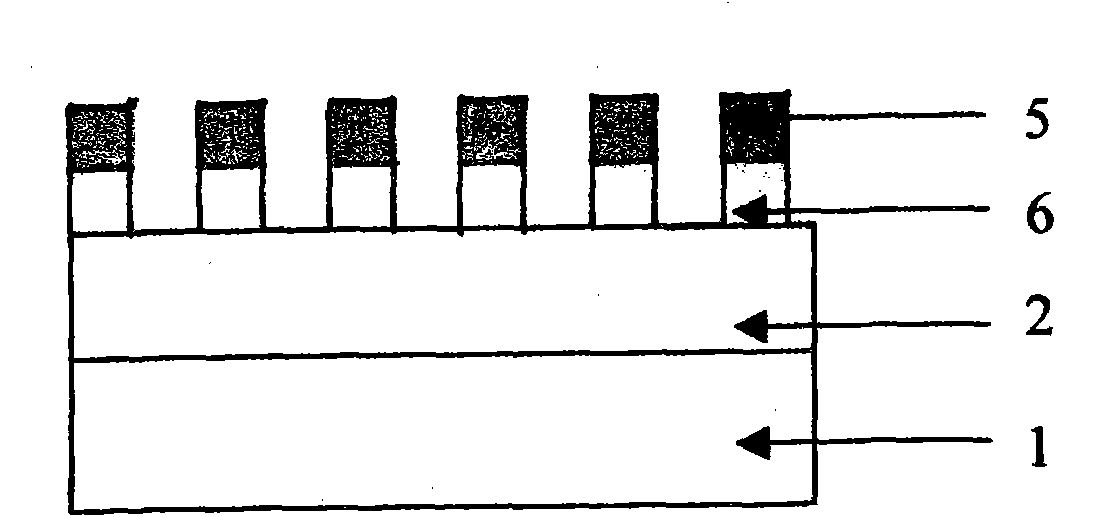

ActiveUS20050208752A1Semiconductor/solid-state device detailsSolid-state devicesPorosityElectrical conductor

A method for fabricating a low k, ultra-low k, and extreme-low k multilayer interconnect structure on a substrate in which the interconnect line features are separated laterally by a dielectric with vertically oriented nano-scale voids formed by perforating it using sub-optical lithography patterning and etching techniques and closing off the tops of the perforations by a dielectric deposition step. The lines are supported either by solid or patterned dielectric features underneath. The method avoids the issues associated with the formation of air gaps after the fabrication of conductor patterns and those associated with the integration of conventional low k, ultra-low k and extreme low k dielectrics which have porosity present before the formation of the interconnect patterns.

Owner:GLOBALFOUNDRIES US INC

Method for fabricating a self-aligned nanocolumnar airbridge and structure produced thereby

InactiveUS20050272341A1Semiconductor/solid-state device detailsSolid-state devicesPorosityElectrical conductor

A method for fabricating a low k, ultra-low k, and extreme-low k multilayer interconnect structure on a substrate in which the interconnect line features are separated laterally by a dielectric with vertically oriented nano-scale voids formed by perforating it using sub-optical lithography patterning and etching techniques and closing off the tops of the perforations by a dielectric deposition step. The lines are supported either by solid or patterned dielectric features underneath. The method avoids the issues associated with the formation of air gaps after the fabrication of conductor patterns and those associated with the integration of conventional low k, ultra-low k and extreme low k dielectrics which have porosity present before the formation of the interconnect patterns.

Owner:GLOBALFOUNDRIES INC

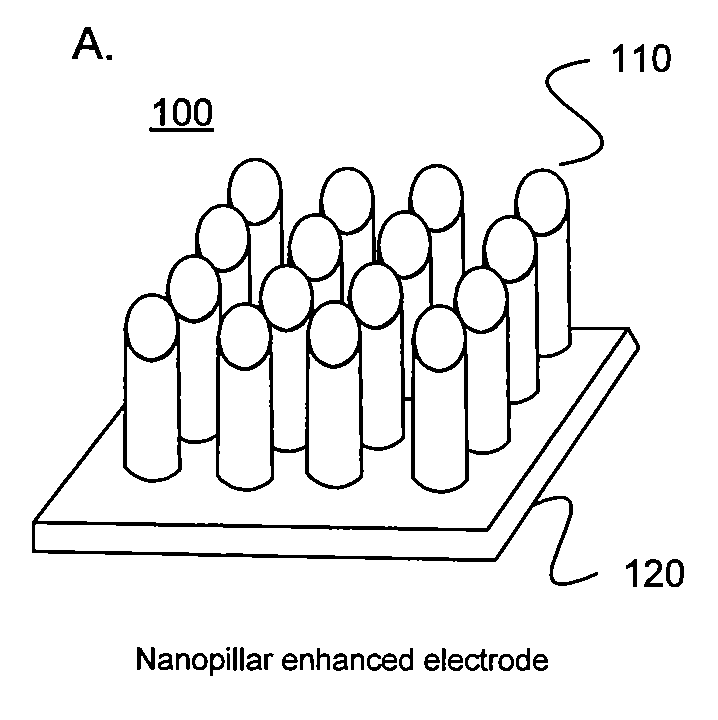

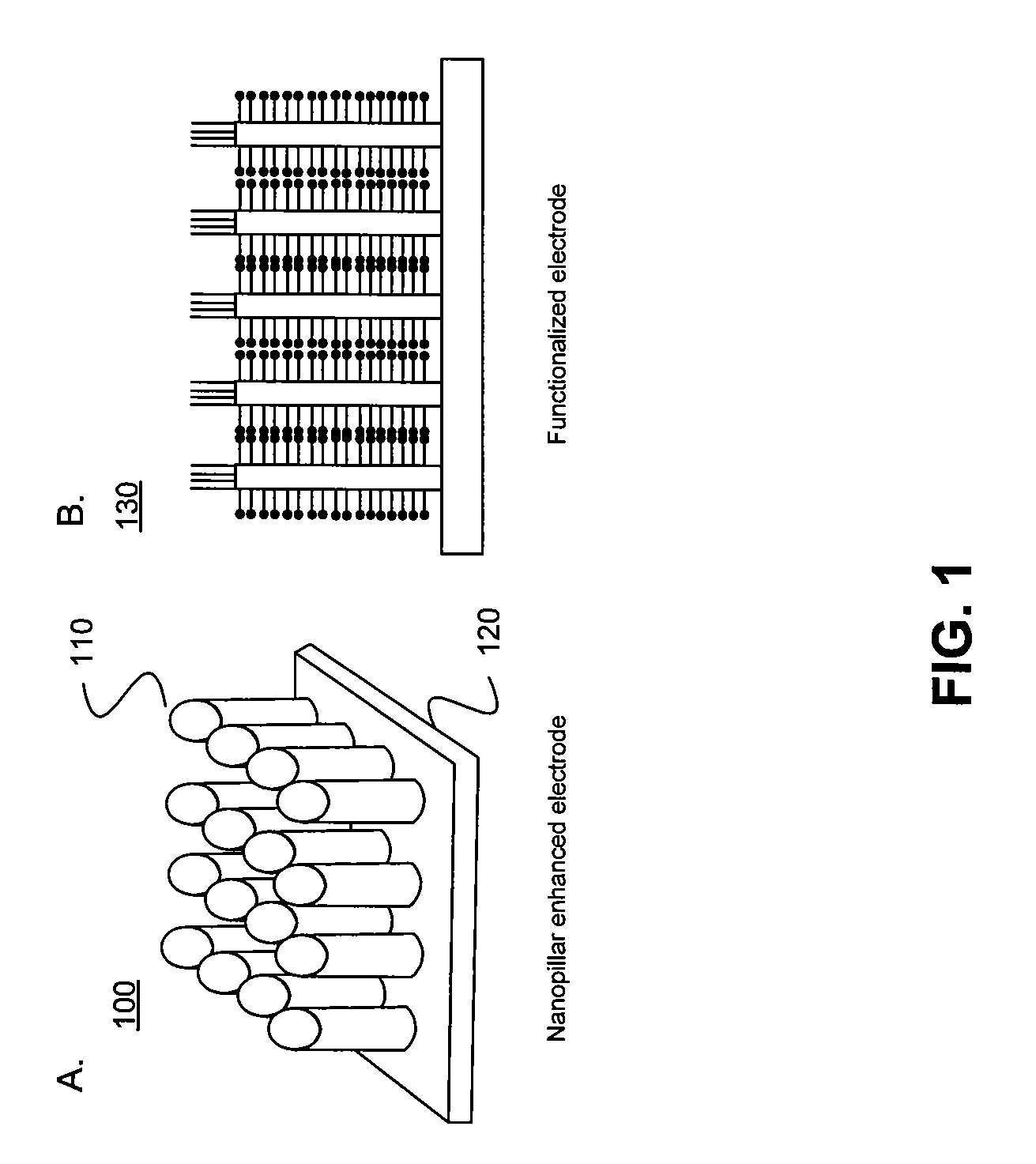

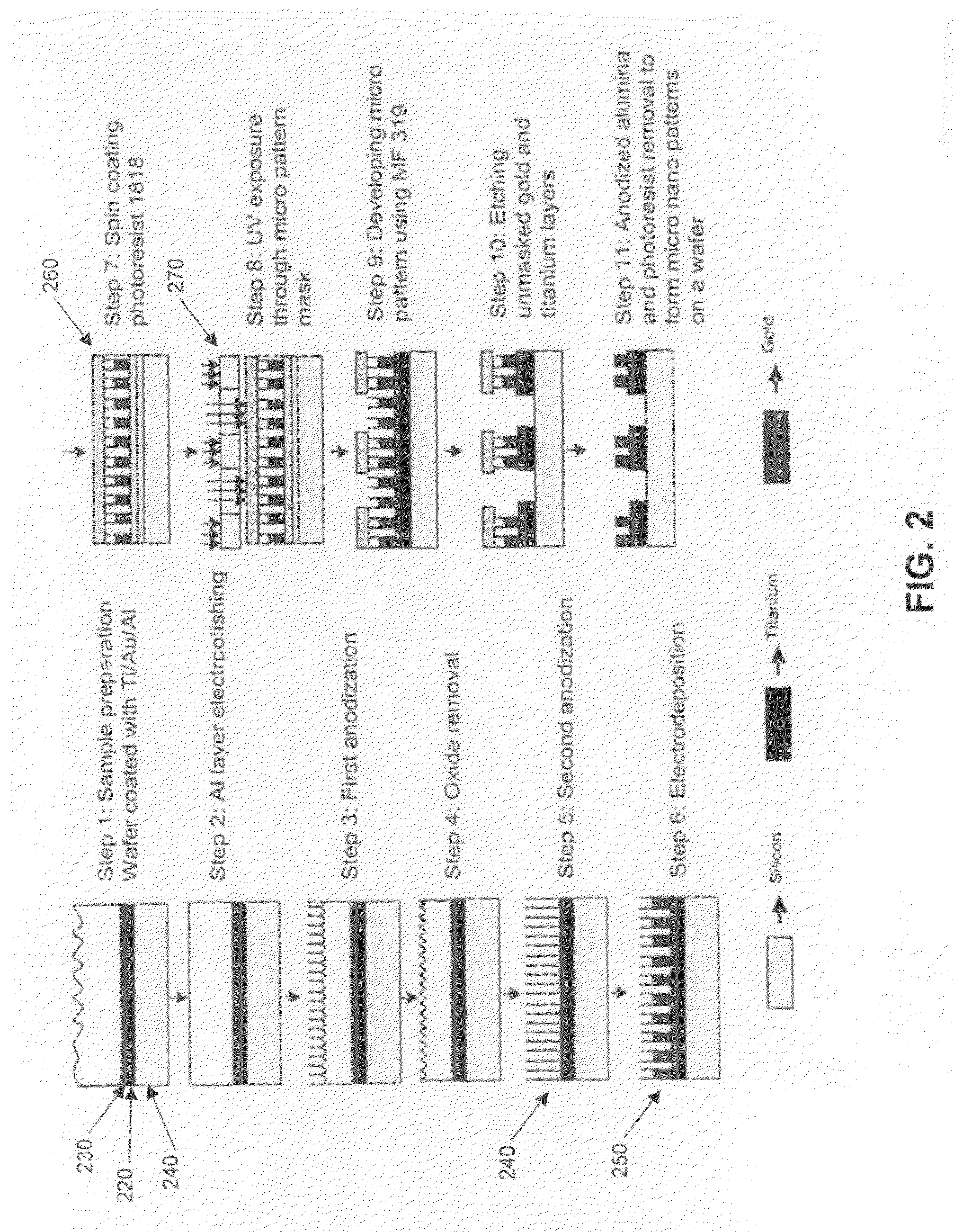

Fabrication of microstructures integrated with nanopillars along with their applications as electrodes in sensors

InactiveUS20100066346A1Improve mechanical propertiesHigh detection sensitivityVibration measurement in solidsAnalysing solids using sonic/ultrasonic/infrasonic wavesNanopillarEngineering

This invention presents microstructures enhanced with nanopillars. The invention also provides ways for manufacturing nanopillar-enhanced microstructures. In some embodiments, the invention also provides methods of use for the nanopillar-enhanced microstructures.

Owner:UNIV OF GEORGIA RES FOUND INC

Surface nanoreplication using polymer nanomasks

ActiveUS20140205766A1Low production costReduce manufacturing costNanoinformaticsPhotomechanical apparatusNanopillarNanometre

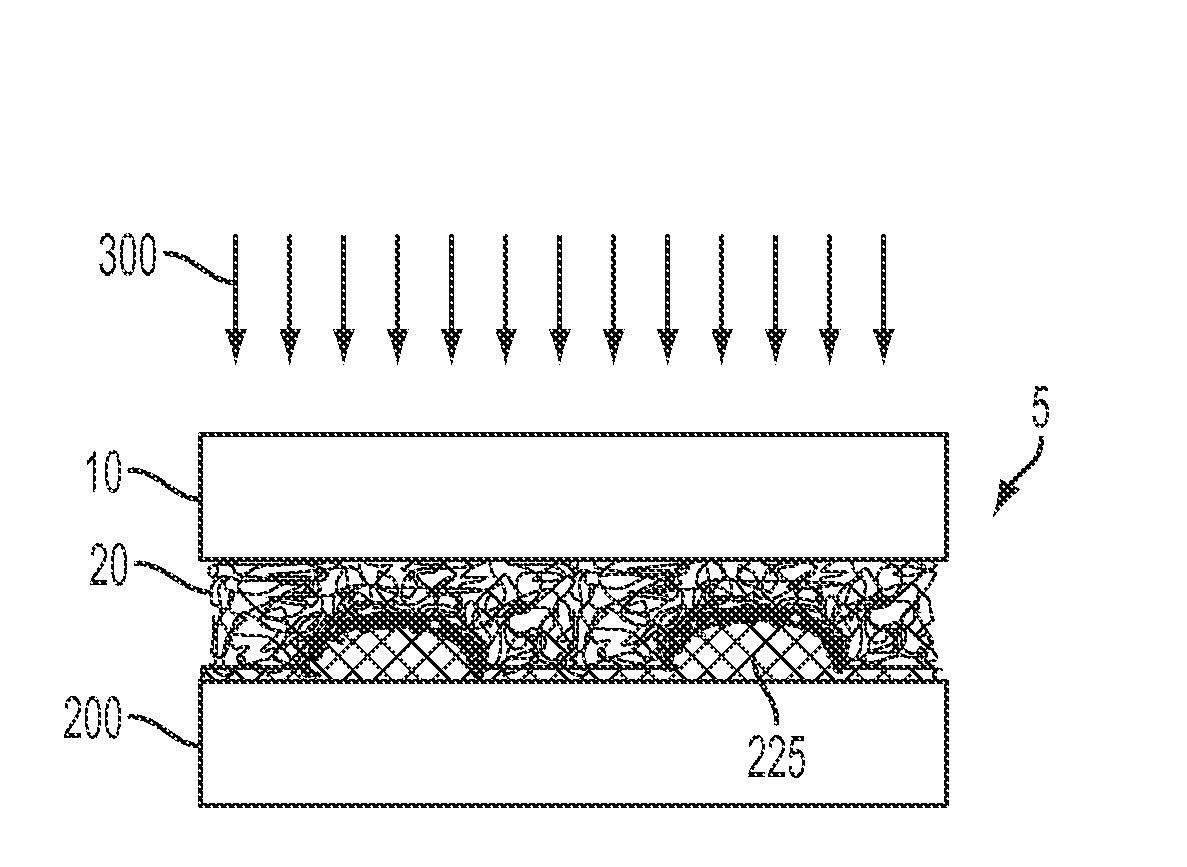

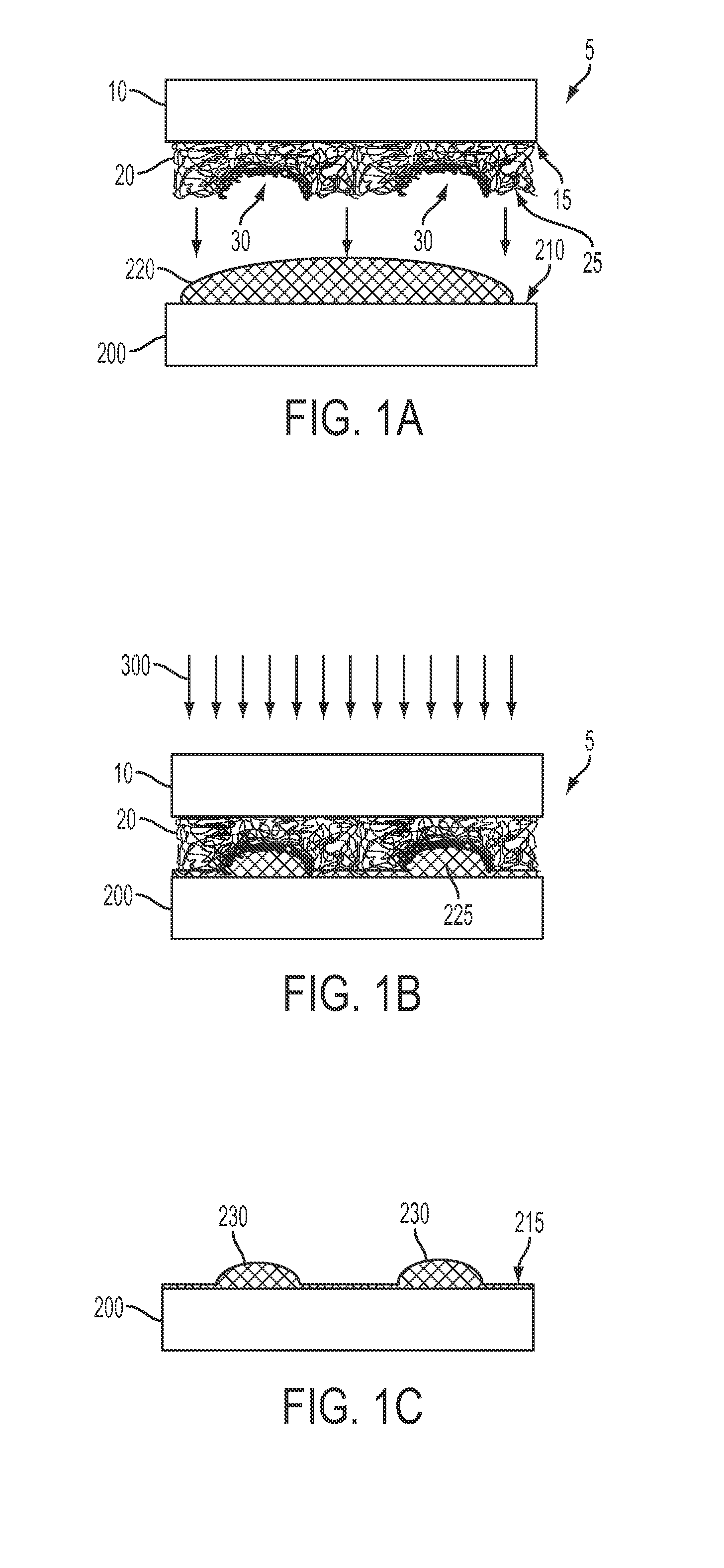

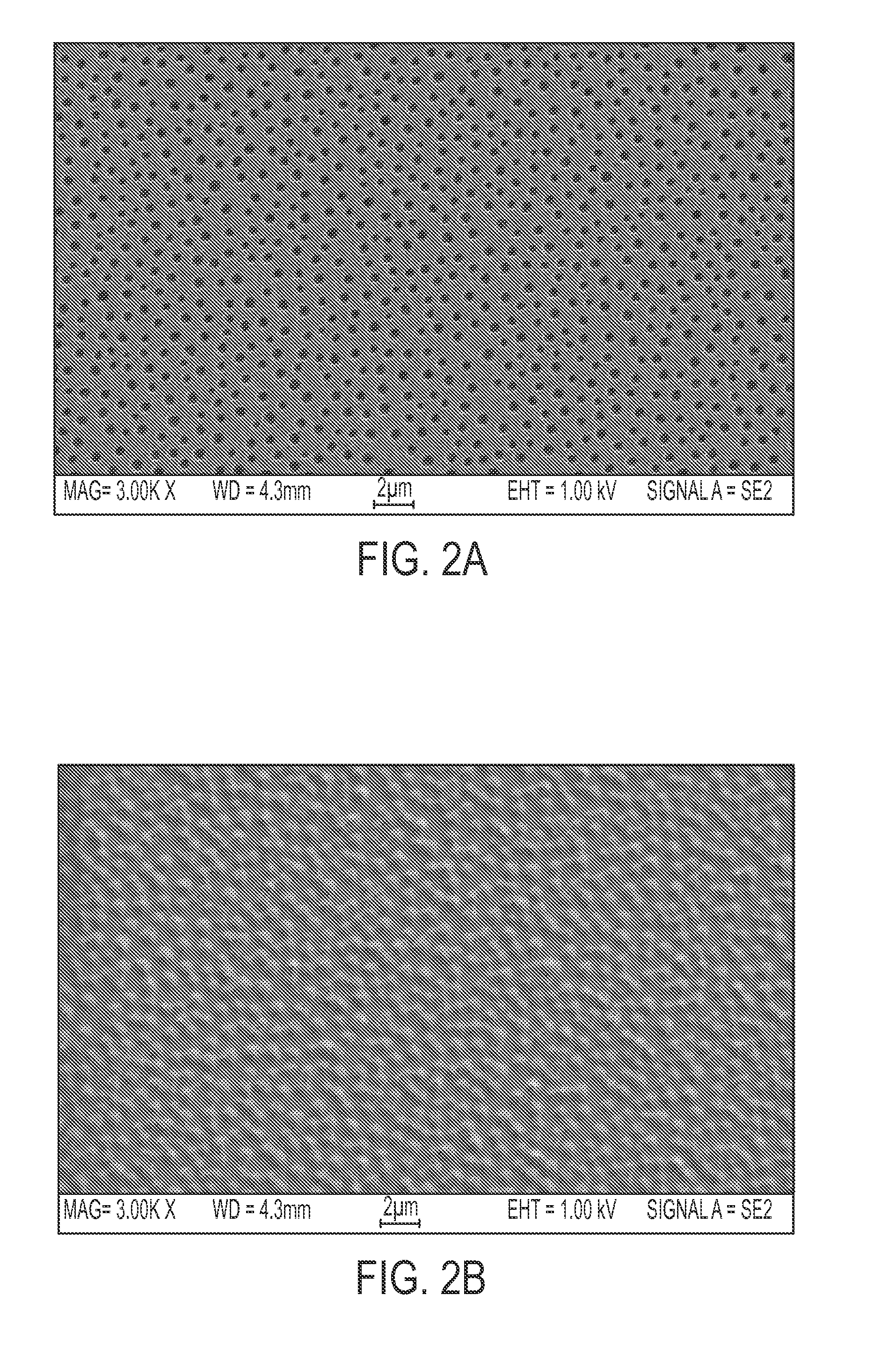

Methods for replicating a nanopillared surface include applying a nanopillar-forming material to a surface of a replica substrate to form a precursor layer on the replica-substrate surface. A template surface of a nanomask may be contacted to the precursor layer. The nanomask may include a self-assembled polymer layer on a nanomask-substrate surface, the template surface being defined in the self-assembled polymer layer. The self-assembled polymer layer may have nano-sized pores with openings at the template surface. The precursor layer may be cured while the template surface remains in contact with the precursor layer. The nanomask is removed to expose a nanopillared surface having a plurality of nanopillars on the replica-substrate surface. The nanopillars on the replica-substrate surface may correspond to the pores in the template surface. Nanopillared surfaces may be replicated on one side of the replica substrate or on two opposing sides of the replica substrate.

Owner:CORNING INC

Nano-VCSEL device and fabrication thereof using nano-colonnades

A nano-colonnade VCSEL device and a method of fabrication utilize a nanowire column grown nearly vertically from a (111) horizontal surface of a first layer to another horizontal surface of a second layer to connect the layers. The VCSEL device includes a first layer having the (111) horizontal surface; a second layer; and an insulator support between the first layer and the second layer that separates the first layer from the second layer. A portion of the second layer overhangs the insulator support, such that a horizontal surface of the overhanging portion is spaced from and faces the (111) horizontal surface of the first layer. The VCSEL device further includes a nanowire column extending nearly vertically from the (111) horizontal surface to the facing horizontal surface, and distributed Bragg mirrors adjacent to opposite end of the nanowire column.

Owner:SAMSUNG ELECTRONICS CO LTD

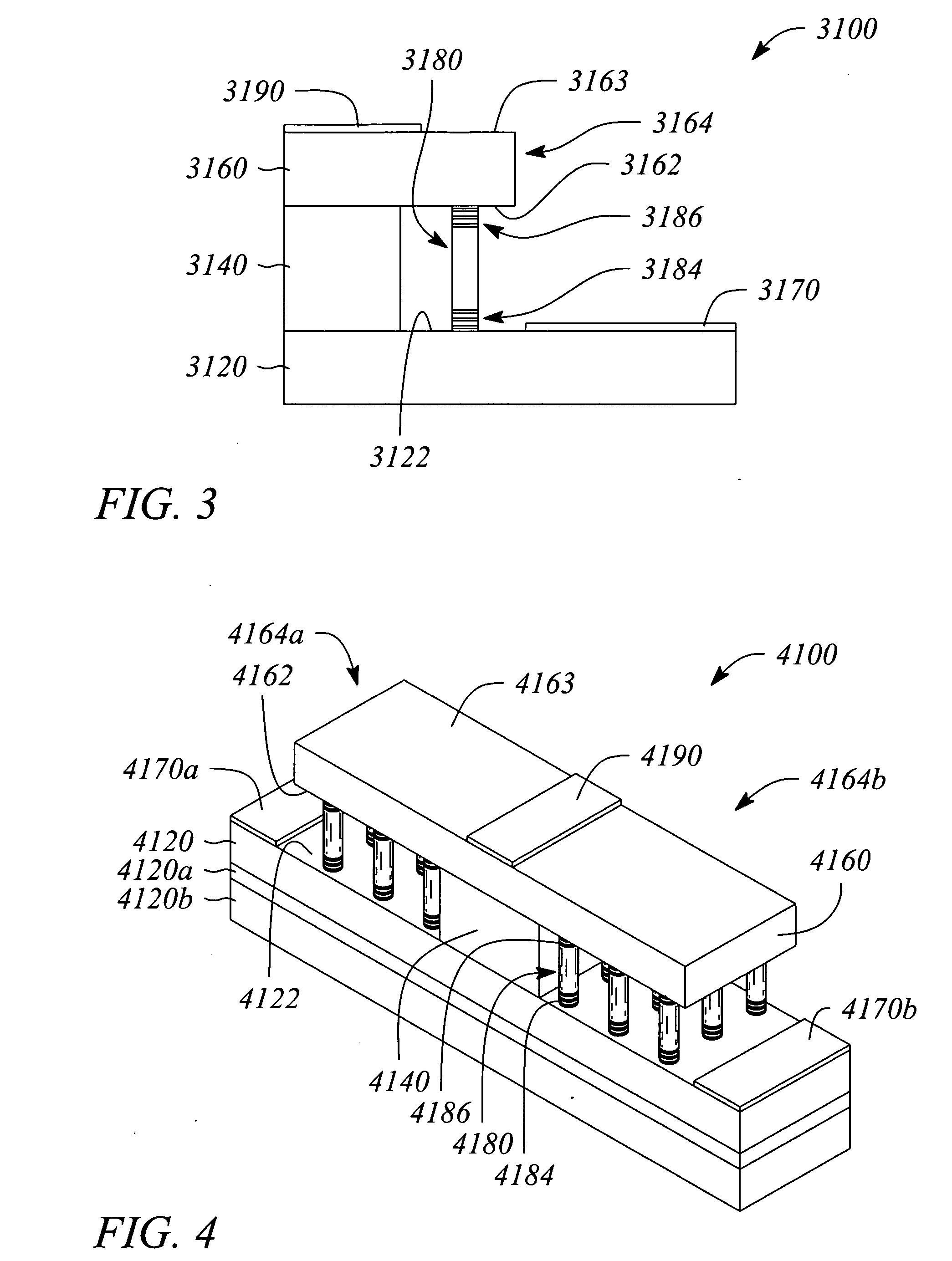

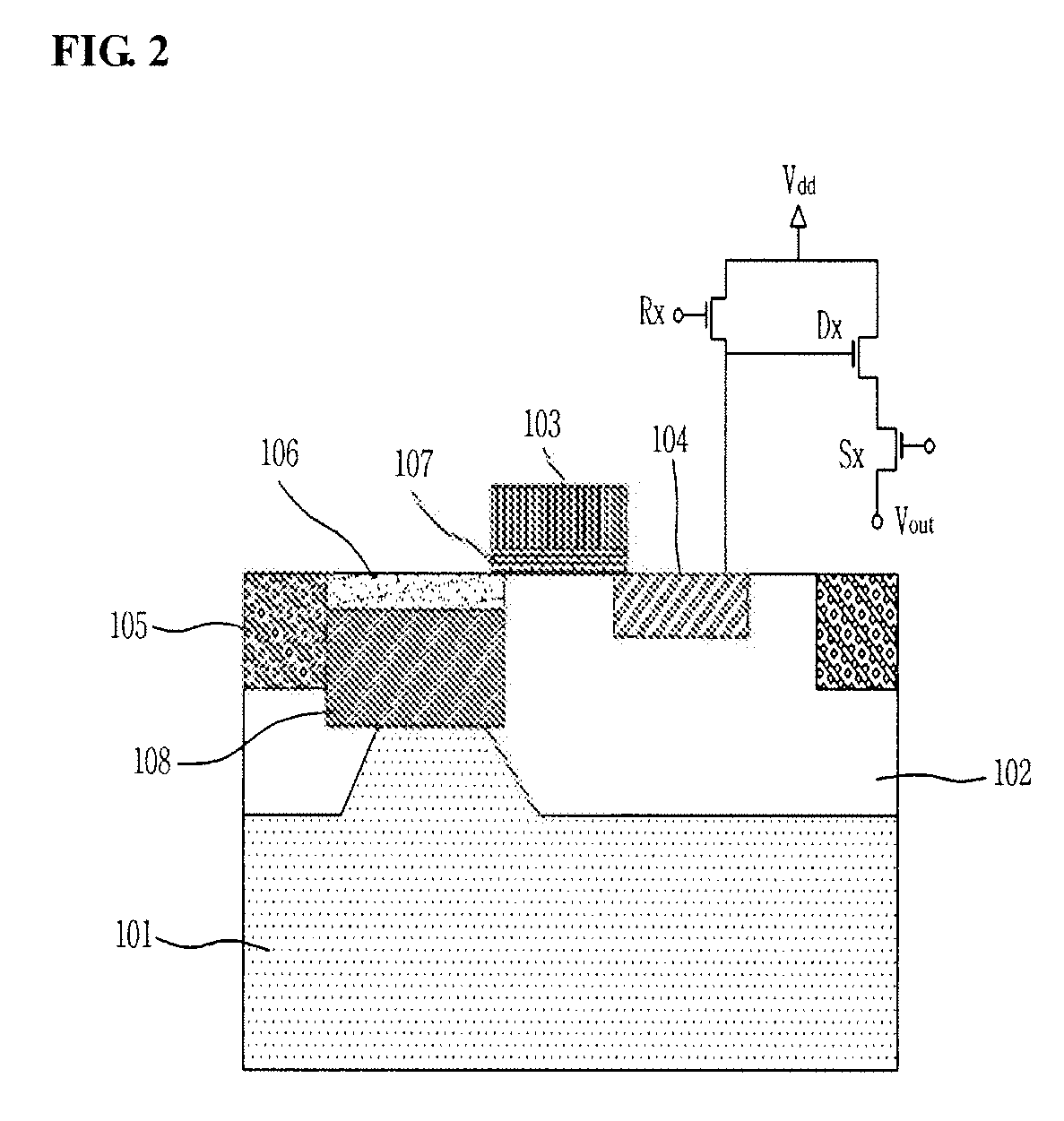

Complementary metal oxide semiconductor image sensor and method for fabricating the same

ActiveUS20070152248A1Increase photosensitivityEasy to integrateNanotechApparel holdersCMOSNanopillar

Provided are a CMOS image sensor and a method for fabricating the same. A nanopillar is plurally formed at an upper end of a light receiving element.

Owner:KOREA ADVANCED INST OF SCI & TECH

Method of making diamond nanopillars

ActiveUS20090233445A1High application potentialMaterial nanotechnologyPolycrystalline material growthNanopillarAlloy substrate

A method for fabricating diamond nanopillars includes forming a diamond film on a substrate, depositing a metal mask layer on the diamond film, and etching the diamond film coated with the metal mask layer to form diamond nanopillars below the mask layer. The method may also comprise forming diamond nuclei on the substrate prior to forming the diamond film. Typically, a semiconductor substrate, an insulating substrate, a metal substrate, or an alloy substrate is used.

Owner:CITY UNIVERSITY OF HONG KONG

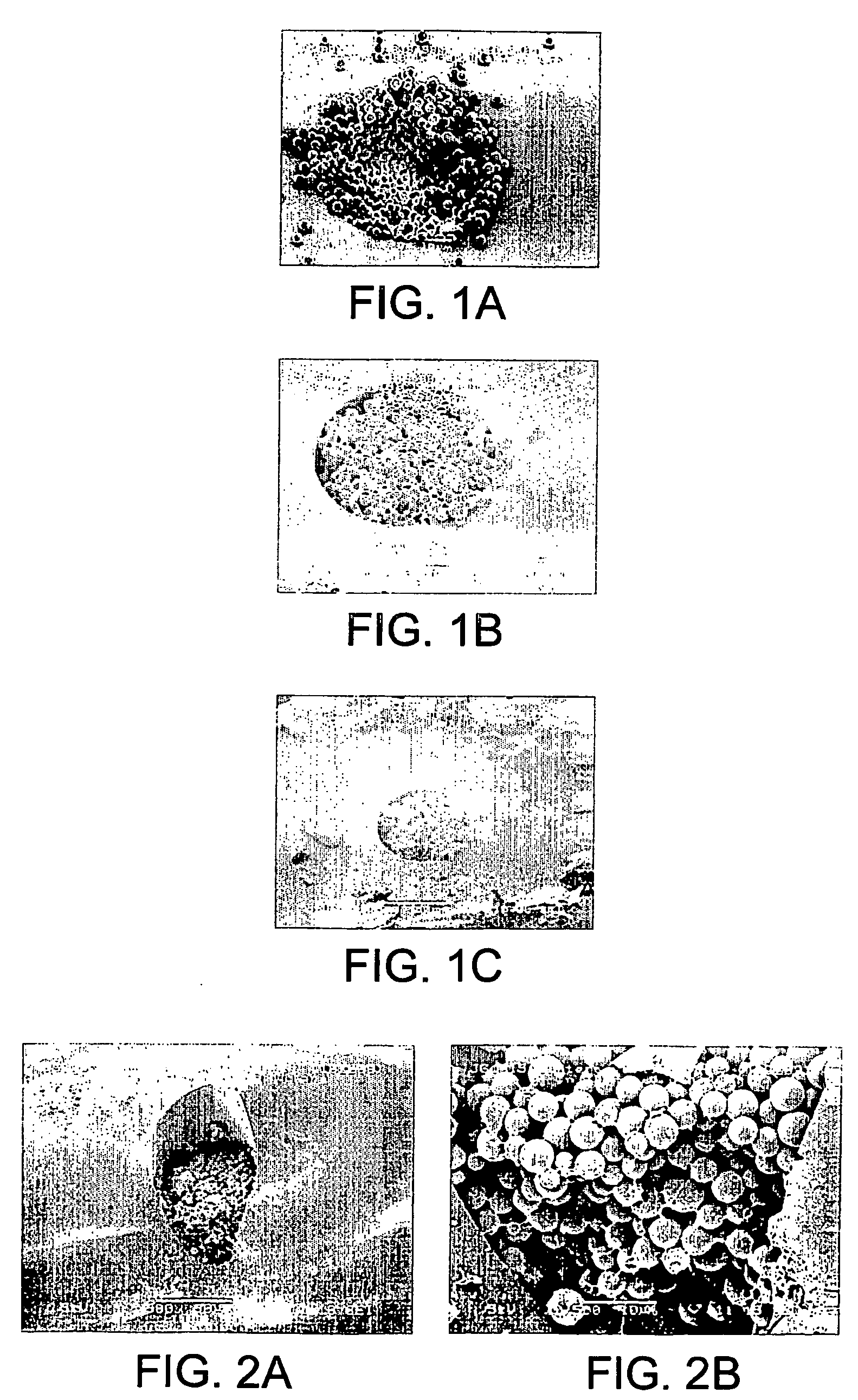

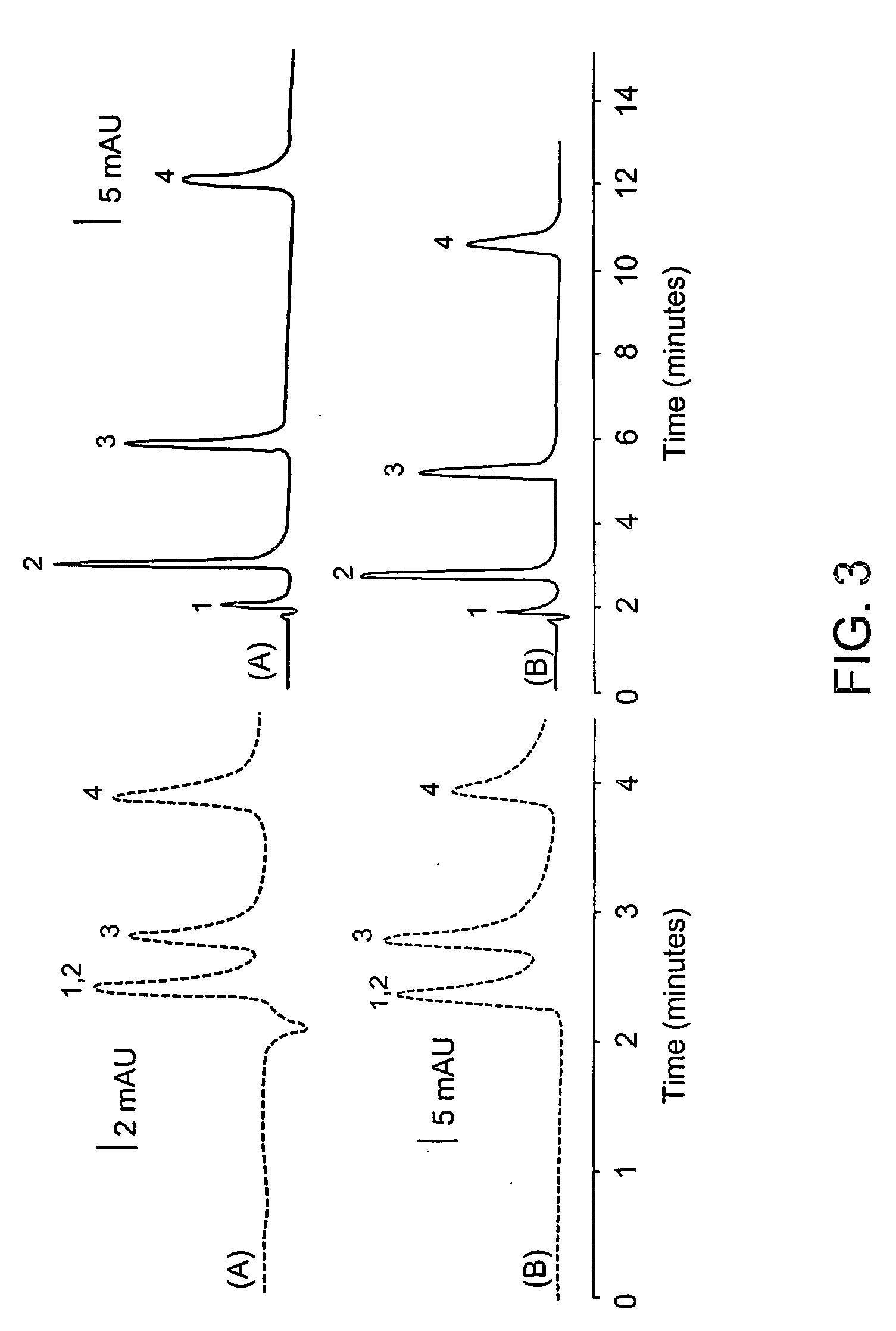

Polymeric solid supports for chromatography nanocolumns

ActiveUS20060144770A1Ion-exchange process apparatusAnalysis using chemical indicatorsStationary phaseParticulates

Nanocolumn chromatography devices useful, e.g., in CEC and nanoLC are disclosed. An exemplary chromatography device of the invention includes a nanocolumn, e.g., a capillary, packed with a particulate stationary phase material and a solid support. The solid support, or in situ frit, is adjacent to and integral with the stationary phase material. An in situ frit of the invention may be a mixture of the stationary phase material and a polymeric network of cross-linked poly(diorganosiloxane), e.g., poly(dimethylsiloxane), which may optionally be sintered. The invention also provides methods of making and using such devices.

Owner:WATERS TECH CORP

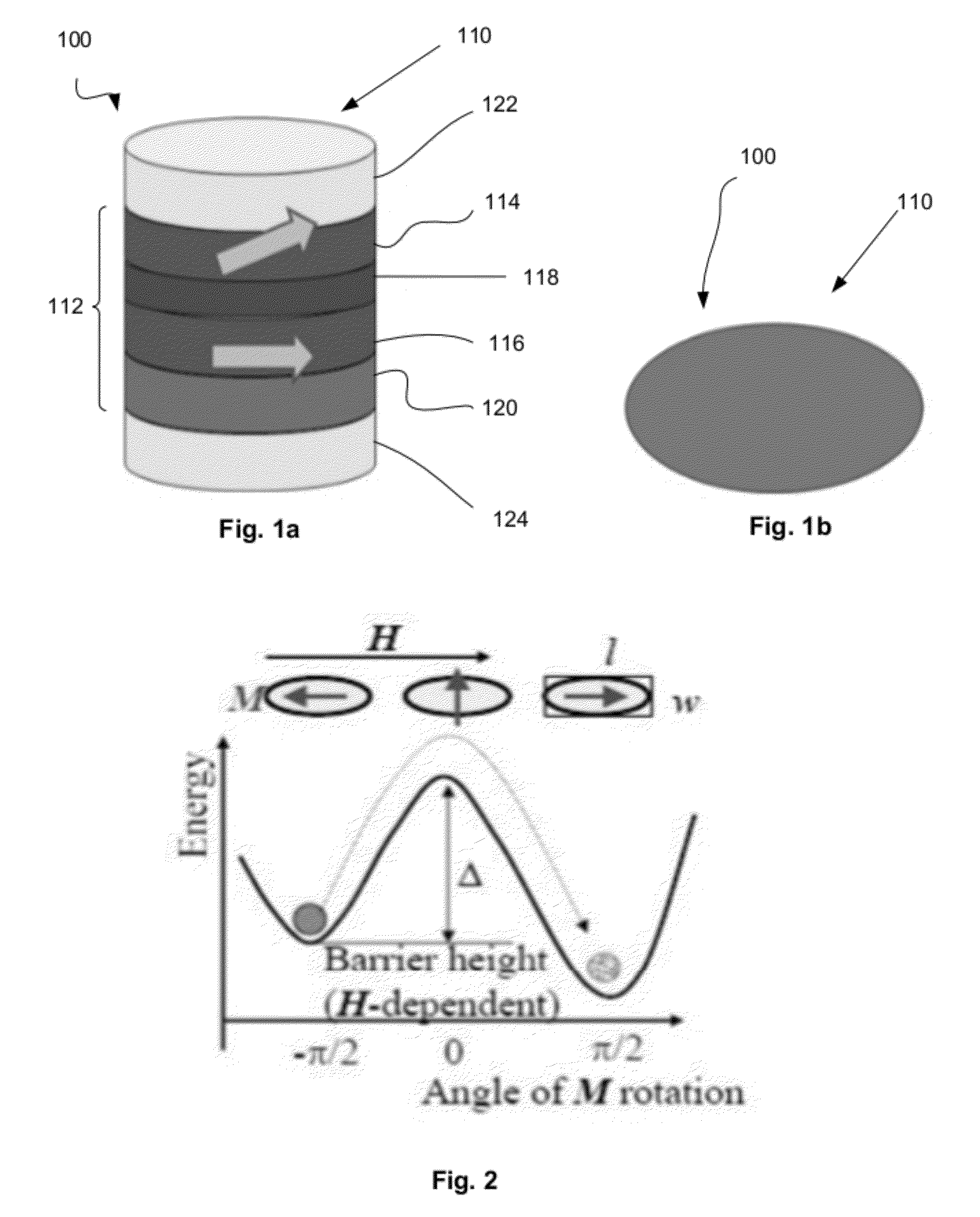

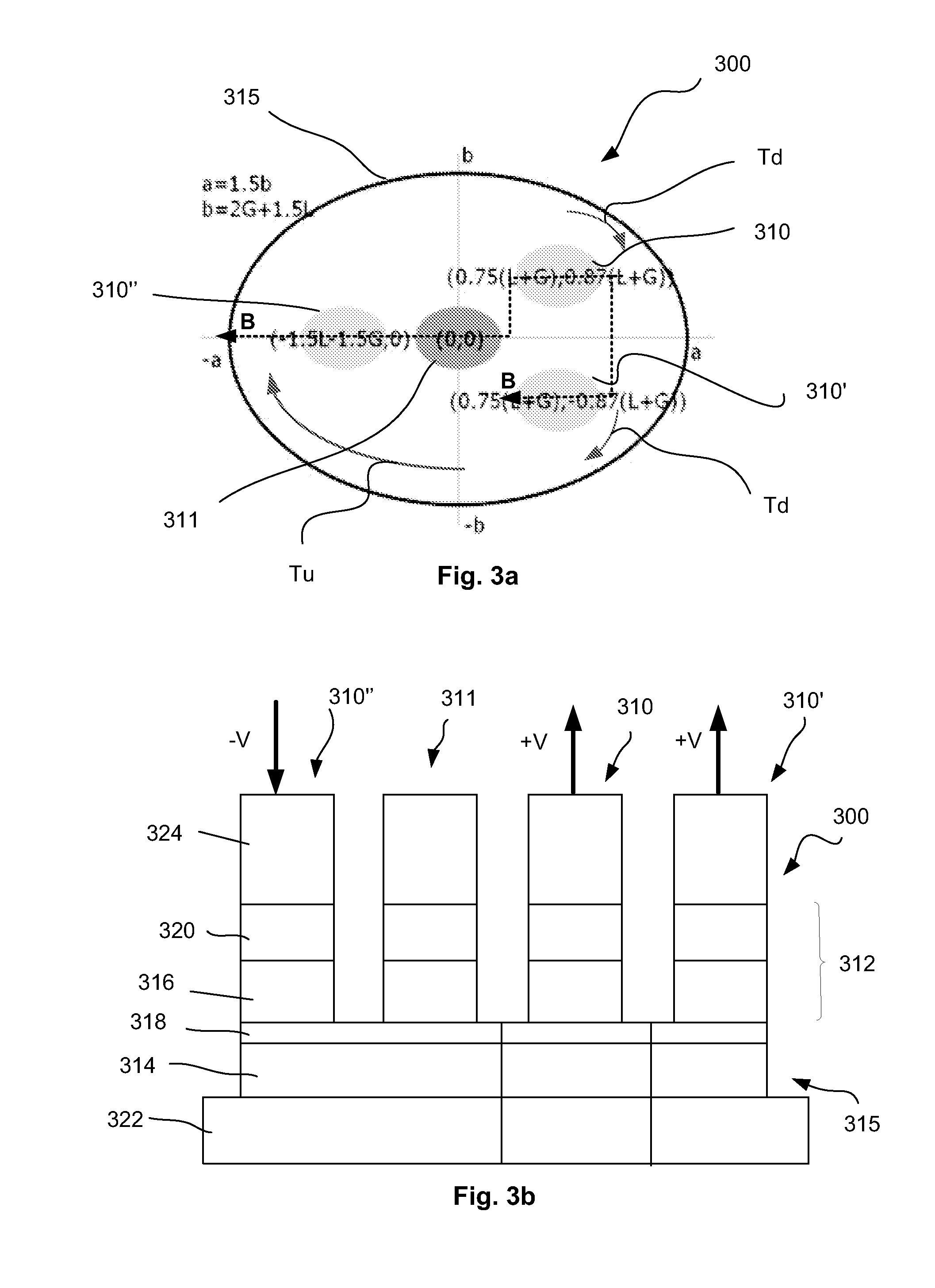

Spin torque oscillator having multiple fixed ferromagnetic layers or multiple free ferromagnetic layers

InactiveUS8604886B2Record information storageInductances/transformers/magnets manufactureNanopillarMicrowave

A spin torque oscillator and a method of making same. The spin torque oscillator is configured to generate microwave electrical oscillations without the use of a magnetic field external thereto, the spin torque oscillator having one of a plurality of input nanopillars and a nanopillar having a plurality of free FM layers.

Owner:INTEL CORP

Three-dimensional coherent plasmonic nanowire arrays for enhancement of optical processes

InactiveUS20120273662A1Avoid large gapsMaterial analysis by optical meansPhotometry using electric radiation detectorsNanowireNanopillar

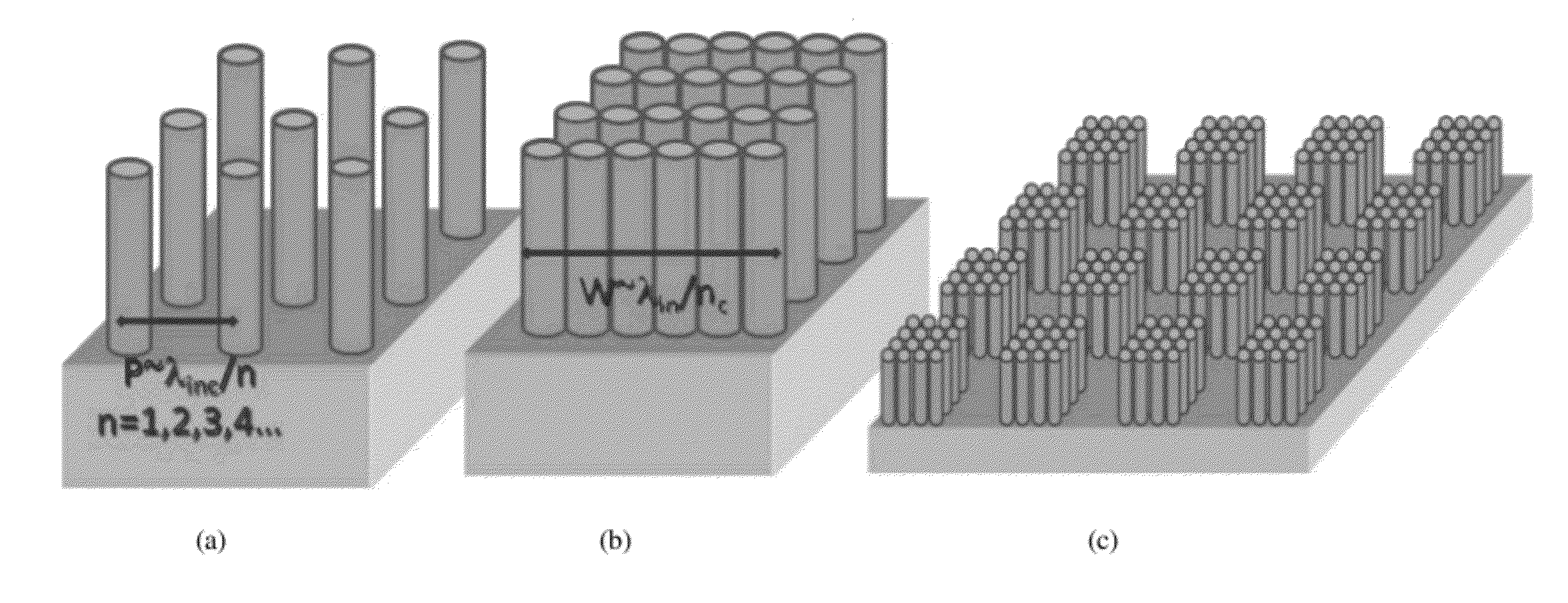

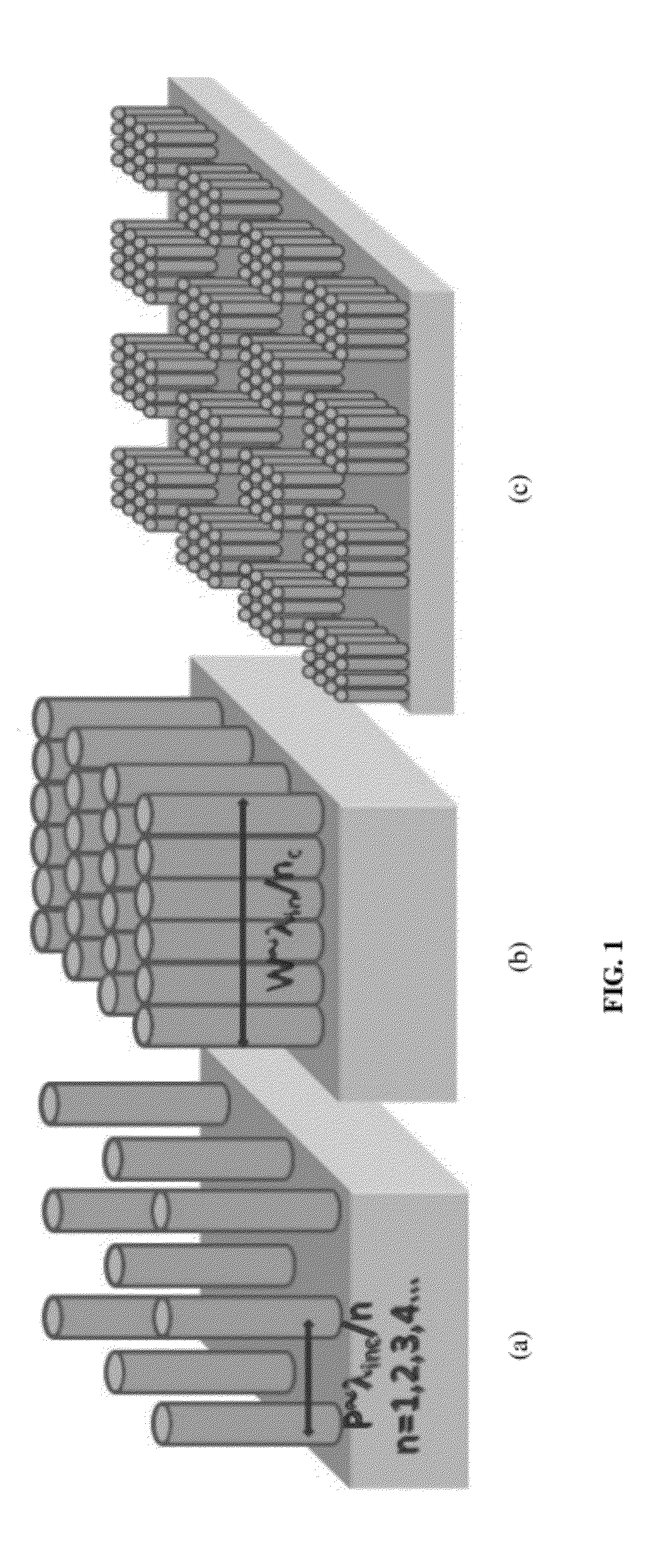

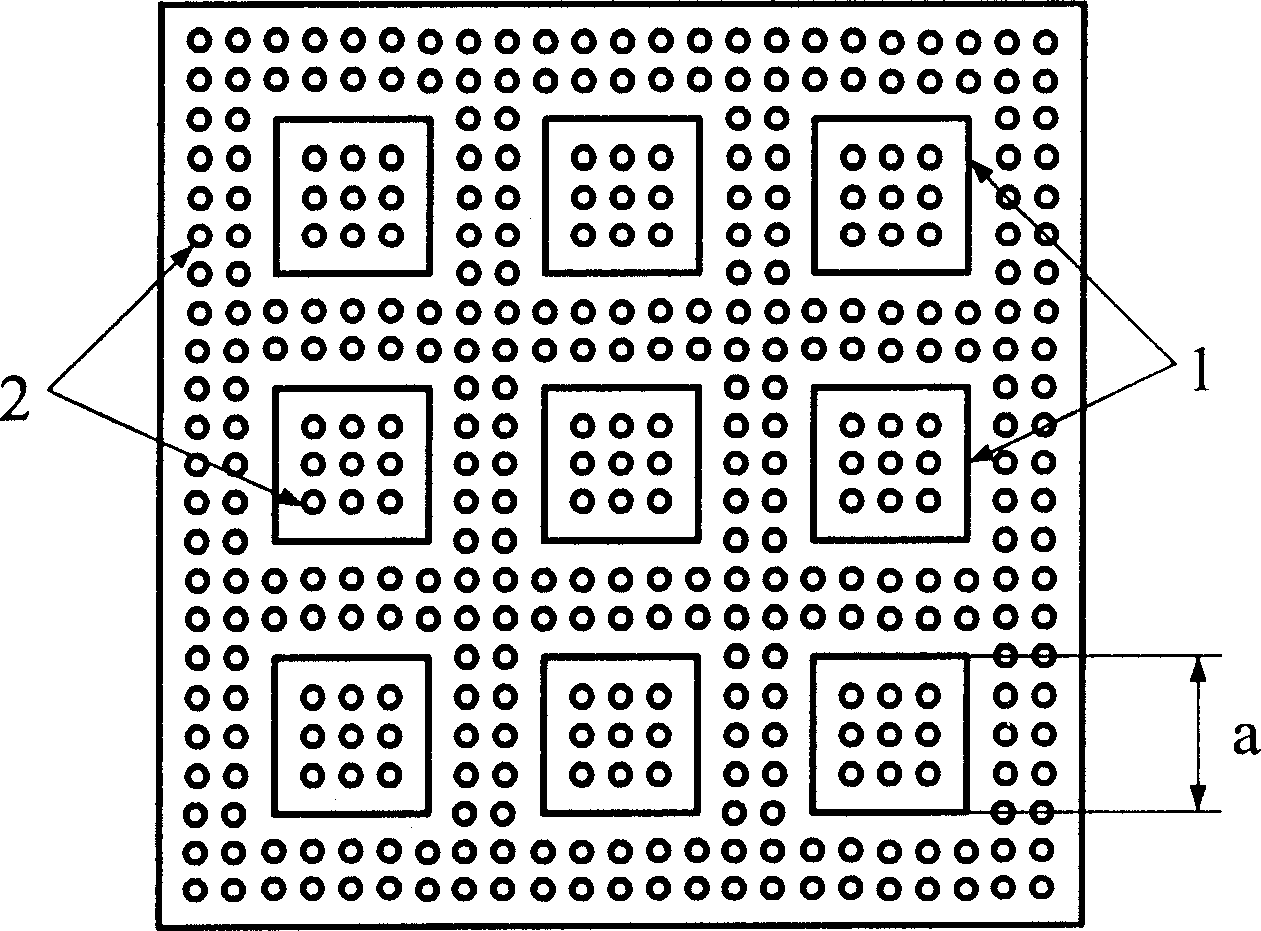

A plasmonic grating sensor having periodic arrays of vertically aligned plasmonic nanopillars, nanowires, or both with an interparticle pitch ranging from λ / 8−2λ, where λ is the incident wavelength of light divided by the effective index of refraction of the sample; a coupled-plasmonic array sensor having vertically aligned periodic arrays of plasmonically coupled nanopillars, nanowires, or both with interparticle gaps sufficient to induce overlap between the plasmonic evanescent fields from neighboring nanoparticles, typically requiring edge-to-edge separations of less than 20 nm; and a plasmo-photonic array sensor having a double-resonant, periodic array of vertically aligned subarrays of 1 to 25 plasmonically coupled nanopillars, nanowires, or both where the subarrays are periodically spaced at a pitch on the order of a wavelength of light.

Owner:THE UNITED STATES OF AMERICA AS REPRESENTED BY THE SECRETARY OF THE NAVY

Super hydrophobic surface possessing dual microtexture and preparation method

InactiveCN1760112AAvoid surface frictionOvercoming wear and tearDecorative surface effectsIndividual molecule manipulationAnodizingNanopillar

A superhydrophobic surface with dual microscopic structures features that the micron-class arrays and nano-class arrays are prepared on the surface of polymer film through microprocessing and anodizing. The length, width, height and gap of microposts in array are 10-100 microns for micron array and 10-100 nm for nano-array. Its template can be cyclically used.

Owner:HUAZHONG UNIV OF SCI & TECH

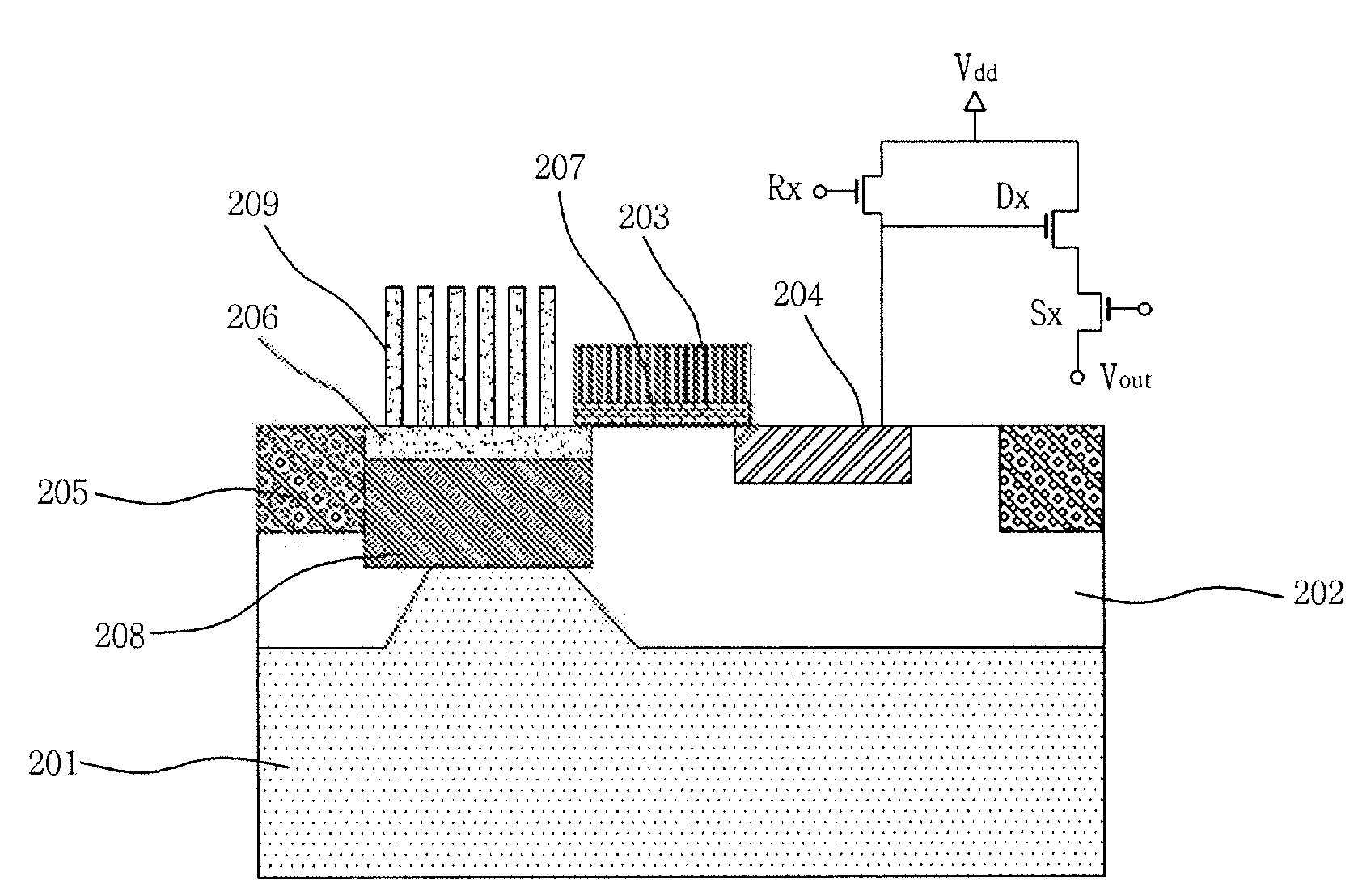

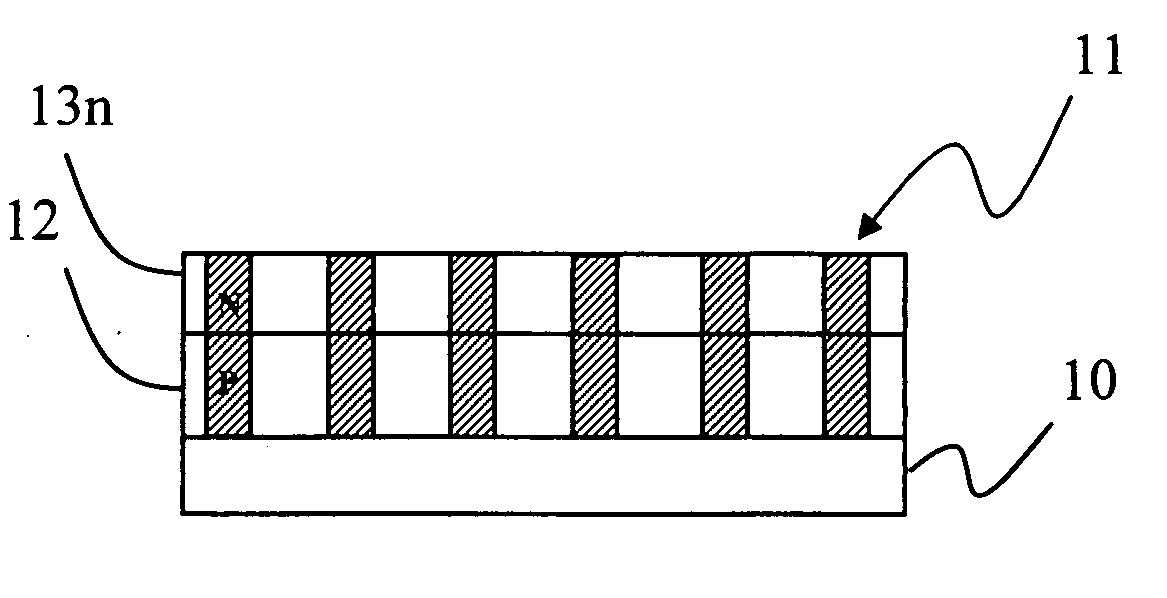

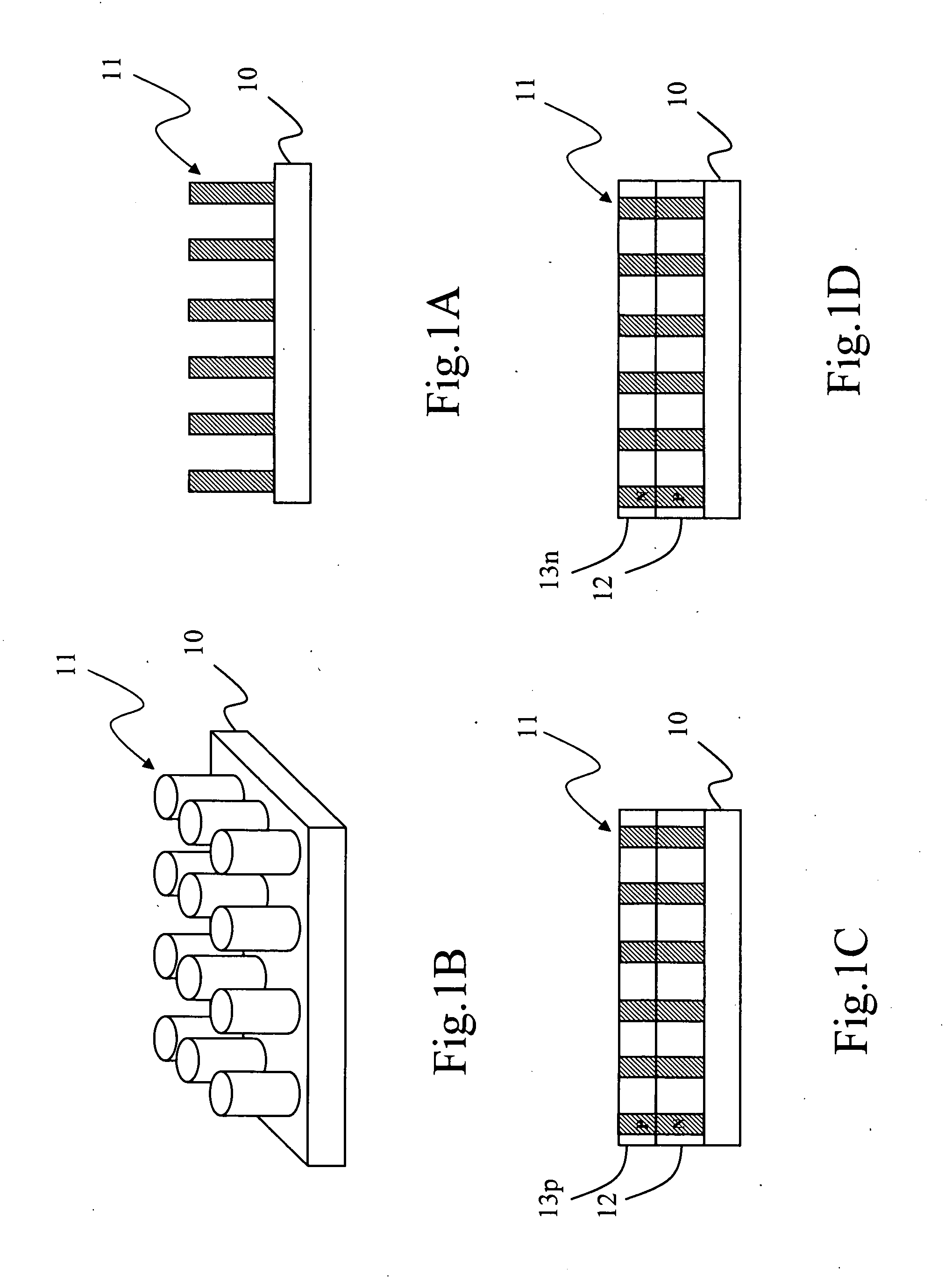

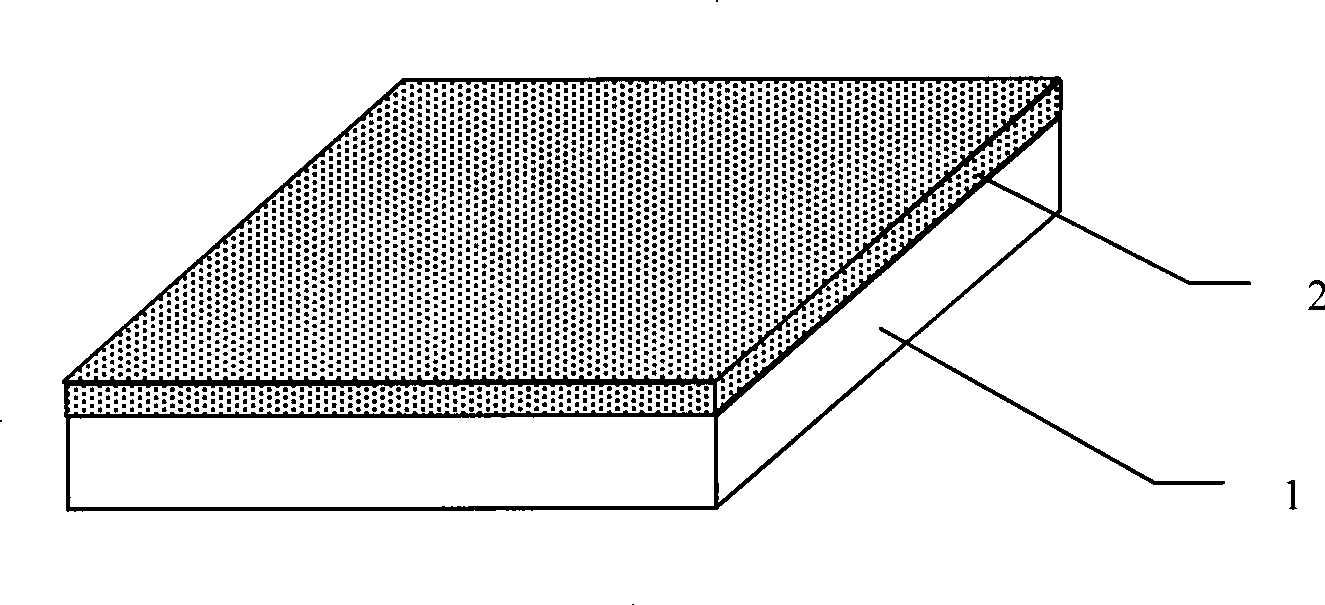

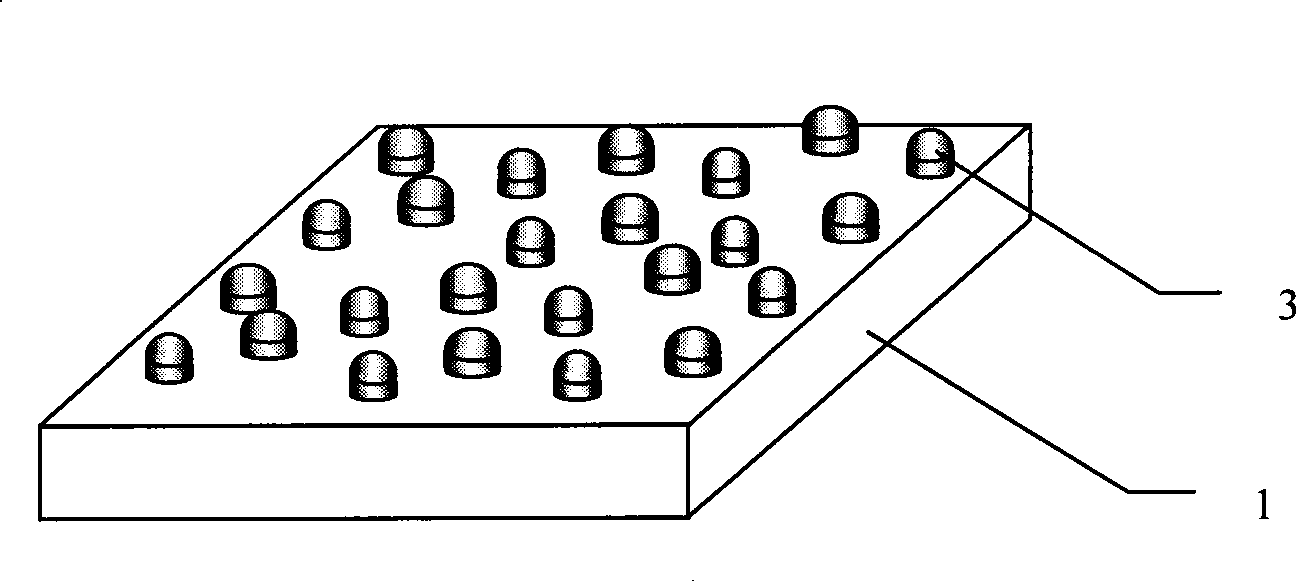

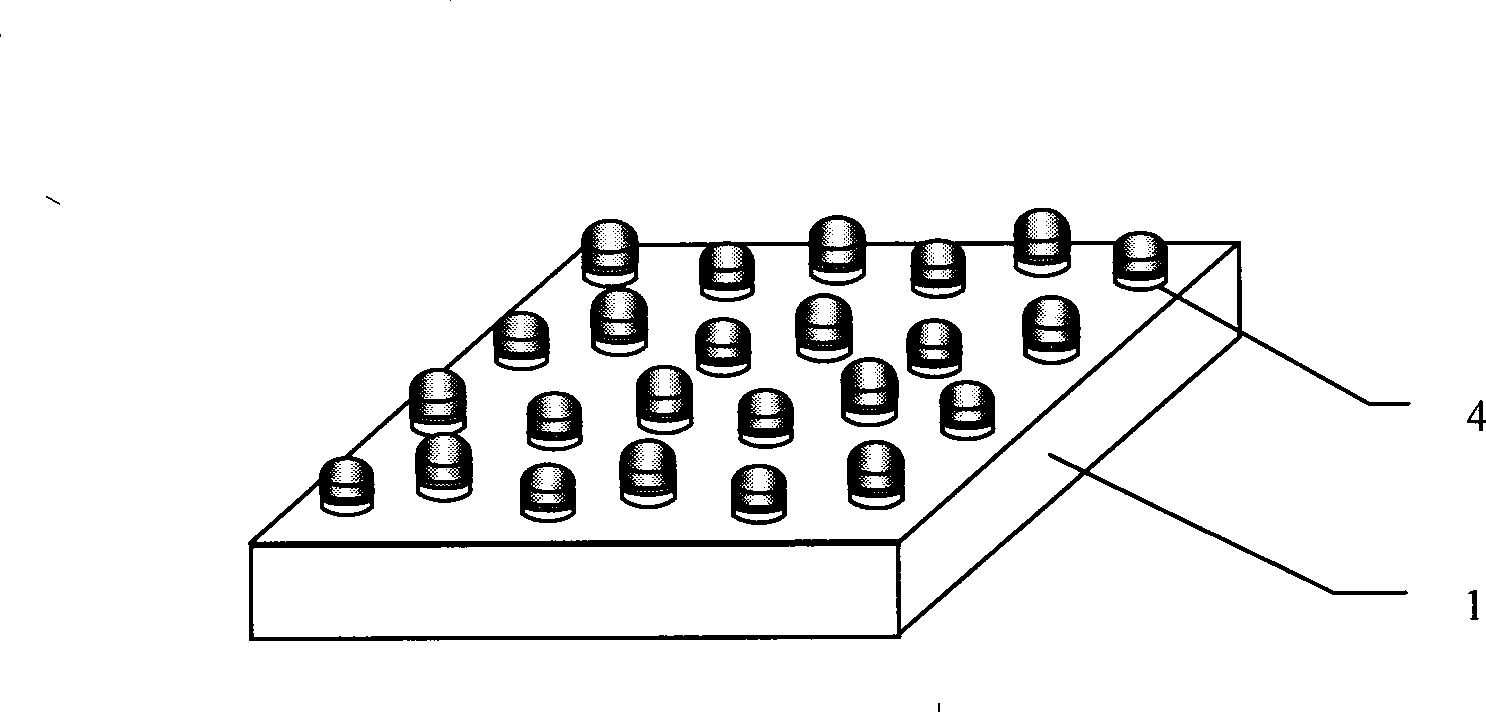

Micro/nanostructure PN junction diode array thin-film solar cell and method for fabricating the same

ActiveUS20100055824A1Save materialSolve the real problemNanoinformaticsSolid-state devicesSemiconductor materialsSource material

The present invention discloses a micro / nanostructure PN junction diode array thin-film solar cell and a method for fabricating the same, wherein a microstructure or sub-microstructure PN junction diode array, such as a nanowire array or a nanocolumns array, is transferred from a source-material wafer to two pieces of transparent substrates, which are respectively corresponding to two electric conduction types, to fabricate a thin-film solar cell. In the present invention, the micro / nanostructure PN junction diode array has advantages of a fine-quality crystalline semiconductor, and the semiconductor substrate can be reused to save a lot of semiconductor material. Besides, the present invention can make the best of sunlight energy via stacking up the solar cells made of different types of semiconductor materials to absorb different wavebands of the sunlight spectrum.

Owner:NAT TAIWAN UNIV

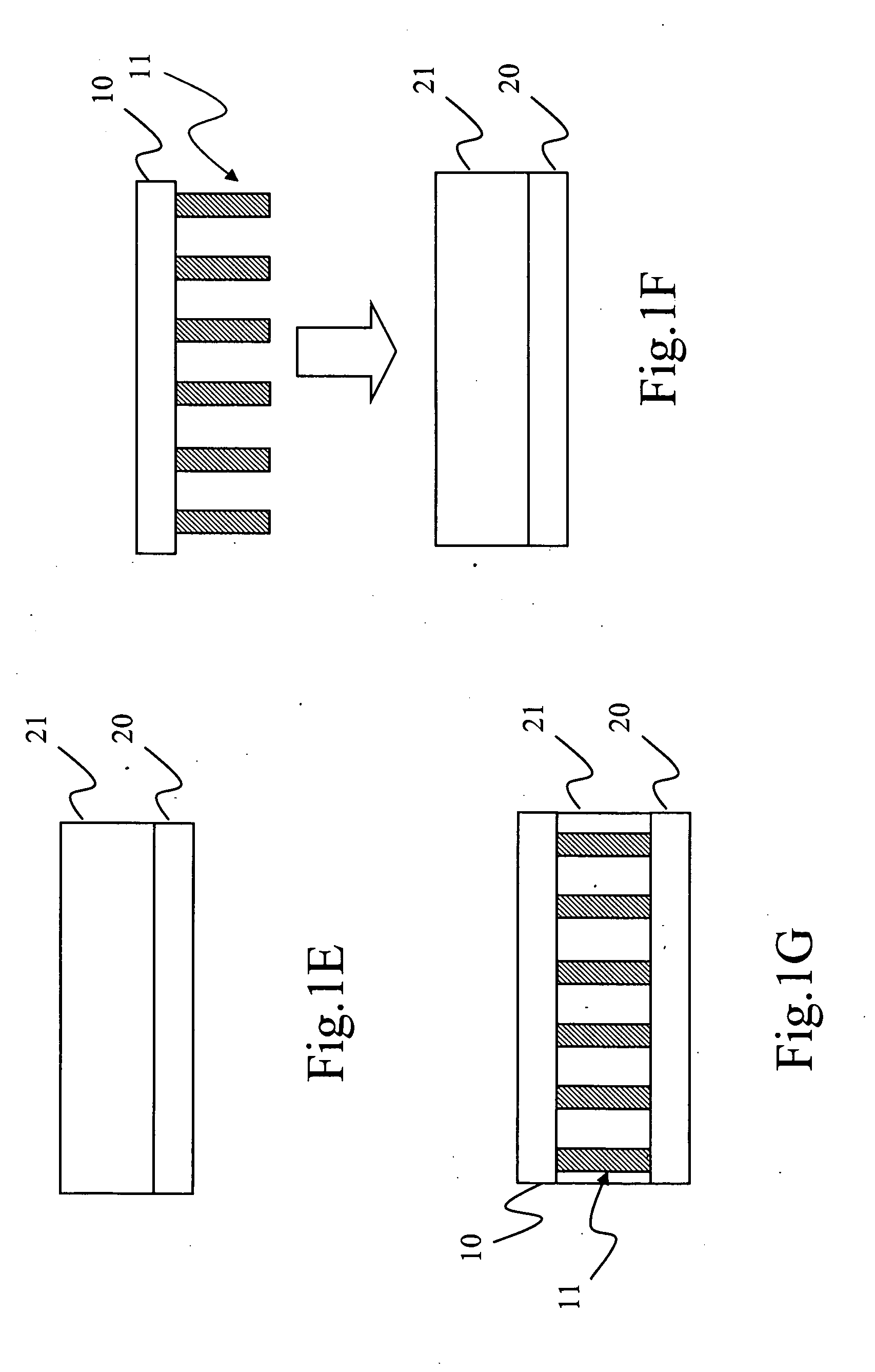

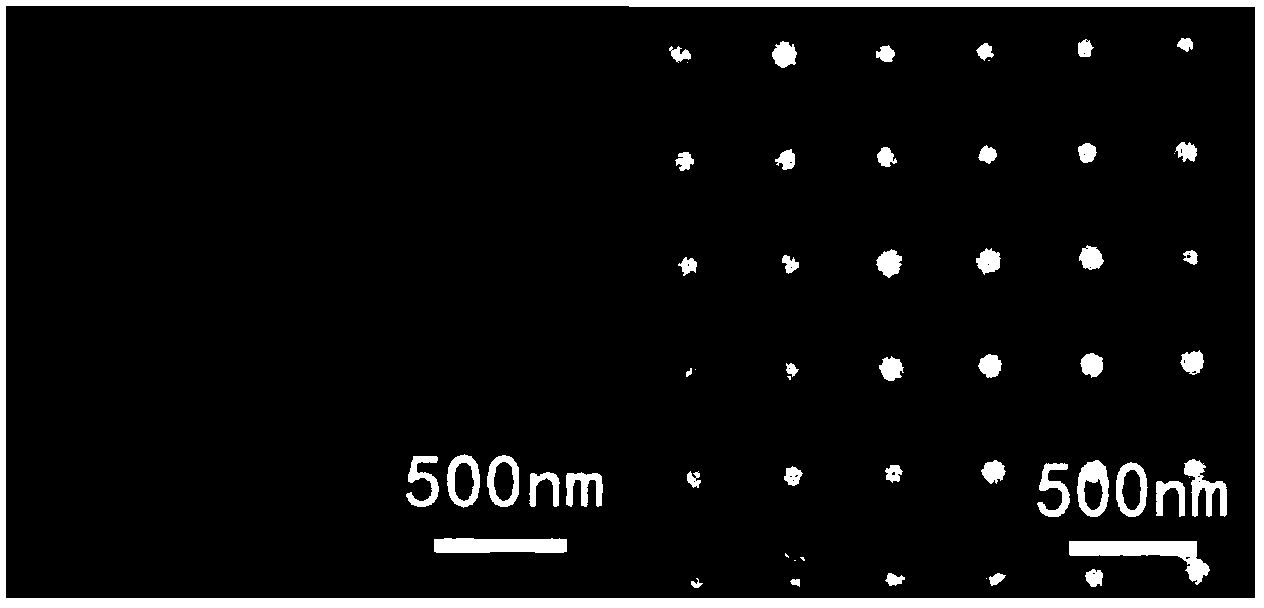

Process for formation of highly uniform arrays of nano-holes and nano-pillars

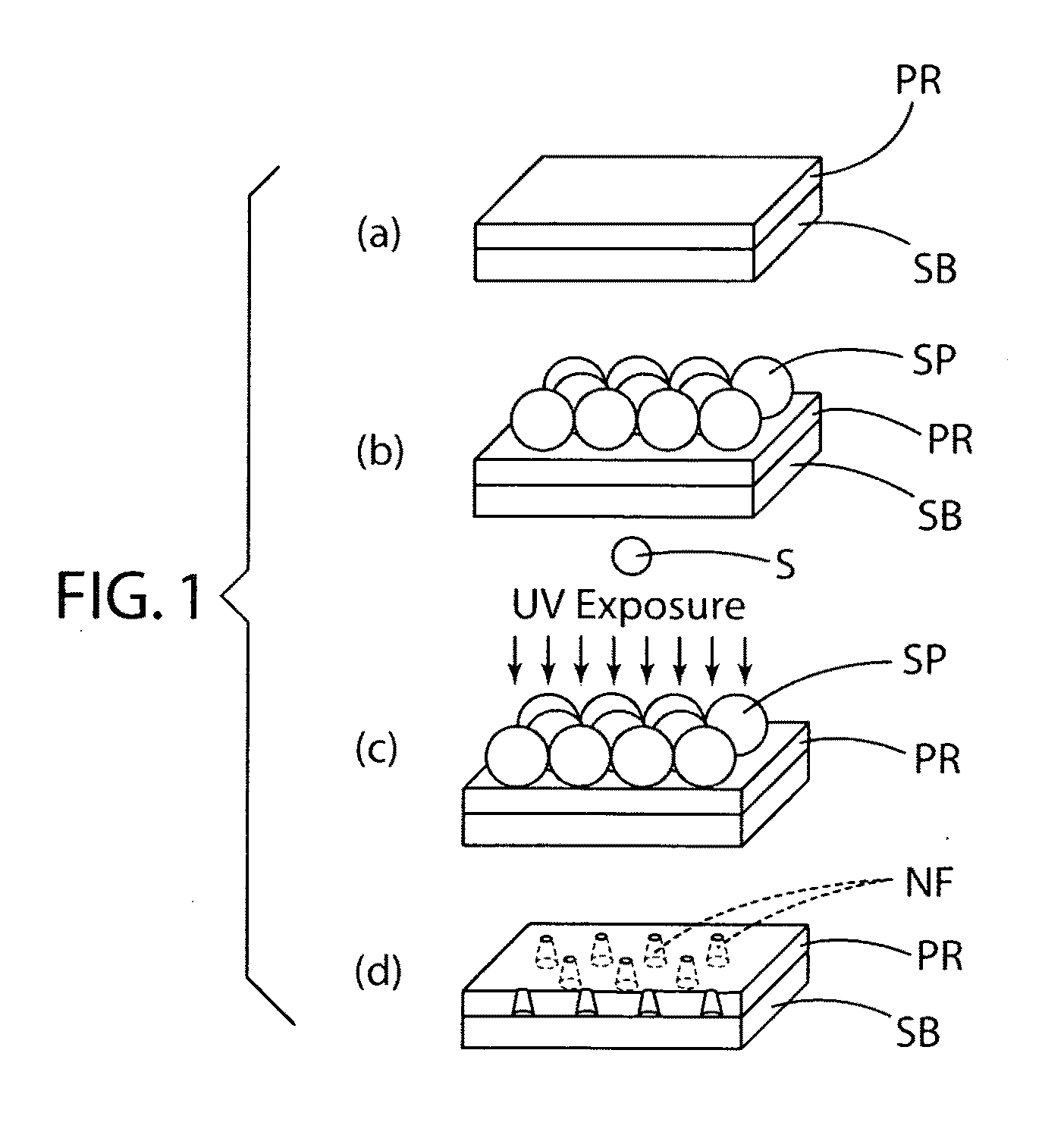

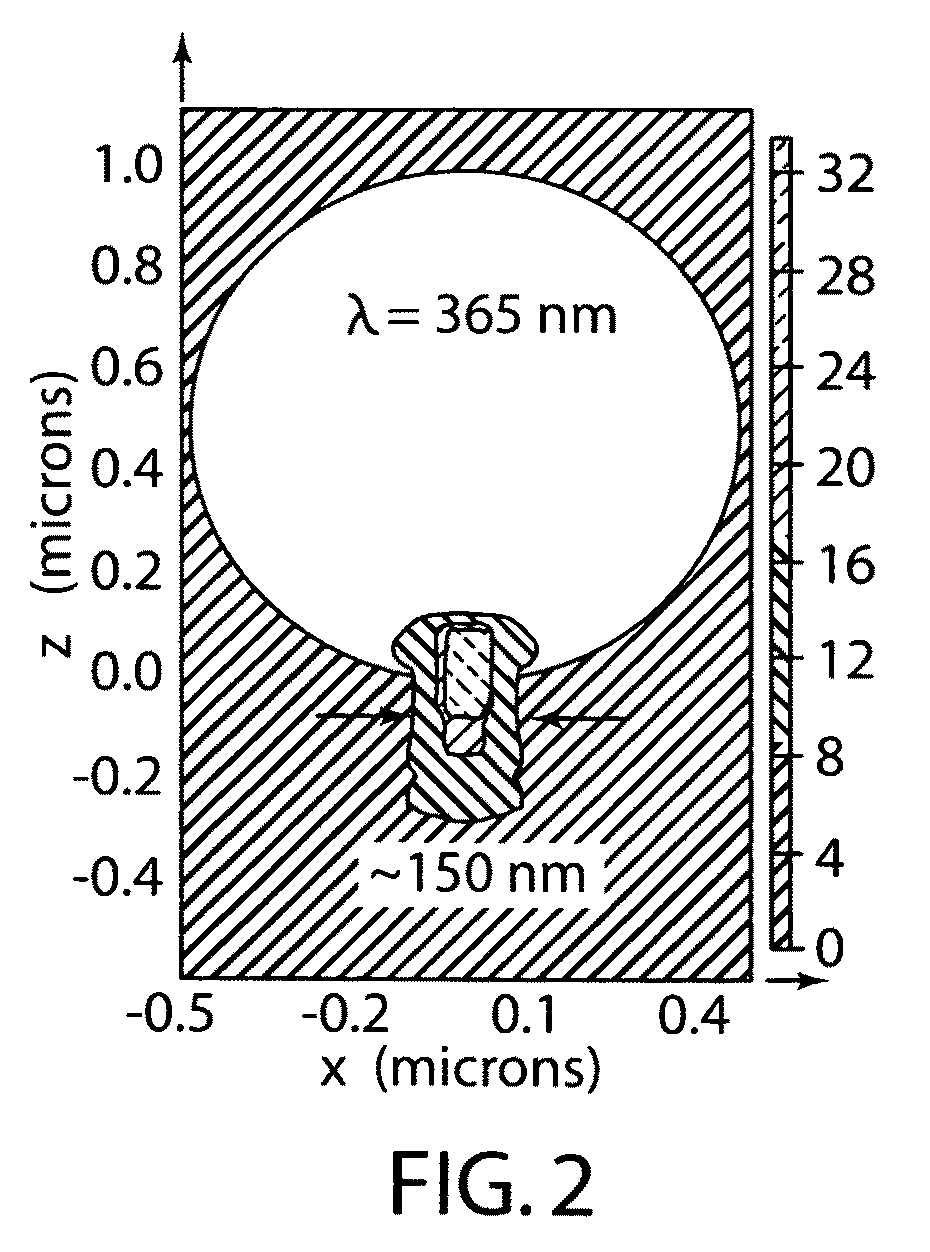

A photolithography method of patterning photoresist involves disposing a two-dimensional array of focusing particles of spherical or other shape on the photoresist and illuminating the particles on the photoresist to generate deep, sub-wavelength patterns on the photoresist. When developed, a positive photoresist layer generates a two-dimensional array of micro- or nano-holes on the developed photoresist. When developed, a negative photoresist layer generates a two-dimensional array of micro- or nano-pillars on the developed photoresist.

Owner:NORTHWESTERN UNIV

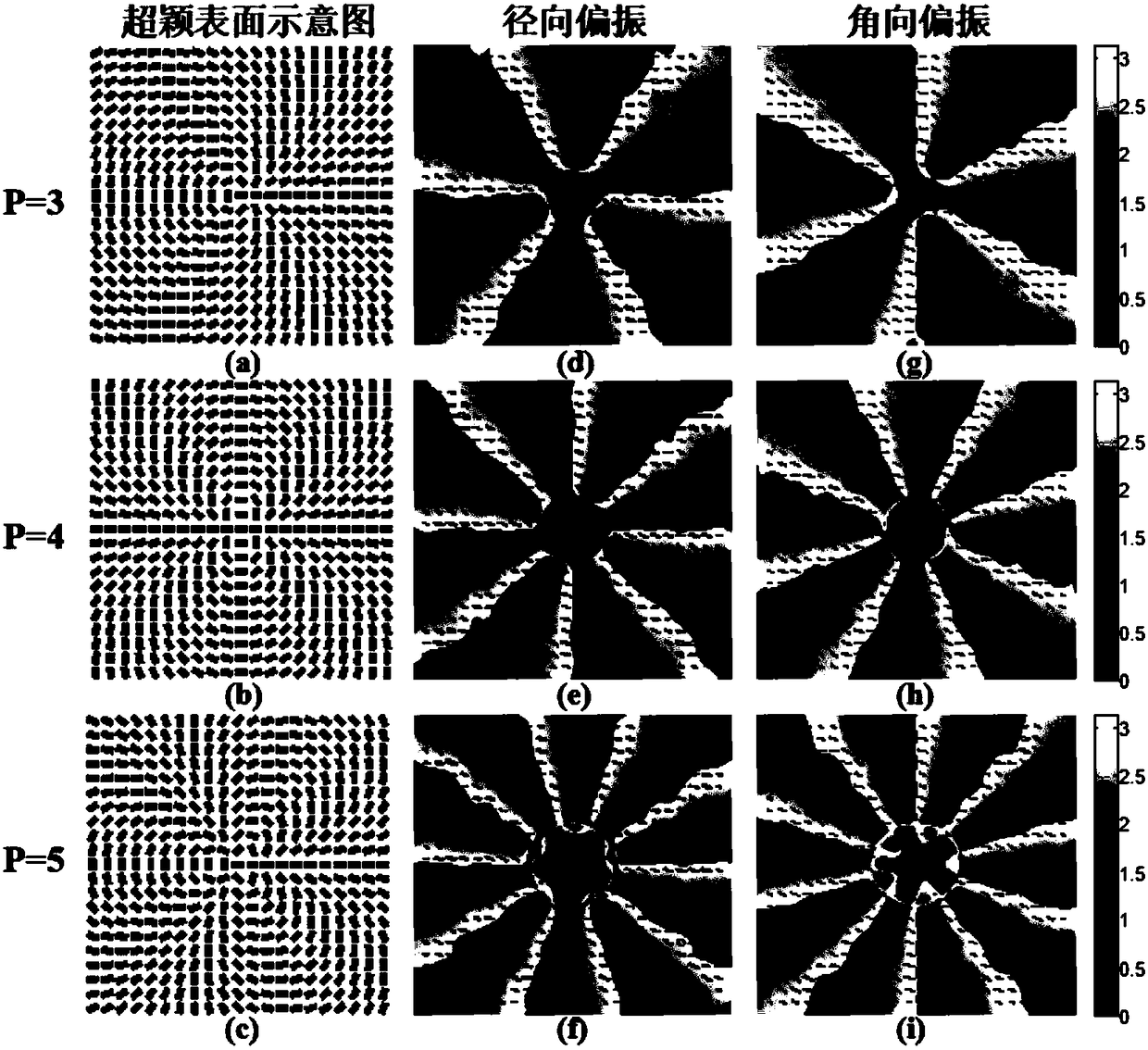

Method for generating vector light beam based on transmission-type medium metasurface

ActiveCN108490603AWith subwavelength pixelsImprove transmission efficiencyDecorative surface effectsChemical vapor deposition coatingMicro nanoLight beam

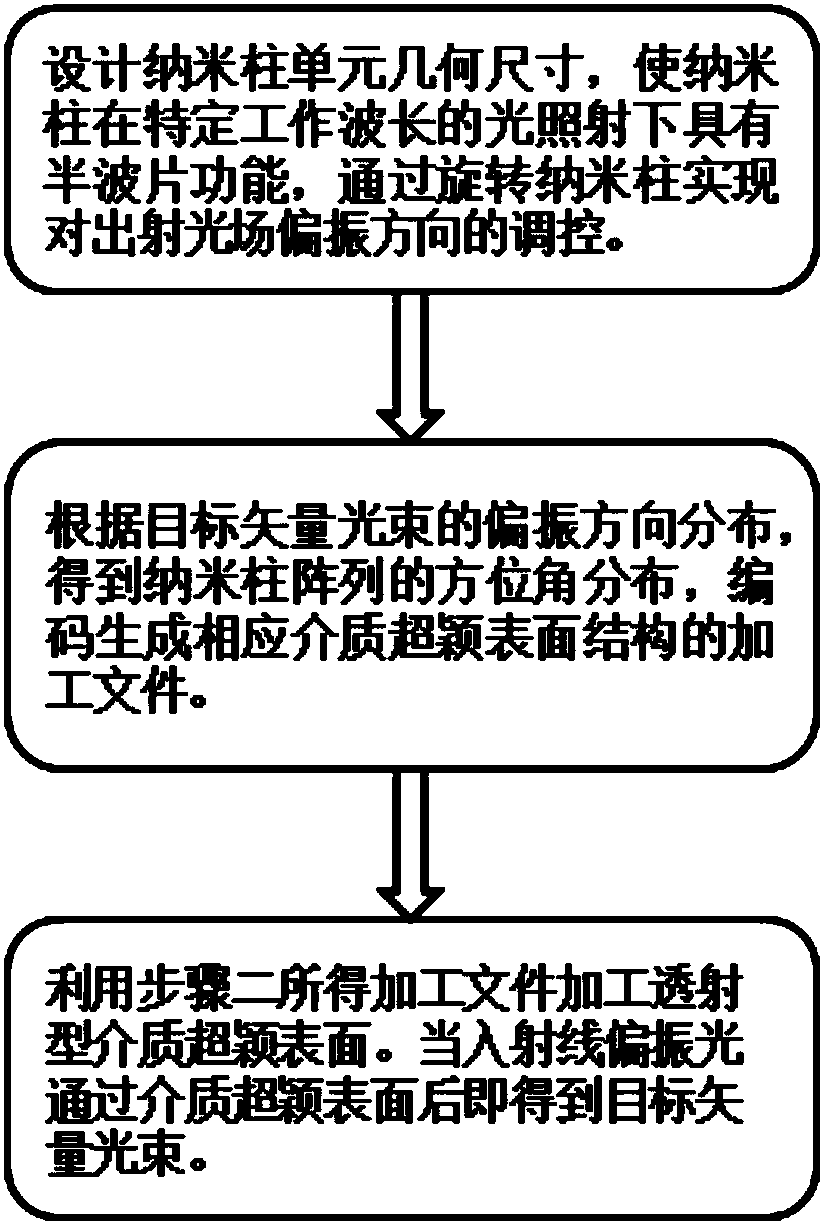

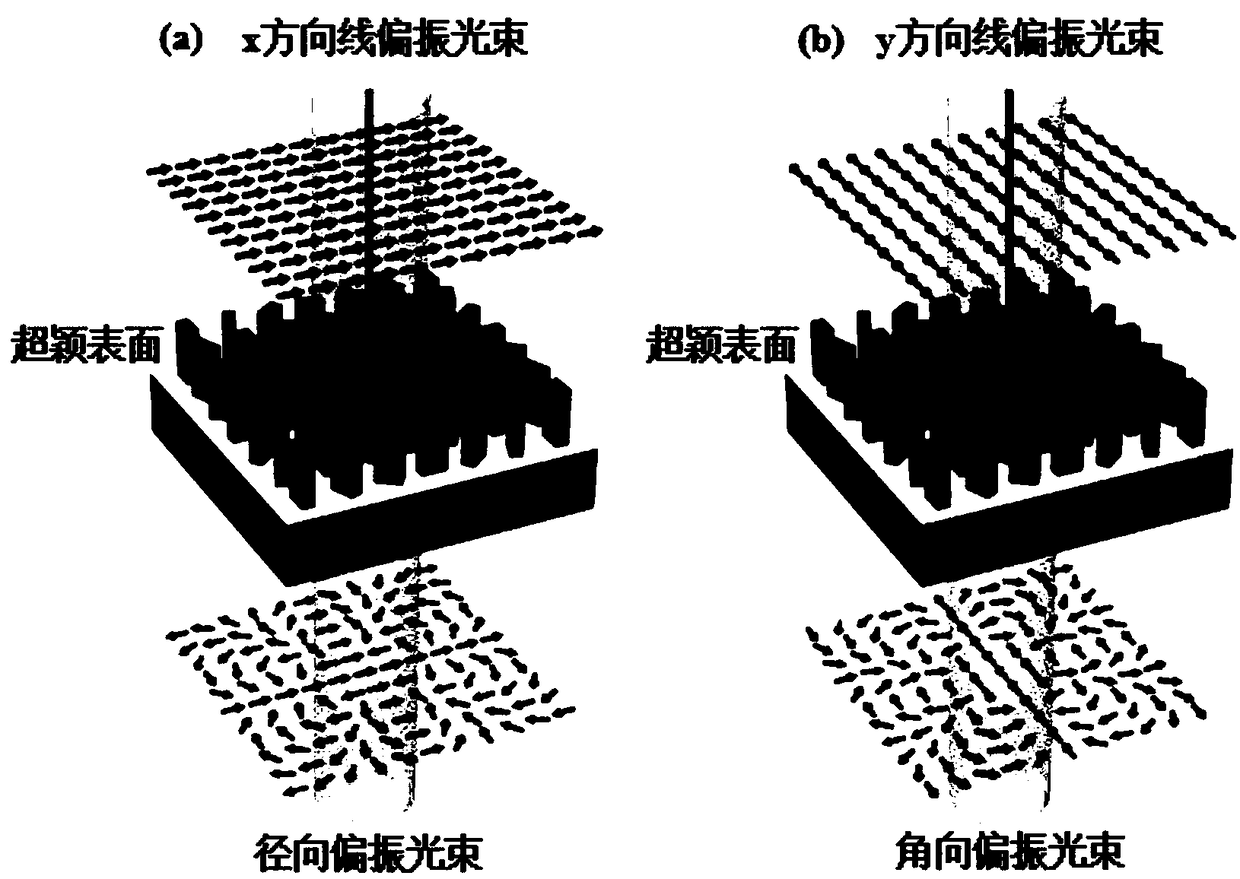

The invention discloses a method for generating a vector light beam based on a transmission-type medium metasurface, and belongs to the field of micro-nano optics. The method comprises the steps: selecting a noncrystalline silicon nanorod as a medium metasurface structure unit, carrying out the designing according to the geometric size of the nanorod, and enabling the nanorod to have a half wave plate function under the irradiation of light with the specific working wavelength; changing an azimuth angle of the nanorod unit and achieving the regulation and control of the polarization directionof an emergent optical field; obtaining the azimuth angle distribution of a nanorod array according to the polarization direction distribution of a target rod vector light beam, generating a processing file through coding, and carrying out the processing; and obtaining the target rod vector light beam after the incident polarization light passes through the medium metasurface. The invention also discloses a method for generating a vector light beam distributed in any polarization direction based on the transmission-type medium metasurface, and the method can be used for enabling a polarizationpattern to be hidden in the vector light beam, and is used for optical anti-fake occasions and polarization encryption occasions. The method can generate any vector light beam in a miniature and compact optical system.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

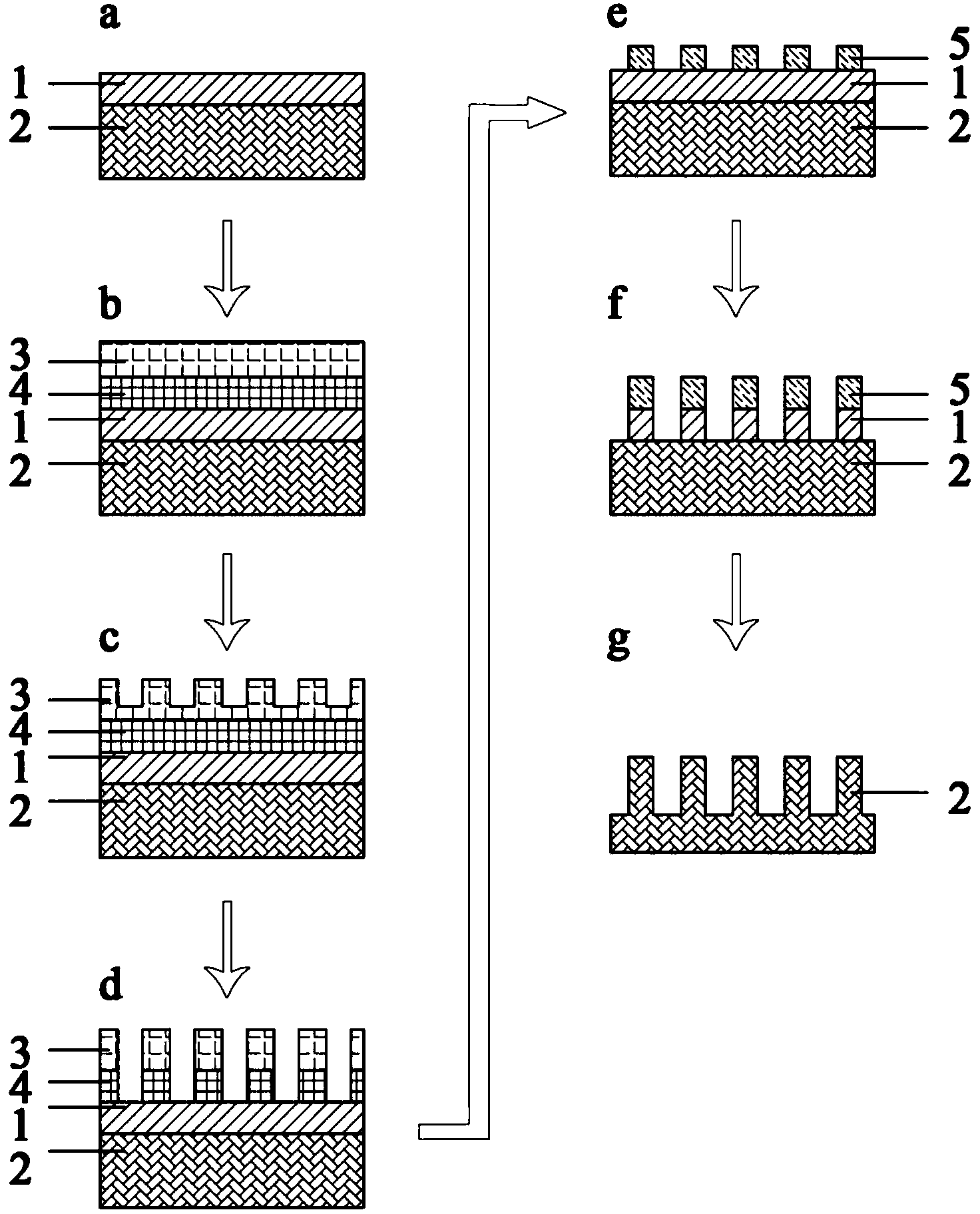

Method for preparing orderly gallium nitride nano pillar array with ultraviolet soft imprinting

ActiveCN103383980AHigh luminous intensityImprove internal quantum efficiencyPhotomechanical apparatusNanotechnologyDielectricNanopillar

Provided is a method for preparing an orderly gallium nitride nano pillar array with ultraviolet soft imprinting. A dielectric film is grown on a gallium nitride substrate, a metal orderly nano pillar (hole) structure is obtained through an ultraviolet soft imprinting double-layer stripping technology, a dielectric film nano pillar (hole) structure with a changeable and adjustable diameter is obtained through a reactive ion etching method, and inductively coupled plasma is used for being etched to obtain the gallium nitride orderly nano pillar (hole) array with different diameters. The dielectric film which comprises SiO2 and SiNx is grown on the gallium nitride substrate, and PMMA and ultraviolet curing glue coat the surface of a substrate sample in a rotary mode in sequence. A large-area low-defect orderly nano hole (pillar) array structure is formed on the ultraviolet curing glue through an ultraviolet soft imprinting technology, residual glue and the PMMA are then etched through a reactive ion etching technology, and the metal nano pillar (hole) array structure is obtained by stripping an evaporated metallic film. A dielectric film layer structure is etched through the reactive ion etching method, and the dielectric nano pillar (hole) structure with the changeable and adjustable diameter is obtained.

Owner:NANJING UNIV

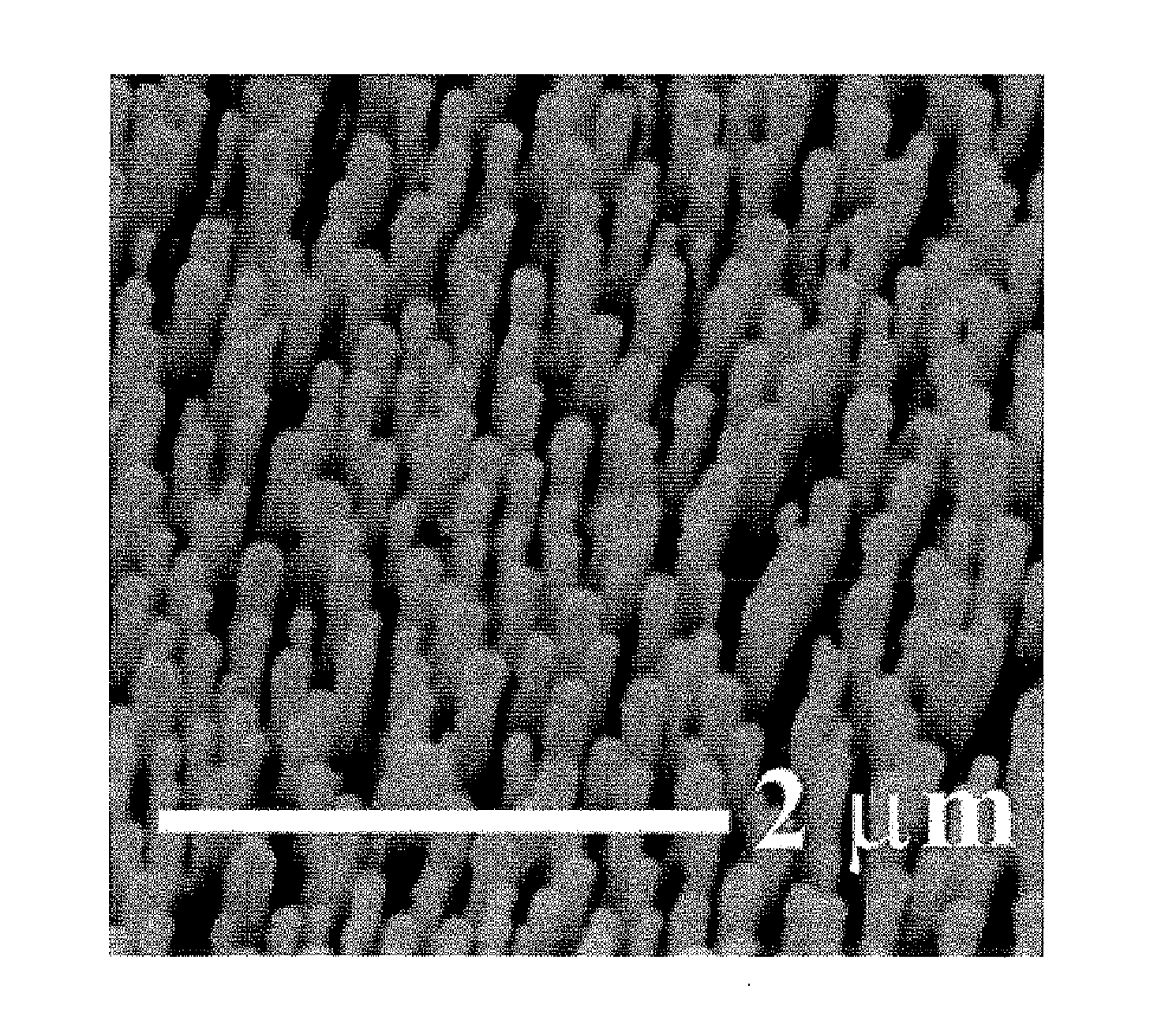

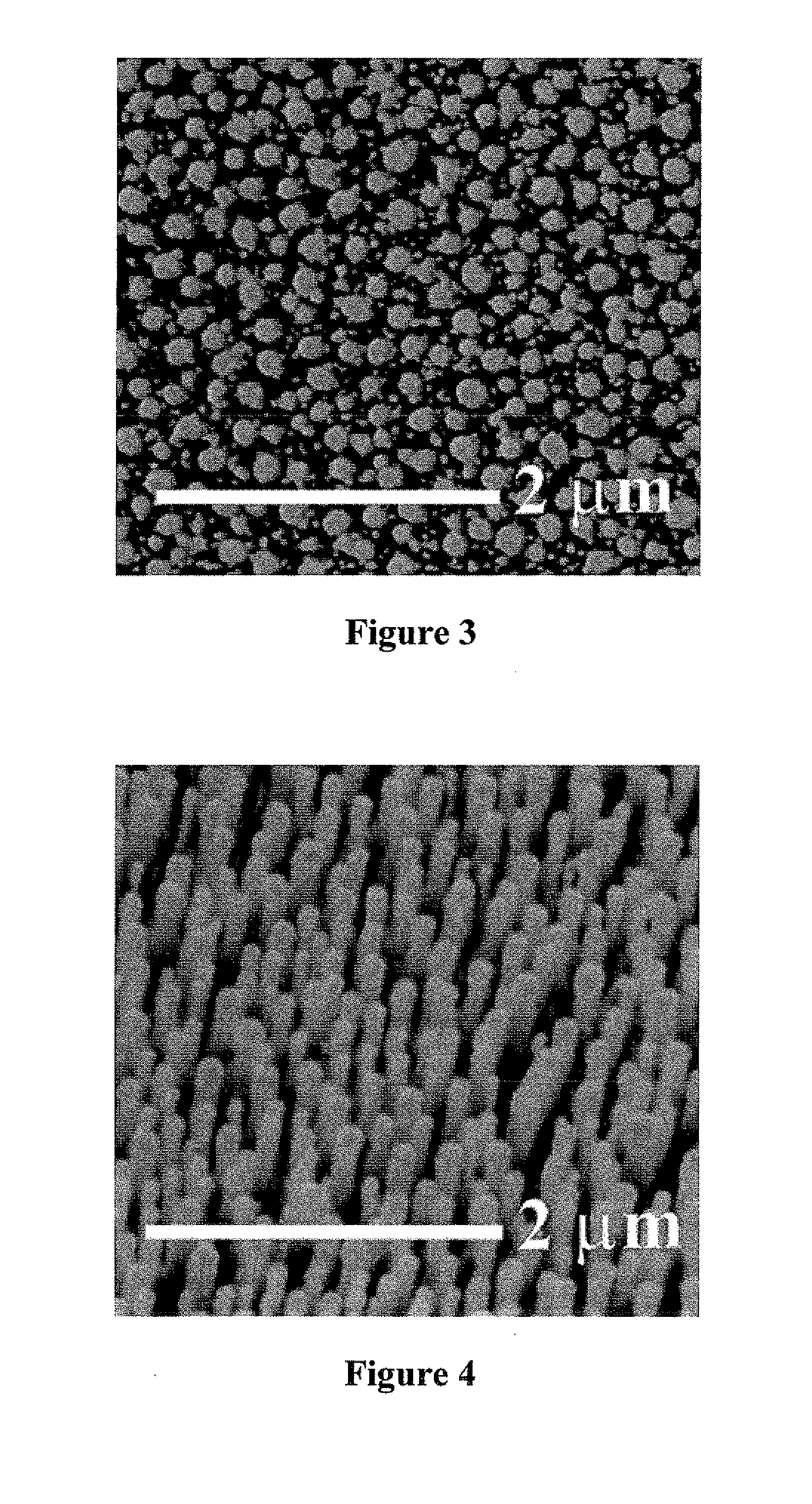

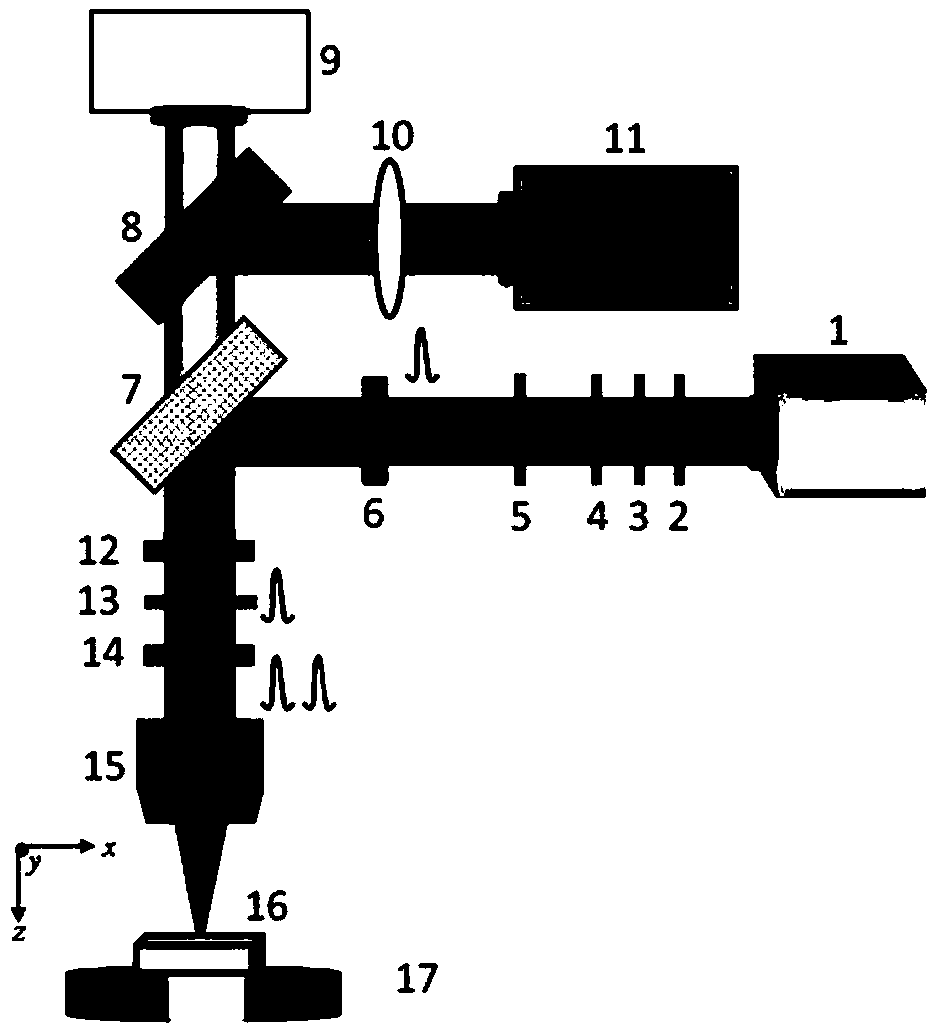

Femtosecond laser-controlled silicon surface nanopillar preparation method based on dual-wavelength electronic dynamic control

ActiveCN105499792AEfficient and precise preparationAchieve optimal controlLaser beam welding apparatusMicro nanoNanopillar

The invention relates to a femtosecond laser-controlled silicon surface nanopillar preparation method based on dual-wavelength electronic dynamic control, and belongs to the technical field of femtosecond laser application. The method comprises the steps that on the basis of local instant electronic exciting dynamic control, the wave length of the fundamental frequency laser is converted into 400 nm from 800 nm through a frequency doubling technology, and the surface micro-nano structural morphology is controlled by adopting a dual-wavelength femtosecond laser, wherein a first beam generates a generic plasma lens structure (PL) on the surface of a material, a second beam generates surface plasma along the edge of the generic PL structure and generates a gradient field distributed along the center of a light spot, and then the material generates the force extruding towards the center under the action of the pulse to form a convex nanopillar structure; preparation of large-area uniform nanopillar arrays is achieved through control over a procedure of a processing platform. Compared with an existing method, the preparation method has the advantages that the nanopillar processing precision and processing efficiency are effectively improved, efficient and precise control over the crystalline silicon surface nano structure is achieved, and the application value on the aspects such as information storage and solar cells is achieved.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

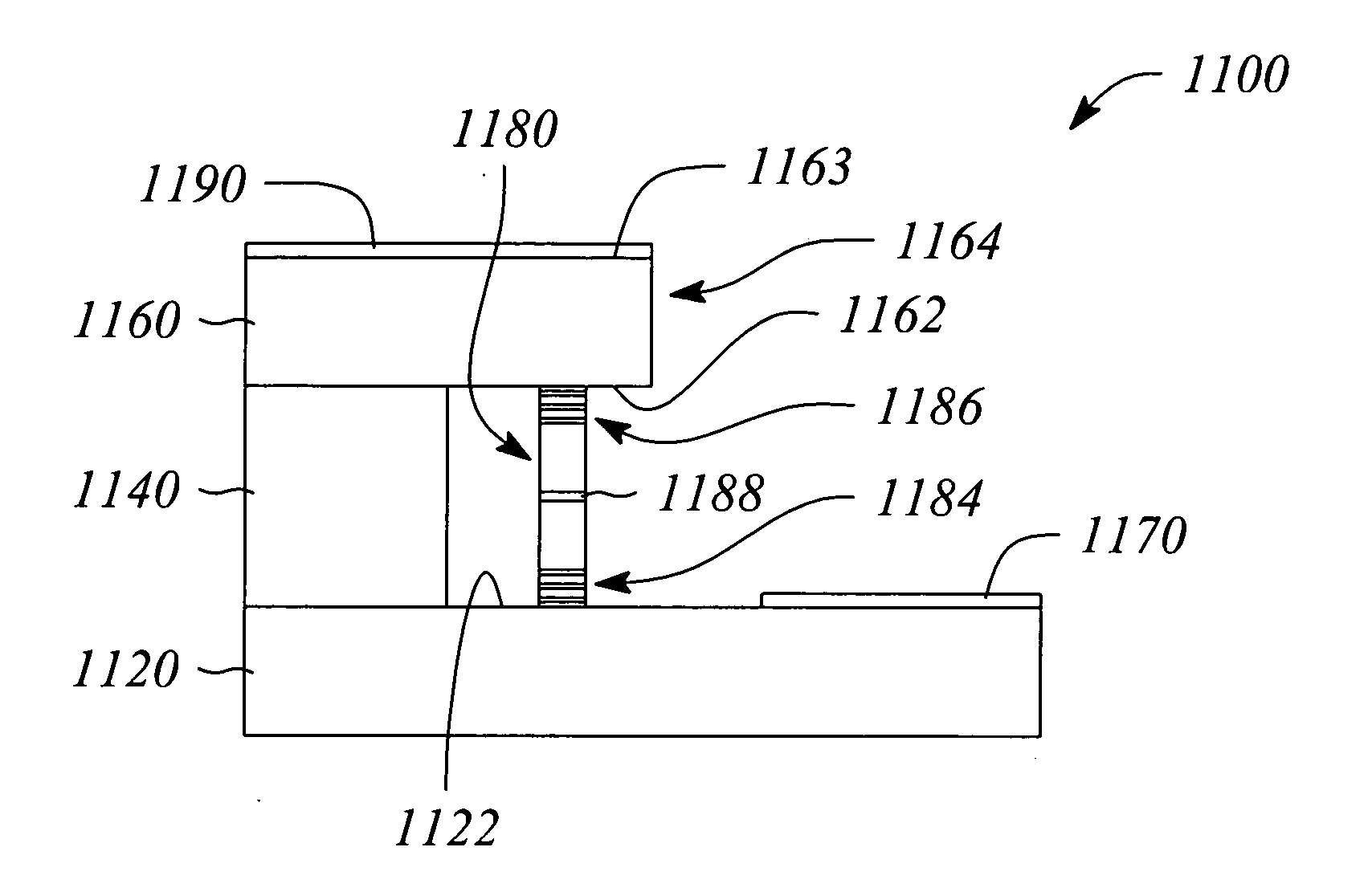

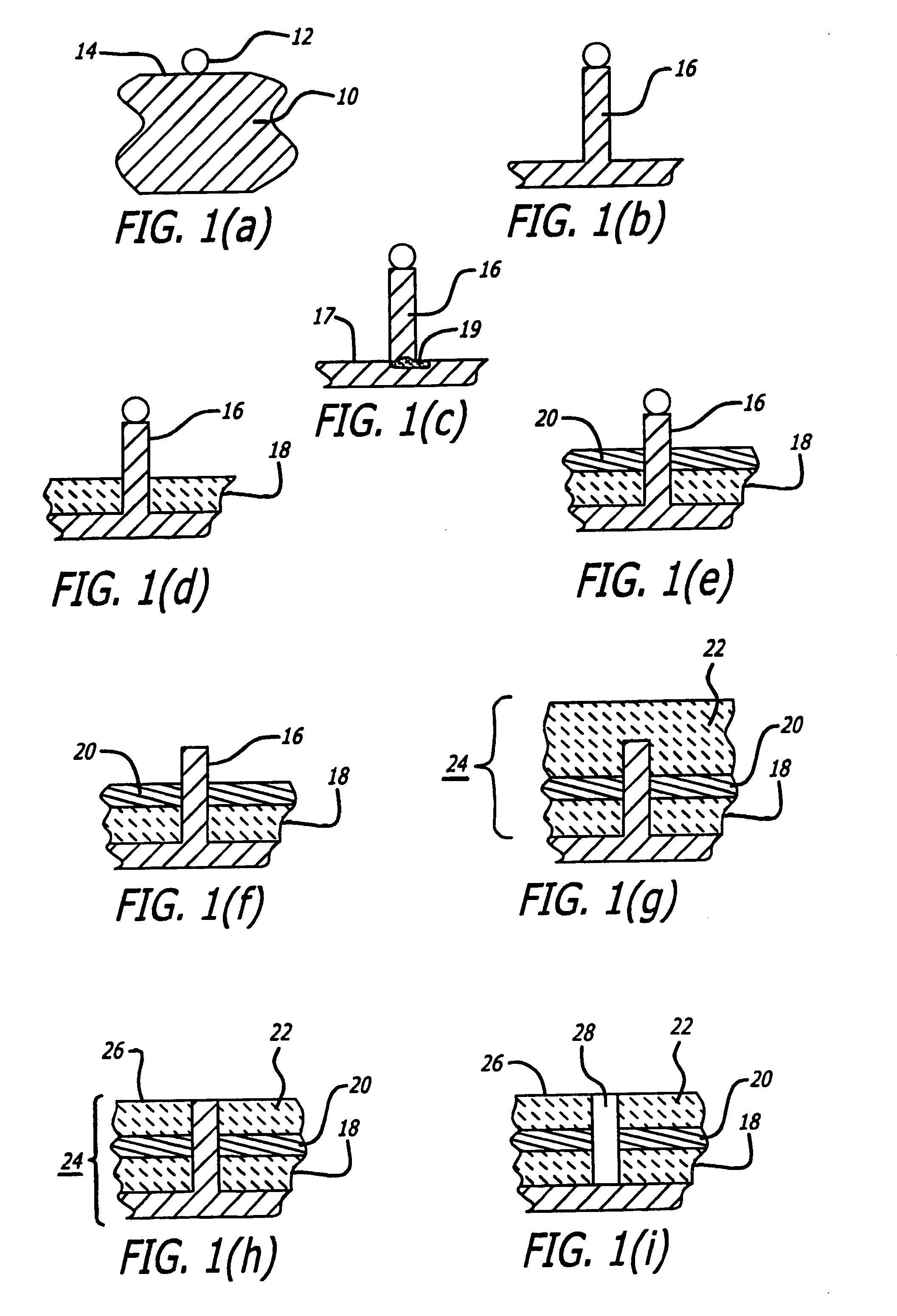

Field effect transistor fabrication including formation of a channel in a pore

A field effect transistor having a narrow channel and a method for forming such a device. An upstanding nanopillar is formed from a substrate by directional etching of the substrate preferentially masked by a nanoparticle. A stack of planar layers of material is formed adjacent and around the nanopillar. The bottom layer, adjacent the substantially planar top substrate surface, comprises insulating material. A conductive gate layer overlies the bottom layer while a second insulating layer overlies the gate layer. The pillar material is etched to leave a nanopore into which semiconductor material is deposited, forming an upstanding channel, after insulating material has been deposited on the interior of the nanopore. The source or drain may be a conductive substrate or a doped region of the substrate formed immediately beneath the nanopillar with the other electrode formed by doping the region adjacent the top of the channel.

Owner:HEWLETT PACKARD DEV CO LP

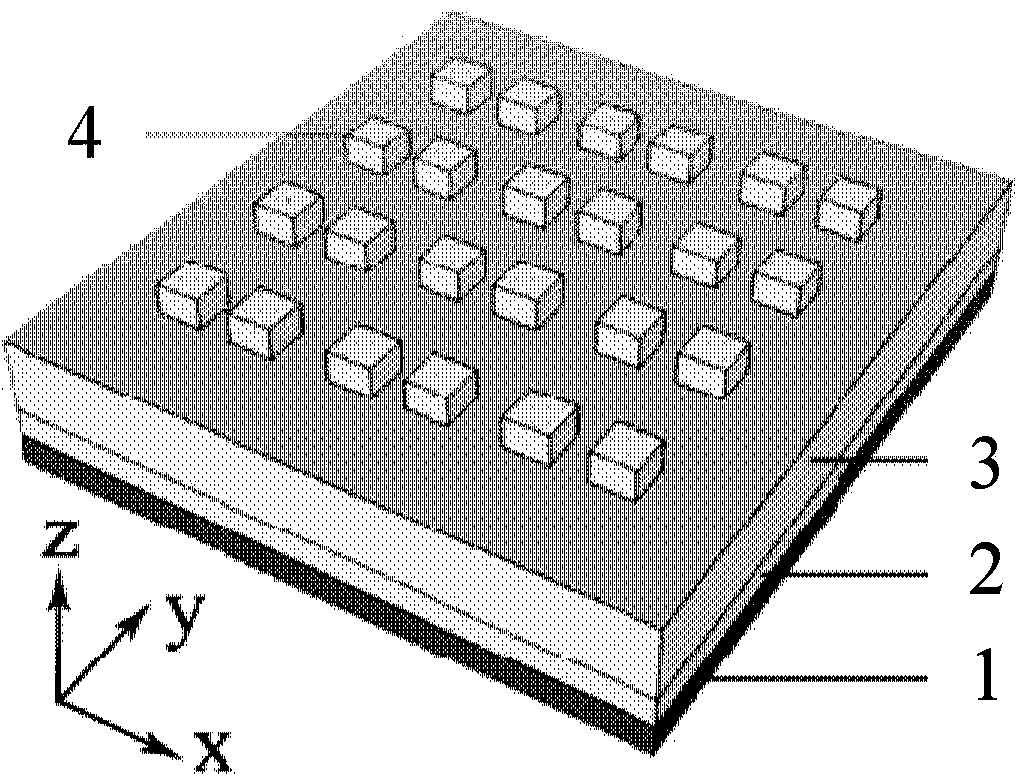

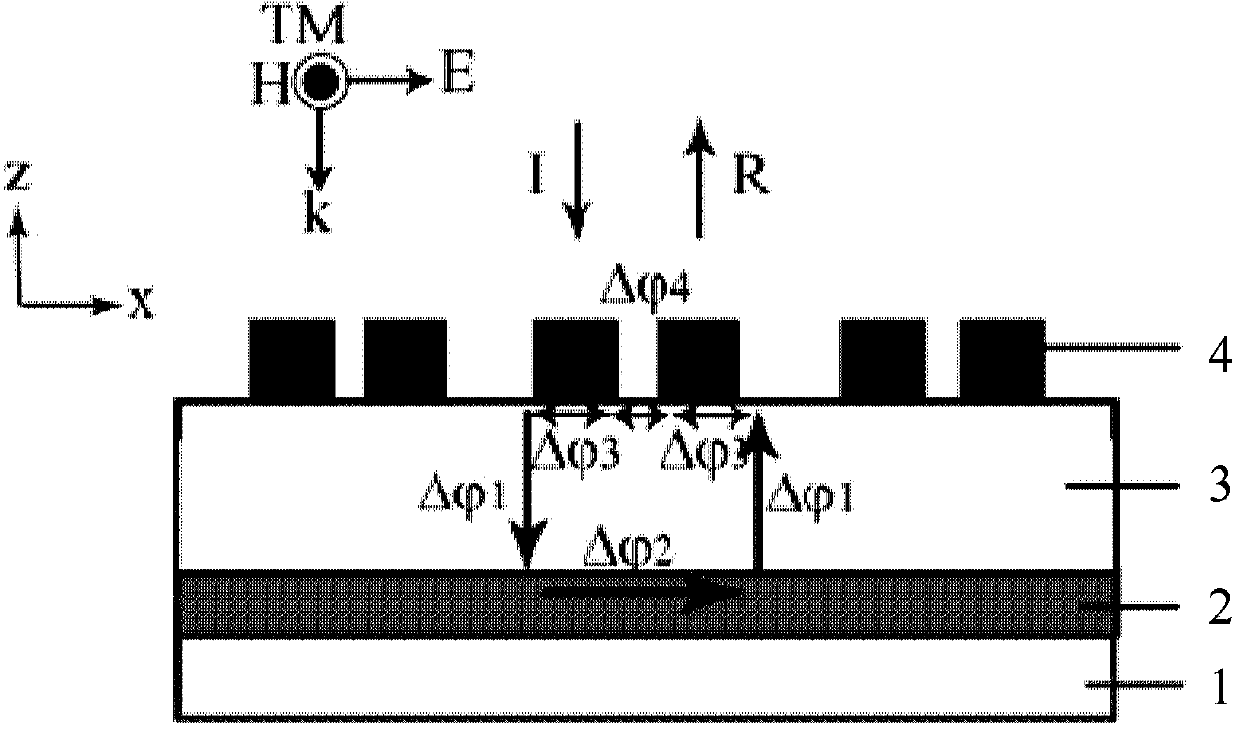

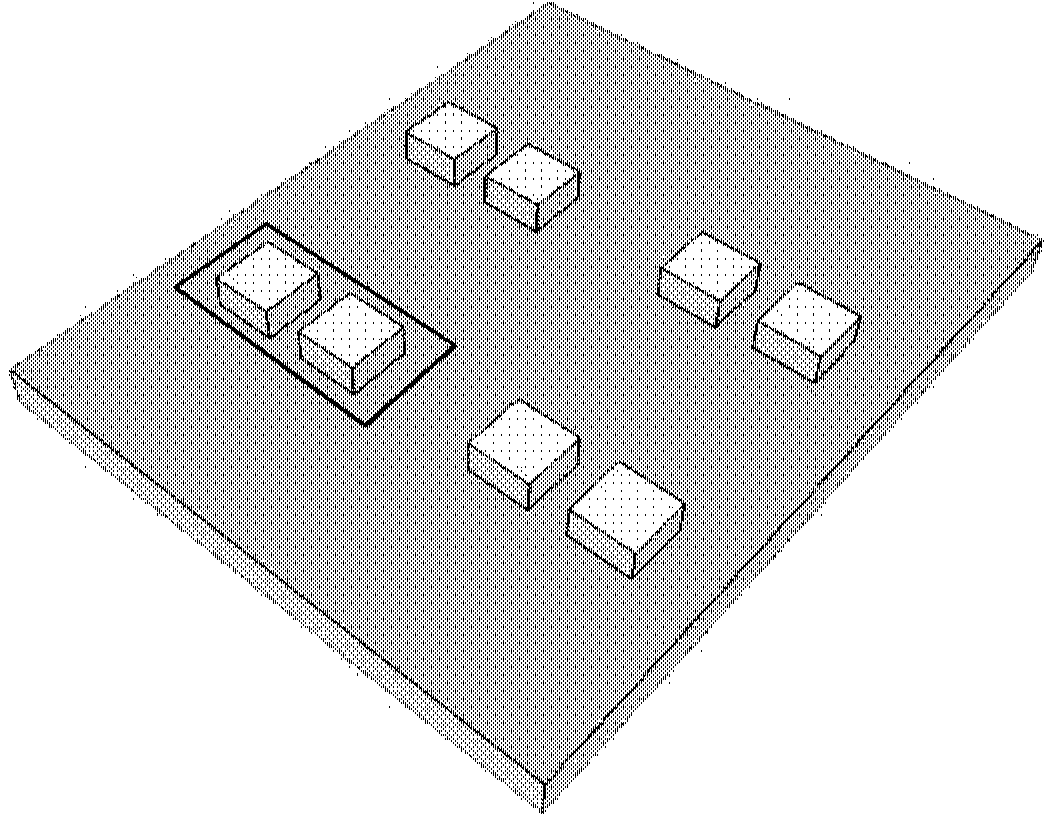

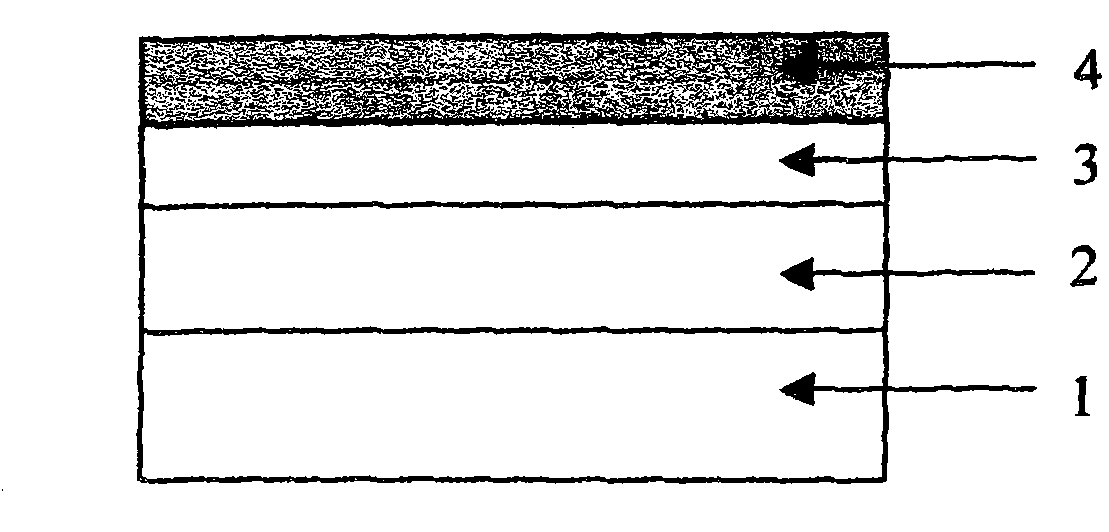

Asymmetric Au particle array and FPcavity coupled refractive index sensor

InactiveCN103808691AReduce FWHMHigh quality factorPhase-affecting property measurementsNanopillarNon symmetric

The invention provides an asymmetric Au particle array and FP cavity coupled refractive index sensor which comprises an insulation substrate, a metal film reflection layer, a transparent medium layer and a two-dimensional metal unit array, wherein at least one surface of the insulation substrate is polished; the metal film reflection layer is deposited on a polishing surface of the substrate; the transparent medium layer is deposited on the metal film reflection layer; the two-dimensional metal unit array is formed on the transparent medium layer, each metal unit in the two-dimensional metal unit array is an asymmetric unit, and is composed of two metal nano columns arranged along the surface of the substrate, and an F-P cavity loop is formed between the two metal nano columns of each metal unit and the metal film reflection layer just below the two metal nano columns. According to the asymmetric Au particle array and FP cavity coupled refractive index sensor, by combining an asymmetric Fano resonance effect and coupling an LSP mode and an FP cavity mode, the full width at half maximum of a resonance valley of the sensor can be reduced, and thus the performance of a local area surface plasma sensor is improved.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

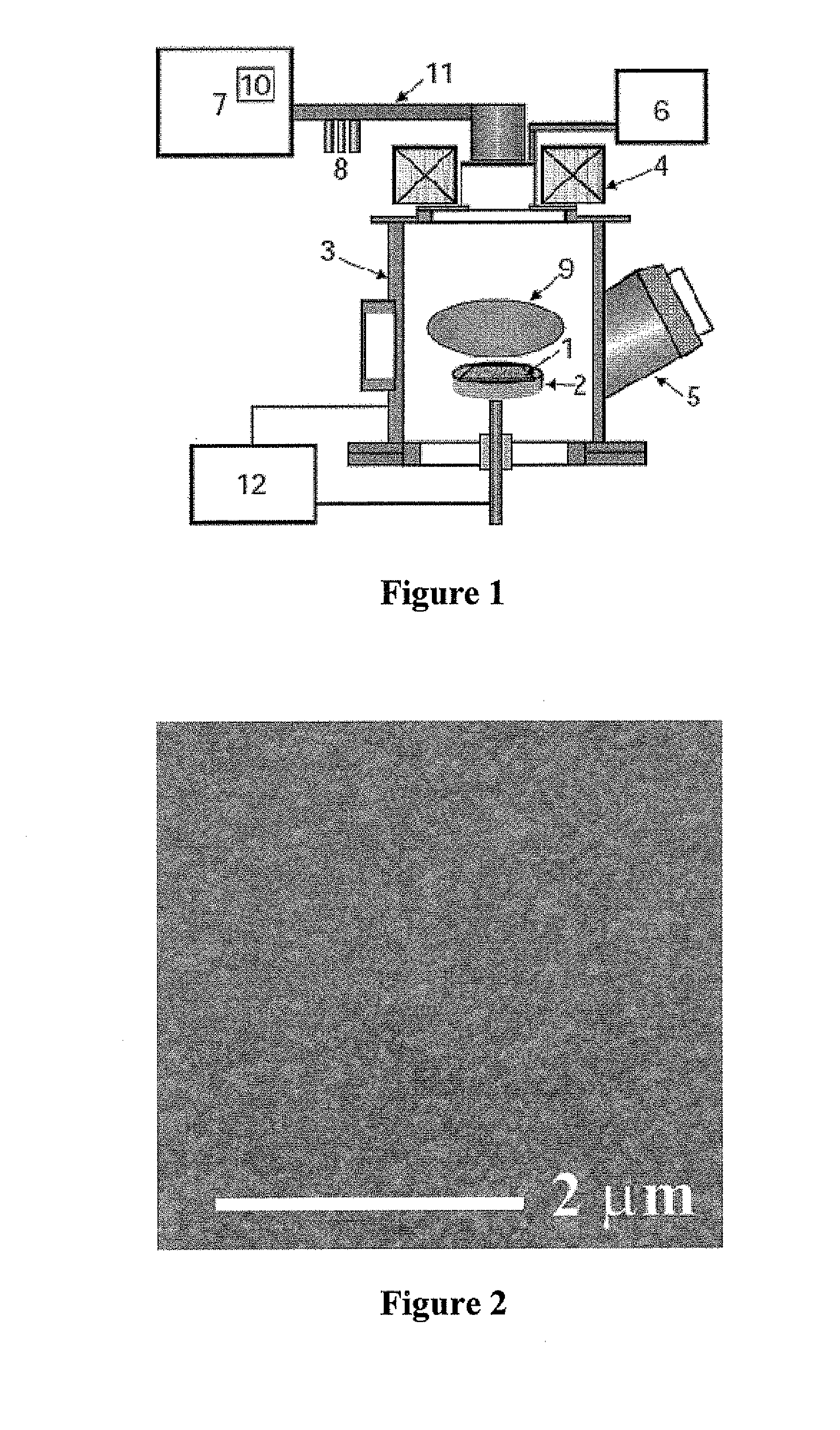

Method for growing group III nitride nanometer material

InactiveCN101898751ALower quality requirementsSimple manufacturing methodNanostructure manufactureNitrogen-metal/silicon/boron binary compoundsNanopillarRapid thermal annealing

The invention relates to a method for growing a group III nitride nanometer material, which comprises the following steps of: (1) epitaxially growing a GaN template, a SiO2 layer and a Ni metal film on a substrate in sequence; (2) enabling the Ni metal film to form self-organized nanometer Ni particles by using a two-step rapid thermal annealing method; (3) and etching the SiO2 layer by a dry method by using the self-organized nanometer Ni particles as a mask to form a SiO2 nanometer column; (4) etching the GaN template by the dry method by using the self-organized nanometer Ni particles and the SiO2 nanometer column formed by etching as masks to form GaN nanometer column array; (5) removing the SiO2 nanometer column and the nanometer Ni particles by using a BOE solution to obtain the GaN nanometer column array; and (6) growing the InN or InGaN group III nitride semiconductor material on the GaN nanometer column array, the side wall thereof and the bottom of the nanometer column array.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

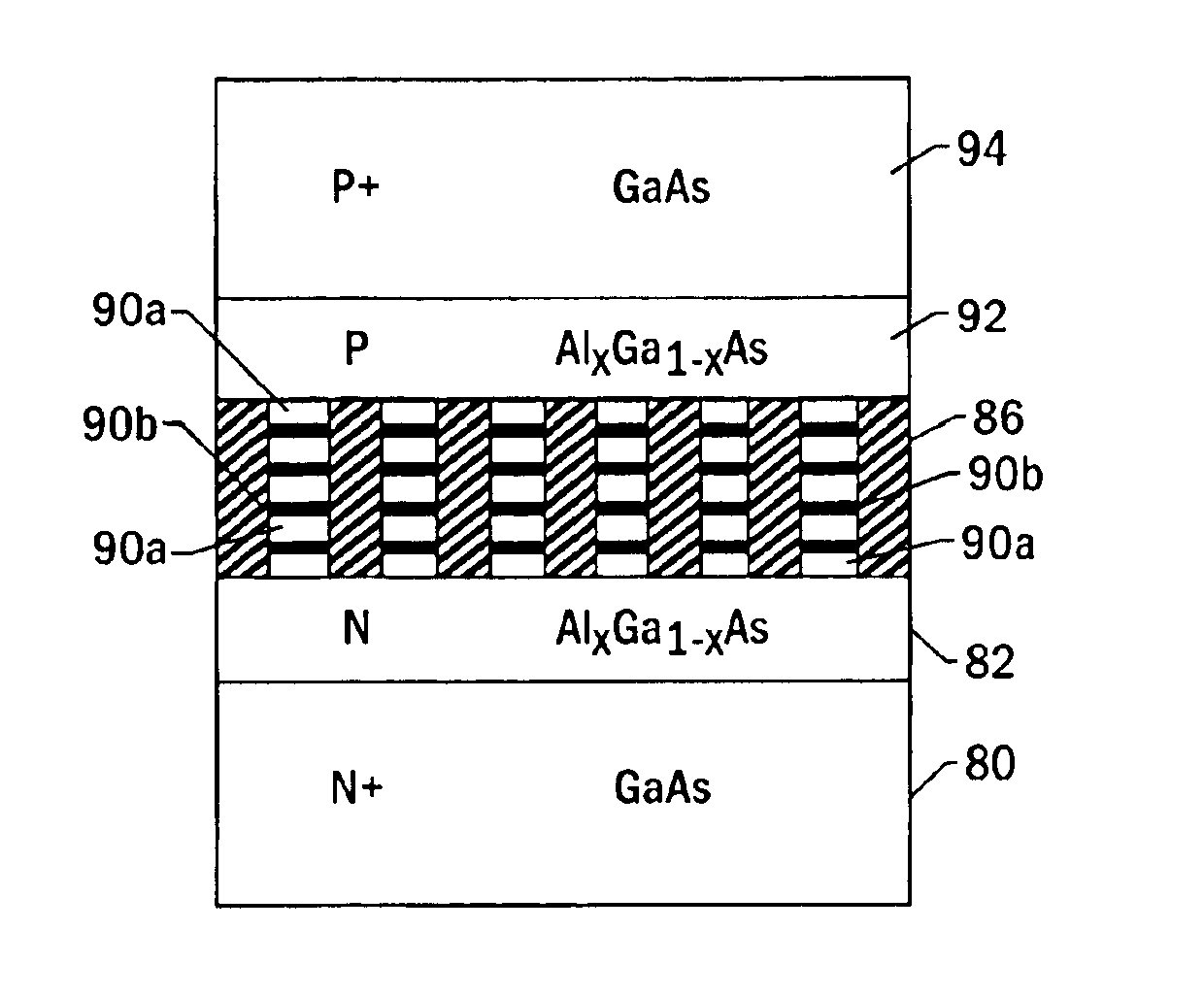

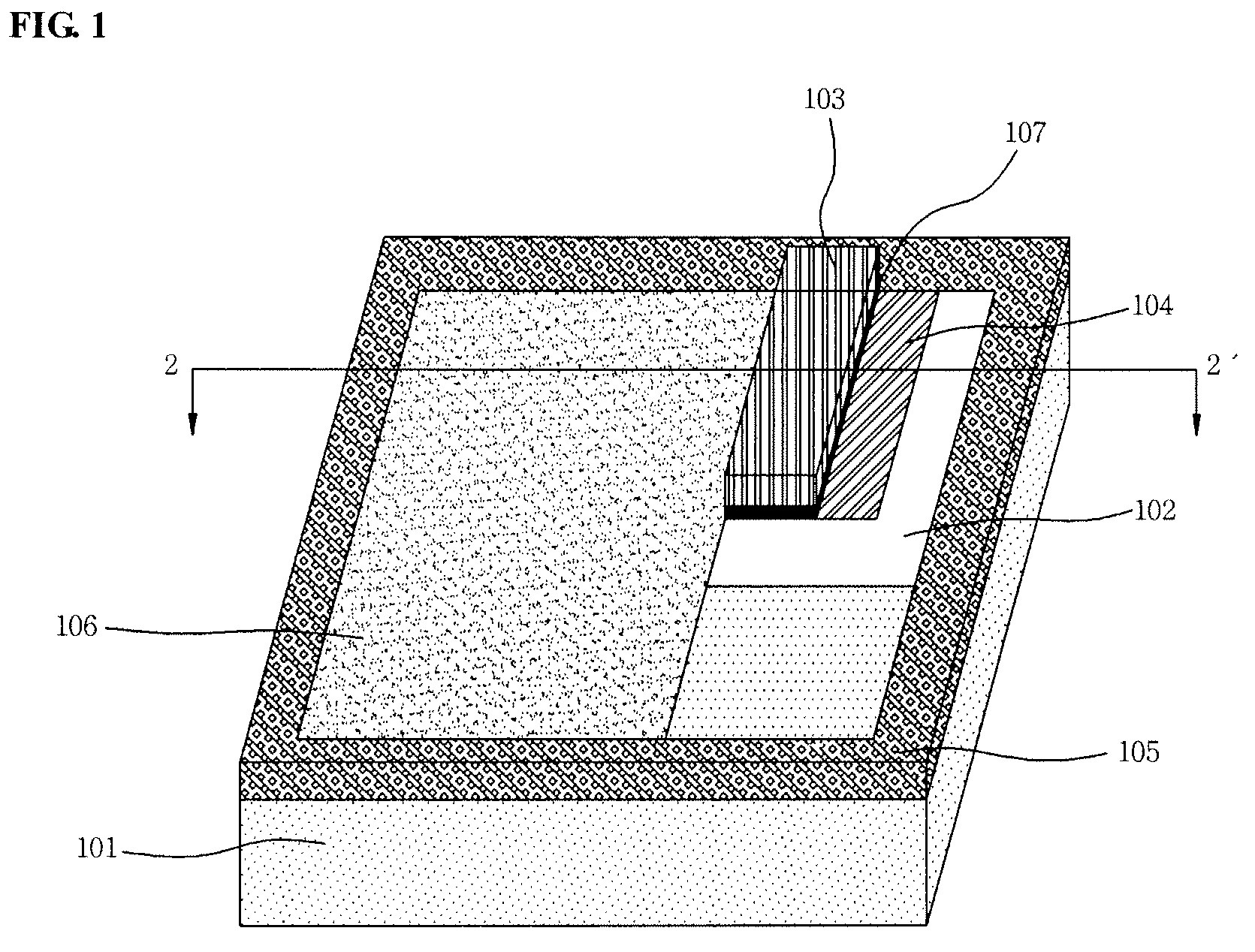

Optoelectronic devices having arrays of quantum-dot compound semiconductor superlattices therein

Methods of forming a nano-scale electronic and optoelectronic devices include forming a substrate having a semiconductor layer therein and a substrate insulating layer on the semiconductor layer. An etching template having a first array of non-photolithographically defined nano-channels extending therethrough, is formed on the substrate insulating layer. This etching template may comprise an anodized metal oxide, such as an anodized aluminum oxide (AAO) thin film. The substrate insulating layer is then selectively etched to define a second array of nano-channels therein. This selective etching step preferably uses the etching template as an etching mask to transfer the first array of nano-channels to the underlying substrate insulating layer, which may be thinner than the etching template. An array of semiconductor nano-pillars is then formed in the second array of nano-channels. The semiconductor nano-pillars in the array may have an average diameter in a range between about 8 nm and about 50 nm. The semiconductor nano-pillars are also preferably homoepitaxial or heteroepitaxial with the semiconductor layer.

Owner:NORTH CAROLINA STATE UNIV

Transversal epitaxial growth method for nano area of semiconductor film

InactiveCN101510504AUniform crystal qualityImprove crystal qualityNanostructure manufactureSemiconductor/solid-state device manufacturingDiffusionEtching

The invention discloses a cross epitaxial growth method of a semiconductor film, which comprises the following steps: (1) a nucleated metallic catalyst film is evaporated on a substrate material and island-shaped metallic catalyst particles which are evenly distributed on the substrate are obtained after the film is annealed; (2) in external equipment, a crystal nucleus is formed on the bottom of island-shaped metallic particles; and then nano-column arrays grow longitudinally; (3) a wet etching method is used for eliminating the metallic catalyst on a nano-column to obtain semiconductor nano-column array structures with the same orientation and height; (4) the etched nano-column is put into the external equipment and a lateral epitaxy technology is used for integrating the nano-column arrays into a flat surface; and then a semiconductor epitaxial film with the required thickness grows on the flat surface. As cross epitaxy occurs in nano area, defects and diffusion of residual stress can be effectively restrained and the quality of film crystals is more uniform than that of film crystals prepared by the traditional method, thus improving the crystal quality of two-dimensional semiconductor films; furthermore, the invention has simple method and wide applicability.

Owner:SUZHOU NANOJOIN PHOTONICS

Tungsten trioxide nano-film with photocatalytic performance, and preparation method thereof

ActiveCN103708559ALarge specific surface areaIncrease profitMaterial nanotechnologyTungsten oxides/hydroxidesNanopillarPhotocatalytic water splitting

The invention discloses a tungsten trioxide nano-film with photocatalytic performance, and a preparation method thereof. The tungsten trioxide nano-film is characterized in that a WO3 nano layer with a WO3 nano structure is grown on a WO3 crystal seed layer, and the WO3 nano structure is shaped like a two-dimensional flying saucer including a middle main sheet and a nano-column. The preparation method of the tungsten trioxide nano-film comprises the steps of preparing a tungsten acid crystal seed layer precursor solution, preparing FTO (Fluorine-doped Tin Oxide) conductive glass with the crystal seed layer, preparing thermal tungsten acid solvent precursor solution, and finally performing hydrothermal synthesis to obtain the tungsten trioxide nano-film. According to the tungsten trioxide nano-film with photocatalytic performance, and the preparation method thereof, the specific surface area of the WO3 nano layer can be effectively enlarged; the efficiency of photocatalytic water splitting can be improved, the performance of photocatalytic water splitting in a photoelectric chemical pool is excellent, and excellent chemical stability can be achieved, the preparation method is simple, and the low-cost and large-scale application can be realized.

Owner:TIANJIN UNIV

Scalable fabrication of one-dimensional and three-dimensional, conducting, nanostructured templates for diverse applications such as battery electrodes for next generation batteries

InactiveUS20140342236A1Electrode manufacturing processesNanoinformaticsNanopillarConductive materials

Articles including an array of one-dimensional or three-dimensional nanopillar arrays disposed on a substrate and methods for the formation thereof. The methods can include filling a plurality of hollow nanopillars, which are supported on a substrate, with a first conductive material and removing the plurality of hollow nanopillars to leave a plurality of vertically-aligned, epitaxial nanopillars, comprising the first conductive material, on the substrate.

Owner:UT BATTELLE LLC

Application of semiconductor quantum dot phosphors in nanopillar light emitting diodes

A quantum well-based p-i-n light emitting diode is provided that includes nanopillars with an average linear dimension of between 50 nanometers and 1 micron. The nanopillars include a laminar layer of quantum wells capable of non-radiative energy transfer to quantum dot nanocrystals. Quantum dot-Quantum well coupling through the side walls of the nanopillar-configured LED structure achieves a close proximity between quantum wells and quantum dots while retaining the overlying contact electrode structures. A white LED with attractive properties relative to conventional incandescent and fluorescence lighting devices is produced.

Owner:PENN STATE RES FOUND

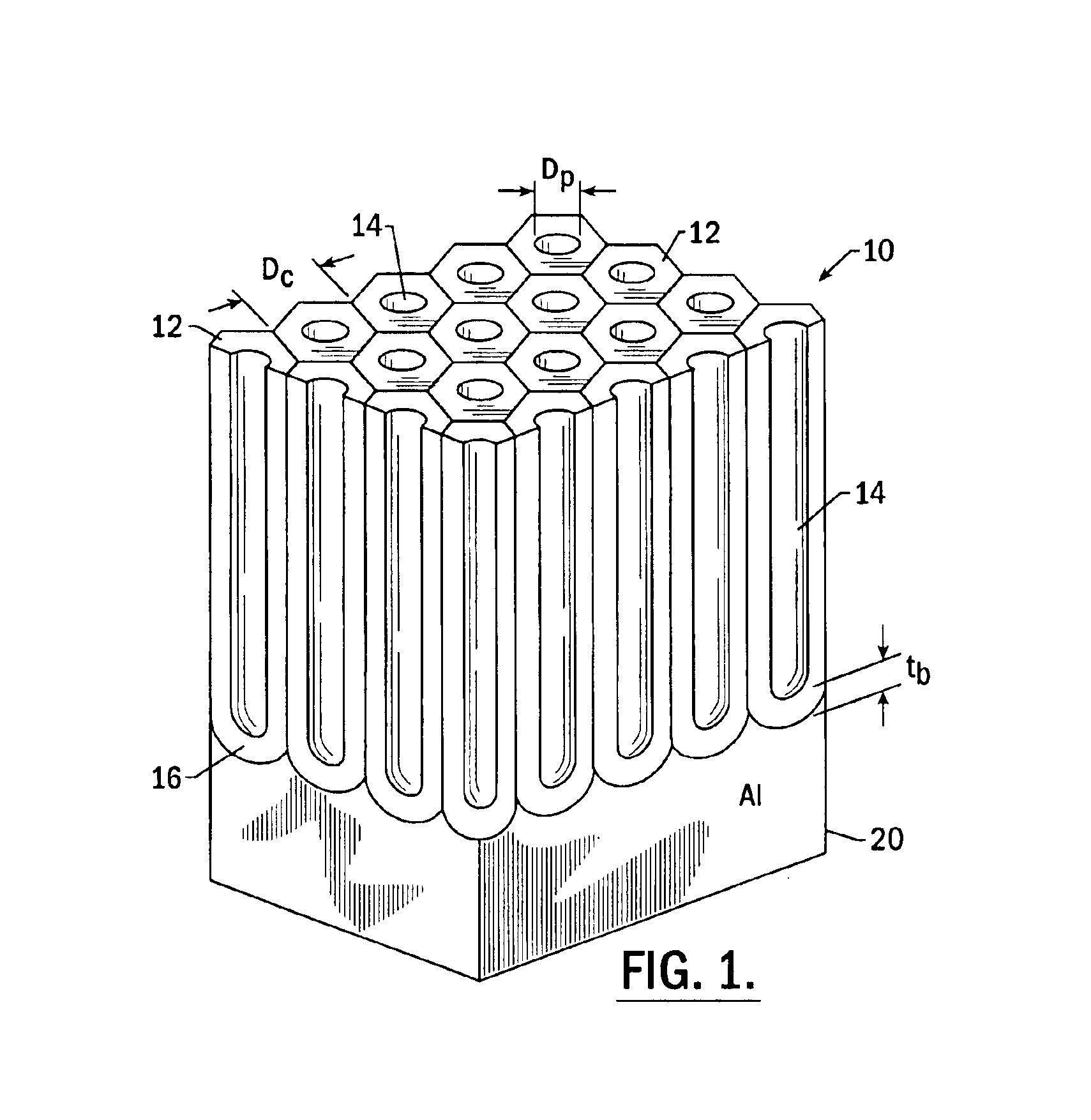

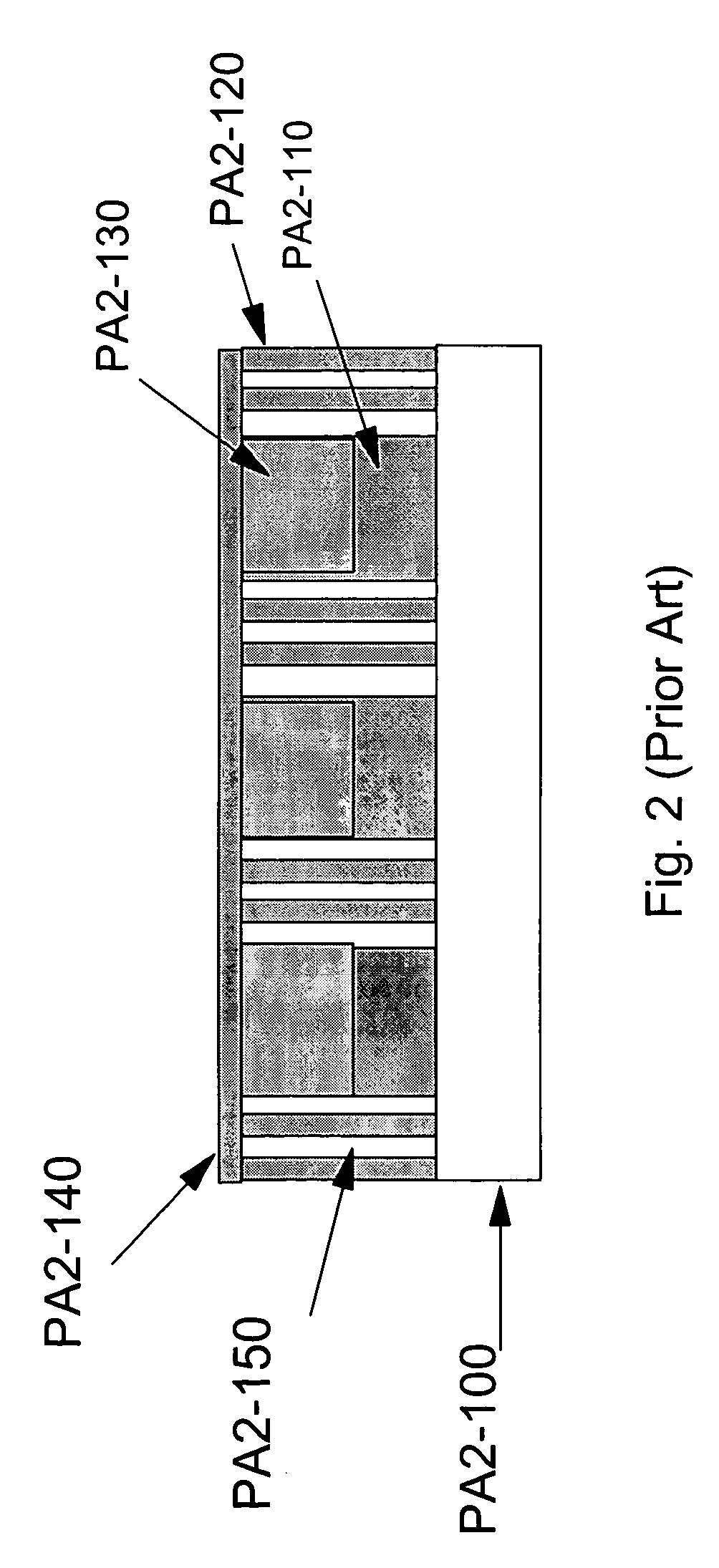

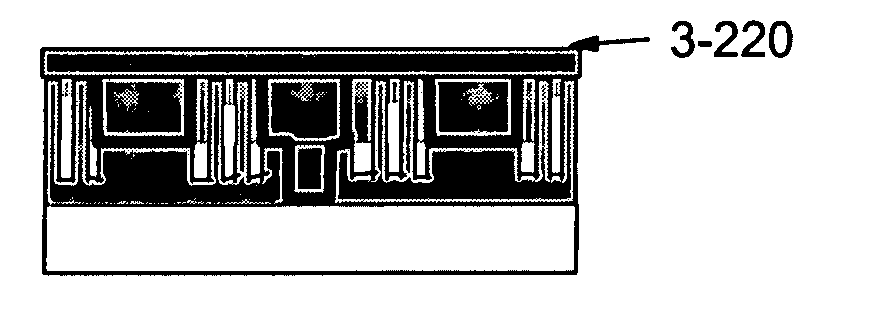

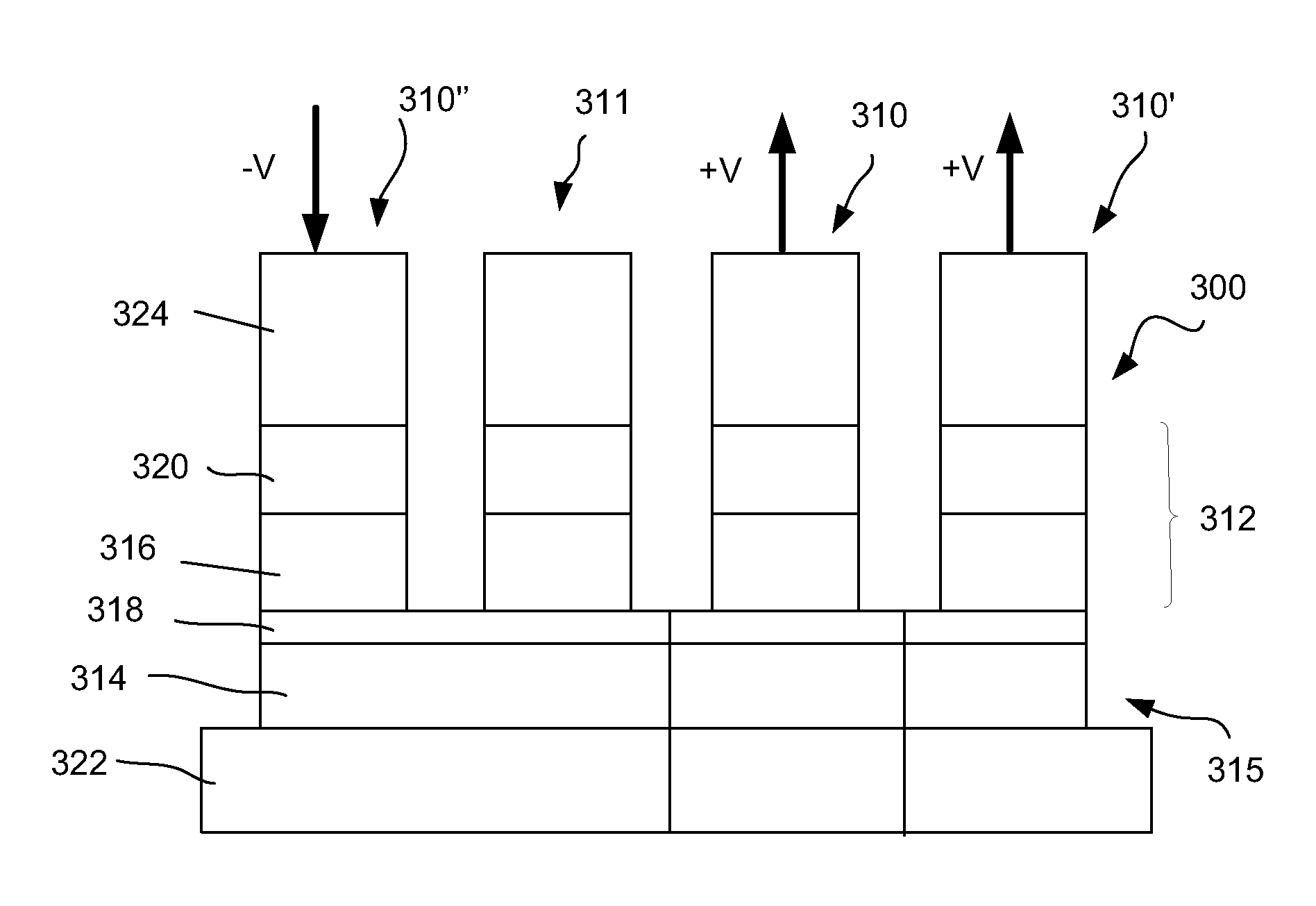

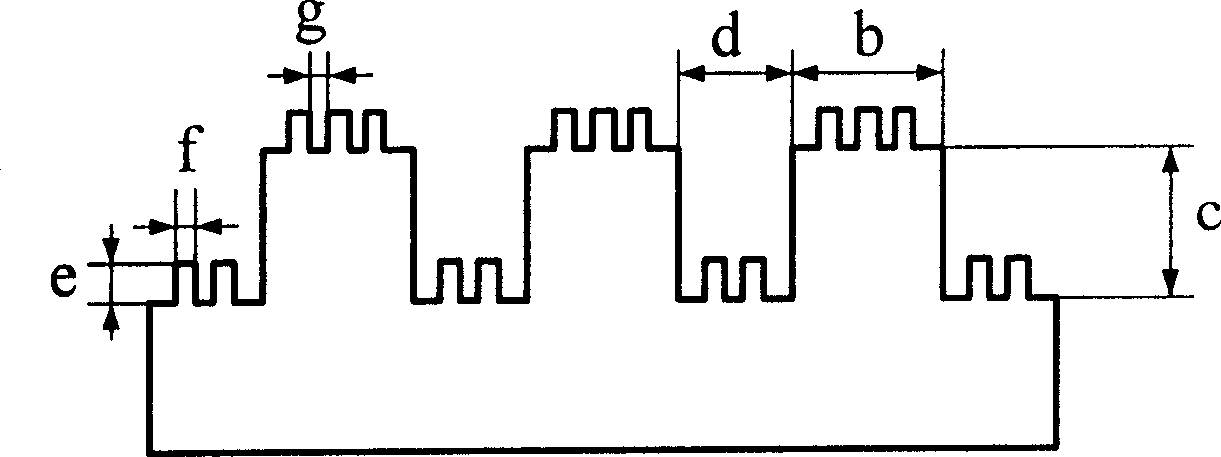

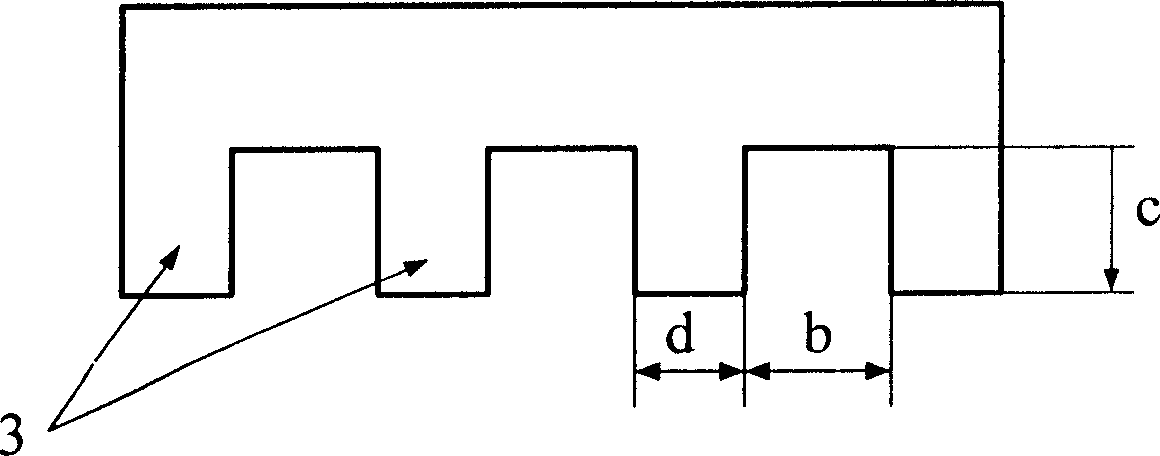

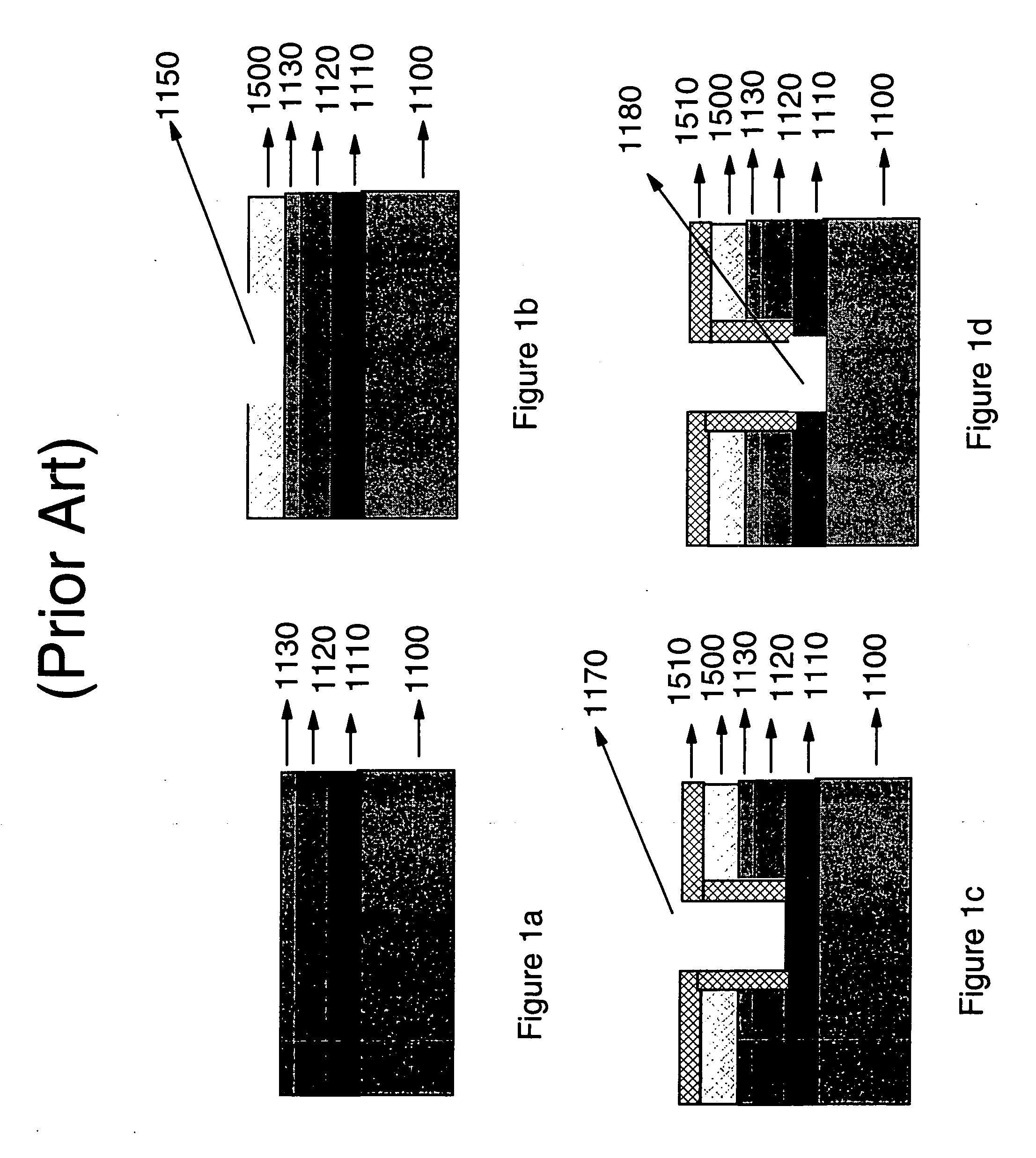

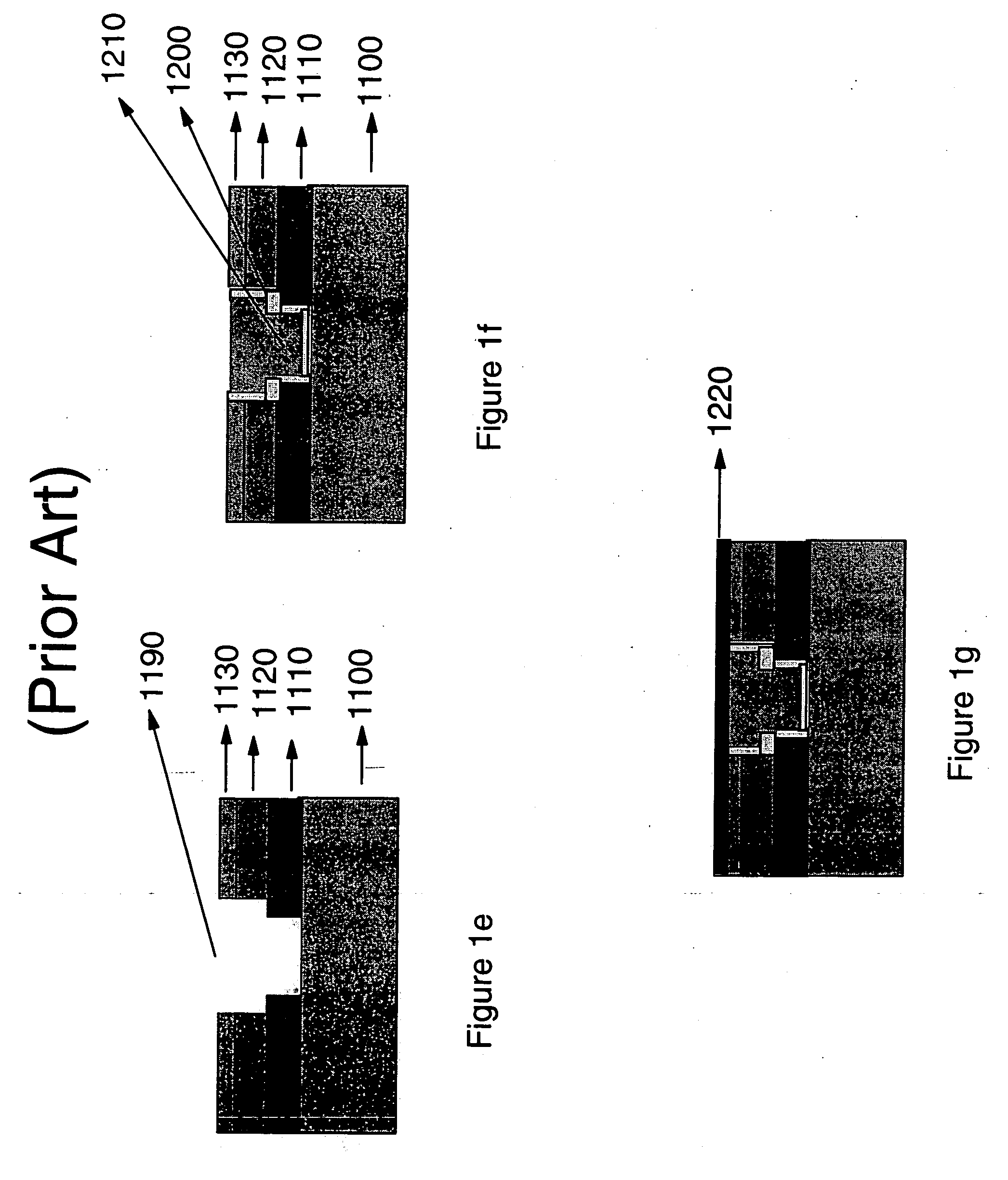

Interconnect structures with engineered dielectrics with nanocolumnar porosity

ActiveUS20050079719A1Lower effective dielectric constantImprove performanceSemiconductor/solid-state device detailsSolid-state devicesPorosityDielectric

A method for forming an interconnect structure with nanocolumnar intermetal dielectric is described involving the construction of an interconnect structure using a solid dielectric, and introducing a regular array of vertically aligned nanoscale pores through stencil formation and etching to form a hole array and subsequently pinching off the tops of the hole array with a cap dielectric. Variations of the method and means to construct a multilevel nanocolumnar interconnect structure are also described.

Owner:GLOBALFOUNDRIES US INC

Nanopillar arrays for electron emission

The present invention provides systems, devices, device components and structures for modulating the intensity and / or energies of electrons, including a beam of incident electrons. In some embodiments, for example, the present invention provides nano-structured semiconductor membrane structures capable of generating secondary electron emission. Nano-structured semiconductor membranes of this aspect of the present invention include membranes having an array of nanopillar structures capable of providing electron emission for amplification, filtering and / or detection of incident radiation, for example secondary electron emission and / or field emission. Nano-structured semiconductor membranes of the present invention are useful as converters wherein interaction of incident primary electrons and nanopillars of the nanopillar array generates secondary emission. Nano-structured semiconductor membranes of this aspect of the present invention are also useful as directed charge amplifiers wherein secondary emission from a nanopillar array provides gain functionality for increasing the intensity of radiation comprising incident electrons.

Owner:WISCONSIN ALUMNI RES FOUND