Patents

Literature

849 results about "Crystalline semiconductor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Semiconductor, any of a class of crystalline solids intermediate in electrical conductivity between a conductor and an insulator. Semiconductors are employed in the manufacture of various kinds of electronic devices, including diodes, transistors, and integrated circuits.

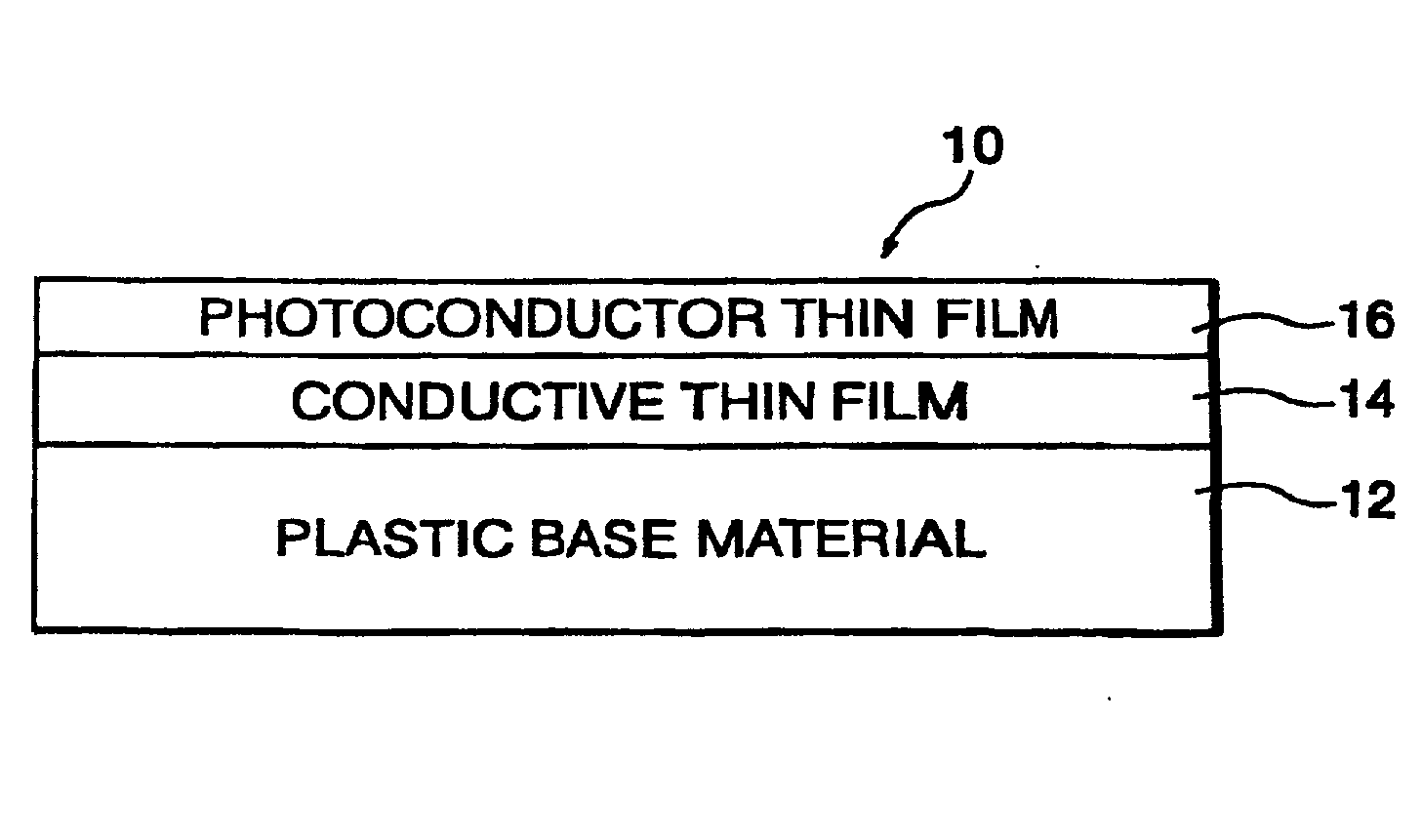

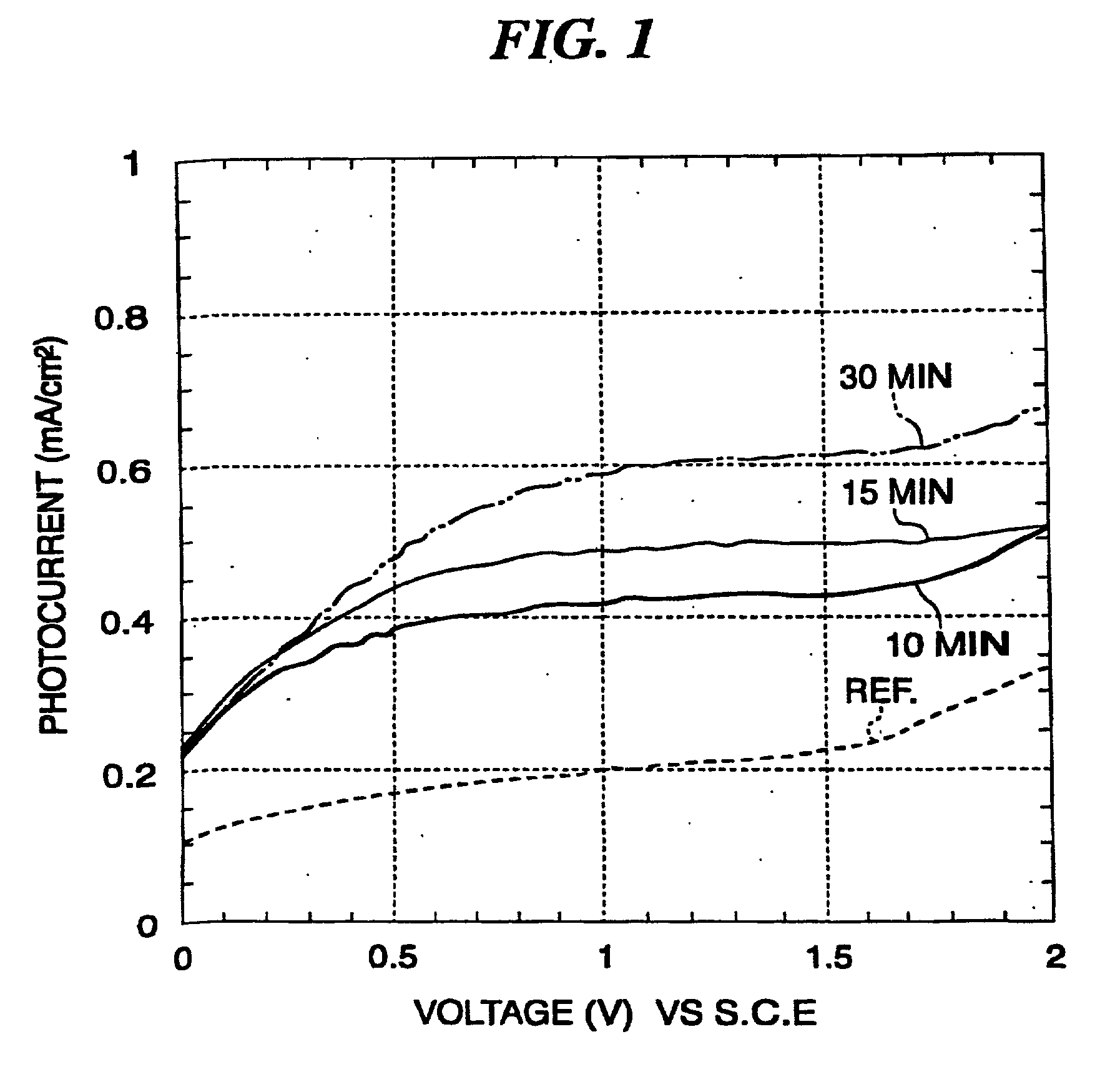

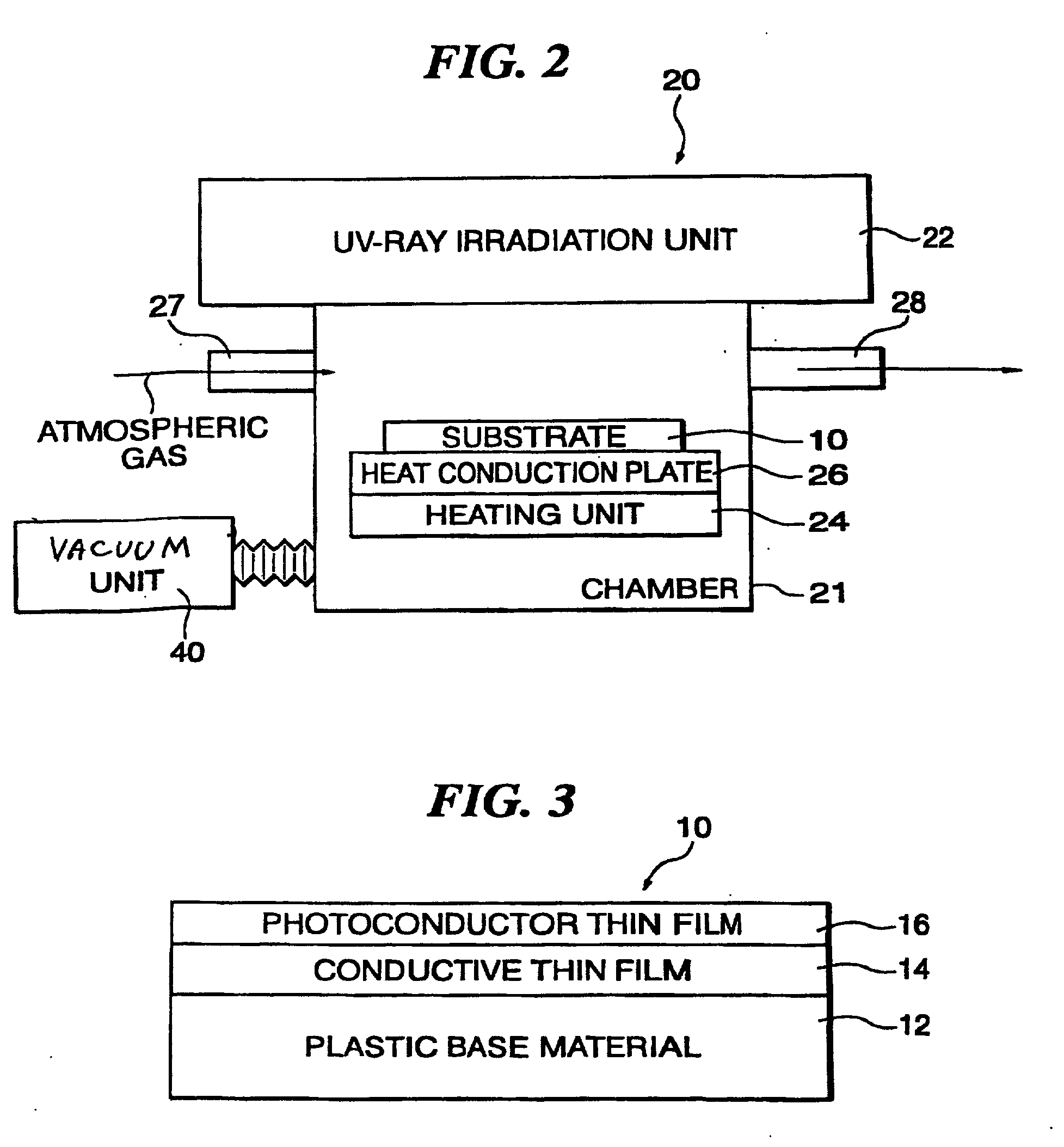

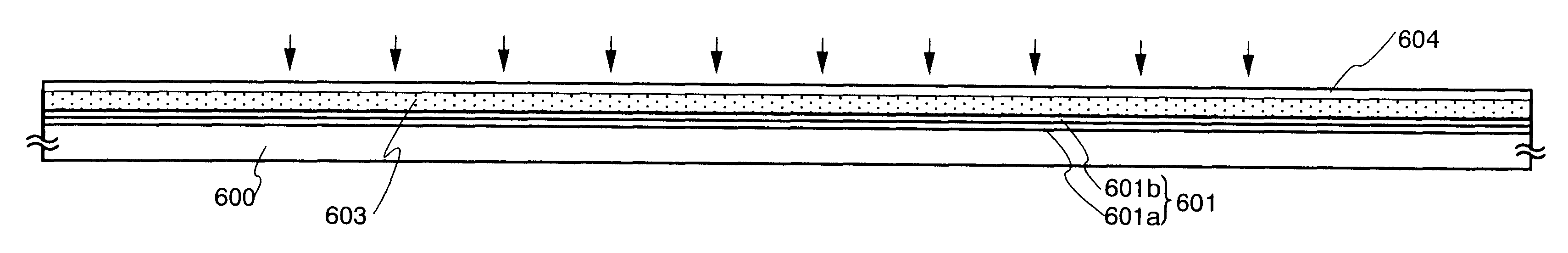

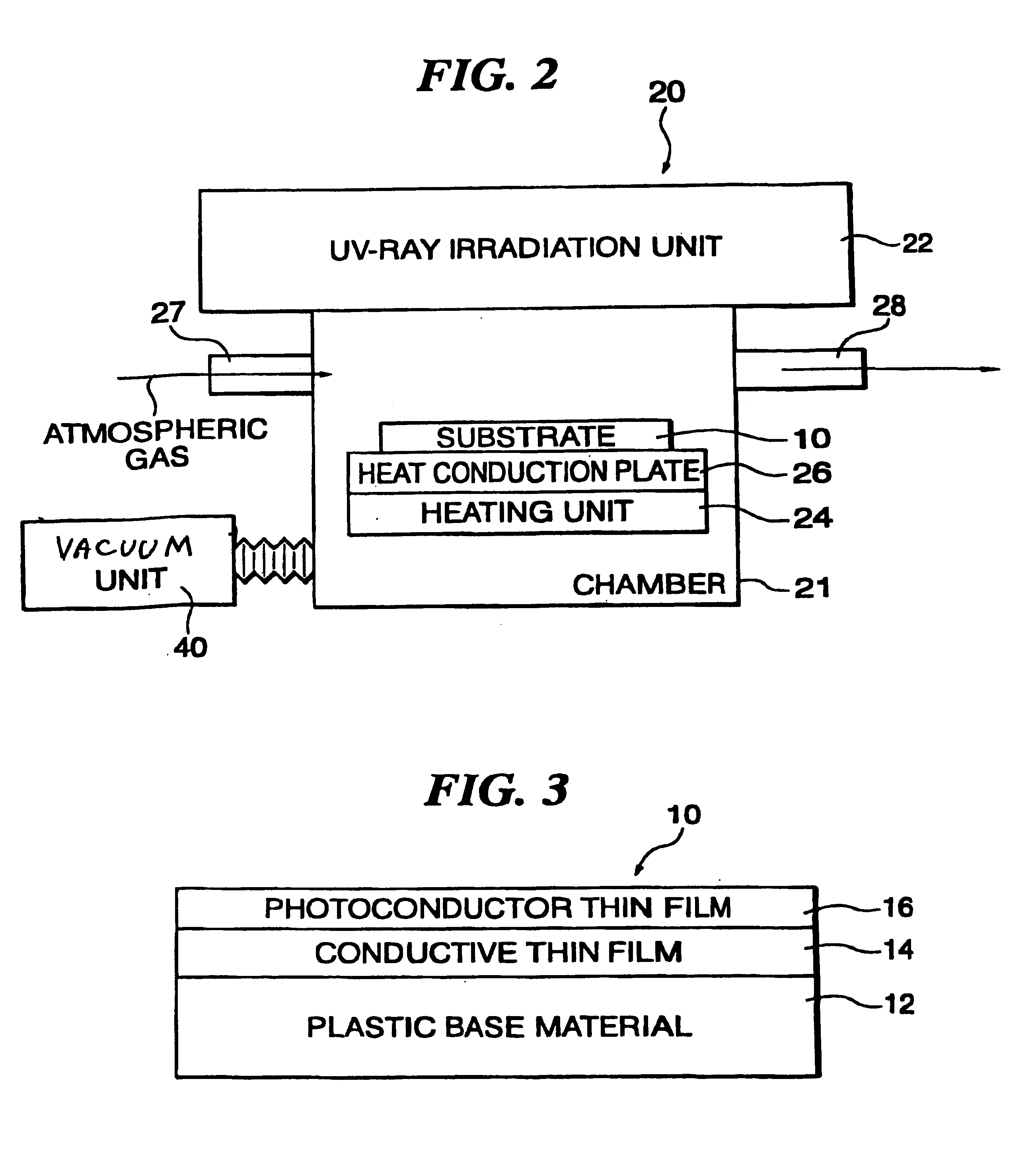

Method of forming crystalline semiconductor thin film on base substrate, lamination formed with crystalline semiconductor thin film and color filter

A method of forming a crystalline semiconductor thin film on a base material which can be prepared at a low temperature by simple step and device, the method including a processing step of applying UV-rays to an amorphous semiconductor thin film provided on a base material while keeping a temperature at not less than 25° C. and not more than 300° C. in a vacuum or a reducing gas atmosphere, as well as a substrate having the semiconductor thin film provided on the base material, a substrate for forming a color filter and a color filter using the substrate.

Owner:FUJIFILM BUSINESS INNOVATION CORP

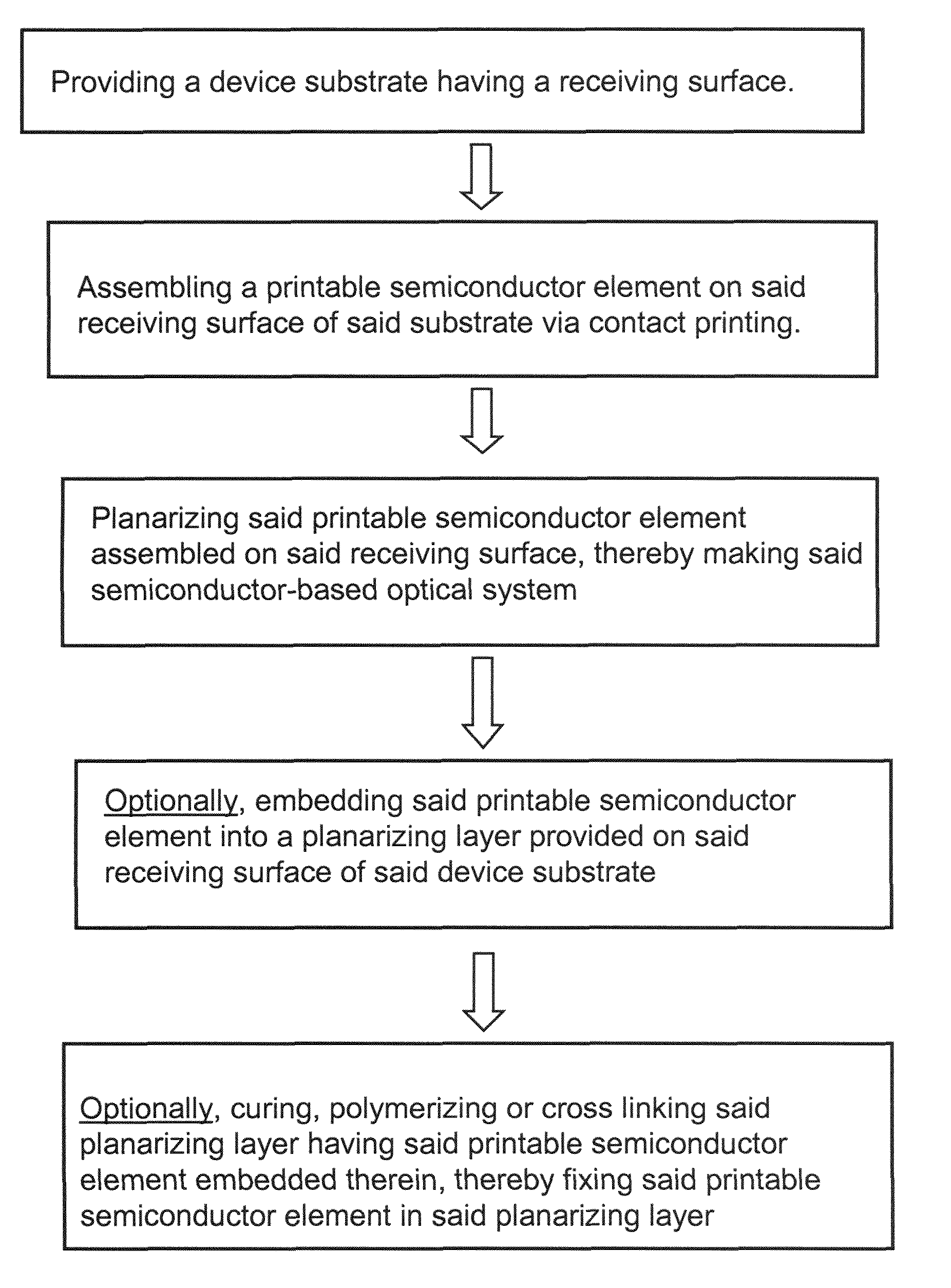

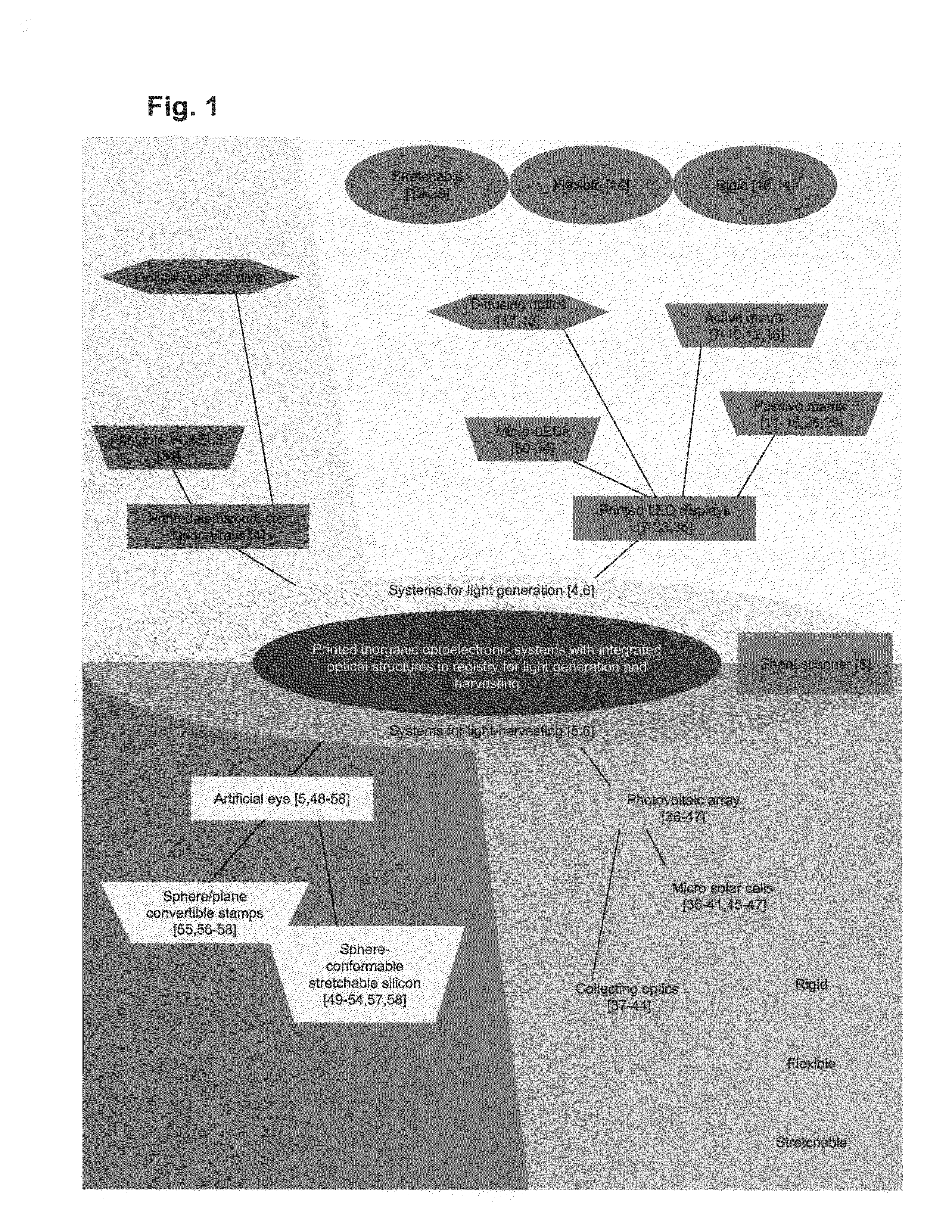

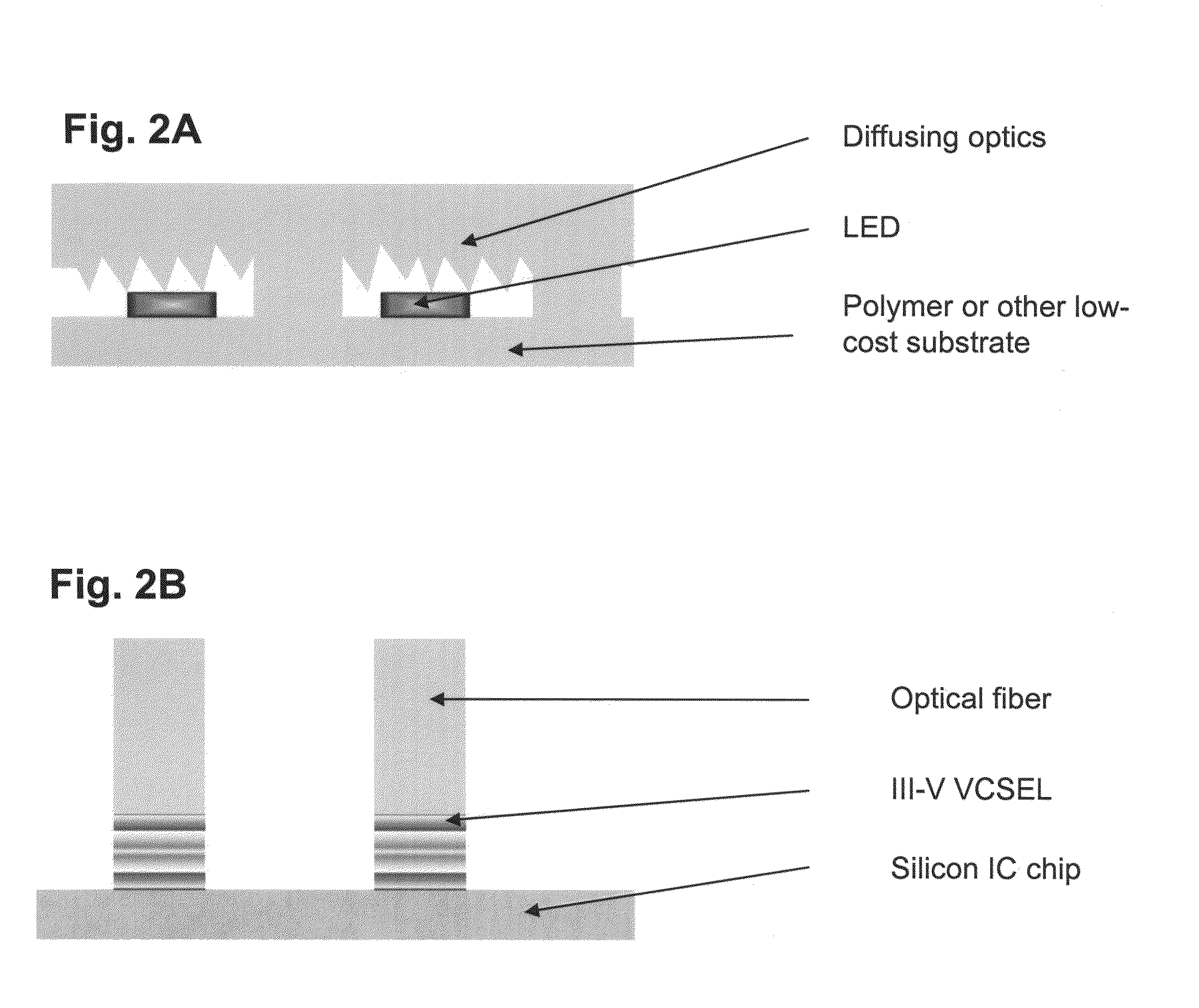

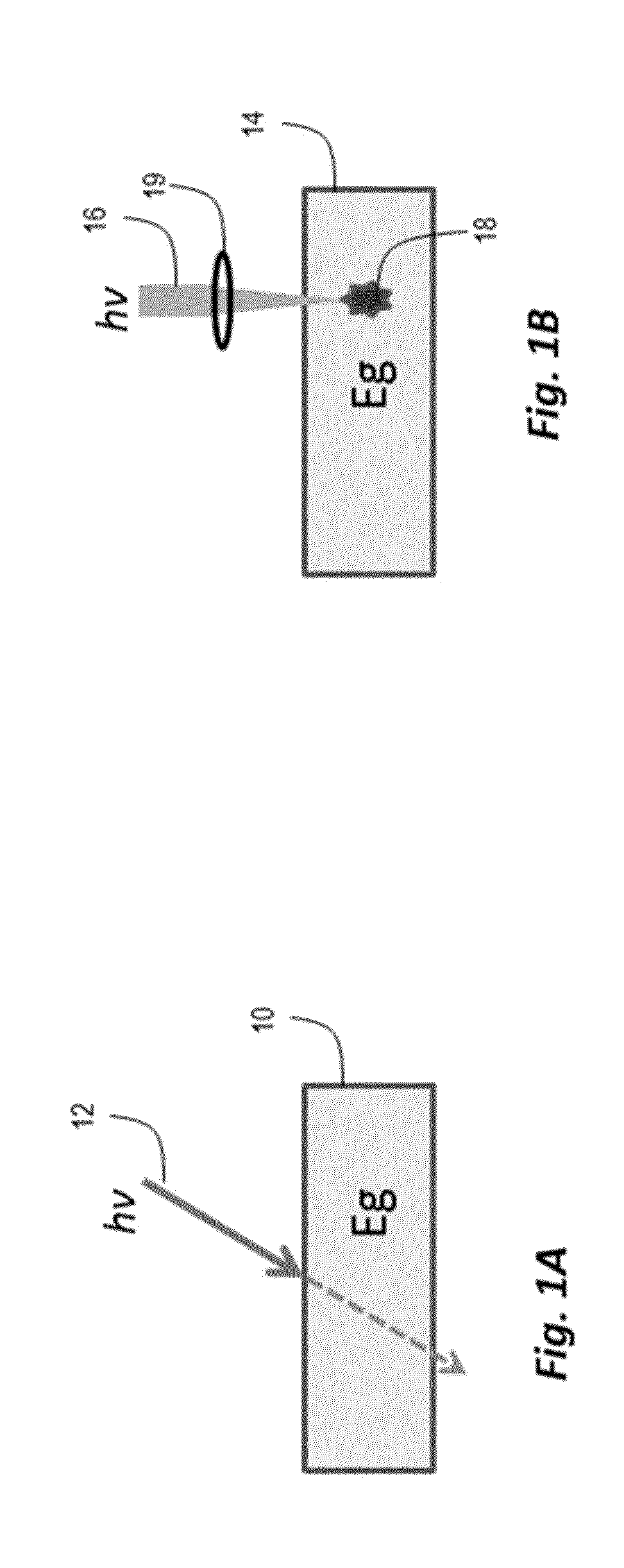

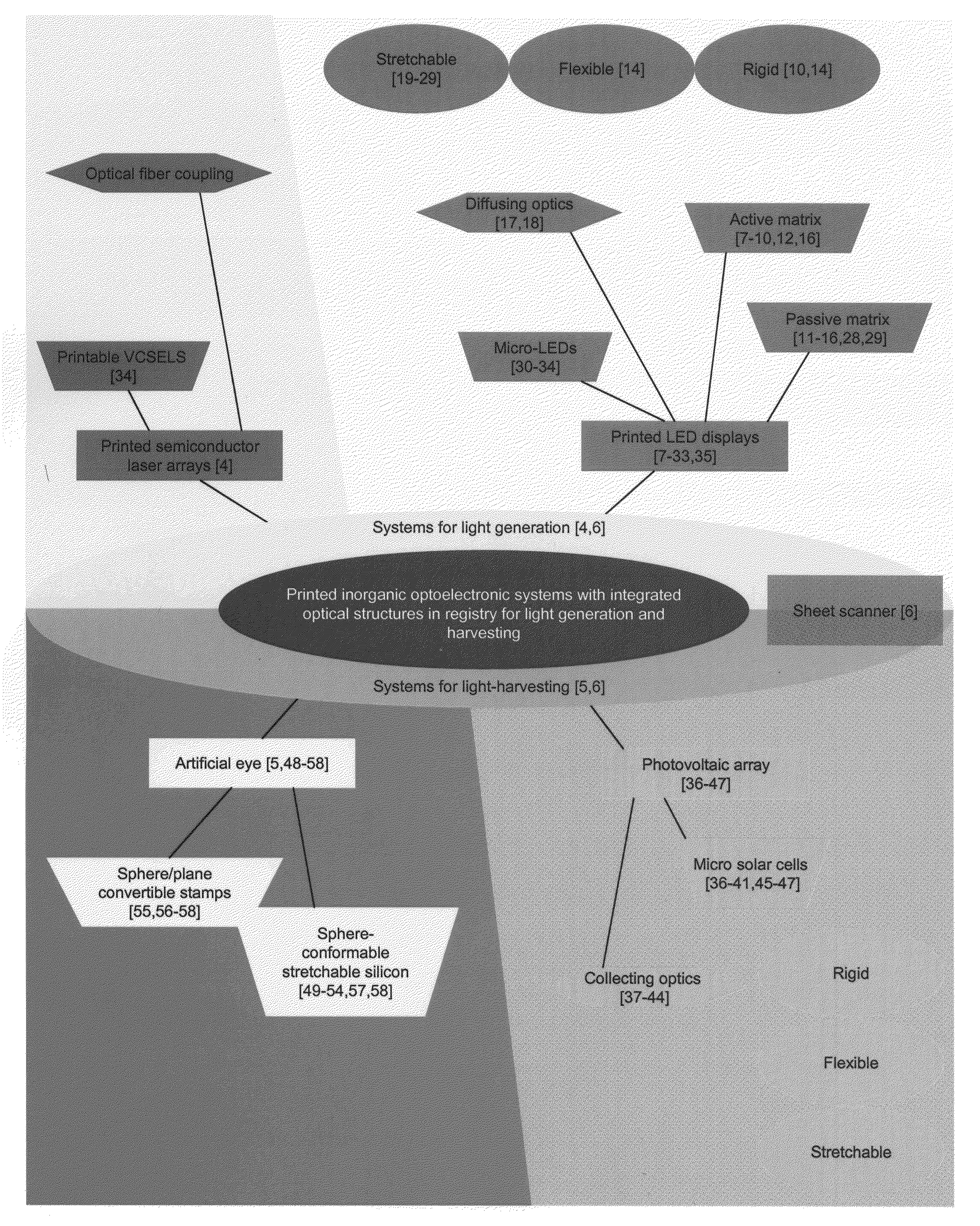

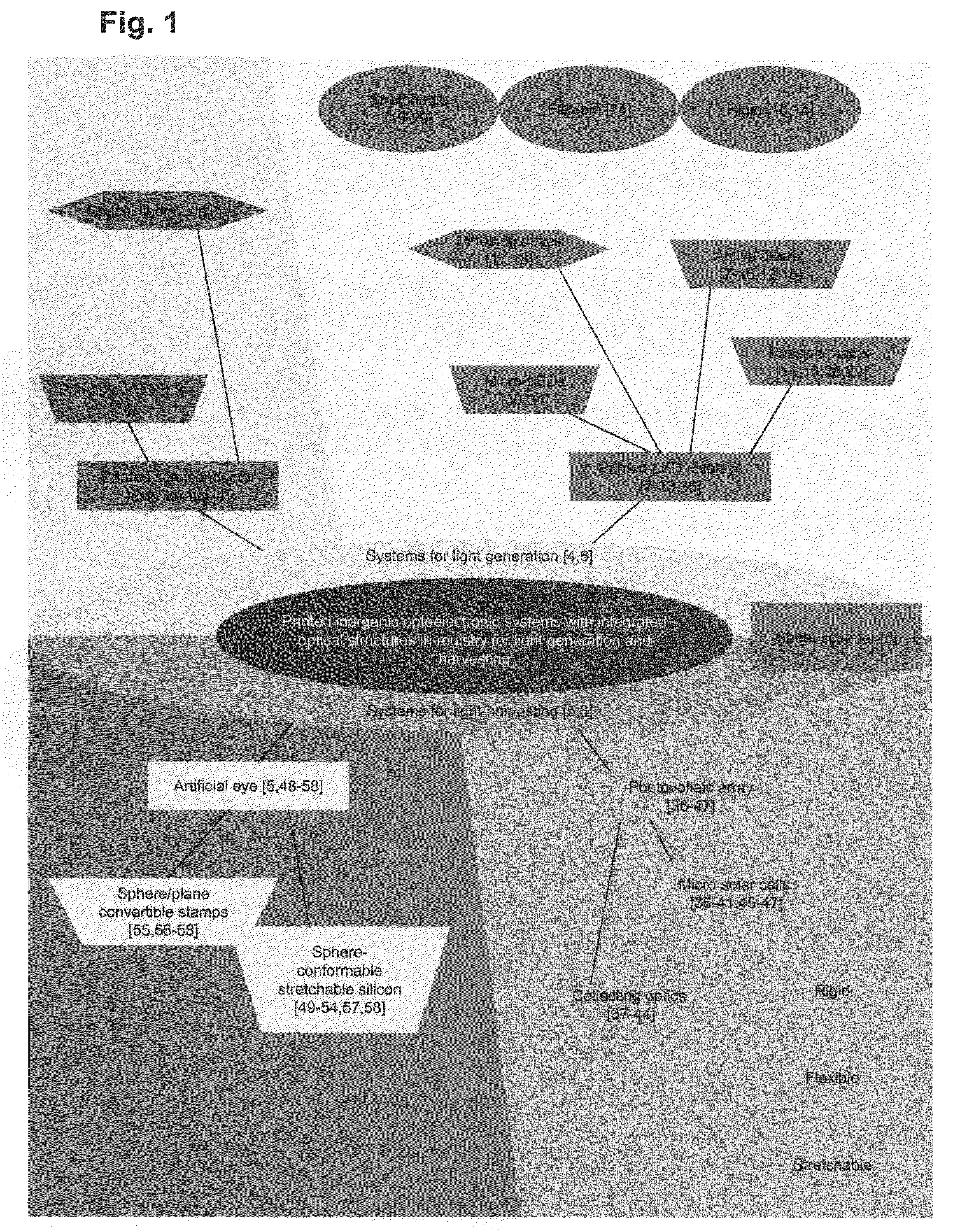

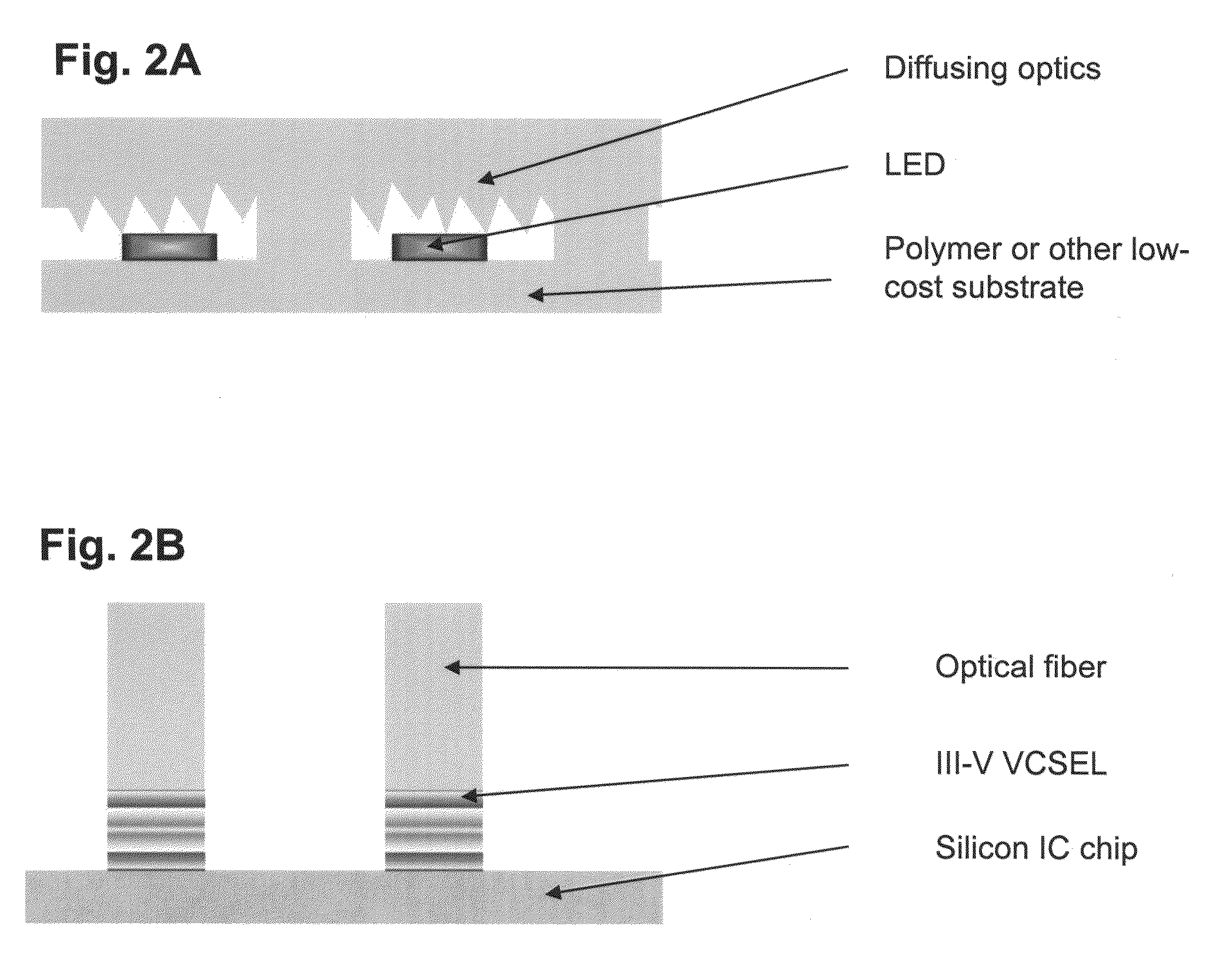

Optical systems fabricated by printing-based assembly

ActiveUS7972875B2Low costImprove performanceFinal product manufactureNanoinformaticsLight sensingSingle crystal

Provided are optical devices and systems fabricated, at least in part, via printing-based assembly and integration of device components. In specific embodiments the present invention provides light emitting systems, light collecting systems, light sensing systems and photovoltaic systems comprising printable semiconductor elements, including large area, high performance macroelectronic devices. Optical systems of the present invention comprise semiconductor elements assembled, organized and / or integrated with other device components via printing techniques that exhibit performance characteristics and functionality comparable to single crystalline semiconductor based devices fabricated using conventional high temperature processing methods. Optical systems of the present invention have device geometries and configurations, such as form factors, component densities, and component positions, accessed by printing that provide a range of useful device functionalities. Optical systems of the present invention include devices and device arrays exhibiting a range of useful physical and mechanical properties including flexibility, shapeability, conformability and stretchablity.

Owner:X DISPLAY CO TECH LTD +1

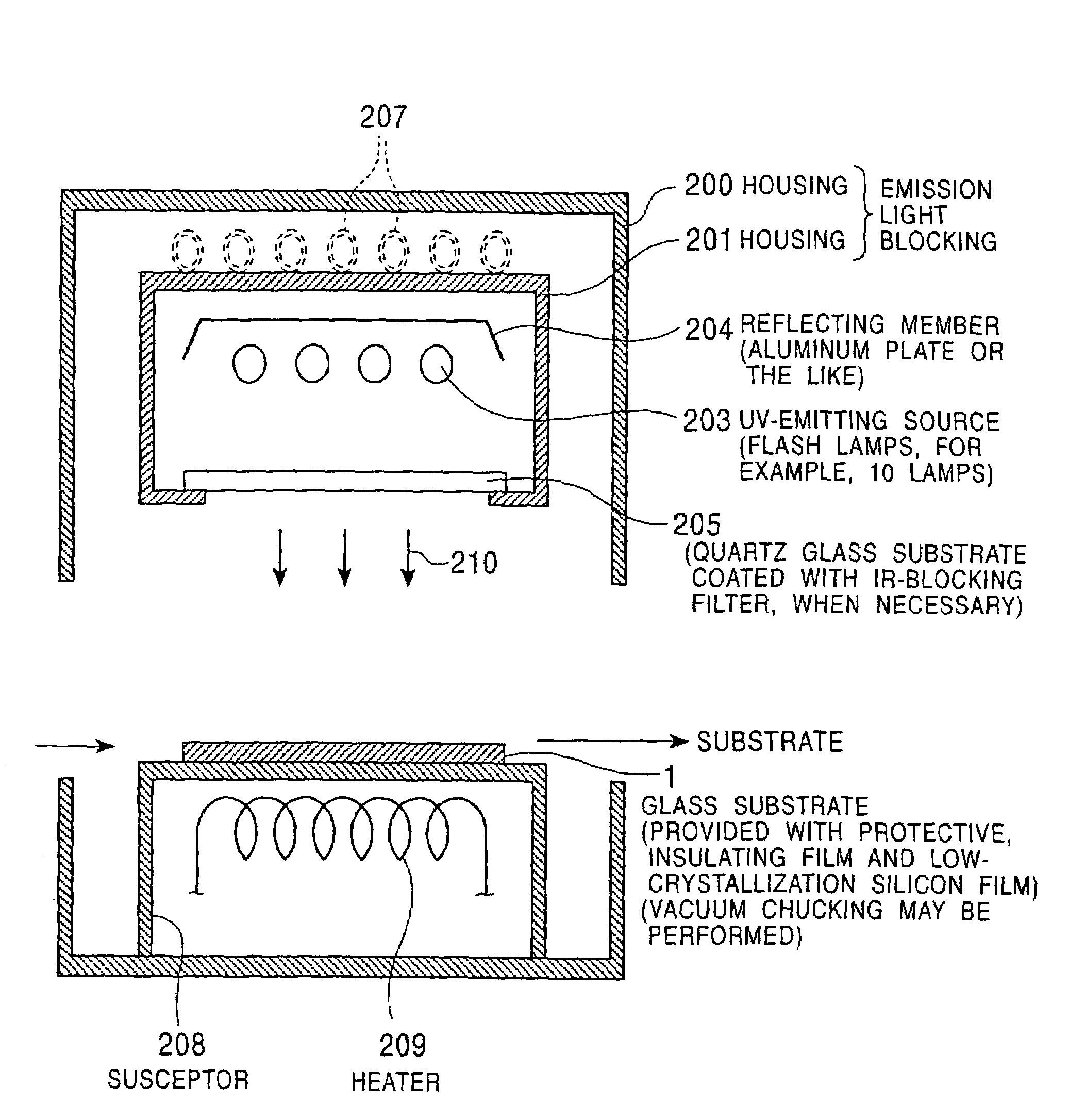

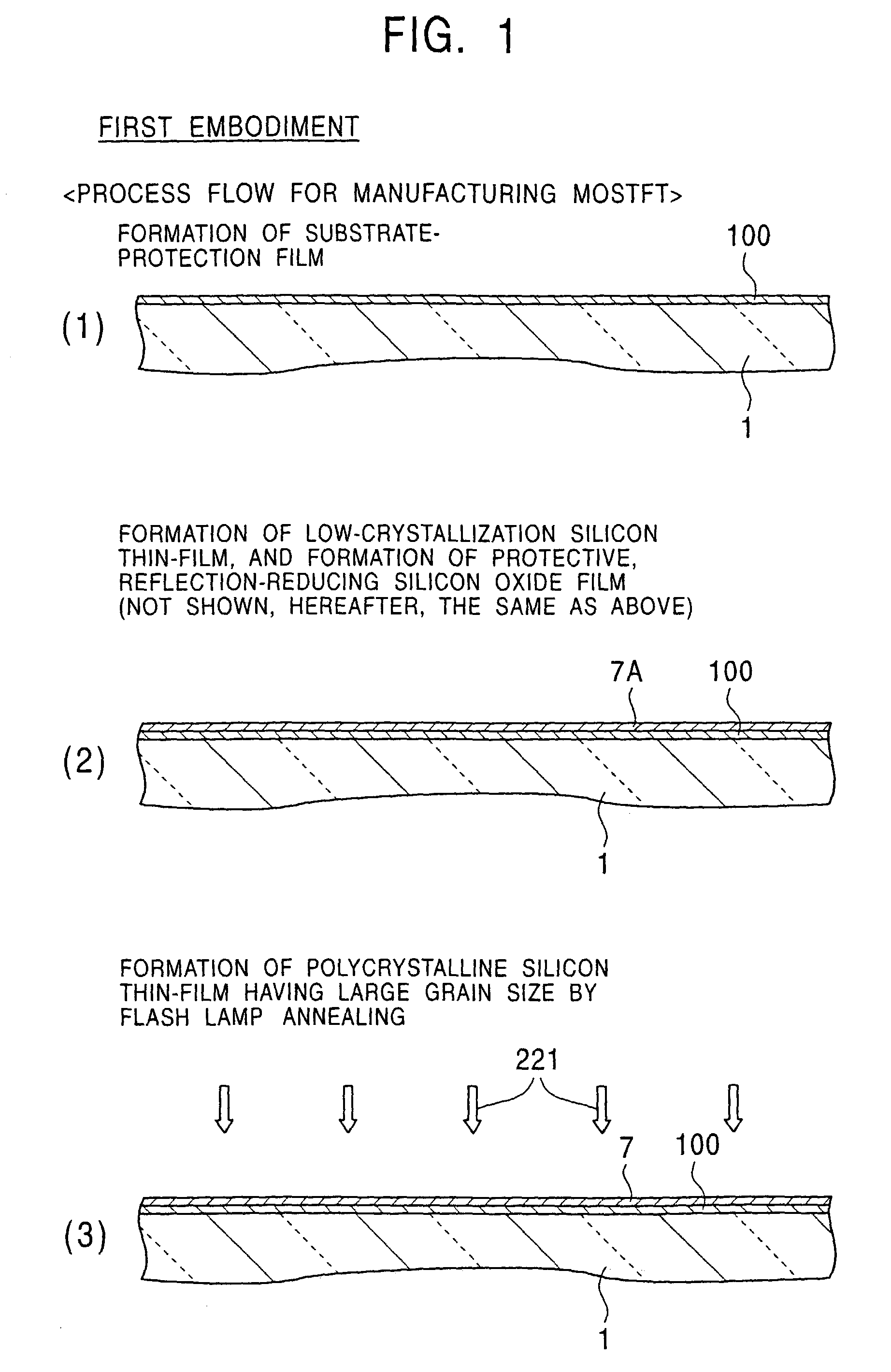

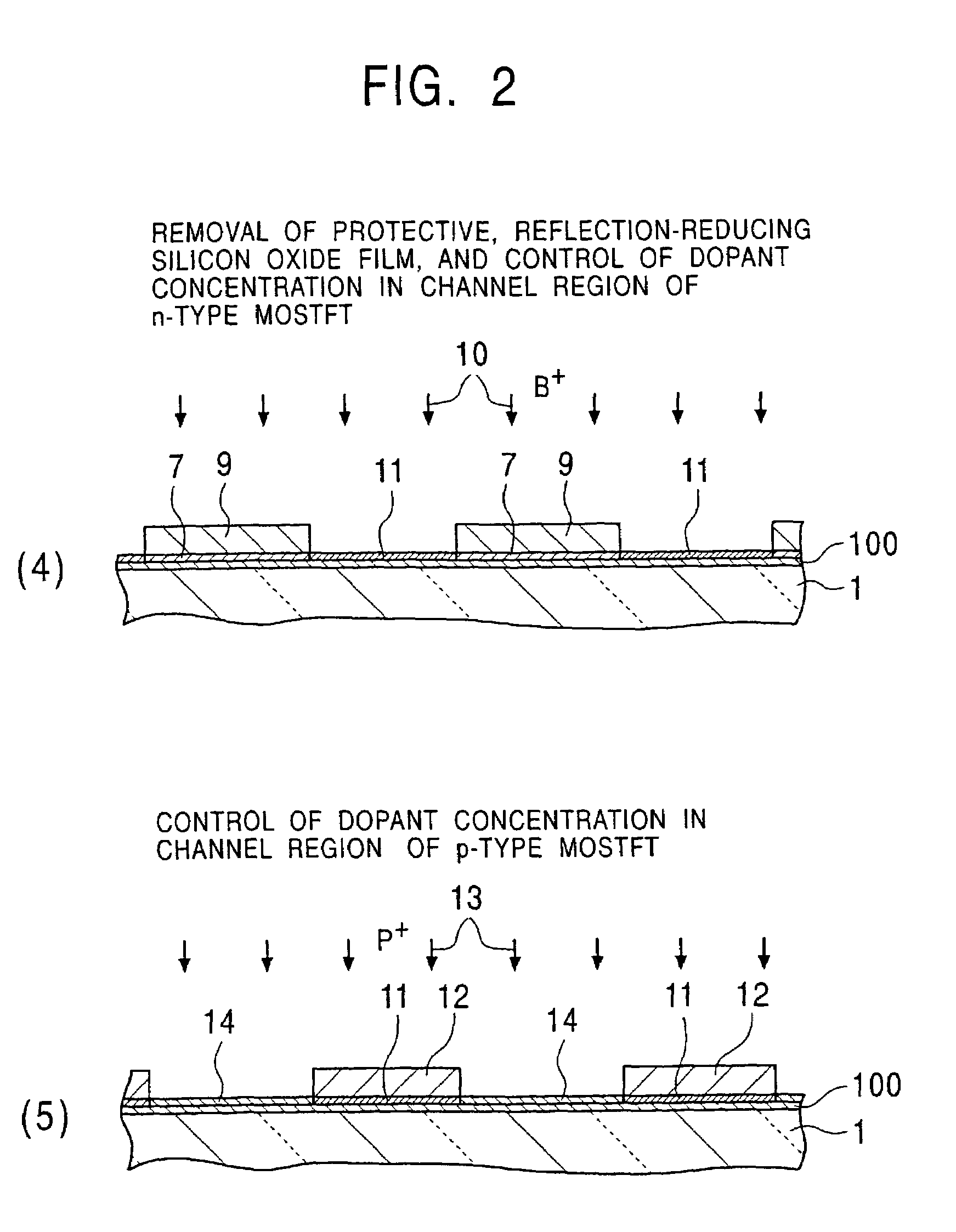

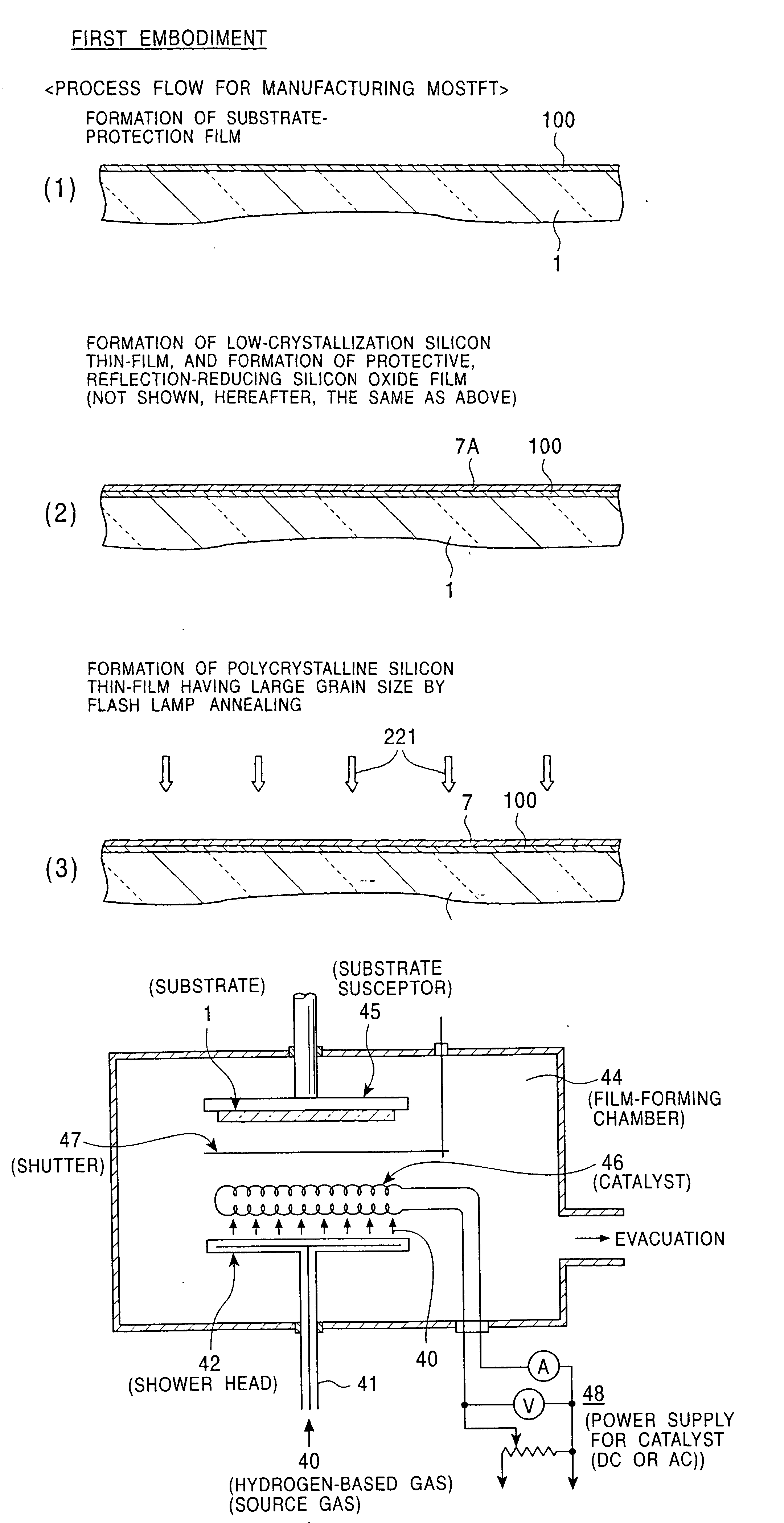

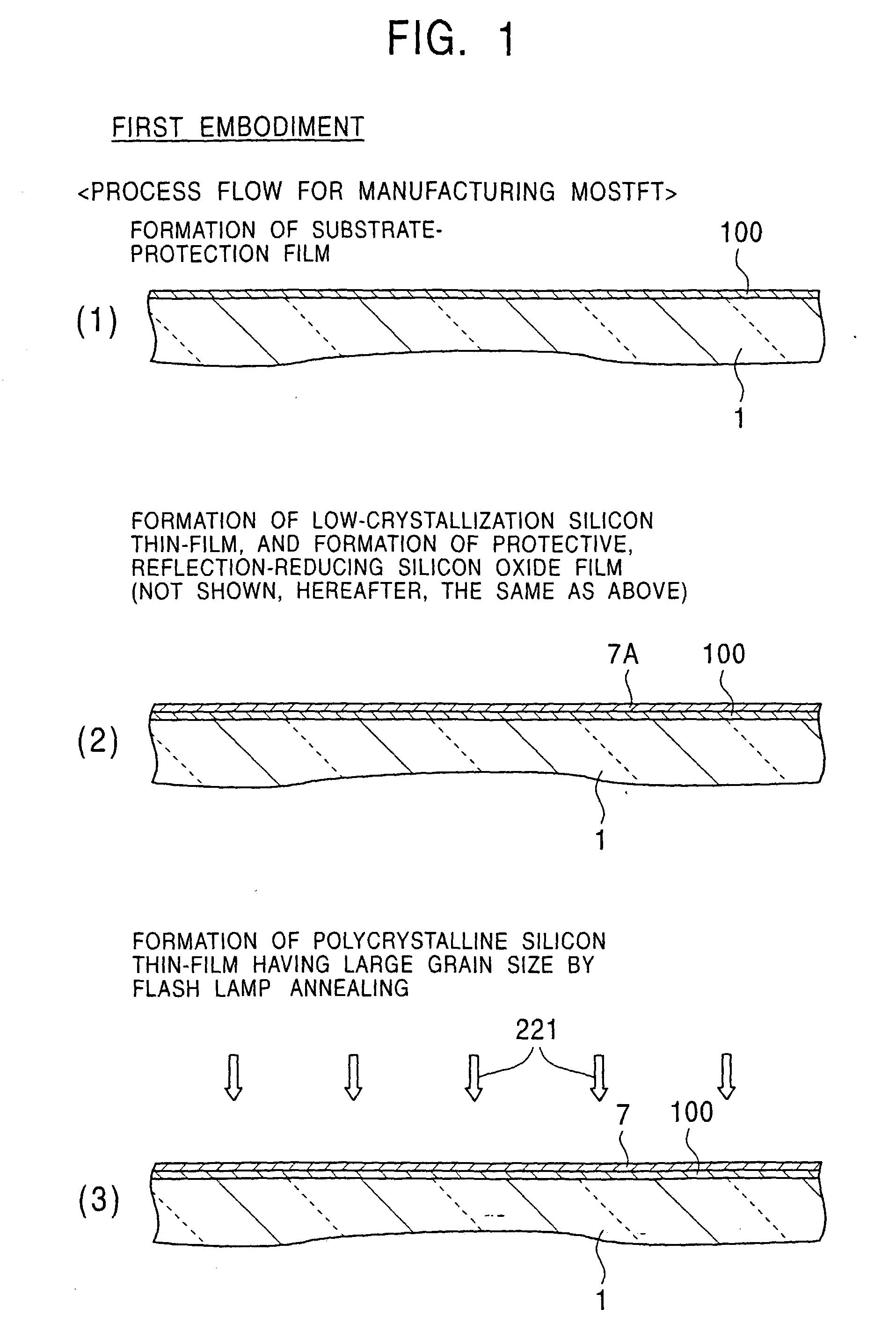

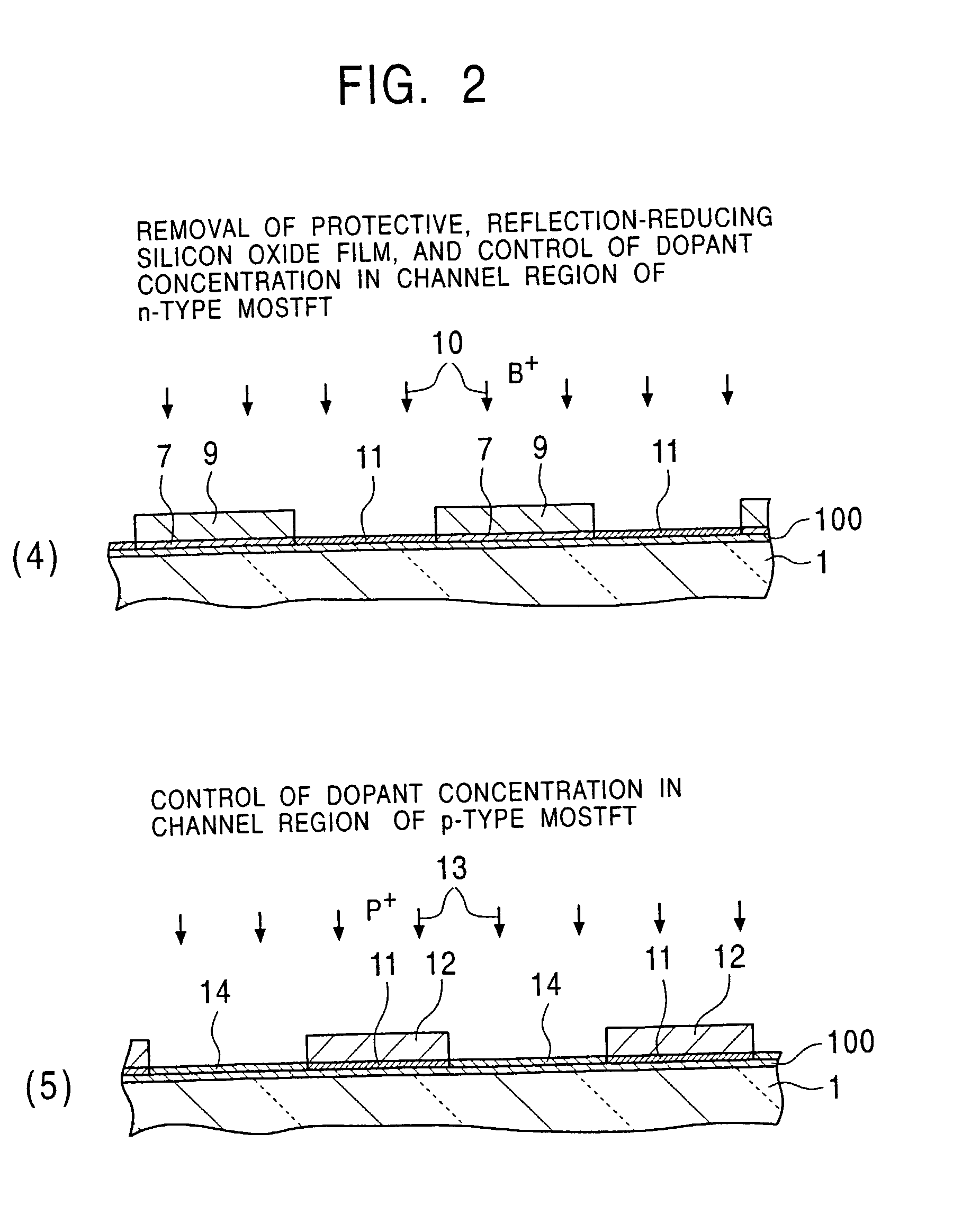

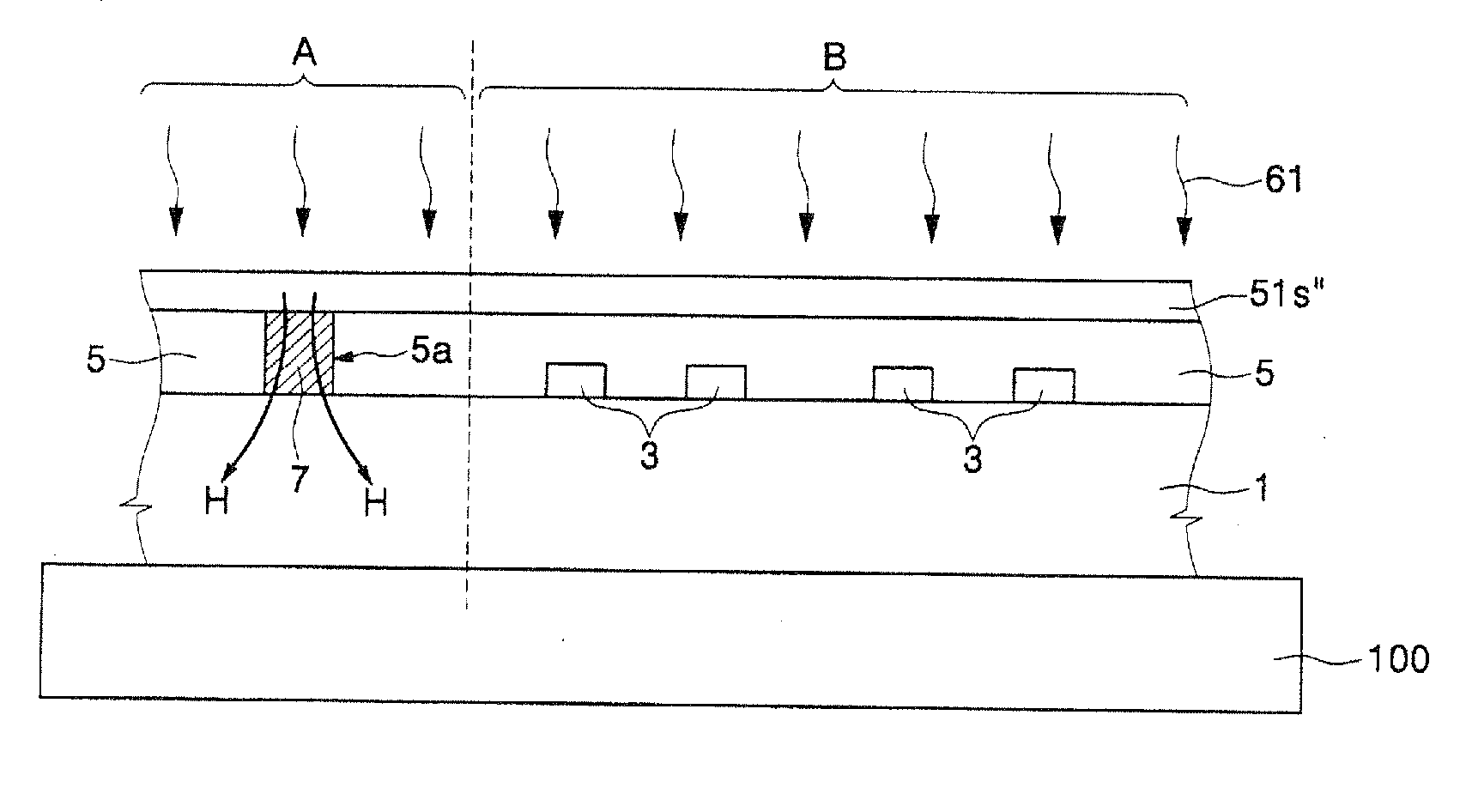

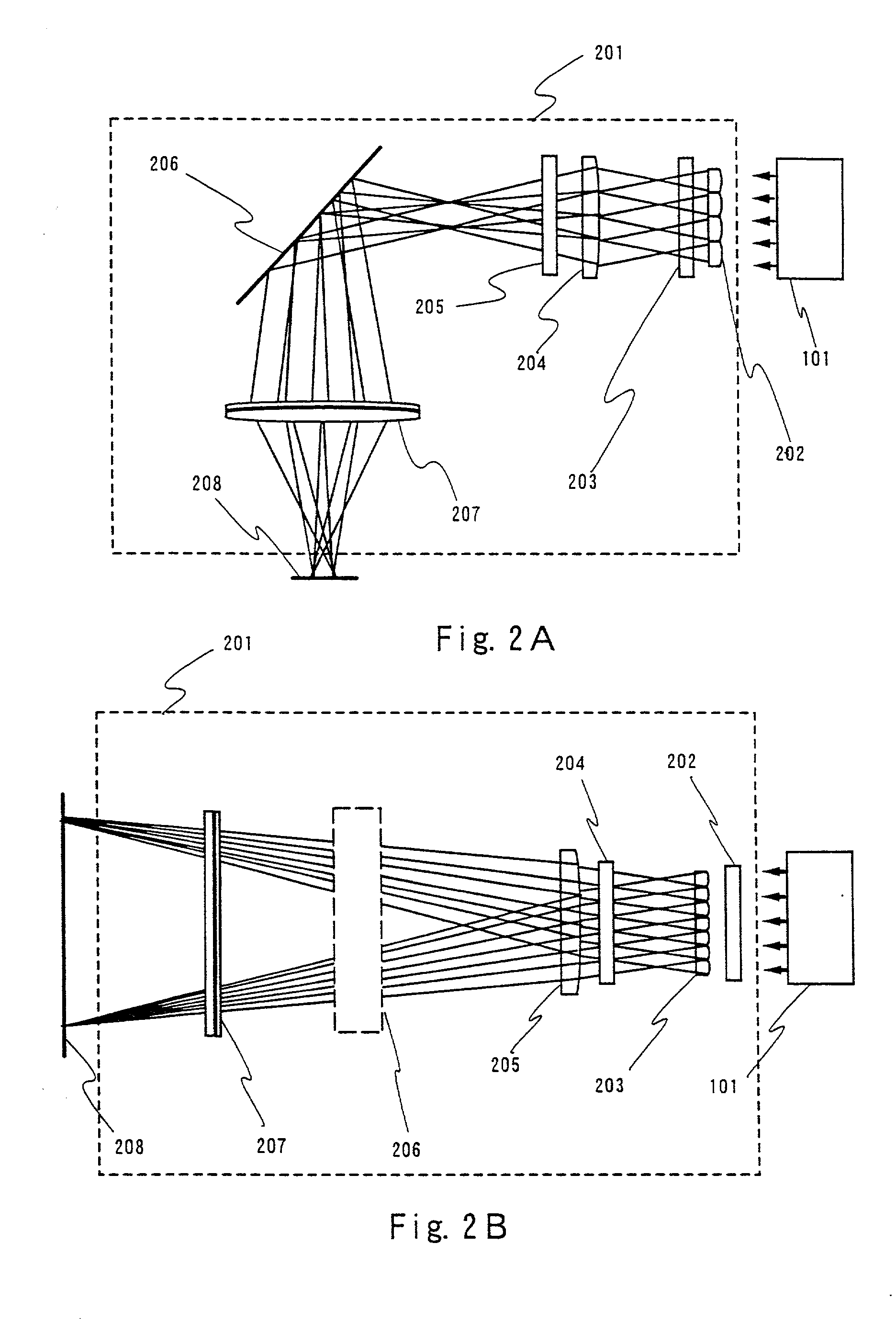

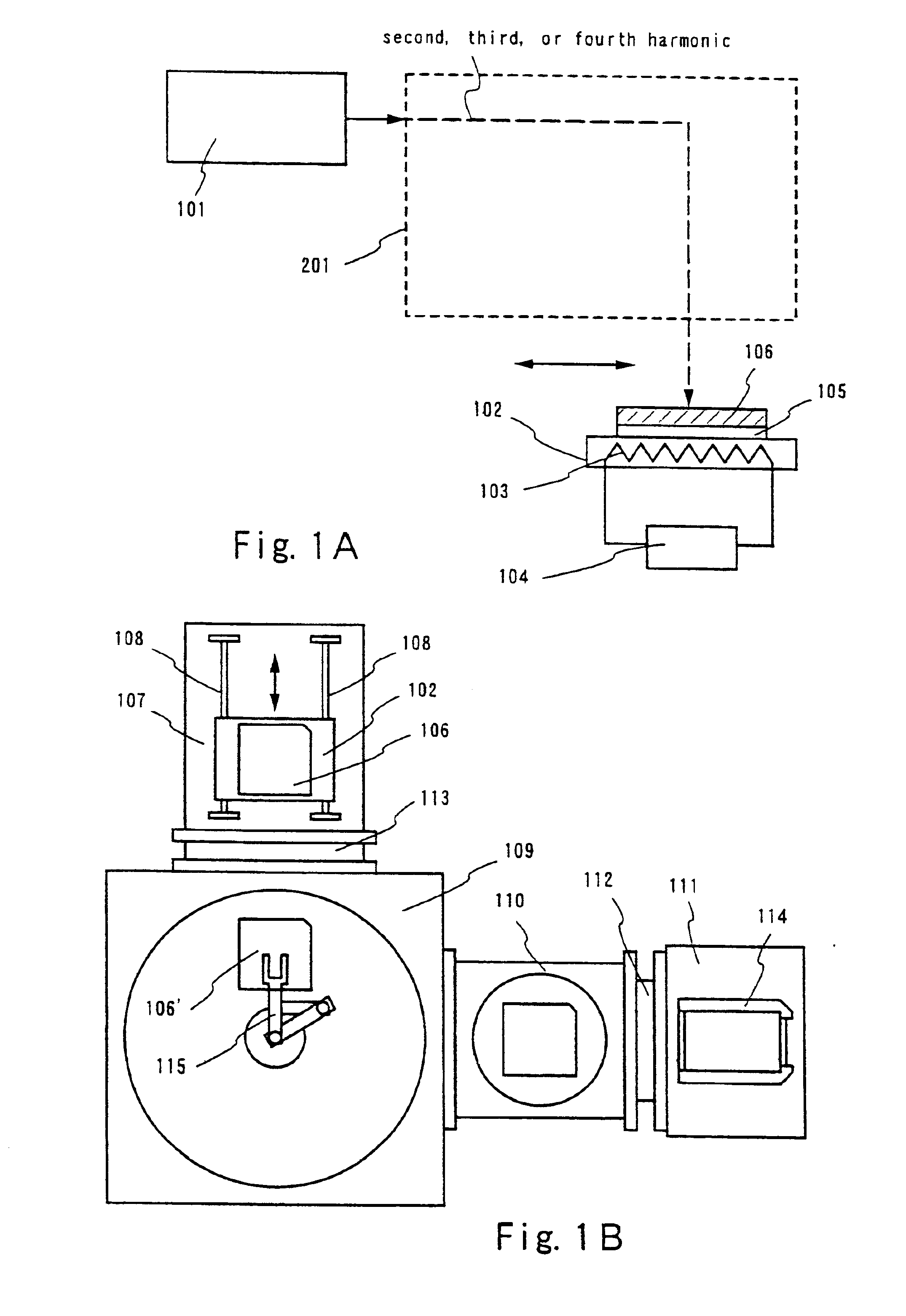

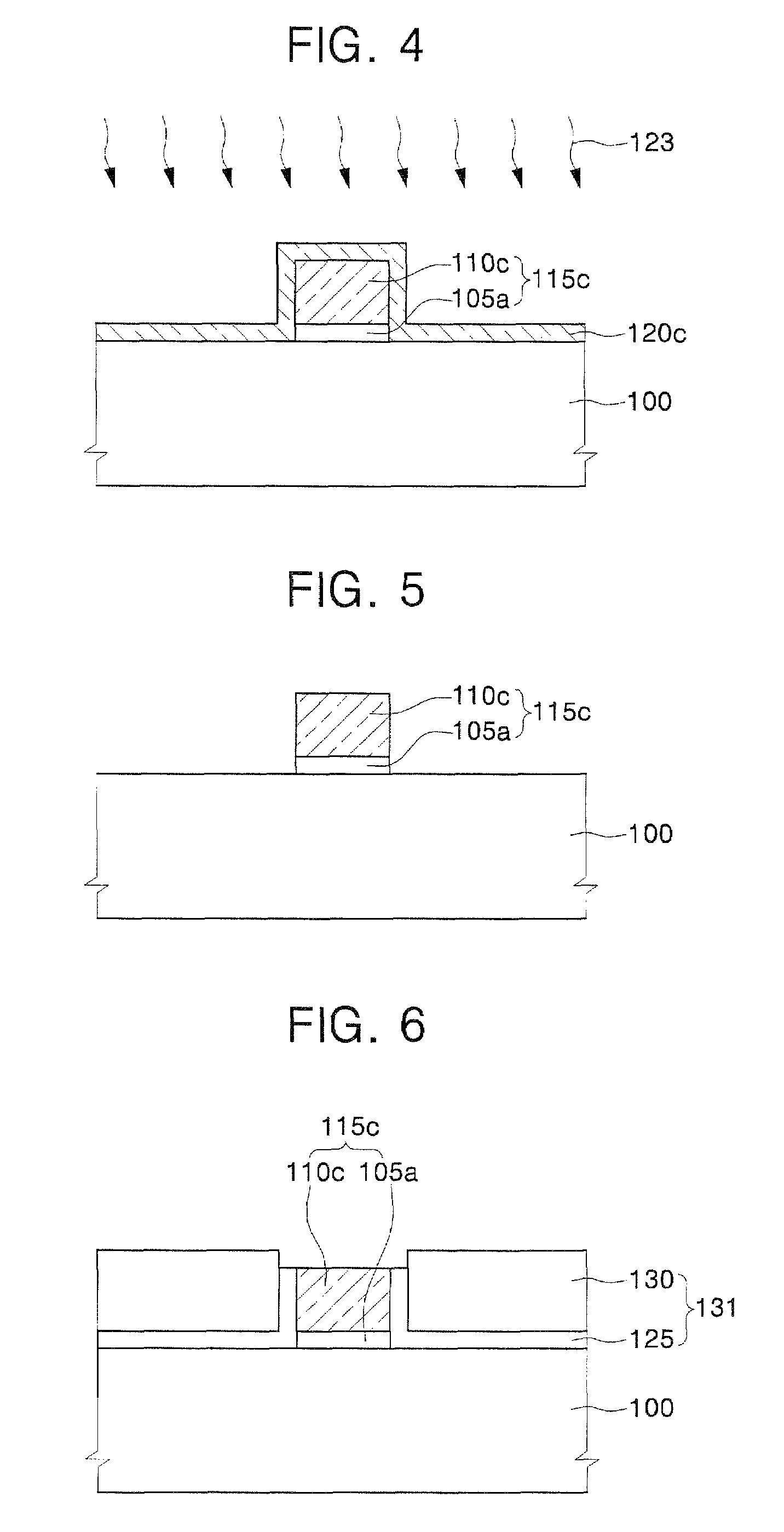

Semiconductor thin film forming method, production methods for semiconductor device and electrooptical device, devices used for these methods, and semiconductor device and electrooptical device

InactiveUS7183229B2Promote crystallizationTransistorDrying solid materials with heatSingle crystalCrystallinity

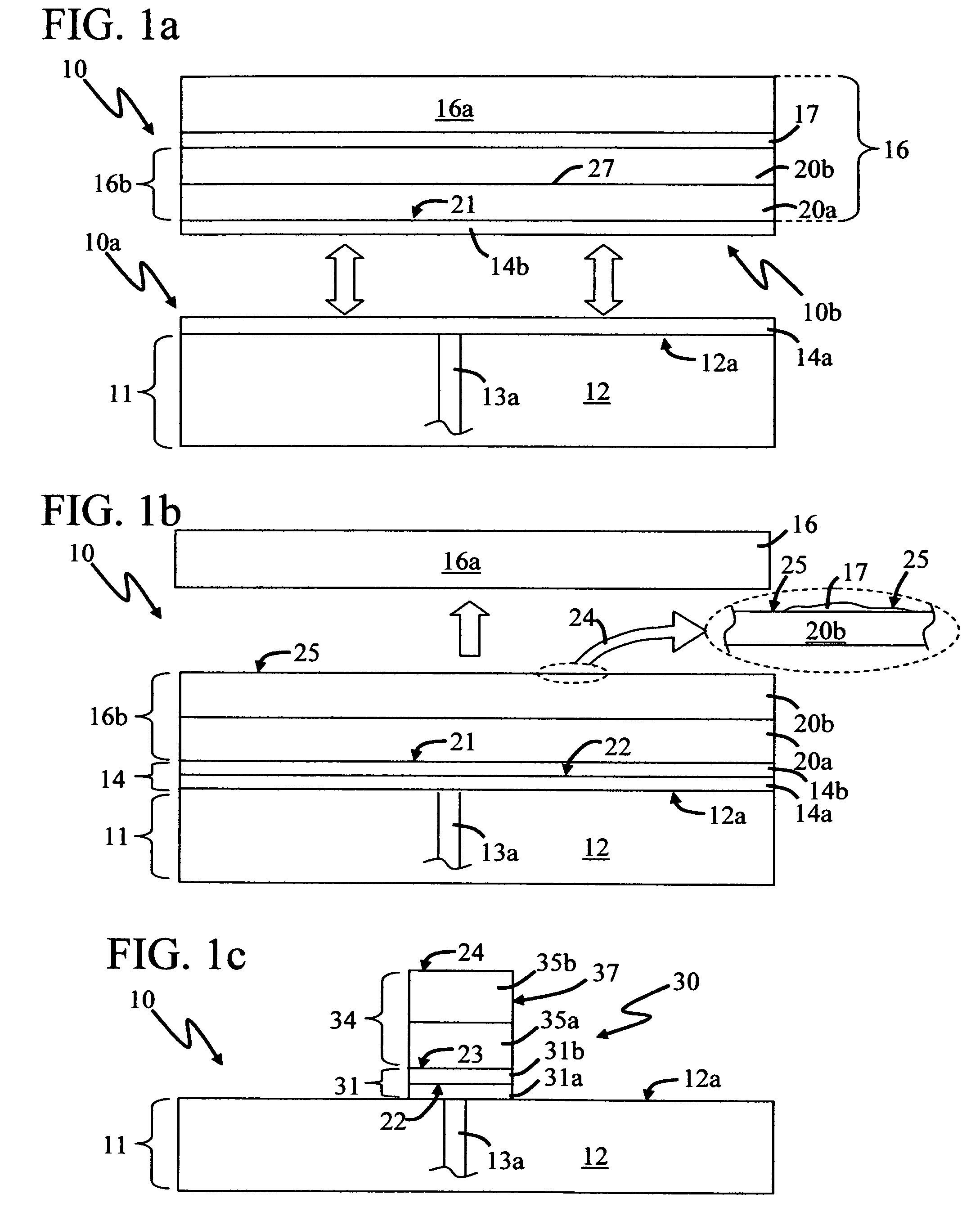

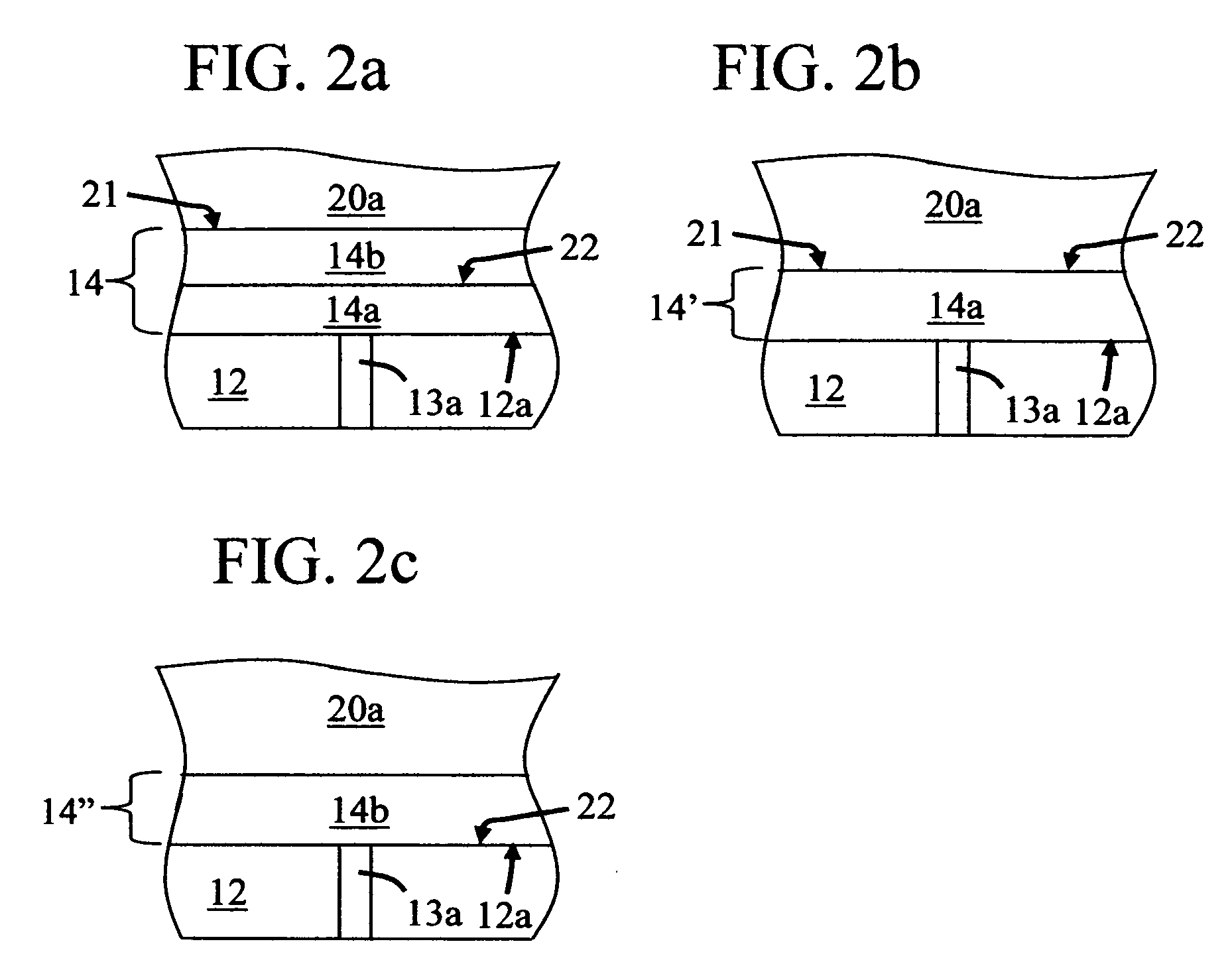

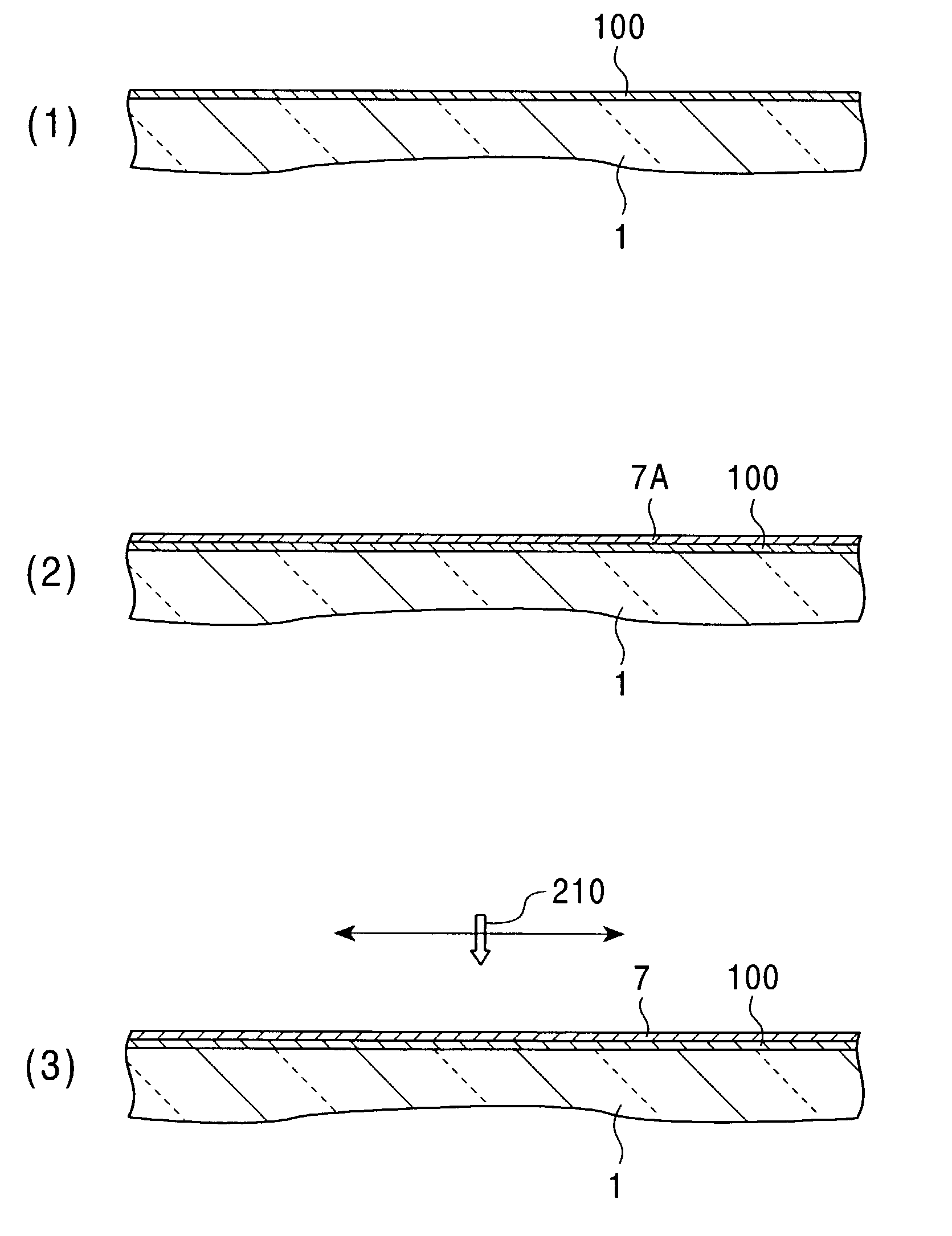

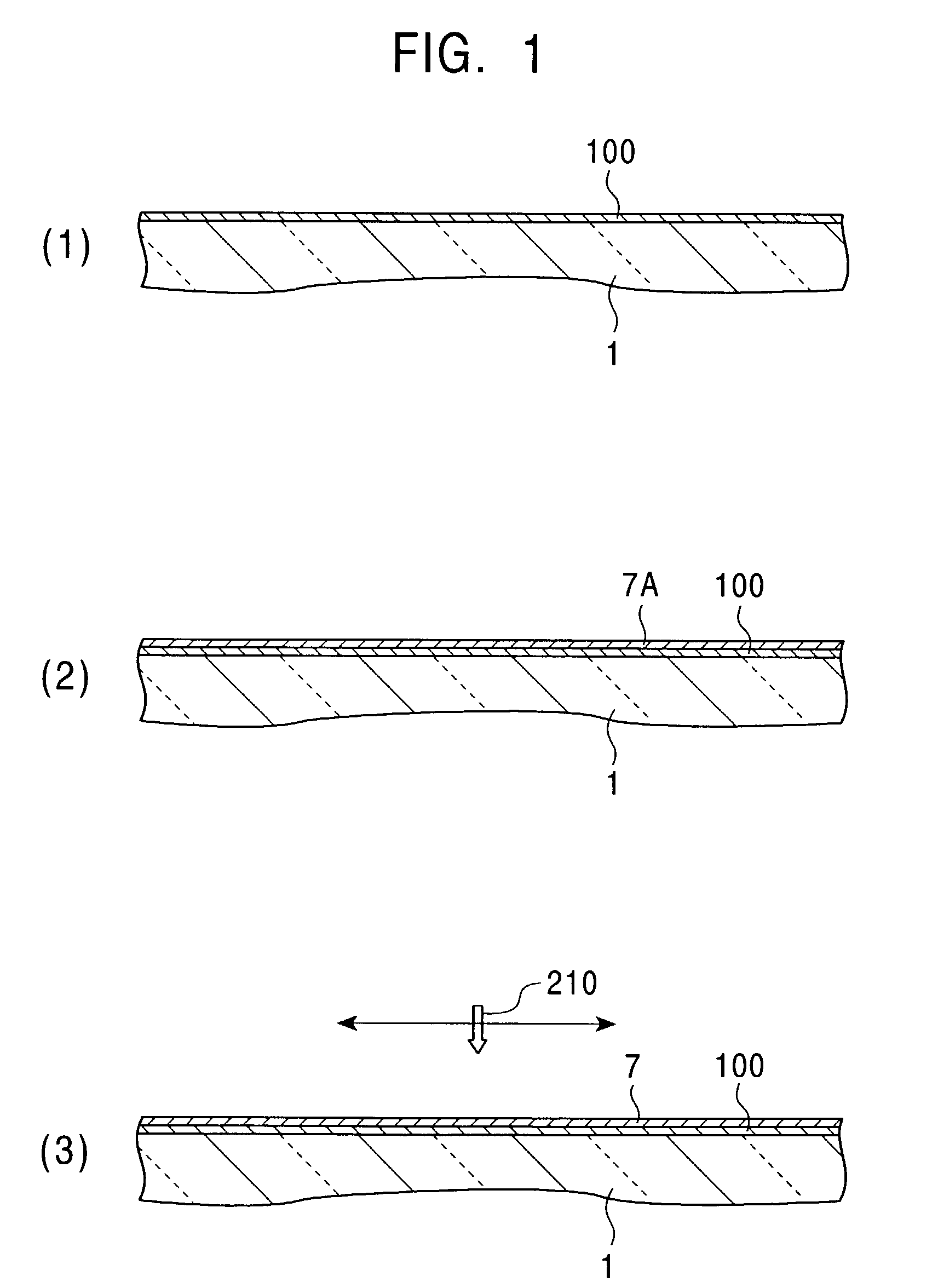

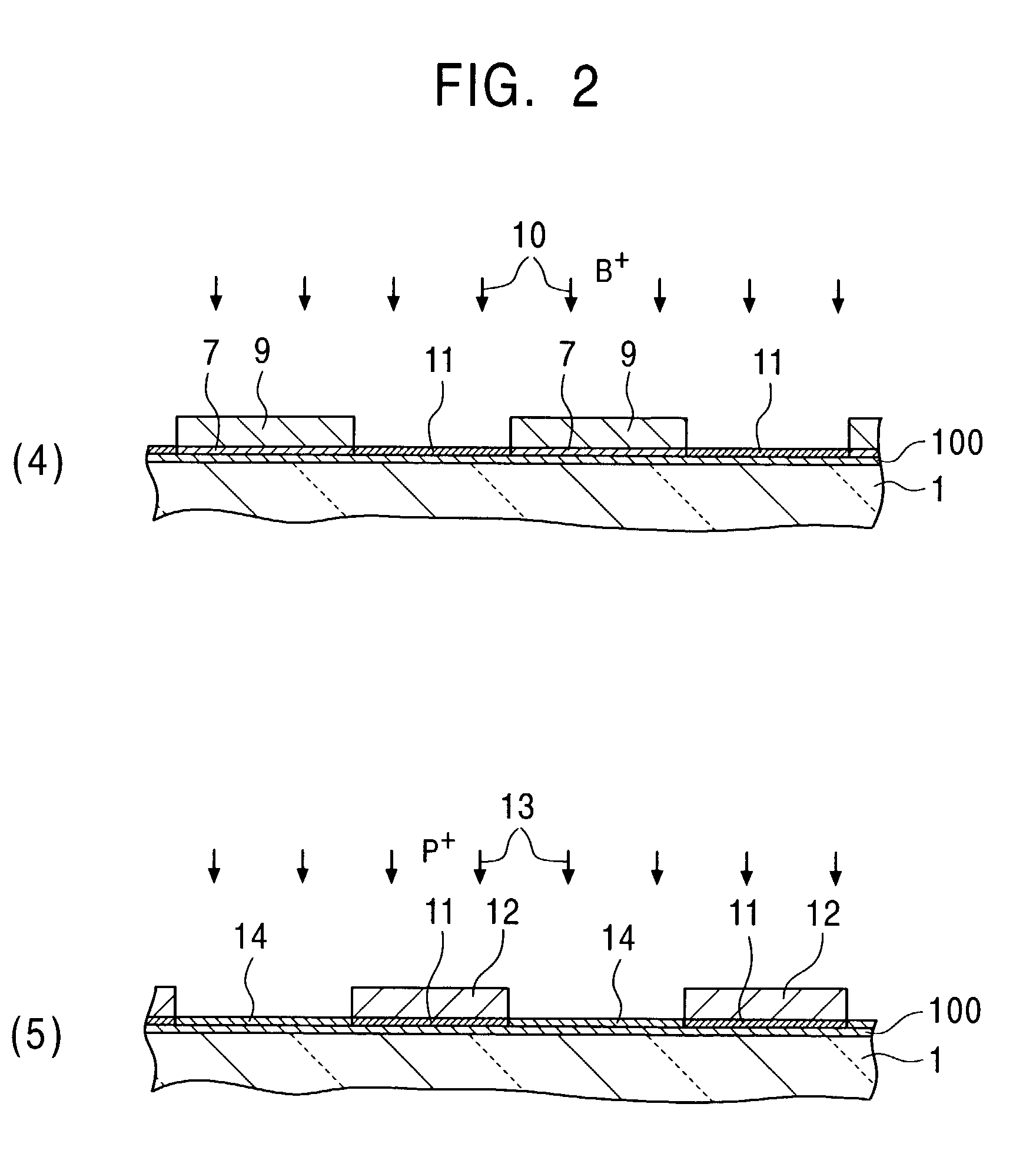

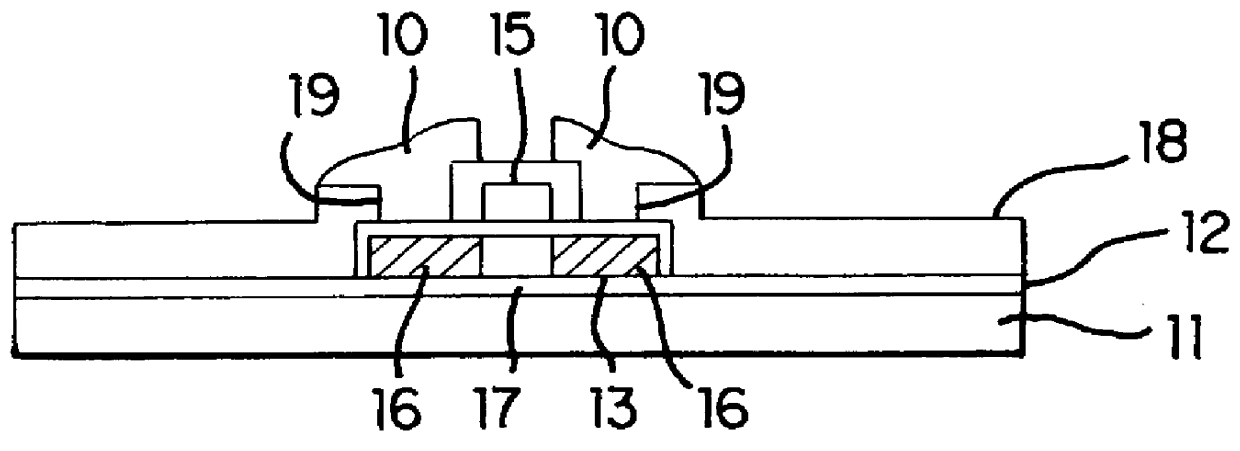

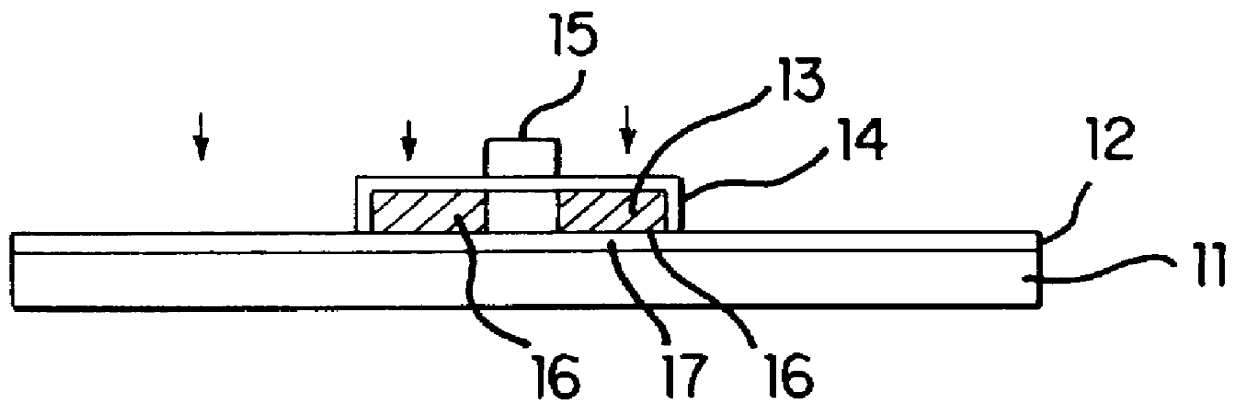

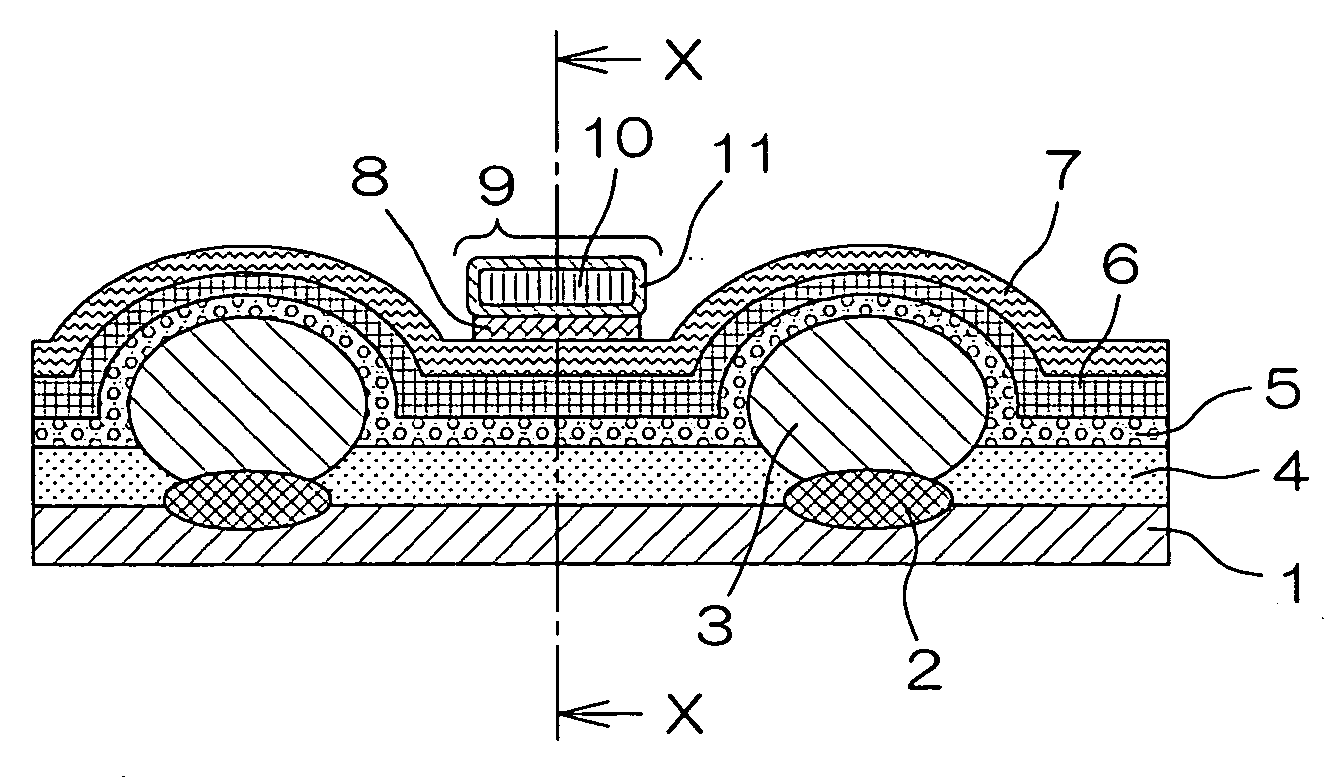

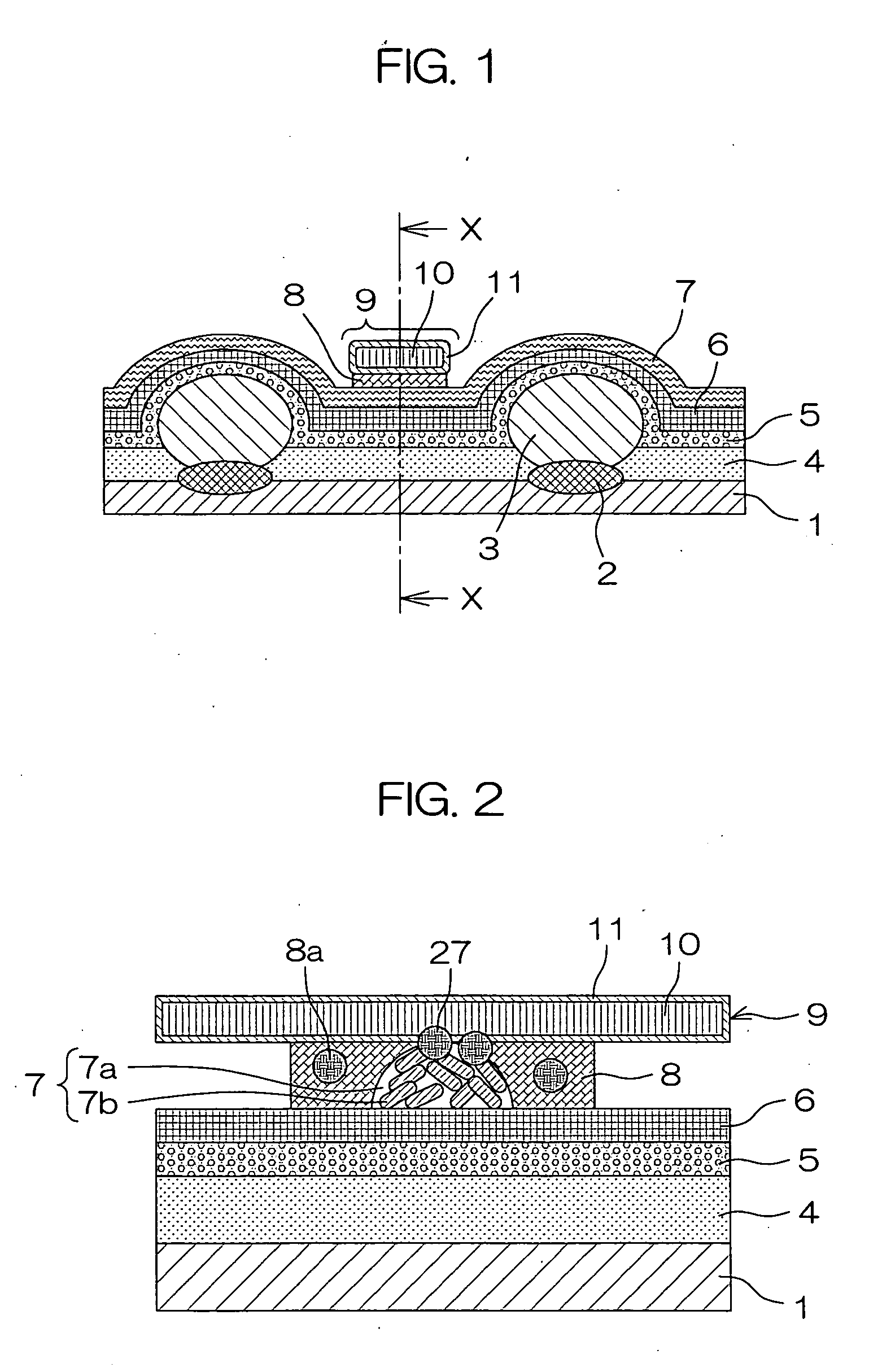

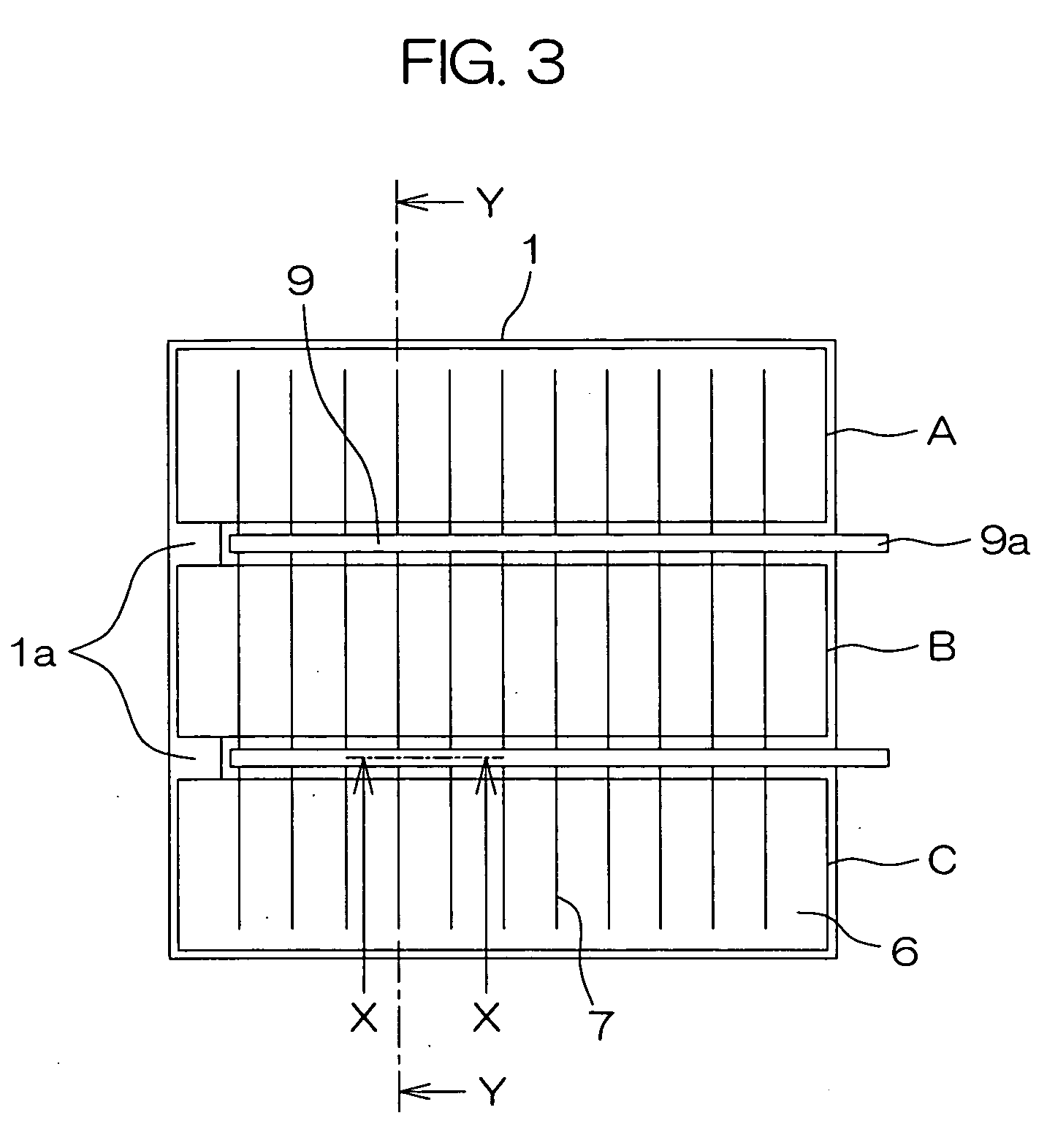

An object of the present invention is to provide a method for easily forming a polycrystalline semiconductor thin-film, such as polycrystalline silicon having high crystallinity and high quality, or a single crystalline semiconductor thin-film at inexpensive cost, the crystalline semiconductor thin-film having a large area, and to provide an apparatus for processing the method described above. In forming a polycrystalline (or single crystalline) semiconductor thin-film (7), such as a polycrystalline silicon thin-film, having high crystallinity and a large grain size on a substrate (1), or in forming a semiconductor device having the polycrystalline (or single crystalline) semiconductor thin-film (7) on the substrate (1), a method comprises forming a low-crystallization semiconductor thin-film (7A) on the substrate (1), and subsequently heating and cooling this low-crystallization semiconductor thin-film (7A) to a fusion, a semi-fusion, or a non-fusion state by flash lamp annealing to facilitate the crystallization of the low-crystallization semiconductor thin-film, whereby a polycrystalline (single crystalline) semiconductor thin-film (7) is obtained. A method for forming the semiconductor device and an apparatus for processing the methods are also disclosed.

Owner:SONY CORP

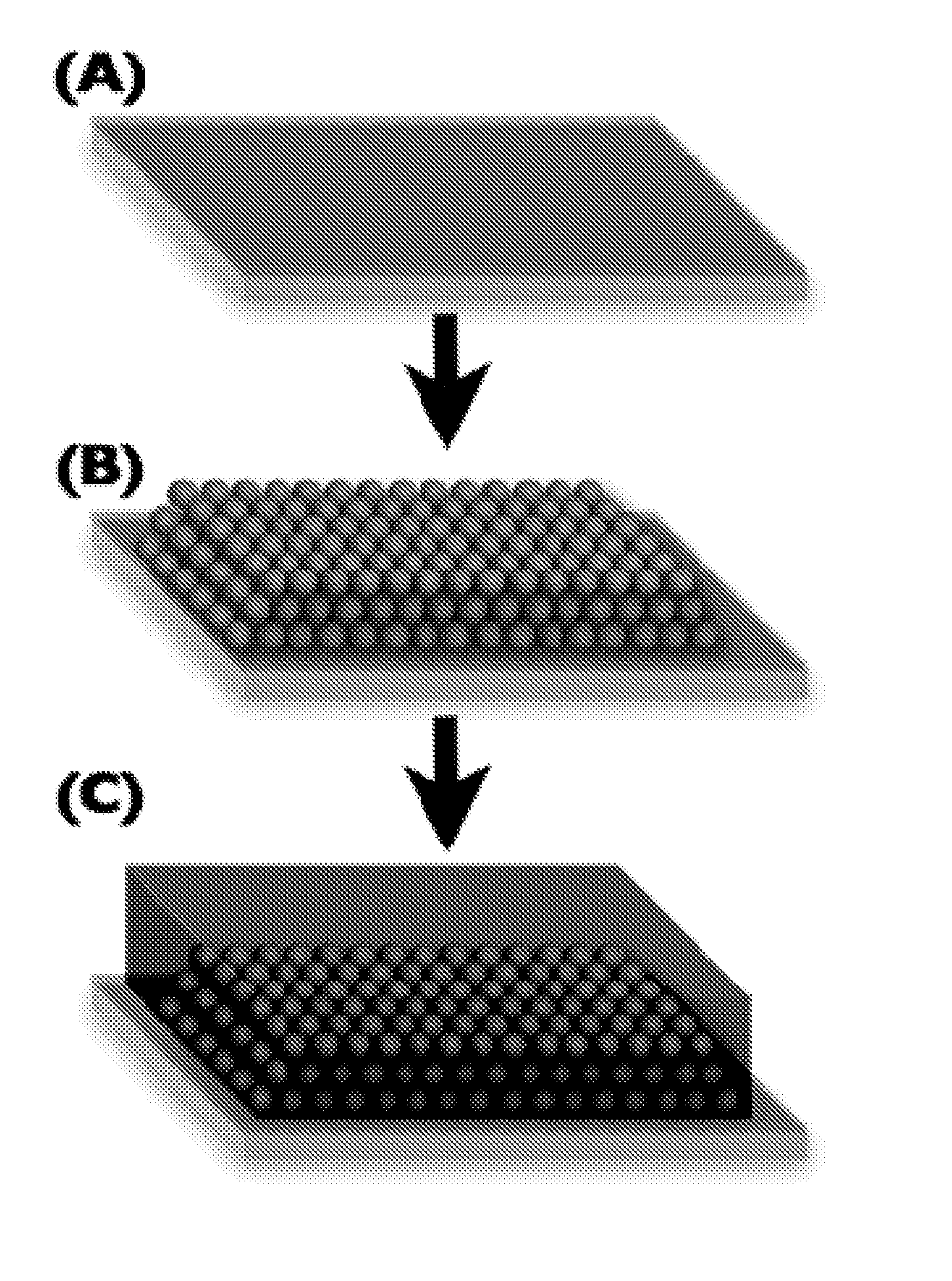

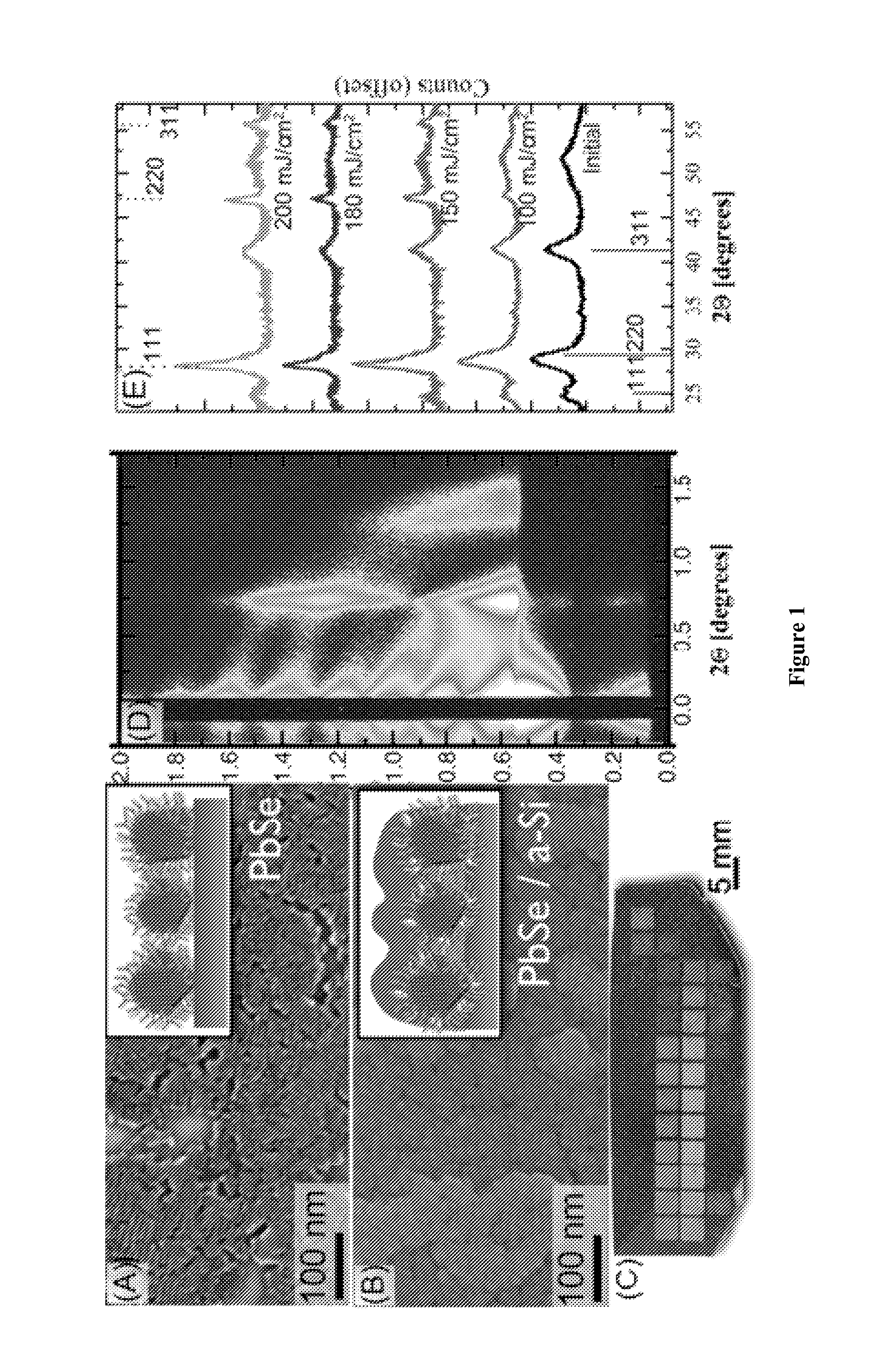

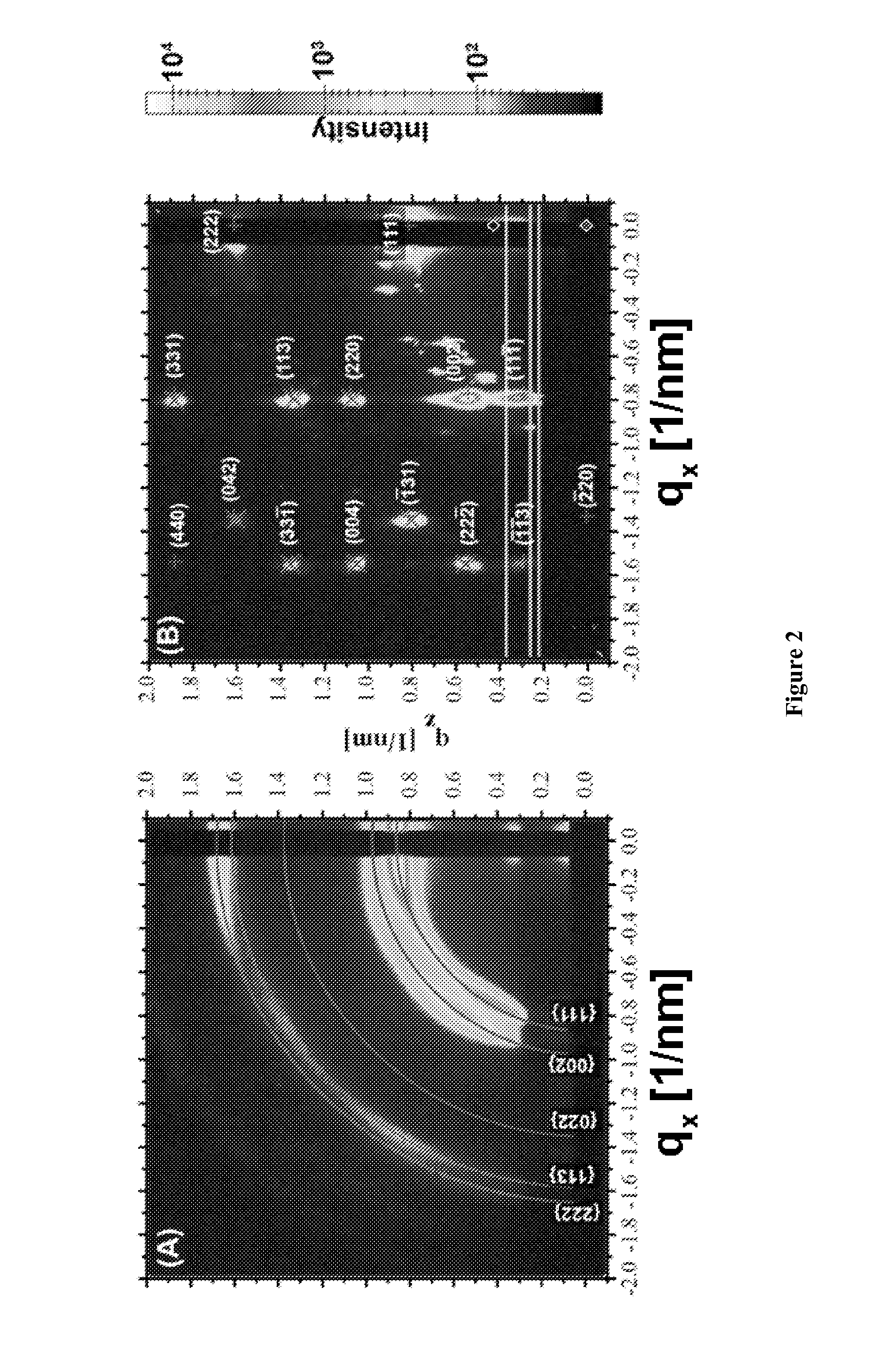

Inorganic Bulk Multijunction Materials and Processes for Preparing the Same

InactiveUS20110220874A1Material nanotechnologyFinal product manufactureAlloySemiconductor nanocrystals

A nanostructured composite material comprising semiconductor nanocrystals in a crystalline semiconductor matrix. Suitable nanocrystals include silicon, germanium, and silicon-germanium alloys, and lead salts such as PbS, PbSe, and PbTe. Suitable crystalline semiconductor matrix materials include Si and silicon-germanium alloys. A process for making the nanostructured composite materials. Devices comprising nanostructured composite materials.

Owner:CORNELL UNIVERSITY

Semiconductor thin film forming method, production methods for semiconductor device and electrooptical device, devices used for these methods, and semiconductor device and electrooptical device

InactiveUS20030013280A1Promote crystallizationTransistorPolycrystalline material growthSingle crystalCrystallinity

An object of the present invention is to provide a method for easily forming a polycrystalline semiconductor thin-film, such as polycrystalline silicon having high crystallinity and high quality, or a single crystalline semiconductor thin-film at inexpensive cost, the crystalline semiconductor thin-film having a large area, and to provide an apparatus for processing the method described above. In forming a polycrystalline (or single crystalline) semiconductor thin-film (7), such as a polycrystalline silicon thin-film, having high crystallinity and a large grain size on a substrate (1), or in forming a semiconductor device having the polycrystalline (or single crystalline) semiconductor thin-film (7) on the substrate (1), a method comprises forming a low-crystallization semiconductor thin-film (7A) on the substrate (1), and subsequently heating and cooling this low-crystallization semiconductor thin-film (7A) to a fusion, a semi-fusion, or a non-fusion state by flash lamp annealing to facilitate the crystallization of the low-crystallization semiconductor thin-film, whereby a polycrystalline (single crystalline) semiconductor thin-film (7) is obtained. A method for forming the semiconductor device and an apparatus for processing the methods are also disclosed.

Owner:SONY CORP

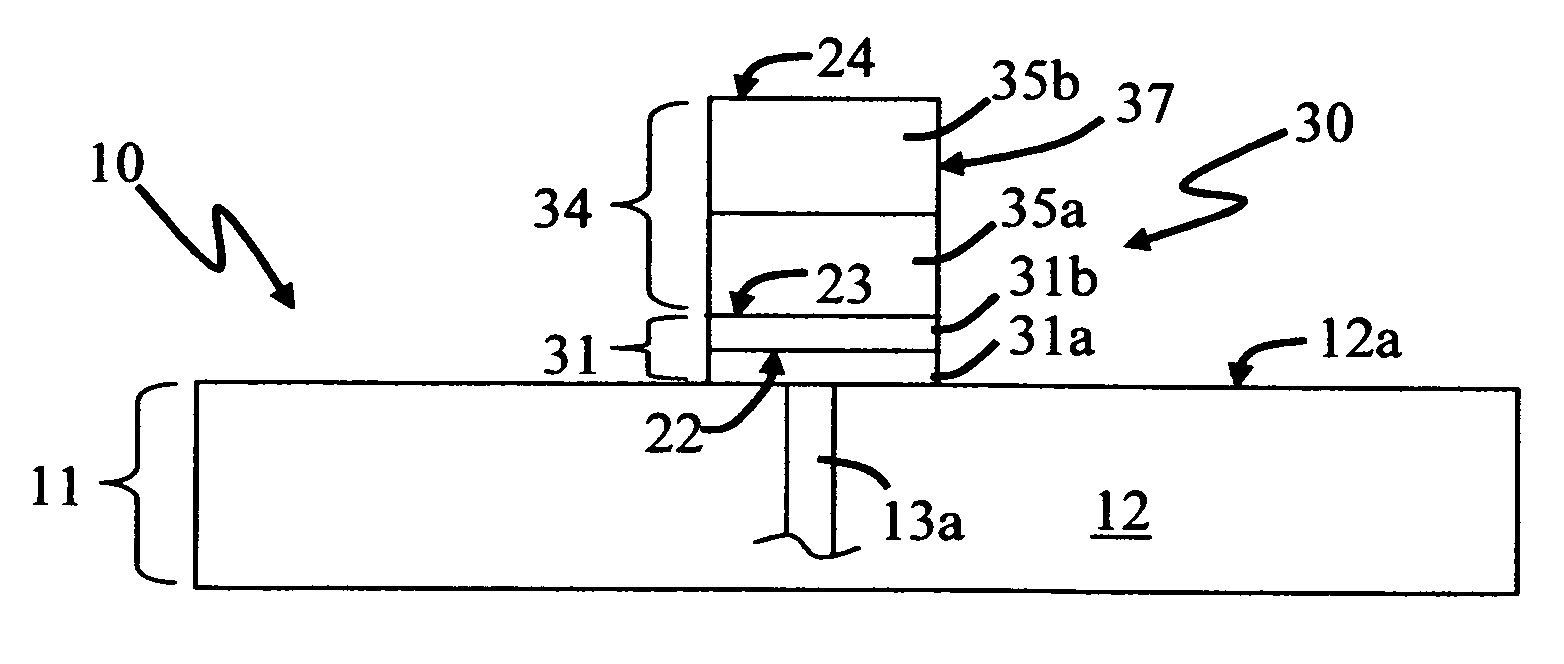

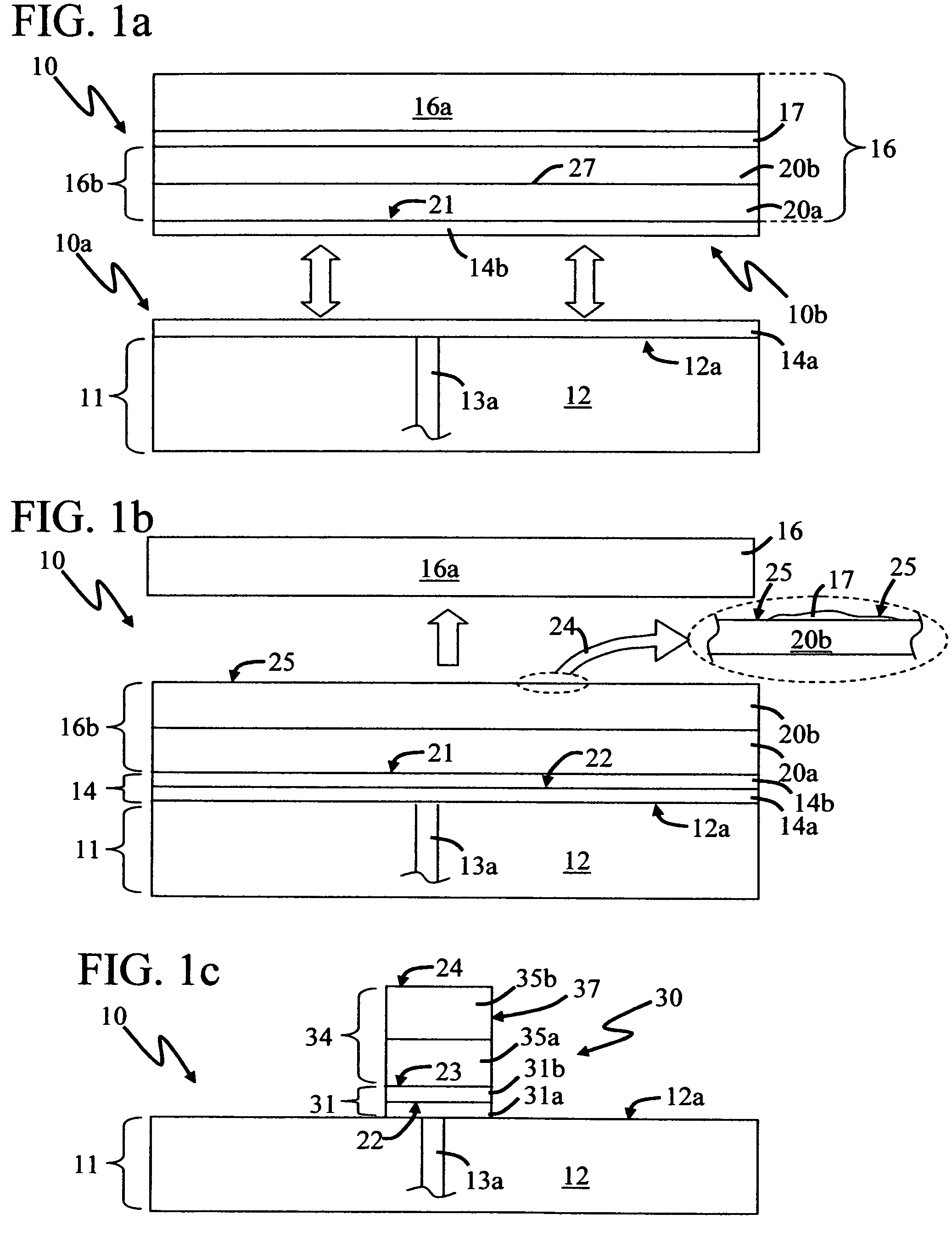

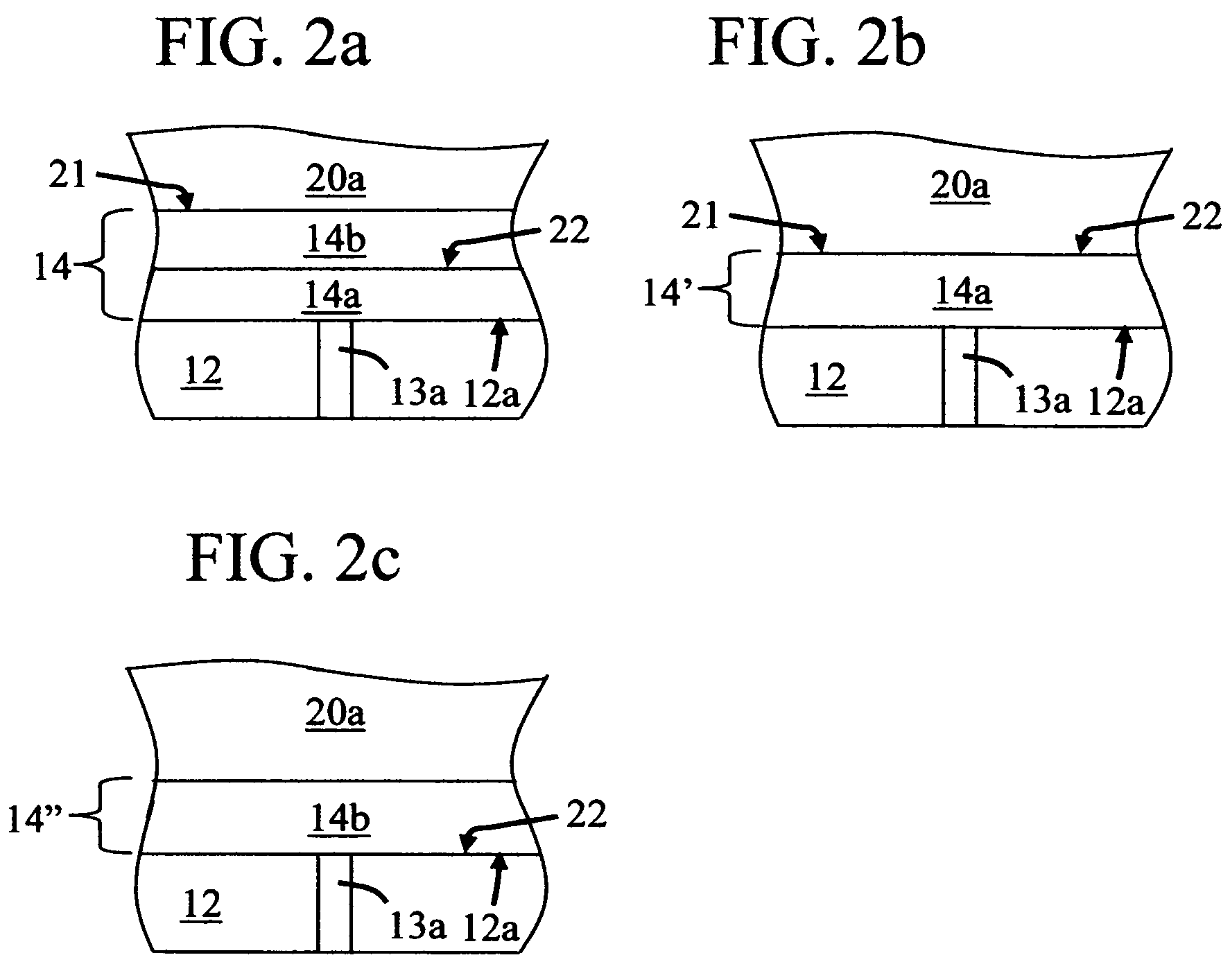

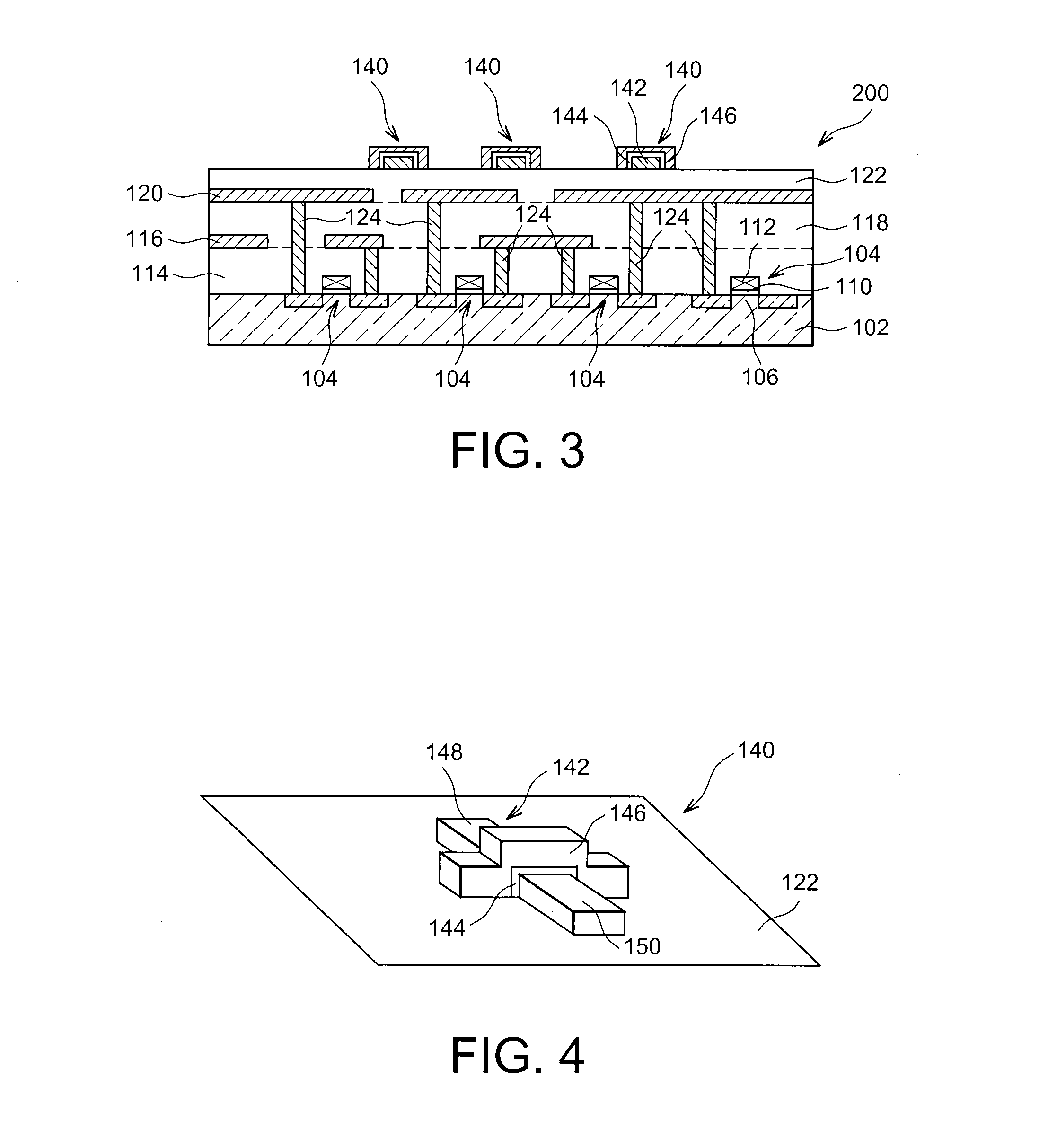

Three-dimensional integrated circuit structure

InactiveUS20070077694A1Solid-state devicesSemiconductor/solid-state device manufacturingSemiconductor structureDevice material

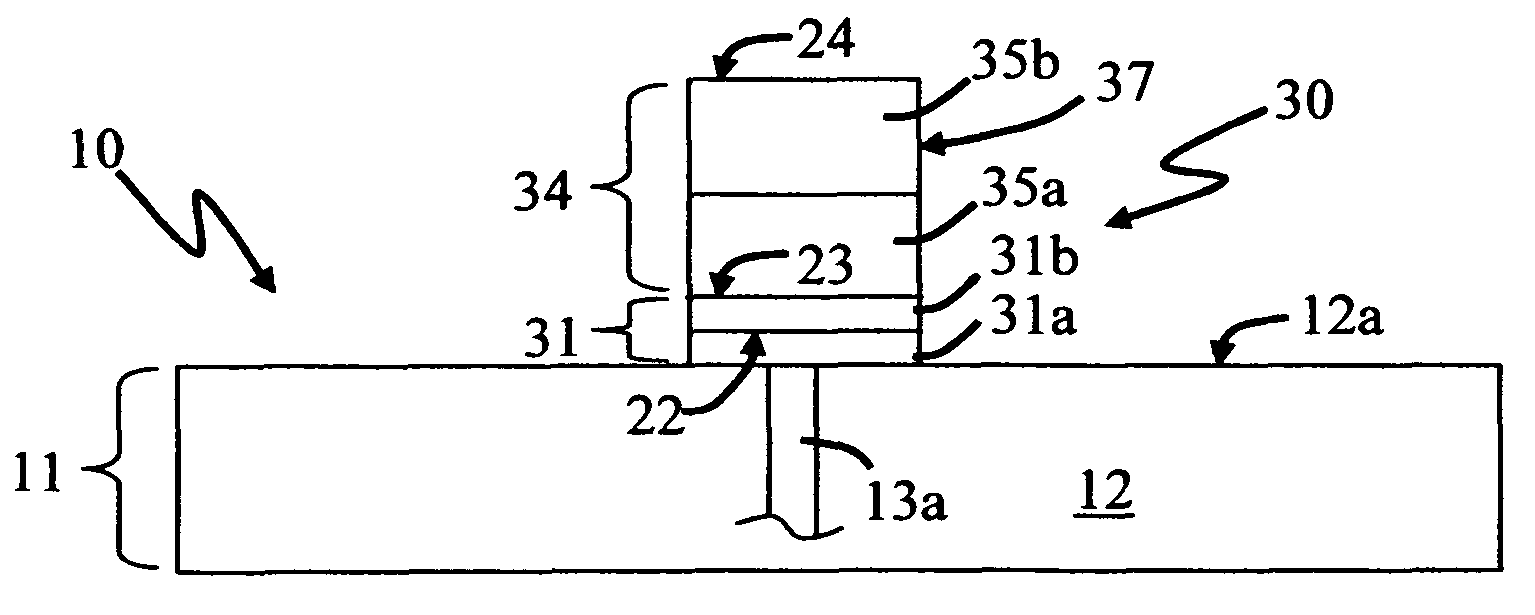

A semiconductor structure includes an interconnect region and a semiconductor stack bonded to the interconnect region through a bonding region. The stack includes at least two semiconductor layers having different electrical properties. The stack also includes single crystalline semiconductor material. The stack can be processed to form a mesa structure and the mesa structure can be processed to from a vertically oriented semiconductor device.

Owner:BESANG

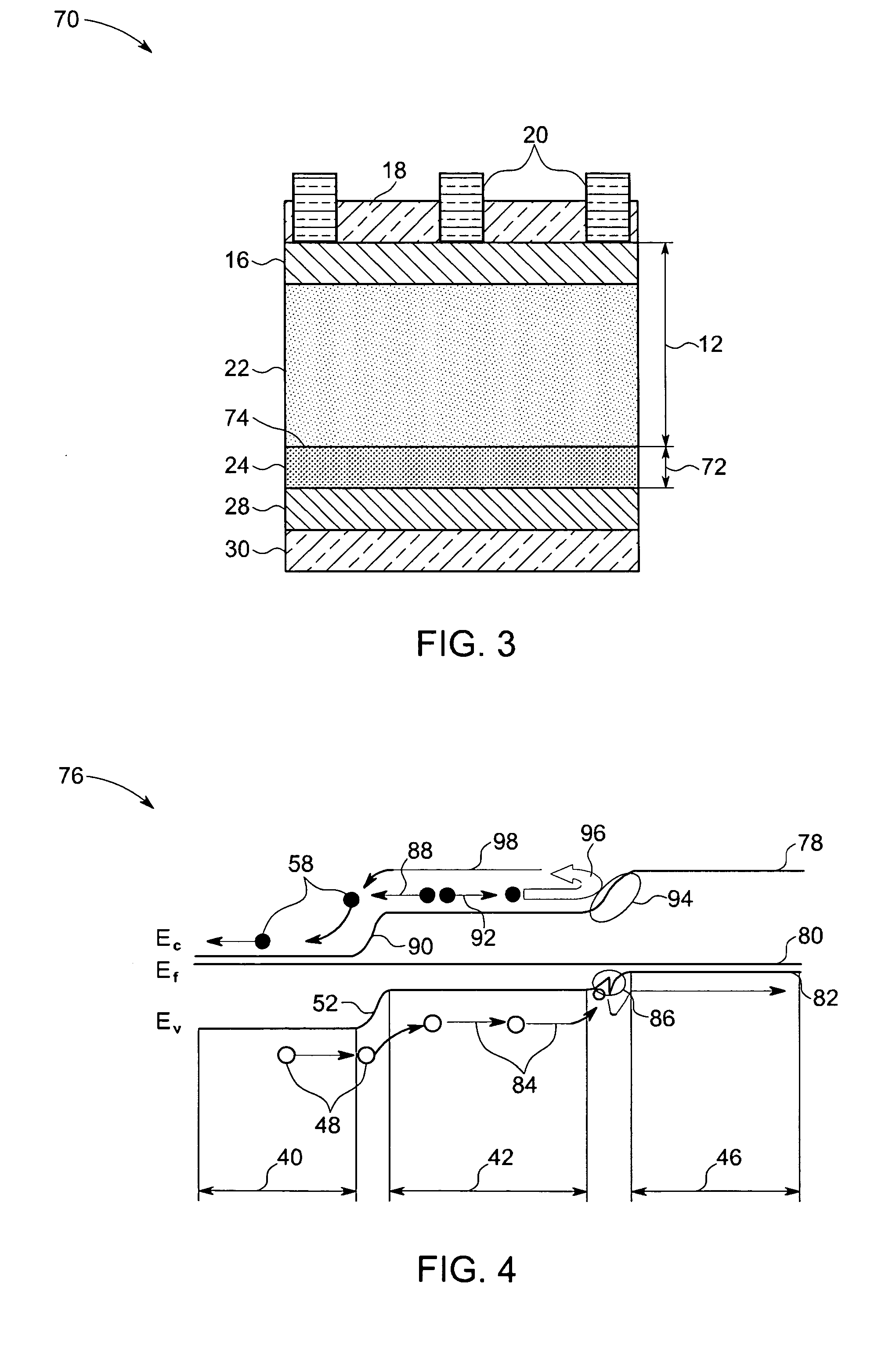

Surface passivated photovoltaic devices

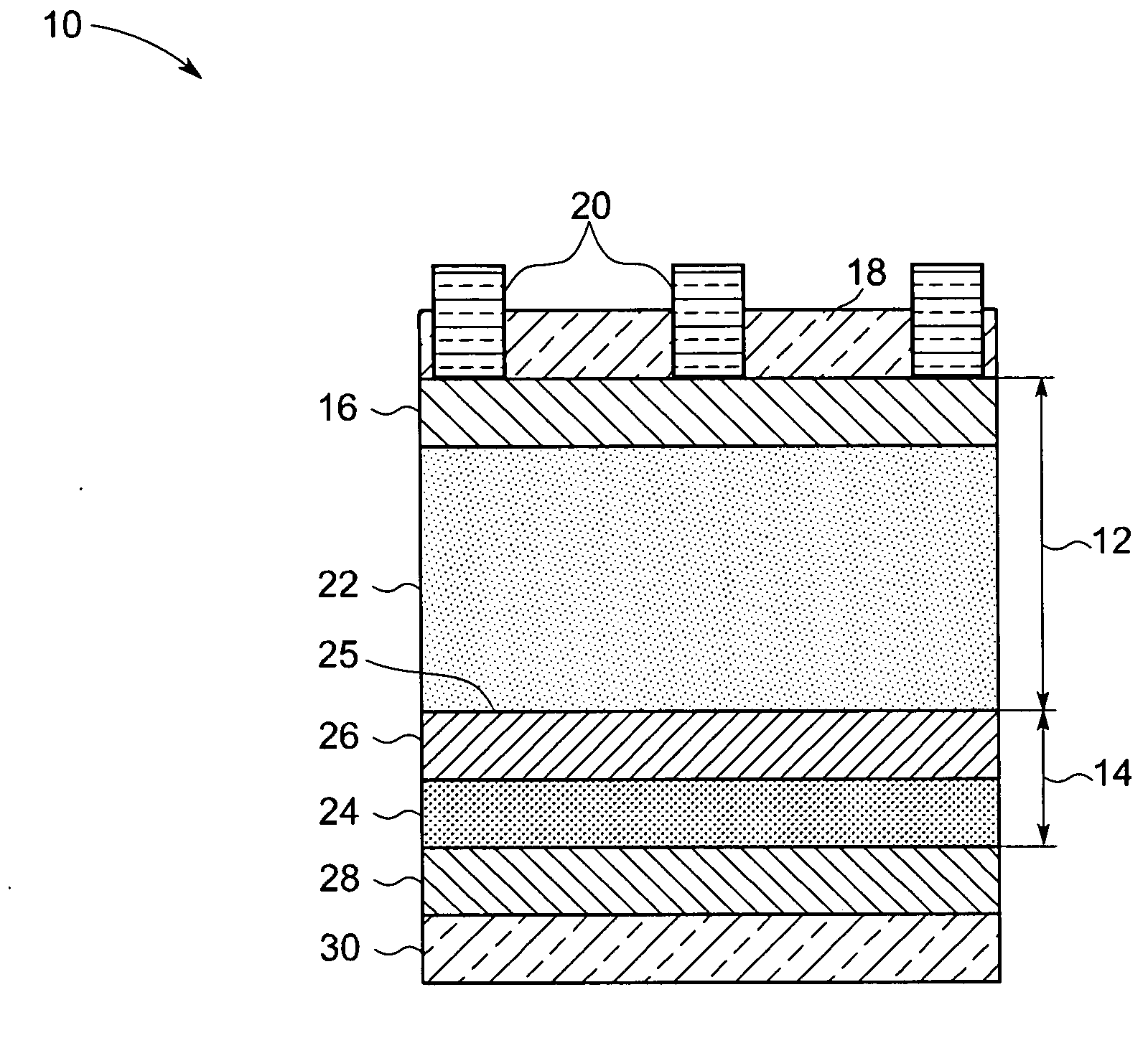

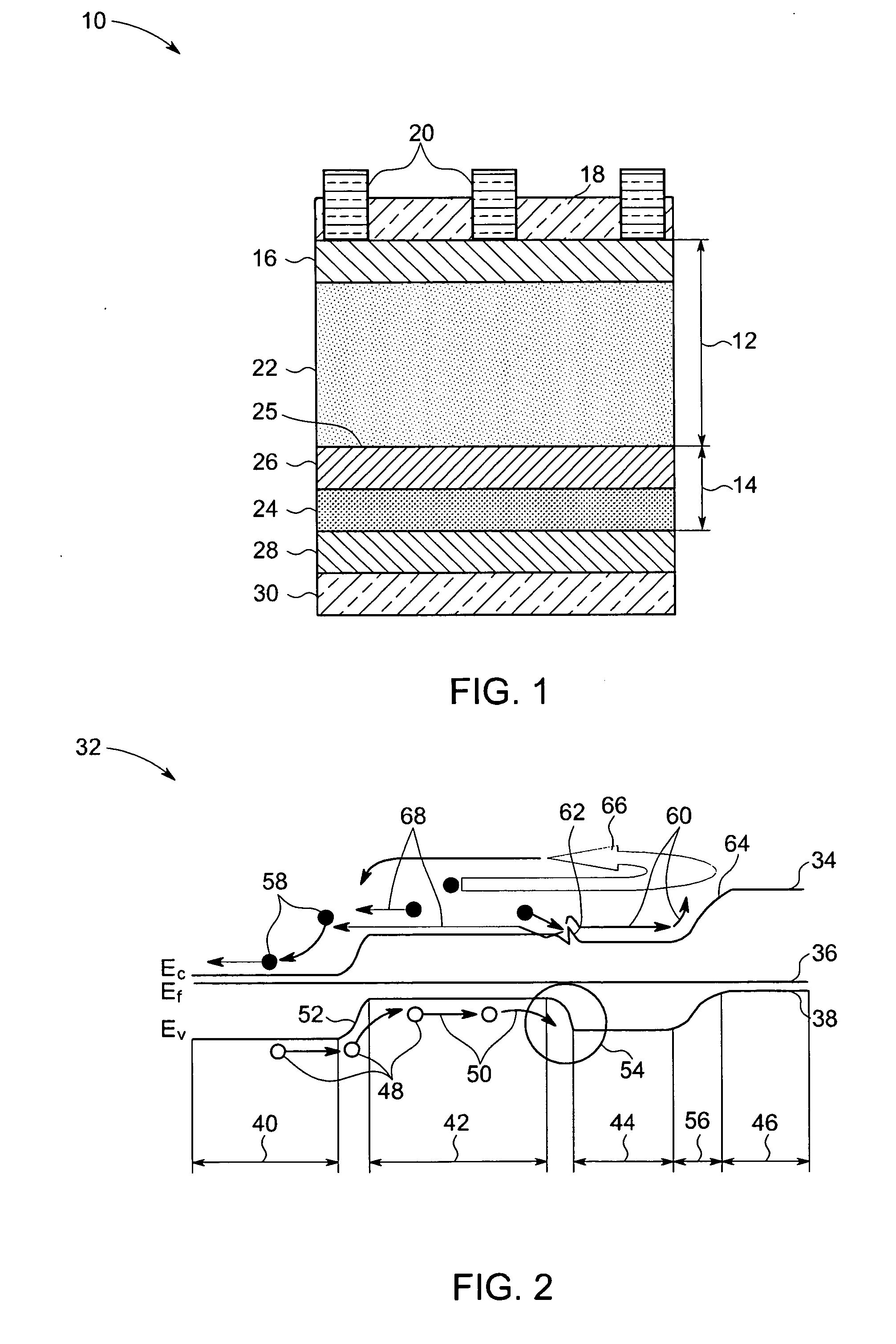

InactiveUS20060255340A1Raise the level of dopingReduce potential barrierSolid-state devicesPhotovoltaic energy generationSemiconductor materialsBack surface field

A photovoltaic device comprising a photovoltaic cell is provided. The photovoltaic cell includes an emitter layer comprising a crystalline semiconductor material and a lightly doped crystalline substrate disposed adjacent the emitter layer. The lightly doped crystalline substrate and the emitter layer are oppositely doped. Further, the photovoltaic device includes a back surface passivated structure coupled to the photovoltaic cell. The structure includes a highly doped back surface field layer disposed adjacent the lightly doped crystalline substrate. The highly doped back surface field layer includes an amorphous or a microcrystalline semiconductor material, wherein the highly doped back surface field layer and the lightly doped crystalline substrate are similarly doped, and wherein a doping level of the highly doped back surface field layer is higher than a doping level of the lightly doped crystalline substrate. Additionally, the structure may also include an intrinsic back surface passivated layer disposed adjacent the lightly doped crystalline substrate, where the intrinsic back surface passivated layer includes an amorphous or a microcrystalline semiconductor material.

Owner:GENERAL ELECTRIC CO

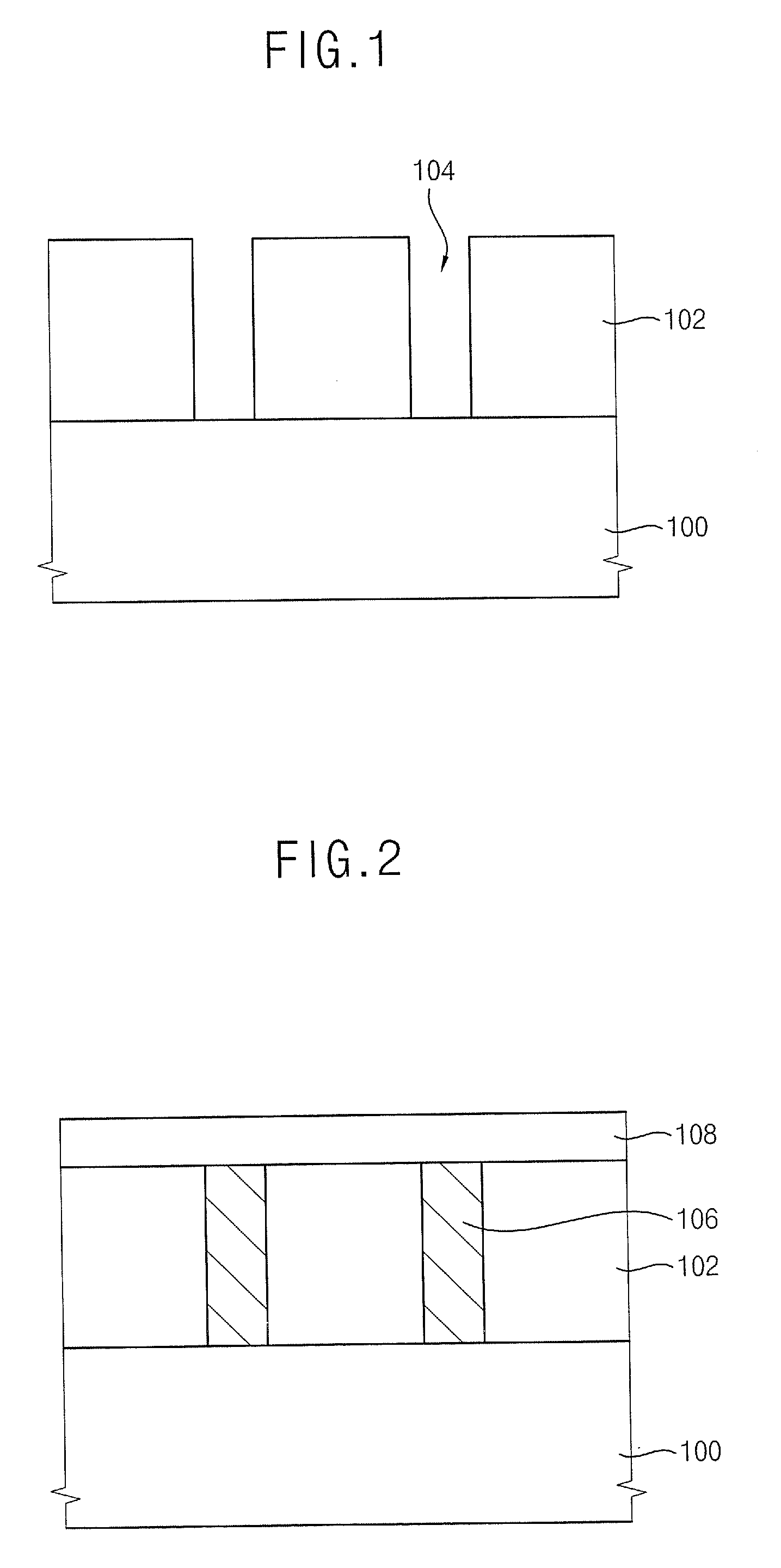

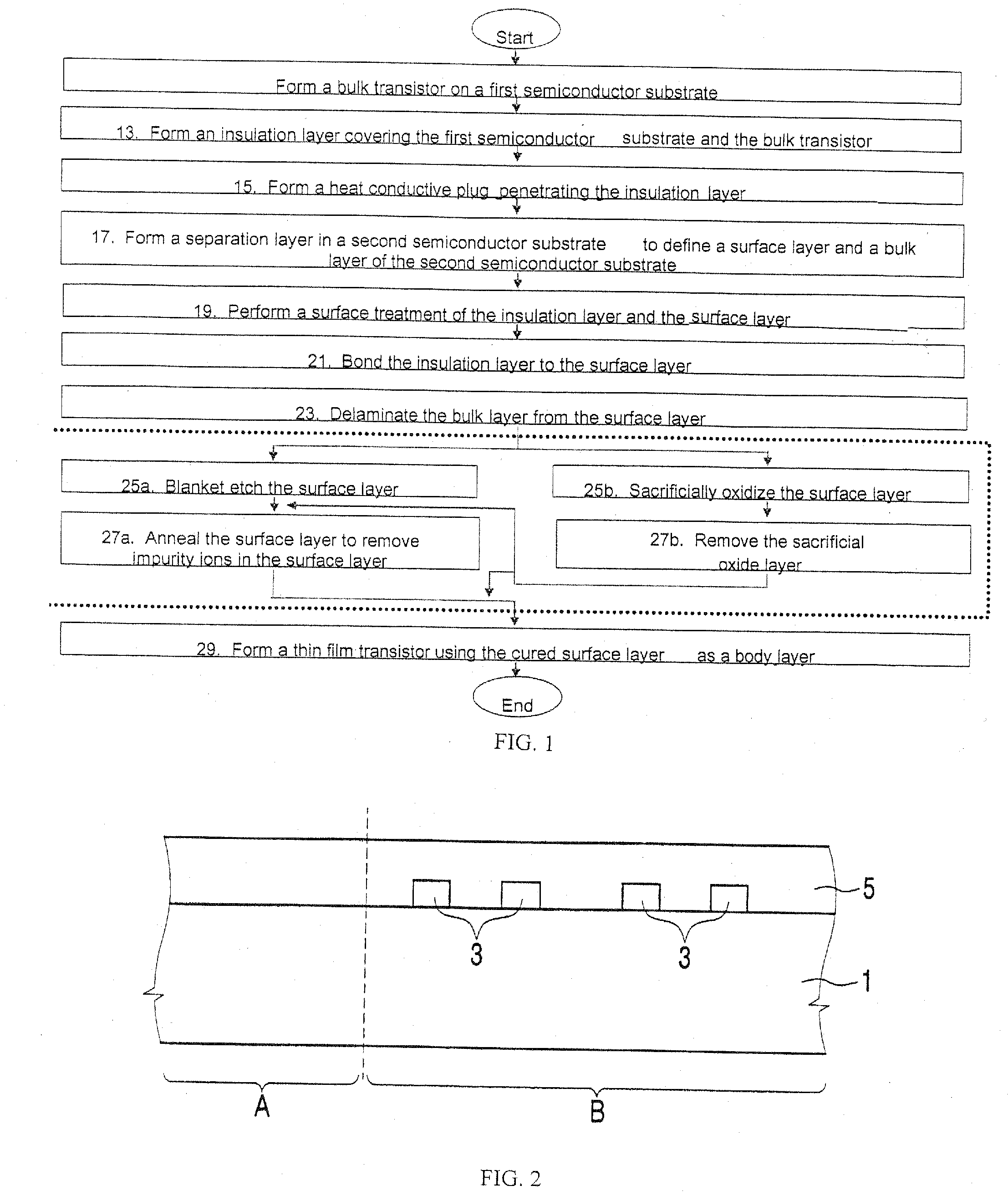

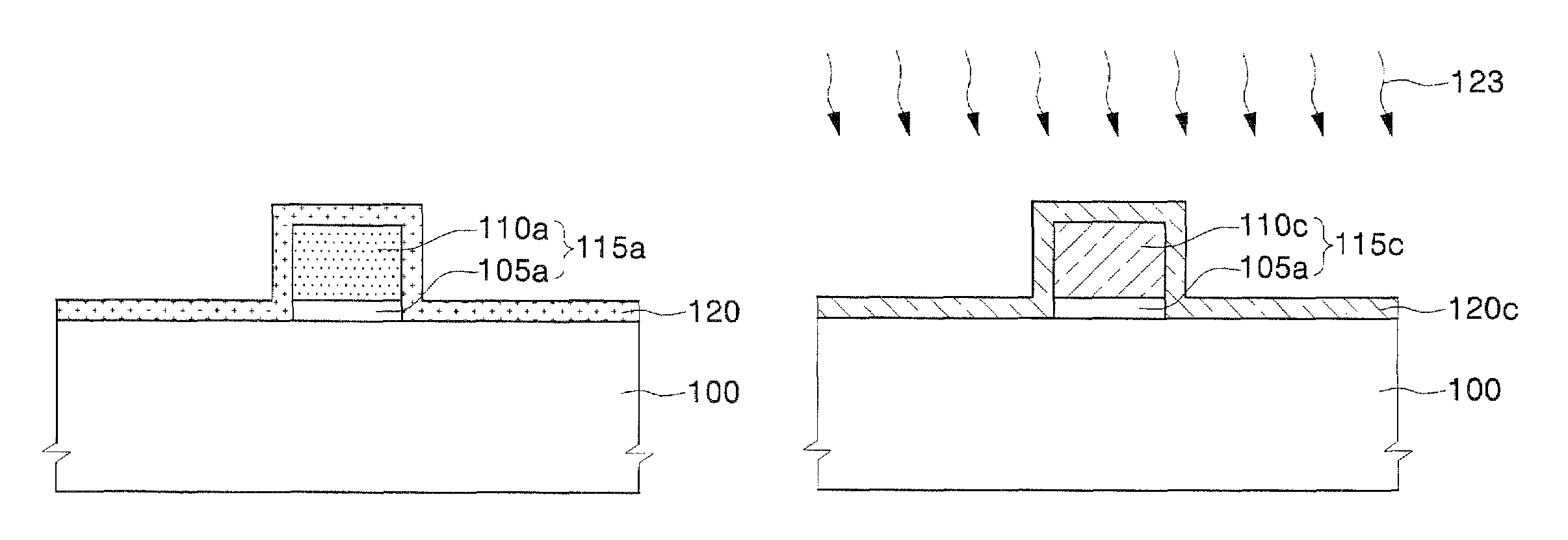

Methods of fabricating semiconductor devices including channel layers having improved defect density and surface roughness characteristics

ActiveUS20080160726A1Improved surface roughness characteristicUniform thicknessSemiconductor/solid-state device detailsSemiconductor/solid-state device manufacturingSurface roughnessSingle crystal

A method of fabricating a semiconductor device including a channel layer includes forming a single crystalline semiconductor layer on a semiconductor substrate. The single crystalline semiconductor layer includes a protrusion extending from a surface thereof. A first polishing process is performed on the single crystalline semiconductor layer to remove a portion of the protrusion such that the single crystalline semiconductor layer includes a remaining portion of the protrusion. A second polishing process different from the first polishing process is performed to remove the remaining portion of the protrusion and define a substantially planar single crystalline semiconductor layer having a substantially uniform thickness. A sacrificial layer may be formed on the single crystalline semiconductor layer and used as a polish stop for the first polishing process to define a sacrificial layer pattern, which may be removed prior to the second polishing process. Related methods of fabricating stacked semiconductor memory devices are also discussed.

Owner:SAMSUNG ELECTRONICS CO LTD

Three-dimensional integrated circuit structure

InactiveUS7888764B2Solid-state devicesSemiconductor/solid-state device manufacturingSemiconductor structureSemiconductor package

Owner:BESANG

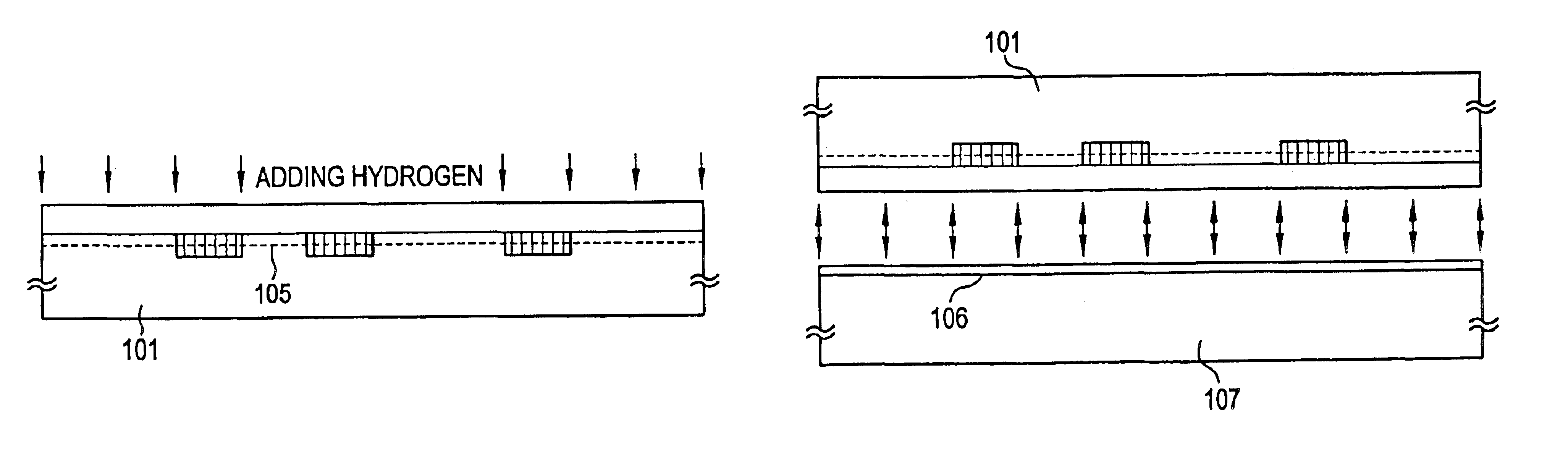

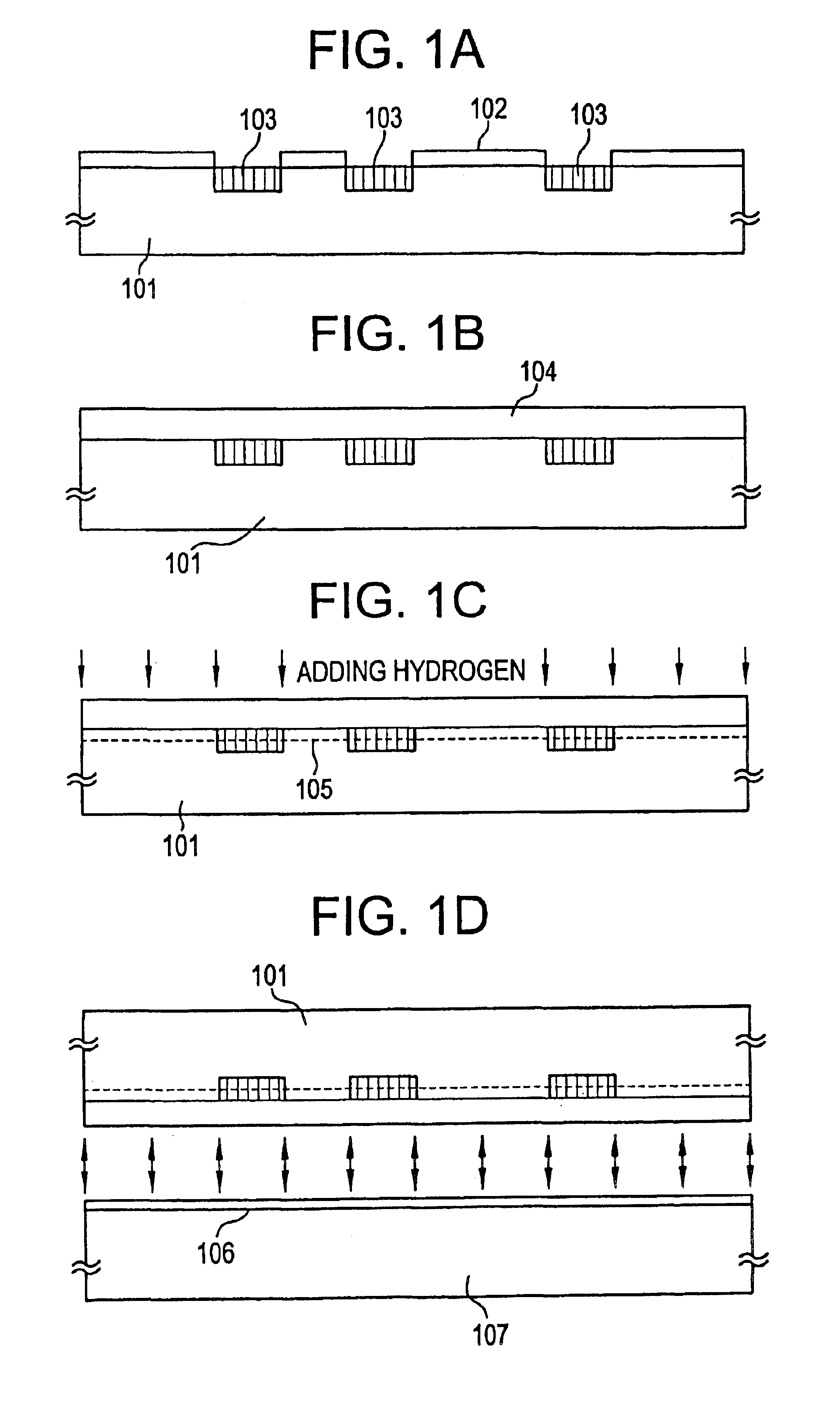

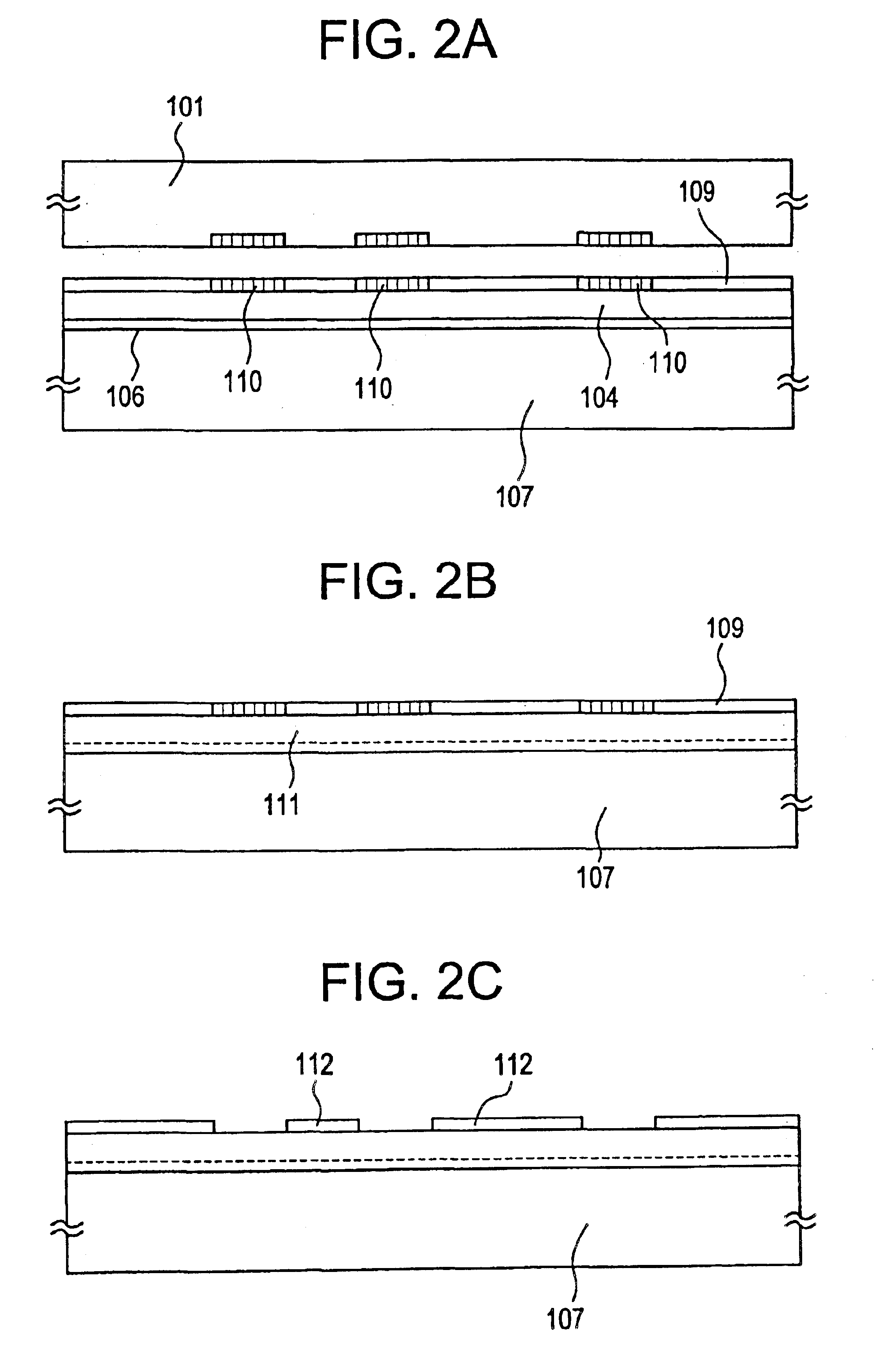

Process for production of SOI substrate and process for production of semiconductor device

A process for producing an adhered SOI substrate without causing cracking and peeling of a single-crystal silicon thin film. The process consists of selectively forming a porous silicon layer in a single-crystal semiconductor substrate, adding hydrogen into the single-crystal semiconductor substrate to form a hydrogen-added layer, adhering the single-crystal semiconductor substrate to a supporting substrate, separating the single-crystal semiconductor substrate at the hydrogen-added layer by thermal annealing, performing thermal annealing again to stabilize the adhering interface, and selectively removing the porous silicon layer to give single-crystal silicon layer divided into islands.

Owner:SEMICON ENERGY LAB CO LTD

Integrated circuit having a junctionless depletion-mode fet device

InactiveUS20130203248A1Elimination of handleEasy to operateSolid-state devicesSemiconductor/solid-state device manufacturingDopantInterconnection

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

Methods of manufacturing a three-dimensional semiconductor device and semiconductor devices fabricated thereby

InactiveUS20070158831A1Prevent degradationSemiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

A method of fabricating a three-dimensional semiconductor device is provided along with a three-dimensional semiconductor device fabricated thereby. The method includes forming a heat conductive plug to channel heat away from devices on a substrate, while high temperature processes are performed on a stacked semiconductor layer. The ability to use high temperature processes on the stacked semiconductor layer without adversely effecting devices on the substrate allows the formation of a high quality single-crystalline stacked semiconductor layer. The high quality single-crystalline semiconductor layer can then be used to fabricate improved thin film transistors.

Owner:SAMSUNG ELECTRONICS CO LTD

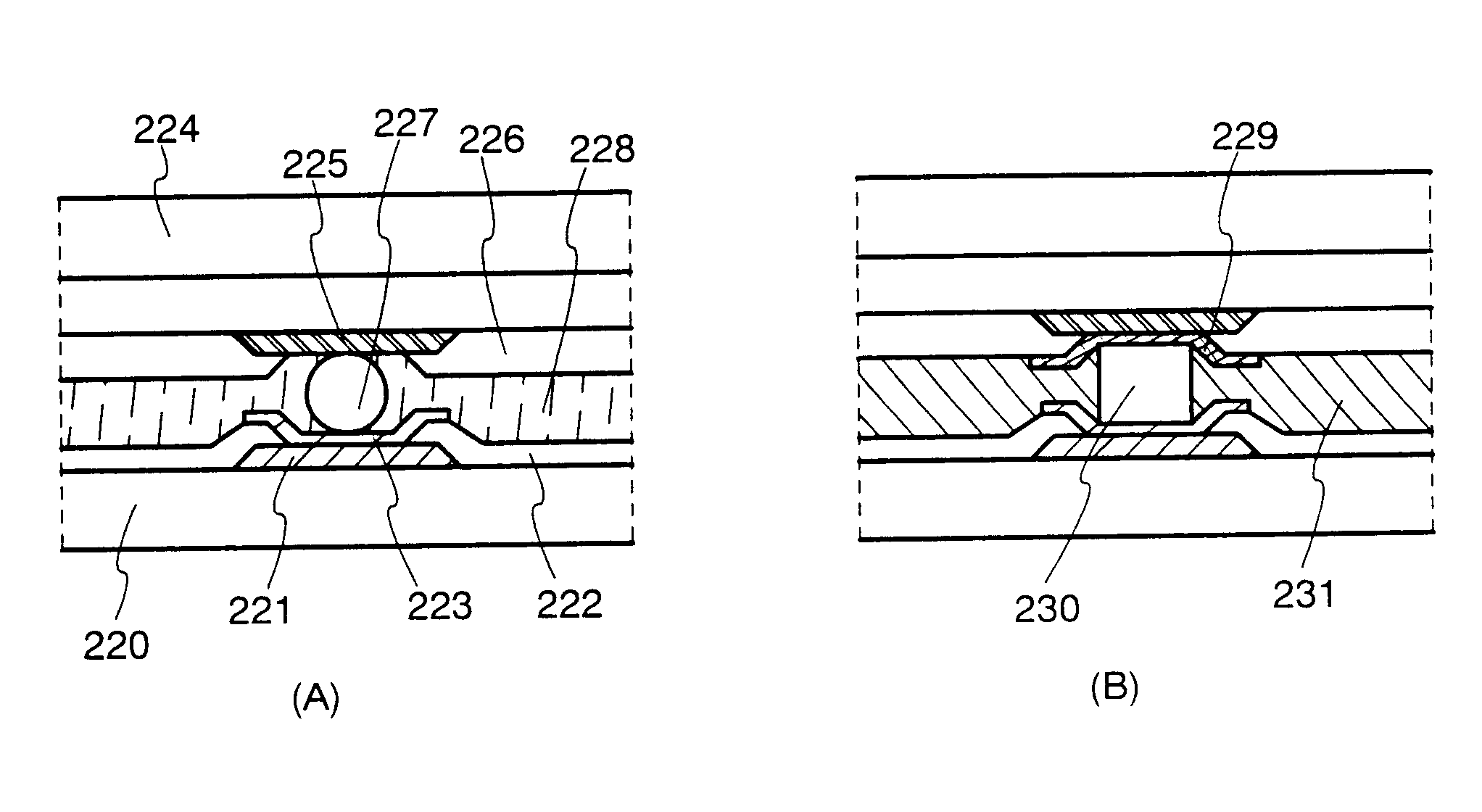

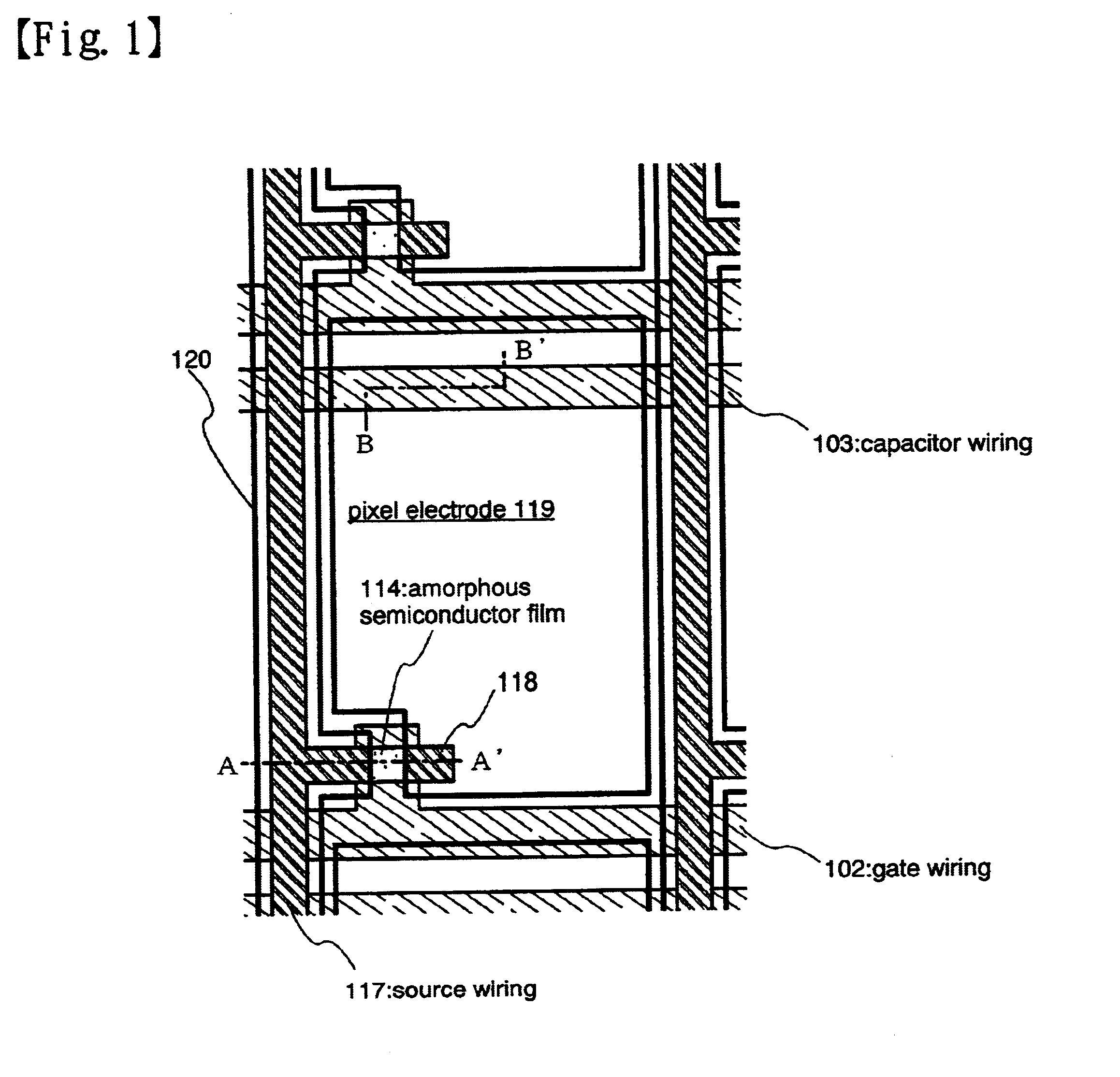

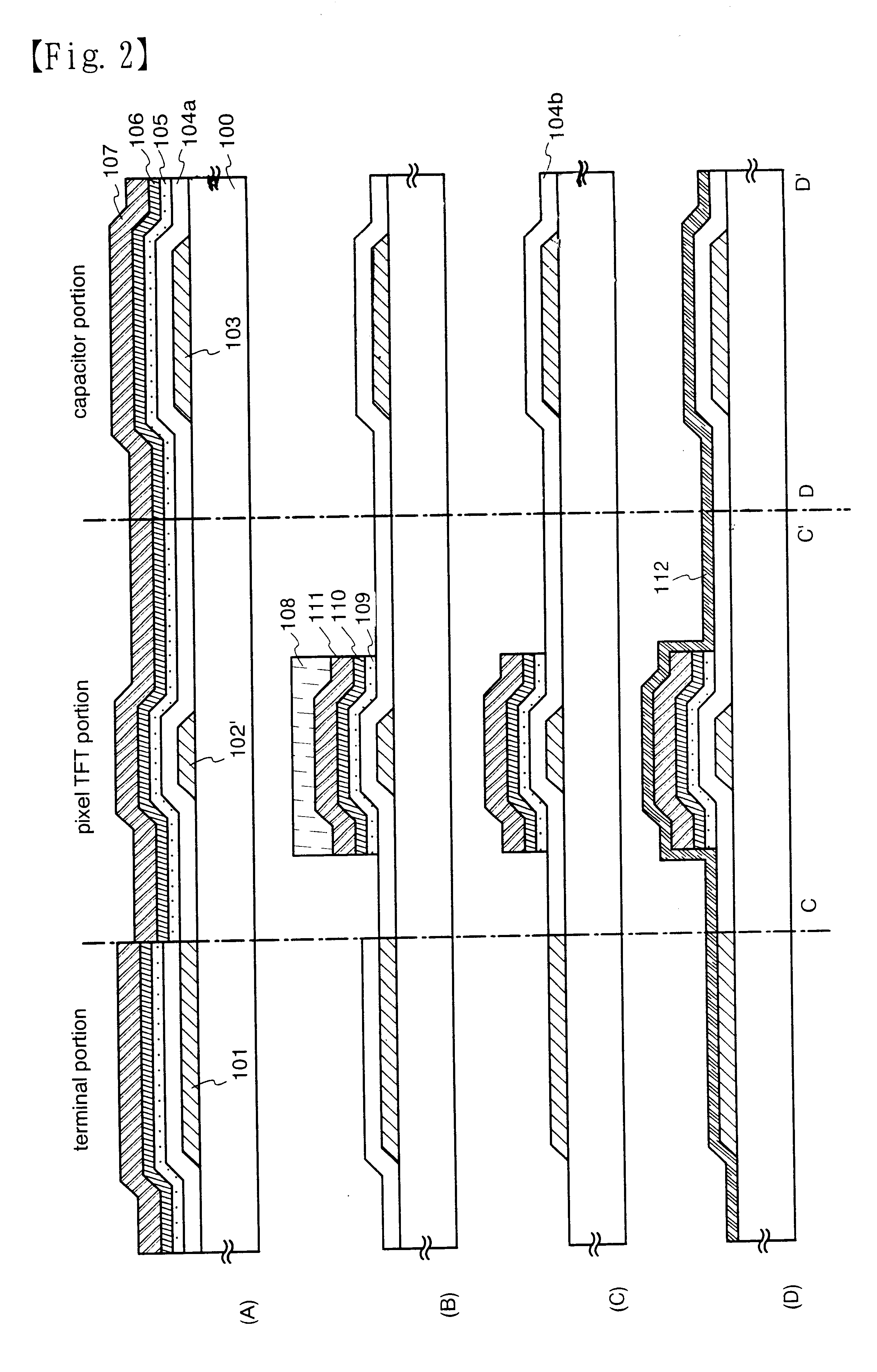

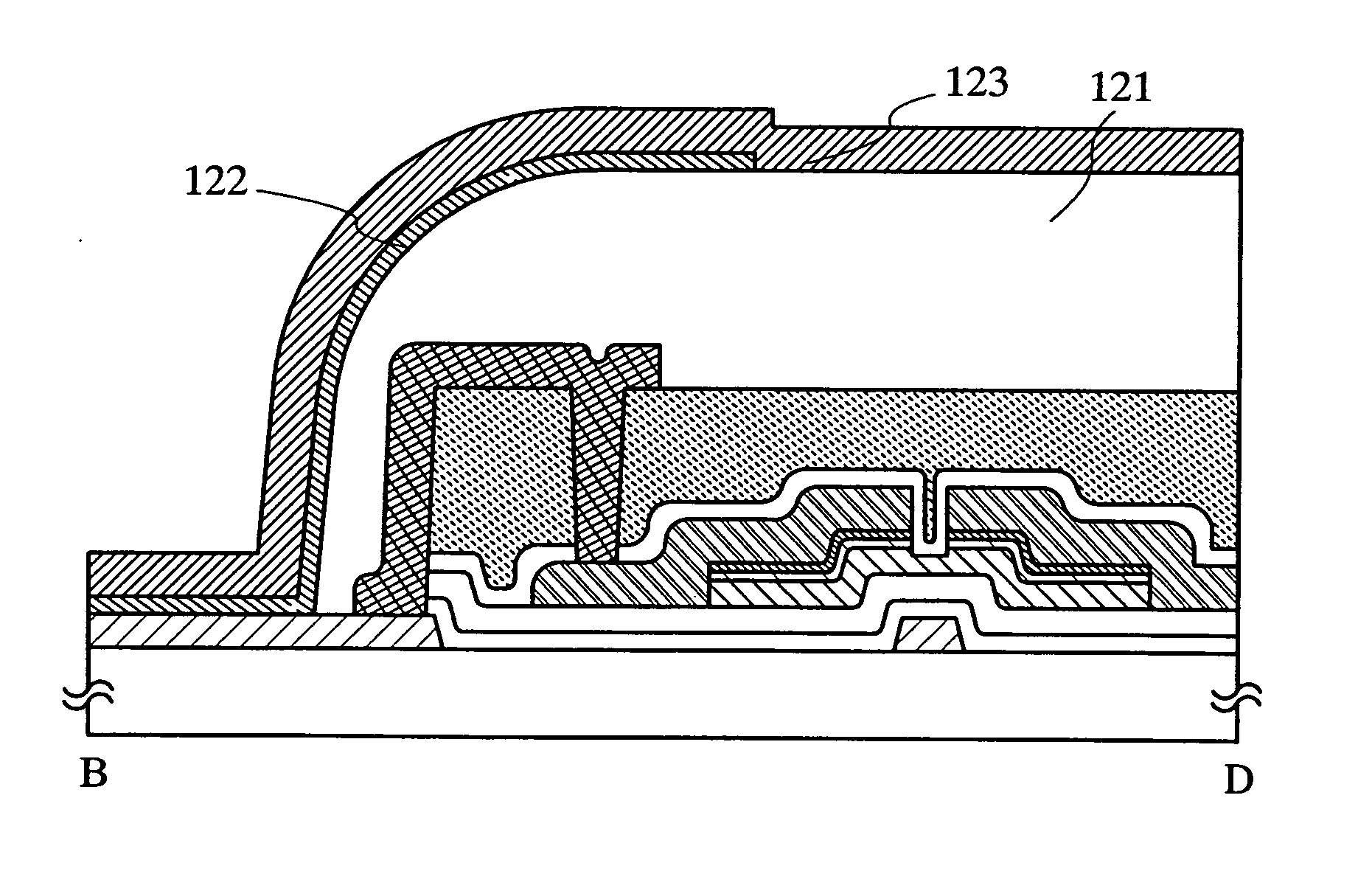

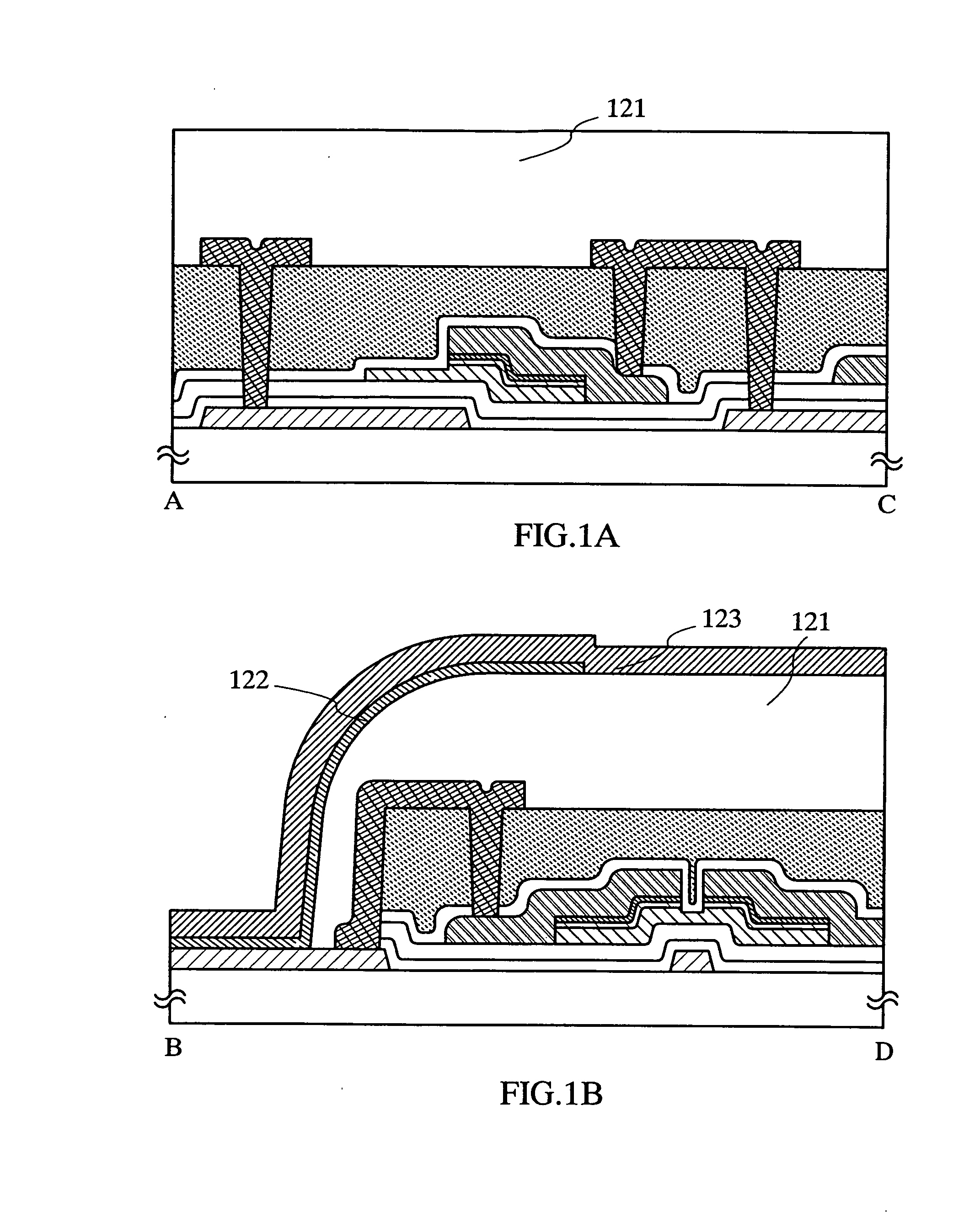

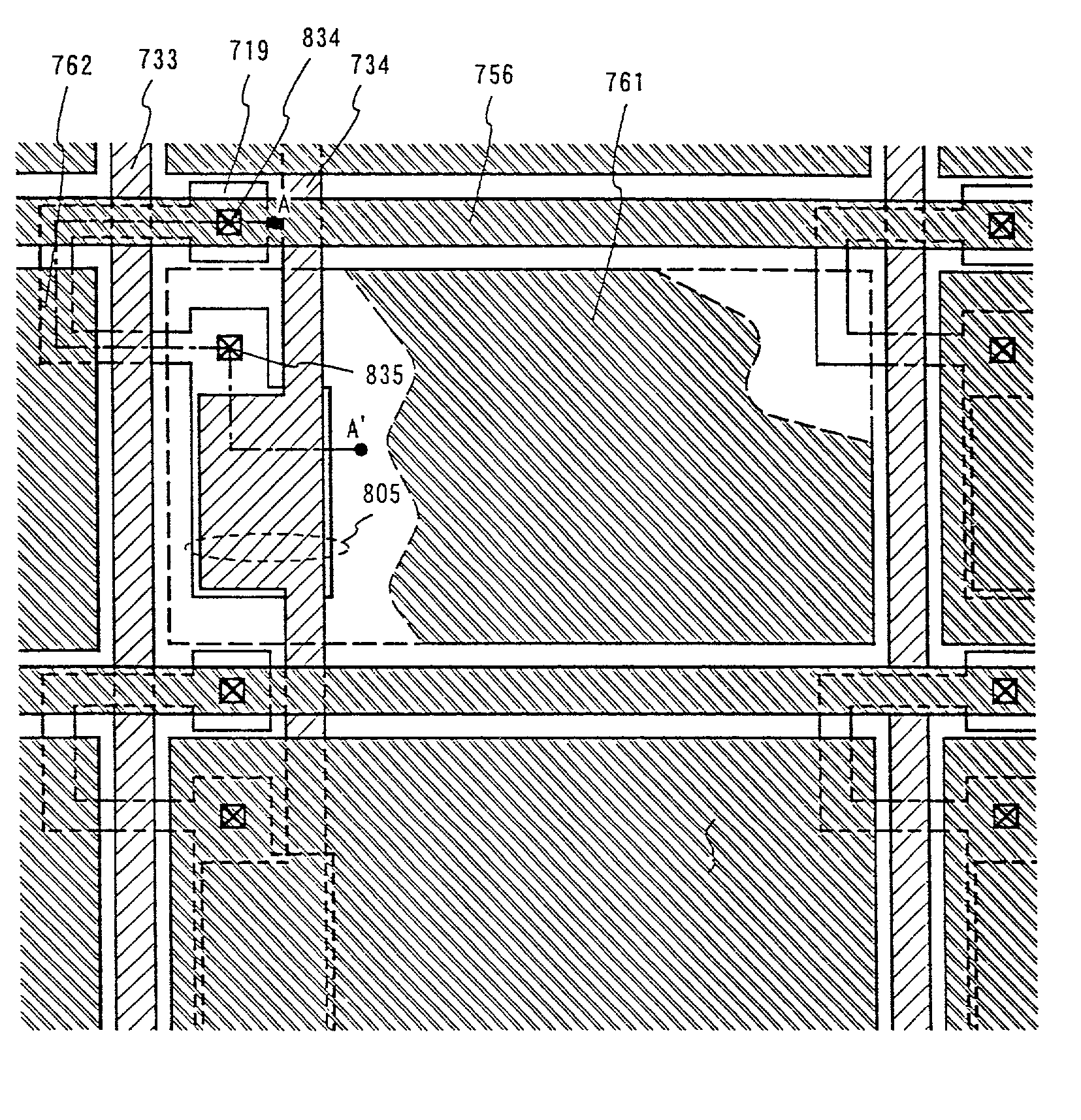

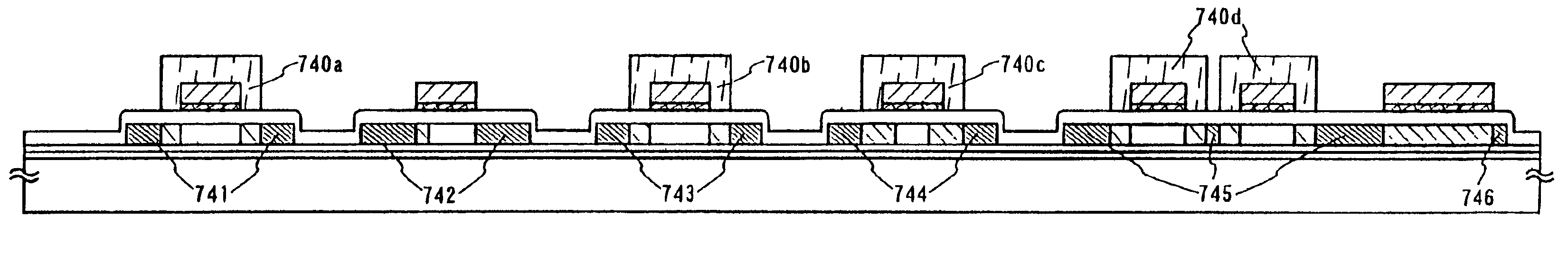

Semiconductor device having stick drivers and a method of manufacturing the same

A pixel TFT formed in a pixel region is formed on a first substrate by a channel etch type reverse stagger type TFT, and patterning of a source region and a drain region, and patterning of a pixel electrode are performed by the same photomask. A driver circuit formed by using TFTs having a crystalline semiconductor layer, and an input-output terminal dependent on the driver circuit, are taken as one unit. A plurality of units are formed on a third substrate, and afterward the third substrate is partitioned into individual units, and the obtained stick drivers are mounted on the first substrate.

Owner:SEMICON ENERGY LAB CO LTD

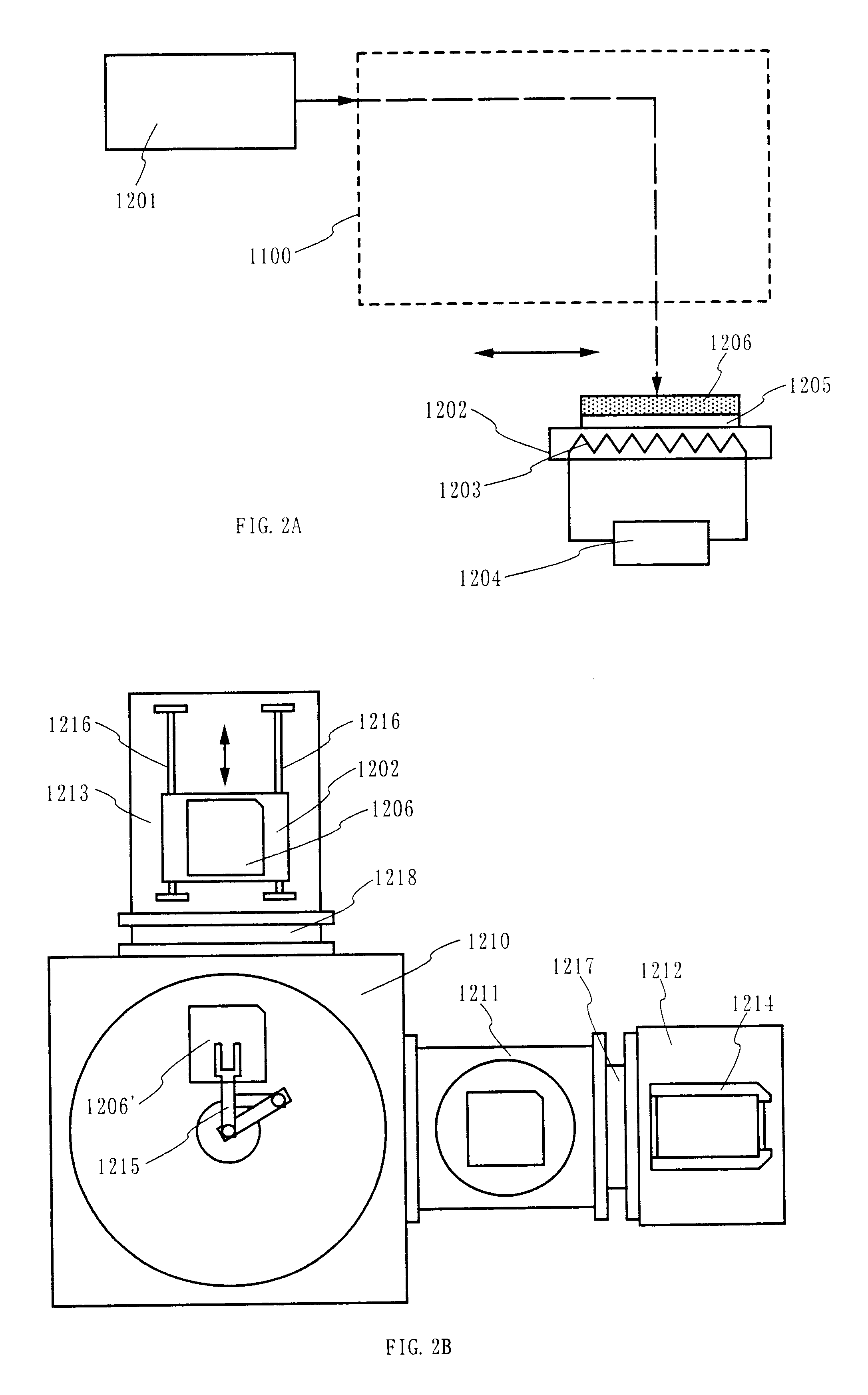

Method for forming thin semiconductor film, method for fabricating semiconductor device, system for executing these methods and electrooptic device

InactiveUS20030148565A1Promote crystallizationEasily realizedTransistorSolid-state devicesMolten stateUltraviolet

The present invention provides a method capable of easily forming a polycrystalline or monocrystalline semiconductor thin film of polycrystalline silicon with a high degree of crystallization and high quality at low cost, and an apparatus for carrying out the method. In a method of forming a polycrystalline (or monocrystalline) semiconductor thin film, a method of manufacturing a semiconductor device and an apparatus for carrying out these methods, in order to form a large-grain polycrystalline (or monocrystalline) semiconductor thin film (7) such as a polycrystalline silicon film with a high degree of crystallization on a substrate (1) or manufacturing a semiconductor device having the polycrystalline (or monocrystalline) semiconductor thin film (7), a low-crystalline semiconductor thin film (7A) is formed on the substrate (1), and then heated in a molten, semi-molten or non-molten state by laser annealing with ultraviolet rays (UV) or / and deep ultraviolet rays (DUV) and cooled to promote crystallization of the low-crystalline semiconductor thin film (7A), obtaining the polycrystalline (or monocrystalline) semiconductor thin film (7).

Owner:SONY CORP

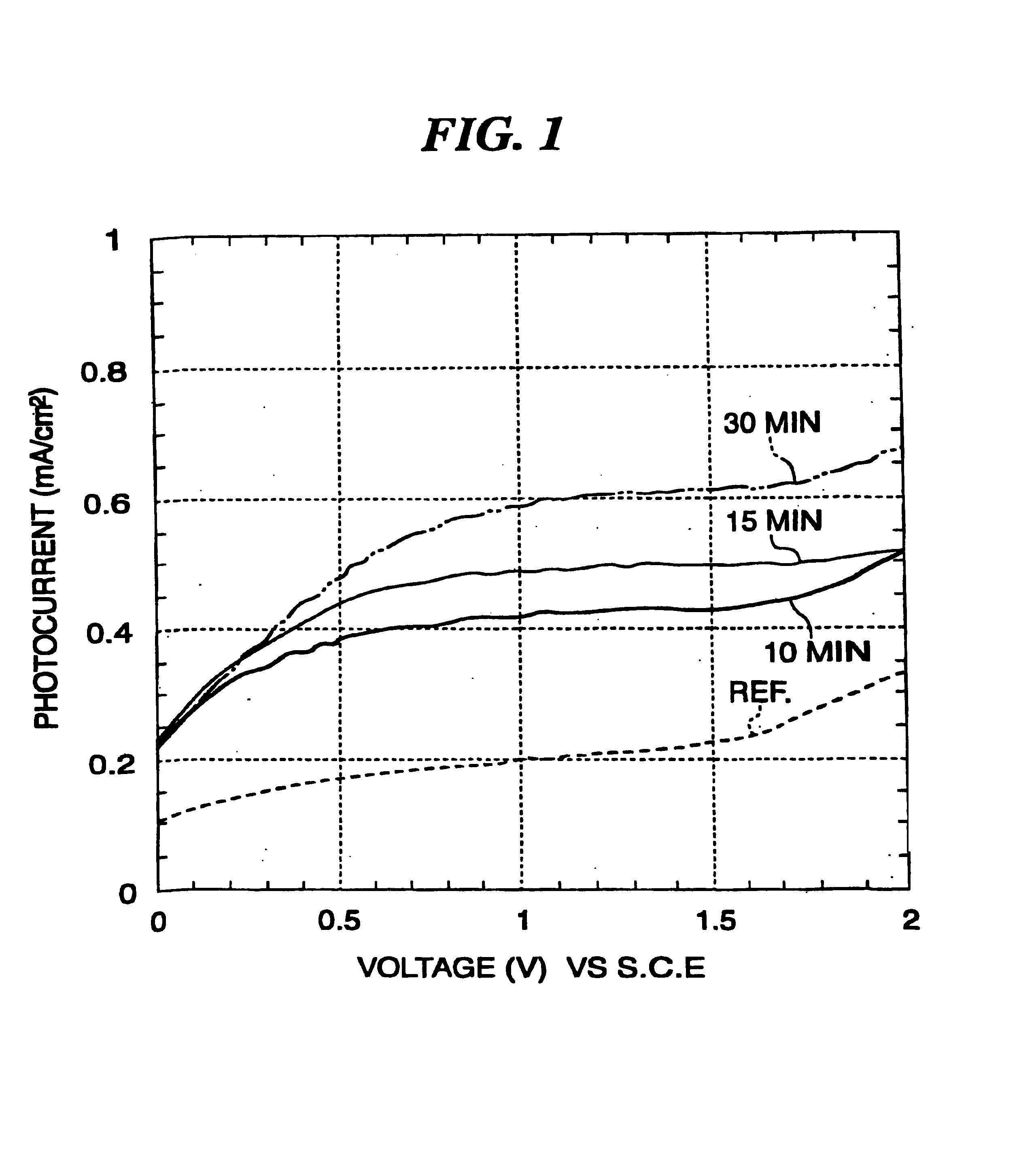

Method for forming crystalline semiconductor layers, a method for fabricating thin film transistors, and method for fabricating solar cells and active matrix liquid crystal devices

InactiveUS6066516AGreat fabricationImprove mobilityTransistorFinal product manufactureActive matrixSolar cell

PCT No. PCT / JP96 / 01775 Sec. 371 Date Jan. 31, 1997 Sec. 102(e) Date Jan. 31, 1997 PCT Filed Jun. 26, 1996 PCT Pub. No. WO97 / 01863 PCT Pub. Date Jan. 16, 1997A crystalline semiconductor layer can be formed by forming a semiconductor film on an inexpensive conventional substrate. Next, perform a first annealing process in which nearly the entire surface of the semiconductor film is exposed to laser irradiation or other forms of irradiation, and then perform a second annealing process consisting of rapid thermal annealing. This enables the formation of a high quality crystalline semiconductor film with high throughput but without subjecting the substrate to undue thermal stress. When this invention is applied to thin film transistors, good transistors having high performance are easily fabricated. When this invention is applied to solar cells, energy conversion efficiency is increased.

Owner:SEIKO EPSON CORP

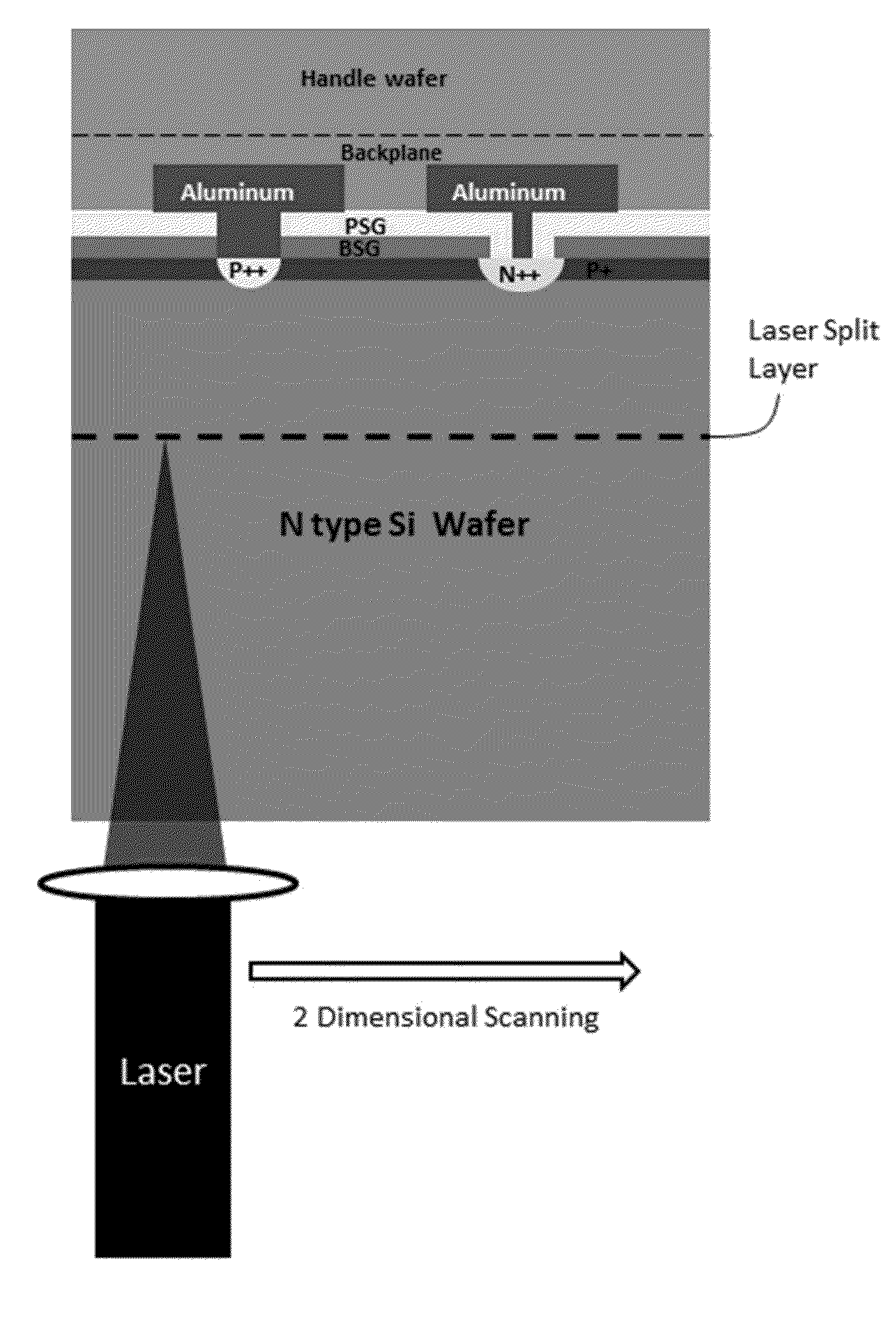

Systems and methods for laser splitting and device layer transfer

ActiveUS20140038392A1Eliminates and reduces disadvantageSolid-state devicesSemiconductor/solid-state device manufacturingIrradiationCrystalline semiconductor

Methods and systems are provided for the split and separation of a layer of desired thickness of crystalline semiconductor material containing optical, photovoltaic, electronic, micro-electro-mechanical system (MEMS), or optoelectronic devices, from a thicker donor wafer using laser irradiation.

Owner:BEAMREACH SOLAR INC

Display device, manufacturing method thereof, and television set

InactiveUS20060027804A1Improve mobilityLow resistivitySolid-state devicesSemiconductor/solid-state device manufacturingContact formationDisplay device

A manufacturing method of a display device having TFTs capable of high-speed operation with few variations of threshold voltage is provided, in which materials are used with high efficiency and a small number of photomasks is required. The display device of the invention comprises a gate electrode layer and a pixel electrode layer formed over an insulating surface, a gate insulating layer formed over the gate electrode layer, a crystalline semiconductor layer formed over the gate insulating layer, a semiconductor layer having one conductivity type formed in contact with the crystalline semiconductor layer, a source electrode layer and a drain electrode layer formed in contact with the semiconductor layer having one conductivity type, an insulating later formed over the source electrode layer, the drain electrode layer, and the pixel electrode layer, a first opening formed in the insulating layer to reach the source electrode layer or the drain electrode layer, a second opening formed in the gate insulating layer and the insulating layer to reach the pixel electrode layer, and a wiring layer formed in the first opening and the second opening to electrically connect the source electrode layer or the drain electrode layer to the pixel electrode layer.

Owner:SEMICON ENERGY LAB CO LTD

Optical systems fabricated by printing-based assembly

ActiveUS20100283069A1Low costImprove performanceFinal product manufactureNanoinformaticsLight sensingPliability

The present invention provides optical devices and systems fabricated, at least in part, via printing-based assembly and integration of device components. In specific embodiments the present invention provides light emitting systems, light collecting systems, light sensing systems and photovoltaic systems comprising printable semiconductor elements, including large area, high performance macroelectronic devices. Optical systems of the present invention comprise semiconductor elements assembled, organized and / or integrated with other device components via printing techniques that exhibit performance characteristics and functionality comparable to single crystalline semiconductor based devices fabricated using conventional high temperature processing methods. Optical systems of the present invention have device geometries and configurations, such as form factors, component densities, and component positions, accessed by printing that provide a range of useful device functionalities. Optical systems of the present invention include devices and device arrays exhibiting a range of useful physical and mechanical properties including flexibility, shapeability, conformability and stretchability. Optical systems of the present invention include, however, devices and device arrays provided on conventional rigid or semi-rigid substrates, in addition to devices and device arrays provided on flexible, shapeable and / or stretchable substrates.

Owner:X DISPLAY CO TECH LTD +1

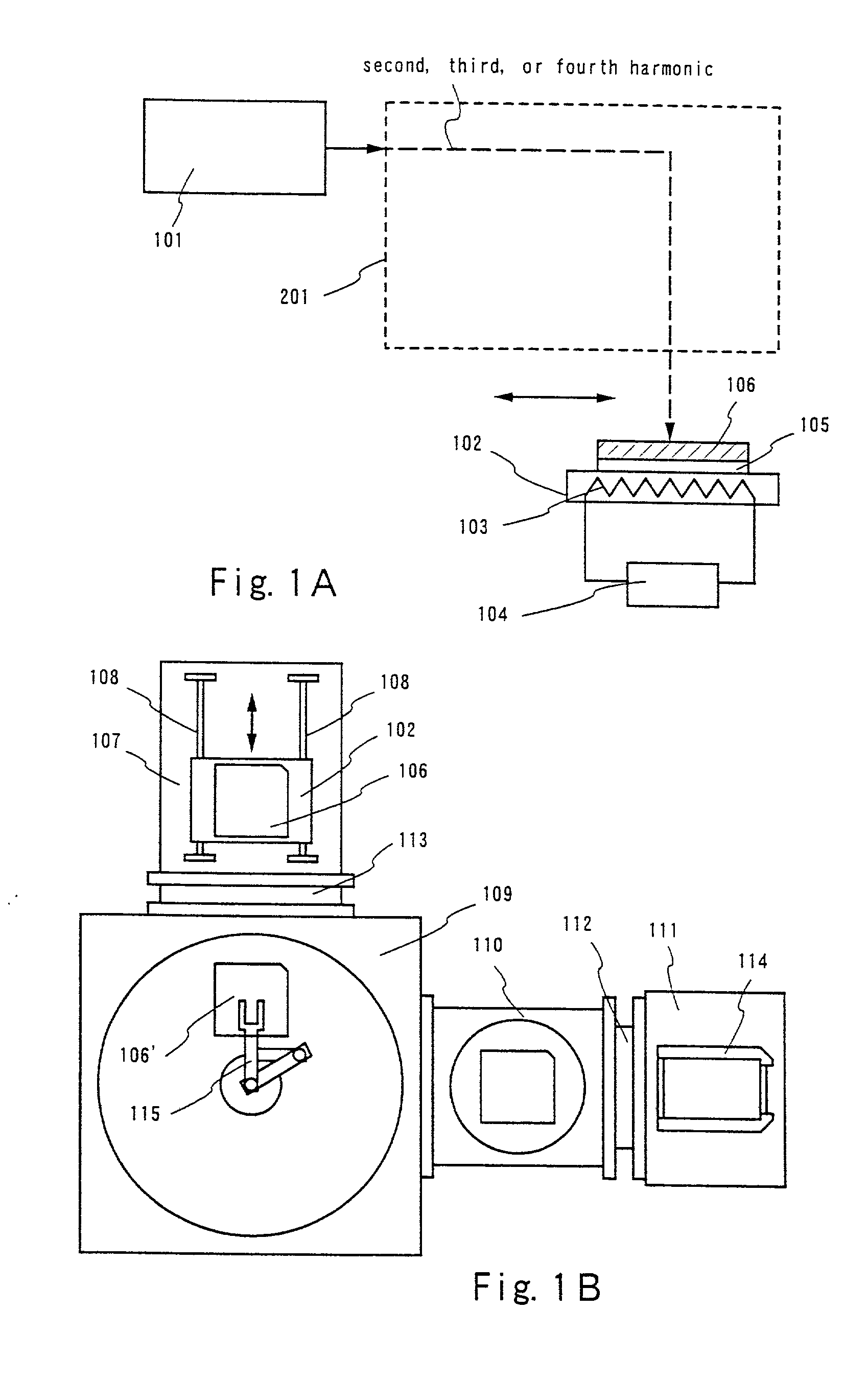

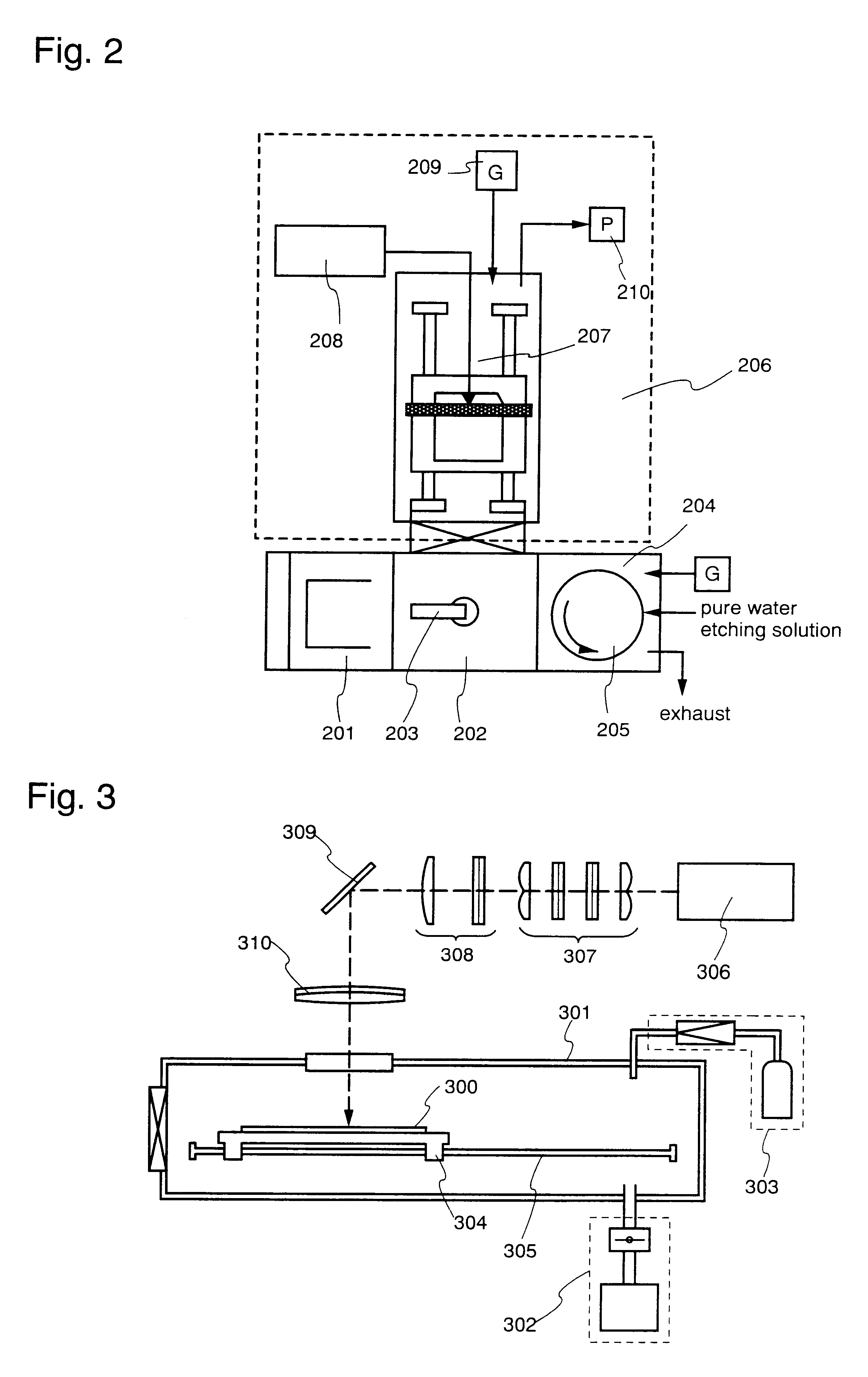

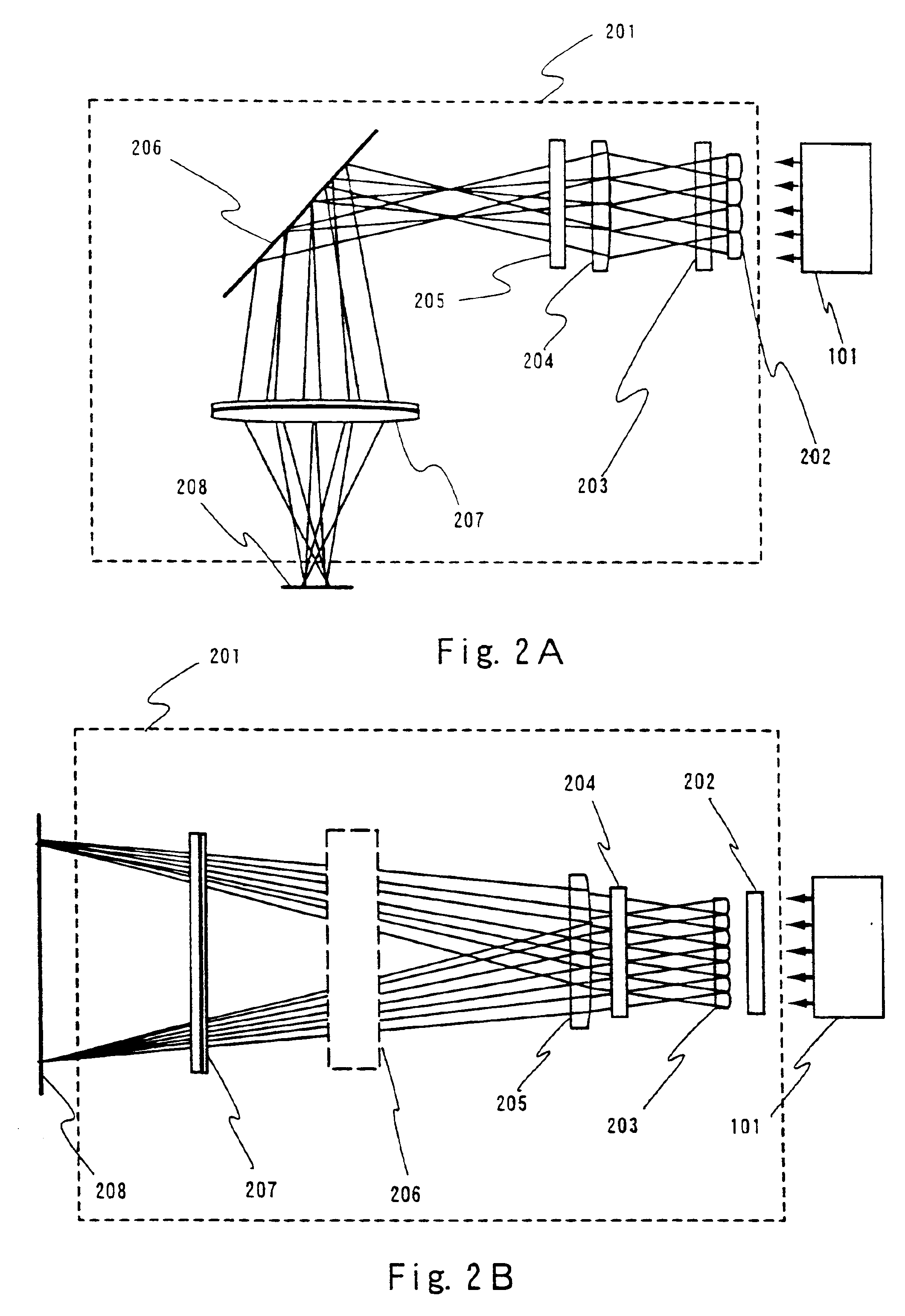

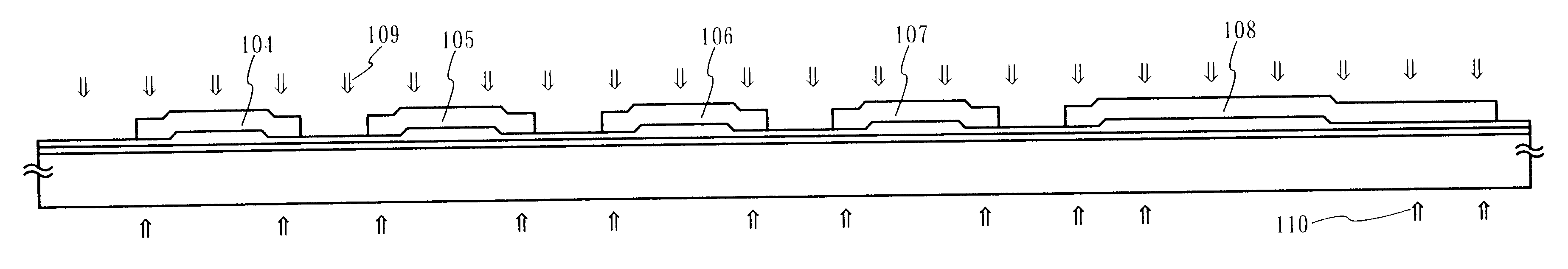

Laser apparatus, laser annealing method, and manufacturing method of a semiconductor device

InactiveUS20020048864A1Solution value is not highIncrease valueSemiconductor/solid-state device testing/measurementSolid-state devicesLaser lightSolid-state laser

To provide a laser apparatus and a laser annealing method with which a crystalline semiconductor film with a larger crystal grain size is obtained and which are low in their running cost. A solid state laser easy to maintenance and high in durability is used as a laser, and laser light emitted therefrom is linearized to increase the throughput and to reduce the production cost as a whole. Further, both the front side and the back side of an amorphous semiconductor film is irradiated with such laser light to obtain the crystalline semiconductor film with a larger crystal grain size.

Owner:SEMICON ENERGY LAB CO LTD

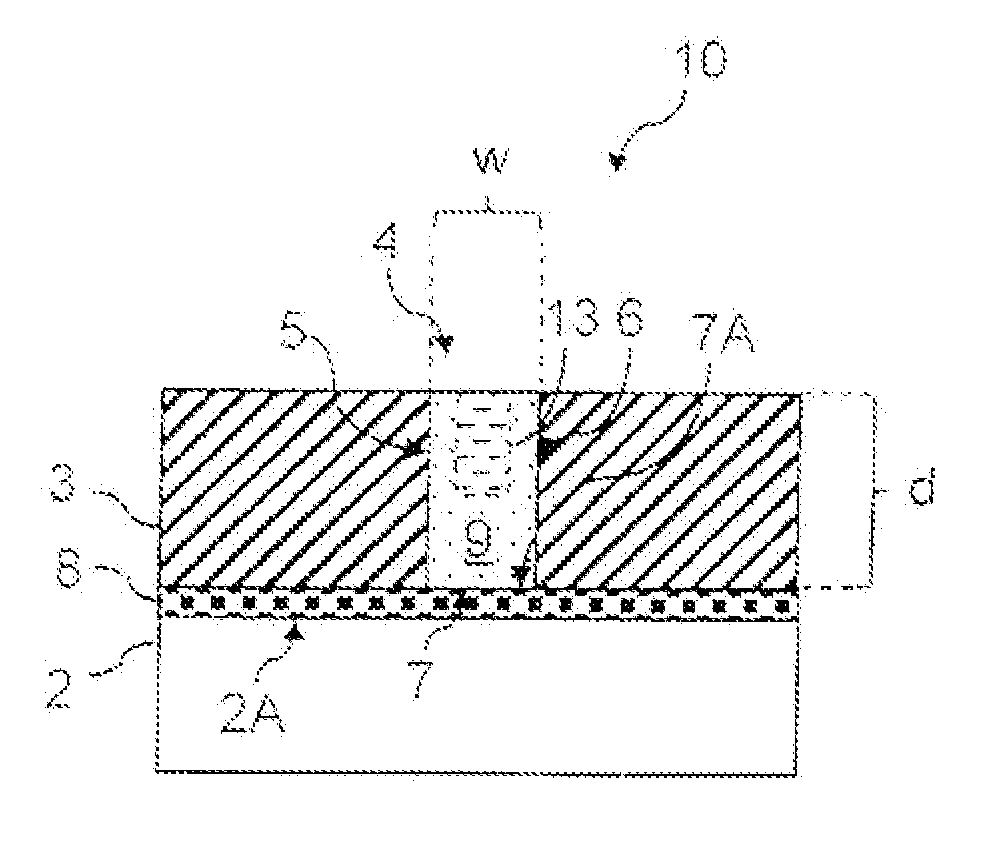

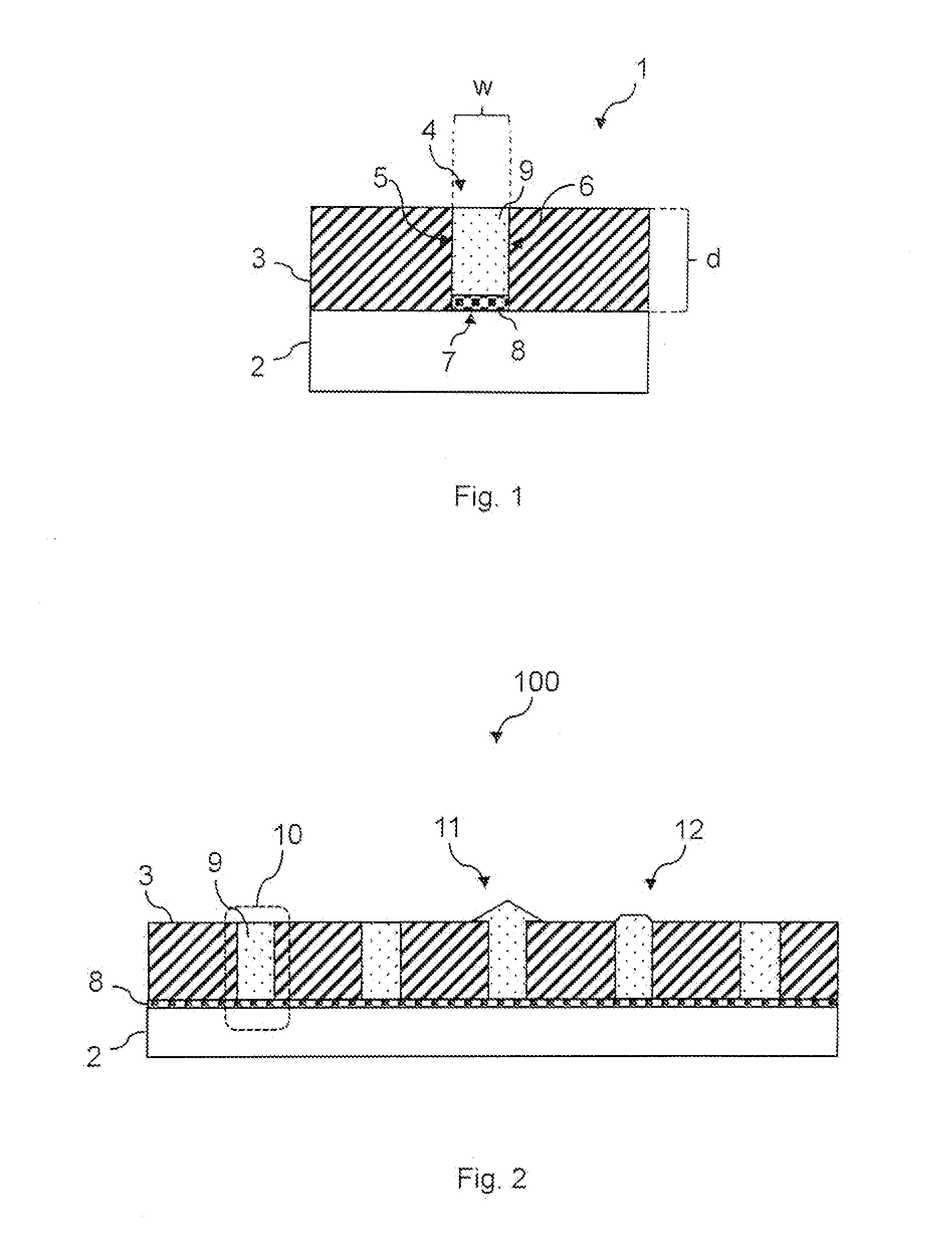

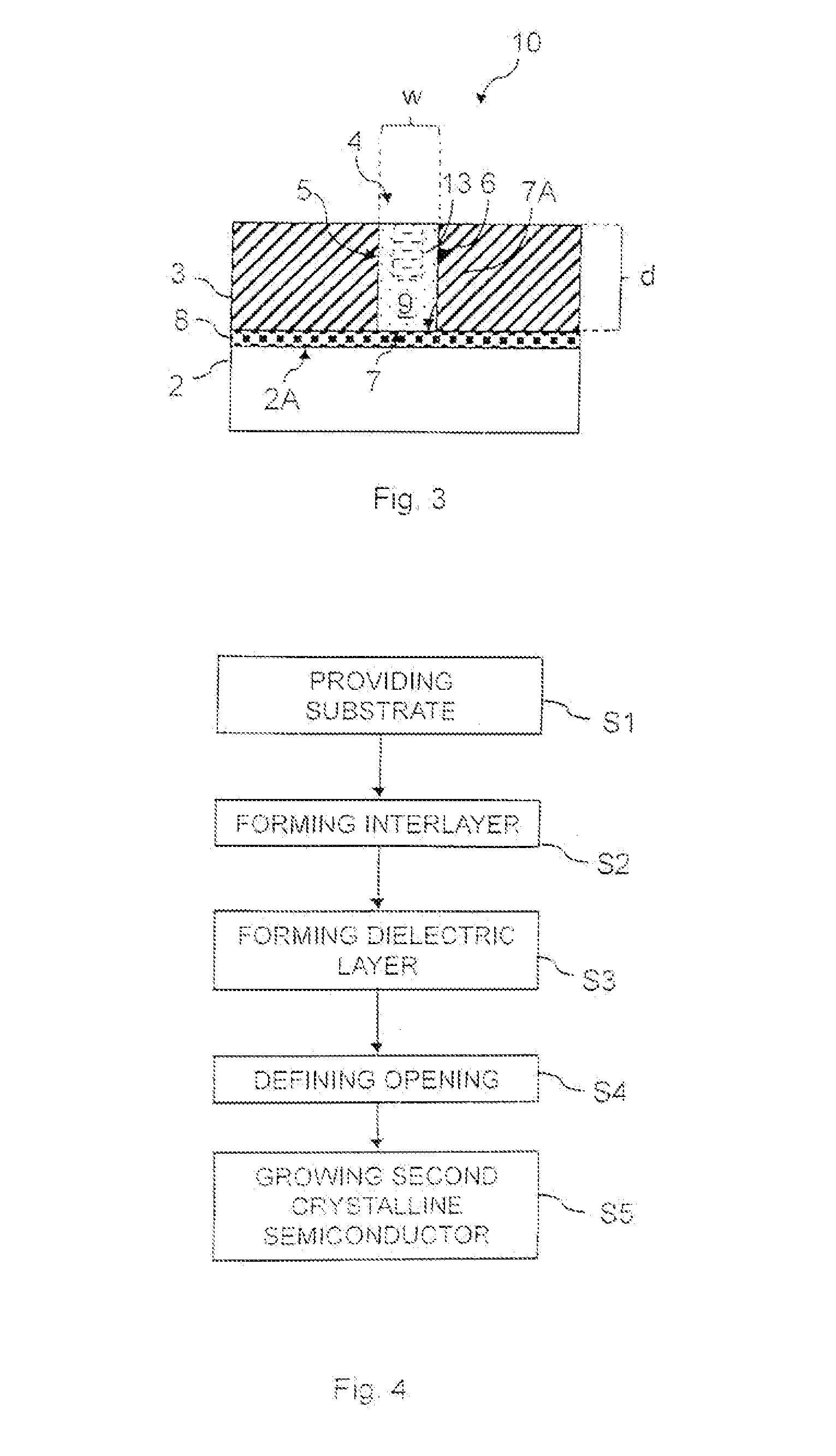

Compound semiconductor structure

InactiveUS20150061078A1Semiconductor/solid-state device manufacturingSemiconductor devicesCrystallographySemiconductor materials

A semiconductor structure comprises a substrate comprising a first crystalline semiconductor material, a dielectric layer, above the substrate, defining an opening, a second crystalline semiconductor material at least partially filling the opening, and a crystalline interlayer between the substrate and the second crystalline semiconductor material. The first crystalline semiconductor material and the second crystalline semiconductor material are lattice mismatched, and the crystalline interlayer comprises an oxygen compound. A method for fabricating semiconductor structure comprises the steps of providing a substrate including a first crystalline semiconductor material, patterning an opening in a dielectric layer above the substrate, the opening having a bottom, forming a crystalline interlayer on the substrate at least partially covering the bottom, and growing a second crystalline semiconductor material on the crystalline interlayer thereby at least partially filling the opening. The crystalline semiconductor materials are lattice mismatched, and the crystalline interlayer comprises an oxygen compound.

Owner:ALSEPHINA INNOVATIONS INC

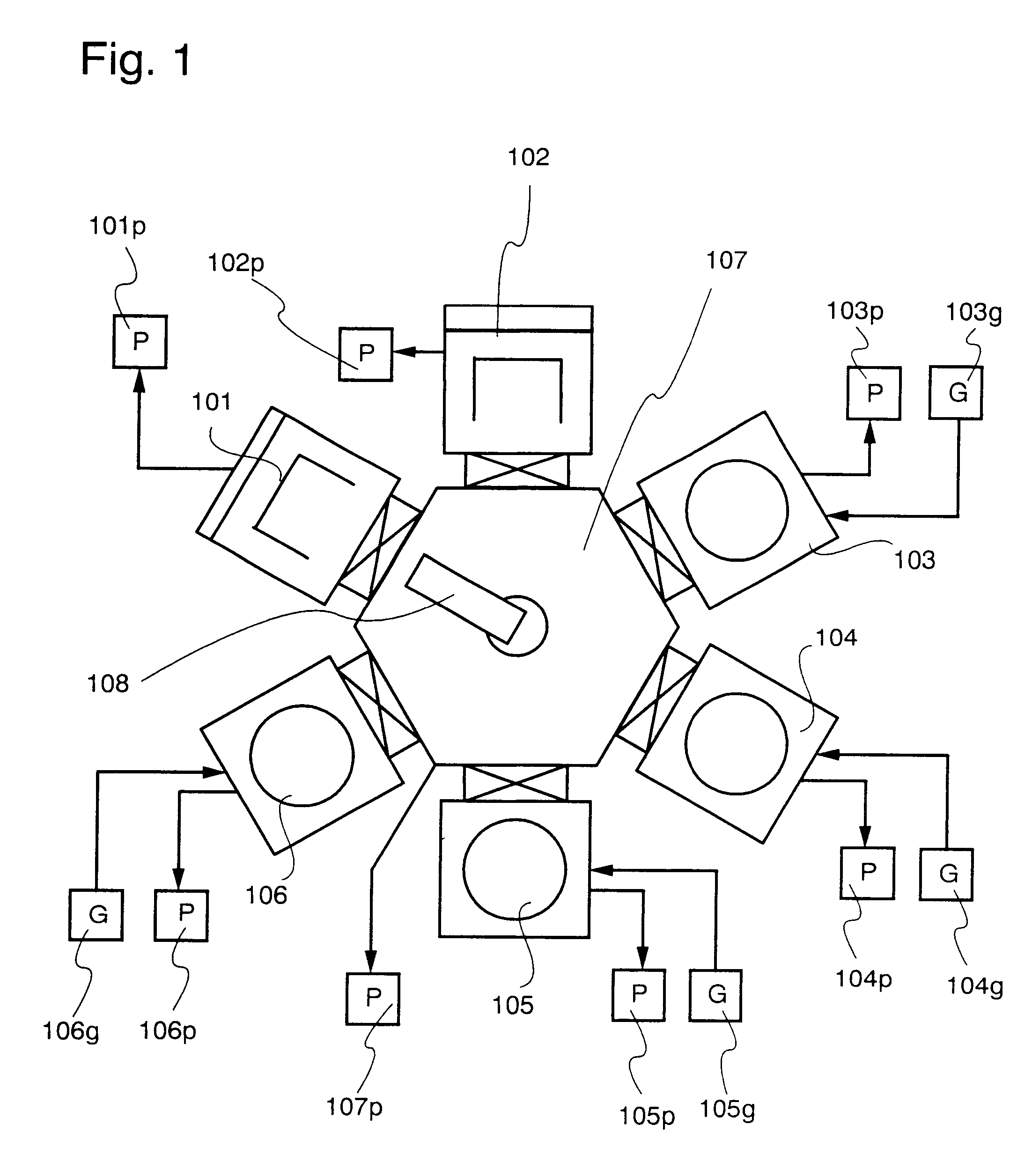

Method of manufacturing a semiconductor device having a crystallized amorphous silicon film

InactiveUS6506636B2Interface is preventedTransistorSolid-state devicesCrystal structureAmorphous silicon

Contamination of an interface of respective films constituting a TFT due to an contaminant impurity in a clean room atmosphere becomes a great factor to lower the reliability of the TFT. Besides, when an impurity is added to a crystalline semiconductor film, its crystal structure is broken. By using an apparatus for manufacturing a semiconductor device including a plurality of treatment chambers, a treatment can be made without being exposed to a clean room atmosphere in an interval between respective treatment steps, and it becomes possible to keep the interface of the respective films constituting the TFT clean. Besides, by carrying out crystallization after an impurity is added to an amorphous semiconductor film, the breakdown of the crystal structure of the crystalline semiconductor film is prevented.

Owner:SEMICON ENERGY LAB CO LTD

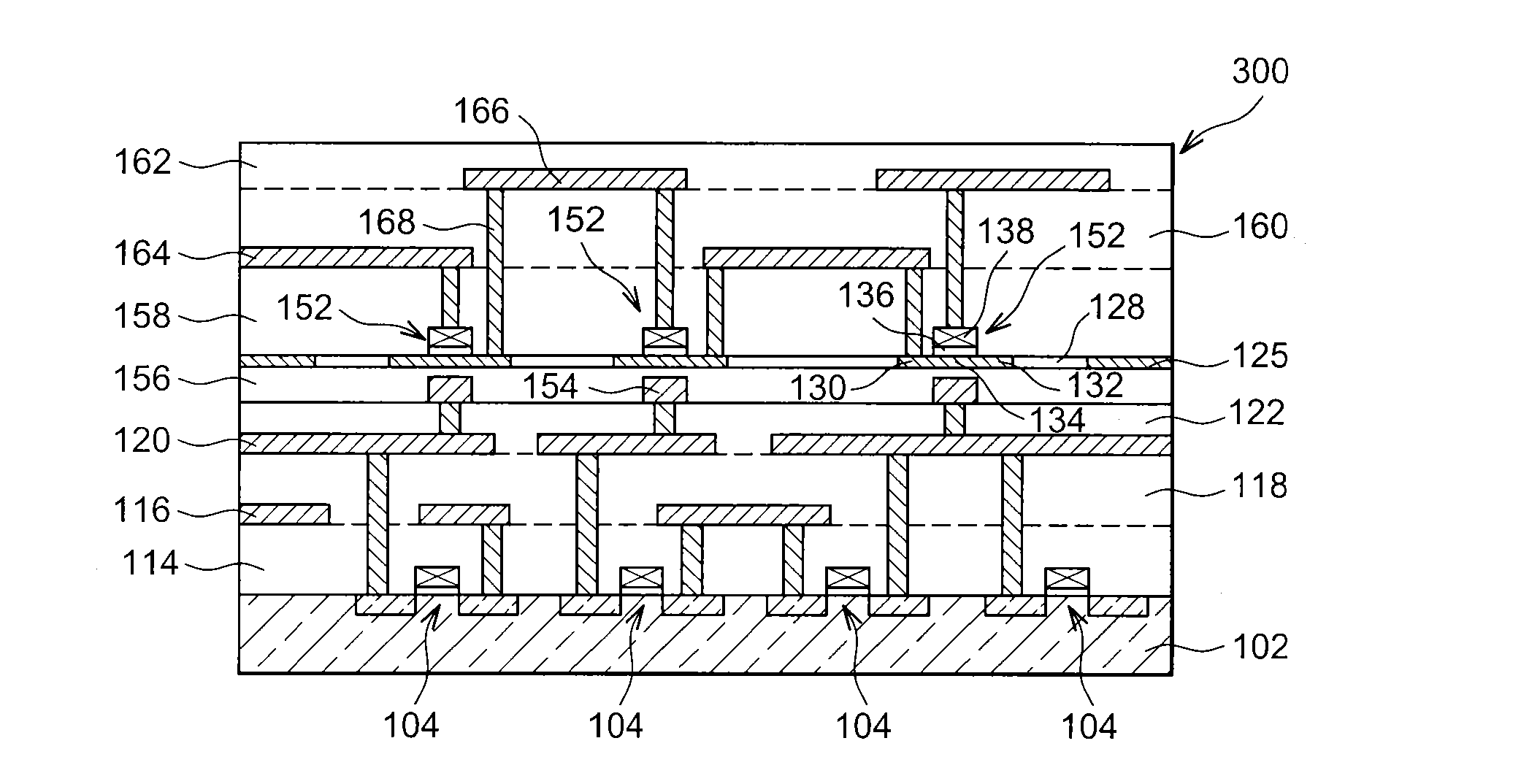

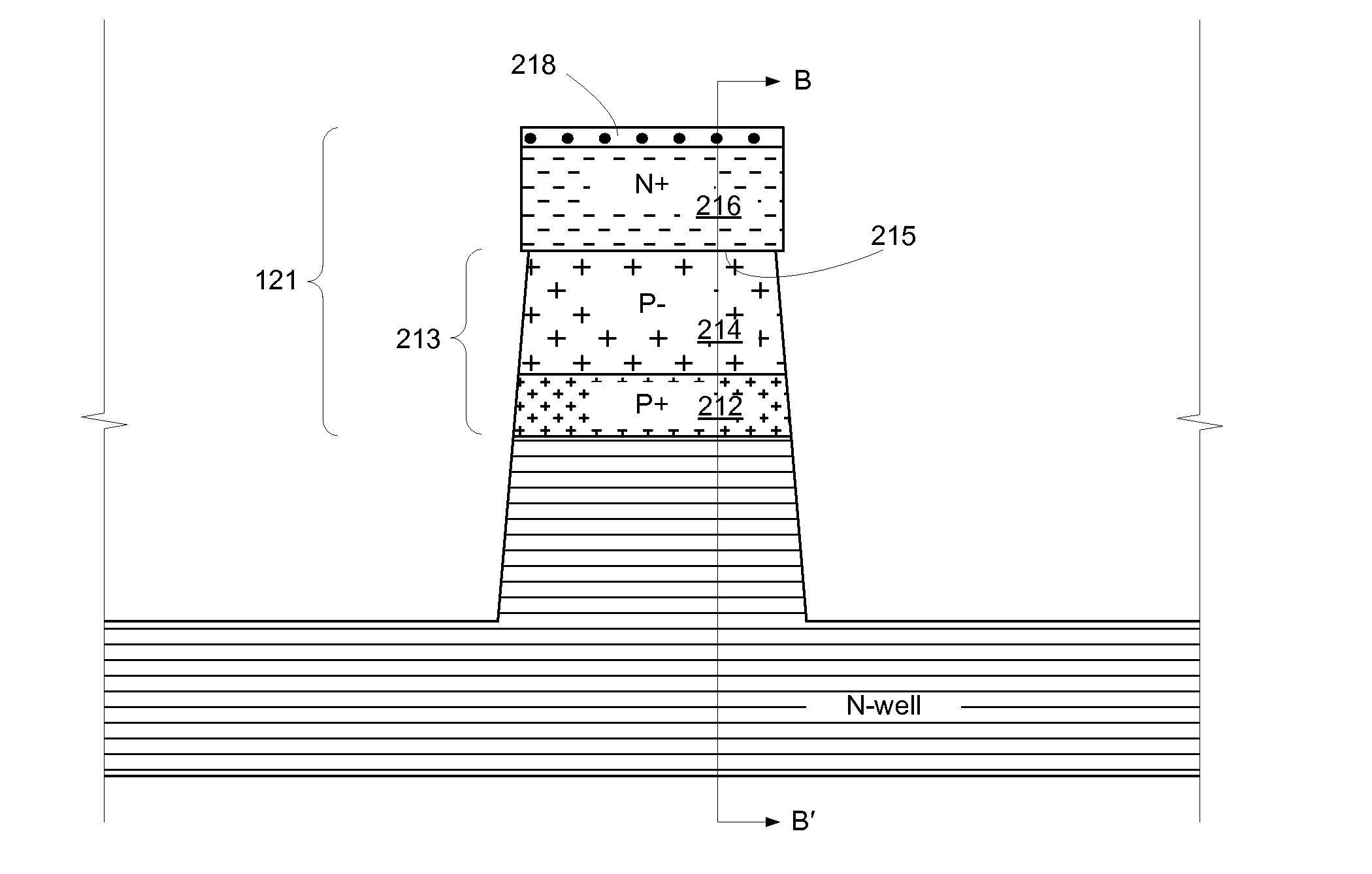

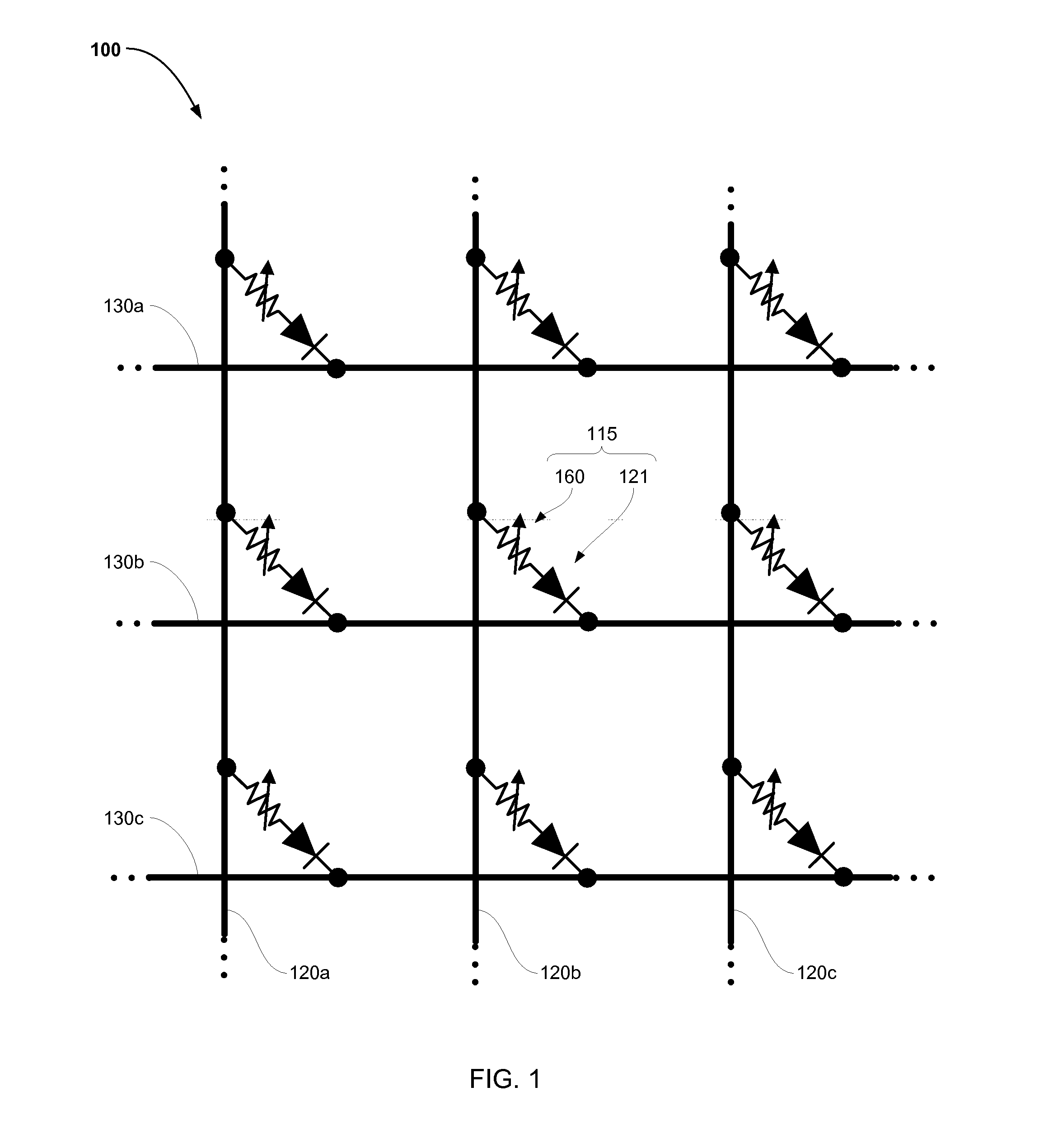

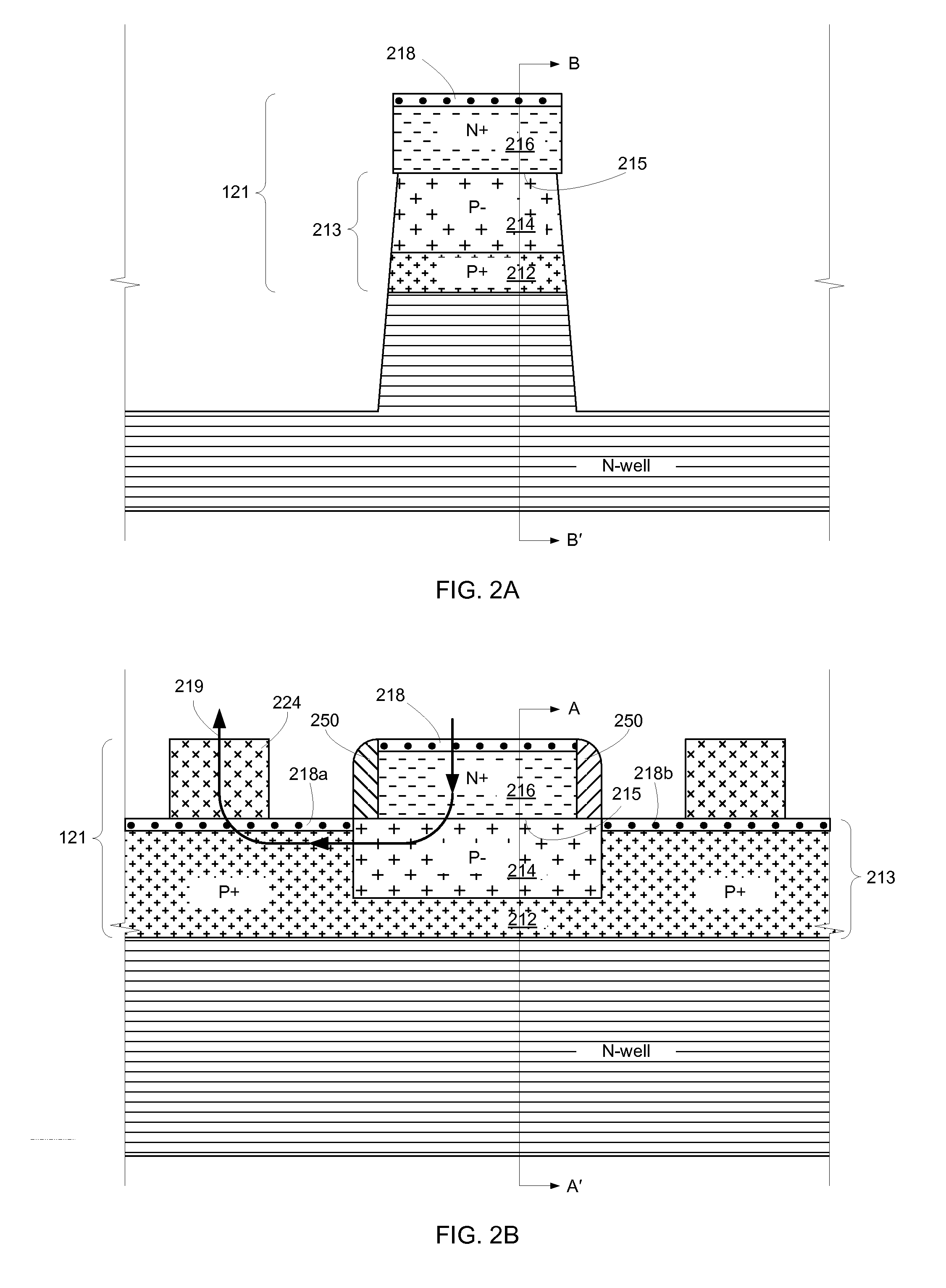

Memory cell access device having a pn-junction with polycrystalline and single-crystal semiconductor regions

ActiveUS20100117048A1Inhibited DiffusionImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingSingle crystalP–n junction

A memory device includes a driver comprising a pn-junction in the form of a multilayer stack including a first doped semiconductor region having a first conductivity type, and a second doped semiconductor region having a second conductivity type opposite the first conductivity type, the first and second doped semiconductors defining a pn-junction therebetween, in which the first doped semiconductor region is formed in a single-crystalline semiconductor, and the second doped semiconductor region includes a polycrystalline semiconductor. Also, a method for making a memory device includes forming a first doped semiconductor region of a first conductivity type in a single-crystal semiconductor, such as on a semiconductor wafer; and forming a second doped polycrystalline semiconductor region of a second conductivity type opposite the first conductivity type, defining a pn-junction between the first and second regions.

Owner:MACRONIX INT CO LTD

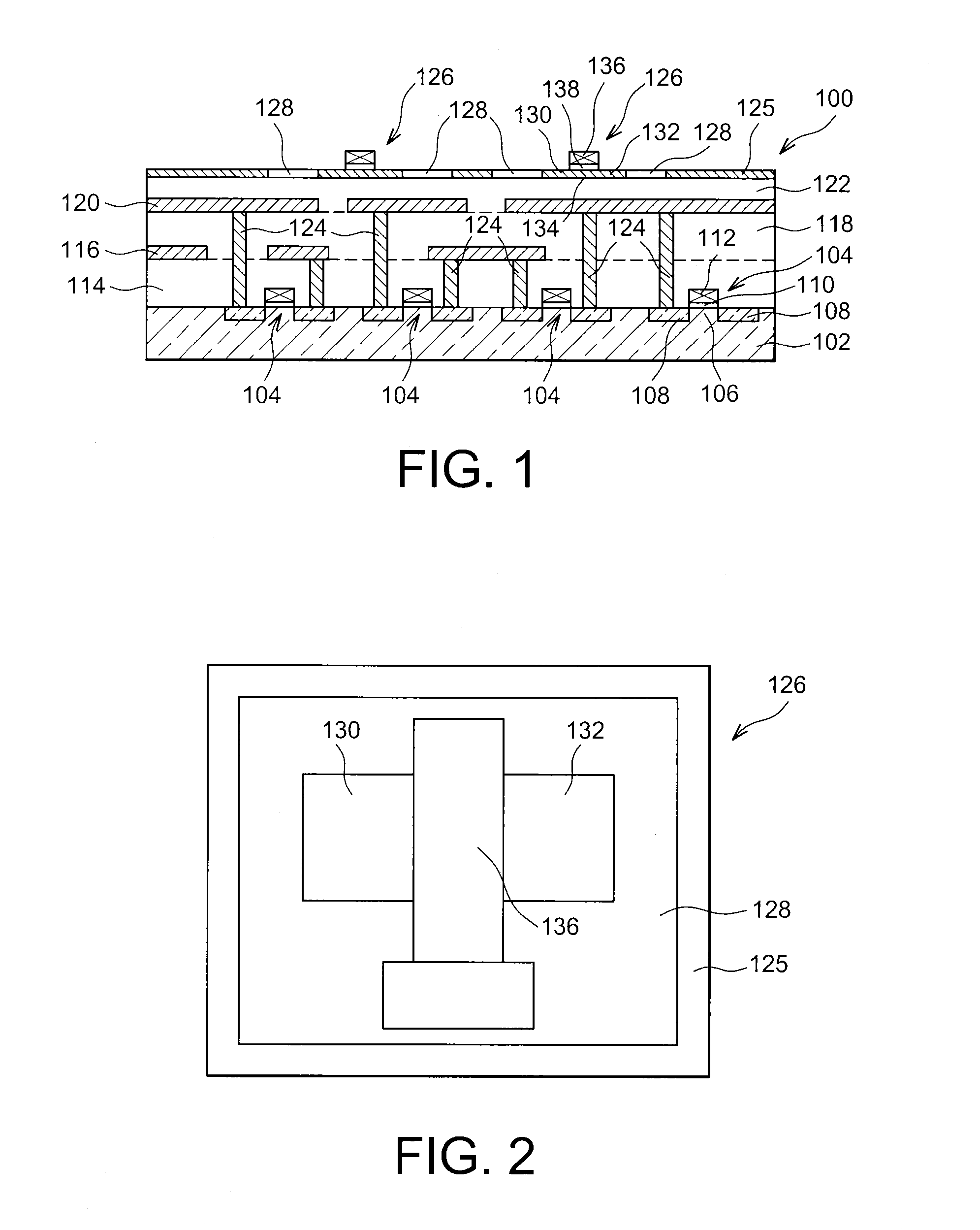

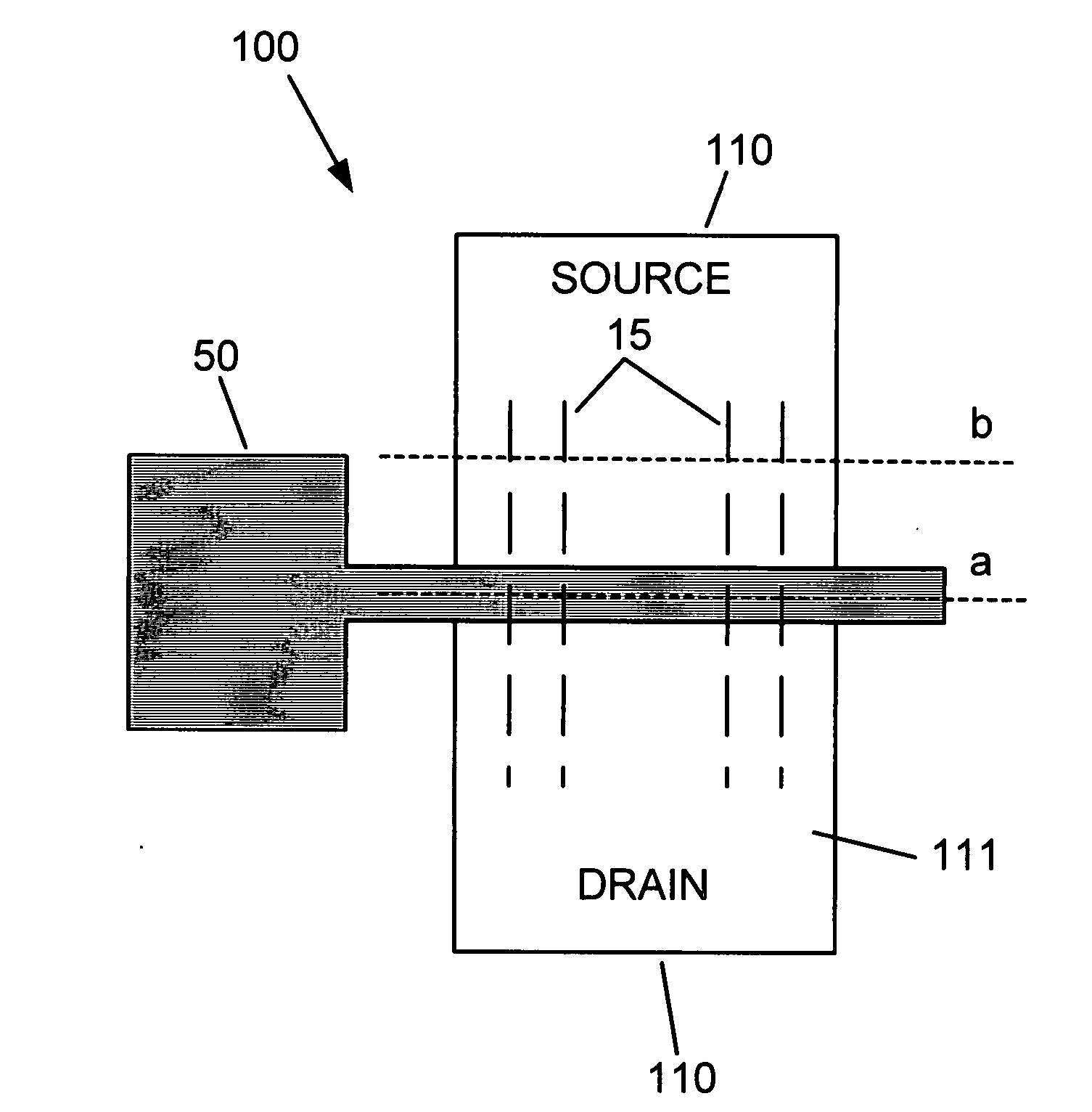

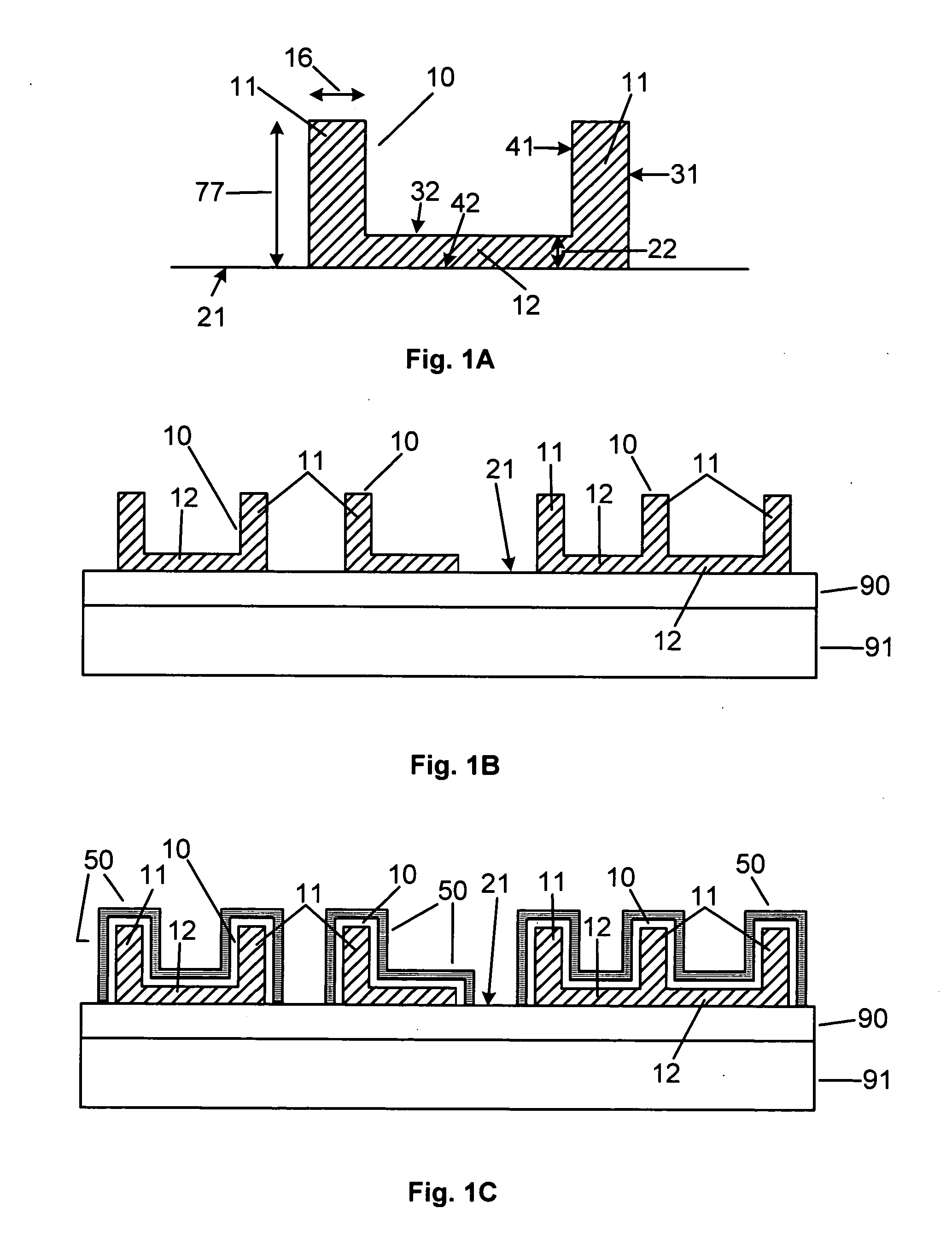

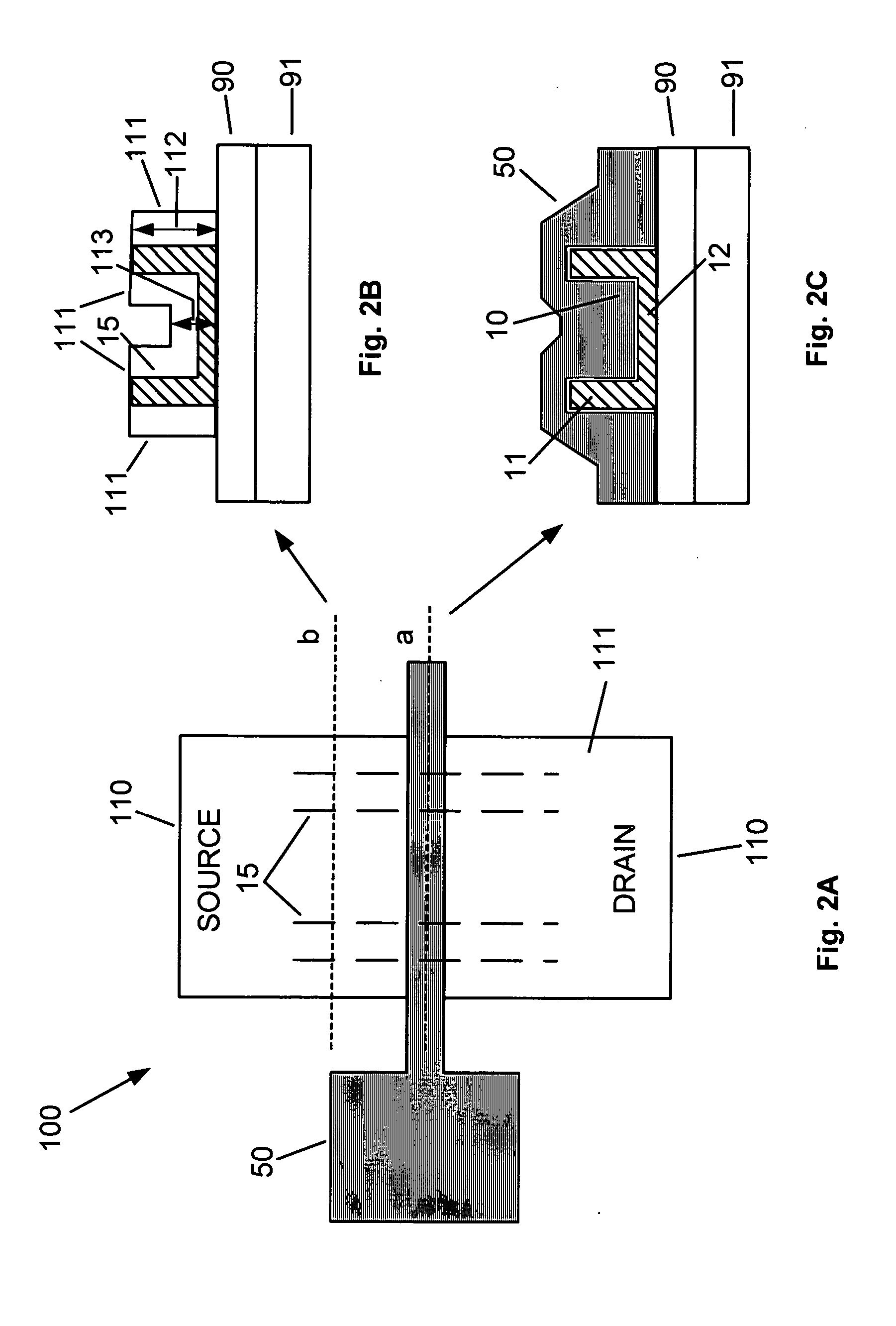

Sectional field effect devices and method of fabrication

ActiveUS20050127362A1Improve the layout densityHigh densityTransistorSolid-state devicesCrystalline semiconductorSilicon on insulator

A field effect device is disclosed which has a body formed of a crystalline semiconductor material and has at least one vertically oriented section and at least one horizontally oriented section. The device is produced in SOI technology by fabricating first a formation of the device in masking insulators, and then transferring this formation through several etching steps into the SOI layer. The segmented field effect device combines FinFET, or fully depleted silicon-on-insulator FETs, type devices with fully depleted planar devices. This combination allows device width control with FinFET type devices. The segmented field effect device gives high current drive for a given layout area. The segmented field effect devices allow for the fabrication of high performance processors.

Owner:GLOBALFOUNDRIES US INC

Laser apparatus, laser annealing method, and manufacturing method of a semiconductor device

InactiveUS6974731B2Large grainLow running costSolid-state devicesSemiconductor/solid-state device manufacturingLaser lightSolid-state laser

To provide a laser apparatus and a laser annealing method with which a crystalline semiconductor film with a larger crystal grain size is obtained and which are low in their running cost. A solid state laser easy to maintenance and high in durability is used as a laser, and laser light emitted therefrom is linearized to increase the throughput and to reduce the production cost as a whole. Further, both the front side and the back side of an amorphous semiconductor film is irradiated with such laser light to obtain the crystalline semiconductor film with a larger crystal grain size.

Owner:SEMICON ENERGY LAB CO LTD

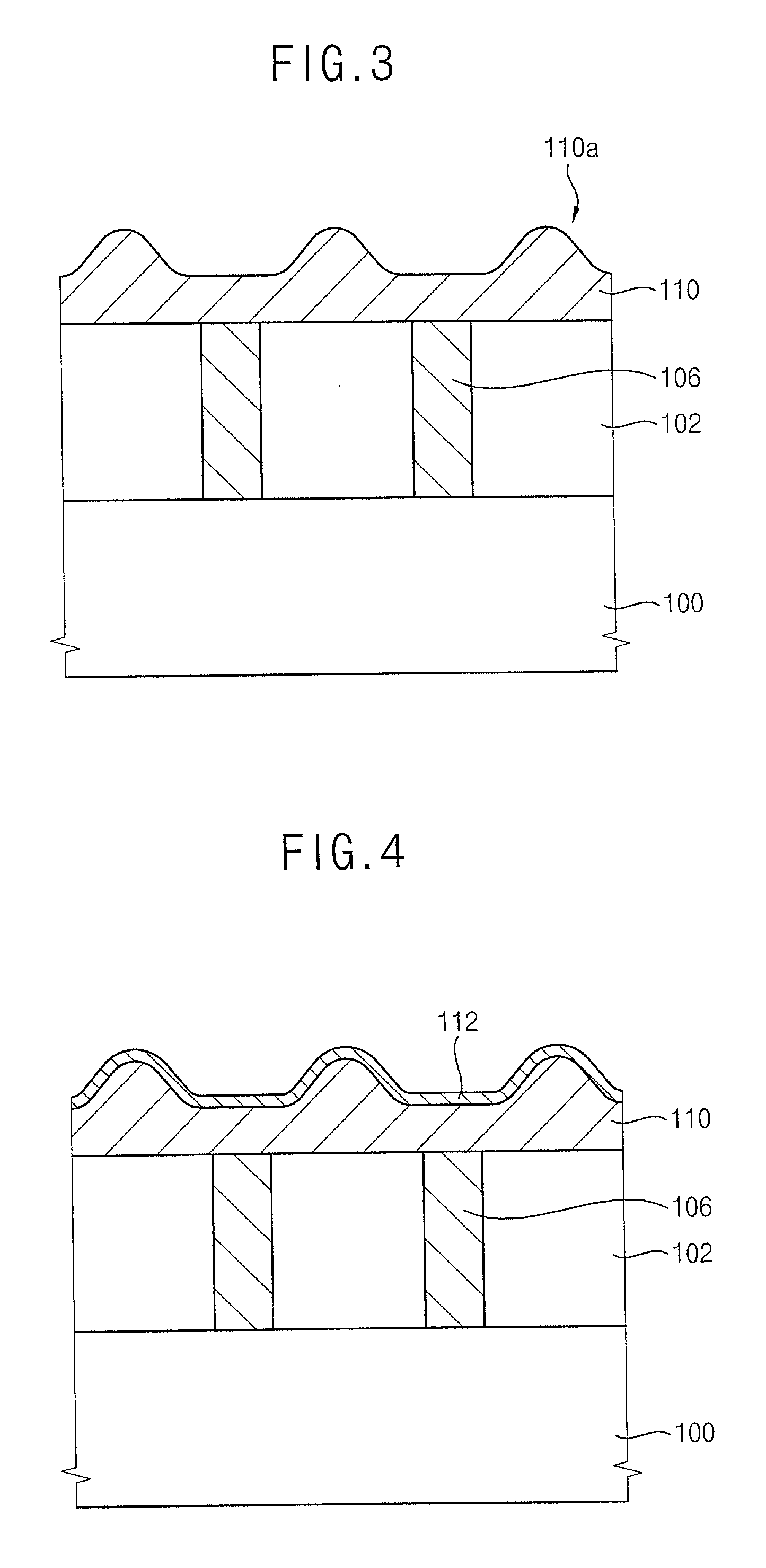

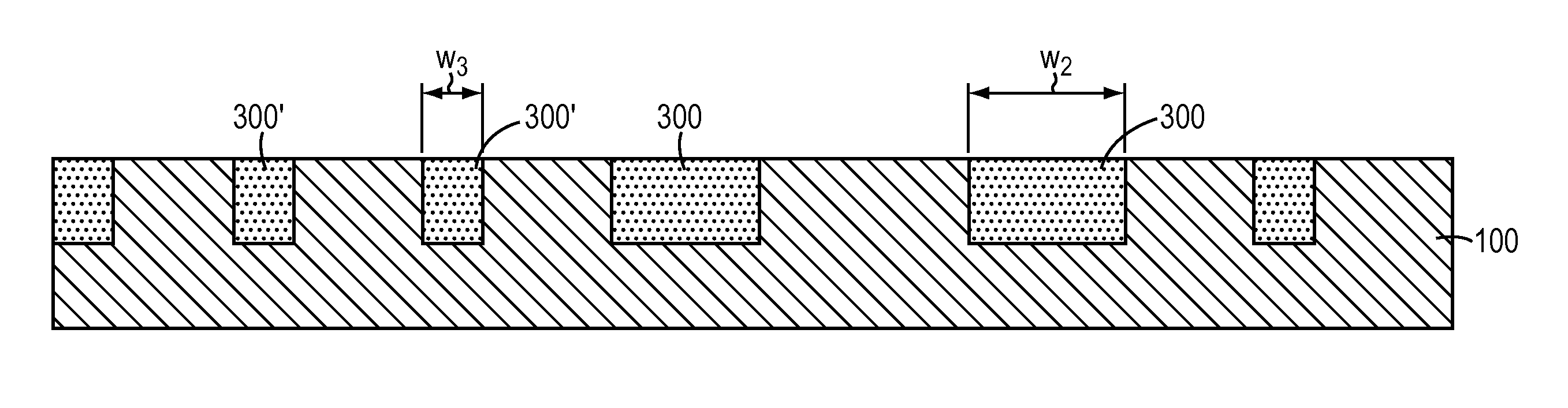

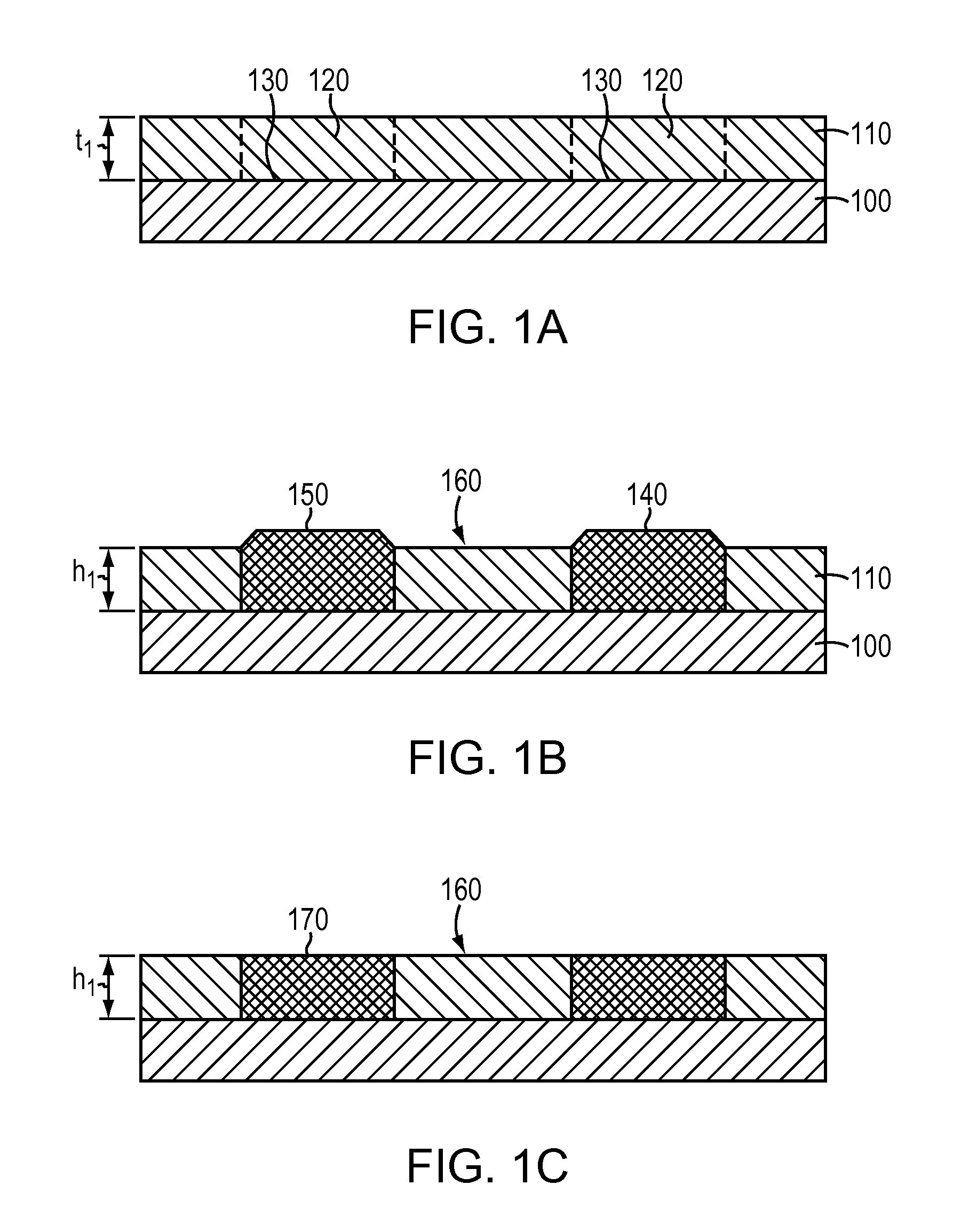

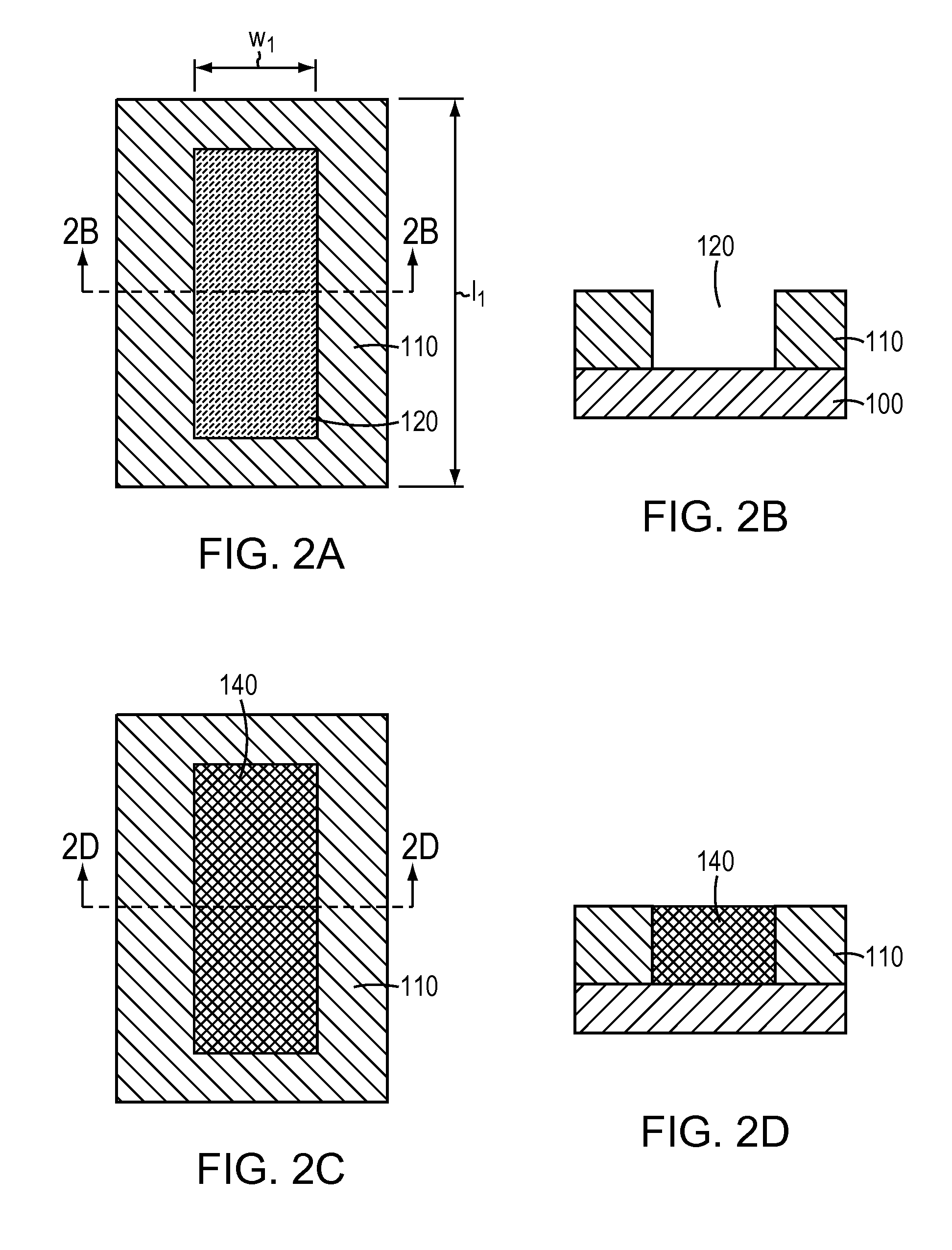

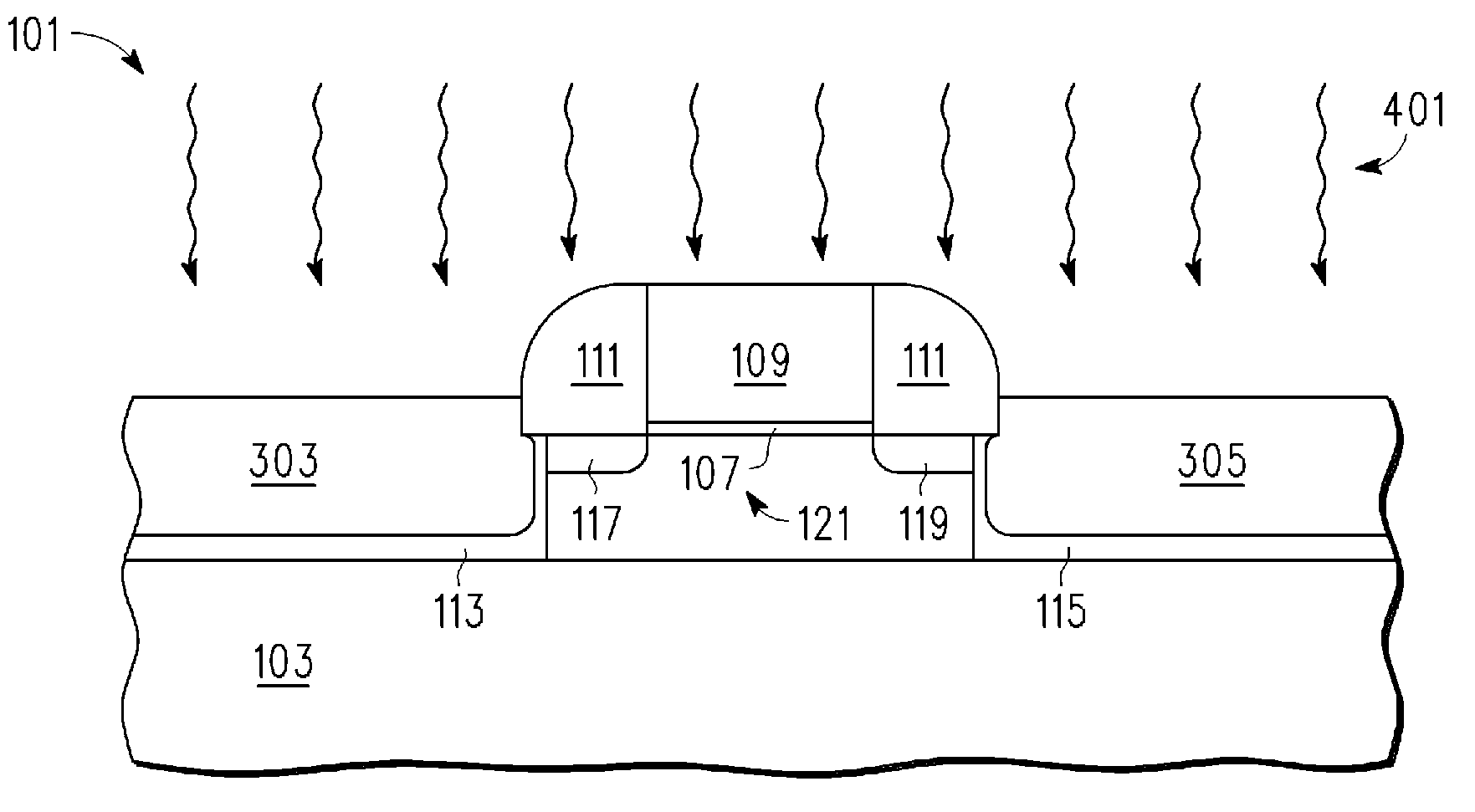

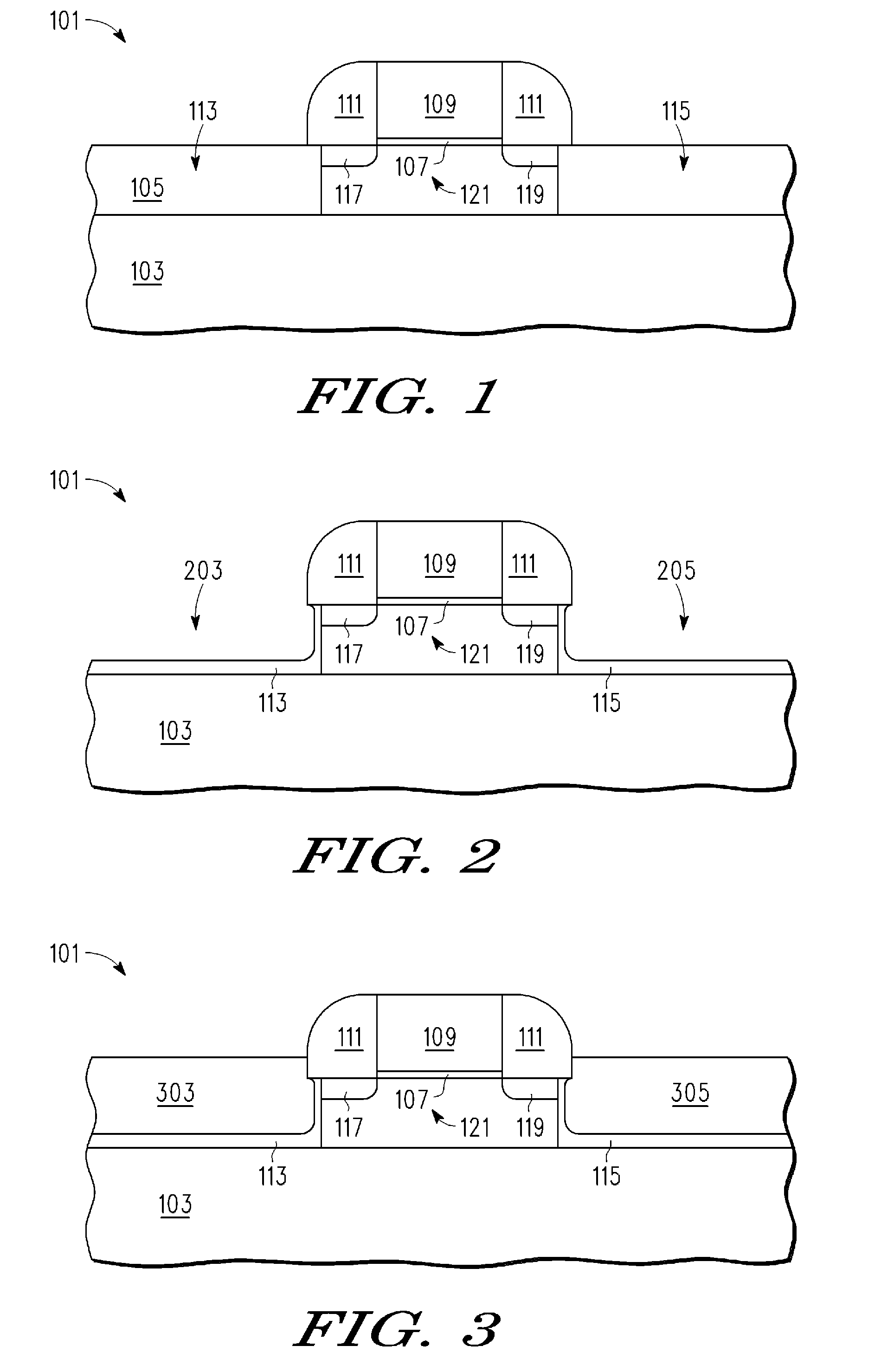

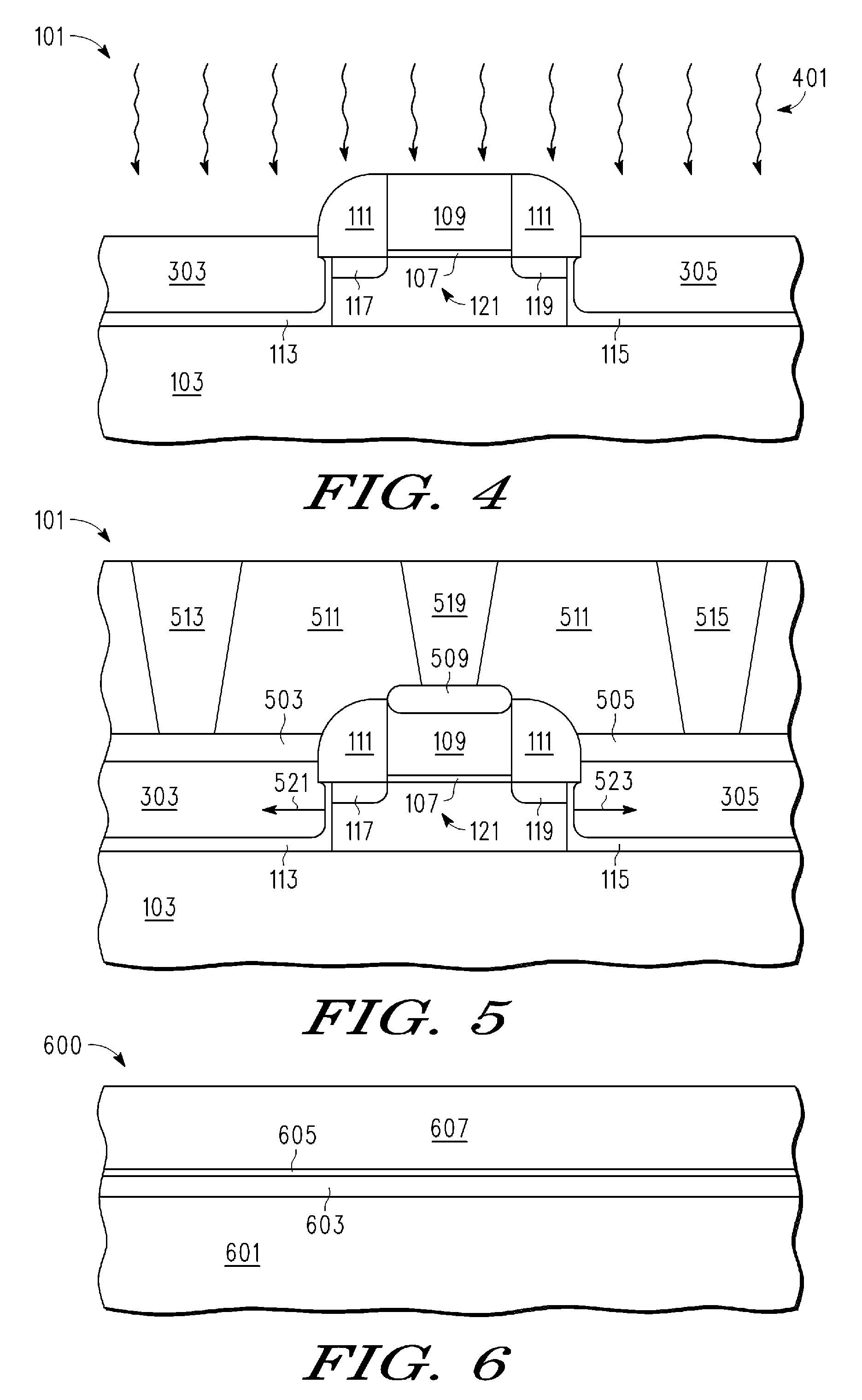

Solutions for integrated circuit integration of alternative active area materials

ActiveUS7626246B2Improve functionalityImprove performanceSemiconductor/solid-state device detailsSolid-state devicesMOSFETOpto electronic

Methods of forming areas of alternative material on crystalline semiconductor substrates, and structures formed thereby. Such areas of alternative material are suitable for use as active areas in MOSFETs or other electronic or opto-electronic devices.

Owner:TAIWAN SEMICON MFG CO LTD

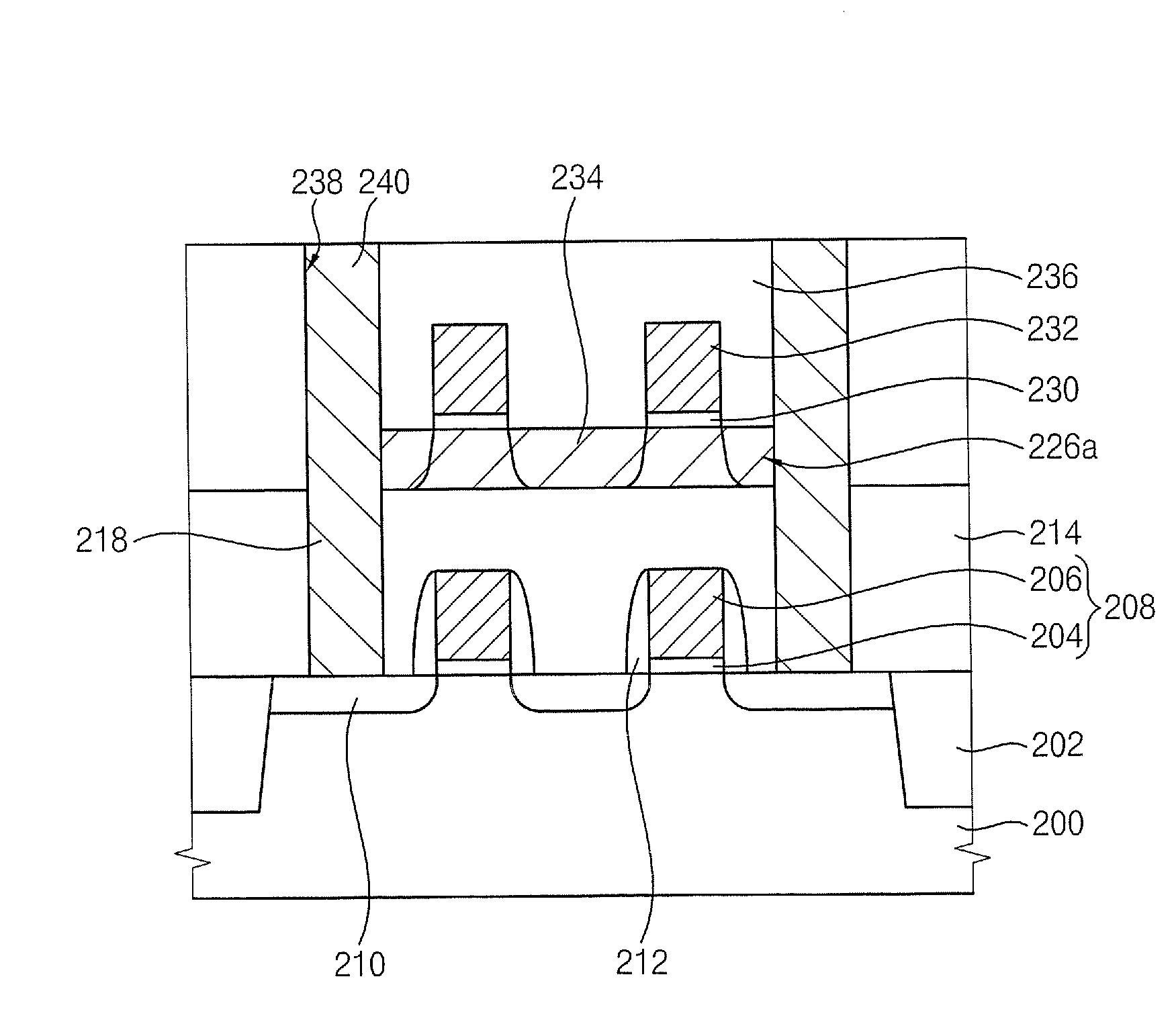

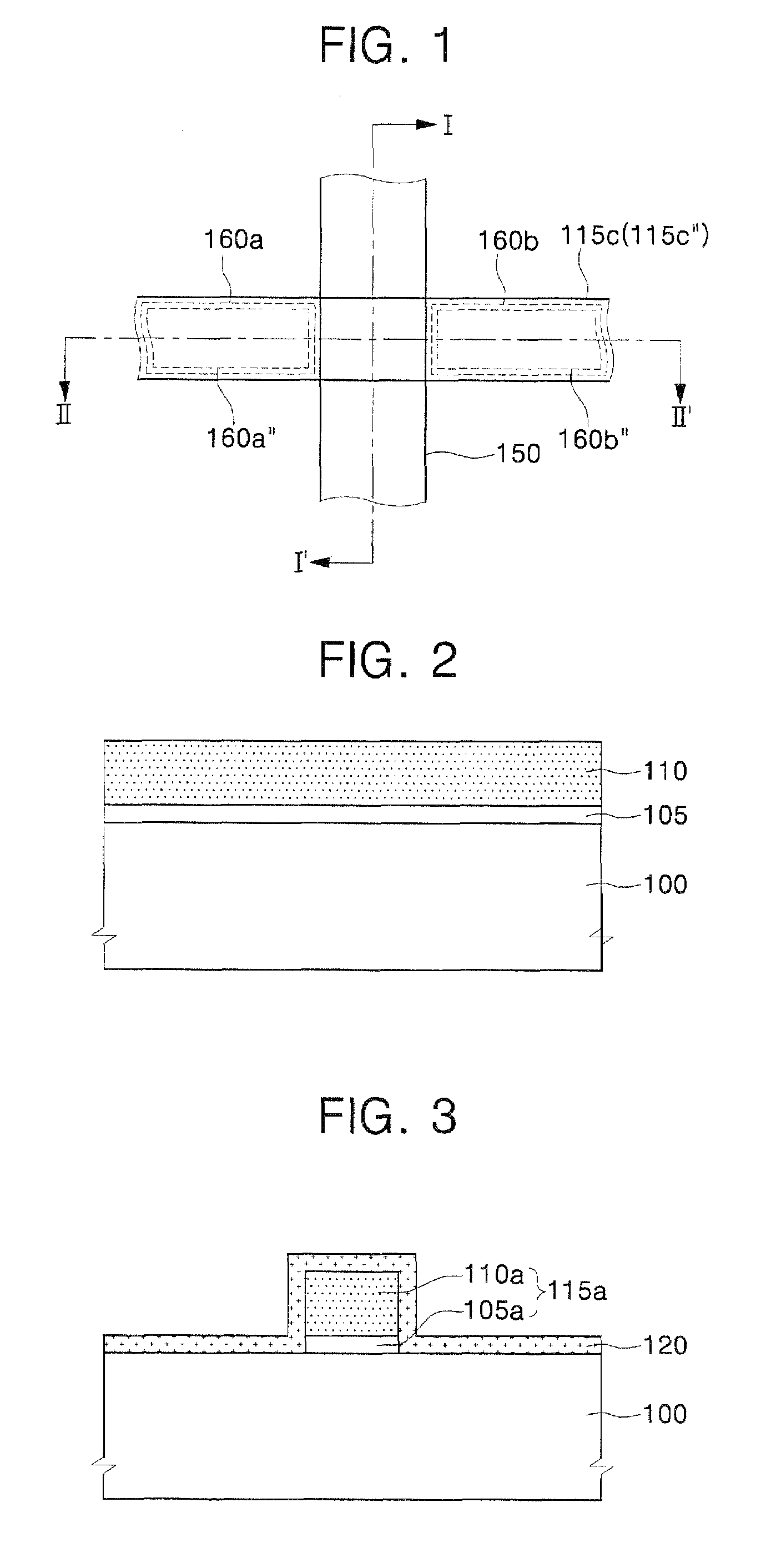

Semiconductor device including a crystal semiconductor layer, its fabrication and its operation

In one embodiment, a method of fabricating a semiconductor device having a crystalline semiconductor layer includes preparing a semiconductor substrate and forming a preliminary active pattern on the semiconductor substrate. The preliminary active pattern includes a barrier pattern and a non-single crystal semiconductor pattern. A sacrificial non-single crystal semiconductor layer covers the preliminary active pattern and the semiconductor substrate. By crystallizing the sacrificial non-single crystal semiconductor layer and the non-single crystal semiconductor pattern, using the semiconductor substrate as a seed layer, the sacrificial non-single crystal semiconductor layer and the non-single crystal semiconductor pattern are changed to a sacrificial crystalline semiconductor layer and a crystalline semiconductor pattern, respectively. The crystalline semiconductor pattern and the barrier pattern constitute an active pattern. The sacrificial crystalline semiconductor layer is removed.

Owner:SAMSUNG ELECTRONICS CO LTD

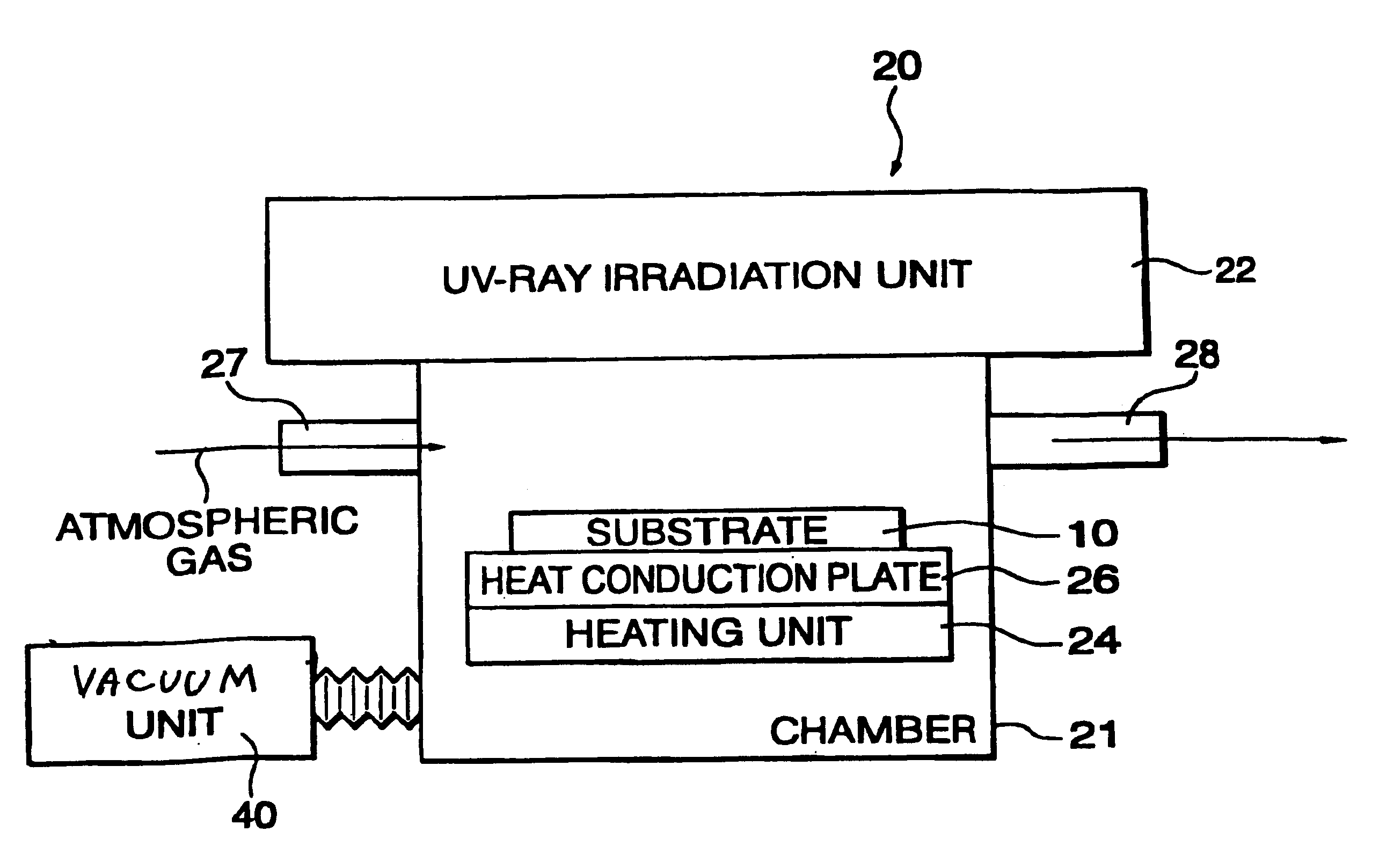

Method of forming crystalline semiconductor thin film on base substrate, lamination formed with crystalline semiconductor thin film and color filter

A method of forming a crystalline semiconductor thin film on a base material which can be prepared at a low temperature by simple step and device, the method including a processing step of applying UV-rays to an amorphous semiconductor thin film provided on a base material while keeping a temperature at not less than 25° C. and not more than 300° C. in a vacuum or a reducing gas atmosphere, as well as a substrate having the semiconductor thin film provided on the base material, a substrate for forming a color filter and a color filter using the substrate.

Owner:FUJIFILM BUSINESS INNOVATION CORP

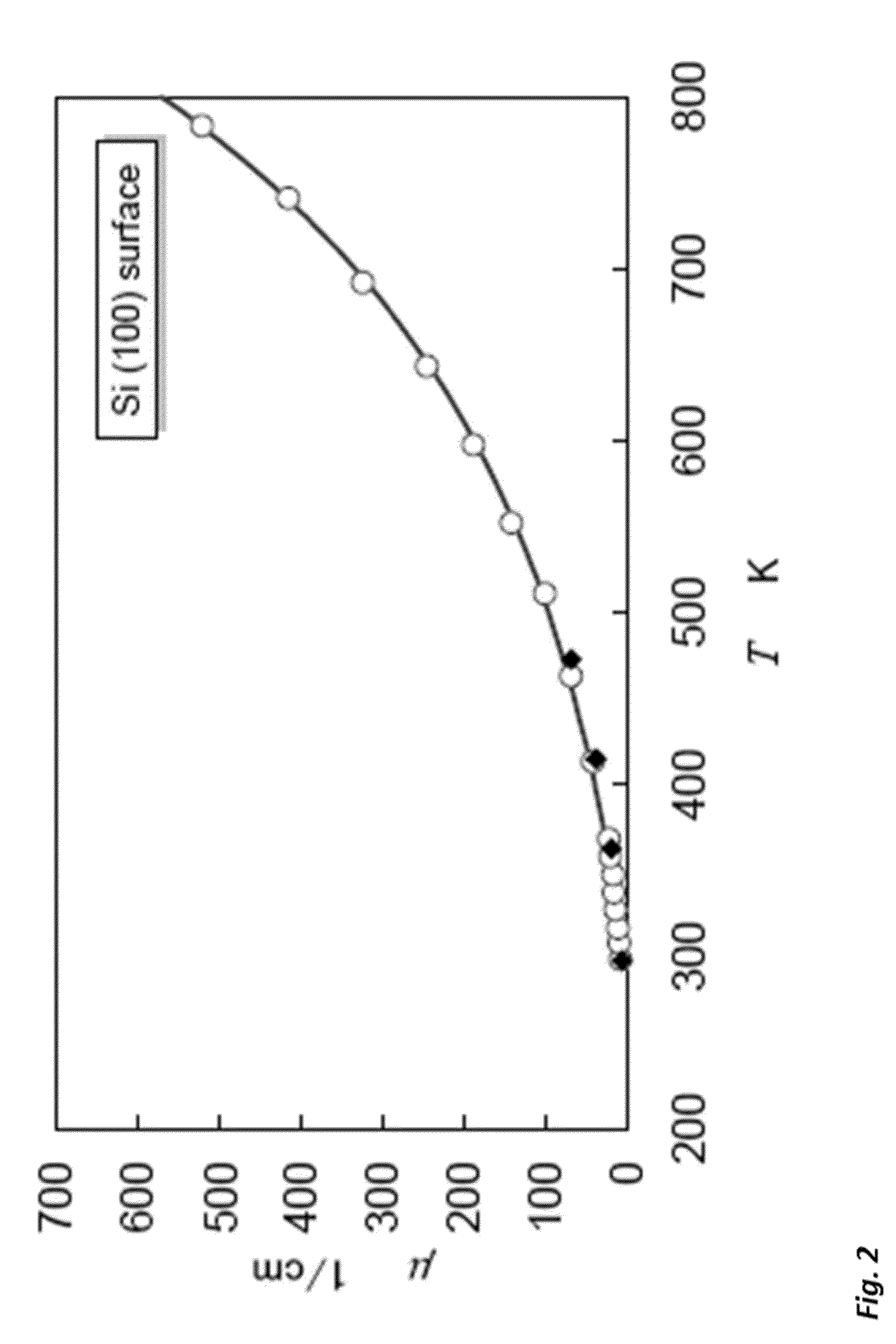

Anneal of epitaxial layer in a semiconductor device

InactiveUS7416605B2From gel statePolycrystalline material growthCharge carrier mobilityDegree Celsius

An anneal of an epitaxially grown crystalline semiconductor layer comprising a combination of group-IV elements. The layer contains at least one of the group of carbon and tin. The layer of epitaxially grown material is annealed at a temperature substantially in a range of 1,000 to 1,400 degrees Celsius for a period not to exceed 100 milliseconds within 10% of the peak temperature. The anneal is performed for example with a laser anneal or a flash lamp anneal. The limited-time anneal may improve carrier mobility of a transistor.

Owner:NORTH STAR INNOVATIONS

Photo-electric conversion cell and array, and photo-electric generation system

InactiveUS20050115602A1Practical to useHigh economic valuePV power plantsPhotovoltaic energy generationElectricityElectrical conductor

A photo-electric conversion array is formed by connecting photo-electric conversion cells in series. Each photo-electric conversion cell includes: a substrate, at least one main surface of which is made of a conductor layer; plural crystalline semiconductor particles provided on the conductor surface of the substrate; an insulation layer filled in clearances among the crystalline semiconductor particles; a transparent electric conducting layer provided above the plural crystalline semiconductor particles; a collector electrode, formed on the transparent electric conducting layer, to collect electricity from the transparent electric conducting layer. The substrate is provided with a substrate electrode portion at one end portion, through which the conductor surface of the substrate is exposed, and a connection electrode is formed by extending the collector electrode, so that the connection electrode in a given photo-electric conversion cell is connected to the substrate electrode portion in another photo-electric conversion cell. It is thus possible to provide a photo-electric conversion array capable of maintaining the reliability as to the adhesion strength, with a good outward appearance as well as excellent reliability and power generation efficiency.

Owner:KYOCERA CORP

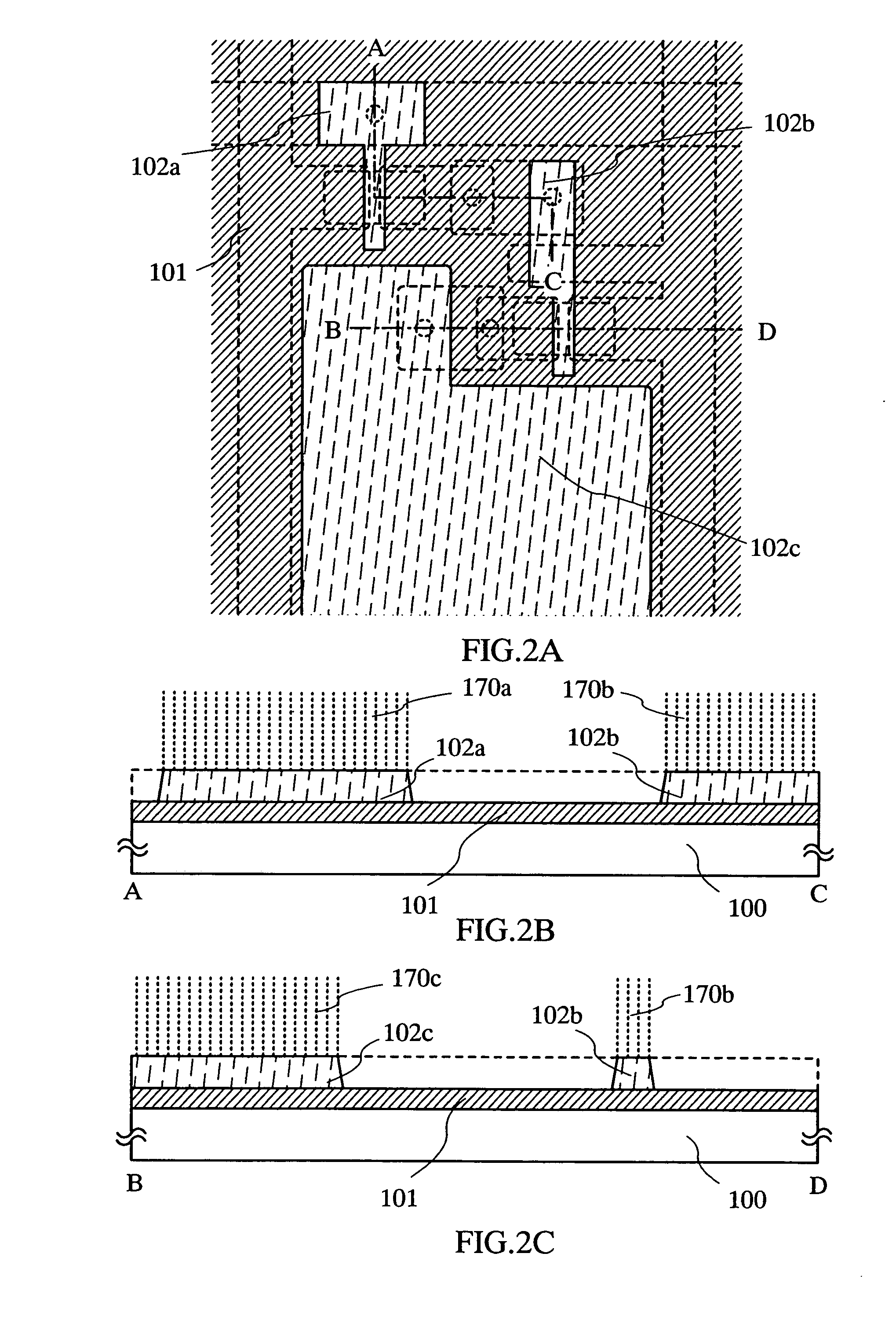

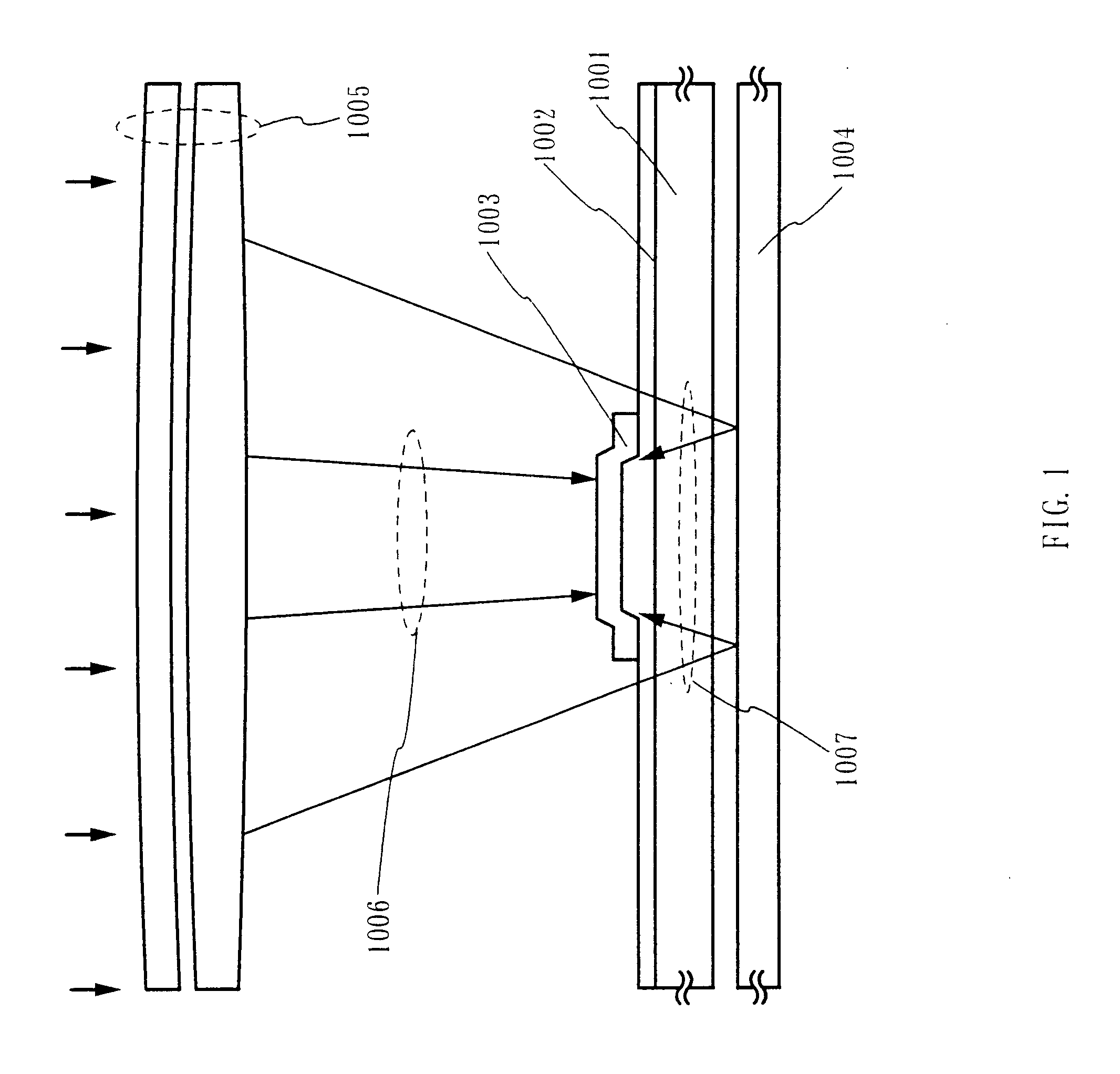

Semiconductor device and method of fabricating the same

A crystalline semiconductor film in which the position and size of a crystal grain is controlled is fabricated, and the crystalline semiconductor film is used for a channel formation region of a TFT, so that a high performance TFT is realized. An island-like semiconductor layer is made to have a temperature distribution, and a region where temperature change is gentle is provided to control the nucleus generation speed and nucleus generation density, so that the crystal grain is enlarged. In a region where an island-like semiconductor layer 1003 overlaps with a base film 1002, a thick portion is formed in the base film 1002. The volume of this portion increases and heat capacity becomes large, so that a cycle of temperature change by irradiation of a pulse laser beam to the island-like semiconductor layer becomes gentle (as compared with other thin portion). Like this, a laser beam is irradiated from the front side and reverse side of the substrate to directly heat the semiconductor layer, and heat conduction from the semiconductor layer to the side of the substrate and heat conduction of the semiconductor layer in the horizontal direction to the substrate are used, so that the increase in the size of the crystal grain is realized.

Owner:SEMICON ENERGY LAB CO LTD