Patents

Literature

438 results about "Polycrystalline semiconductor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Semiconductor thin film forming method, production methods for semiconductor device and electrooptical device, devices used for these methods, and semiconductor device and electrooptical device

InactiveUS7183229B2Promote crystallizationTransistorDrying solid materials with heatSingle crystalCrystallinity

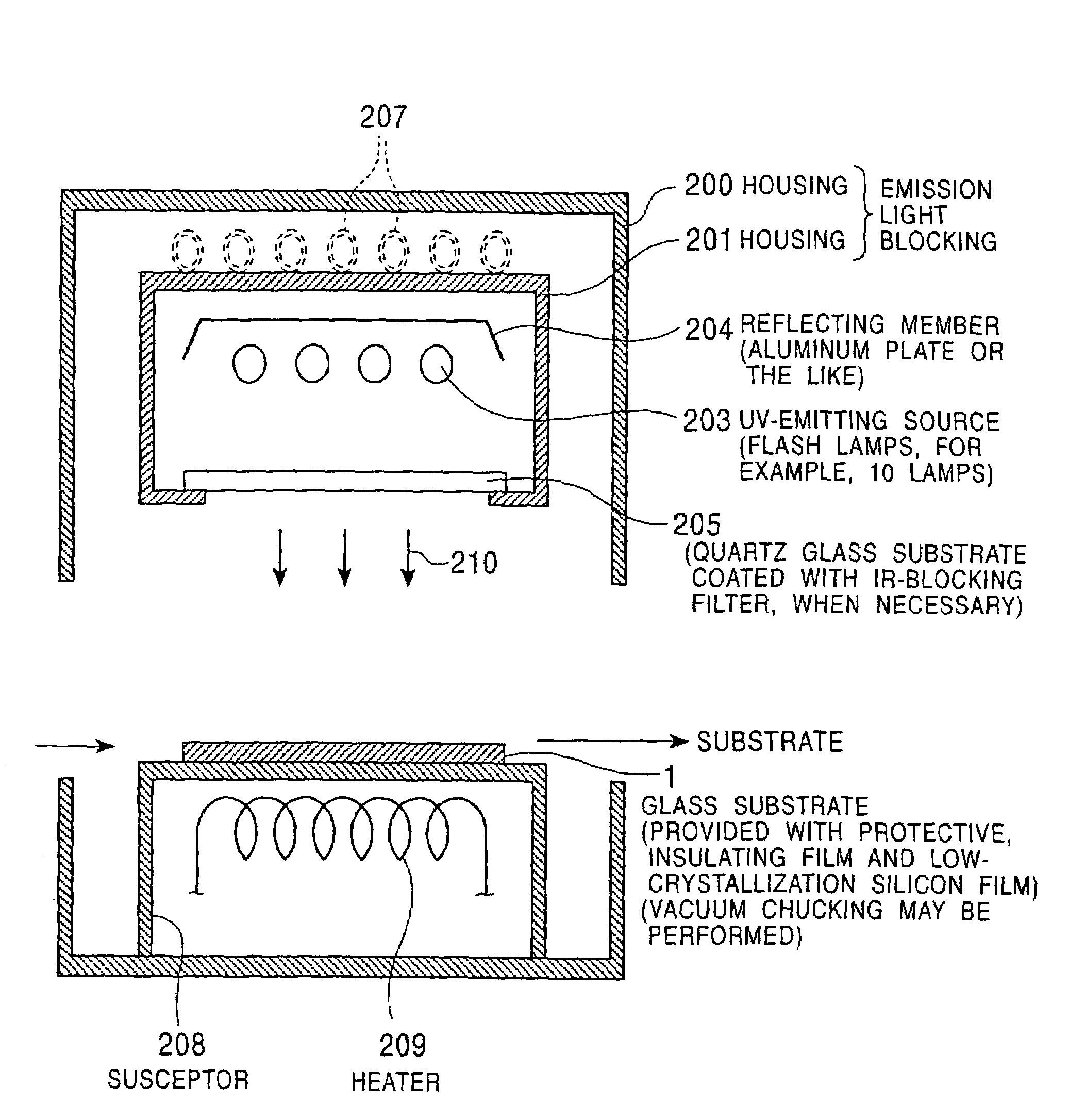

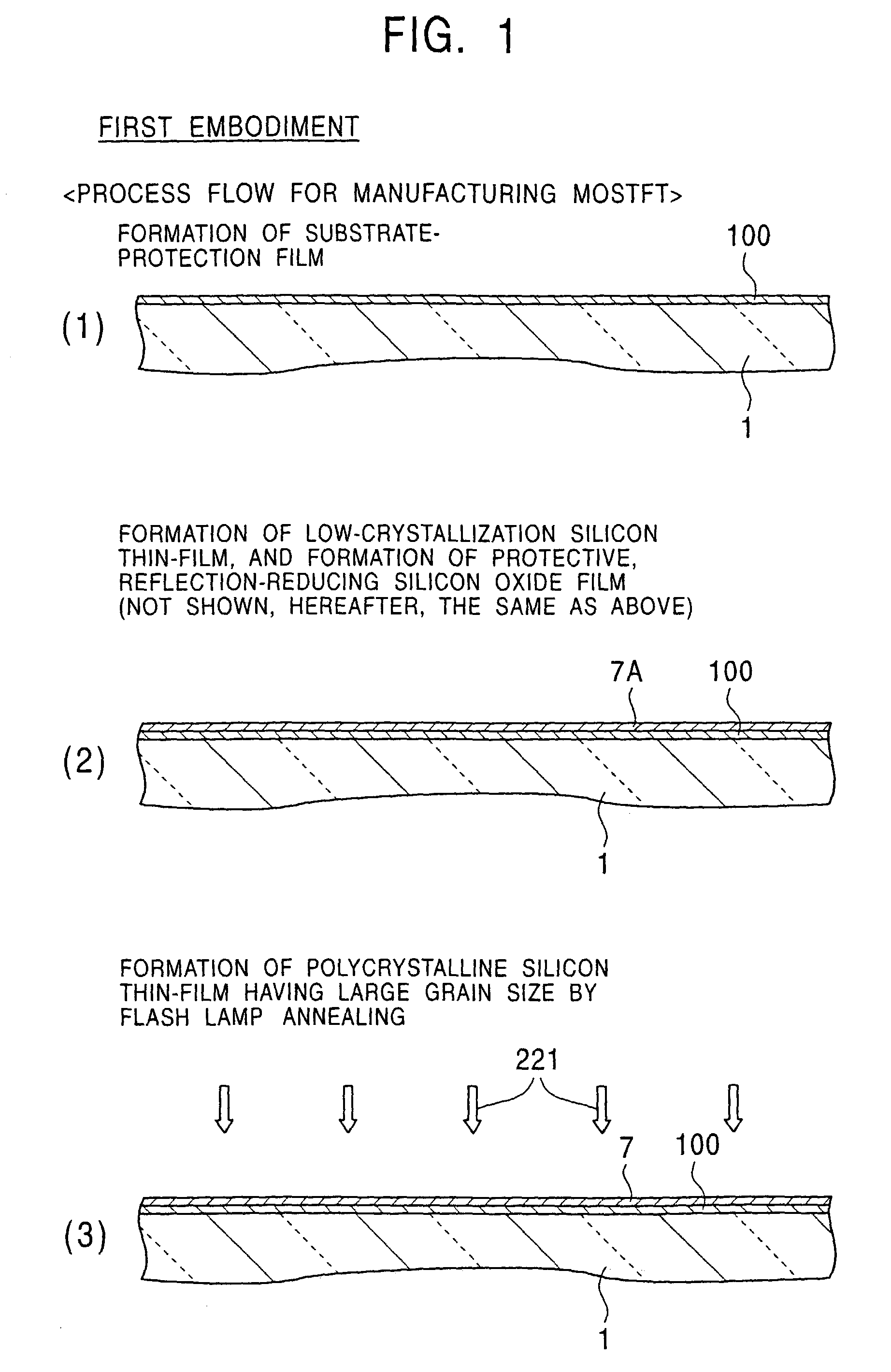

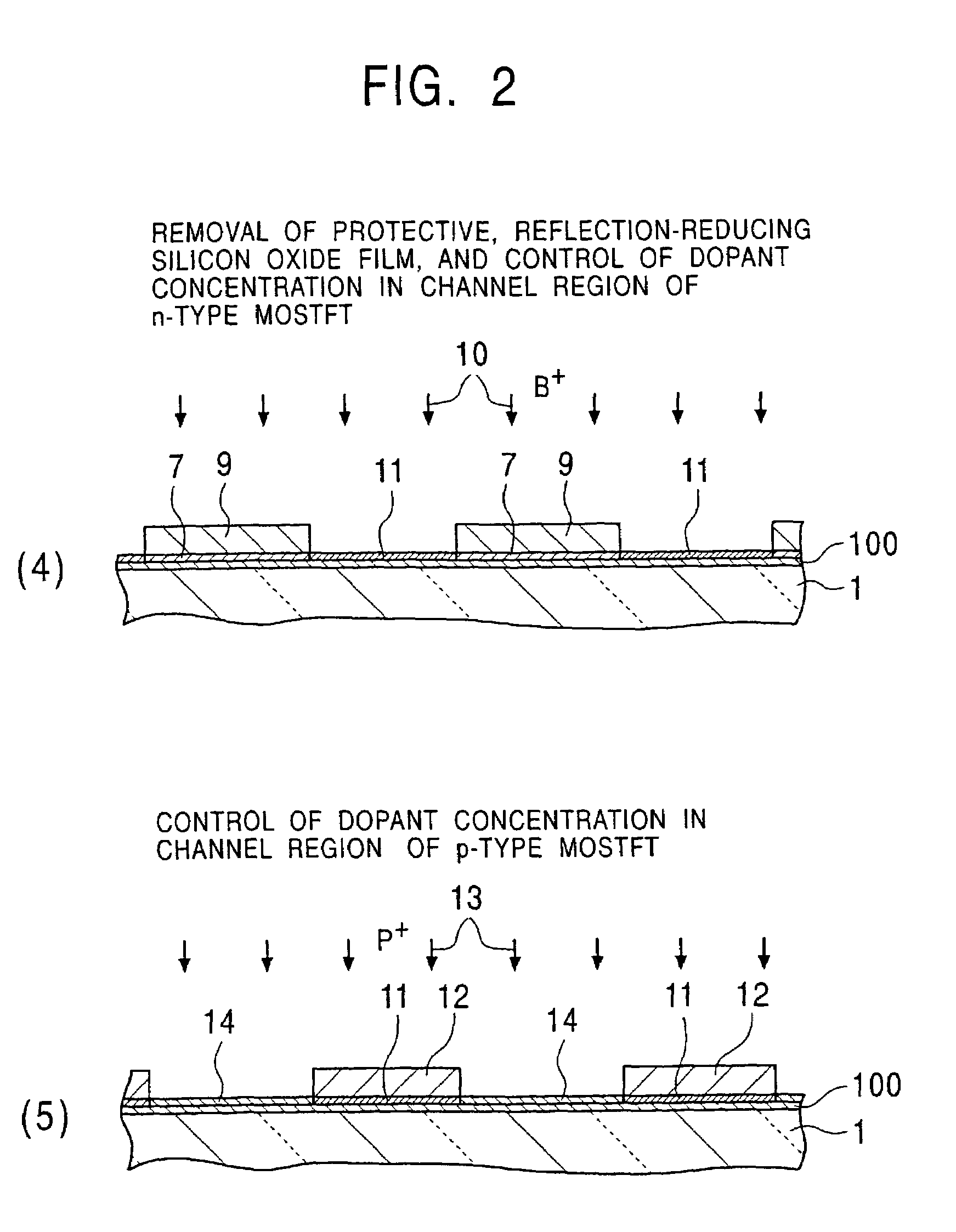

An object of the present invention is to provide a method for easily forming a polycrystalline semiconductor thin-film, such as polycrystalline silicon having high crystallinity and high quality, or a single crystalline semiconductor thin-film at inexpensive cost, the crystalline semiconductor thin-film having a large area, and to provide an apparatus for processing the method described above. In forming a polycrystalline (or single crystalline) semiconductor thin-film (7), such as a polycrystalline silicon thin-film, having high crystallinity and a large grain size on a substrate (1), or in forming a semiconductor device having the polycrystalline (or single crystalline) semiconductor thin-film (7) on the substrate (1), a method comprises forming a low-crystallization semiconductor thin-film (7A) on the substrate (1), and subsequently heating and cooling this low-crystallization semiconductor thin-film (7A) to a fusion, a semi-fusion, or a non-fusion state by flash lamp annealing to facilitate the crystallization of the low-crystallization semiconductor thin-film, whereby a polycrystalline (single crystalline) semiconductor thin-film (7) is obtained. A method for forming the semiconductor device and an apparatus for processing the methods are also disclosed.

Owner:SONY CORP

Process for the production of thin semiconductor material films

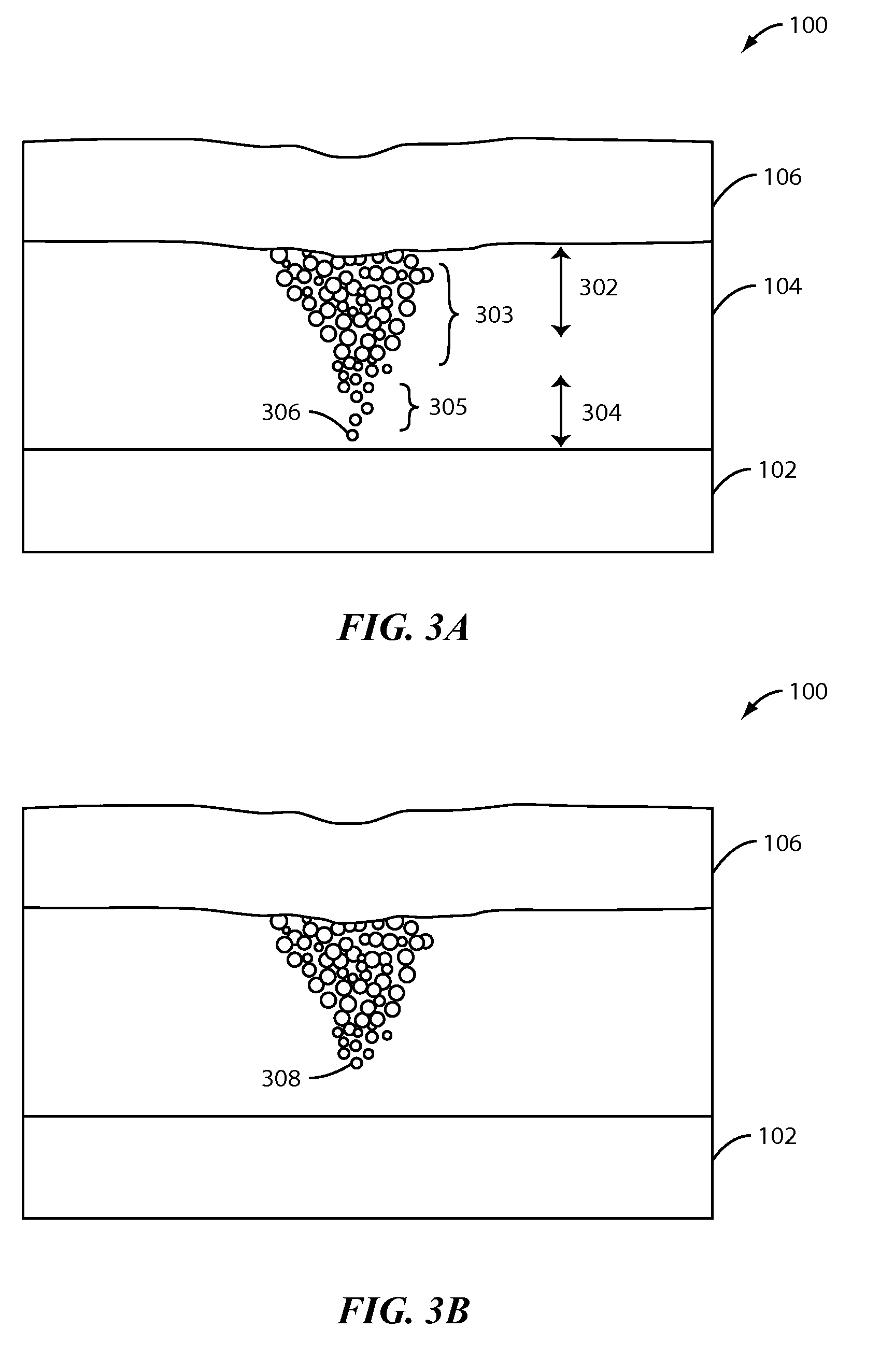

InactiveUSRE39484E1Uniform and controlled thicknessHigh implantationFluid pressure measurement by electric/magnetic elementsSolid-state devicesIon bombardmentMicrobubbles

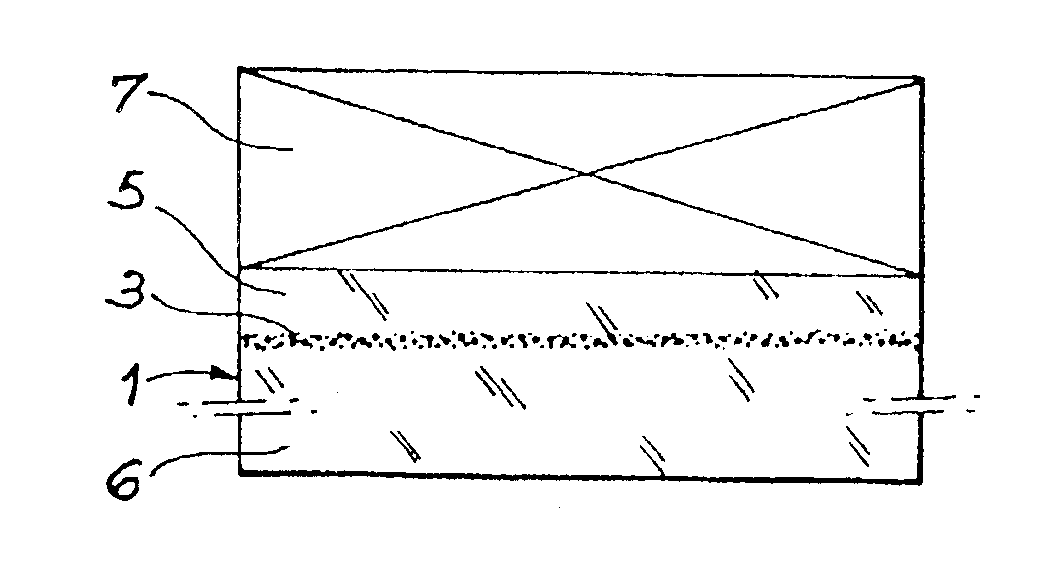

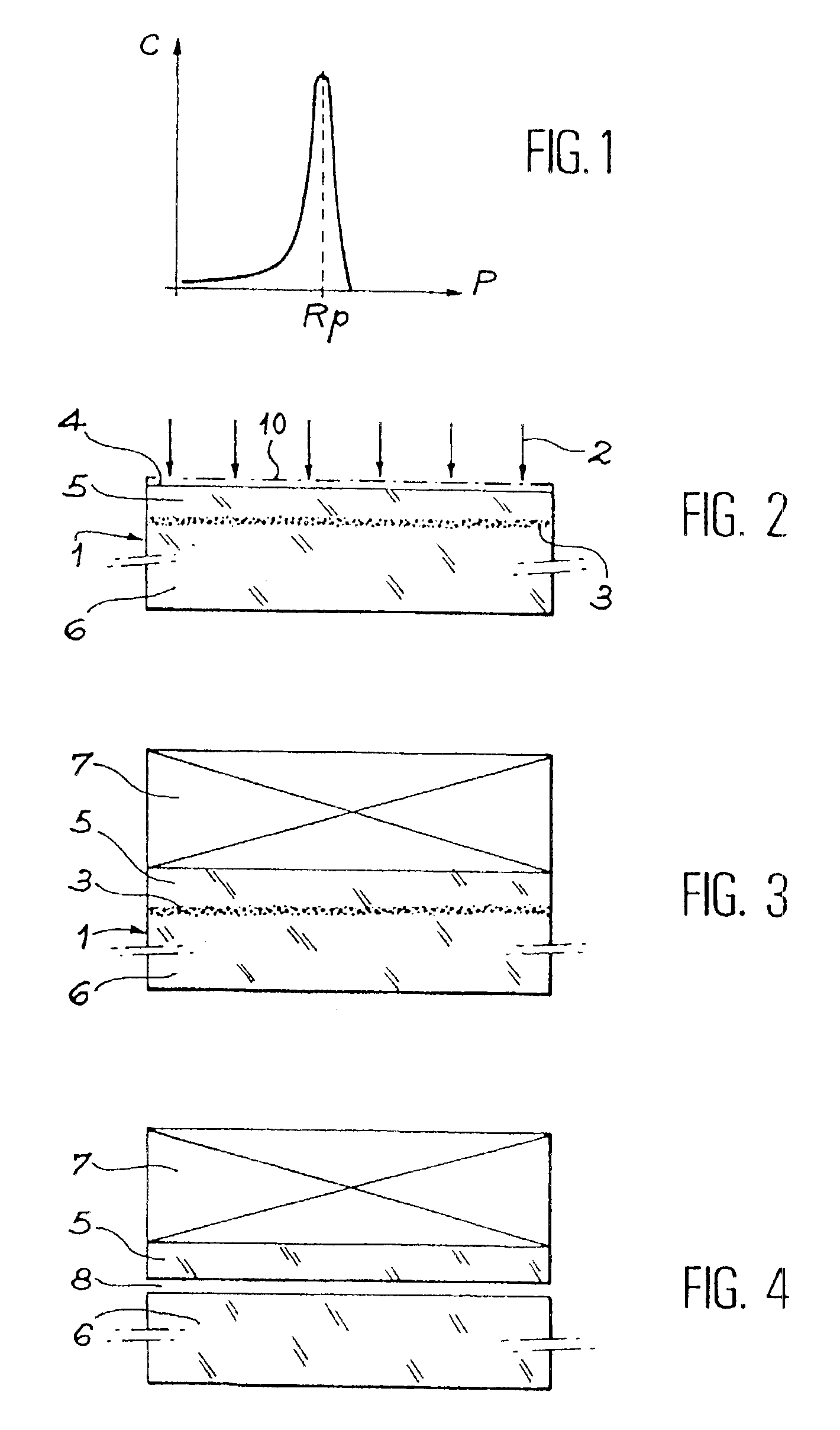

Process for the preparation of thin monocrystalline or polycrystalline semiconductor material films, characterized in that it comprises subjecting a semiconductor material wafer having a planar face to the three following stages: a first stage of implantation by bombardment (2) of the face (4) of the said wafer (1) by means of ions creating in the volume of said wafer a layer (3) of gaseous microbubbles defining in the volume of said wafer a lower region (6) constituting the mass of the substrate and an upper region (5) constituting the thin film, a second stage of intimately contacting the planar face (4) of said wafer with a stiffener (7) constituted by at least one rigid material layer, a third stage of heat treating the assembly of said wafer (1) and said stiffener (7) at a temperature above that at which the ion bombardment (2) was carried out and sufficient to create by a crystalline rearrangement effect in said wafer (1) and a pressure effect in the said microbubbles, a separation between the thin film (5) and the mass of the substrate (6).

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

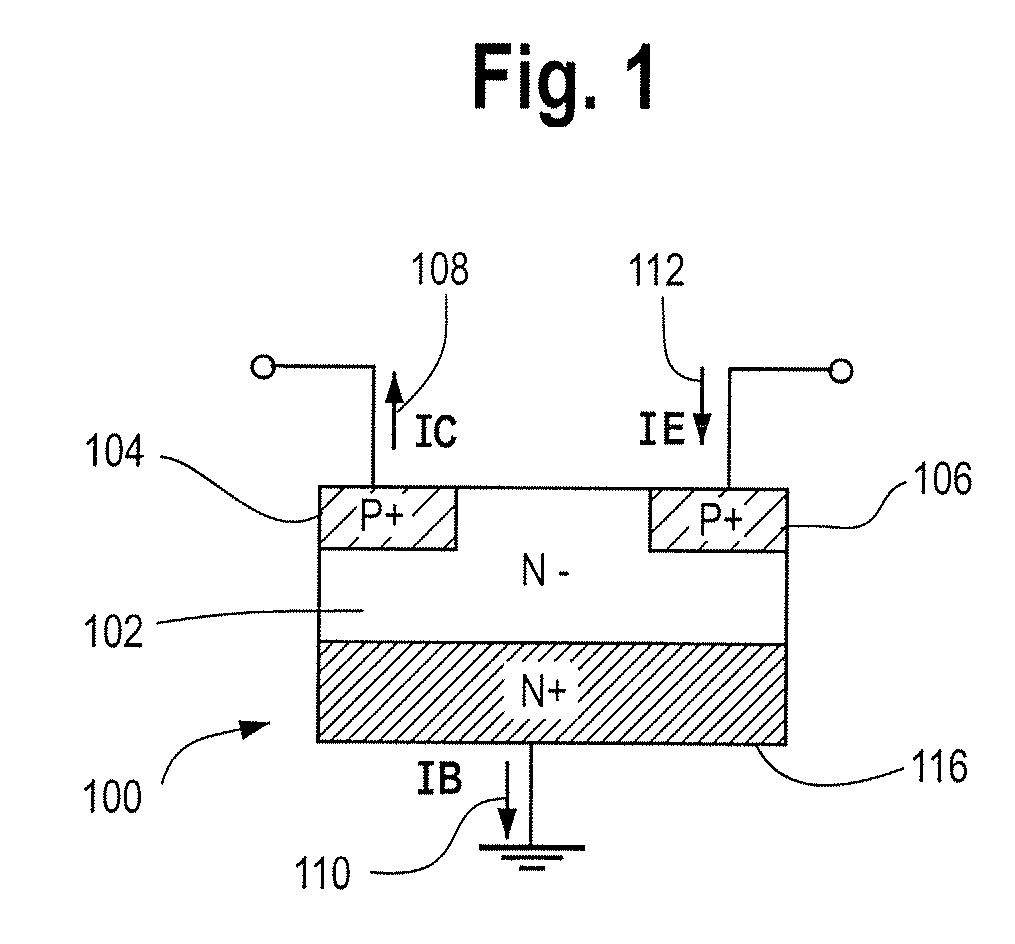

Semiconductor device

InactiveUS7795619B2Inhibit deteriorationPrevent short-circuitingSemiconductor/solid-state device detailsSolid-state devicesTransistorPhysics

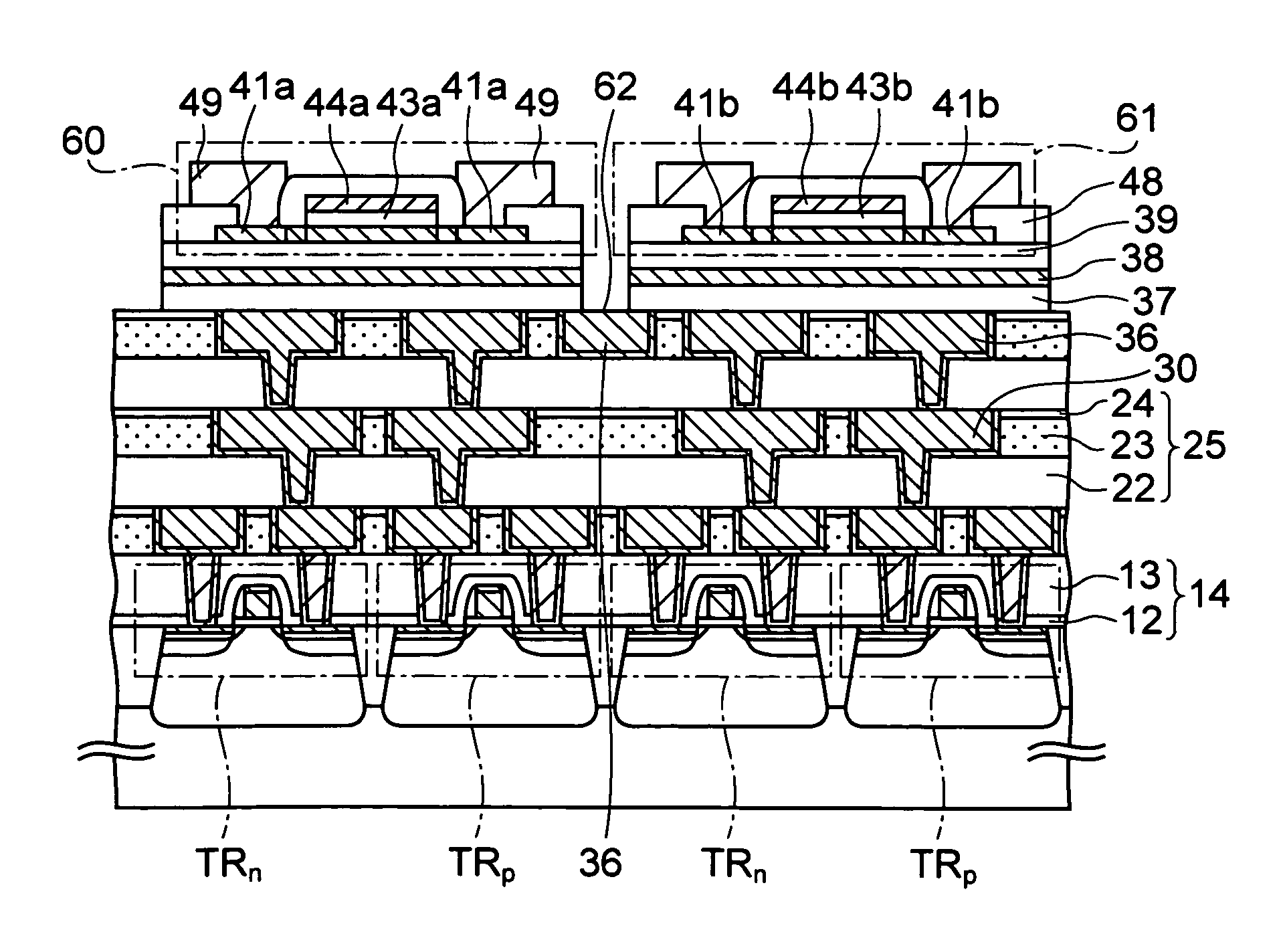

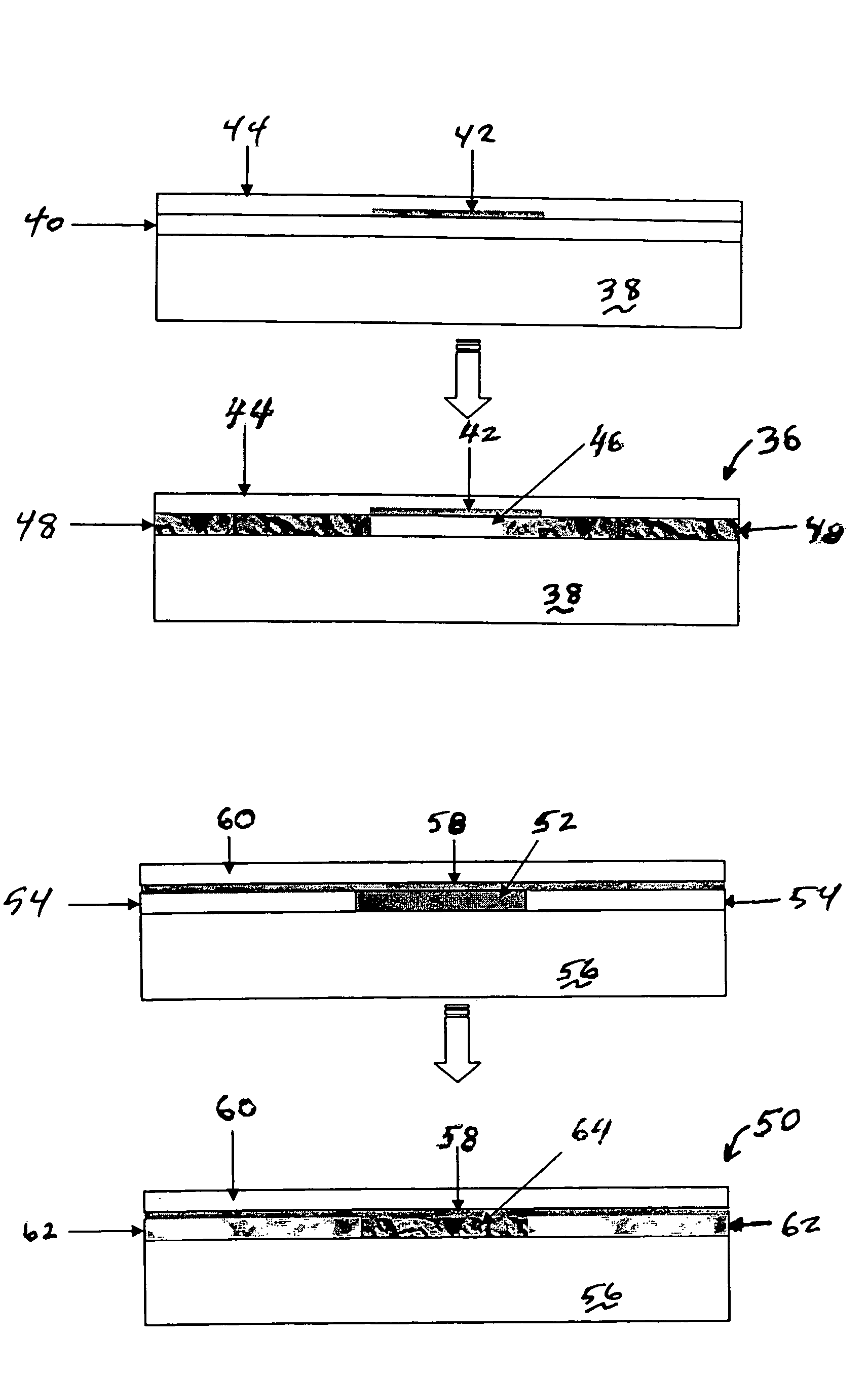

A method for manufacturing a semiconductor device, including the steps of: forming a shielding film 38 on a first insulating film 37; sequentially forming a second insulating film 39 and an amorphous semiconductor film 40 on the shielding film 38; melting the amorphous semiconductor film 40 at least in portions to be channels of thin-film transistors by irradiating an energy beam onto the amorphous semiconductor film 40, and converting the amorphous semiconductor film 40 into a polycrystalline semiconductor film 41; sequentially forming a gate insulating film 43a and a gate electrode 44a on the polycrystalline semiconductor film 41 on the channels; and forming source and drain regions 41a in the polycrystalline semiconductor film 41 on sides of the gate electrode 44a, and forming a TFT 60 by use of the source and drain regions 41a, the gate insulating film 43a, and the gate electrode 44a.

Owner:FUJITSU SEMICON LTD

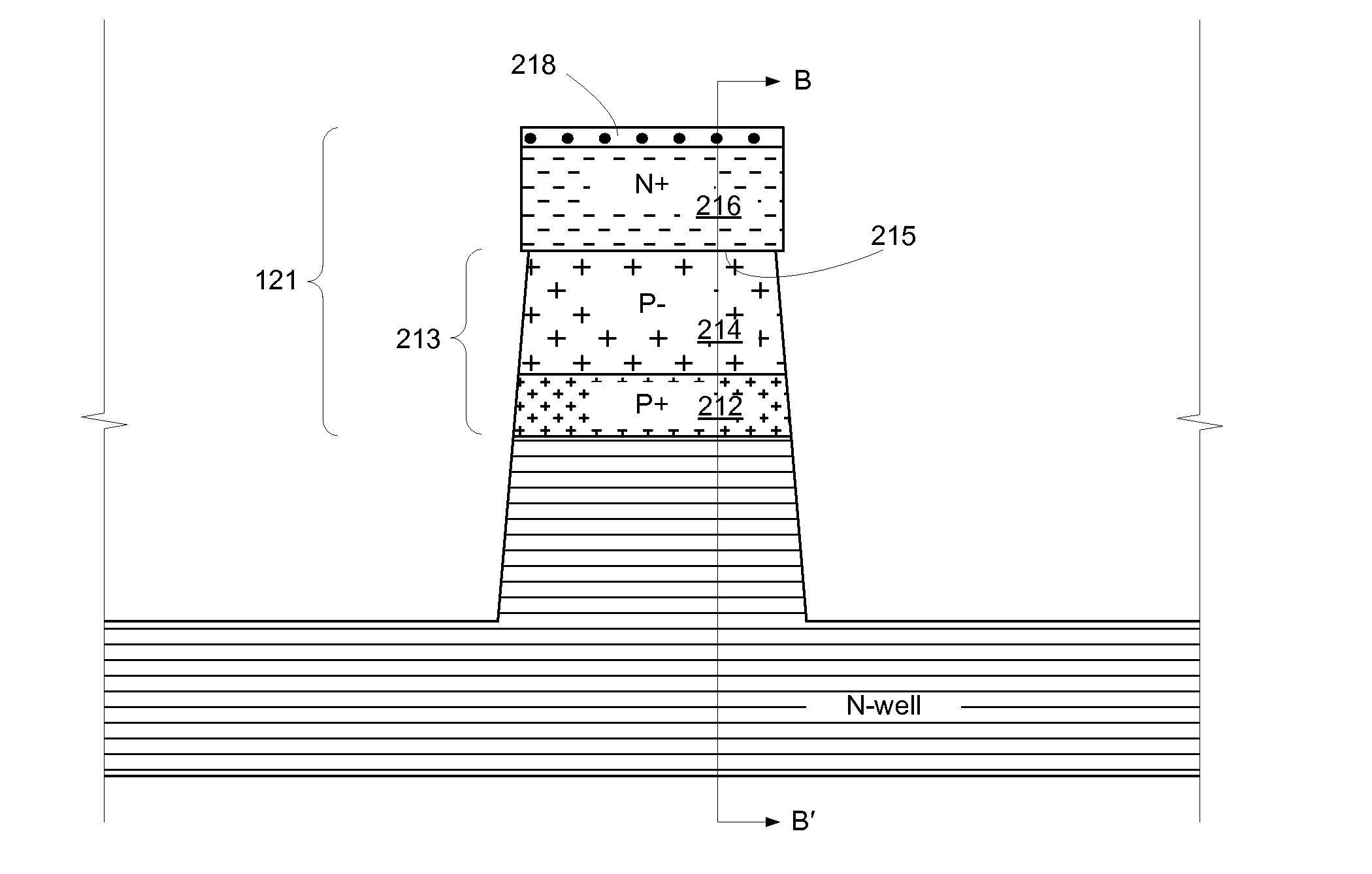

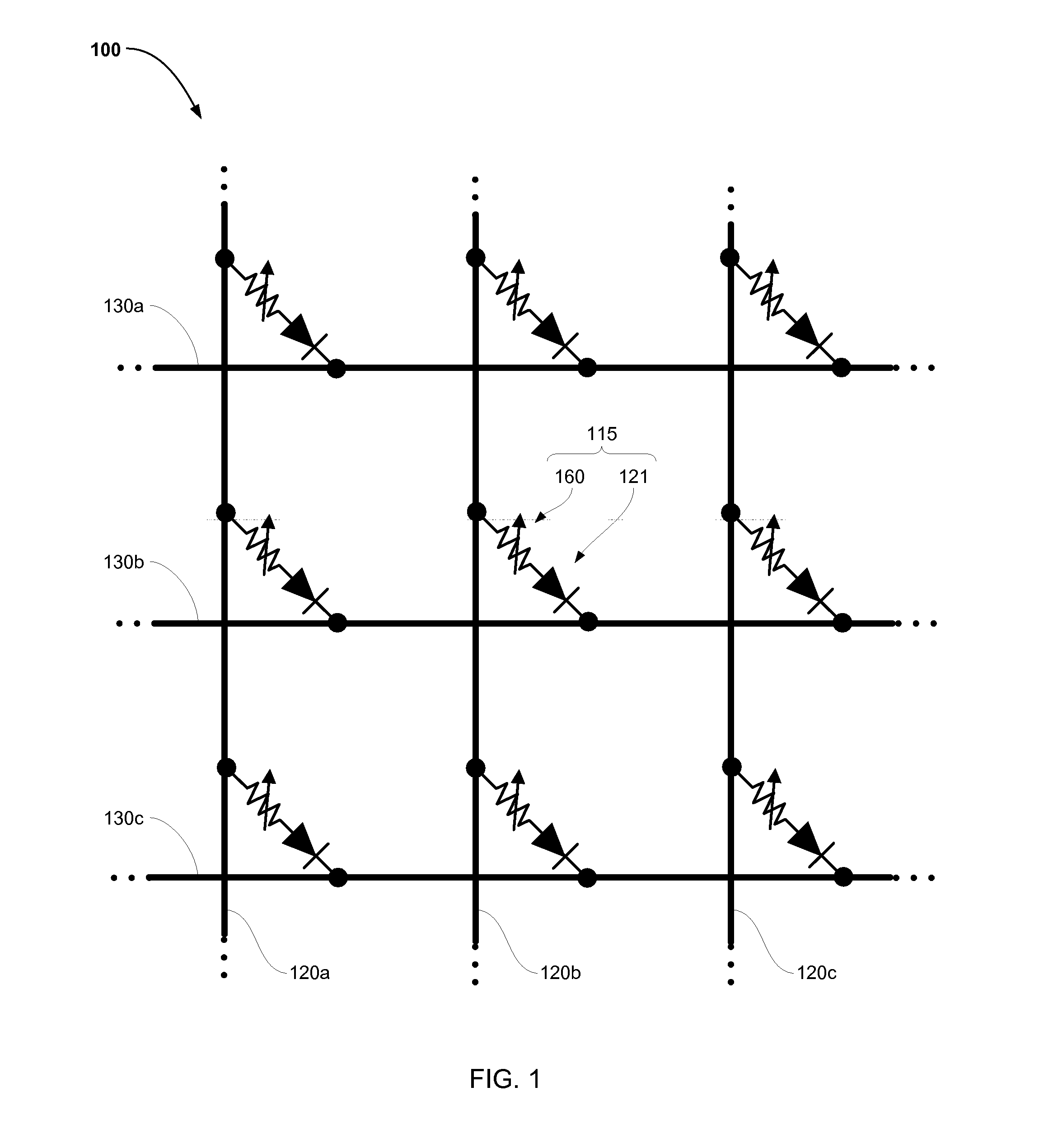

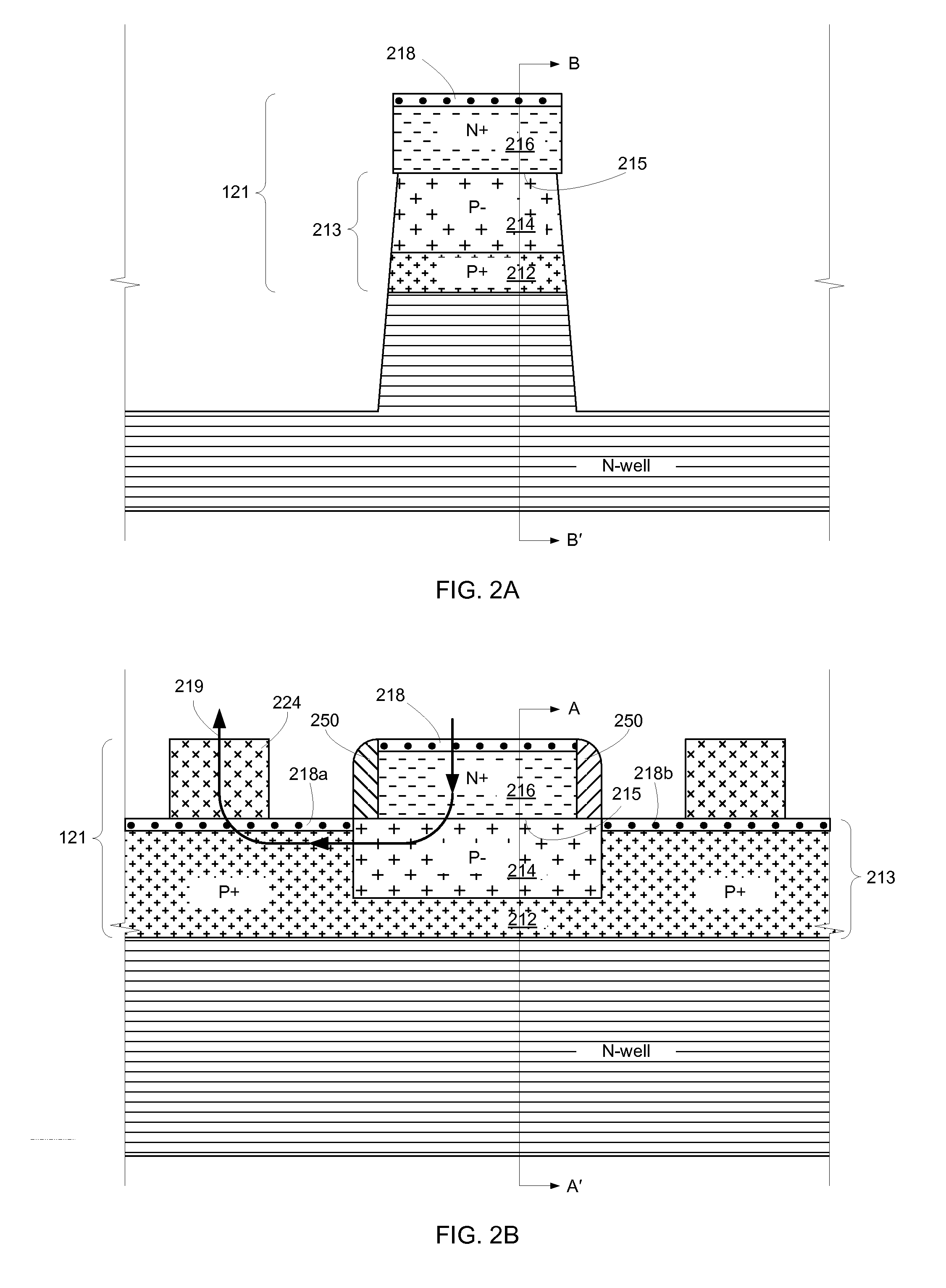

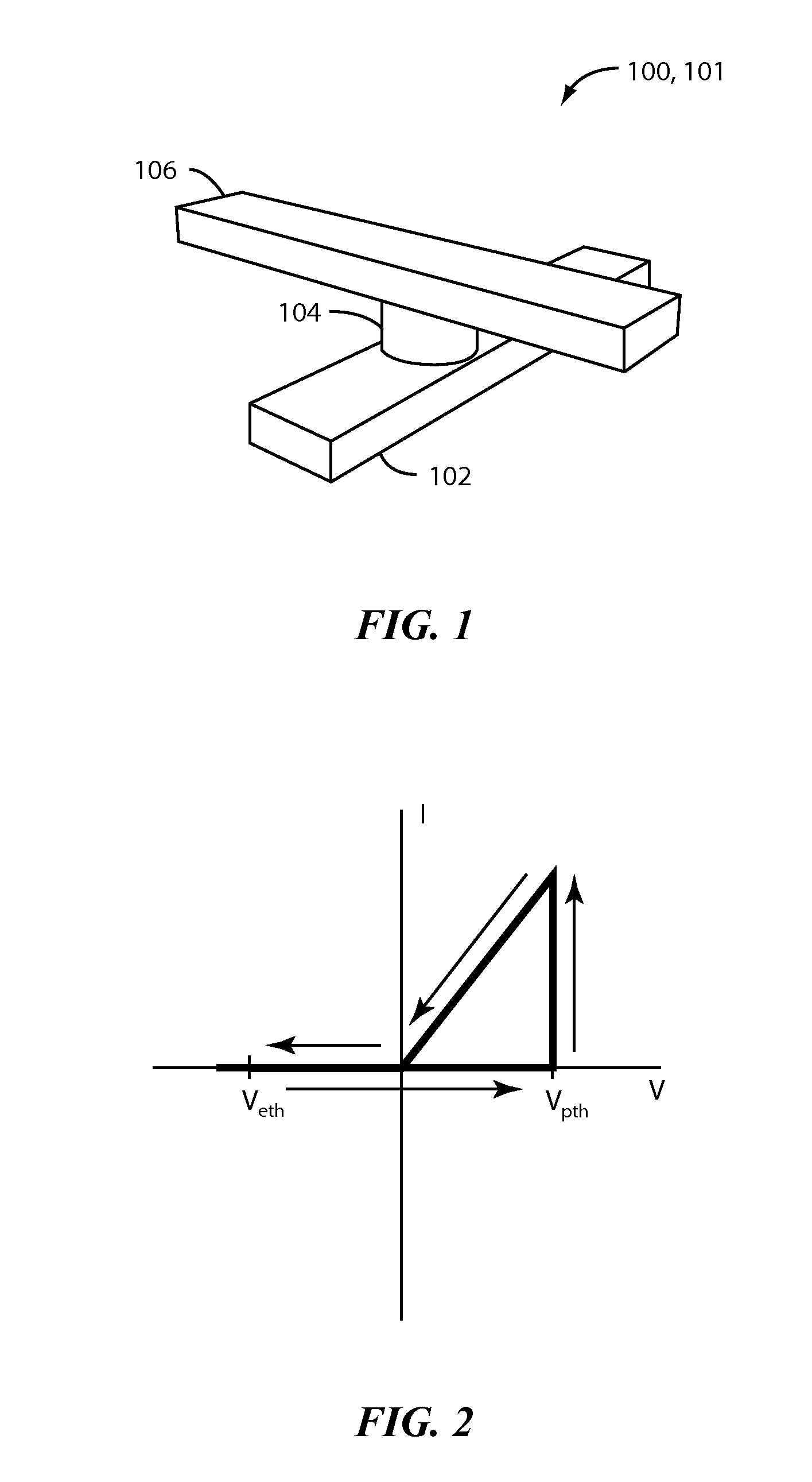

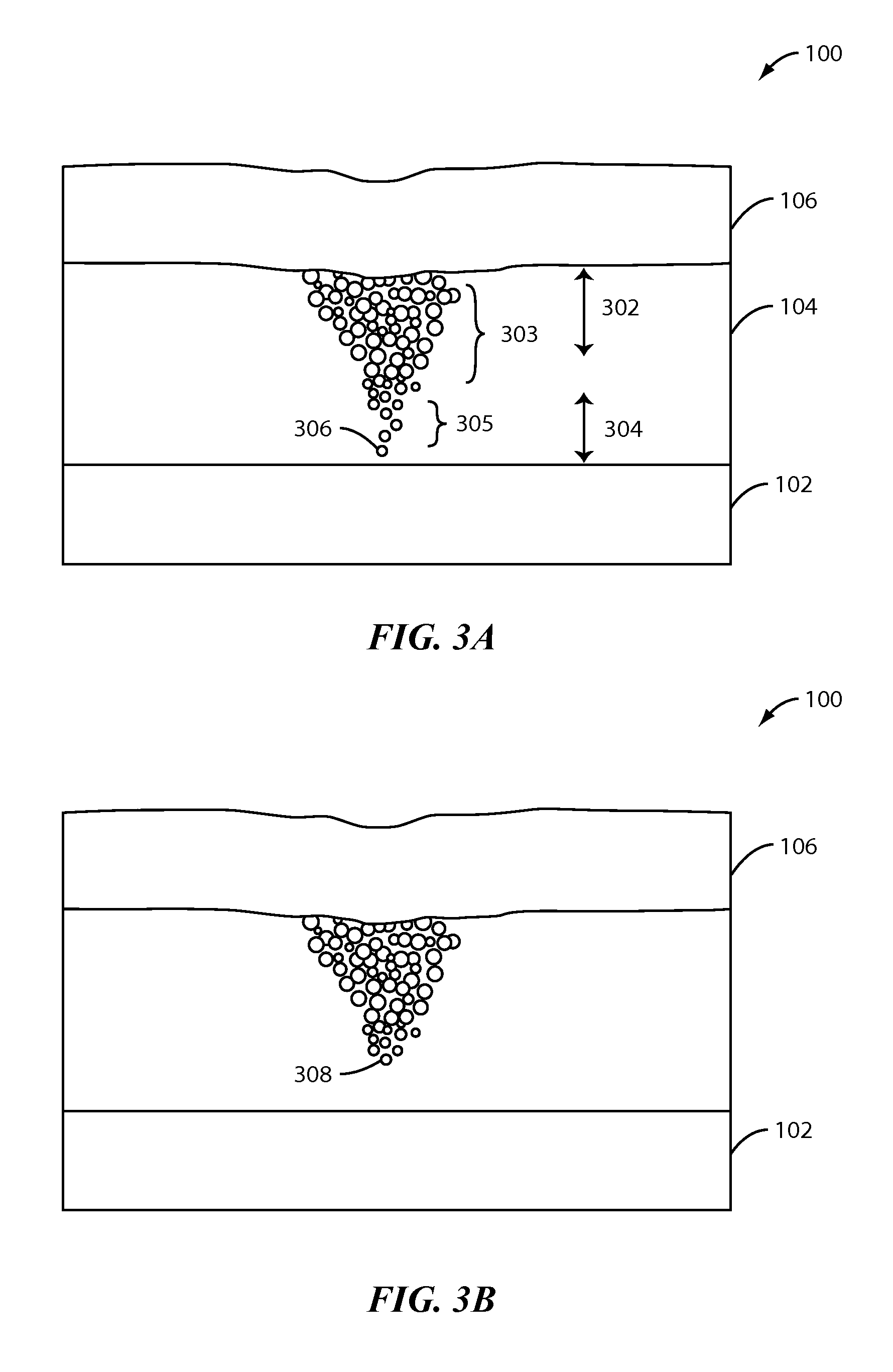

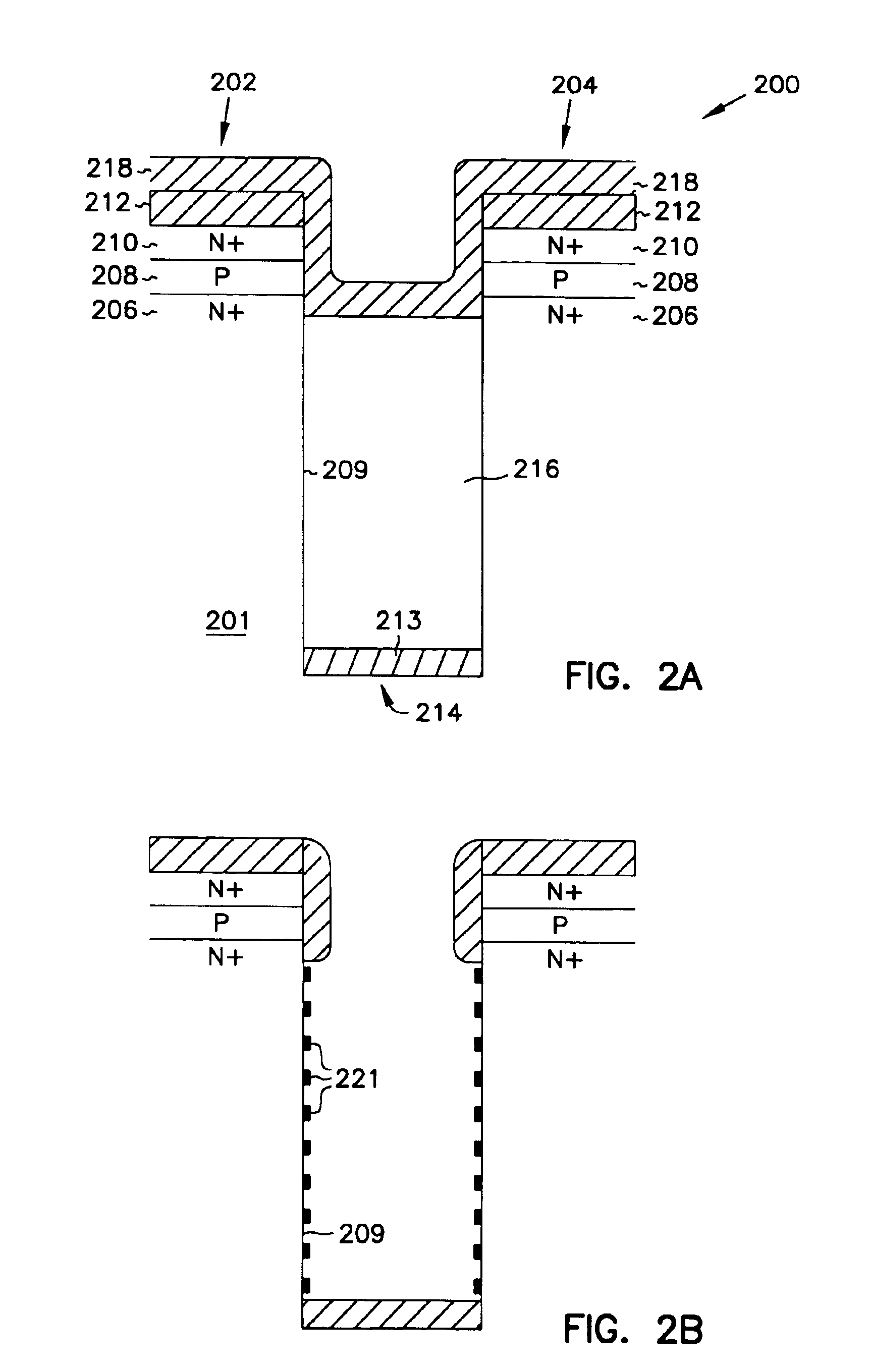

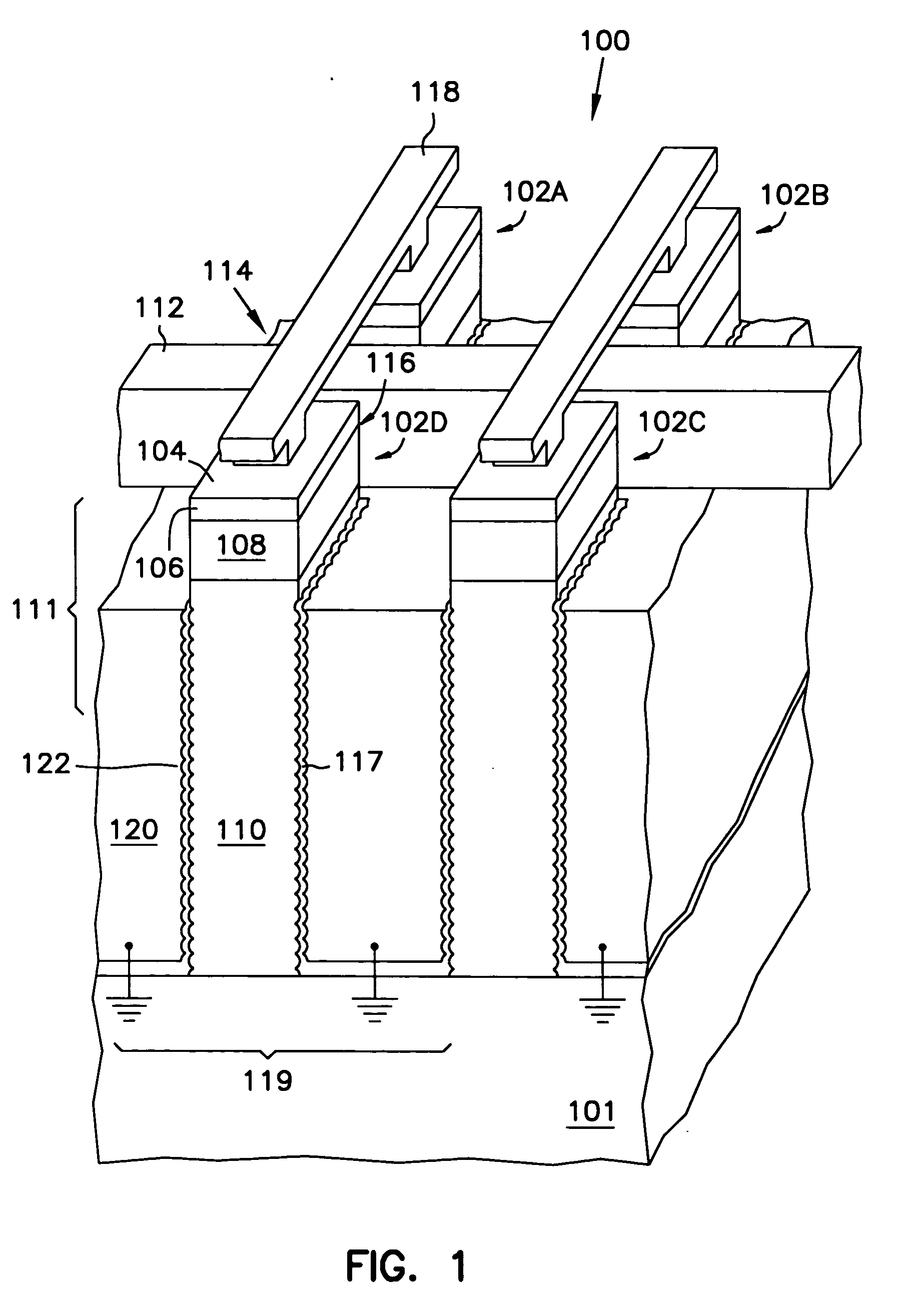

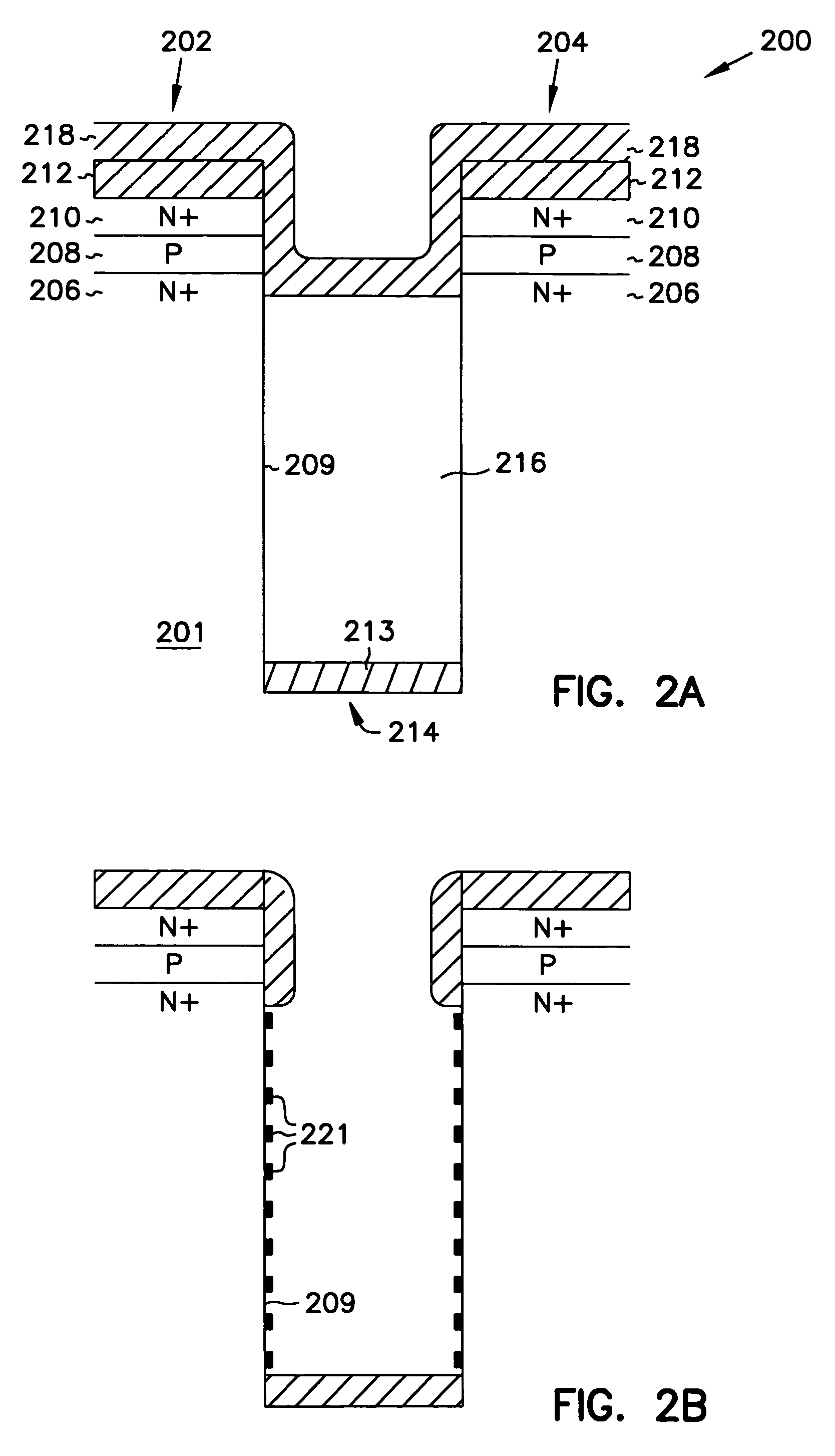

Memory cell access device having a pn-junction with polycrystalline and single-crystal semiconductor regions

ActiveUS20100117048A1Inhibited DiffusionImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingSingle crystalP–n junction

A memory device includes a driver comprising a pn-junction in the form of a multilayer stack including a first doped semiconductor region having a first conductivity type, and a second doped semiconductor region having a second conductivity type opposite the first conductivity type, the first and second doped semiconductors defining a pn-junction therebetween, in which the first doped semiconductor region is formed in a single-crystalline semiconductor, and the second doped semiconductor region includes a polycrystalline semiconductor. Also, a method for making a memory device includes forming a first doped semiconductor region of a first conductivity type in a single-crystal semiconductor, such as on a semiconductor wafer; and forming a second doped polycrystalline semiconductor region of a second conductivity type opposite the first conductivity type, defining a pn-junction between the first and second regions.

Owner:MACRONIX INT CO LTD

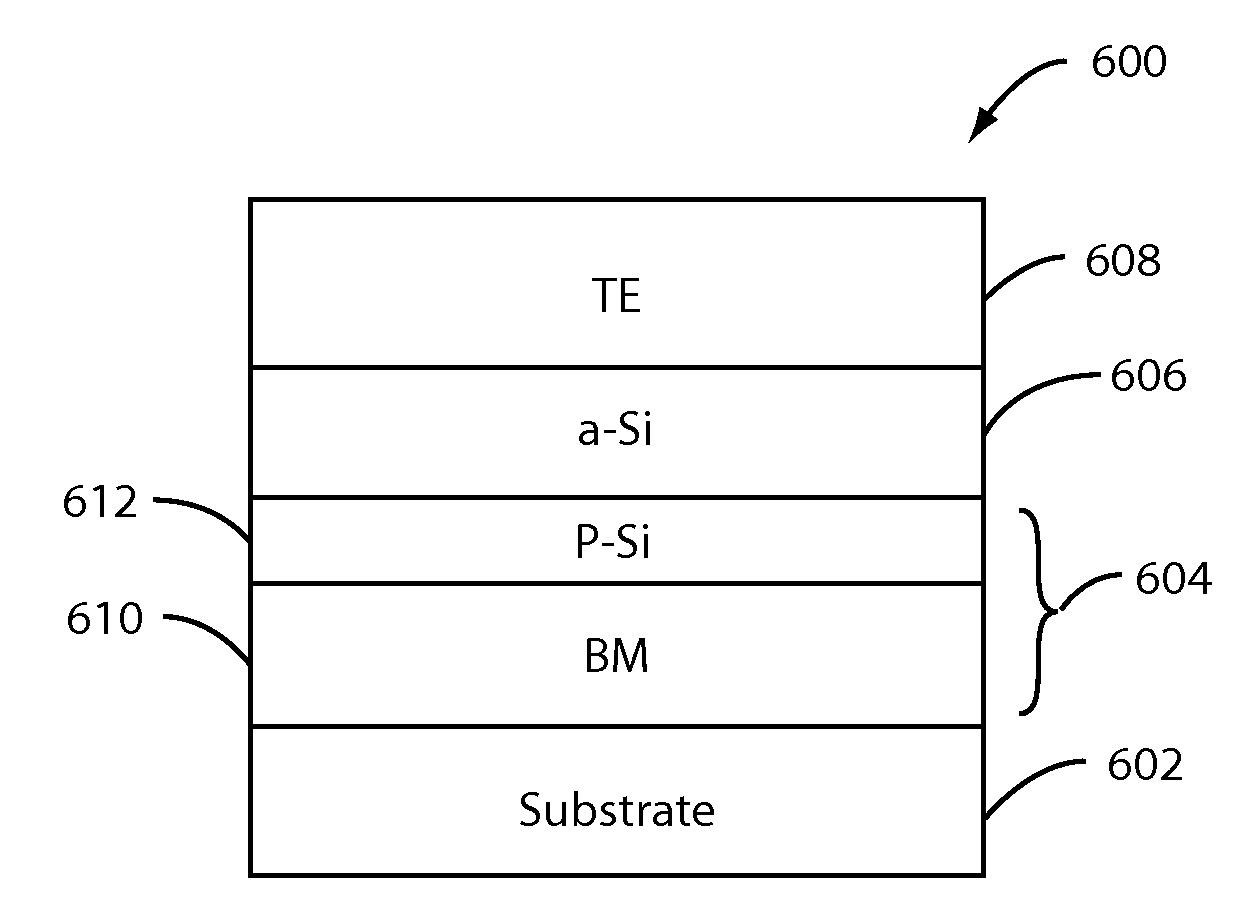

RESTIVE MEMORY USING SiGe MATERIAL

ActiveUS20120008366A1Solid-state devicesSemiconductor/solid-state device manufacturingAmorphous siliconCrystalline silicon

A resistive memory device includes a first electrode; a second electrode having a polycrystalline semiconductor layer that includes silicon; a non-crystalline silicon structure provided between the first electrode and the second electrode. The first electrode, second electrode and non-crystalline silicon structure define a two-terminal resistive memory cell.

Owner:INNOSTAR SEMICON SHANGHAI CO LTD

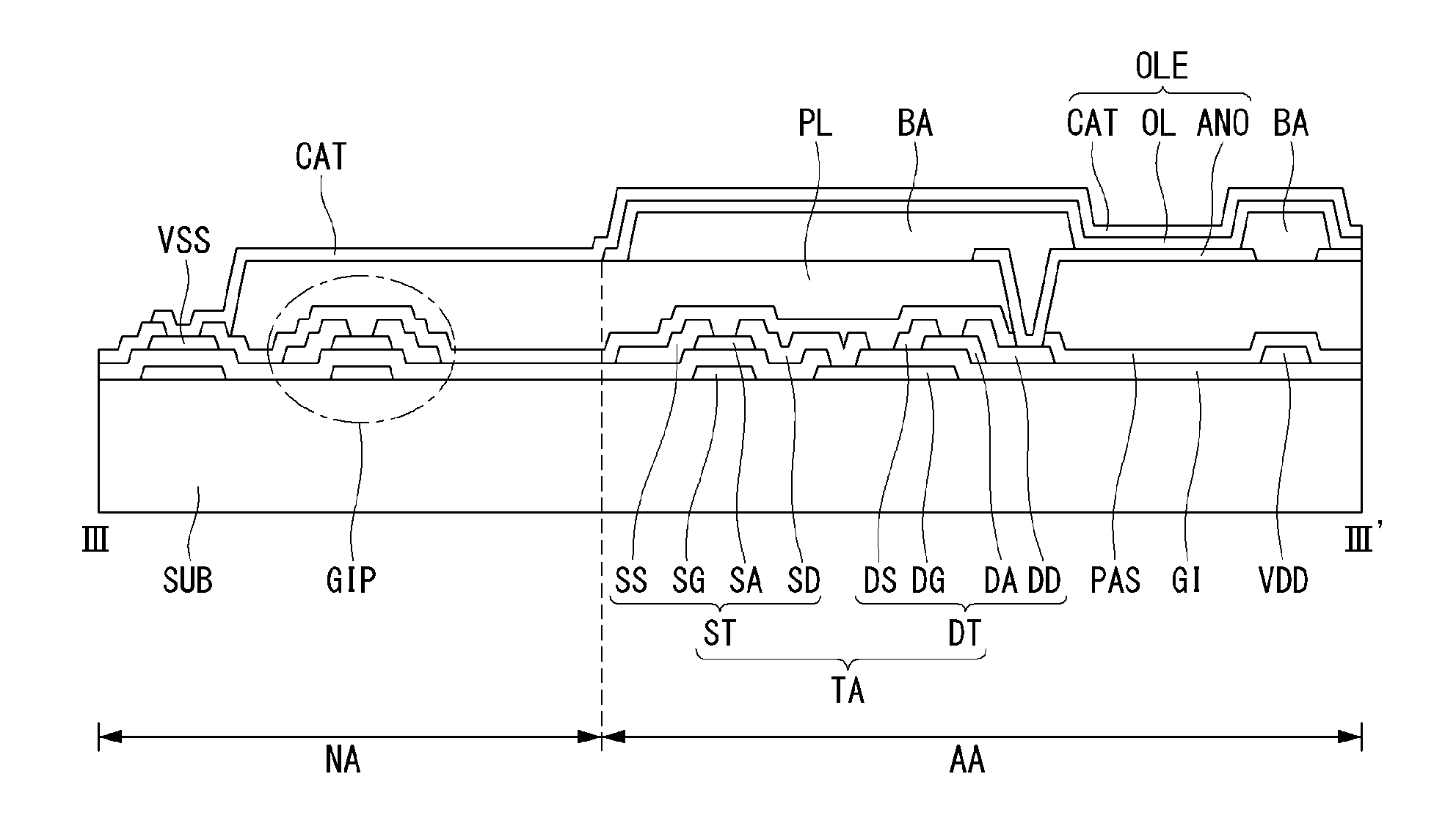

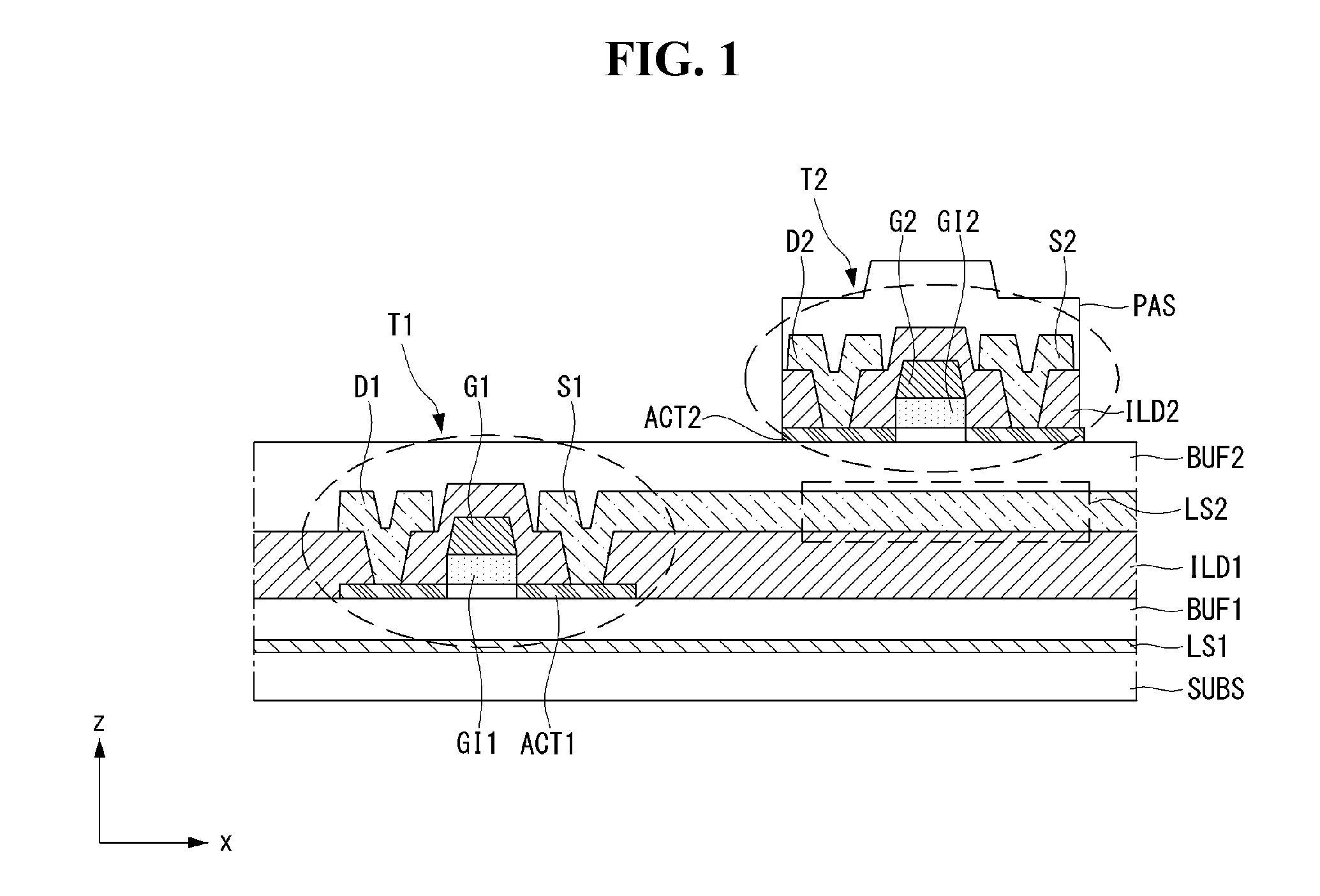

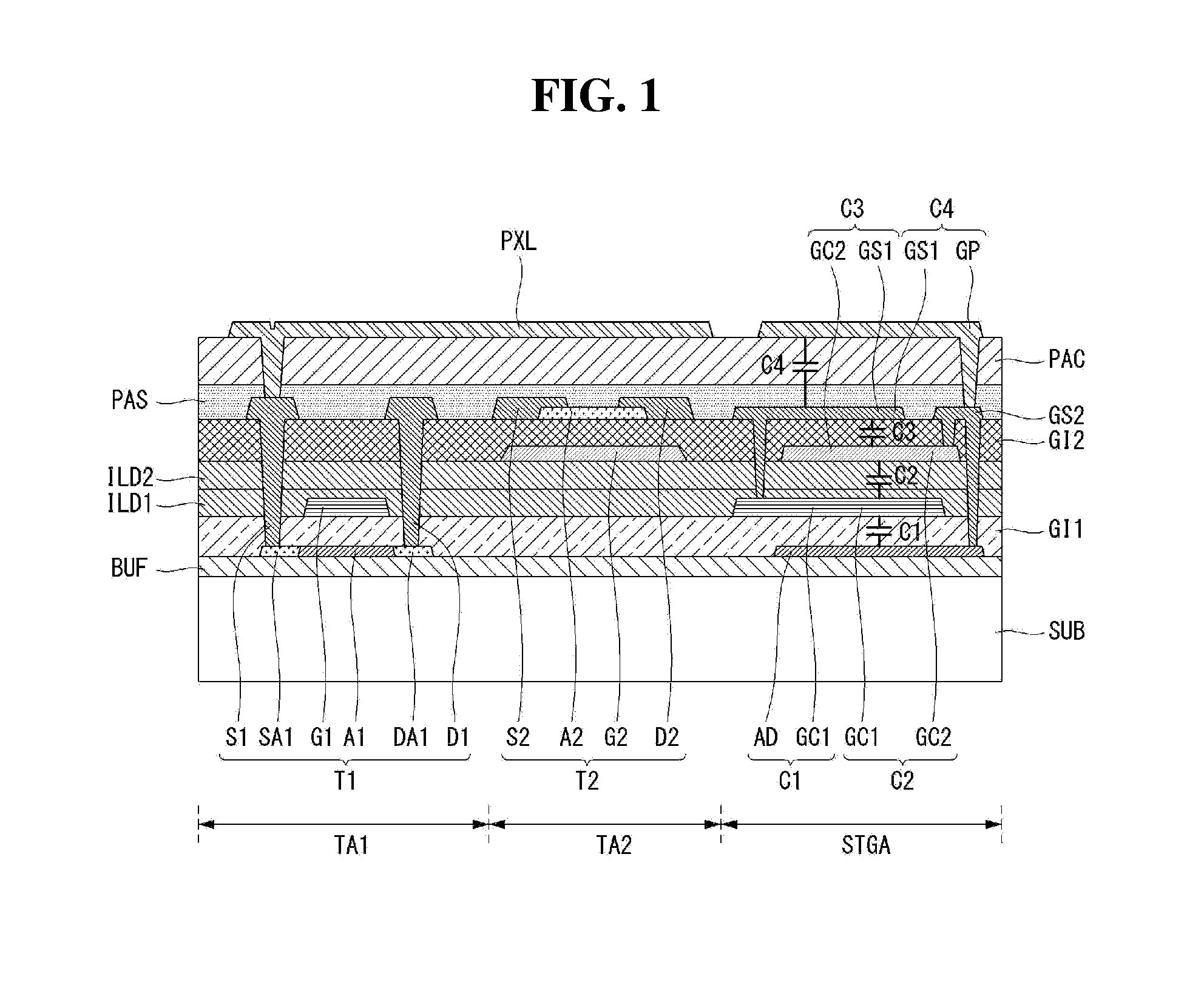

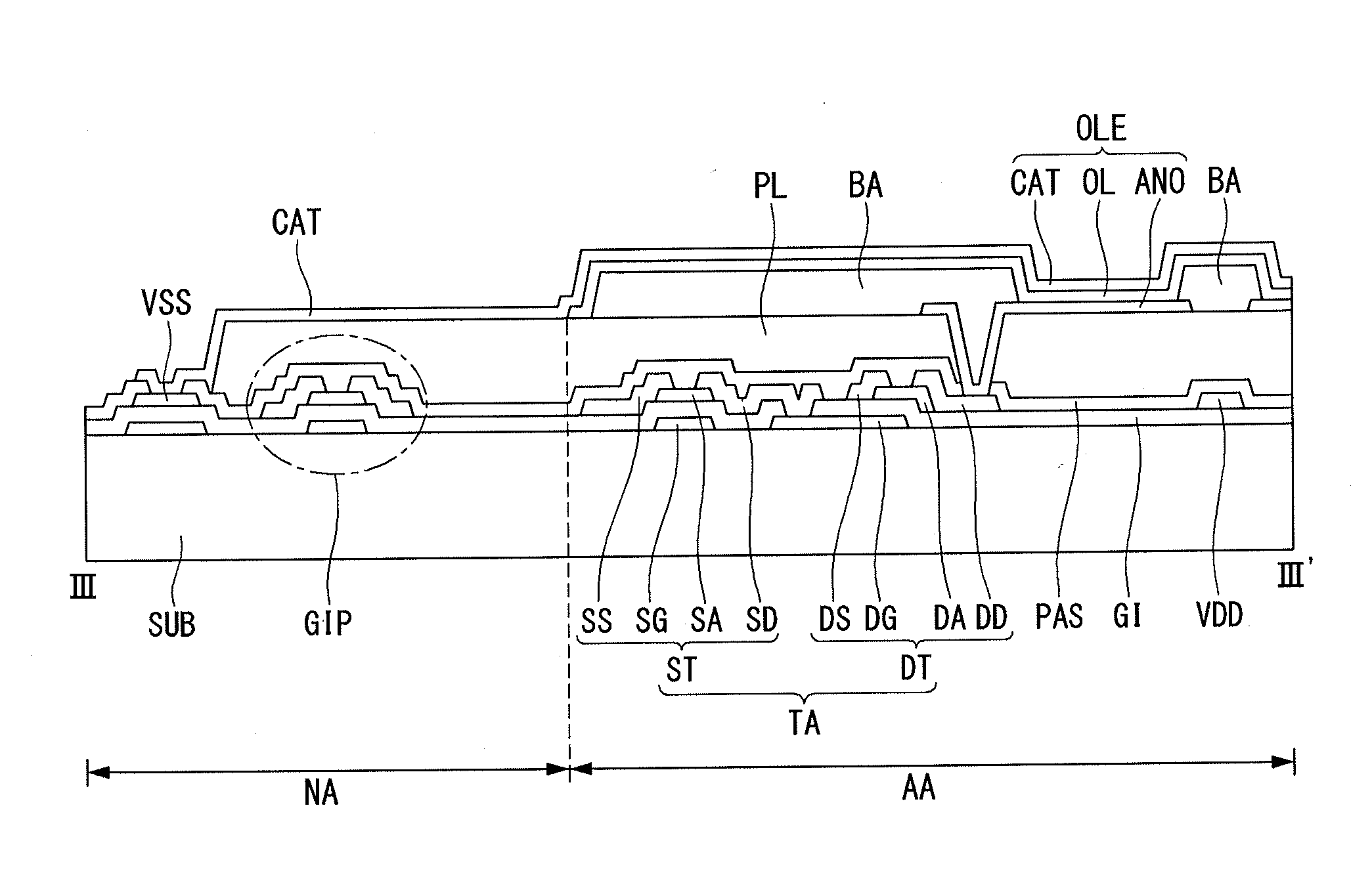

Thin film transistor substrate and display device using the same

ActiveUS20160064421A1Efficient preparationReduce in quantityTransistorSolid-state devicesDisplay deviceEngineering

A thin film transistor (TFT) substrate and a display device using the same are disclosed. The TFT substrate includes a base substrate, a first TFT having a polycrystalline semiconductor and disposed on the base substrate, and a second TFT having an oxide semiconductor and disposed on the first TFT. The second TFT overlaps at least a portion of the first TFT in a plan view.

Owner:LG DISPLAY CO LTD

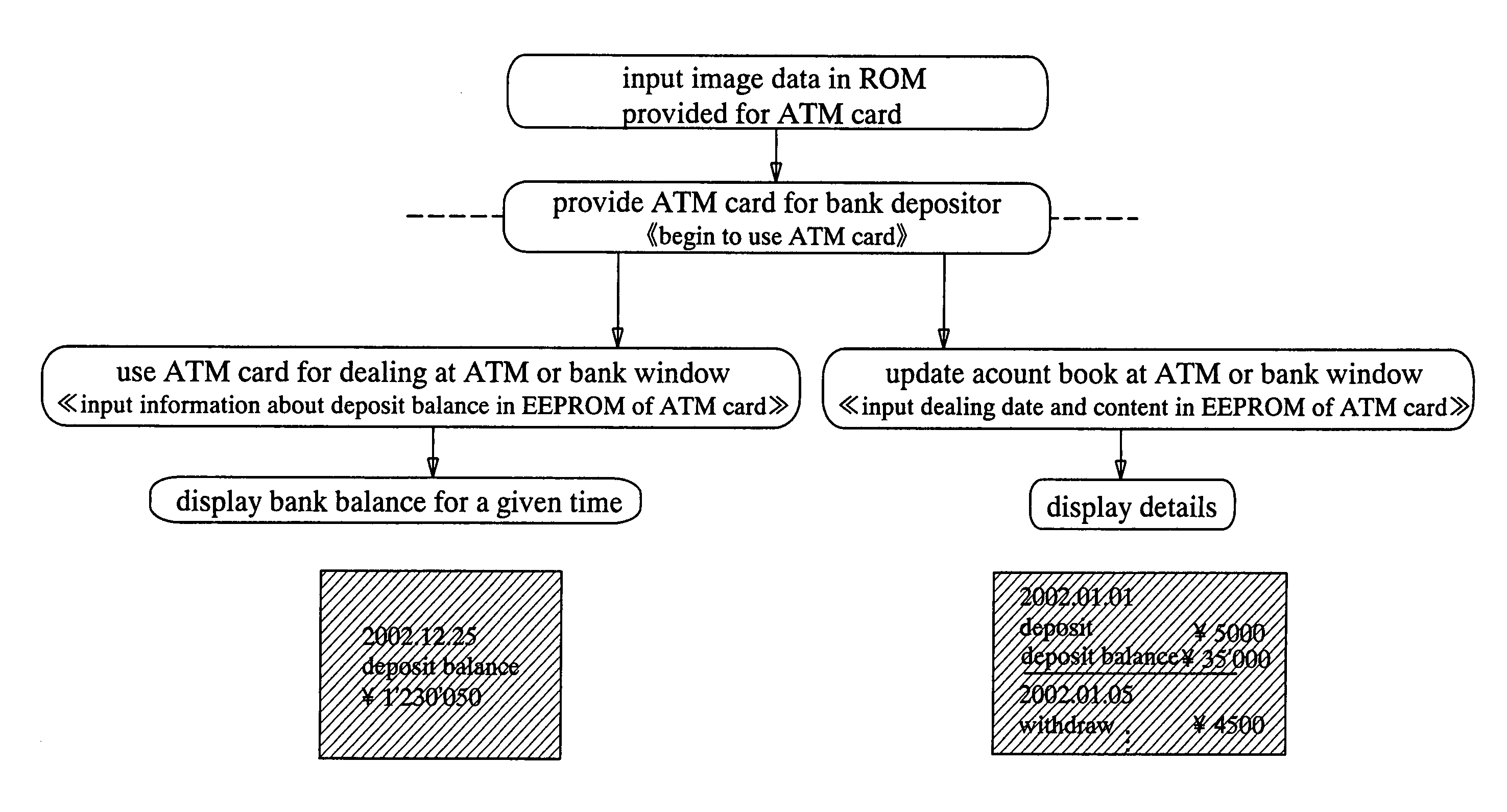

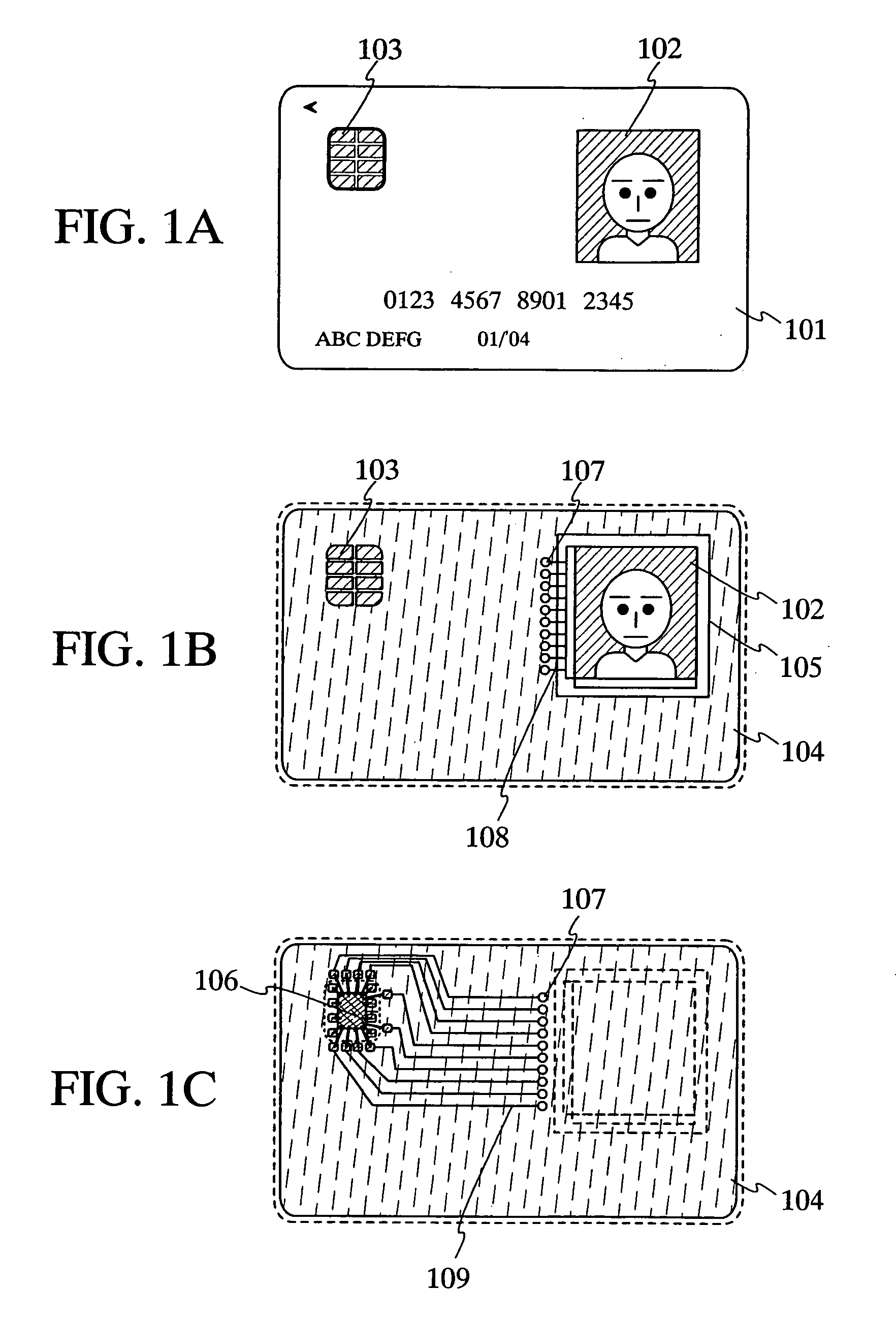

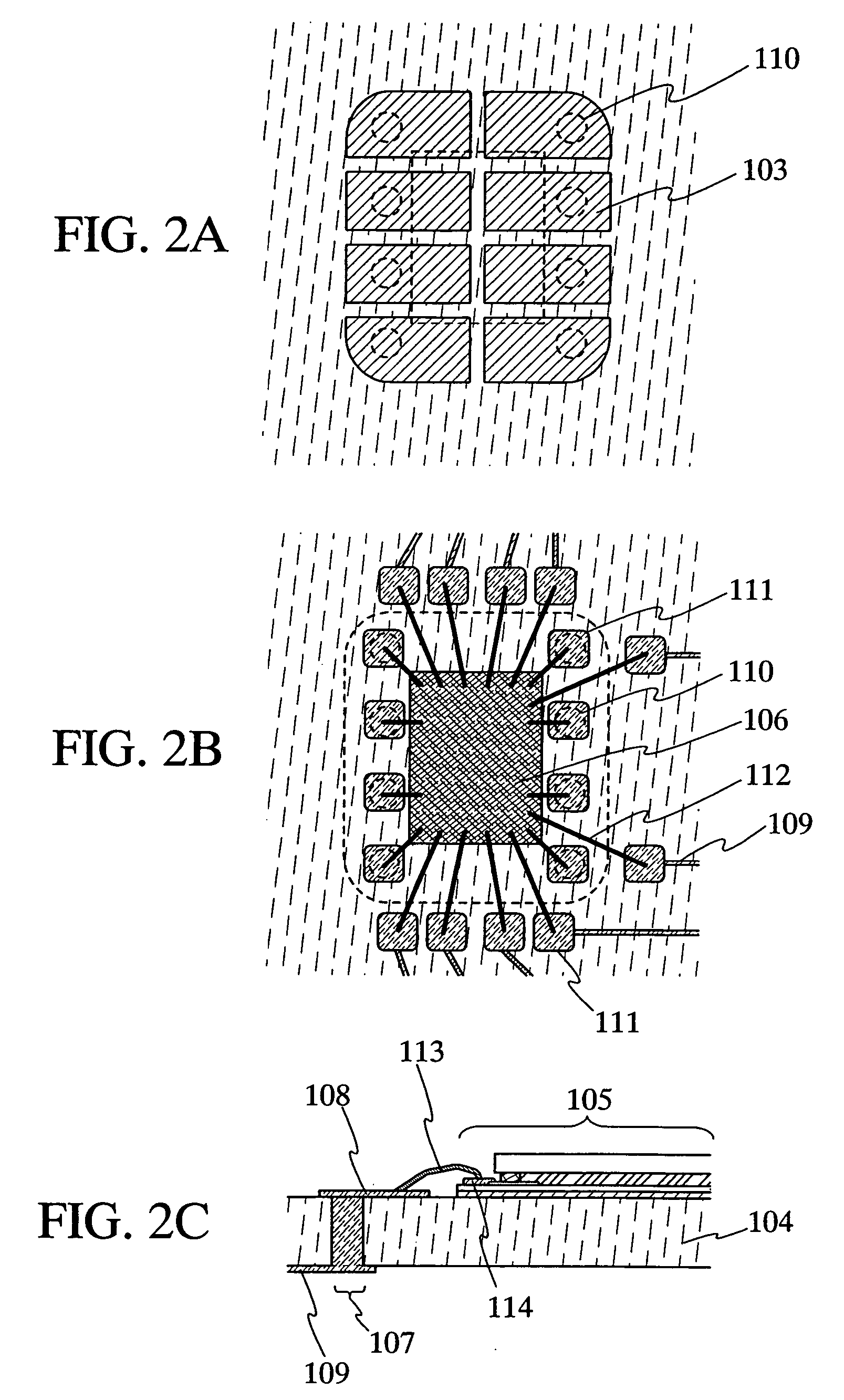

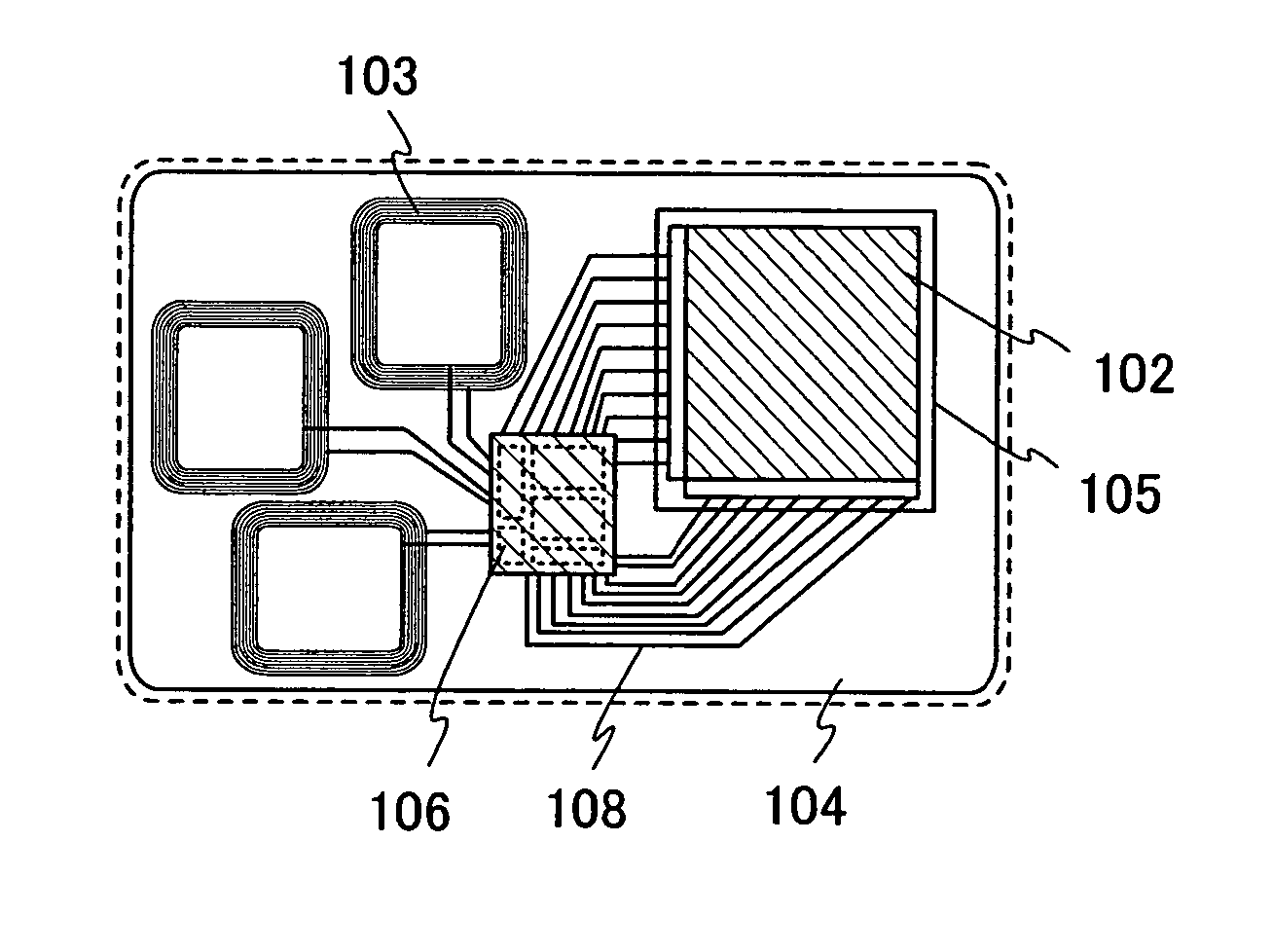

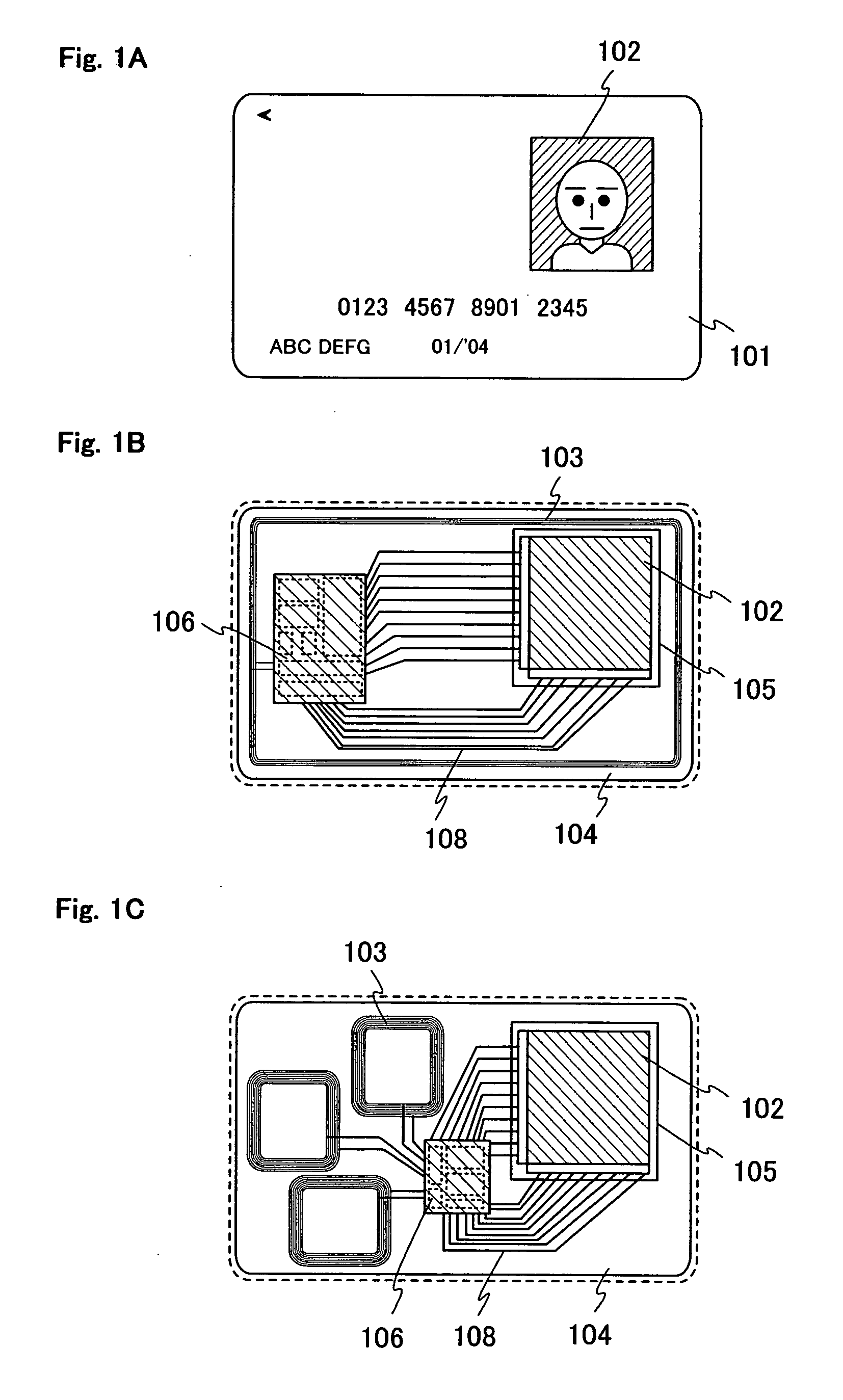

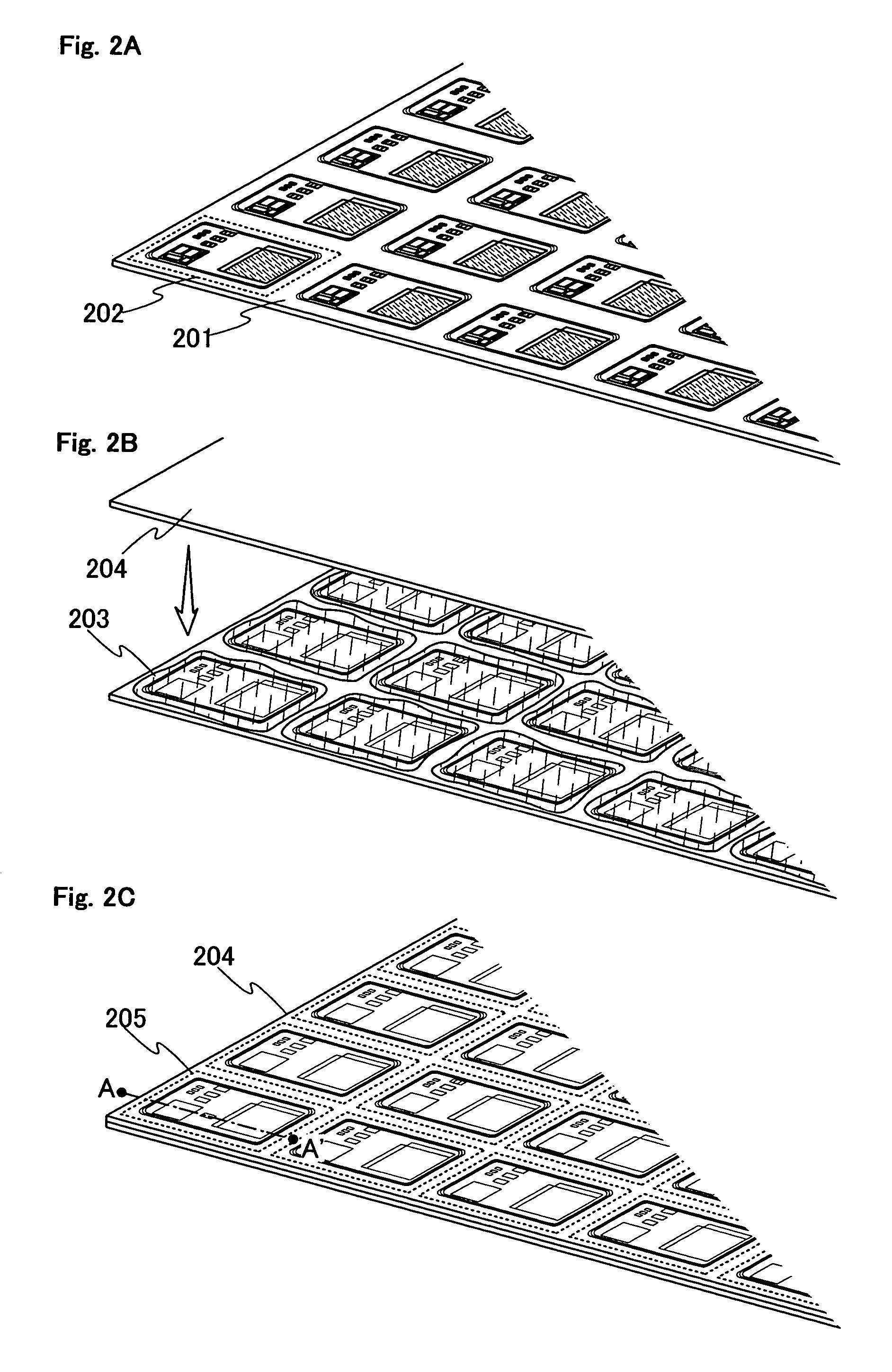

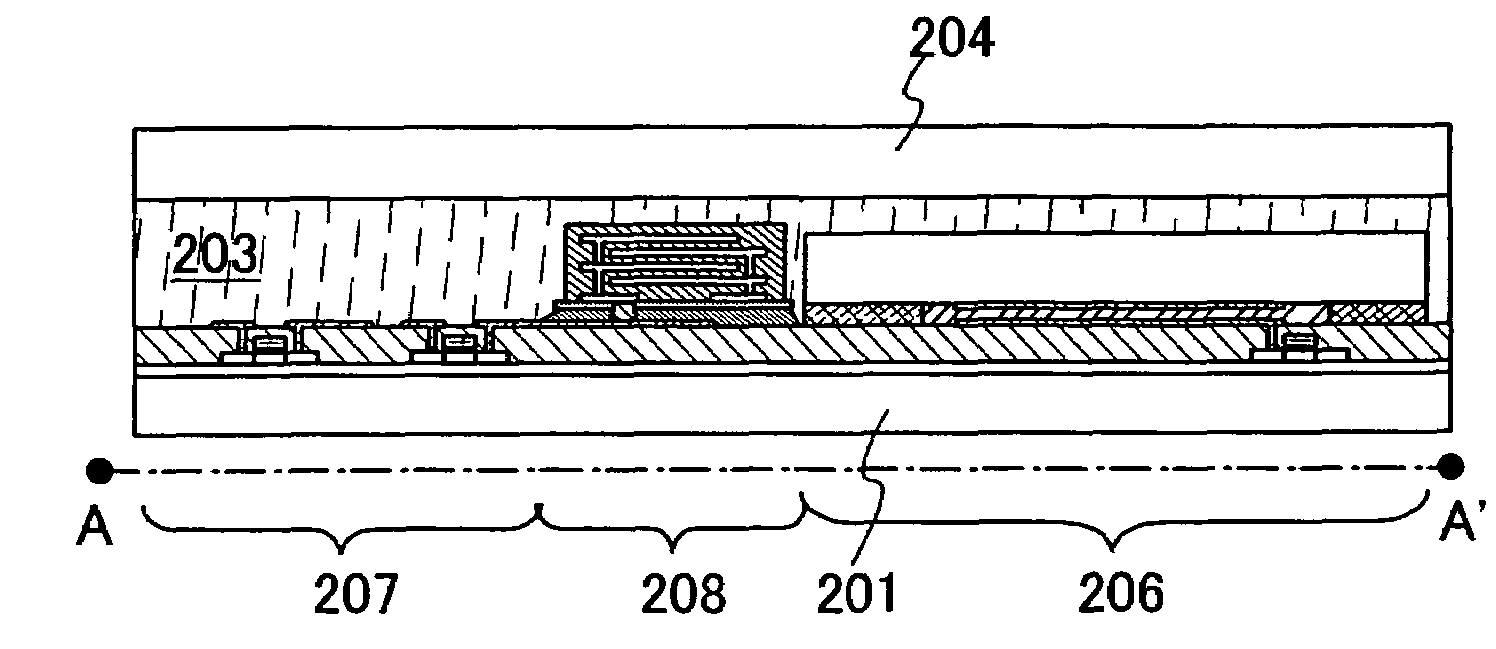

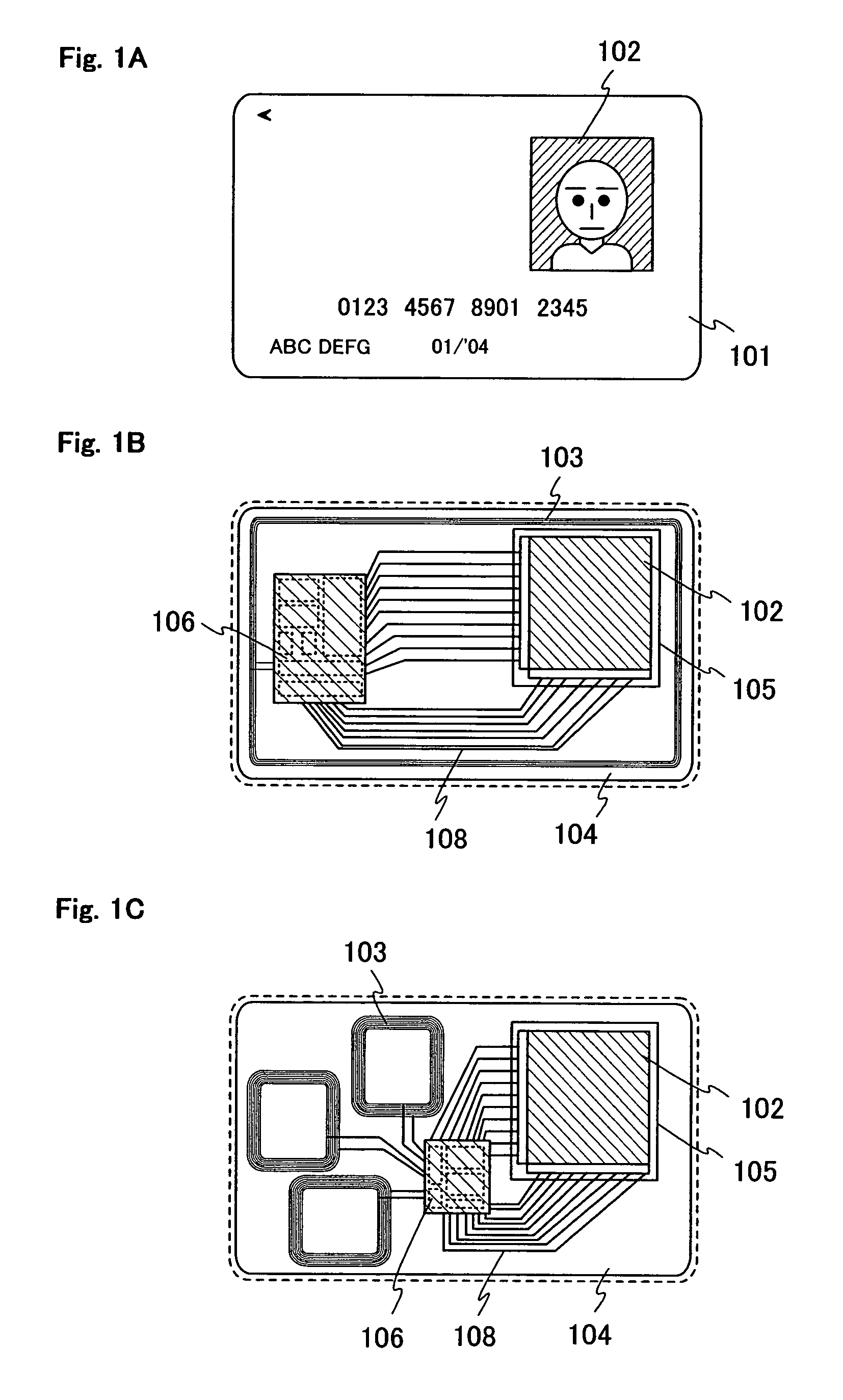

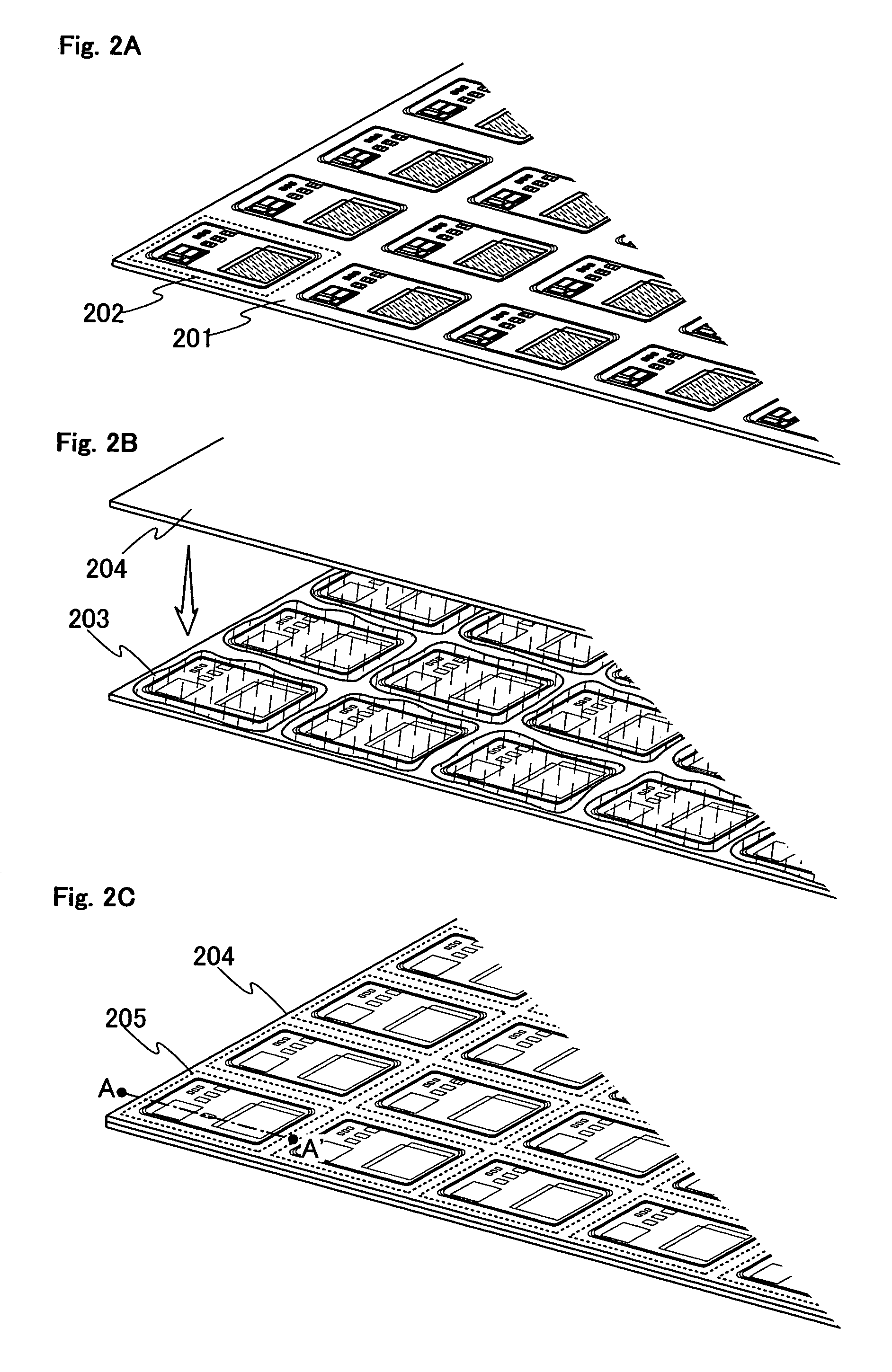

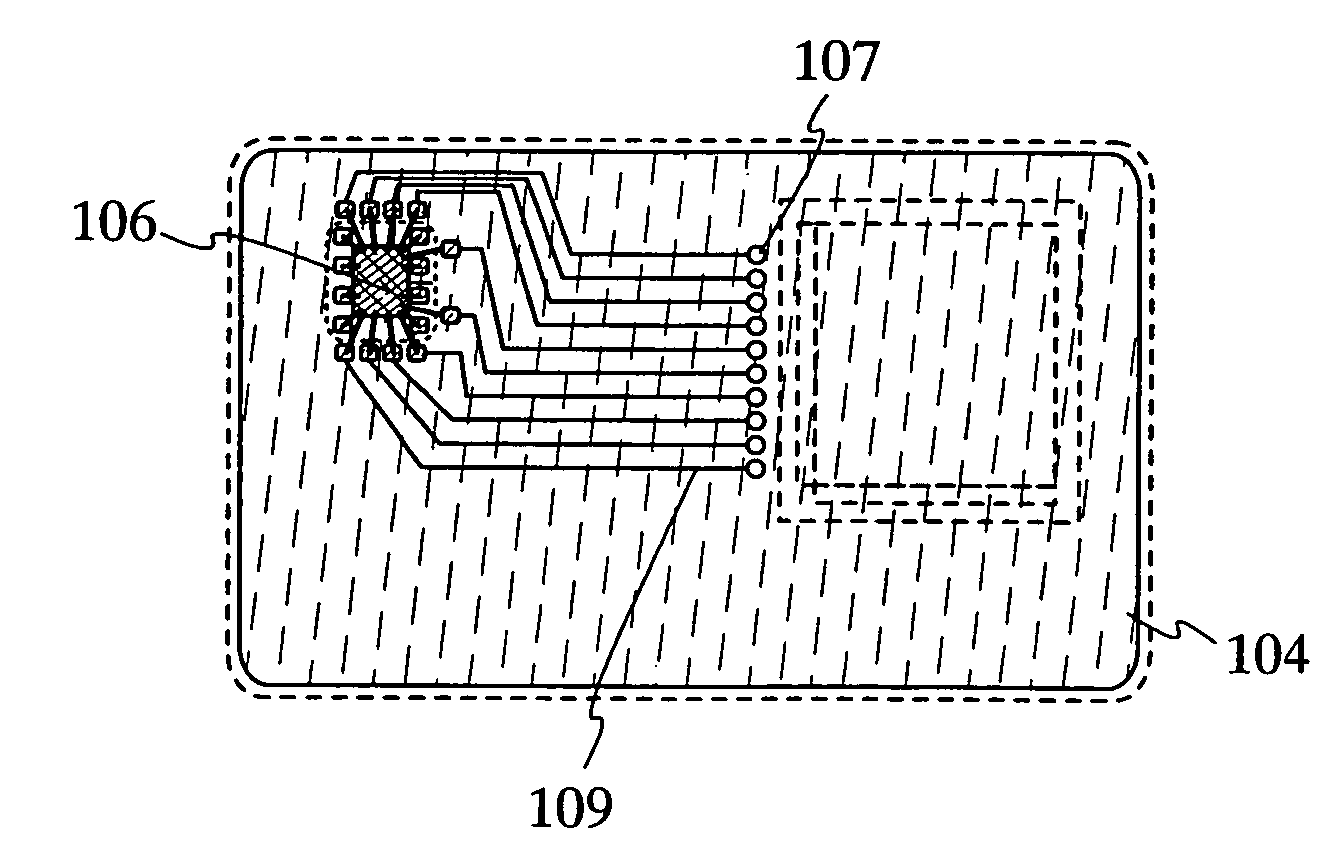

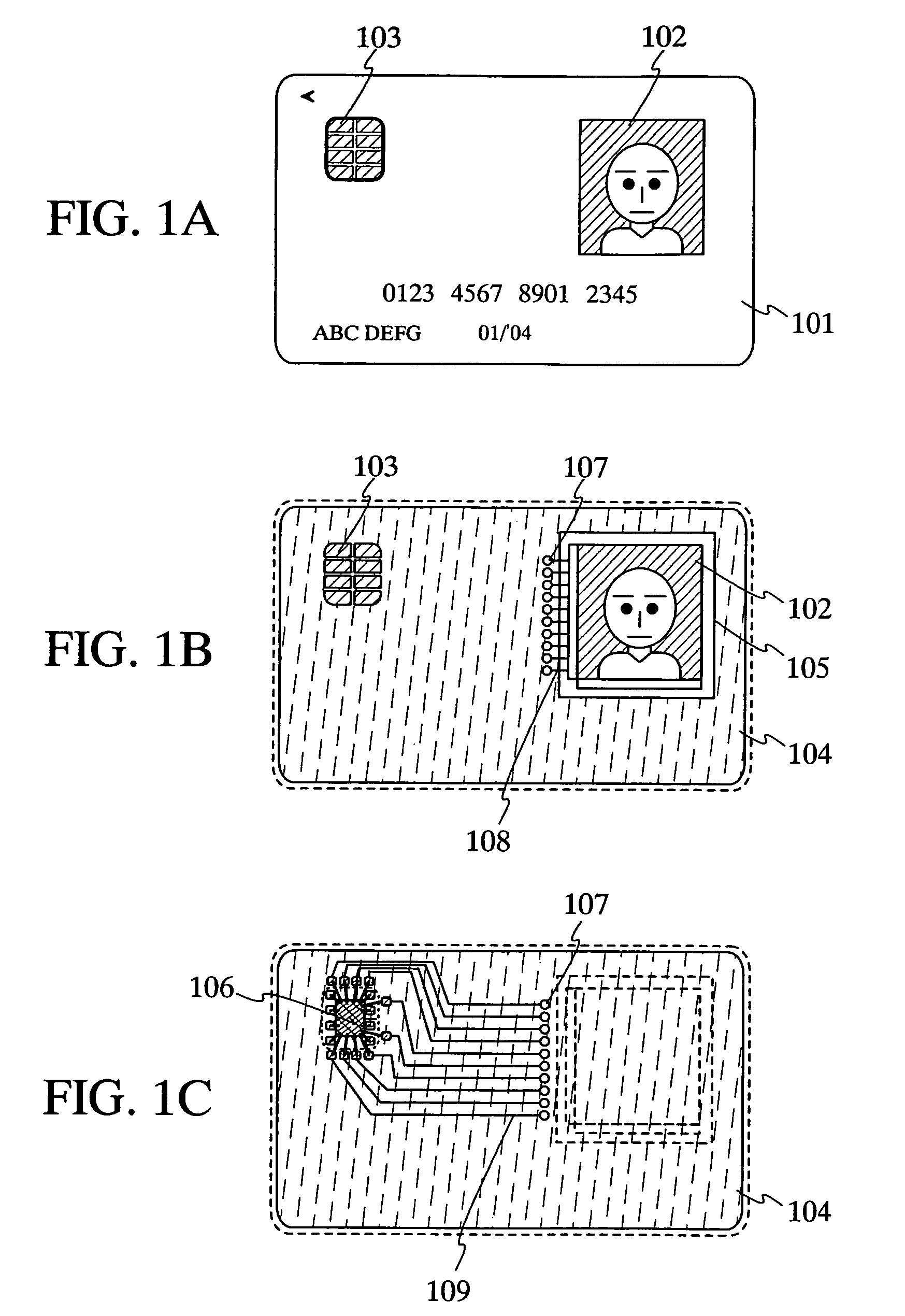

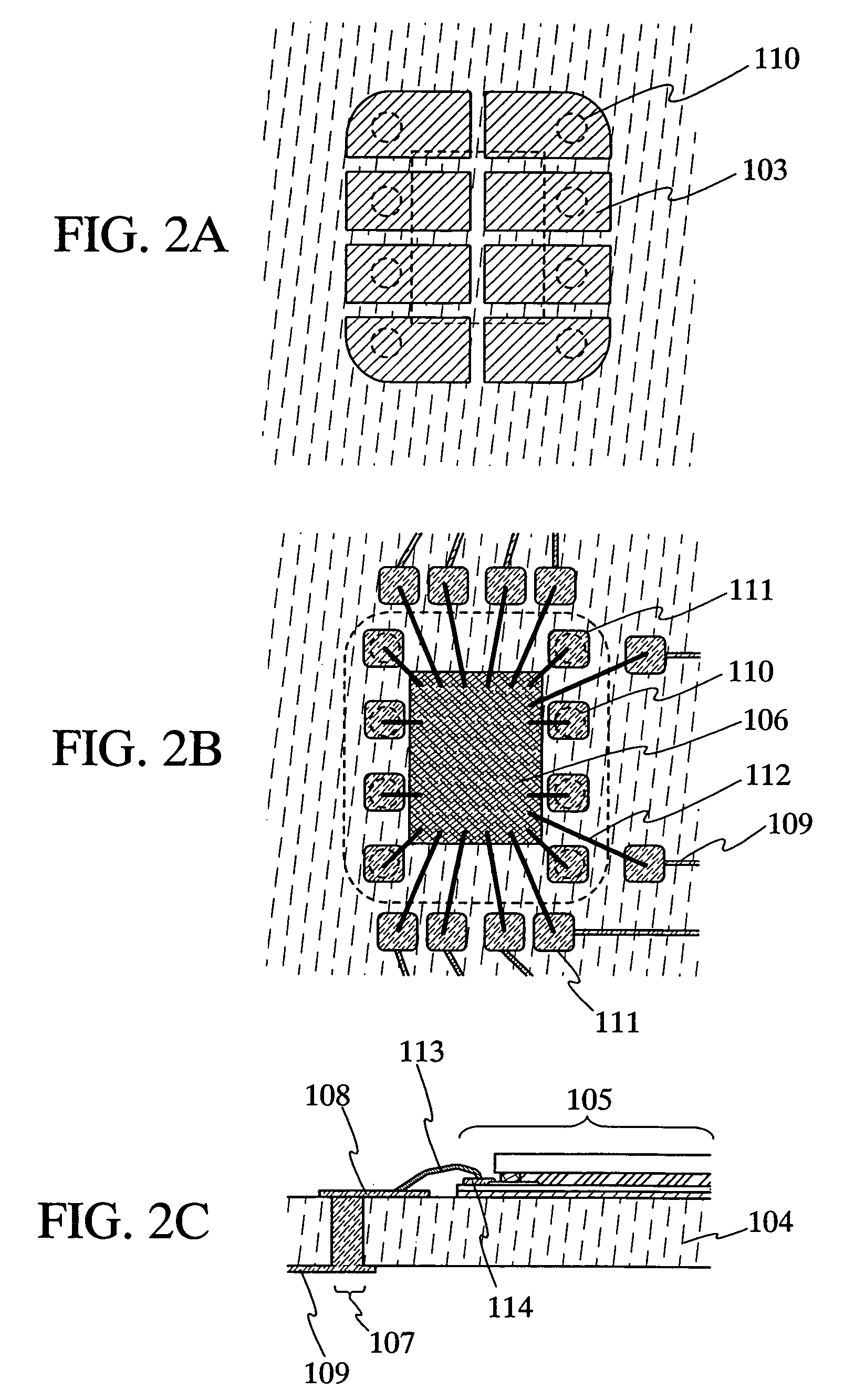

IC card and booking-account system using the IC card

InactiveUS20040128246A1Improve rigidityAvoid damageFinanceStatic indicating devicesDisplay deviceEngineering

It is an object of the present invention to provide a highly sophisticated functional IC card that can ensure security by preventing forgery such as changing a picture of a face, and display other images as well as the picture of a face. An IC card comprising a display device and a plurality of thin film integrated circuits; wherein driving of the display device is controlled by the plurality of thin film integrated circuits; a semiconductor element used for the plurality of thin film integrated circuits and the display device is formed by using a polycrystalline semiconductor film; the plurality of thin film integrated circuits are laminated; the display device and the plurality of thin film integrated circuits are equipped for the same printed wiring board; and the IC card has a thickness of from 0.05 mm to 1 mm.

Owner:SEMICON ENERGY LAB CO LTD

IC card and booking account system using the IC card

InactiveUS20040129450A1Poor heat resistanceImprove brittlenessSolid-state devicesPayment architectureDisplay deviceIntegrated circuit

It is an object of the present invention to provide a highly sophisticated functional card that can ensure security by preventing forgery such as changing a picture of a face, and display other images as well as the picture of a face. A card comprising a display device and a thin film integrated circuit; wherein driving of the display device is controlled by the thin film integrated circuit; a semiconductor element used for the thin film integrated circuit and the display device is formed by using a polycrystalline semiconductor film; the thin film integrated circuit and the display device are sealed with a resin between a first substrate and a second substrate of the card; and the first substrate and the second substrate are plastic substrates.

Owner:SEMICON ENERGY LAB CO LTD

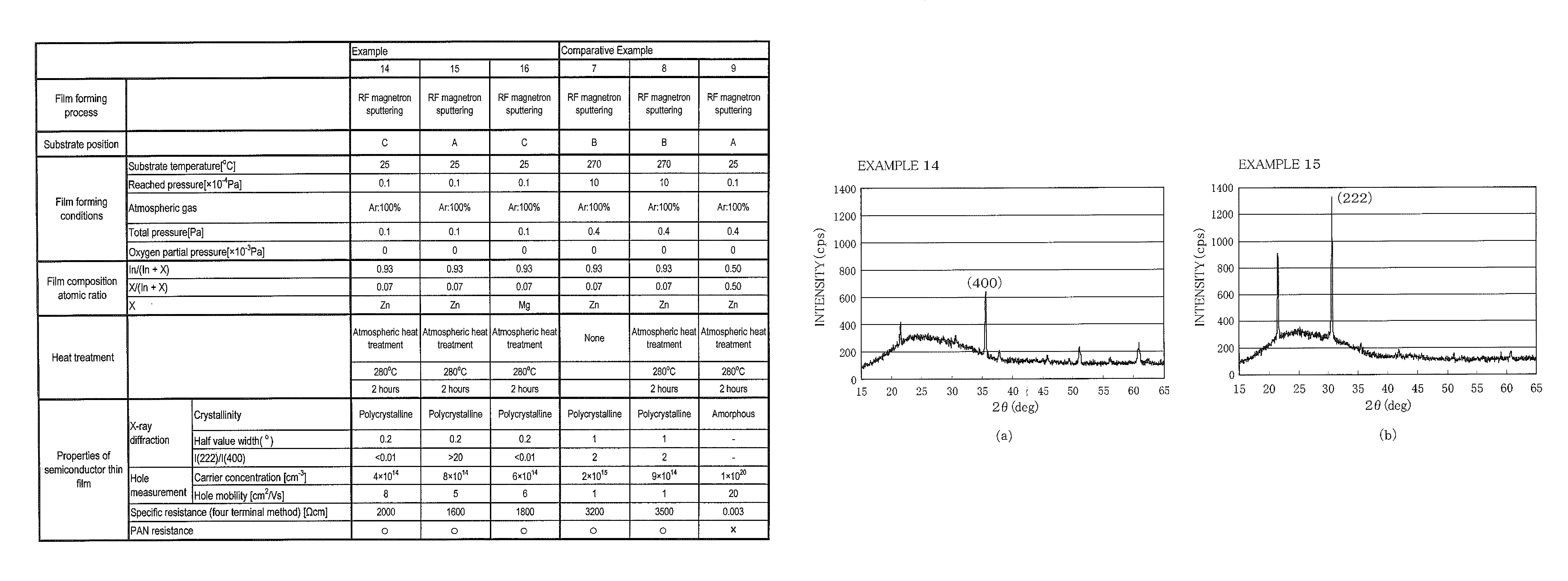

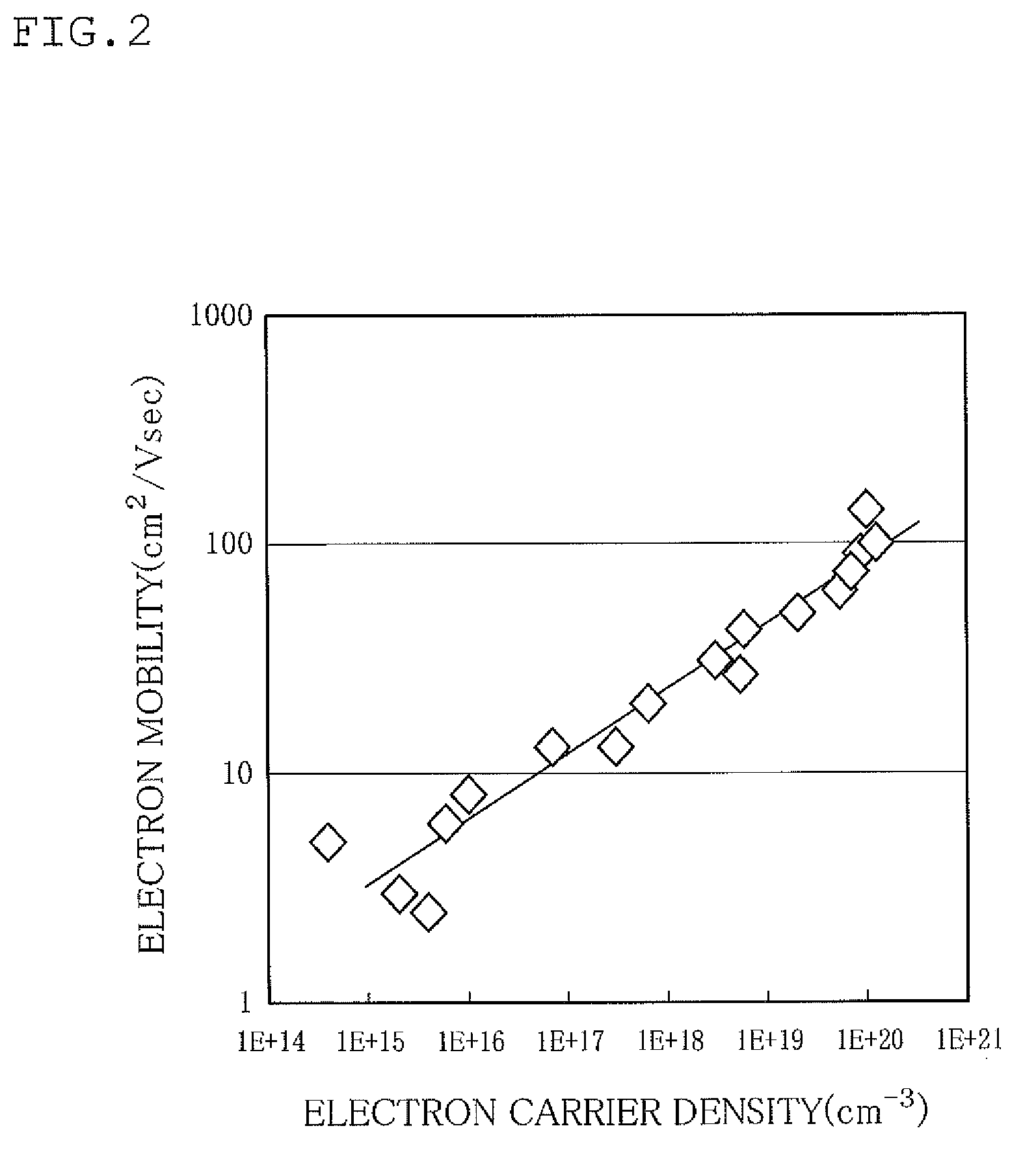

Semiconductor device, polycrystalline semiconductor thin film, process for producing polycrystalline semiconductor thin film, field effect transistor, and process for producing field effect transistor

ActiveUS8158974B2Easy to produceEasily enlargedSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialHeat resistance

An object of the present invention is to provide a novel semiconductor device which is excellent in stability, uniformity, reproducibility, heat resistance, durability and the like, and can exert excellent transistor properties. The semiconductor device is a thin-film transistor, and this thin-film transistor uses, as an active layer, a polycrystalline oxide semiconductor thin film containing In and two or more metals other than In and having an electron carrier concentration of less than 1×1018 / cm3.

Owner:IDEMITSU KOSAN CO LTD

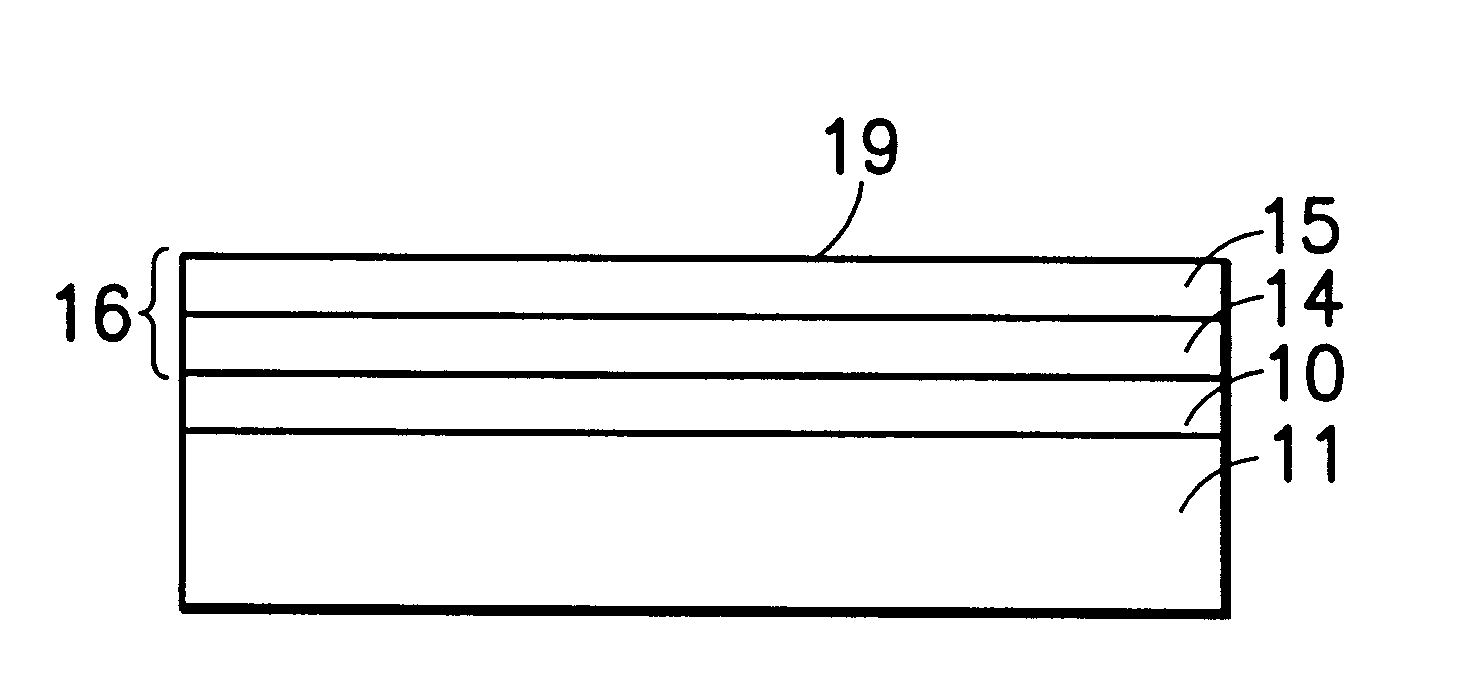

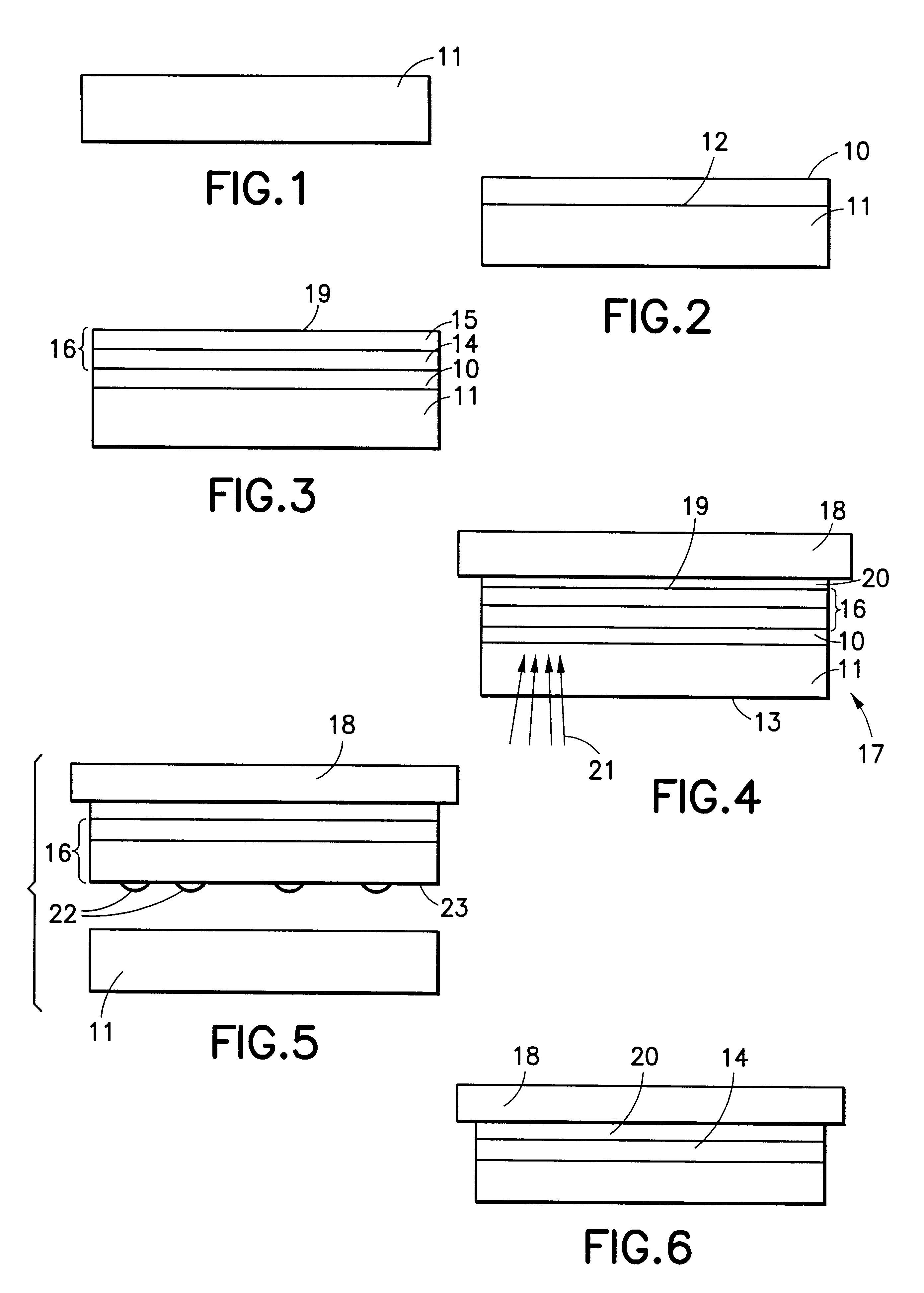

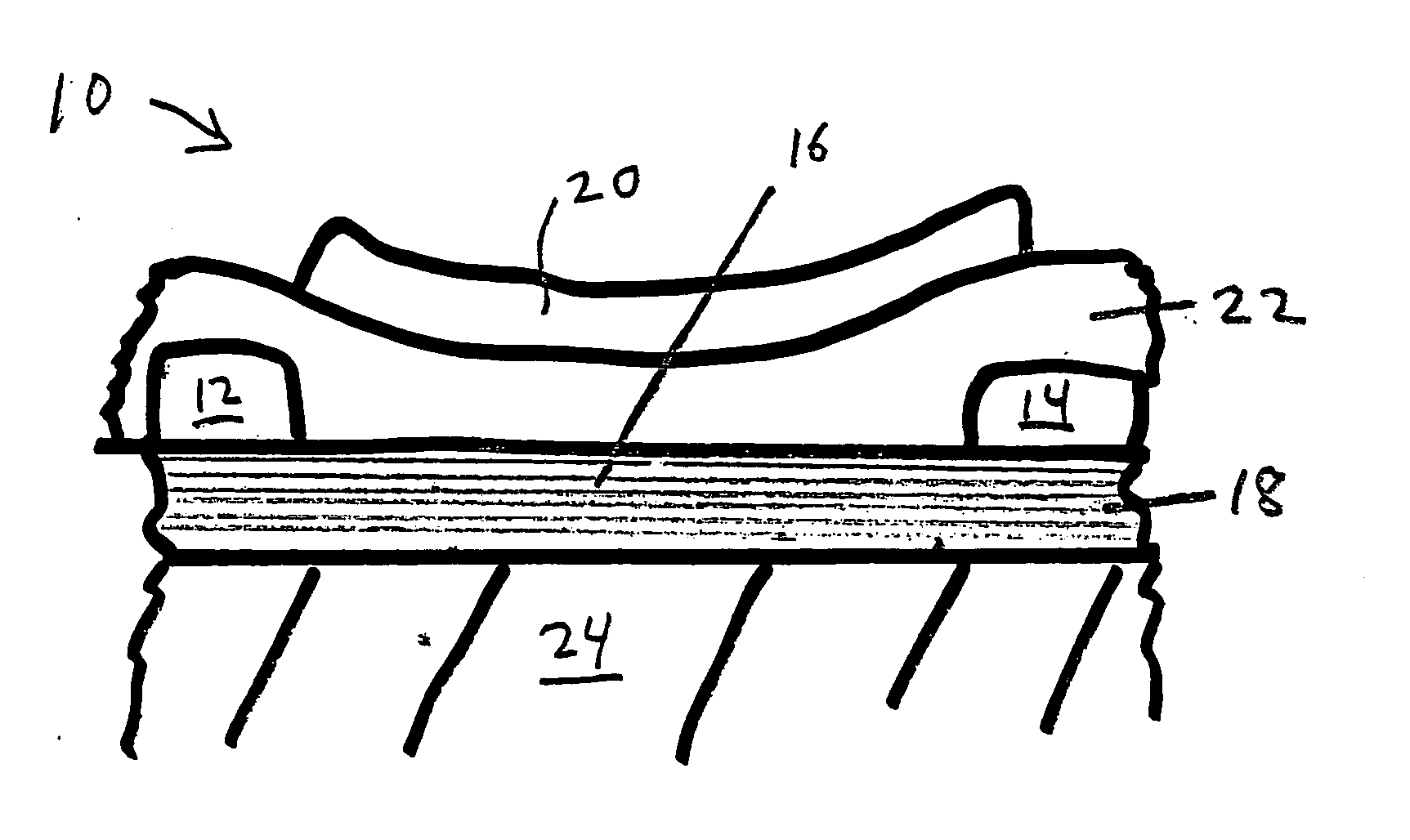

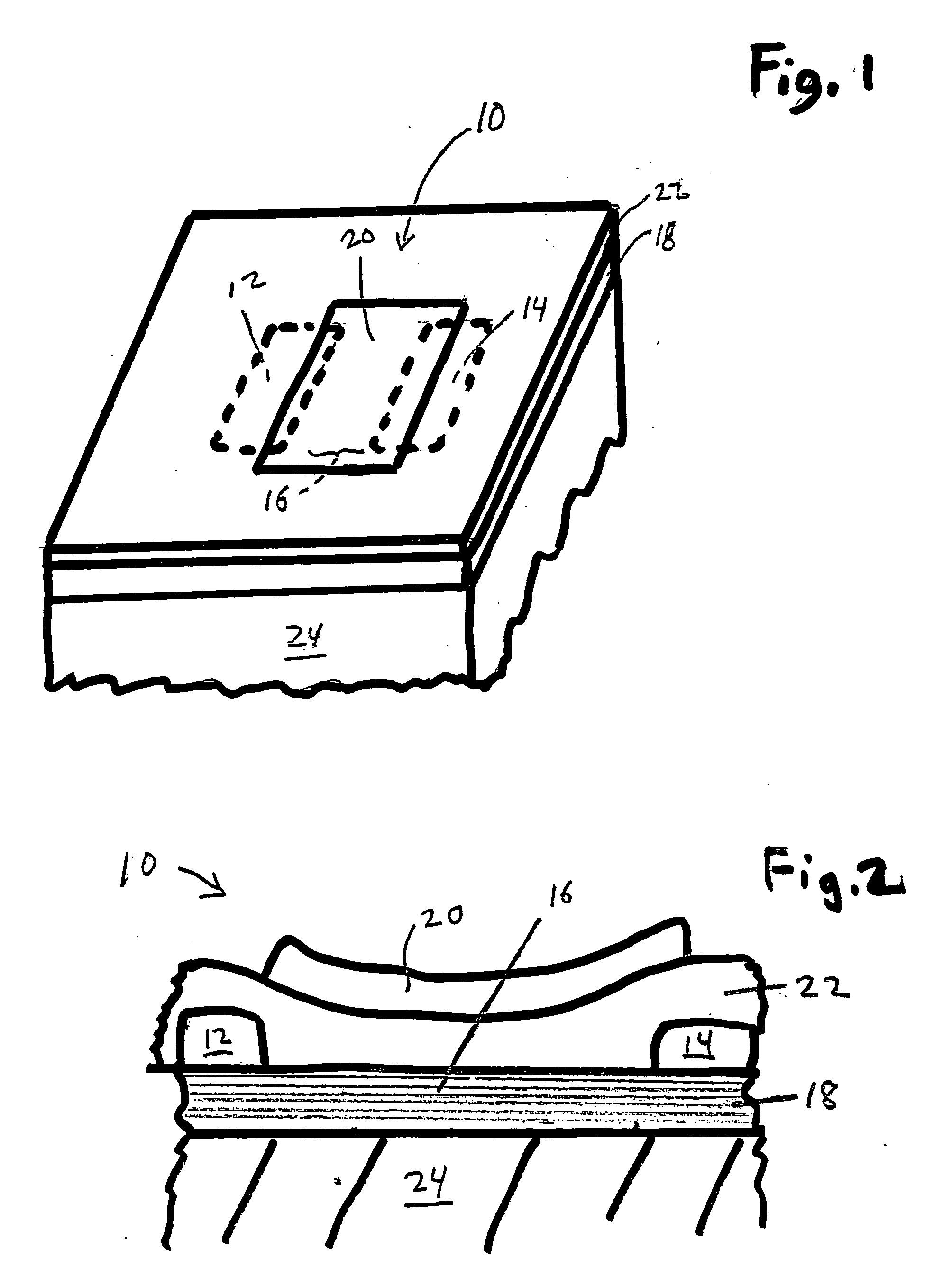

Product and process for forming a semiconductor structure on a host substrate

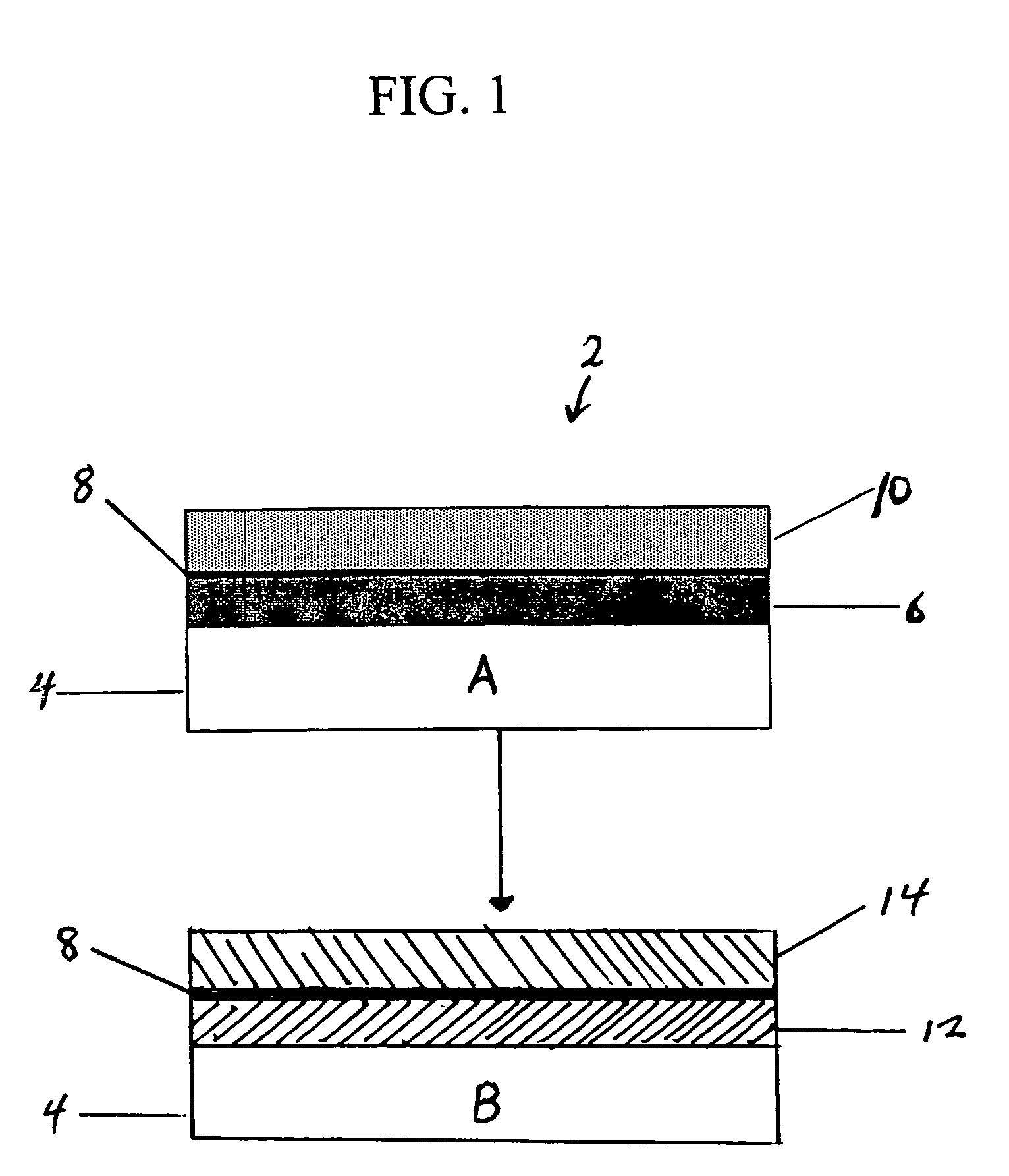

InactiveUS6210479B1Polycrystalline material growthSemiconductor/solid-state device manufacturingSemiconductor structureNitrogen

A process for cheaply fabricating a substantially single crystal or a polycrystalline semiconductor structure on a host substrate. The process begins by depositing a layer of wide band gap nitride material 10, such as gallium nitride, aluminum nitride and / or indium nitride, on a sapphire substrate 11. The semiconductor structure 14 is then grown on the nitride layer. Next, the host substrate 15 is attached with a bonding agent to an exposed surface area of the semiconductor structure 14. The sapphire substrate is lifted off by irradiation in which nitrogen is dissociated from the nitride layer.

Owner:IBM CORP

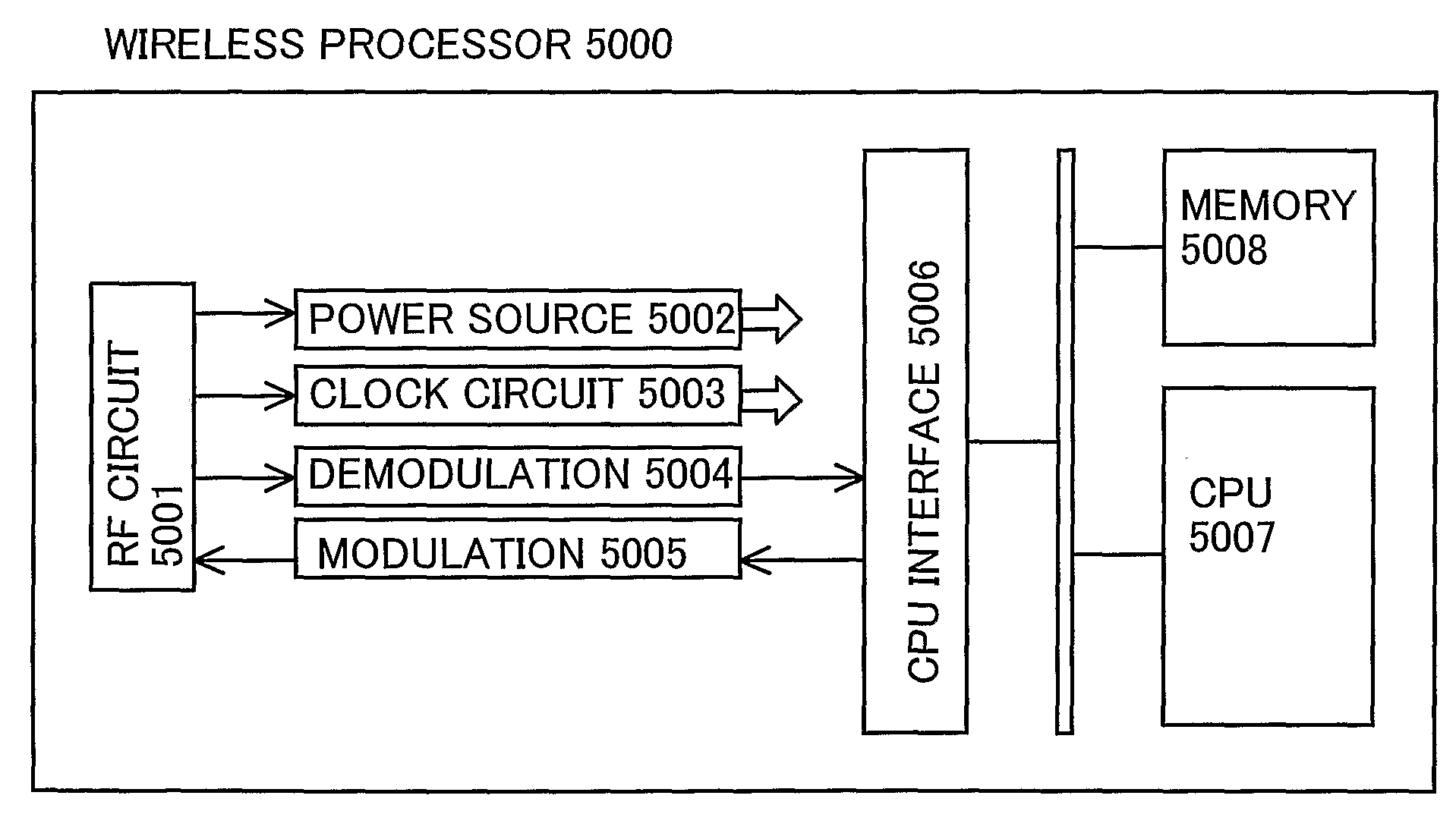

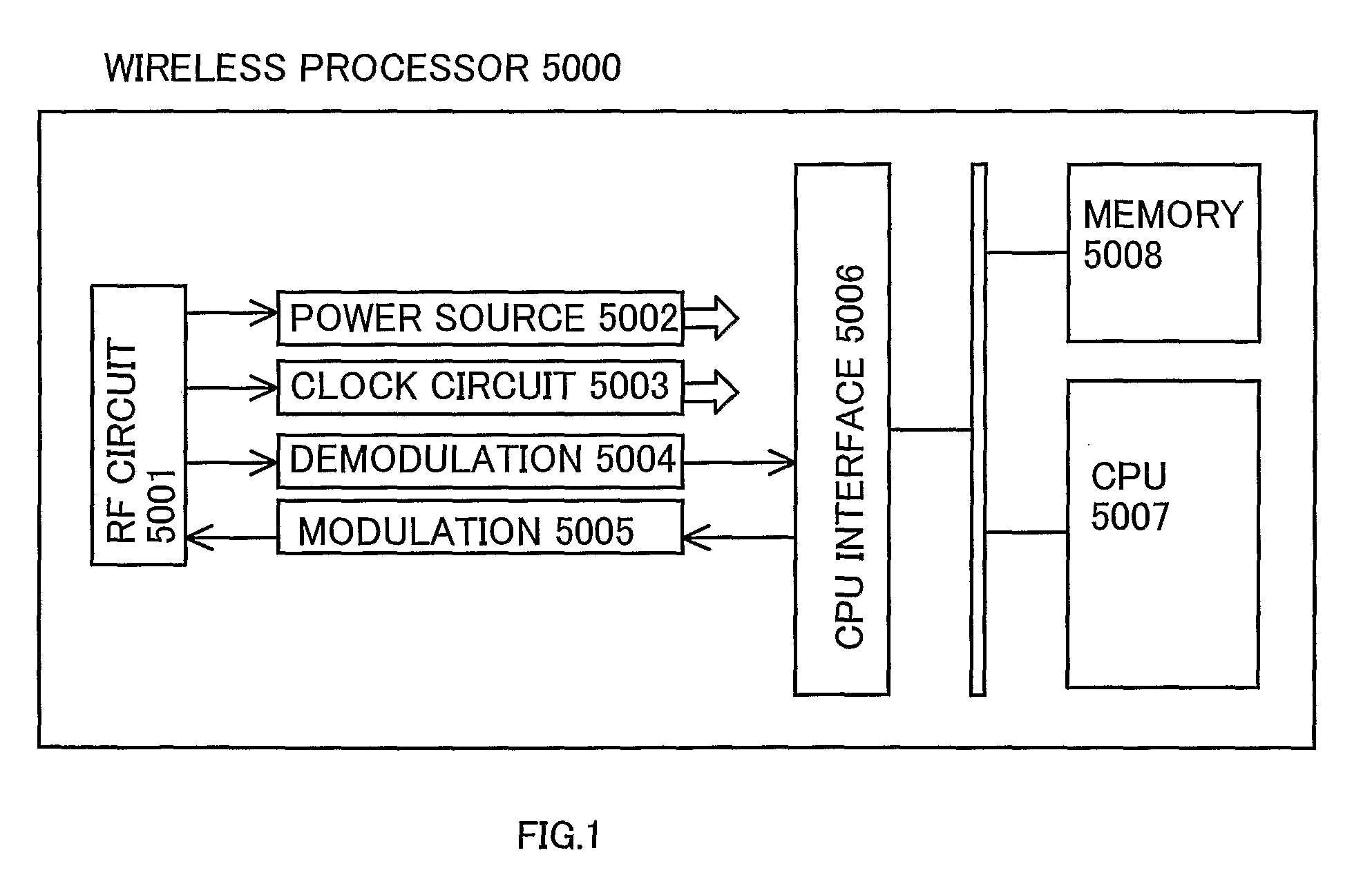

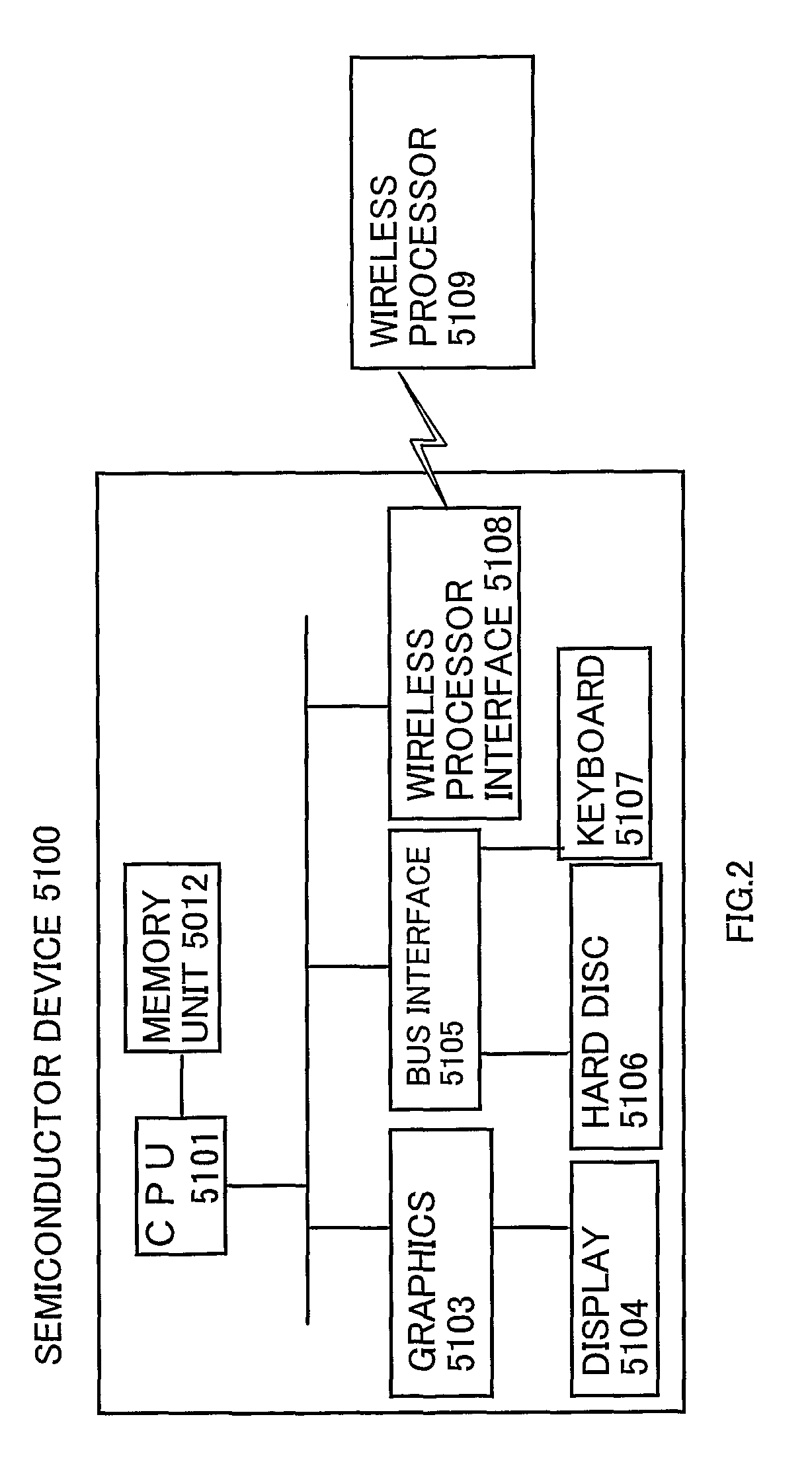

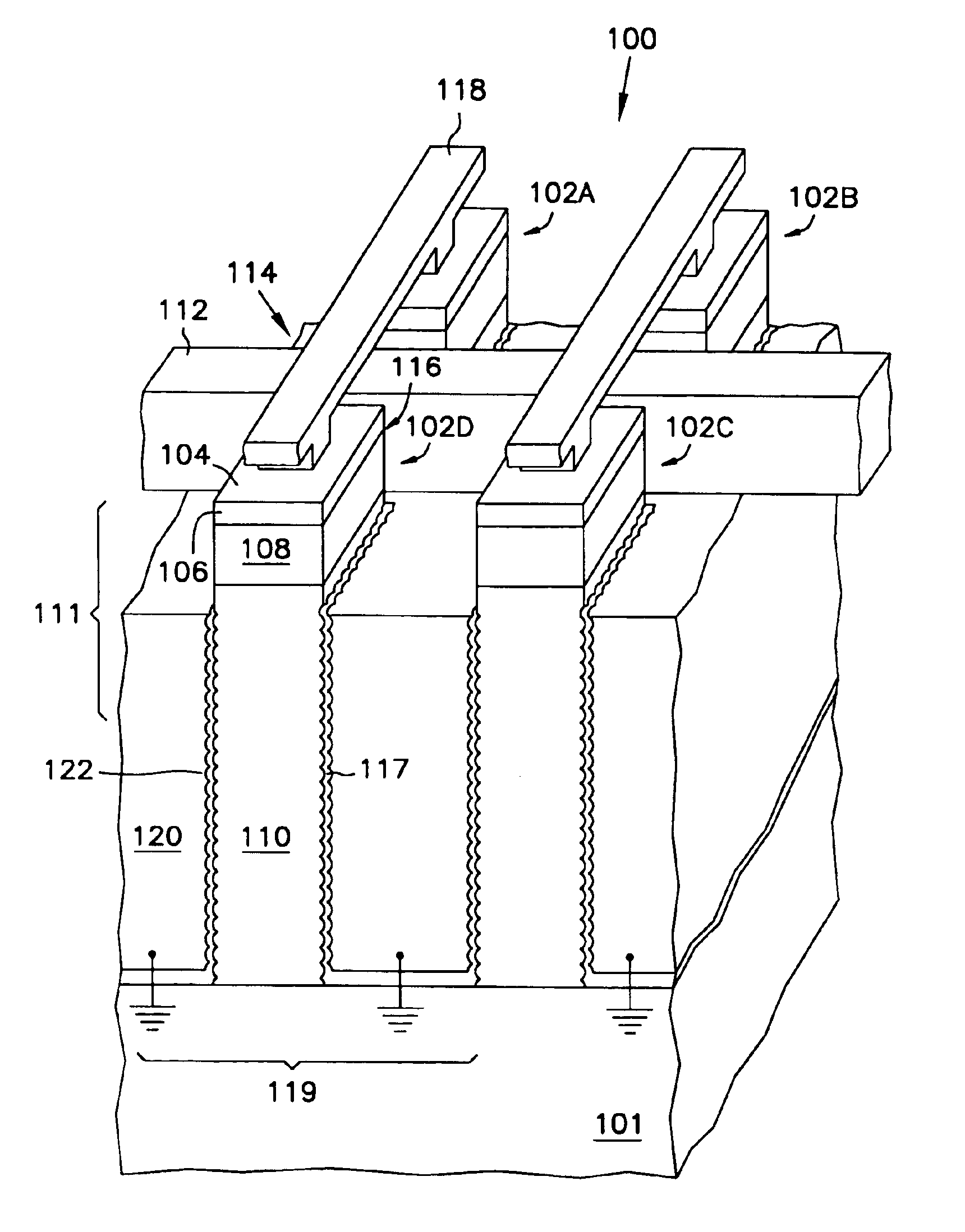

Wireless Processor, Wireless Memory, Information System, And Semiconductor Device

InactiveUS20080093454A1Increase valueEasy to optimizeSemiconductor/solid-state device detailsSolid-state devicesInformation processingEngineering

The invention provides a processor obtained by forming a high functional integrated circuit using a polycrystalline semiconductor over a substrate which is sensitive to heat, such as a plastic substrate or a plastic film substrate. Moreover, the invention provides a wireless processor, a wireless memory, and an information processing system thereof which transmit and receive power or signals wirelessly. According to the invention, an information processing system includes an element forming region including a transistor which has at least a channel forming region formed of a semiconductor film separated into islands with a thickness of 10 to 200 nm, and an antenna. The transistor is fixed on a flexible substrate. The wireless processor in which a high functional integrated circuit including the element forming region is formed and the semiconductor device transmit and receive data through the antenna.

Owner:SEMICON ENERGY LAB CO LTD

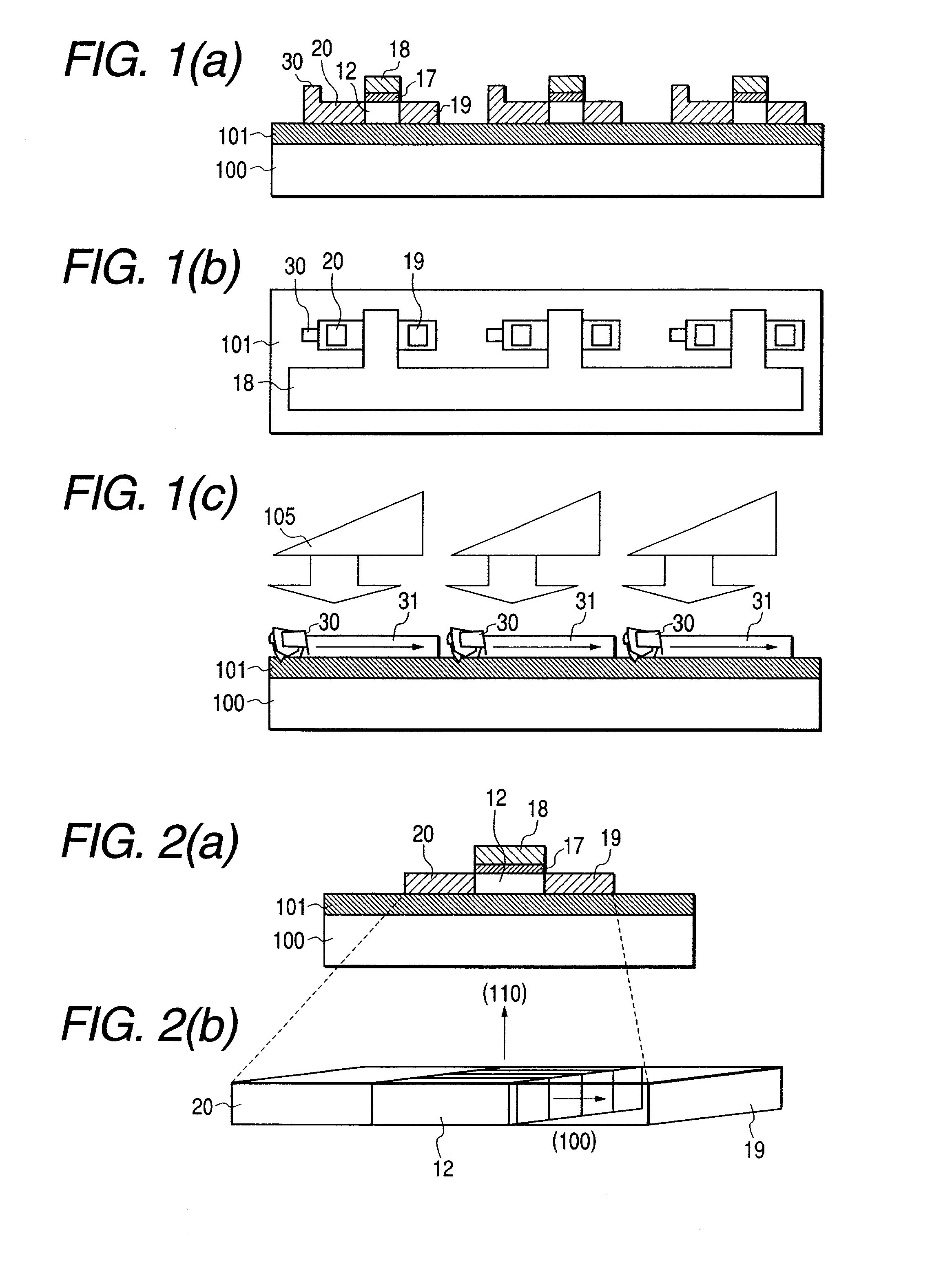

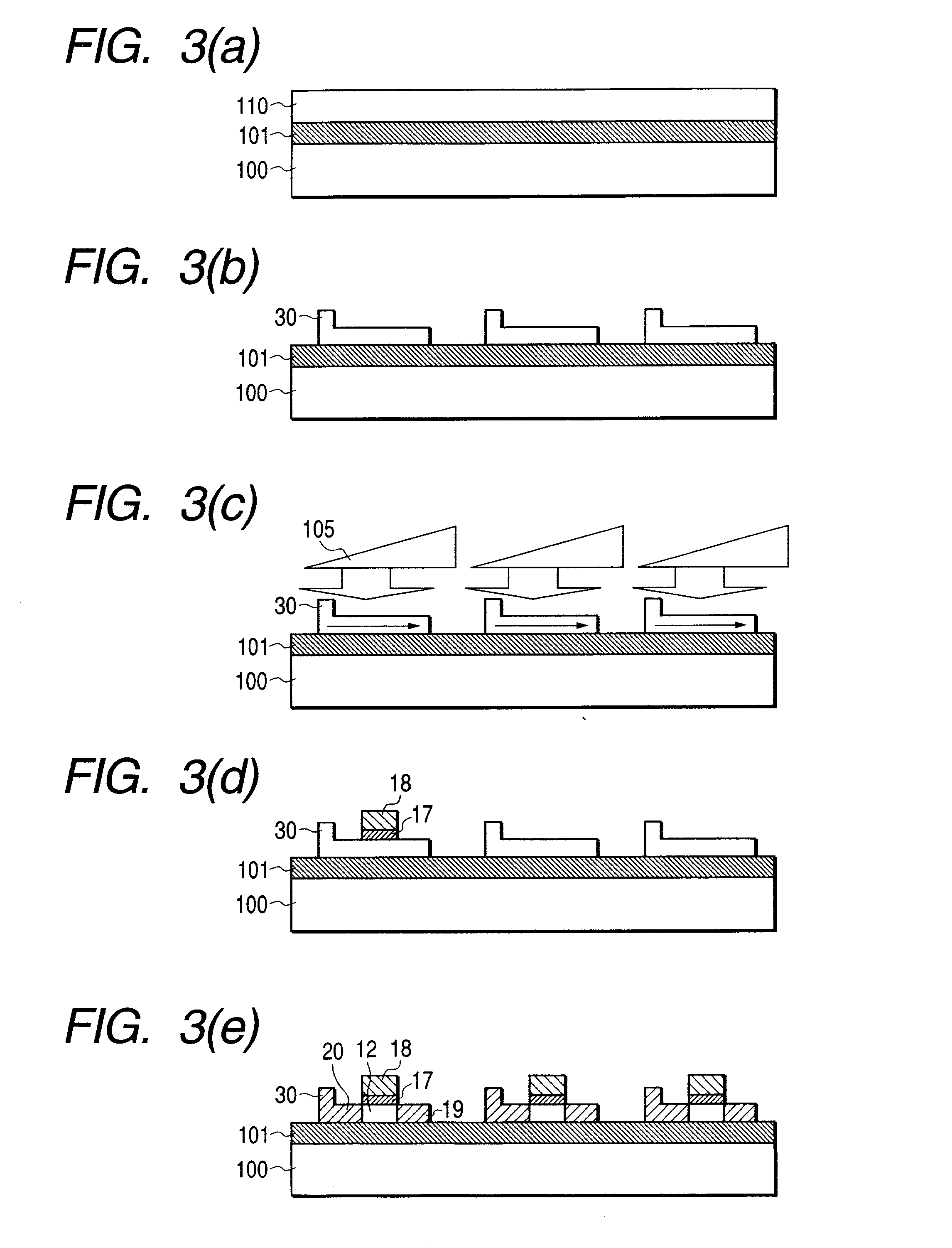

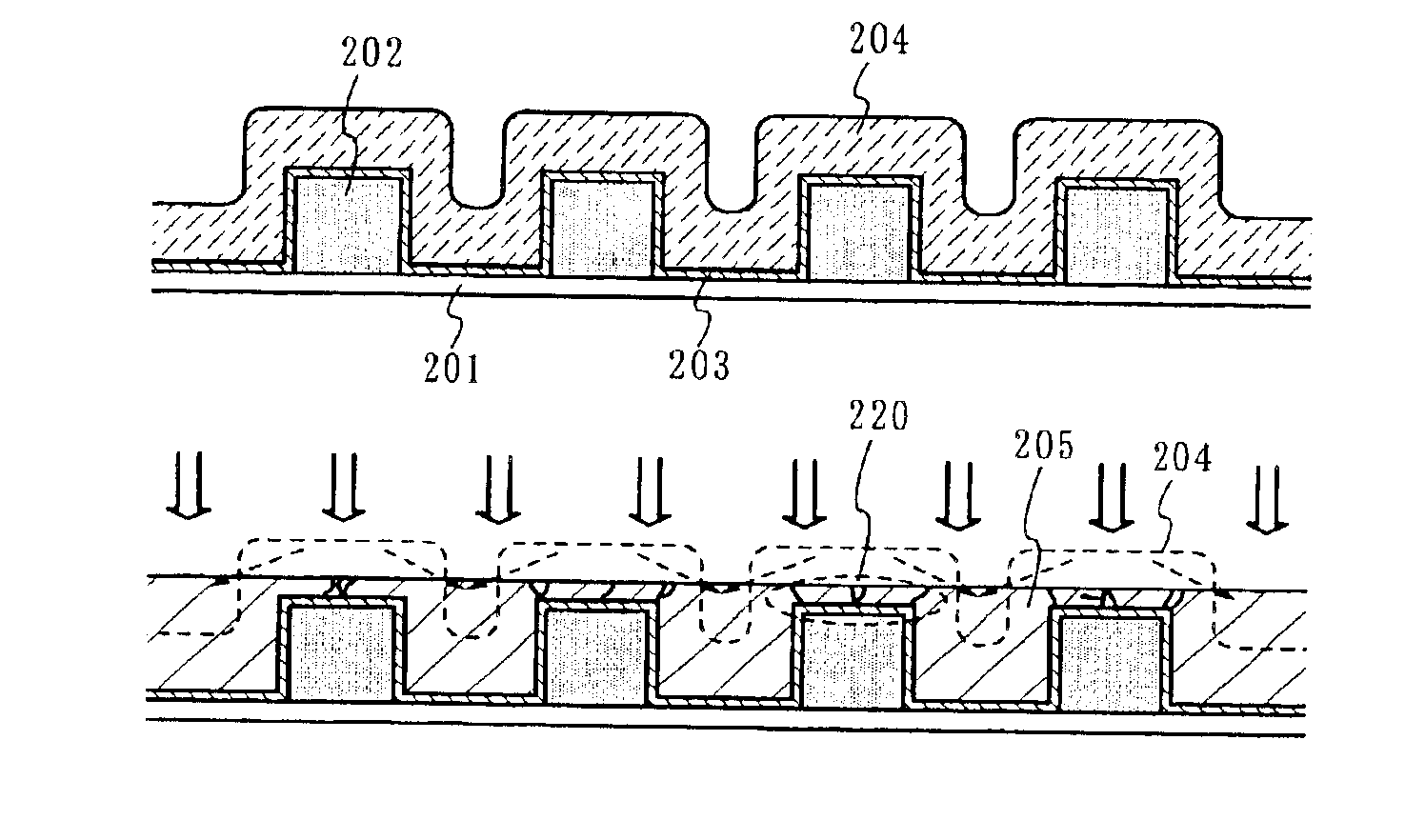

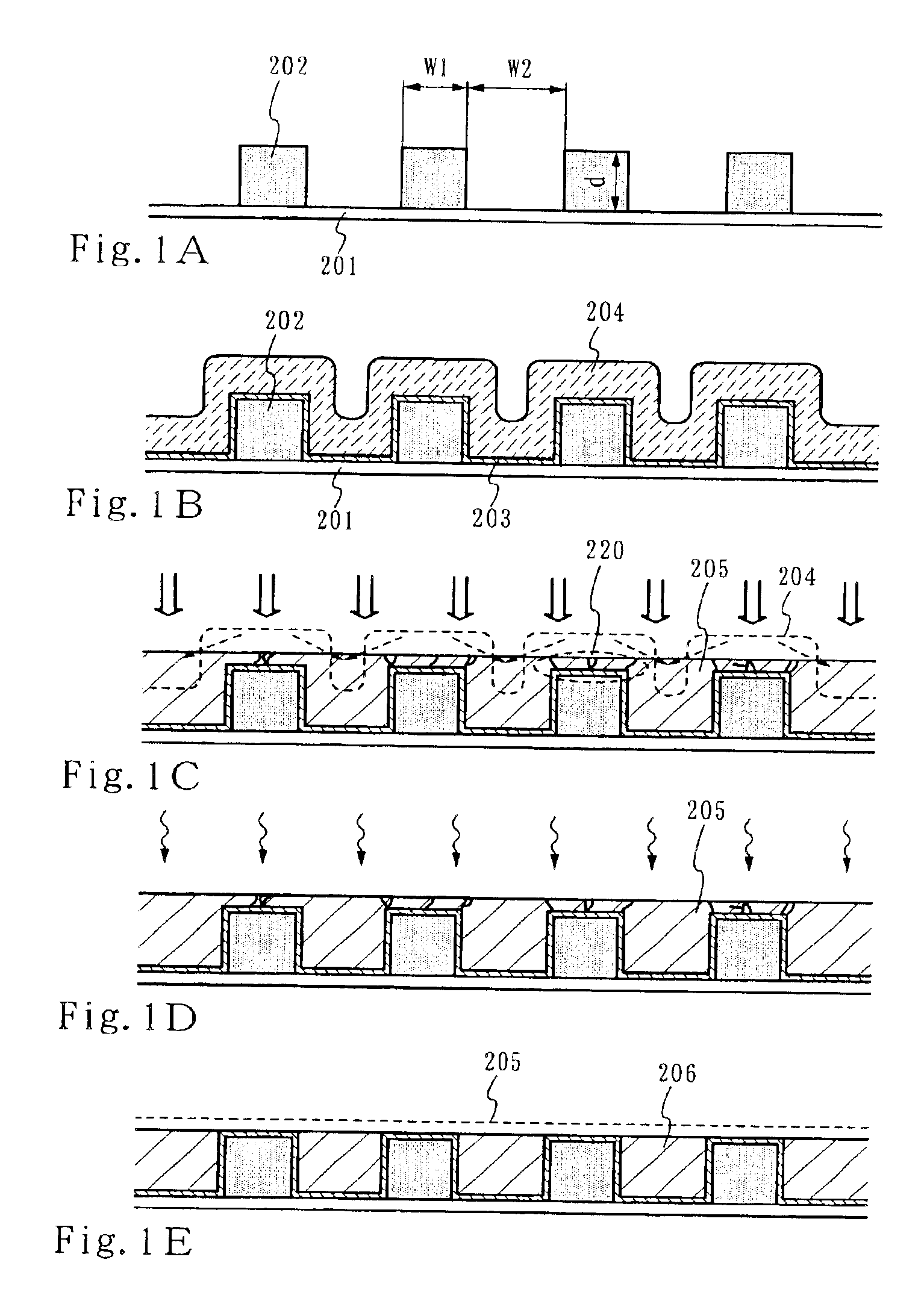

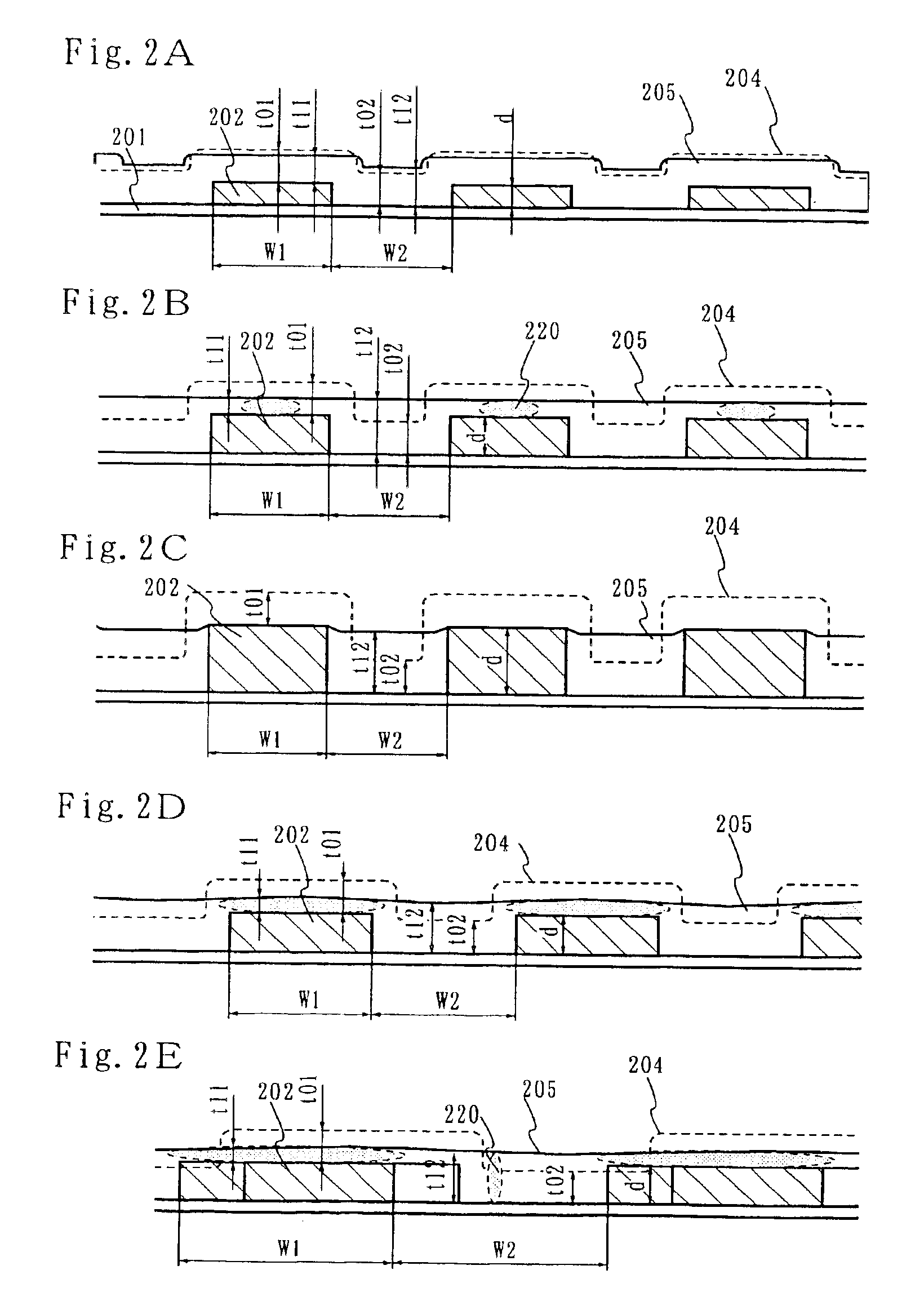

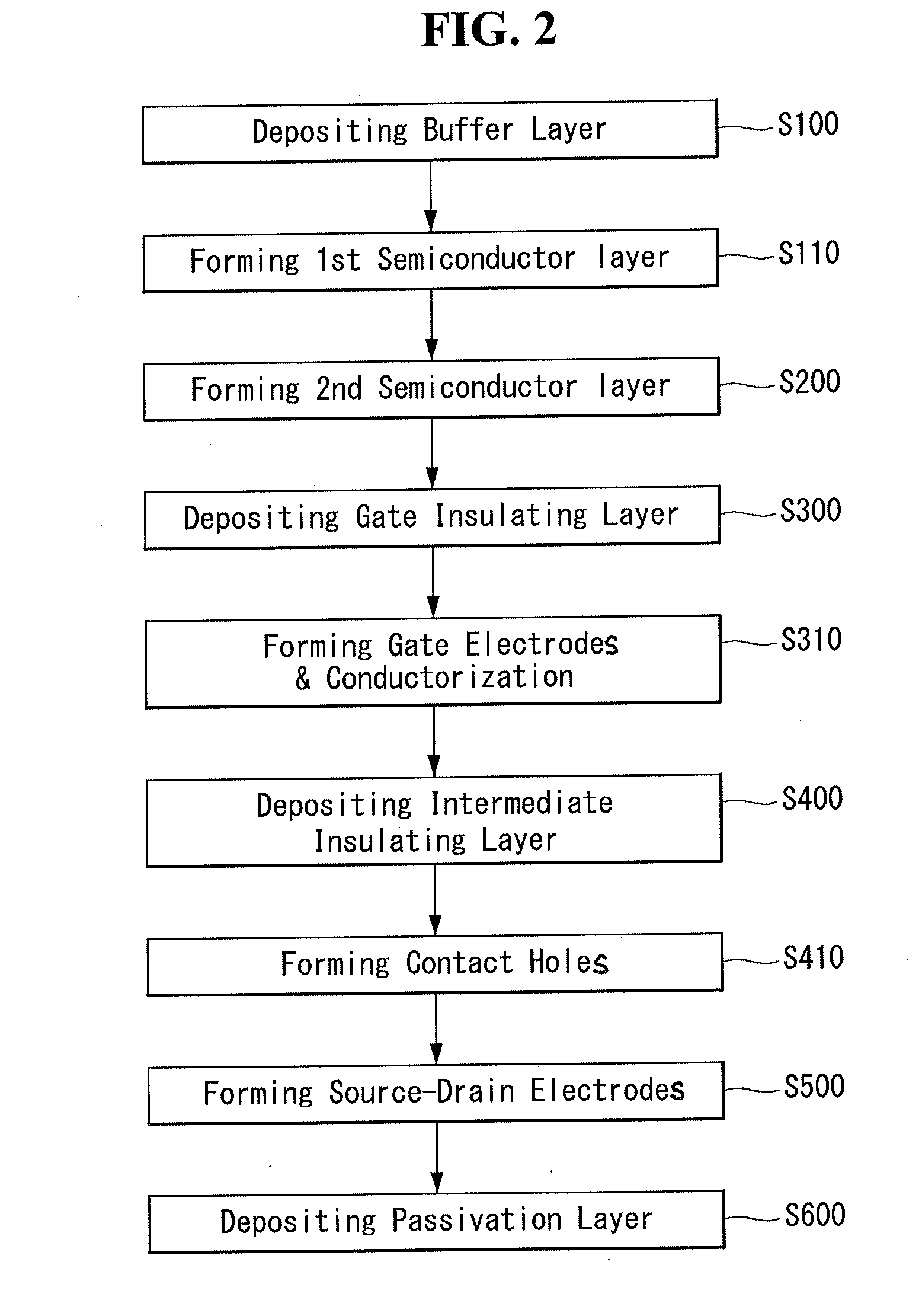

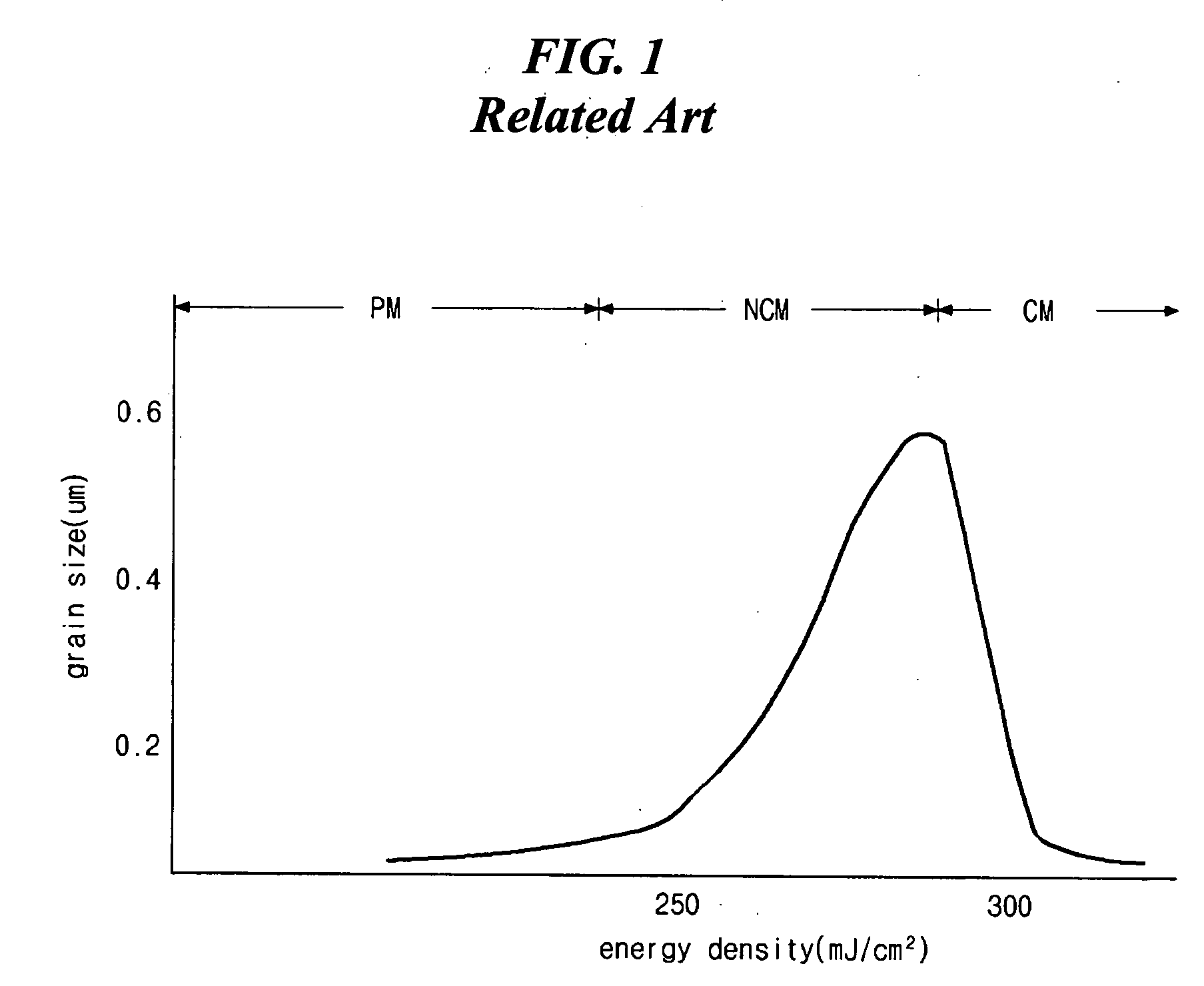

Thin film semiconductor device, polycrystalline semiconductor thin film production process and production apparatus

InactiveUS20020119609A1Reduce in quantityQuality improvementTransistorFrom solid stateElectrical conductorCrystal orientation

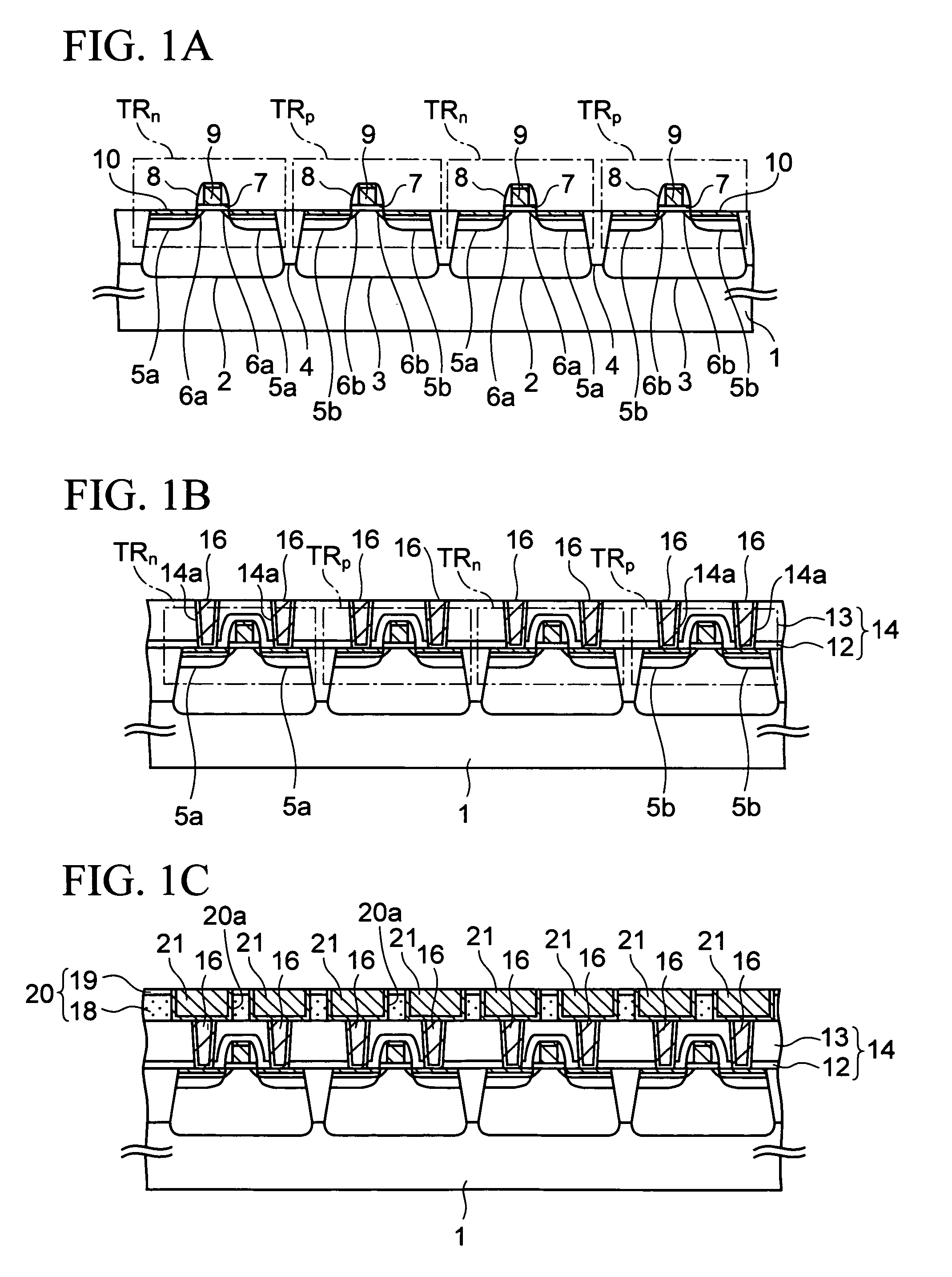

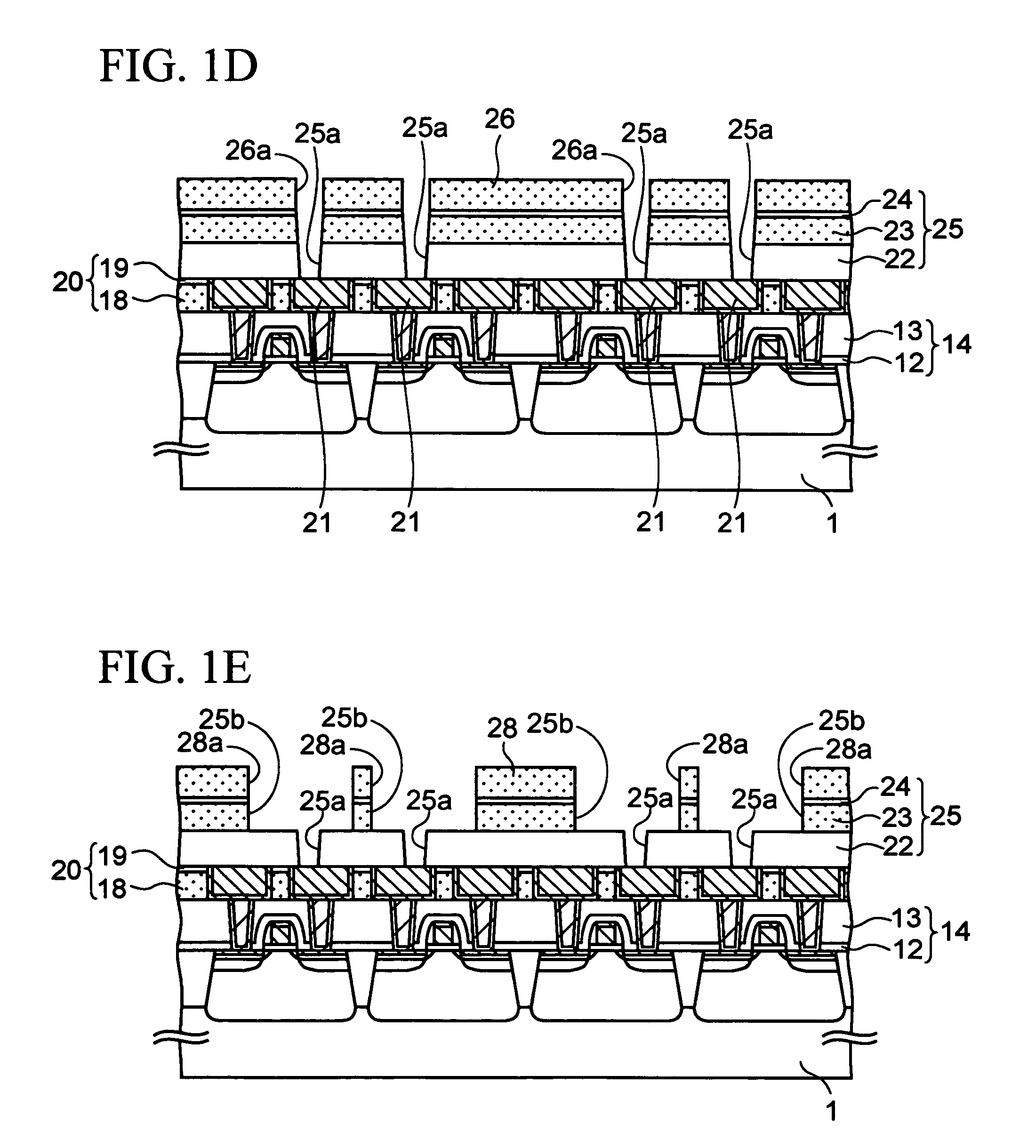

In an MIS field effect transistor having a gate electrode formed on a first semiconductor layer which is a polycrystalline silicon film on an insulating substrate through a gate insulating film, a channel region formed in the semiconductor layer and a source region and a drain region arranged on both sides of the channel region, a thin film semiconductor device has a main orientation of at least the channel region of {110} with respect to the surface of the gate insulating film. Further, a polycrystalline semiconductor film having a main orientation of the surface almost perpendicular to a direction for connecting the source and drain regions of {100} is preferably used in the channel of a semiconductor device. According to the present invention, a semiconductor device having a high-quality polycrystalline semiconductor film whose grain boundary, grain size and crystal orientation can be controlled and whose film roughness and crystal defects formed by crystallization have been reduced can be obtained on the insulating substrate.

Owner:PANASONIC LIQUID CRYSTAL DISPLAY CO LTD +1

Semiconductor device, polycrystalline semiconductor thin film, process for producing polycrystalline semiconductor thin film, field effect transistor, and process for producing field effect transistor

ActiveUS20100140609A1Easy to produceEasily enlargedSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialHeat resistance

An object of the present invention is to provide a novel semiconductor device which is excellent in stability, uniformity, reproducibility, heat resistance, durability and the like, and can exert excellent transistor properties. The semiconductor device is a thin-film transistor, and this thin-film transistor uses, as an active layer, a polycrystalline oxide semiconductor thin film containing In and two or more metals other than In and having an electron carrier concentration of less than 1×1018 / cm3.

Owner:IDEMITSU KOSAN CO LTD

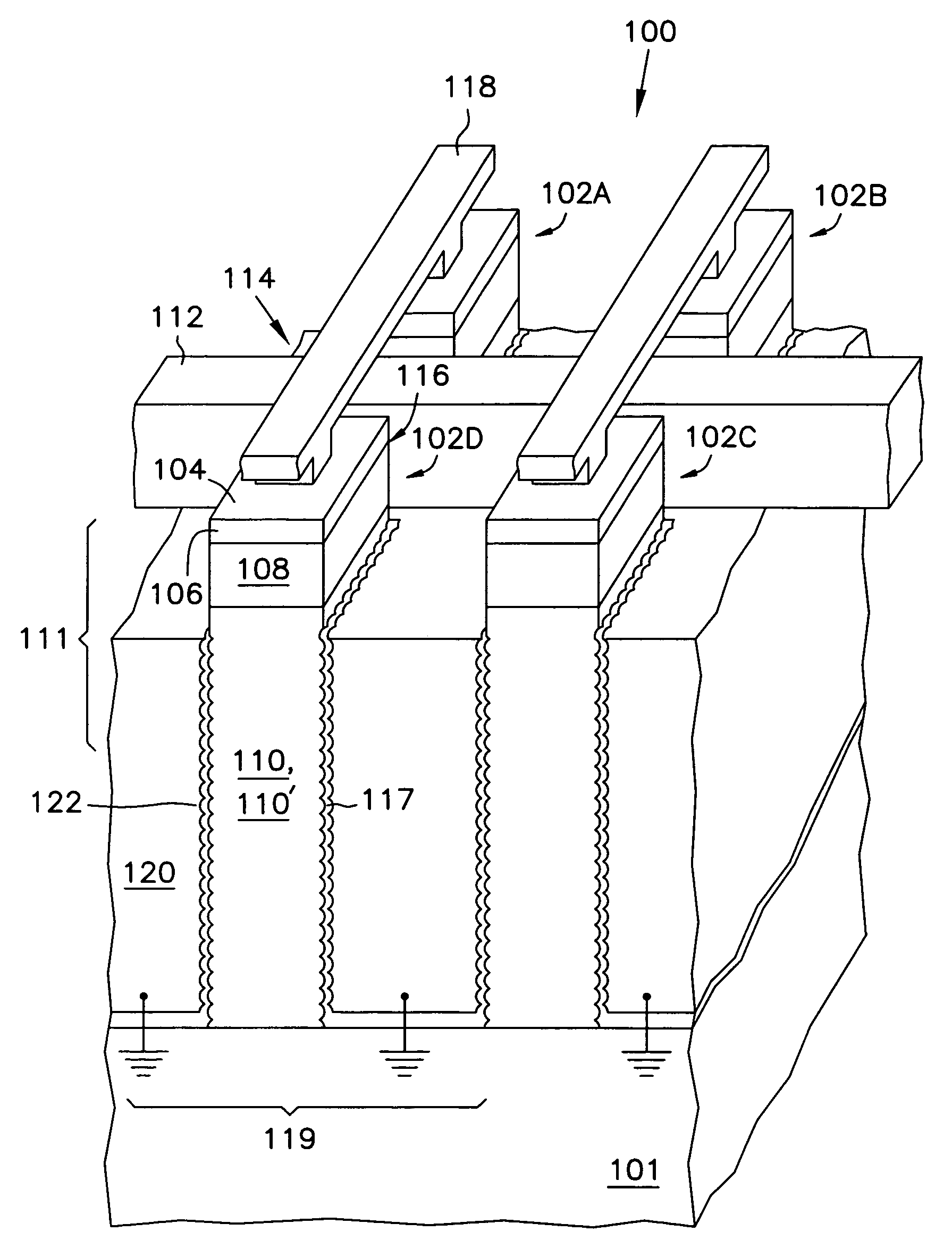

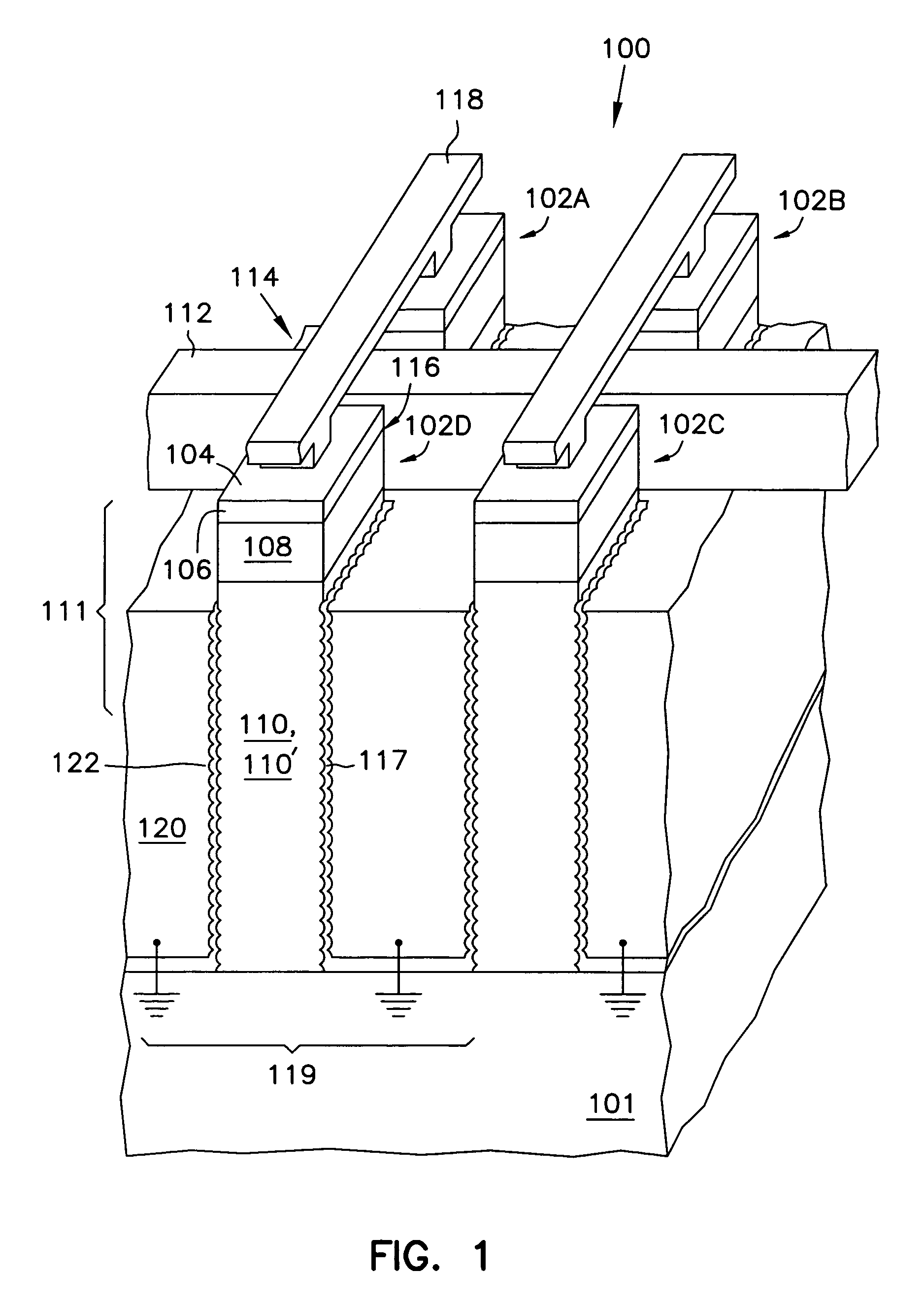

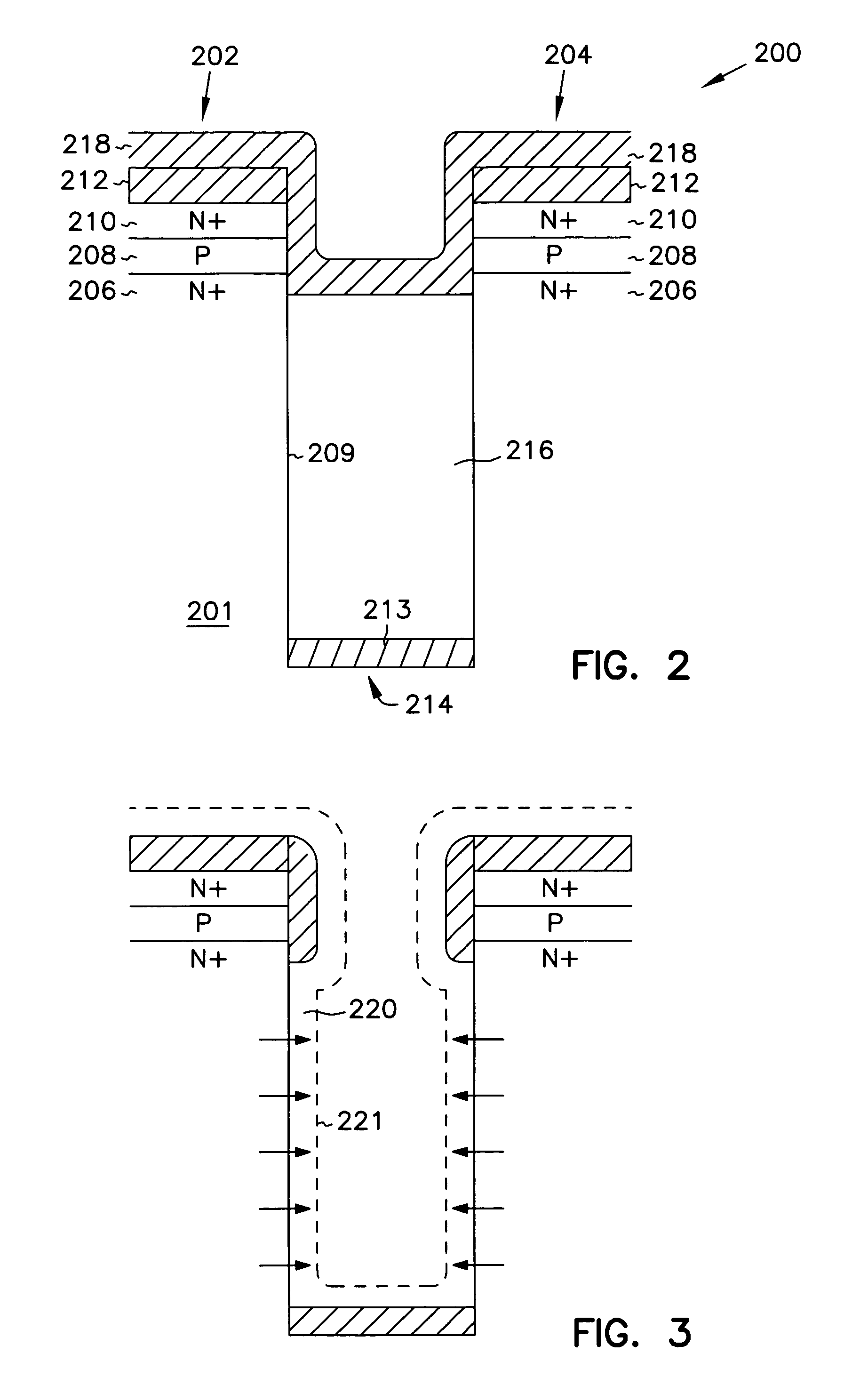

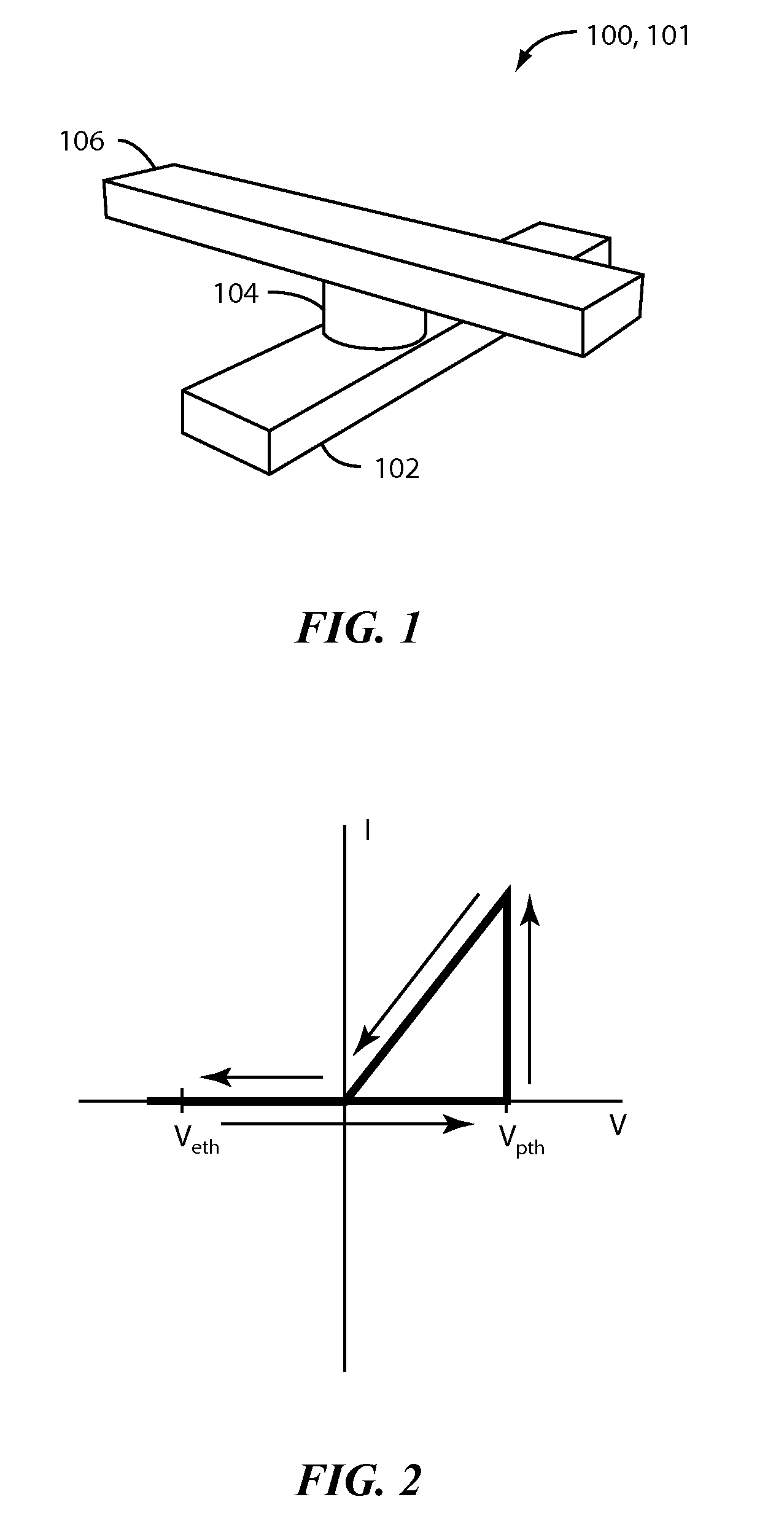

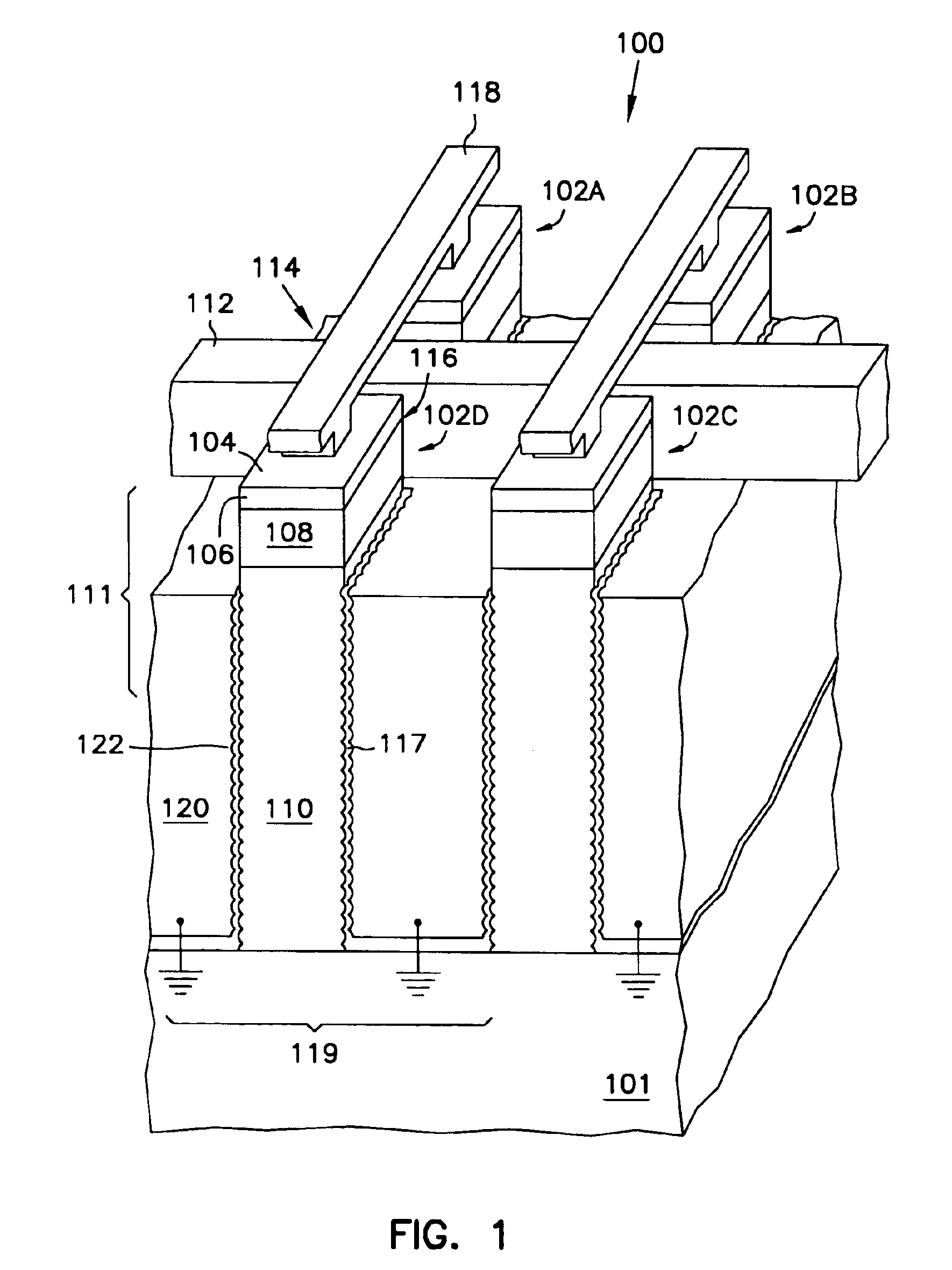

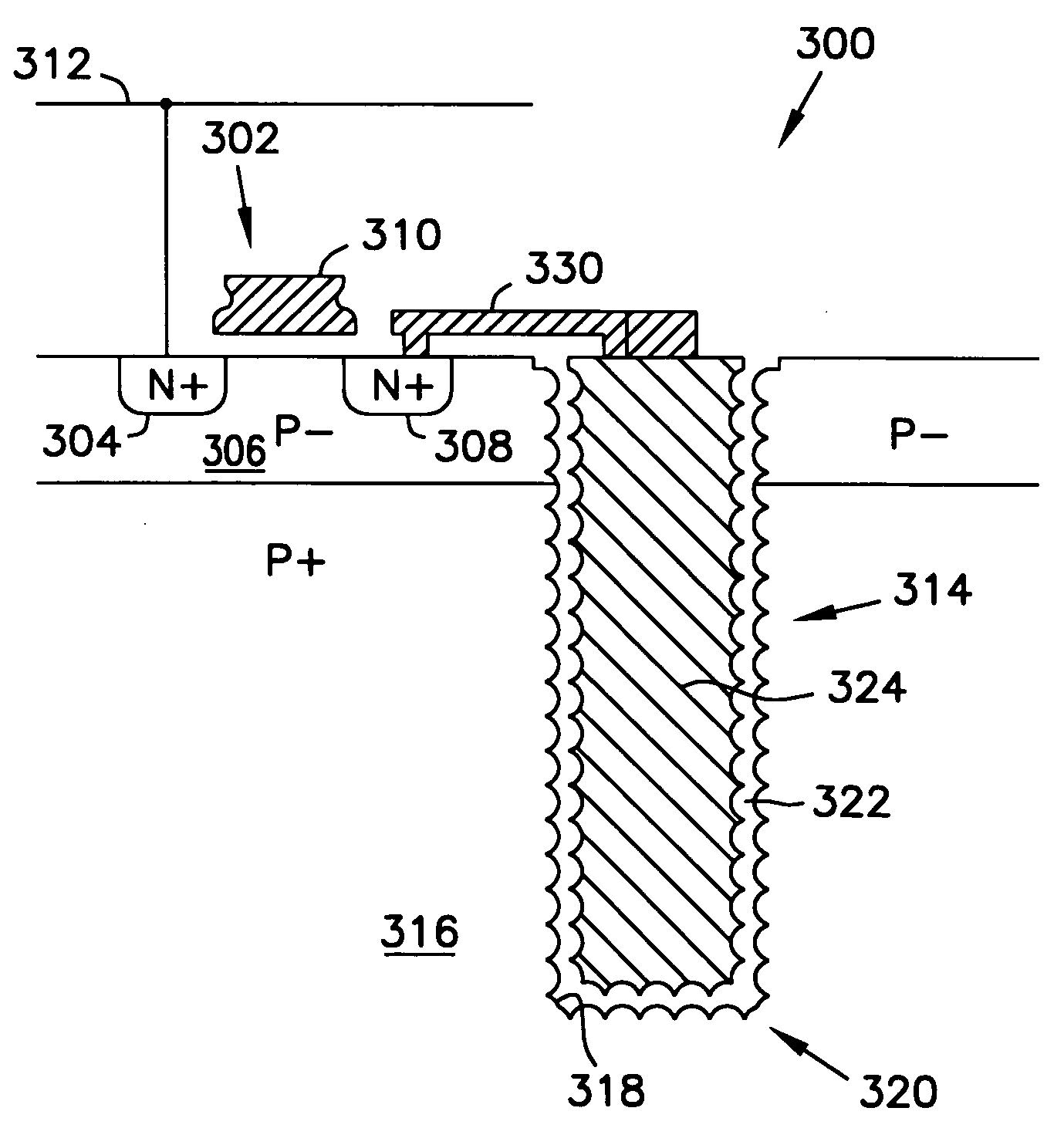

Circuits with a trench capacitor having micro-roughened semiconductor surfaces

A method for forming a trench capacitor. The method includes forming a trench in a semiconductor substrate. A conformal layer of semiconductor material is deposited in the trench. The surface of the conformal layer of semiconductor material is roughened. An insulator layer is formed outwardly from the roughened, conformal layer of semiconductor material. A polycrystalline semiconductor plate is formed outwardly from the insulator layer in the trench.

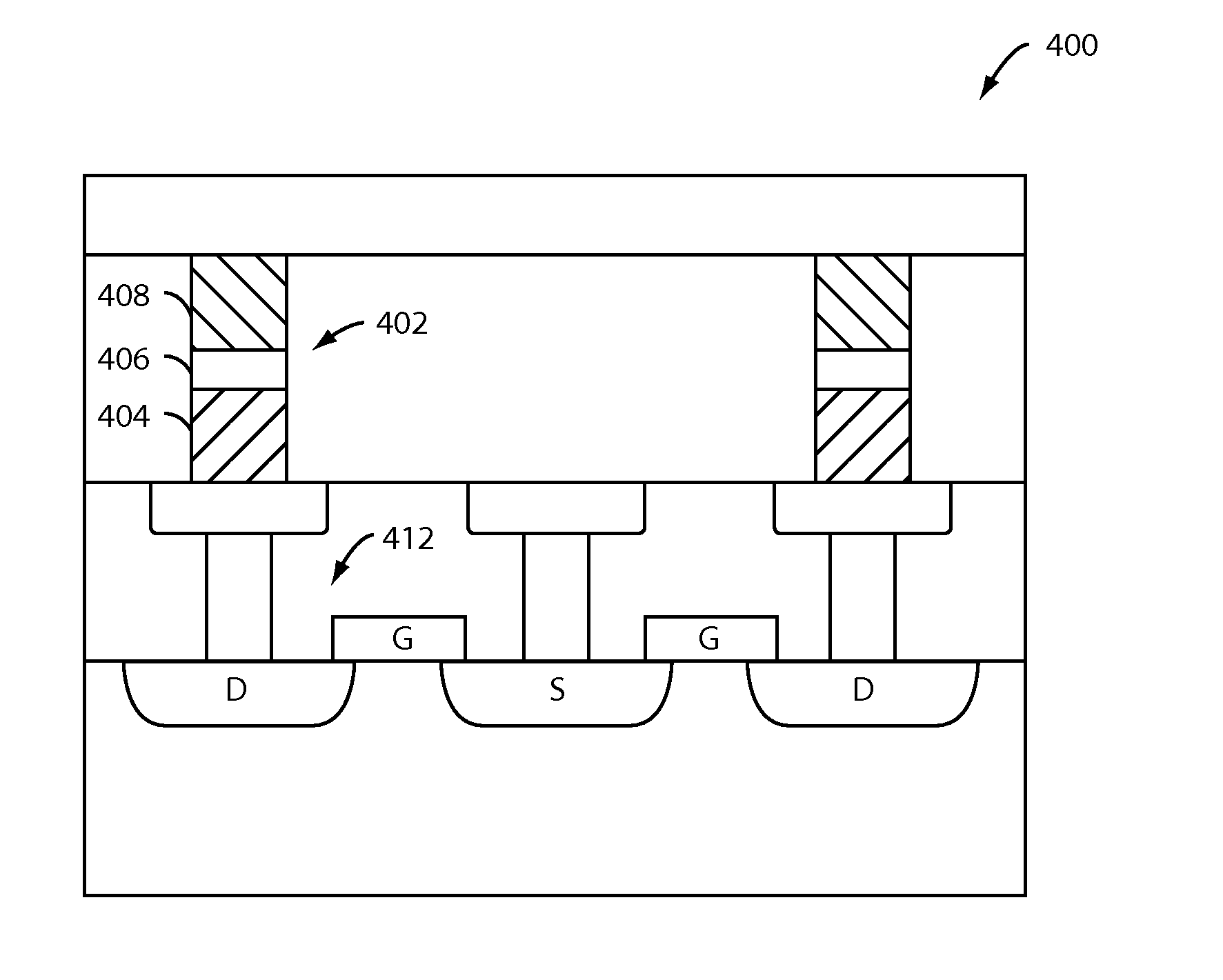

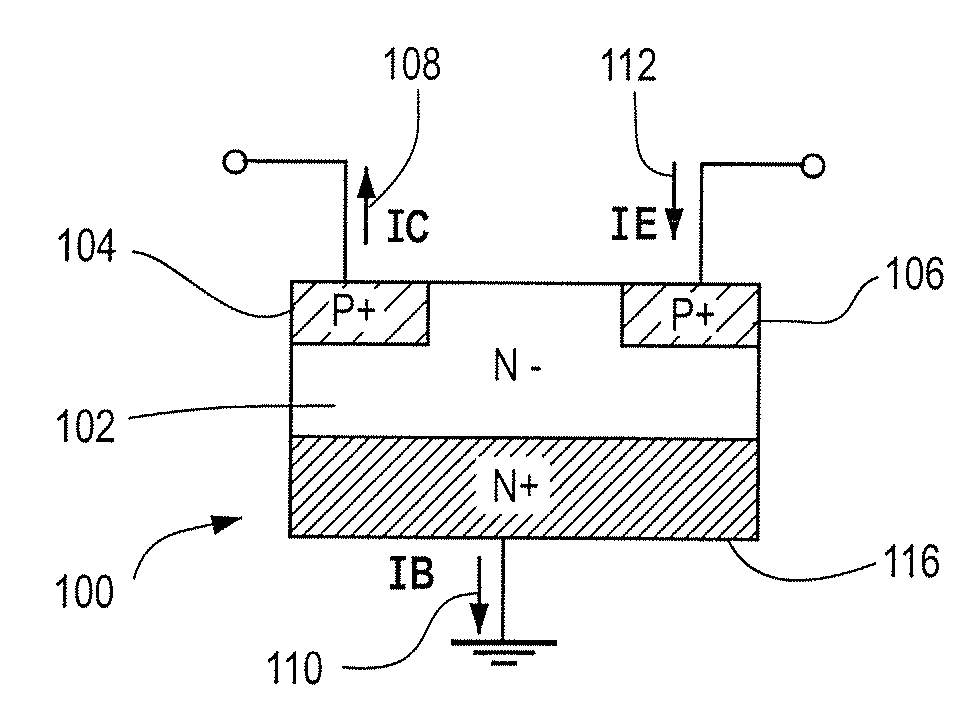

Method for forming polycrystalline thin film bipolar transistors

ActiveUS20080311722A1Read-only memoriesSemiconductor/solid-state device manufacturingGermanideMaterials science

A method is described for forming a semiconductor device comprising a bipolar transistor having a base region, an emitter region and a collector region, wherein the base region comprises polycrystalline semiconductor material formed by crystallizing silicon, germanium or silicon germanium in contact with a silicide, germanide or silicide germanide. The emitter region and collector region also may be formed from polycrystalline semiconductor material formed by crystallizing silicon, germanium or silicon germanium in contact with a silicide, germanide or silicide germanide forming metal. The polycrystalline semiconductor material is preferably silicided polysilicon, which is formed in contact with C49 phase titanium silicide.

Owner:SANDISK TECH LLC

Resistive memory using SiGe material

Owner:INNOSTAR SEMICON SHANGHAI CO LTD

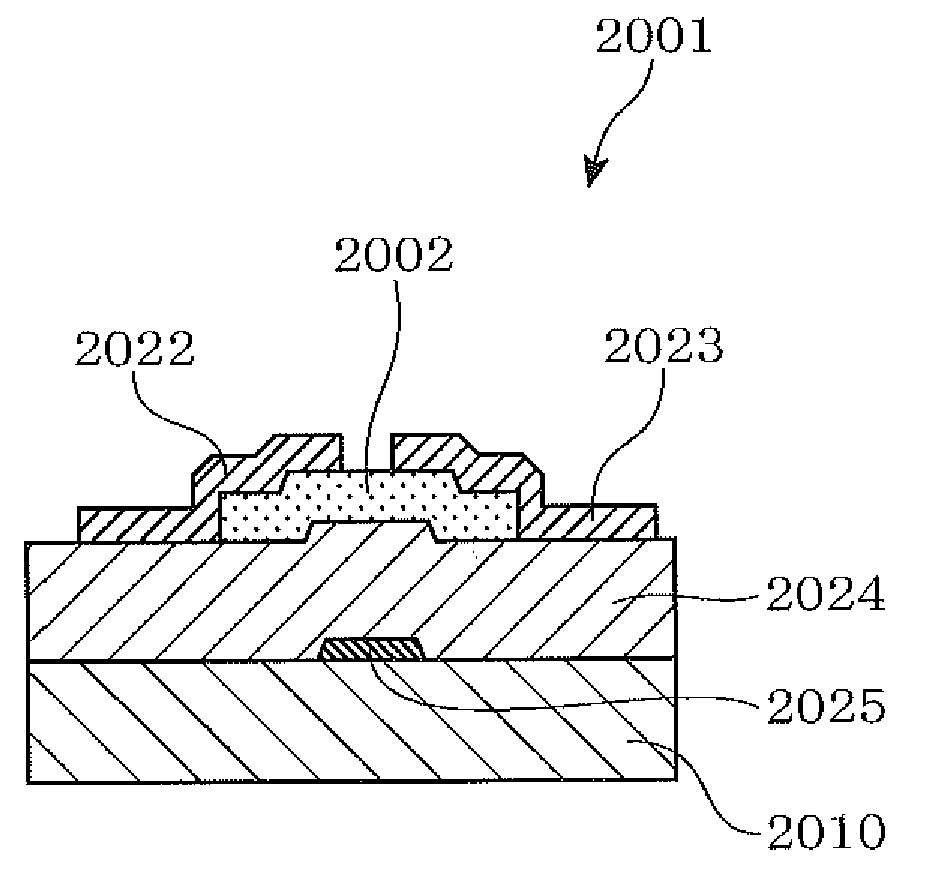

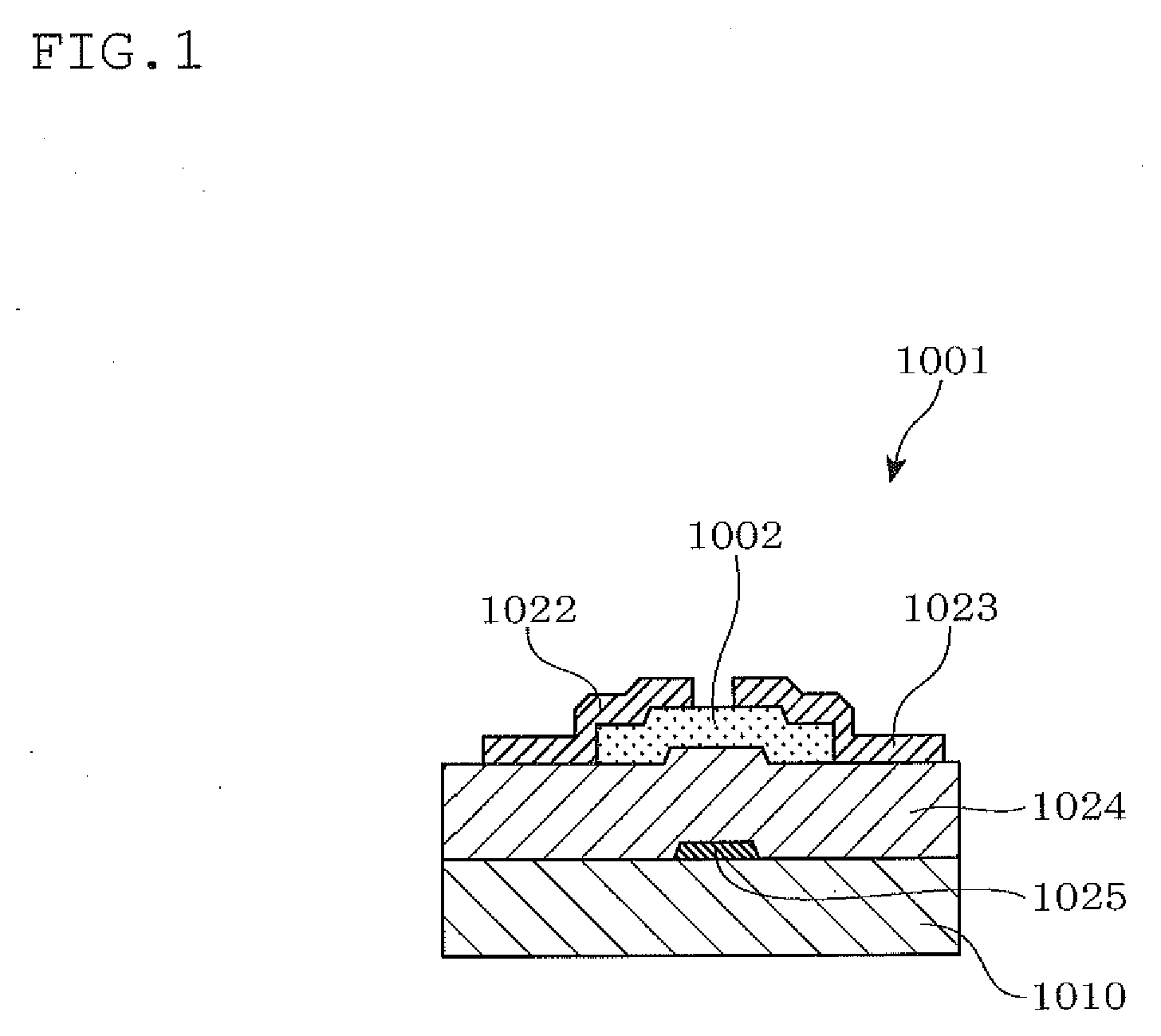

Semiconductor device, its manufacturing method, and electronic device

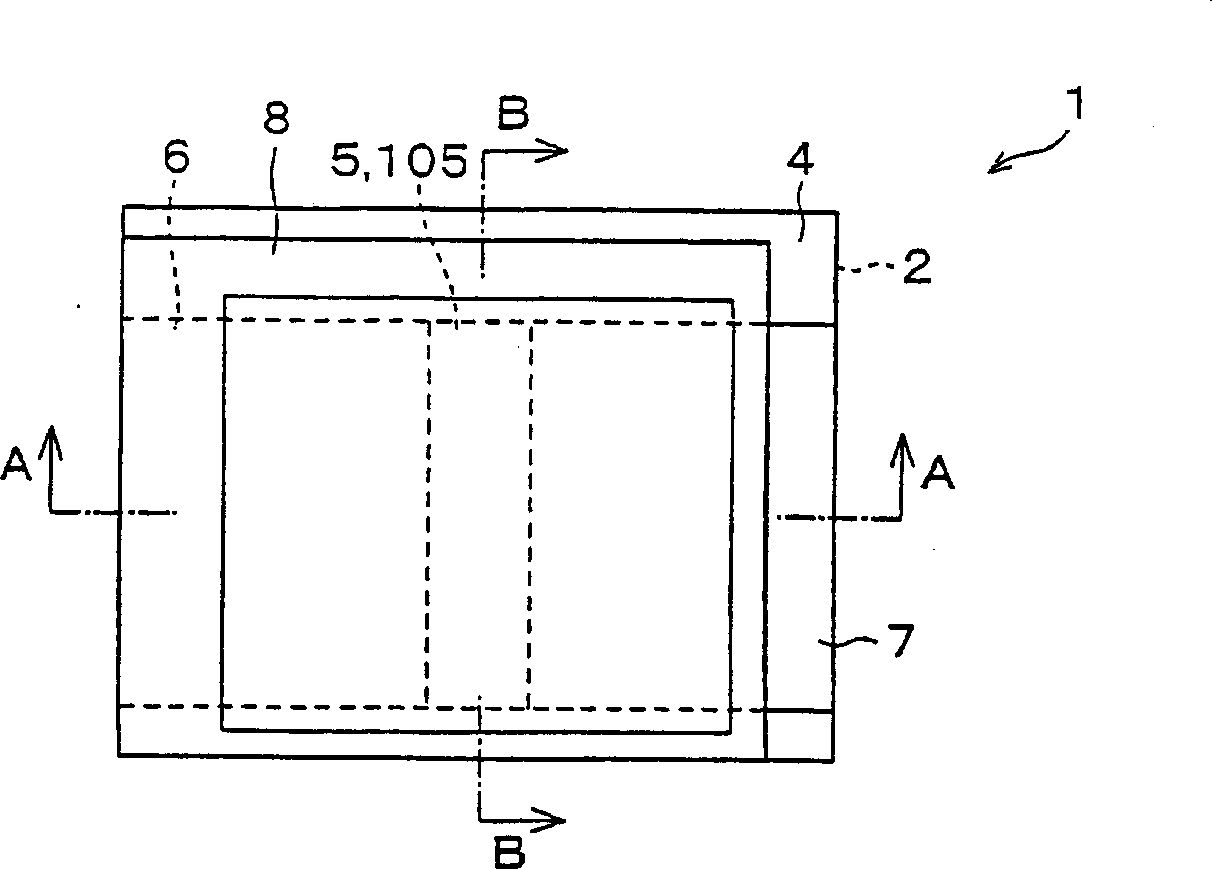

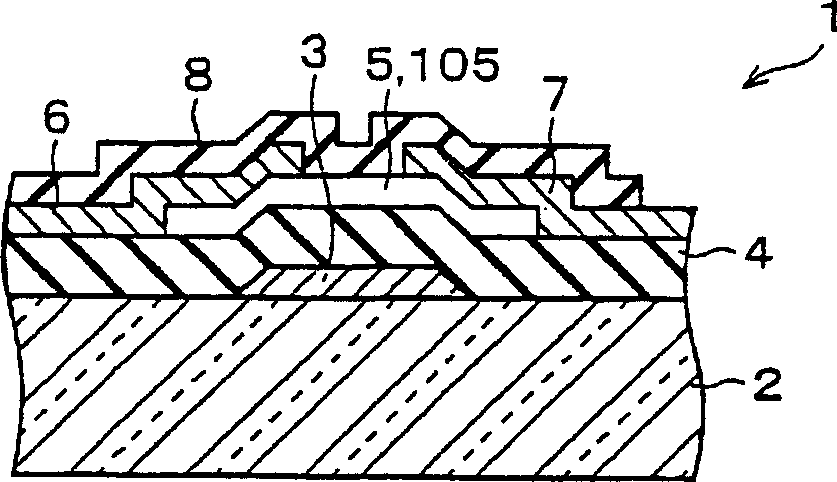

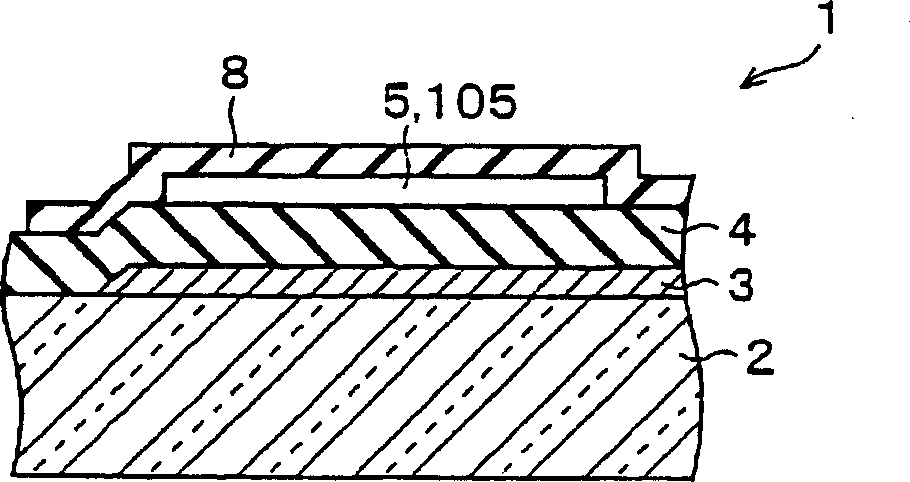

InactiveCN1806322ATransistorSemiconductor/solid-state device manufacturingIntrinsic resistanceGate voltage

A thin film transistor (1) wherein a gate electrode (3) is formed on an insulative substrate (2), a gate insulating layer (4) is formed on the gate electrode (3), a semiconductor layer (5) is formed on the gate insulating layer (4), a source electrode (6) and a drain electrode (7) are formed on the semiconductor layer (5), and a protective layer (8) covering them are formed. The semiconductor layer (5) is isolated from the atmosphere. The semiconductor layer (5) (active layer) is formed of a ZnO polycrystalline semiconductor doped with, for example, a group V element. Since the surface state of the ZnO semiconductor is reduced thanks to the protective layer (8) and inward expansion of the depletion layer is prevented, the ZnO semiconductor is of an n-type showing its intrinsic resistance value and contains excessive free electrons. The added element acts as acceptor impurities in the ZnO semiconductor, decreasing the excessive electrons. Thus the gate voltage to eliminate the excessive free electrons lowers, thereby making the threshold voltage around 0 V. A semiconductor device using a zinc oxide for an active layer and having a protective layer for isolating the active layer from the atmosphere can be actually used.

Owner:SHARP KK +2

IC card and booking account system using the IC card

InactiveUS7518692B2Ensure safetySolid-state devicesPayment architectureDisplay deviceIntegrated circuit

It is an object of the present invention to provide a highly sophisticated functional card that can ensure security by preventing forgery such as changing a picture of a face, and display other images as well as the picture of a face. A card comprising a display device and a thin film integrated circuit; wherein driving of the display device is controlled by the thin film integrated circuit; a semiconductor element used for the thin film integrated circuit and the display device is formed by using a polycrystalline semiconductor film; the thin film integrated circuit and the display device are sealed with a resin between a first substrate and a second substrate of the card; and the first substrate and the second substrate are plastic substrates.

Owner:SEMICON ENERGY LAB CO LTD

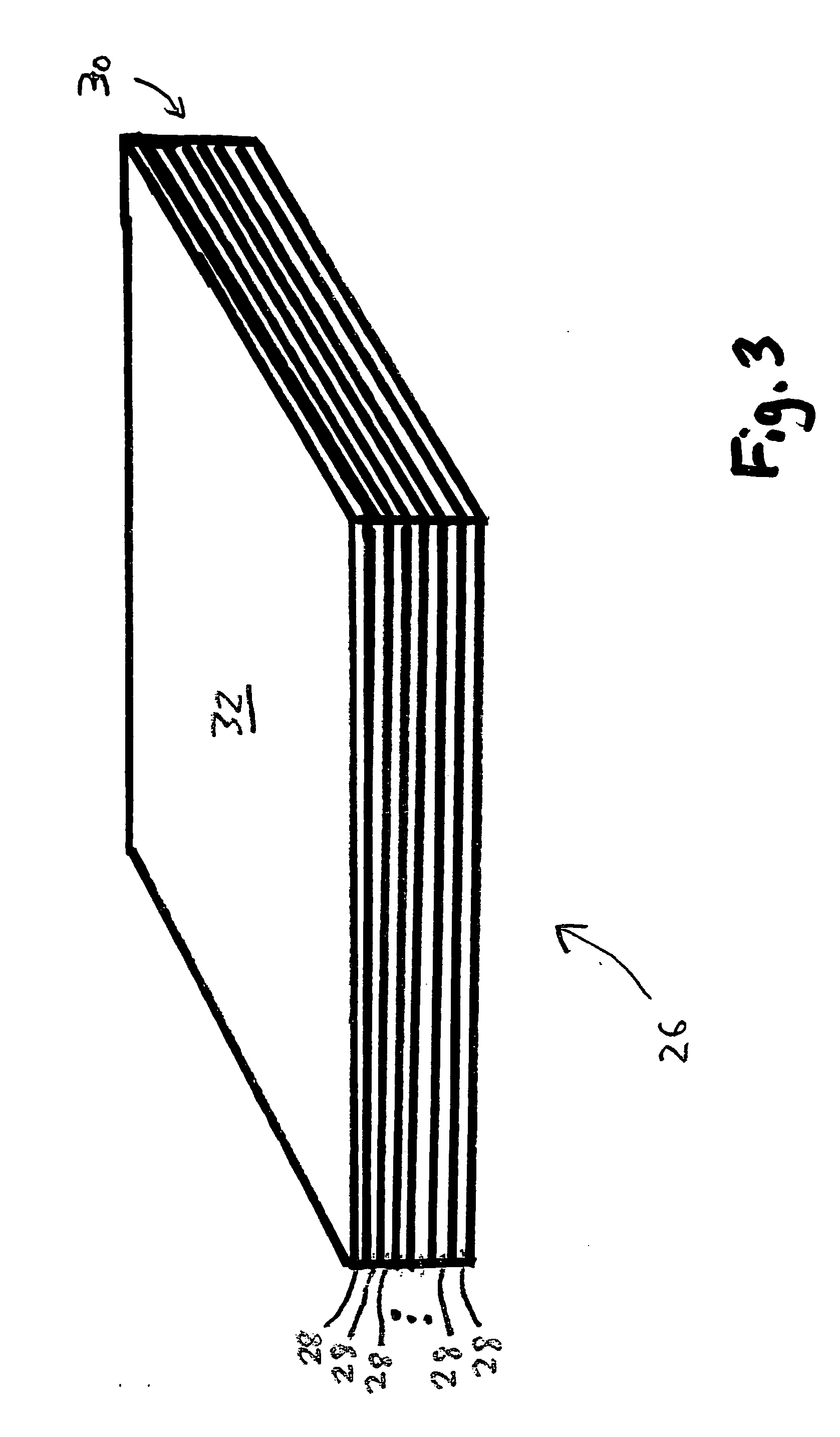

Method and structure for high capacitance memory cells

InactiveUS6927122B2Increase capacitanceMaterial nanotechnologyNanoinformaticsCapacitanceHigh capacitance

A method and structure for high capacitance memory cells is provided. The method includes forming a trench capacitor in a semiconductor substrate. A self-structured mask is formed on the interior surface of the trench. The interior surface of the trench is etched to form an array of silicon pillars. The self-structured mask is removed. Then an insulator layer is formed on the array of silicon pillars. A polycrystalline semiconductor plate extends outwardly from the insulator layer in the trench.

Owner:MICRON TECH INC

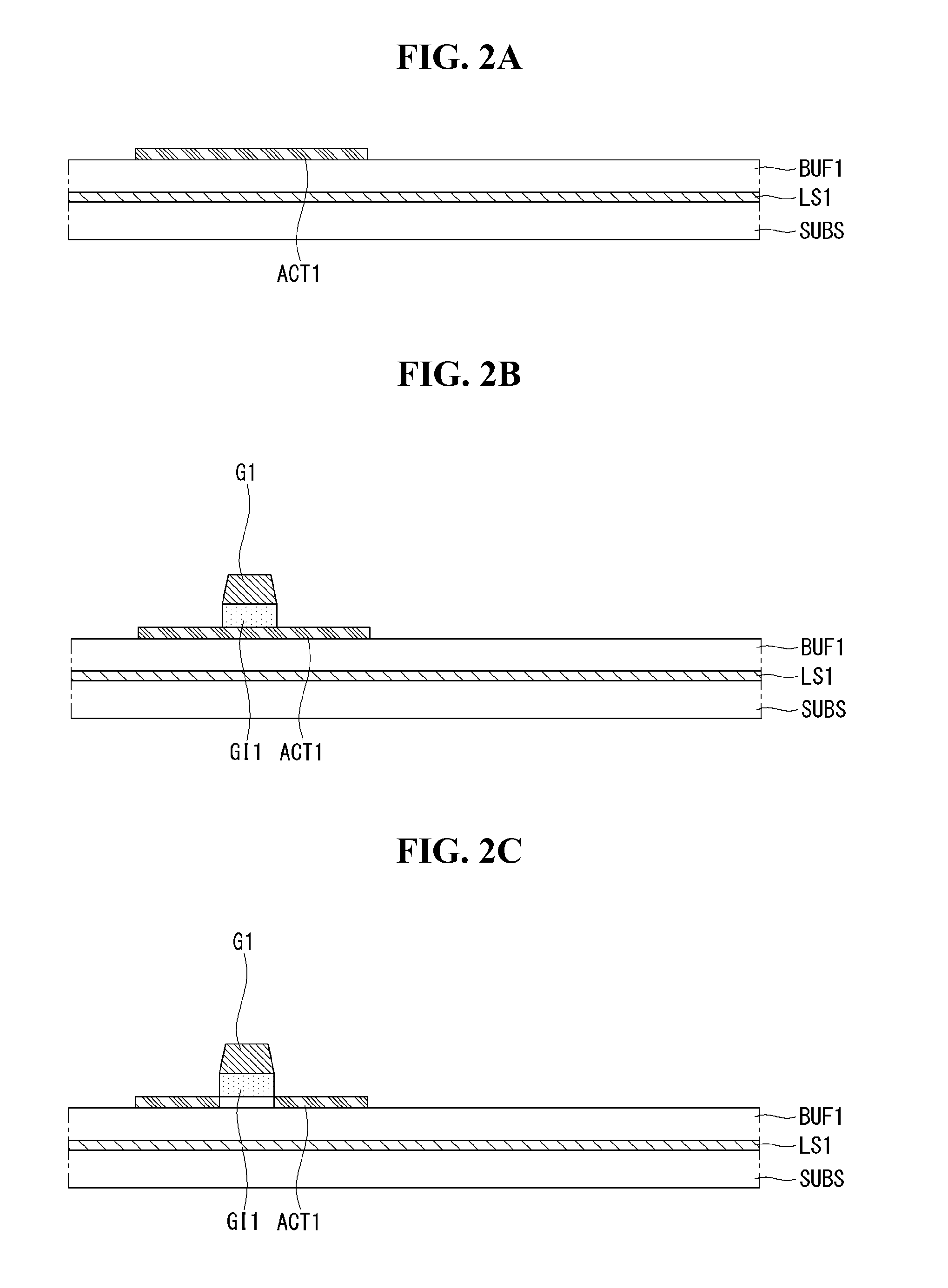

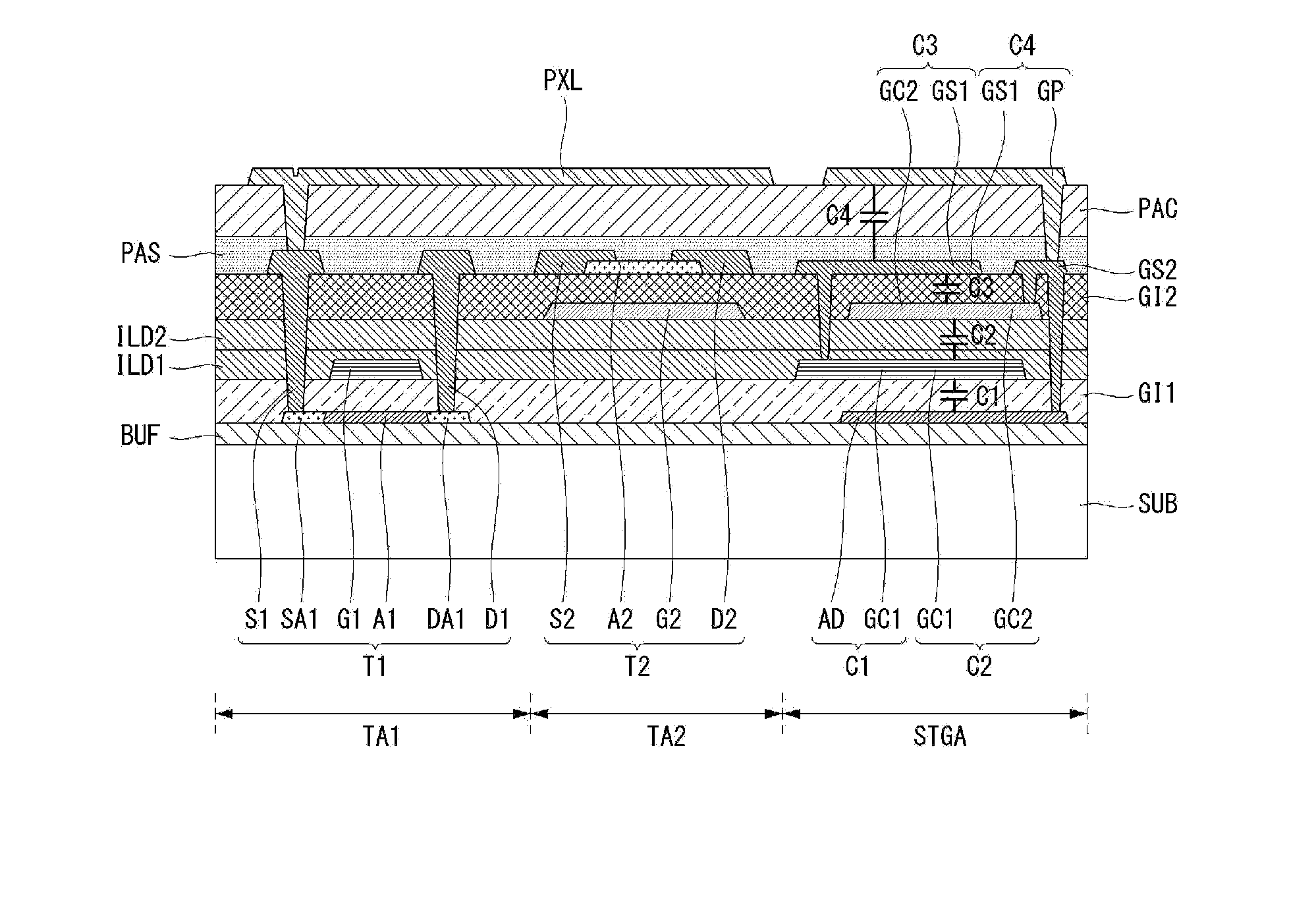

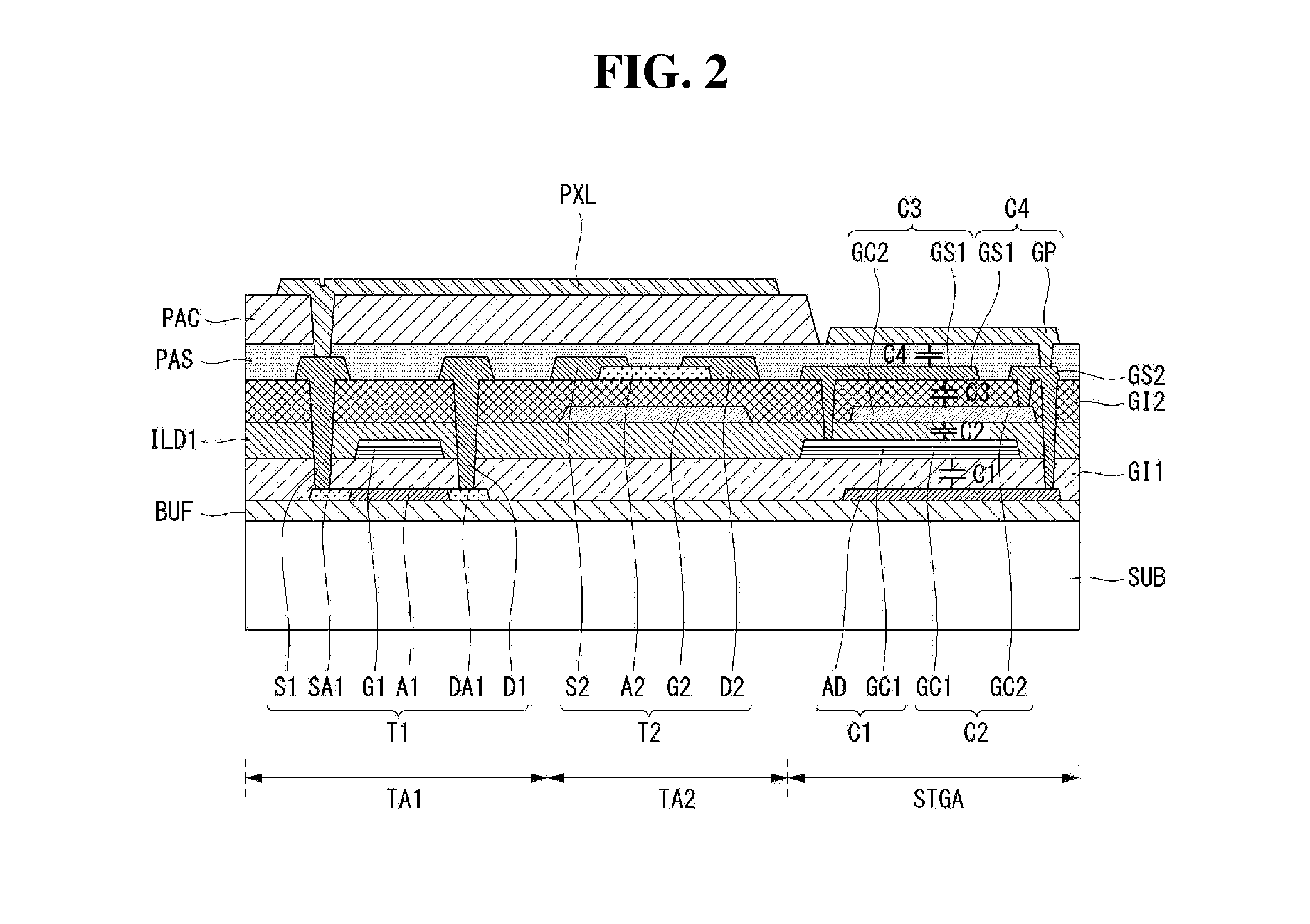

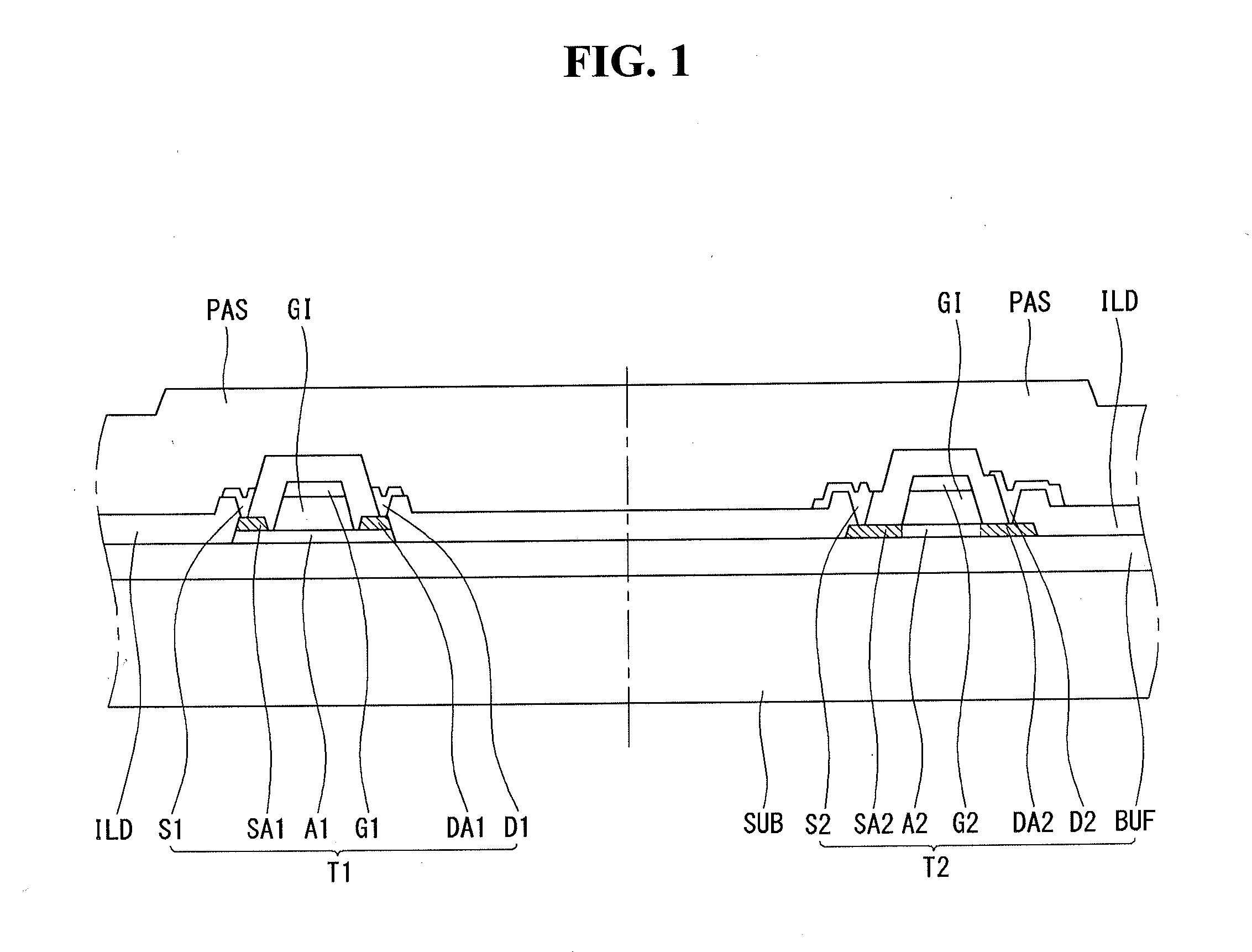

Thin film transistor substrate and display device using the same

ActiveUS20160372497A1Improve image qualitySolid-state devicesNon-linear opticsDisplay deviceCapacitor

A thin film transistor (TFT) substrate and a display device using the same are disclosed. The TFT substrate includes a first TFT including a polycrystalline semiconductor layer, a first gate electrode, a first source electrode, and a first drain electrode deposited on a substrate, a second TFT separated from the first TFT, the second TFT including a second gate electrode, an oxide semiconductor layer, a second source electrode, and a second drain electrode deposited on the first gate electrode, and a plurality of storage capacitors separated from the first and second TFTs, each storage capacitor including a first dummy semiconductor layer, a first gate insulating layer on the first dummy semiconductor layer, a first dummy gate electrode on the first gate insulating layer, and an intermediate insulating layer on the first dummy gate electrode.

Owner:LG DISPLAY CO LTD

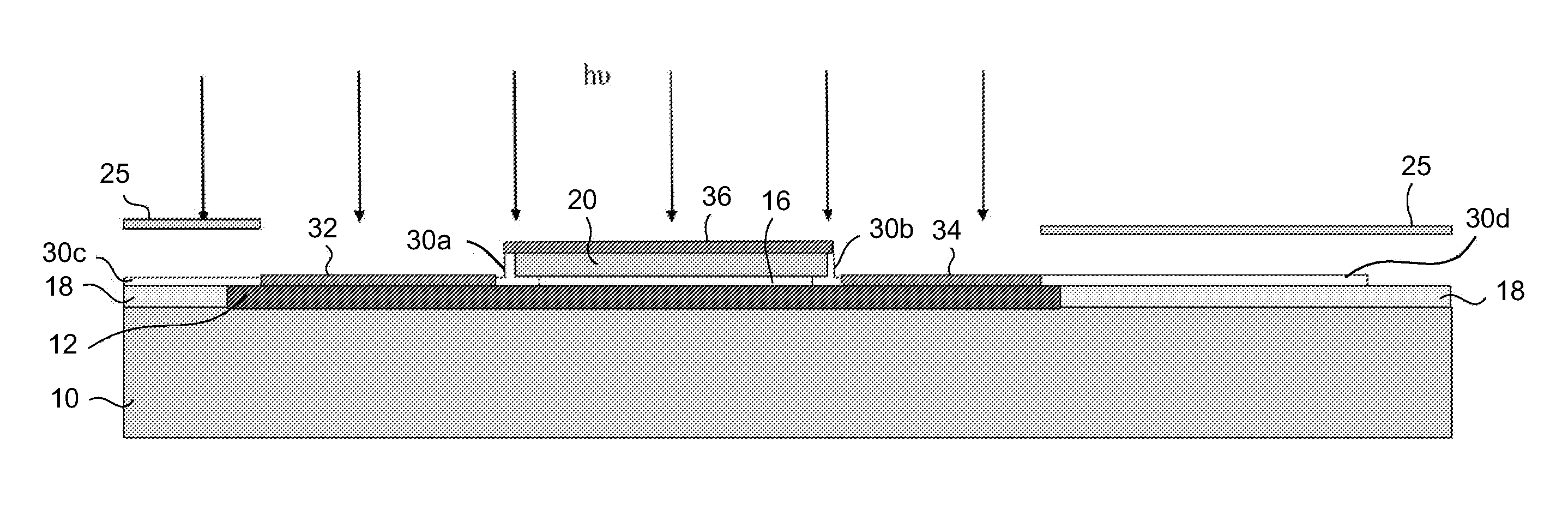

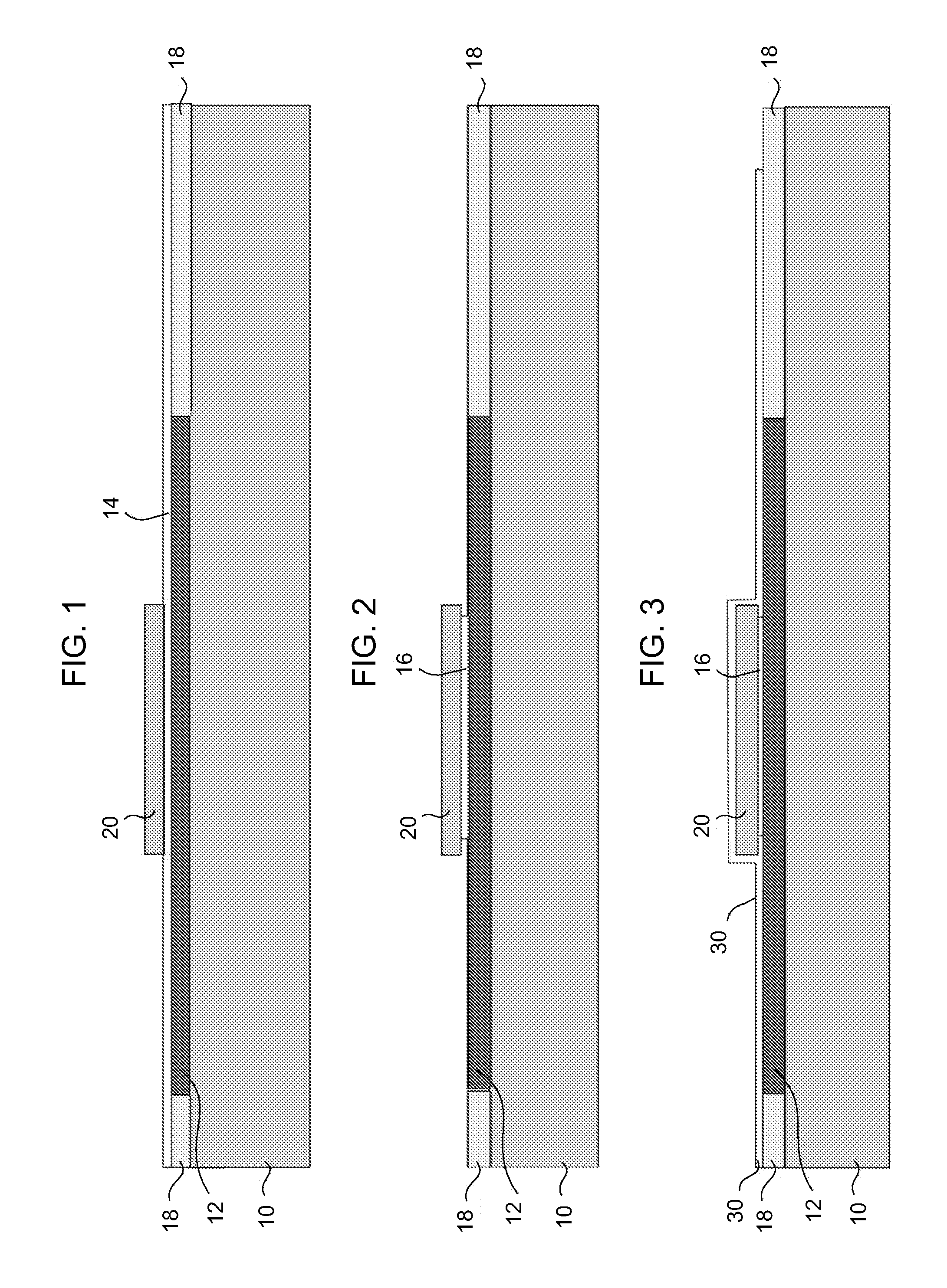

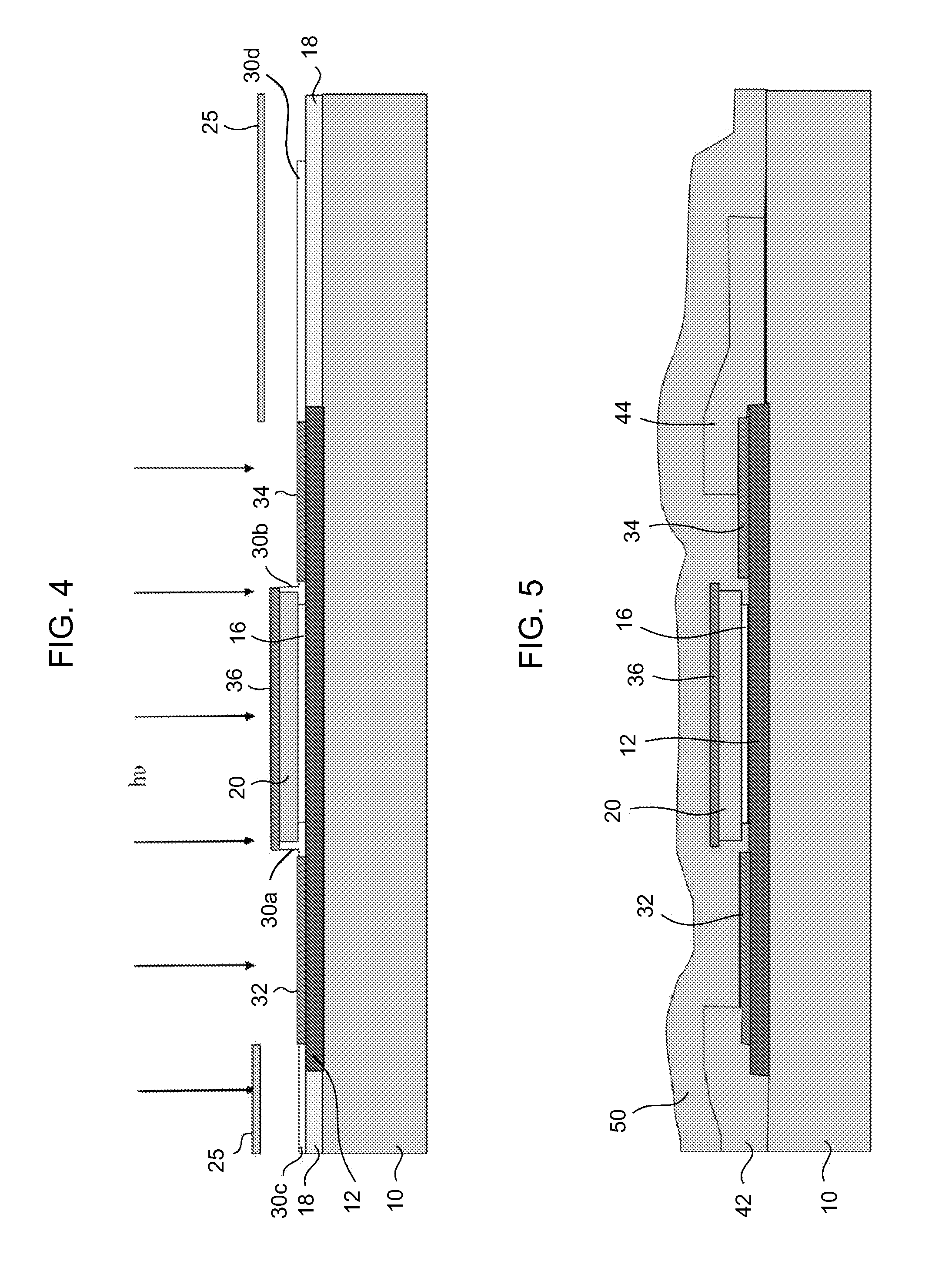

MOS transistor with self-aligned source and drain, and method for making the same

InactiveUS7619248B1Low costReliable and commercially acceptable electrical characteristicSemiconductor devicesSemiconductor materialsEngineering

A MOS transistor with self-aligned source / drain terminals, and methods for its manufacture. The transistor generally includes an electrically functional substrate, a dielectric film on portions of the substrate, a gate on the dielectric film, and polycrystalline source and drain terminals self-aligned with the gate. The method generally includes forming an amorphous semiconductor material on a gate and on exposed portions of an electrically functional substrate, irradiating an upper surface of the amorphous semiconductor material to form self-aligned polycrystalline semiconducting source / drain terminal layers, and (optionally) selectively removing the non-irradiated amorphous semiconductor material portions. The present invention advantageously provides MOS thin film transistors having reliable electrical characteristics quickly, efficiently, and / or at a low cost by eliminating one or more conventional photolithographic steps.

Owner:ENSURGE MICROPOWER ASA

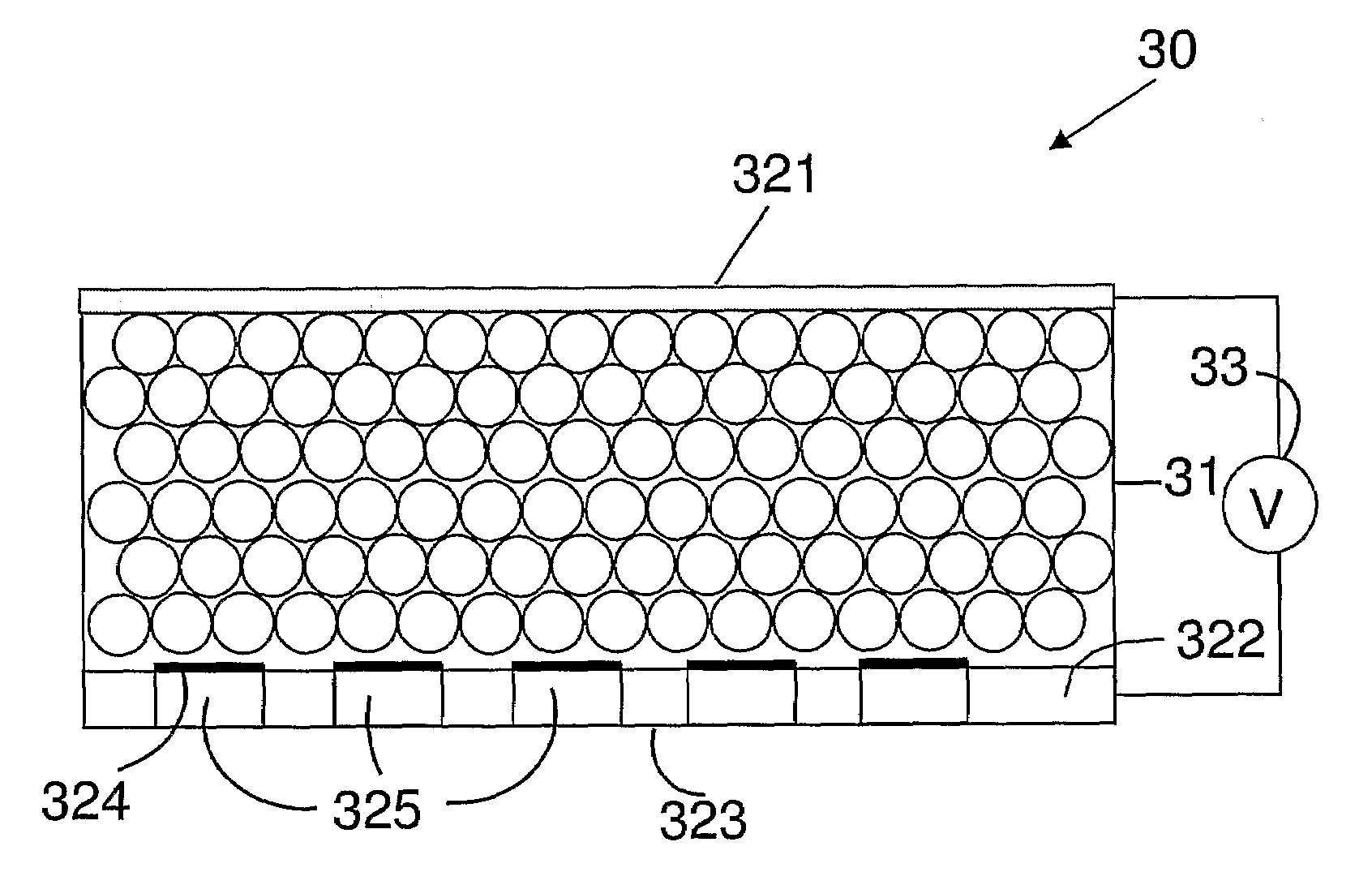

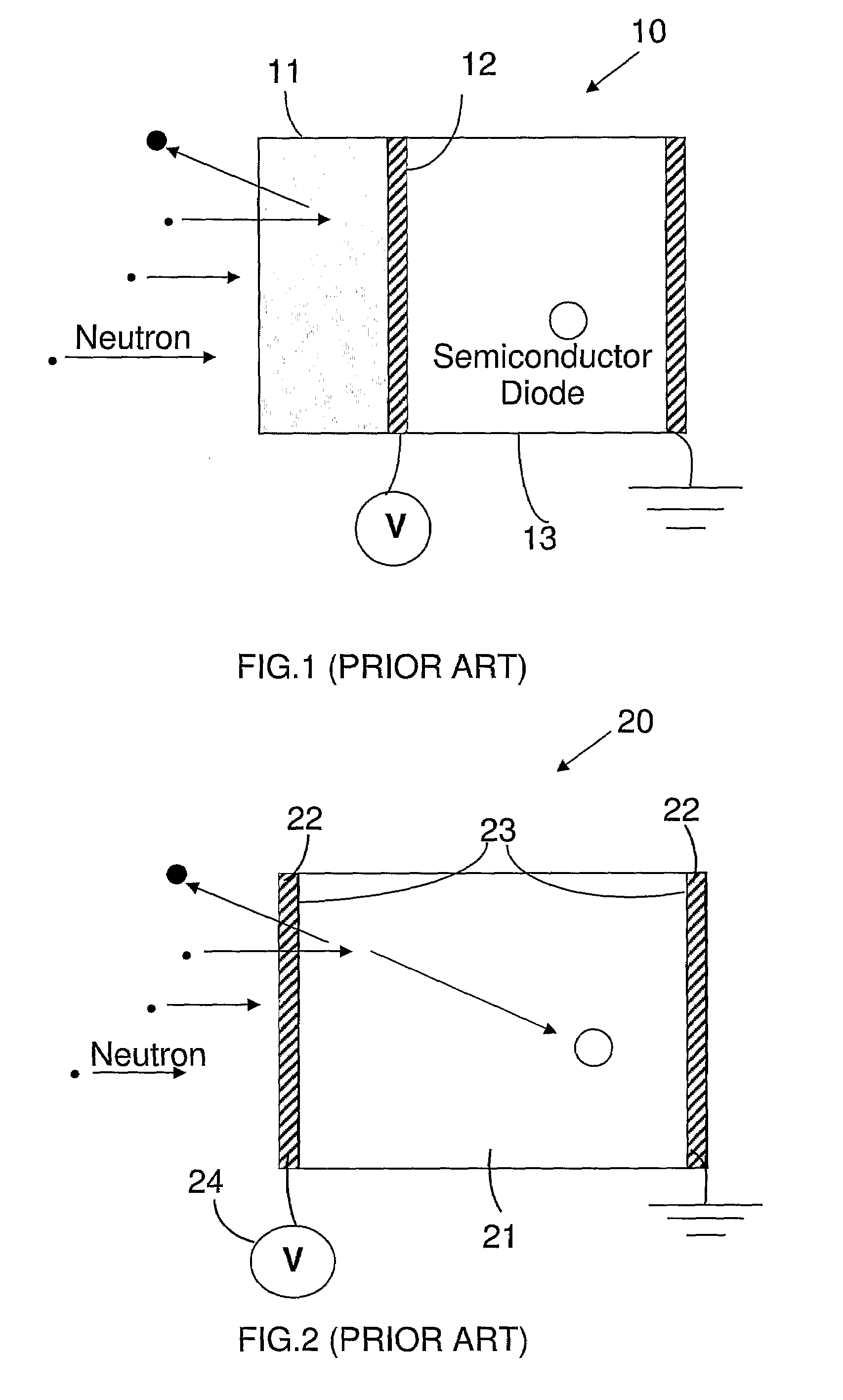

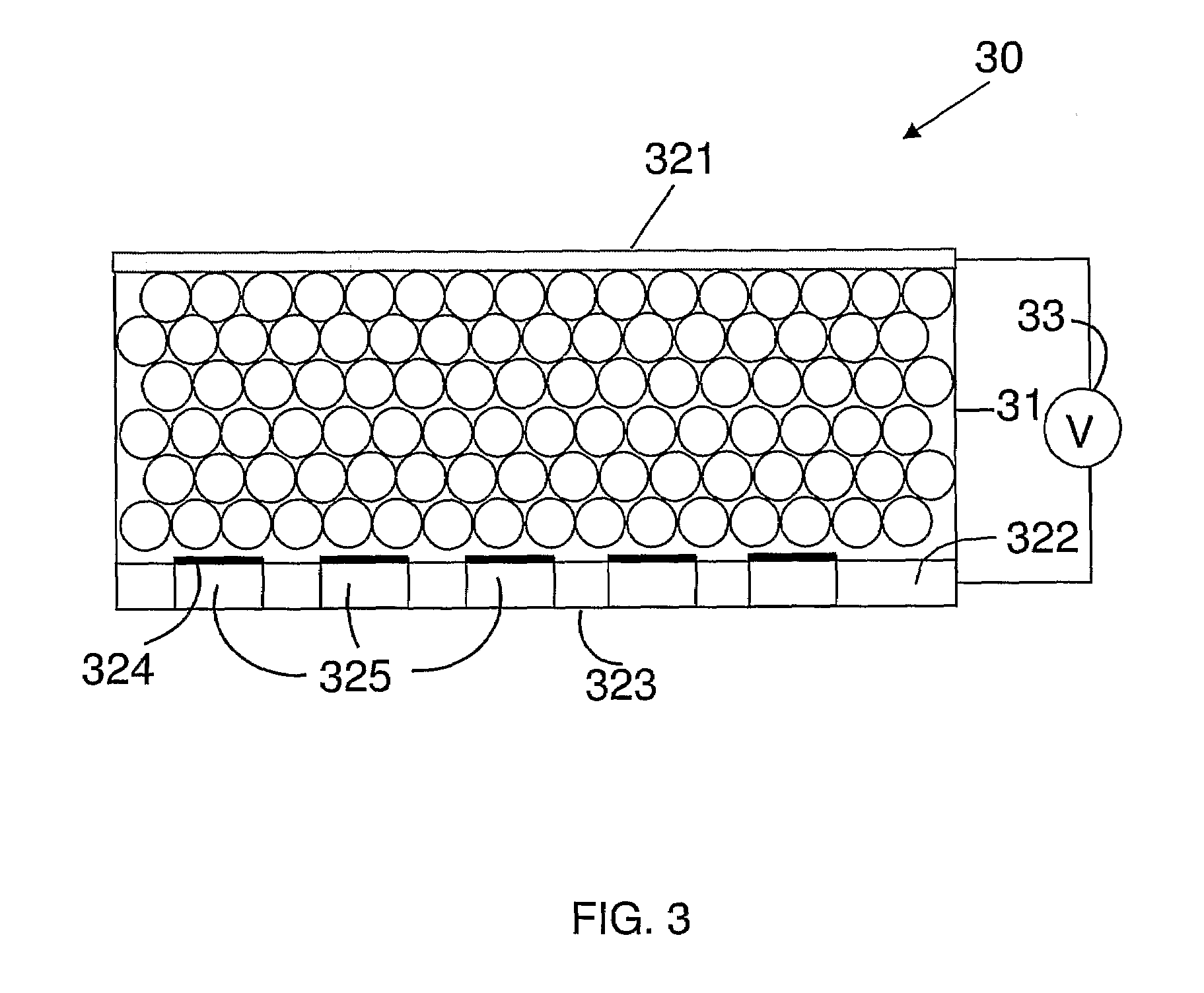

Solid-state neutron and alpha particles detector and methods for manufacturing and use thereof

InactiveUS20090302226A1Optimize detection resultsMeasurement with semiconductor devicesSolid-state devicesParticulatesSemiconductor materials

A solid-state detector for detection of neutron and alpha particles detector and methods for manufacturing and use thereof are described. The detector has an active region formed of a polycrystalline semiconductor compound comprising a particulate semiconductor material sensitive to neutron and alpha particles radiation imbedded in a binder. The particulate semiconductor material contains at least one element sensitive to neutron and alpha particles radiation, selected from a group including 10Boron, 6Lithium, 113Cadmium, 157Gadolinium and 199Mercury. The semiconductor compound is sandwiched between an electrode assembly configured to detect the neutron and alpha particles interacting with the bulk of the active region. The binder can be either an organic polymer binder or inorganic binder. The organic polymer binder comprises at least one polymer that can be selected from the group comprising polystyrene, polypropylene, Humiseal™ and Nylon-6. The inorganic binder can be selected from B2O3, PbO / B2O3 / , Bi2O3 / PbO, Borax glass, Bismuth Borate glass and Boron Oxide based glass.

Owner:YISSUM RES DEV CO OF THE HEBREWUNIVERSITY OF JERUSALEM LTD

Article having display device

InactiveUS7652359B2Increased complexityEnsure safetyFinanceStatic indicating devicesDisplay deviceEngineering

It is an object of the present invention to provide a highly sophisticated functional IC card that can ensure security by preventing forgery such as changing a picture of a face, and display other images as well as the picture of a face. An IC card comprising a display device and a plurality of thin film integrated circuits; wherein driving of the display device is controlled by the plurality of thin film integrated circuits; a semiconductor element used for the plurality of thin film integrated circuits and the display device is formed by using a polycrystalline semiconductor film; the plurality of thin film integrated circuits are laminated; the display device and the plurality of thin film integrated circuits are equipped for the same printed wiring board; and the IC card has a thickness of from 0.05 mm to 1 mm.

Owner:SEMICON ENERGY LAB CO LTD

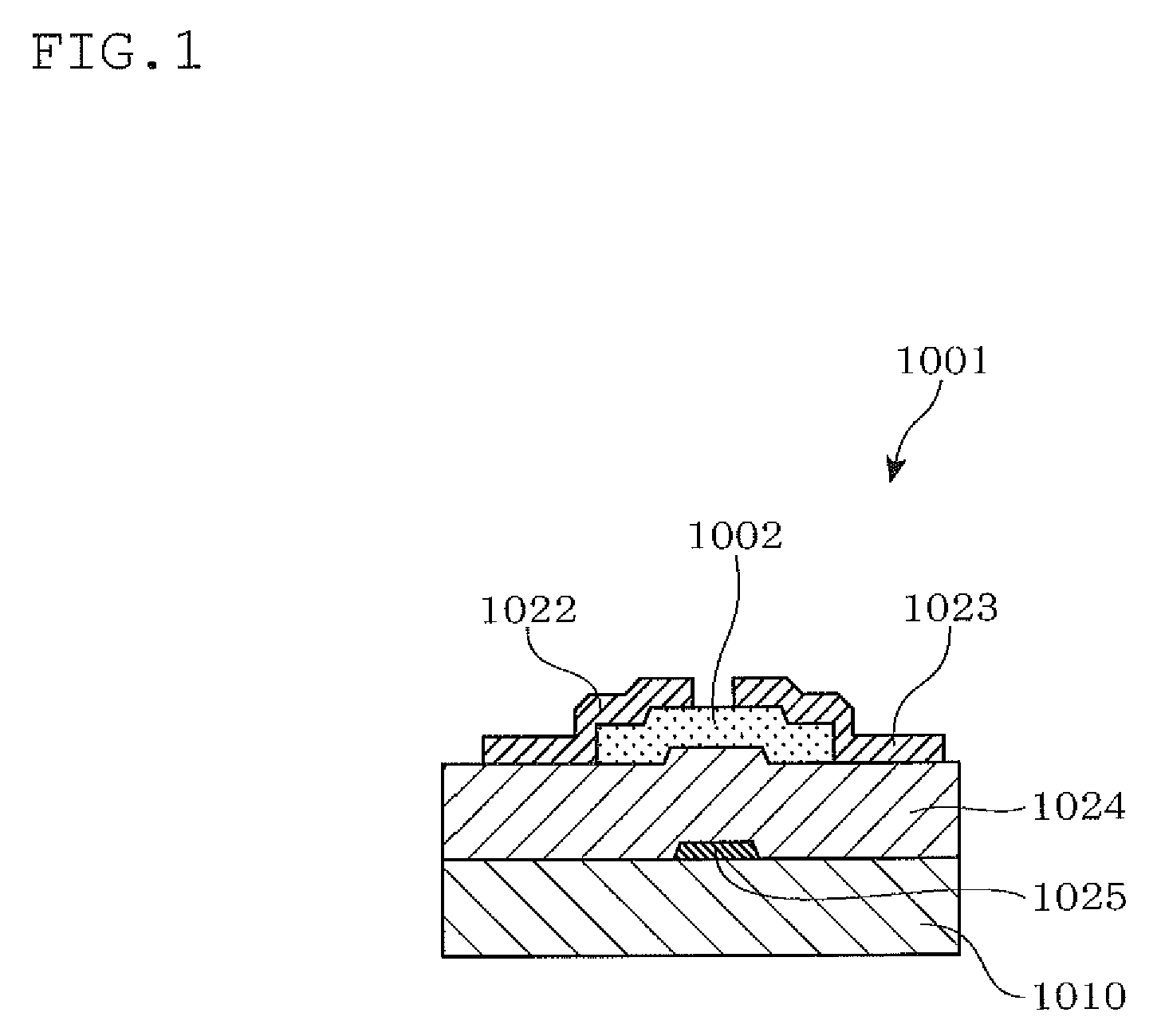

Semiconductor device and method of manufacturing the same

InactiveUS7148092B2Increase speedLess fluctuationTransistorSolid-state devicesEngineeringCrystalline semiconductor

Owner:SEMICON ENERGY LAB CO LTD

Field-effect transistors with weakly coupled layered inorganic semiconductors

InactiveUS20050062082A1Improve mobilityExhibit mechanical flexibilityTransistorSolid-state devicesSemiconductor materialsField-effect transistor

A field-effect transistor includes source, drain, and gate electrodes; a crystalline or polycrystalline layer of inorganic semiconductor; and a dielectric layer. The layer of inorganic semiconductor has an active channel portion physically extending from the source electrode to the drain electrode. The inorganic semiconductor has a stack of 2-dimensional layers in which intra-layer bonding forces are covalent and / or ionic. Adjacent ones of the layers are bonded together by forces substantially weaker than covalent and ionic bonding forces. The dielectric layer is interposed between the gate electrode and the layer of inorganic semiconductor material. The gate electrode is configured to control a conductivity of an active channel part of the layer of inorganic semiconductor.

Owner:RUTGERS THE STATE UNIV +1

Method and structure for high capacitance memory cells

InactiveUS20050026360A1Increase capacitanceIncrease in capacitance levelMaterial nanotechnologyNanoinformaticsCapacitanceHigh capacitance

A method and structure for high capacitance memory cells is provided. The method includes forming a trench capacitor in a semiconductor substrate. A self-structured mask is formed on the interior surface of the trench. The interior surface of the trench is etched to form an array of silicon pillars. The self-structured mask is removed. Then an insulator layer is formed on the array of silicon pillars. A polycrystalline semiconductor plate extends outwardly from the insulator layer in the trench.

Owner:MICRON TECH INC

Thin film transistor substrate and display using the same

ActiveUS20160064465A1Simple preparation processReduce in quantityTransistorSolid-state devicesSemiconductor materialsDisplay device

The present invention relates to a thin film transistor substrate having two different types of semiconductor materials on the same substrate, and a display using the same. A disclosed display may include a substrate, a first thin film transistor having a polycrystalline semiconductor material on the substrate and a second thin film transistor having an oxide semiconductor material on the substrate.

Owner:LG DISPLAY CO LTD

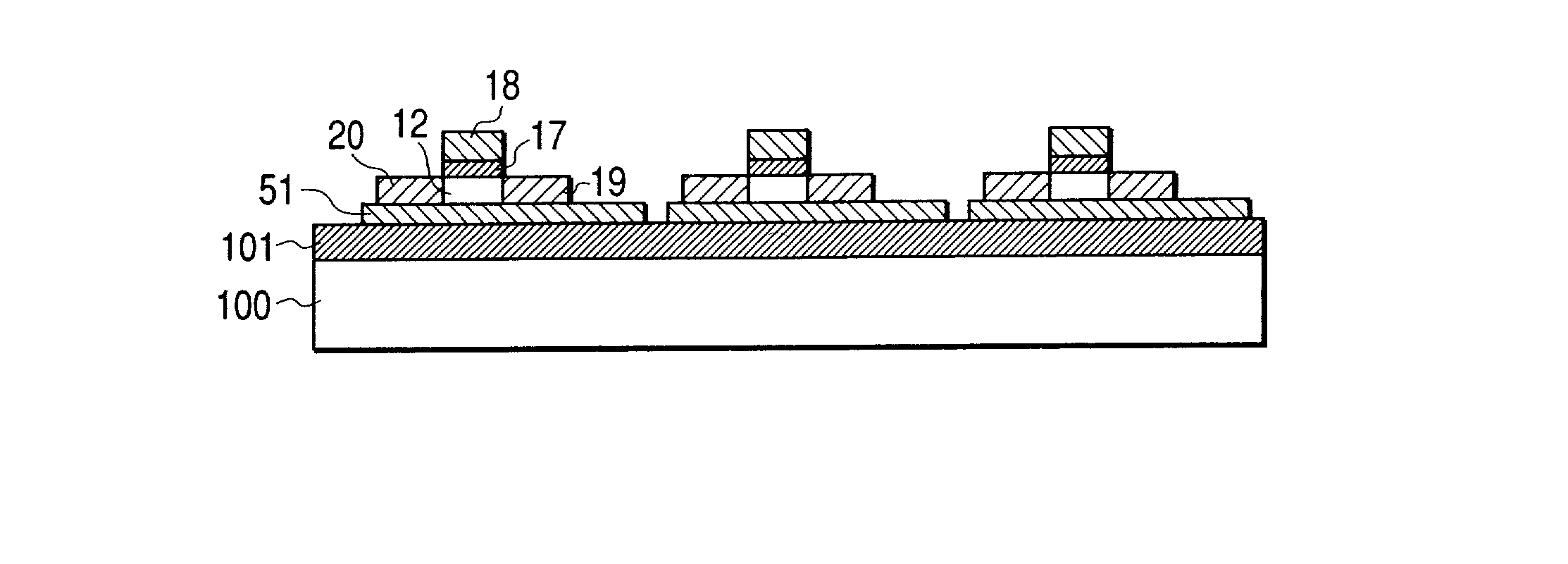

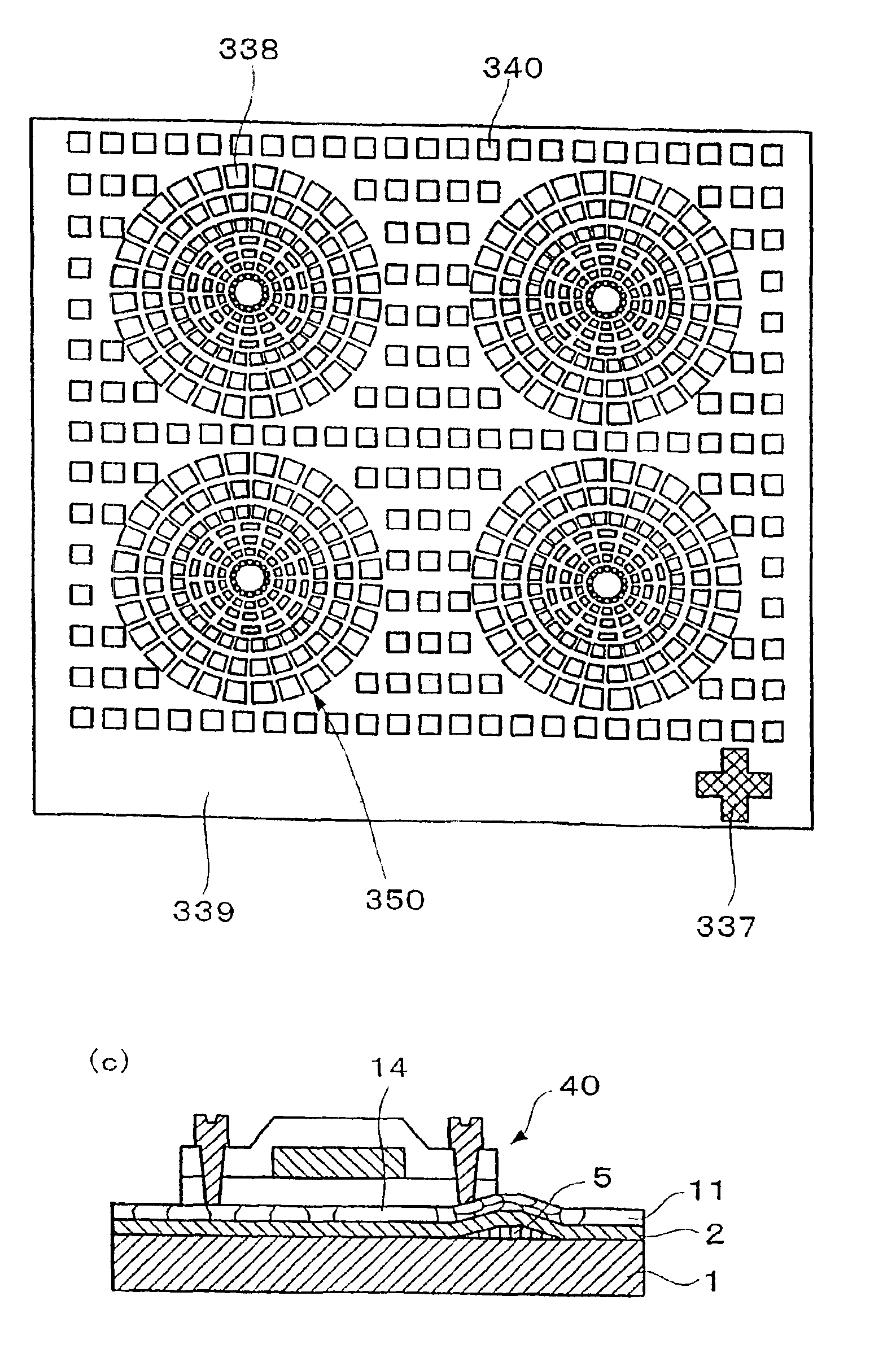

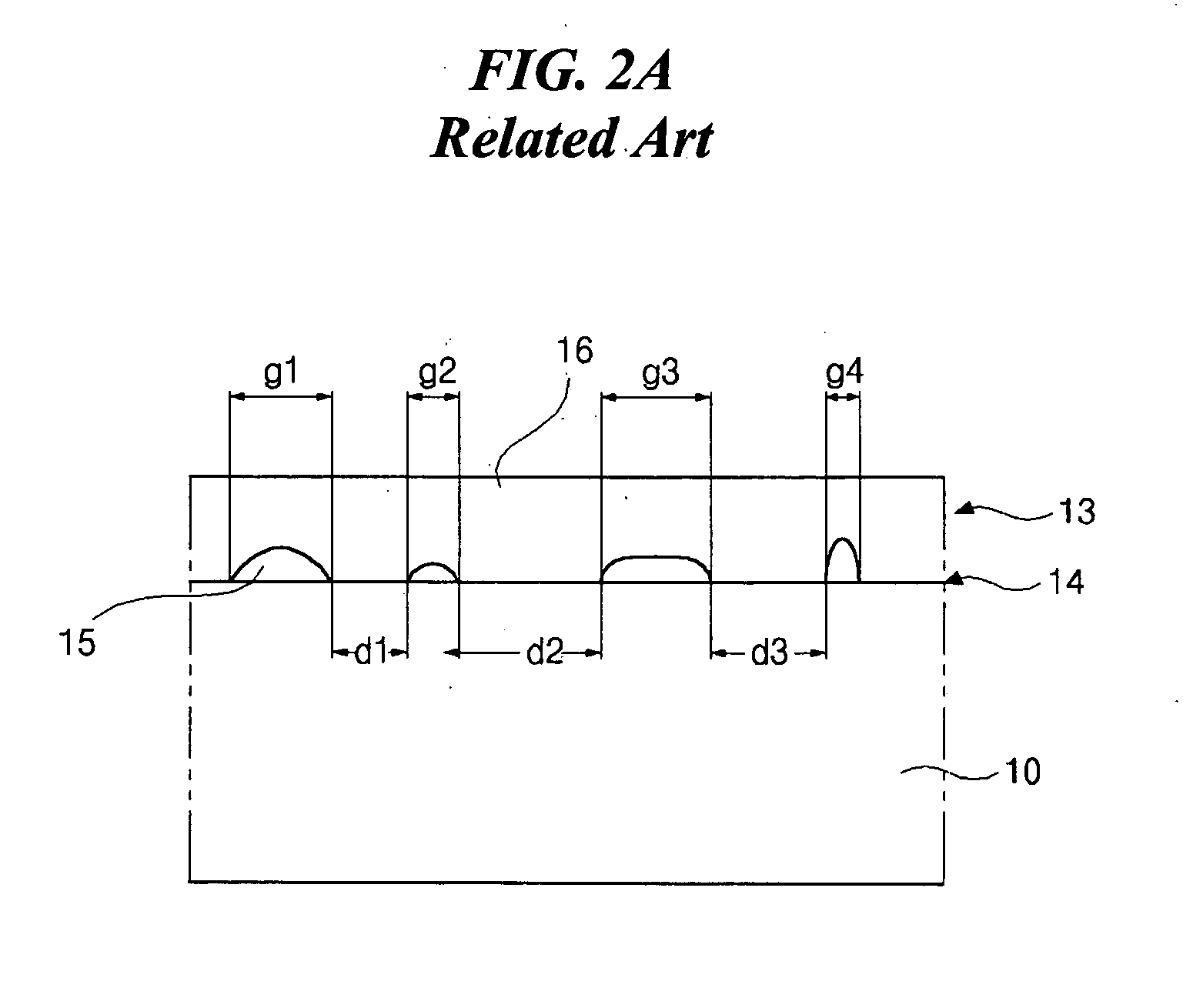

Semiconductor device, liquid crystal display device, EL display device, method for fabricating semiconductor thin film, and method for manufacturing the semiconductor device

This invention concerns with a semiconductor device which is characterized in that the device is provided with a thin film transistor 40 having a polycrystalline semiconductor layer 11, the semiconductor layer 11 including a channel area 22, highly doped drain areas 24, 17 positioned on both sides of the channel area 22 and LDD areas 18a, 18b positioned between the channel area 22 and the highly doped drain areas 24, 17 and lower in dopant density than the highly doped drain areas 24, 17, wherein any diameter of the crystal 14 at least partly existing in the LDD area 18b is larger than the size of other crystals 15.

Owner:JOLED INC

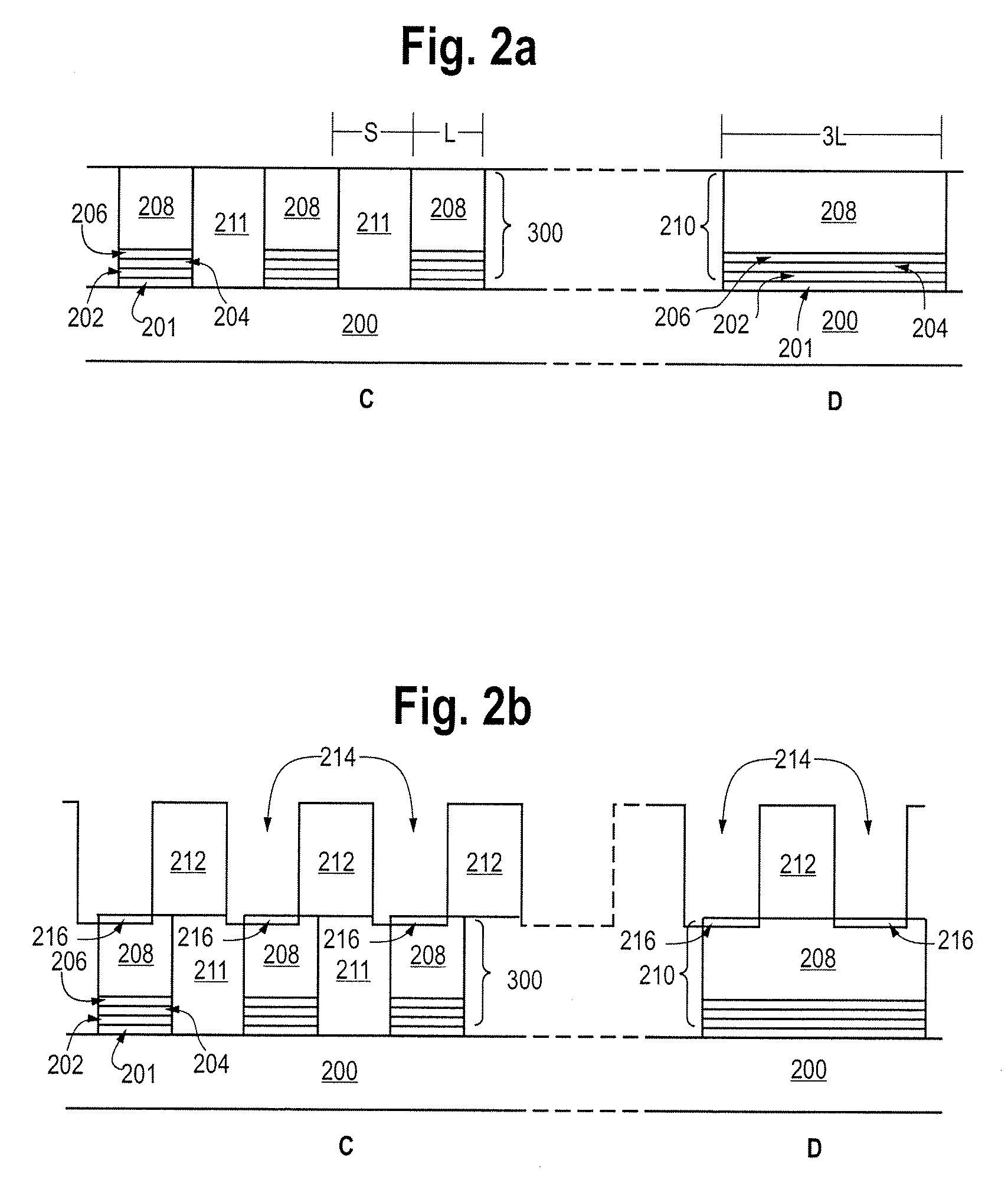

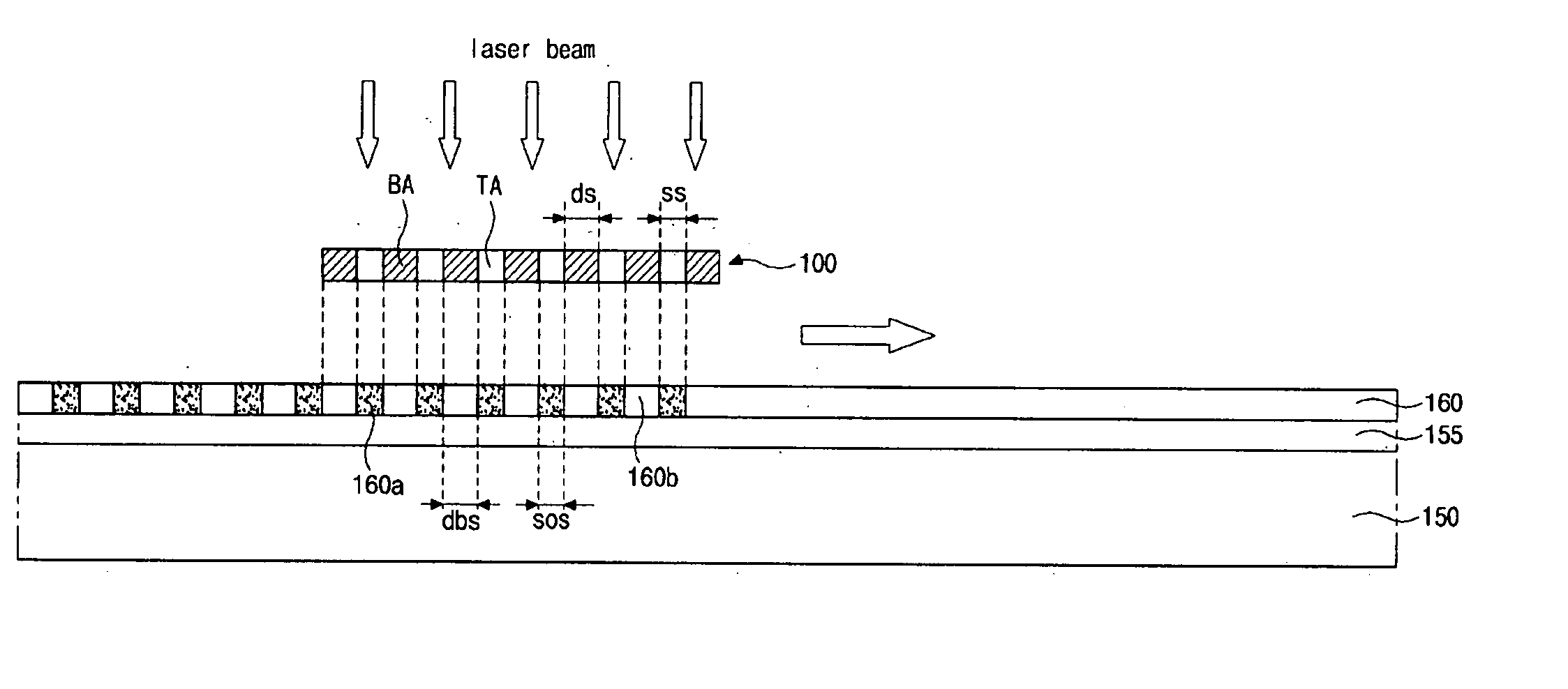

Method of forming polycrystalline semiconductor layer and thin film transistor using the same

ActiveUS20050059222A1Uniform particle sizeUniform distanceTransistorSolid-state devicesAmorphous siliconOptoelectronics

A method of forming a polycrystalline semiconductor layer includes forming a semiconductor layer of amorphous silicon on a substrate, forming a plurality of spot seeds in the semiconductor layer by irradiating a first laser beam through a crystallization mask, each of the plurality of spot seeds being equally spaced from one another and each having equal area, and forming a polycrystalline silicon layer along an entire surface of the substrate by irradiating a second laser beam onto the semiconductor layer.

Owner:LG DISPLAY CO LTD

Low temperature production of large-grain polycrystalline semiconductors

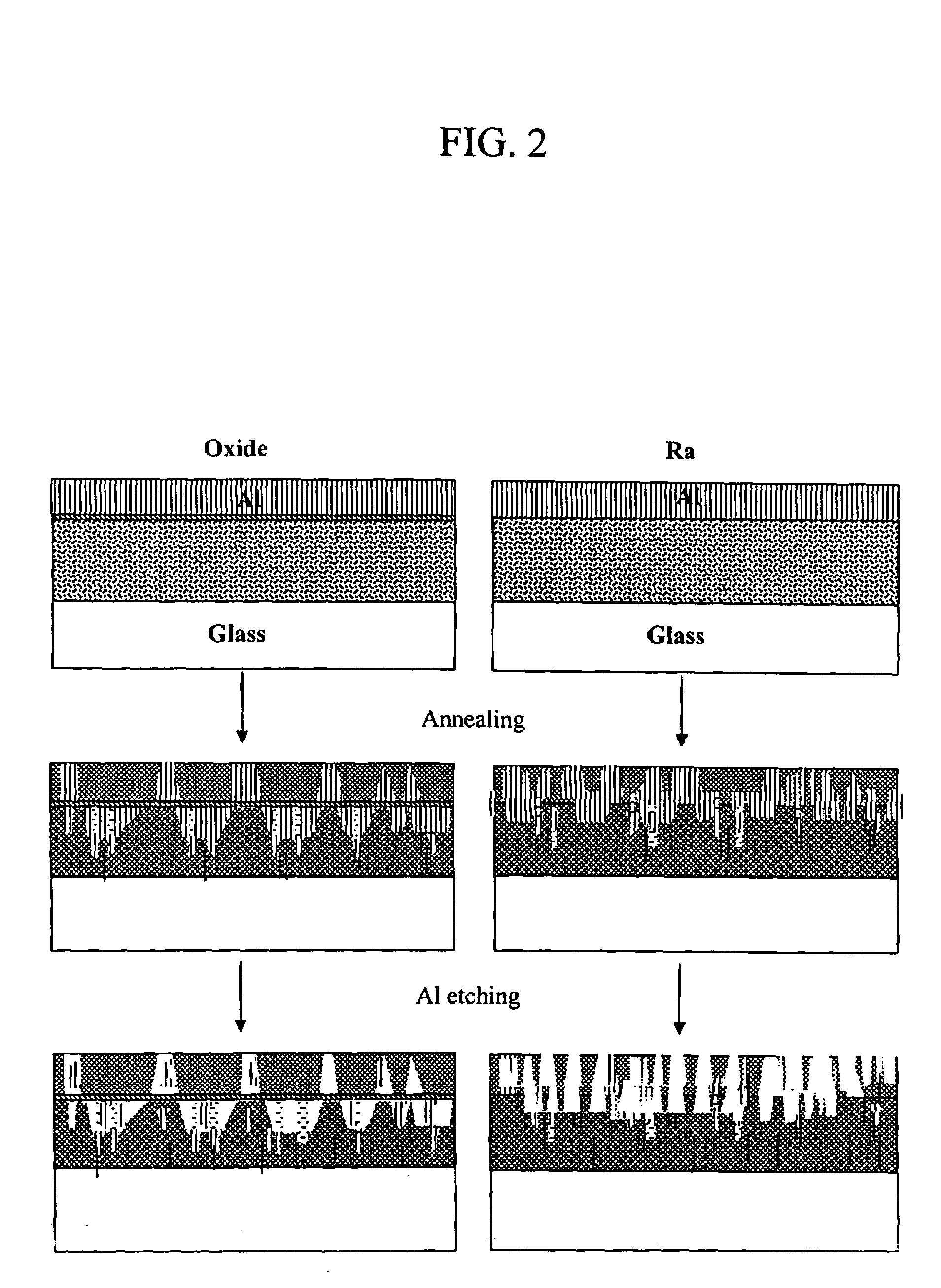

InactiveUS7202143B1Final product manufactureSemiconductor/solid-state device manufacturingSolar cellSilicon dioxide

An oxide or nitride layer is provided on an amorphous semiconductor layer prior to performing metal-induced crystallization of the semiconductor layer. The oxide or nitride layer facilitates conversion of the amorphous material into large grain polycrystalline material. Hence, a native silicon dioxide layer provided on hydrogenated amorphous silicon (a-Si:H), followed by deposited Al permits induced crystallization at temperatures far below the solid phase crystallization temperature of a-Si. Solar cells and thin film transistors can be prepared using this method.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ARKANSAS