Patents

Literature

1181 results about "Polycrystalline silicon thin films" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Semiconductor thin film forming method, production methods for semiconductor device and electrooptical device, devices used for these methods, and semiconductor device and electrooptical device

InactiveUS7183229B2Promote crystallizationTransistorDrying solid materials with heatSingle crystalCrystallinity

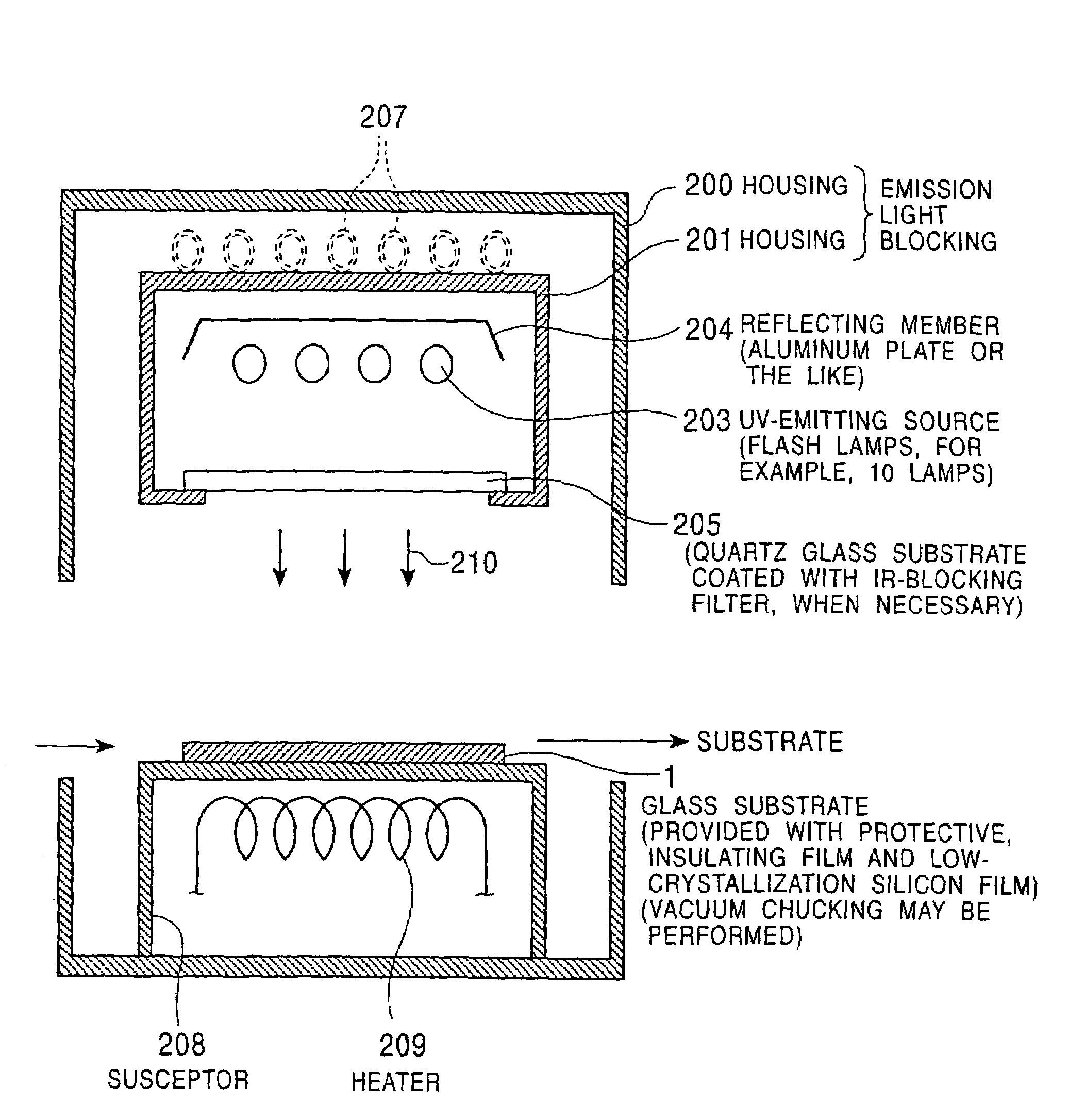

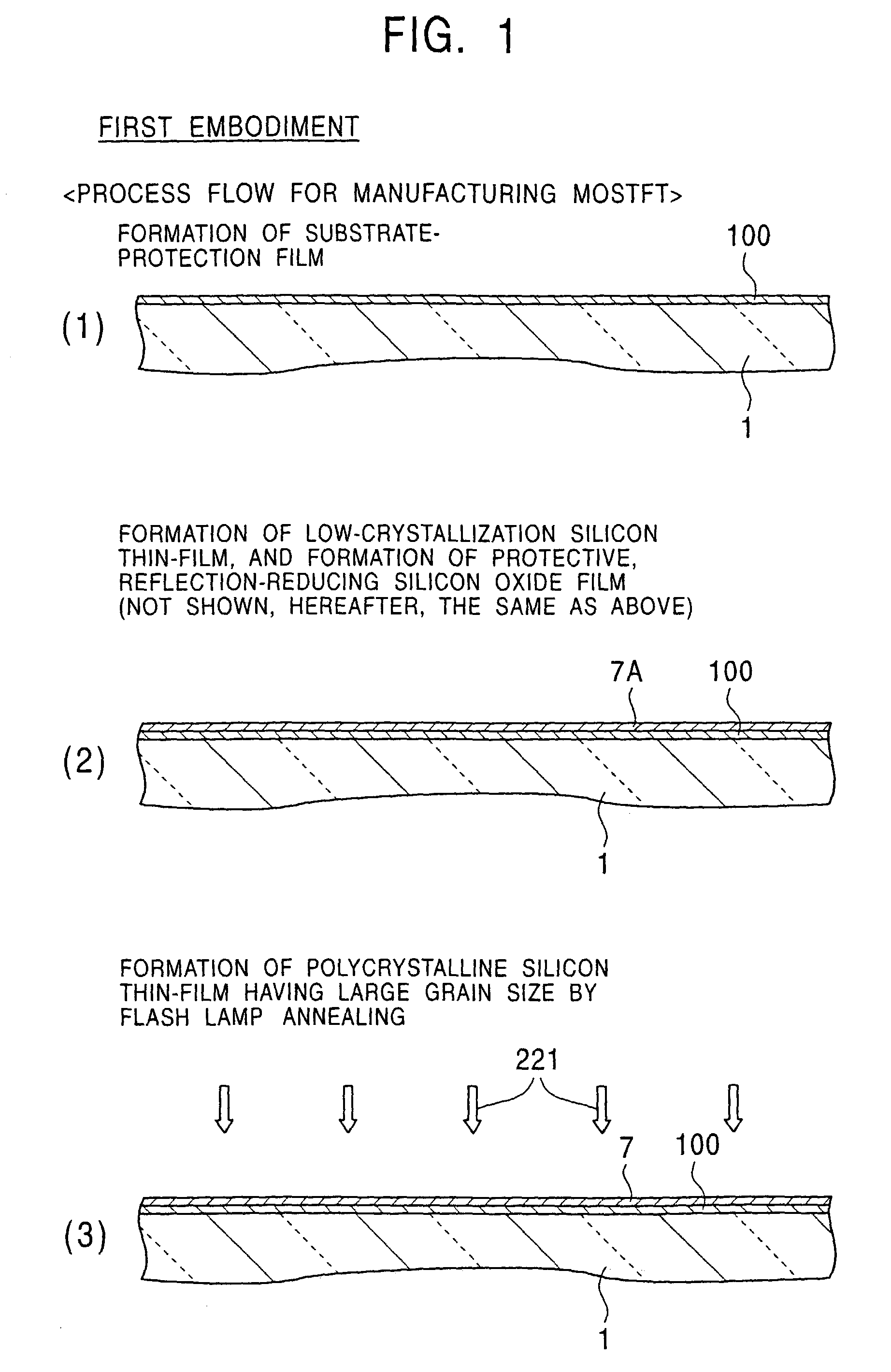

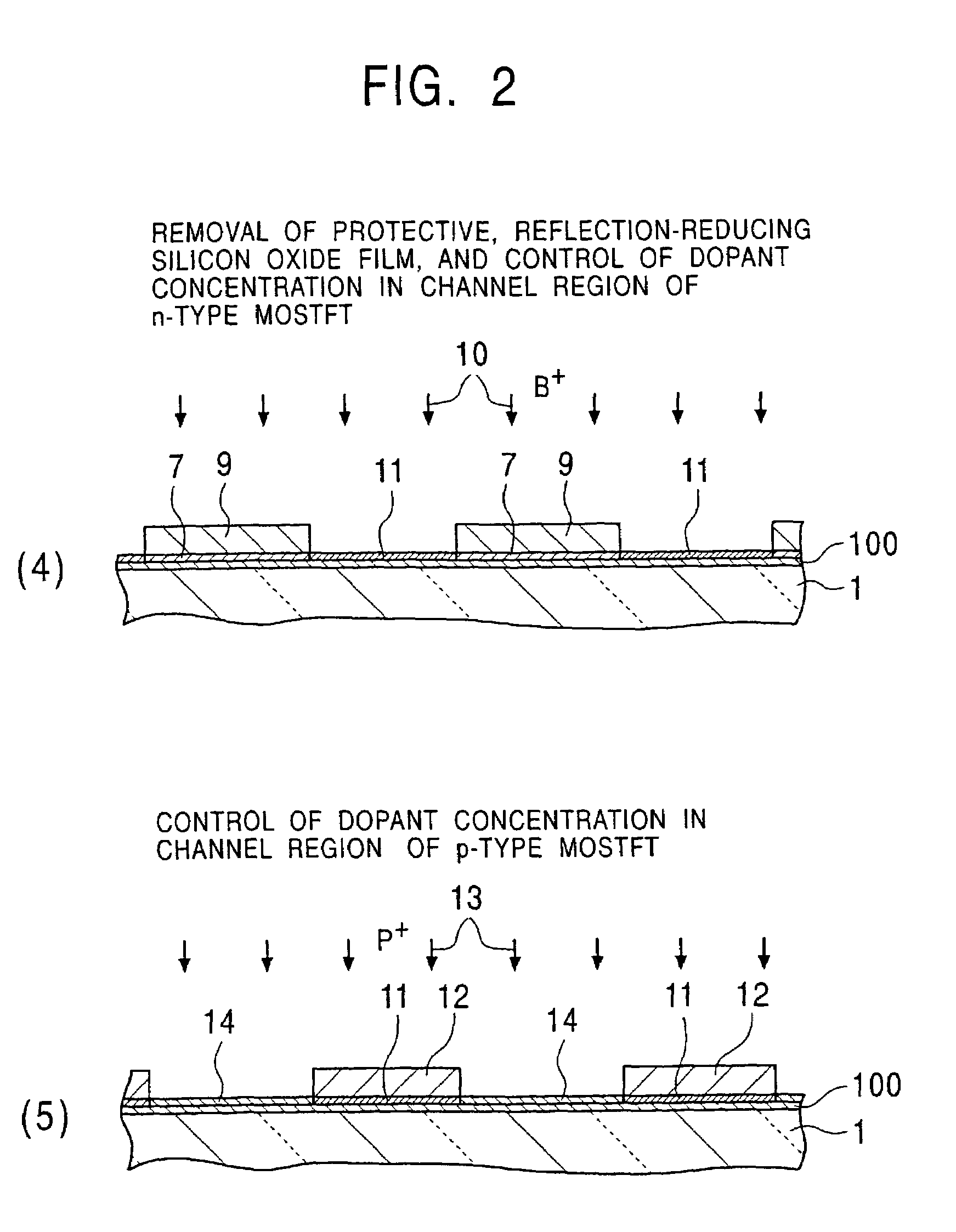

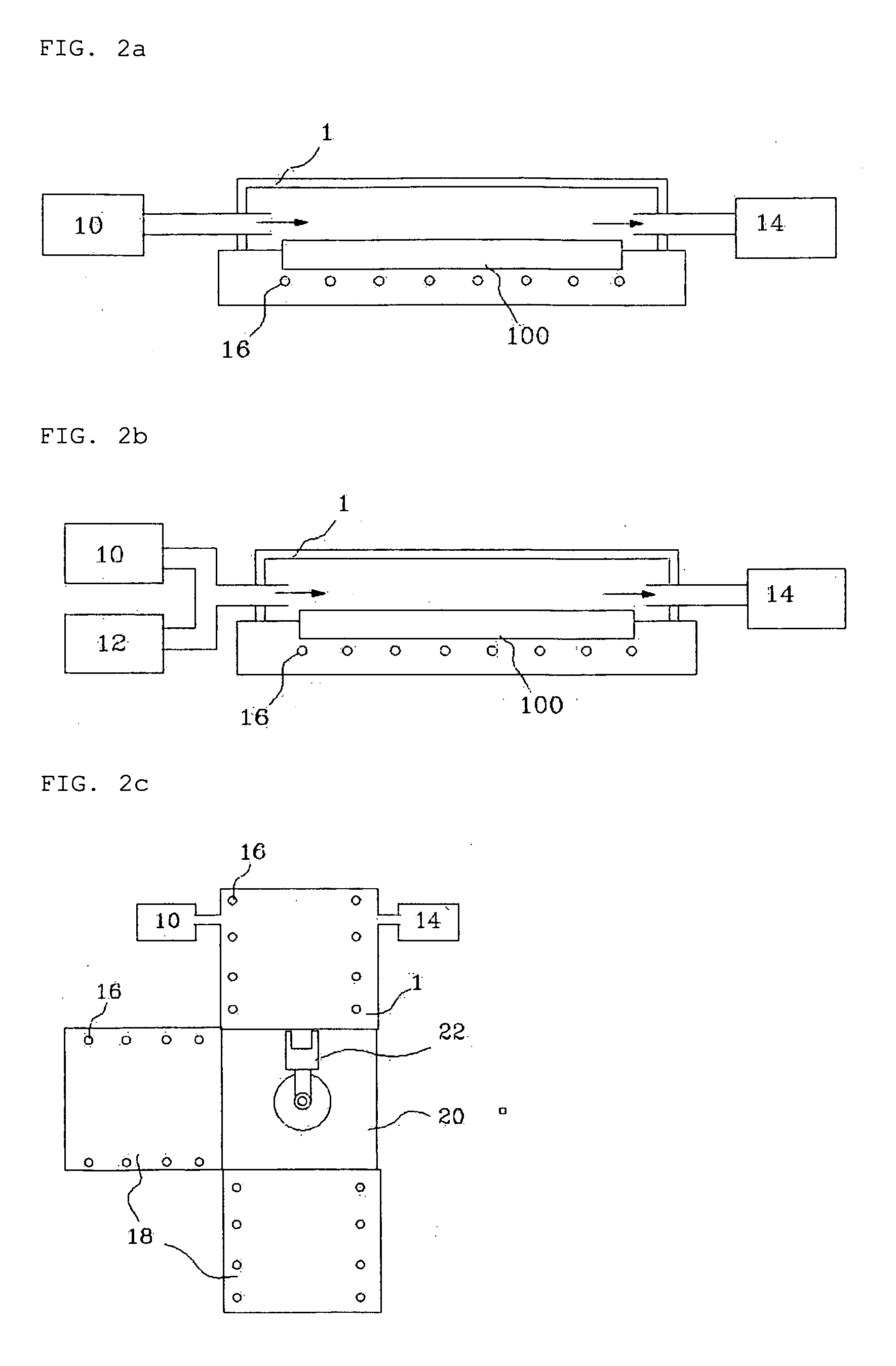

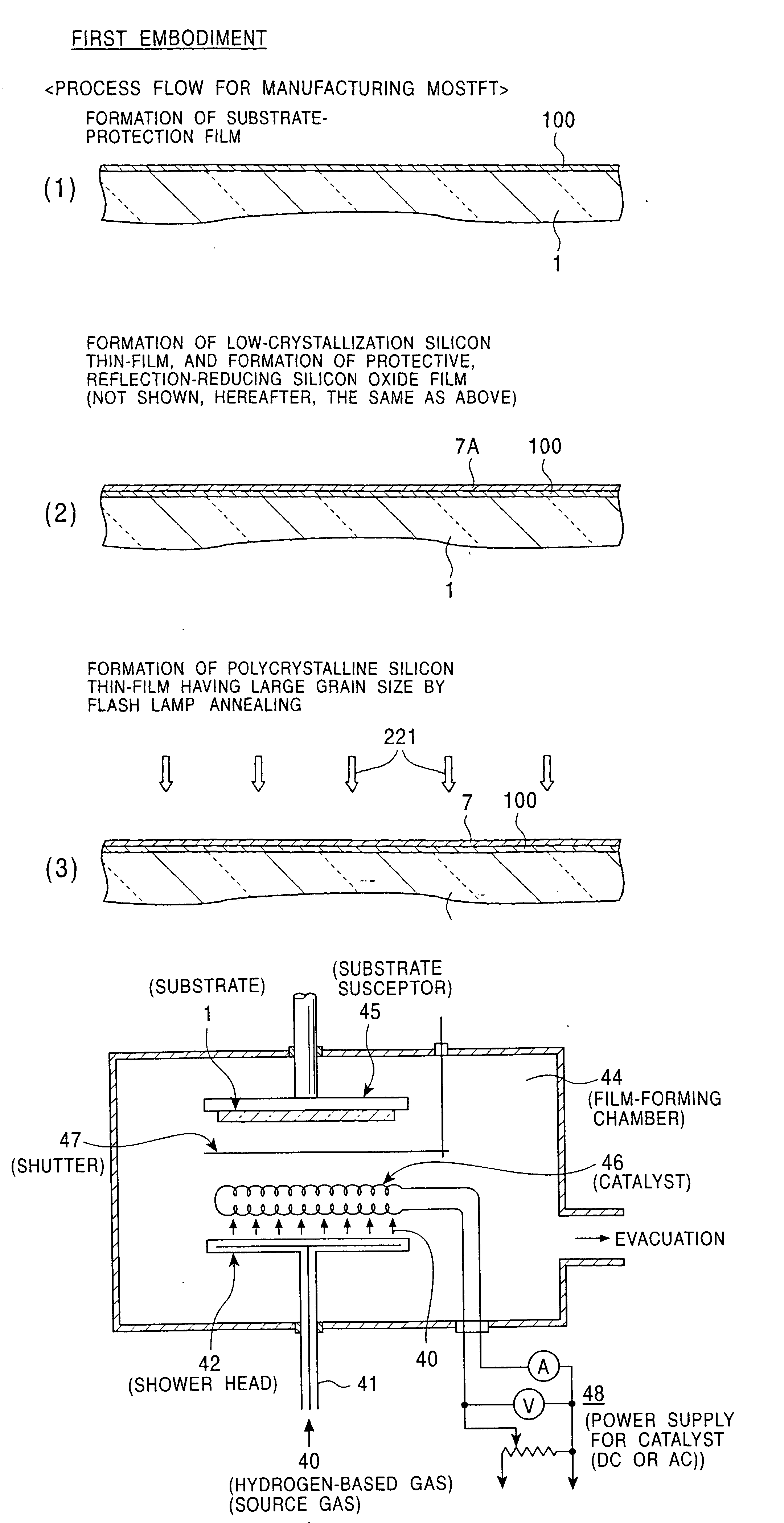

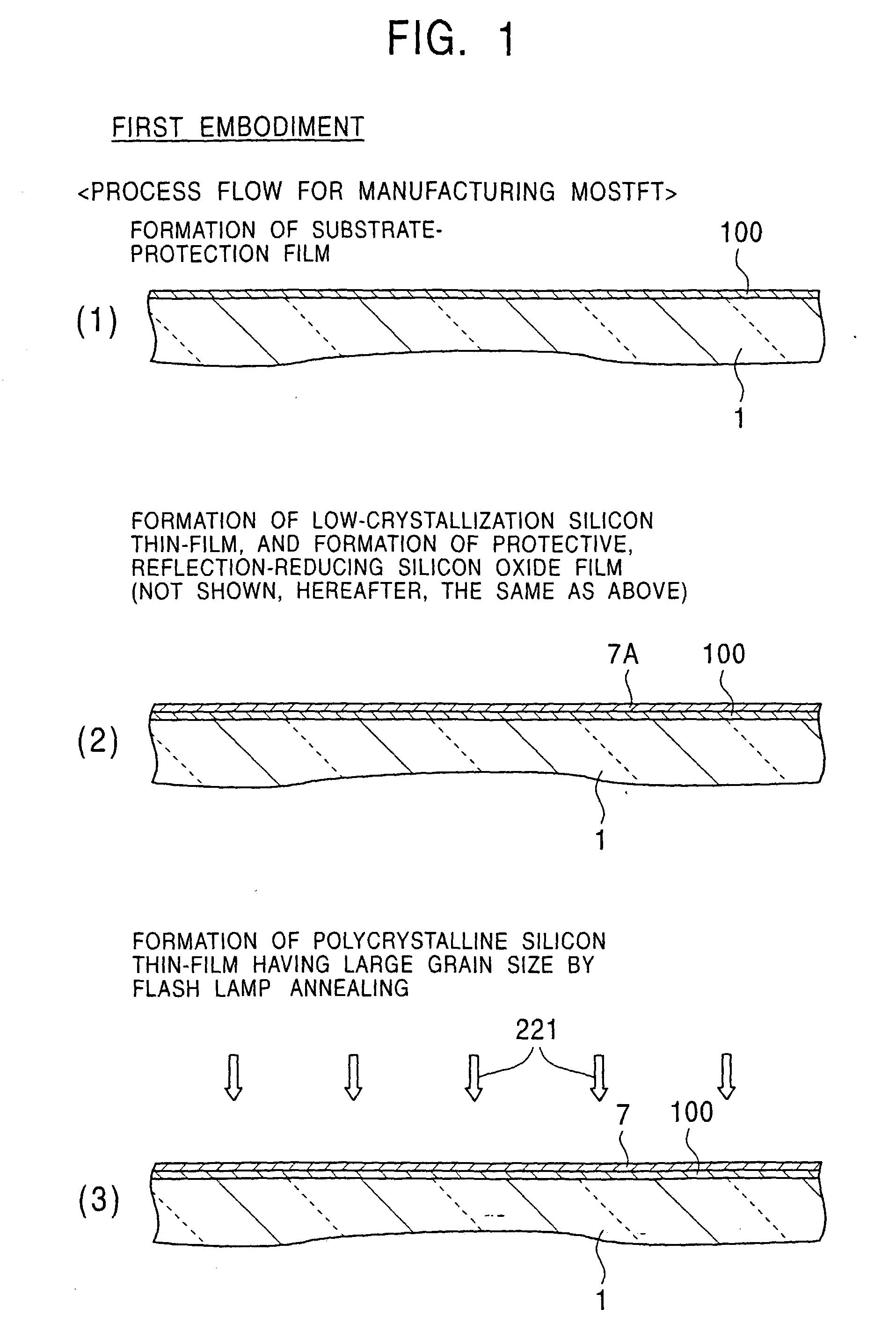

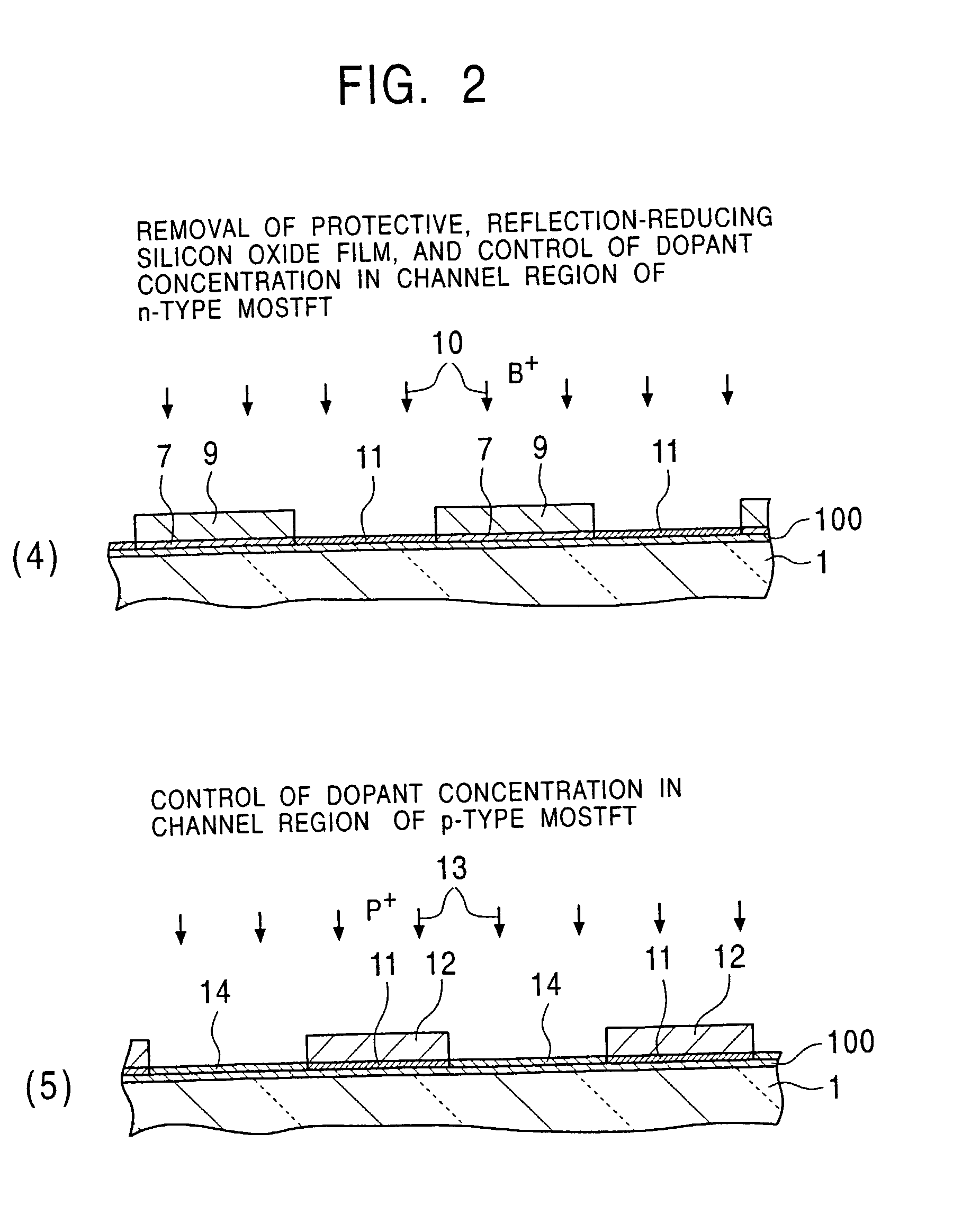

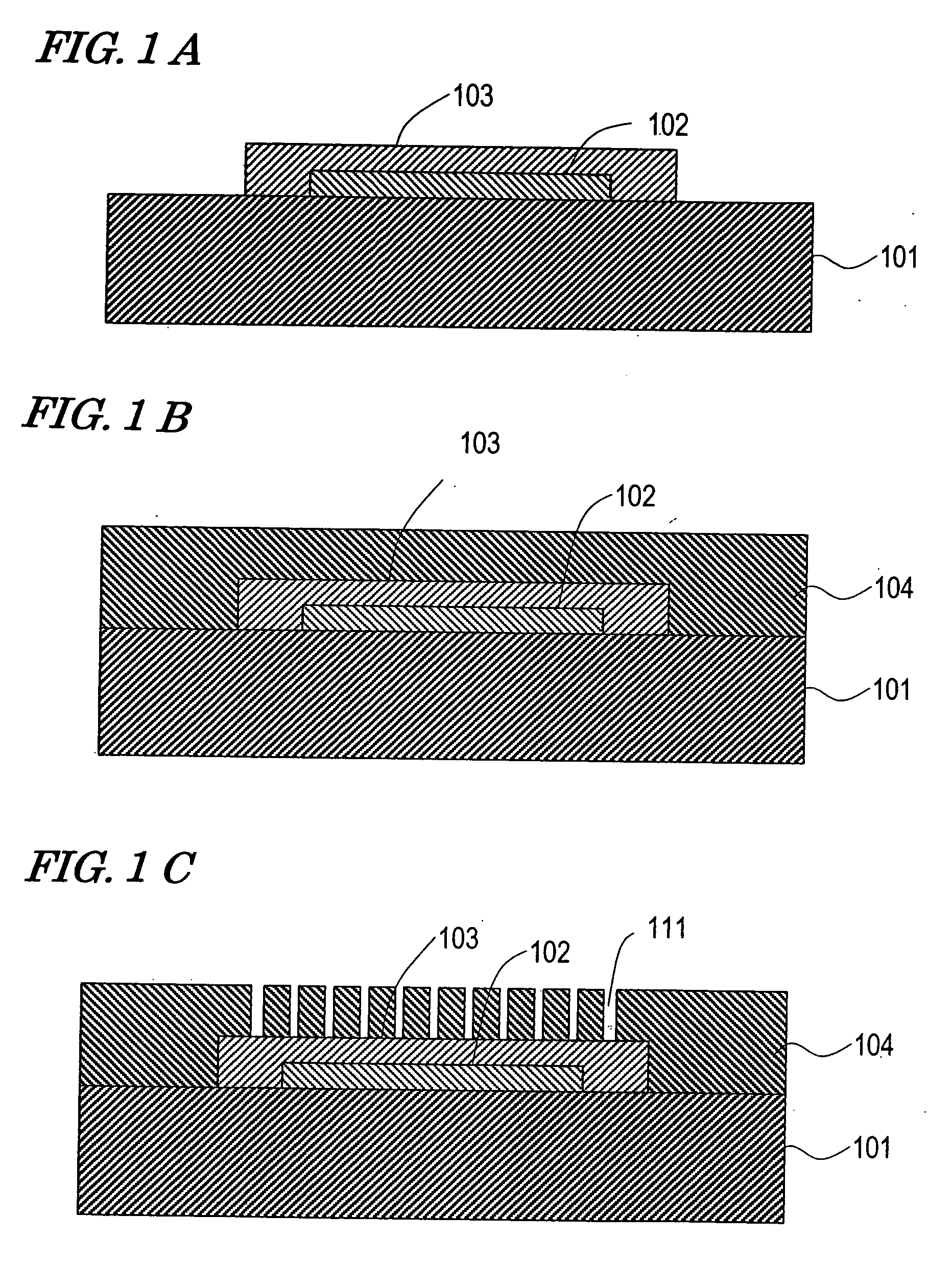

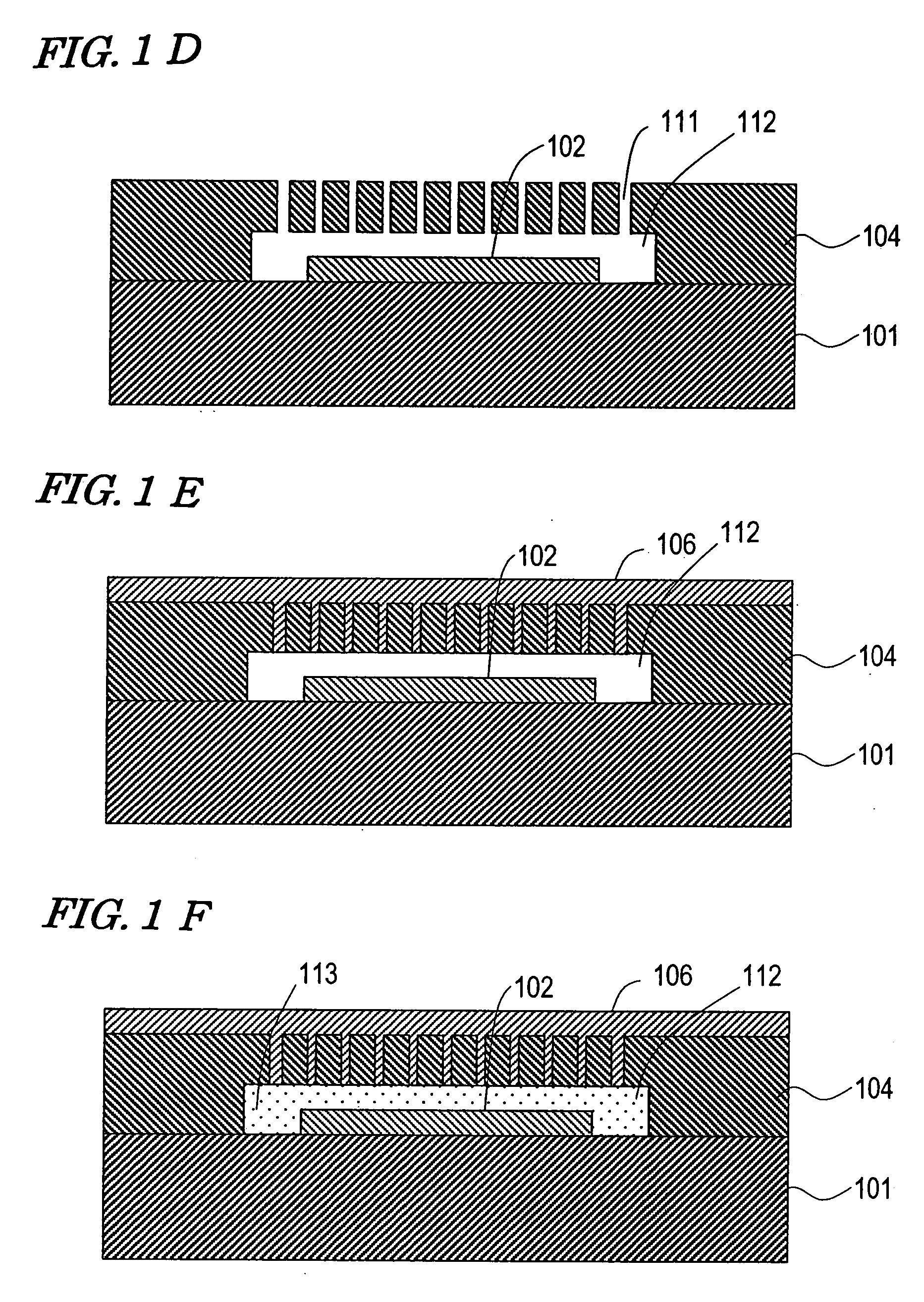

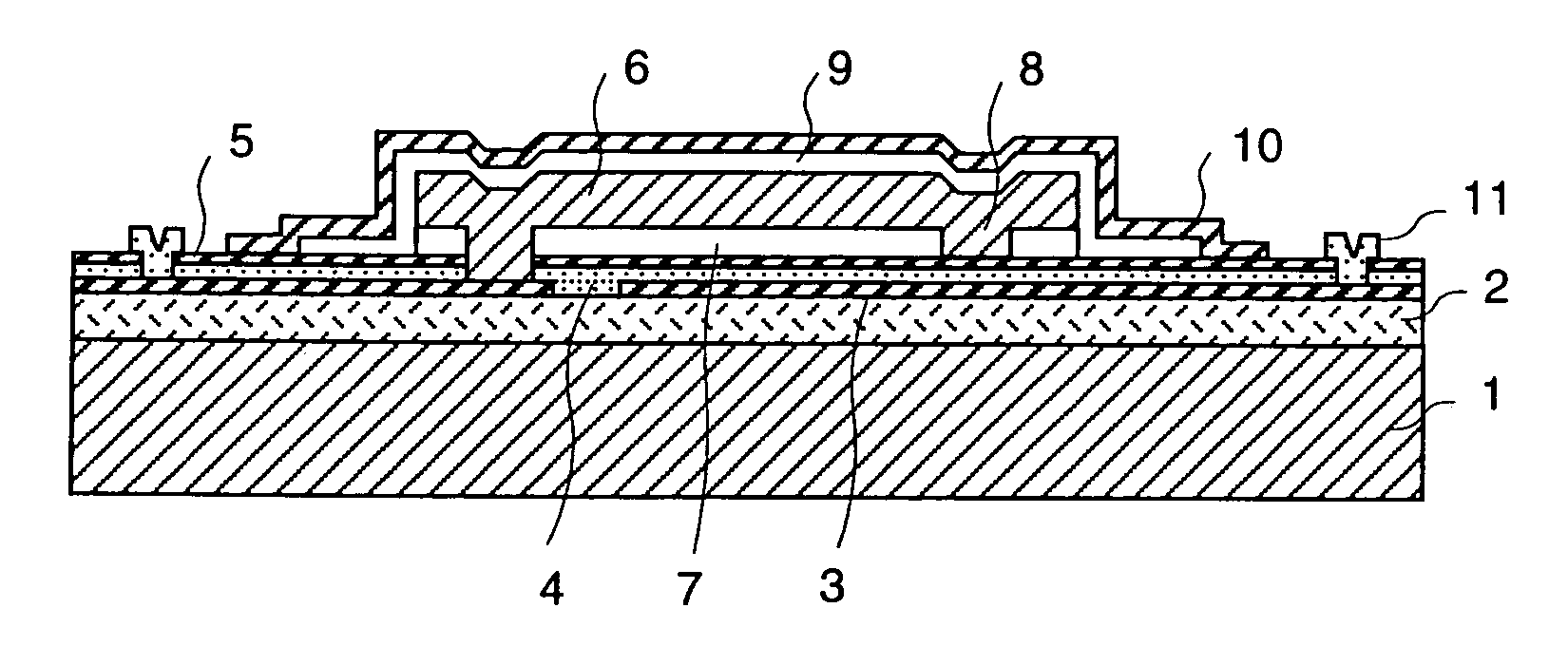

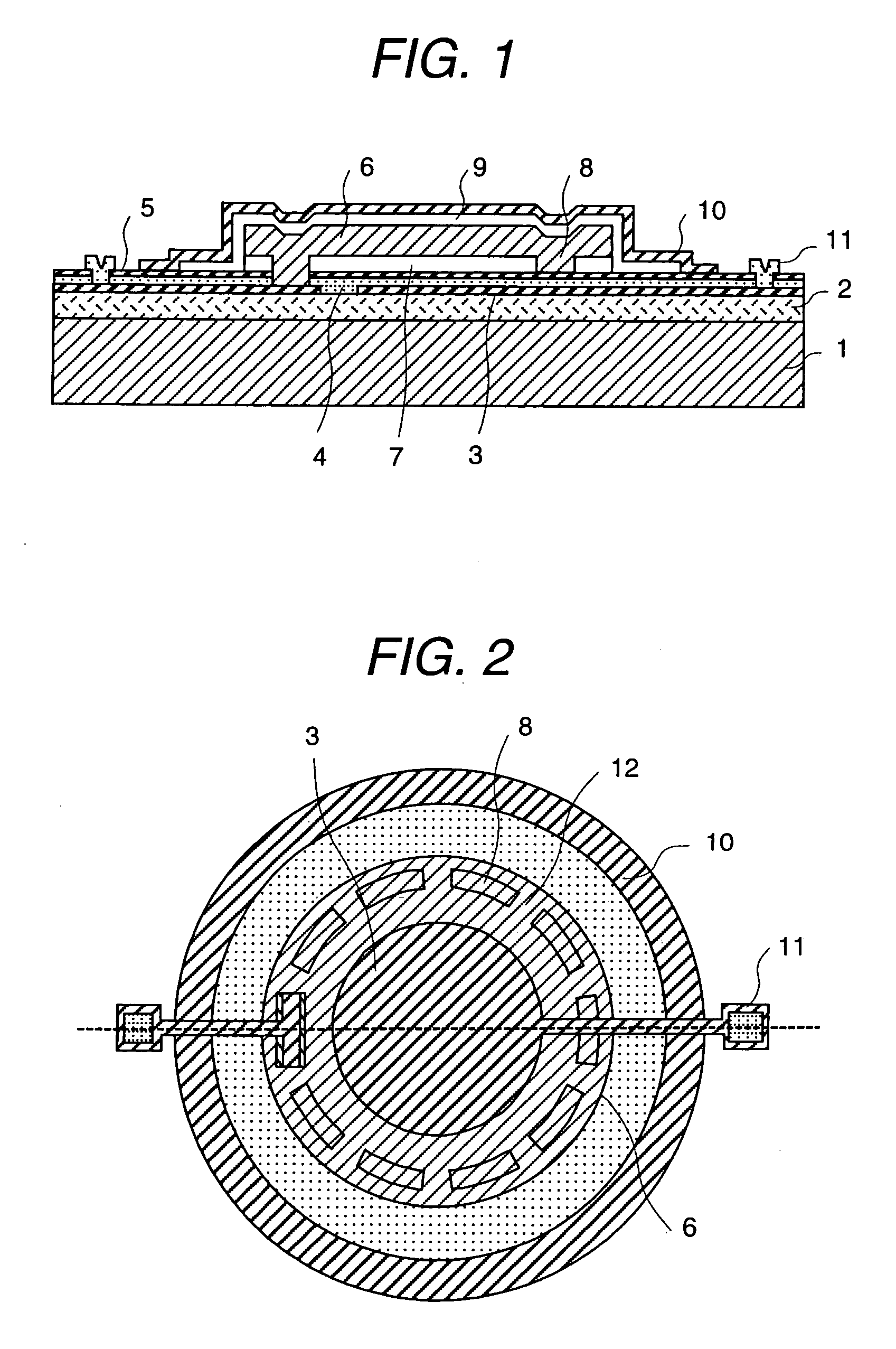

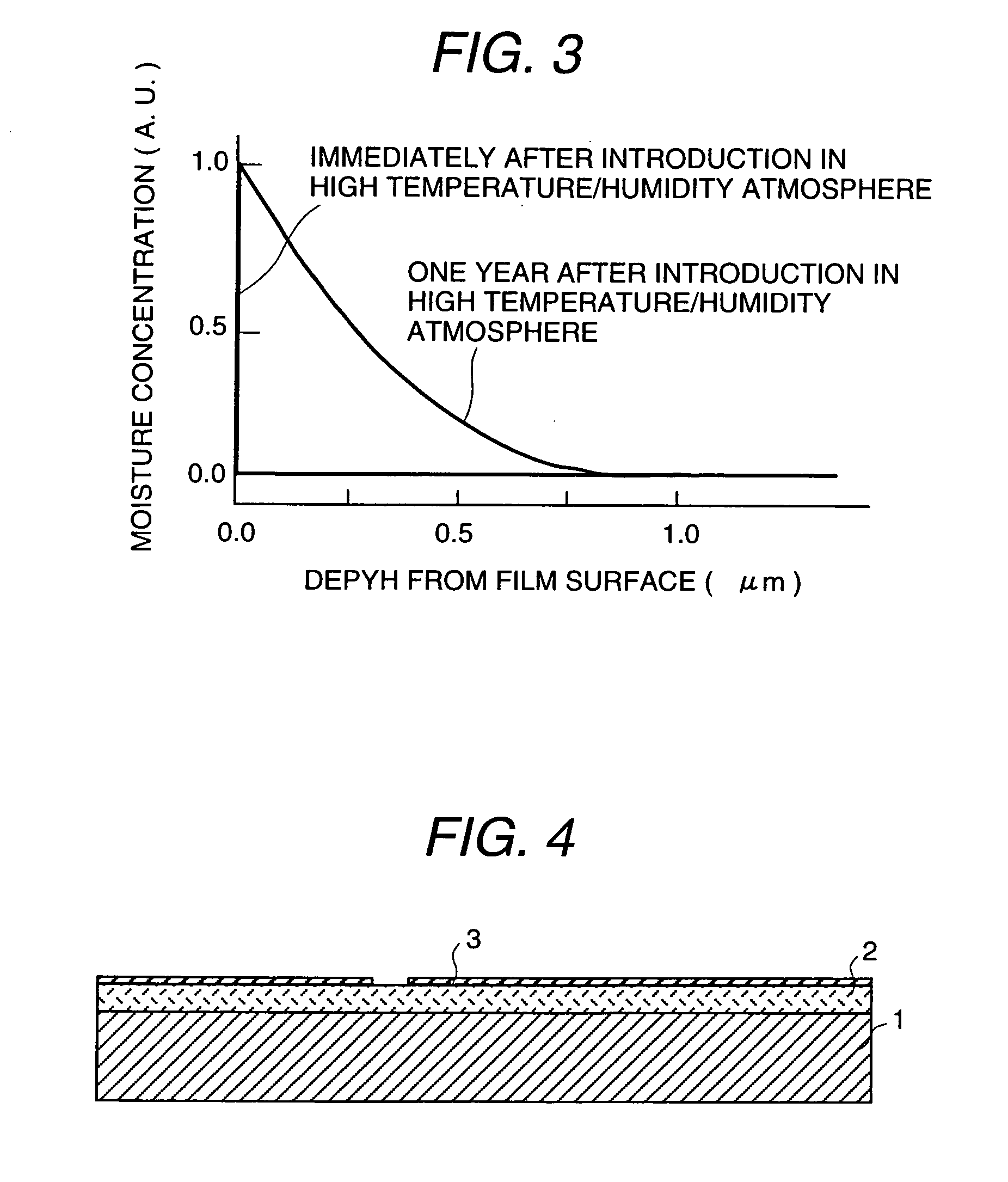

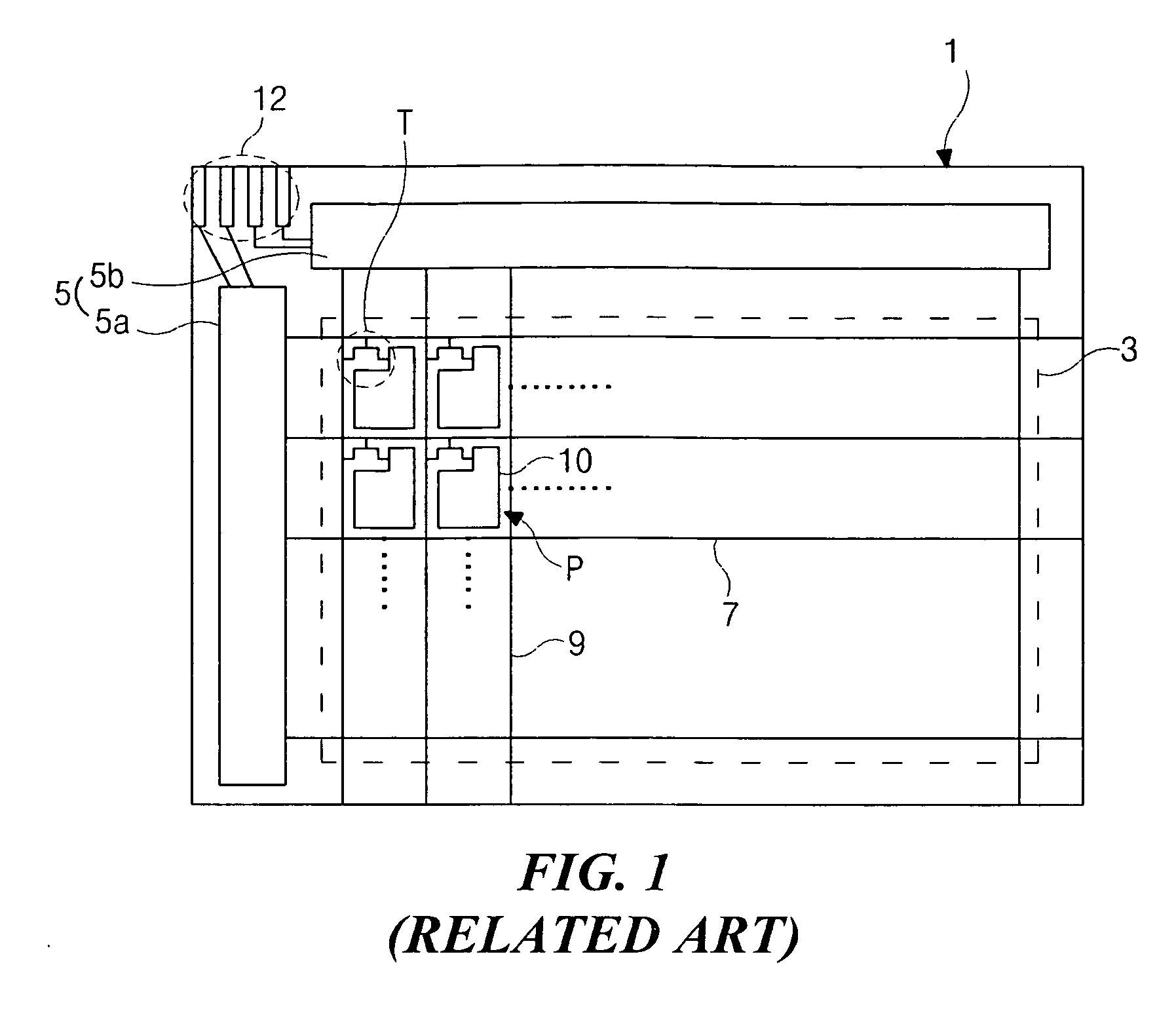

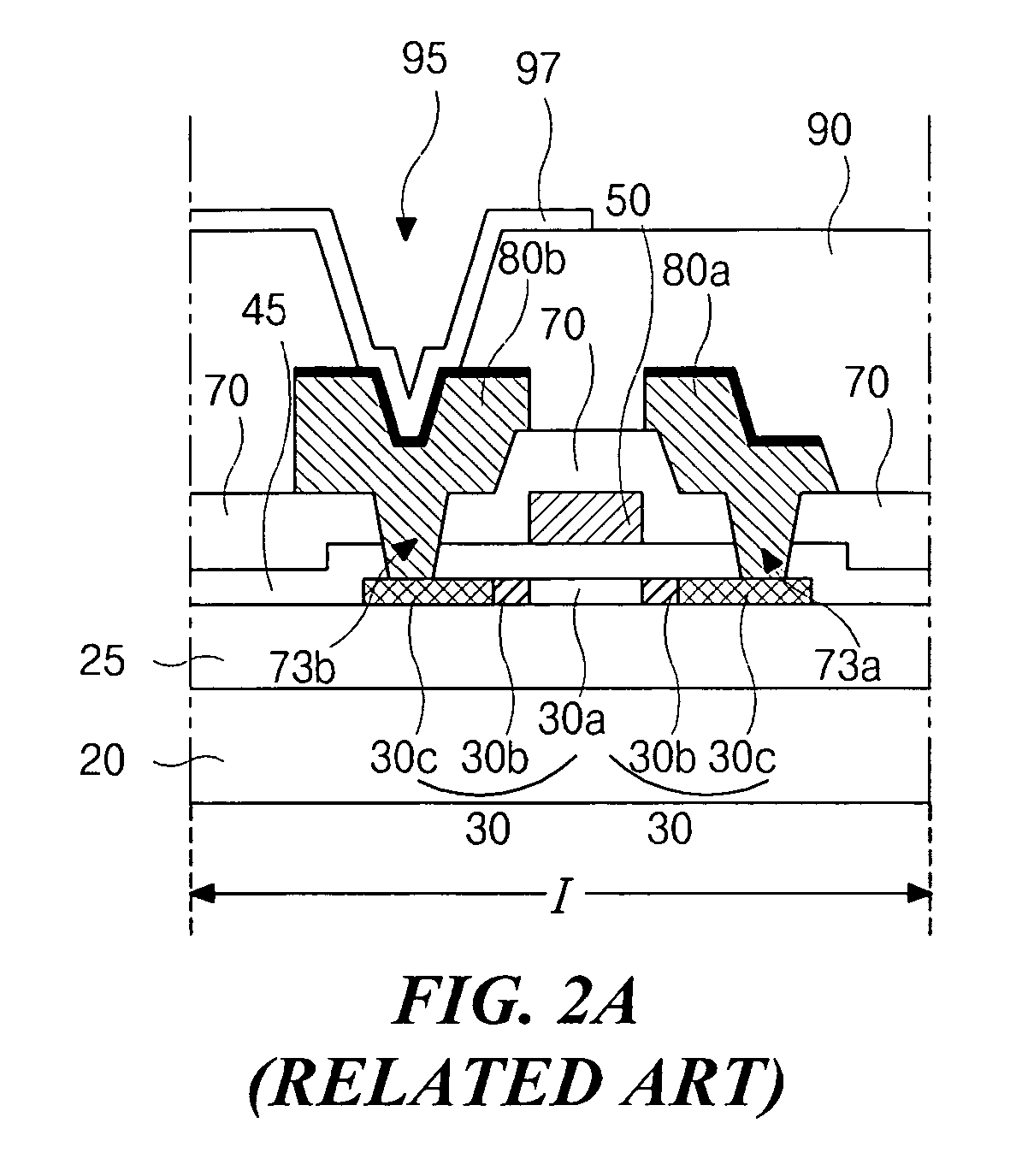

An object of the present invention is to provide a method for easily forming a polycrystalline semiconductor thin-film, such as polycrystalline silicon having high crystallinity and high quality, or a single crystalline semiconductor thin-film at inexpensive cost, the crystalline semiconductor thin-film having a large area, and to provide an apparatus for processing the method described above. In forming a polycrystalline (or single crystalline) semiconductor thin-film (7), such as a polycrystalline silicon thin-film, having high crystallinity and a large grain size on a substrate (1), or in forming a semiconductor device having the polycrystalline (or single crystalline) semiconductor thin-film (7) on the substrate (1), a method comprises forming a low-crystallization semiconductor thin-film (7A) on the substrate (1), and subsequently heating and cooling this low-crystallization semiconductor thin-film (7A) to a fusion, a semi-fusion, or a non-fusion state by flash lamp annealing to facilitate the crystallization of the low-crystallization semiconductor thin-film, whereby a polycrystalline (single crystalline) semiconductor thin-film (7) is obtained. A method for forming the semiconductor device and an apparatus for processing the methods are also disclosed.

Owner:SONY CORP

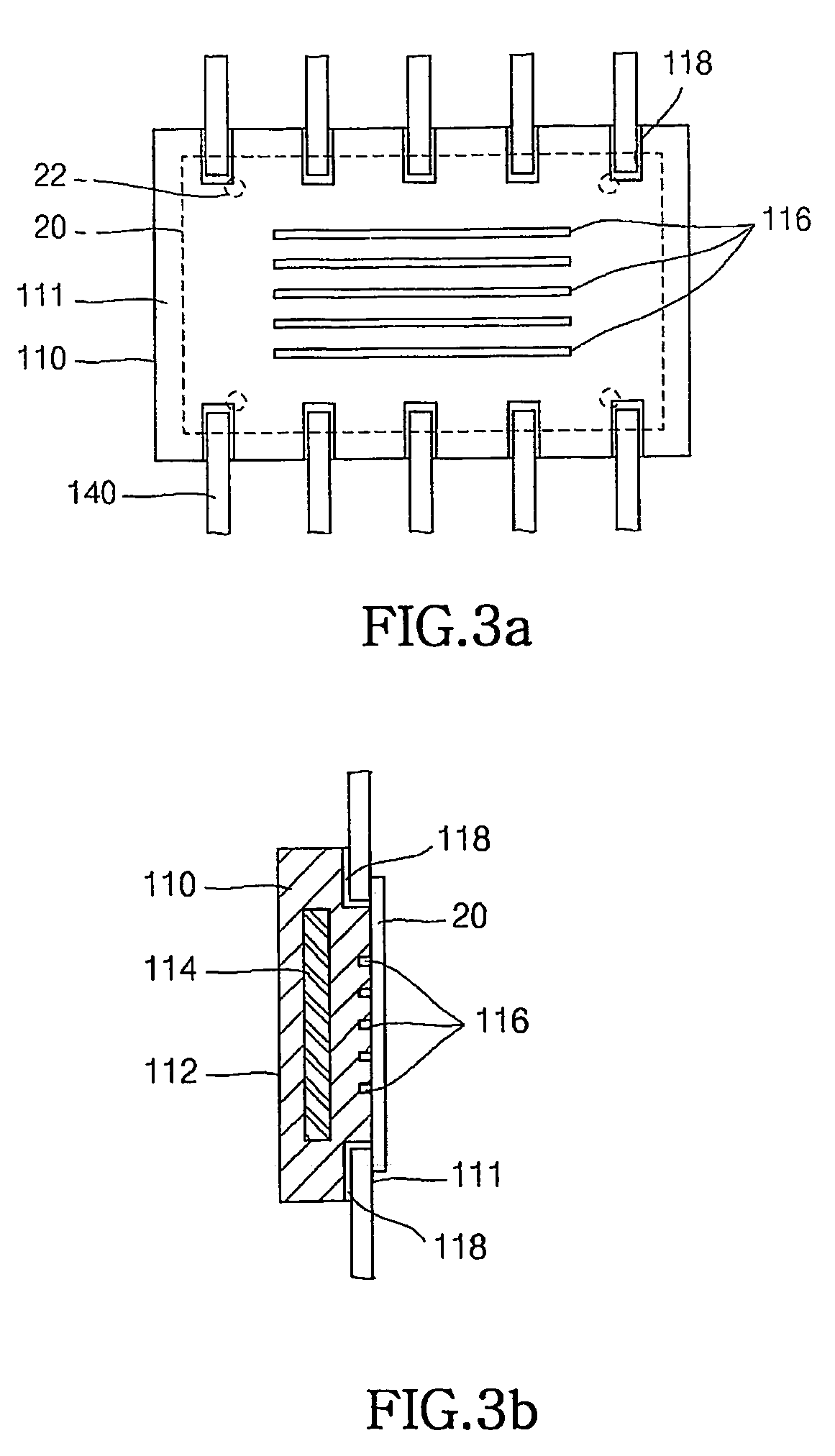

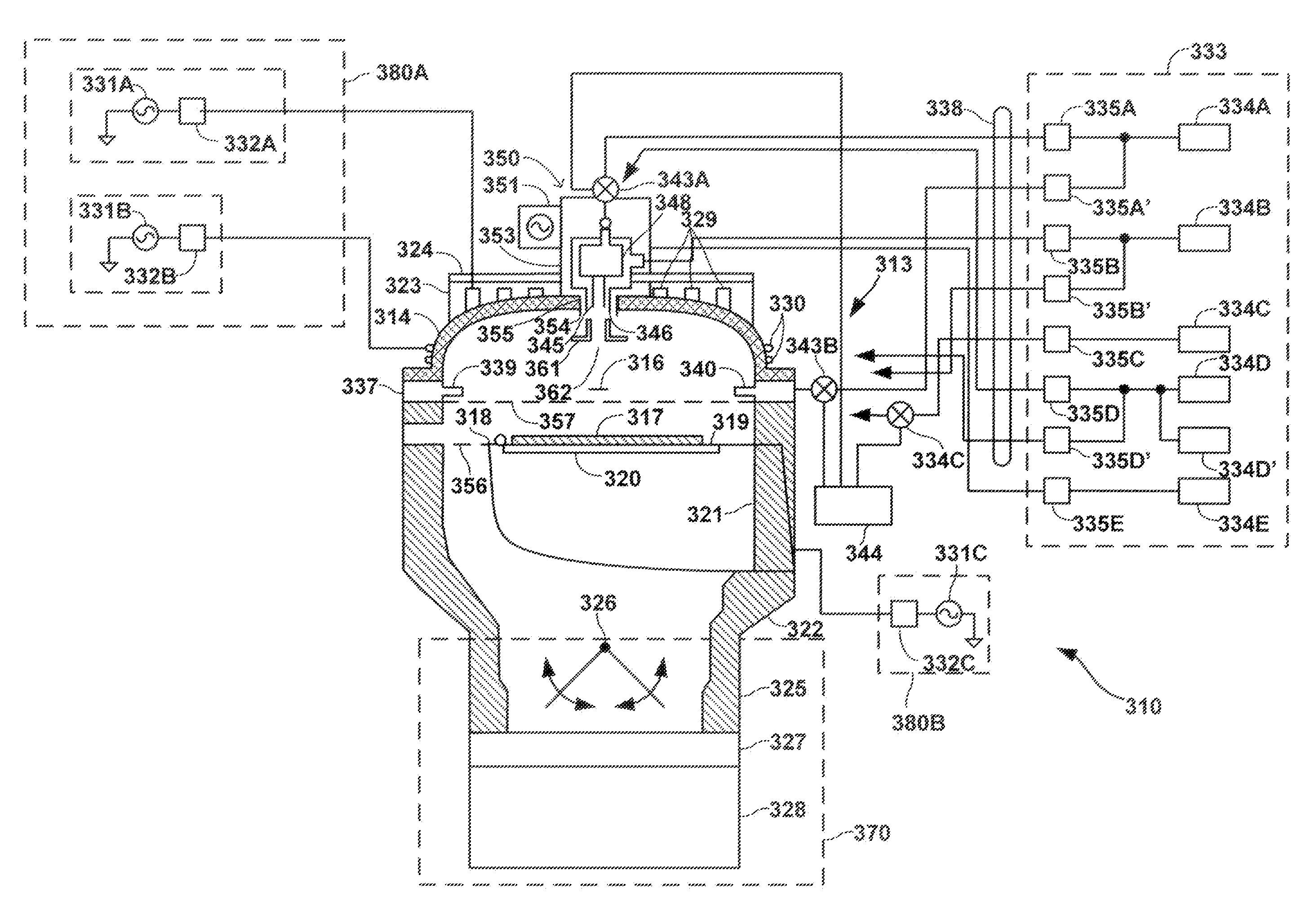

Apparatus and method for forming polycrystalline silicon thin film

ActiveUS20070054499A1Increase the rate of crystallizationDecrease in crystallization temperatureAfter-treatment apparatusSemiconductor/solid-state device manufacturingGas phaseAmorphous silicon

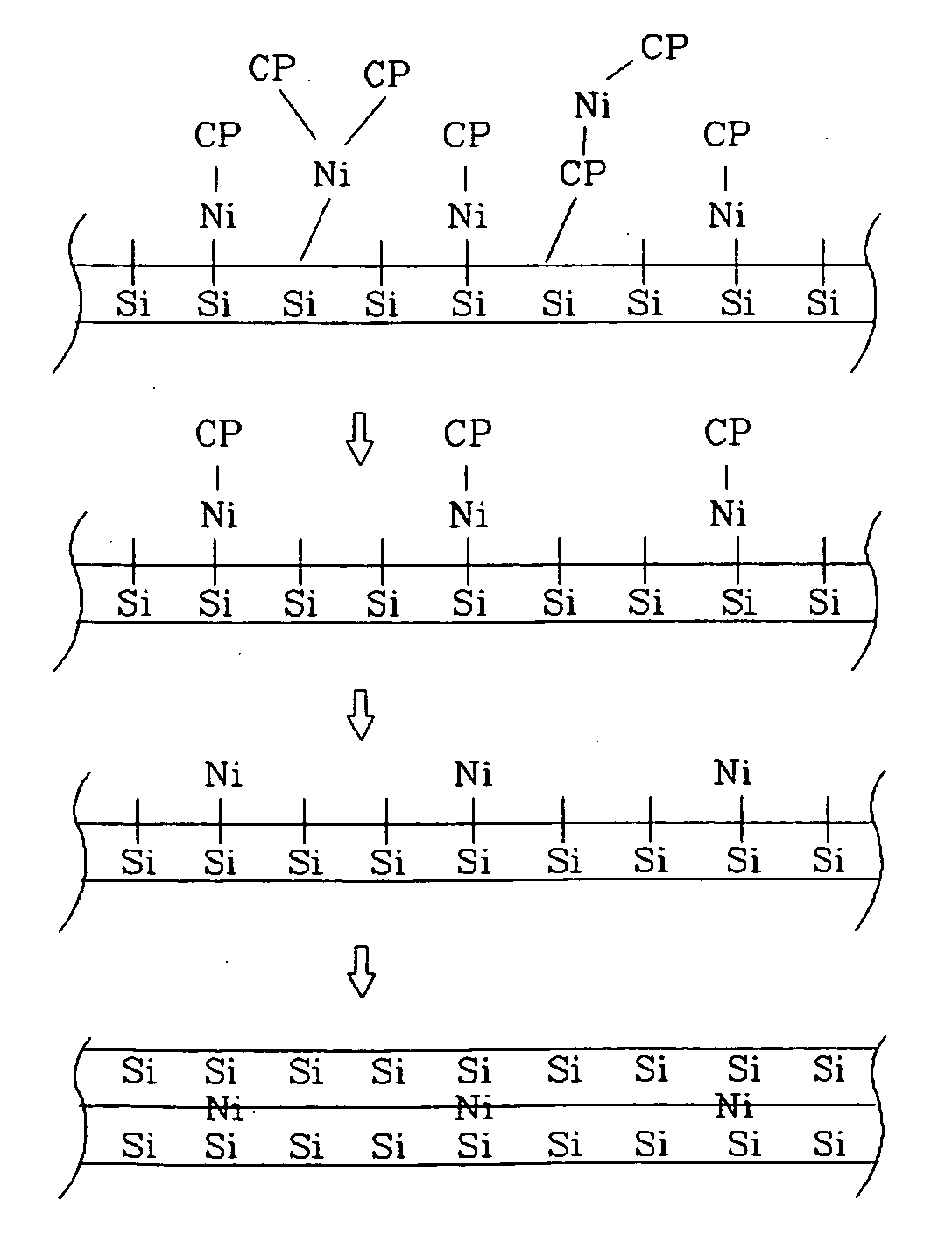

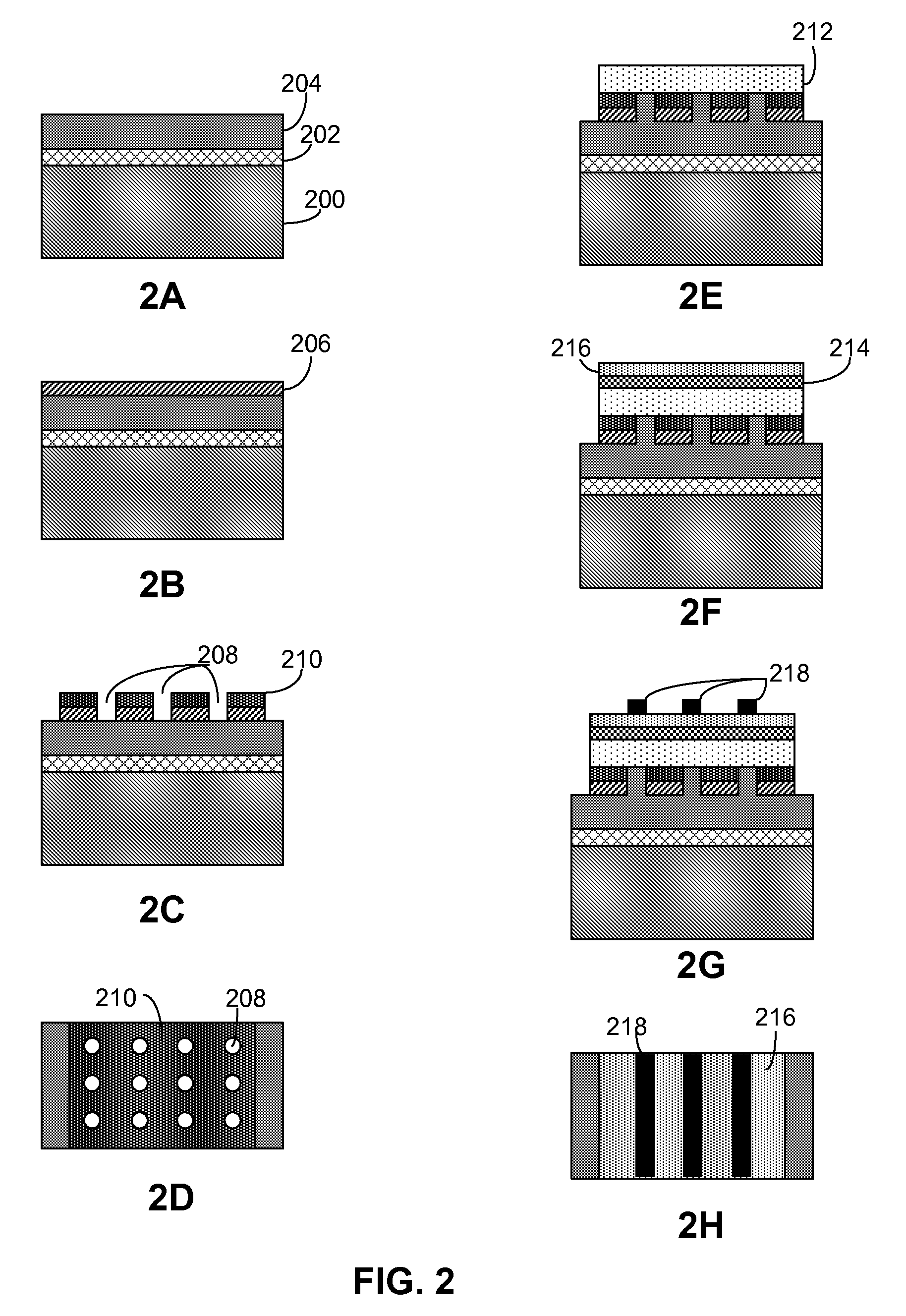

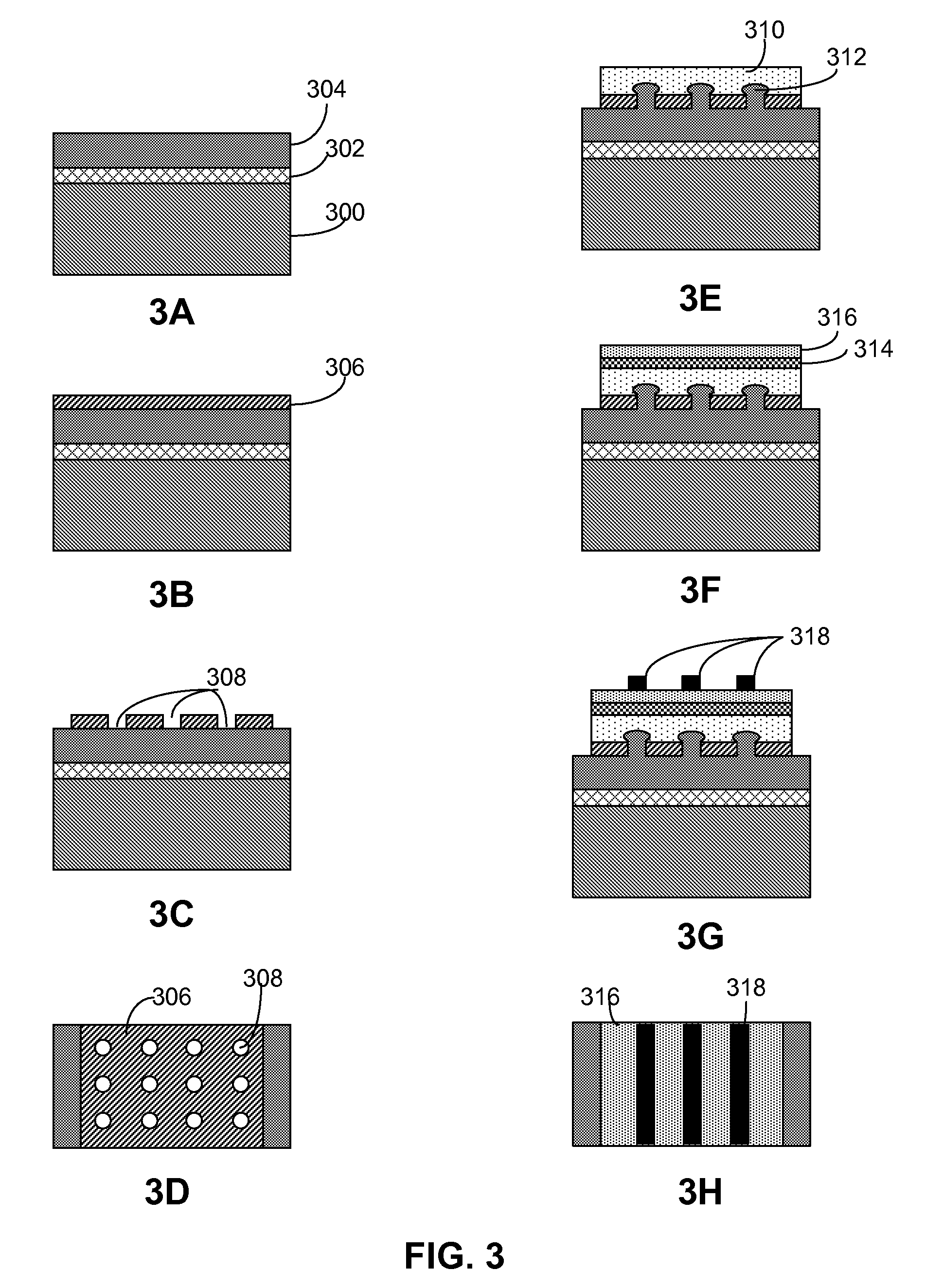

Apparatus and method for forming a polycrystalline silicon thin film by converting an amorphous silicon thin film into the polycrystalline silicon thin film using a metal are provided. The method includes: a metal nucleus adsorbing step of introducing a vapor phase metal compound into a process space where the glass substrate having the amorphous silicon formed thereon is disposed, to adsorb a metal nucleus contained in the metal compound into the amorphous silicon layer; a metal nucleus distribution region-forming step of forming a community region including a plurality of silicon particles every metal nucleus in a plane boundary region occupied by the metal compound by a self-limited mechanism due to the adsorption of the metal nucleus; and an excess gas removing step of purging and removing an excess gas which is not adsorbed in the metal nucleus distribution region-forming step.

Owner:WONIK IPS CO LTD

Semiconductor thin film forming method, production methods for semiconductor device and electrooptical device, devices used for these methods, and semiconductor device and electrooptical device

InactiveUS20030013280A1Promote crystallizationTransistorPolycrystalline material growthSingle crystalCrystallinity

An object of the present invention is to provide a method for easily forming a polycrystalline semiconductor thin-film, such as polycrystalline silicon having high crystallinity and high quality, or a single crystalline semiconductor thin-film at inexpensive cost, the crystalline semiconductor thin-film having a large area, and to provide an apparatus for processing the method described above. In forming a polycrystalline (or single crystalline) semiconductor thin-film (7), such as a polycrystalline silicon thin-film, having high crystallinity and a large grain size on a substrate (1), or in forming a semiconductor device having the polycrystalline (or single crystalline) semiconductor thin-film (7) on the substrate (1), a method comprises forming a low-crystallization semiconductor thin-film (7A) on the substrate (1), and subsequently heating and cooling this low-crystallization semiconductor thin-film (7A) to a fusion, a semi-fusion, or a non-fusion state by flash lamp annealing to facilitate the crystallization of the low-crystallization semiconductor thin-film, whereby a polycrystalline (single crystalline) semiconductor thin-film (7) is obtained. A method for forming the semiconductor device and an apparatus for processing the methods are also disclosed.

Owner:SONY CORP

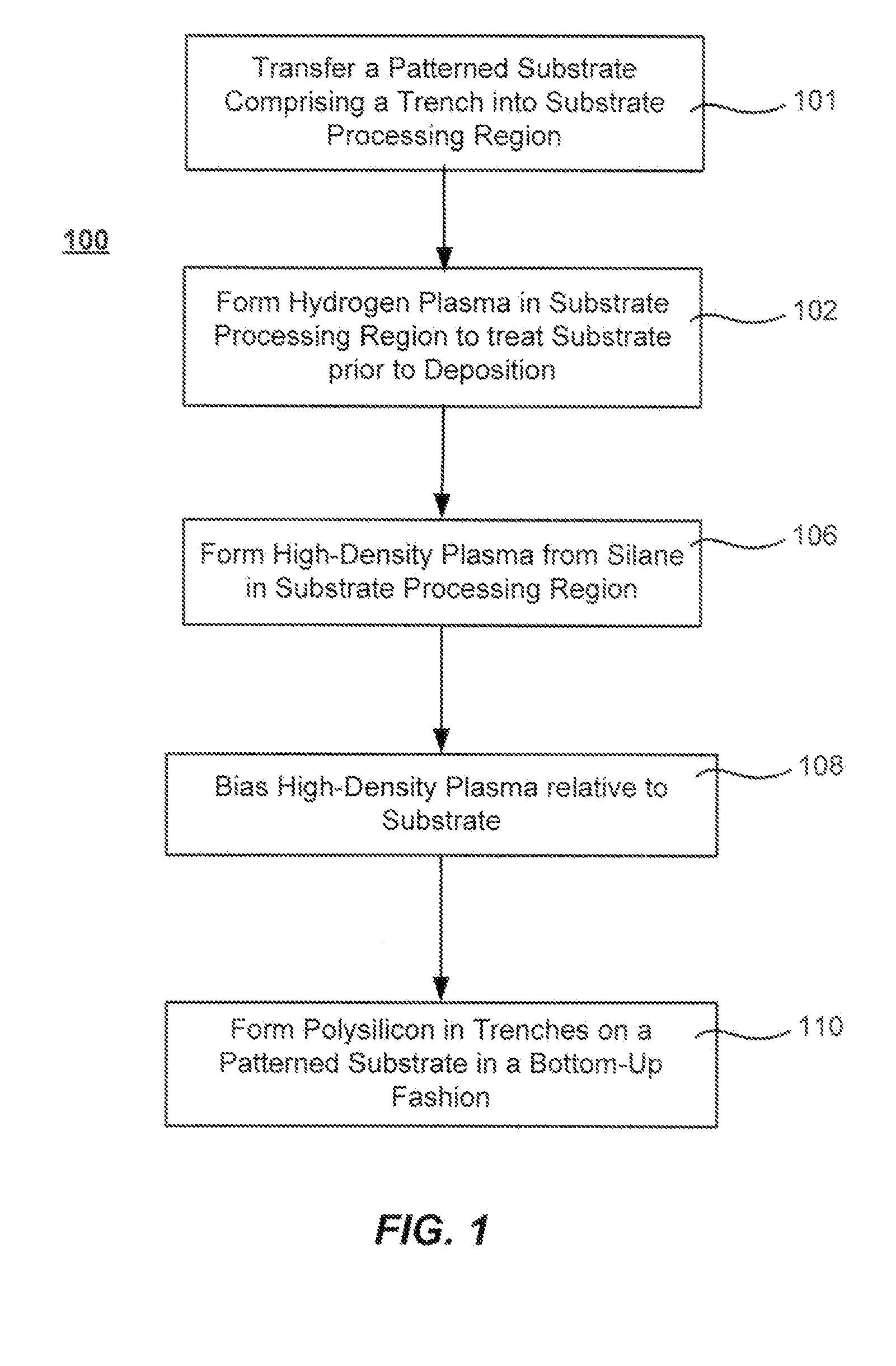

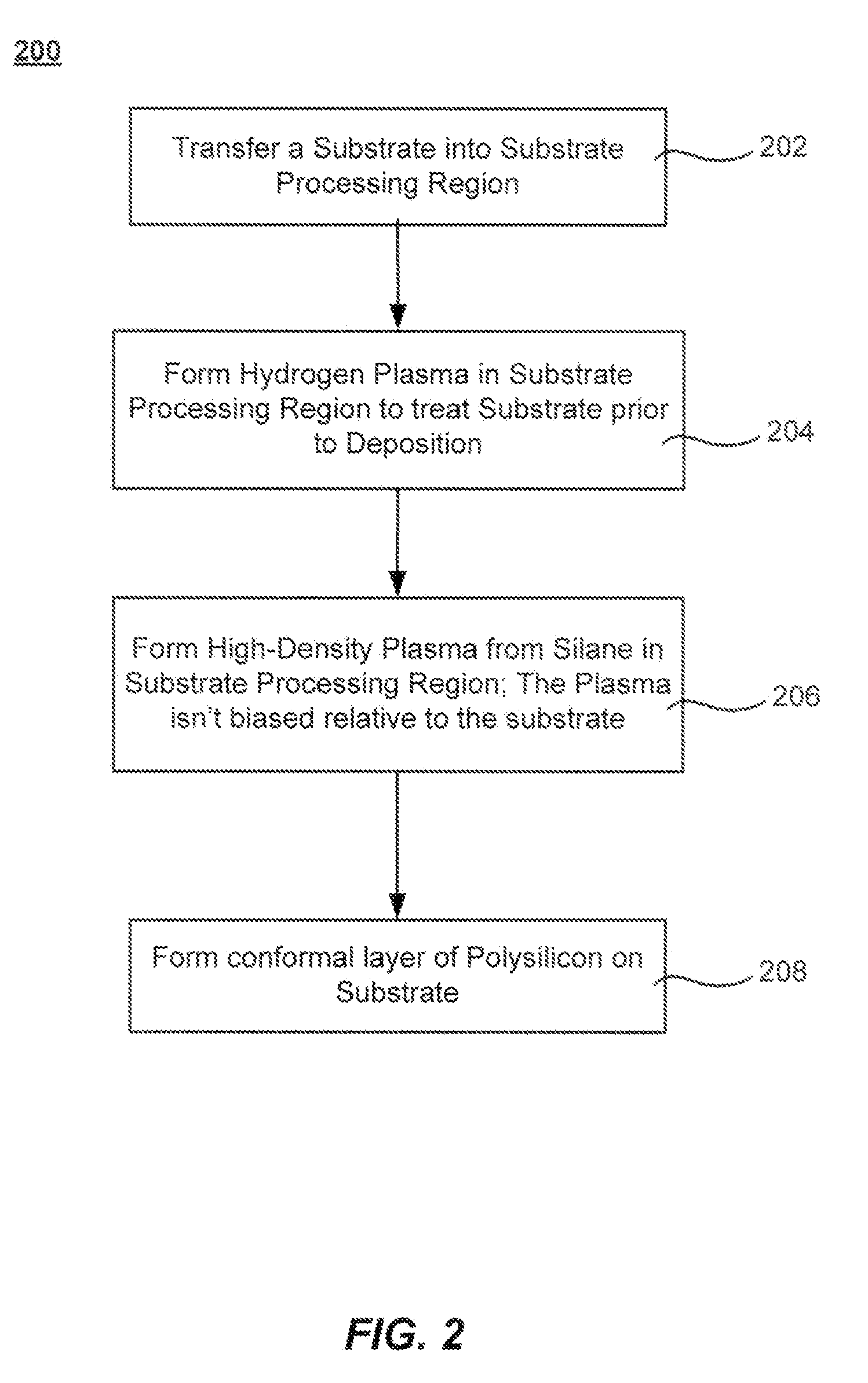

Polysilicon films by HDP-CVD

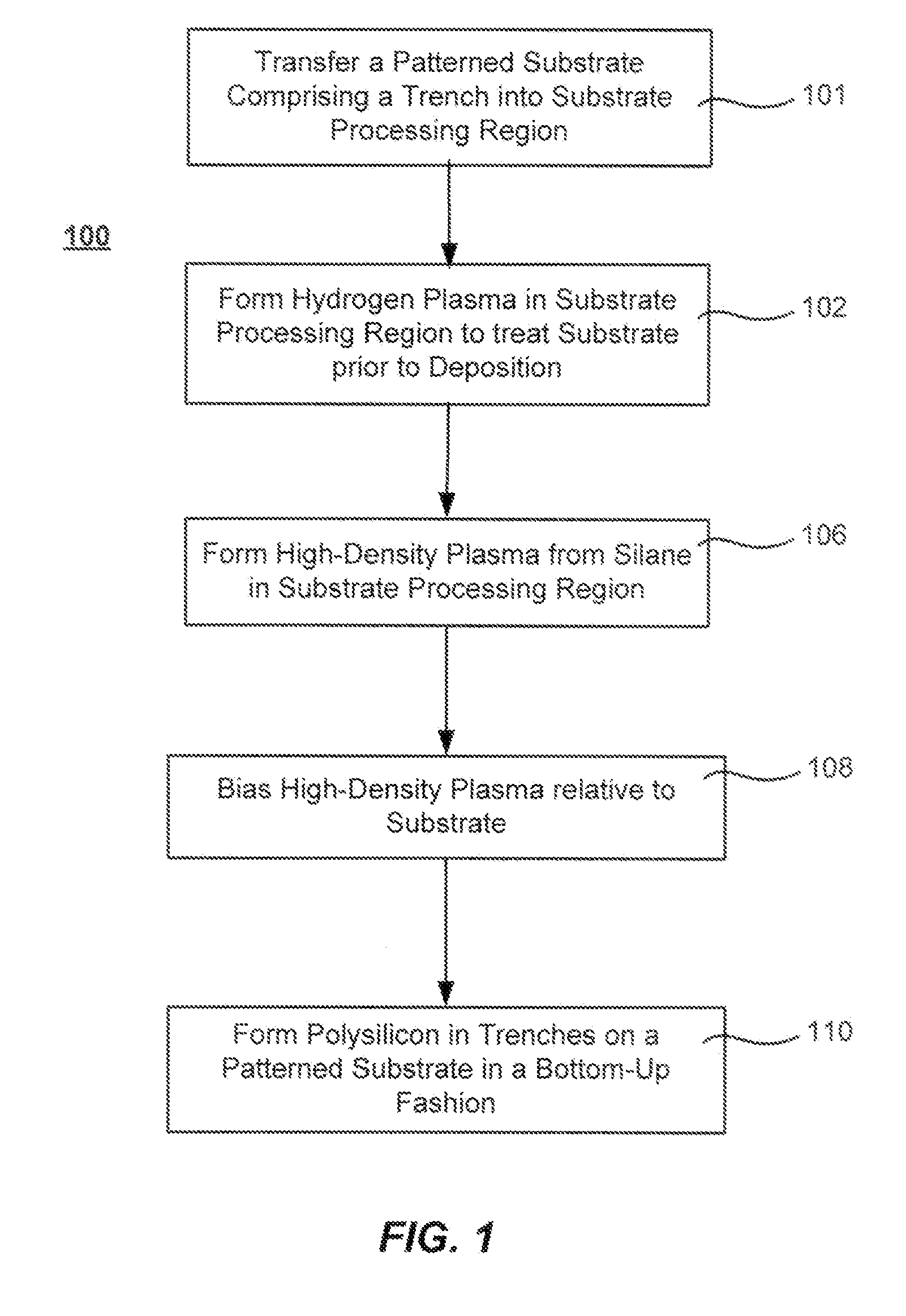

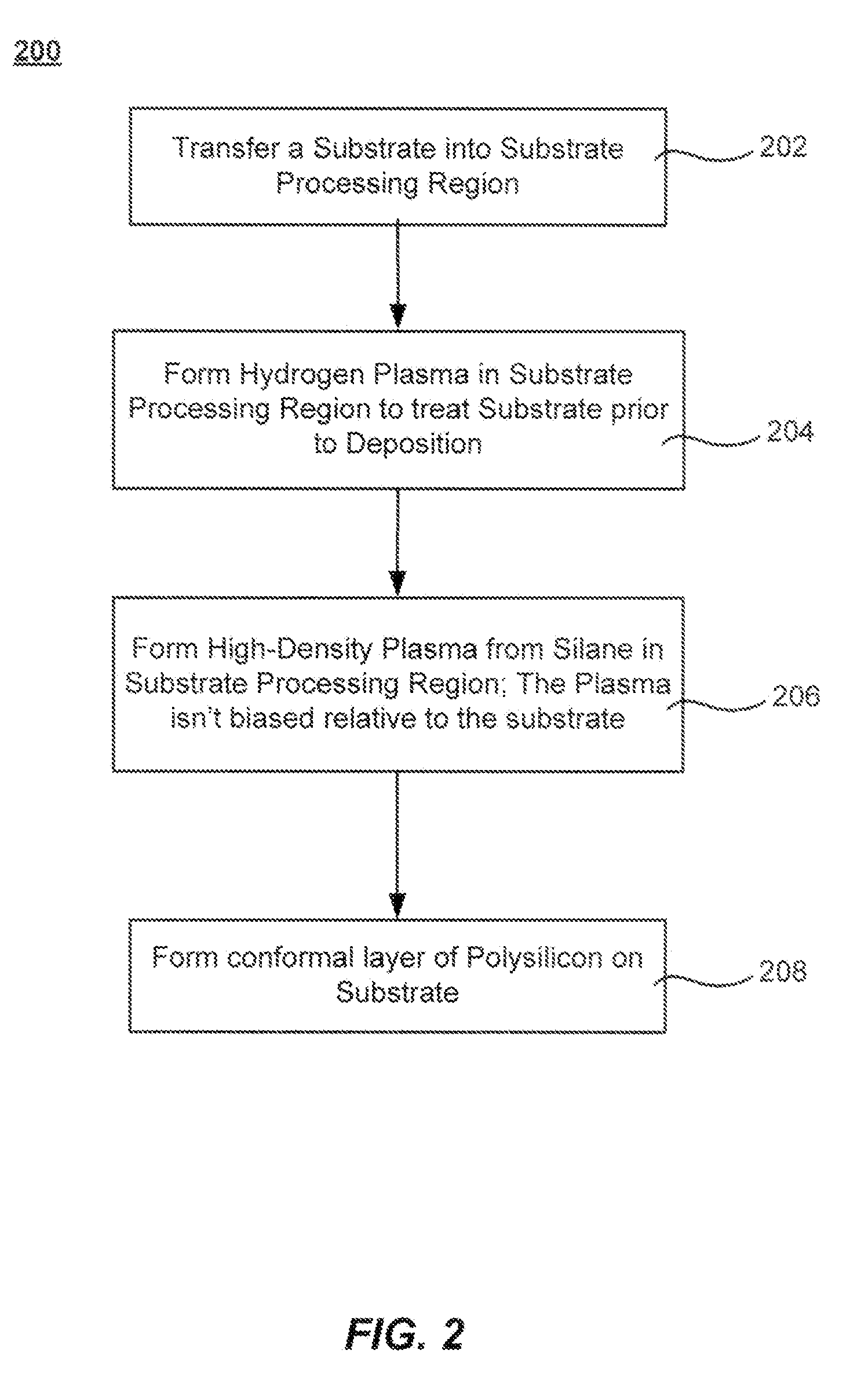

InactiveUS8450191B2Semiconductor/solid-state device manufacturingChemical vapor deposition coatingDopantHigh density

Methods of forming polysilicon layers are described. The methods include forming a high-density plasma from a silicon precursor in a substrate processing region containing the deposition substrate. The described methods produce polycrystalline films at reduced substrate temperature (e.g. <500° C.) relative to prior art techniques. The availability of a bias plasma power adjustment further enables adjustment of conformality of the formed polysilicon layer. When dopants are included in the high density plasma, they may be incorporated into the polysilicon layer in such a way that they do not require a separate activation step.

Owner:APPLIED MATERIALS INC

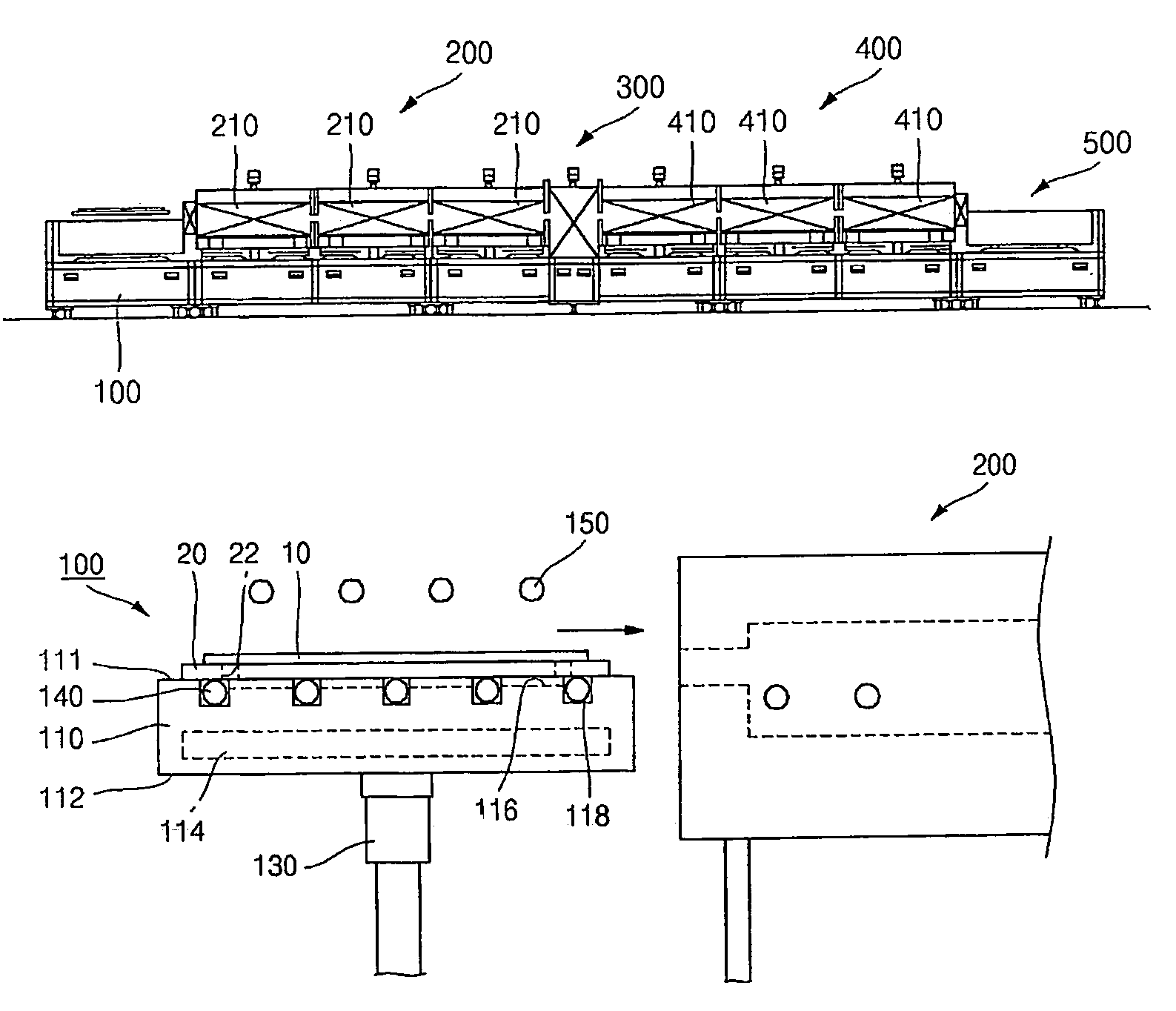

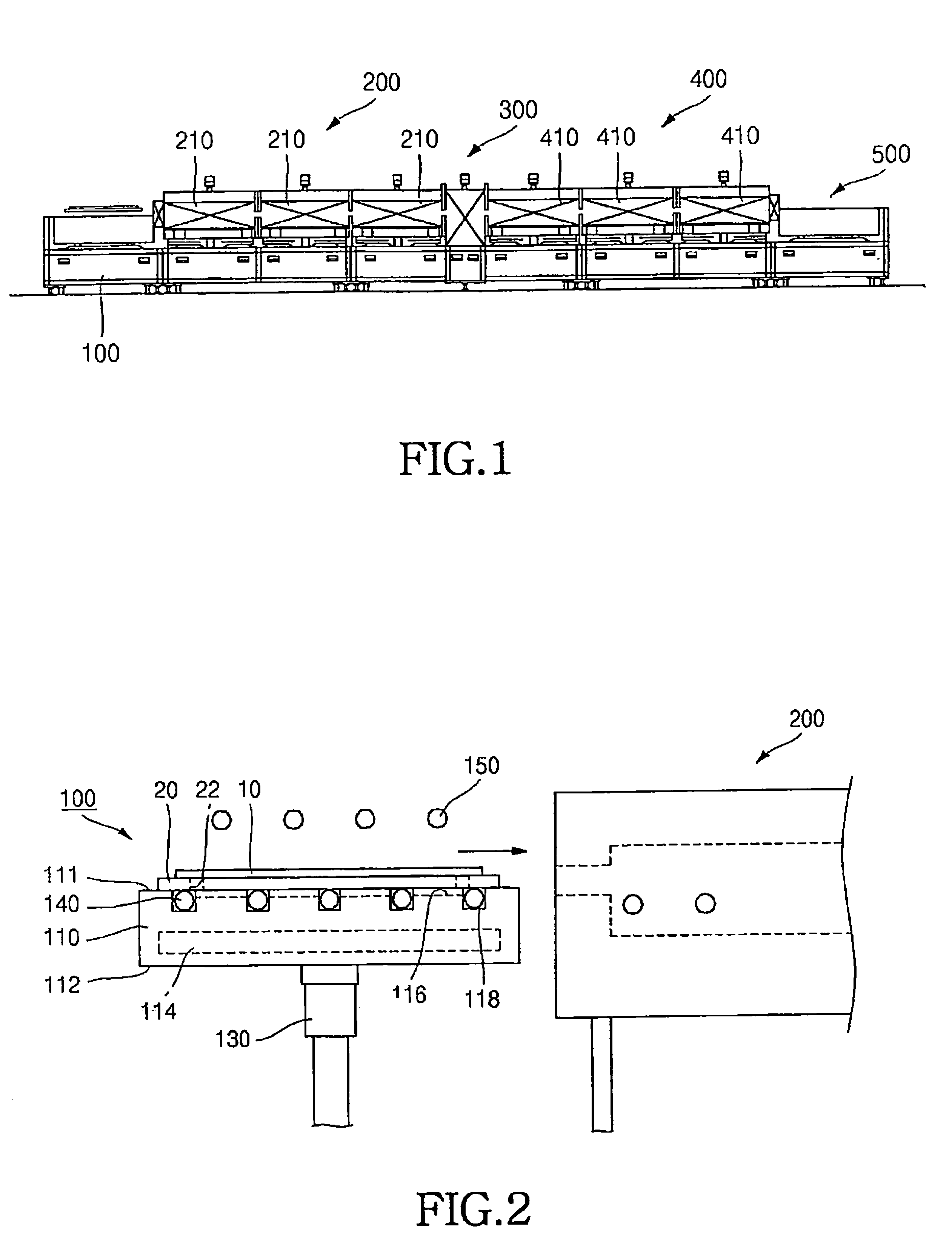

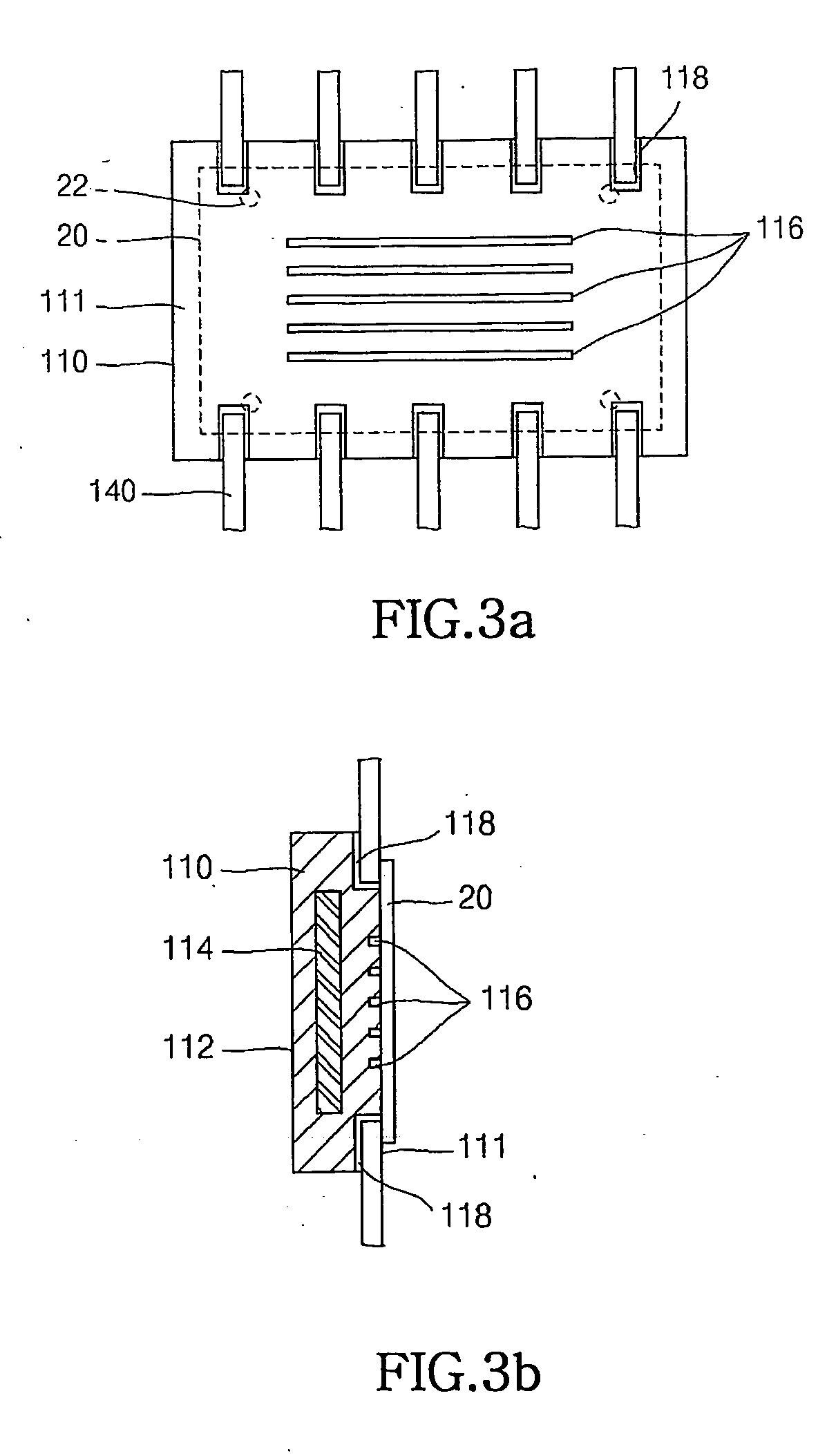

System for heat treatment of semiconductor device

InactiveUS7989736B2Avoid damageIncrease temperatureFurnaces without endless coreSemiconductor/solid-state device manufacturingElectromotive forceSilicon thin film

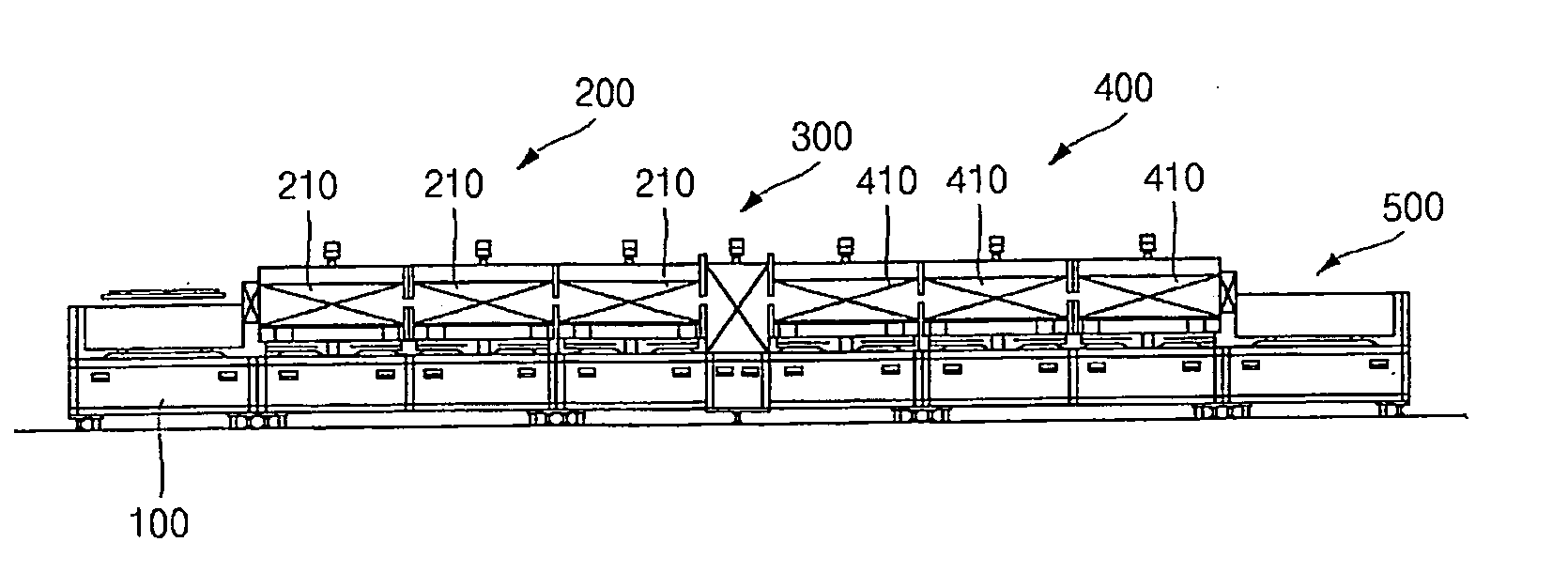

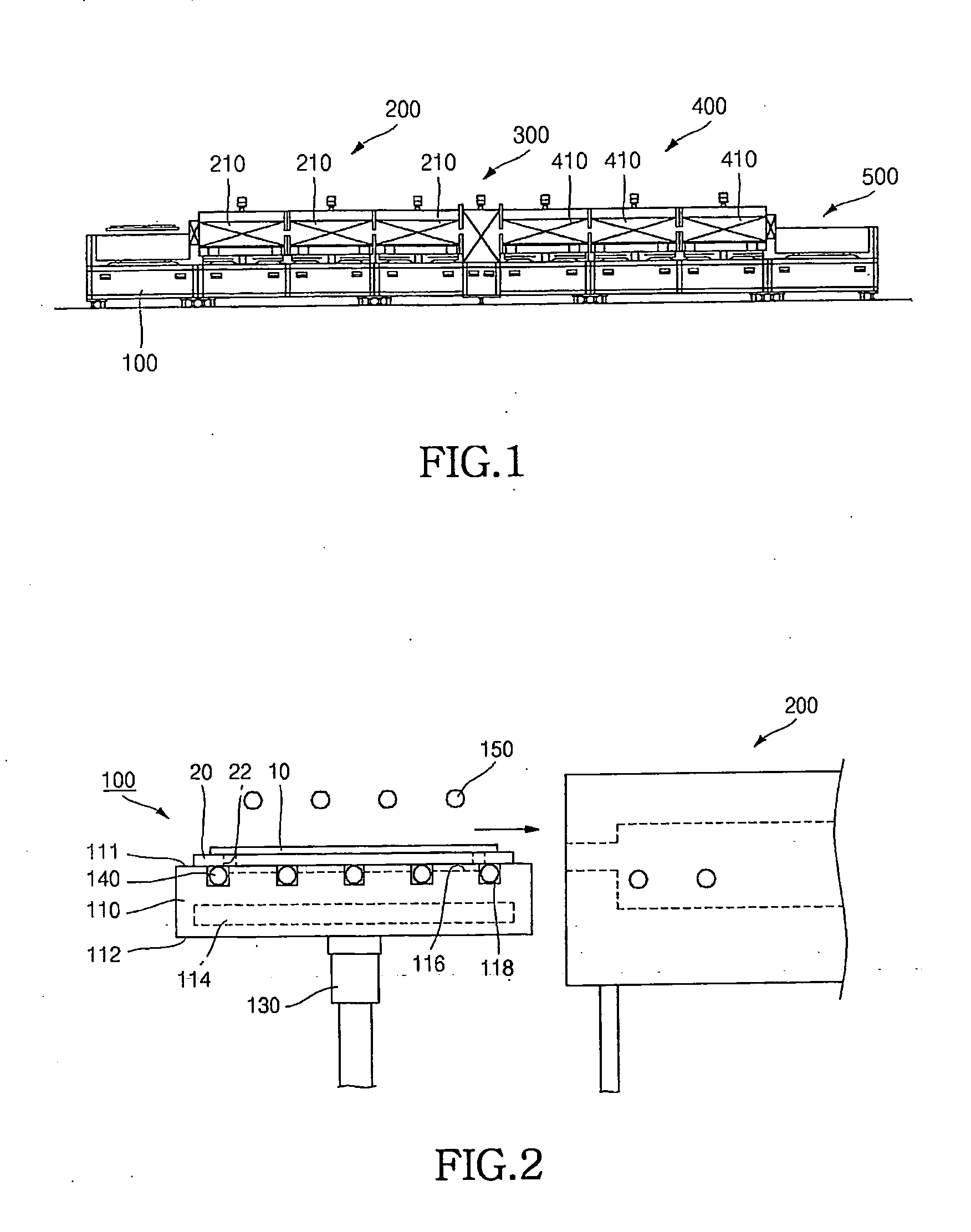

Disclosed is a heat treatment system for semiconductor devices. The heat treatment system is used in a heat treatment process for semiconductor devices, such as a crystallization process for an amorphous silicon thin film or a dopant activation process for a poly-crystalline silicon thin film formed on a surface of a glass substrate of a flat display panel including a liquid crystal display (LCD) or an organic light emitting device (OLED). The heat treatment system transfers a semiconductor device after uniformly preheating the semiconductor device in order to prevent deformation of the semiconductor device during the heat treatment process, rapidly performs the heat treatment process under the high temperature condition by heating the semiconductor device using a lamp heater and induction heat derived from induced electromotive force, and unloads the semiconductor device after uniformly cooling the semiconductor device such that the semiconductor device is prevented from being deformed when the heat treatment process has been finished. The heat treatment system rapidly performs the heat treatment process while preventing deformation of the semiconductor device by gradually heating or cooling the semiconductor device.

Owner:VIATRON TECH INC

Polysilicon films by hdp-cvd

InactiveUS20120190178A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingMetallurgyPolycrystalline silicon thin films

Methods of forming polysilicon layers are described. The methods include forming a high-density plasma from a silicon precursor in a substrate processing region containing the deposition substrate. The described methods produce polycrystalline films at reduced substrate temperature (e.g. <500° C.) relative to prior art techniques. The availability of a bias plasma power adjustment further enables adjustment of conformality of the formed polysilicon layer. When dopants are included in the high density plasma, they may be incorporated into the polysilicon layer in such a way that they do not require a separate activation step.

Owner:APPLIED MATERIALS INC

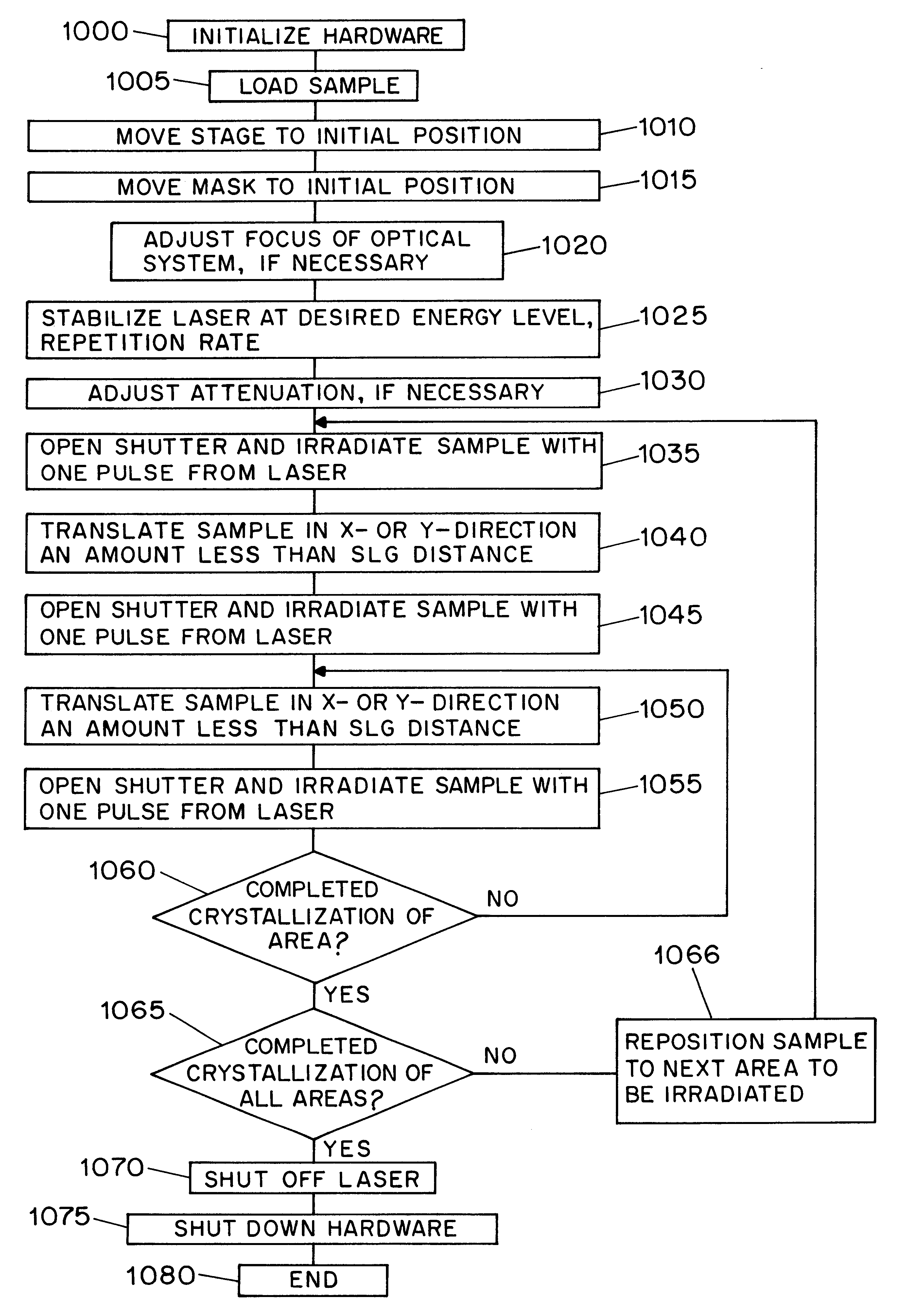

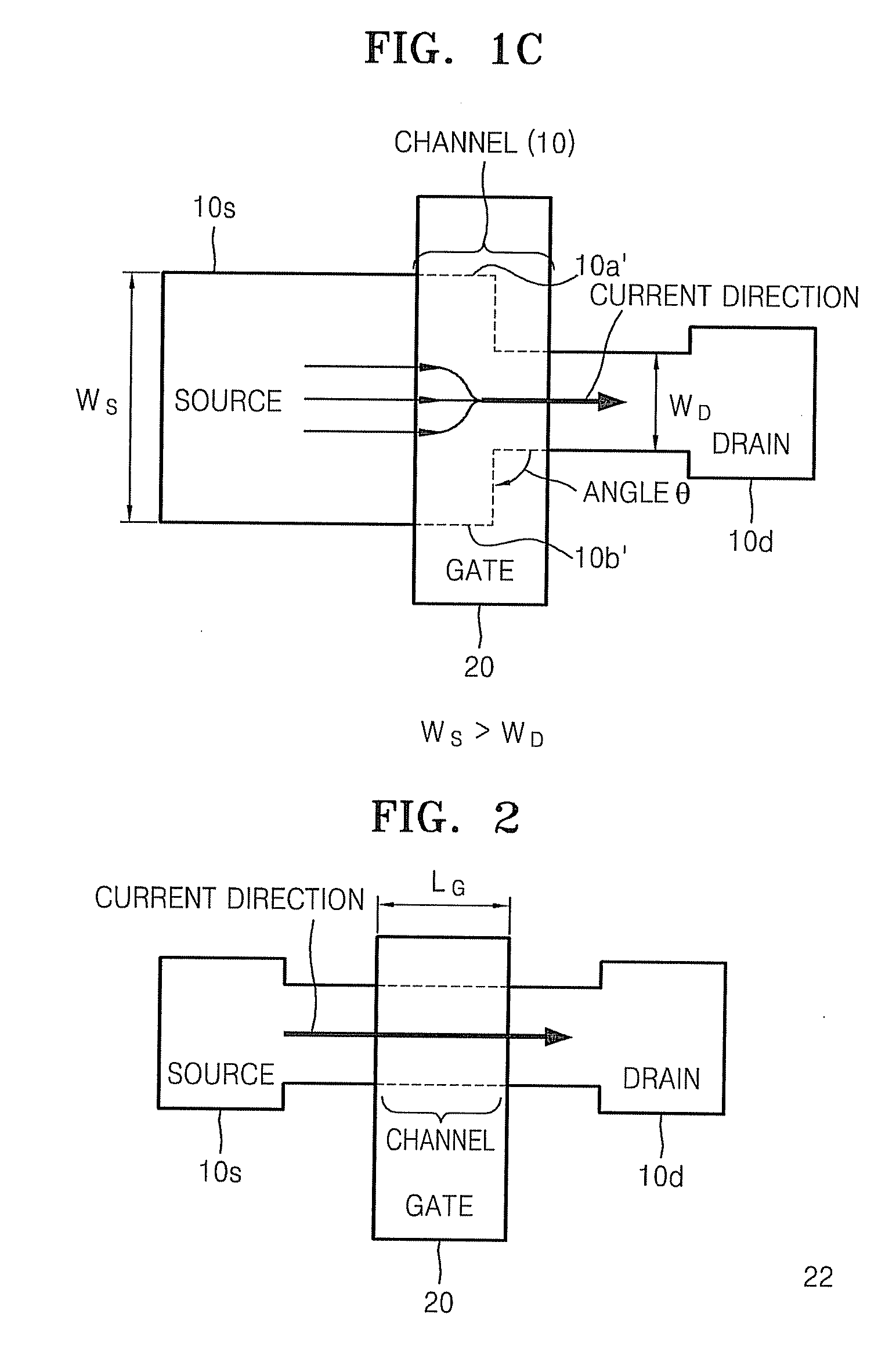

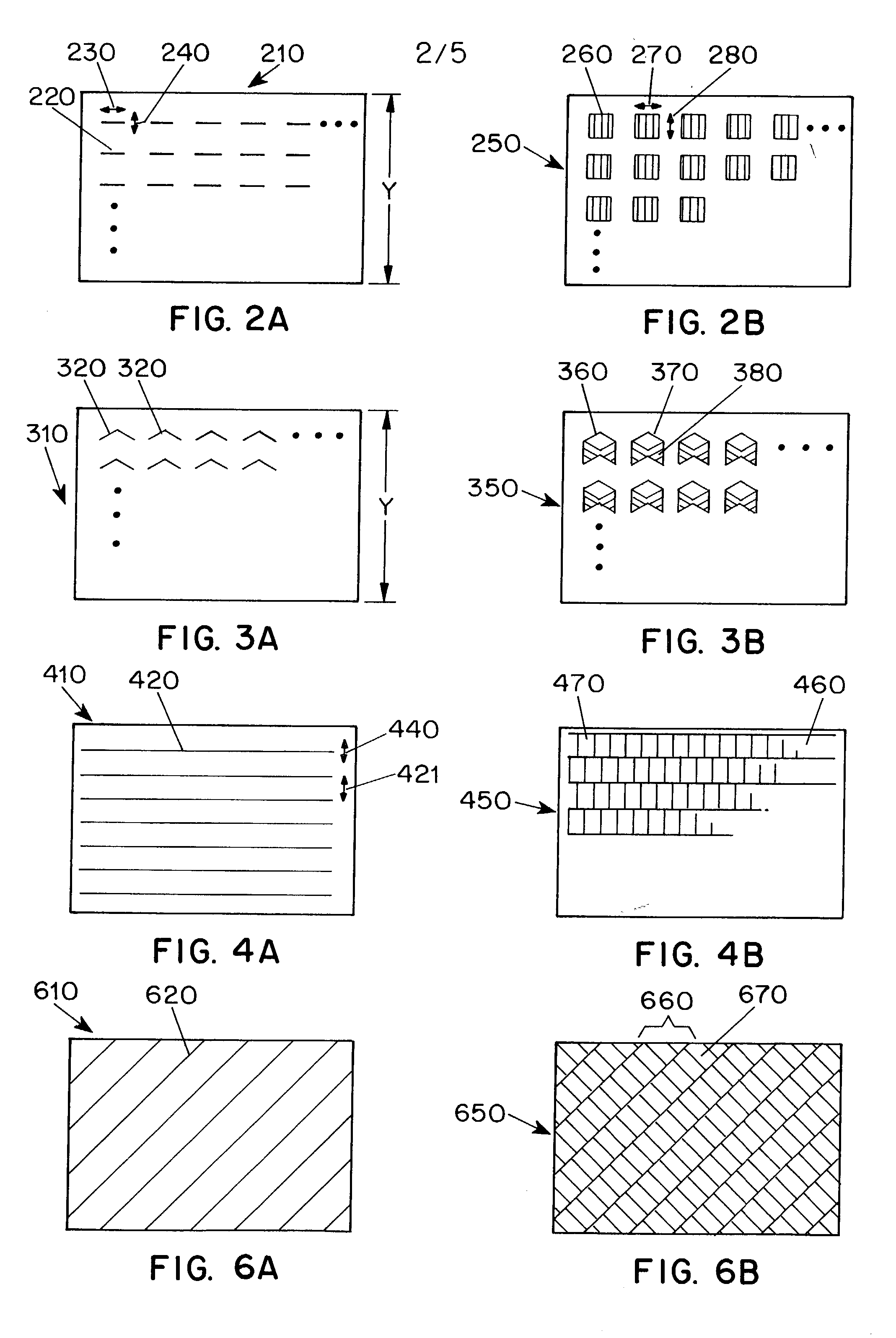

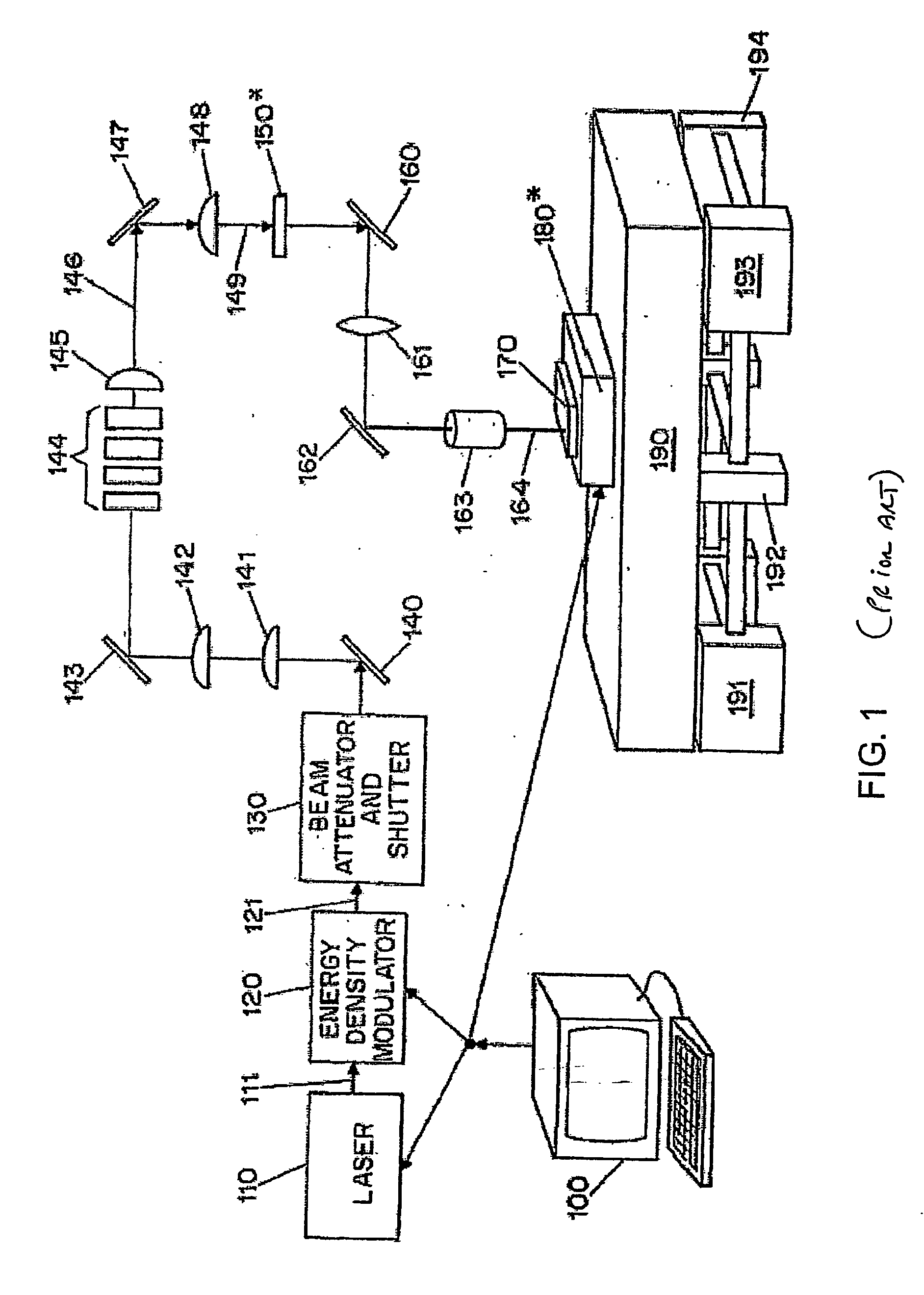

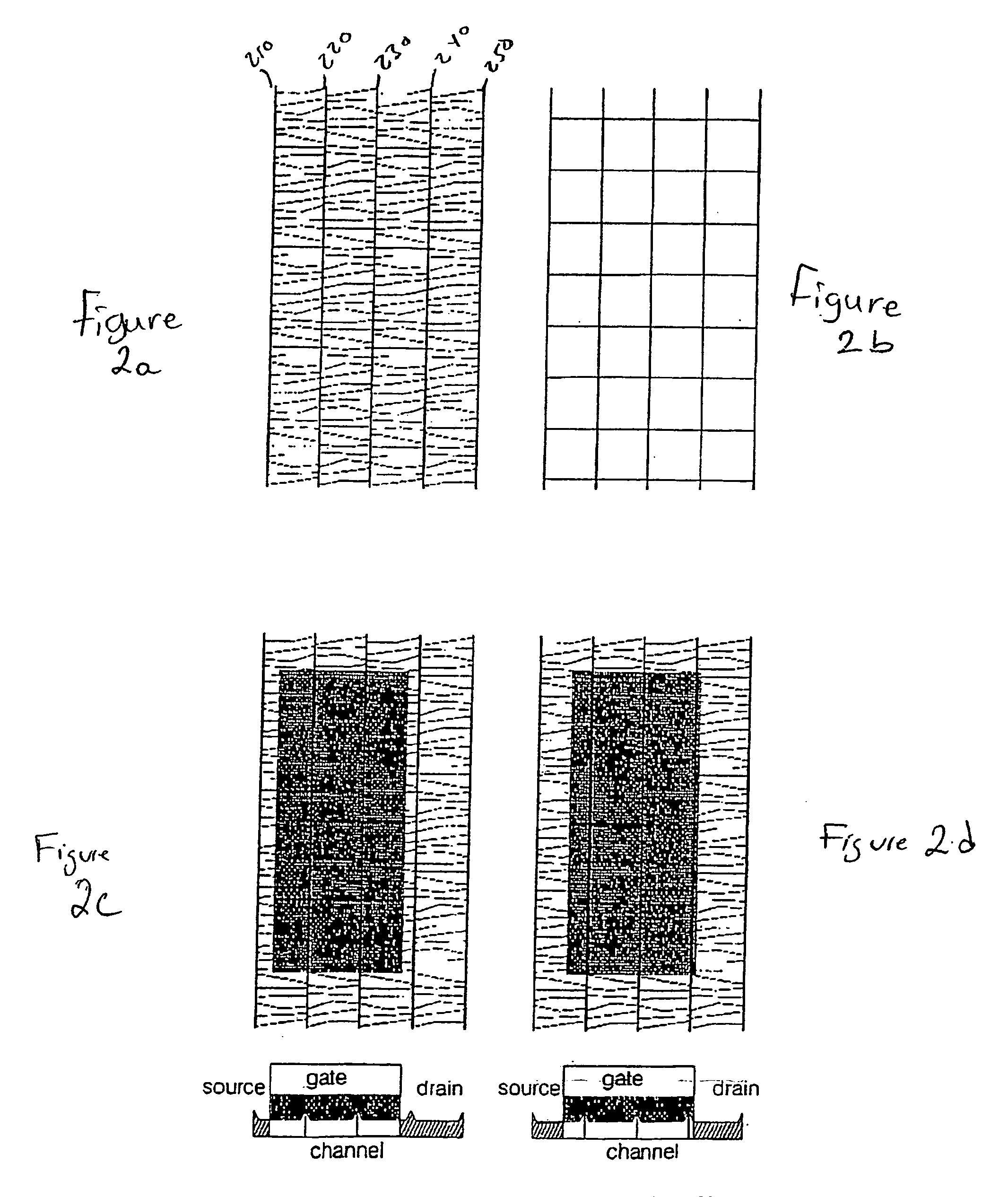

Methods for producing uniform large-grained and grain boundary location manipulated polycrystalline thin film semiconductors using sequential lateral solidification

Methods for processing an amorphous silicon thin film sample into a polycrystalline silicon thin film are disclosed. In one preferred arrangement, a method includes the steps of generating a sequence of excimer laser pulses, controllably modulating each excimer laser pulse in the sequence to a predetermined fluence, homoginizing each modulated laser pulse in the sequence in a predetermined plane, masking portions of each homogenized fluence controlled laser pulse in the sequence with a two dimensional pattern of slits to generate a sequence of fluence controlled pulses of line patterned beamlets, each slit in the pattern of slits being sufficiently narrow to prevent inducement of significant nucleation in region of a silicon thin film sample irradiated by a beam let corresponding to the slit, irradiating an amorphous silicon thin film sample with the sequence of fluence controlled slit patterned beamlets to effect melting of portions thereof corresponding to each fluence controlled patterned beamlet pulse in the sequence of pulses of patterned beamlets, and controllably sequentially translating a relative position of the sample with respect to each of the fluence controlled pulse of slit patterned beamlets to thereby process the amorphous silicon thin film sample into a single or polycrystalline silicon thin film.

Owner:THE TRUSTEES OF COLUMBIA UNIV IN THE CITY OF NEW YORK

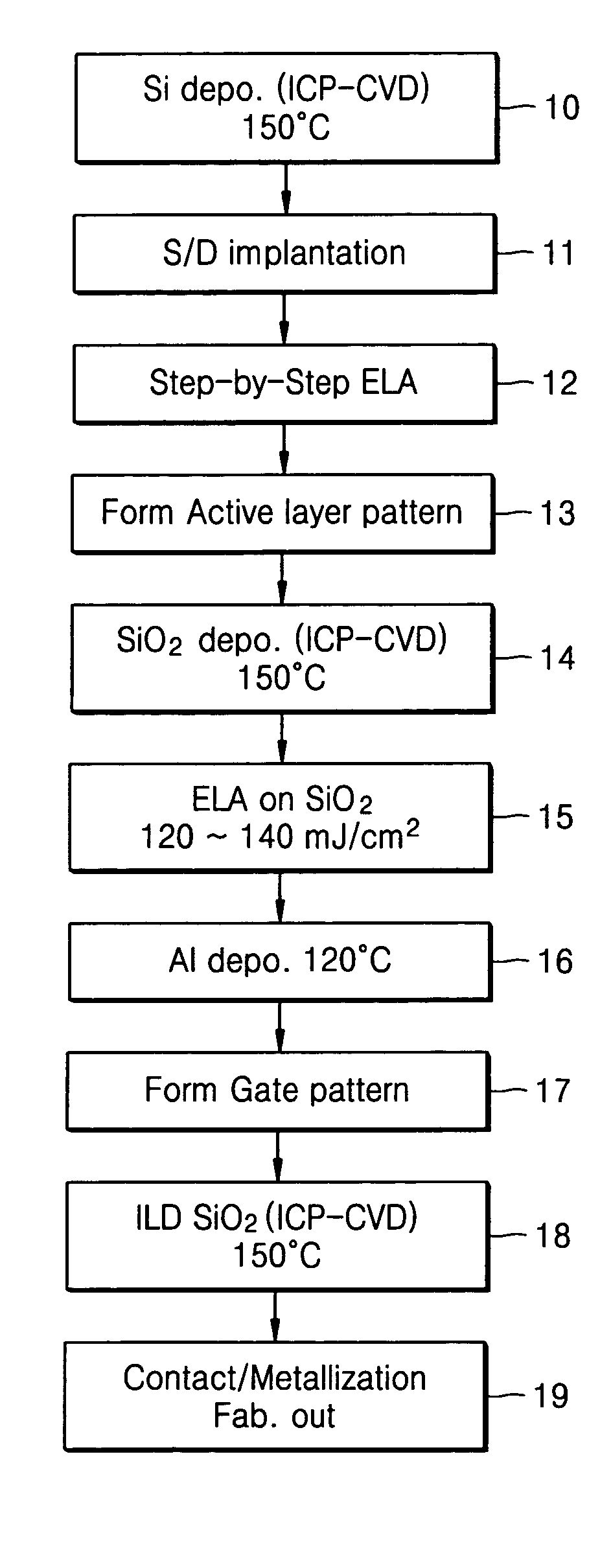

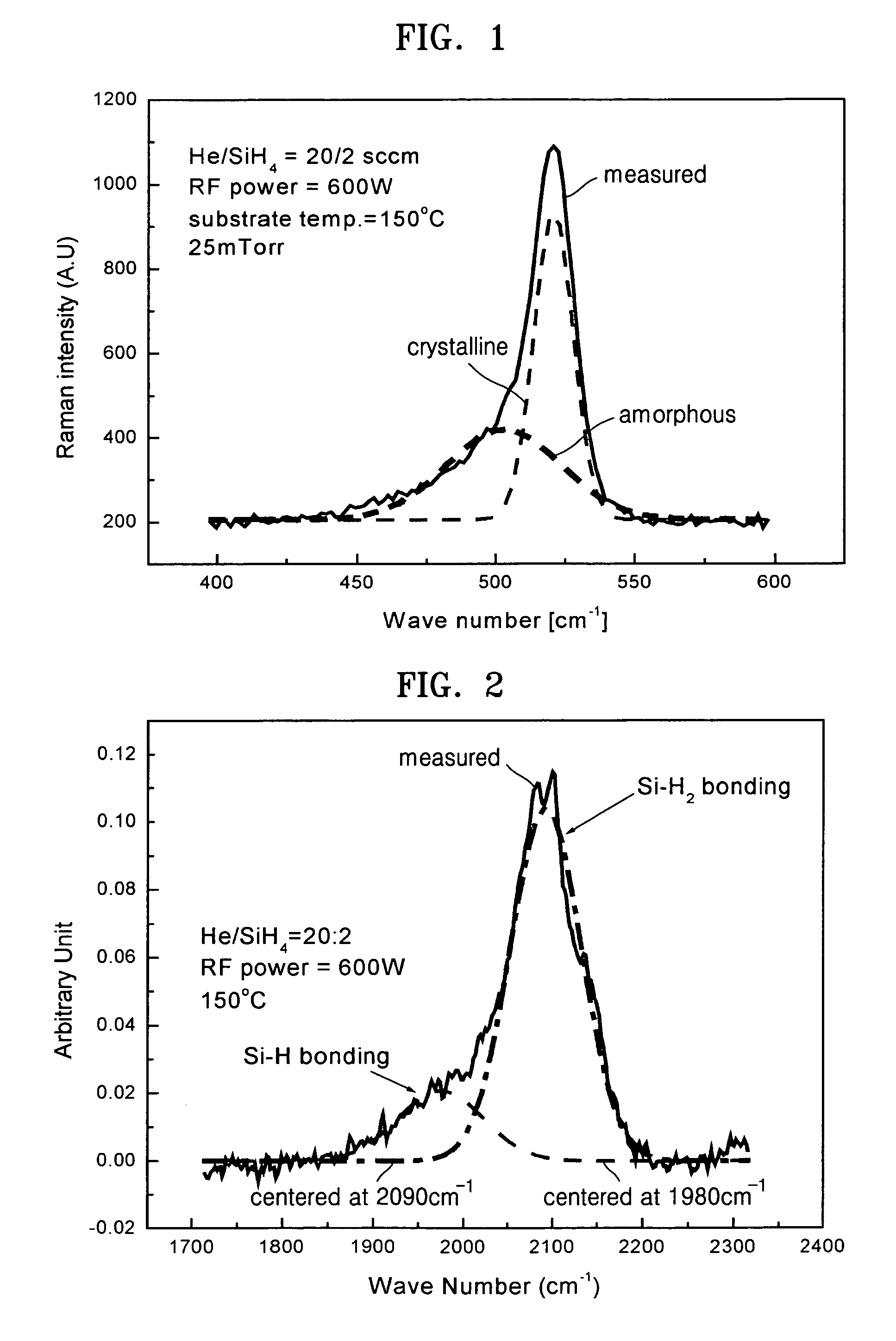

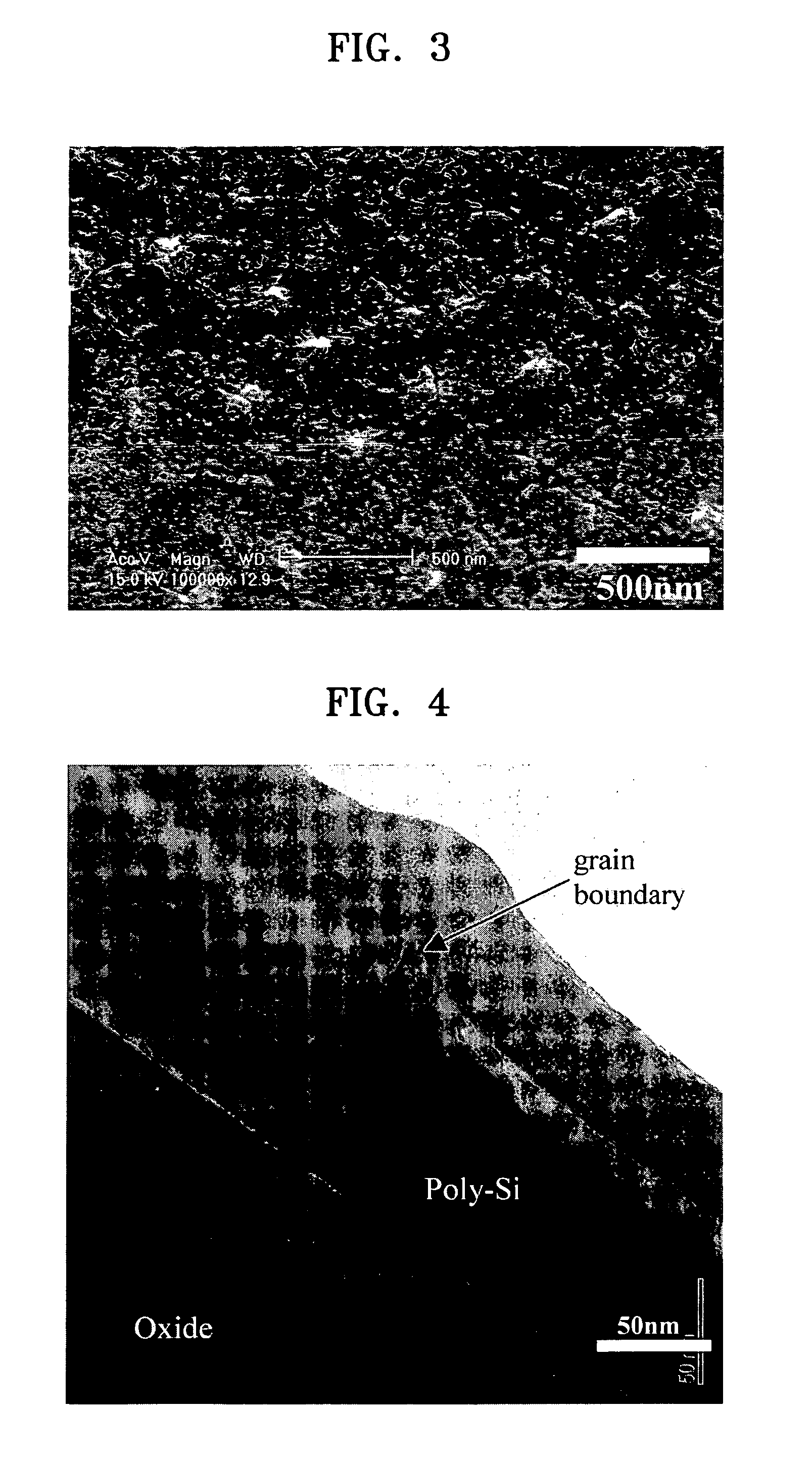

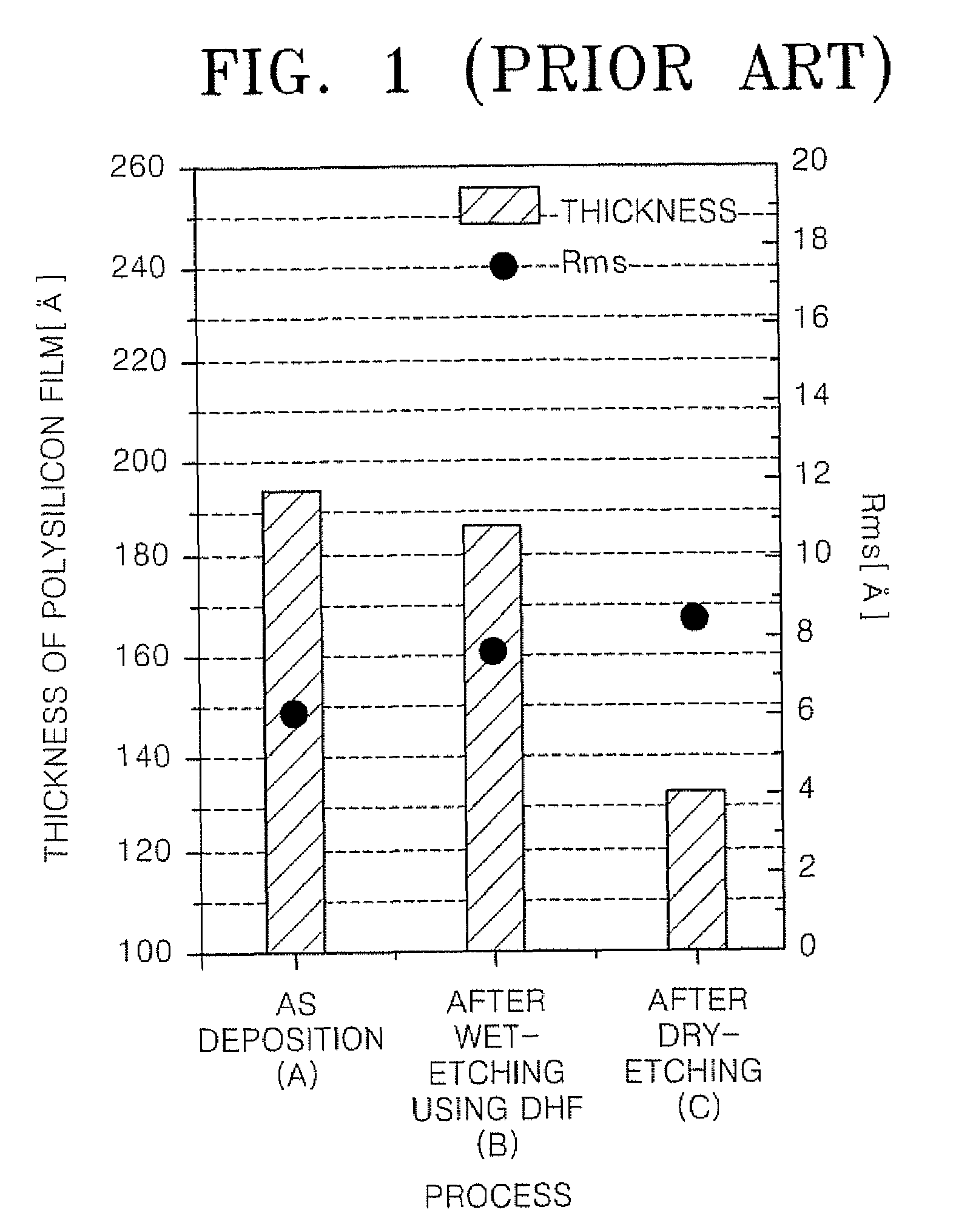

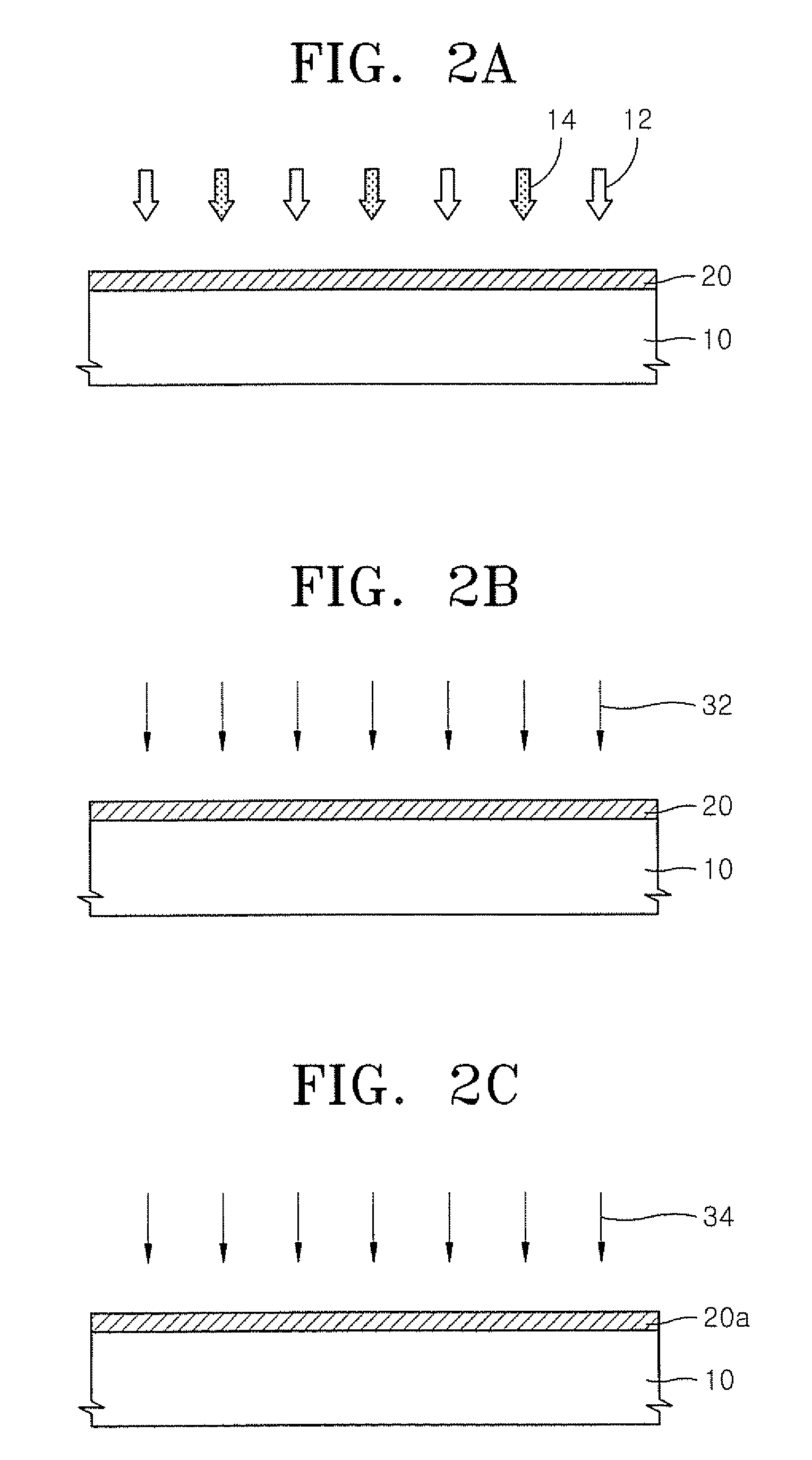

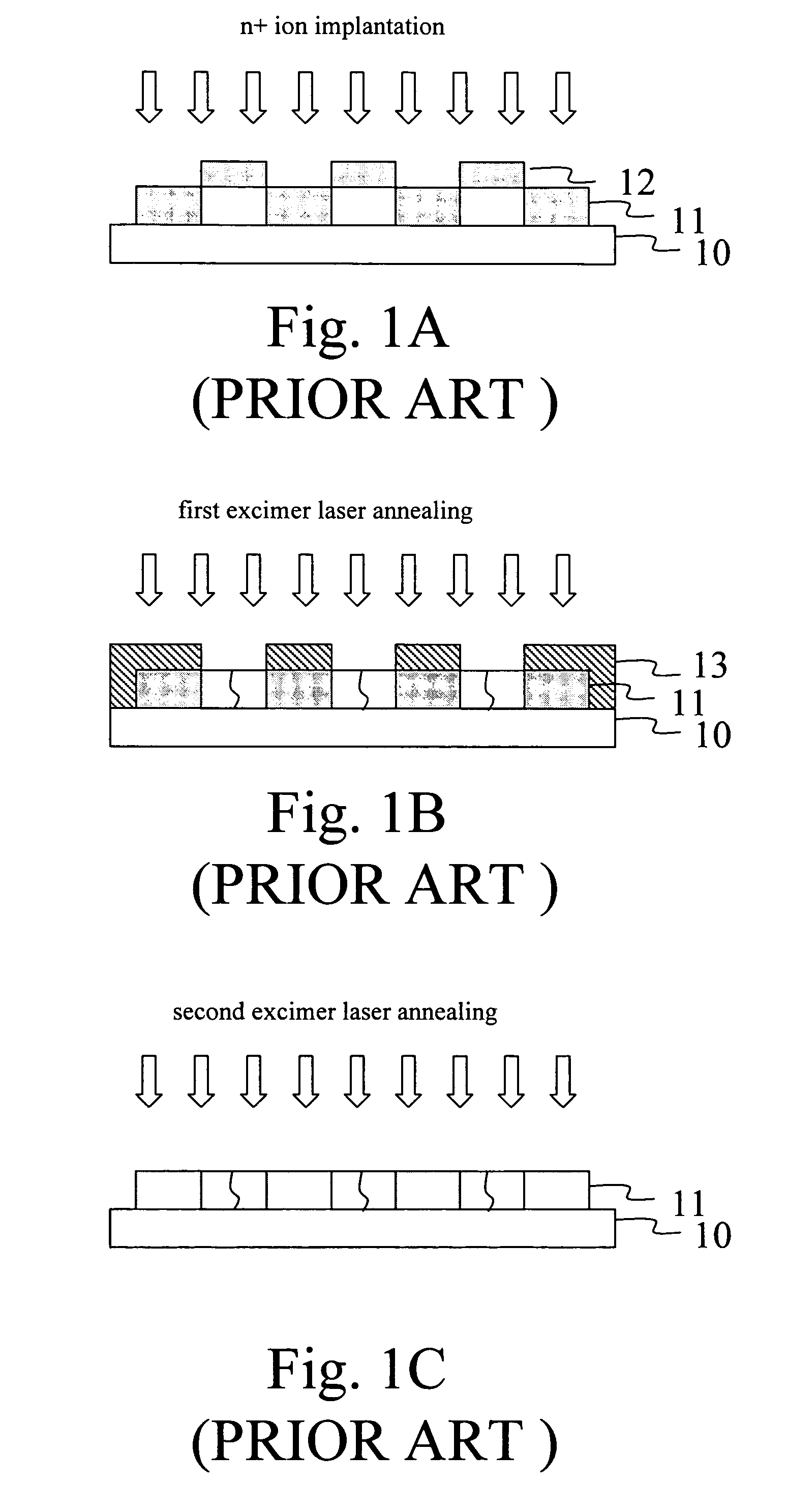

Method of fabricating poly-crystalline silicon thin film and method of fabricating transistor using the same

InactiveUS7563659B2Refined grain sizeHigh energyTransistorSemiconductor/solid-state device manufacturingInductively coupled plasmaSilicon thin film

A method of fabricating a poly-Si thin film and a method of fabricating a poly-Si TFT using the same are provided. The poly-Si thin film is formed at a low temperature using inductively coupled plasma chemical vapor deposition (ICP-CVD). After the ICP-CVD, excimer laser annealing (ELA) is performed while increasing energy by predetermined steps. A poly-Si active layer and a SiO2 gate insulating layer are deposited at a temperature of about 150° C. using ICP-CVD. The poly-Si has a large grain size of about 3000 Å or more. An interface trap density of the SiO2 can be as high as 1011 / cm2. A transistor having good electrical characteristics can be fabricated at a low temperature and thus can be formed on a heat tolerant plastic substrate.

Owner:SAMSUNG ELECTRONICS CO LTD

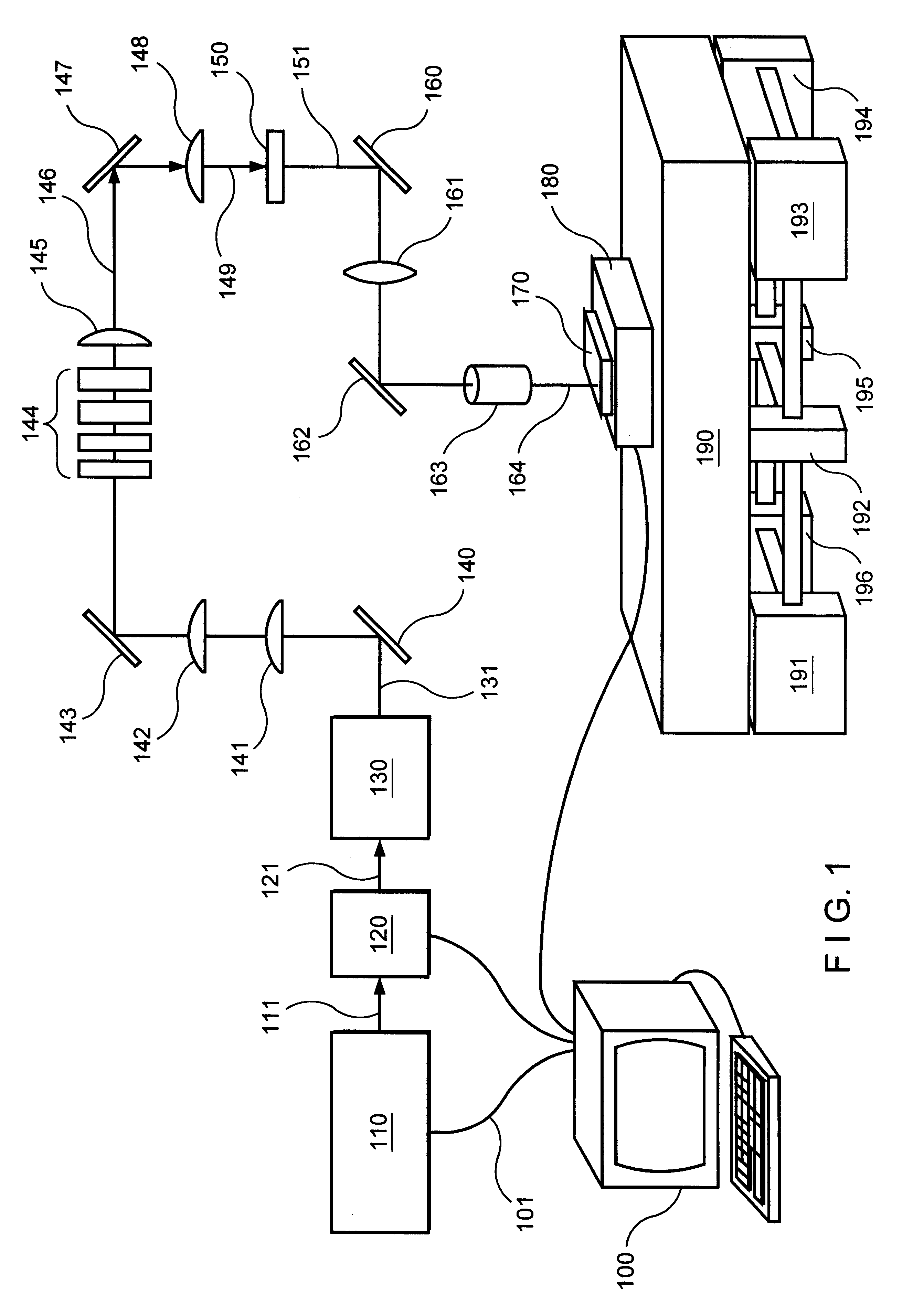

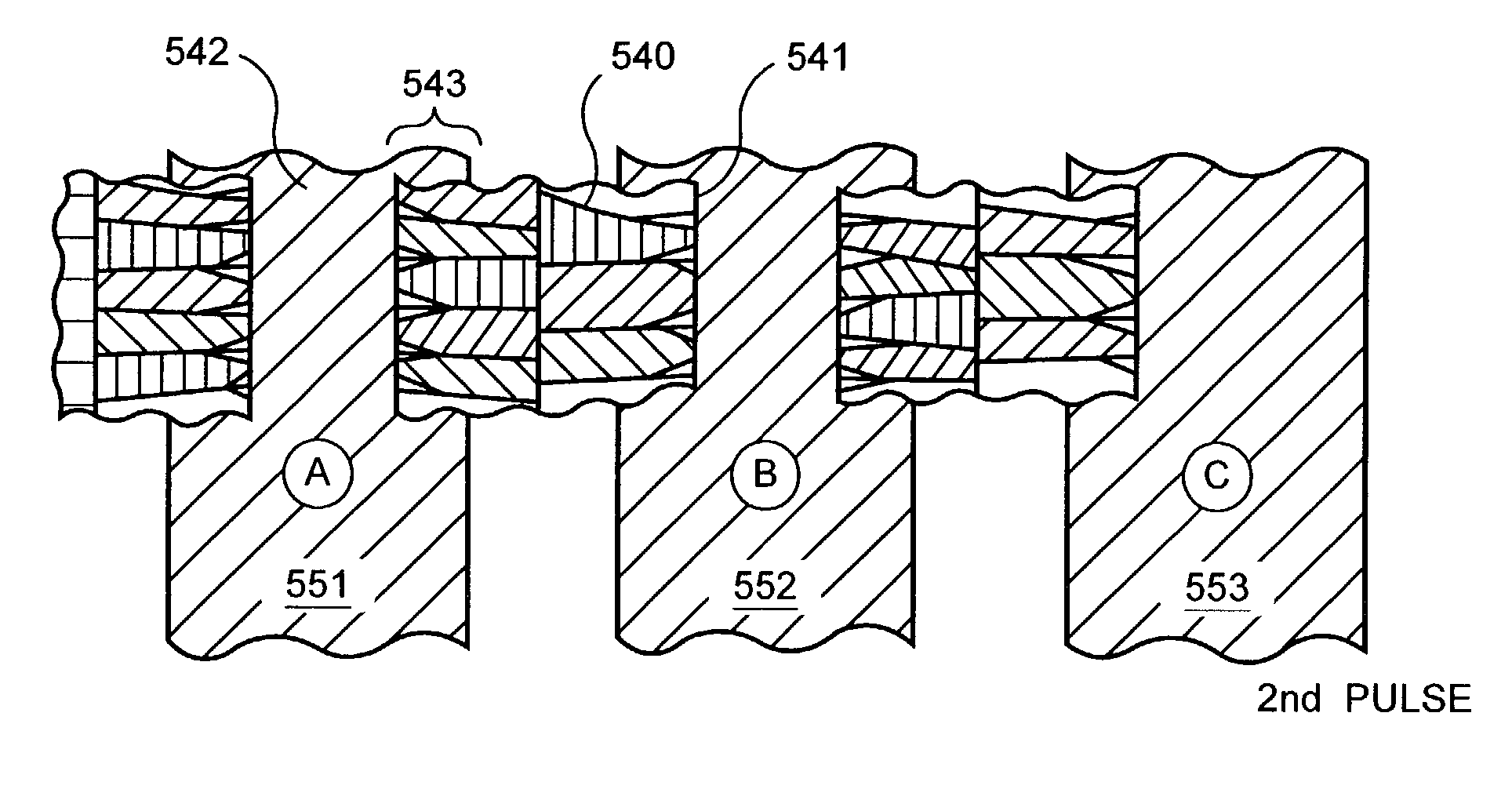

Systems and methods using sequential lateral solidification for producing single or polycrystalline silicon thin films at low temperatures

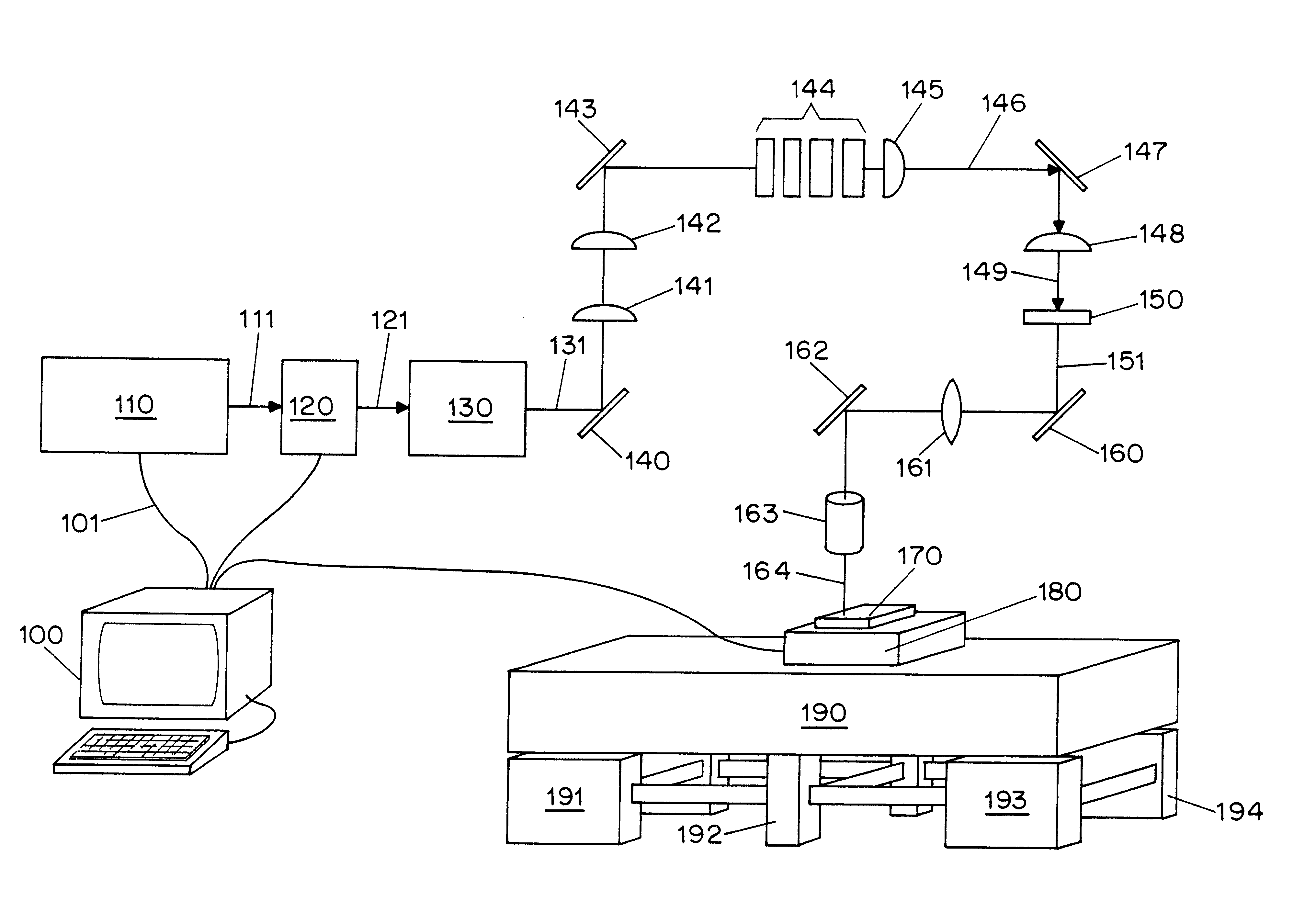

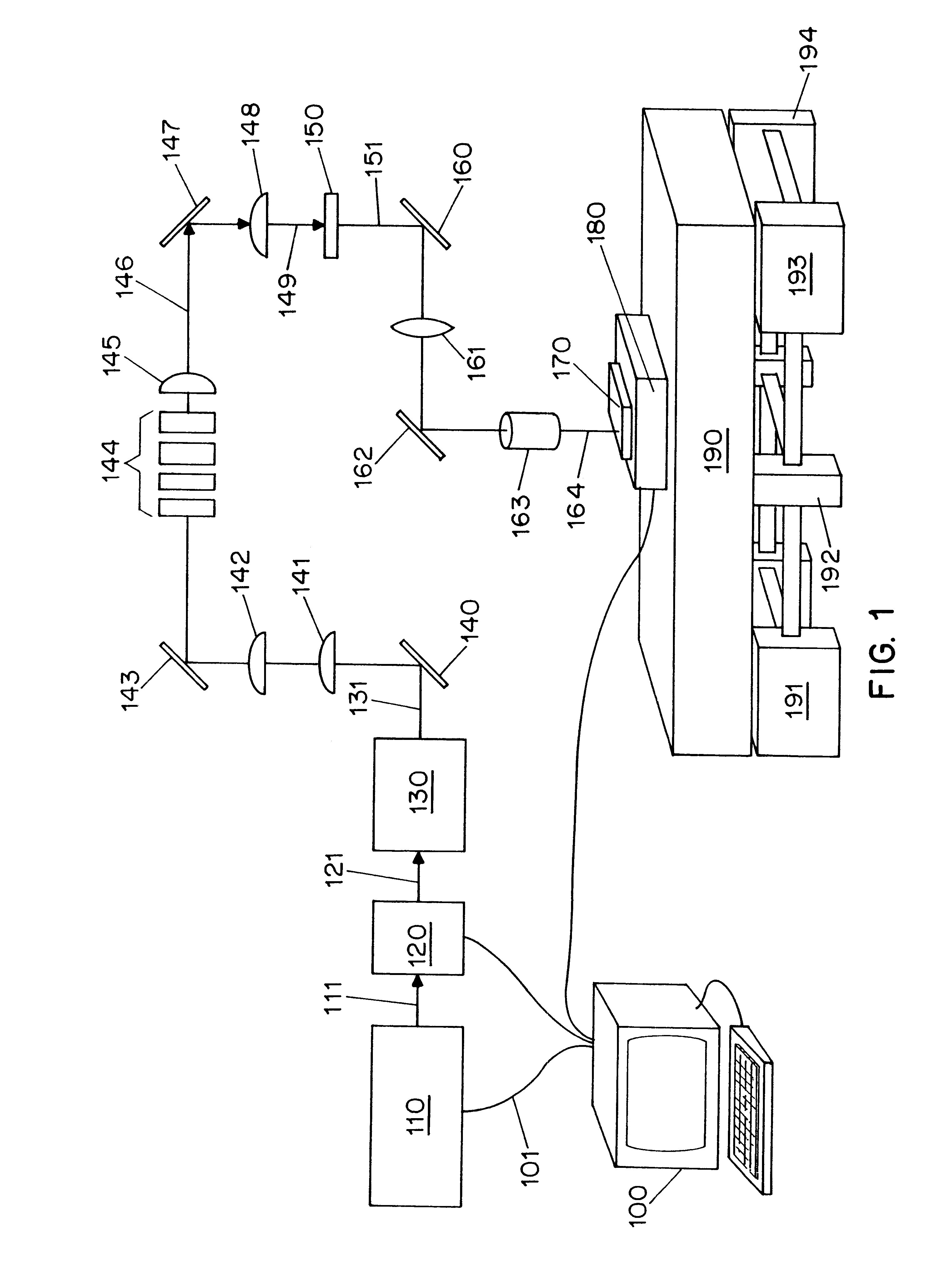

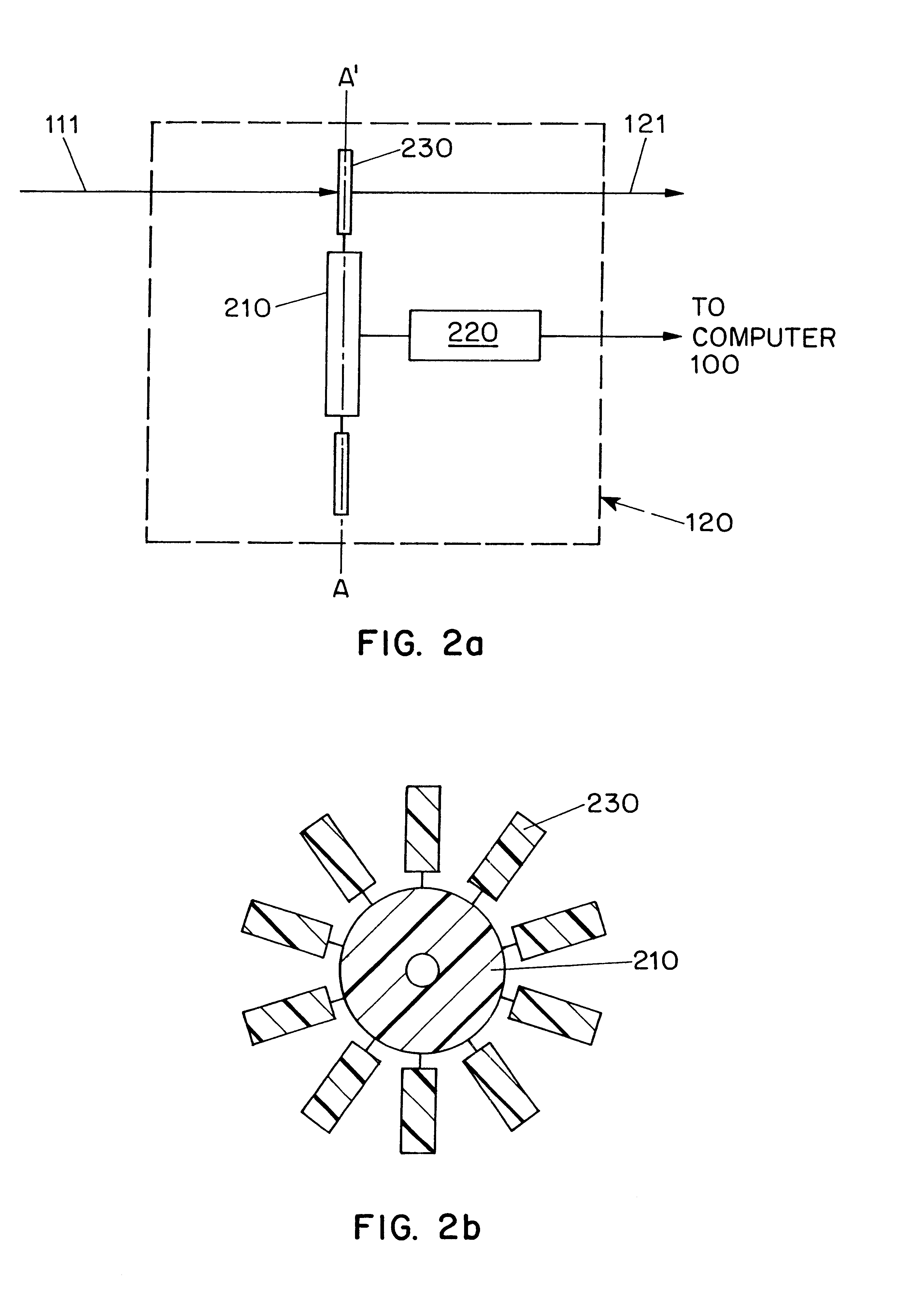

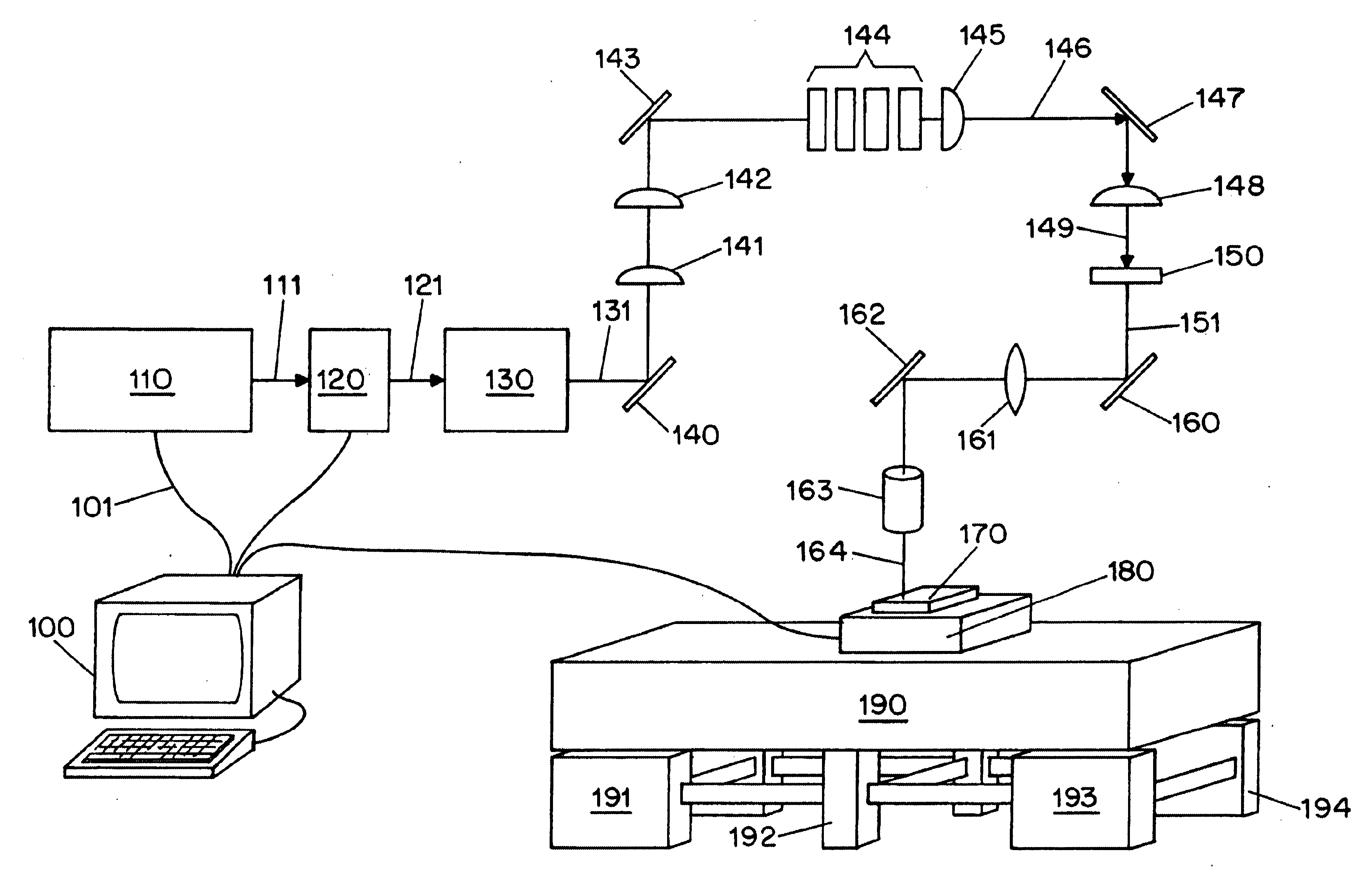

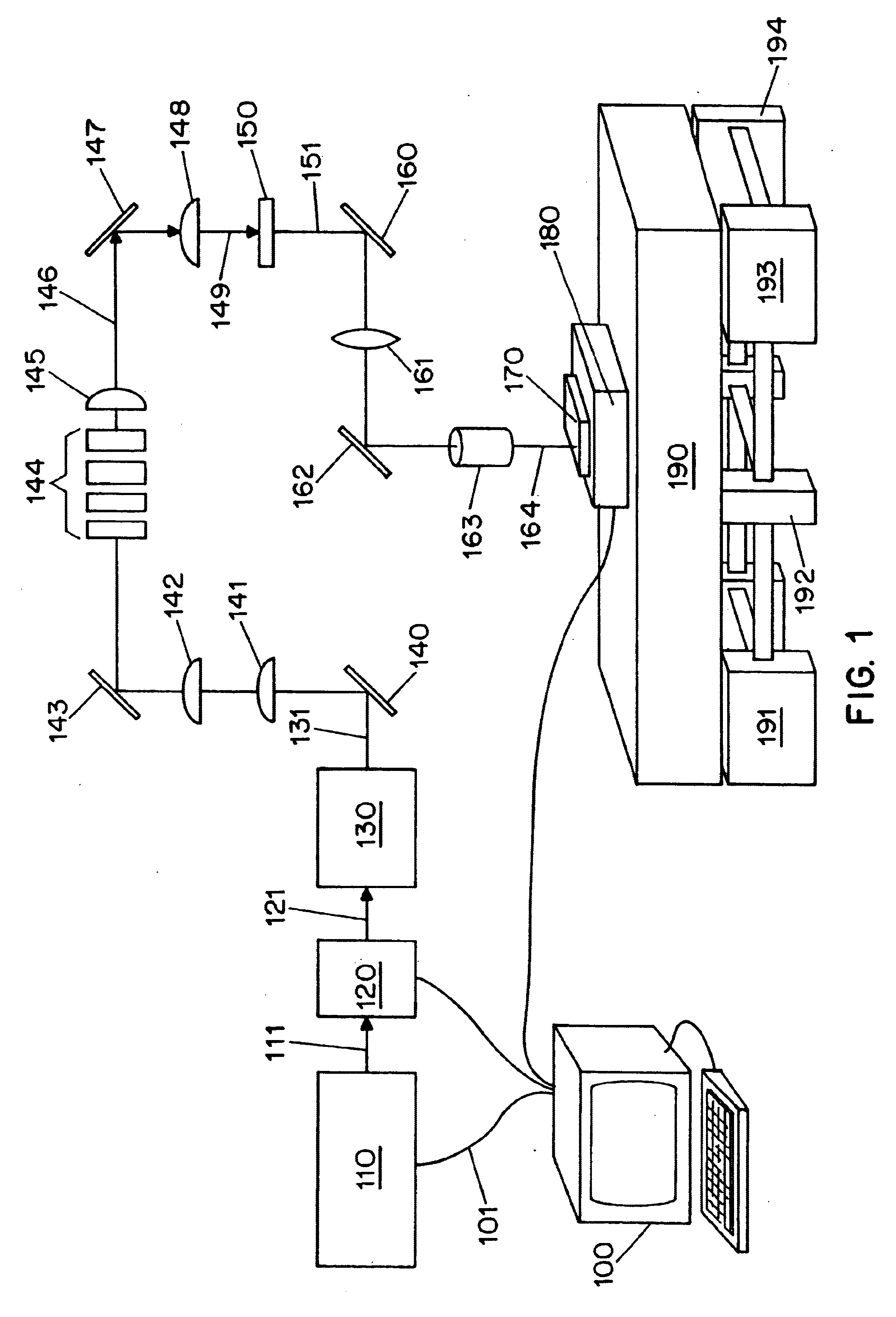

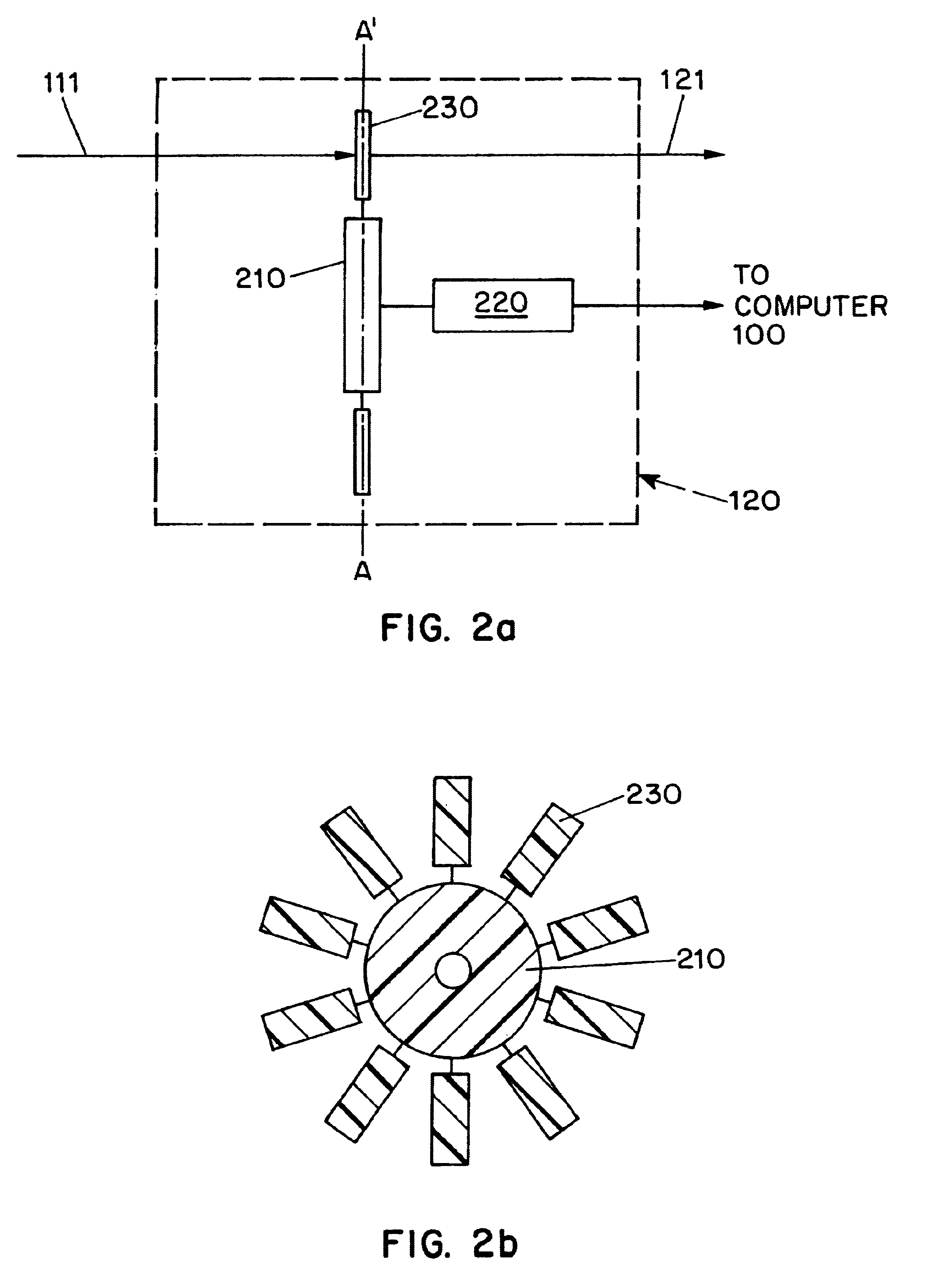

System and methods for processing an amorphous silicon thin film sample into a single or polycrystalline silicon thin film are disclosed. The system includes an excimer laser for generating a plurality of excimer laser pulses of a predetermined fluence, an energy density modulator for controllably modulating fluence of the excimer laser pulses, a beam homoginizer for homoginizing modulated laser pulses in a predetermined plane, a mask for masking portions of the homoginized modulated laser pulses into patterned beamlets, a sample stage for receivingthe patterned beamlets to effect melting of portions of any amorphous silicon thin film sample placed thereon corresponding to the beamlets, translating means for controllably translating a relative position of the sample stage with respect to a position of the mask and a computer for controlling the controllable fluence modulation of the excimer laser pulses and the controllable relative positions of the sample stage and mask, and for coordinating excimer pulse generation and fluence modulation with the relative positions of the sample stage and mask, to thereby process amorphous silicon thin film sample into a single or polycrystalline silicon thin film by sequential translation of the sample stage relative to the mask and irradiation of the sample by patterned beamlets of varying fluence at corresponding sequential locations thereon.

Owner:THE TRUSTEES OF COLUMBIA UNIV IN THE CITY OF NEW YORK

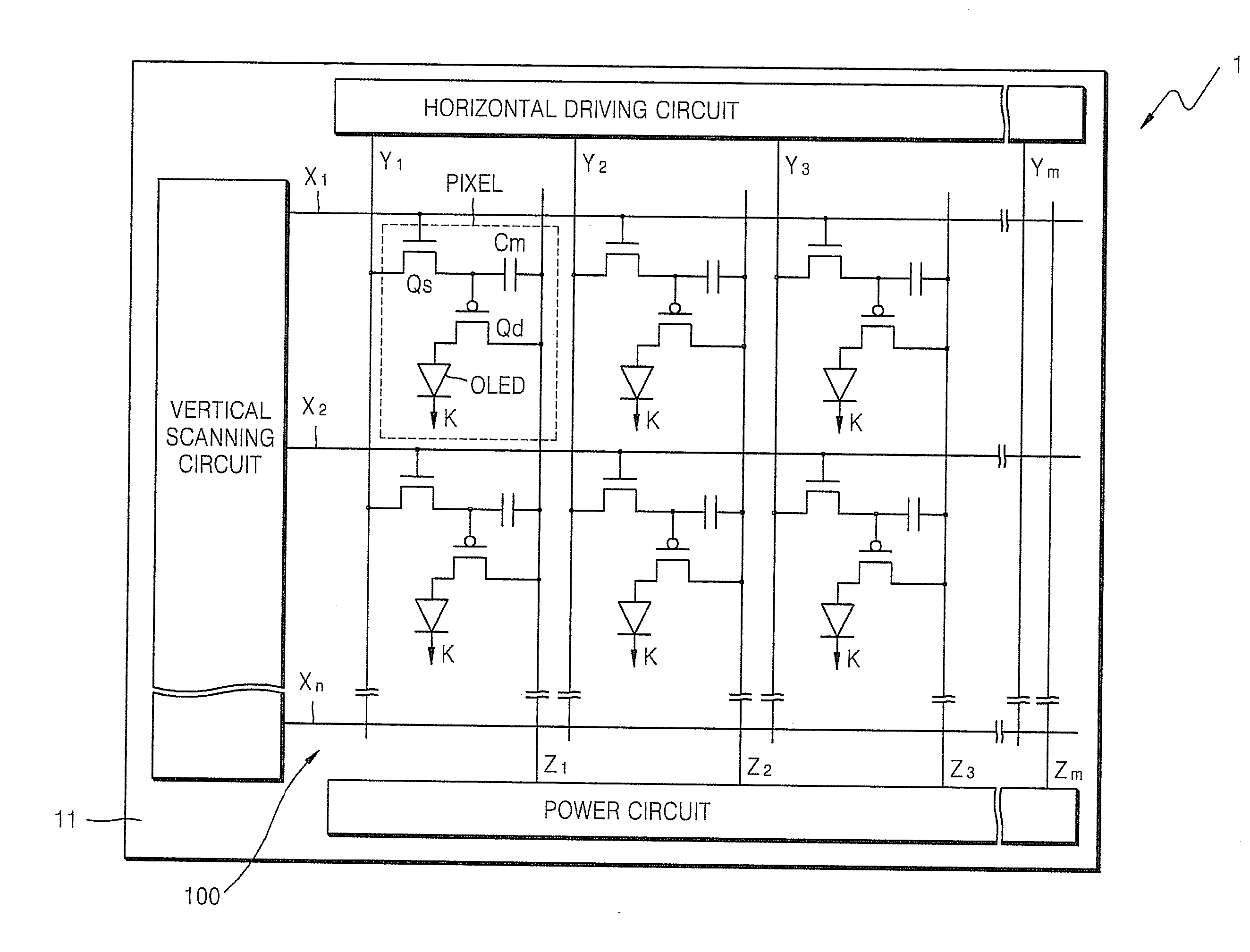

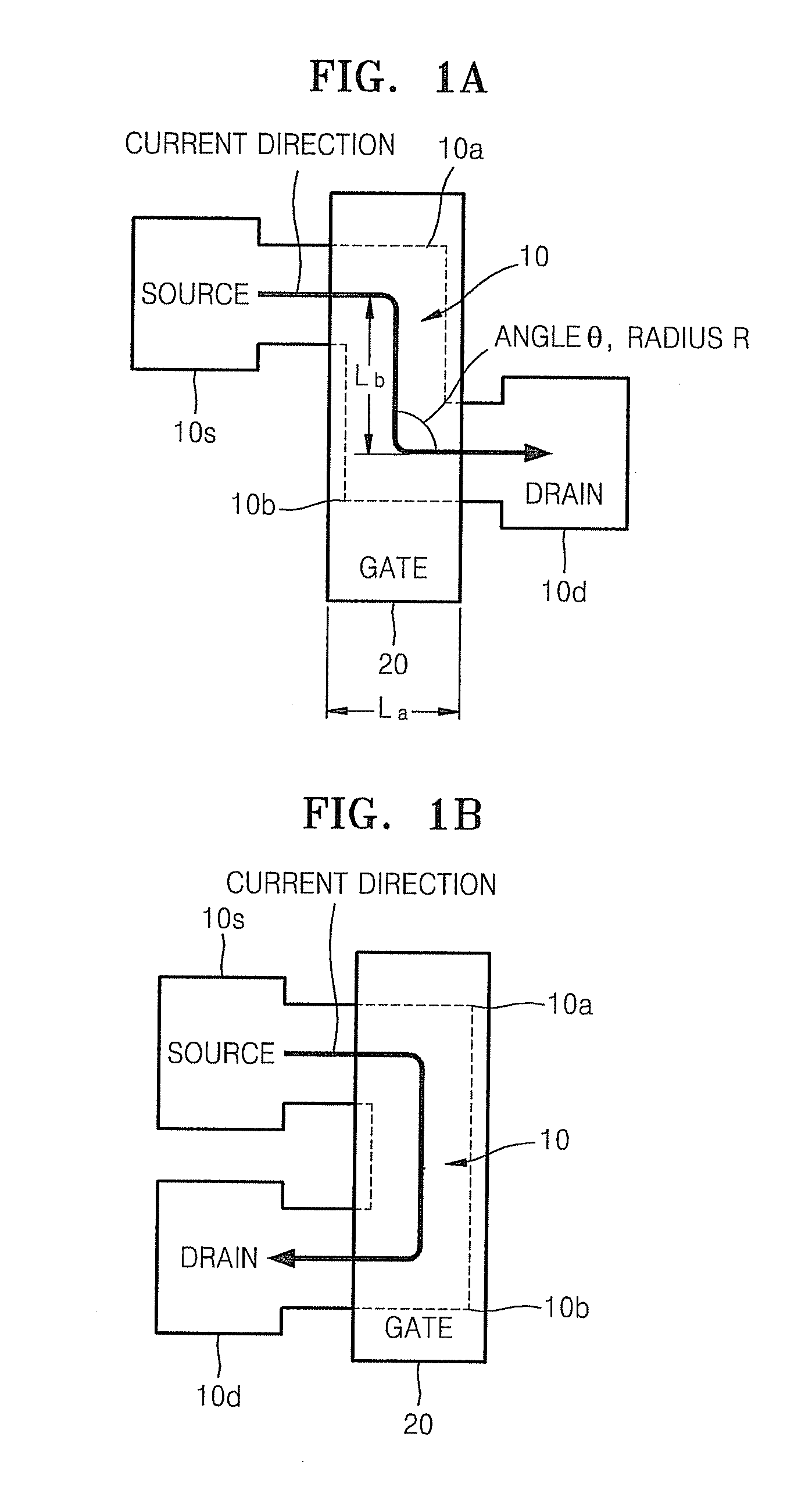

POLY-Si THIN FILM TRANSISTOR AND ORGANIC LIGHT-EMITTING DISPLAY HAVING THE SAME

ActiveUS20070128777A1Reduce leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingElectronTransistor

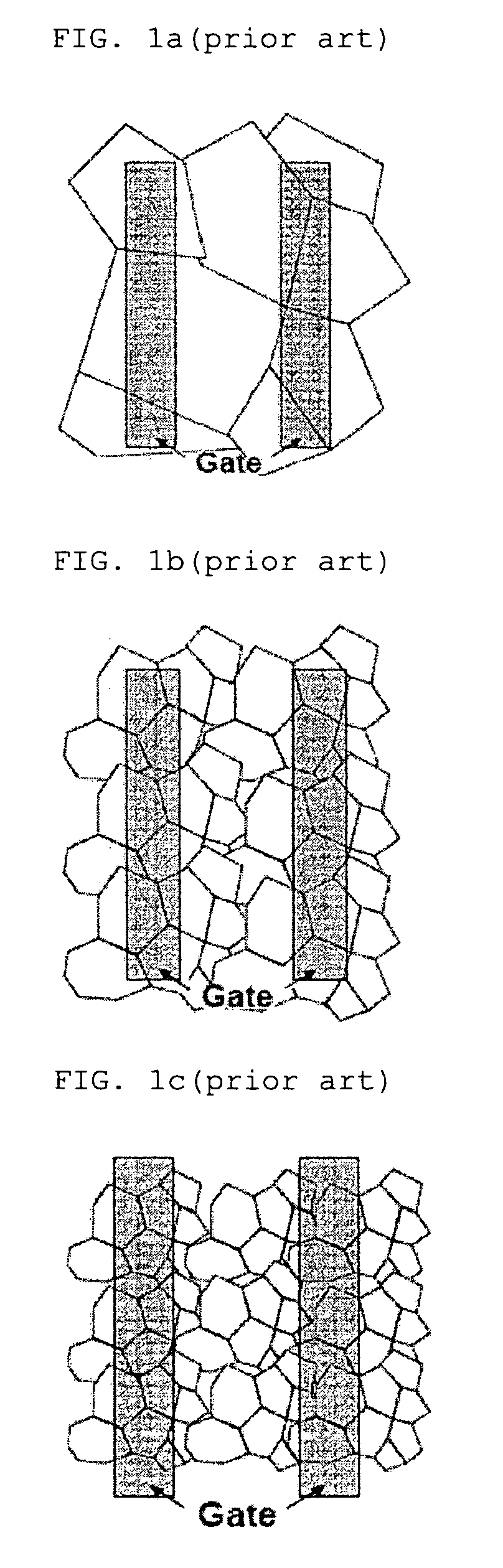

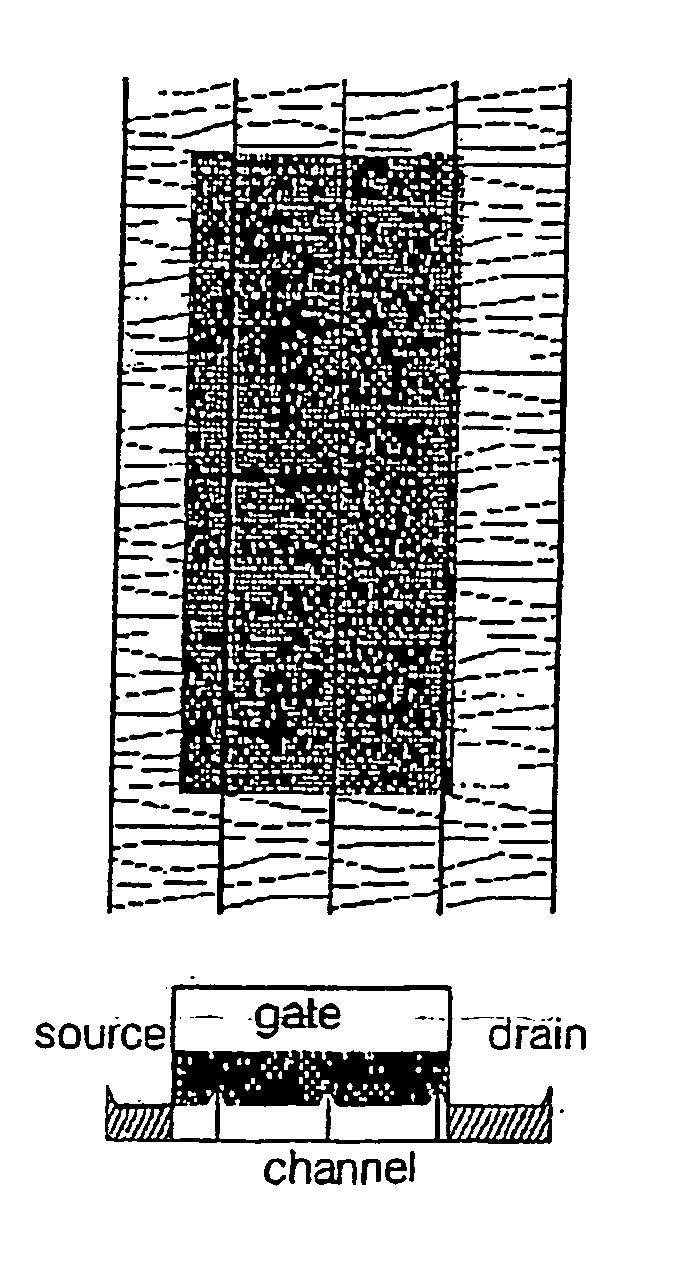

A thin film transistor comprises an Si-based channel having a nonlinear electron-moving path, a source and a drain disposed at both sides of the channel, a gate disposed above the channel, an insulator interposed between the channel and the gate, and a substrate supporting the channel and the source and the drain disposed at either side of the channel respectively.

Owner:SAMSUNG ELECTRONICS CO LTD

Methods for producing uniform large-grained and grain boundary location manipulated polycrystalline thin film semiconductors using sequential lateral solidification

Owner:THE TRUSTEES OF COLUMBIA UNIV IN THE CITY OF NEW YORK

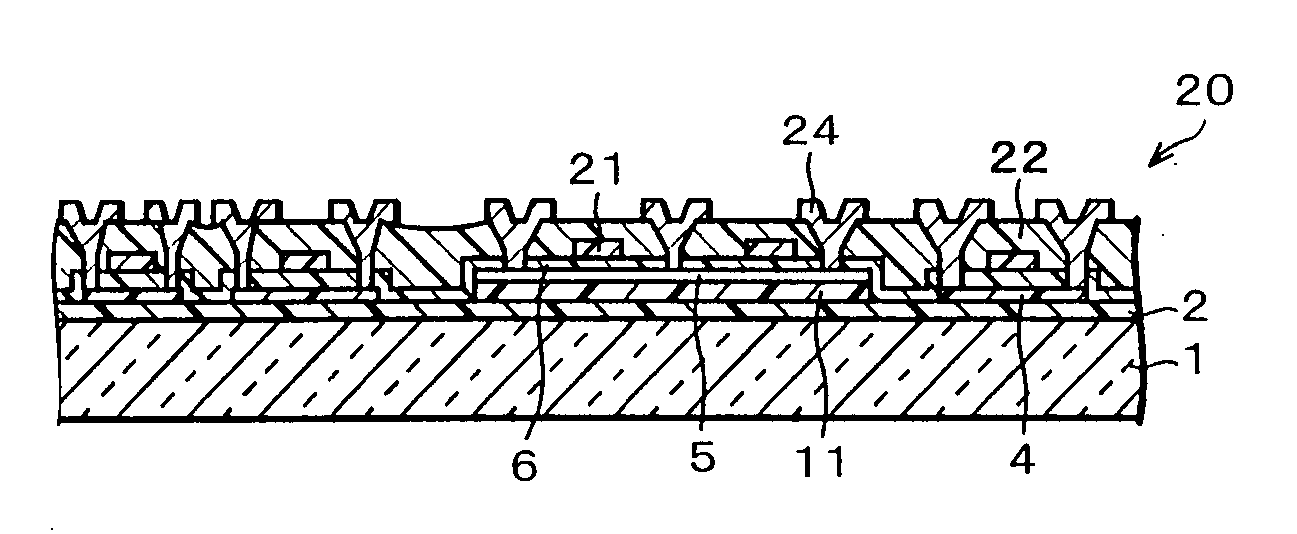

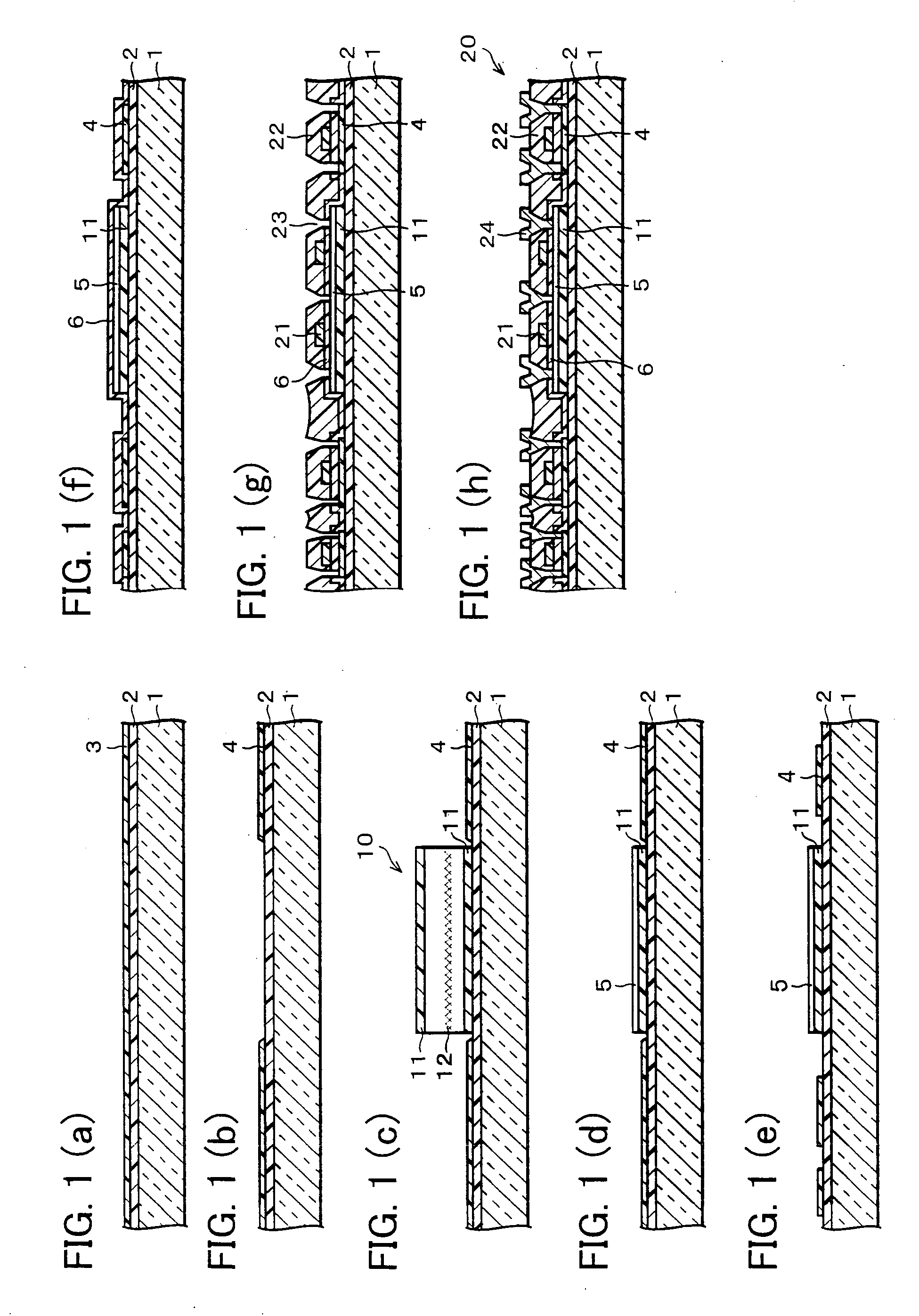

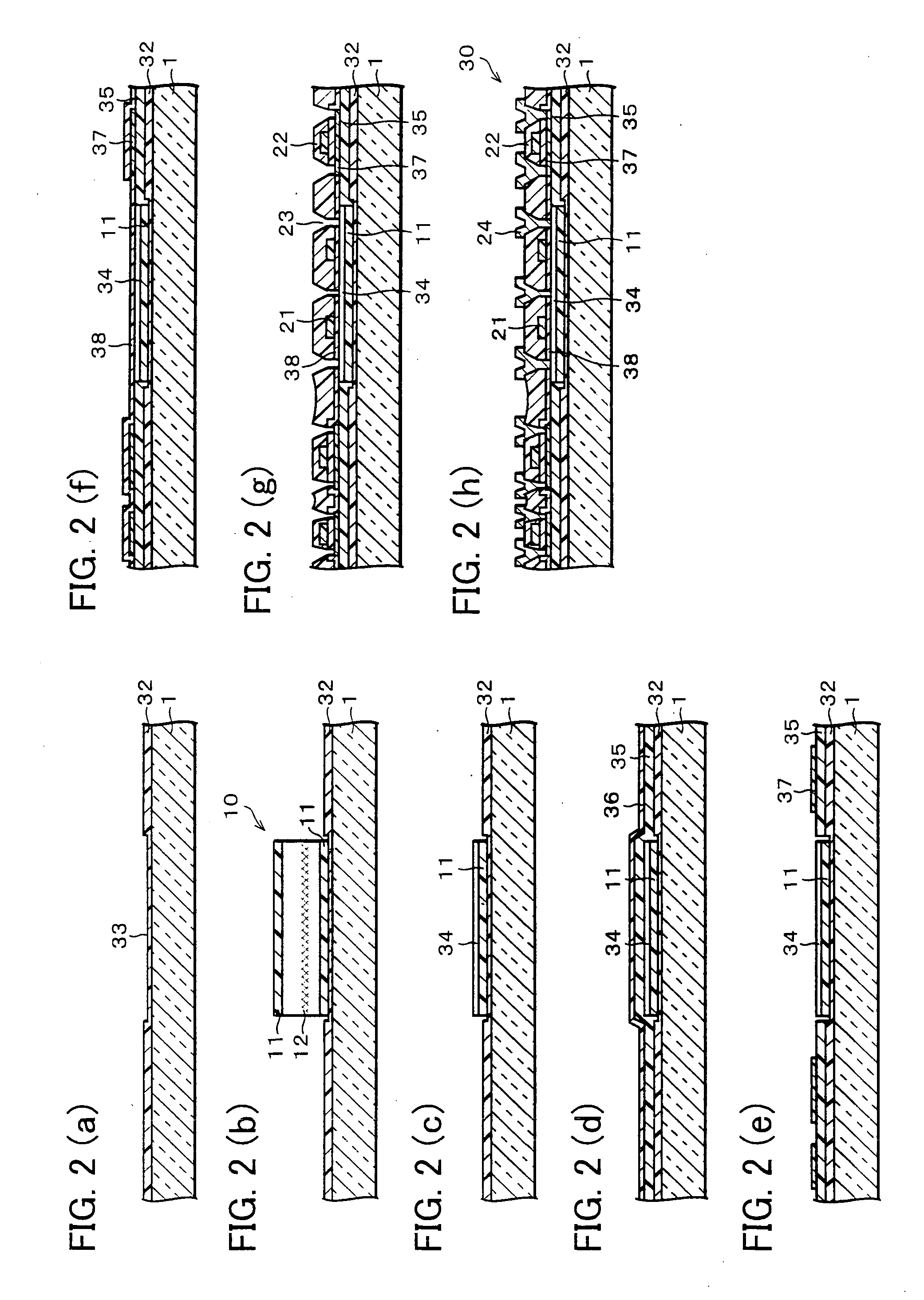

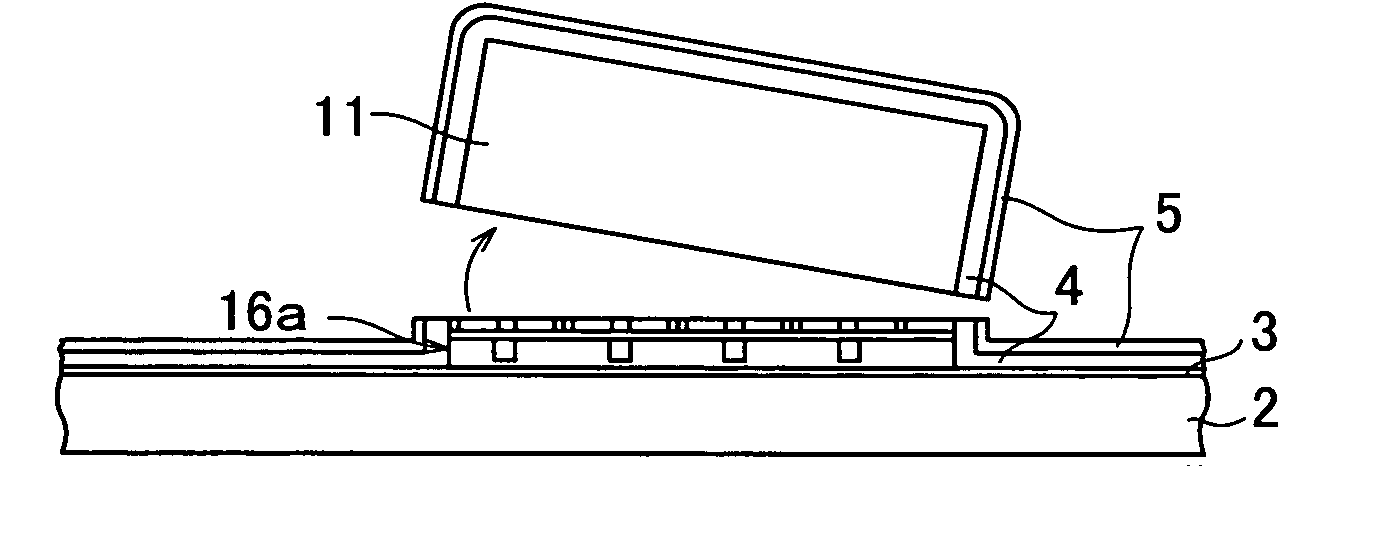

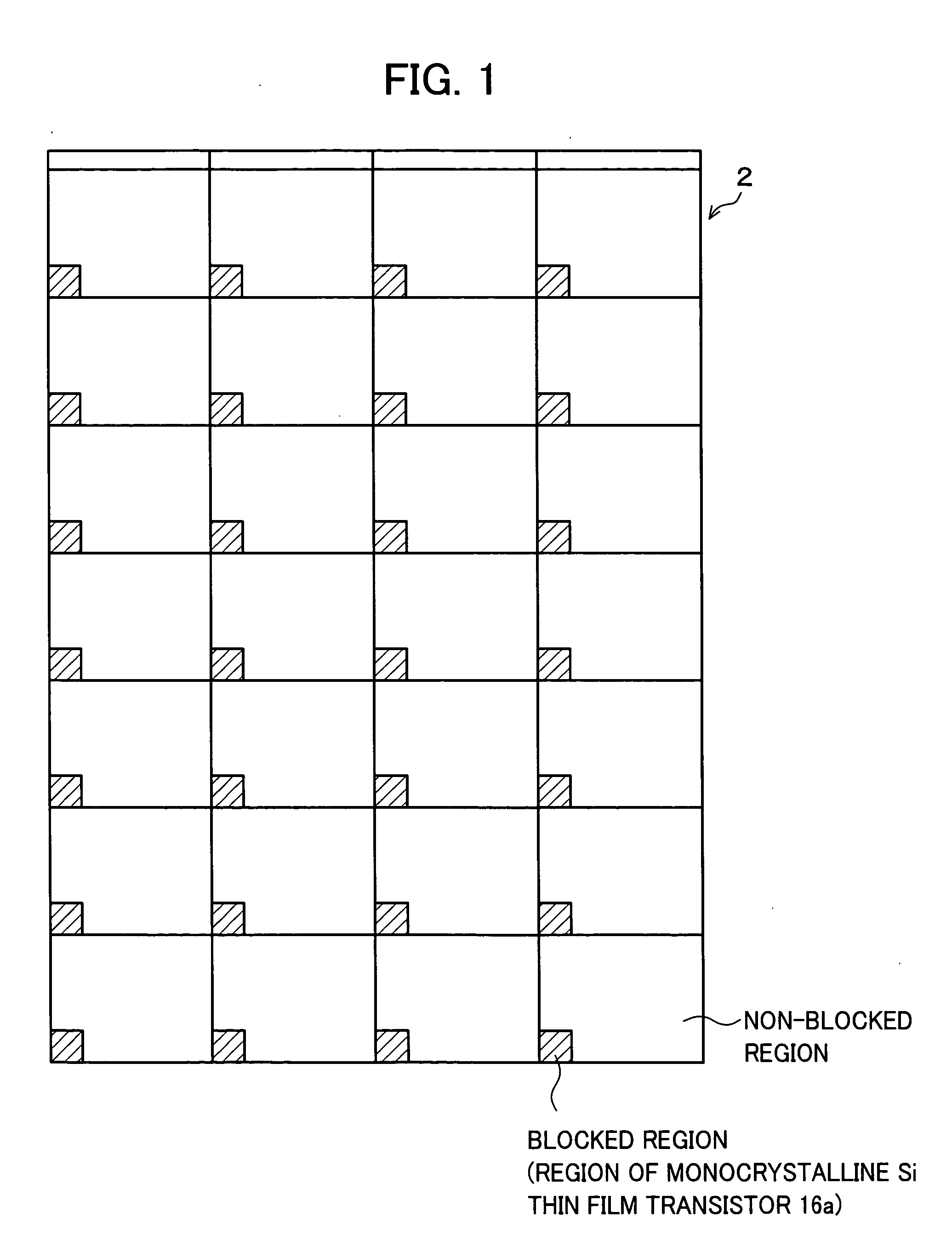

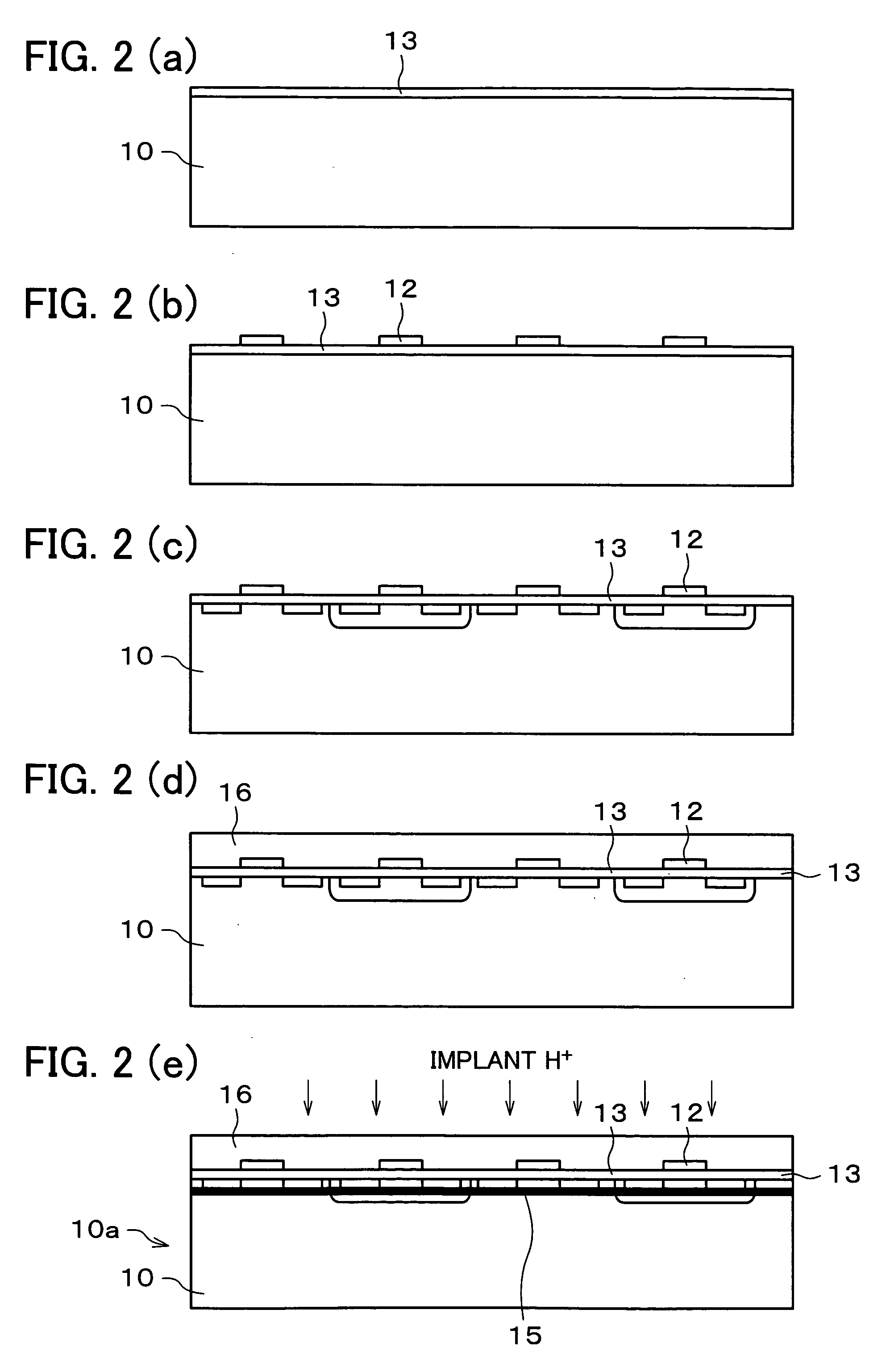

Semiconductor device and manufacturing method thereof, SOI substrate and display device using the same, and manufacturing method of the SOI substrate

A polycrystalline Si thin film and a single crystal Si thin film are formed on an SiO2 film deposited on an insulating substrate. A polycrystalline Si layer is grown by thermally crystallizing an amorphous Si thin film so as to form the polycrystalline Si thin film. A single crystal Si substrate, having (a) an SiO2 film thereon and (b) a hydrogen ion implantation portion therein, is bonded to an area of the polycrystalline Si thin film that has been subjected to etching removal, and is subjected to a heating process. Then, the single crystal Si substrate is divided at the hydrogen ion implantation portion in an exfoliating manner, so as to form the single crystal Si thin film. As a result, it is possible to provide a large-size semiconductor device, having the single crystal Si thin film, whose property is stable, at a low cost.

Owner:SHARP KK

Method for producing uniform large-grained and grain boundary location manipulated polycrystalline thin film semiconductors using sequential lateral solidification

Methods for processing an amorphous silicon thin film sample into a polycrystalline silicon thin film are disclosed. In one preferred arrangement, a method includes the steps of generating a sequence of excimer laser pulses, controllably modulating each excimer laser pulse in the sequence to a predetermined fluence, homoginizing each modulated laser pulse in the sequence in a predetermined plane, masking portions of each homoginized fluence controlled laser pulse in the sequence with a two dimensional pattern of slits to generate a sequence of fluence controlled pulses of line patterned beamlets, each slit in the pattern of slits being sufficiently narrow to prevent inducement of significant nucleation in region of a silicon thin film sample irradiated by a beamlet corresponding to the slit, irradiating an amorphous silicon thin film sample with the sequence of fluence controlled slit patterned beamlets to effect melting of portions thereof corresponding to each fluence controlled patterned beamlet pulse in the sequence of pulses of patterned beamlets, and controllably sequentially translating a relative position of the sample with respect to each of the fluence controlled pulse of slit patterned beamlets to thereby process the amorphous silicon thin film sample into a single or polycrystalline silicon thin film.

Owner:IM JAMES S +2

Systems and methods using sequential lateral solidification for producing single or polycrystalline silicon thin films at low temperatures

Owner:THE TRUSTEES OF COLUMBIA UNIV IN THE CITY OF NEW YORK

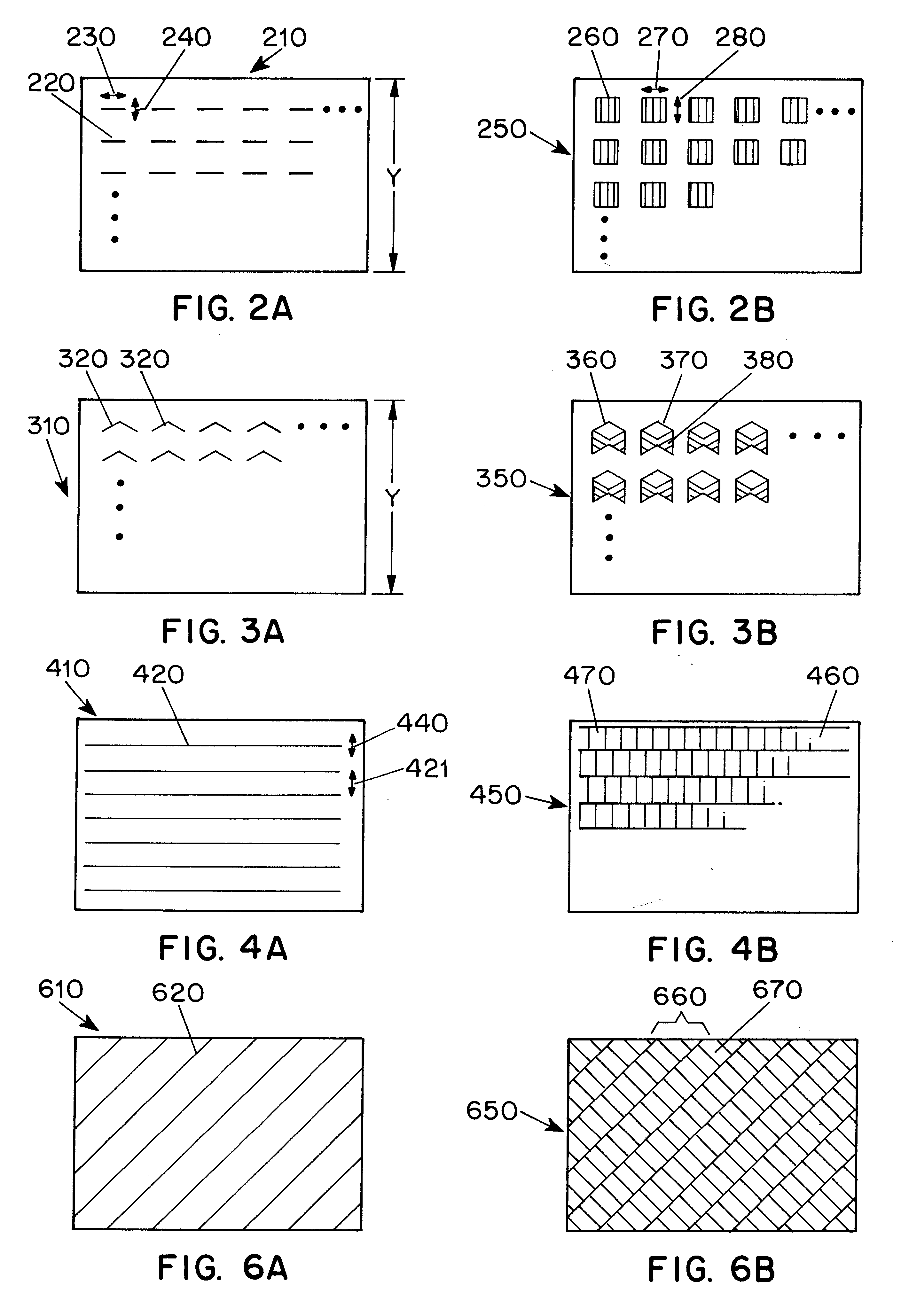

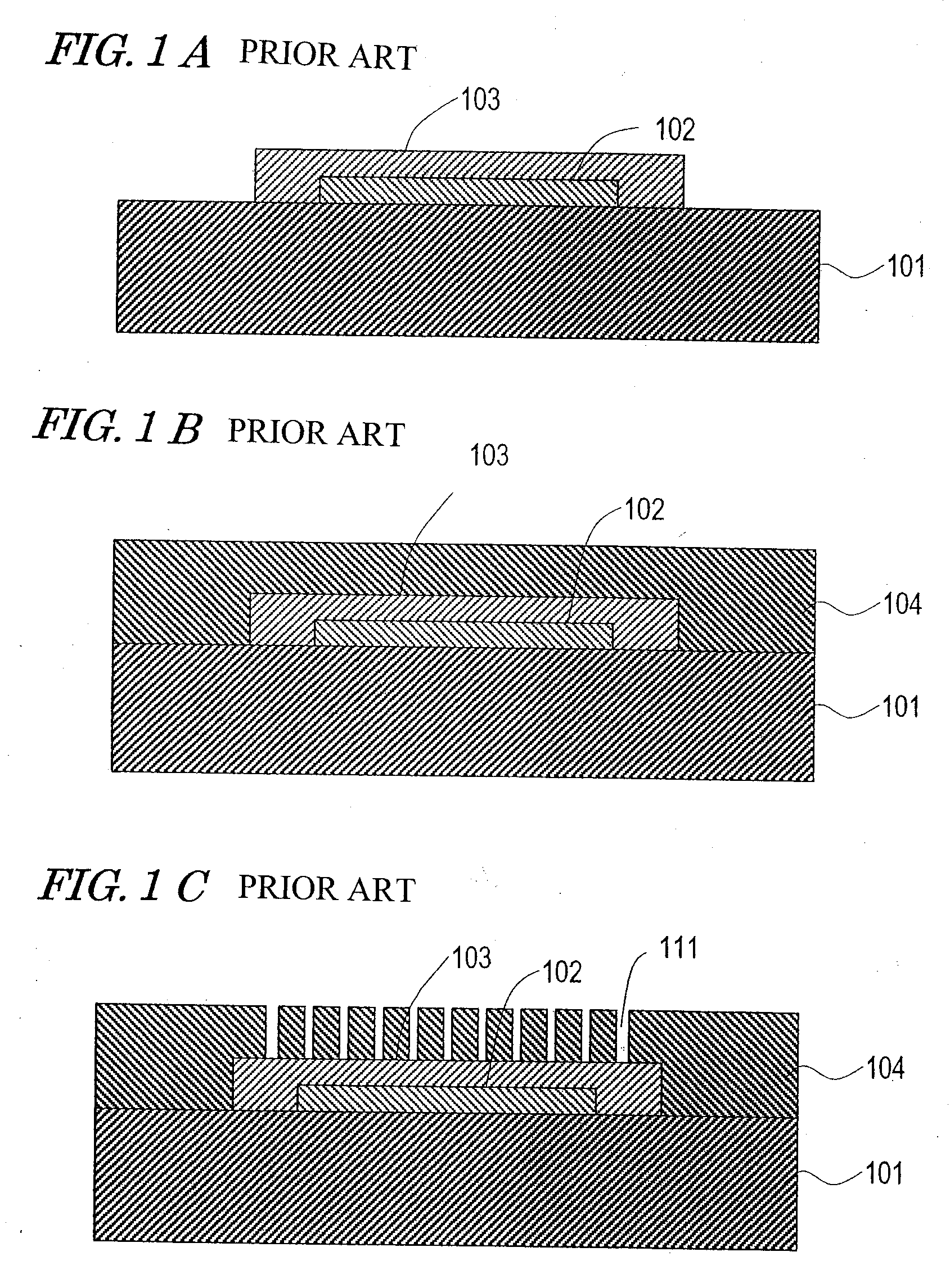

Polycrystalline tft uniformity through microstructure mis-alignment

InactiveUS20050034653A1Provide uniformityUniformityTransistorPolycrystalline material growthOptoelectronicsGrain structure

Methods of making a polycrystalline silicon thin-film transistor having a uniform microstructure. One exemplary method requires receiving a polycrystalline silicon thin film having a grain structure which is periodic in at least a first direction, and placing at least portions (410, 420) of one or more thin-film transistors on the received film such that they are tilted relative to the periodic structure of the thin film.

Owner:THE TRUSTEES OF COLUMBIA UNIV IN THE CITY OF NEW YORK

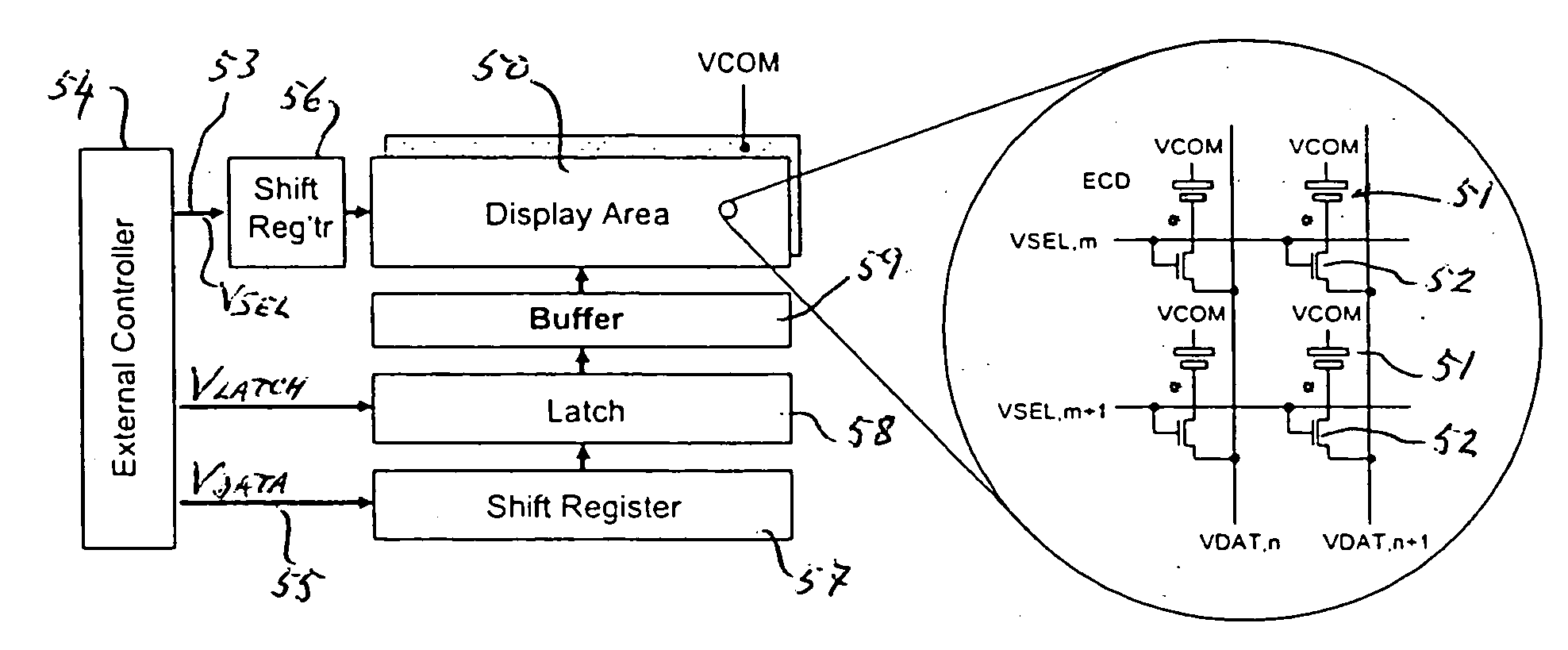

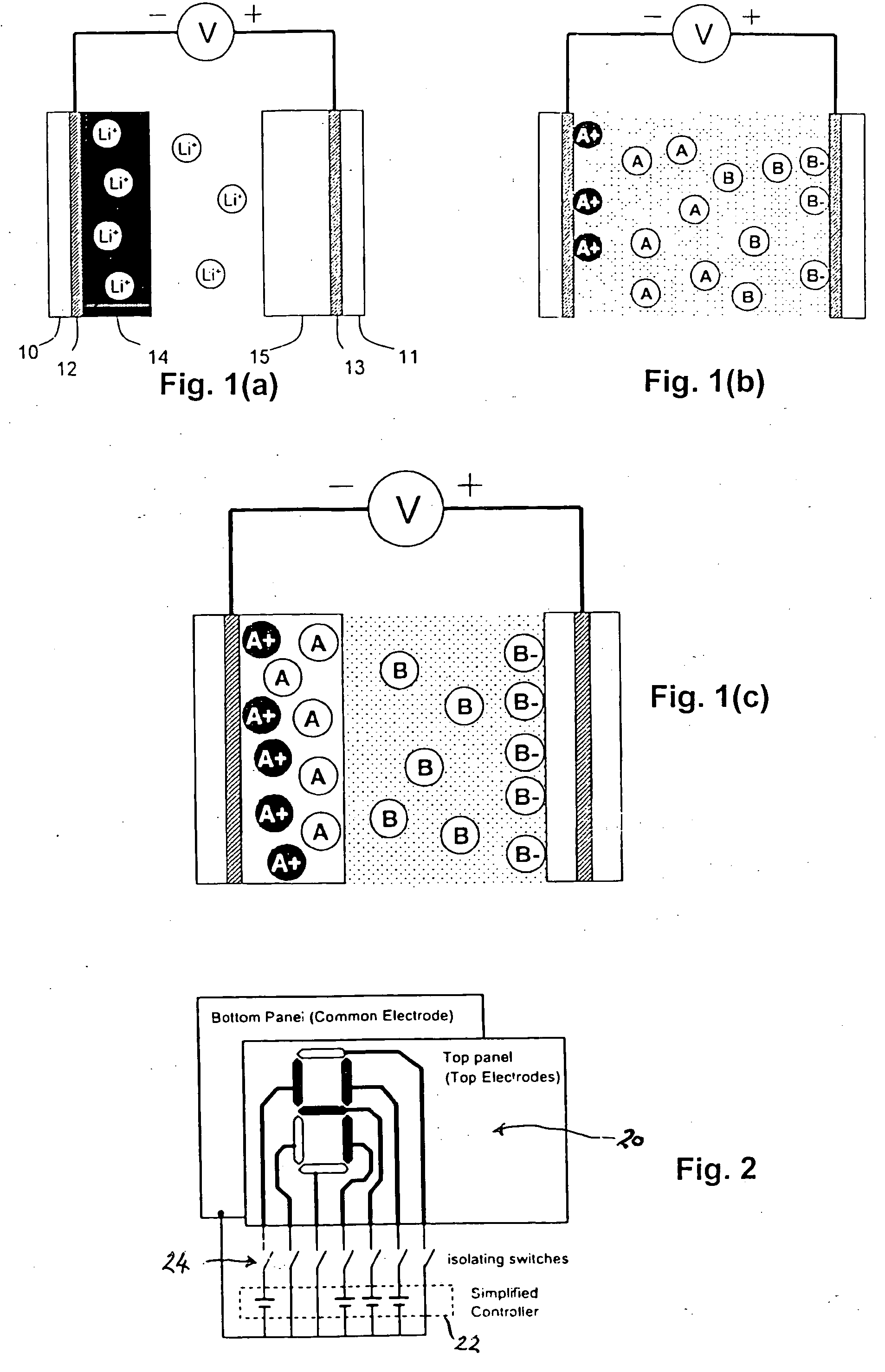

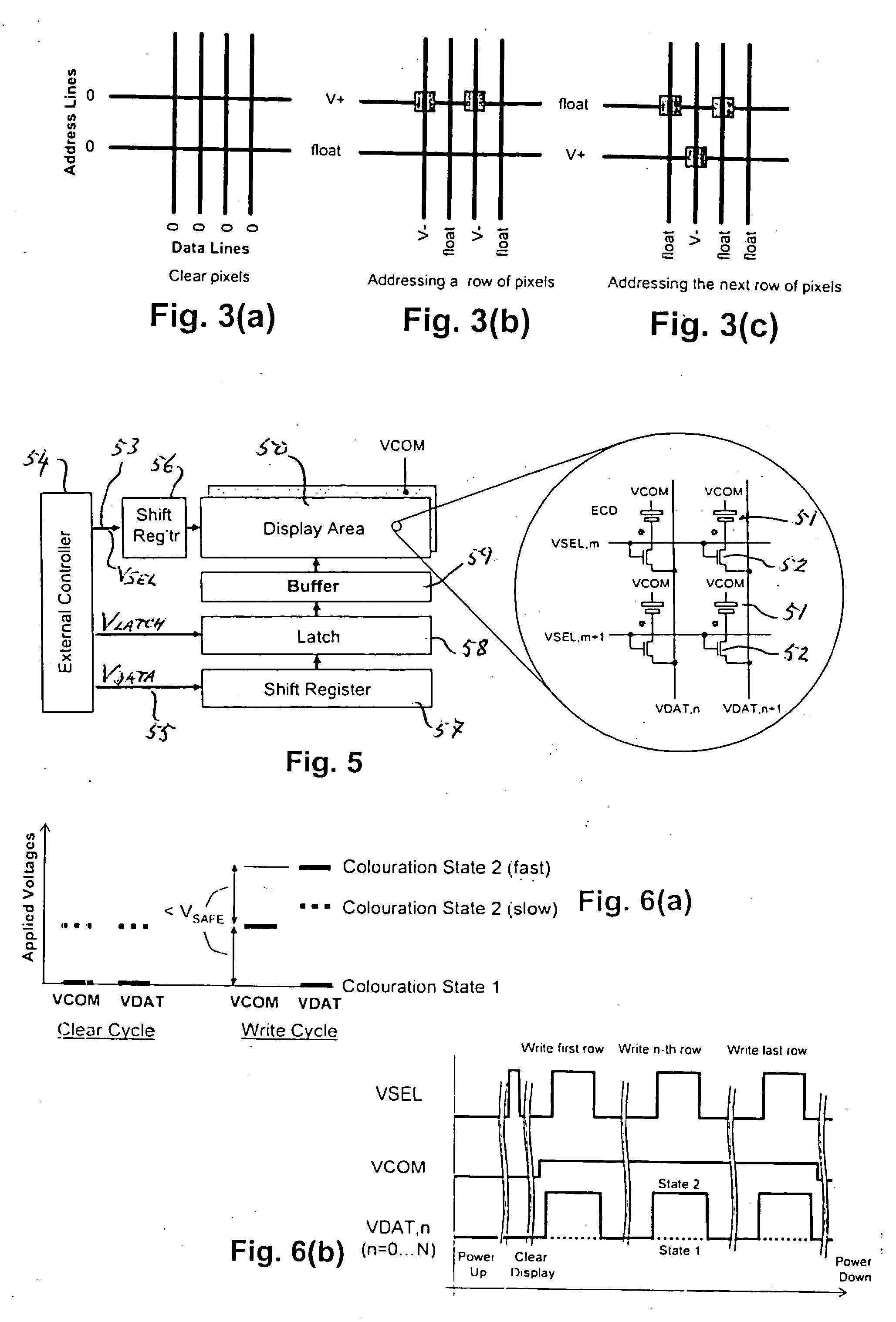

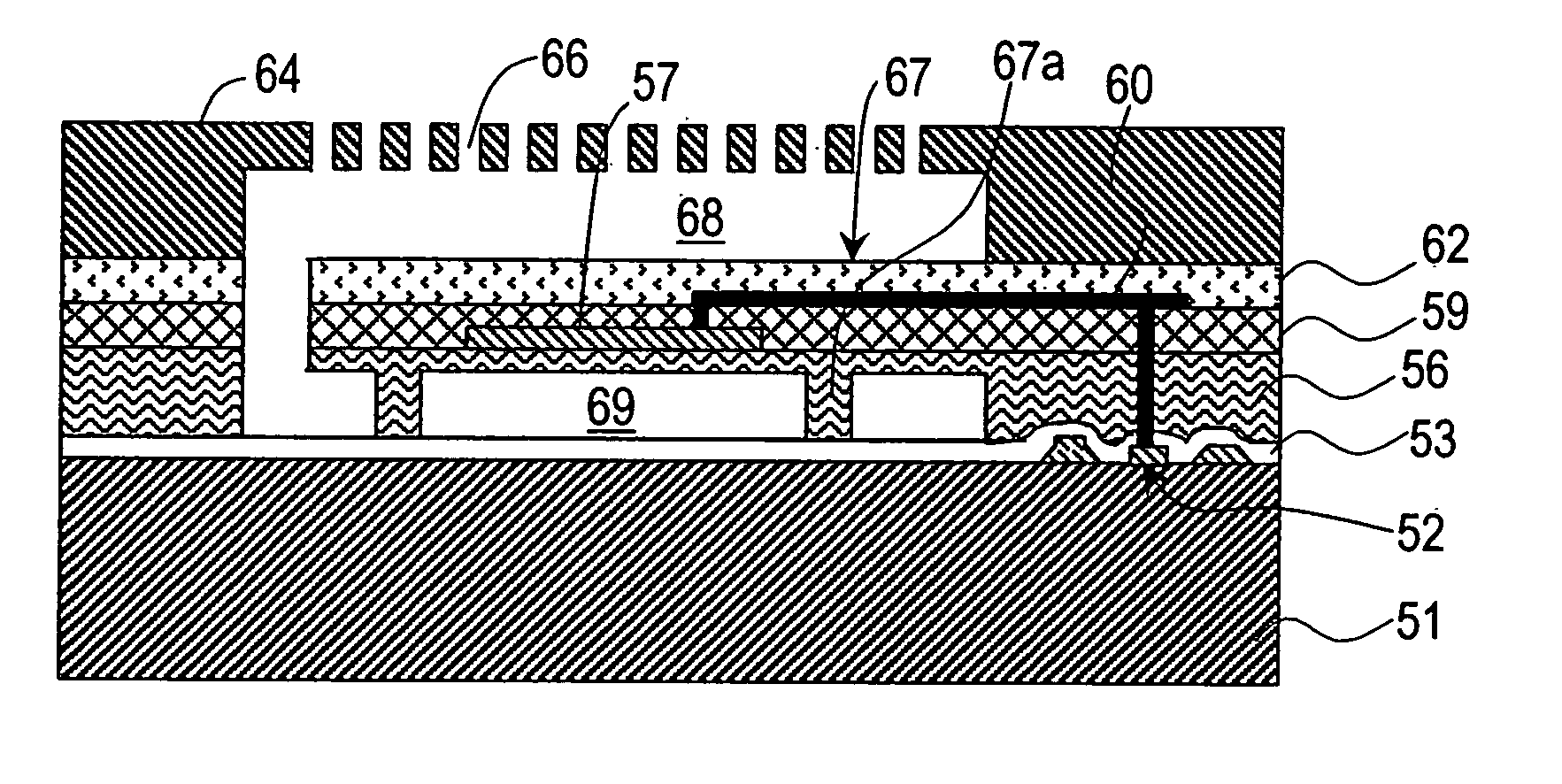

Electro-optical arrangement

An electro-optical arrangement includes an electrochromic device which can take either a cleared (transparent) state, a first display state or a second display state, and a driving stage which provides first and second electrode-drive signals to drive the first and second electrodes of the device. At least one of the electrode-drive signals is supplied by way of a polysilicon thin-film buffer. The driving stage in an initial clearing operation outputs approximately equal voltages to the electrodes, which places the device into its transparent state. Subsequently the driver stage applies voltages to the electrodes, such that the device assumes either the first display state or the second display state. In either state it is arranged for the device not to be subjected to more than a safe operating voltage. Preferably, in one of the electrochromic device's two display states one of its electrodes is supplied with a voltage which is higher than the voltage (Vcom) on the other electrode, while in the other of its two display states the one electrode is supplied with a voltage which is lower than the voltage (Vcom) on the other electrode, the two voltage differences being less than the safe operating voltage. The second display state may itself be a transparent state, while the first display state may be a colored state. Alternatively, the two states may be differently colored states.

Owner:SEIKO EPSON CORP +1

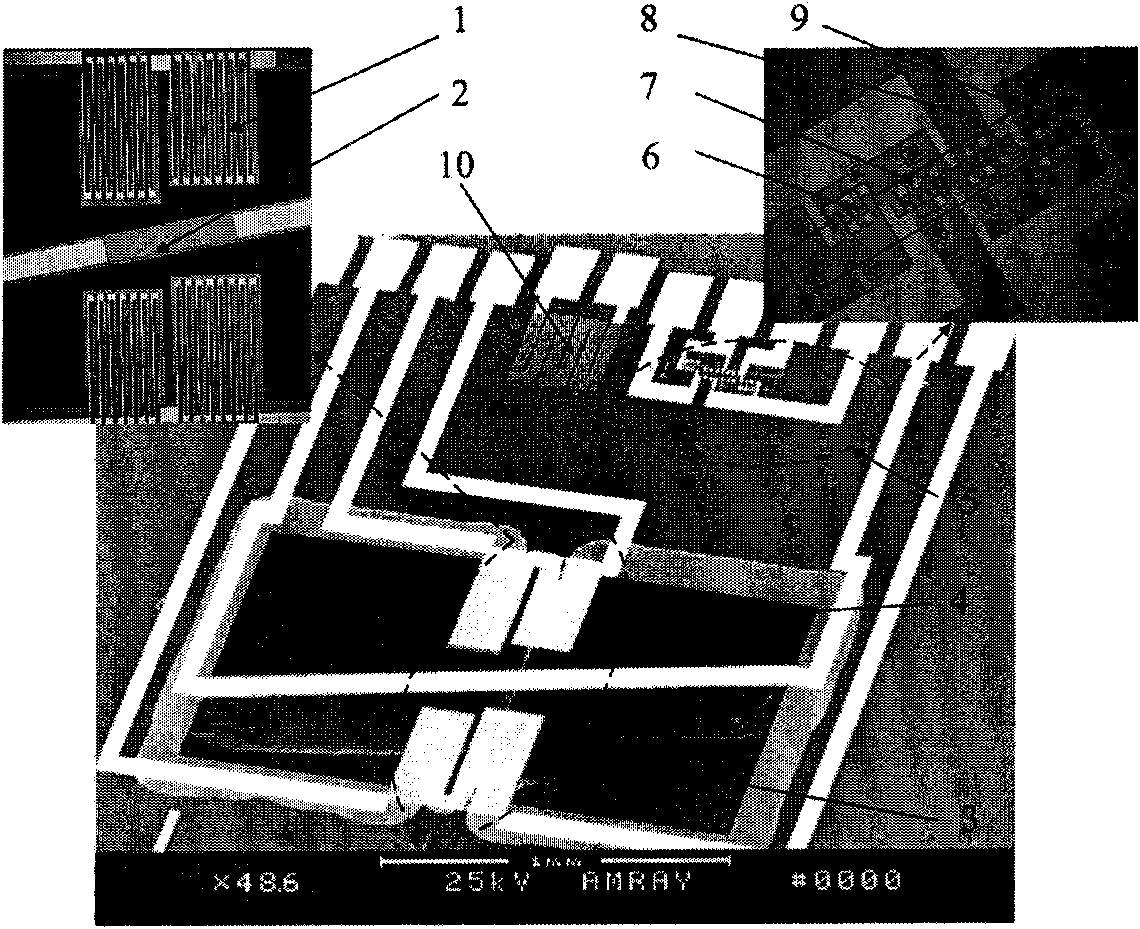

Electronic device and method of manufacturing the same

ActiveUS20050176179A1Small openingTelevision system detailsThermoelectric device with dielectric constant thermal changeSputteringHydrofluoric acid

In the present invention, an etching hole 21 is formed in a polysilicon film 14 as a cavity-wall member. Through the etching hole 21, hydrofluoric acid is injected, so as to dissolve a silicon oxide film 13, thereby forming a cavity 22. In the cavity 22, a detecting unit 12 of a sensor is in an exposed condition. Next, by sputtering, an Al film 16 is deposited in the etching hole 21 and on an upper face of a substrate. Thereafter, a portion of the Al film 16 positioned on the polysilicon film 14 is removed by etching back, thereby leaving only a metal closure 16a of Al which closes the etching hole. The sputtering step is performed under a pressure of 5 Pa or less, so that the pressure in the cavity can be held to be low.

Owner:PANASONIC CORP

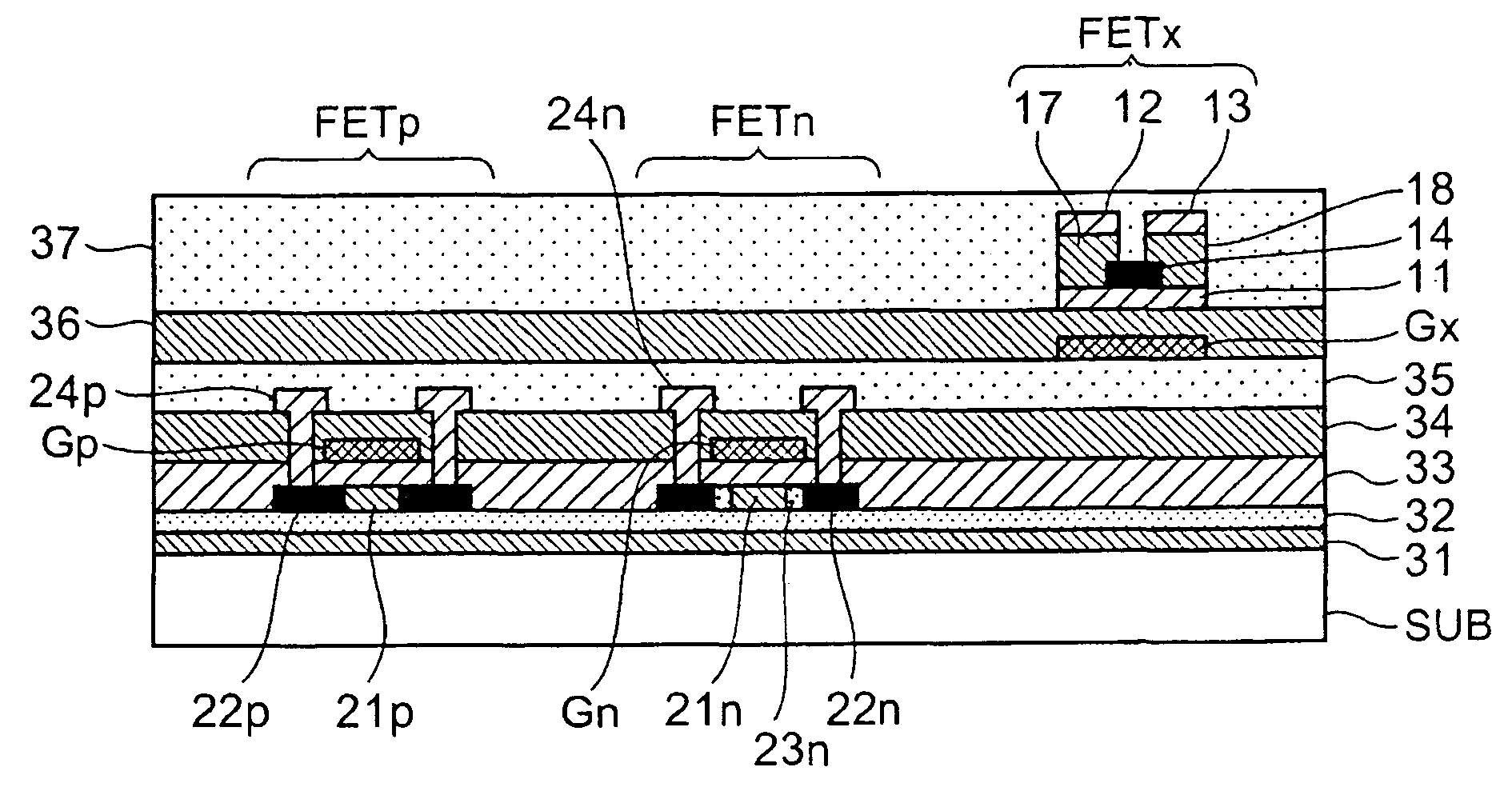

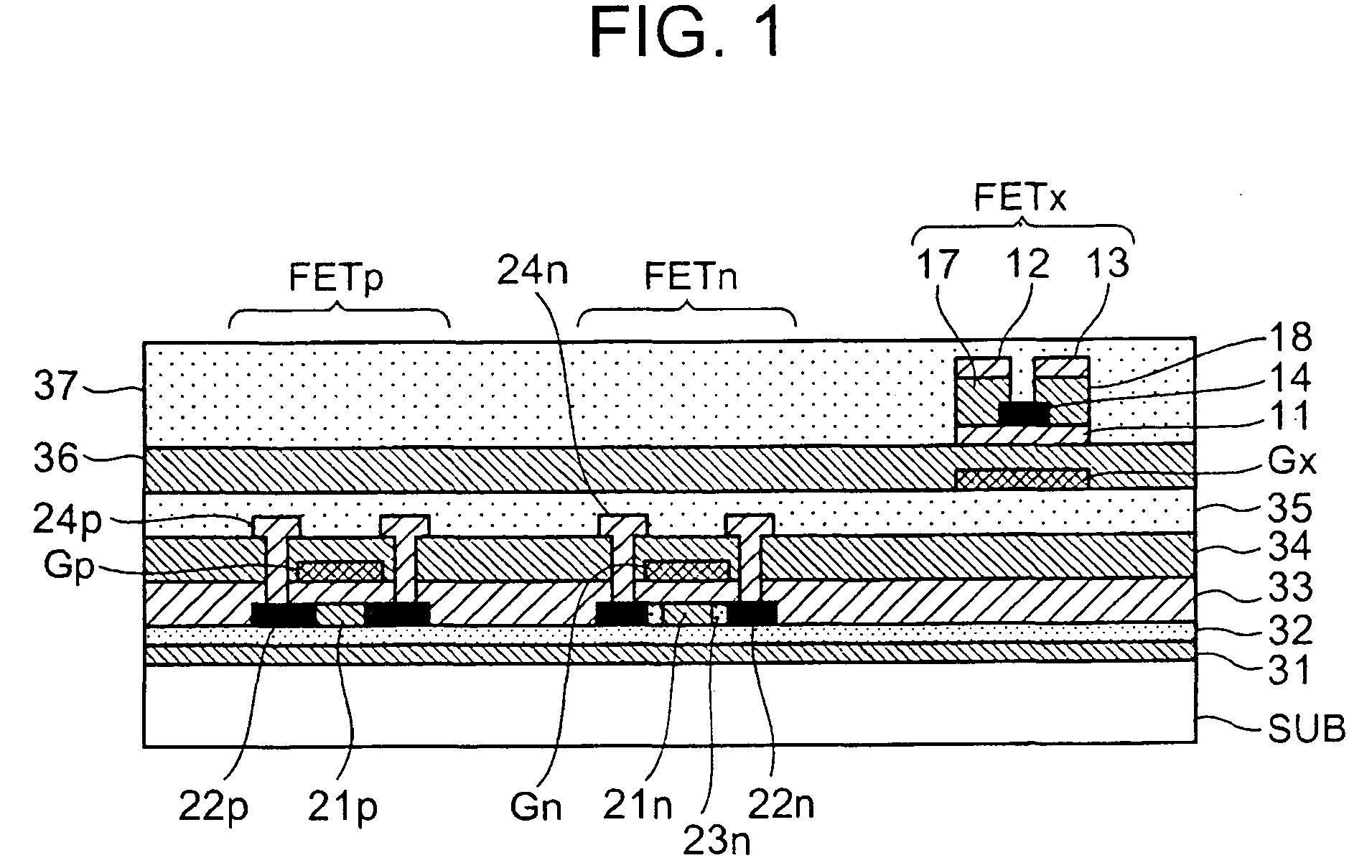

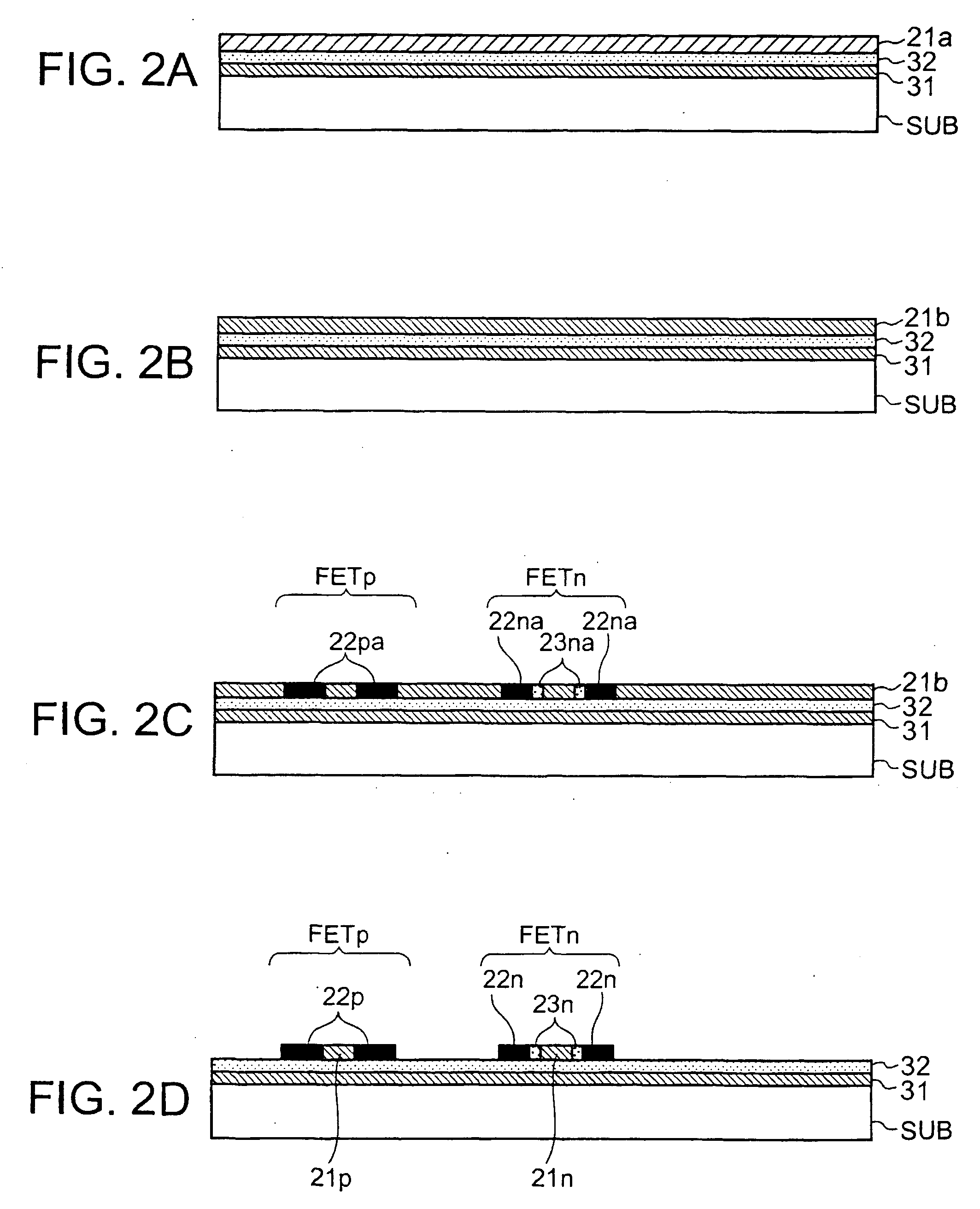

Transistor arrray, manufacturing method thereof and image processor

ActiveUS20050176194A1Highly reliable operating characteristicReduce component countSemiconductor/solid-state device detailsSolid-state devicesTransistor arrayElectrical conductor

An image processor by way of a transistor array in which a plurality of transistors are formed on a substrate comprising a plurality of polysilicon thin-film transistors using a first semiconductor layer composed of polysilicon formed on the substrate and functional devices having a plurality of amorphous silicon thin-film transistors using a second semiconductor layer composed of amorphous silicon which are formed in an upper layer more superior than the first semiconductor layer. The polysilicon thin-film transistors and functional devices include a plurality of electrode layers composed of a conductor layer, for instance, the functional devices at least of any one of the electrode layers are formed in the same layer as any one the electrode layers of the polysilicon thin-film transistors.

Owner:BOE TECH GRP CO LTD

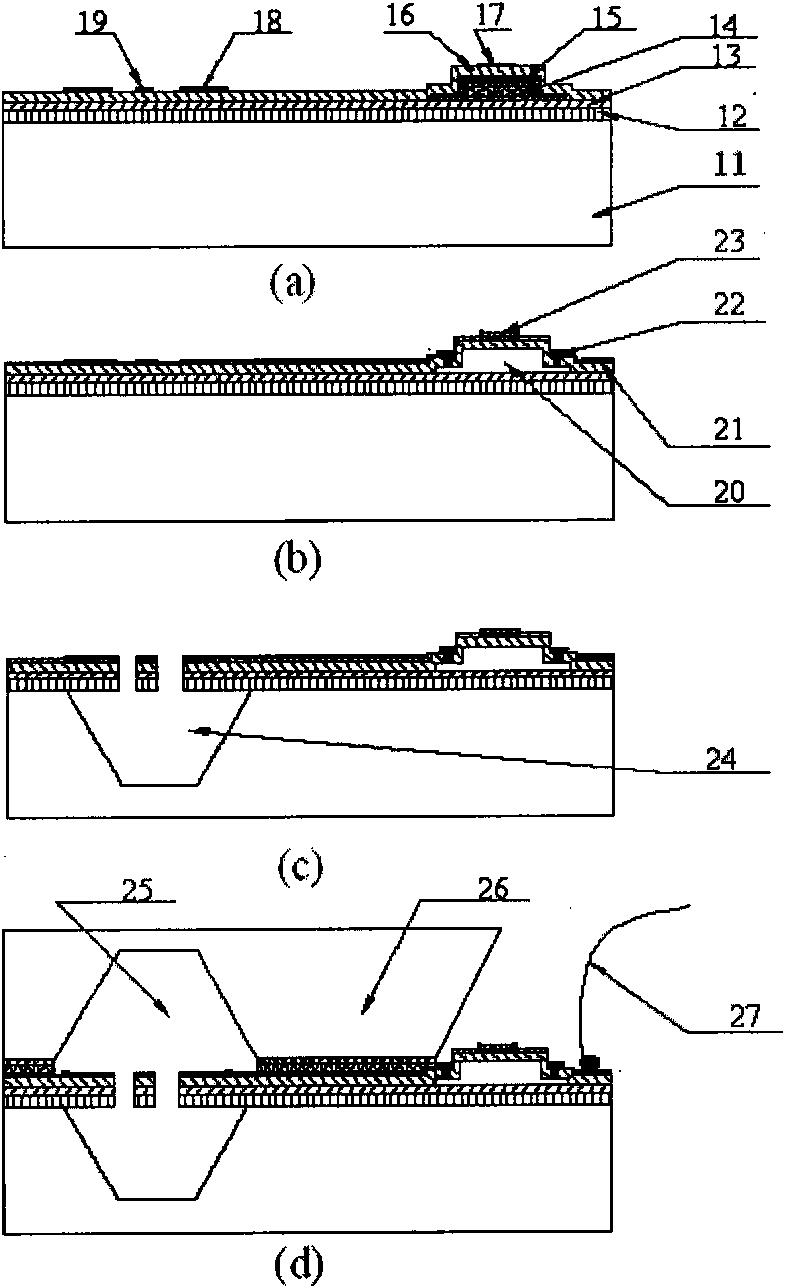

Integrated silicon chip for testing acceleration, pressure and temperature, and manufacturing method thereof

ActiveCN101551403AHigh sensitivityImprove stabilityFluid pressure measurement using ohmic-resistance variationDecorative surface effectsAccelerometerThermopile

The invention relates to an integrated silicon chip for testing acceleration, pressure and temperature, and the manufacturing method thereof. The invention is characterized in manufacturing the pressure sensor, temperature sensor and accelerometers of thermoelectric pile on to one chip by the same micro processing technology. The acceleration is detected by adopting thermal convection type accelerometers, using polysilicon resistor as heater, using a thermoelectric pile composed of two pairs of metals (such as aluminium and tungsten-titanium) and P type or N type polysilicon to detect the temperature difference in the sealed cavity caused by acceleration. The high accurate absolute pressure sensor is manufactured by using silicon nitride film with low stress as the core structure layer of the pressure sensor chip, and forming force sensitive resistor track by polysilicon film, forming vacuum reference cavity by TEOS bolt in LPCVD furnace. At the same time, the temperature sensor is composed by using polysilicon thermistor to detect temperature change. The integrated chip achieves the advantages of microminiaturization, low cost, high precision, high reliability and high stability.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Methods of forming conductive polysilicon thin films via atomic layer deposition and methods of manufacturing semiconductor devices including such polysilicon thin films

Owner:SAMSUNG ELECTRONICS CO LTD

Polysilicon thin film fabrication method

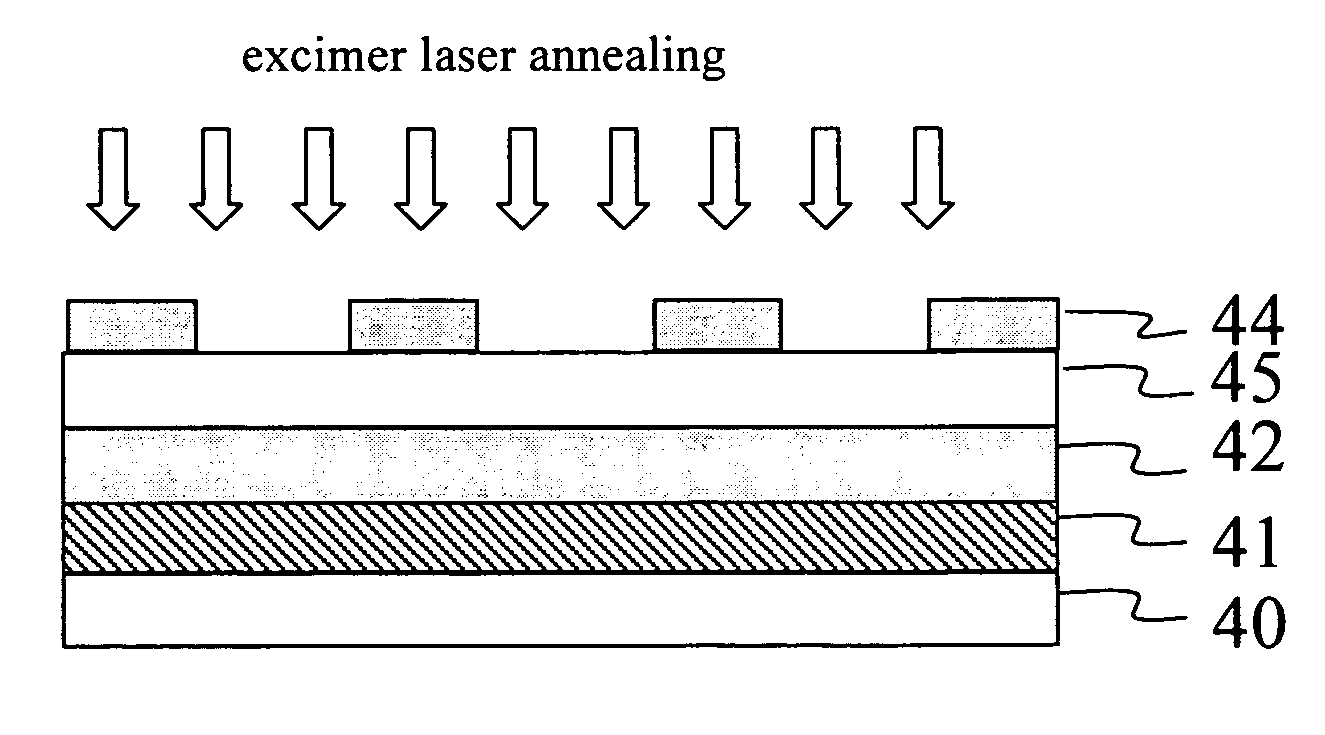

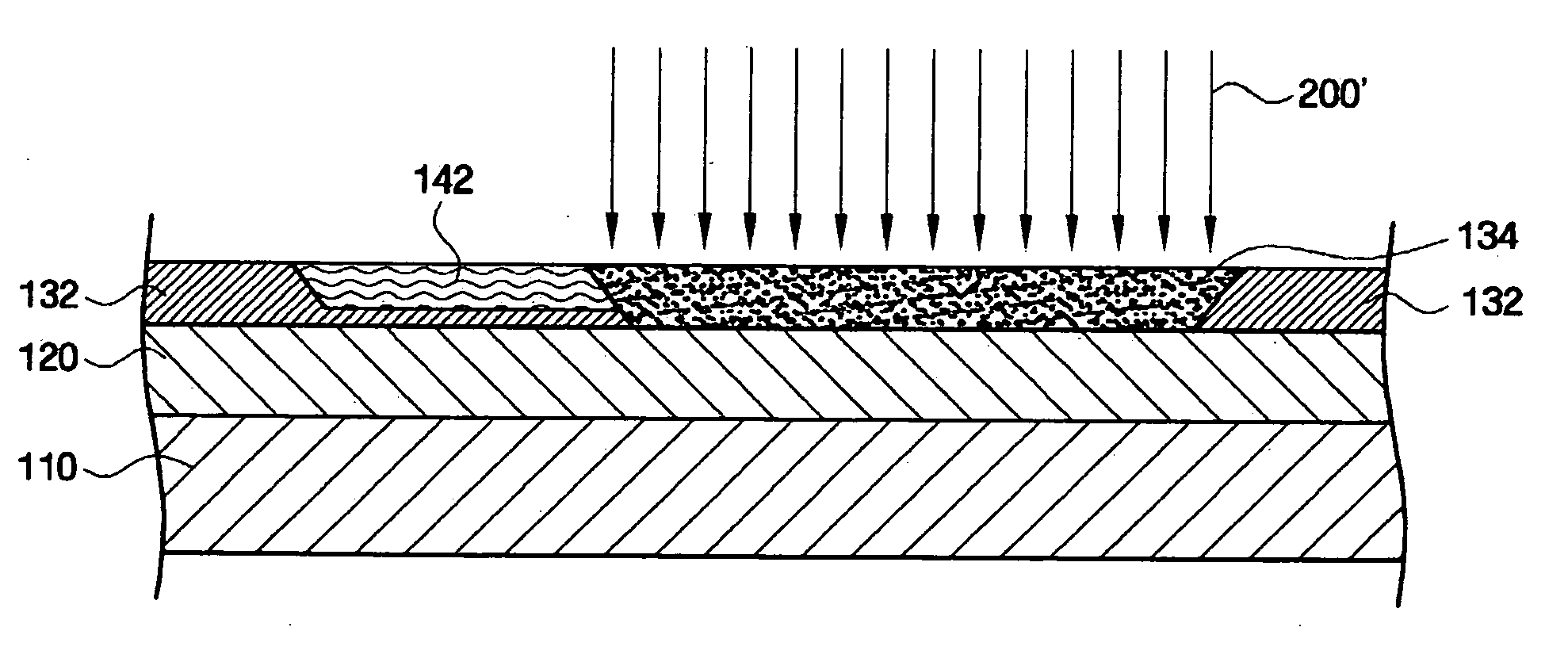

ActiveUS7192818B1Excellent electrical propertiesElectrical uniformitySolid-state devicesSemiconductor/solid-state device manufacturingHeat conductingAmorphous silicon

A polysilicon thin film fabrication method is provided, in which a heat-absorbing layer is used to provide sufficient heat for grain growth of an amorphous silicon thin film, and an insulating layer is used to isolate the heat-absorbing layer and the amorphous silicon thin film. A regular heat-conducting layer is used as a cooling source to control the crystallization position and grain size of the amorphous silicon thin film. Therefore, the amorphous silicon thin film can crystallize into a uniform polysilicon thin film, and the electrical characteristics of the polysilicon thin film can be stably controlled.

Owner:NAT TAIWAN UNIV

Semiconductor pressure sensor and pressure sensing device

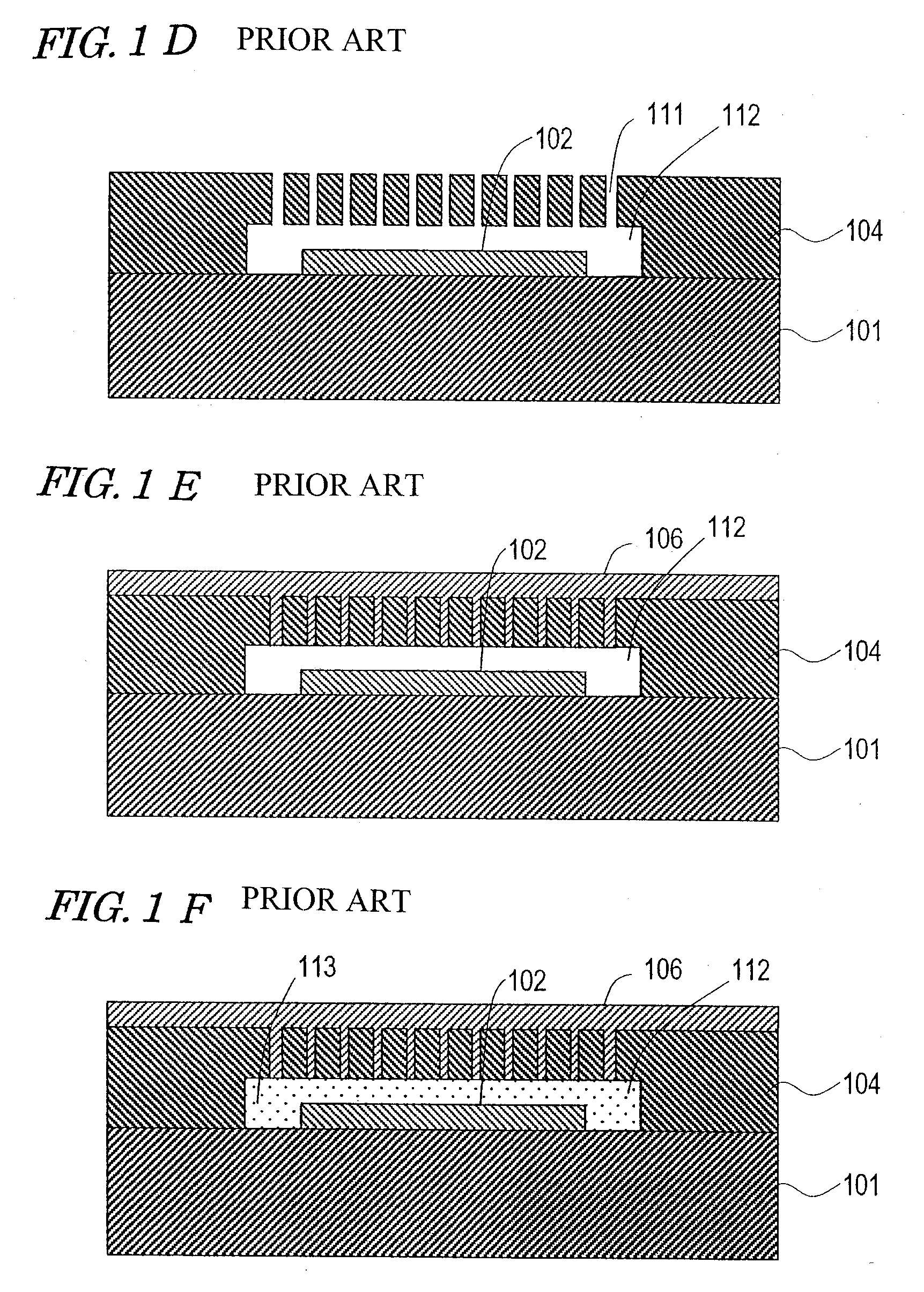

InactiveUS6892582B1Increase productivityIncreased durabilityFluid pressure measurement using elastically-deformable gaugesFluid pressure measurement by electric/magnetic elementsPressure senseEngineering

The object of the present invention is to propose an etch channel sealing structure characterized by excellent impermeability to moisture and resistance to temporal change of the diaphragm in the pressure sensor produced according to the sacrificial layer etching technique, and to provide a pressure sensor characterized by excellent productivity and durability. After a very small gap is formed by the sacrificial layer etching technique, silicon oxide film is deposited by the CVD technique or the like, thereby sealing the etch channel. Further, impermeable thin film of polysilicon or the like is formed to cover the oxide film.This allows an etch channel sealing structure to be simplified in the pressure sensor produced according to the sacrificial layer etching technique, and prevents entry of moisture into the cavity, thereby improving moisture resistance. Moreover, sealing material with small film stress reduces temporal deformation of the diaphragm.

Owner:HITACHI LTD +1

System for heat treatment of semiconductor device

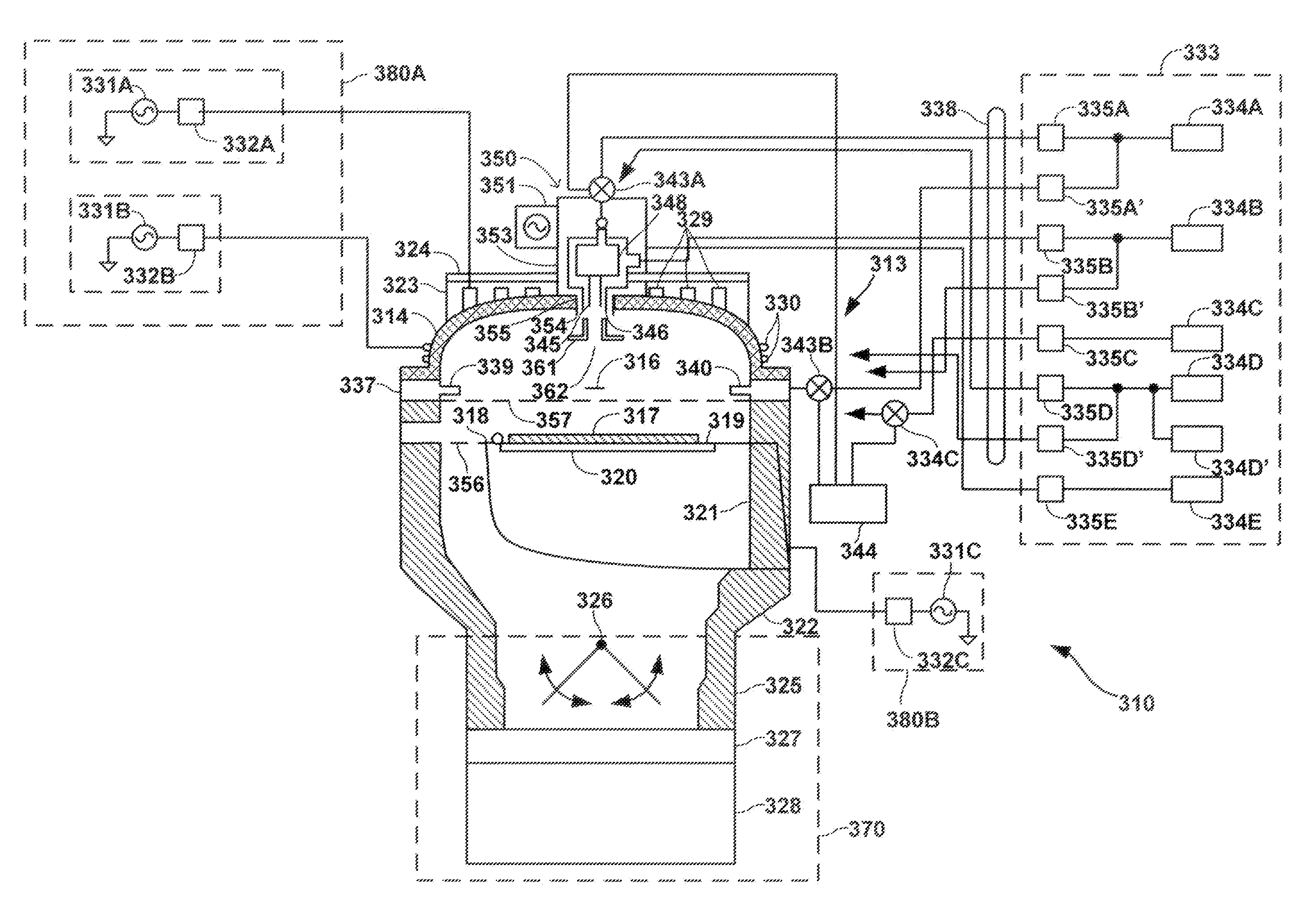

InactiveUS20070122936A1Avoid damageIncrease temperatureFurnaces without endless coreSemiconductor/solid-state device manufacturingDevice materialElectromotive force

Disclosed is a heat treatment system for semiconductor devices. The heat treatment system is used in a heat treatment process for semiconductor devices, such as a crystallization process for an amorphous silicon thin film or a dopant activation process for a poly-crystalline silicon thin film formed on a surface of a glass substrate of a flat display panel including a liquid crystal display (LCD) or an organic light emitting device (OLED). The heat treatment system transfers a semiconductor device after uniformly preheating the semiconductor device in order to prevent deformation of the semiconductor device during the heat treatment process, rapidly performs the heat treatment process under the high temperature condition by heating the semiconductor device using a lamp heater and induction heat derived from induced electromotive force, and unloads the semiconductor device after uniformly cooling the semiconductor device such that the semiconductor device is prevented from being deformed when the heat treatment process has been finished. The heat treatment system rapidly performs the heat treatment process while preventing deformation of the semiconductor device by gradually heating or cooling the semiconductor device.

Owner:VIATRON TECH INC

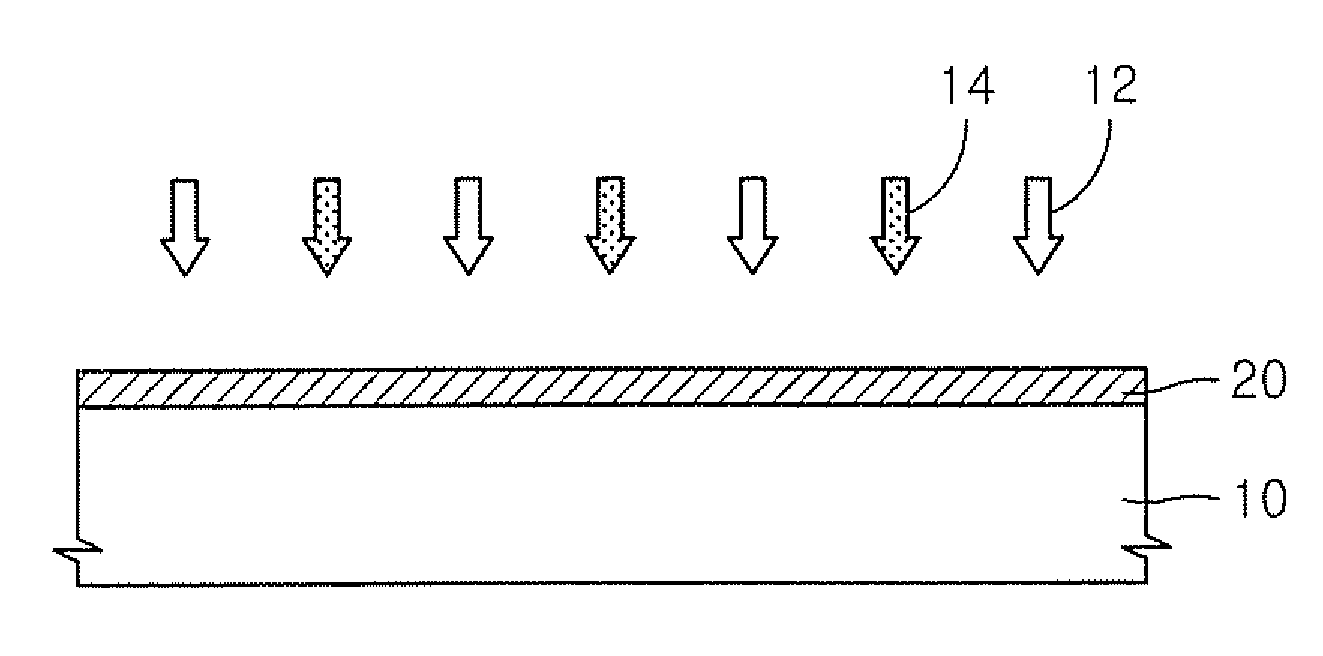

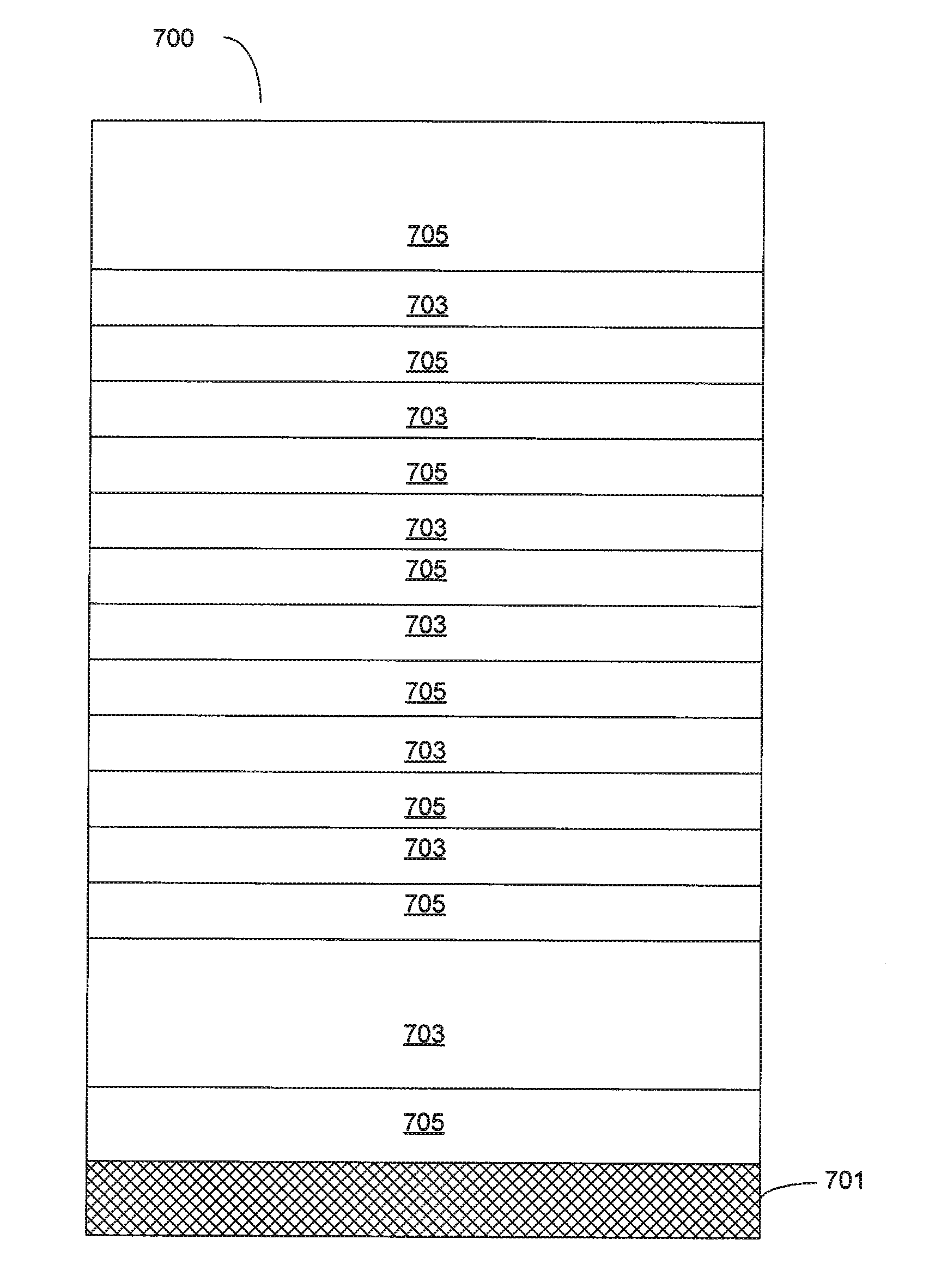

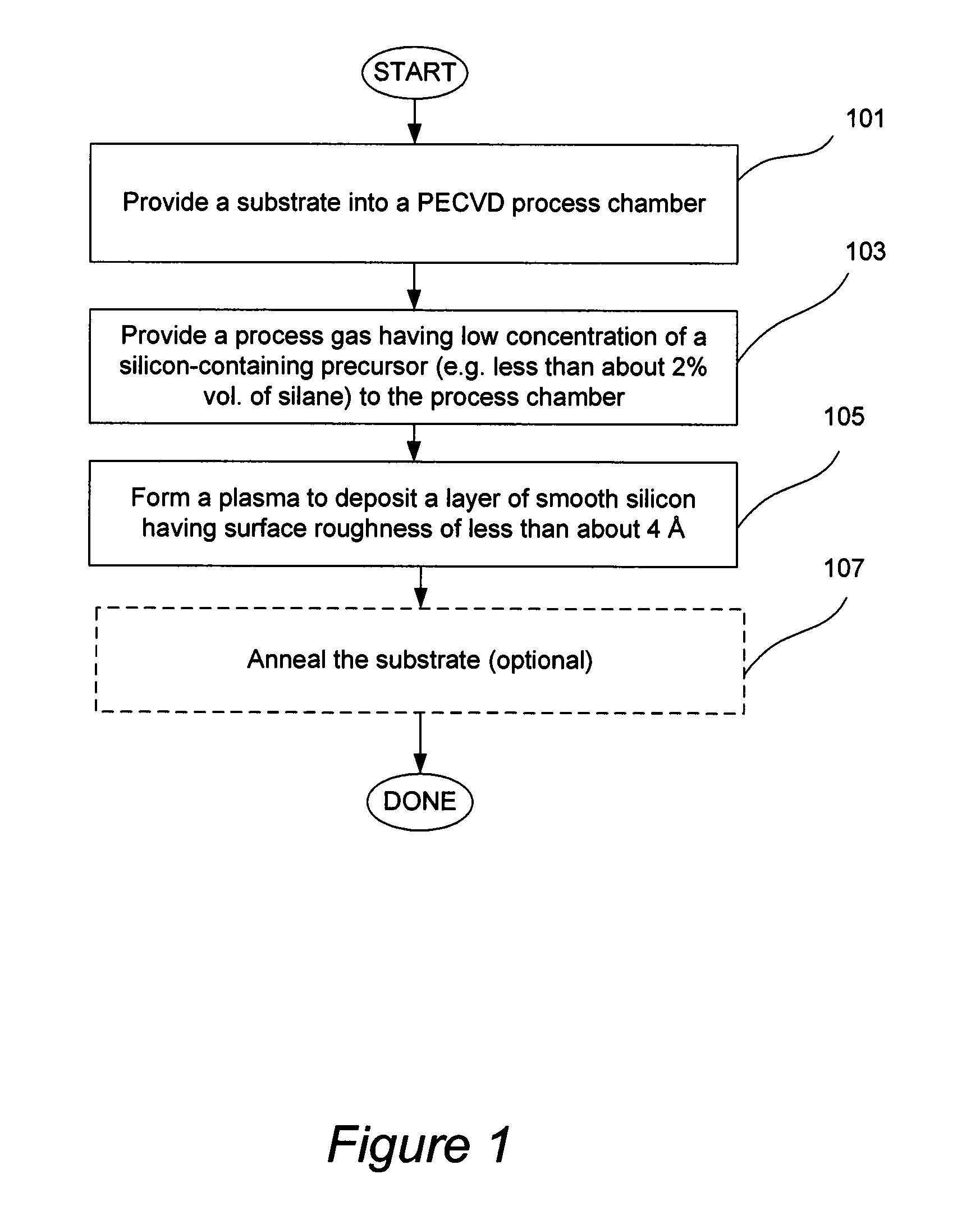

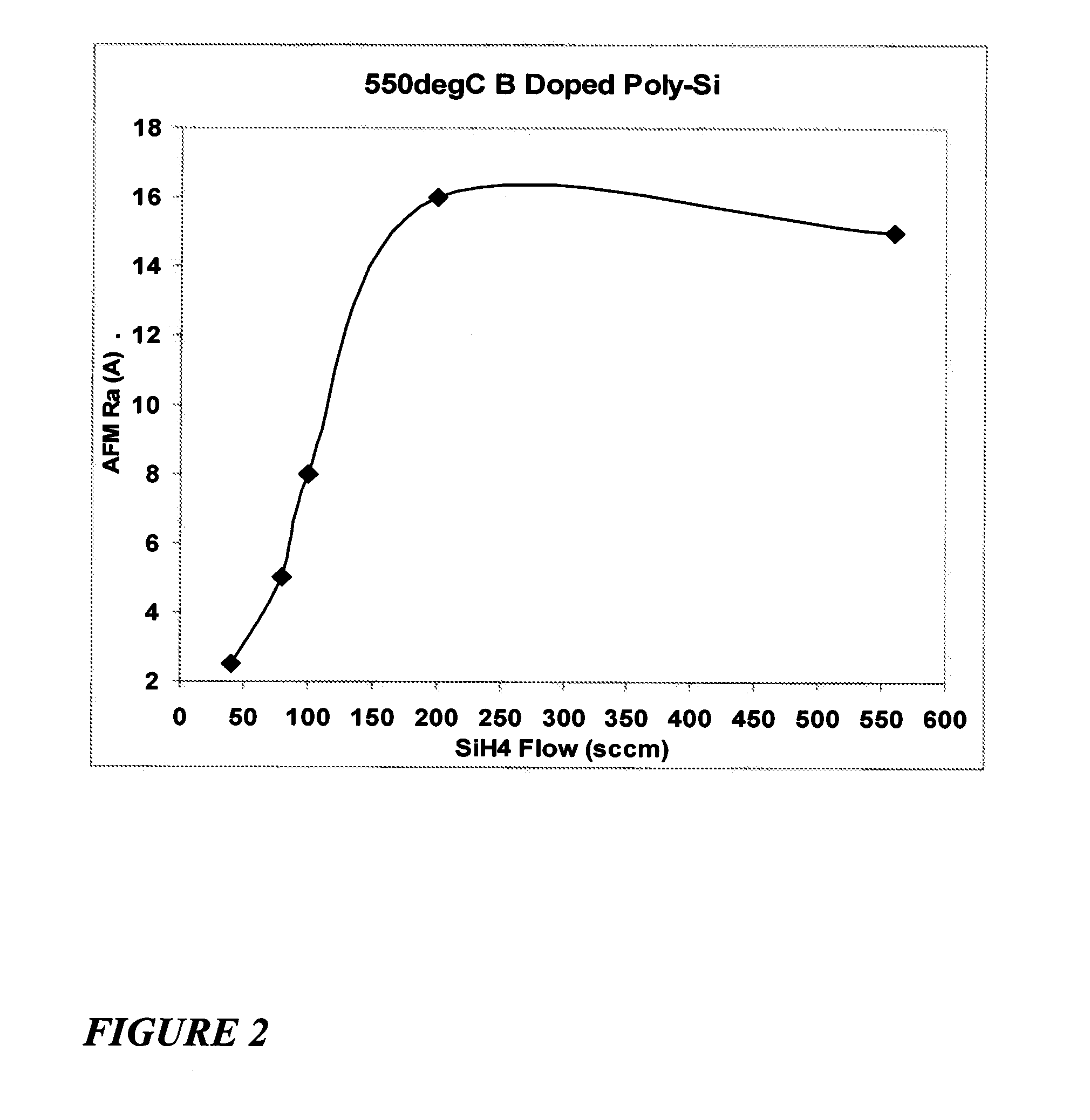

Pecvd deposition of smooth polysilicon films

InactiveUS20120142172A1Beneficial for thermal budgetReduced stabilityLiquid surface applicatorsSemiconductor/solid-state device manufacturingDopantSilicon oxide

Smooth silicon and silicon germanium films are deposited by plasma enhanced chemical vapor deposition (PECVD). The films are characterized by roughness (Ra) of less than about 4 Å. In some embodiments, smooth silicon films are undoped and doped polycrystalline silicon films. The dopants can include boron, phosphorus, and arsenic. In some embodiments the smooth polycrystalline silicon films are also highly conductive. For example, boron-doped polycrystalline silicon films having resistivity of less than about 0.015 Ohm cm and Ra of less than about 4 Å can be deposited by PECVD. In some embodiments smooth silicon films are incorporated into stacks of alternating layers of doped and undoped polysilicon, or into stacks of alternating layers of silicon oxide and doped polysilicon employed in memory devices. Smooth films can be deposited using a process gas having a low concentration of silicon-containing precursor and / or a process gas comprising a silicon-containing precursor and H2.

Owner:NOVELLUS SYSTEMS

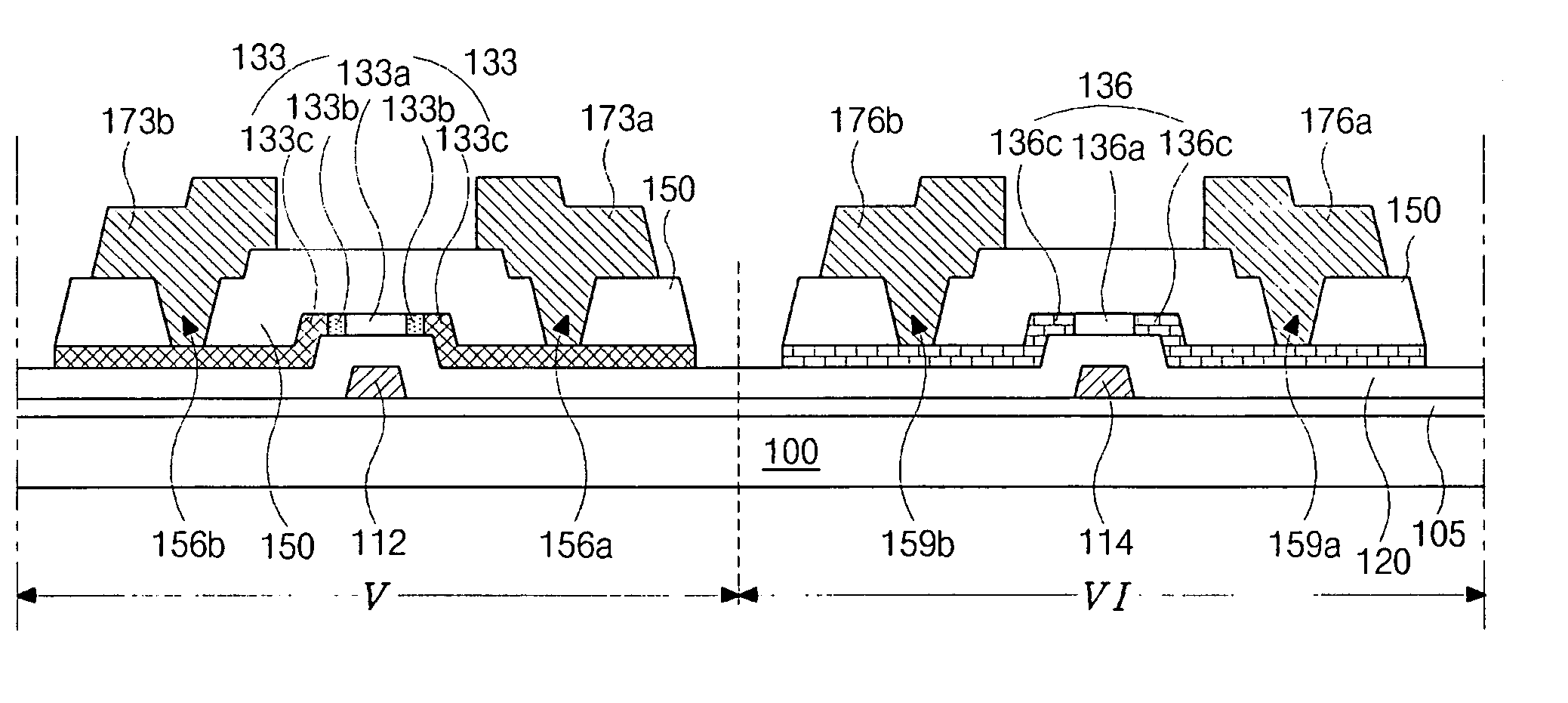

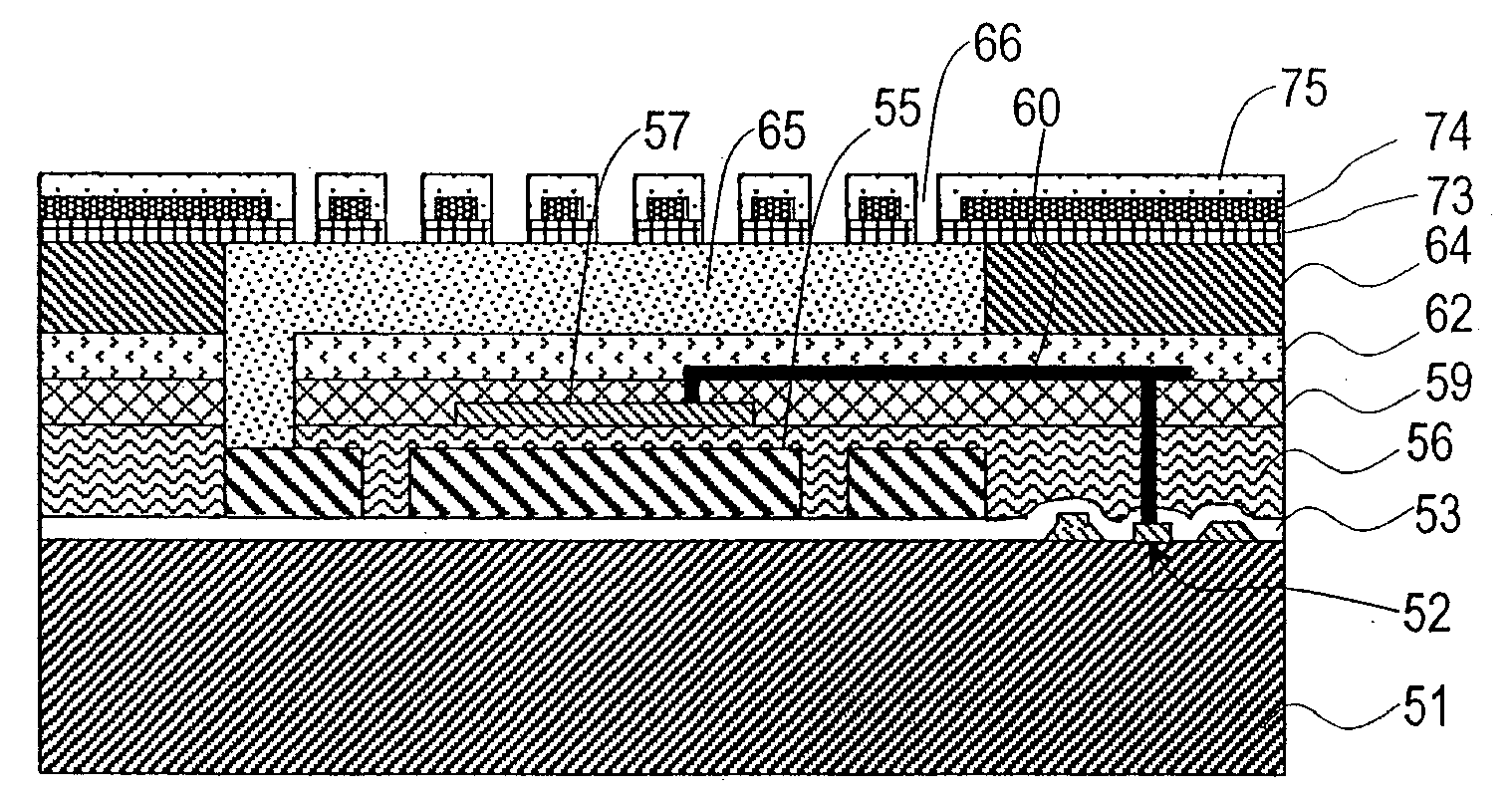

Liquid crystal display device including polycrystalline silicon thin film transistor and method of fabricating the same

ActiveUS20050099551A1Low production costImprove production yieldTransistorStatic indicating devicesCMOSLiquid-crystal display

A liquid crystal display device having a switching element in a pixel portion and a CMOS element in a driving portion includes: a substrate; a gate electrode on the substrate; a gate insulating layer on the gate electrode; a polycrystalline silicon layer on the gate insulating layer, the polycrystalline silicon layer having an active region in a central portion corresponding to the gate electrode and an ohmic contact region at side portions of the active region; an interlayer insulating layer having a set of contact holes for contacting the polycrystalline silicon layer at the side portions; and source and drain electrodes spaced apart from each other on the interlayer insulating layer, the source and drain electrodes contacting the polycrystalline silicon layer through the set of contact holes.

Owner:LG DISPLAY CO LTD

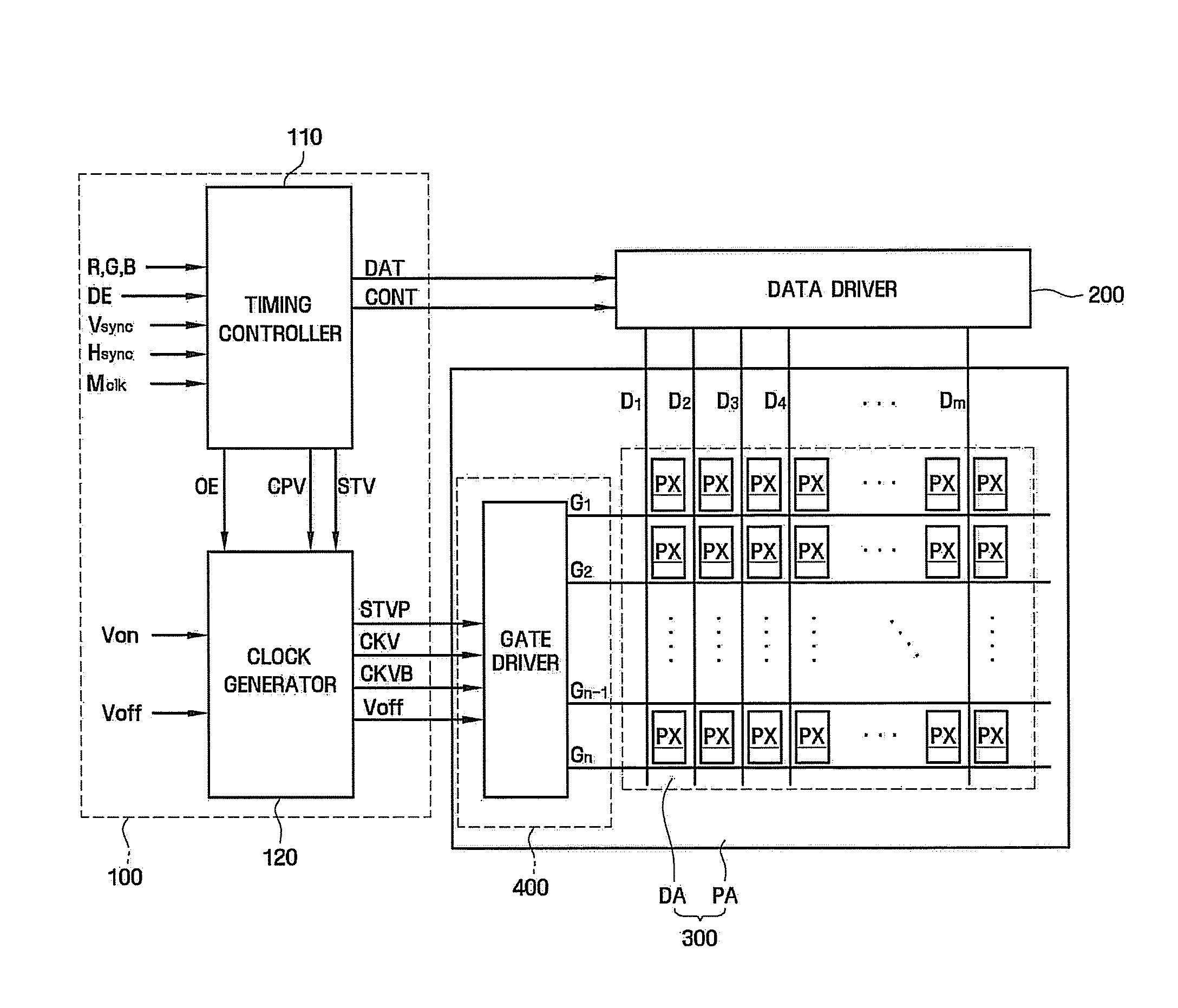

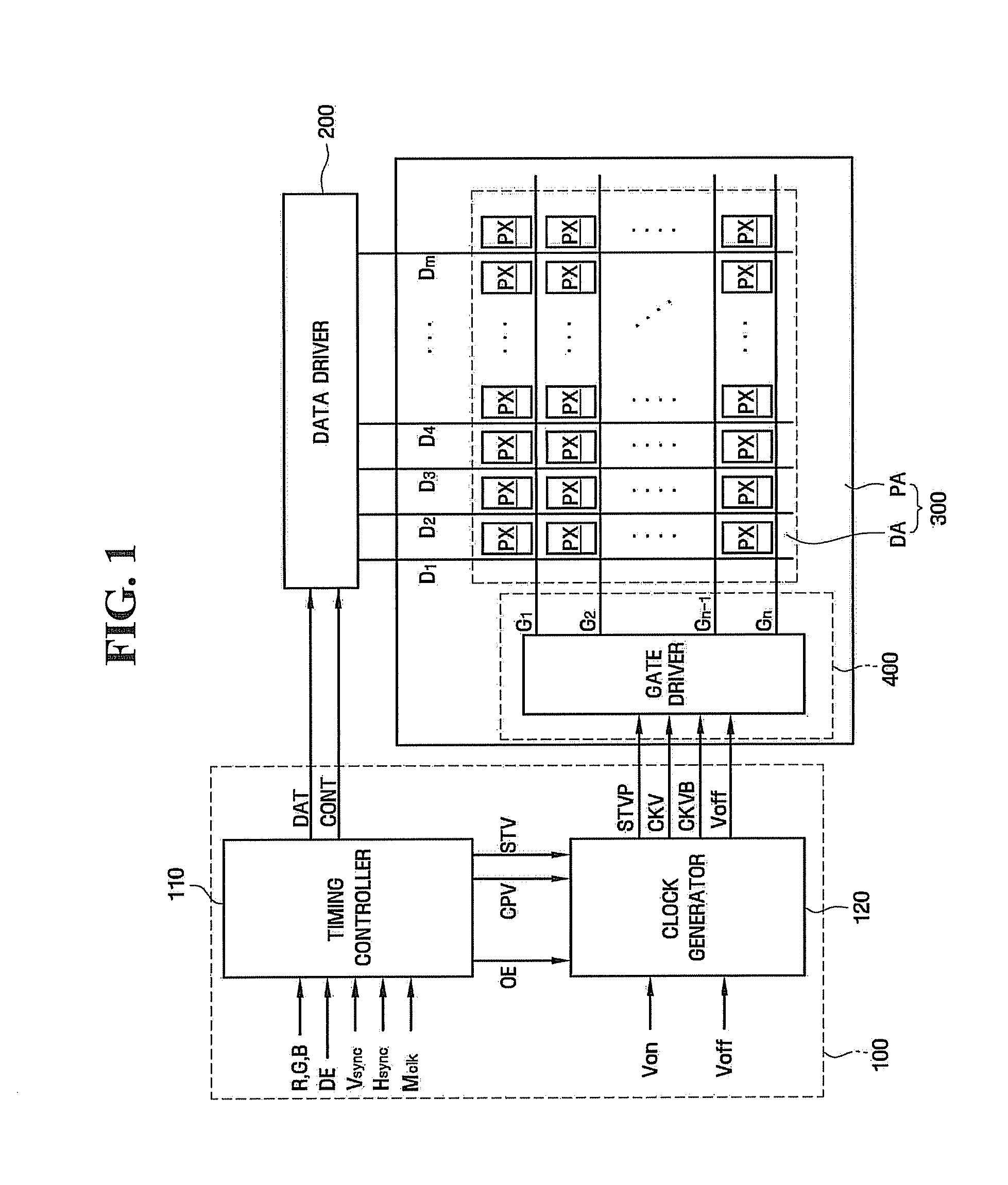

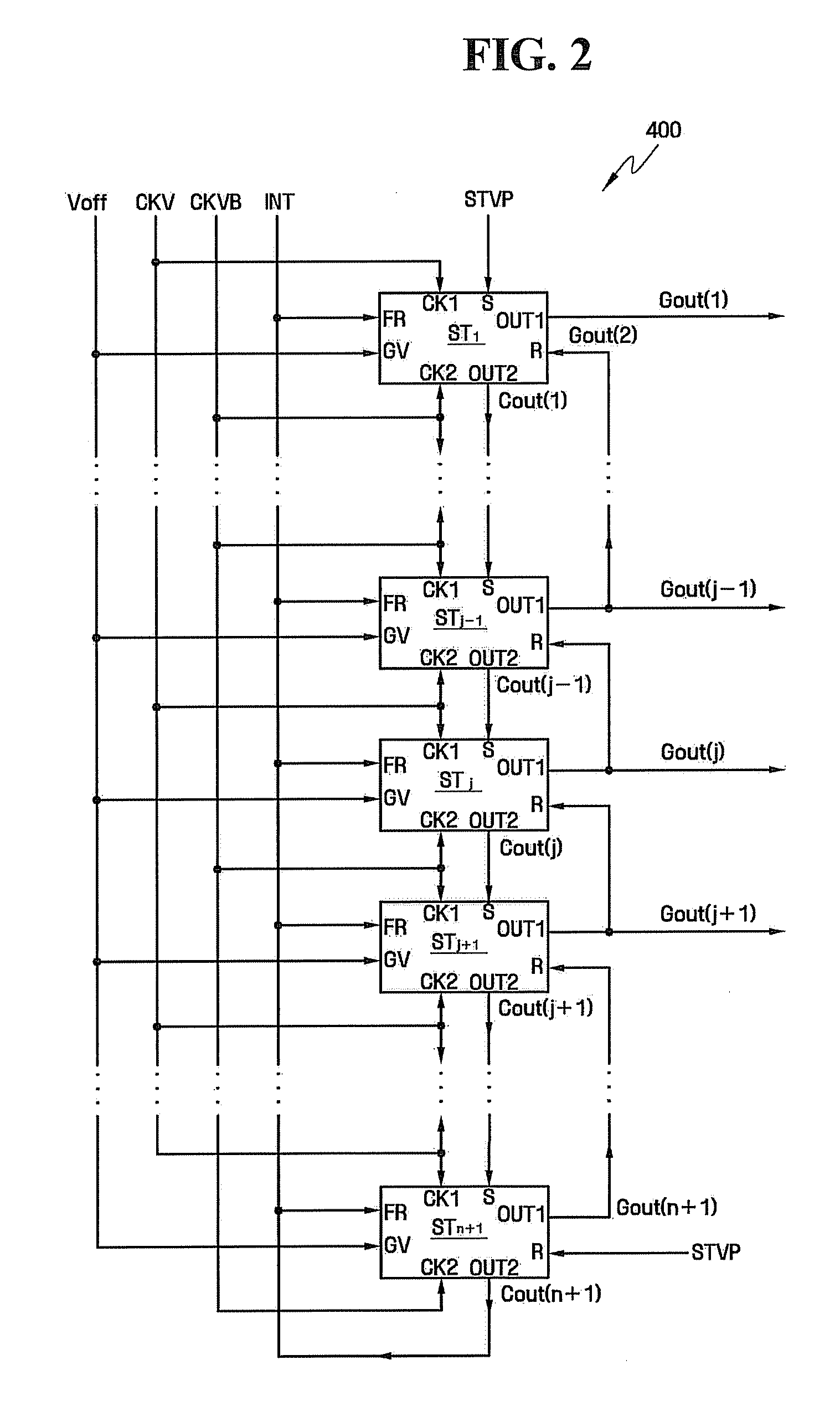

Gate driving circuit, display device having the same, and method for manufacturing the display device

ActiveUS20100026669A1Without lowering driving capabilityEnsure reliabilitySemiconductor/solid-state device manufacturingCathode-ray tube indicatorsShift registerDisplay device

A gate driving circuit having improved driving capability and maintaining reliability even after a prolonged period of use includes a shift register having a plurality of stages cascaded to one another, each of the plurality of stages including a pull-up unit, a pull-down unit, a discharging unit, and a holding unit, wherein at least one of the discharging unit and the holding unit includes an amorphous silicon thin film transistor and a polysilicon thin film transistor connected in parallel to each other.

Owner:SAMSUNG DISPLAY CO LTD

Electronic device and method of manufacturing the same

ActiveUS20070298534A1Reduce internal pressureTelevision system detailsThermoelectric device with dielectric constant thermal changeSputteringHydrofluoric acid

In the present invention, an etching hole 21 is formed in a polysilicon film 14 as a cavity-wall member. Through the etching hole 21, hydrofluoric acid is injected, so as to dissolve a silicon oxide film 13, thereby forming a cavity 22. In the cavity 22, a detecting unit 12 of a sensor is in an exposed condition. Next, by sputtering, an Al film 16 is deposited in the etching hole 21 and on an upper face of a substrate. Thereafter, a portion of the Al film 16 positioned on the polysilicon film 14 is removed by etching back, thereby leaving only a metal closure 16a of Al which closes the etching hole. The sputtering step is performed under a pressure of 5 Pa or less, so that the pressure in the cavity can be held to be low.

Owner:PANASONIC CORP

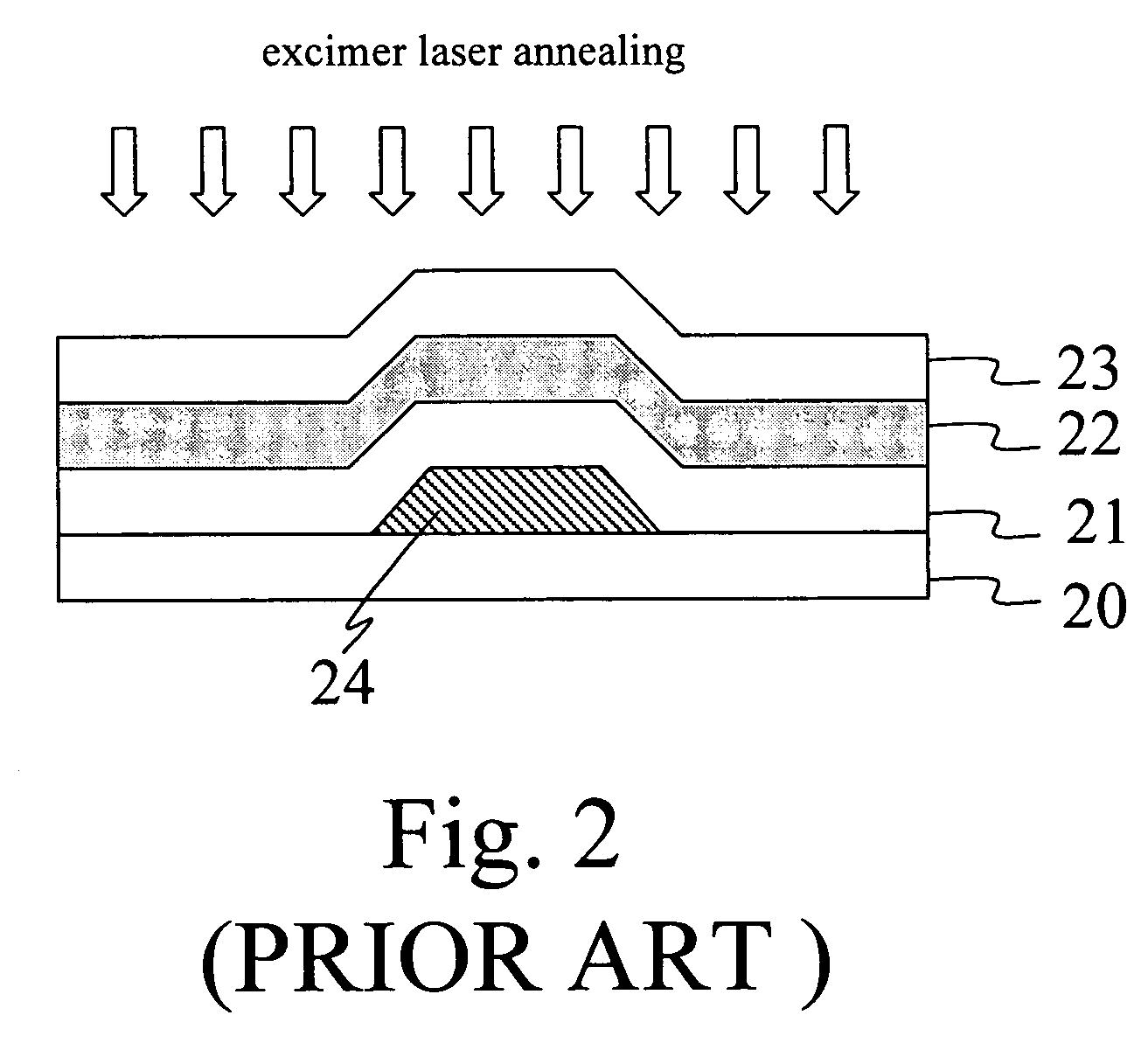

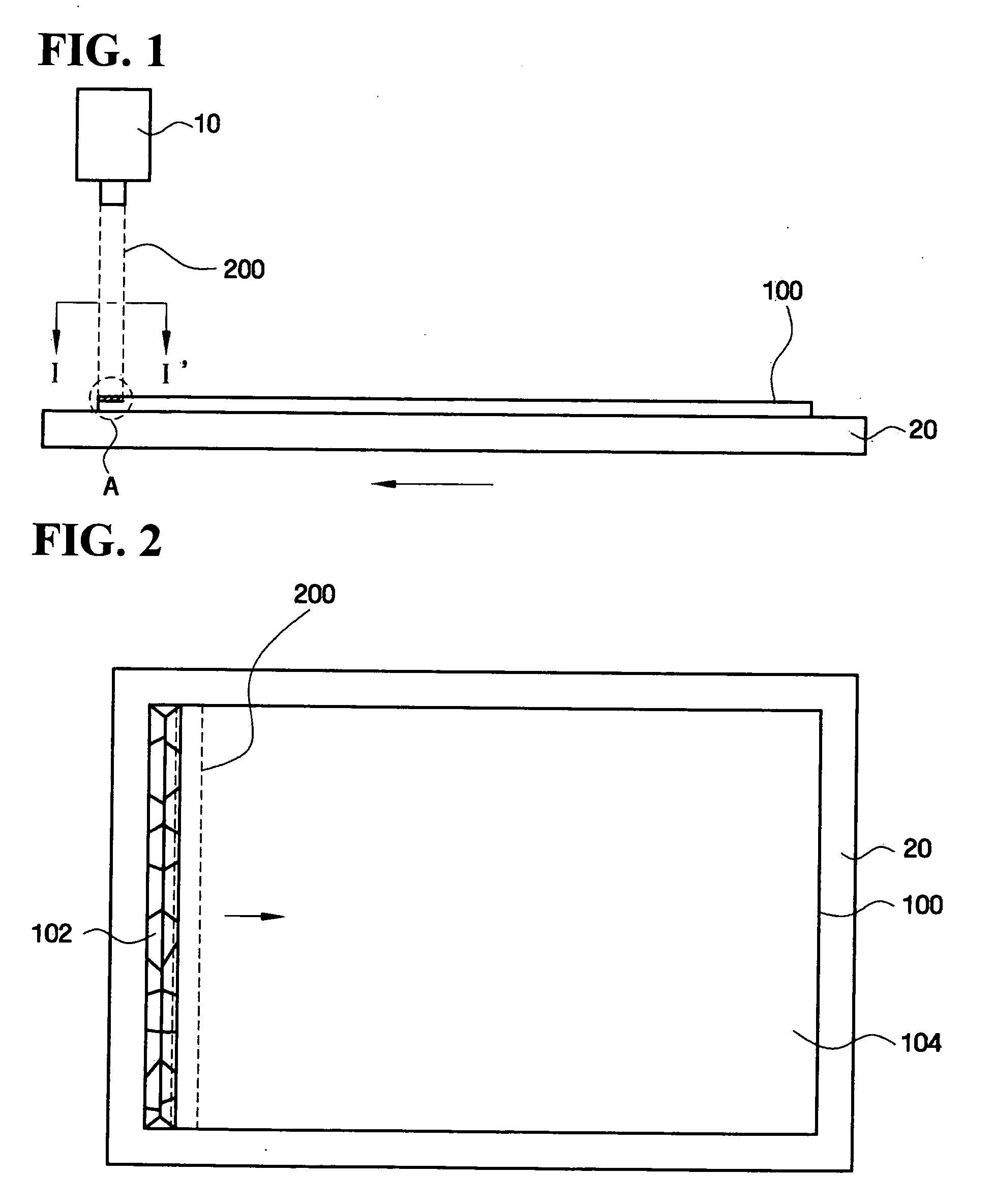

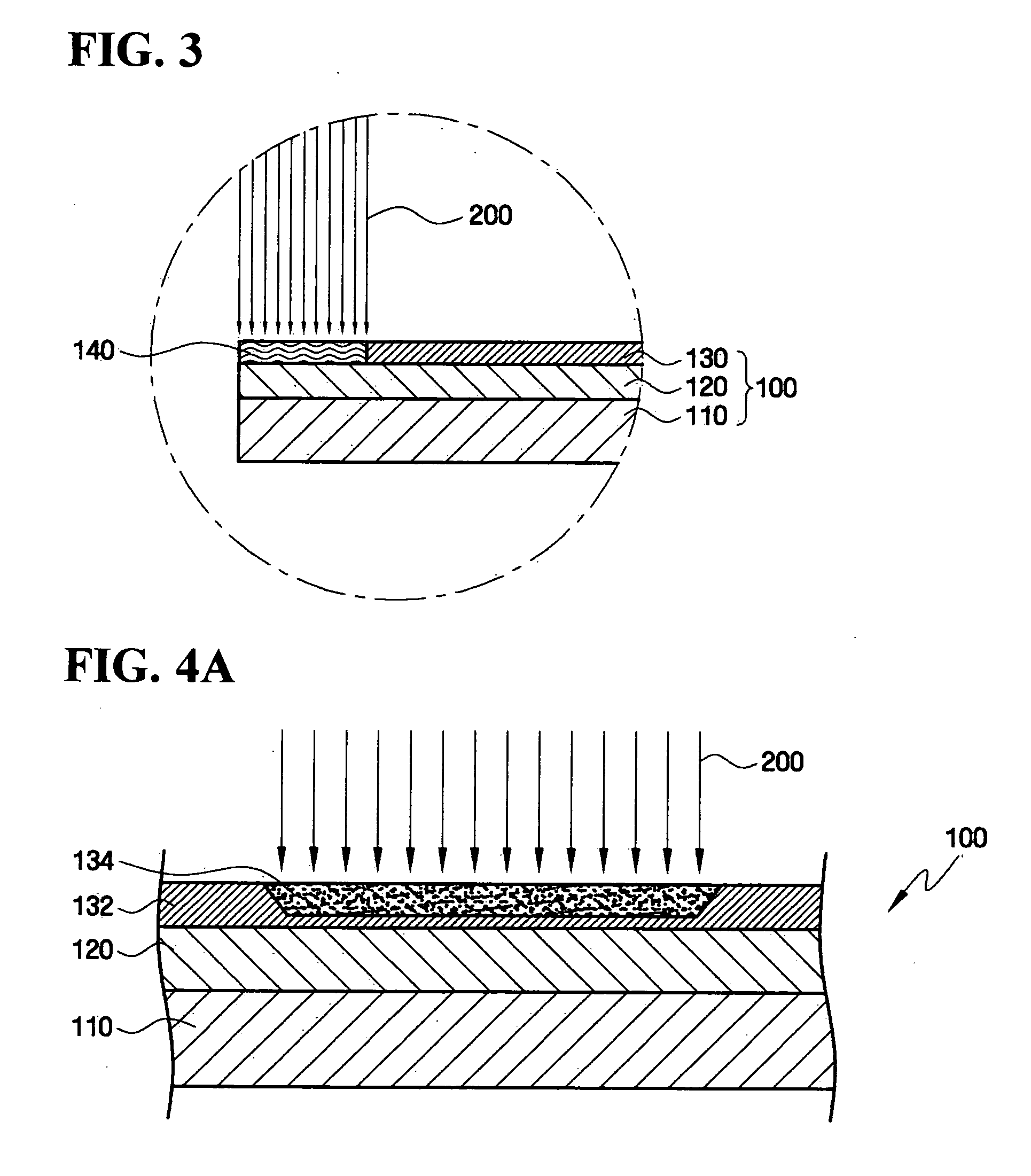

Method of forming polycrystalline silicon thin film and method of manufacturing thin film transistor using the method

ActiveUS20070054477A1Excellent electrical propertiesSolid-state devicesSemiconductor/solid-state device manufacturingHigh energyLaser beams

Provided are a method of forming a polycrystalline silicon thin film with improved electrical characteristics and a method of manufacturing a thin film transistor using the method of forming the polycrystalline silicon thin film. The method includes forming an amorphous silicon thin film on a substrate, partially melting a portion of the amorphous silicon thin film by irradiating the portion of the amorphous silicon thin film with a laser beam having a low energy density, forming polycrystalline silicon grains with a predetermined crystalline arrangement by crystallizing the partially molten portion of the amorphous silicon thin film, completely melting a portion of the polycrystalline silicon grains and a portion of the amorphous silicon thin film by irradiation of a laser beam having a high energy density while repeatedly moving the substrate by a predetermined distance, and growing the polycrystalline silicon grains by crystallizing the completely molten silicon homogeneously with the predetermined crystalline arrangement.

Owner:SAMSUNG DISPLAY CO LTD

Fabrication method of semiconductor device

InactiveUS20050032283A1Avoid damageNot to damageSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialSingle crystal

An insulating substrate is bonded to a monocrystalline Si substrate that includes a monocrystalline Si thin film transistor and a hydrogen ion implanted portion. After depositing an amorphous Si thin film, the amorphous Si thin film is modified into a polycrystalline Si thin film by irradiation of the excimer laser. In laser irradiation, the irradiation of the laser beam on the monocrystalline Si thin film transistor is blocked either by inserting a mask in part of the optical path of the laser beam, or by irradiating the laser beam before unnecessary portions of the monocrystalline Si substrate is detached. In this way, the irradiation of the laser beam for forming the polycrystalline Si thin film will not damage the monocrystalline Si thin film transistor in a semiconductor device in which the monocrystalline Si thin film transistor, which has been transferred, and the polycrystalline Si thin film transistor, which has been formed on the insulating substrate, are formed on the insulating substrate.

Owner:SHARP KK

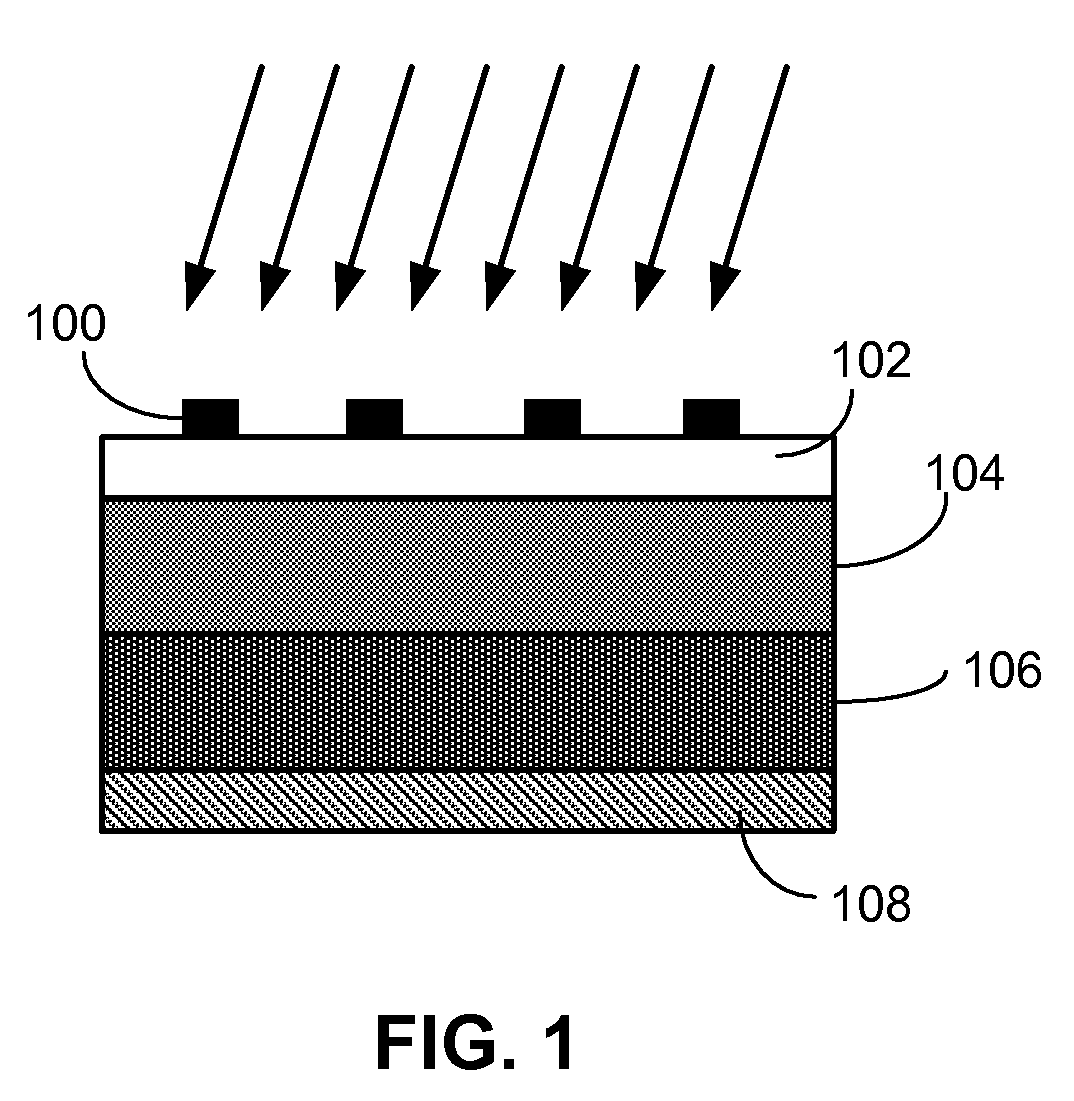

Solar cell fabricated by silicon liquid-phase deposition

InactiveUS20090255574A1Final product manufactureSemiconductor/solid-state device manufacturingHeterojunctionContact layer

One embodiment of the present invention provides a solar cell. The solar cell includes a substrate; a polycrystalline Si (poly-Si) thin-film layer which includes a p+ layer situated above the substrate, wherein the poly-Si thin-film layer is hydrogenated; a contact under-layer situated between the foreign substrate and the poly-Si thin-film layer; a metal layer situated below the contact layer, wherein part of the metal layer reaches the p+ layer through the contact under-layer; an n-type doped amorphous-Si (a-Si) thin-film layer situated above the poly-Si thin-film layer forming a heterojunction; an optional intrinsic layer situated between the poly-Si thin-film layer and the n-type doped a-Si thin-film layer; a transparent conductive layer situated above the n-type doped a-Si thin-film layer; and a front-side electrode situated above the transparent conductive layer.

Owner:SILEVO