Patents

Literature

47results about How to "Electrical uniformity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

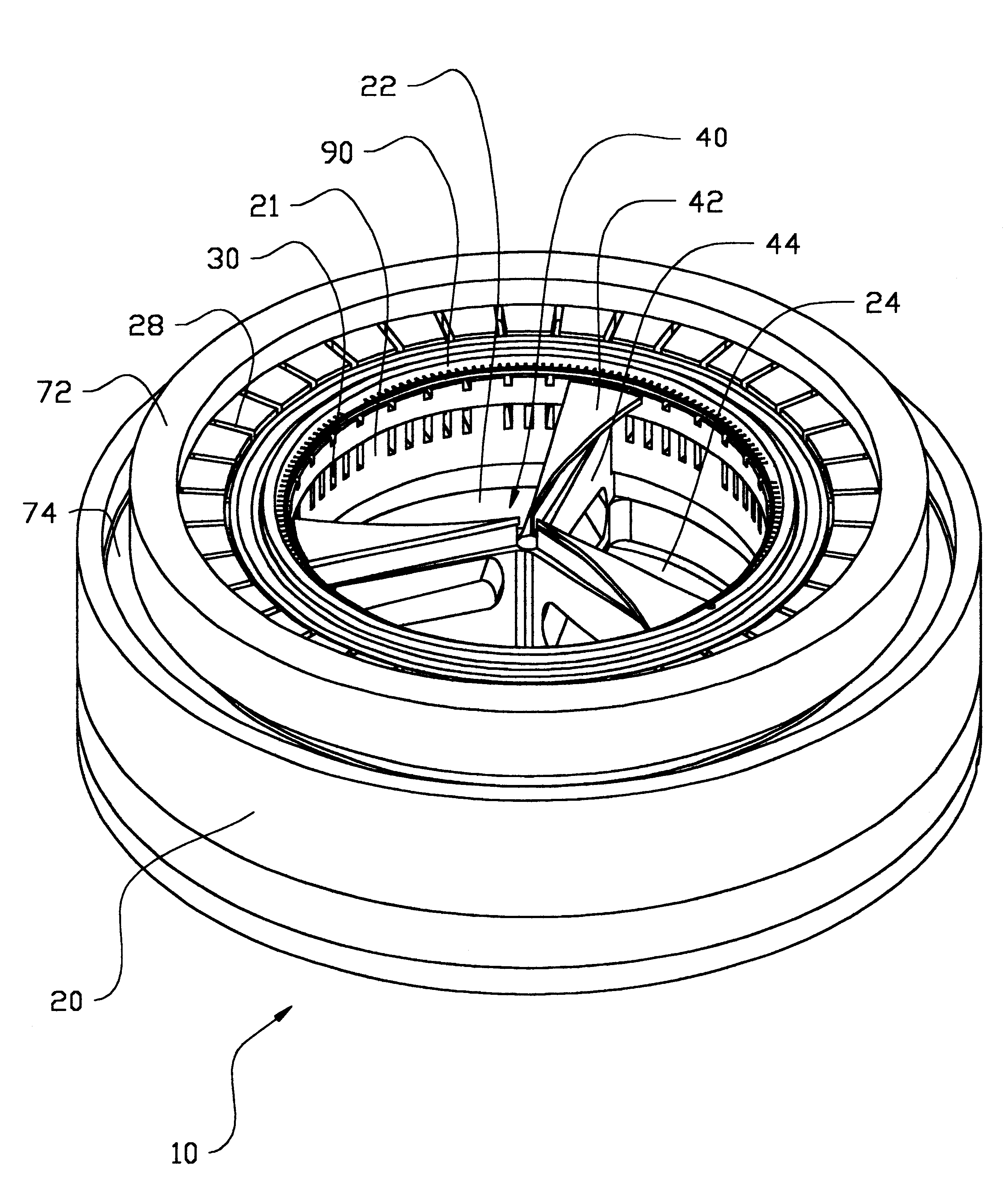

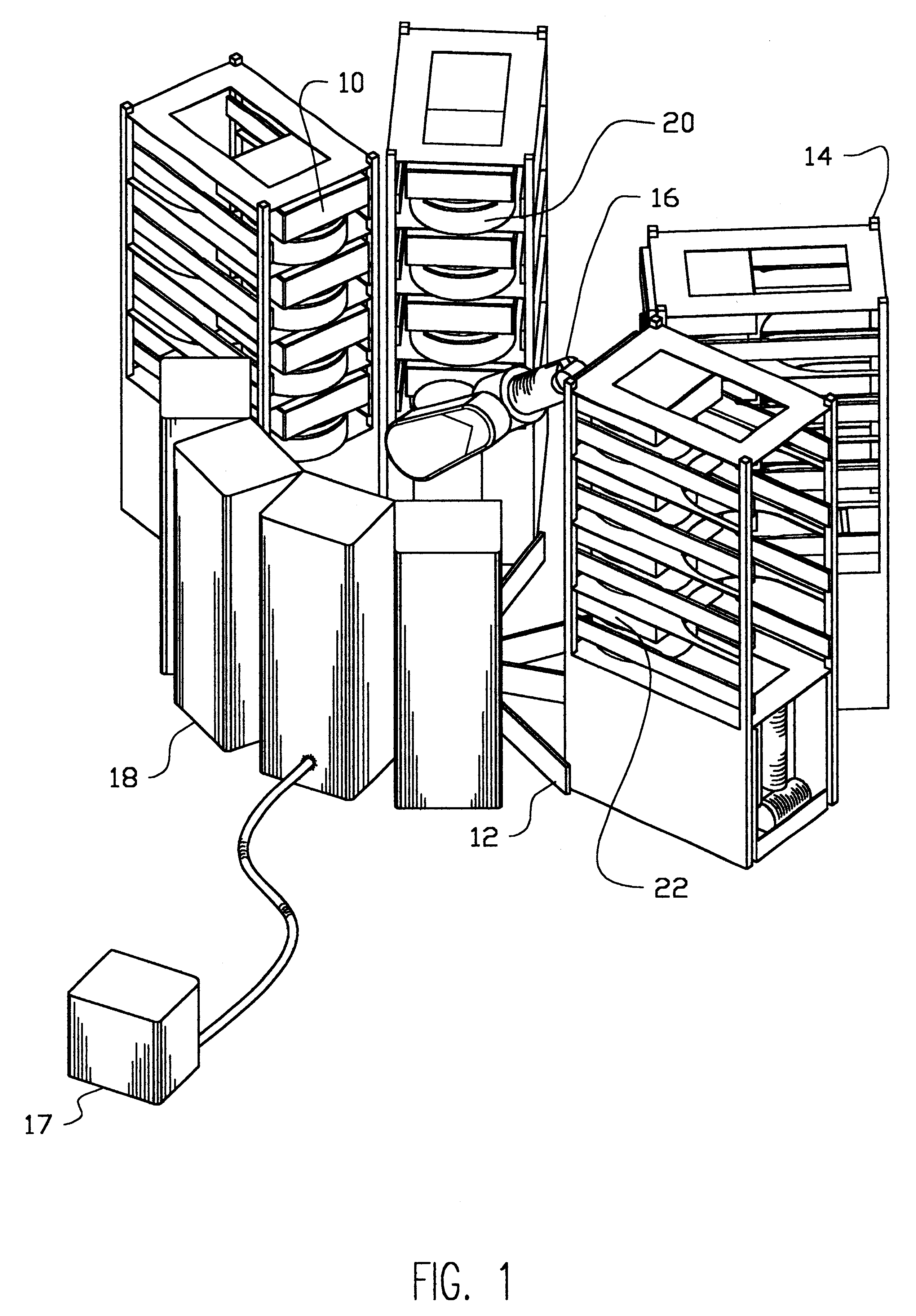

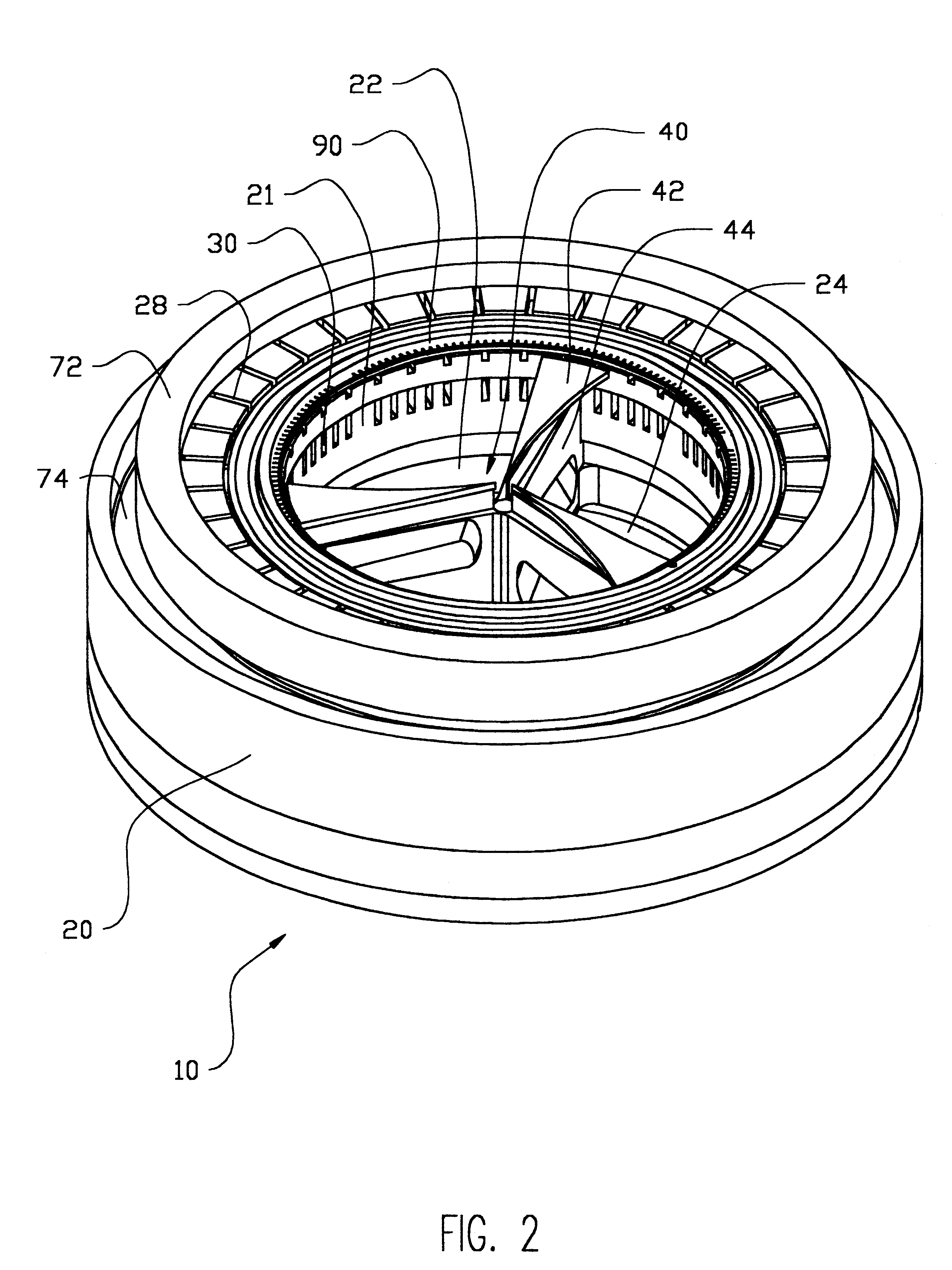

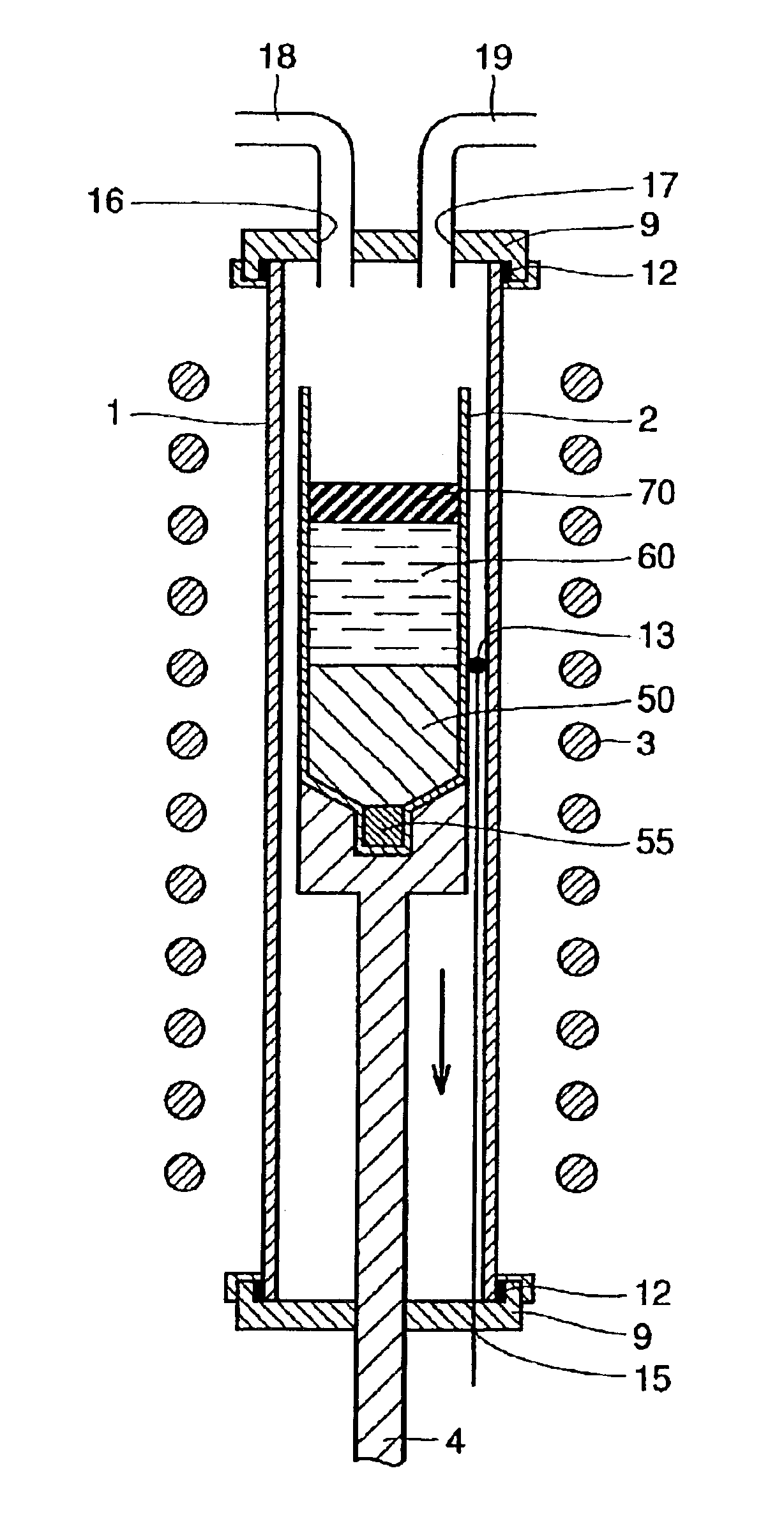

Method of and apparatus for controlling fluid flow and electric fields involved in the electroplating of substantially flat workpieces and the like and more generally controlling fluid flow in the processing of other work piece surfaces as well

A novel method and apparatus of wet processing workpieces, such as electroplating semiconductor wafers and the like, that incorporates reciprocating processing fluid agitation to control fluid flow at the workpiece, and where electric fields are involved as in such electroplating, controlling the electric field distribution.

Owner:HERCULES TECH GROWTH CAPITAL +1

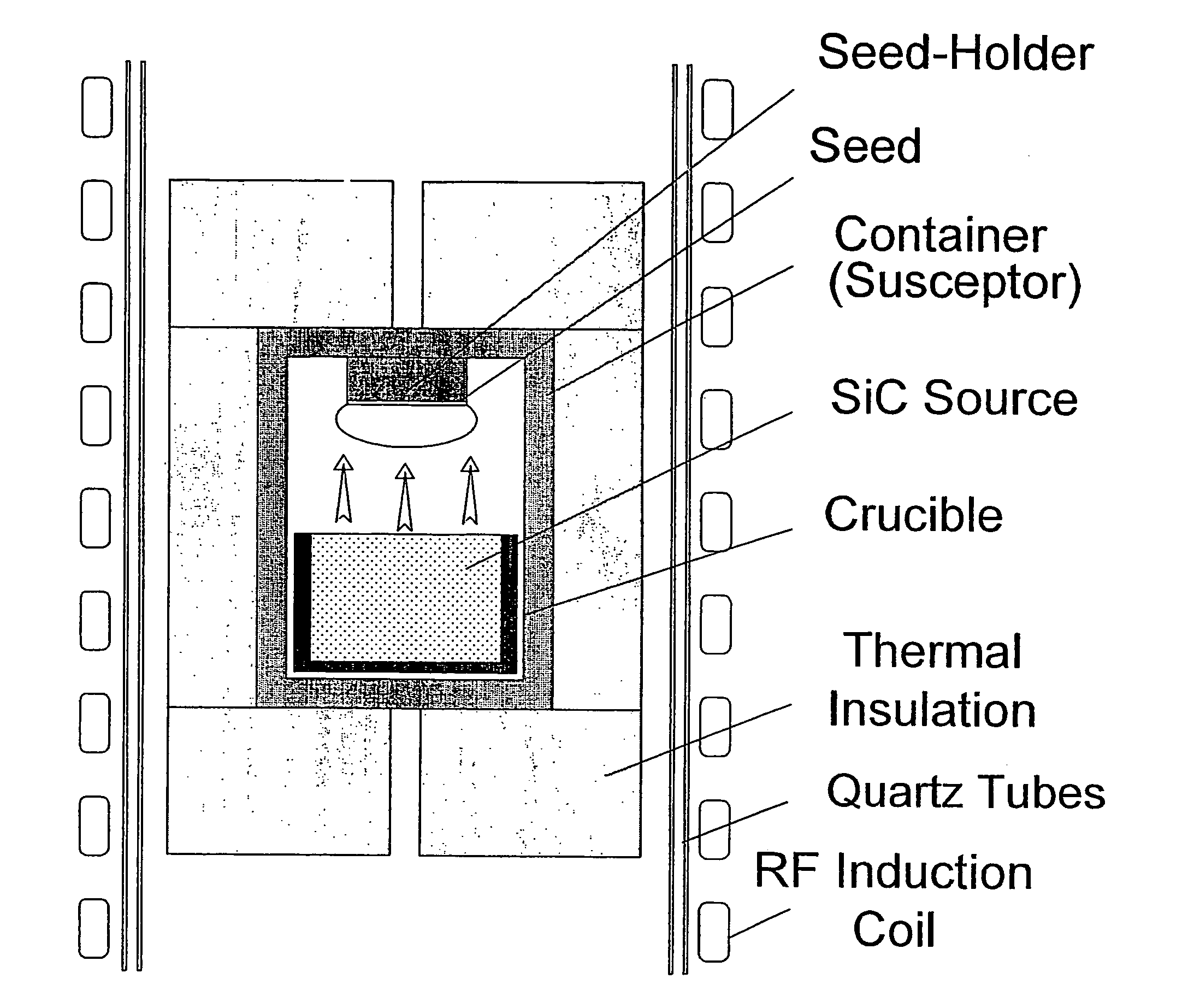

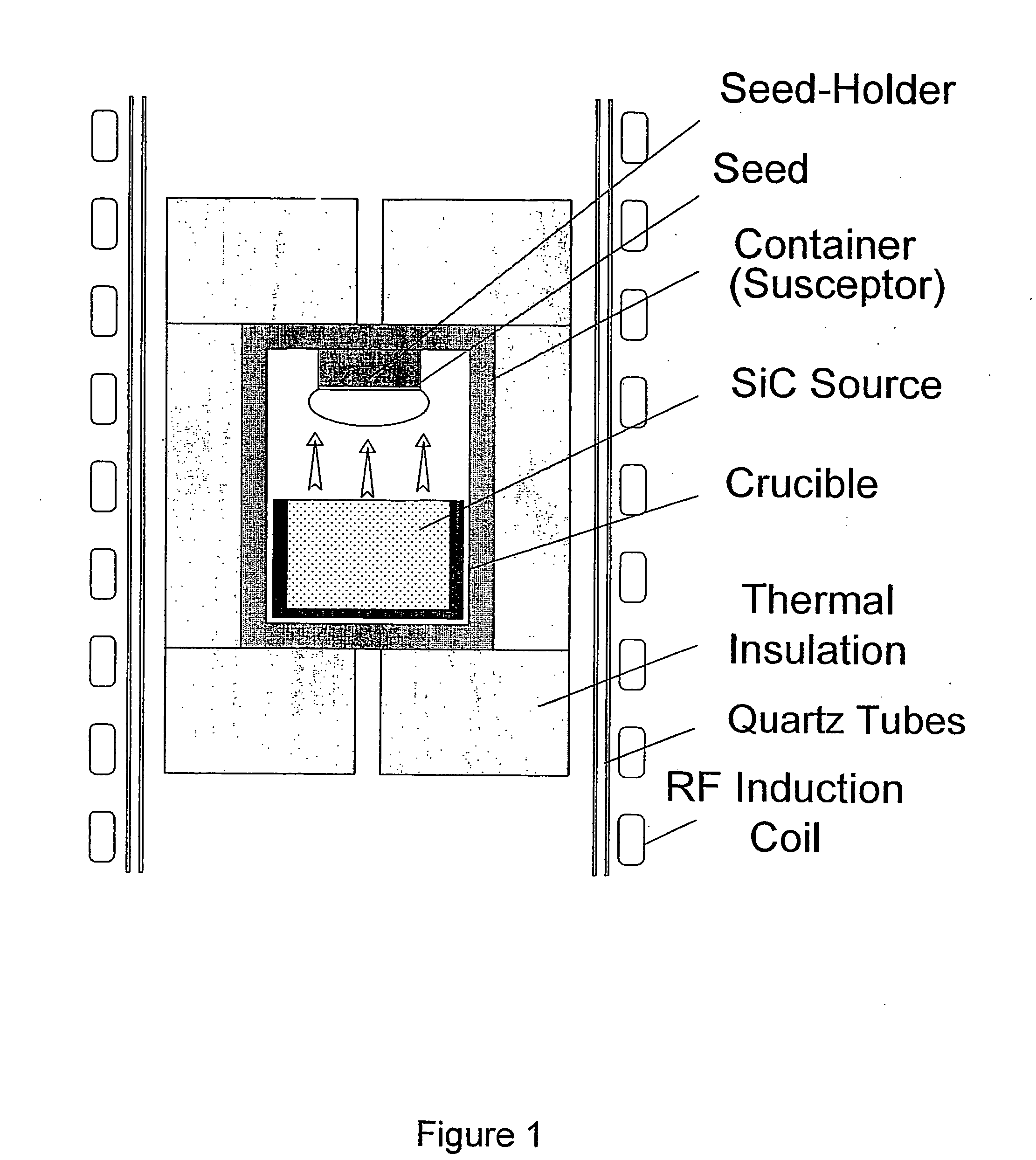

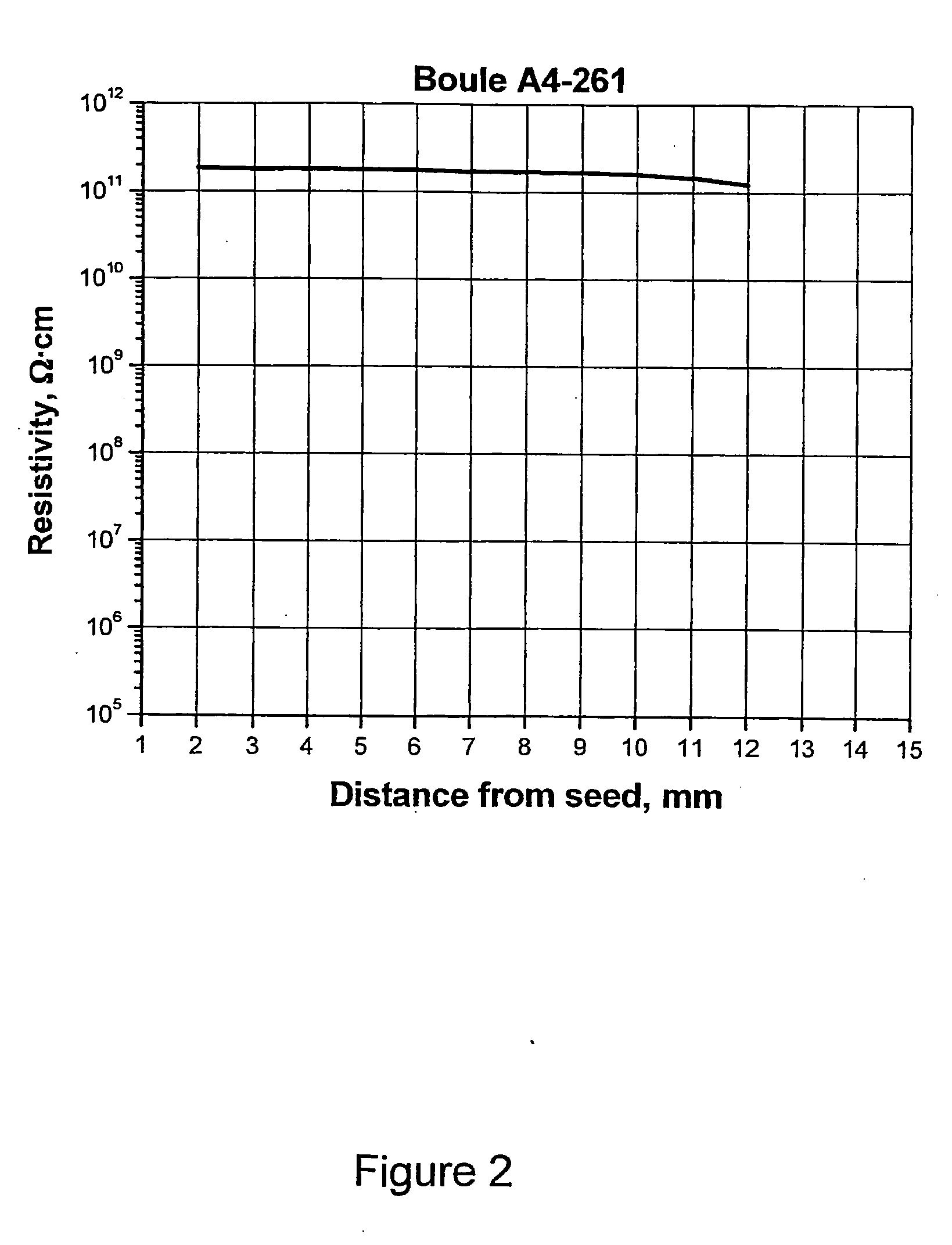

Low-Doped Semi-Insulating Sic Crystals and Method

InactiveUS20080190355A1Overcome disadvantagesIncrease capacitanceNon-metal conductorsPolycrystalline material growthCapacitanceDeep level

The invention relates to substrates of semi-insulating silicon carbide used for semiconductor devices and a method for making the same. The substrates have a resistivity above 106 Ohm-cm, and preferably above 108 Ohm-cm, and most preferably above 109 Ohm-cm, and a capacitance below 5 pF / mm2 and preferably below 1 pF / mm2. The electrical properties of the substrates are controlled by a small amount of added deep level impurity, large enough in concentration to dominate the electrical behavior, but small enough to avoid structural defects. The substrates have concentrations of unintentional background impurities, including shallow donors and acceptors, purposely reduced to below 5·1016 cm−3, and preferably to below 1·1016 cm−3, and the concentration of deep level impurity is higher, and preferably at least two times higher, than the difference between the concentrations of shallow acceptors and shallow donors. The deep level impurity comprises one of selected metals from the periodic groups IB, IIB, IIIB, IVB, VB, VIB, VIIB and VIIIB. Vanadium is a preferred deep level element. In addition to controlling the resistivity and capacitance, a further advantage of the invention is an increase in electrical uniformity over the entire crystal and reduction in the density of crystal defects.

Owner:II VI

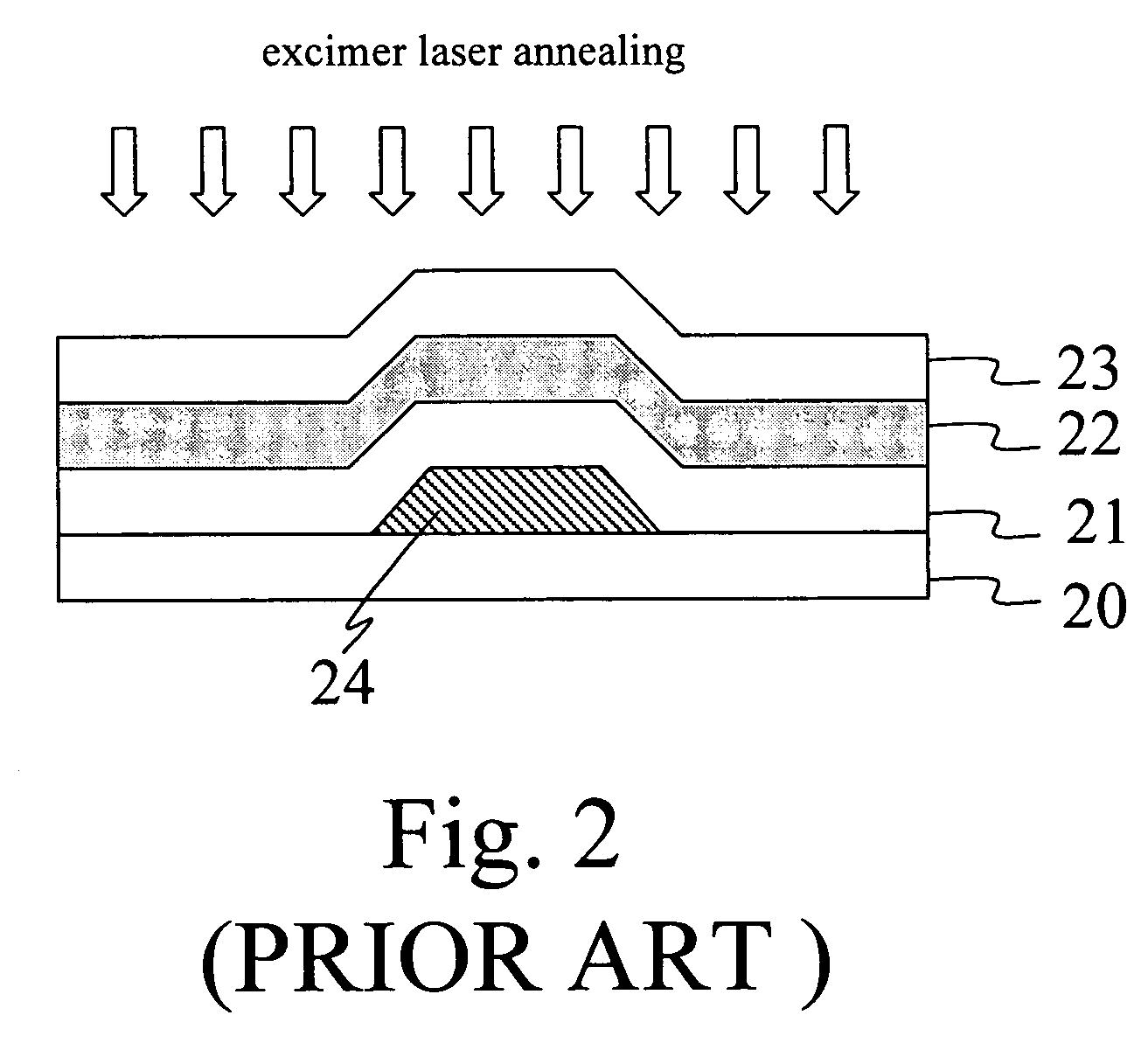

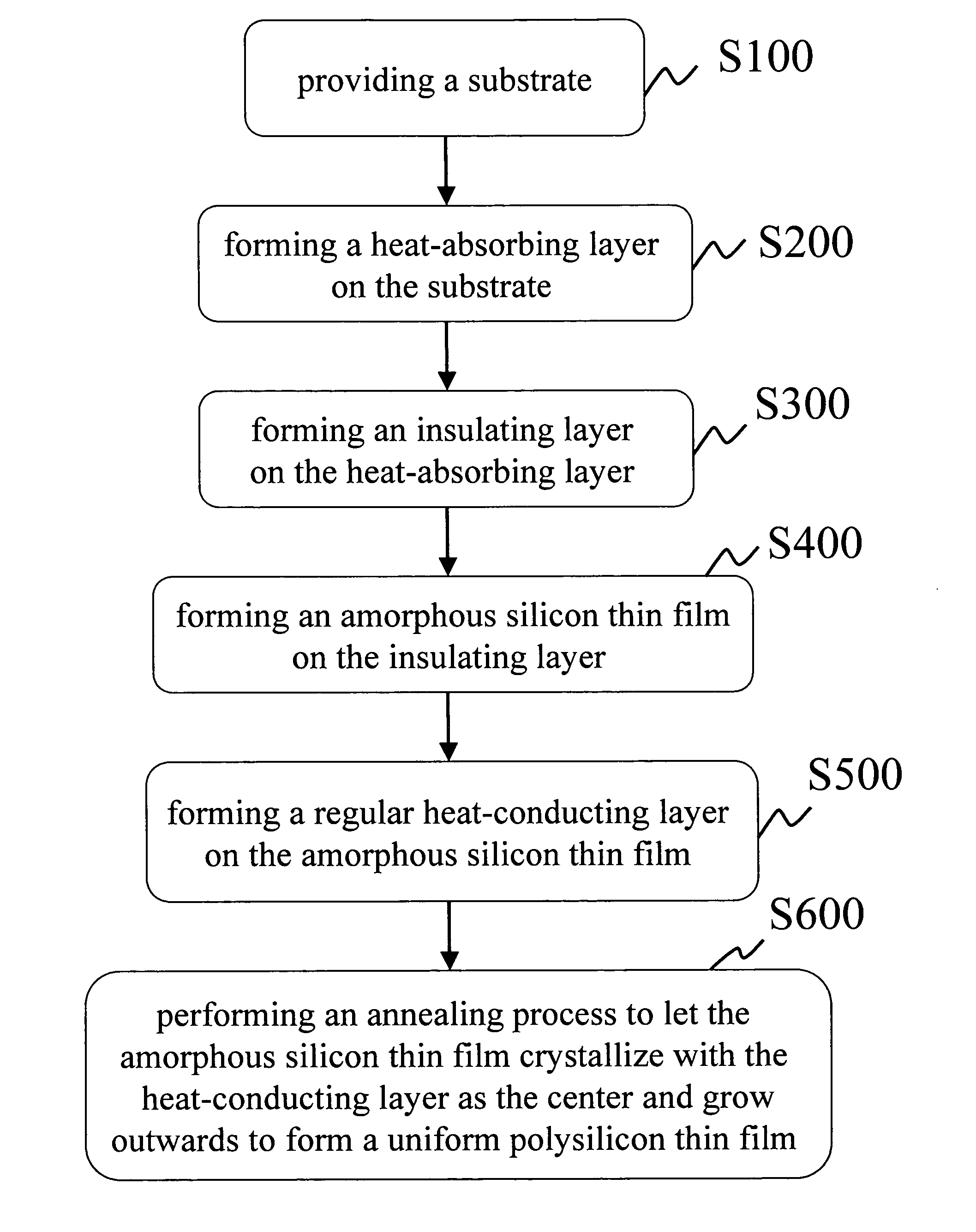

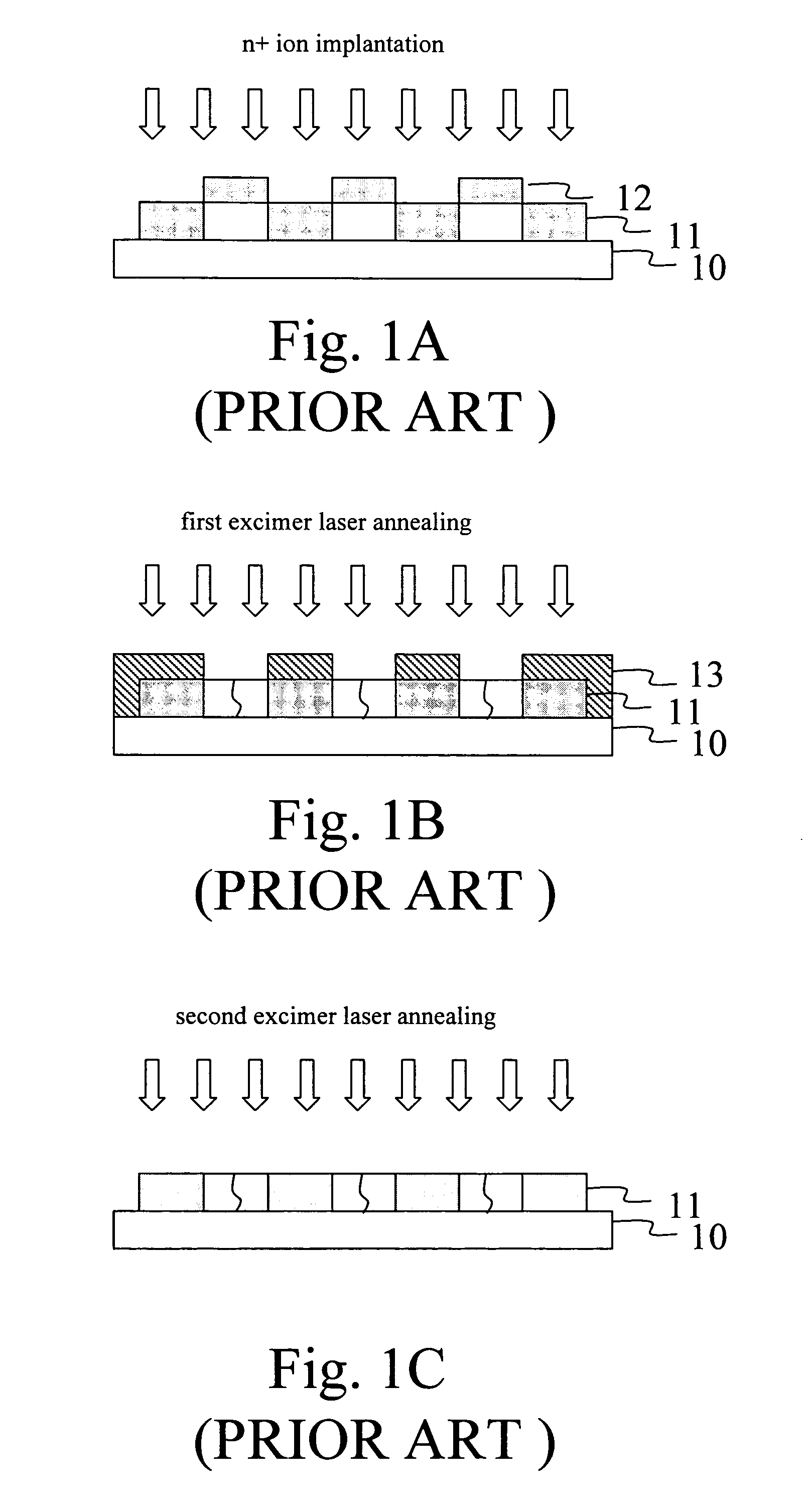

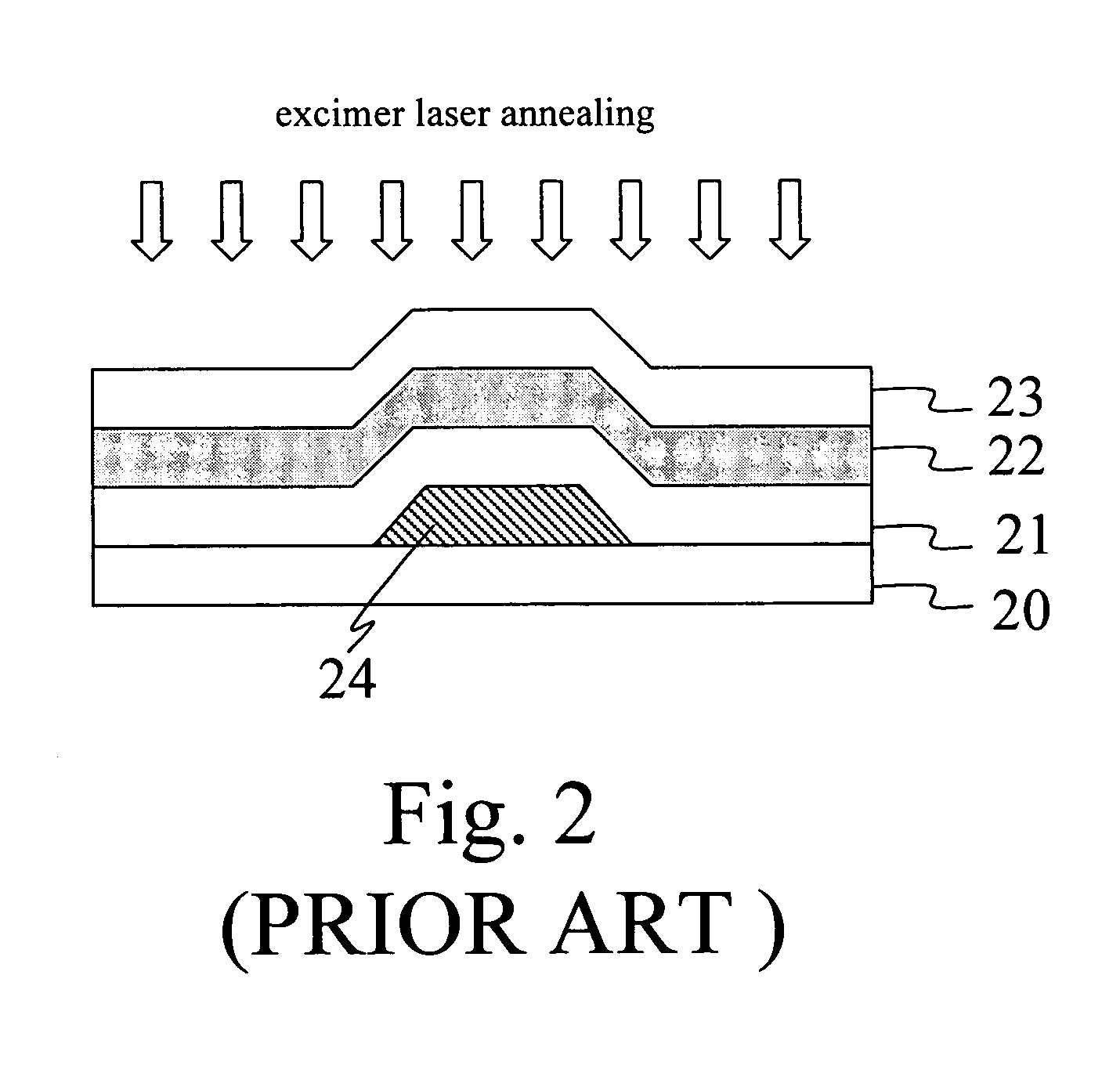

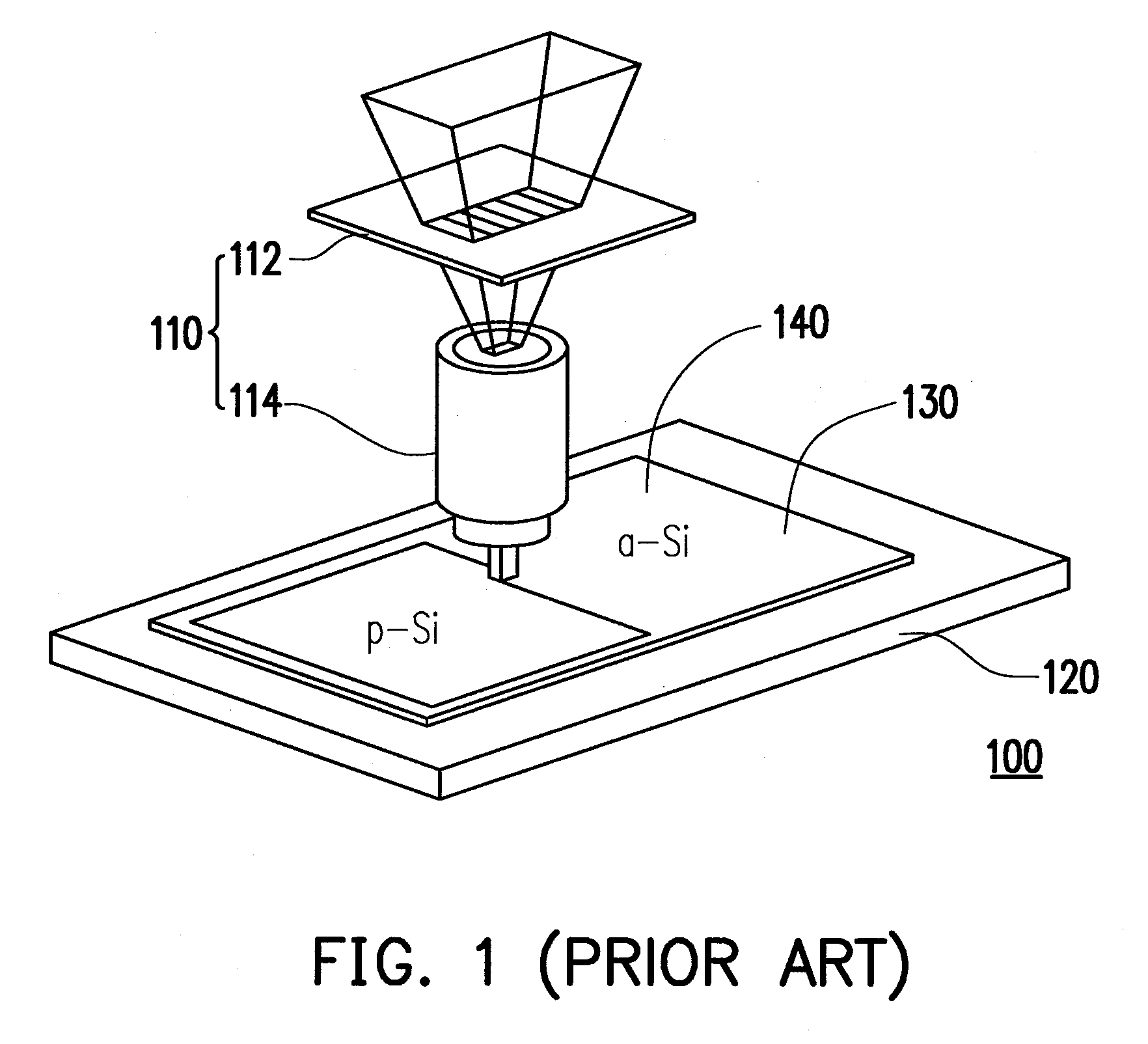

Polysilicon thin film fabrication method

ActiveUS7192818B1Excellent electrical propertiesElectrical uniformitySolid-state devicesSemiconductor/solid-state device manufacturingHeat conductingAmorphous silicon

A polysilicon thin film fabrication method is provided, in which a heat-absorbing layer is used to provide sufficient heat for grain growth of an amorphous silicon thin film, and an insulating layer is used to isolate the heat-absorbing layer and the amorphous silicon thin film. A regular heat-conducting layer is used as a cooling source to control the crystallization position and grain size of the amorphous silicon thin film. Therefore, the amorphous silicon thin film can crystallize into a uniform polysilicon thin film, and the electrical characteristics of the polysilicon thin film can be stably controlled.

Owner:NAT TAIWAN UNIV

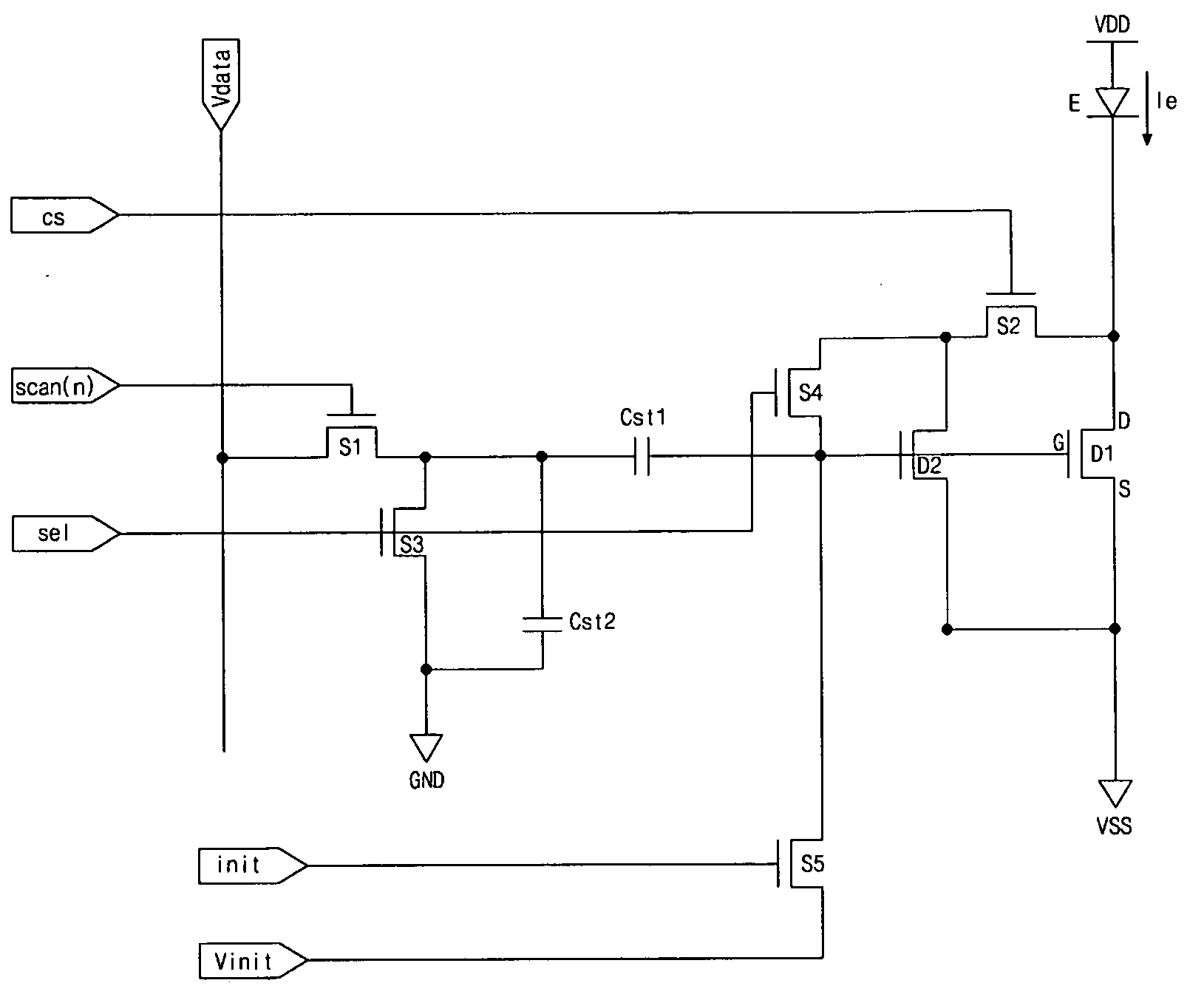

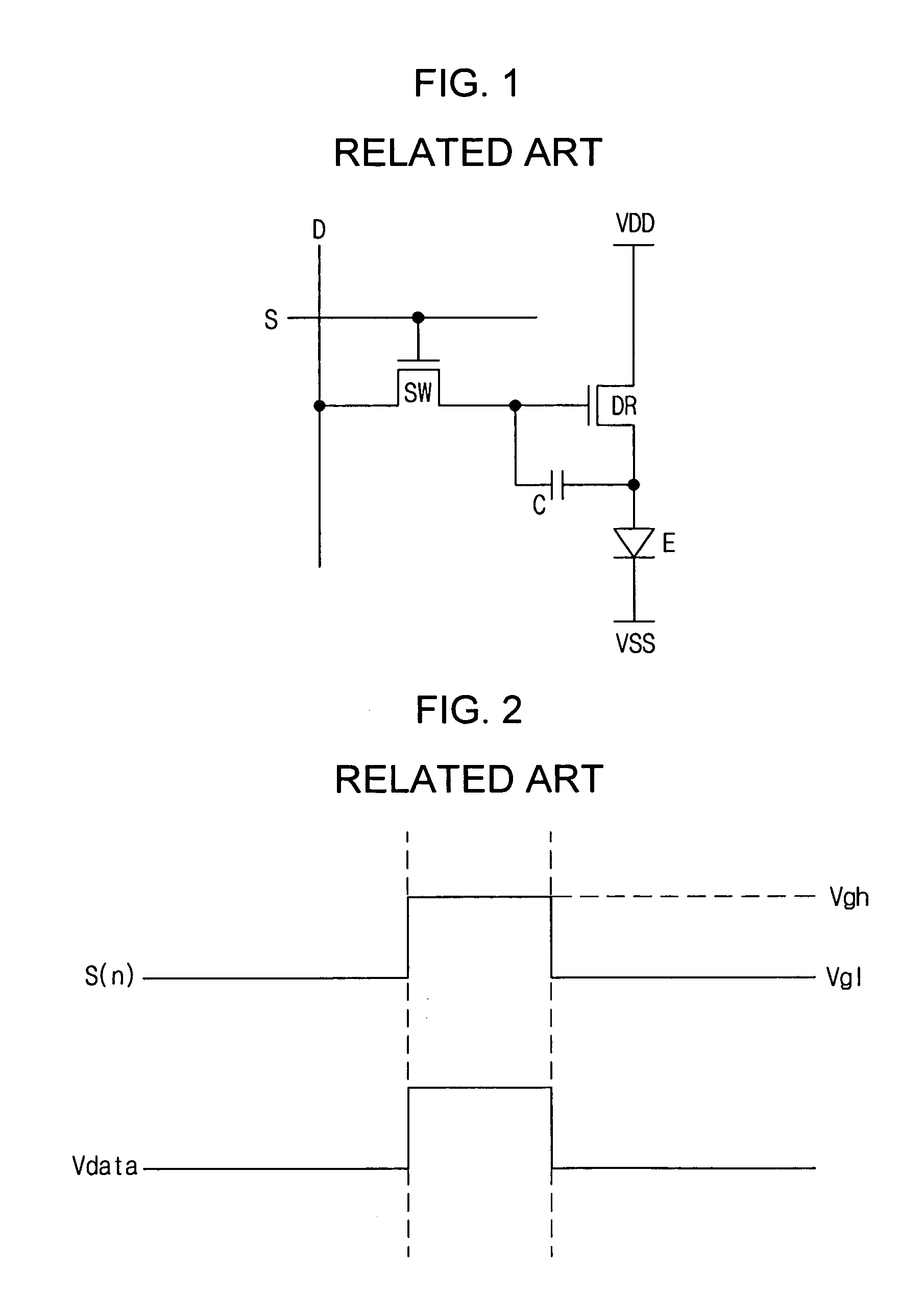

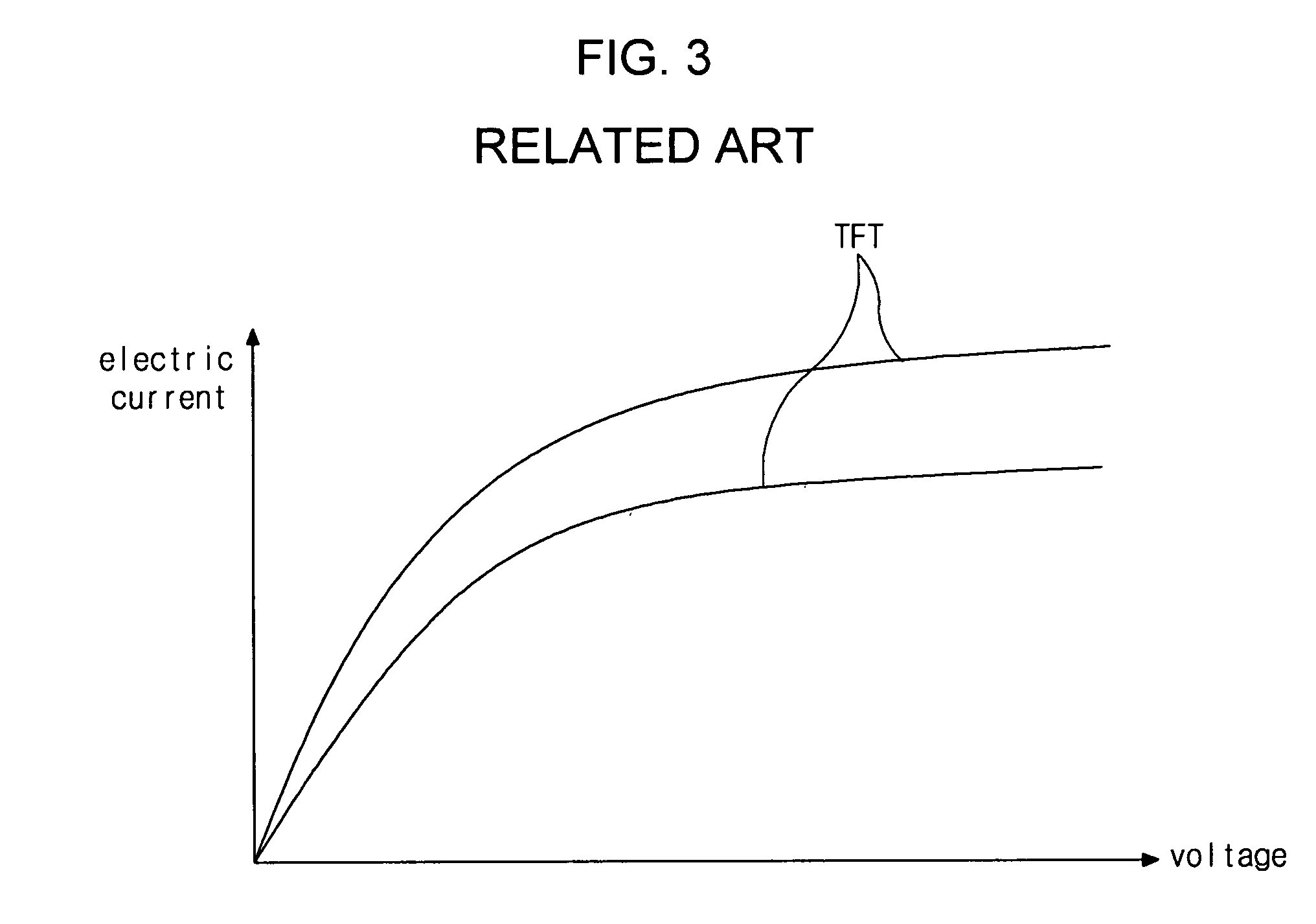

Organic electroluminescent display device and method of driving the same

ActiveUS20100123700A1Uniform brightnessElectrical uniformitySolid-state devicesCathode-ray tube indicatorsDriving currentEngineering

An organic electroluminescent display device includes an organic electroluminescent diode receiving a driving voltage and a first ground voltage; first and second driving thin film transistors for providing a driving current to the organic electroluminescent diode, each of the first and second driving thin film transistors receiving one of the driving voltage and the first ground voltage; a first switching thin film transistor receiving a data voltage and switched by an nth scan signal to output the data voltage; a second switching thin film transistor switched by a current providing signal to provide the one of the driving voltage and the first ground voltage to the second driving thin film transistor; a third switching thin film transistor receiving a second ground voltage and switched by a selection signal to output the second ground voltage to an output terminal of the first switching thin film transistor; a fourth switching thin film transistor disposed among an output terminal of the second switching thin film transistor, a gate terminal of the first driving thin film transistor and a gate terminal of the second driving thin film transistor and switched by the selection signal; and a first capacitor disposed among the output terminal of the first switching thin film transistor, the gate terminal of the first driving thin film transistor and the gate terminal of the second driving thin film transistor, wherein “n” is a positive integer.

Owner:LG DISPLAY CO LTD

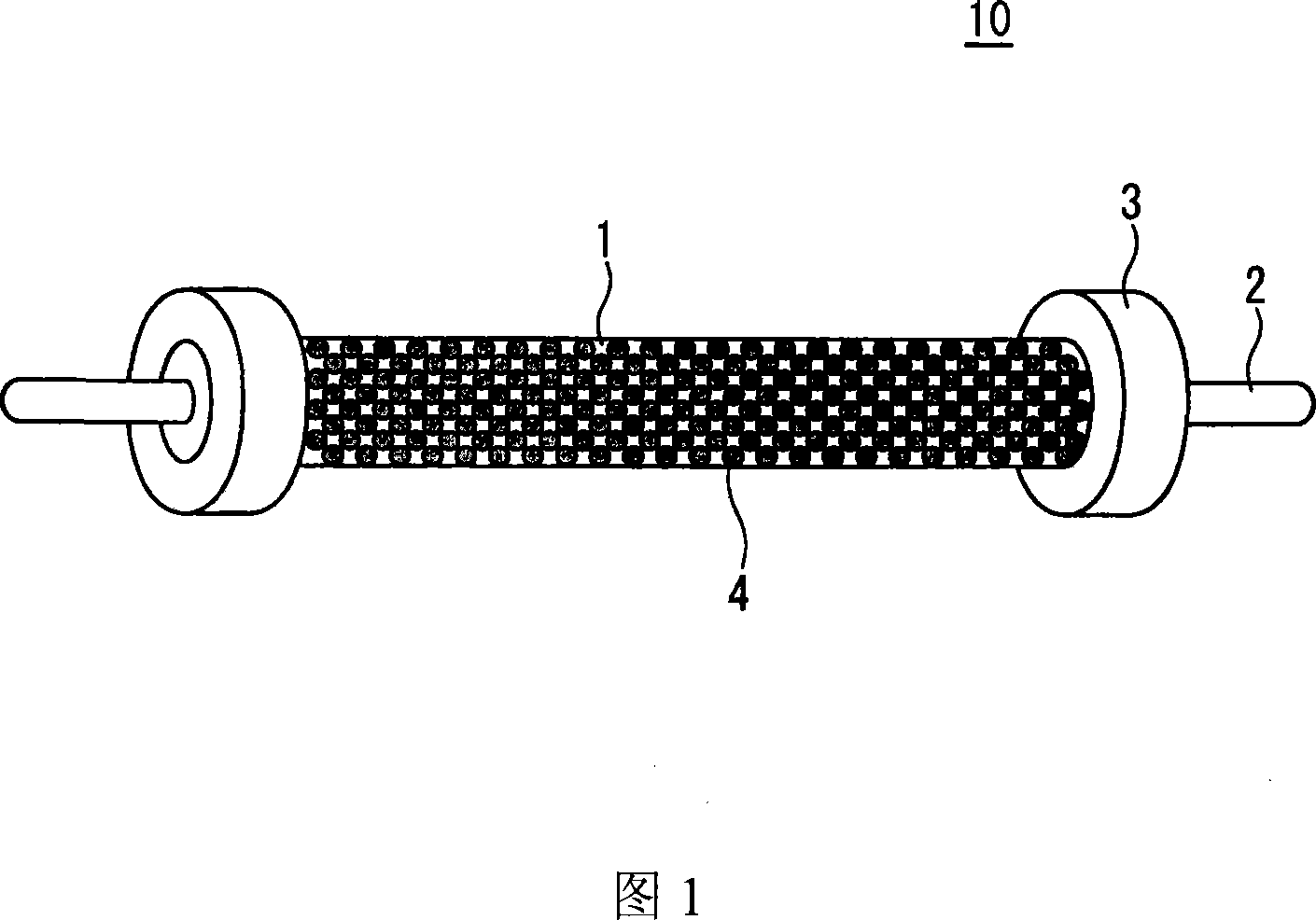

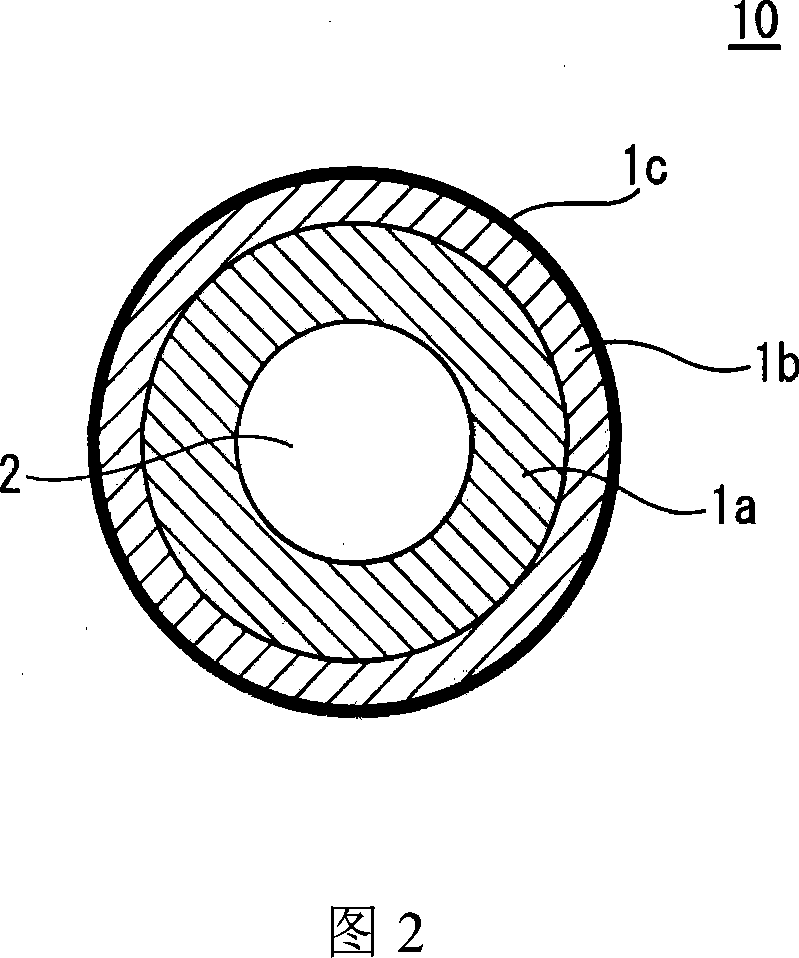

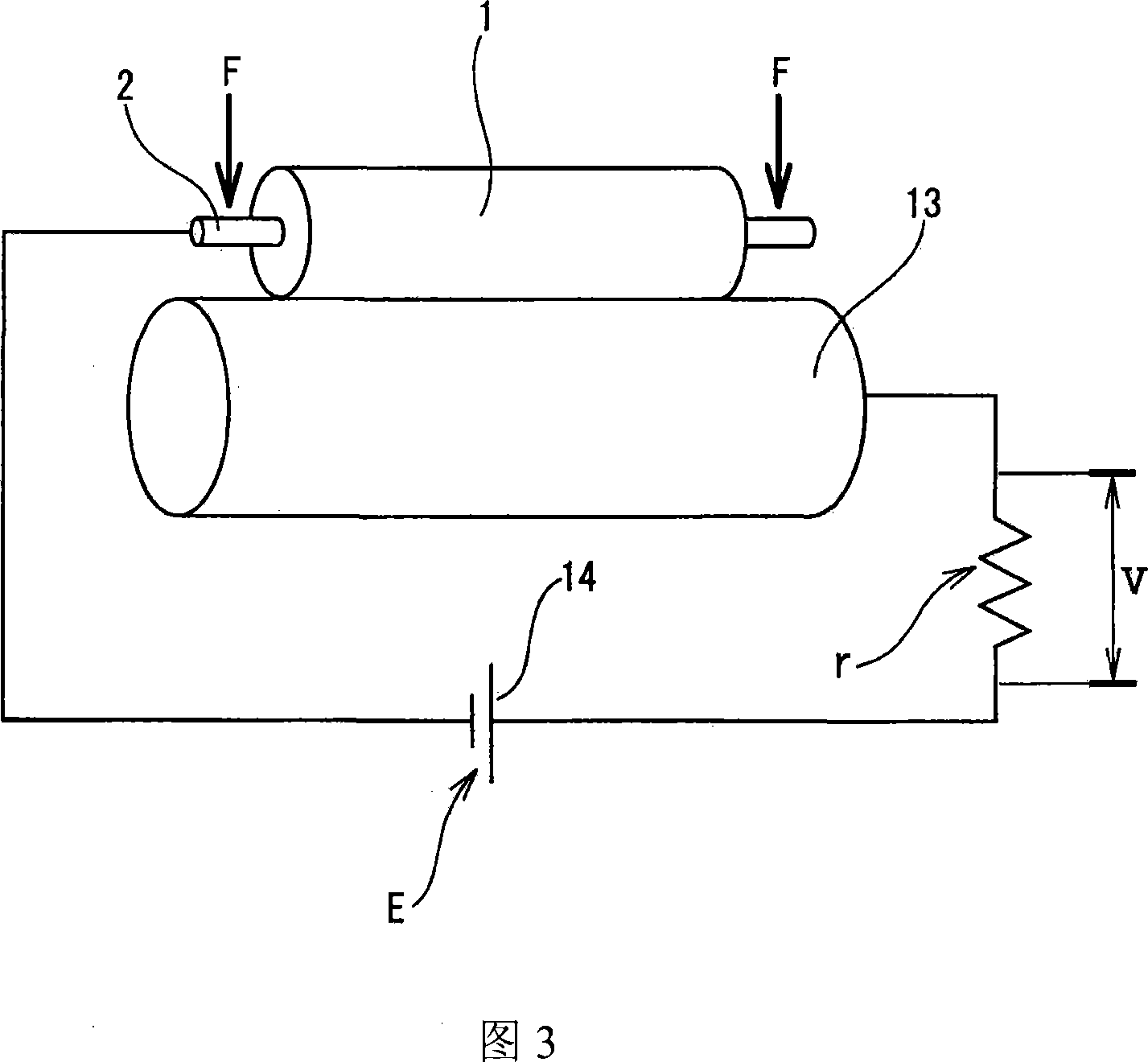

Semiconductor rubber member and developing roller composed of semiconductor rubber member

InactiveCN101055455AElectrical uniformityLower the resistance valueElectrographic process apparatusElectrical resistance and conductanceSurface layer

The present invention provides a developing roller including a semiconductive rubber member having not less than two vulcanized layers including a base layer composed of a vulcanized electro-conductive rubber composition and a surface layer composed of a vulcanized rubber composition. An electric resistance value of the base layer is set to not more than 10<7>Omega, when the electric resistance value of the base layer is measured by applying a voltage of 100V thereto at a temperature of 10 DEG C. and a relative humidity of 20%. An electric resistance value of a laminate of all layers including the base layer and the surface layer is set not more than 10<7>Omega in the same condition as the above-described condition in which the electric resistance value of the base layer is measured.

Owner:SUMITOMO RUBBER IND LTD

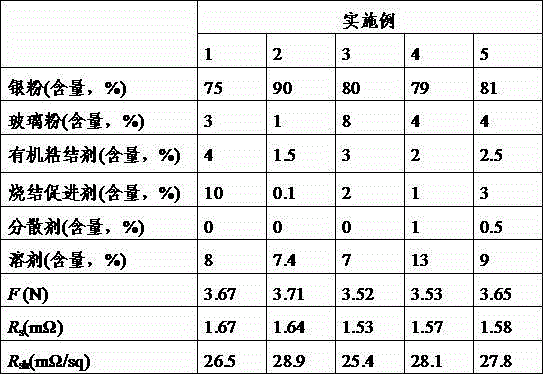

Doping type solar cell front silver paste

ActiveCN103559938AIncrease lytic activityHigh bonding strengthNon-conductive material with dispersed conductive materialSemiconductor devicesSilver pasteIndium

The invention relates to a doping type solar cell front silver paste. The composition and weight percentage of the paste is 75% to 90% of silver powder, 1% to 8% of glass powder, 1.5% to 4% of organic binder, 0.1 % to 10% of compound containing indium and zinc, 0% to 1% of dispersing agent, and a solvent as a surplus, wherein the glass powder is la, boron, and zinc glass system, the compound containing indium and zinc is A(Zn(CH3(CH2)16COO)2), and A comprises the element In. According to the doping type solar cell front silver paste, since the la, boron, and zinc glass system glass powder is employed, the compound containing indium and zinc is added at the same time, the bonding strength between an electrode and a silicon substrate is strengthened, and the series resistance and sheet resistance are reduced. At the same time, in the compound containing indium and zinc, a zinc component is hard zinc stearate, the effect of surface tension of a contact interface between the compound containing indium and zinc and the organic binder and the solvent, and the electric performance of the electrode is more uniform.

Owner:JIANGSU RUIDE NEW ENERGY TECH

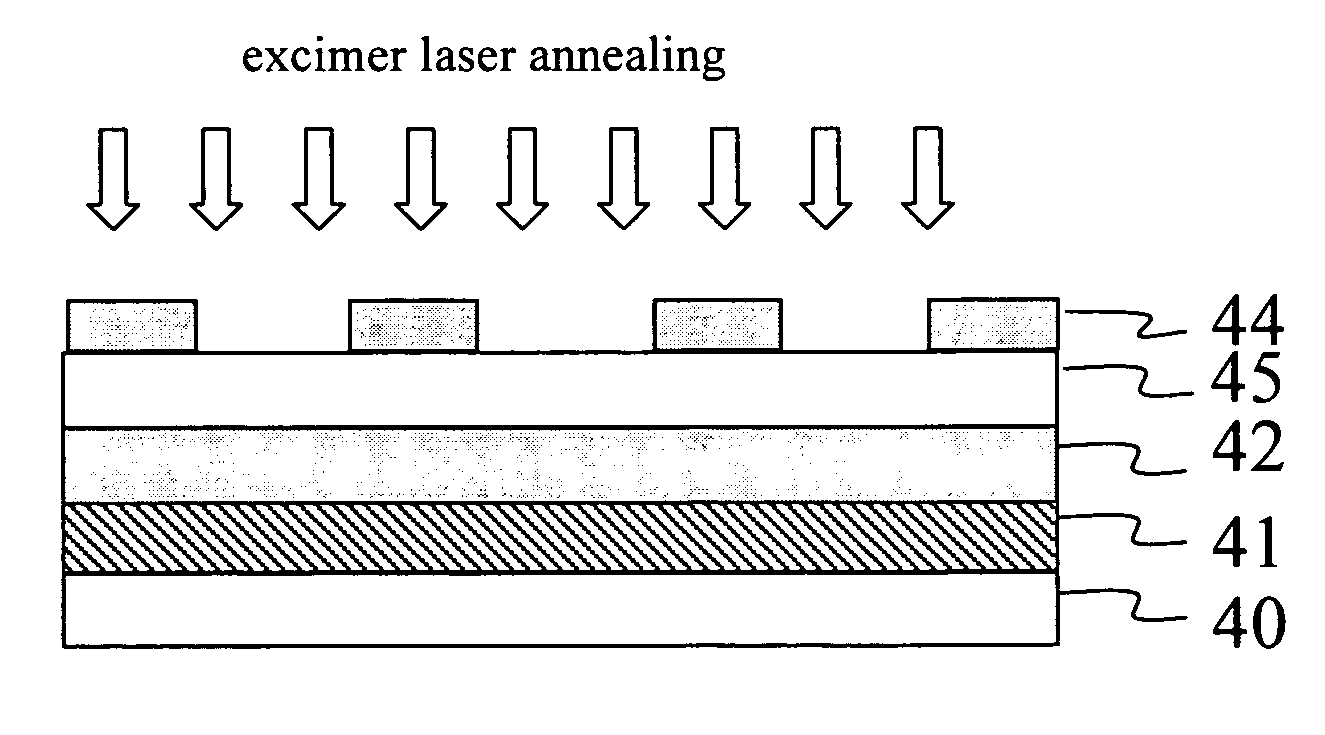

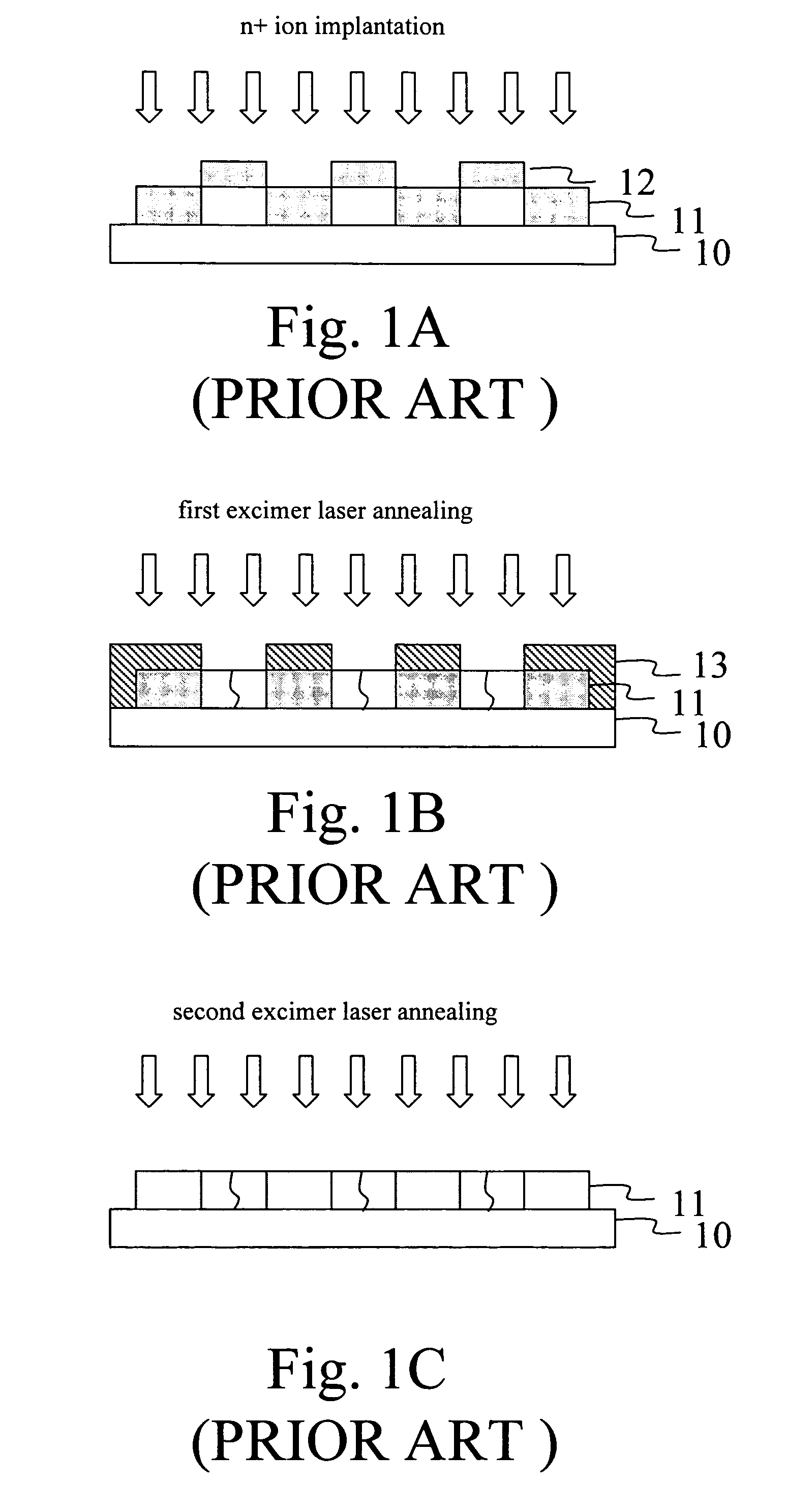

Polysilicon thin film fabrication method

ActiveUS20070065998A1Excellent electrical propertiesElectrical uniformitySolid-state devicesSemiconductor/solid-state device manufacturingHeat conductingAmorphous silicon

A polysilicon thin film fabrication method is provided, in which a heat-absorbing layer is used to provide sufficient heat for grain growth of an amorphous silicon thin film, and an insulating layer is used to isolate the heat-absorbing layer and the amorphous silicon thin film. A regular heat-conducting layer is used as a cooling source to control the crystallization position and grain size of the amorphous silicon thin film. Therefore, the amorphous silicon thin film can crystallize into a uniform polysilicon thin film, and the electrical characteristics of the polysilicon thin film can be stably controlled.

Owner:NAT TAIWAN UNIV

Large size semiconductor crystal with low dislocation density

InactiveUS6866714B2Easy to getElectrical uniformityAfter-treatment apparatusPolycrystalline material growthVolumetric Mass DensitySingle crystal

A large semiconductor crystal has a diameter of at least 6 inches and a low dislocation density of not more than 1×104 cm−2. The crystal is preferably a single crystal of GaAs, or one of CdTe, InAs, GaSb, Si or Ge, and may have a positive boron concentration of not more than 1×1016 cm−3 and a carbon concentration of 0.5×1015 cm−3 to 1.5×1015 cm−3 with a uniform concentration throughout the crystal. Such a crystal can form a very thin wafer with a low dislocation density. A special method and apparatus for producing such a crystal is also disclosed.

Owner:SUMITOMO ELECTRIC IND LTD

Liquid crystal display device

ActiveCN106647074AImprove cooling effectElectrical uniformityNon-linear opticsThermal conductivityLiquid-crystal display

The invention provides a liquid crystal display device. A first epitaxial electrode layer which is used for connecting a conduction point and extends towards the outer side of an array substrate is arranged at the edge of the array substrate, a second epitaxial electrode layer which extends towards the outer side of a color film substrate is arranged at the edge of the color film substrate, at the same time a conduction light-shielding layer which is coated with graphene and light-shielding materials is arranged at the broadside of a liquid crystal display panel, wherein the conduction light-shielding layer is capable of shielding the light leakage around the liquid crystal display device, and is capable of simultaneously connecting the first epitaxial electrode layer and the second epitaxial electrode layer so that breakover is achieved between the array substrate and the color film substrate. Compared with the prior art, conducive gold gum does not need to be produced, the producing time is short, and the product cost is short; meanwhile, due to the fact that graphene has high thermal conductivity efficiency and high electricity conductivity rate, the heat dissipation capability around the liquid crystal display device can be promoted, and the liquid crystal display device is uniform in overall electricity, good in display effect, and has an anti-static function.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

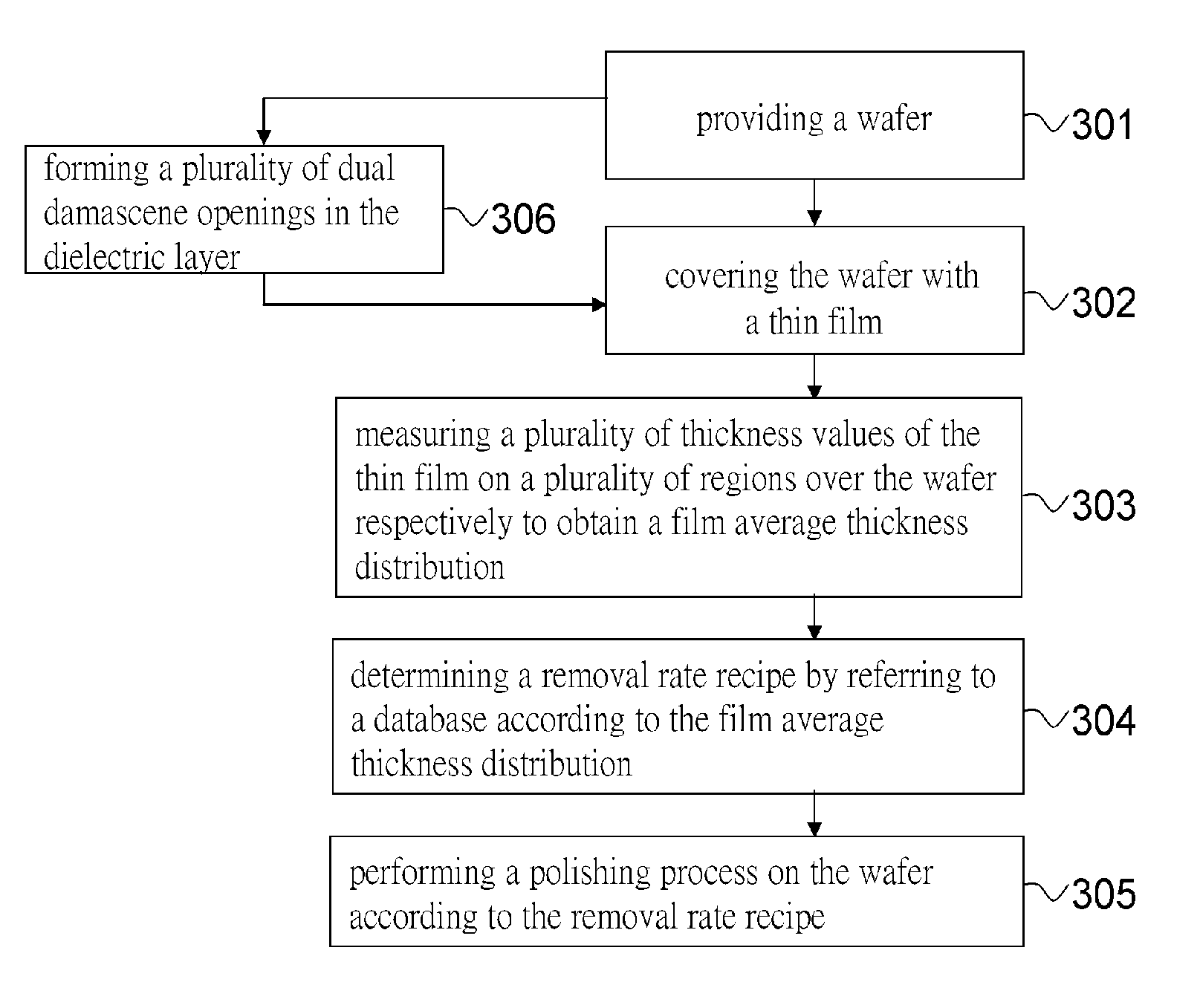

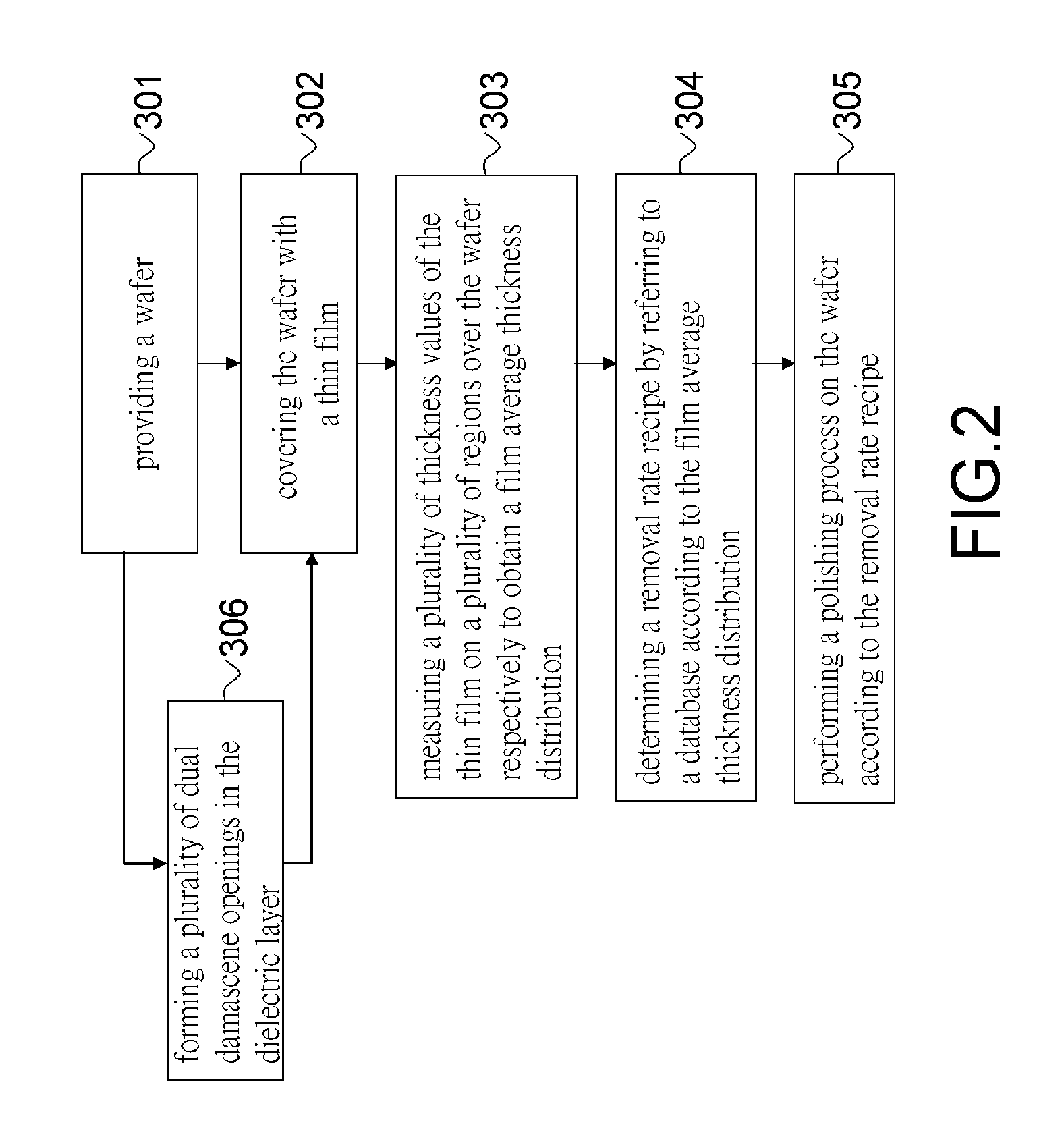

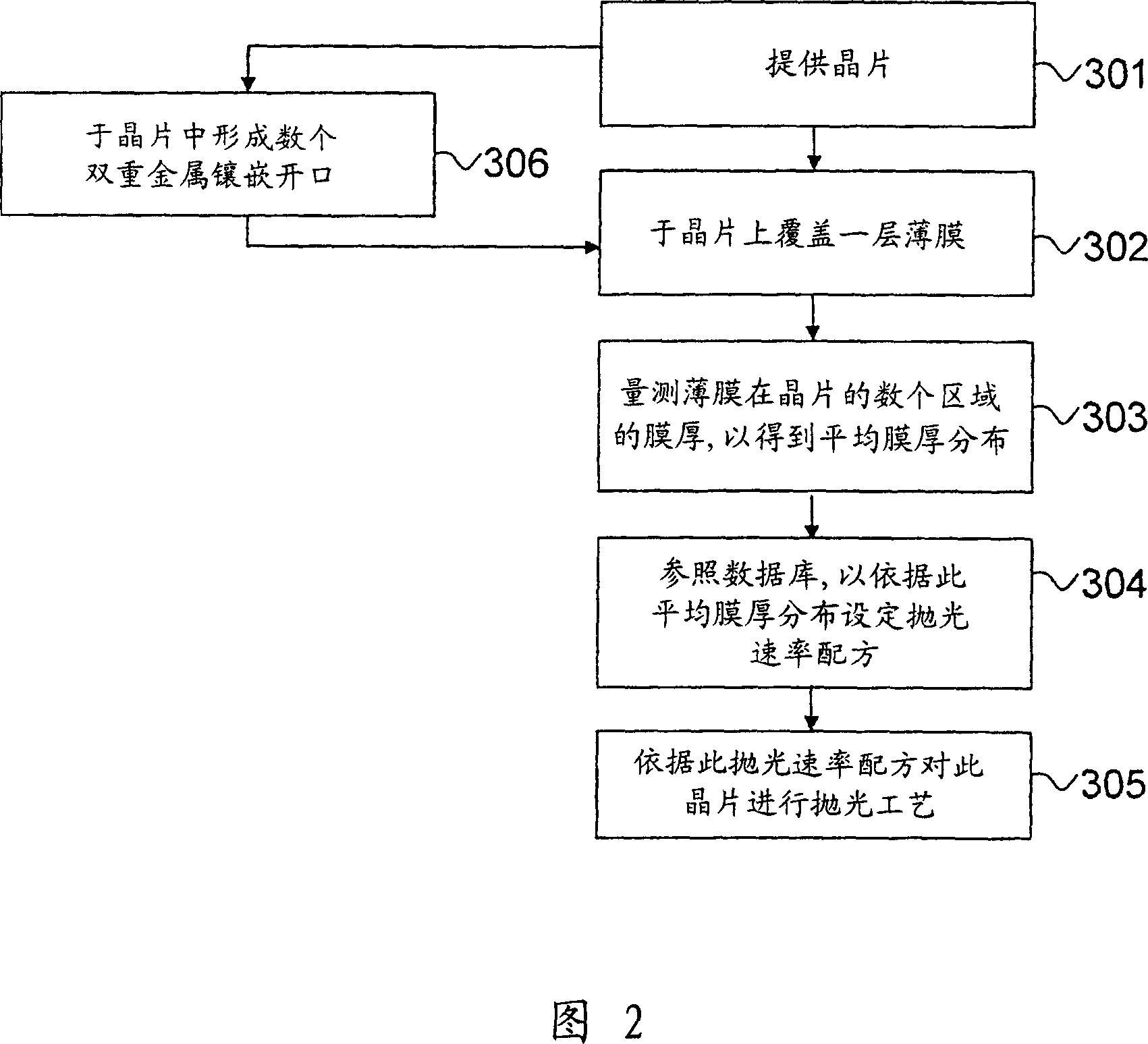

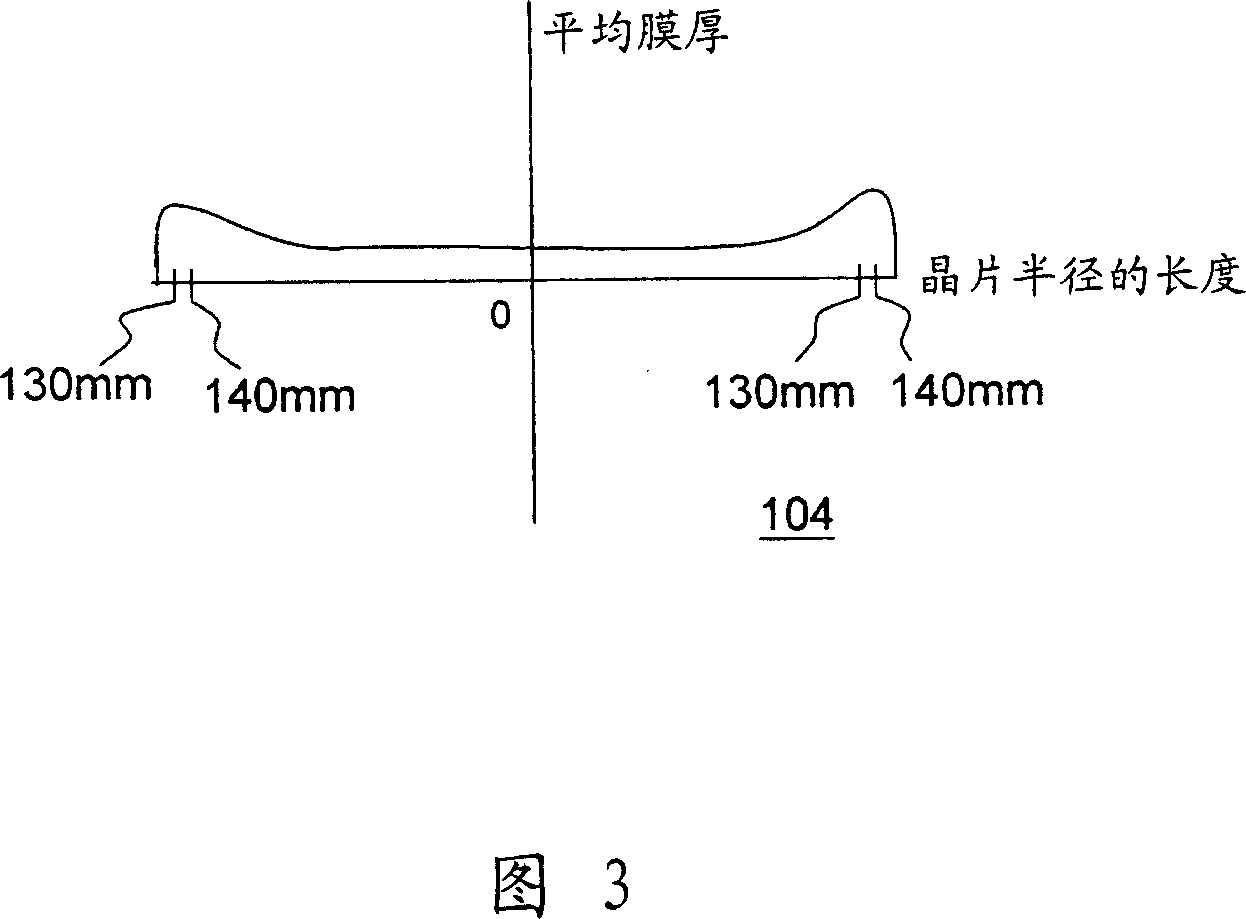

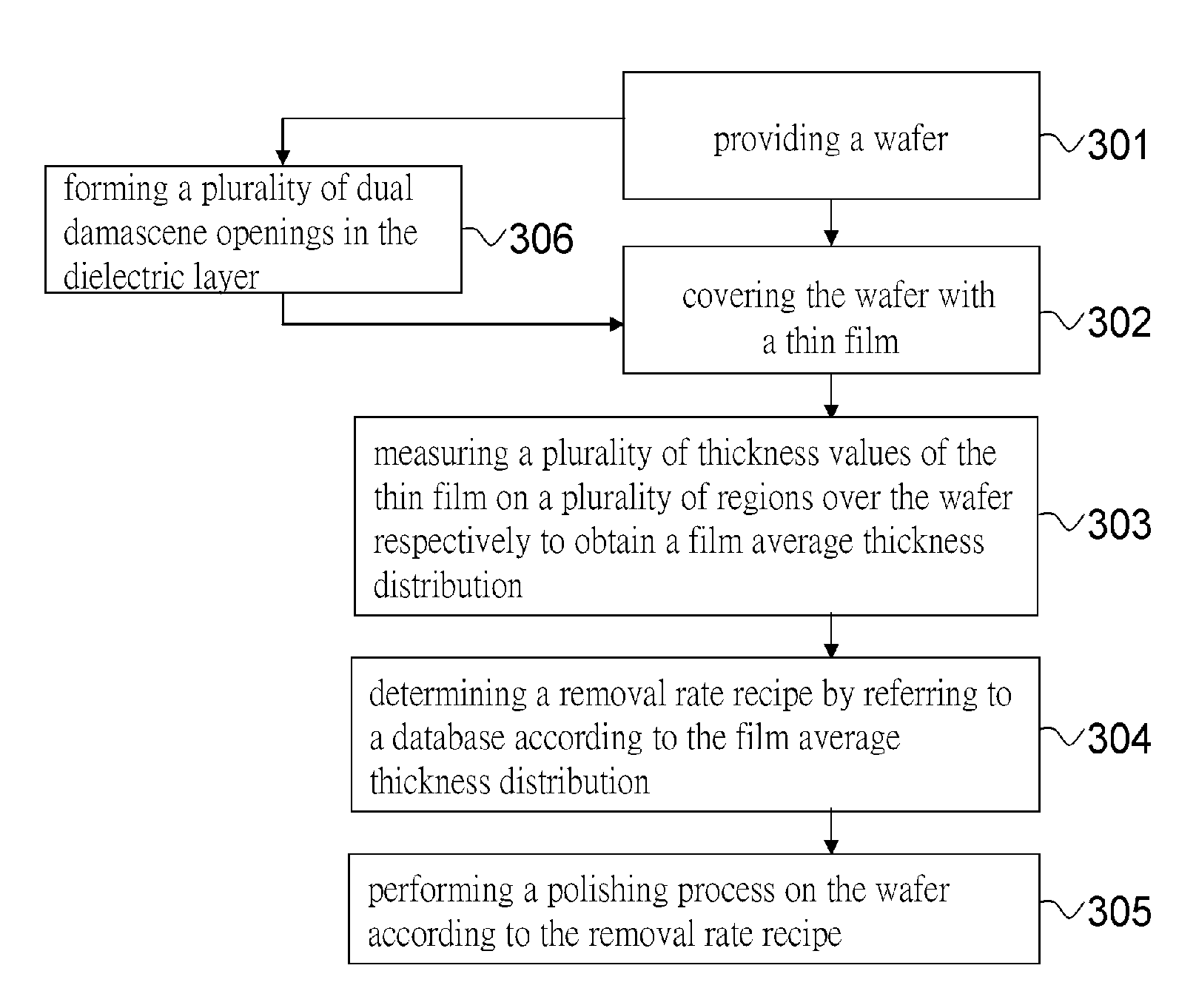

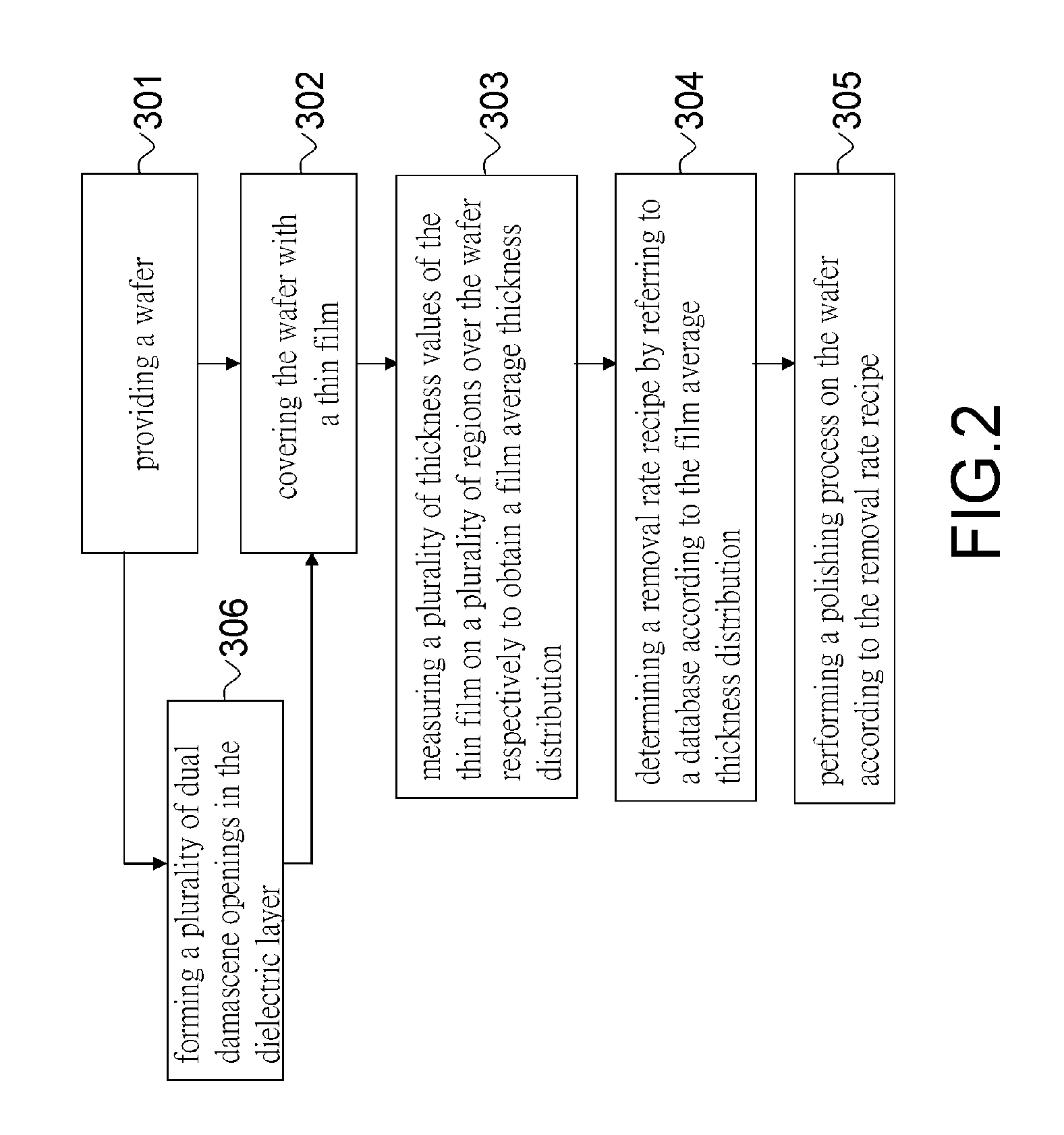

Method for controlling polishing process

ActiveUS20070138140A1Improve uniformityCopper remaining on the wafer edge, over polishing and dishingSemiconductor/solid-state device testing/measurementDecorative surface effectsEngineeringElectrical and Electronics engineering

The invention is directed to a method for controlling a polishing process. The method comprises steps of providing a first wafer, wherein a thin film is located over the first wafer. A film average thickness distribution is obtained by measuring a plurality of thickness values of the thin film on a plurality regions over the wafer respectively. A removal rate recipe is determined according to the film average thickness distribution. A polishing process is performed according to the removal rate recipe.

Owner:UNITED MICROELECTRONICS CORP

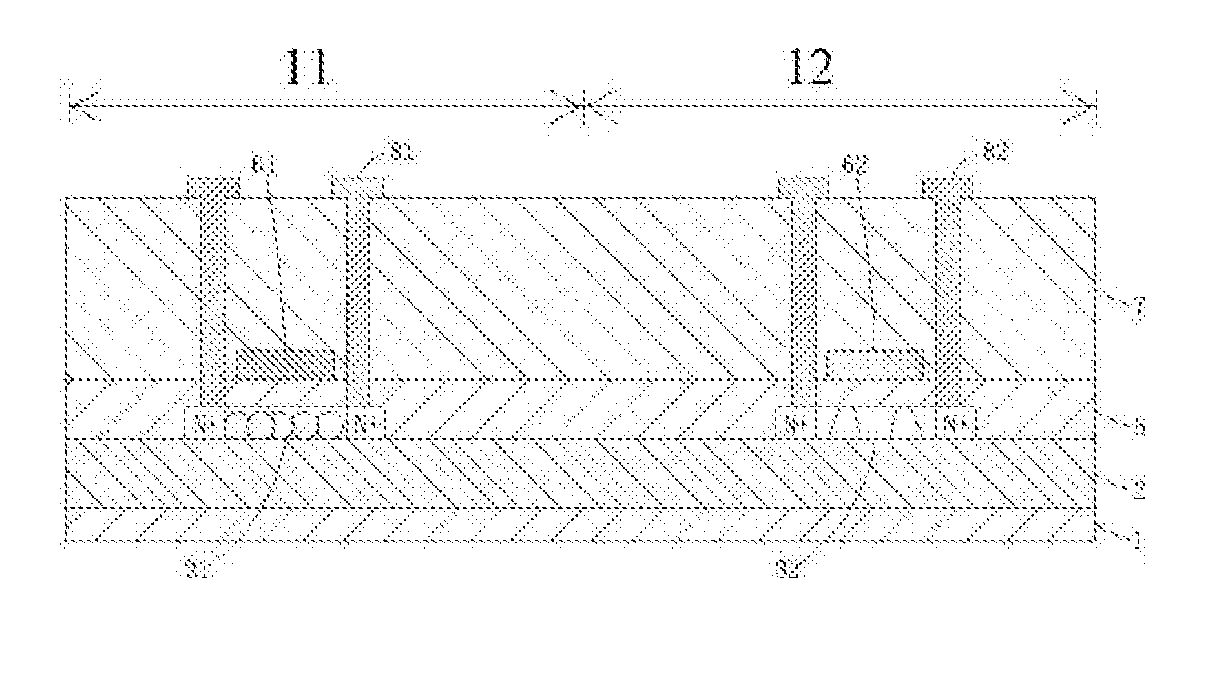

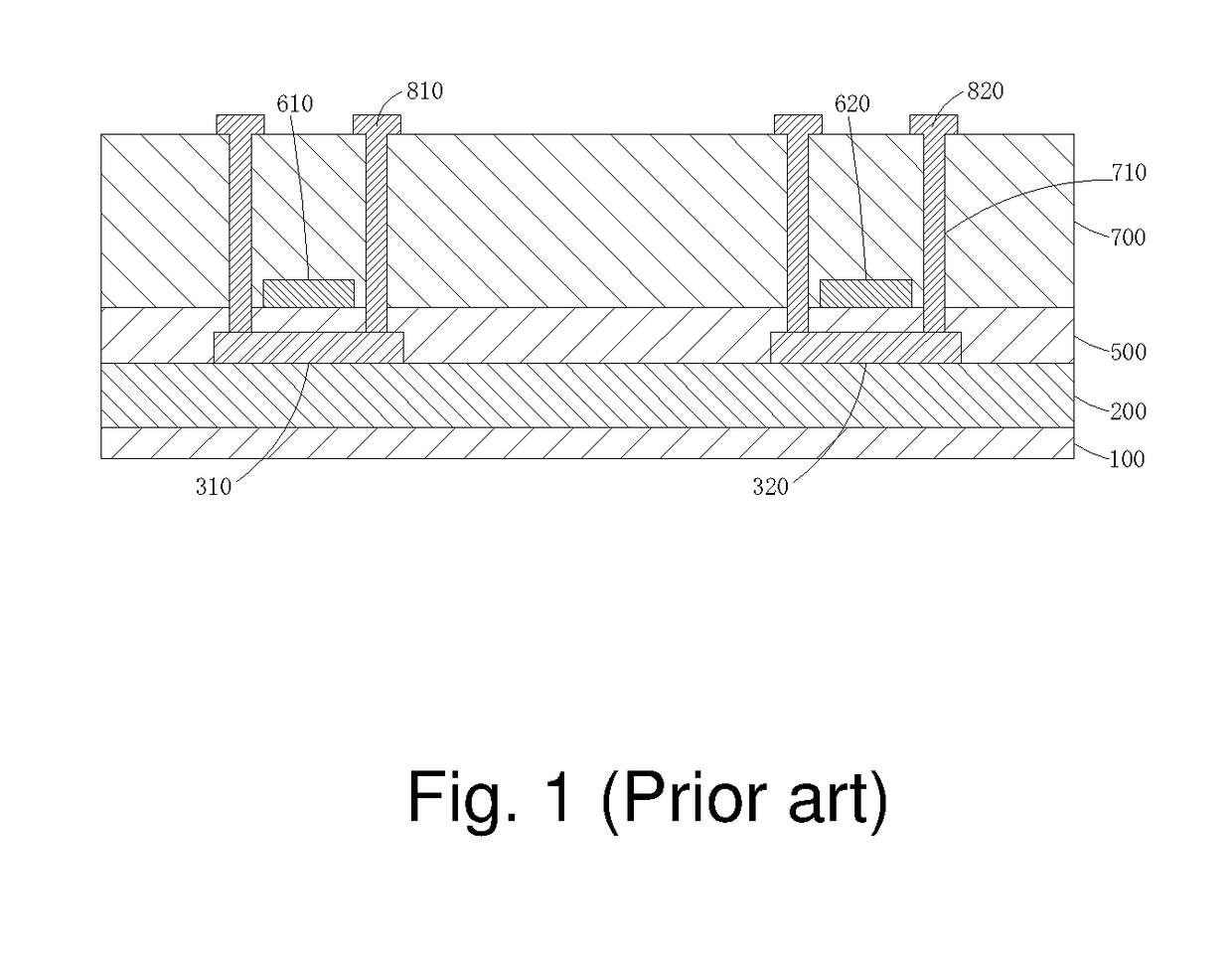

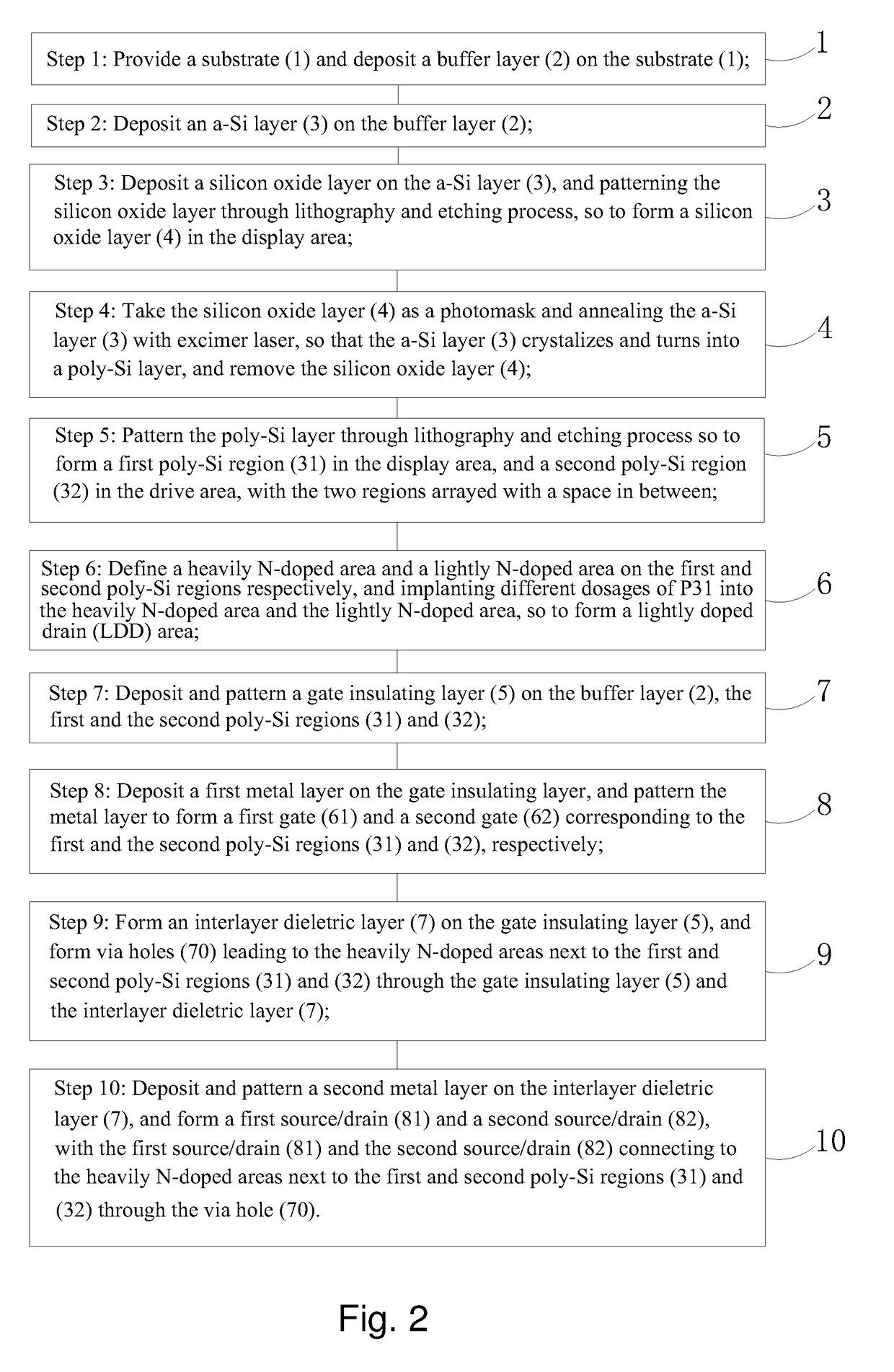

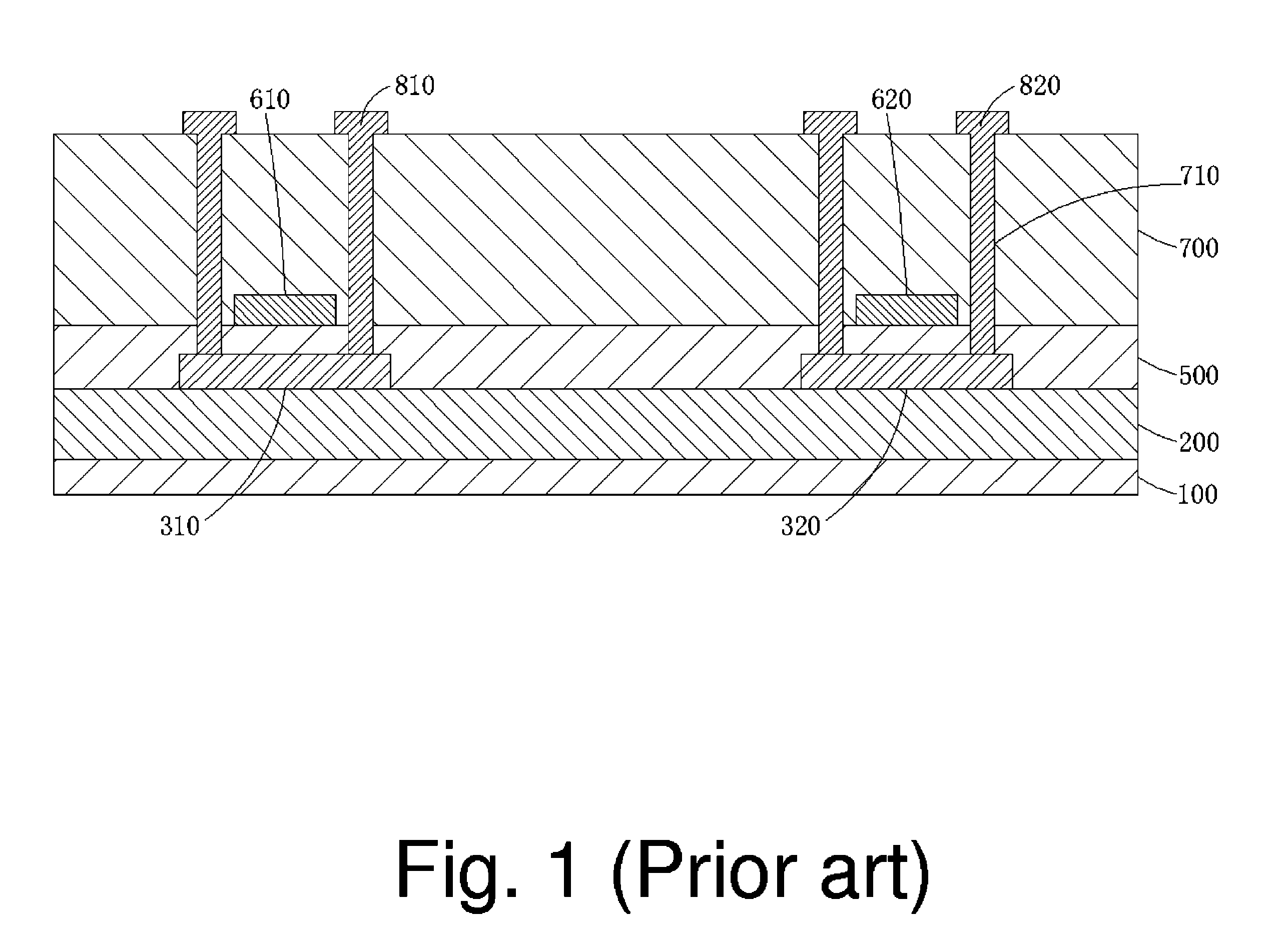

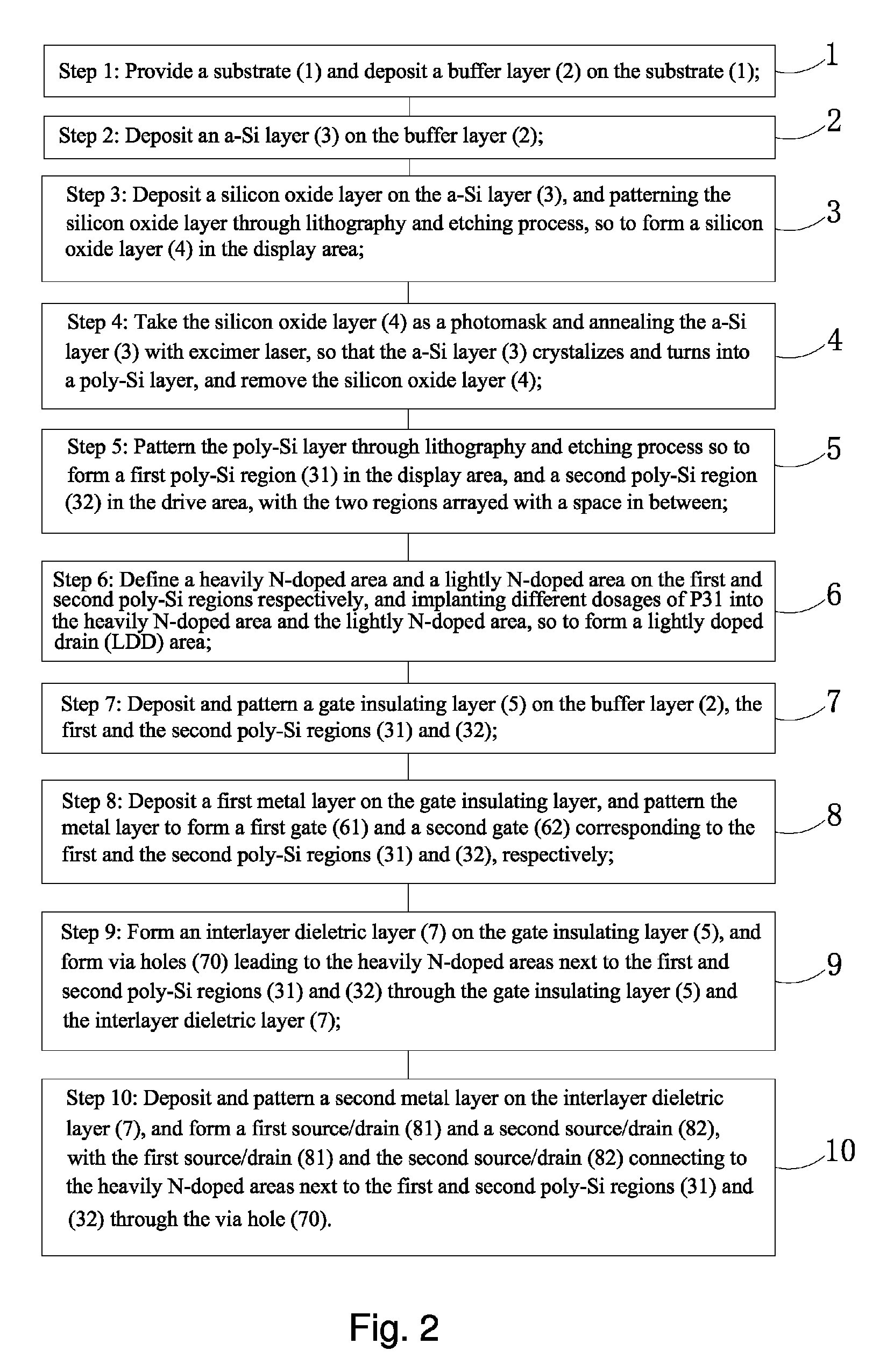

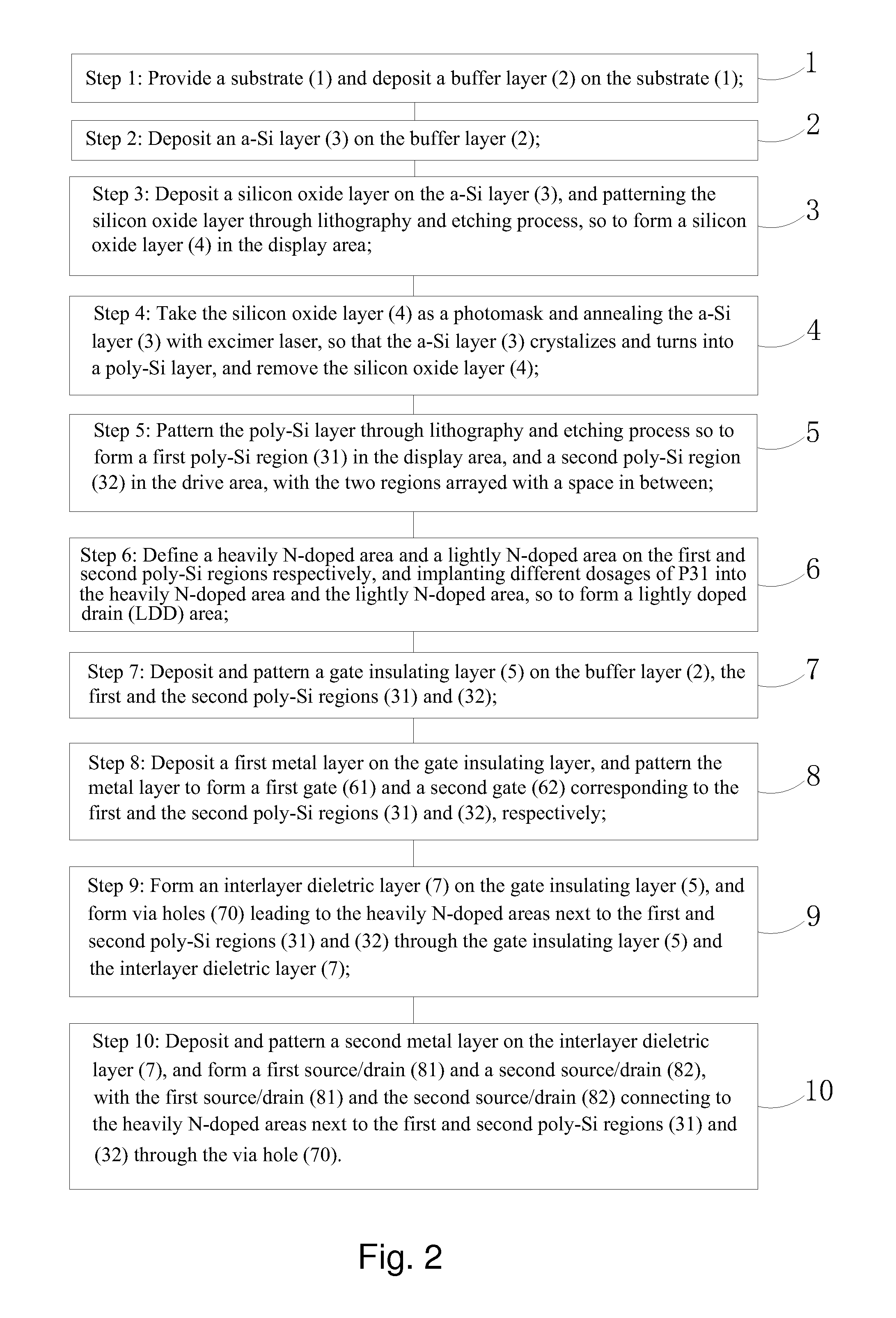

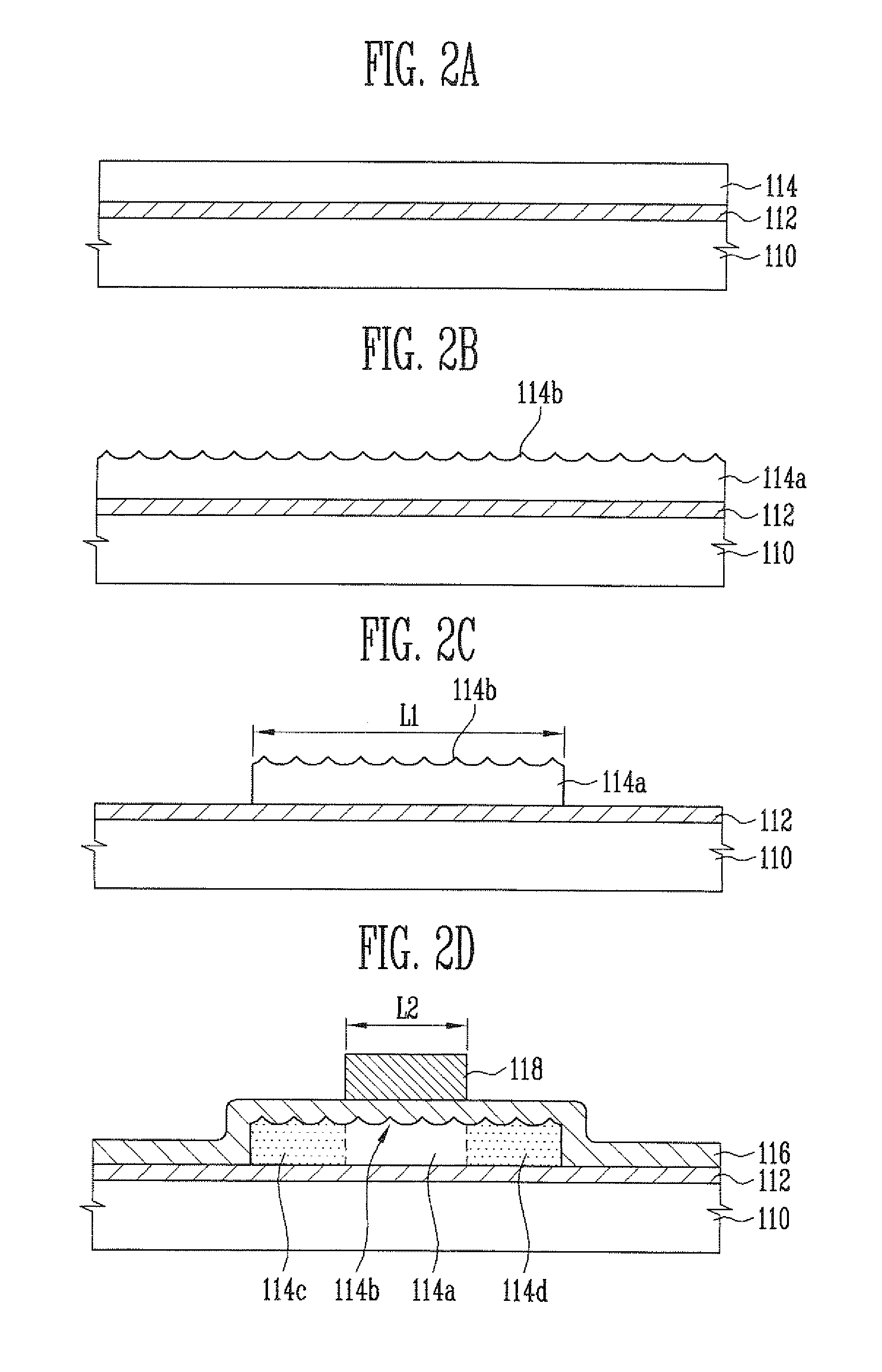

LTPS TFT Substrate Structure and Method of Forming the Same

ActiveUS20170110489A1Large poly-SiHigh electron mobilityTransistorSemiconductor/solid-state device detailsOptoelectronicsSilicon oxide

A method of forming an LTPS TFT substrate includes: Step 1: providing a substrate and depositing a buffer layer; Step 2: depositing an a-Si layer; Step 3: depositing and patterning a silicon oxide layer; Step 4: taking the silicon oxide layer as a photomask and annealing the a-Si layer with excimer laser, so that the a-Si layer crystalizes and turns into a poly-Si layer; Step 5: forming a first poly-Si region and a second poly-Si region; Step 6: defining a heavily N-doped area and a lightly N-doped area on the first and second poly-Si regions, and forming an LDD area; Step 7: depositing and patterning a gate insulating layer; Step 8: forming a first gate and a second gate; Step 9: forming via holes; and Step 10: forming a first source / drain and a second source / drain.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

Control method of polishing technology

ActiveCN1992178AAvoid unevennessElectrical uniformitySemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingMaterials scienceProcess control

It is a polishing process control method. First, provide a chip, and the chip has been covered with a thin film layer. Measuring thin film thickness on the chip's several regions, in order to obtain the average film thickness distribution. Thereafter, according to the average film thickness distribution, it sets a polishing rate formula. Then, based on this polishing rate formula, it processes the polishing technique to the chip. This method can improve the film thickness uniformity after polishing, and furthermore improve the efficiency of polishing technique and yield of the chip.

Owner:UNITED MICROELECTRONICS CORP

Method for forming channel of thin film transistor and compensating circuit

InactiveCN103325688AElectrical uniformityTransistorStatic indicating devicesAmorphous siliconTemperature difference

The invention discloses a method for forming a channel of a thin film transistor and a compensating circuit. The method for forming the channel of the thin film transistor comprises the steps of (1) forming amorphous silicon layers on a substrate; (2) carrying out etching processing on the amorphous silicon layer to form an amorphous silicon graph which comprises a plurality of amorphous silicon layers, wherein each amorphous silicon layer of the amorphous silicon graph is of a bent structure; (3) forming two disconnected spaces in each amorphous silicon layer of the amorphous silicon layer, wherein every two disconnected spaces are formed at adjacent bent positions of each amorphous silicon layer respectively; (4) carrying out laser irradiation processing on the amorphous silicon graph which has the disconnected spaces so as to enable crystal grains, on the two sides of each disconnected space, of each amorphous silicon layer to grow towards a corresponding disconnected space under the action of the temperature difference, and carrying out crystallization to form the channel of the thin film transistor in each disconnected space. The method for forming the channel of the thin film transistor and the compensating circuit can improve the electron mobility of the formed channel, and the electrical property is more even.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

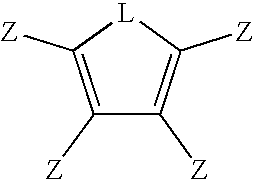

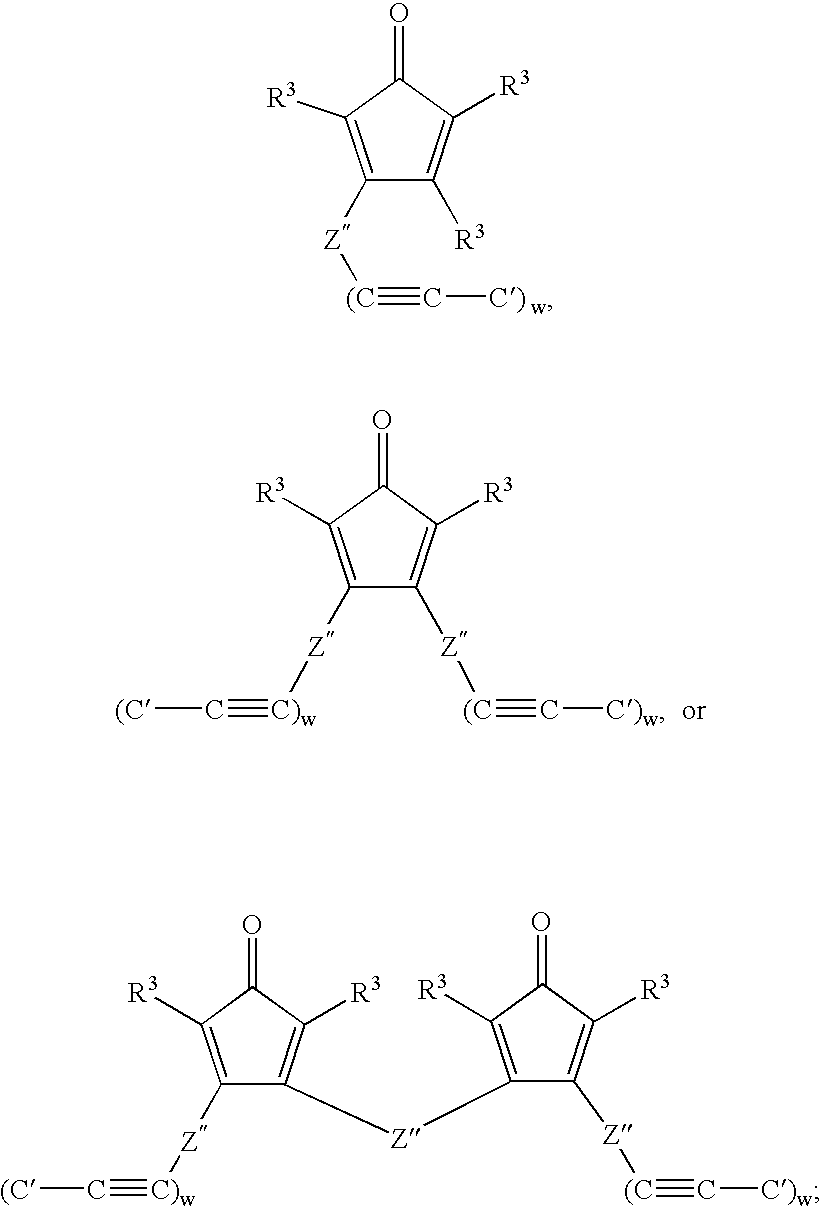

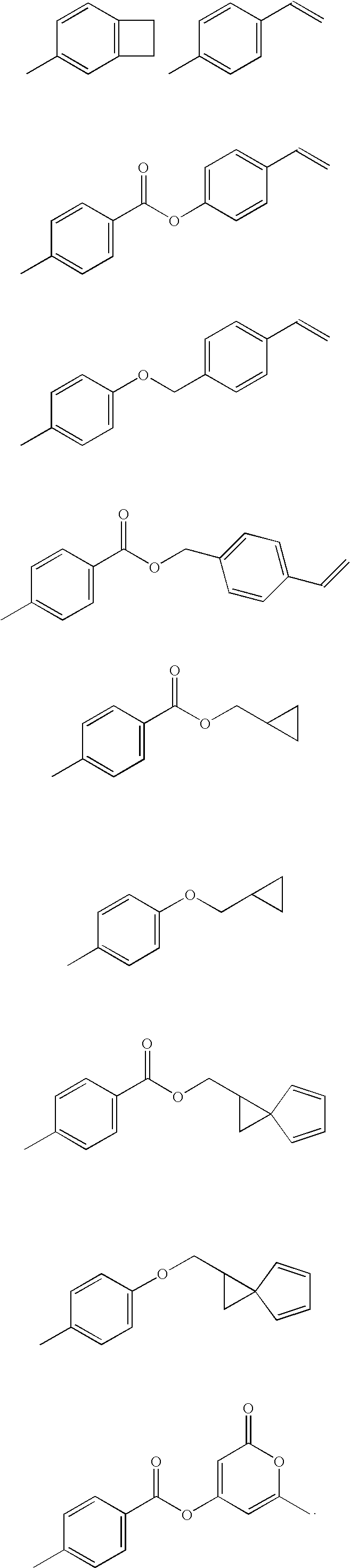

Multifunctional Monomers Containing Bound Poragens and Polyarylene Compositions Therefrom

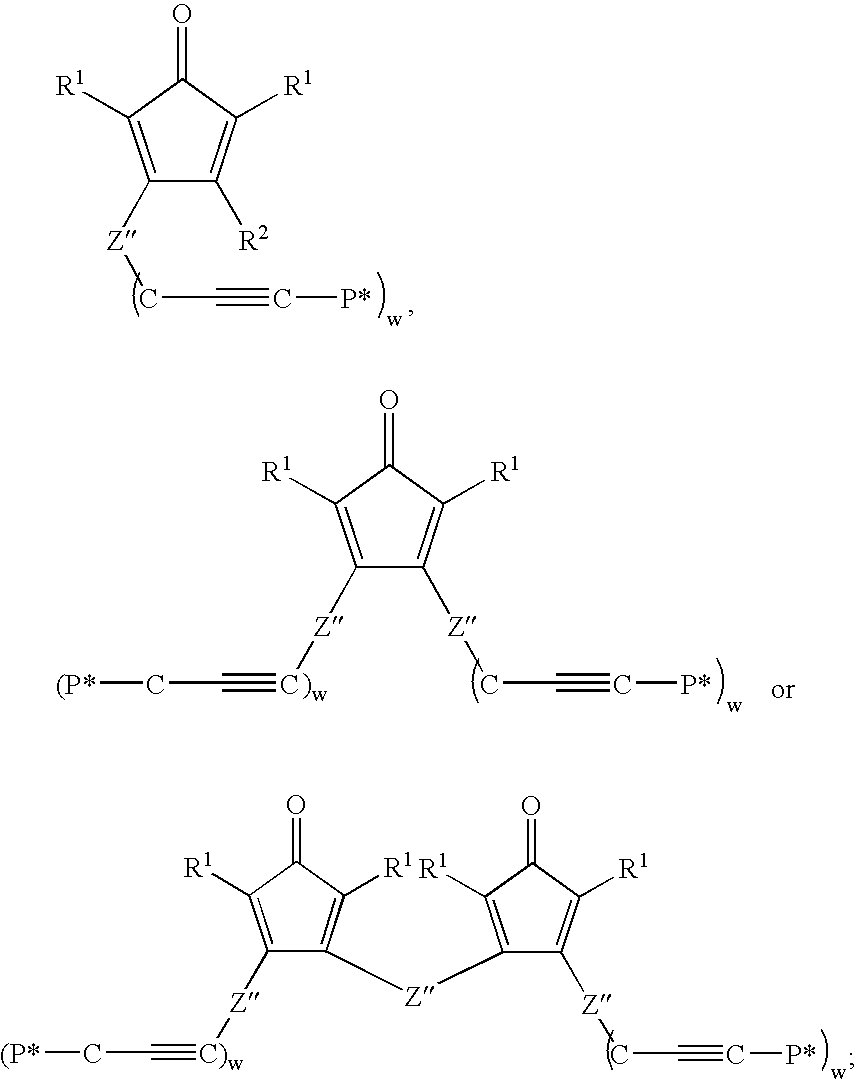

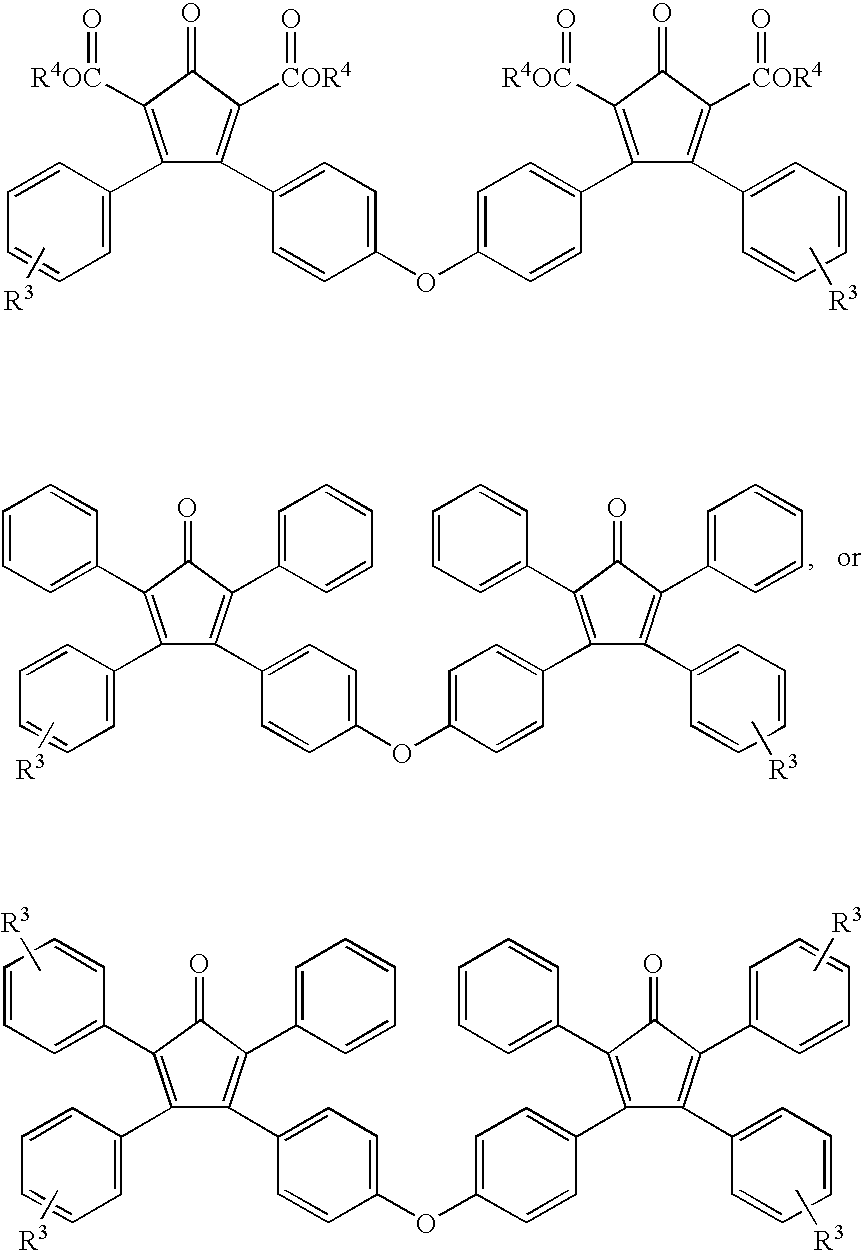

InactiveUS20080227882A1Reduced potential for pore collapse and coalescenceElectrical uniformityOrganic compound preparationCarbonyl compound preparationPolymer scienceCycloaddition

A compound (monomer) comprising i) one or more dienophile groups (A-functional groups), ii) one or more ring structures comprising two conjugated carbon-to-carbon double bonds and a leaving group L (B-functional groups), and iii) one or more chemically bound poragens, characterized in that the A-functional group of one monomer is capable of reaction under cycloaddition reaction conditions with the B-functional group of a second monomer to thereby form a cross-linked, polyphenylene polymer.

Owner:HAHNFELD JERRY L +2

Multifunctional menomers and polyarylene compsotions therefrom

InactiveUS20070037894A1Reduce potentialUniform electrical propertyOrganic compound preparationCarbonyl compound preparation by oxidationChemistryDouble bond

A compound comprising i) one or more dienophile groups (A-functional groups), ii) one or more ring structures comprising two conjugated carbon-to-carbon double bonds and a leaving group L (B-functional groups), and iii) one or more addition polymerizable, telechelic, or graftable functional groups, excluding groups capable of cycloaddition reactions with acetylenic- or conjugated diene functionality (C′-functional groups), characterized in that the A-functional group of one monomer is capable of reaction under cycloaddition reaction conditions with the B-functional group of a second monomer to thereby form a polymer.

Owner:HAHNFELD JERRY L +2

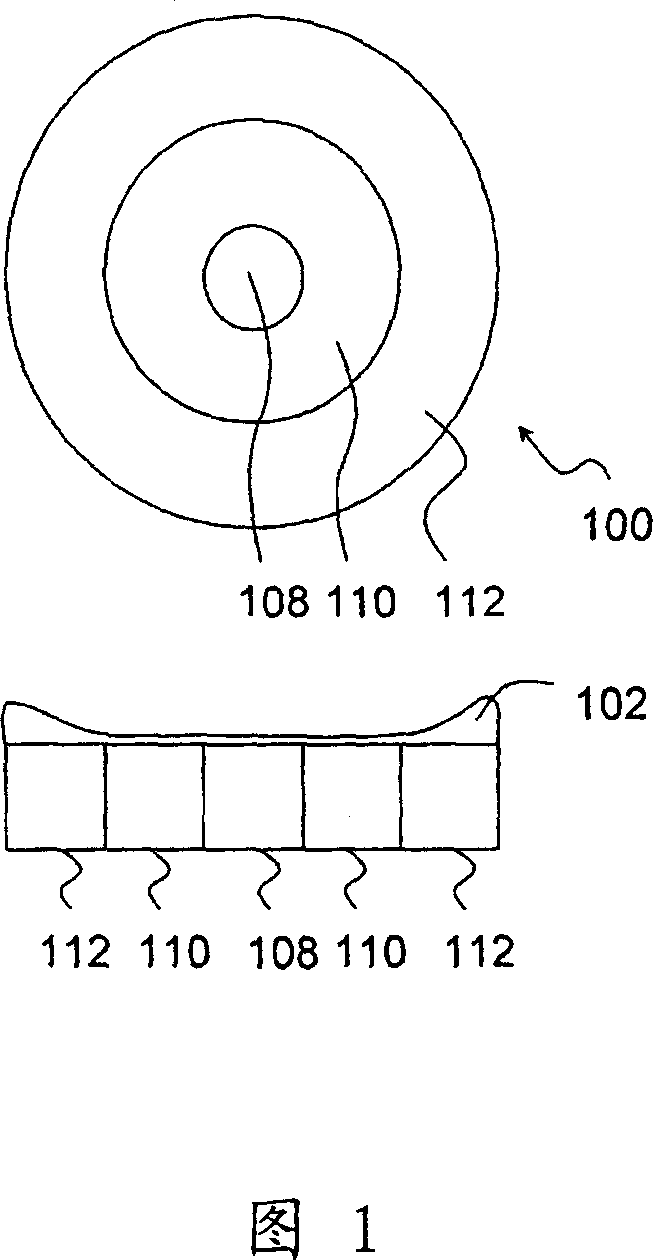

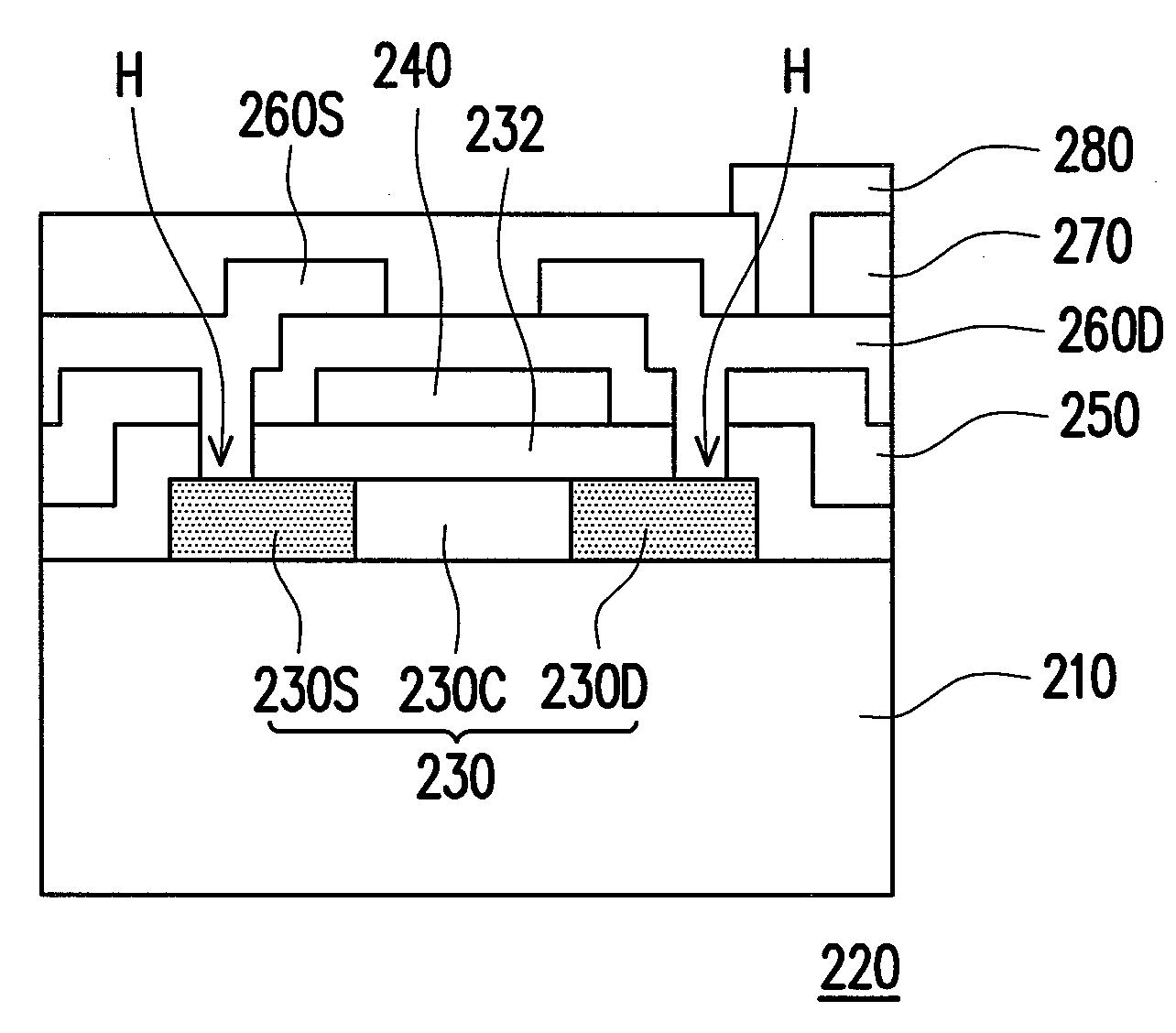

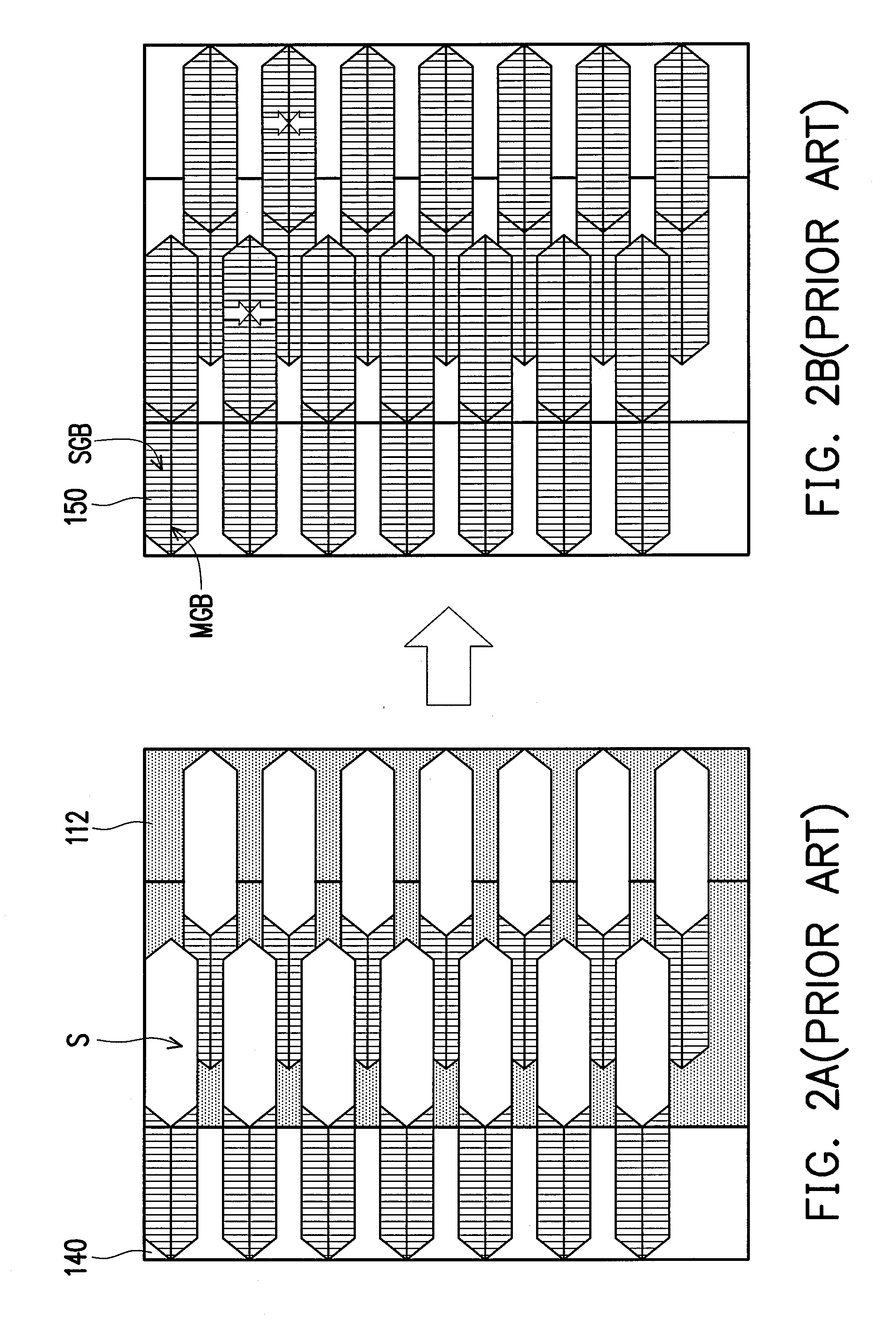

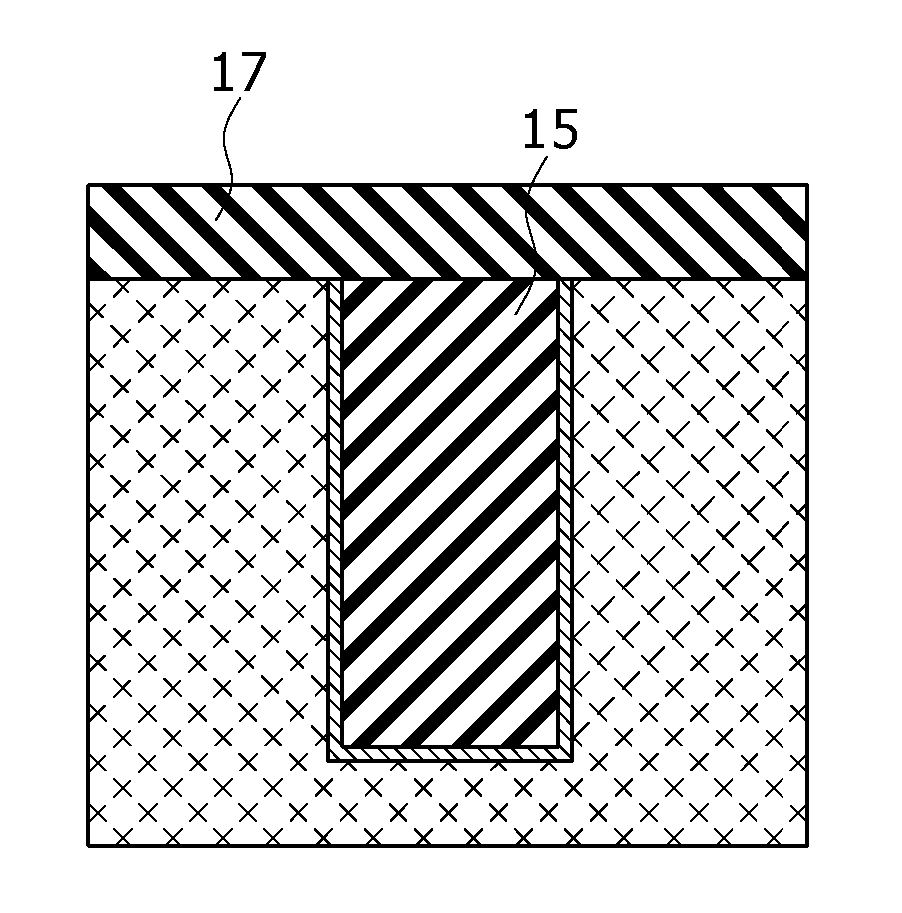

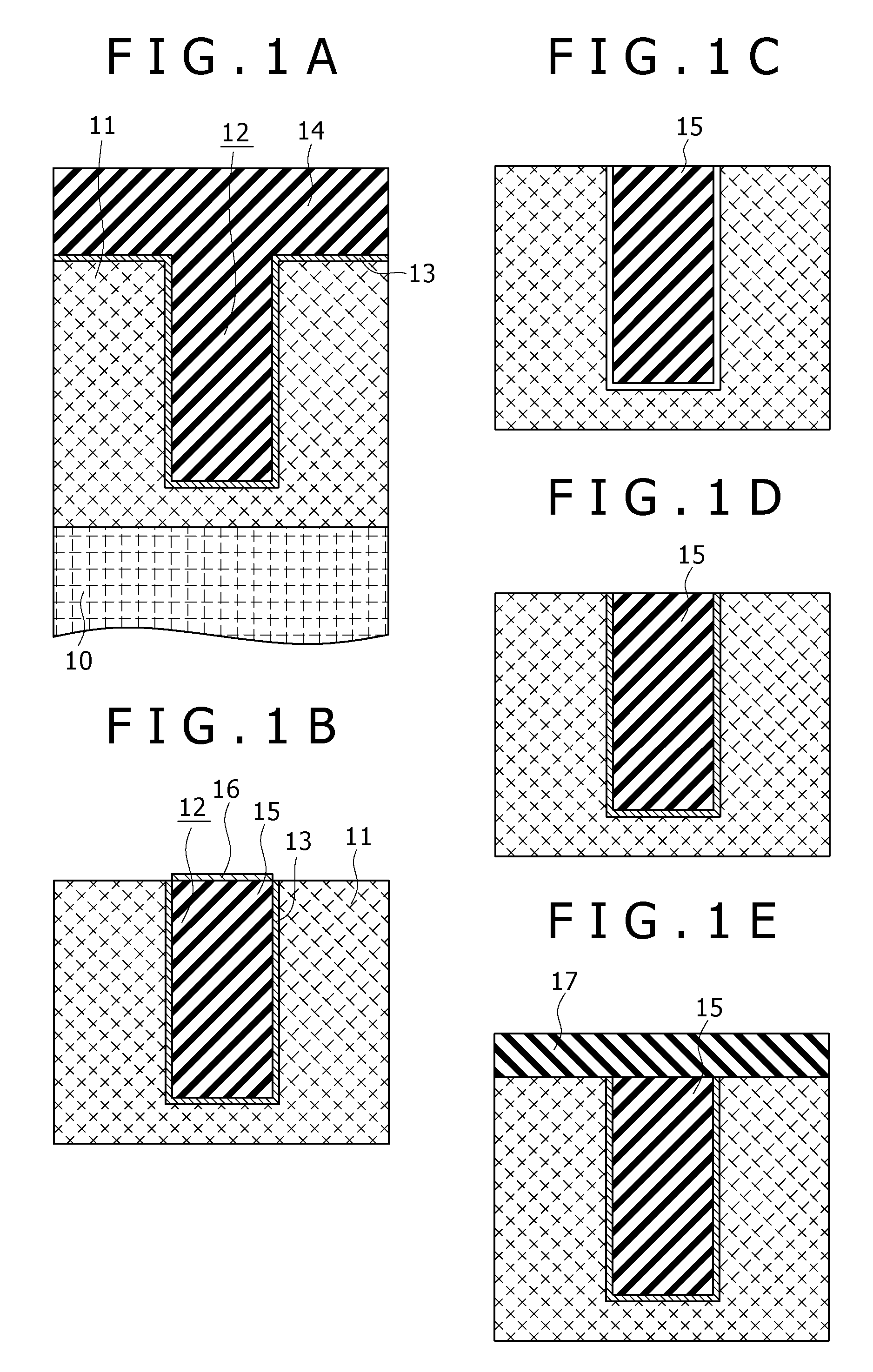

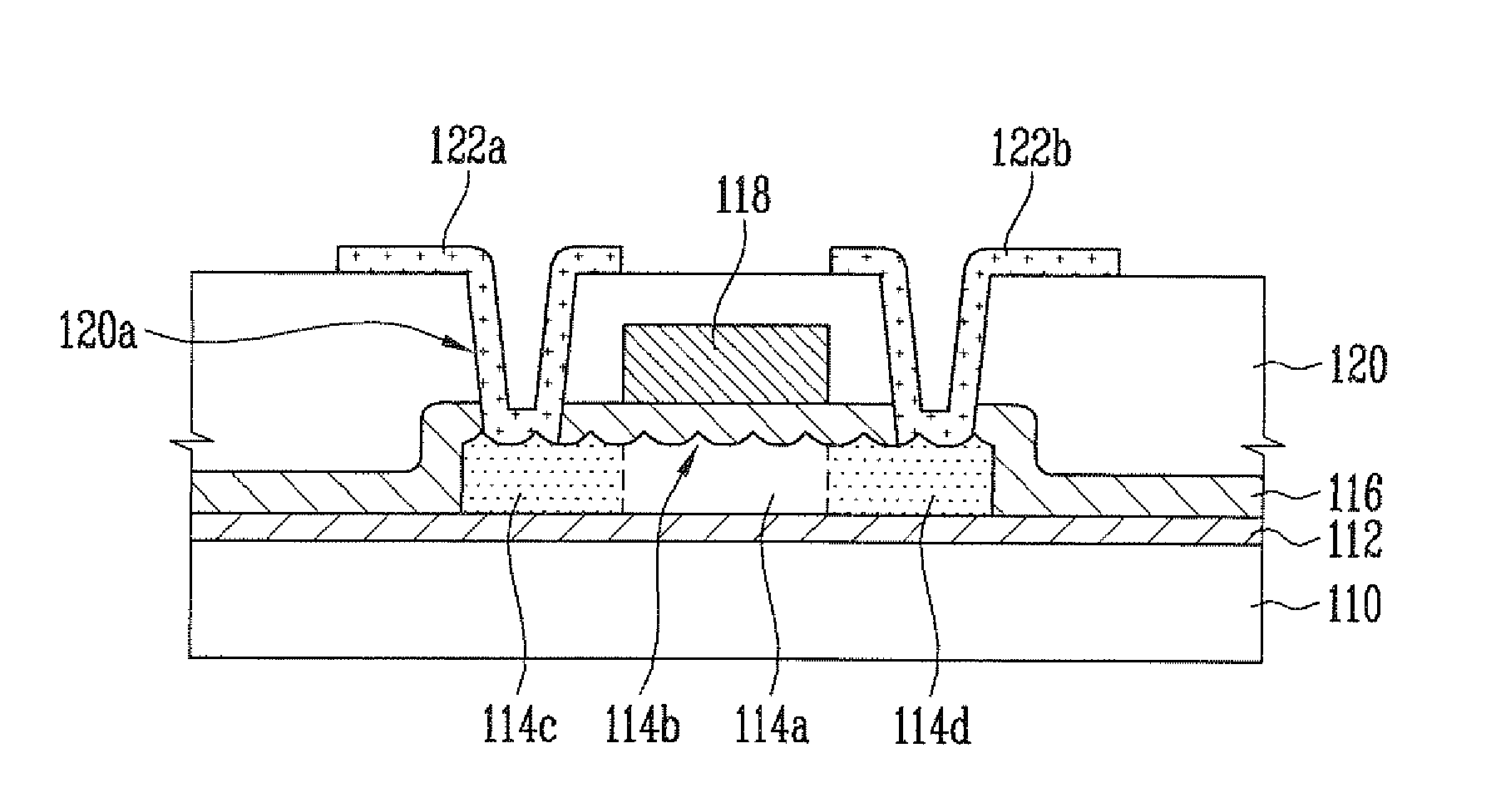

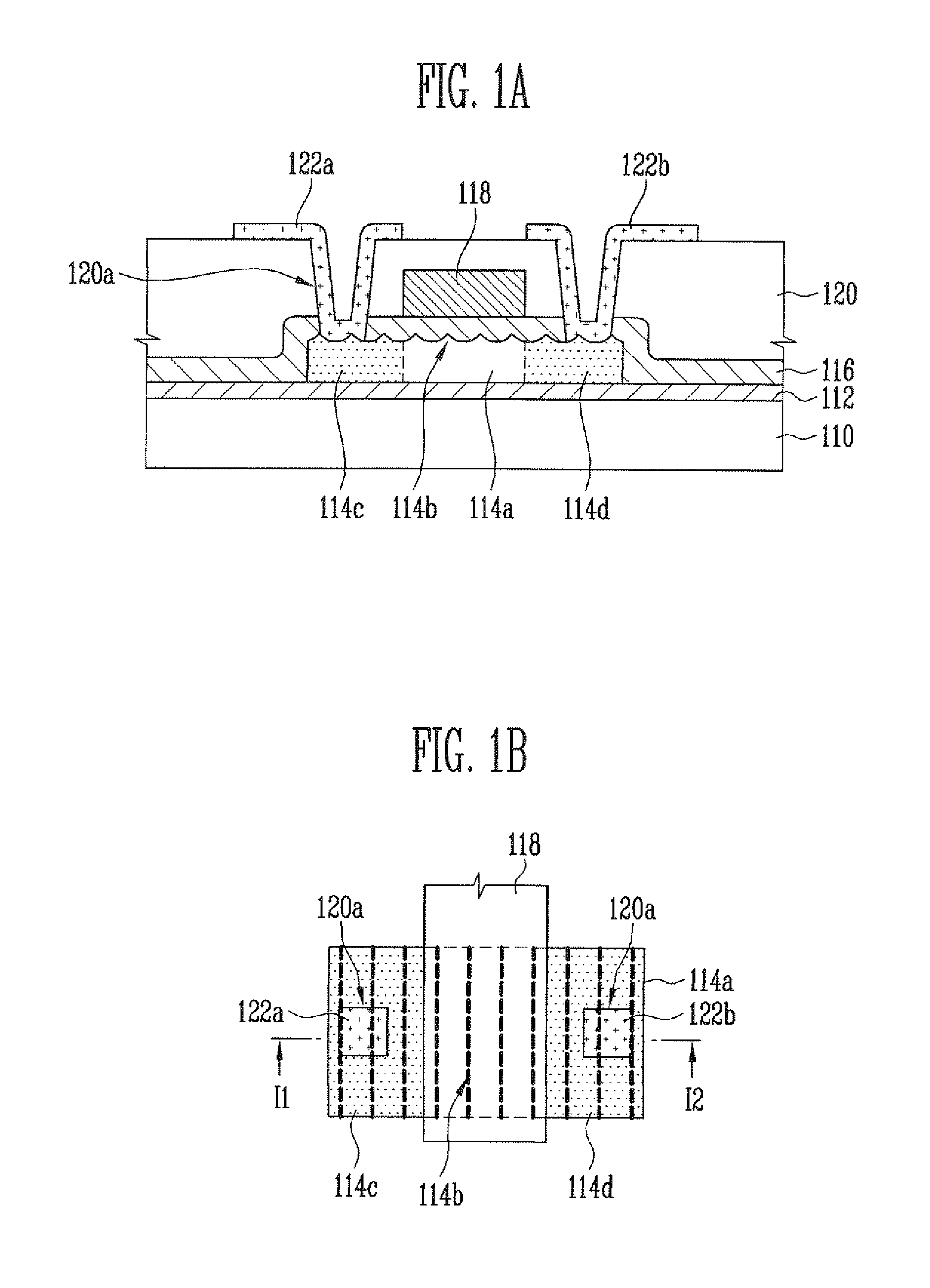

Thin film transistor substrate, electronic apparatus, and methods for fabricating the same

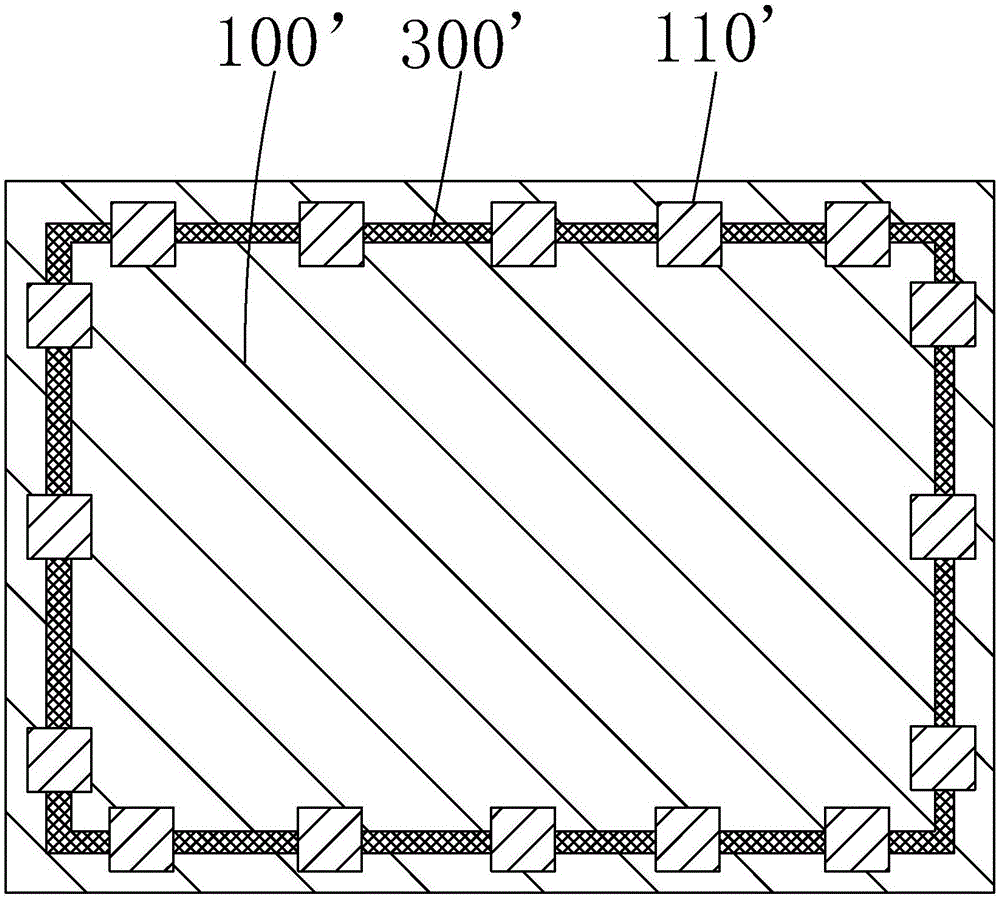

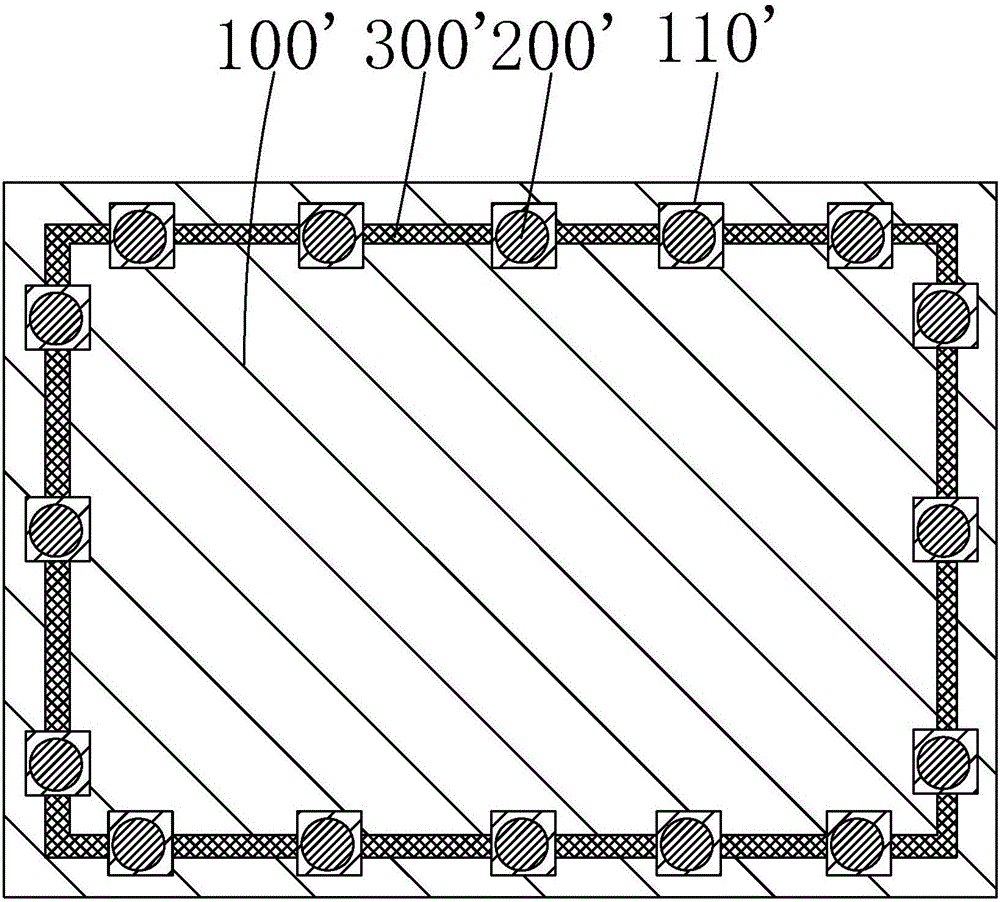

ActiveUS20100019243A1Electrical uniformityImprove uniformitySolid-state devicesSemiconductor/solid-state device manufacturingEngineeringGrain boundary

A TFT substrate includes a substrate and at least a TFT disposed thereon. The TFT includes a semiconductor island and at least a gate. The semiconductor island has a source region, a drain region, and a channel region interposed therebetween. The semiconductor island has sub-grain boundaries. The gate corresponds to the channel region. A first included angle between an extending direction of the gate and a line connecting the centroid of the source region with the centroid of the drain region is not substantially equal to 90 degrees. A second included angle between the sub-grain boundaries in the channel region and the line connecting the centroid of the source region with the centroid of the drain region is not substantially equal to 0 degree or 90 degrees. Additionally, a method of fabricating a TFT substrate, an electronic apparatus, and a method of fabricating the electronic apparatus are also provided.

Owner:AU OPTRONICS CORP

Method for controlling polishing process

ActiveUS7432205B2Improve uniformityCopper remaining on the wafer edge, over polishing and dishingSemiconductor/solid-state device testing/measurementDecorative surface effectsEngineeringElectrical and Electronics engineering

Owner:UNITED MICROELECTRONICS CORP

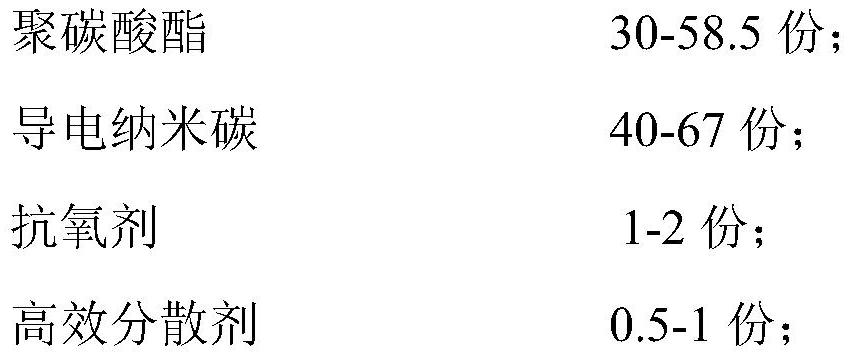

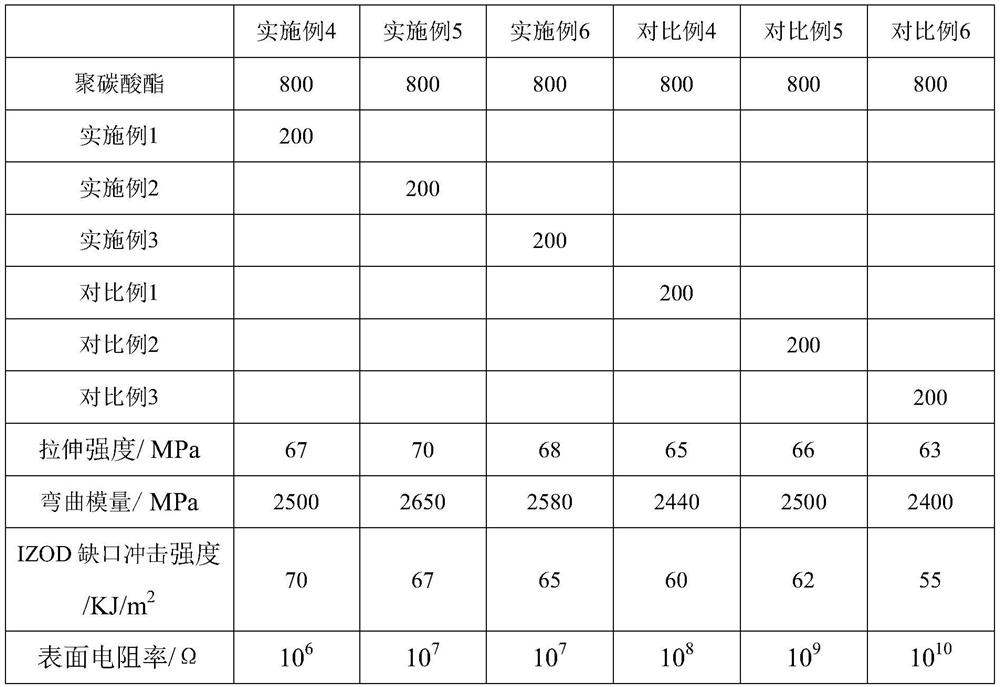

Ultrahigh-conductivity nano carbon masterbatch as well as preparation method and application thereof

The invention discloses ultrahigh-conductivity nano-carbon masterbatch as well as a preparation method and application thereof. The ultrahigh-conductivity nano-carbon masterbatch is prepared from 30-58.5 parts of polycarbonate, 40 to 67 parts of conductive nano carbon masterbatch, 1-2 parts of an antioxidant and 0.5-1 parts of an efficient dispersant through steps of internal mixing, extrusion andgranulation. The conductive nano carbon is formed by compounding multi-walled carbon nanotubes, porous graphene and a coupling agent. The multi-walled carbon nanotubes and the porous graphene are matched for use, and due to the existence of vacancies, the multi-walled carbon nanotubes can be embedded into the porous graphene with the vacancies to play a bridging role, so that the whole system ismore communicated, and the electrical property is better; then the efficient dispersant is added to reduce agglomeration of the conductive nano carbon; compared with the direct twin-screw extrusion ofconductive materials, the method has the advantages that the agglomeration is reduced, the distribution of the conductive material is more uniform, the conductive network is smoother, and the electrical property is more uniform, so that the surface resistivity of the material is greatly reduced.

Owner:HEFEI GENIUS NEW MATERIALS

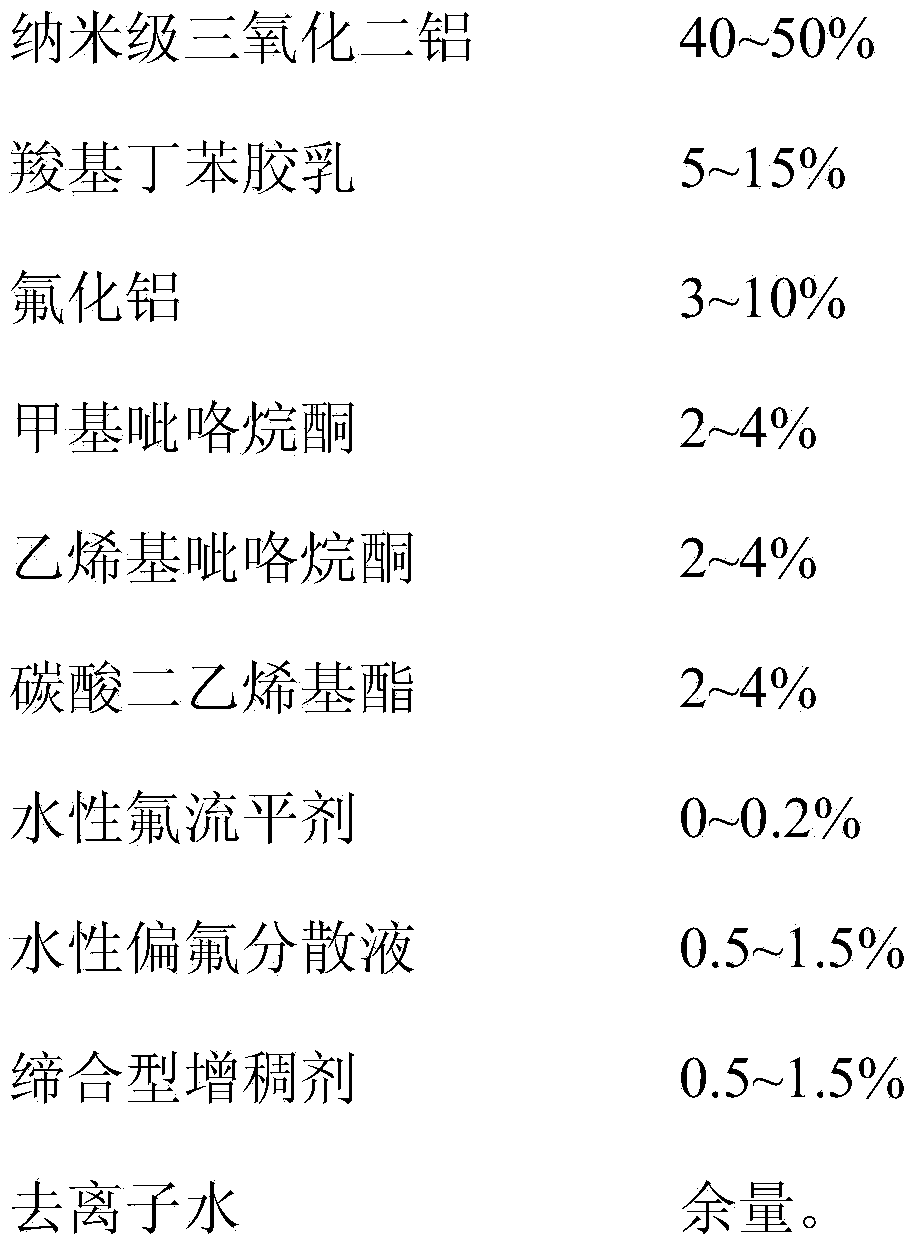

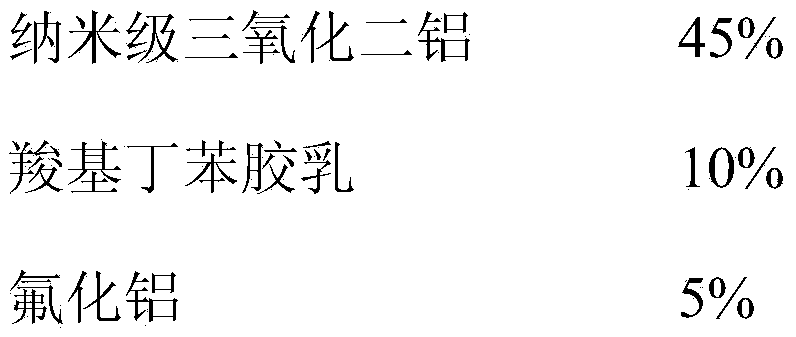

Slurry for coating isolating membrane of lithium ion battery, isolating membrane and preparation method of slurry

InactiveCN104143616ACoating molecular dispersion is goodUniform thicknessSecondary cellsStarch coatingsElectrical batterySlurry

The invention provides slurry for coating an isolating membrane of a lithium ion battery. The slurry comprises the following components: nano-grade aluminum oxide, carboxylic butadiene-styrene latex, aluminum fluoride, N-methylpyrrolidone, vinyl pyrrolidinone, divinyl carbonate, an aqueous fluorine flatting agent, aqueous fluoride dispersing liquid, an associated thickening agent and the balance being deionized water. The invention further provides a preparation of the slurry. By virtue of combination of the components in special ratios, the slurry for coating the isolating membrane of the lithium ion battery has excellent properties of resisting high temperature up to 250 DEG C and low temperature up to -80 DEG C, and meanwhile, by virtue of spherical ultrasonic dispersion treatment used when the slurry is prepared and the special process that the basic isolating membrane is coated with the slurry, the prepared isolating membrane has the characteristics that the coating is good in molecular dispersivity, uniform in thickness and uniform in electrical property.

Owner:ZHEJIANG JINMEI ENERGY SCI & TECH

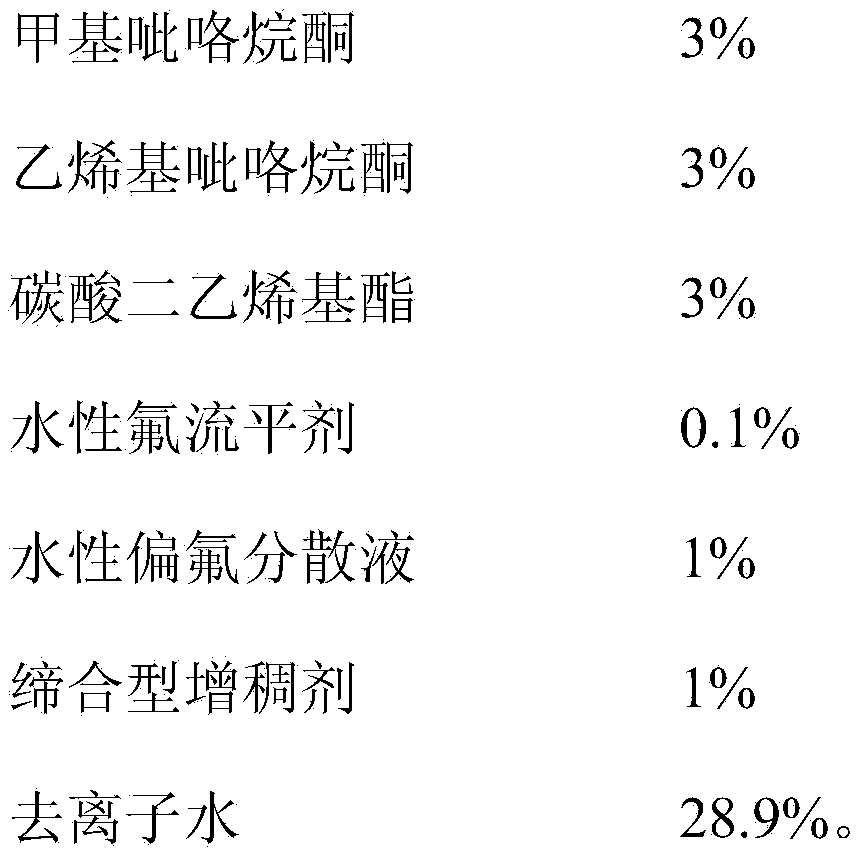

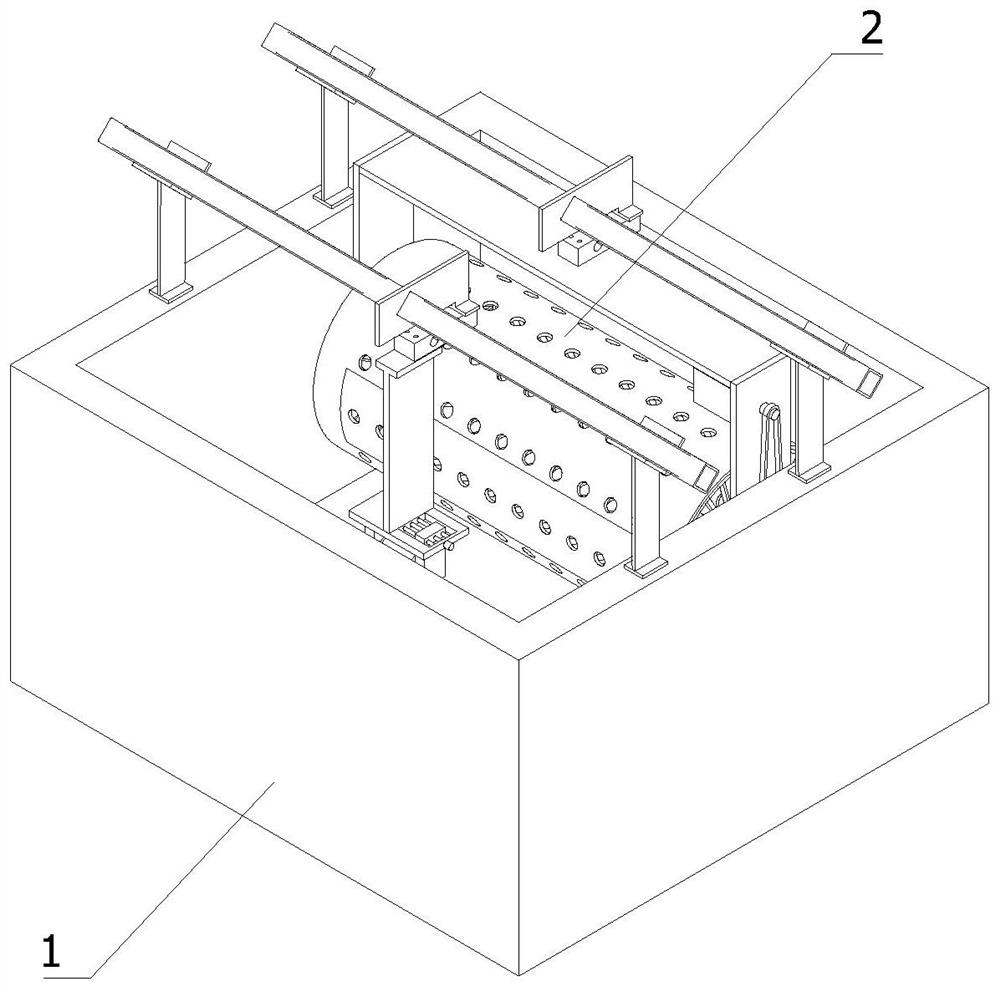

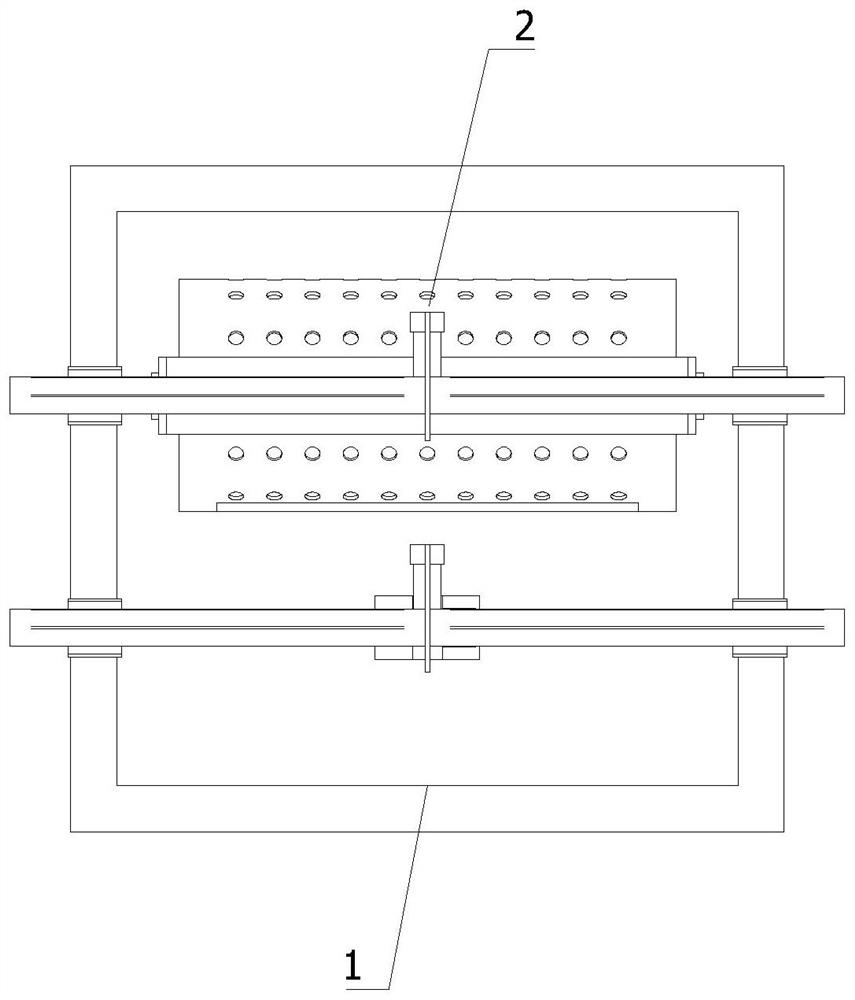

Electroplating process of neodymium-iron-boron magnet

ActiveCN114277410ACalculate real-time thicknessEasy to increase or decreaseCellsProcess efficiency improvementMetallurgyElectric current flow

The invention relates to an electroplating process of a neodymium iron boron magnet, electroplating equipment is used in the electroplating process, the electroplating equipment comprises an electroplating pool, a placing frame capable of being placed in the electroplating pool, and a weight detection mechanism used for detecting the weight of the magnet in electroplating liquid before and after electroplating, and the electroplating process comprises the following steps: S1, carrying out electroplating; the pretreated magnet is placed on the placing frame; s2, placing the shelf in an electroplating tank; s3, electroplating the magnet under the action of current; s4, a weight detection mechanism monitors the weight of the magnet before and after electroplating in real time and sends a signal to the controller; s5, the controller passes through a formula (h is the thickness of the plating layer; delta m is the weight of the plating layer; rho is the plating layer density; and S: the surface area of the magnet), the real-time thickness of the plating layer is calculated until the plating layer reaches the preset thickness, and the real-time weight of the plating layer is monitored through the weight detection mechanism, so that the real-time thickness of the plating layer is calculated, the increase and decrease of the current density are controlled, and the electroplating efficiency is improved.

Owner:宁波市信泰科技有限公司

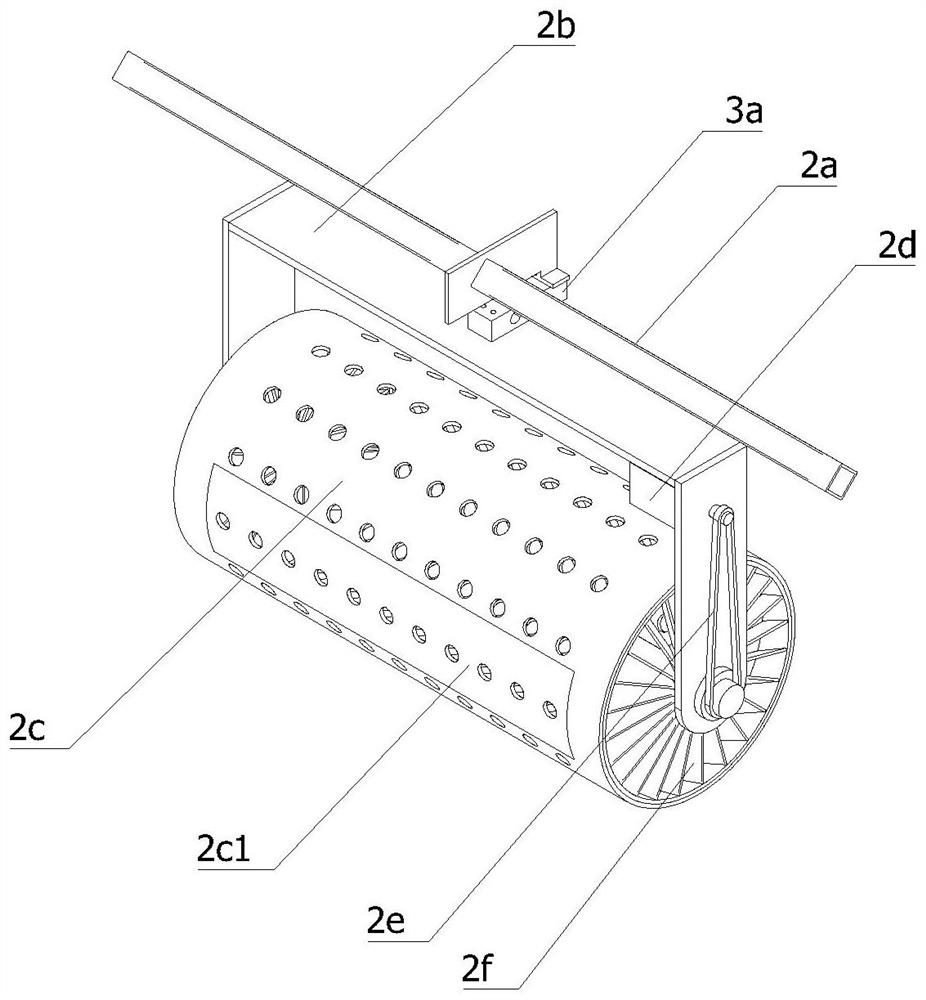

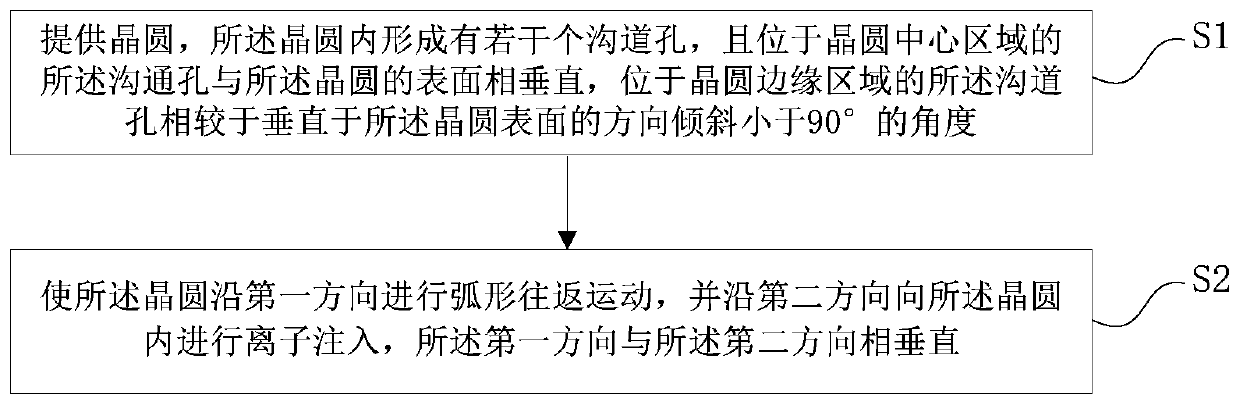

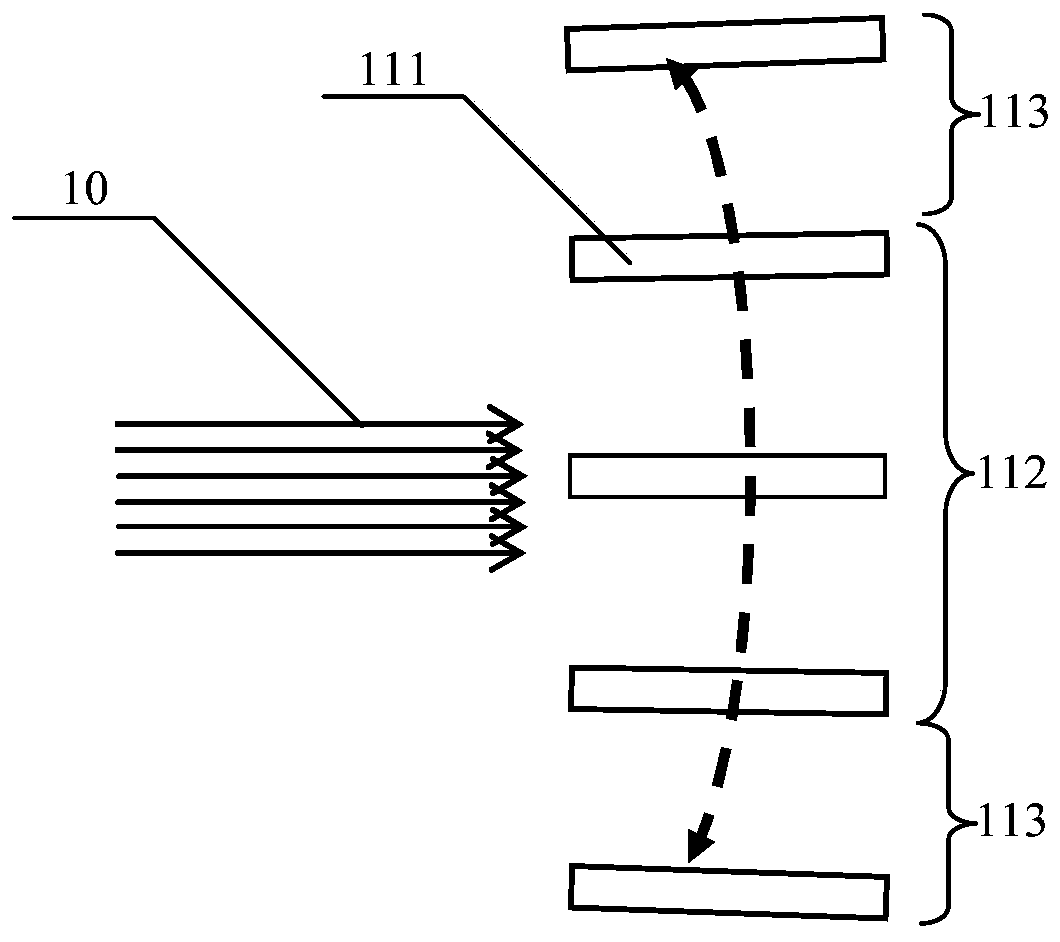

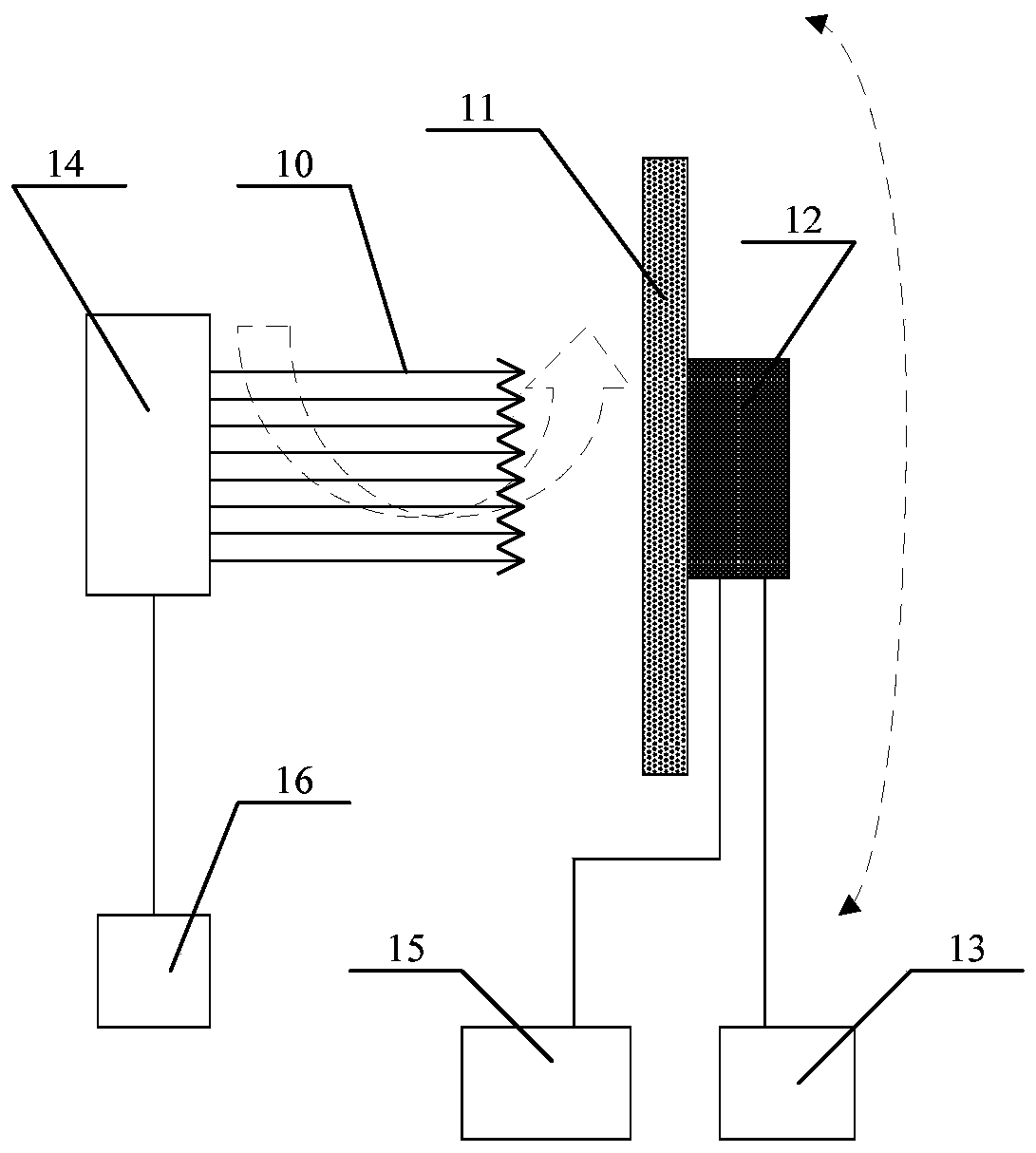

Ion implantation method and ion implantation system

ActiveCN111162003AElectrical uniformityThe amount of ion implantation is the sameSemiconductor/solid-state device manufacturingWaferEngineering

The invention provides an ion implantation method and an ion implantation system. The ion implantation method comprises the following steps of providing a wafer, wherein a plurality of channel holes are formed in the wafer, the communication holes located in the center area of the wafer are perpendicular to the surface of the wafer, and the channel holes located in the edge area of the wafer incline by an angle smaller than 90 degrees relative to the direction perpendicular to the surface of the wafer; and enabling the wafer to perform arc reciprocating motion along a first direction, and carrying out ion implantation in the wafer along a second direction, wherein the first direction is perpendicular to the second direction. According to the ion implantation method provided by the invention, in the process of carrying out ion implantation along the second direction to enable the wafer to do arc-shaped reciprocating motion along the first direction vertical to the second direction, theions can be ensured to be injected into the bottom of each channel hole, so that the ion implantation quantities of the bottoms of the channel holes are the same, the influence of different inclination degrees of the channel holes in different regions of the wafer relative to the direction perpendicular to the surface of the wafer on the ion implantation effect is eliminated, the electrical property and yield of a device can be ensured, and the whole wafer has better and more uniform electrical property.

Owner:YANGTZE MEMORY TECH CO LTD

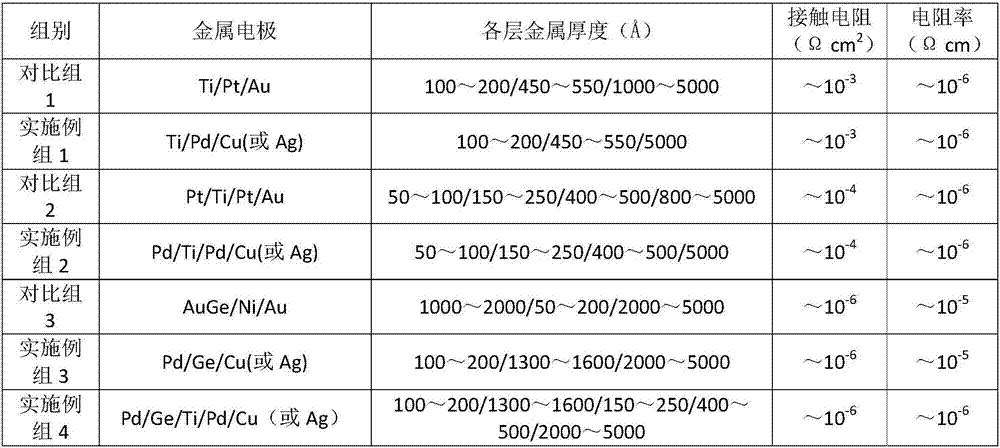

Compound semiconductor metal contact electrode

InactiveCN107403833AImproved lateral uniformity and stabilityGood for device sizeSemiconductor devicesBlock layerType metal

The invention belongs to the technical field of a semiconductor, and discloses a compound semiconductor metal contact electrode. Platinum Pt and gold germanium AuGe in the conventional non-alloy metal electrodes Ti / Pt / Au, Pt / Ti / Pt / Au and alloy type metal electrodes AuGe / Ni / Au are replaced by palladium Pd or palladium germanium Pd / Ge, and top layer noble metal Au is replaced by copper Cu or silver Ag to obtain two kinds of metal contact electrodes which comprise a metal conductive layer and a bonding layer, and comprise a metal conductive layer, a diffusion blocking layer and a bonding layer, wherein the metal conductive layer is a Cu or Ag layer; the diffusion blocking layer is a Pd or Ti / Pd layer; and the bonding layer is a Ti, Pd or Pd / Ge layer. The compound semiconductor metal contact electrode disclosed in the invention has the advantages of low contact resistance, high intrinsic conductivity, high thermal stability, strong adhesive force in connection with the semiconductor, low production and manufacturing cost and the like.

Owner:SUZHOU LIANG DONGXIN MICROELECTRONICS CO LTD

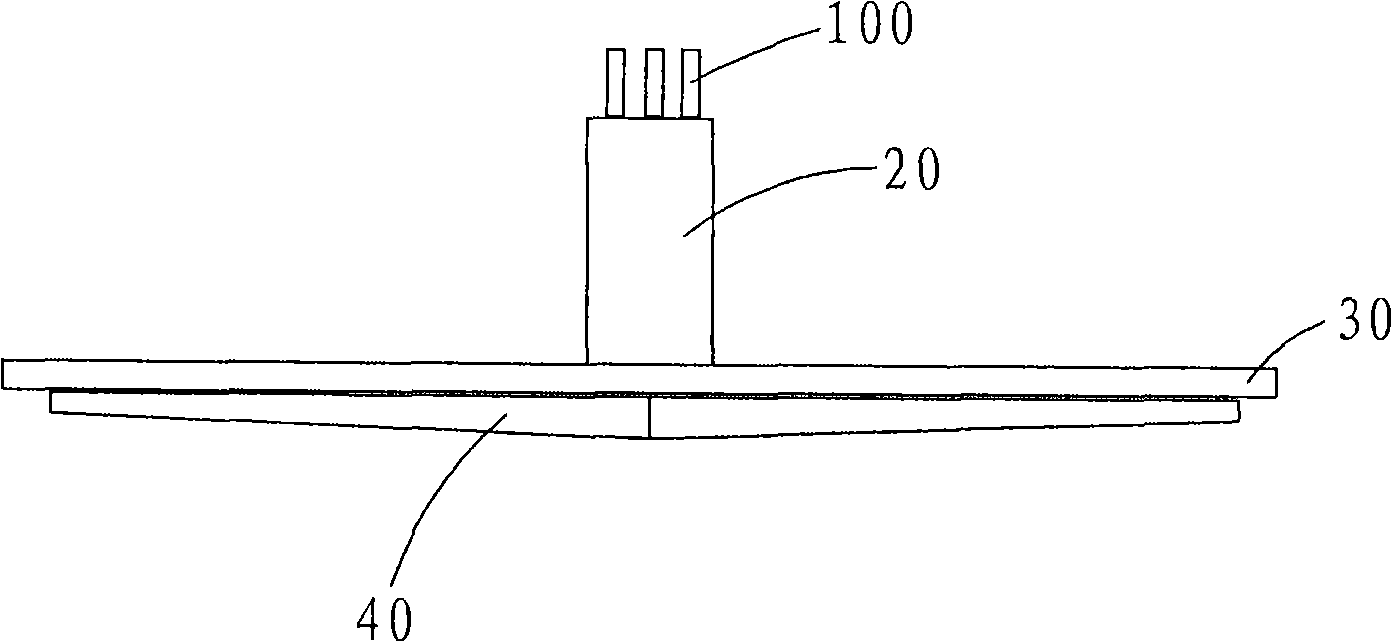

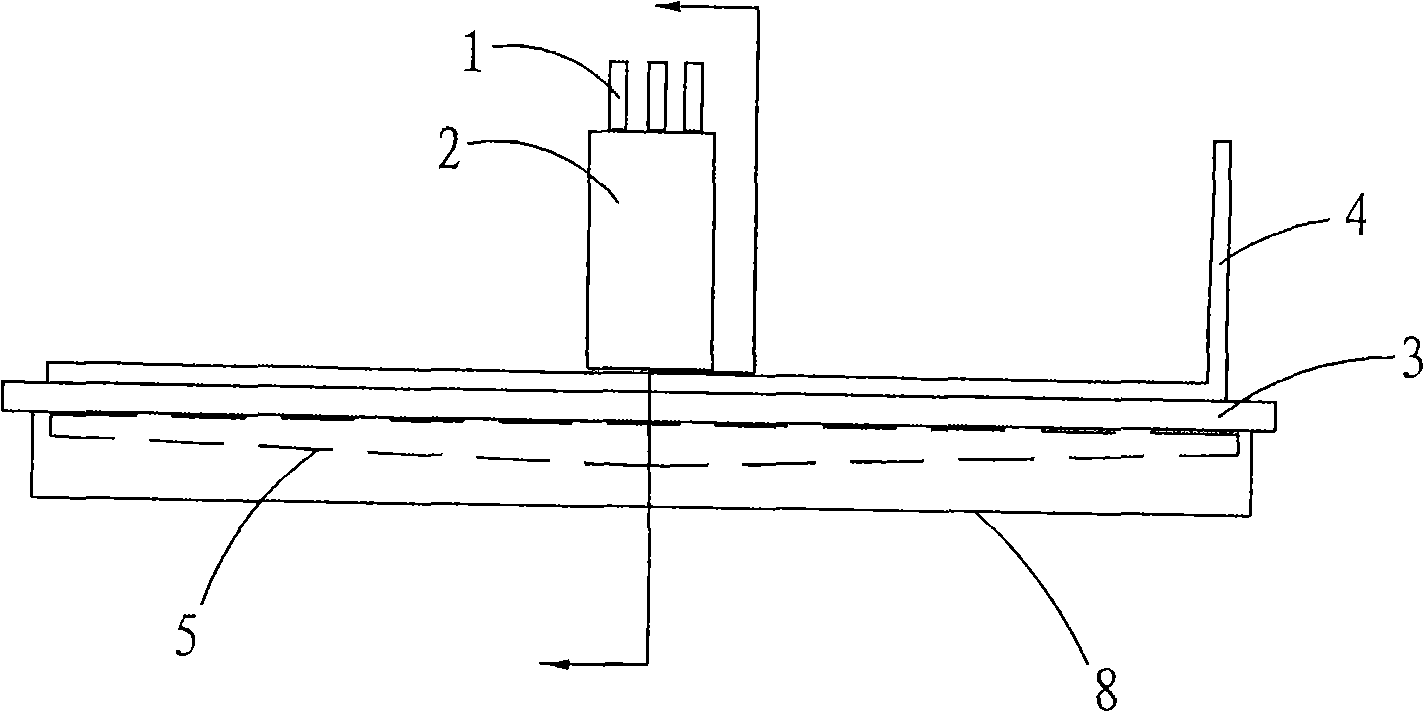

Nozzle system capable of continuously evening chemical vapour deposition of large area

InactiveCN101492812AAdequate responseWell mixedChemical vapor deposition coatingDeposition temperatureGas phase

The invention discloses a spray head system capable of continuously homogenizing chemical vapor deposition in large area. The system comprises a conveying tube, a fixed panel, a primary reaction gas mixing cavity and a jet tube, wherein the primary reaction gas mixing cavity is arranged at the upper part of the fixed panel; the jet tube is arranged at the lower part of the fixed panel; the jet tube is provided with a jet exhaust; a circulating water cooling system is also arranged at the upper part of the fixed panel; a secondary reaction gas mixing cavity is also arranged at the lower part of the fixed panel; the jet tube is covered in the secondary reaction gas mixing cavity; the cross section of the secondary reaction gas mixing cavity is in a V shape; a monolete nozzle is arranged on the bottom of the secondary reaction gas mixing cavity; and raw material gas enters the primary reaction gas mixing cavity through the conveying tube, enters the jet tube, then enters the secondary reaction gas mixing cavity after the gas is sprayed from the jet exhaust of the jet tube, and finally is sprayed out from the monolete nozzle. The system can lower the deposition temperature so as to lead homogenization of a film to be easily controlled during large-area deposition, thereby ensuring normal running of continuous large-scale production.

Owner:CHUANGDA SOLAR ENERGY TECH OF ZHANGZHOU DEV ZONE INVESTMENT PROMOTION BUREAU

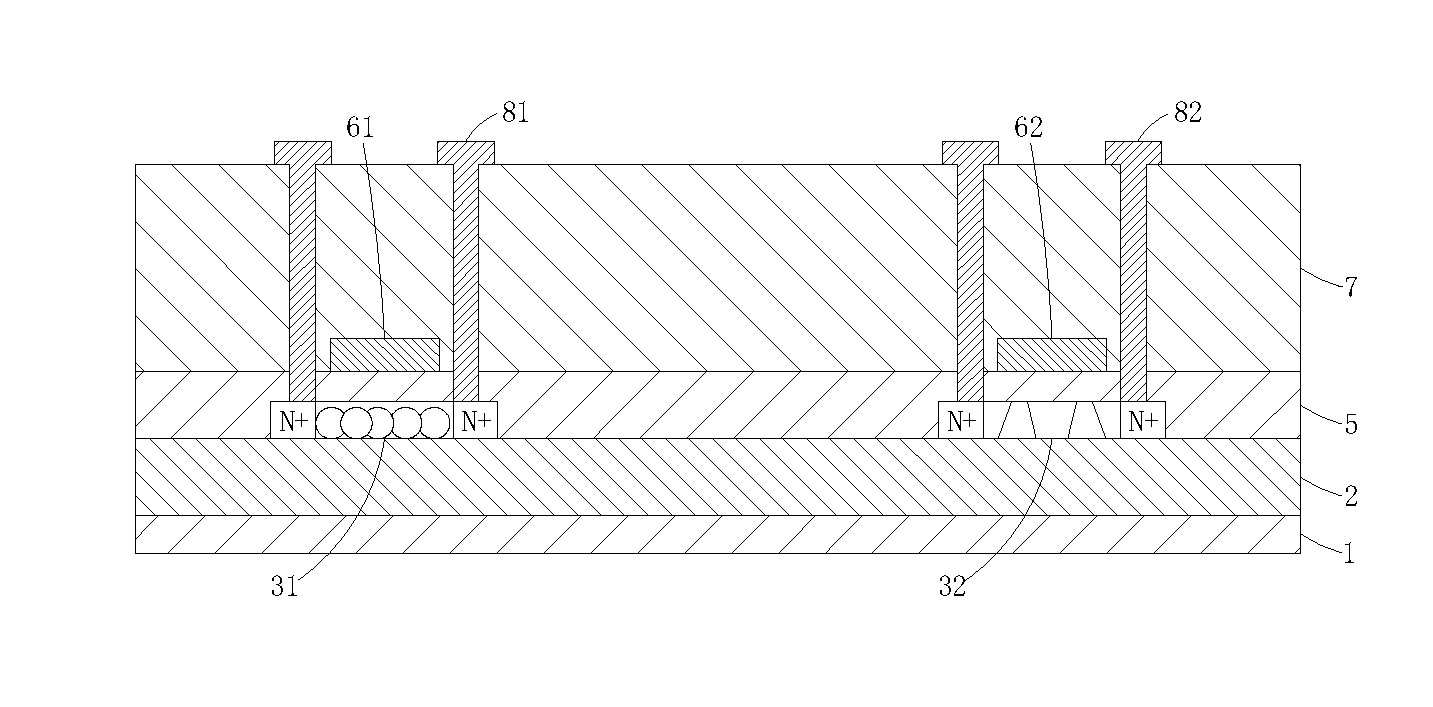

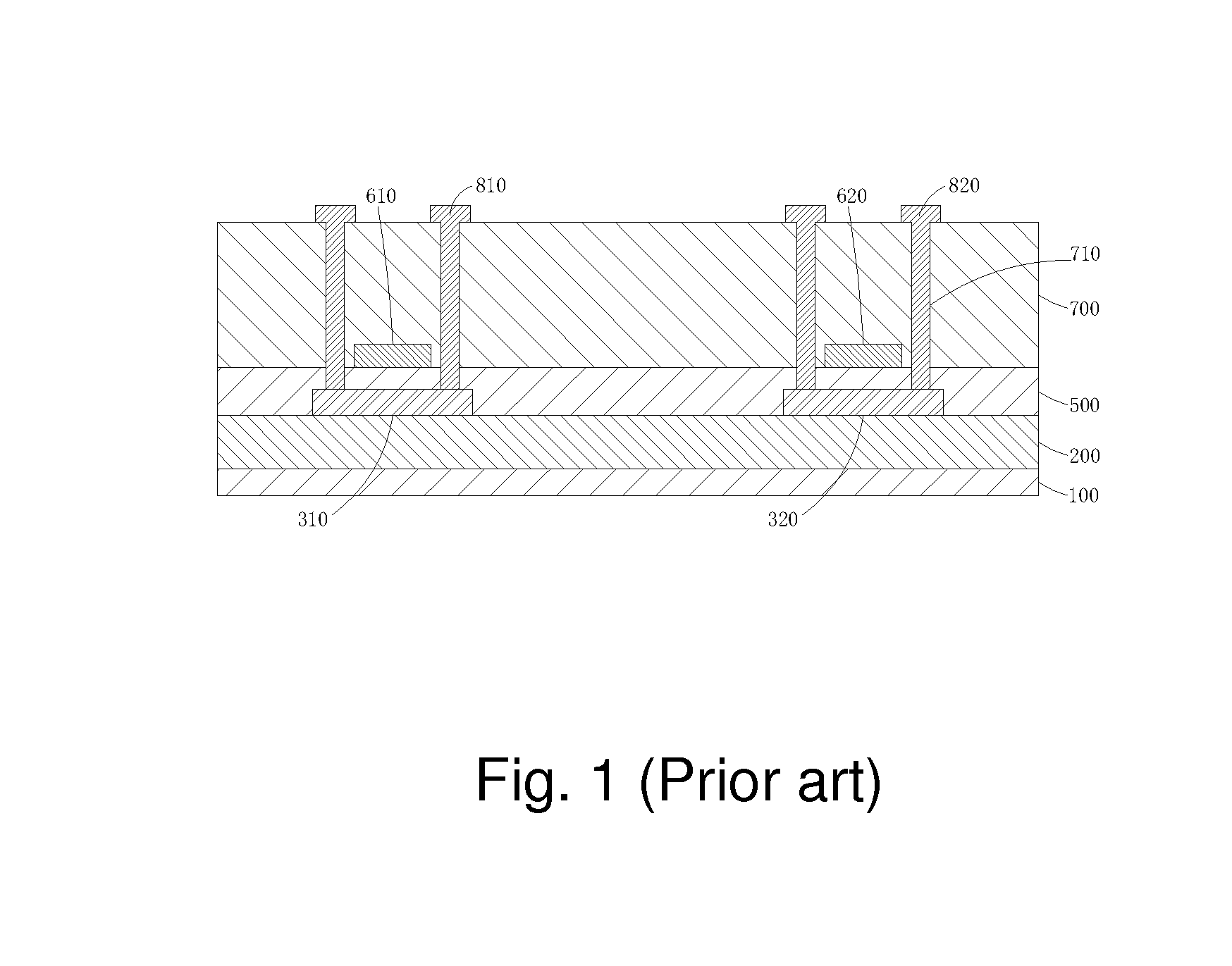

LTPS TFT substrate structure and method of forming the same

ActiveUS9589985B2Large poly-SiHigh electron mobilityTransistorSemiconductor/solid-state device detailsOptoelectronicsSilicon oxide

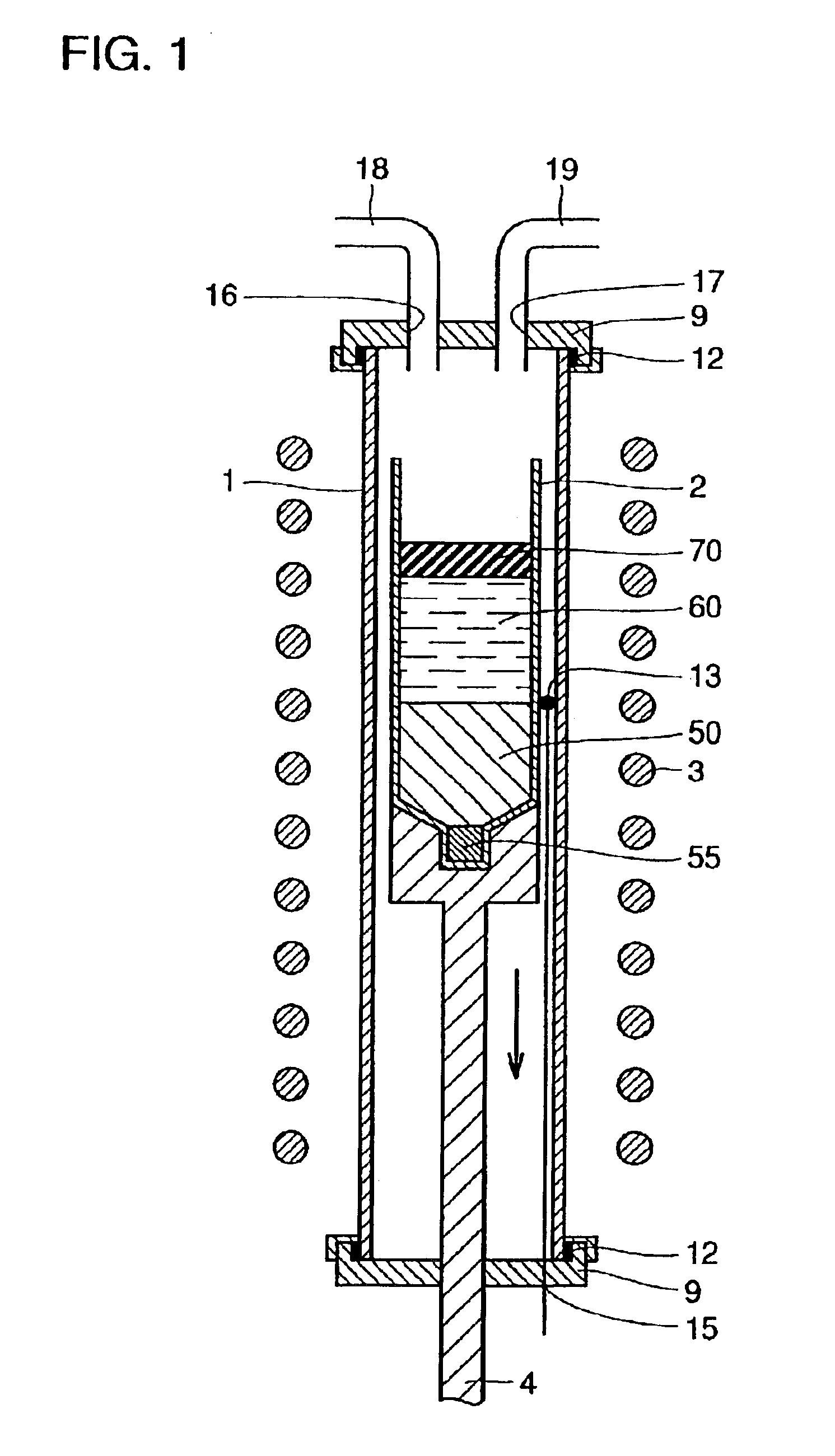

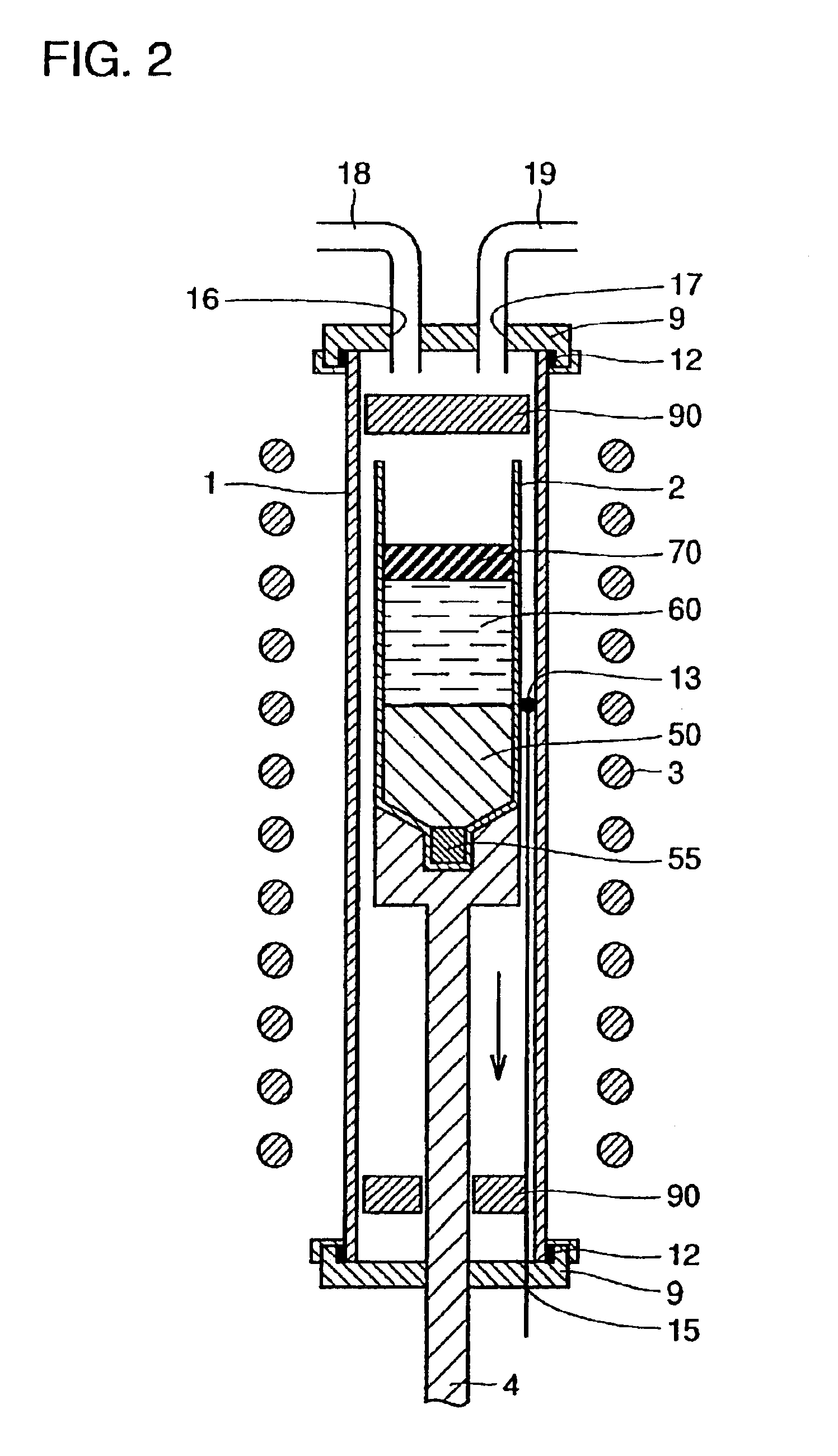

A method of forming an LTPS TFT substrate includes: Step 1: providing a substrate (1) and depositing a buffer layer (2); Step 2: depositing an a-Si layer (3); Step 3: depositing and patterning a silicon oxide layer (4); Step 4: taking the silicon oxide layer (4) as a photomask and annealing the a-Si layer (3) with excimer laser, so that the a-Si layer crystalizes and turns into a poly-Si layer; Step 5: forming a first poly-Si region (31) and a second poly-Si region (32); Step 6: defining a heavily N-doped area and a lightly N-doped area on the first and second poly-Si regions (31) and (32), and forming an LDD area; Step 7: depositing and patterning a gate insulating layer (5); Step 8: forming a first gate (61) and a second gate (62); Step 9: forming via holes (70); and Step 10: forming a first source / drain (81) and a second source / drain (82).

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

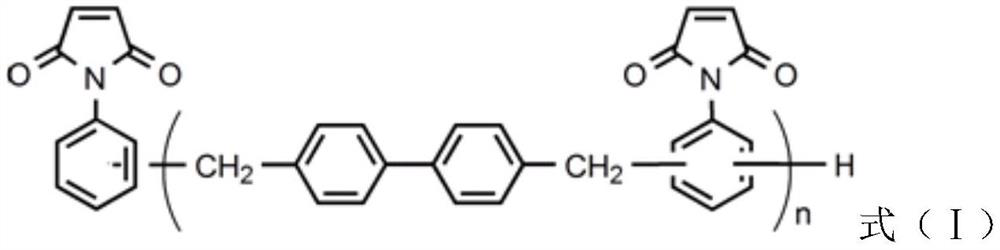

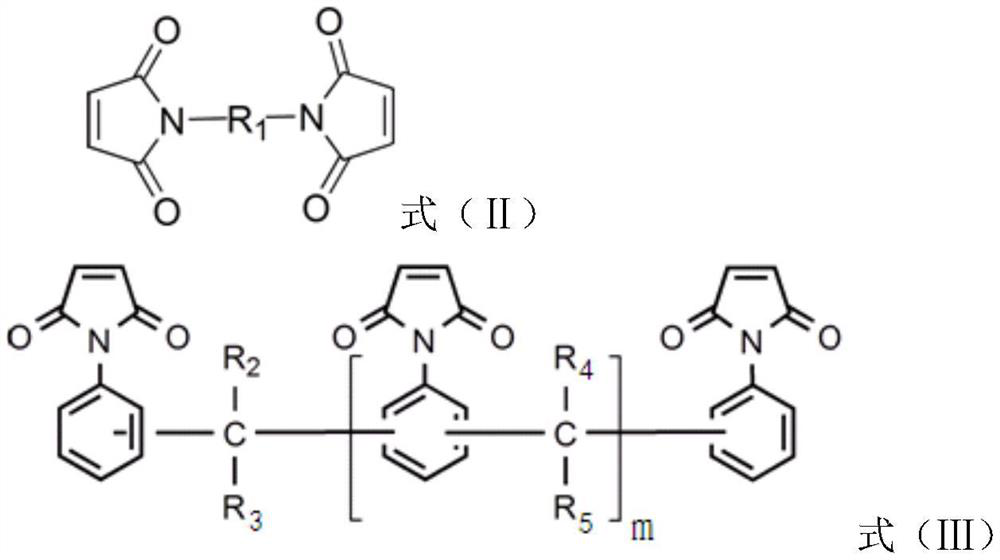

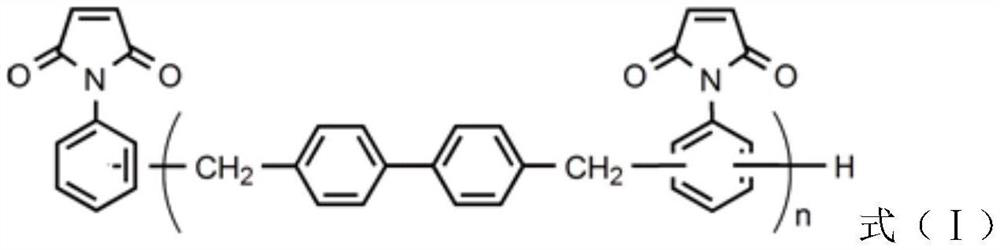

Maleimide resin composition and application thereof

ActiveCN113980272AUniform toughnessElectrical uniformityPrinted circuit detailsSynthetic resin layered productsImidePolymer science

The invention discloses a maleimide resin composition and application thereof, and belongs to the technical field of high polymer materials. The composition comprises the following components in parts by weight: 10-40 parts by mass of maleimide resin with the structure shown in the description, 30-70 parts by mass of one or a mixture of two of maleimide resin with the structures shown in the description and 10-40 parts by mass of a cross-linking agent, wherein n is an integer of 1-5, R1 is an organic group with 1-20 carbon atoms, R2 to R5 are independently hydrogen atoms or alkyl groups containing 1-4 carbon atoms, and m is an integer of 1-6. According to the invention, the maleimide resin with different structures are compounded by utilizing the trifunctional cross-linking agent containing a rigid benzene ring structure, the toughness, the electrical property and the heat resistance of the maleimide resin composition are balanced under the optimal proportion, and the maleimide resin composition is used for electronic product components such as prepregs, copper-clad laminated boards or printed circuit boards.

Owner:NANYA NEW MATERIAL TECH CO LTD

LTPS TFT Substrate Structure and Method of Forming the Same

ActiveUS20160190169A1Avoid smallHigh electron mobilityTransistorSemiconductor/solid-state device detailsOptoelectronicsSilicon oxide

A method of forming an LTPS TFT substrate includes: Step 1: providing a substrate (1) and depositing a buffer layer (2); Step 2: depositing an a-Si layer (3); Step 3: depositing and patterning a silicon oxide layer (4); Step 4: taking the silicon oxide layer (4) as a photomask and annealing the a-Si layer (3) with excimer laser, so that the a-Si layer crystalizes and turns into a poly-Si layer; Step 5: forming a first poly-Si region (31) and a second poly-Si region (32); Step 6: defining a heavily N-doped area and a lightly N-doped area on the first and second poly-Si regions (31) and (32), and forming an LDD area; Step 7: depositing and patterning a gate insulating layer (5); Step 8: forming a first gate (61) and a second gate (62); Step 9: forming via holes (70); and Step 10: forming a first source / drain (81) and a second source / drain (82).

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

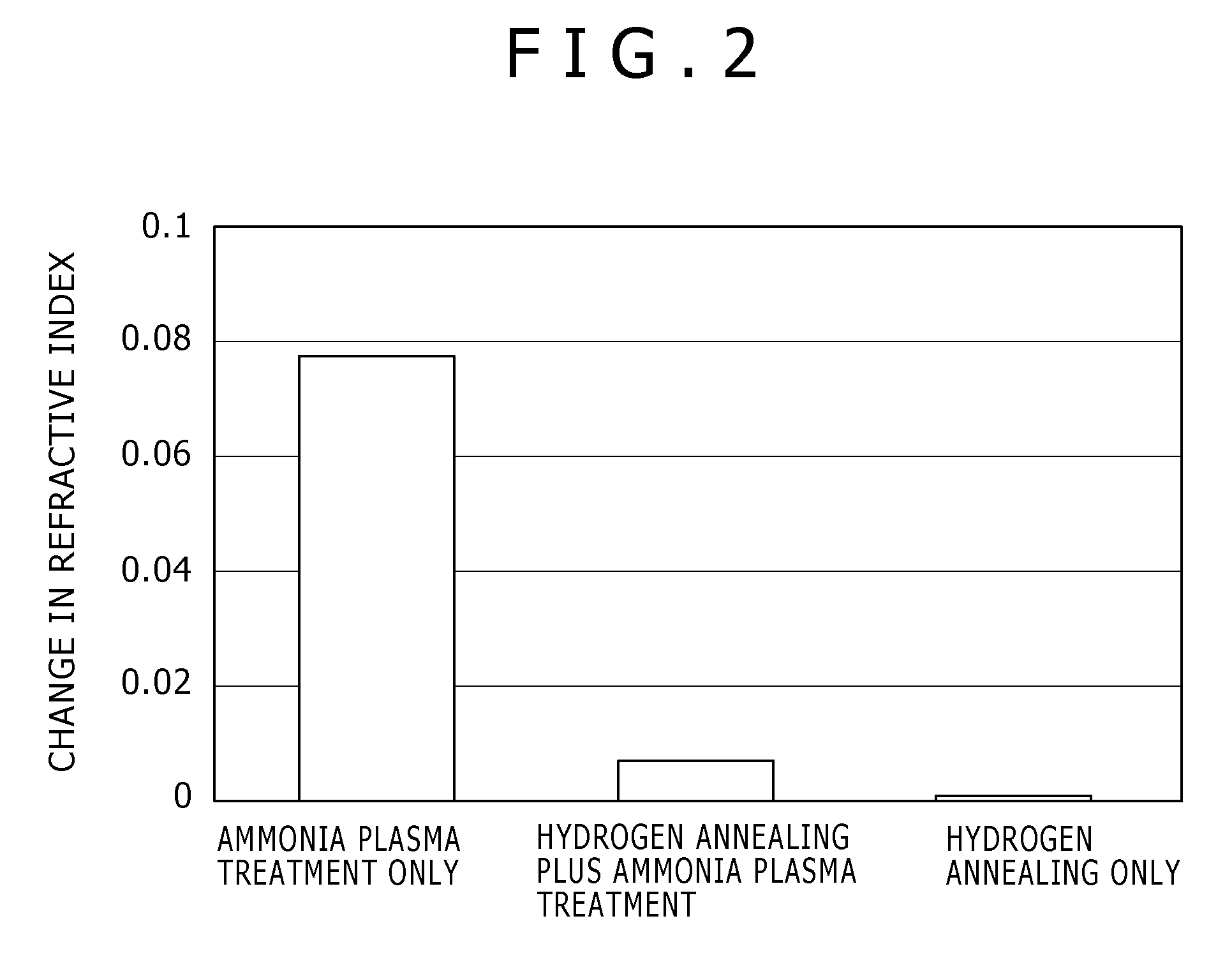

Method for production of semiconductor devices

InactiveUS7670941B2Minimal damageCut surfaceSemiconductor/solid-state device manufacturingHydrogenCopper

A method for production of semiconductor devices which includes the steps of forming, on an interlayer insulating film formed on a substrate, a copper-containing conductive layer in such a way that its surface is exposed, performing heat treatment with a reducing gas composed mainly of hydrogen on the surface of the conductive layer, performing plasma treatment with a reducing gas on the surface of the conductive layer, thereby permitting the surface of the conductive layer to be reduced and the hydrogen adsorbed by the heat treatment to be released, and forming an oxidation resistance film that covers the surface of the conductive layer such that the surface of the conductive layer is not exposed to an oxygen-containing atmospheric gas after the plasma treatment.

Owner:SONY CORP

Thin Film Transistor, Method of Manufacturing the Same, and Display Device Having Thin Film Transistor

ActiveUS20110221991A1Minimizing leakage currentMinimize leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingOxide thin-film transistorImaging quality

A thin film transistor, a manufacturing method thereof, and a display device having the same are disclosed. The thin film transistor includes a semiconductor layer formed on a substrate, a gate insulating layer formed on the substrate including the semiconductor layer, a gate electrode formed on the gate insulating above the semiconductor layer, source and drain electrodes connected to the semiconductor layer, and 3.5 to 4.5 protrusions formed on the semiconductor layer overlapped with the gate electrode. Malfunction of the thin film transistor and inferior image quality of the display device can be prevented by adjusting the number of protrusions to minimize leakage current and defects.

Owner:SAMSUNG DISPLAY CO LTD

Nozzle system capable of continuously evening chemical vapour deposition of large area

InactiveCN101492812BAdequate responseWell mixedChemical vapor deposition coatingDeposition temperatureGas phase

Owner:CHUANGDA SOLAR ENERGY TECH OF ZHANGZHOU DEV ZONE INVESTMENT PROMOTION BUREAU

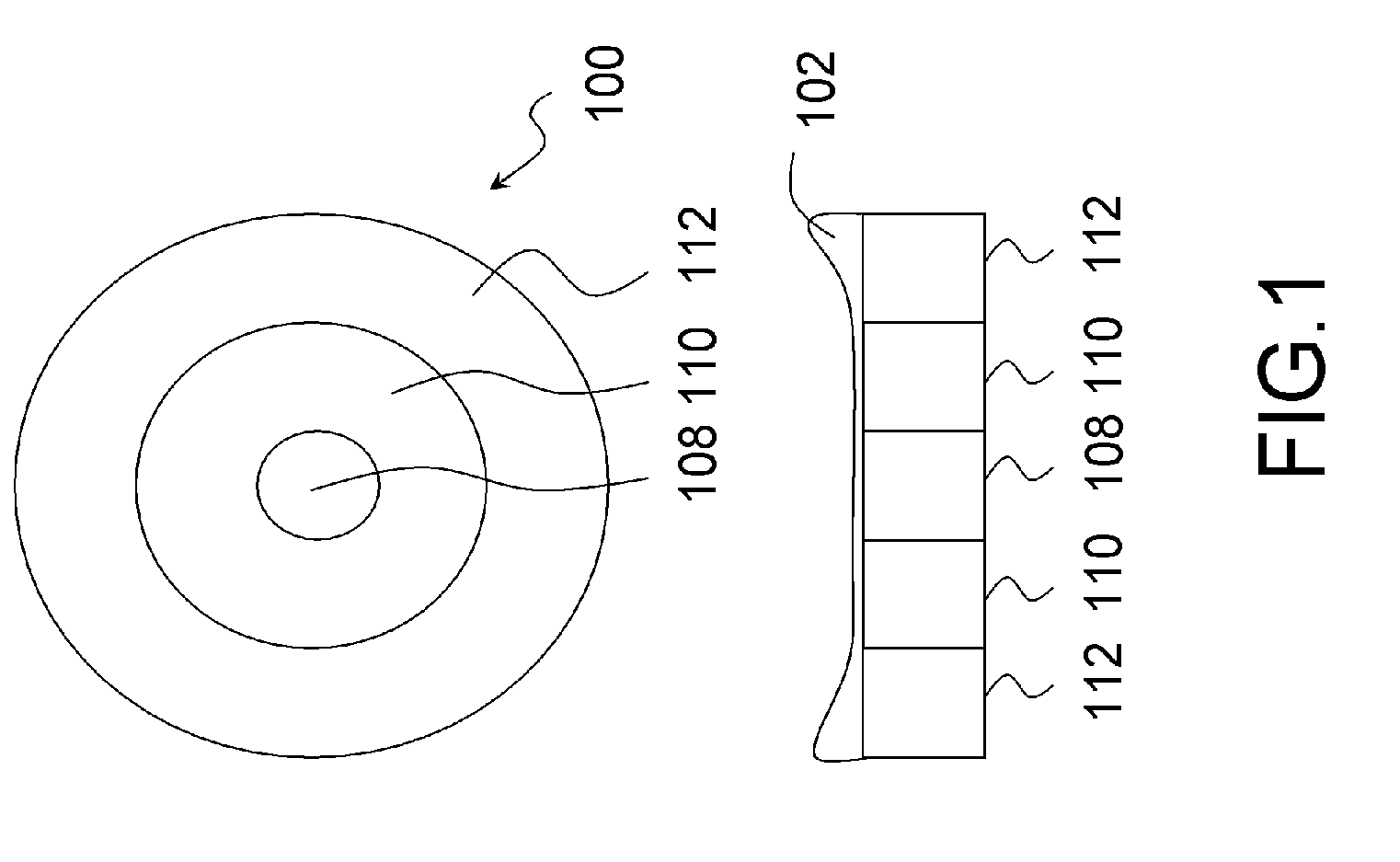

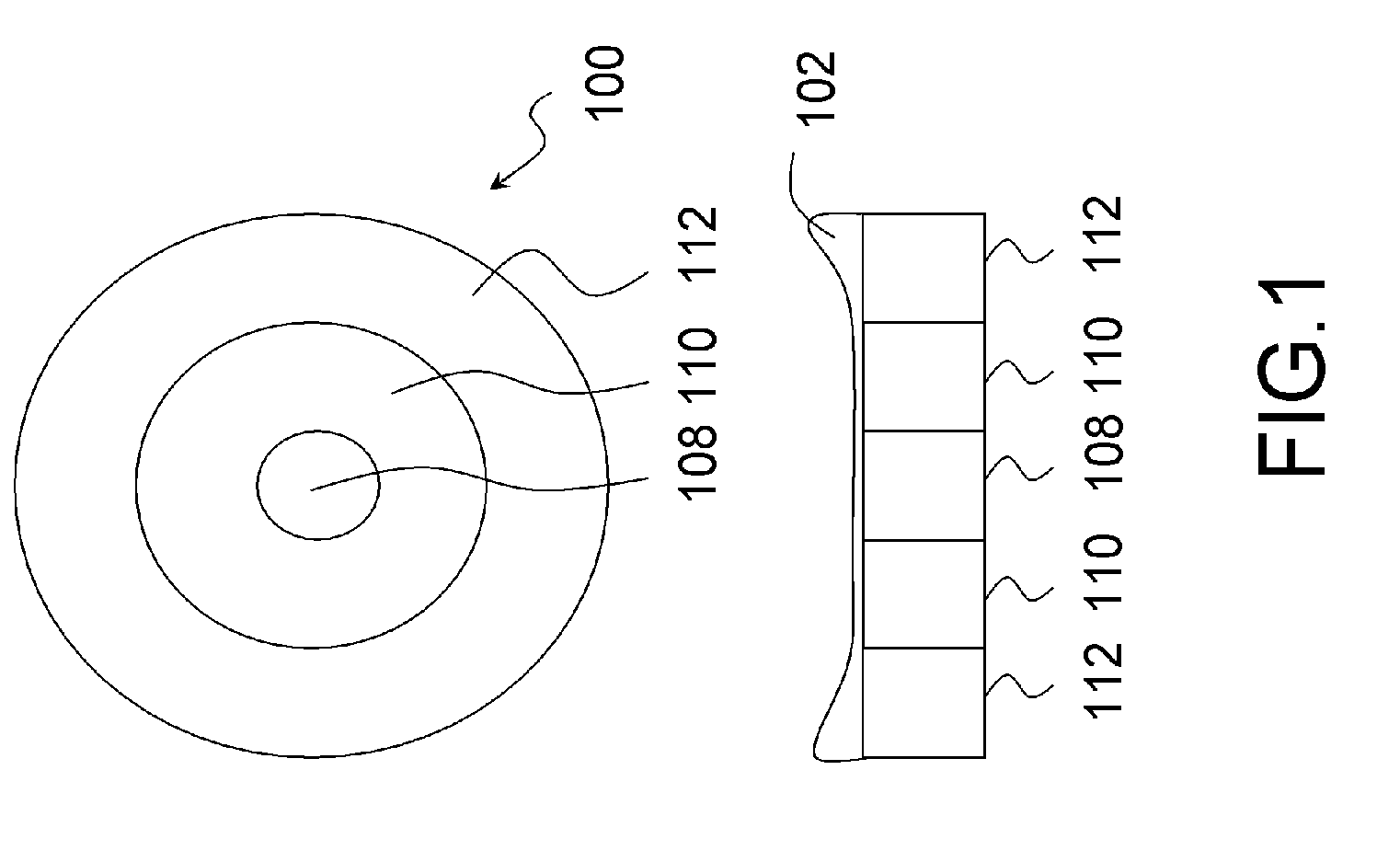

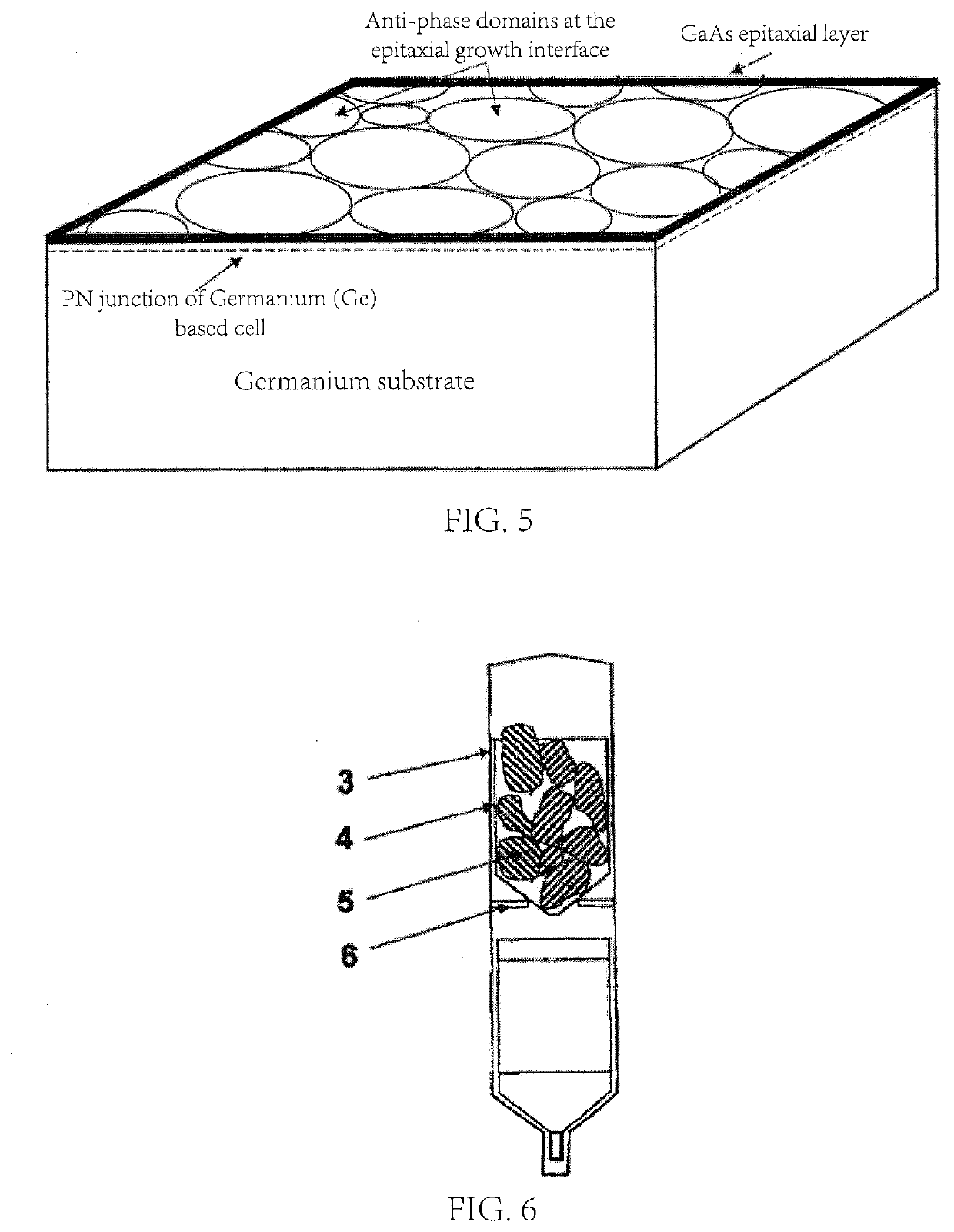

Germanium single-crystal wafer, method for preparing germanium single-crystal wafer, method for preparing crystal bar, and use of single-crystal wafer

PendingUS20220238746A1Uniform concentrationEqually distributedEdge grinding machinesPolycrystalline material growthWaferingSingle crystal

A germanium single-crystal wafer comprises silicon with an atomic concentration of from 3×1014 atoms / cc to 10×1013 atoms / cc, boron with an atomic concentration of from 1×1016 atoms / cc to 10×1018 atoms / cc, and gallium with an atomic concentration of from 1×1016 atoms / cc to 10×1019 atoms / cc. Further provided are a method for preparing the germanium single-crystal wafer, a method for preparing a germanium single-crystal ingot, and the use of the germanium single-crystal wafer for increasing the open-circuit voltage of a solar cell. The germanium single-crystal wafer has an improved electrical property in that it has a smaller difference in resistivity and carrier concentration.

Owner:BEIJING TONGMEI XTAL TECH CO LTD