Patents

Literature

2179results about How to "Excellent electrical properties" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

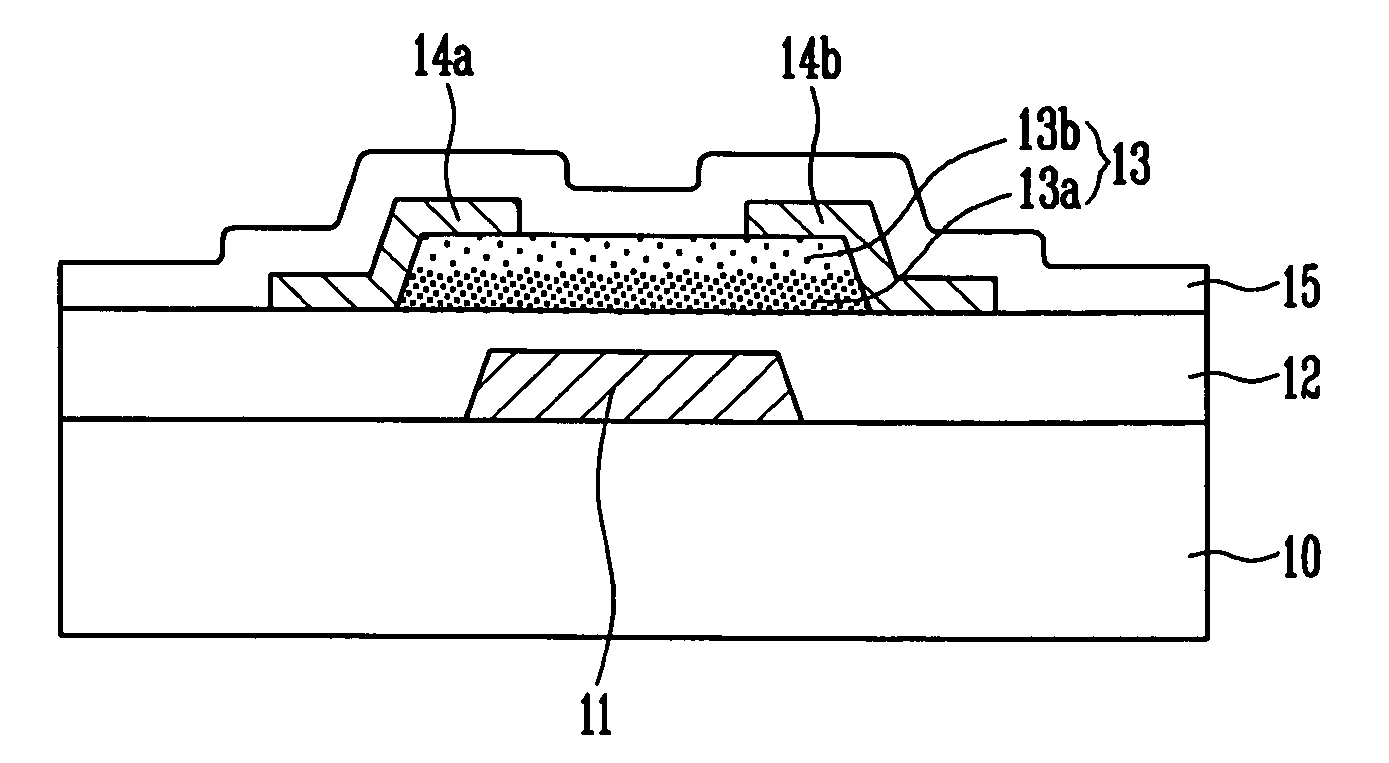

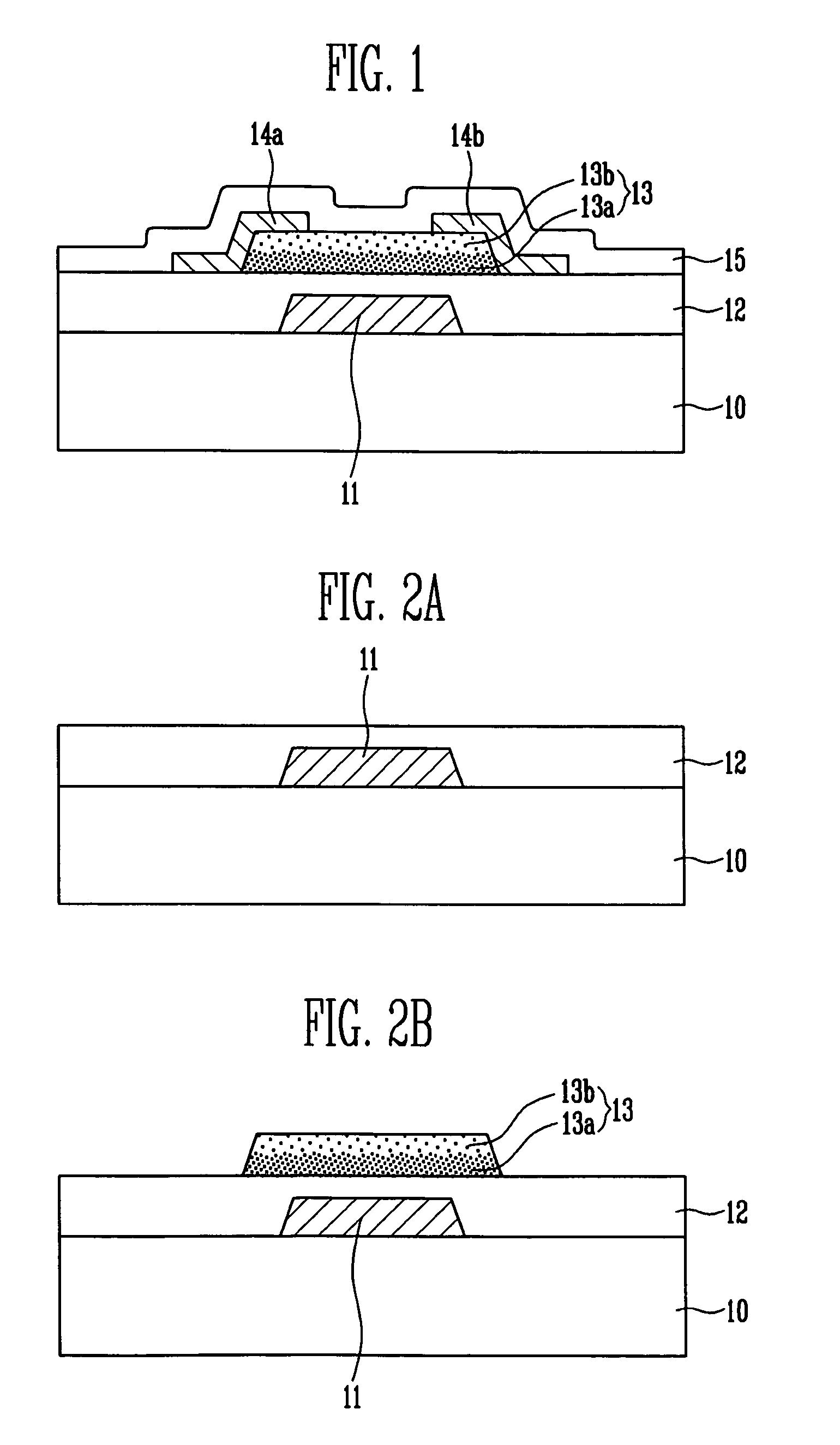

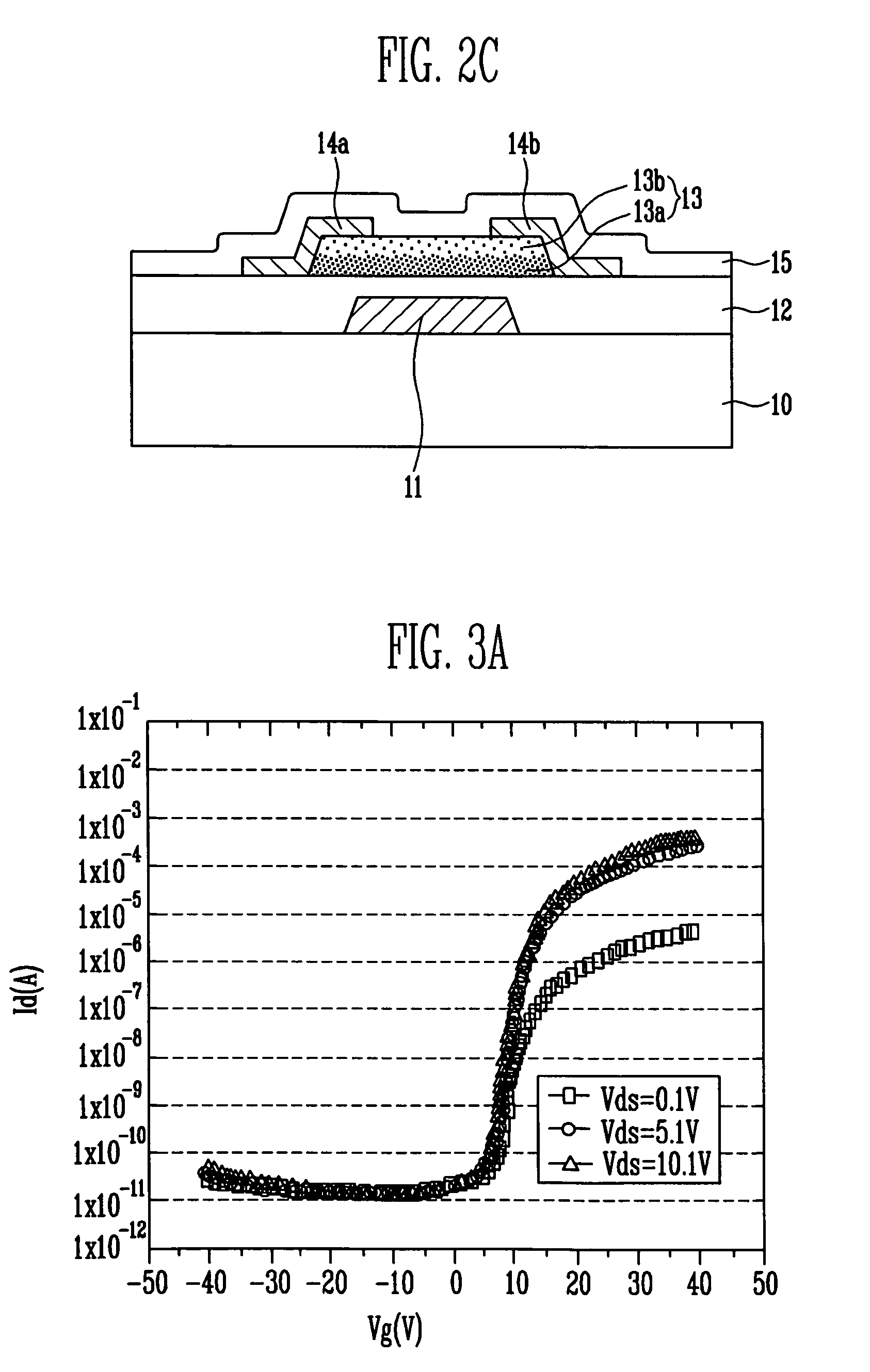

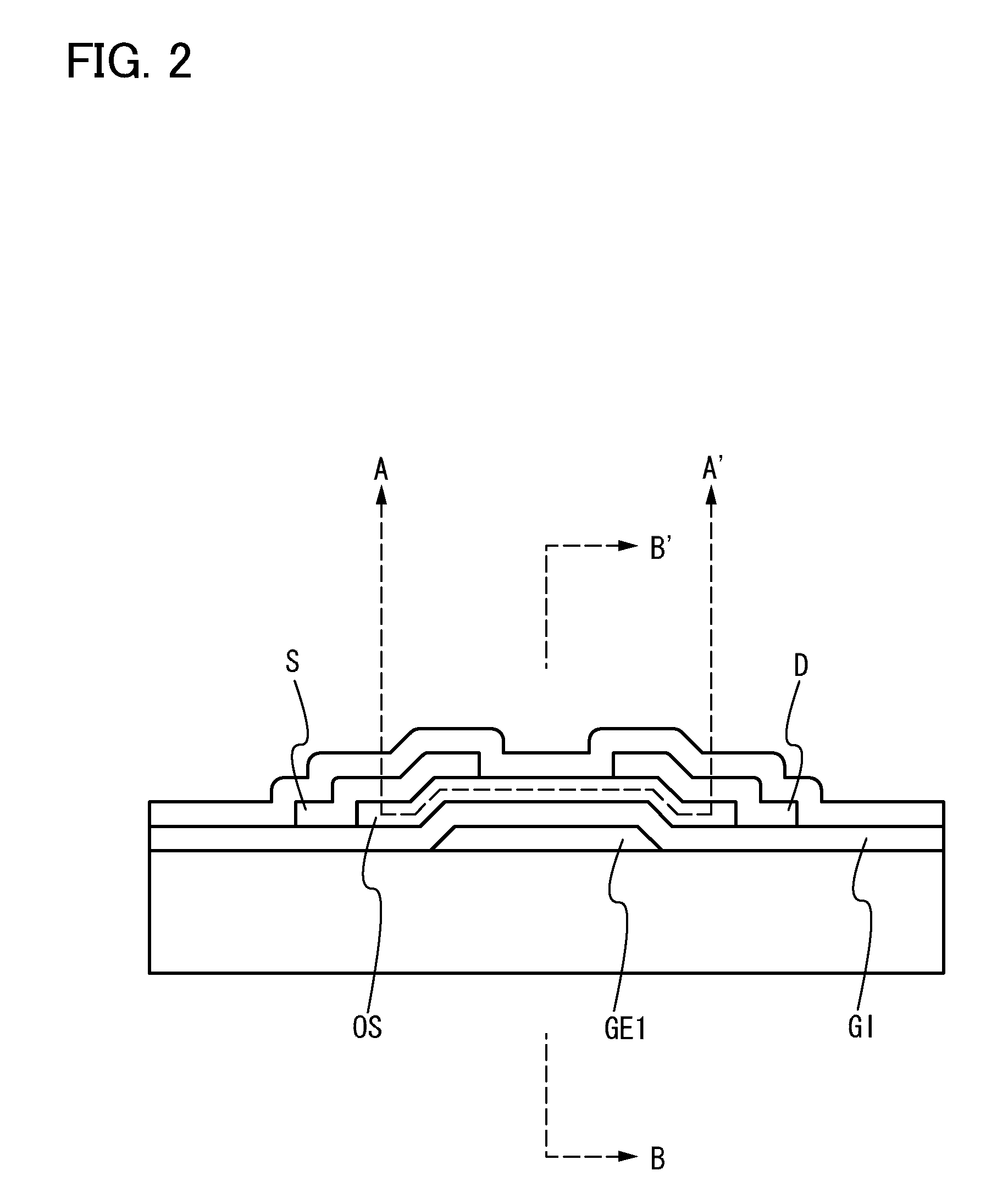

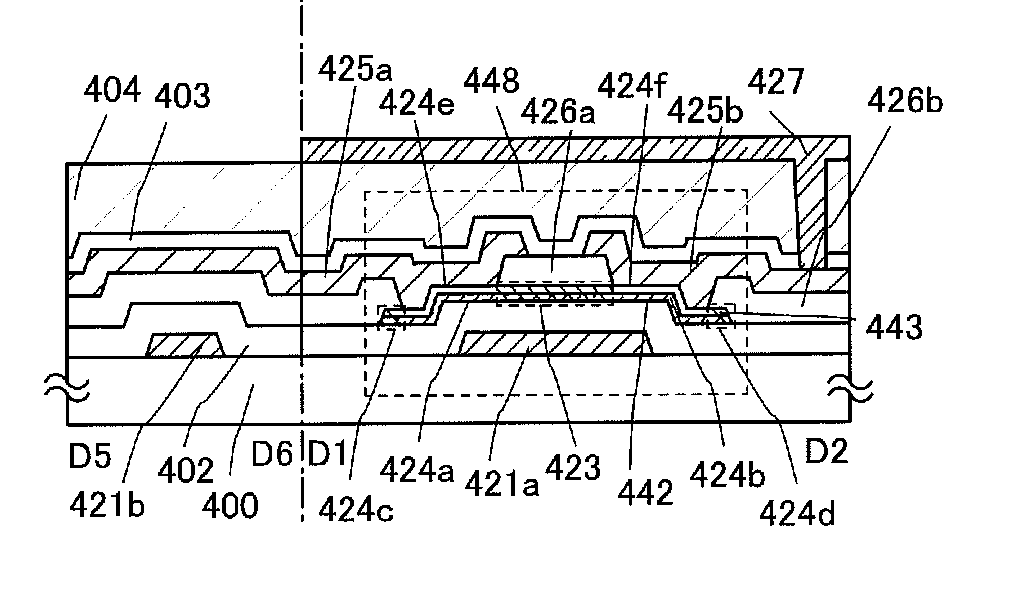

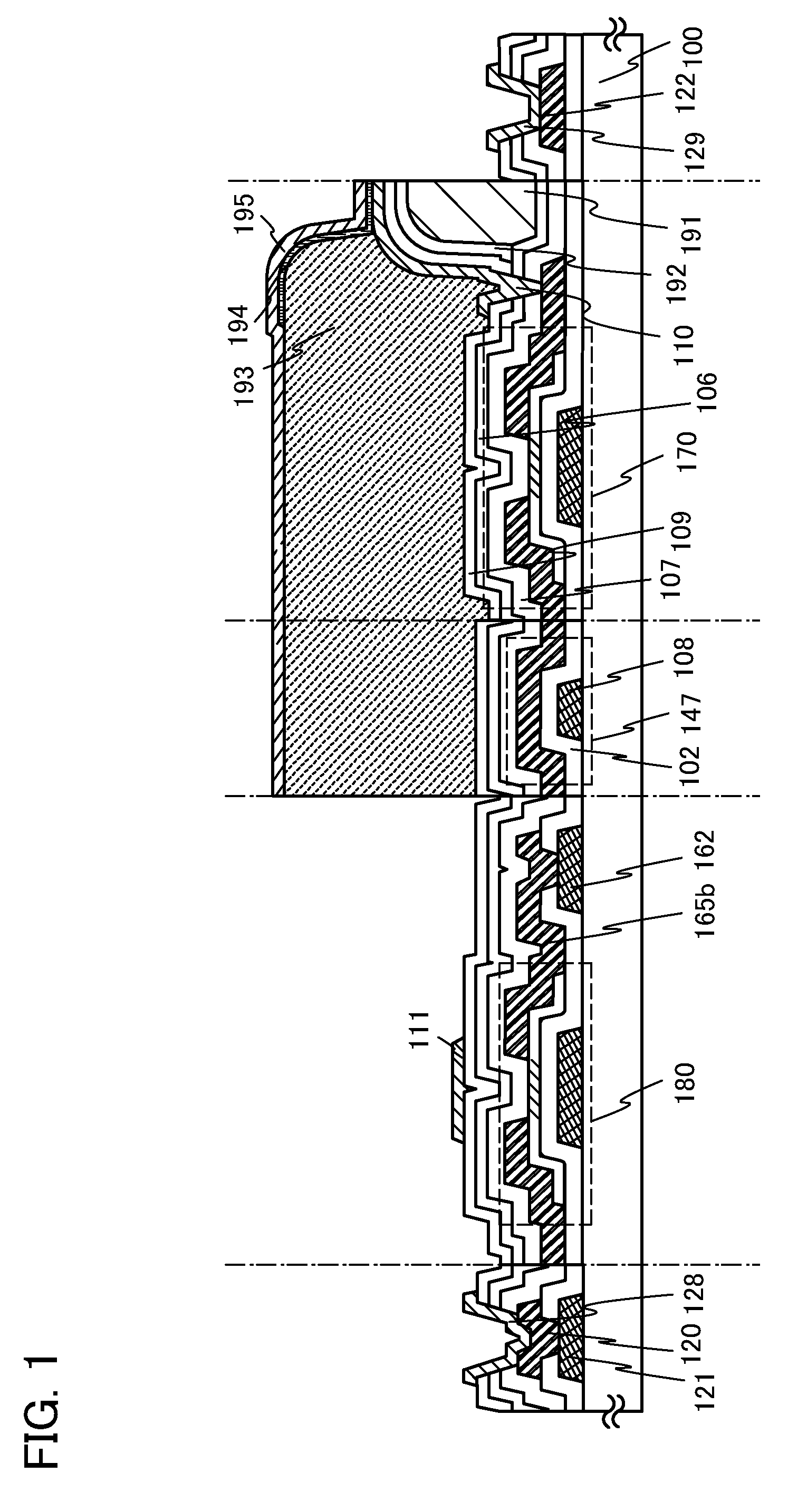

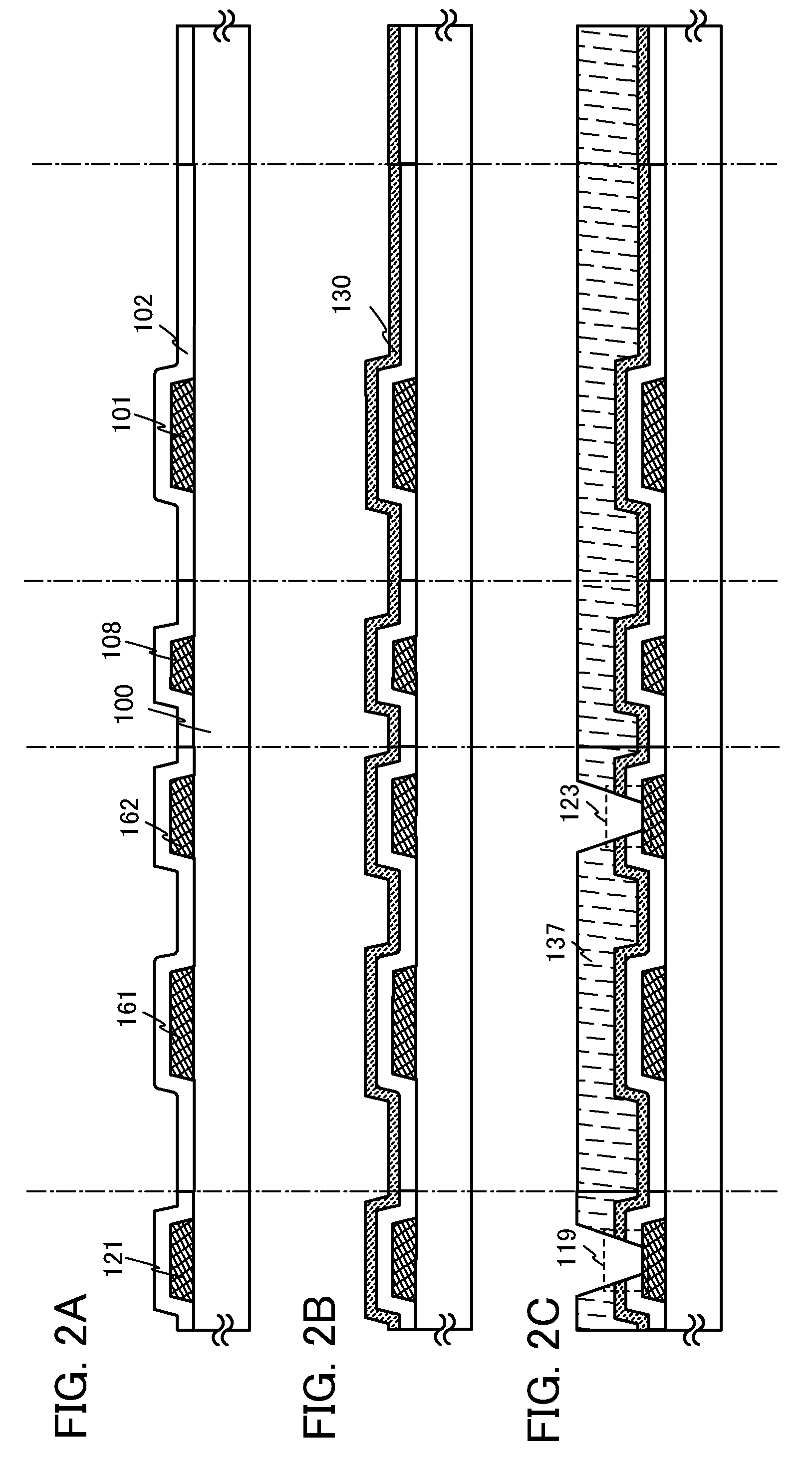

Thin film transistor, display device, including the same, and associated methods

InactiveUS8058645B2Excellent electrical propertiesMinimize damageSolid-state devicesSemiconductor/solid-state device manufacturingIndiumDisplay device

A thin film transistor (TFT), including a substrate, a gate electrode on the substrate, an oxide semiconductor layer including a channel region, a source region, and a drain region, a gate insulating layer between the gate electrode and the oxide semiconductor layer, and source and drain electrodes in contact with the source and drain regions of the oxide semiconductor layer, respectively, wherein the oxide semiconductor layer has a GaInZnO (GIZO) bilayer structure including a lower layer and an upper layer, and the upper layer has a different indium (In) concentration than the lower layer.

Owner:SAMSUNG DISPLAY CO LTD

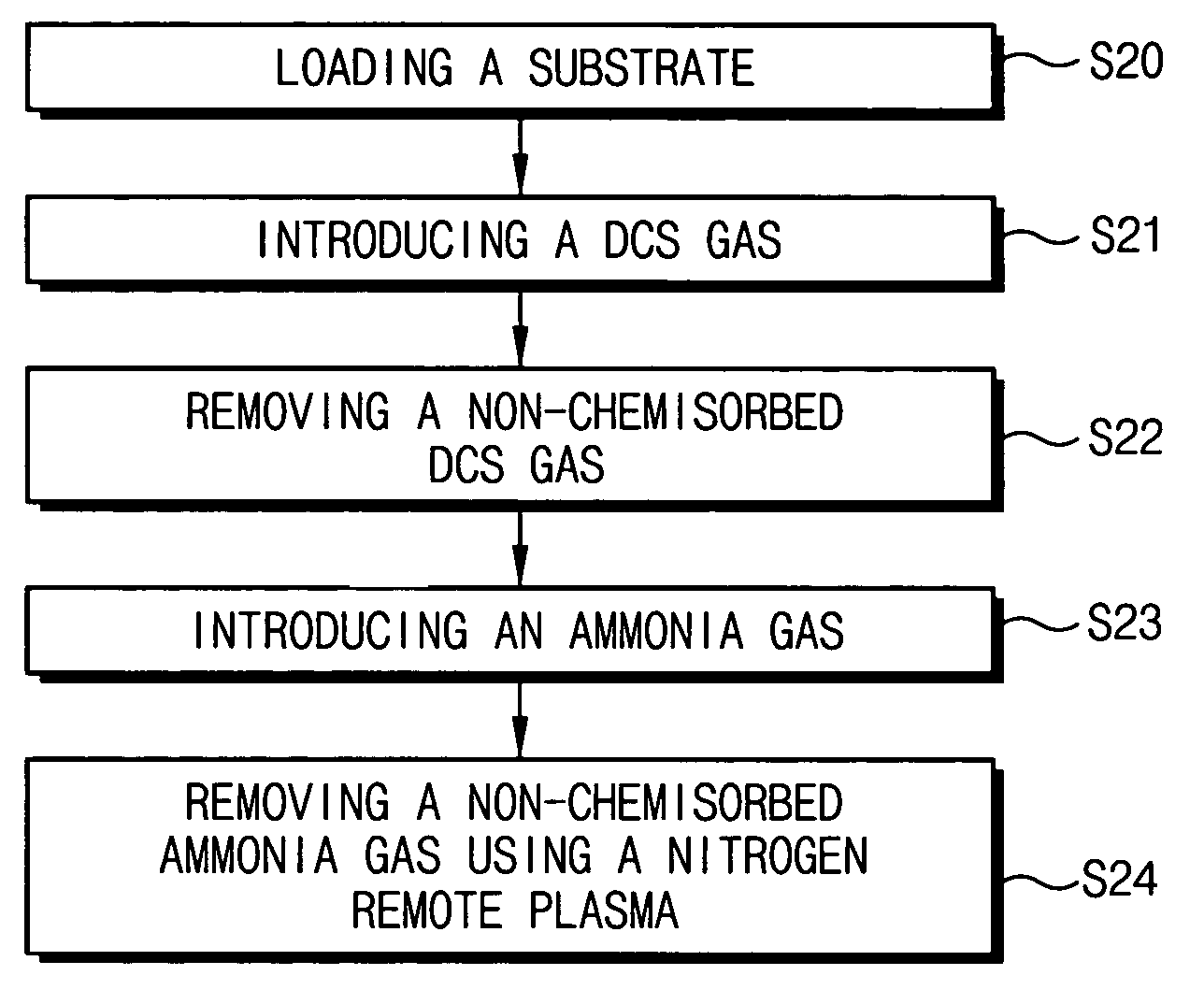

Method of forming a layer and forming a capacitor of a semiconductor device having the same layer

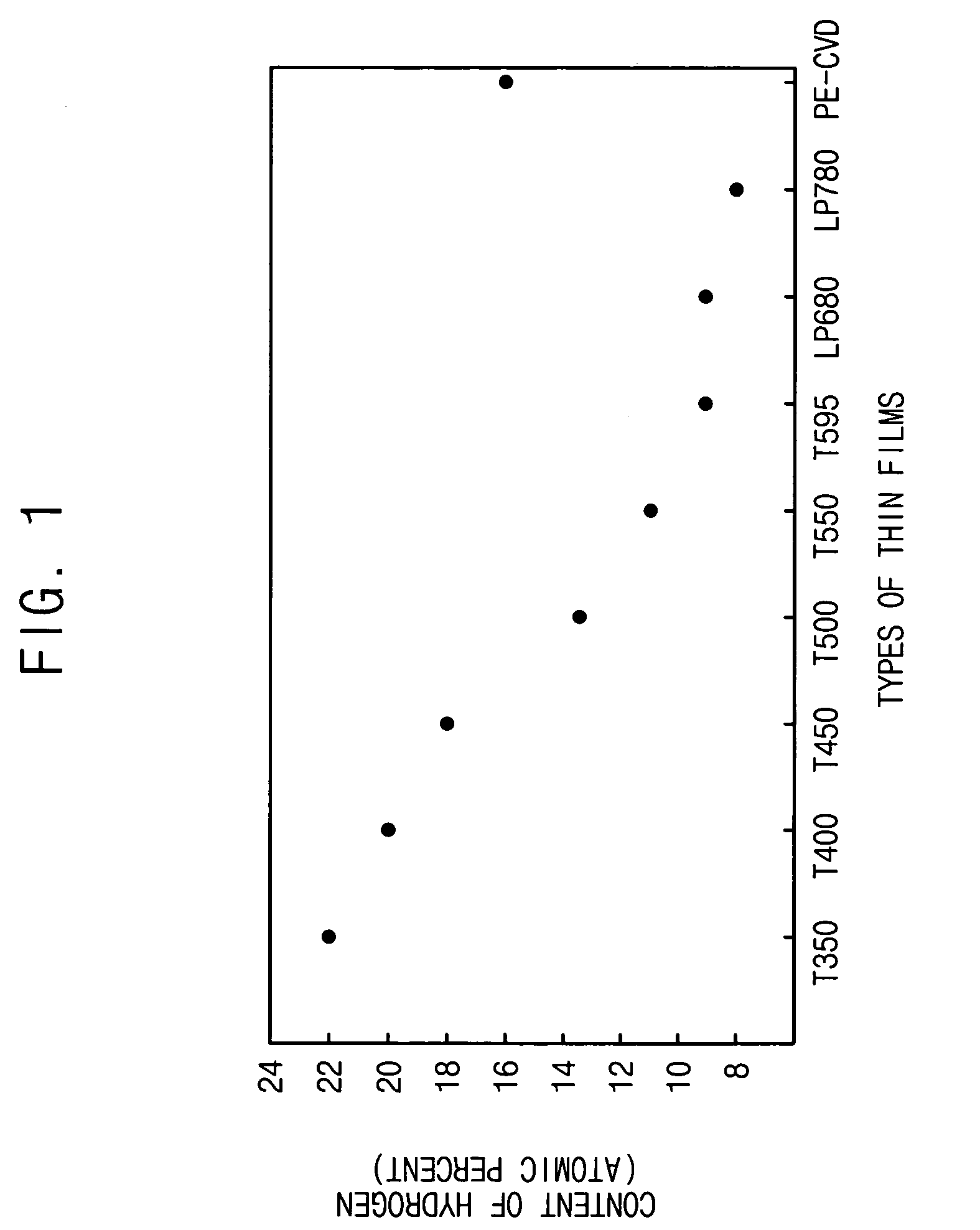

InactiveUS20060014384A1Low hydrogen contentReduce leakage currentSemiconductor/solid-state device manufacturingCapacitorsChemical reactionDevice material

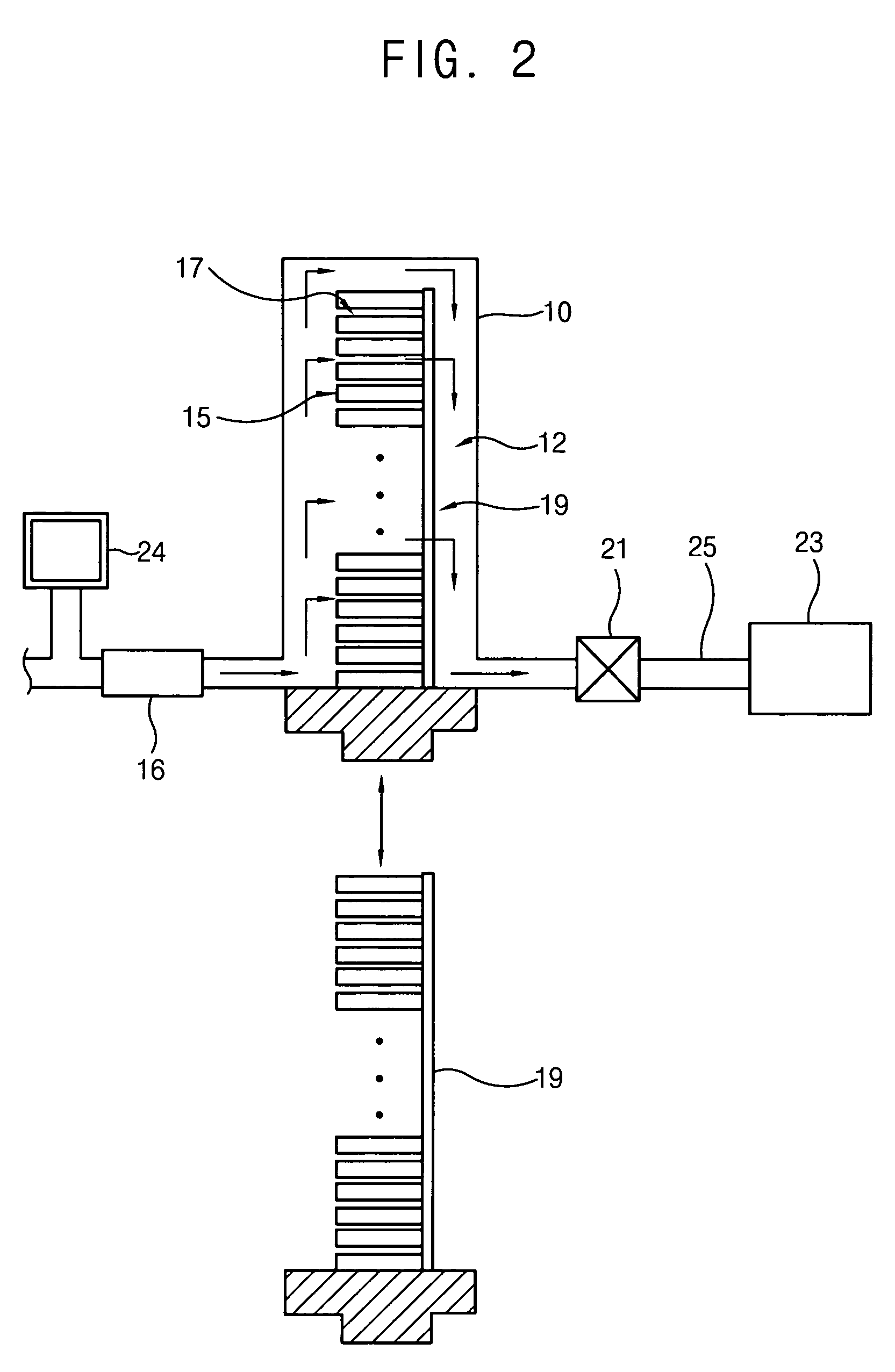

In a method of forming a layer using an atomic layer deposition process, after a substrate is loaded into a chamber, a first reactant is provided onto the substrate. The first reactant is partially chemisorbed on the substrate. A second reactant is introduced into the chamber to form a preliminary layer on the substrate by chemically reacting the second reactant with the chemisorbed first reactant. Impurities in the preliminary layer and unreacted reactants are simultaneously removed using a plasma for removing impurities to thereby form the layer on the substrate. The impurities in the layer may be effectively removed so that the layer may have reduced leakage current.

Owner:SAMSUNG ELECTRONICS CO LTD

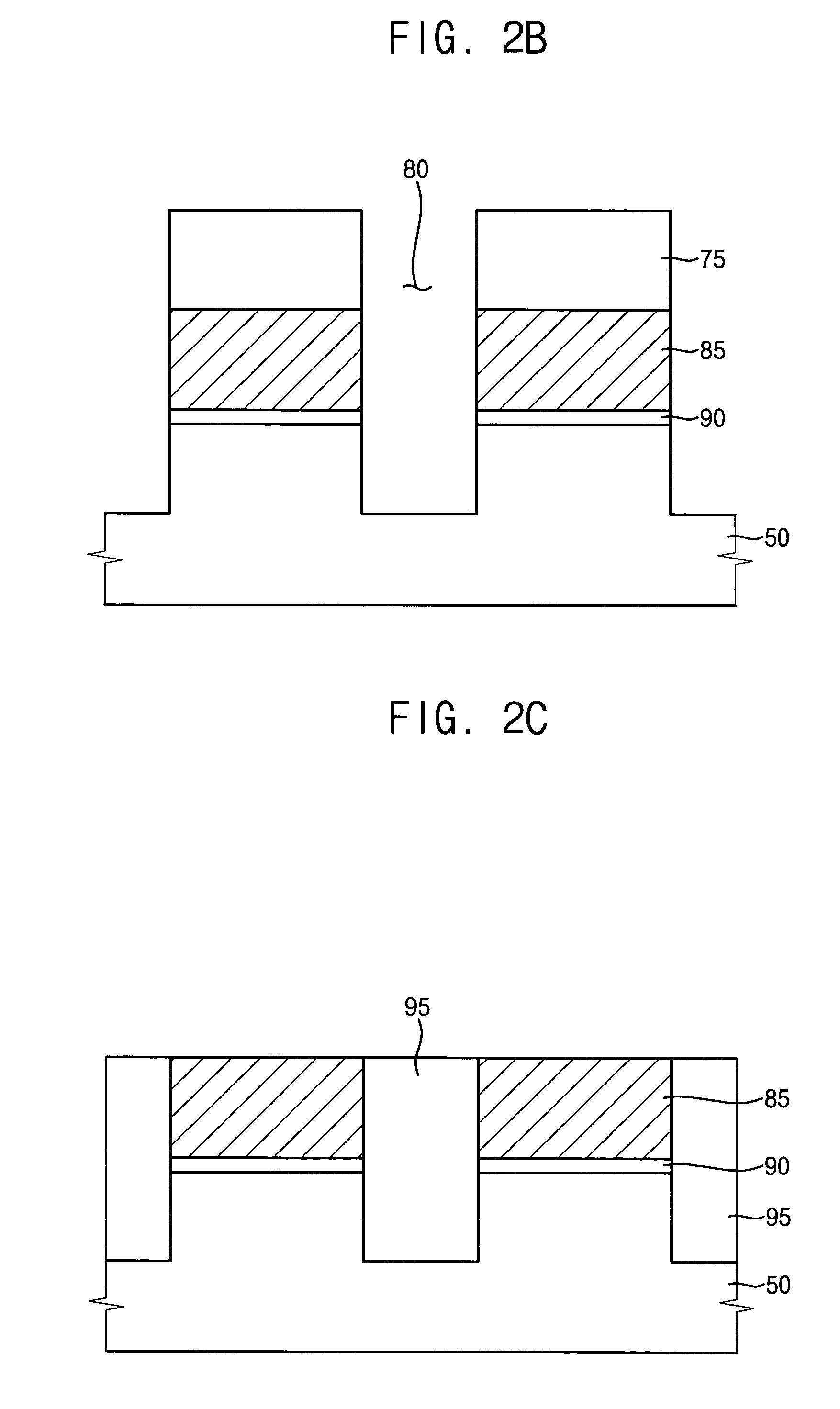

Methods of forming a thin film structure, and a gate structure and a capacitor including the thin film structure

InactiveUS20060013946A1Well formedHigh dielectric constantSemiconductor/solid-state device manufacturingSpecial surfacesChemical reactionSilicon oxide

A thin film structure is formed that includes hafnium silicon oxide using an atomic layer deposition process. A first reactant including tetrakis ethyl methyl amino hafnium (TEMAH) is introduced onto a substrate. A first portion of the first reactant is chemisorbed to the substrate, whereas a second portion of the first reactant is physorbed to the first portion of the first reactant. A first oxidant is provided onto the substrate. A first thin film including hafnium oxide is formed on the substrate by chemically reacting the first oxidant with the first portion of the first reactant. A second reactant including amino propyl tri ethoxy silane (APTES) is introduced onto the first thin film. A first portion of the second reactant is chemisorbed to the first thin film, whereas a second portion of the second reactant is physorbed to the first portion of the second reactant. A second oxidant is provided onto the first thin film. A second thin film including silicon oxide is formed on the first thin film by chemically reacting the second oxidant with the first portion of the second reactant.

Owner:SAMSUNG ELECTRONICS CO LTD

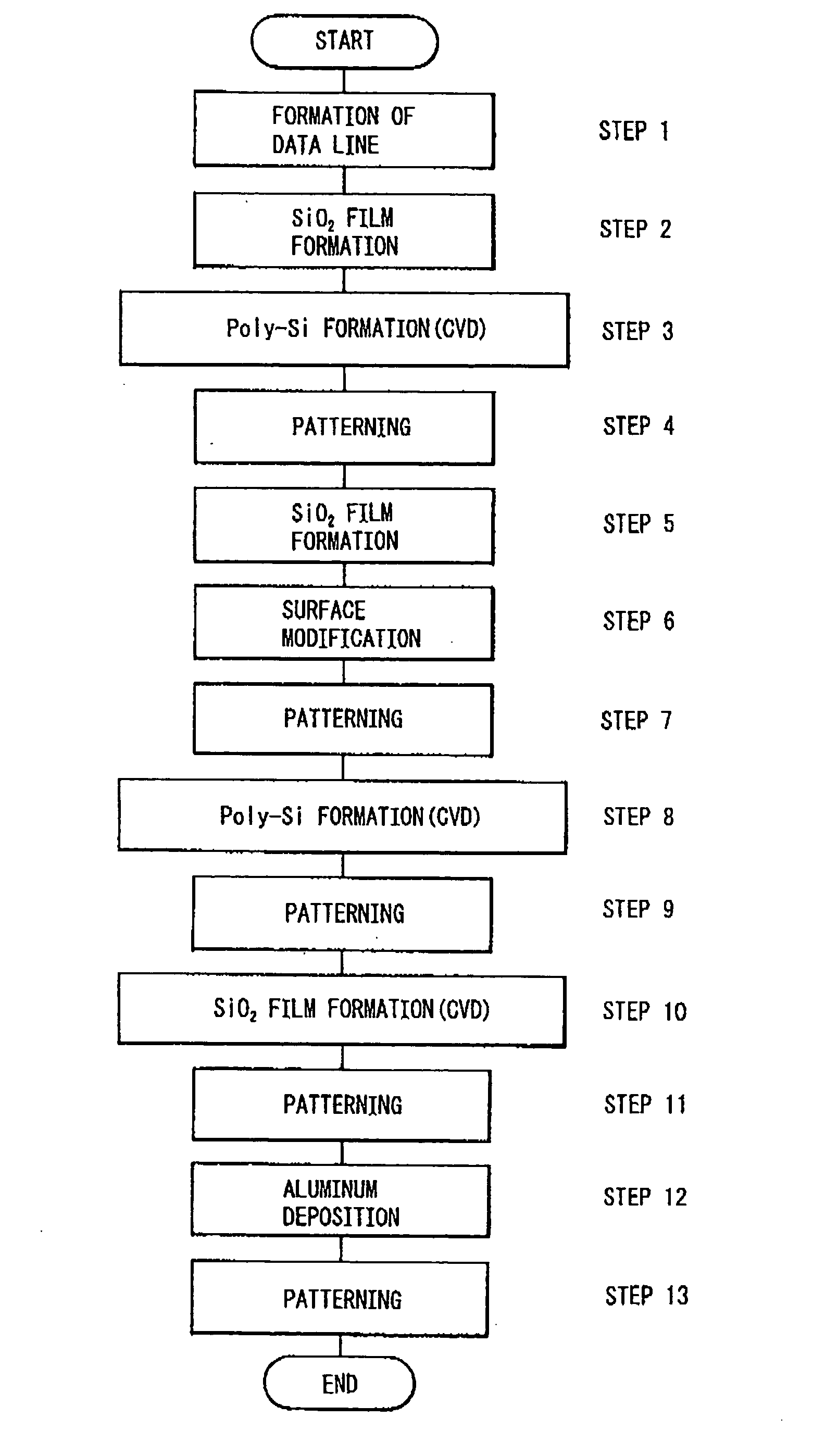

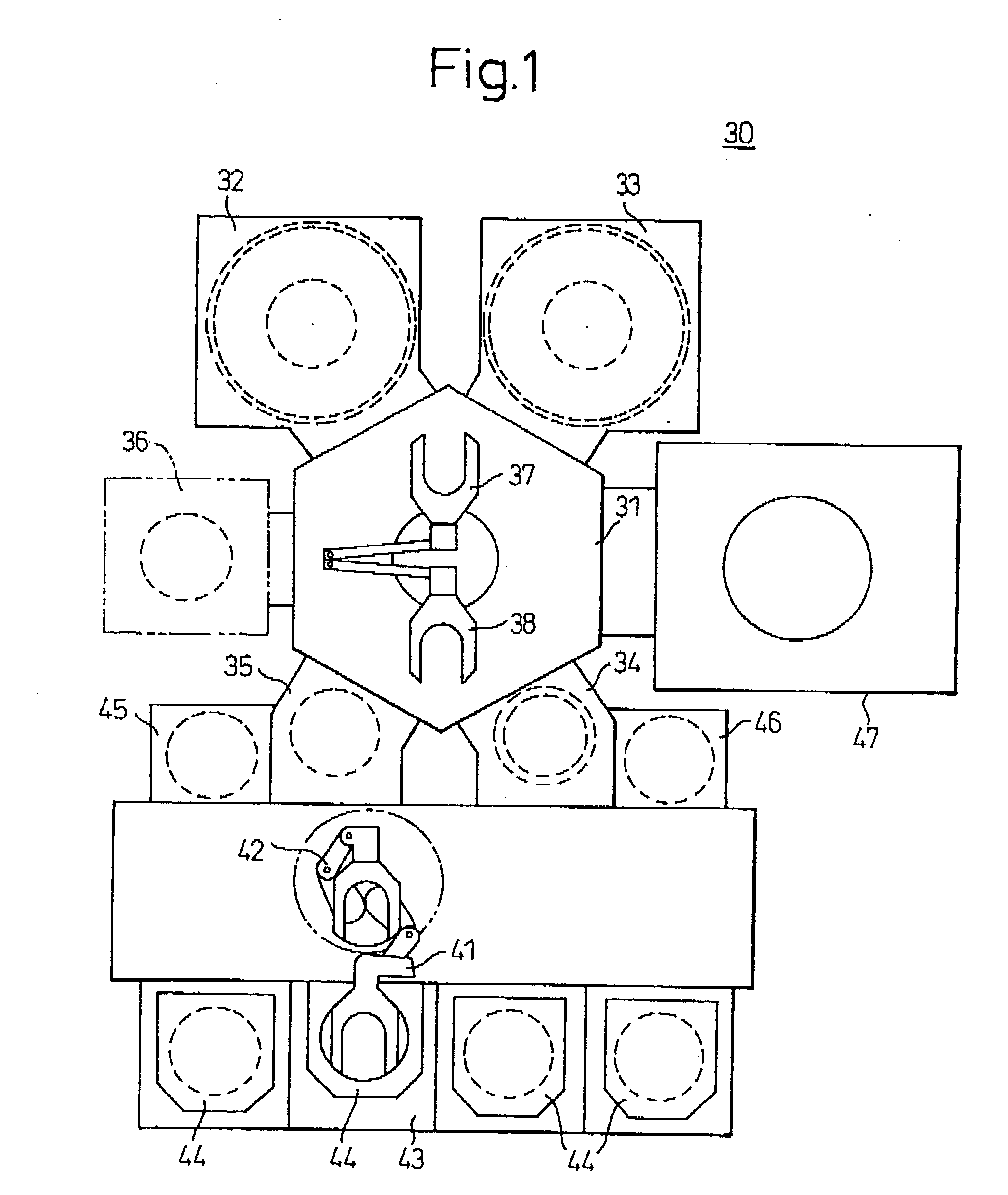

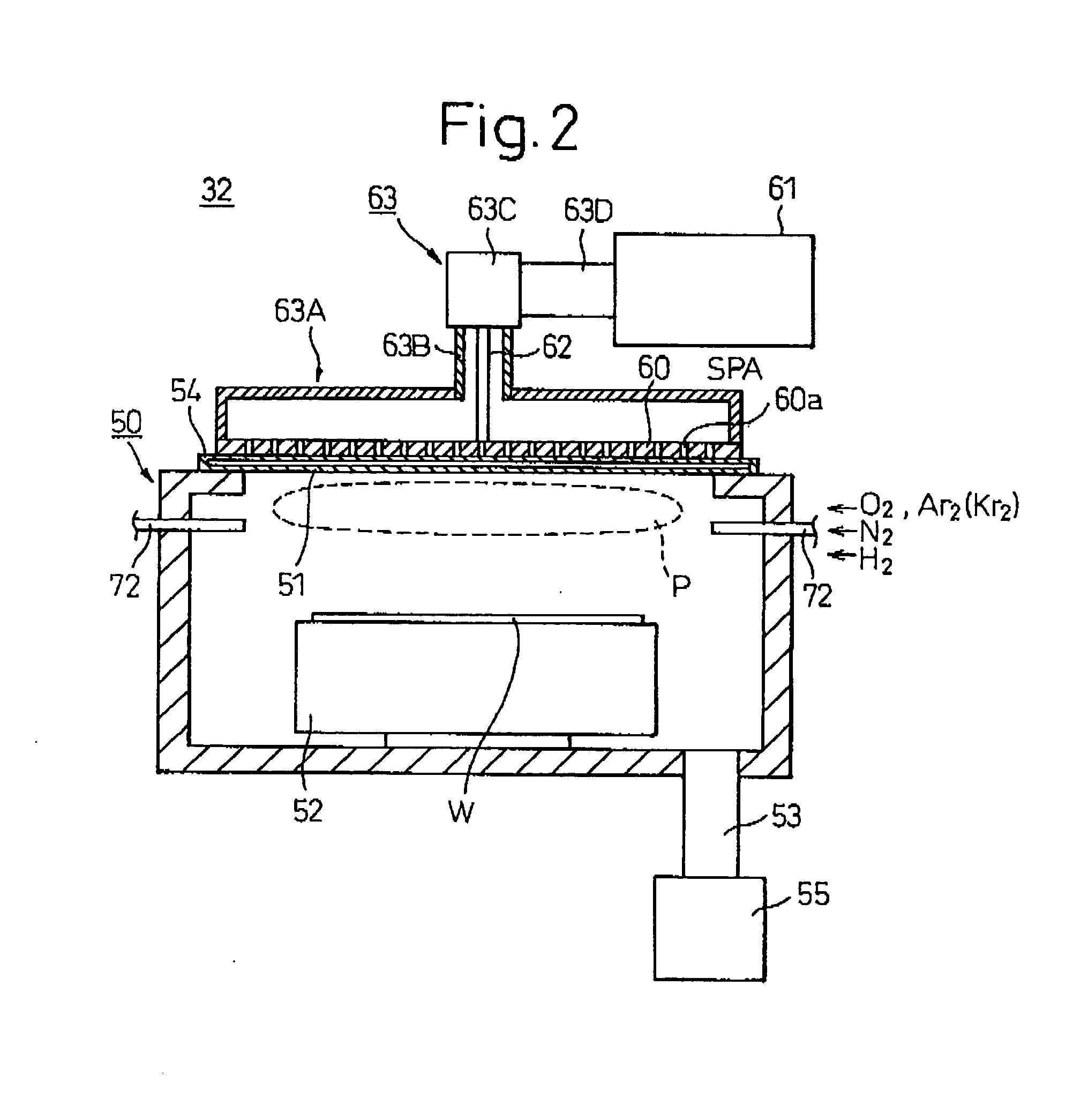

Method of producing electronic device material

InactiveUS20040048452A1High densityLow electron temperatureElectric discharge tubesSemiconductor/solid-state device manufacturingDevice materialEngineering

A process for producing an electronic device material of a high quality MOS-type semiconductor comprising an insulating layer and a semiconductor layer excellent in the electrical characteristic. The process includes: a step of CVD-treating a substrate to be processed comprising single-crystal silicon as a main component, to thereby form an insulating layer; and a step of exposing the substrate to be processed to a plasma which has been generated from a process gas on the basis of microwave irradiation via a plane antenna member having a plurality of slots, to thereby modify the insulating film by using the thus generated plasma.

Owner:TOKYO ELECTRON LTD

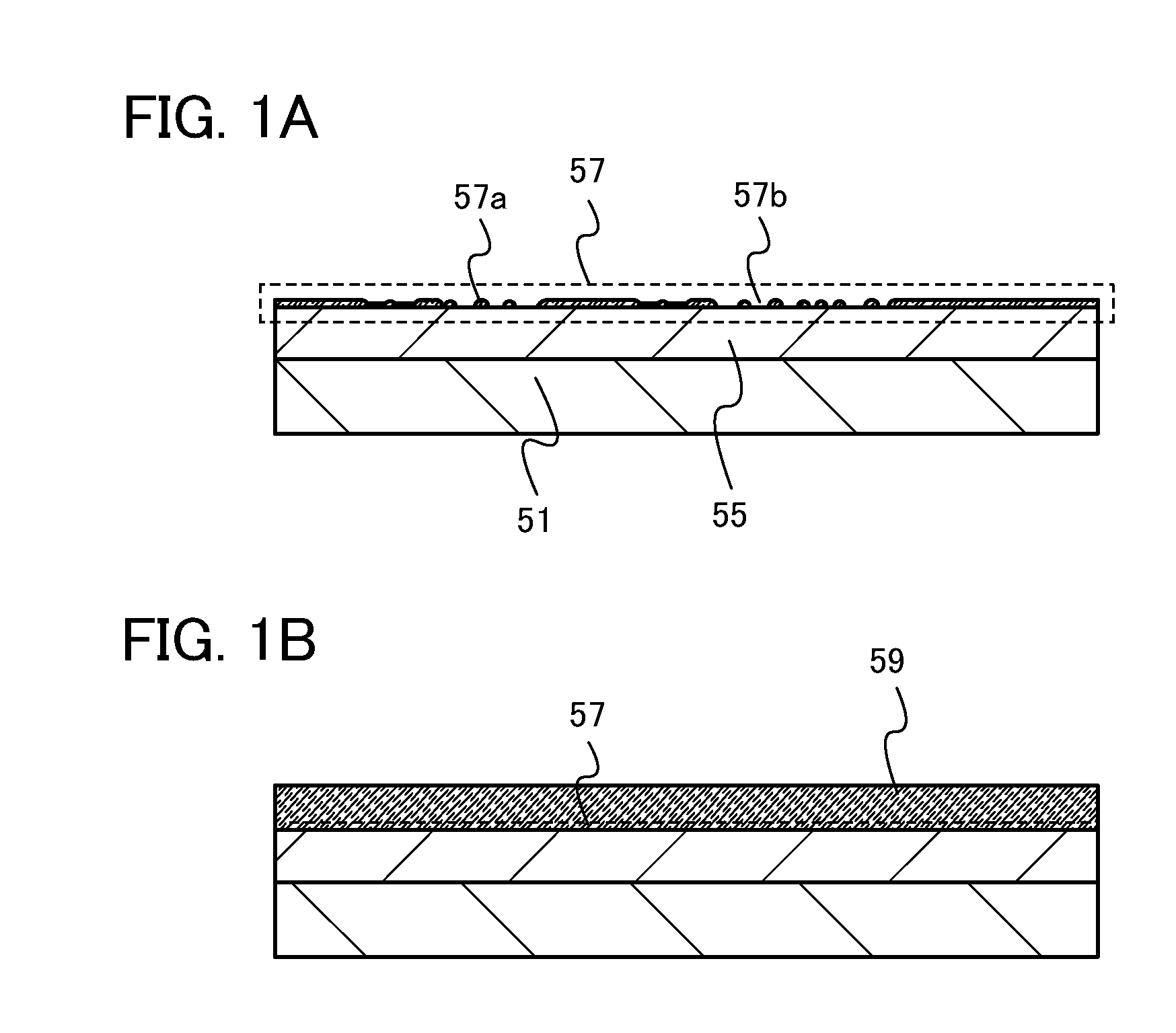

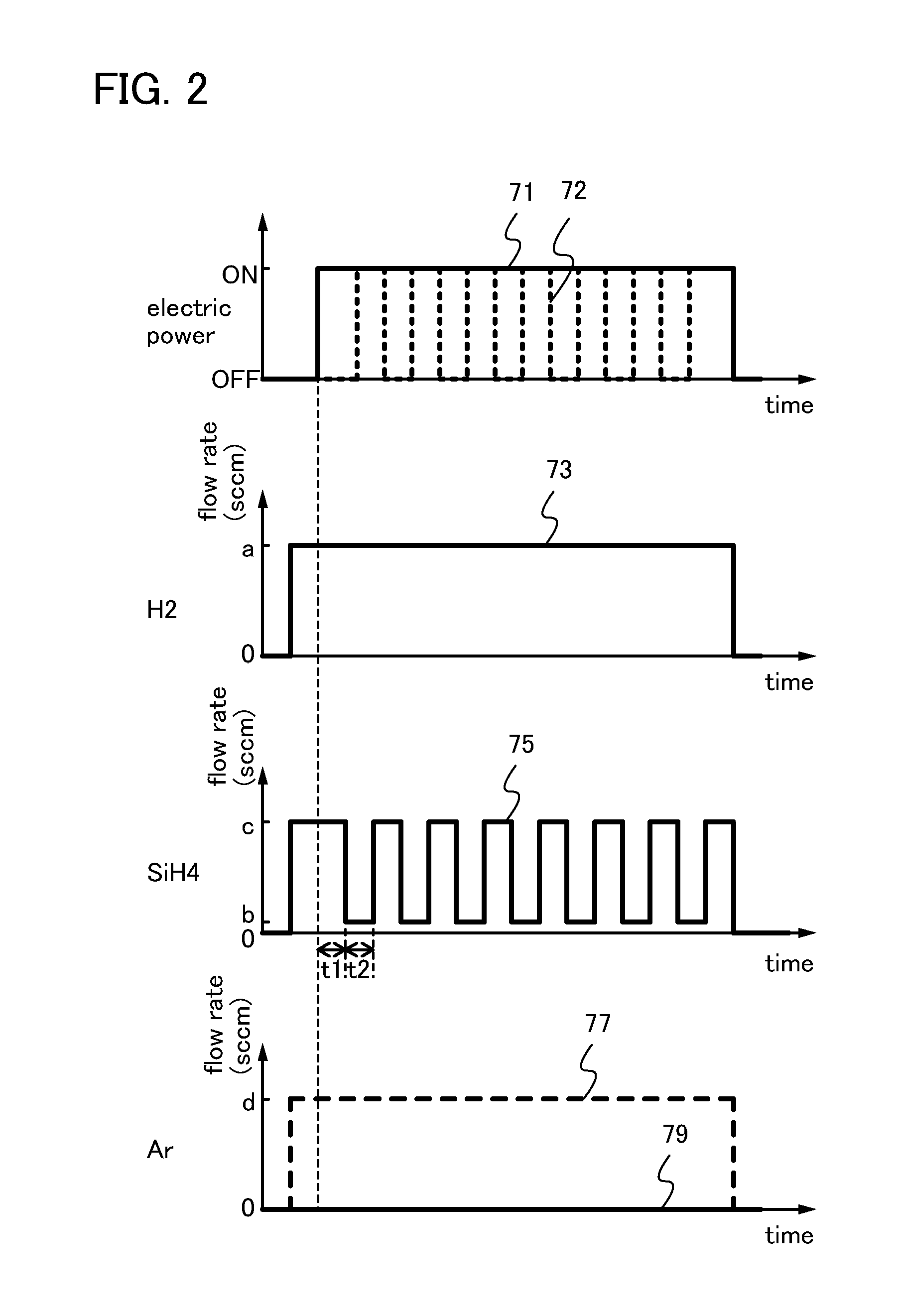

Method for manufacturing semiconductor device

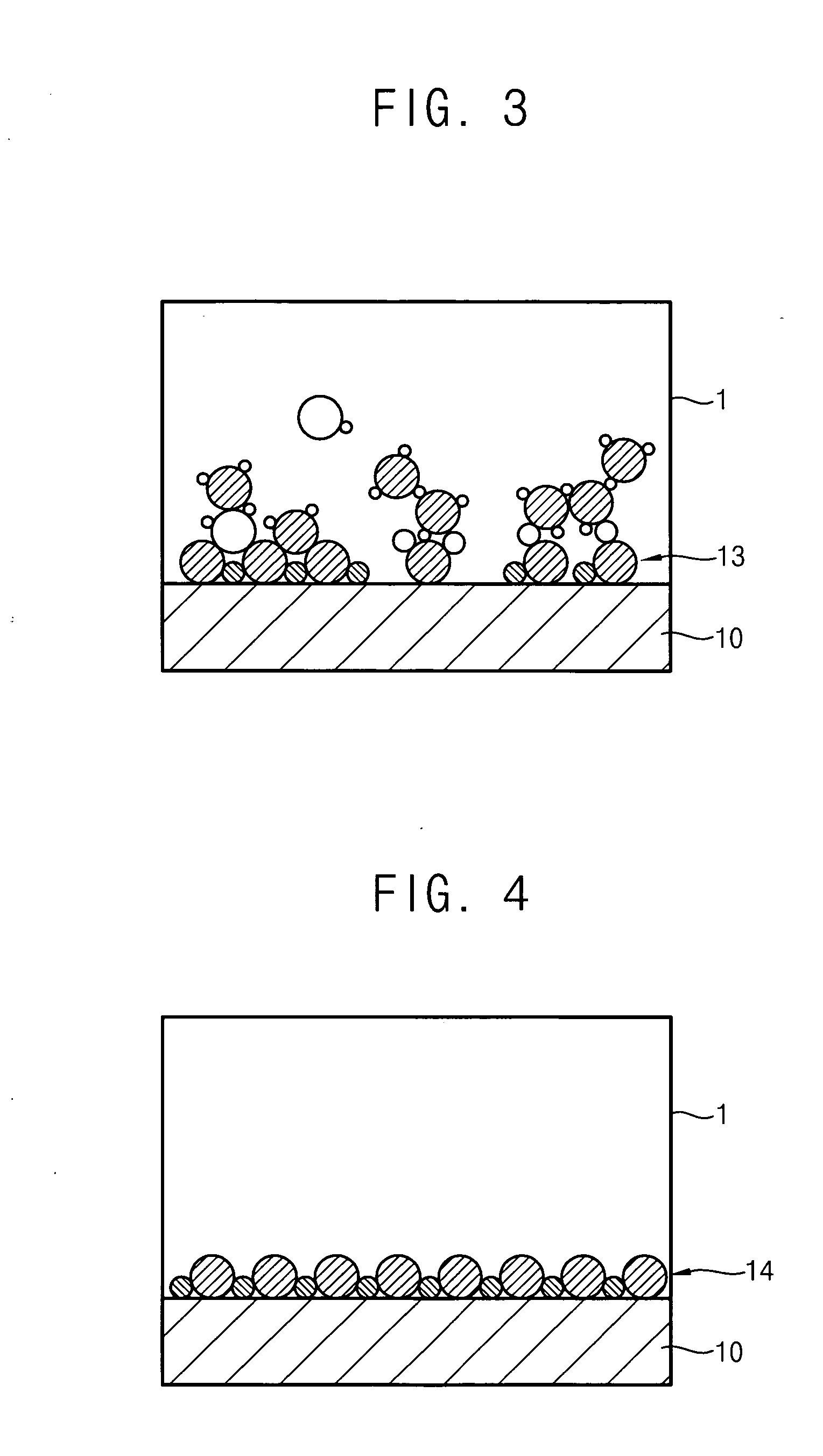

InactiveUS20110318888A1High crystallinityExcellent electrical propertiesSemiconductor/solid-state device manufacturingChemical vapor deposition coatingHydrogenEngineering

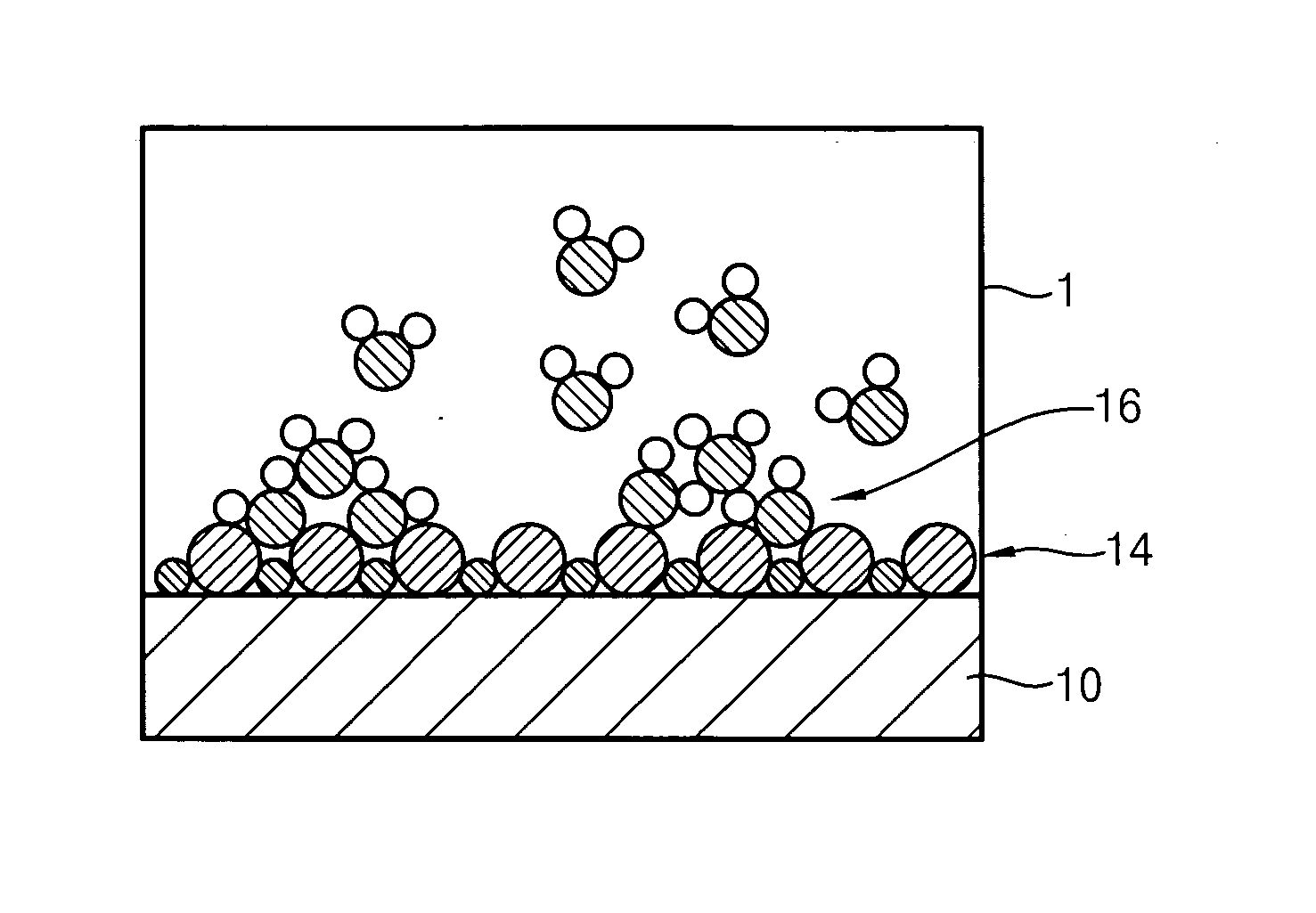

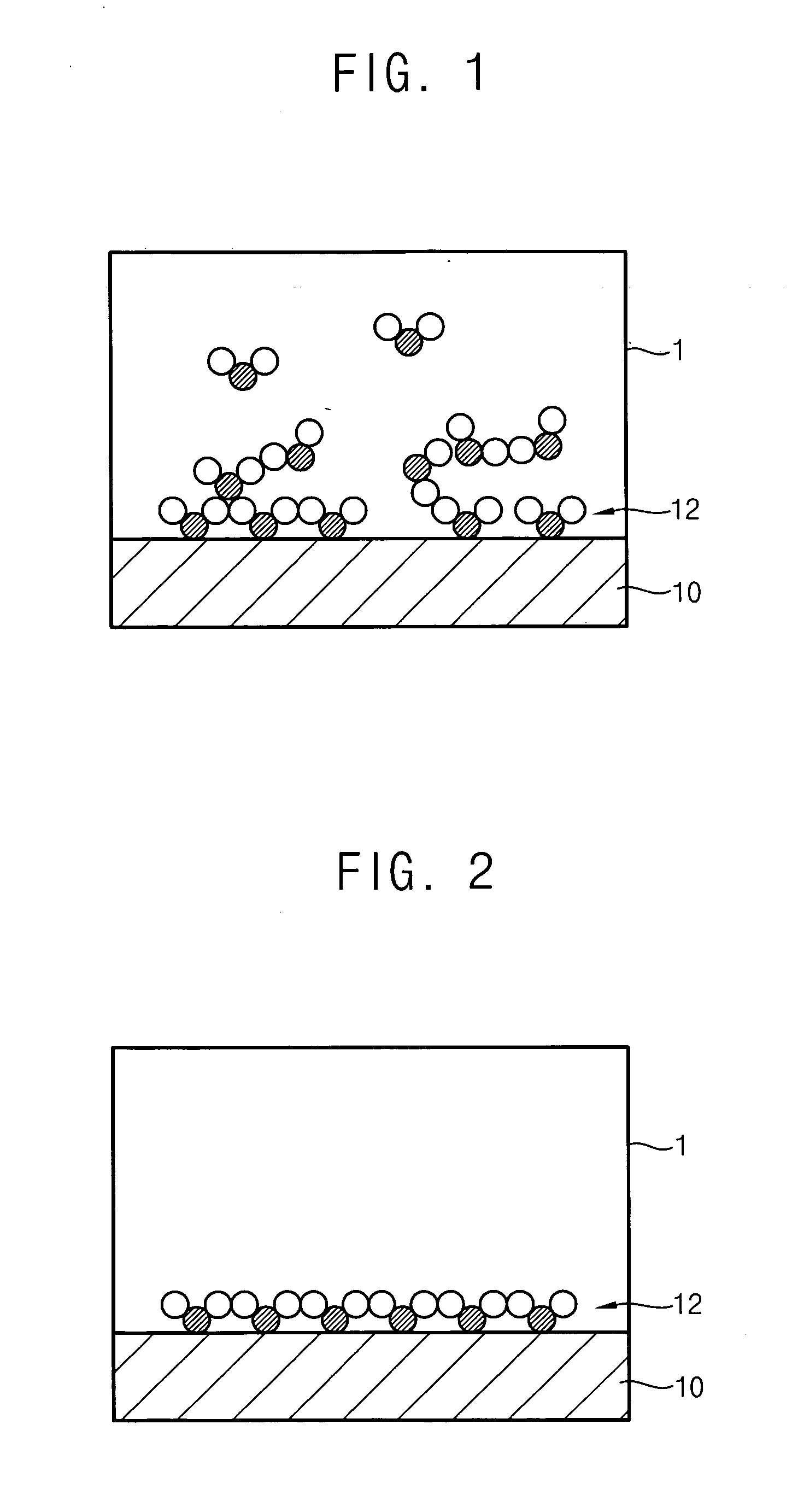

A method for manufacturing a semiconductor device comprises the steps of forming a seed over the insulating film by introducing hydrogen and a deposition gas into a first treatment chamber under a first condition and forming a microcrystalline semiconductor film over the seed by introducing hydrogen and the deposition gas into a second treatment chamber under a second condition: a second flow rate of the deposition gas is periodically changed between a first value and a second value; and a second pressure in the second treatment chamber is higher than or equal to 1.0×102 Torr and lower than or equal to 1.0×103 Torr.

Owner:SEMICON ENERGY LAB CO LTD

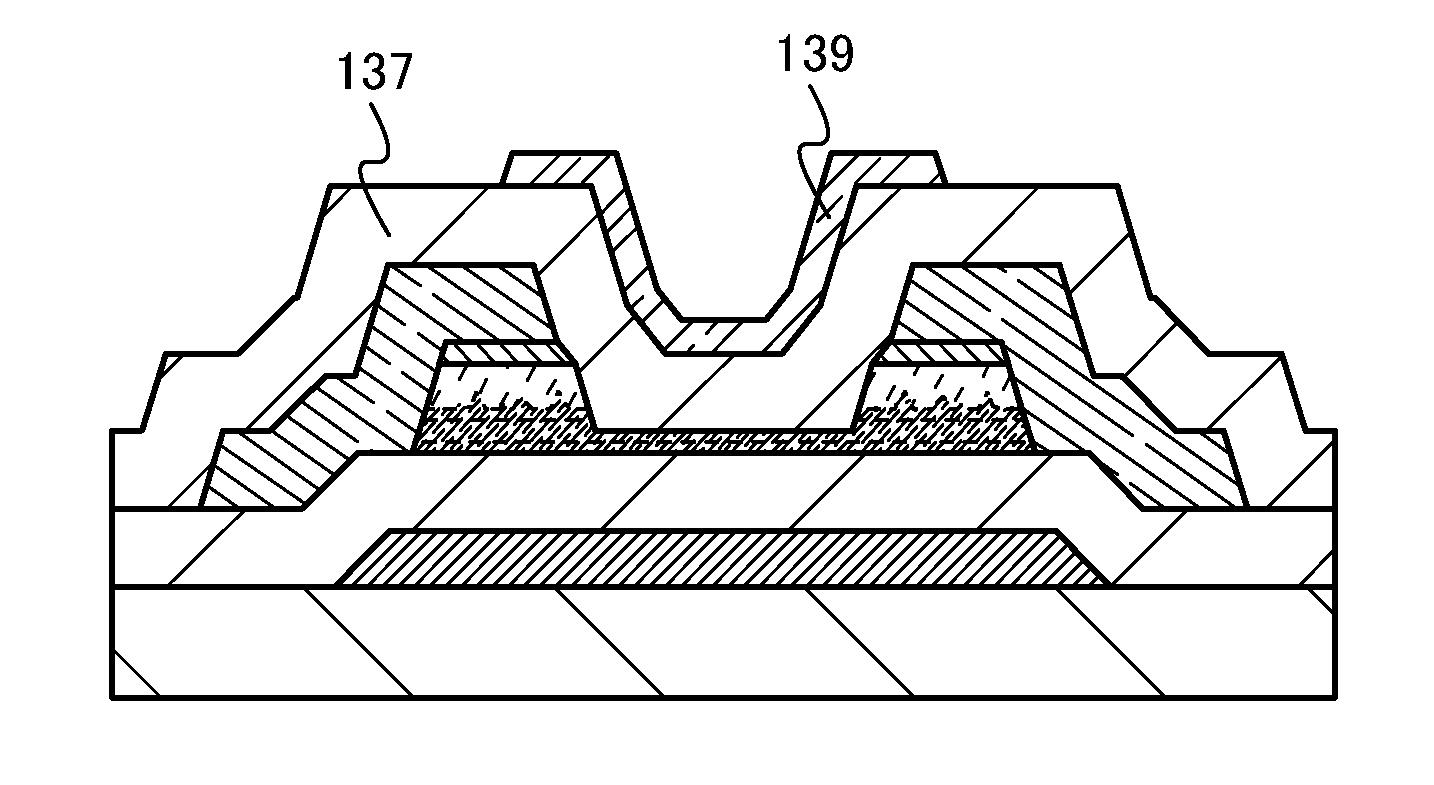

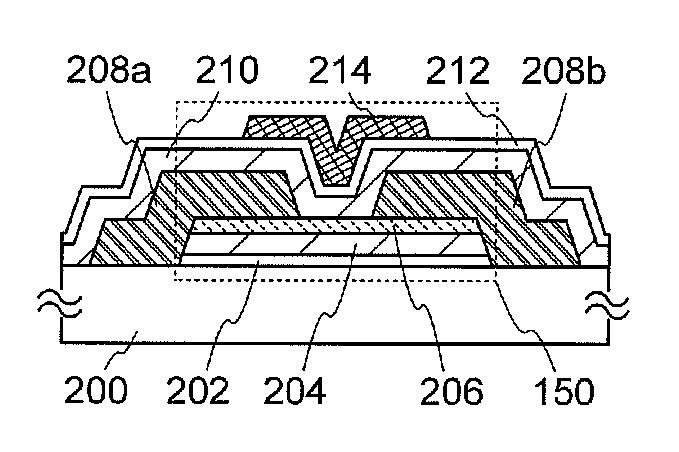

Semiconductor device and manufacturing method thereof

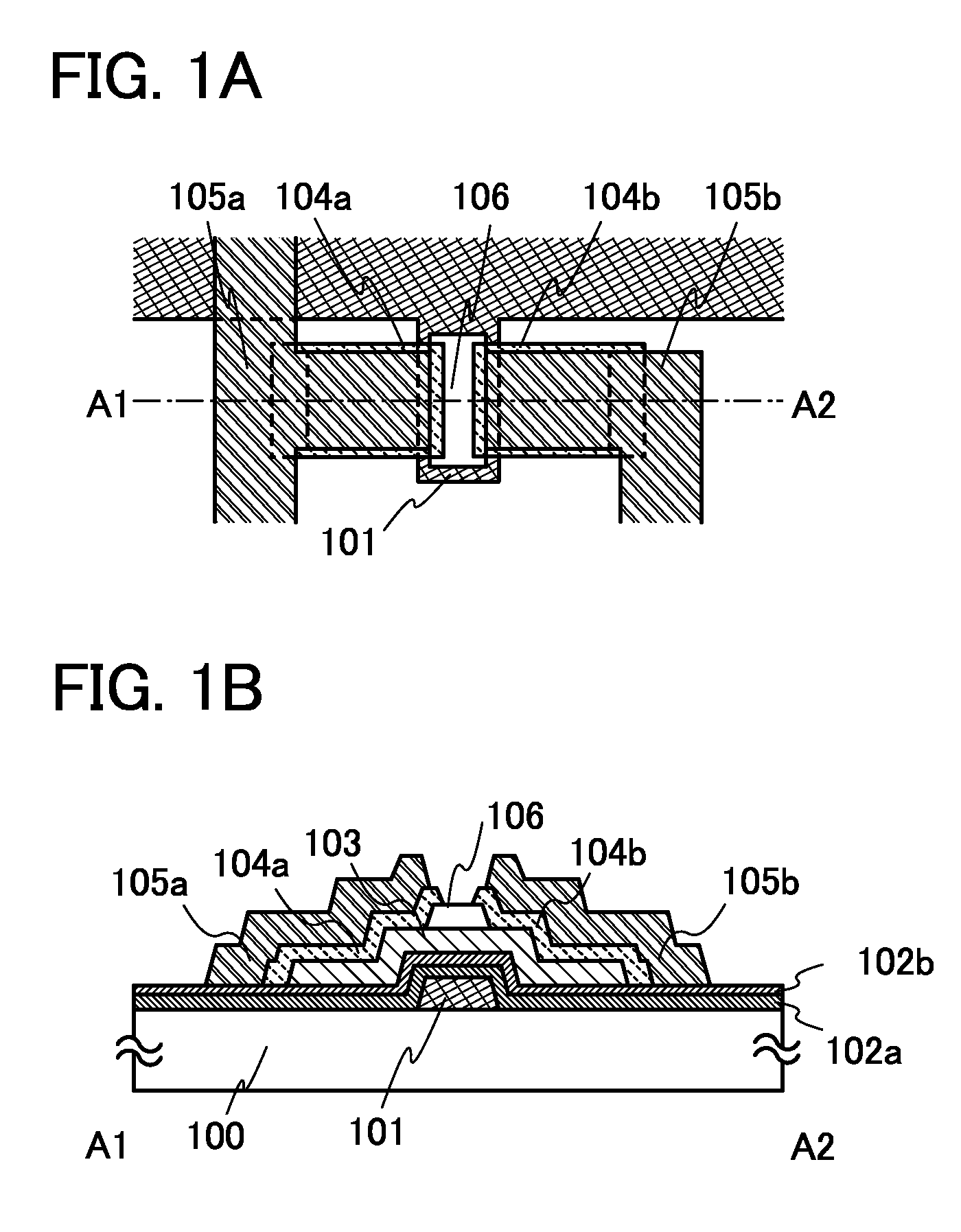

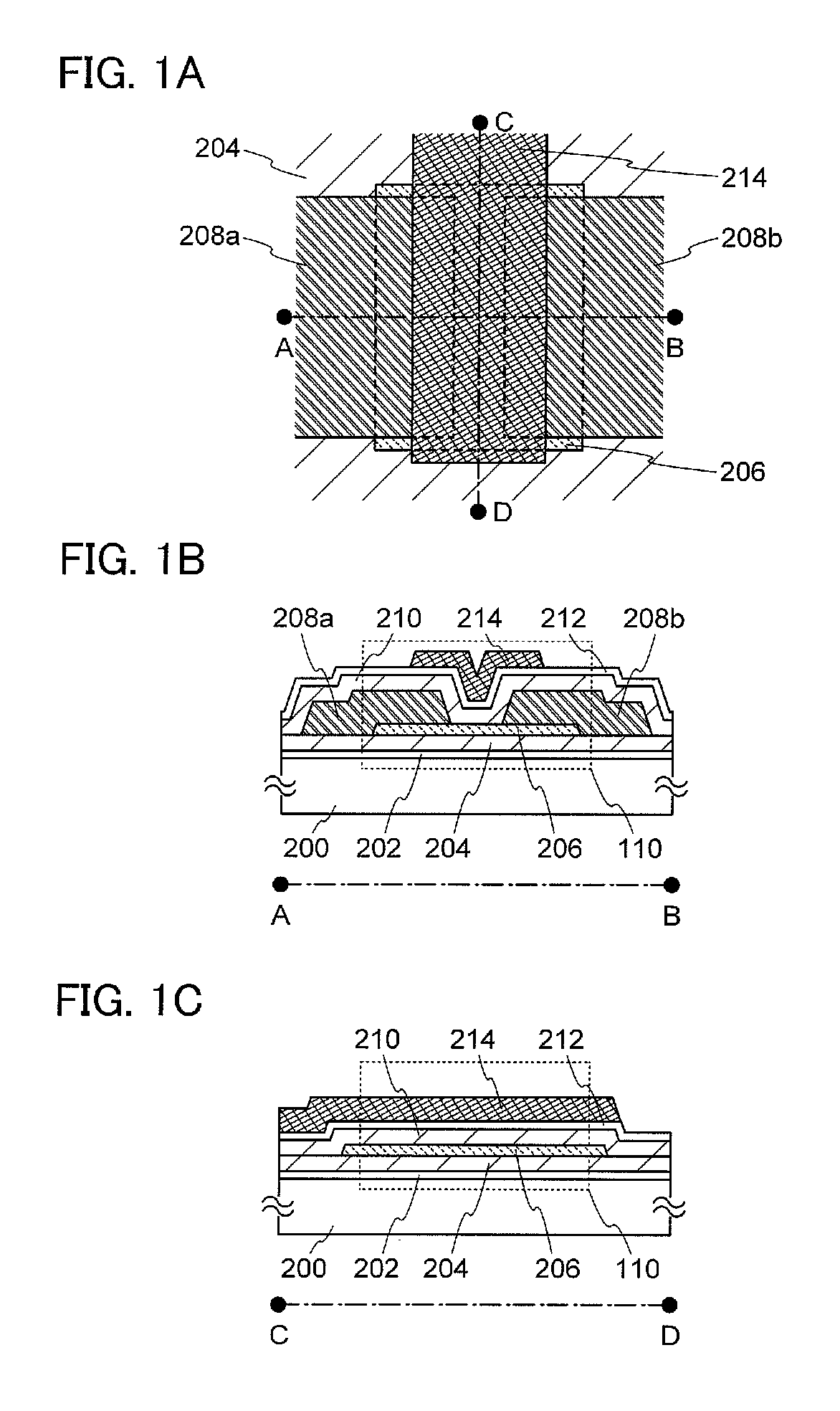

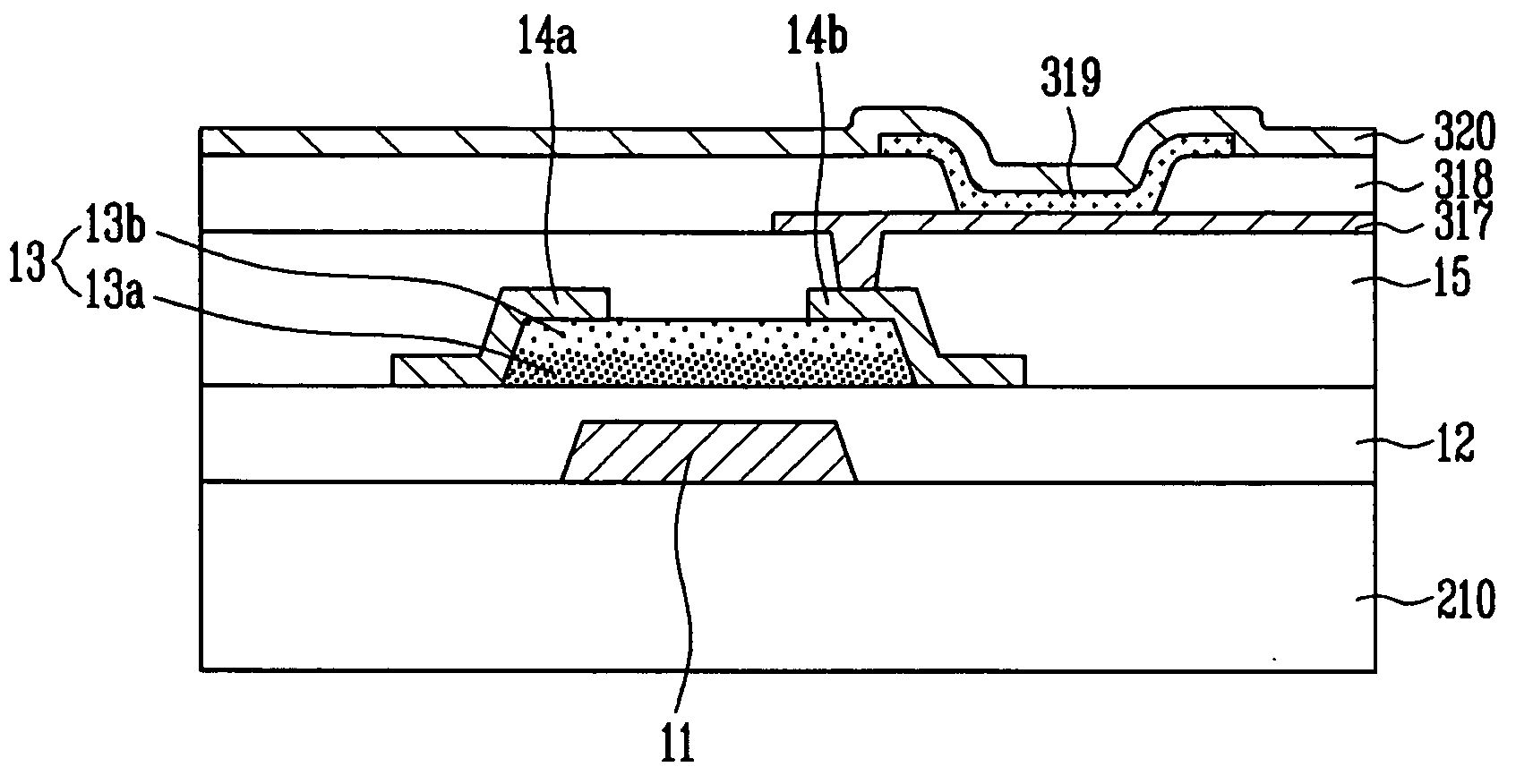

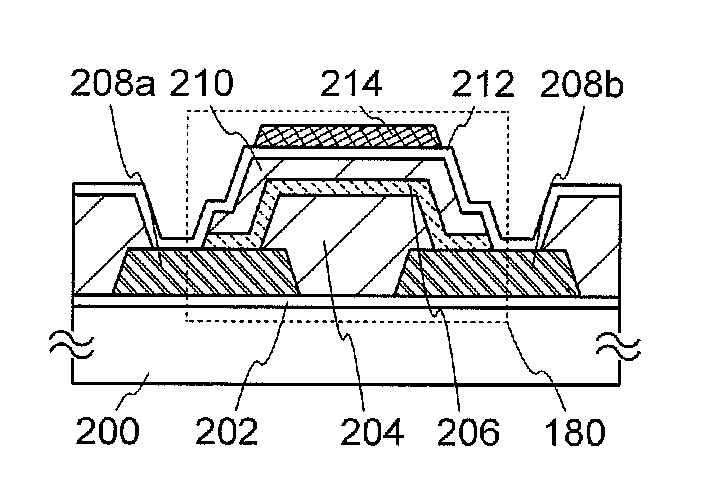

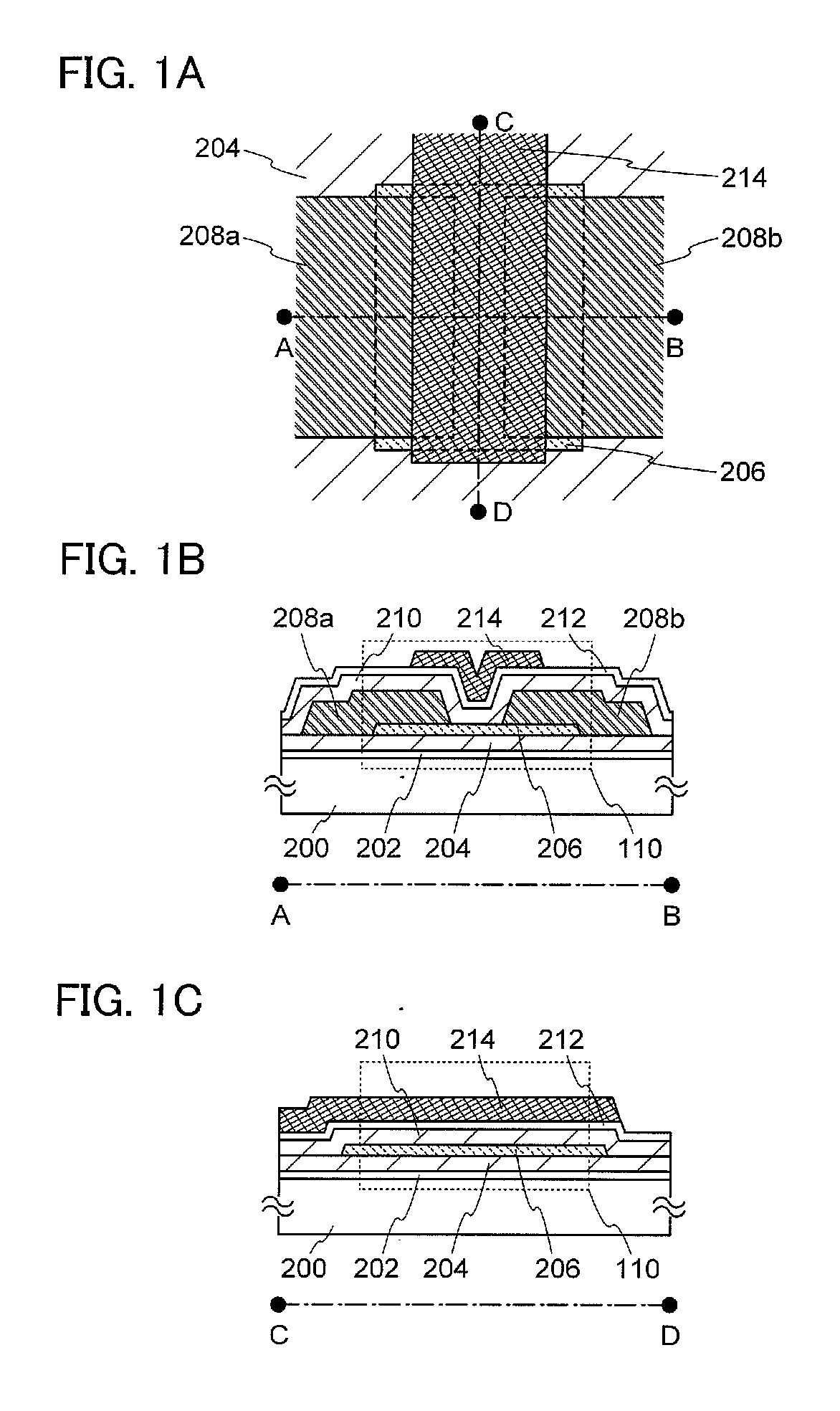

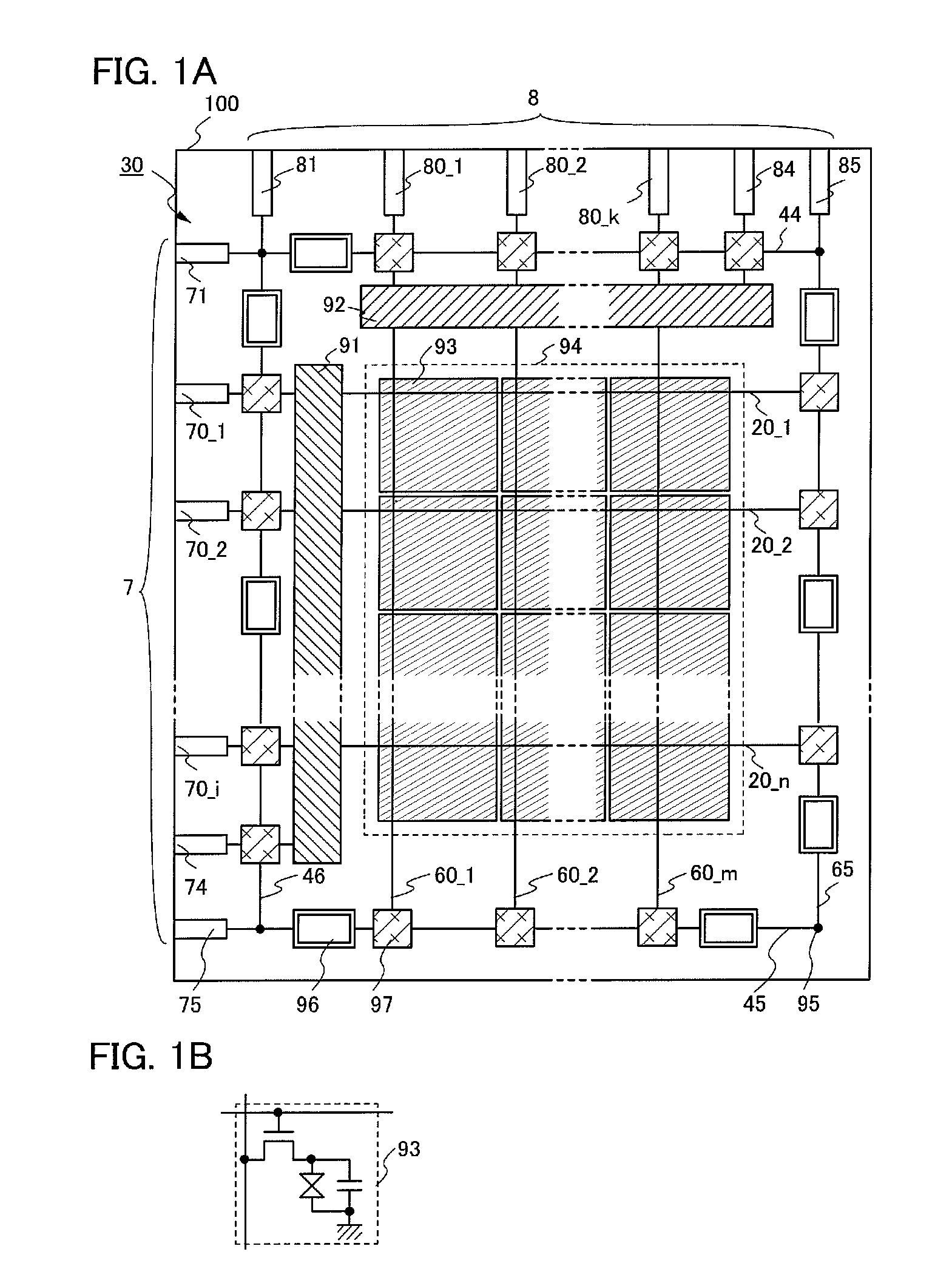

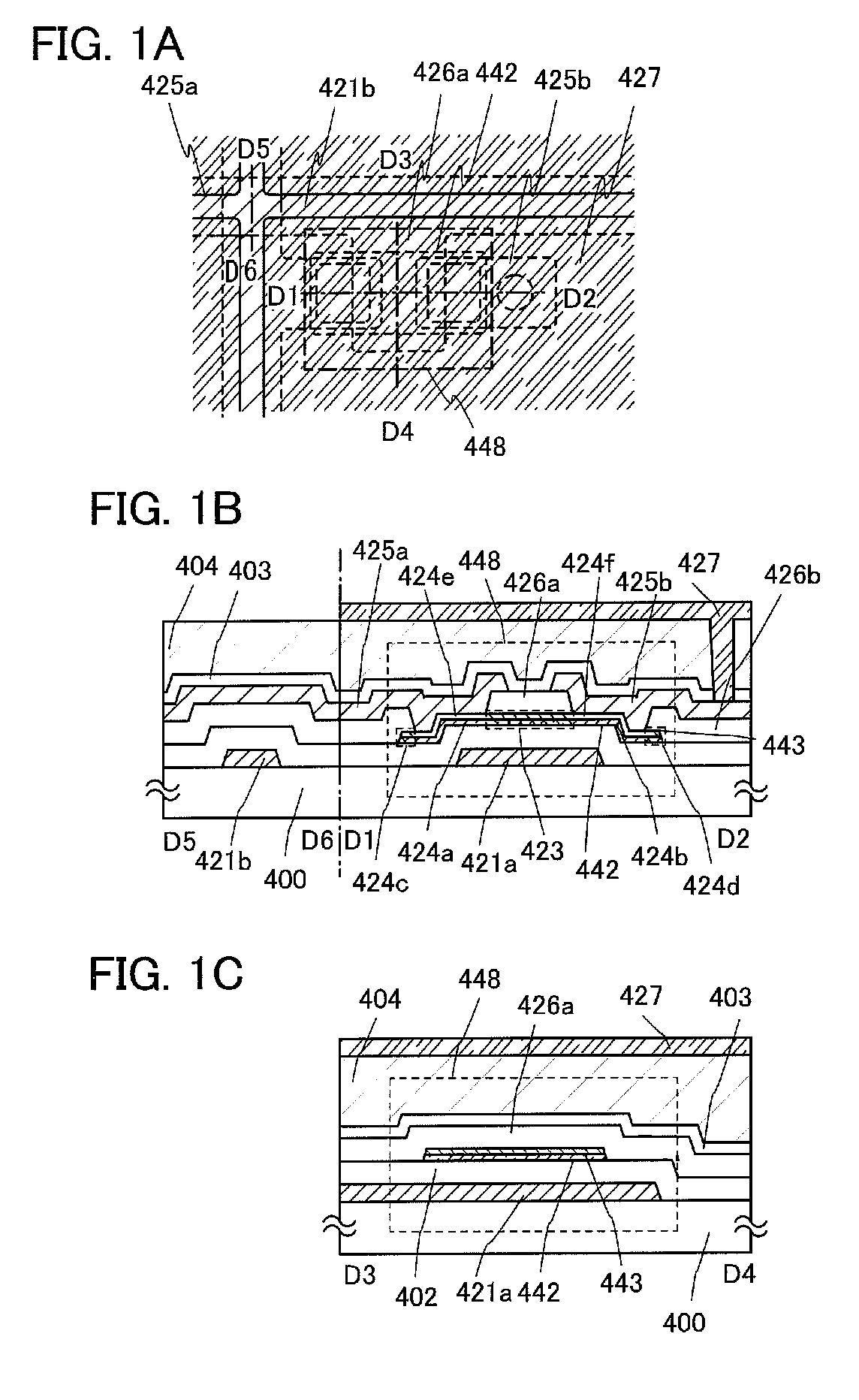

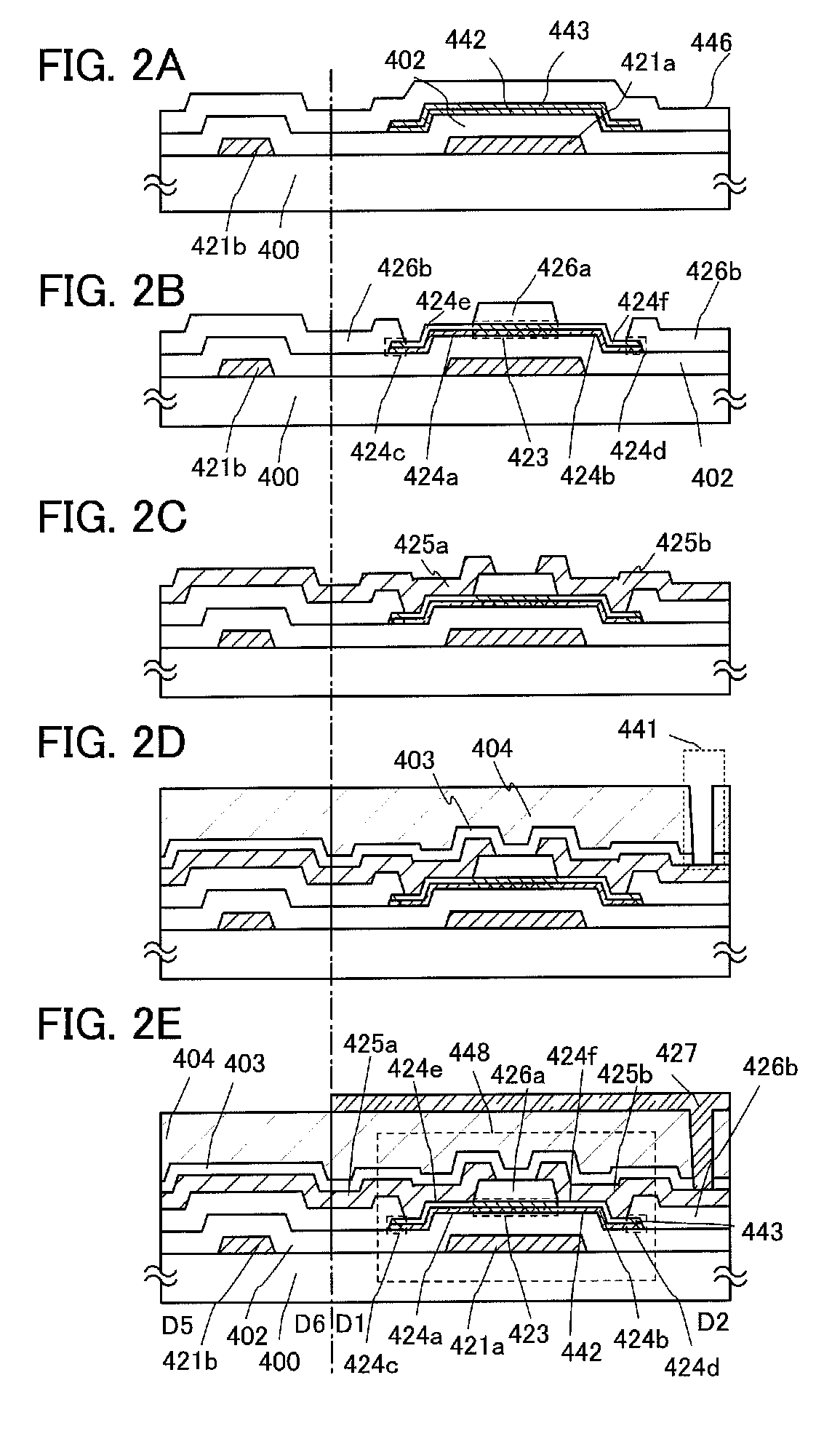

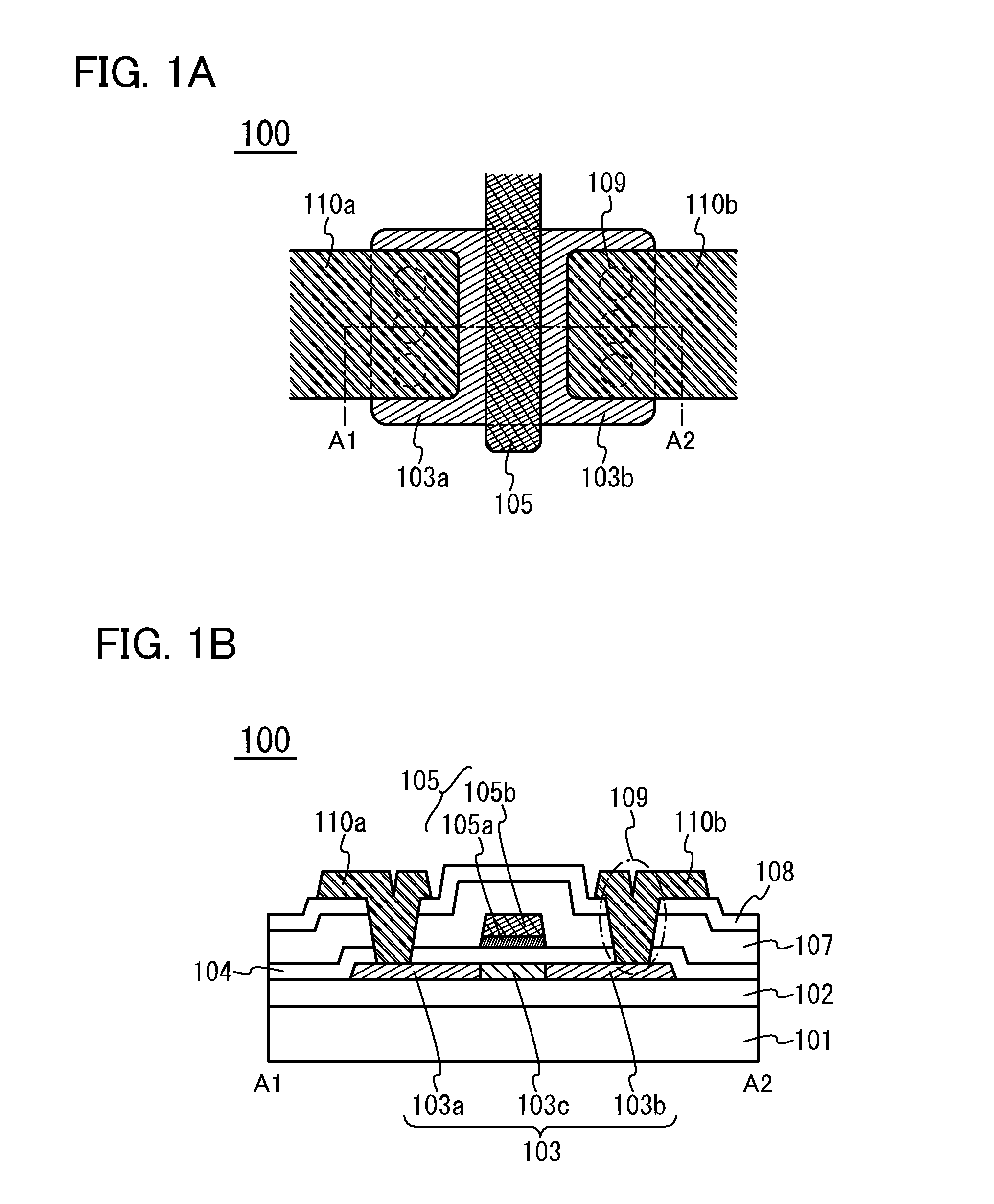

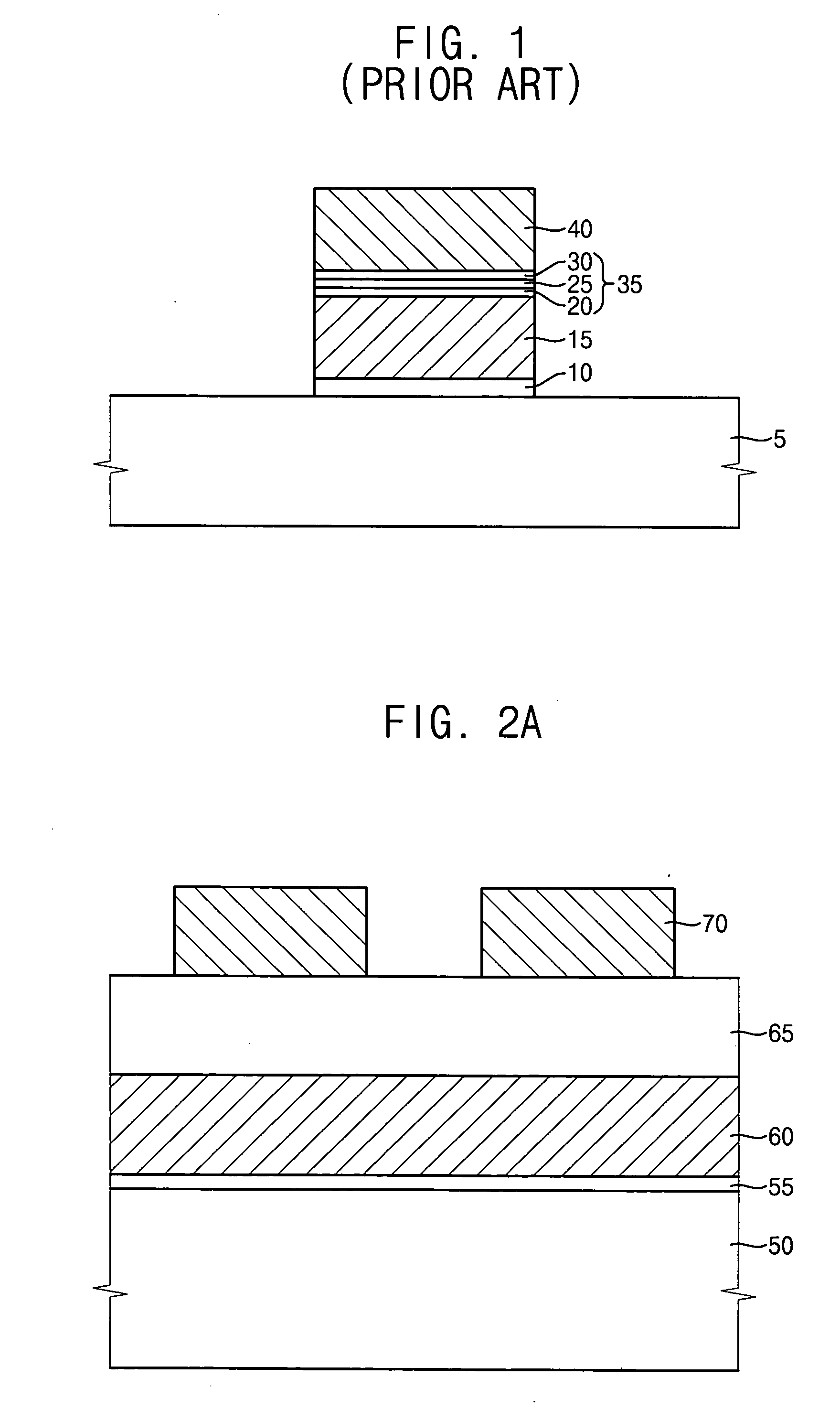

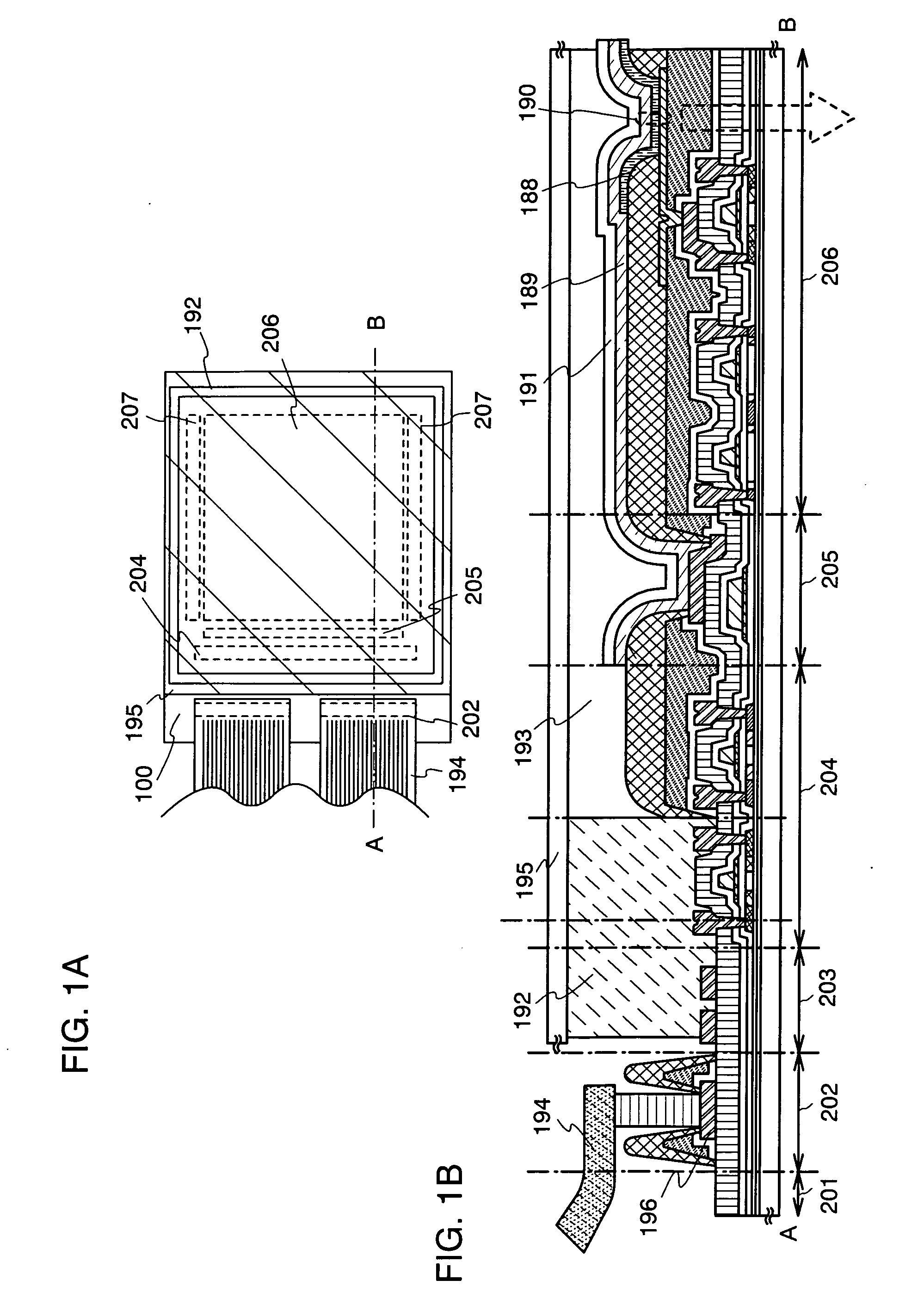

ActiveUS20100025677A1Small amount of photocurrentReduce parasitic capacitanceTransistorElectroluminescent light sourcesProduction rateCharge carrier

To provide a semiconductor device including a thin film transistor having excellent electric characteristics and high reliability and a manufacturing method of the semiconductor device with high mass productivity. The summary is that an inverted-staggered (bottom-gate) thin film transistor is included in which an oxide semiconductor film containing In, Ga, and Zn is used as a semiconductor layer, a channel protective layer is provided in a region that overlaps a channel formation region of the semiconductor layer, and a buffer layer is provided between the semiconductor layer and source and drain electrodes. An ohmic contact is formed by intentionally providing the buffer layer having a higher carrier concentration than the semiconductor layer between the semiconductor layer and the source and drain electrodes.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device and method for manufacturing the same

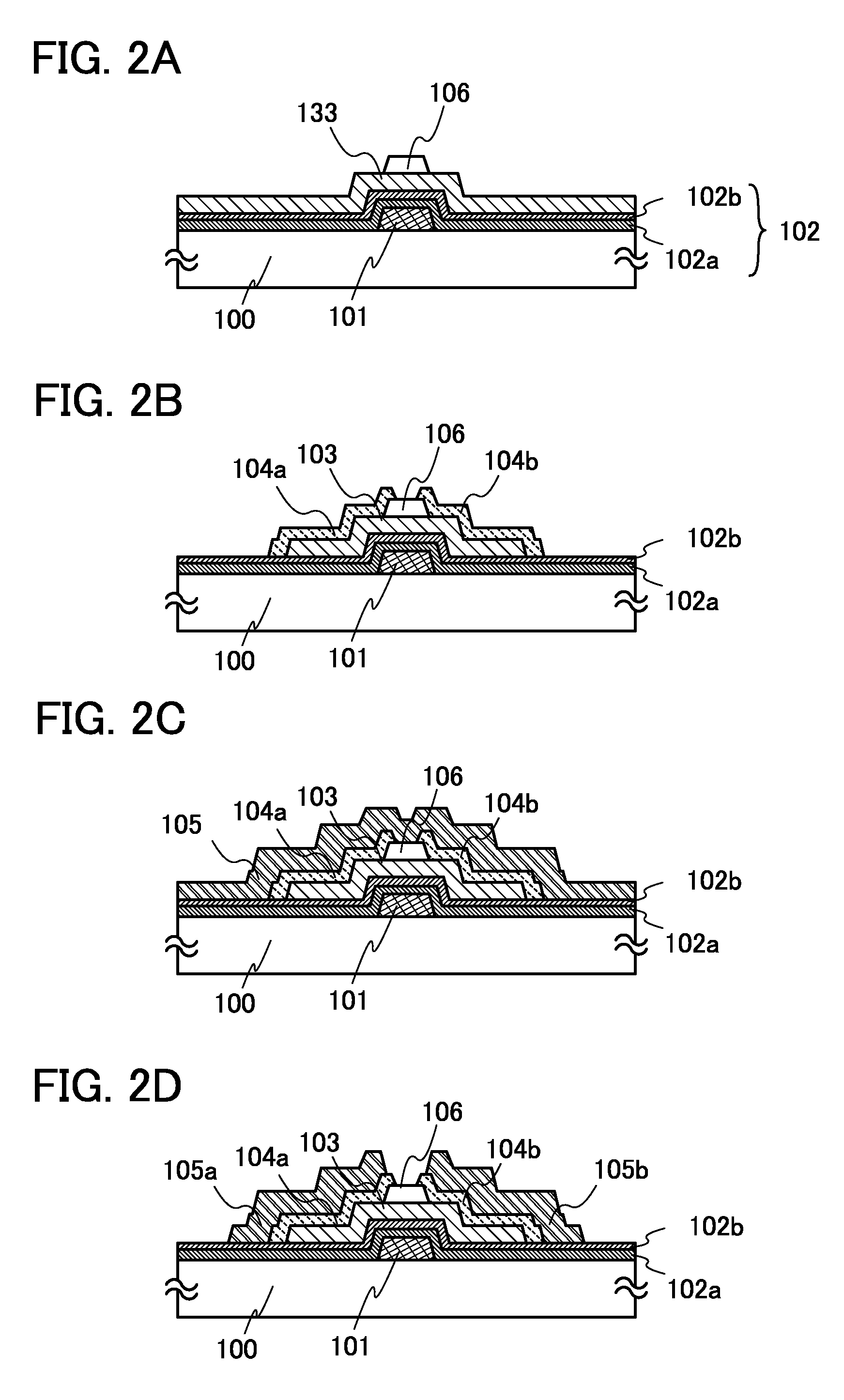

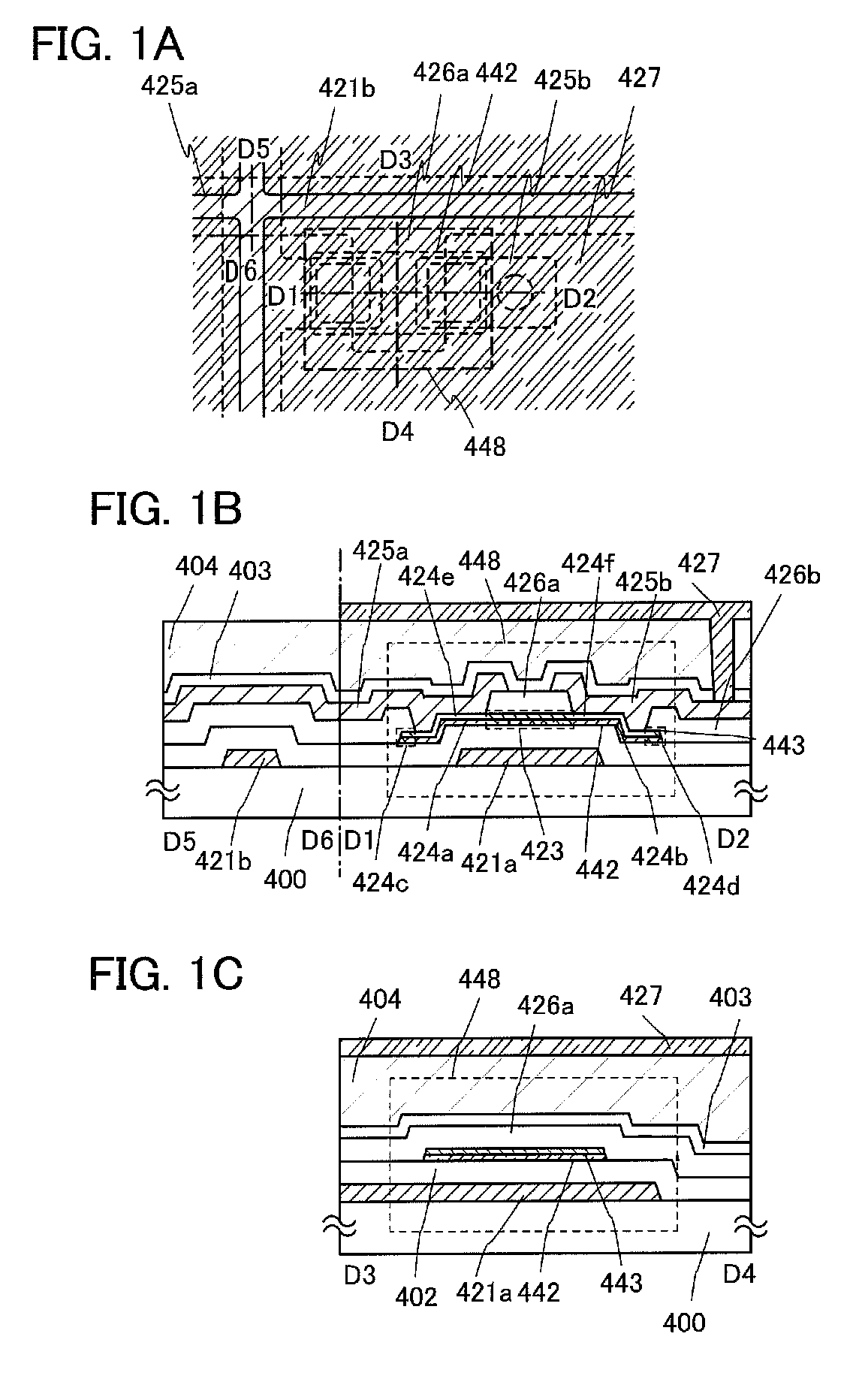

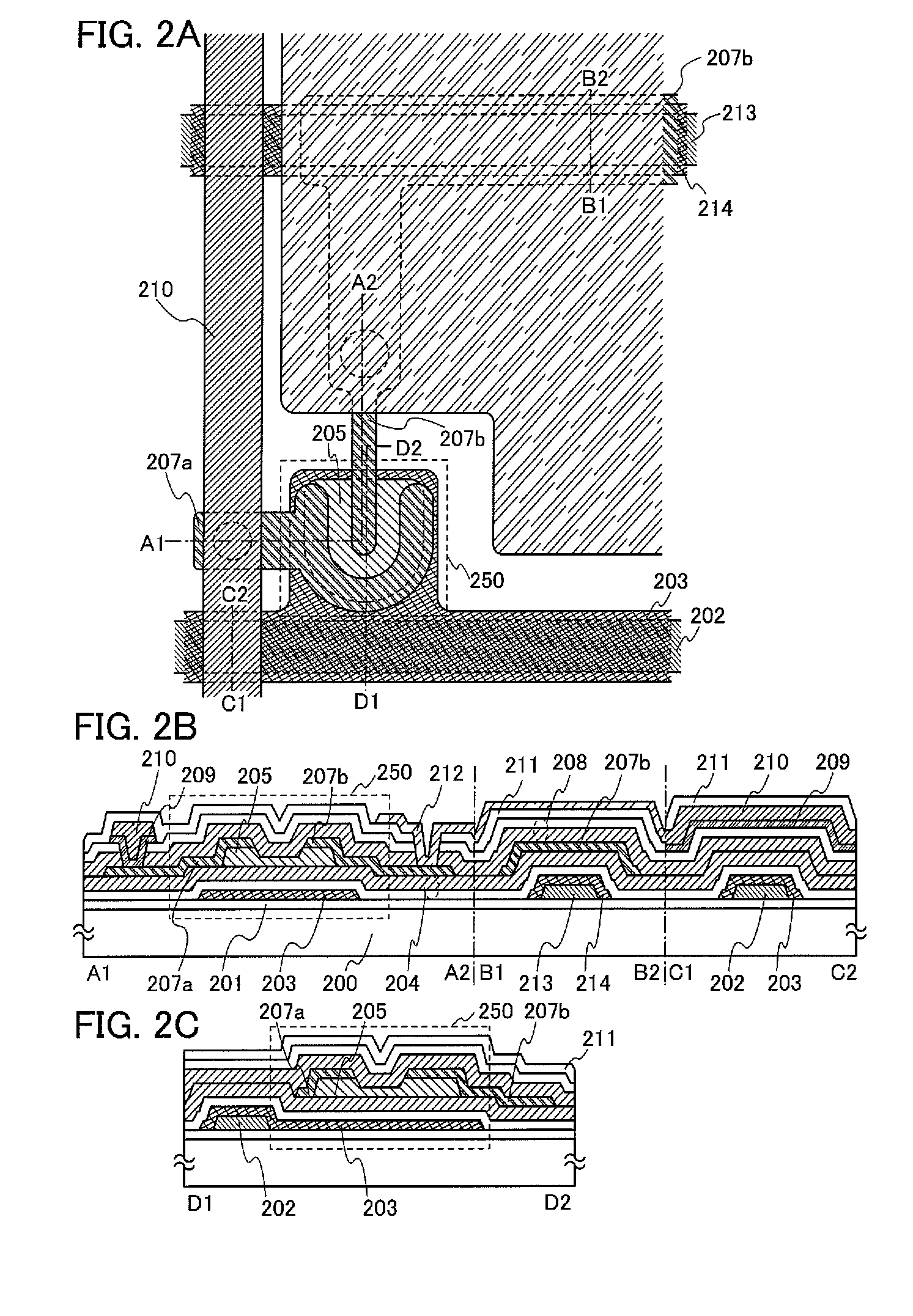

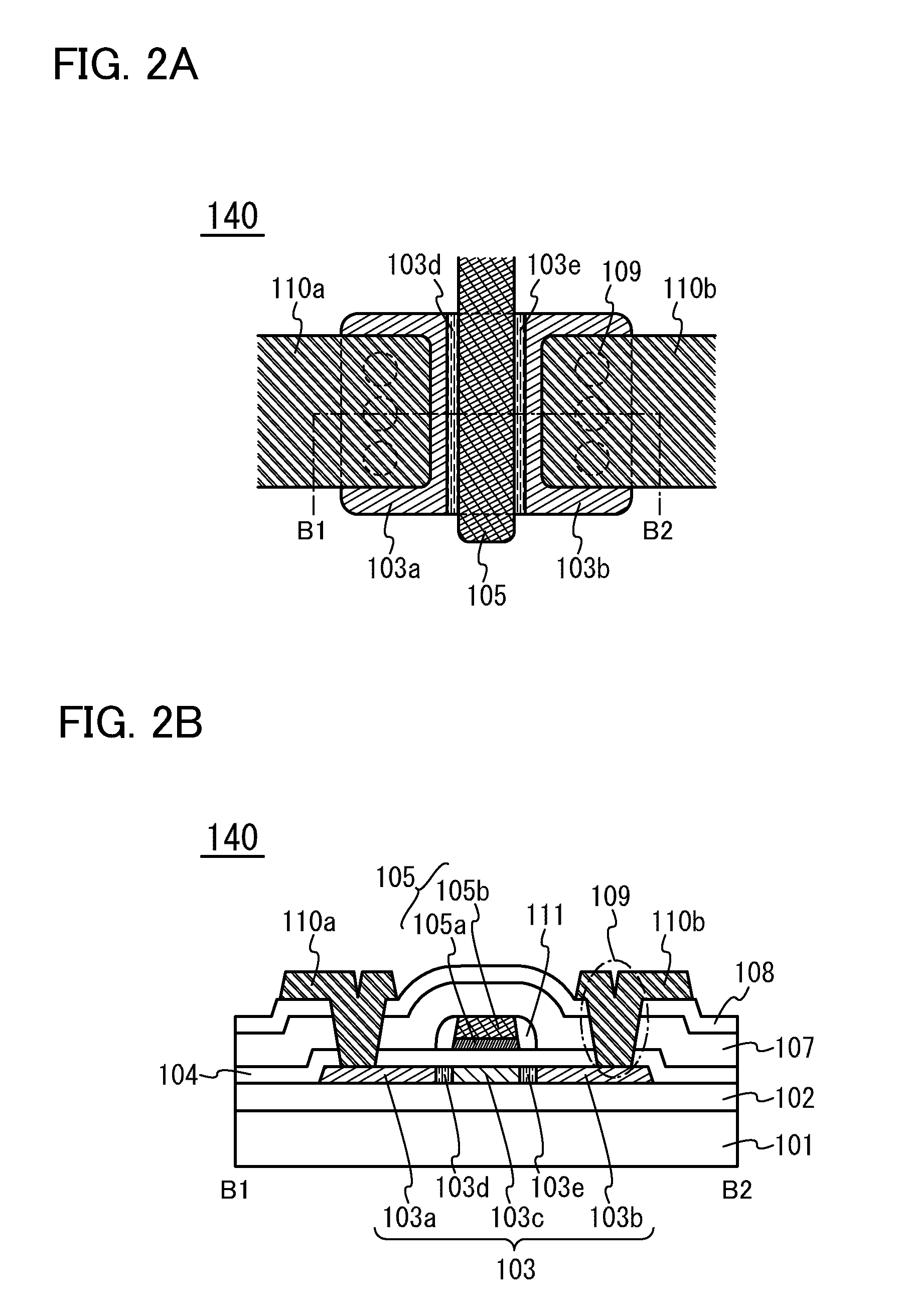

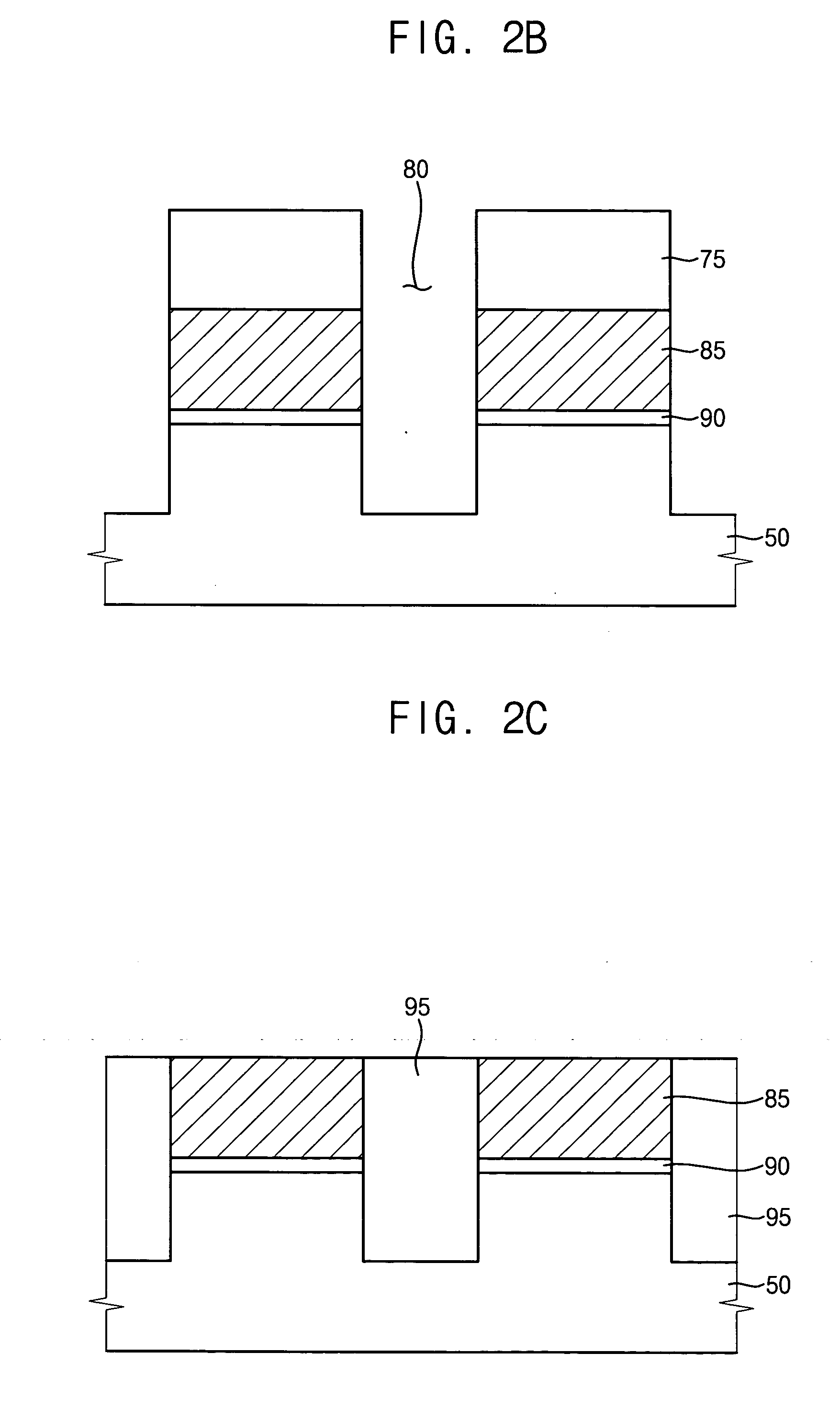

ActiveUS20110037068A1Manufacturing cost be reduceEasily breakTransistorSolid-state devicesOxide semiconductorOxide

One object is to provide a semiconductor device with a structure which enables reduction in parasitic capacitance sufficiently between wirings. In a bottom-gate type thin film transistor including a stacked layer of a first layer which is a metal thin film oxidized partly or entirely and an oxide semiconductor layer, the following oxide insulating layers are formed together: an oxide insulating layer serving as a channel protective layer which is over and in contact with a part of the oxide semiconductor layer overlapping with a gate electrode layer; and an oxide insulating layer which covers a peripheral portion and a side surface of the stacked oxide semiconductor layer.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device and manufacturing method thereof

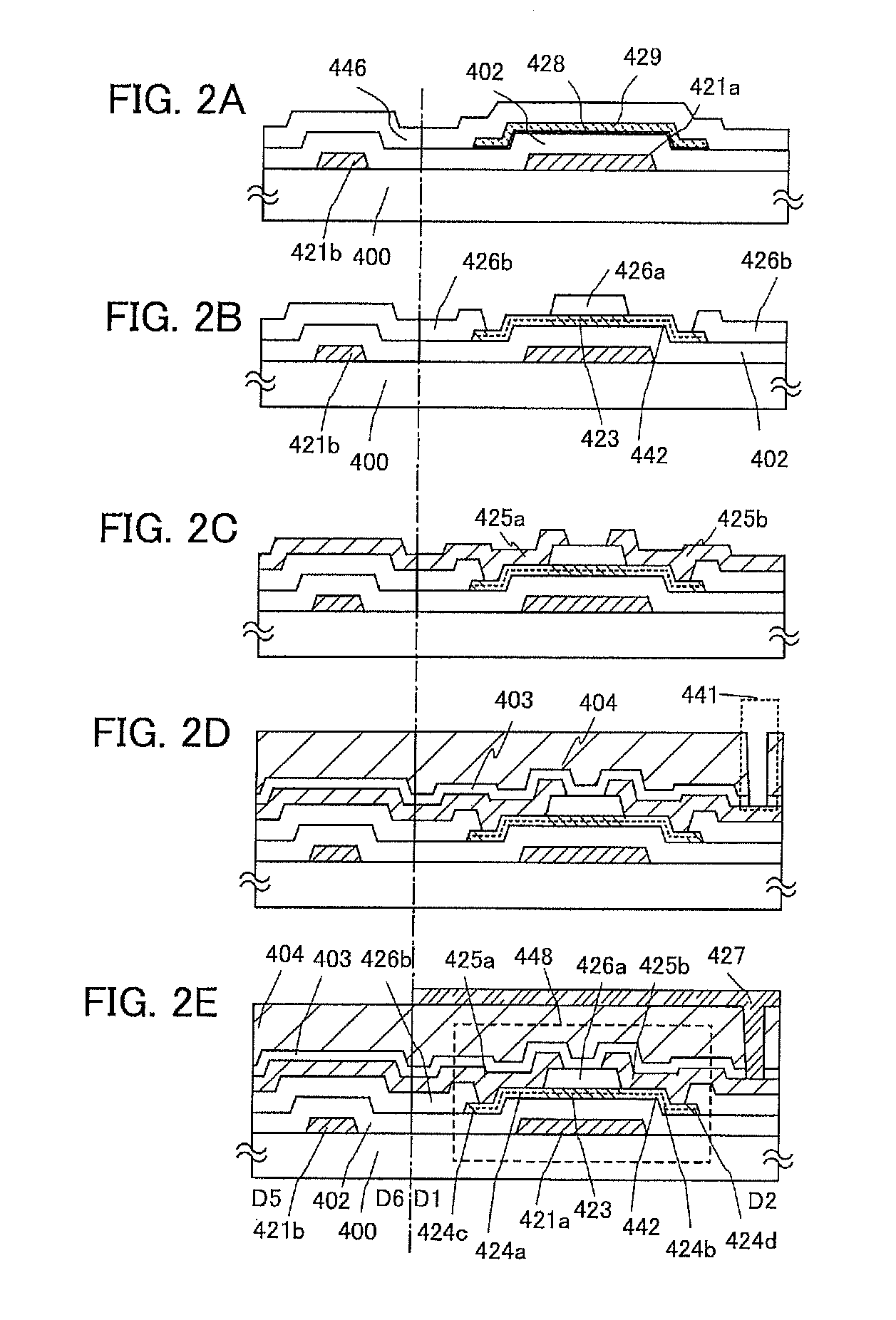

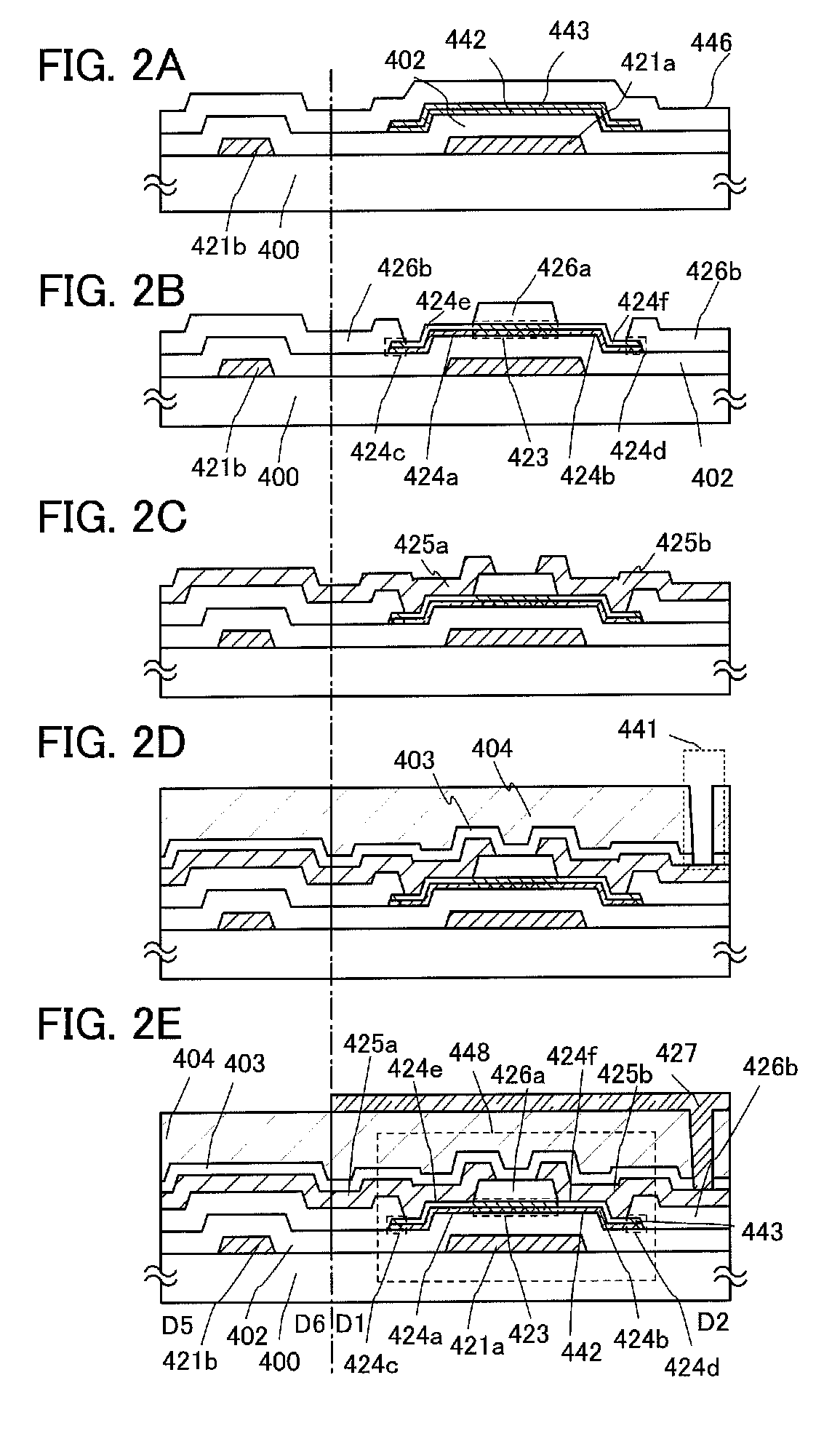

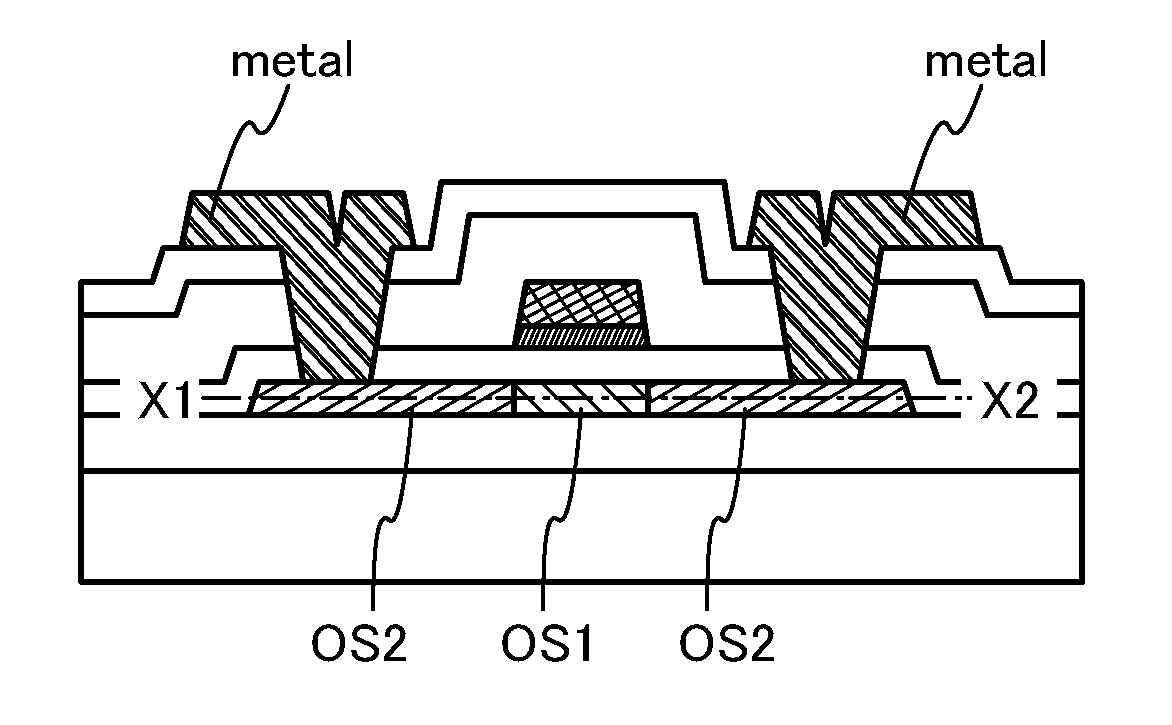

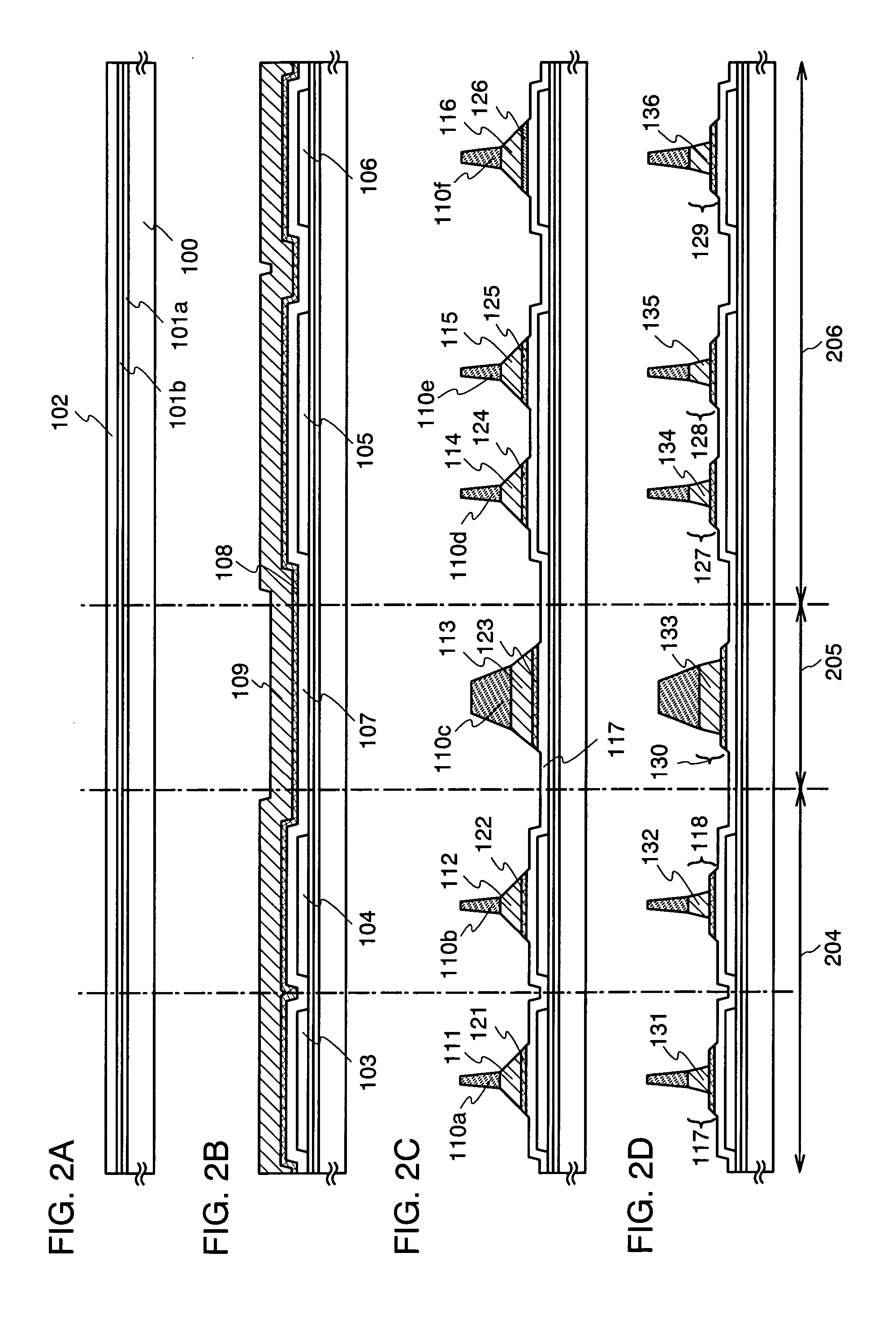

ActiveUS20110024751A1Reduce manufacturing costEasily brokenTransistorSolid-state devicesBottom gateSemiconductor

In a bottom-gate thin film transistor using the stack of the first oxide semiconductor layer and the second oxide semiconductor layer, an oxide insulating layer serving as a channel protective layer is formed over and in contact with part of the oxide semiconductor layer overlapping with a gate electrode layer. In the same step as formation of the insulating layer, an oxide insulating layer covering a peripheral portion (including a side surface) of the stack of the oxide semiconductor layers is formed.

Owner:SEMICON ENERGY LAB CO LTD

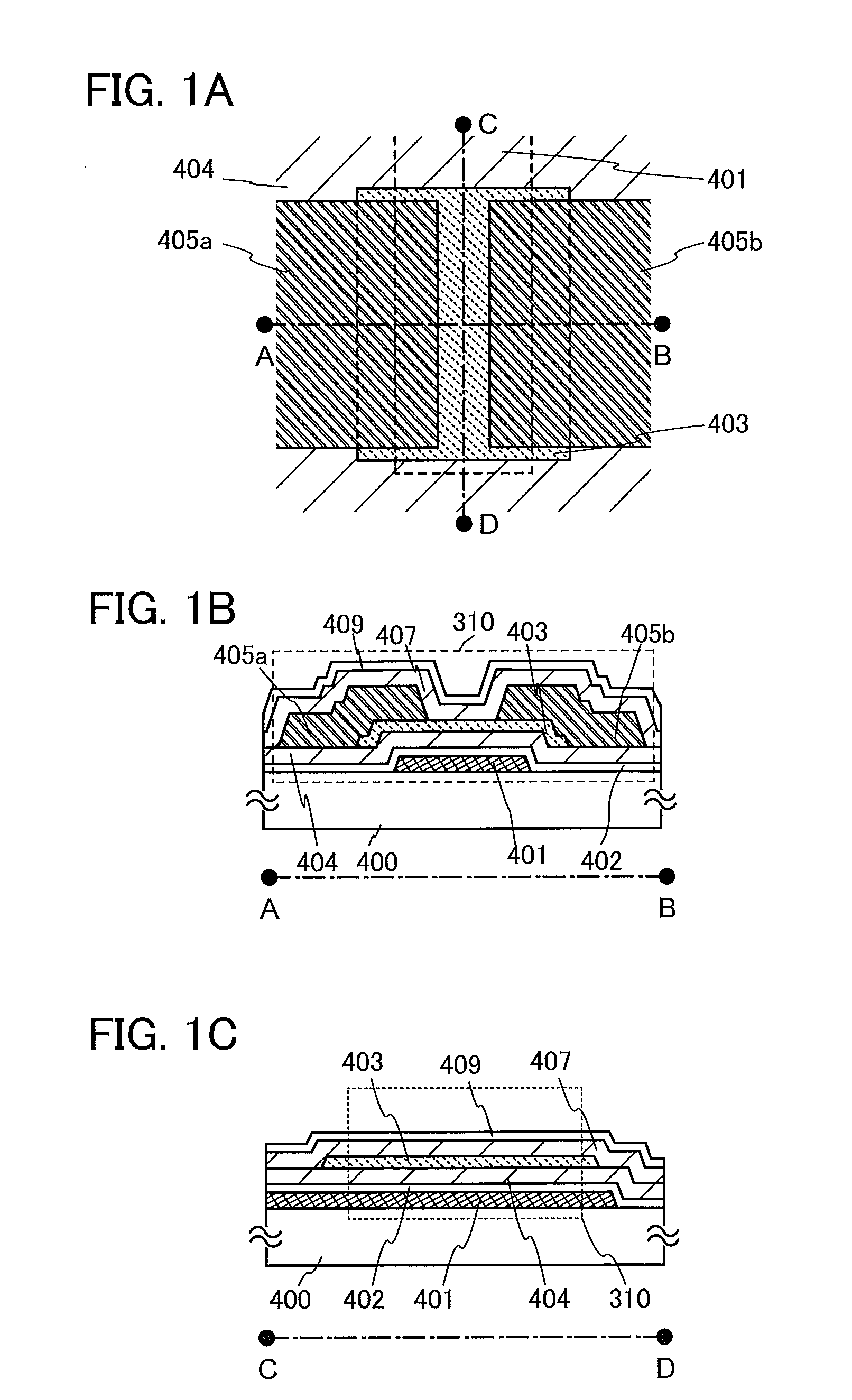

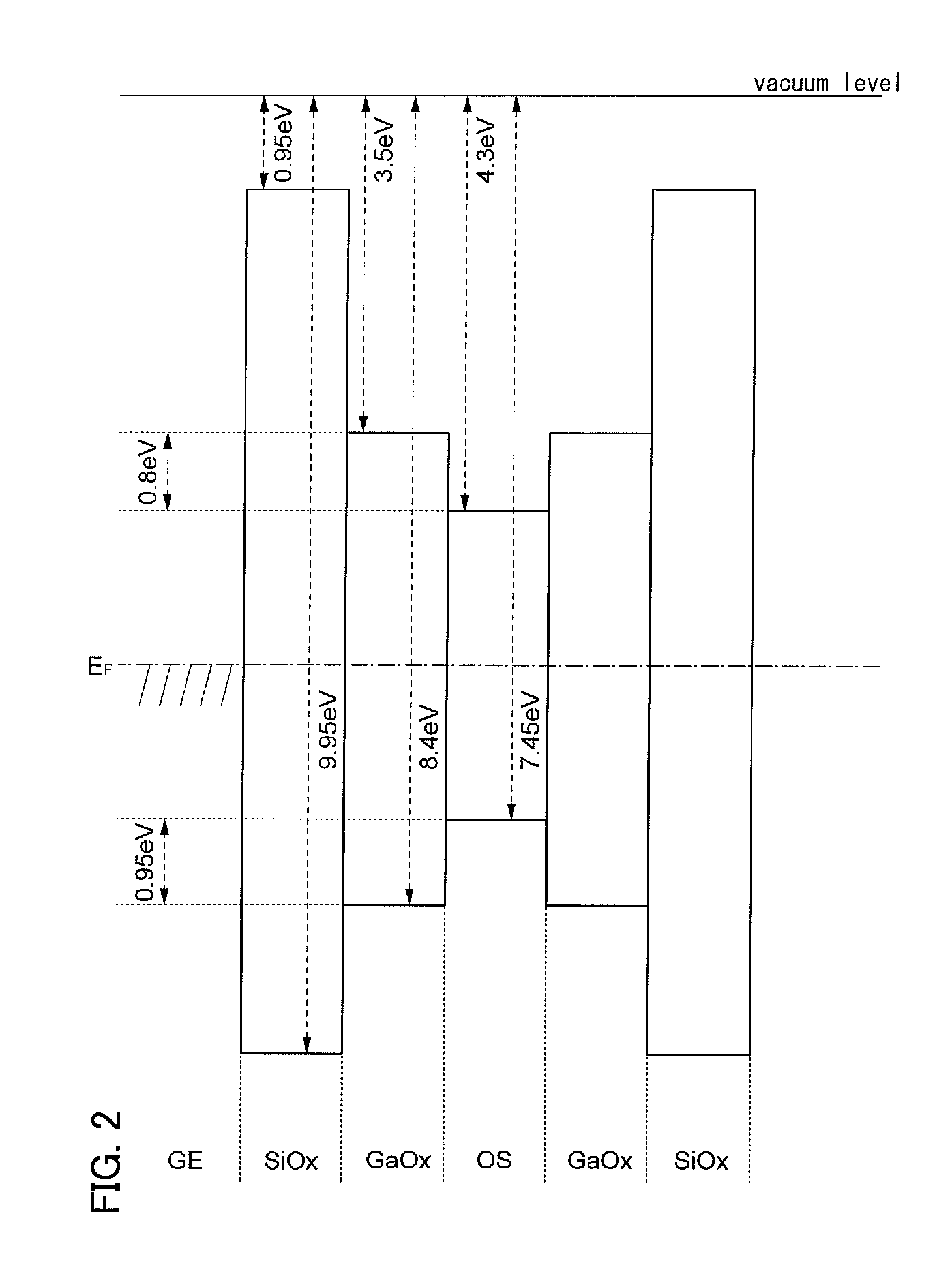

Semiconductor device

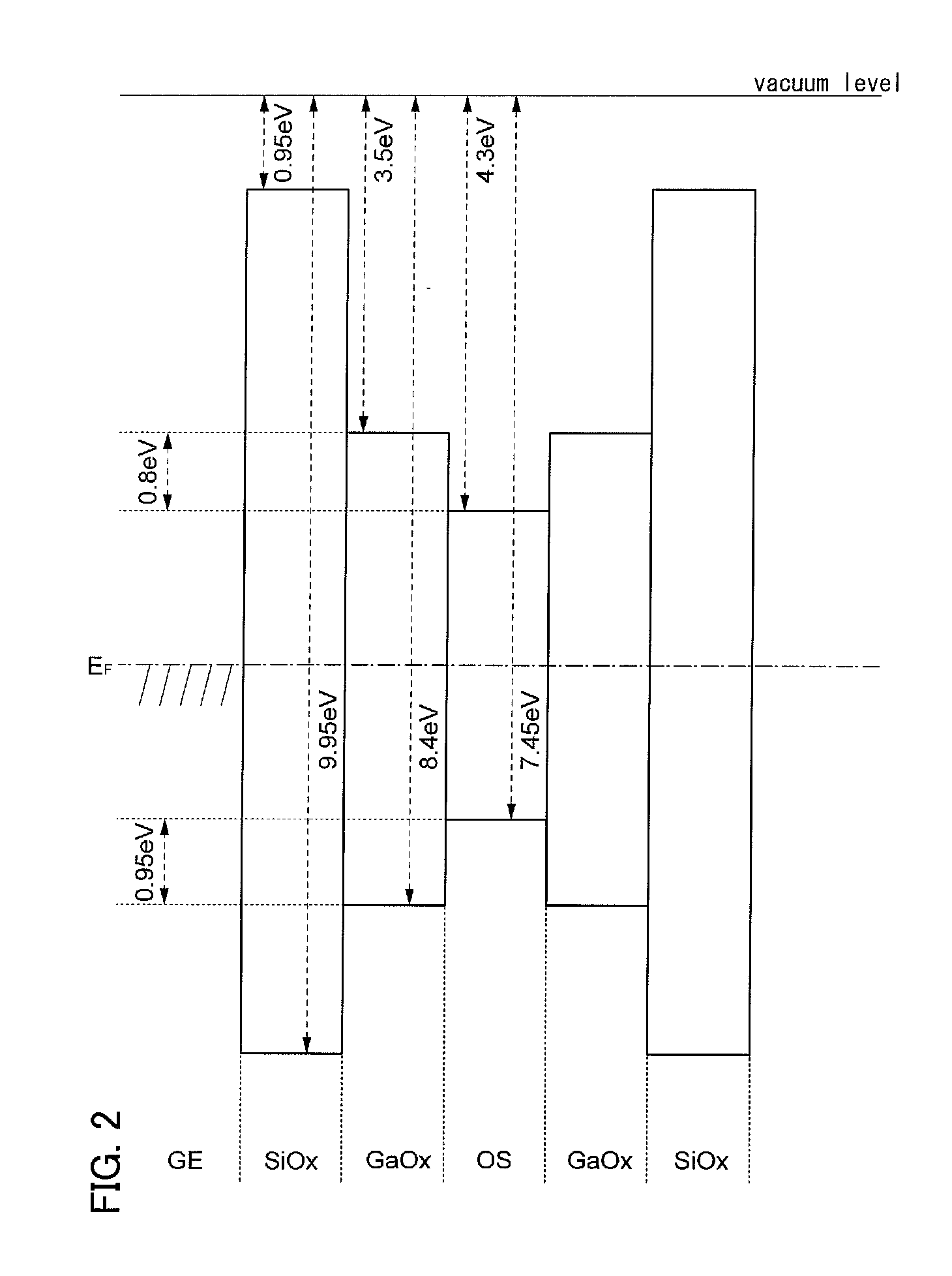

ActiveUS20110240991A1Stable electrical characteristicsExcellent electrical propertiesTransistorElectroluminescent light sourcesHydrogenOxygen

The oxide semiconductor film has the top and bottom surface portions each provided with a metal oxide film containing a constituent similar to that of the oxide semiconductor film. An insulating film containing a different constituent from the metal oxide film and the oxide semiconductor film is further formed in contact with a surface of the metal oxide film, which is opposite to the surface in contact with the oxide semiconductor film The oxide semiconductor film used for the active layer of the transistor is an oxide semiconductor film highly purified to be electrically i-type (intrinsic) by removing impurities such as hydrogen, moisture, a hydroxyl group, and hydride from the oxide semiconductor and supplying oxygen which is a major constituent of the oxide semiconductor and is simultaneously reduced in a step of removing impurities.

Owner:SEMICON ENERGY LAB CO LTD

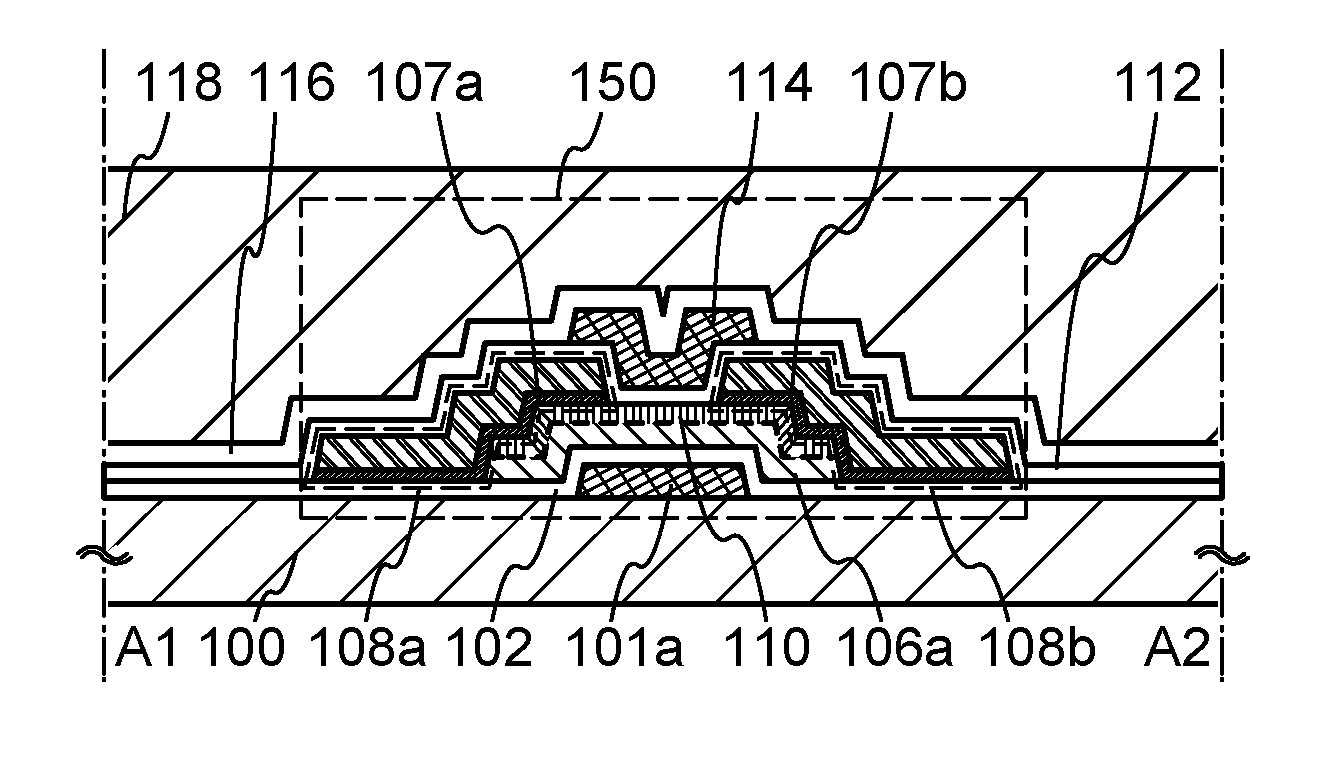

Semiconductor device with two metal oxide films and an oxide semiconductor film

ActiveUS8502221B2Improve reliabilityExcellent electrical propertiesTransistorSolid-state devicesSemiconductorMetal

An object is to stabilize electric characteristics of a semiconductor device including an oxide semiconductor to increase reliability. The semiconductor device includes an insulating film; a first metal oxide film on and in contact with the insulating film; an oxide semiconductor film partly in contact with the first metal oxide film; source and drain electrodes electrically connected to the oxide semiconductor film; a second metal oxide film partly in contact with the oxide semiconductor film; a gate insulating film on and in contact with the second metal oxide film; and a gate electrode over the gate insulating film.

Owner:SEMICON ENERGY LAB CO LTD

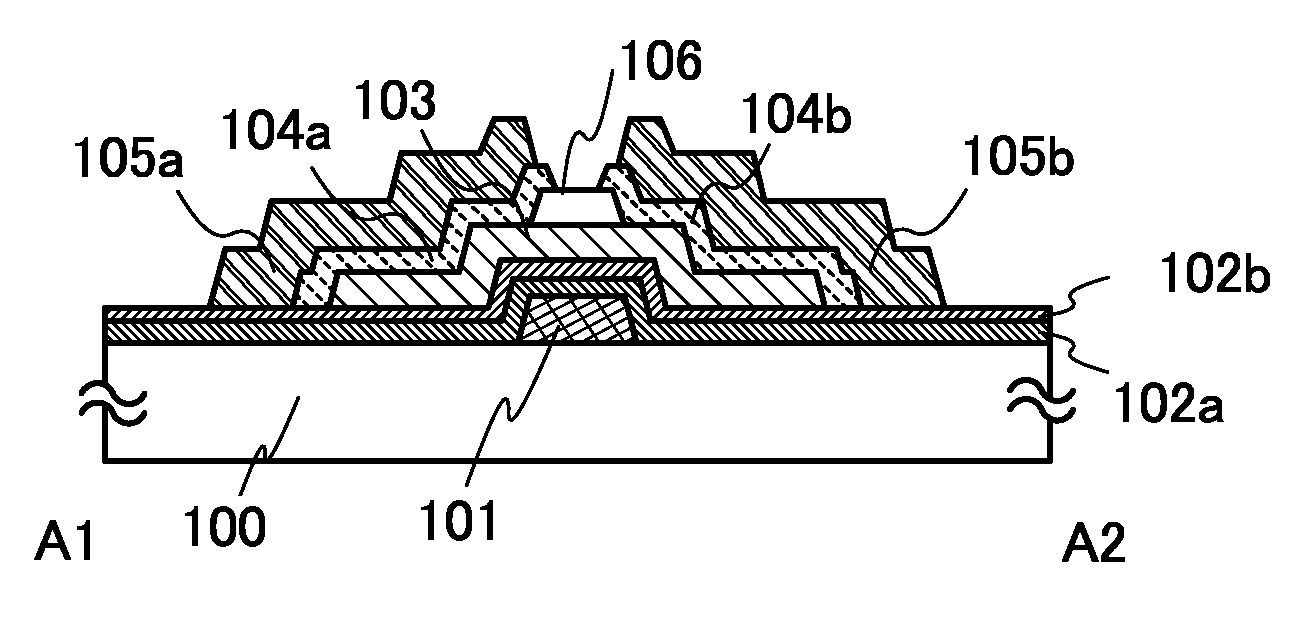

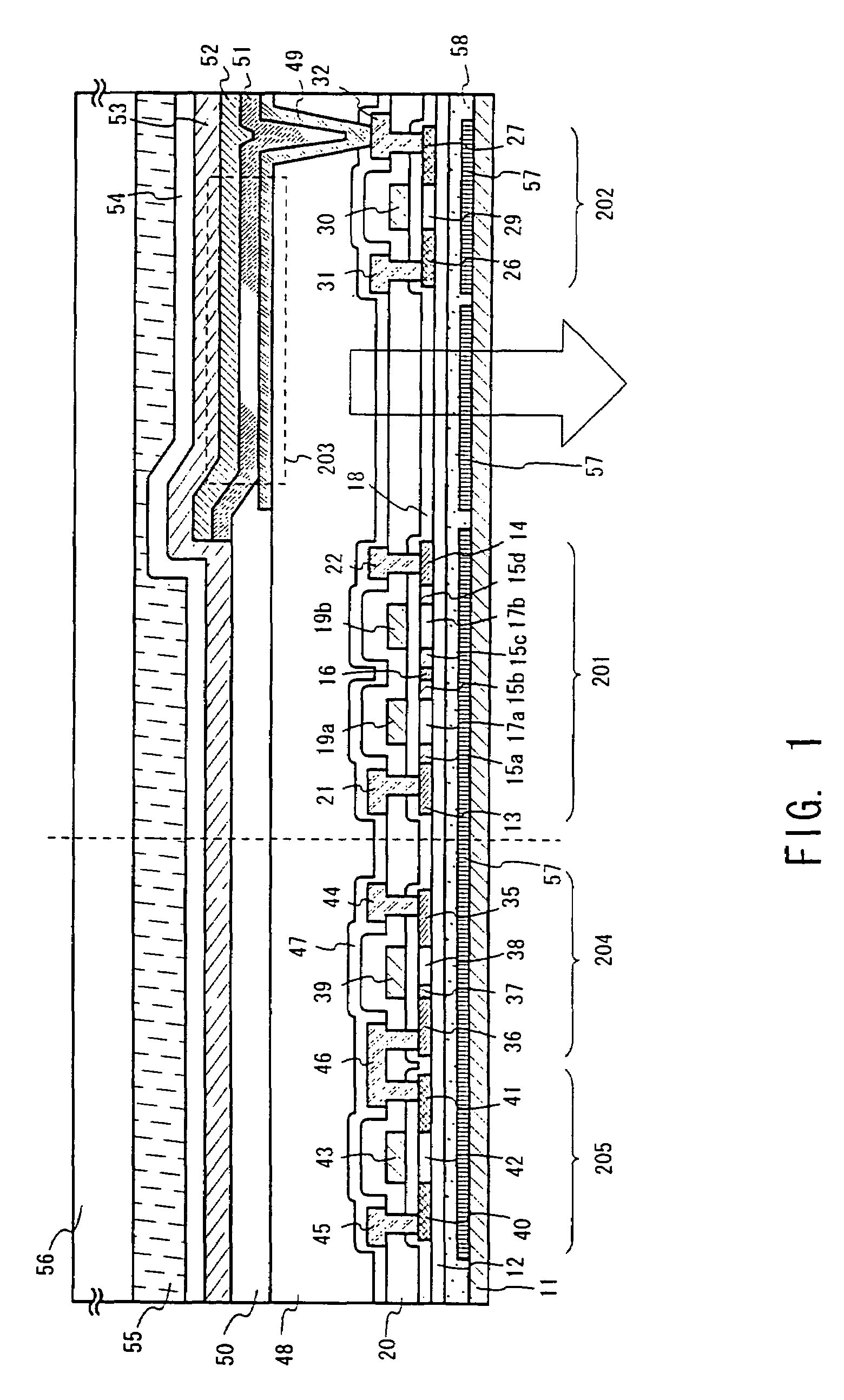

Semiconductor device and manufacturing method thereof

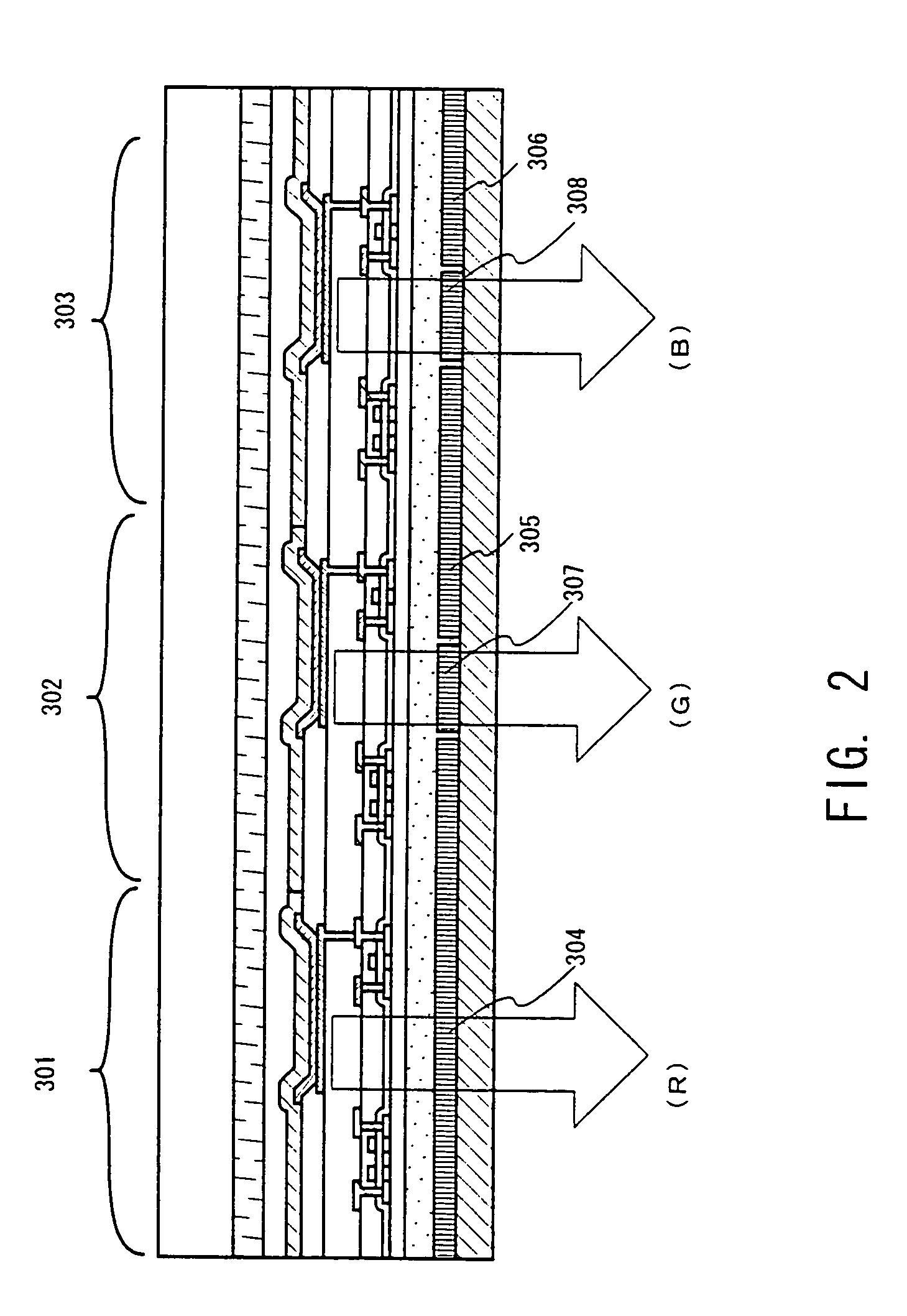

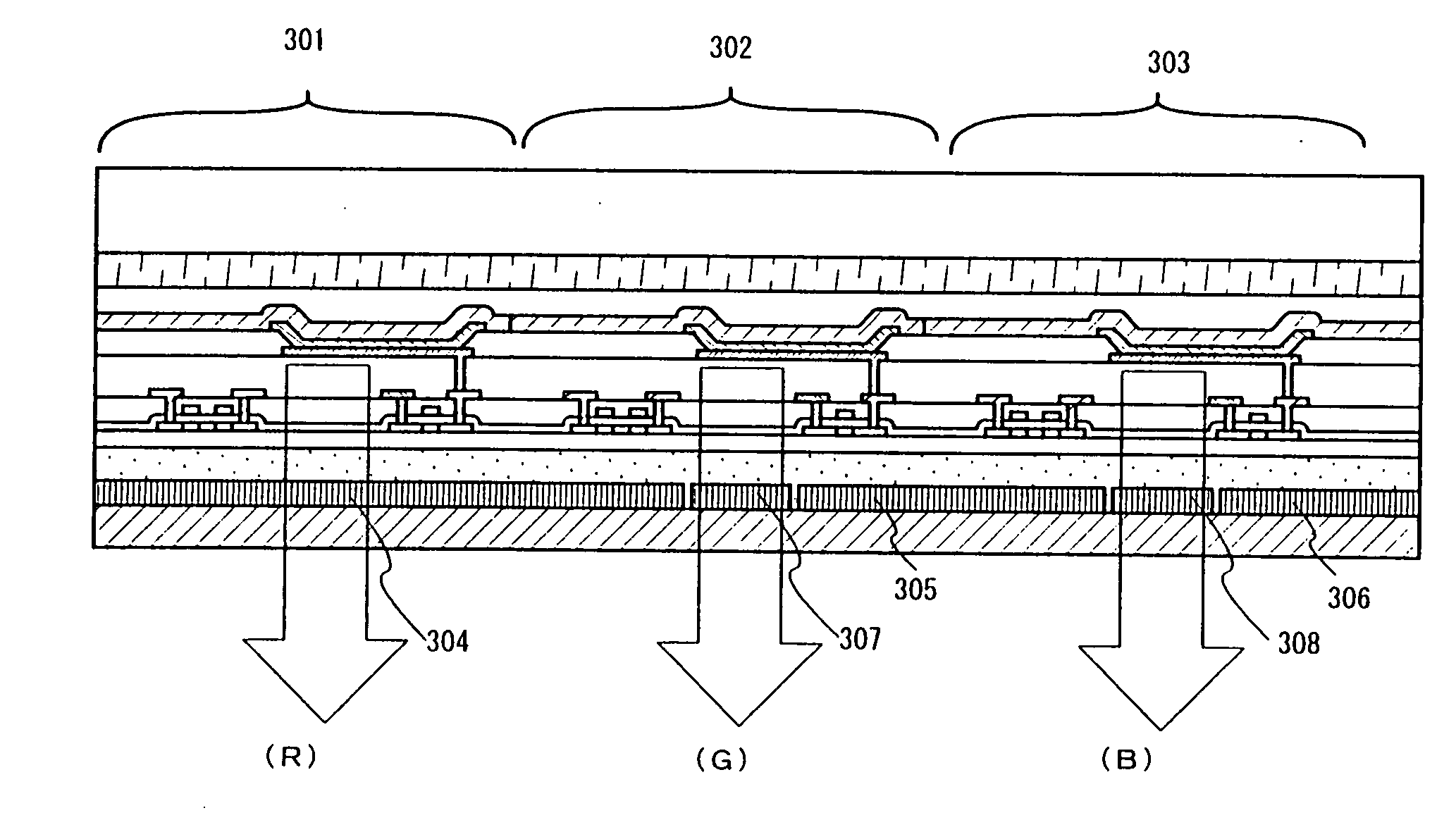

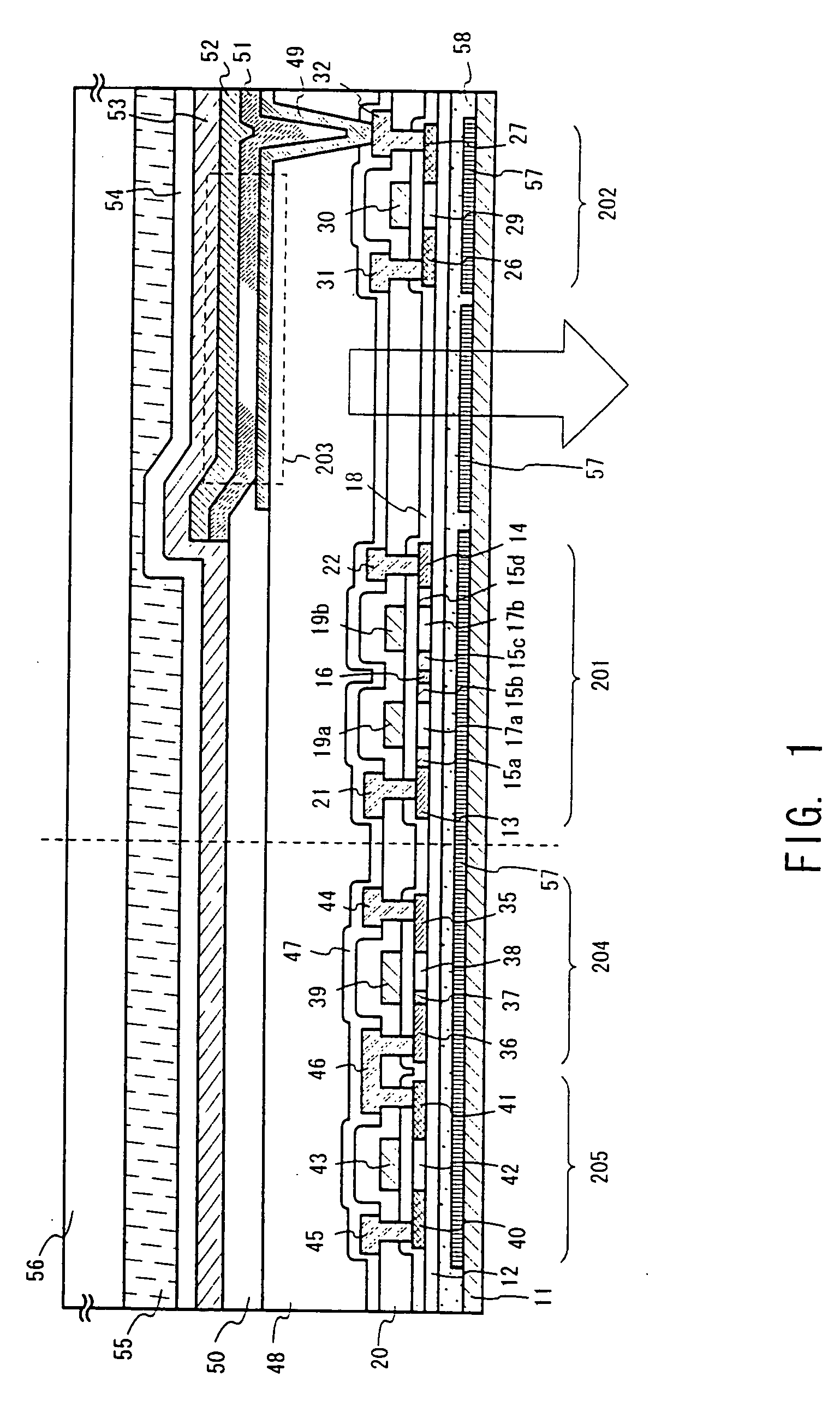

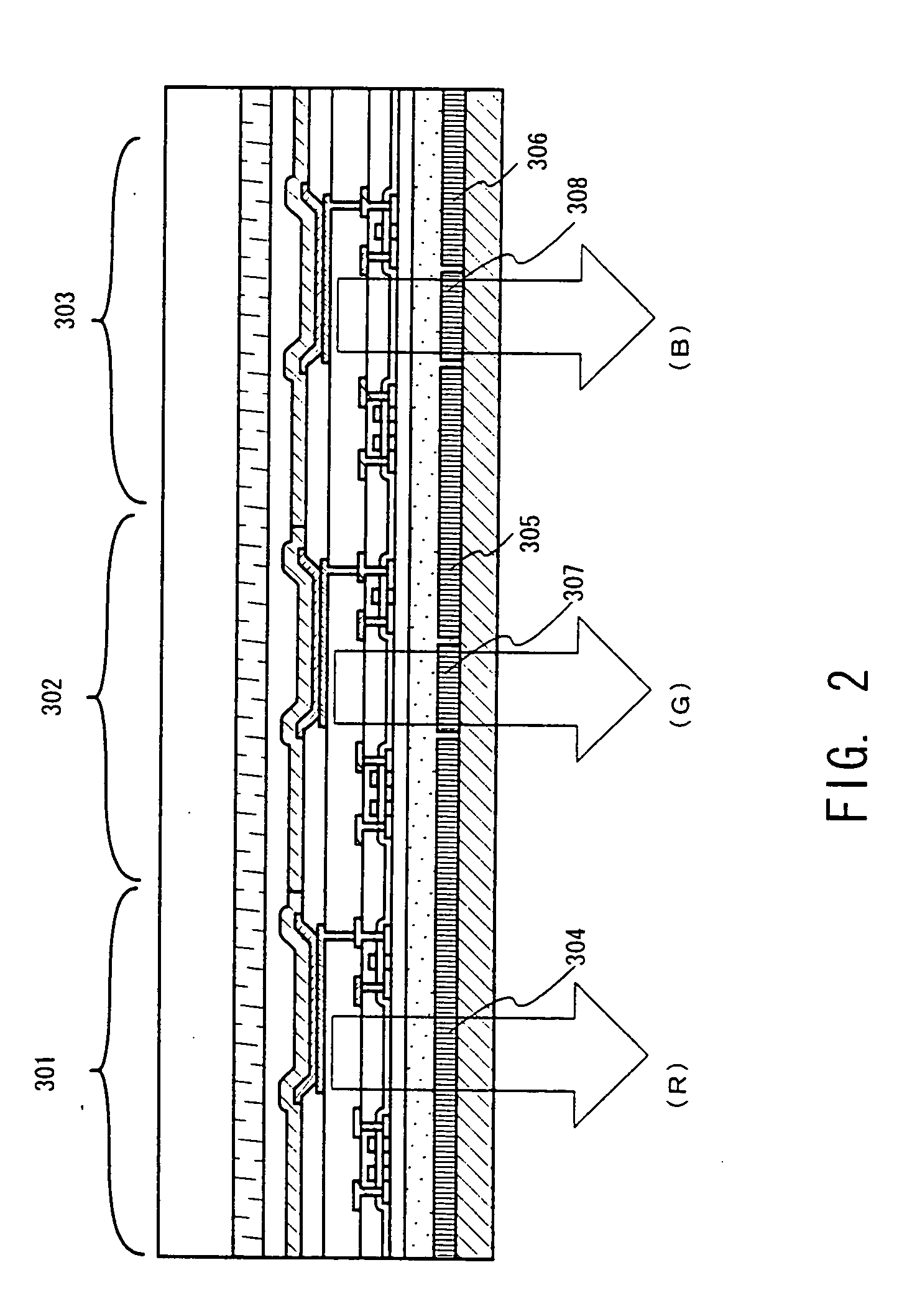

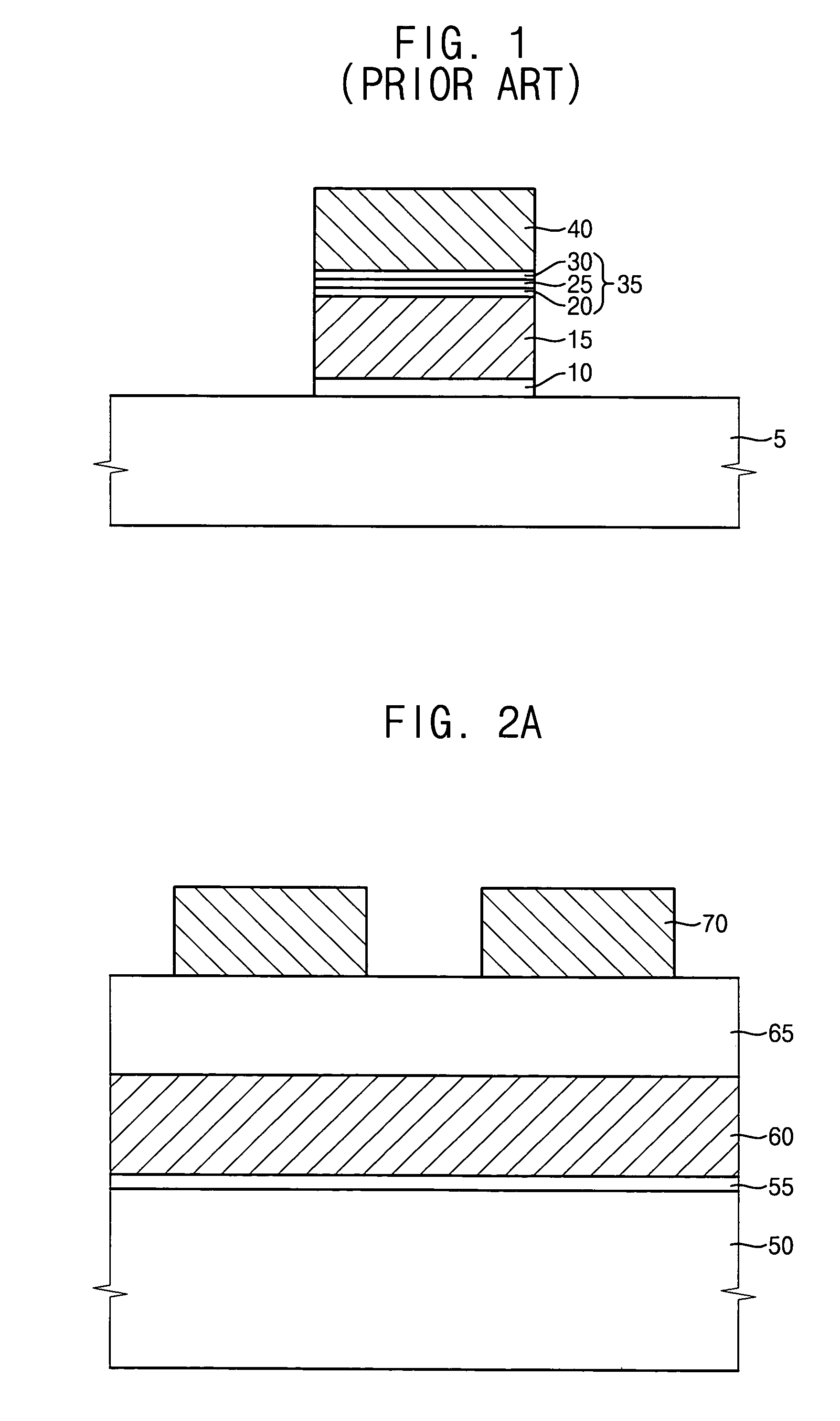

InactiveUS7119364B2Improve heat resistanceExcellent electrical propertiesFinal product manufactureElectroluminescent light sourcesHeat resistanceColor film

A high performance electric device which uses an adhesive layer over a substrate. A color filter is over a substrate, and an adhesive layer is also located over the substrate and color film. An insulating layer is over the adhesive layer, and thin film transistors cover the insulating film and the color filters. Light emitting elements cover the thin film transistors and emit light through the substrate that is through the adhesive layer and color filter. The substrate may be plastic, thus increasing the heat resistance.

Owner:SEMICON ENERGY LAB CO LTD

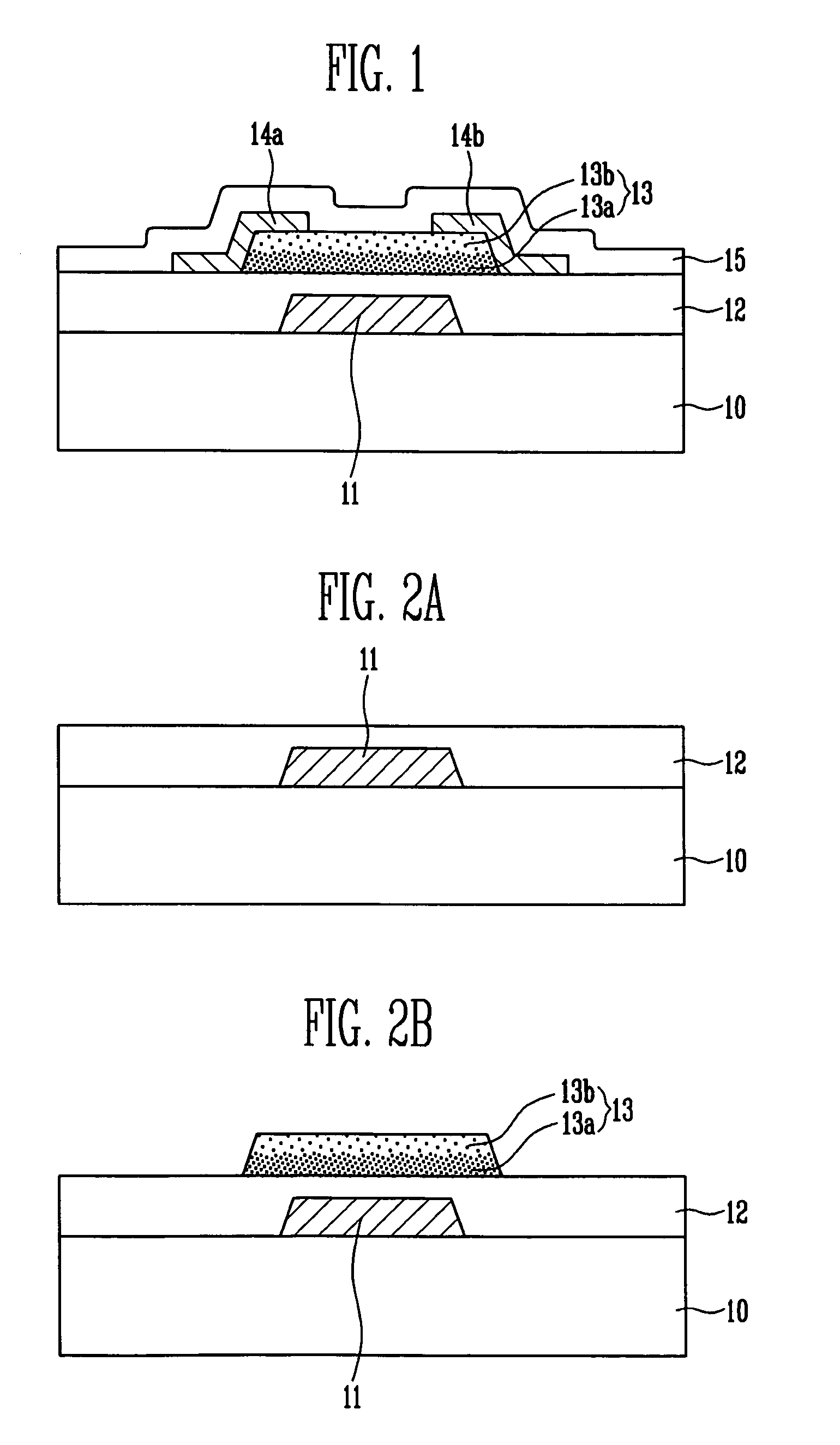

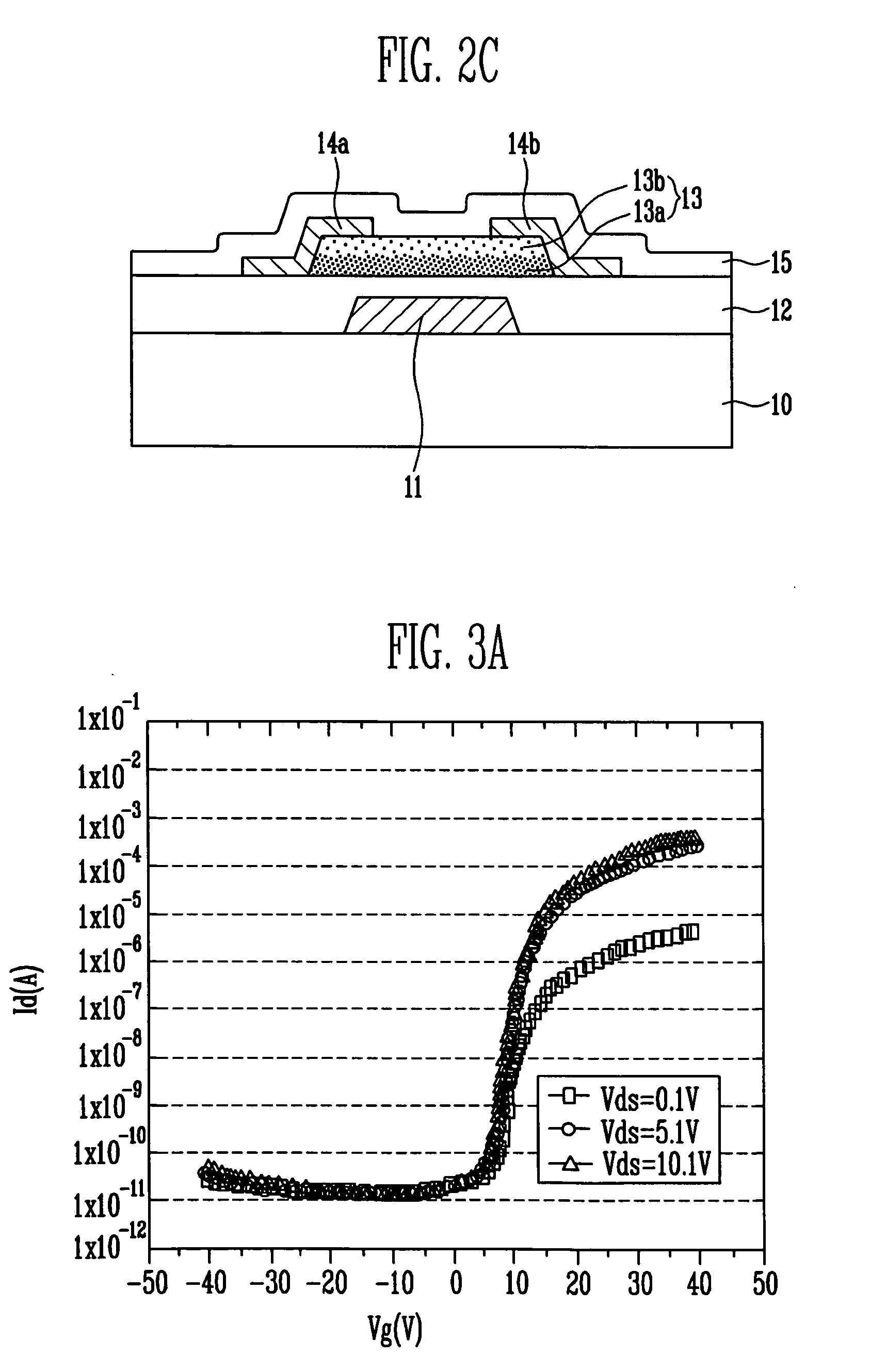

Thin film transistor, display device, including the same, and associated methods

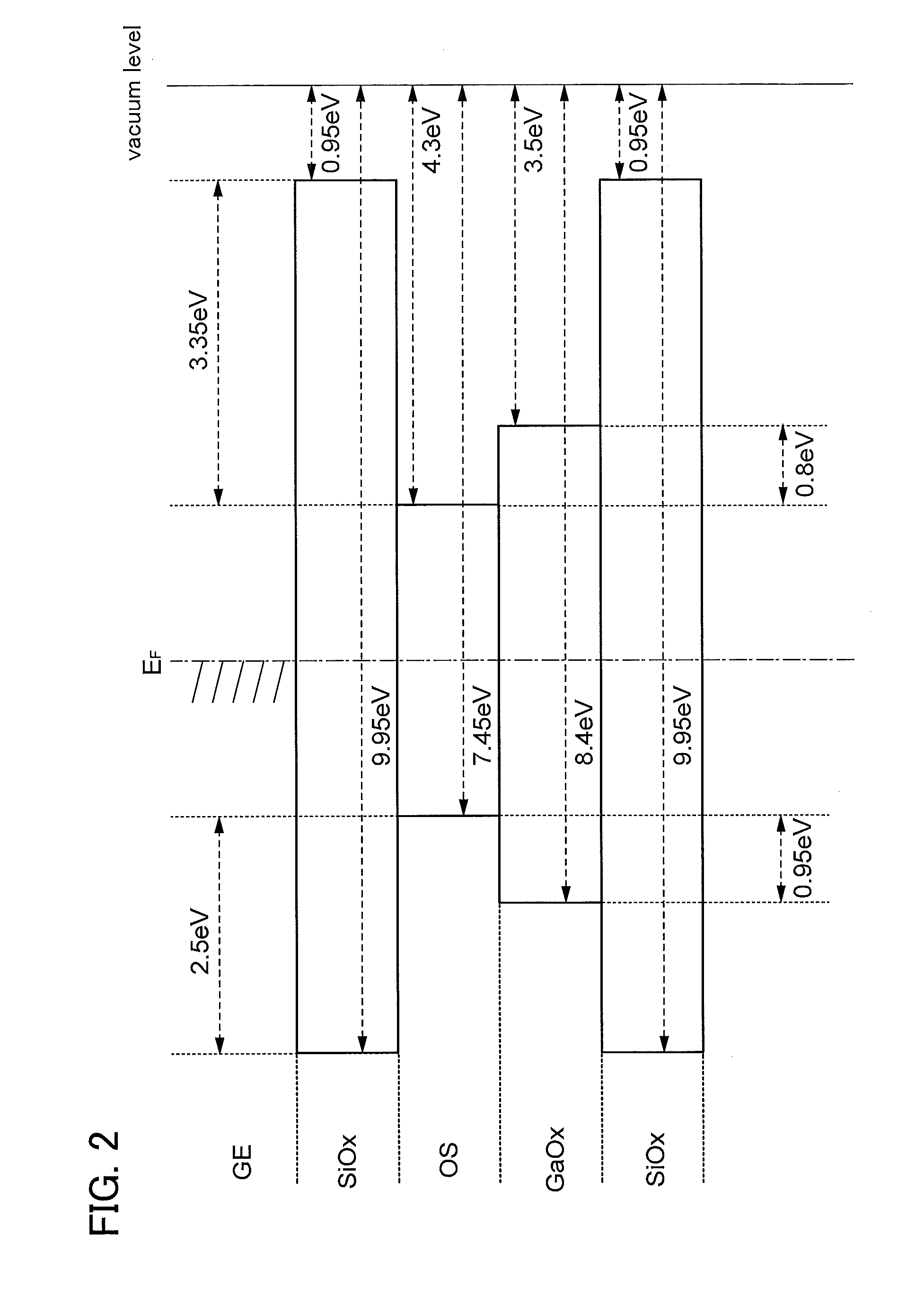

InactiveUS20090250693A1Excellent electrical propertiesMinimized plasma damageTransistorSolid-state devicesIndiumDisplay device

A thin film transistor (TFT), including a substrate, a gate electrode on the substrate, an oxide semiconductor layer including a channel region, a source region, and a drain region, a gate insulating layer between the gate electrode and the oxide semiconductor layer, and source and drain electrodes in contact with the source and drain regions of the oxide semiconductor layer, respectively, wherein the oxide semiconductor layer has a GaInZnO (GIZO) bilayer structure including a lower layer and an upper layer, and the upper layer has a different indium (In) concentration than the lower layer.

Owner:SAMSUNG DISPLAY CO LTD

Semiconductor device

ActiveUS20110240990A1Improve reliabilityExcellent electrical propertiesTransistorSolid-state devicesPower semiconductor deviceSemiconductor

An object is to stabilize electric characteristics of a semiconductor device including an oxide semiconductor to increase reliability. The semiconductor device includes an insulating film; a first metal oxide film on and in contact with the insulating film; an oxide semiconductor film partly in contact with the first metal oxide film; source and drain electrodes electrically connected to the oxide semiconductor film; a second metal oxide film partly in contact with the oxide semiconductor film; a gate insulating film on and in contact with the second metal oxide film; and a gate electrode over the gate insulating film.

Owner:SEMICON ENERGY LAB CO LTD

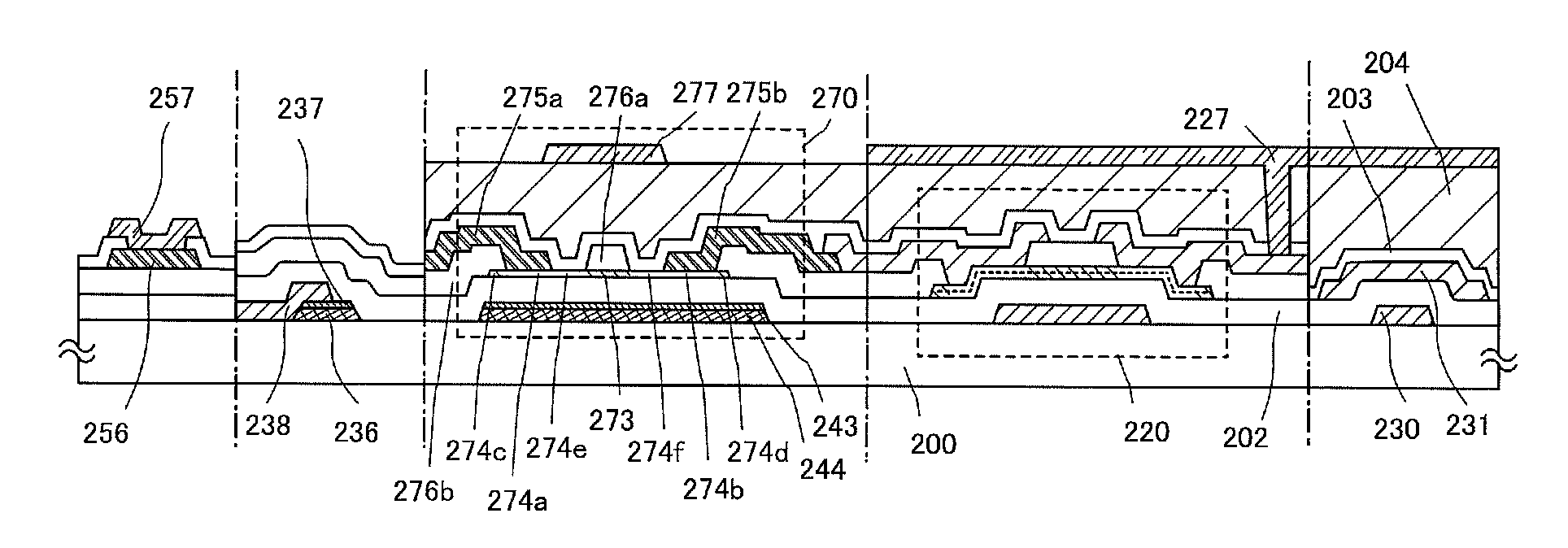

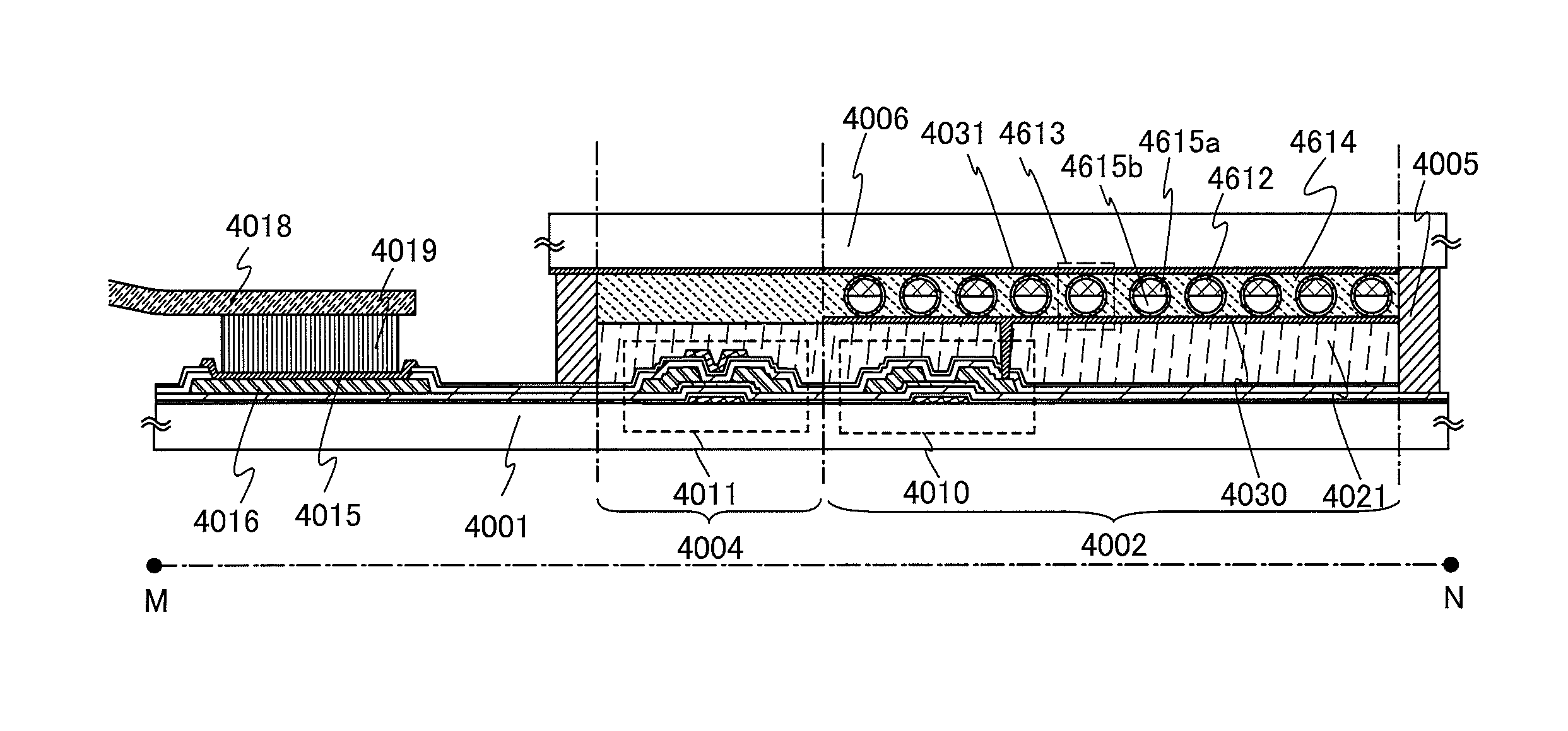

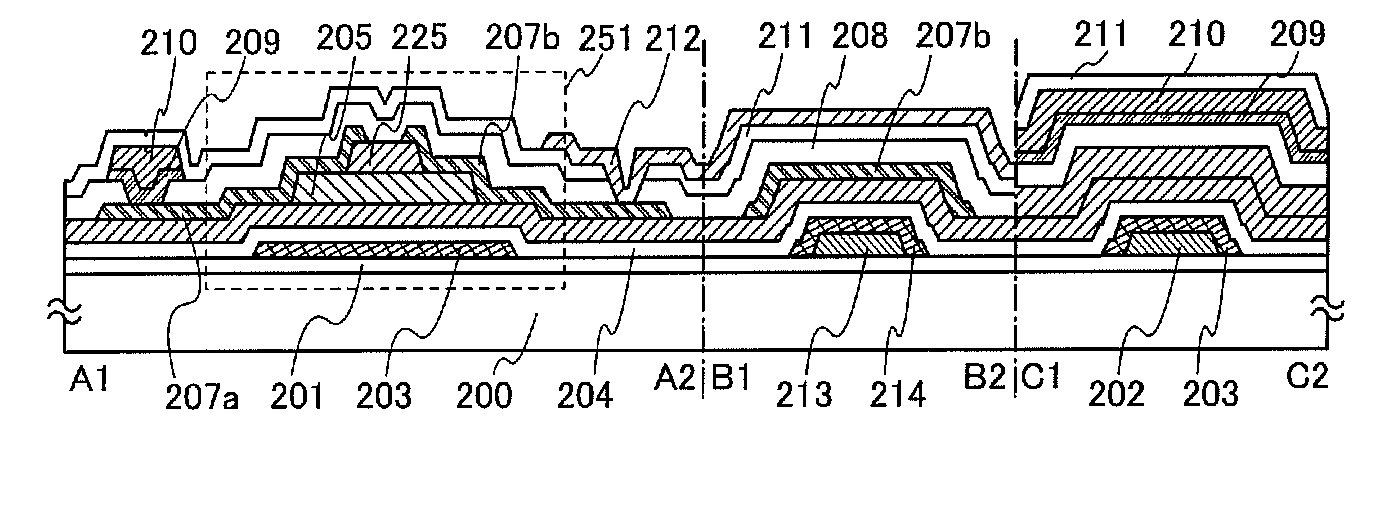

Semiconductor device and method for manufacturing the same

ActiveUS20110084267A1Excellent electrical propertiesEasy to displaySolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceSemiconductor

By using a conductive layer including Cu as a long lead wiring, increase in wiring resistance is suppressed. Further, the conductive layer including Cu is provided in such a manner that it does not overlap with the oxide semiconductor layer in which a channel region of a TFT is formed, and is surrounded by insulating layers including silicon nitride, whereby diffusion of Cu can be prevented; thus, a highly reliable semiconductor device can be manufactured. Specifically, a display device which is one embodiment of a semiconductor device can have high display quality and operate stably even when the size or definition thereof is increased.

Owner:SEMICON ENERGY LAB CO LTD

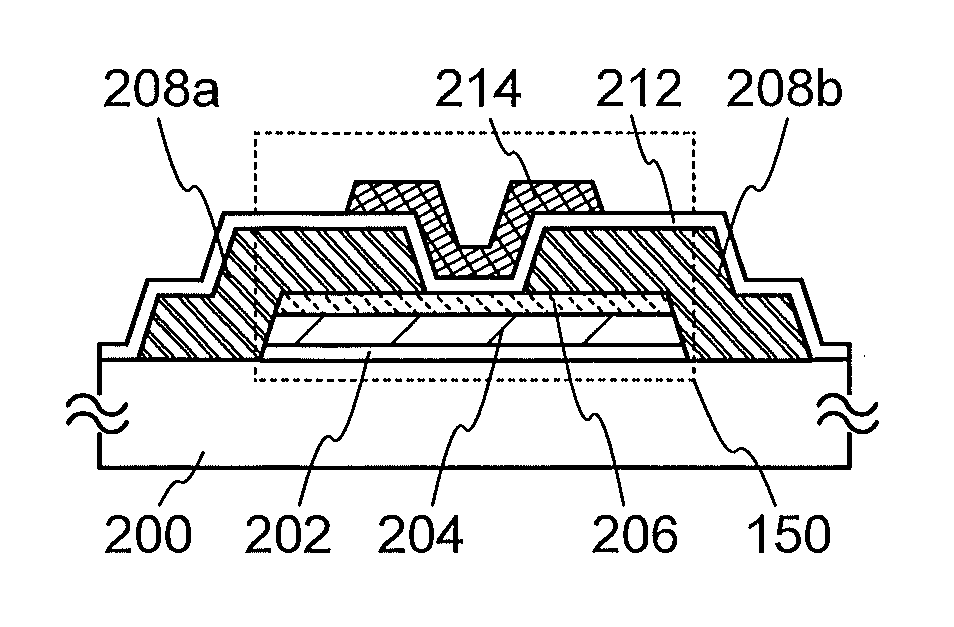

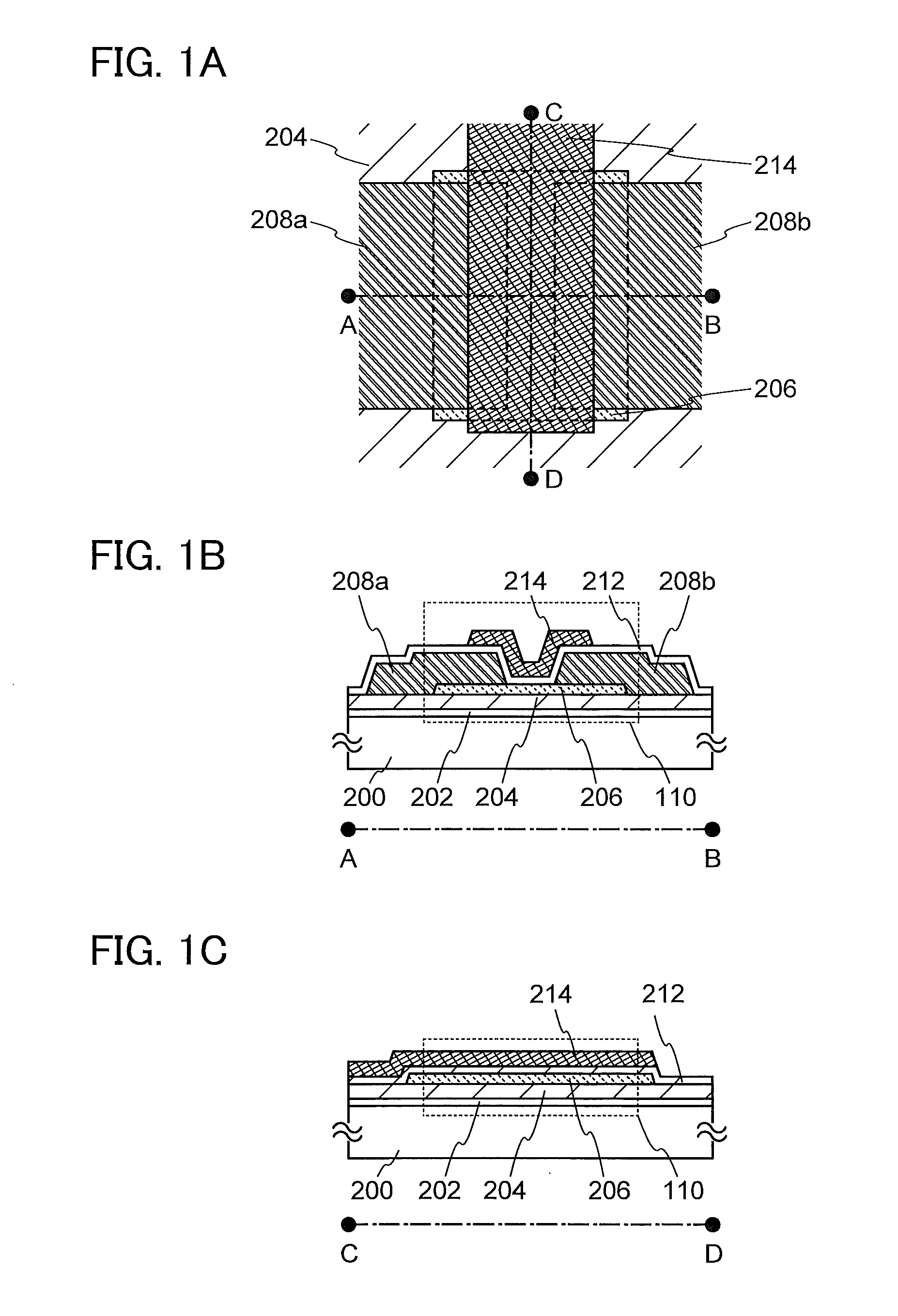

Semiconductor device and manufacturing method thereof

ActiveUS20110133191A1Improve insulation performanceExcellent electrical propertiesTransistorSolid-state devicesDevice materialSemiconductor

A semiconductor device includes an oxide semiconductor layer including a crystalline region over an insulating surface, a source electrode layer and a drain electrode layer in contact with the oxide semiconductor layer, a gate insulating layer covering the oxide semiconductor layer, the source electrode layer, and the drain electrode layer, and a gate electrode layer over the gate insulating layer in a region overlapping with the crystalline region. The crystalline region includes a crystal whose c-axis is aligned in a direction substantially perpendicular to a surface of the oxide semiconductor layer.

Owner:SEMICON ENERGY LAB CO LTD

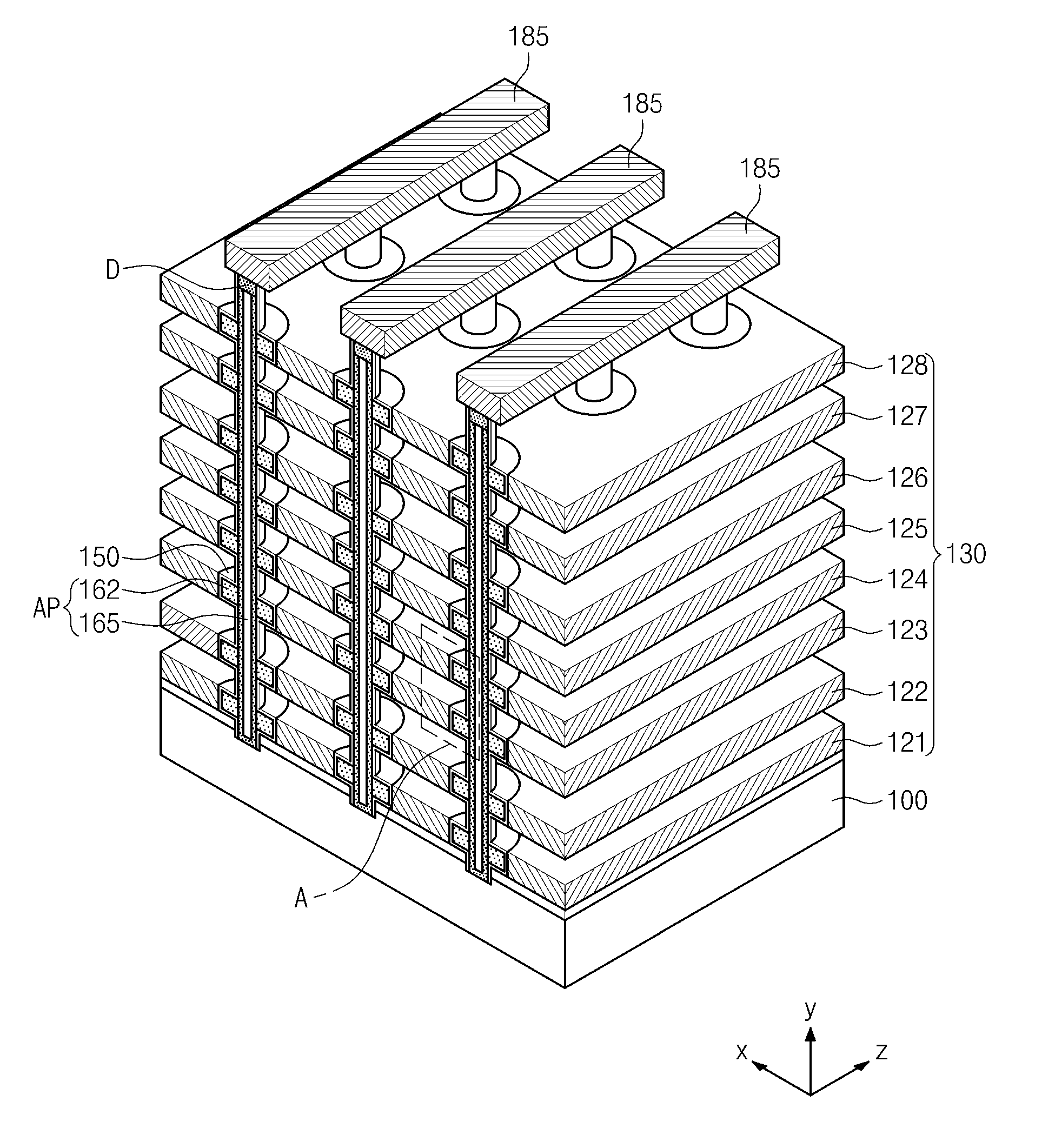

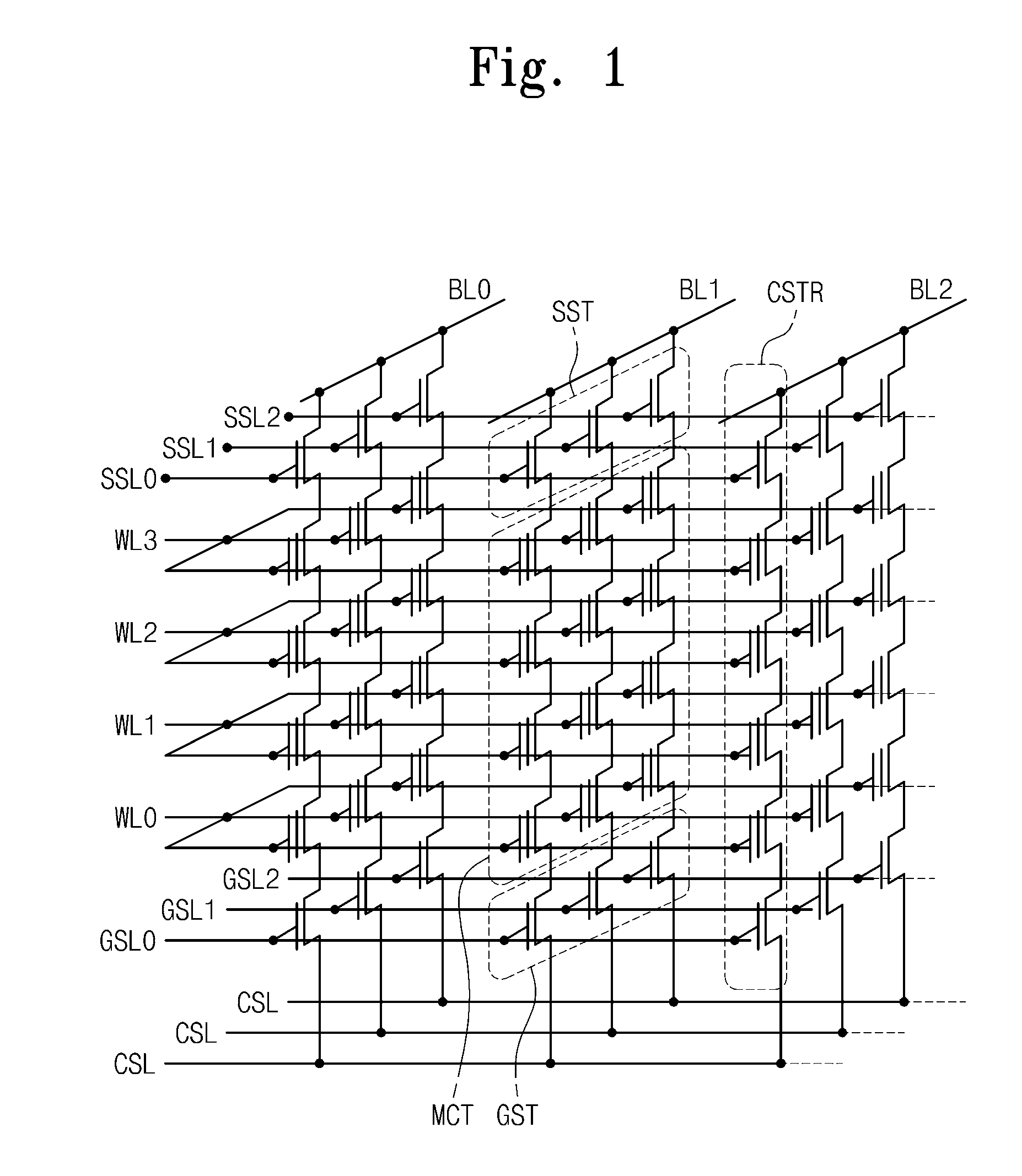

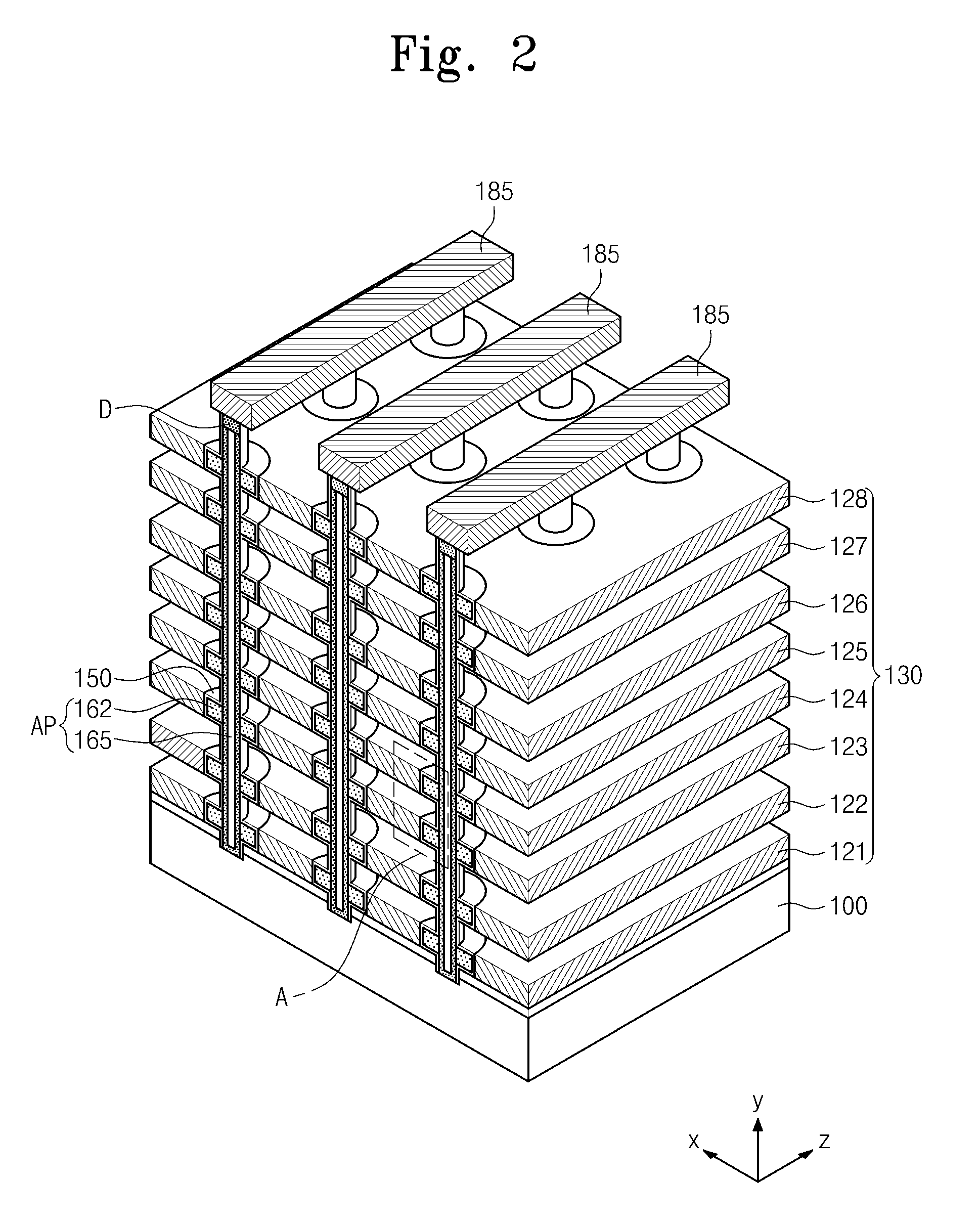

Three-dimensional semiconductor memory device and method for manufacturing the same

ActiveUS20110294290A1Improved electrical characteristicExcellent electrical propertiesSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor memory

A three-dimensional semiconductor memory device includes a stacked structure including a plurality of conductive patterns, an active pillar penetrating the stacked structure, and a data storage pattern between the active pillar and the conductive patterns, wherein the active pillar includes a vertical semiconductor pattern penetrating the stacked structure and protruding semiconductor patterns between the vertical semiconductor pattern and the data storage pattern, the protruding semiconductor patterns having a different crystalline structure from that of the vertical semiconductor pattern.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor device with two oxide semiconductor layers and manufacturing method thereof

In a bottom-gate thin film transistor using the stack of the first oxide semiconductor layer and the second oxide semiconductor layer, an oxide insulating layer serving as a channel protective layer is formed over and in contact with part of the oxide semiconductor layer overlapping with a gate electrode layer. In the same step as formation of the insulating layer, an oxide insulating layer covering a peripheral portion (including a side surface) of the stack of the oxide semiconductor layers is formed.

Owner:SEMICON ENERGY LAB CO LTD

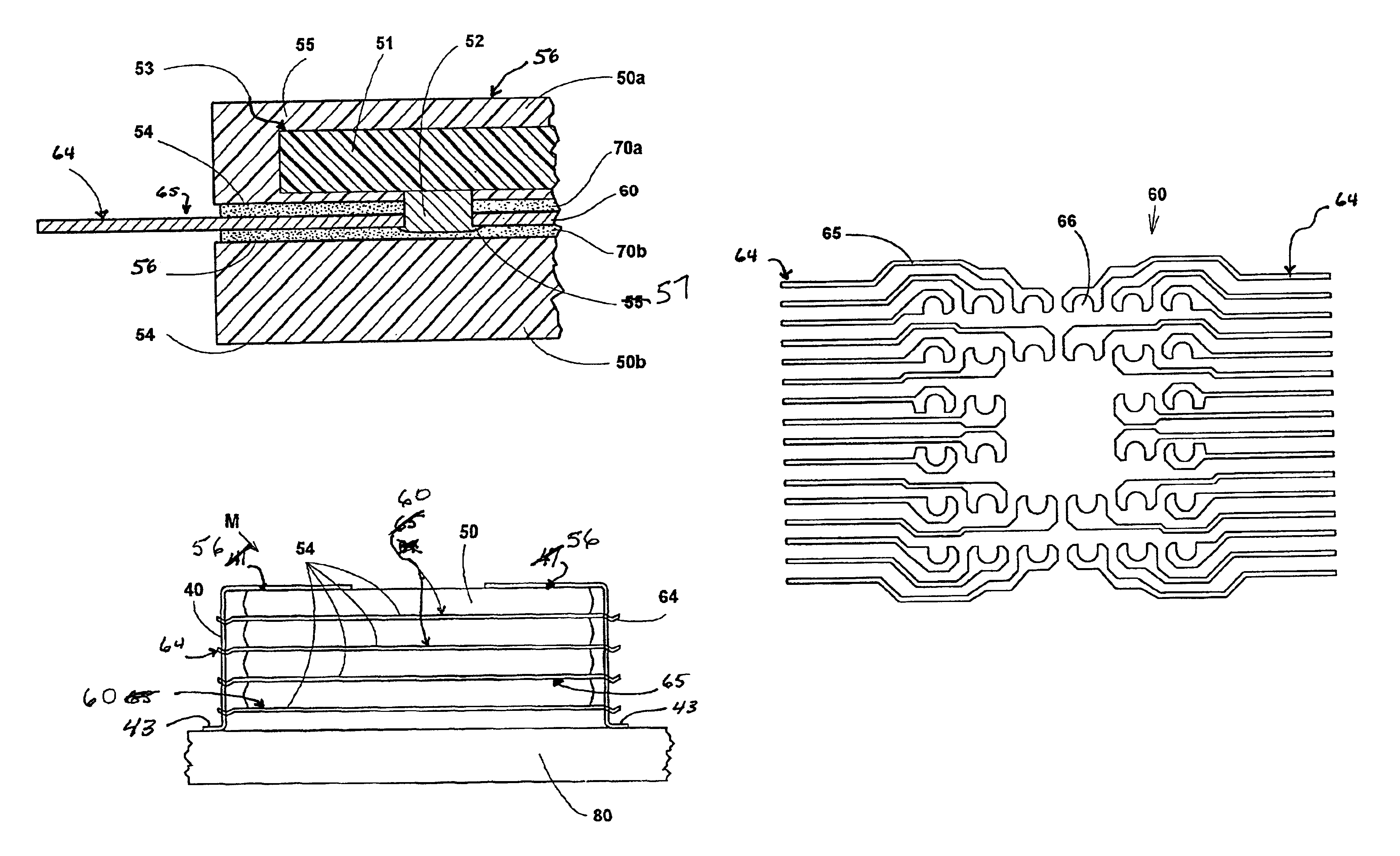

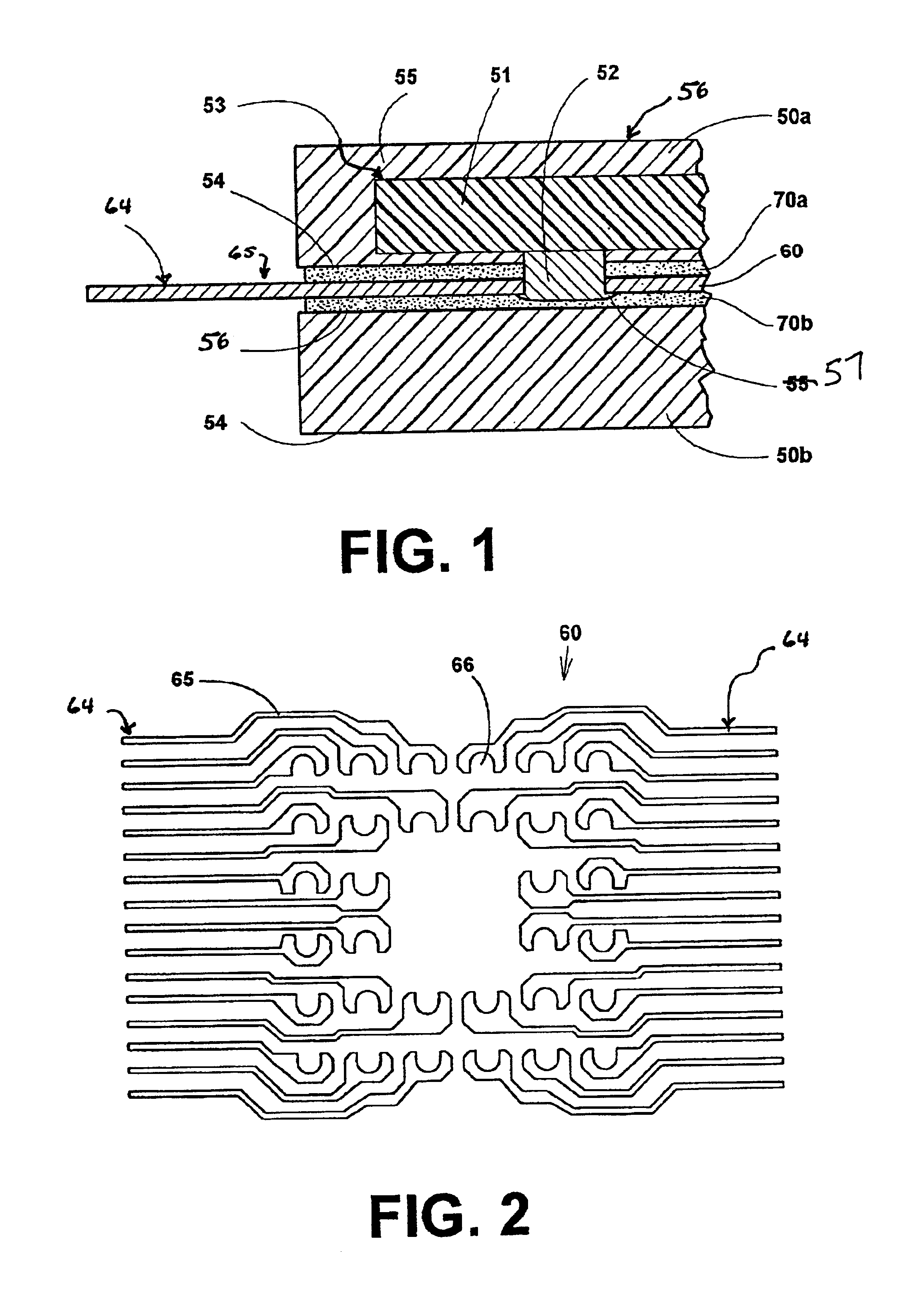

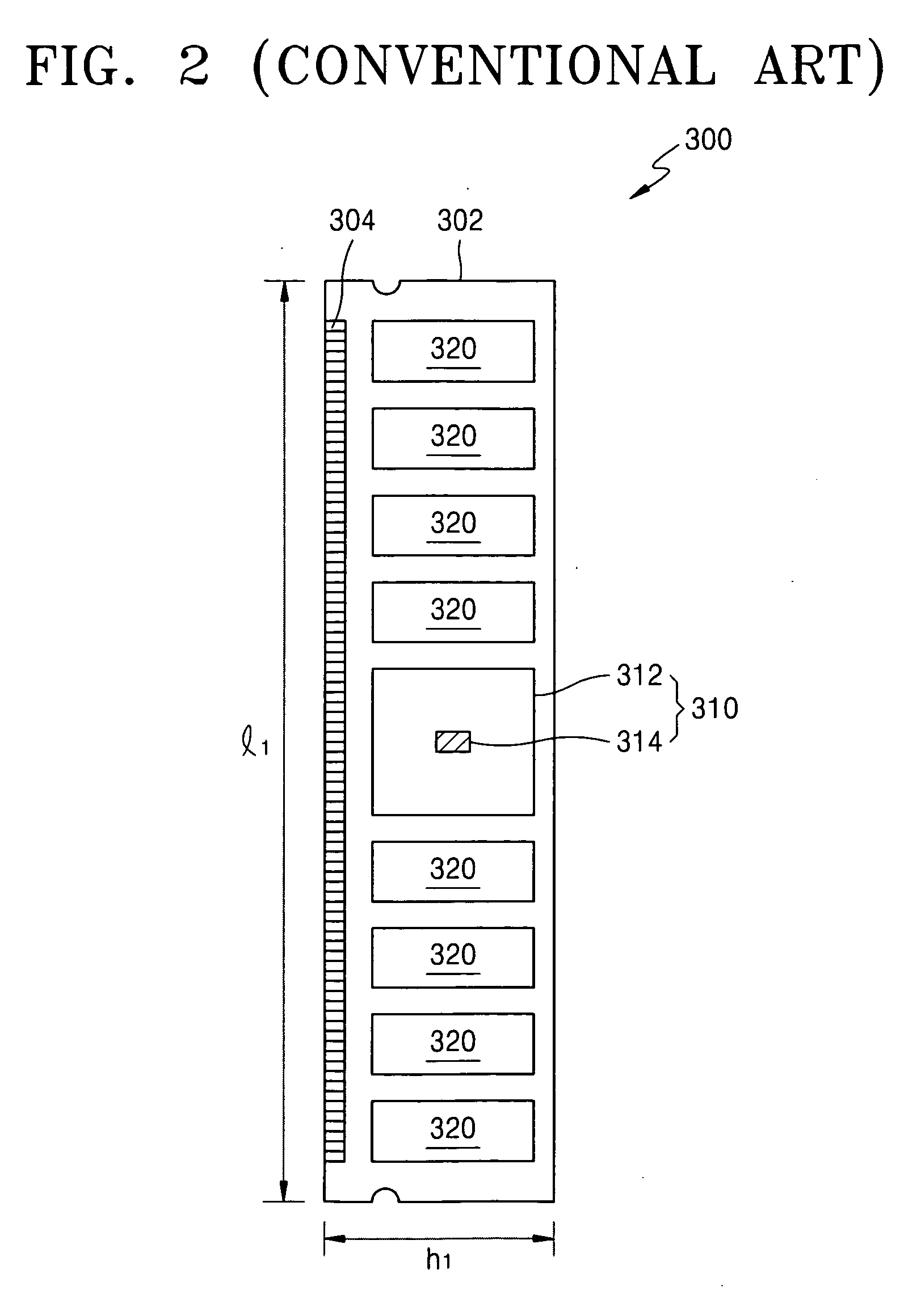

High density integrated circuit module

InactiveUS6919626B2Improve cooling effectImprove space efficiencyPrinted circuit assemblingLine/current collector detailsAdhesiveFlexible circuits

The present invention provides a method and apparatus for fabricating densely stacked ball-grid-array packages into a three-dimensional multi-package array. Integrated circuit packages are stacked on one another to form a module. Lead carriers provide an external point of electrical connection to buried package leads. Lead carriers are formed with apertures that partially surround each lead and electrically and thermally couple conductive elements or traces in the lead carrier to each package lead. Optionally thin layers of thermally conductive adhesive located between the lead carrier and adjacent packages facilitates the transfer of heat between packages and to the lead carrier. Lead carriers may be formed of custom flexible circuits having multiple layers of conductive material separated by a substrate to provide accurate impedance control and providing high density signal trace routing and ball-grid array connection to a printed wiring board.

Owner:OVID DATA CO

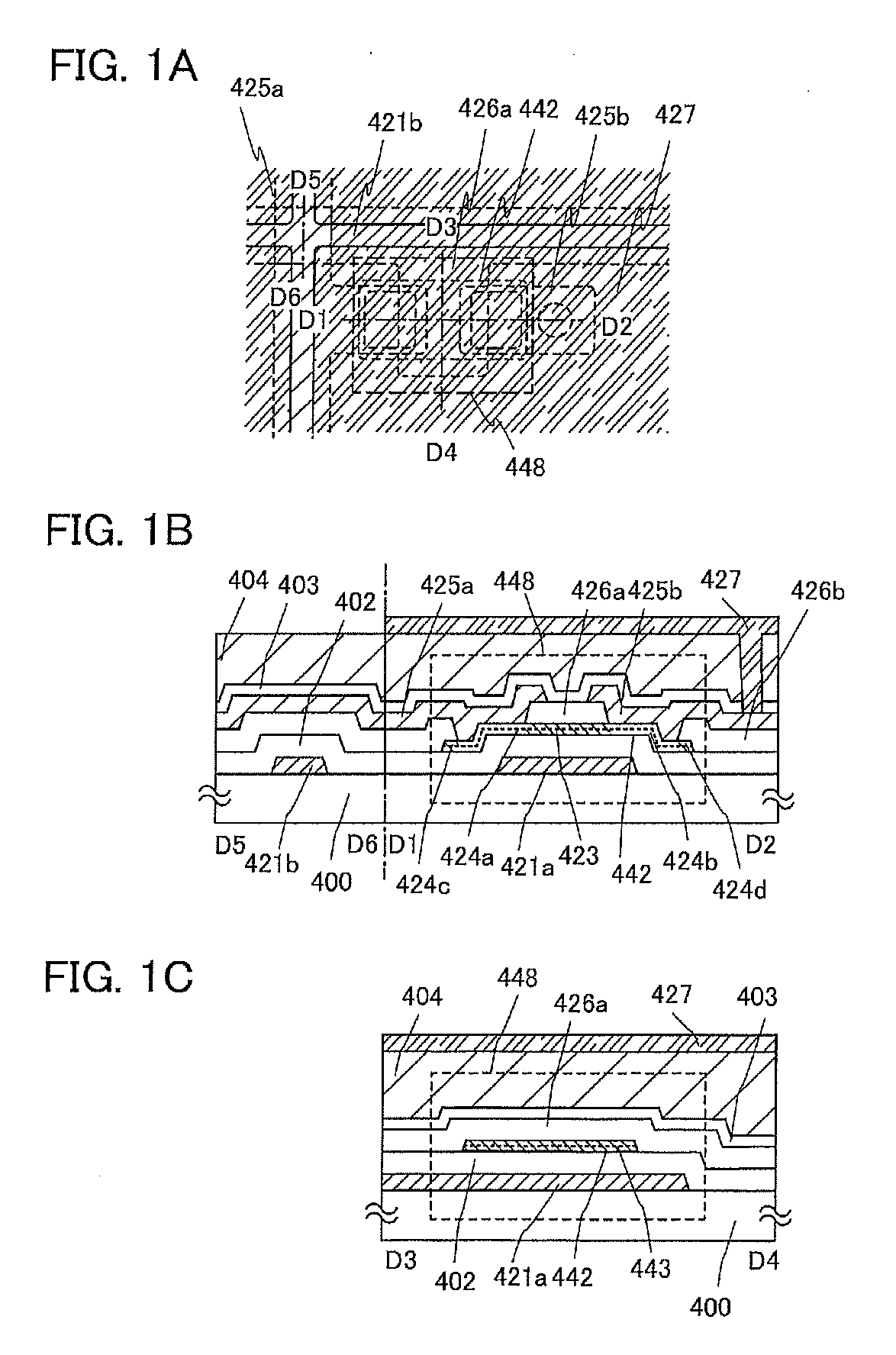

Semiconductor device and manufacturing method thereof

ActiveUS20120161125A1Excellent electrical propertiesMiniaturizationSolid-state devicesSemiconductor/solid-state device manufacturingOxide semiconductorIon doping

A semiconductor device capable of high speed operation is provided. Further, a highly reliable semiconductor device is provided. An oxide semiconductor having crystallinity is used for a semiconductor layer of a transistor. A channel formation region, a source region, and a drain region are formed in the semiconductor layer. The source region and the drain region are formed in such a manner that one or more of elements selected from rare gases and hydrogen are added to the semiconductor layer by an ion doping method or an ion implantation method with the use of a channel protective layer as a mask.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device and manufacturing method thereof

InactiveUS20050017255A1Improve heat resistanceExcellent electrical propertiesFinal product manufactureElectroluminescent light sourcesHeat resistanceColor film

A high performance electric device which uses an adhesive layer over a substrate. A color filter is over a substrate, and an adhesive layer is also located over the substrate and color film. An insulating layer is over the adhesive layer, and thin film transistors cover the insulating film and the color filters. Light emitting elements cover the thin film transistors and emit light through the substrate that is through the adhesive layer and color filter. The substrate may be plastic, thus increasing the heat resistance.

Owner:SEMICON ENERGY LAB CO LTD

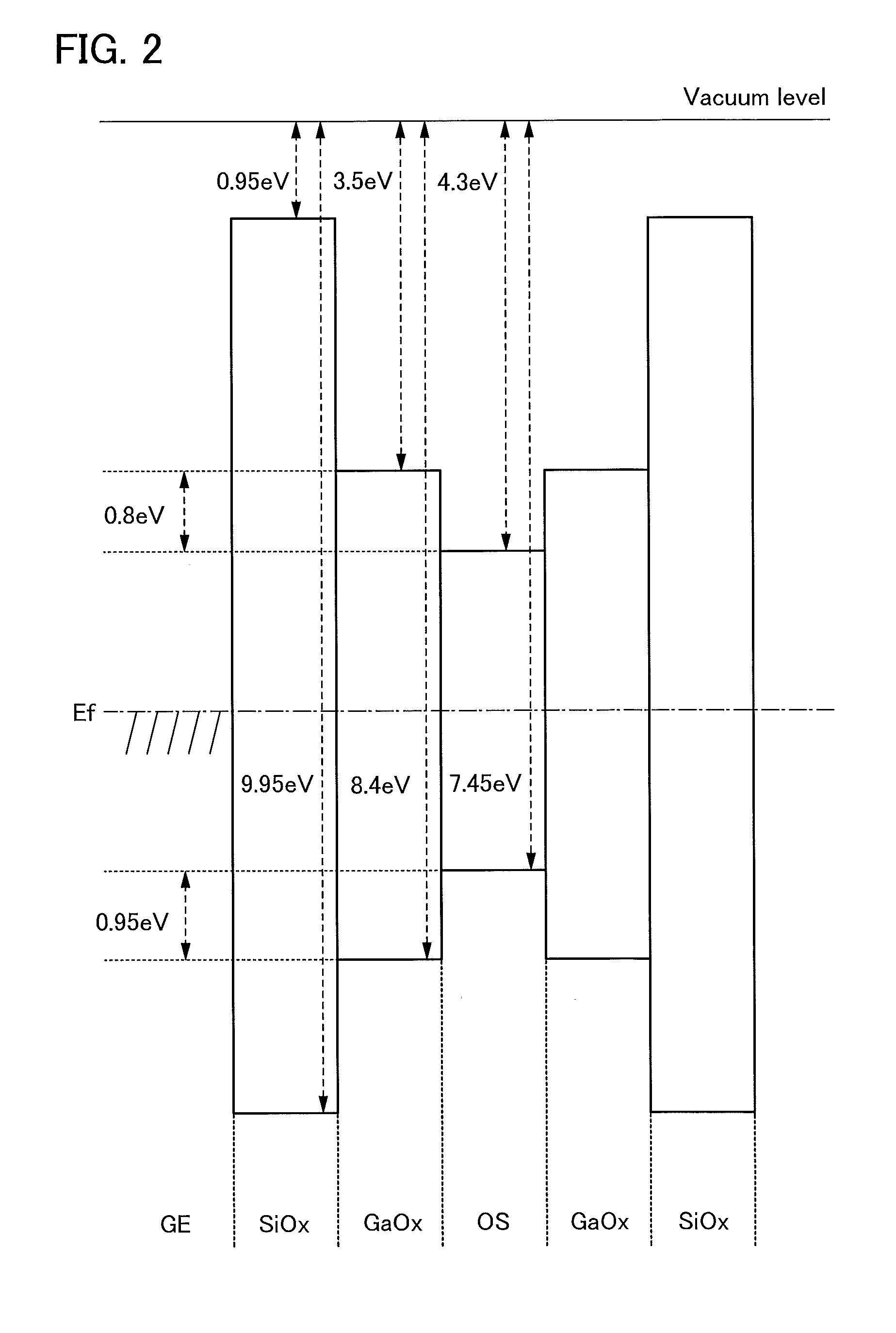

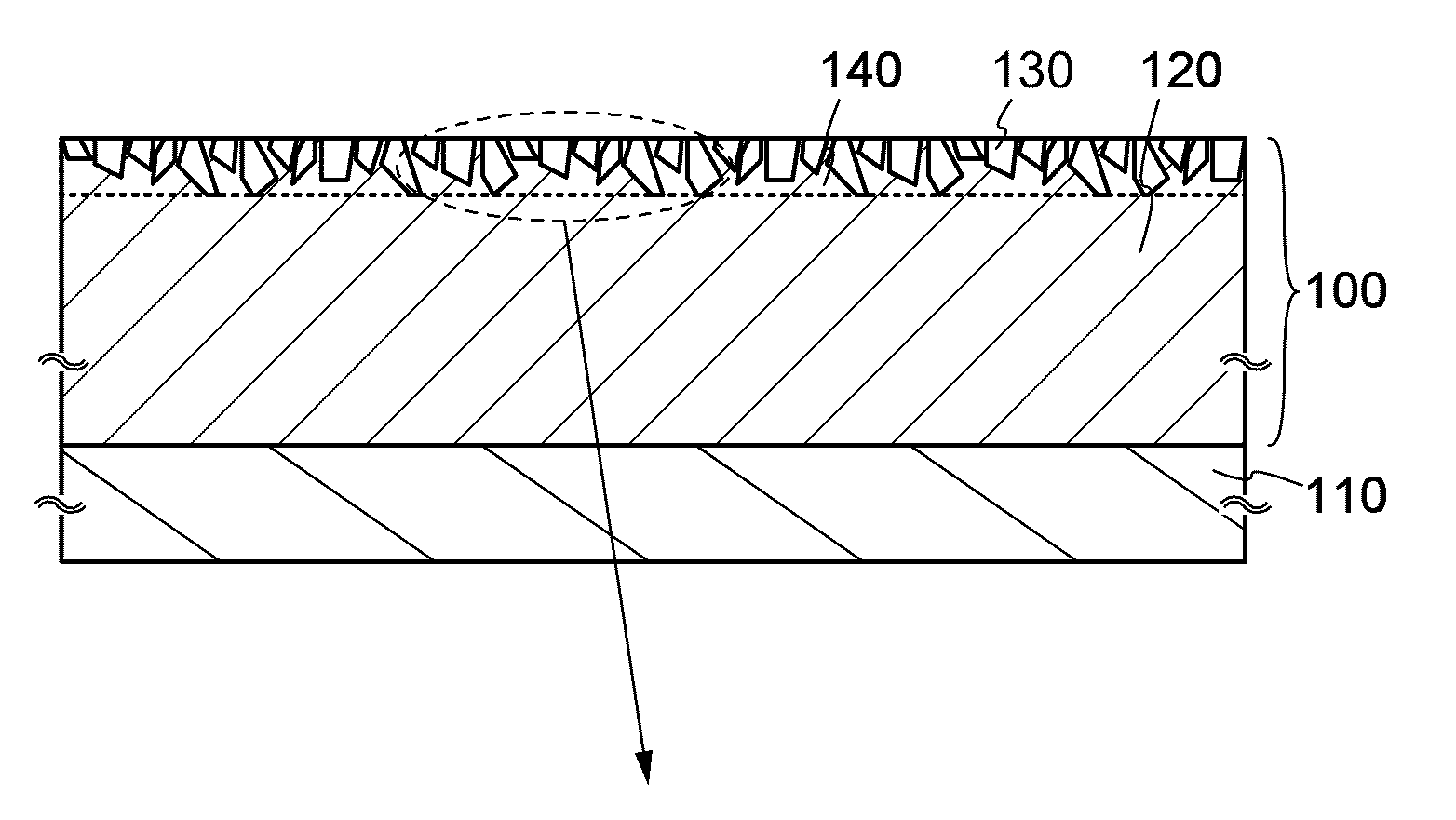

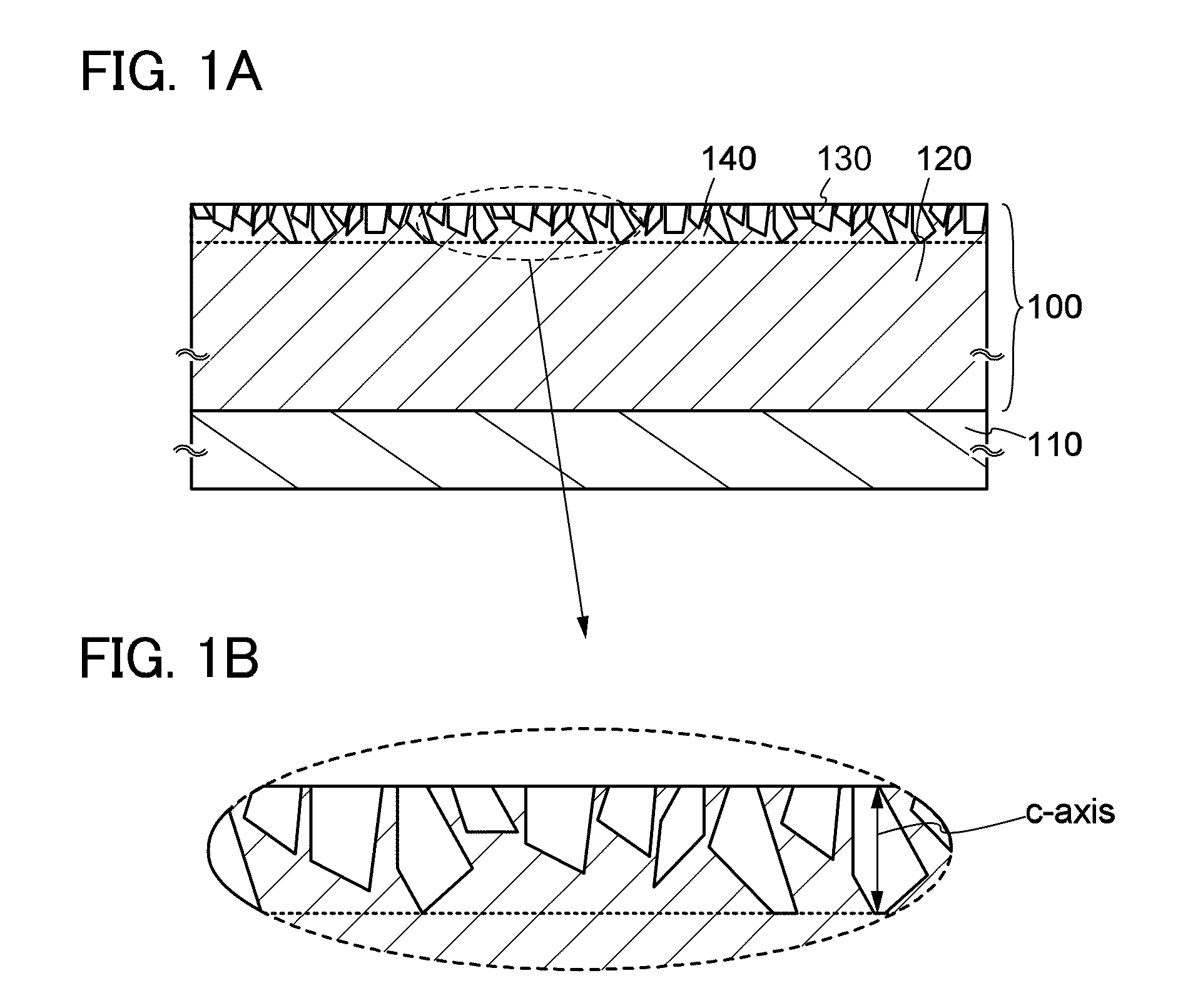

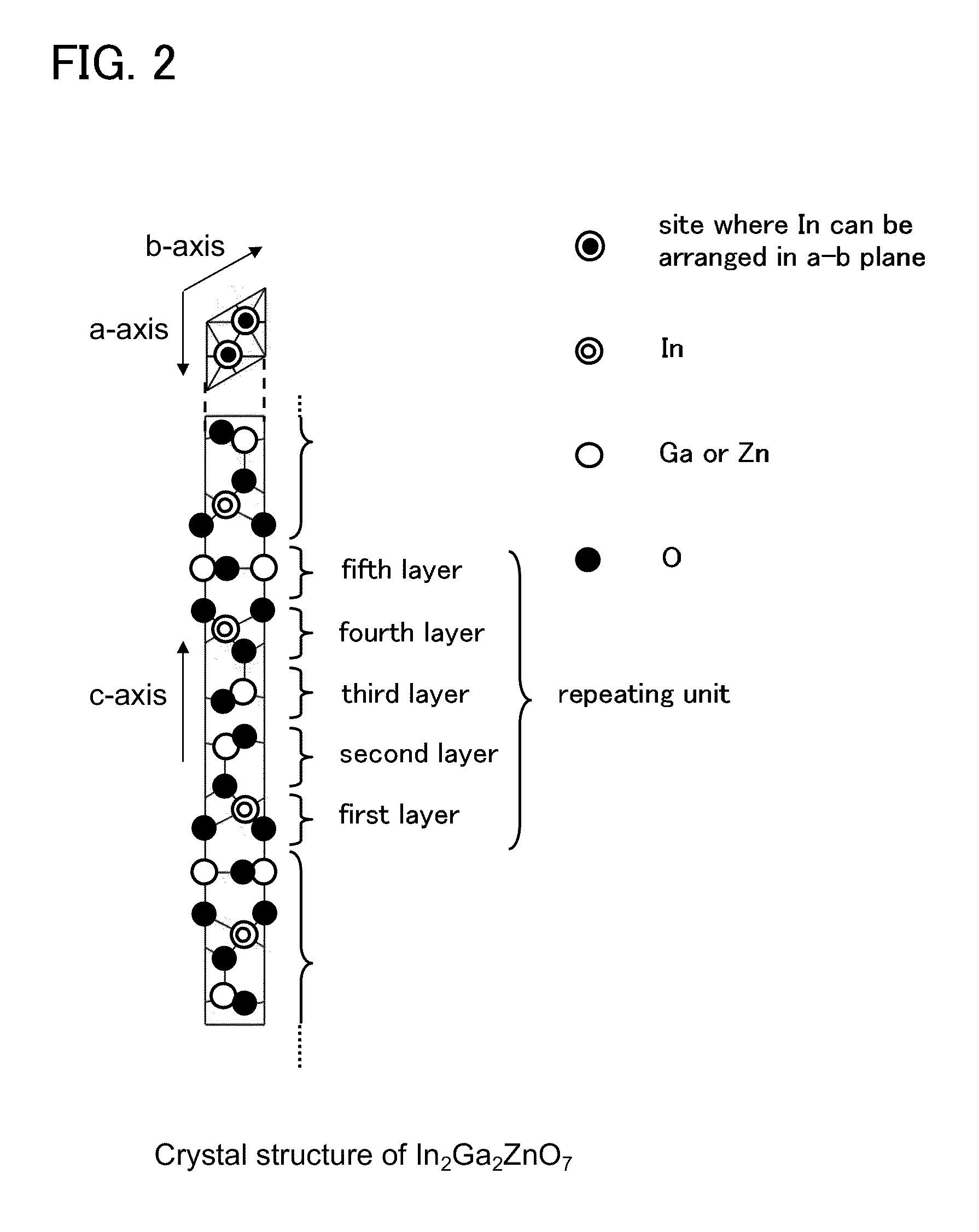

Oxide semiconductor layer and semiconductor device

ActiveUS20110084264A1Improve conductivityExcellent electrical propertiesSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductorSemiconductor device

An object is to provide an oxide semiconductor layer having a novel structure which is preferably used for a semiconductor device. Alternatively, another object is to provide a semiconductor device using an oxide semiconductor layer having the novel structure. An oxide semiconductor layer includes an amorphous region which is mainly amorphous and a crystal region containing crystal grains of In2Ga2ZnO7 in a vicinity of a surface, in which the crystal grains are oriented so that the c-axis is almost vertical with respect to the surface. Alternatively, a semiconductor device uses such an oxide semiconductor layer.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device

ActiveUS20110240992A1Improve reliabilityExcellent electrical propertiesTransistorElectroluminescent light sourcesOxygenActive layer

A transistor is provided in which the bottom surface portion of an oxide semiconductor film is provided with a metal oxide film containing a constituent similar to that of the oxide semiconductor film, and an insulating film containing a different constituent from the metal oxide film and the oxide semiconductor film is formed in contact with a surface of the metal oxide film, which is opposite to the surface in contact with the oxide semiconductor film In addition, the oxide semiconductor film used for the active layer of the transistor is an oxide semiconductor film highly purified to be electrically i-type (intrinsic) through heat treatment in which impurities such as hydrogen, moisture, hydroxyl, and hydride are removed from the oxide semiconductor and oxygen which is one of main component materials of the oxide semiconductor is supplied and is also reduced in a step of removing impurities.

Owner:SEMICON ENERGY LAB CO LTD

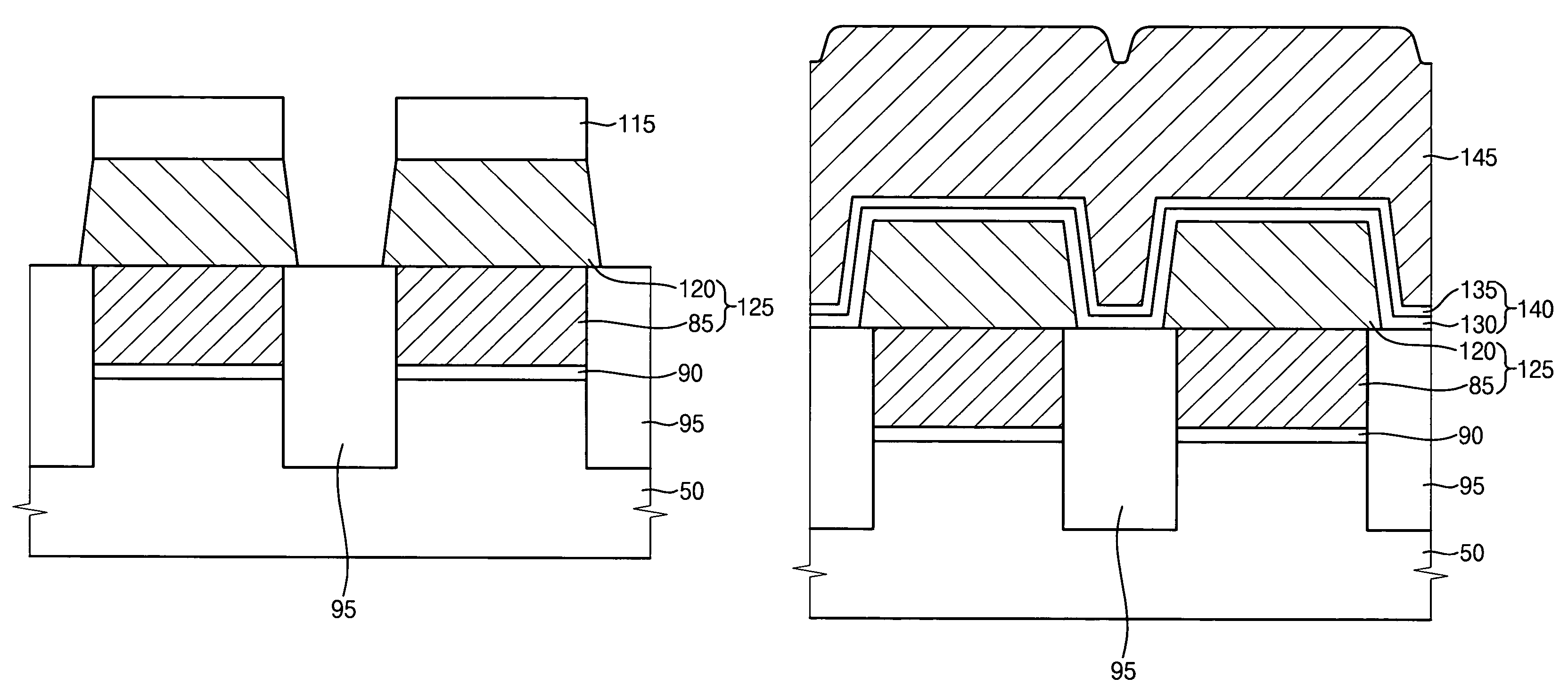

Dielectric structures having high dielectric constants, methods of forming the dielectric structures, non-volatile semiconductor memory devices having the dielectric structures and methods of manufacturing the non-volatile semiconductor memory devices

ActiveUS20060244147A1High dielectric constantImprove heat resistanceRoofingSemiconductor/solid-state device detailsCapacitanceLow leakage

In a method of manufacturing a dielectric structure, after a tunnel oxide layer pattern is formed on a substrate, a floating gate is formed on the tunnel oxide layer. After a first dielectric layer pattern including a metal silicon oxide and a second dielectric layer pattern including a metal silicon oxynitride are formed, a control gate is formed on the dielectric structure. Since the dielectric structure includes at least one metal silicon oxide layer and at least one metal silicon oxynitride layer, the dielectric structure may have a high dielectric constant and a good thermal resistance. A non-volatile semiconductor memory device including the dielectric structure may have good electrical characteristics such as a large capacitance and a low leakage current.

Owner:SAMSUNG ELECTRONICS CO LTD

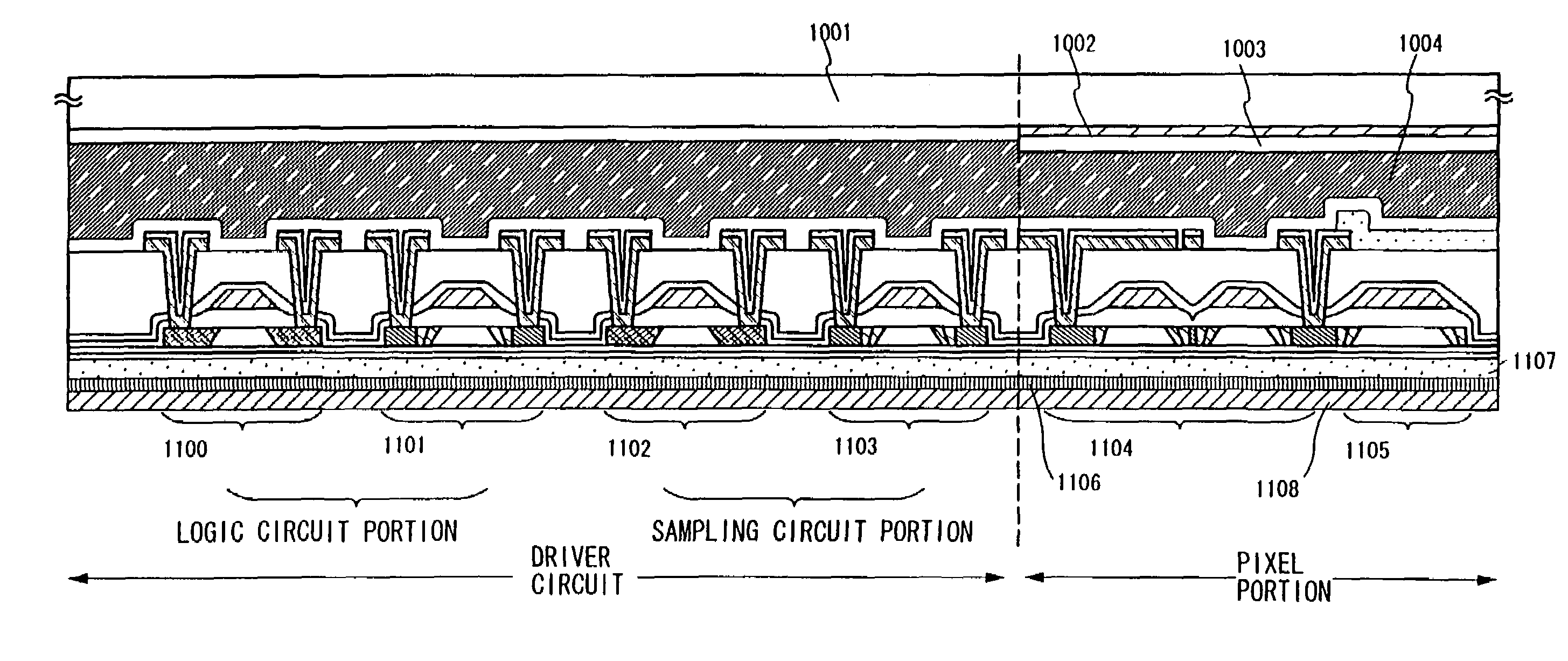

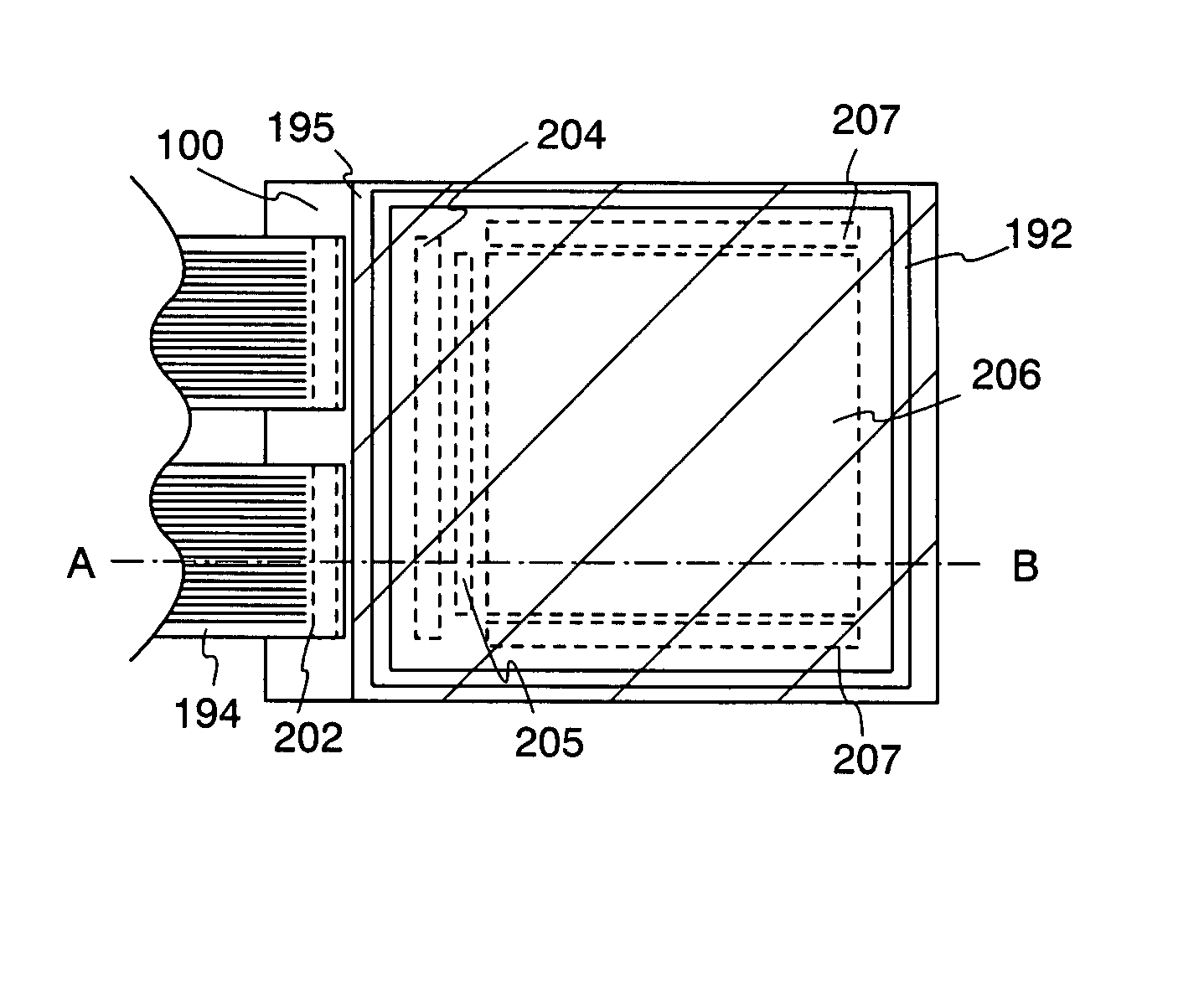

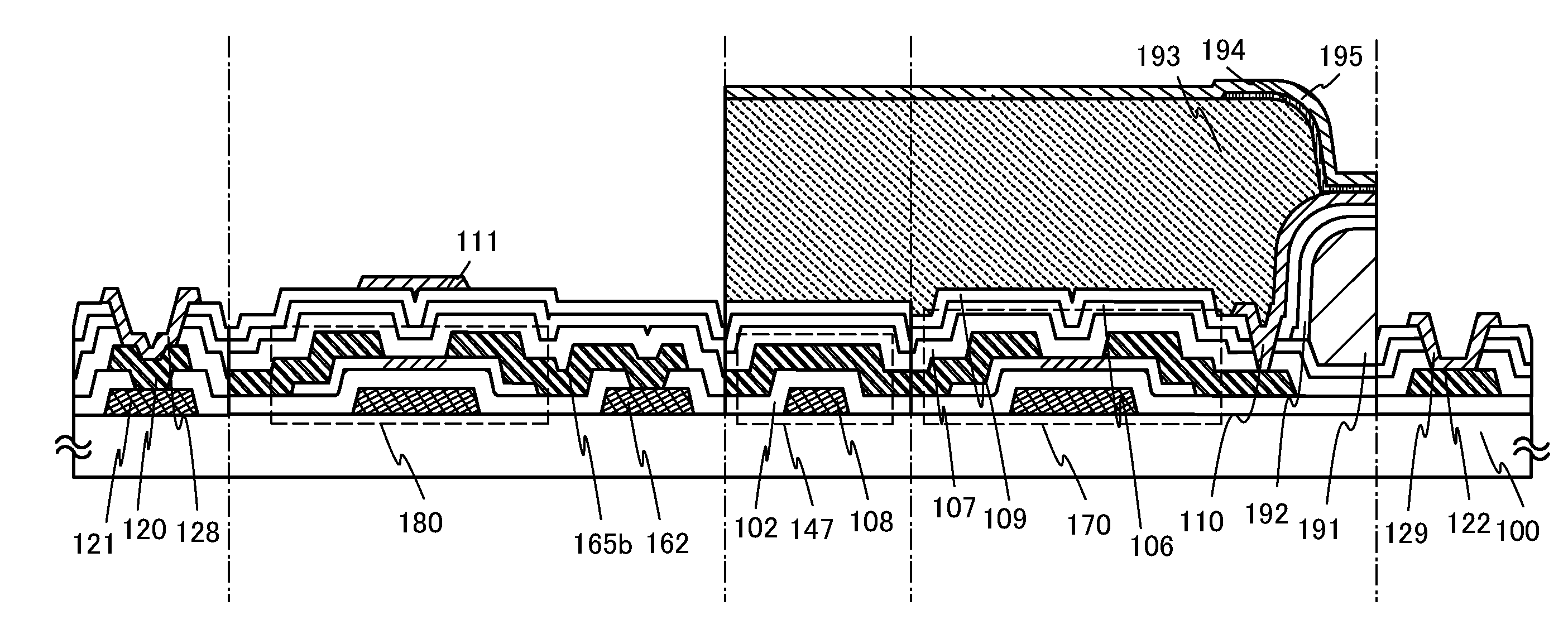

Display device and method for manufacturing the same

ActiveUS20060043510A1Improve reliabilitySimple processInput/output for user-computer interactionTelevision system detailsDriver circuitDisplay device

The present invention provides a method for manufacturing a highly reliable display device at a low cost with high yield. According to the present invention, a step due to an opening in a contact is covered with an insulating layer to reduce the step, and is processed into a gentle shape. A wiring or the like is formed to be in contact with the insulating layer and thus the coverage of the wiring or the like is enhanced. In addition, deterioration of a light-emitting element due to contaminants such as water can be prevented by sealing a layer including an organic material that has water permeability in a display device with a sealing material. Since the sealing material is formed in a portion of a driver circuit region in the display device, the frame margin of the display device can be narrowed.

Owner:SEMICON ENERGY LAB CO LTD

Dielectric structures having high dielectric constants, and non-volatile semiconductor memory devices having the dielectric structures

ActiveUS7482677B2High dielectric constantImprove heat resistanceSemiconductor/solid-state device detailsRoofingCapacitanceLow leakage

In a method of manufacturing a dielectric structure, after a tunnel oxide layer pattern is formed on a substrate, a floating gate is formed on the tunnel oxide layer. After a first dielectric layer pattern including a metal silicon oxide and a second dielectric layer pattern including a metal silicon oxynitride are formed, a control gate is formed on the dielectric structure. Since the dielectric structure includes at least one metal silicon oxide layer and at least one metal silicon oxynitride layer, the dielectric structure may have a high dielectric constant and a good thermal resistance. A non-volatile semiconductor memory device including the dielectric structure may have good electrical characteristics such as a large capacitance and a low leakage current.

Owner:SAMSUNG ELECTRONICS CO LTD

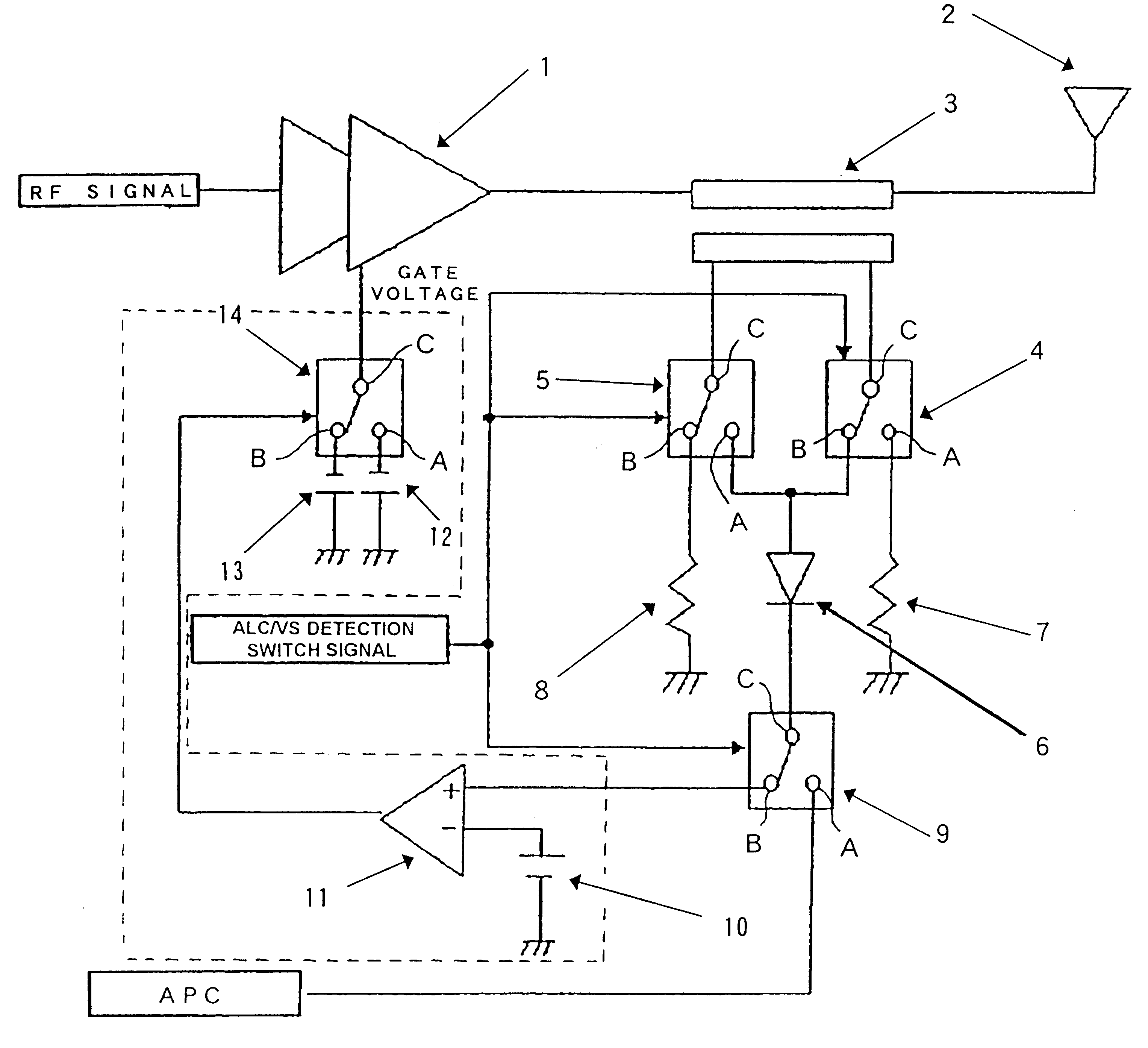

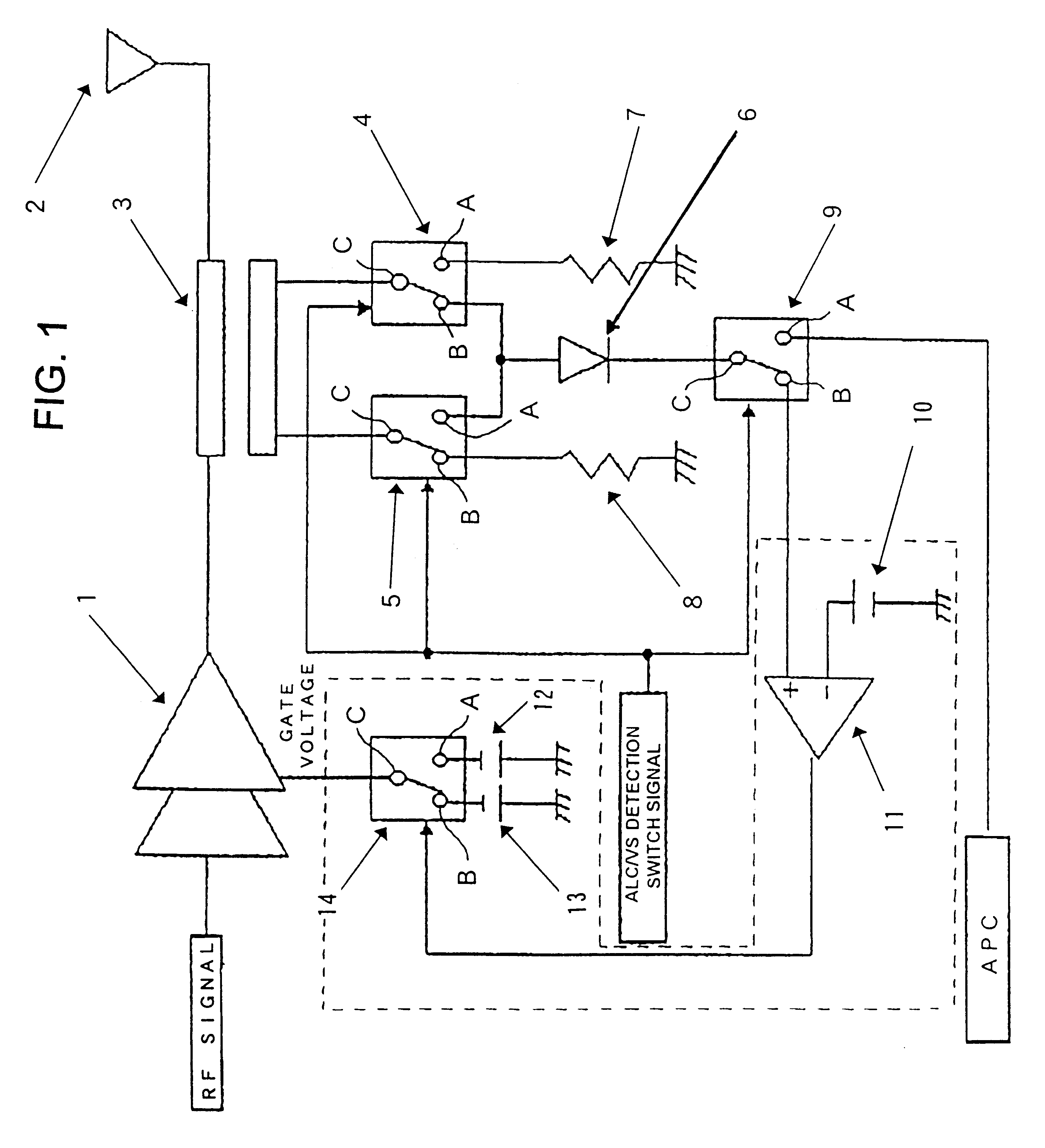

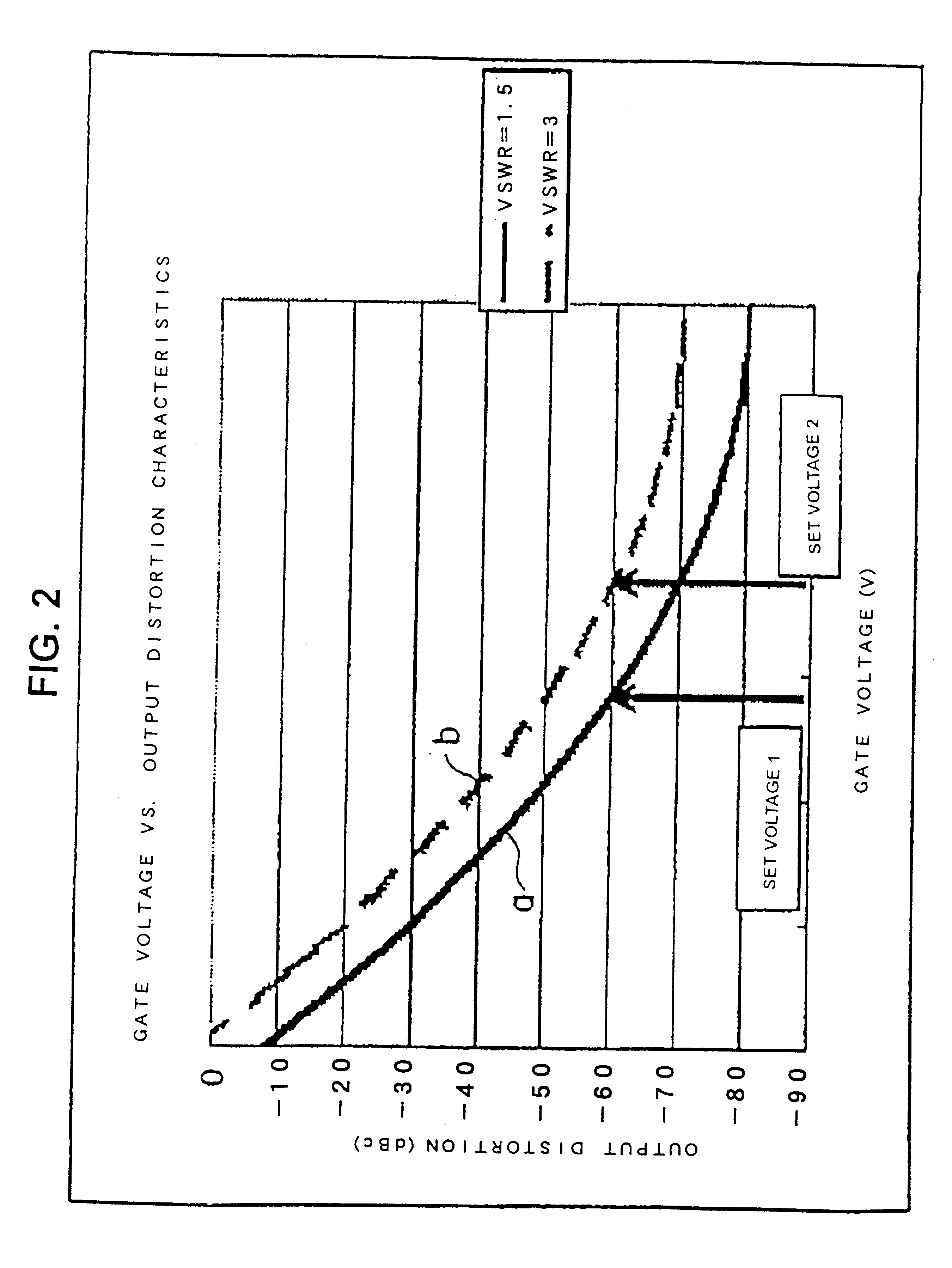

Radio frequency transmitting circuit

InactiveUS6329880B2Excellent electrical propertiesMiniaturize a mobile communication equipmentGain controlEmergency protective circuit arrangementsAudio power amplifierReflected waves

An object of the present invention is to allow the miniaturization of a mobile communication equipment and the reduction of consumption power, and to improve the electrical characteristics of a final stage amplifier. An inputted RF signal is amplified to a specified transmission output by a final stage amplifier, the output power and a reflected wave generated by mismatching between an output impedance of the final stage amplifier and a load impedance connected to an output side of the final stage amplifier are detected by a directional coupler. Two switches are selectively switched in a time division manner, a DC voltage corresponding to the reflected wave is selected, a comparator compares a threshold voltage with the DC voltage, a switch is switched by an output of the comparator outputted in accordance with the comparison, and gate voltages are selectively applied to the final stage amplifier.

Owner:NEC CORP

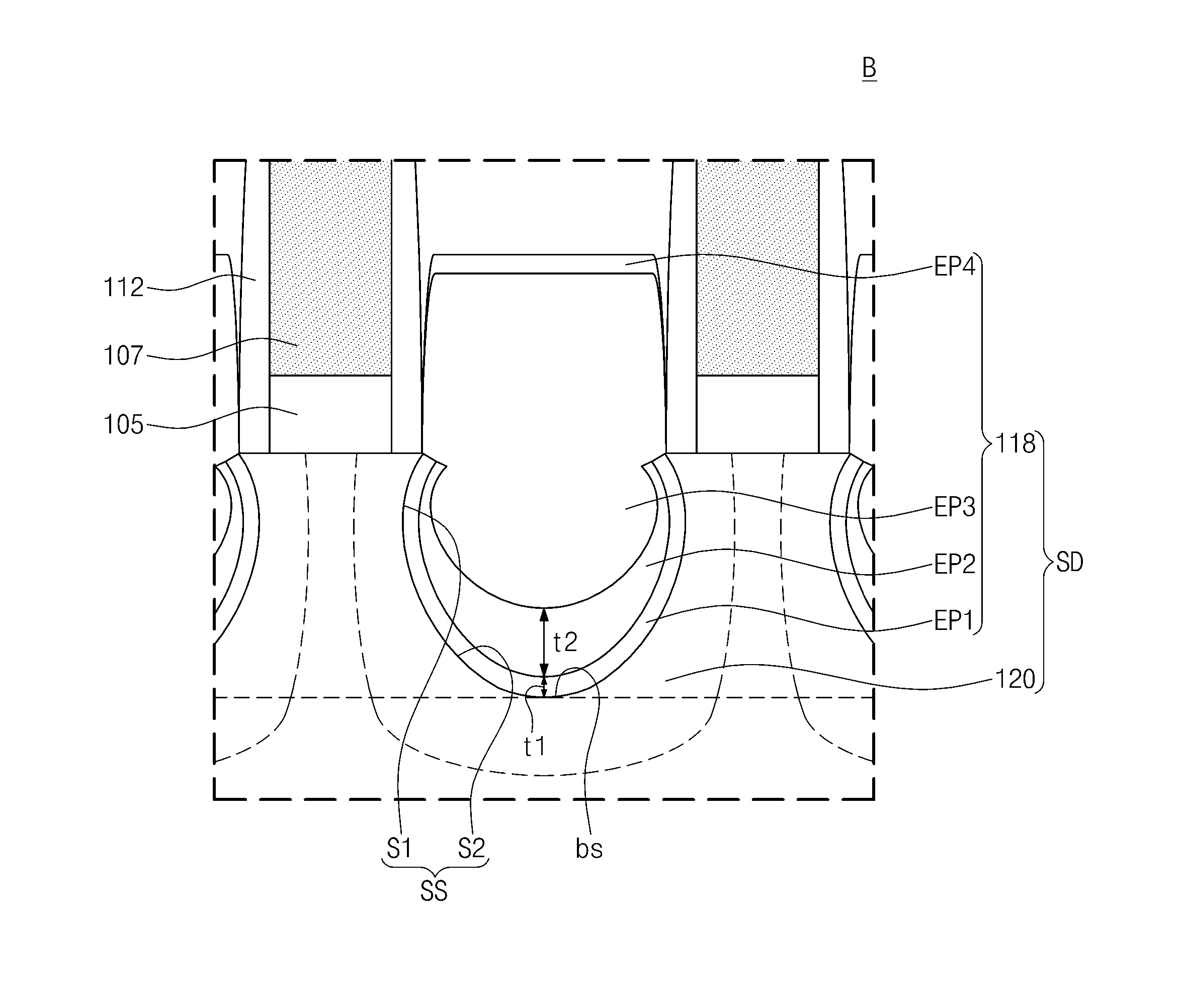

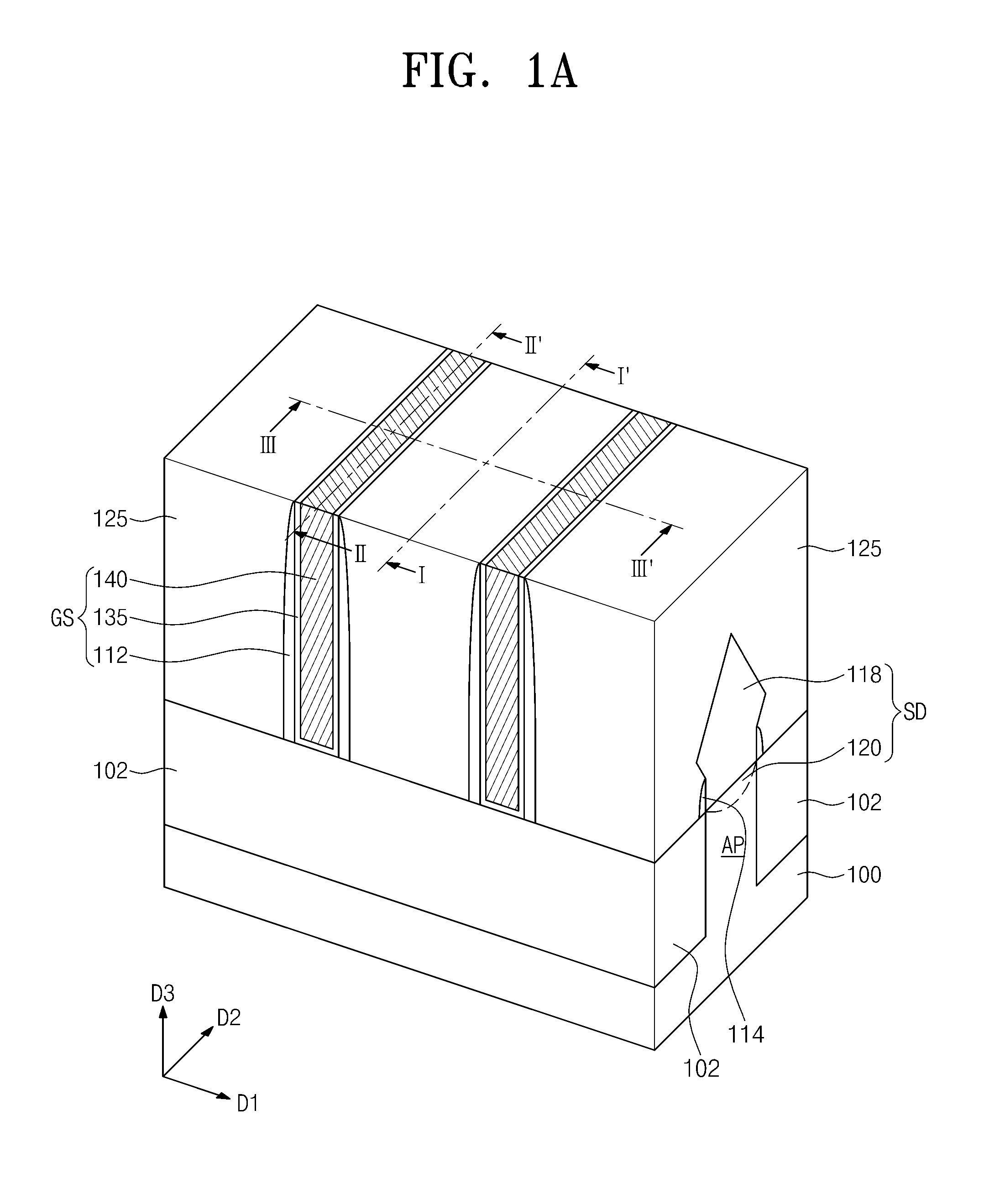

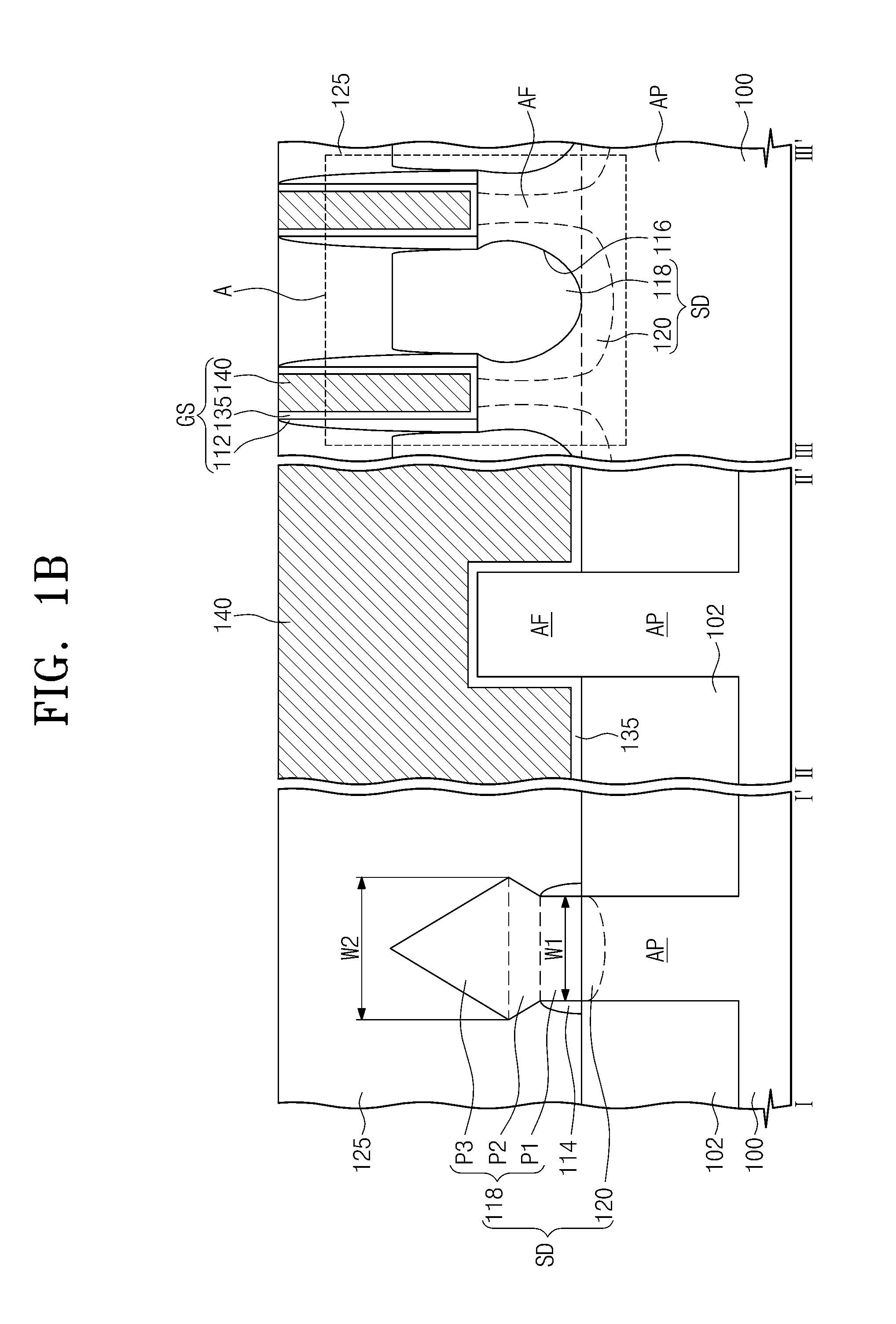

Semiconductor device and method of fabricating the same

ActiveUS20160087104A1Excellent electrical propertiesSemiconductor/solid-state device manufacturingSemiconductor devicesImpurity diffusionDevice material

Provided are a semiconductor device and a method of fabricating the same. The device may include an active pattern protruding from a substrate, gate structures crossing the active pattern, and a source / drain region provided between adjacent ones of the gate structures. The source / drain region may include a source / drain epitaxial layer in a recessed region, which is formed in the active pattern between the adjacent ones of the gate structures. Further, an impurity diffusion region may be provided in the active pattern to enclose the source / drain epitaxial layer along inner surfaces of the recessed region.

Owner:SAMSUNG ELECTRONICS CO LTD

Light-emitting device and manufacturing method thereof

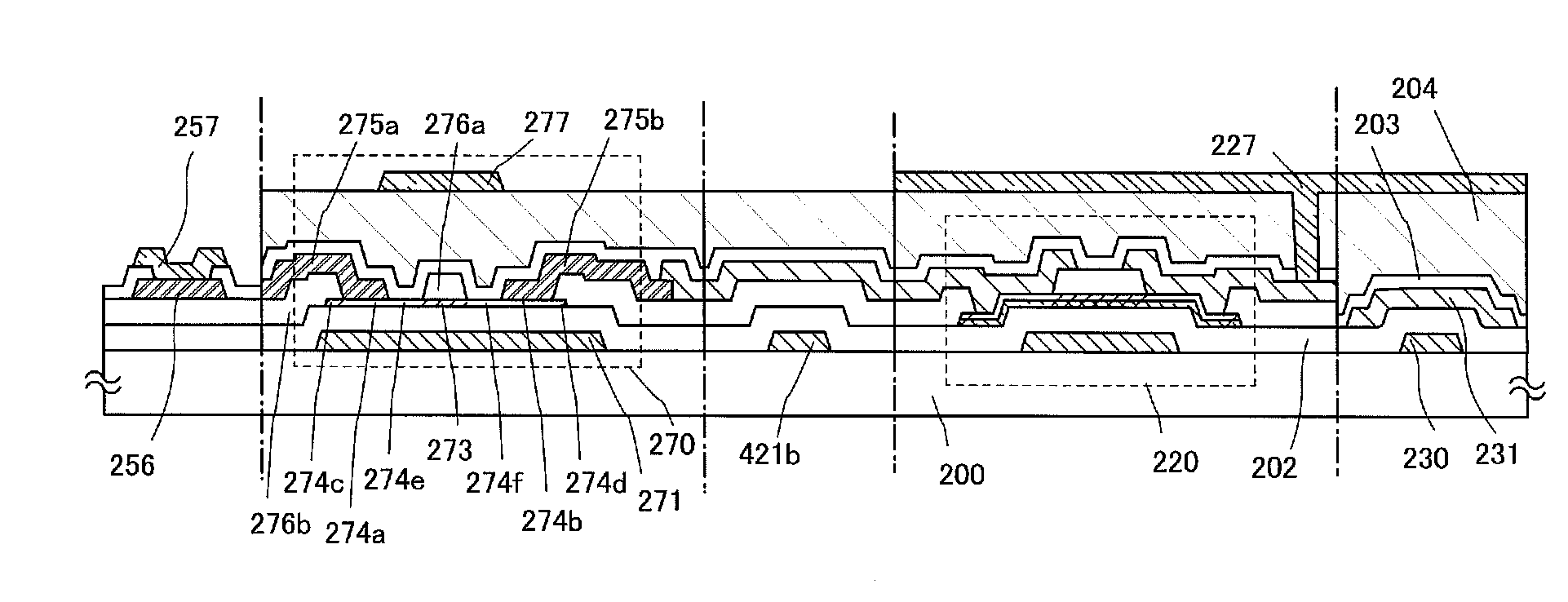

ActiveUS20110062434A1Excellent electrical propertiesImprove reliabilityFinal product manufactureSolid-state devicesEngineeringLight emitting device

An object of the invention is to improve the reliability of a light-emitting device. Another object of the invention is to provide flexibility to a light-emitting device having a thin film transistor using an oxide semiconductor film. A light-emitting device has, over one flexible substrate, a driving circuit portion including a thin film transistor for a driving circuit and a pixel portion including a thin film transistor for a pixel. The thin film transistor for a driving circuit and the thin film transistor for a pixel are inverted staggered thin film transistors including an oxide semiconductor layer which is in contact with a part of an oxide insulating layer.

Owner:SEMICON ENERGY LAB CO LTD

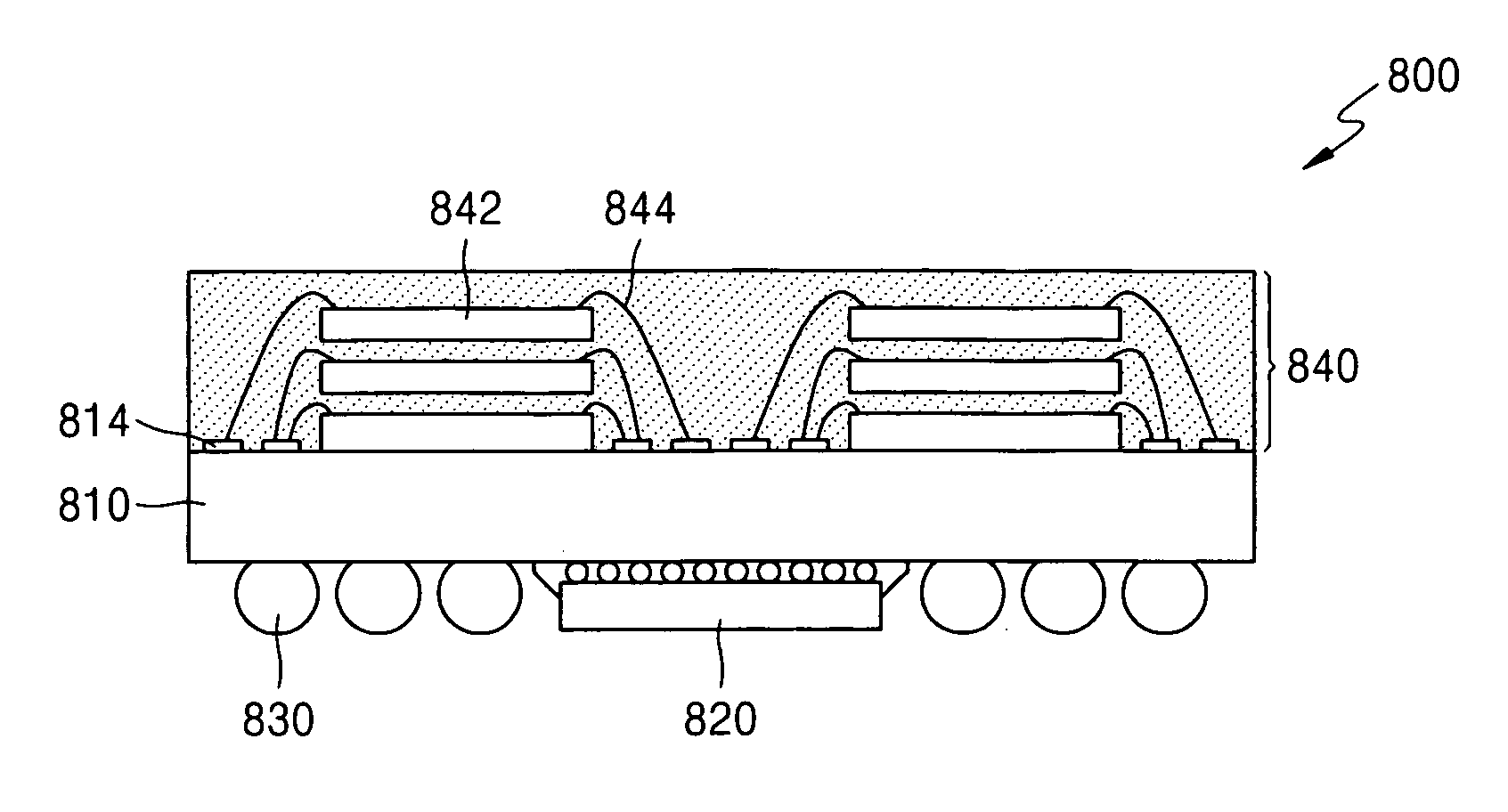

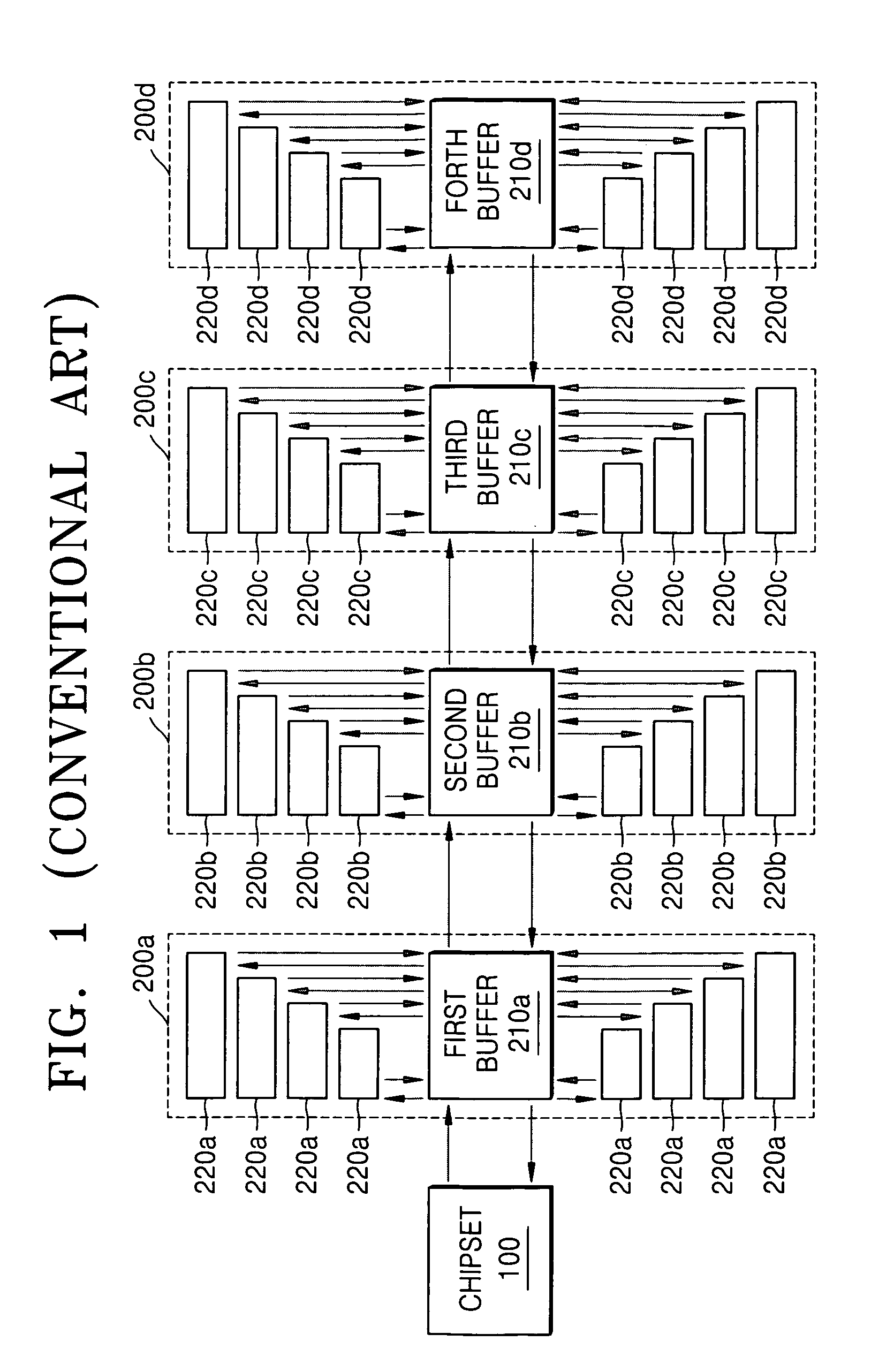

Semiconductor device package having buffered memory module and method thereof

ActiveUS20050224948A1Excellent electrical propertiesReduce distanceSemiconductor/solid-state device detailsPrinted circuit aspectsMemory chipDevice material

A method and apparatus of fabricating a semiconductor device are disclosed. The semiconductor device may include a buffer chip package having a buffer chip mounted on a buffer chip substrate and at least one memory package mounted on the buffer chip substrate, wherein the at least one memory package may include a plurality of memory chips. Further, the buffer chip package may have a plurality of external connection terminals.

Owner:SAMSUNG ELECTRONICS CO LTD

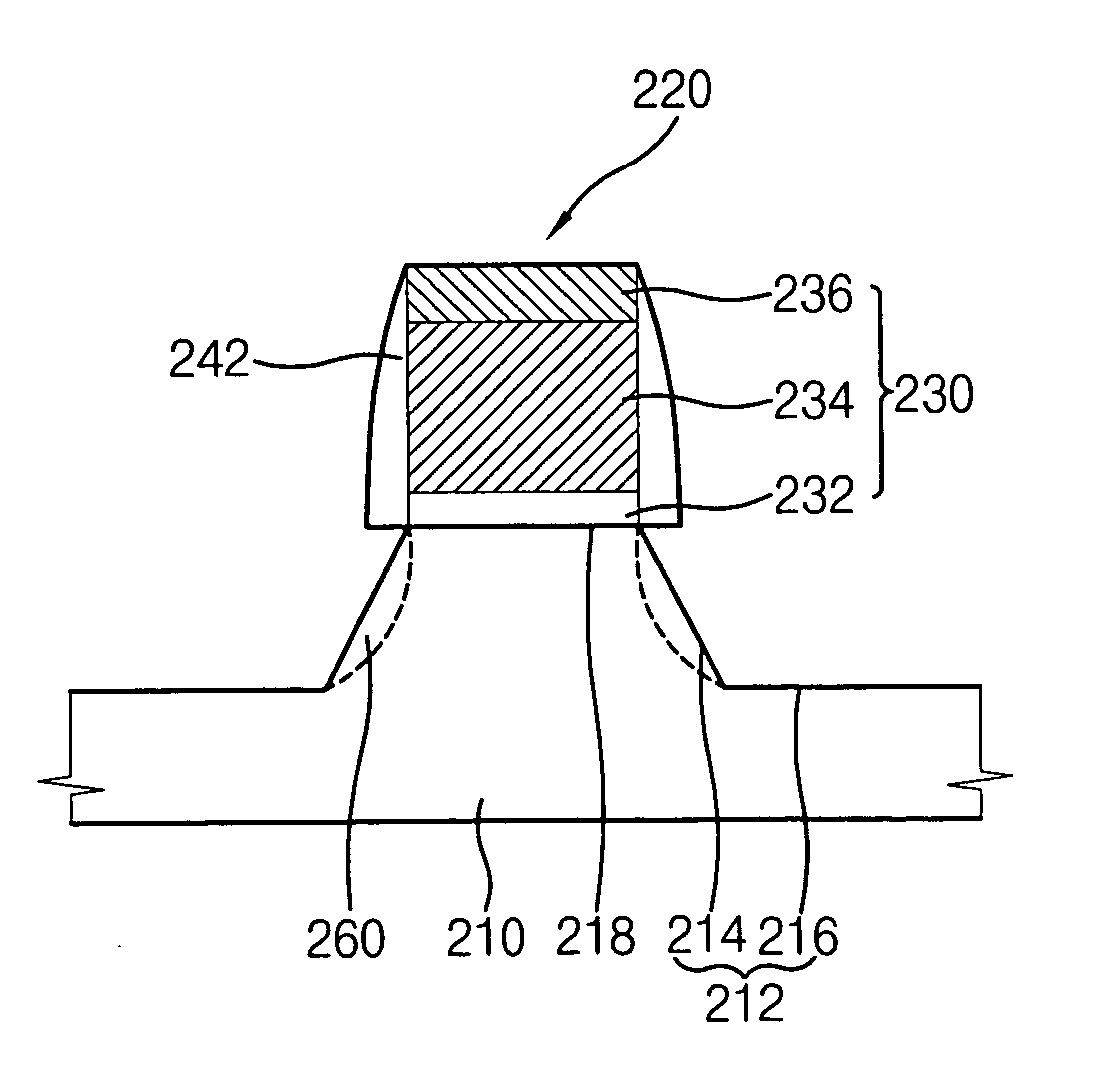

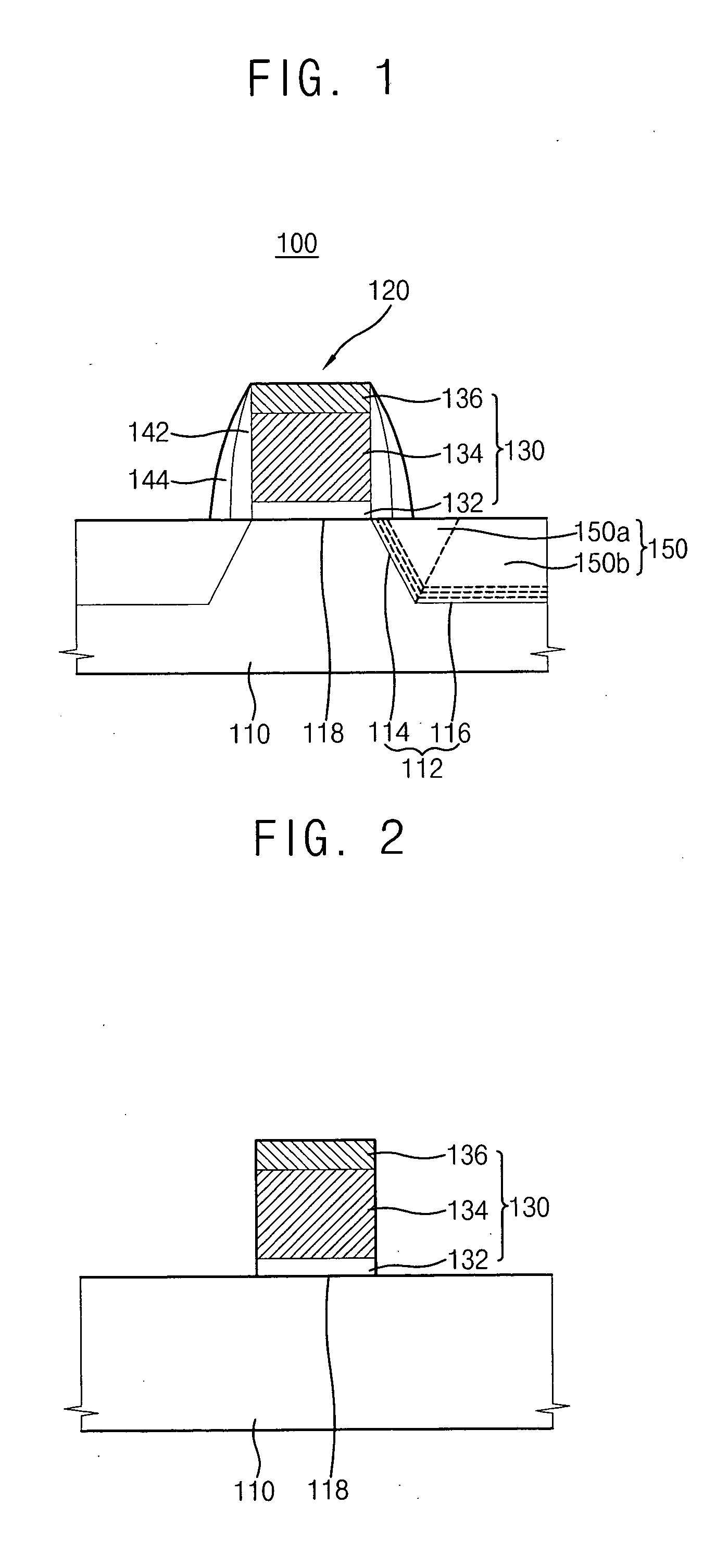

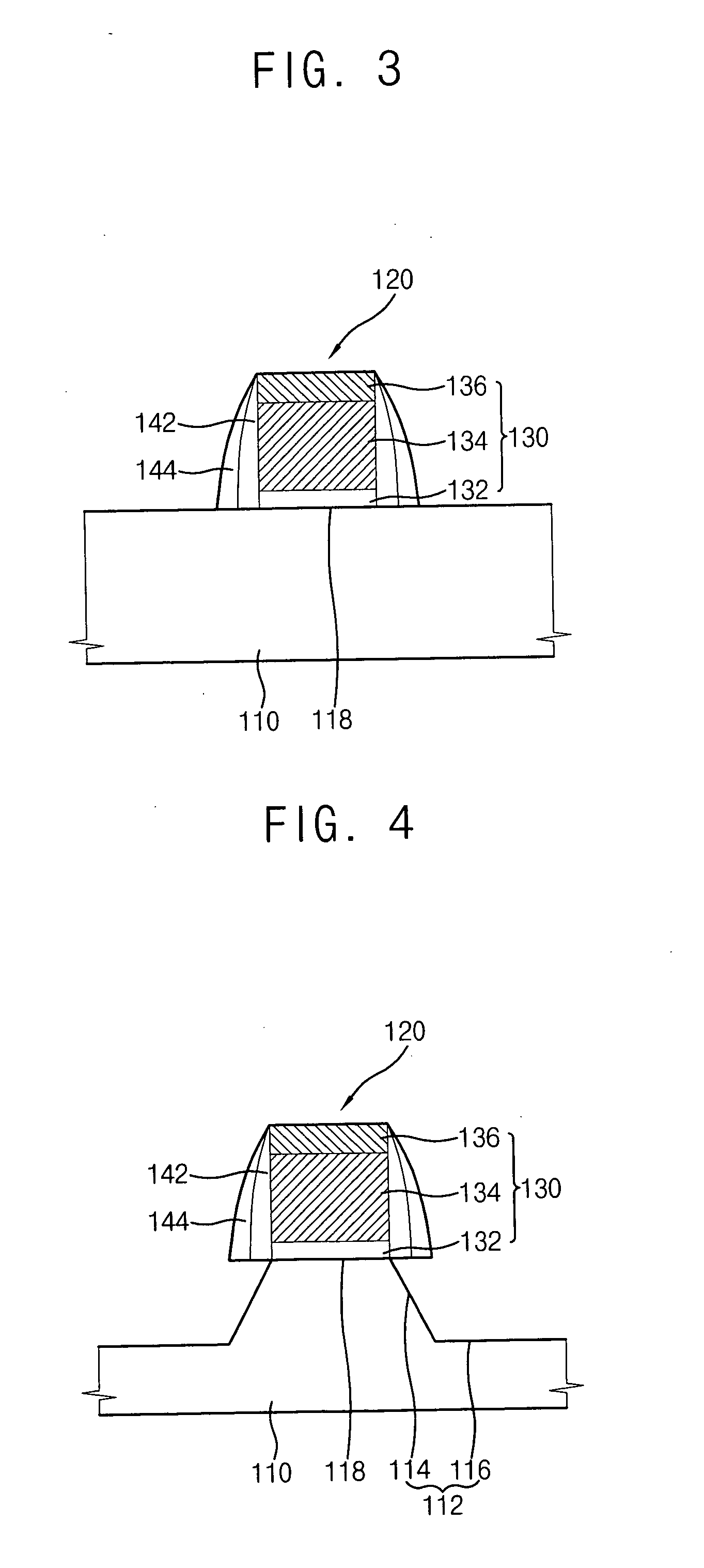

Transistor and method of manufacturing the same

ActiveUS20060038230A1Improved structureExcellent electrical characteristicTransistorSolid-state devicesCrystal planeShort-channel effect

A transistor includes a semiconductor substrate that has a first surface of a {100} crystal plane, a second surface of the {100} crystal plane having a height lower than that of the first surface, and a third surface of a {111} crystal plane connecting the first surface to the second surface. First heavily doped impurity regions are formed under the second surface. A gate structure is formed on the first surface. An epitaxial layer is formed on the second surface and the third surface. Second heavily doped impurity regions are formed at both sides of the gate structure. The second heavily doped impurity regions have side faces of the {111} crystal plane so that a short channel effect generated between the impurity regions may be prevented.

Owner:SAMSUNG ELECTRONICS CO LTD