Patents

Literature

943 results about "Dielectric structure" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

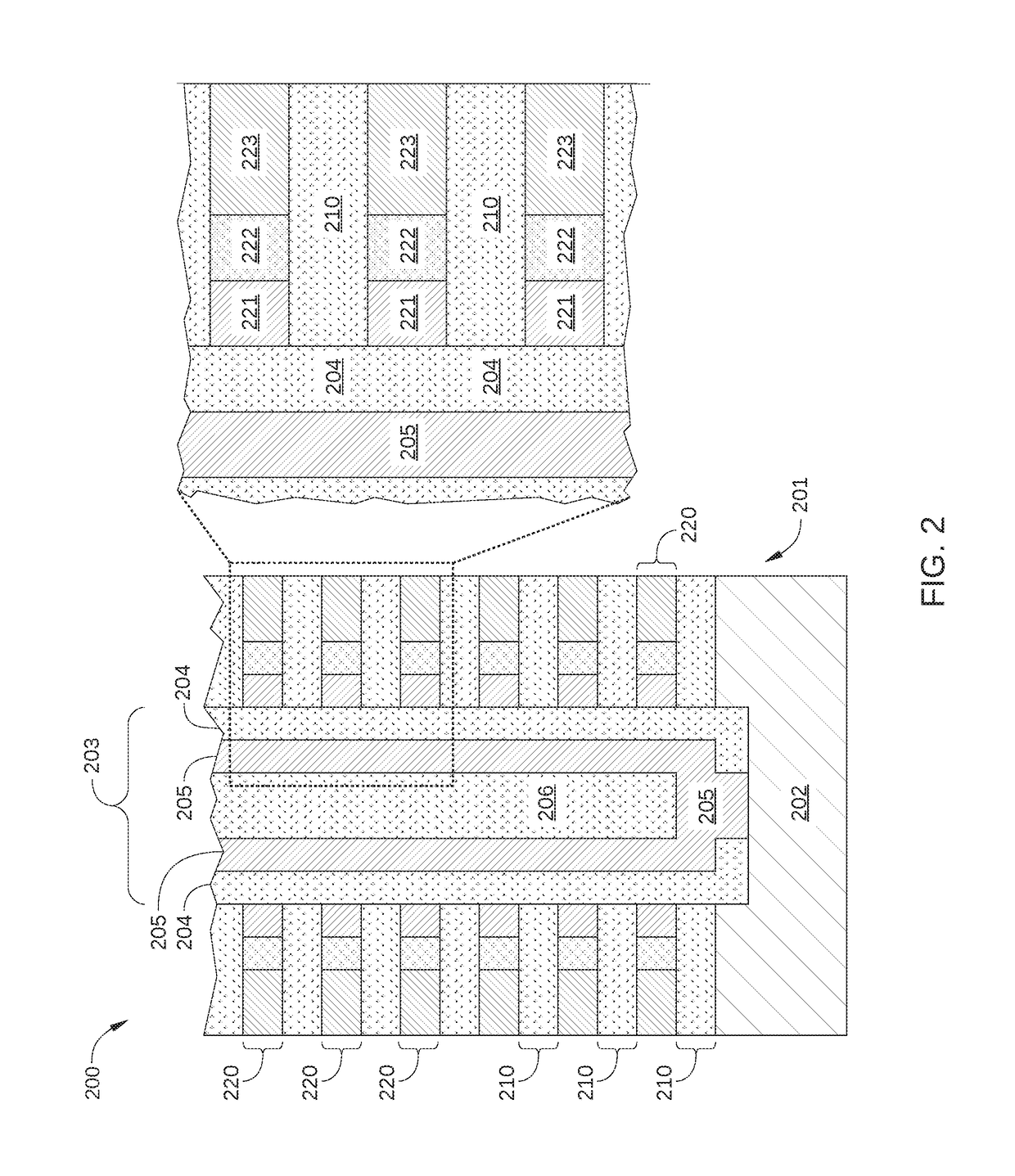

Reconfigurable tactile sensor input device

InactiveUS20070257821A1Low production costSmall sizeInput/output for user-computer interactionElectronic switchingCapacitanceDisplay device

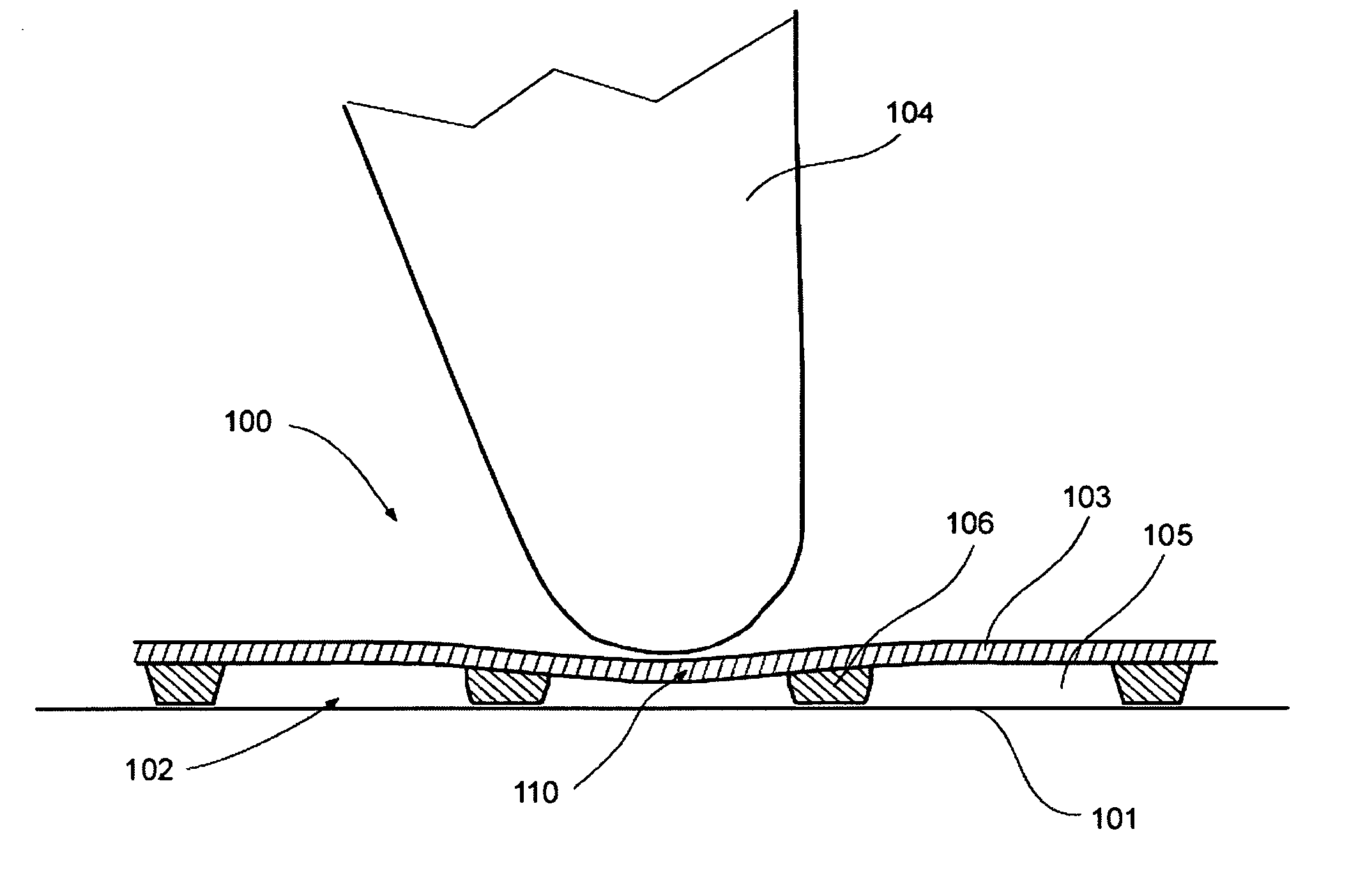

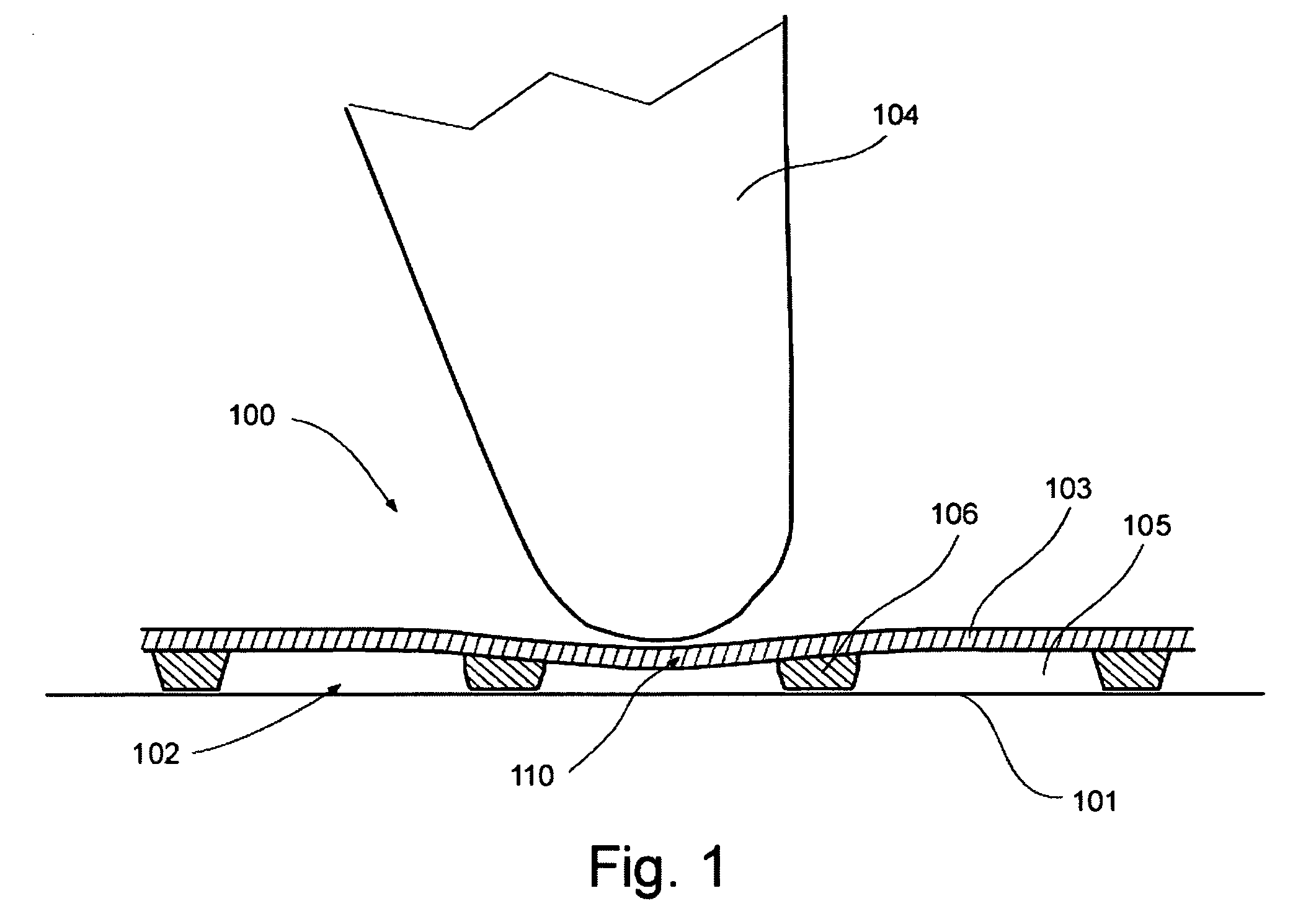

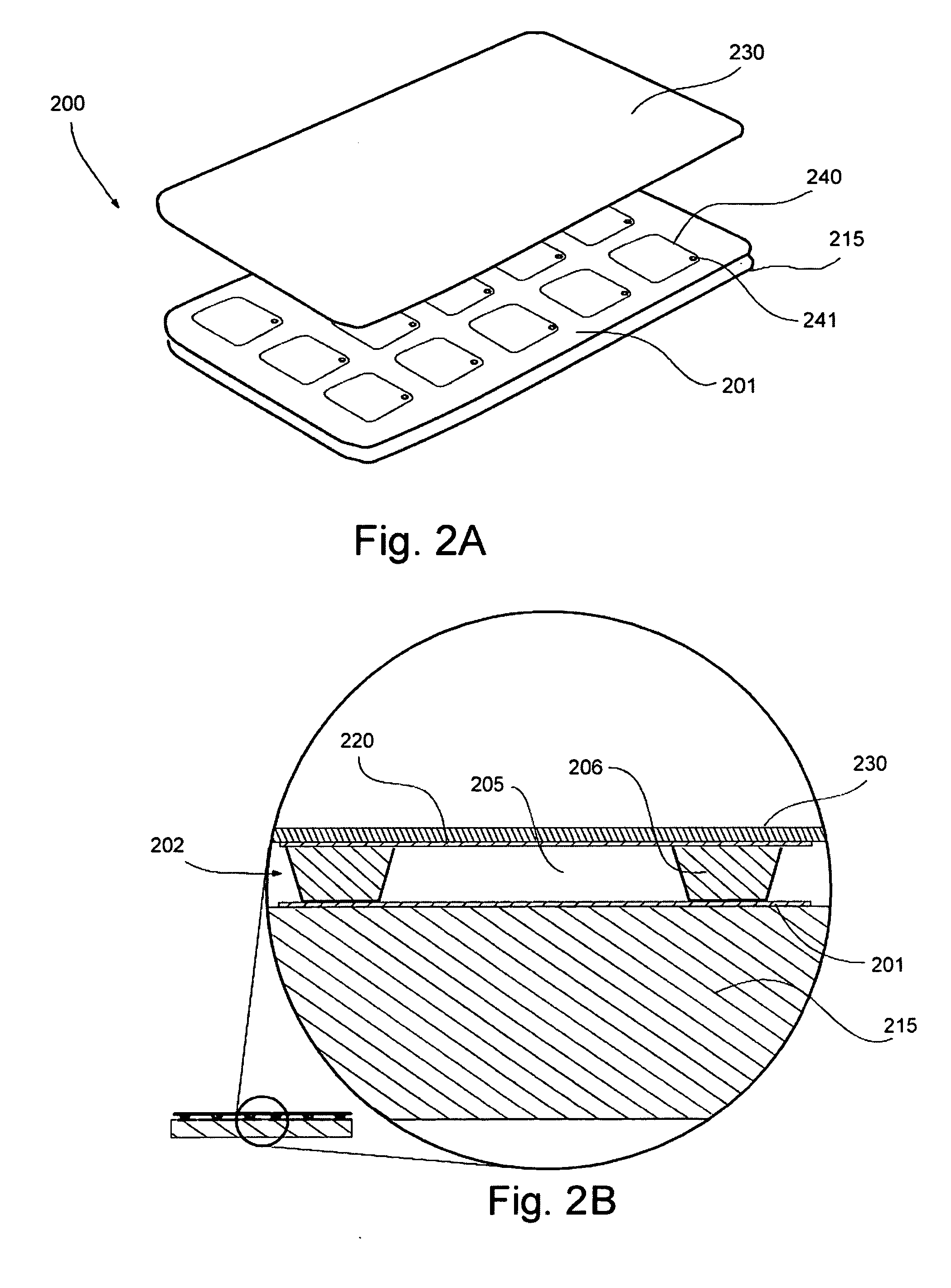

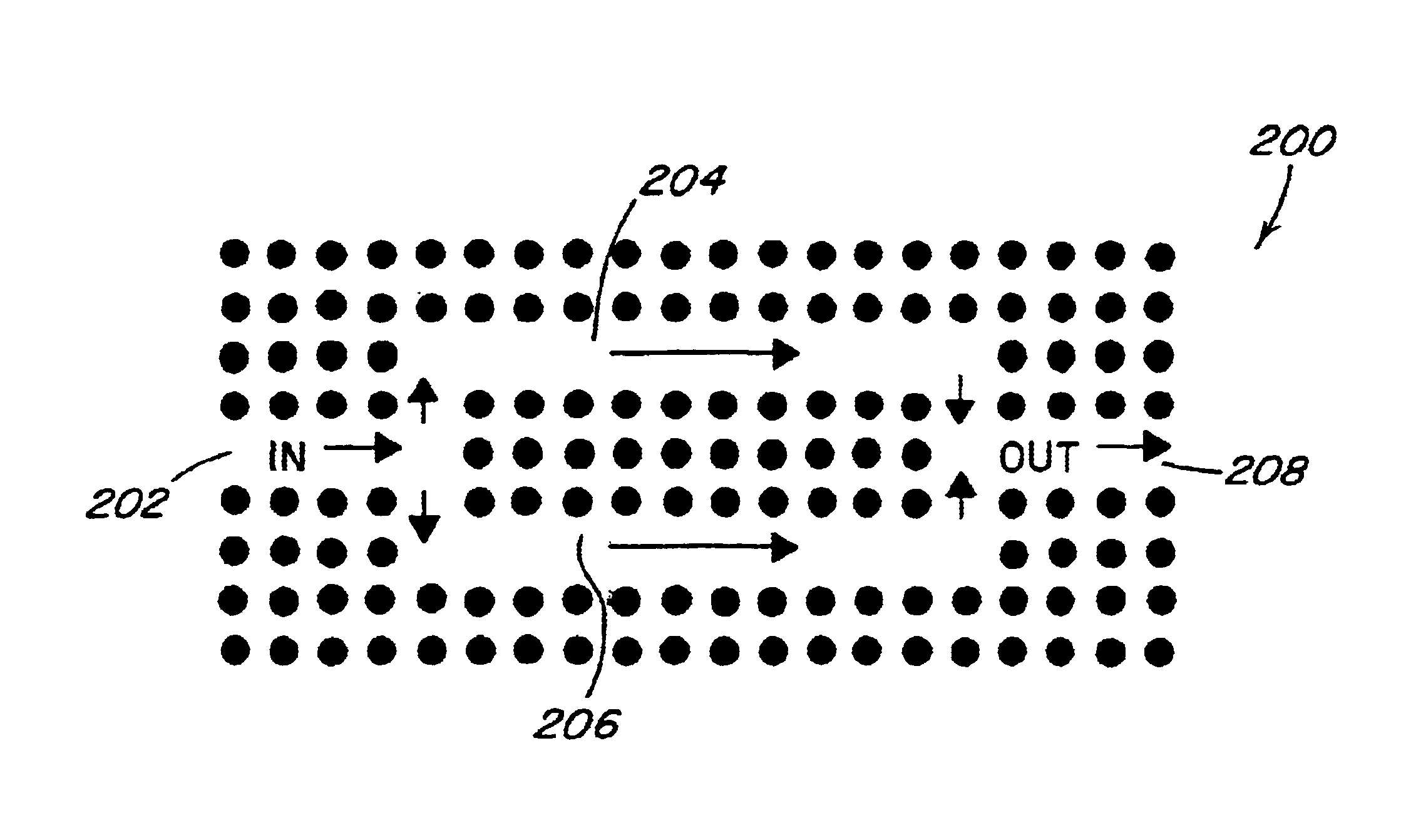

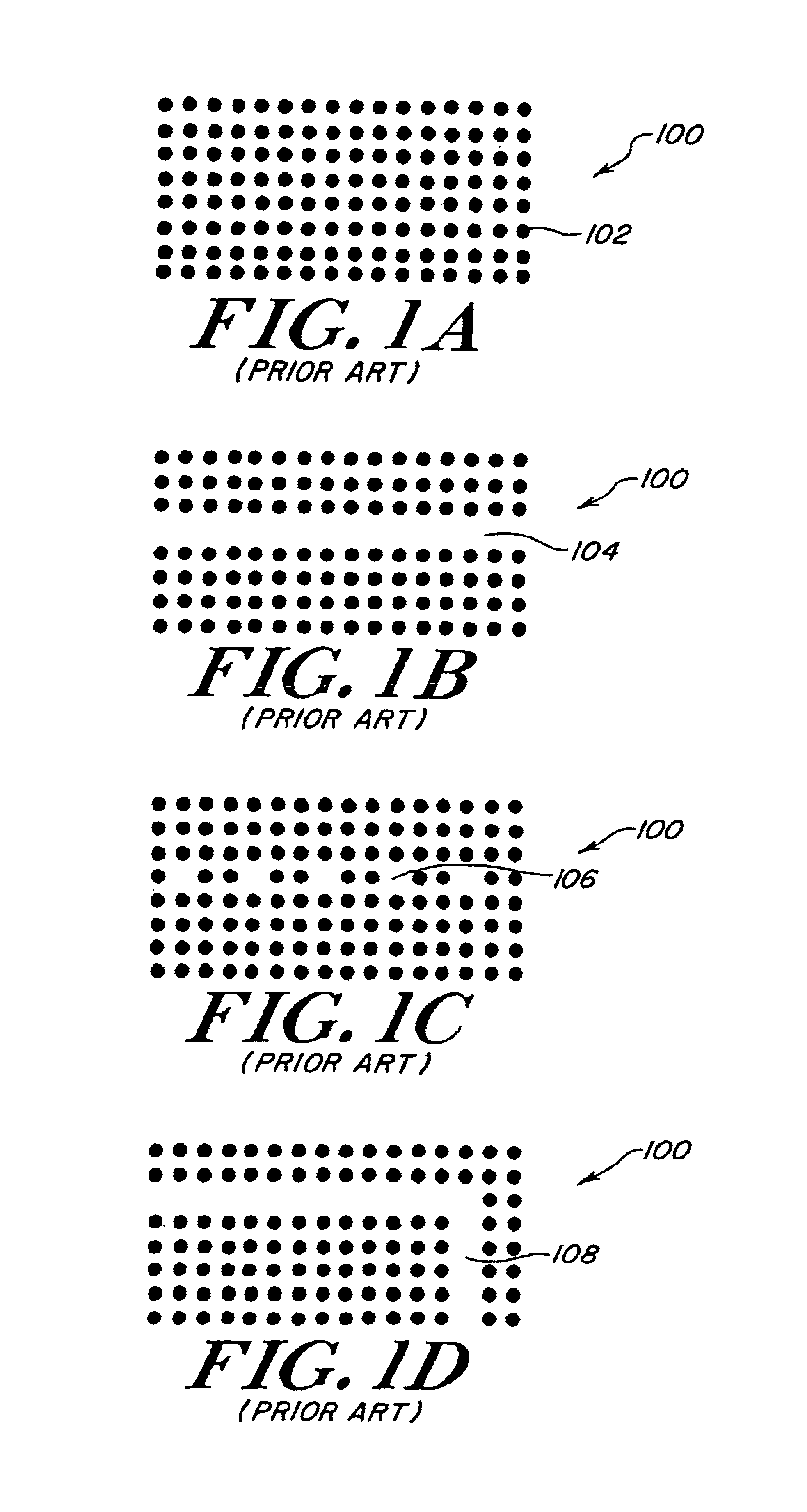

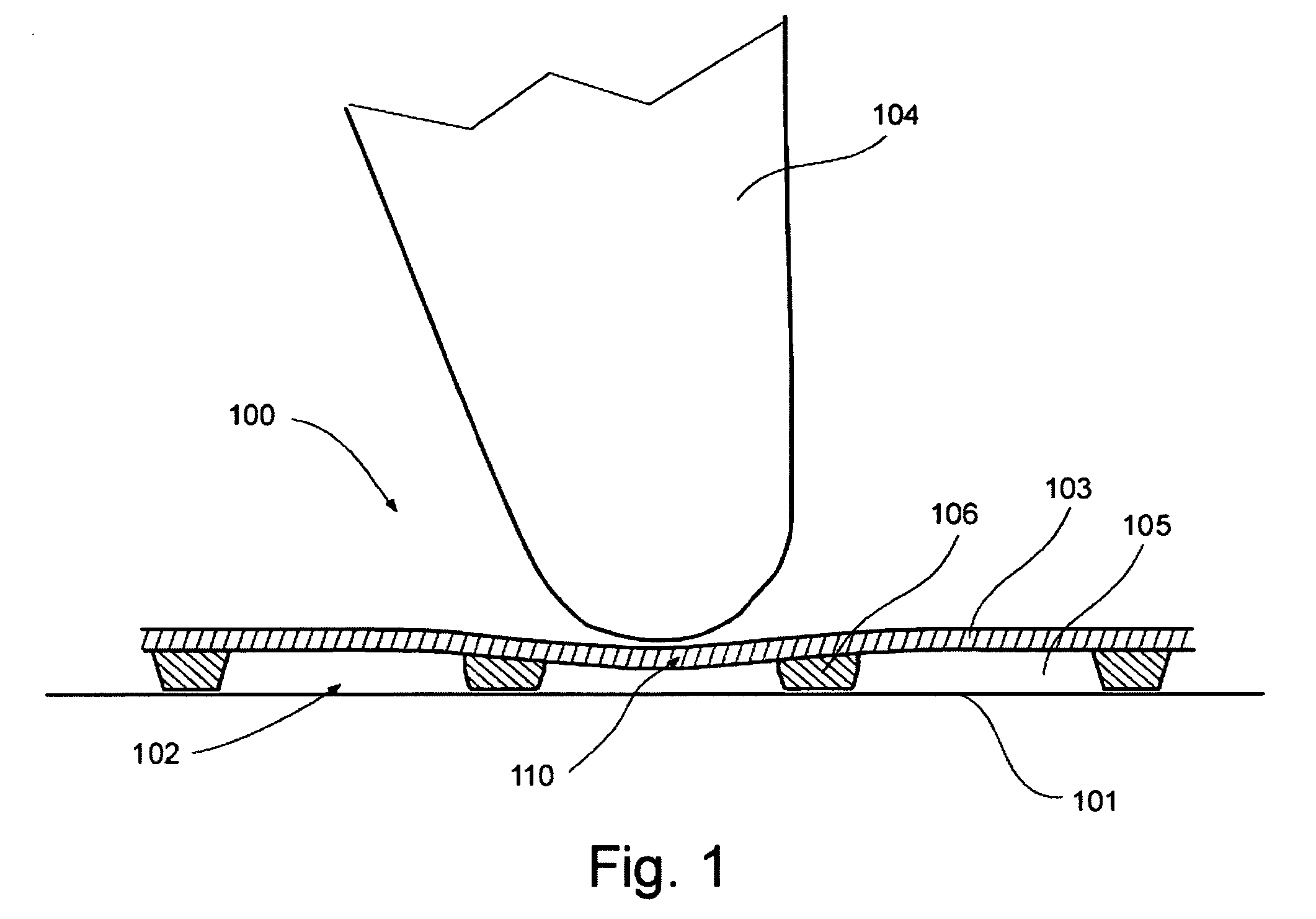

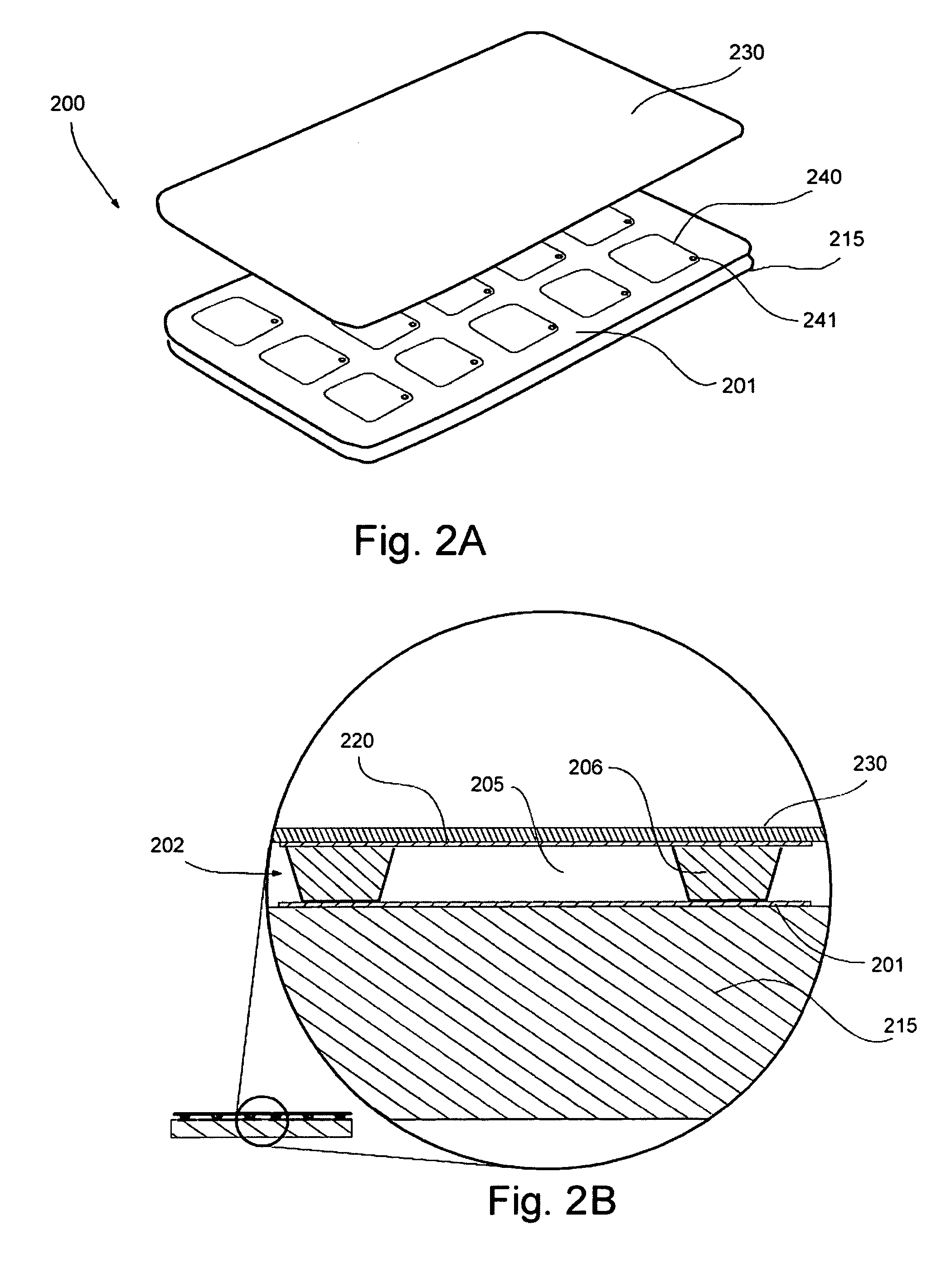

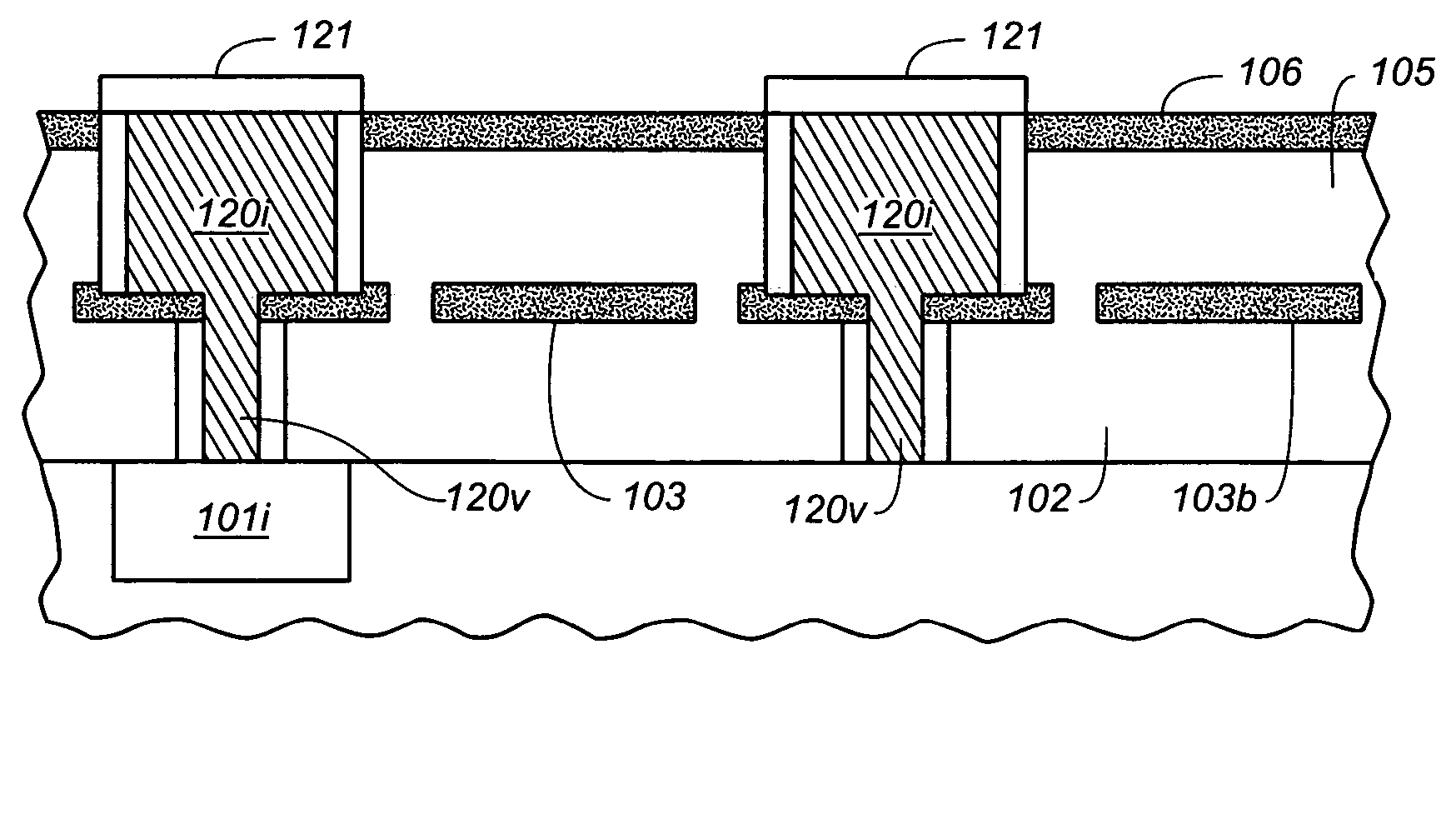

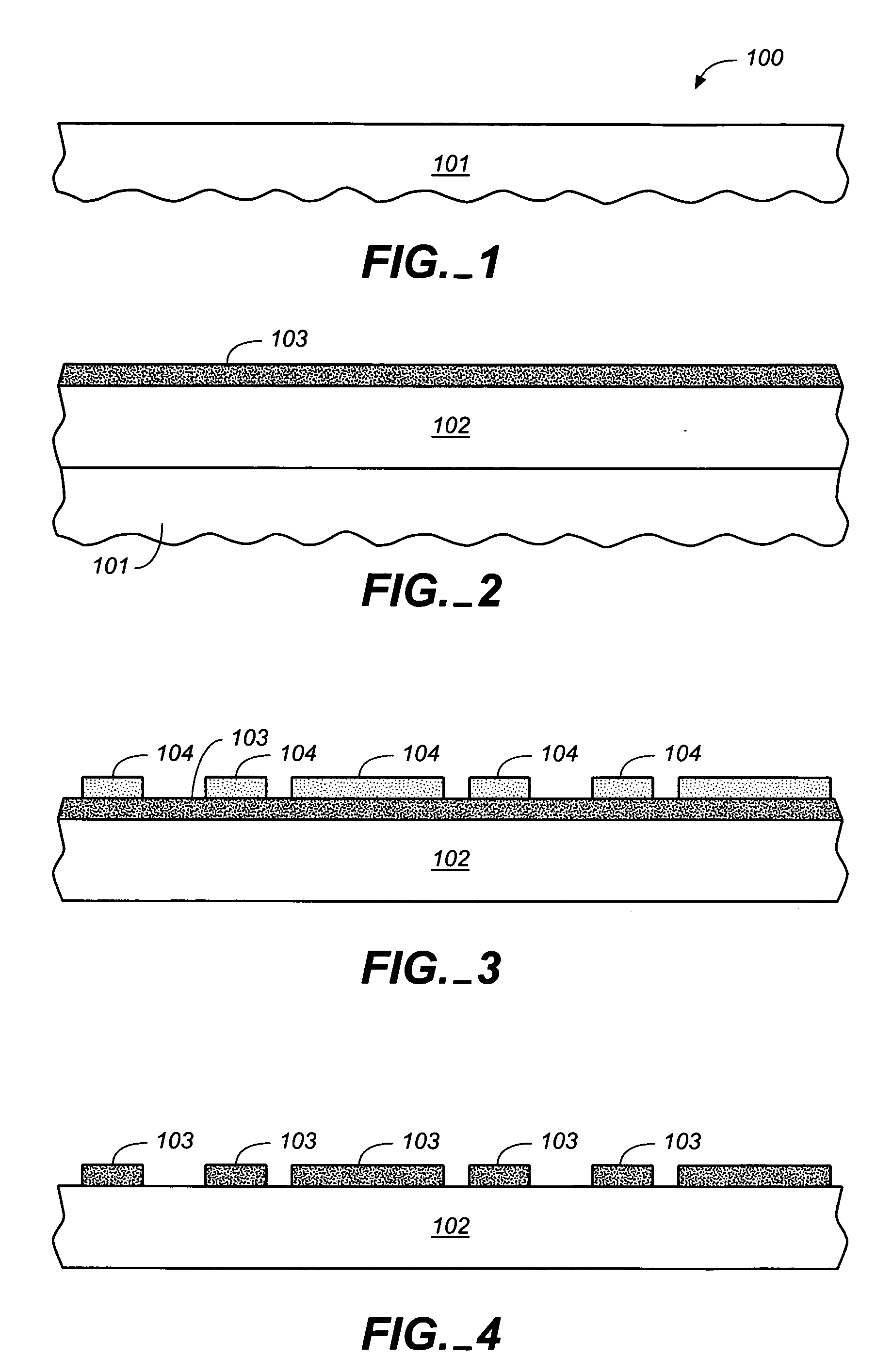

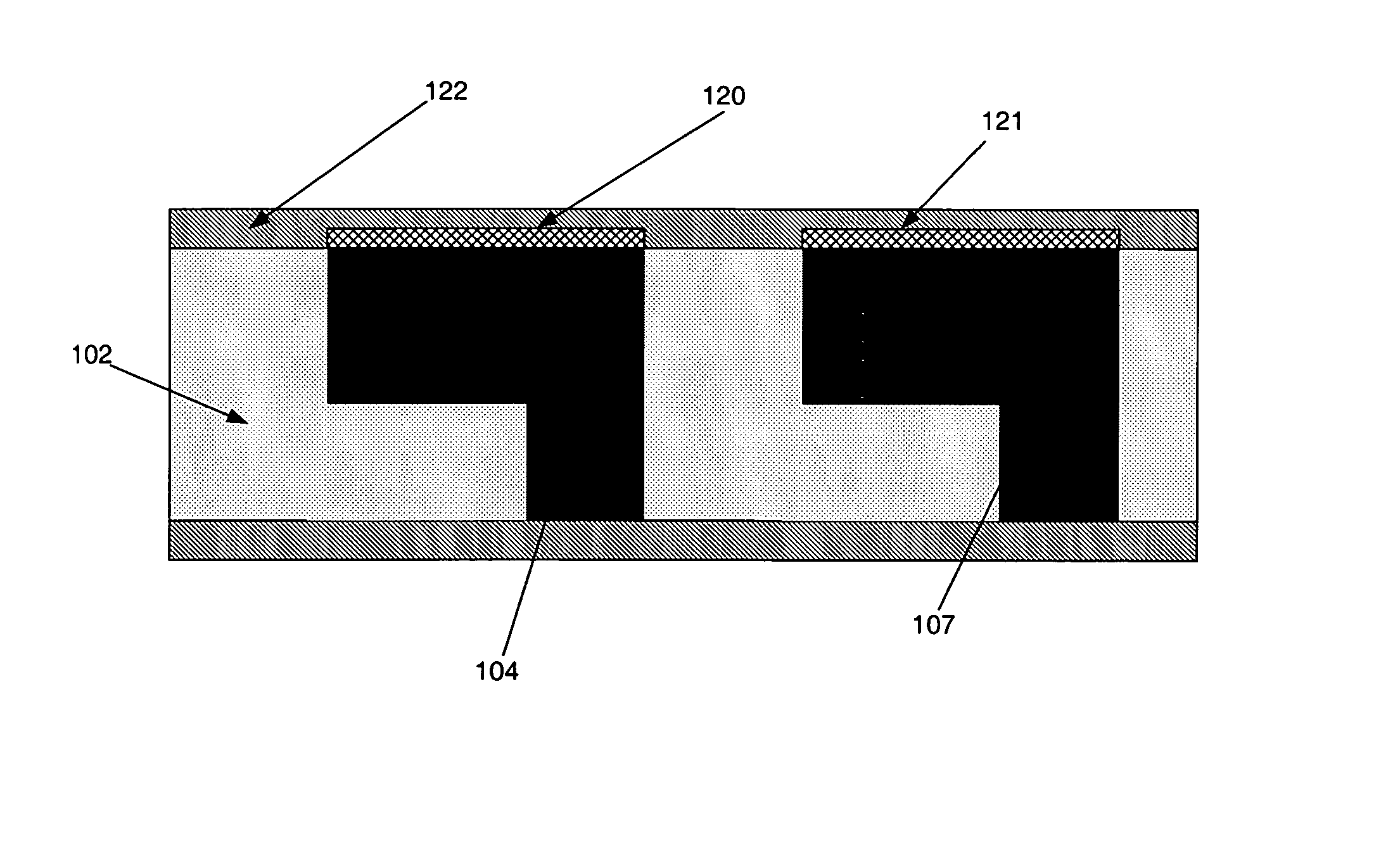

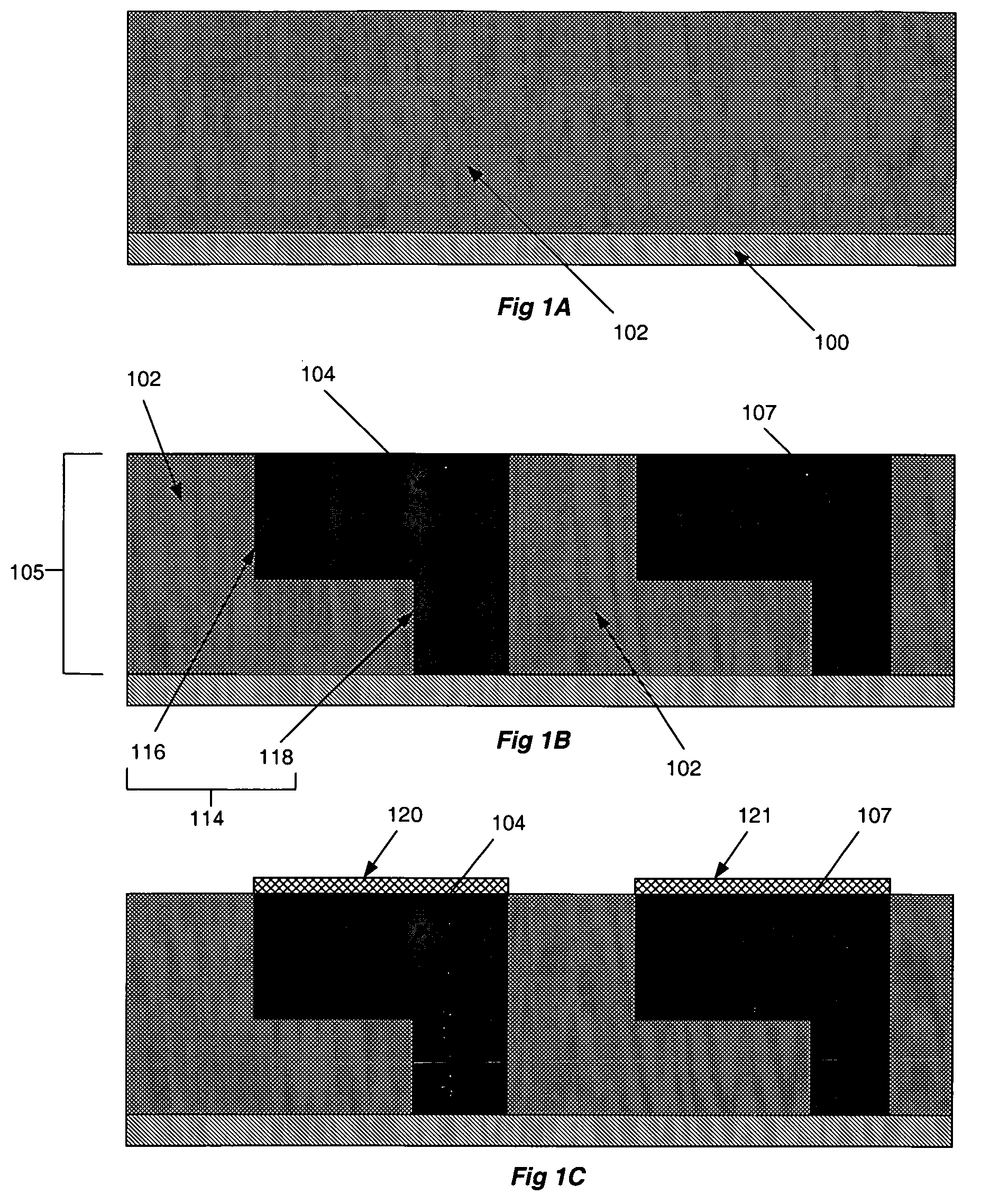

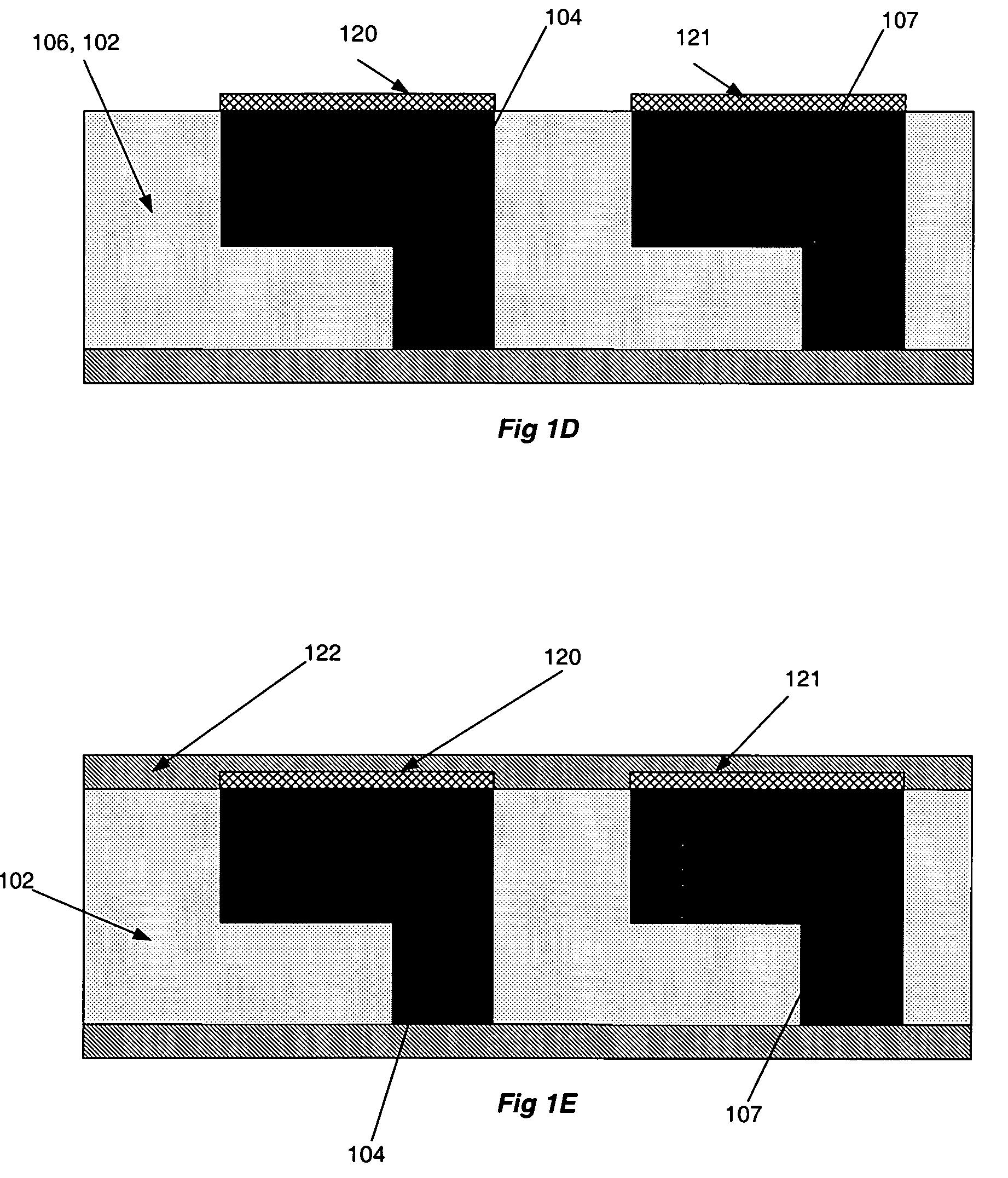

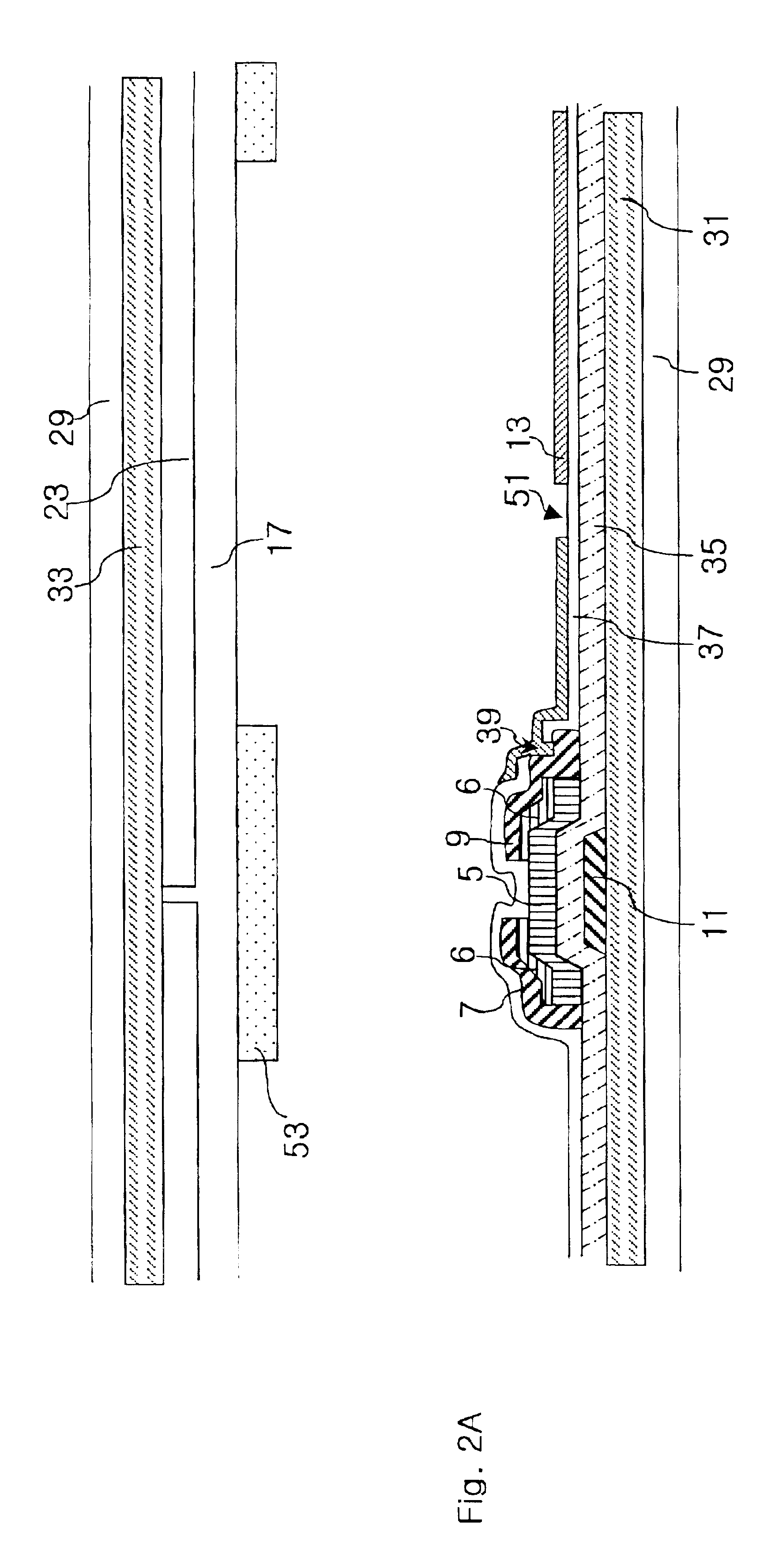

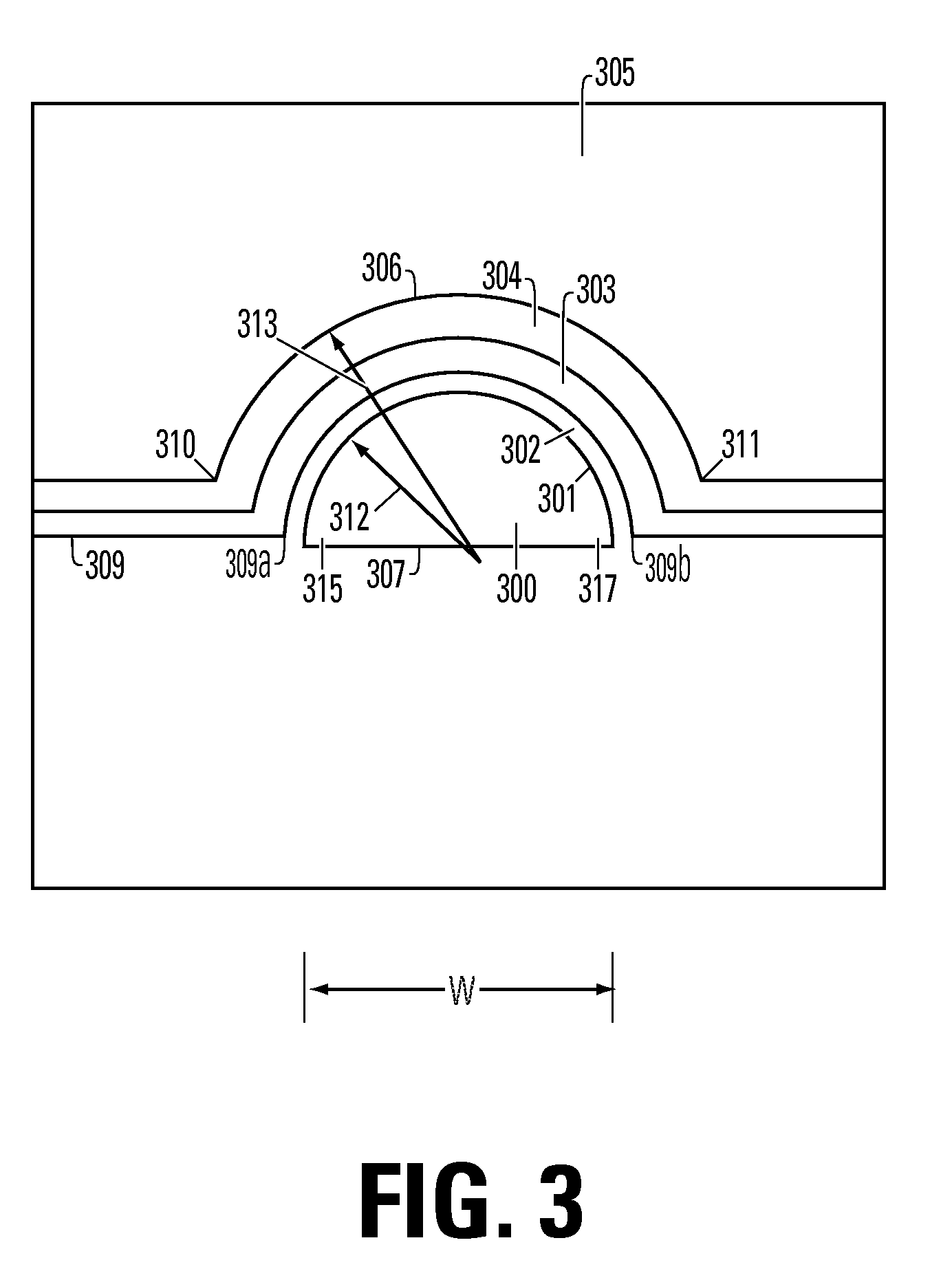

A reconfigurable tactile input device includes a first rigid electrode layer, a compressible dielectric structure, and a second flexible electrode layer forming together a tactile sensor with appropriate electrode connection means to a control means. The control means may include a mixed-signal IC mounted next to the input device in a compact package and capable of measuring capacitance in real time. The dielectric structure may include a matrix of compressible geometric elements with voids therebetween optionally vented to atmosphere, making the entire assembly thin and facilitating its use for mobile phones and other small, portable electronic devices. Some embodiments provide the user wit tactile feedback upon compression of the electrodes. An optional flexible display may be mounted over the input device to indicate the present configuration to the user.

Owner:WISETOUCH CO LTD

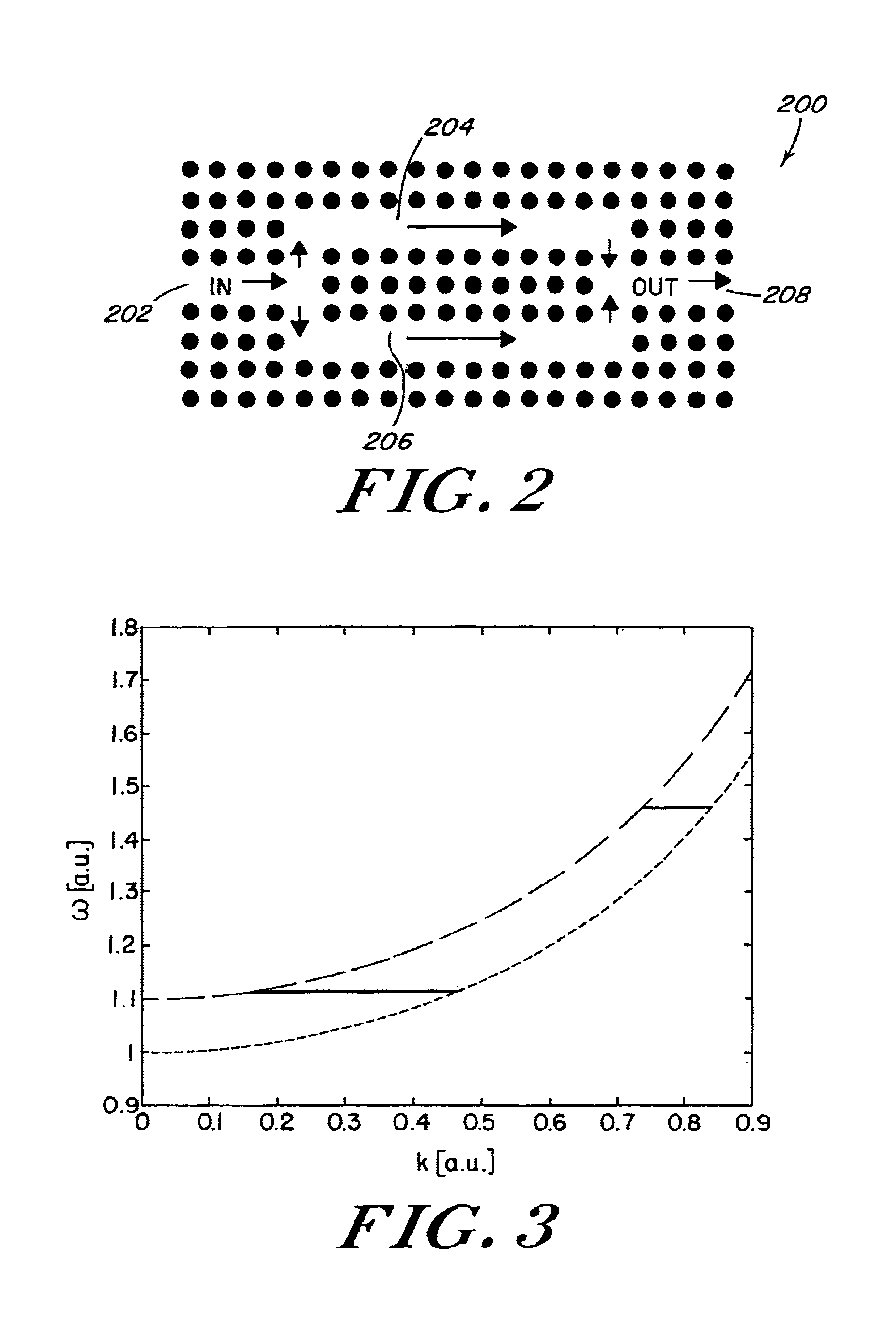

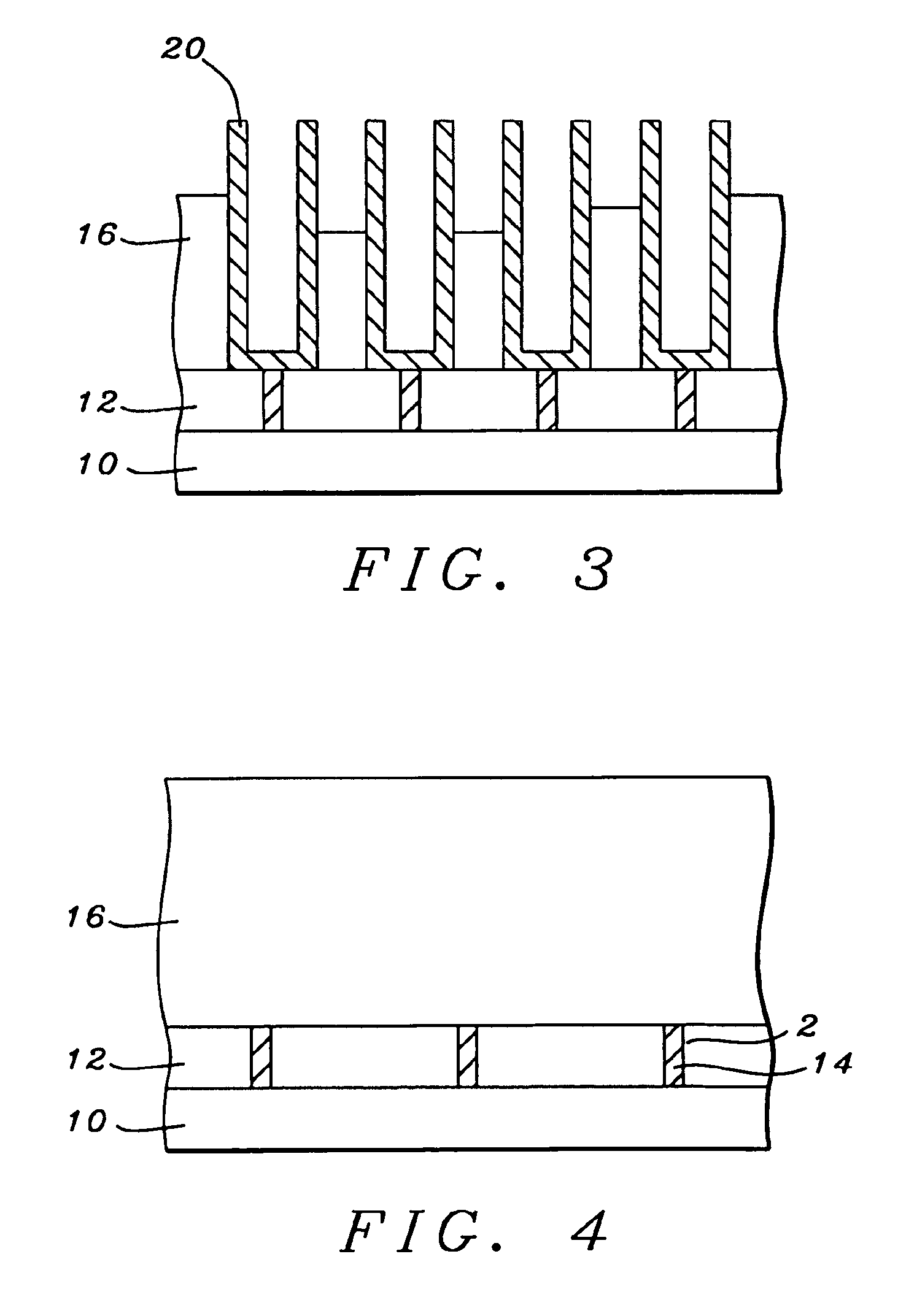

Mach-Zehnder interferometer using photonic band gap crystals

InactiveUS6917431B2Small sizeLarge operating bandwidthLaser detailsLaser optical resonator constructionPhotonic crystalMach–Zehnder interferometer

A photonic crystal optical switch having a periodic dielectric structure including at least one input waveguide. First and second waveguide arms branch from the input waveguide in which the relative optical path lengths of electromagnetic radiation within the arms are controlled by stimuli. At least one output waveguide that combines the electromagnetic radiation propagating within the first and second waveguide arms.

Owner:MASSACHUSETTS INST OF TECH

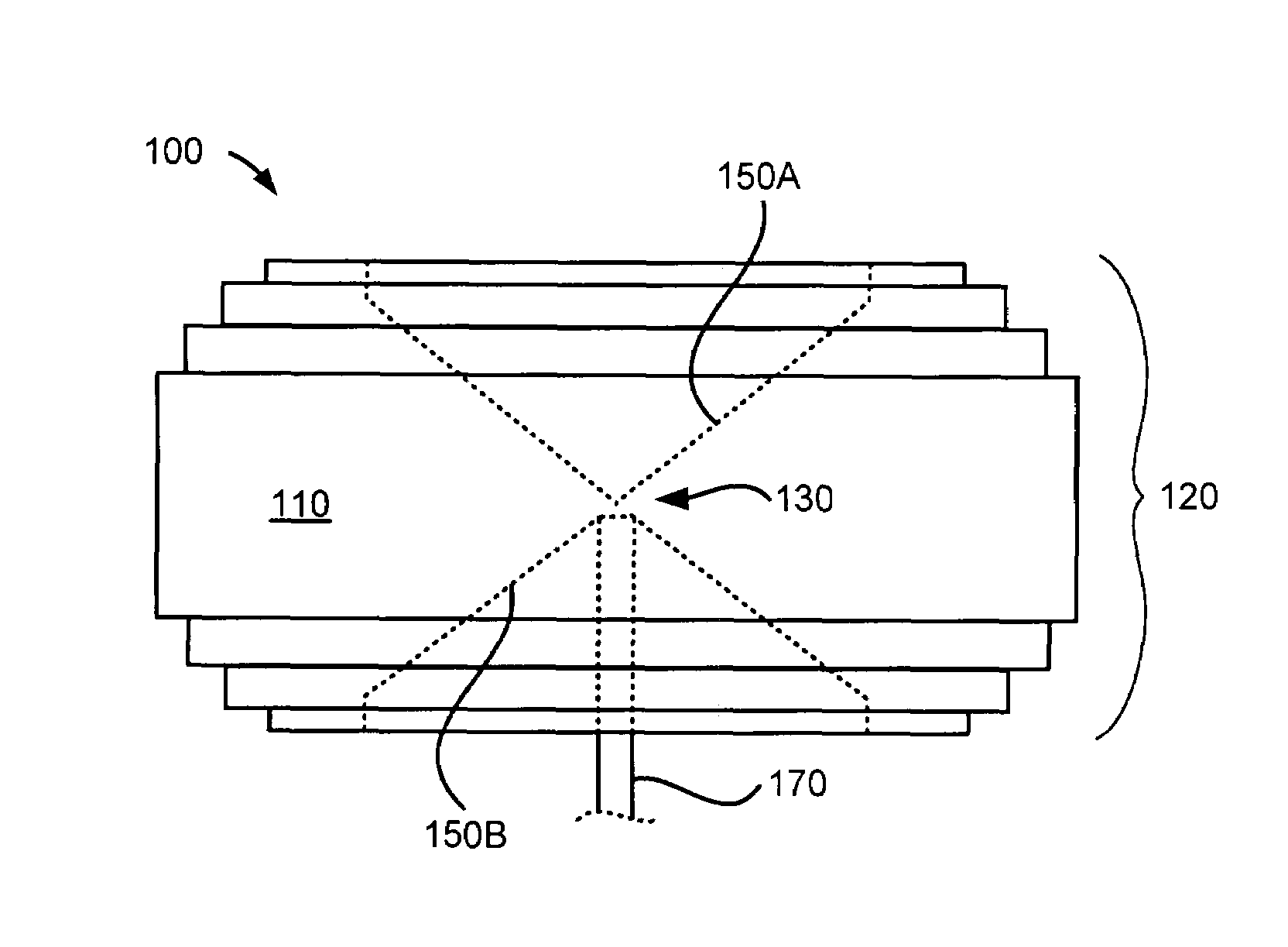

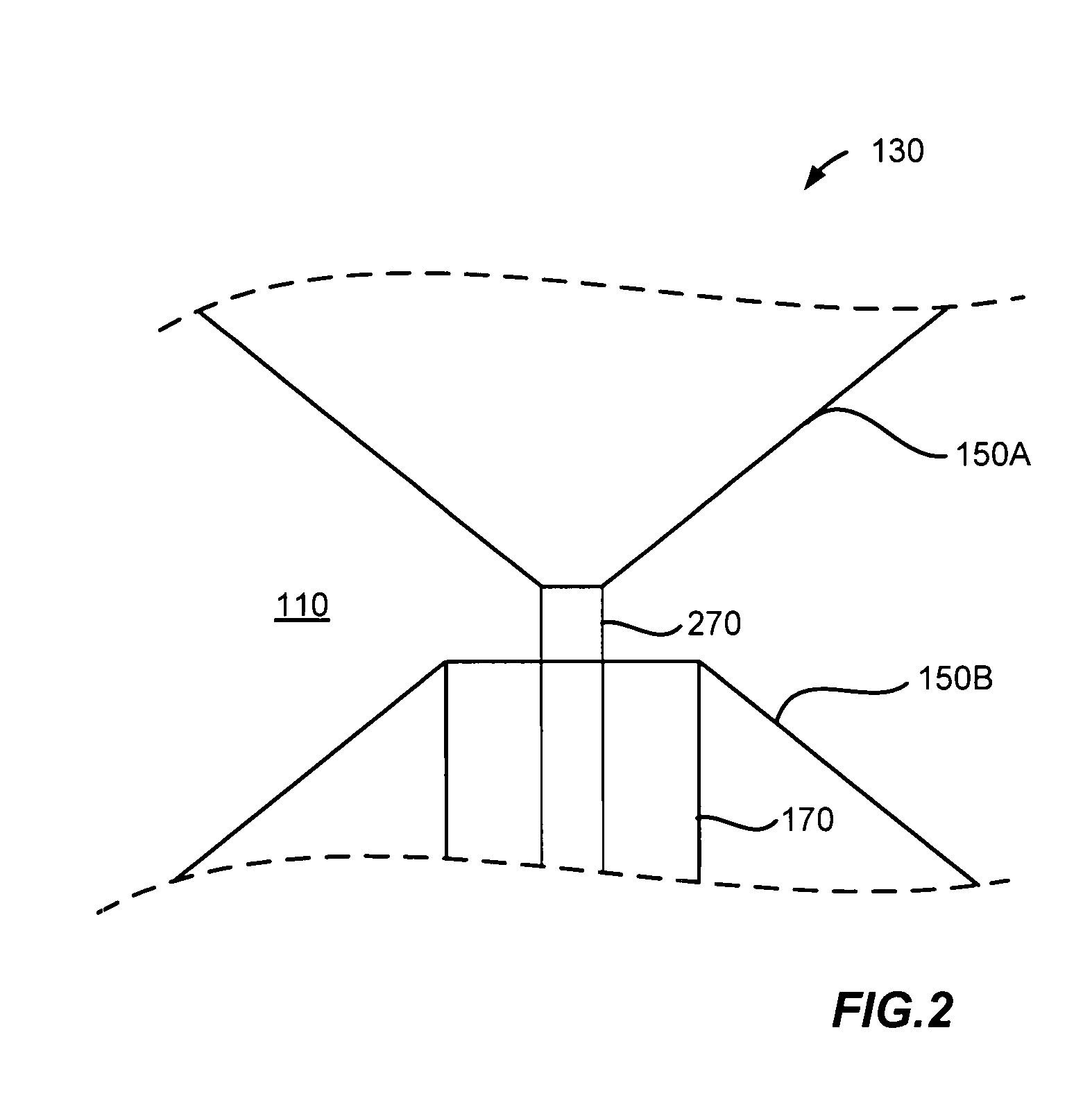

Bicone pattern shaping device

ActiveUS7525501B2Low costHigh gainAntenna feed intermediatesElectromagnetic radiationOmni directional

A broadband omni-directional bicone antenna. The antenna can comprise conductive surfaces of conical voids provided within a solid dielectric structure. The outside surface of the solid structure can support a radio frequency (RF) lens geometry operable for beam forming. The beam forming can modify the elevation pattern of the electromagnetic radiation from the bicone antenna. The solid dielectric structure may be machined or molded from a single piece of material. The conical voids provided within the solid structure can be metallized to provide conductive bicone radiators. The outer surface beam shaping lenses can be zoned or continuous and can provide elevation patterns with increased gain, cosecant squared falloff, or various other patterns. The beam shaping lens may be formed from any low-loss dielectric. Alternatively, the lens may be formed from a less dense material such as dielectric foam that can support radial conductive beam forming vanes.

Owner:EMS TECHNOLOGIES

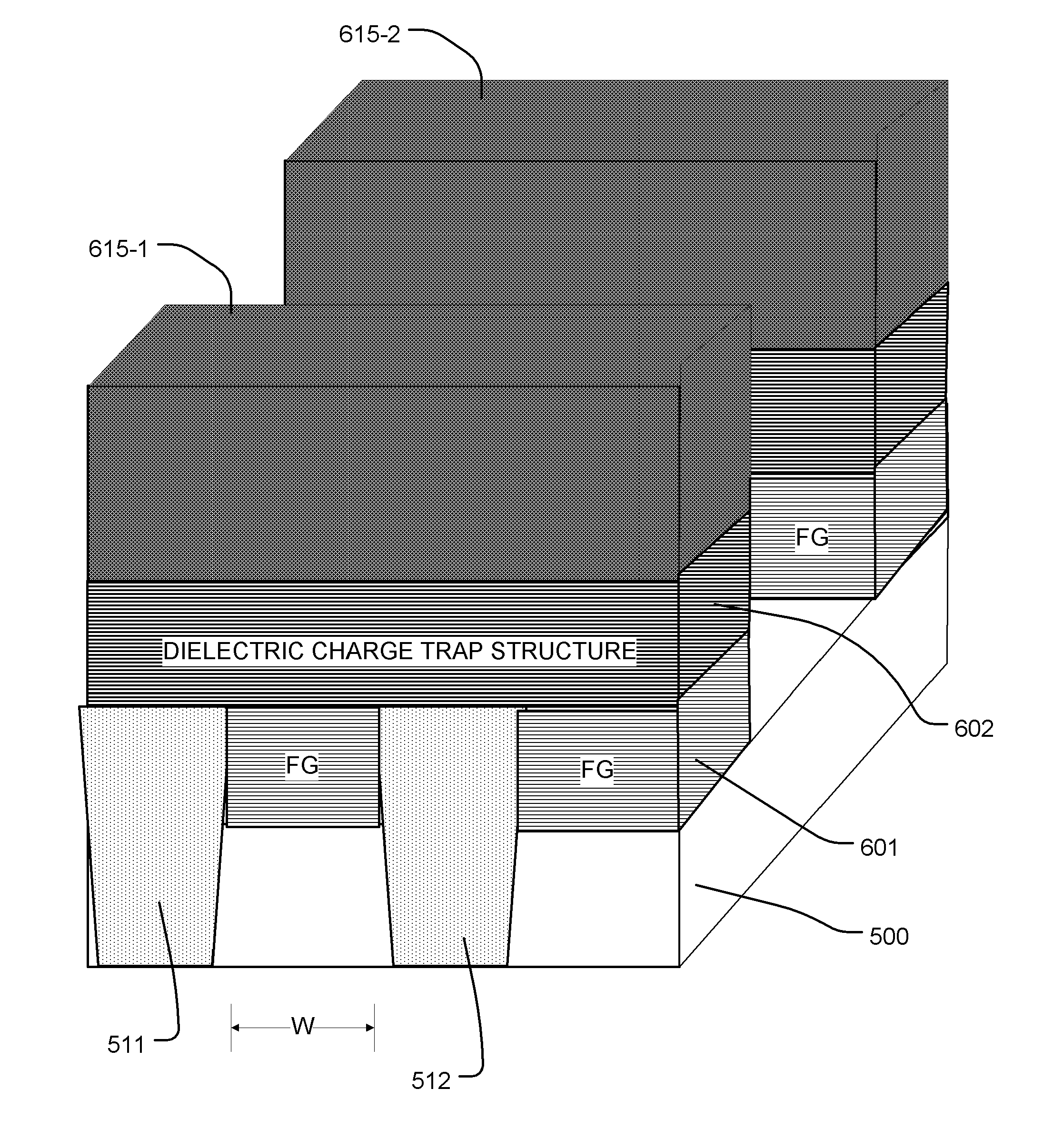

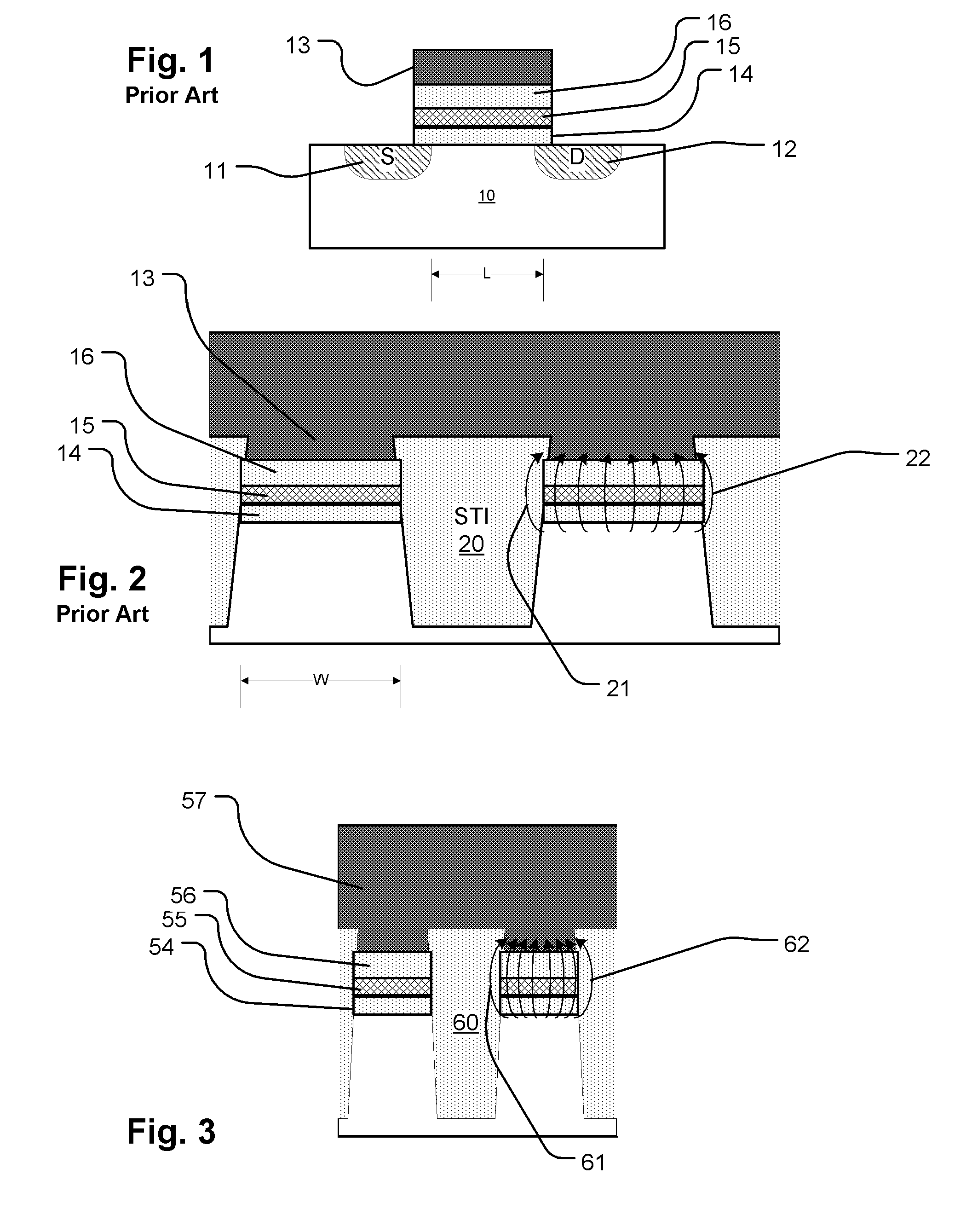

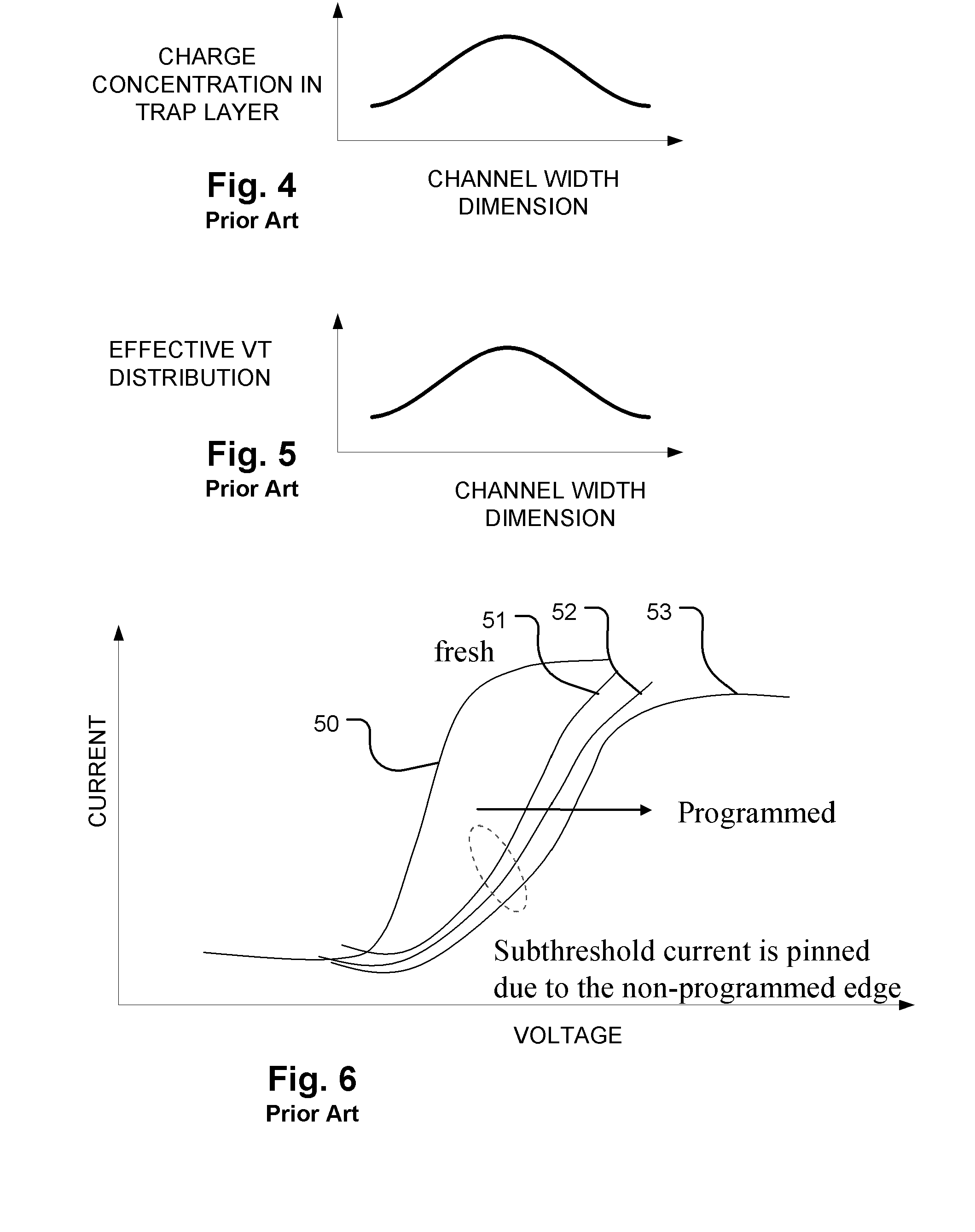

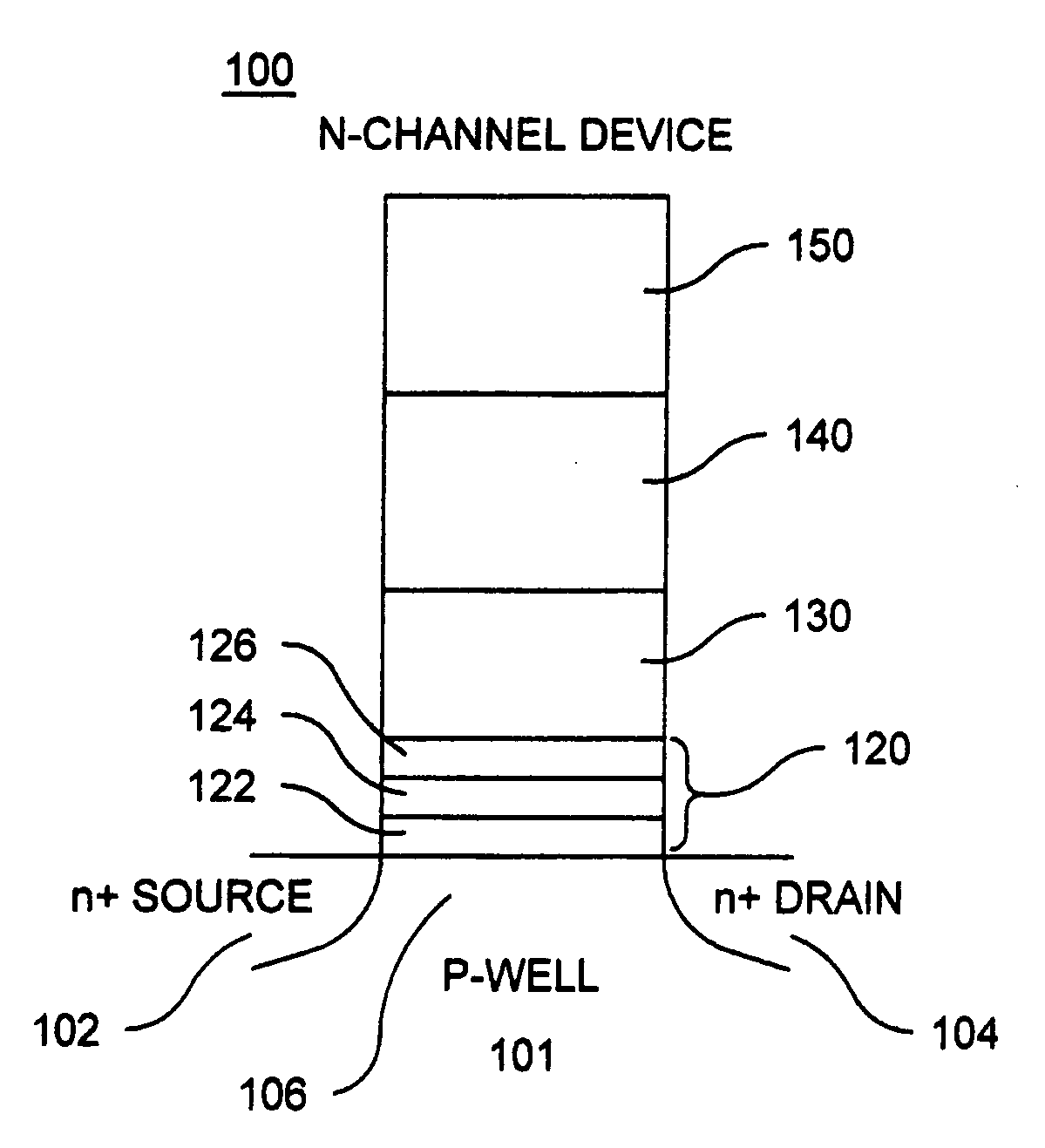

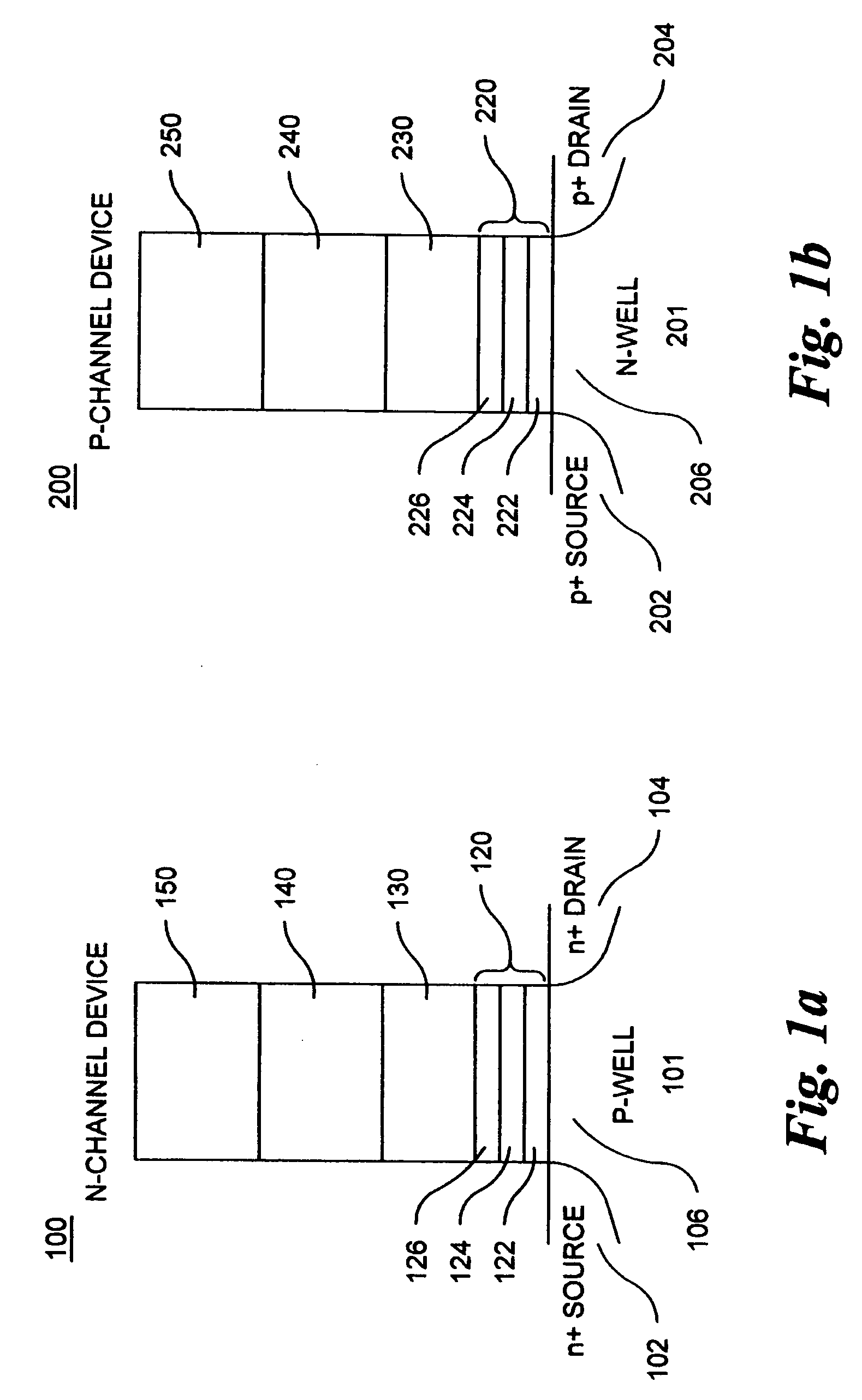

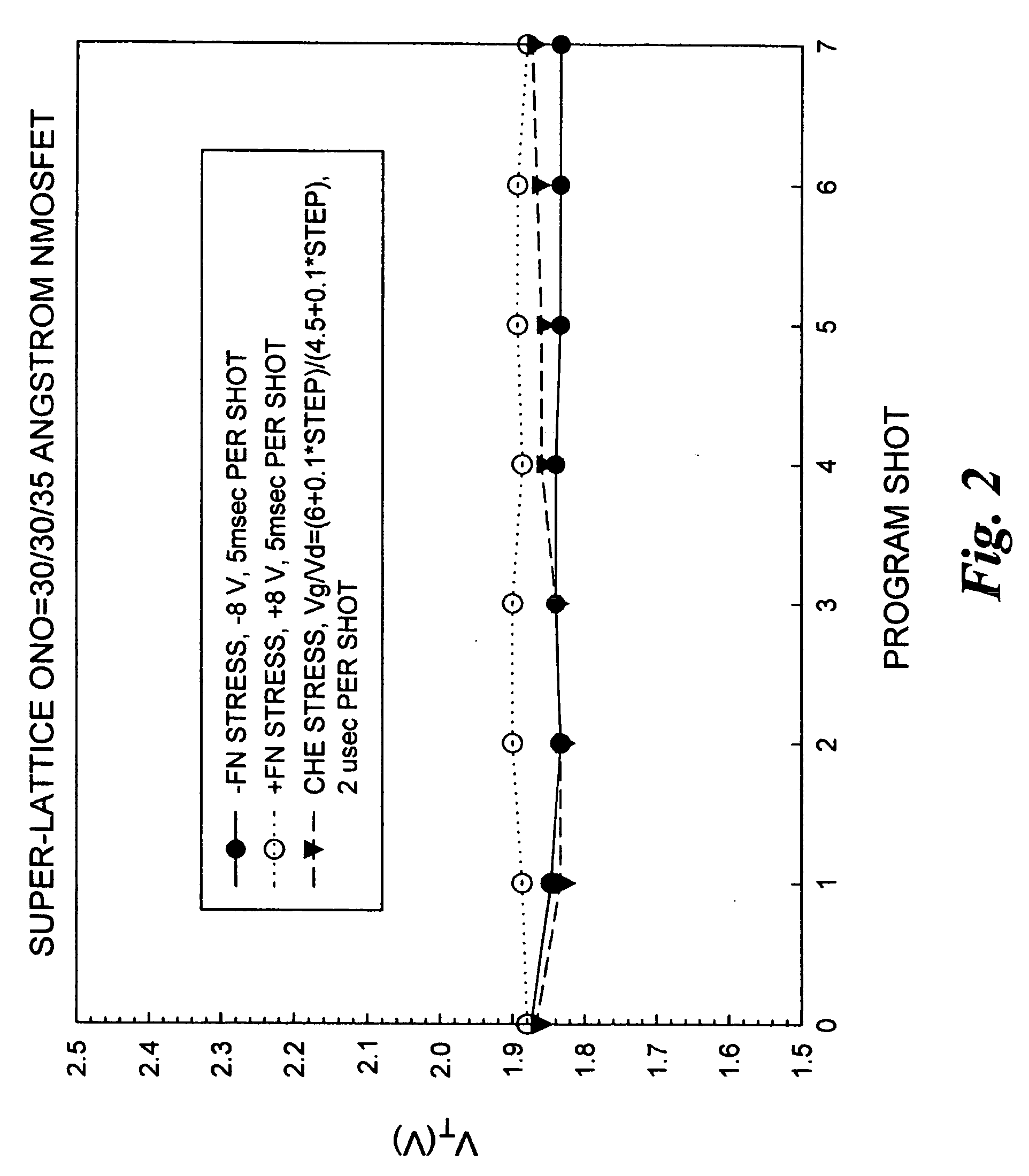

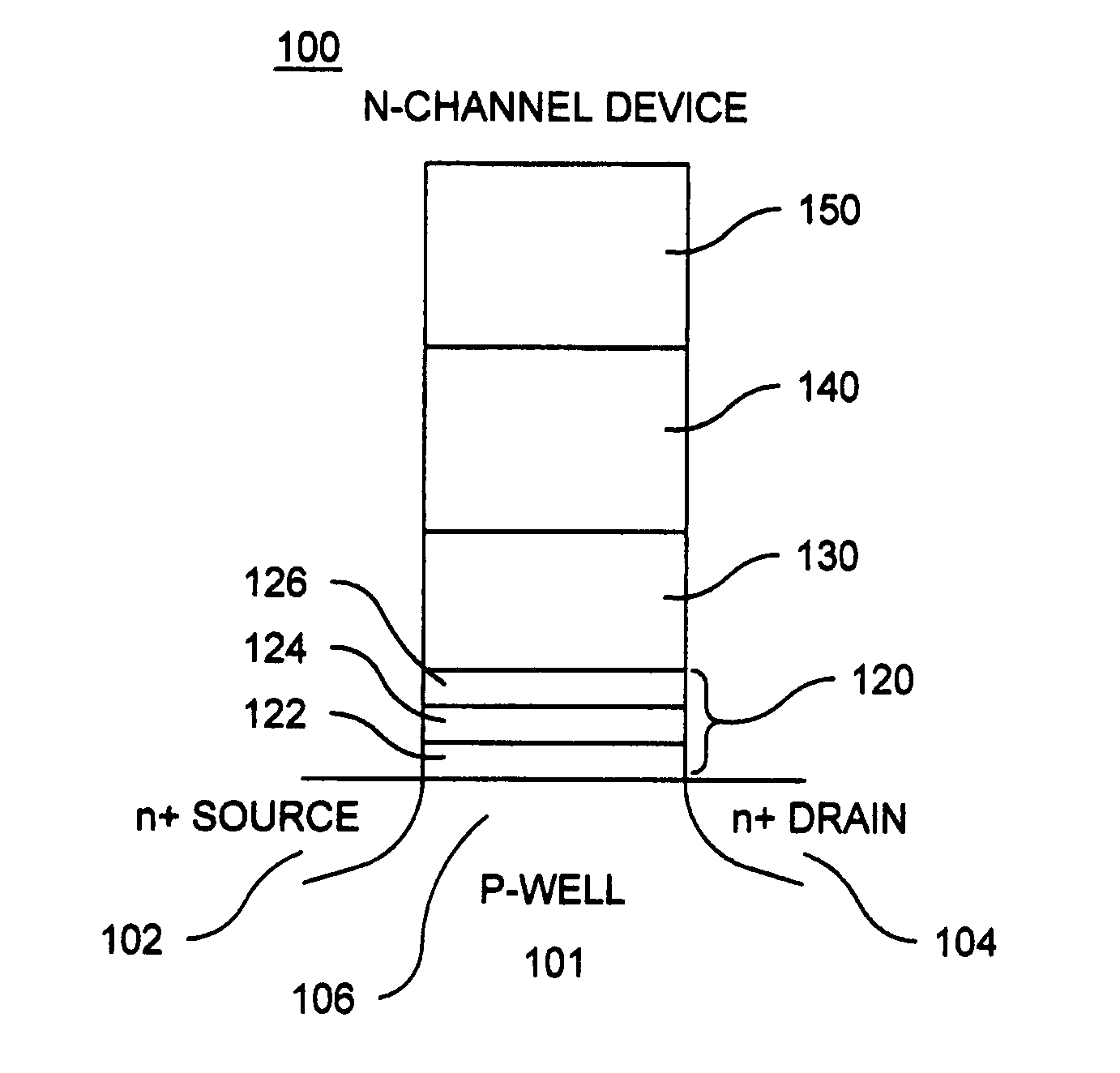

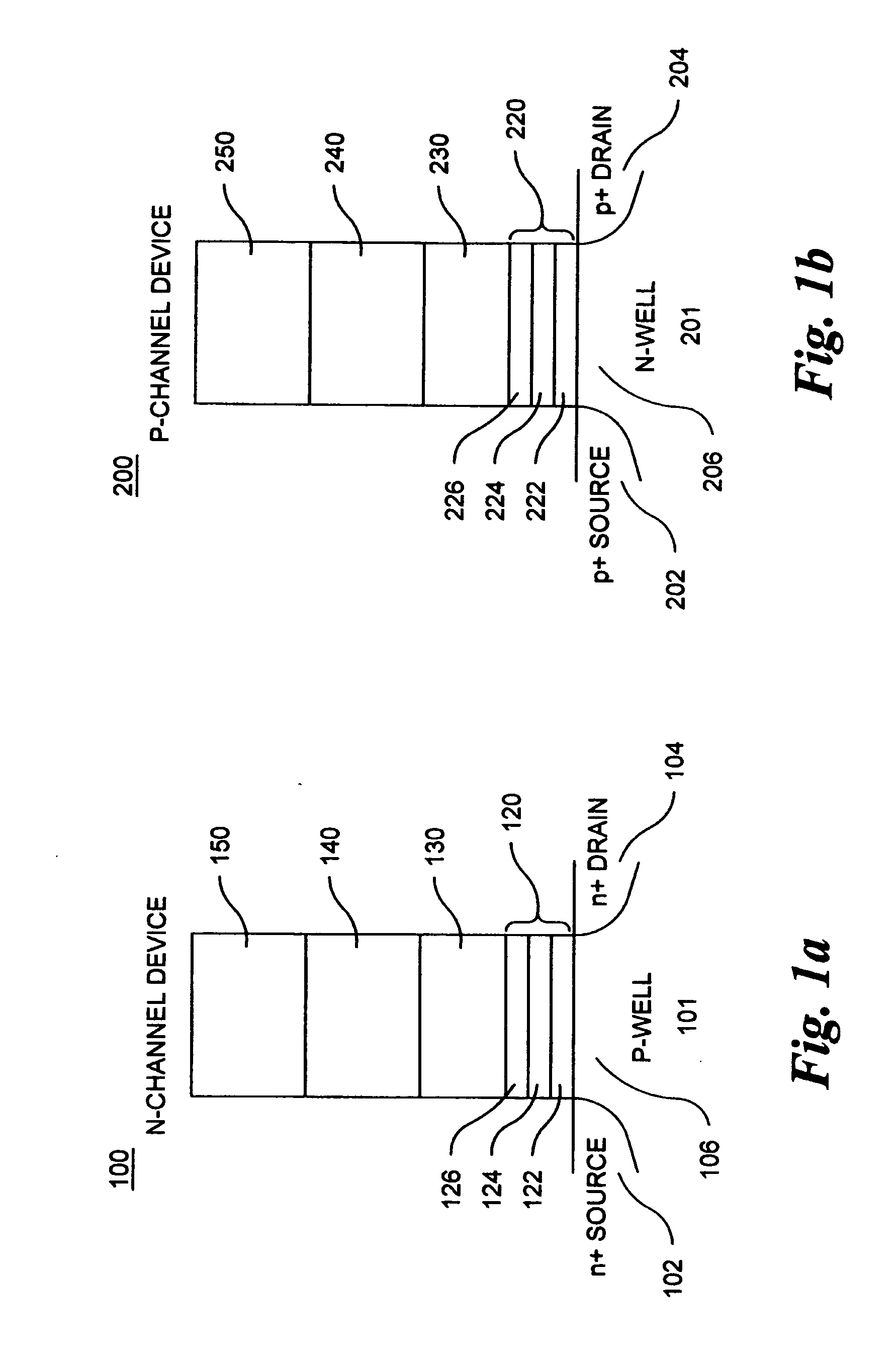

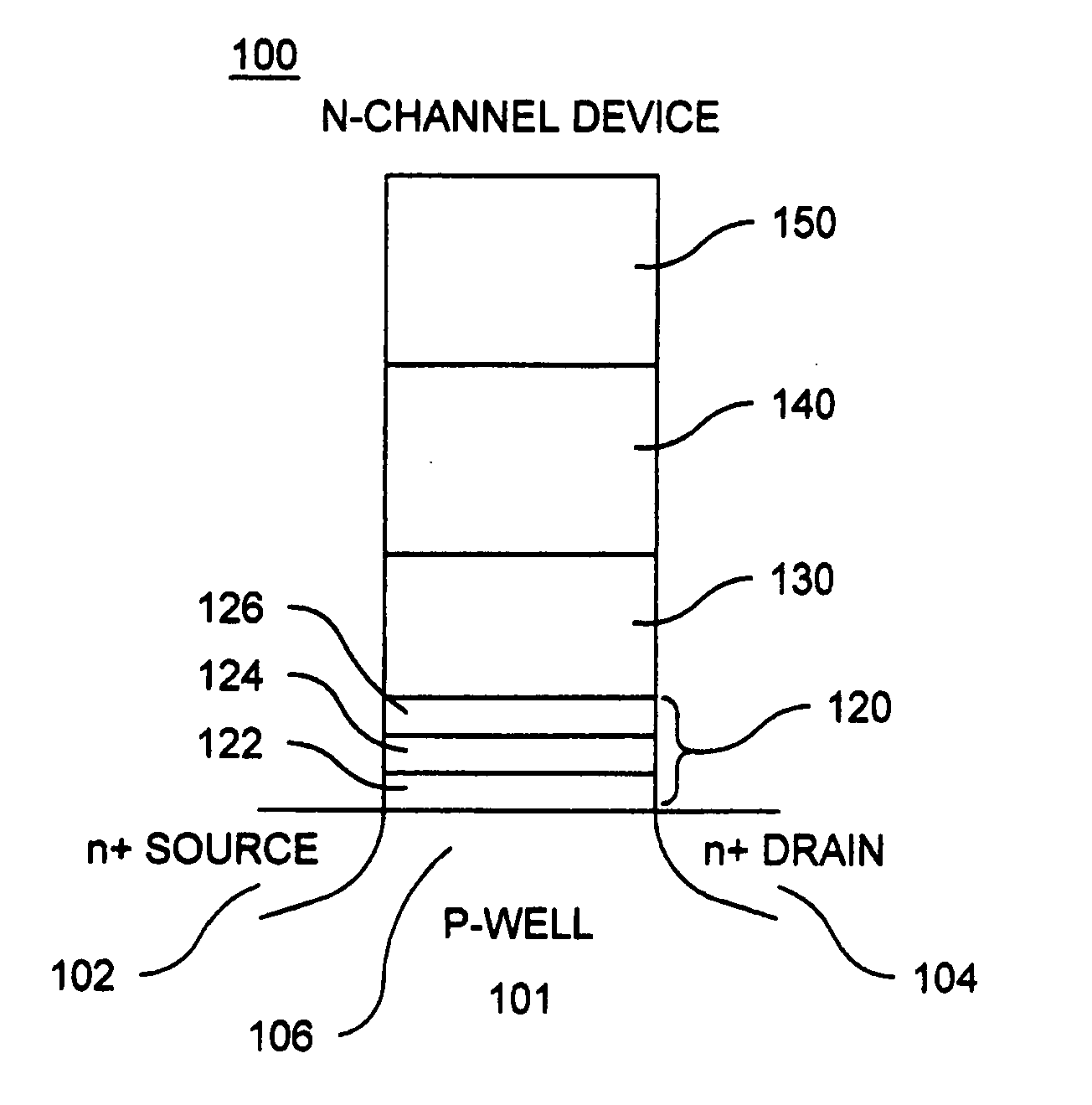

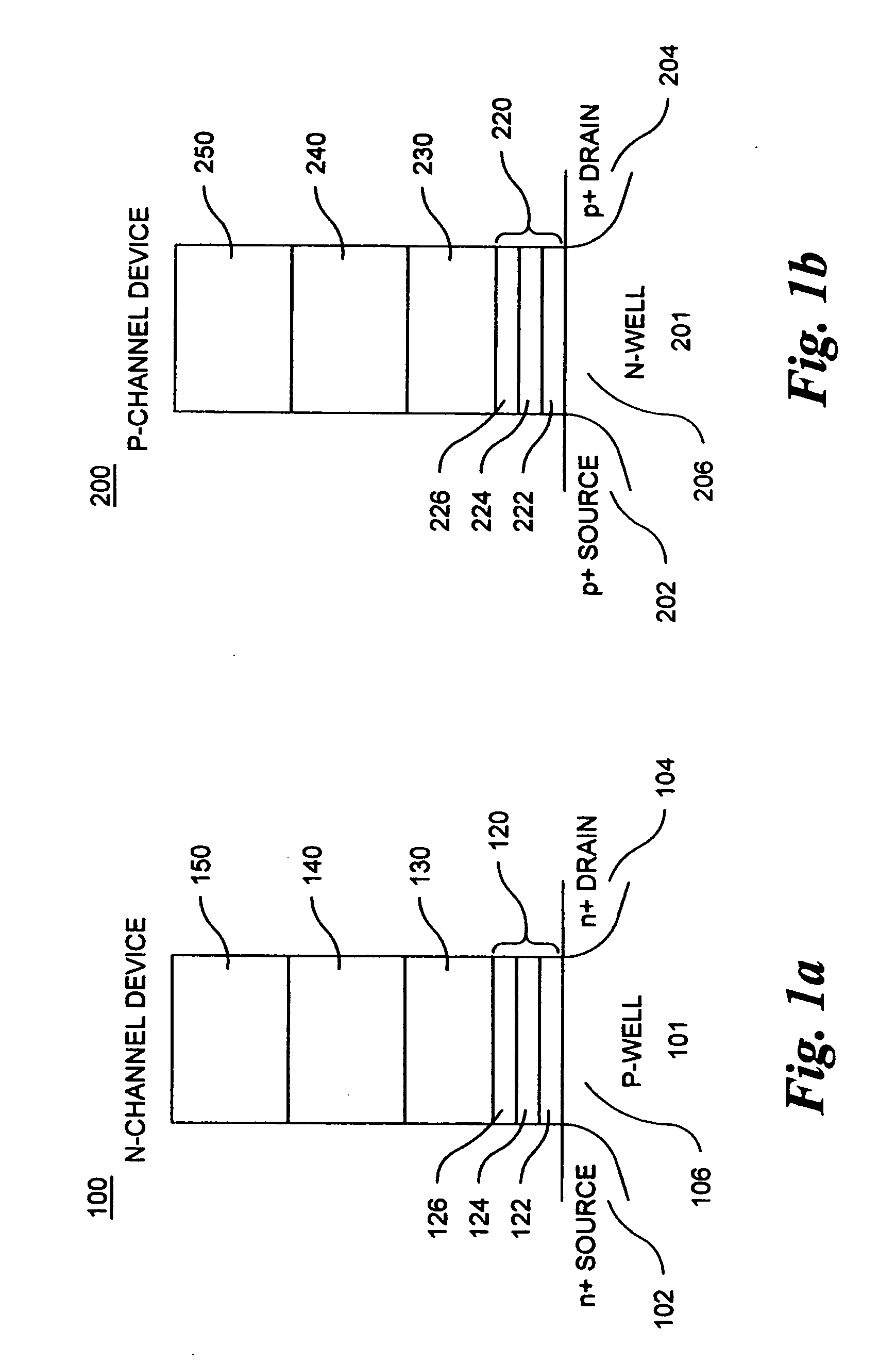

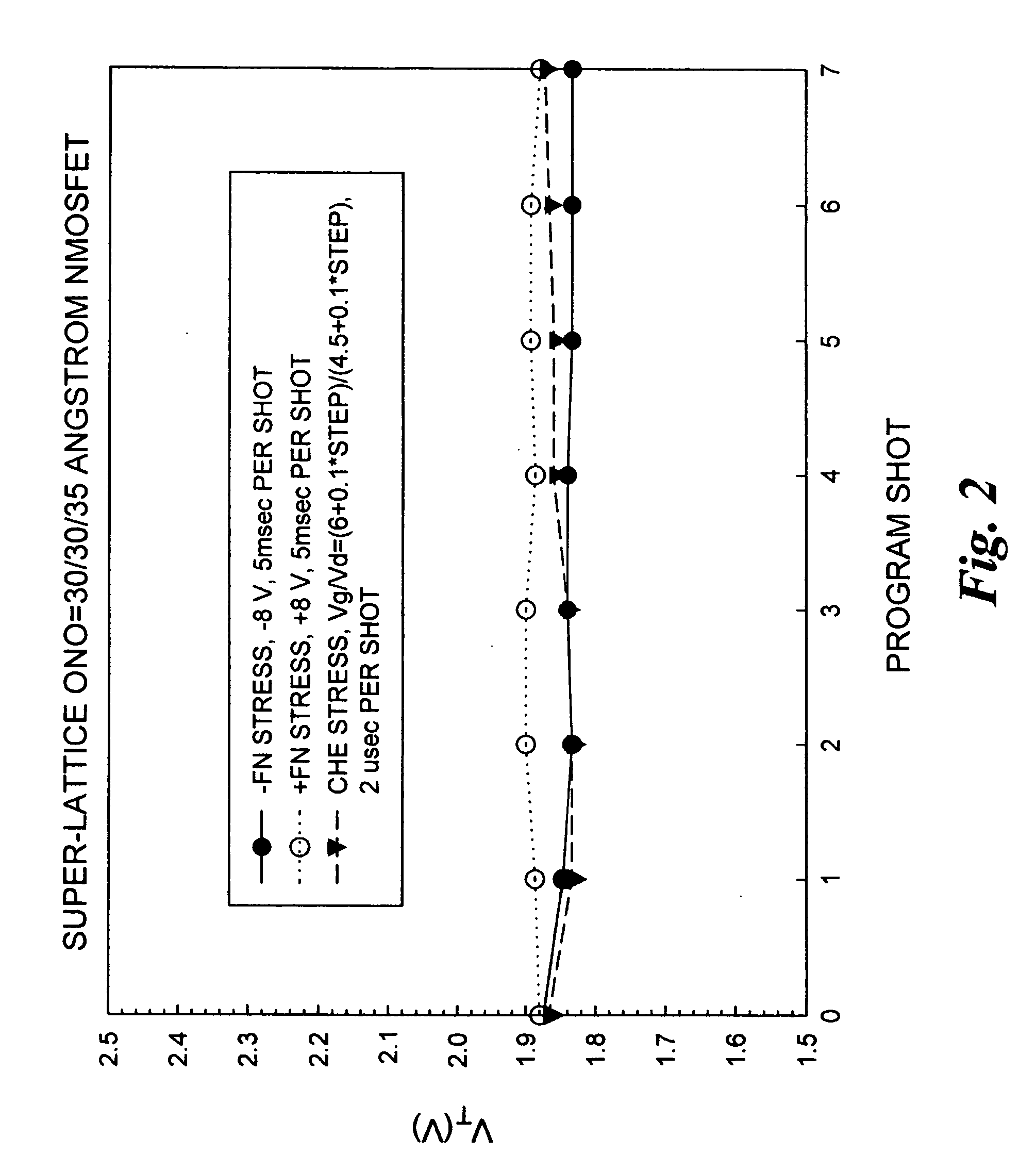

Floating gate memory device with interpoly charge trapping structure

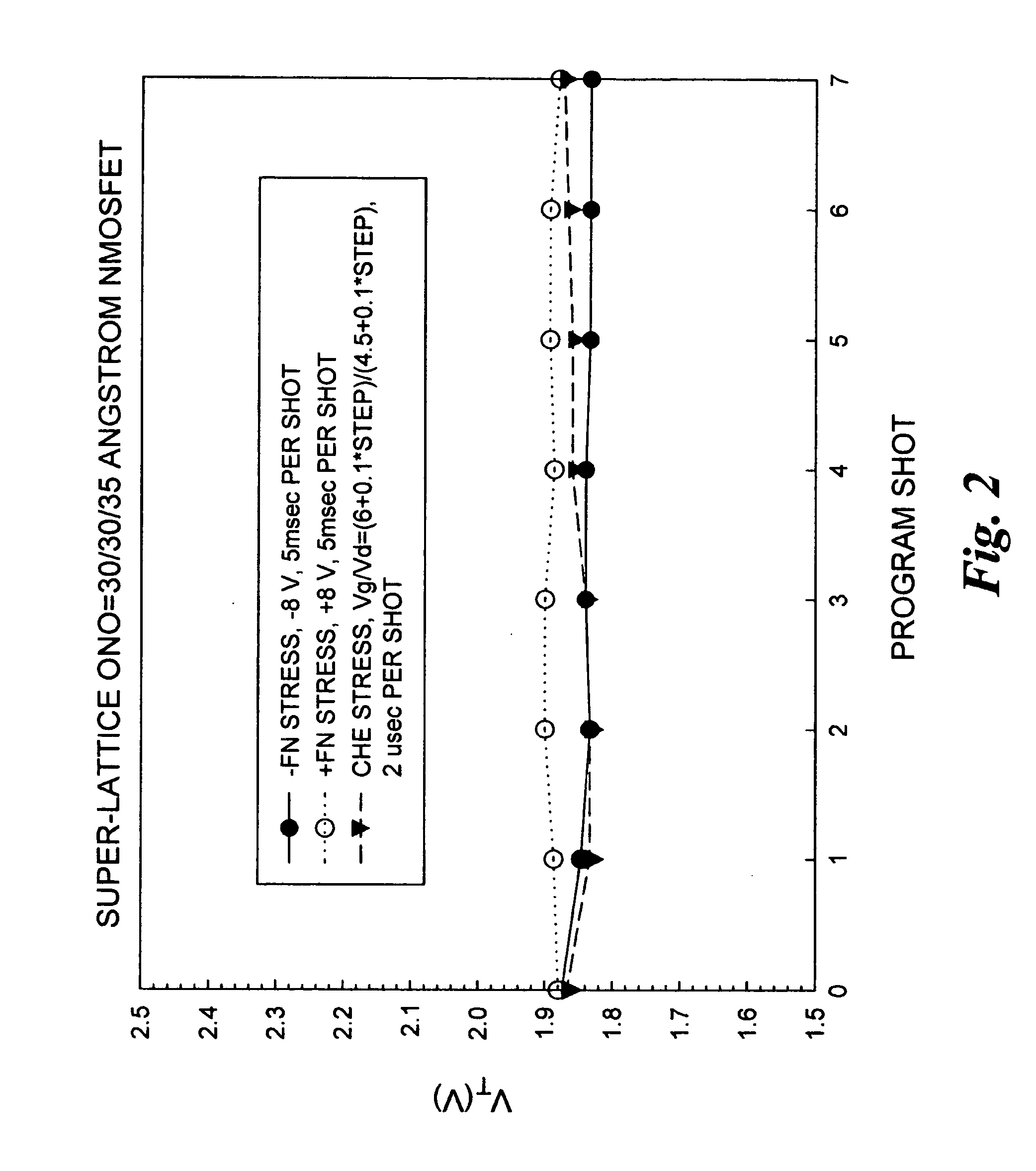

ActiveUS20090262583A1Constant threshold voltageReduce distractionsTransistorSolid-state devicesElectrical conductorTrapping

A charge trapping floating gate is described with asymmetric tunneling barriers. The memory cell includes a source region and a drain region separated by a channel region. A first tunneling barrier structure is disposed above the channel region. A floating gate is disposed above the first tunneling barrier structure covering the channel region. A second tunneling barrier is disposed above the floating gate. A dielectric charge trapping structure disposed above the second tunneling barrier and a blocking dielectric structure is disposed above the charge trapping structure. A top conductive layer disposed above the top dielectric structure acts as a gate. The second tunneling barrier is a more efficient conductor of tunneling current, under bias conditions applied for programming and erasing the memory cell, than the first tunneling barrier structure.

Owner:MACRONIX INT CO LTD

Reconfigurable tactile sensor input device

InactiveUS7609178B2Low production costSmall sizeInput/output for user-computer interactionElectronic switchingCapacitanceAtmospheric air

A reconfigurable tactile input device includes a first rigid electrode layer, a compressible dielectric structure, and a second flexible electrode layer forming together a tactile sensor with appropriate electrode connection means to a control means. The control means may include a mixed-signal IC mounted next to the input device in a compact package and capable of measuring capacitance in real time. The dielectric structure may include a matrix of compressible geometric elements with voids therebetween optionally vented to atmosphere, making the entire assembly thin and facilitating its use for mobile phones and other small, portable electronic devices. Some embodiments provide the user wit tactile feedback upon compression of the electrodes. An optional flexible display may be mounted over the input device to indicate the present configuration to the user.

Owner:WISETOUCH CO LTD

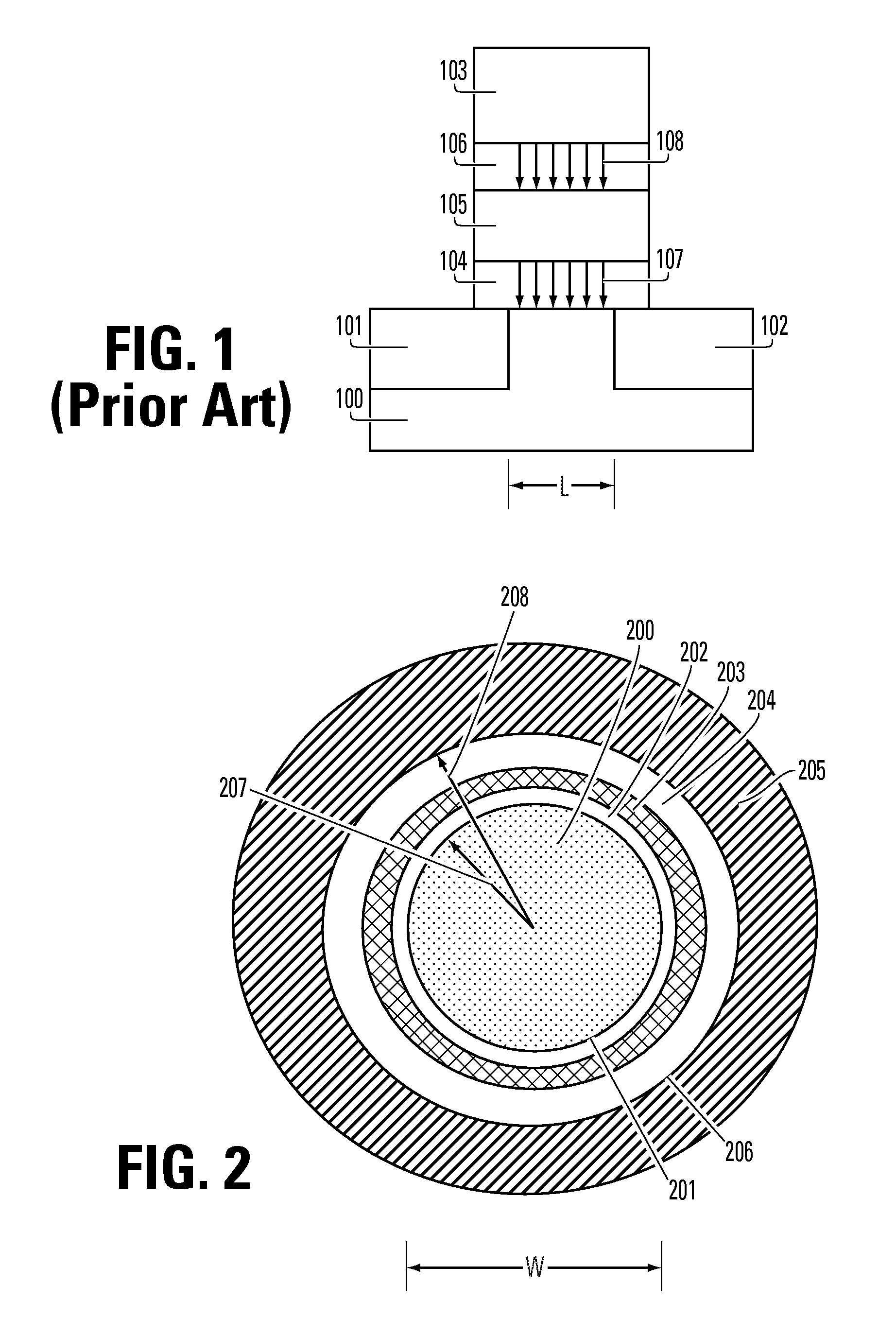

Extreme low-K interconnect structure and method

InactiveUS20060006538A1Improve methodSimple structureSemiconductor/solid-state device detailsSolid-state devicesEngineeringDielectric structure

Embodiments of the invention include an extreme low-K circuit structure formed on a substrate having a plurality of electrically conductive structures. A lattice structure of bracing material configured to support the electrically conductive structures is formed on the substrate and also can define regions of extreme low-K dielectric space between the electrically conductive structures. Additionally, methods for creating dielectric structures on a substrate are disclosed.

Owner:LSI CORPORATION

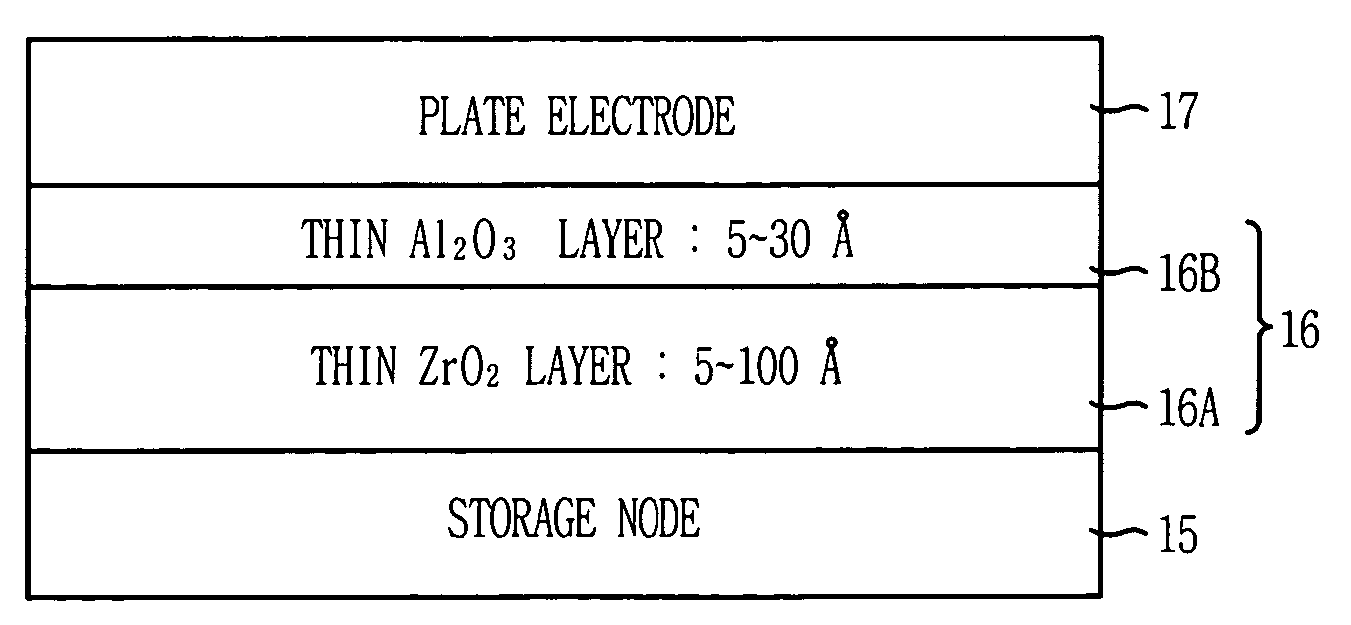

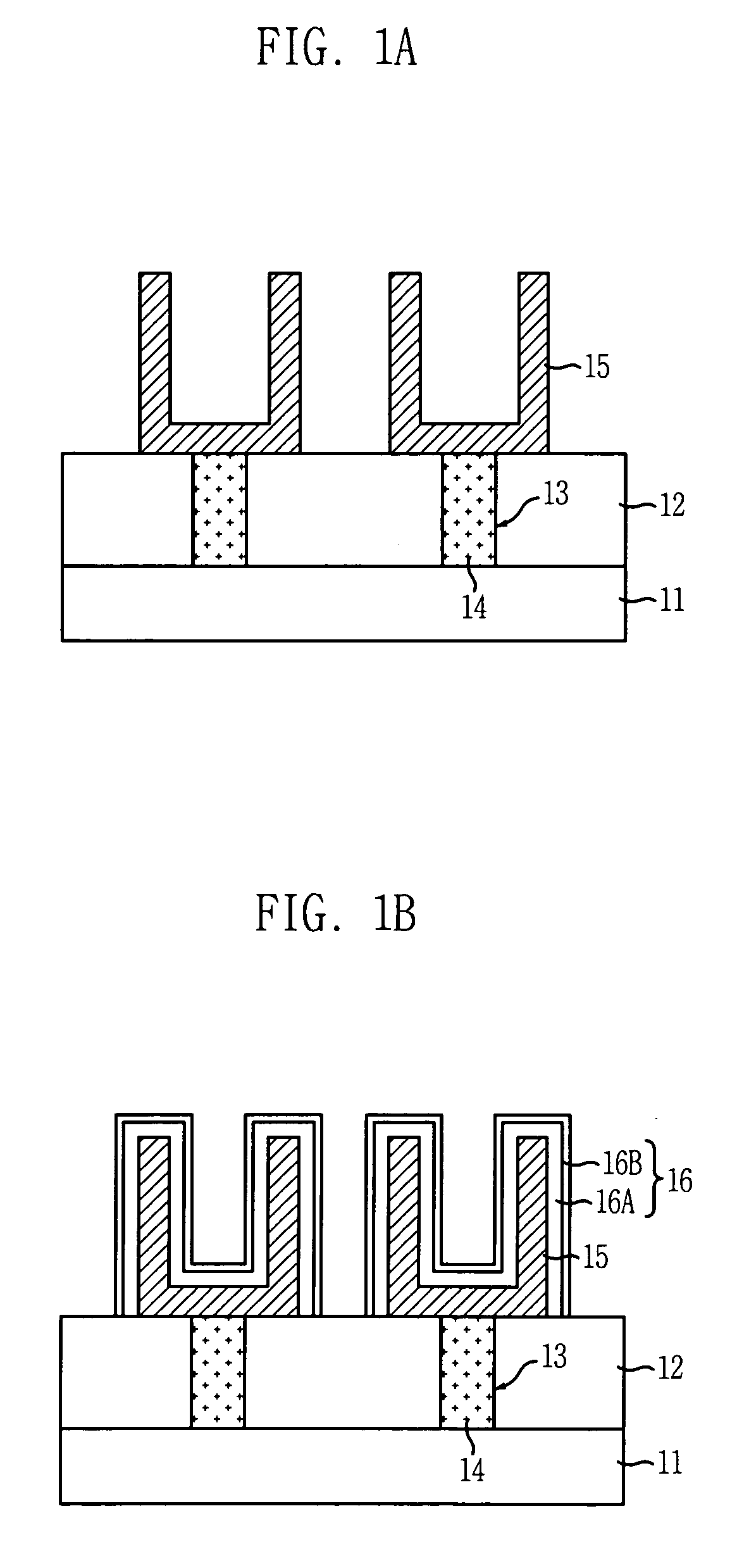

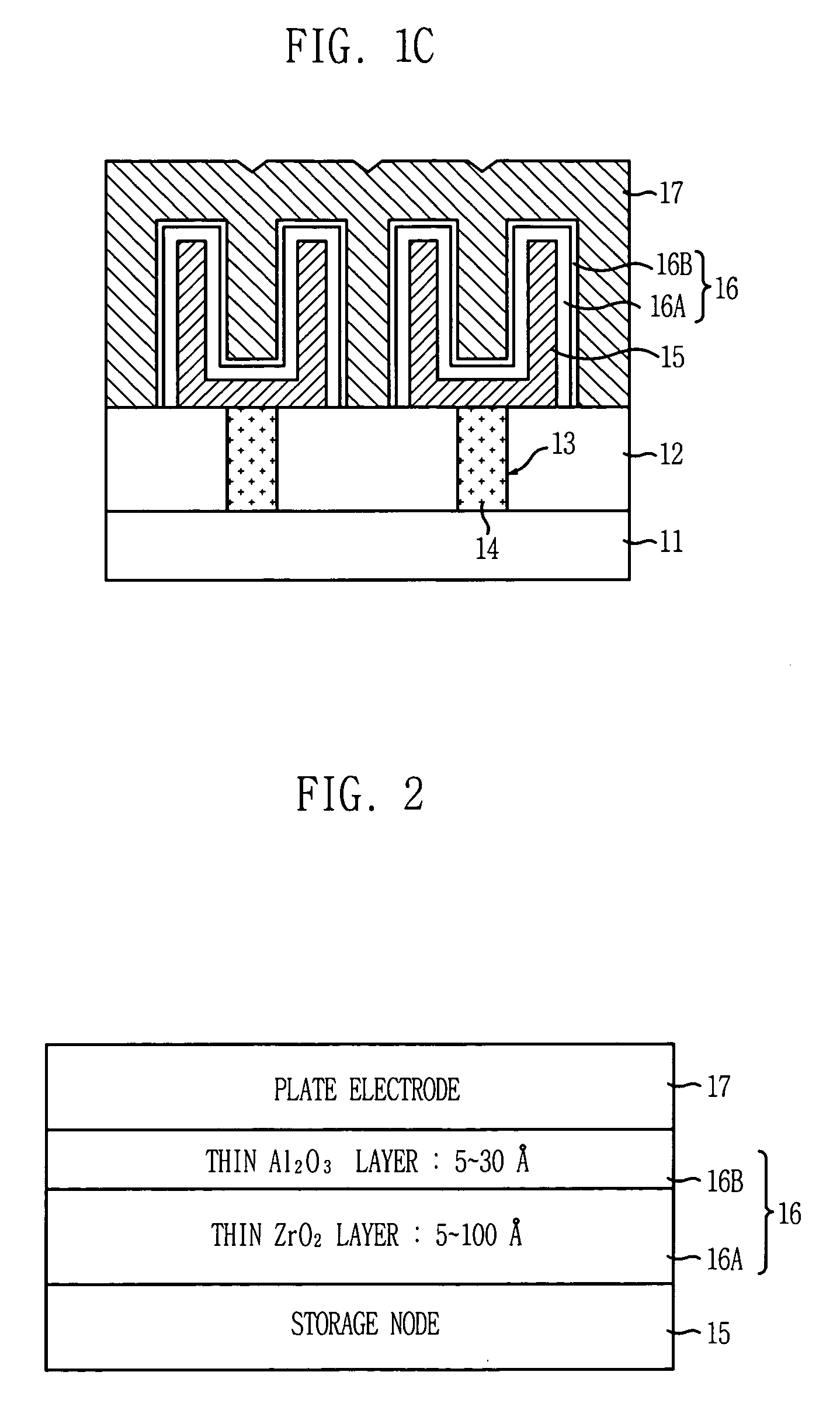

Capacitor with zirconium oxide and method for fabricating the same

ActiveUS20060097305A1Secure leakage current characteristicSecure capacitance levelTransistorSolid-state devicesOptoelectronicsDielectric structure

A capacitor with zirconium oxide and a method for fabricating the same are provided. The method includes: forming a storage node; forming a multi-layered dielectric structure on the storage node, the multi-layered dielectric structure including a zirconium oxide (ZrO2) layer and an aluminum oxide (Al2O3) layer; and forming a plate electrode on the multi-layered dielectric structure.

Owner:SK HYNIX INC

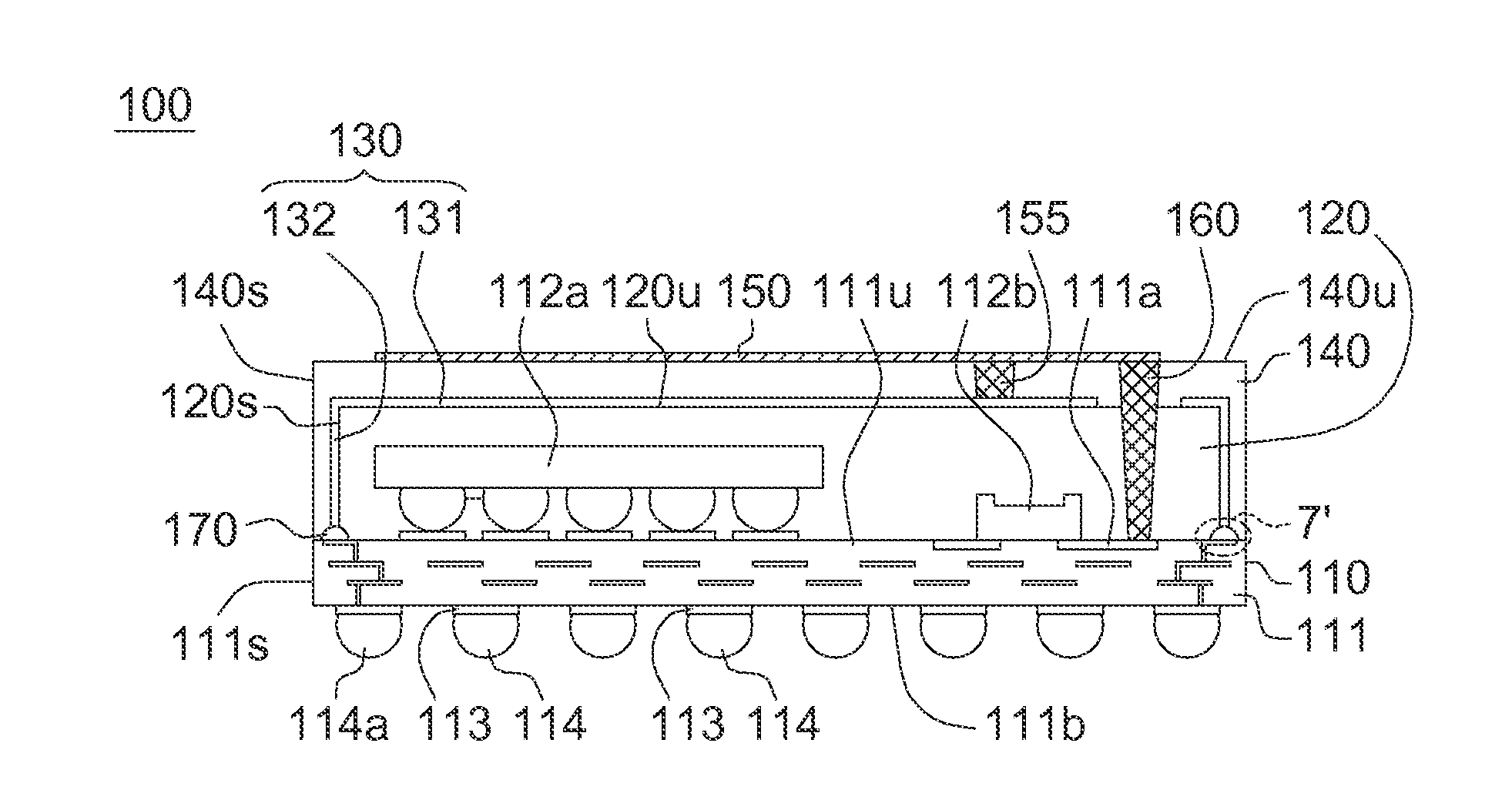

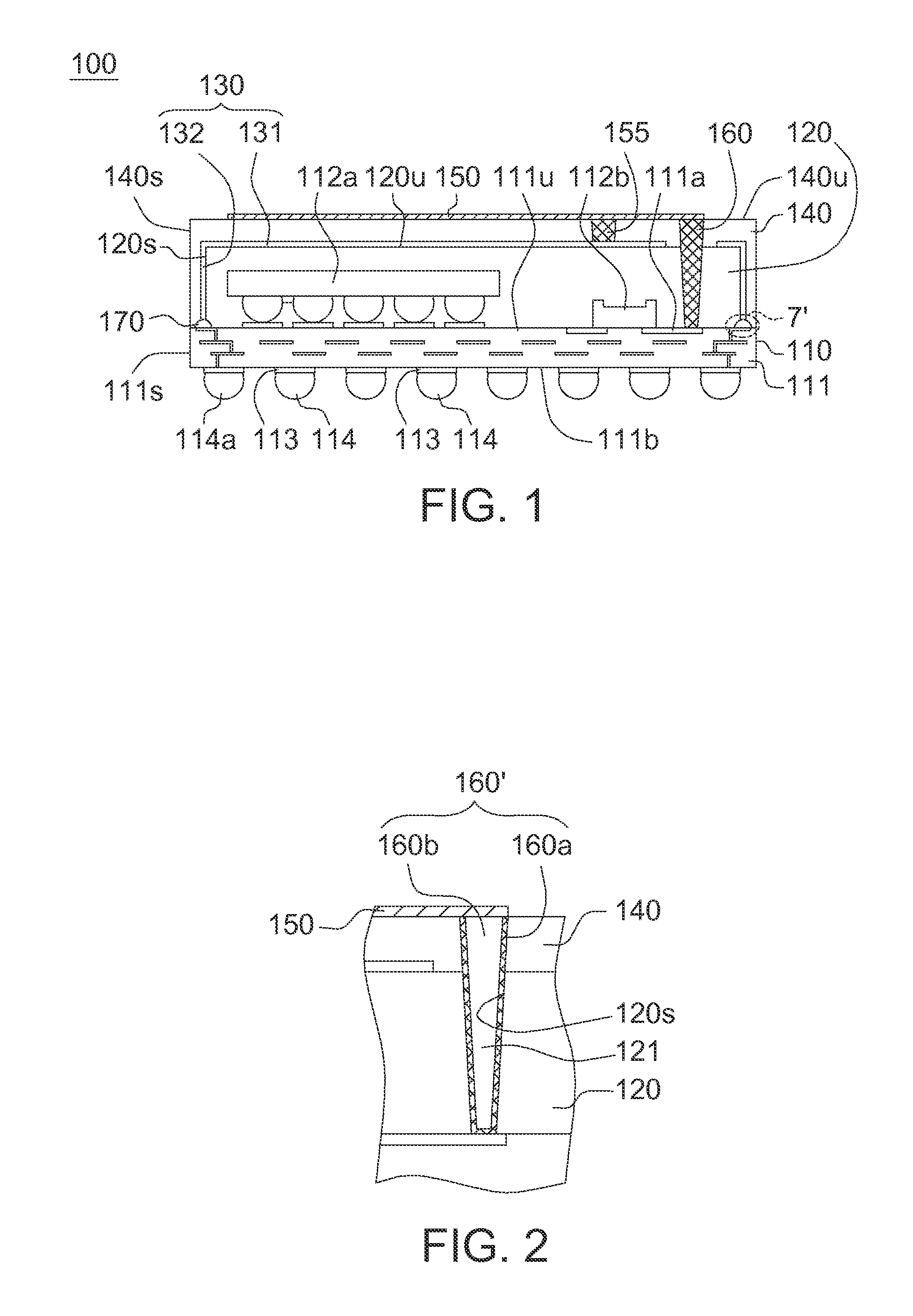

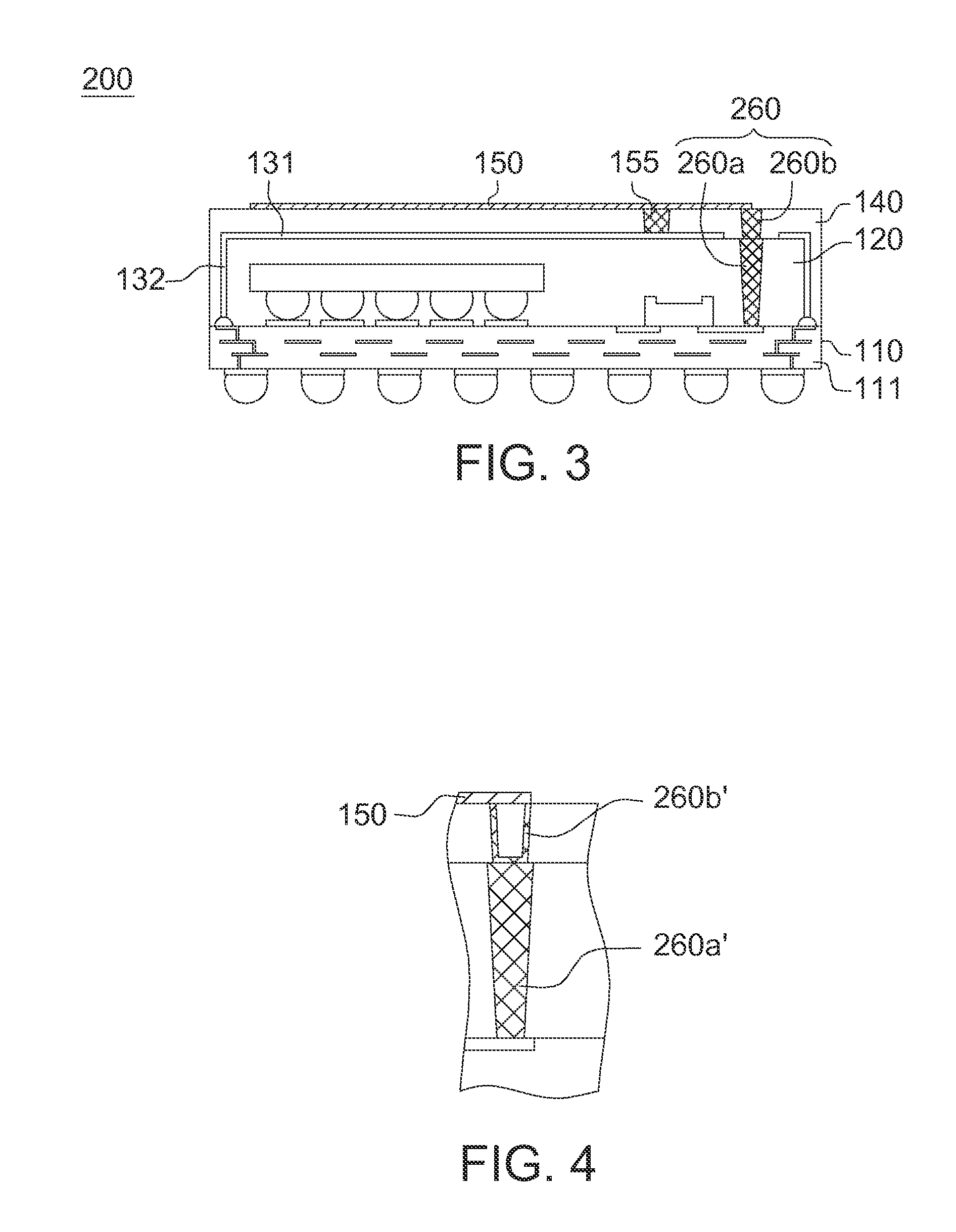

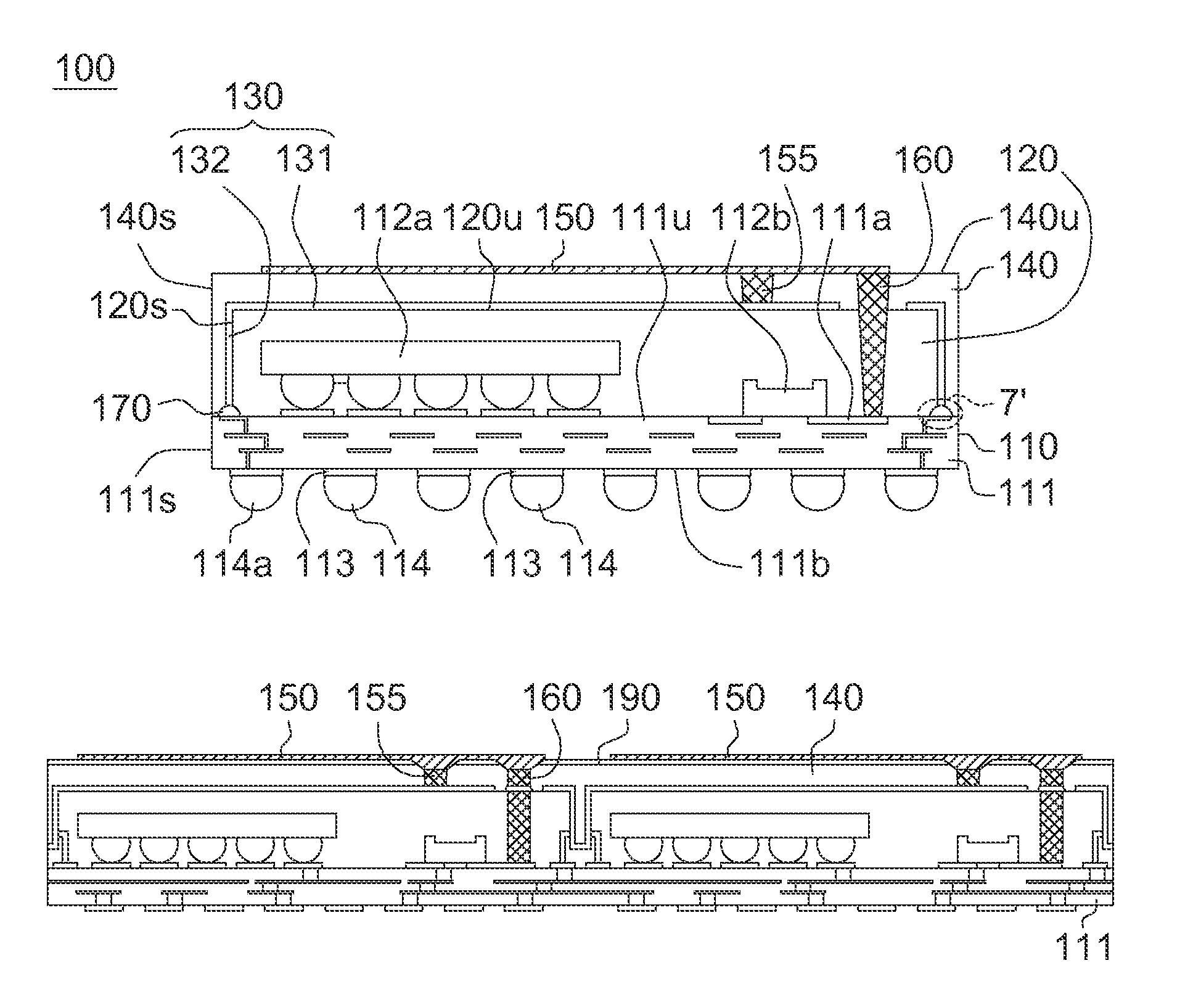

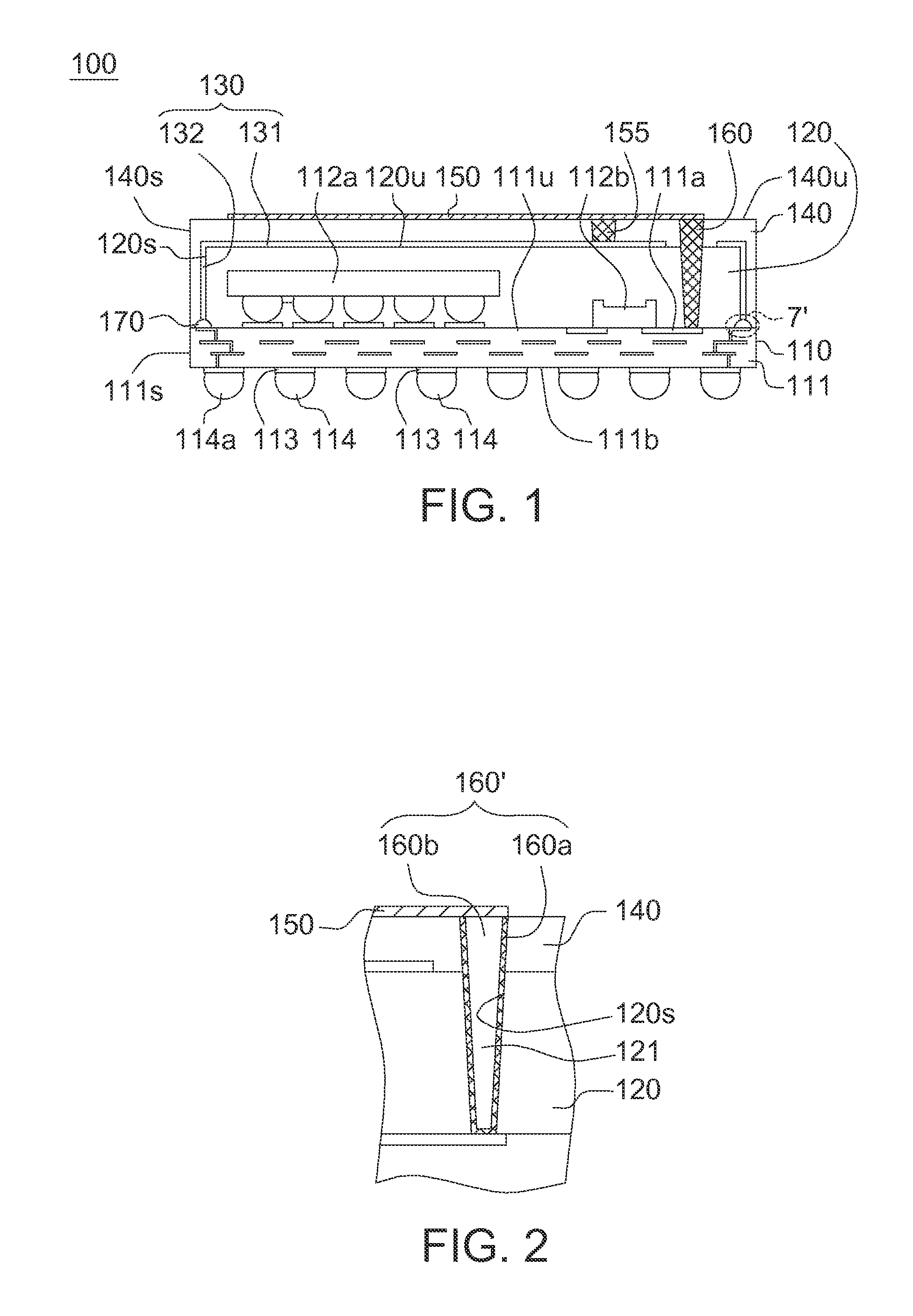

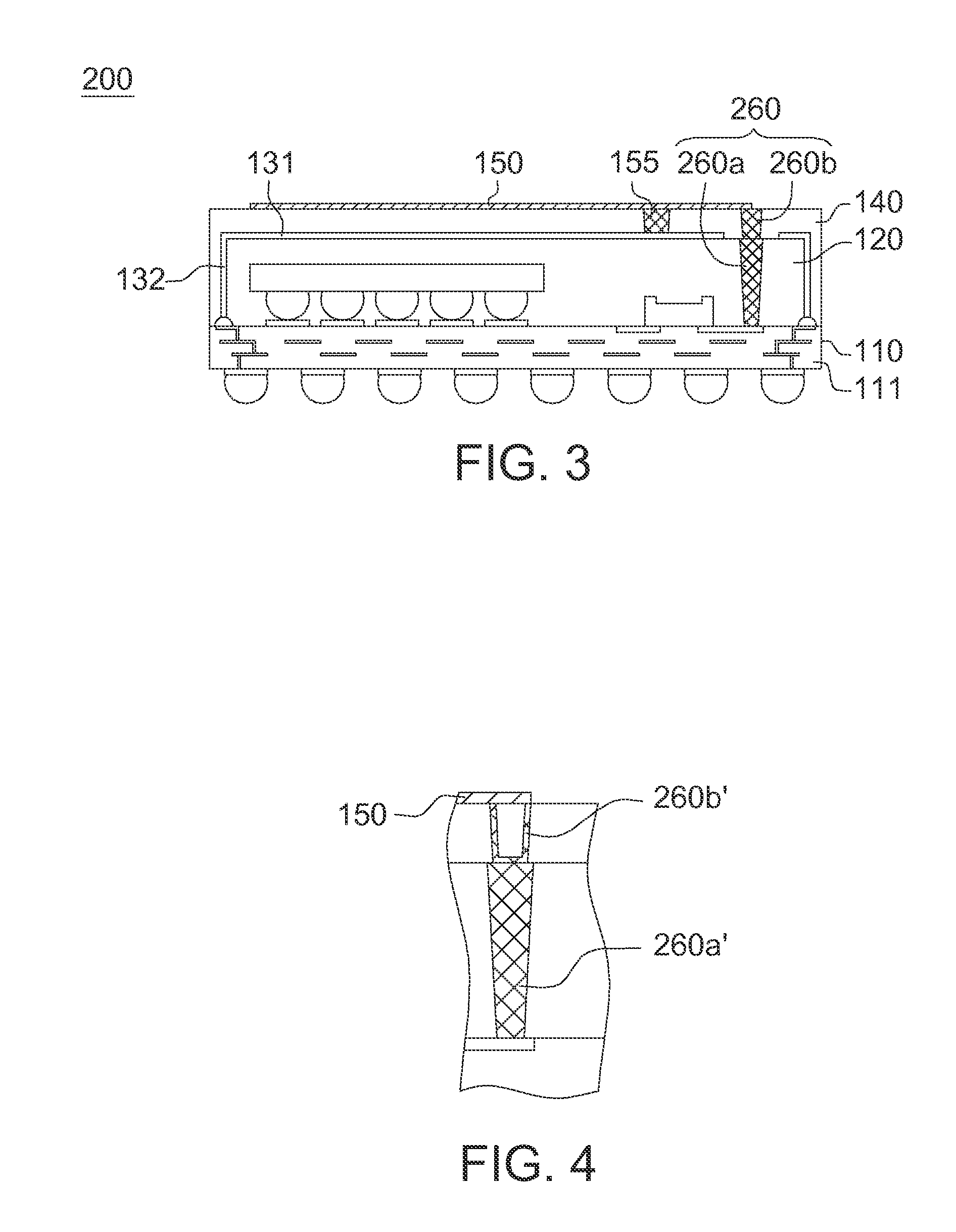

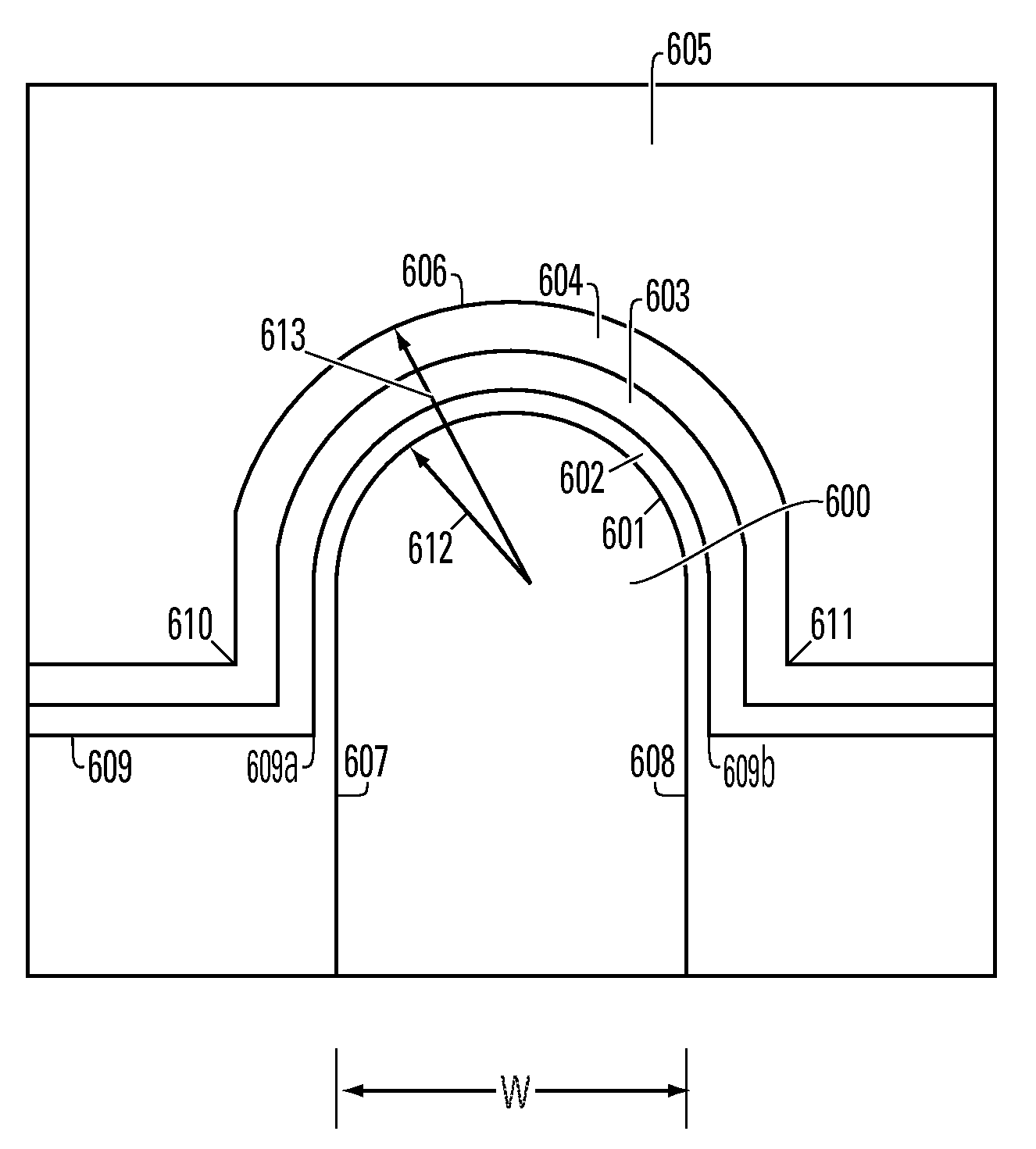

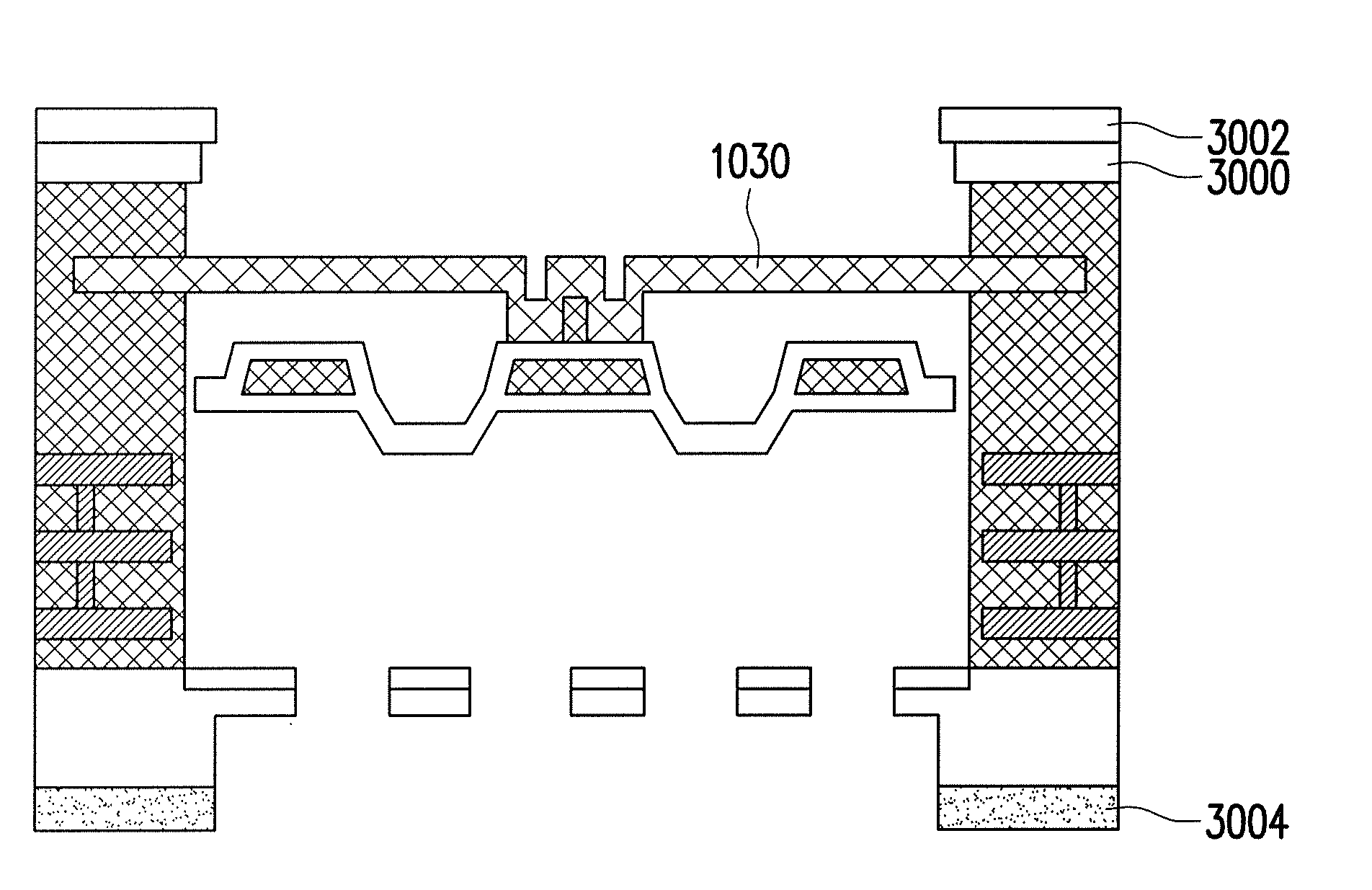

Semiconductor package integrated with conformal shield and antenna

ActiveUS20130292808A1High dielectric constantSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageElectromagnetic interference

A semiconductor package includes a substrate, a semiconductor die, a package body, an electromagnetic interference shield, a dielectric structure and an antenna element. The substrate comprises a grounding segment and a feeding point. The semiconductor die is disposed on the substrate. The package body encapsulates the semiconductor die. The electromagnetic interference shield is formed on the package body. The dielectric structure encapsulates the electromagnetic interference shield. The antenna element is formed on the dielectric structure and electrically connecting the grounding segment of the substrate and the feeding point.

Owner:ADVANCED SEMICON ENG INC

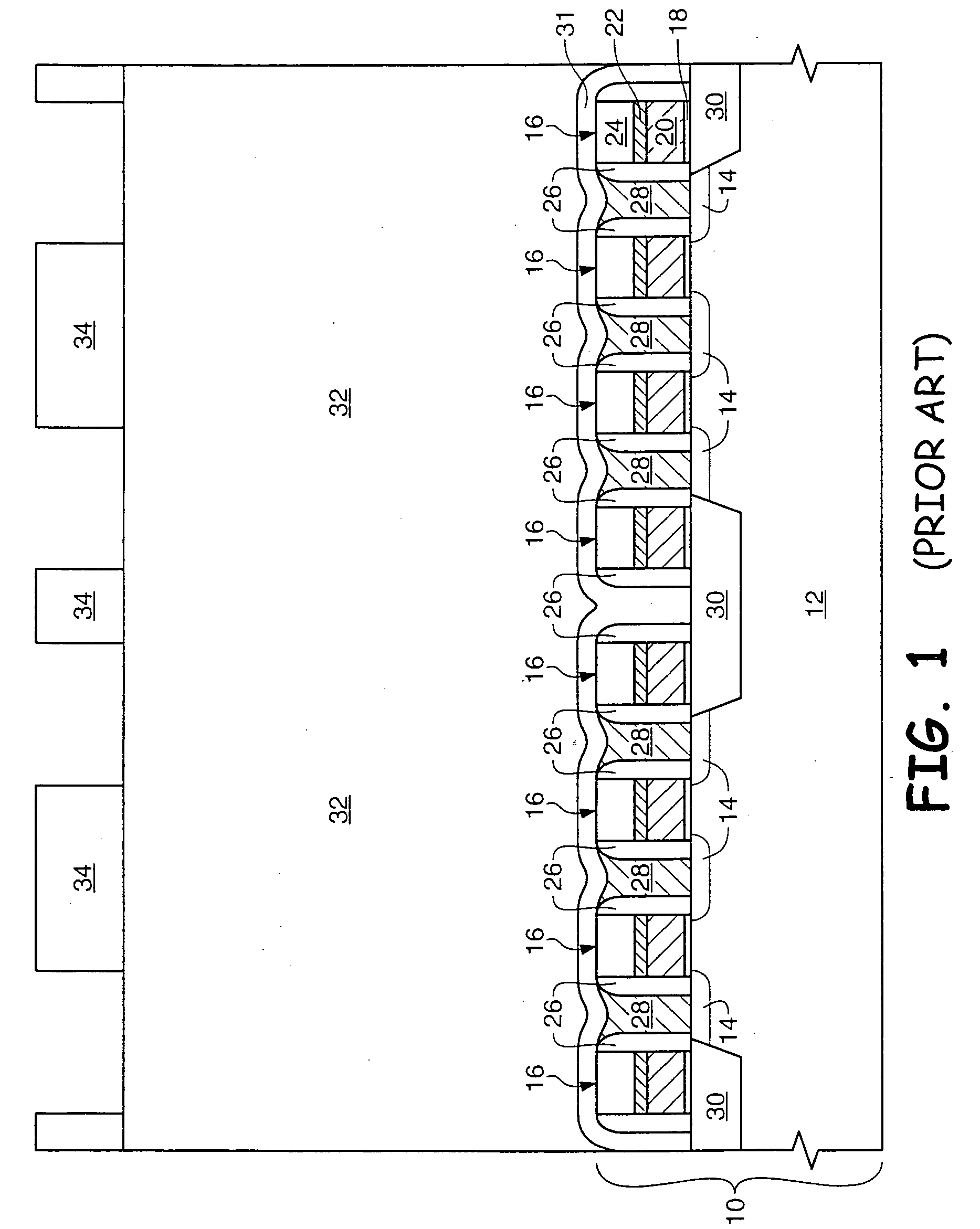

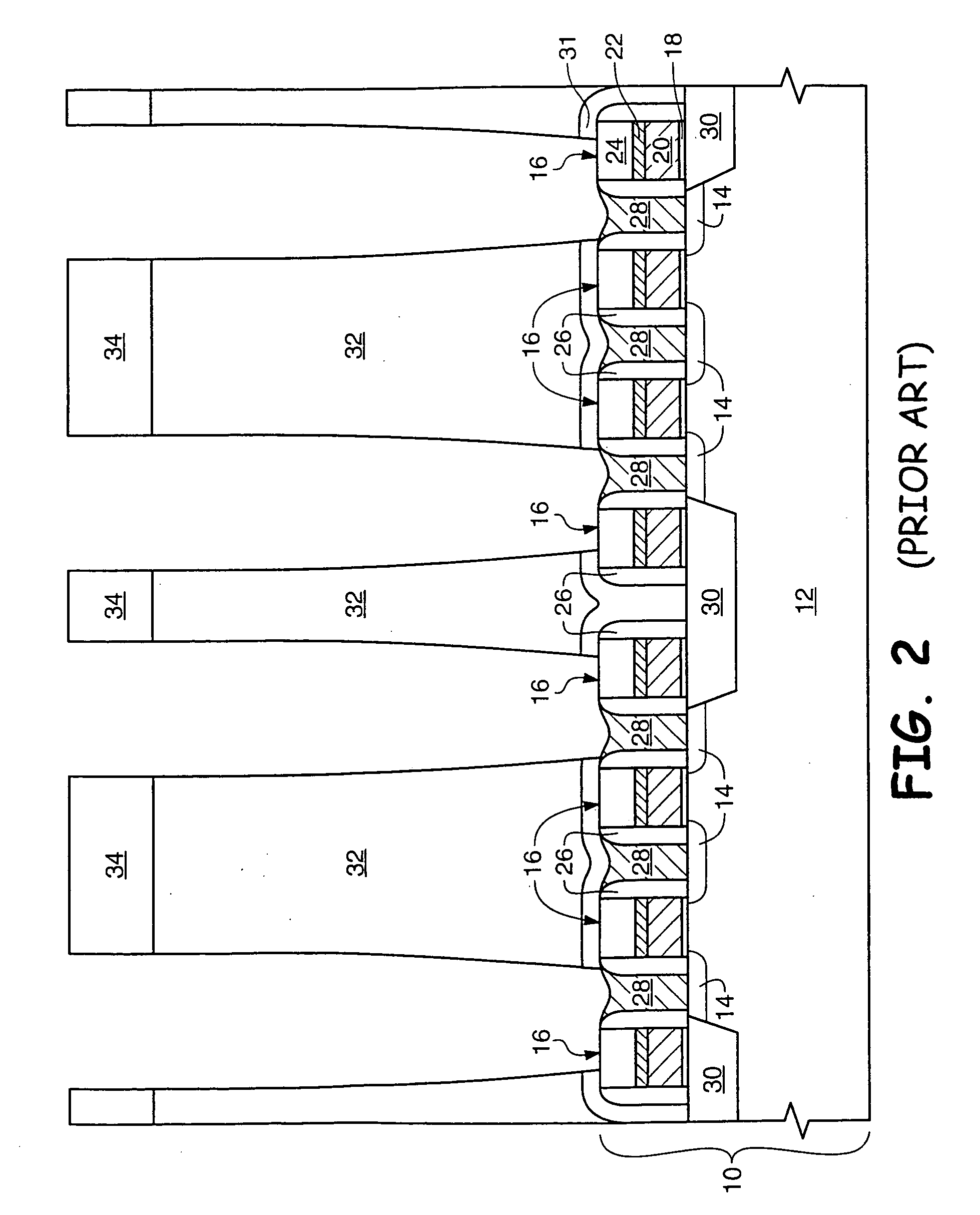

Non-volatile memory cells, memory arrays including the same and methods of operating cells and arrays

ActiveUS20060202261A1Easy to eraseLarge operating windowSolid-state devicesRead-only memoriesEngineeringDielectric structure

Memory cells comprising: a semiconductor substrate having a source region and a drain region disposed below a surface of the substrate and separated by a channel region; a tunnel dielectric structure disposed above the channel region, the tunnel dielectric structure comprising at least one layer having a small hole-tunneling-barrier height; a charge storage layer disposed above the tunnel dielectric structure; an insulating layer disposed above the charge storage layer; and a gate electrode disposed above the insulating layer are described along with arrays thereof and methods of operation.

Owner:MACRONIX INT CO LTD

Non-volatile memory cells, memory arrays including the same and methods of operating cells and arrays

ActiveUS20060198190A1Easy to optimizeEasy to eraseSolid-state devicesRead-only memoriesDielectric structureCondensed matter physics

Memory cells comprising: a semiconductor substrate having a source region and a drain region disposed below a surface of the substrate and separated by a channel region; a tunnel dielectric structure disposed above the channel region, the tunnel dielectric structure comprising at least one layer having a small hole-tunneling-barrier height; a charge storage layer disposed above the tunnel dielectric structure; an insulating layer disposed above the charge storage layer; and a gate electrode disposed above the insulating layer are described along with arrays thereof and methods of operation.

Owner:MACRONIX INT CO LTD

Metal-insulator-metal capacitor for copper damascene process and method of forming the same

A capacitor structure formed on a semiconductor substrate may include a first interconnect wiring (such as copper damascene) and a first conductive barrier layer in contact with the first interconnect wiring. A first capacitor plate, a capacitor dielectric structure and a second capacitor plate may also be included over the first conductive barrier layer. A second conductive barrier layer may be formed on the second capacitor plate and a second planar insulating structure may be formed over the second capacitor plate. Finally, a second interconnect wiring may be embedded within a second planar insulator structure.

Owner:IBM CORP

Non-volatile memory cells, memory arrays including the same and methods of operating cells and arrays

InactiveUS20060198189A1Easy to eraseLarge operating windowRead-only memoriesDigital storageDielectric structureCondensed matter physics

Memory cells comprising: a semiconductor substrate having a source region and a drain region disposed below a surface of the substrate and separated by a channel region; a tunnel dielectric structure disposed above the channel region, the tunnel dielectric structure comprising at least one layer having a small hole-tunneling-barrier height; a charge storage layer disposed above the tunnel dielectric structure; an insulating layer disposed above the charge storage layer; and a gate electrode disposed above the insulating layer are described along with arrays thereof and methods of operation.

Owner:MACRONIX INT CO LTD

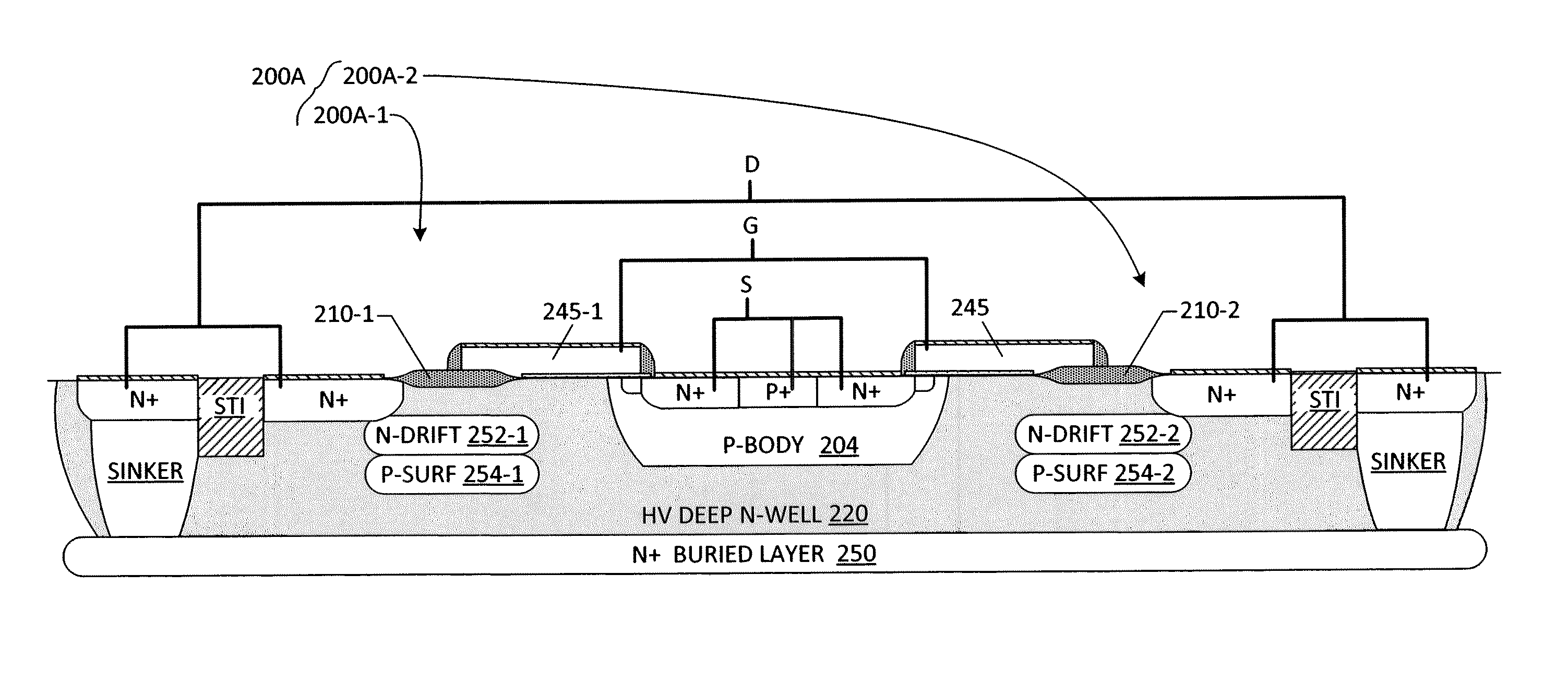

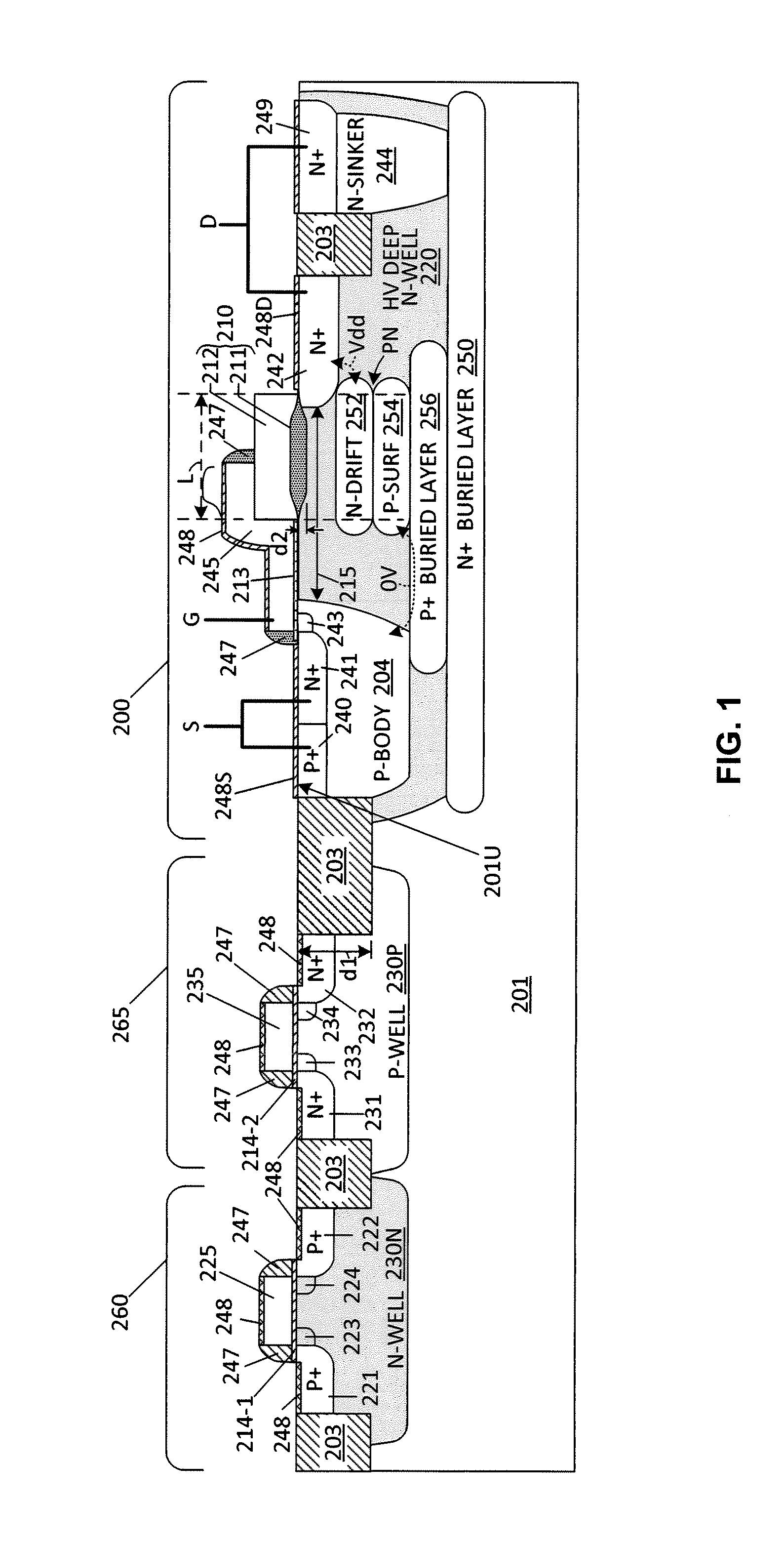

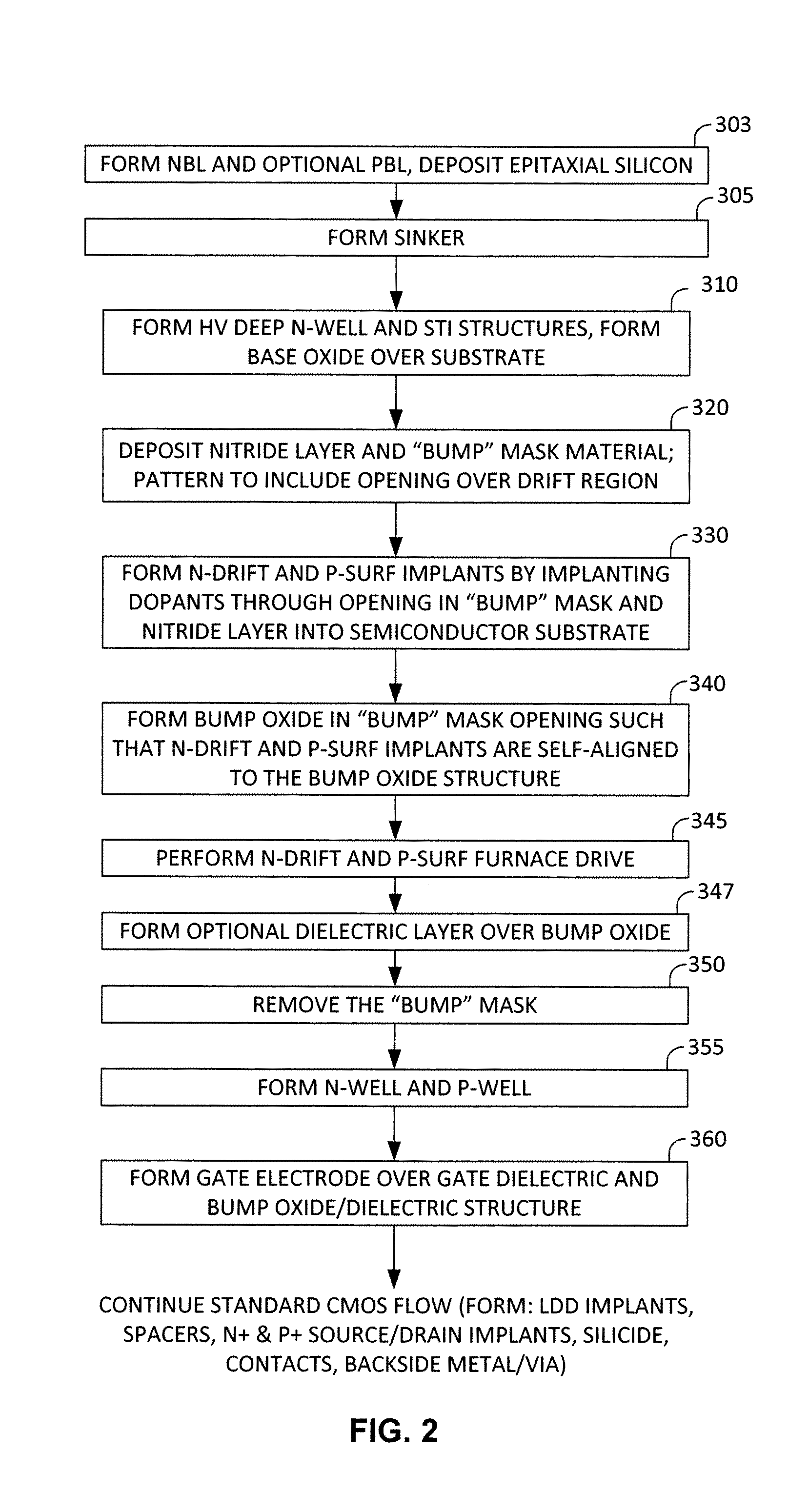

Double-Resurf LDMOS With Drift And PSURF Implants Self-Aligned To A Stacked Gate "BUMP" Structure

ActiveUS20140070315A1Ideal overall performanceHighest possible BVTransistorSolid-state devicesLDMOSGate dielectric

A double-RESURF LDMOS transistor has a gate dielectric structure including a shallow field “bump” oxide region and an optional raised dielectric structure that provides a raised support for the LDMOS transistor's polysilicon gate electrode. Fabrication of the shallow field oxide region is performed through a hard “bump” mask and controlled such that the bump oxide extends a minimal depth into the LDMOS transistor's drift (channel) region. The hard “bump” mask is also utilized to produce an N-type drift (N-drift) implant region and a P-type surface effect (P-surf) implant region, whereby these implants are “self-aligned” to the gate dielectric structure. The N-drift implant is maintained at Vdd by connection to the LDMOS transistor's drain diffusion. An additional Boron implant is utilized to form a P-type buried layer that connects the P-surf implant to the P-body region of the LDMOS transistor, whereby the P-surf implant is maintained at 0V.

Owner:TOWER SEMICONDUCTOR

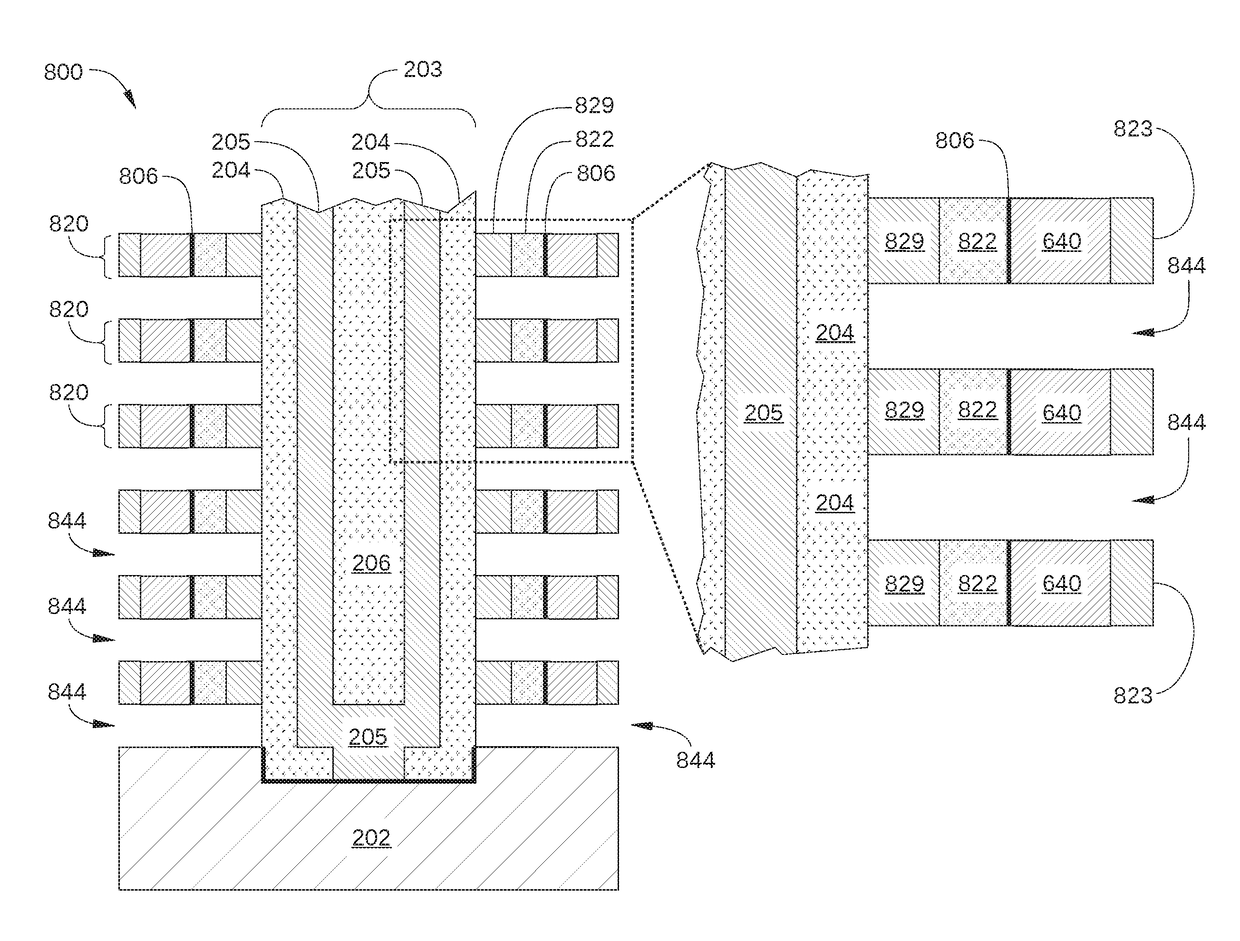

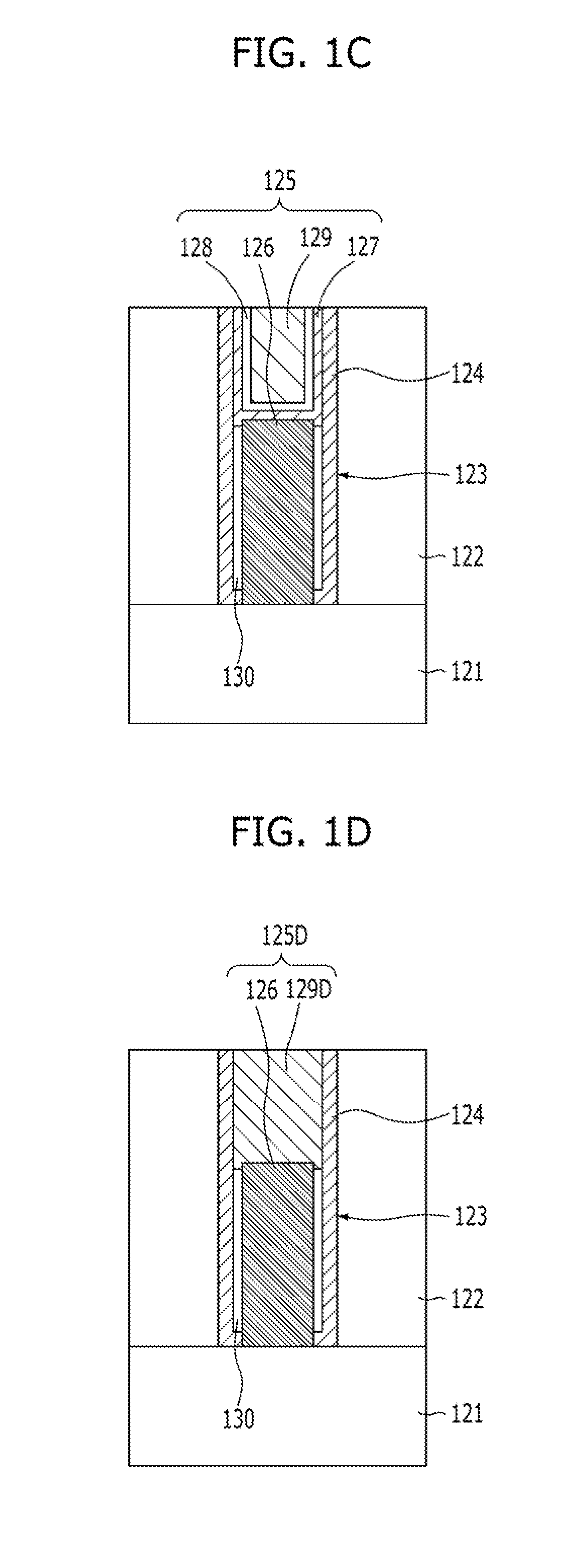

Charge-trap layer separation and word-line isolation for enhanced 3-D NAND structure

ActiveUS9960045B1Solid-state devicesSemiconductor/solid-state device manufacturingVacuum gapSilicon oxide

In a 3D NAND device, the charge trap region of a memory cell is formed as a separate charge-trap “island.” As a result, the charge-trap region of one memory cell is electrically isolated from charge-trap regions in adjacent memory cells. The charge trap region of one memory cell is separated from the charge trap regions of adjacent memory cells by a dielectric structure, such as a silicon oxide film. Alternatively, the charge trap region of a memory cell is separated from the charge trap regions of adjacent memory cells by an air, gas, or vacuum gap.

Owner:APPLIED MATERIALS INC

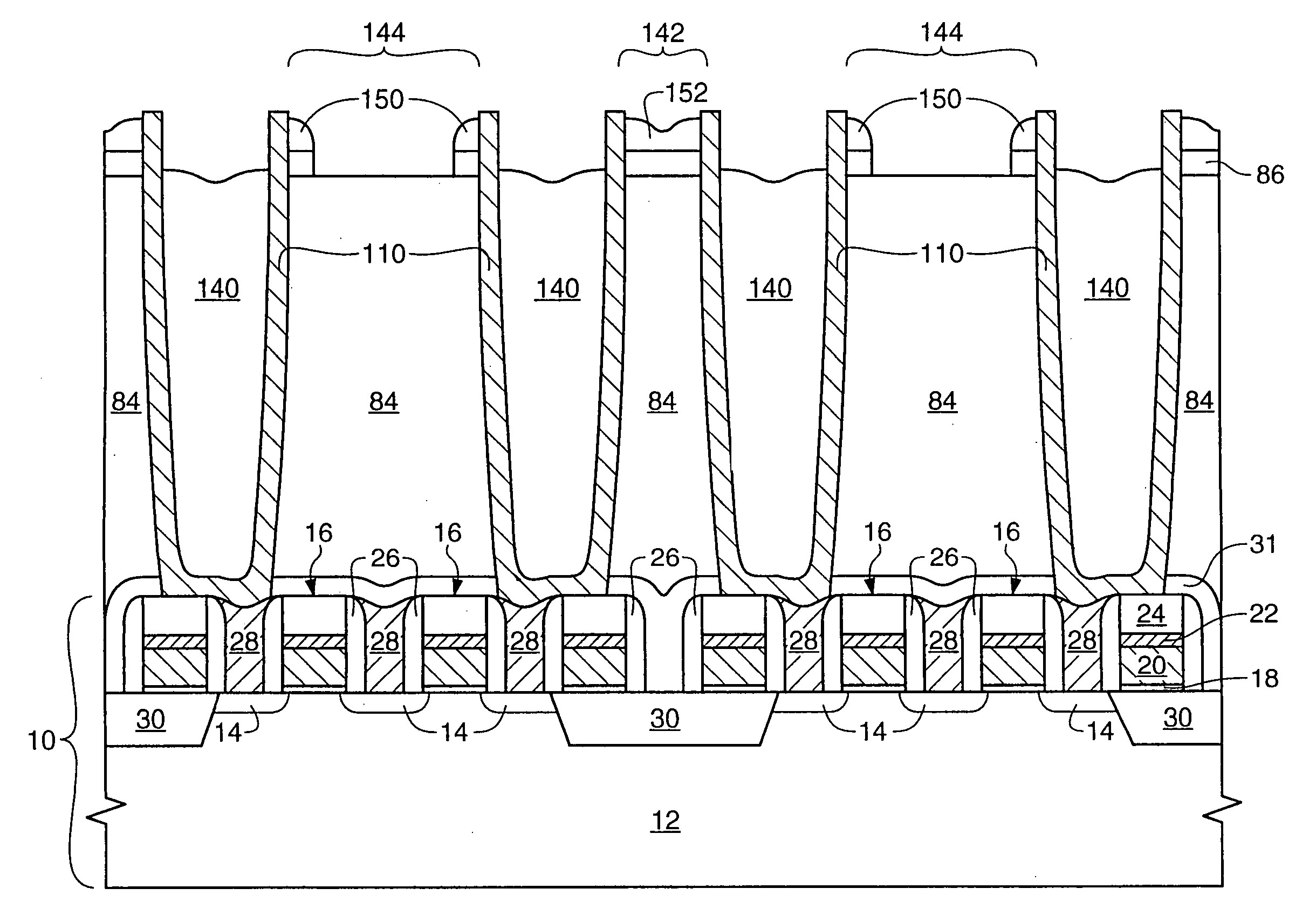

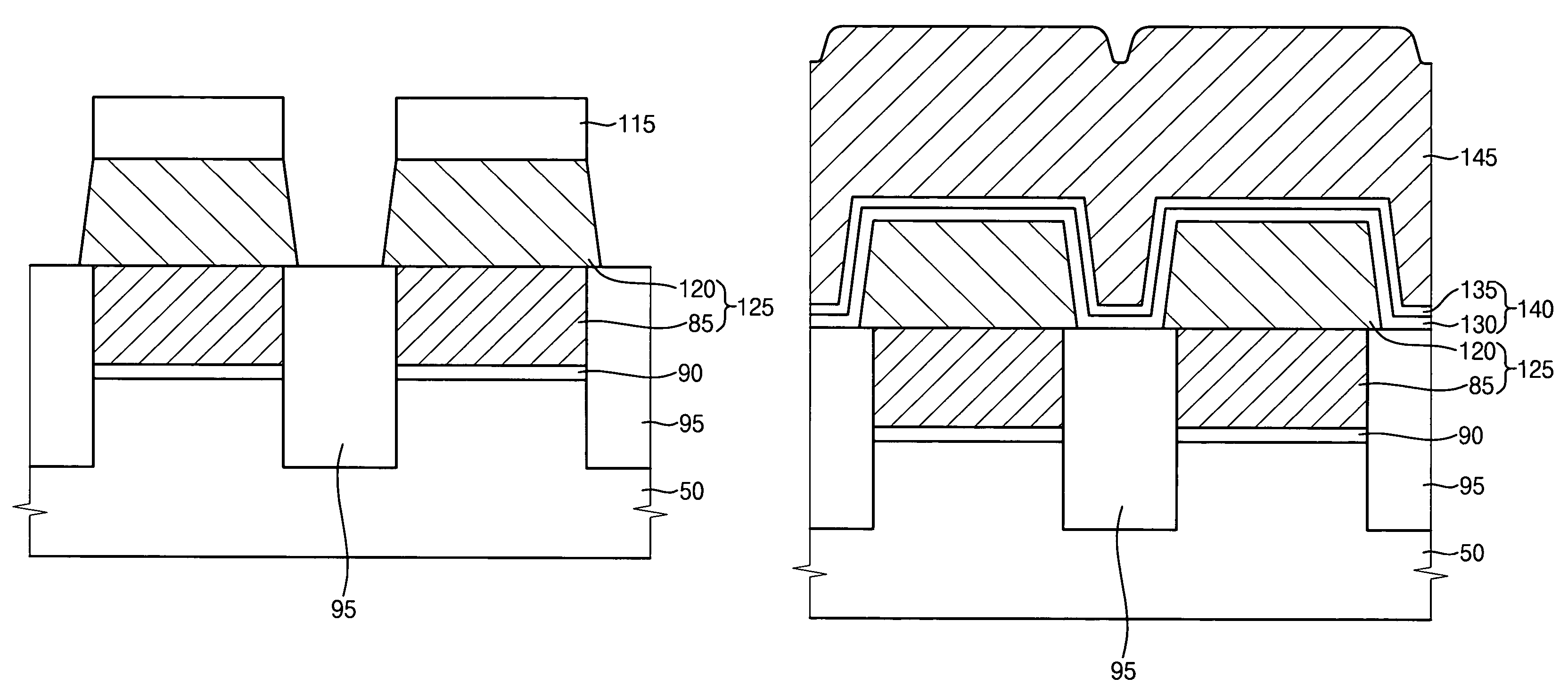

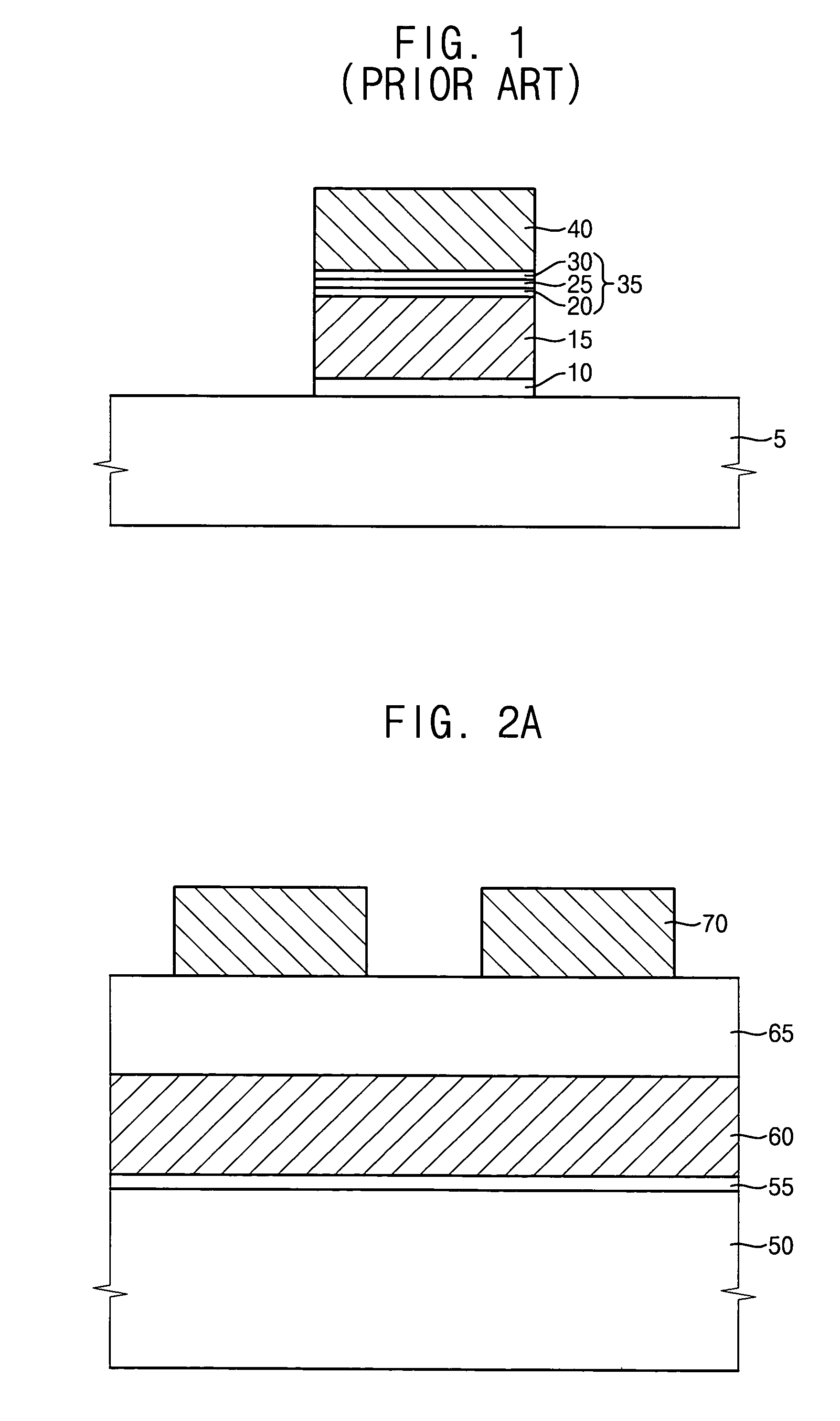

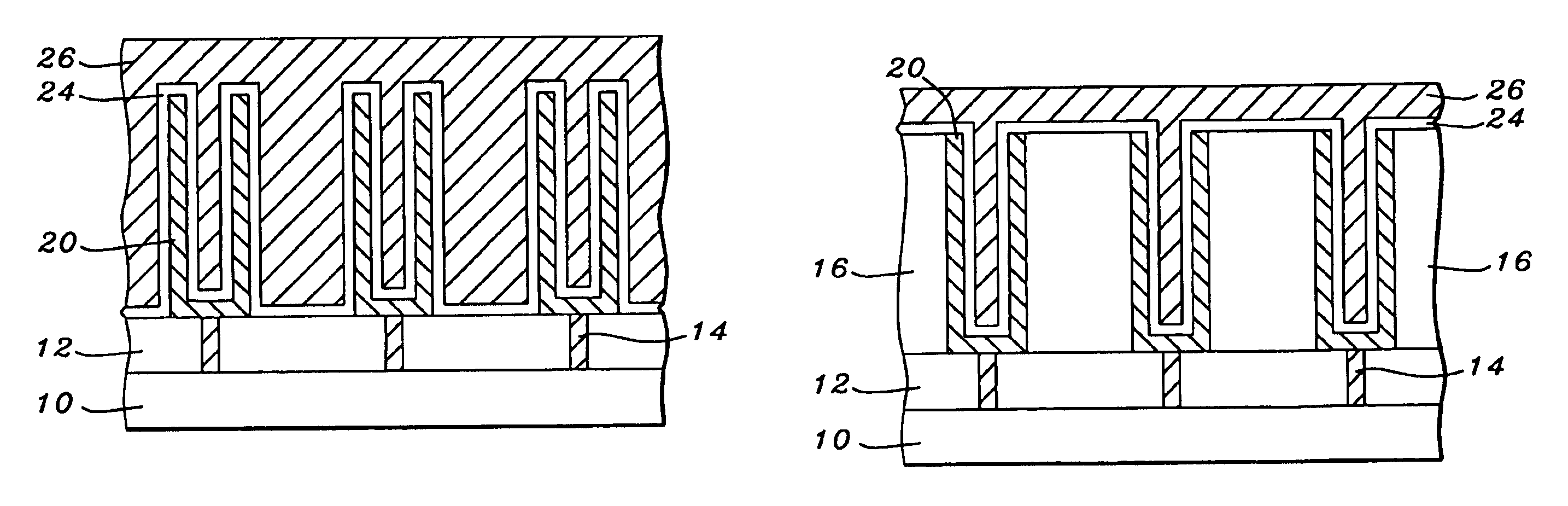

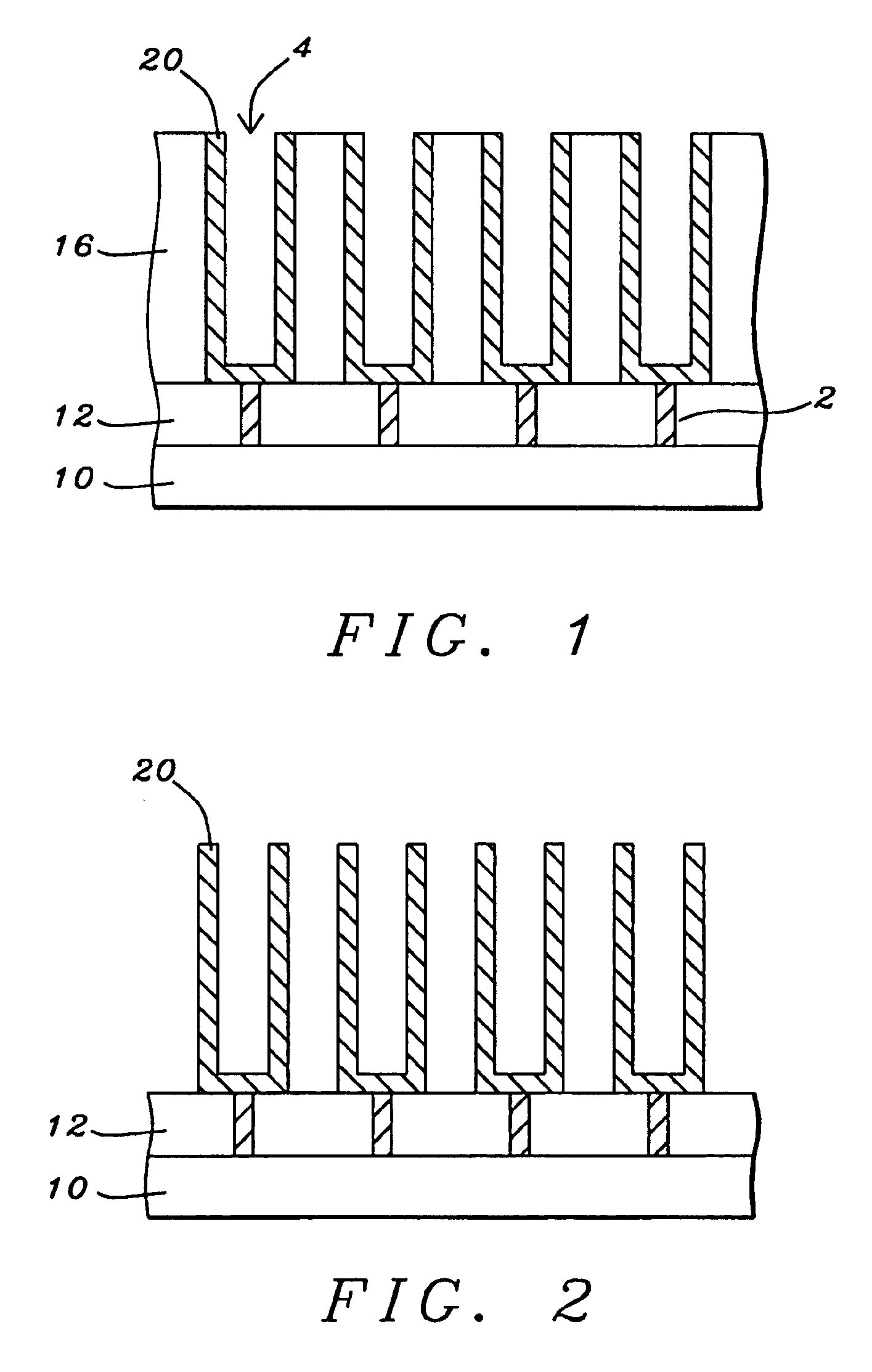

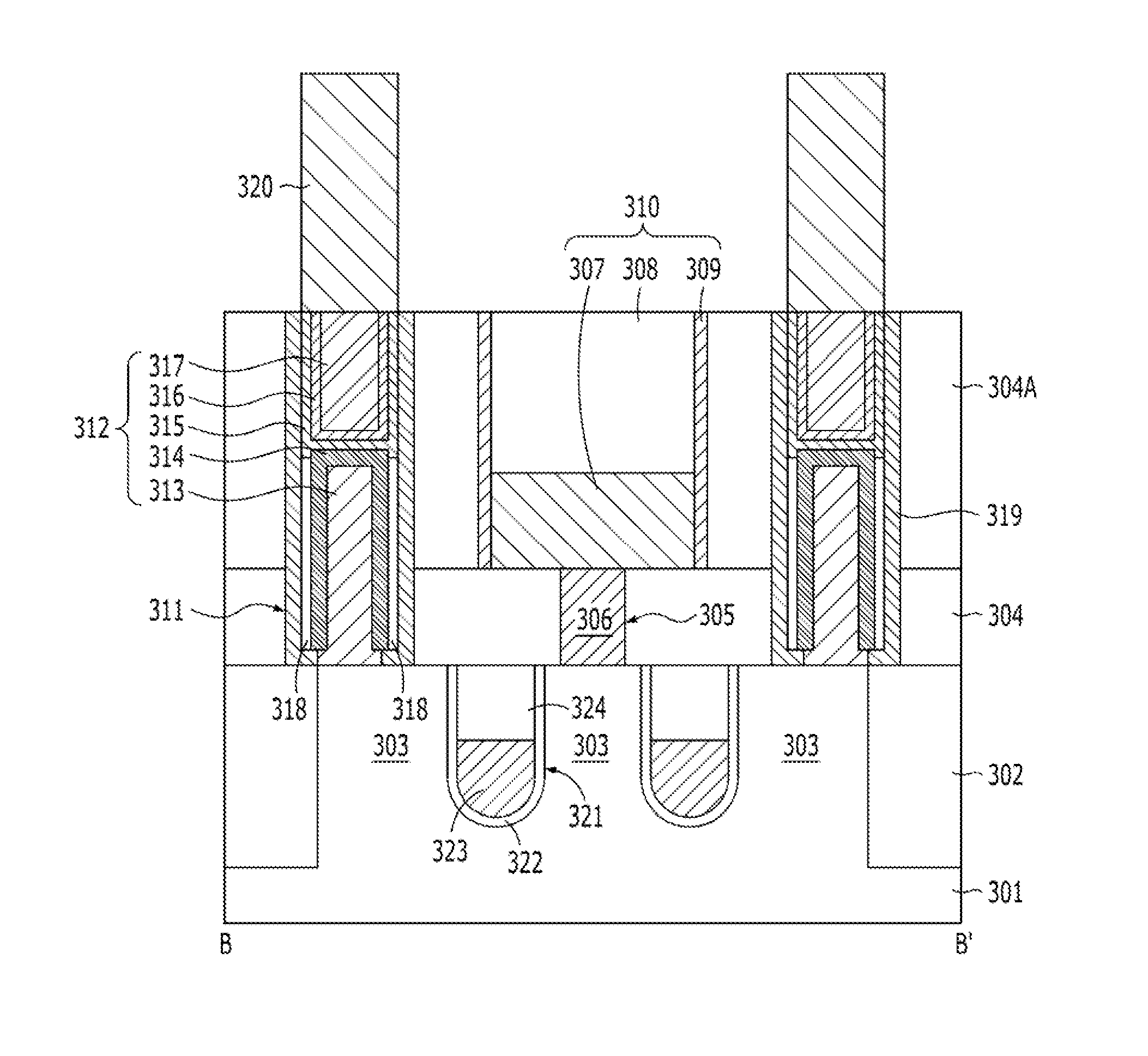

Semiconductor devices

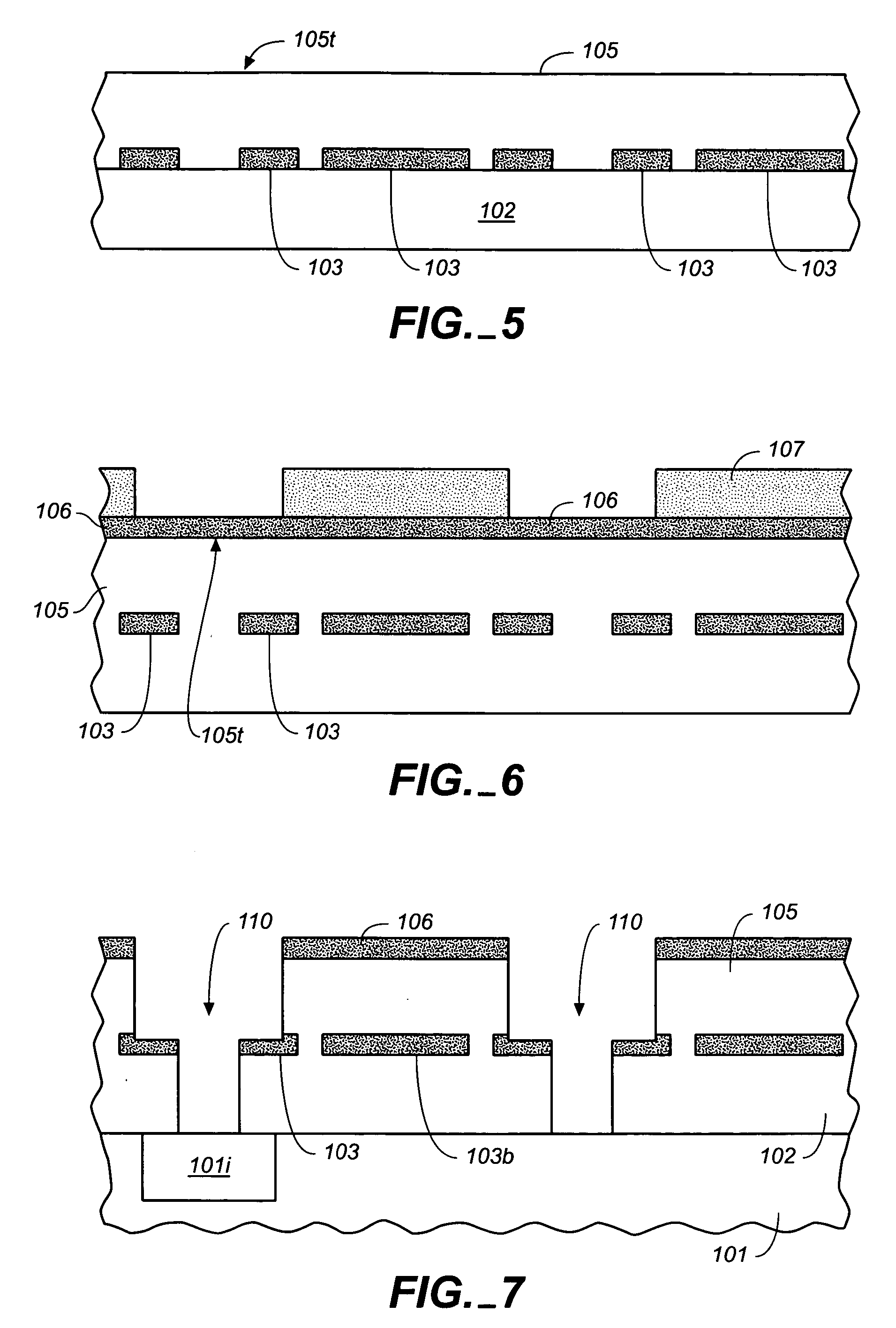

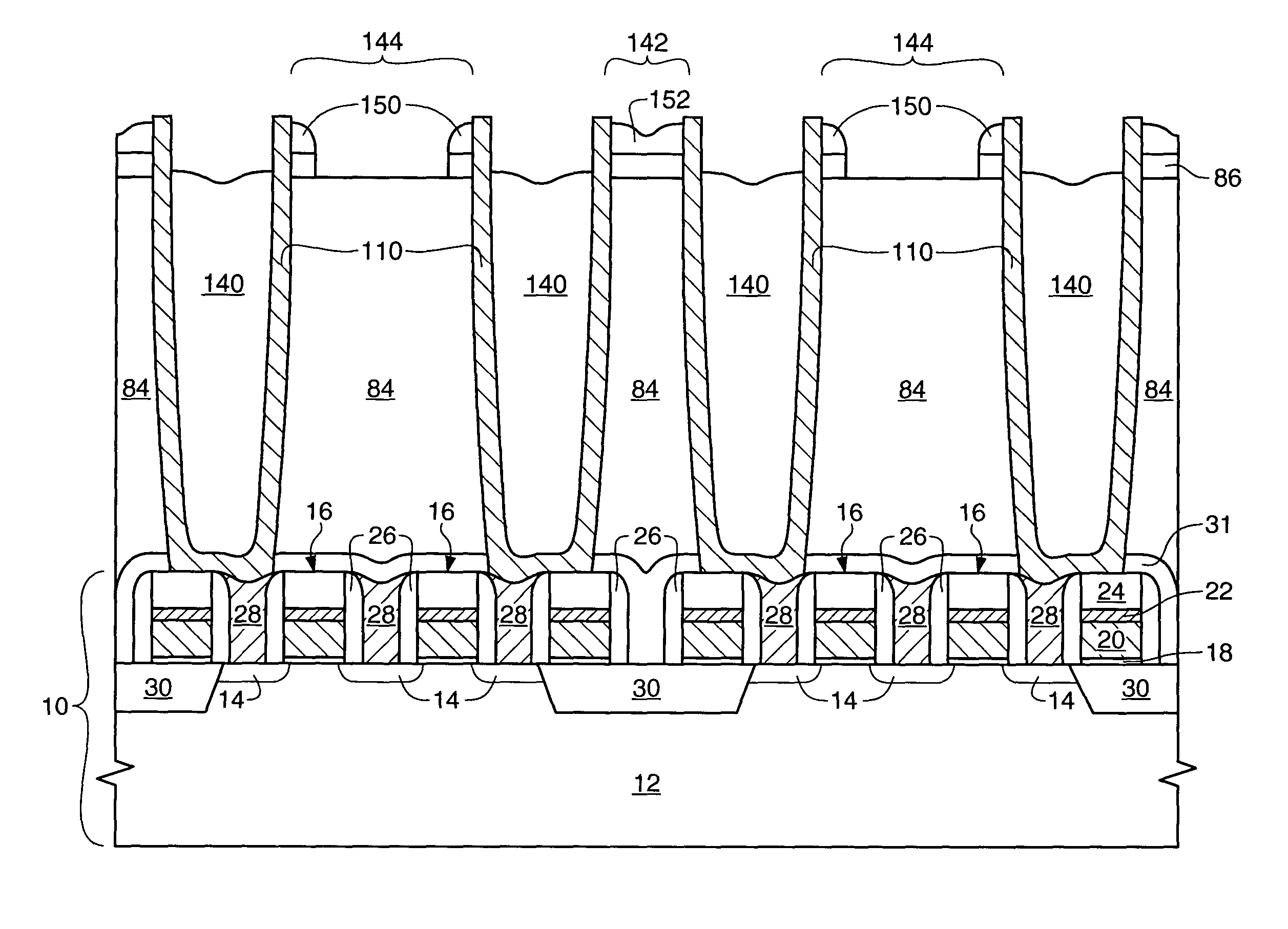

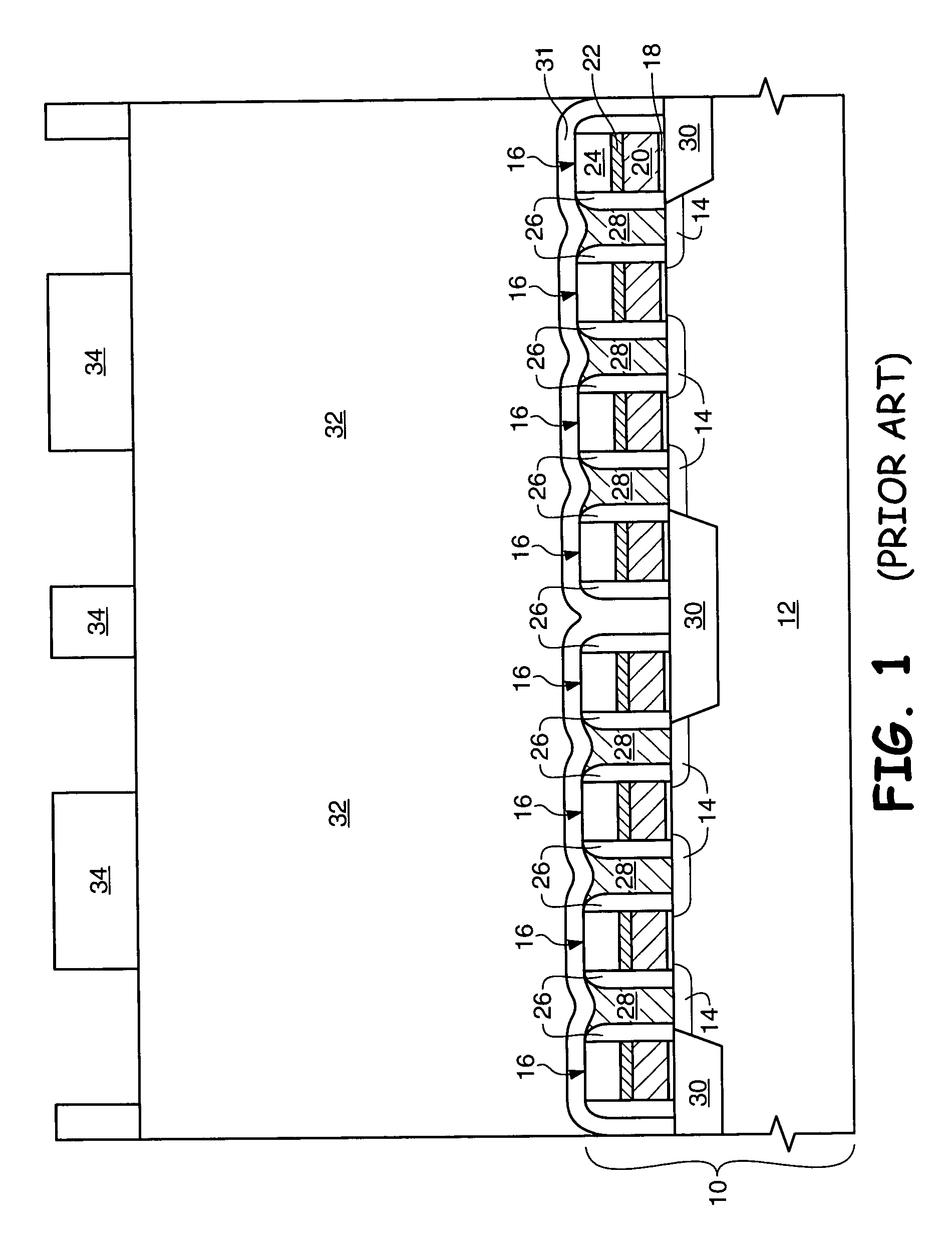

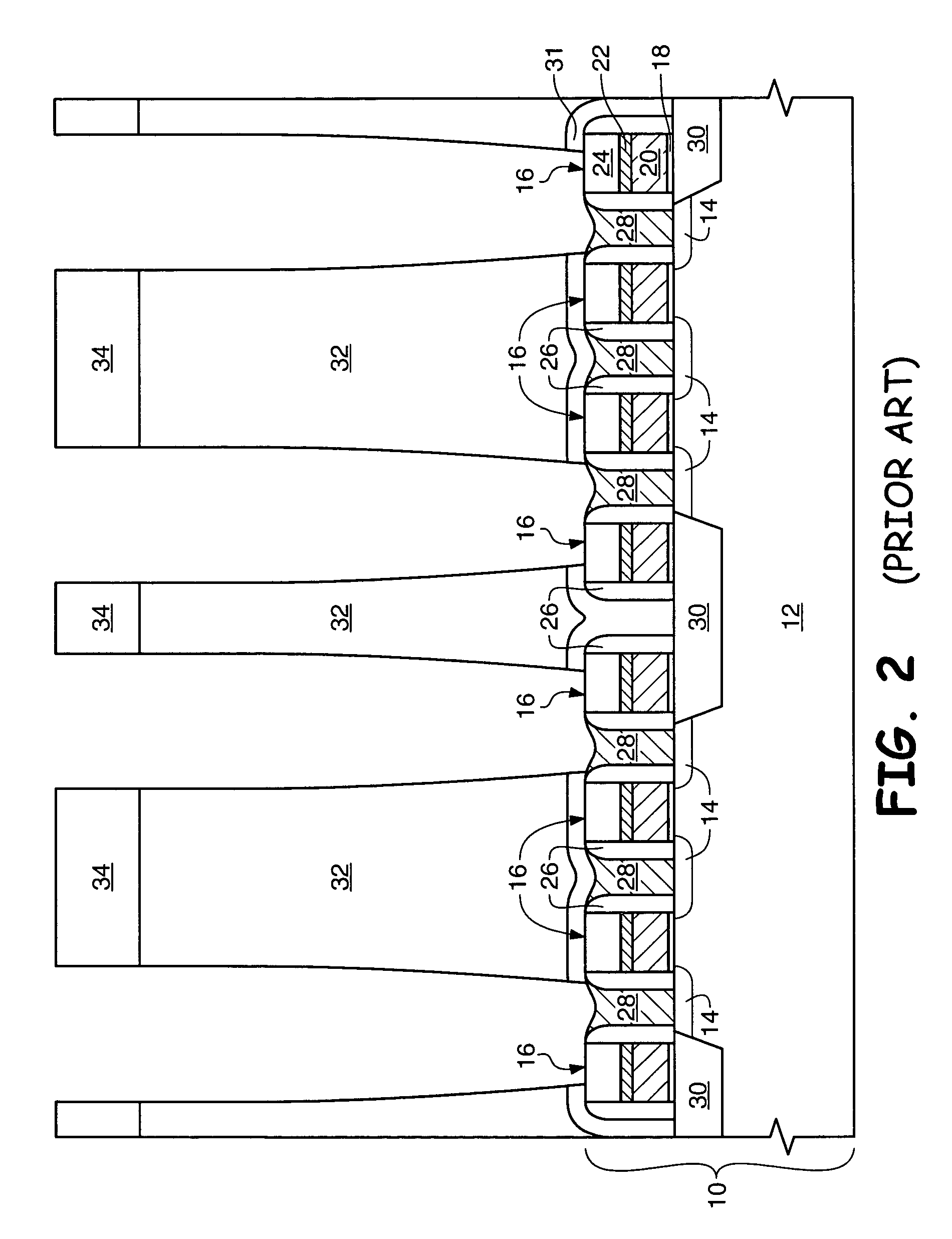

A method for forming double-sided capacitors for a semiconductor device includes forming a dielectric structure which supports capacitor bottom plates during wafer processing. The structure is particularly useful for supporting the bottom plates during removal of a base dielectric layer to expose the outside of the bottom plates to form a double-sided capacitor. The support structure further supports the bottom plates during formation of a cell dielectric layer, a capacitor top plate, and final supporting dielectric. An inventive structure is also described.

Owner:ROUND ROCK RES LLC

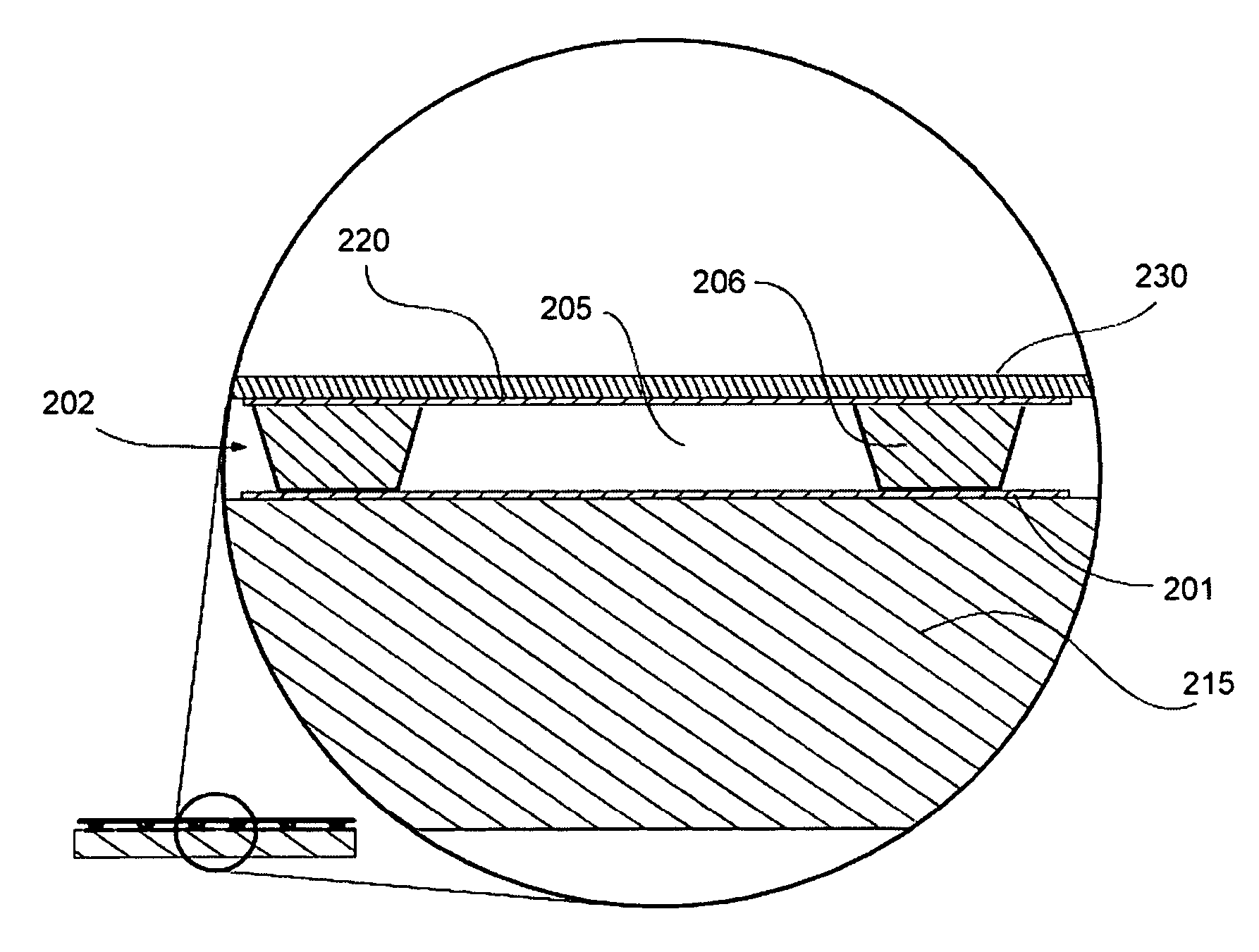

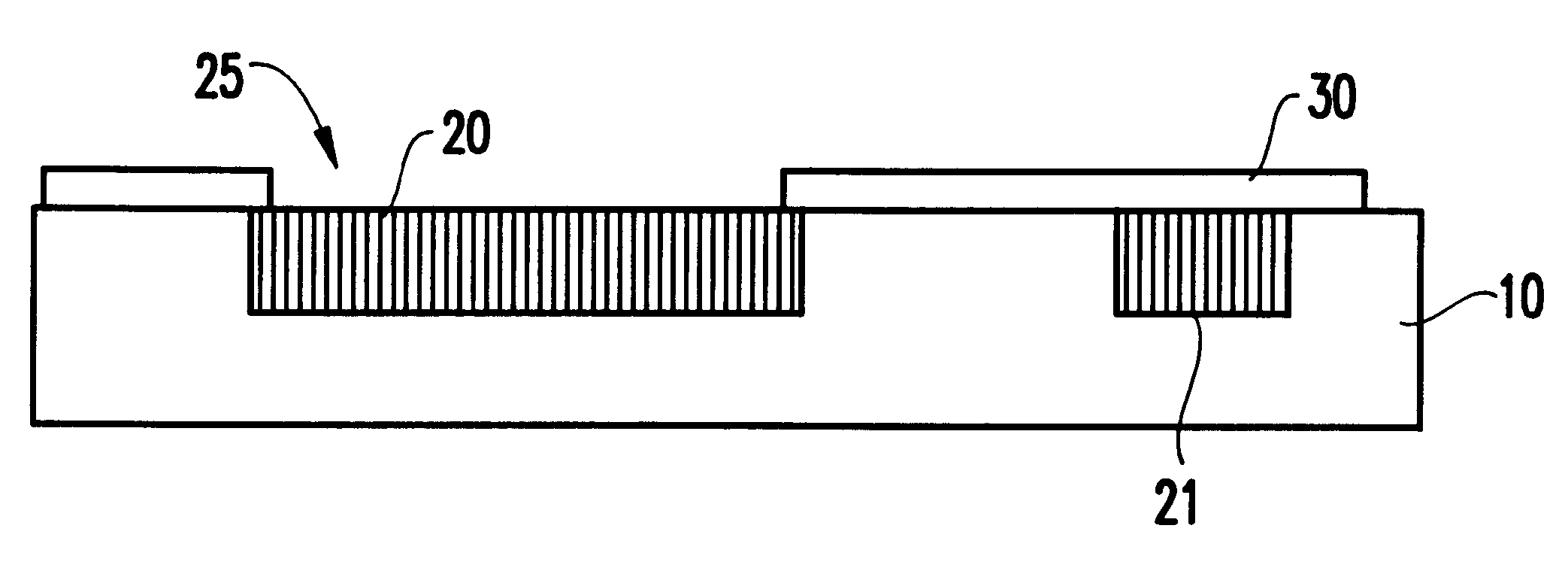

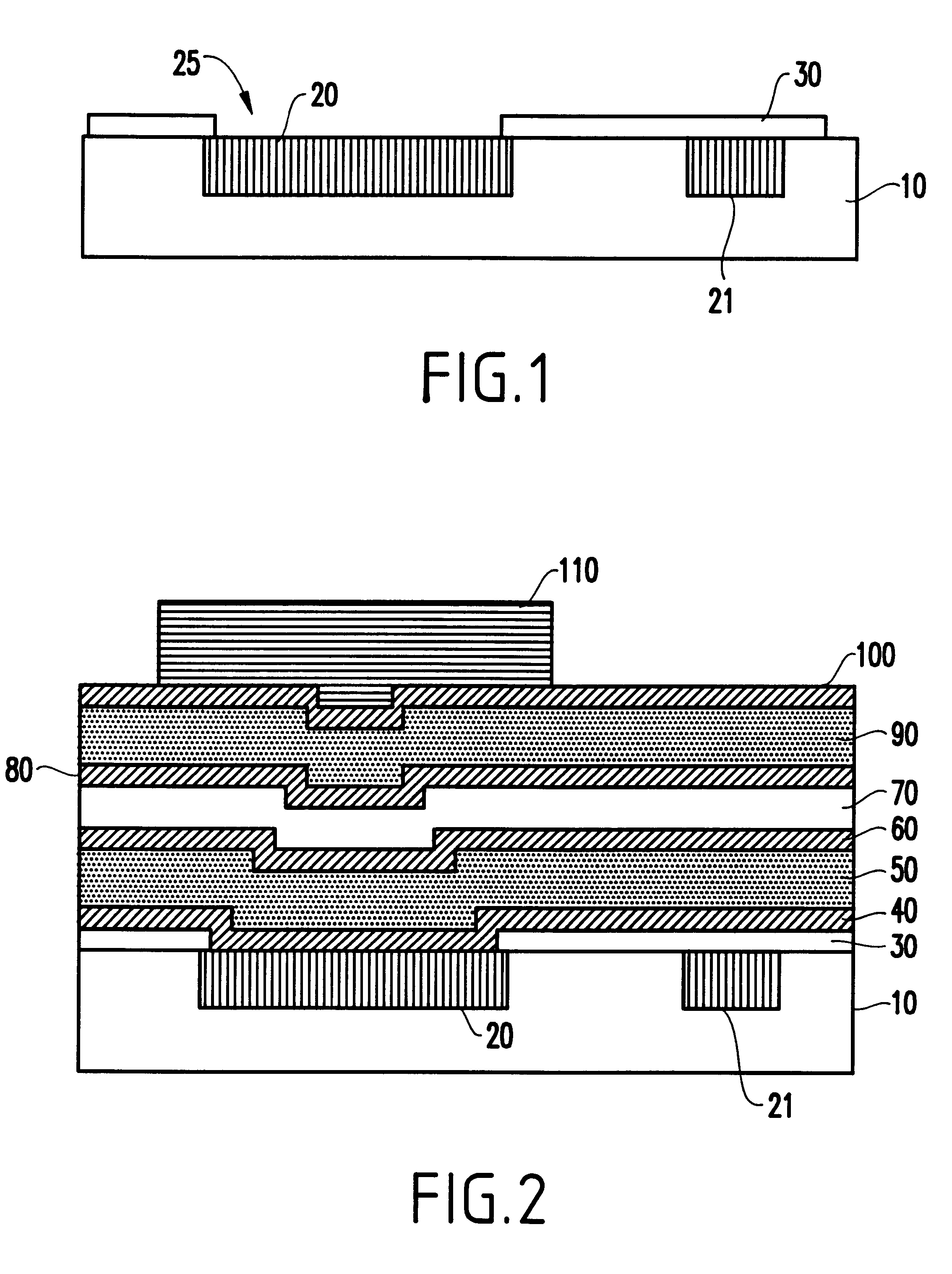

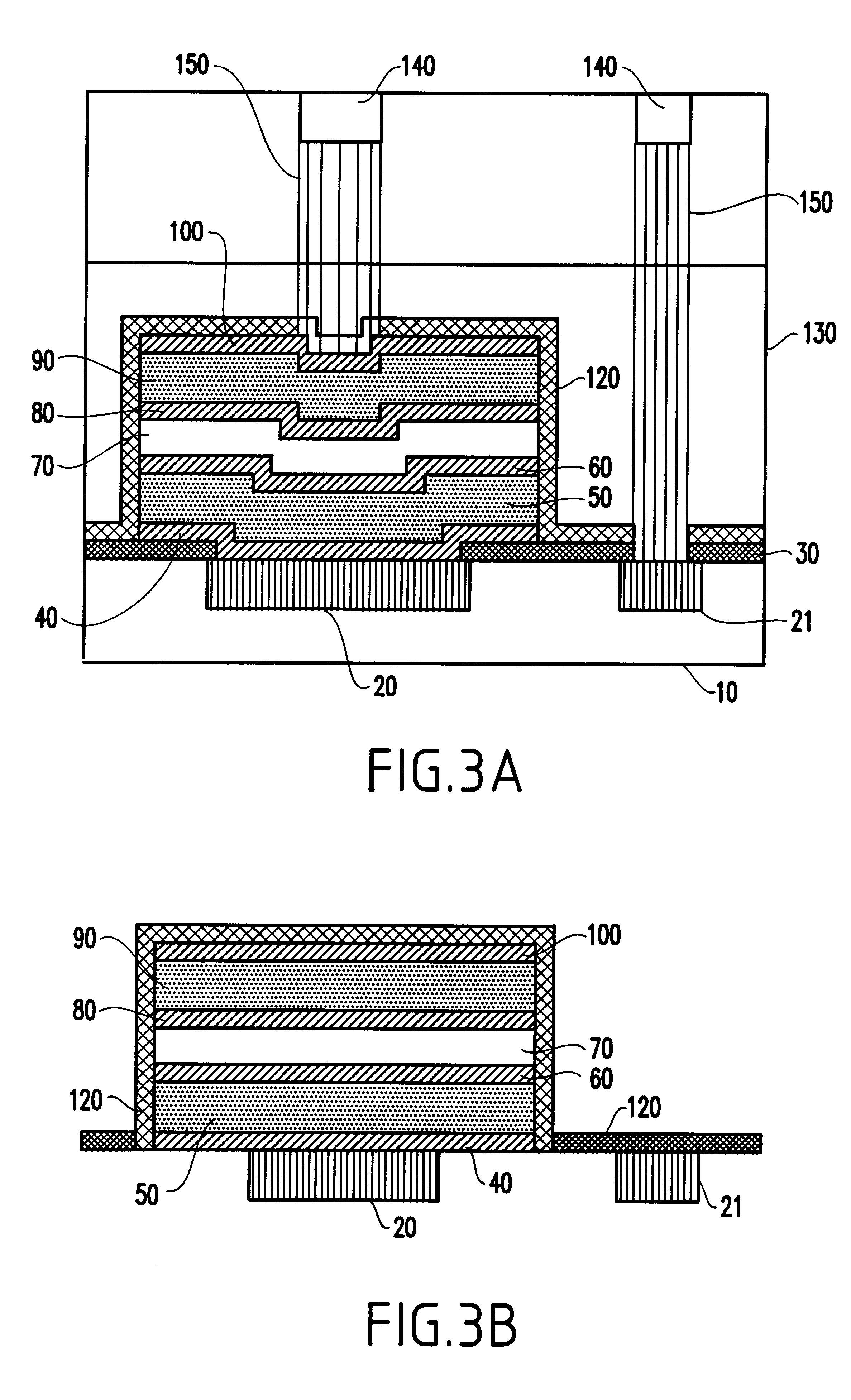

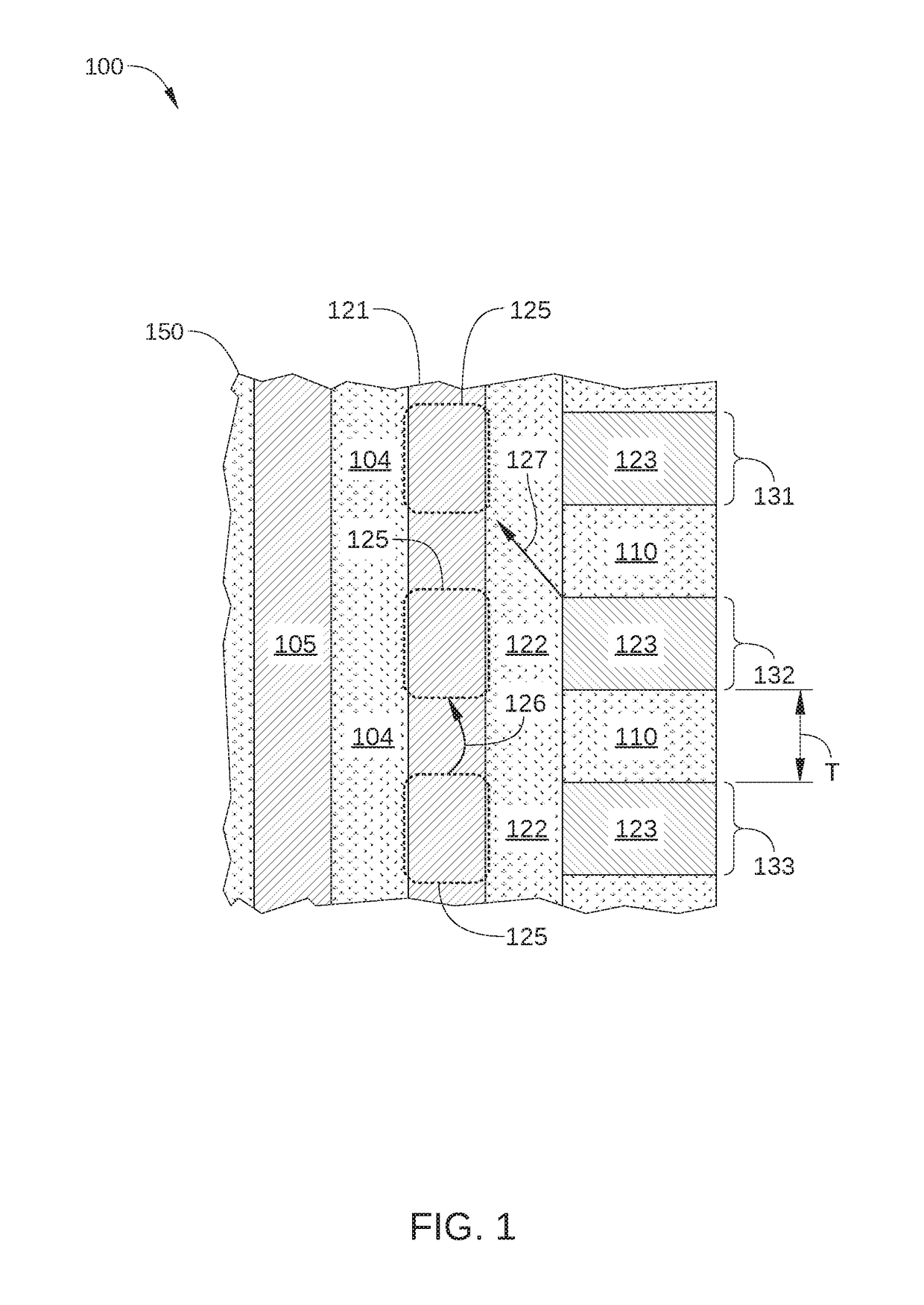

Support for vertically oriented capacitors during the formation of a semiconductor device

A method for forming double-sided capacitors for a semiconductor device includes forming a dielectric structure which supports capacitor bottom plates during wafer processing. The structure is particularly useful for supporting the bottom plates during removal of a base dielectric layer to expose the outside of the bottom plates to form a double-sided capacitor. The support structure further supports the bottom plates during formation of a cell dielectric layer, a capacitor top plate, and final supporting dielectric. An inventive structure is also described.

Owner:ROUND ROCK RES LLC

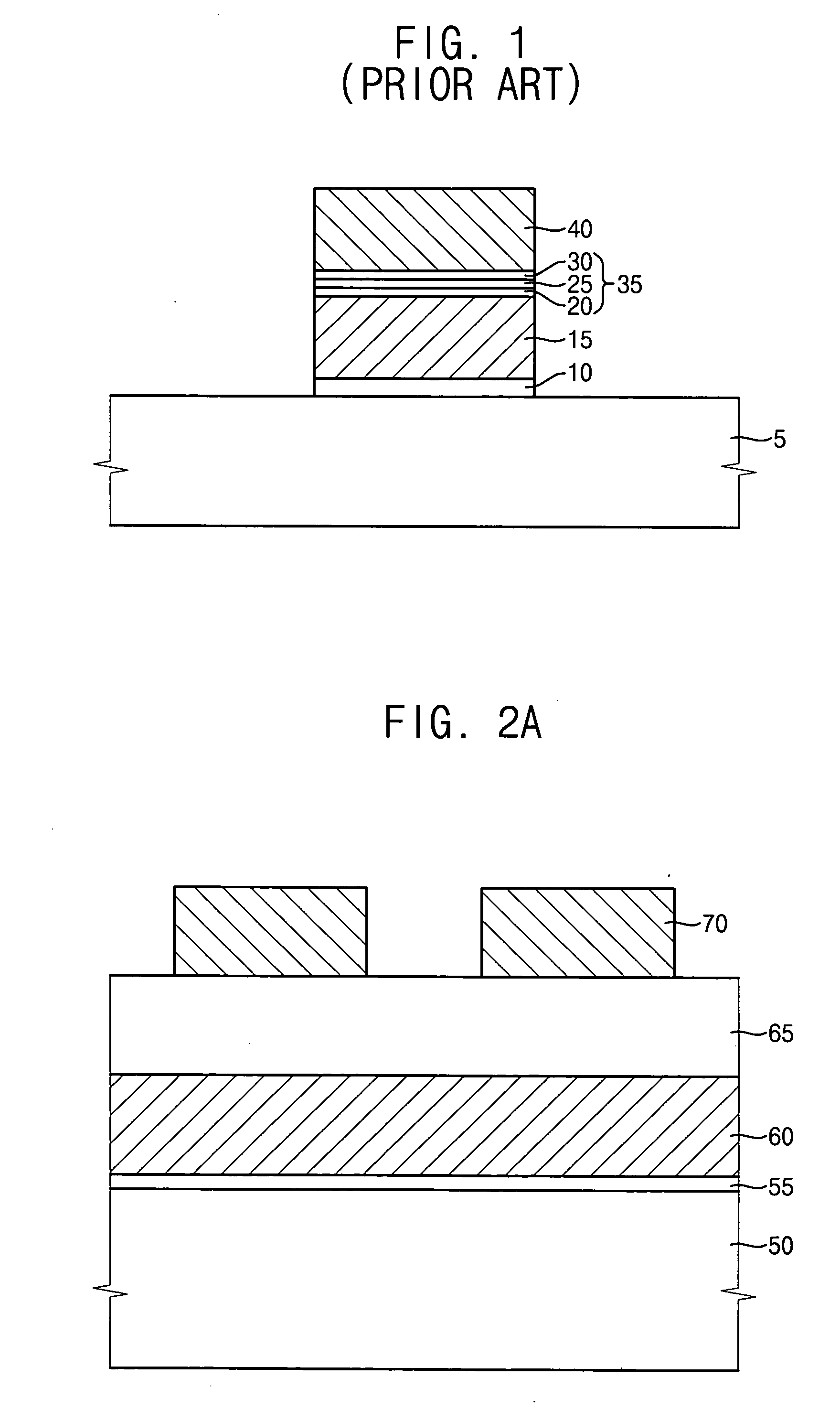

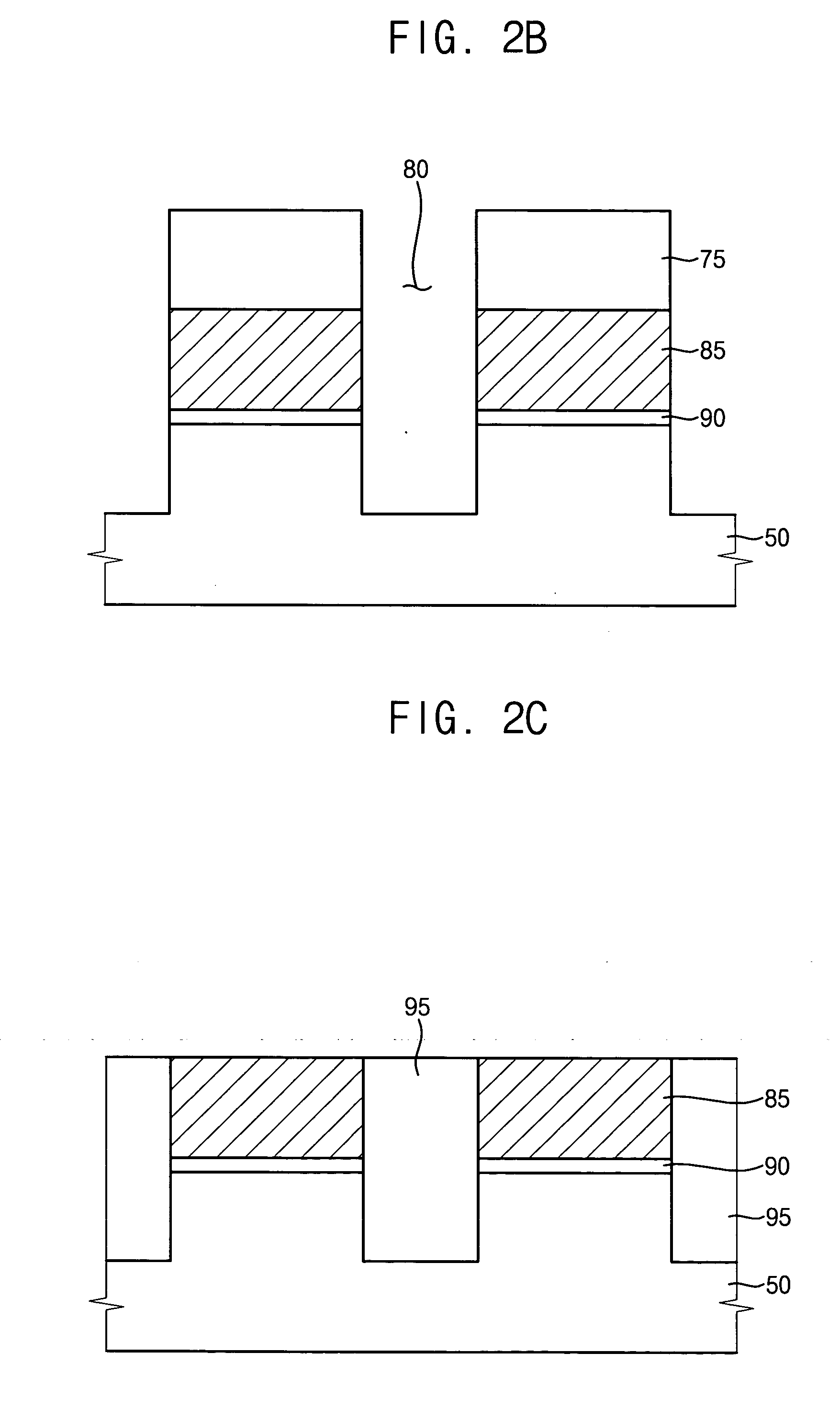

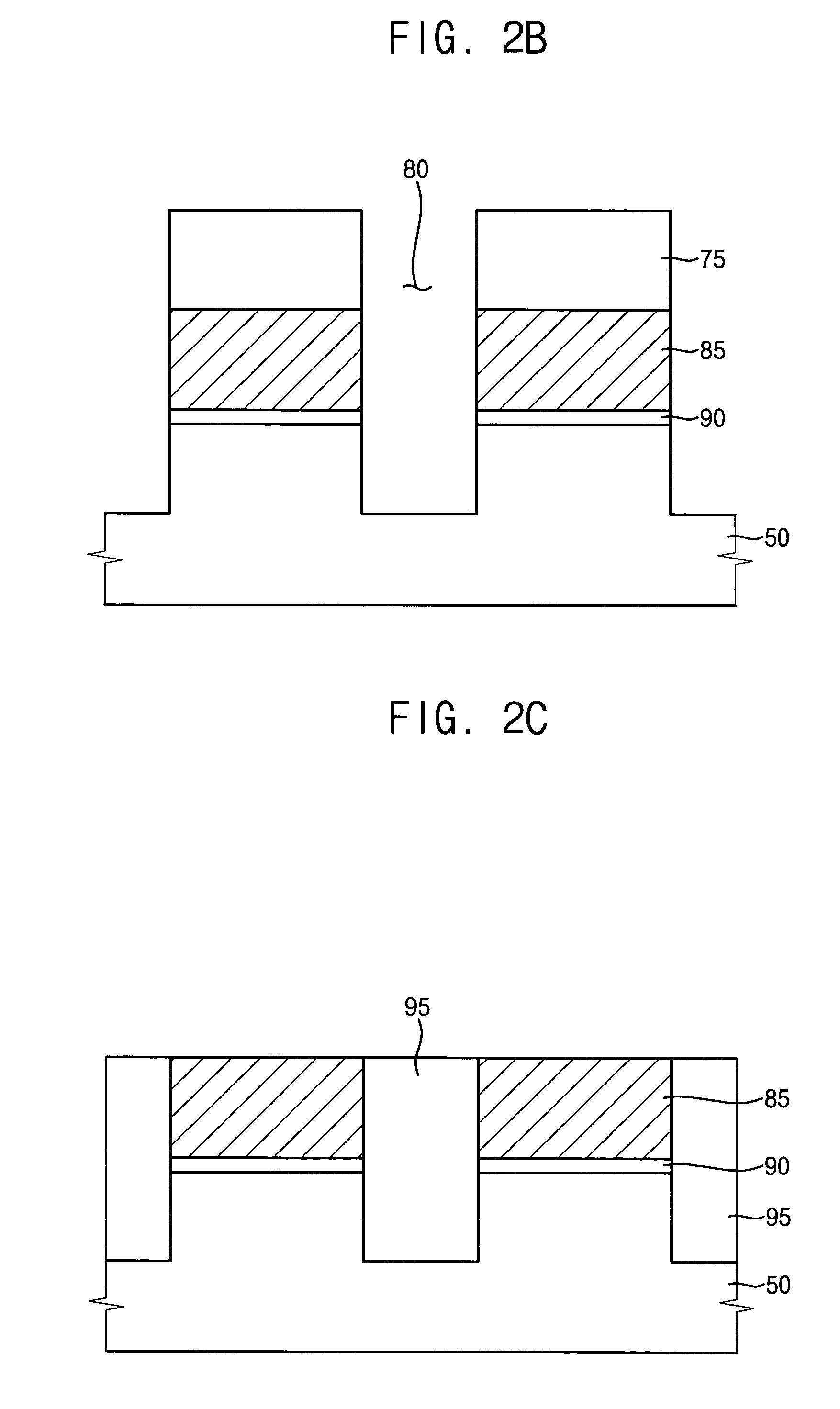

Dielectric structures having high dielectric constants, methods of forming the dielectric structures, non-volatile semiconductor memory devices having the dielectric structures and methods of manufacturing the non-volatile semiconductor memory devices

ActiveUS20060244147A1High dielectric constantImprove heat resistanceRoofingSemiconductor/solid-state device detailsCapacitanceLow leakage

In a method of manufacturing a dielectric structure, after a tunnel oxide layer pattern is formed on a substrate, a floating gate is formed on the tunnel oxide layer. After a first dielectric layer pattern including a metal silicon oxide and a second dielectric layer pattern including a metal silicon oxynitride are formed, a control gate is formed on the dielectric structure. Since the dielectric structure includes at least one metal silicon oxide layer and at least one metal silicon oxynitride layer, the dielectric structure may have a high dielectric constant and a good thermal resistance. A non-volatile semiconductor memory device including the dielectric structure may have good electrical characteristics such as a large capacitance and a low leakage current.

Owner:SAMSUNG ELECTRONICS CO LTD

Dielectric structures having high dielectric constants, and non-volatile semiconductor memory devices having the dielectric structures

ActiveUS7482677B2High dielectric constantImprove heat resistanceSemiconductor/solid-state device detailsRoofingCapacitanceLow leakage

In a method of manufacturing a dielectric structure, after a tunnel oxide layer pattern is formed on a substrate, a floating gate is formed on the tunnel oxide layer. After a first dielectric layer pattern including a metal silicon oxide and a second dielectric layer pattern including a metal silicon oxynitride are formed, a control gate is formed on the dielectric structure. Since the dielectric structure includes at least one metal silicon oxide layer and at least one metal silicon oxynitride layer, the dielectric structure may have a high dielectric constant and a good thermal resistance. A non-volatile semiconductor memory device including the dielectric structure may have good electrical characteristics such as a large capacitance and a low leakage current.

Owner:SAMSUNG ELECTRONICS CO LTD

Method of forming a selectively converted inter-layer dielectric using a porogen material

InactiveUS7018918B2Solid-state devicesSemiconductor/solid-state device manufacturingPorosityInter layer

An inter-layer dielectric structure and method of making such structure are disclosed. A composite dielectric layer, initially comprising a porous matrix and a porogen, is formed. Subsequent to other processing treatments, the porogen is decomposed and removed from at least a portion of the porous matrix, leaving voids defined by the porous matrix in areas previously occupied by the porogen. The resultant structure has a desirably low k value as a result of the porosity and materials comprising the porous matrix and porogen. The composite dielectric layer may be used in concert with other dielectric layers of varying porosity, dimensions, and material properties to provide varied mechanical and electrical performance profiles.

Owner:INTEL CORP

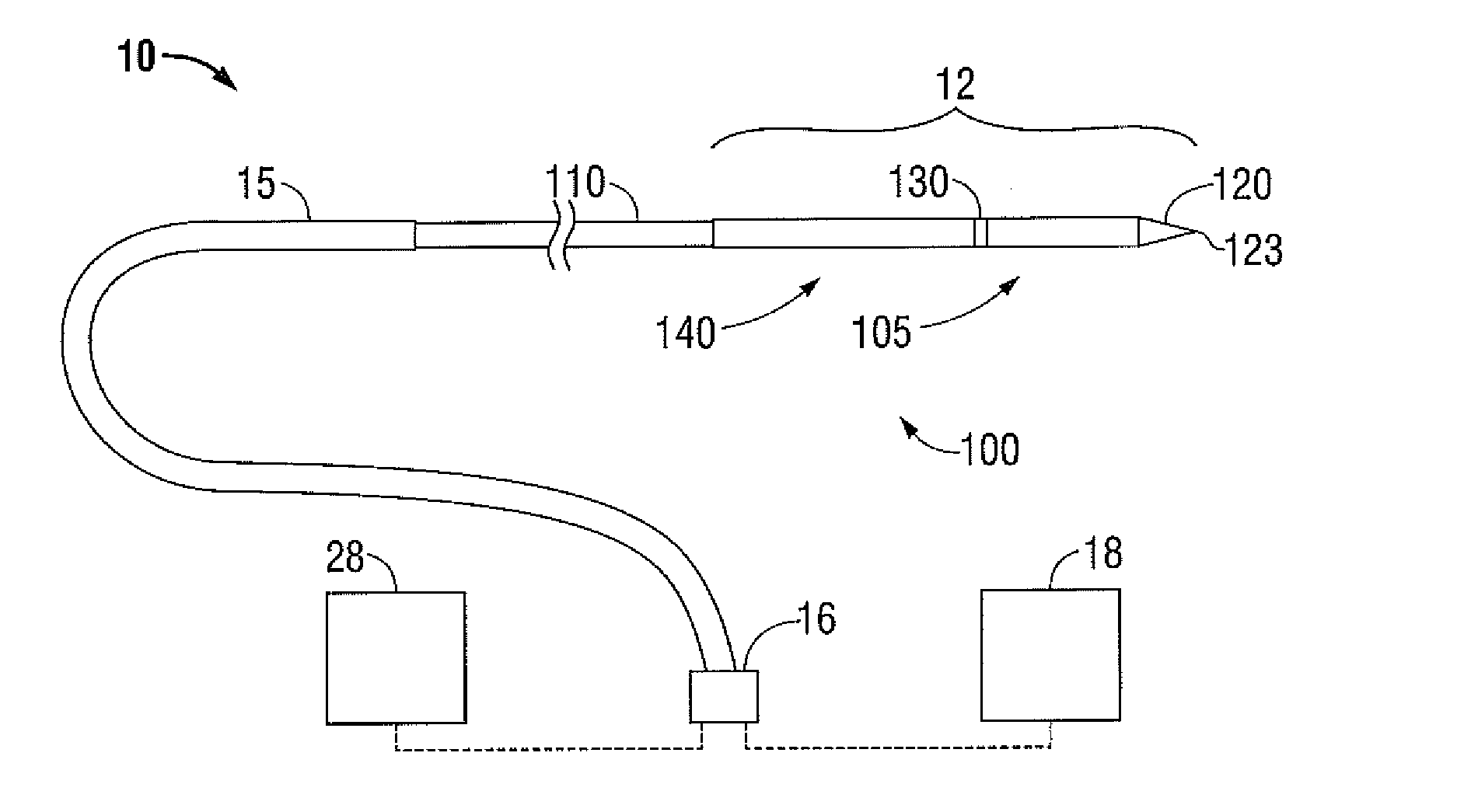

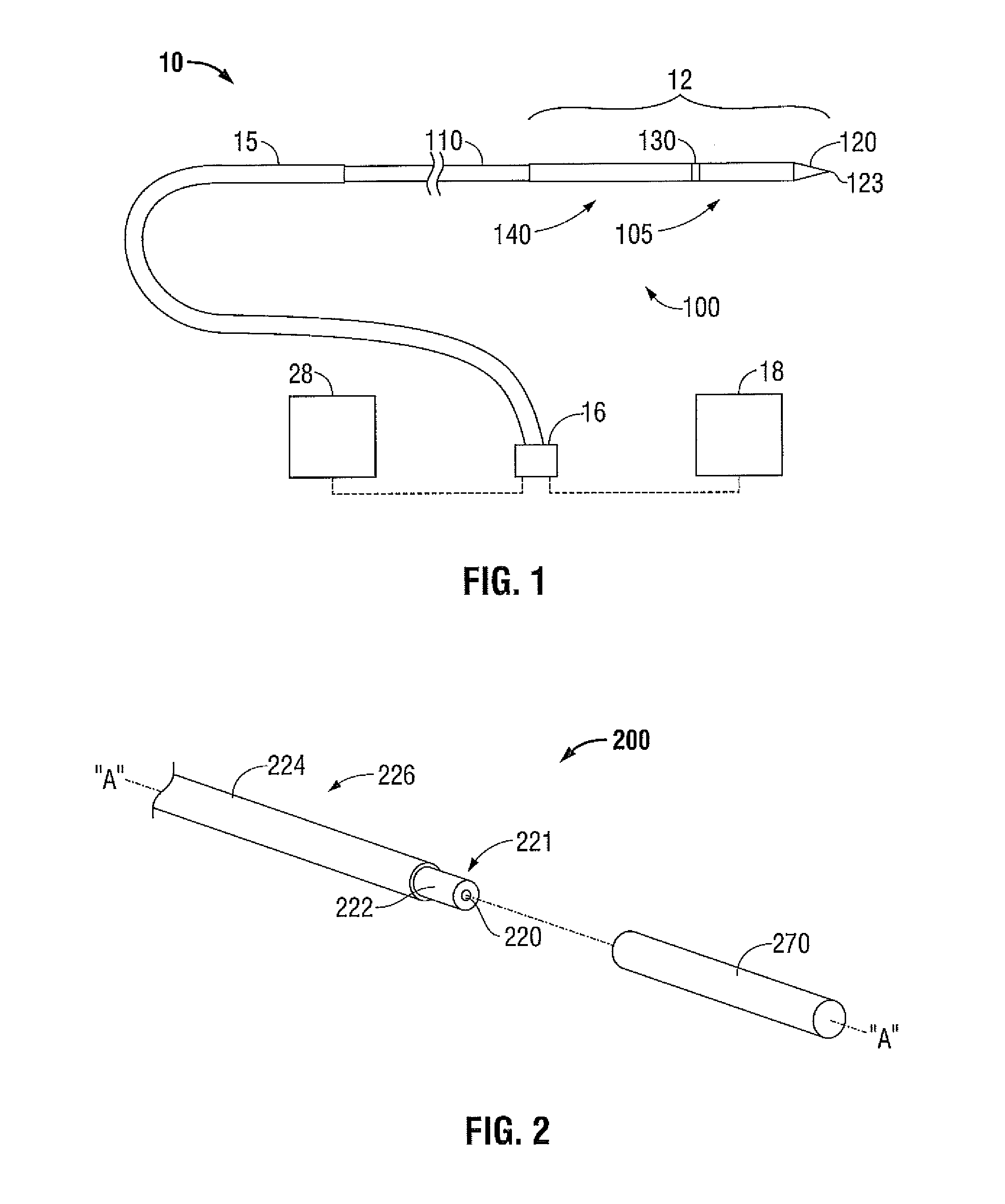

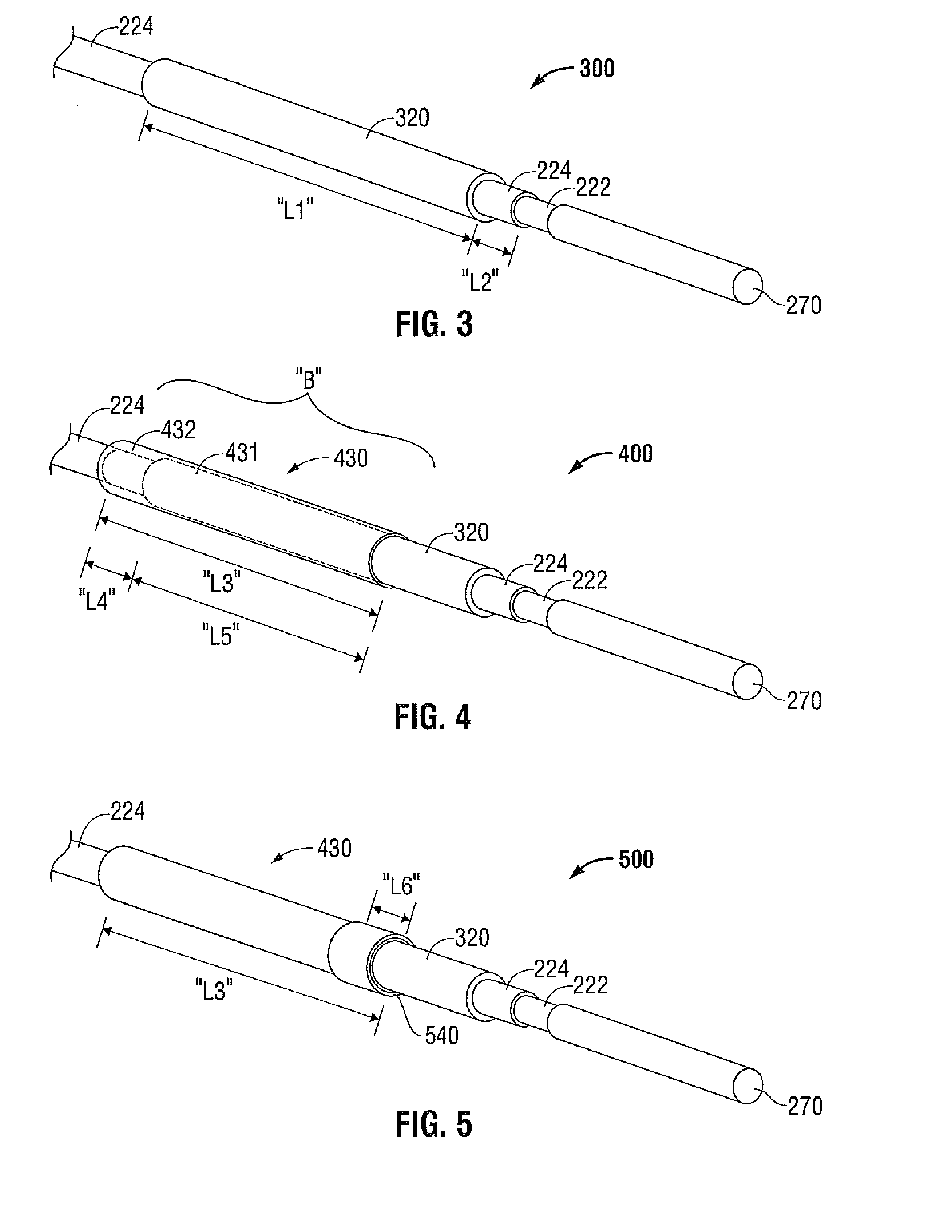

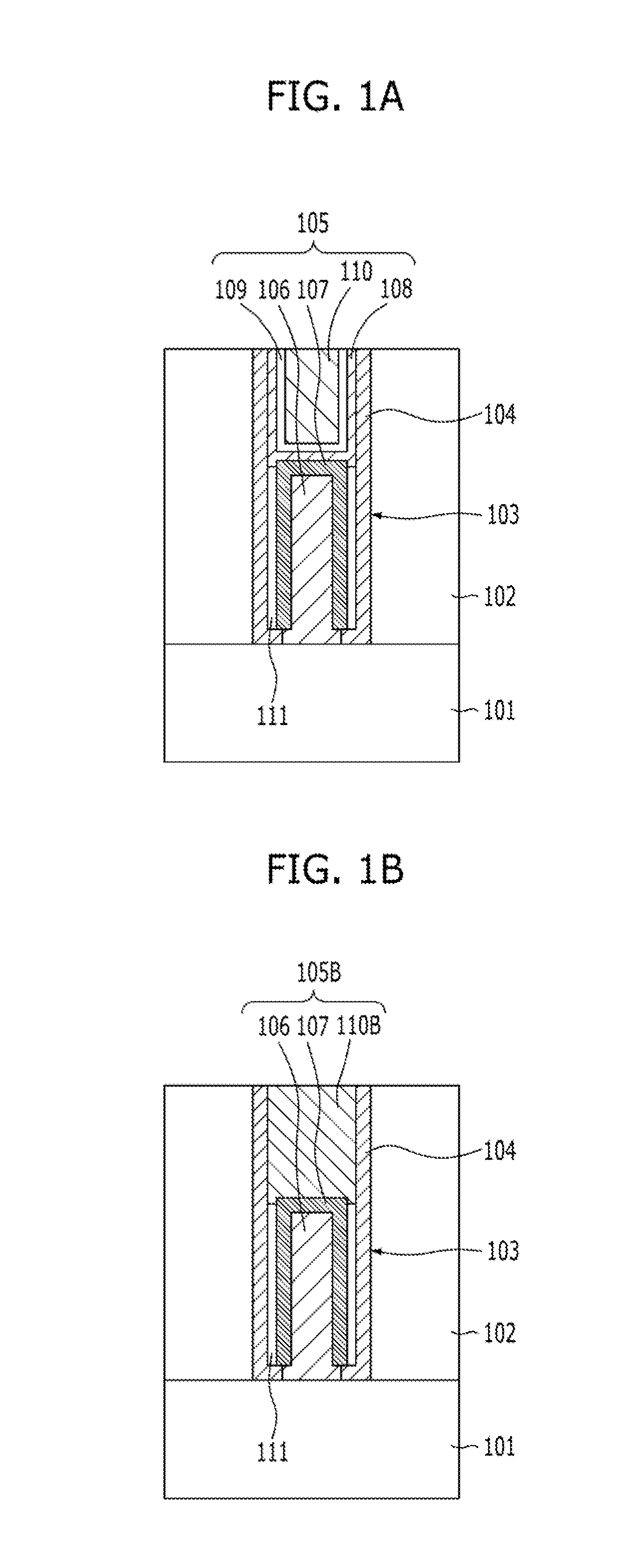

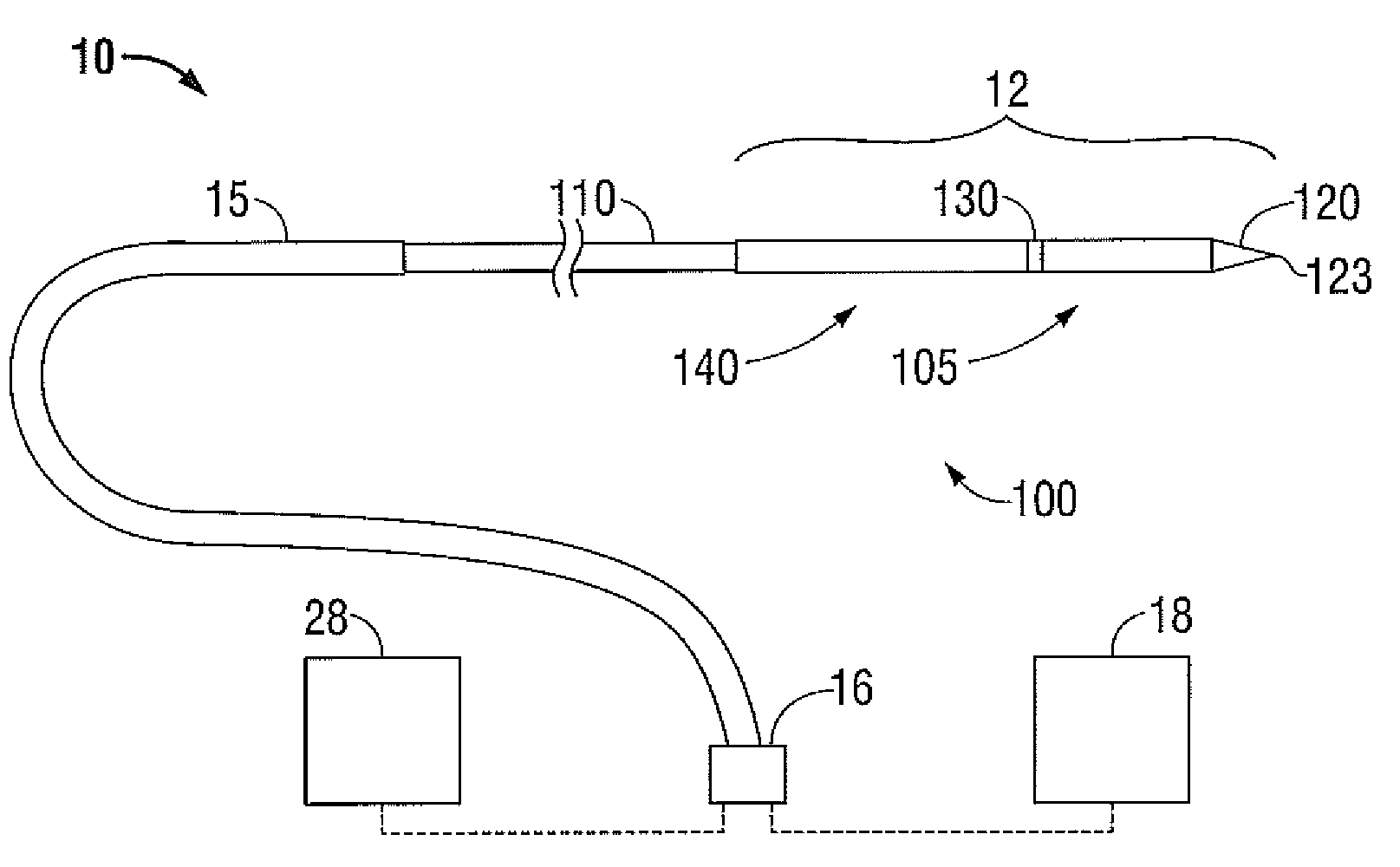

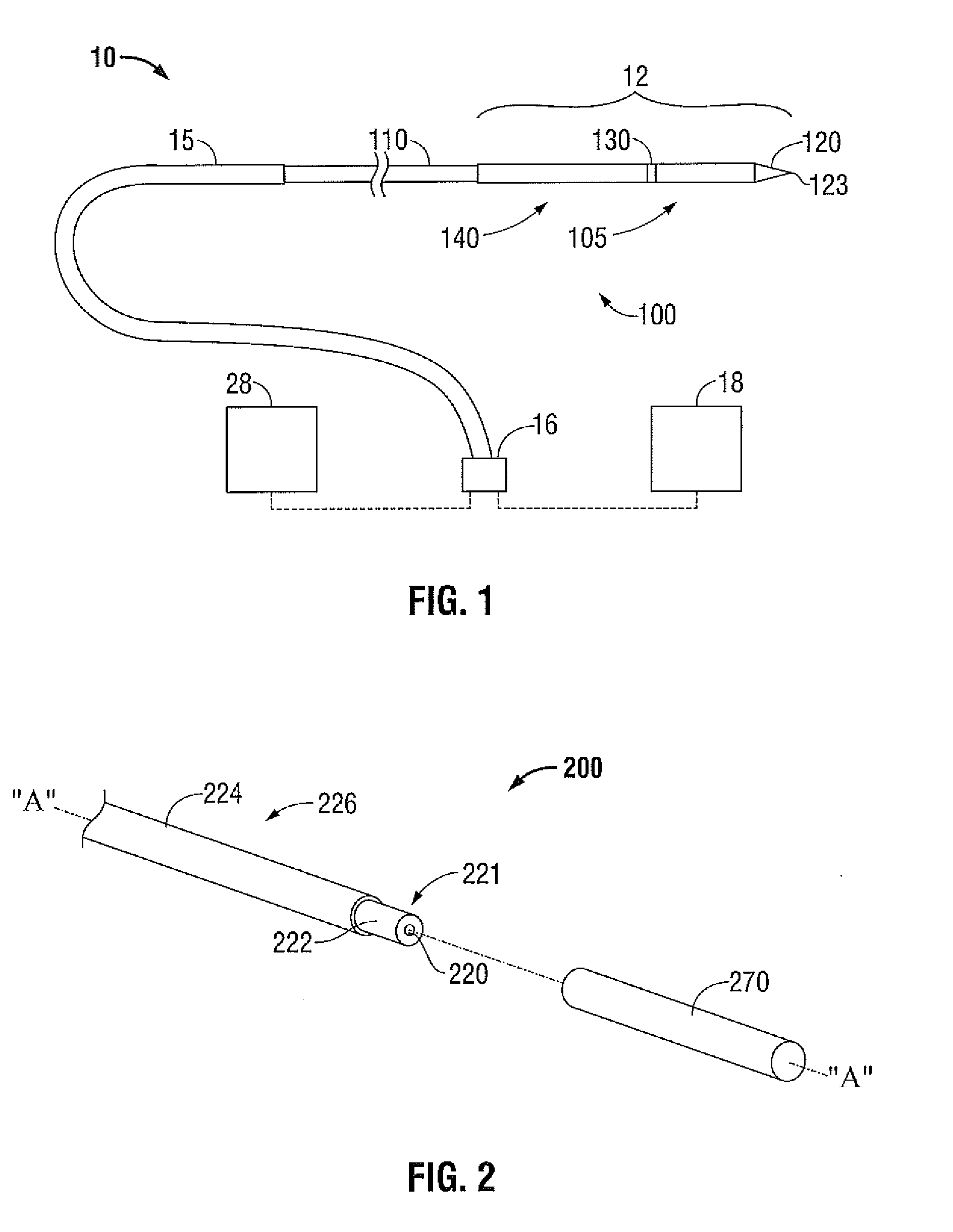

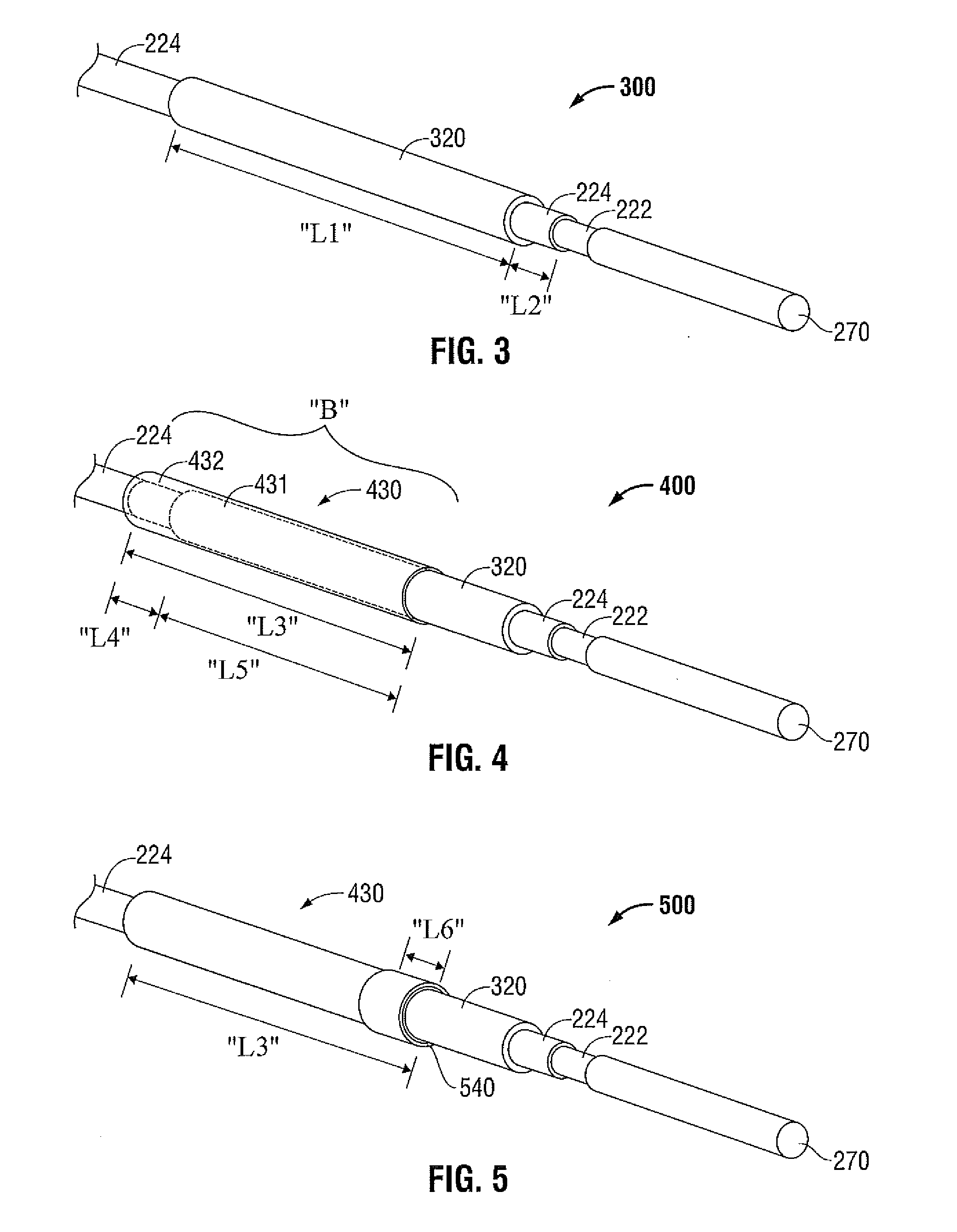

Surface Ablation Antenna with Dielectric Loading

An electrosurgical device for directing energy to a target volume of tissue includes a coaxial feedline having an inner conductor, an outer conductor coaxially disposed around the inner conductor, and a dielectric material disposed therebetween. An elongated electrically-conductive member is longitudinally disposed at a distal end of the inner conductor; a balun structure is disposed on the outer conductor. An electrically-conductive cylinder is coaxially disposed around a distal portion of the balun structure and a dielectric structure is disposed substantially adjacent to a distal end of the electrically-conductive cylinder and configured to extend to a distal end of the electrically-conductive member. An elongated handle assembly is coaxially disposed around a portion of the outer conductor proximal to the dielectric structure and a shell assembly is disposed at a distal end of the elongated handle assembly. A portion of the shell assembly is configured to extend distally beyond the distal end of the electrically-conductive member.

Owner:TYCO HEALTHCARE GRP LP

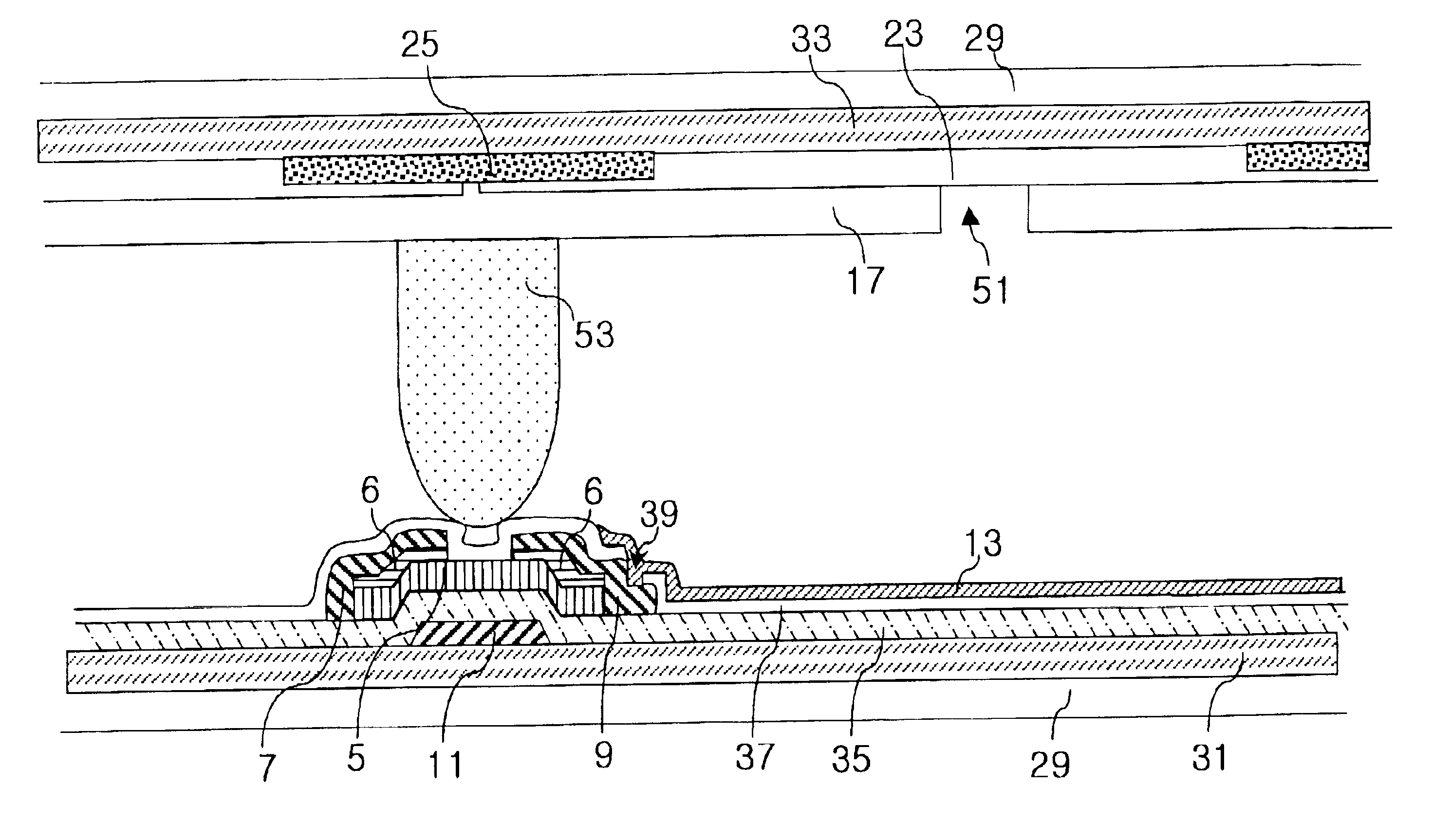

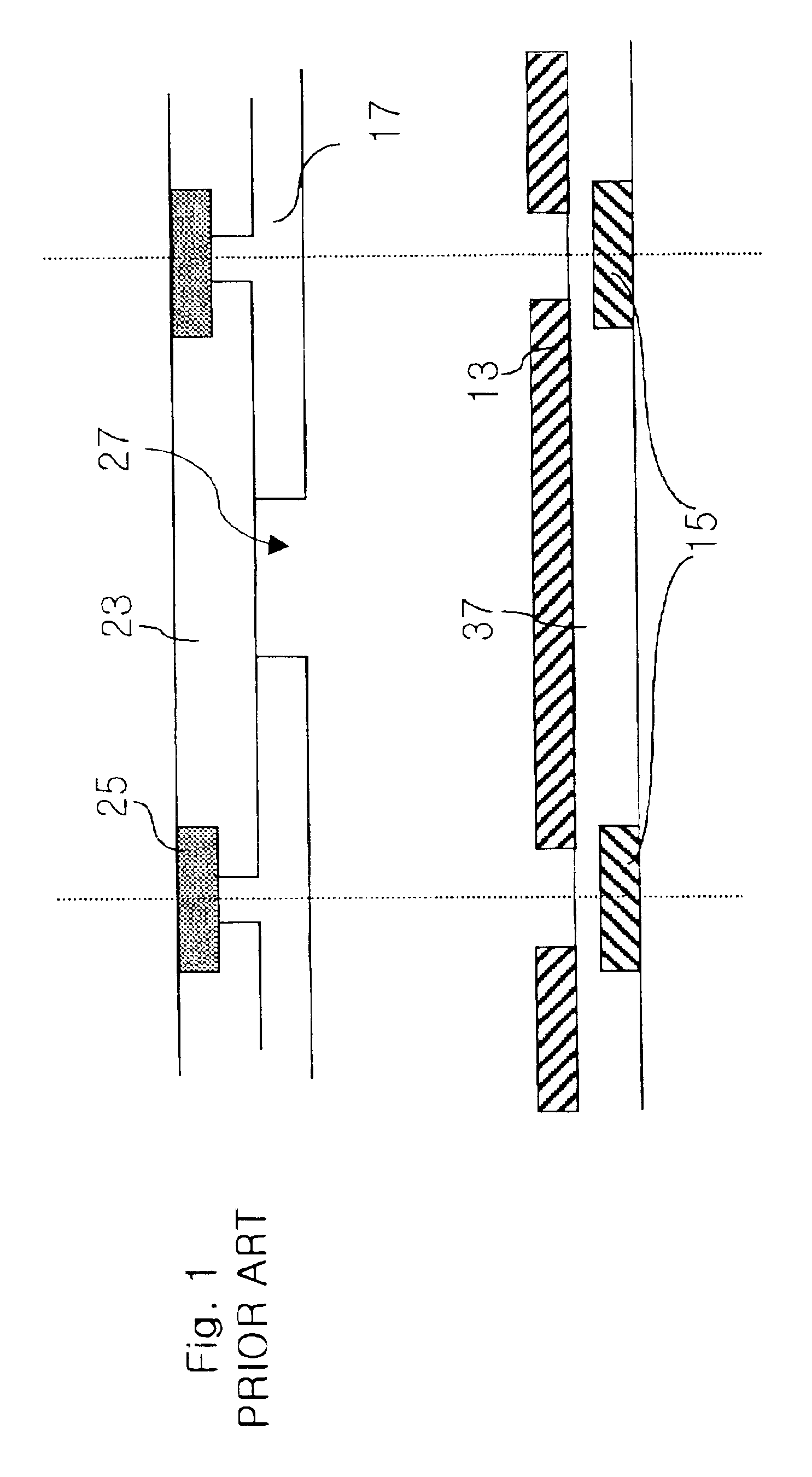

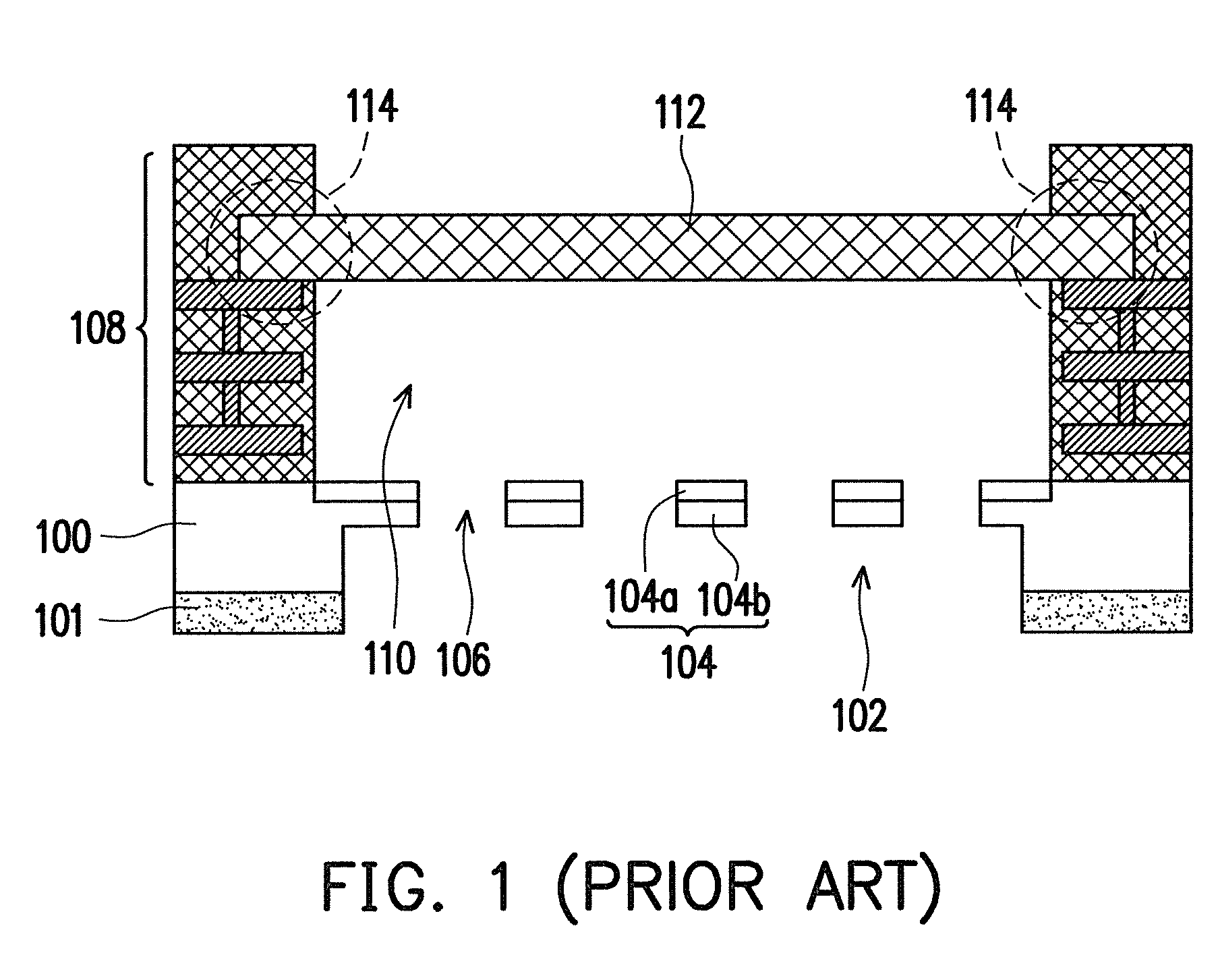

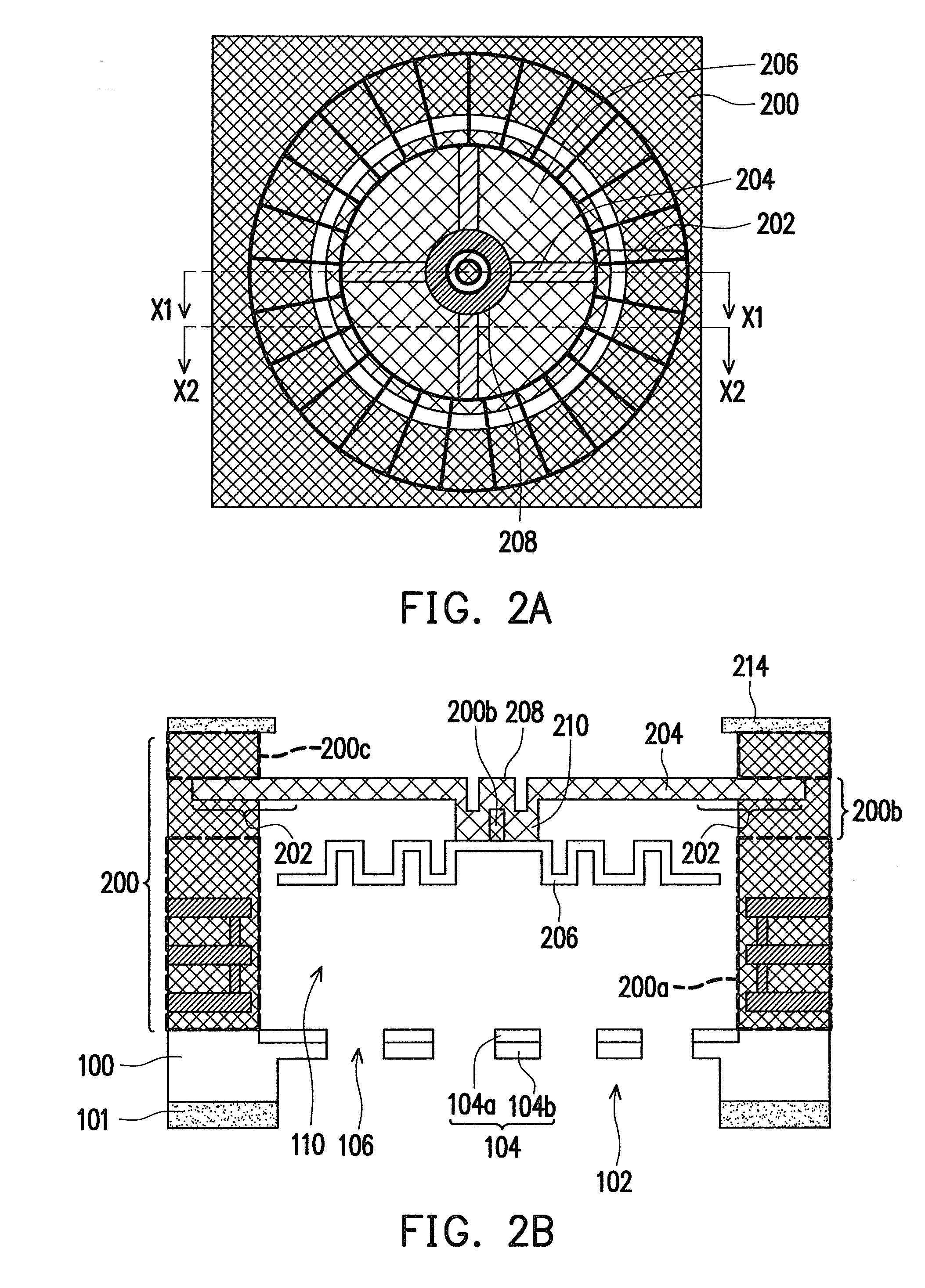

Multi-domain liquid crystal display device with particular dielectric structures

InactiveUS6900869B1Uniform gapHigh response time characteristicNon-linear opticsLiquid-crystal displayDielectric structure

A multi-domain liquid crystal display device includes first and second substrates facing each other and a liquid crystal layer between the first and second substrates. A plurality of gate bus lines are arranged in a first direction on the first substrate and a plurality of data bus lines are arranged in a second direction on the first substrate to define a pixel region. A pixel electrode is electrically charged through the data bus line in the pixel region. A dielectric frame is in a region other than a region where the pixel electrode is formed, and distorts electric field applied to the liquid crystal layer. A common electrode is on the second substrate, and an alignment layer is on at least one substrate between the first and second substrates.

Owner:LG DISPLAY CO LTD

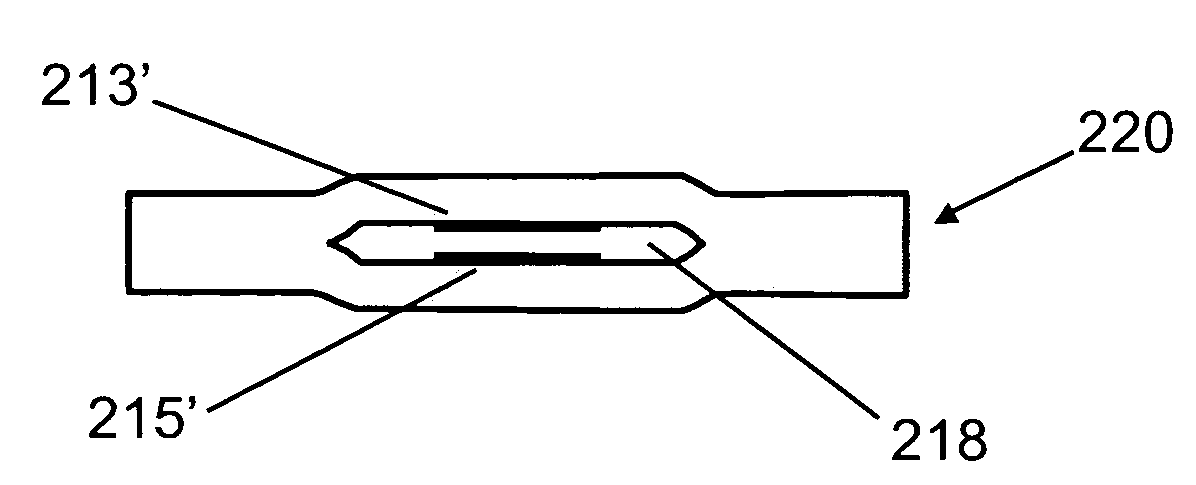

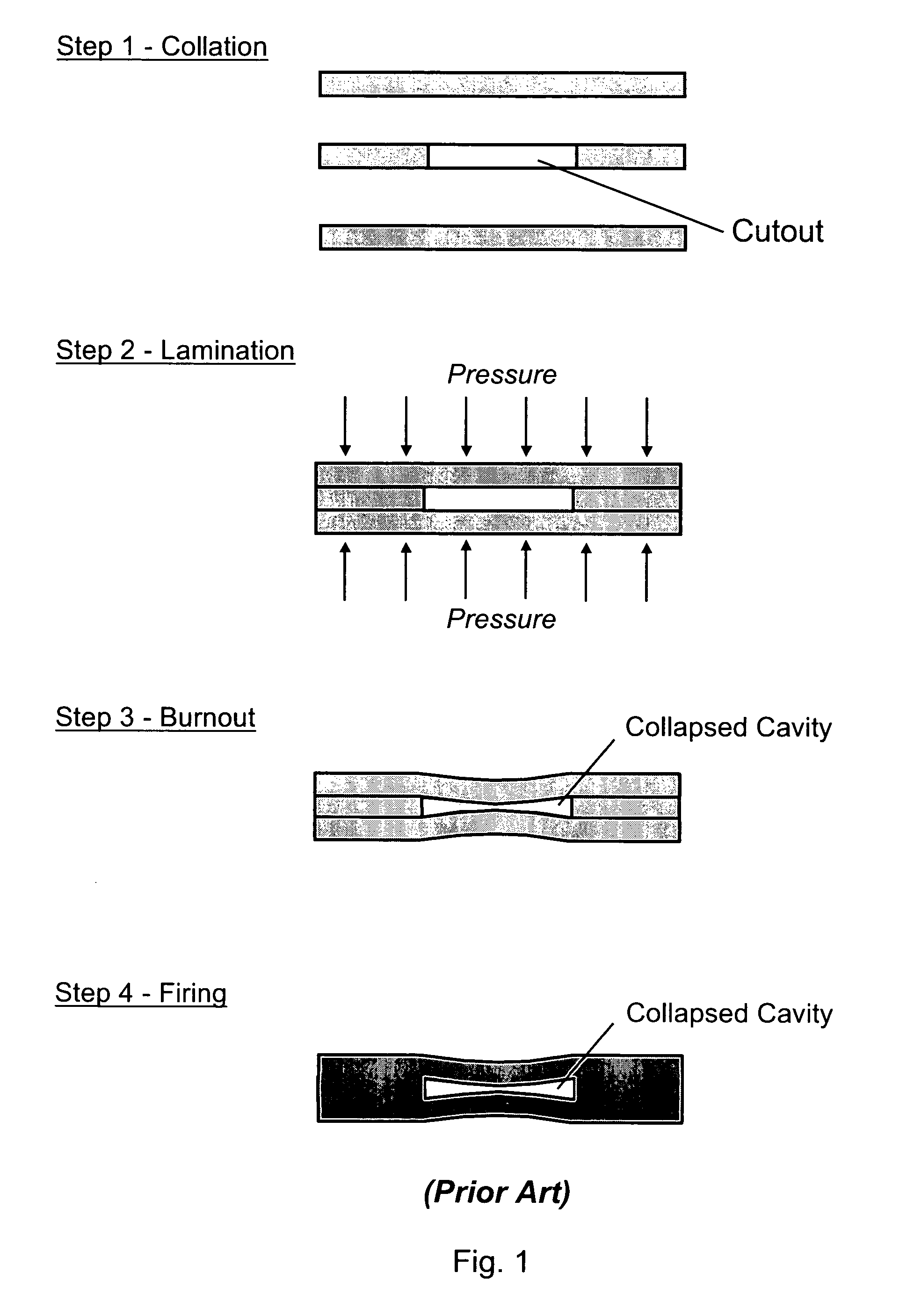

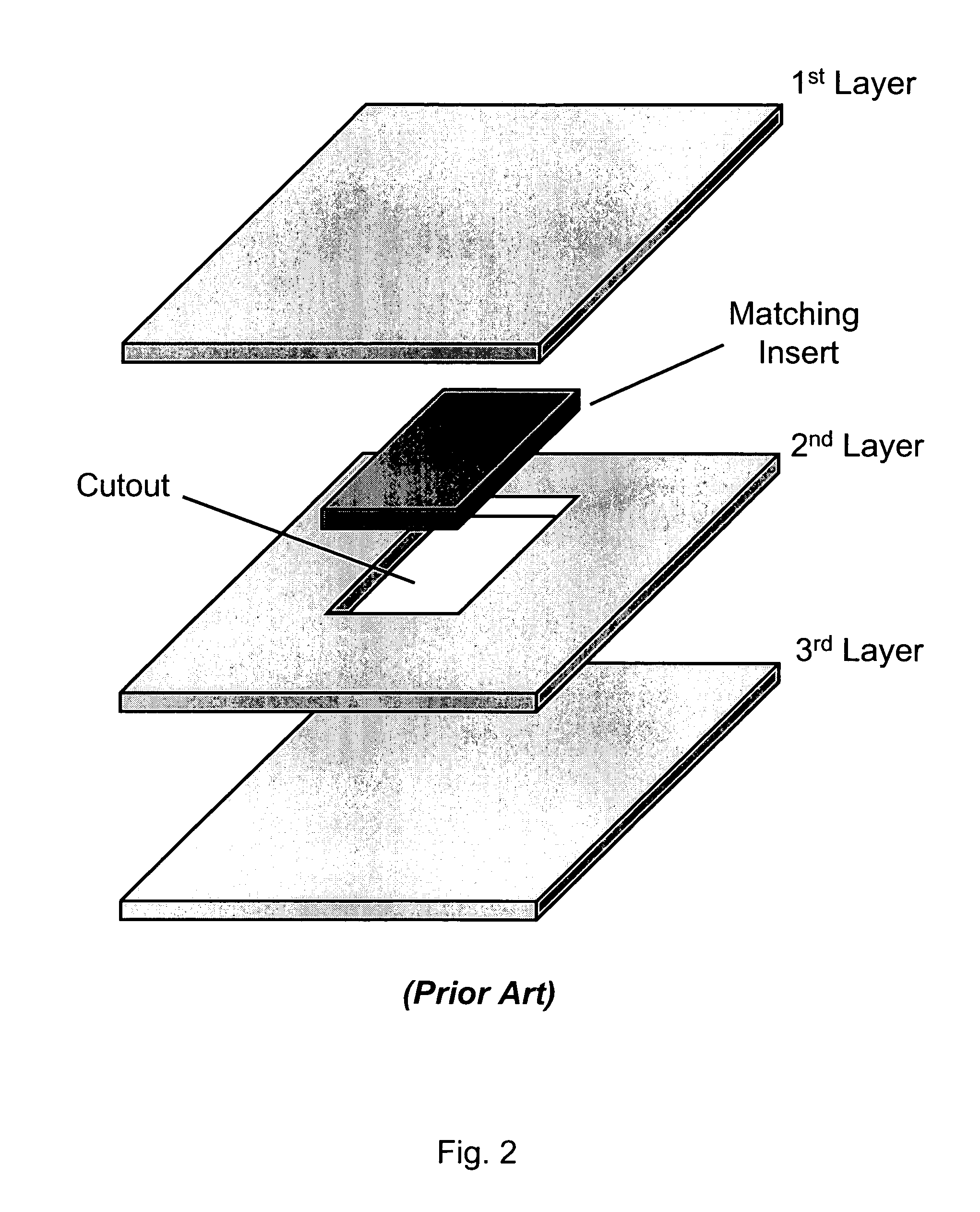

Method of using sacrificial materials for fabricating internal cavities in laminated dielectric structures

A method of using sacrificial materials for fabricating internal cavities and channels in laminated dielectric structures, which can be used as dielectric substrates and package mounts for microelectronic and microfluidic devices. A sacrificial mandrel is placed in-between two or more sheets of a deformable dielectric material (e.g., unfired LTCC glass / ceramic dielectric), wherein the sacrificial mandrel is not inserted into a cutout made in any of the sheets. The stack of sheets is laminated together, which deforms the sheet or sheets around the sacrificial mandrel. After lamination, the mandrel is removed, (e.g., during LTCC burnout), thereby creating a hollow internal cavity in the monolithic ceramic structure.

Owner:NAT TECH & ENG SOLUTIONS OF SANDIA LLC

Semiconductor package integrated with conformal shield and antenna

ActiveUS8786060B2Semiconductor/solid-state device detailsSolid-state devicesElectromagnetic interferenceSemiconductor package

Owner:ADVANCED SEMICON ENG INC

Method of forming DRAM capacitors with protected outside crown surface for more robust structures

A method for fabricating a high-density array of crown capacitors with increased capacitance while reducing process damage to the bottom electrodes is achieved. The process is particularly useful for crown capacitors for future DRAM circuits with minimum feature sizes of 0.18 micrometer or less. A conformal conducting layer is deposited over trenches in an interlevel dielectric (ILD) layer, and is polished back to form capacitor bottom electrodes. A novel photoresist mask and etching are then used to pattern the ILD layer to provide a protective interlevel dielectric structure between capacitors. The protective structures prevent damage to the bottom electrodes during subsequent processing. The etching also exposes portions of the outer surface of bottom electrodes for increased capacitance (>50%). In a first embodiment the ILD structure is formed between pairs of adjacent bottom electrodes, and in a second embodiment the ILD structure is formed between four adjacent bottom electrodes.

Owner:TAIWAN SEMICON MFG CO LTD

Cylindrical channel charge trapping devices with effectively high coupling ratios

ActiveUS20080099830A1Read-only memoriesSemiconductor/solid-state device manufacturingCylindrical channelElectrical conductor

A memory cell comprising: a source region and a drain region separated by a semiconductor channel region, the channel region having a channel surface having an area A1 including a first cylindrical region, a first dielectric structure on the channel surface, a dielectric charge trapping structure on the first dielectric structure, a second dielectric structure on the dielectric charge trapping structure, a conductive layer having a conductor surface having an area A2 including a second cylindrical region on the second dielectric structure, the conductor surface overlying the dielectric charge trapping structure and the channel surface of the channel region, and the ratio of the area A2 to the area A1 being greater than or equal to 1.2 are described along with devices thereof and methods for manufacturing.

Owner:MACRONIX INT CO LTD

Micro-electro-mechanical systems (MEMS) device and method for fabricating the same

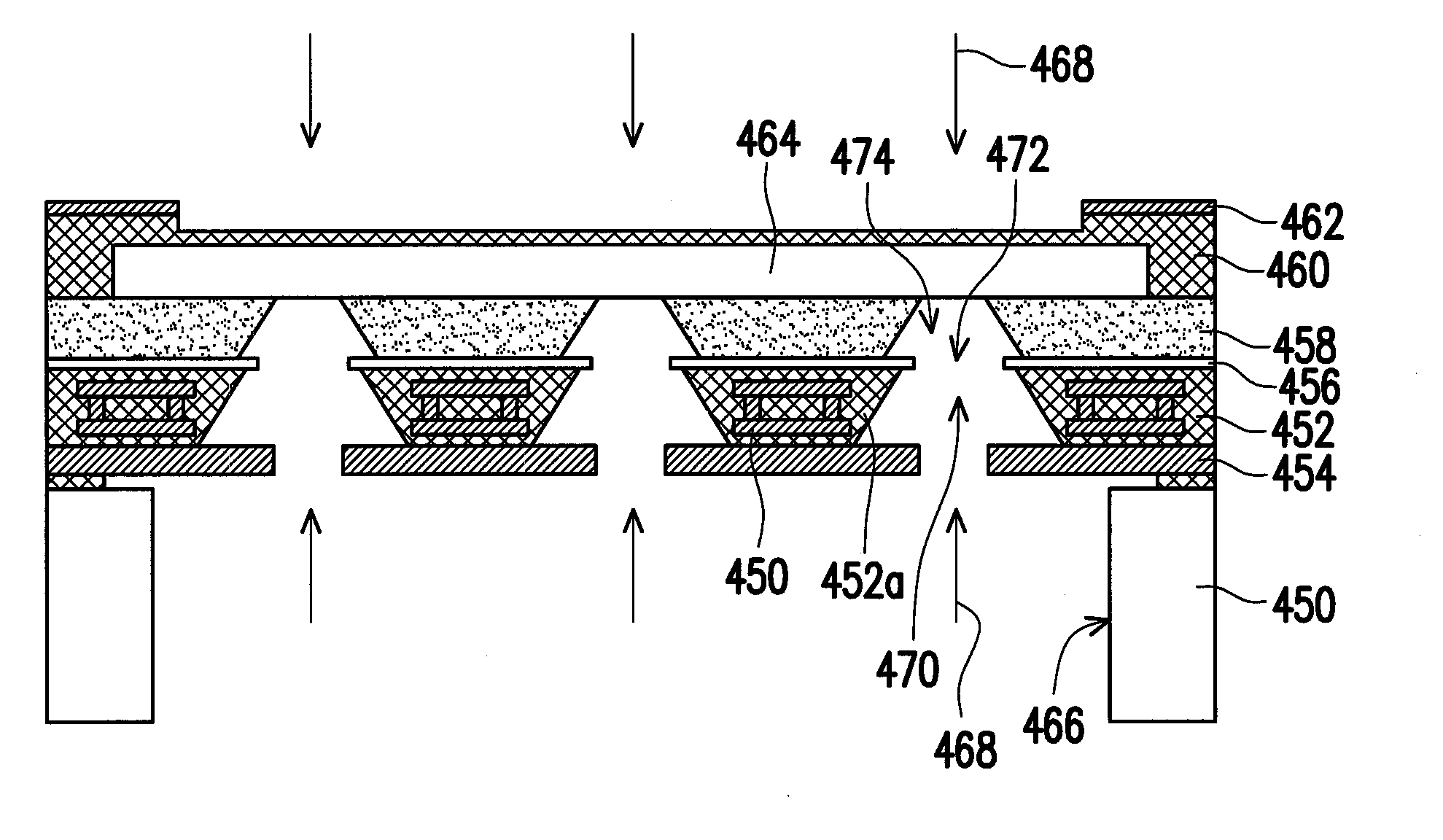

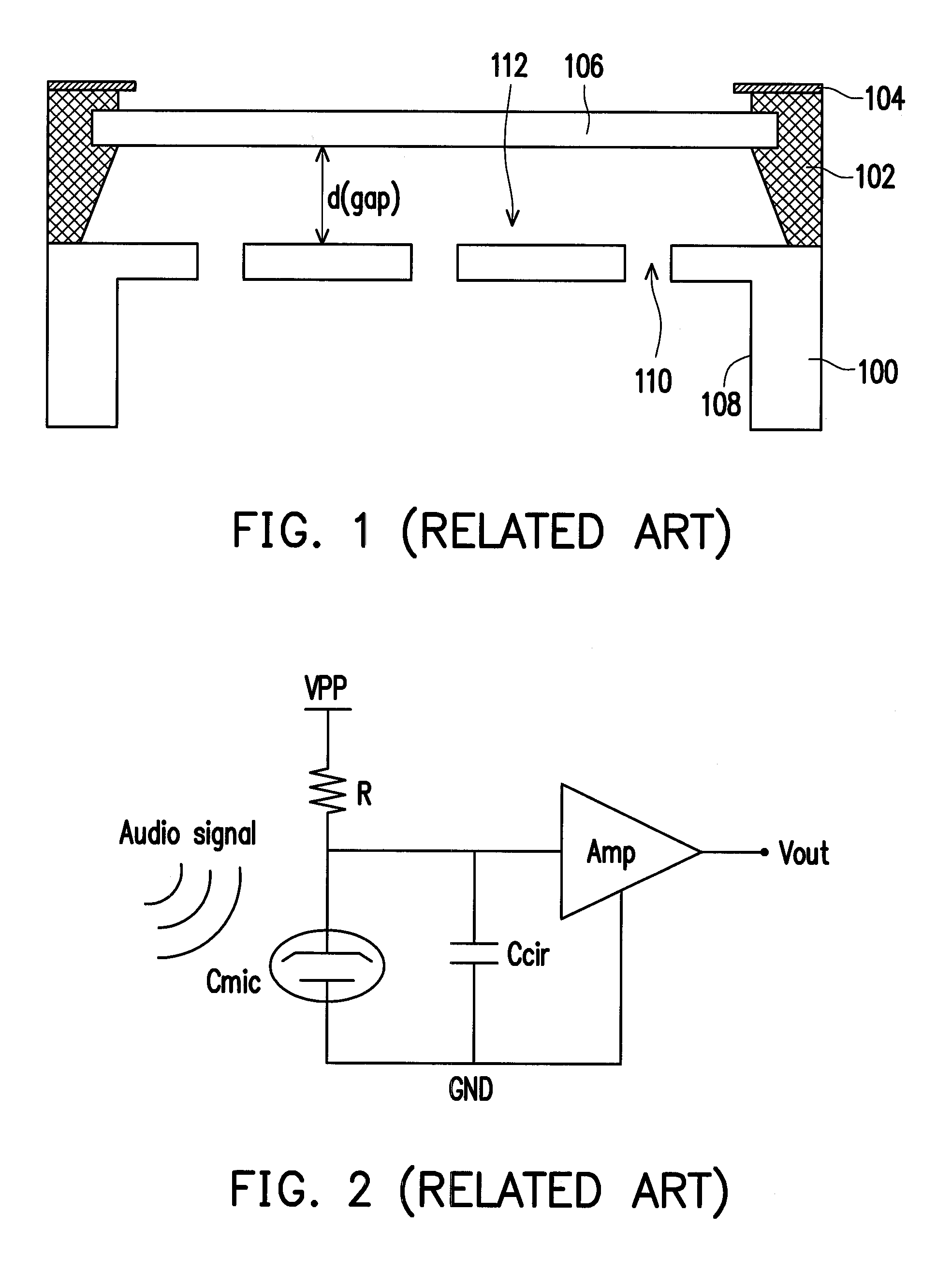

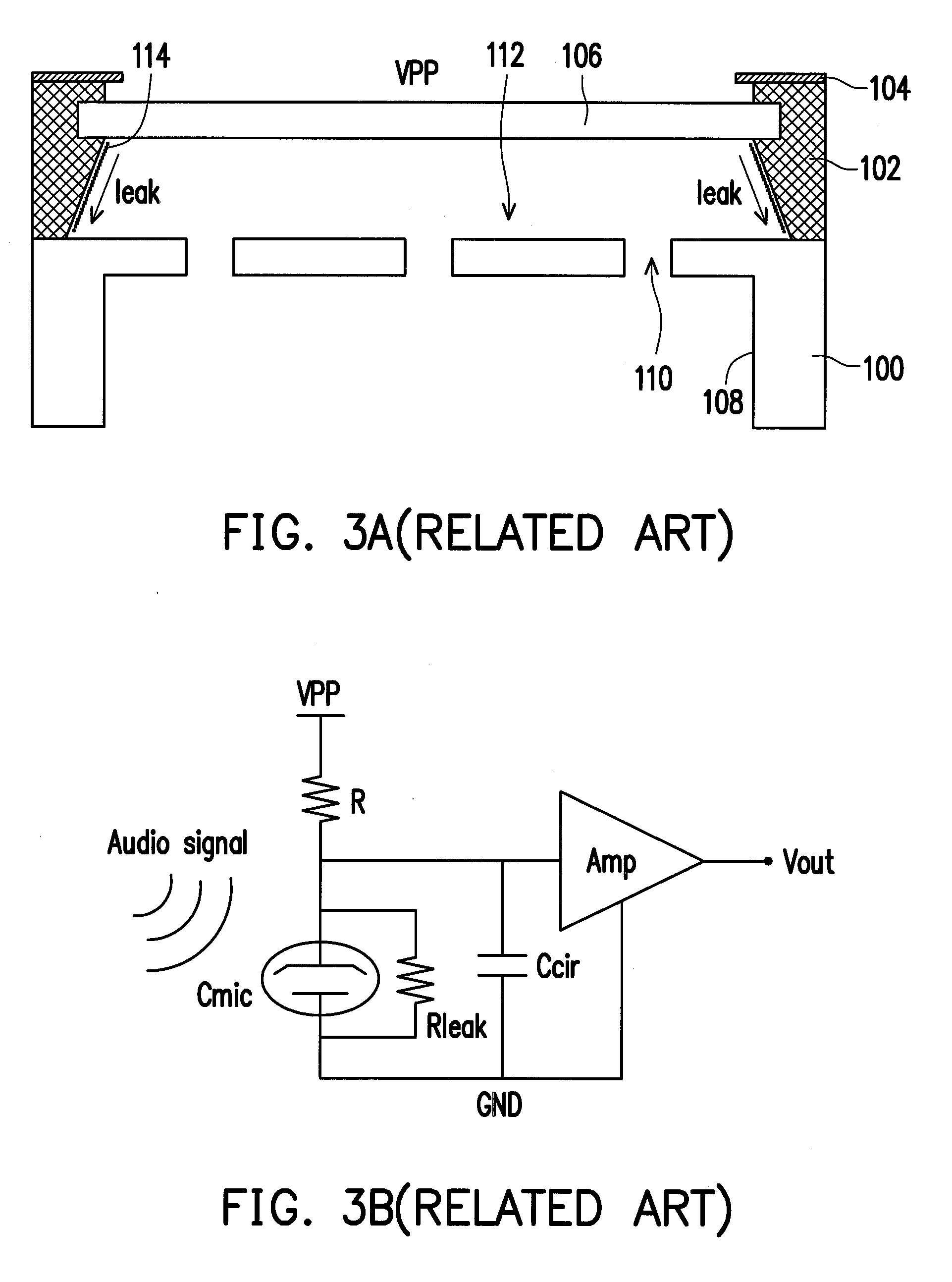

ActiveUS20130056841A1Increase capacitanceReduce thicknessSemiconductor electrostatic transducersCapacitor with electrode distance variationMicro electrical mechanical systemsEngineering

A MEMS device includes a substrate. The substrate has a plurality of through holes in the substrate within a diaphragm region and optionally an indent space from the second surface at the diaphragm region. A first dielectric structural layer is then disposed over the substrate from the first surface, wherein the first dielectric structural layer has a plurality of openings corresponding to the through holes, wherein each of the through holes remains exposed by the first dielectric structural layer. A second dielectric structural layer with a chamber is disposed over the first dielectric structural layer, wherein the chamber exposes the openings of the first dielectric structural layer and the through holes of the substrate to connect to the indent space. A MEMS diaphragm is embedded in the second dielectric structural layer above the chamber, wherein an air gap is formed between the substrate and the MEMS diaphragm.

Owner:SOLID STATE SYST

Method for fabricating micro-electro-mechanical system (MEMS) device

ActiveUS20100072561A1Compact integrationSemiconductor electrostatic transducersFluid pressure measurement by electric/magnetic elementsOptoelectronicsDielectric structure

A micro-electro-mechanical system (MEMS) device includes a substrate, having a first side and second side, the second side has a cavity and a plurality of venting holes in the substrate at the second side with connection to the cavity. However, the cavity is included in option without absolute need. A structural dielectric layer has a dielectric structure and a conductive structure in the dielectric structure. The structural dielectric layer has a chamber in connection to the cavity by the venting holes. A suspension structure layer is formed above the chamber. An end portion is formed in the structural dielectric layer in fix position. A diaphragm has a first portion of the diaphragm fixed on the suspension structure layer while a second portion of the diaphragm is free without being fixed.

Owner:SOLID STATE SYST

Semiconductor device with air gap and method for fabricating the same

ActiveUS20150014759A1Reduce sheet resistanceIncrease resistanceTransistorSemiconductor/solid-state device detailsEngineeringDielectric structure

A semiconductor device includes a dielectric structure which has an opening exposing a surface of a substrate; and a conductive structure which is formed in the opening, wherein the conductive structure comprises: a first conductive pattern recessed in the opening; a second conductive pattern covering a top surface and sidewalls of the first conductive pattern; an air gap defined between sidewalls of the opening and the second conductive pattern; and a third conductive pattern capping the second conductive pattern and the air gap.

Owner:SK HYNIX INC

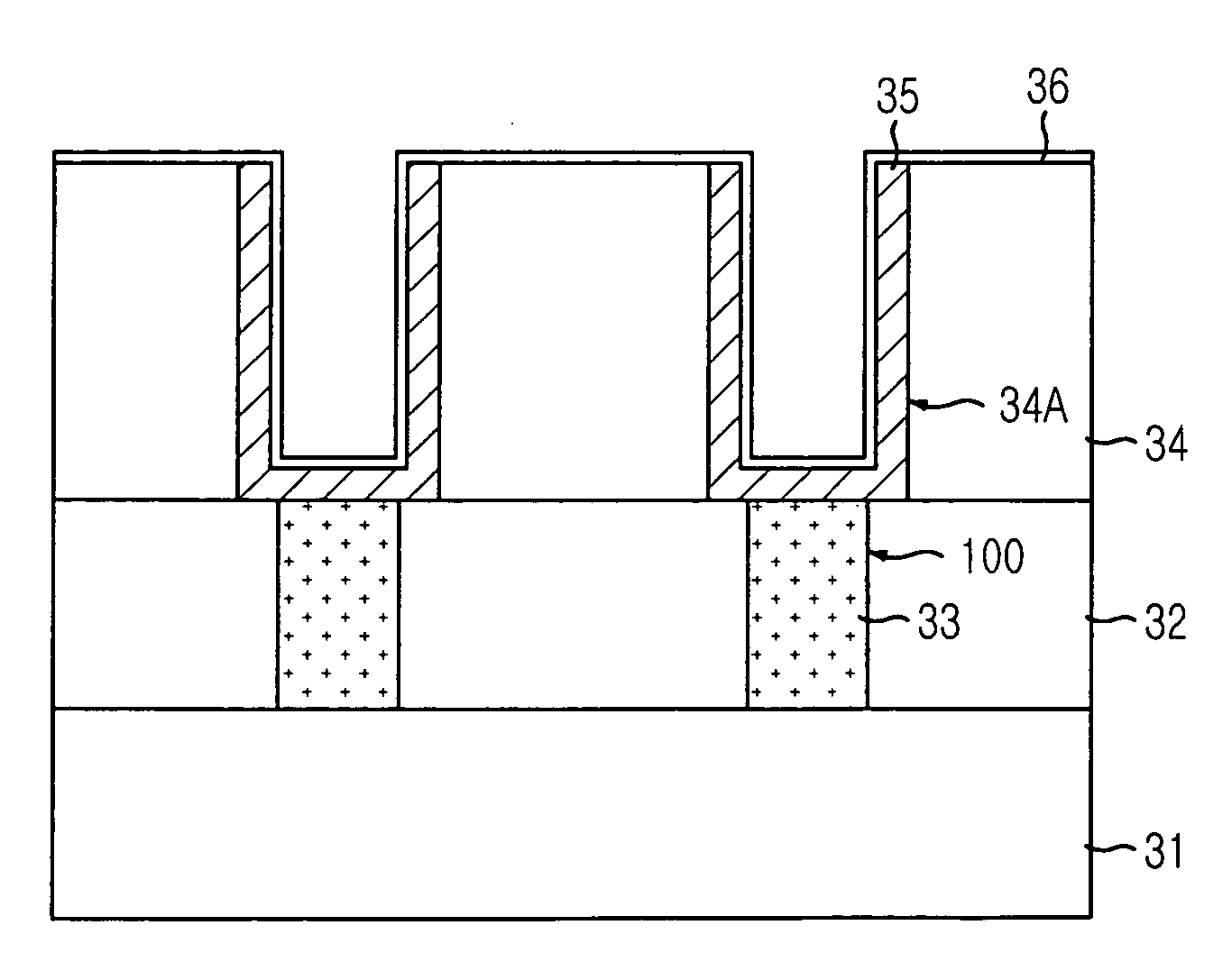

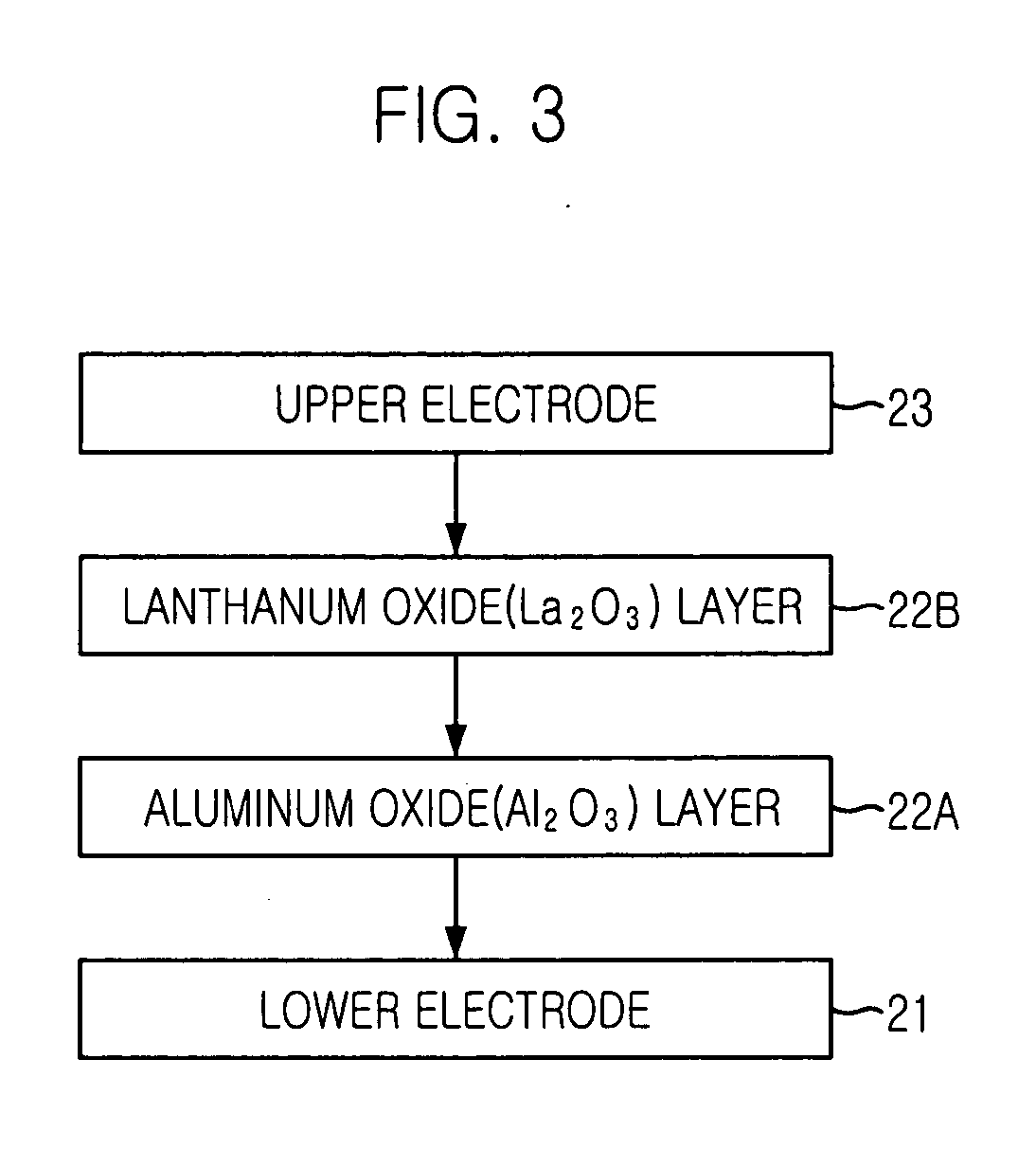

Capacitor with aluminum oxide and lanthanum oxide containing dielectric structure and fabrication method thereof

InactiveUS20050141168A1Reduce equivalent oxide thicknessReduce thicknessFixed capacitor dielectricSolid-state devicesHigh energyDielectric structure

Disclosed is a capacitor with a dielectric structure having an aluminum oxide layer and a lanthanum oxide layer and a fabrication method thereof. The capacitor includes: a lower electrode; a first dielectric layer with a high energy band gap formed on the lower electrode; a second dielectric layer formed on the first dielectric layer, the second dielectric layer with a high dielectric constant, wherein an energy band gap of the second dielectric layer is lower than the energy band gap of the first dielectric layer; and an upper electrode formed on the second dielectric layer.

Owner:SK HYNIX INC

Directive Window Ablation Antenna with Dielectric Loading

An electrosurgical device for directing energy to a target volume of tissue includes a coaxial feedline having an inner conductor, an outer conductor coaxially disposed around the inner conductor, and a dielectric material disposed therebetween. An elongated electrically-conductive member is longitudinally disposed at a distal end of the inner conductor. A balun structure is disposed on the outer conductor. The device also includes an electrically-conductive cylinder coaxially disposed around a distal portion of the balun structure, and a dielectric structure disposed substantially adjacent to a distal end of the electrically-conductive cylinder, wherein the dielectric structure longitudinally extends from the distal end of the electrically-conductive cylinder to a distal end of the electrically-conductive member.

Owner:TYCO HEALTHCARE GRP LP