Patents

Literature

242 results about "Cylindrical channel" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

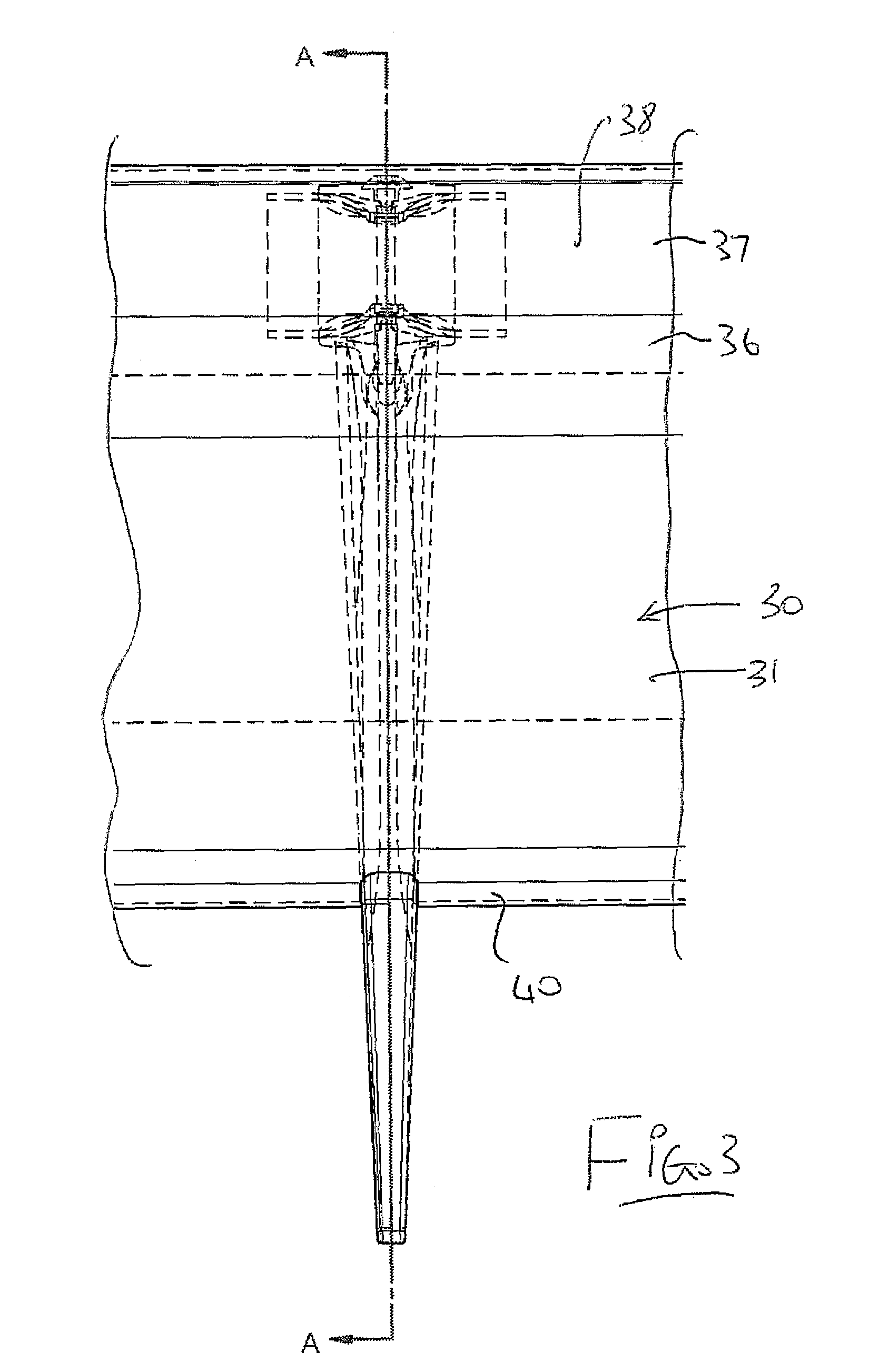

Marking and guidance method and system for flexible fixation of a spine

ActiveUS20050065515A1Easy constructionSimple designInternal osteosythesisEar treatmentSpinal columnCylindrical channel

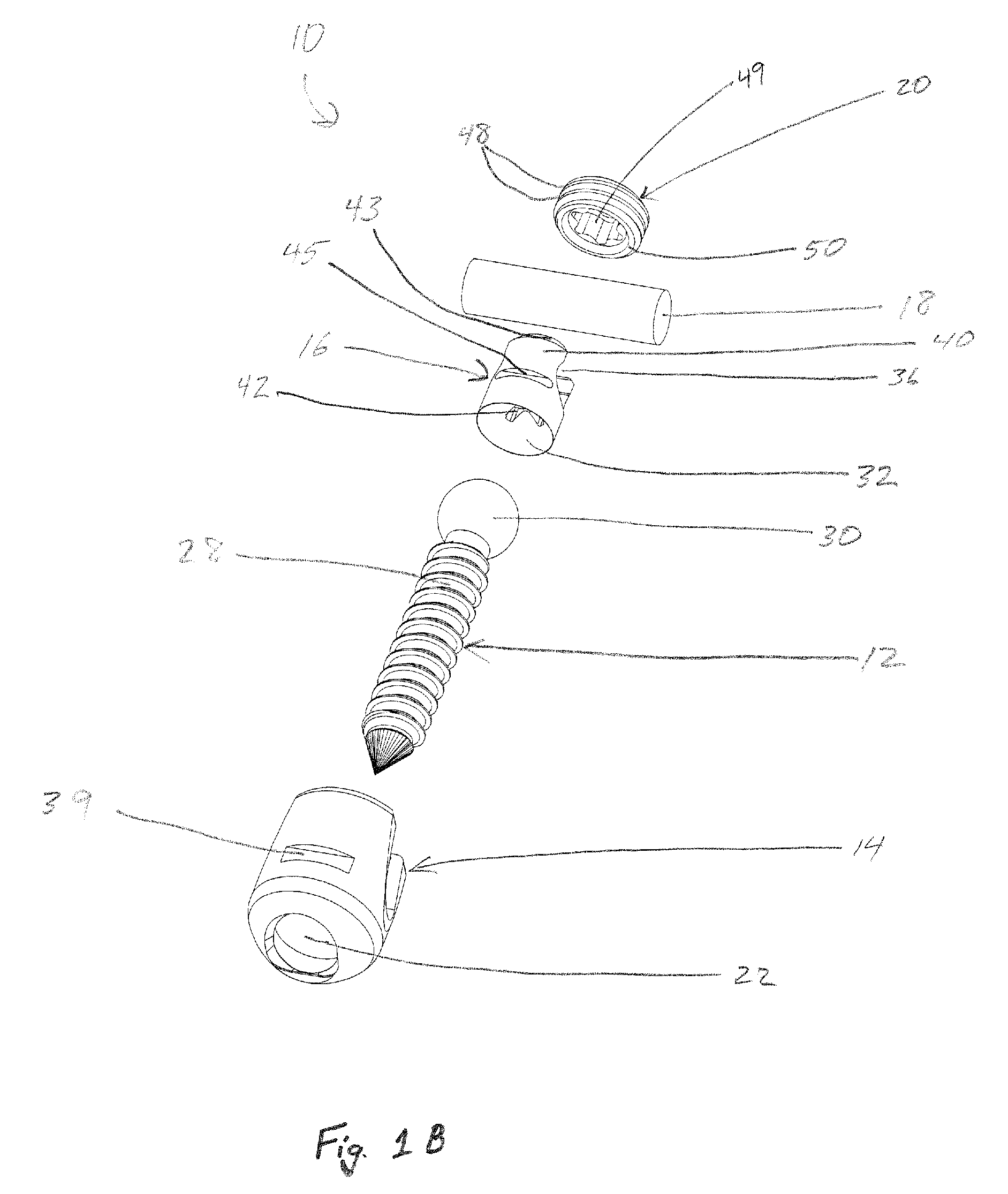

A method and system for marking and guiding the insertion of securing members (e.g., pedicle screws) of a spinal fixation device. In one embodiment, the marking and guidance method and system includes the use of a guide tube configured to be inserted into a patient's back until a first end reaches an entry point on or near a vertebral bone of the patient's spinal column, wherein the guide tube includes a hollow cylindrical channel along its longitudinal center axis; a penetrating device configured to be positioned within the cylindrical channel of the guide tube and having a sharp tip configured to protrude outwardly from the first end of the guide tube so as to allow the first end of the guide tube to penetrate through the patient's back muscle and tissue and reach the vertebral bone at the entry point; a marking pin configured to be inserted through the cylindrical channel of the guide tube, after removal of the penetrating device, until a first end of the marking pin having a sharp tip reaches the entry point; and a pushing device configured to be inserted through the cylindrical channel of the guide tube and provide a driving force at a second end of the marking pin, opposite the first end, so as to drive and secure the first end of the marking pin into the vertebral bone, wherein the marking pin identifies the location of the entry point on the vertebral bone for subsequent implantation of a securing member of a spinal fixation device.

Owner:N SPINE INC

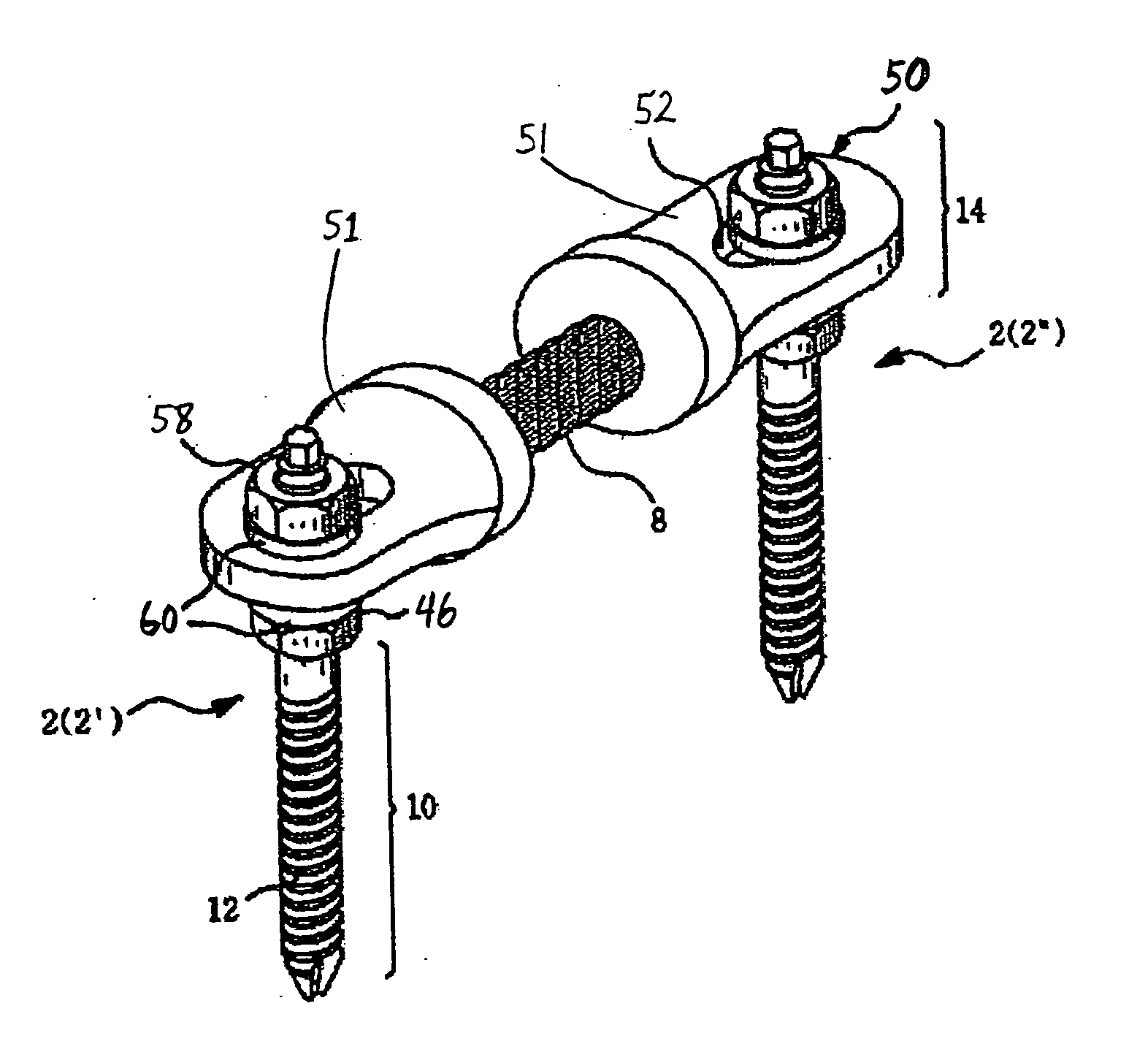

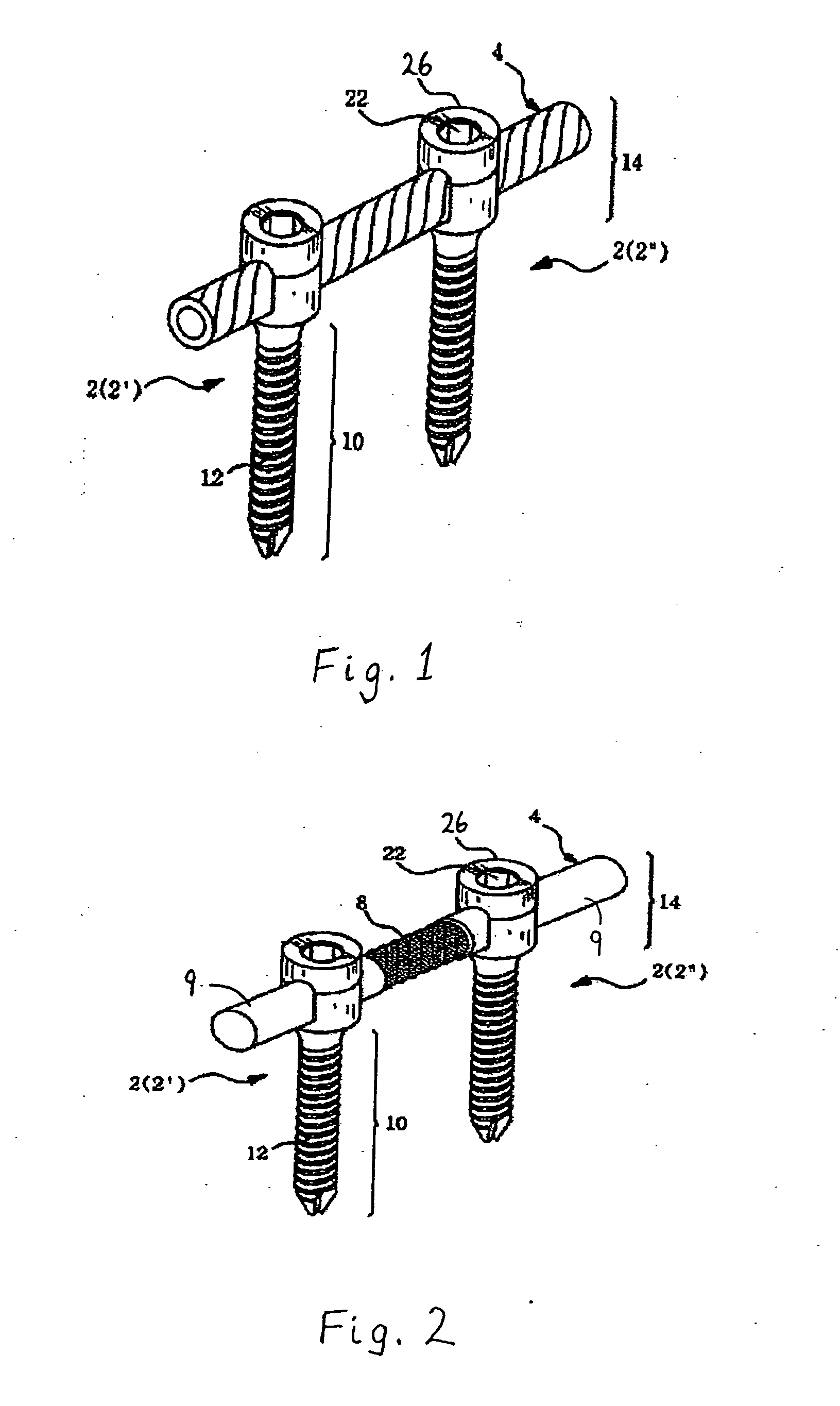

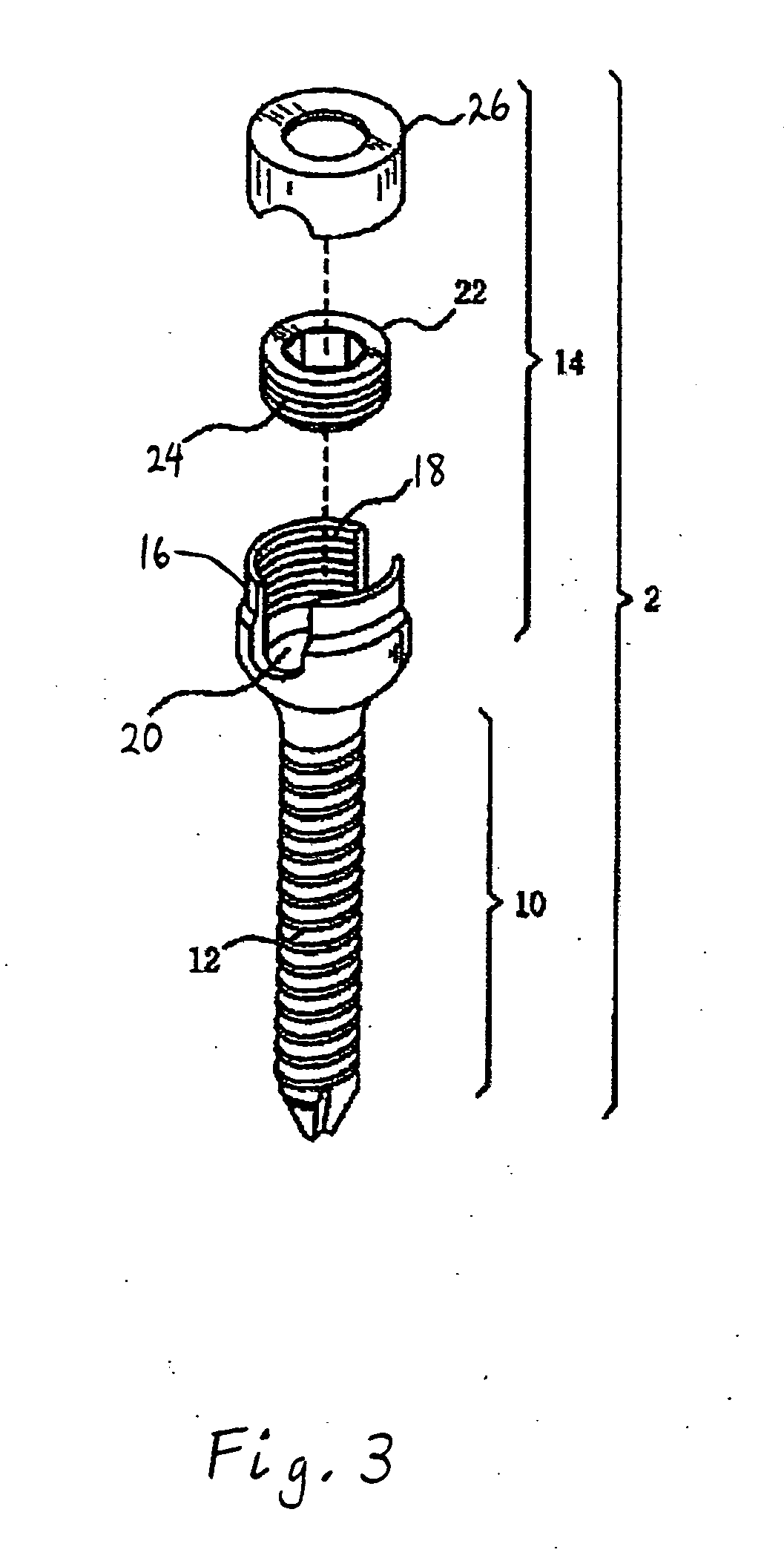

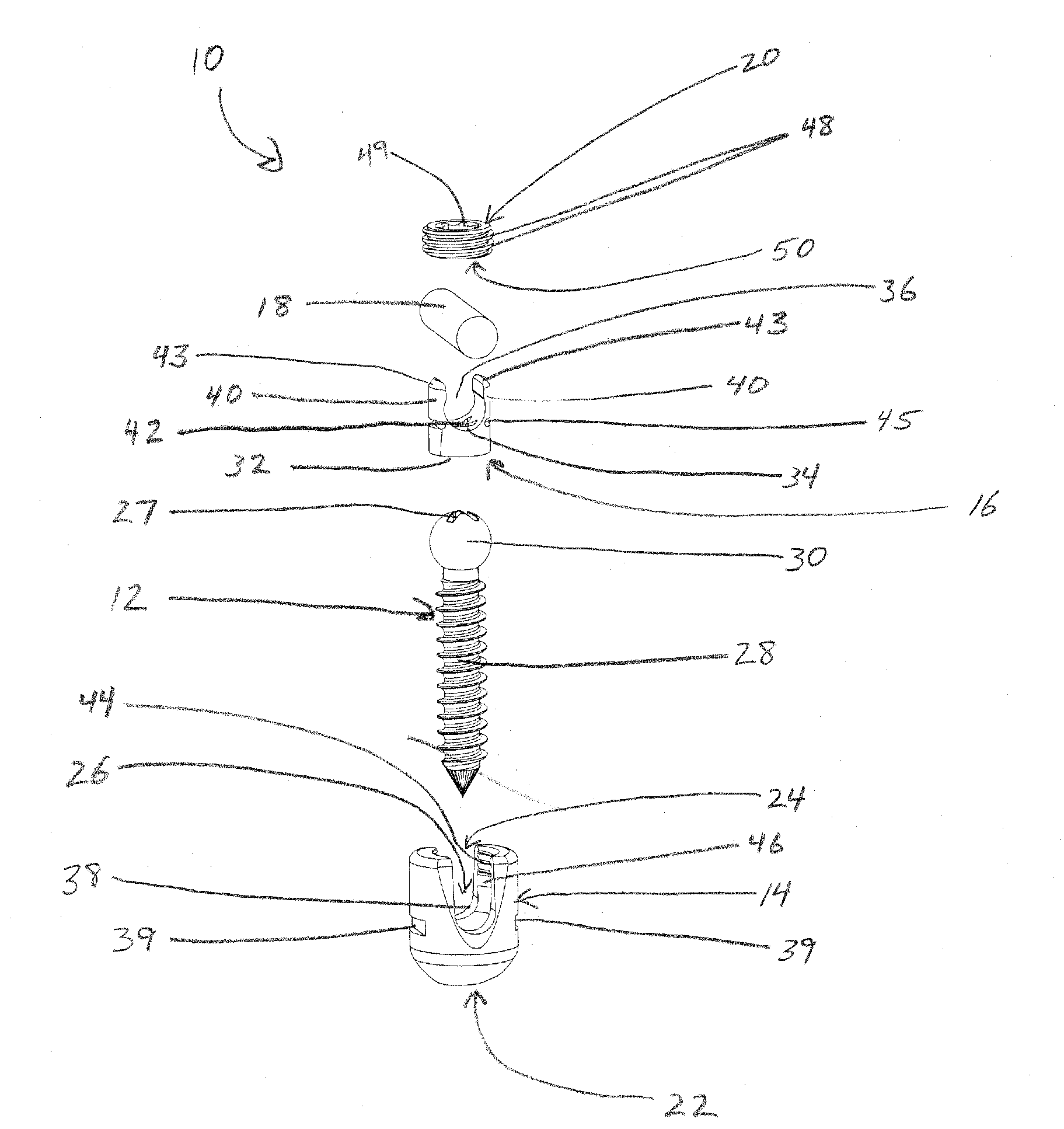

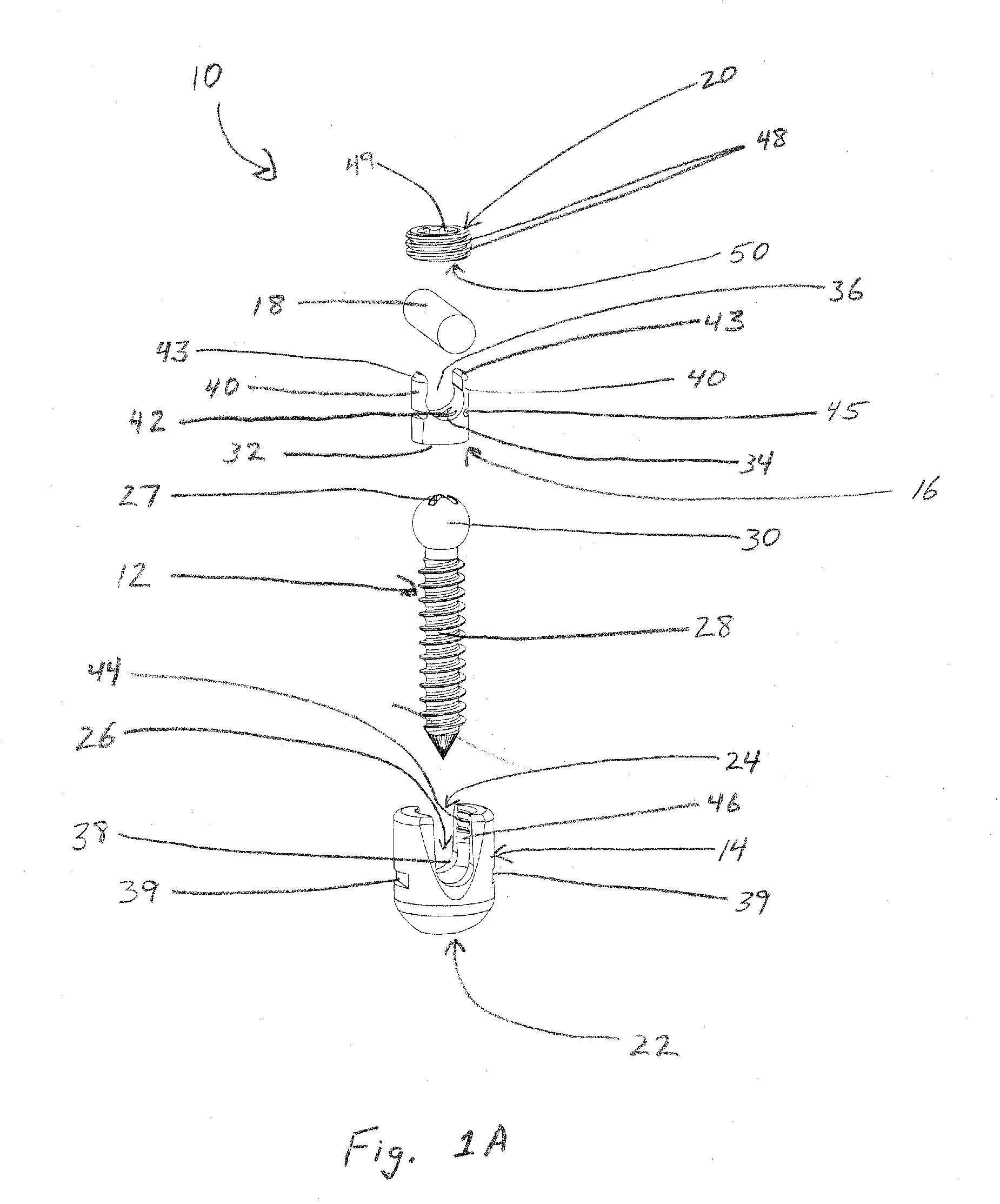

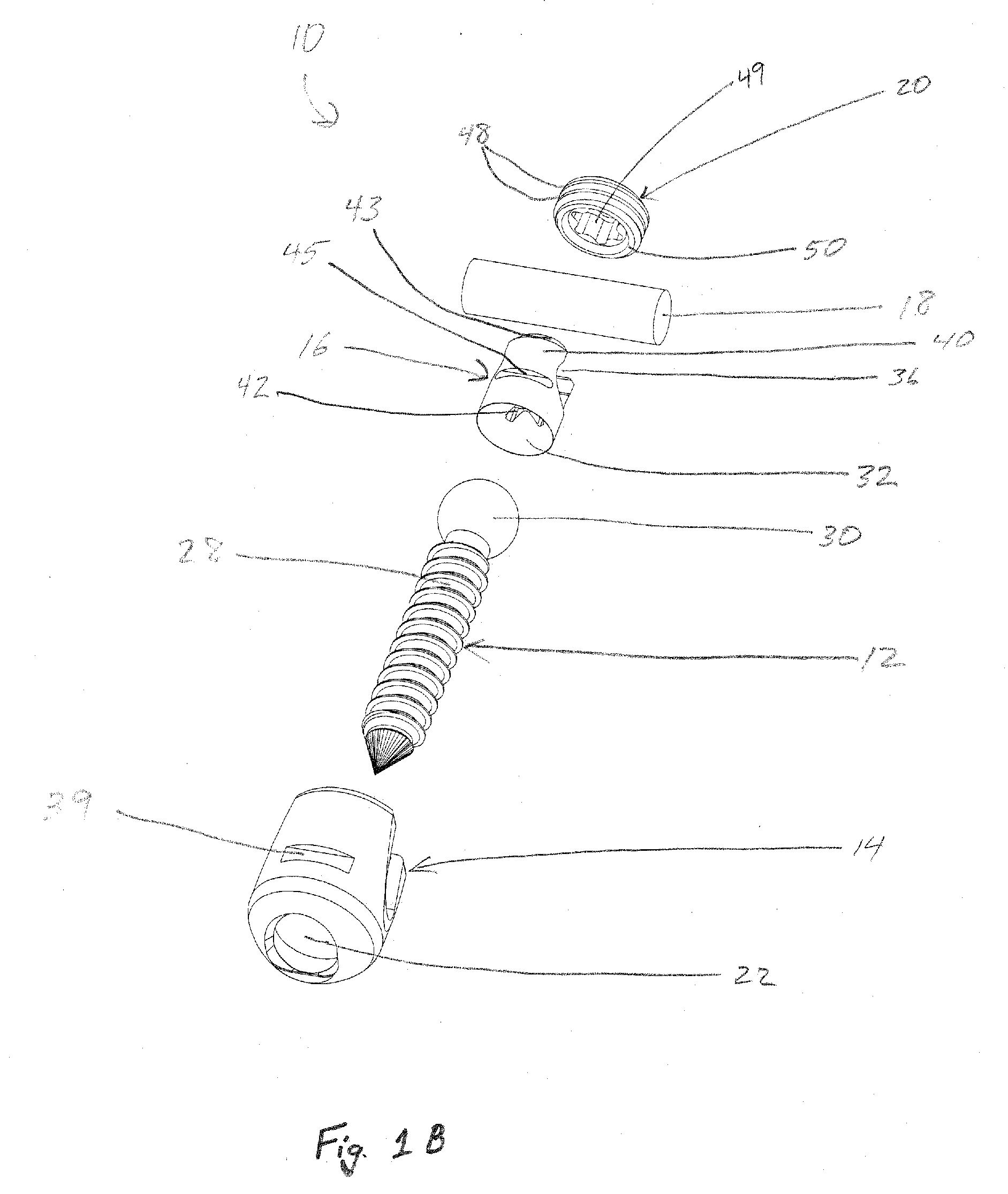

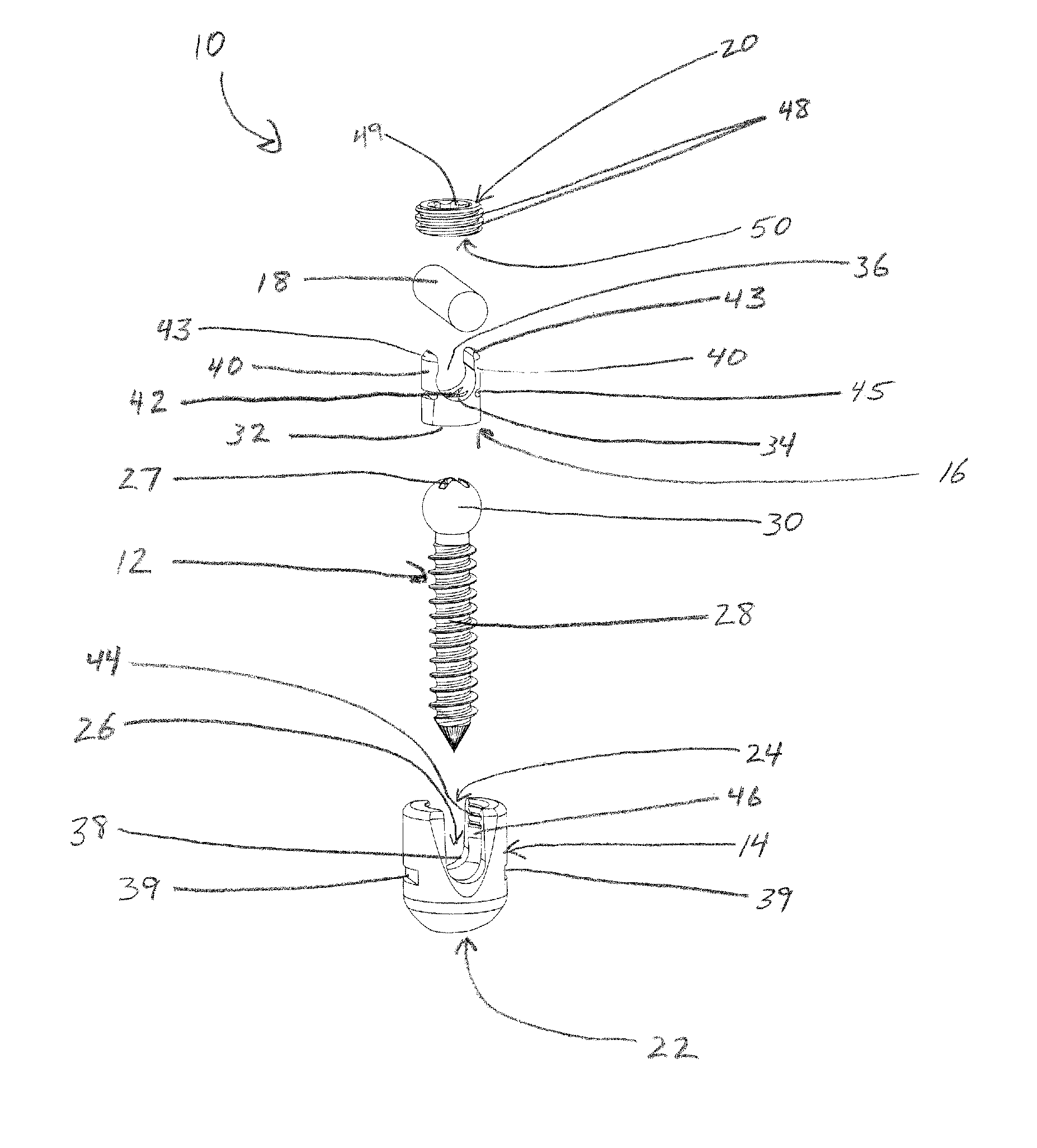

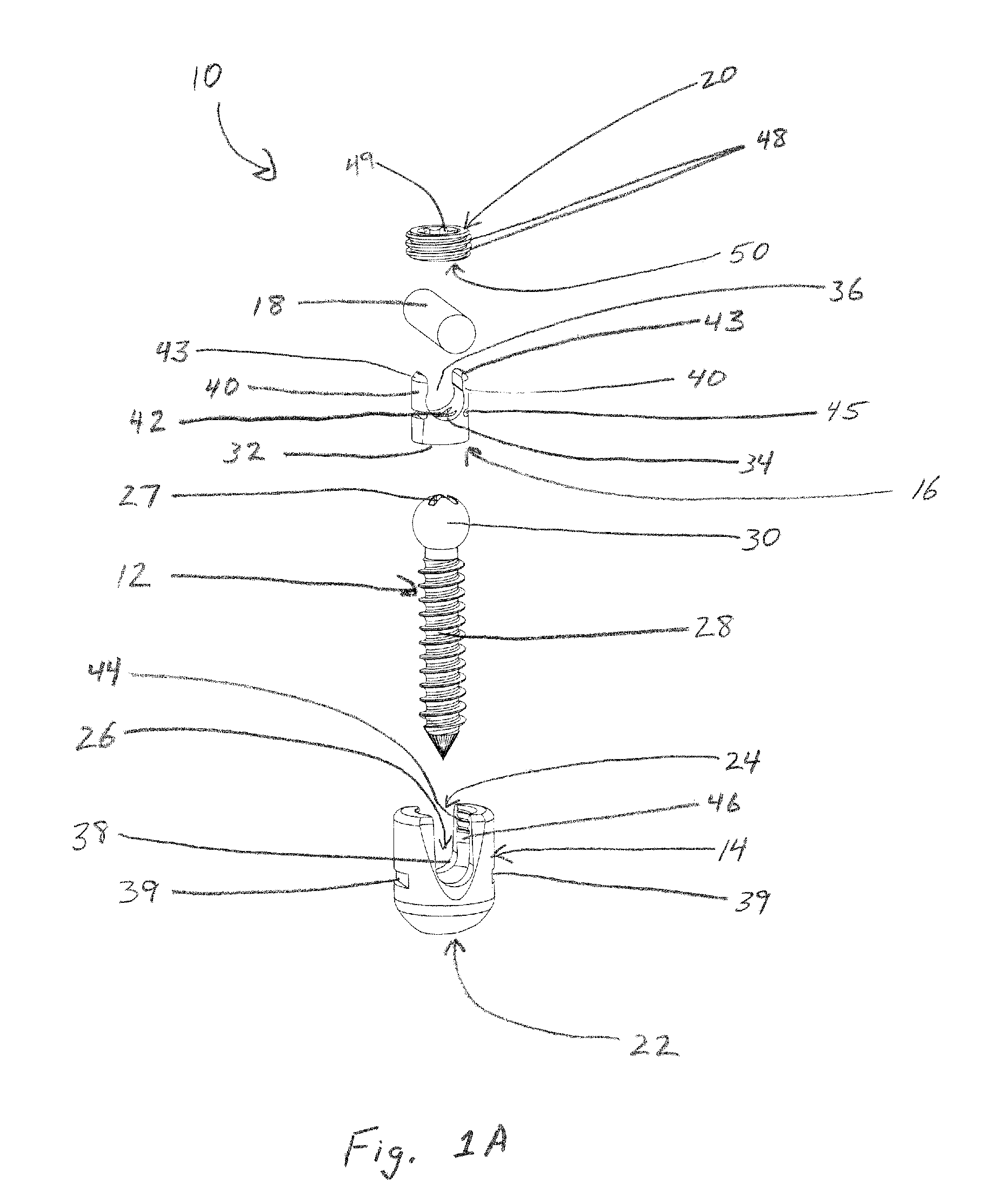

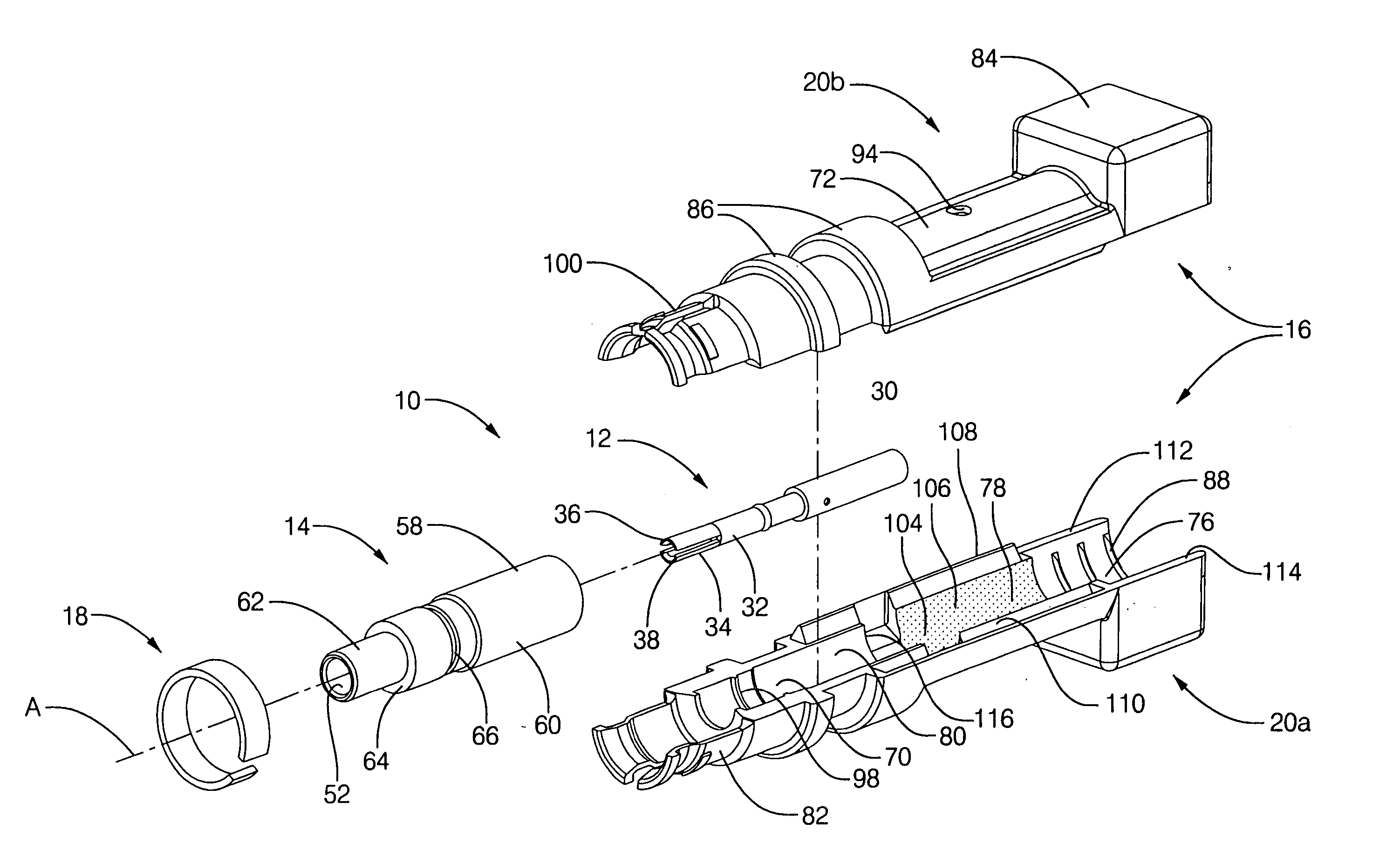

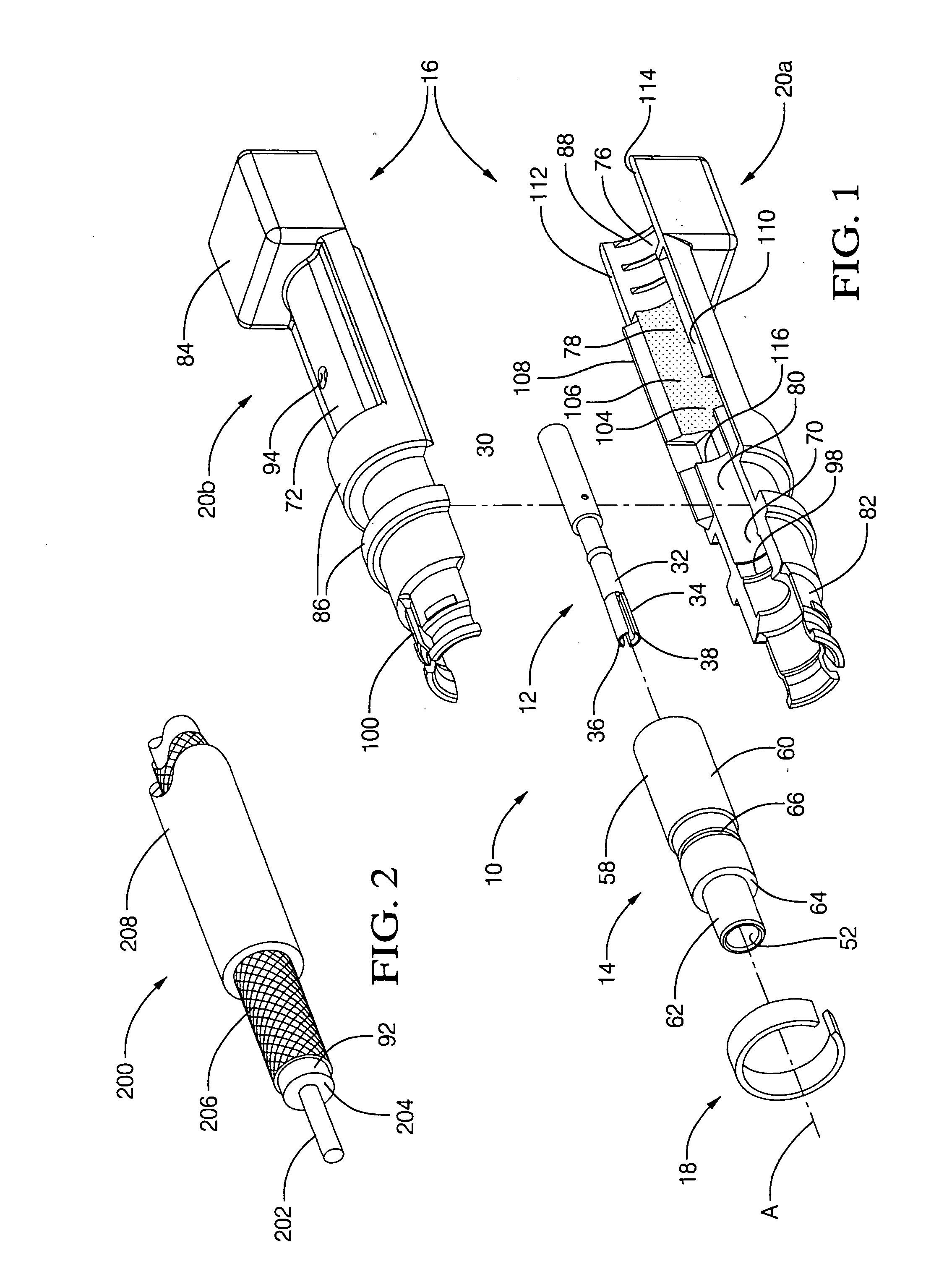

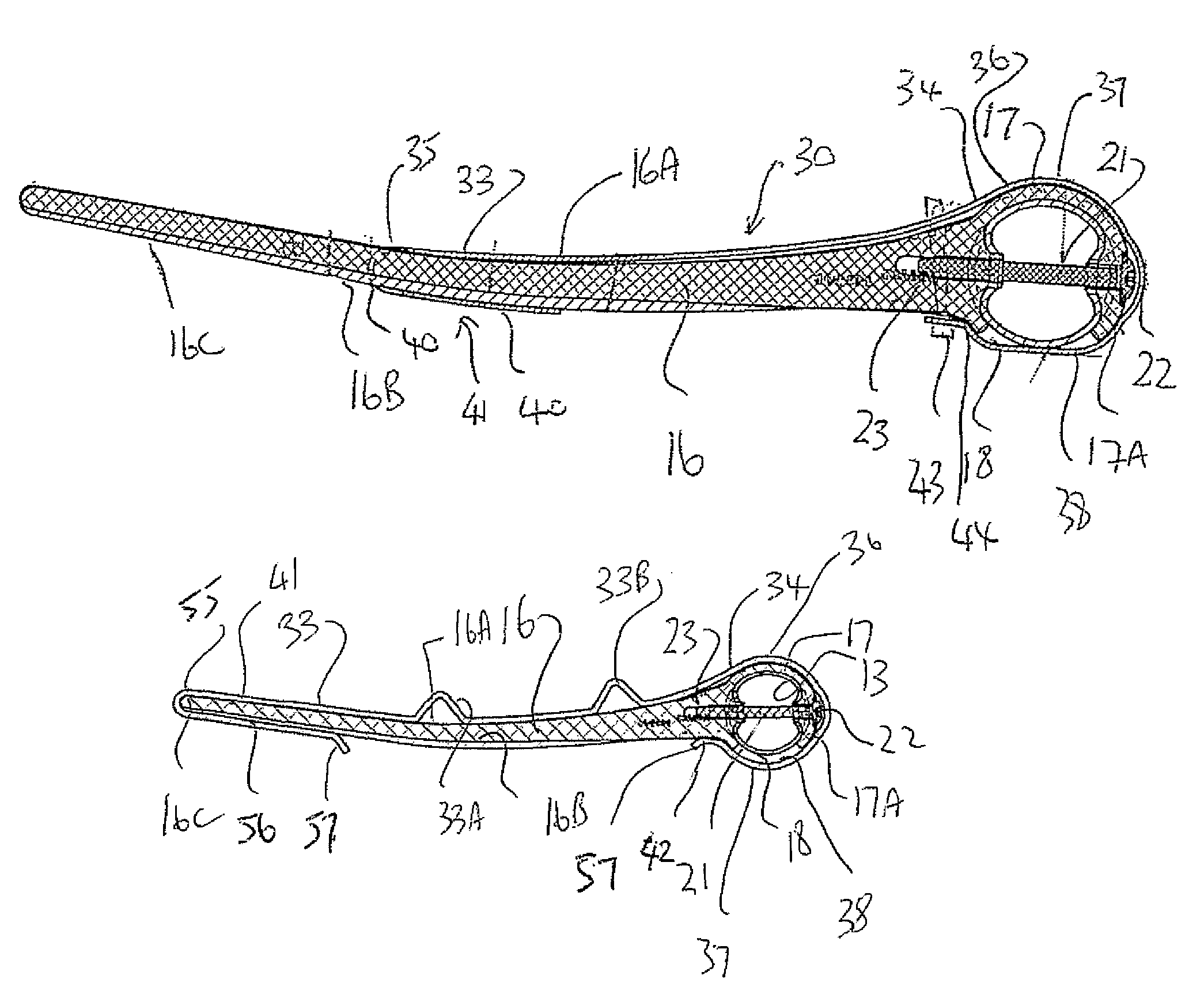

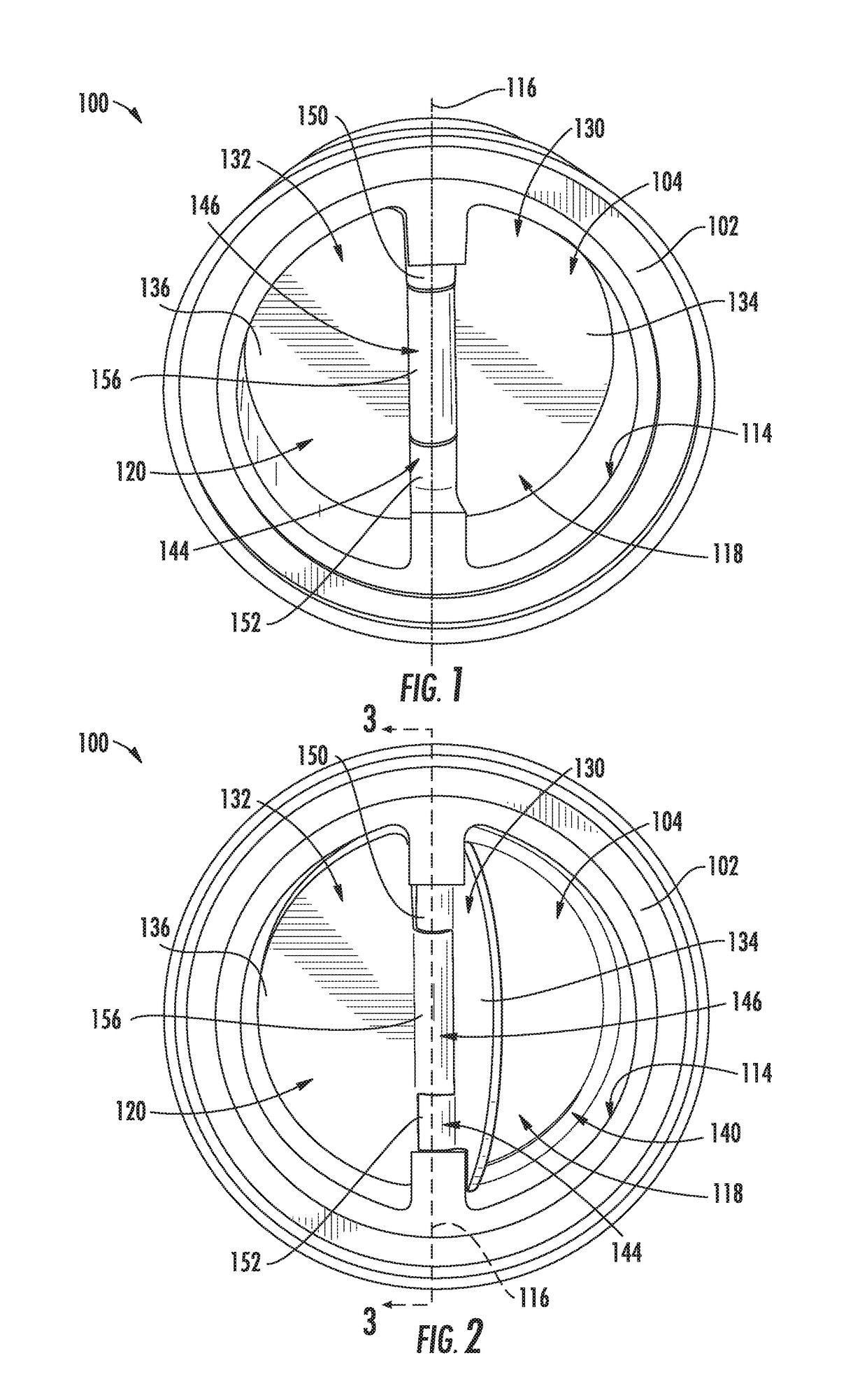

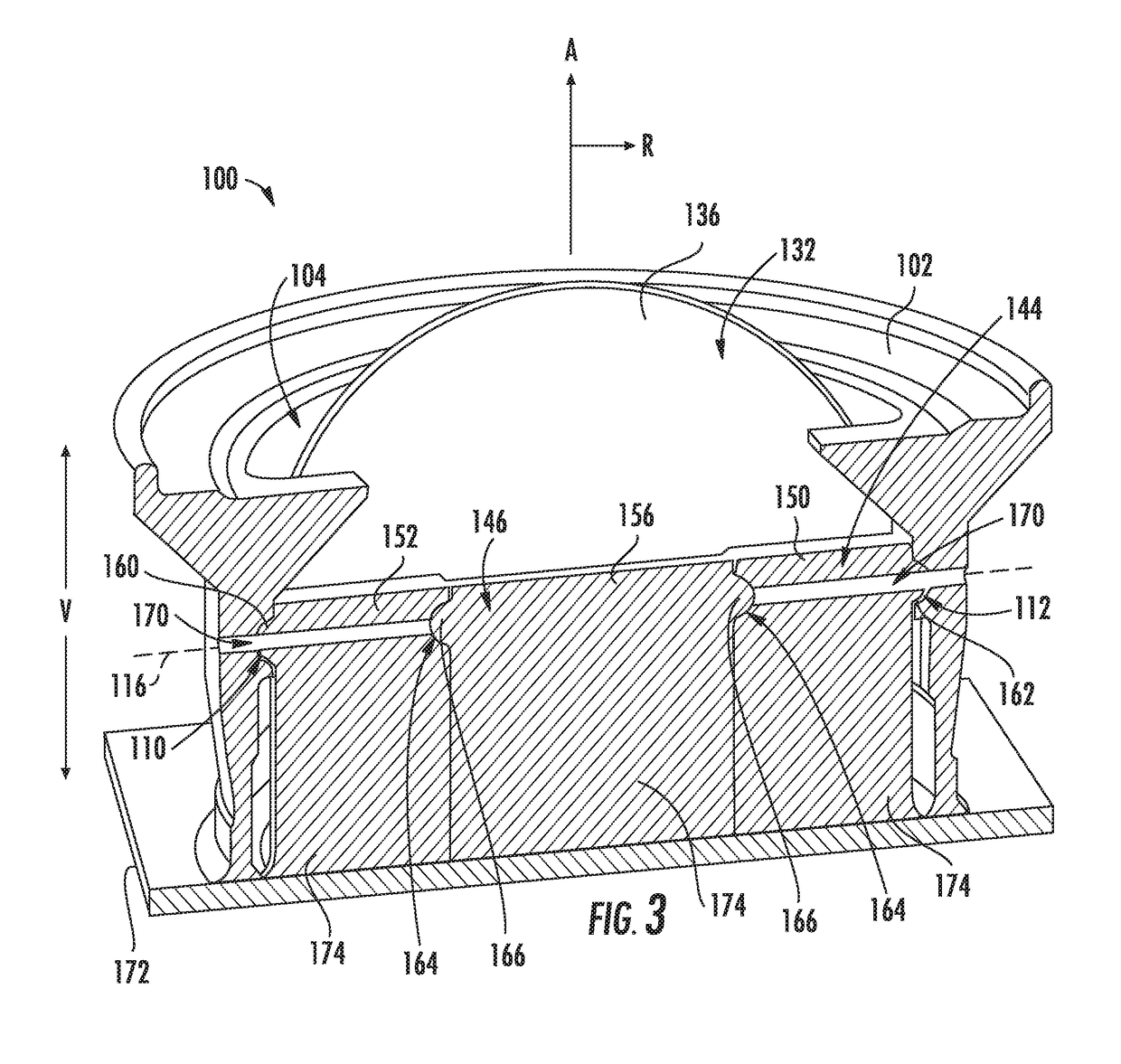

Bone Screw and Associated Assembly and Methods of Use Thereof

ActiveUS20080161859A1Increased amount of allowable angulationMinimize damageSuture equipmentsInternal osteosythesisSet screwCylindrical channel

A bone screw assembly comprises a bone screw having a shaft and a head, a stabilizer retainer, a set screw, and a housing having a proximal opening, biased to one side, and a distal opening that open on an interior cavity. The stabilizer retainer has a cylindrical channel that receives a stabilizer. The retainer has flexible portions that allow passage of the stabilizer into the channel. An arcuate wall of the channel maintains contact with the stabilizer within the channel. The housing is adapted to receive the bone screw, the stabilizer retainer and the set screw in the interior cavity. The housing has a channel that permits passage of the stabilizer though the housing. The set screw is engaged in the distal opening. The set screw and stabilizer retainer engage and prevent movement of the flexible portions, preventing movement of the stabilizer from the stabilizer retainer.

Owner:INNOVATIVE DELTA TECH LLC

Bone screw and associated assembly and methods of use thereof

ActiveUS8167910B2Increased amount of allowable angulationMinimize damageSuture equipmentsInternal osteosythesisCylindrical channelBiomedical engineering

A bone screw assembly comprises a bone screw having a shaft and a head, a stabilizer retainer, a set screw, and a housing having a proximal opening, biased to one side, and a distal opening that open on an interior cavity. The stabilizer retainer has a cylindrical channel that receives a stabilizer. The retainer has flexible portions that allow passage of the stabilizer into the channel. An arcuate wall of the channel maintains contact with the stabilizer within the channel. The housing is adapted to receive the bone screw, the stabilizer retainer and the set screw in the interior cavity. The housing has a channel that permits passage of the stabilizer though the housing. The set screw is engaged in the distal opening. The set screw and stabilizer retainer engage and prevent movement of the flexible portions, preventing movement of the stabilizer from the stabilizer retainer.

Owner:INNOVATIVE DELTA TECH LLC

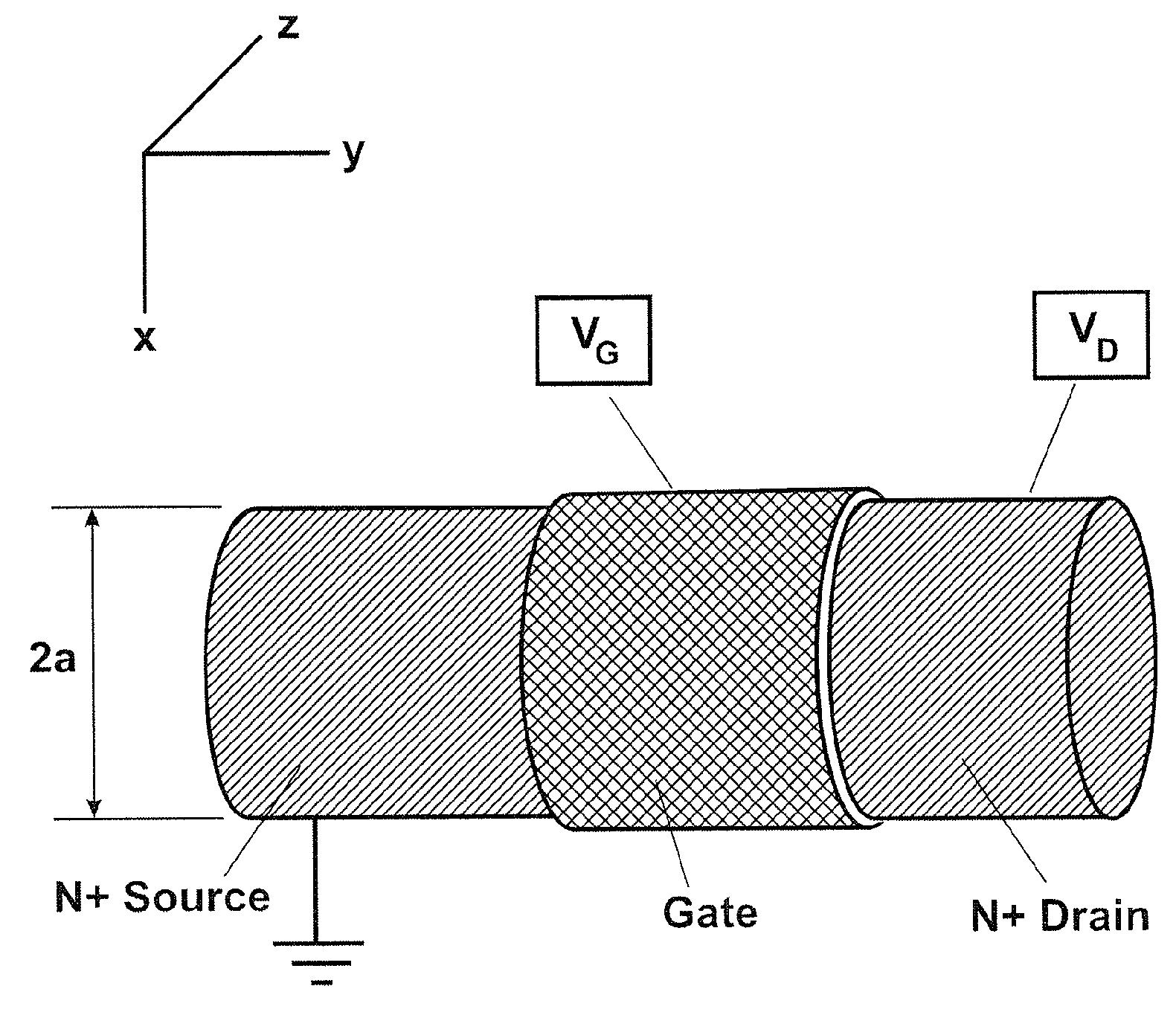

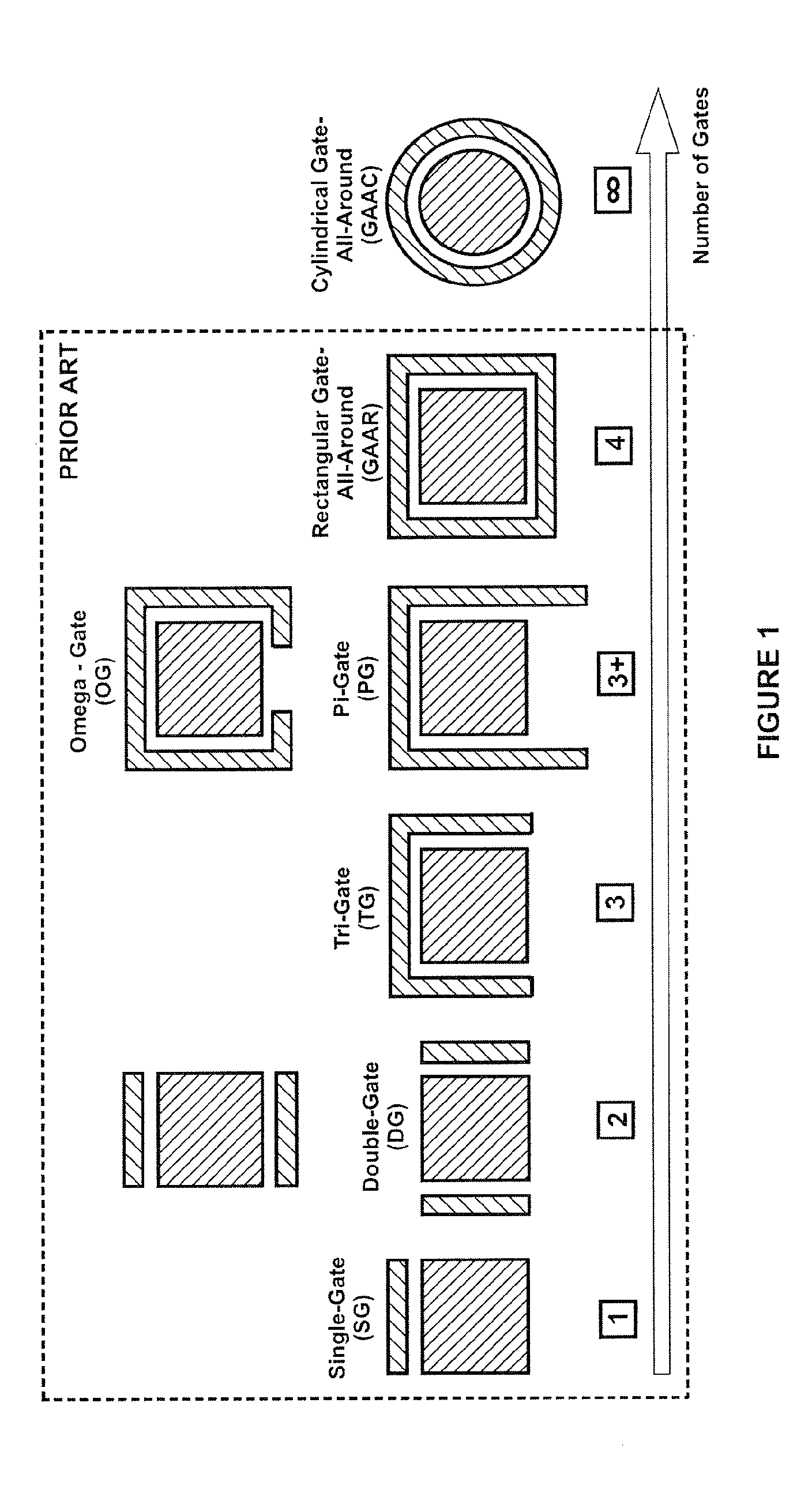

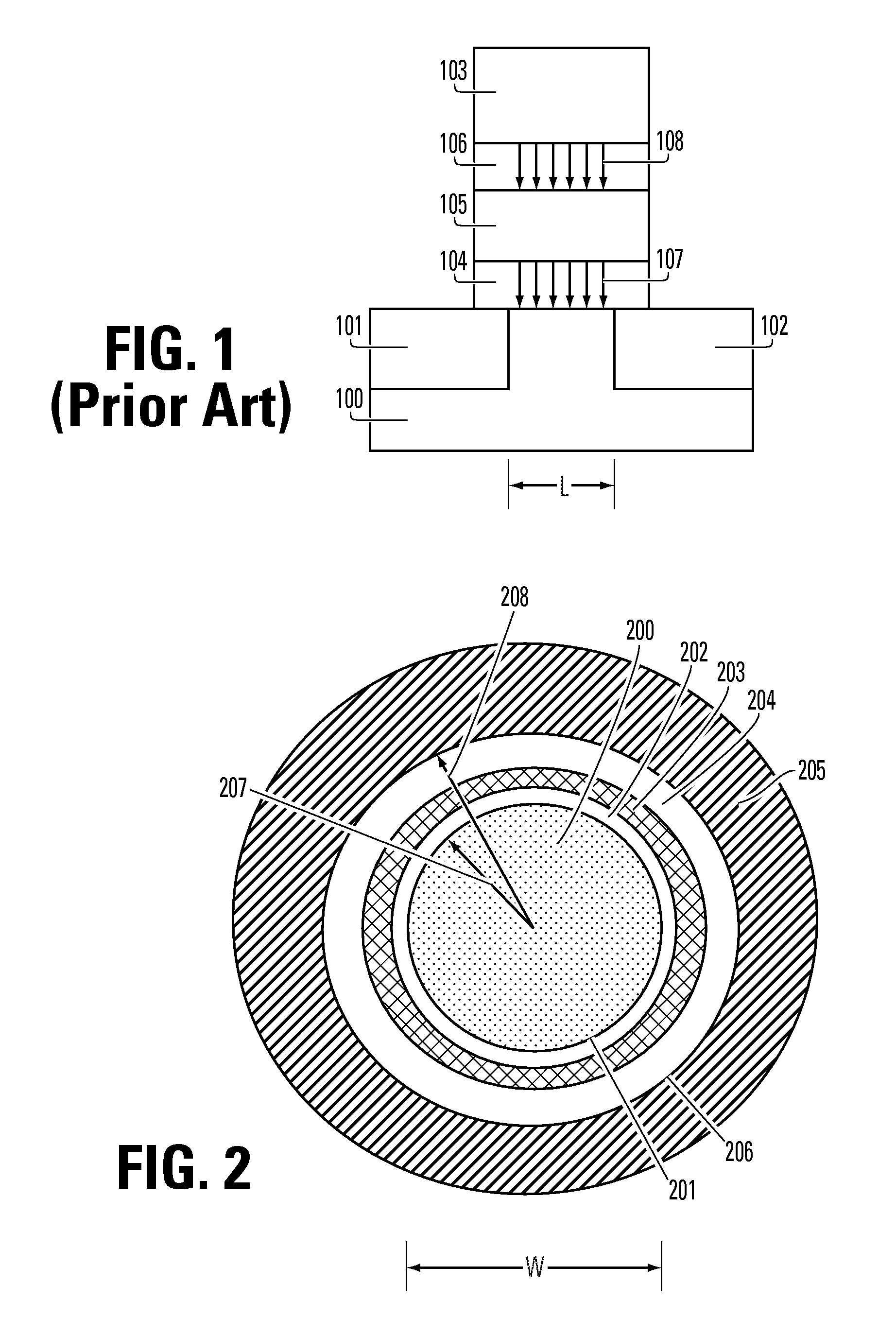

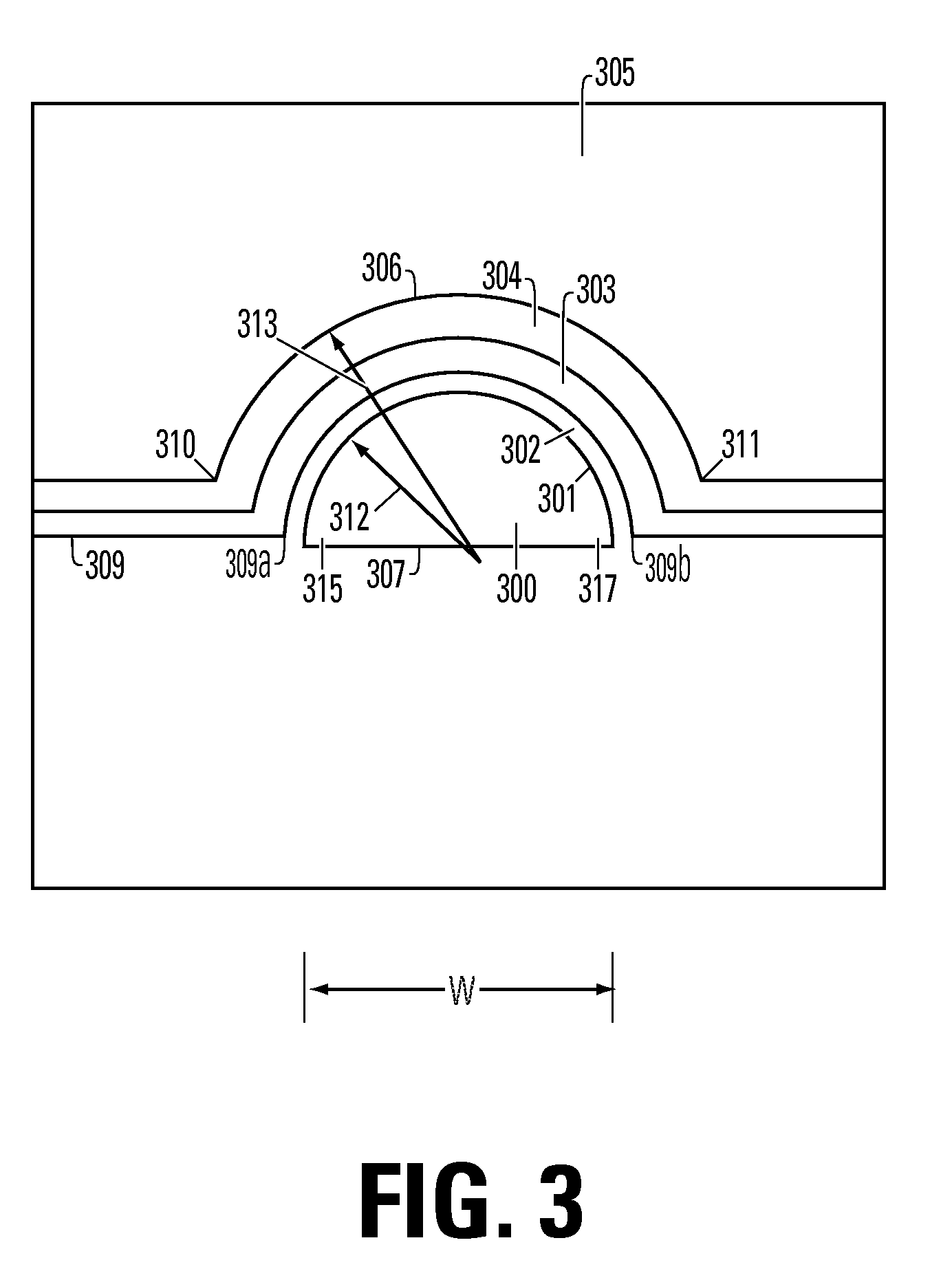

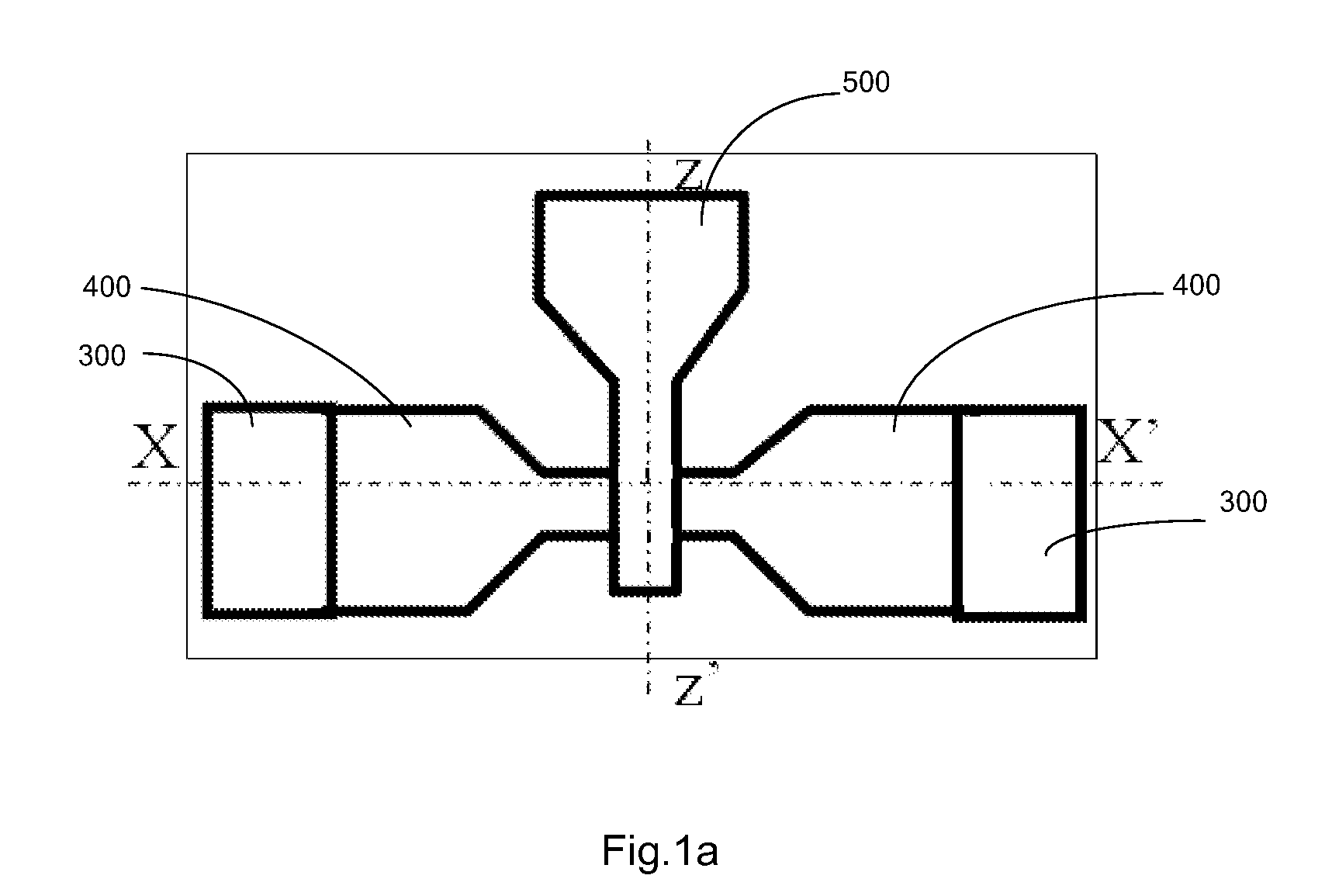

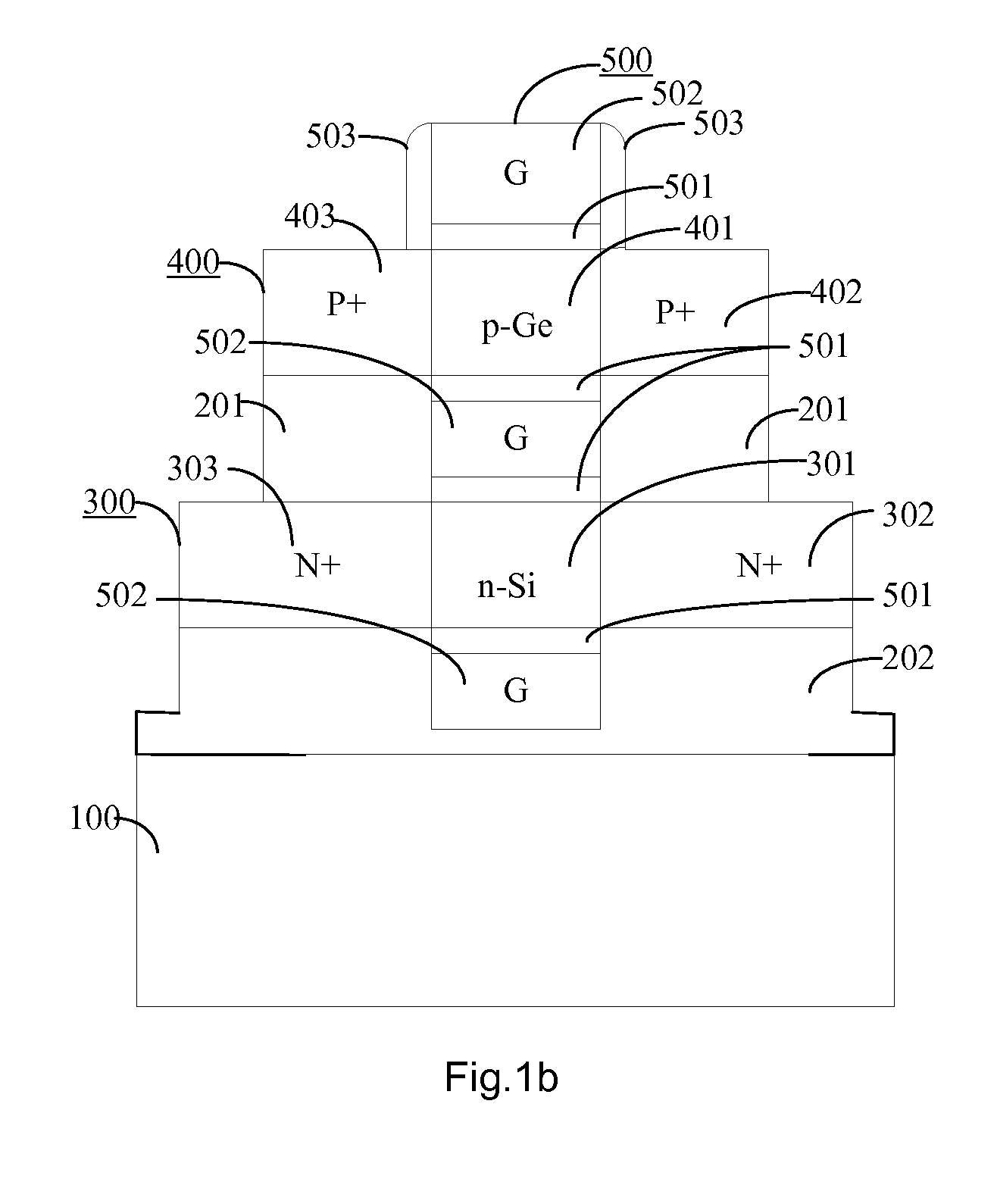

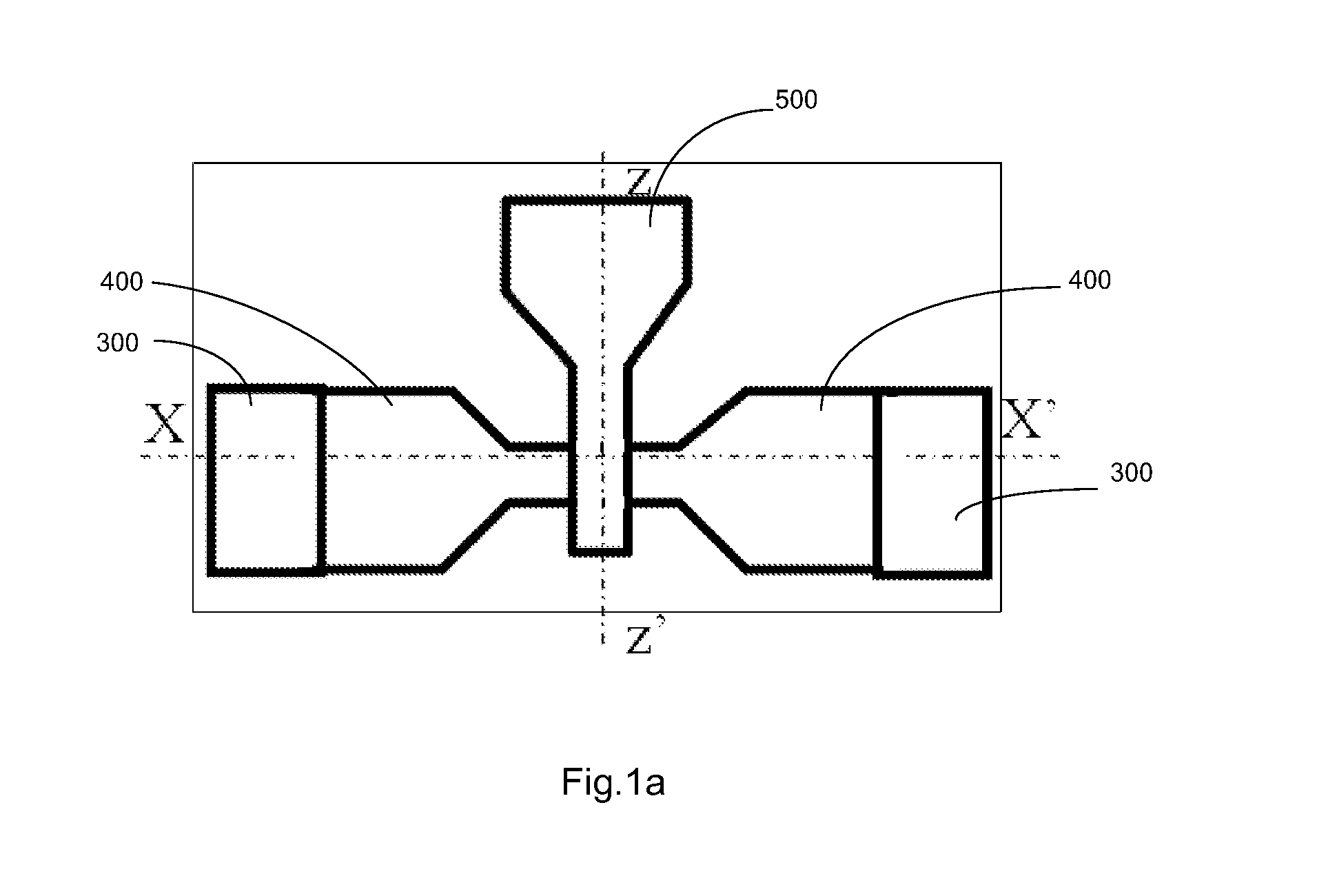

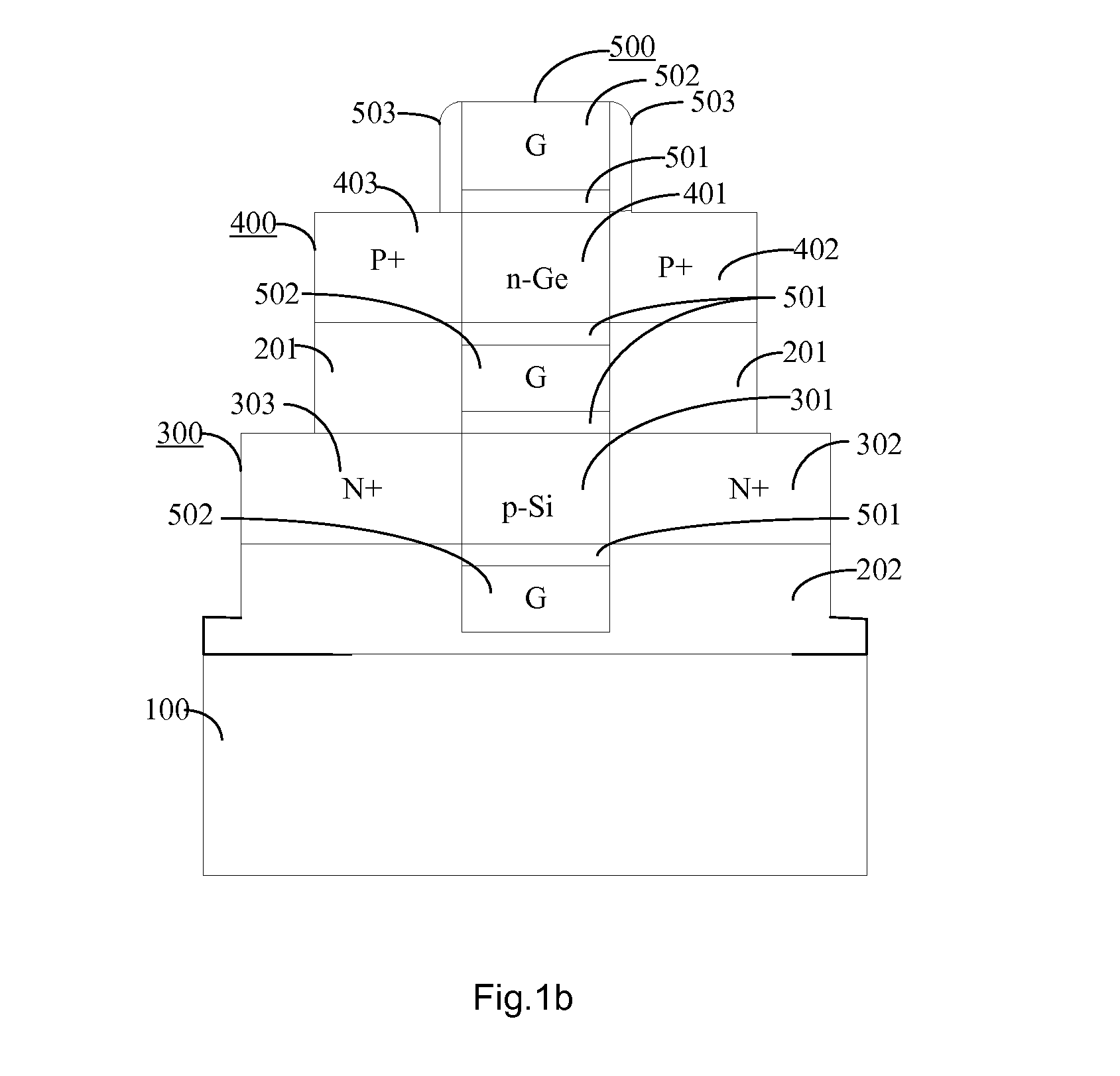

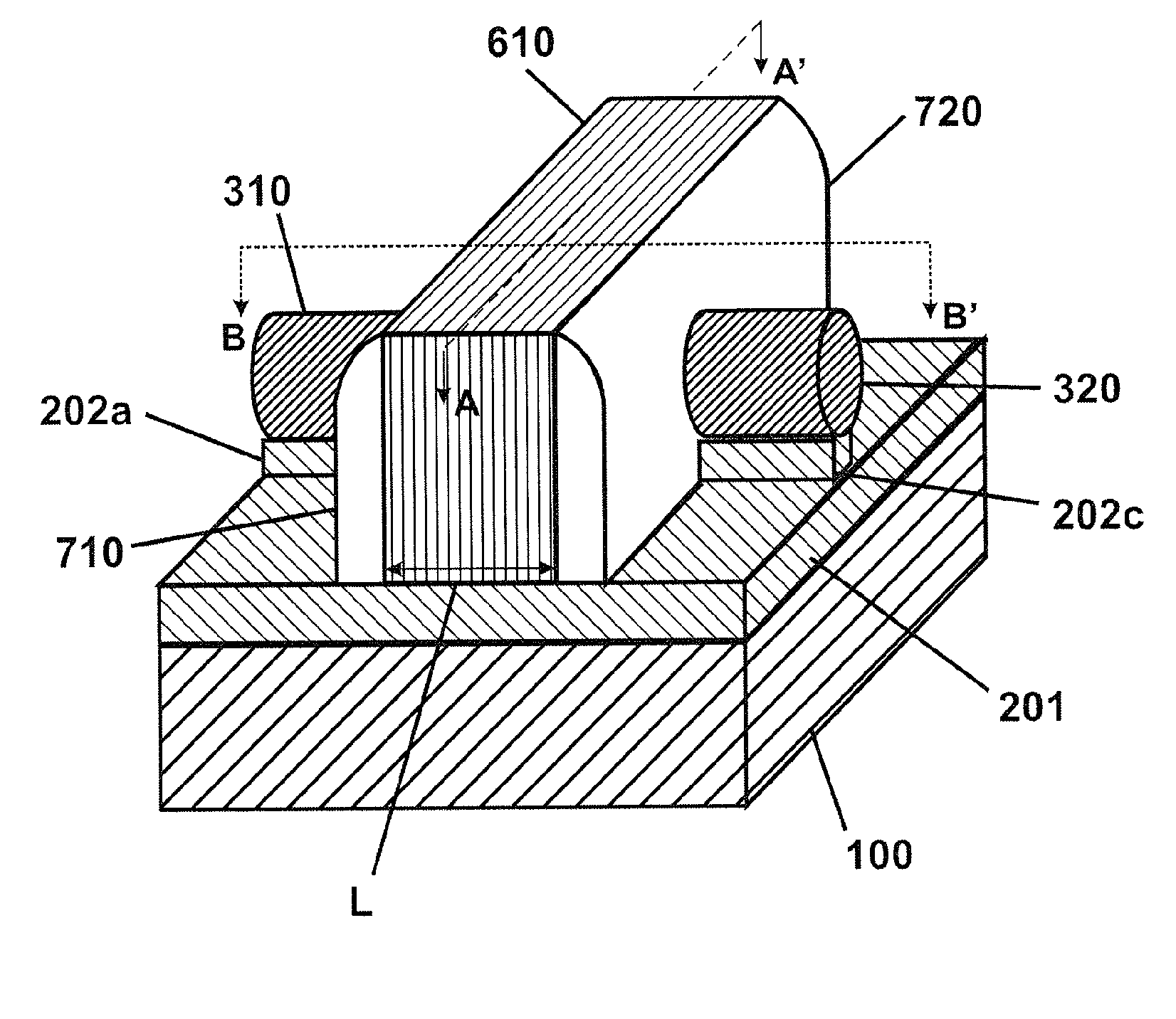

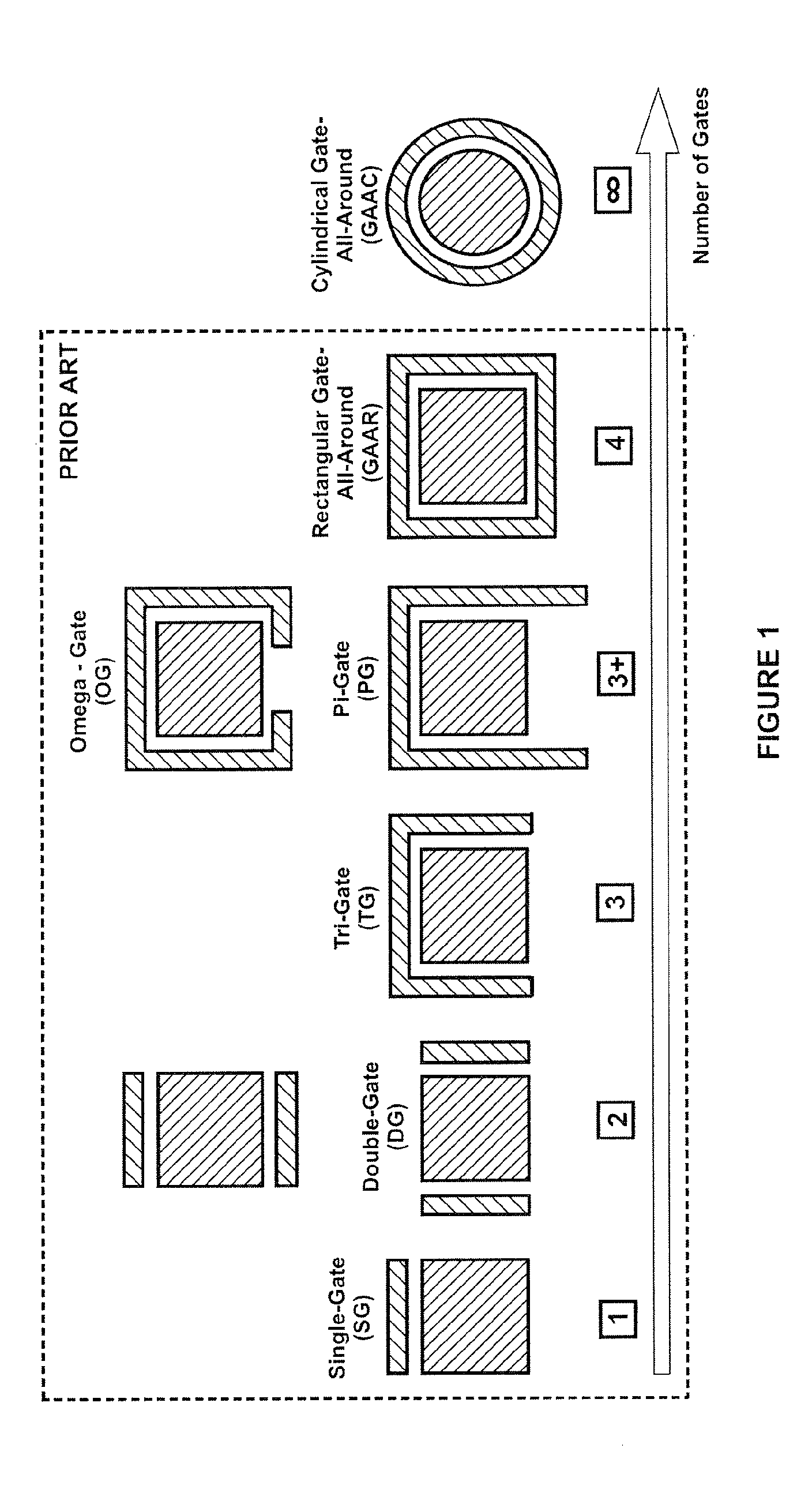

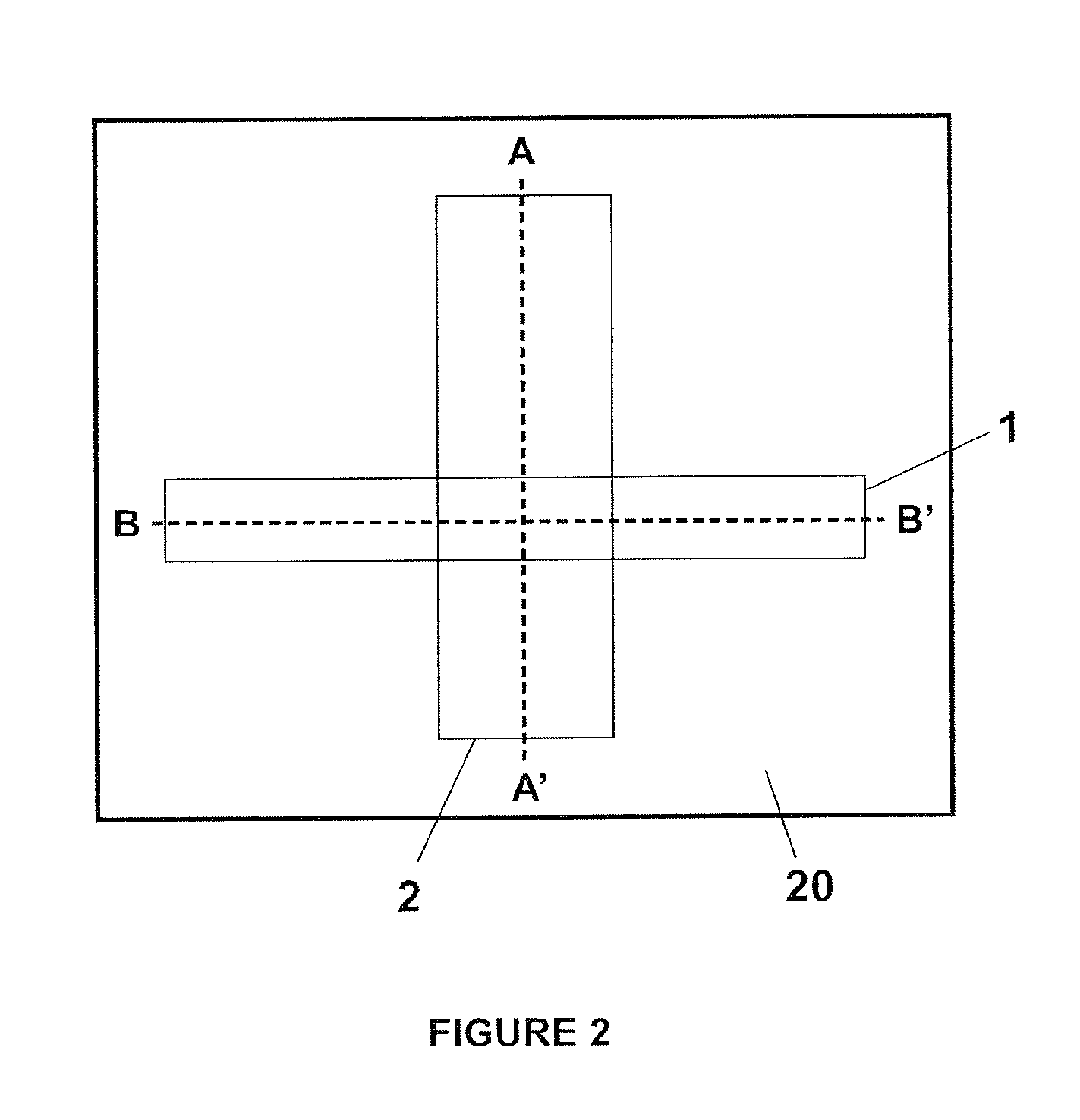

System and method for integrated circuits with cylindrical gate structures

ActiveUS20110291190A1Improve rendering capabilitiesImprove performanceNanoinformaticsSolid-state devicesCylindrical channelNanowire

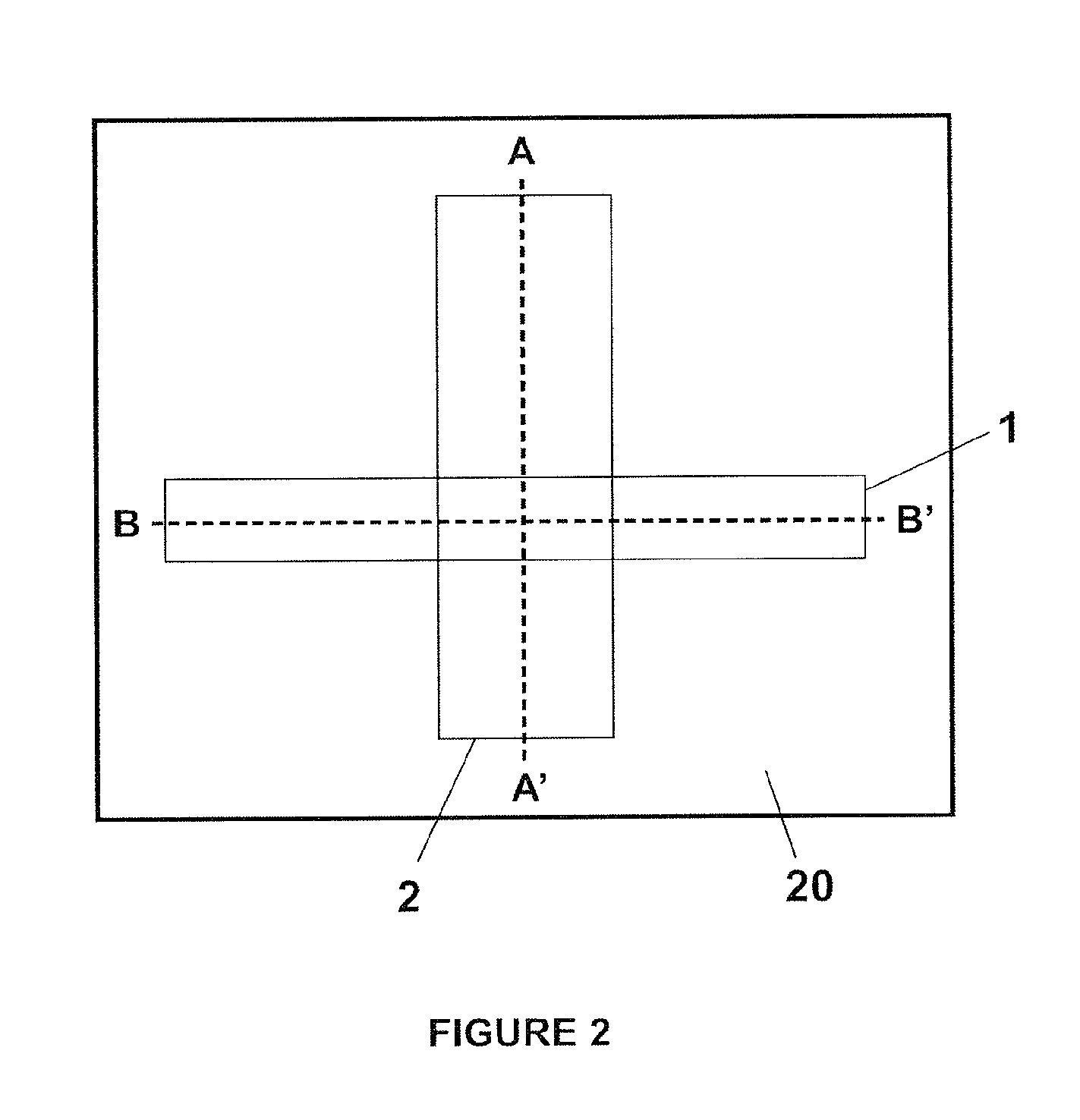

A system and method for integrated circuits with surrounding gate structures are disclosed. The integrated circuits system includes a transistor having a gate all around cylindrical (GAAC) nanowire channel with an interposed dielectric layer. The cylindrical nanowire channel being in a middle section of a semiconductor wire pattern connects the source and drain region positioned at the two opposite end sections of the same wire pattern. A method is provided for manufacturing the integrate circuits system with a GAAC transistor including forming an SOI layer wire pattern on the buried oxide layer of an SOI wafer; forming a cavity underneath the middle section of the wire pattern and shaping the middle section to cylindrically shaped channel; forming a gate electrode surrounding the cylindrical channel region with an interposed gate dielectric layer, the gate electrode being positioned on the buried oxide layer vertically towards the wire pattern; forming the source / drain regions at the two opposite end sections of the wire pattern on either sides of the gate electrode and channel.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

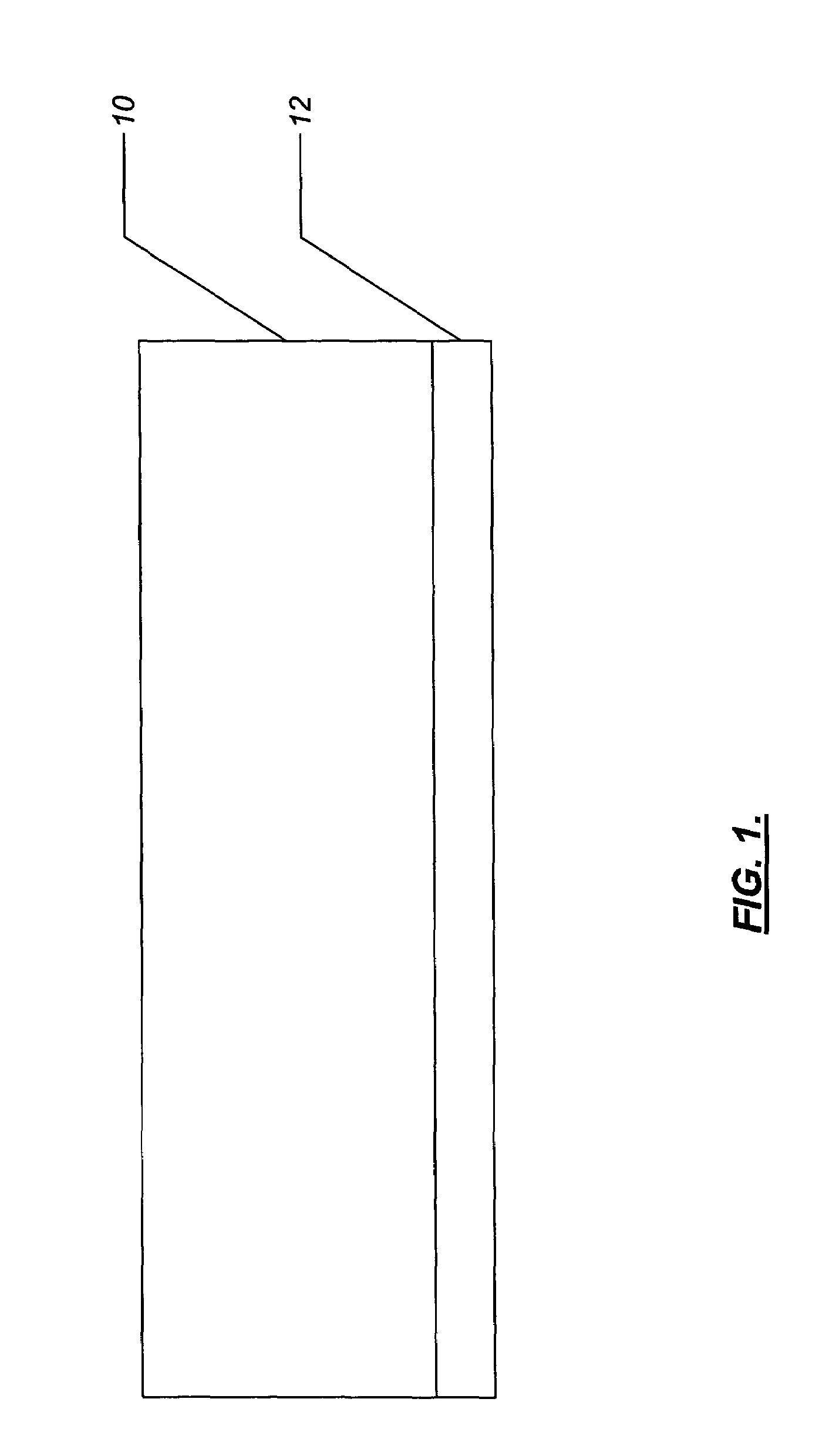

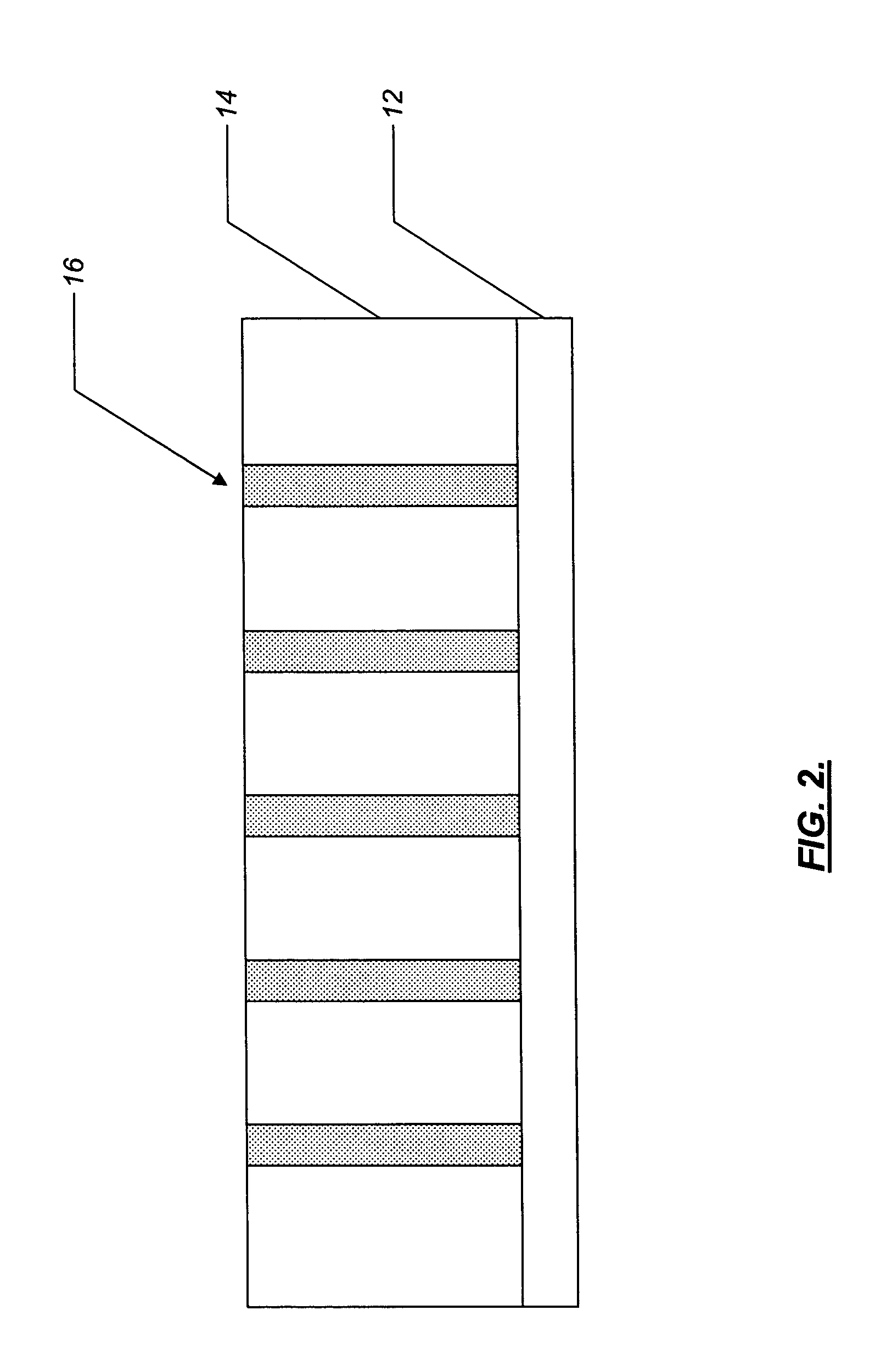

Nanopatterned templates from oriented degradable diblock copolymer thin films

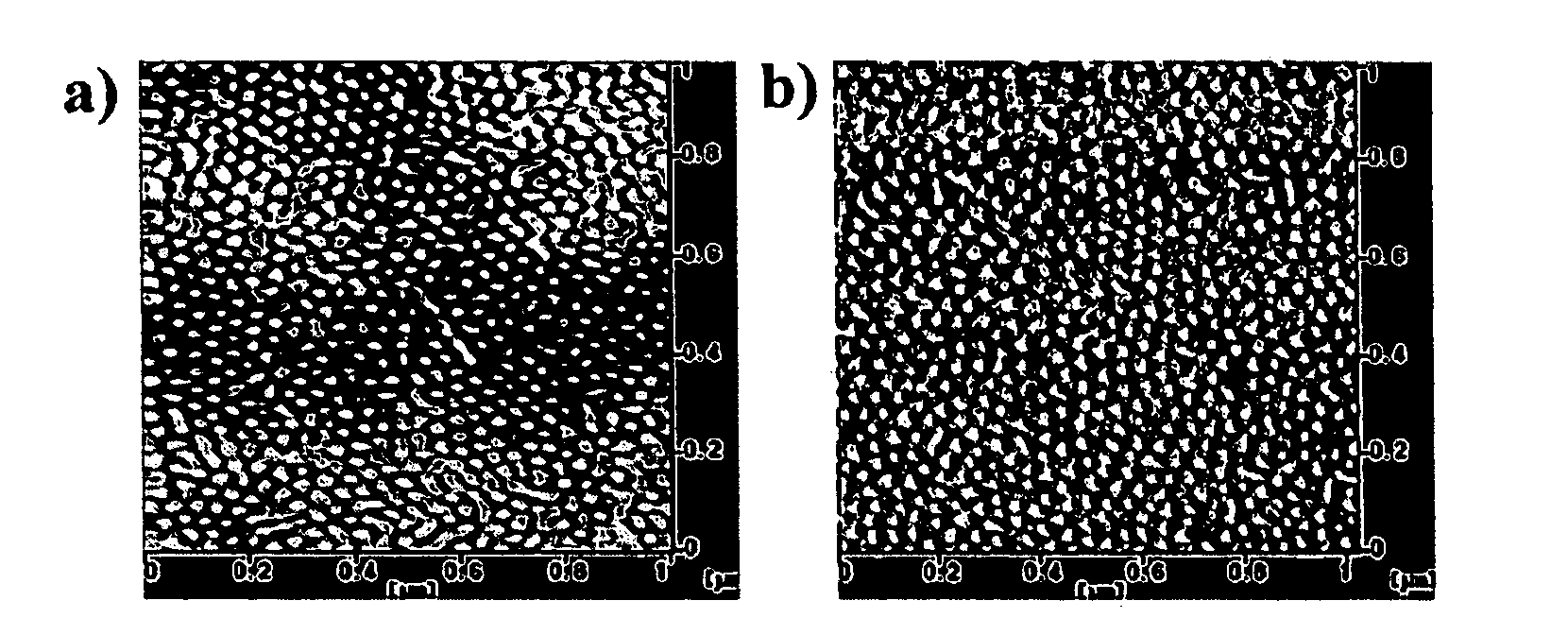

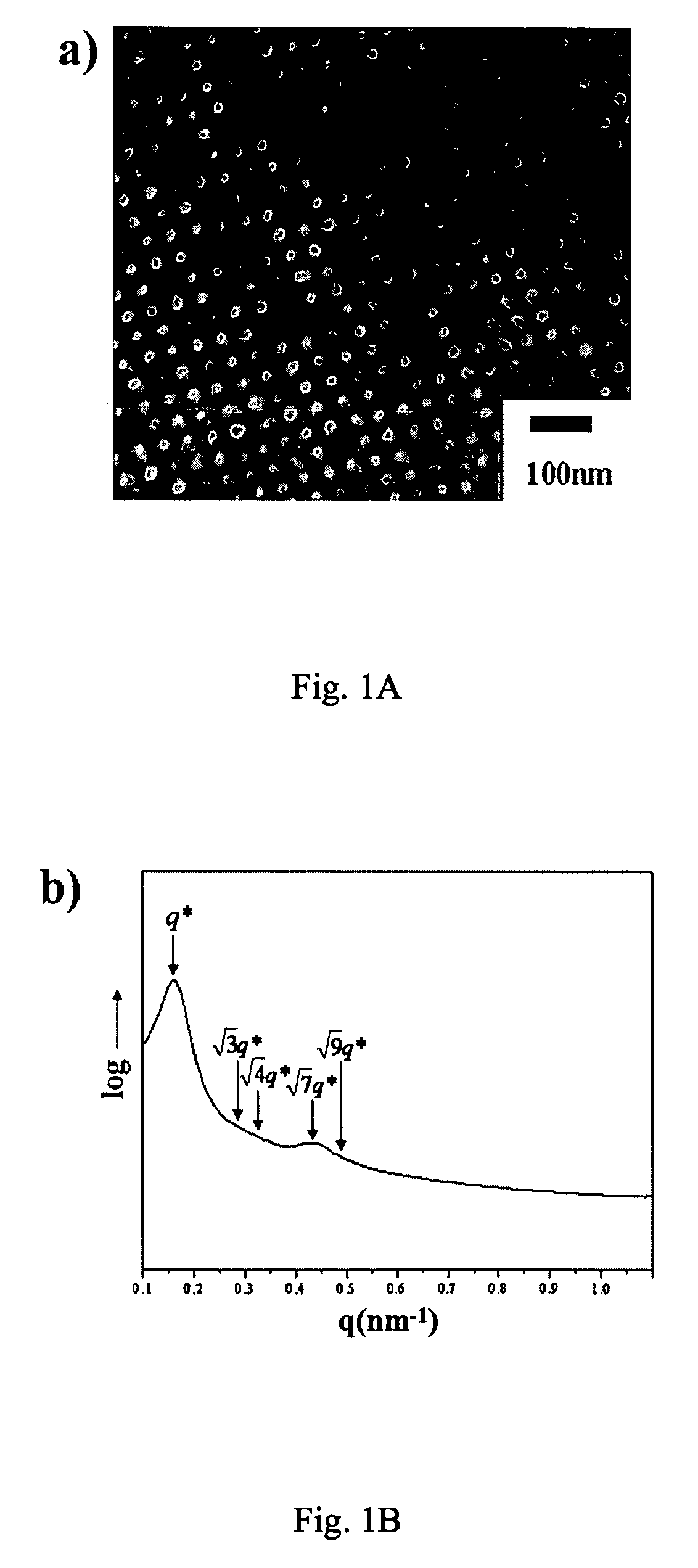

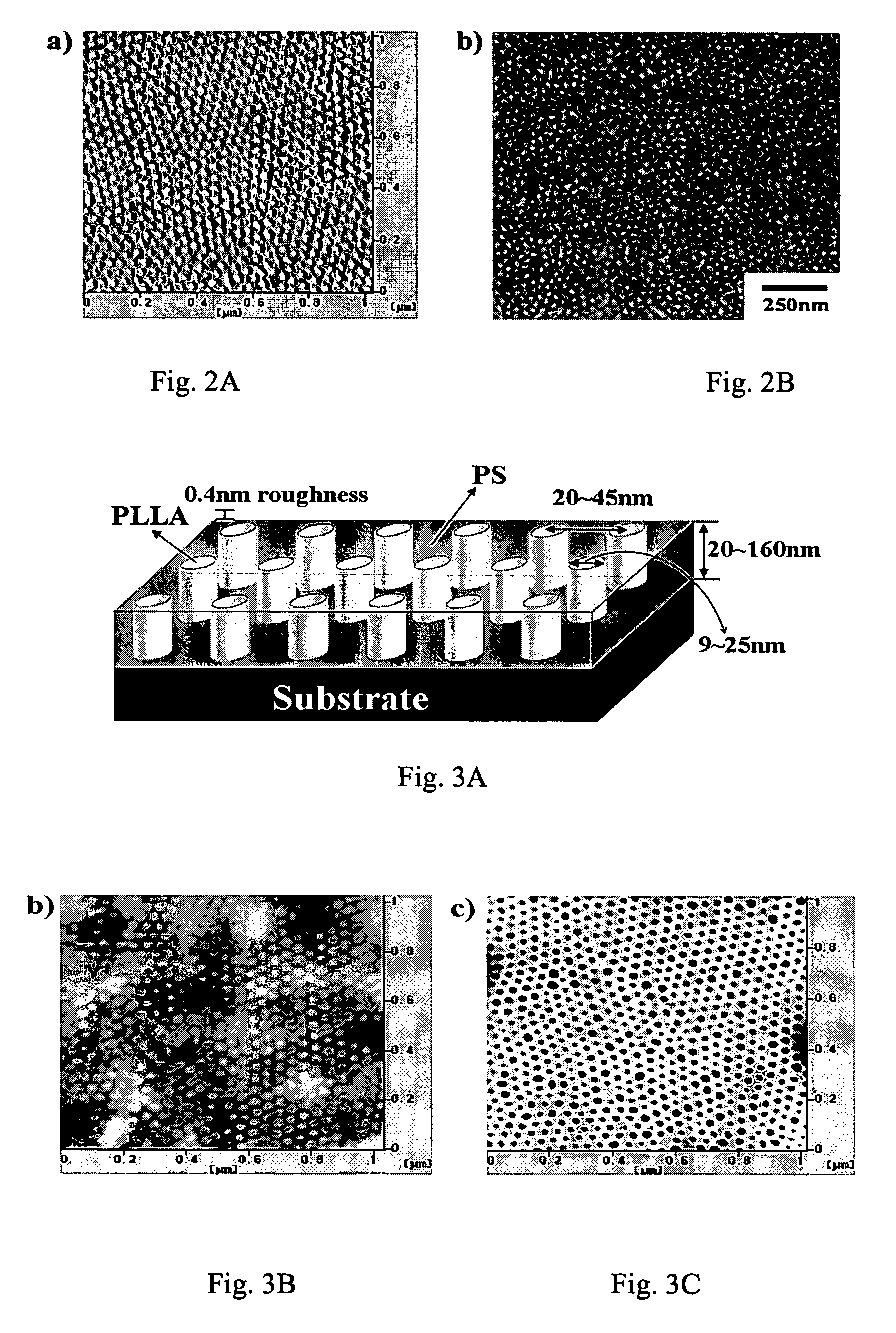

InactiveUS7632544B2Improve applicabilityAverage thicknessMaterial nanotechnologyDecorative surface effectsCylindrical channelPolymer science

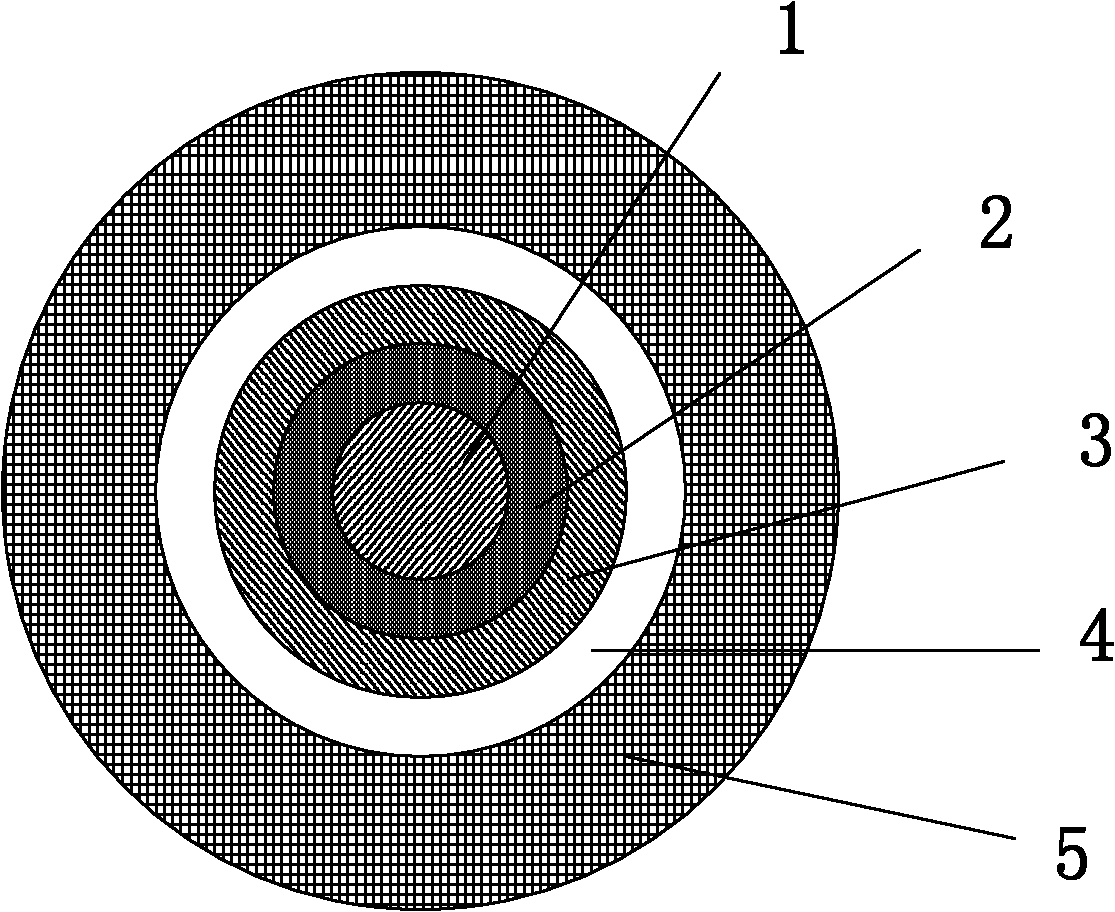

A nanopatterned template for use in manufacturing nanoscale objects. The nanopatterned template contains a nanoporous thin film with a periodically ordered porous geomorphology which is made from a process comprising the steps of: (a) using a block copolymerization process to prepare a block copolymer comprising first and second polymer blocks, the first and second polymer blocks being incompatible with each other; (b) forming a thin film under conditions such that the first polymer blocks form into a periodically ordered topology; and (c) selectively degrading the first polymer blocks to cause the thin film to become a nanoporous material with a periodically ordered porous geomorphology. In a preferred embodiment, the block copolymer is poly(styrene)-poly(L-lactide) (PS-PLLA) chiral block copolymer, the first polymer is poly(L-lactide), and the second polymer is polystyrene. Experimental results show that the first polymer blocks can be formed into a hexagonal cylindrical geomorphology with its axis perpendicular to a surface of the thin film. After hydrolysis to selectively degrade the first polymer blocks, a thin film having a series of repeated nanoscale hexagonal-cylindrical channels is obtained.

Owner:IND TECH RES INST

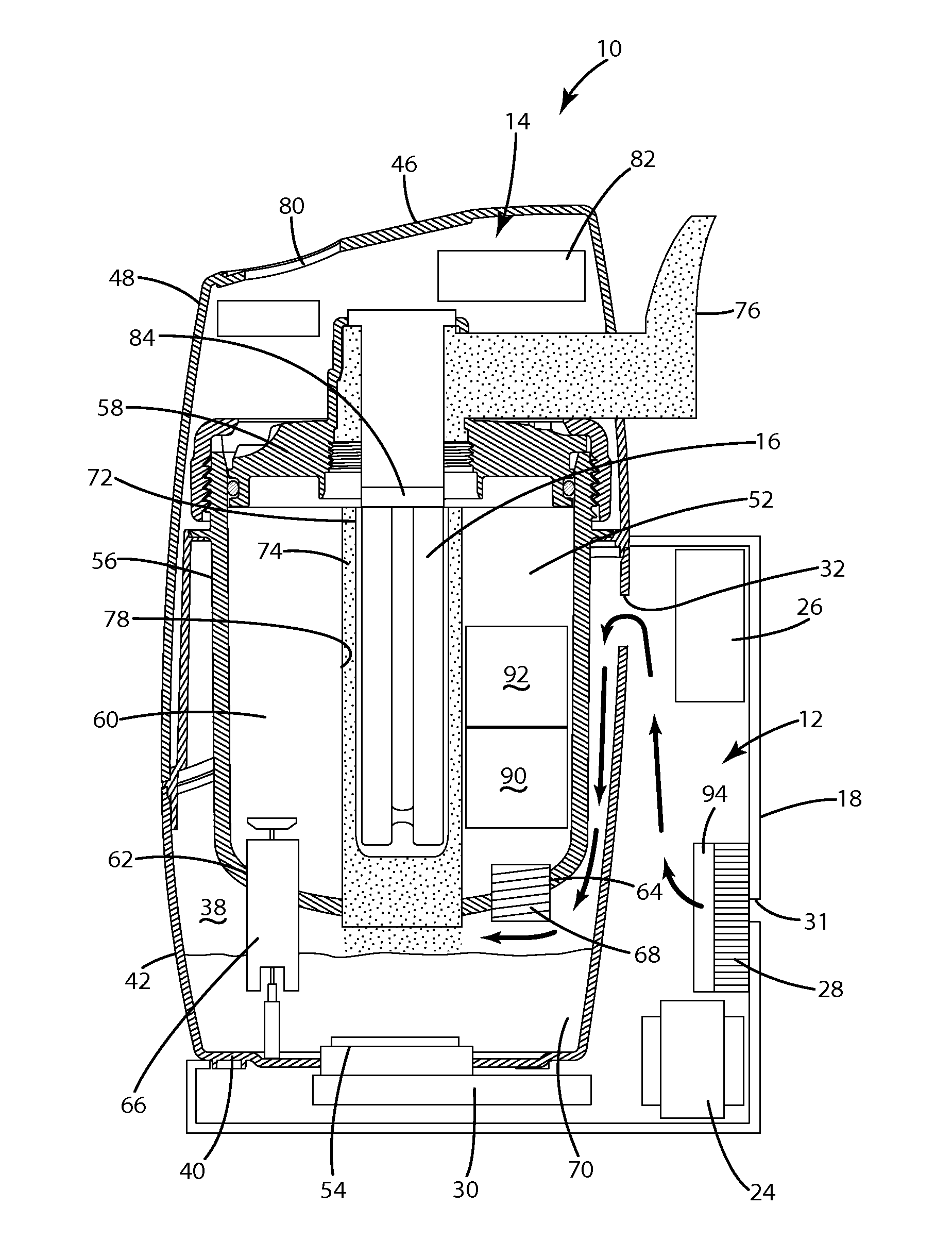

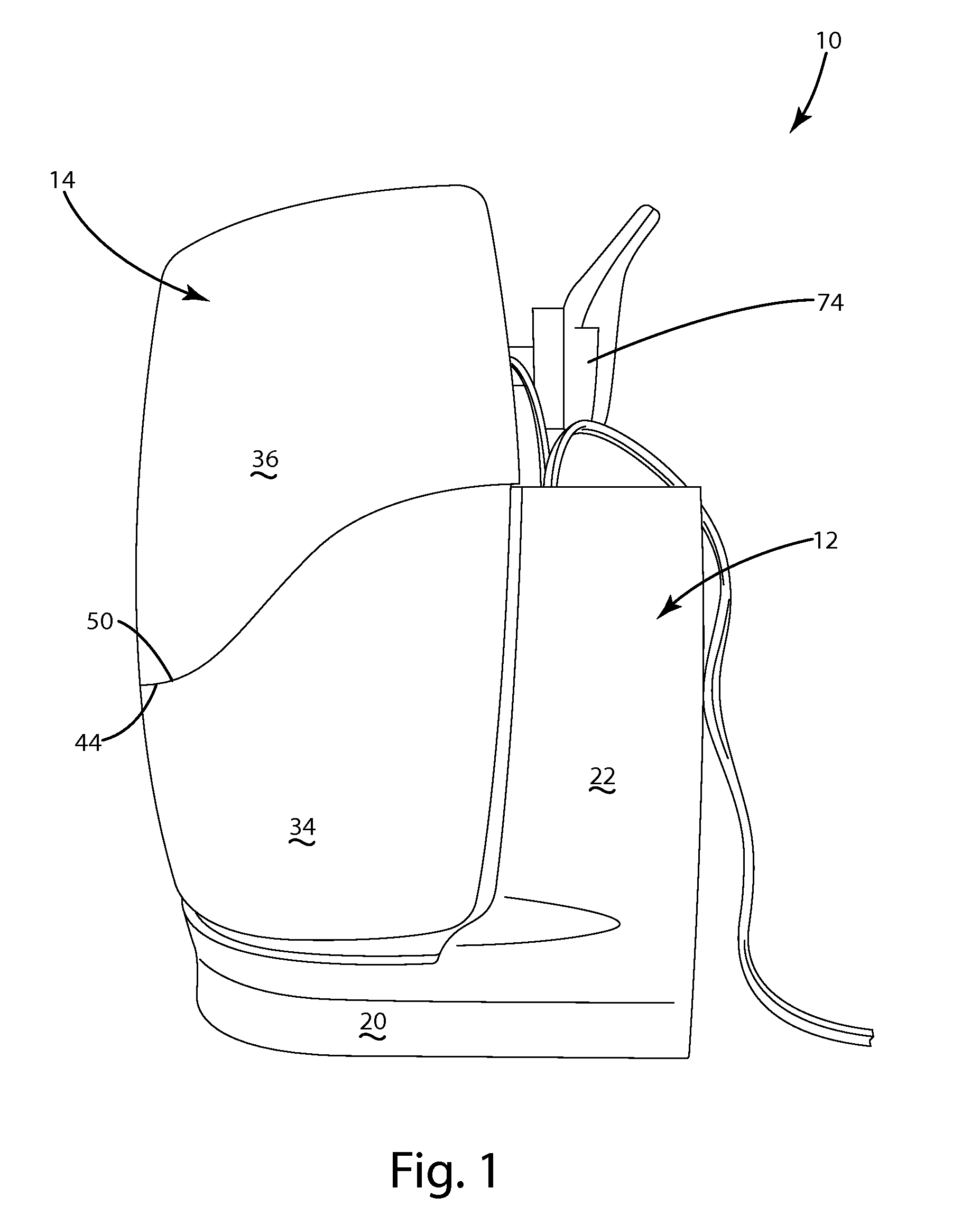

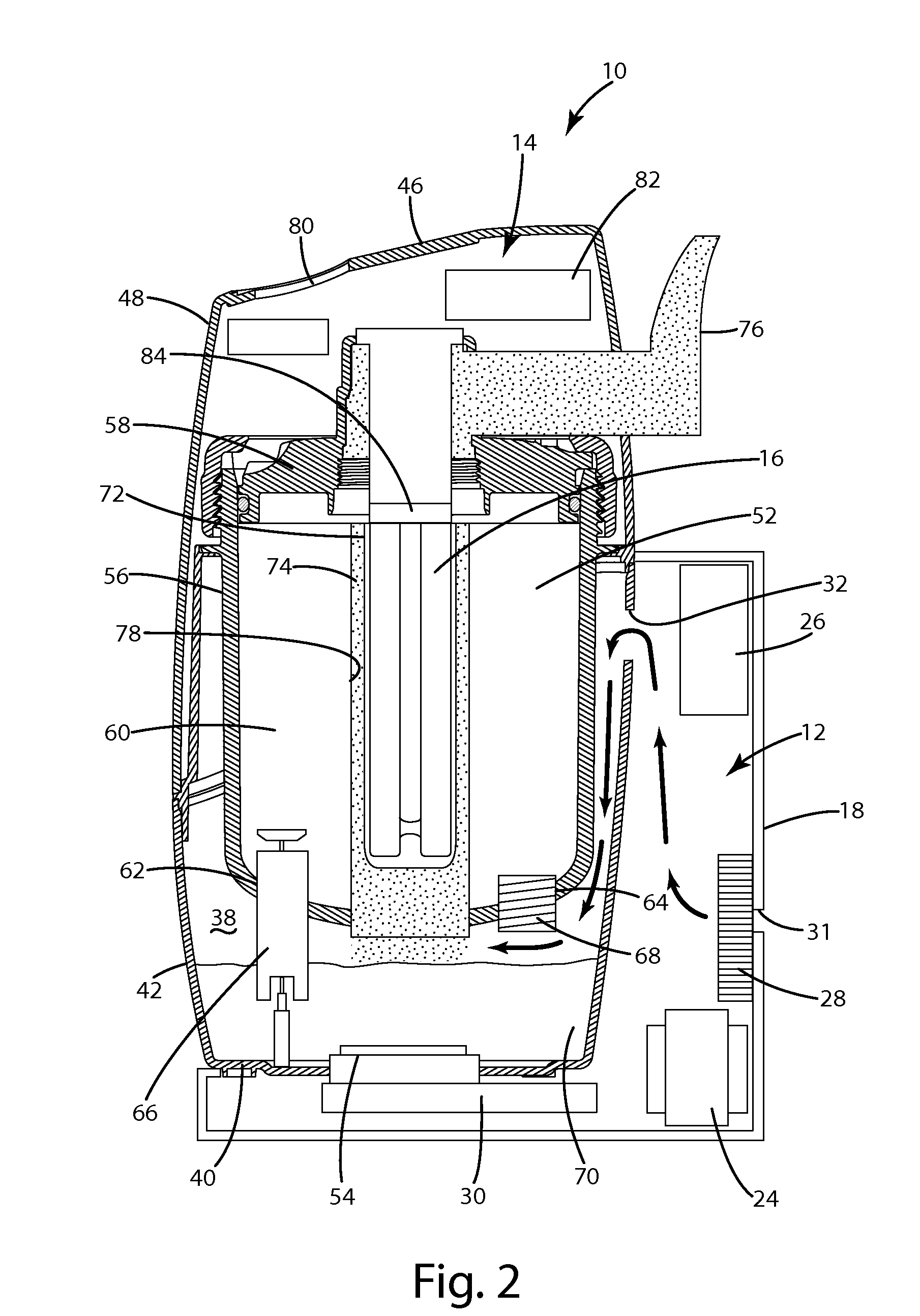

Humidifier with ultraviolet disinfection

ActiveUS20120234166A1Increase moisture contentAvoid effectivenessCombination devicesMechanical apparatusCylindrical channelUltraviolet lights

A humidifier for treating humidified air with germicidal light is provided. The humidifier includes a water reservoir, an atomizer to atomize a supply of water, and an ultraviolet light source to expose the atomized water to germicidal light. The ultraviolet light source extends vertically within a cylindrical channel to irradiate the atomized water dissipating upwardly from the atomizer. The water reservoir can include a carbon filter and a hardness-removing module for removing containments and metal oxides from the water supply. A control panel indicates the remaining useful life of the ultraviolet light source, the carbon filter and the hardness-removing module based on historical humidifier usage and water quality levels.

Owner:ACCESS BUSINESS GRP INT LLC

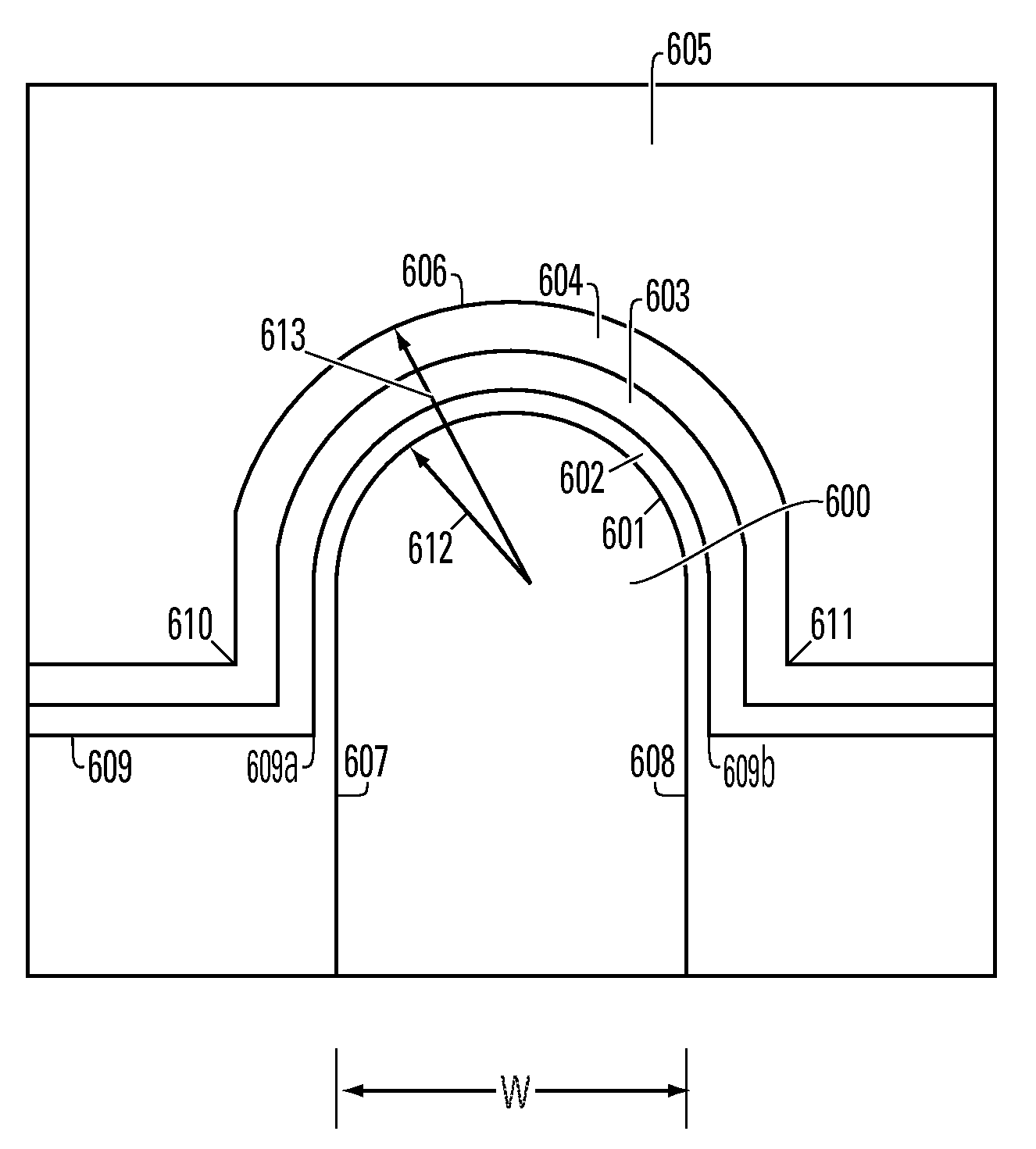

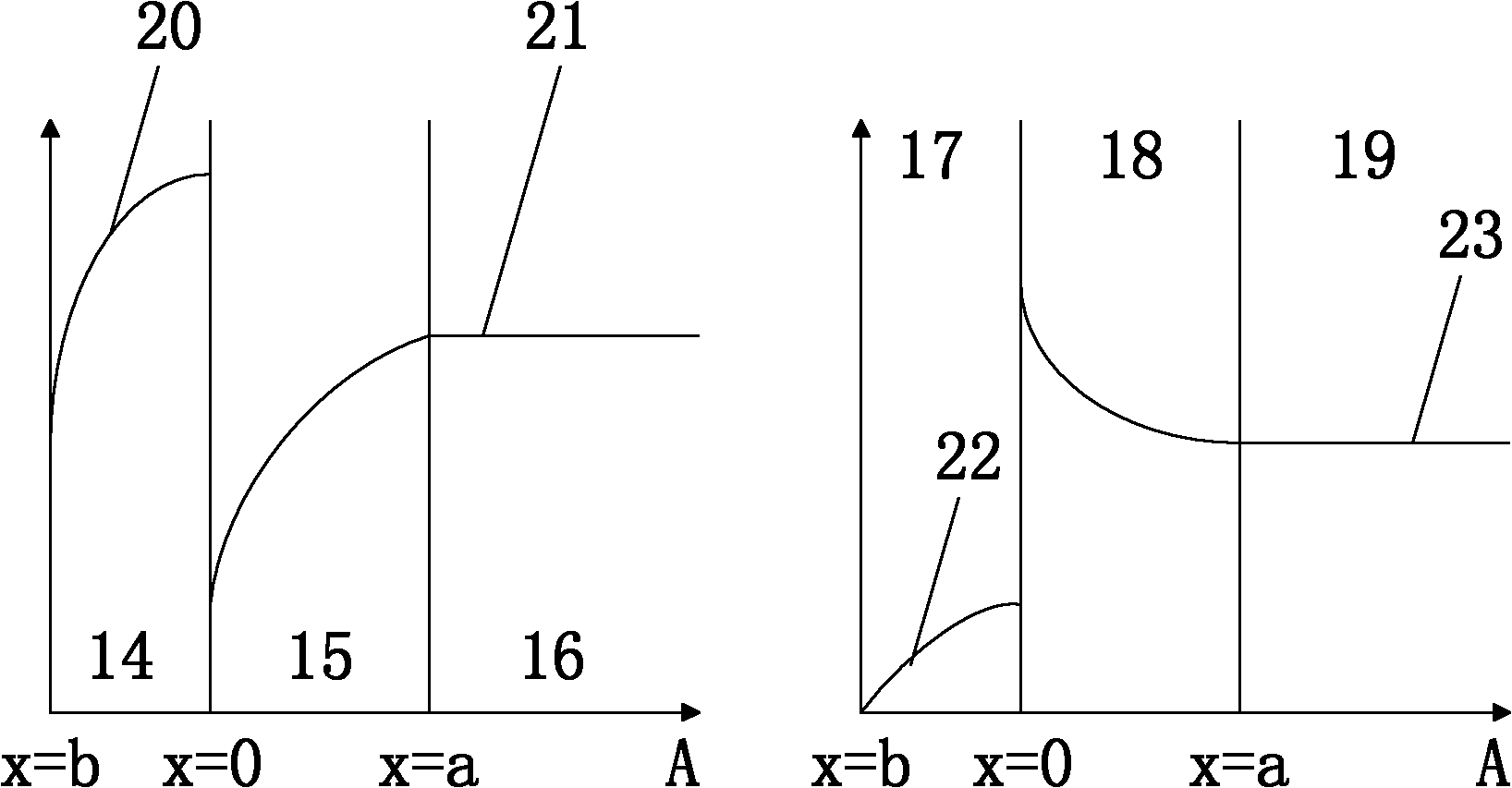

Cylindrical channel charge trapping devices with effectively high coupling ratios

ActiveUS20080099830A1Read-only memoriesSemiconductor/solid-state device manufacturingCylindrical channelElectrical conductor

A memory cell comprising: a source region and a drain region separated by a semiconductor channel region, the channel region having a channel surface having an area A1 including a first cylindrical region, a first dielectric structure on the channel surface, a dielectric charge trapping structure on the first dielectric structure, a second dielectric structure on the dielectric charge trapping structure, a conductive layer having a conductor surface having an area A2 including a second cylindrical region on the second dielectric structure, the conductor surface overlying the dielectric charge trapping structure and the channel surface of the channel region, and the ratio of the area A2 to the area A1 being greater than or equal to 1.2 are described along with devices thereof and methods for manufacturing.

Owner:MACRONIX INT CO LTD

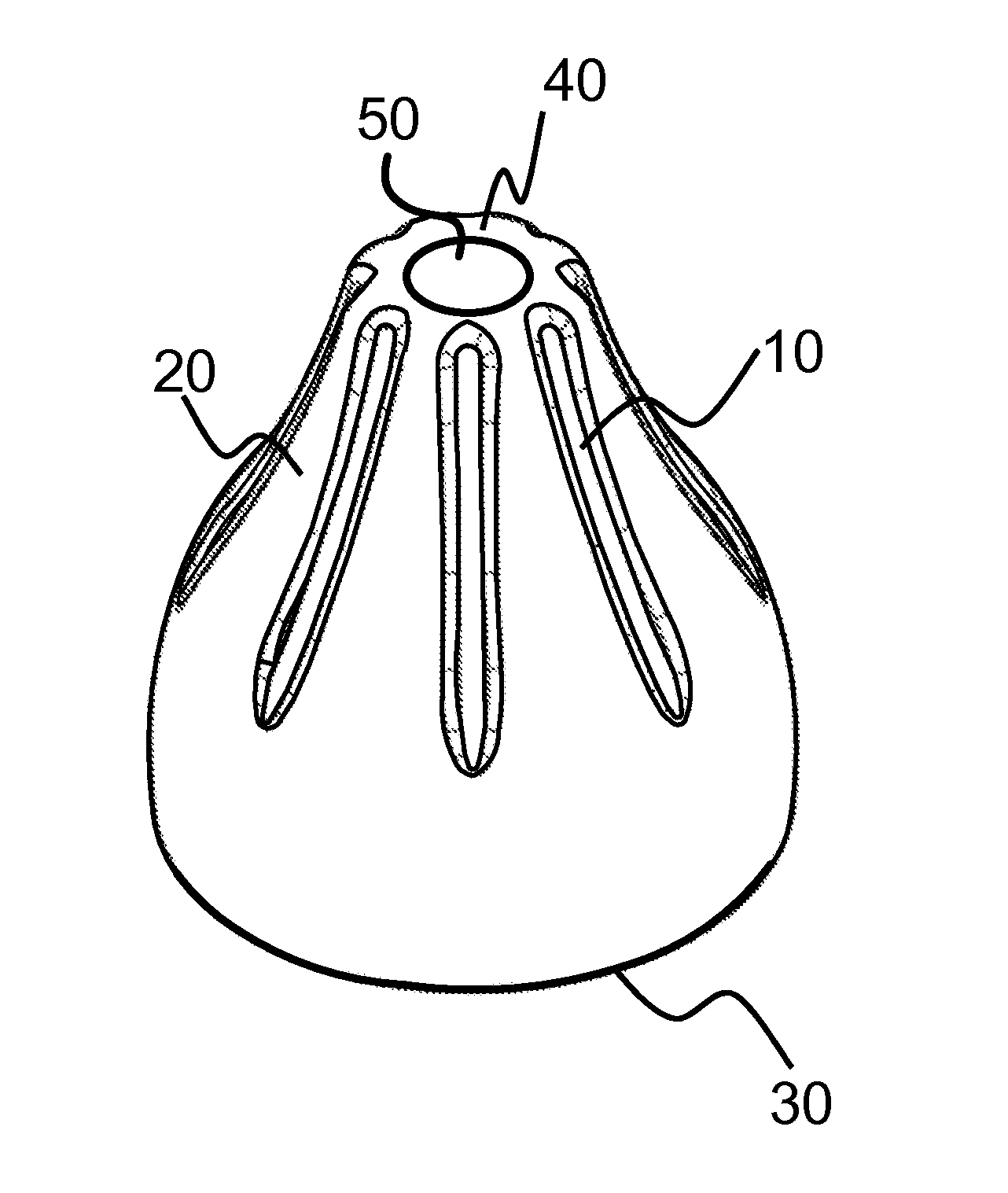

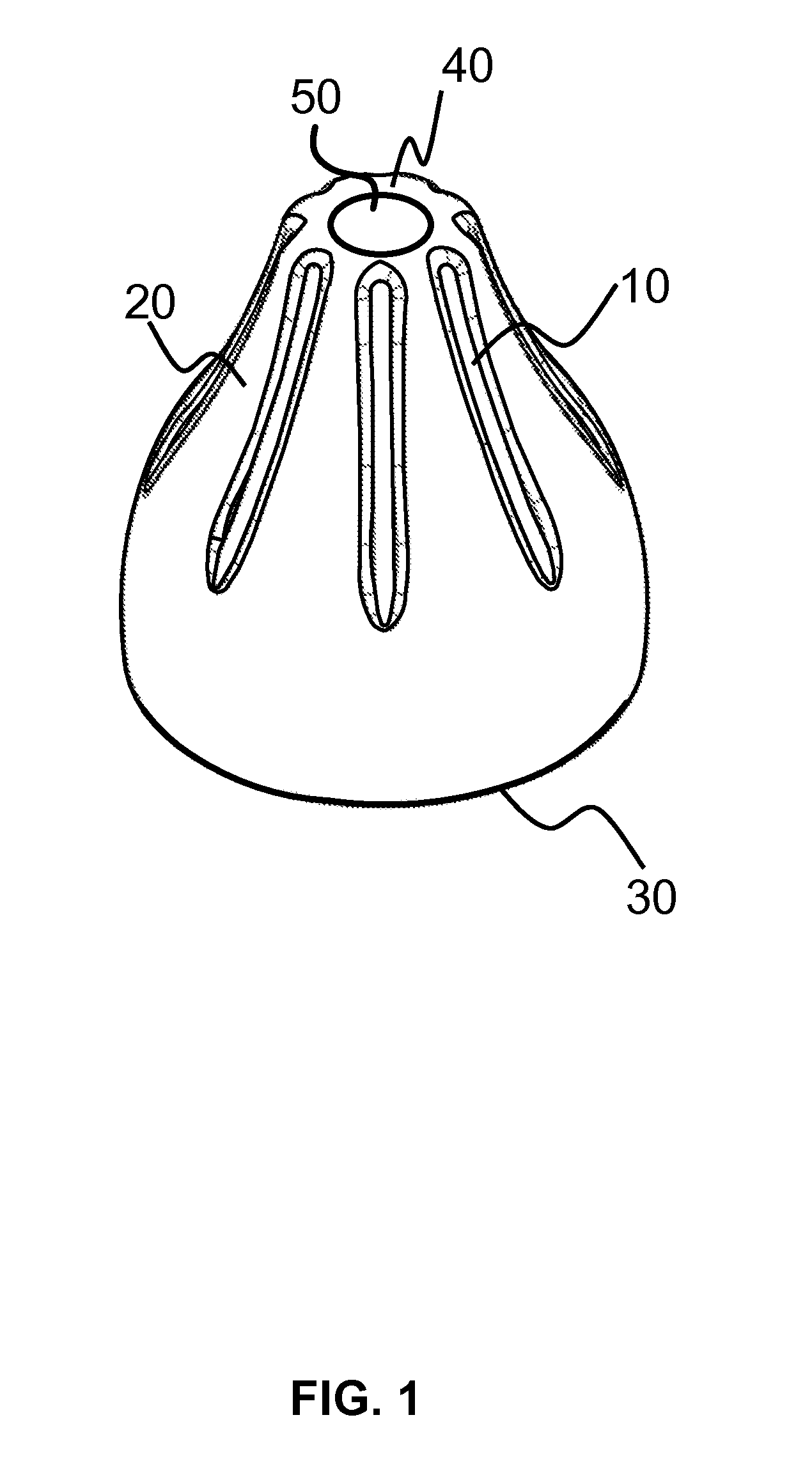

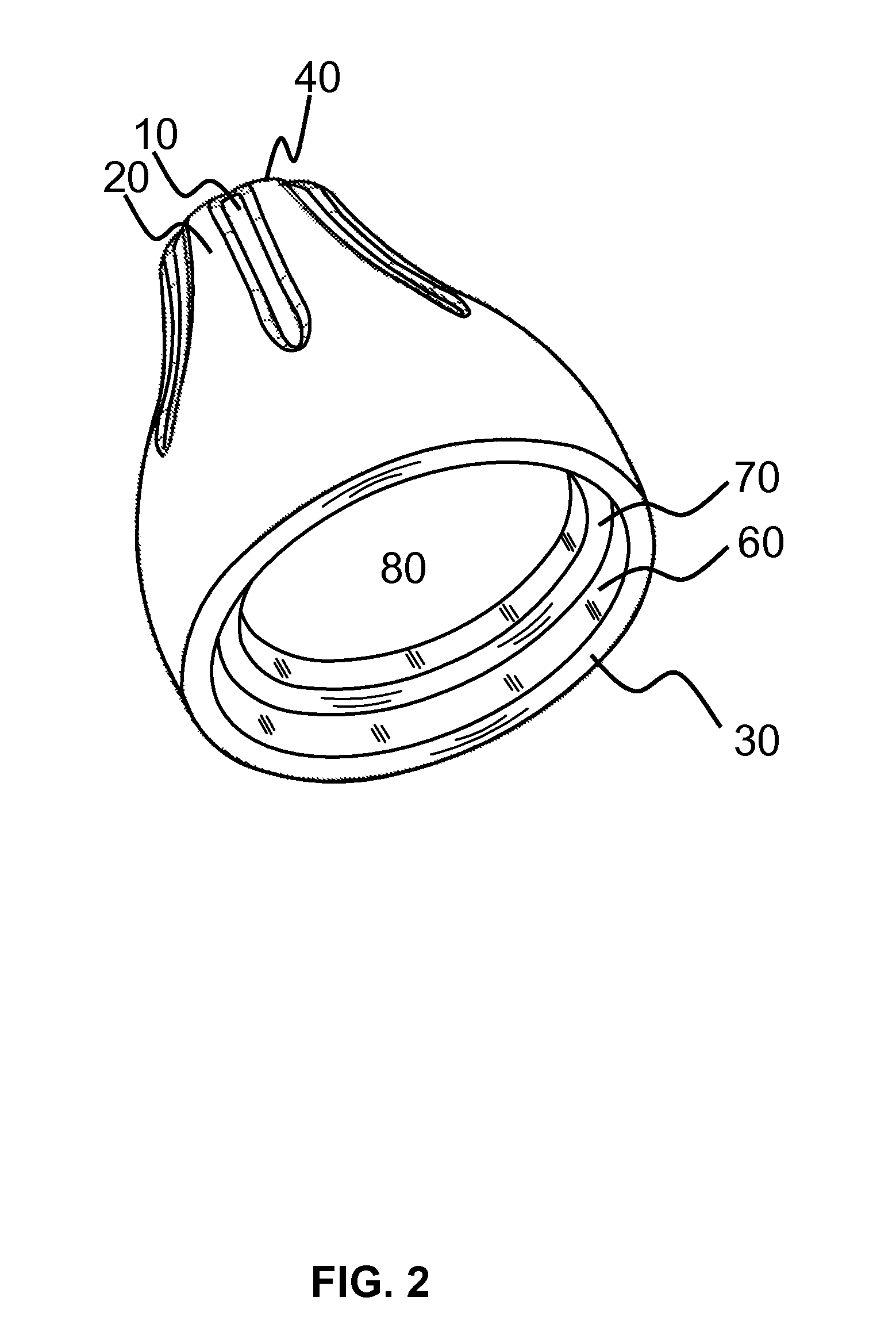

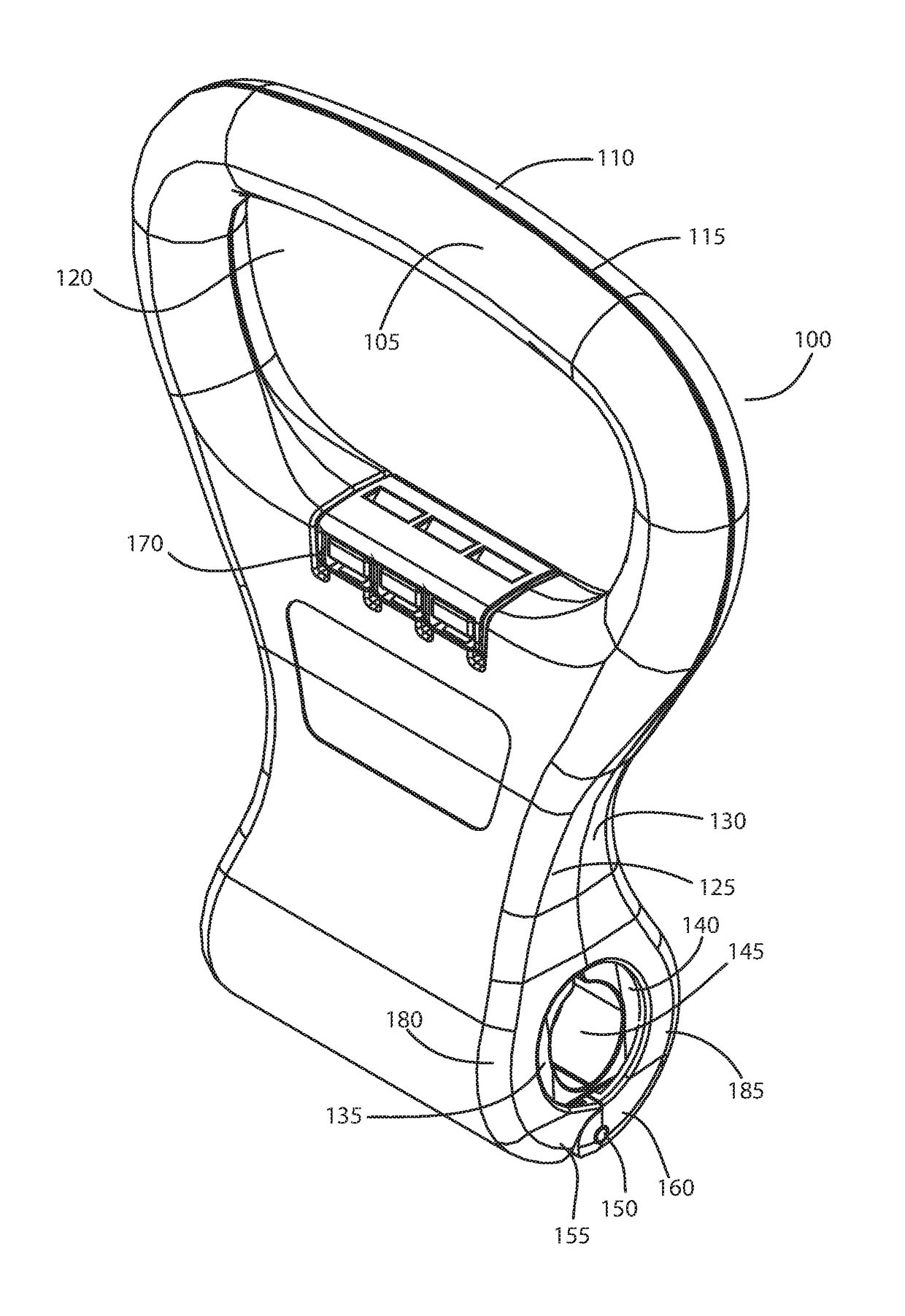

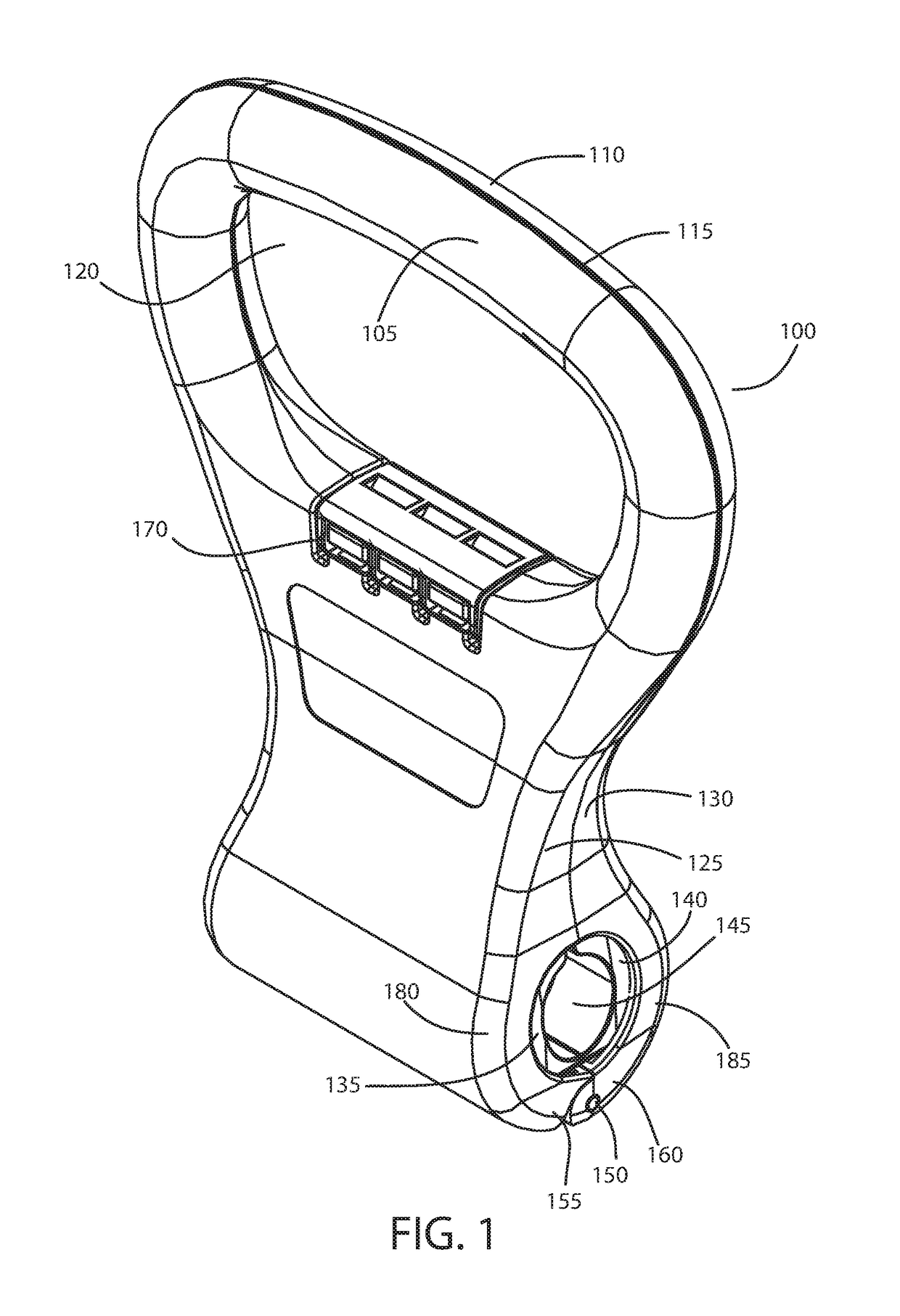

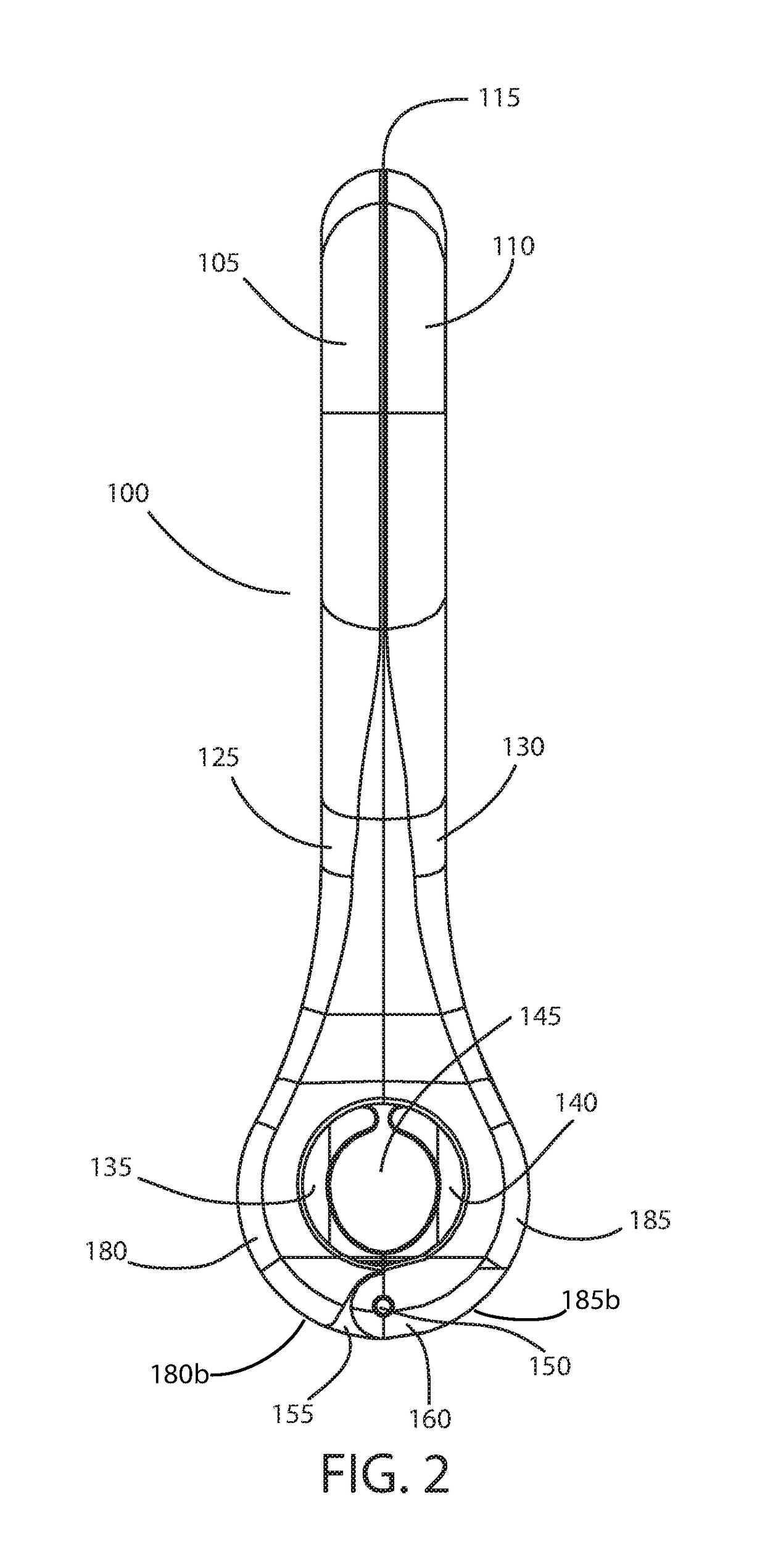

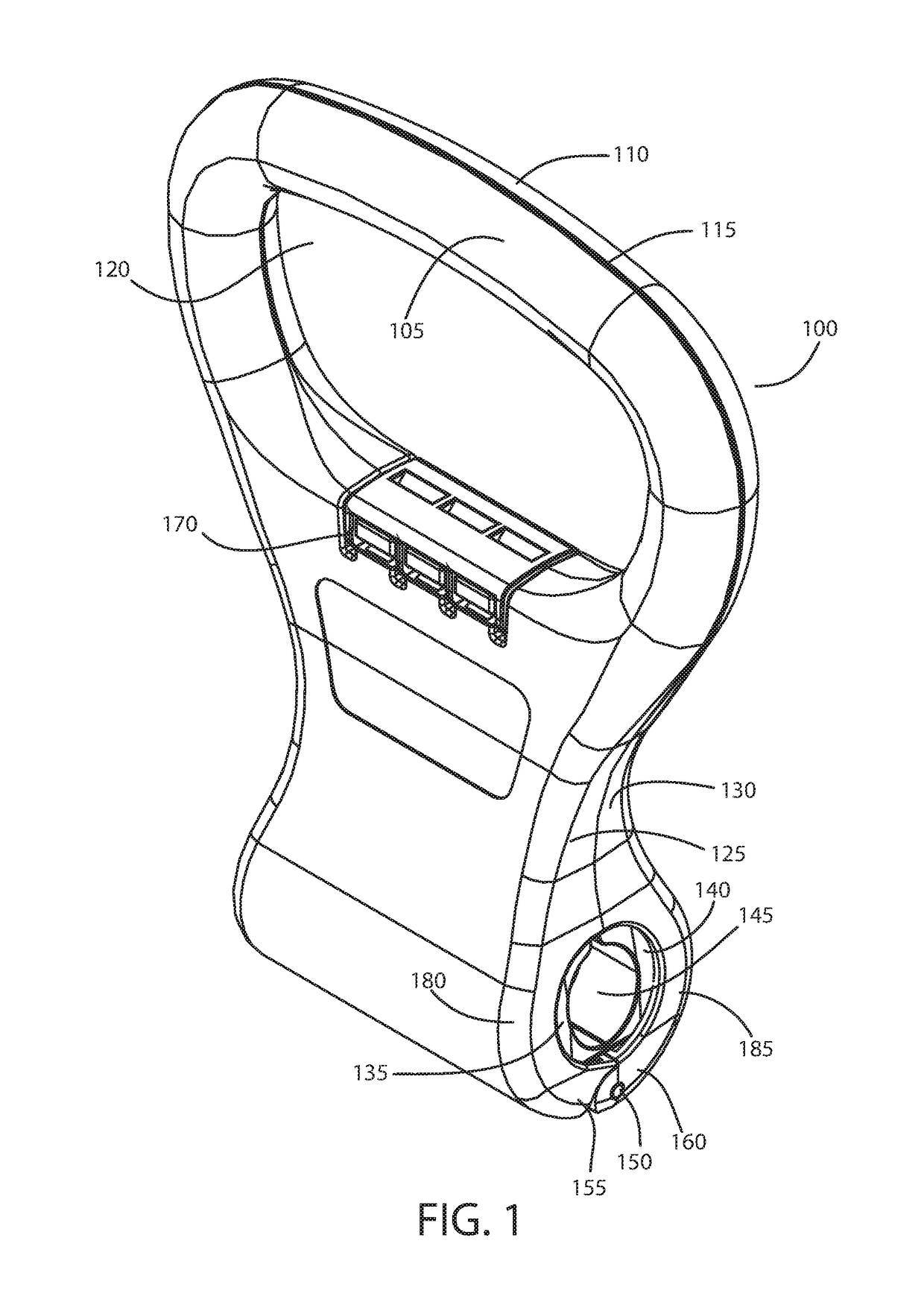

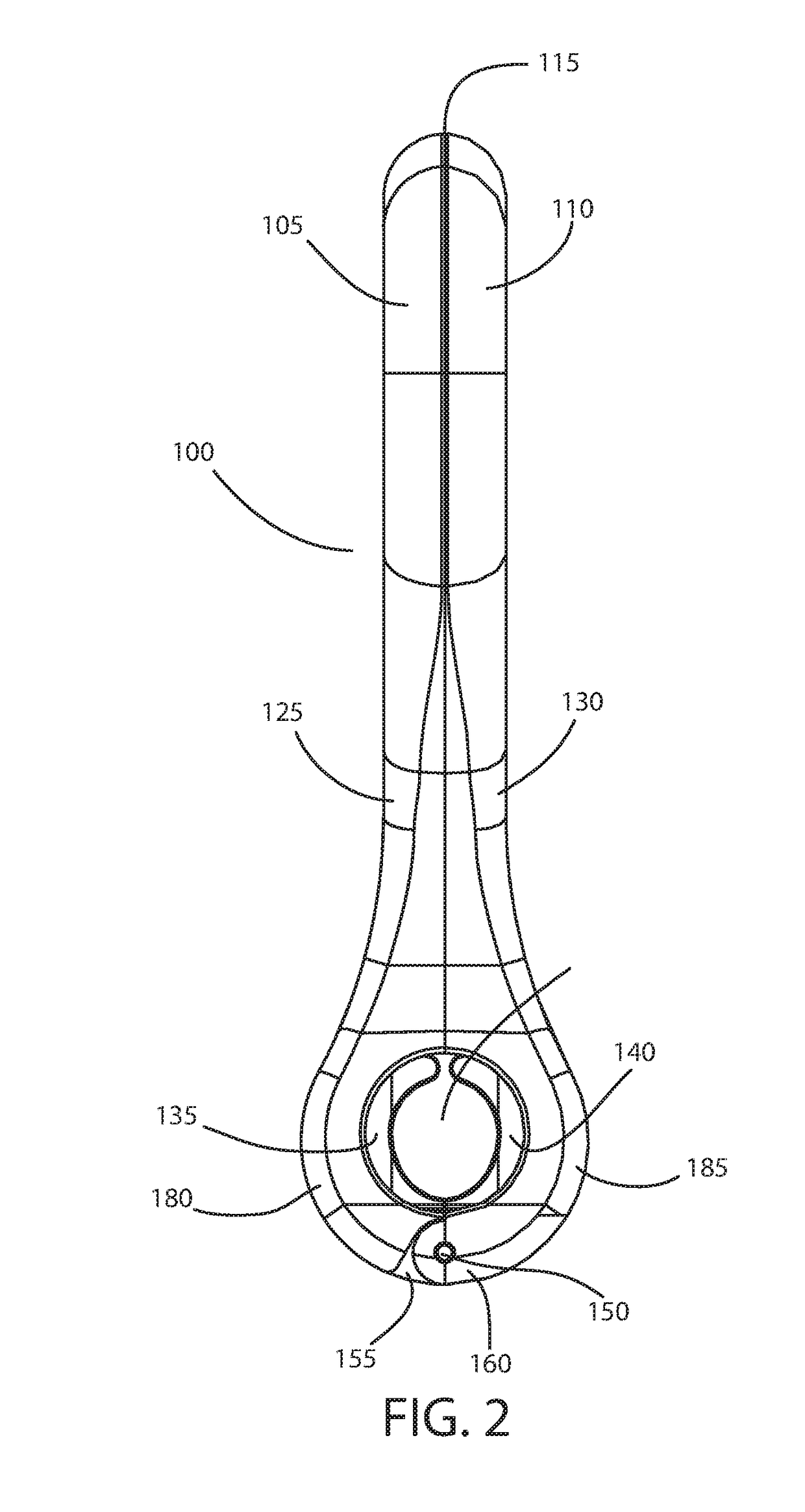

Partially Occluding Ergonomic Earbud Adapter

A partially occluding ergonomic earbud adapter is formed from low durometer materials. The exterior of the adapter is frustoconical and tear-drop shaped and formed with several fluted recesses which set apart finger-like flanges extending from an open base toward the tip of the adapter. The ergonomic flanges grip the inside of the ear canal as a result of elastic restoring forces of the flanges against each other and against the ear canal to form an ergonomic seal partially occluding sound from the ear canal while providing isolation. The inside wall of the adapter is formed to enclose and secure the earphone in a parabolic concavity formed by an undercut rib at the base. The cavity is abutted by a cylindrical channel extending through the adapter to an orifice at the tip to deliver high fidelity audio into a user's ear canal from the headset or another audio listening device.

Owner:VASQUEZ RAFAEL

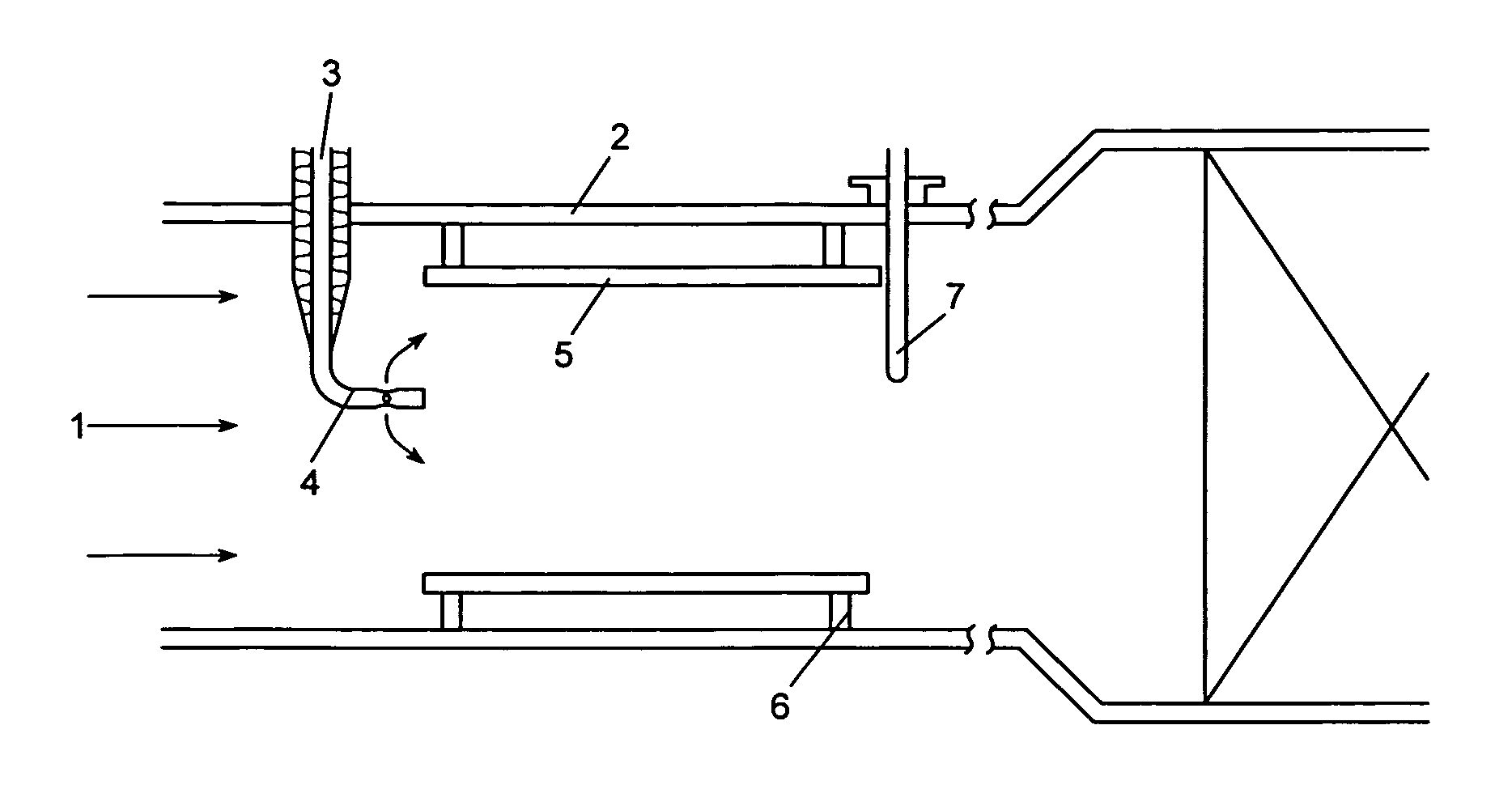

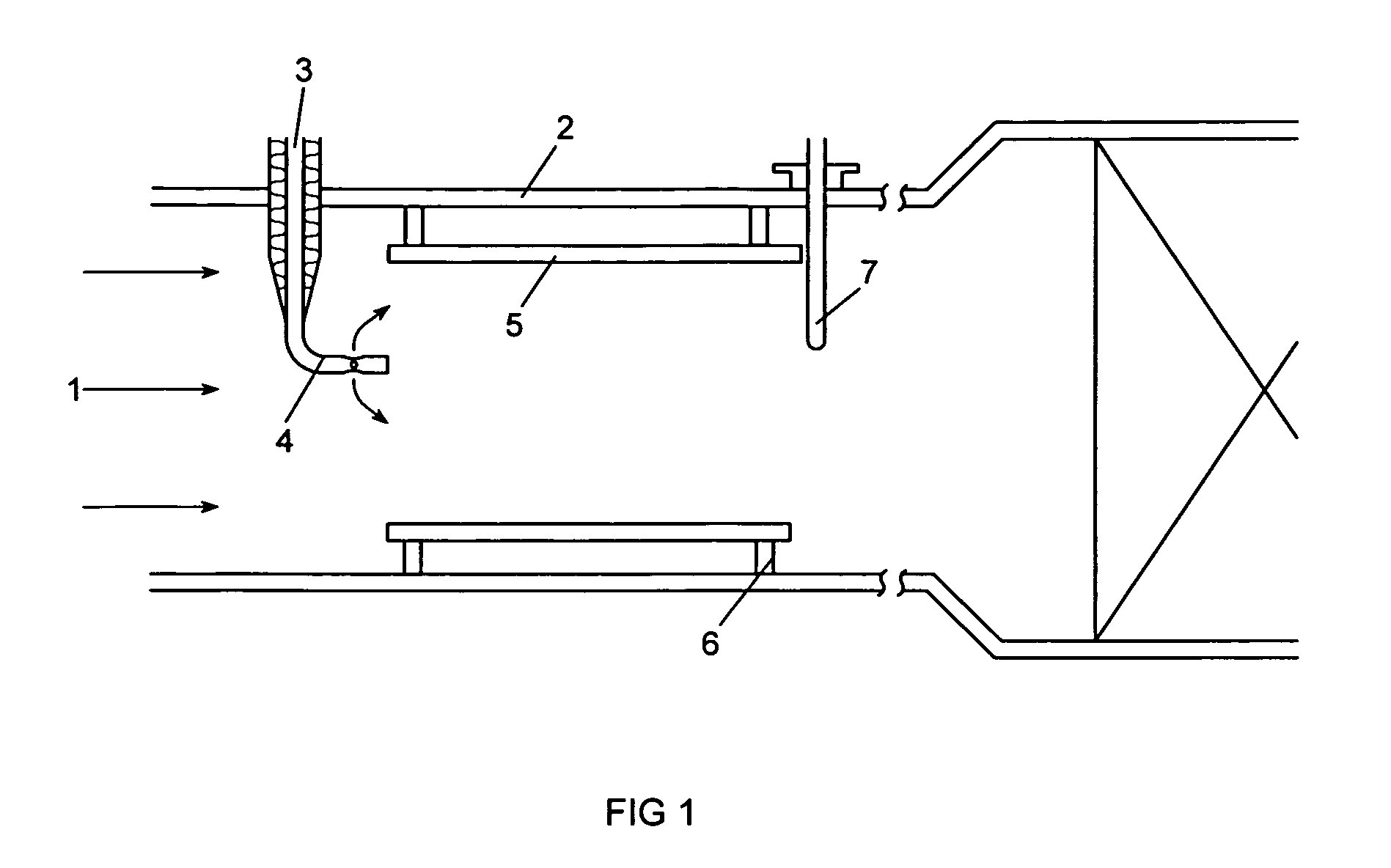

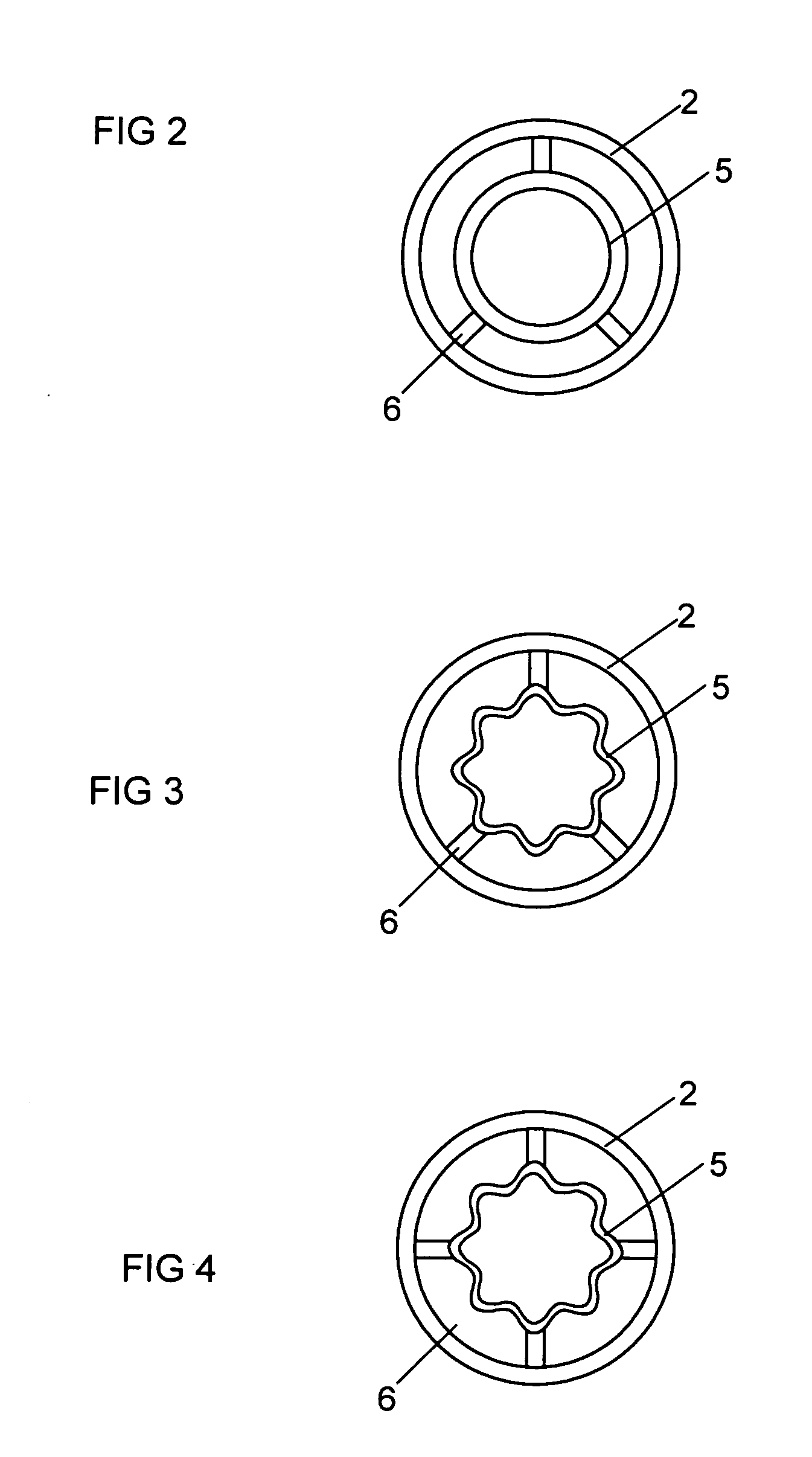

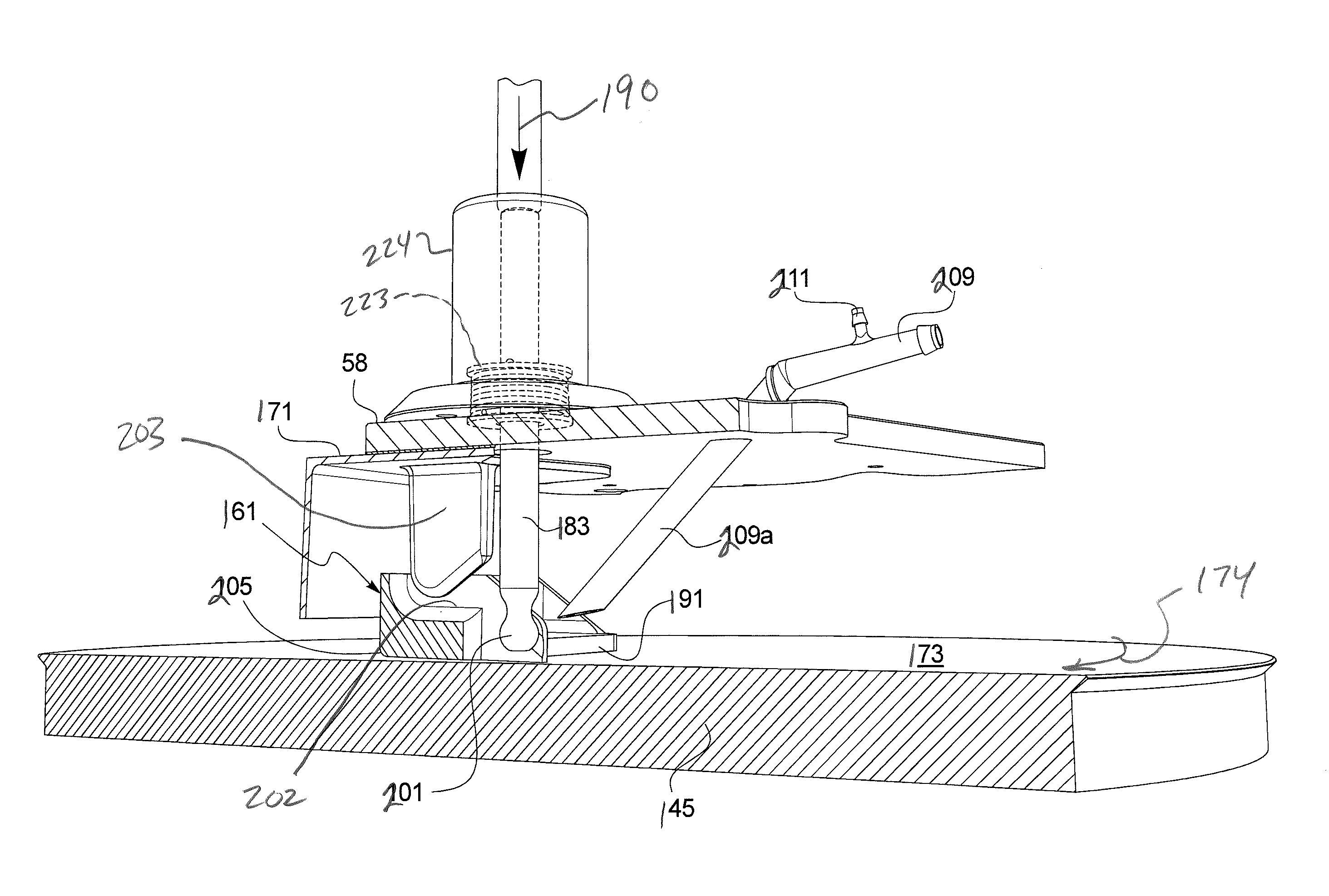

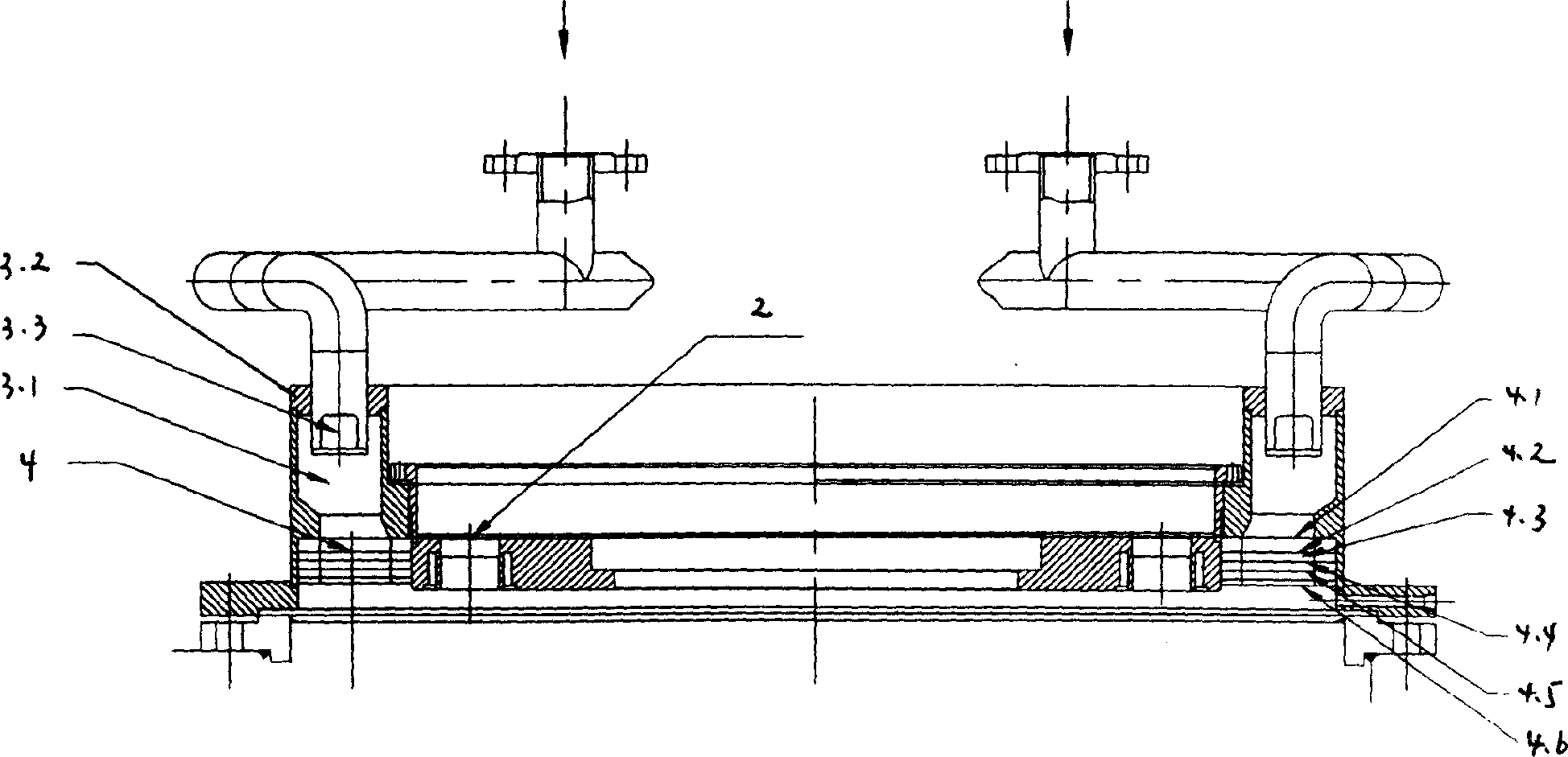

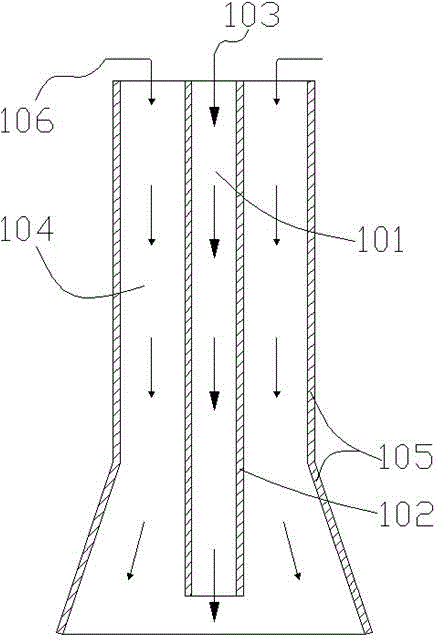

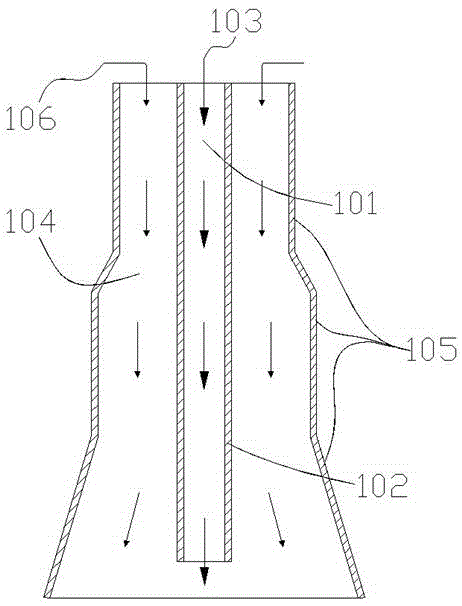

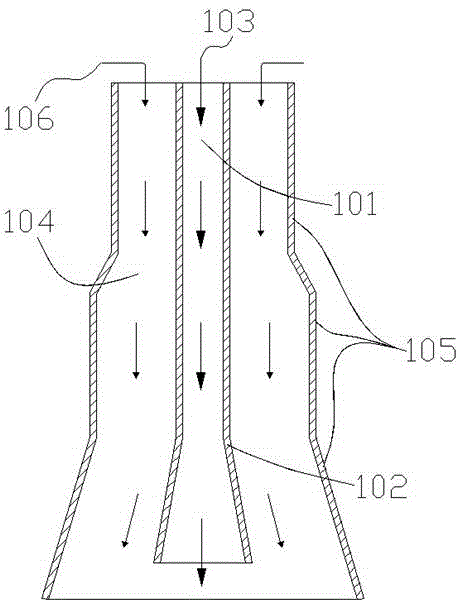

Method and system for injection of a solution into a gas stream

ActiveUS20060275192A1Reduce contentNitrogen compoundsInternal combustion piston enginesCylindrical channelInterior space

The invention provides a method and a system for injection of a solution of a compound into a gas at elevated temperature, evaporating the solution and decomposing the compound in the gas at the elevated temperature, comprising injecting the solution into an injection channel being provided into at least a portion of an outer channel and being surrounded by and spaced apart from the outer channel, passing the gas along space between inner wall of the outer channel and outer wall of the injection channel and along inner space of the injection channel, evaporating the solution in and on inner wall of the injection channel and decomposing the compound in and on the inner wall of the injection channel and in the gas. The solution can be an aqueous solution comprising urea or ammonia, the gas is an exhaust gas from combustion and the injection channel typically is a cylindrical channel concentrically installed in the outer channel.

Owner:UMICORE AG & CO KG

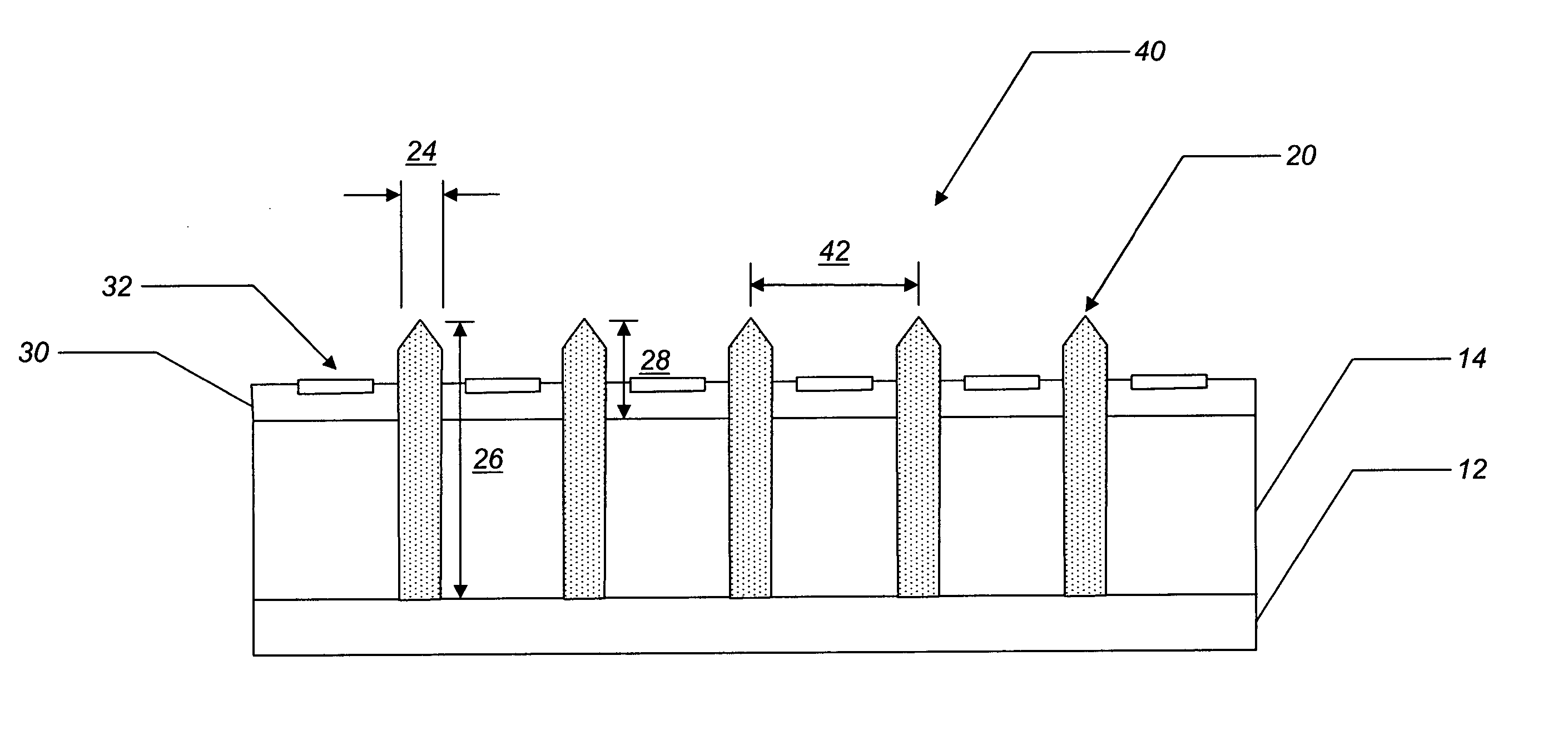

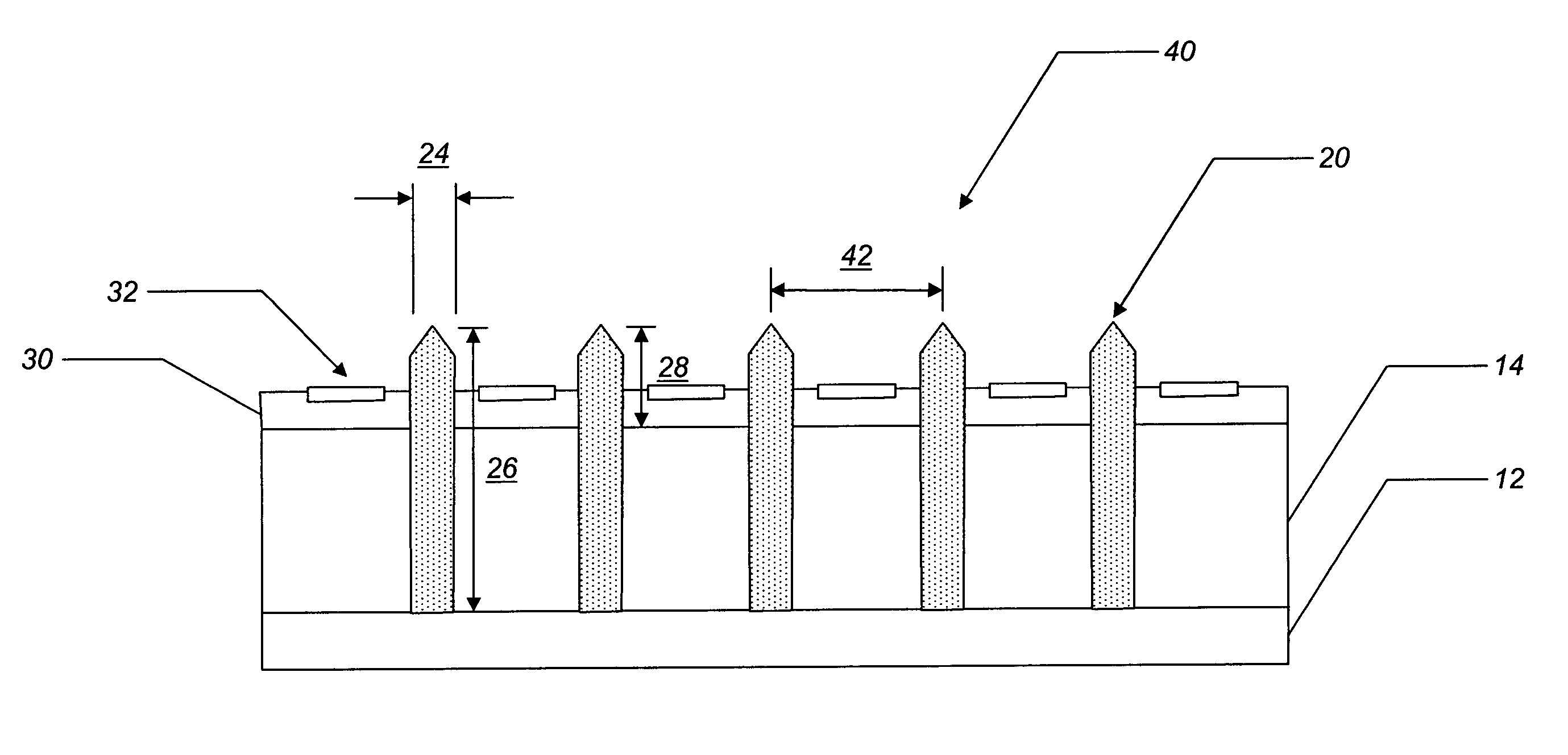

Self-aligned gated rod field emission device and associated method of fabrication

ActiveUS20050067935A1Discharge tube luminescnet screensLamp detailsCylindrical channelField emission device

A self-aligned gated field emission device and an associated method of fabrication are described. The device includes a substrate and a porous layer disposed adjacent to the surface of the substrate, wherein the porous layer defines a plurality of substantially cylindrical channels, each of the plurality of substantially cylindrical channels aligned substantially parallel to one another and substantially perpendicular to the surface of the substrate. The device also includes a plurality of substantially rod-shaped structures disposed within at least a portion of the plurality of substantially cylindrical channels defined by the porous layer and adjacent to the surface of the substrate, wherein a portion of each of the plurality of substantially rod-shaped structures protrudes above the surface of the porous layer. The device further includes a gate dielectric layer disposed on the surface of the porous layer, wherein the gate dielectric layer is disposed between the plurality of substantially rod-shaped structures. The device still further includes a conductive layer selectively disposed on the surface of the gate dielectric layer, wherein the conductive layer is selectively disposed between the plurality of substantially rod-shaped structures.

Owner:GENERAL ELECTRIC CO

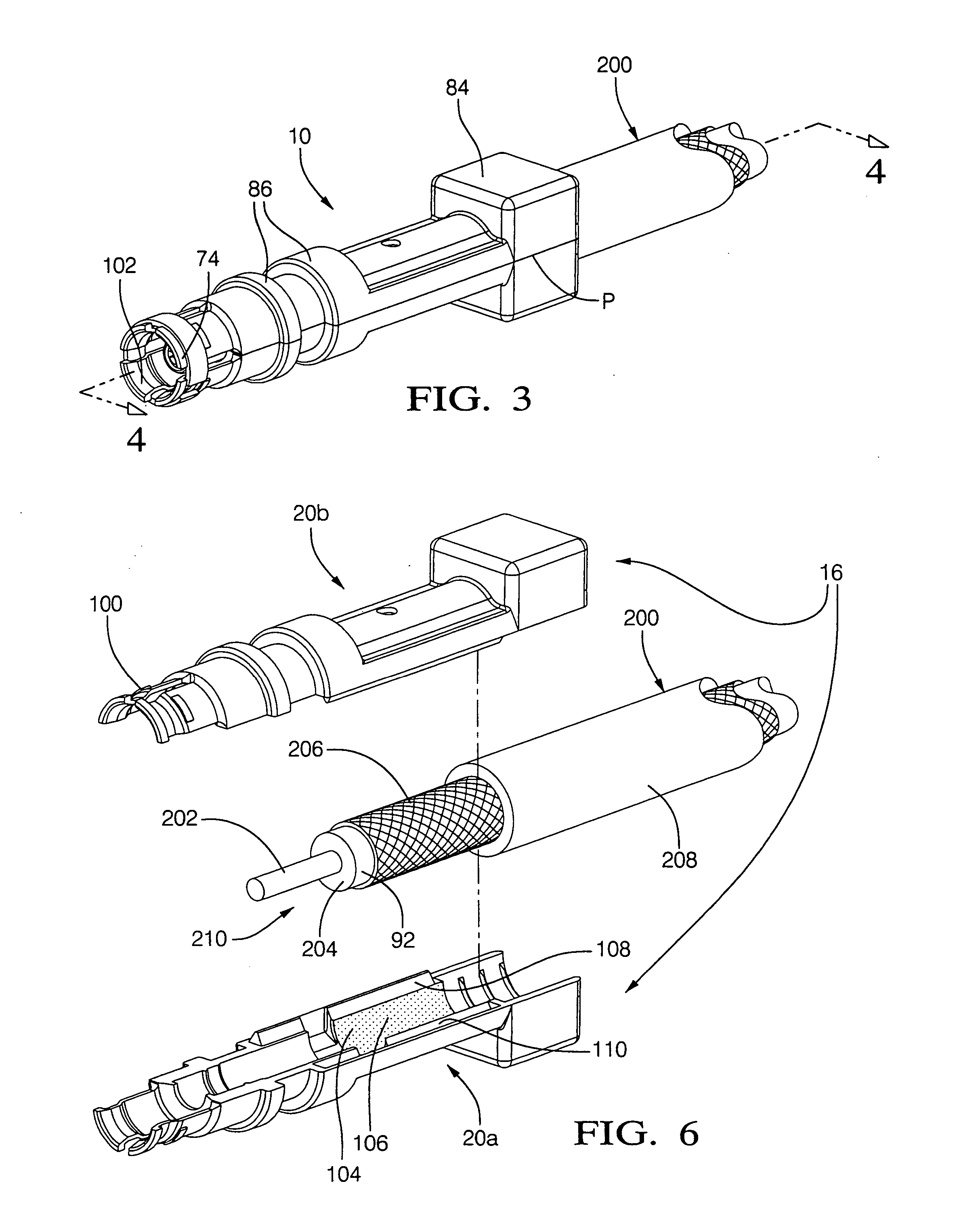

Terminal assembly for a coaxial cable

InactiveUS20050054237A1Coupling device detailsSoldered/welded conductive connectionsDielectricCylindrical channel

A terminal for a coaxial cable includes an electrically conductive core mounted in a dielectric member. The dielectric member along with the conductive core are positioned within an electrically conductive ground shield. The ground shield includes two identical split-barrel housing members which are joined together. When joined, the housing members form a cylindrical channel having surfaces which intimately contact an exposed length of cable outer conductor layer, creating a conductive connection between the outer conductor layer and the ground shield and structurally maintaining the outer conductor layer concentric to the dielectric sheath and inner conductor of the cable.

Owner:DELPHI TECH INC

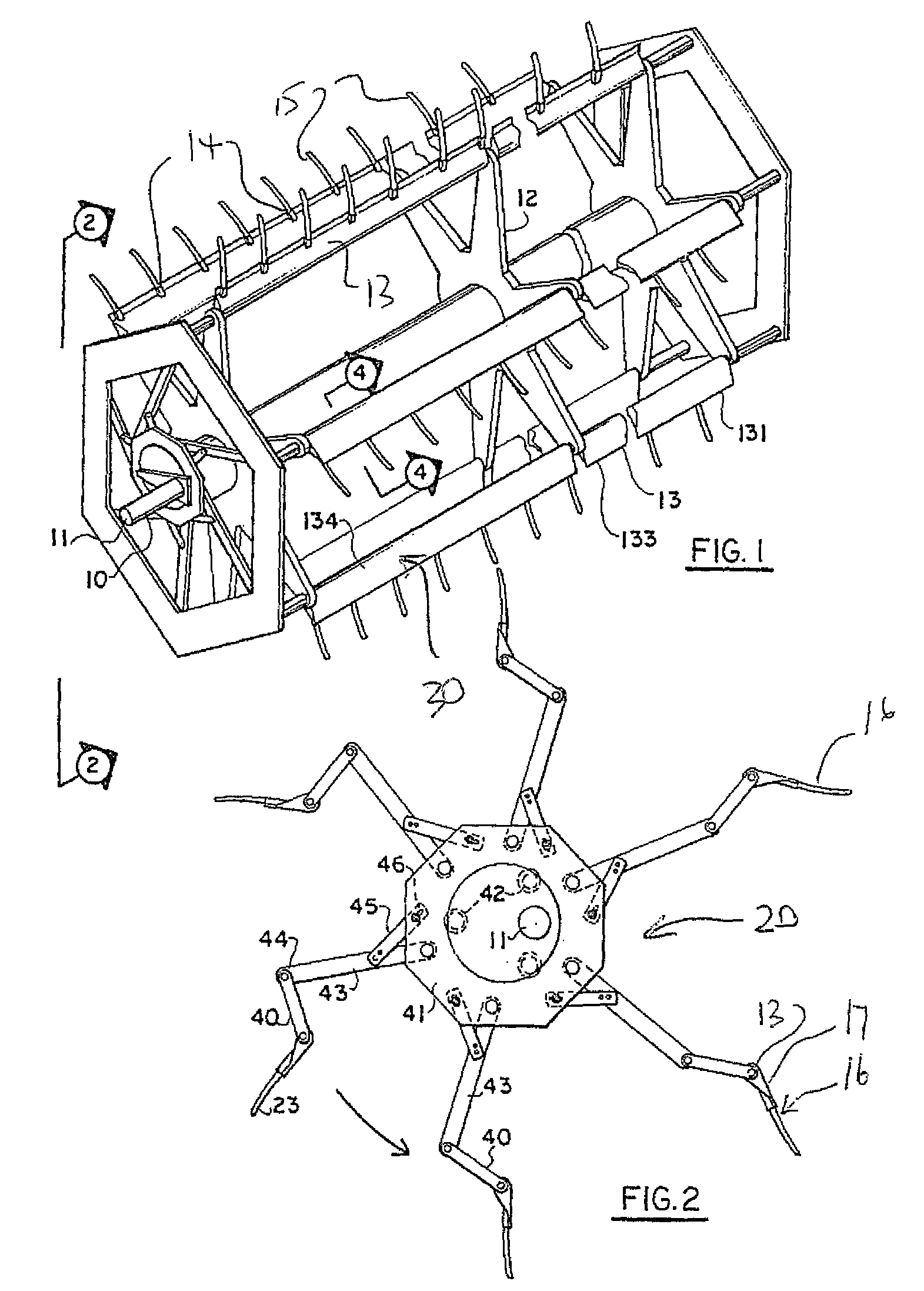

Extruded bat for the reel of a crop harvesting header

A removable bat attachment to be applied when required over the tine tubes and fingers of reel of a harvesting machine is formed by an elongate flexible plastic extruded member having a first wall lying against the leading face of the plurality of fingers, a second wall at the inner edge of the first wall wrapping around the tine tube to define a generally cylindrical channel shaped receptacle to receive the tine tube therein and a third wall at the outer edge. In one arrangement the outer edge wraps around an outer end of the fingers and is snap fit onto the outer ends of the fingers and on to the tine tube so as to be held in place thereon by the snap fit. In another arrangement the outer edge has an end wall with a series of holes one for each finger so that the fingers project outwardly from the outer edge.

Owner:MACDON INDS

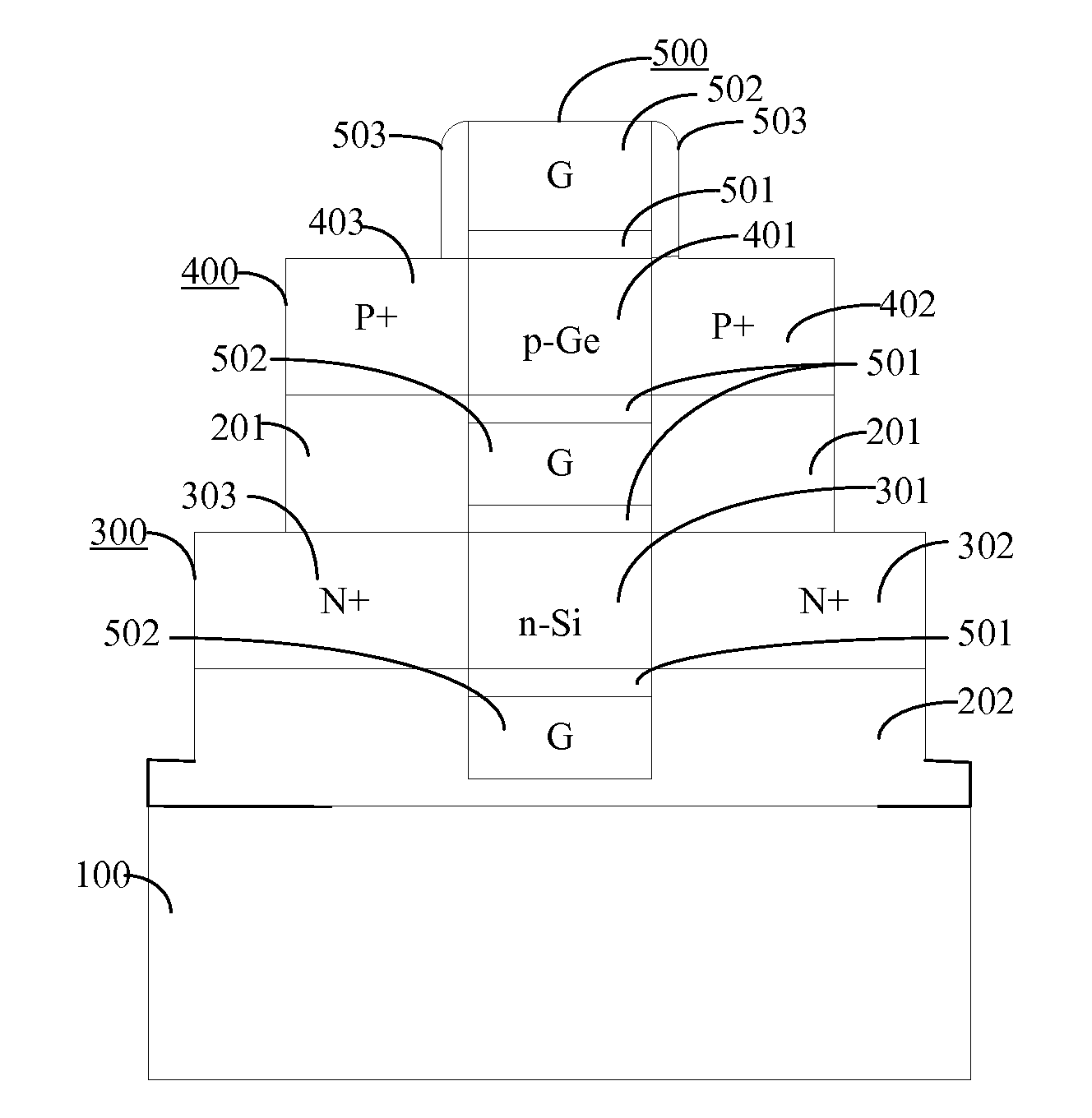

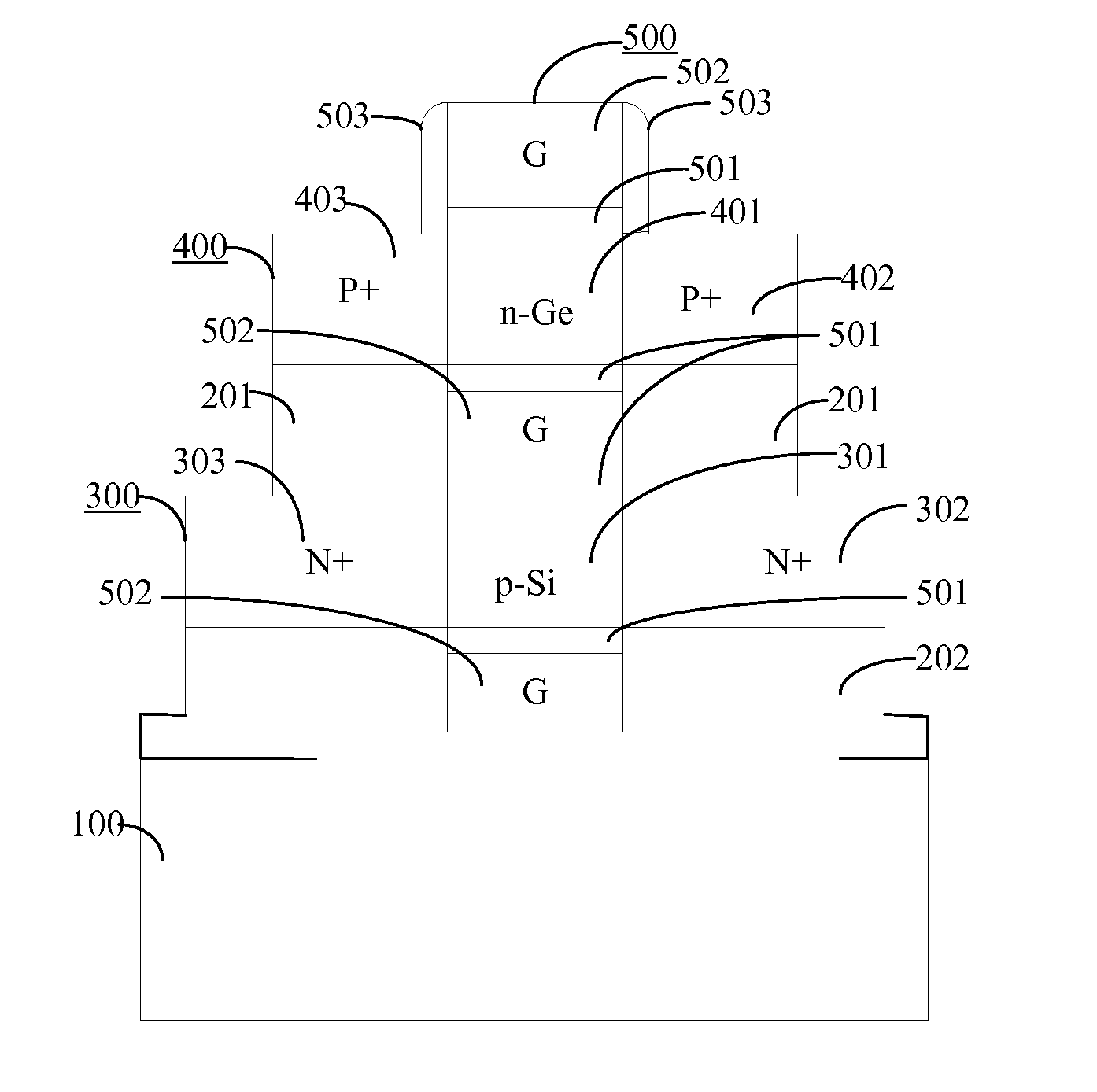

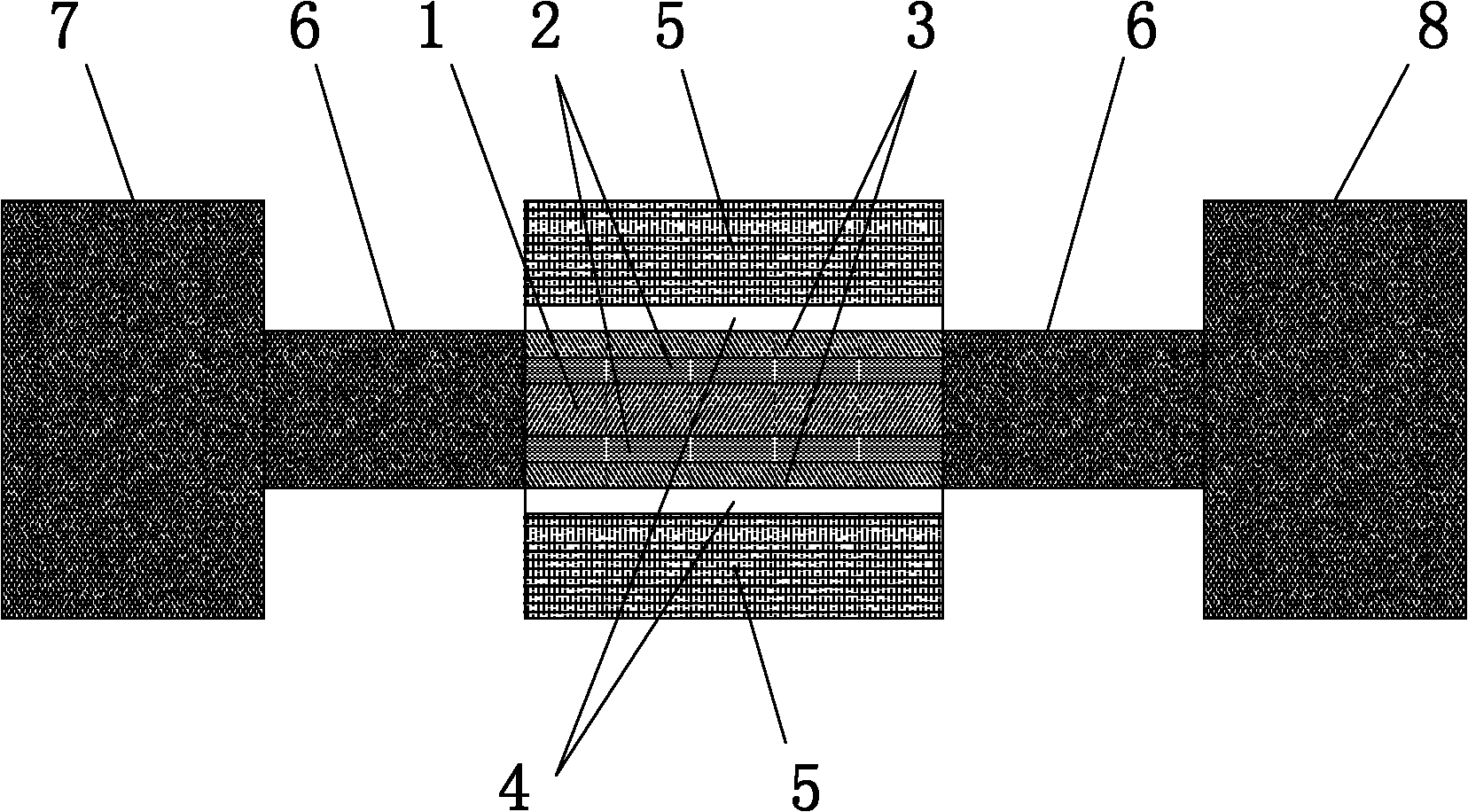

Hybrid material accumulation mode GAA CMOSFET

InactiveUS20110254099A1Raise the threshold voltageEasy to integrateTransistorSolid-state devicesCylindrical channelCharge carrier mobility

A Ge and Si hybrid material accumulation mode GAA (Gate-All-Around) CMOSFET includes a PMOS region having a first channel, an NMOS region having a second channel and a gate region. The first channel and the second channel have a circular-shaped cross section and are formed of p-type Ge and n-type Si, respectively; the surfaces of the first channel and the second channel are substantially surrounded by the gate region; a buried oxide layer is disposed between the PMOS region and the NMOS region and between the PMOS or NMOS region and the Si substrate to isolate them from one another. In an accumulation mode, current flows through the overall cylindrical channel, so as to achieve high carrier mobility, reduce low-frequency noises, prevent polysilicon gate depletion and short channel effects and increase the threshold voltage of the device.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

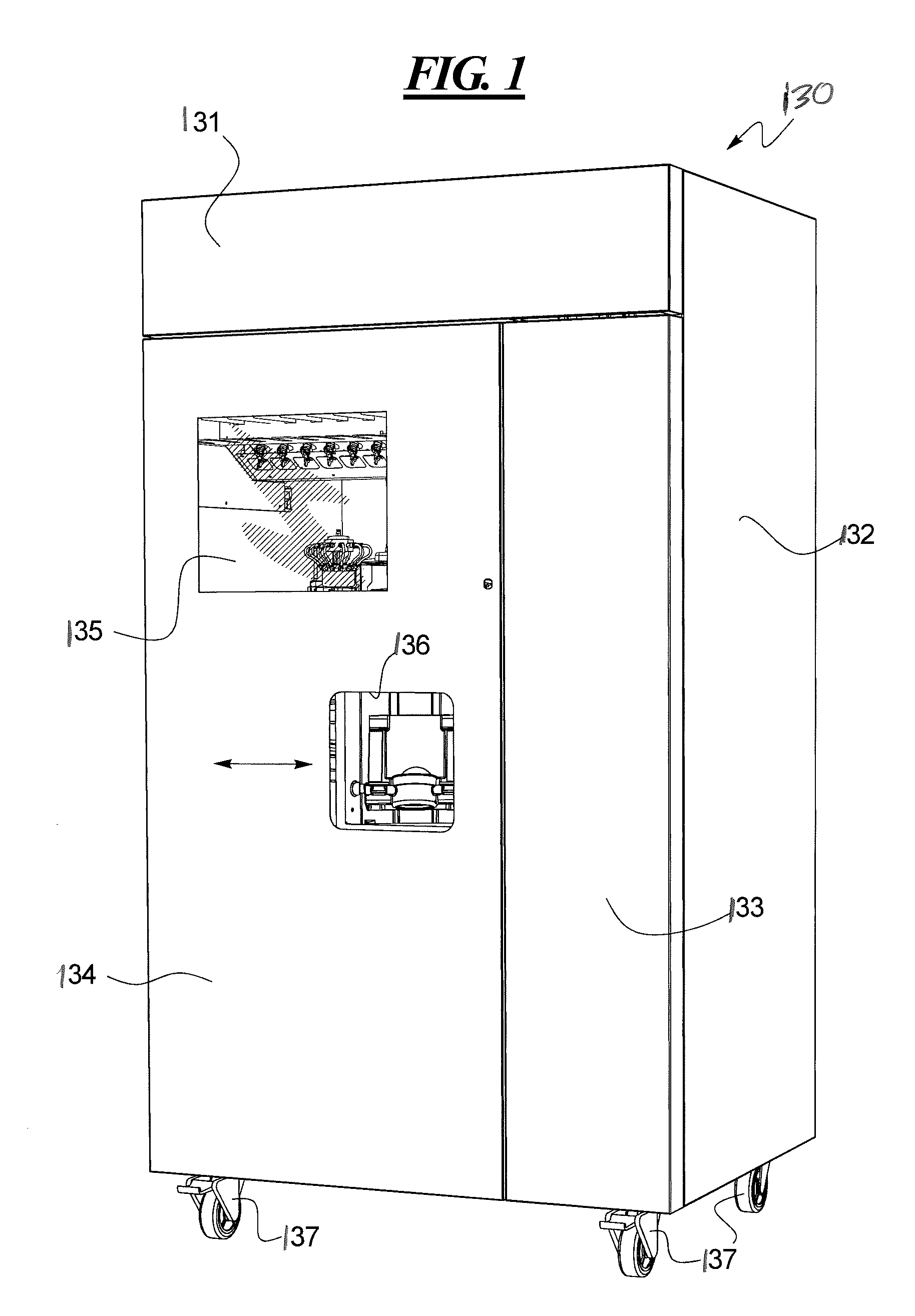

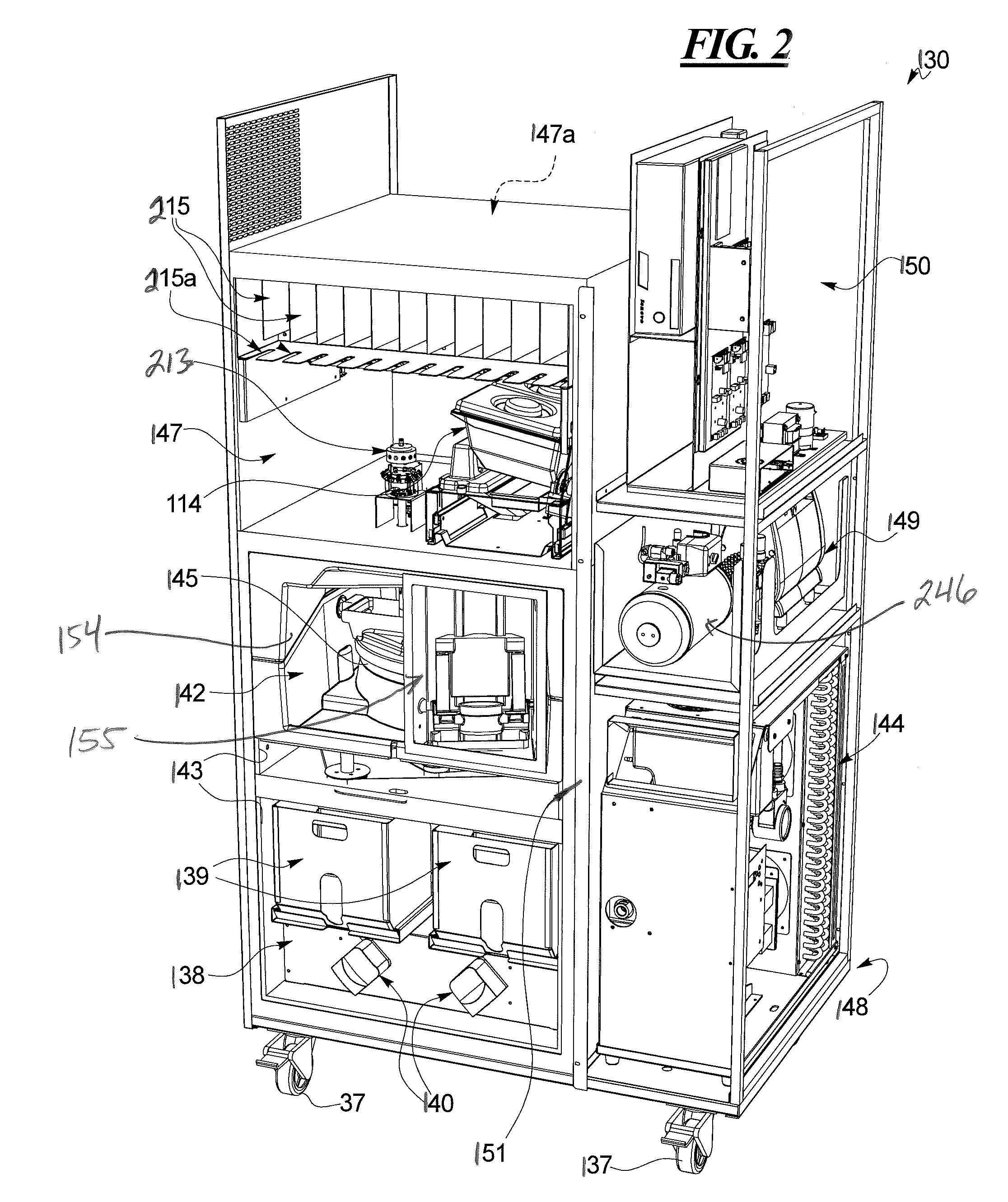

Point of sale method and apparatus for making and dispensing aerated frozen food products

ActiveUS20100062128A1Avoid stickingReduce humidityMilk preservationLighting and heating apparatusLeading edgeCylindrical channel

An apparatus for making and dispensing frozen aerated products includes a rotating horizontal freeze plate with an upper surface for receiving a chilled aerated mix. The chilled aerated mix includes, in one embodiment, a base that has been sufficiently aerated, and at least one flavor. The horizontal freeze plate rotates about its central axis. The apparatus also includes a spreader body for distributing the chilled aerated mix on the rotating freeze plate. The spreader body extends radially across at least a portion of the upper surface of the freeze plate. The apparatus further includes a scraper for scraping frozen aerated mix off of the rotating freeze plate. The scraper includes a scraper blade with a leading edge that extends radially across the portion of the freeze plate and that engages the upper surface of the freeze plate. The scraper blade is directed opposite the direction of rotation of the freeze plate. The scraper further includes a body that forms an elongated semi-cylindrical channel above the scraper blade that extends radially above the freeze plate for the collection of scraped, frozen and aerated mix. The apparatus also includes a plow for pushing the scraped, frozen and aerated mix through the channel towards a cup held by a cup-lifter mechanism disposed at an end of the channel. The action of the plow pushes the scraped frozen aerated mix through the channel and into the cup resulting in a generally round scoop of scraped frozen aerated mix in the cup that resembles a serving scoop experienced at a traditional ice cream shop.

Owner:FLUID MANAGEMENT LLC

Hybrid material inversion mode gaa cmosfet

InactiveUS20110254101A1Easy to integrateLess-high frequency noiseTransistorSolid-state devicesCylindrical channelCharge carrier mobility

A Ge and Si hybrid material inversion mode GAA (Gate-All-Around) CMOSFET includes a PMOS region having a first channel, an NMOS region having a second channel and a gate region. The first channel and the second channel have a circular-shaped cross section and are formed of n-type Ge and p-type Si, respectively; the surfaces of the first channel and the second channel are substantially surrounded by the gate region; a buried oxide layer is disposed between the PMOS region and the NMOS region and between the PMOS or NMOS region and the Si substrate to isolate them from one another. In an inversion mode, current flows through the overall cylindrical channel, so as to achieve high carrier mobility, reduce low-frequency noises, prevent polysilicon gate depletion and short channel effects and increase the threshold voltage of the device.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

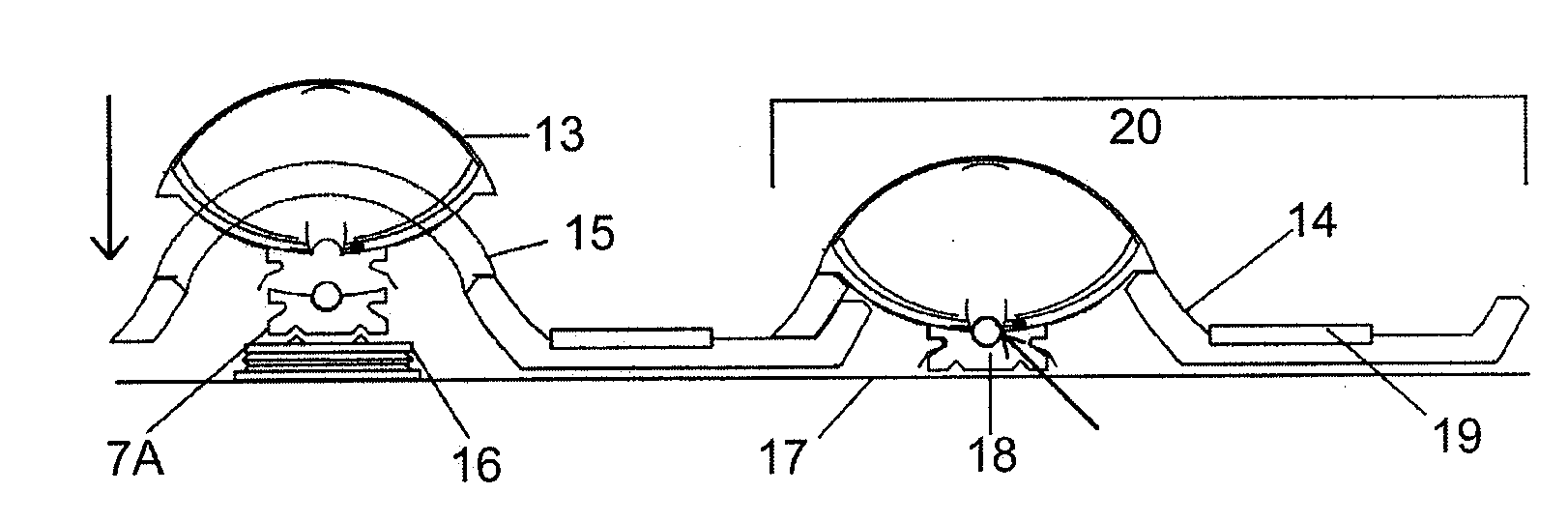

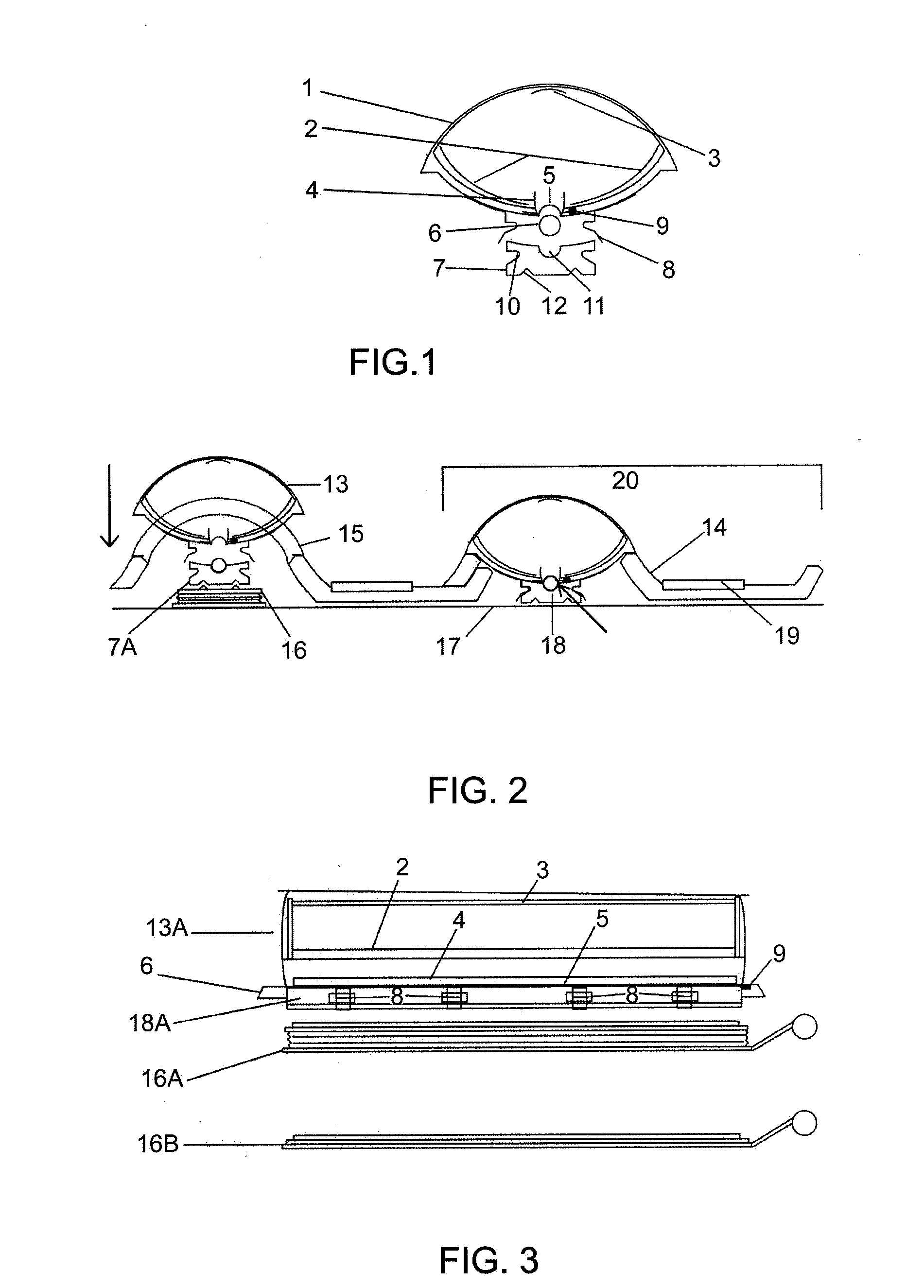

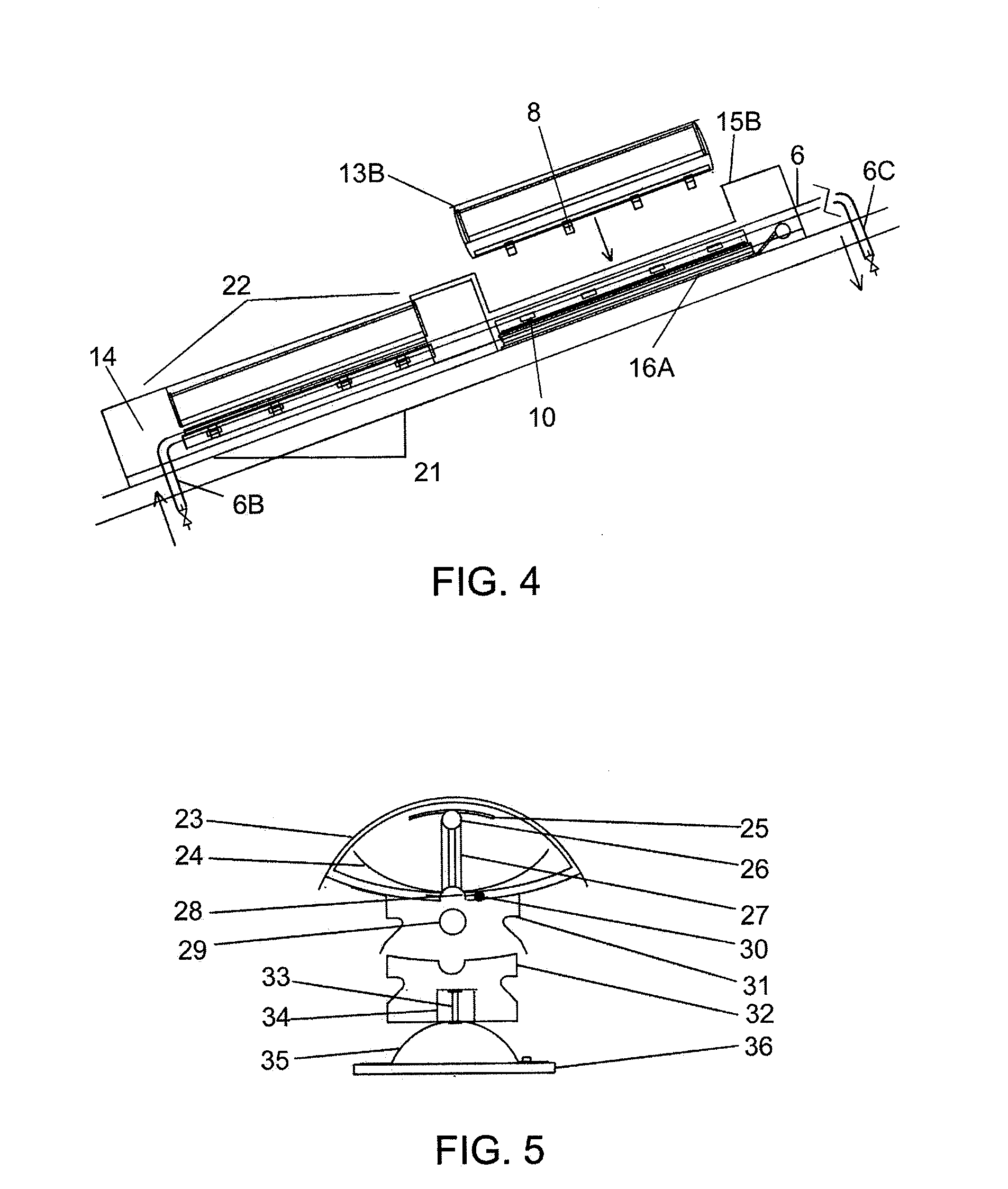

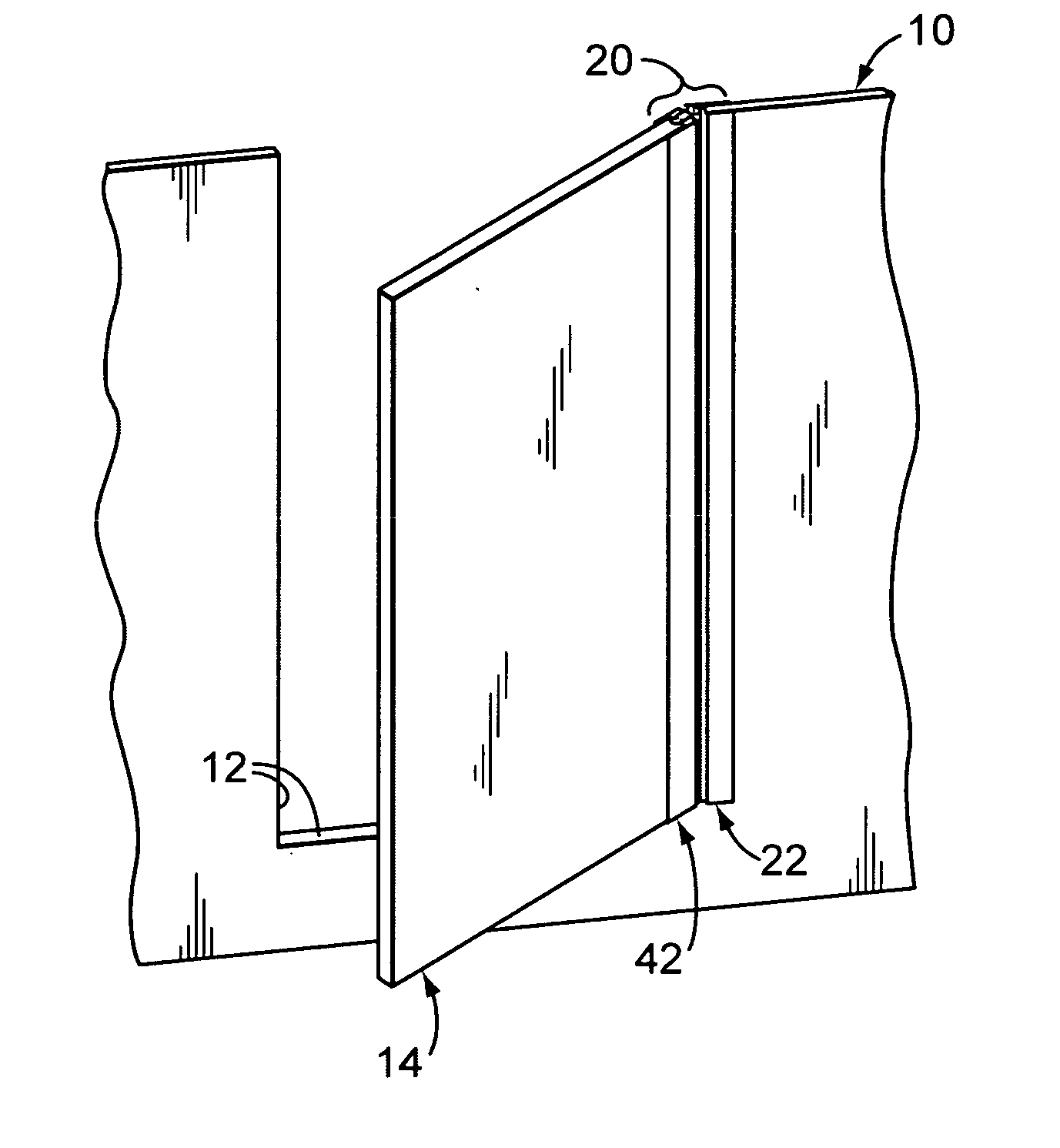

Solar Energy Collection Device for Tiled Roofs, and a Method for Mounting the Same

InactiveUS20080308093A1Facilitates hermetic anchorEasy to usePhotovoltaic supportsRoof covering using slabs/sheetsCylindrical channelEngineering

The device part of the embodiment over the tiles (14) with wide openings(15) which mainly involves, openings (15) in which are houses both irregular bodies (1-13), of transparent glass, hermetically closed and vacuum filled, which establish surface continuity through the upper face with the rest of the tile (14) and in whose interior are established parabolic cylinder reflectors (2-3) which conduct solar radiation to a concentration funnel (5) which defines a semi-cylindrical channel and adapting to the heat transfer tube (6), which rests over a support cradle (7) which in turn is pressed against aforementioned tube (6) by a bellows lifting device (16), also keeping the support cradle (7) and irregular bodies (1) fixed using anchor elements (8). Thus simple mounting of the collection devices is achieved by a simple pressure coupling system, achieving close contact with the heat transfer tubes which remain hidden and protected below the tiles.

Owner:GIANASSO ROLAND +1

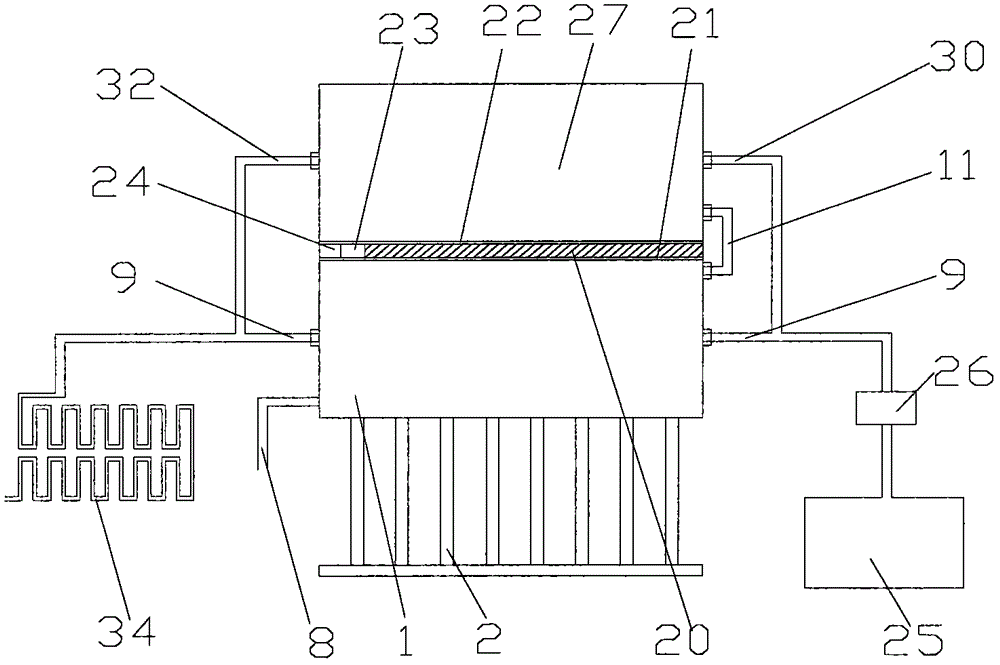

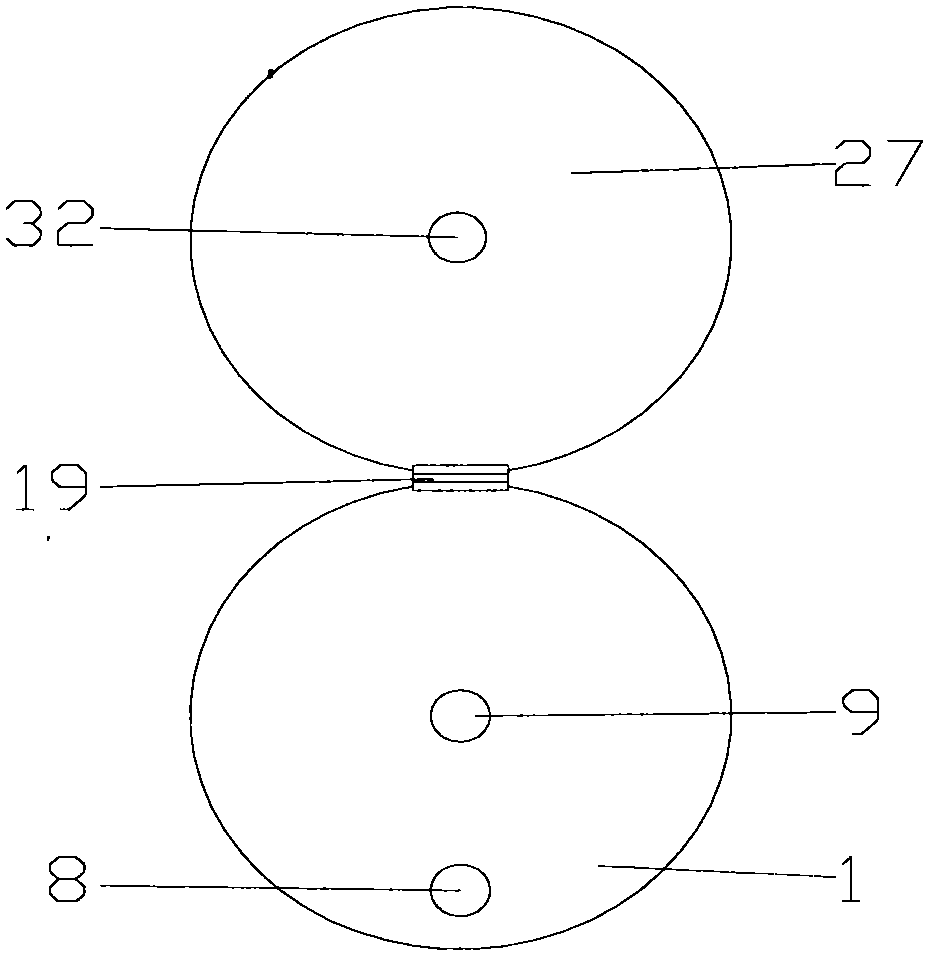

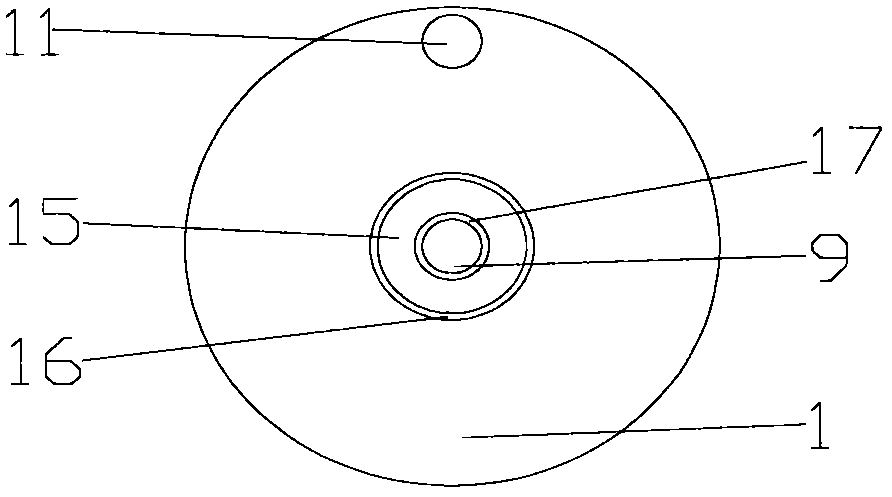

Double-thermoelectric power generation device for solar water heater

InactiveCN104567022ASolve wasteSolar heating energyBatteries circuit arrangementsElectricityCylindrical channel

The invention discloses a double-thermoelectric power generation device for a solar water heater. The double-thermoelectric power generation device mainly comprises a solar heat water, a first thermoelectric power generation module, a second thermoelectric power generation module and a cold water circulating system, wherein a cylindrical channel is reserved at the center in a heat-insulating hot water tank of the solar heat water; the first thermoelectric power generation module having a cylindrical shape is mounted in the cylindrical channel; a cylindrical channel is also reserved at the center of the first thermoelectric power generation module; a first cold water pipe passes through the cylindrical channel at the center of the first thermoelectric power generation module; a first cold end face of the first thermoelectric power generation module is in contact with the first cold water pipe while a first hot end face is in contact with the hot water in the heat-insulating hot water tank; the second thermoelectric power generation module is arranged between the heat-insulating hot water tank and a cold water tank; a second cold end face of the second thermoelectric power generation module is in contact with the cold water tank while a second hot end face is in contact with the heat-insulating hot water tank; the heat-insulating hot water tank is connected with the cold water tank through a lower water pipe; the cold water tank is connected with a cold water source, a water pump and a heating radiator through the water pipe. The double-thermoelectric power generation device is capable of supplying hot water and generating electricity, is energy-saving and environment-friendly, is safe and high-efficient and is capable of effectively solving the problem of energy waste caused by hot water evaporation.

Owner:ANHUI UNIVERSITY OF ARCHITECTURE

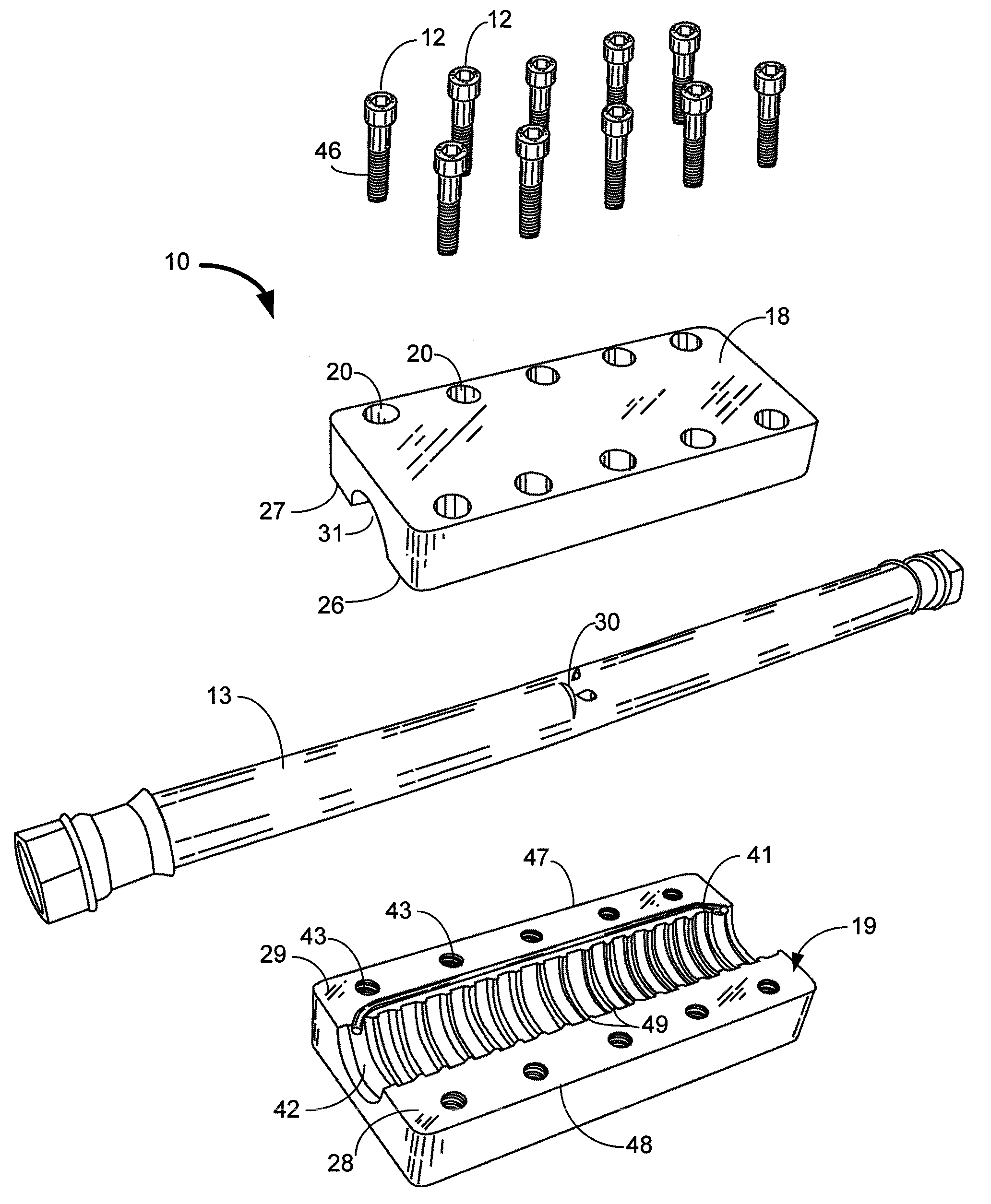

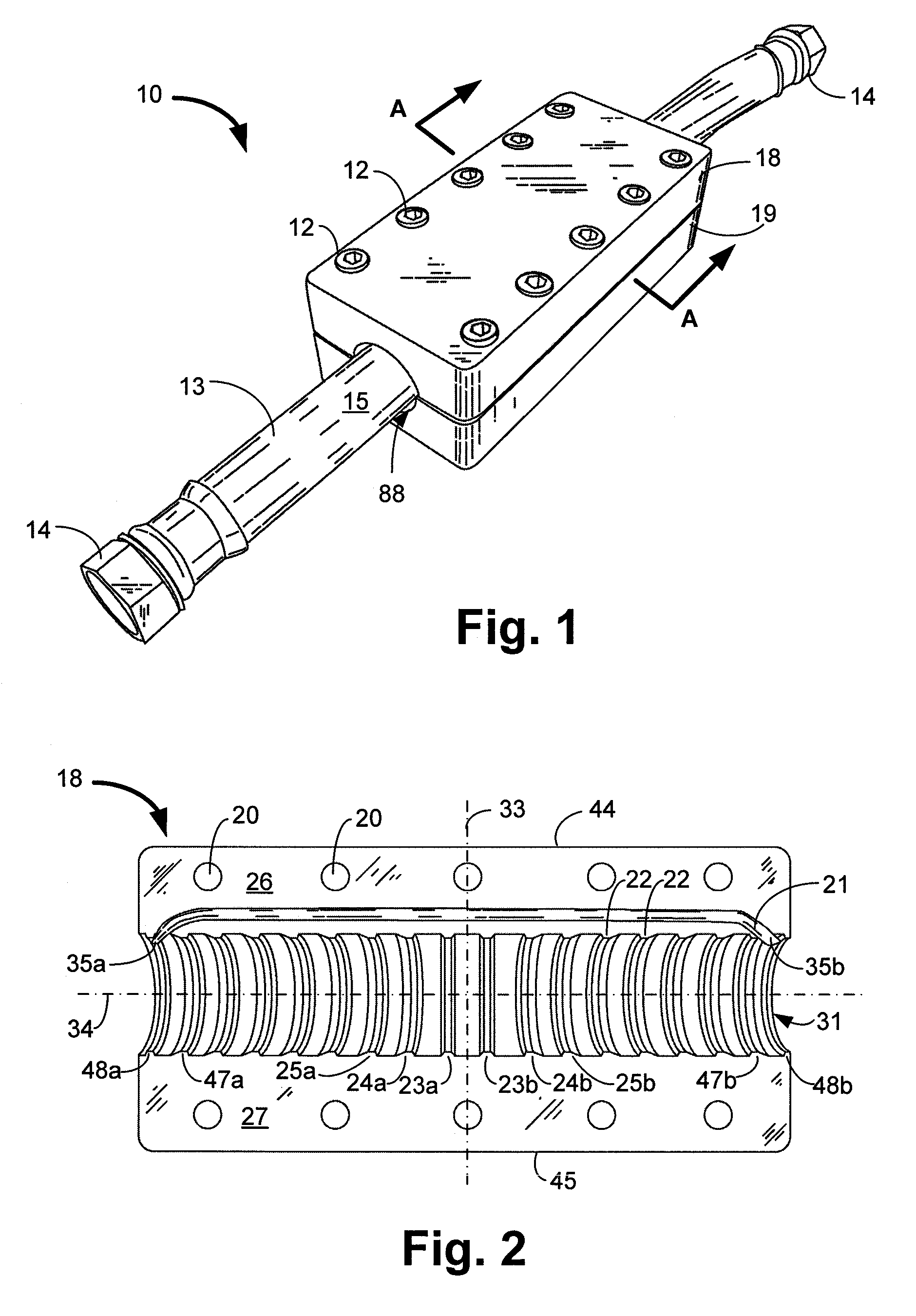

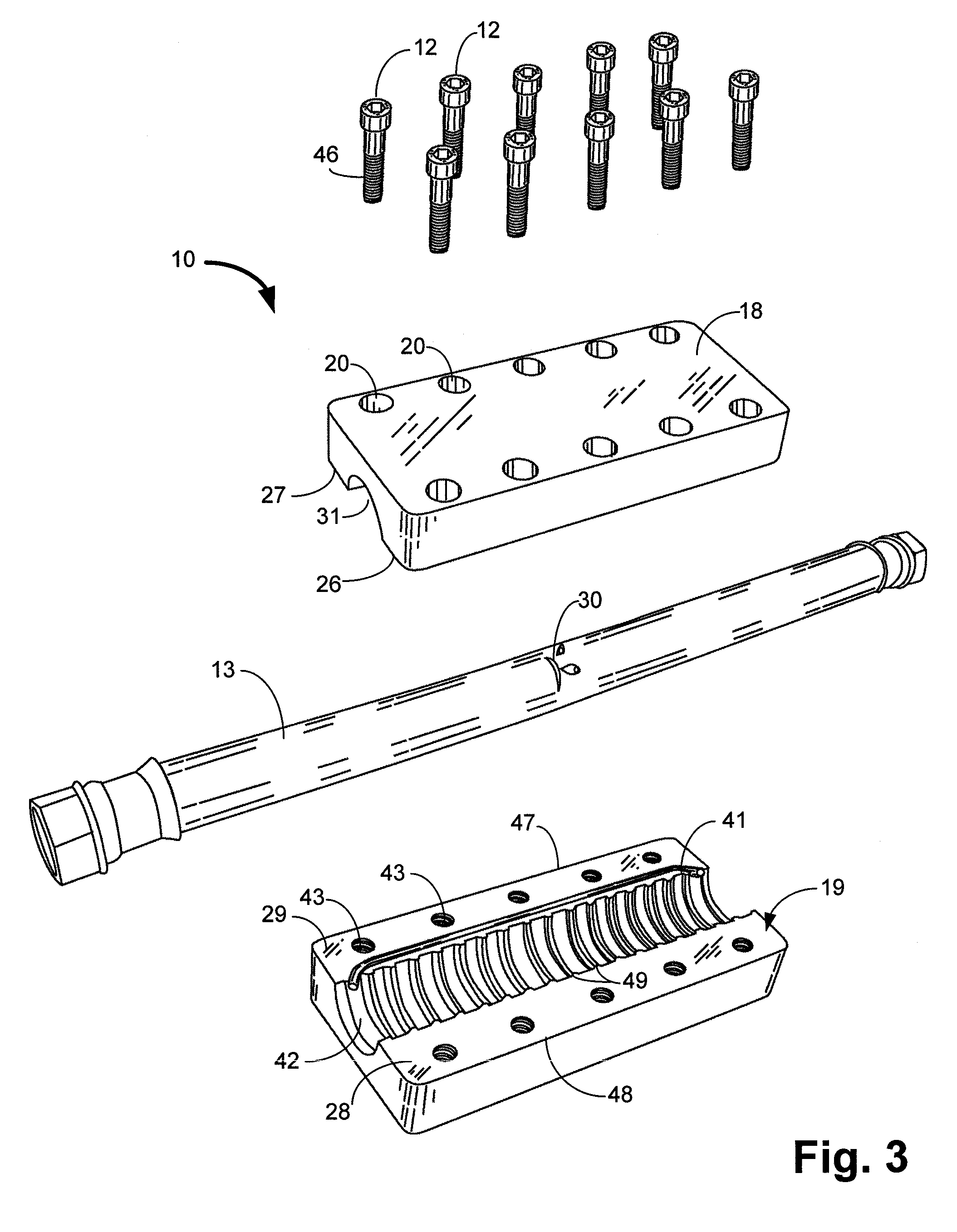

Hose Repair Clamp

A hose clamp for repairing high pressure hydraulic hoses comprises a first clamp portion mated to a second clamp portion around a hose. The first and second clamp portions each comprise a semi-cylindrical channel extending longitudinally along an inner surface of the clamp. The hose is received within the channel and a plurality of fasteners releasably affix the clamp portions together. A plurality of barbs extending circumferentially around the channel compress the hose to minimize leakage from the hose.

Owner:HOSEBEE

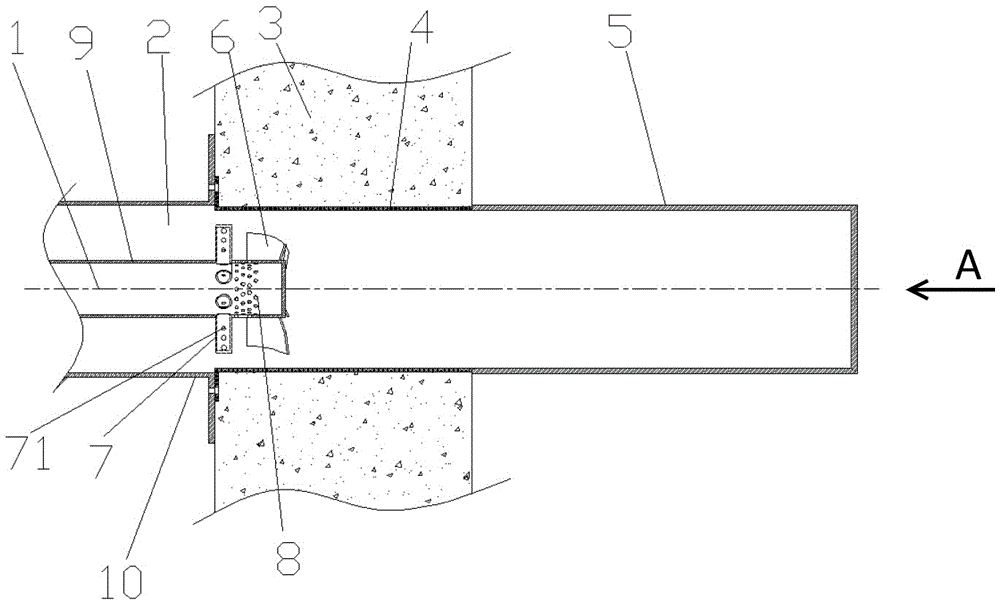

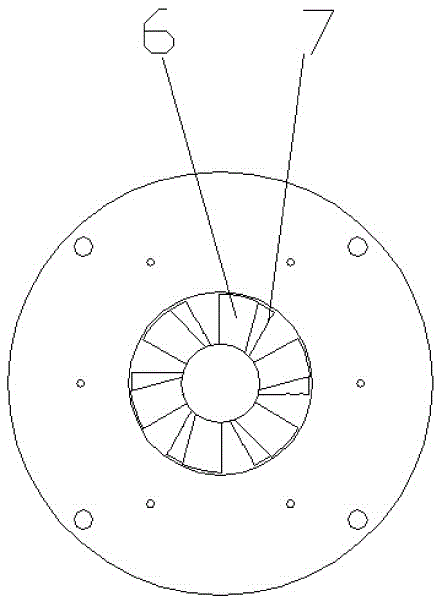

Metal surface combustor and gas premixing method thereof

InactiveCN105546533AShorten the mixing distanceImprove mixing uniformityGaseous fuel burnerCycloneCylindrical channel

The invention discloses a metal surface combustor and a gas premixing method thereof, solves the technical problem that the combustor can uniformly mix gas with combustion air in a shorter premixing channel, and belongs to the technical field of combustion of metal surface combustors. The metal surface combustor is characterized in that a metal throat is a cylindrical channel; the outer side surface is connected with a boiler front wall; one part extending into a hearth is an end-sealed microhole metal cylinder; the other end is connected with an air pipe as a whole; multiple gas spray guns and multiple cyclone blades are arranged at the tail end of the gas pipe in sequence; the gas uniformly enters the throat by spray holes in the gas spray guns and gas pipe holes in the gas pipes; meanwhile, the combustion air and the gas are hedged and uniformly mixed in the throat; and under stirring of the cyclone blades at the end part of the gas pipe, the uniform mixing is further accelerated, so that the mixing distance is shortened, the flame temperature nonuniformity caused by nonuniform gas mixing is effectively prevented, and the NOx emission is reduced.

Owner:新疆海天祥瑞环保工程有限公司

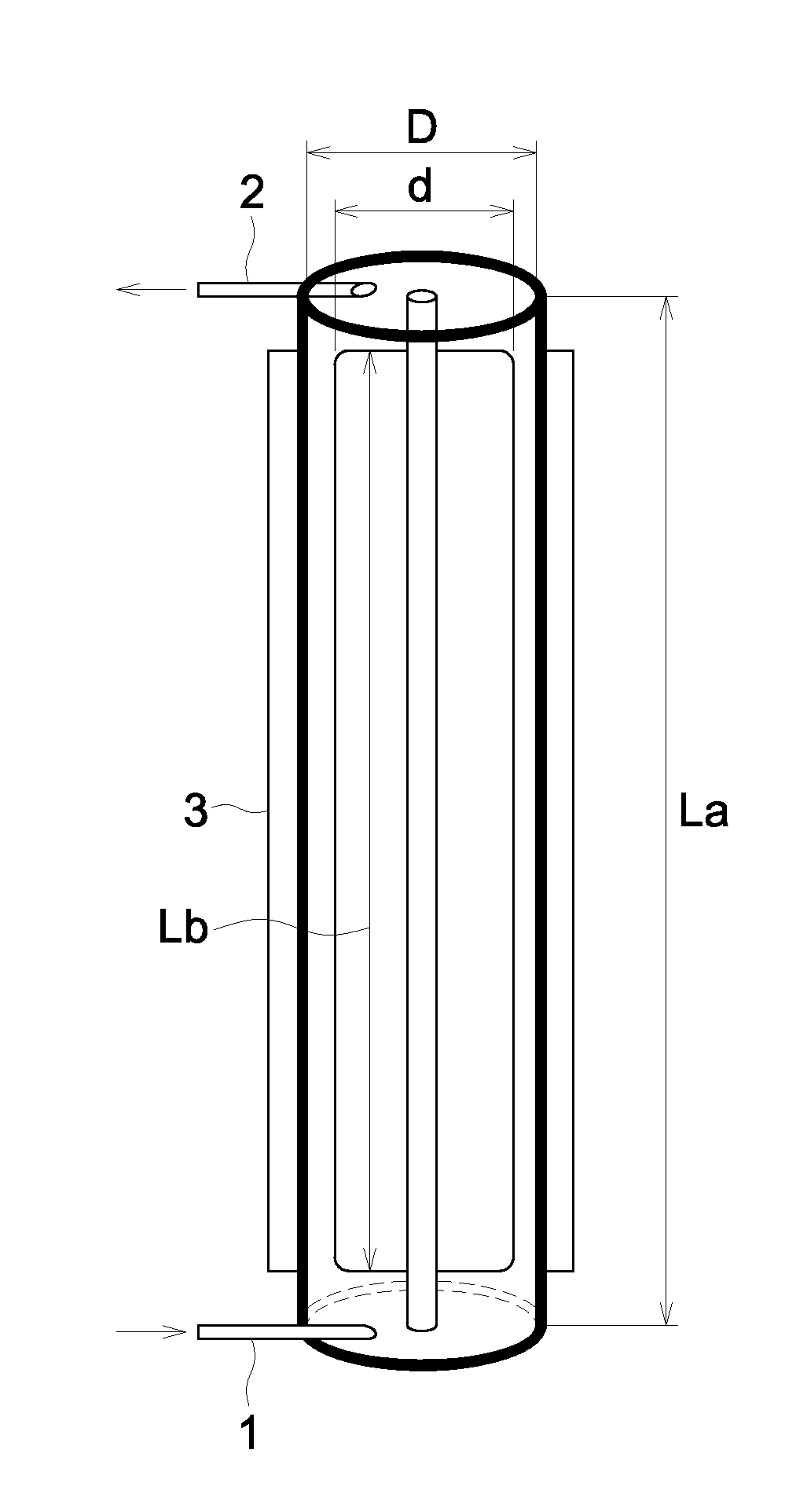

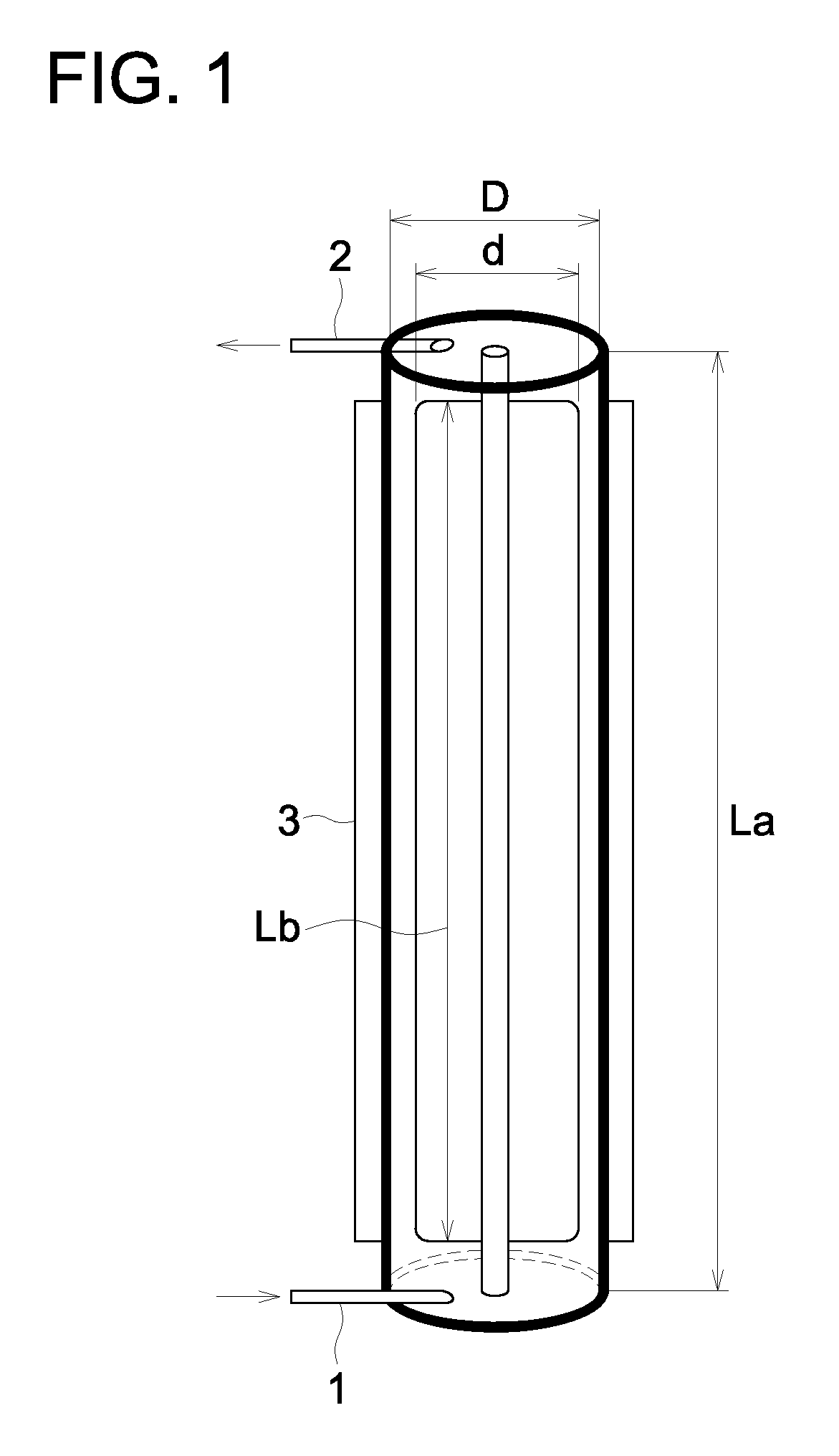

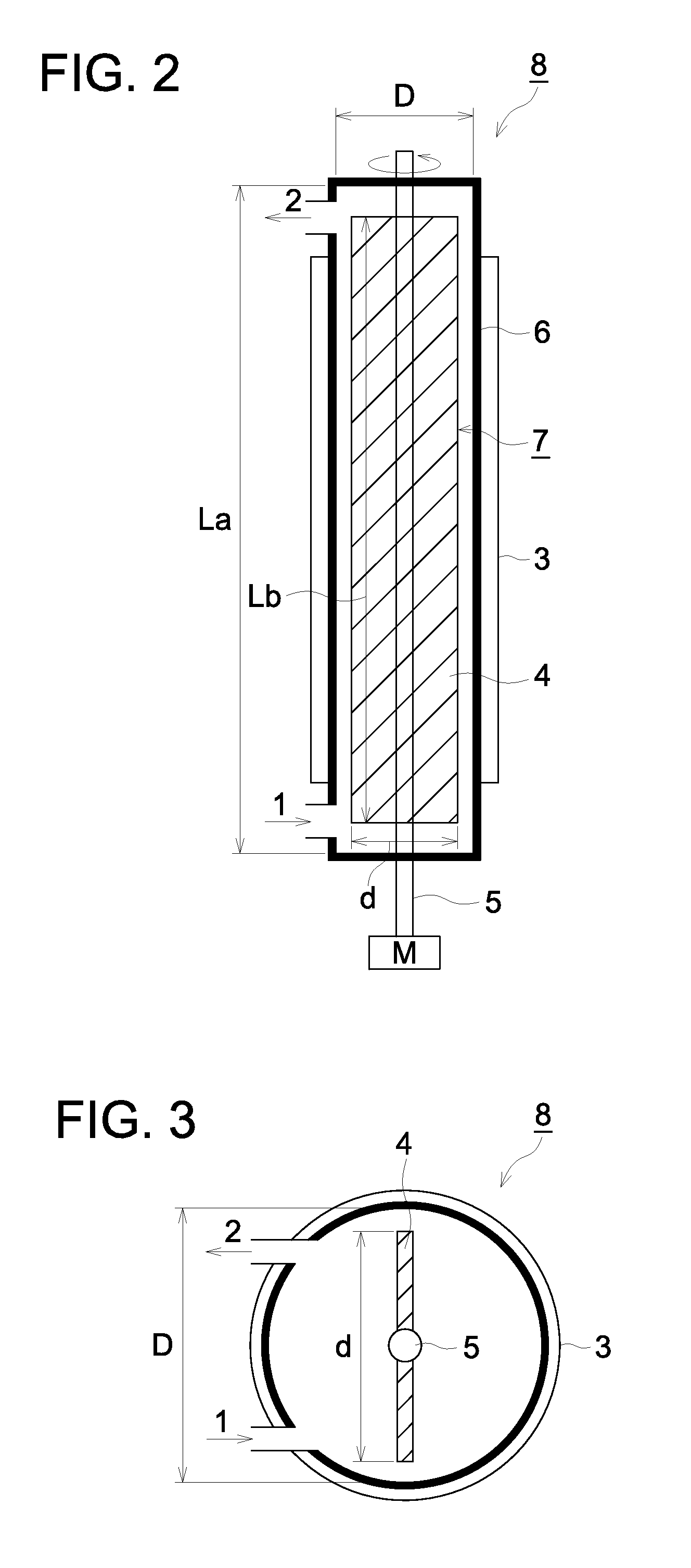

Tubular flow reactor and method of manufacturing polymeric resin fine particle

ActiveUS8148477B2Maintain liquidityNarrow molecular weight distributionRotary stirring mixersTransportation and packagingCylindrical channelPolymer science

In the present invention, a tubular flow reactor can maintain a plug flow property even though the tubular flow reactor is downsized, and provided is the tubular flow reactor with which uniform resin fine particles exhibiting a narrow particle size distribution and a narrow molecular weight distribution can be prepared when the tubular flow reactor is used for preparation of the resin fine particle via emulsion polymerization or the like. Disclosed is a tubular flow reactor possessing a stirring blade and a cylindrical channel, wherein a ratio d / D is 0.3-0.9 when a diameter of the stirring blade is represented by d and an inner diameter of the cylindrical channel is represented by D, and a ratio Lb / La is 0.80-0.99 when a length of the stirring blade is represented by Lb and a length of the cylindrical channel is represented by La.

Owner:KONICA MINOLTA BUSINESS TECH INC

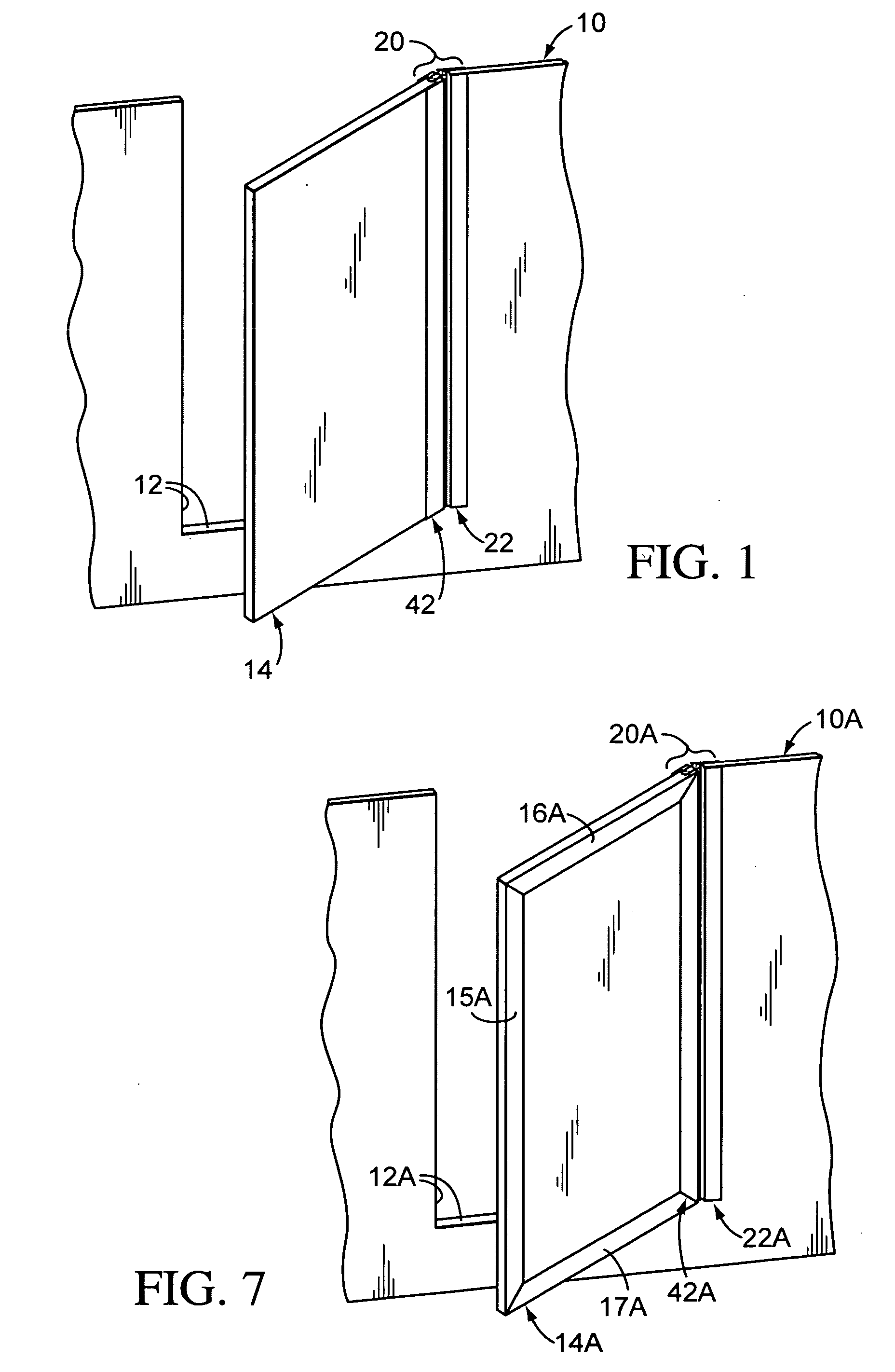

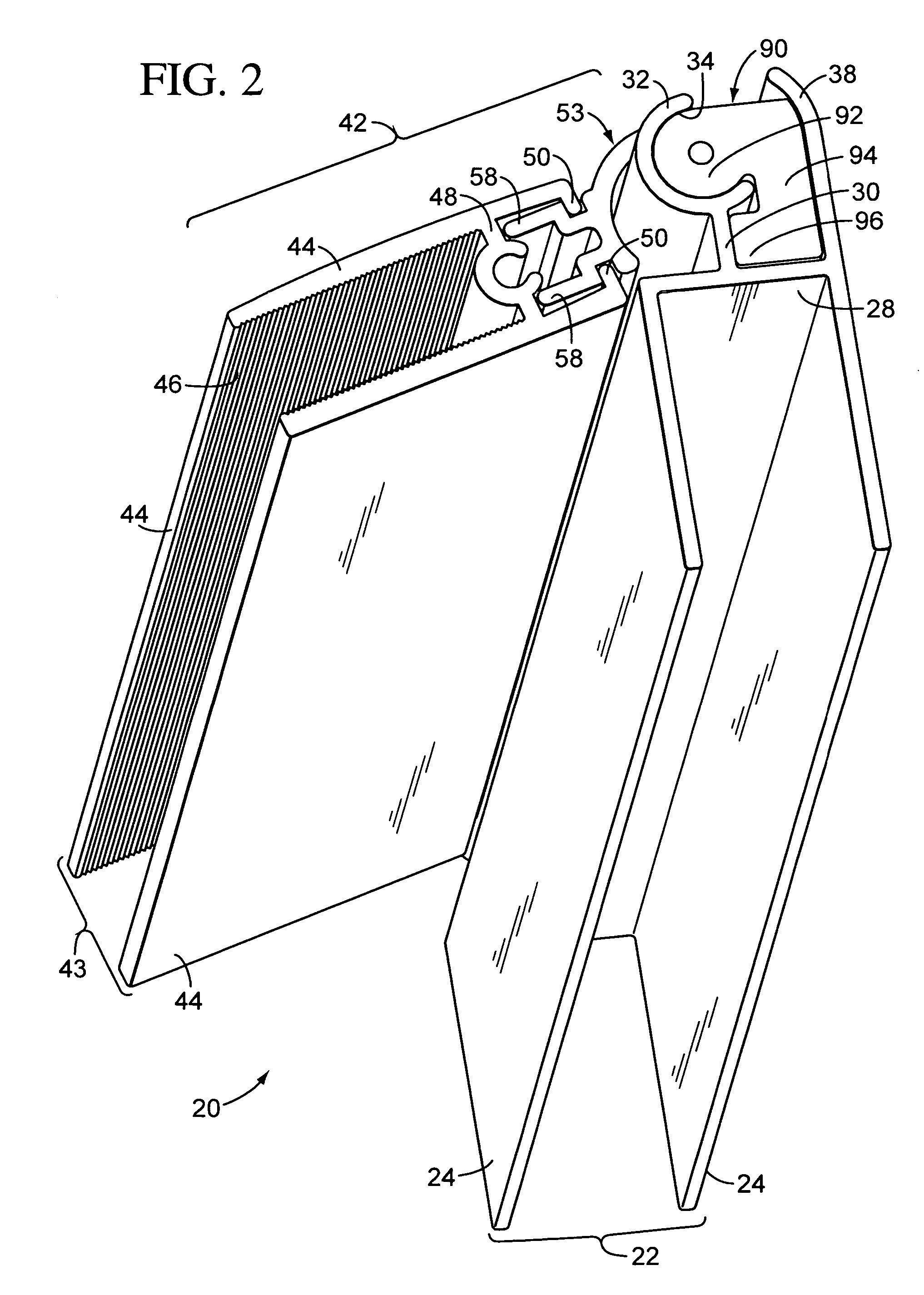

Continuous hinge for swing door

A hinge is provided for connecting a swing door to an adjacent support structure. The hinge includes a first attachment structure for being mounted to either the door or the adjacent support structure and has a partially cylindrical channel defining a longitudinal pivot axis. A second attachment structure is mounted to the other of the door and adjacent support structure, and has a longitudinally extending mounting arm projecting into the partially cylindrical channel of the first attachment structure. A bushing (1) is mounted on the arm of the second attachment structure, (2) is disposed in the partially cylindrical channel of the first attachment structure, and (3) has a partially cylindrical exterior surface which (a) is defined around the pivot axis for engaging the partially cylindrical channel of the first attachment structure, and (b) has a surface hardness that is less than the surface hardness of the partially cylindrical channel.

Owner:JOHN STERLING , A CORP OF IL

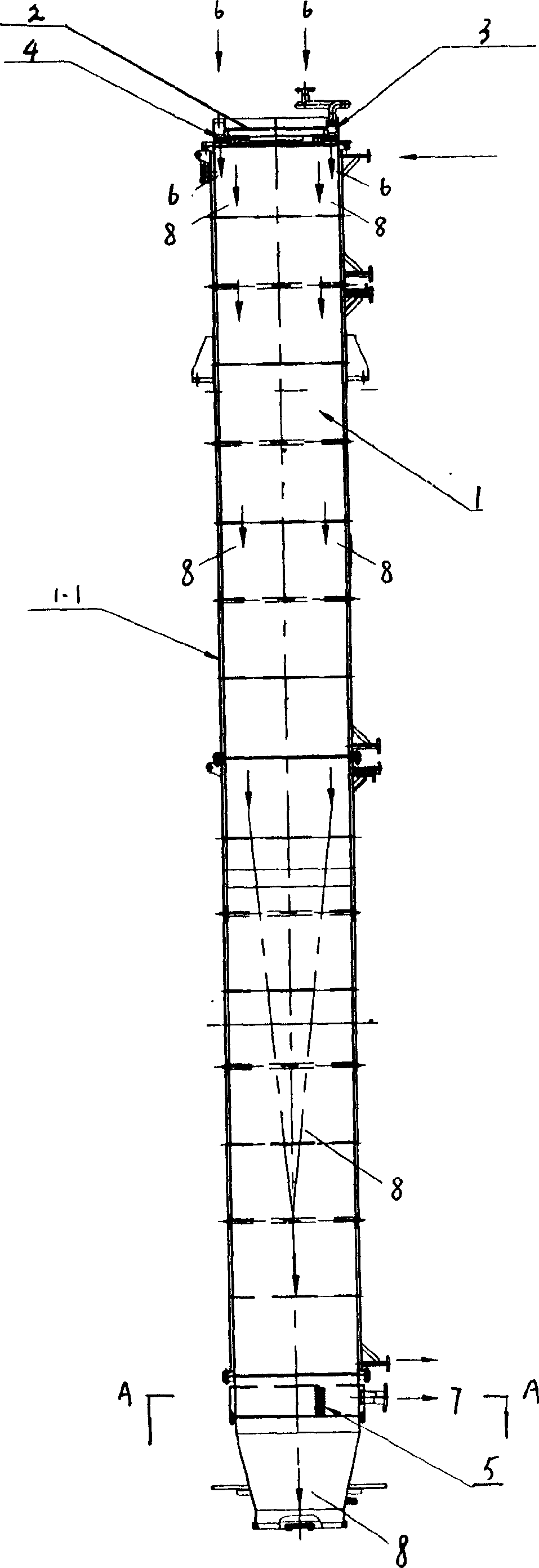

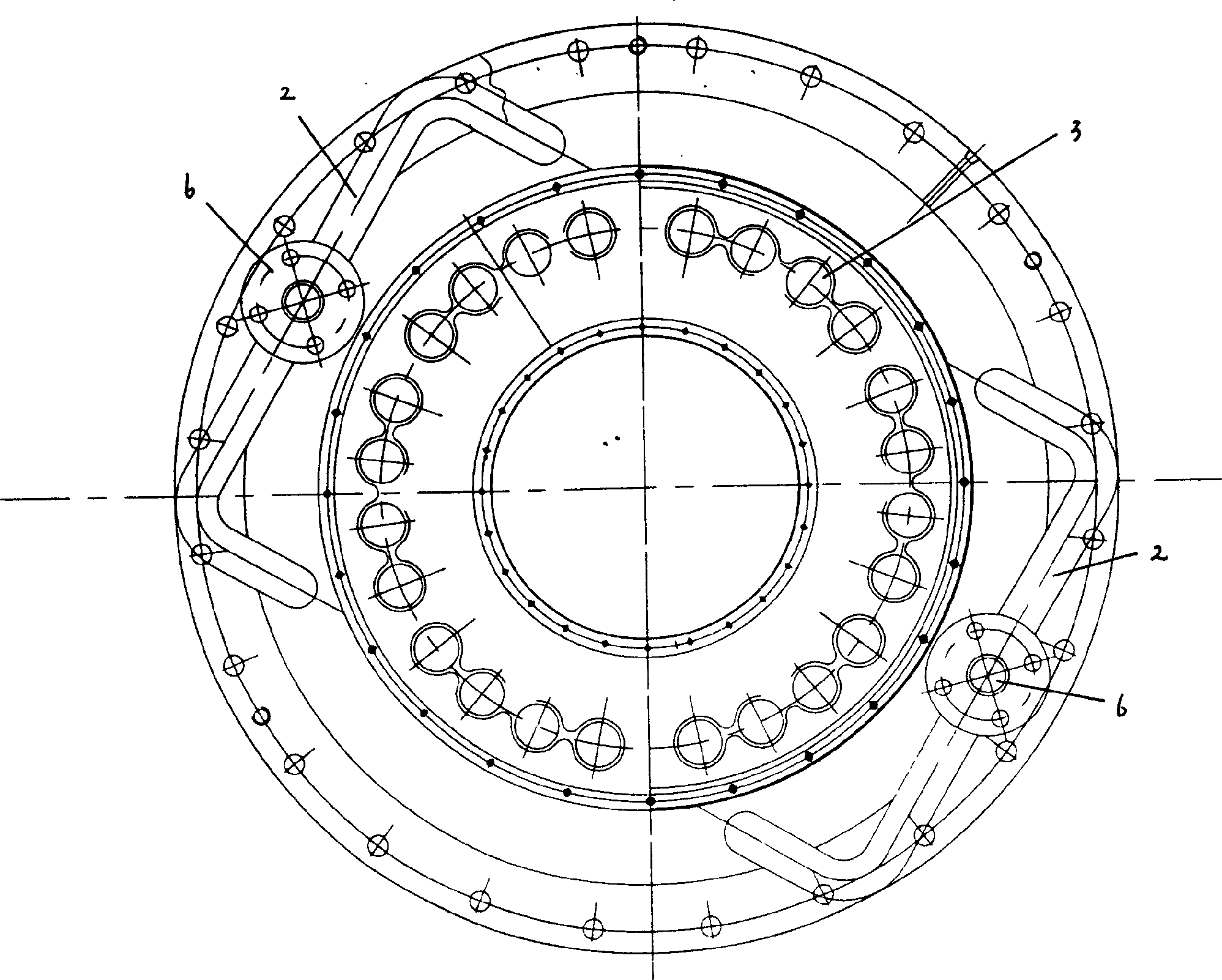

Circular corridor for spinning of urethane elastic fiber

ActiveCN1727529AAvoid interferenceAvoid intertwiningMonocomponent polyurethanes artificial filamentFilament/thread formingCylindrical channelFiber

A circular channel for spinning polyurethane fibers is composed of cylindrical channel, spinneret plate module, annular air blower, annular air inlet flow-regulator, annular air-returning flow-regulator, hot airflow inlet and hot airflow outlet. Its advantages are high airflow stability, distribution uniformity and spinning quality.

Owner:JIANGYIN L V CHEM FIBER PROCESS TECH

Self-aligned gated rod field emission device and associated method of fabrication

ActiveUS7239076B2Small emitter tipSimple and efficientDischarge tube luminescnet screensLamp detailsCylindrical channelField emission device

A self-aligned gated field emission device and an associated method of fabrication are described. The device includes a substrate and a porous layer disposed adjacent to the surface of the substrate, wherein the porous layer defines a plurality of substantially cylindrical channels, each of the plurality of substantially cylindrical channels aligned substantially parallel to one another and substantially perpendicular to the surface of the substrate. The device also includes a plurality of substantially rod-shaped structures disposed within at least a portion of the plurality of substantially cylindrical channels defined by the porous layer and adjacent to the surface of the substrate, wherein a portion of each of the plurality of substantially rod-shaped structures protrudes above the surface of the porous layer. The device further includes a gate dielectric layer disposed on the surface of the porous layer, wherein the gate dielectric layer is disposed between the plurality of substantially rod-shaped structures. The device still further includes a conductive layer selectively disposed on the surface of the gate dielectric layer, wherein the conductive layer is selectively disposed between the plurality of substantially rod-shaped structures.

Owner:GENERAL ELECTRIC CO

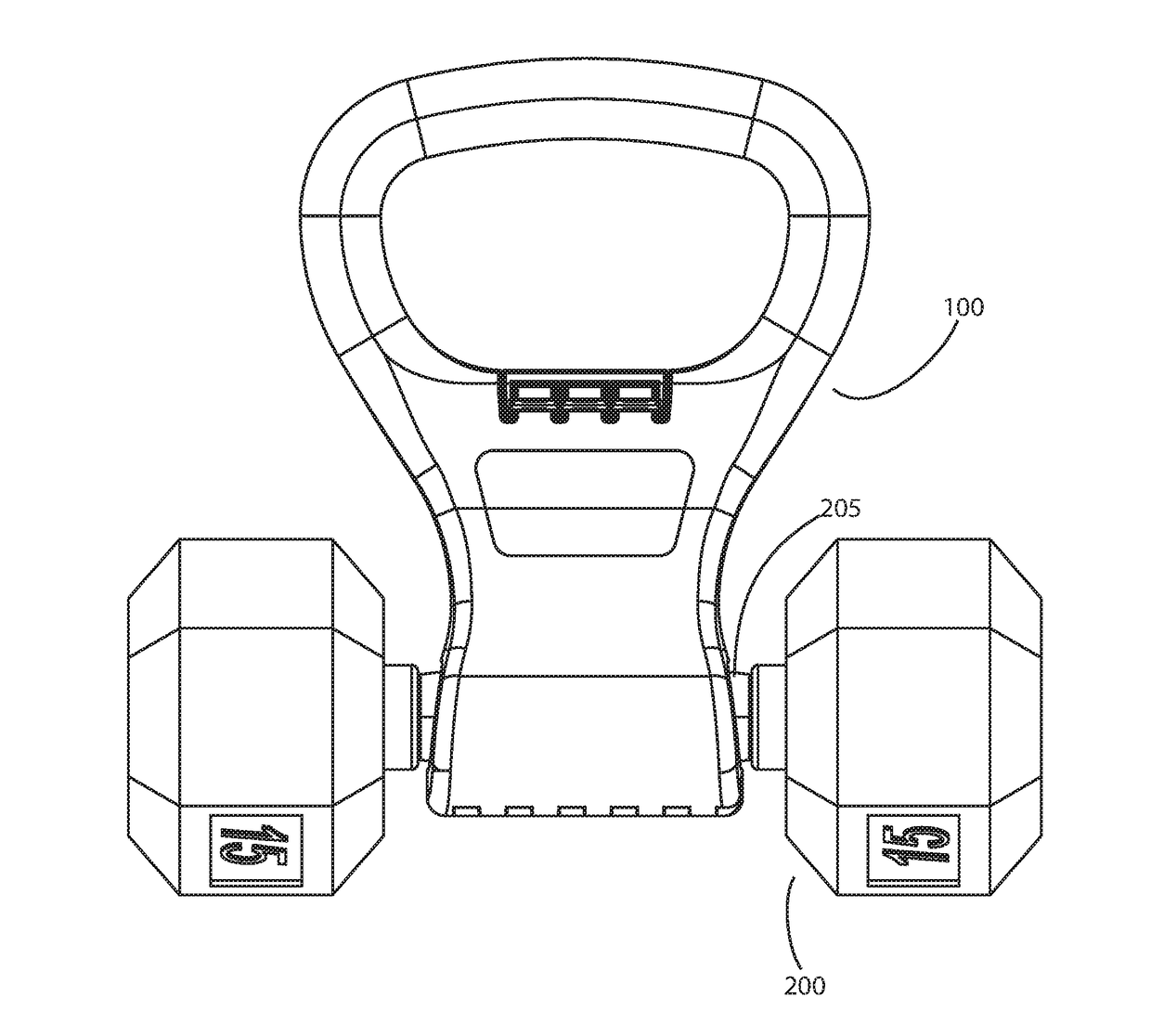

Bottom-hinged intermediate-locking barbell holder

A bottom-hinged intermediate-locking barbell holder includes a pair of opposed holding bodies connected along their bottoms by a hinge. In a closed position, the handle sections form a handle for gripping and the bases define a generally cylindrical channel, near the hinged bottom, in which compressible gaskets and a handle of a dumbbell may be received and securely contained. A cam latch releasably secures the intermediate sections together.

Owner:PANGOLIN DESIGN GRP LLC

System and method for integrated circuits with cylindrical gate structures

ActiveUS8884363B2Improve rendering capabilitiesImprove performanceTransistorNanoinformaticsCylindrical channelNanowire

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Bottom-hinged intermediate-locking barbell holder

A bottom-hinged intermediate-locking barbell holder includes a pair of opposed holding bodies (bodies) connected along their bottoms by a hinge. In a closed position, the handle sections form a handle for gripping and the bases define a generally cylindrical channel, near the hinged bottom, in which compressible gaskets and a handle of a dumbbell may be received and securely contained. A cam latch releasably secures the intermediate sections together.

Owner:PANGOLIN DESIGN GRP LLC

Dual-channel nozzle structure capable of controlling reactant uniform distribution

ActiveCN103981512AImprove uniformityMeet the needs of uniform growthChemical vapor deposition coatingCylindrical channelSubstrate surface

The invention discloses a dual-channel nozzle structure capable of controlling reactant uniform distribution. The structure comprises a first channel and a second channel; wherein the first channel is an equal diameter cylindrical channel or a variable diameter cylindrical channel, the reactant gas in the first channel is GaCl; the second channel is arranged in the center position of the first channel, the gas in the second channel can be N2 or a mixed gas of GaCl and N2, the second channel can be a cylindrical channel, or the second channel can be composed of two sections, the upper section is in a cylindrical shape and the lower section is in an inverse circular truncated cone shape, and the diameters of the upper section and the lower section on the joint part are equal. The dual-channel structure can improve the reactant GaCl radial distribution uniformity near the substrate surface through optimizing the gas flows in the two channels, and thus the uniform growth of GaN crystal material on a large area substrate is achieved.

Owner:SINO NITRIDE SEMICON +1

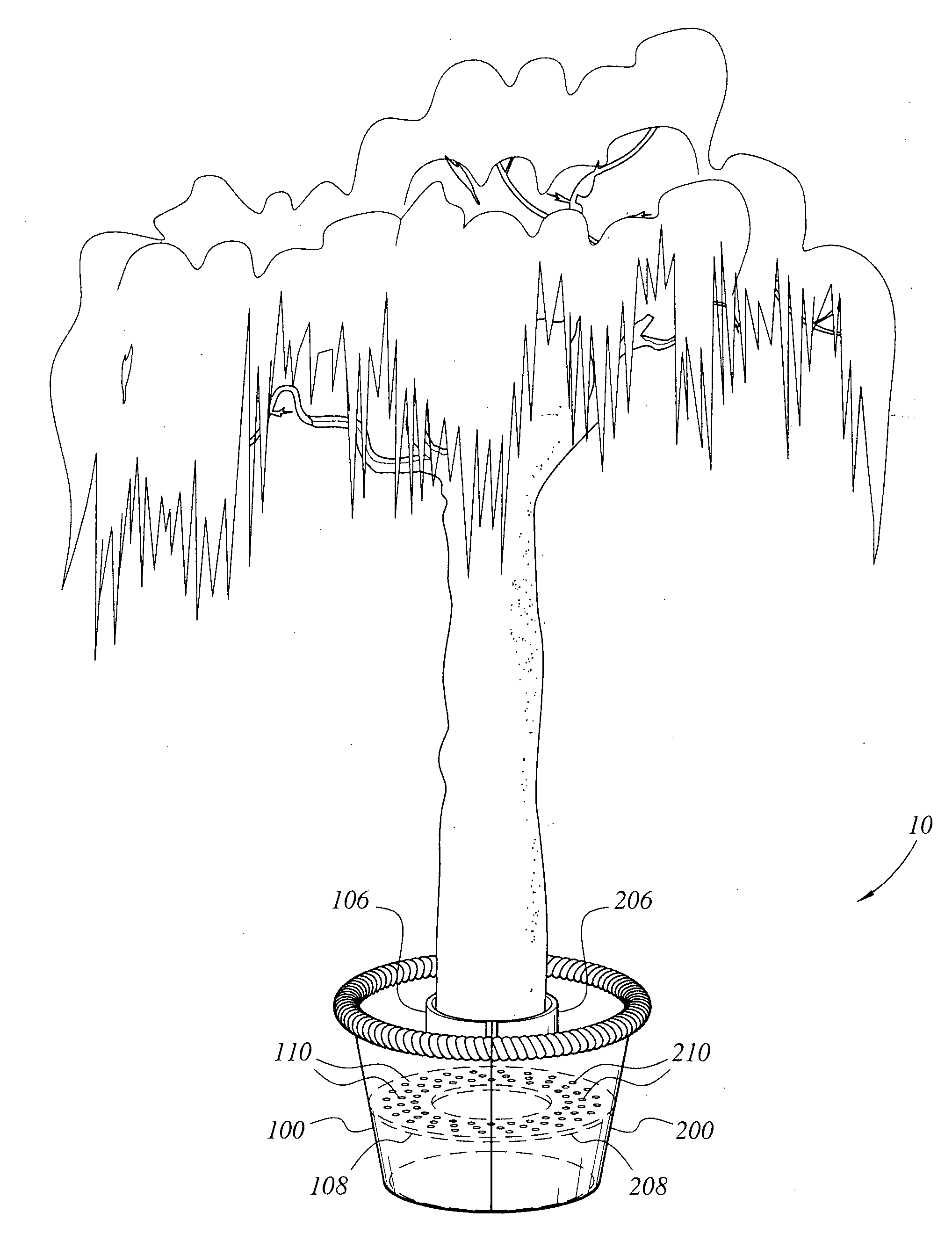

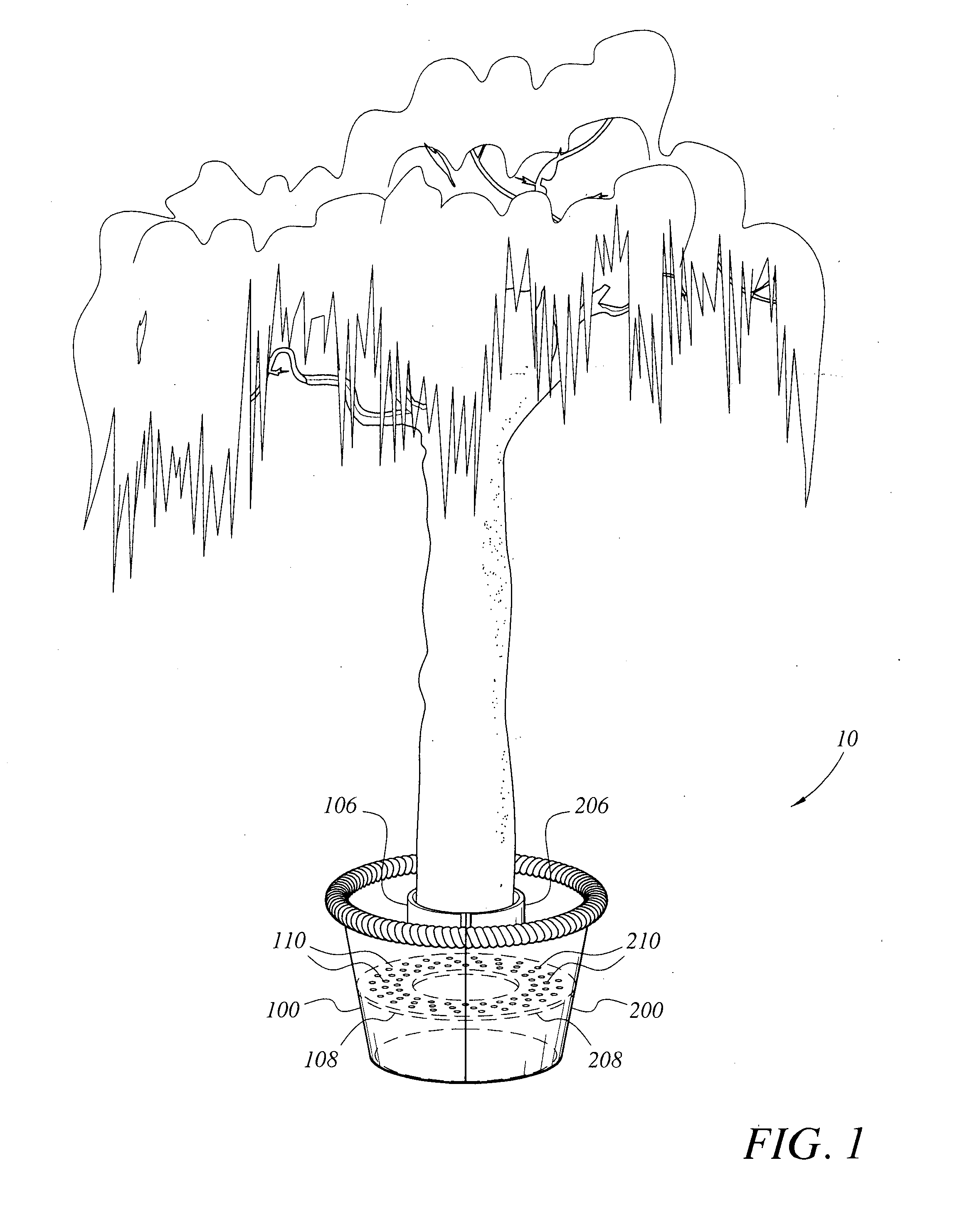

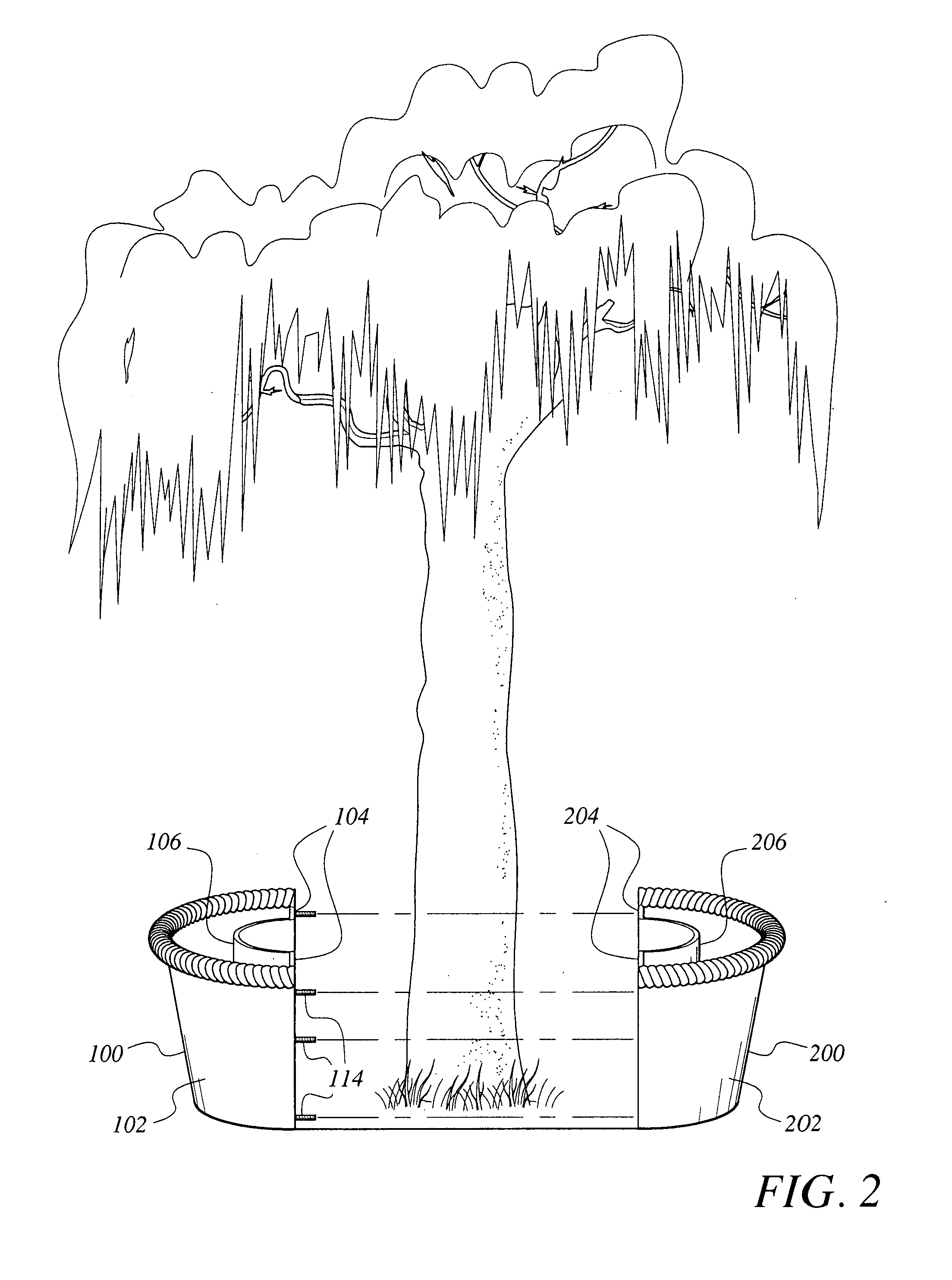

Wraparound flower planter

InactiveUS20070227068A1Readily apparentCultivating equipmentsReceptacle cultivationCylindrical channelEngineering

The wraparound flower planter includes two almost-identical semicylindrical members and releasable fasteners for securing the two members together so that the wraparound flower planter is maintained in a closed position around the base of a tree, or other columnar support. Each of the semicylindrical pot members has an open upper end, an open lower end, and a surrounding sidewall. A pair of diametrically opposed interior planar walls extend radially inward from the sidewall. A substantially semicylindrical inner wall coaxial with the sidewall extends between inner edges of the interior planar walls from the open upper end to the bottom edge of the interior planar walls, defining a cylindrical channel extending through the pot. A shelf extends between the sidewall and the inner wall, forming the floor of a generally U-shaped peripheral channel. The shelf has a plurality of drainage apertures disposed therethrough.

Owner:CATALDI RUSSELL

Oxidizing-dephlegmation-based silicon-based wrap gate transistor with buried-channel structure and preparation method thereof

ActiveCN102157556AImprove mobilityReduce the impactSemiconductor/solid-state device manufacturingSemiconductor devicesCylindrical channelSilicon nanowires

The invention provides a silicon-based wrap gate transistor with a buried-channel structure, and belongs to the field of electronic semiconductor devices. The transistor comprises a channel region, a gate medium, a gate region, a source region, a drain region and a source / drain terminal epitaxial region, wherein the channel region has a silicon nanowire structure with three layers, a cylindrical channel region lower layer is arranged inside the channel region, and the channel region and the channel region upper layer are wrapped outside the channel region lower layer respectively; impurities with opposite types are mixed into the channel region upper layer and the channel region lower layer; a layer of gate medium region is covered outside the channel region upper layer; and the gate region is positioned on the outer layer of the gate medium. In a preparation method, the silicon-based wrap gate transistor with the buried-channel structure which is suitable to be applied to high-speed circuits is prepared on the basis of an oxidizing dephlegmation technology, so that the phenomena of descending in mobility and serious random telegraph noise which are caused by the polycrystal orientation of wrap gate devices are avoided.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

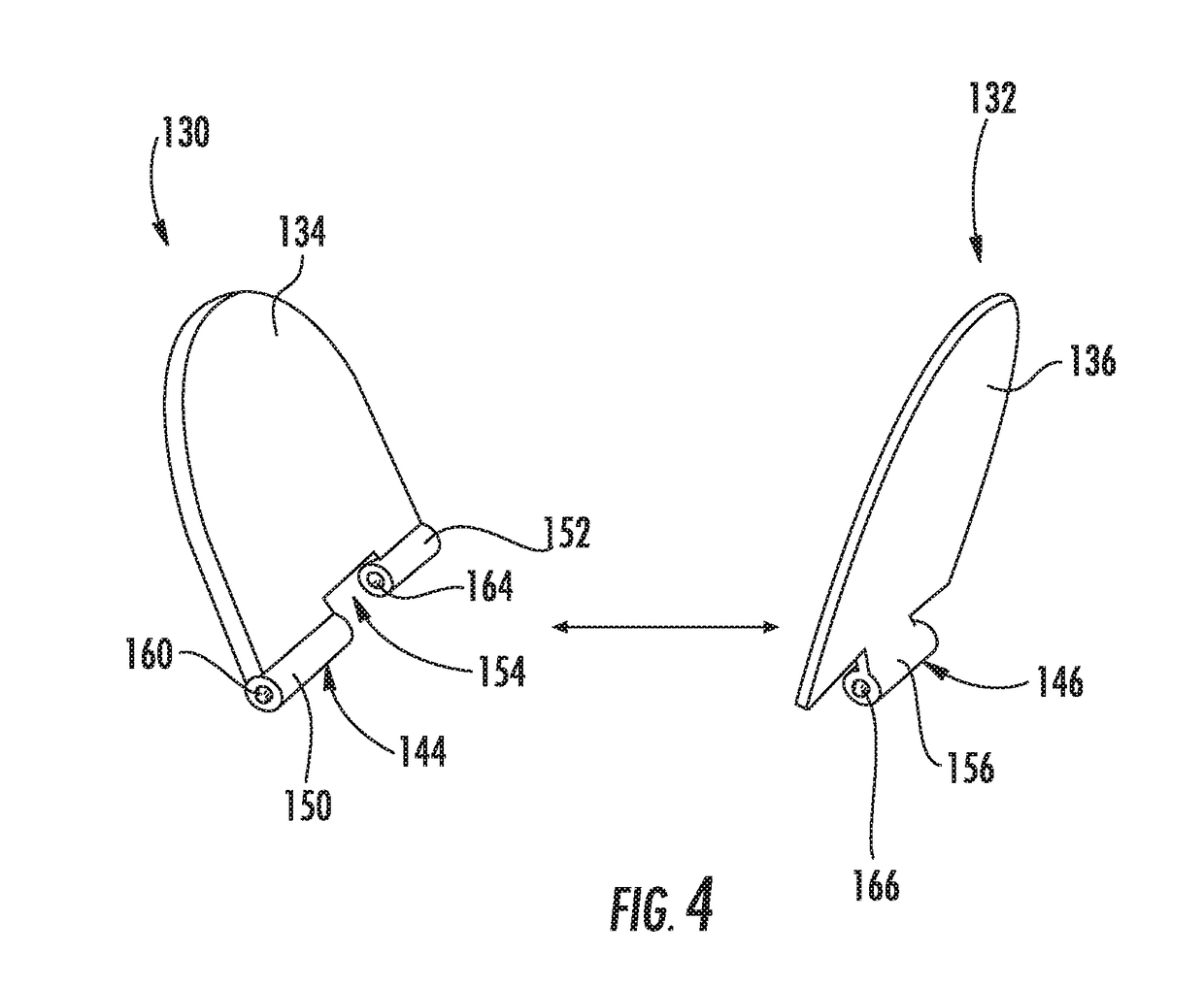

Additively manufactured valve assembly

A valve assembly and a method of additively manufacturing the same are provided. The valve assembly includes a valve housing defining first and second mounting features, such as recessed dimples or protruding bumps, positioned on opposite sides of a substantially cylindrical channel to define a hinge axis. One or more valve flaps are positioned within the cylindrical channel, each valve flap including a hinge member extending along the hinge axis and defining two or more complementary features or coupling members for engaging either the mounting features of the valve housing or an adjacent hinge member.

Owner:GENERAL ELECTRIC CO