Oxidizing-dephlegmation-based silicon-based wrap gate transistor with buried-channel structure and preparation method thereof

A transistor, silicon-based technology, applied in the field of buried-channel structure silicon-based gate-surrounding transistors, can solve the problems of reducing carrier mobility, random telegraph noise, aggravating carrier scattering noise, etc. The effect of increasing the transmission speed and improving the mobility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

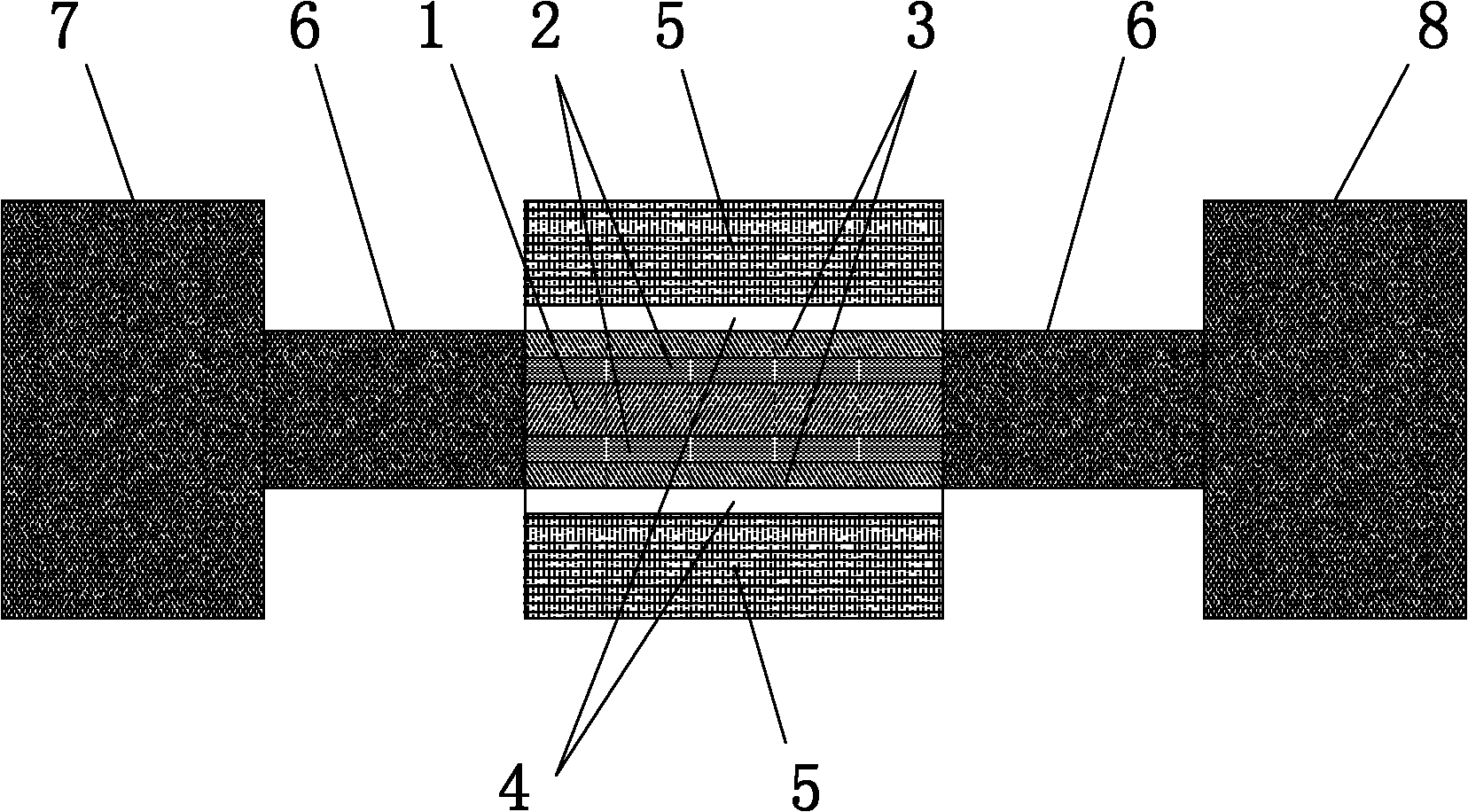

[0039] Below in conjunction with accompanying drawing and specific embodiment the present invention is described in further detail:

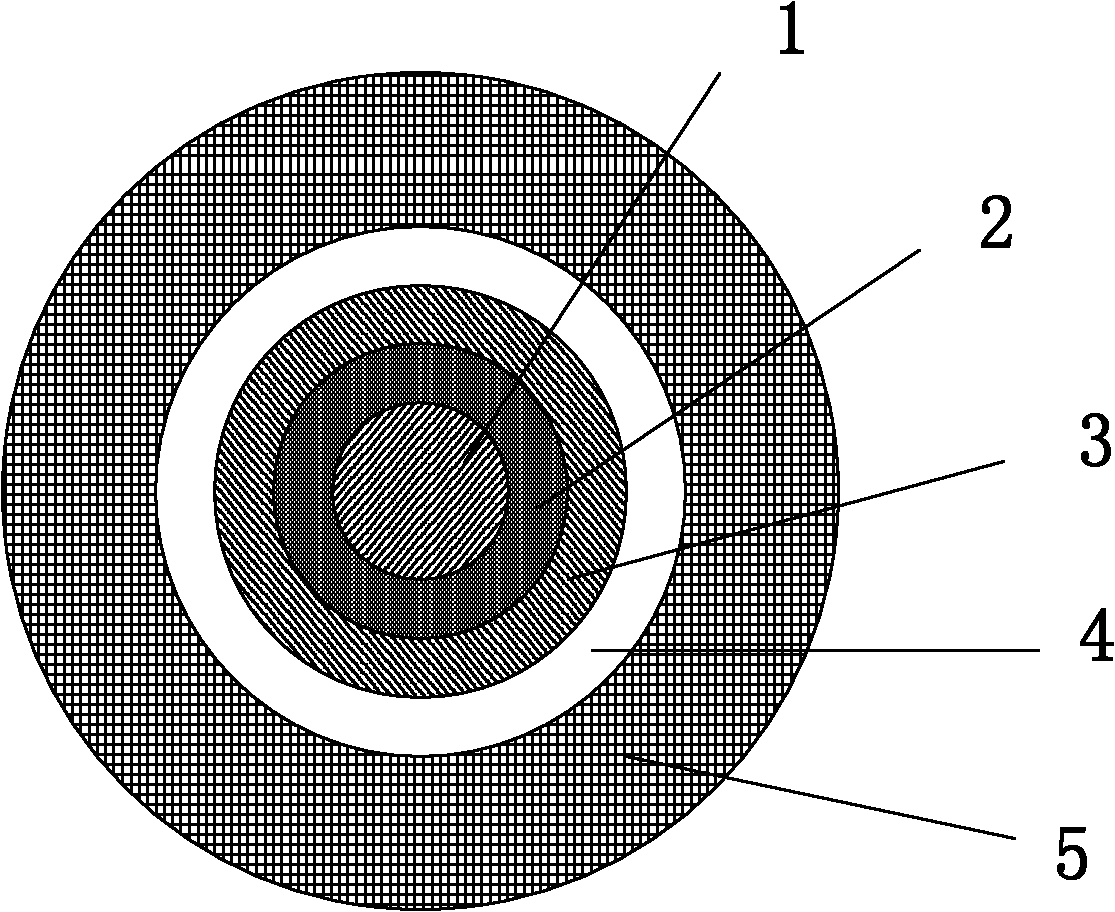

[0040] Figure 1 Knot The structure is a top cross-sectional schematic view of the core part of the buried trench structure silicon-based surrounding gate transistor based on the oxidation segregation technology introduced in the present invention. Its structure is different from the general conventional silicon-based surrounding gate transistors in that:

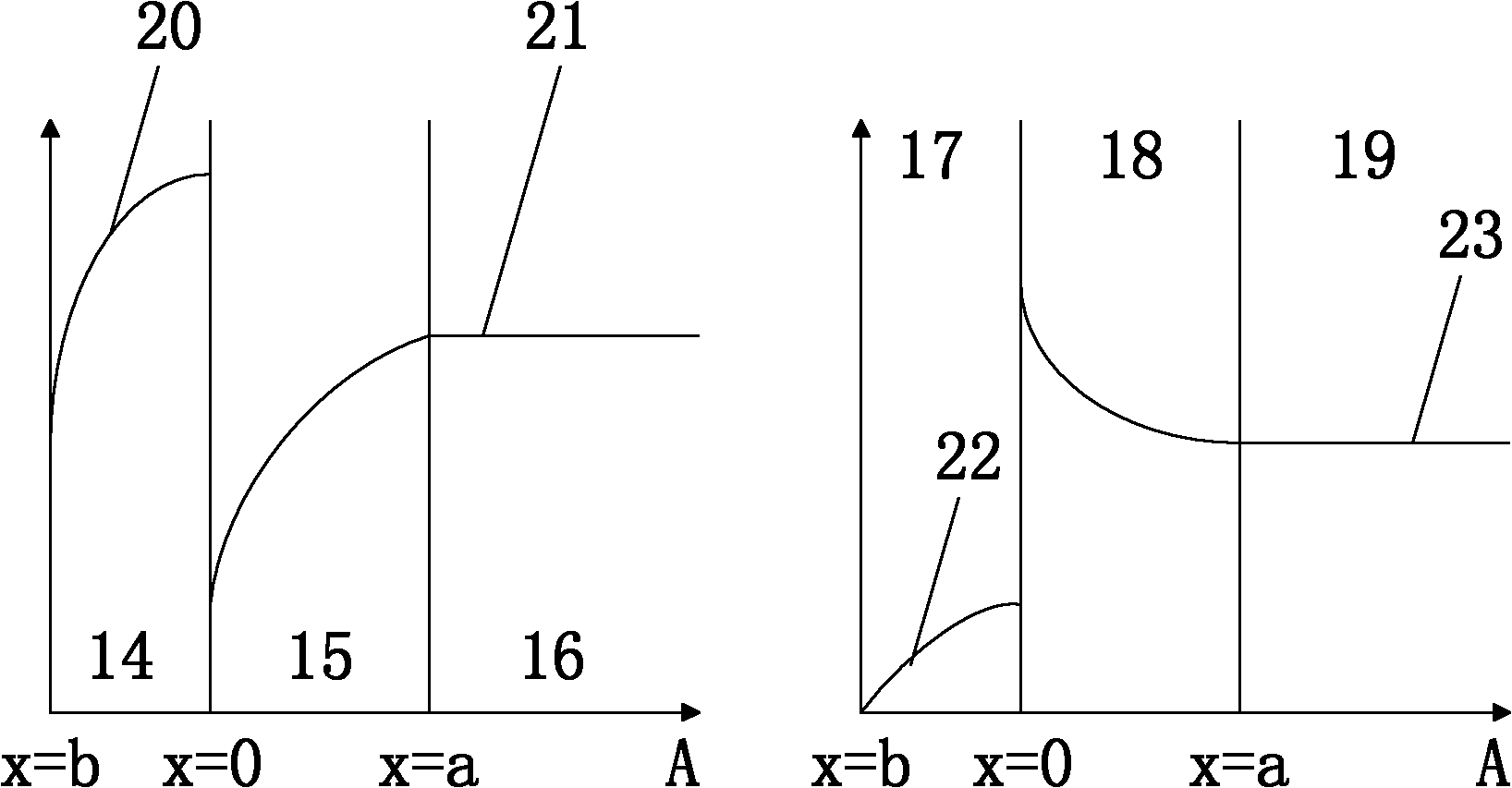

[0041] The channel is divided into three layers: the channel area, the upper layer of the channel area, and the lower layer of the channel area. These three layers form a buried trench structure that keeps the carrier flow path away from the silicon-silicon dioxide interface. Thus, the influence of the traps at the silicon-silicon dioxide interface on the carriers is reduced. At the same time, the influence of surface roughness on the mobility is avoided.

[0042] Its structure is differe...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More