Patents

Literature

115824 results about "Impurity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Impurities are chemical substances inside a confined amount of liquid, gas, or solid, which differ from the chemical composition of the material or compound. Impurities are either naturally occurring or added during synthesis of a chemical or commercial product. During production, impurities may be purposely, accidentally, inevitably, or incidentally added into the substance.

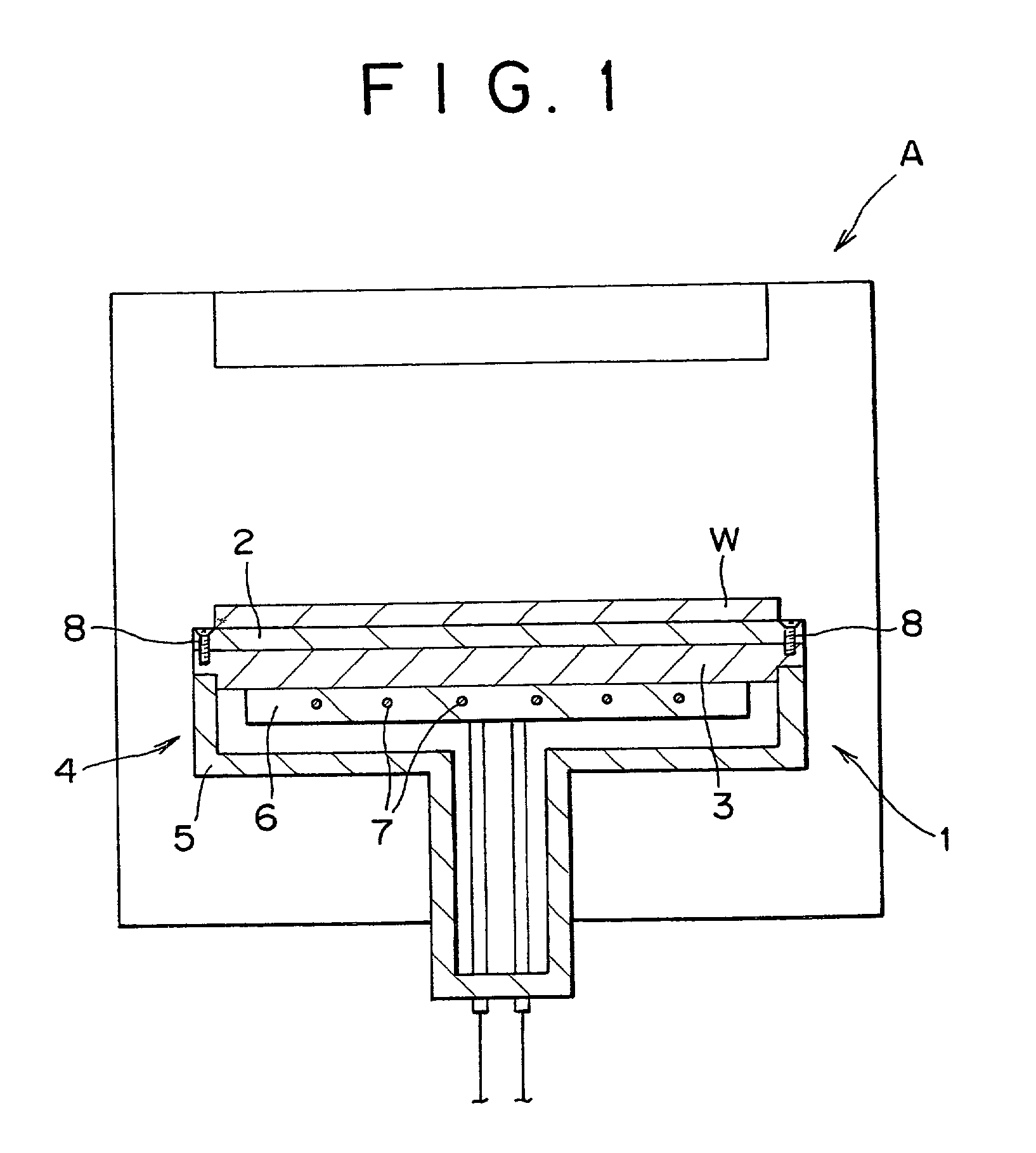

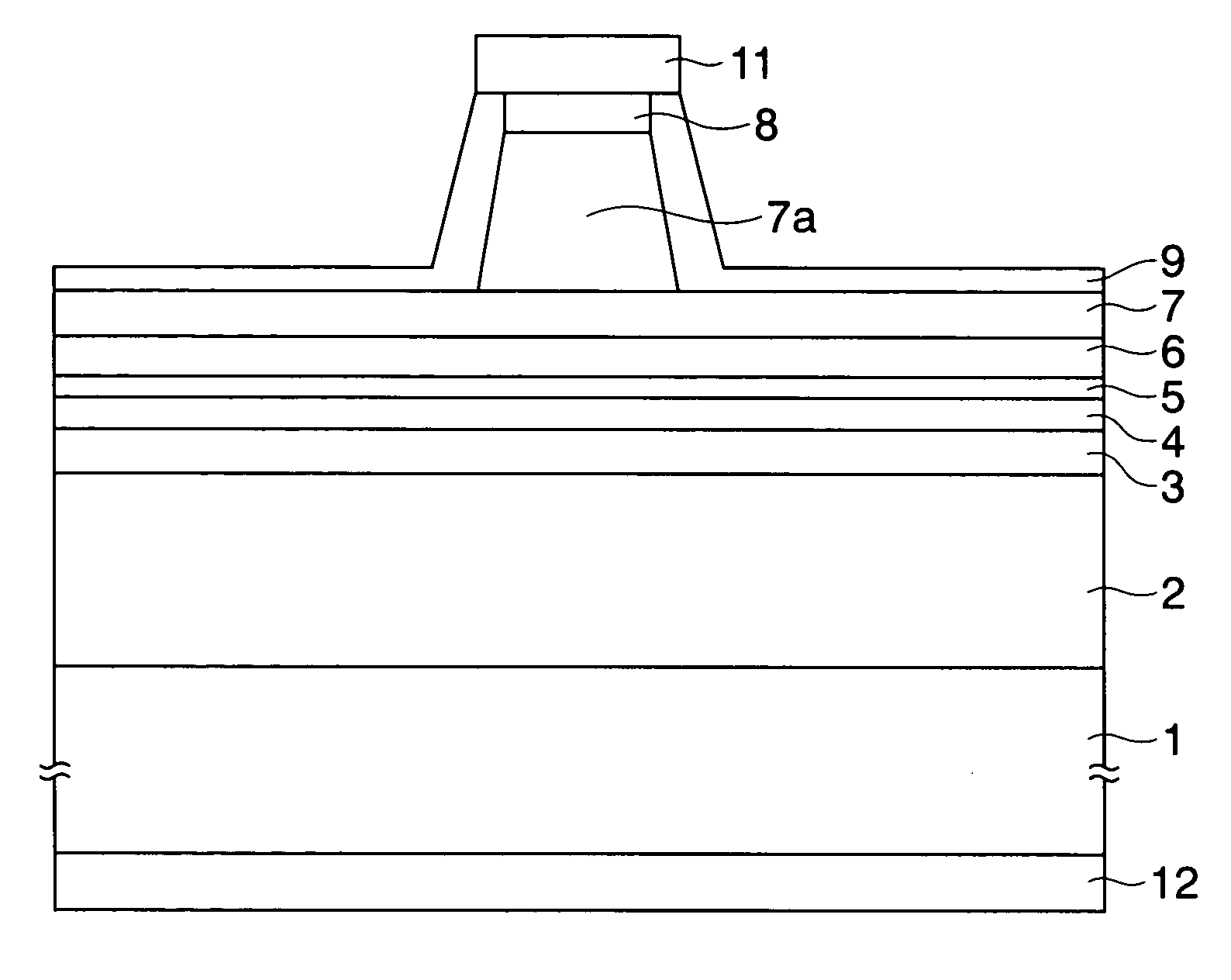

Semiconductor device, manufacturing method, and electronic device

ActiveUS20060244107A1Stabilize element propertyEasy to manufactureTransistorSemiconductor/solid-state device detailsSurface levelIntrinsic resistance

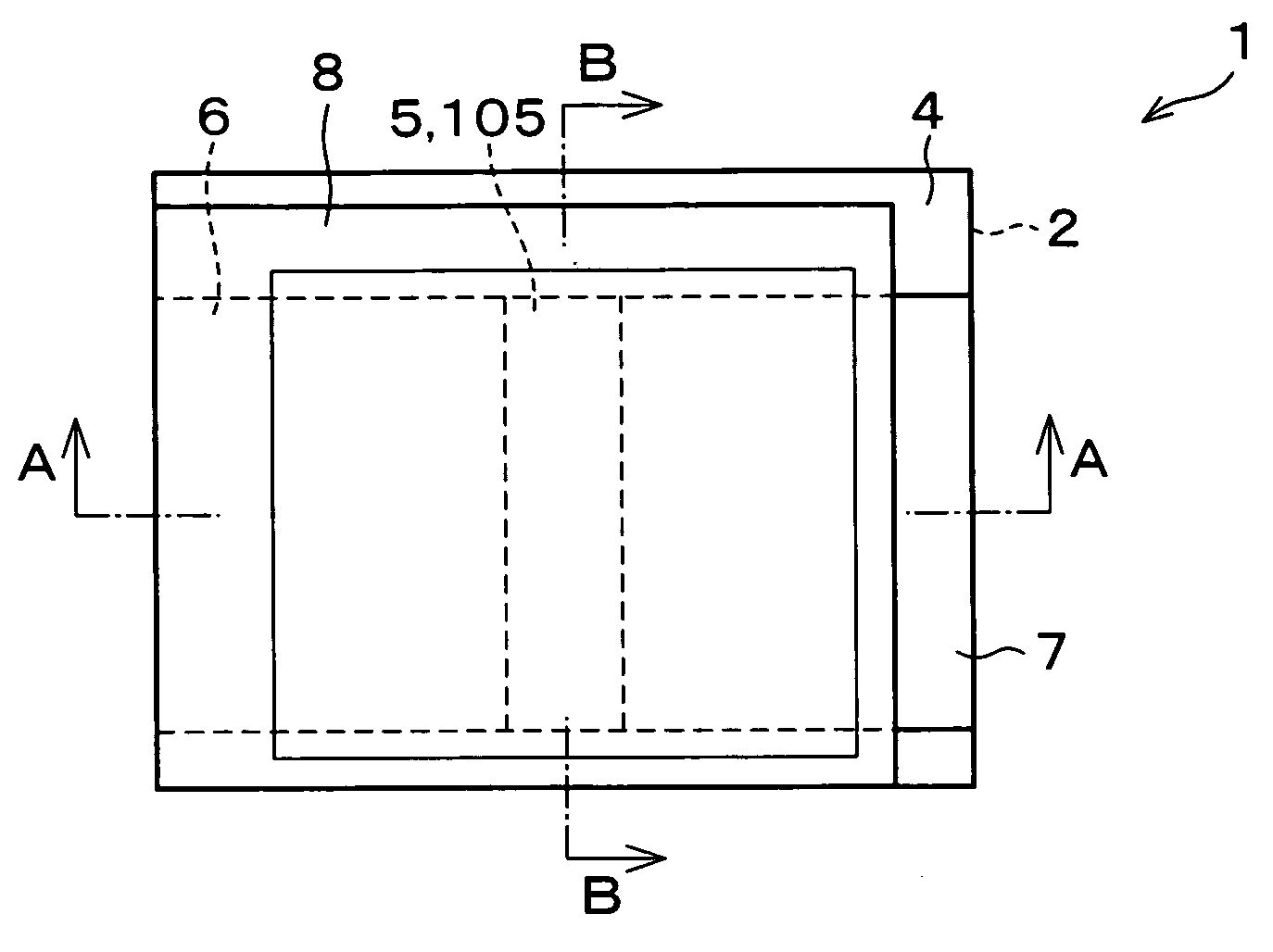

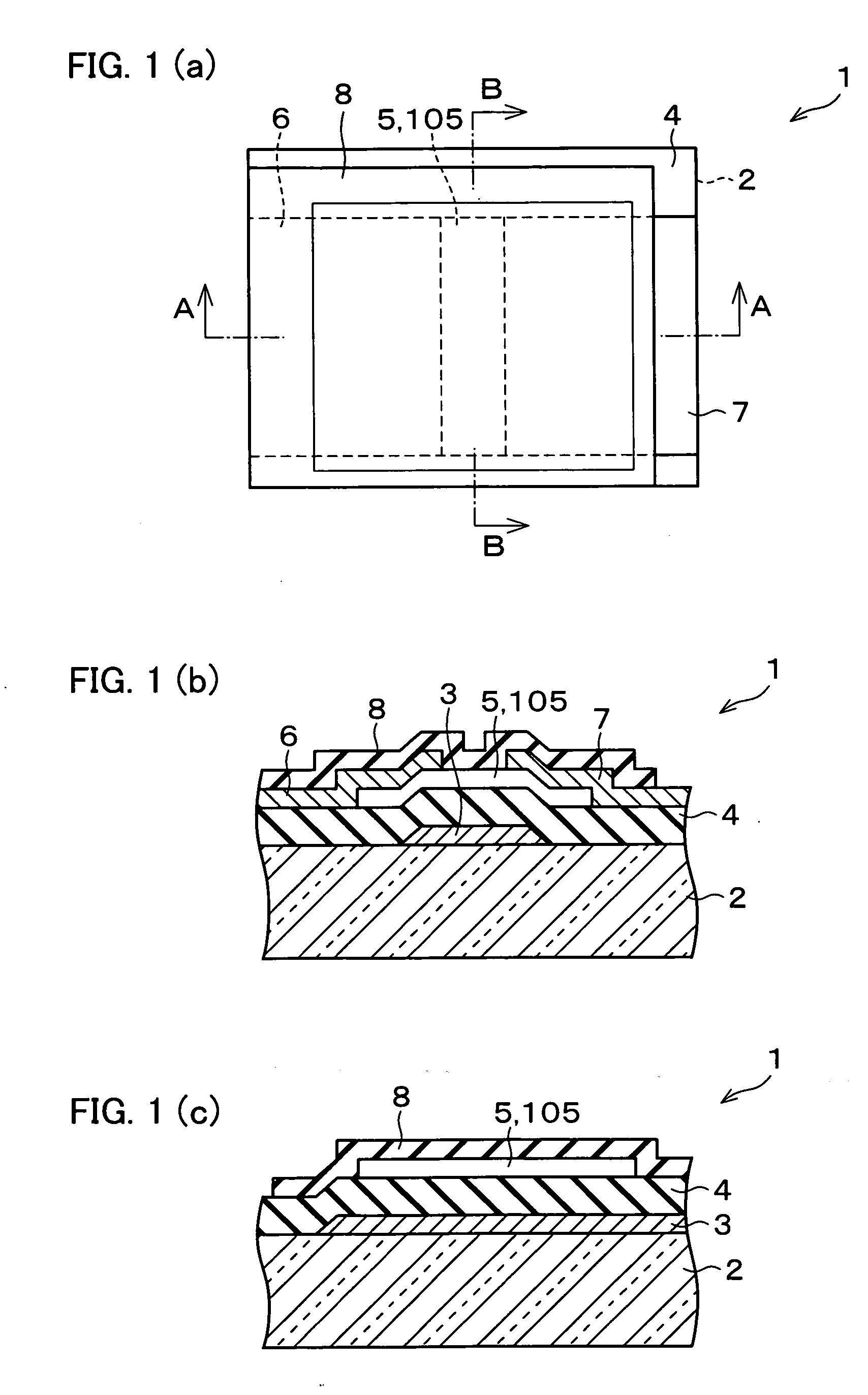

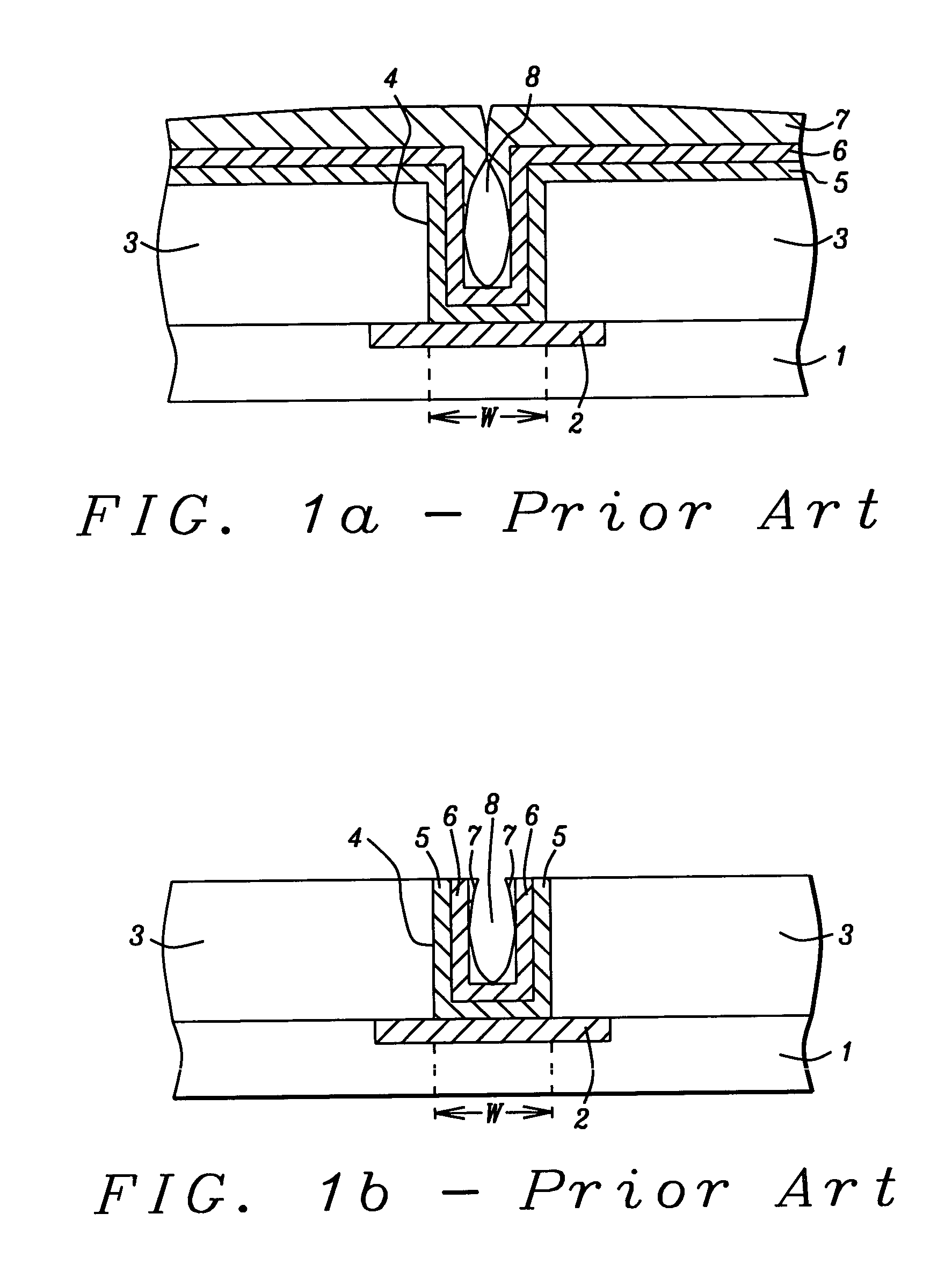

In a thin film transistor (1), a gate insulating layer (4) is formed on a gate electrode (3) formed on an insulating substrate (2). Formed on the gate insulating layer (4) is a semiconductor layer (5). Formed on the semiconductor layer (5) are a source electrode (6) and a drain electrode (7). A protective layer (8) covers them, so that the semiconductor layer (5) is blocked from an atmosphere. The semiconductor layer (5) (active layer) is made of, e.g., a semiconductor containing polycrystalline ZnO to which, e.g., a group V element is added. The protective layer (8) thus formed causes decrease of a surface level of the semiconductor layer (5). This eliminates a depletion layer spreading therewithin. Accordingly, the ZnO becomes an n-type semiconductor indicating an intrinsic resistance, with the result that too many free electrons are generated. However, the added element works on the ZnO as an accepter impurity, so that the free electrons are reduced. This decreases a gate voltage required for removal of the free electrons, so that the threshold voltage of the thin film transistor (1) becomes on the order of 0V. This allows practical use of a semiconductor device which has an active layer made of zinc oxide and which includes an protective layer for blocking the active layer from an atmosphere.

Owner:SHARP KK +2

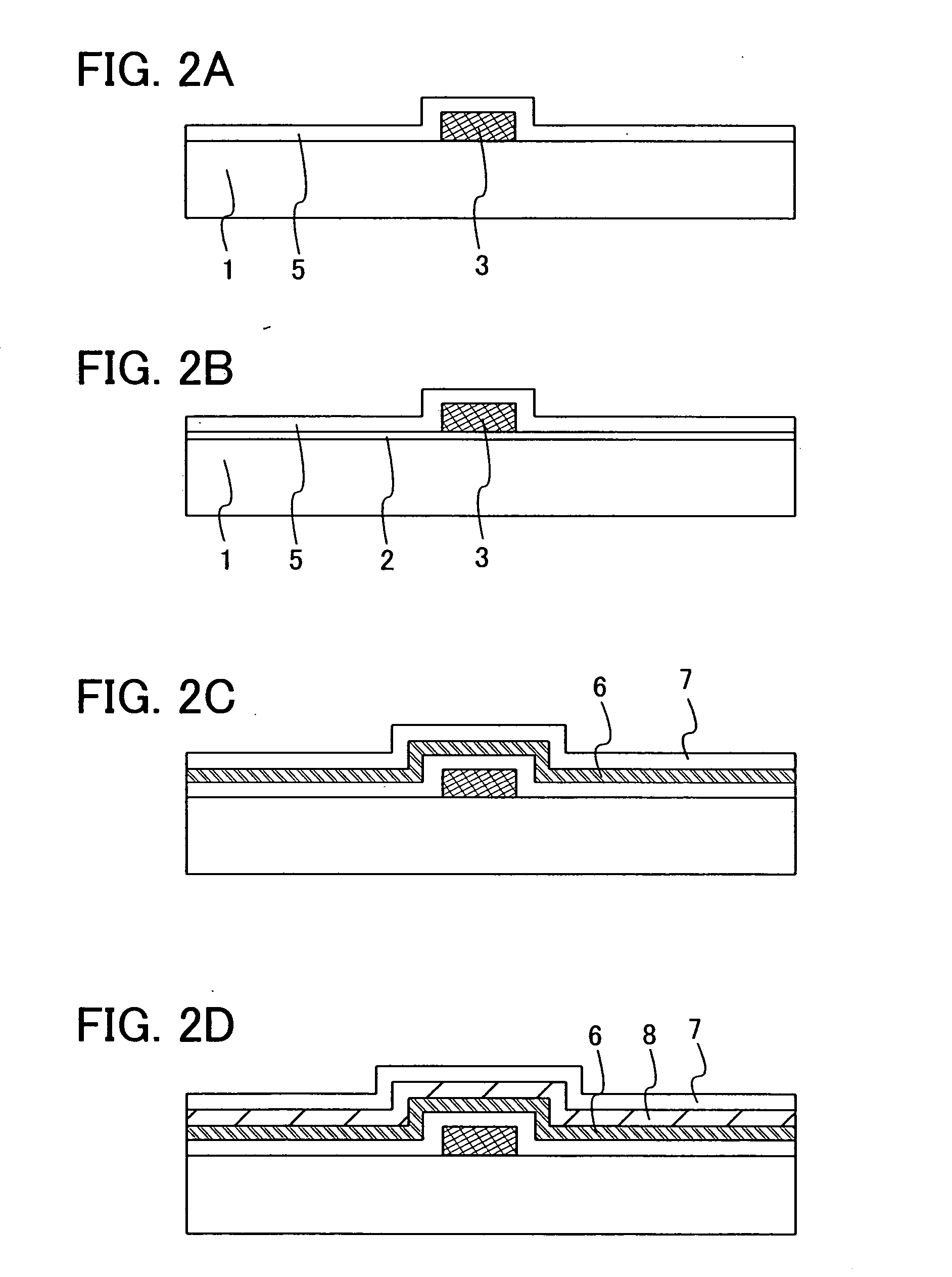

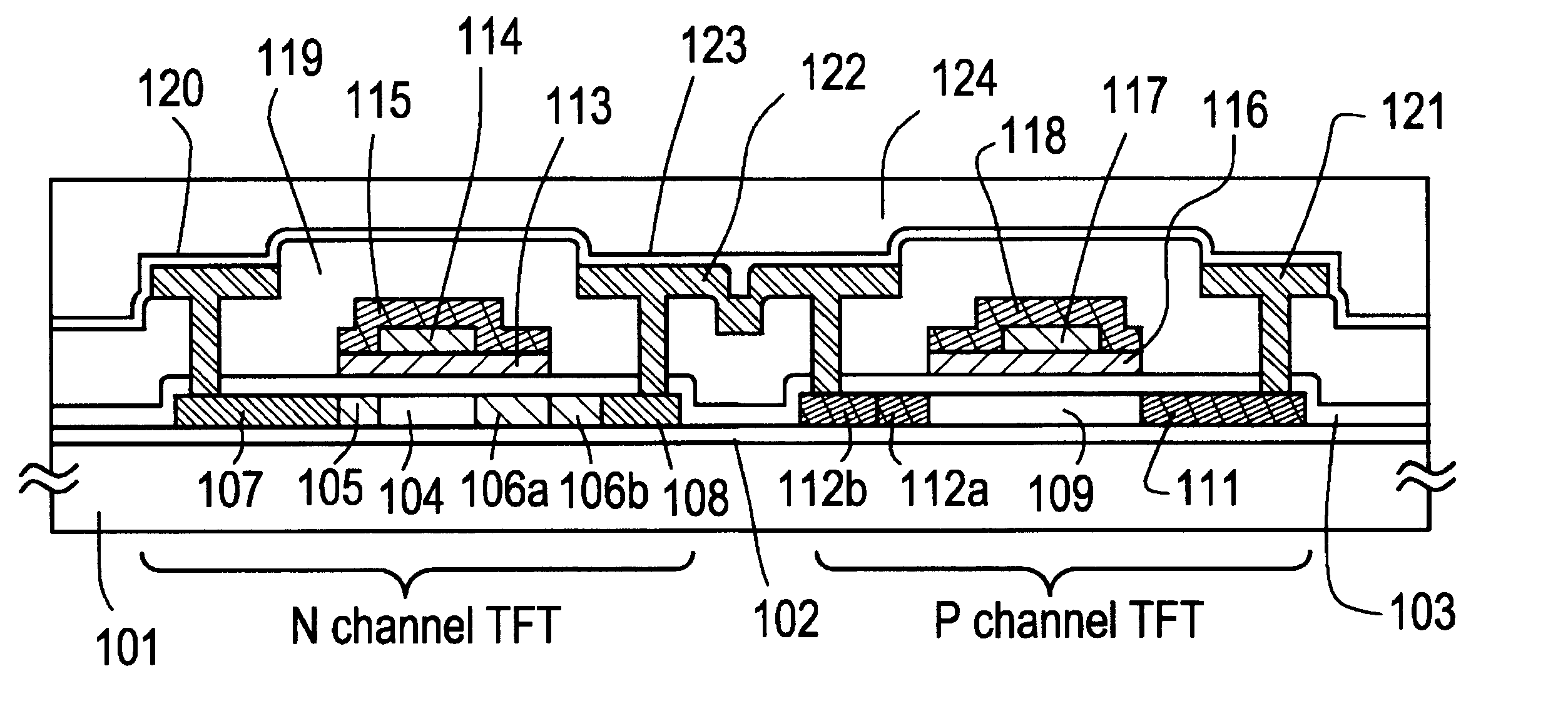

Semiconductor device and manufacturing method thereof

ActiveUS20070108446A1Low resistance of wireLower resistanceTransistorElectroluminescent light sourcesAlloySilicon oxide

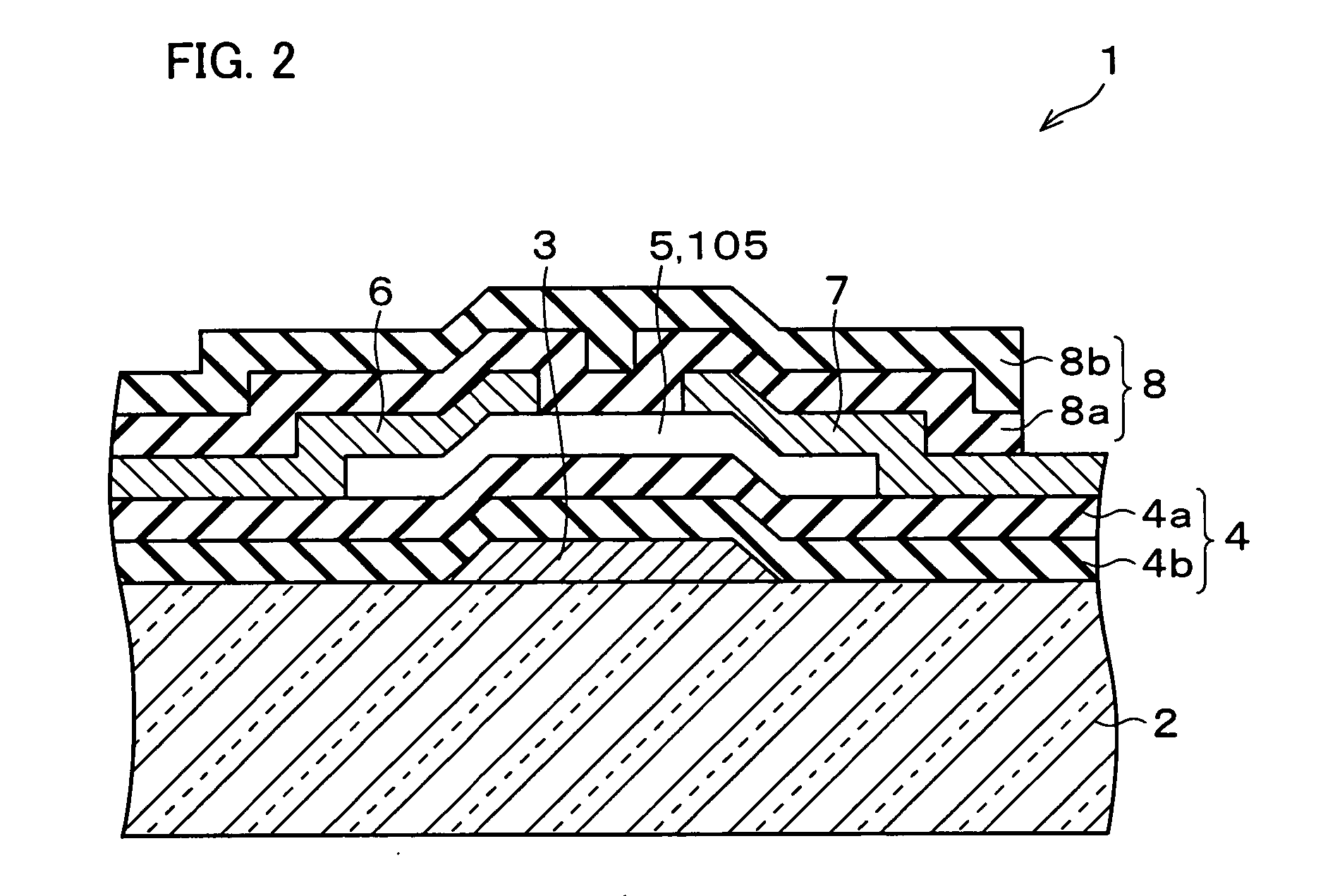

To provide a semiconductor device in which a defect or fault is not generated and a manufacturing method thereof even if a ZnO semiconductor film is used and a ZnO film to which an n-type or p-type impurity is added is used for a source electrode and a drain electrode. The semiconductor device includes a gate insulating film formed by using a silicon oxide film or a silicon oxynitride film over a gate electrode, an Al film or an Al alloy film over the gate insulating film, a ZnO film to which an n-type or p-type impurity is added over the Al film or the Al alloy film, and a ZnO semiconductor film over the ZnO film to which an n-type or p-type impurity is added and the gate insulating film.

Owner:SEMICON ENERGY LAB CO LTD

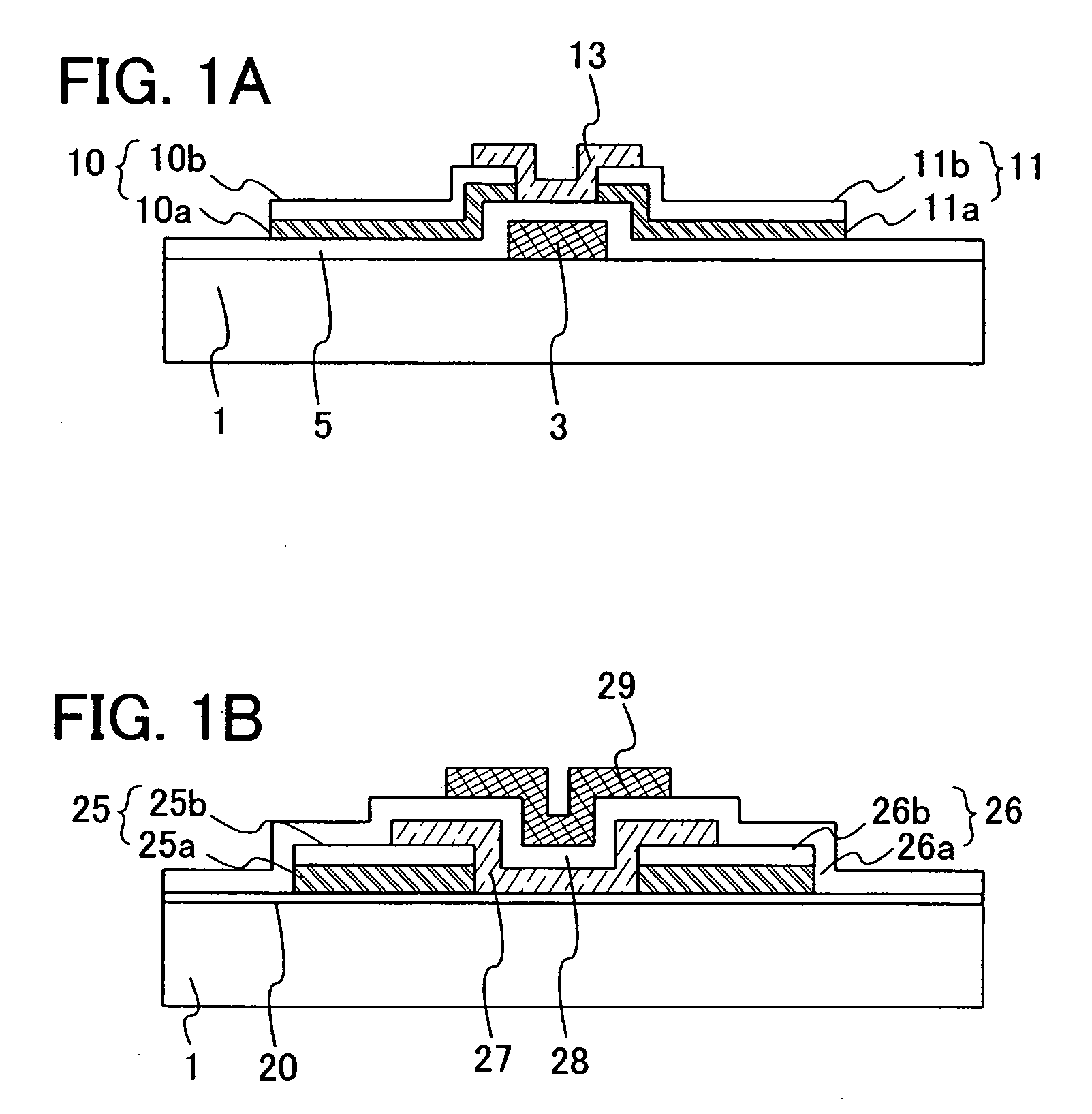

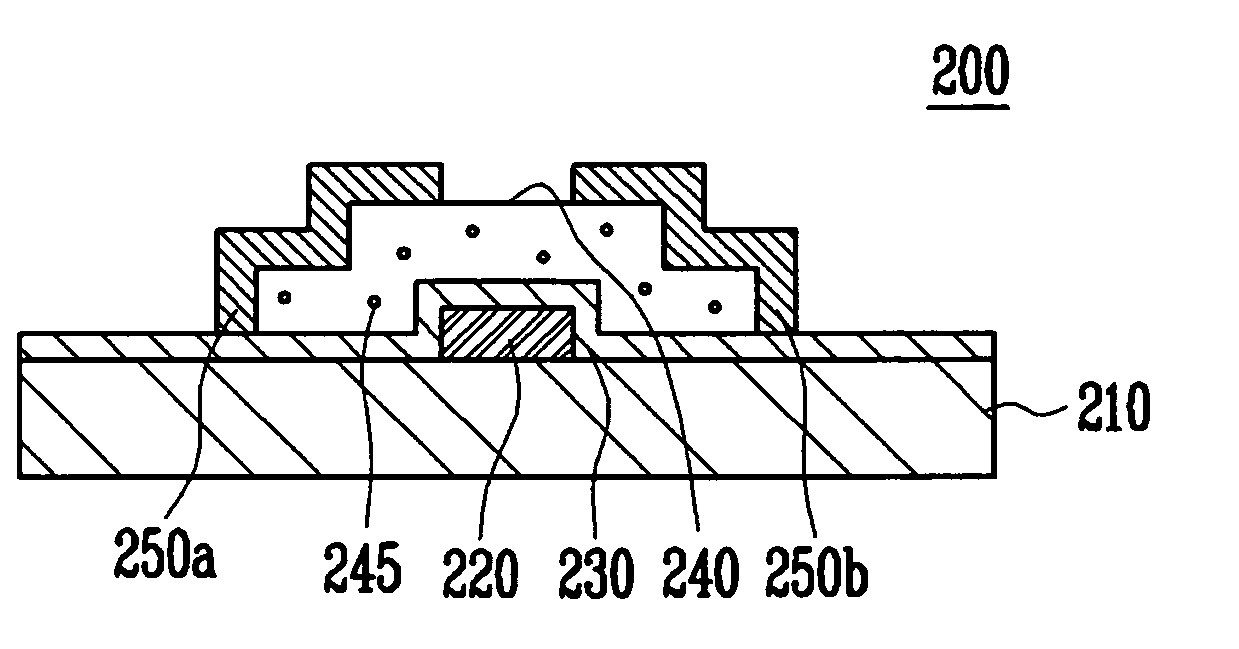

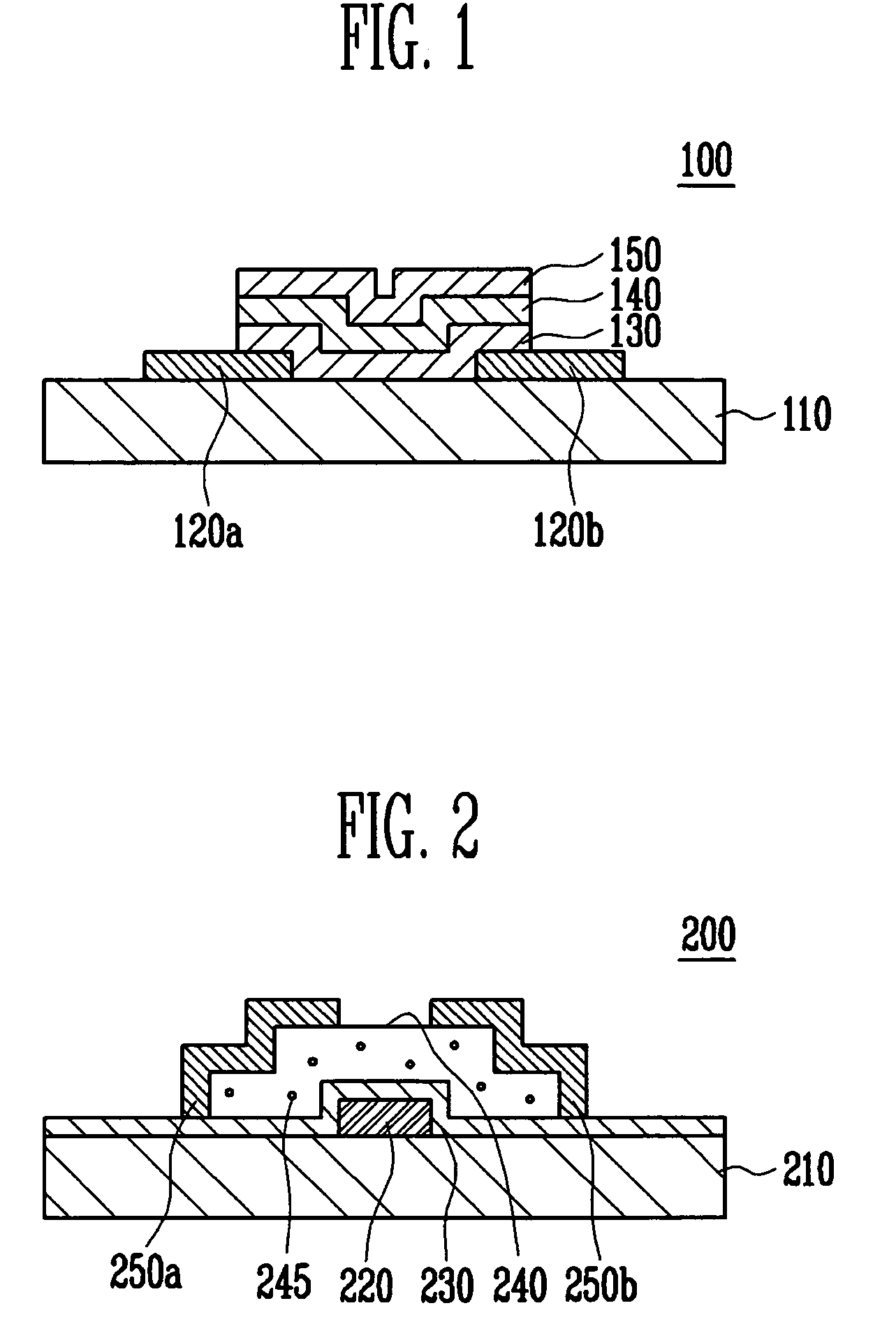

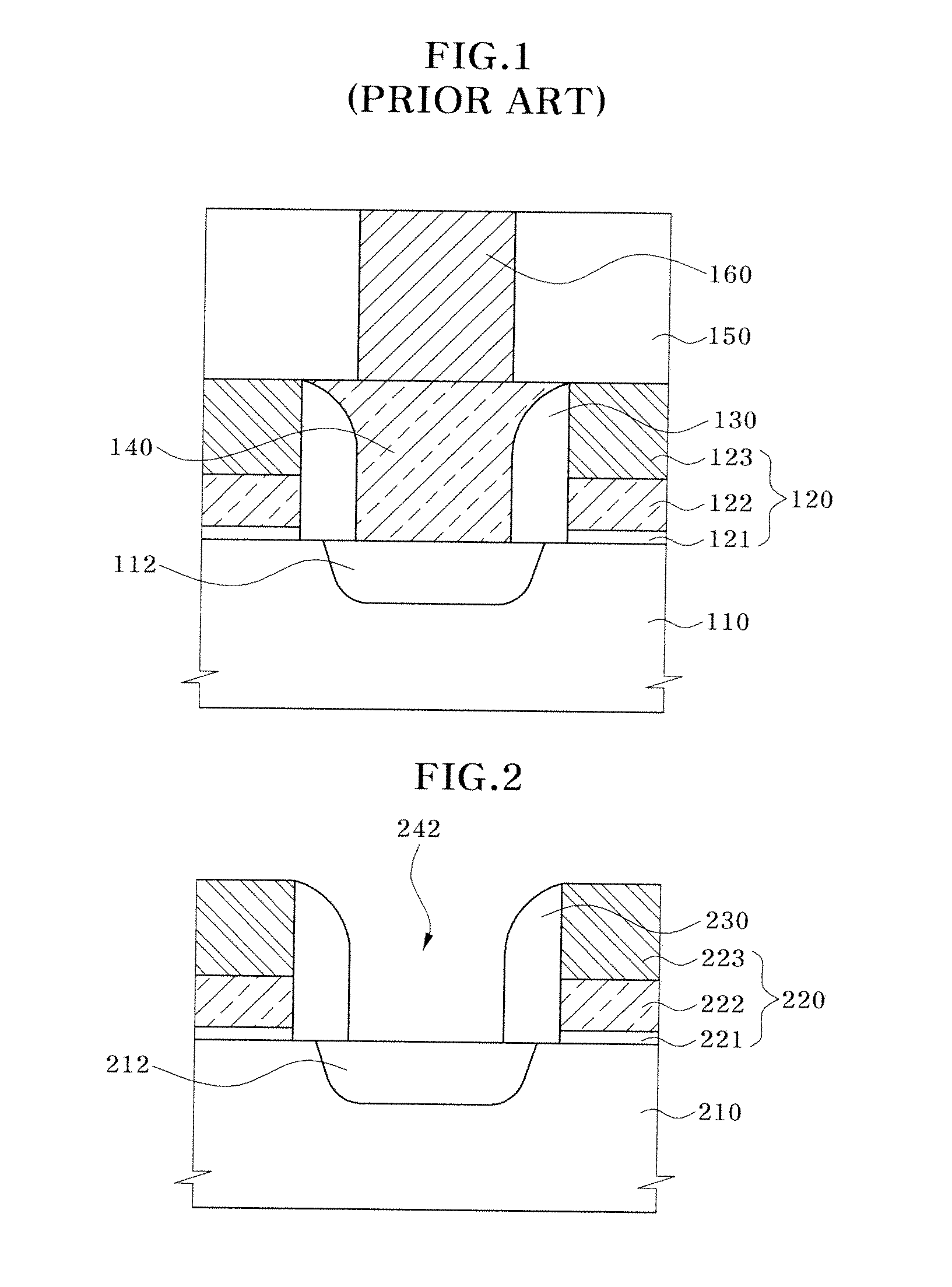

Thin film transistor, method of manufacturing the same, and flat panel display having the same

ActiveUS20080258141A1Improve stabilityUniform characteristicsSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceEngineering

A thin film transistor (TFT), a method of manufacturing the TFT, and a flat panel display comprising the TFT are provided. The TFT includes a gate, a gate insulating layer that contacts the gate, a channel layer that contacts the gate insulating layer and faces the gate with the gate insulating layer therebetween, a source that contacts an end of the channel layer; and a drain that contacts an other end of the channel layer, wherein the channel layer is an amorphous oxide semiconductor layer, and each of the source and the drain is a conductive oxide layer comprising an oxide semiconductor layer having a conductive impurity in the oxide semiconductor layer. A low resistance metal layer can further be included on the source and drain. A driving circuit of a unit pixel of a flat panel display includes the TFT.

Owner:SAMSUNG ELECTRONICS CO LTD

Thin film transistor and organic light-emitting display device having the thin film transistor

InactiveUS20080224133A1Solid-state devicesSemiconductor/solid-state device manufacturingNitrogenDisplay device

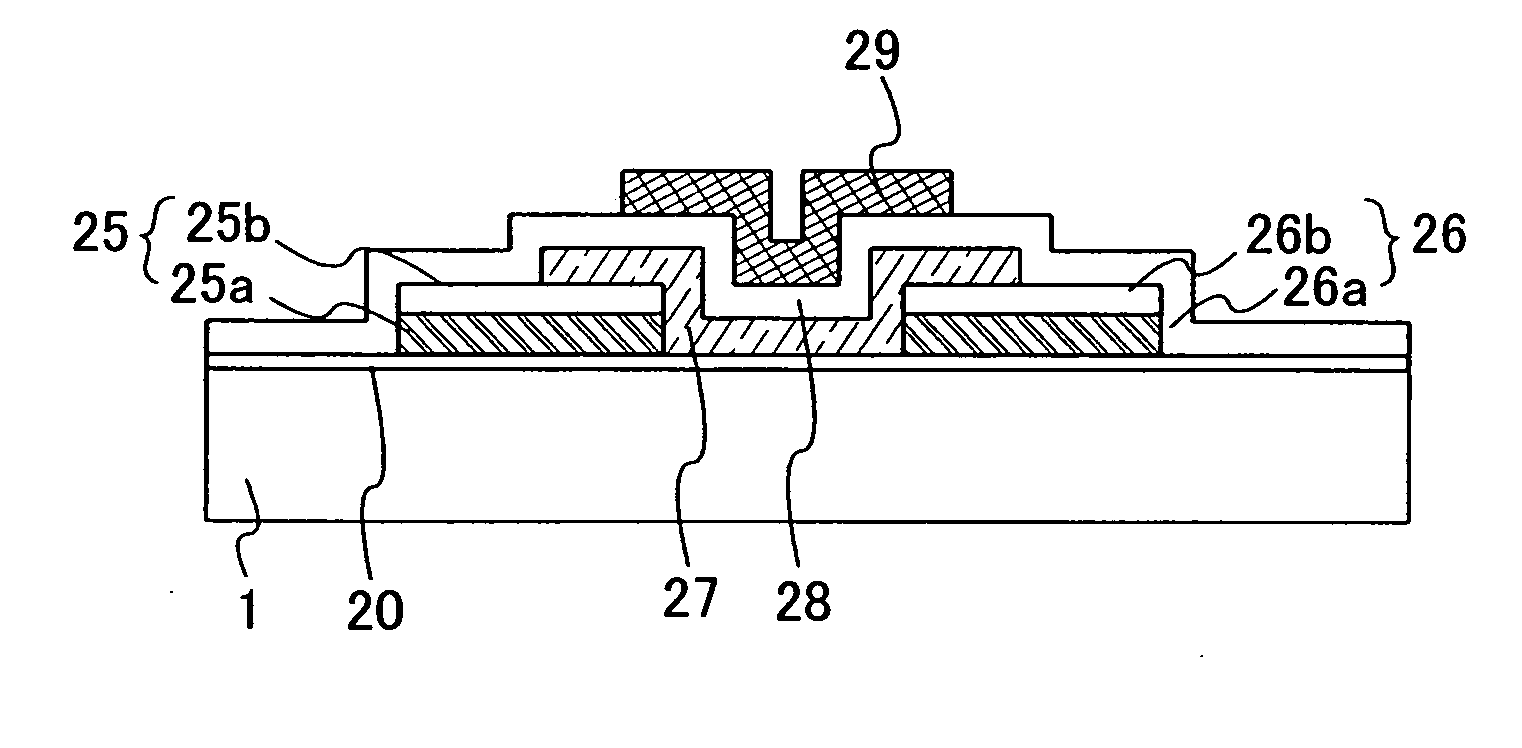

Disclosed is a thin film transistor including a P-type semiconductor layer, and an organic light-emitting display device having the thin film transistor. The present invention provides a thin film transistor including a substrate, a semiconductor layer, and a gate electrode and a source / drain electrode formed on the substrate, wherein the semiconductor layer is composed of P-type ZnO:N layers through a reaction of a mono-nitrogen gas with a zinc precursor, and the ZnO:N layer includes an un-reacted impurity element at a content of 3 at % or less.

Owner:SAMSUNG MOBILE DISPLAY CO LTD

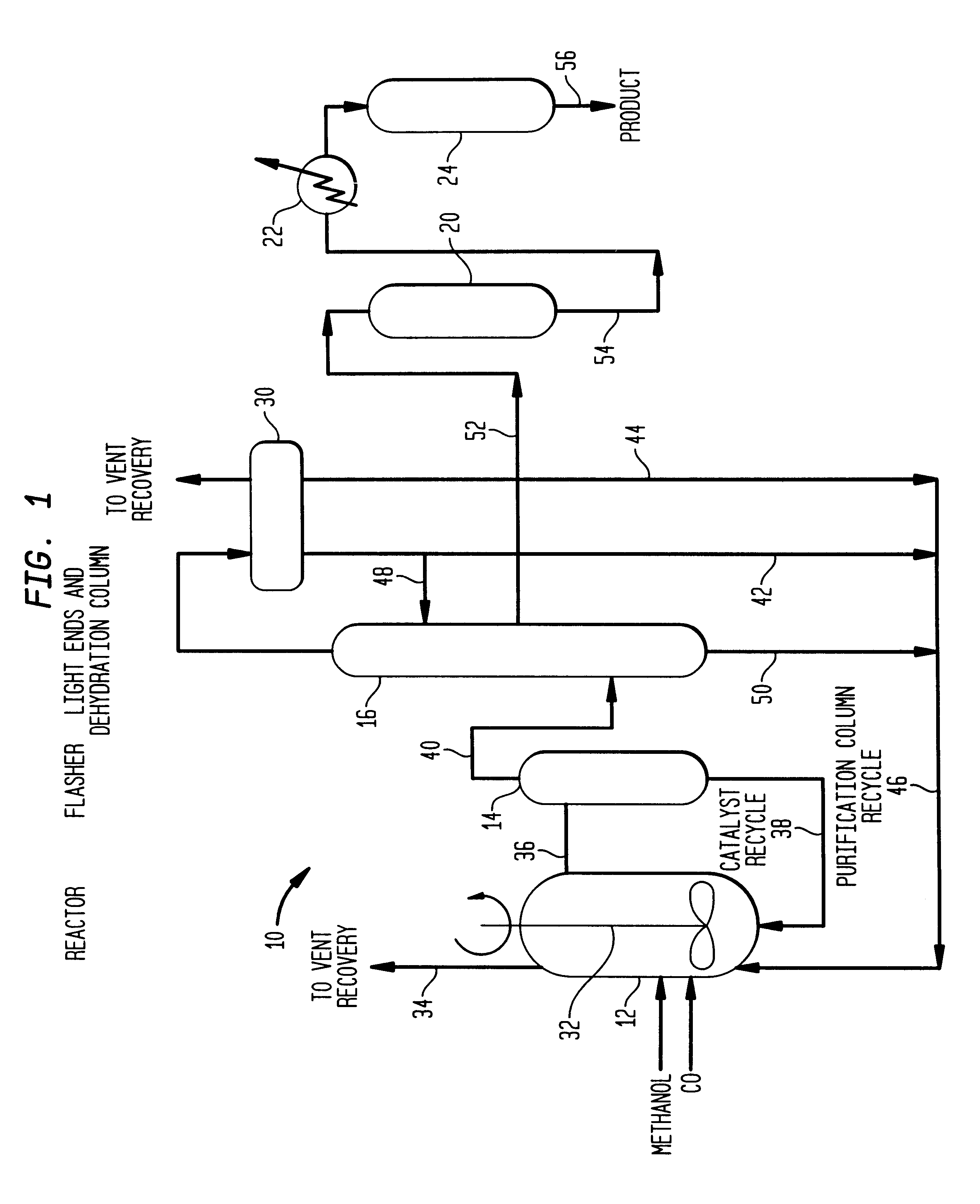

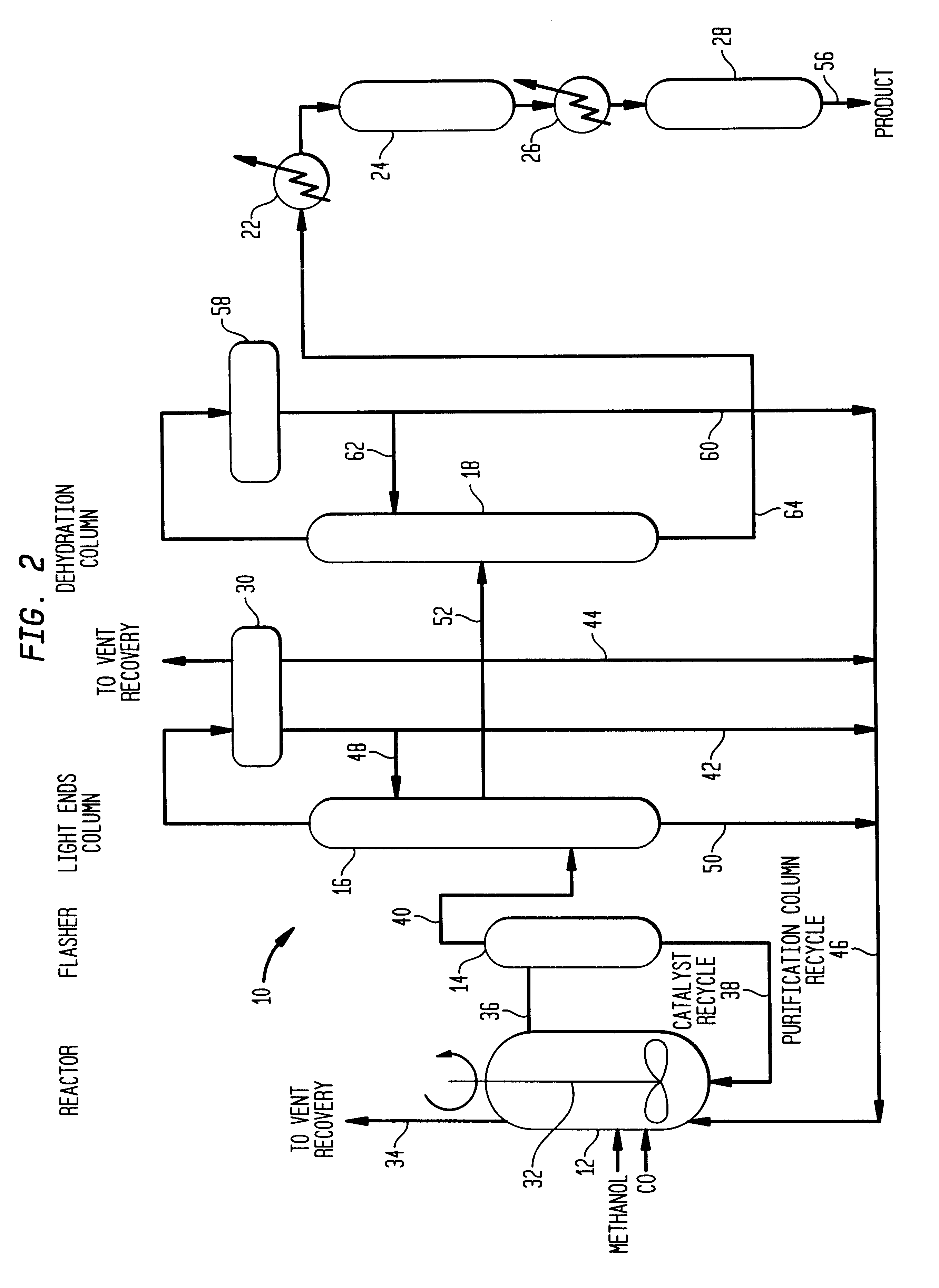

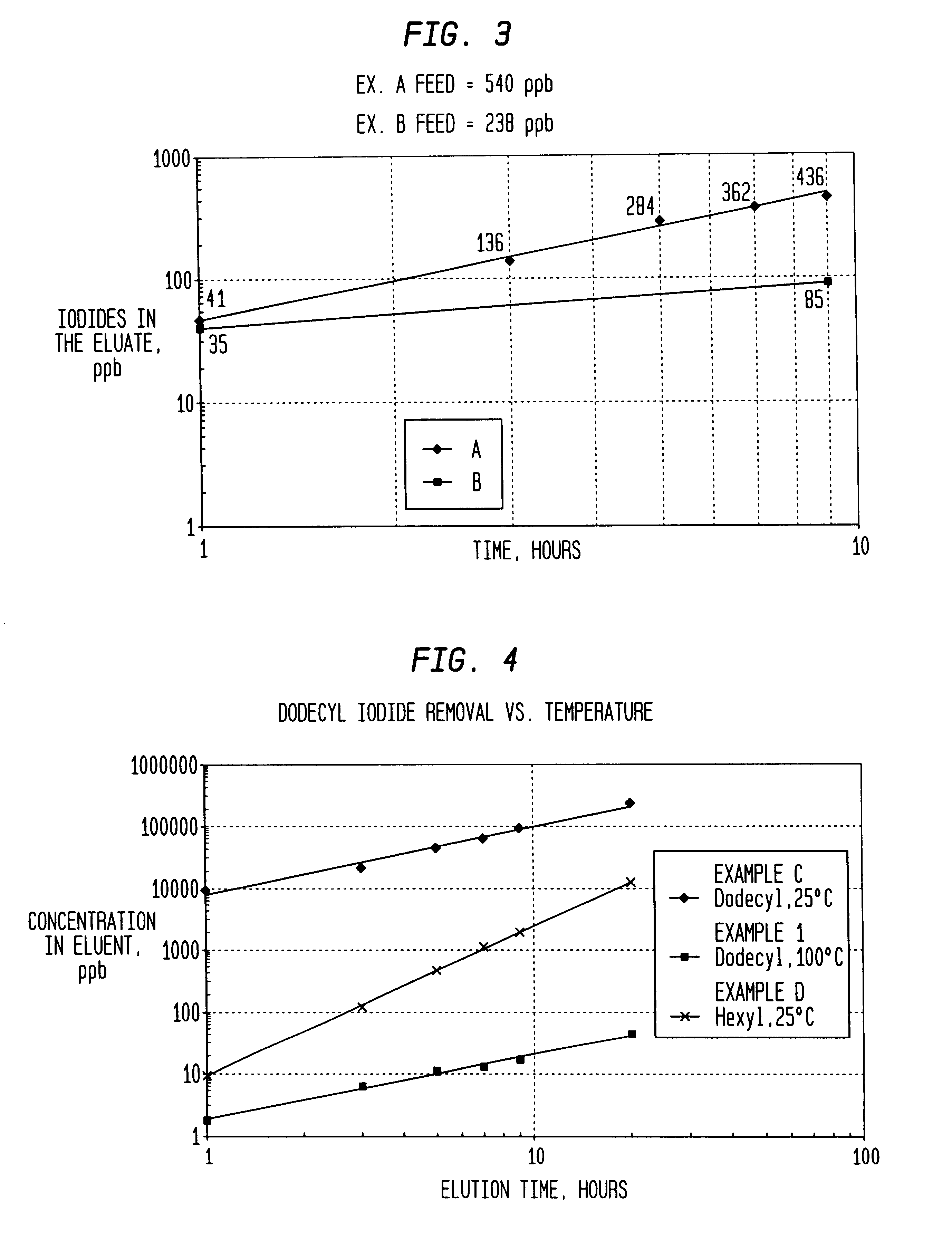

Low energy carbonylation process

InactiveUS6657078B2Weaken energyHigh purityOrganic compound preparationOrganic chemistry methodsPropanoic acidIodide

A low energy process for producing acetic acid by the carbonylation of methanol is disclosed. The process involves a rhodium-catalyzed system operated at less than about 14% water utilizing up to 2 distillation columns. The process is preferably controlled such that the product stream has a low level of propionic acid impurity and the level of aldehyde impurities is minimized by way of aldehyde removal or minimizing aldehyde generation. The level of iodides is controlled by contacting the product, at elevated temperatures, with ion exchange resins. In preferred embodiments, at least one silver or mercury exchanged macroreticular strong acid ion exchange resin is used to purify the product. The high temperature treatment provides the added benefit of controlling the Color Value (Pt-Co units) of the product stream.

Owner:CELANESE INT CORP

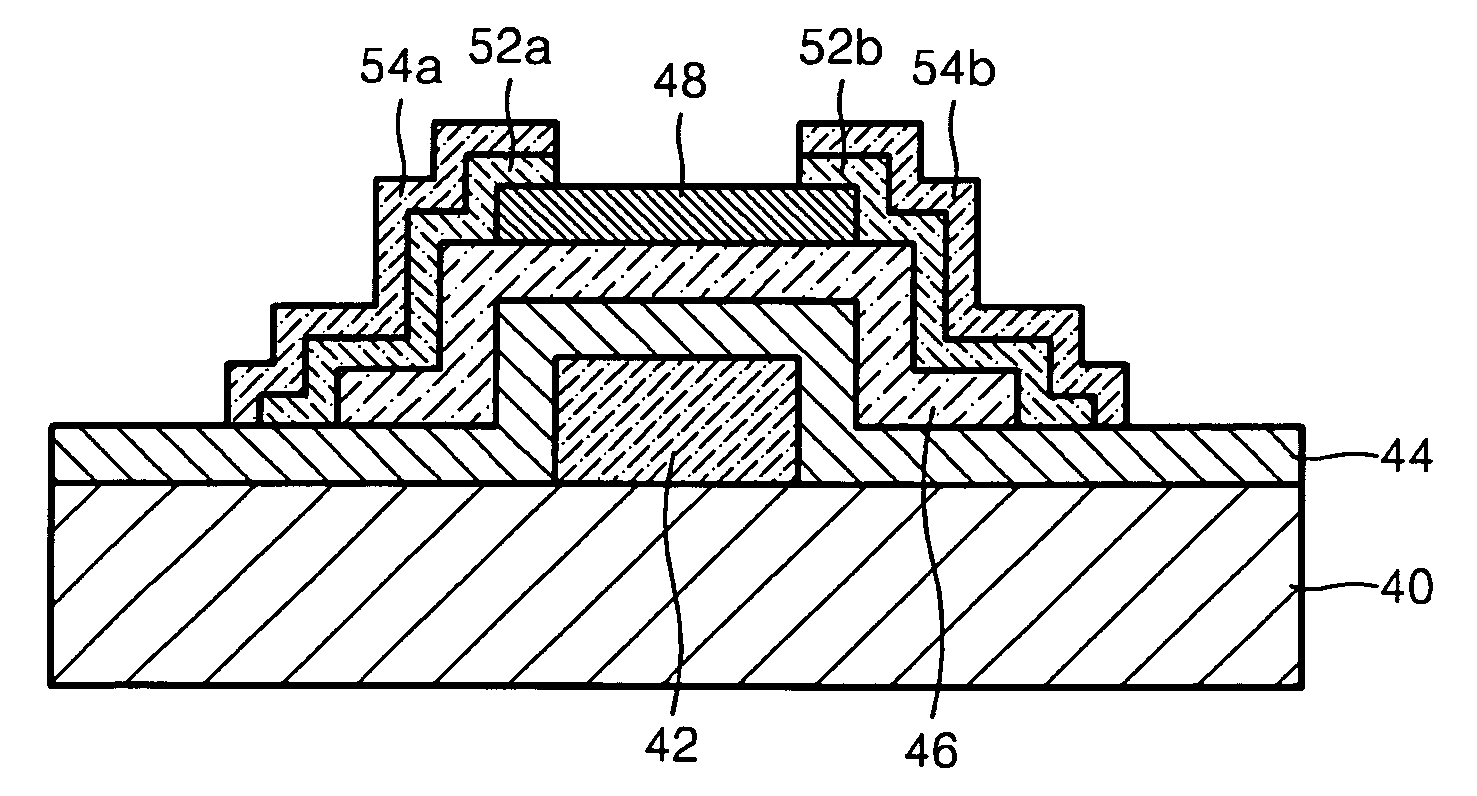

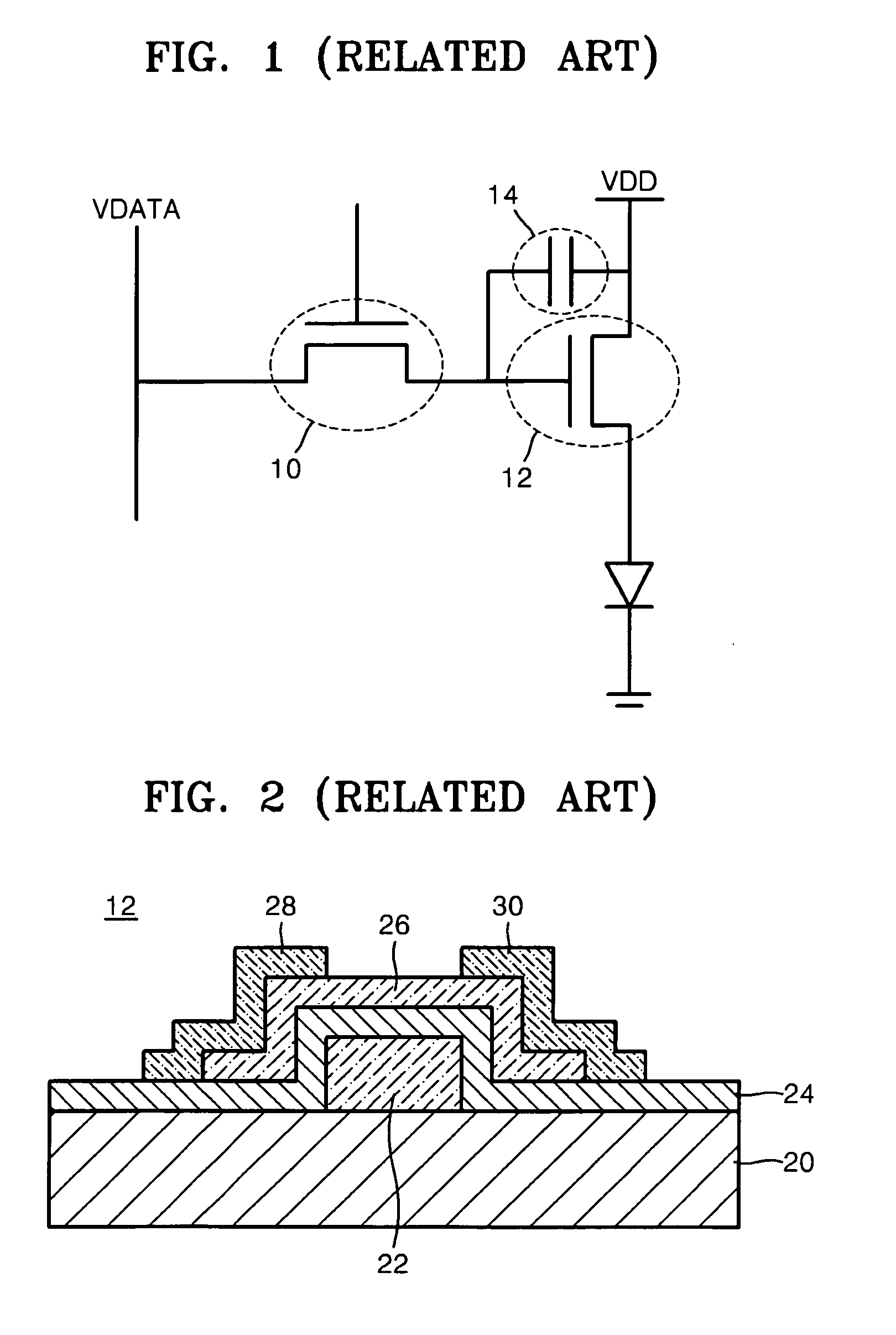

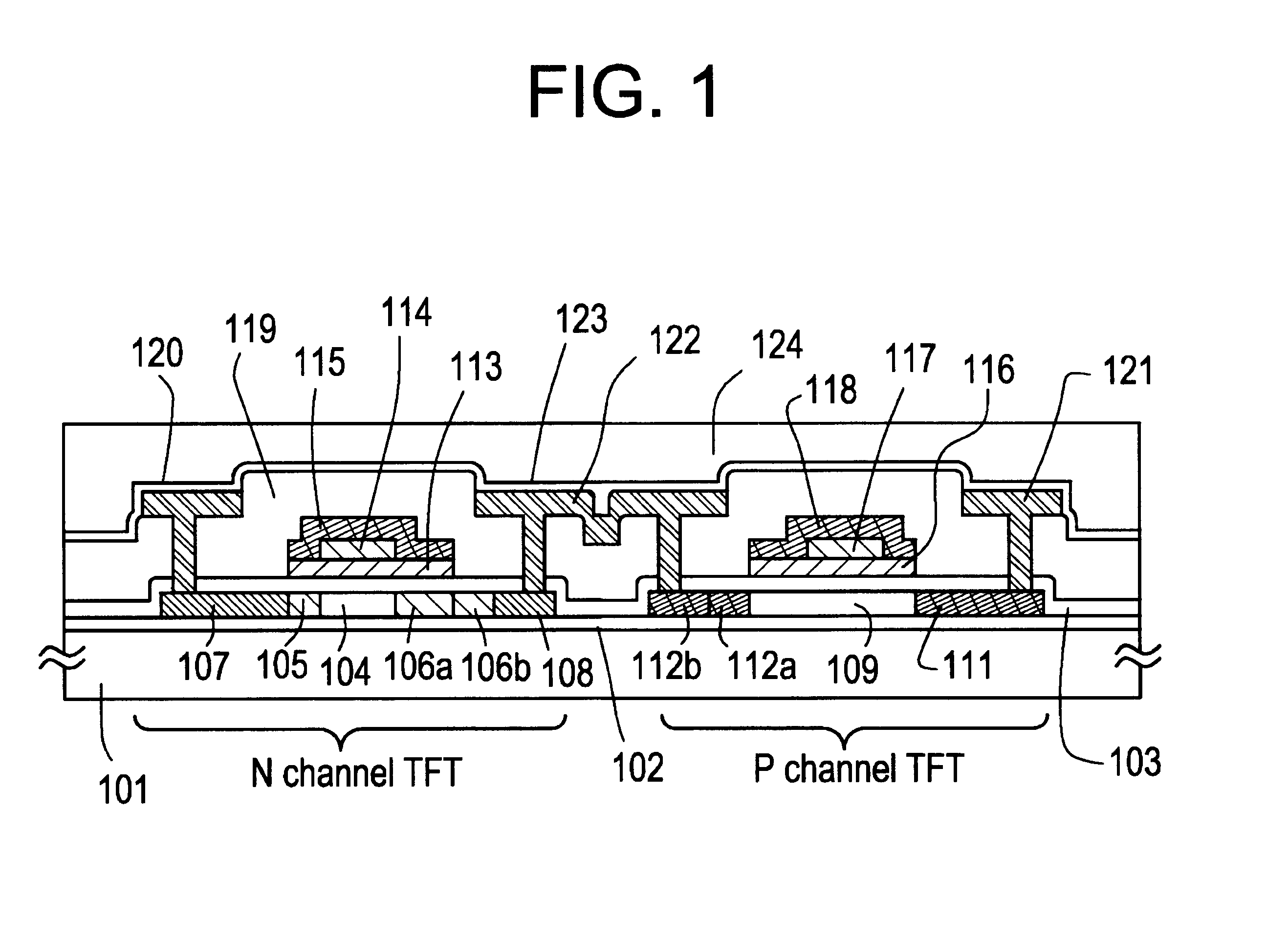

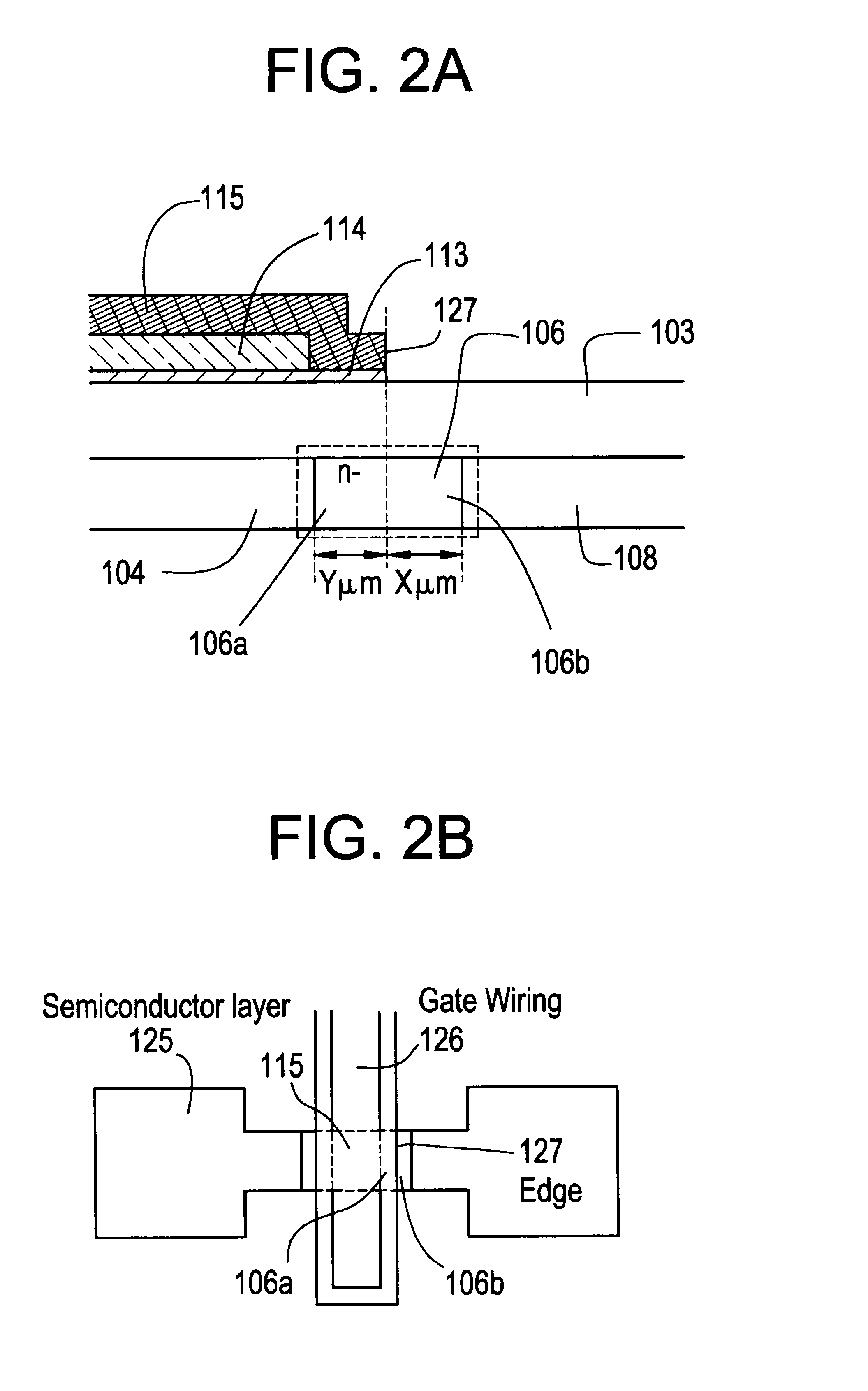

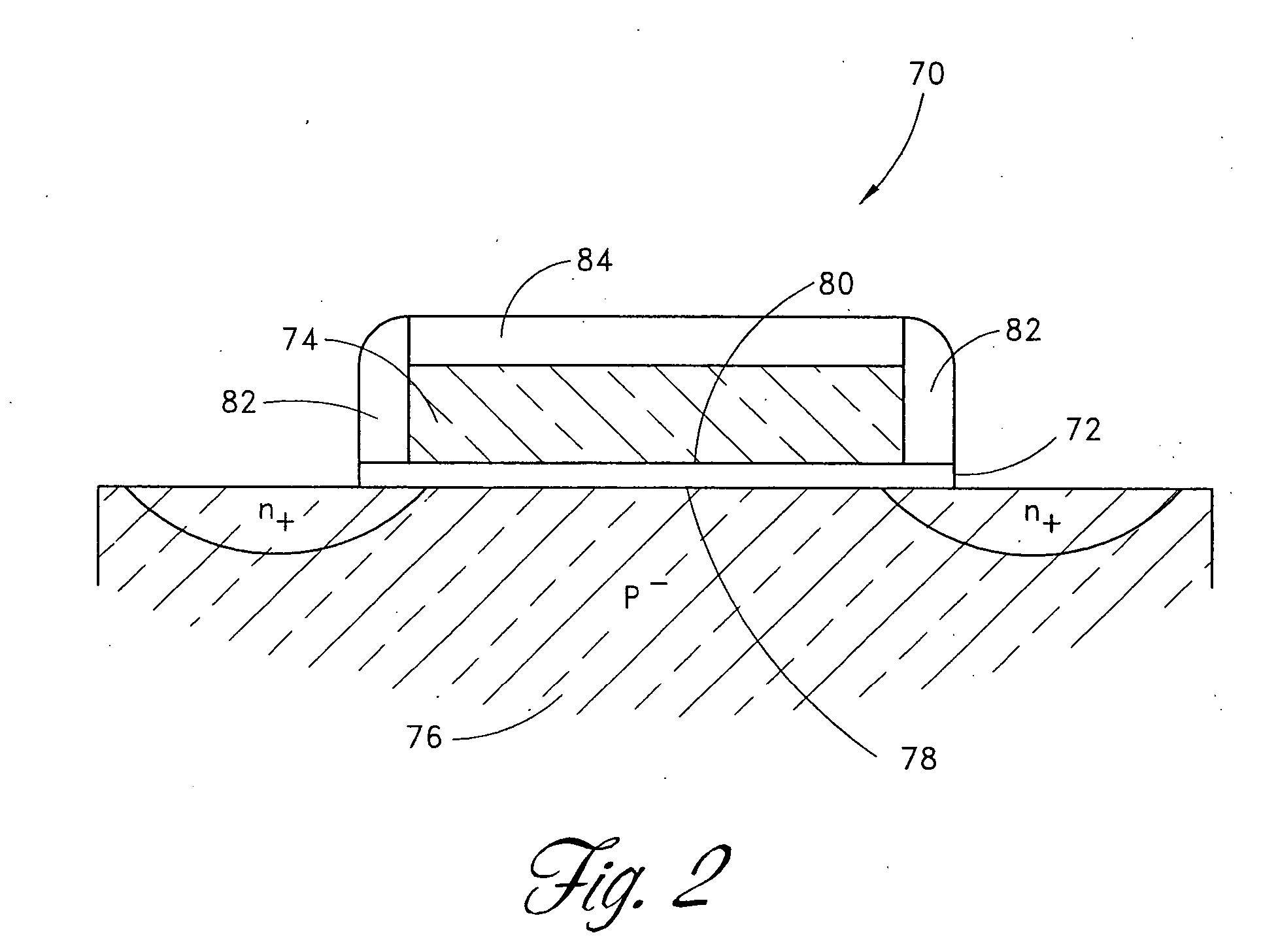

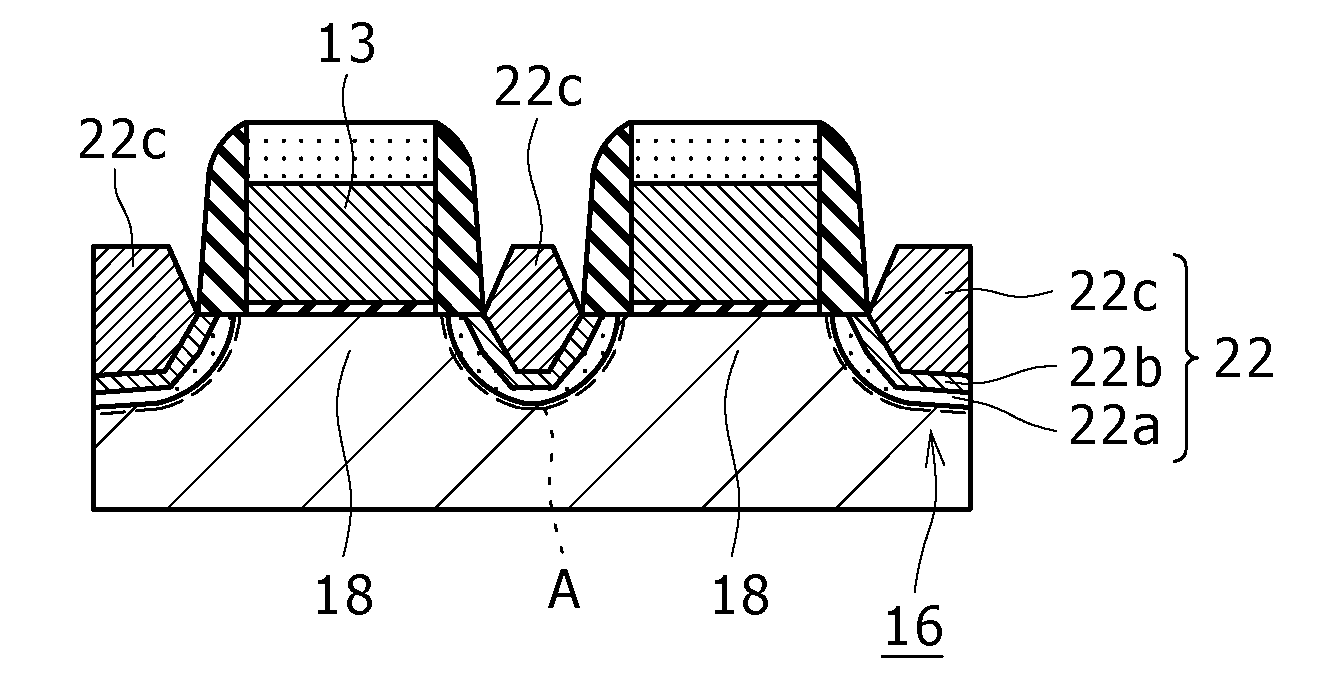

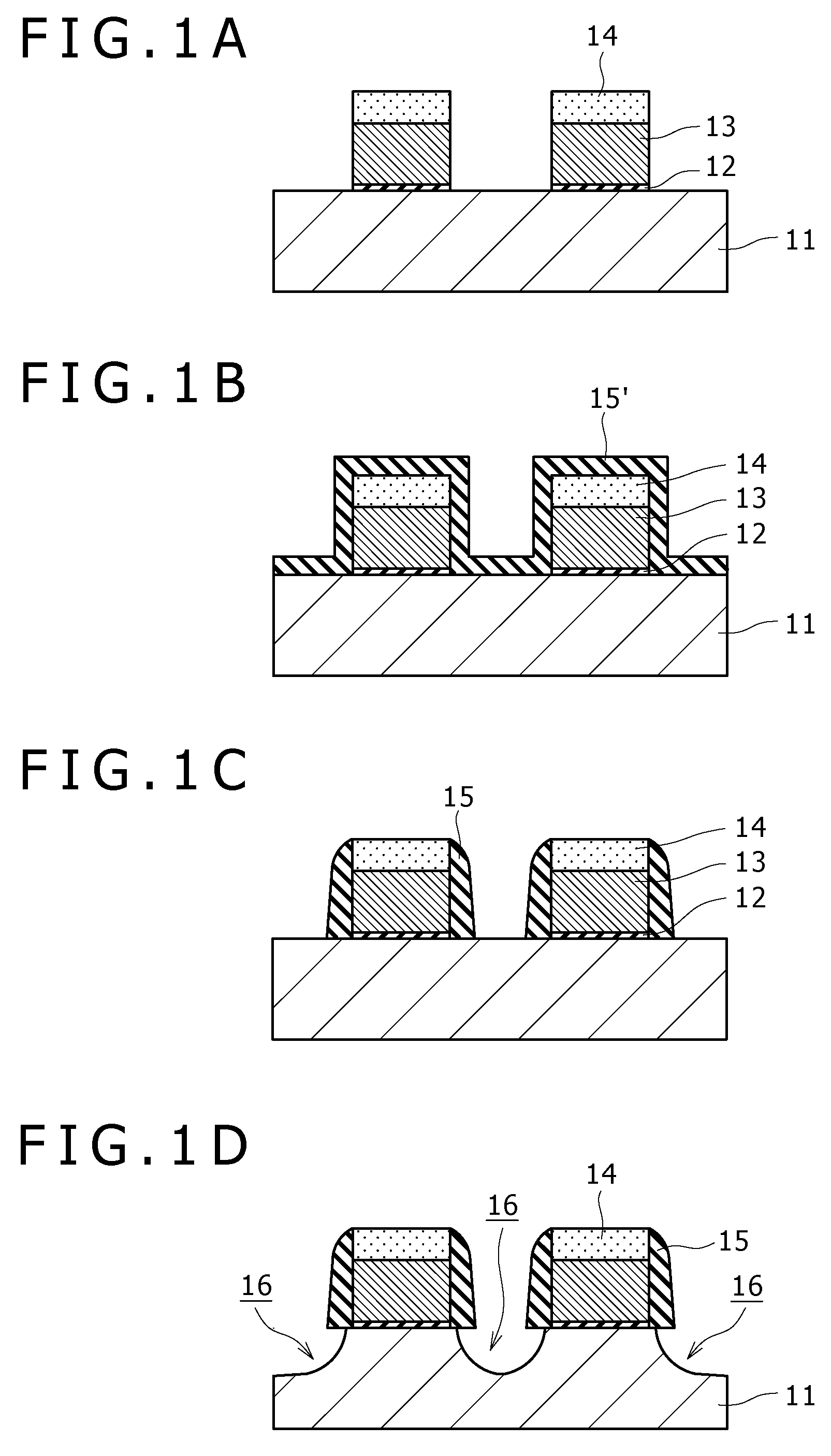

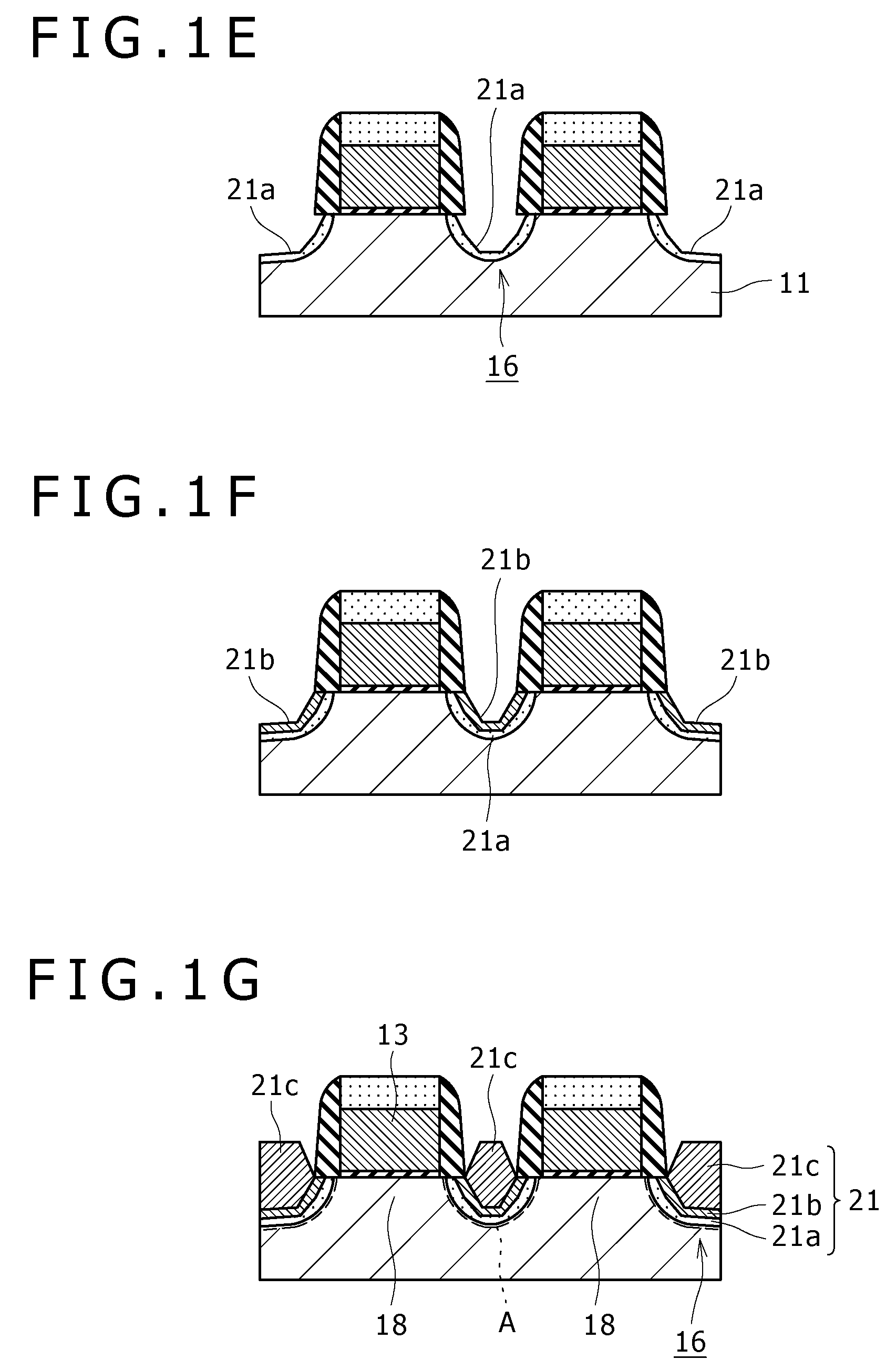

Semiconductor device

The gate electrode of a crystalline TFT is constructed as a clad structure which consists of a first gate electrode, a second gate electrode and a third gate electrode, thereby to enhance the thermal resistance of the gate electrode. Besides, an n-channel TFT is provided with a low-concentration impurity region which adjoins a channel forming region, and which includes a subregion overlapped by the gate electrode and a subregion not overlapped by the gate electrode, thereby to mitigate a high electric field near the drain of the TFT and to simultaneously prevent the OFF current of the TFT from increasing.

Owner:SEMICON ENERGY LAB CO LTD

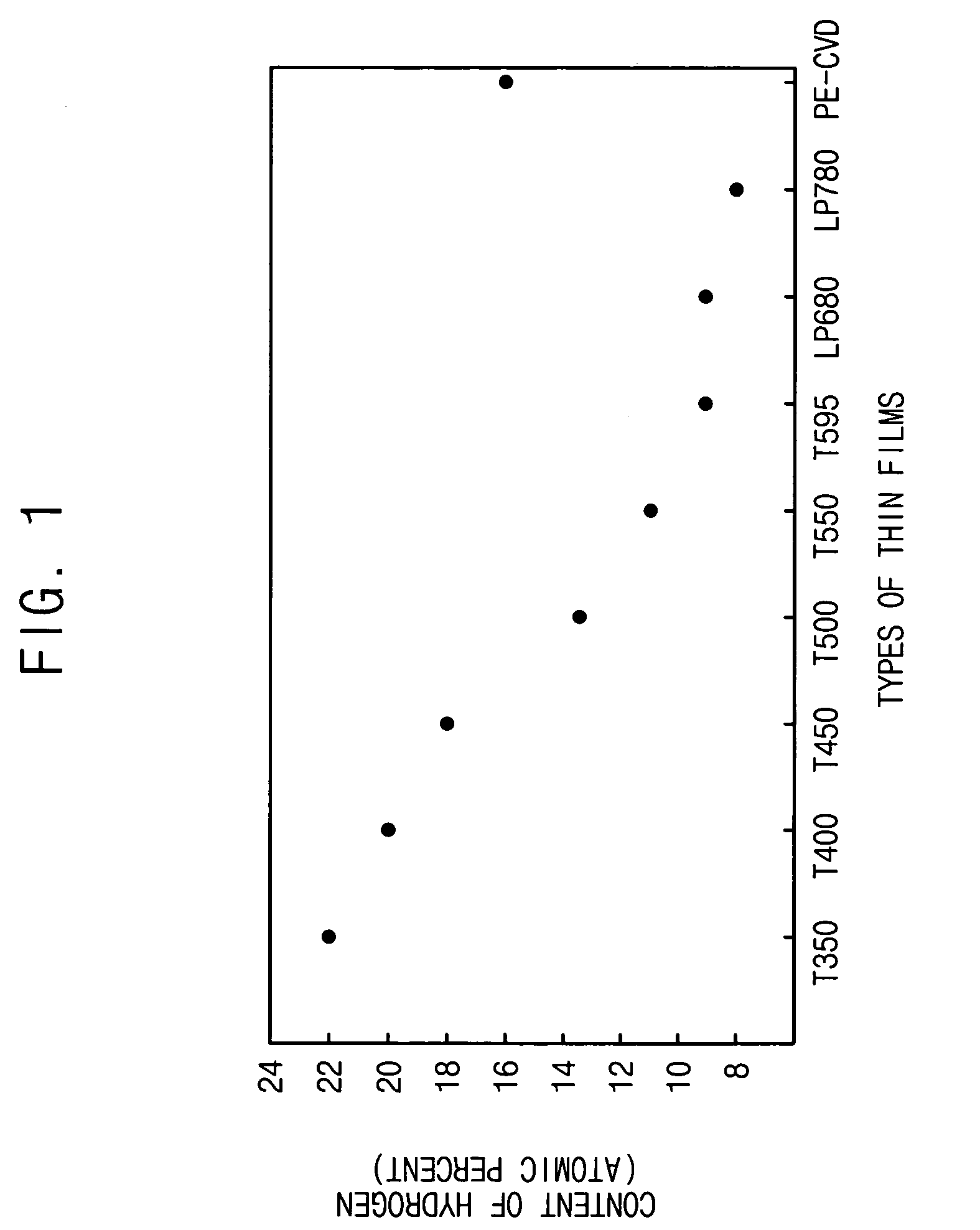

Thin films

InactiveUS20050181555A1Quality improvementHigh dielectric constantSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricSilicon oxide

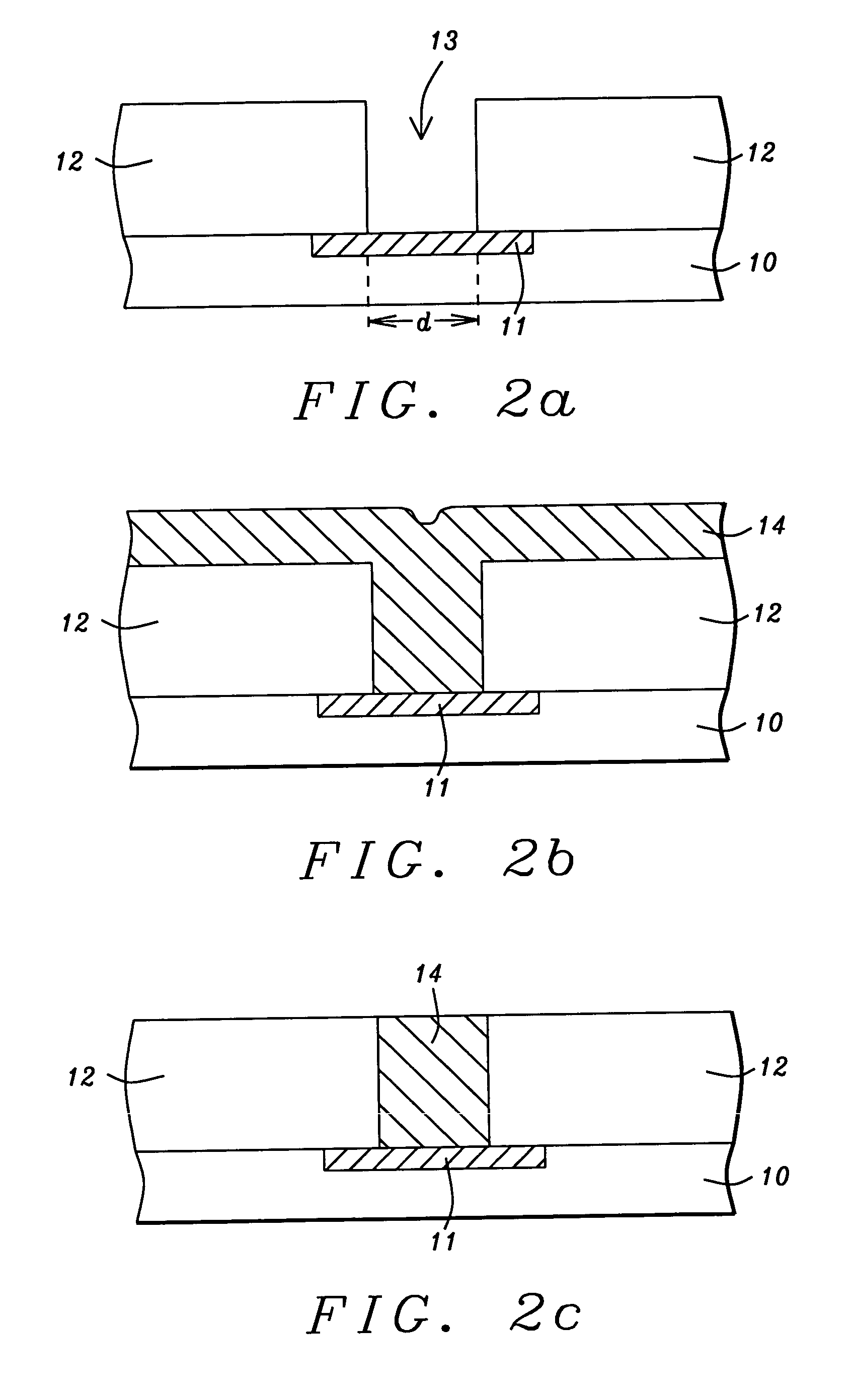

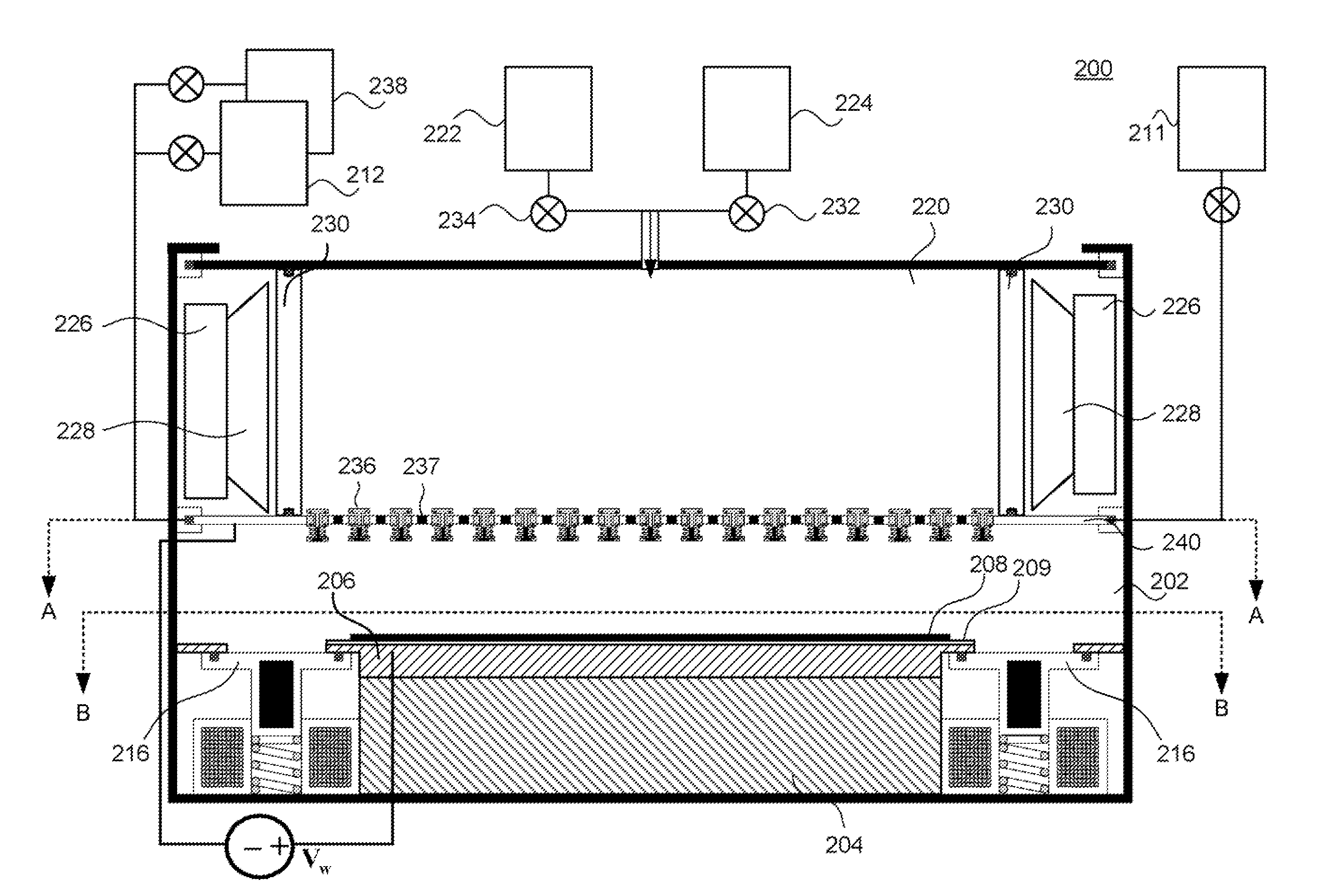

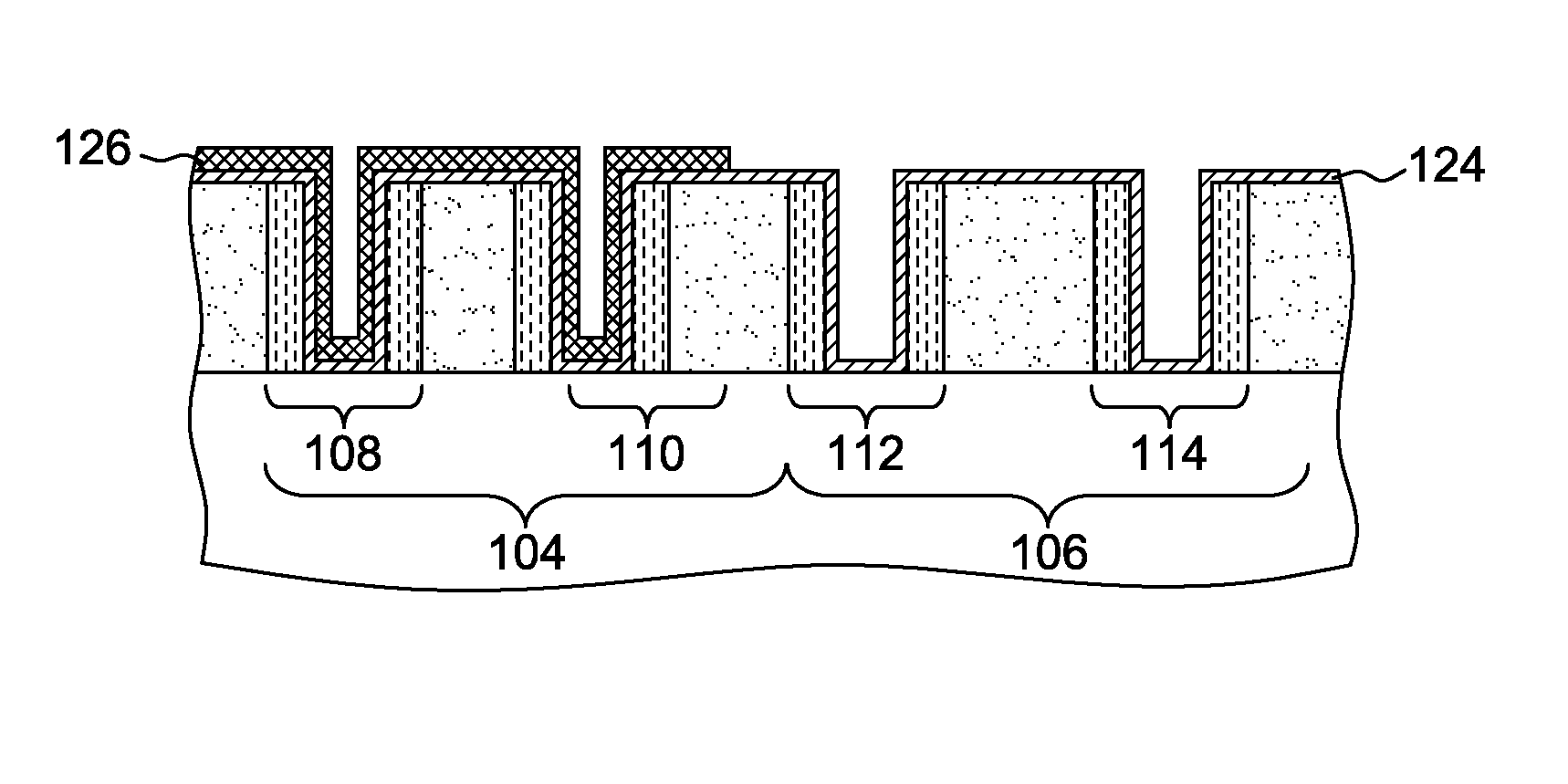

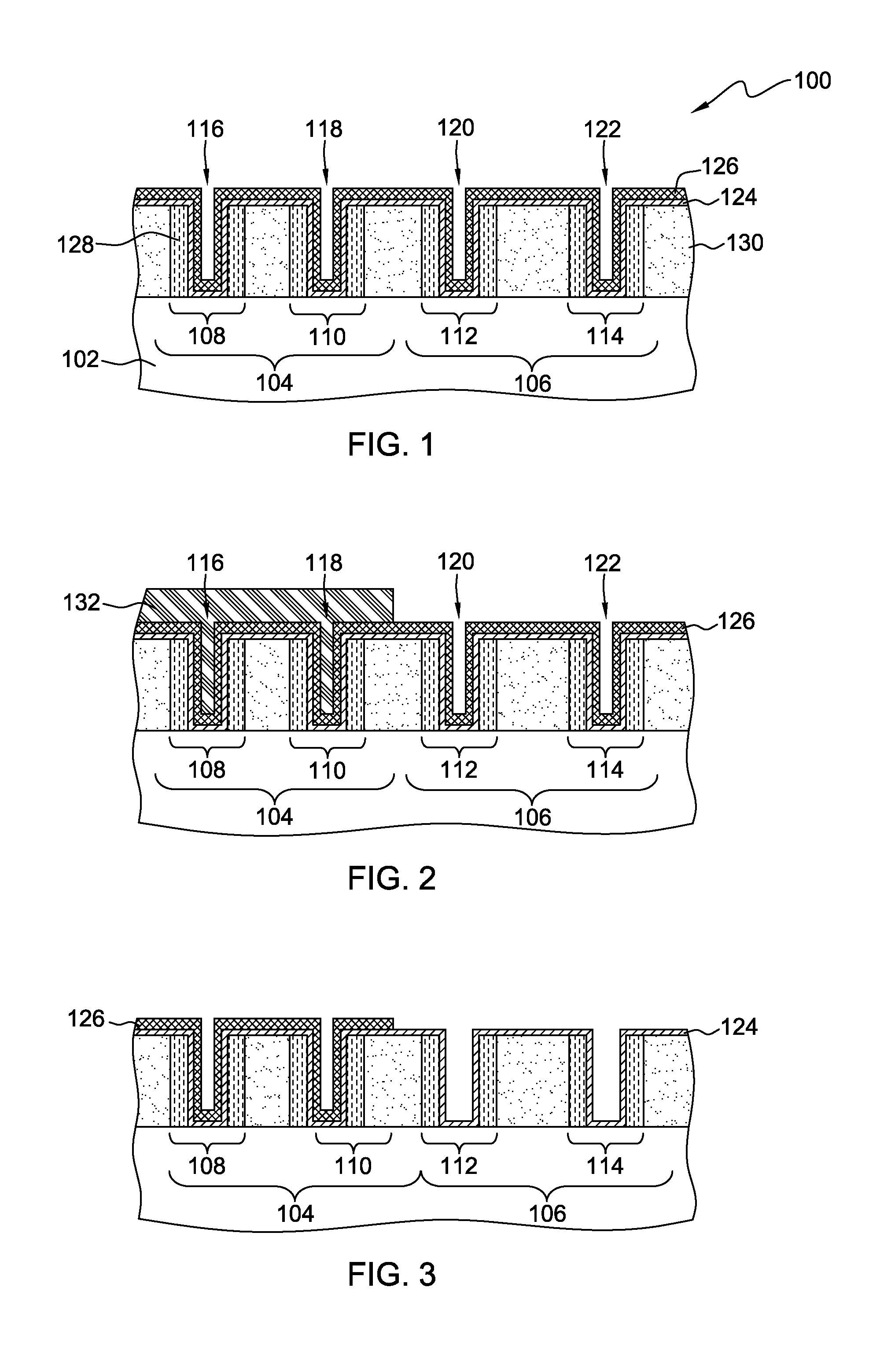

Thin films are formed by formed by atomic layer deposition, whereby the composition of the film can be varied from monolayer to monolayer during cycles including alternating pulses of self-limiting chemistries. In the illustrated embodiments, varying amounts of impurity sources are introduced during the cyclical process. A graded gate dielectric is thereby provided, even for extremely thin layers. The gate dielectric as thin as 2 nm can be varied from pure silicon oxide to oxynitride to silicon nitride. Similarly, the gate dielectric can be varied from aluminum oxide to mixtures of aluminum oxide and a higher dielectric material (e.g., ZrO2) to pure high k material and back to aluminum oxide. In another embodiment, metal nitride (e.g., WN) is first formed as a barrier for lining dual damascene trenches and vias. During the alternating deposition process, copper can be introduced, e.g., in separate pulses, and the copper source pulses can gradually increase in frequency, forming a transition region, until pure copper is formed at the upper surface. Advantageously, graded compositions in these and a variety of other contexts help to avoid such problems as etch rate control, electromigration and non-ohmic electrical contact that can occur at sharp material interfaces. In some embodiments additional seed layers or additional transition layers are provided.

Owner:ASM INTERNATIONAL

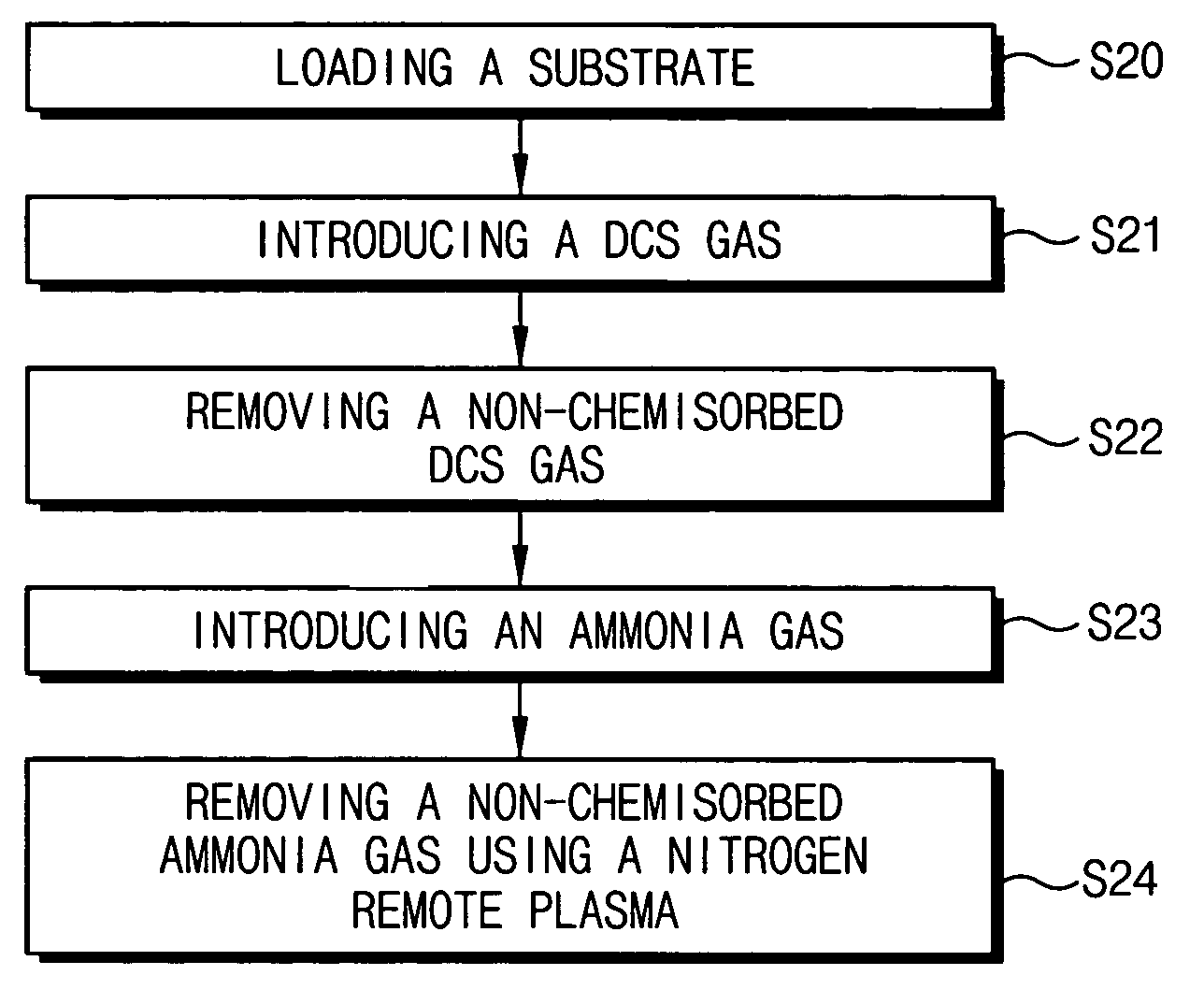

Method of forming a layer and forming a capacitor of a semiconductor device having the same layer

InactiveUS20060014384A1Low hydrogen contentReduce leakage currentSemiconductor/solid-state device manufacturingCapacitorsChemical reactionDevice material

In a method of forming a layer using an atomic layer deposition process, after a substrate is loaded into a chamber, a first reactant is provided onto the substrate. The first reactant is partially chemisorbed on the substrate. A second reactant is introduced into the chamber to form a preliminary layer on the substrate by chemically reacting the second reactant with the chemisorbed first reactant. Impurities in the preliminary layer and unreacted reactants are simultaneously removed using a plasma for removing impurities to thereby form the layer on the substrate. The impurities in the layer may be effectively removed so that the layer may have reduced leakage current.

Owner:SAMSUNG ELECTRONICS CO LTD

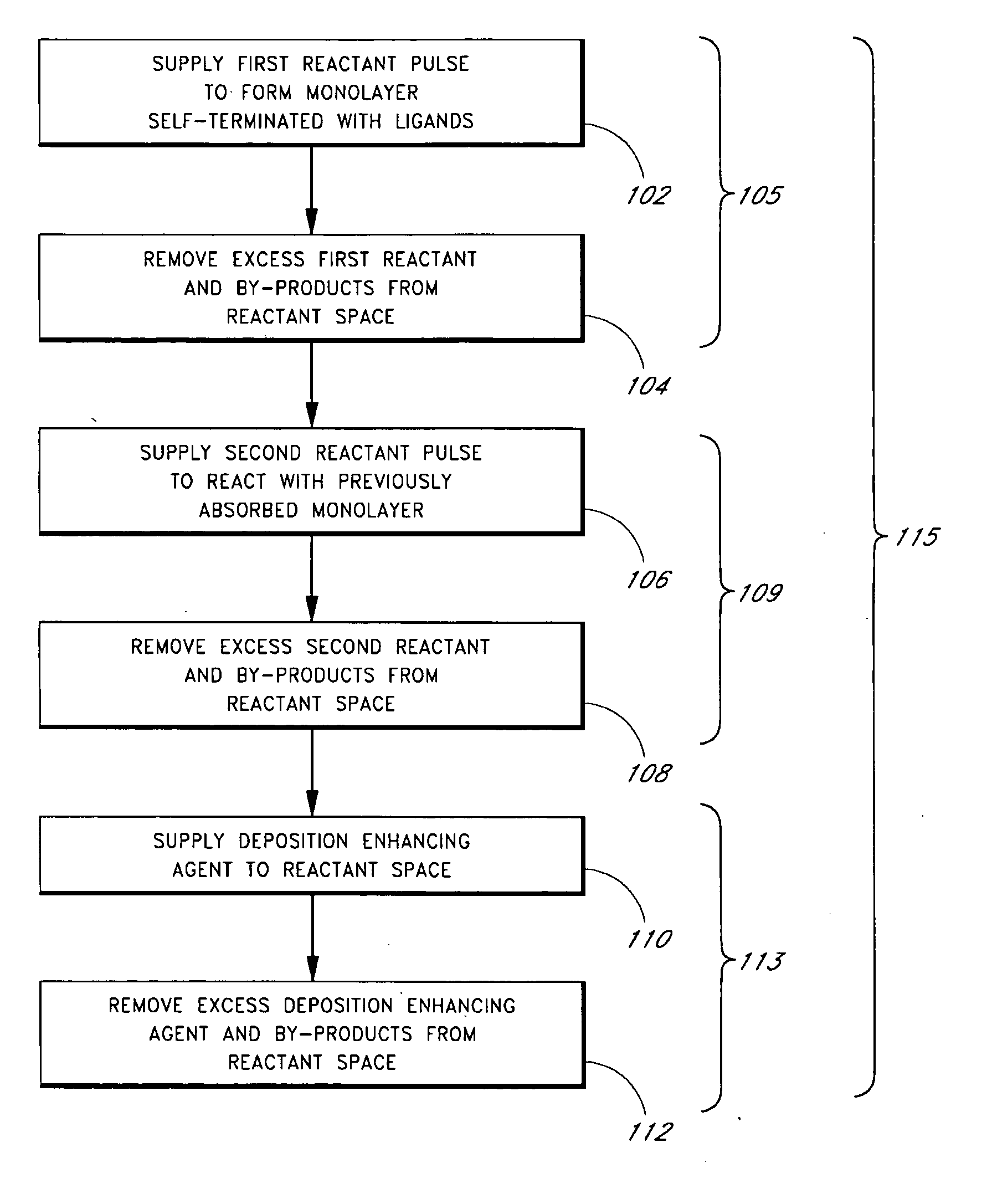

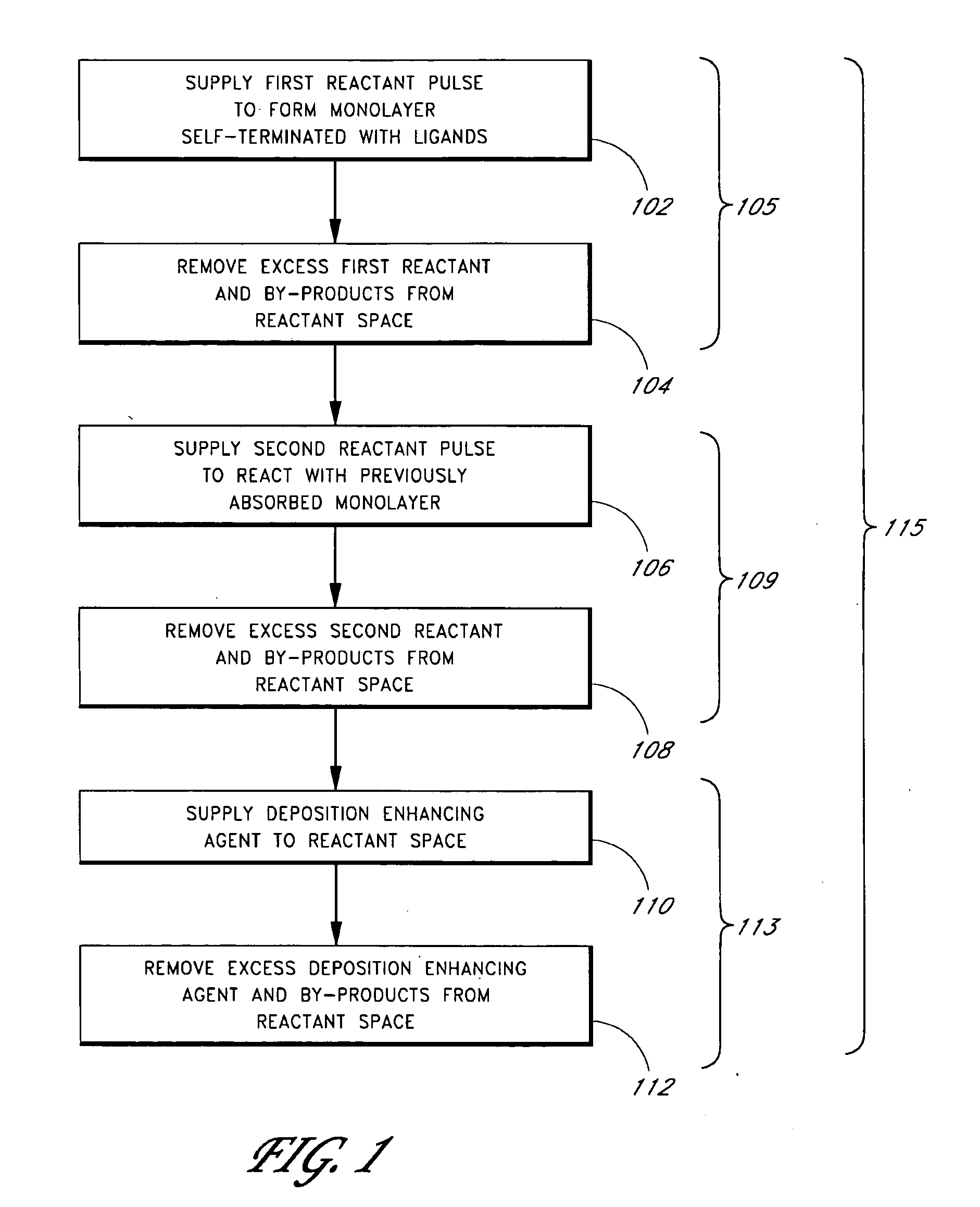

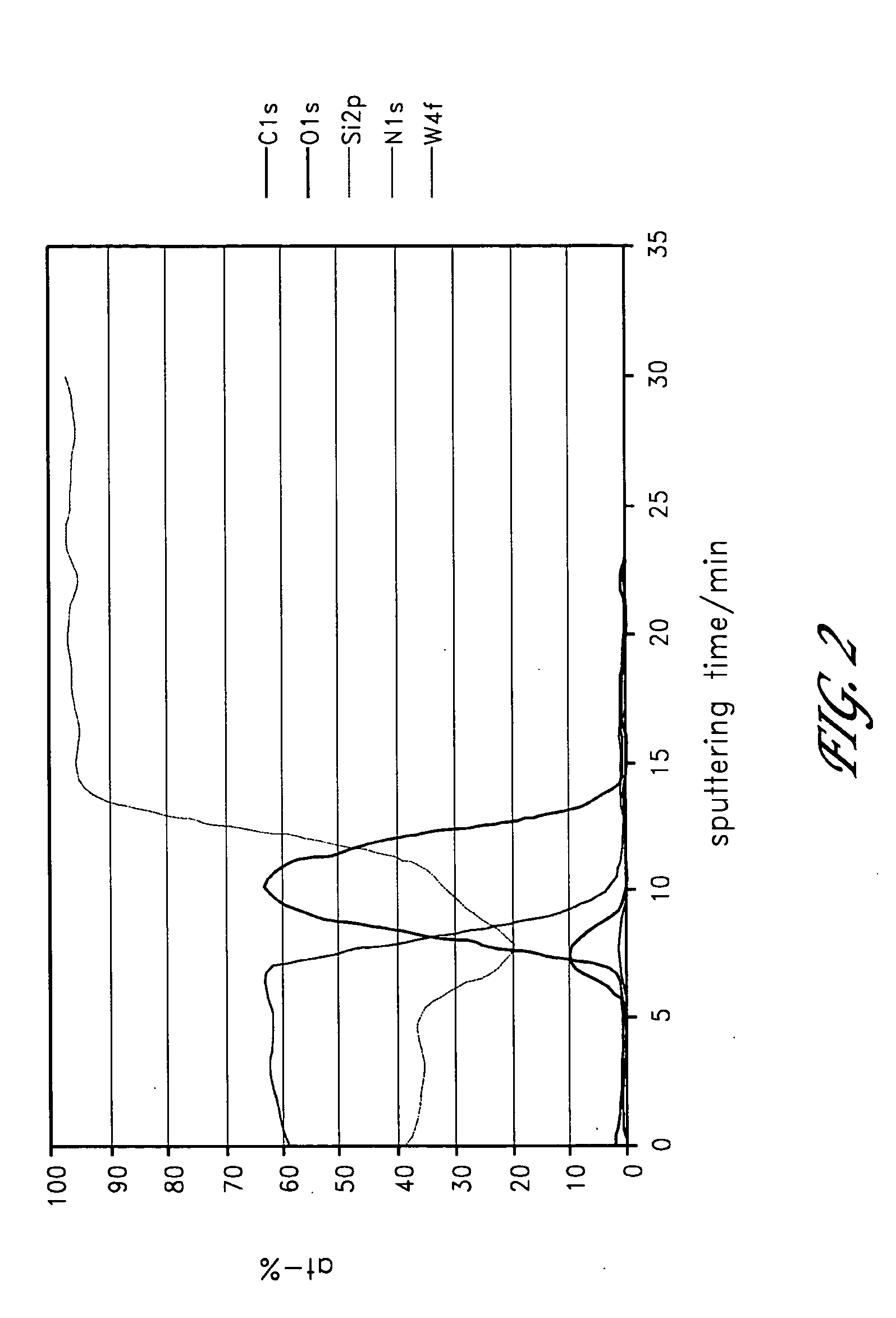

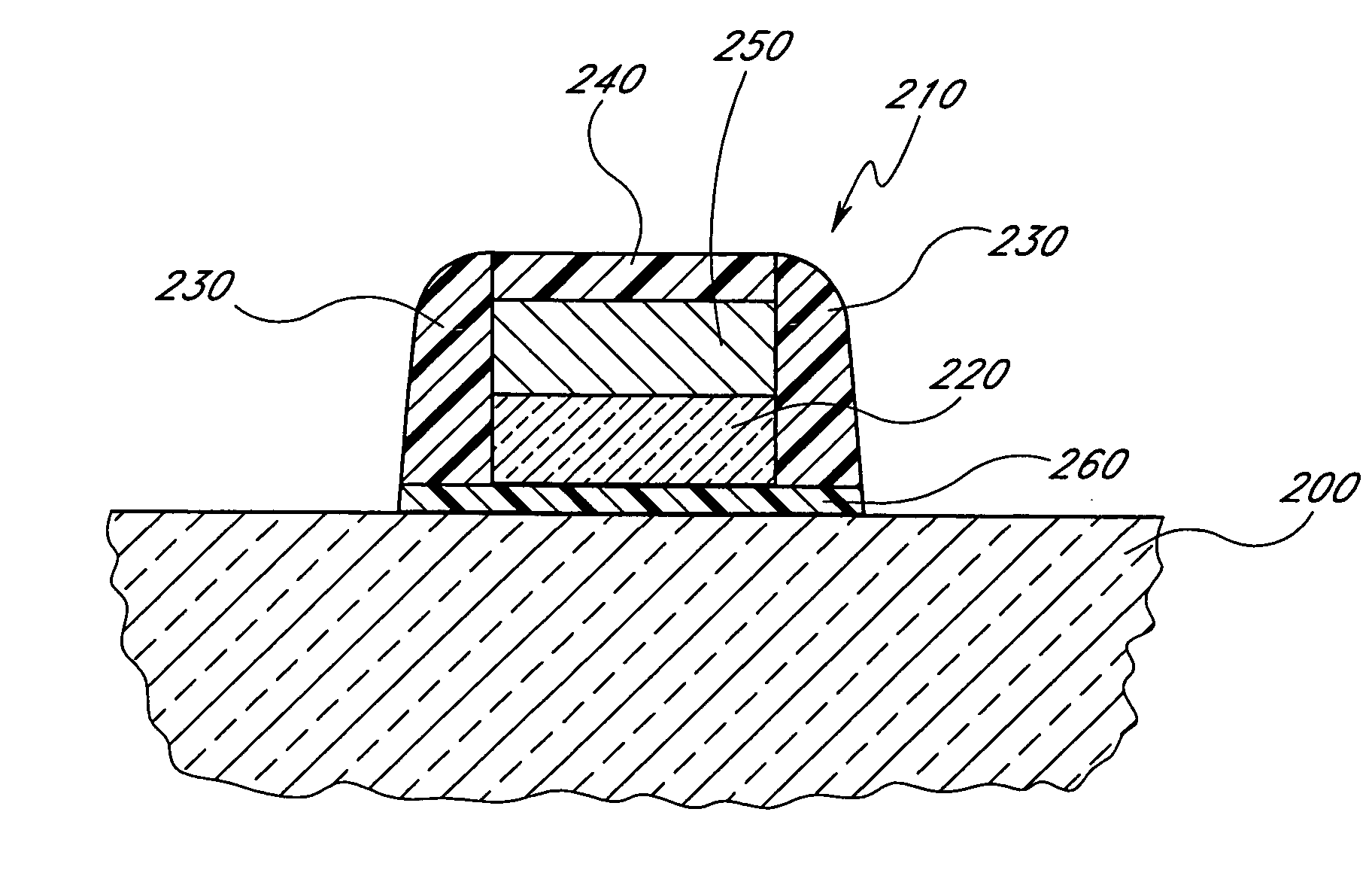

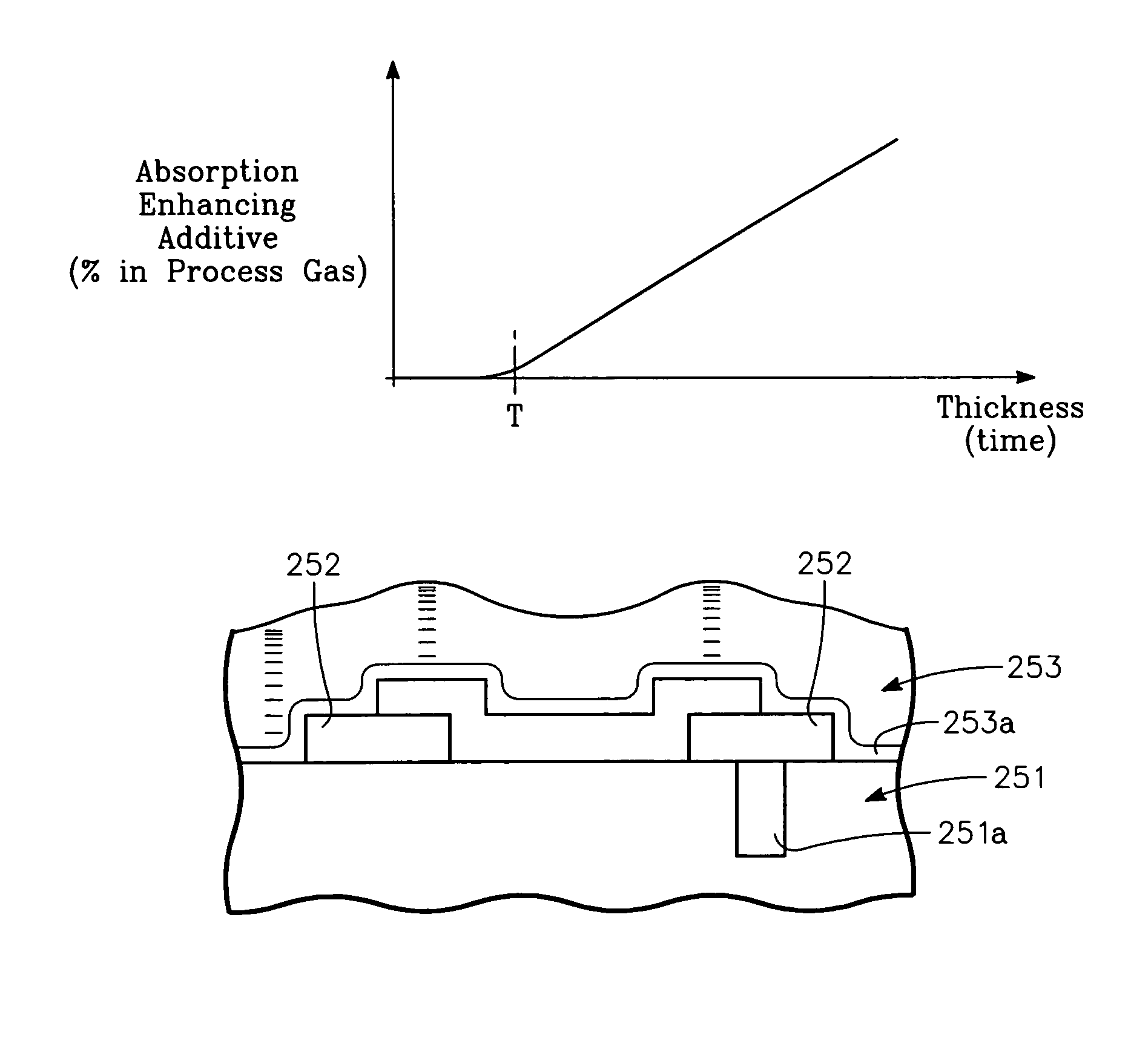

Enhanced thin film deposition

ActiveUS20070148350A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingSilanesNitrogen

Methods of producing metal-containing thin films with low impurity contents on a substrate by atomic layer deposition (ALD) are provided. The methods preferably comprise contacting a substrate with alternating and sequential pulses of a metal source chemical, a second source chemical and a deposition enhancing agent. The deposition enhancing agent is preferably selected from the group consisting of hydrocarbons, hydrogen, hydrogen plasma, hydrogen radicals, silanes, germanium compounds, nitrogen compounds, and boron compounds. In some embodiments, the deposition-enhancing agent reacts with halide contaminants in the growing thin film, improving film properties.

Owner:ASM INTERNATIONAL

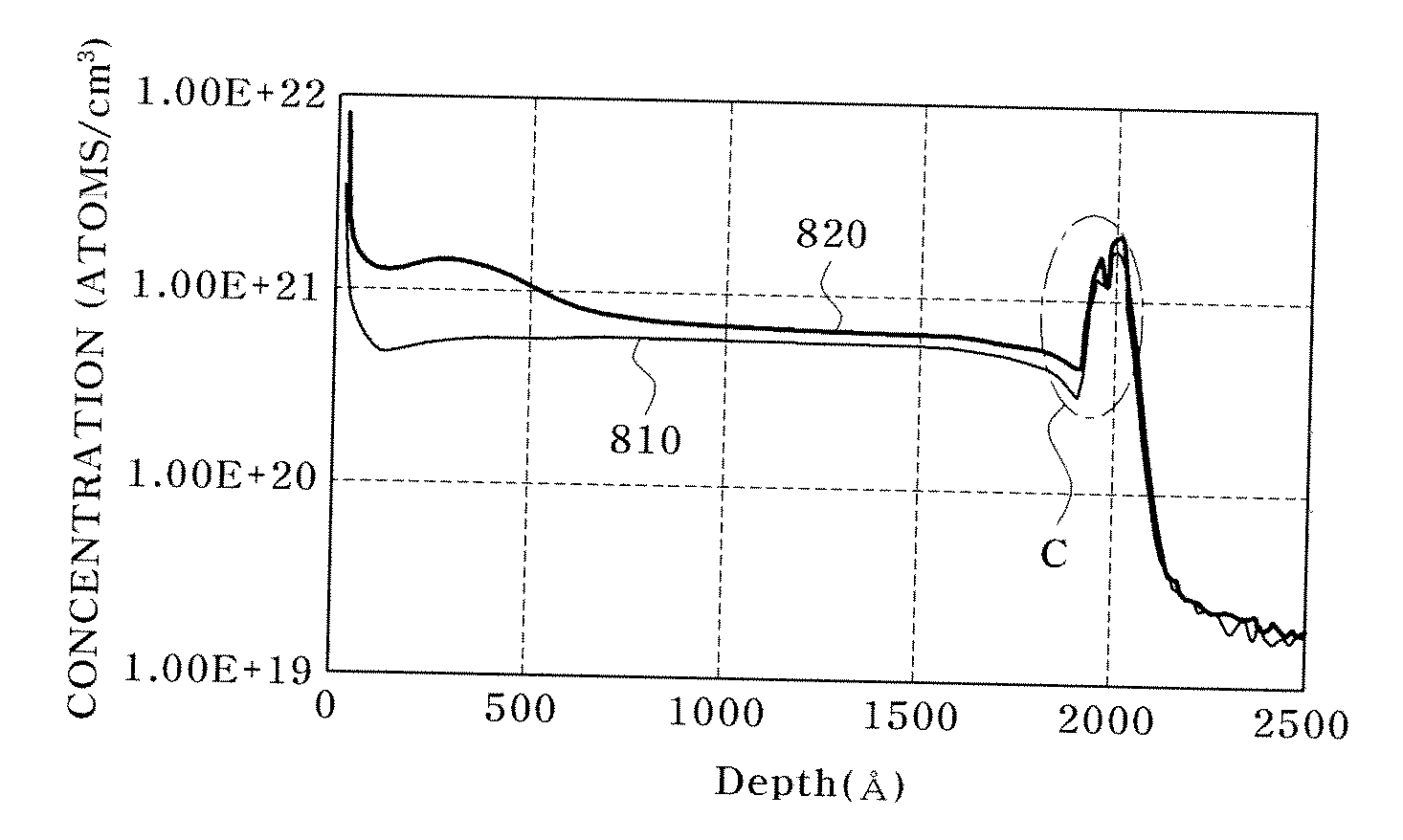

Incorporation of nitrogen into high k dielectric film

InactiveUS20050212119A1Semiconductor/solid-state device detailsSolid-state devicesDielectricCyclic process

A high k dielectric film and methods for forming the same are disclosed. The high k material includes two peaks of impurity concentration, particularly nitrogen, such as at a lower interface and upper interface, making the layer particularly suitable for transistor gate dielectric applications. The methods of formation include low temperature processes, particularly CVD using a remote plasma generator and atomic layer deposition using selective incorporation of nitrogen in the cyclic process. Advantageously, nitrogen levels are tailored during the deposition process and temperatures are low enough to avoid interdiffusion and allow maintenance of the desired impurity profile.

Owner:ASM IP HLDG BV

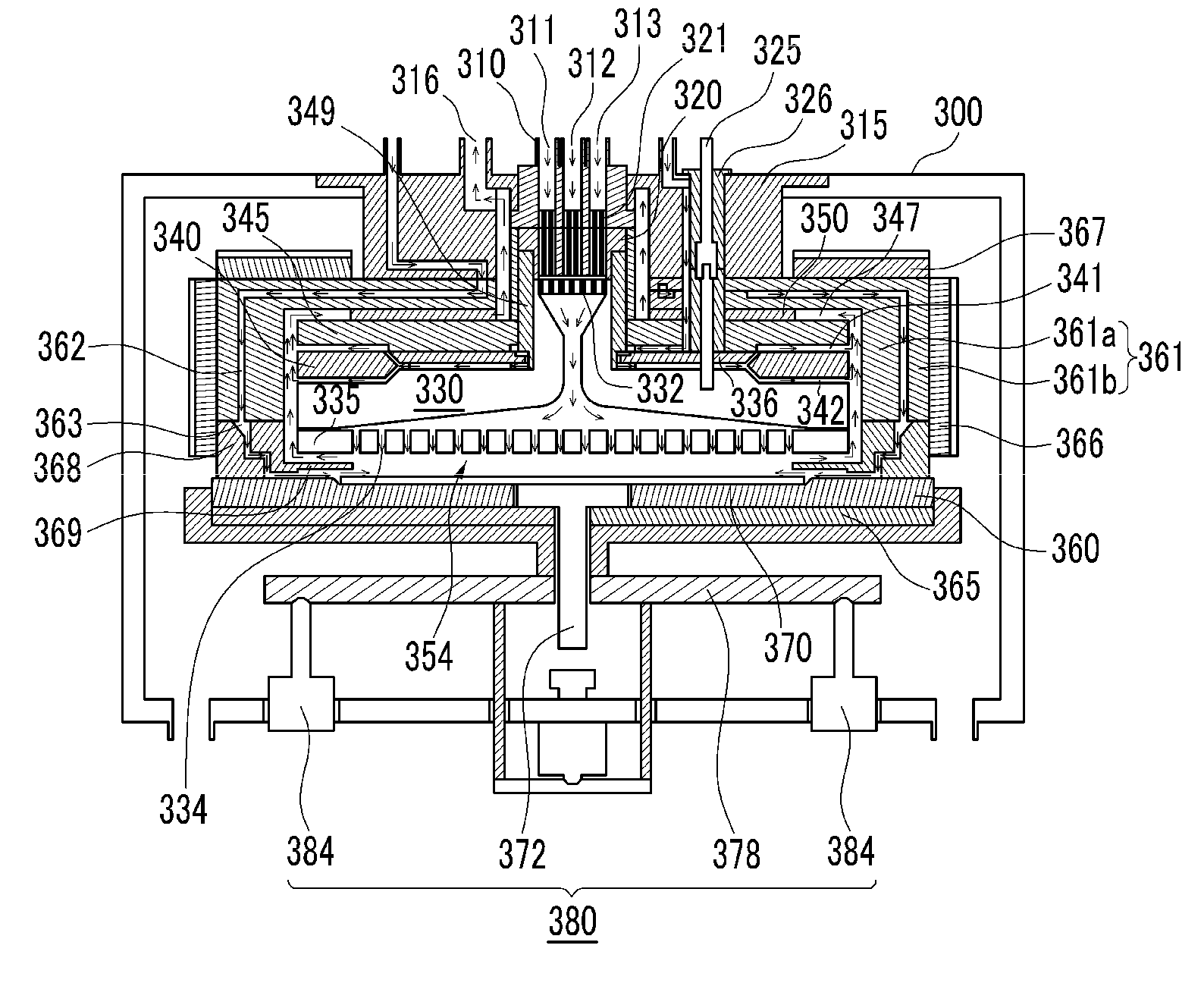

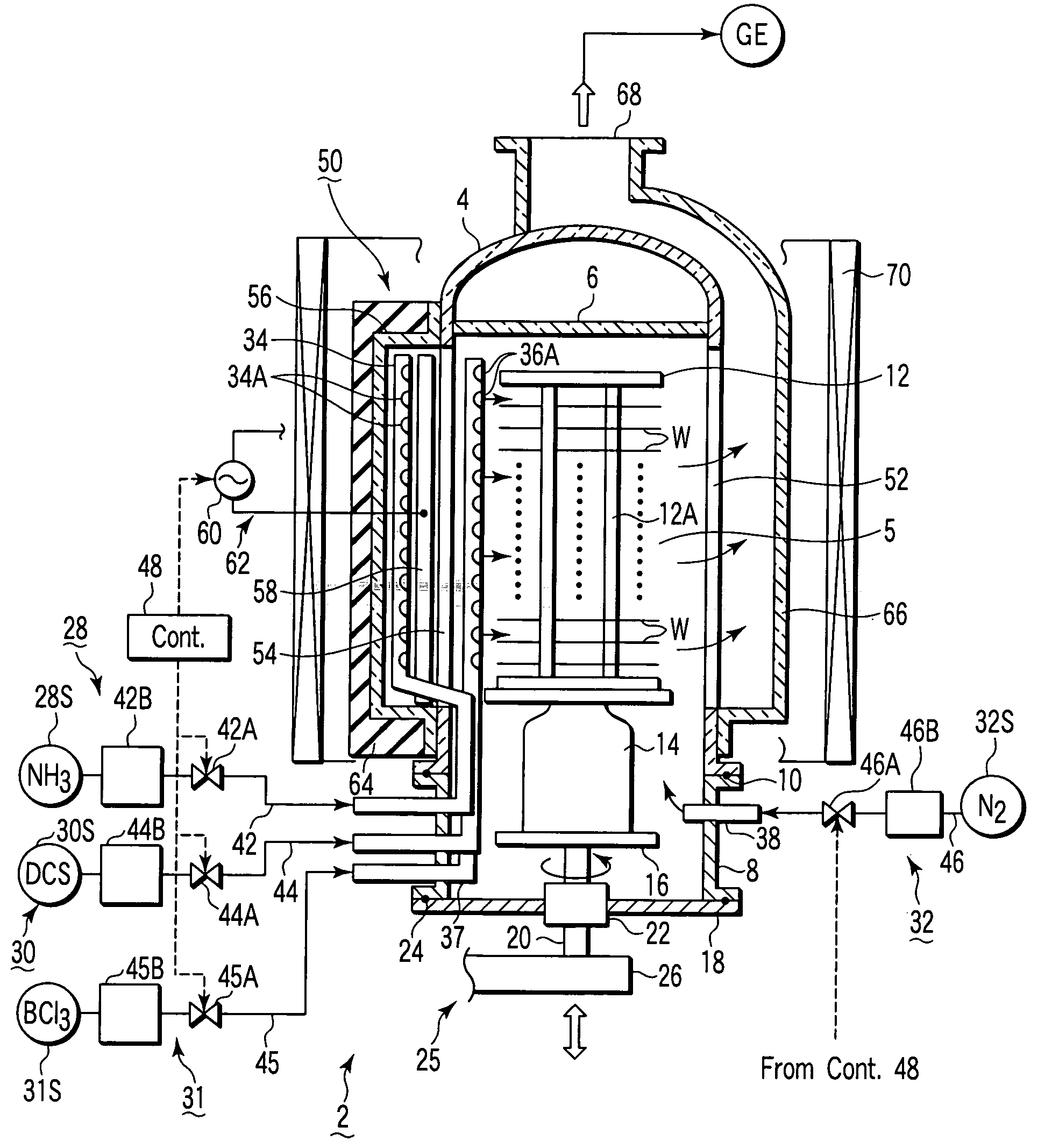

Deposition apparatus

ActiveUS20090156015A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingProduct gasEngineering

A deposition apparatus configured to form a thin film on a substrate includes: a reactor wall; a substrate support positioned under the reactor wall; and a showerhead plate positioned above the substrate support. The showerhead plate defines a reaction space together with the substrate support. The apparatus also includes one or more gas conduits configured to open to a periphery of the reaction space at least while an inert gas is supplied therethrough. The one or more gas conduits are configured to supply the inert gas inwardly toward the periphery of the substrate support around the reaction space. This configuration prevents reactant gases from flowing between a substrate and the substrate support during a deposition process, thereby preventing deposition of an undesired thin film and impurity particles on the back side of the substrate.

Owner:ASM KOREA LTD

Chamber material made of Al alloy and heater block

InactiveUS20010019777A1Not be restrictElectric discharge tubesSemiconductor/solid-state device manufacturingHigh-temperature corrosionContamination

A chamber material made of Al alloy excellent in thermal cracking resistance and chemical and / or physical corrosion resistance and capable of reducing contamination excellently and further having excellent and wide applicable brazing property in a high temperature corrosive circumstance, in which the substrate aluminum material for the chamber material made of Al alloy having an anodized film comprises 0.1 to 2.0% Si, 0.1 to 3.5% Mg, 0.02 to 4.0% Cu on the mass % basis and the balance of Al and impurity element with Cr in the impurity elements being less than 0.04%. Preferably, Fe is 0.1% or less and Mn is 0.04% or less in the impurity element and, further, the total sum of impurity elements other than Cr and Mn being restricted to 0.1$ or less. This invention can be utilized suitably to various materials used in high temperature corrosive circumstance, particularly, in high temperature corrosive gas or plasma atmosphere.

Owner:KOBE STEEL LTD

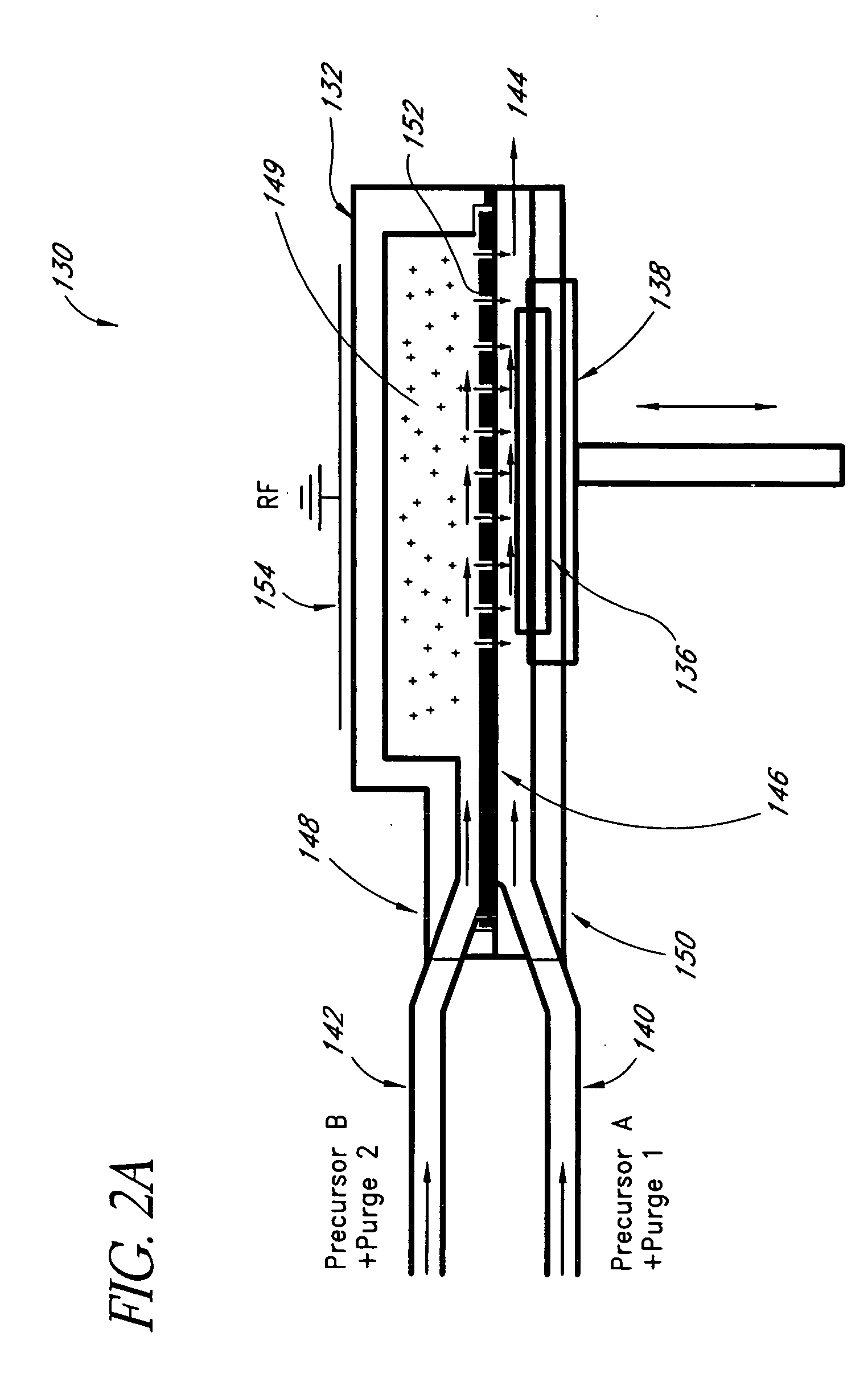

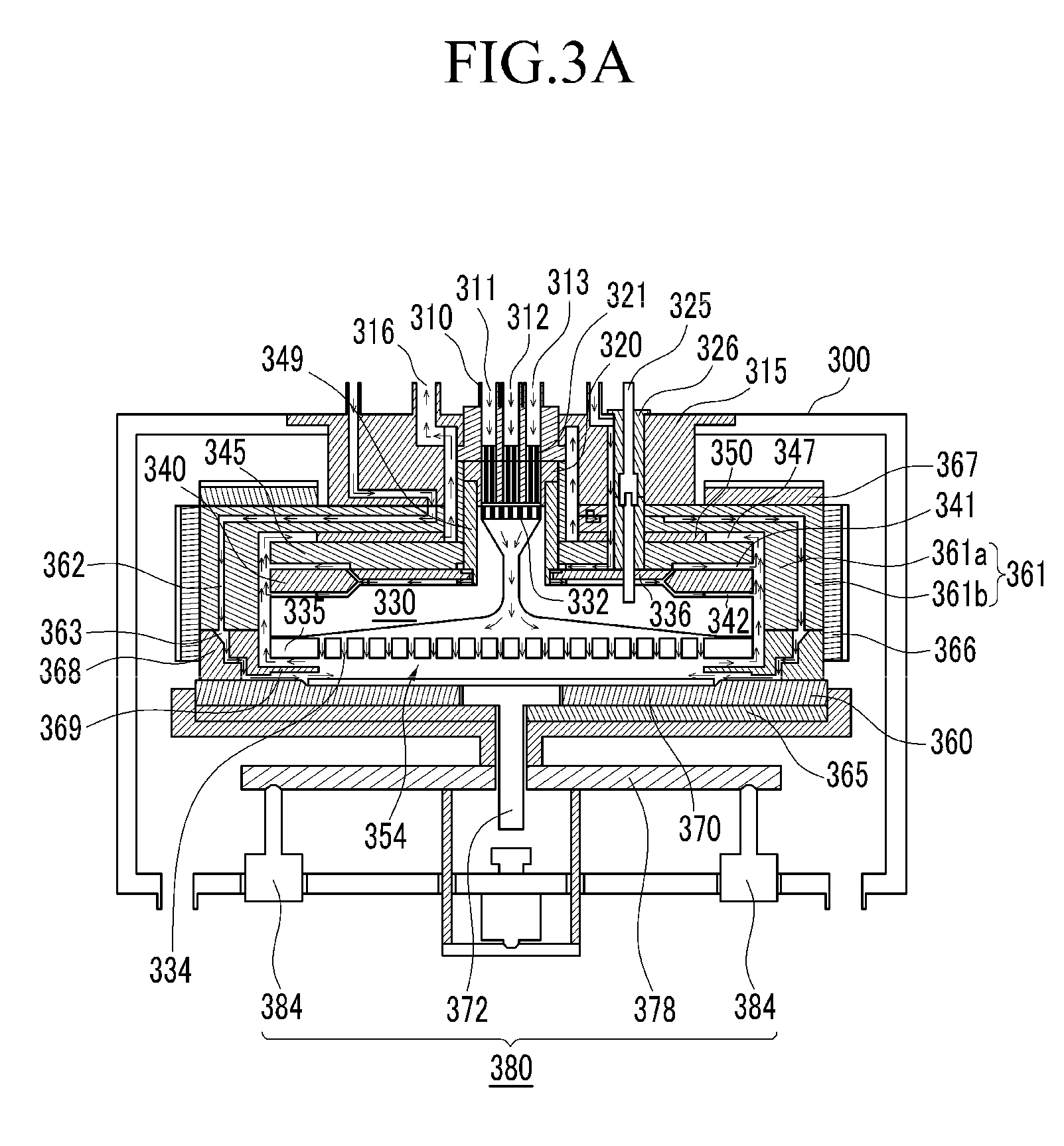

Semiconductor junction formation process including low temperature plasma deposition of an optical absorption layer and high speed optical annealing

A method of forming semiconductor junctions in a semiconductor material of a workpiece includes ion implanting dopant impurities in selected regions of the semiconductor material, introducing an optical absorber material precursor gas into a chamber containing the workpiece, generating an RF oscillating toroidal plasma current in a reentrant path that includes a process zone overlying the workpiece by applying RF source power, so as to deposit a layer of an optical absorber material on the workpiece, and optically annealing the workpiece so as to activate dopant impurities in the semiconductor material.

Owner:APPLIED MATERIALS INC

Method of manufacturing a contact interconnection layer containing a metal and nitrogen by atomic layer deposition for deep sub-micron semiconductor technology

ActiveUS7235482B2Good step coverageSafe handlingSemiconductor/solid-state device detailsSolid-state devicesAtomic layer depositionContamination

An atomic layer deposition method is used to deposit a TiN or TiSiN film having a thickness of about 50 nm or less on a substrat. A titanium precursor which is tetrakis(dimethylamido)titanium (TDMAT), tetrakis(diethylamido)titanium (TDEAT), or Ti{OCH(CH3)2}4 avoids halide contamination from a titanium halide precursor and is safer to handle than a titanium nitrate. After a monolayer of the titanium precursor is deposited on a substrate, a nitrogen containing reactant is introduced to form a TiN monolayer which is followed by a second purge. For TiSiN, a silicon source gas is fed into the process chamber after the TiN monolayer formation. The process is repeated several times to produce a composite layer comprised of a plurality of monolayers that fills a contact hole. The ALD method is cost effective and affords an interconnect with lower impurity levels and better step coverage than conventional PECVD or CVD processes.

Owner:TAIWAN SEMICON MFG CO LTD

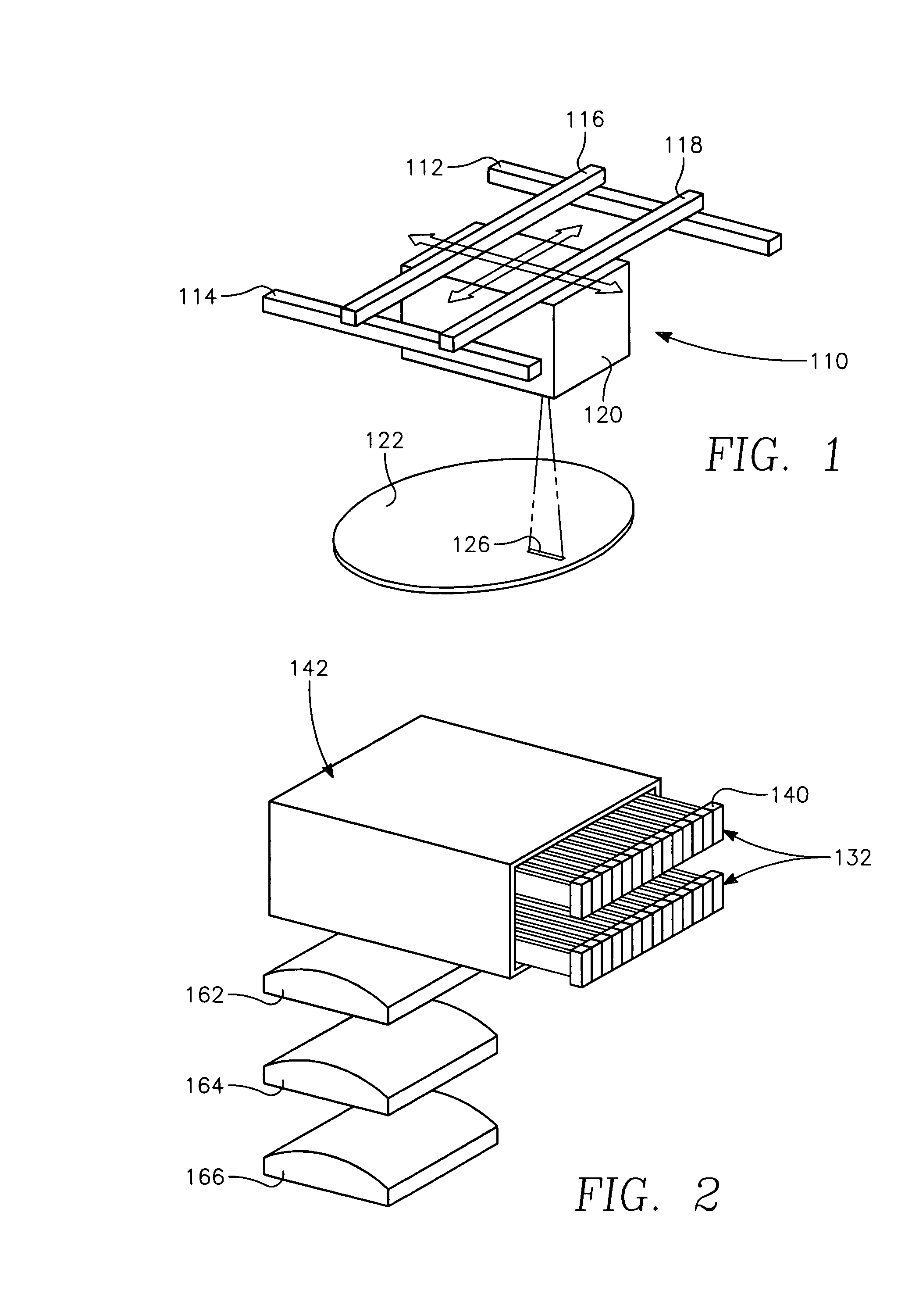

Flash Heating in Atomic Layer Deposition

InactiveUS20070281082A1Control performanceSave stepsSolid-state devicesPretreated surfacesMetallurgyAtomic layer deposition

System and methods for flash heating of materials deposited using atomic layer deposition techniques are disclosed. By flash heating the surface of the deposited material after each or every few deposition cycles, contaminants such as un-reacted precursors and byproducts can be released from the deposited material. A higher quality material is deposited by reducing the incorporation of impurities. A flash heating source is capable of quickly raising the temperature of the surface of a deposited material without substantially raising the temperature of the bulk of the substrate on which the material is being deposited. Because the temperature of the bulk of the substrate is not significantly raised, the bulk acts like a heat sink to aid in cooling the surface after flash heating. In this manner, processing times are not significantly increased in order to allow the surface temperature to reach a suitably low temperature for deposition.

Owner:SANDISK TECH LLC

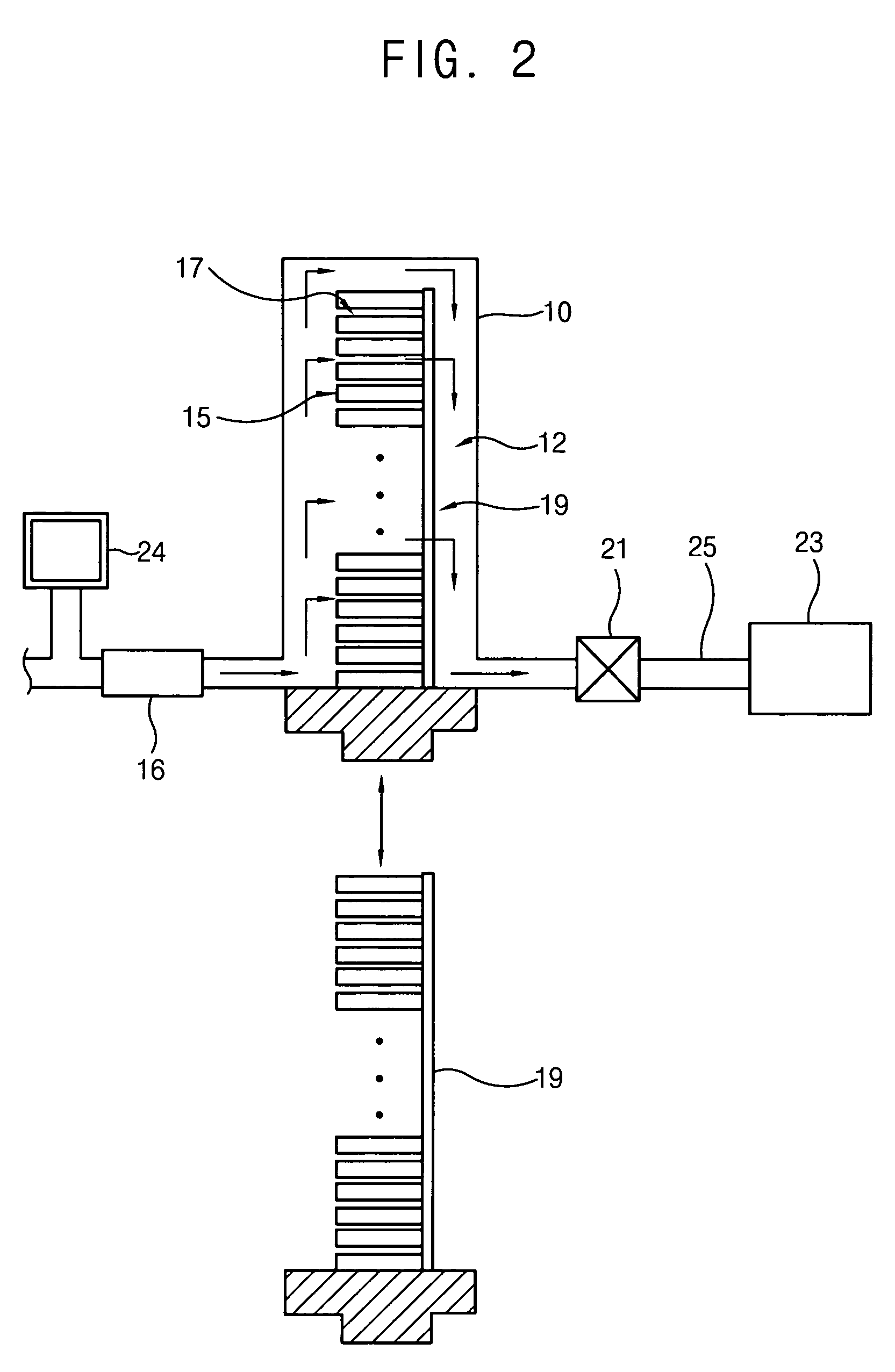

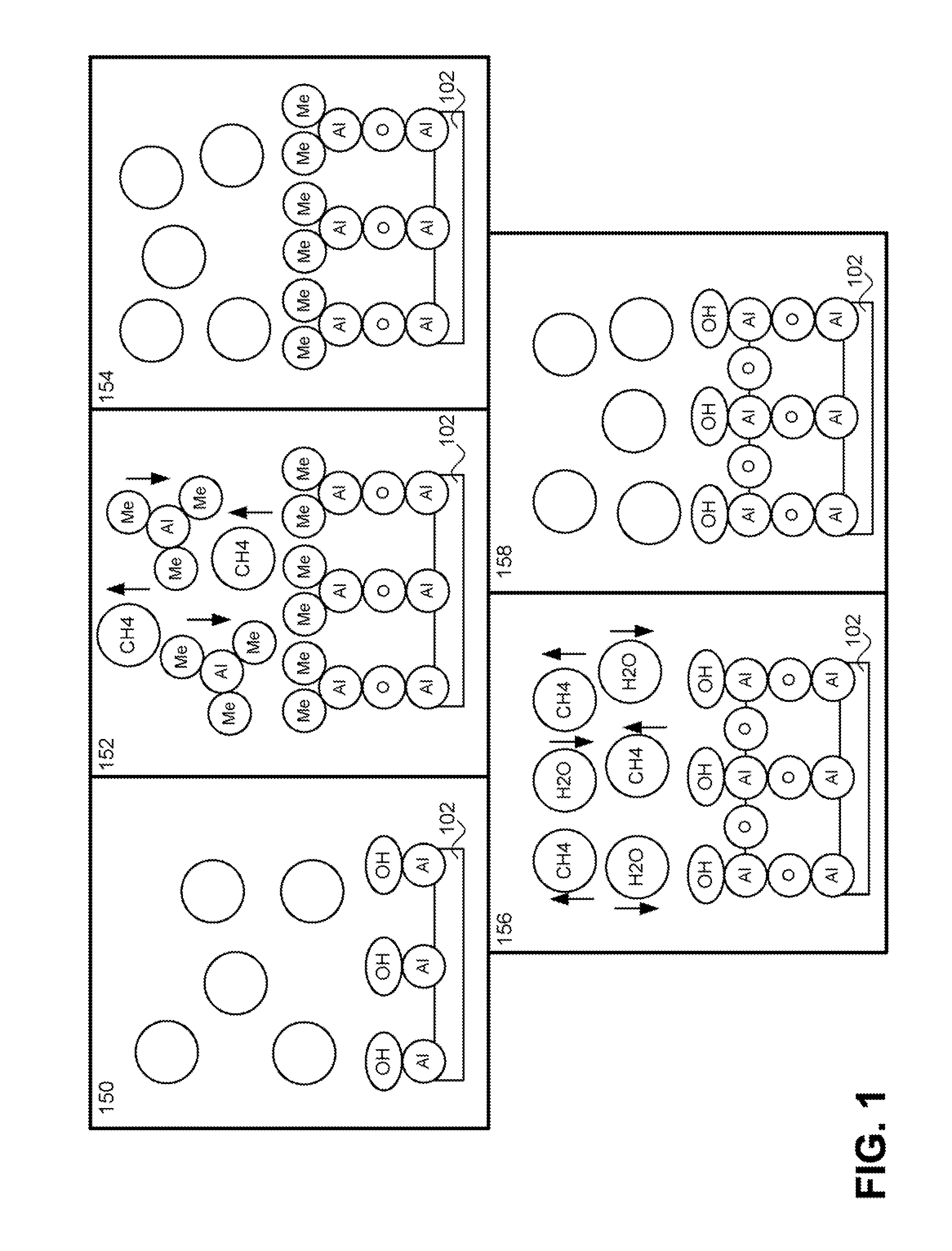

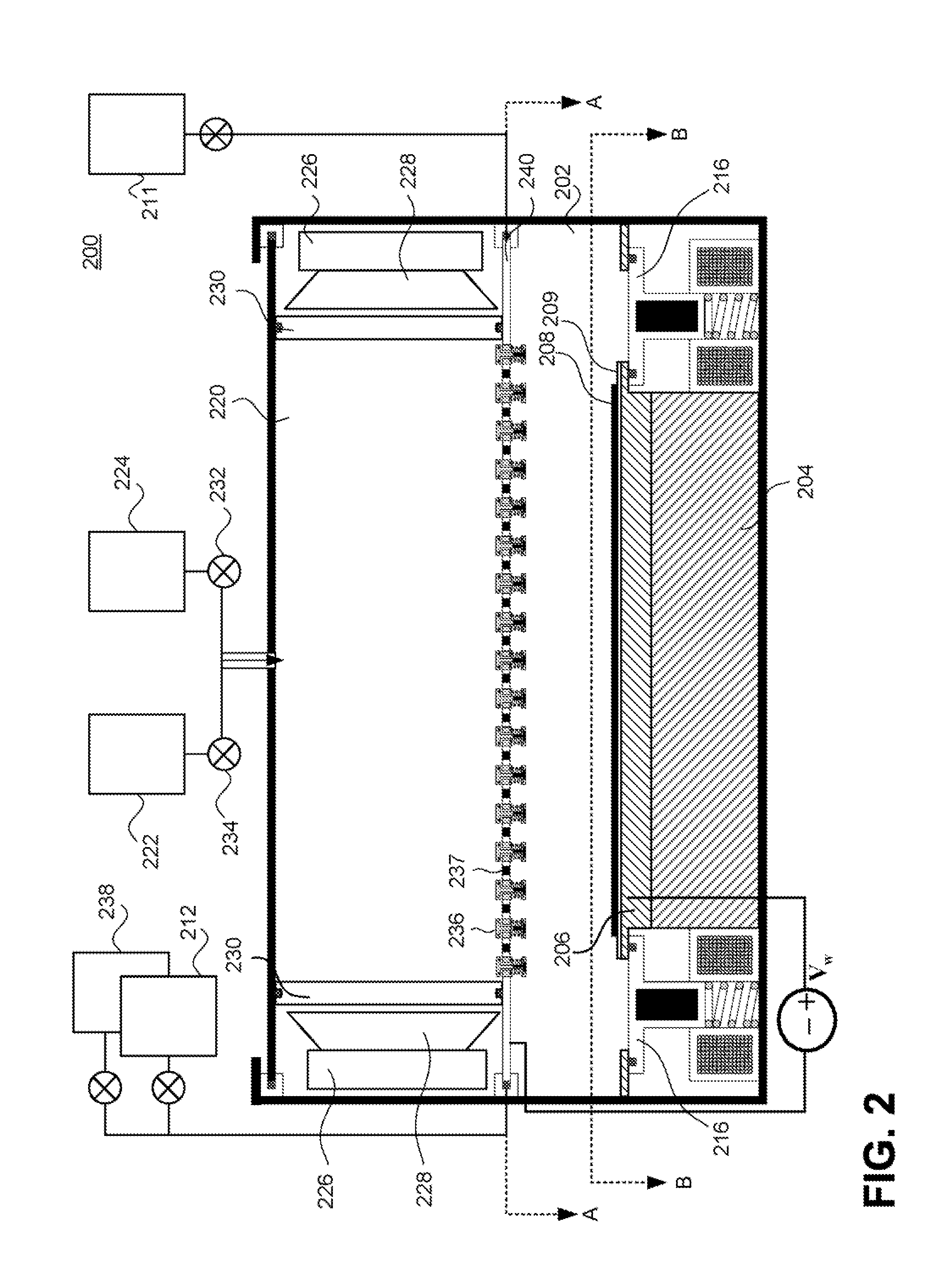

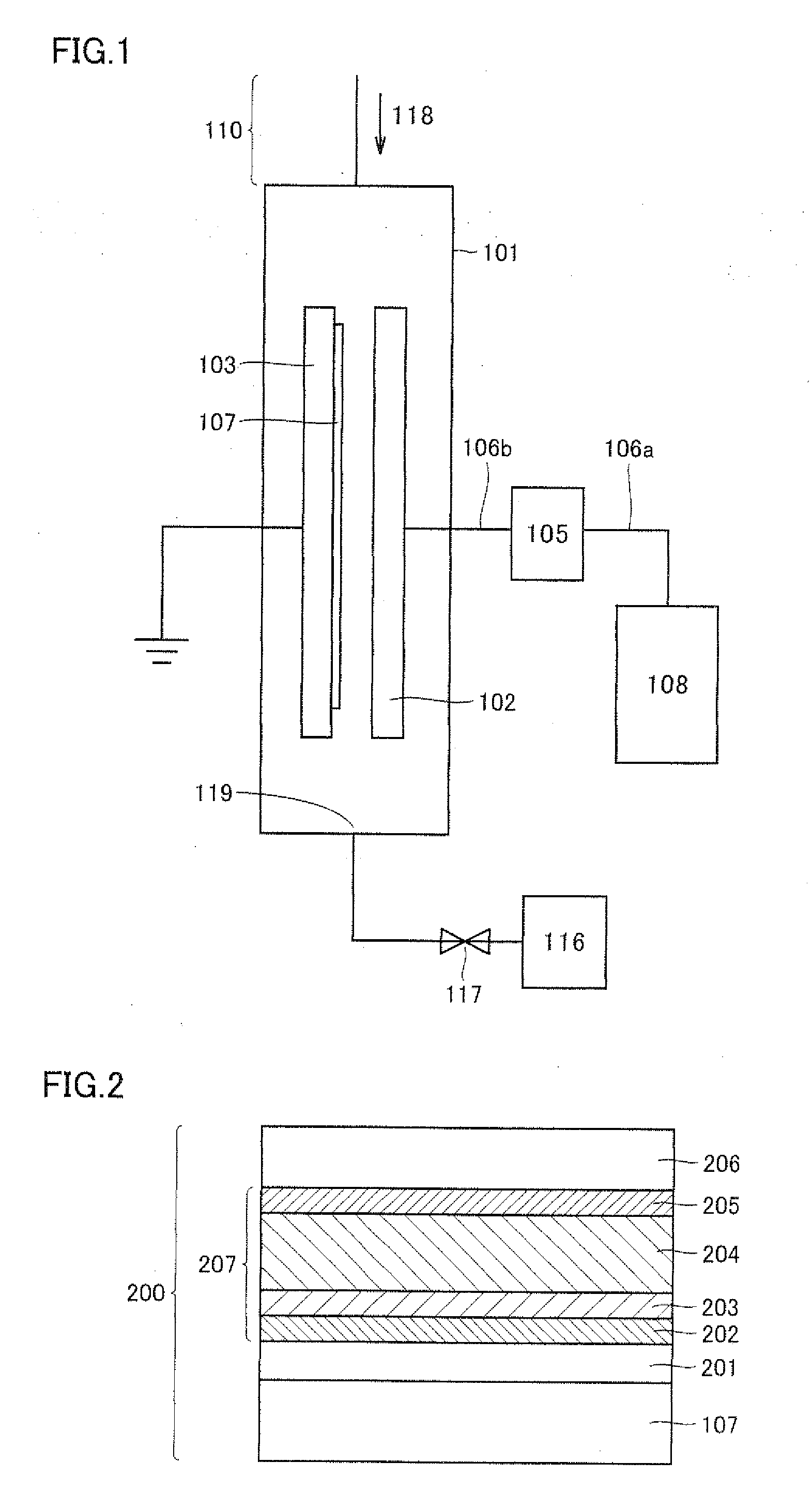

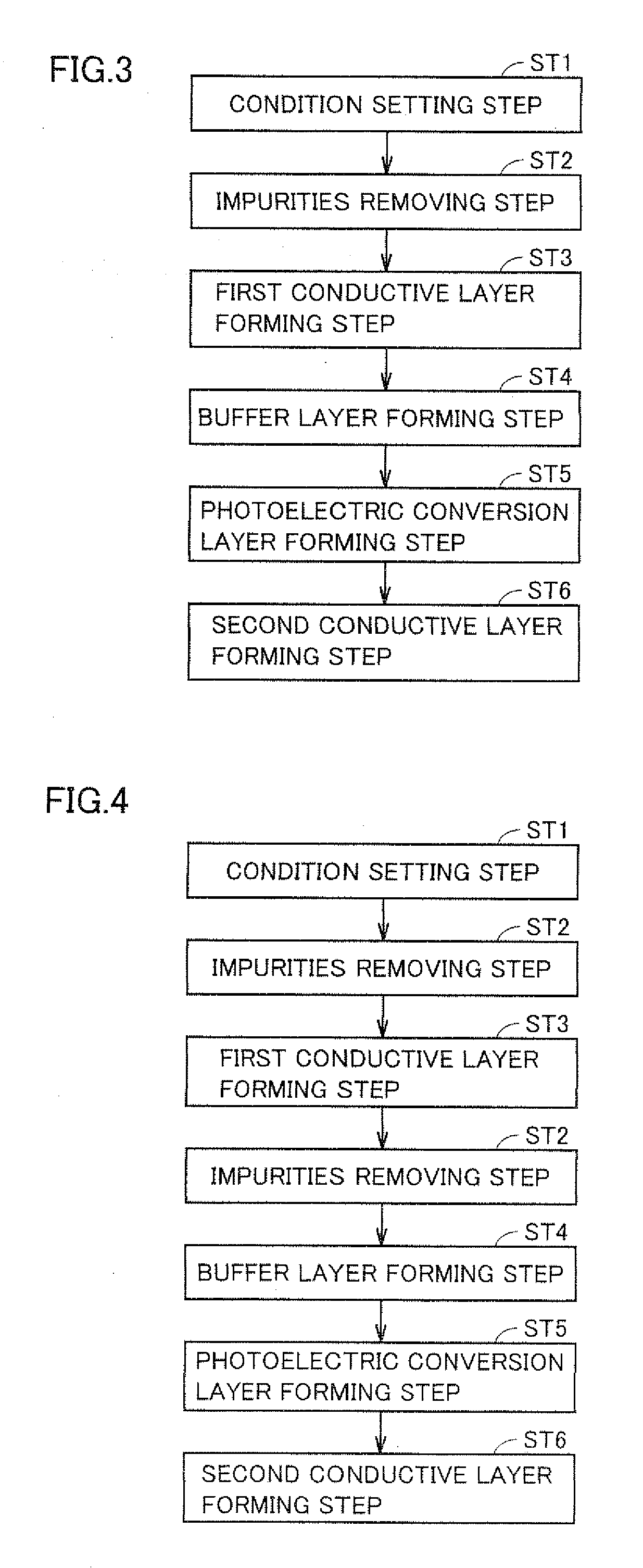

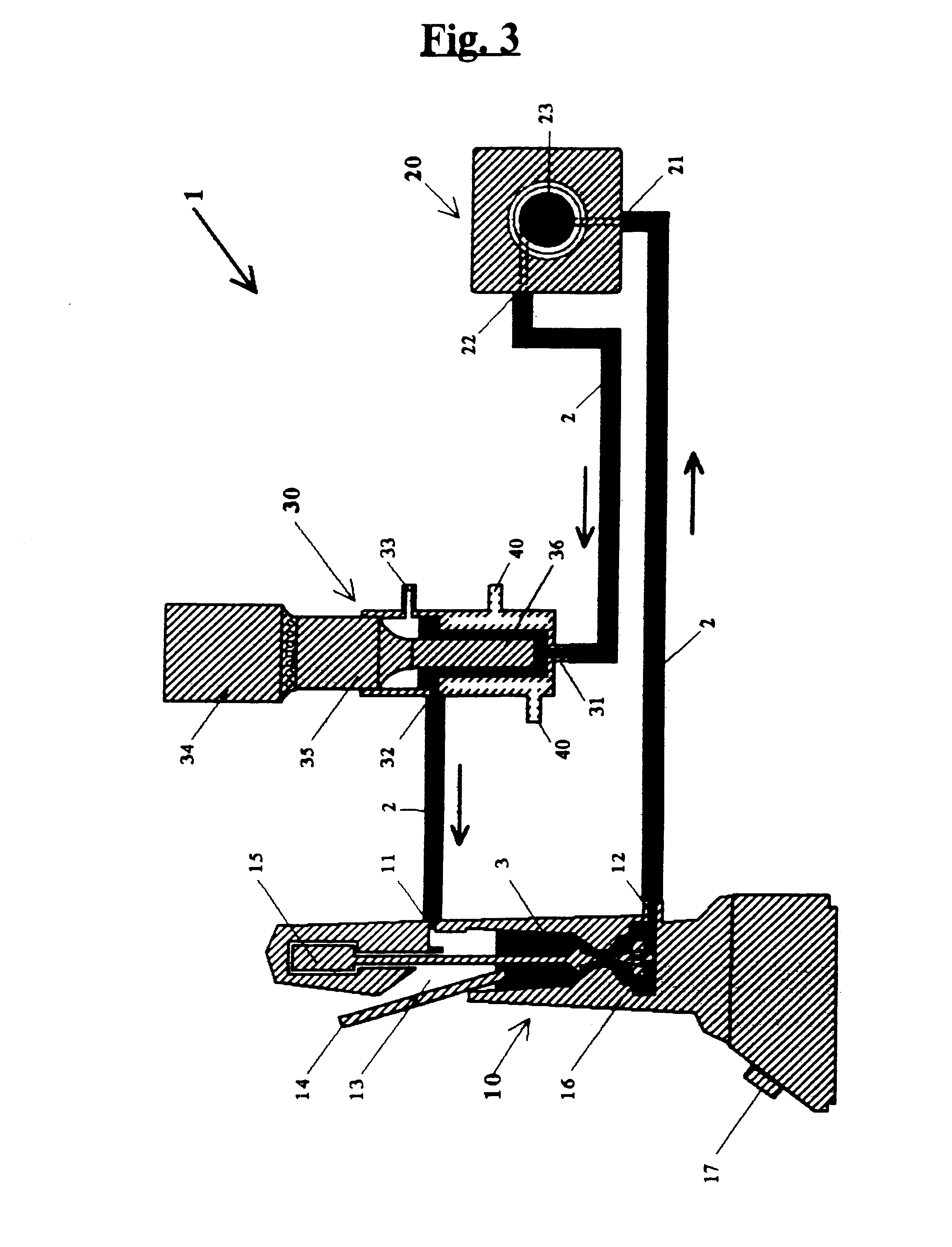

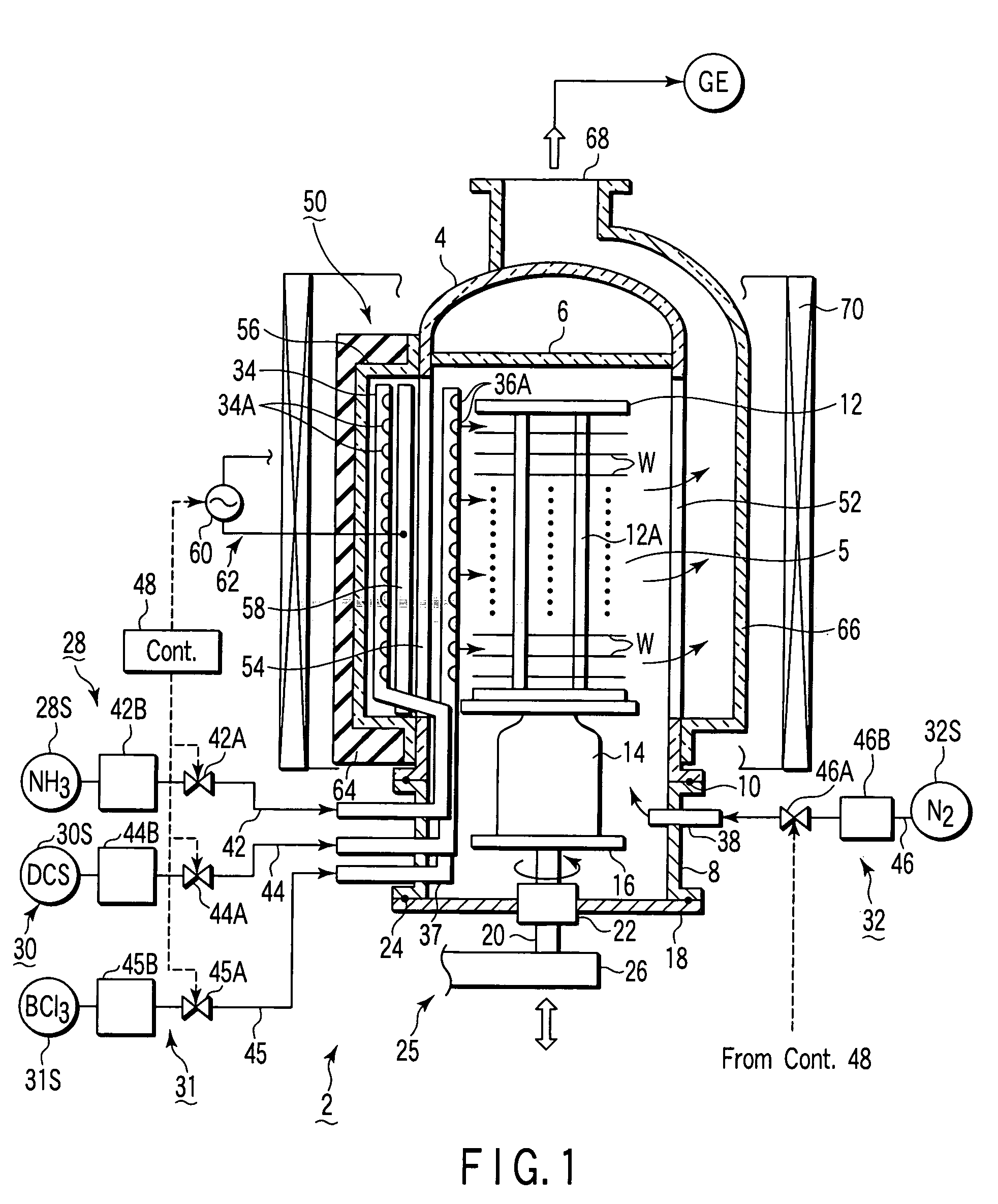

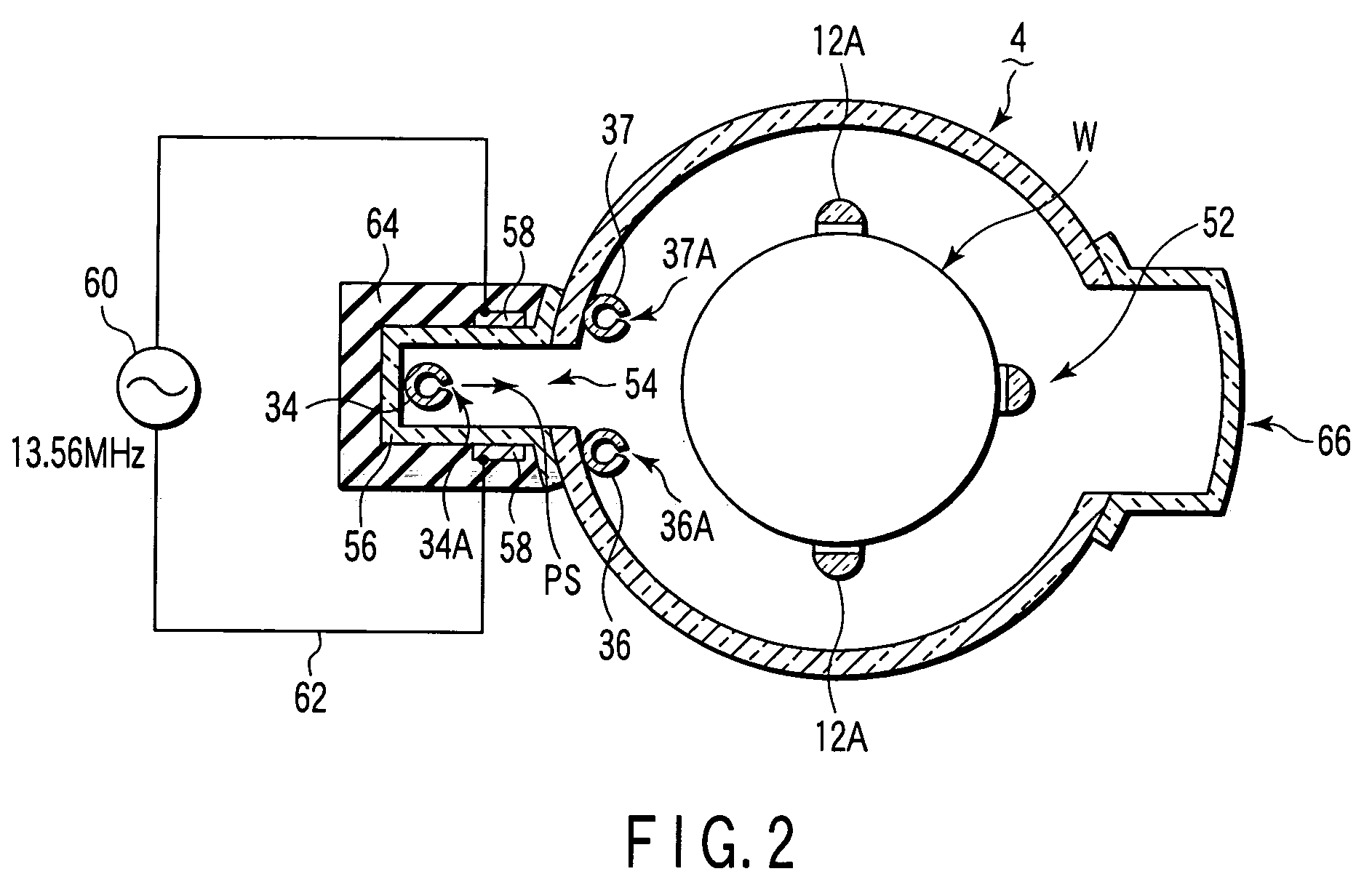

Semiconductor layer manufacturing method, semiconductor layer manufacturing apparatus, and semiconductor device manufactured using such method and apparatus

InactiveUS20100024872A1Quality improvementImprove batch productivityLiquid surface applicatorsFinal product manufactureHermetic sealManufactured apparatus

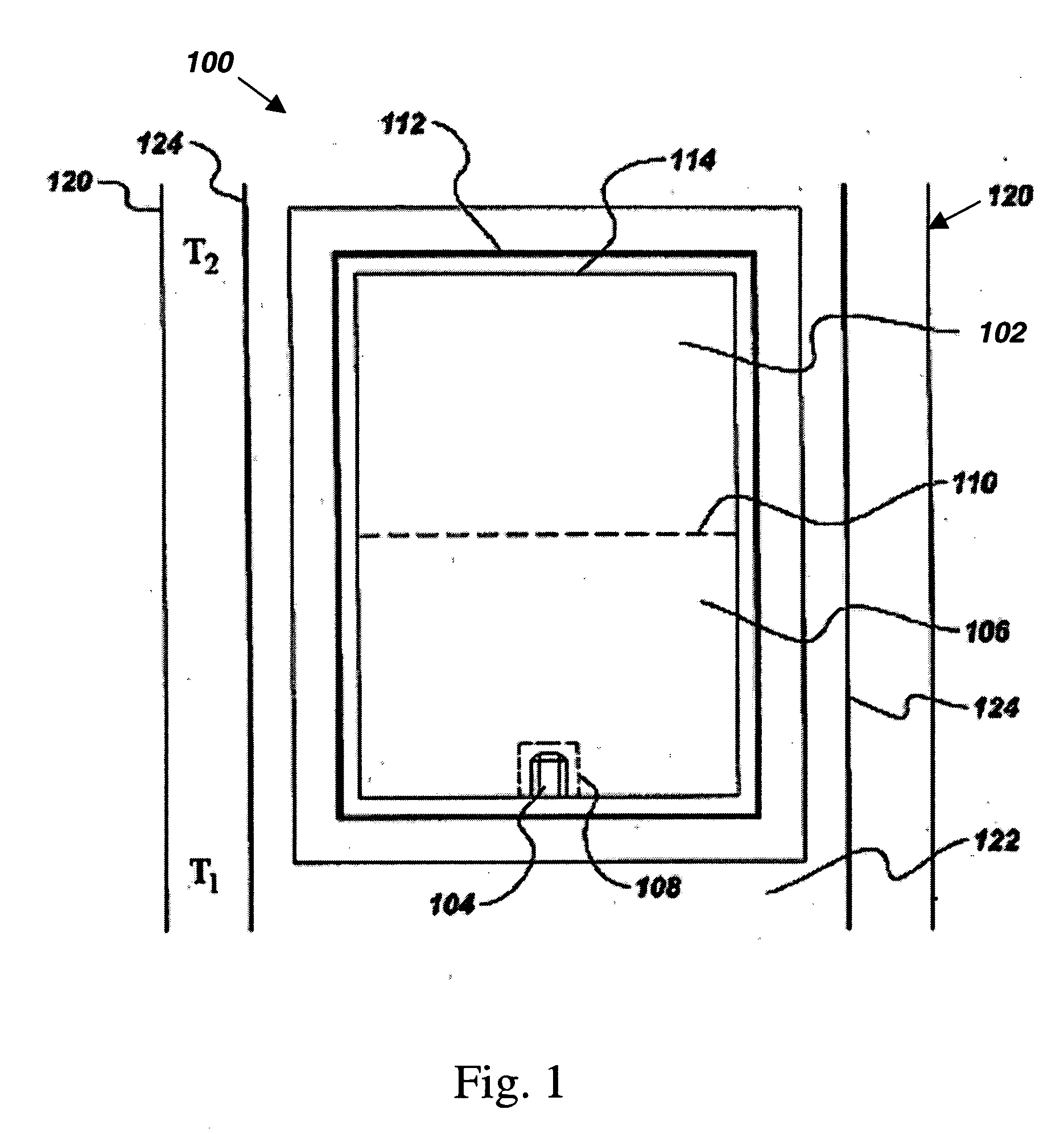

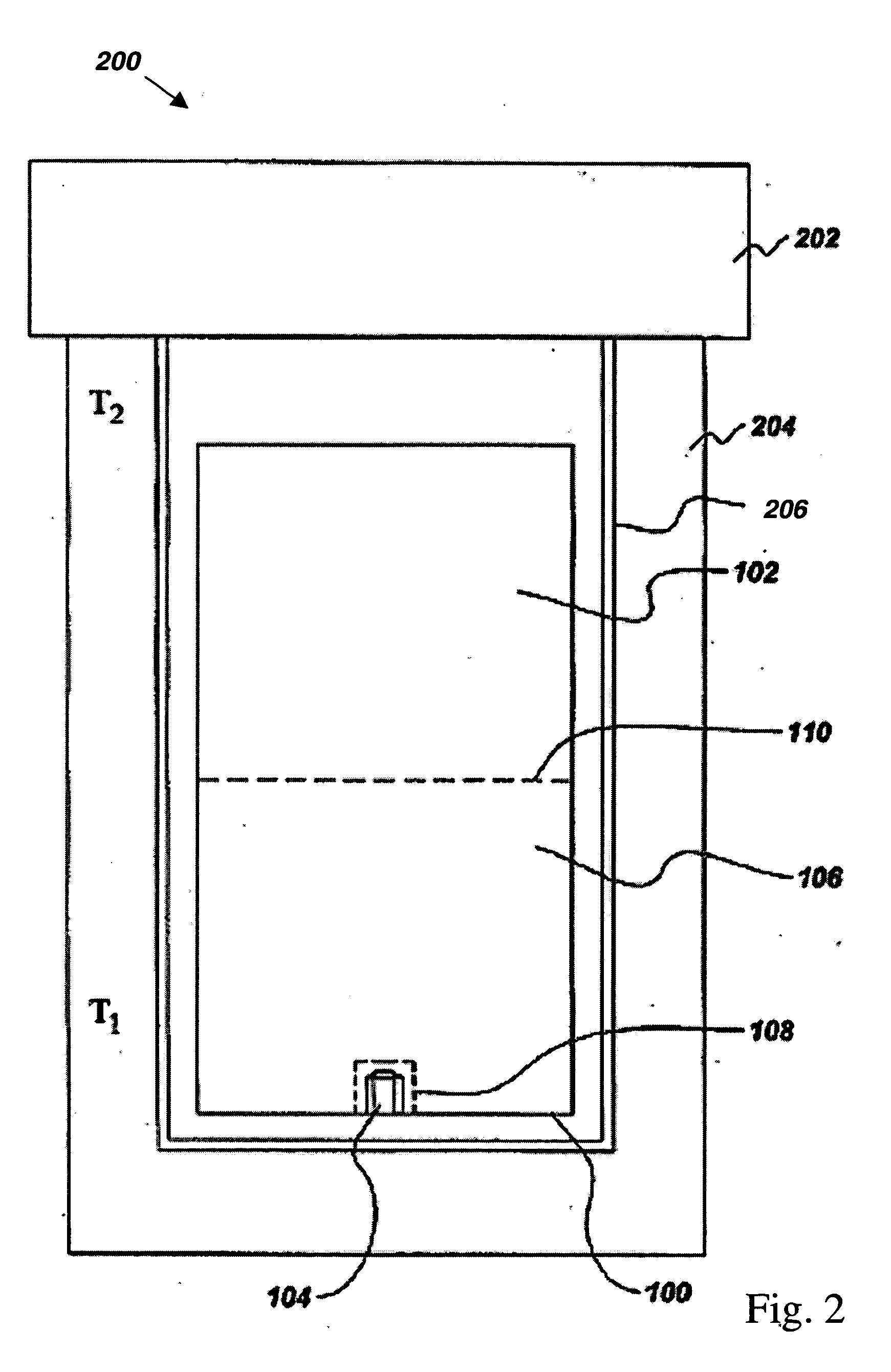

Provided are a semiconductor layer manufacturing method and a semiconductor manufacturing apparatus capable of forming a high quality semiconductor layer even by a single chamber system, with a shortened process time required for reducing a concentration of impurities that exist in a reaction chamber before forming the semiconductor layer. A semiconductor device manufactured using such a method and apparatus is also provided. The present invention relates to a semiconductor layer manufacturing method of forming a semiconductor layer inside a reaction chamber (101) capable of being hermetically sealed, including an impurities removing step of removing impurities inside the reaction chamber (101) using a replacement gas, and a semiconductor layer forming step of forming the semiconductor layer, the impurities removing step being a step in which a cycle composed of a replacement gas introducing step of introducing the replacement gas into the reaction chamber (101) and an exhausting step of exhausting the replacement gas is repeated a plurality of times, the impurities removing step being performed at least before the semiconductor layer forming step.

Owner:SHARP KK

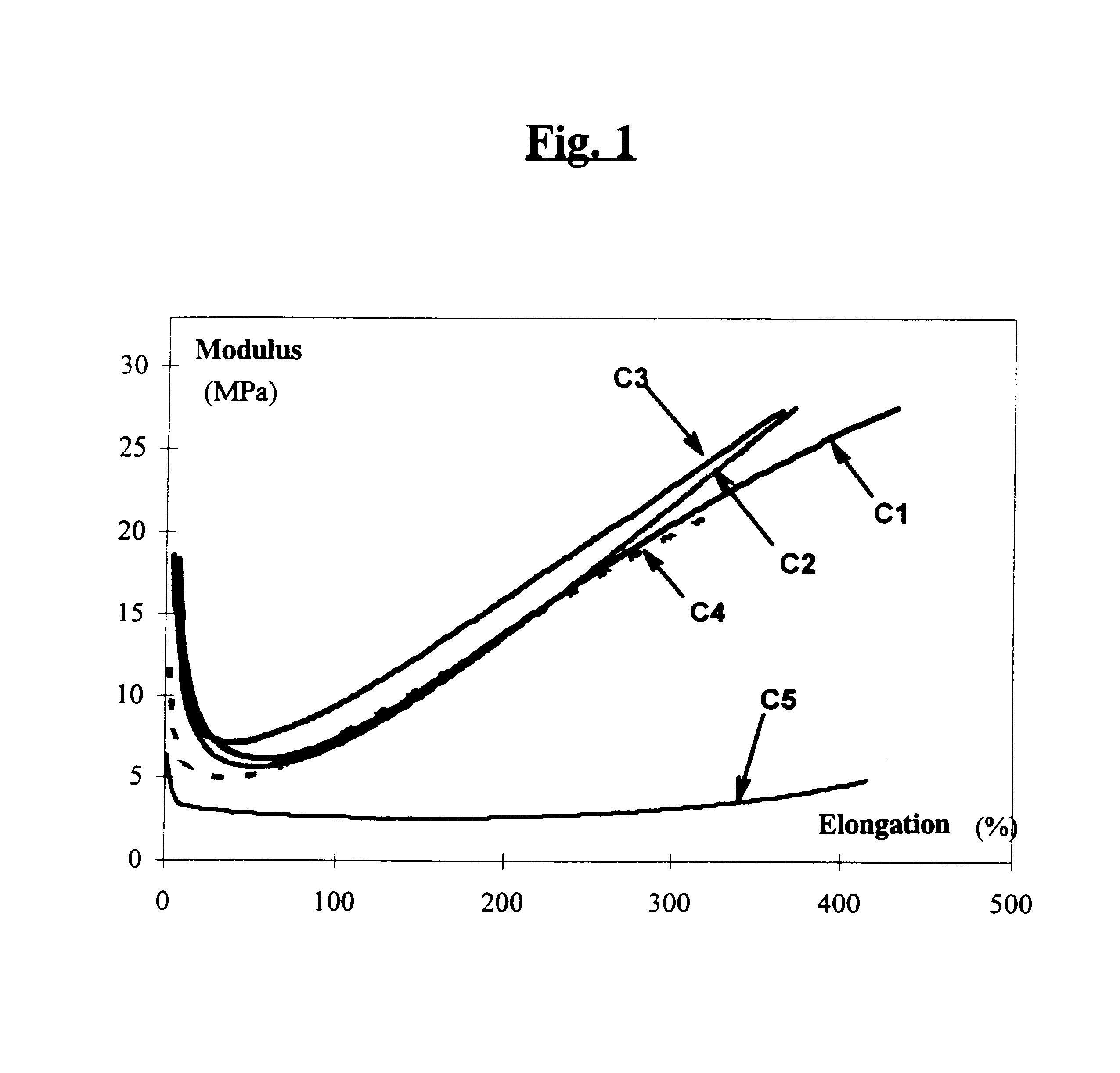

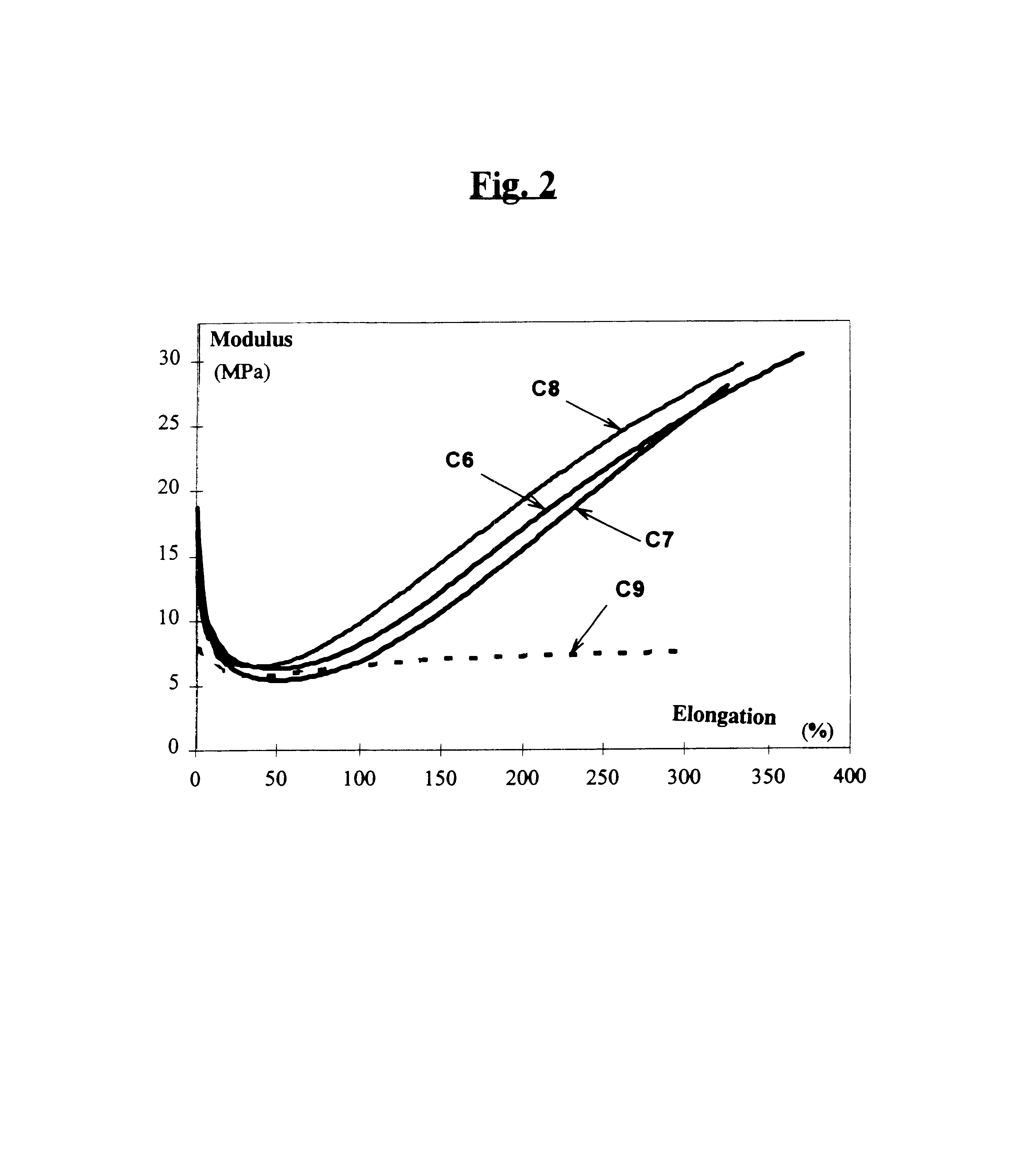

Reinforcing aluminum-based filler and rubber composition comprising such a filter

A reinforcing aluminum-based filler which can be used for reinforcing diene rubber compositions intended for the manufacture of tires, comprising an aluminum (oxide-)hydroxide corresponding, with the exception of any impurities and the water of hydration, to the general formula (a and b being real numbers):the specific BET surface area of which is between 30 and 400 m2 / g, the average particle size (by mass) dw of which is between 20 and 400 nm and the disagglomeration rate, alpha, of which, measured via an ultrasound disagglomeration test at 100% power of a 600-watt ultrasonic probe, is greater than 5x10-3 mum-1 / s is provided. A rubber composition suitable for the manufacture of tires comprising said aluminum-based filler as reinforcing filler.

Owner:MICHELIN & CO CIE GEN DES ESTAB MICHELIN

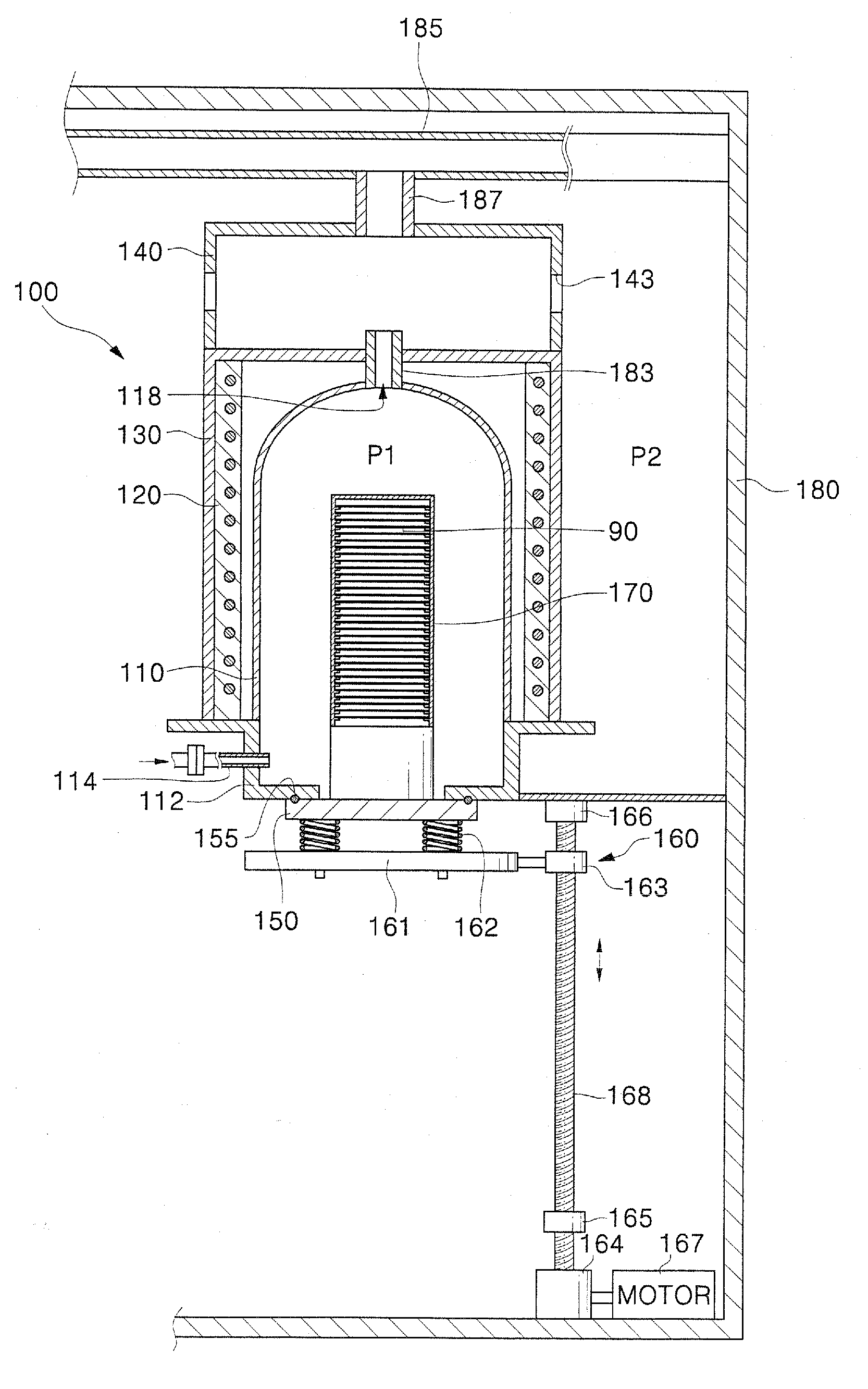

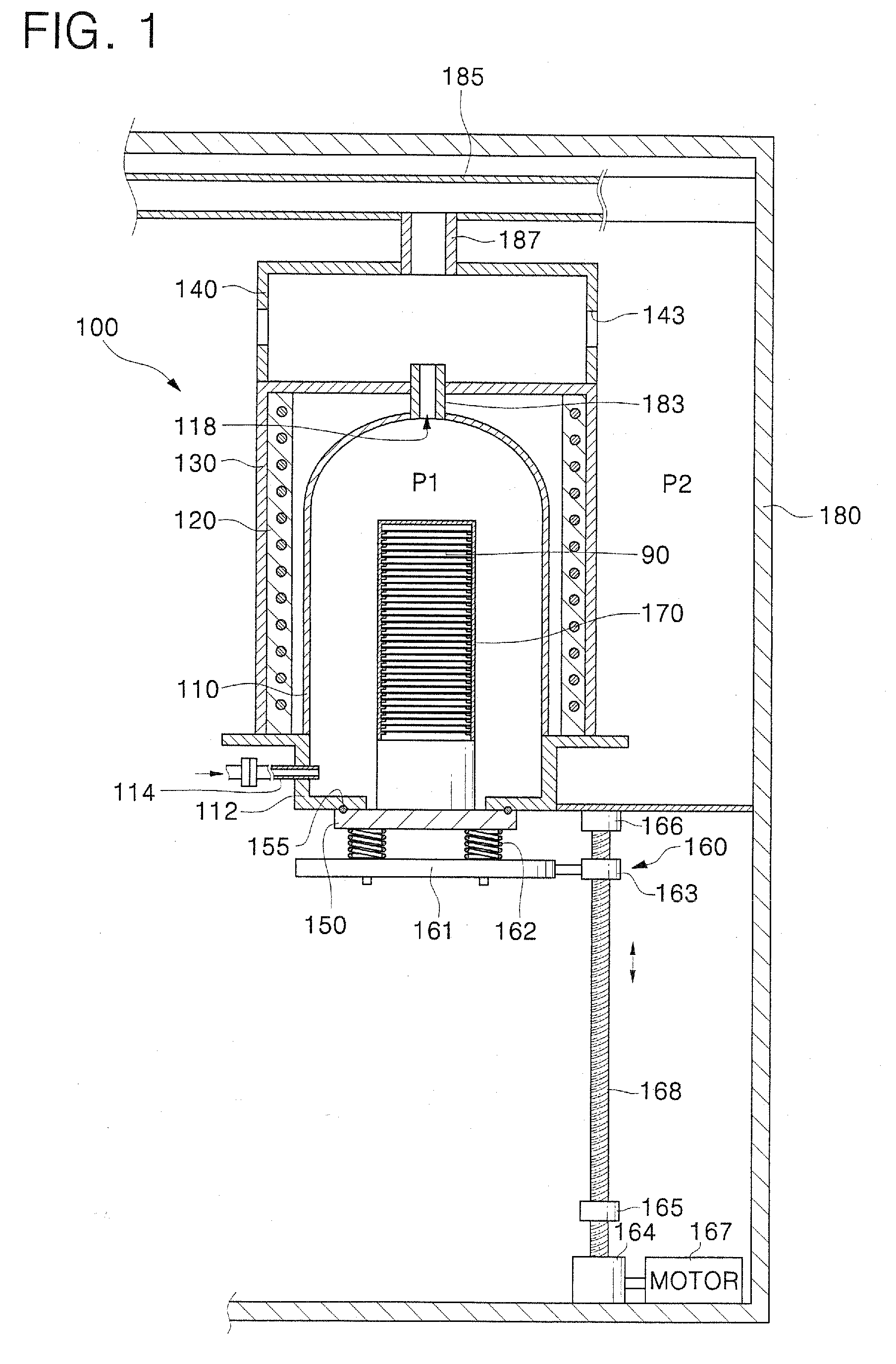

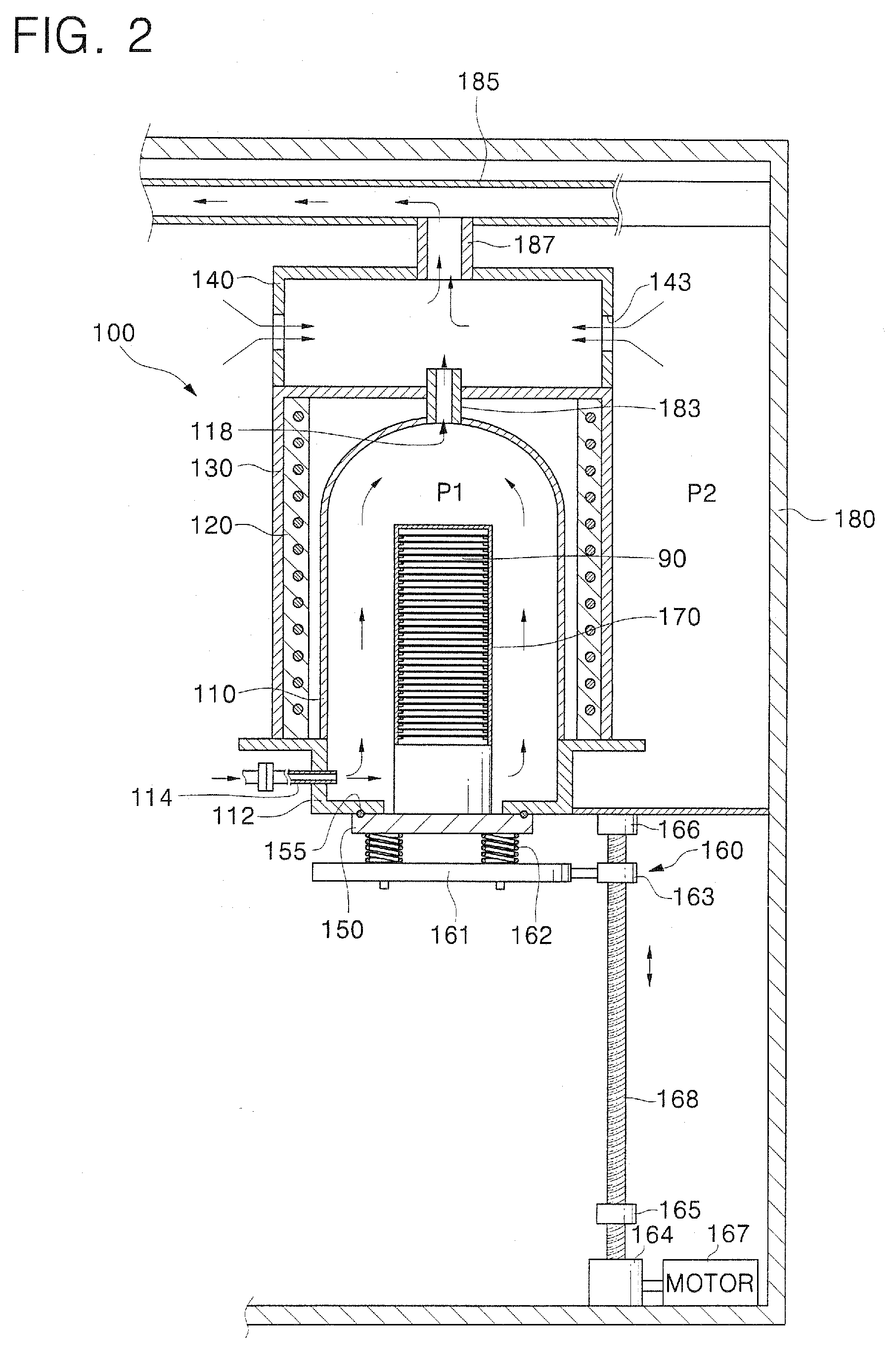

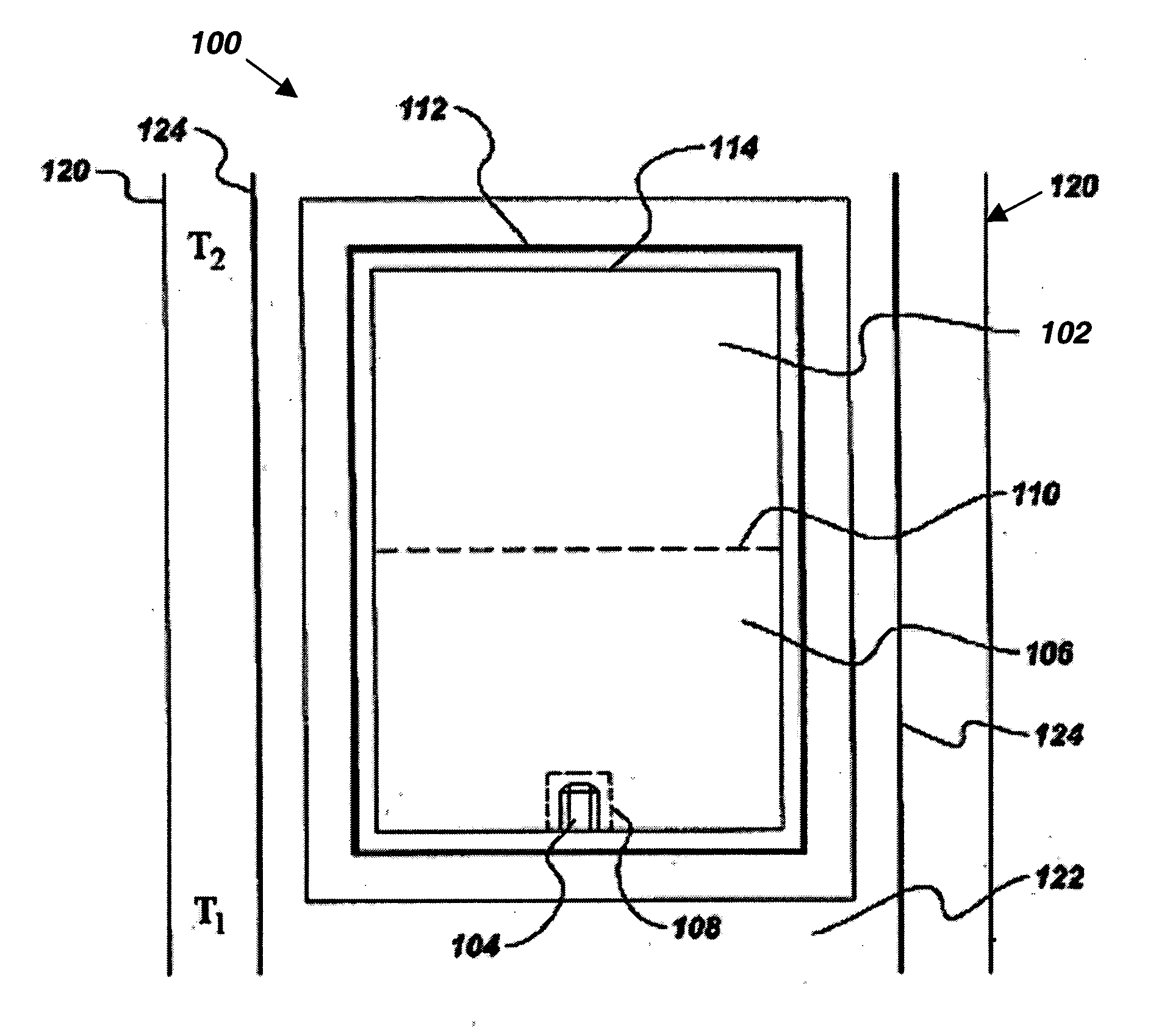

Heat treatment equipment

InactiveUS7850449B2Growth inhibitionReduce processing stepsMuffle furnacesBaking ovenProcess engineeringPressure controlled ventilation

In an embodiment, heat treatment equipment comprises a process tube, an exhaust duct connected to the process tube, and, during operation, exhausting gases present within the process tube. The heat treatment equipment also comprises a hollow pressure control member interposed between the process tube and the exhaust duct, the pressure control member being operatively connected to the process tube and the exhaust duct respectively, and including one or a number of openings. Negative pressure is avoided in the process tube during heat treatment processes so that unwanted gas and impurities cannot enter the process tube from outside.

Owner:SAMSUNG ELECTRONICS CO LTD

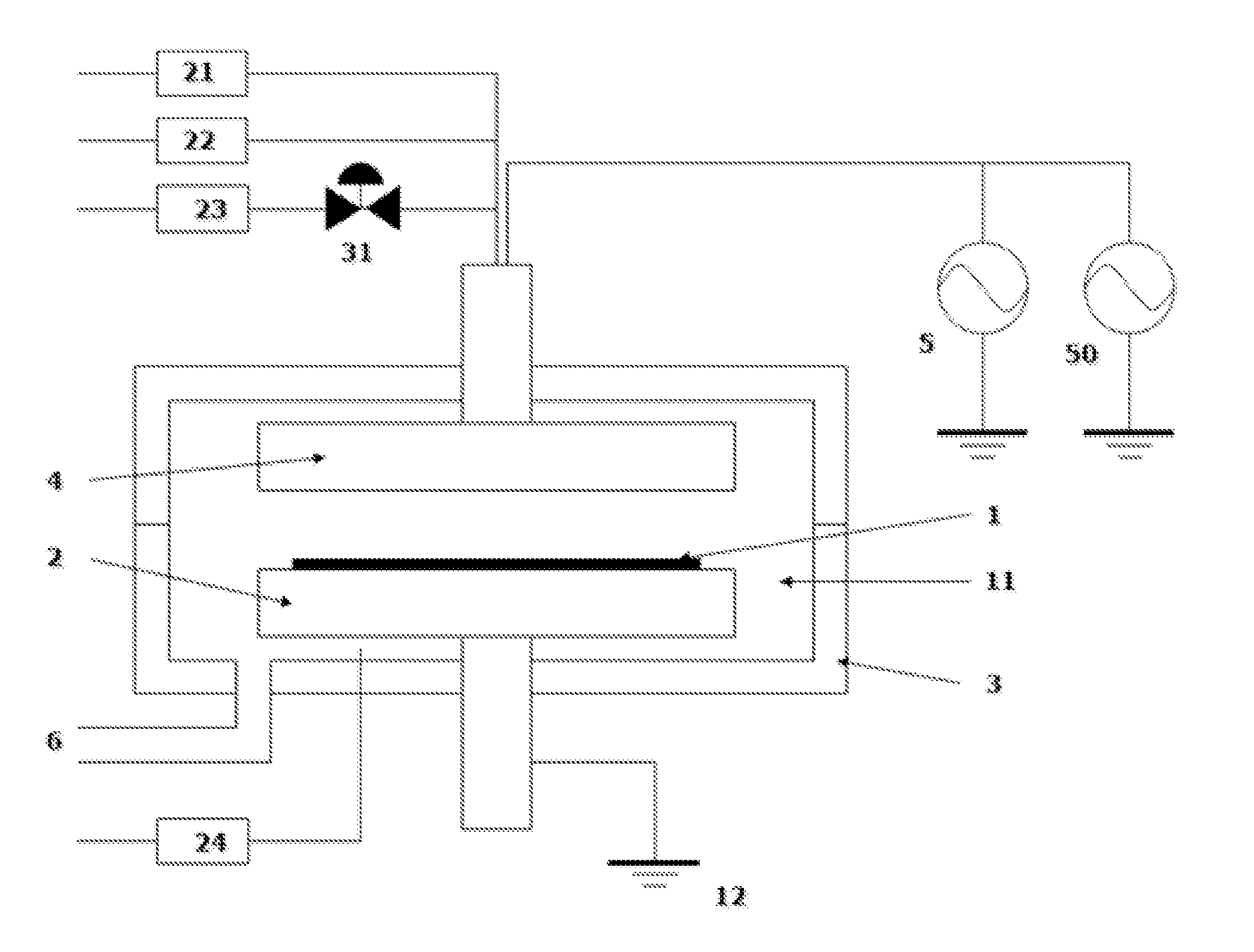

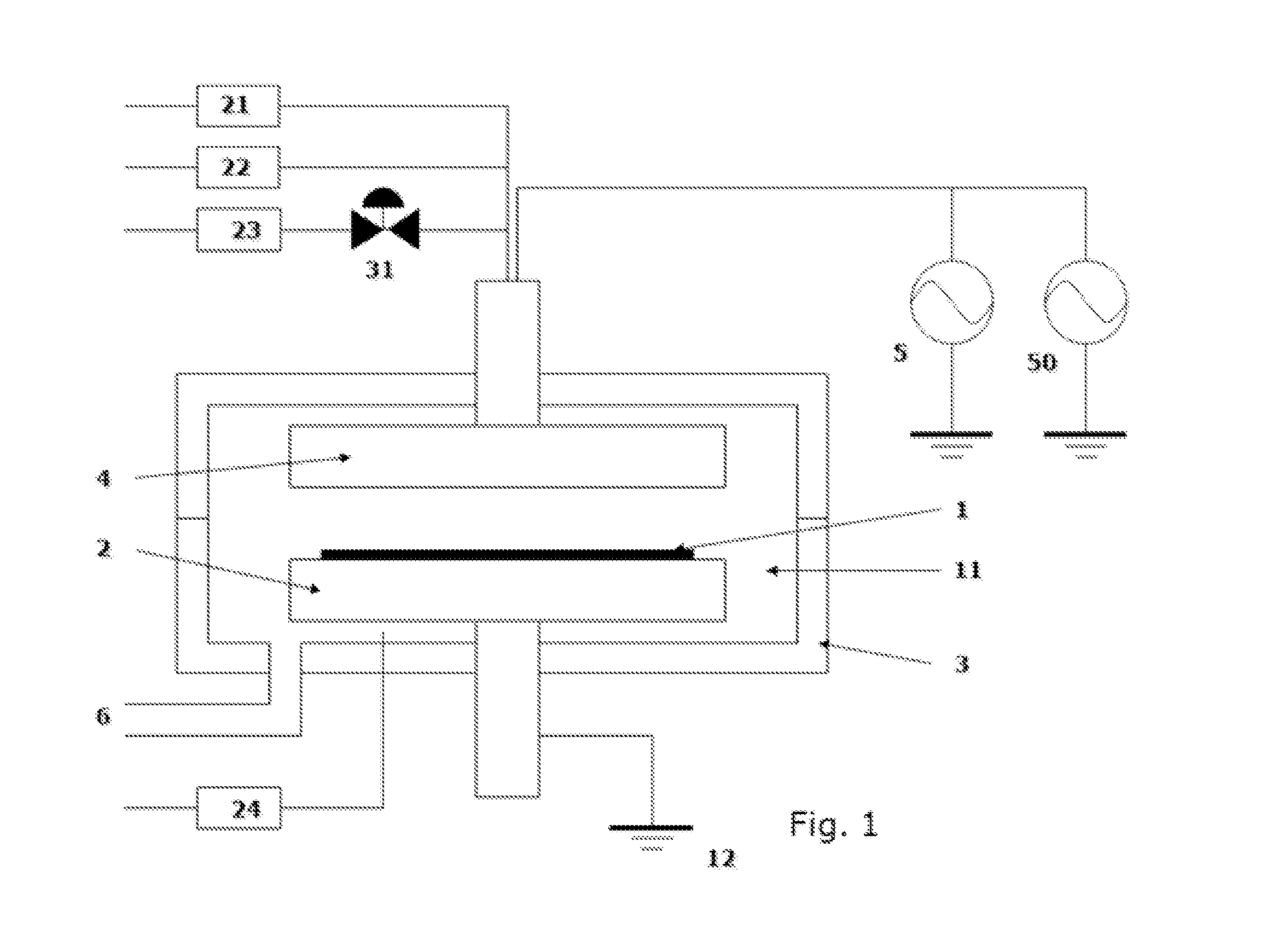

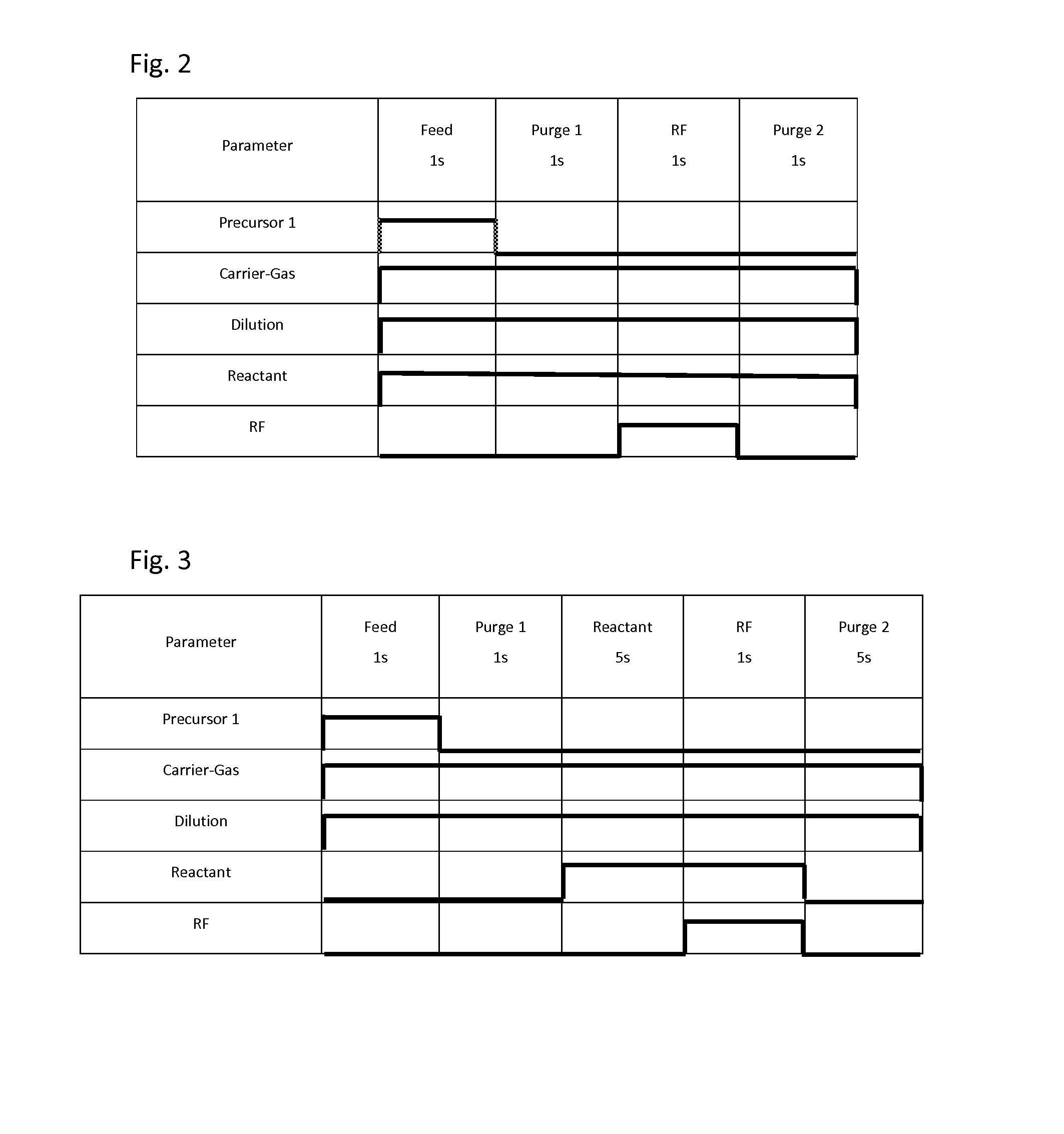

Method for depositing metal-containing film using particle-reduction step

InactiveUS20160168699A1Reduce surface roughnessSolve the lack of resistanceChemical vapor deposition coatingPlasma techniqueAMINO BASENitride

A method for forming a metal oxide or nitride film on a substrate by plasma-enhanced atomic layer deposition (PEALD), includes: introducing an amino-based metal precursor in a pulse to a reaction space where a substrate is placed, using a carrier gas; and continuously introducing a reactant gas to the reaction space; applying RF power in a pulse to the reaction space wherein the pulse of the precursor and the pulse of RF power do not overlap, wherein conducted is at least either step (a) comprising passing the carrier gas through a purifier for reducing impurities before mixing the carrier gas with the precursor, or step (b) introducing the reactant gas at a flow rate such that a partial pressure of the reactant gas relative to the total gas flow provided in the reaction space is 15% or less.

Owner:ASM IP HLDG BV

Single crystal and quasi-single crystal, composition, apparatus, and associated method

InactiveUS20060037529A1Material nanotechnologyPolycrystalline material growthMischmetalSource material

Owner:SORAA

Common fabrication of different semiconductor devices with different threshold voltages

A multi-device semiconductor structure including a p-type logic device, a p-type memory device, a n-type logic device and a n-type memory device are provided on a bulk silicon substrate. Each of these devices includes a dielectric layer and either a n-type or a p-type work function layer disposed over the dielectric layer. Some of the various device types of the multi-device semiconductor structure are protected, and impurities, such as aluminum and / or nitrogen, are added to the exposed work function layers to achieve one or more other desired work functions with different threshold voltages.

Owner:GLOBALFOUNDRIES INC

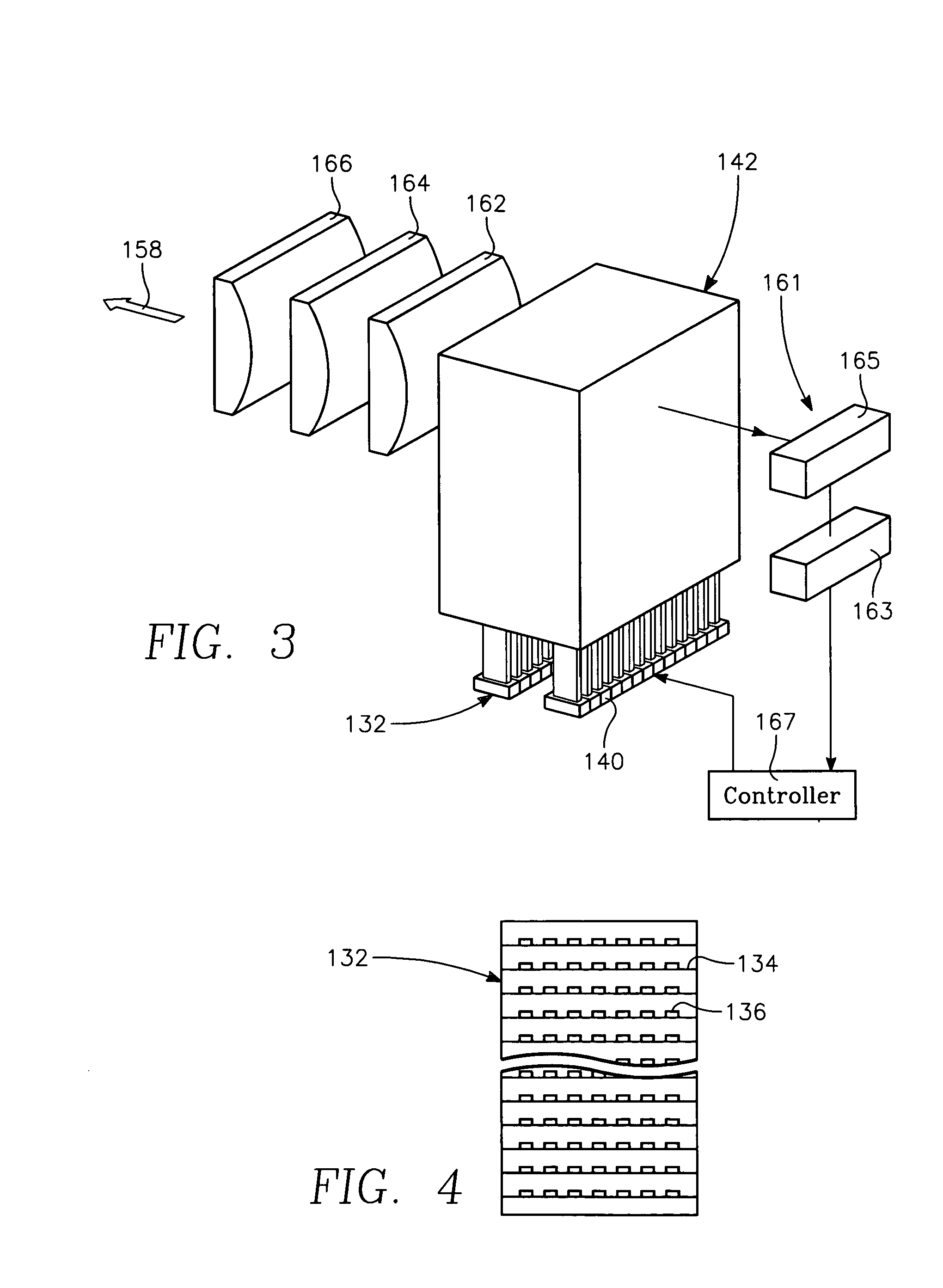

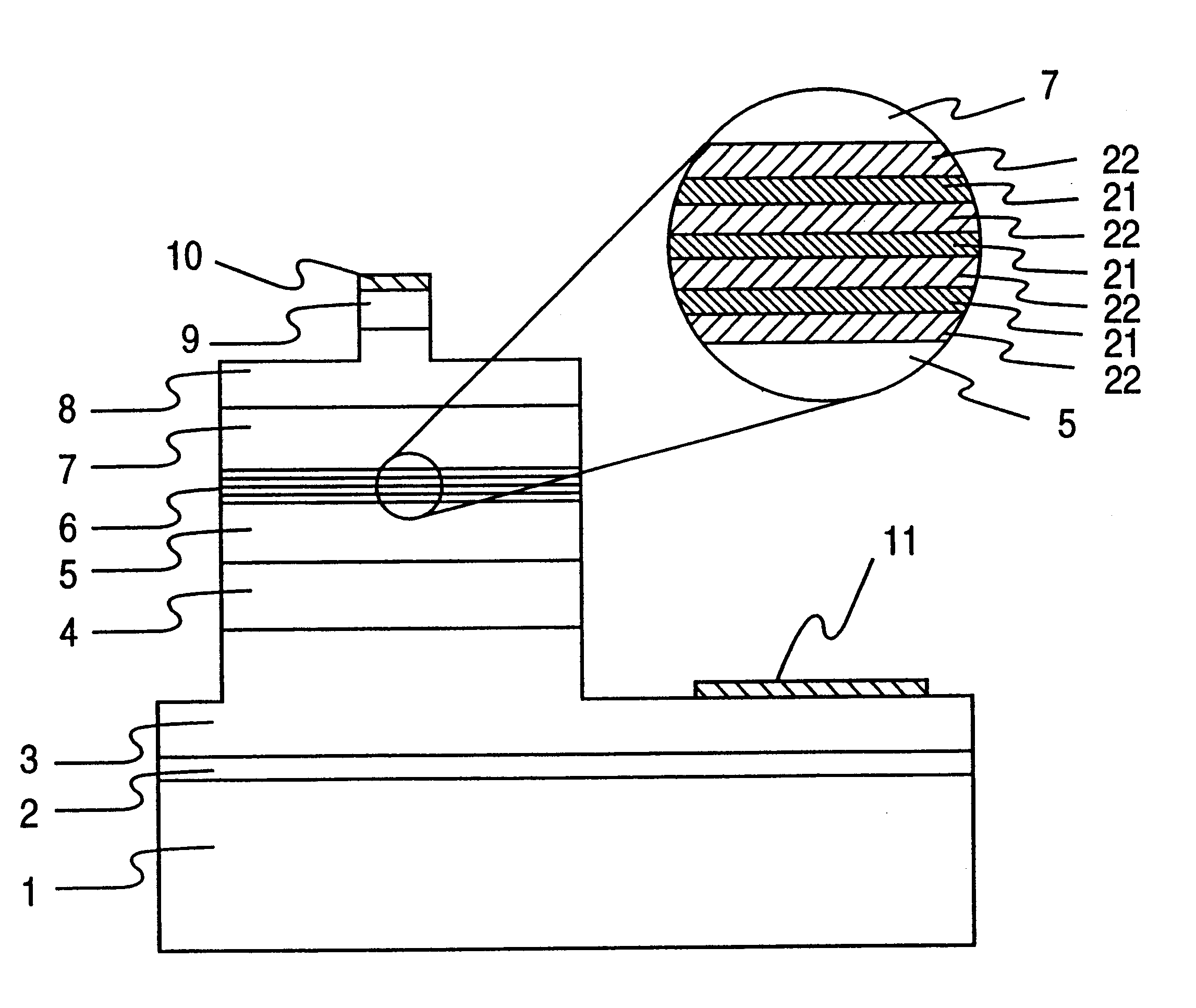

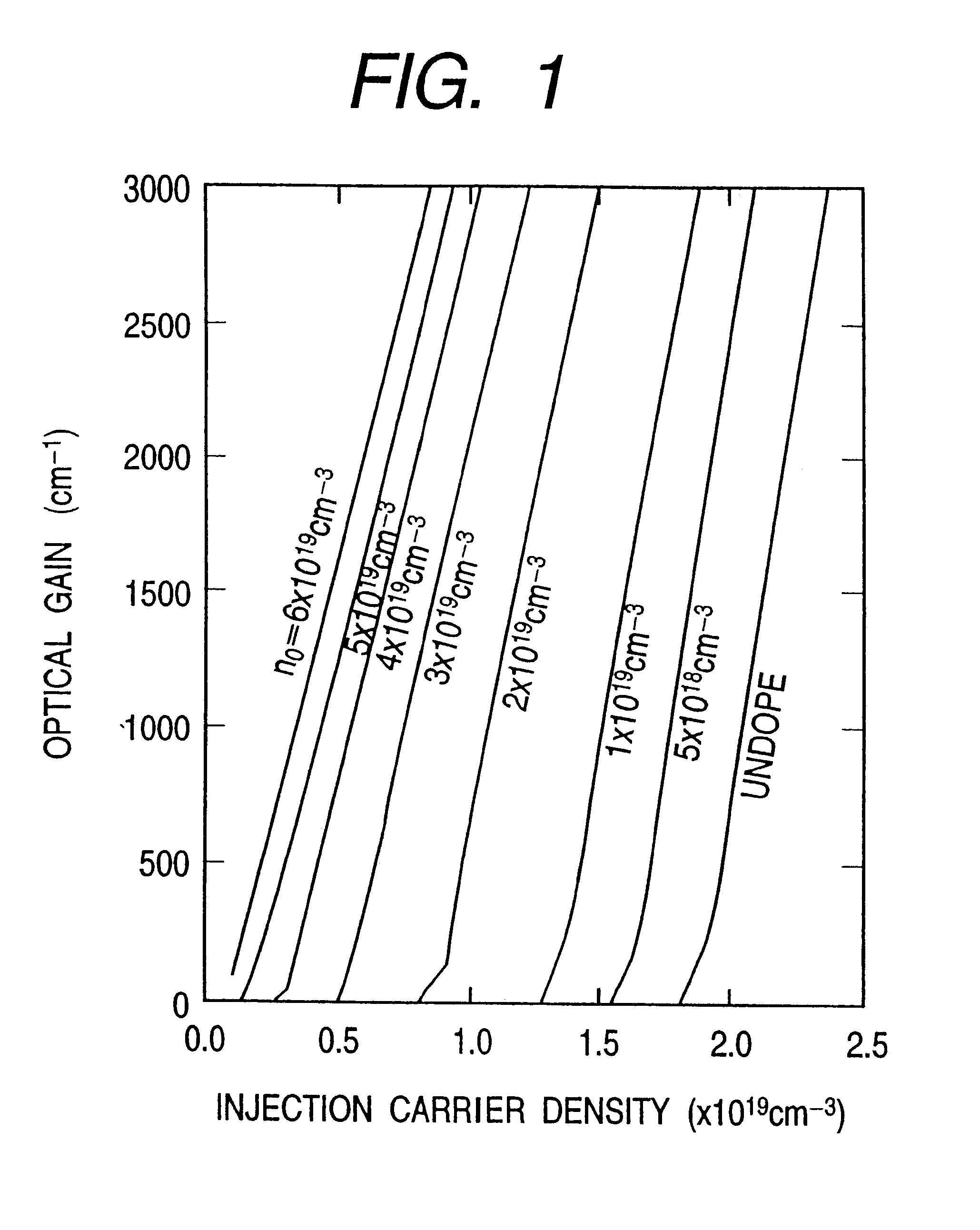

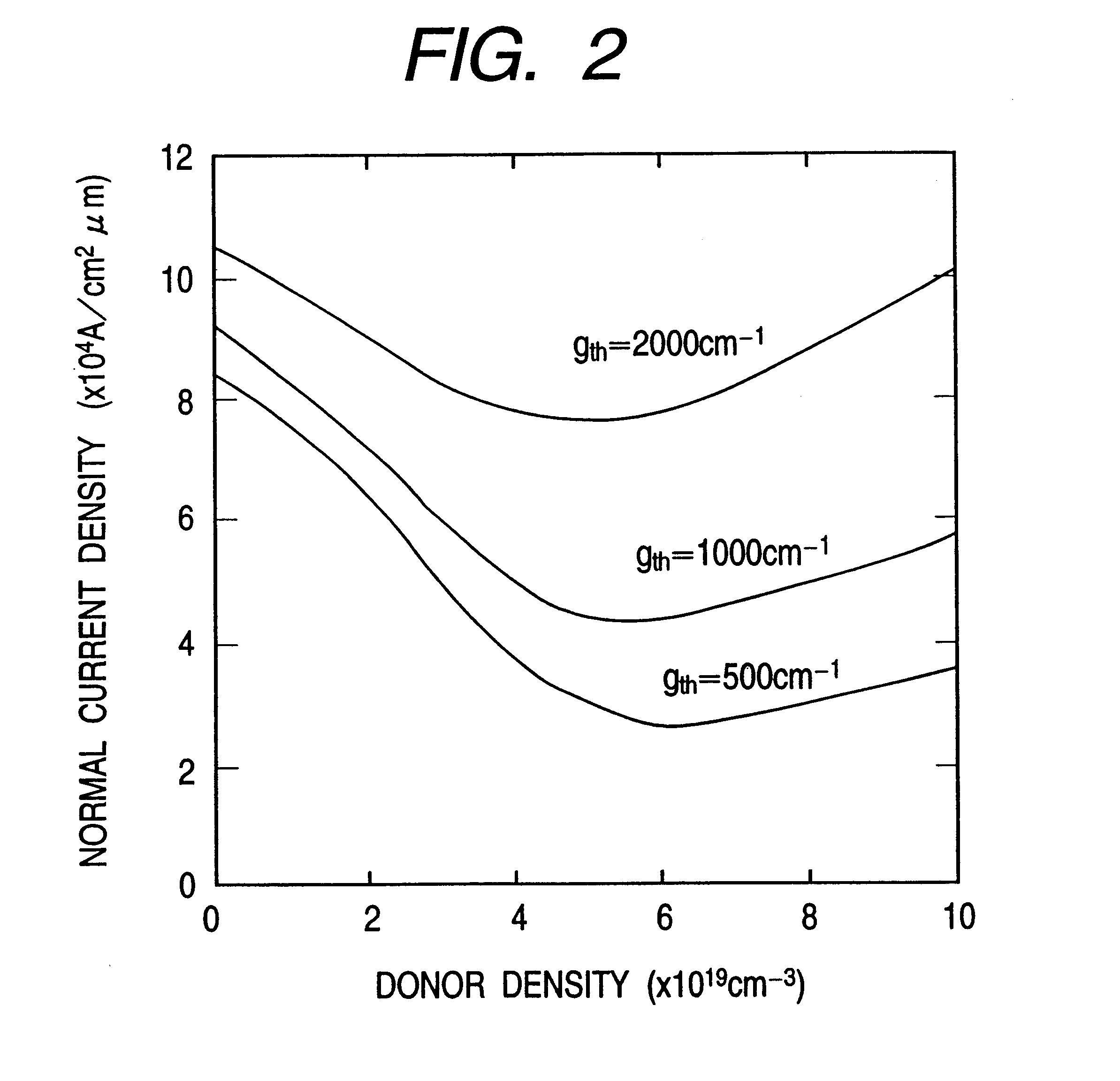

Optical information processing equipment and semiconductor light emitting device suitable therefor

An information processor of a high reliability and a high recording density, and a blue color, blue-violet color and violet color based semiconductor light emitting device operable at a low threshold current density, used for the same, are provided. An optical information processor of a high reliability and a high recording density enables a moving picture, such as a high-definition television picture, to be recorded and reproduced satisfactorily. A barrier layer in a quantum-well active layer of a semiconductor light emitting device is doped with n-type impurities at a high density. Alternatively, the face orientation of a quantum-well active layer of a semiconductor light emitting device is a plane inclined from the (0001) plane, whereby the threshold current value of the semiconductor light emitting device can be decreased. The semiconductor light emitting device is typified by a gallium nitride based compound semiconductor laser device.

Owner:USHIO OPTO SEMICON

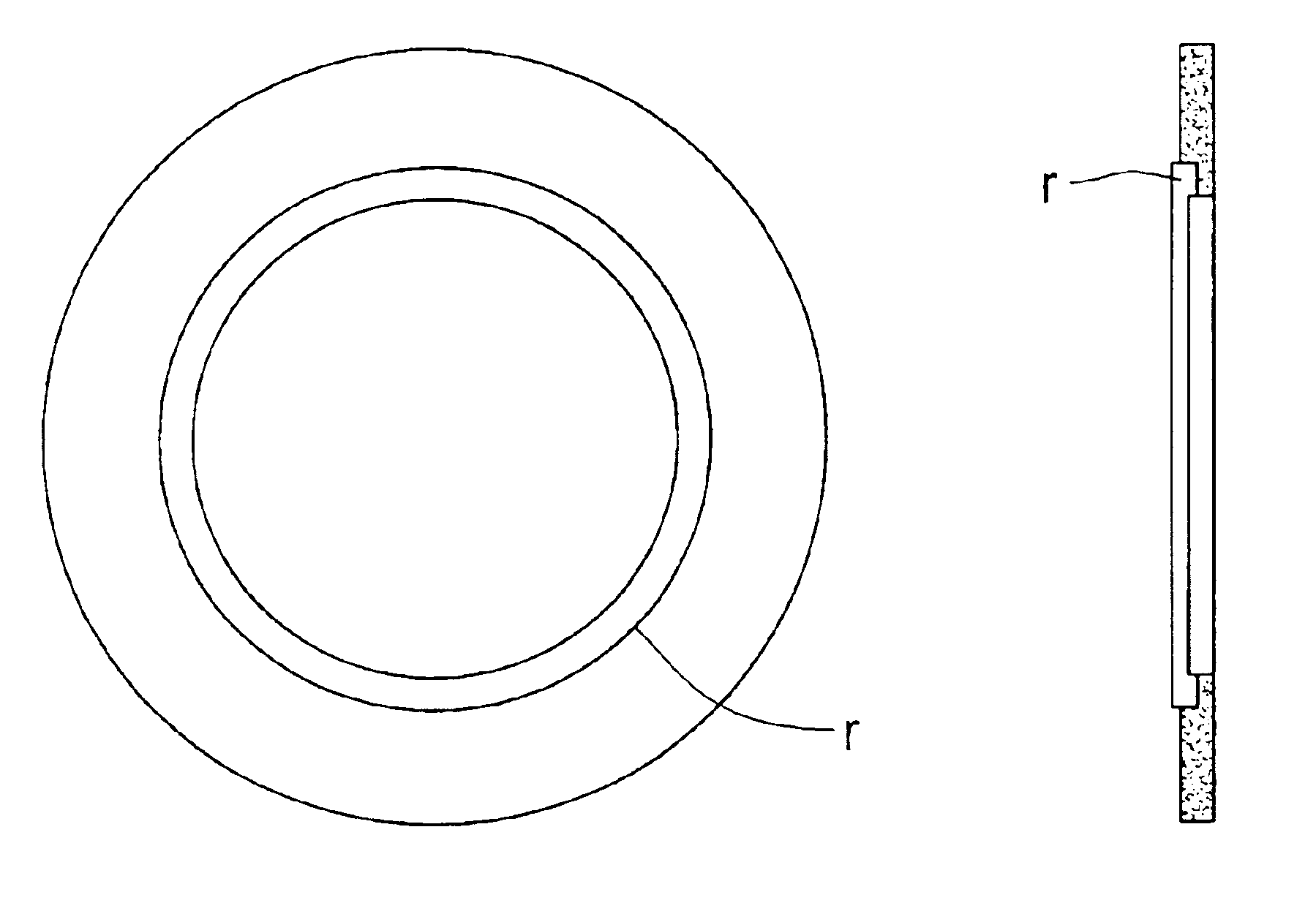

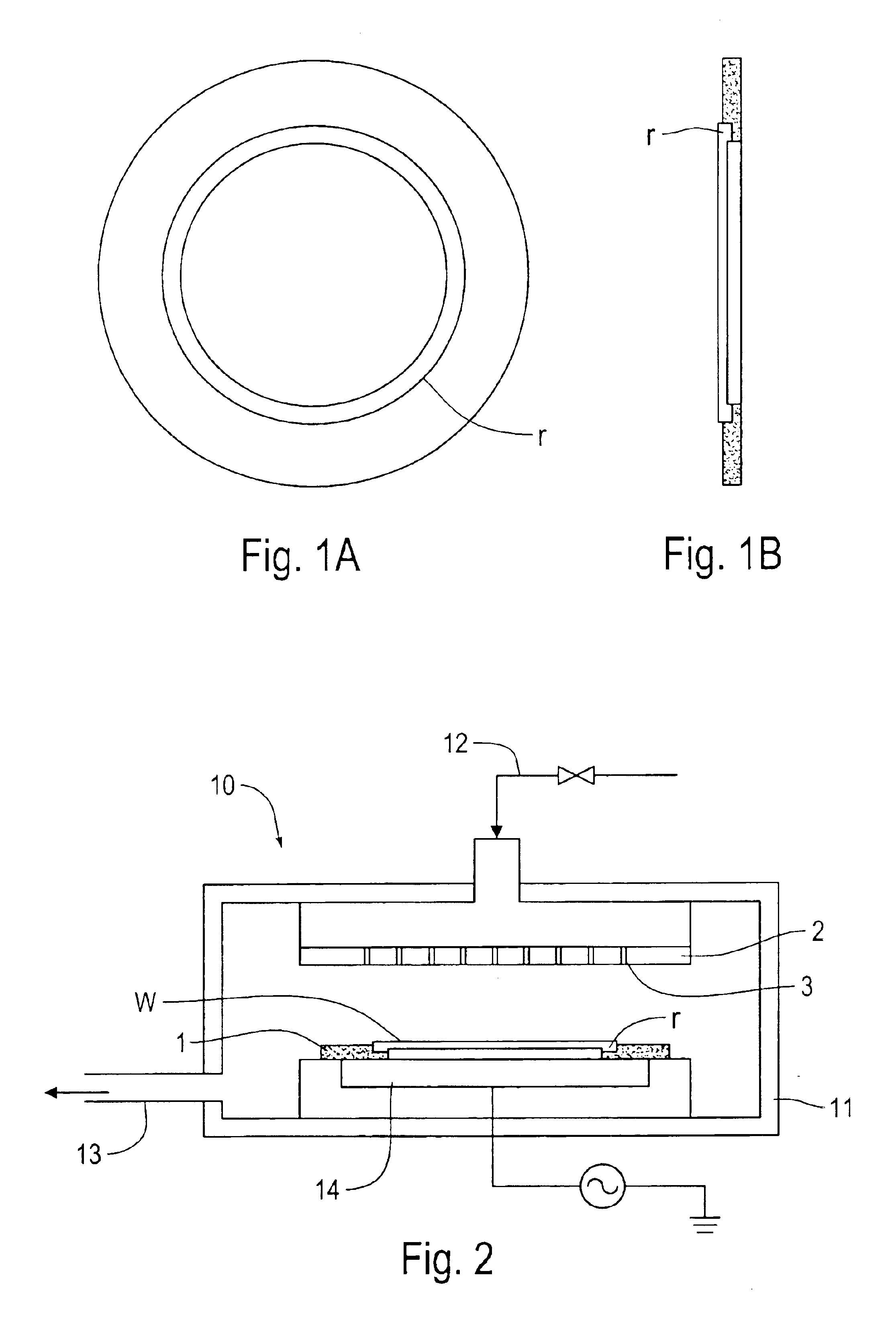

Silicon focus ring and method for producing the same

InactiveUS6815352B1Reduce Particle GenerationAvoid roughnessPolycrystalline material growthElectric discharge tubesCzochralski methodSingle crystal

There is disclosed a silicon focus ring consisting of silicon single crystal used as a silicon focus ring in a plasma apparatus, wherein concentration of interstitial oxygen contained in the silicon focus ring is not less than 5x10<17 >atoms / cm<3 >and not more than 1.5x10<18 >atoms / cm<3>, and a producing method for a silicon focus ring used for a plasma apparatus, wherein a single crystal silicon wherein concentration of interstitial oxygen contained in the silicon focus ring is not less than 5x10<17 >atoms / cm<3 >and not more than 1.5x10<18 >atoms / cm<3 >is grown by a Czochralski method, the single crystal silicon is processed in a circle, and a silicon focus ring is produced. There can be provided a silicon focus ring, which can prevent disadvantage due to impurities such as heavy metal.

Owner:SHIN ETSU CHEM IND CO LTD

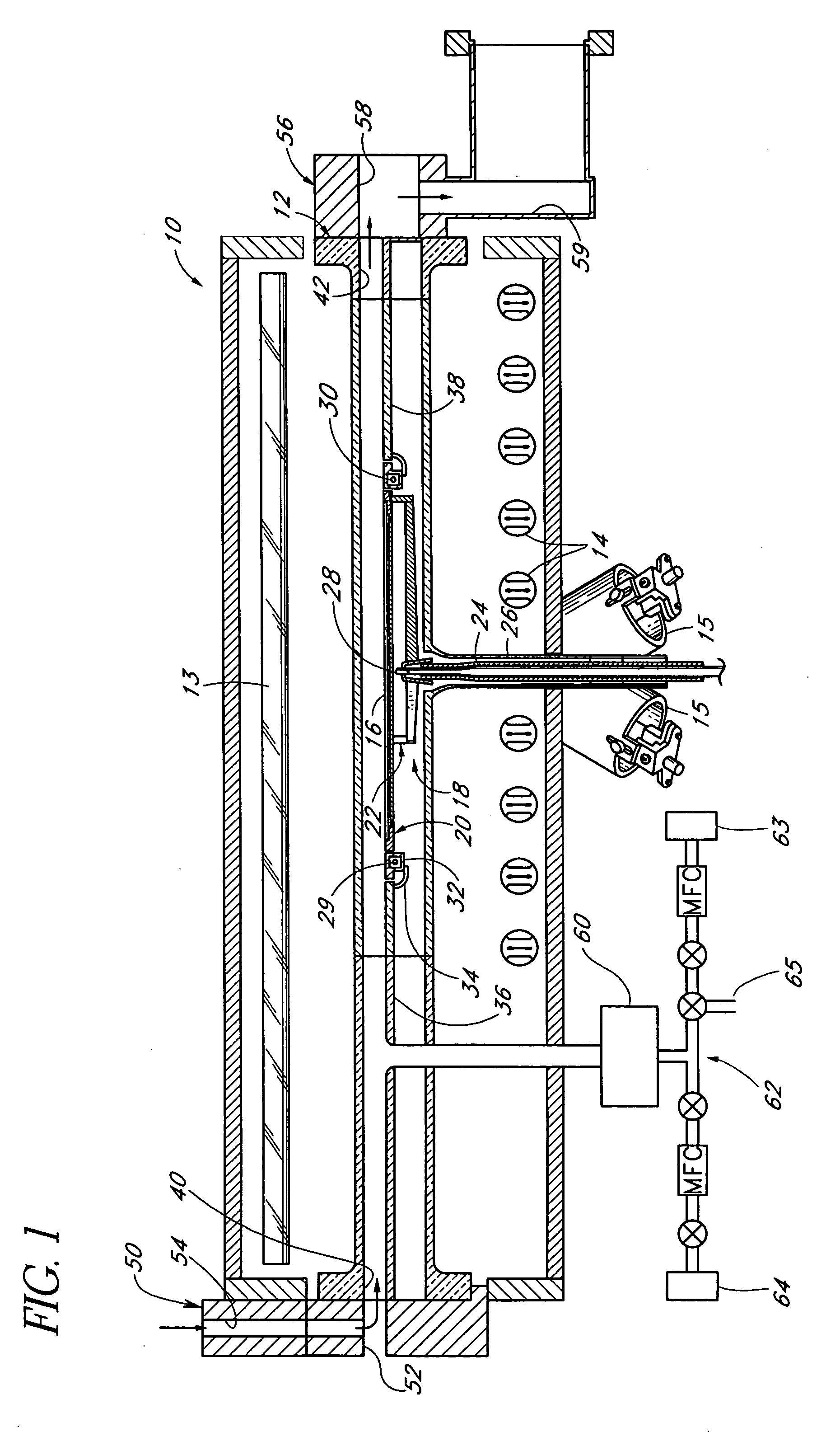

Film formation method and apparatus for semiconductor process

ActiveUS20060032443A1Low dielectric constantImprove corrosion resistanceSemiconductor/solid-state device manufacturingChemical vapor deposition coatingSilanesProcess engineering

An impurity-doped silicon nitride or oxynitride film is formed on a target substrate by CVD, in a process field to be selectively supplied with a first process gas containing a silane family gas, a second process gas containing a nitriding or oxynitriding gas, and a third process gas containing a doping gas. This method alternately includes first to fourth steps. The first step performs supply of the first and third process gases to the field. The second step stops supply of the first to third process gases to the field. The third step performs supply of the second process gas to the field while stopping supply of the first and third process gases to the field, and includes an excitation period of exciting the second process gas by an exciting mechanism. The fourth step stops supply of the first to third process gases to the field.

Owner:TOKYO ELECTRON LTD

Method of manufacturing semiconductor device, and semiconductor device

ActiveUS20070254414A1Sufficient carrier mobilityImpurity will diffuseSemiconductor/solid-state device manufacturingSemiconductor devicesSurface layerConcentration gradient

A method of manufacturing a semiconductor device includes: the first step of forming a gate electrode over a silicon substrate, with a gate insulating film; and the second step of digging down a surface layer of the silicon substrate by etching conducted with the gate electrode as a mask. The method of manufacturing the semiconductor device further includes the third step of epitaxially growing, on the surface of the dug-down portion of the silicon substrate, a mixed crystal layer including silicon and atoms different in lattice constant from silicon so that the mixed crystal layer contains an impurity with such a concentration gradient that the impurity concentration increases along the direction from the silicon substrate side toward the surface of the mixed crystal layer.

Owner:SONY CORP

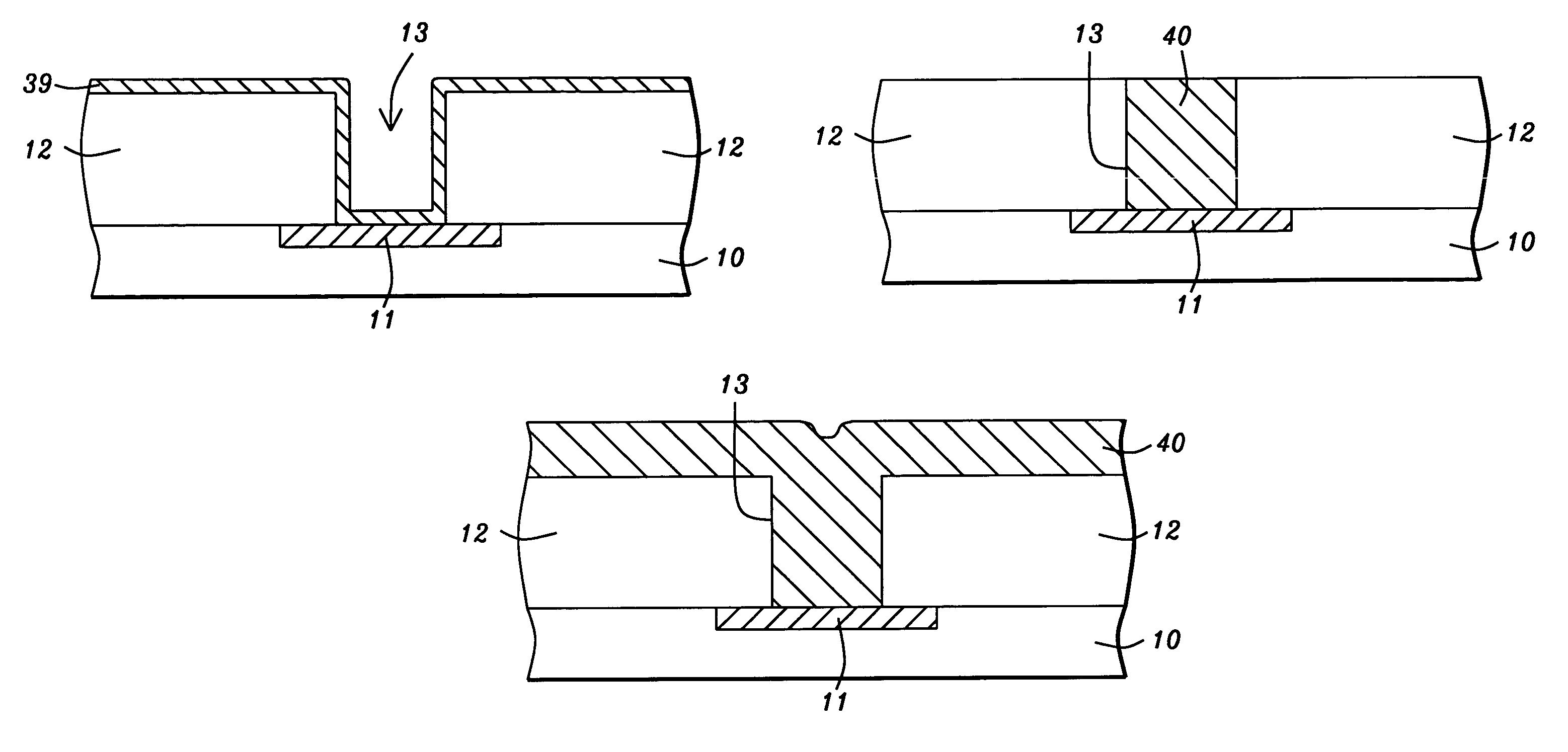

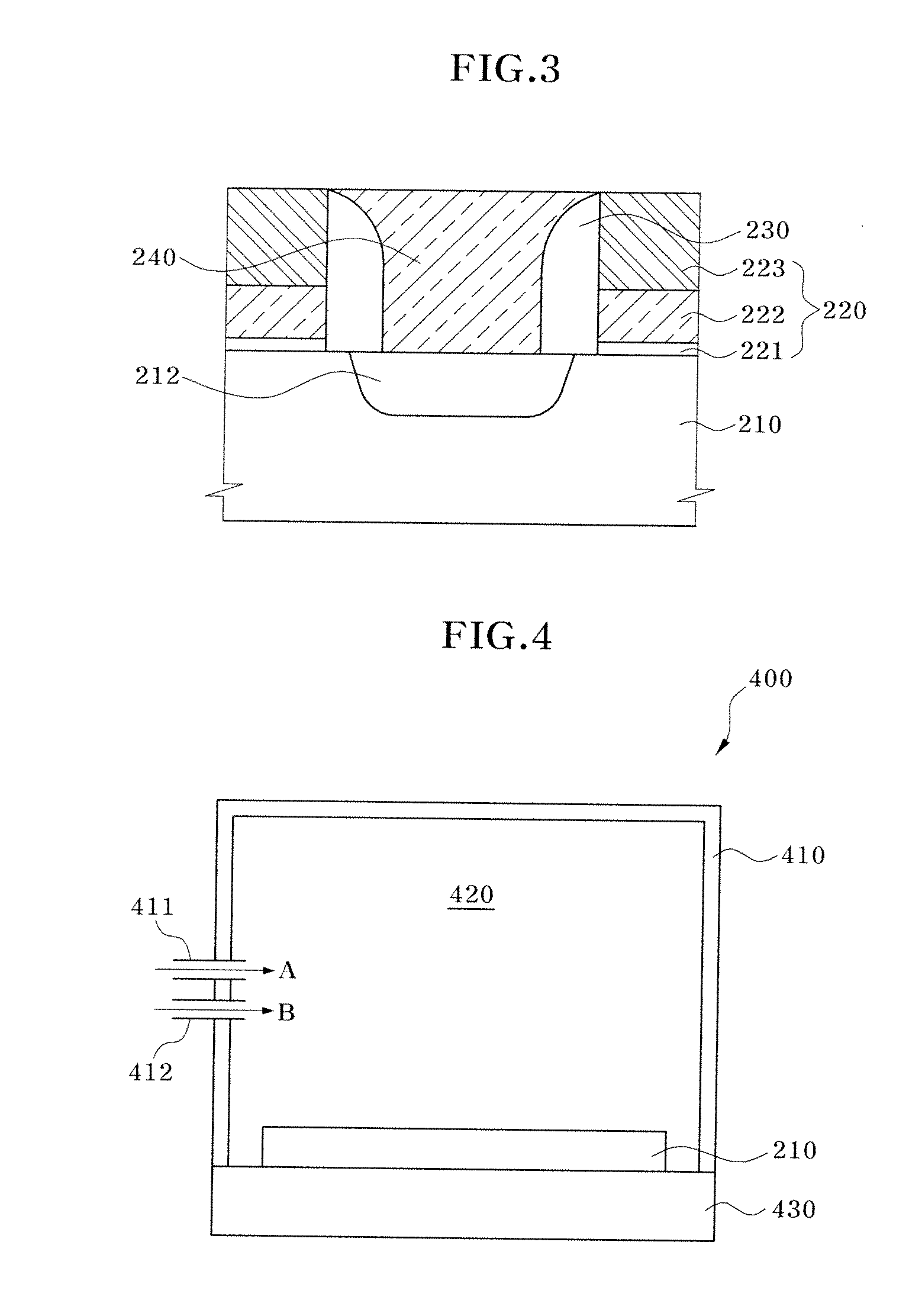

Method of Fabricating Landing Plug in Semiconductor Device

InactiveUS20100330801A1Improve resistance performanceSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

A method of fabricating a landing plug in a semiconductor memory device, which in one embodiment includes forming a landing plug contact hole on a semiconductor substrate having an impurity region to expose the impurity region; forming a landing plug by filling the landing plug contact hole with a polysilicon layer, wherein the landing plug is divided into a first region, a second region, a third region, and a fourth region from a lower portion of the landing plug, and the first region is doped with a first doping concentration that is relatively lowest, the second region is doped with a second doping concentration that is higher than the first doping concentration, the third region is doped with a third doping concentration that is higher than the second doping concentration and the fourth region is not doped; and annealing the resulting product formed with the landing plug.

Owner:SK HYNIX INC

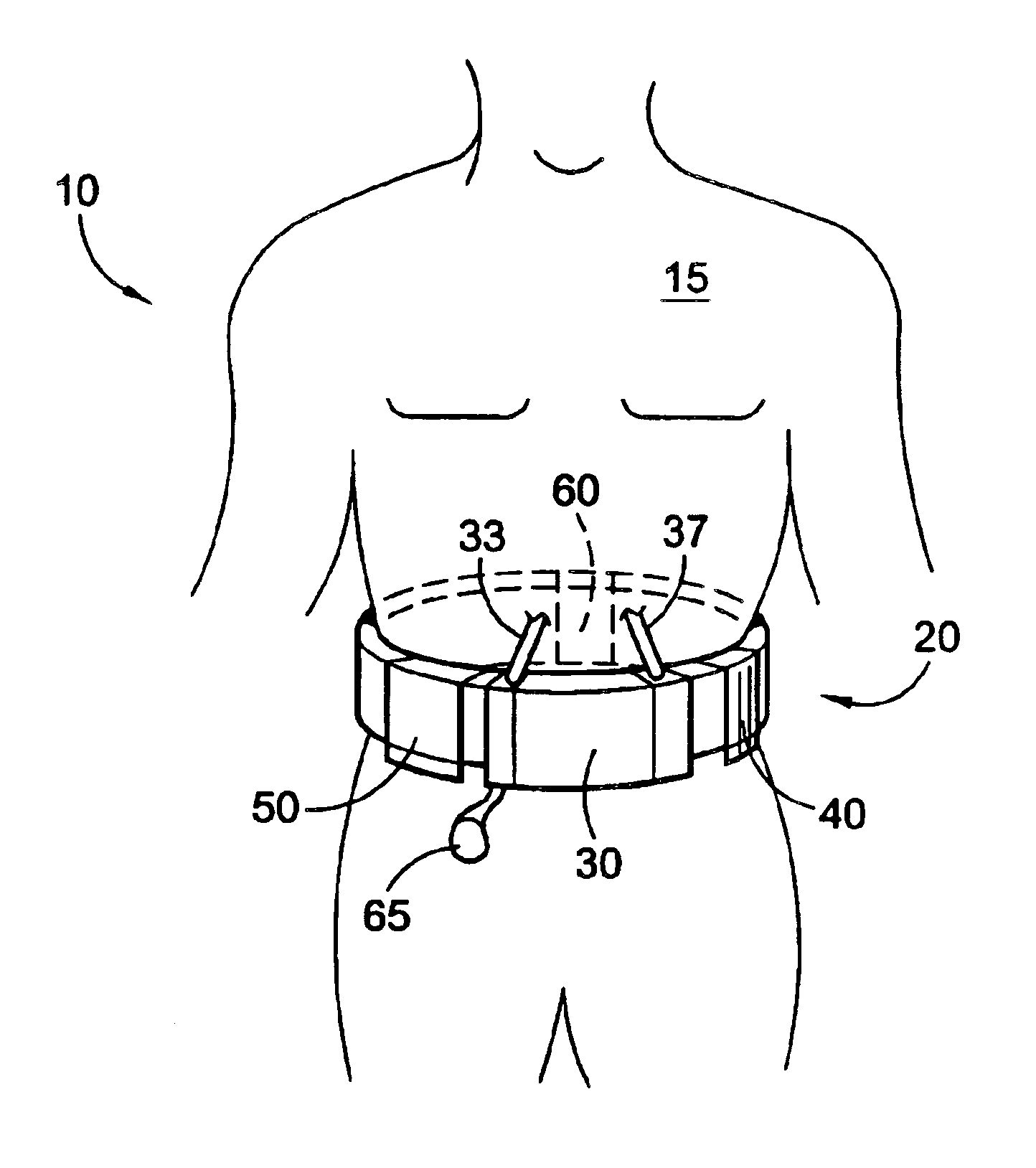

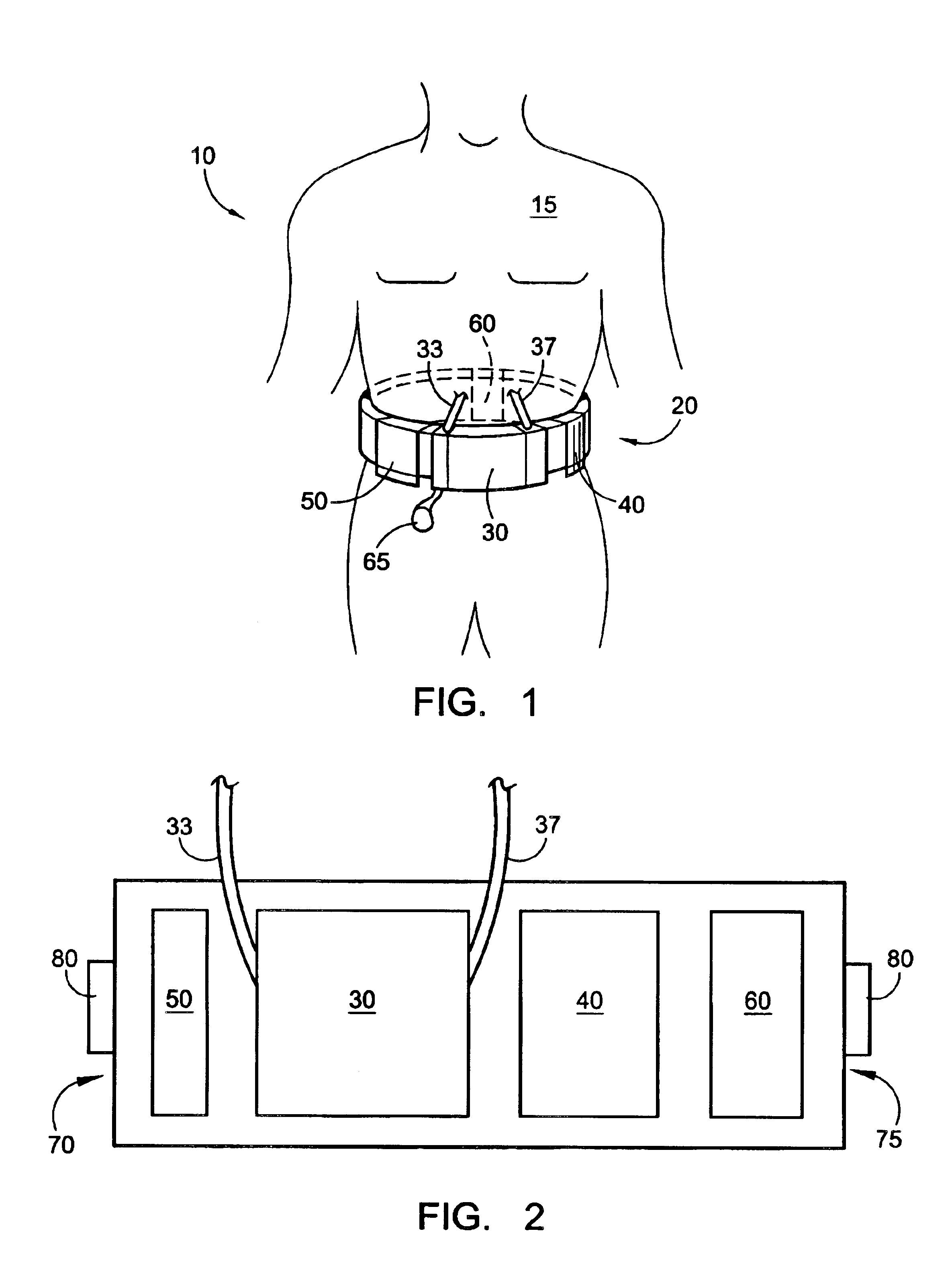

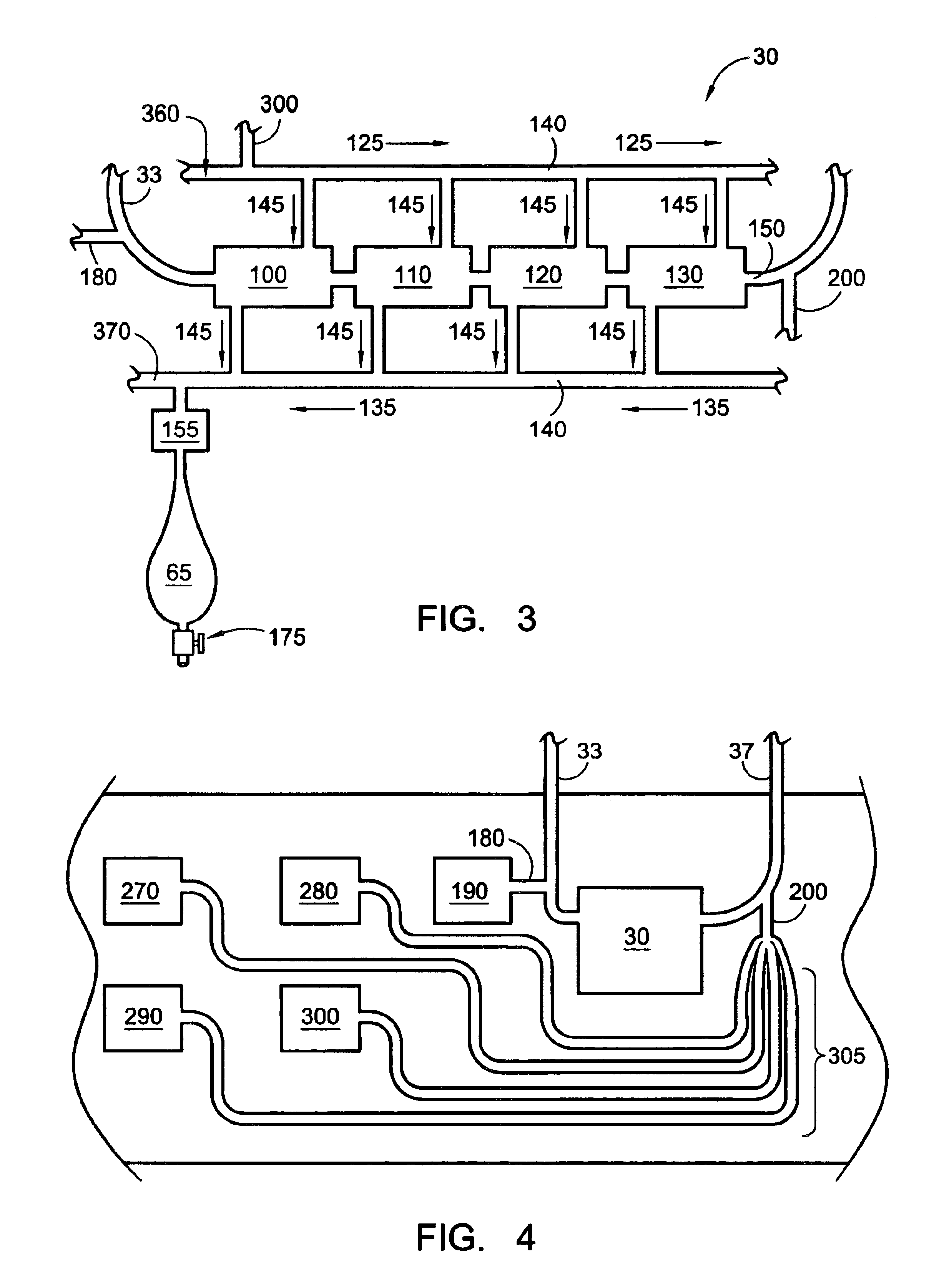

Wearable continuous renal replacement therapy device

A continuous renal replacement therapy device adapted to be worn on a portion of the body of a patient, including: a plurality of contoured dialyzers, which are connected in series and utilize dialysate to remove impurities from the blood of the patient; and a plurality of contoured sorbent device, which are connected in series and are for regenerating the spent dialysate.

Owner:FRESENIUS MEDICAL CARE HLDG INC

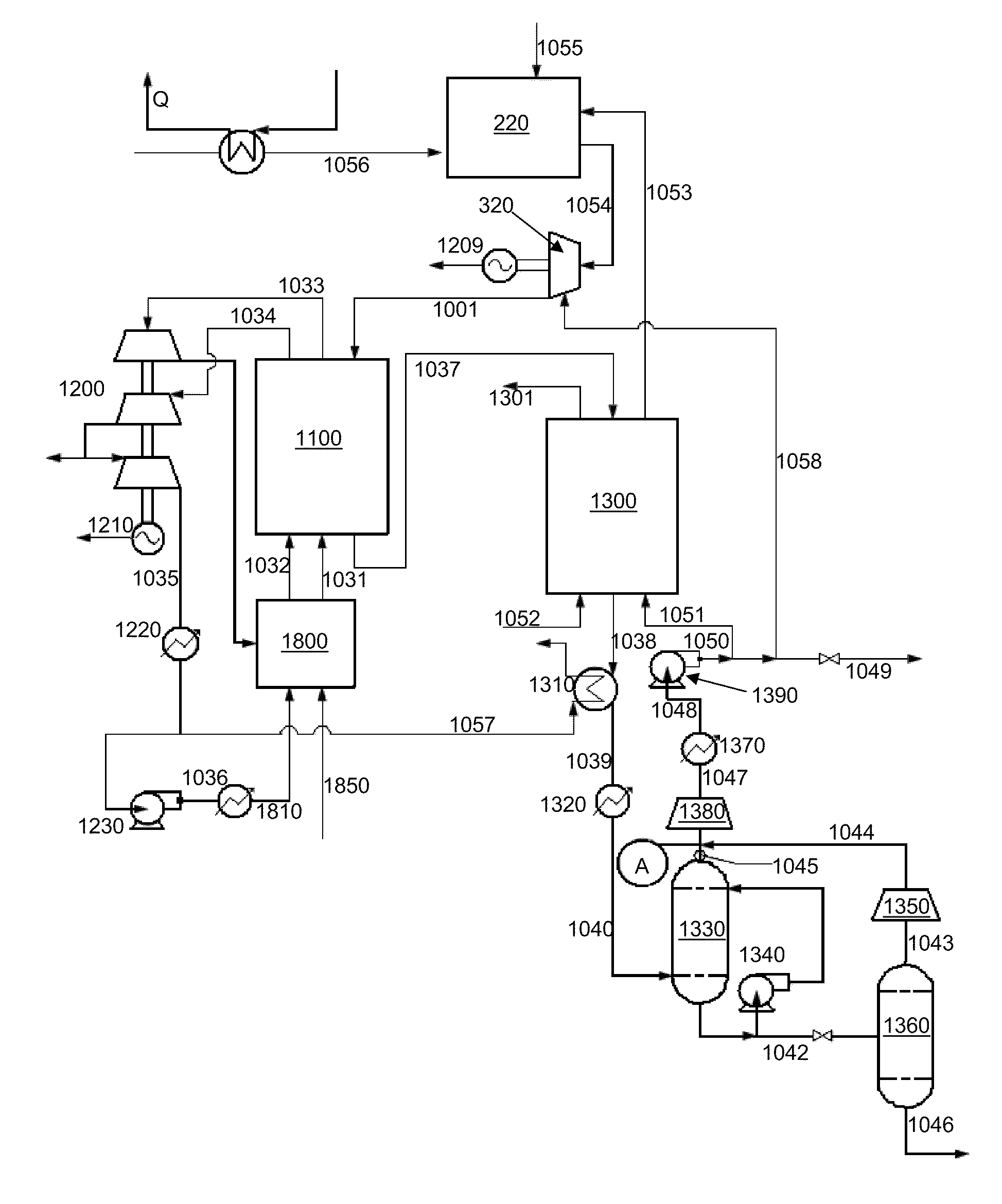

System and method for high efficiency power generation using a carbon dioxide circulating working fluid

ActiveUS20110179799A1Improve efficiencyIncrease pressure ratioSolidificationLiquefactionWorking fluidCombustor

The present invention provides methods and system for power generation using a high efficiency combustor in combination with a CO2 circulating fluid. The methods and systems advantageously can make use of a low pressure ratio power turbine and an economizer heat exchanger in specific embodiments. Additional low grade heat from an external source can be used to provide part of an amount of heat needed for heating the recycle CO2 circulating fluid. Fuel derived CO2 can be captured and delivered at pipeline pressure. Other impurities can be captured.

Owner:8 RIVERS CAPTTAL LLC

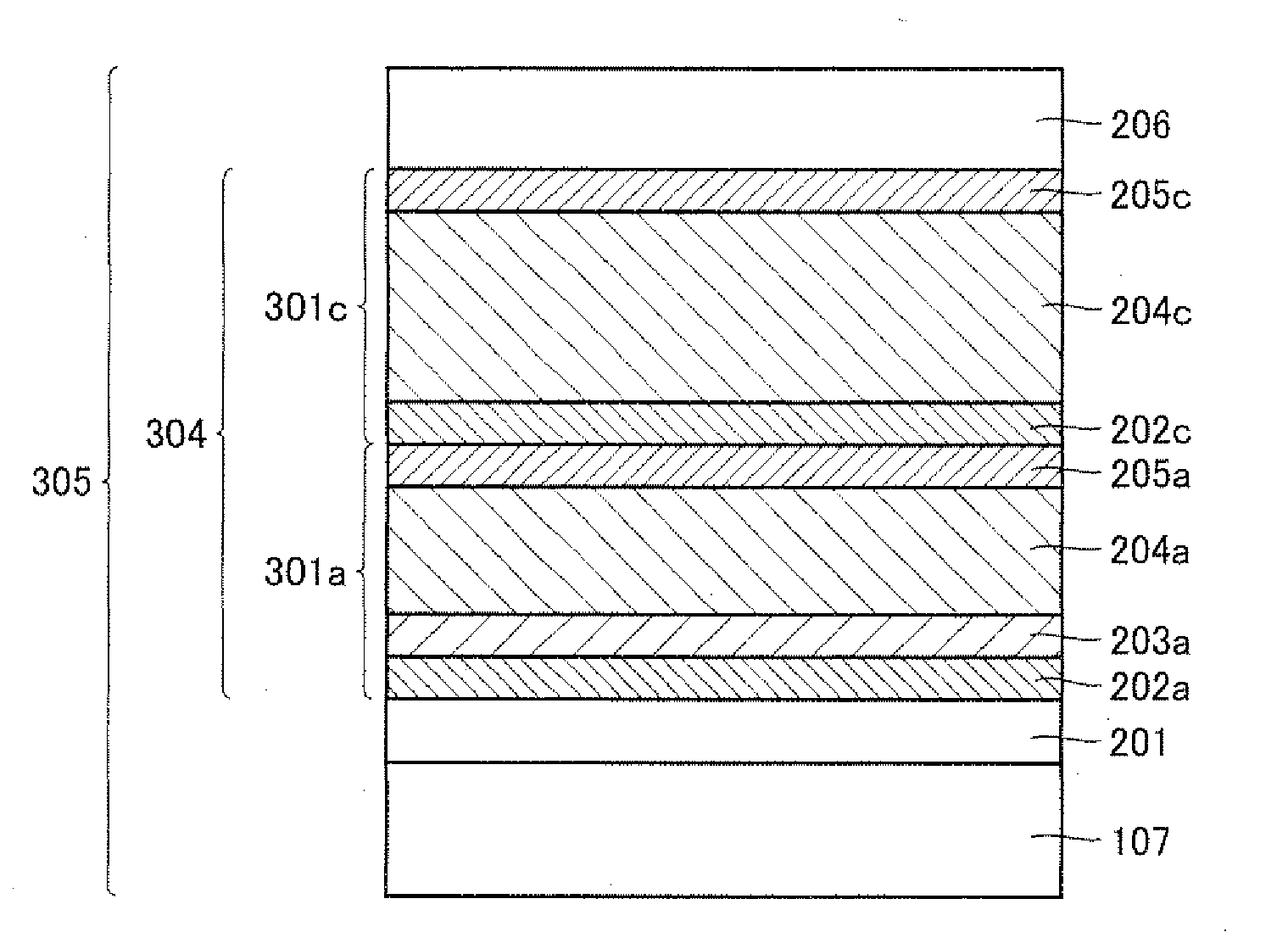

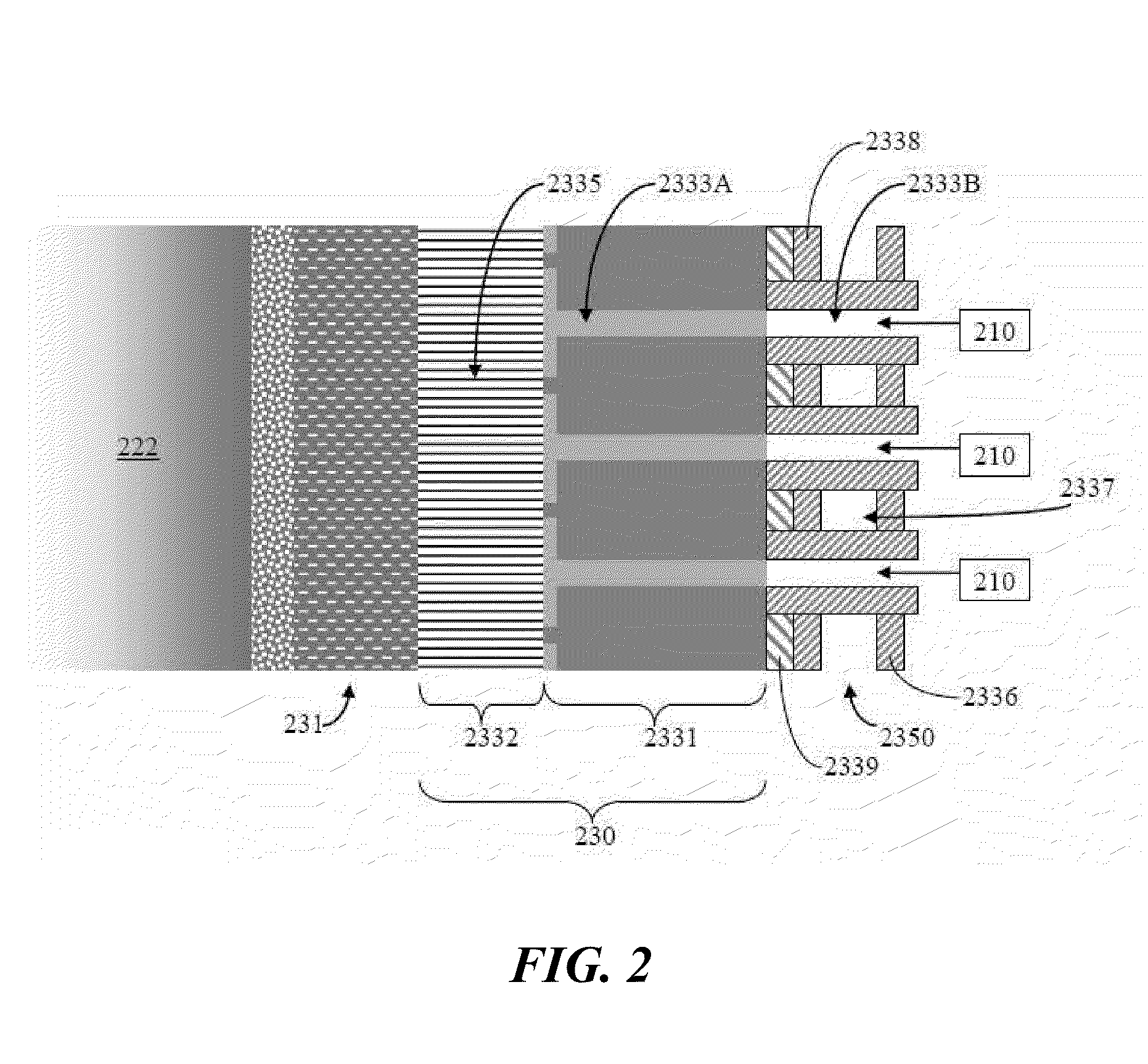

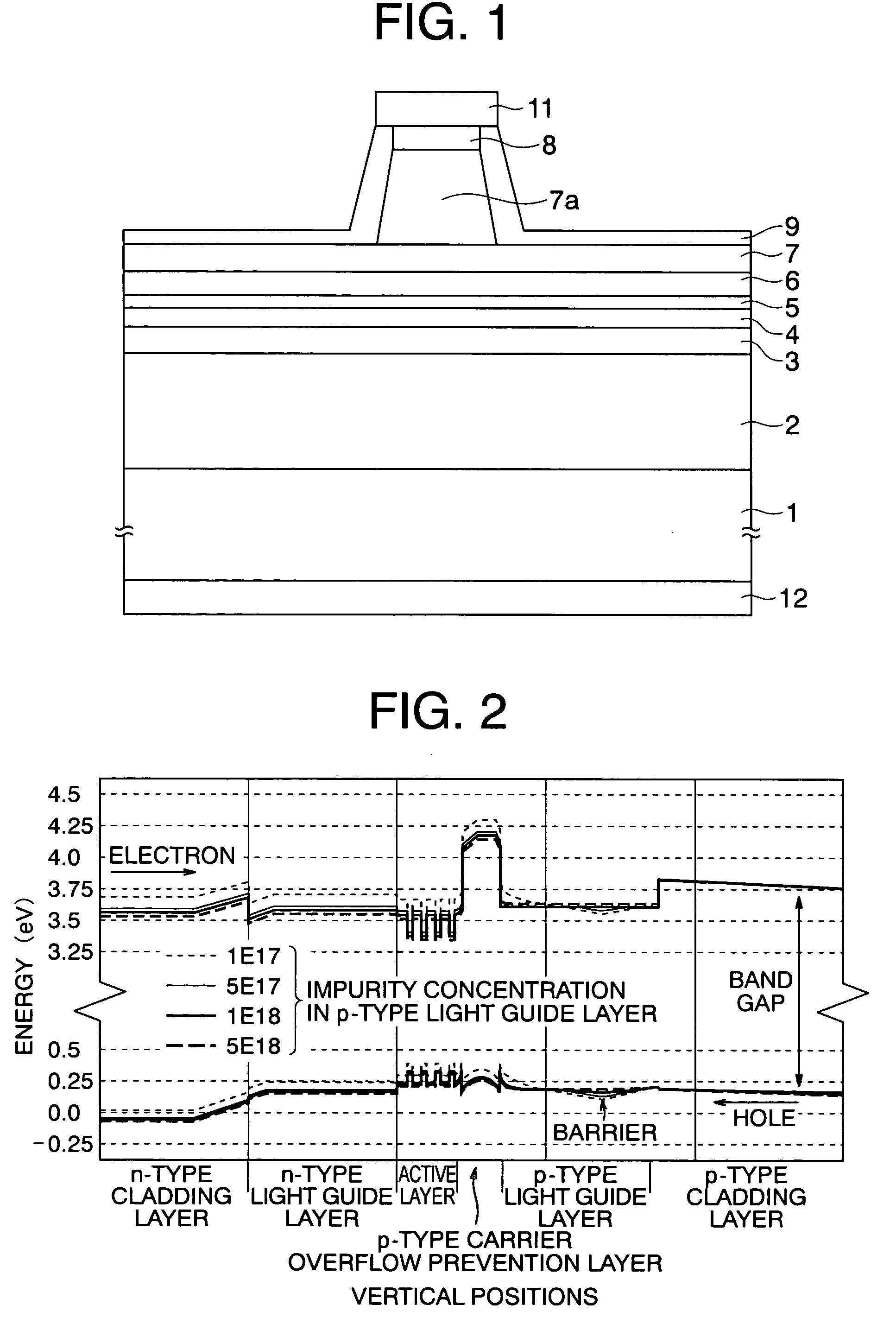

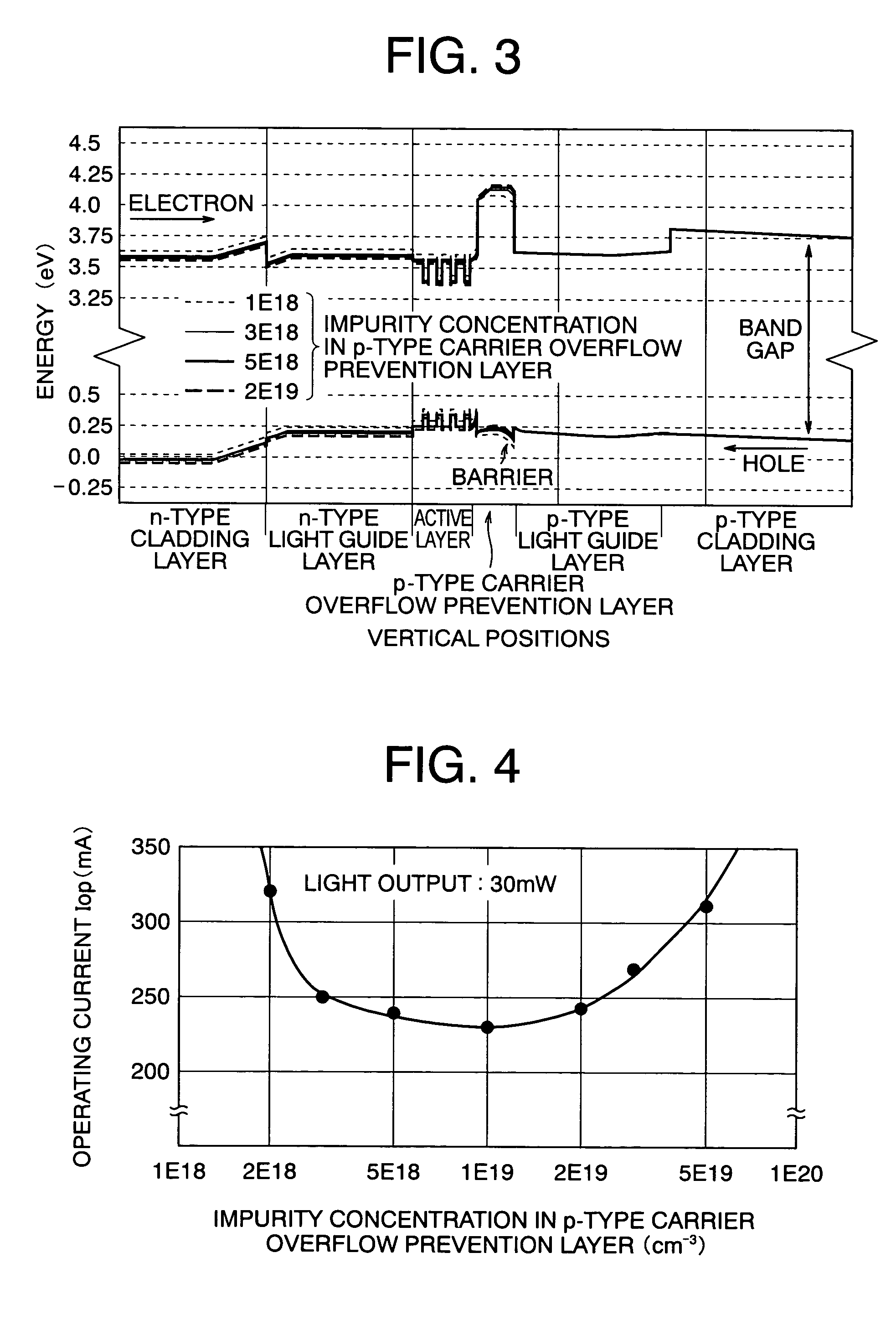

Semiconductor light-emitting element and method of manufacturing the same

Disclosed is a semiconductor light-emitting element, comprising an n-type-cladding layer; a light guide layer positioned on the n-type cladding layer; a multiple quantum well structure active layer positioned on the light guide layer; a p-type carrier overflow prevention layer positioned on the active layer and having an impurity concentration of 5×1018 cm−3 to not more than 3×1019 cm−3; a p-type light guide layer positioned on the p-type carrier overflow prevention layer and-having an impurity concentration of 1×1018 cm−3 or more and less-than that of the p-type carrier overflow prevention layer; and a p-type cladding layer positioned on the p-type light guide layer and having a band gap narrower than the p-type carrier overflow prevention layer, and a method of manufacturing the same.

Owner:KK TOSHIBA

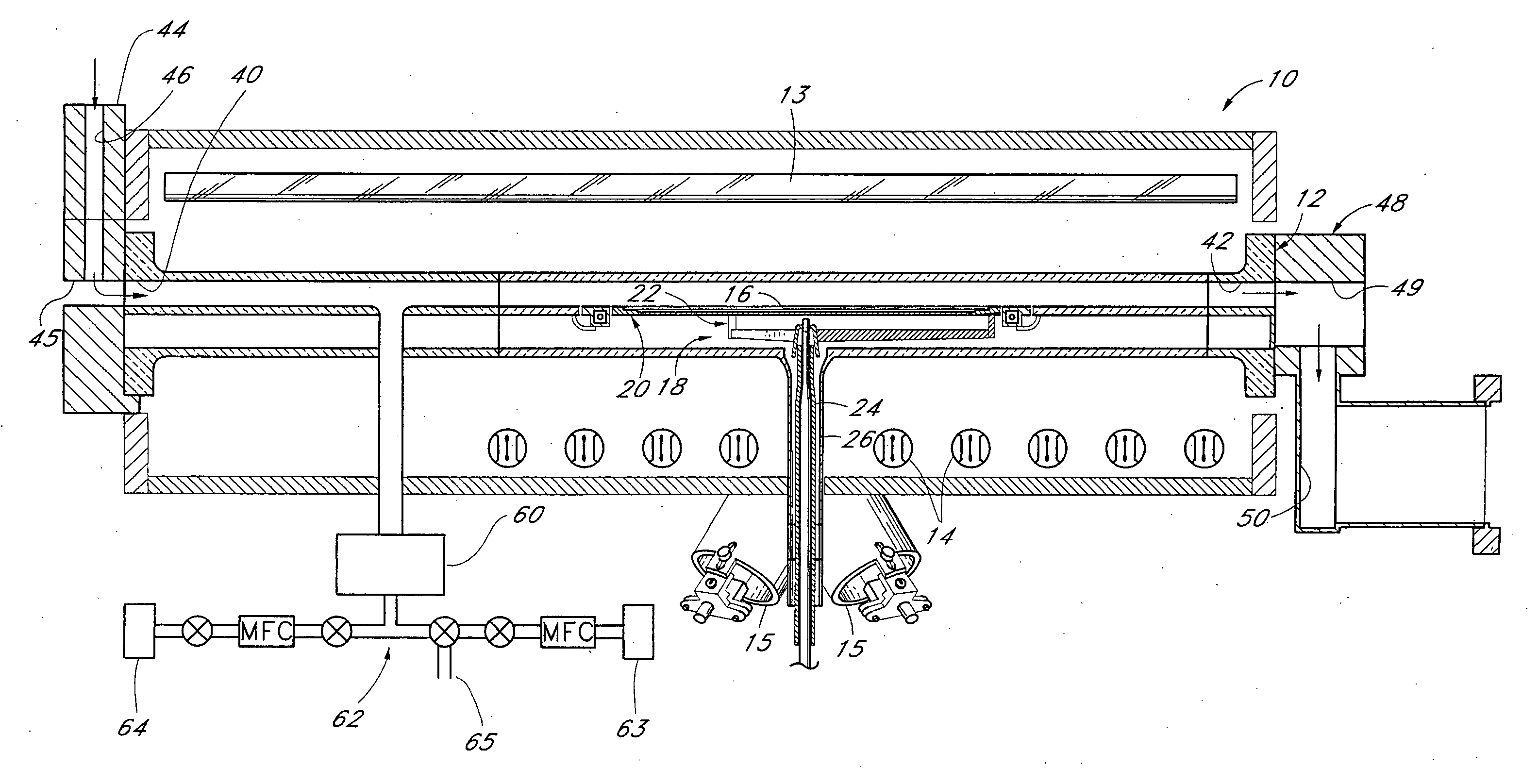

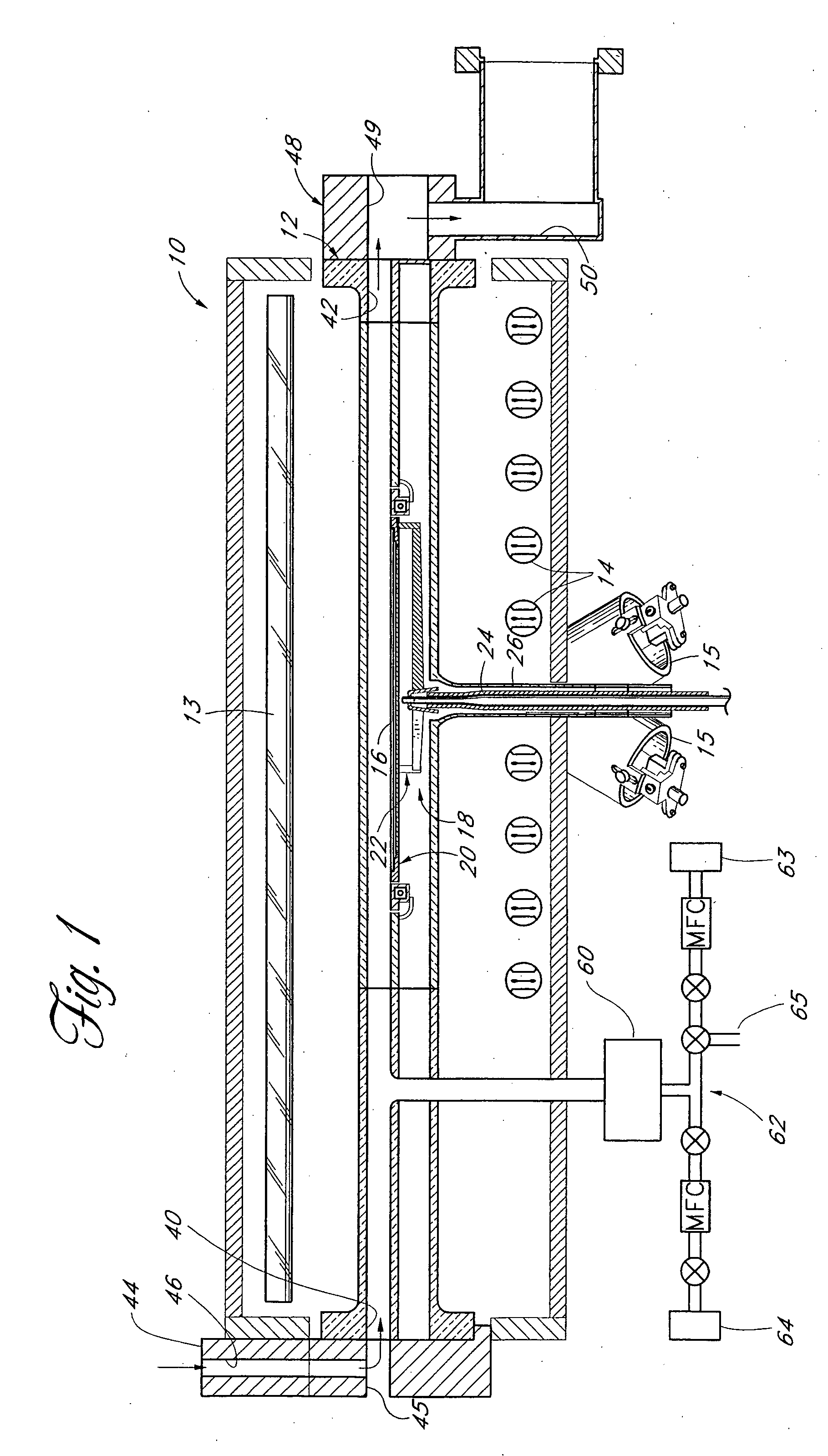

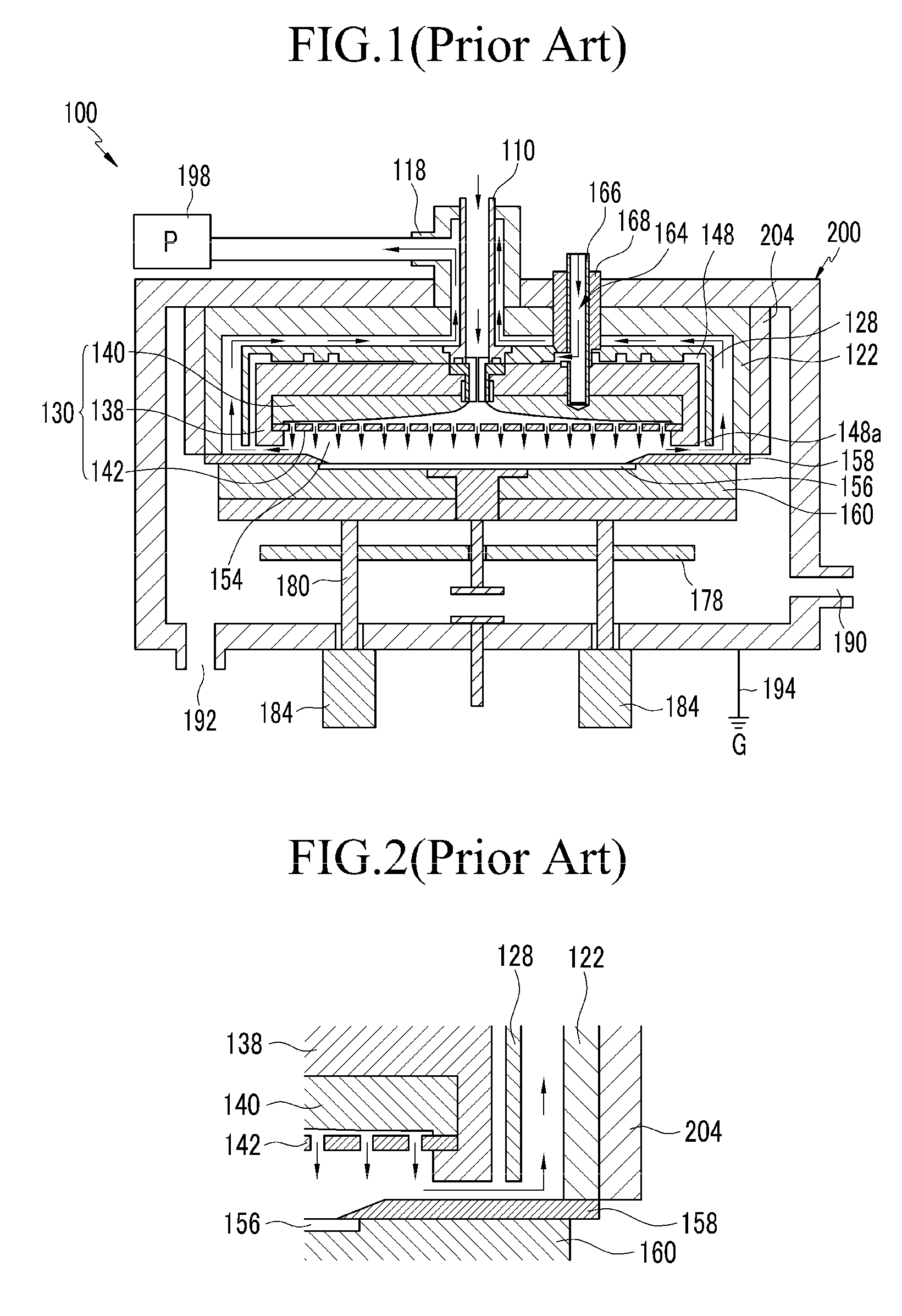

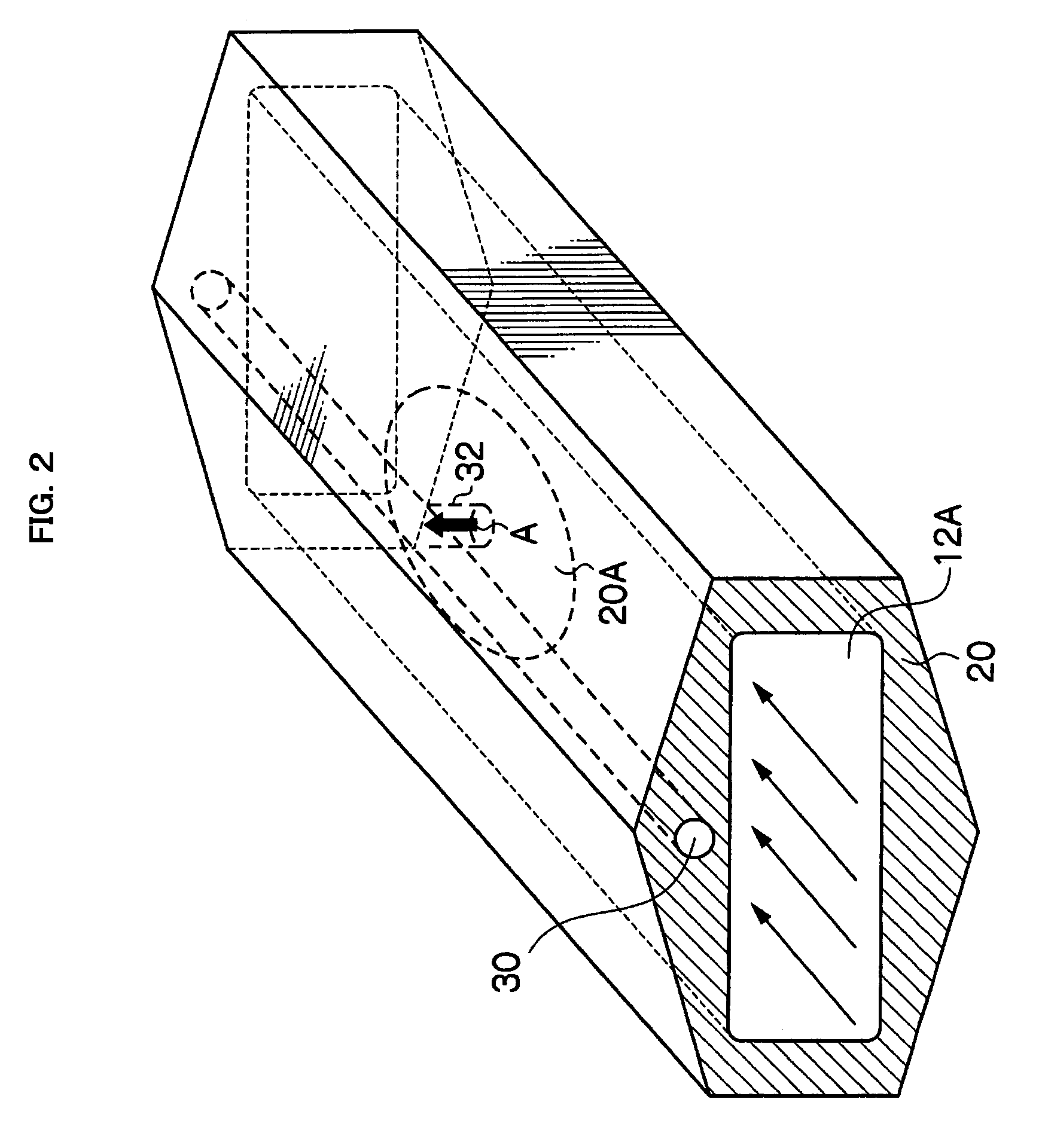

Apparatus for manufacturing semiconductor thin film

InactiveUS20090229519A1Improve in-plane evennessPolycrystalline material growthSemiconductor/solid-state device manufacturingIn planeSusceptor

The present invention provides an apparatus for manufacturing a semiconductor thin film that is capable of manufacturing an even thin film with substantially no adhesion of impurities, and is capable of improving in-plane evenness of a grown thin film. The invention is an apparatus for manufacturing a semiconductor thin film includes a reaction tube 12, a susceptor 20 disposed in the reaction tube 12, and a negative pressure generator, the negative pressure generator applying a negative pressure to a substrate 22A placed on the susceptor 20 to hold the substrate, and the substrate 22A is placed so that an angle of a normal line to a crystal growth face of the substrate 22A to a vertical downward direction is less than 180°.

Owner:TOYOTA JIDOSHA KK