Patents

Literature

6484 results about "Inter layer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

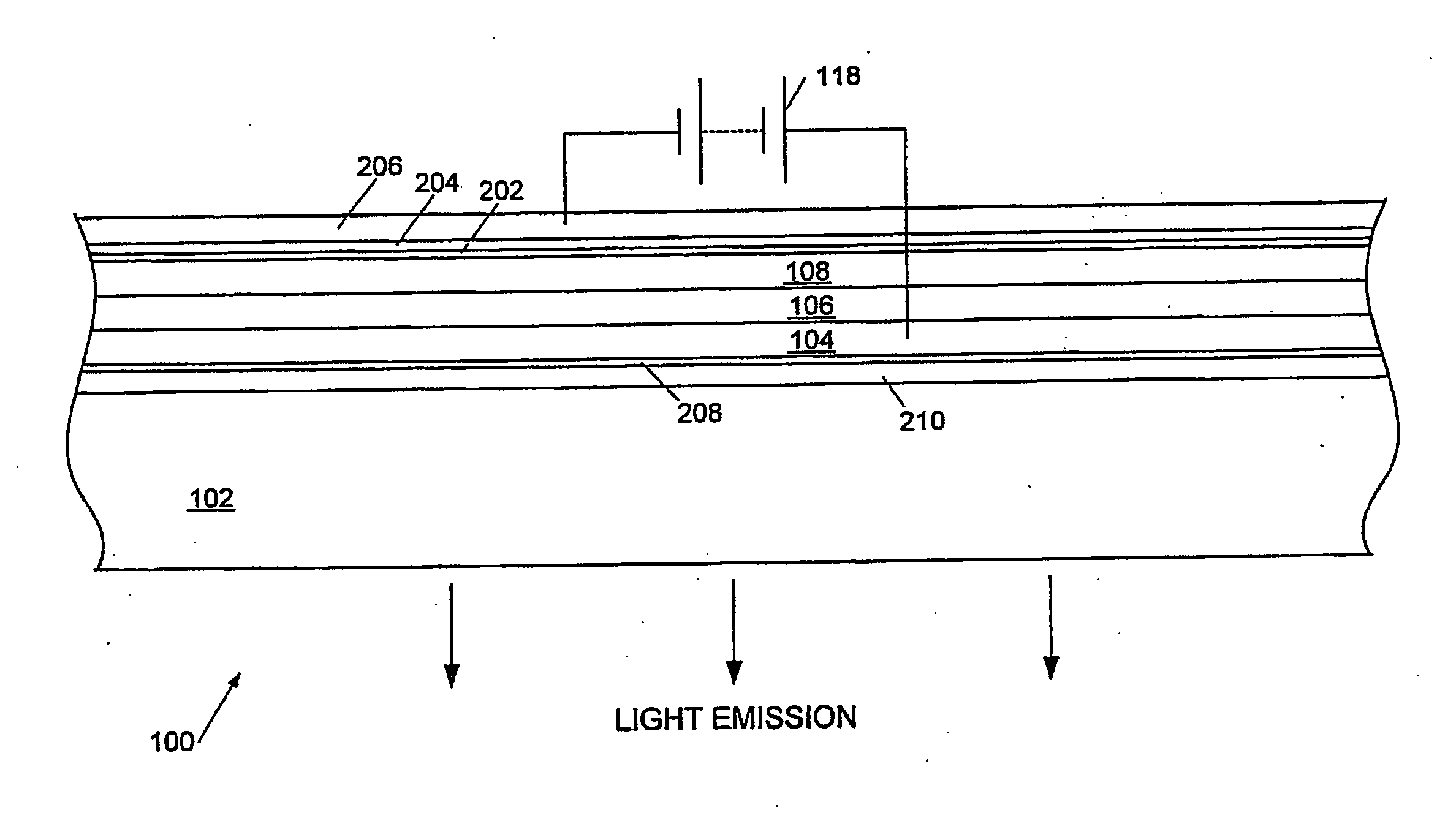

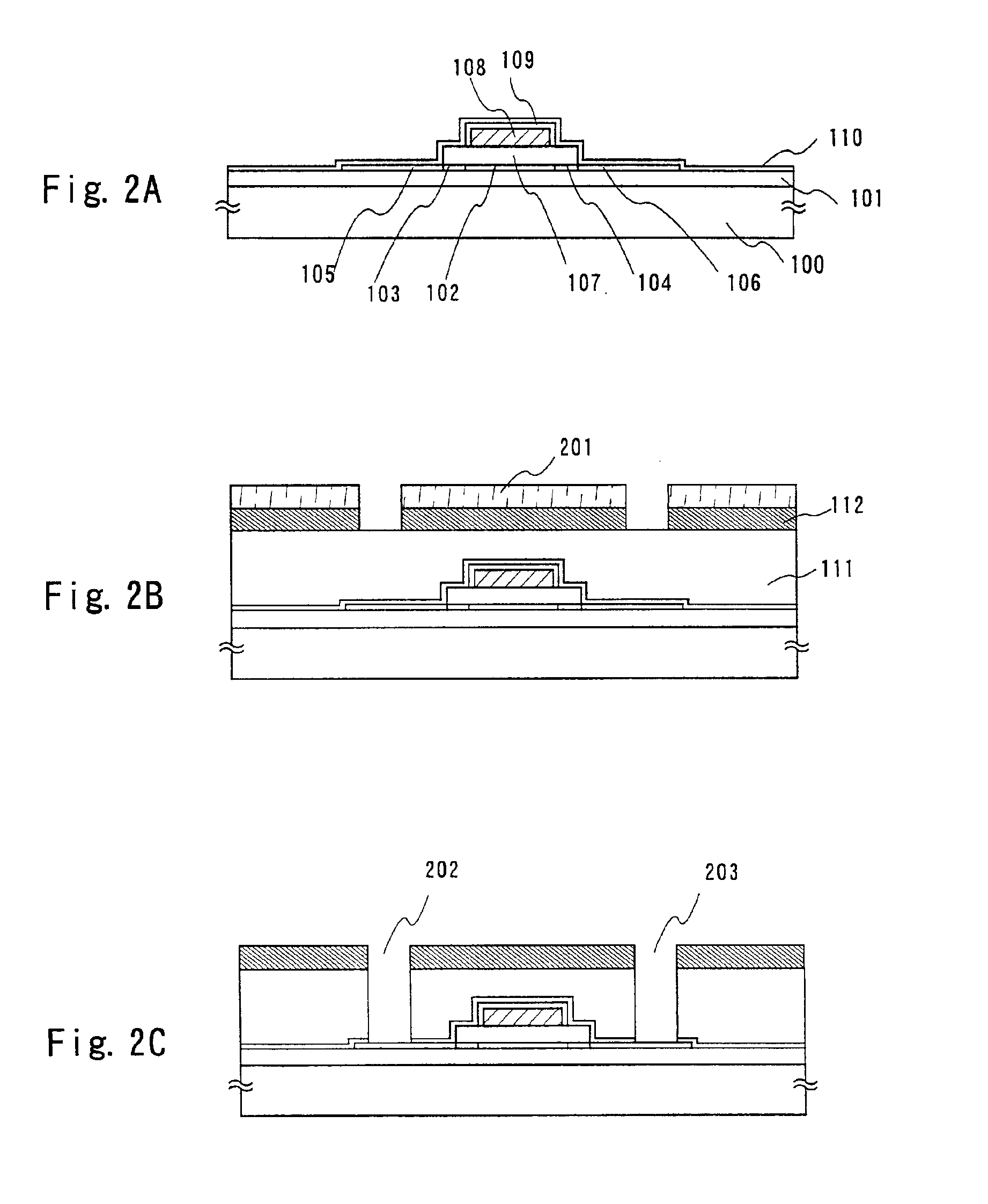

Manufacturing Apparatus and Manufacturing Method of Lighting Device

InactiveUS20100236691A1Improve efficiencyReduce manufacturing costVacuum evaporation coatingSolid-state devicesInter layerManufactured apparatus

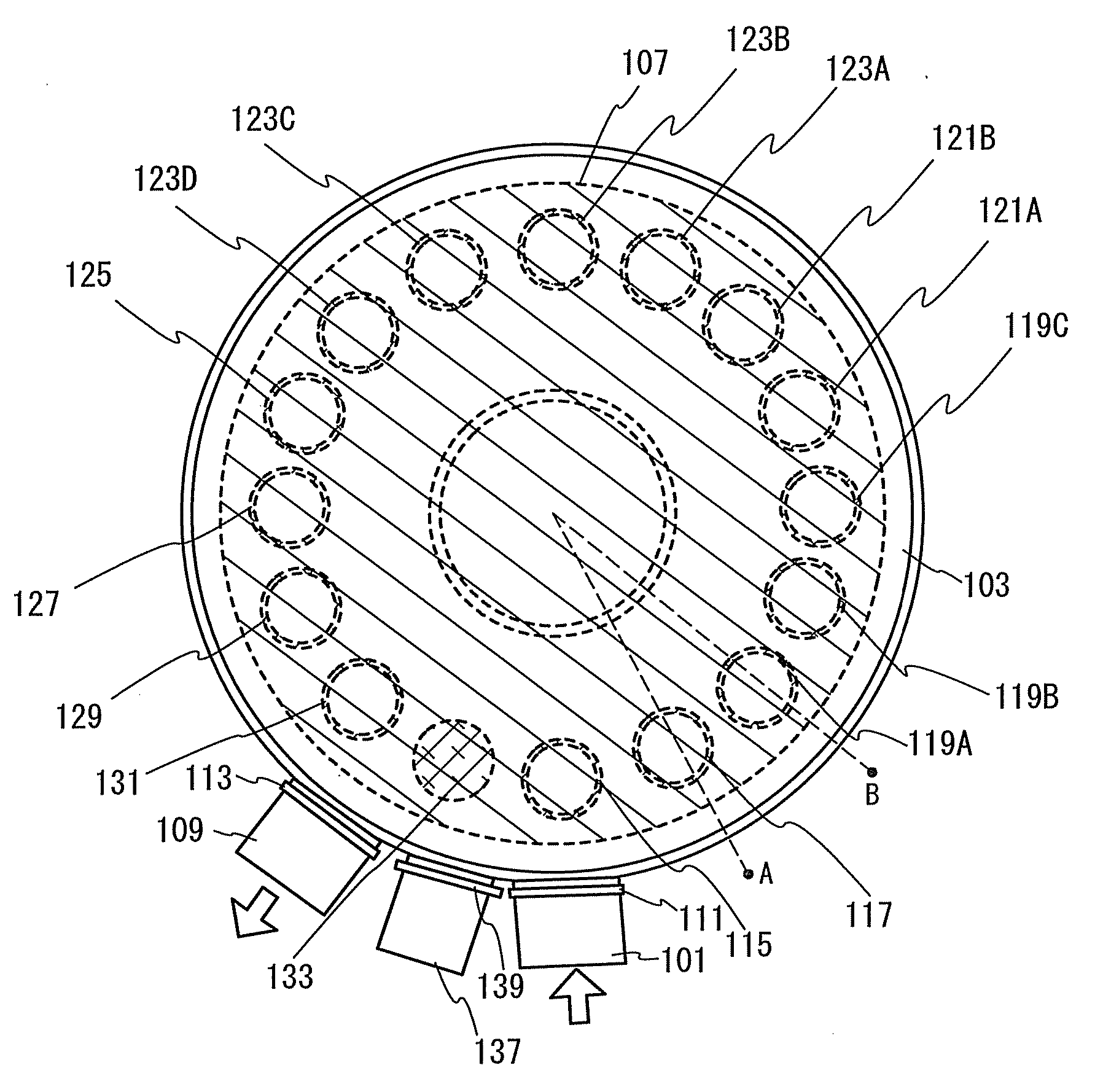

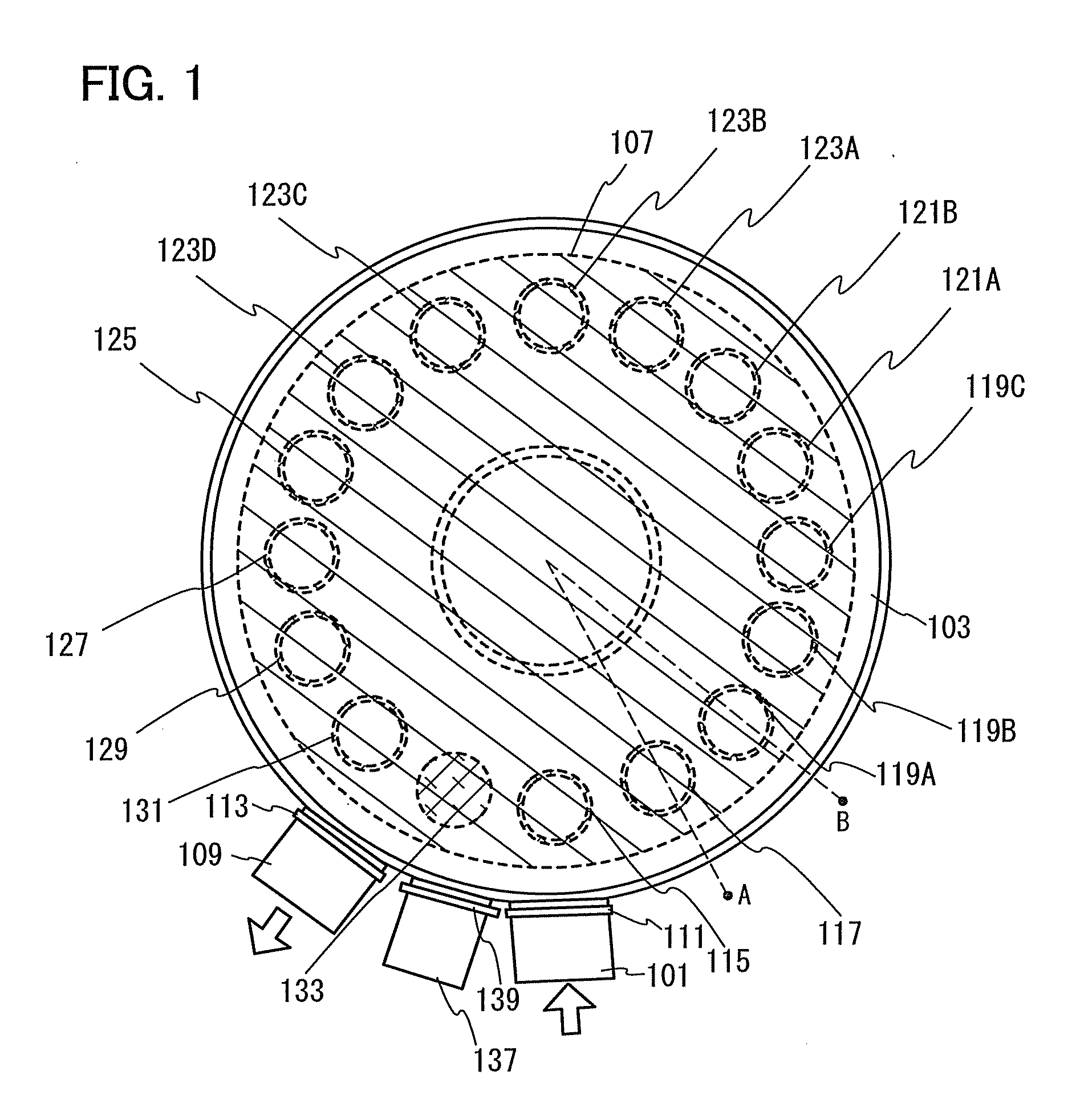

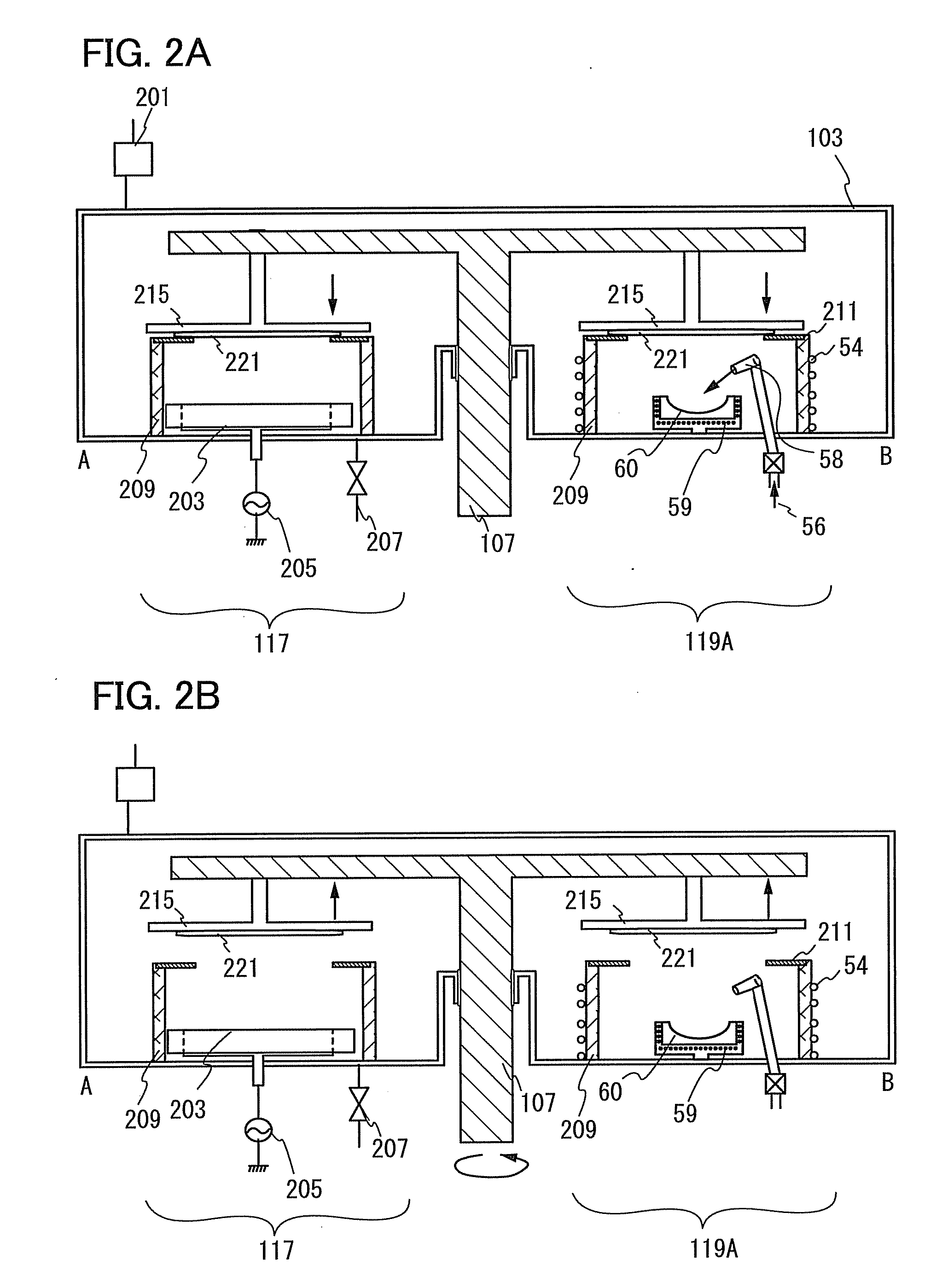

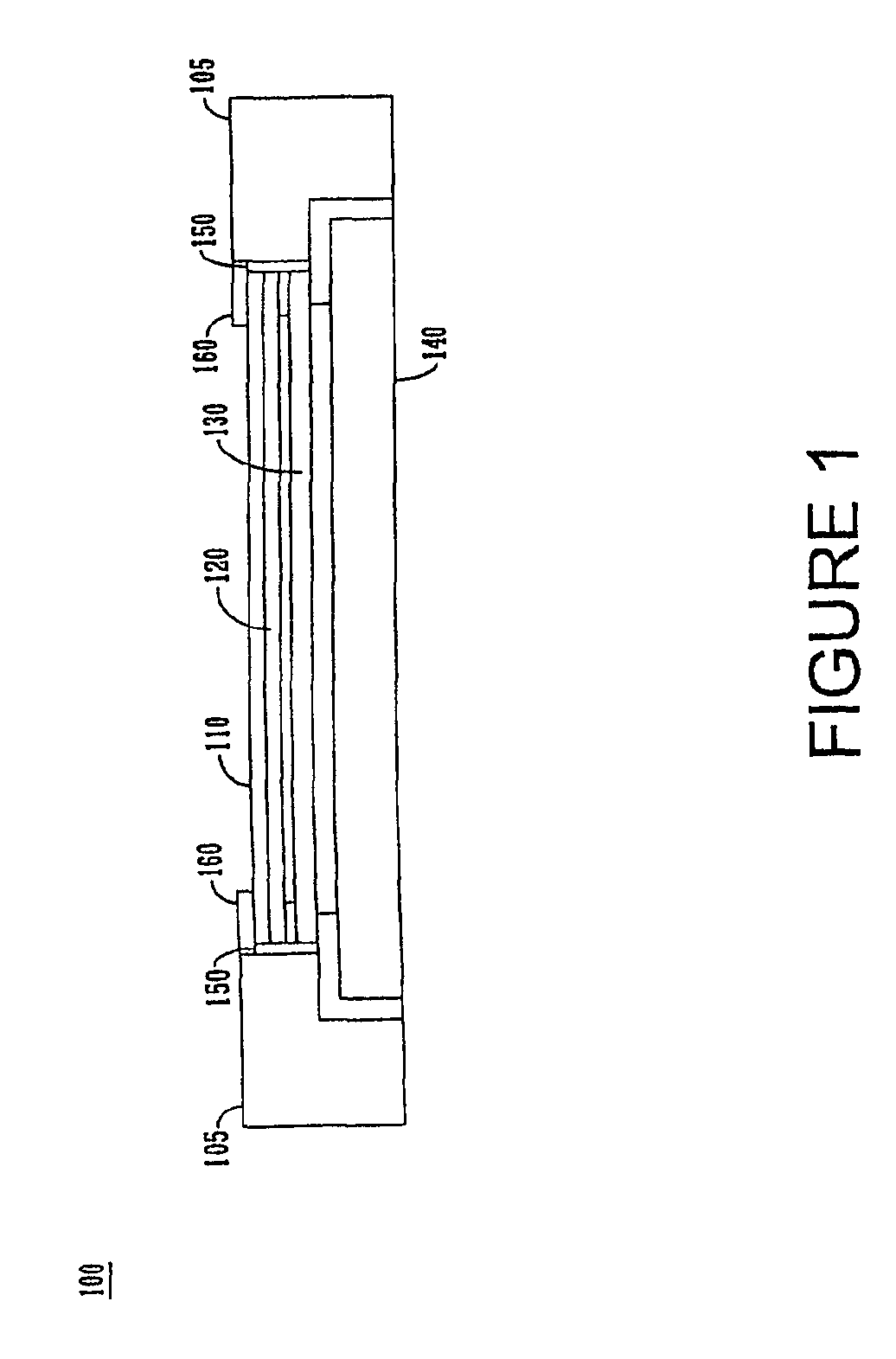

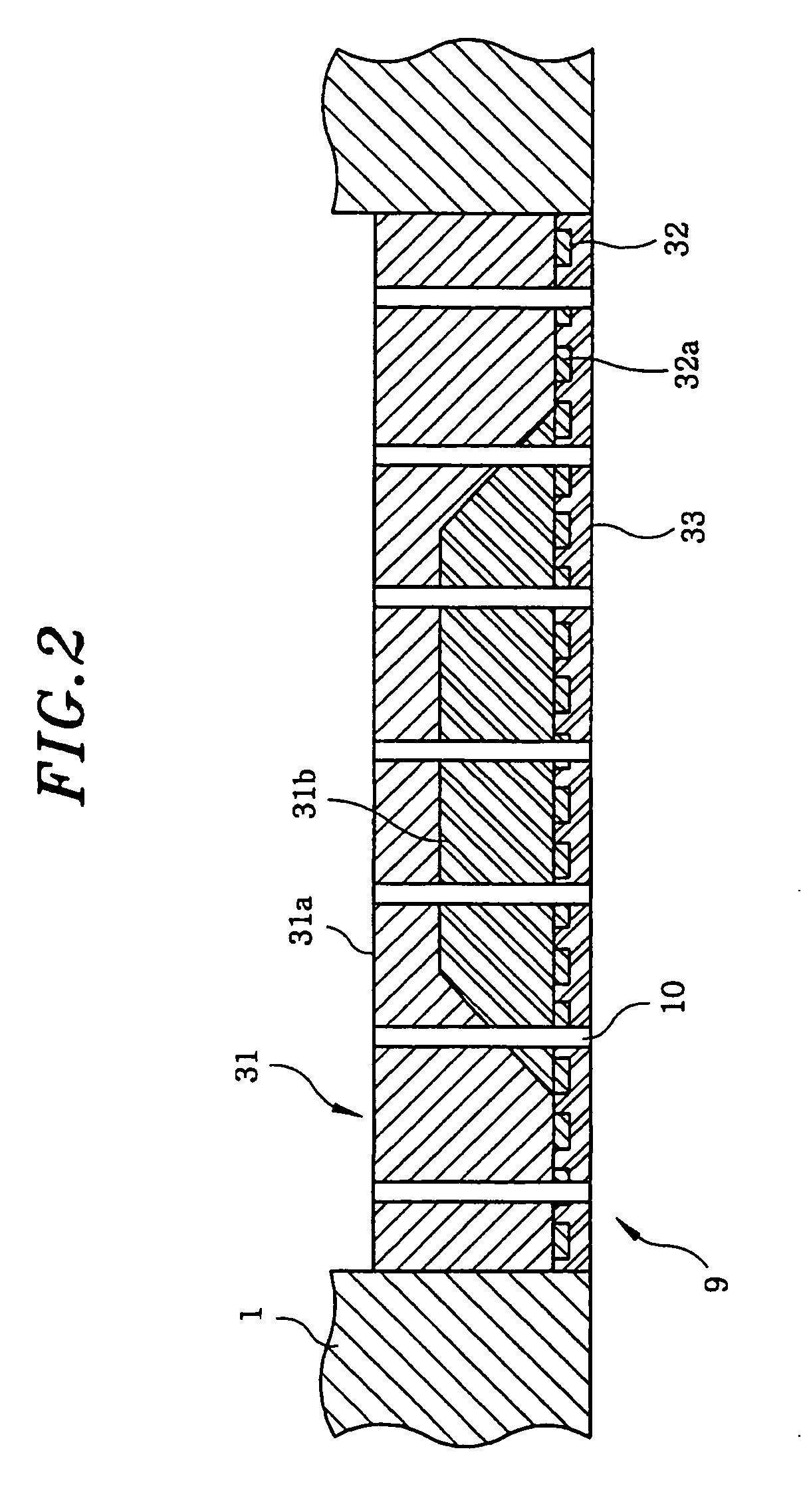

A manufacturing apparatus of a lighting device, including a vacuum chamber, an exhaust system by which the vacuum chamber is set to a reduced-pressure state, and a transfer chamber from which a substrate is transferred to the vacuum chamber is provided. The vacuum chamber of the manufacturing apparatus includes a plurality of deposition chambers in which a first electrode, a first light-emitting unit including at least a light-emitting layer, an intermediate layer, a second light-emitting unit including at least a light-emitting layer, a second electrode, a sealing film are formed, and a substrate transfer means by which the substrate is sequentially transferred to the deposition chambers.

Owner:SEMICON ENERGY LAB CO LTD

High transparency integrated enclosure touch screen assembly for a portable hand held device

InactiveUS6992659B2Eliminates exposed seamHigh light transmittanceCathode-ray tube indicatorsNon-linear opticsInter layerHand held

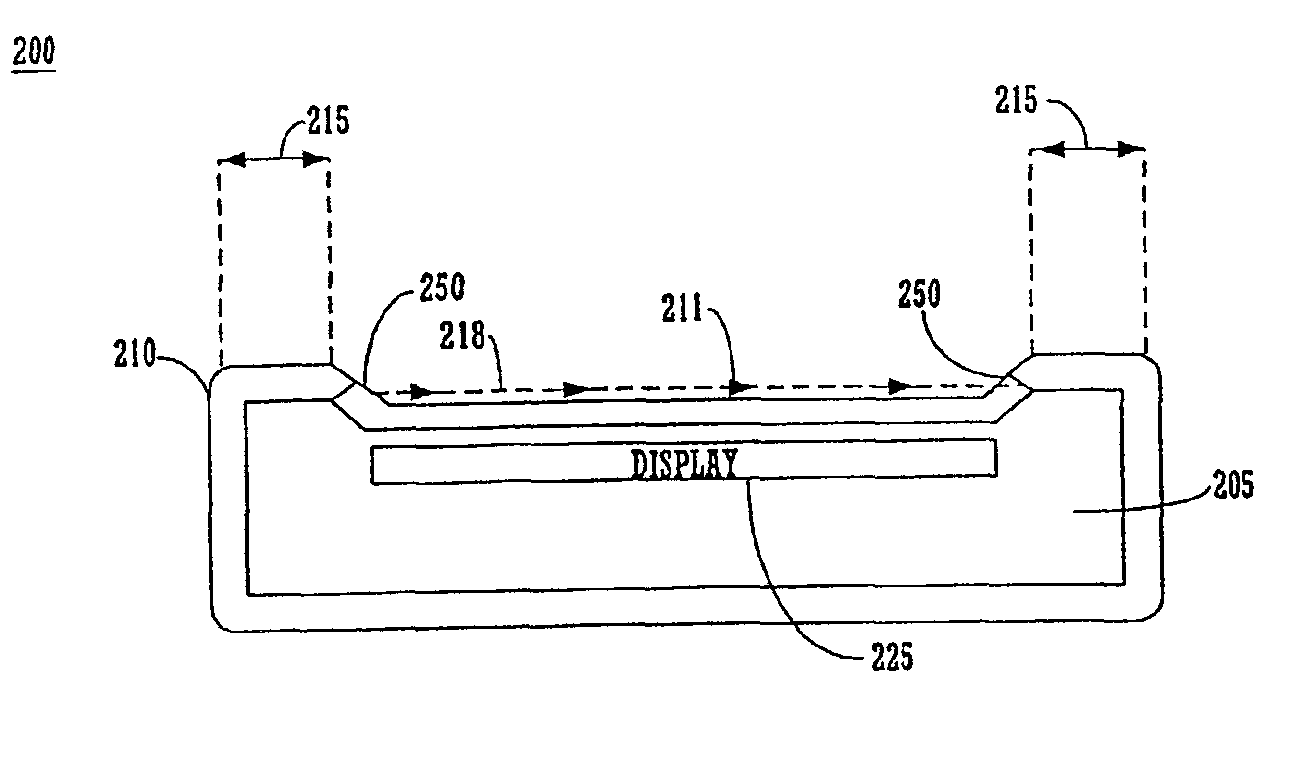

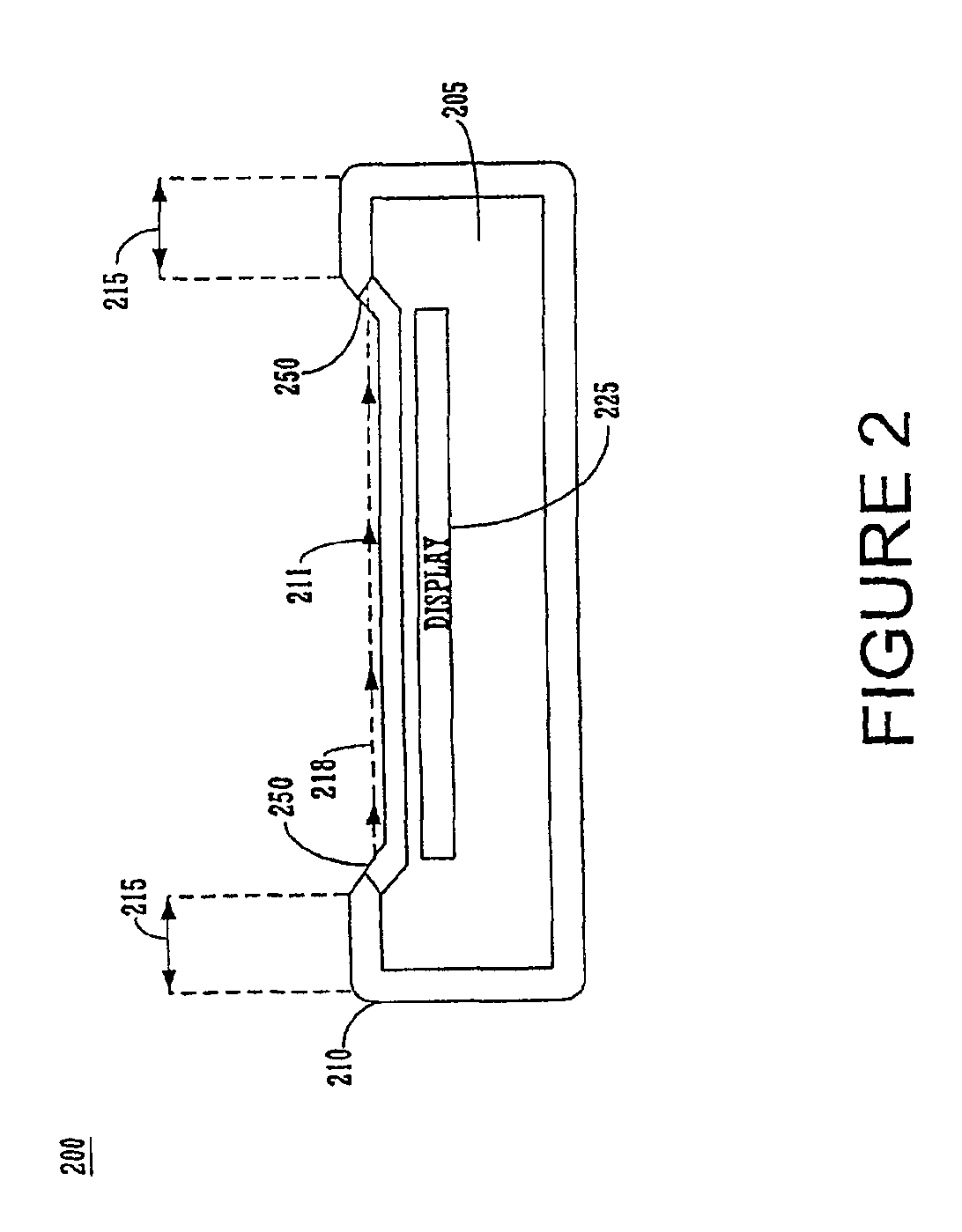

An integrated enclosure / touch screen assembly. A touch screen assembly consisting of a display mechanism and optical sensor mechanism are enclosed within a single piece cover. The optical sensor mechanism consists of lens structure and optical sensor couple to the lens structure. The single piece cover includes a transparent top surface and the lens structure is embedded within the transparent top surface. The transparent top surface of the single piece cover provides an enclosure that is both dust free and waterproof.The lens structure of the single piece cover functions by columnating light across the transparent surface. The optical touch sensor is coupled to the lens structure to register contact with the transparent surface via the lens structure by detecting disturbances in the columnated light. In one embodiment, the single piece cover is constructed by embedding the lens structure directly into the transparent surface. This process forms the single piece cover and also may be used to provide various shapes for the outer edges of the cover. The single piece cover eliminates exposed seams of the touch screen assembly. Additionally, the transparent surface is disposed directly above the display without any intervening layers, thereby improving the transmission of light to the display.

Owner:QUALCOMM INC

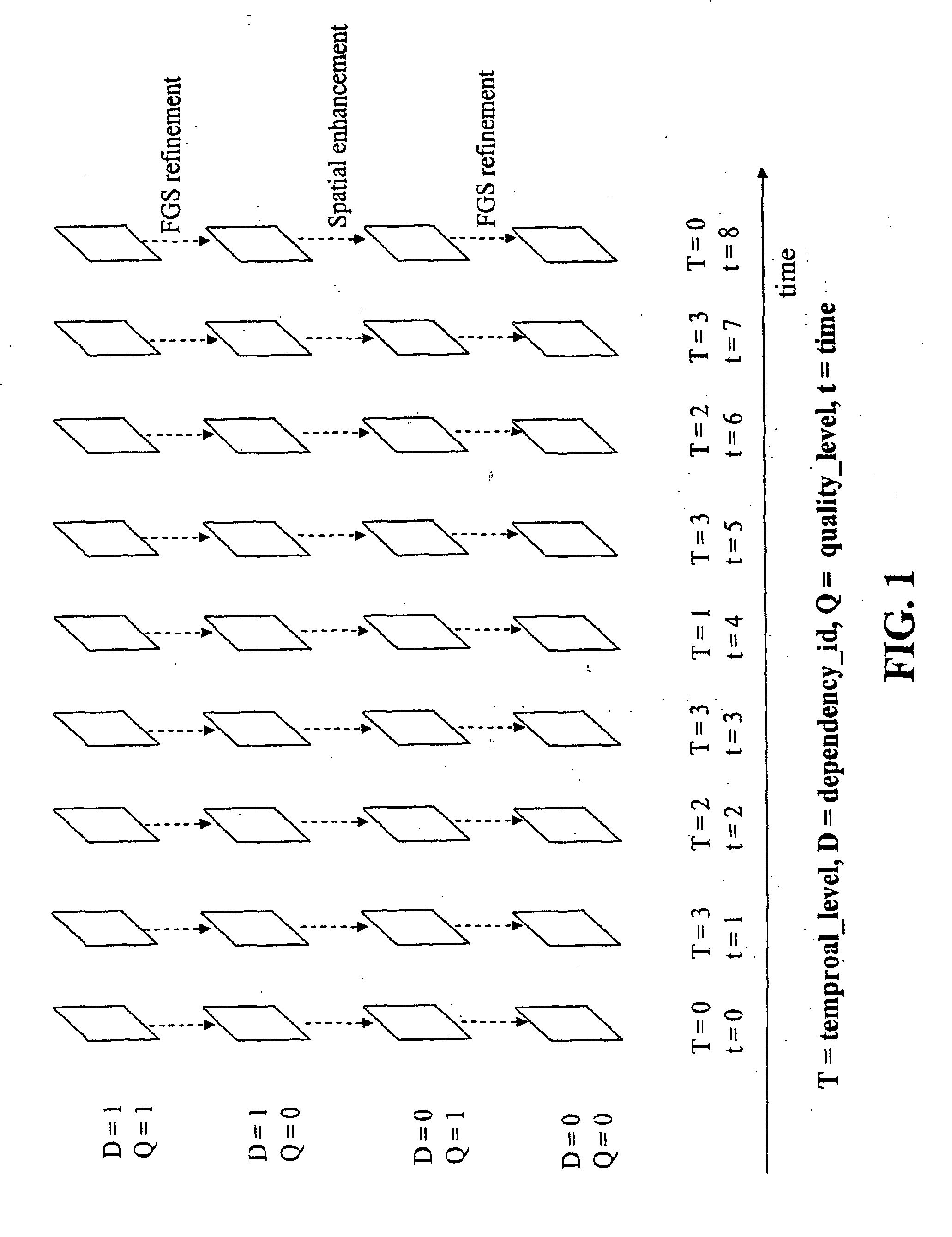

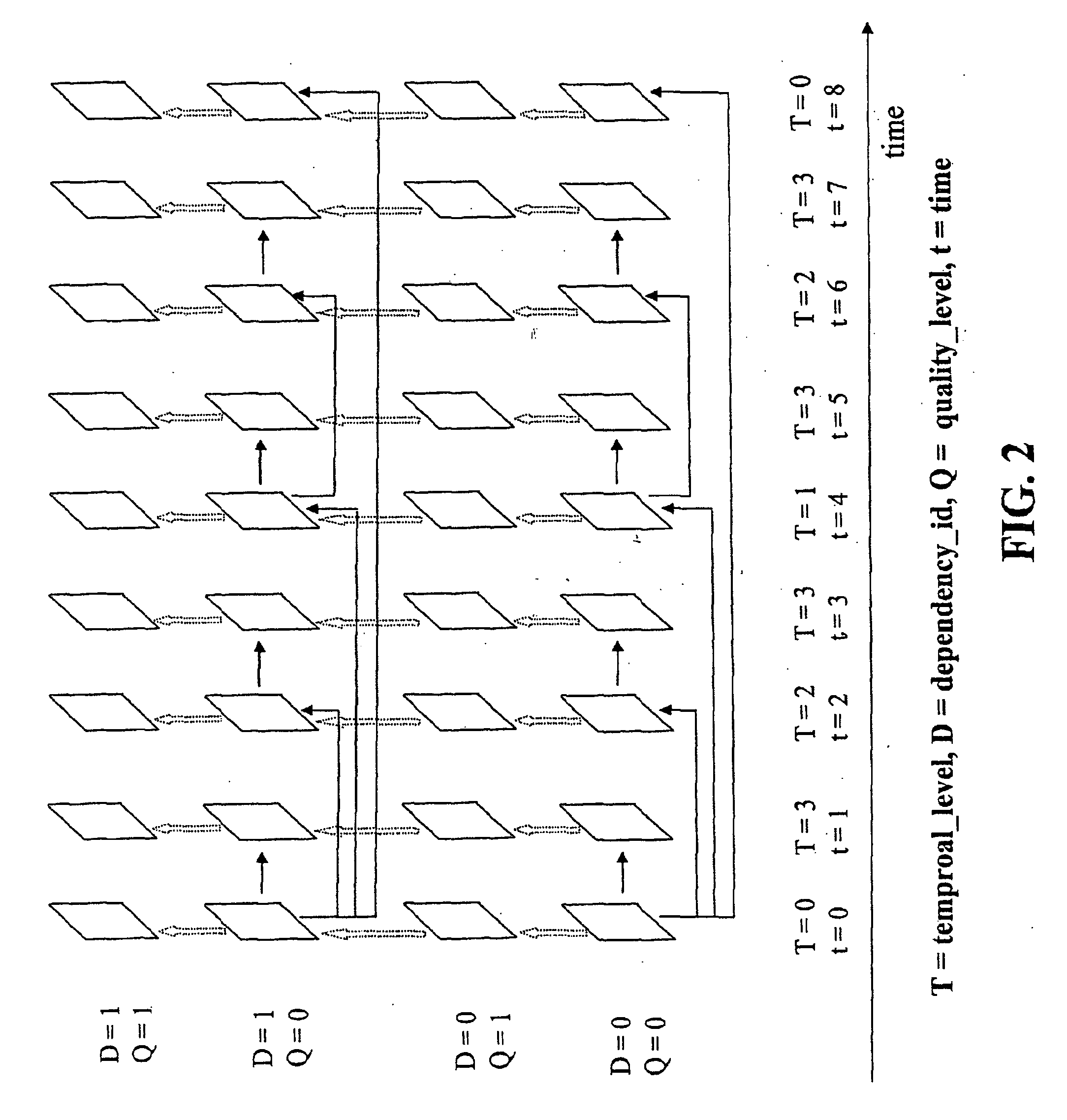

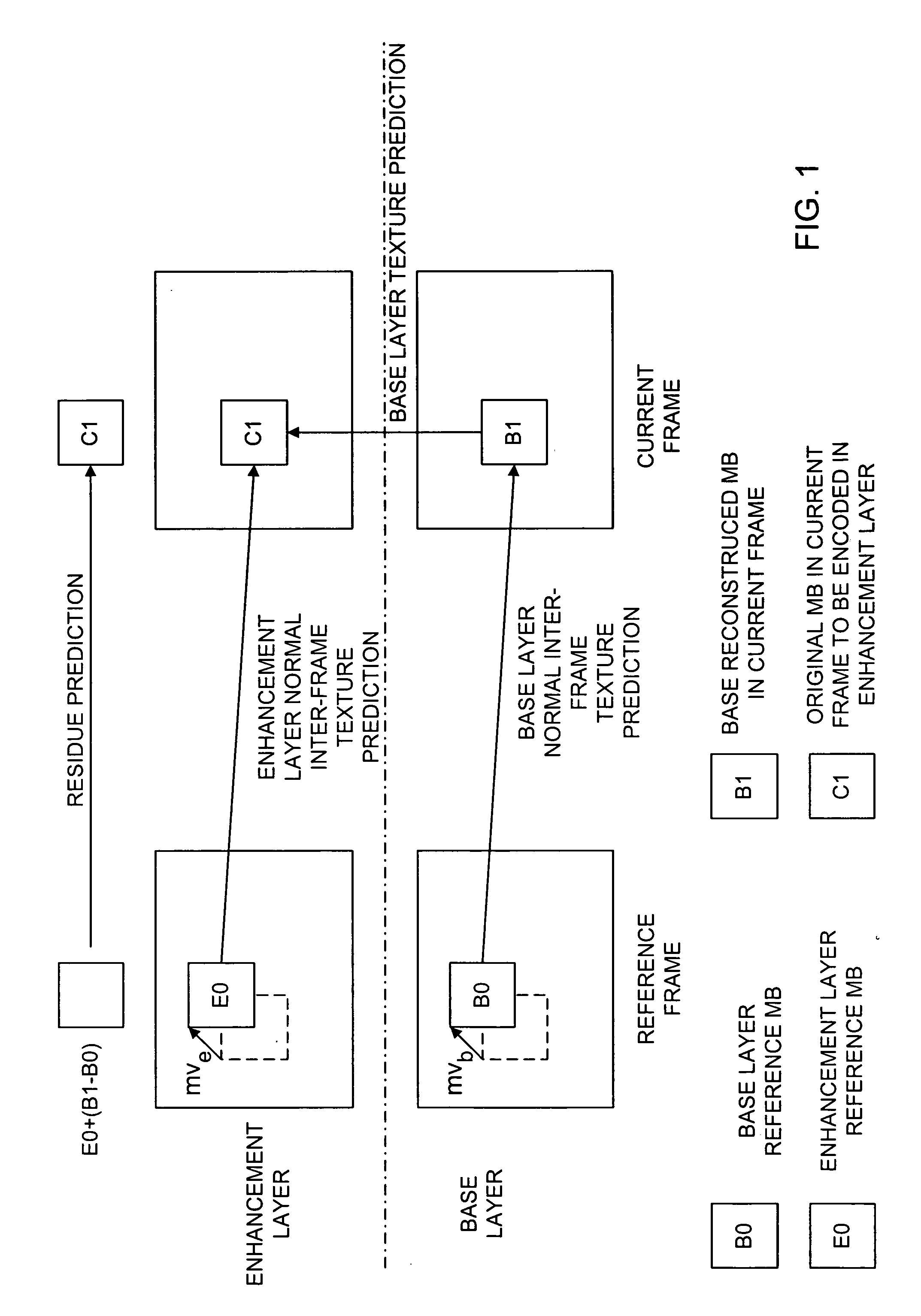

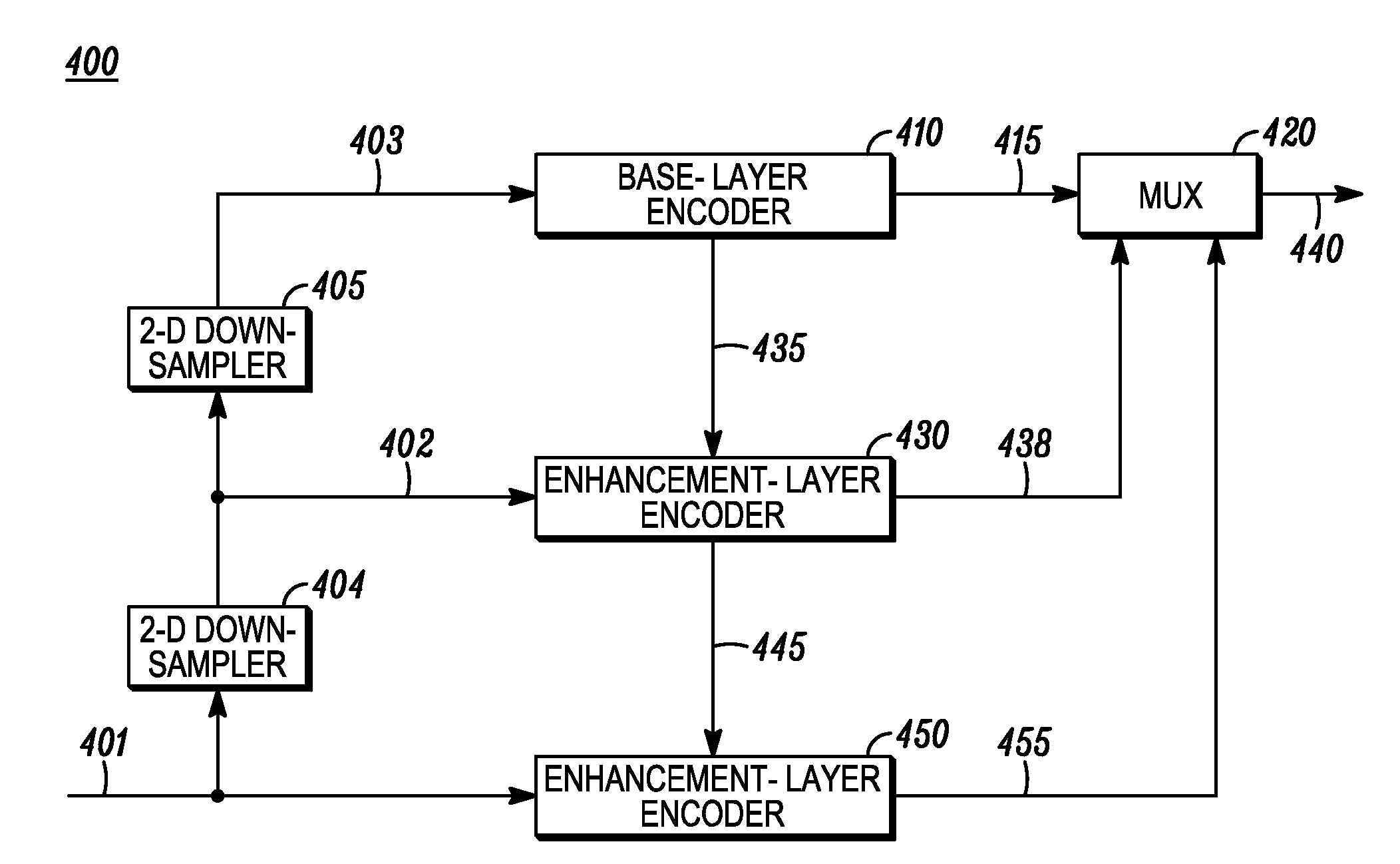

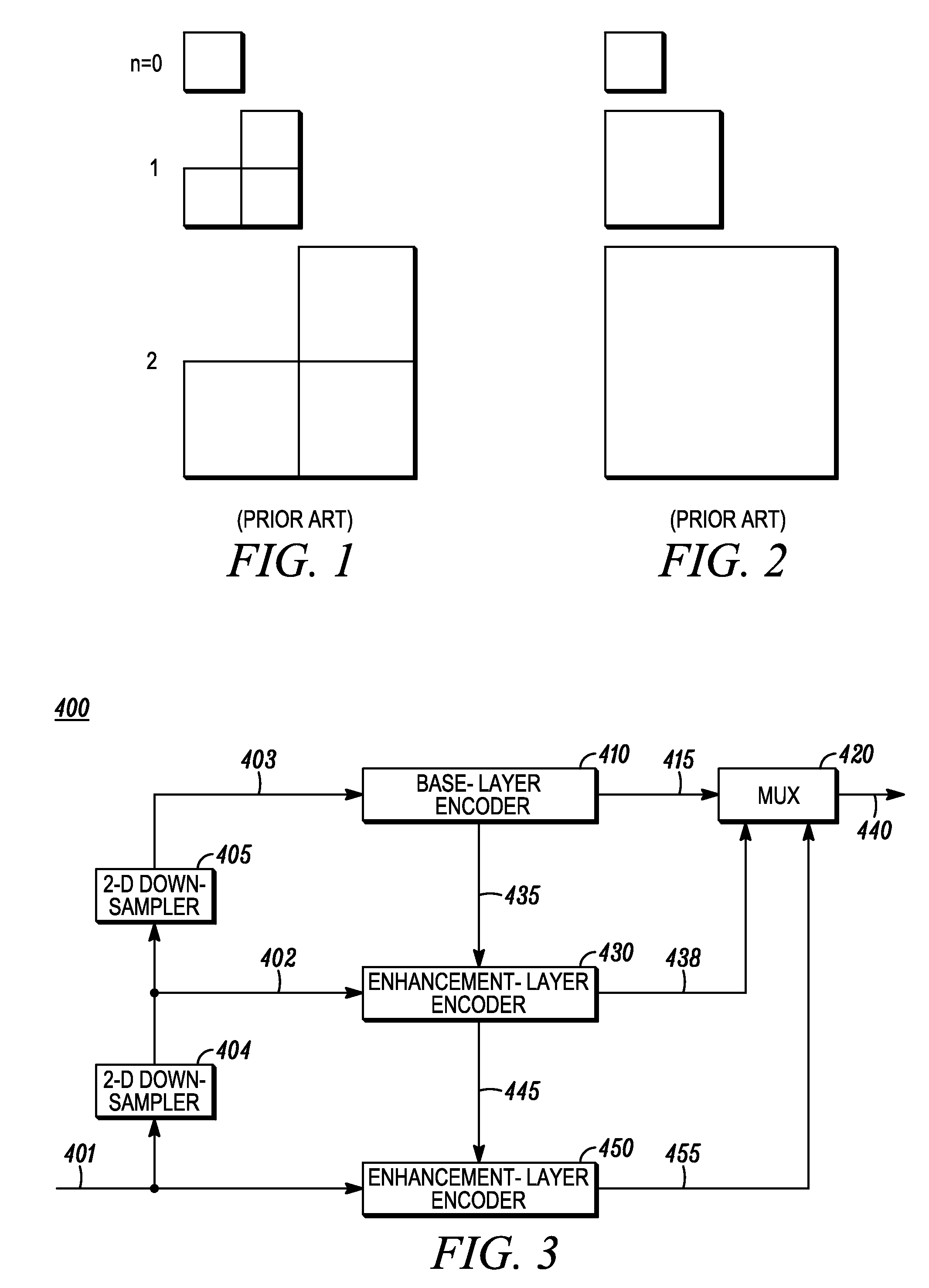

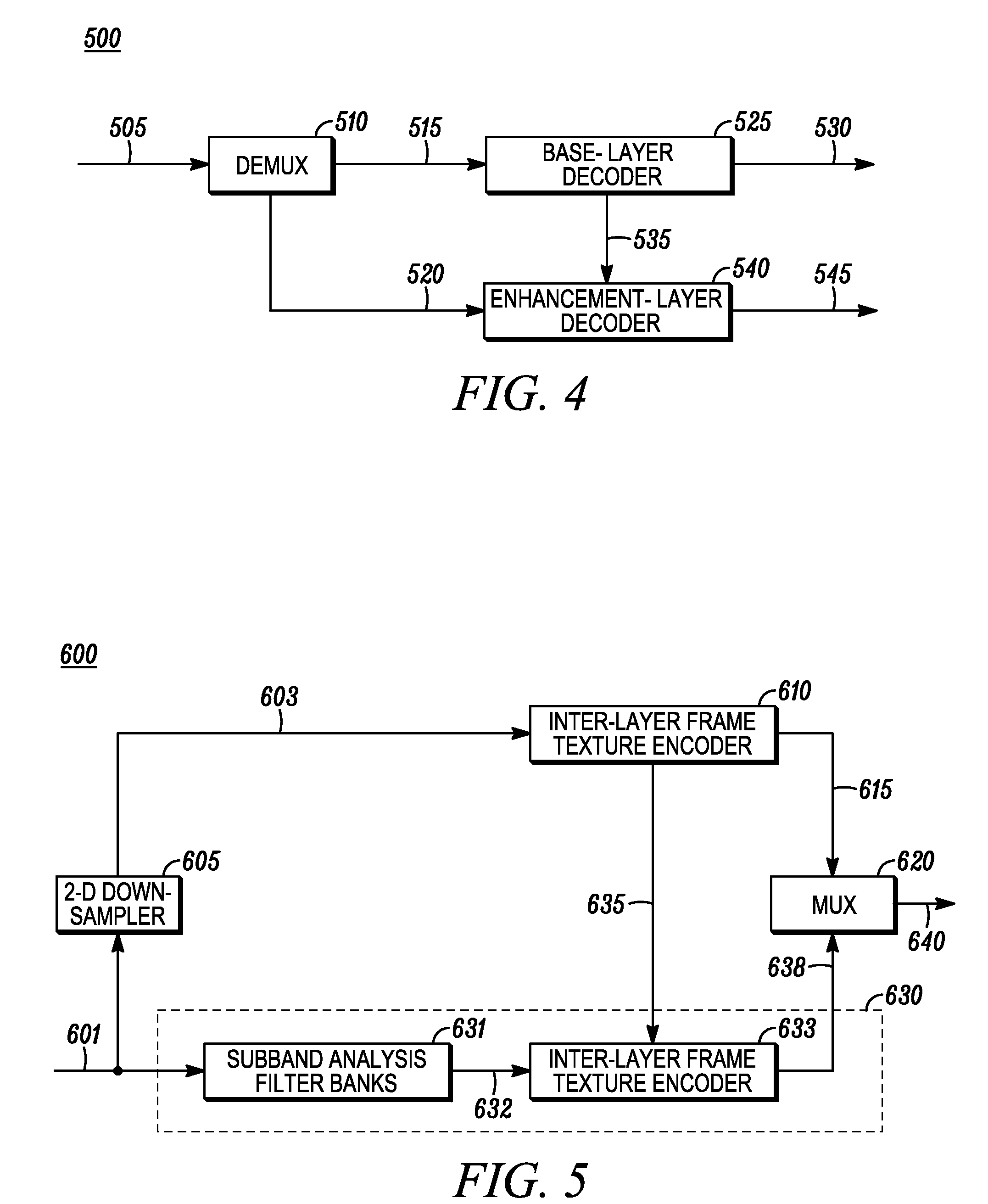

Inter-layer prediction for extended spatial scalability in video coding

ActiveUS20080165855A1Improving inter-layer predictionReduce computational complexityColor television with pulse code modulationColor television with bandwidth reductionInter layerMotion vector

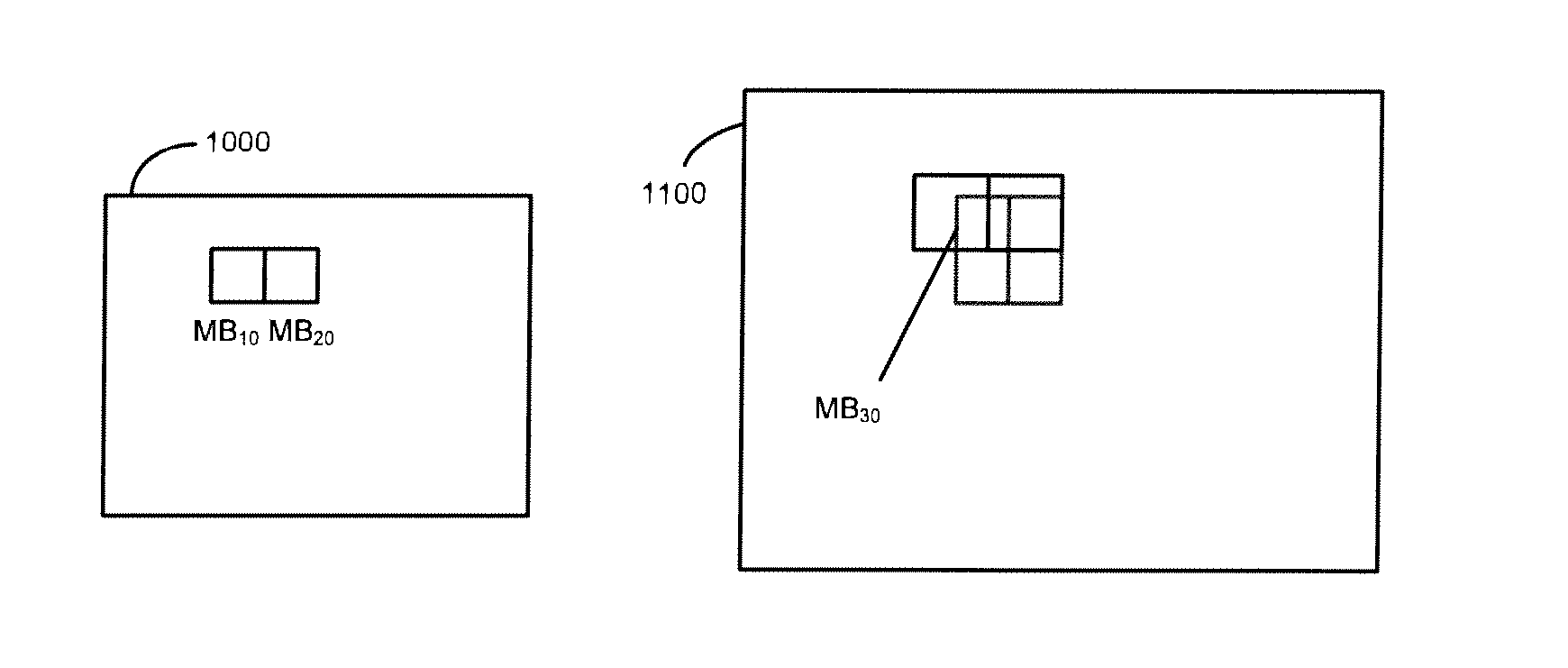

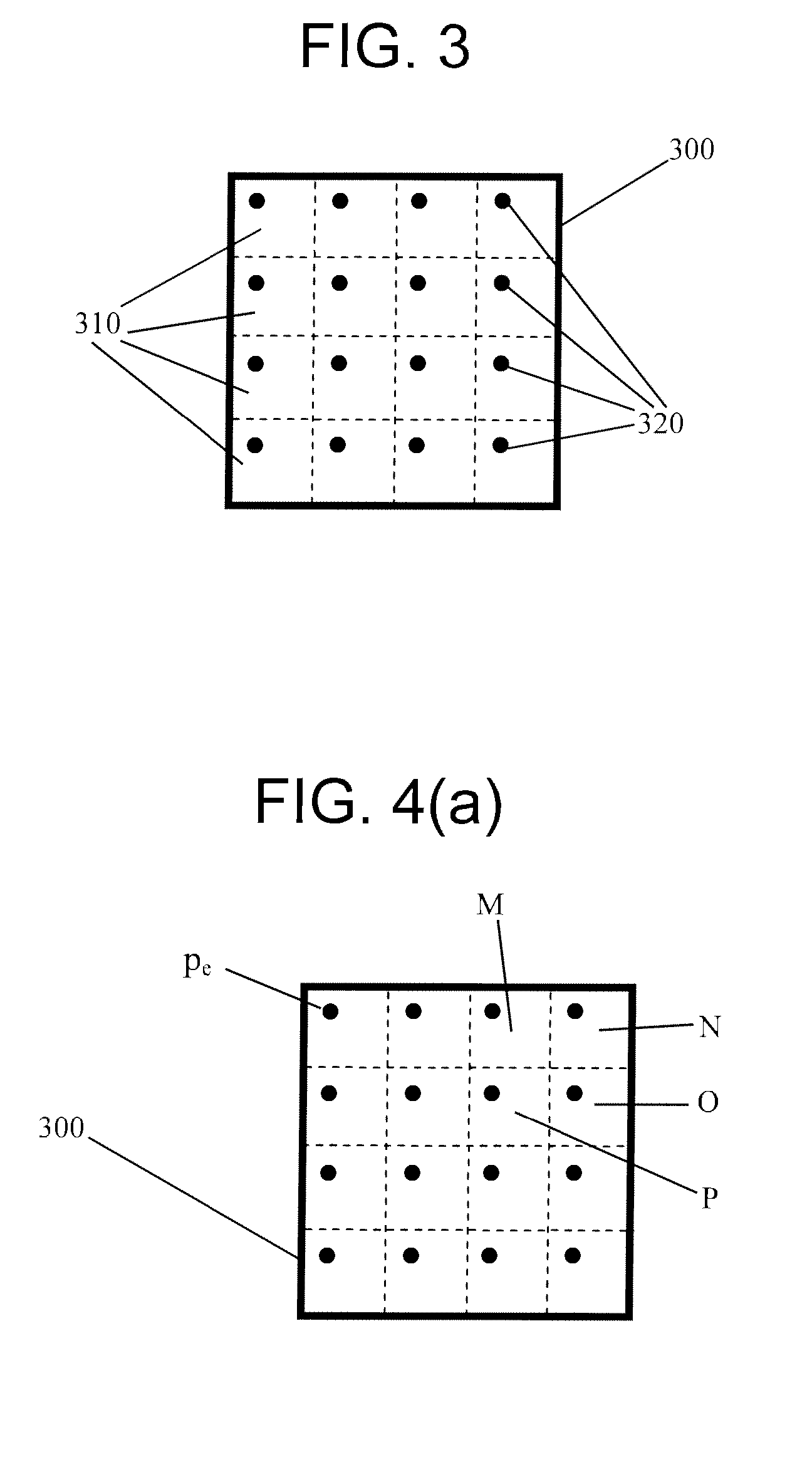

An improved system and method for providing improved inter-layer prediction for extended spatial scalability in video coding, as well as improving inter-layer prediction for motion vectors in the case of extended spatial scalability. In various embodiments, for the prediction of macroblock mode, the actual reference frame index and motion vectors from the base layer are used in determining if two blocks should be merged. Additionally, multiple representative pixels in a 4×4 block can be used to represent each 4×4 block in a virtual base layer macroblock. The partition and motion vector information for the relevant block in the virtual base layer macroblock can be derived from all of the partition information and motion vectors of those 4×4 blocks.

Owner:NOKIA TECHNOLOGLES OY

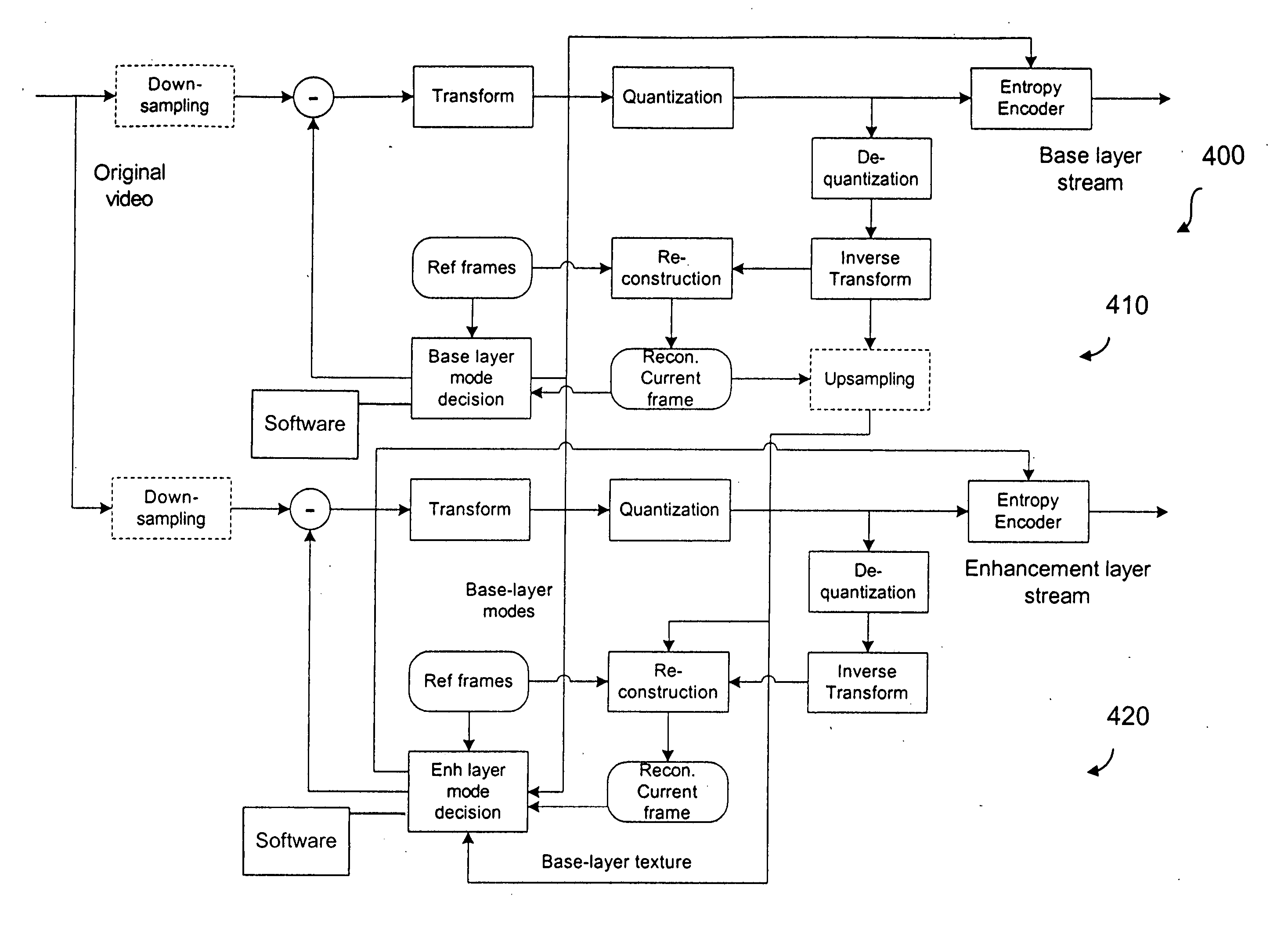

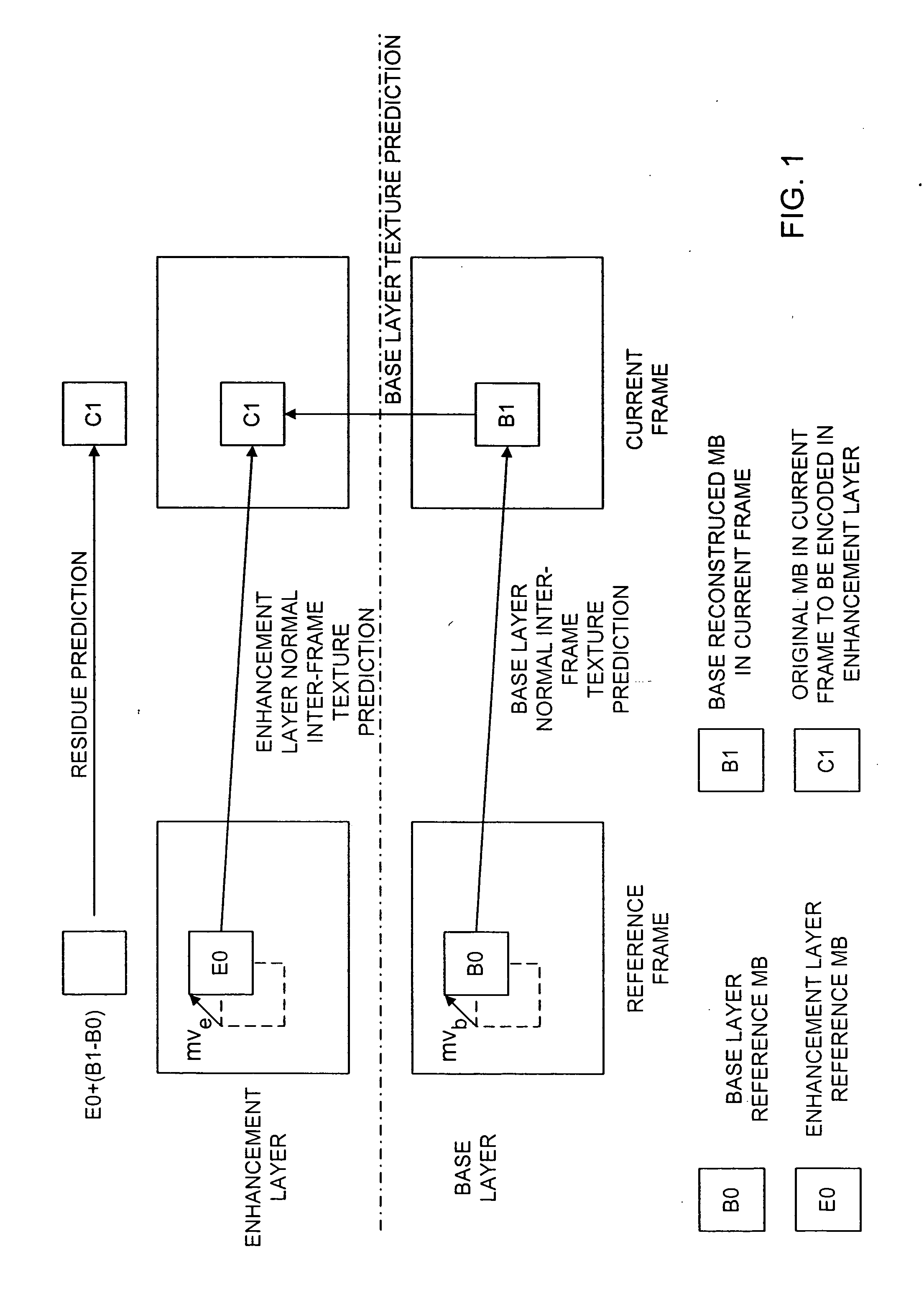

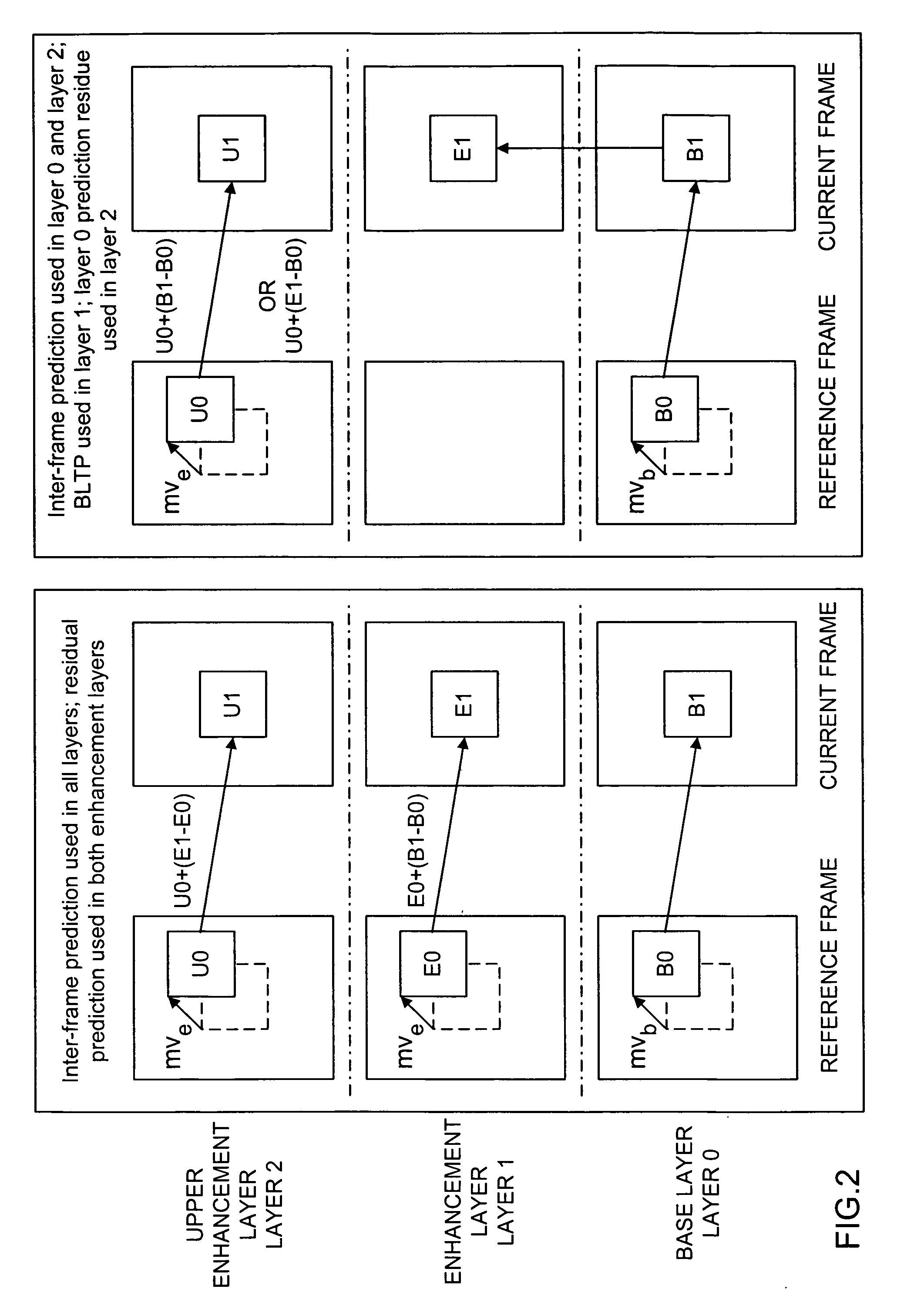

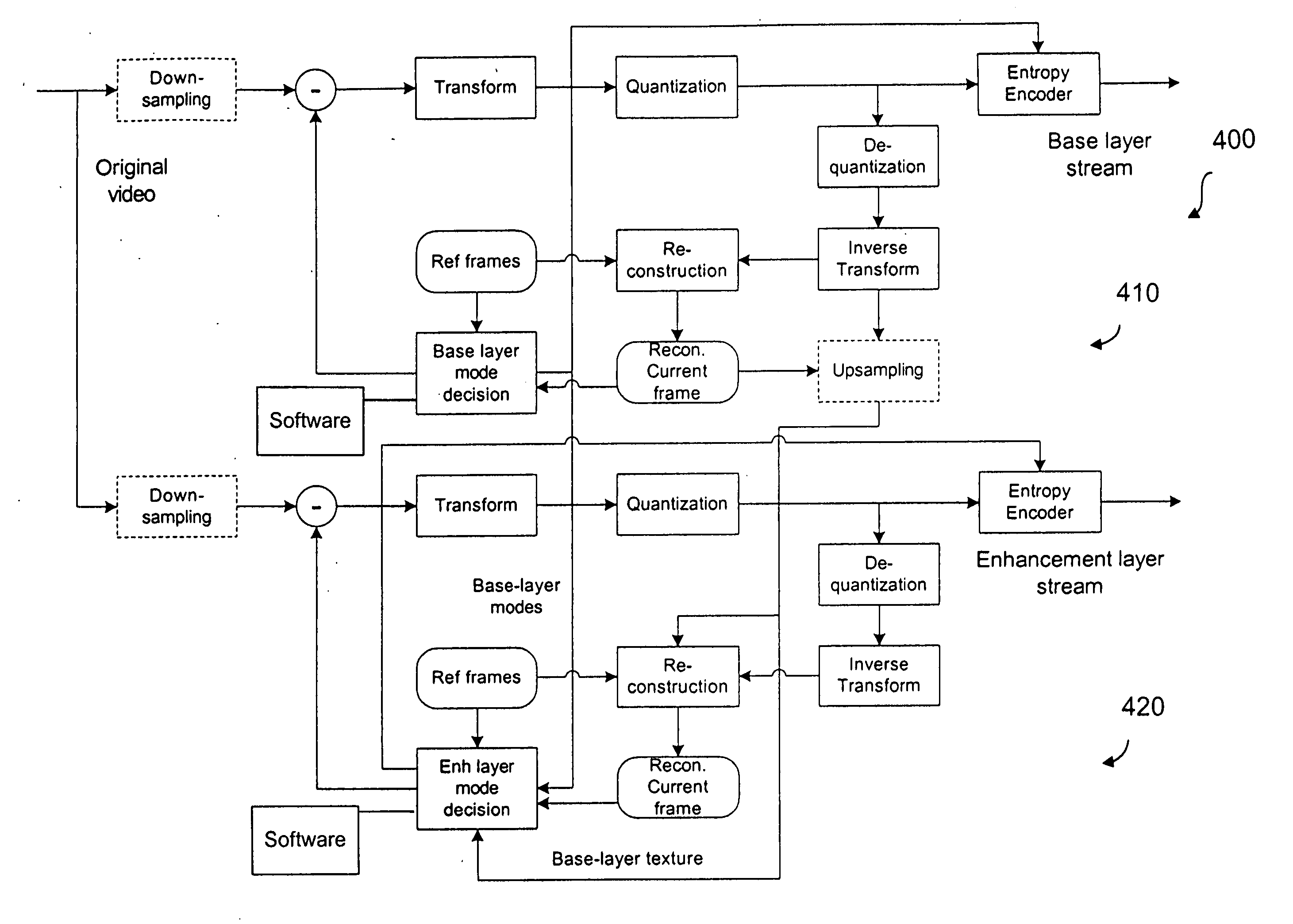

Method and system for inter-layer prediction mode coding in scalable video coding

InactiveUS20060153295A1Eliminate redundancyImproving inter-layer prediction modeColor television with pulse code modulationColor television with bandwidth reductionComputer architectureInter layer

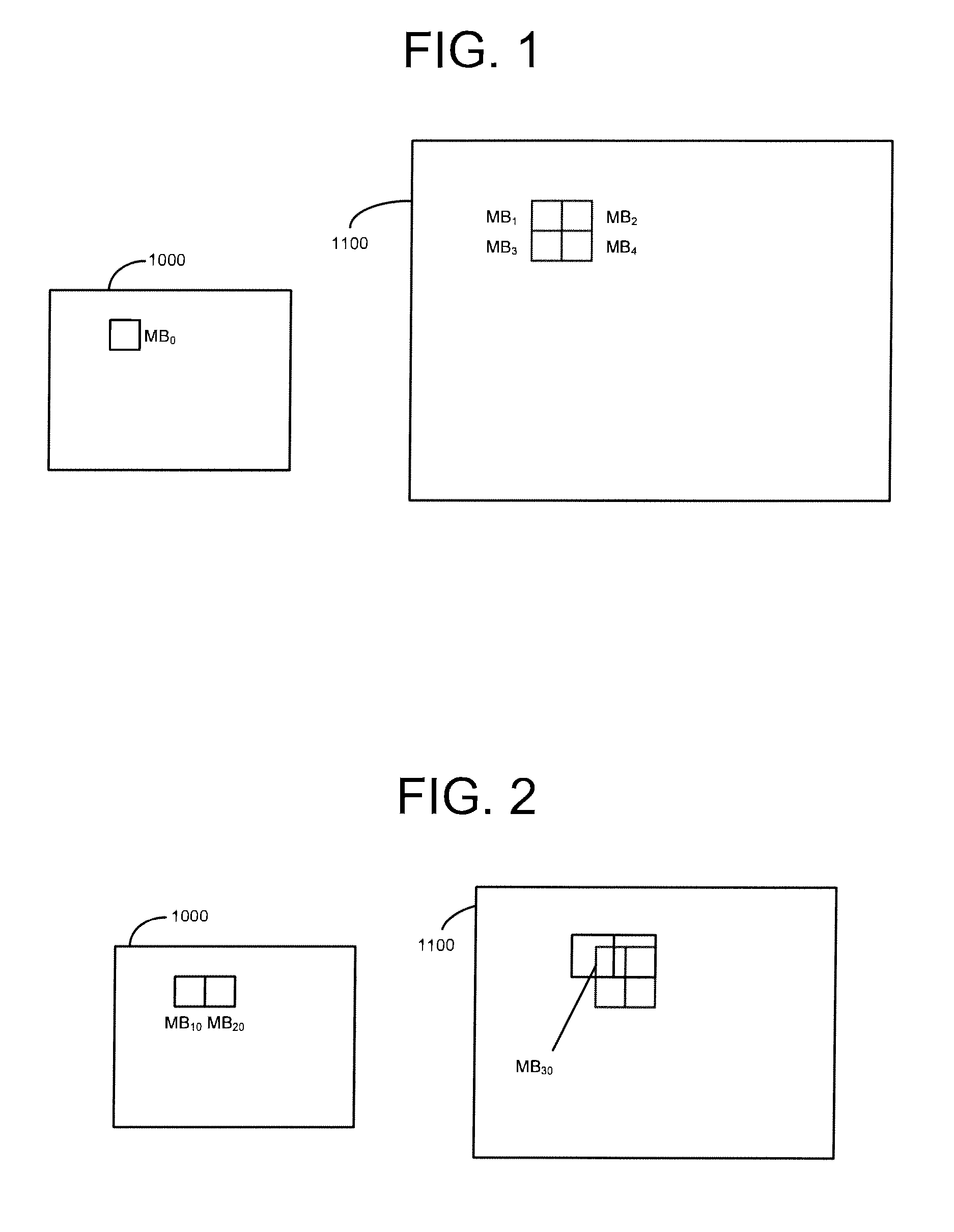

The present invention improves residue prediction by using MI even when the base layer MB is encoded in intra mode such as copying intra 4×4 mode of one 4×4 block in the base layer to multiple neighboring 4×4 blocks in the enhancement layer if the base layer resolution is lower than the enhancement layer resolution, using the intra 4×4 mode as intra 8×8 mode if the base layer resolution is lower than the enhancement layer resolution and the base layer resolution is half of the enhancement layer resolution in both dimensions, carrying out direct calculation of the base layer prediction residue used in RP, clipping of prediction residue for reducing memory requirement and tunneling of prediction residue in BLTP mode; and conditional coding of RP flag to save flag bits and reduce implementation complexity

Owner:NOKIA CORP

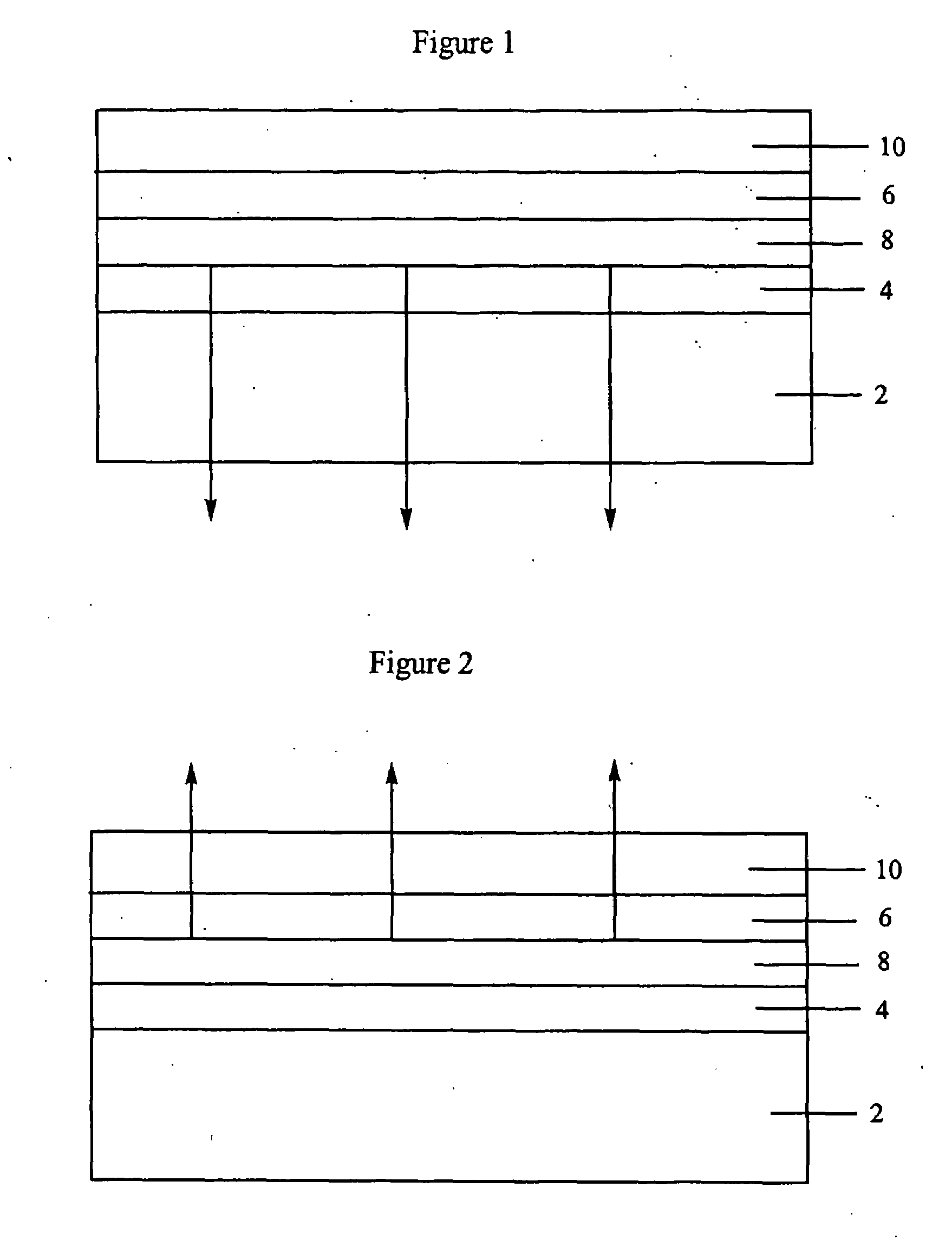

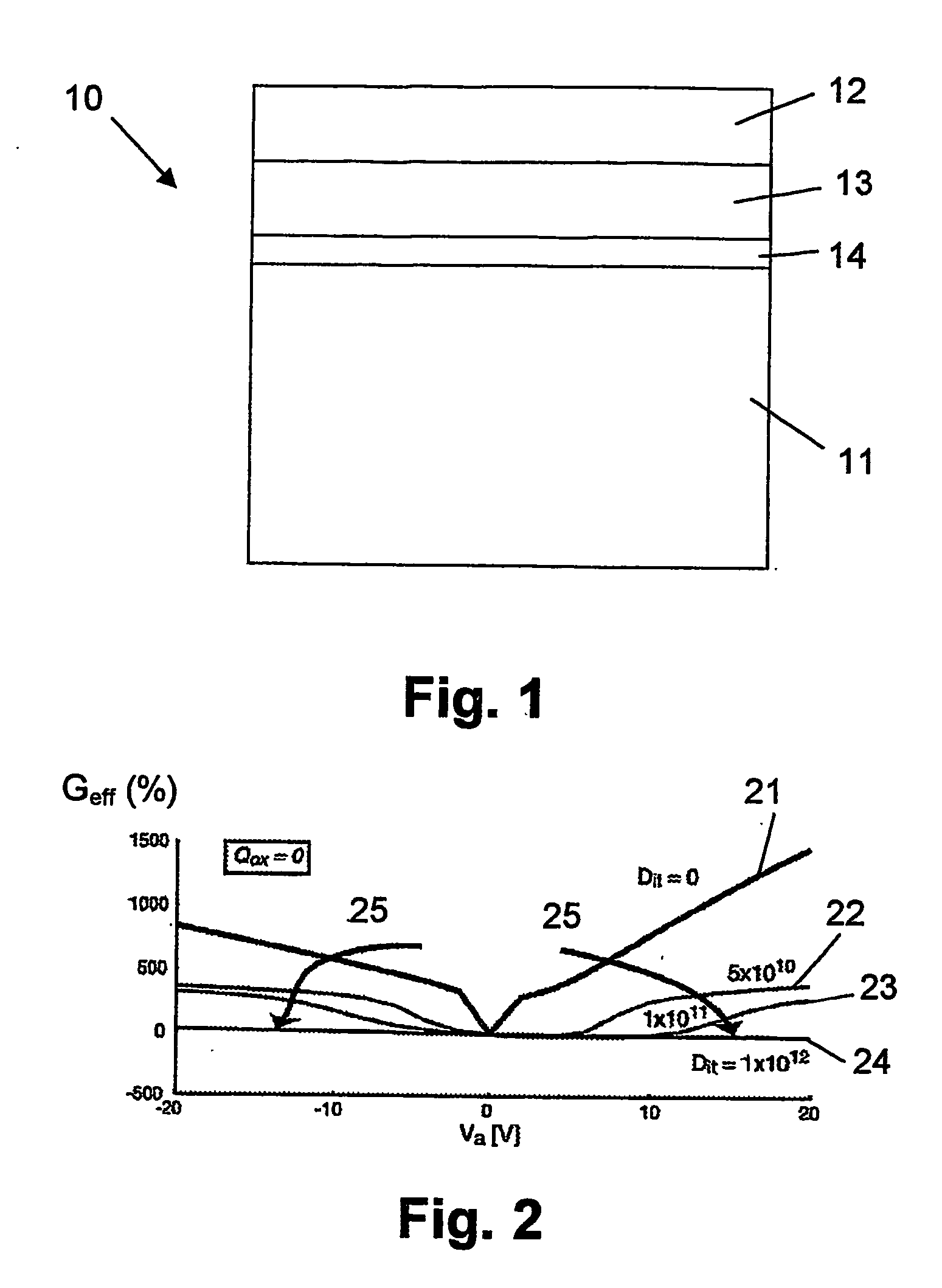

Organic Electroluminescent Device

ActiveUS20110042696A1Improve light outcoupling efficiencyHigh color puritySolid-state devicesVacuum evaporation coatingInter layerRefractive index

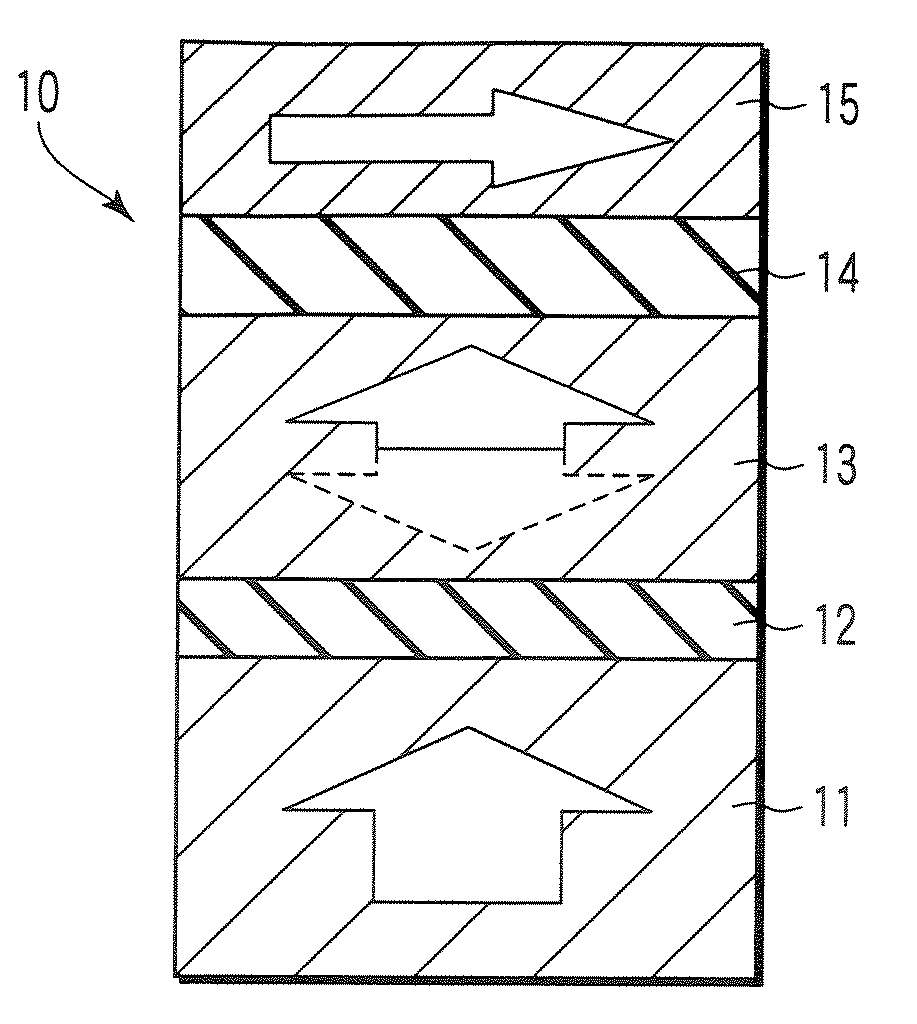

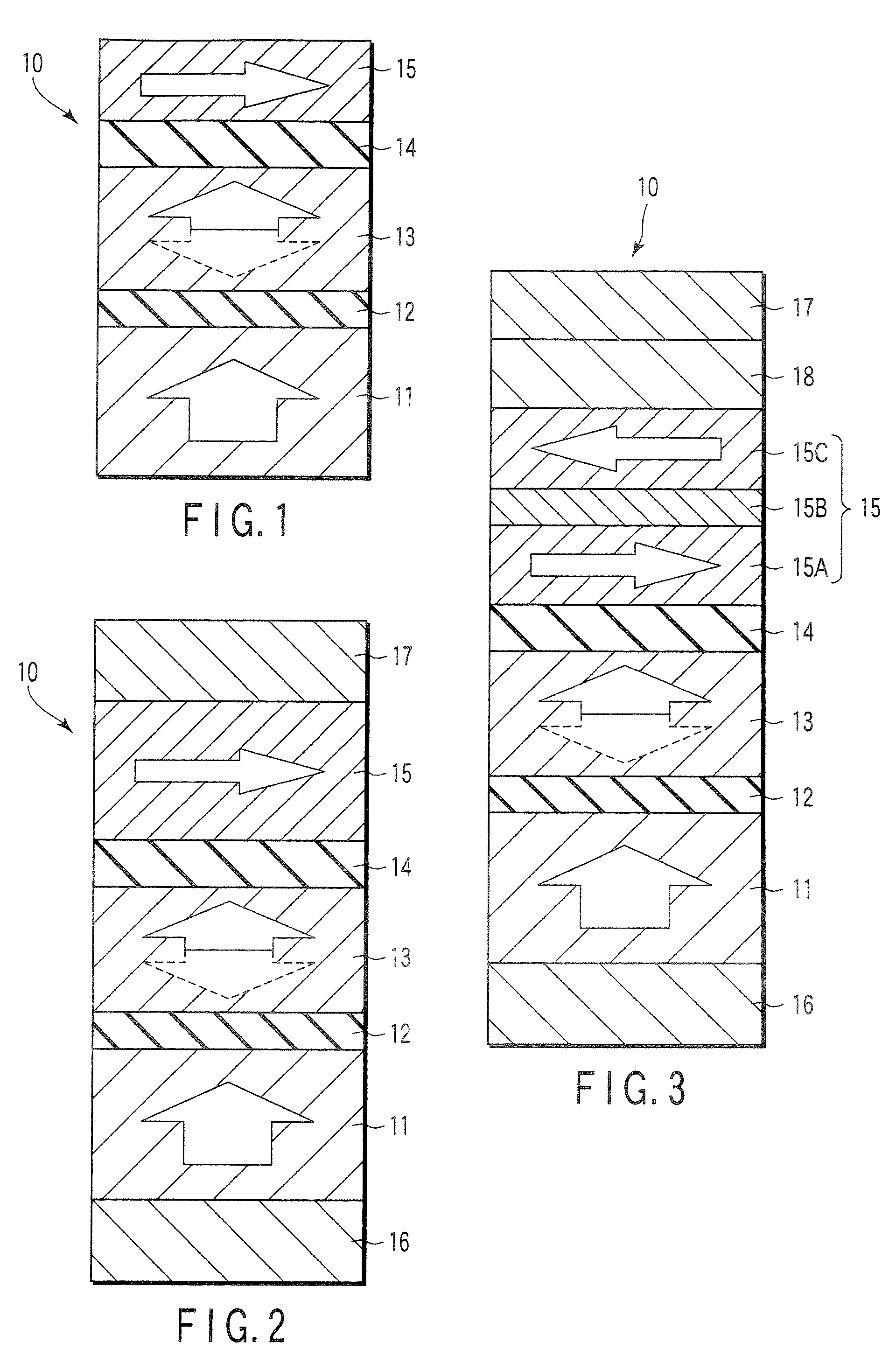

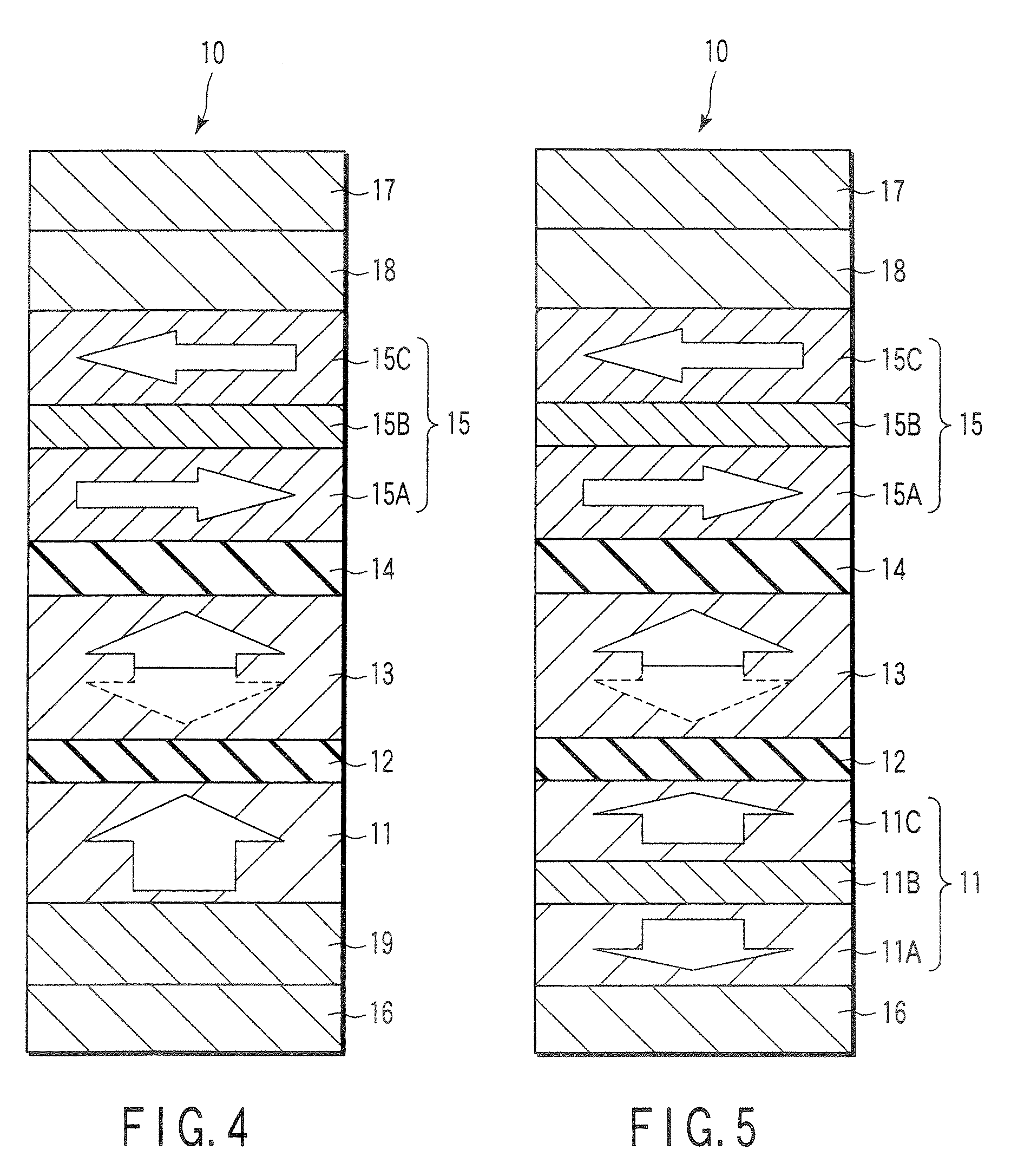

An organic electroluminescent device cfomprising: a transparent substrate; a first electrode disposed over the substrate for injecting charge of a first polarity; a second electrode disposed over the first electrode for injecting charge of a second polarity opposite to said first polarity; an organic light-emitting layer disposed between the first and the second electrode, wherein the second electrode is reflective, the first electrode is transparent or semi-transparent, and one or more intermediate layers of dielectric material with a refractive index greater than 1.8 or a metal material is disposed between the substrate and the first electrode forming a semi-transparent mirror whereby a microcavity is provided between the reflective second electrode and the semi-transparent mirror, all the intermediate layers disposed between the substrate and the first electrode having a surface nearest the organic light-emitting layer not more than 150 nm from a surface of the first electrode nearest the organic light-emitting layer.

Owner:CAMBRIDGE DISPLAY TECH LTD

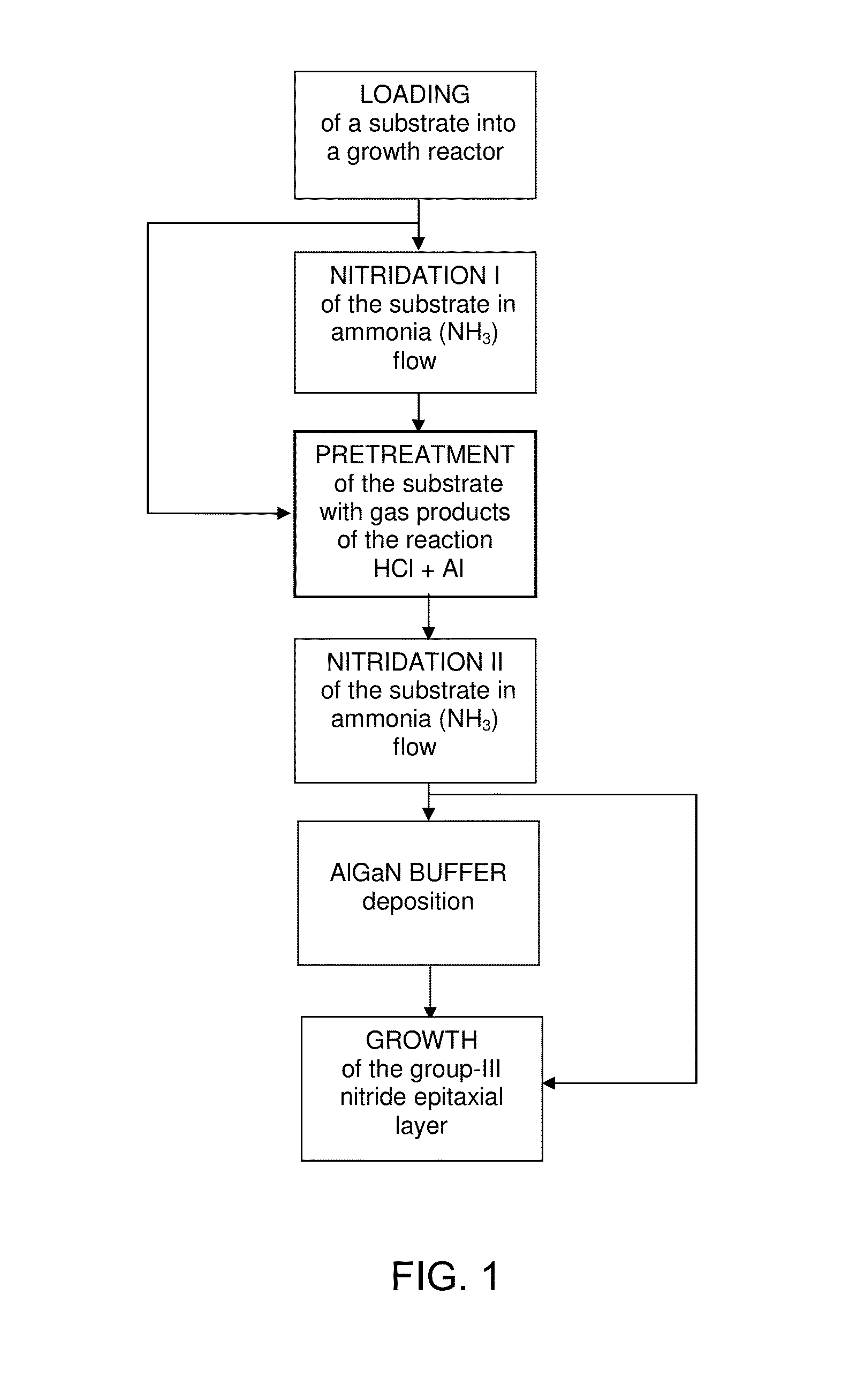

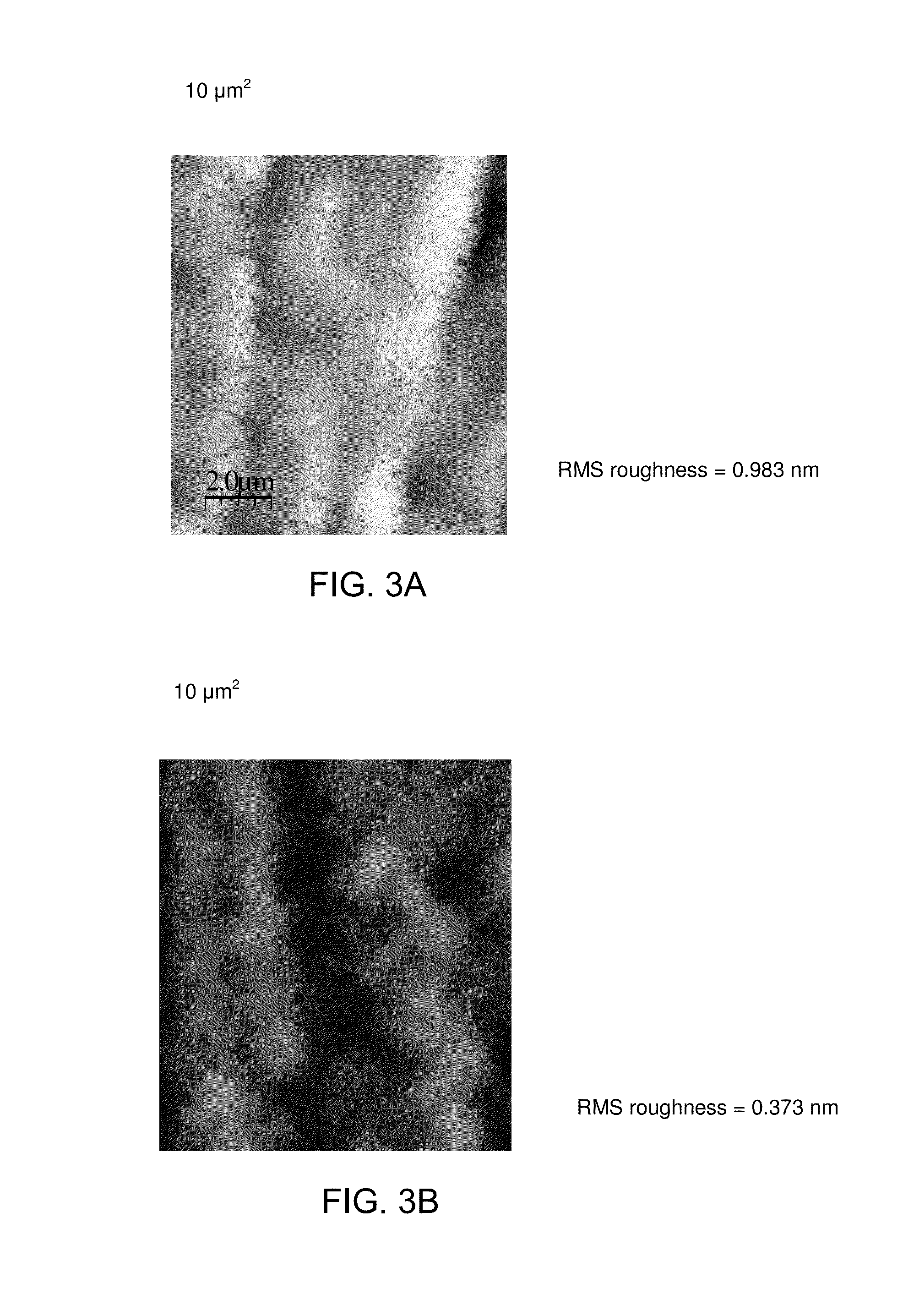

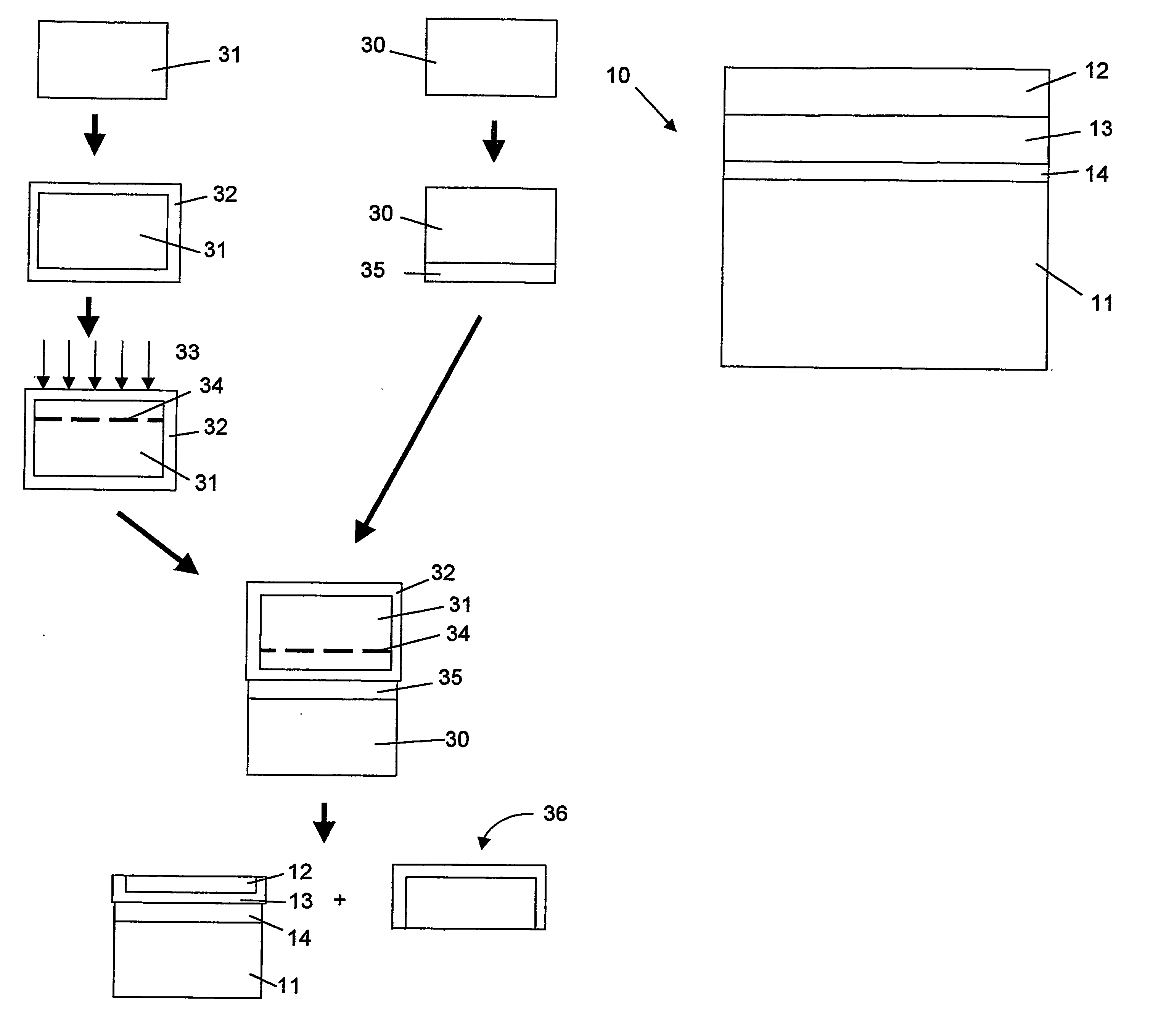

Method for Substrate Pretreatment To Achieve High-Quality III-Nitride Epitaxy

The present invention relates to a method for producing a modified surface of a substrate that stimulates the growth of epitaxial layers of group-III nitride semiconductors with substantially improved structural perfection and surface flatness. The modification is conducted outside or inside a growth reactor by exposing the substrate to a gas-product of the reaction between hydrogen chloride (HCl) and aluminum metal (Al). As a single-step or an essential part of the multi-step pretreatment procedure, the modification gains in coherent coordination between the substrate and group-III nitride epitaxial structure to be deposited. Along with epilayer, total epitaxial structure may include buffer inter-layer to accomplish precise substrate-epilayer coordination. While this modification is a powerful tool to make high-quality group-III nitride epitaxial layers attainable even on foreign substrates having polar, semipolar and nonpolar orientation, it remains gentle enough to keep the surface of the epilayer extremely smooth. Various embodiments are disclosed.

Owner:OSTENDO TECH INC

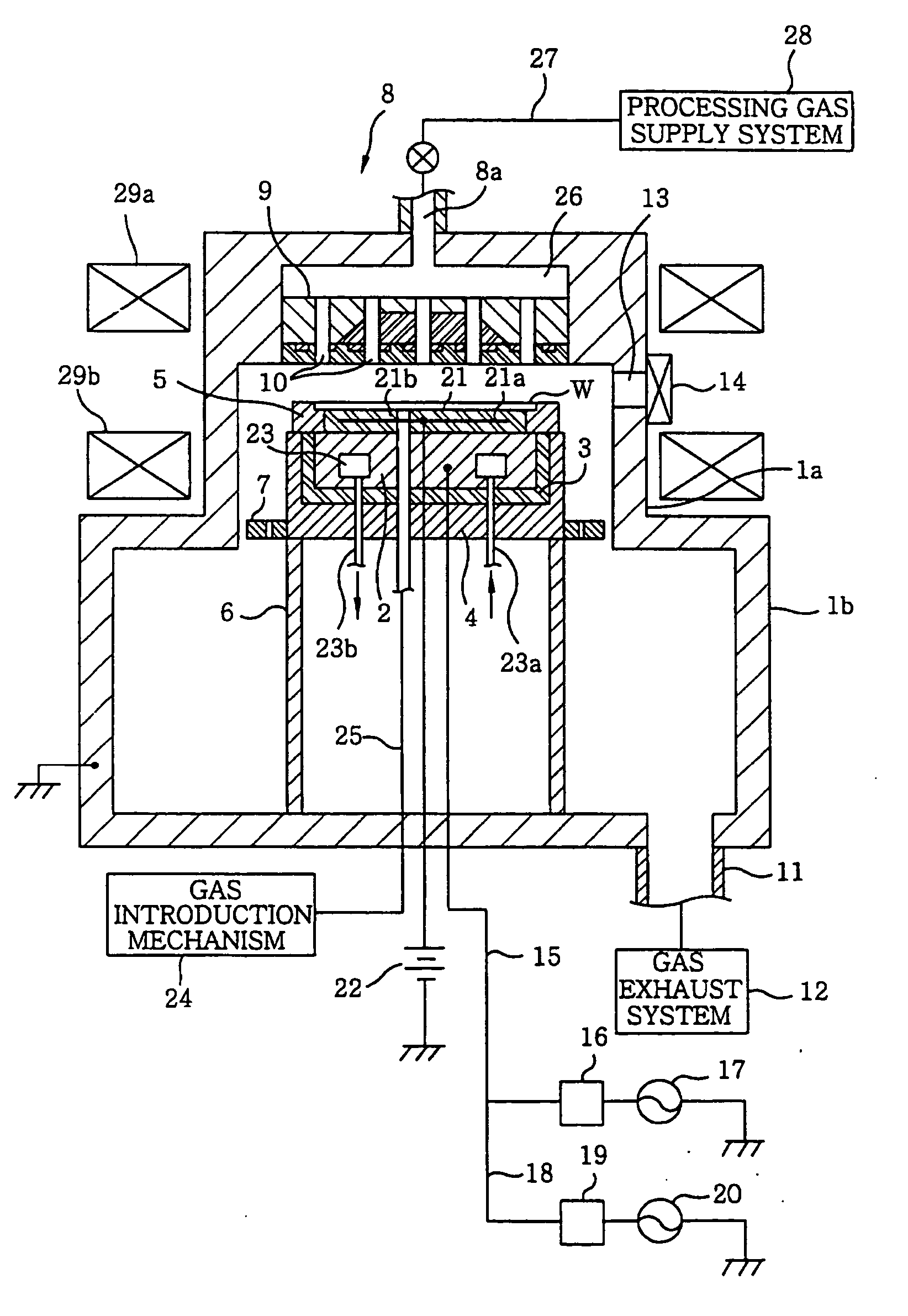

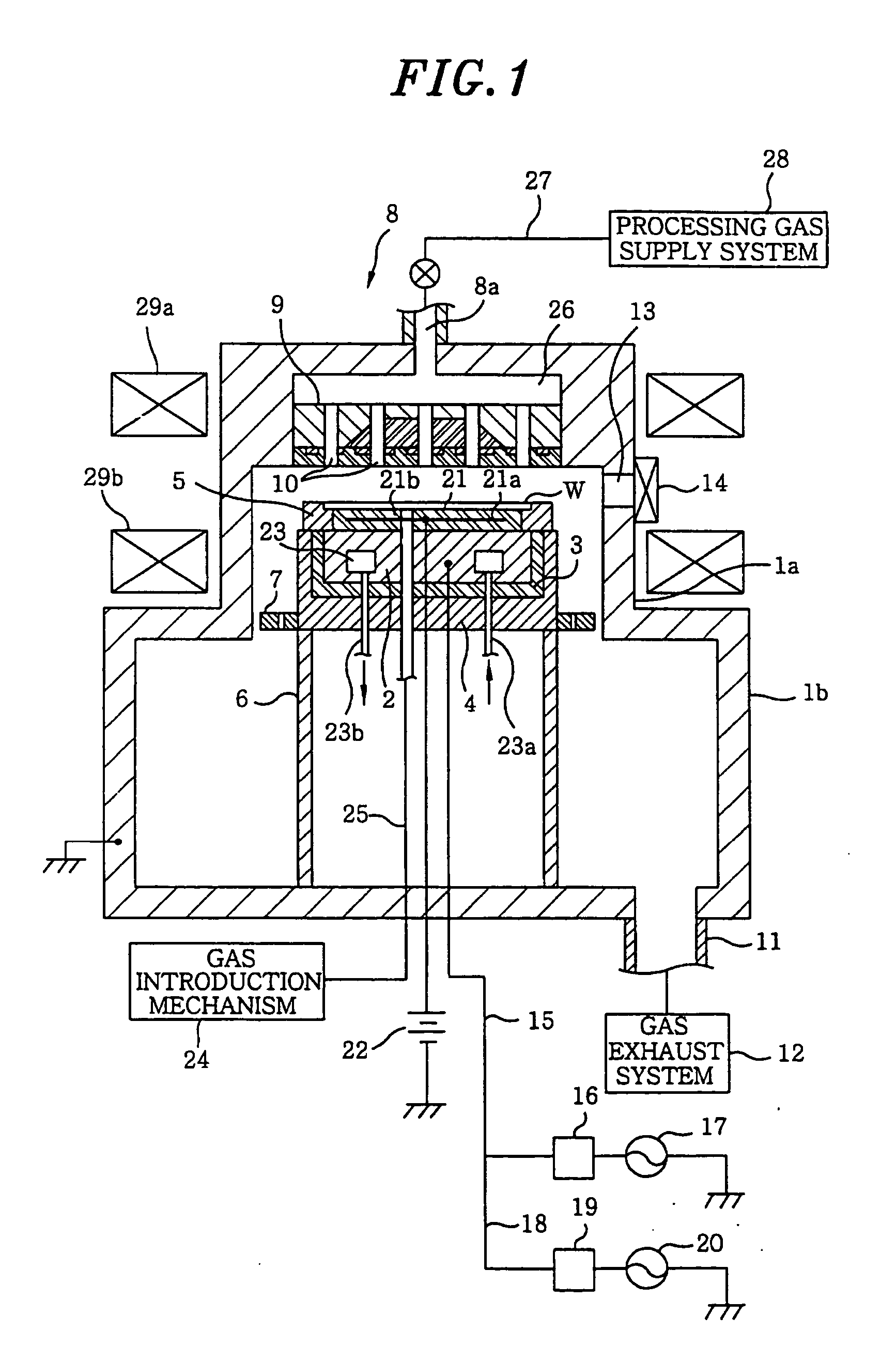

Thermally sprayed member, electrode and plasma processing apparatus using the electrode

ActiveUS20050211384A1High-frequency powerAvoid flowMolten spray coatingElectric discharge tubesThermal sprayingInter layer

A thermally sprayed member or an electrode includes a basic material, a thermally sprayed film formed on the surface of the basic material, the thermally sprayed film being made of an insulating ceramic and a metallic intermediate layer provided between the basic material and the thermally sprayed film for increasing a bonding force therebetween, wherein the thermally sprayed film side of the member is exposed to a high frequency plasma atmosphere and the electrode is intended to form a high frequency plasma on the side of the thermally sprayed film. The basic material includes a base portion made of a conductive material and a dielectric portion provided to include a part of a surface of the basic material. Further, the intermediate layer is comprised of a plurality of island-shaped parts isolated from each other.

Owner:TOKYO ELECTRON LTD

Magnetoresistive element and magnetic memory

InactiveUS20070297220A1Easily magnetizedNanomagnetismMagnetic-field-controlled resistorsIn planeInter layer

A magnetoresistive includes a first magnetic reference layer having a fixed magnetization direction, a magnetic free layer having a magnetization direction which is changeable by being supplied with spin polarized electrons, a second magnetic reference layer having a fixed magnetization direction, a first intermediate layer provided between the first magnetic reference layer and the magnetic free layer, and a second intermediate layer provided between the magnetic free layer and the second magnetic reference layer. The magnetic free layer and the first magnetic reference layer have directions of easy magnetization perpendicular or parallel to an in-plane direction. The first magnetic reference layer and the second magnetic reference layer have directions of easy magnetization perpendicular to each other.

Owner:KK TOSHIBA

Cutting elements formed from ultra hard materials having an enhanced construction

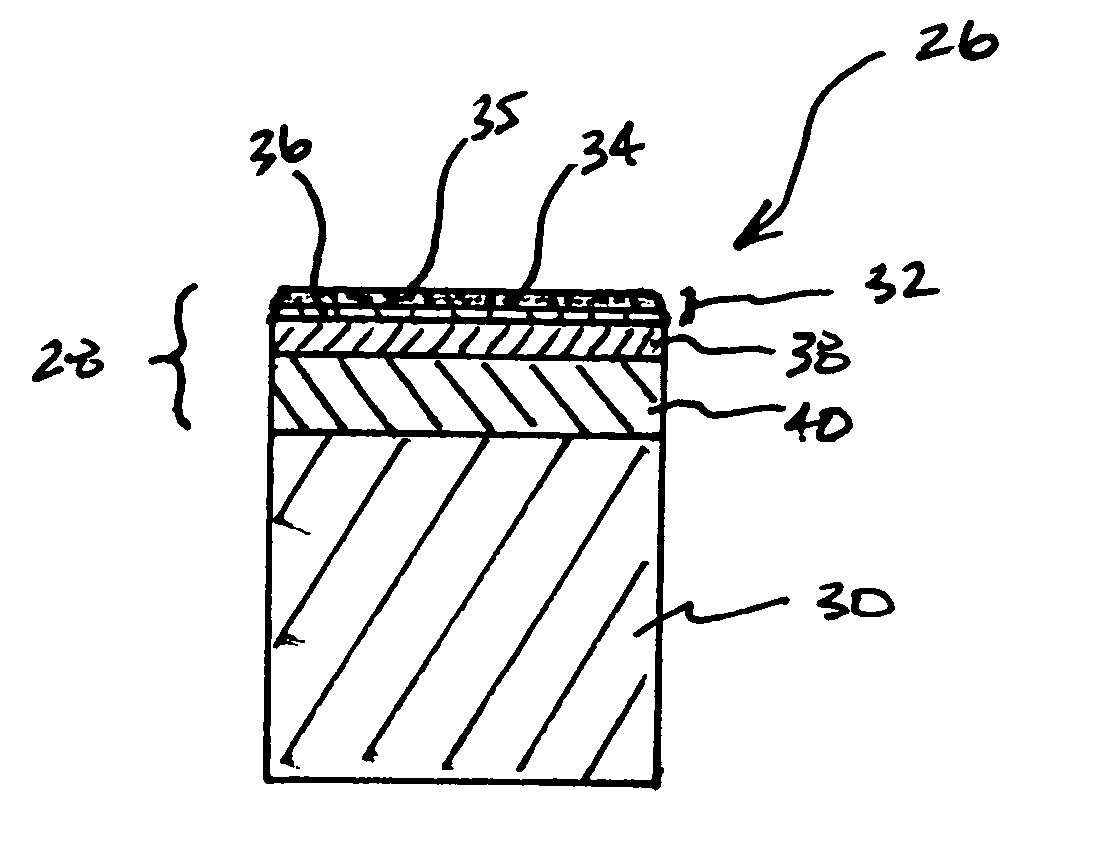

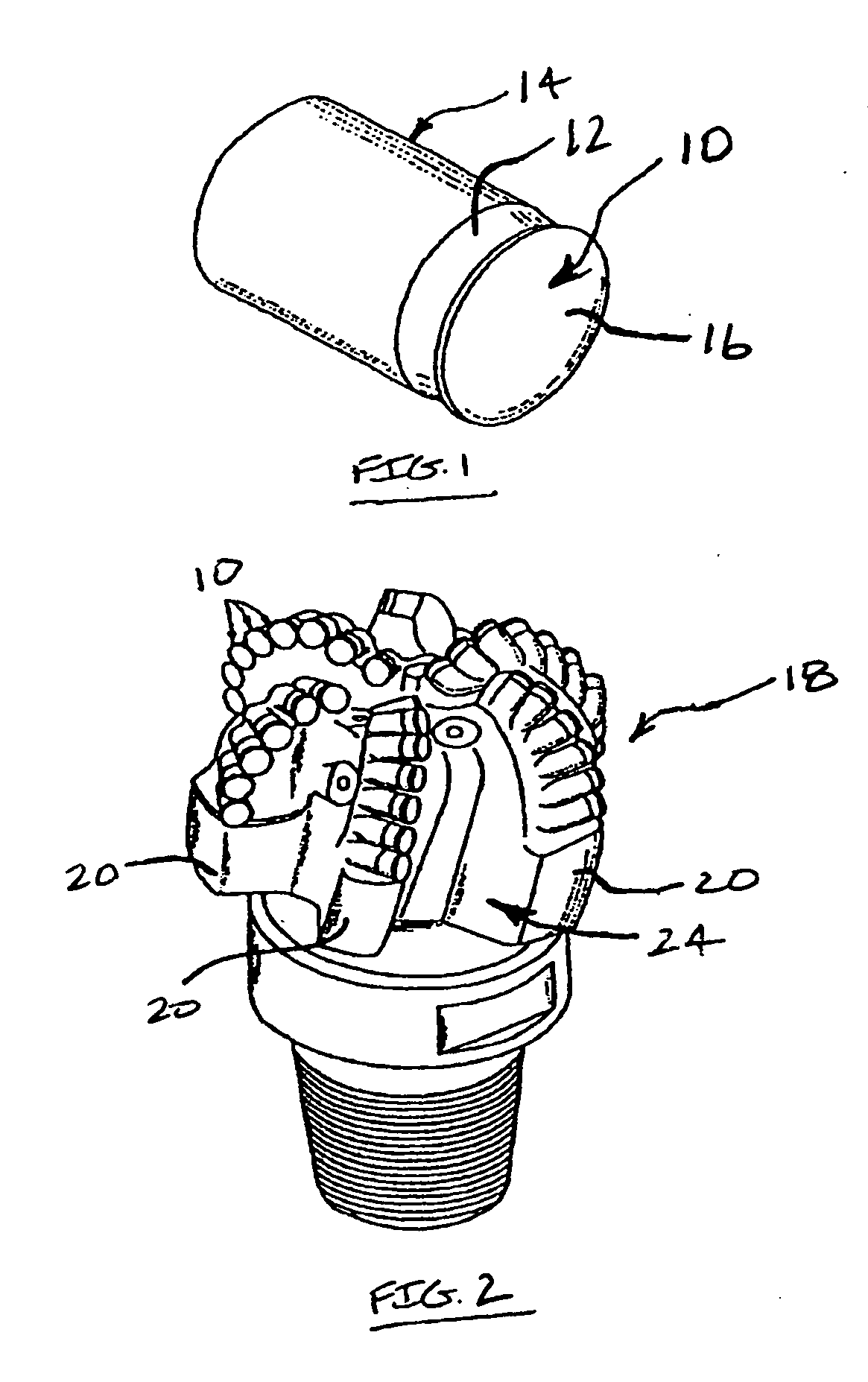

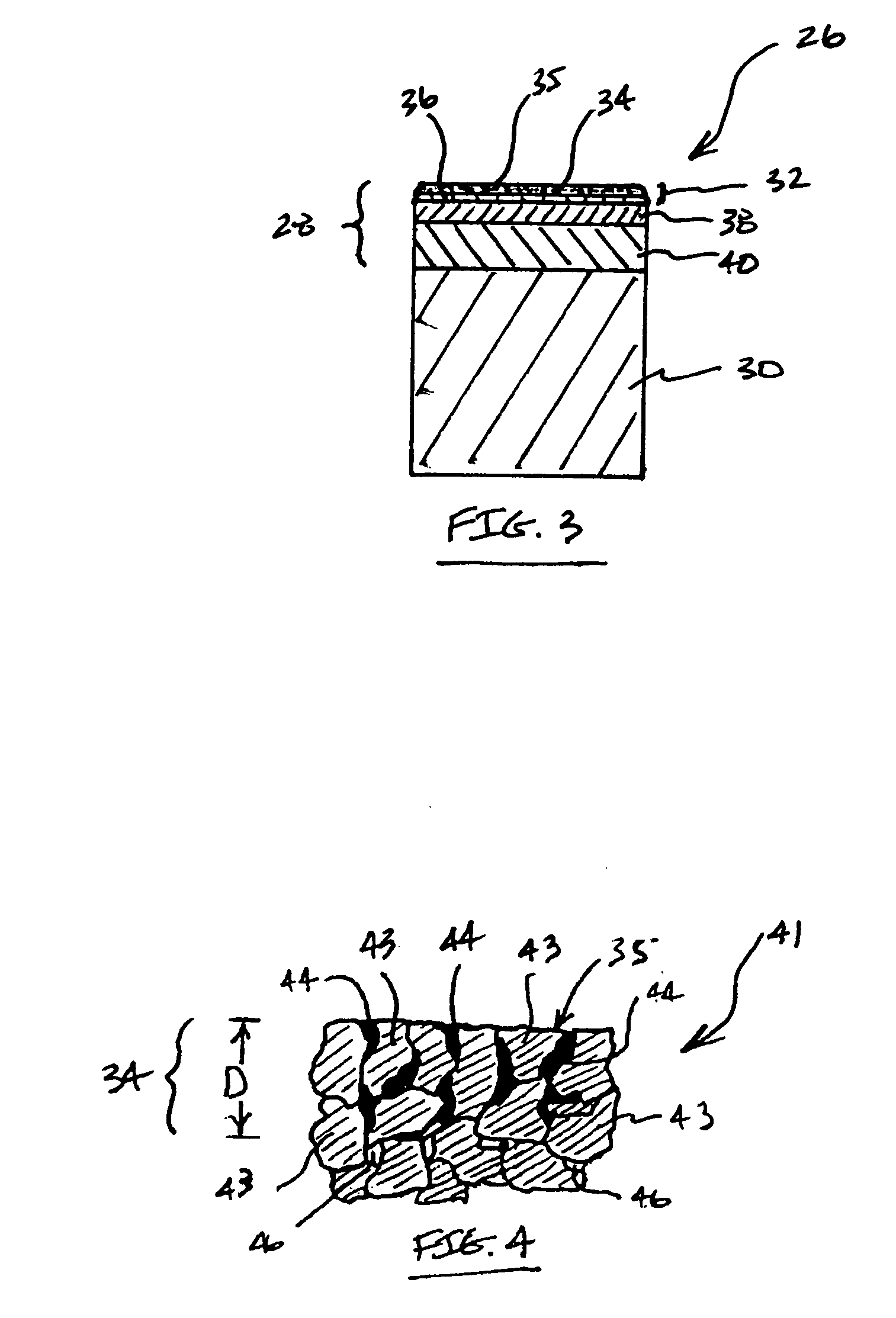

InactiveUS20060162969A1Eliminate or resist any cracking during useDifferential wear resistanceDrill bitsConstructionsSuperhard materialInter layer

Cutting elements of this invention include an ultra hard body joined with a metallic substrate. The body includes an uppermost layer comprising a plurality of bonded ultra hard crystals and interstitial regions, and that defines a body working surface. The uppermost layer includes an outer region that is relatively more thermally stable than a remaining portion of the uppermost layer. The body further includes an intermediate layer joined to the uppermost layer, comprising a plurality of bonded ultra hard crystals, and having a wear resistance less than that of the uppermost layer remaining region. The body may additionally include a lowermost PCD layer that is interposed between and attached to the intermediate layer and the substrate.

Owner:SMITH INT INC

Efficient decoded picture buffer management for scalable video coding

InactiveUS20070086521A1Color television with pulse code modulationColor television with bandwidth reductionInter layerComputer graphics (images)

A system and method for enabling the removal of decoded pictures from a decoded picture buffer as soon as the decoded pictures are no longer needed for prediction reference and future output. An indication is introduced into the bitstream as to whether a picture may be used for inter-layer prediction reference, as well as a decoded picture buffer management method which uses the indication. The present invention includes a process for marking a picture as being used for inter-layer reference or unused for inter-layer reference, a storage process of decoded pictures into the decoded picture buffer, a marking process of reference pictures, and output and removal processes of decoded pictures from the decoded picture buffer.

Owner:NOKIA CORP

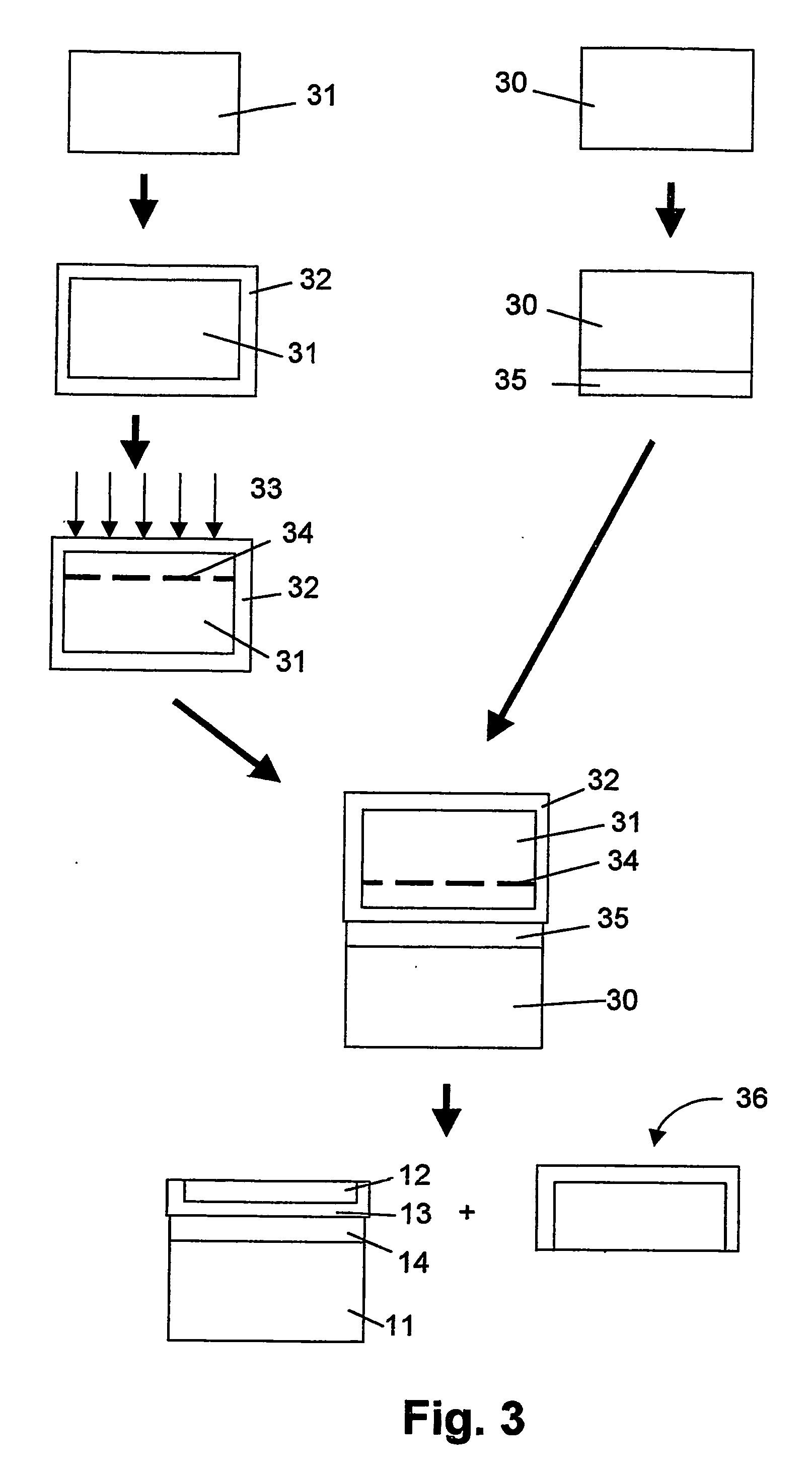

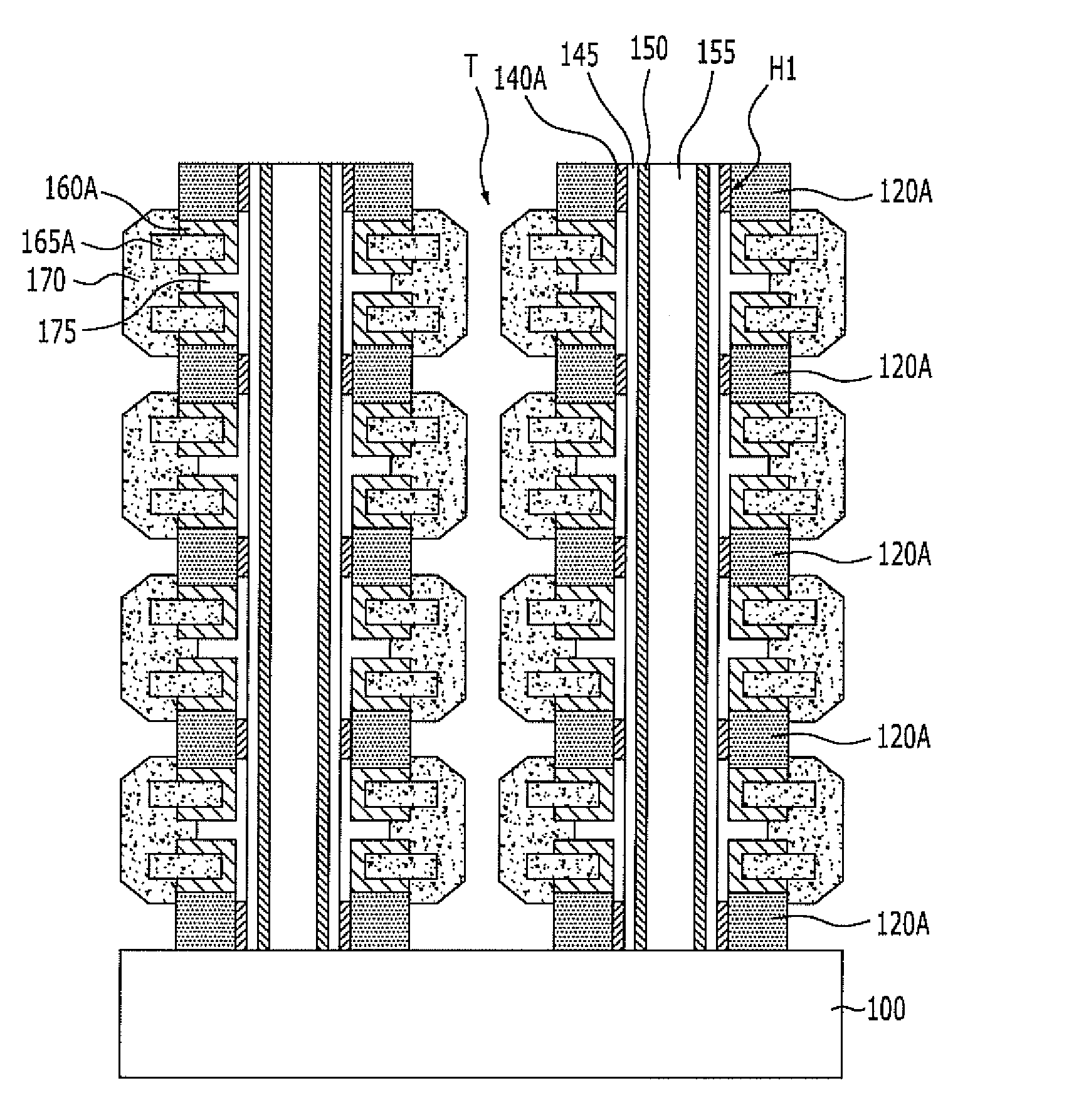

Method of manufacturing a multilayer semiconductor structure with reduced ohmic losses

InactiveUS20070032040A1Reduce and minimiseElectrical losses are reducedSolid-state devicesSemiconductor/solid-state device manufacturingInter layerSemiconductor structure

The present invention provides a method of manufacturing a multilayer semiconductor structure featuring reduced ohmic losses with respect to standard multilayer semiconductor structures. The semiconductor structure comprises a high resistivity silicon substrate with resistivity higher than 3 KΩ.cm, an active semiconductor layer and an insulating layer in between the silicon substrate and the active semiconductor layer. The method comprises suppressing ohmic losses inside the high resistivity silicon substrate by increasing, with regard to prior art devices, charge trap density between the insulating layer and the silicon substrate. In particular this may be obtained by applying an intermediate layer in between the silicon substrate and the insulating layer, the intermediate layer comprising grains having a size, wherein the mean size of the grains of the intermediate layer is smaller than 150 nm, preferably smaller than 50 nm.

Owner:UNIV CATHOLIQUE DE LOVAIN

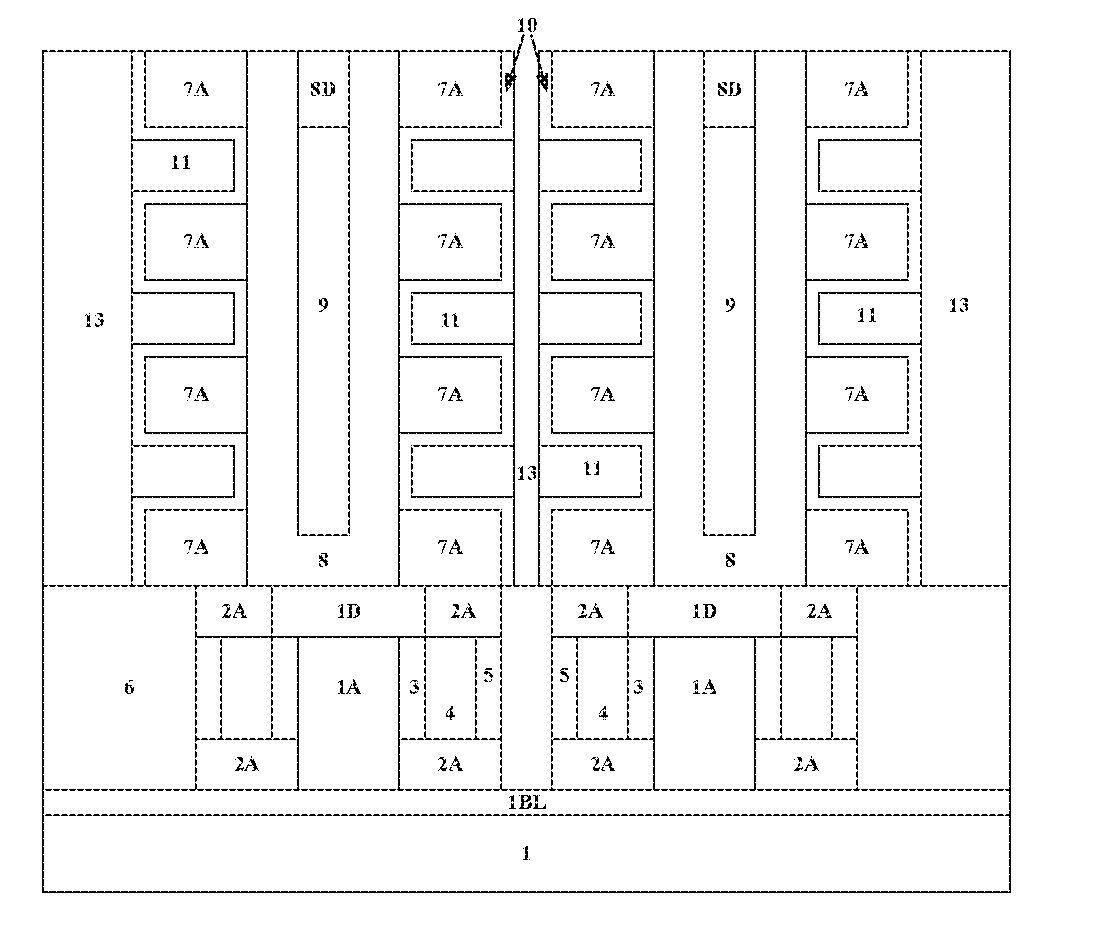

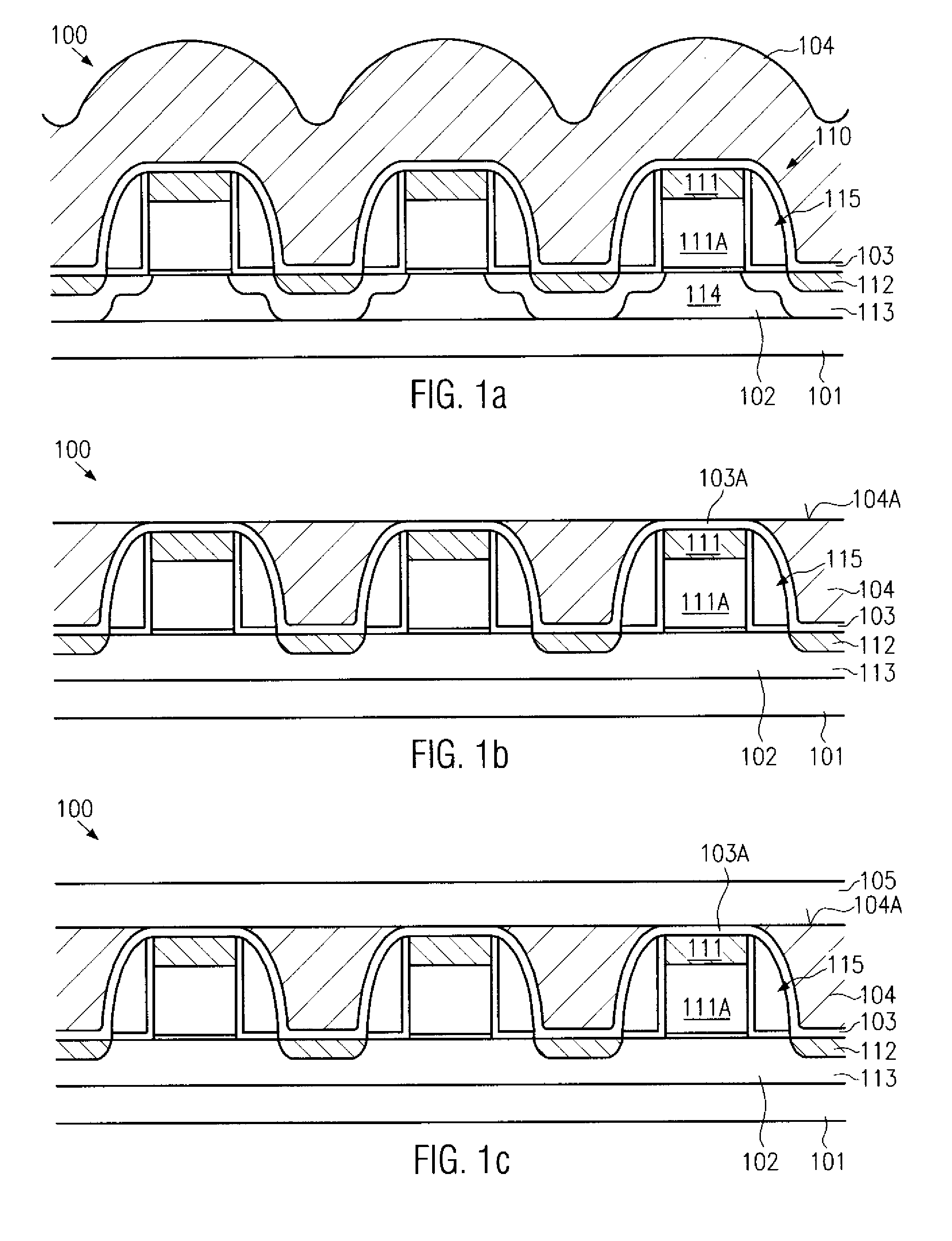

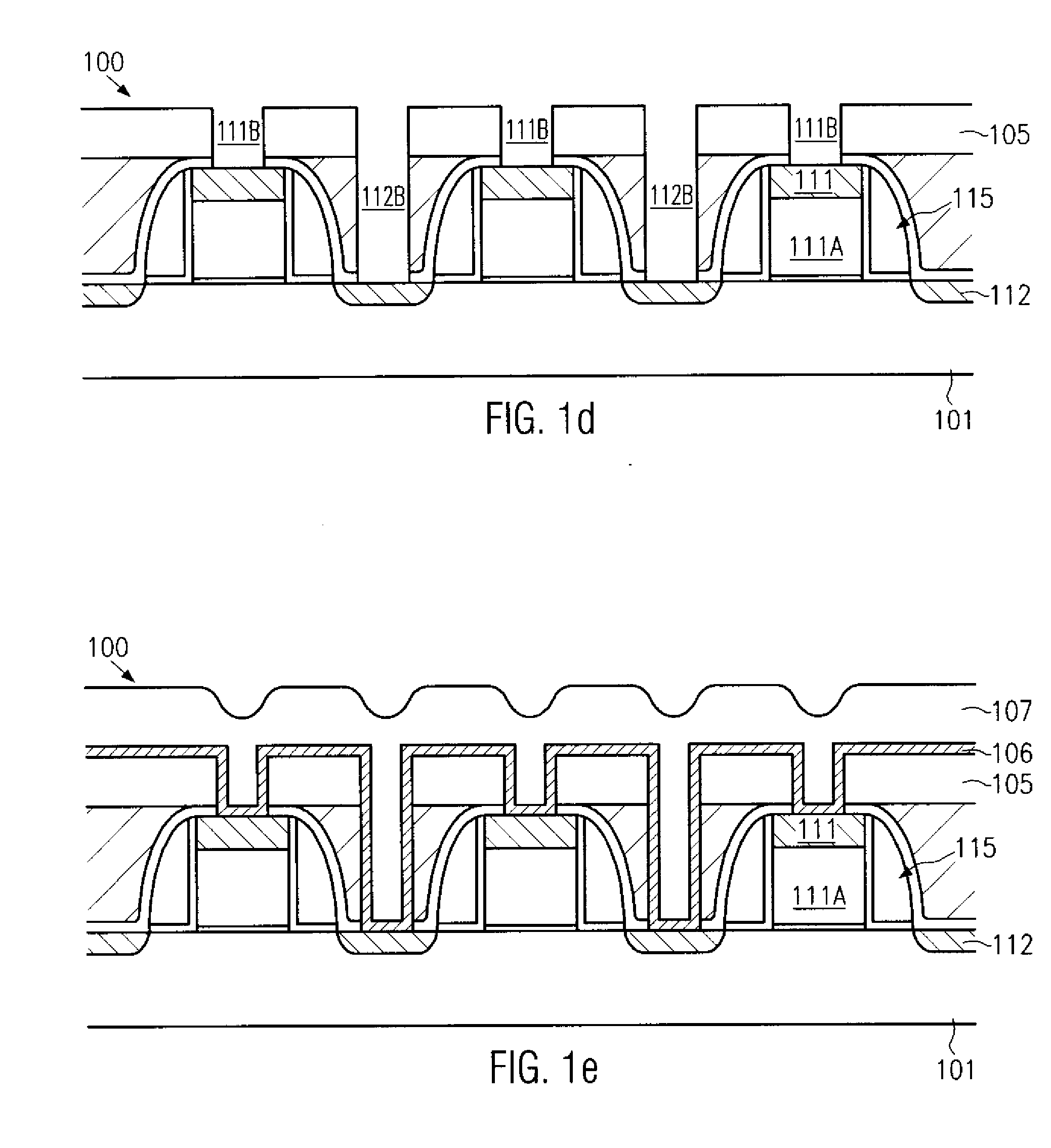

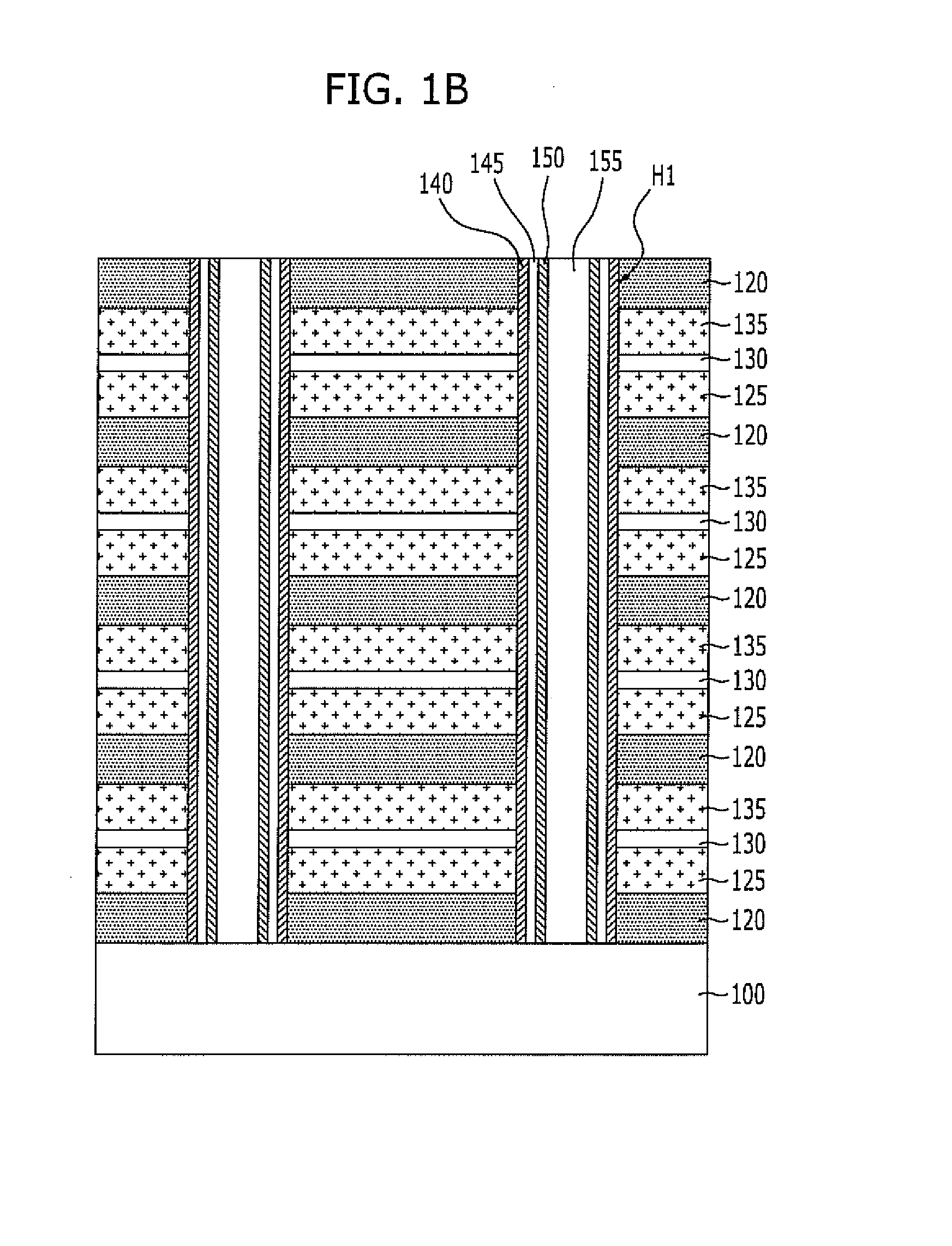

Three-Dimensional Semiconductor Device and Manufacturing Method Therefor

InactiveUS20170154895A1Improve control characteristicsReduce off-state leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETEtching

A three-dimensional semiconductor device, comprising a plurality of memory cell transistors and a plurality of select transistors at least partially overlapped in the vertical direction, wherein each select transistor comprises a first drain, an active region and a common source formed in the substrate, distributed along the vertical direction, as well as a metal gate distributed around the active region; wherein each memory cell transistor comprises a channel layer distributed perpendicularly to the substrate surface, a plurality of inter-layer insulating layers and a plurality of gate stack structures alternately stacked along the sidewalls of said channel layer, a second drain located on top of said channel layer; wherein said channel layer and said the first drain are electrically connected. In accordance with the three-dimensional semiconductor memory device and manufacturing method of the present invention, the multi-gate MOSFET is formed beneath the stack structure of the memory cell string including vertical channel to serve as the select transistor, this can improve the control characteristics of the gate threshold voltage, reduce the off-state leakage current, prevent the substrate from over-etching, and effectively improve the reliability of the device.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

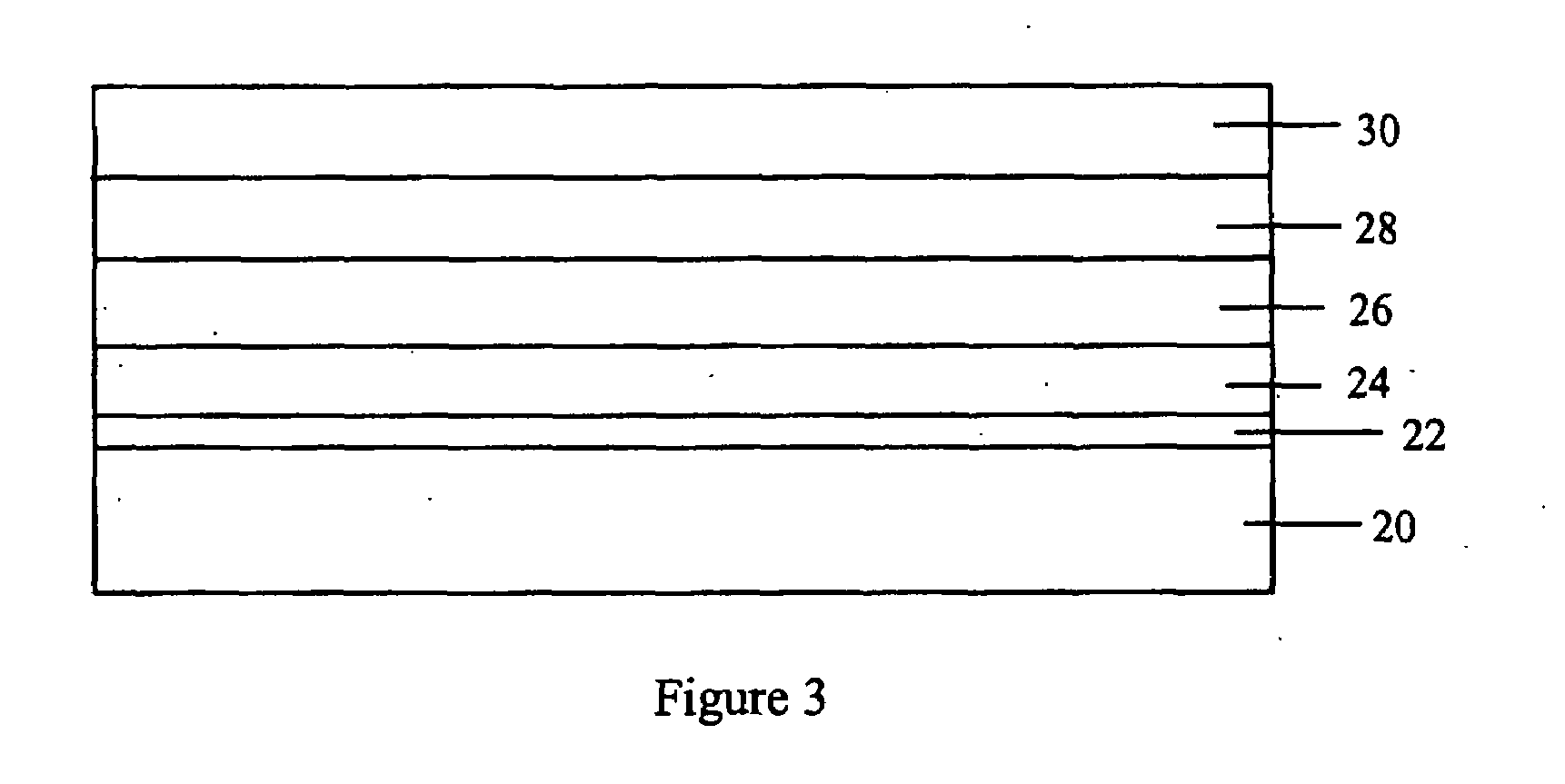

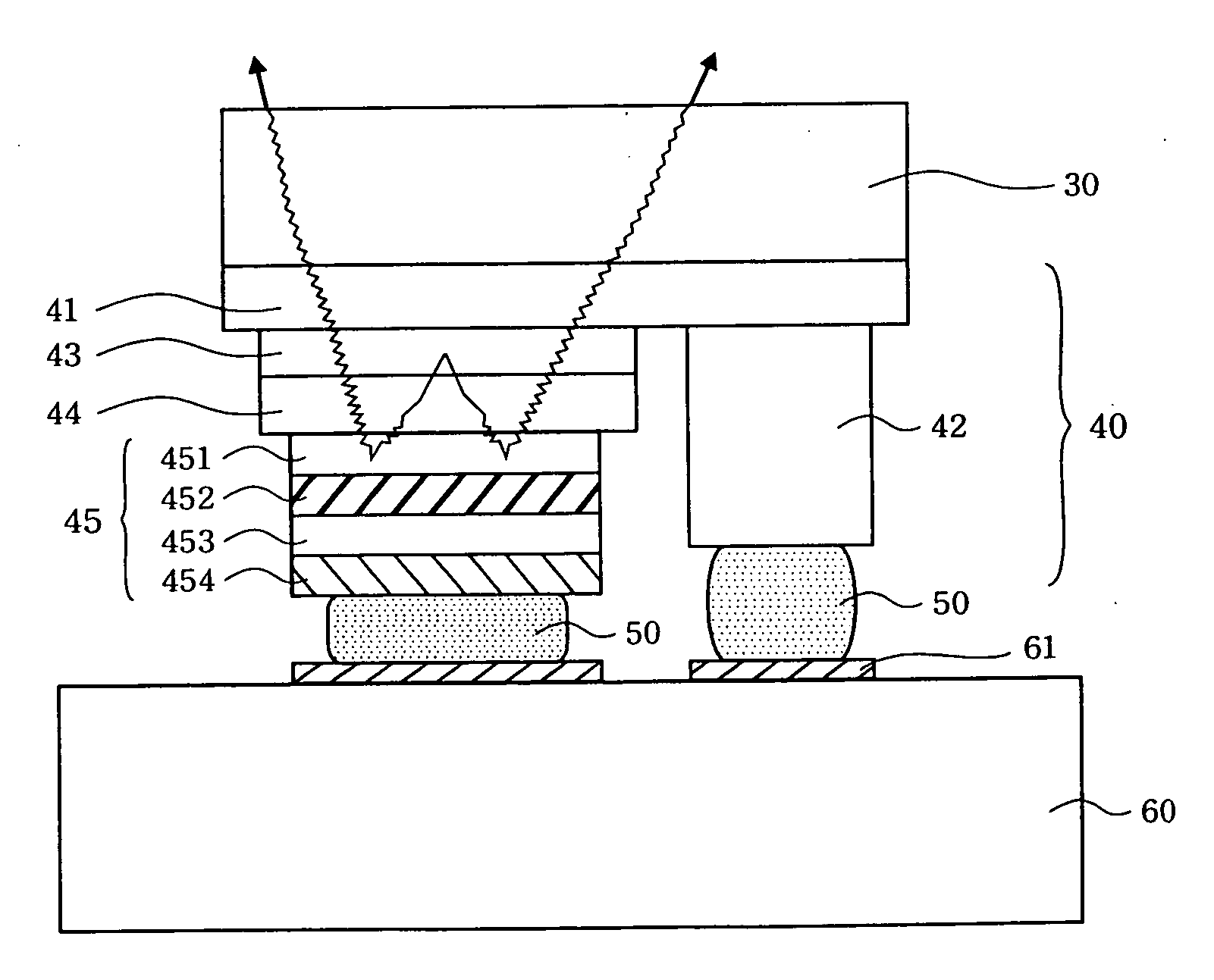

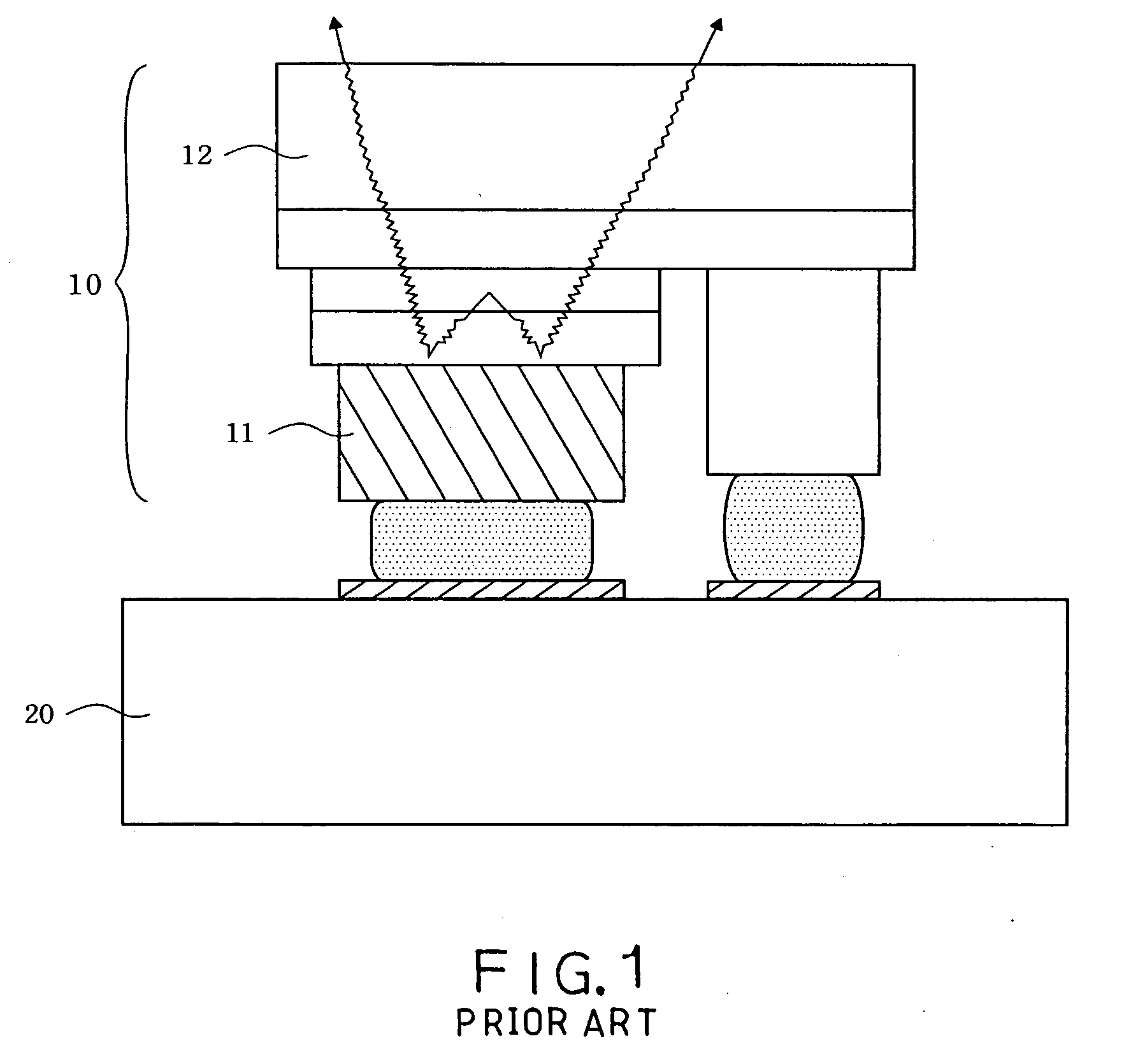

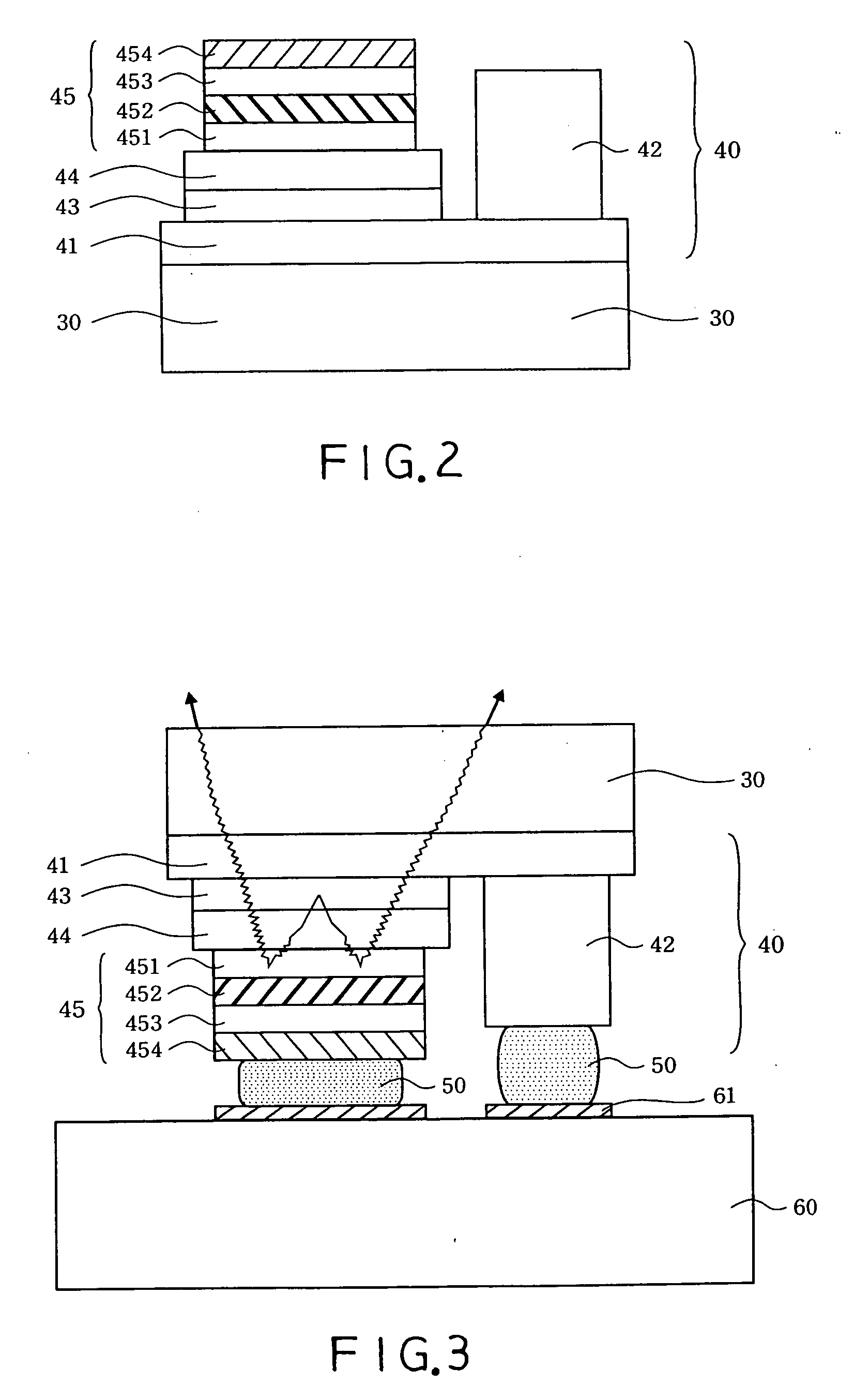

Flip-chip electrode light-emitting element formed by multilayer coatings

InactiveUS20060081869A1High reflective functionLuminous efficiencySolid-state devicesSemiconductor devicesInter layerOhmic contact

A flip-chip electrode light-emitting element formed by multilayer coatings where a translucent conducting layer and a highly reflective metal layer acts as flip-chip electrode for enhancing the LED luminous efficiency. The flip-chip electrode light-emitting element includes a translucent substrate, a semiconductor die structure attached on the translucent substrate and made of group III nitride compounds, and an intermediate layer adapted to support the inverted semiconductor die structure on a submount. The flip-chip electrode formed by multiplayer coatings includes a current-spreading transparent conducting layer formed on a top side of the second type semiconductor layer, a highly reflective metal layer formed on a top side of the transparent conducting layer, a metallic diffusion barrier layer formed on a top side of the highly reflective metal layer, and a bonding layer electrically coupled to the intermediate layer and formed on a top side of the barrier layer. Moreover, an ohmic contact layer is formed on the transparent conducting layer. And a passivation layer encloses the die structure for insulating p / n interface and for avoiding the creation of the leakage current.

Owner:ARIMA OPTOELECTRONICS

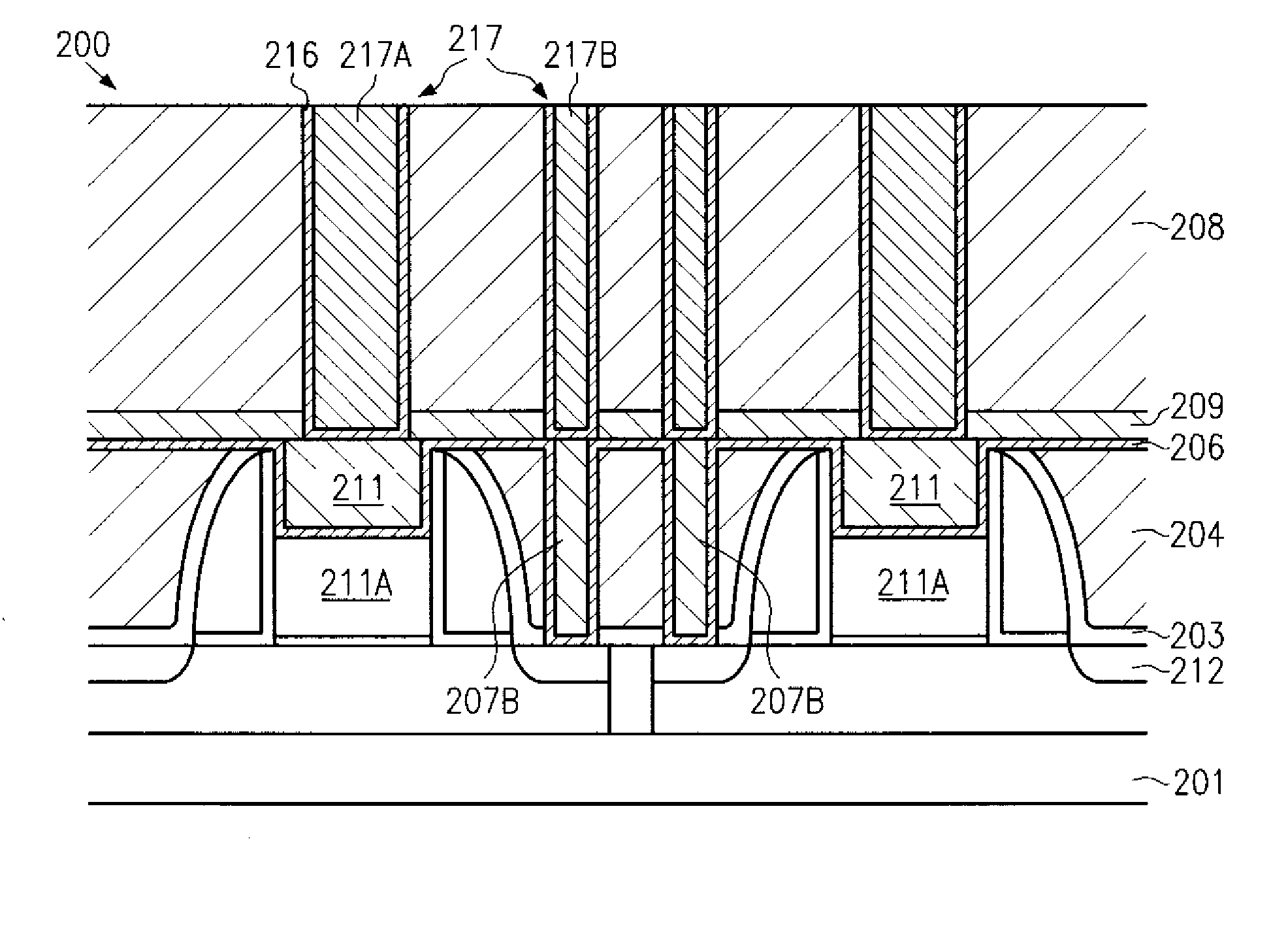

Semiconductor device comprising a contact structure based on copper and tungsten

ActiveUS20070099414A1Reduce resistanceLower resistanceTransistorSemiconductor/solid-state device detailsInter layerDevice material

By providing contact plugs having a lower plug portion, formed on the basis of well-established tungsten-based technologies, and an upper plug portion, which may comprise a highly conductive material such as copper or a copper alloy, a significant increase in conductivity of the contact structure may be achieved. For this purpose, after the deposition of a first dielectric layer of the inter-layer stack, a planarization process may be performed so as to allow the formation of the lower plug portions on the basis of tungsten, while, after the deposition of the second dielectric layer, a corresponding copper-based technology may be used for forming the upper plug portions of significantly enhanced conductivity.

Owner:GLOBALFOUNDRIES US INC

Non-volatile memory device and method for fabricating the same

InactiveUS20130161726A1Improve erase operation characteristicImprove operating characteristicsSolid-state devicesSemiconductor/solid-state device manufacturingInter layerDielectric layer

A non-volatile memory device includes a channel layer vertically extending from a substrate, a plurality of inter-layer dielectric layers and a plurality of gate electrodes that are alternately stacked along the channel layer, and an air gap interposed between the channel layer and each of the plurality of gate electrodes. The non-volatile memory device may improve erase operation characteristics by suppressing back tunneling of electrons by substituting a charge blocking layer interposed between a gate electrode and a charge storage layer with an air gap, and a method for fabricating the non-volatile memory device.

Owner:SK HYNIX INC

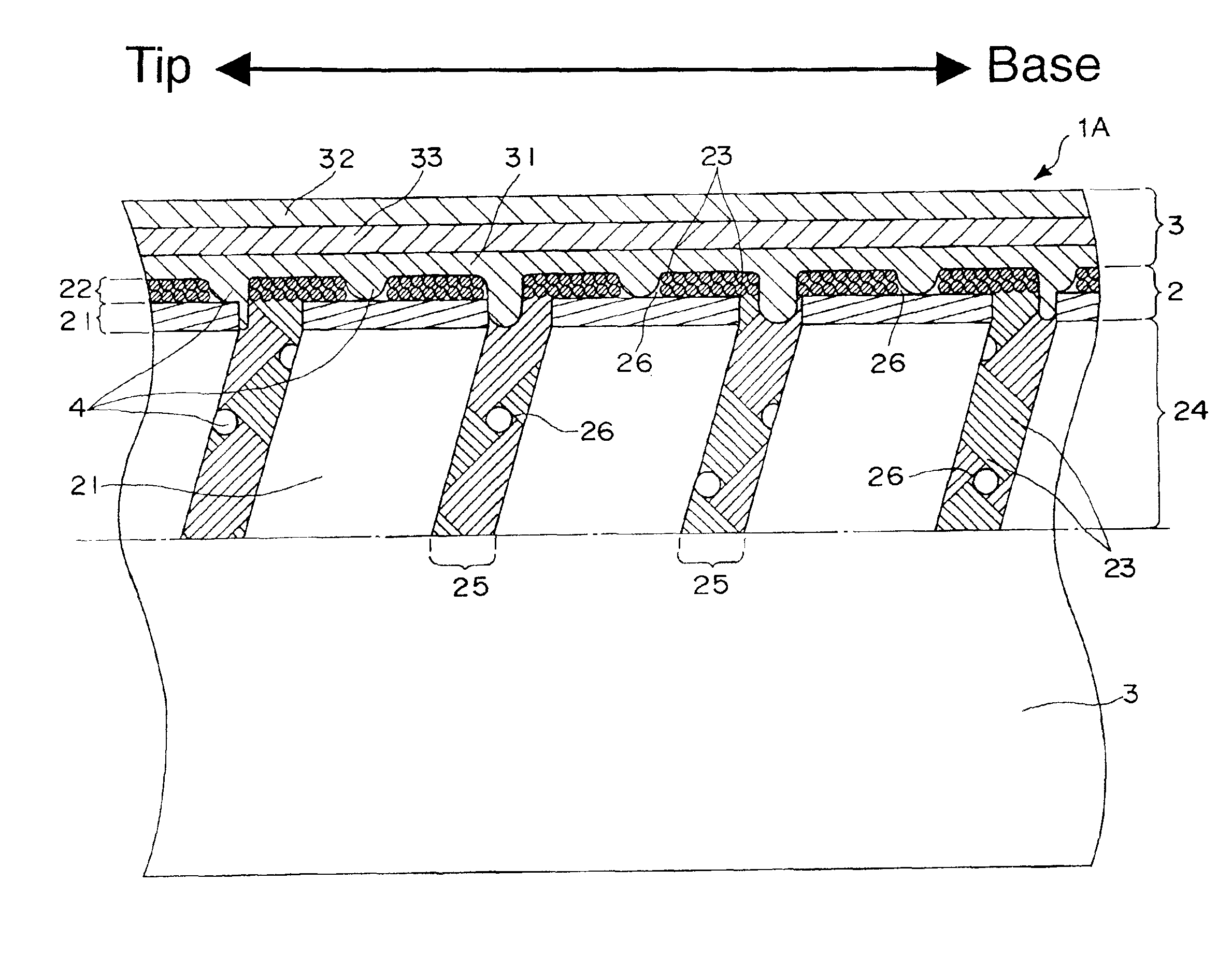

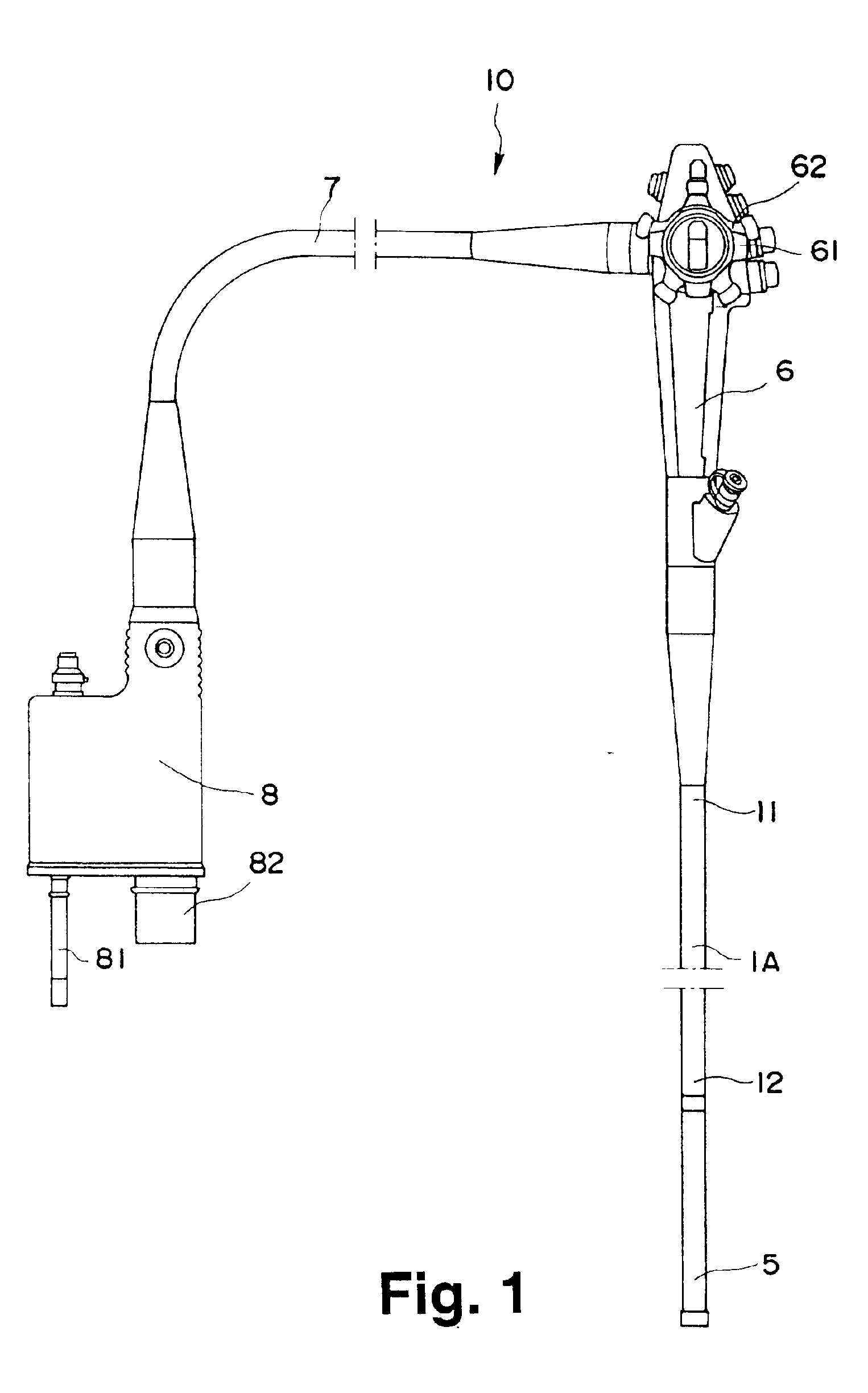

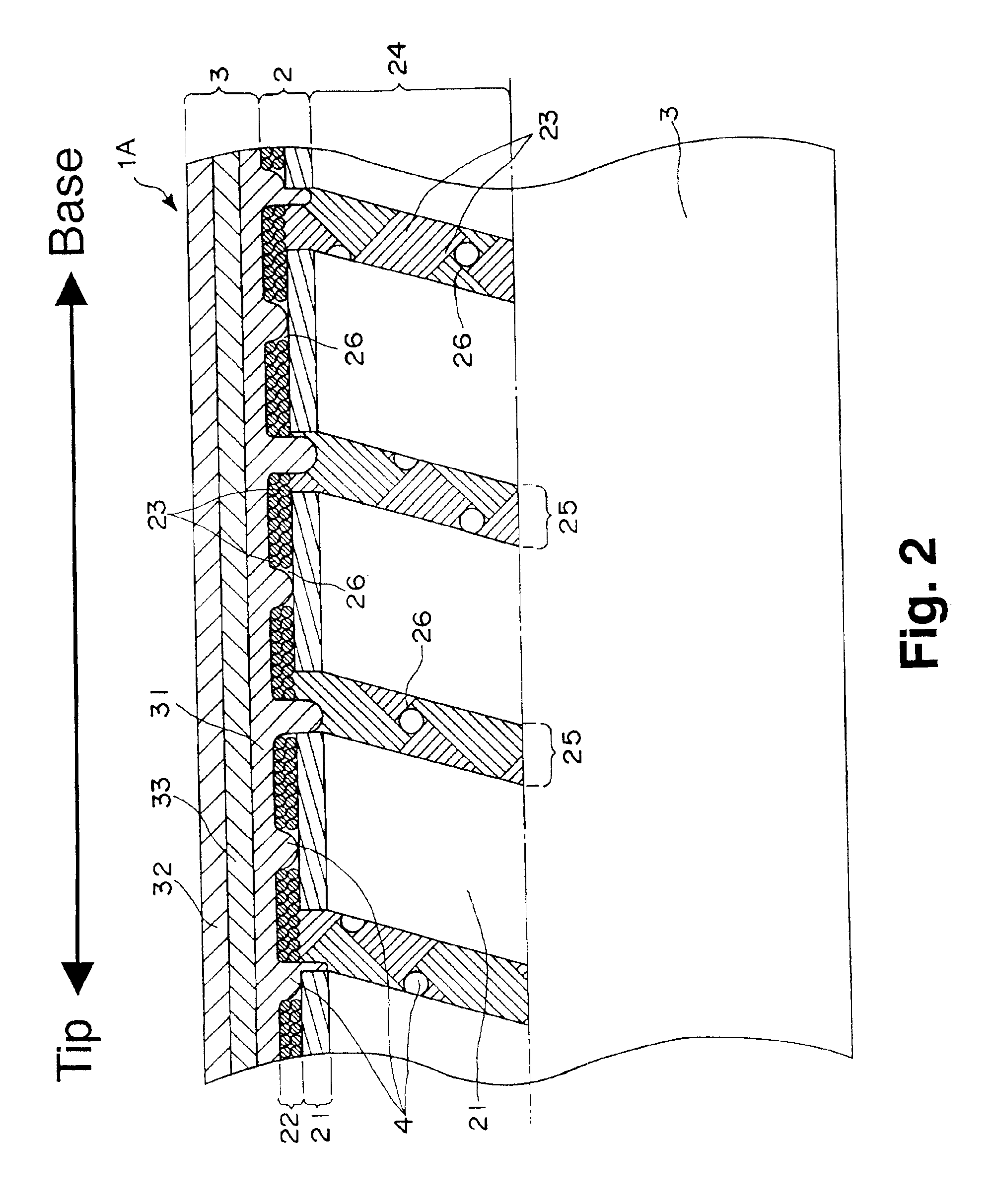

Flexible tube for an endoscope

InactiveUS6860849B2Excellent in operability of insertion and resistance to chemicalIncrease flexibilitySurgerySynthetic resin layered productsInter layerEngineering

A flexible tube for an endoscope has an elongated tubular core body, and an outer cover which is provided over the core body. The outer cover is composed of an inner layer, an outer layer and at least one intermediate layer. In this flexible tube, any one of the layers is different from one of the other layers in its property. Further, at least one of the layers has a thickness-varying region where the thickness of the layer varies in its longitudinal direction. In addition, the inner layer of the outer cover has projections which are integrally formed on the inner layer so that the projections project into holes and / or the recesses formed on the core body. This structure makes it possible to produce a flexible tube for an endoscope that has high durability, high flexibility and high chemical resistance as well as excellent operationability.

Owner:HOYA CORP

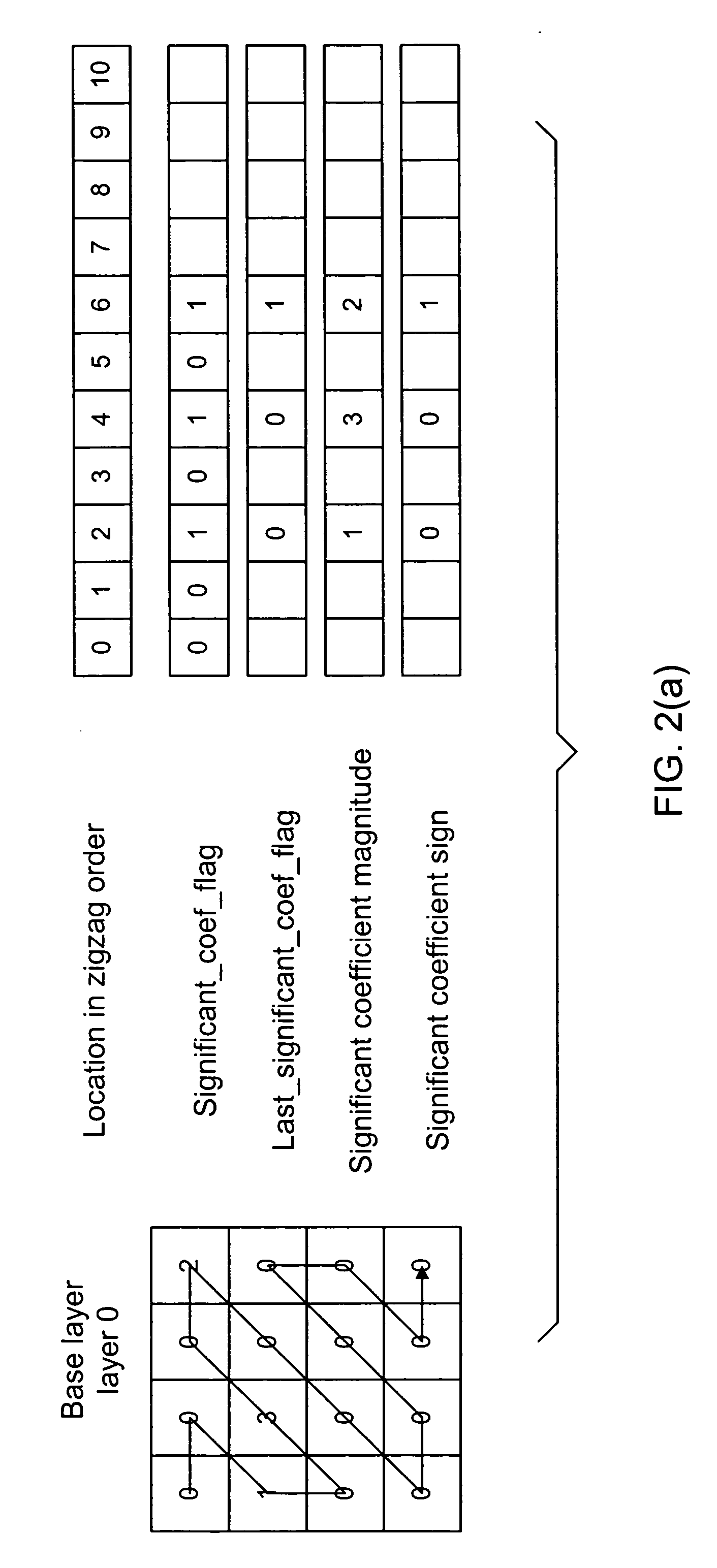

Inter-layer coefficient coding for scalable video coding

InactiveUS20060153294A1Pixel predictorImprove the overall coefficientColor television with pulse code modulationColor television with bandwidth reductionInter layerComputer architecture

A scalable video coding method and apparatus for coding a video sequence, wherein the coefficients in the enhancement layer is classified as belonging to a significant pass when the corresponding coefficient in the base layer is zero, and classified as belonging to a refinement pass when the corresponding coefficient in the base layer is non-zero. For coefficients classified as belonging to the significance pass, an indication is coded to indicate whether the coefficient is zero or non-zero, and if the coefficient is non-zero, coding an indication of the sign of the coefficient. A last_significant_coeff_flag is used to indicate the coding of remaining coefficients in the scanning order can be skipped. For coefficients classified as belonging to the refinement pass, a value to refine the magnitude of the corresponding coefficient in the base layer is coded, and if the coefficient is non-zero, a sign bit may be coded.

Owner:NOKIA CORP

Semiconductor device

InactiveUS6445059B1Capacity producedReduce capacityTransistorSemiconductor/solid-state device detailsInter layerSilicon oxide

A resin material having low dielectric constant is used as an inter-layer insulating film and its bottom surface is contacted with a silicon oxide film across the whole surface thereof. Thereby, the surface may be flattened and capacity produced between a thin film transistor and an pixel electrode may be reduced. Further, it allows to avoid a problem that impurity ions and moisture infiltrate into the lower surface of the resin material, thus degrading the reliability of whole semiconductor device.

Owner:SEMICON ENERGY LAB CO LTD

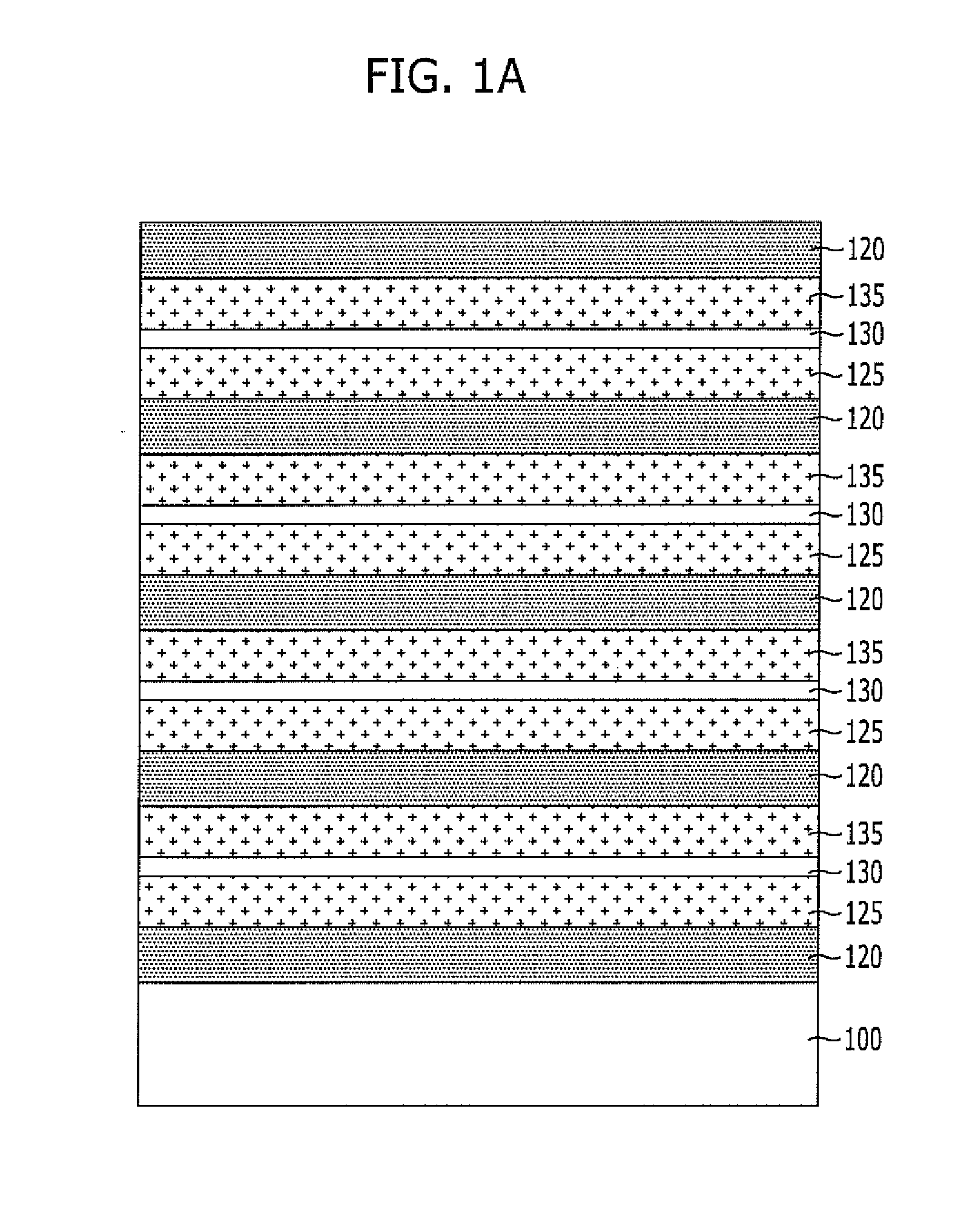

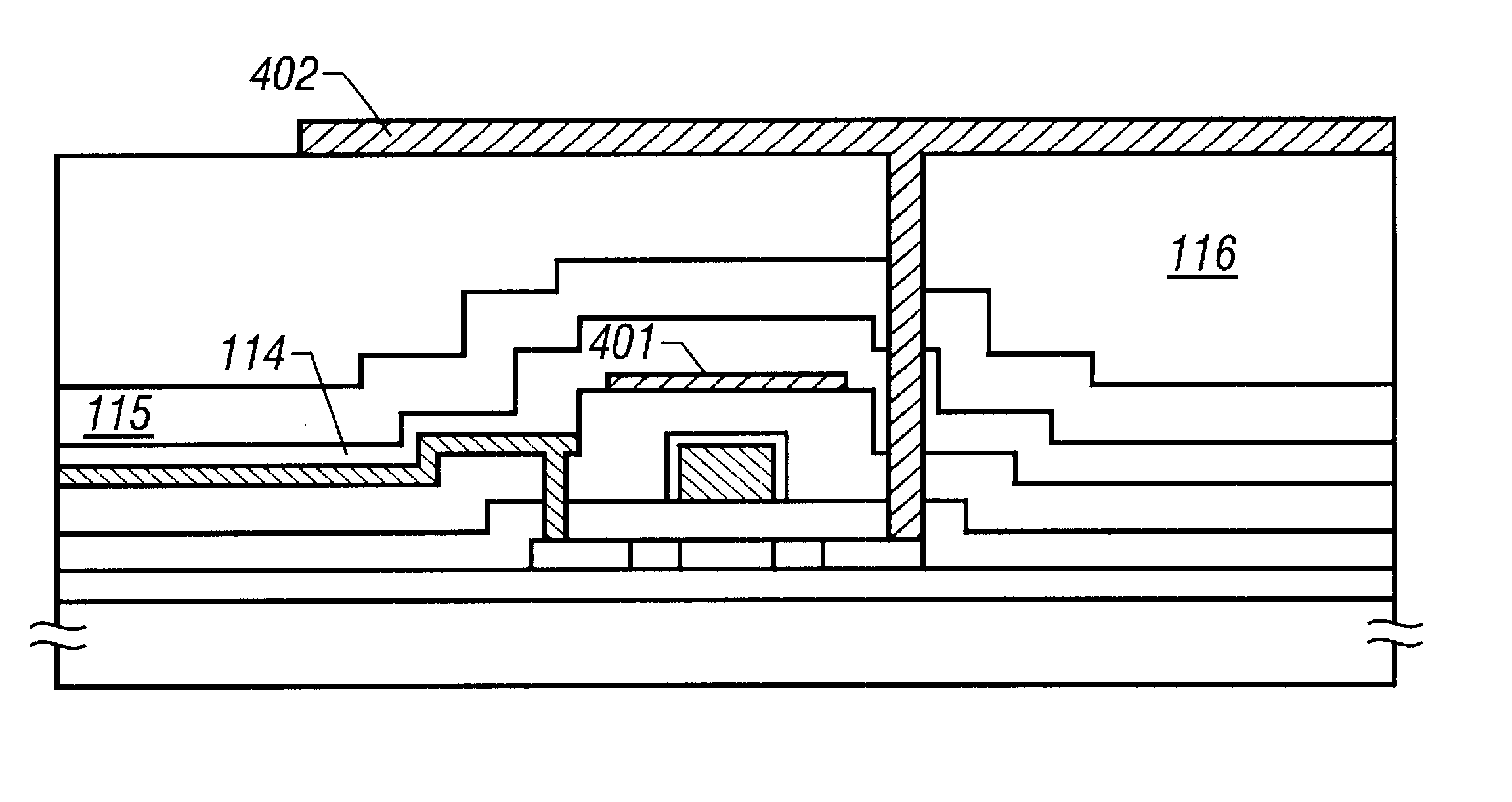

Semiconductor device having multi-layer wiring

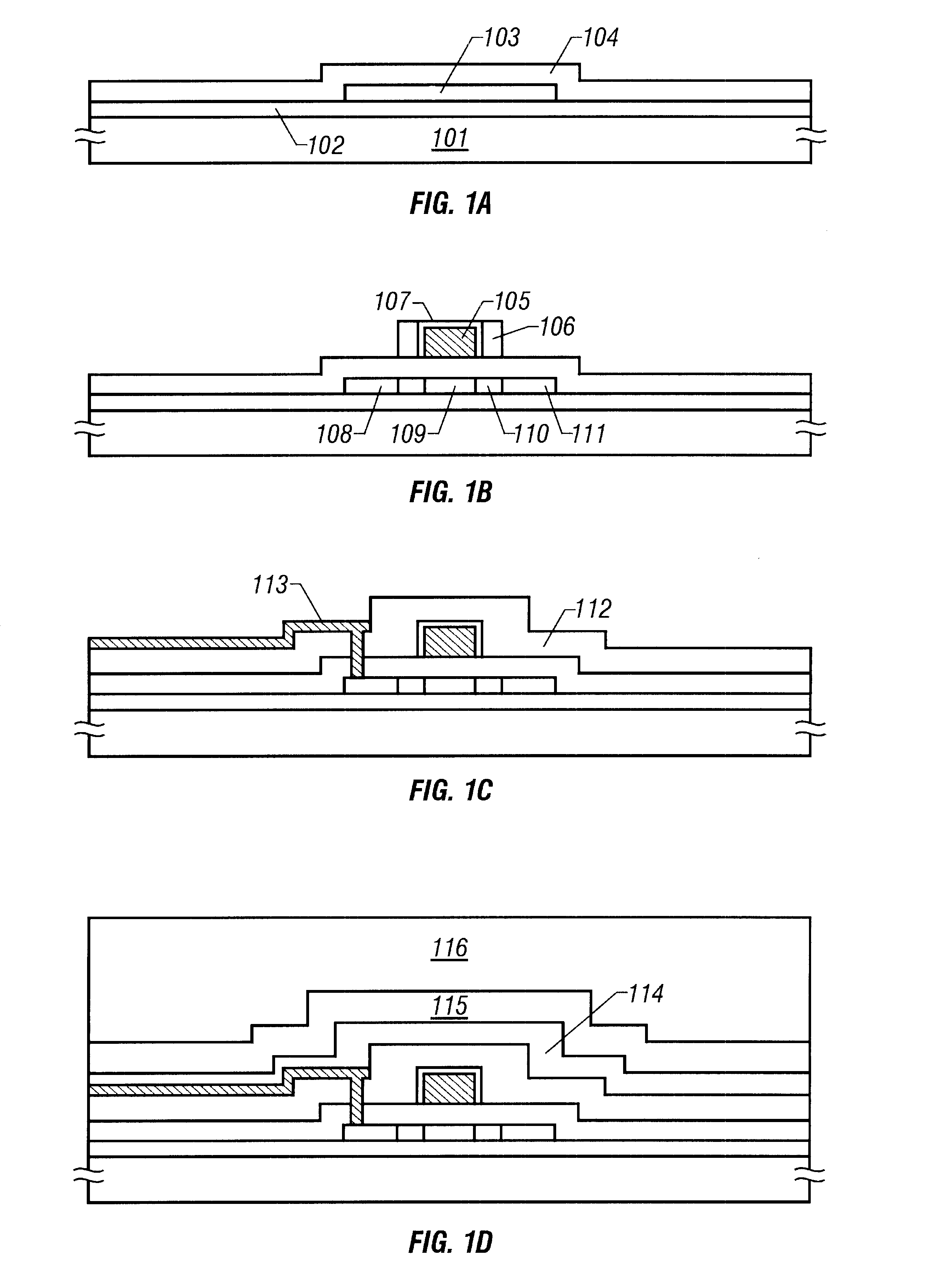

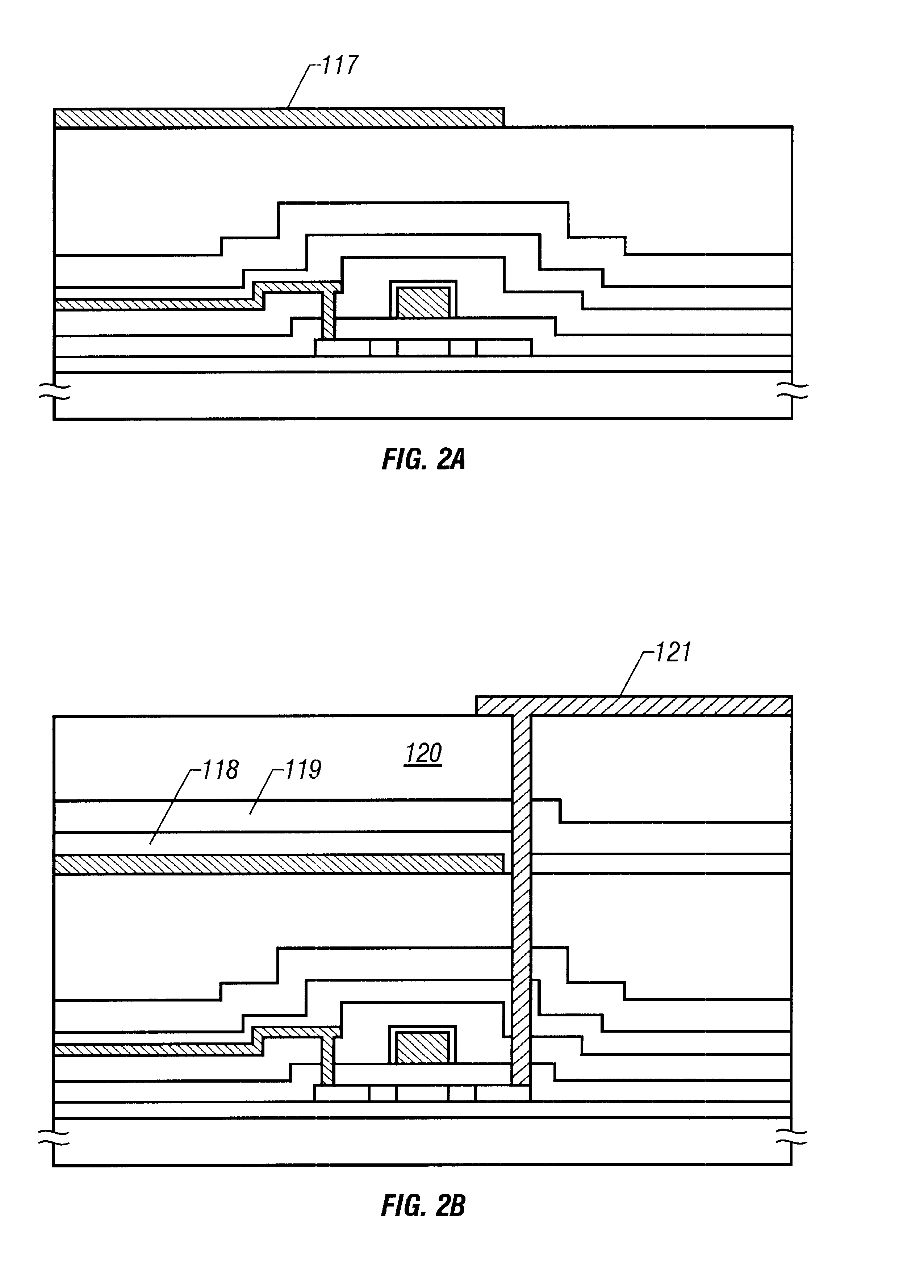

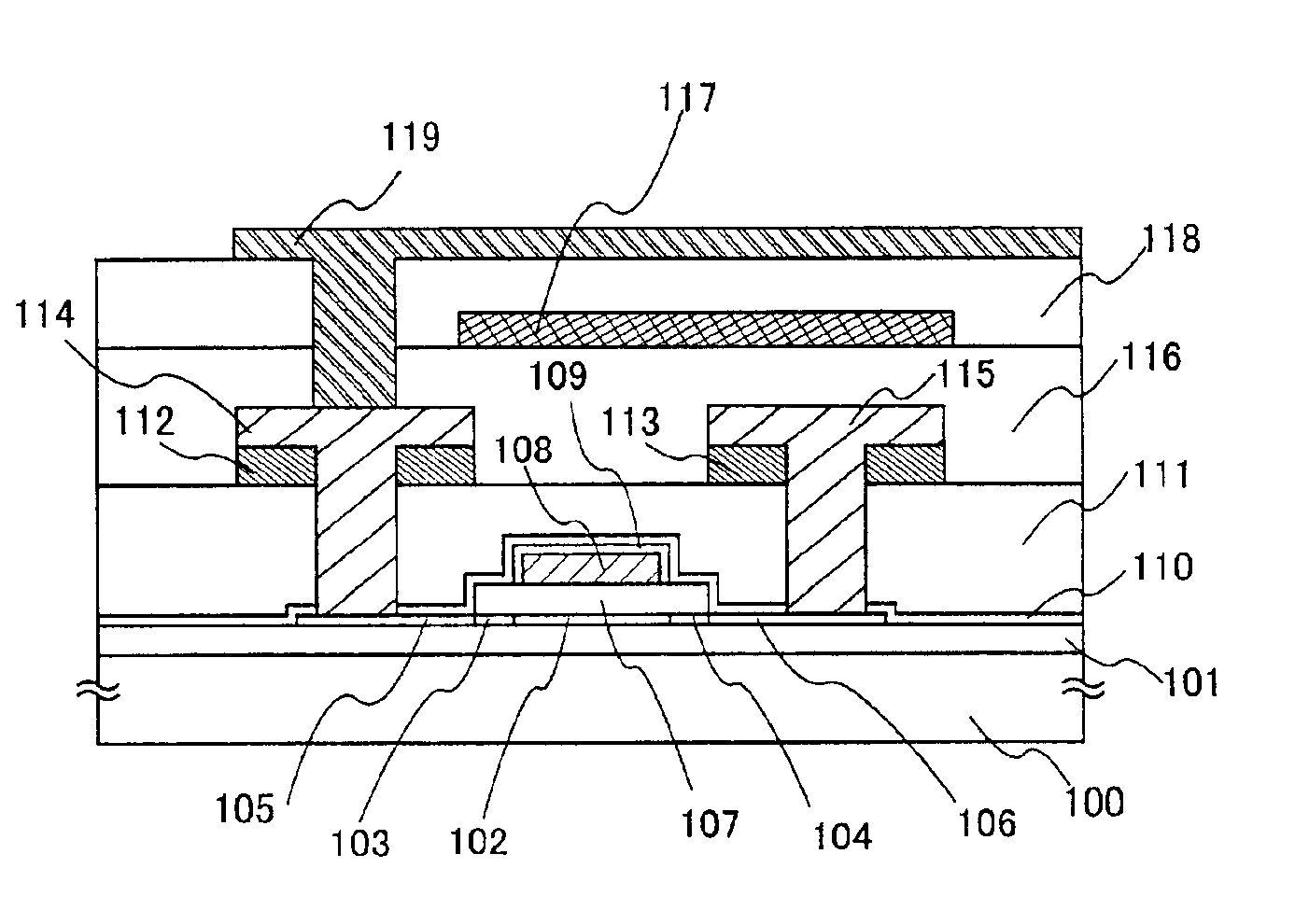

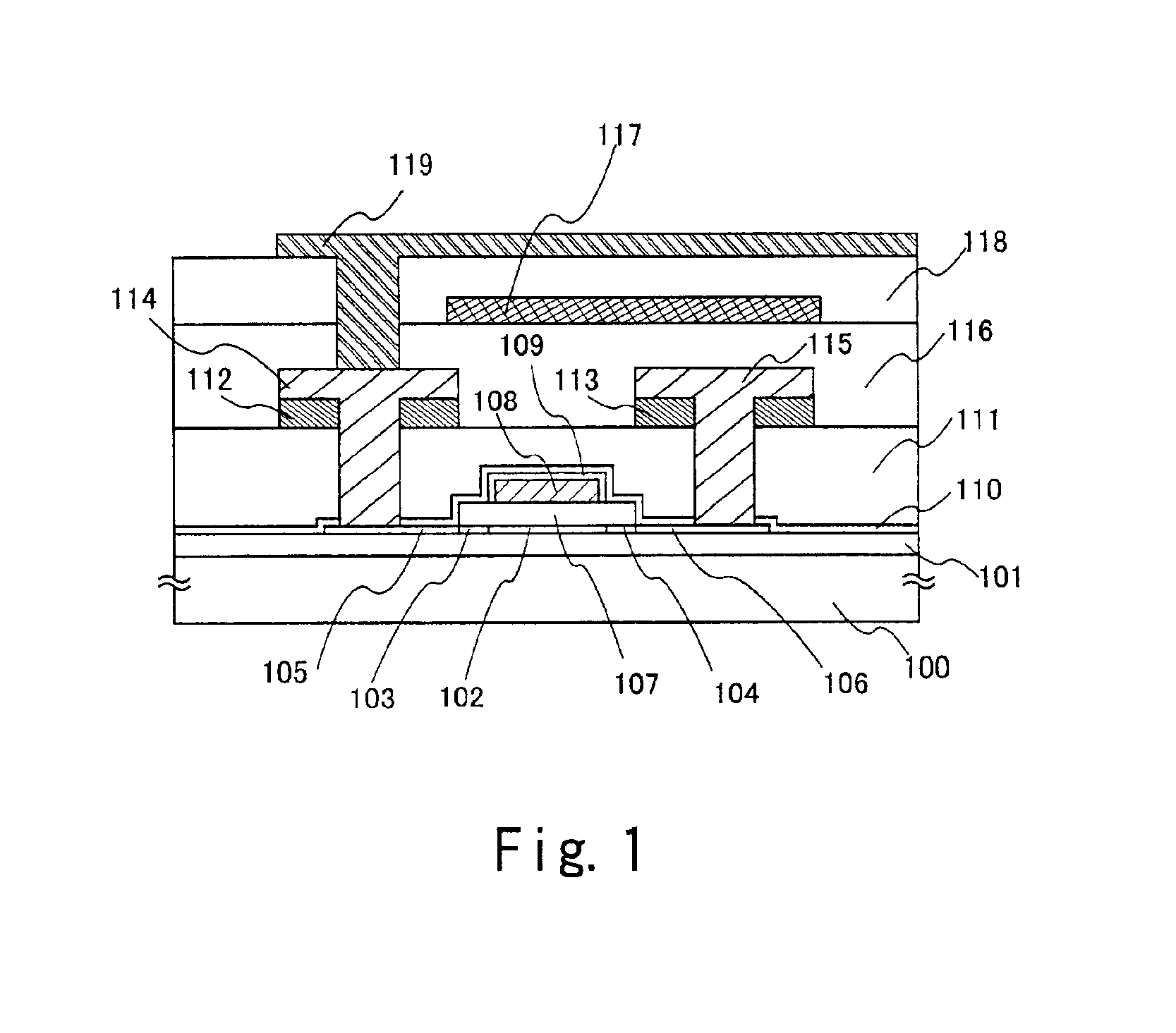

InactiveUS6861670B1Lower resistanceIncrease contactTransistorSemiconductor/solid-state device detailsInter layerDevice material

The object is to pattern extremely fine integrated circuits by forming fine contact holes. The dry etching method is employed to form contact holes to pattern a wiring (114), using a mask made of metallic film (112) and an organic material as an inter-layer insulating film (111) for covering switching elements and each of the wirings.

Owner:SEMICON ENERGY LAB CO LTD

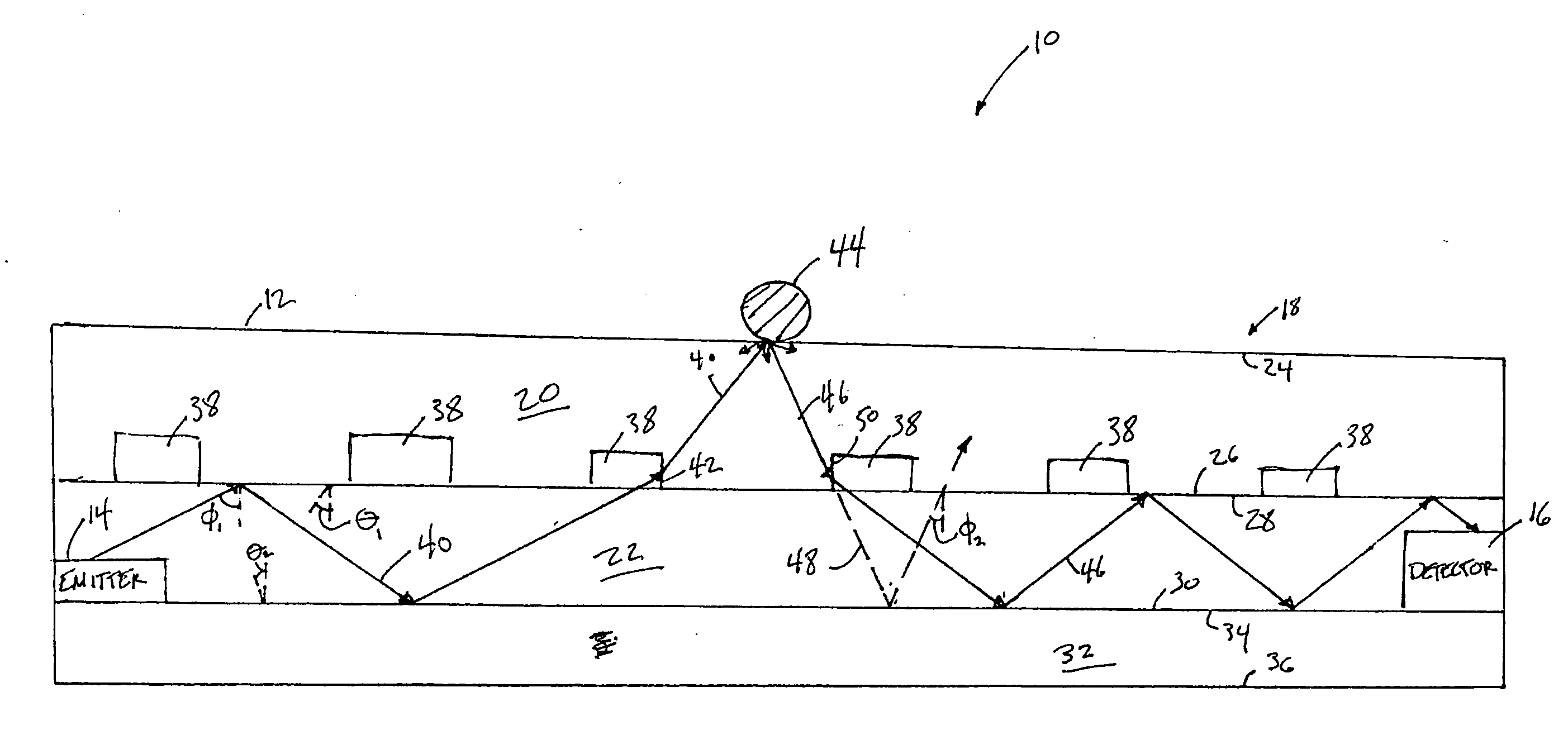

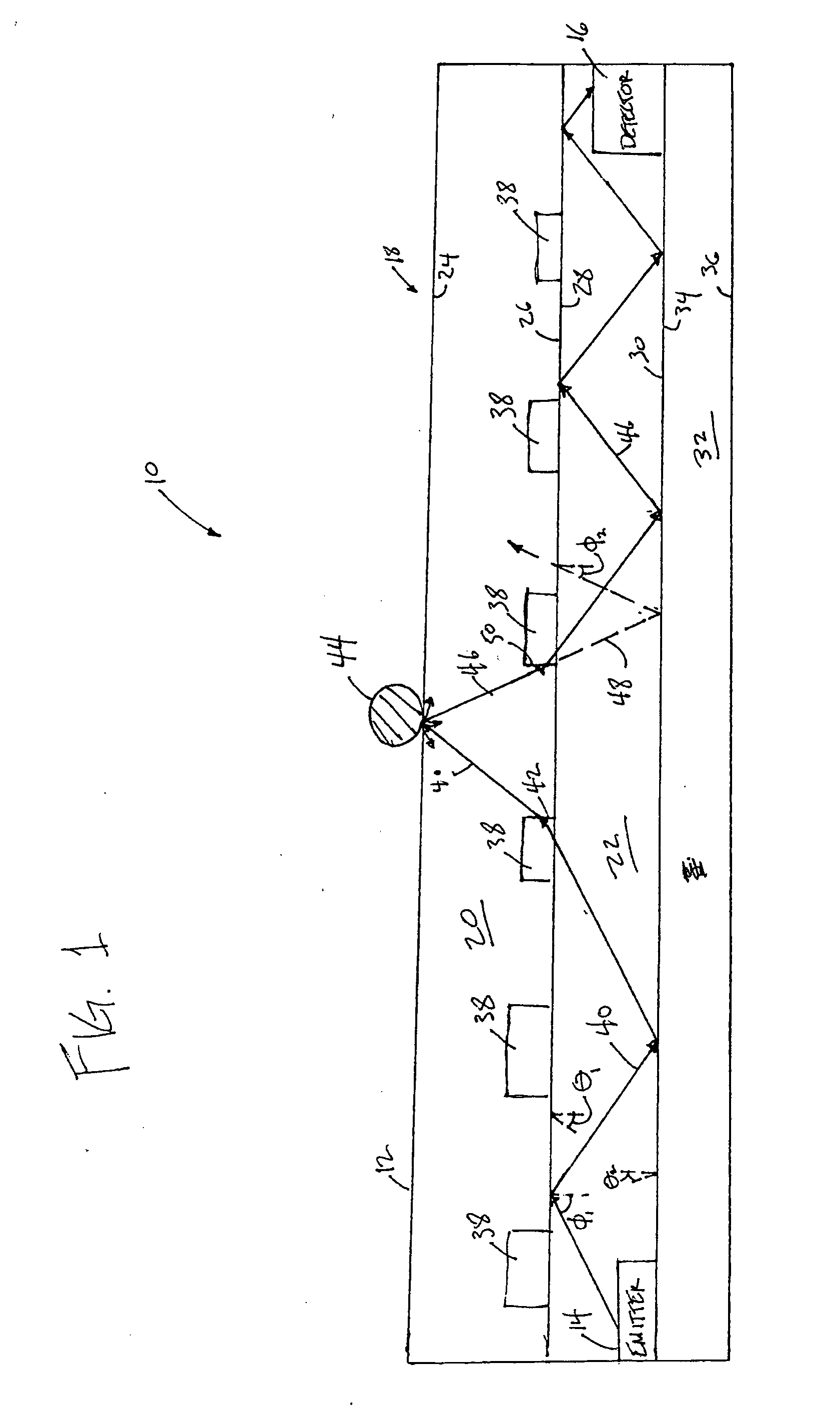

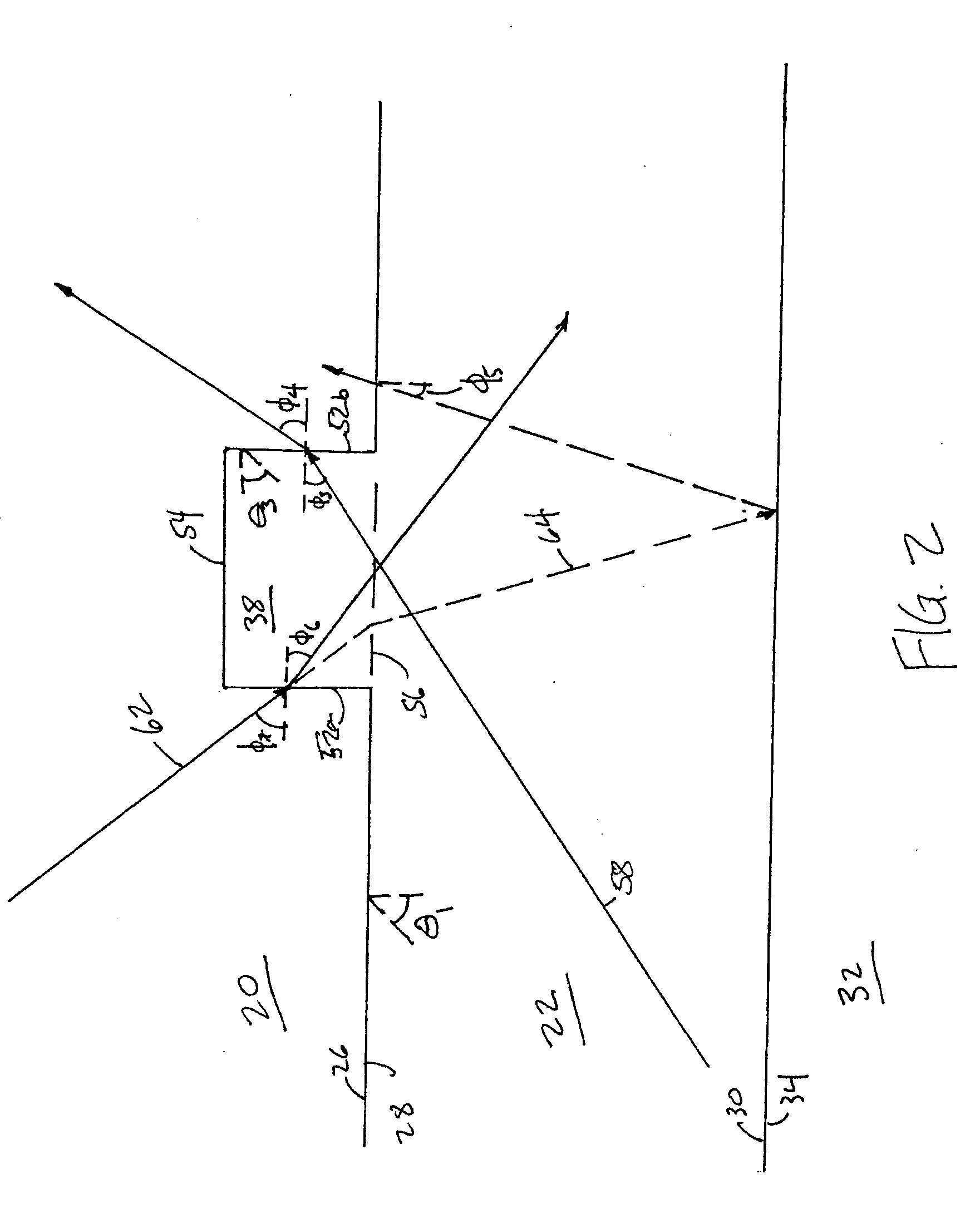

Optical touchpad system and waveguide for use therein

InactiveUS20080007541A1Easy to controlReduce Optical NoiseElectronic switchingInput/output processes for data processingInter layerRefractive index

An optical touchpad system that includes a waveguide having a plurality of waveguide layers. For example, the waveguide may include an intervening layer, a signal layer, and / or other layers. The intervening layer may be defined by a first surface, a second surface and a substantially transparent material having a first index of refraction disposed between the first and the second surface of the interface layer. The signal layer may be defined by a first surface, a second surface and a substantially transparent material having a second index of refraction that is greater than the first index of refraction.

Owner:O PEN

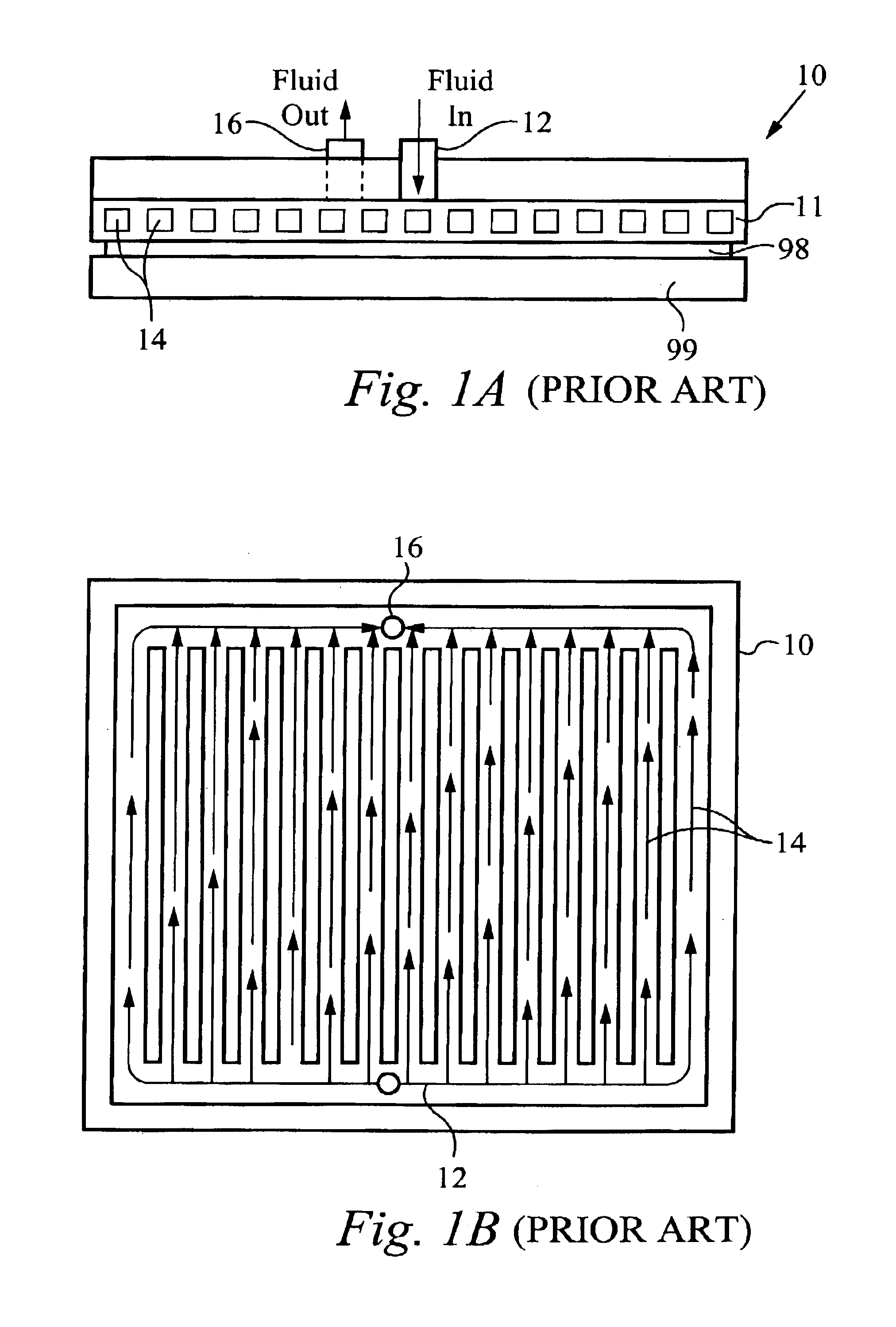

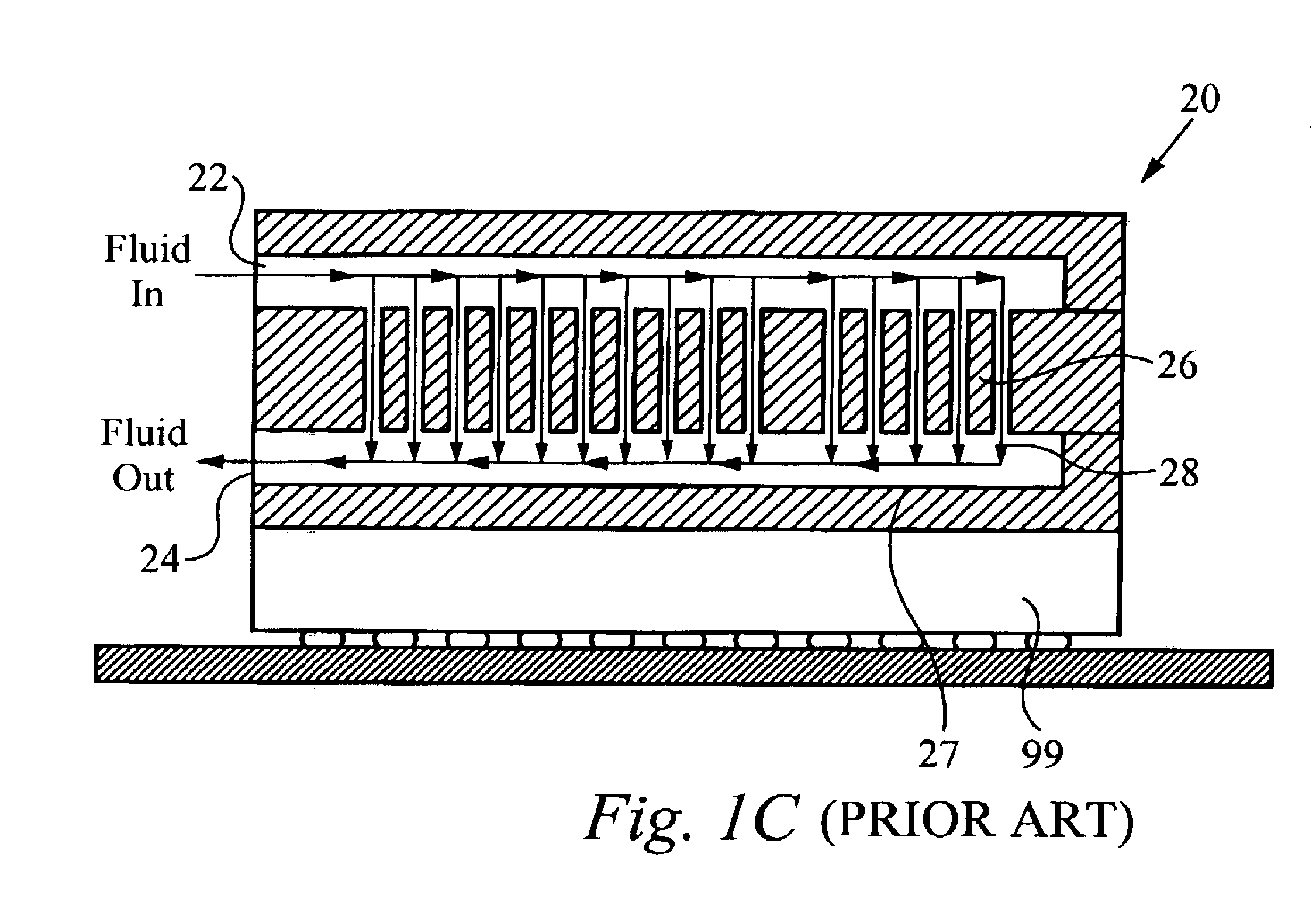

Method and apparatus for flexible fluid delivery for cooling desired hot spots in a heat producing device

InactiveUS6988534B2Temperatue controlSemiconductor/solid-state device detailsInter layerInterface layer

A heat exchanger apparatus and method of manufacturing comprising: an interface layer for cooling a heat source and configured to pass fluid therethrough, the interface layer having an appropriate thermal conductivity and a manifold layer for providing fluid to the interface layer, wherein the manifold layer is configured to achieve temperature uniformity in the heat source preferably by cooling interface hot spot regions. A plurality of fluid ports are configured to the heat exchanger such as an inlet port and outlet port, whereby the fluid ports are configured vertically and horizontally. The manifold layer circulates fluid to a predetermined interface hot spot region in the interface layer, wherein the interface hot spot region is associated with the hot spot. The heat exchanger preferably includes an intermediate layer positioned between the interface and manifold layers and optimally channels fluid to the interface hot spot region.

Owner:VERTIV CORP

Sound reducing wedge shaped polymer interlayers

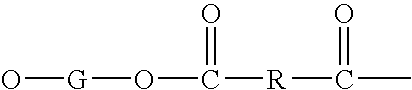

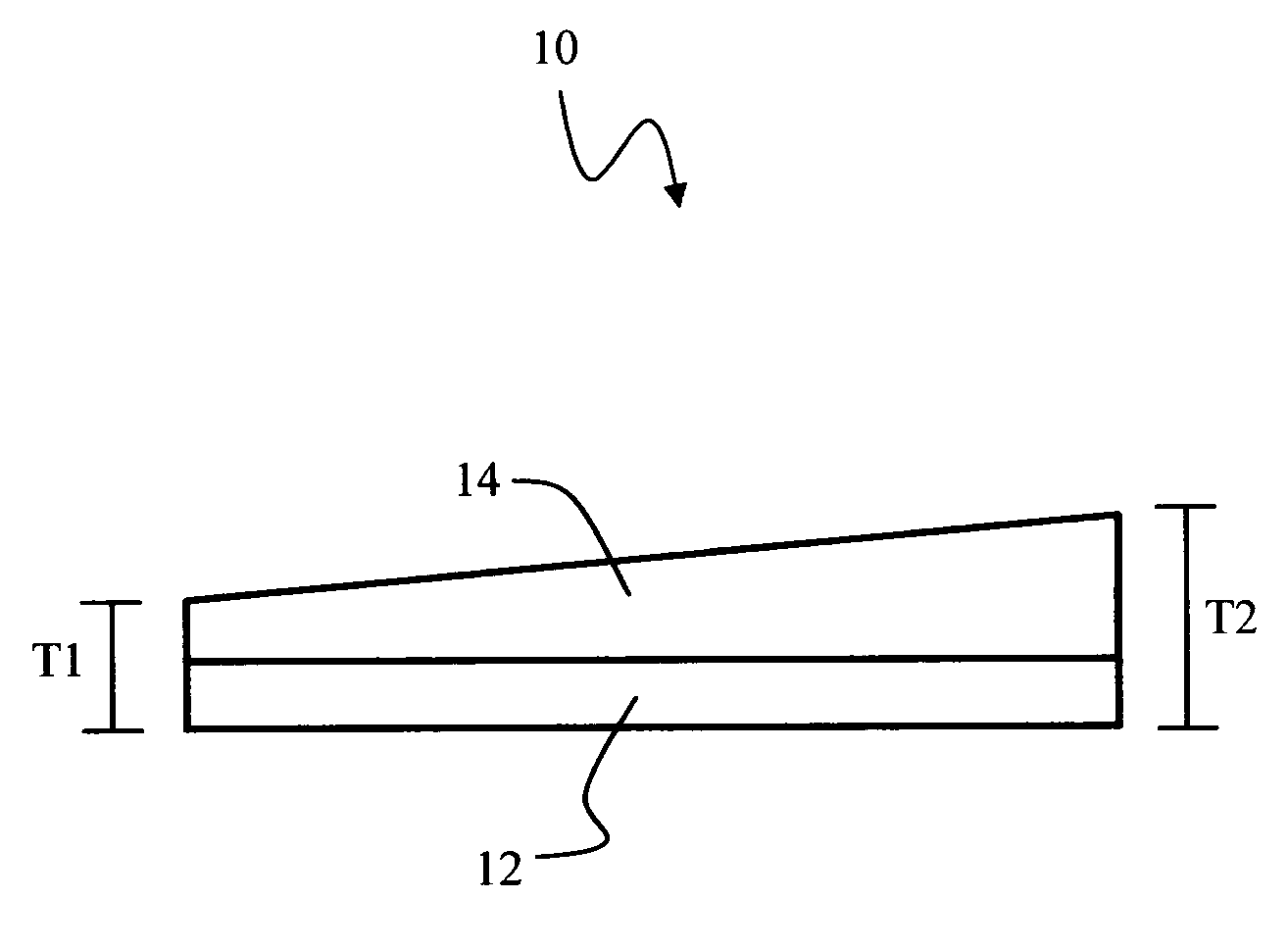

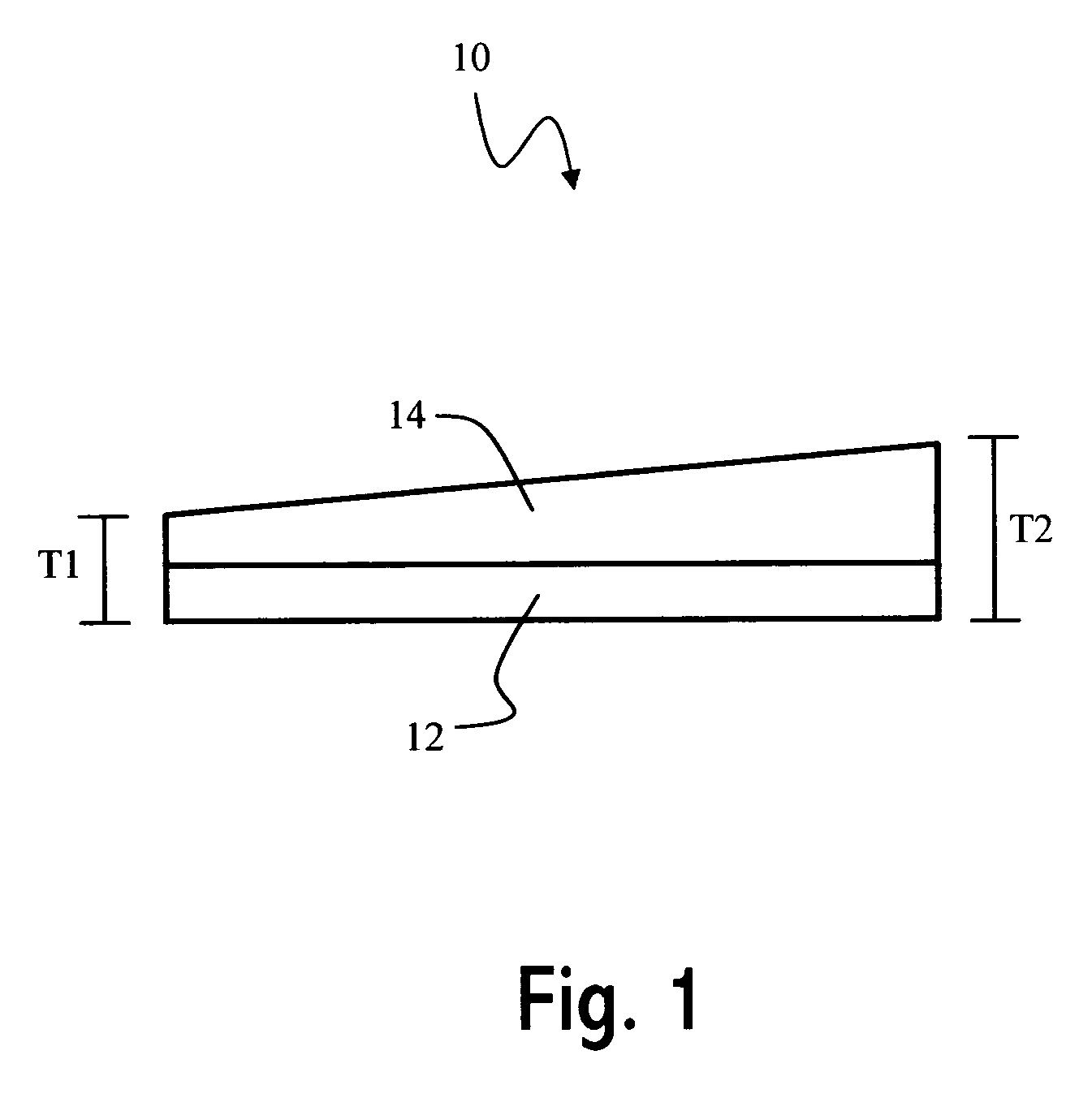

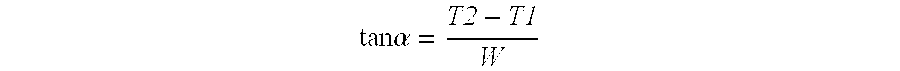

ActiveUS20060210776A1Reduce the amount requiredGlass/slag layered productsMonocoque constructionsPolymer scienceInter layer

The present invention is in the field of polymer interlayers and multiple layer glass panels comprising polymer interlayers, and, more specifically, the present invention is in the field of wedge shaped polymer interlayers.

Owner:SOLUTIA INC

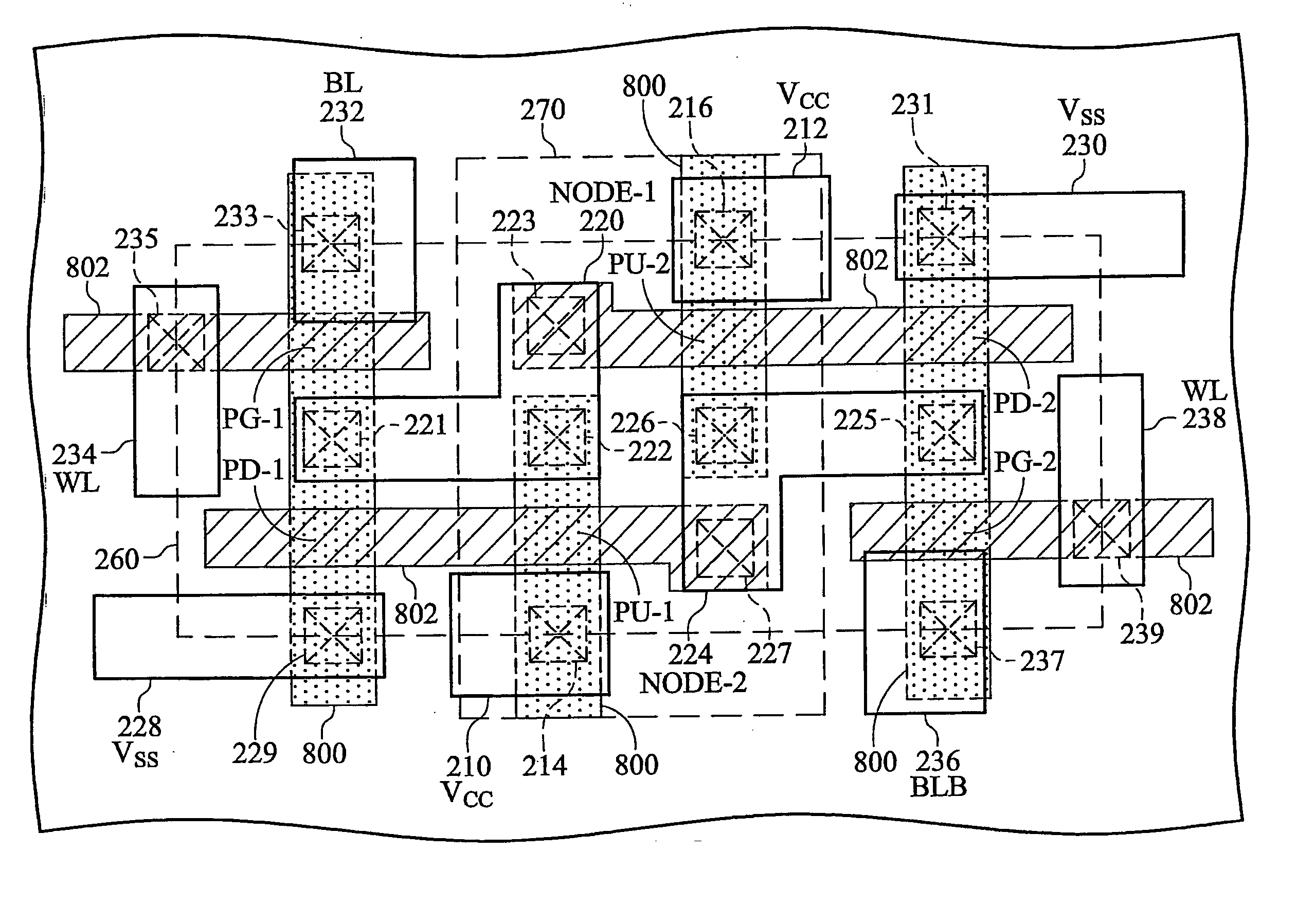

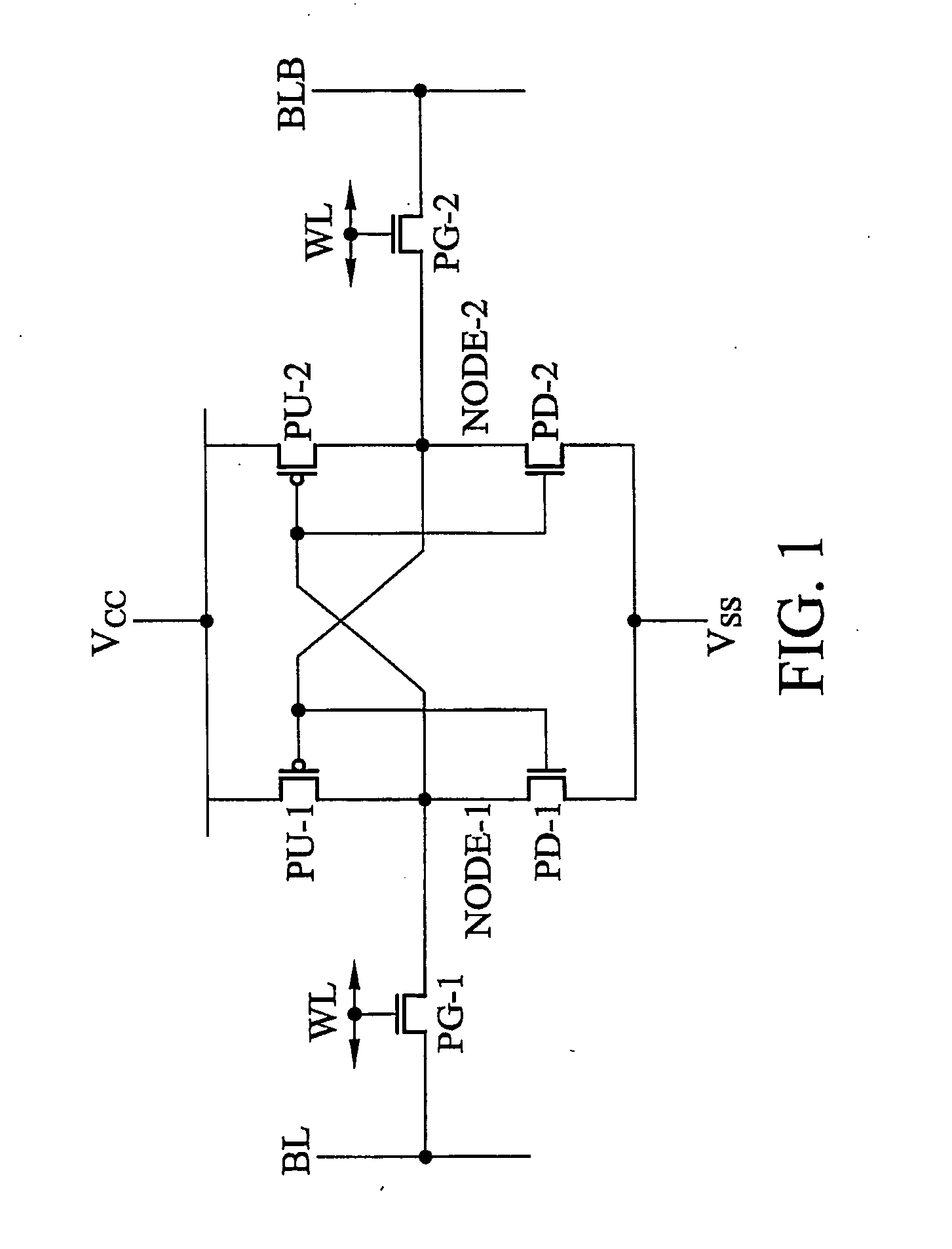

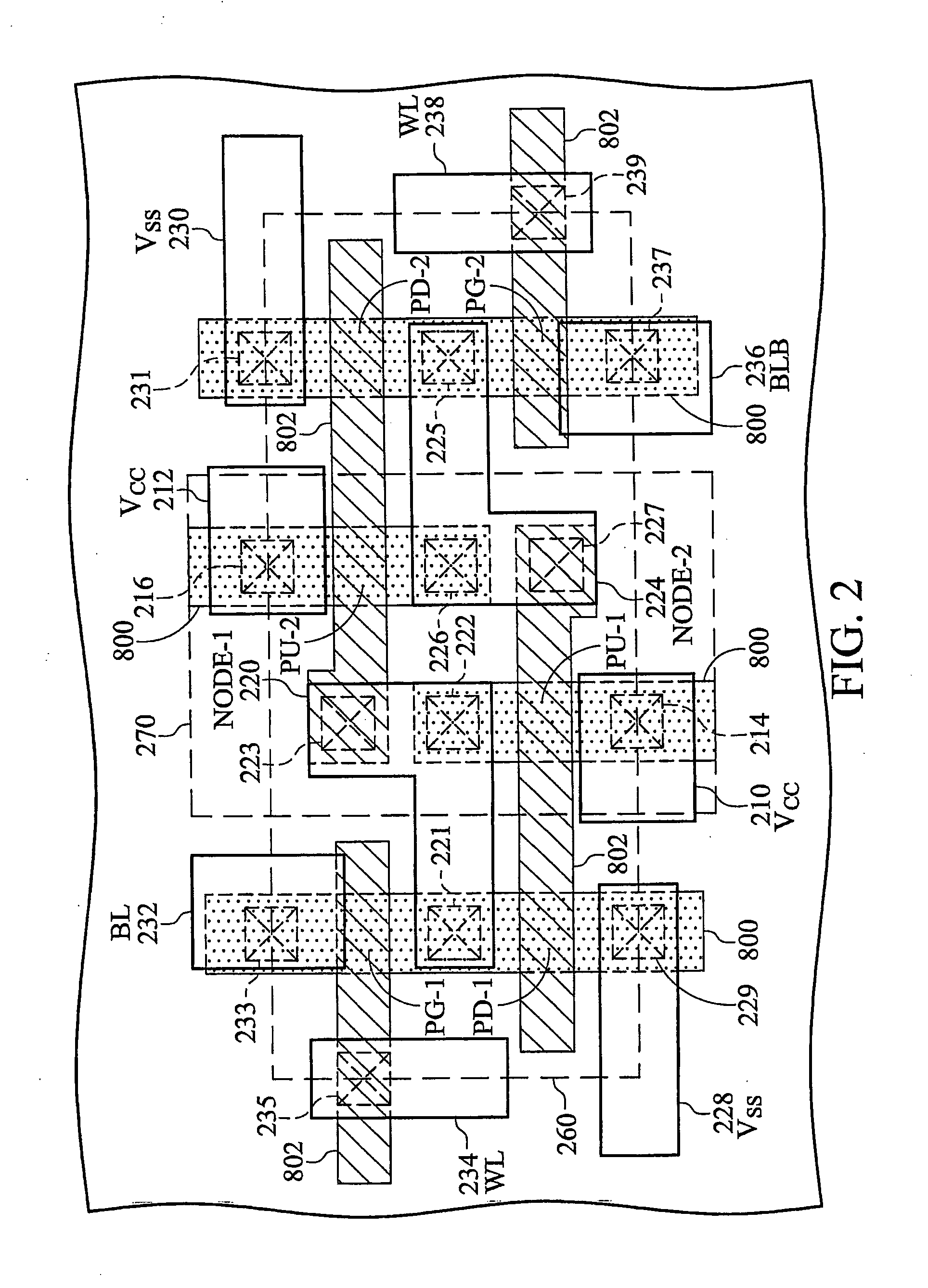

Memory cell structure

An SRAM device includes an SRAM cell in a deep NWELL region in a substrate. PWELL regions in the SRAM cell occupy less than about 65% of the cell area of the SRAM cell. A ratio of a longer side of a cell area of the SRAM cell to a shorter side of the SRAM cell is larger than about 1.8. A total area of the active regions in the plurality of NMOS transistors in the SRAM cell occupies less than about 25% of the SRAM cell area. A ratio of the channel width of a pull up transistor in the SRAM cell to the channel width of a pull down transistor in the SRAM cell is greater than about 0.8. The SRAM cell further includes a boron free inter-layer-dielectric layer, an inter-metal-dielectric layer with dielectric constant less than about 3, and a polyimide layer with a thickness of less than about 20 microns.

Owner:TAIWAN SEMICON MFG CO LTD

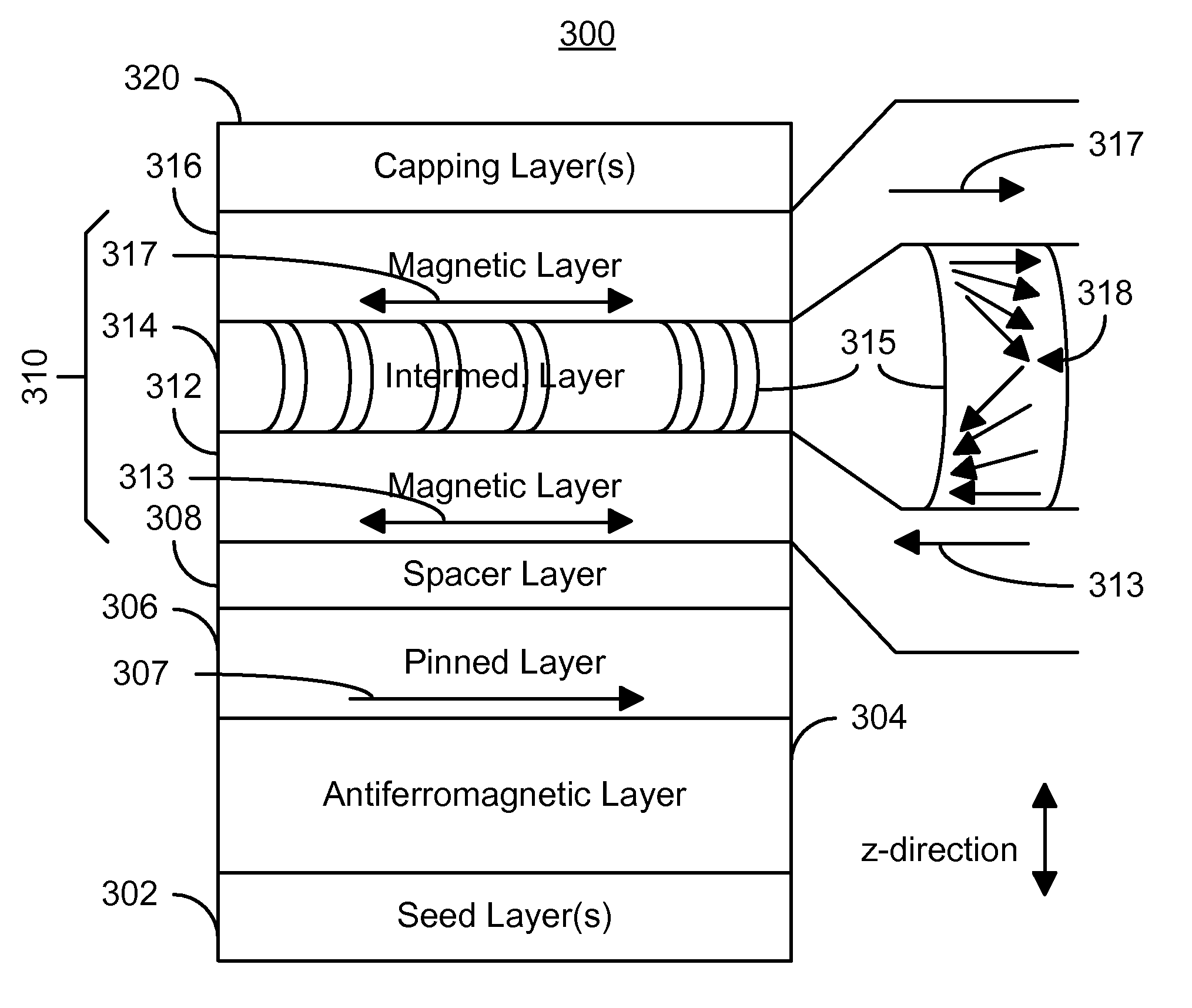

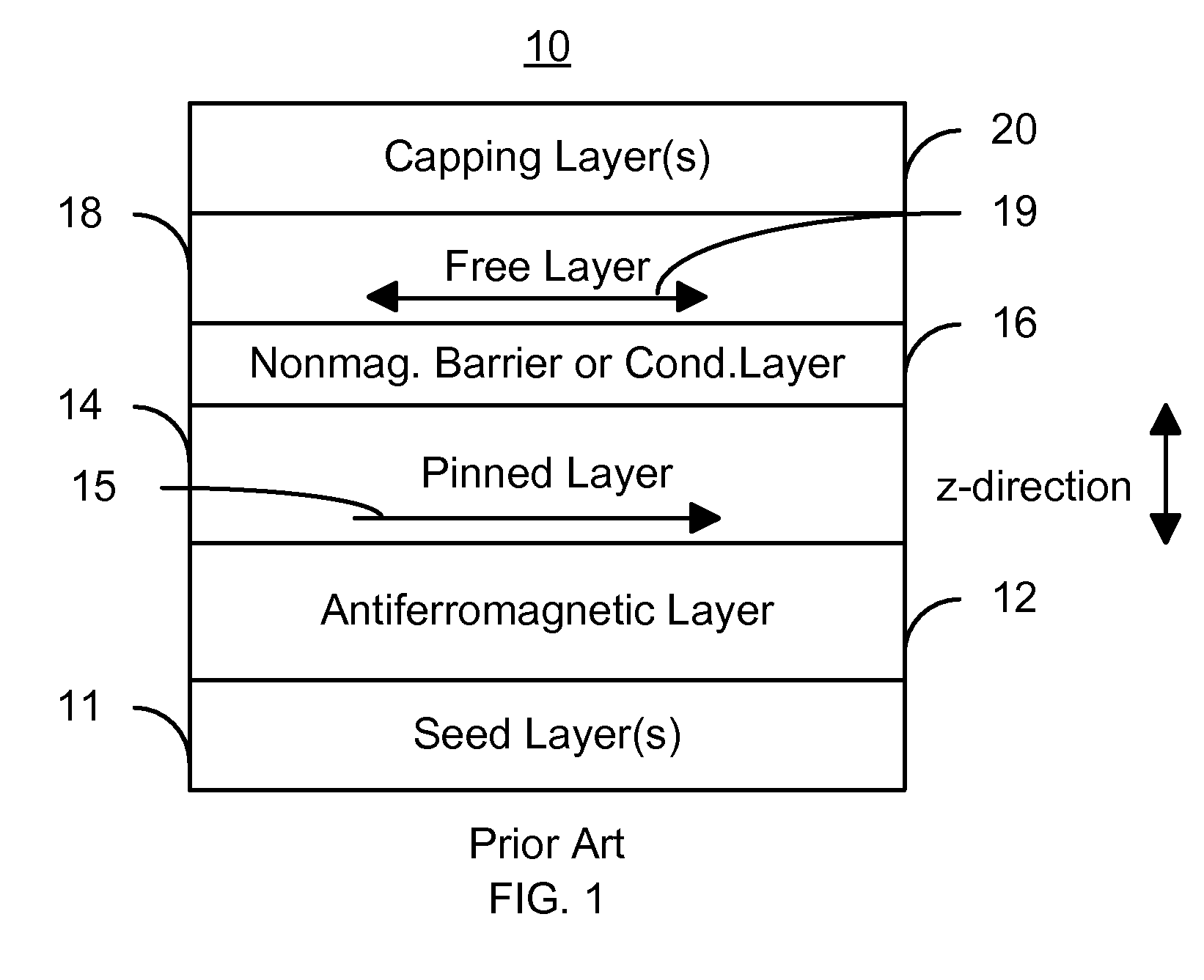

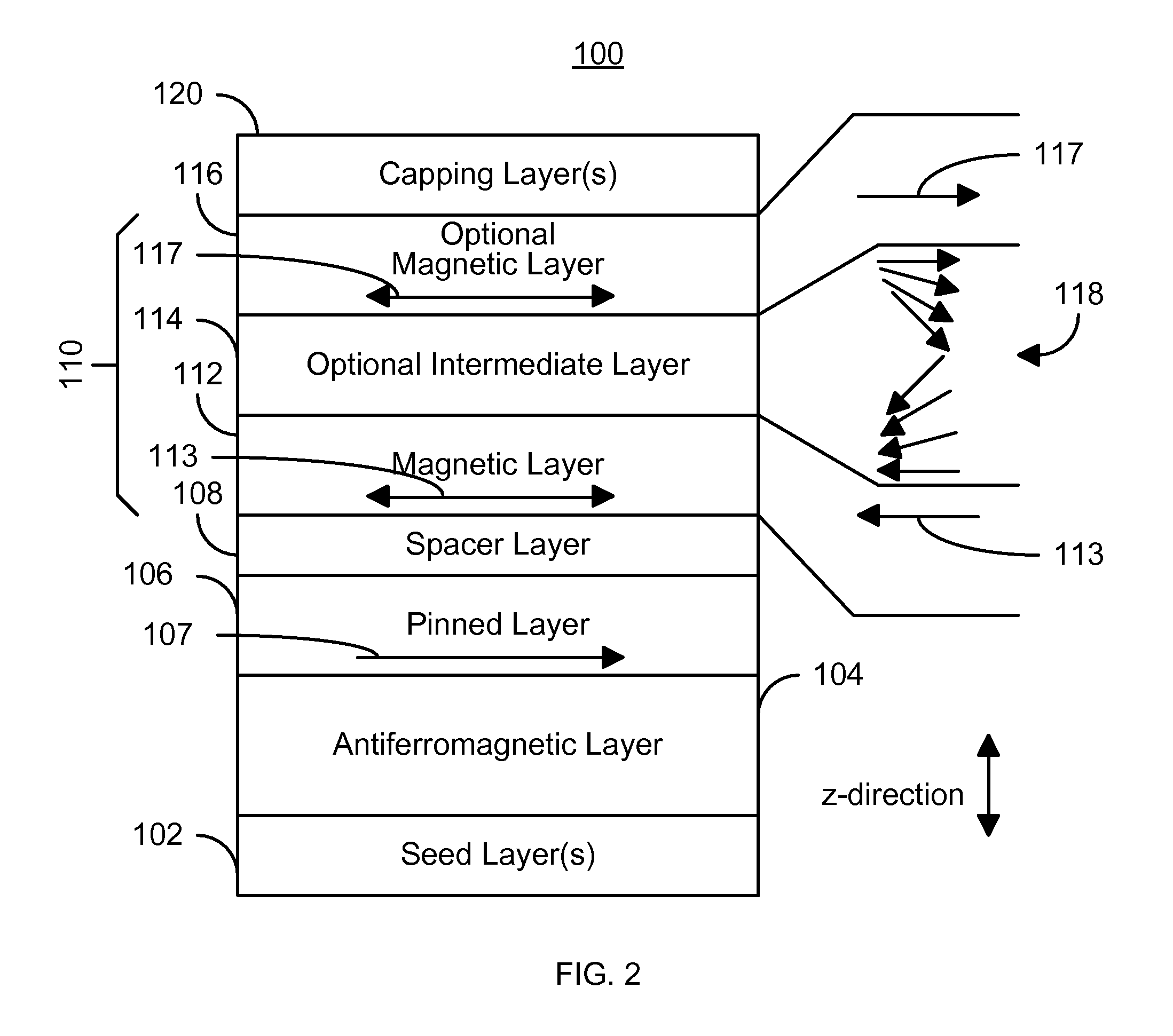

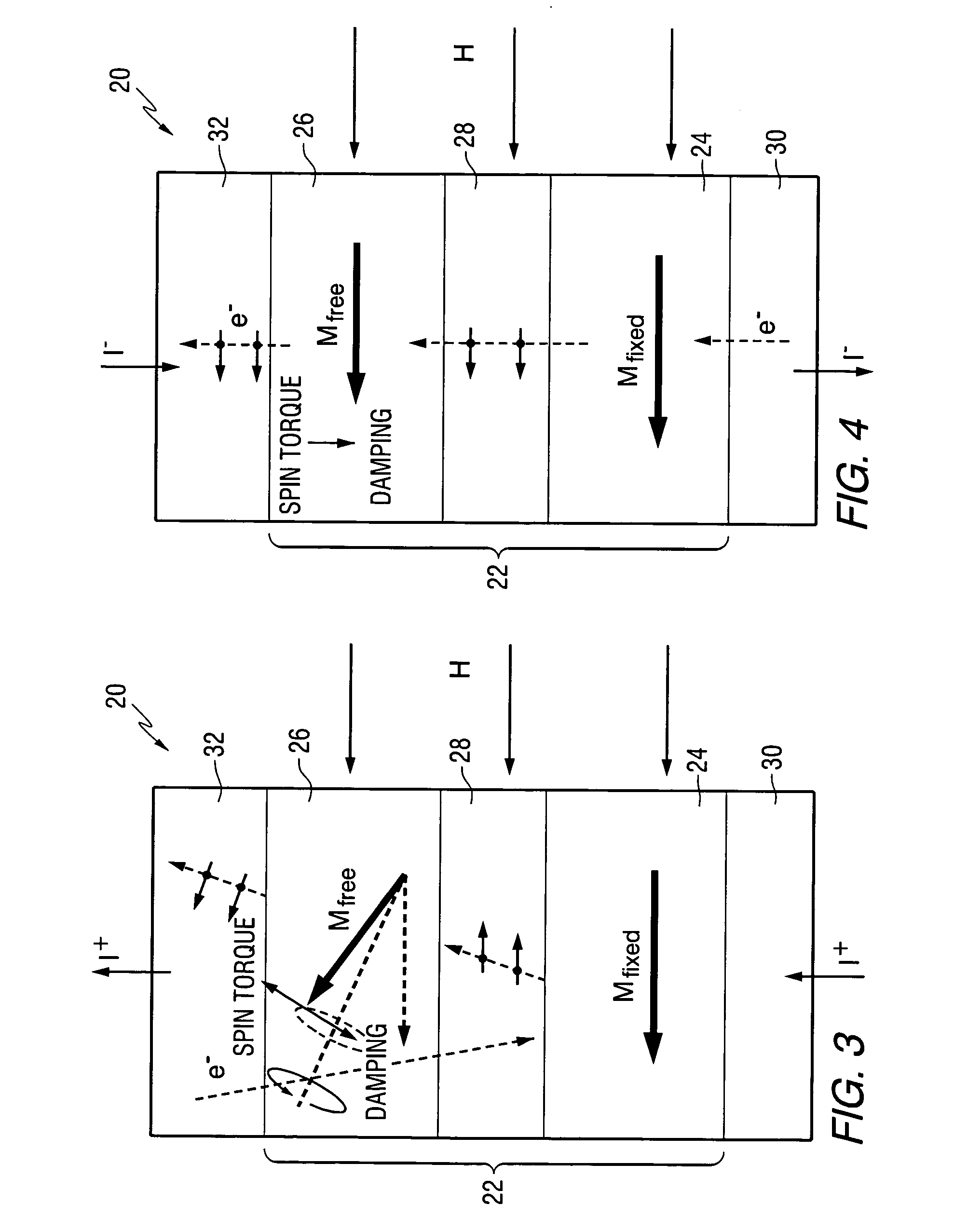

Method and system for providing domain wall assisted switching of magnetic elements and magnetic memories using such magnetic elements

A method and system for providing a magnetic element is described. The magnetic element includes a pinned layer, a spacer layer, and a free layer. The spacer layer is nonferromagnetic and resides between the pinned layer and the free layer. The free layer includes a first magnetic layer and at least one of a second magnetic layer and an intermediate layer. The intermediate layer would reside between the first and second magnetic layers. The free layer also includes at least one domain wall therein during switching. In addition, the magnetic element is configured to allow the free layer to be switched at least in part due to spin transfer when a write current is passed through the magnetic element.

Owner:SAMSUNG SEMICON

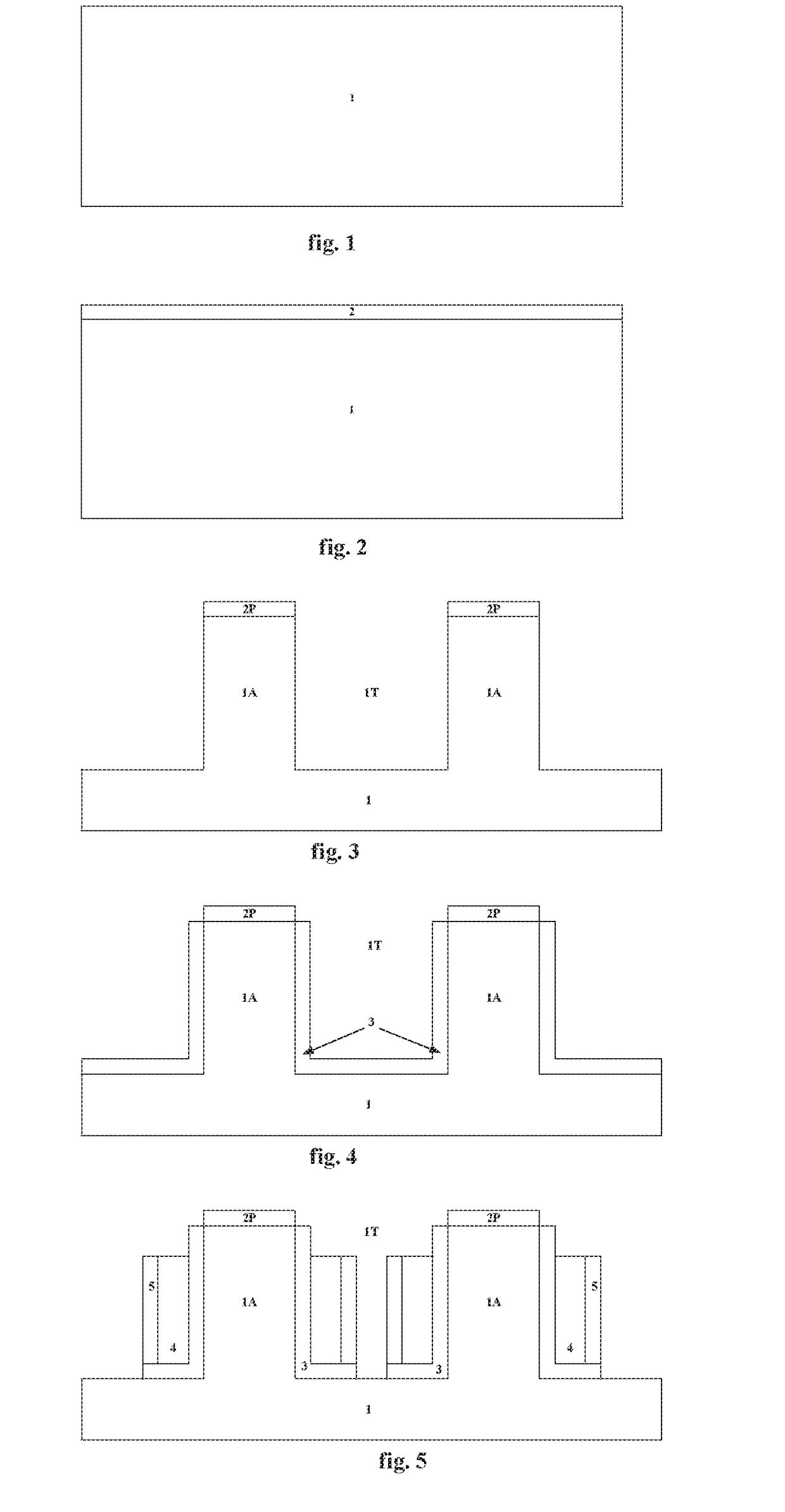

Method of making a lithographic printing plate

ActiveUS8232043B2High degree of polymerizationQuality improvementPlaten pressesPhotosensitive materialsInter layerEngineering

A method of making a lithographic printing plate includes the steps of a) providing a lithographic printing plate precursor including (i) a support having a hydrophilic surface or which is provided with a hydrophilic layer, (ii) a coating on the support including a photopolymerizable layer, and, optionally, an intermediate layer between the photopolymerizable layer and the support, b) image-wise exposing the coating in a plate setter, c) optionally, heating the precursor in a preheating unit, and d) developing the precursor off-press in a gumming unit by treating the coating of the precursor with a gum solution, thereby removing the non-exposed areas of the coating from the support, wherein the coating further includes a compound capable of interacting with the support, the compound being present in the photopolymerizable layer and / or in the intermediate layer.

Owner:AGFA OFFSET BV

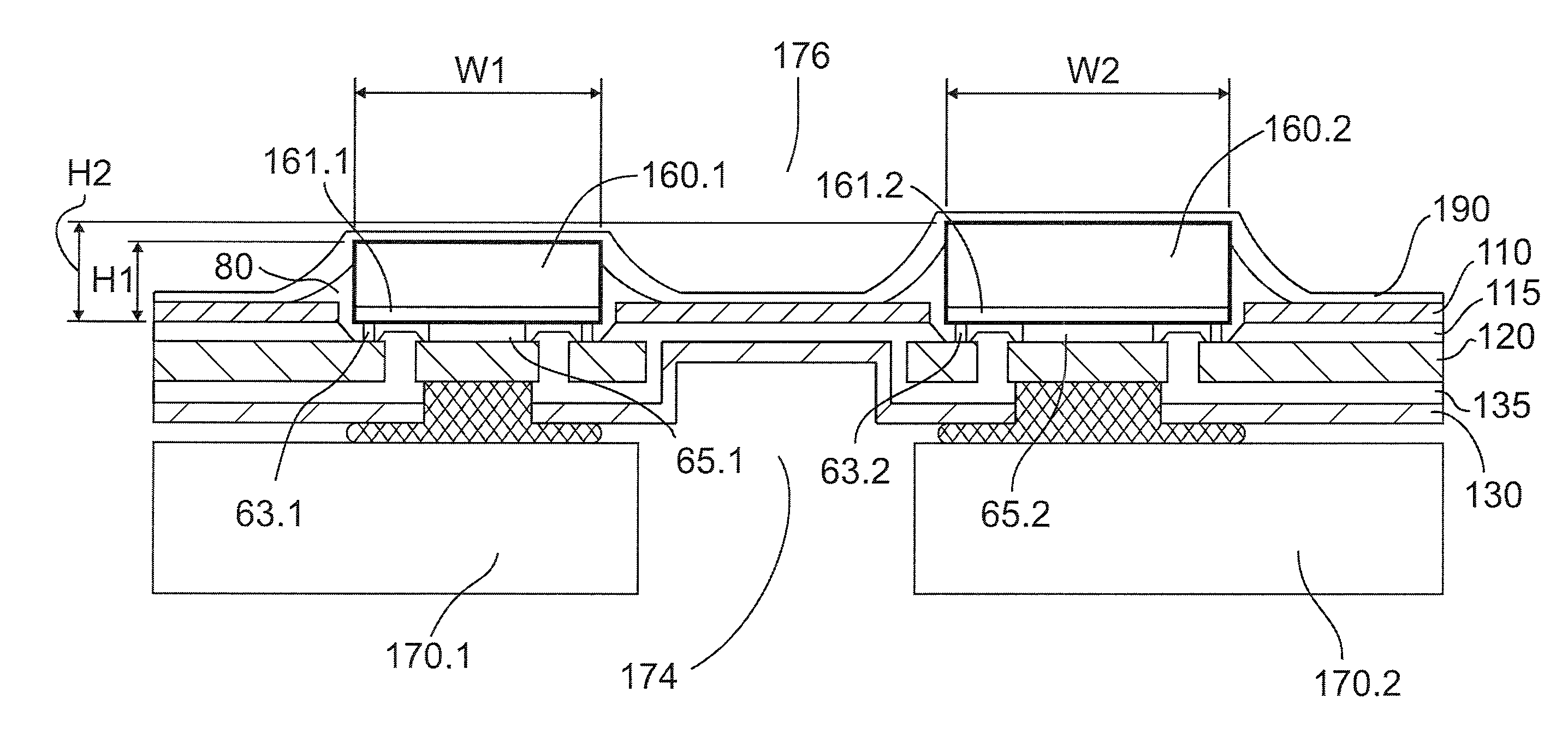

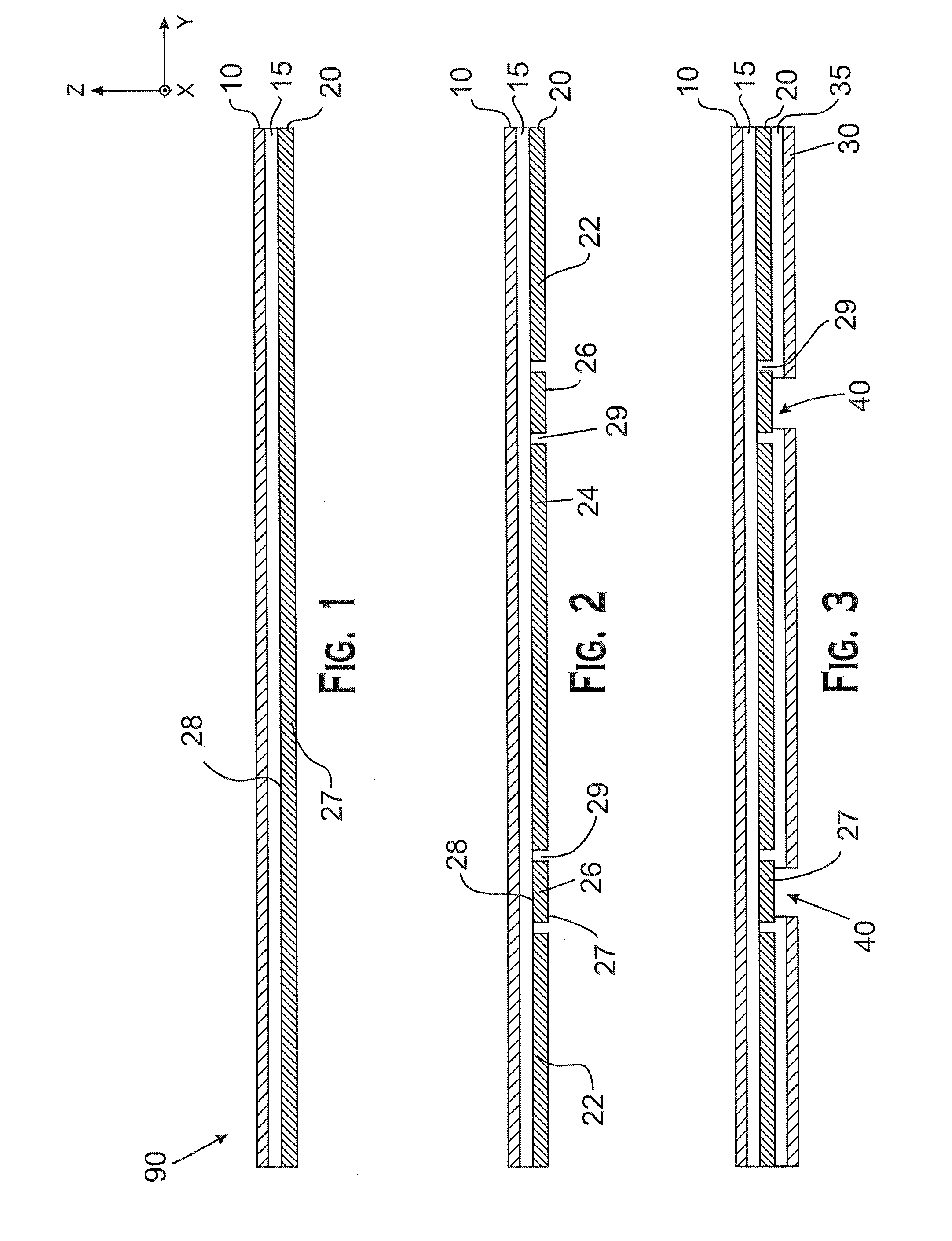

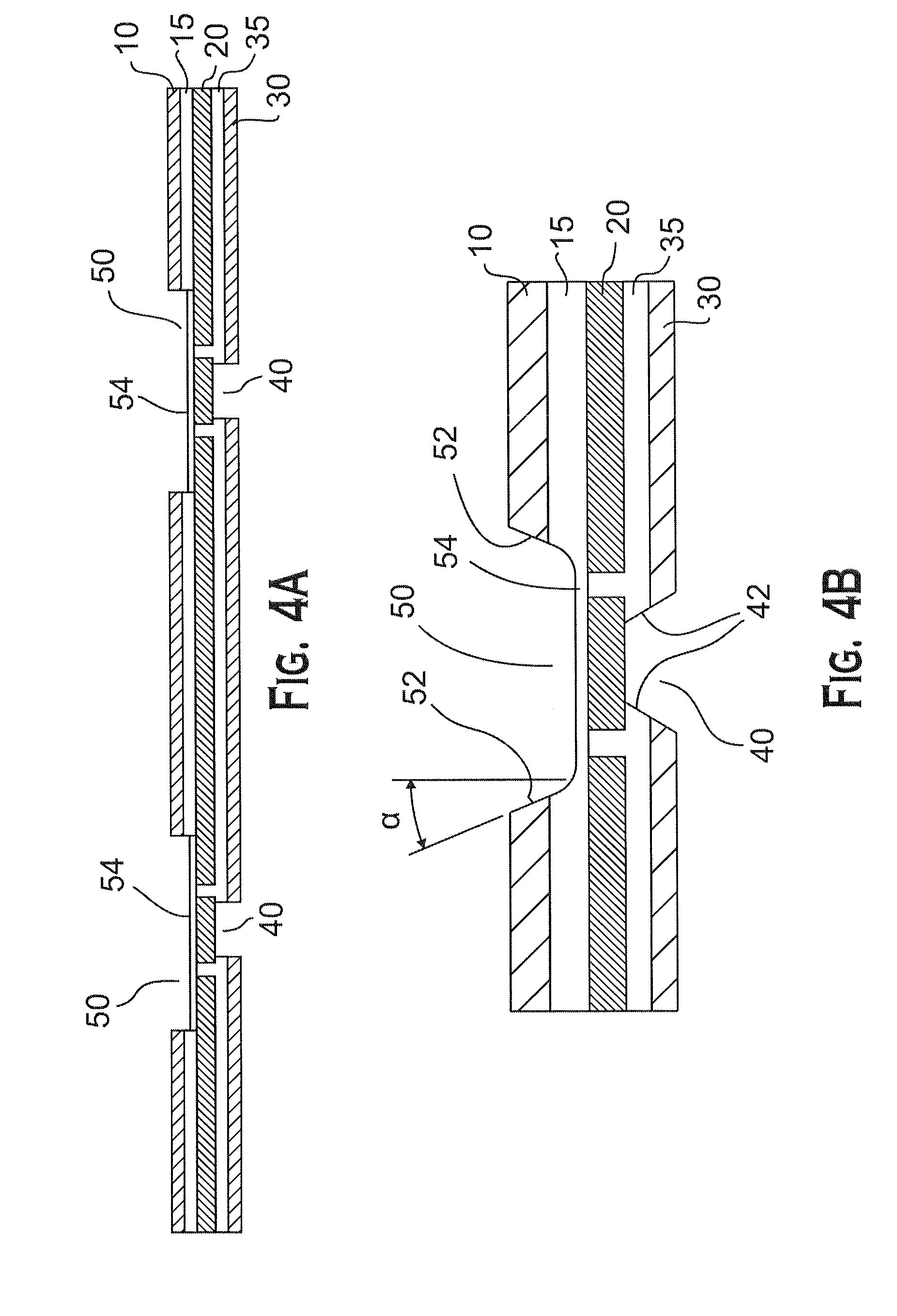

Flexible electronic assembly and method of manufacturing the same

ActiveUS20140268780A1Intuitive imagePrinted circuit assemblingLighting support devicesInter layerFlexible circuits

A flexible circuit assembly for accommodating a plurality of power electronic devices, including an insulating cover layer having first openings for power electronic devices, a flexible conductive layer arranged under the insulating cover layer and attached with a first adhesive to the insulating cover layer, an intermediate insulating layer arranged under the flexible conductive layer and attached with a second adhesive to the flexible conductive layer, the intermediate insulating layer having second openings, a plurality of heat-conductive elements arranged inside the second openings, a first thin heat sink layer, the heat-conductive elements arranged to be in contact with an upper surface of the thin heat sink layer and the lower surface of the islands via heat-conductive material; and a second thin heat sink layer, upper surfaces of the power electronic devices arranged to be in contact with a lower surface of the thin heat sink layer and the lower surface of the islands via heat-conductive material.

Owner:SUMITOMO ELECTRIC PRINTED CIRCUITS INC +1

Method and apparatus for highly scalable intraframe video coding

ActiveUS20090175333A1Color television with pulse code modulationColor television with bandwidth reductionComputer architectureInter layer

An apparatus and method is provided for highly scalable intraframe video coding. The conventional macroblock DCT tools are integrated with the subband filter banks for the improved efficiency of scalable compression. The enhancement layers are represented in a subband domain and coded by an inter-layer frame texture coder utilizing inter-layer prediction signal formed by the decoded previous layer. Each quality enhancement layer is additionally scalable in resolution.

Owner:GOOGLE TECH HLDG LLC

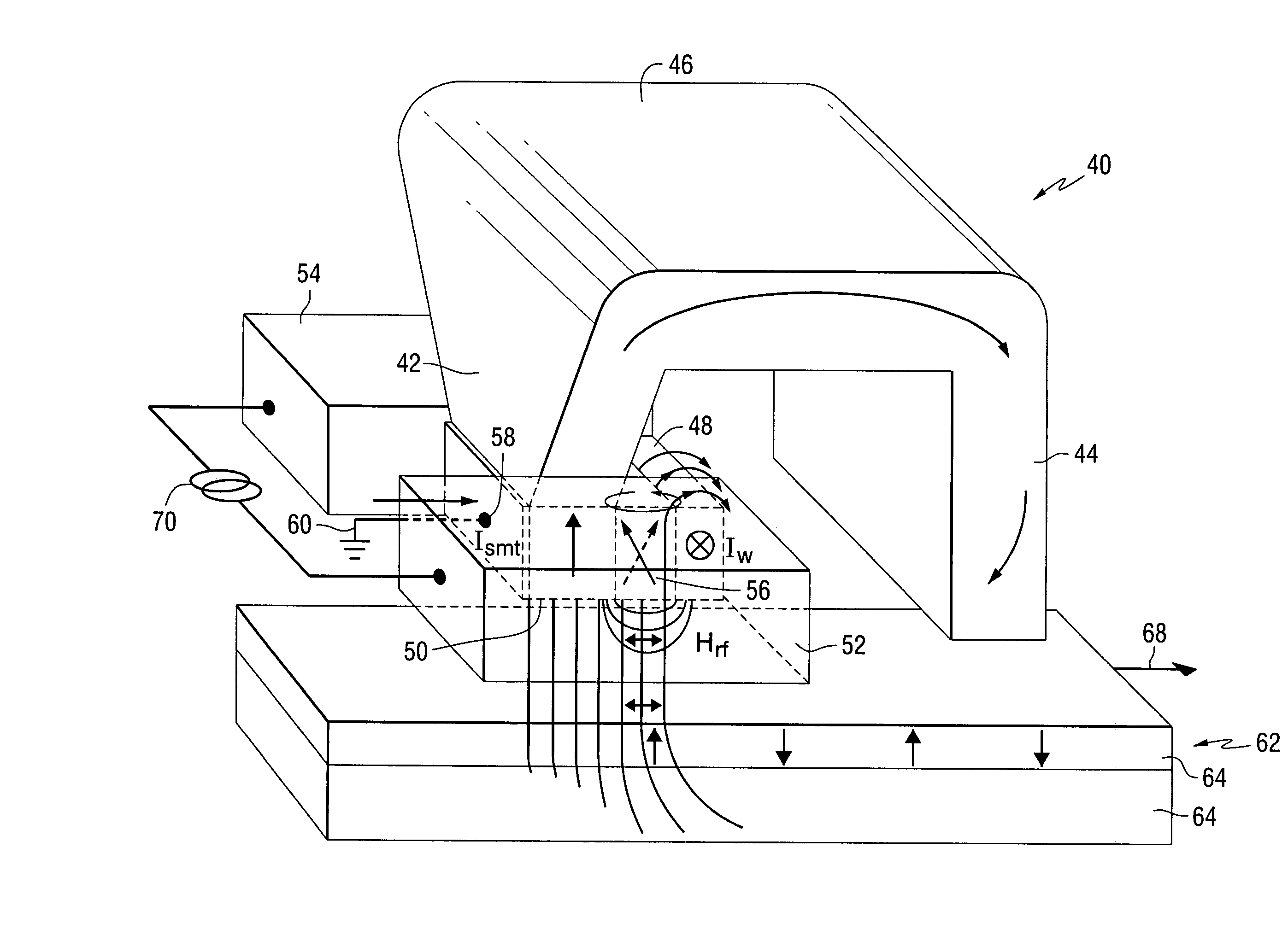

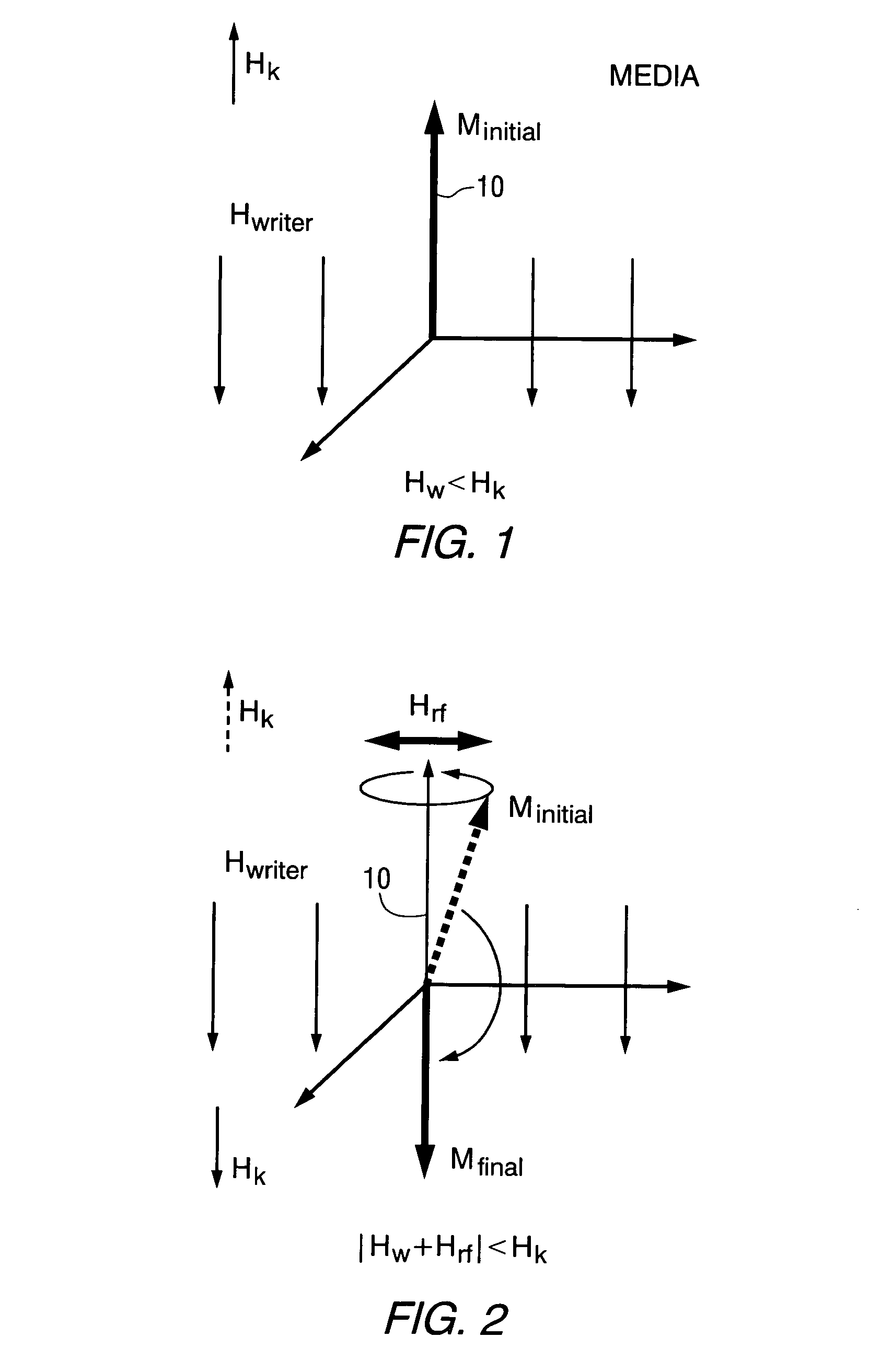

WAMR writer with an integrated spin momentum transfer driven oscillator for generating a microwave assist field

InactiveUS20080112087A1Record information storageManufacture of flux-sensitive headsInter layerSpins

Owner:SEAGATE TECH LLC

Method for estimating and/or reducing uncertainty in reservoir models of potential petroleum reservoirs

ActiveUS7254091B1Reduce uncertaintyGreat constraintSeismic signal processingSpecial data processing applicationsSoil scienceInter layer

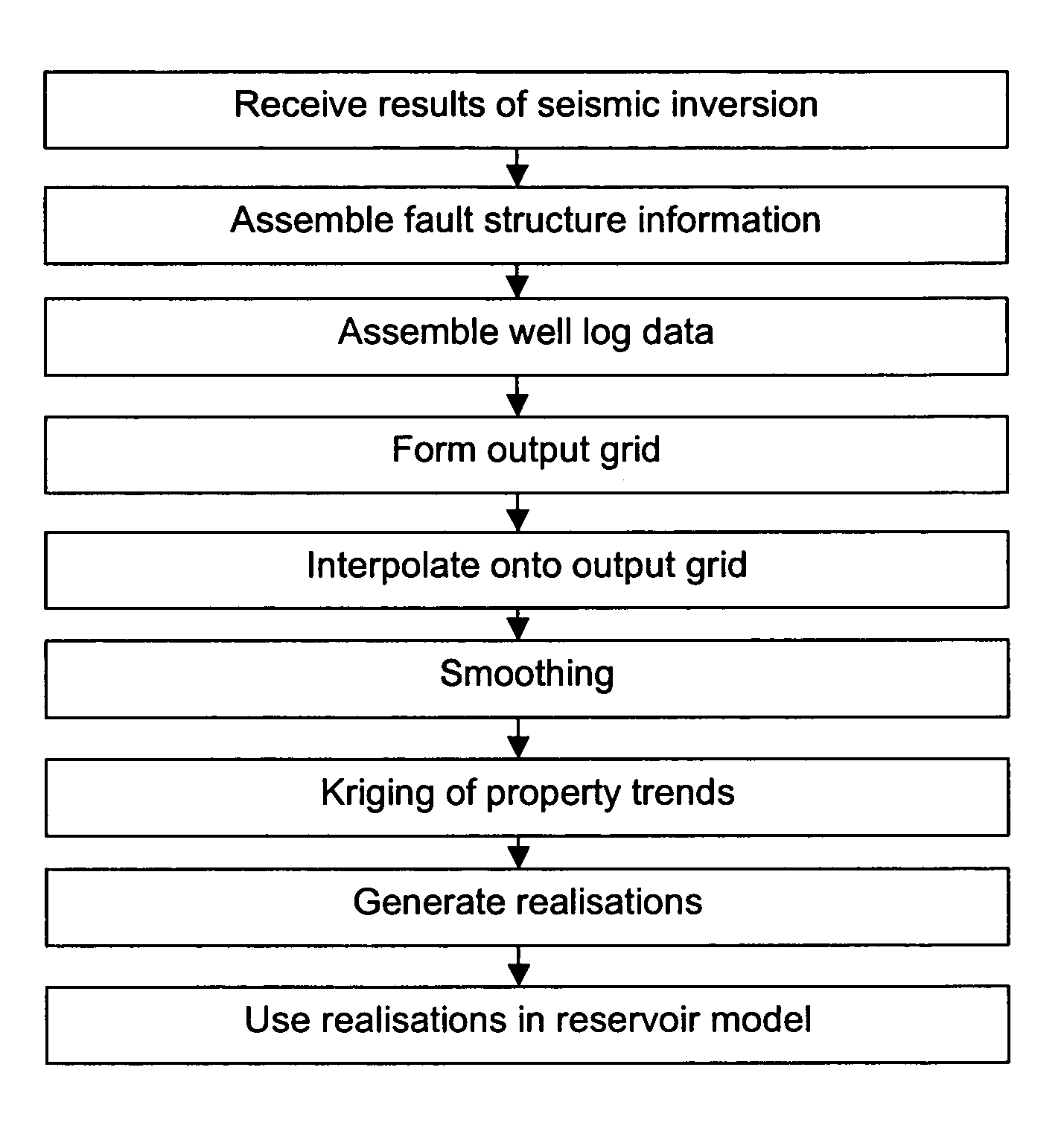

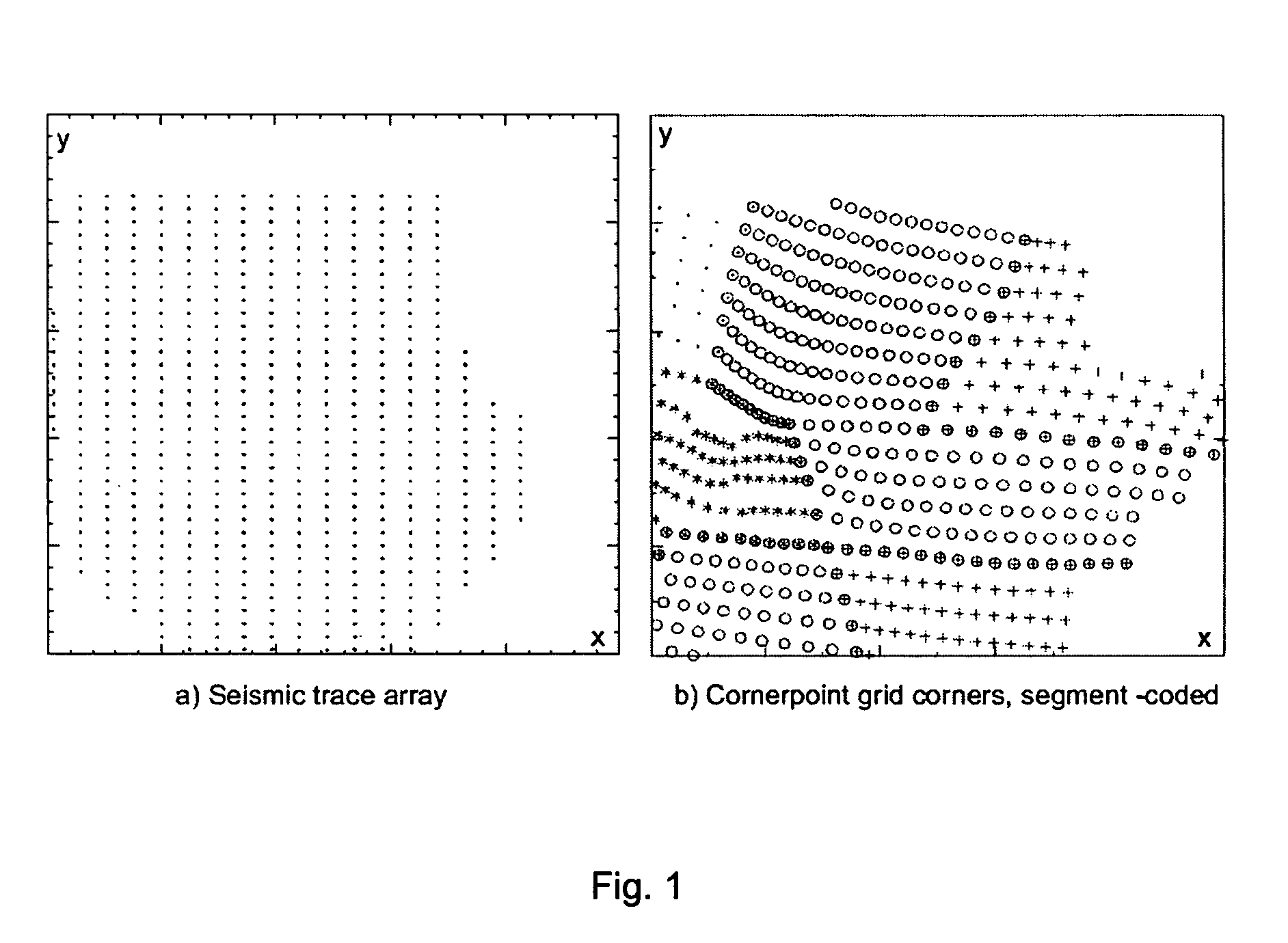

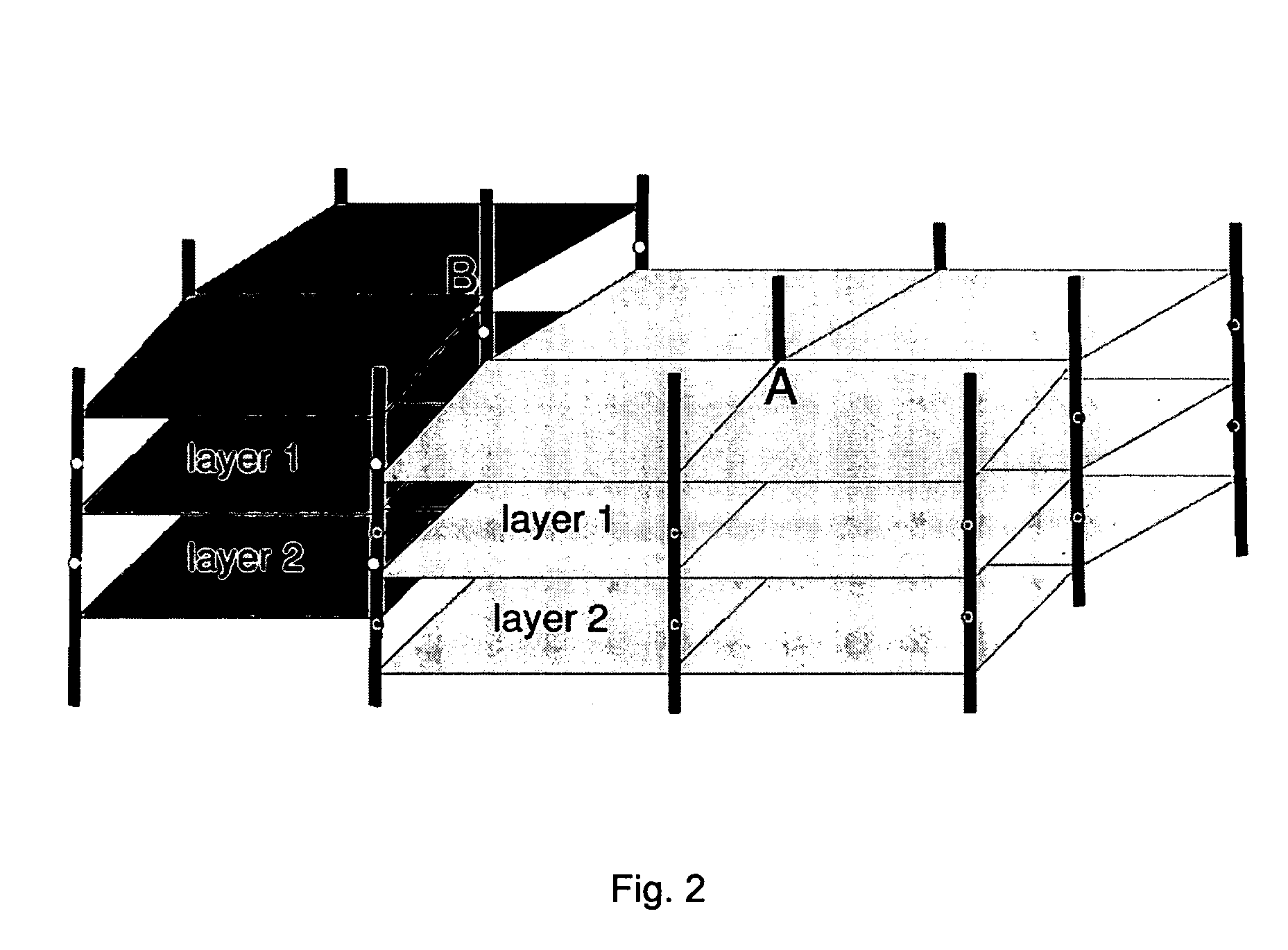

A method for estimating and / or reducing uncertainty in reservoir models of potential petroleum reservoirs comprises receiving the results of a stochastic seismic inversion, and transforming the inversion data into a form suitable for reservoir modelling and flow simulations, while honoring inter-property and inter-layer correlations in the inversion data as well as measured well data and other geological constraints.

Owner:BHP BILLITON INNOVATION PTY LTD