Patents

Literature

270 results about "Sign bit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computer science, the sign bit is a bit in a signed number representation that indicates the sign of a number. Although only signed numeric data types have a sign bit, it is invariably located in the most significant bit position, so the term may be used interchangeably with "most significant bit" in some contexts.

Apparatus and method for saturating decoder values

InactiveUS7073118B2Television system detailsData representation error detection/correctionSign bitSignomial

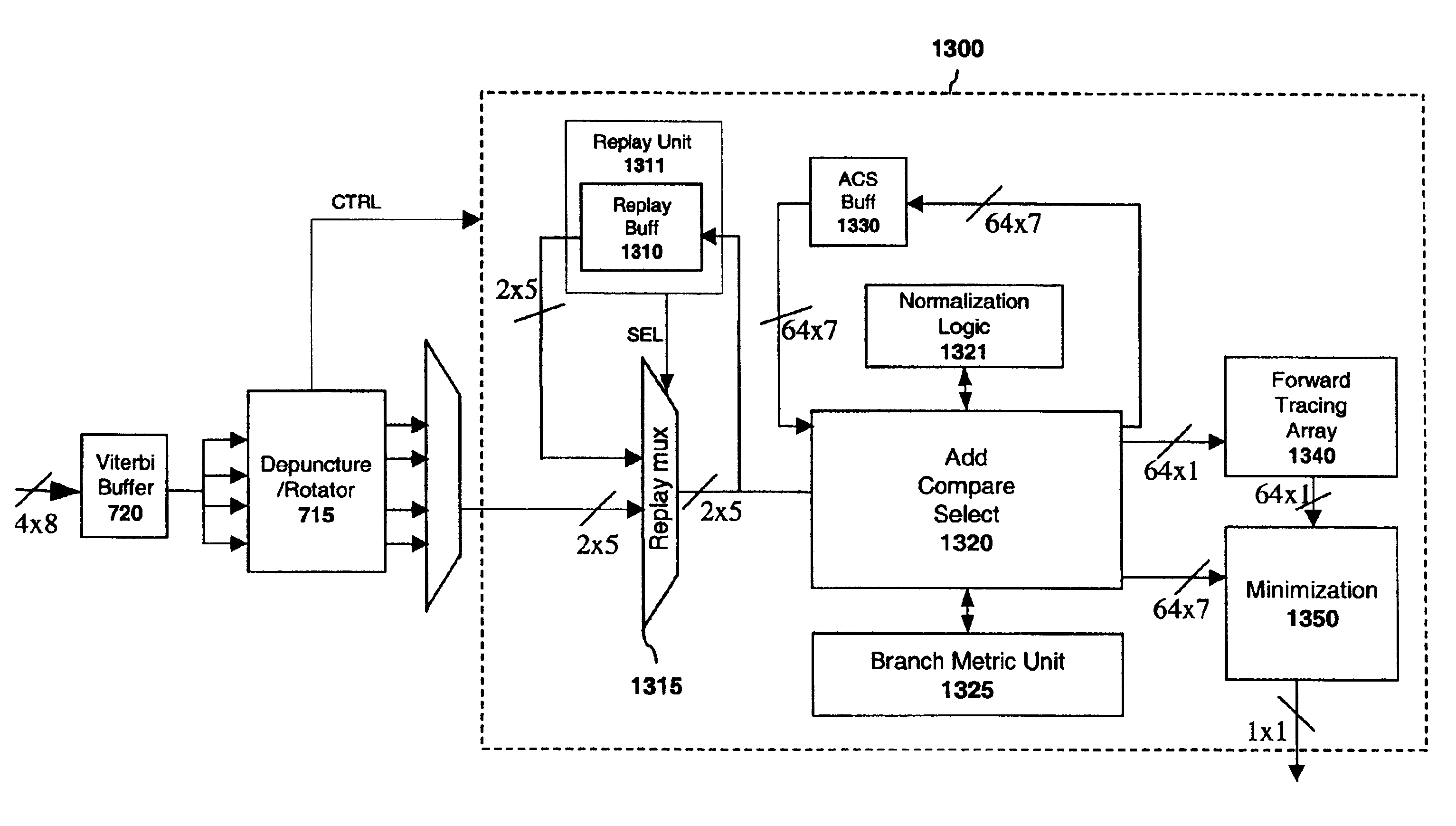

In one embodiment of the invention, during add-compare-select computations, the output of the adders is guaranteed to be a positive value because the only time normalization logic subtracts a normalization amount is when all accumulators are greater than the normalization amount. As such, the detection of overflow is greatly simplified. Overflow in the add-compare-select unit may be indicated simply by the value of the most significant bit (“MSB”) (i.e., the sign bit) of the result. If the MSB of the result of the adder is set then, in one embodiment, the output of the adder gets forced the maximum possible value given the number of bits. For example, this value will be forced to 7h7f if the value is represented by 7-bits. That is to say, if an overflow is detected, then the accumulator is saturated to the maximum value.

Owner:ARRIS ENTERPRISES LLC

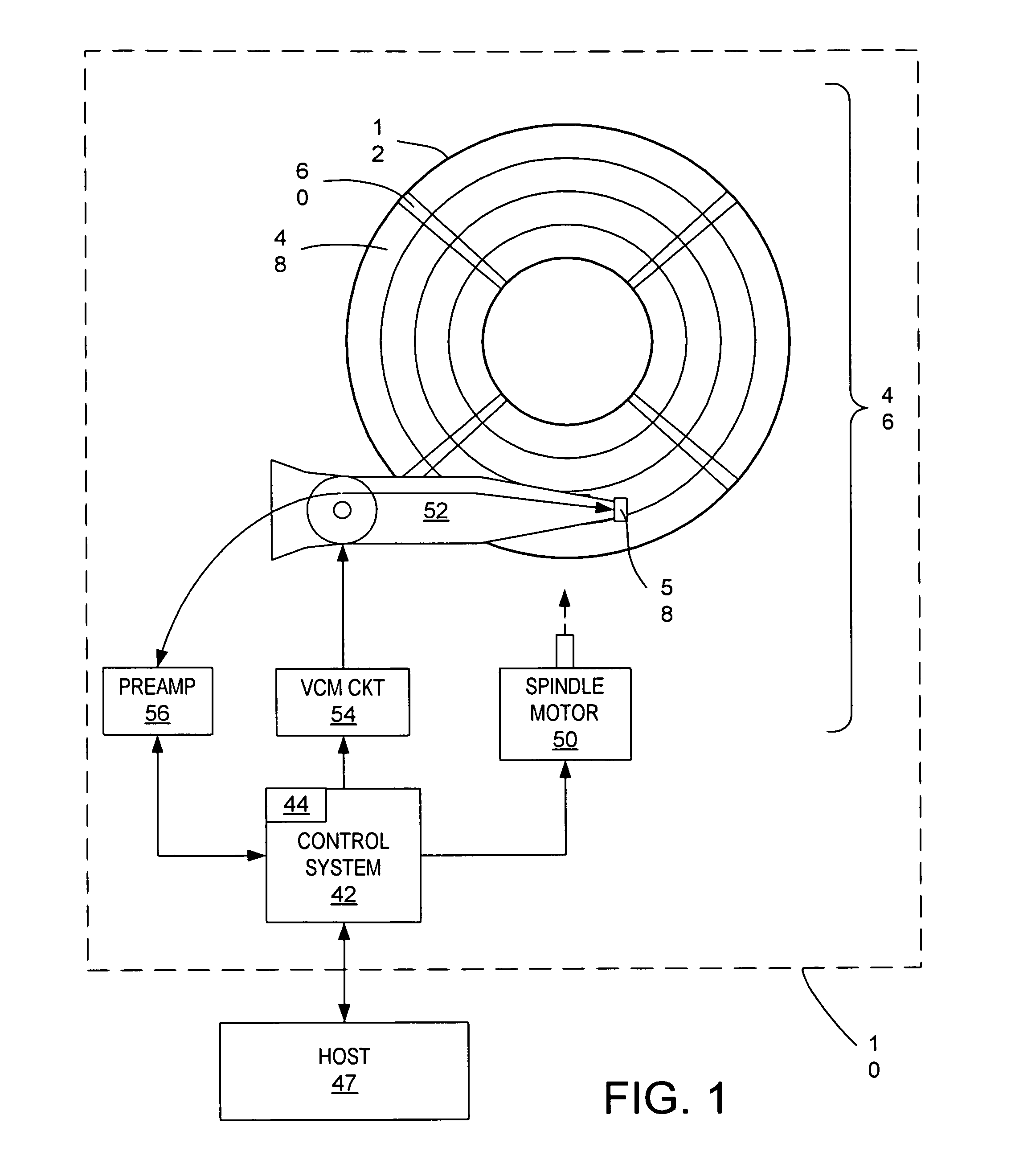

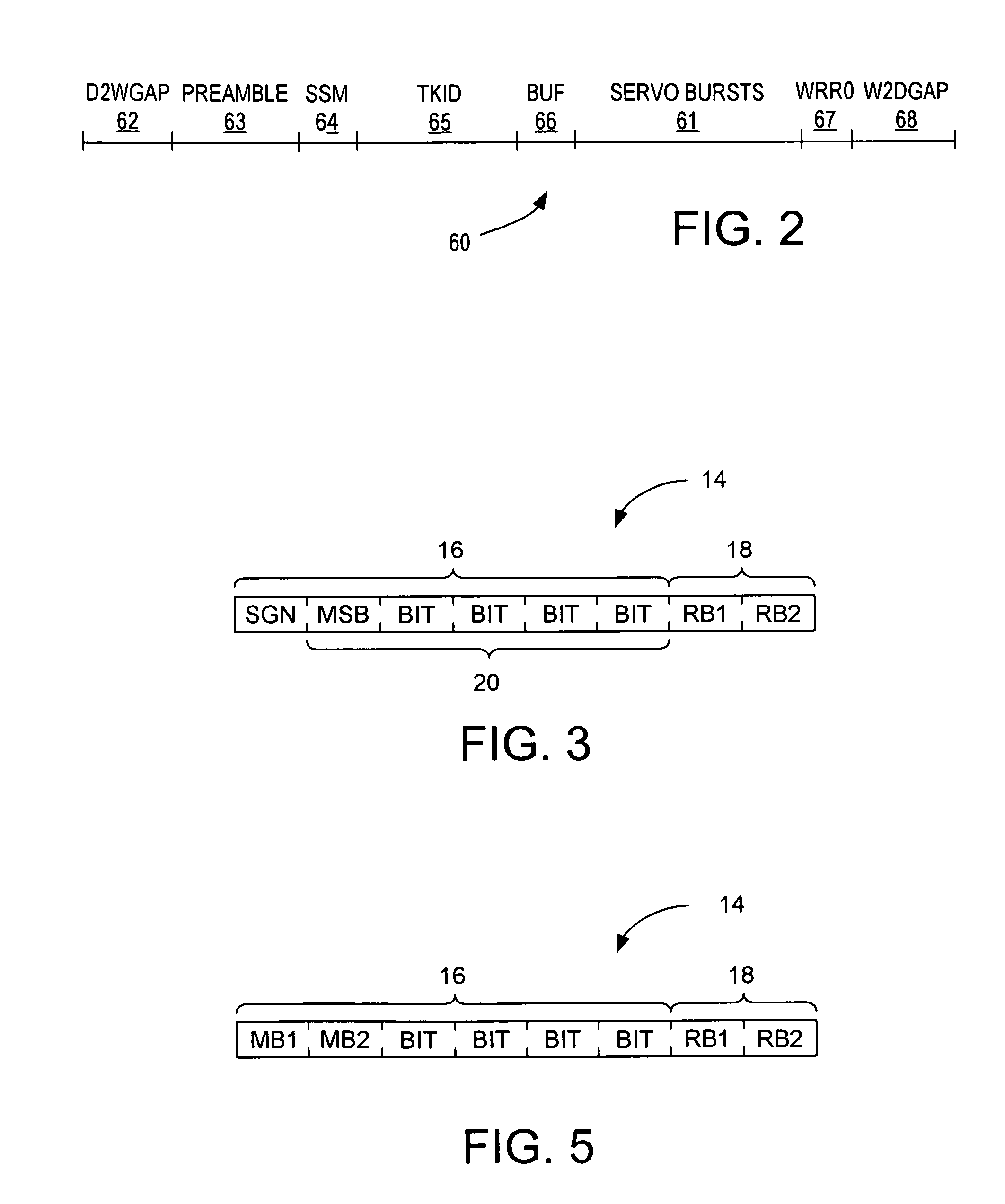

Magnetic disk having efficiently stored WRRO compensation value redundancy information and method for using the redundancy information

InactiveUS7580212B1Record information storageAlignment for track following on disksBit fieldSign bit

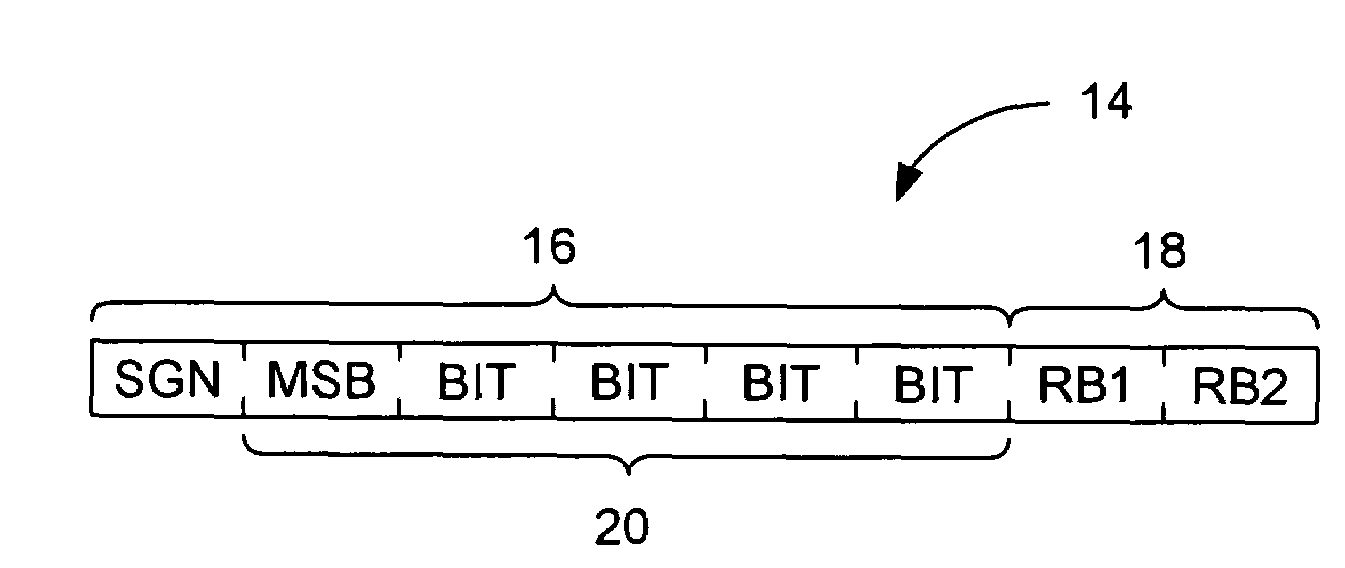

The present invention may be embodied in a magnetic disk, of a disk drive, having eight-bit fields storing wedge repeatable runout (WRRO) compensation values and redundancy information. The WRRO compensation value of each field includes a six-bit binary value of which five bits represent a compensation magnitude and one bit represents a sign bit indicating a compensation direction. The redundancy information of each field has a first bit based on the sign bit.

Owner:WESTERN DIGITAL TECH INC

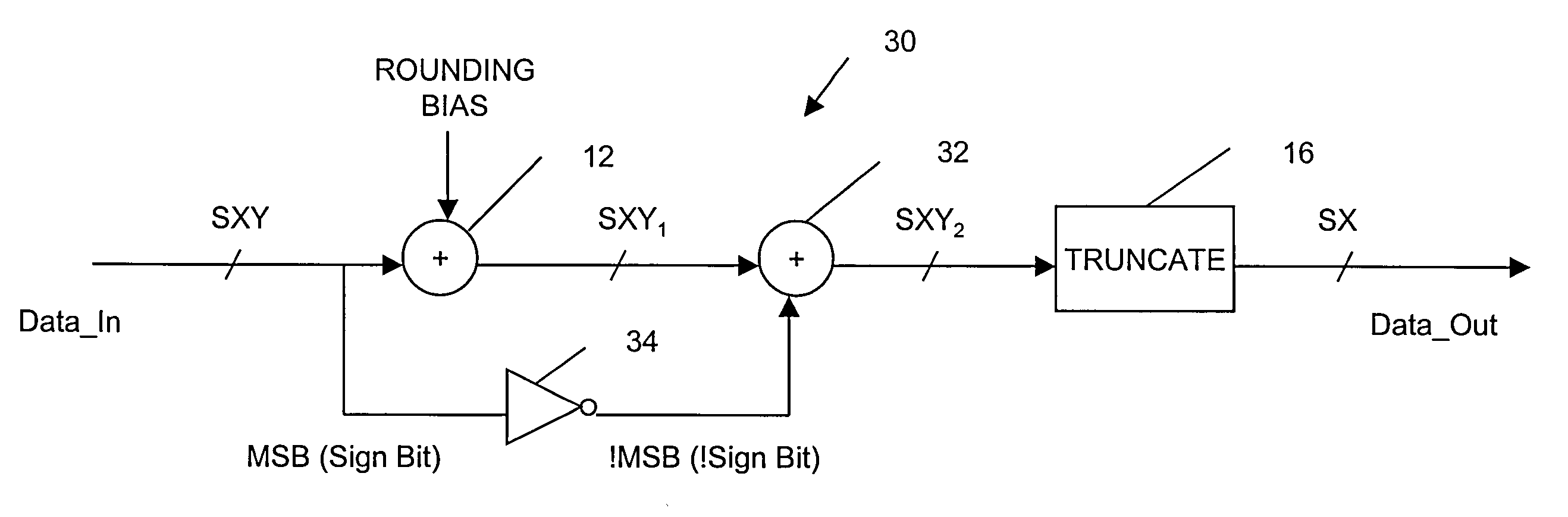

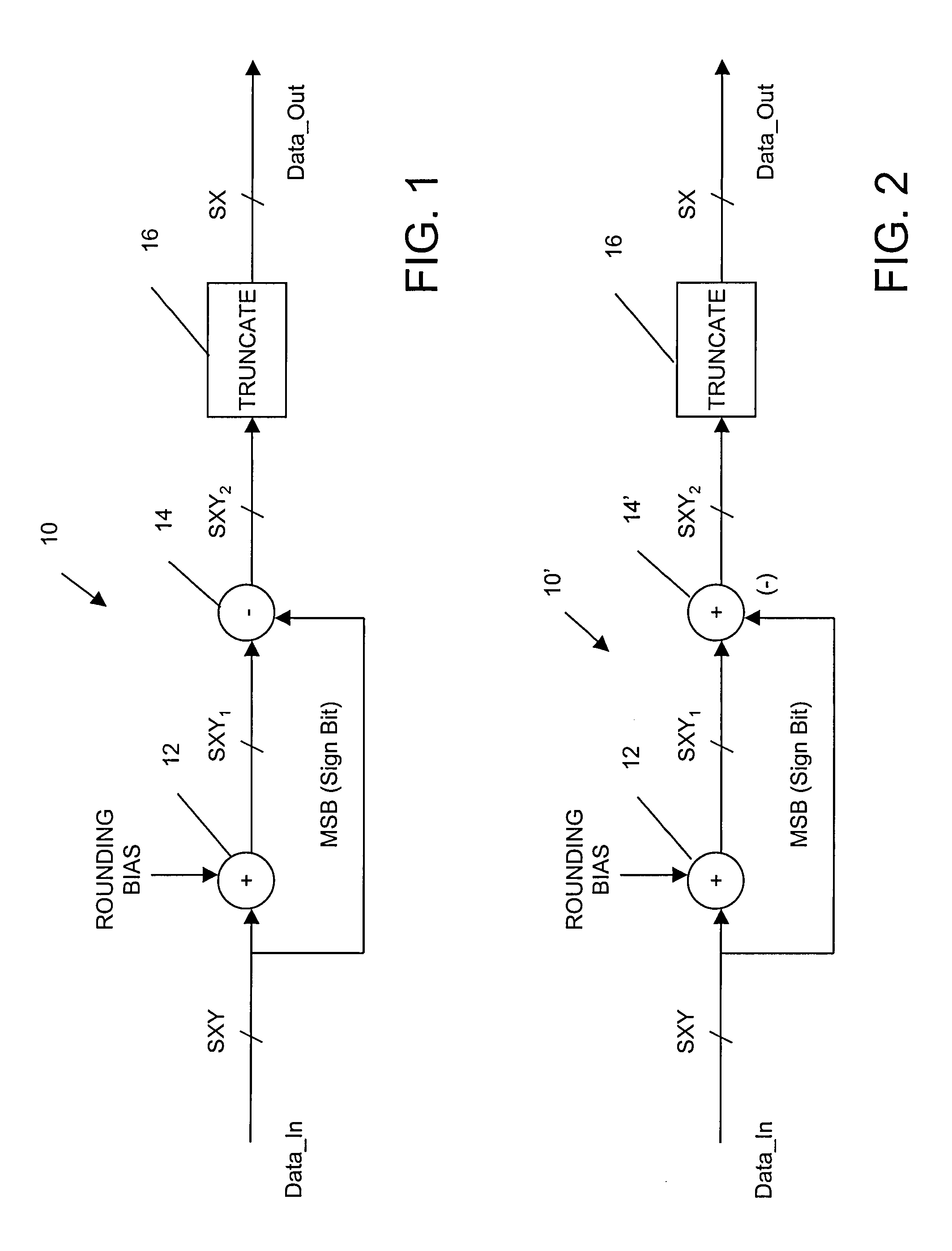

N-BIT 2's COMPLEMENT SYMMETRIC ROUNDING METHOD AND LOGIC FOR IMPLEMENTING THE SAME

InactiveUS20080028014A1Computation using denominational number representationSign bitComputer science

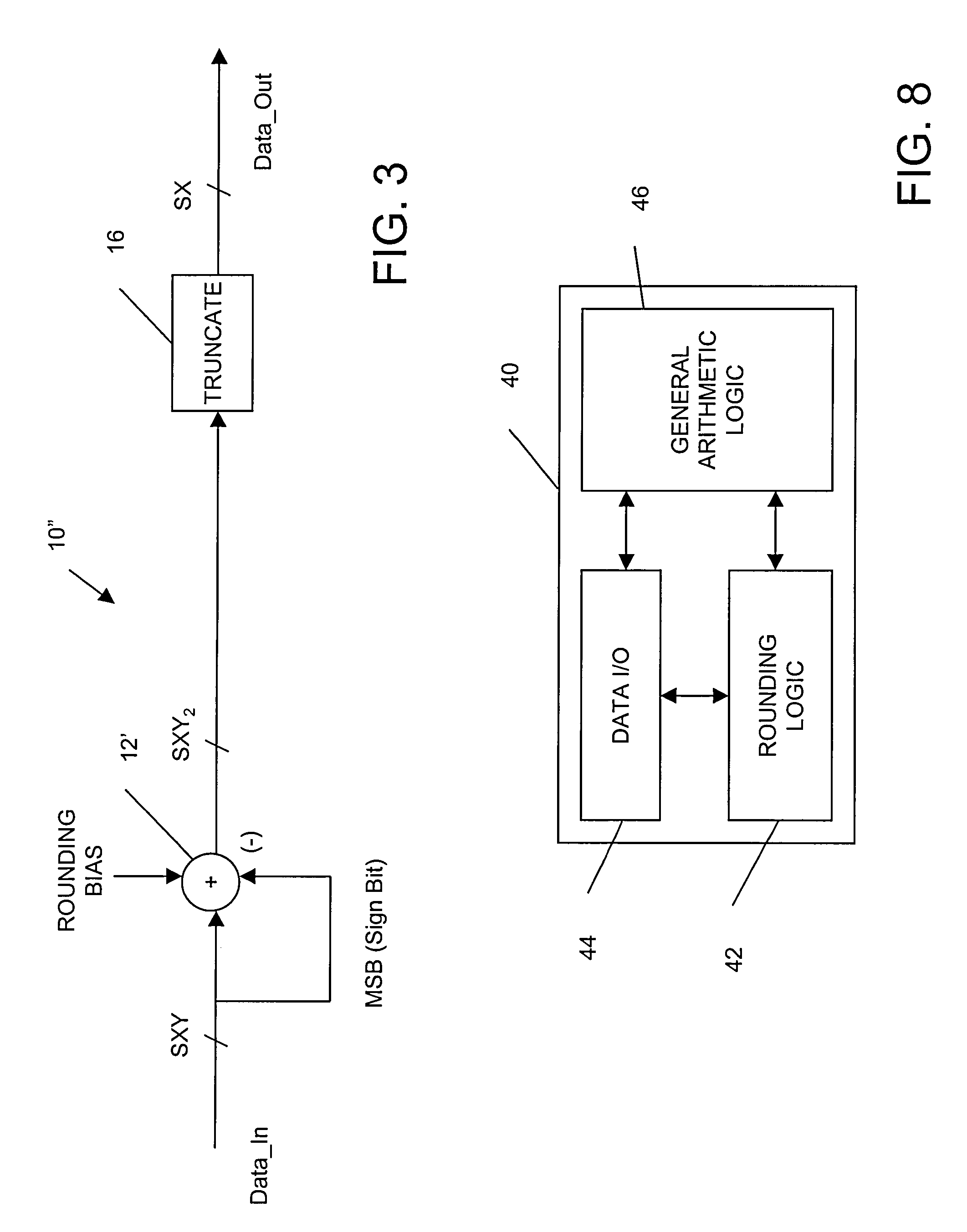

A rounding circuit is provided that includes an input for receiving a 2's complement number to be rounded. The 2's complement number has a format SXY, where S represents a sign bit, X represents one or more bits to round and keep, and Y represents one or more bits to be discarded. The rounding circuit also includes first logic for adding a rounding bias to the 2's complement number, and second logic for at least one of subtracting the sign bit S from the 2's complement number, or adding the inverted sign bit !S to the 2's complement number. Moreover, the rounding circuit includes third logic for truncating Y bits from a result produced by the first and second logic to produce a rounded 2's complement number having a format SX.

Owner:RAYTHEON CO

Entropy coding method and decoding method based on text

InactiveCN1980395AReduce redundancyHigh compressibilityTelevision systemsDigital video signal modificationDecoding methodsNonzero coefficients

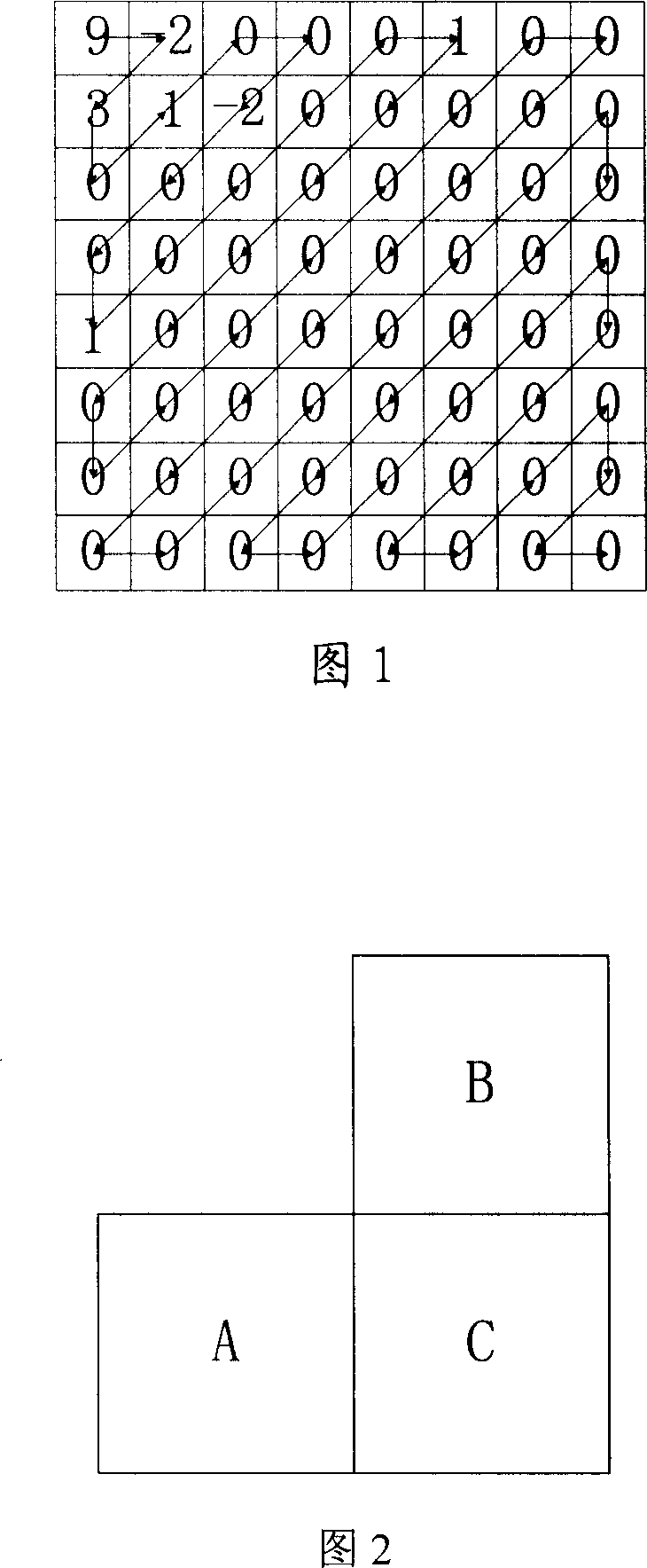

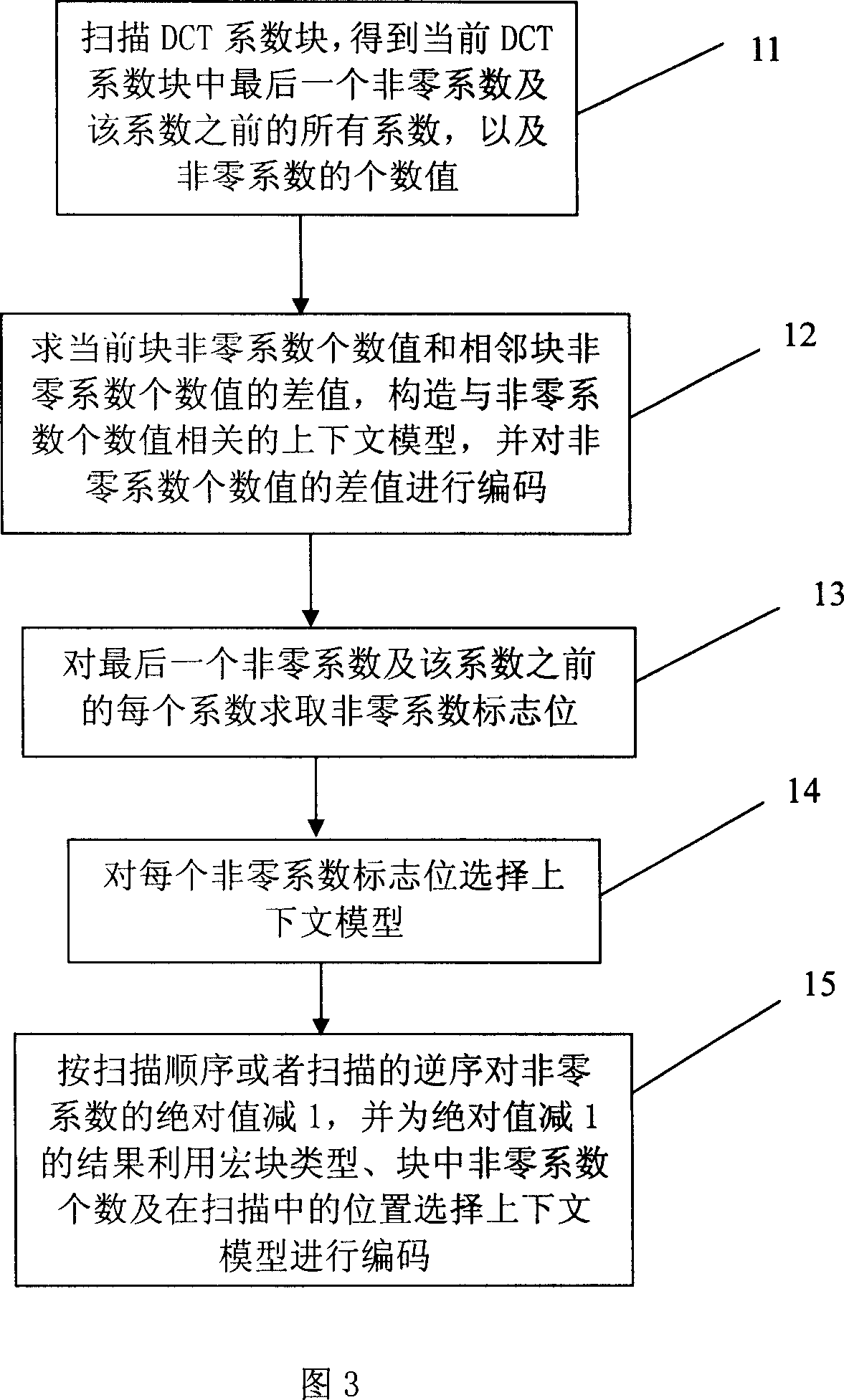

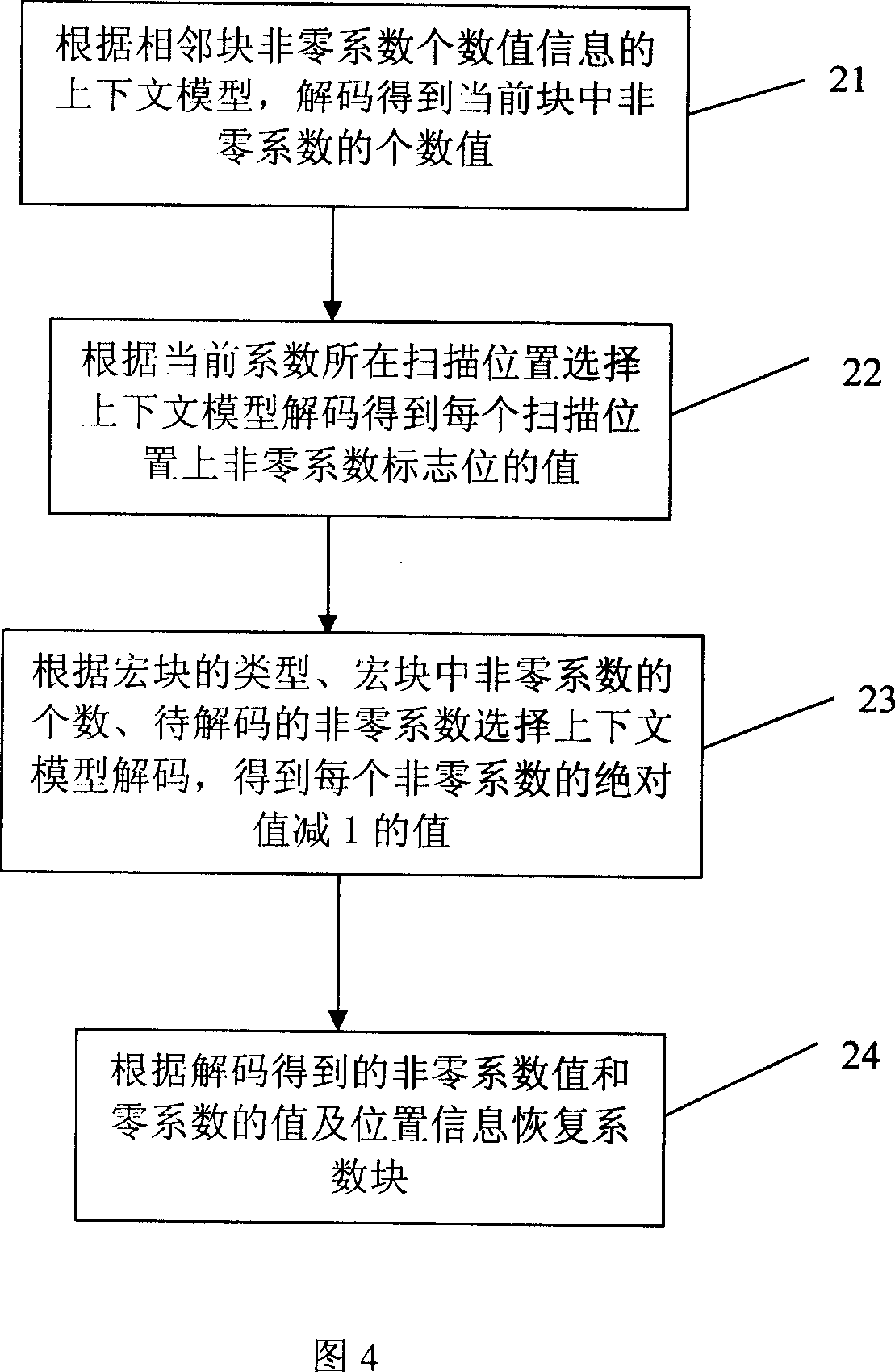

The method includes following steps: scanning DCT coefficient blocks according to sequence so as to obtain last one nonzero coefficient (NC) and the coefficient in front of the last one NC in coefficient block, and number value of NC; based on the number value of NC to calculate difference value between number value of NC in this block and number value of NC in adjacent block, and constructing context model for number value of NC; calculating flag bit of NC for last one NC and coefficients before the last one NC; selecting context model to encode flag bit of NC; subtracting 1 from absolute value of NC according to scanning sequence or scanning inverted sequence; and selecting context model to encode number value of NC, and its position in the scan etc; encoding sign bit. The invention also discloses corresponding decoding method.

Owner:联合信源数字音视频技术(北京)有限公司

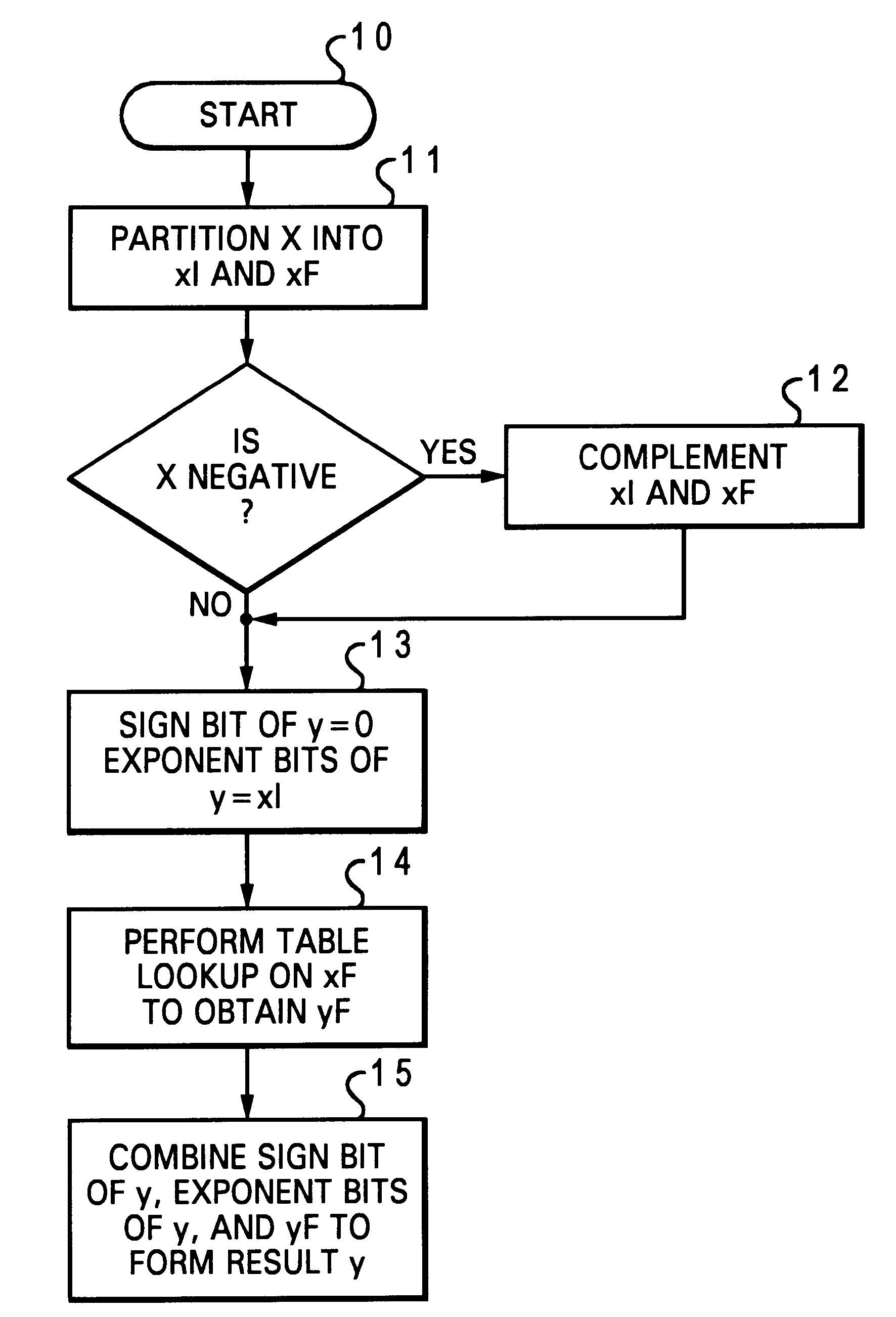

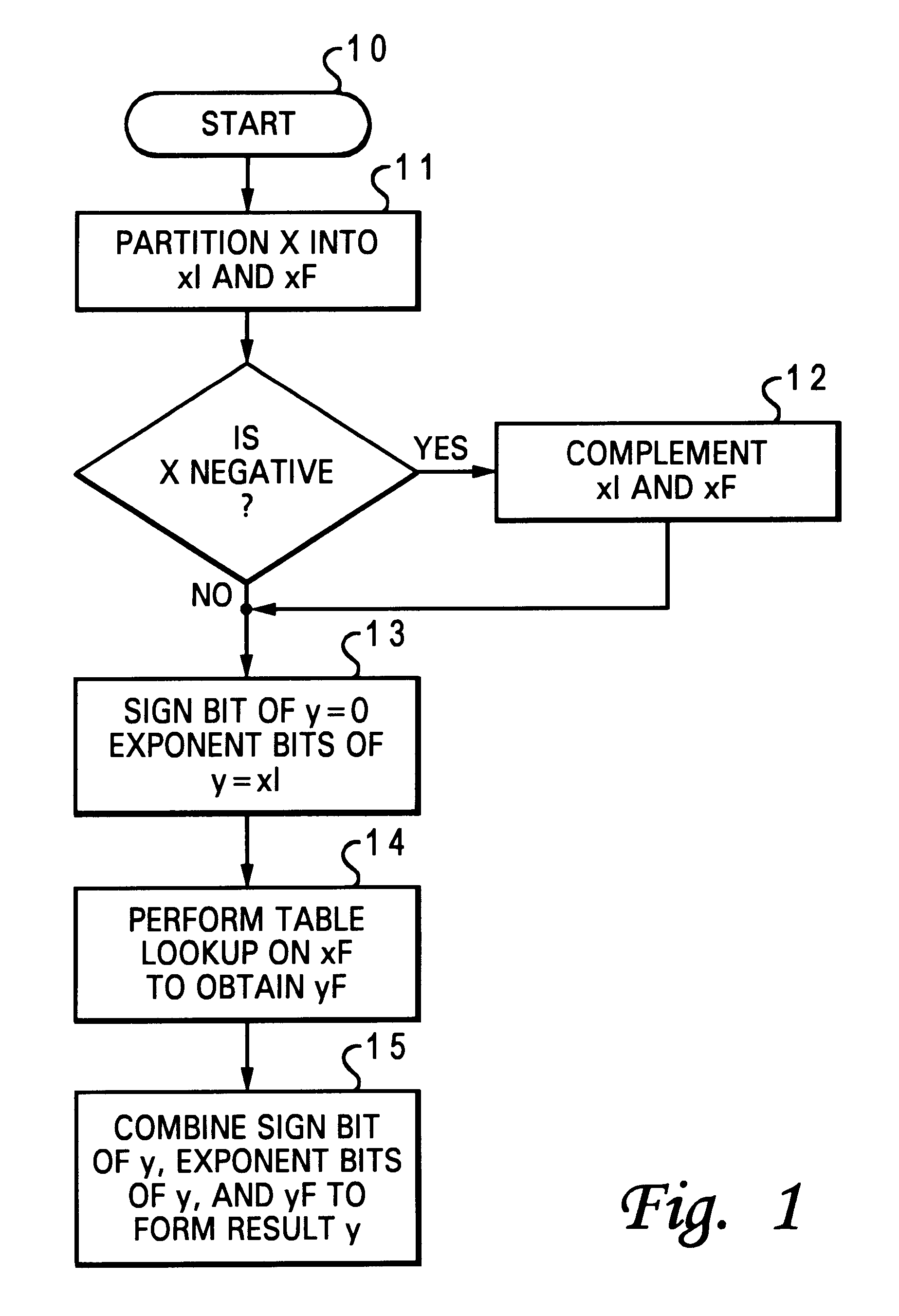

Method and system for performing a power of two estimation within a data processing system

InactiveUS6178435B1Computation using non-contact making devicesDigital function generatorsData processing systemSign bit

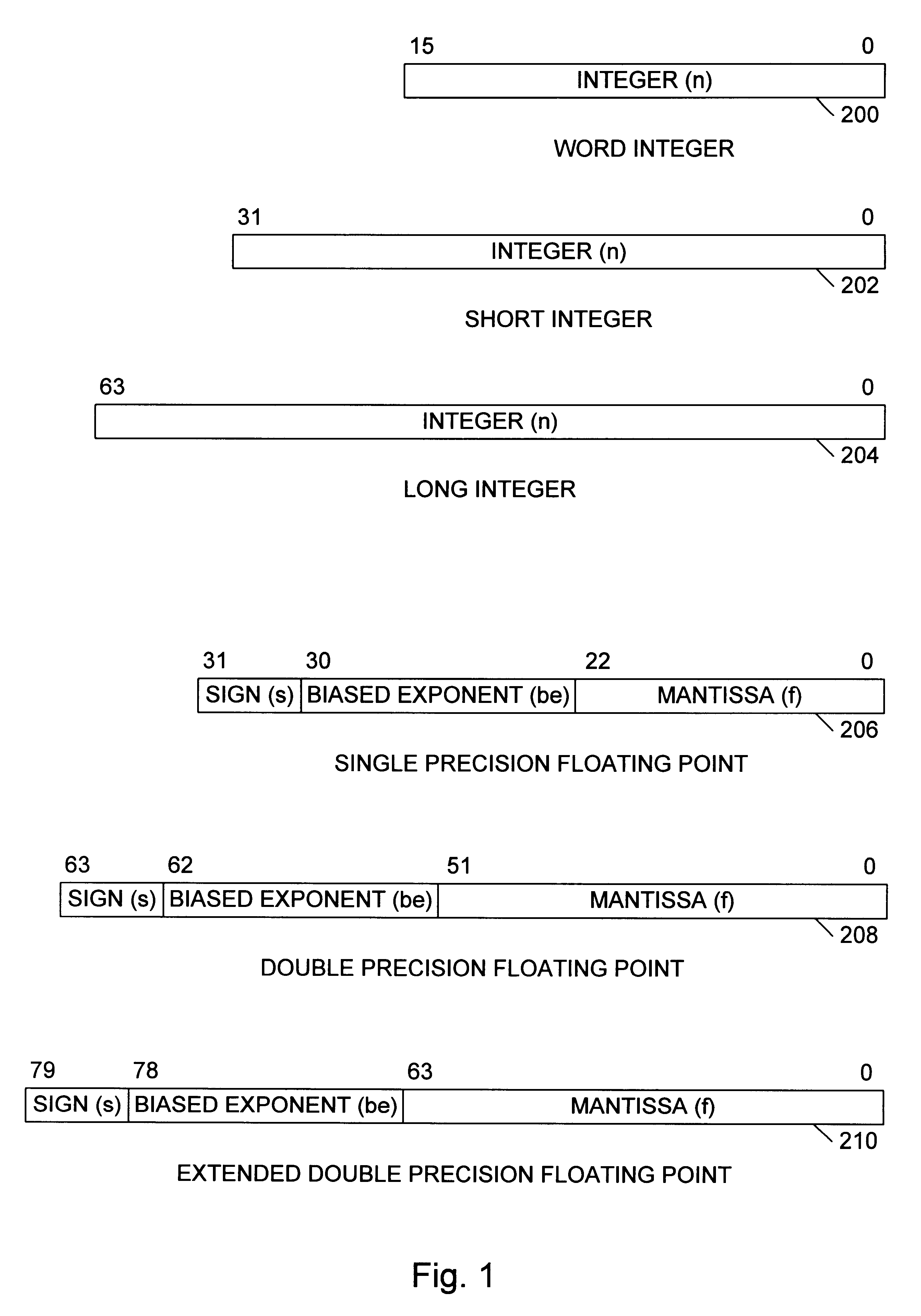

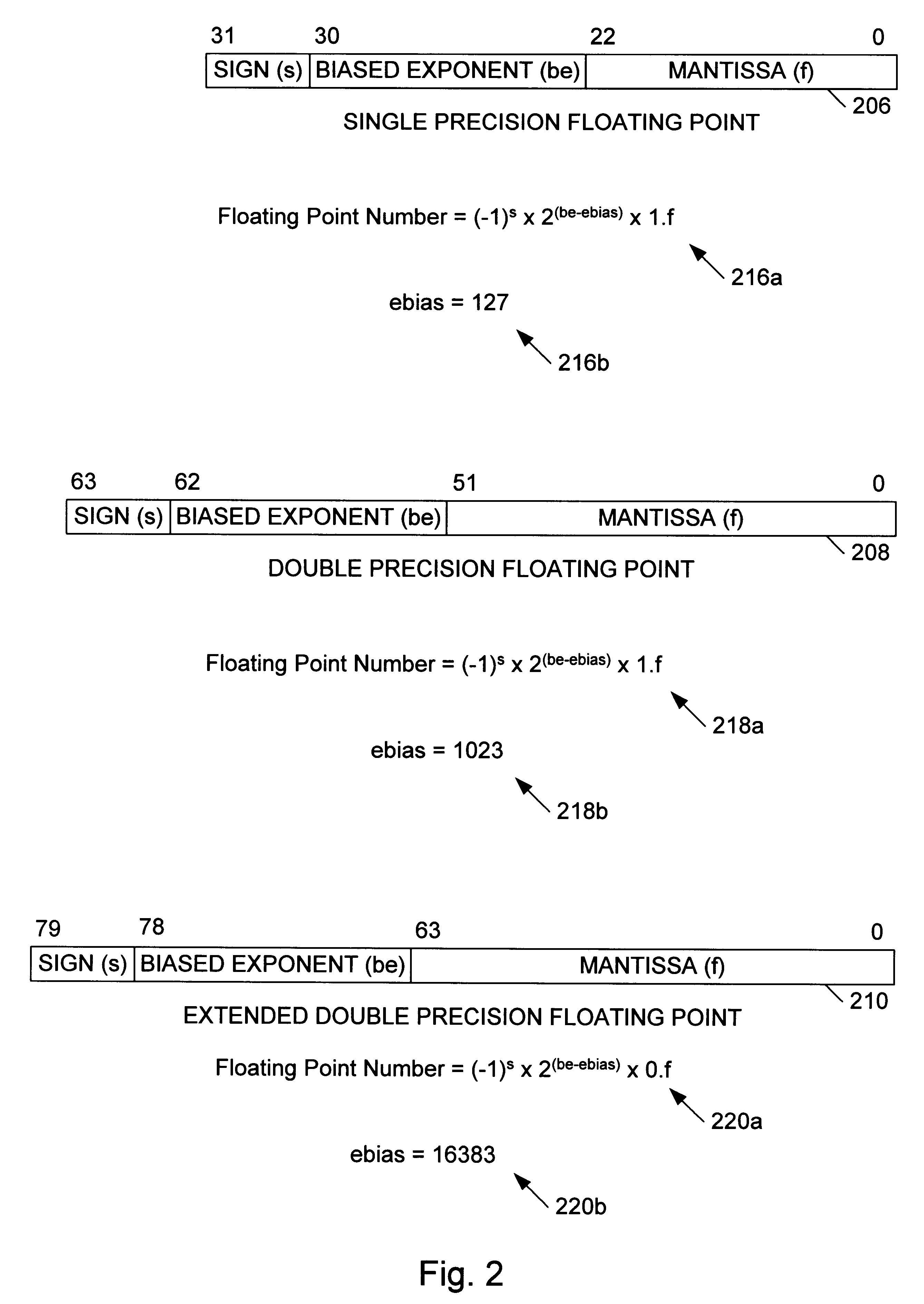

A method for performing a power of two estimation on a floating-point number within a data processing system is disclosed. The floating-point number includes a sign bit, multiple exponent bits, and a mantissa having an implied one and multiple fraction bits. In order to estimate the power of two of the floating-point number, the mantissa is partitioned into an integer part and a fraction part, based on the value of the exponent bits. A floating-point result is formed by assigning the integer part of the floating-point number as an unbiased exponent of the floating-point result, and by converting the fraction part of the floating-point number via a table lookup to become a fraction part of the floating-point result.

Owner:IBM CORP

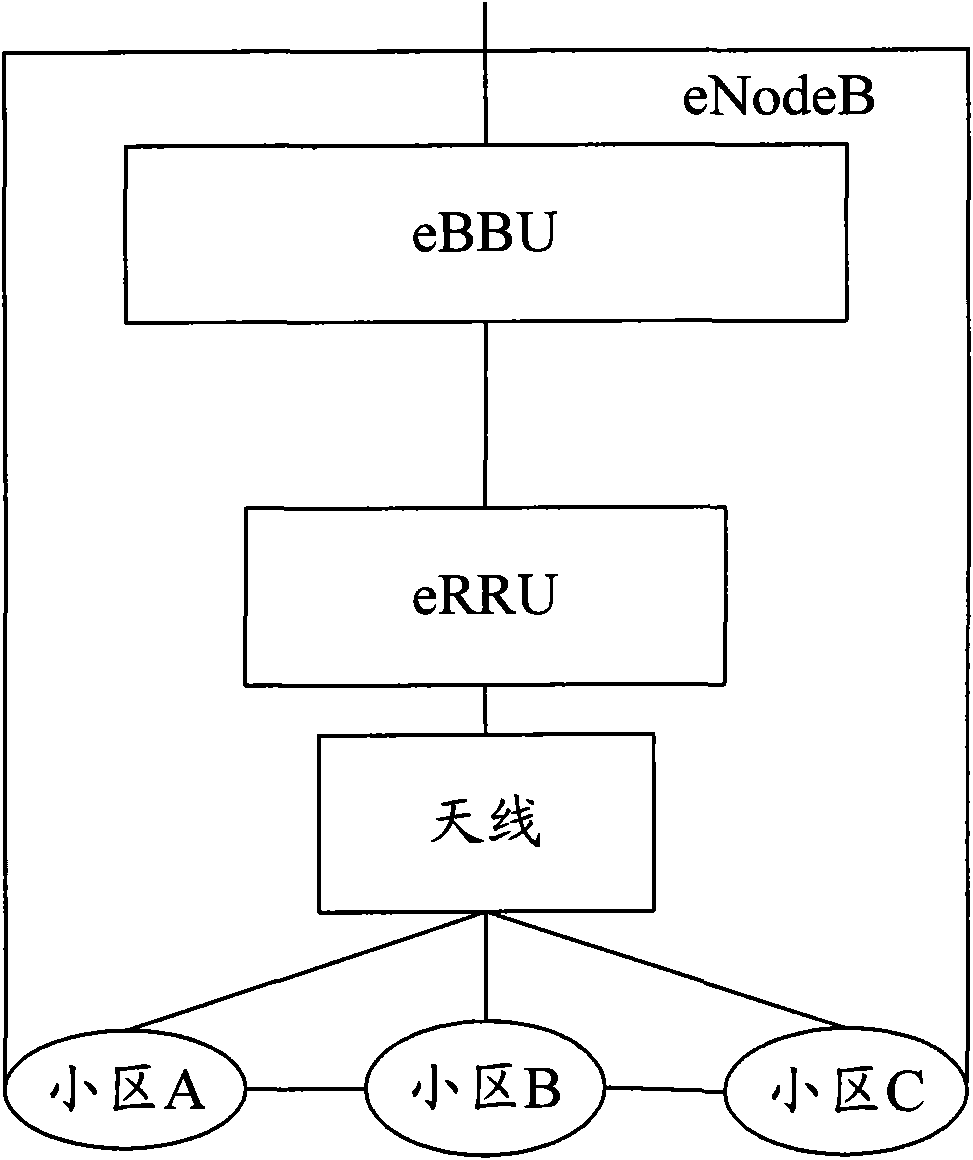

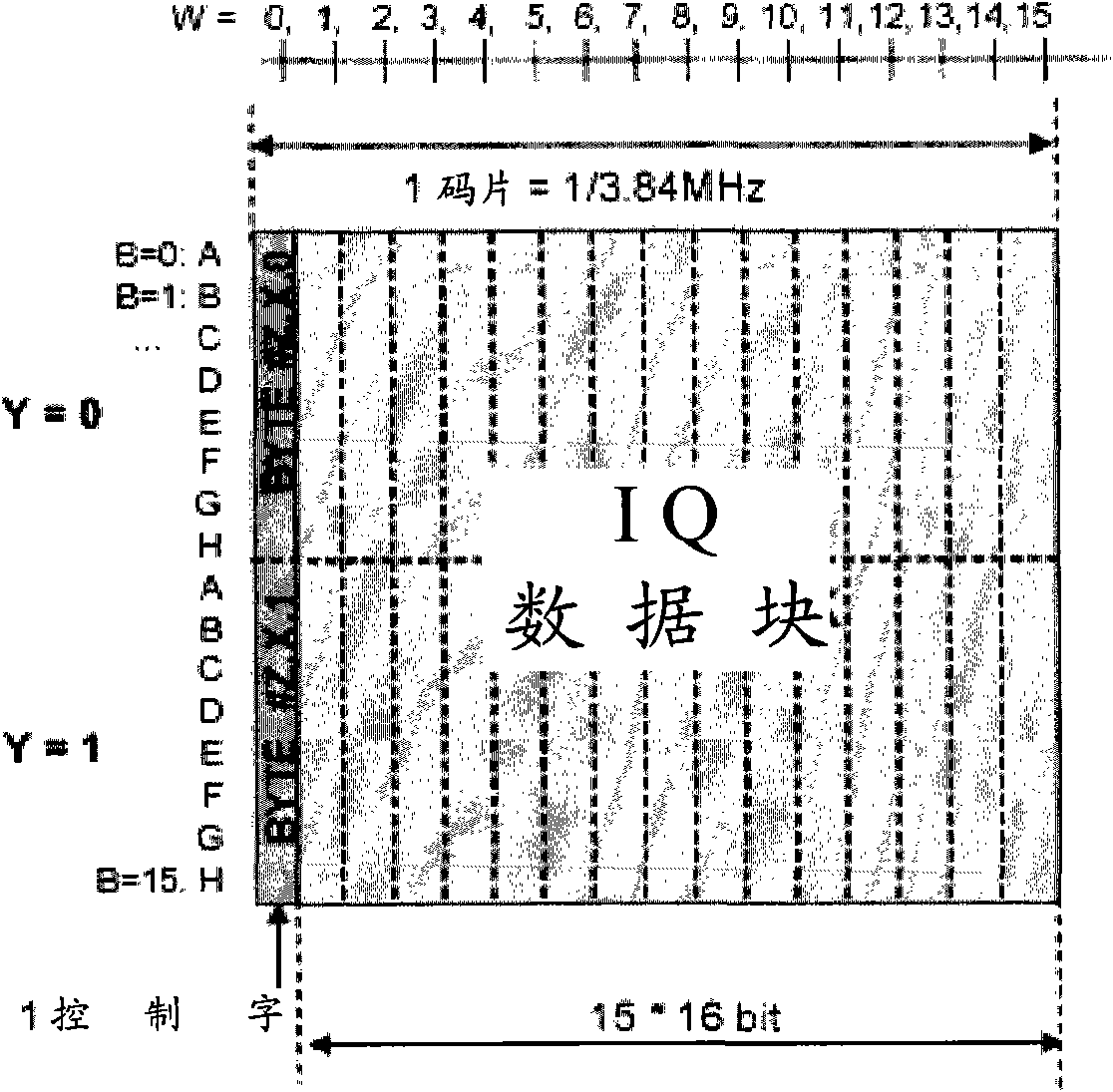

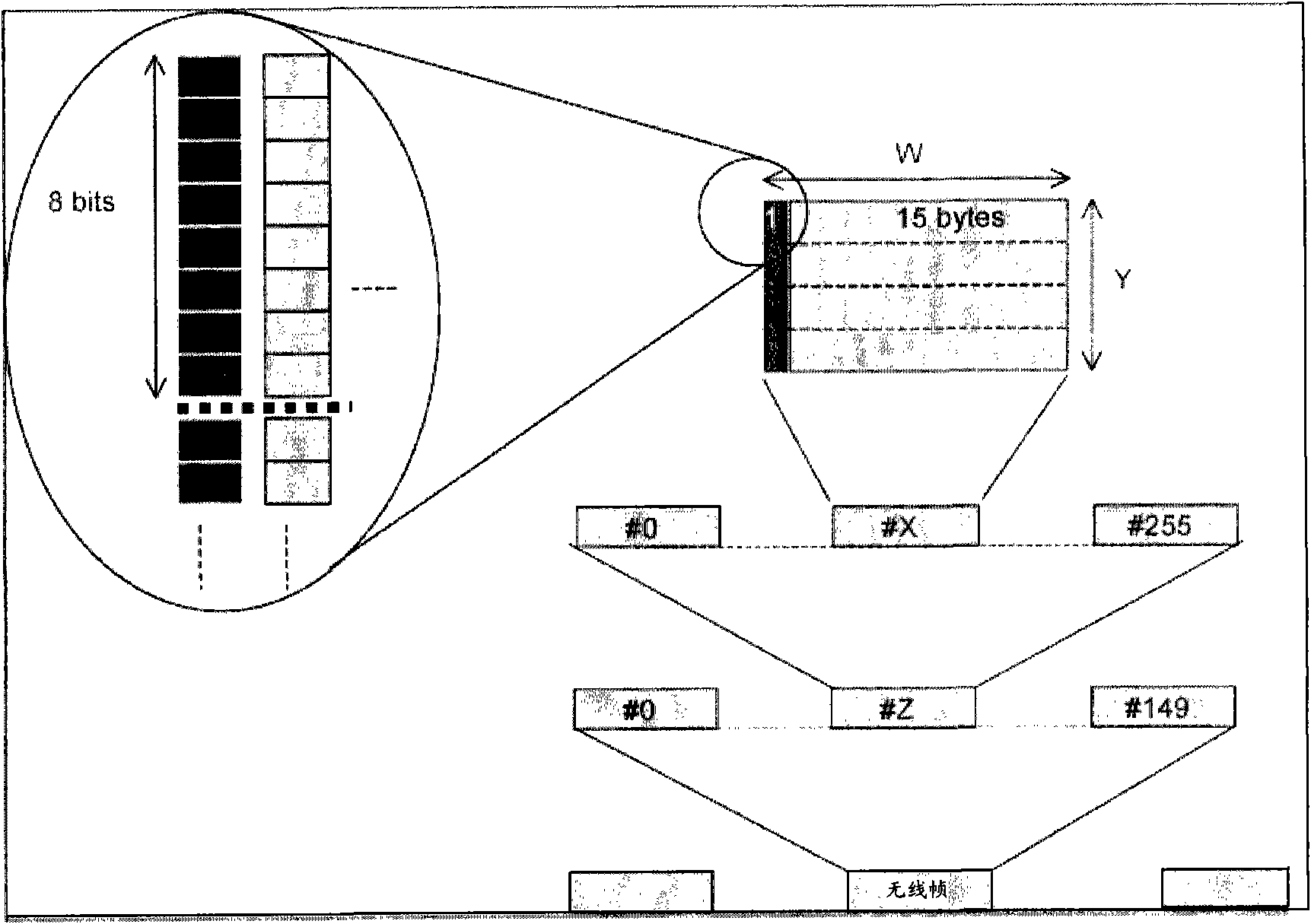

Inphase quadrature signal intelligence quotient (IQ) data compression method and device

ActiveCN102075467ALow costReduce demandError preventionTransmitter/receiver shaping networksData compressionOptical Module

The invention discloses an intelligence quotient (IQ) data compression method and a device. The method comprises the following steps of: dividing m continuous IQ data into one group, and obtaining data with the maximum numerical value in each group of data; intercepting continuous n-bit seniority effective data and sign bits of the data with the maximum numerical value in the group of data, and deleting the rest low-bit data in the data with the maximum numerical value; intercepting the continuous n bit seniority effective data and sign bits of the other m-1 data in the group of data, and deleting the rest low-bit data in the other m-1 data; and determining compression factors of the group according to the bit number of the deleted low-bit data, and sending the compression factors and the compressed IQ data. When the technical scheme of the invention is adopted, the requirement of eNodeB wireless equipment on optical modules and optical fiber can be effectively reduced, and the cost of base station equipment is reduced.

Owner:ZTE CORP

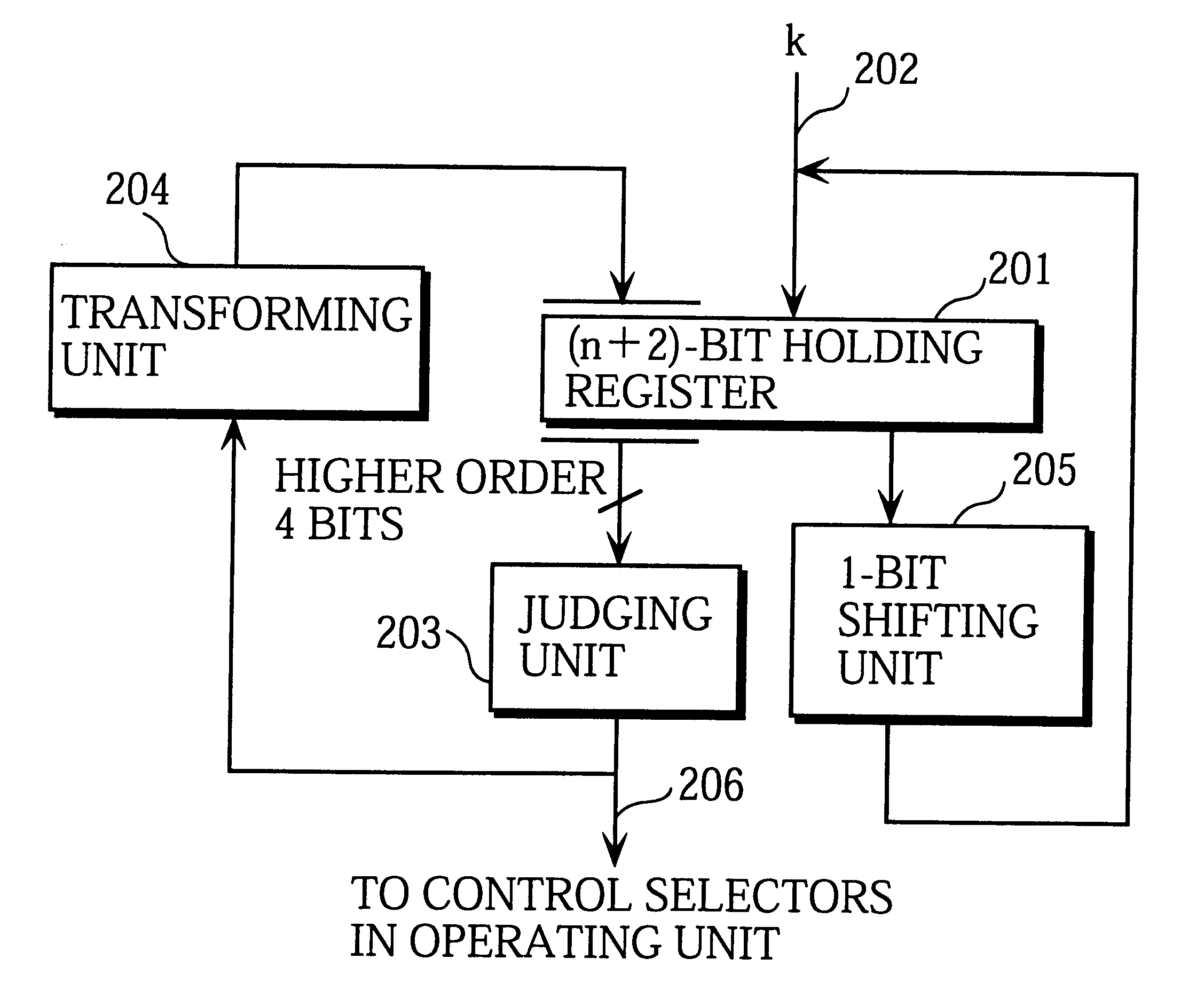

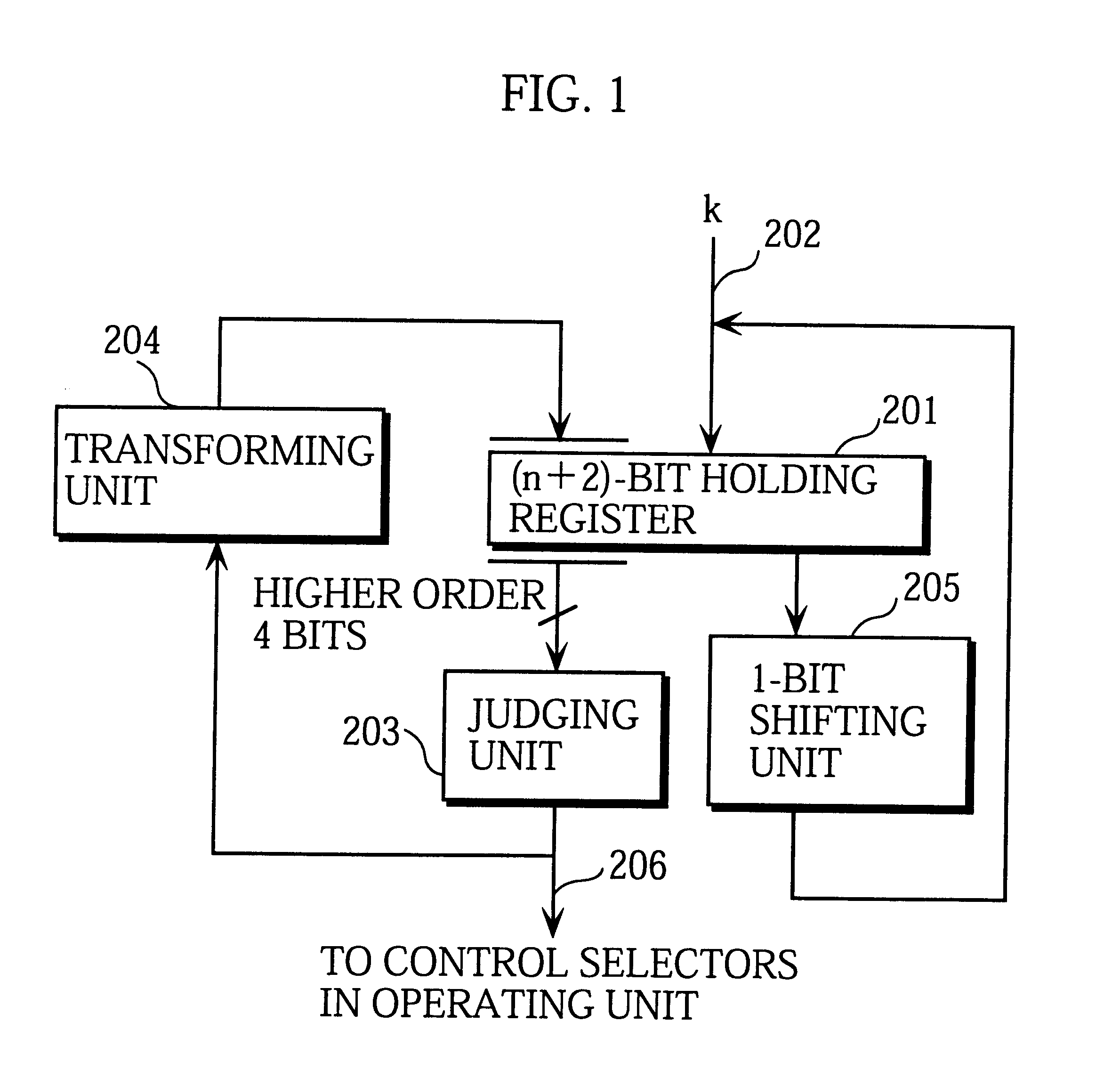

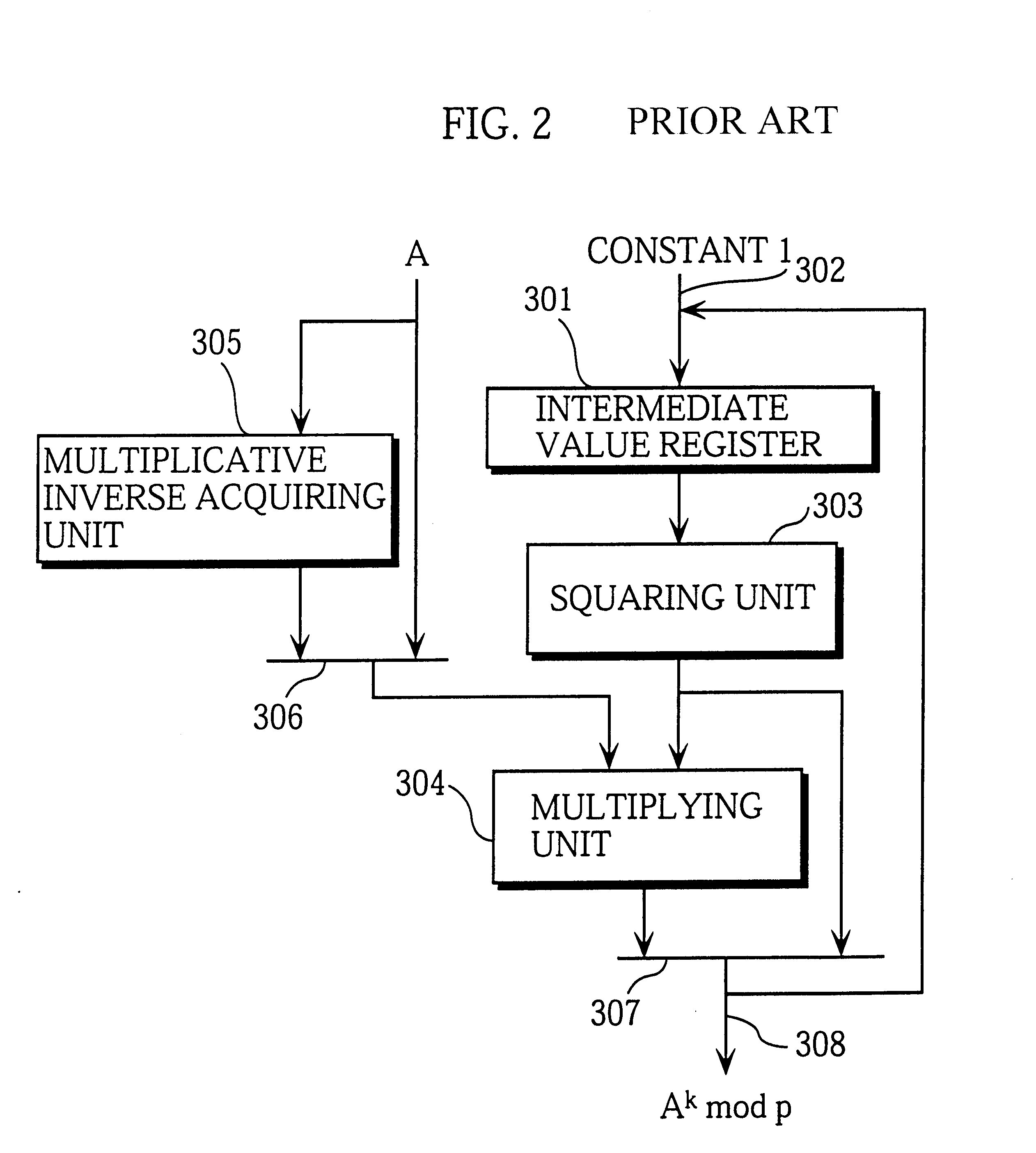

Device, method, and storage medium for exponentiation and elliptic curve exponentiation

InactiveUS6567832B1Reduce in quantityKeep sizeComputations using residue arithmeticComputation using denominational number representationComputer hardwareSign bit

An exponent preprocessing unit preprocesses an n-bit exponent k and exponentiates a base A by the preprocessed exponent k. A bit string storing unit stores a bit string including a sign bit and the exponent k. A reading unit reads a bit pattern composed of the sign bit and a bit sequence made up of a predetermined number of bits. A bit pattern generating unit generates a new bit pattern from the read bit pattern. An operation pattern specifying unit specifies an operation pattern based on the read bit pattern. An operating unit performs an operation according to the specified operation pattern and writes the new bit pattern over the previous bit pattern. The reading unit reads a next bit sequence starting from a different bit in the bit string storing unit. A repeat controlling unit repeats these procedures n+1 times.

Owner:PANASONIC CORP

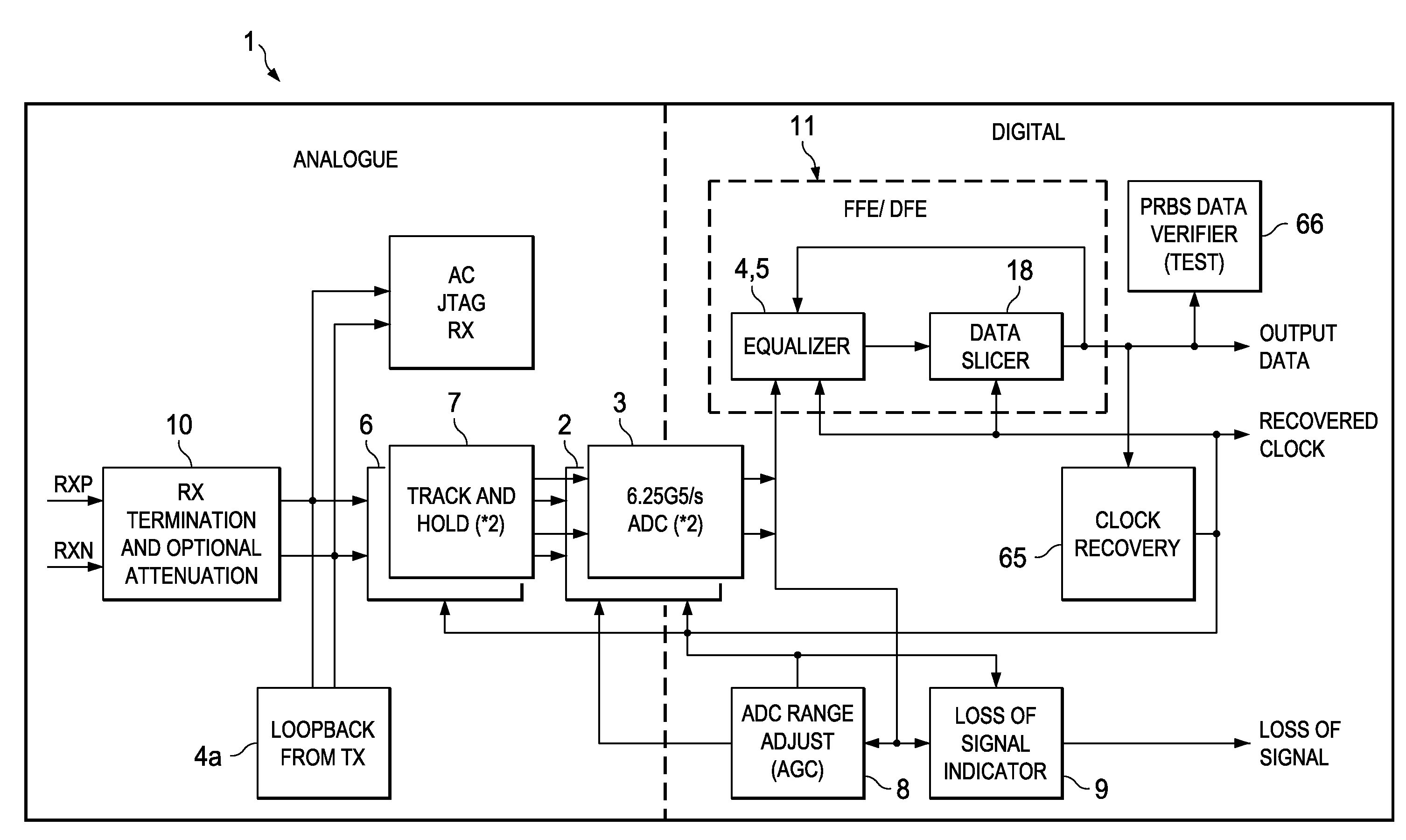

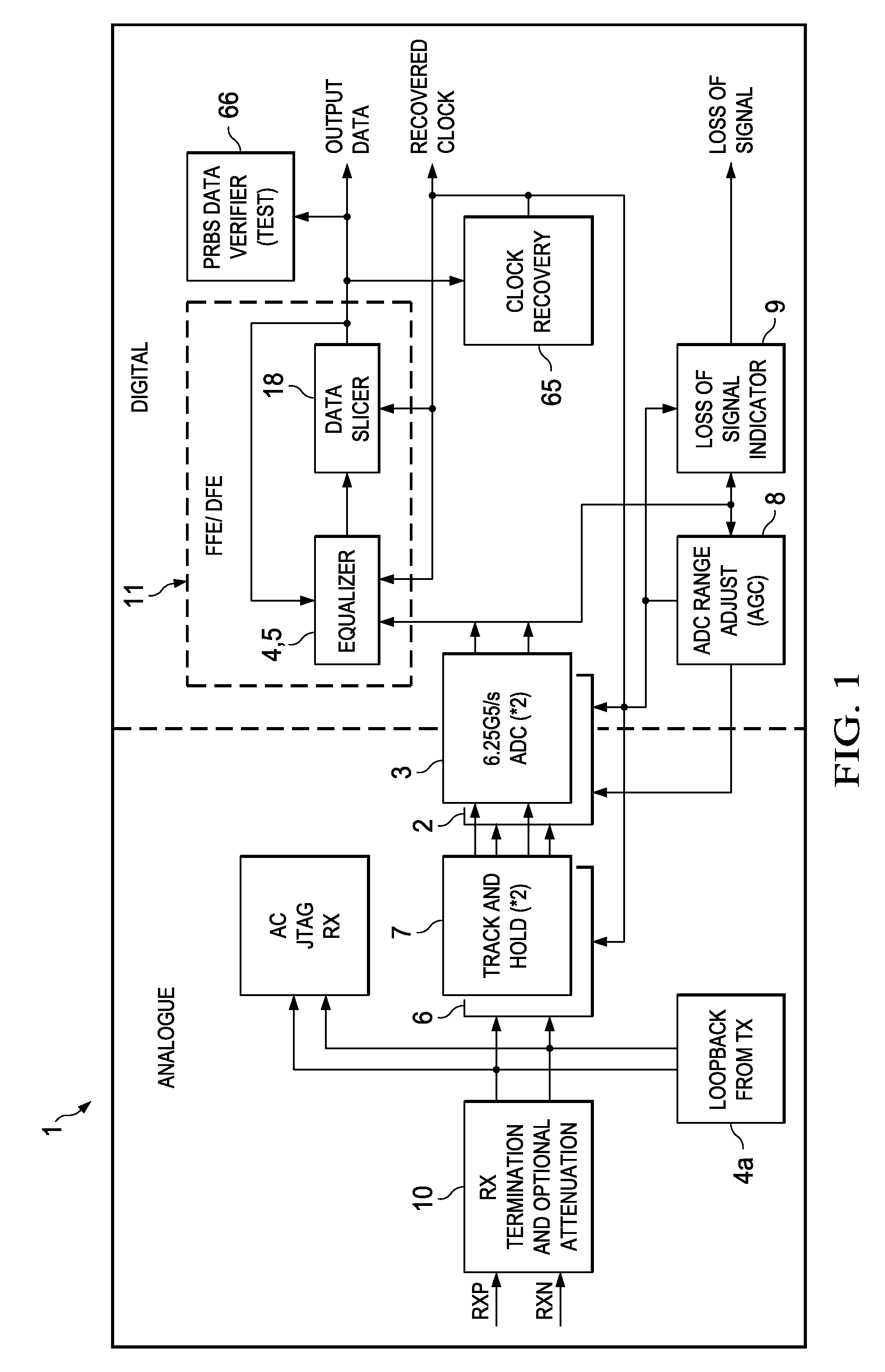

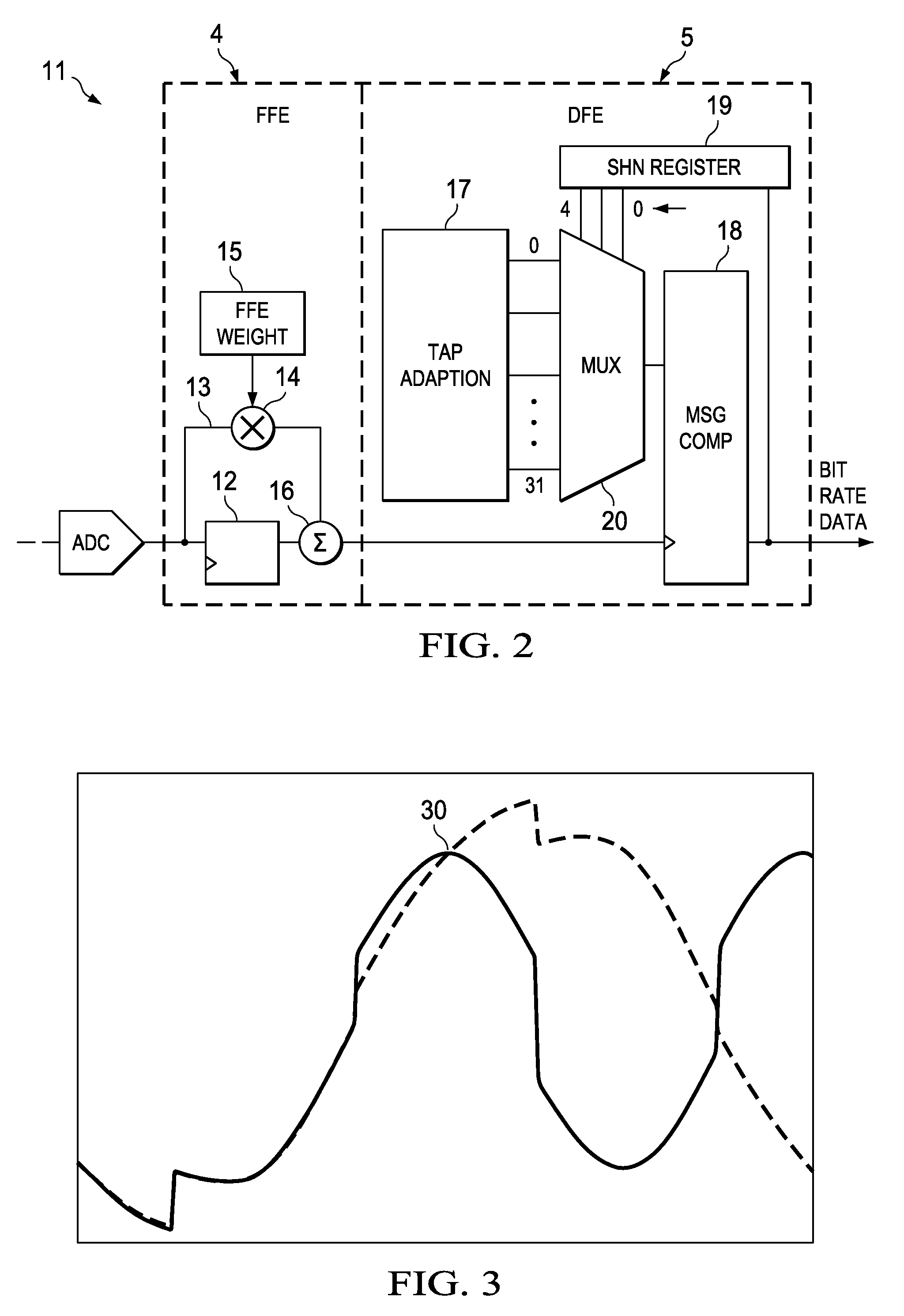

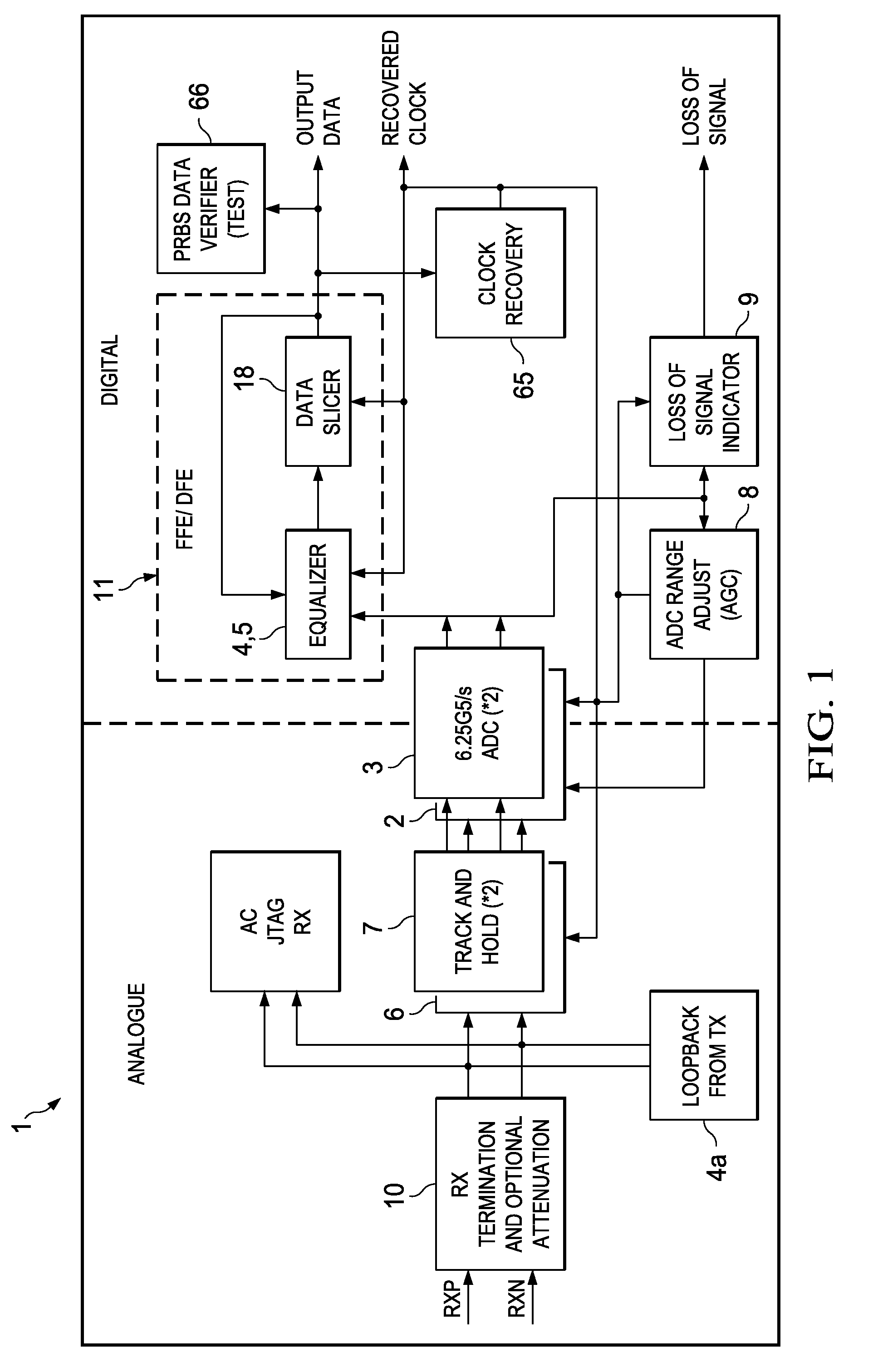

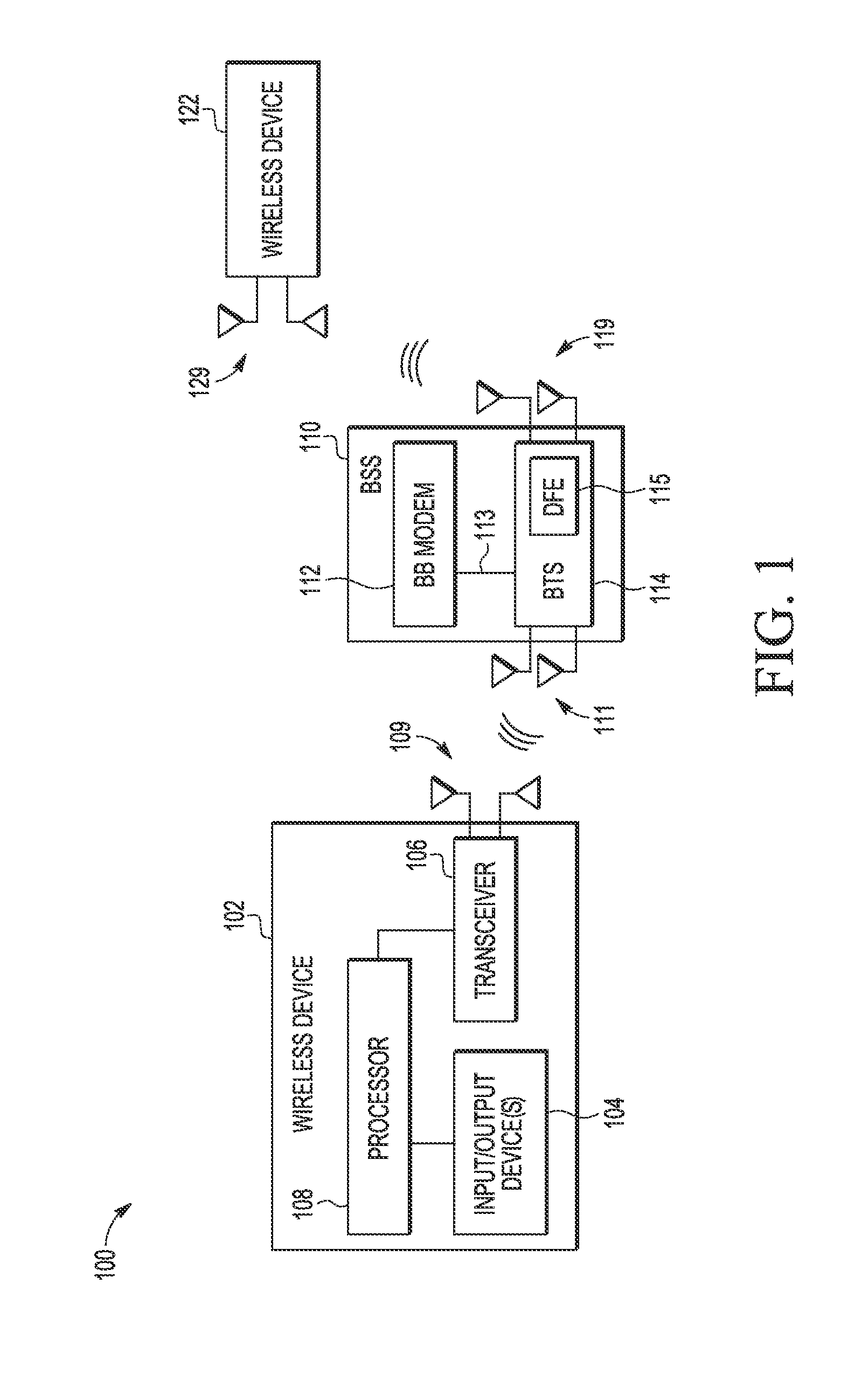

Receiver Circuit

InactiveUS20080219390A1Increase clock frequencyGood tracking effectElectric digital data processingSynchronising arrangementComputer hardwareSign bit

A thermometer code to sign and magnitude converter that is particularly useful in a flash ADC is provided. This comprises two conversion units. The first is a thermometer code to Gray code converter and the second a Gray code to sign and magnitude converter. Preferably, the Gray code is of a kind that has a sign bit and has the other bits symmetrically disposed about zero. This form is easily converted to a sign and magnitude code, which is advantageous as it reduces the latency of the converter, which is particularly useful at high data rates.

Owner:TEXAS INSTR INC

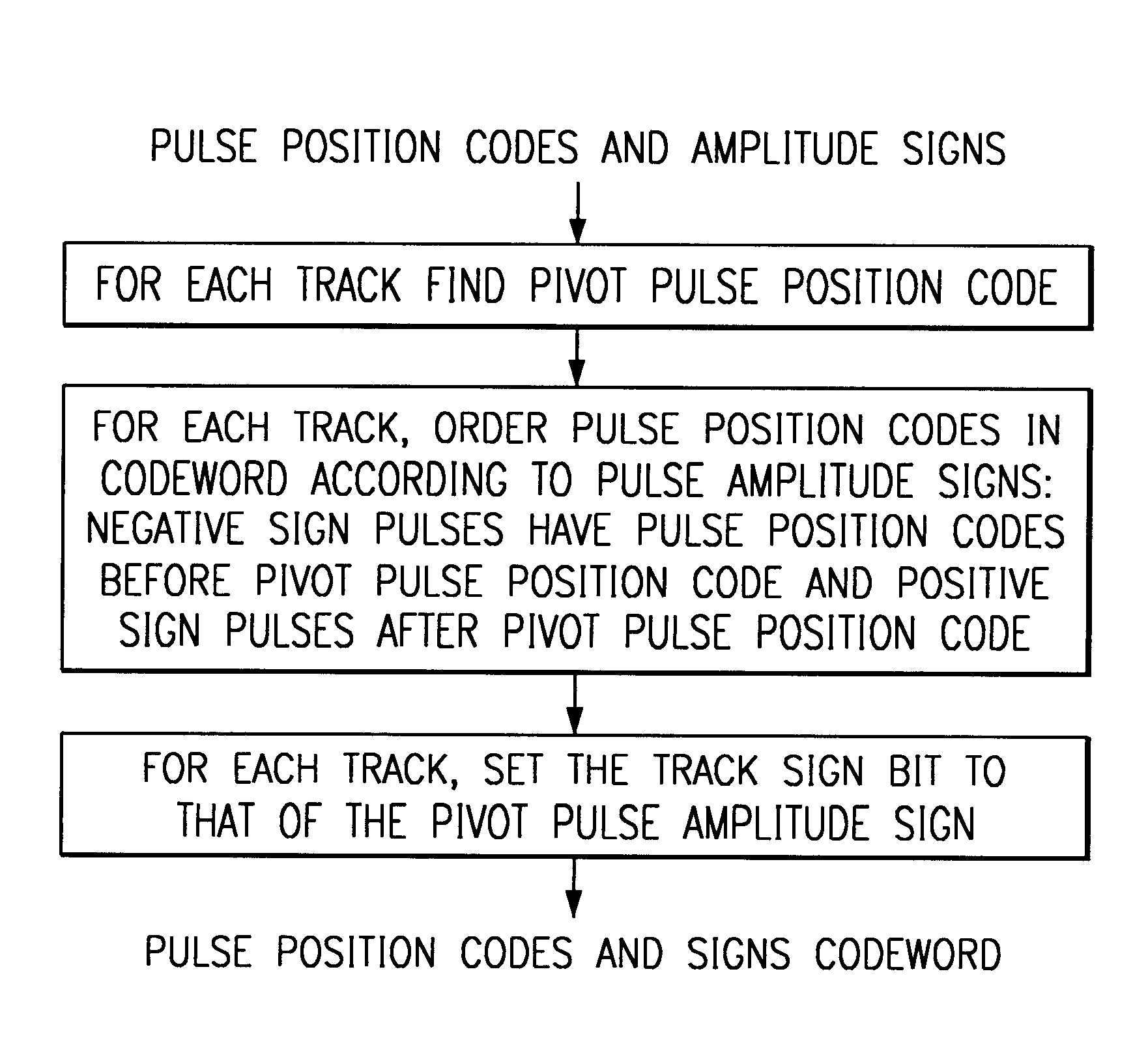

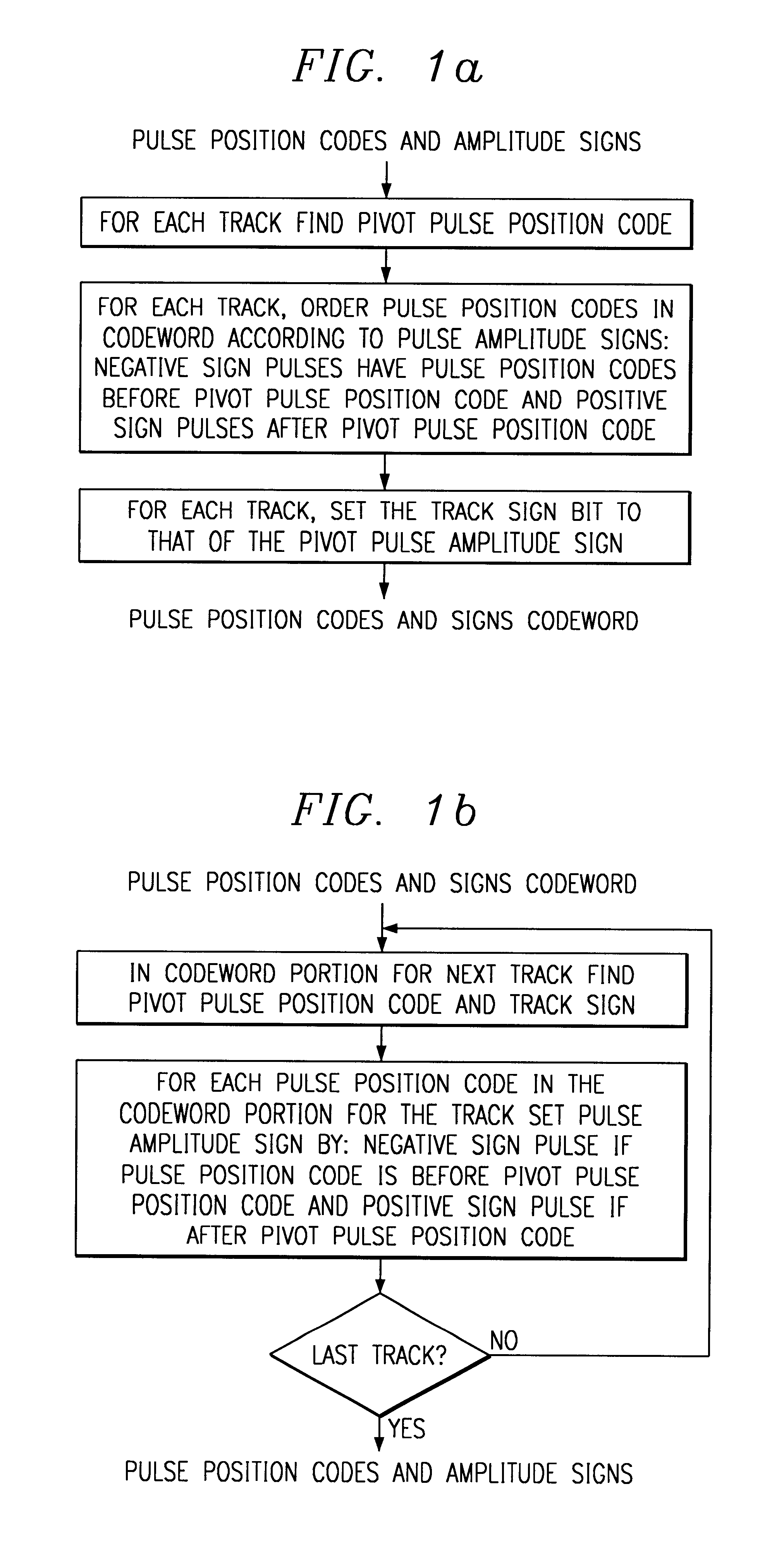

Algebraic codebook system and method

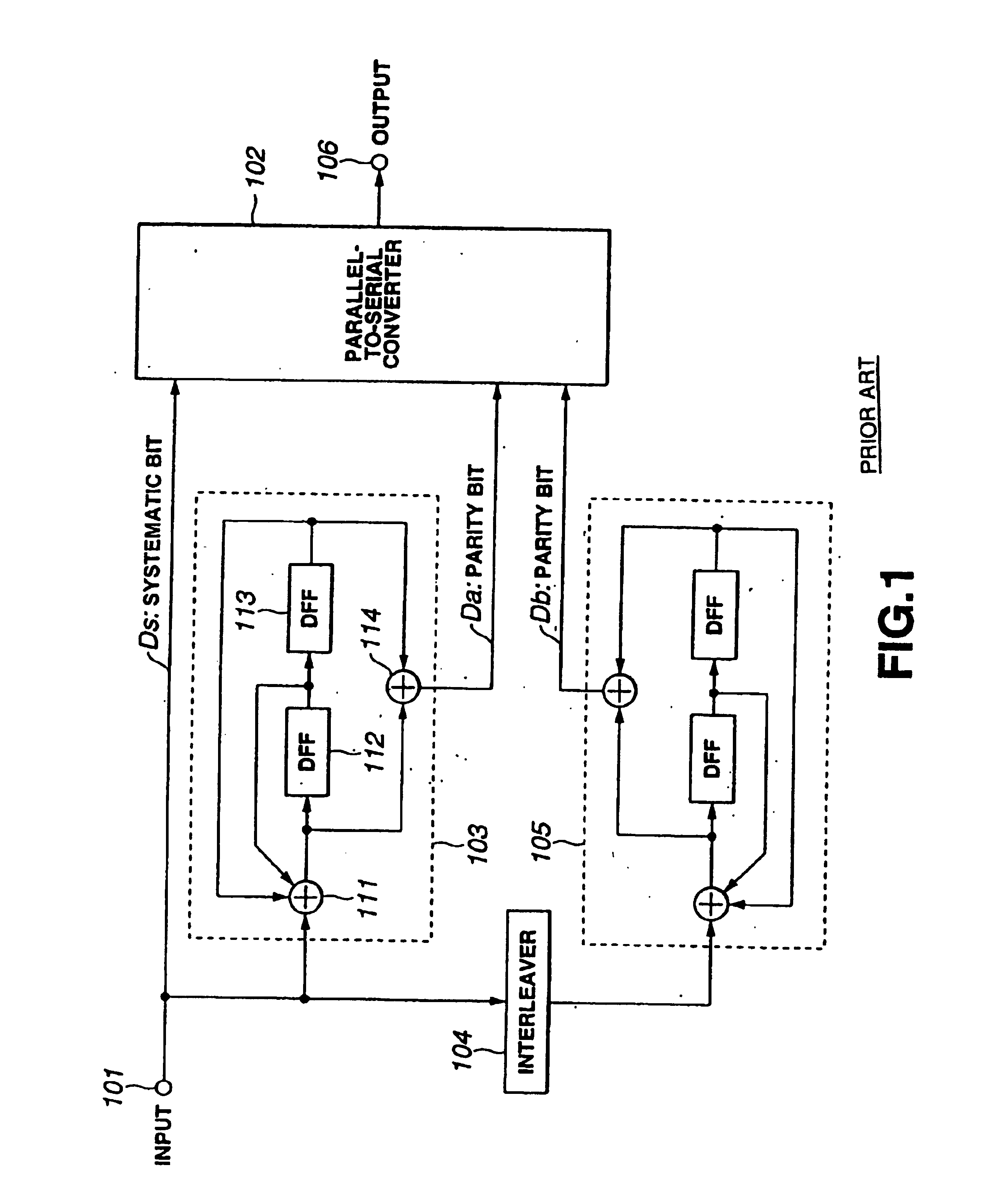

Code-excited linear prediction speech encoders / decoders with excitation including an algebraic codebook contribution encoded with a single sign bit for each track of pulses by inferring pulse amplitude signs from the pulse position code ordering within a codeword.

Owner:TEXAS INSTR INC

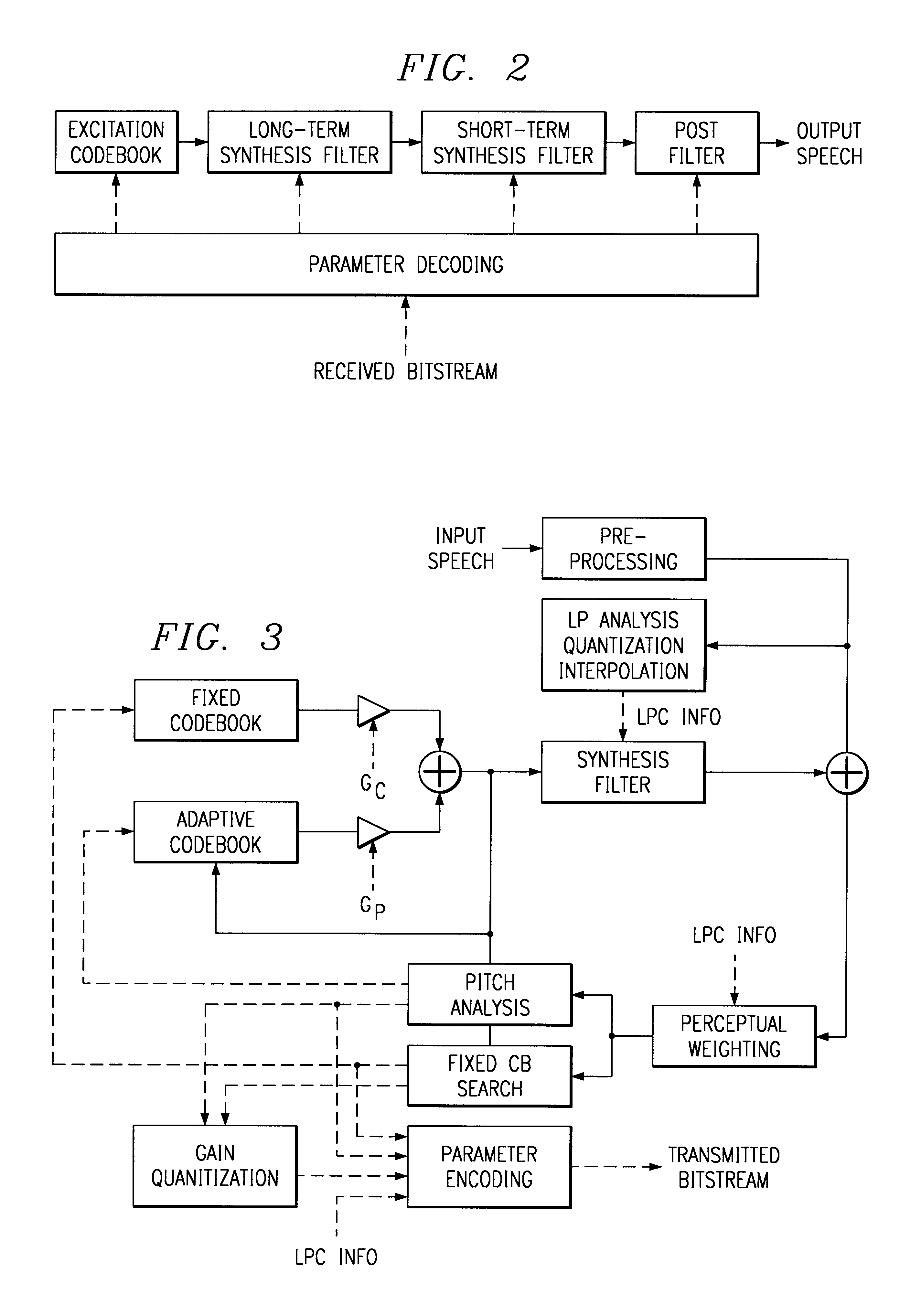

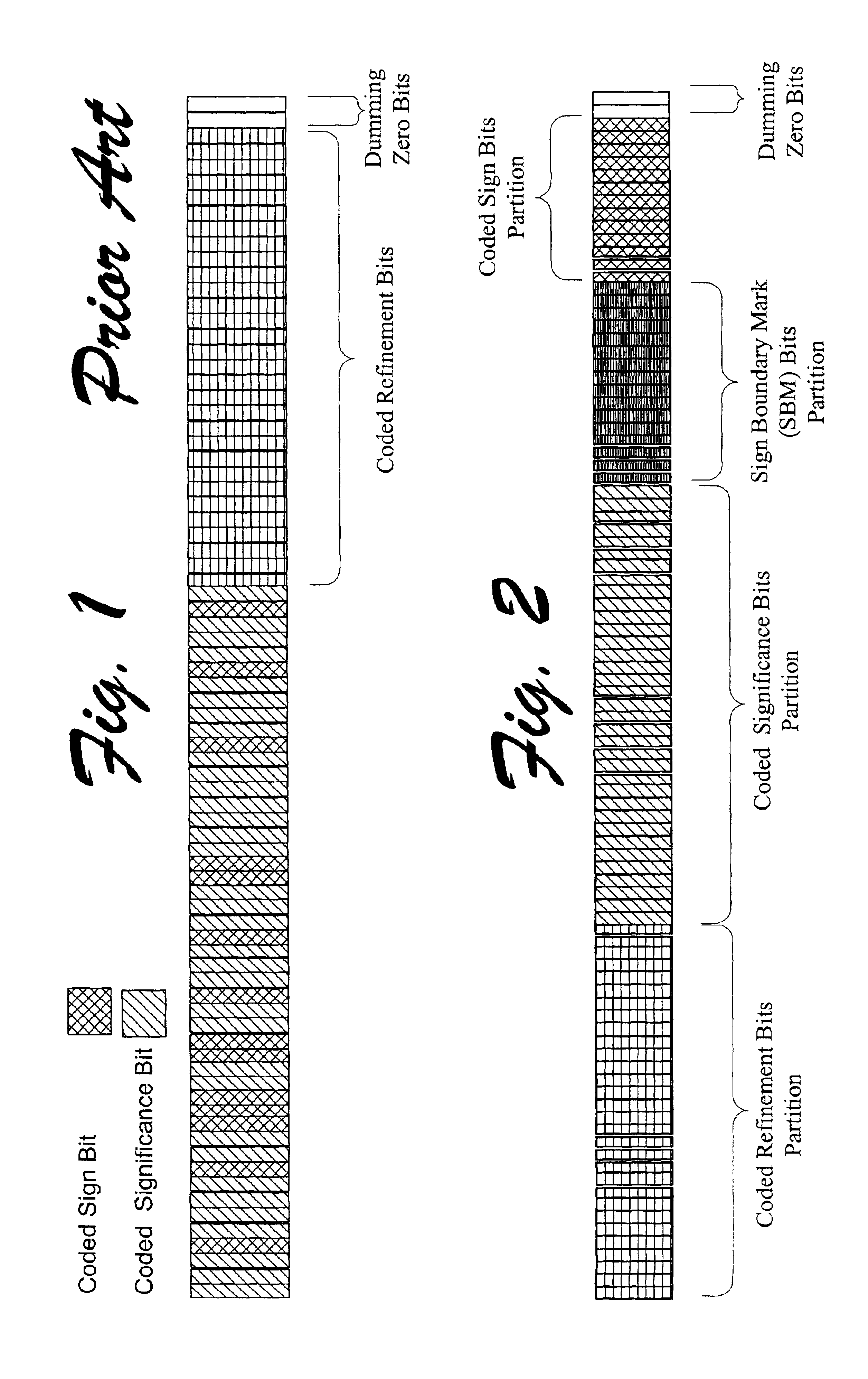

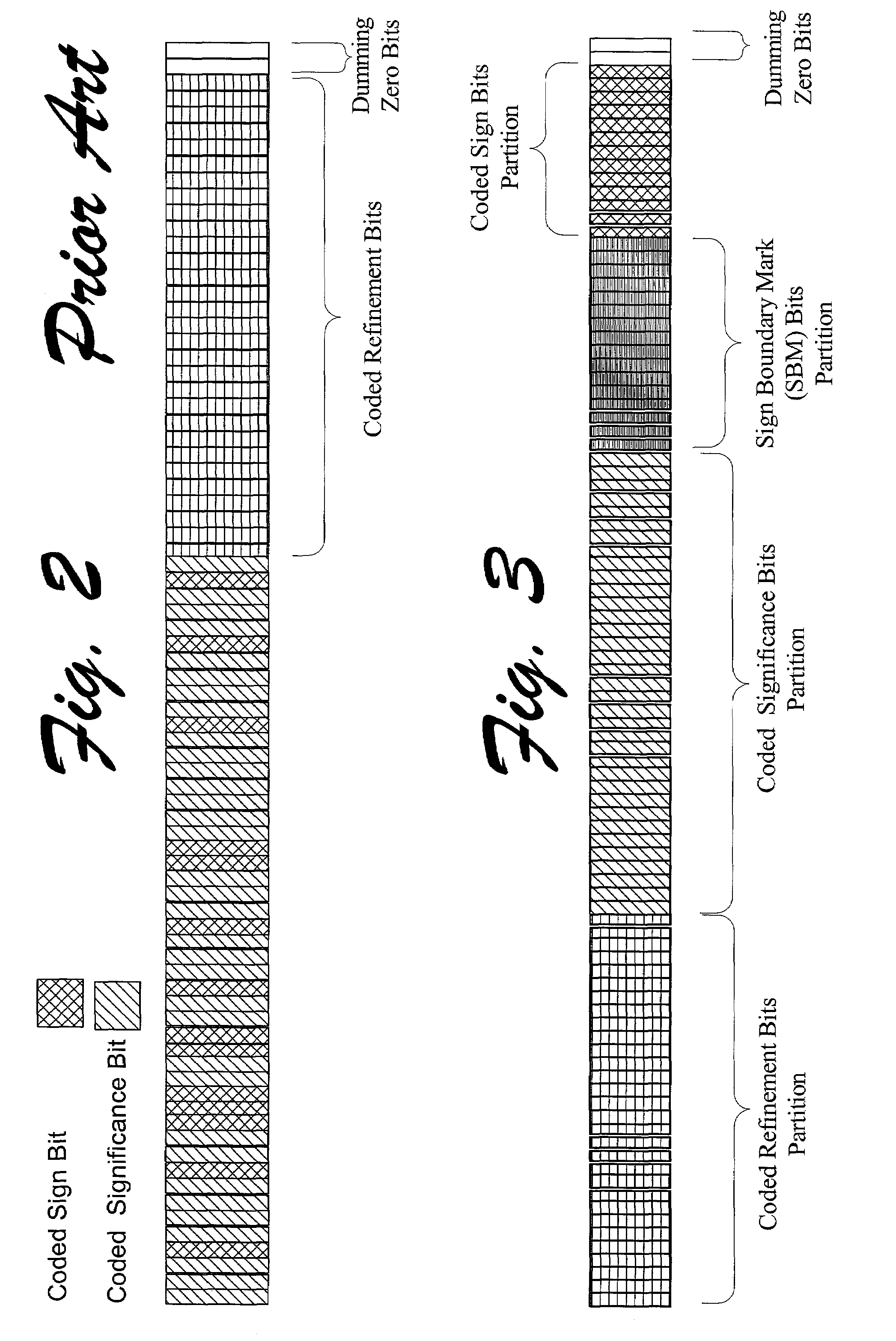

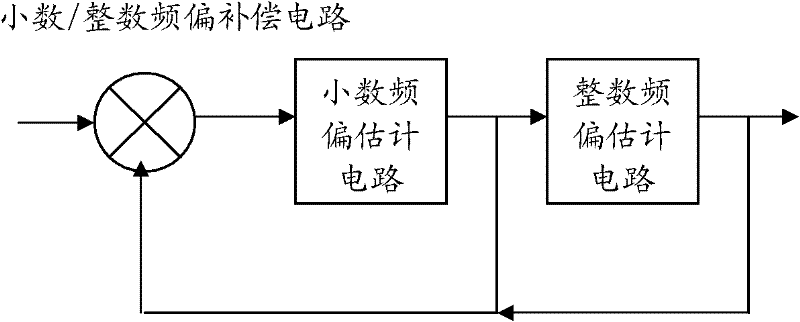

Error resilient scalable audio coding

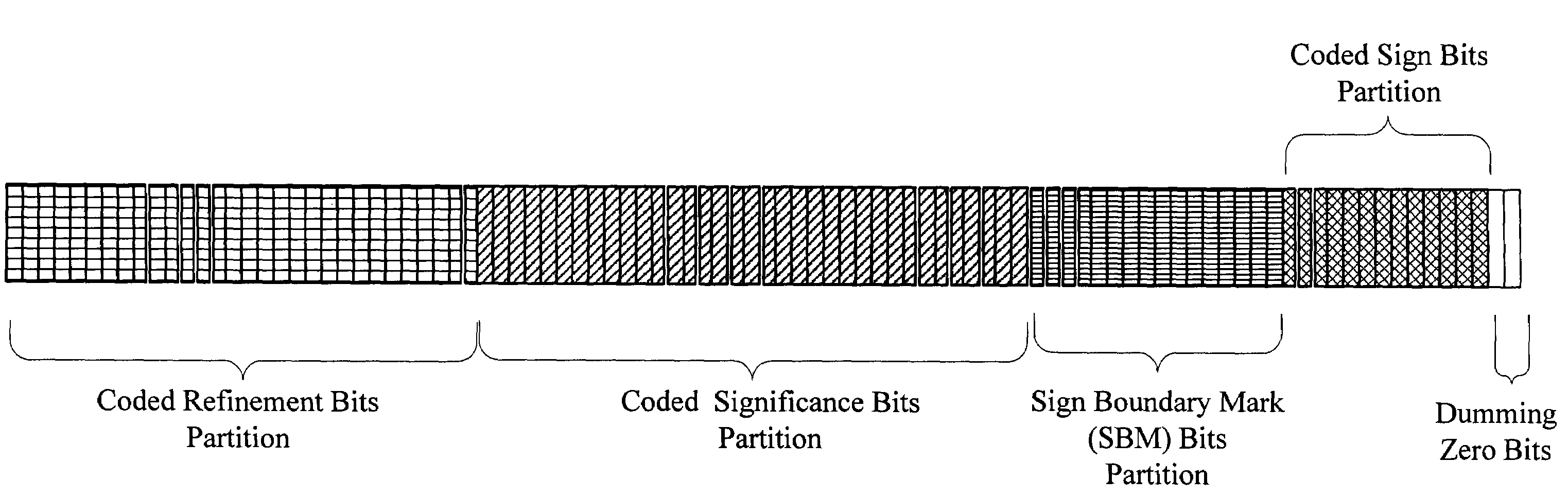

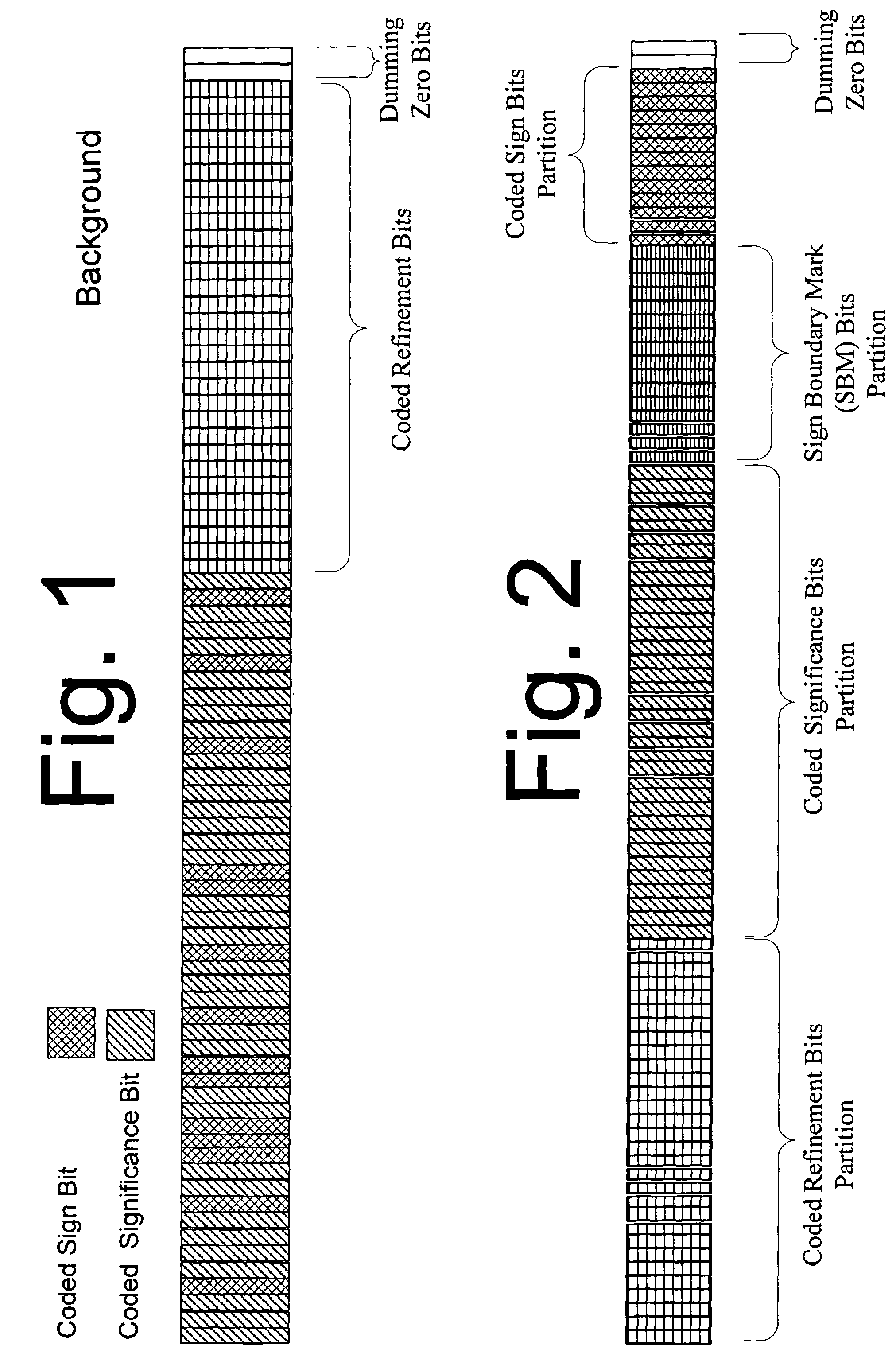

A scalable audio codec processes, quantizes and encodes audio signals into an embedded audio bitstream of bit-planes each having a data unit. The data unit has a beginning refinement bits partition, a second significance bits partition, a third sign boundary mark bits partition, and a fourth sign bits partition. The second and fourth partitions form a boundary for the third partition. The quantizing uses a variable length coding algorithm. The third partition is an invalid codeword for a predetermined encoding method being used to encode. The codec uses a decoder to decode the embedded audio bitstream of bit-planes using Reversible exponential Golomb (Exp-Golomb) codes in a Reversible Variable Length Code (RVLC) algorithm to produce quantized data of weighted subbands. An inverse quantizer dequantizes the quantized data into audio signals.

Owner:MICROSOFT TECH LICENSING LLC

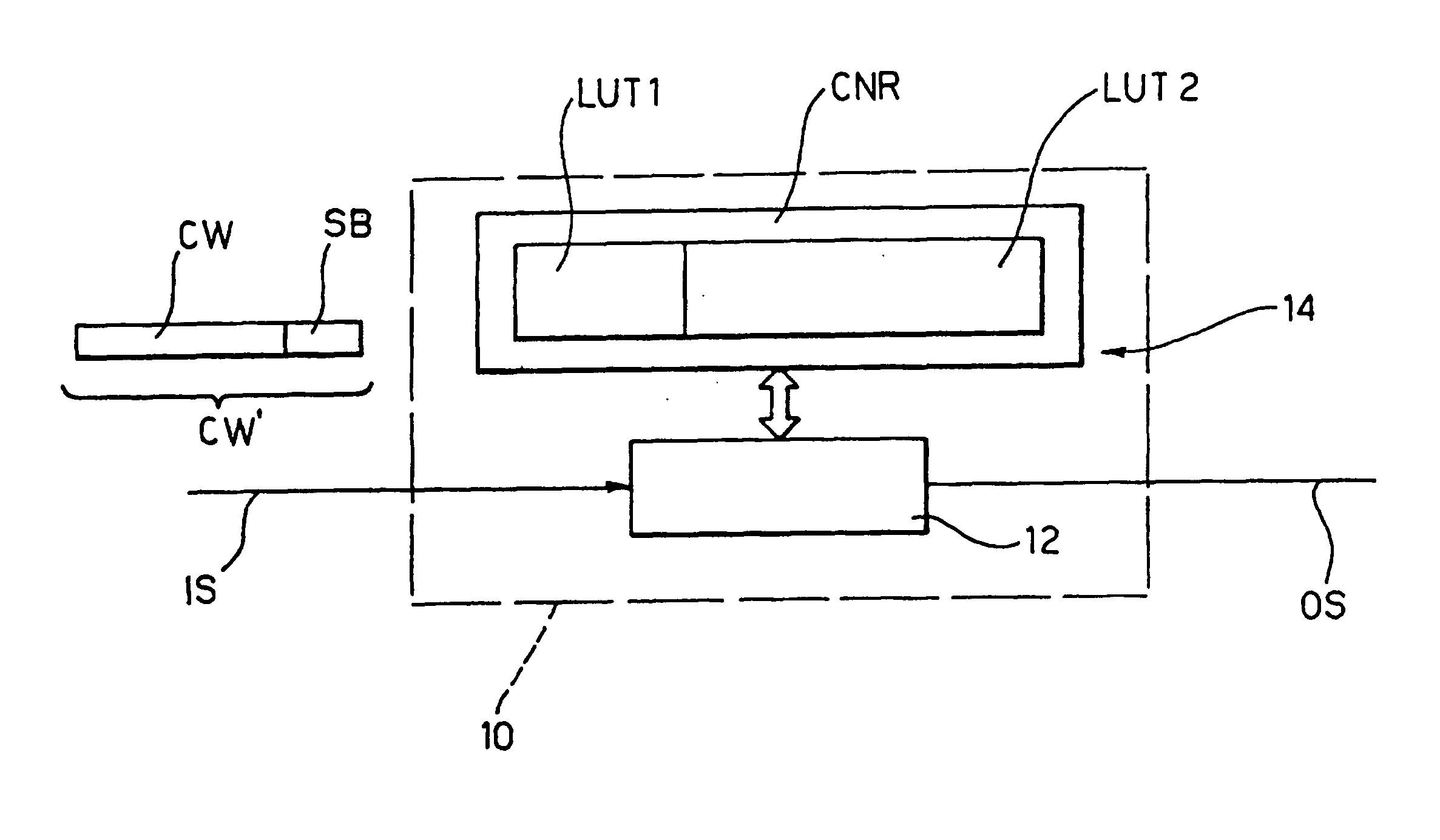

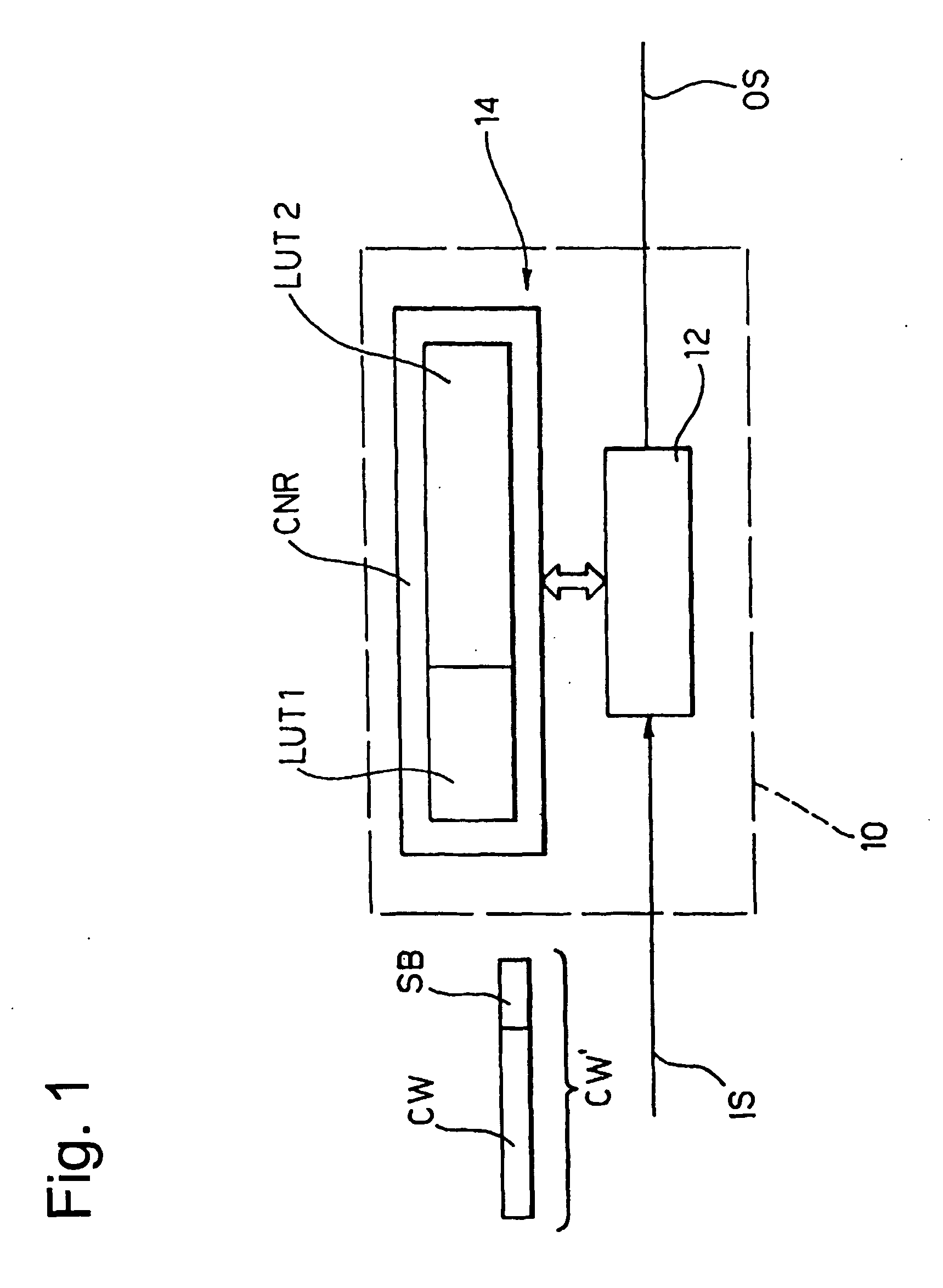

Method and system for decoding variable length encoded signals, computer program product therefor

InactiveUS20070057825A1Down decoding processHeavy memory requirementCode conversionTelevision systemsComputer hardwareVariable-length code

A system adapted for use, e.g. in an MPEG audio-video decoder for decoding variable-length (e.g. Huffman) encoded codewords, each having associated a respective set of sign bits. The system operates on the basis of a signed decoding codebook including extended signed codewords. Each extended codeword includes a respective codeword in the original codebook plus the associated set of sign bits. The variable-length encoded codewords are decoded on the basis of the signed decoding codebook, whereby the codewords are decoded together with the sign bit set associated therewith. Preferably, the codewords are partitioned in “short” and “long” codewords with respect to a given threshold. The short codewords are decoded by means of a single lookup step in a first lookup table. The long words are decoded by means of a multi-step lookup process involving at least one second lookup table. The lookup tables are preferably arranged as nested lookup tables within a container table.

Owner:TELECOM ITALIA SPA

Data processing method, circuit, and apparatus with increased accuracy

InactiveUS20030110444A1More accuracyMore simplicityTelevision system detailsDigital computer detailsData miningComputer science

In a data processing method of converting (nxm-1)-bit data to multi-level data of m symbols of n bits per symbol, n and m being integers satisfying n>=2 and m>=2, respectively, the m symbols each comprising n-bit data are arranged in m columns in an nxm matrix, with a value of each of the m symbols being set to an even or odd number, by creating the m symbols each including (n-1)-bit data of the (nxm-1)-bit data, arranging the m symbols in the m columns so that the {(n-1)xm}-bit data is arranged in upper-side {(n-1)xm} bits of the nxm matrix, and converting the remaining (m-1)-bit data of the (nxm-1)-bit data to m-bit data so that the m-bit data is arranged in a row in lower-side m bits of the nxm matrix.

Owner:RICOH KK

Decoding apparatus and decoding method, and data receiving apparatus and data receiving method

InactiveUS6904555B2Improve error correction performanceGeneration of error can be suppressedError prevention/detection by using return channelTelevision system detailsDecoding methodsComputer hardware

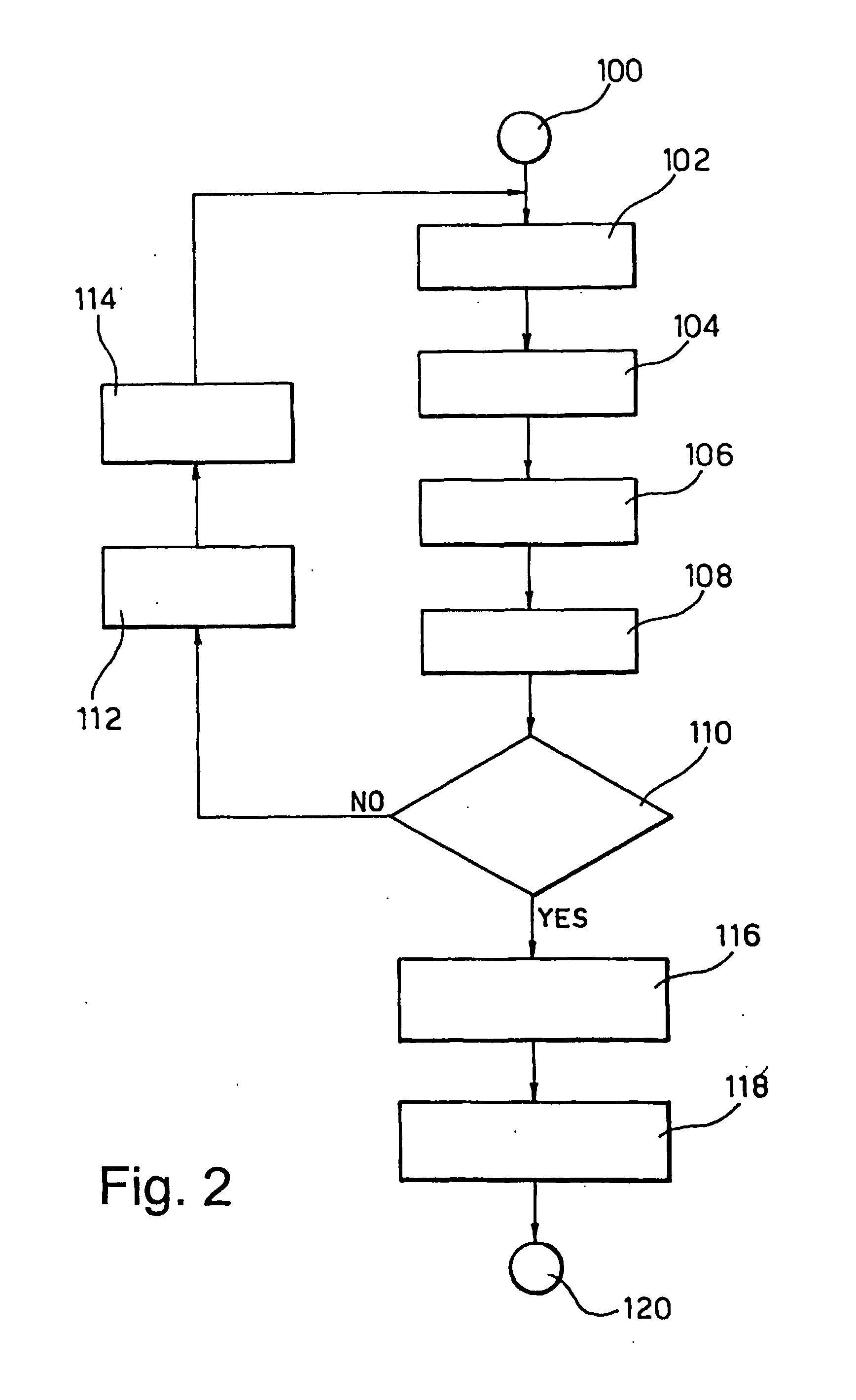

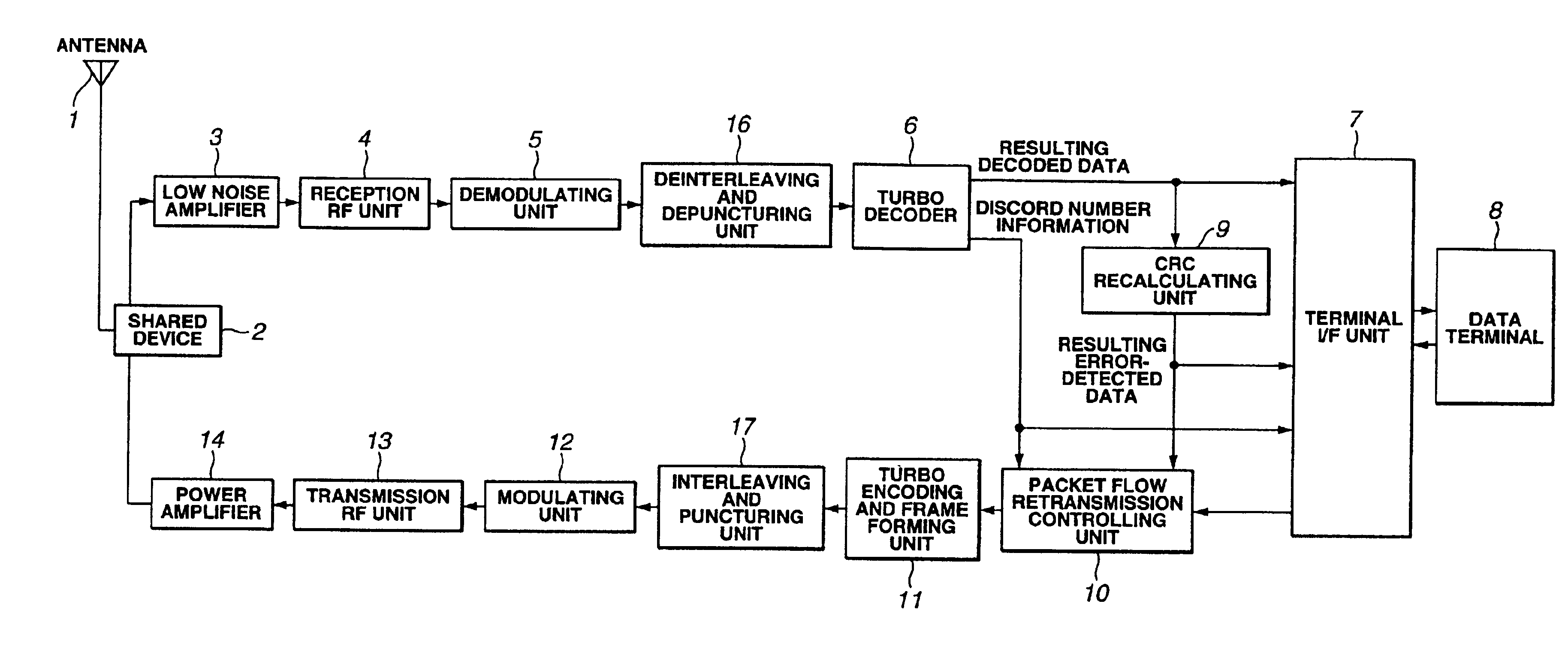

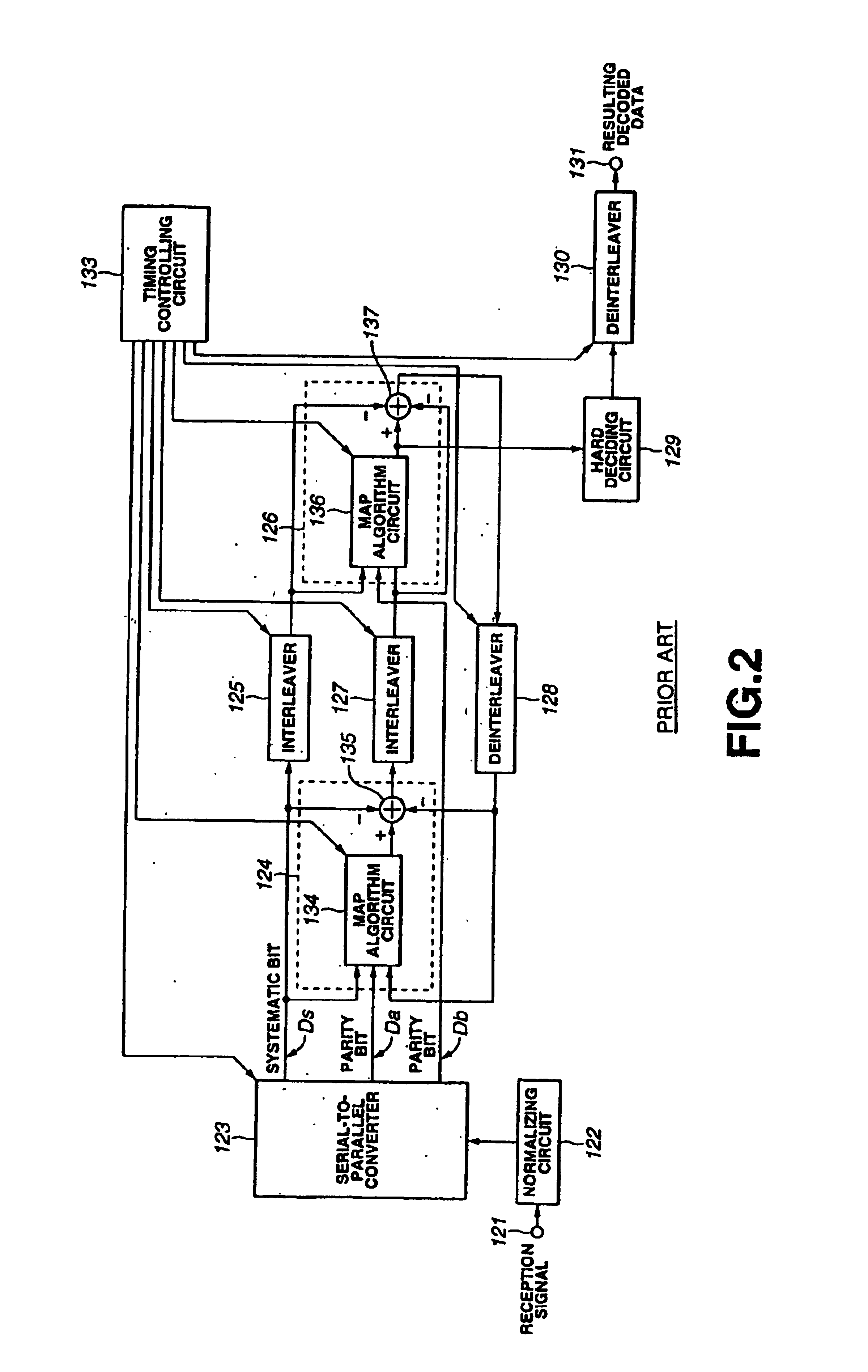

Removing adverse effects in case error detection using error detection codes cannot be performed correctly, and improving the data transmission efficiency. The turbo decoder 6 compares data which is decoded this time with data which is decoded previous time, both of which are decoded in repetitive decoding processing, to obtain discord number information indicative of the number of discordant sign bits, and sends the information to a terminal I / F unit 7 and a packet flow retransmission controlling unit 10. Even though it is determined that error detection result from a CRC recalculating unit 9 shows that there exists no bit error, in case the number of discordant sign bits is larger than a predetermined threshold value, it is determined that there is generated error. And, a packet flow retransmission controlling unit 10 sends a signal requesting retransmission of data. Furthermore, data amount to be retransmitted is varied in accordance with the number of discordant sign bits to improve the data transmission efficiency.

Owner:SONY CORP

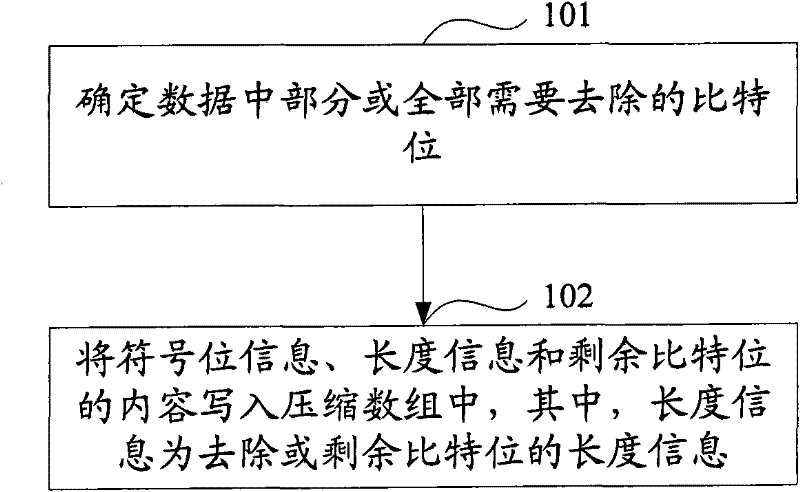

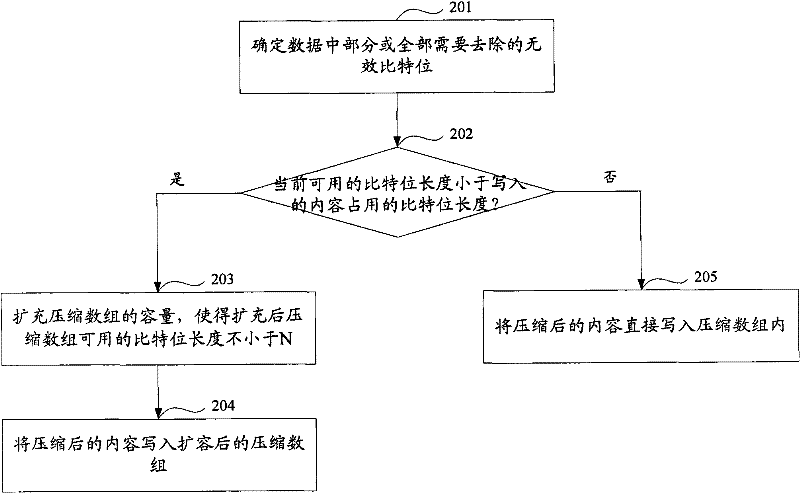

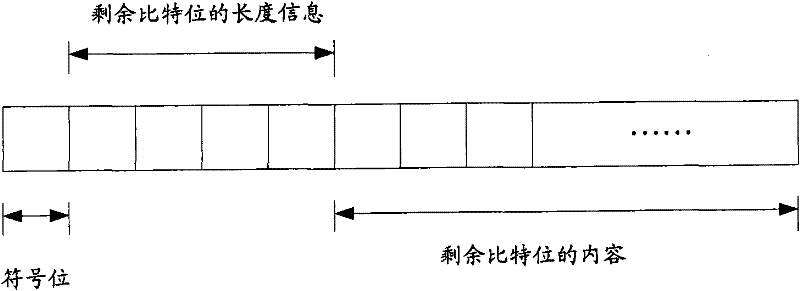

Data compression and decompression method and equipment

ActiveCN102457283AImprove compression efficiencySmall footprintCode conversionData compressionComputer hardware

The application discloses a data compression and decompression method and equipment. The data compression and decompression method comprises the following step that: when data is compressed, part or the whole of invalid bits in the data are removed, the content, the length information and the sign bits of the rest of bits are only written into the compressed data to be stored and transmitted. According to the scheme of the application, as the whole invalid bits of the data do not need to be stored, the occupied space of the stored data can be reduced, further, the data compression efficiency is higher, and the quantity of the stored and transmitted data can be reduced.

Owner:TAOBAO CHINA SOFTWARE

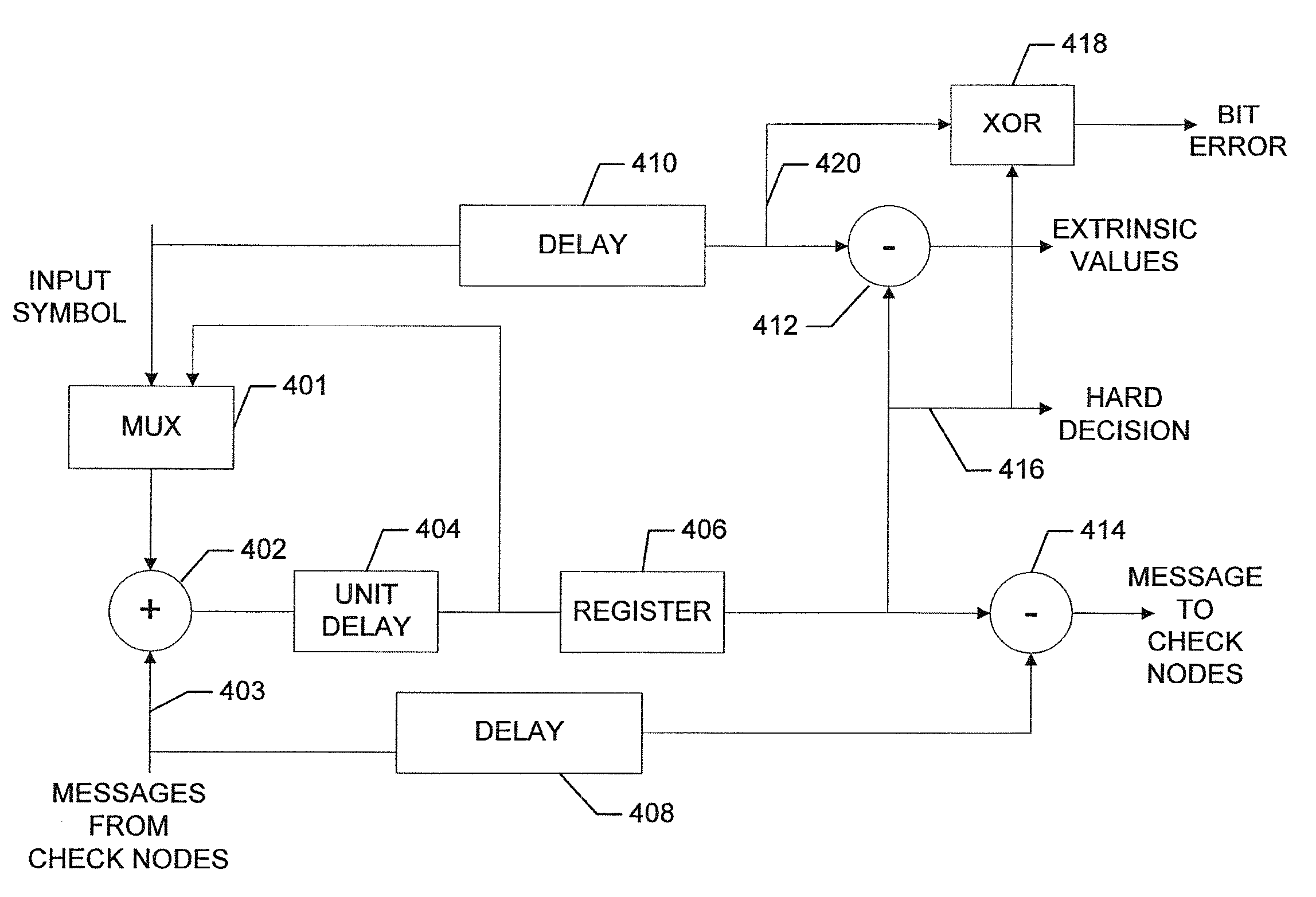

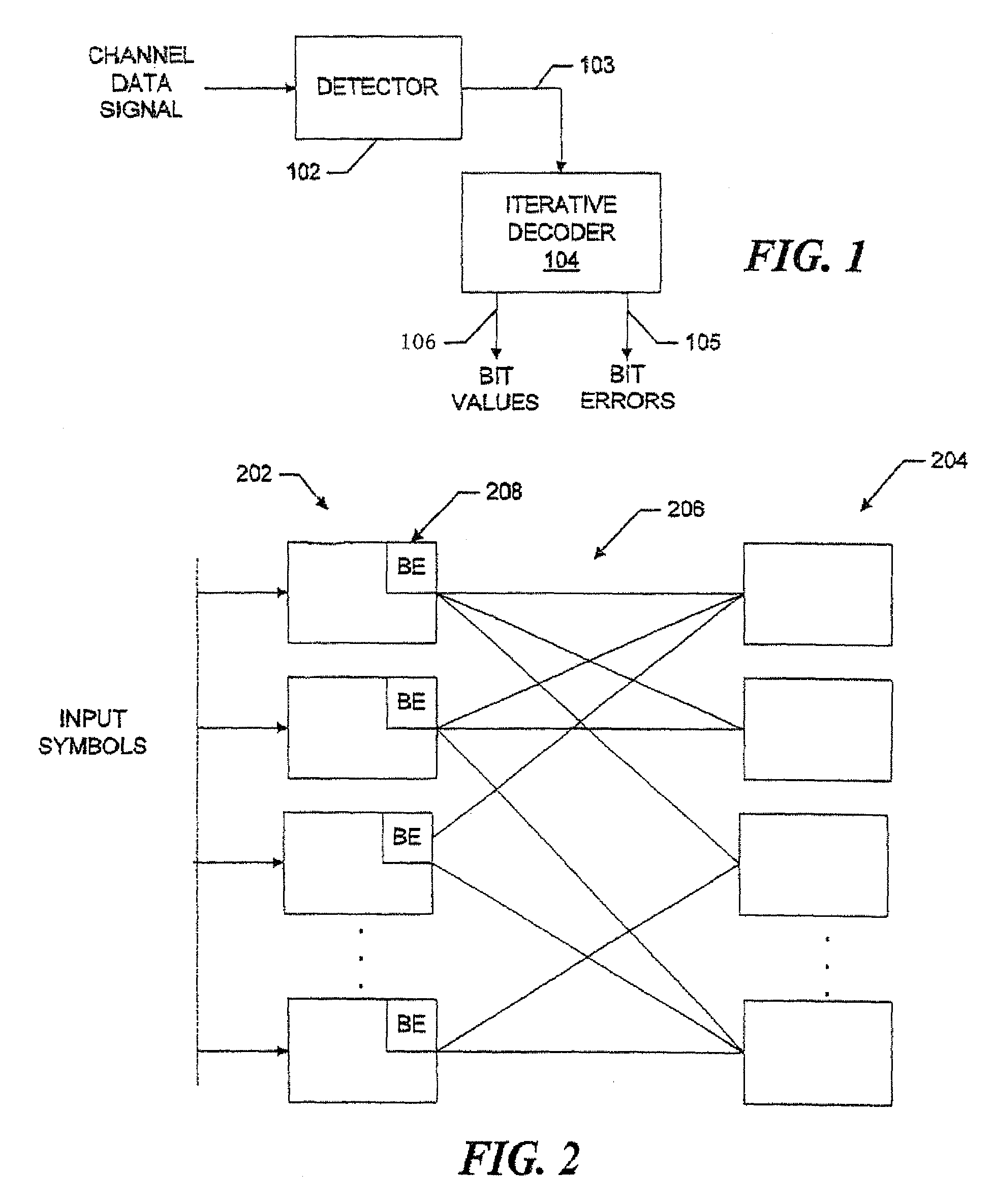

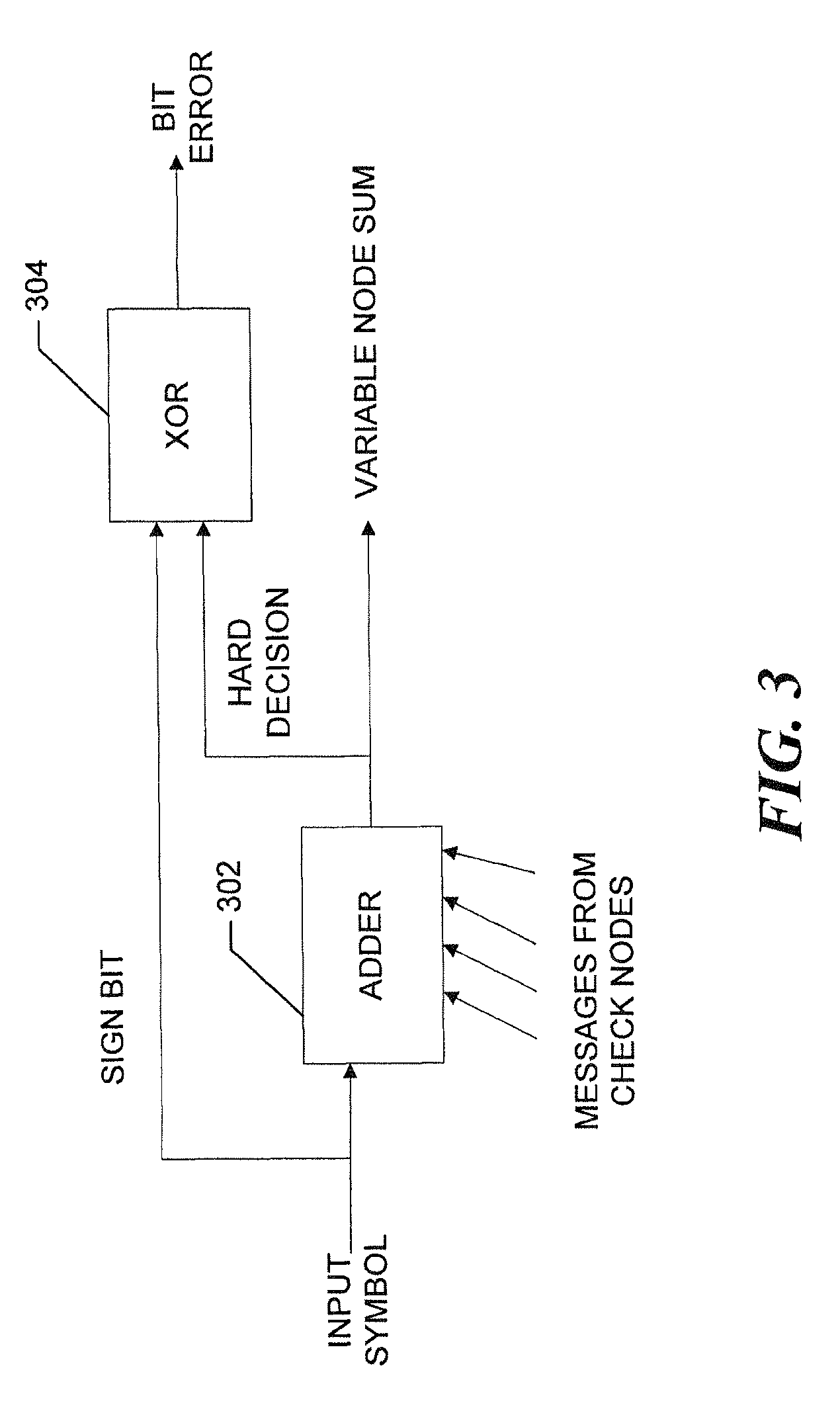

Bit error detector for iterative ECC decoder

Owner:SEAGATE TECH LLC

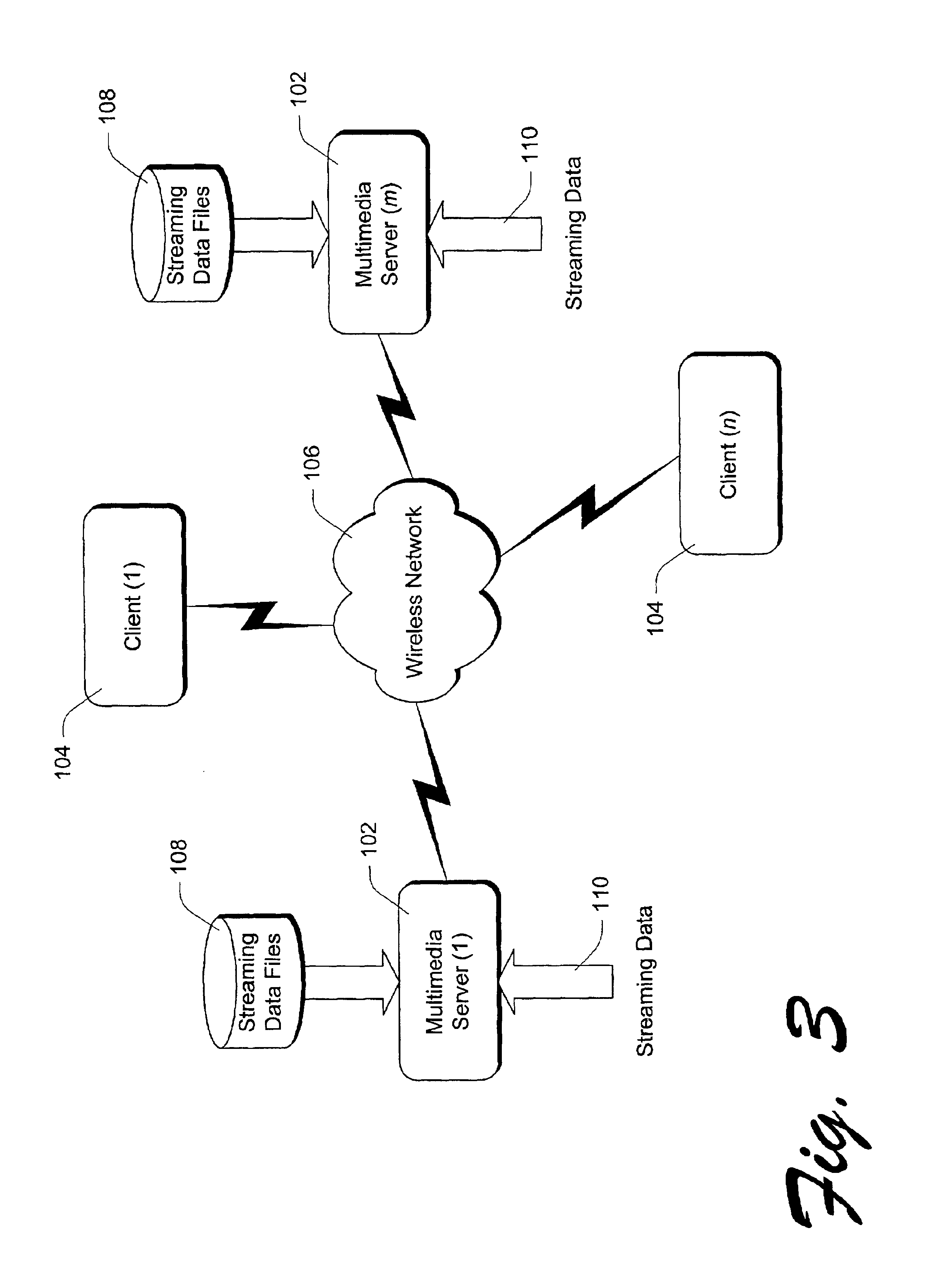

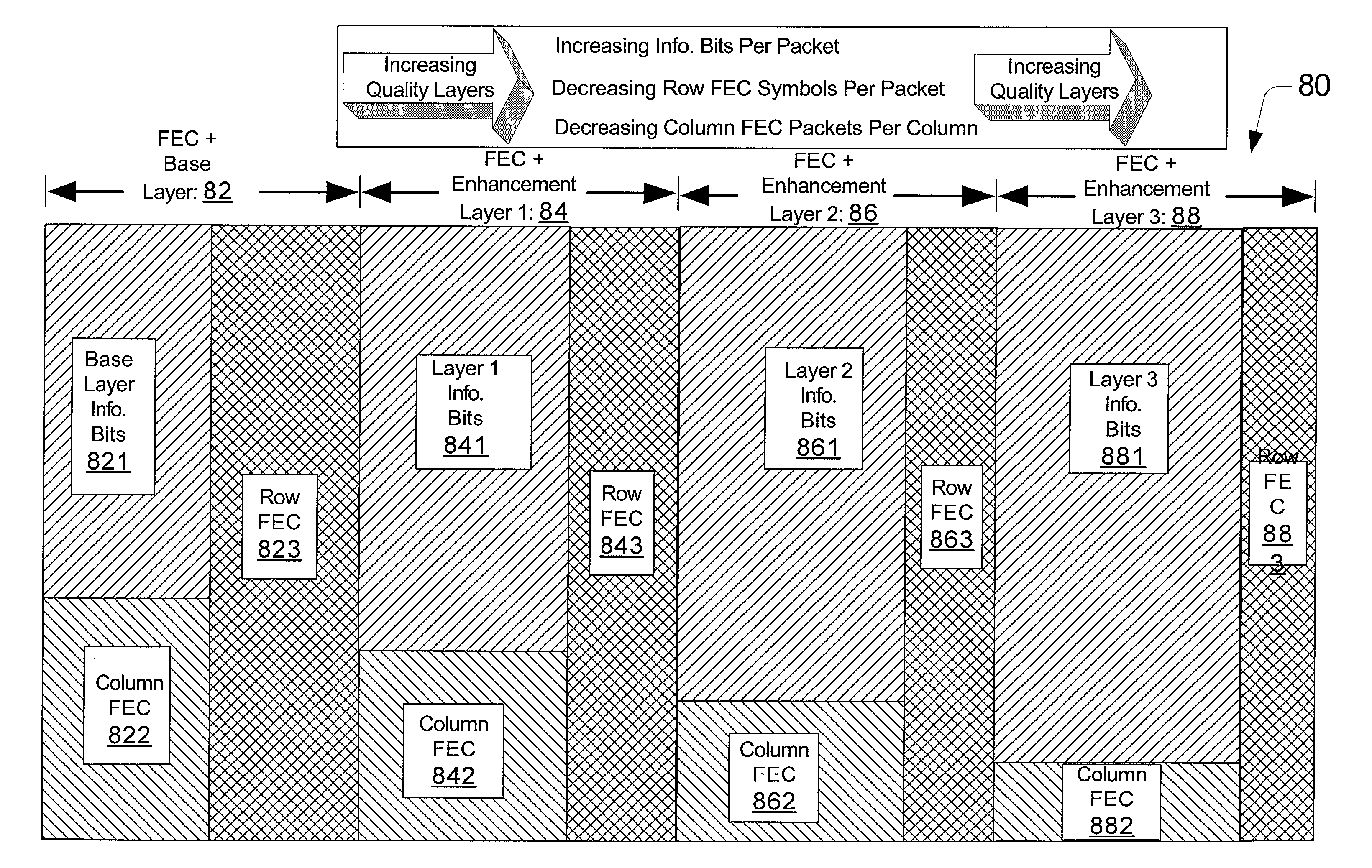

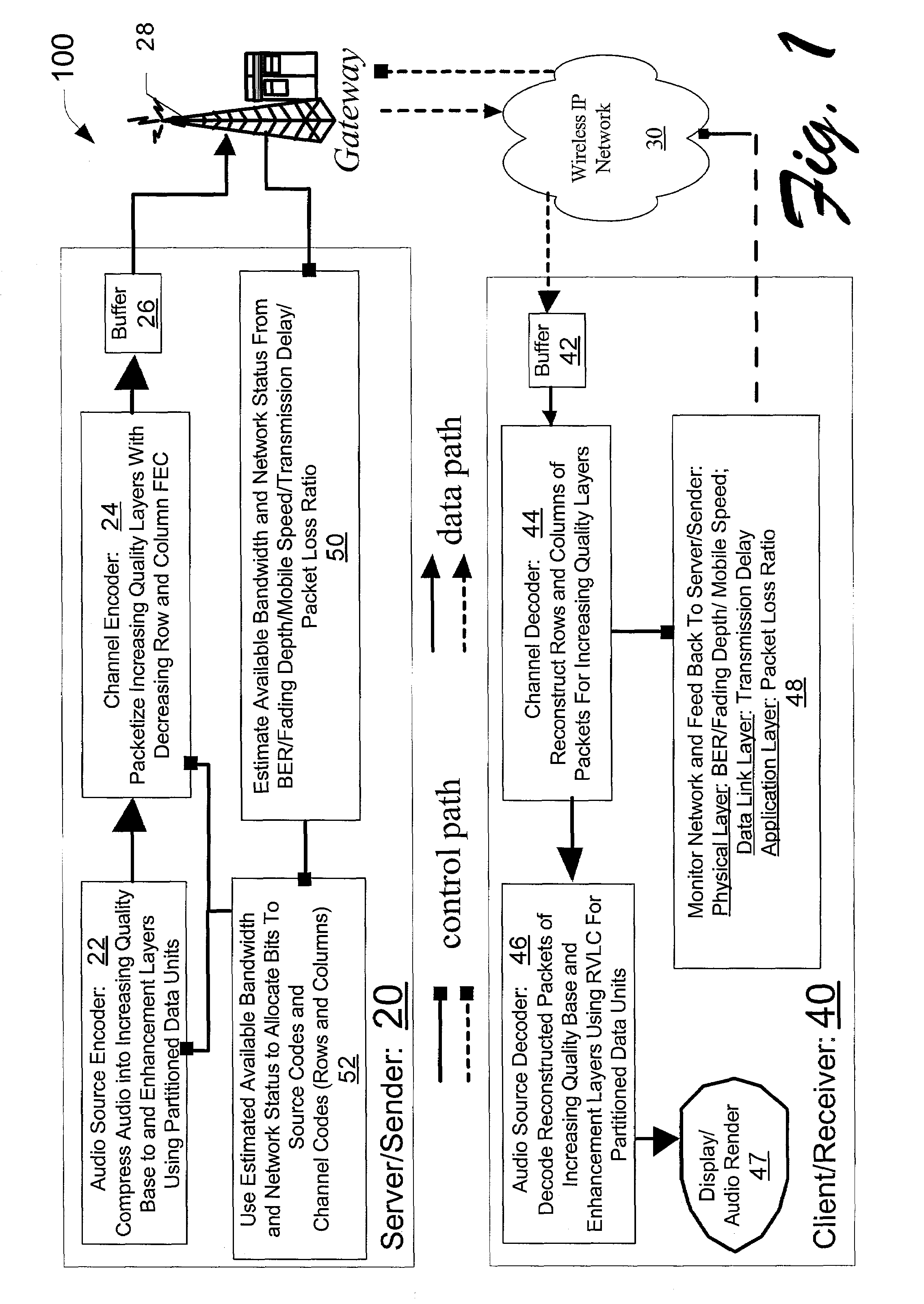

Scalable audio communications utilizing rate-distortion based end-to-end bit allocation

InactiveUS7283966B2Minimize expected end-to-end distortionImprove scalabilitySpeech analysisSign bitBit allocation

A source encoder encodes audio signals into increasing quality layers defined in bit planes. Each bit plane has a data unit that includes a beginning partition having one or more contiguous refinement bits, a second partition having one or more contiguous coded significance bits, a third partition having one or more contiguous sign boundary mark bits, and a fourth partition having one or more contiguous coded sign bits. A channel encoder encodes the bit planes into respective columns containing multiple rows. Unequal error protection coding is provided according to the quality of each layer such that each row has row and column channel protection codes for the respective row and column that correspond to the respective quality layer. For the corresponding row and column, each row contains the row channel protection codes and either the compressed audio data from the respective layer or the column channel protection codes. A server machine can use a network feedback transmission to allocate bits to the source encoder and the channel encoder.

Owner:MICROSOFT TECH LICENSING LLC

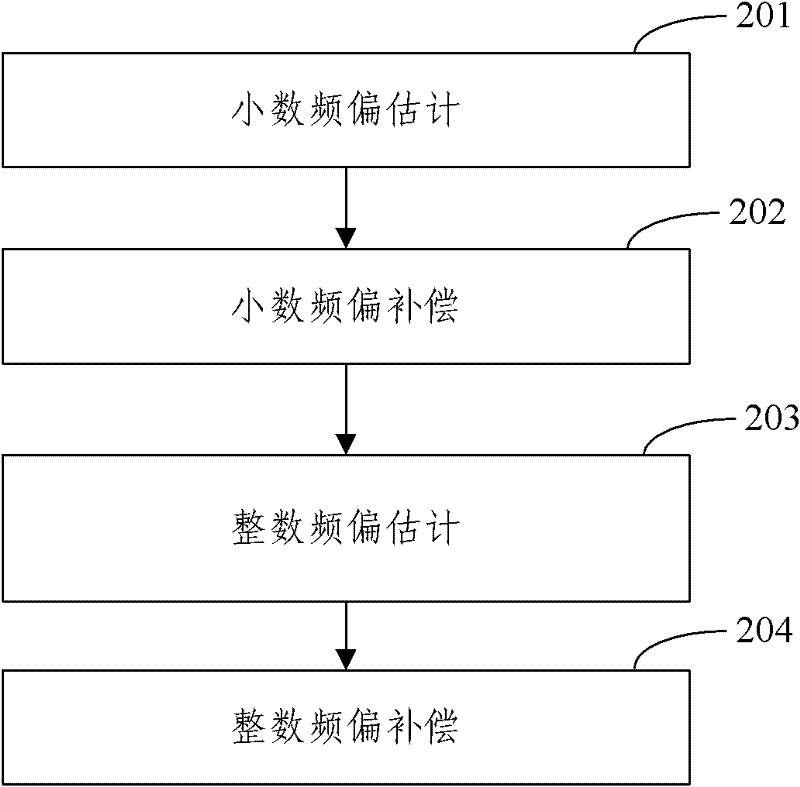

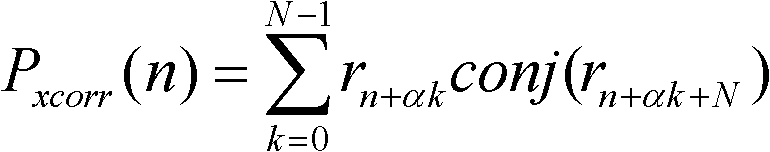

Carrier frequency synchronous circuit and method of OFDM (Orthogonal Frequency Division Multiplexing) system

ActiveCN102480452AReduce overheadSmall amount of calculationMulti-frequency code systemsHigh energyFourier transform on finite groups

The invention discloses a carrier frequency synchronous circuit and method of an OFDM (Orthogonal Frequency Division Multiplexing) system. The carrier frequency synchronous circuit comprises a decimal fraction frequency offset estimation circuit, a decimal fraction frequency offset compensation circuit, an integer frequency offset estimation circuit, an integer frequency offset compensation circuit and other circuits; correspondingly, the method comprises the following steps of decimal fraction frequency offset estimation, decimal fraction frequency offset compensation, integer frequency offset estimation and integer frequency offset compensation; a cross-correlation value of two adjacent synchronous sequences to be sampled of a frequency domain is subjected to normalization treatment to obtain a decimal fraction frequency offset estimation value, and decimal fraction frequency offset compensation correction is carried out by utilizing the estimation value; then, the high energy carrier sign bit of each OFDM sign subjected to fast Fourier transform (FFT) treatment is subjected to self-correlation computation, the self-correlation of a plurality of OFDM signs is subjected to summation computation to obtain an integer frequency offset estimation value, and then integer frequency offset compensation is carried out according to the integer frequency offset estimation value. By adopting the synchronous circuit and method, the computational burden can be reduced, the influence of noise to frequency offset estimation can be lowered, and low-power equipment is favorably designed and realized.

Owner:北京思凌科半导体技术有限公司

High speed divider and method thereof for implementing high speed division arithmetic

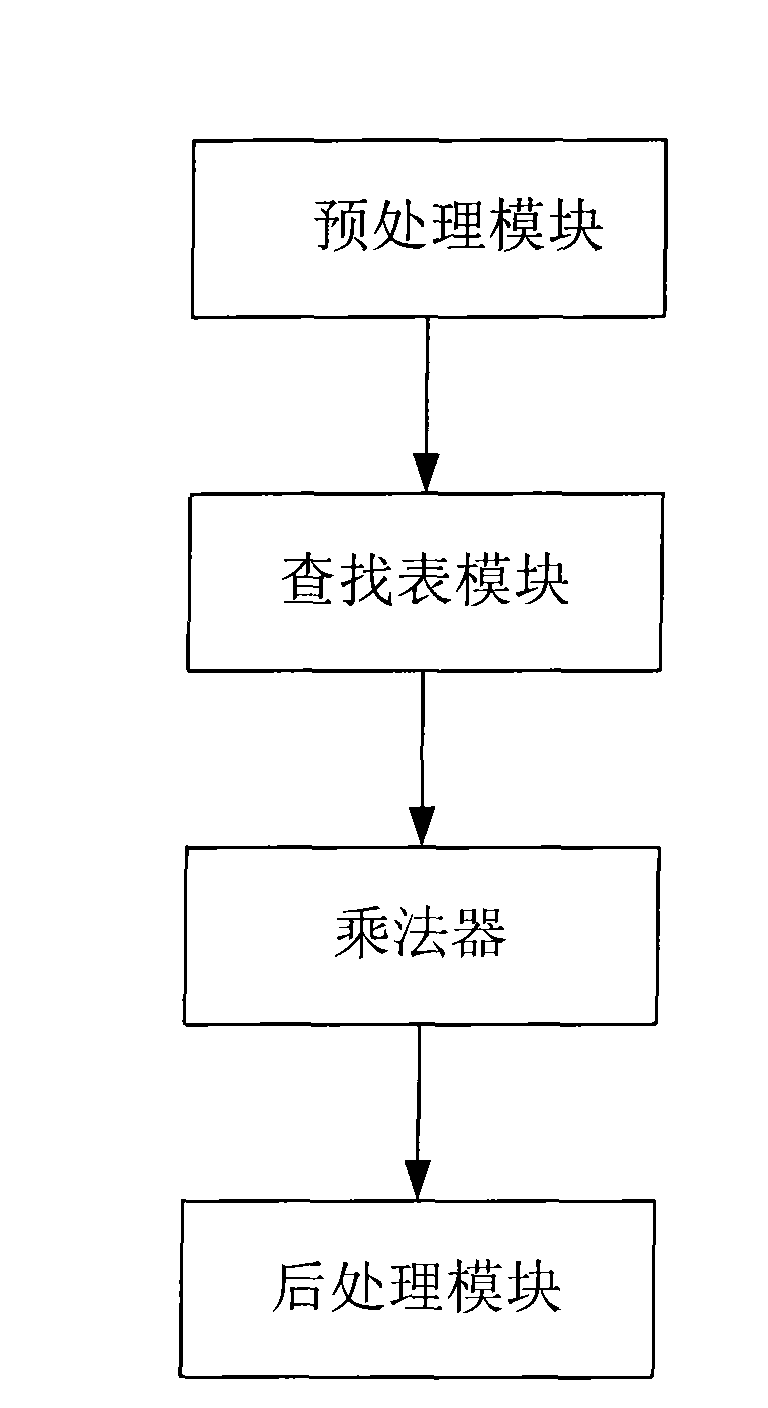

InactiveCN101493760AMeet the requirements of various applicationsReduce clock cyclesComputation using non-contact making devicesCode conversionComputer engineering

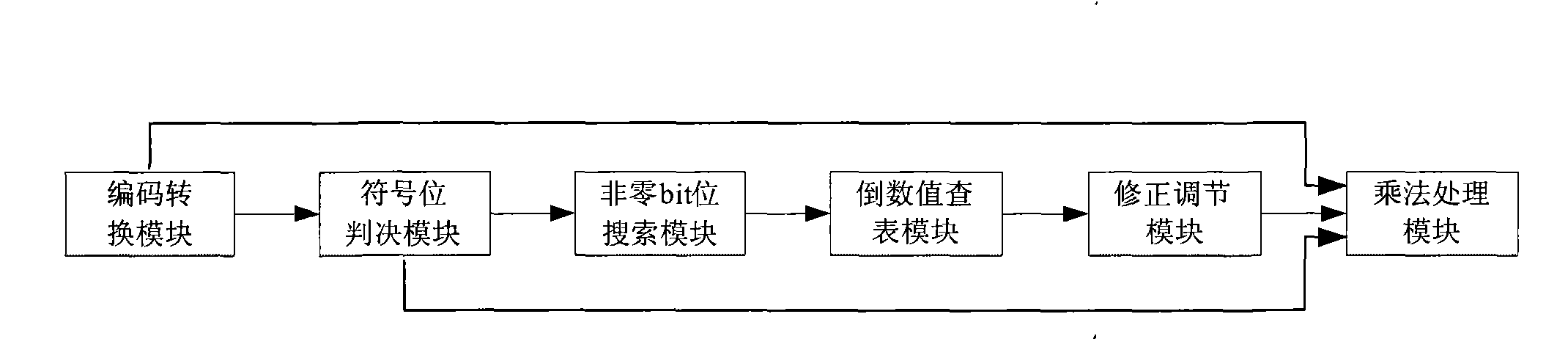

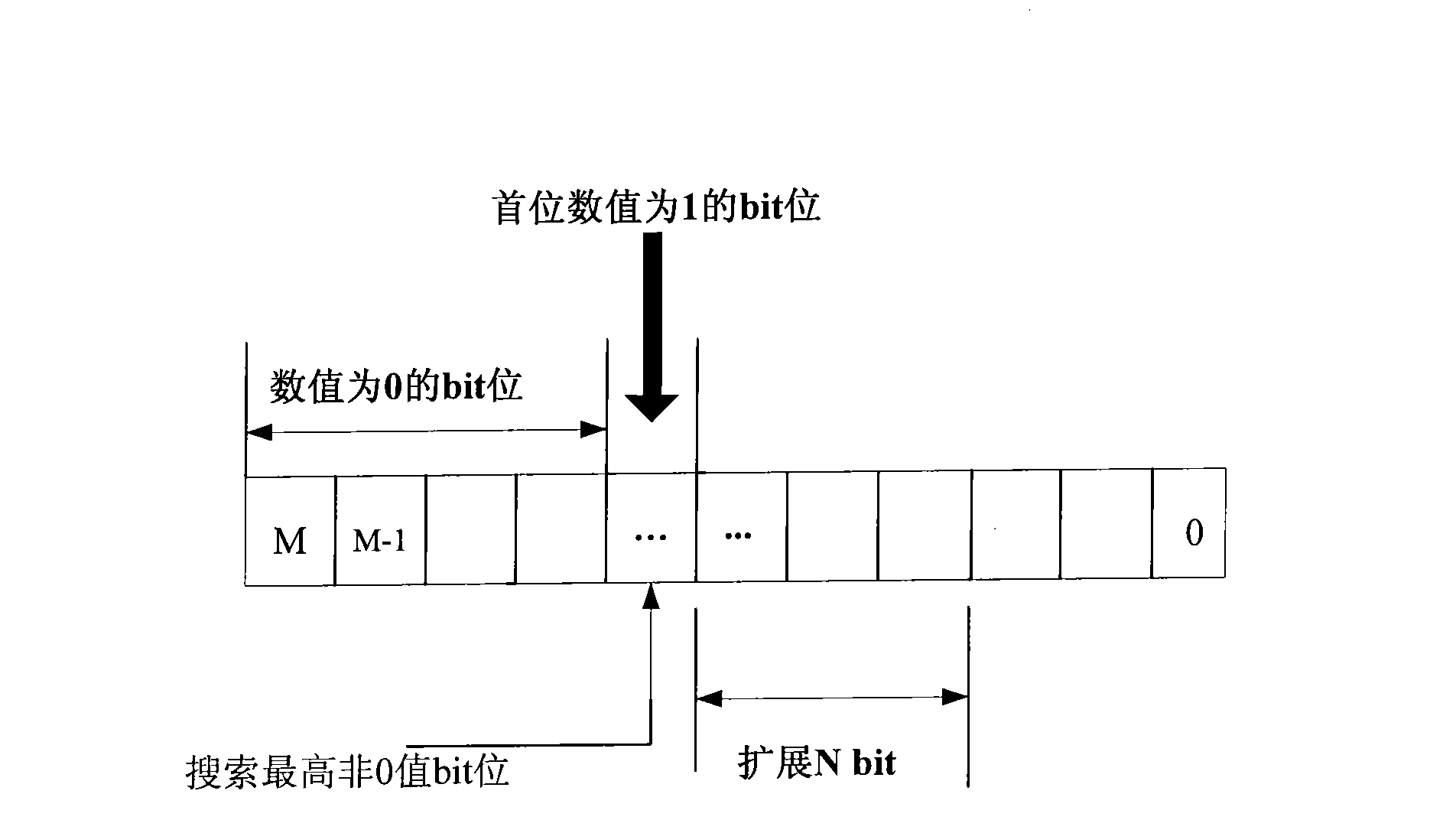

The invention provides a high-speed divider comprising a coded conversion module, a sign bit decision module, a nonzero bit search module, a reciprocal value lookup module, a correction adjusting module and a multiplication processing module. The coded conversion module is sequentially connected with the sign bit decision module, the nonzero bit search module, the reciprocal value lookup module, the correction adjusting module and the multiplication processing module; the coded conversion module, the sign bit decision module are respectively connected with the multiplication processing module; and the output end of the multiplication processing module outputs the results of division operation. The high-speed divider has controllable operation accuracy, not only can freely set the corresponding operation accuracy according to the actual application requirements, but also can be used for high-speed mathematical operation processing with short operation time and small processed delay, and has simple structure and good feasibility.

Owner:COMBA TELECOM SYST CHINA LTD

Divider and division operation method

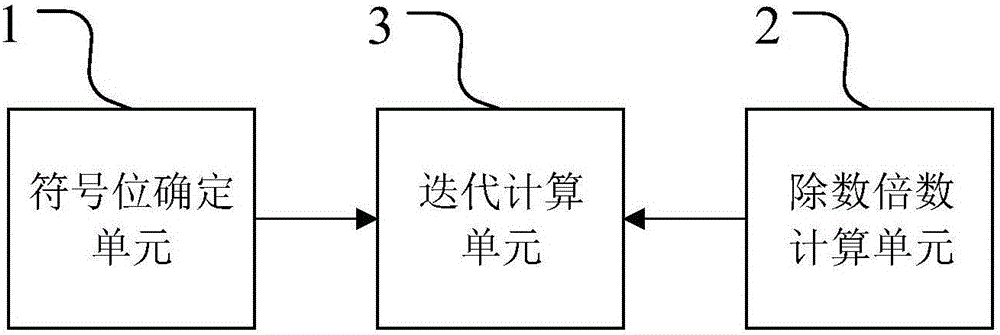

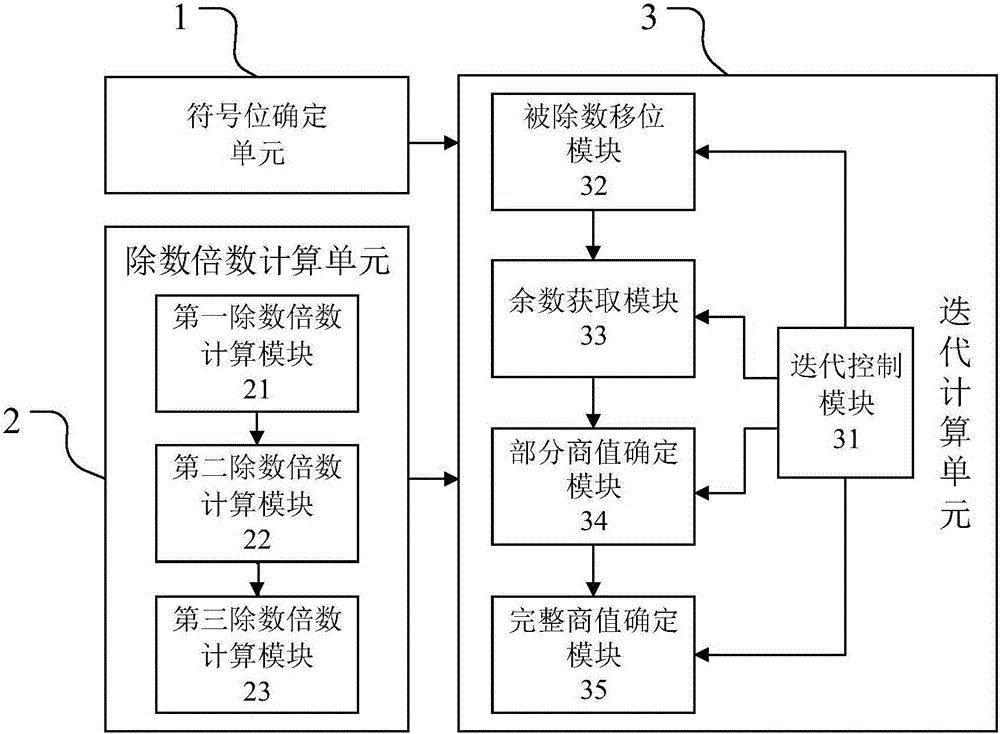

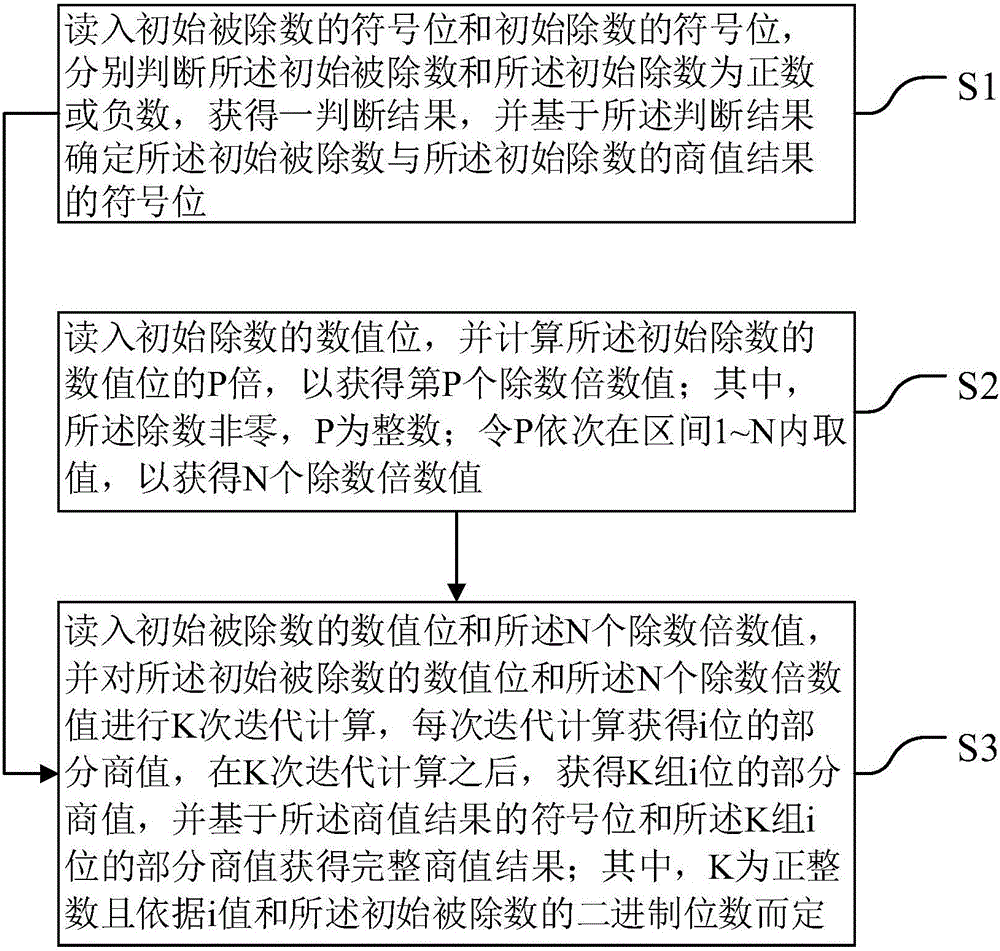

ActiveCN105955706AReduce computing timeDigital data processing detailsDigital signal processingSign bit

The invention discloses a divider and a divider operation method, and belongs to the technical field of the digital signal processing circuit. The divider adopts a cardinal number N algorithm, wherein N is 2i, i is a positive integer greater than or equal to 3, and the quotient of an initial dividend and an initial divisor is greater than or equal to -N or less than or equal to N. The divider comprises a sign bit determining unit (1), a divisor multiple calculation unit (2) and an iterative computation unit (3), wherein the sign bit determining unit (1) is used for judging the sign bit of a quotient result of the initial dividend and the initial divisor; the divisor multiple calculation unit (2) is used for calculating the P times of a numerical value bit of a non-zero initial divisor to obtain a Pth numerical value multiple value, wherein P takes an integral value successively in an interval 1-N so as to obtain N divisor multiple values; and the iterative computation unit (3) is used for carrying out K-time iterative computation on the numerical value bit of the initial dividend and N divisor multiple values to obtain an initial quotient value result. During the iterative computation of the divider, the bit of the quotient generated each time can be flexibly selected, and excessive hardware areas are not occupied while a quick operation is carried out.

Owner:WUHAN SYNTEK CO LTD

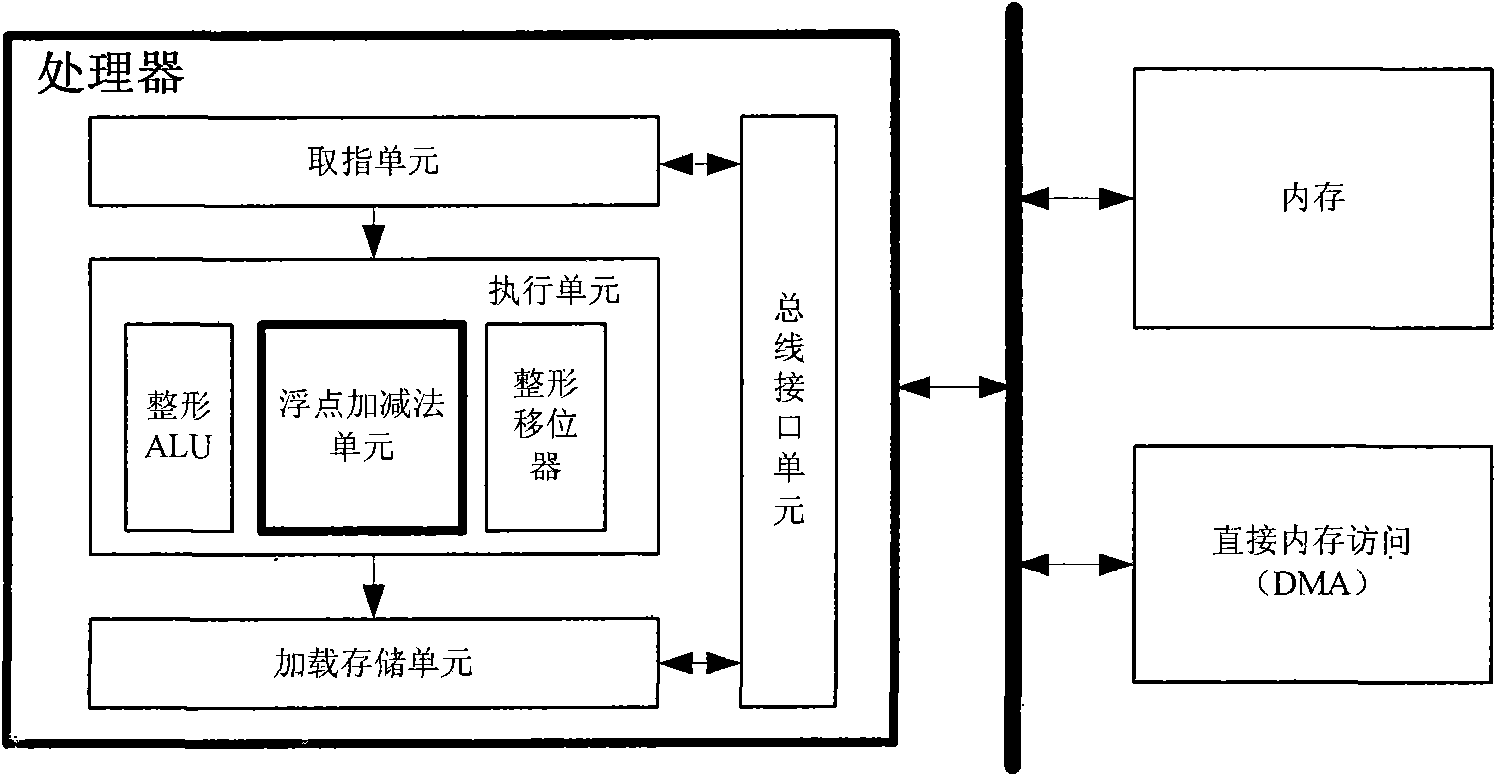

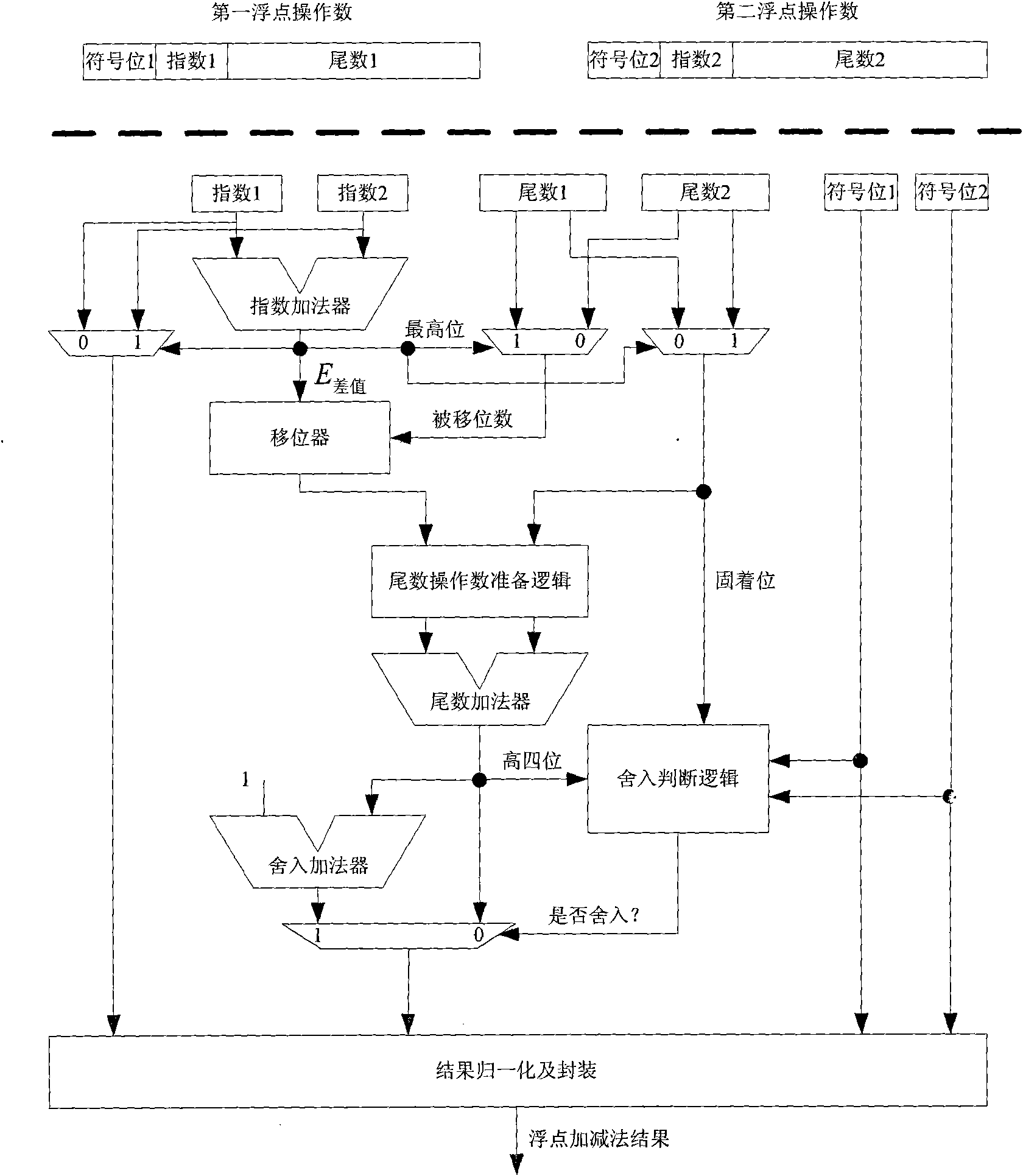

Floating point addition device based on complement rounding

InactiveCN101650642AAvoid preparationAvoid rounding judgment logicComputation using non-contact making devicesLogic complexityRounding

The invention relates to a floating point addition device based on complement rounding, which supports the floating point addition operation and the floating point subtraction operation. The floatingpoint addition device comprises an exponent adder, a mantissa shifter, a mantissa operand preparation logic unit, a mantissa adder, a rounding judgment logic unit and a rounding adder, wherein the mantissa operand preparation logic unit is used for processing the mantissa operand according to sign bits and the exponent difference of the first floating point operand and the second floating point operand, the rounding judgment logic unit is used for executing the uniform rounding judgment on a mantissa addition result, judging the positive and the negative of the mantissa sum according to the highest bit output by the mantissa adder, determining a constant bit for the rounding judgment according to the highest four bits output by the mantissa adder, and unifying original code rounding plus 1judgment logic and complement rounding plus 0 judgment logic; and the rounding adder is used for rounding the mantissa addition result of the floating point and finishing the code extraction and complement operation to the mantissa sum. The invention has the uniform mechanism, avoids the special complex mantissa operand preparation and rounding judgment logic of the floating point addition, and reduces the logic complexity.

Owner:C SKY MICROSYST CO LTD

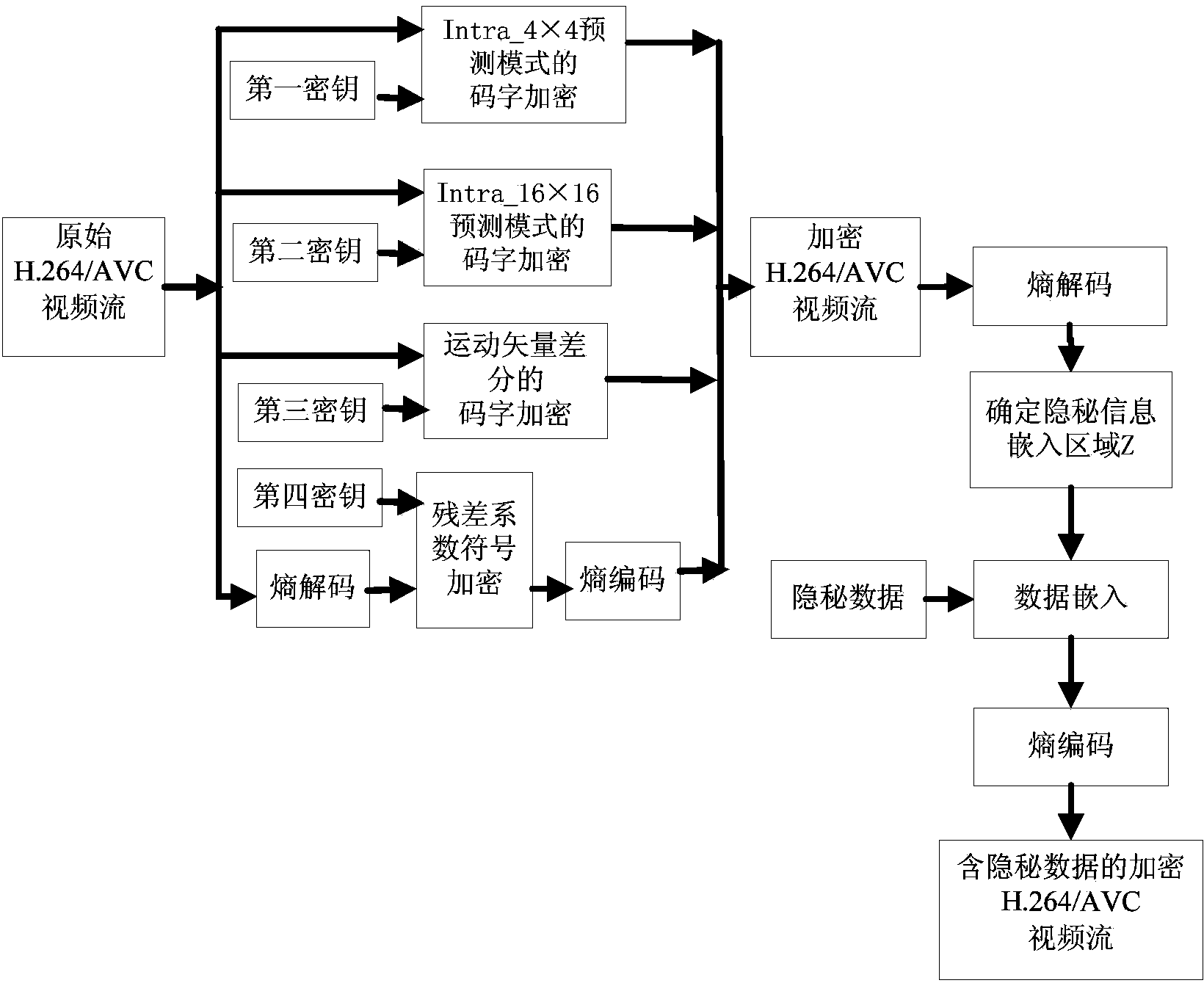

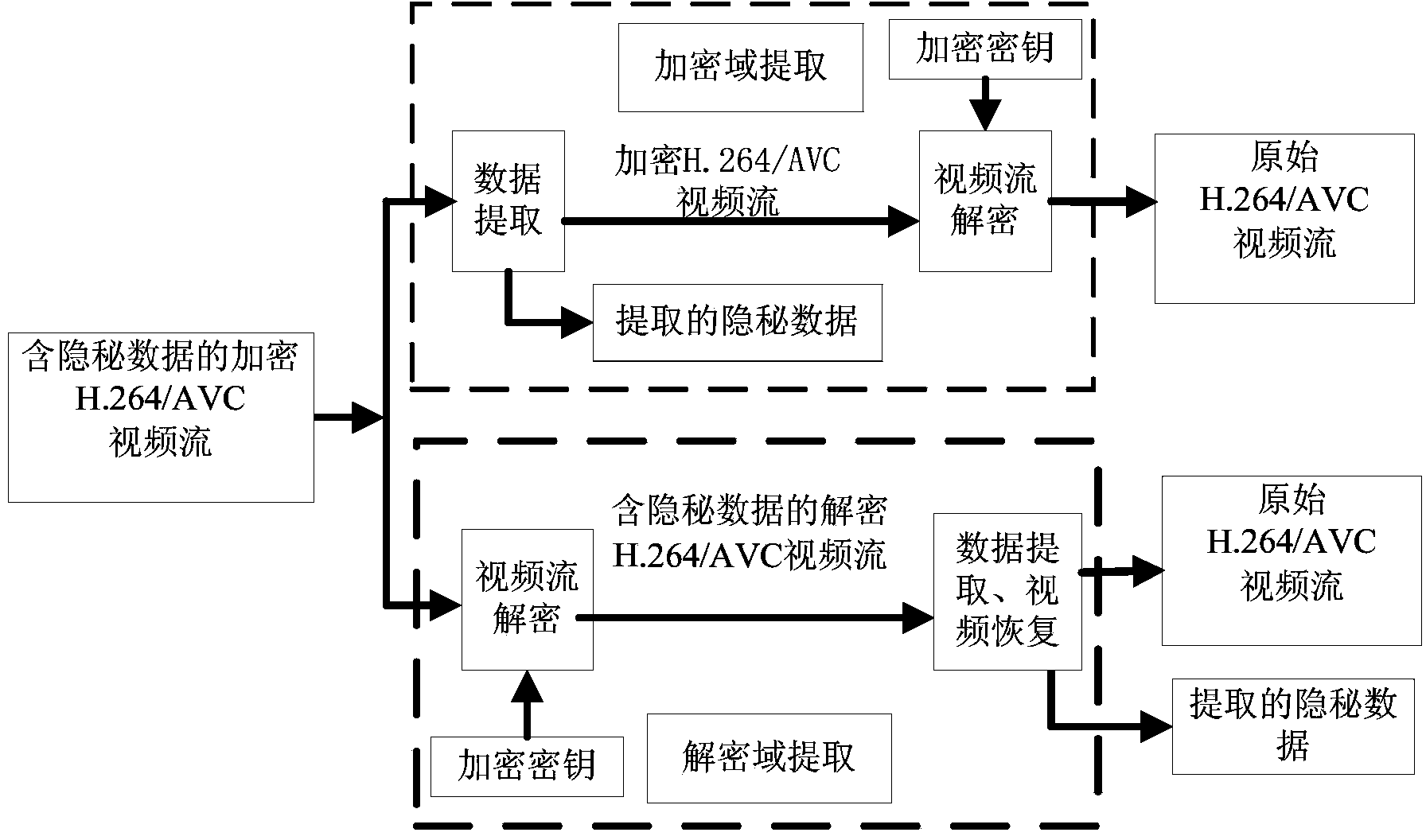

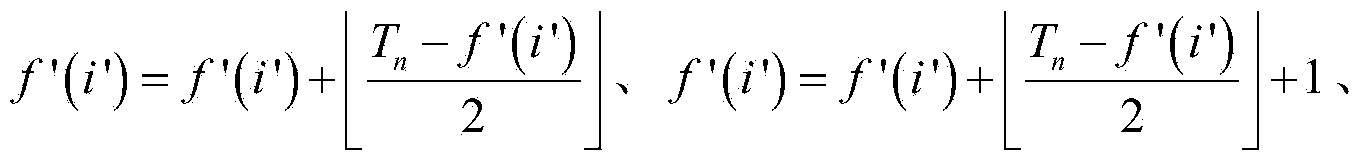

Encryption domain H.264/AVC video reversible data hiding method

ActiveCN103826128AMeet application needsLittle impact on code rateDigital video signal modificationComputation complexityData expansion

The invention discloses an encryption domain H.264 / AVC video reversible data hiding method. Under the premise that the encryption domain H.264 / AVC video reversible data hiding method is compatible with an H.264 / AVC video compressed encoding standard, code words of prediction modes, Exp-Golomb code words of motion vector difference and sign bits of residual error coefficients are selected to be encrypted, computation complexity is low, the application demands of real-time videos are met, and encryption safety is high. Meanwhile, influences of encryption on the code rate of code streams of H.264 / AVC videos are quite small, and the problem of data expansion in the video encryption process is solved. A data hiding person can embed private information in the H.264 / AVC videos of an encryption domain directly, and thus the problems of video content safety and privacy disclosure can be solved effectively. The hidden data can be extracted effectively from the encryption domain and can also be extracted effectively from a decryption domain, namely, data extraction and data decryption are separated completely, and practicality is high. In addition, the encryption domain H.264 / AVC video reversible data hiding method is completely revisable, and original videos can be restored without damage after the hidden information is decrypted and extracted.

Owner:NINGBO UNIVERSITY OF TECHNOLOGY

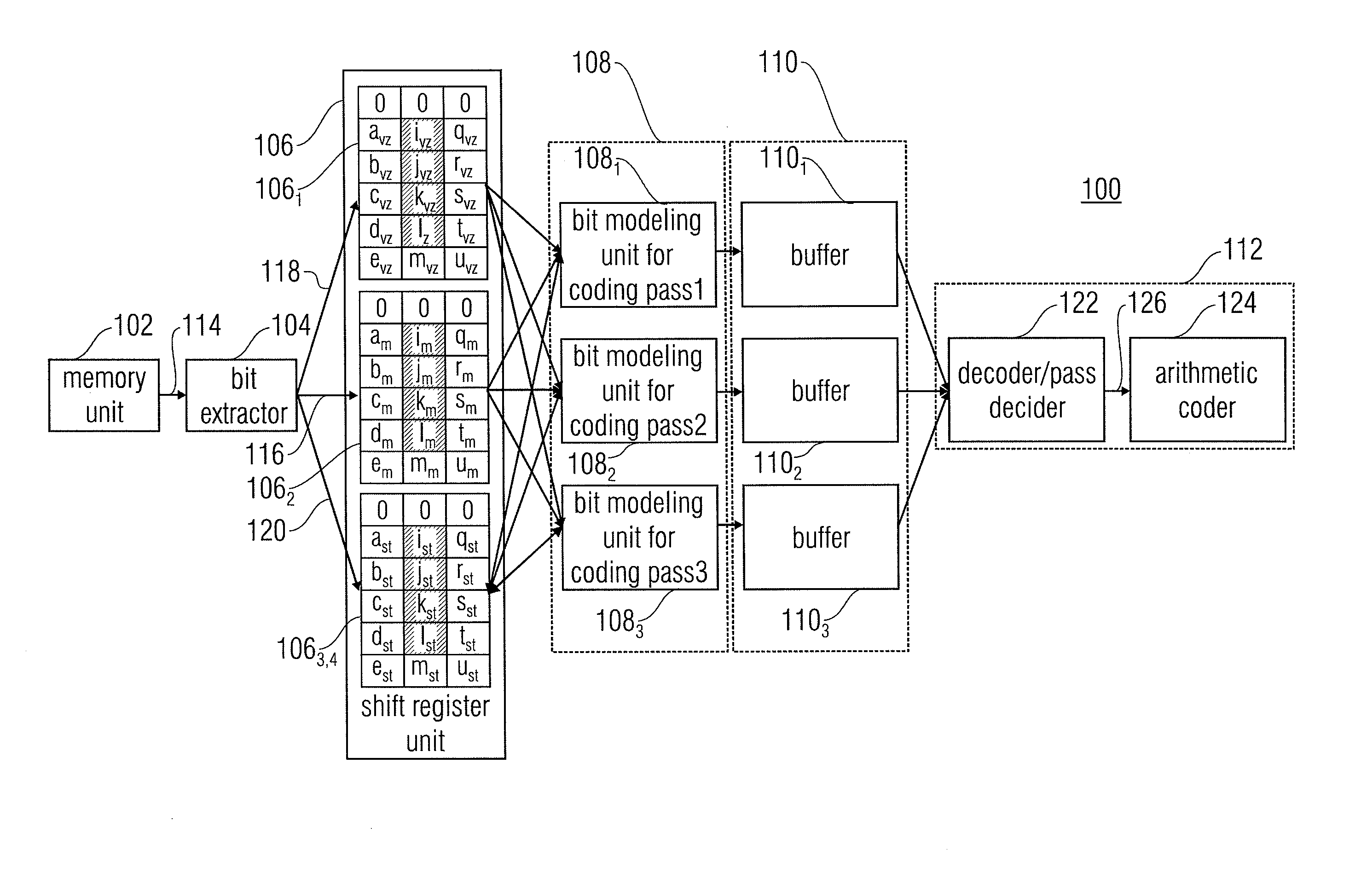

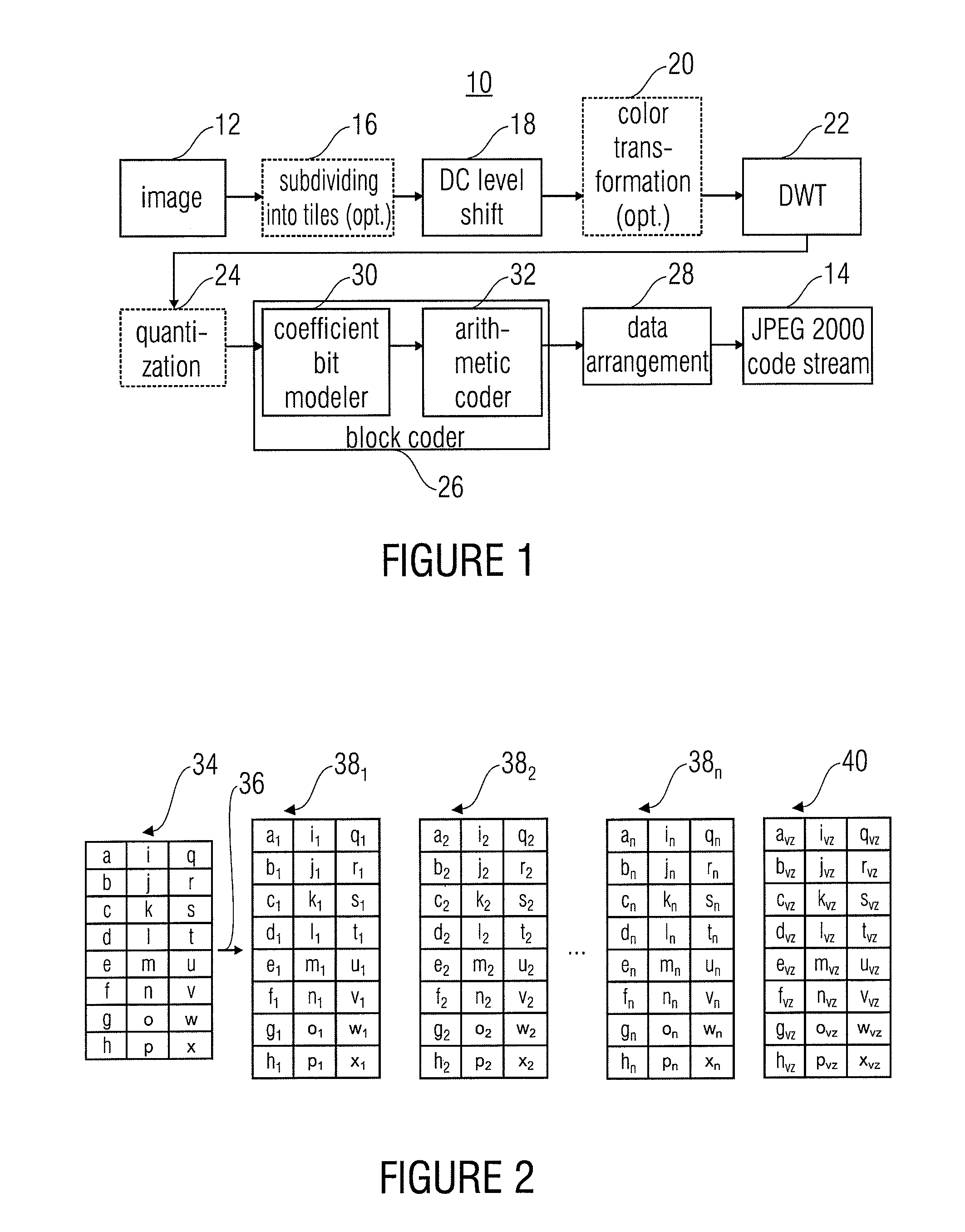

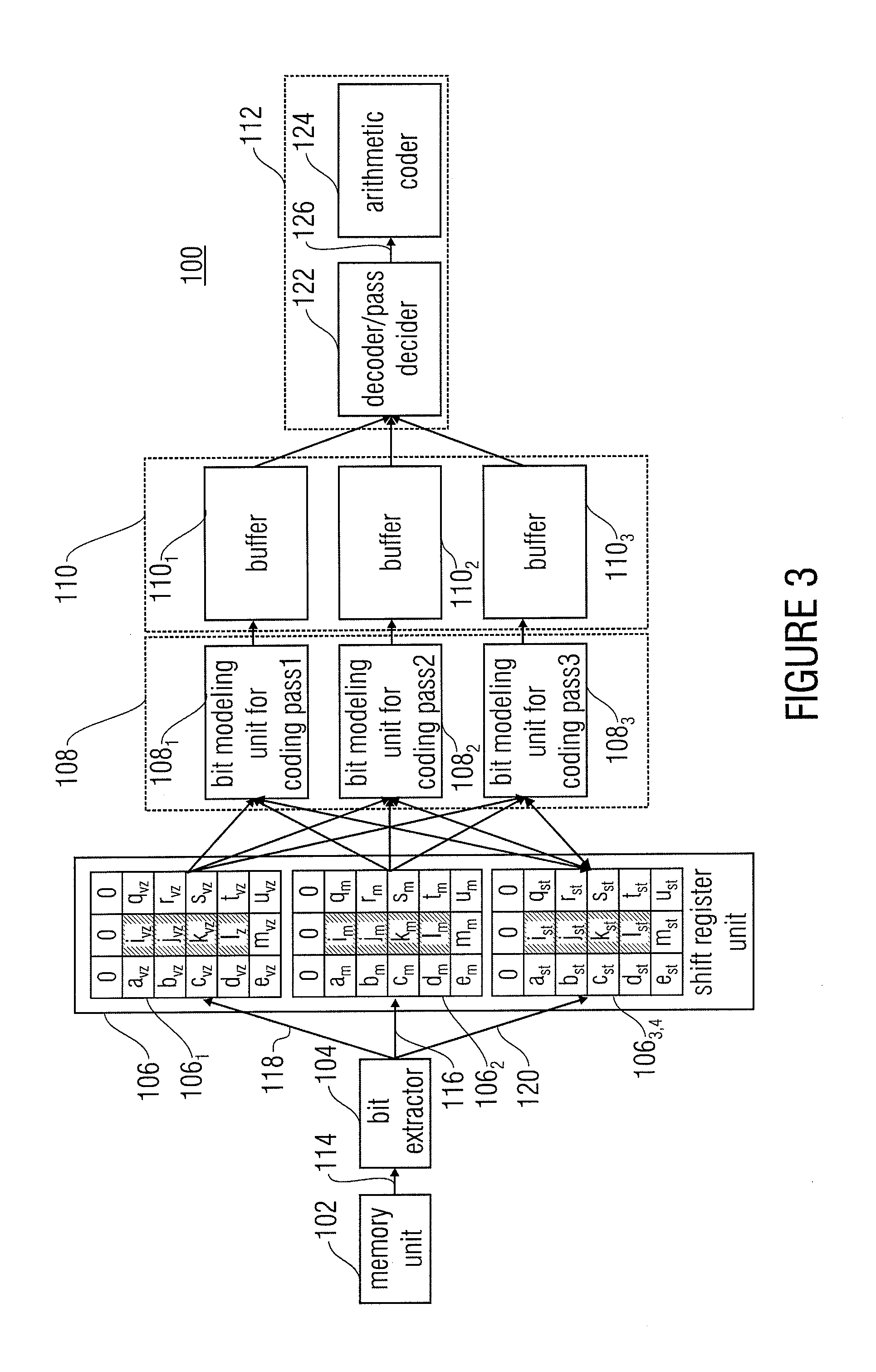

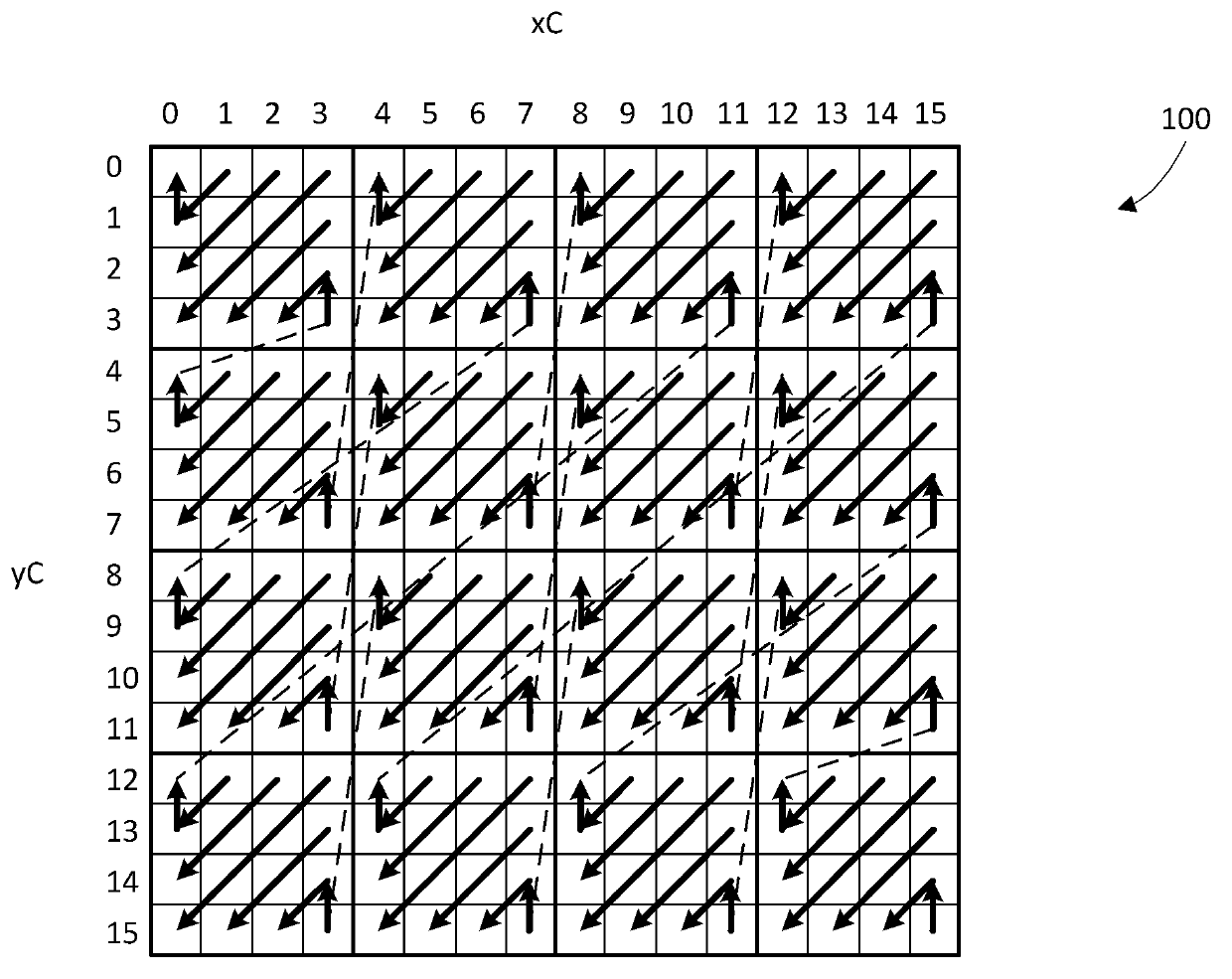

Device and Method for Coding a Transformation Coefficient Block

InactiveUS20100111432A1Promote quick completionEfficient and effectiveImage codingCharacter and pattern recognitionData streamSign bit

A coding of a block of transformation coefficients wherein a precoder traverses the magnitude bits of a predetermined one of magnitude bit planes in tuples of a plurality of adjacent magnitude bits, and codes predetermined ones of the magnitude bits of the tuples into data words such that a predetermined magnitude bit is coded along with an associated sign bit into one of the data words, or that a predetermined magnitude bit is coded along with any other predetermined magnitude bit of the same tuple, into one of the data words. A data word buffer temporarily stores the data words and an entropy coder codes the data words from the data word buffer into a coded data stream. Alternative coding aspects are also presented. According to one alternative aspect, a running window buffer is filled with status bits while traversing the coefficients.

Owner:FRAUNHOFER GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG EV

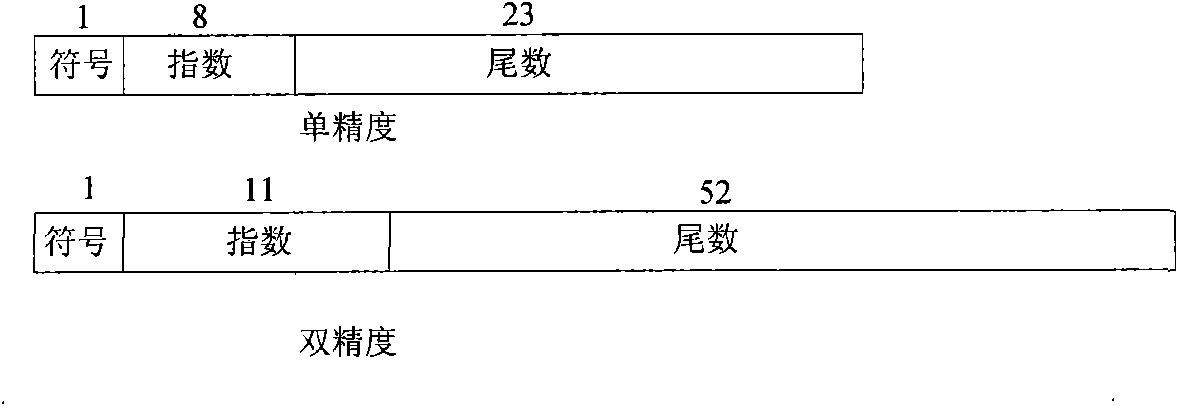

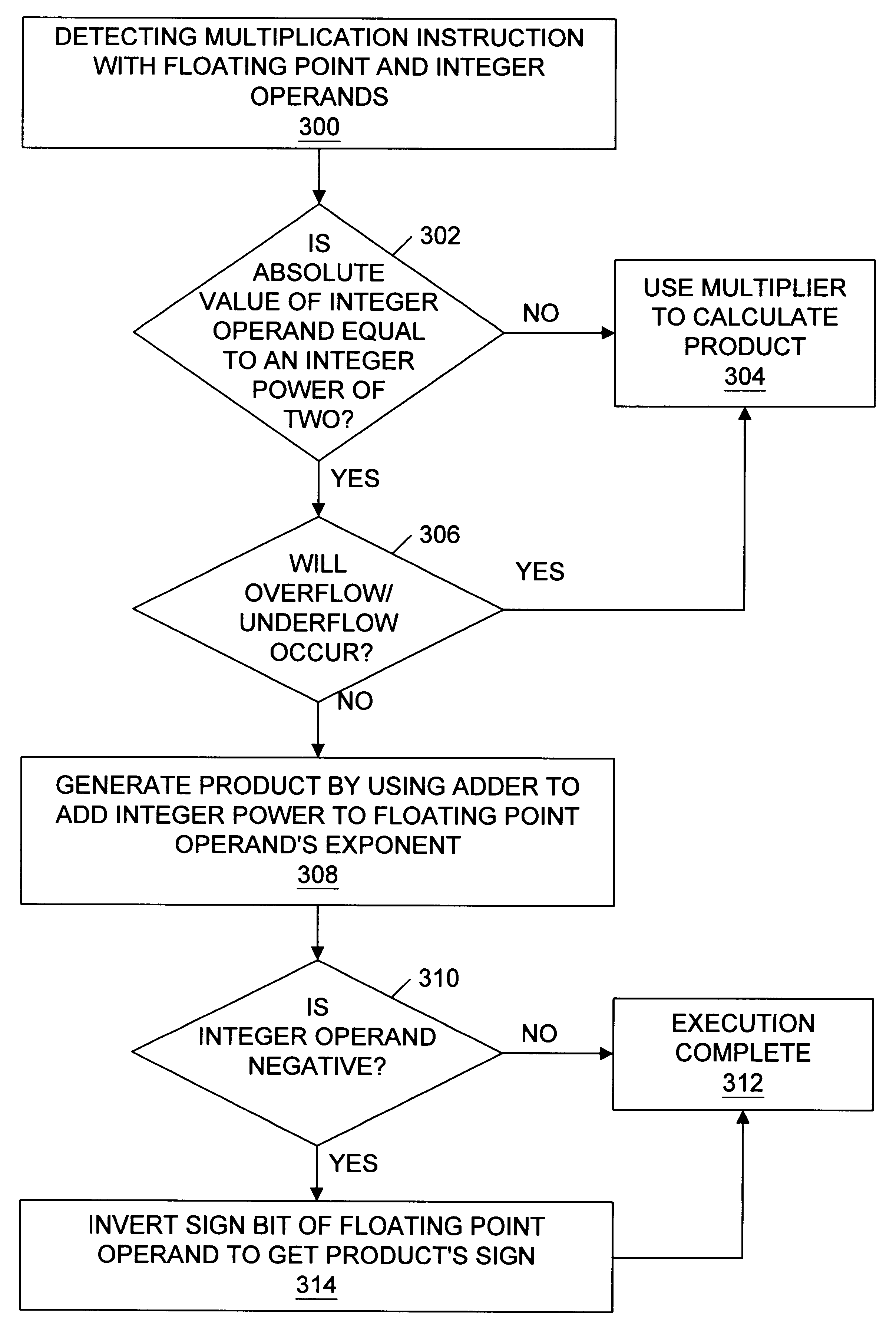

Fast multiplication of floating point values and integer powers of two

InactiveUS6233595B1Computations using contact-making devicesComputation using non-contact making devicesSign bitOperand

A method for performing fast multiplication in a microprocessor is disclosed. The method comprises detecting multiplication operations that have a floating point operand and an integer operand, wherein the integer operand is an integer power of two. Once detected, a multiplication operation meeting these criteria may be executed by using an integer adder to sum the integer power and the floating point operand's exponent to from a product exponent. The bias of the integer operand's exponent may also be subtracted. A product mantissa is simply copied from the floating point operand's mantissa. The floating point operand's sign bit may be inverted to form the product's sign bit if the integer operand is negative. Advantageously, the product is generated using integer addition which is faster than floating point multiplication. The method may be implemented in hardware or software.

Owner:ADVANCED MICRO DEVICES INC

Error resistant scalable audio coding partitioned for determining errors

InactiveUS7308402B2Improve scalabilityError resiliencePicture reproducers using cathode ray tubesCode conversionVariable-length codeSign bit

A scalable audio codec processes, quantizes and encodes audio signals into an embedded audio bitstream of bit-planes each having a data unit. The data unit has a beginning refinement bits partition, a second significance bits partition, a third sign boundary mark bits partition, and a fourth sign bits partition. The second and fourth partitions form a boundary for the third partition. The quantizing uses a variable length coding algorithm. The third partition is an invalid codeword for a predetermined encoding method being used to encode. The codec uses a decoder to decode the embedded audio bitstream of bit-planes using Reversible exponential Golomb (Exp-Golomb) codes in a Reversible Variable Length Code (RVLC) algorithm to produce quantized data of weighted subbands. An inverse quantizer dequantizes the quantized data into audio signals.

Owner:MICROSOFT TECH LICENSING LLC

Fused floating point datapath with correct rounding

ActiveUS9348557B1Improve efficiencySmall area consumptionComputation using non-contact making devicesDatapath circuitsSign bit

In accordance with some embodiments, a floating point number datapath circuitry, e.g., within an integrated circuit programmable logic device is provided. The datapath circuitry may be used for computing a rounded absolute value of a mantissa of a floating point number. The floating point datapath circuitry may have only a single adder stage for computing a rounded absolute value of a mantissa of the floating point number based on one or more bits of an unrounded mantissa of the floating point number. The unrounded and rounded mantissas may include a sign bit, a sticky bit, a round bit, and / or a least significant bit, and / or other bits. The unrounded mantissa may be in a format that includes negative numbers (e.g., 2's complement) and the rounded mantissa may be in a format that may include a portion of the floating point number represented as a positive number, (e.g., signed magnitude).

Owner:TAHOE RES LTD

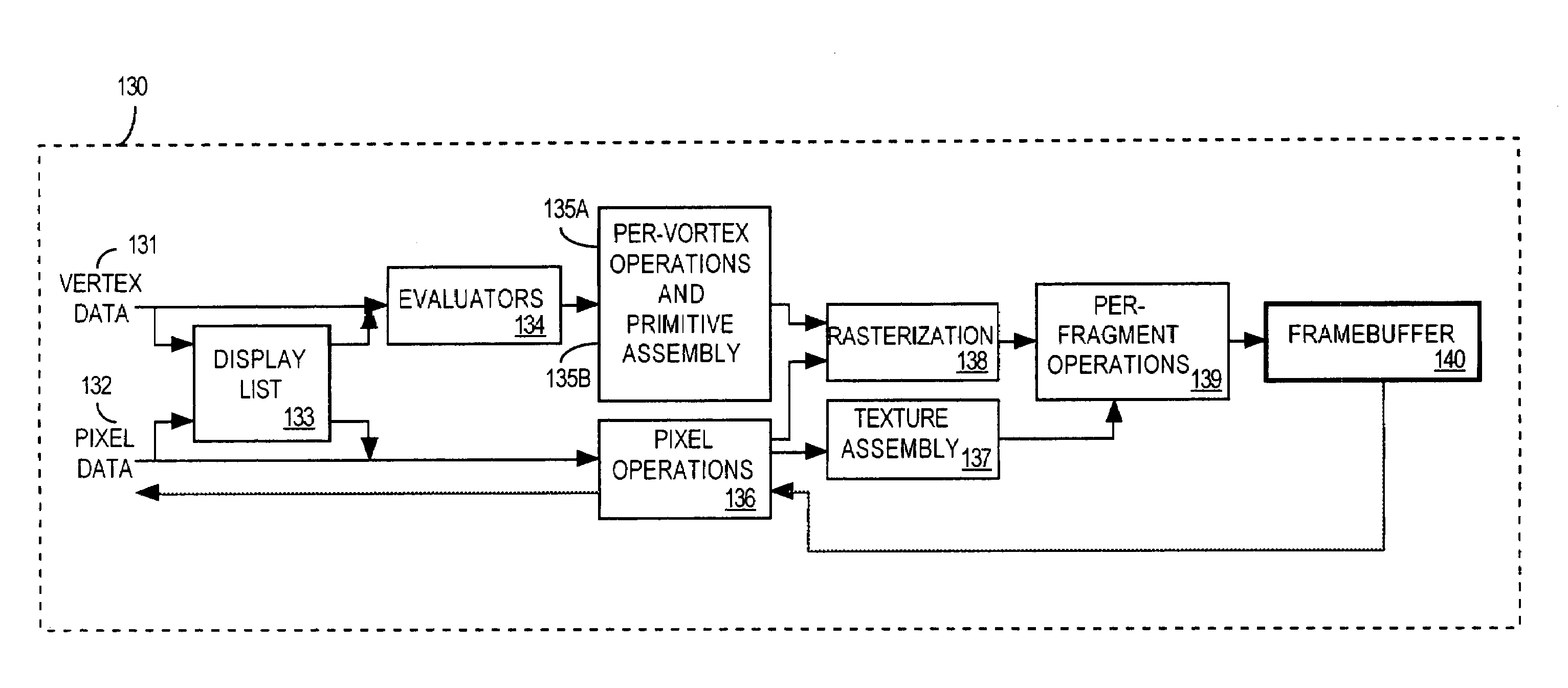

Gray Code to Sign and Magnitude Converter

ActiveUS20080191910A1Electric signal transmission systemsAnalogue-digital convertersComputer hardwareWave shape

The present invention relates to Gray Codes and their conversion to sign and magnitude representation. Gray codes are used in flash ADCs (analogue to digital converters), which convert an analogue waveform into a sampled binary value. This can be done via a thermometer code, and the present invention addresses the issue of the propagation of error due to an indeterminant thermometer code value. In particular the invention provides a Gray code to sign and magnitude converter arranged to produce for the bits of its output other than the sign bit the same code for the Gray codes that are the same distance from the boundary where the sign bit changes value when the Gray codes are arranged in order of their value.

Owner:TEXAS INSTR INC

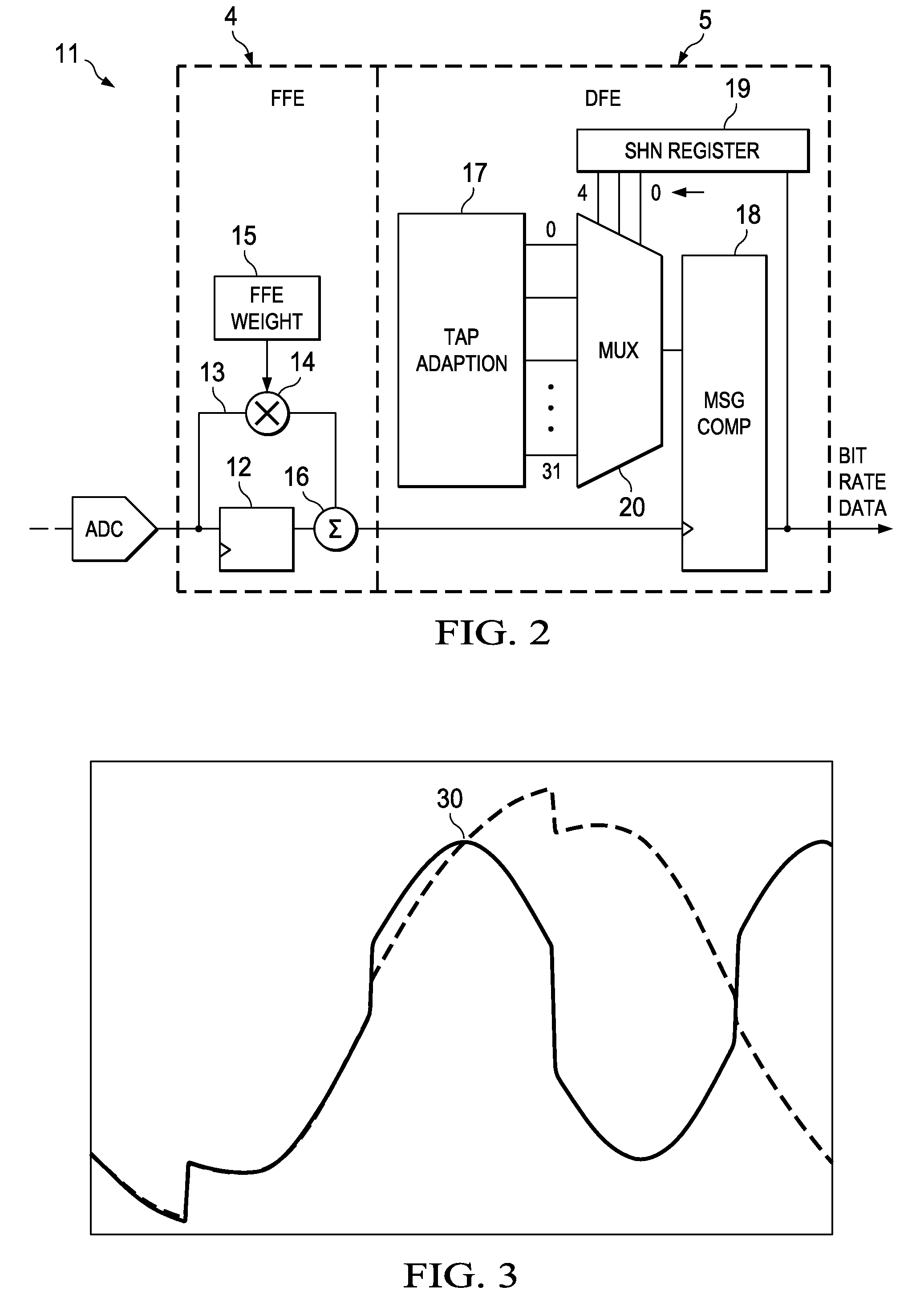

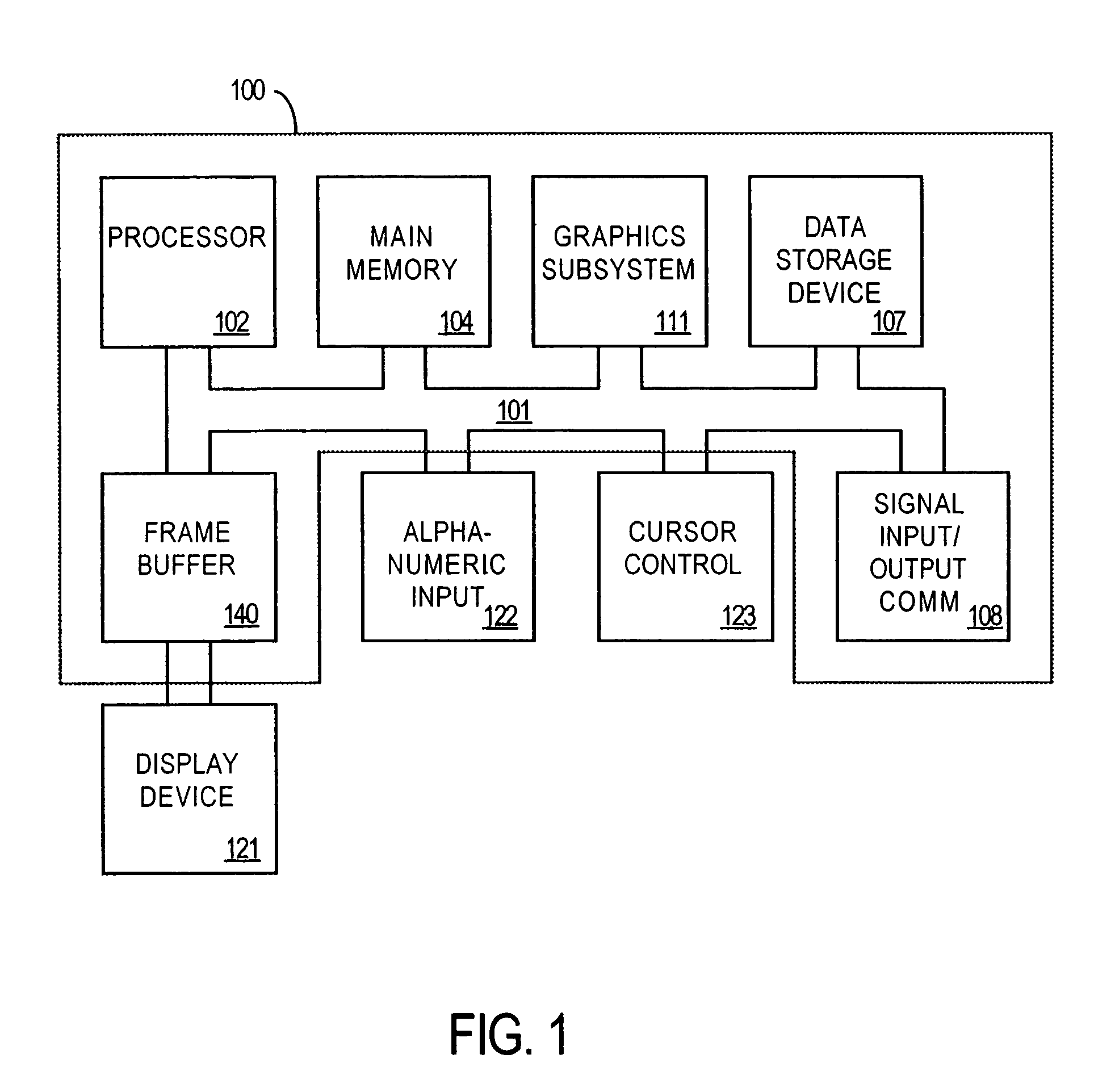

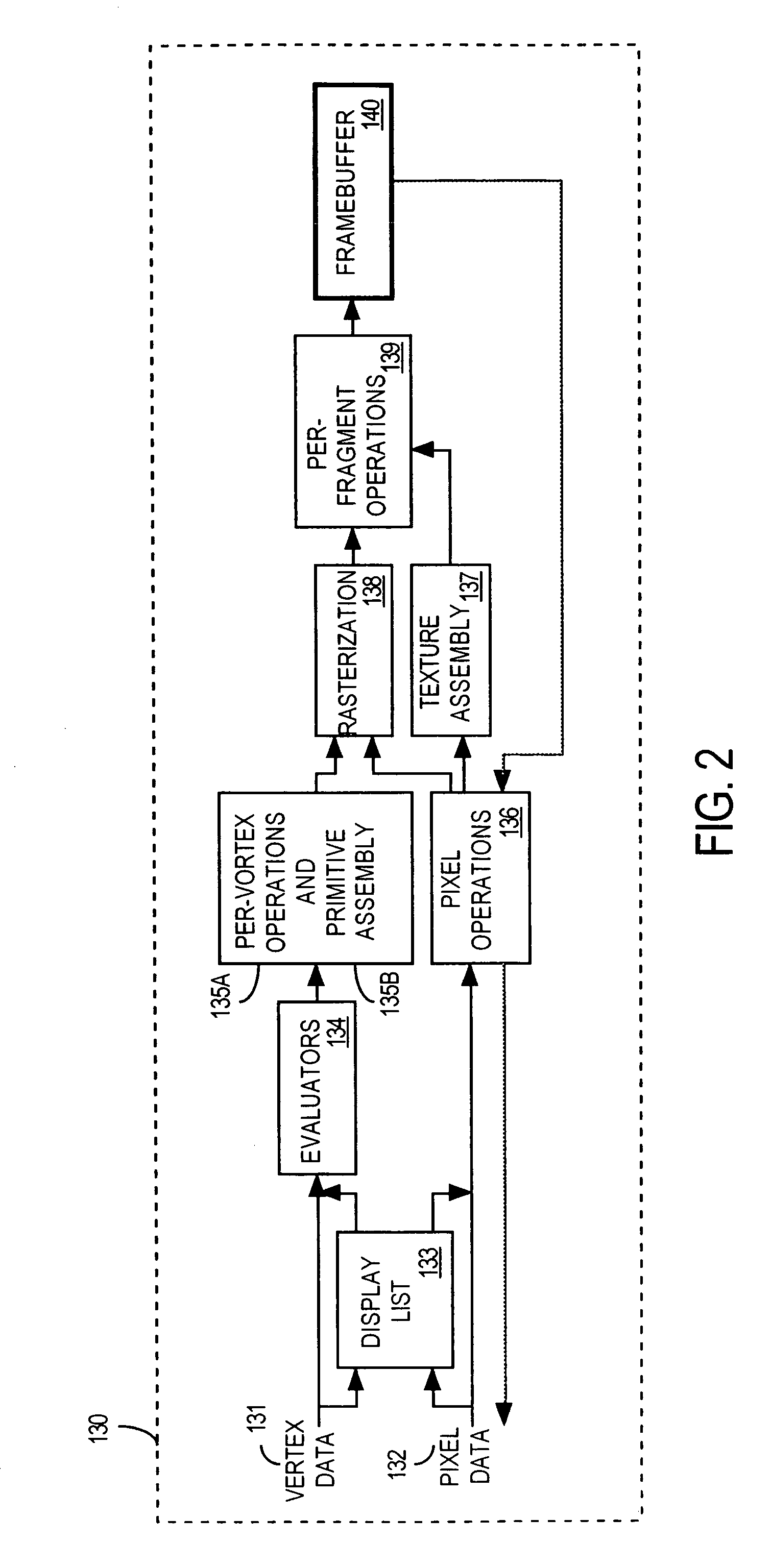

Display system having floating point rasterization and floating point framebuffering

InactiveUS7518615B1Loss of accuracyMemory adressing/allocation/relocationCathode-ray tube indicatorsGraphicsSign bit

A floating point rasterization and frame buffer in a computer system graphics program. The rasterization, fog, lighting, texturing, blending, and antialiasing processes operate on floating point values. In one embodiment, a 16-bit floating point format consisting of one sign bit, ten mantissa bits, and five exponent bits (s10e5), is used to optimize the range and precision afforded by the 16 available bits of information. In other embodiments, the floating point format can be defined in the manner preferred in order to achieve a desired range and precision of the data stored in the frame buffer. The final floating point values corresponding to pixel attributes are stored in a frame buffer and eventually read and drawn for display. The graphics program can operate directly on the data in the frame buffer without losing any of the desired range and precision of the data.

Owner:RPX CORP +1

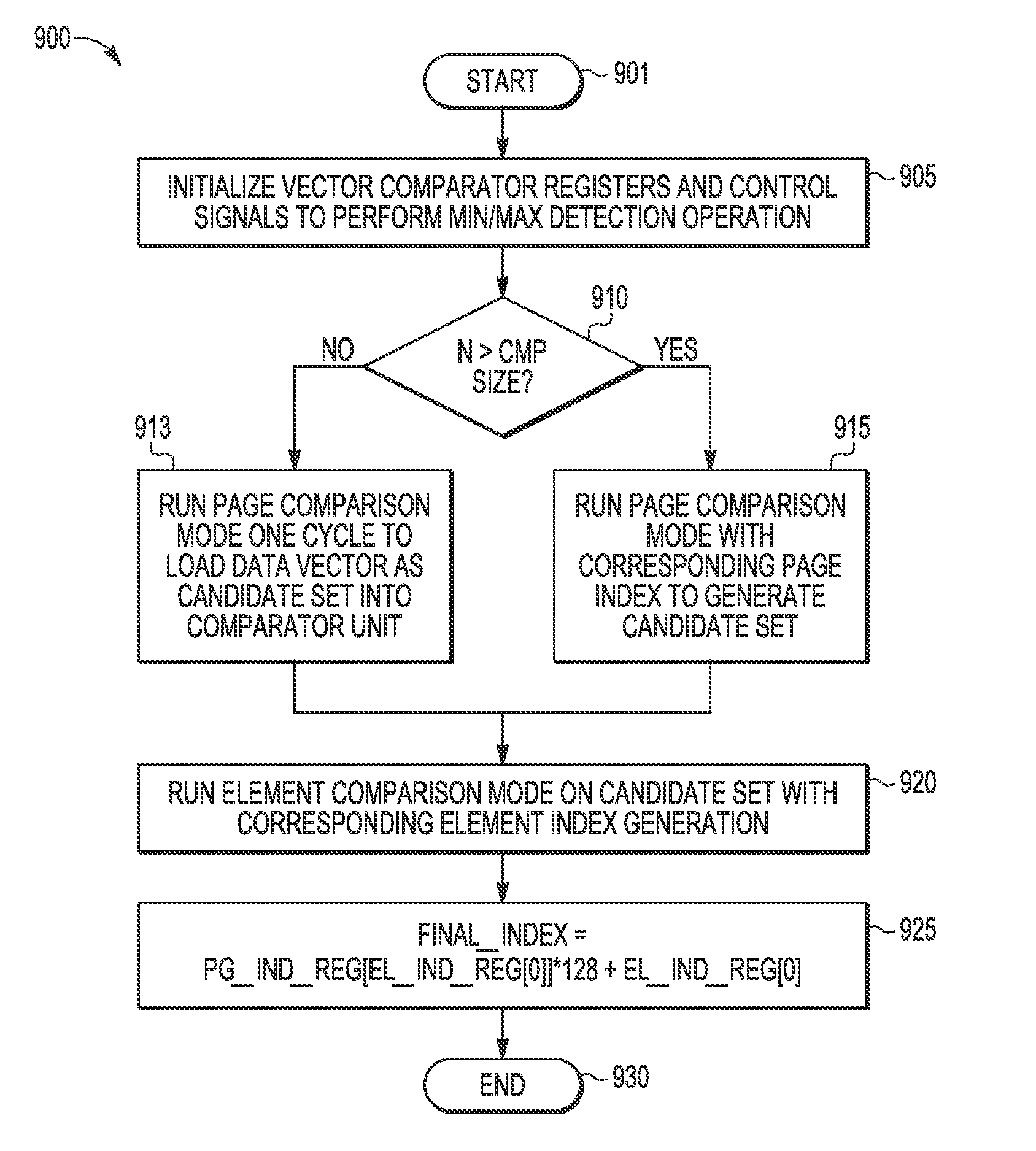

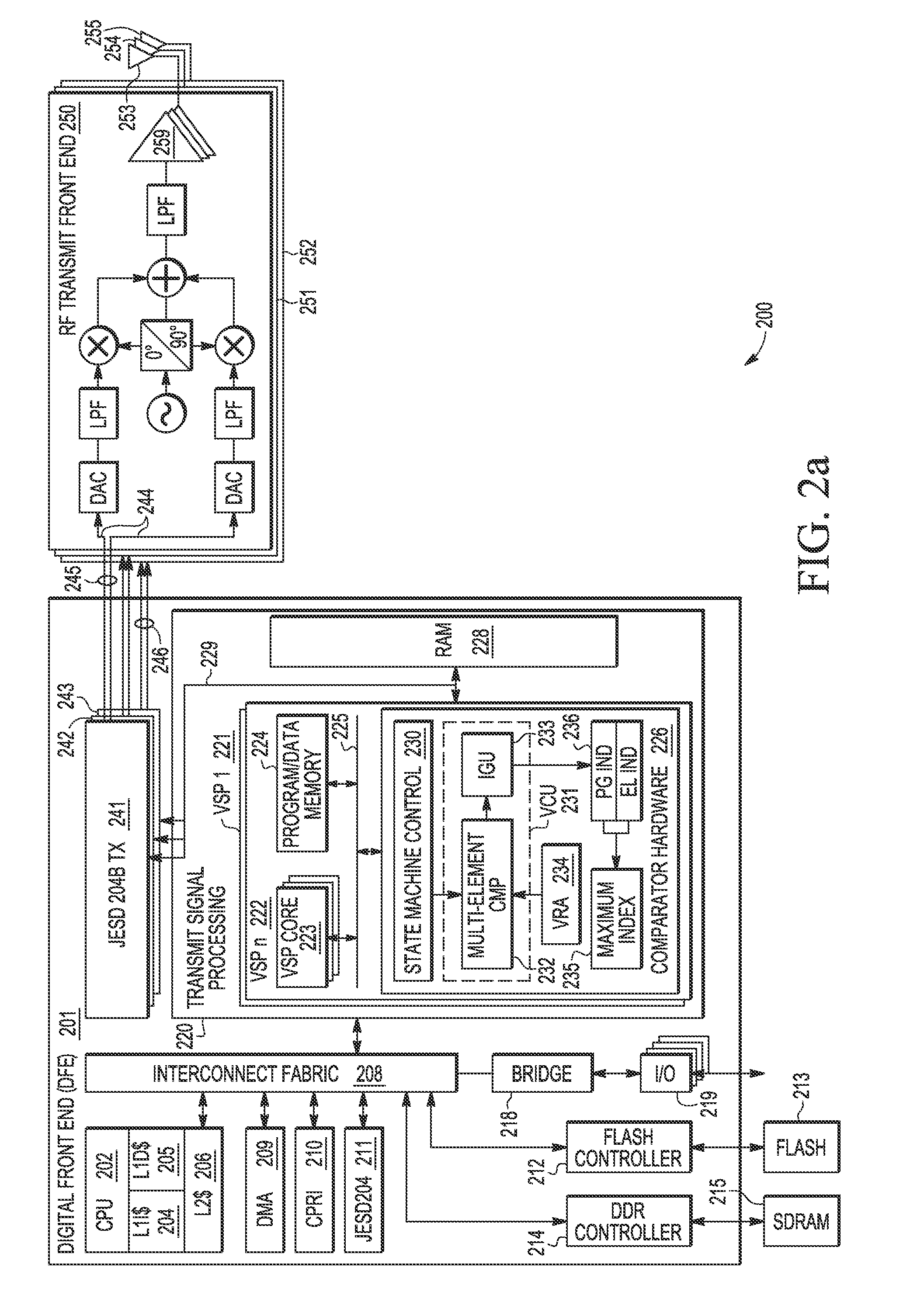

Vector Comparator System for Finding a Peak Number

A comparator (231) for determining a peak number, representing a maximum or minimum of a set of numbers, includes a multi-element comparator (232) for comparing different pages of the set of numbers in a page comparison mode to output a candidate set of winning numbers, and for automatically switching to a leaf / tree search of the candidate set of winning numbers in an element comparison mode. Operating in parallel with the multi-element comparator (232), an index generation unit (233) processes flag / sign bits from the multi-element comparator in conjunction with state machine control logic (230) to keep track of the index / indices for the peak value. Upon completion of final stage, the index generation unit returns the absolute index (235) of the peak value.

Owner:NXP USA INC

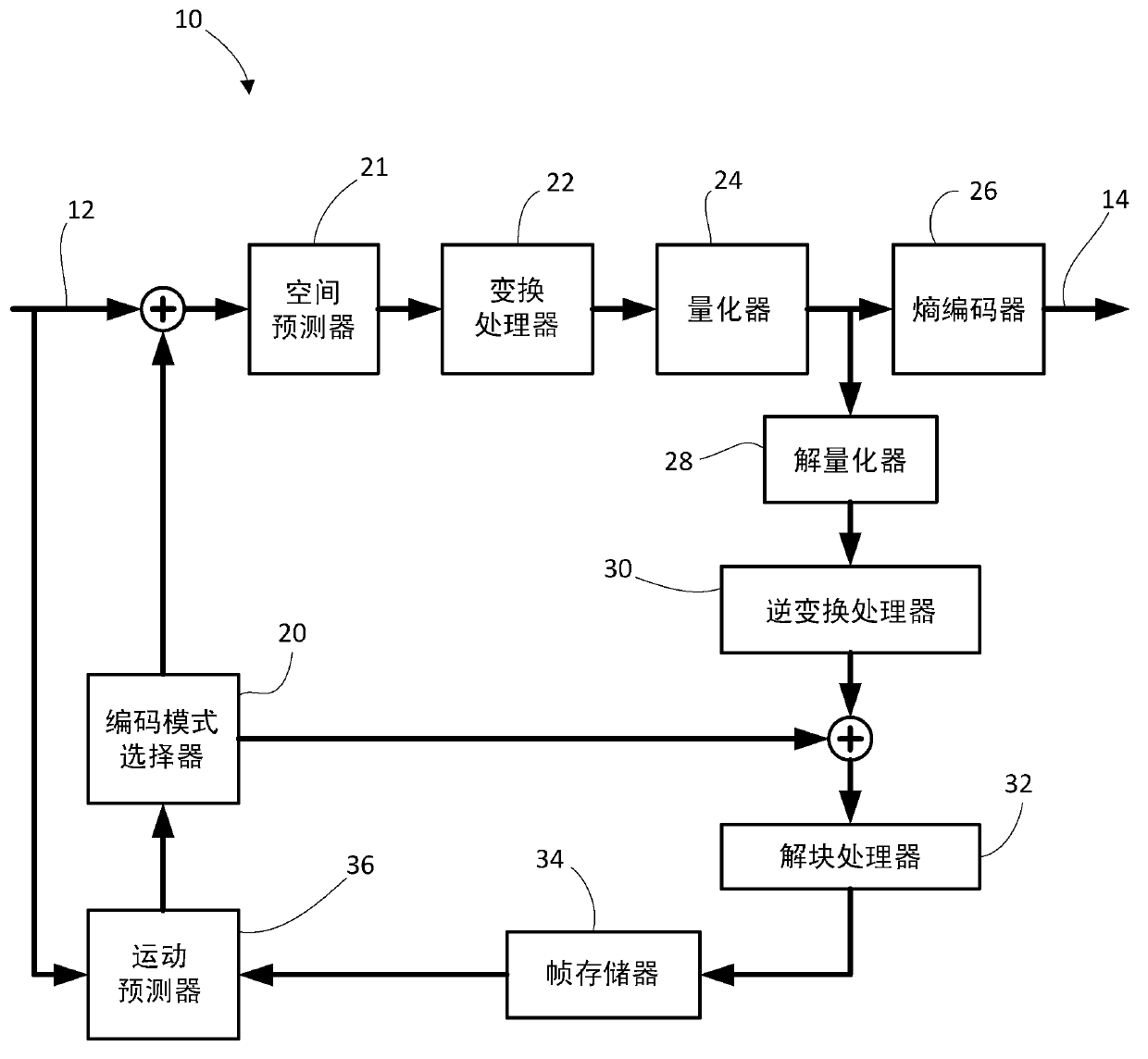

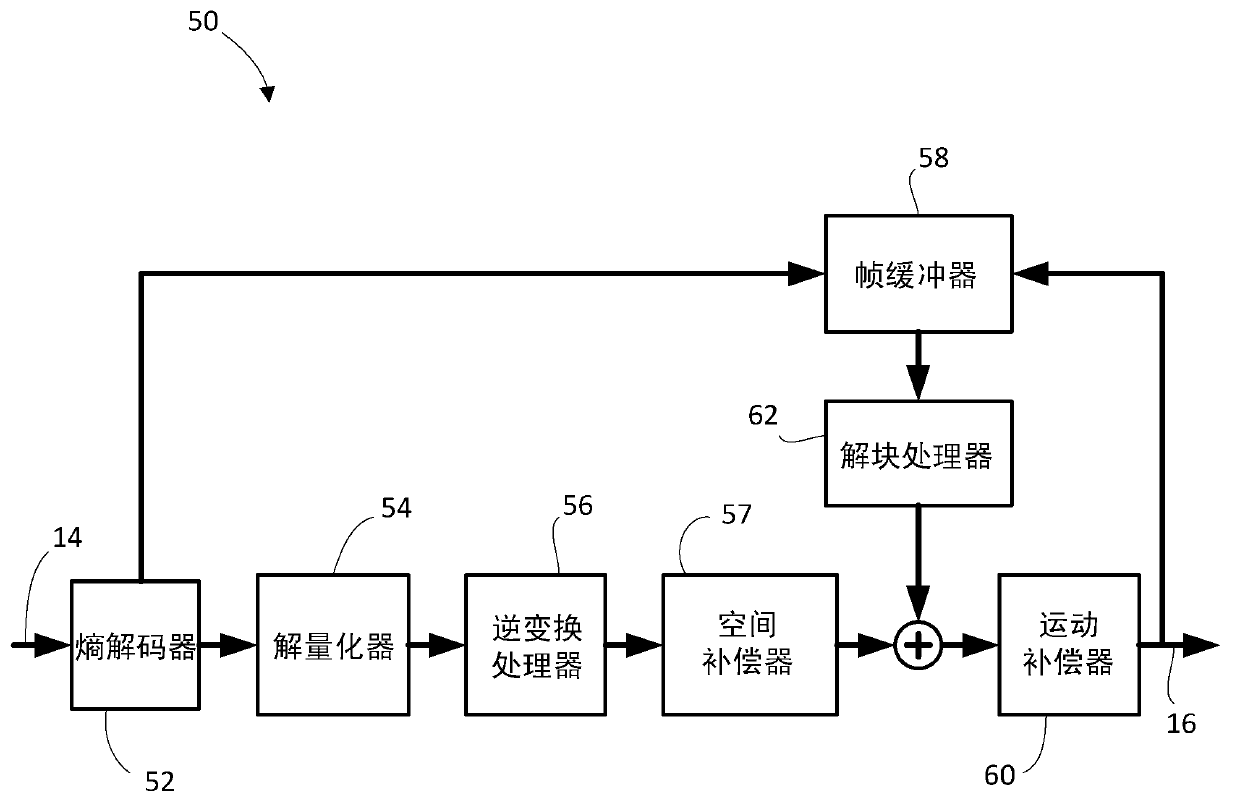

Multiple sign bit hiding within a transform unit

Methods of encoding and decoding for video data are described for encoding or decoding coefficients for a transform unit. In particular, the sign bits for the non-zero coefficients are encoded using sign bit hiding. Two or more sets of coefficients are defined for the transform unit and a sign bit may be hidden for each set, subject to satisfaction of a threshold test. The sets may correspond to coefficient groups that are otherwise used in multi-level significance map encoding and decoding.

Owner:VELOS MEDIA INT LTD

Computation units for functions based on lookup tables

ActiveUS20210096816A1Reduce processing requirementsImprove accuracyDigital data processing detailsOther databases indexingSign bitSoftware engineering

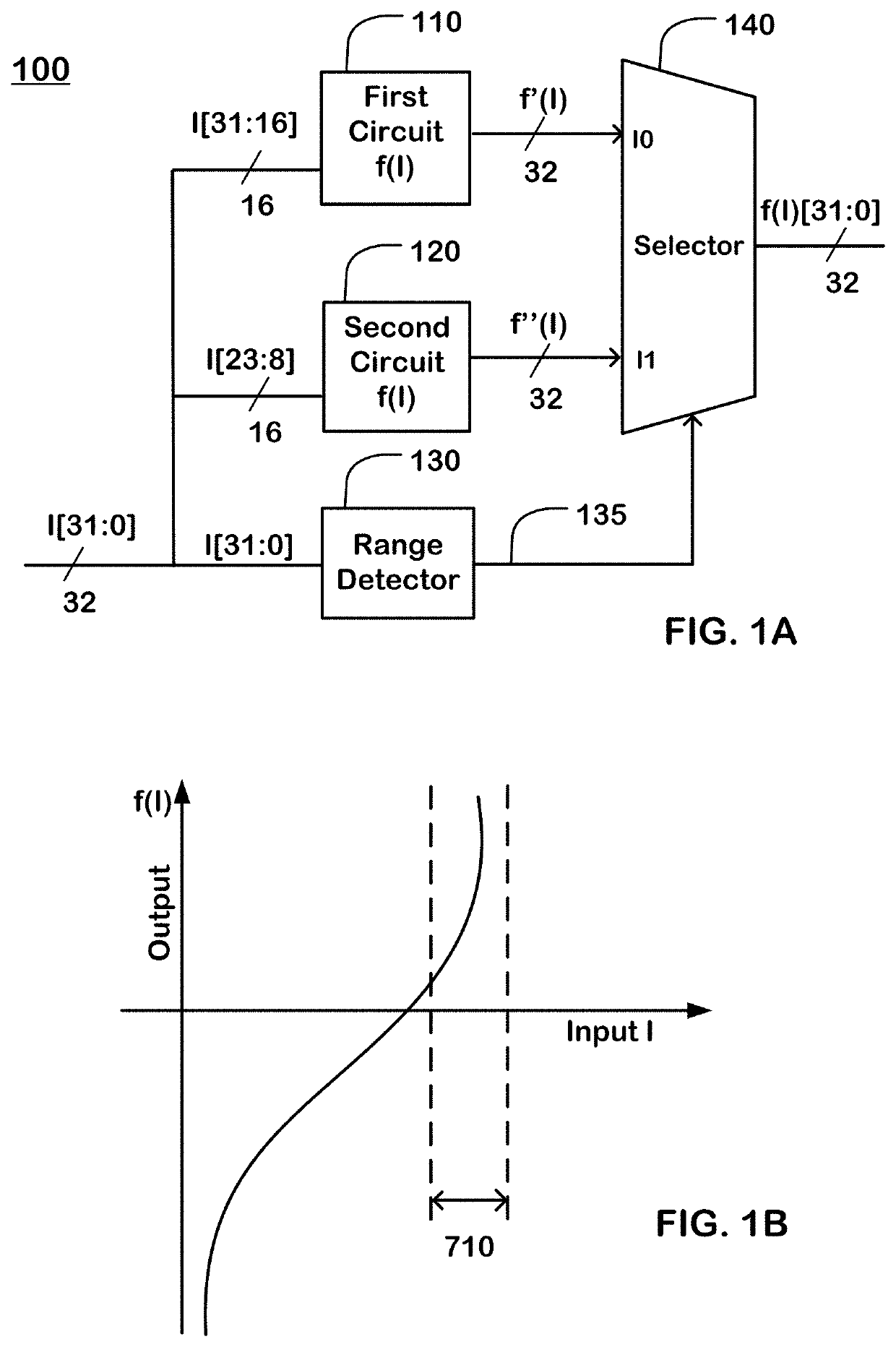

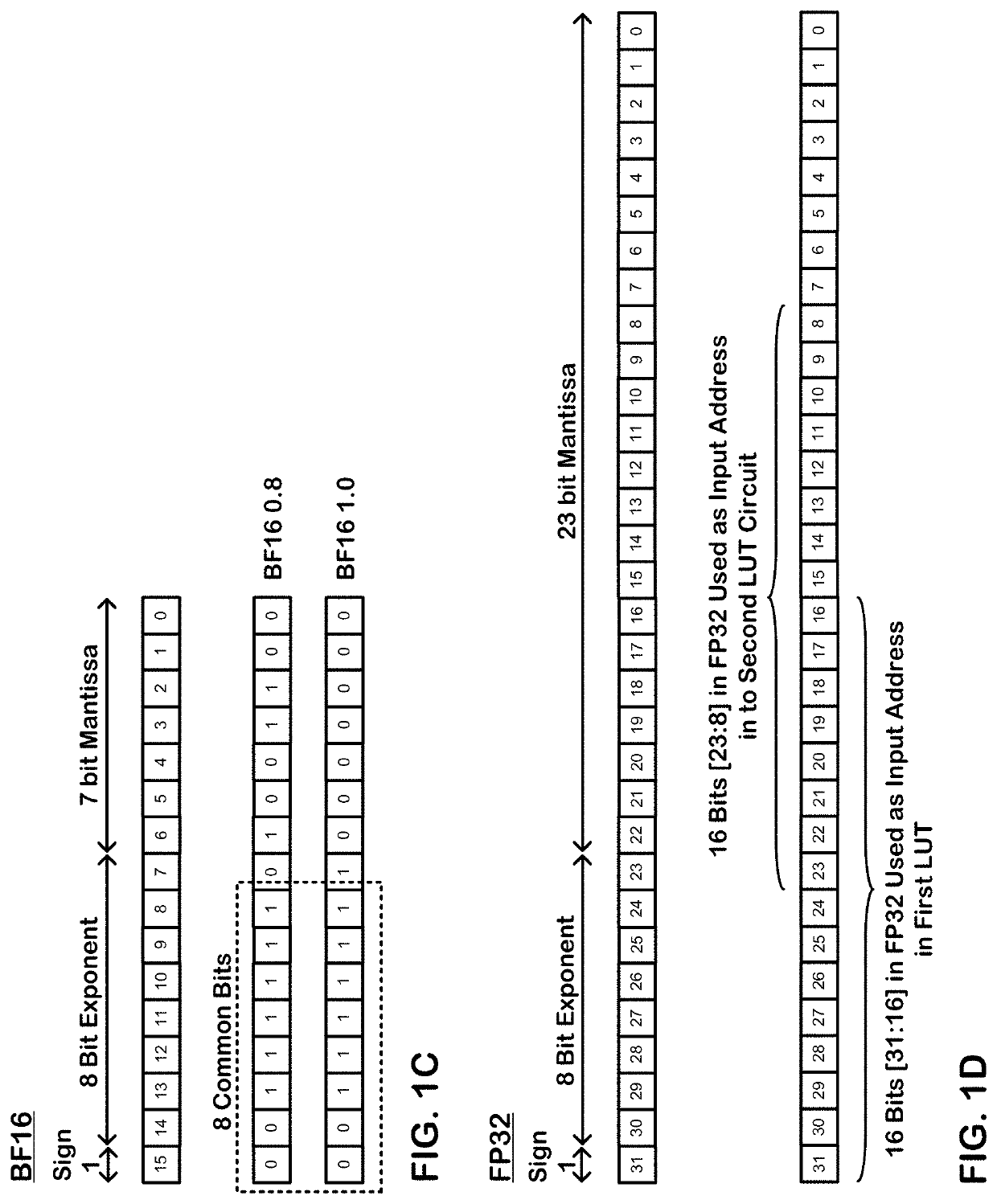

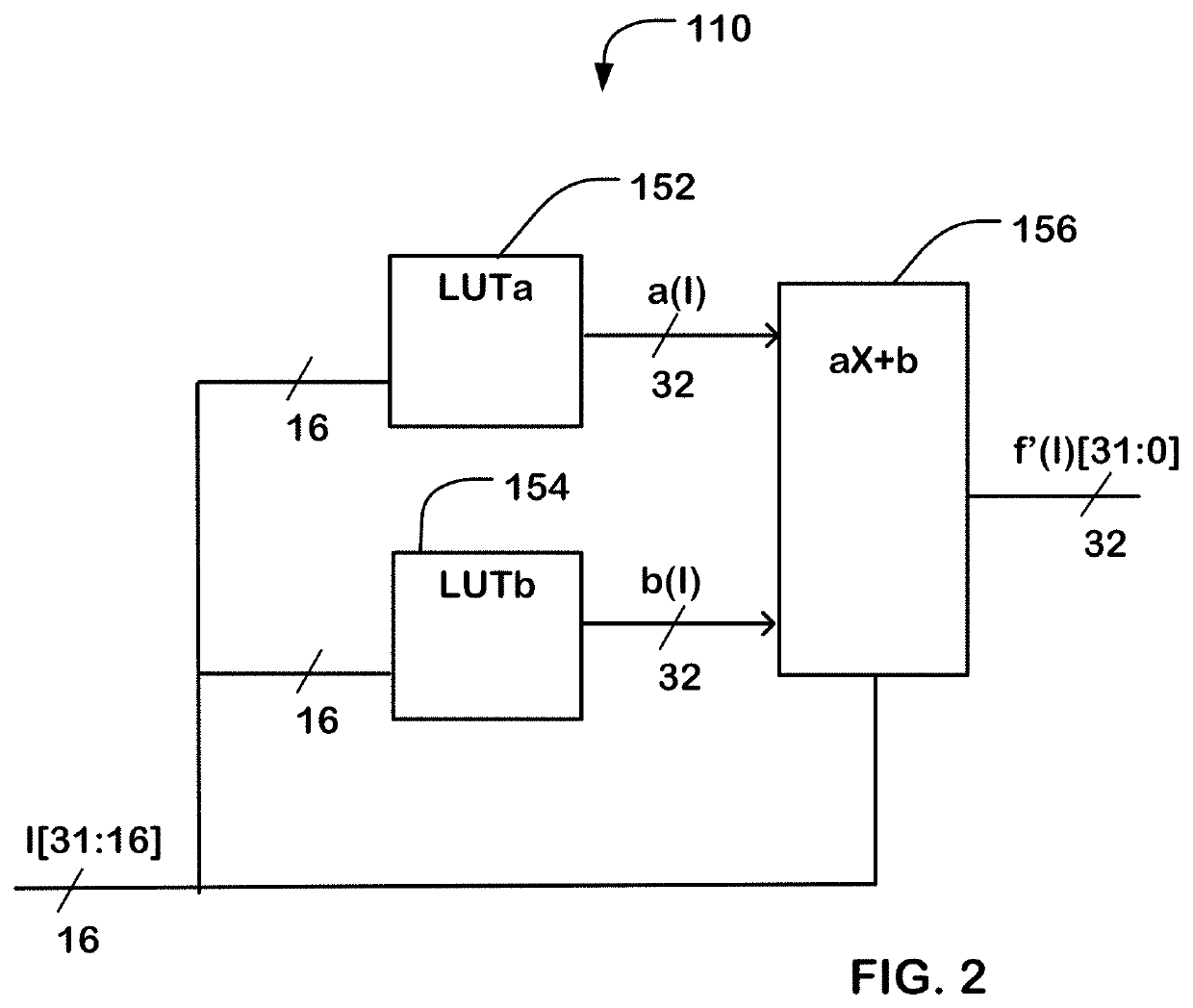

A computation unit comprises a floating point input having X bits including a sign bit, an E bit exponent and an M bit mantissa. A first circuit is operatively coupled to receive X-N bits of the input, including e1 bits of the exponent and ml bits of the mantissa, where e1≤E, and m1≤M, to output values over a first domain of the input. A second circuit is operatively coupled to receive X-K bits of the input, including e2 bits of the exponent, e2<e1, and m2 bits of the mantissa, m2>m1, to output values, over a second domain of the input. A range detector is operatively coupled to the input, to indicate a range in response to a value of the input. A selector can select the output of the first circuit or of the second circuit in response to the range detector.

Owner:SAMBANOVA SYST INC