Patents

Literature

1322 results about "Bit plane" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

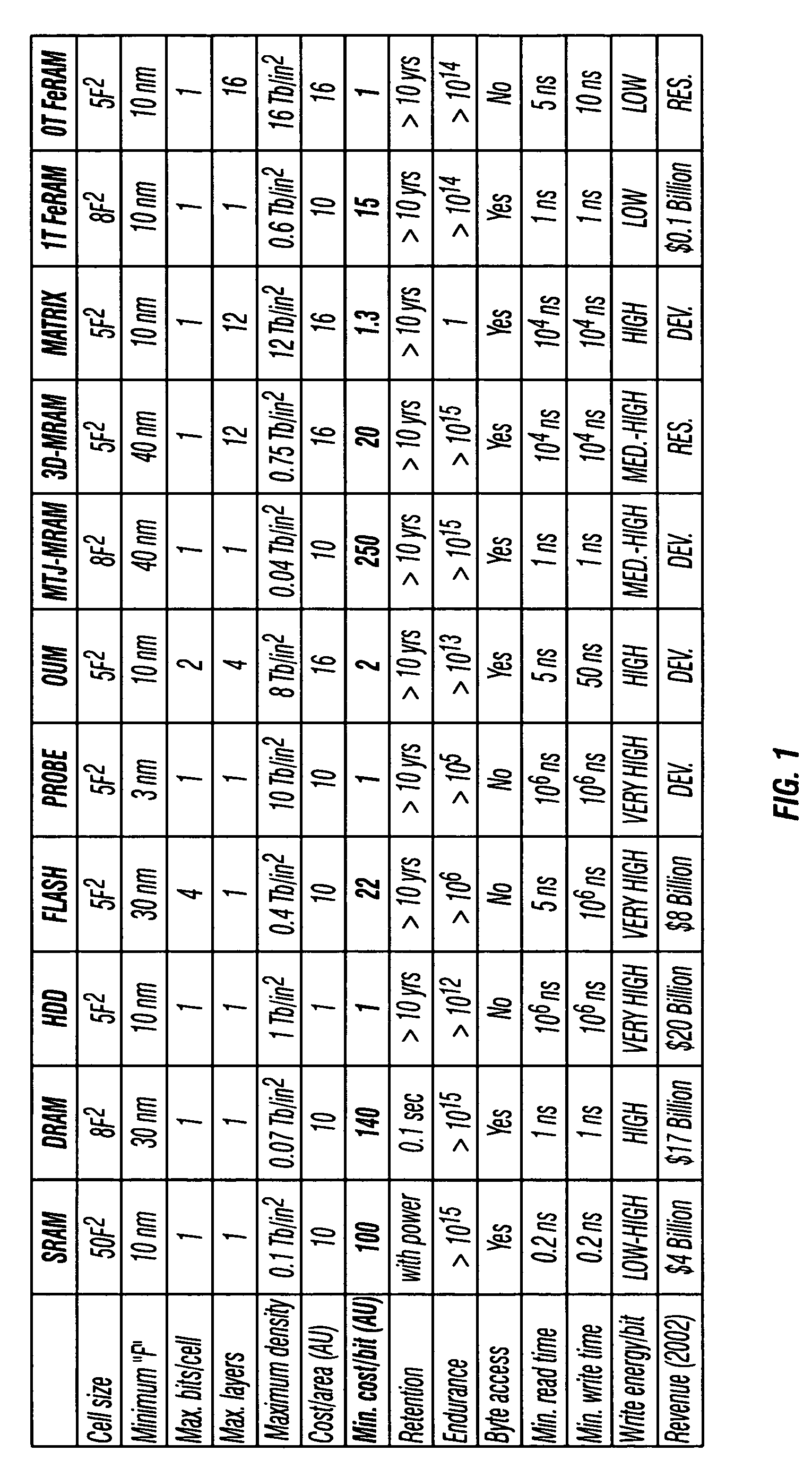

A bit plane of a digital discrete signal (such as image or sound) is a set of bits corresponding to a given bit position in each of the binary numbers representing the signal. For example, for 16-bit data representation there are 16 bit planes: the first bit plane contains the set of the most significant bit, and the 16th contains the least significant bit.

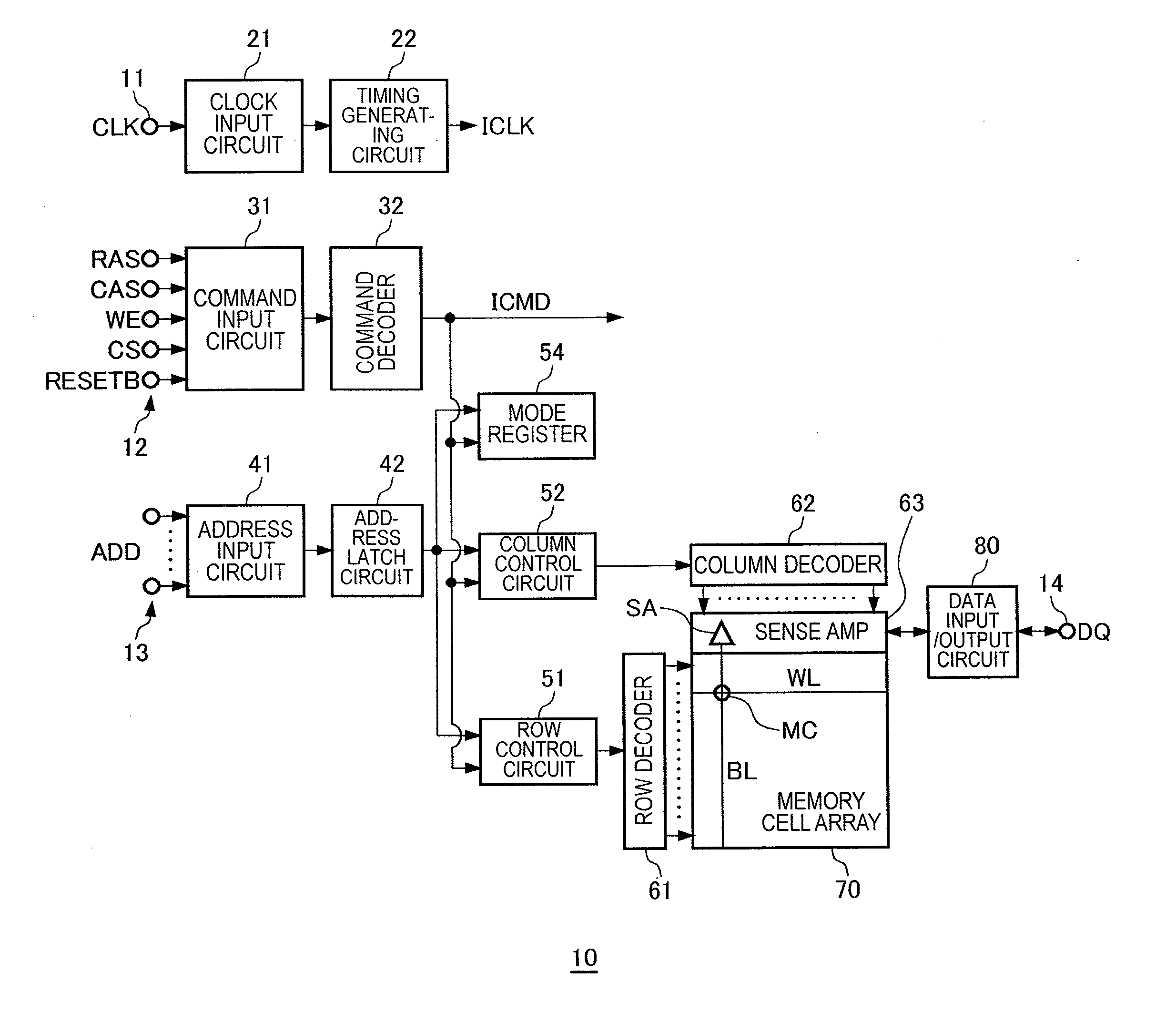

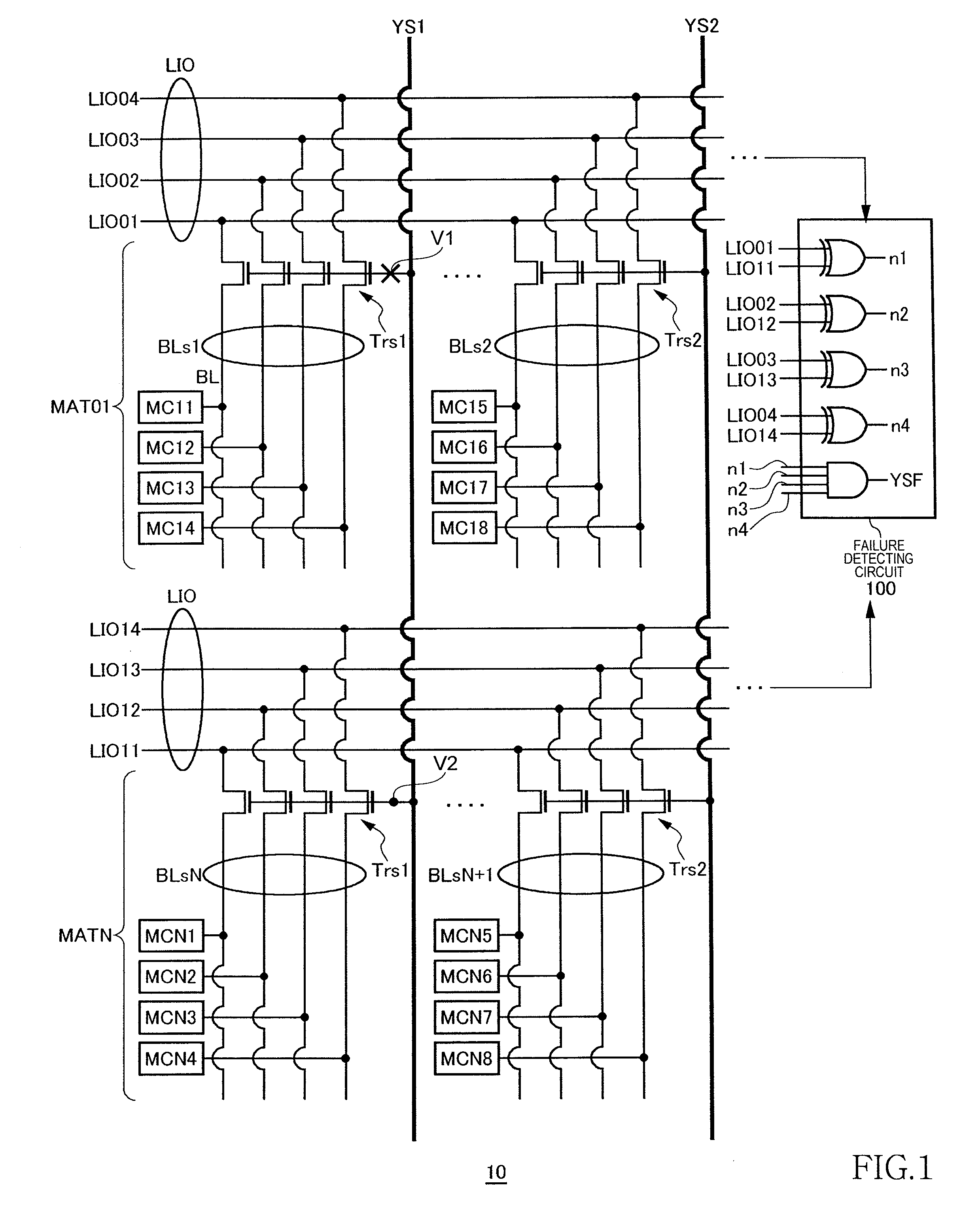

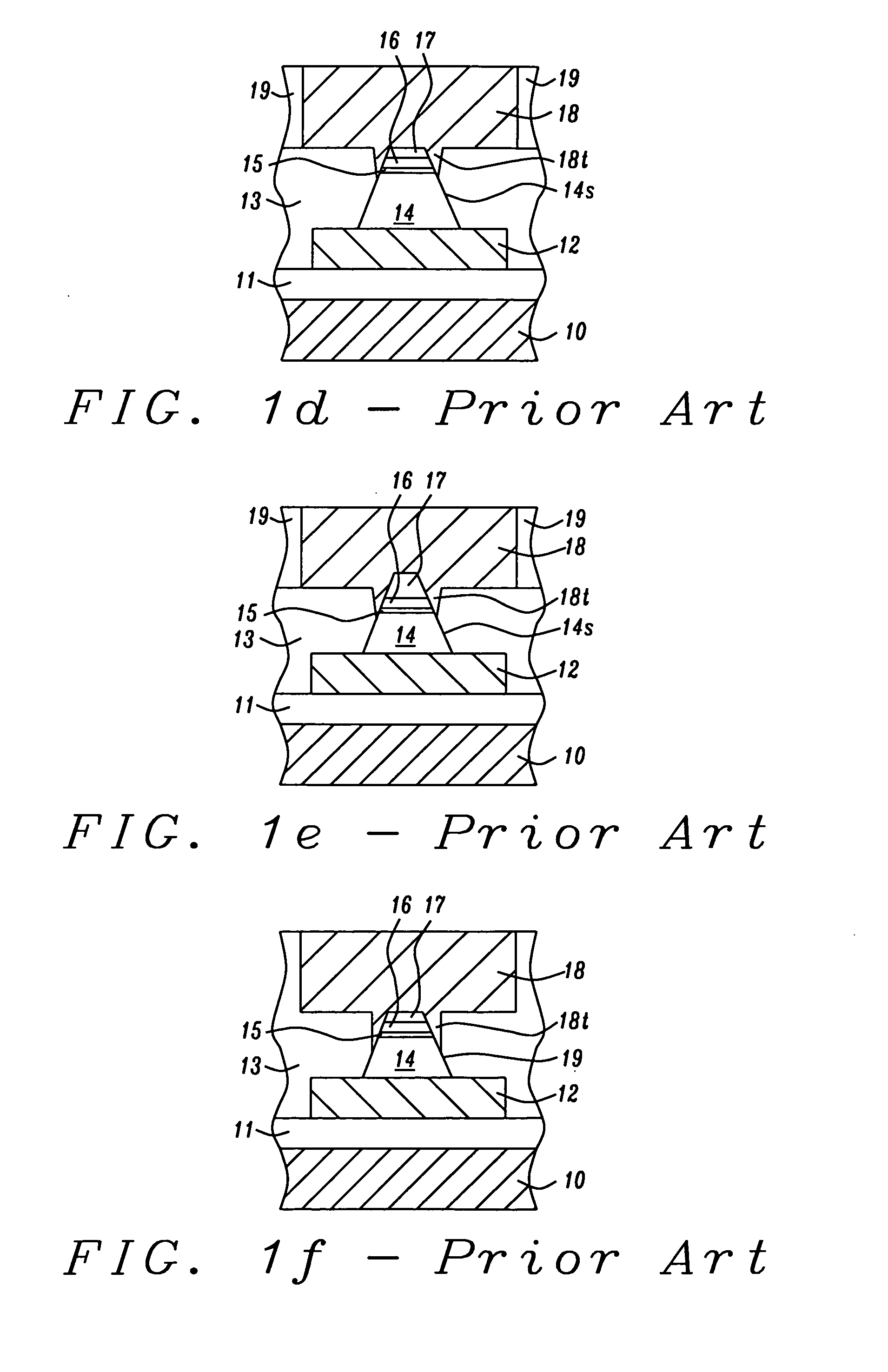

Semiconductor device having bit lines and local I/O lines

InactiveUS20120120705A1Facilitates discrimination of failureFacilitates efficient discriminationDigital storageBit lineContact failure

The present invention efficiently decides line failure and contact failure in a semiconductor device. The semiconductor device has a plurality of bit line groups in which connection with local I / O lines is controlled by the same column selection signal line. A failure detecting circuit compares a first data group read from a first bit line group and a second data group read from a second bit line group to detect whether or not connection failure (contact failure) with the column selection signal line occurs in one of the first and second bit line groups.

Owner:LONGITUDE SEMICON S A R L

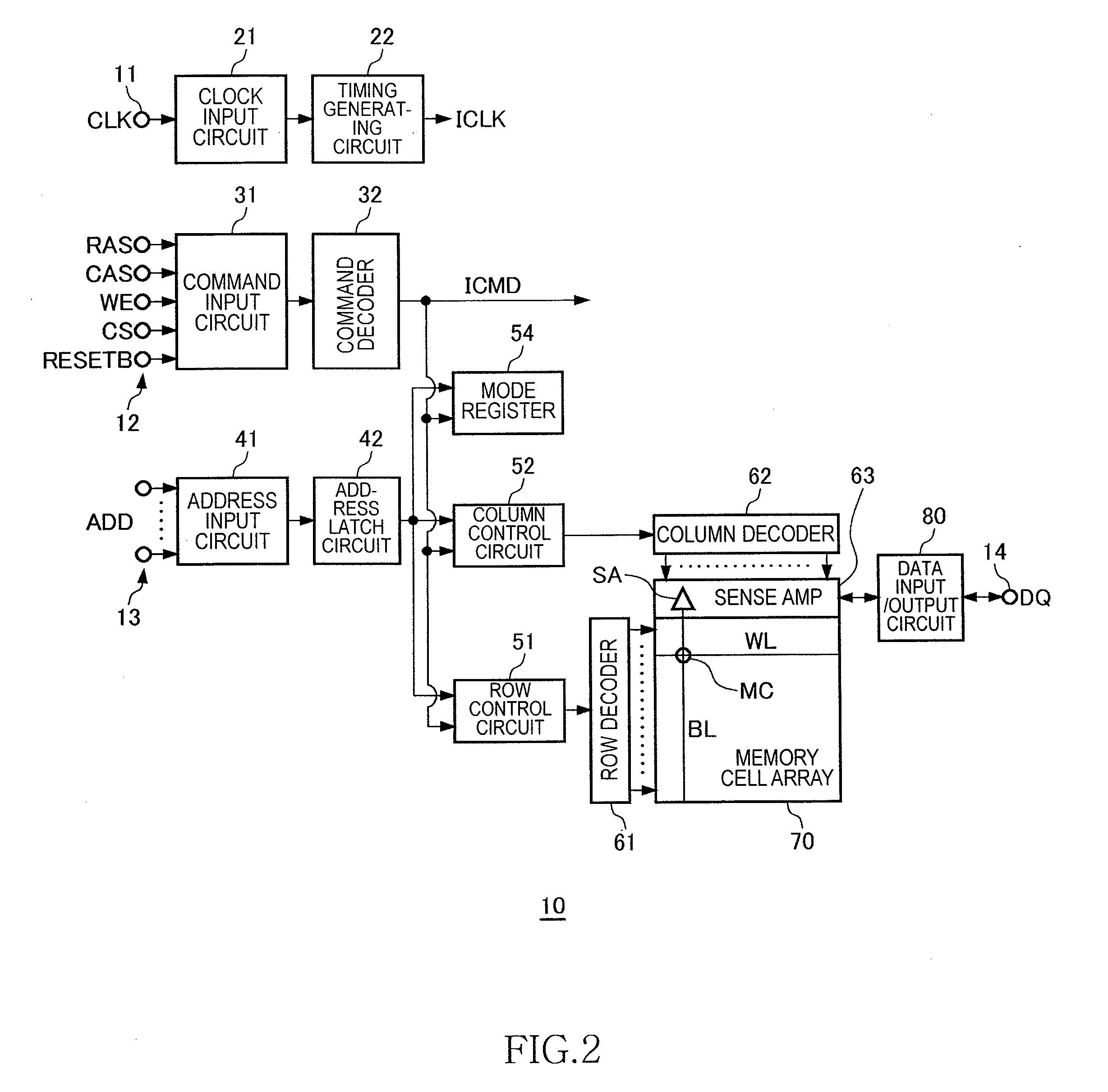

Semiconductor device

ActiveUS20110134683A1Easily multivaluedNovel structureTransistorSolid-state devicesPower semiconductor deviceDriver circuit

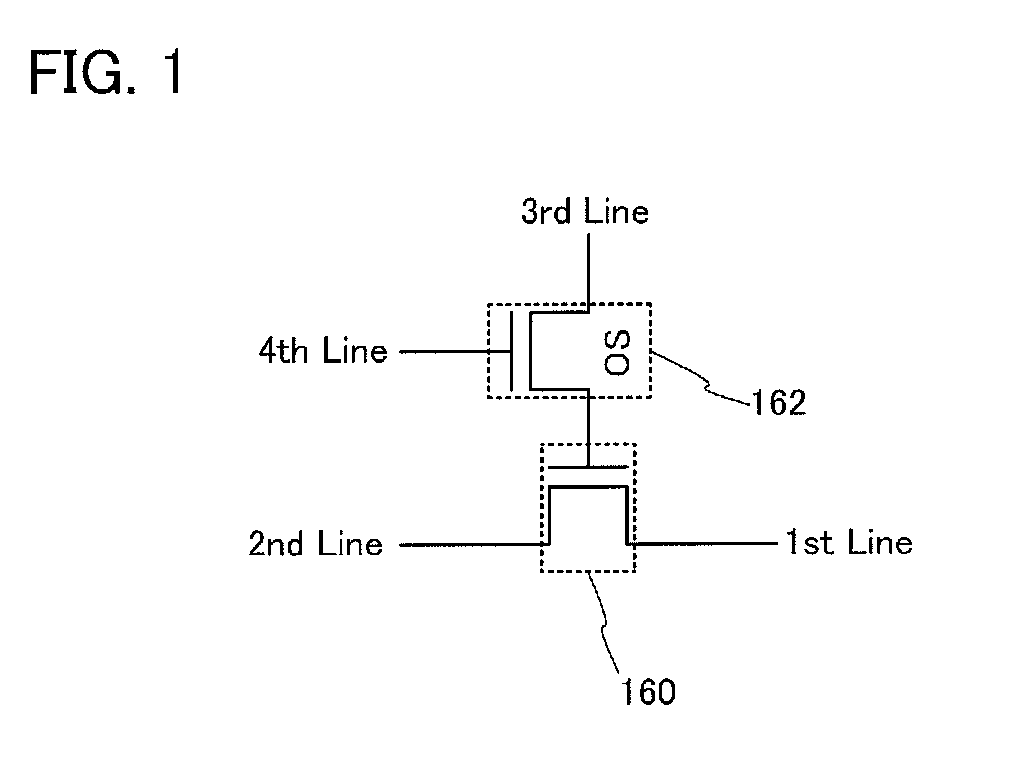

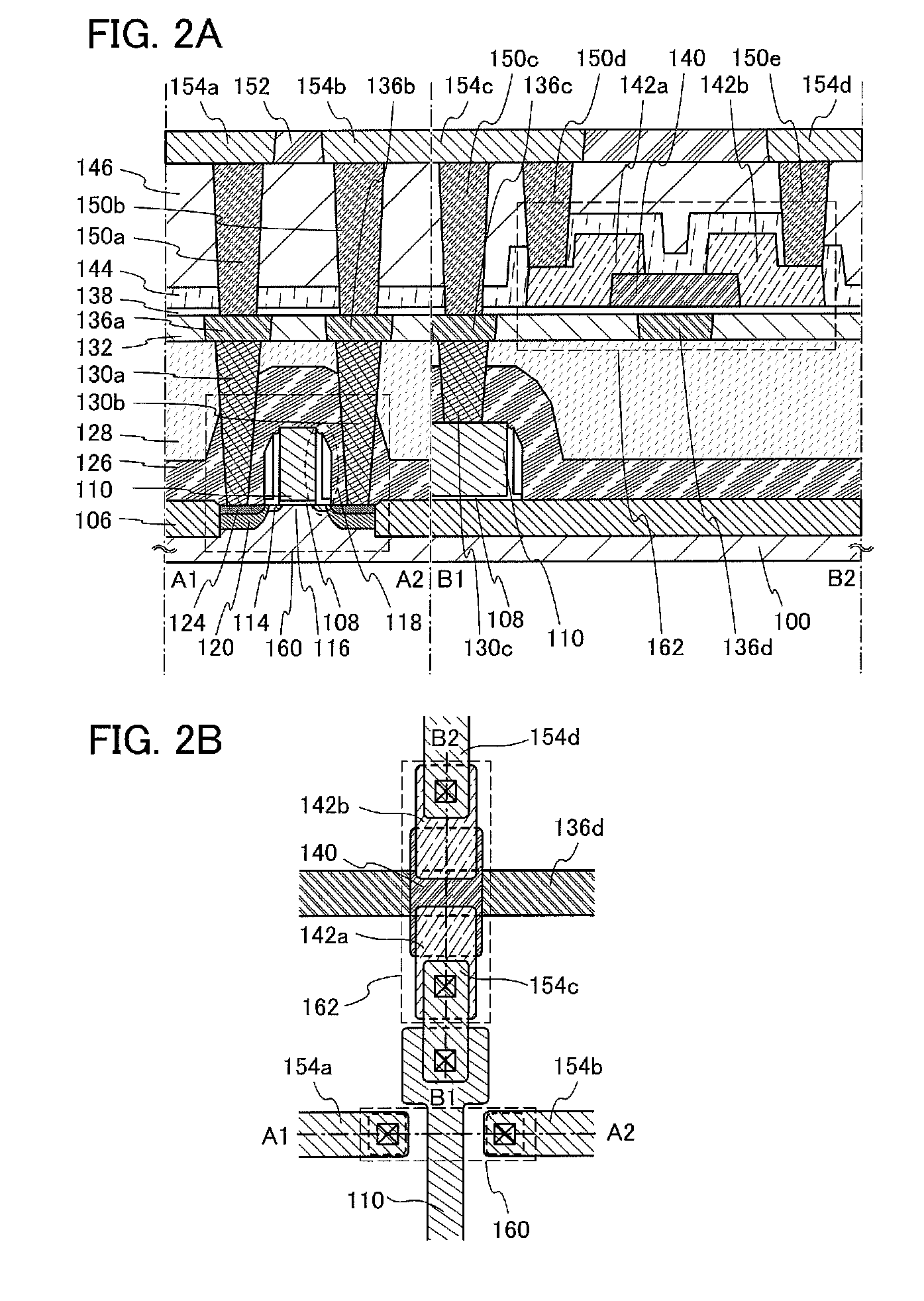

Disclosed is a semiconductor device functioning as a multivalued memory device including: memory cells connected in series; a driver circuit selecting a memory cell and driving a second signal line and a word line; a driver circuit selecting any of writing potentials and outputting it to a first signal line; a reading circuit comparing a potential of a bit line and a reference potential; and a potential generating circuit generating the writing potential and the reference potential. One of the memory cells includes: a first transistor connected to the bit line and a source line; a second transistor connected to the first and second signal line; and a third transistor connected to the word line, bit line, and source line. The second transistor includes an oxide semiconductor layer. A gate electrode of the first transistor is connected to one of source and drain electrodes of the second transistor.

Owner:SEMICON ENERGY LAB CO LTD

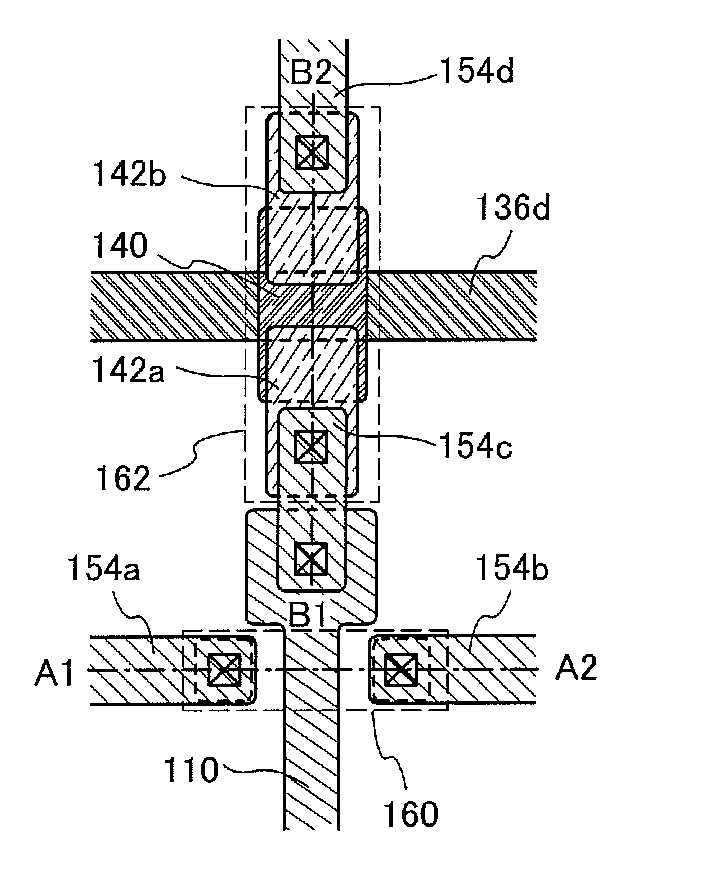

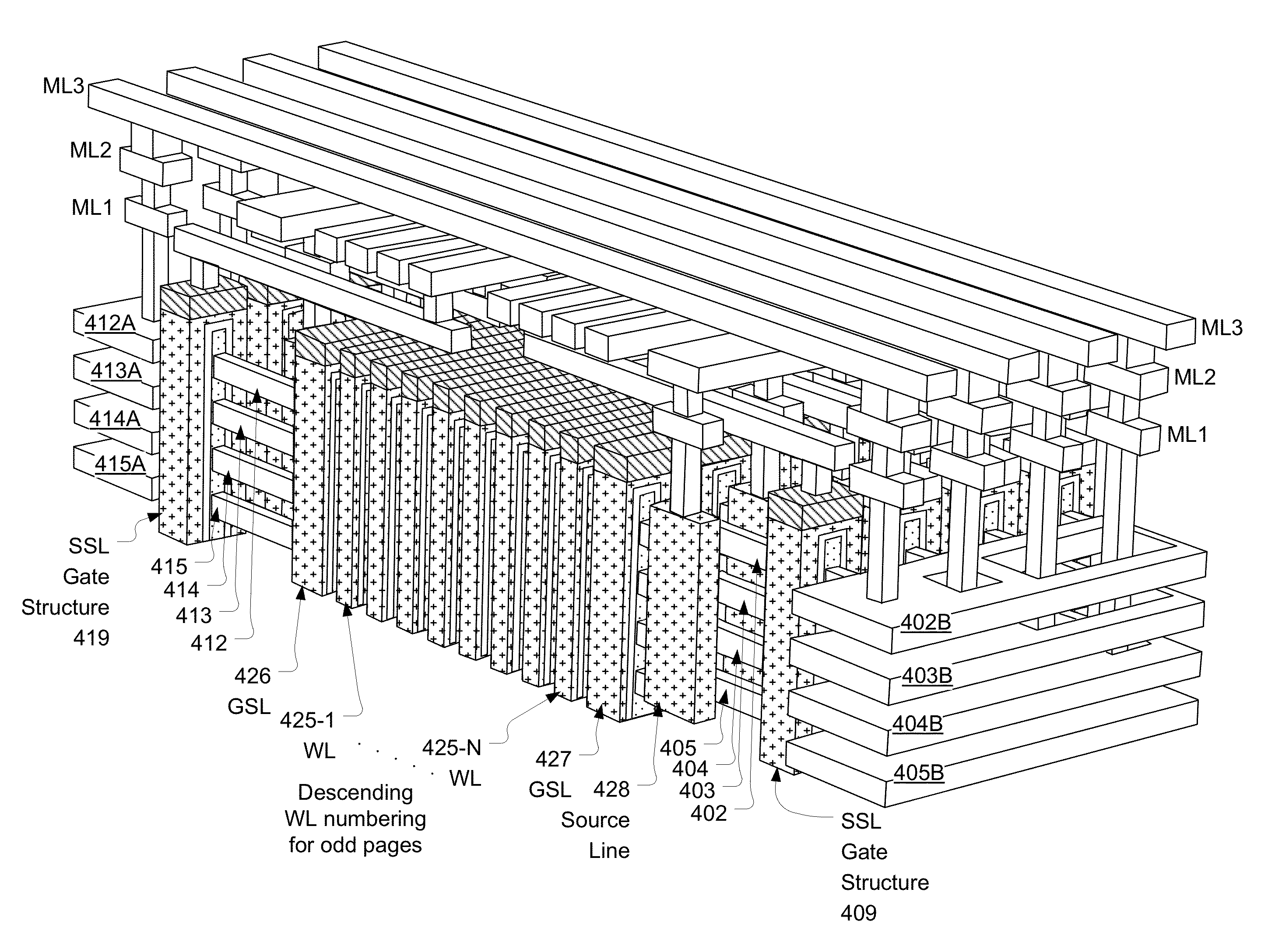

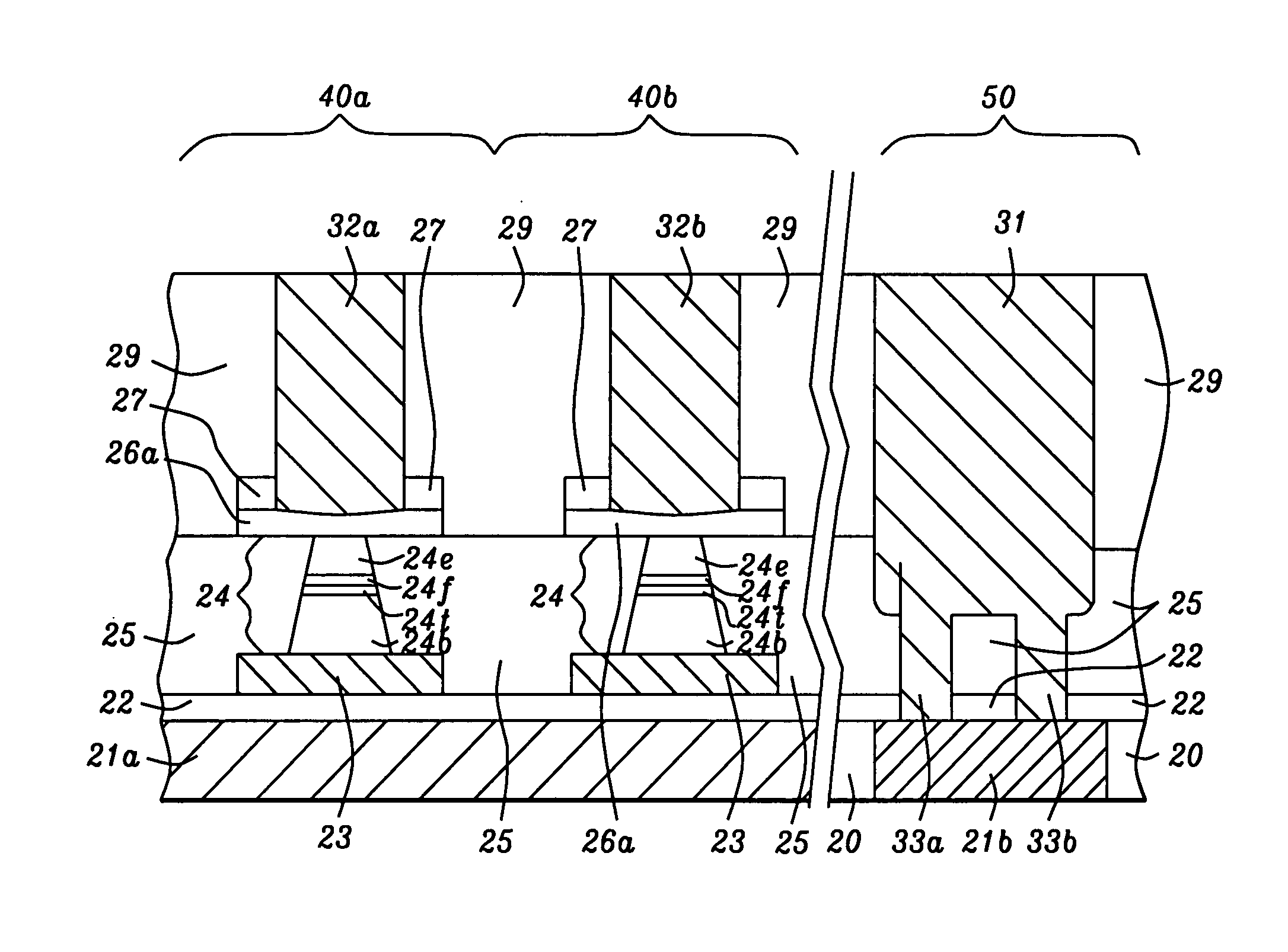

Memory Device, Manufacturing Method and Operating Method of the Same

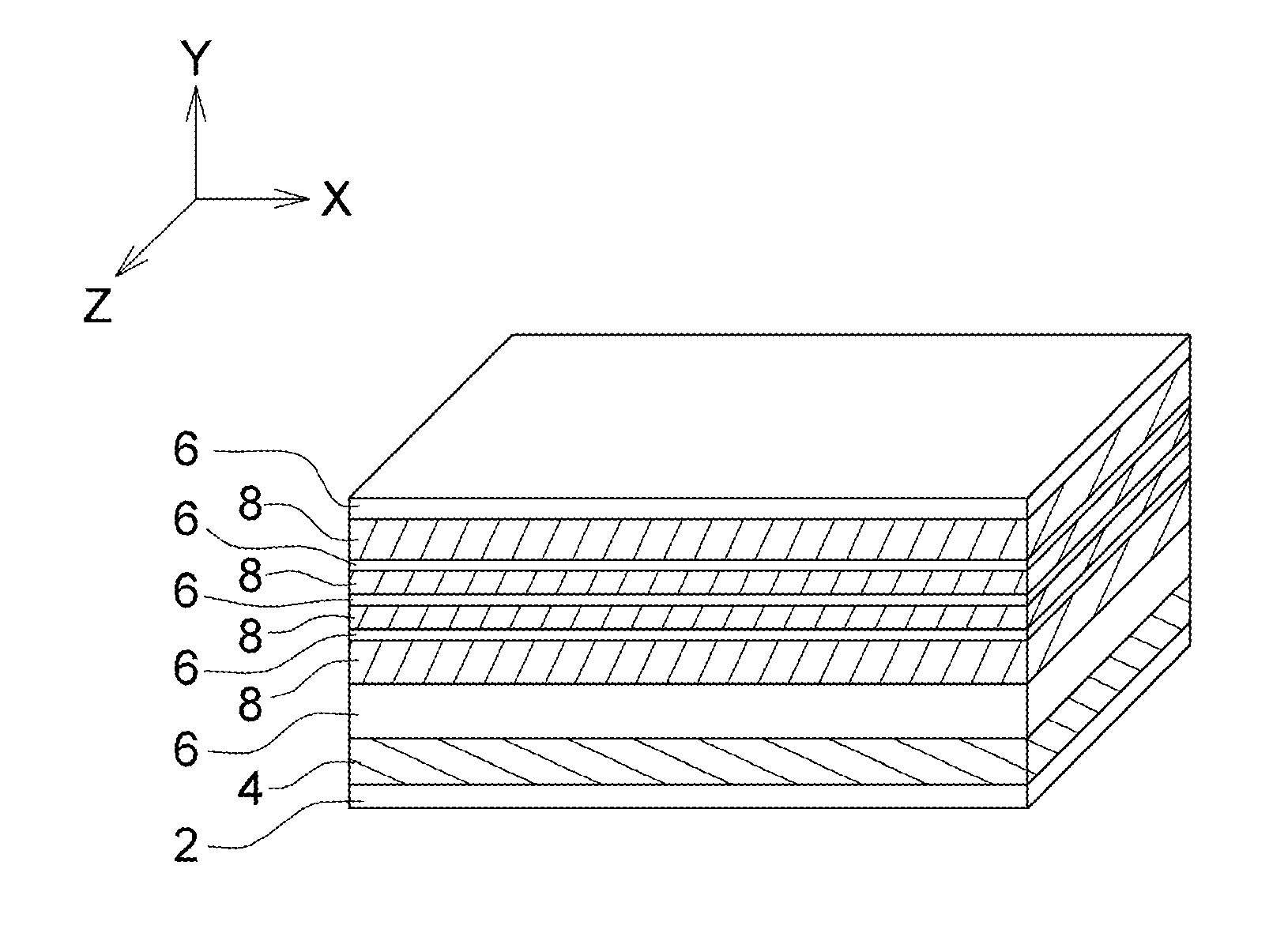

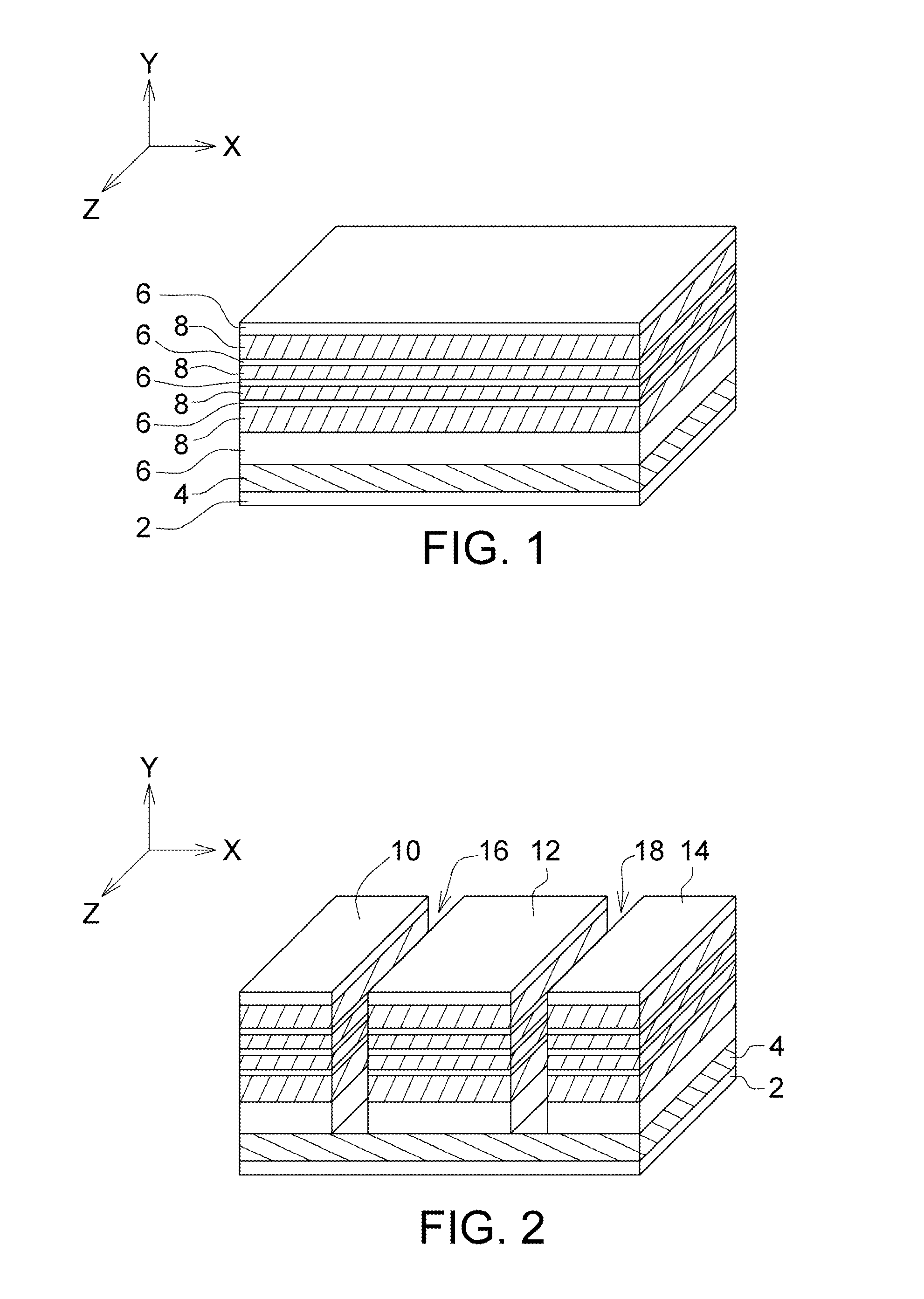

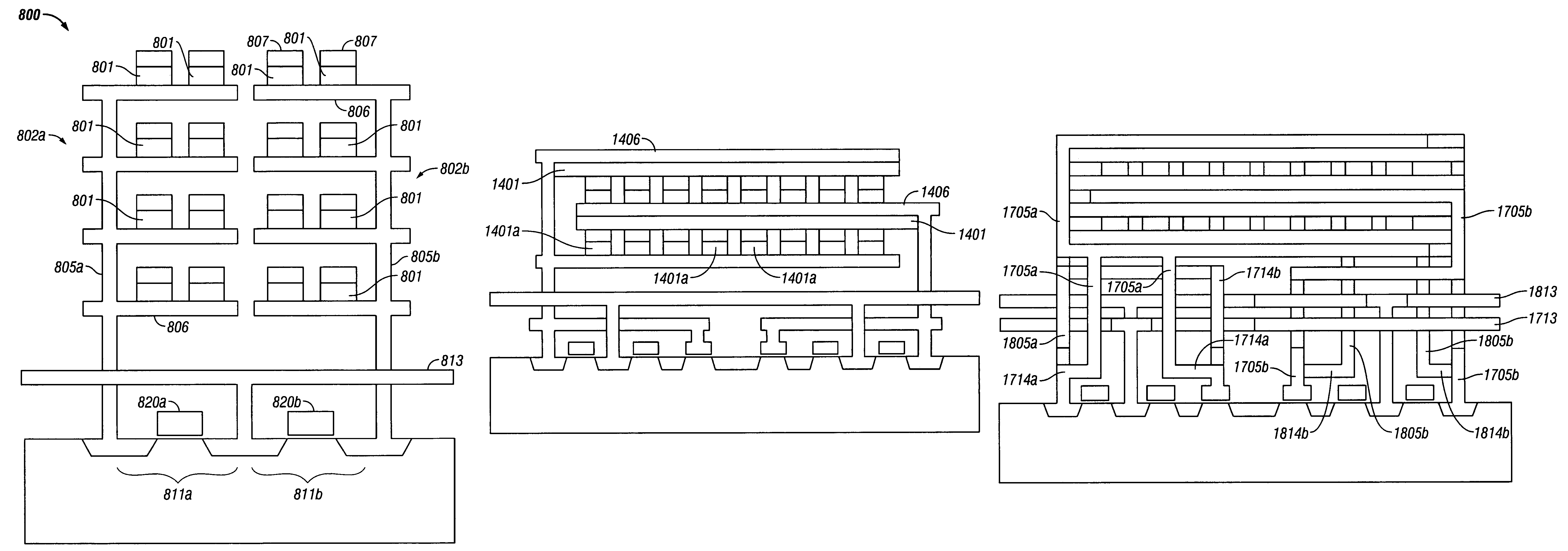

ActiveUS20120182808A1Small scaling featureImprove performanceSolid-state devicesRead-only memoriesDielectricSource element

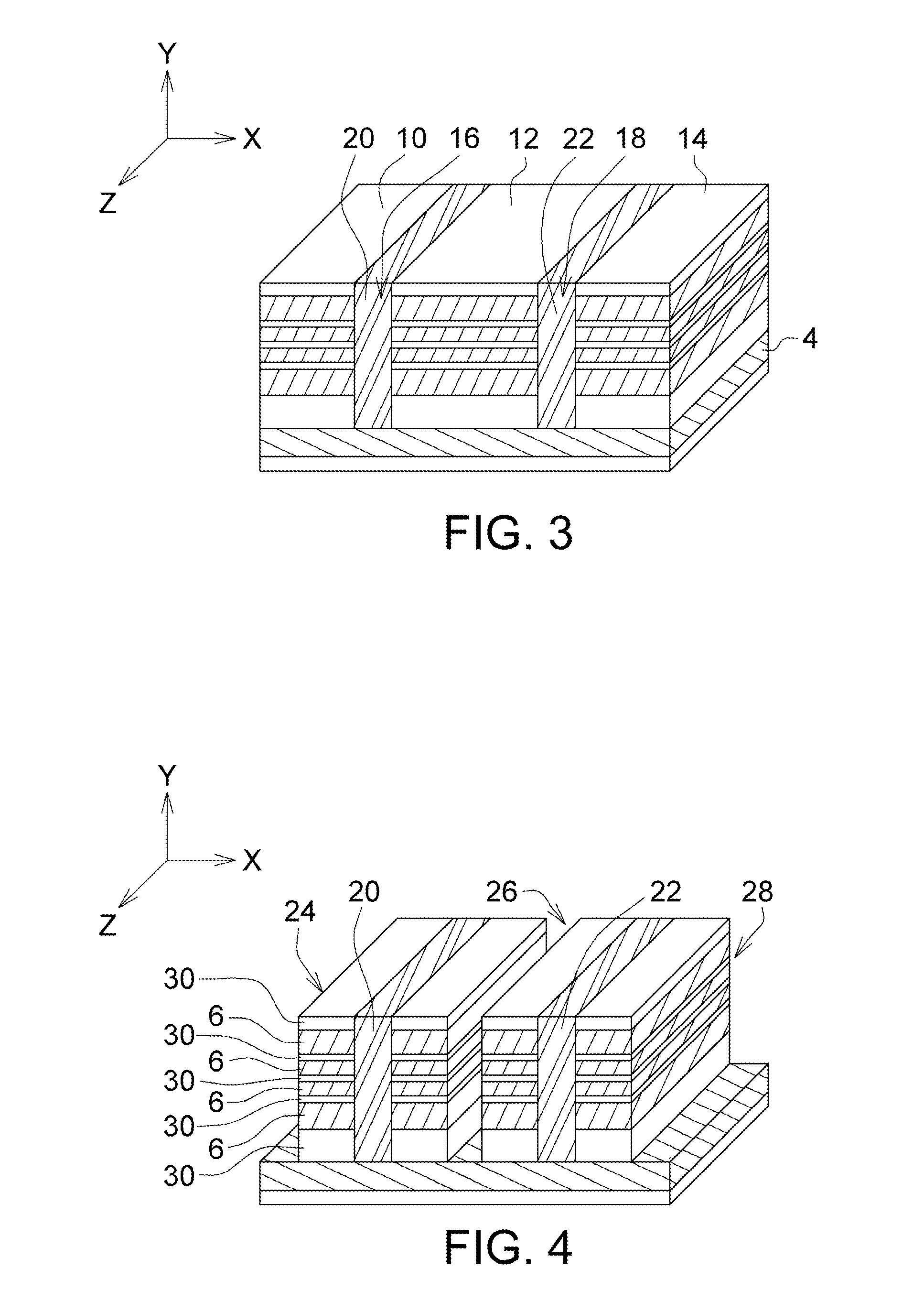

A memory device, a manufacturing method and an operating method of the same are provided. The memory device includes a substrate, stacked structures, a channel element, a dielectric element, a source element, and a bit line. The stacked structures are disposed on the substrate. Each of the stacked structures includes a string selection line, a word line, a ground selection line and an insulating line. The string selection line, the word line and the ground selection line are separated from each other by the insulating line. The channel element is disposed between the stacked structures. The dielectric element is disposed between the channel element and the stacked structure. The source element is disposed between the upper surface of the substrate and the lower surface of the channel element. The bit line is disposed on the upper surface of the channel element.

Owner:MACRONIX INT CO LTD

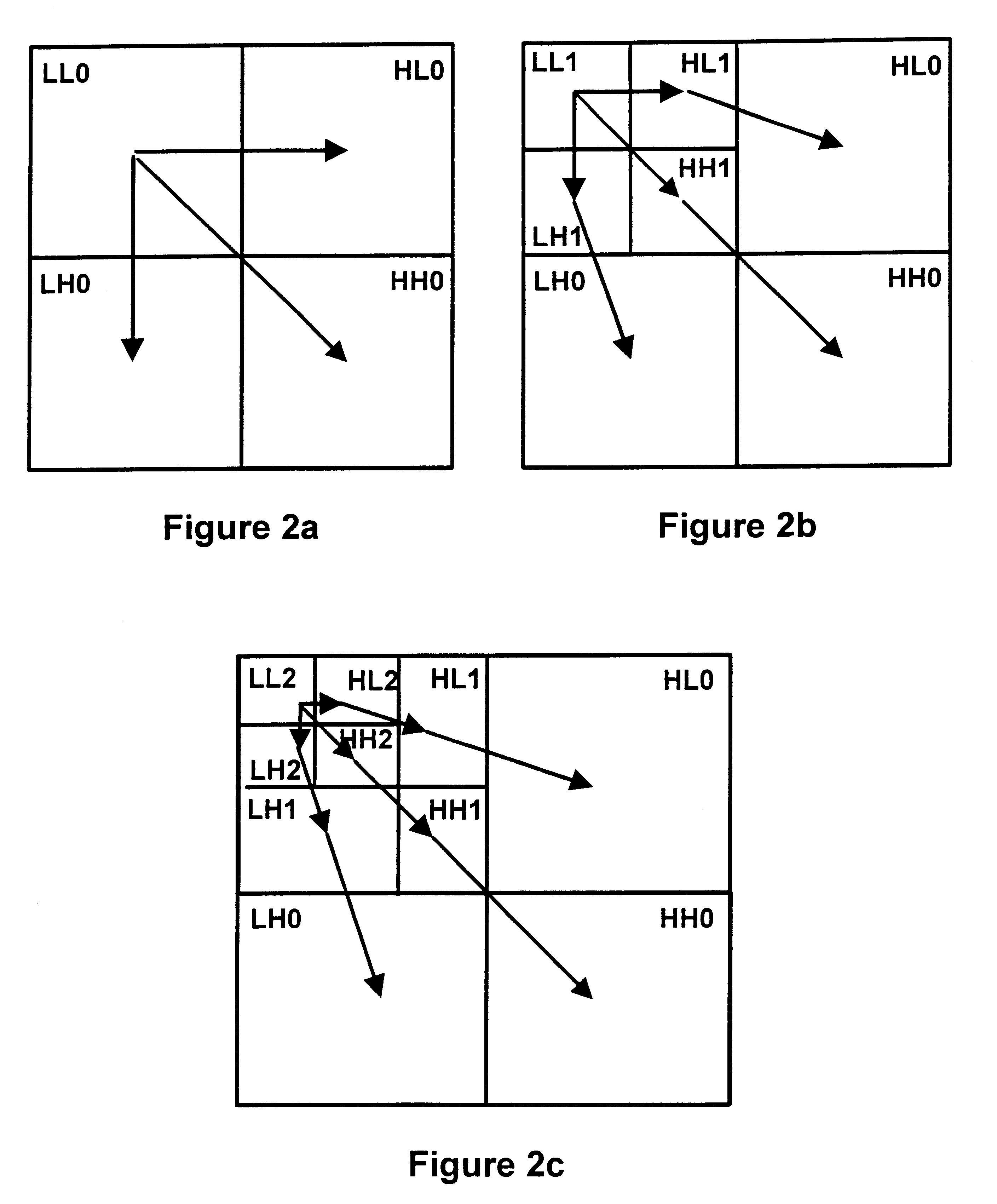

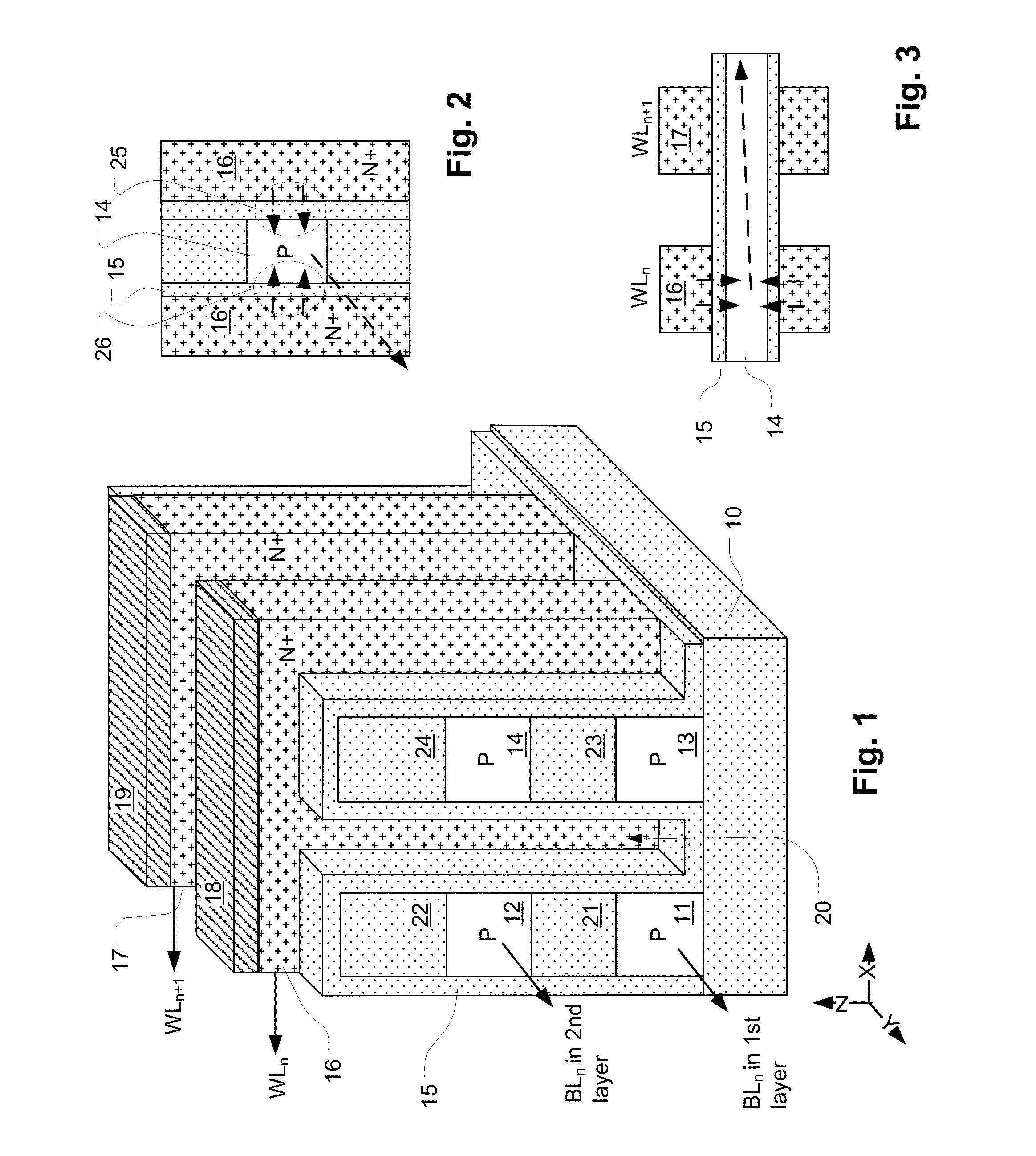

Memory Architecture of 3D Array With Alternating Memory String Orientation and String Select Structures

ActiveUS20120182806A1Increase pitchImproved gate structureSolid-state devicesRead-only memoriesArray data structureConductive materials

Owner:MACRONIX INT CO LTD

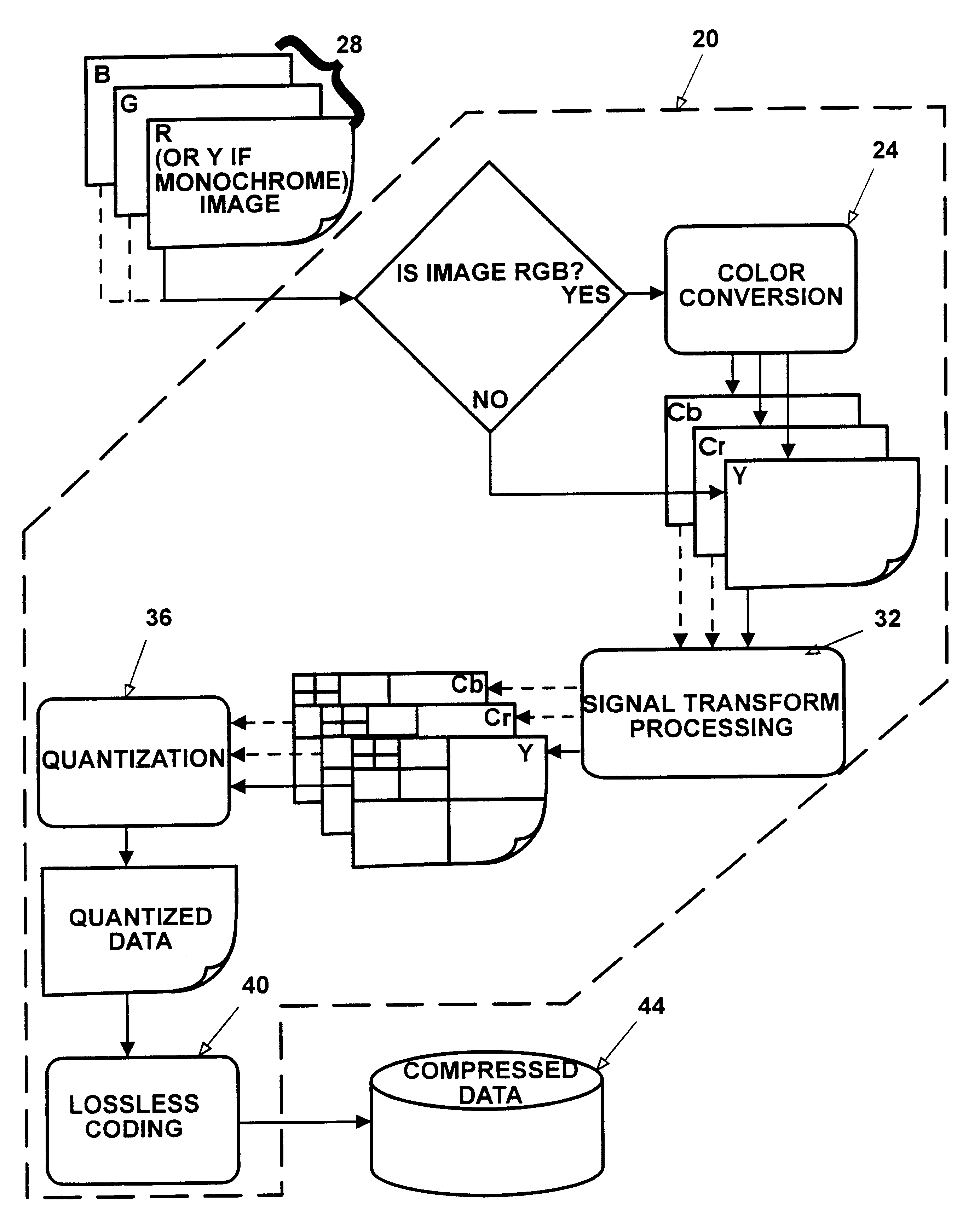

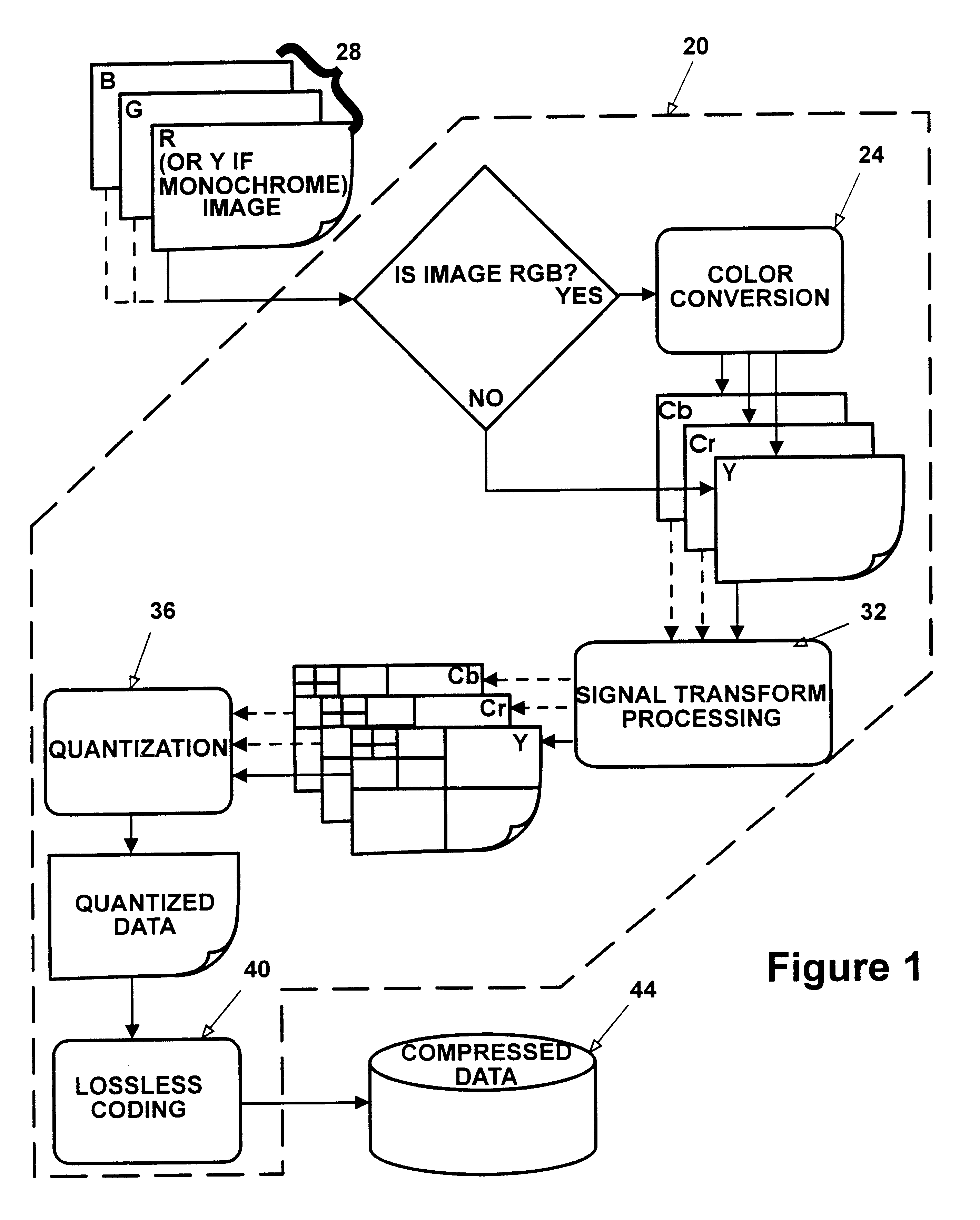

Method apparatus and system for compressing data that wavelet decomposes by color plane and then divides by magnitude range non-dc terms between a scalar quantizer and a vector quantizer

InactiveUS6865291B1Color television with pulse code modulationColor television with bandwidth reductionData compressionImaging quality

An apparatus and method for image data compression performs a modified zero-tree coding on a range of image bit plane values from the largest to a defined smaller value, and a vector quantizer codes the remaining values and lossless coding is performed on the results of the two coding steps. The defined smaller value can be adjusted iteratively to meet a preselected compressed image size criterion or to meet a predefined level of image quality, as determined by any suitable metric. If the image to be compressed is in RGB color space, the apparatus converts the RGB image to a less redundant color space before commencing further processing.

Owner:WDE

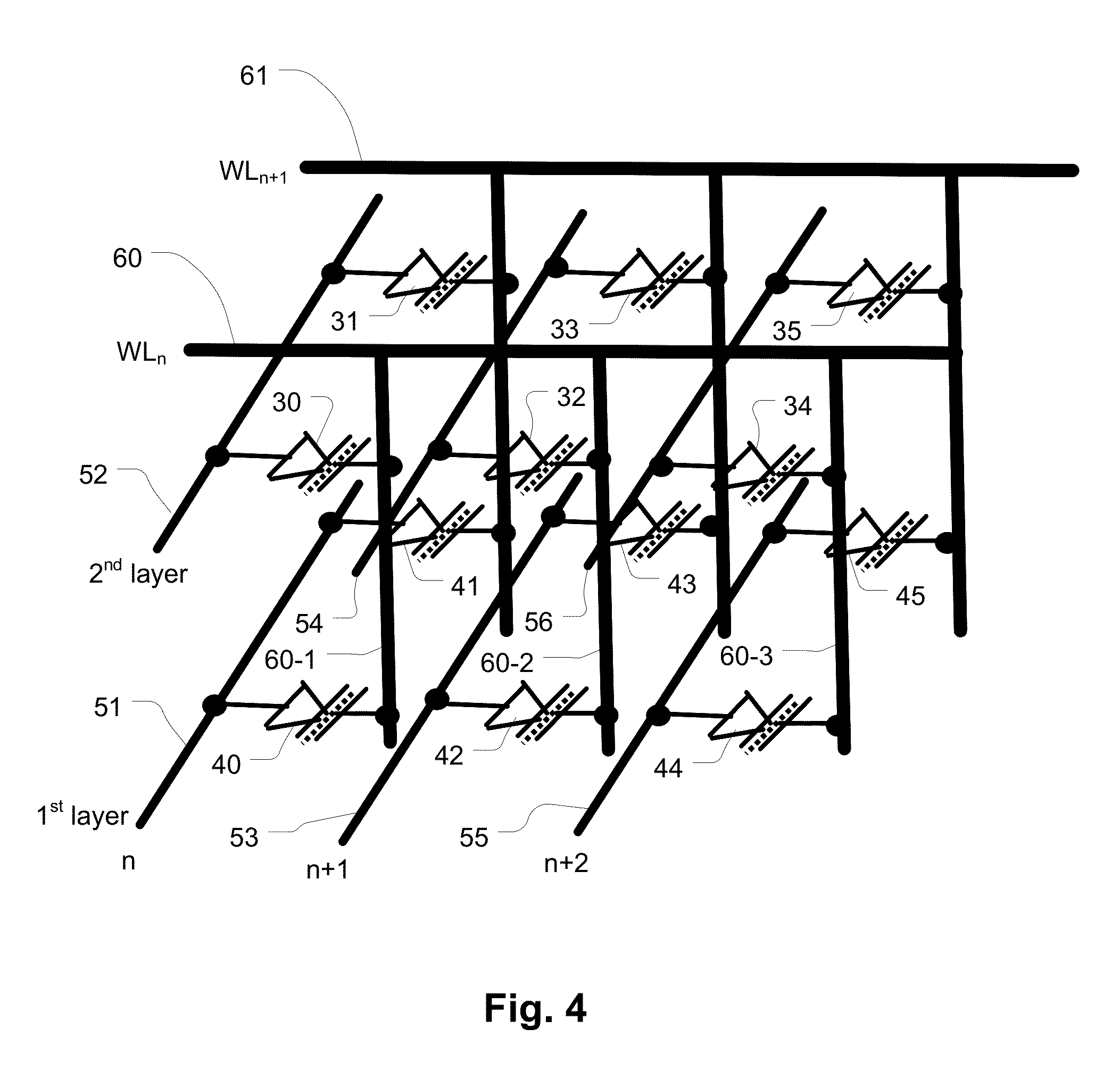

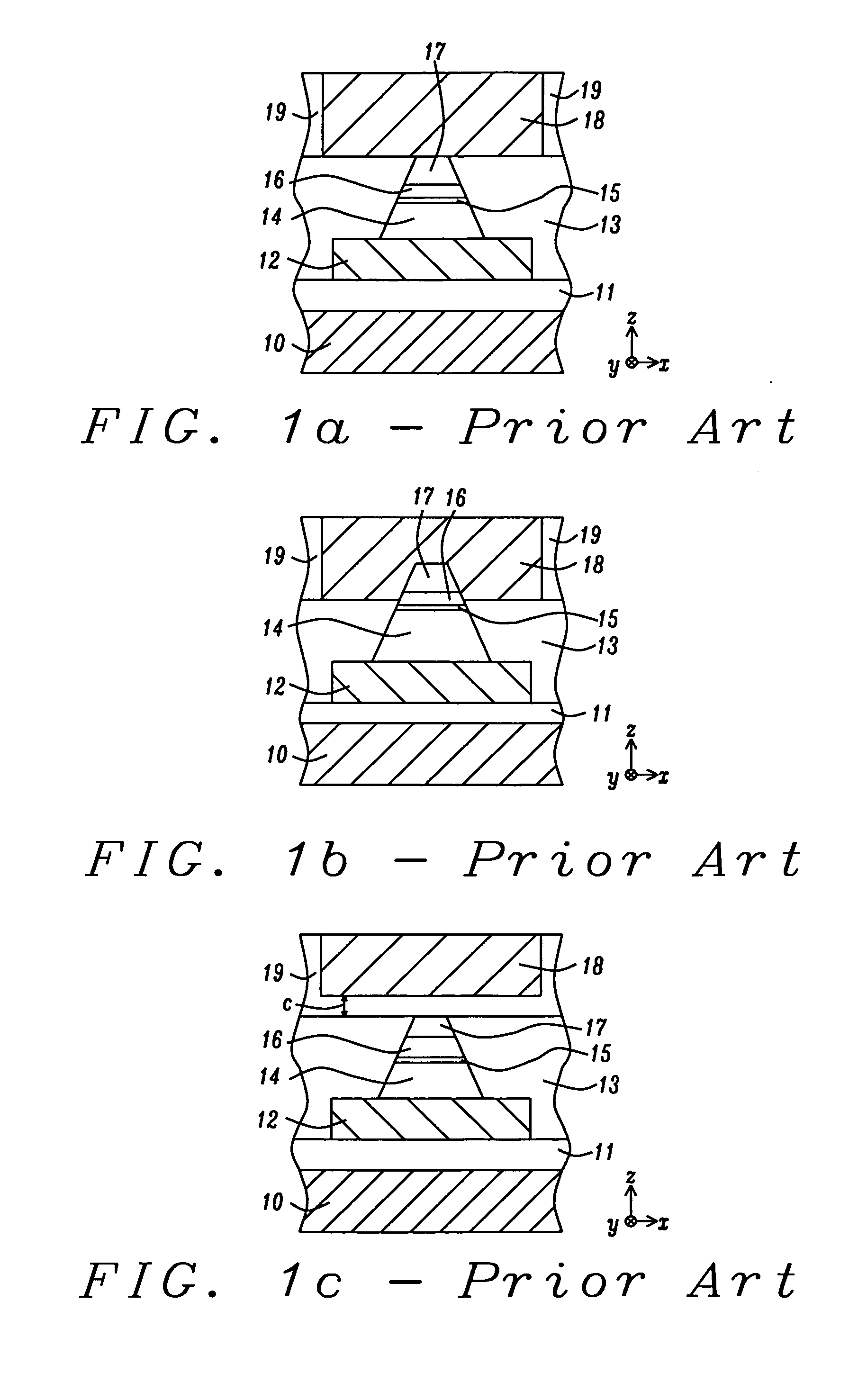

Memory architecture of 3D array with alternating memory string orientation and string select structures

ActiveUS8503213B2Increase pitchPitch is improvedSolid-state devicesRead-only memoriesAudio power amplifierConductive materials

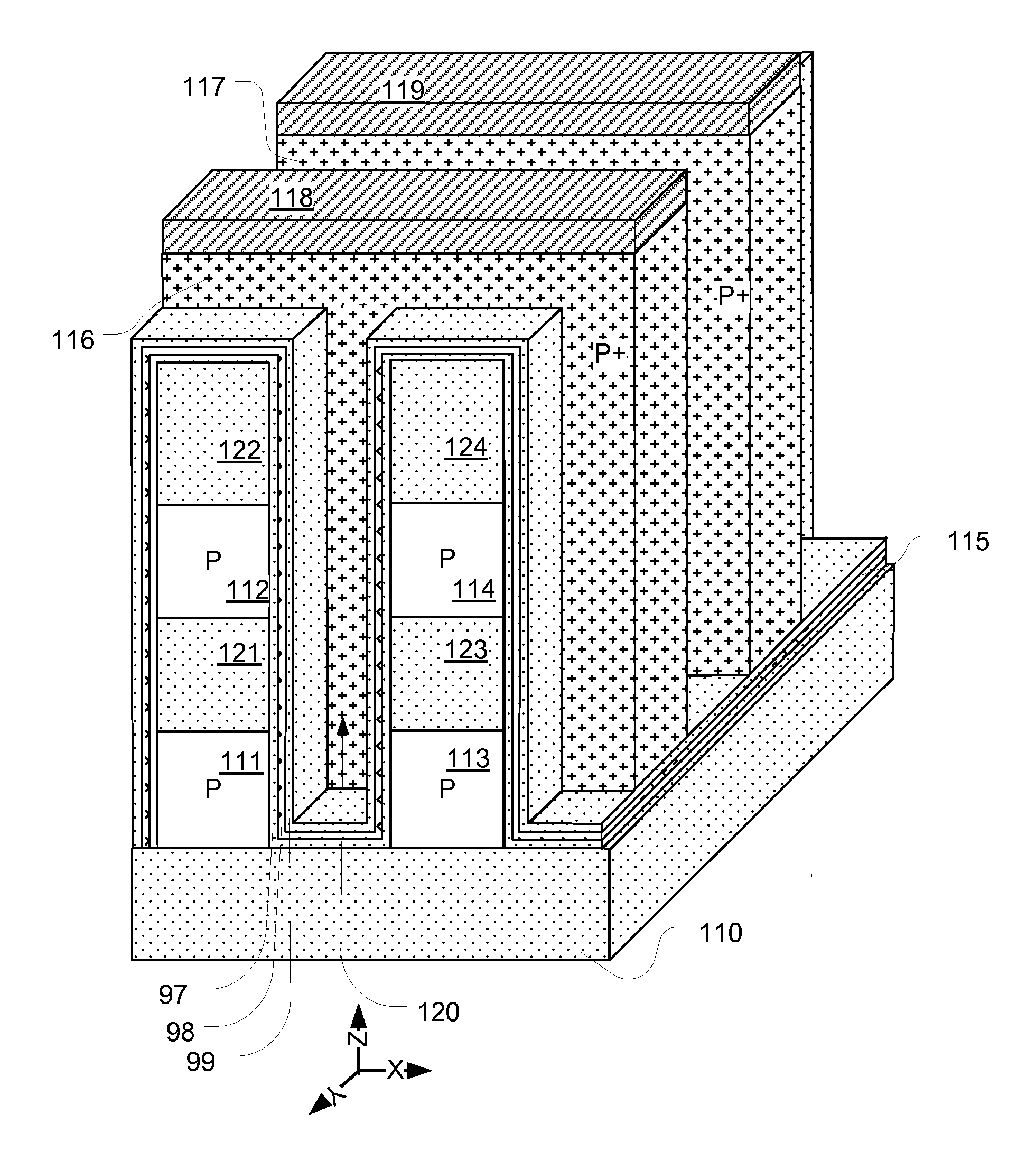

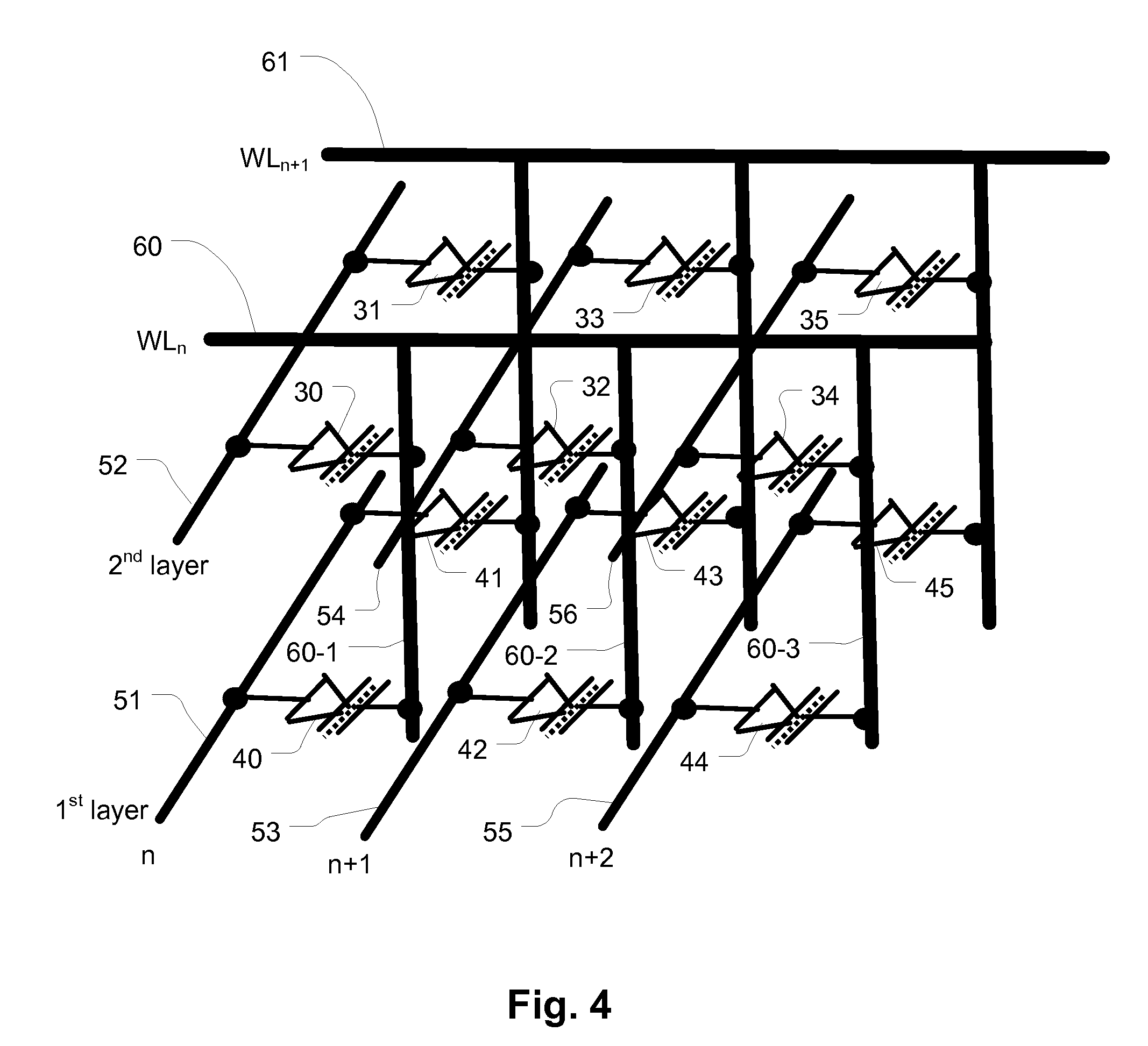

A 3D memory device includes a plurality of ridge-shaped stacks, in the form of multiple strips of conductive material separated by insulating material, arranged as bit lines which can be coupled through decoding circuits to sense amplifiers. Diodes are connected to the bit lines at either the string select of common source select ends of the strings. The strips of conductive material have side surfaces on the sides of the ridge-shaped stacks. A plurality of word lines, which can be coupled to row decoders, extends orthogonally over the plurality of ridge-shaped stacks. Memory elements lie in a multi-layer array of interface regions at cross-points between side surfaces of the semiconductor strips on the stacks and the word lines.

Owner:MACRONIX INT CO LTD

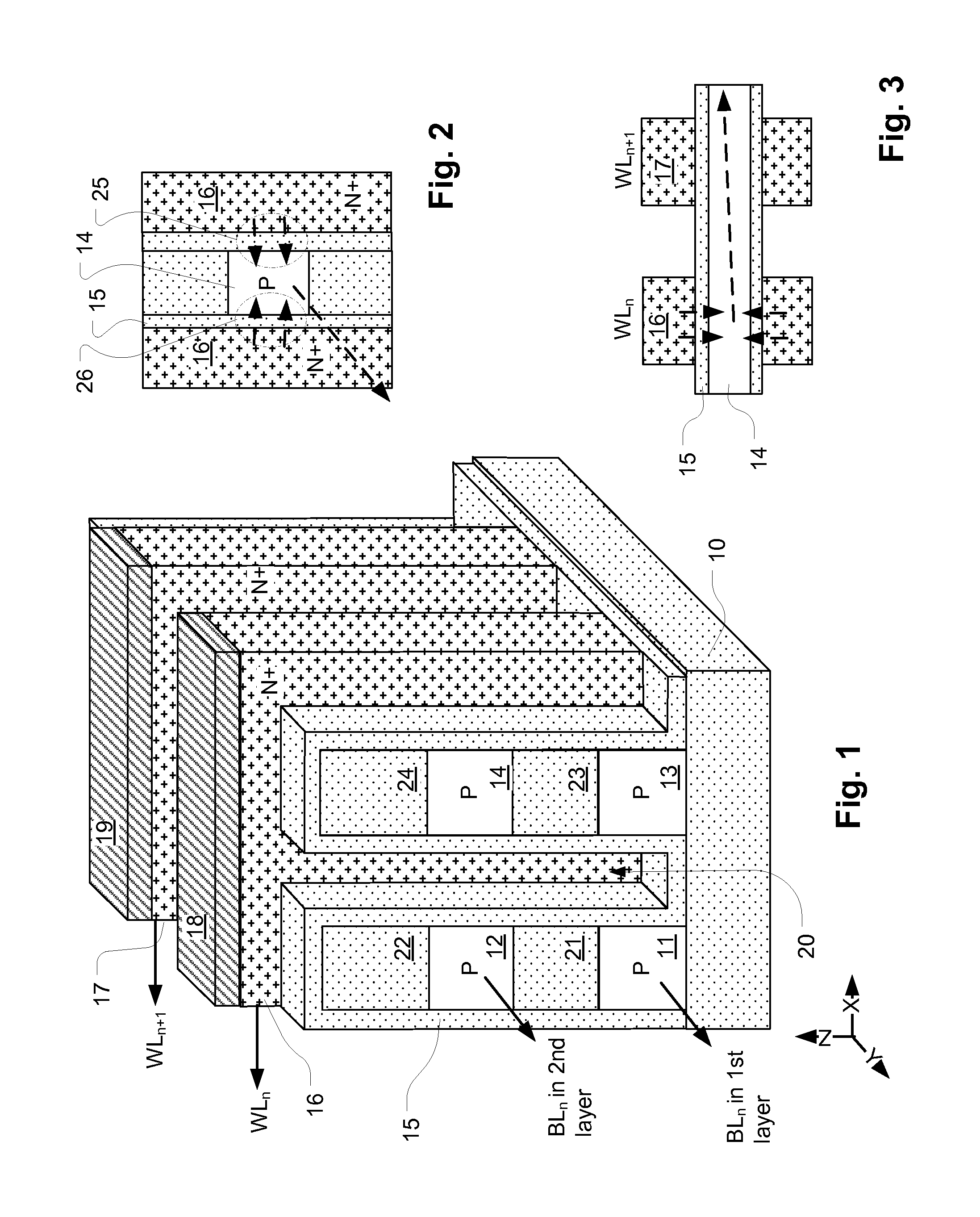

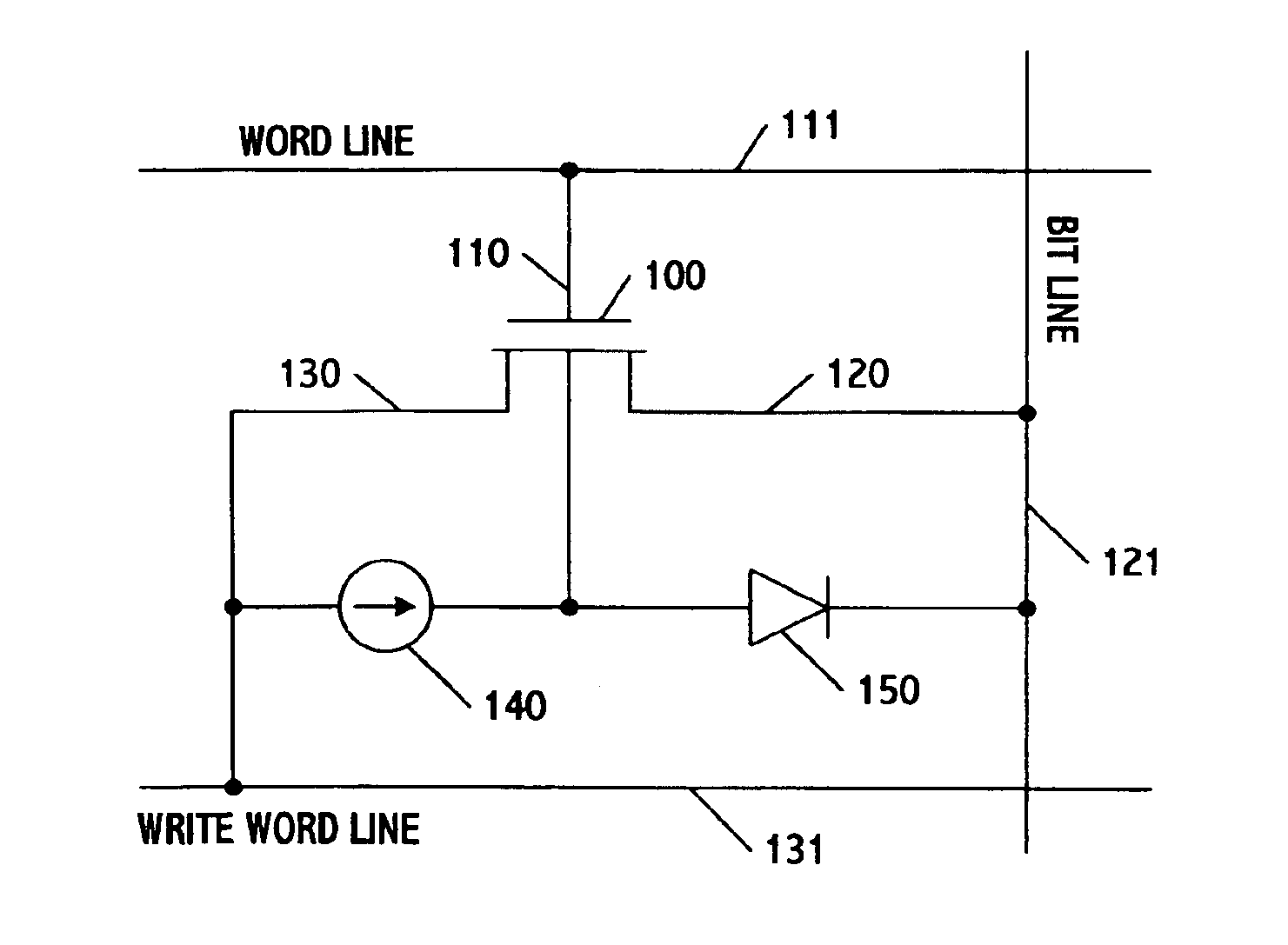

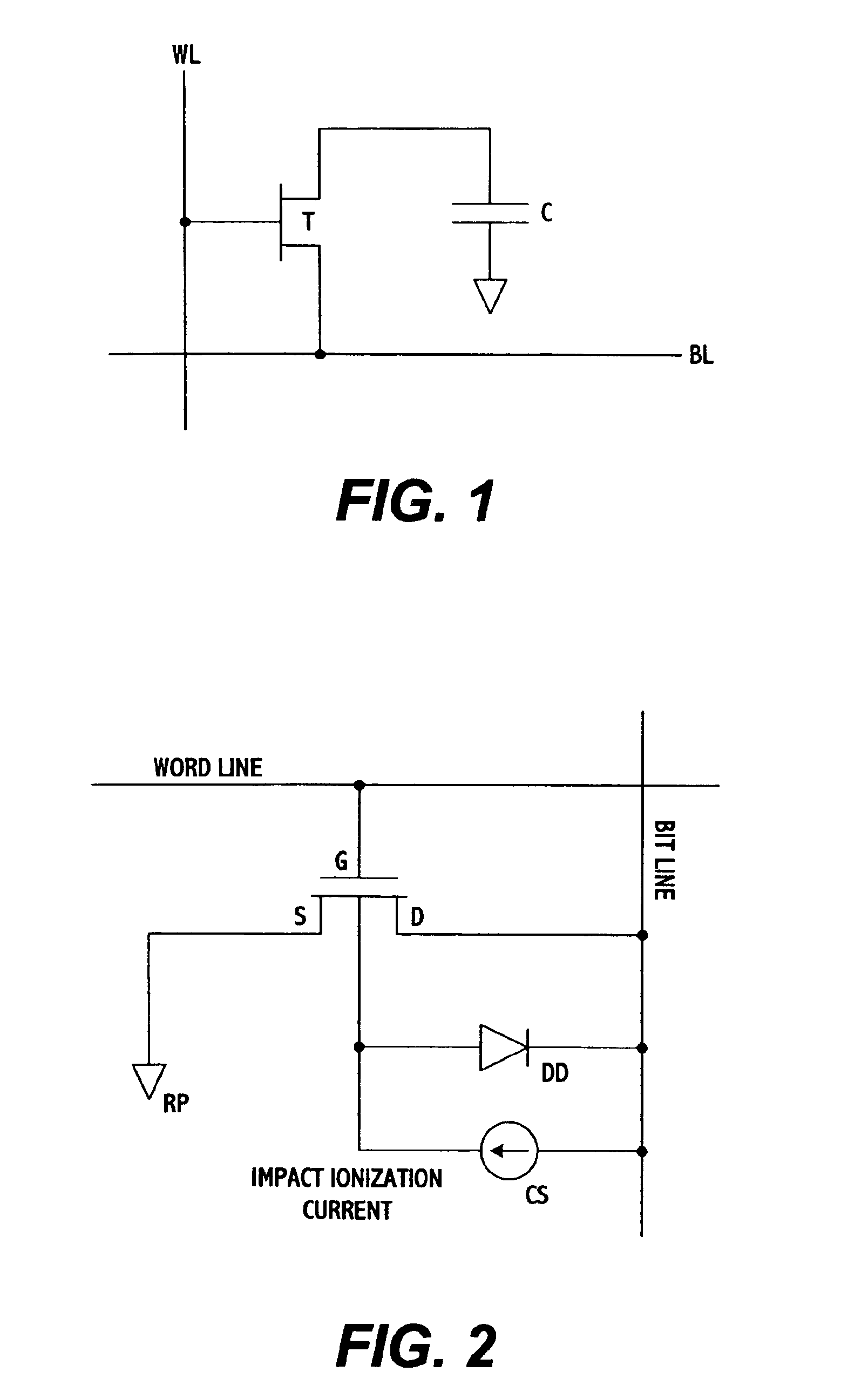

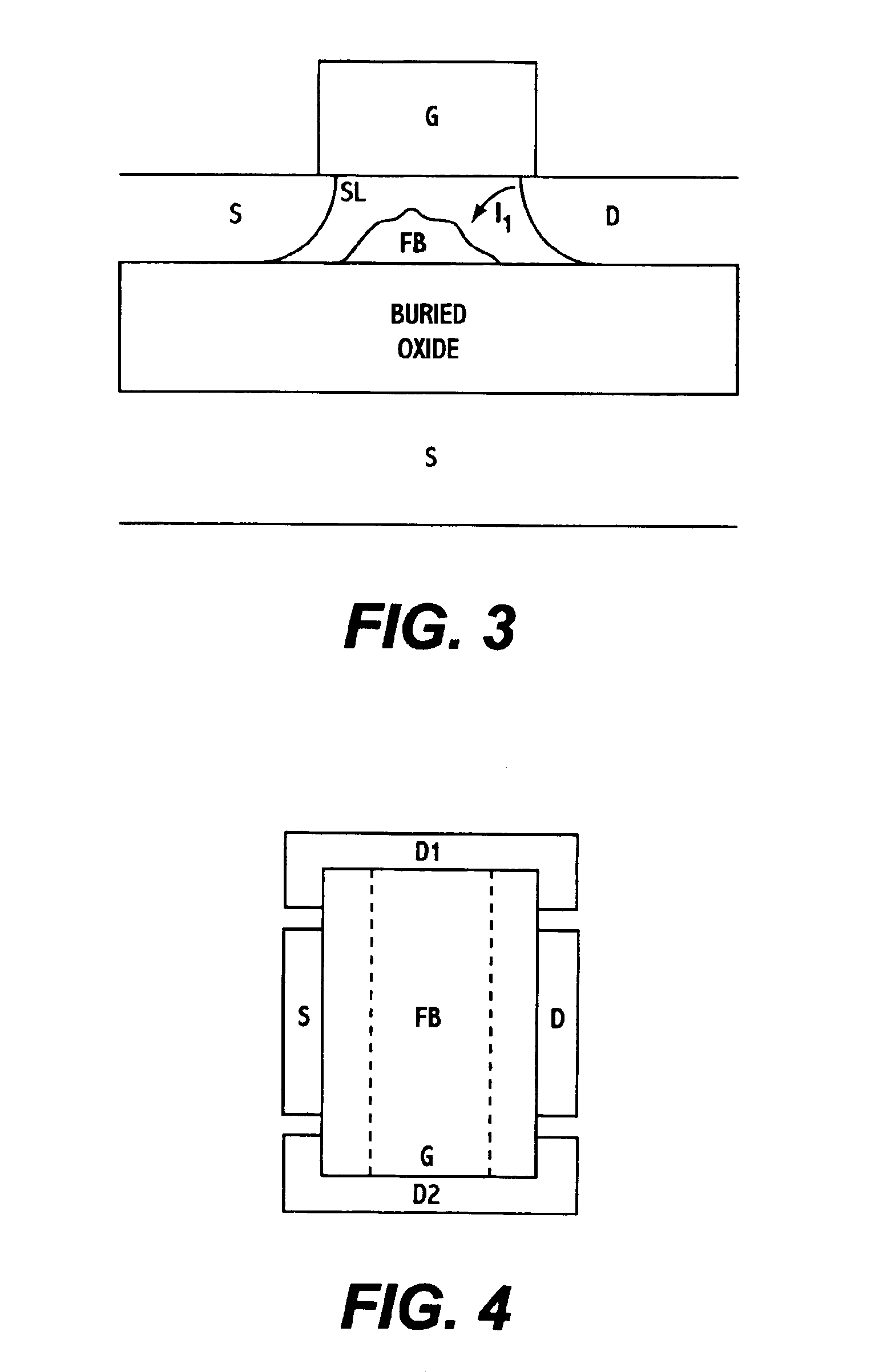

Floating-body DRAM using write word line for increased retention time

A DRAM memory cell uses a single transistor to perform the data storage and switching functions of a conventional cell. The transistor has a floating channel body which stores a potential that corresponds to one of two digital data values. The transistor further includes a gate connected to a first word line, a drain connected to a second word line, and a source connected to a bit line. By setting the word and bit lines to specific voltage states, the channel body stores a digital one potential as a result of impact ionization and a digital zero value as a result of forward bias of body-to-source junction.

Owner:INTEL CORP

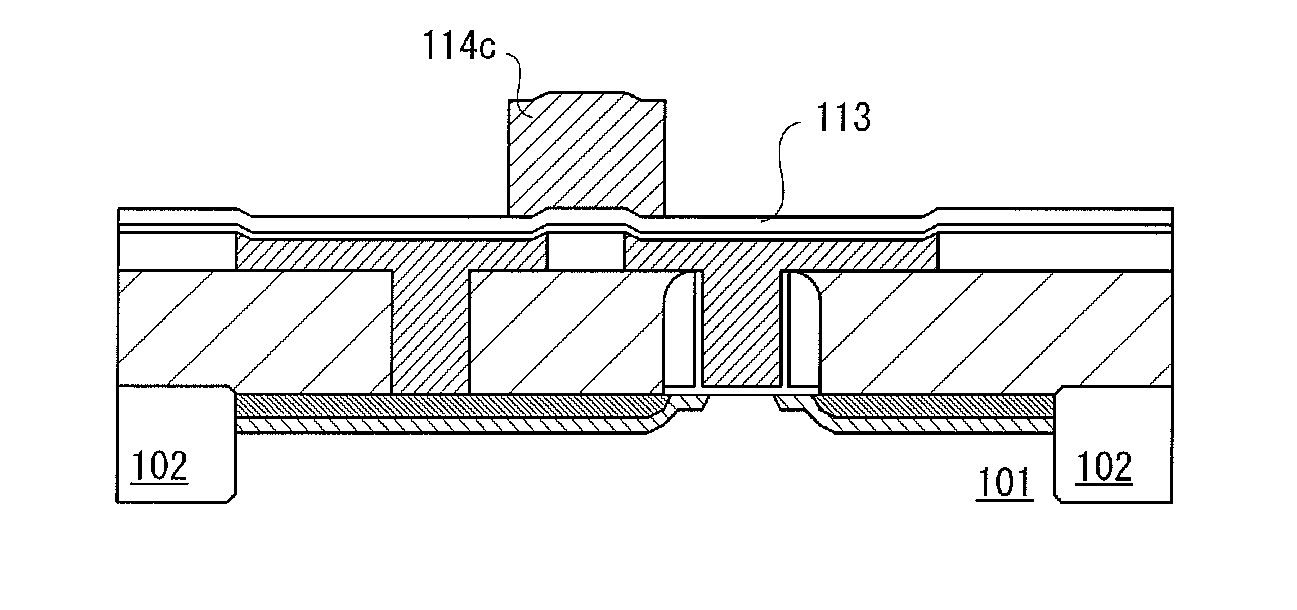

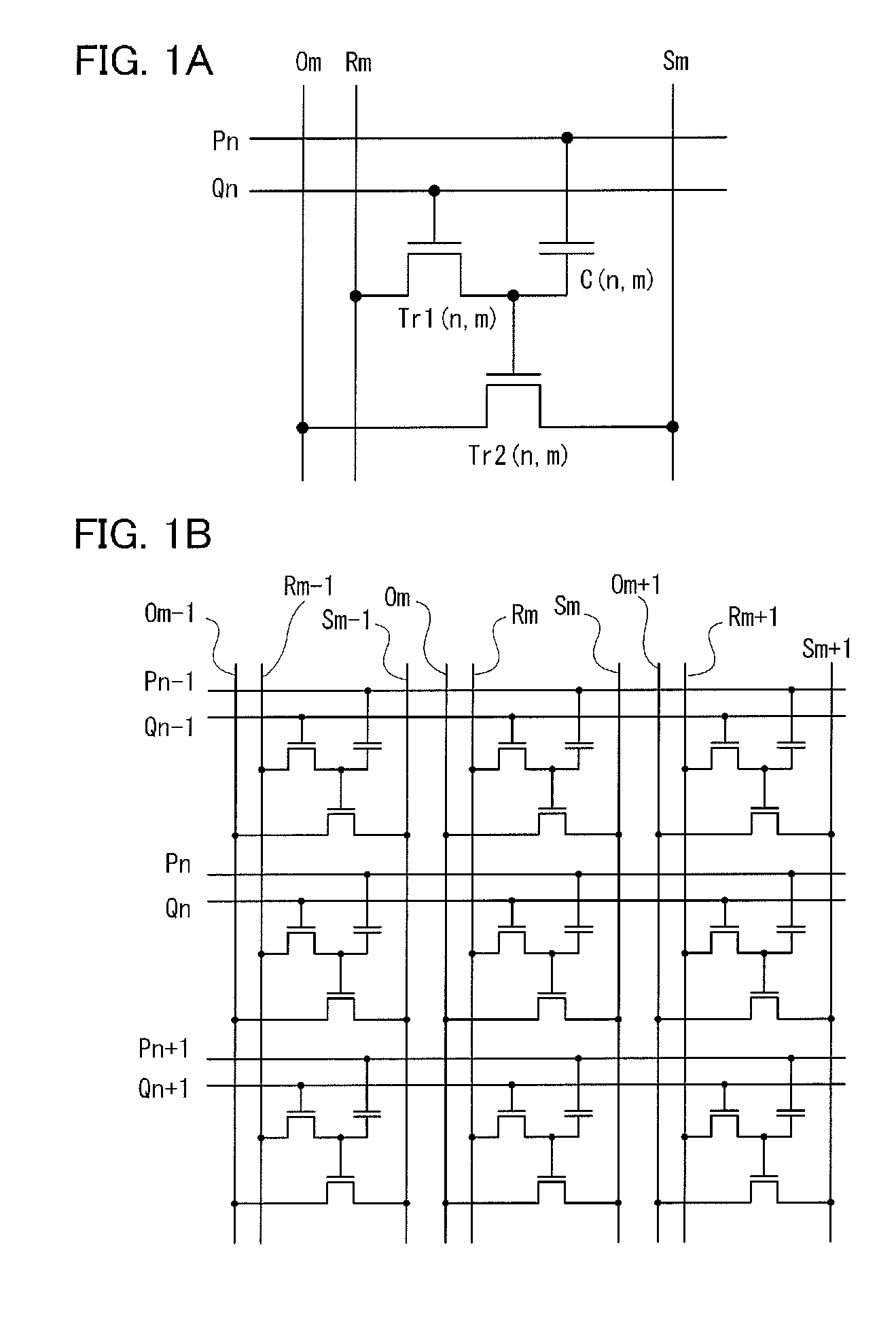

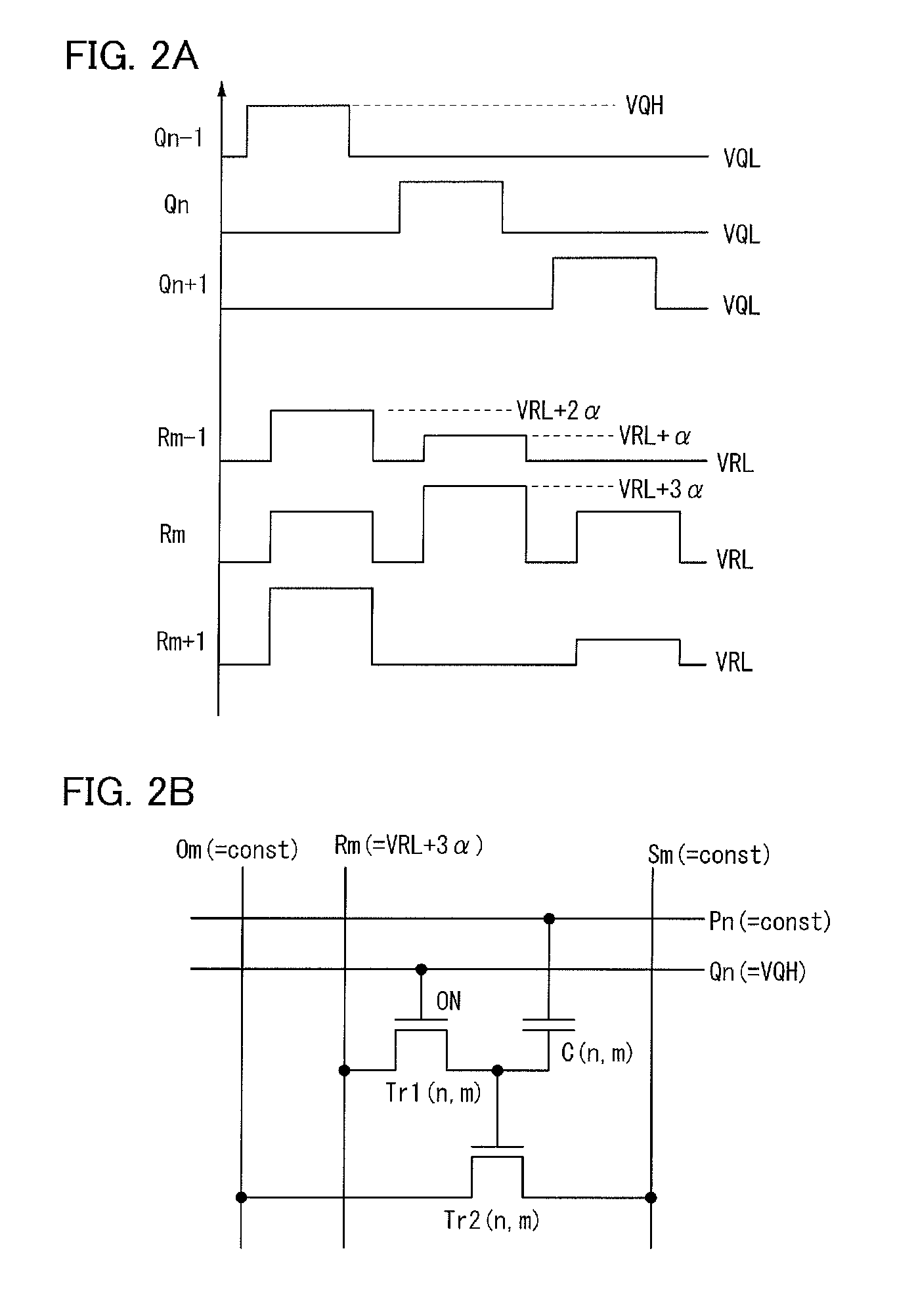

Semiconductor memory device and driving method thereof

ActiveUS20110182110A1Reduce power consumptionNovel structureSolid-state devicesRead-only memoriesWrite bitEngineering

A semiconductor device which stores data by using a transistor whose leakage current between source and drain in an off state is small as a writing transistor. In a matrix including a plurality of memory cells in which a drain of the writing transistor is connected to a gate of a reading transistor and the drain of the writing transistor is connected to one electrode of a capacitor, a gate of the writing transistor is connected to a writing word line; a source of the writing transistor is connected to a writing bit line; and a source and a drain of the reading transistor are connected to a reading bit line and a bias line. In order to reduce the number of wirings, the writing bit line or the bias line is substituted for the reading bit line in another column.

Owner:SEMICON ENERGY LAB CO LTD

JPEG2000 self-adapted rate control system and method based on pre-allocated code rate

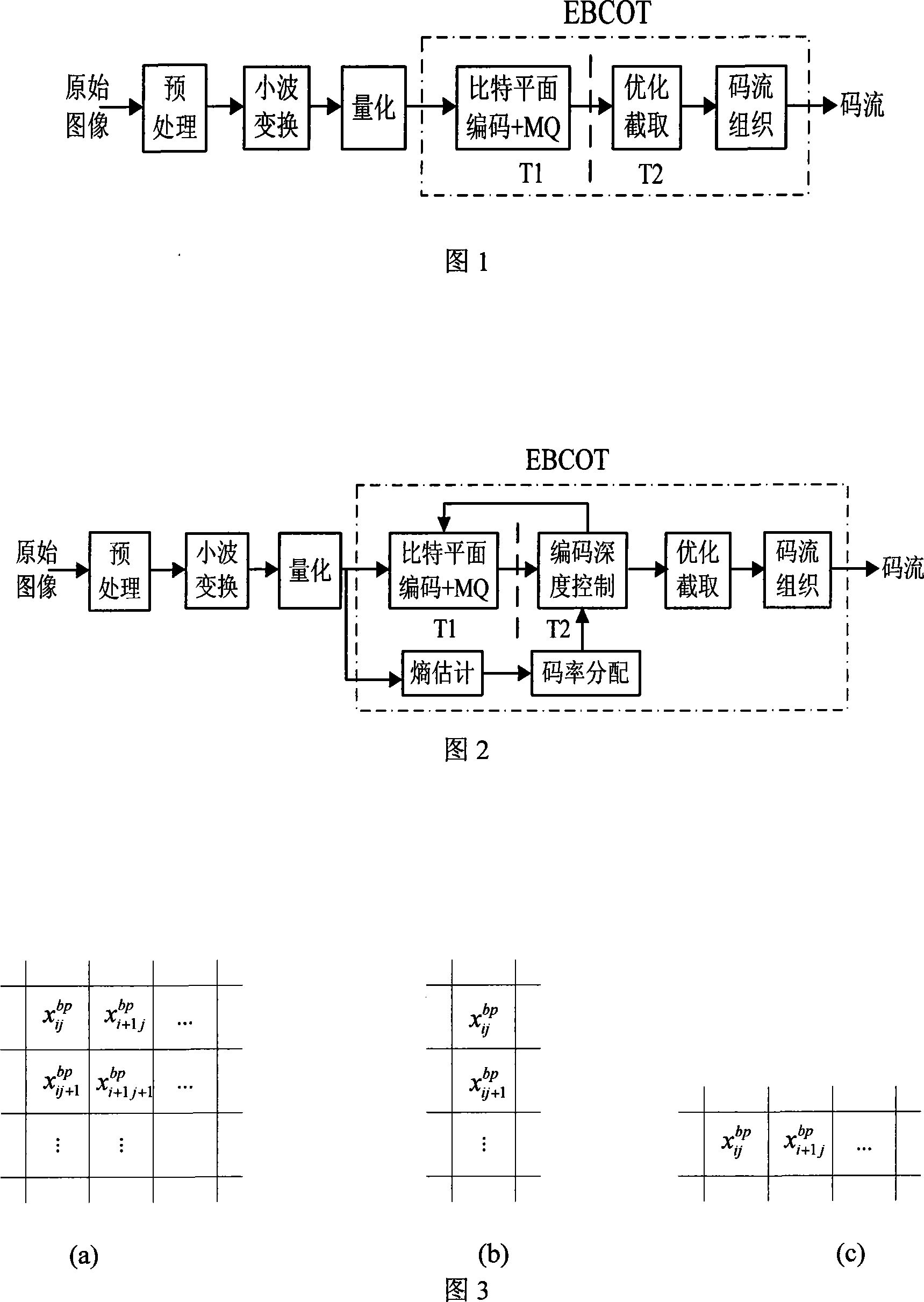

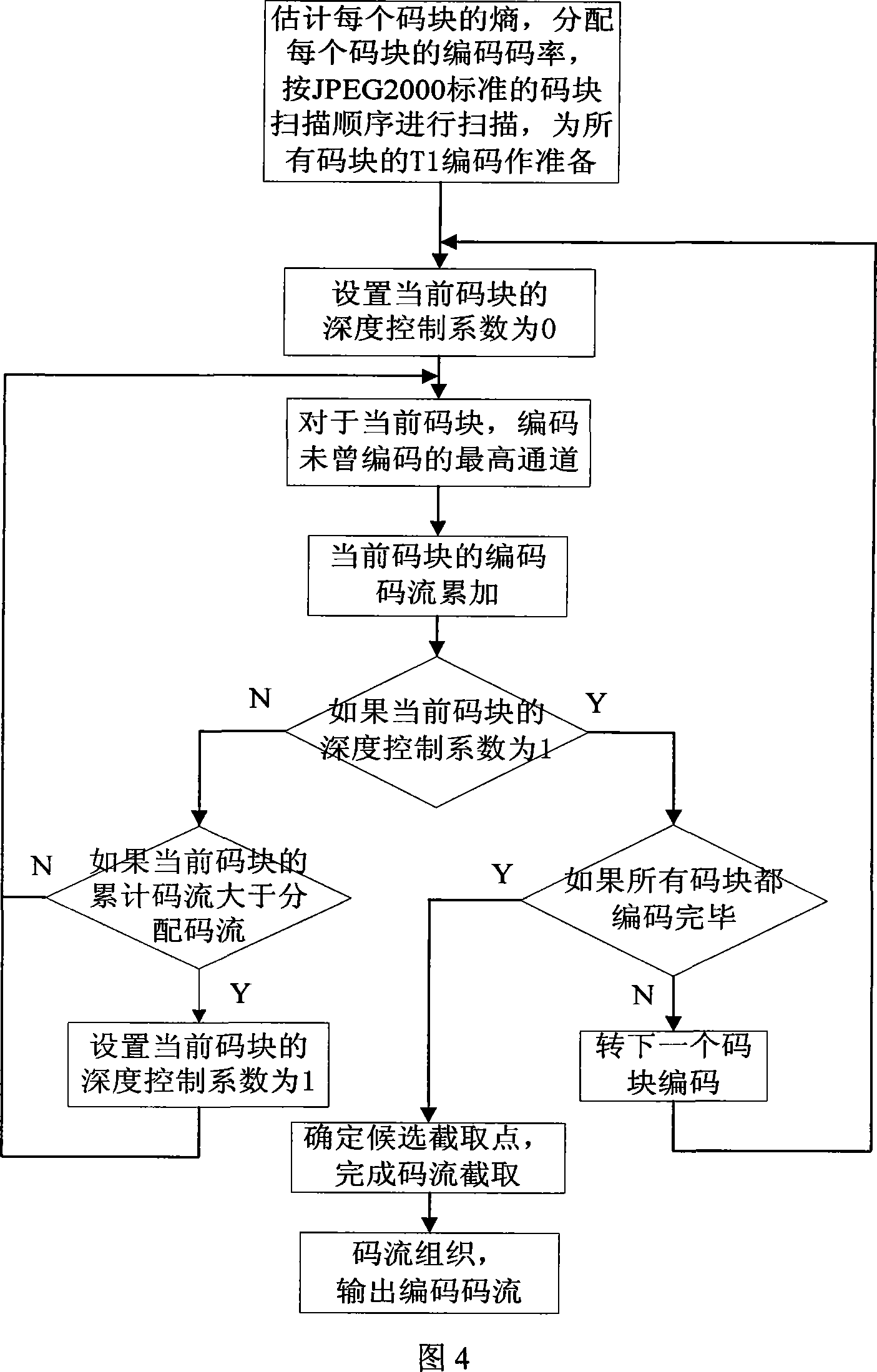

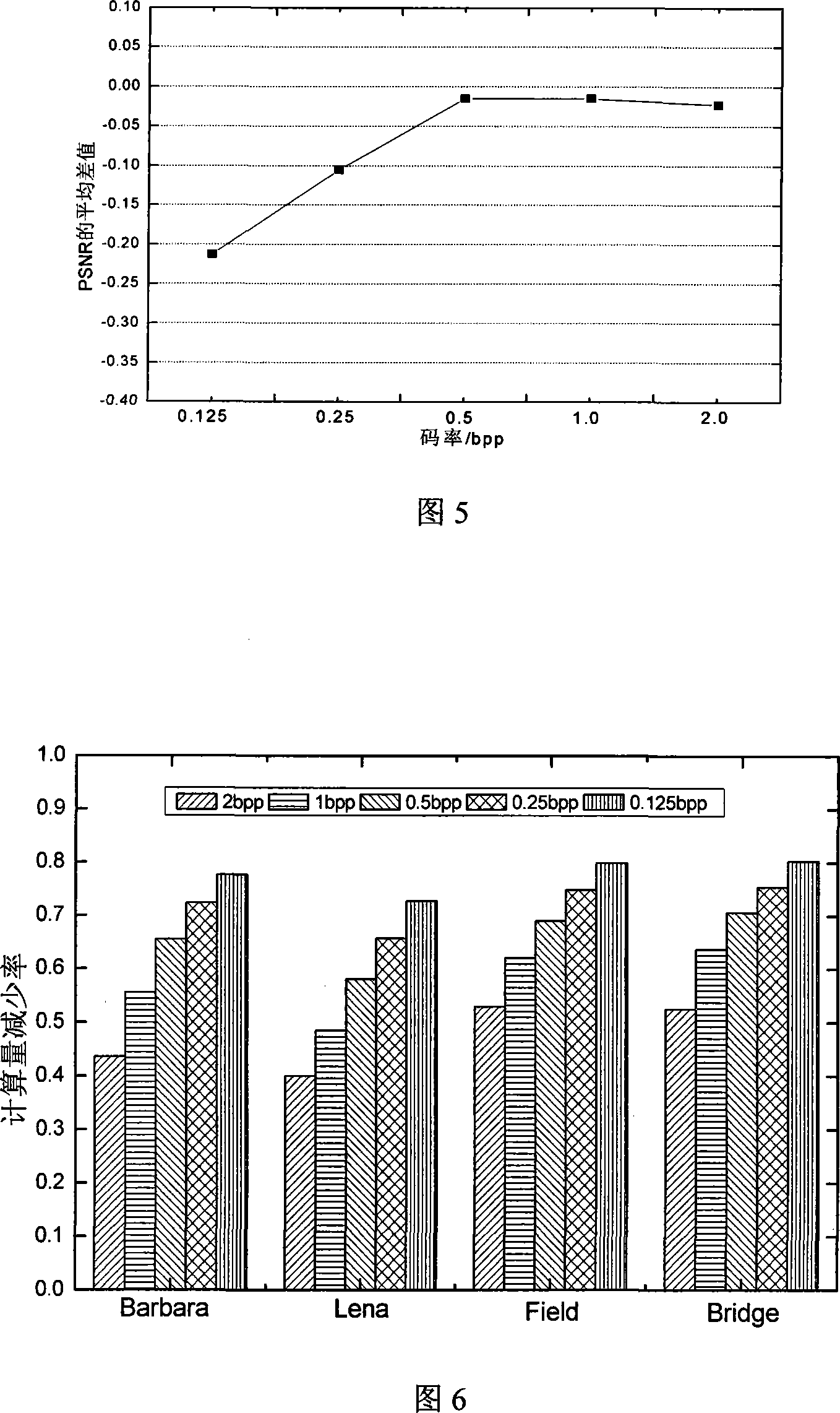

InactiveCN101106711AAccurate code rate pre-allocationPre-allocated precisionTelevision systemsDigital video signal modificationCoding blockControl system

The invention discloses a JPEG2000 self-adapting rate control system and a method based on pre-assignment of code rate, mainly solving the problem of large calculation amount and large memory size of JPEG2000 encoding method. The code block of the original image after pretreatment, wavelet transformation and quantification is output by two lines, one line directly enters the bit plane and MQ coder; for the other line, the entropy of each code block is estimated by the entropy estimate module, sent to the code rate assignment module to assign code rate, and the code rate of each code block is feed back to the bit plane and MQ coder through the encoding depth control module, after the code blocks are encoded by the bit plane, further feed back to the encoding depth control module to determine the output code stream of each encoded code block, and the output code stream is under optimal interception and code stream organization to output the ultimate code stream. At the same time, the invention can change the threshold value of the encoding depth control coefficient as required, to flexibly control the encoding depth in order to improve the image compression quality. The invention has the advantages of low complexity and easiness for hardware implementation, and is suitable for various JPEG2000 image real-time compression systems.

Owner:SHANDONG HUAYU AEROSPACE TECH CO LTD

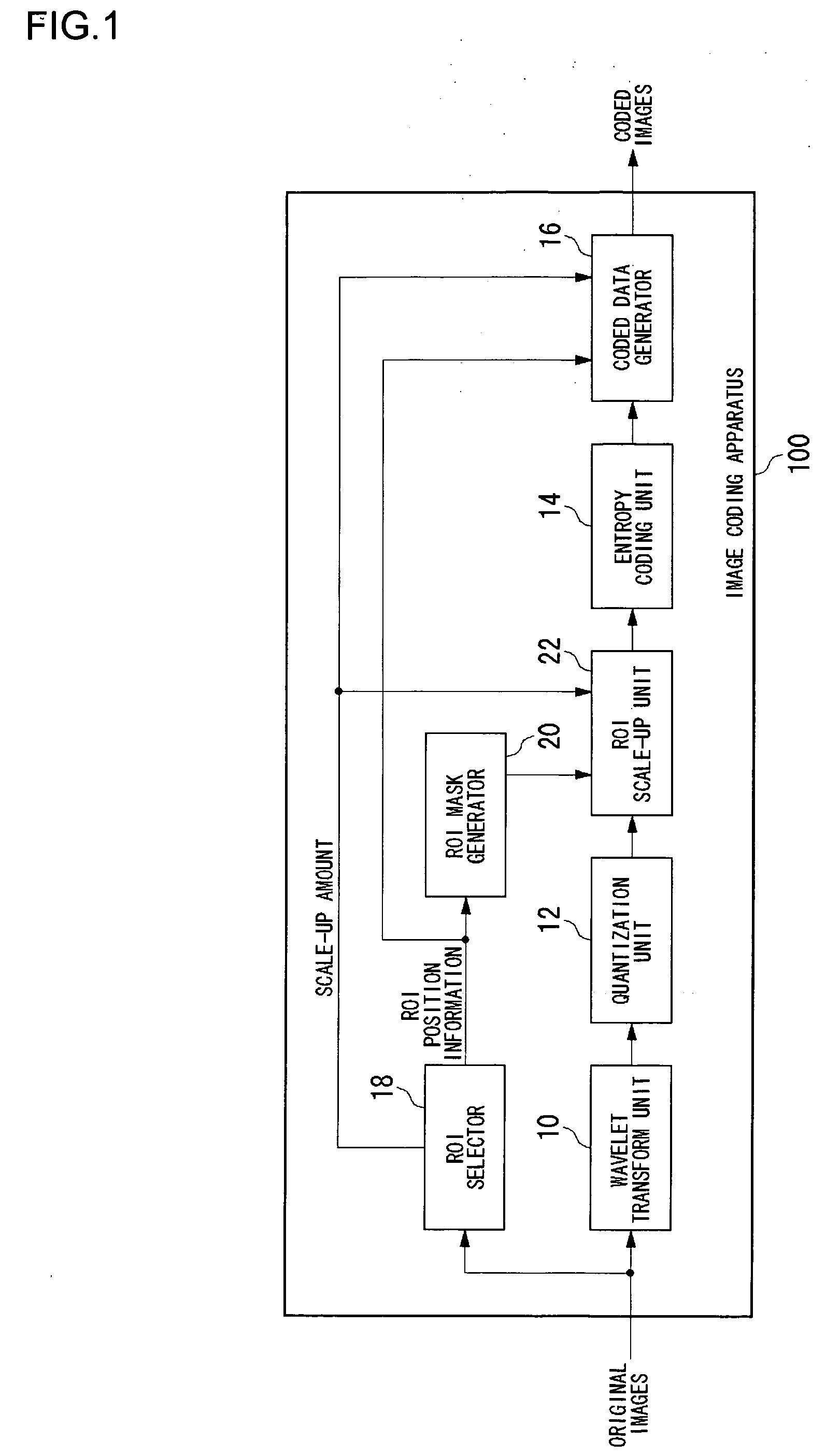

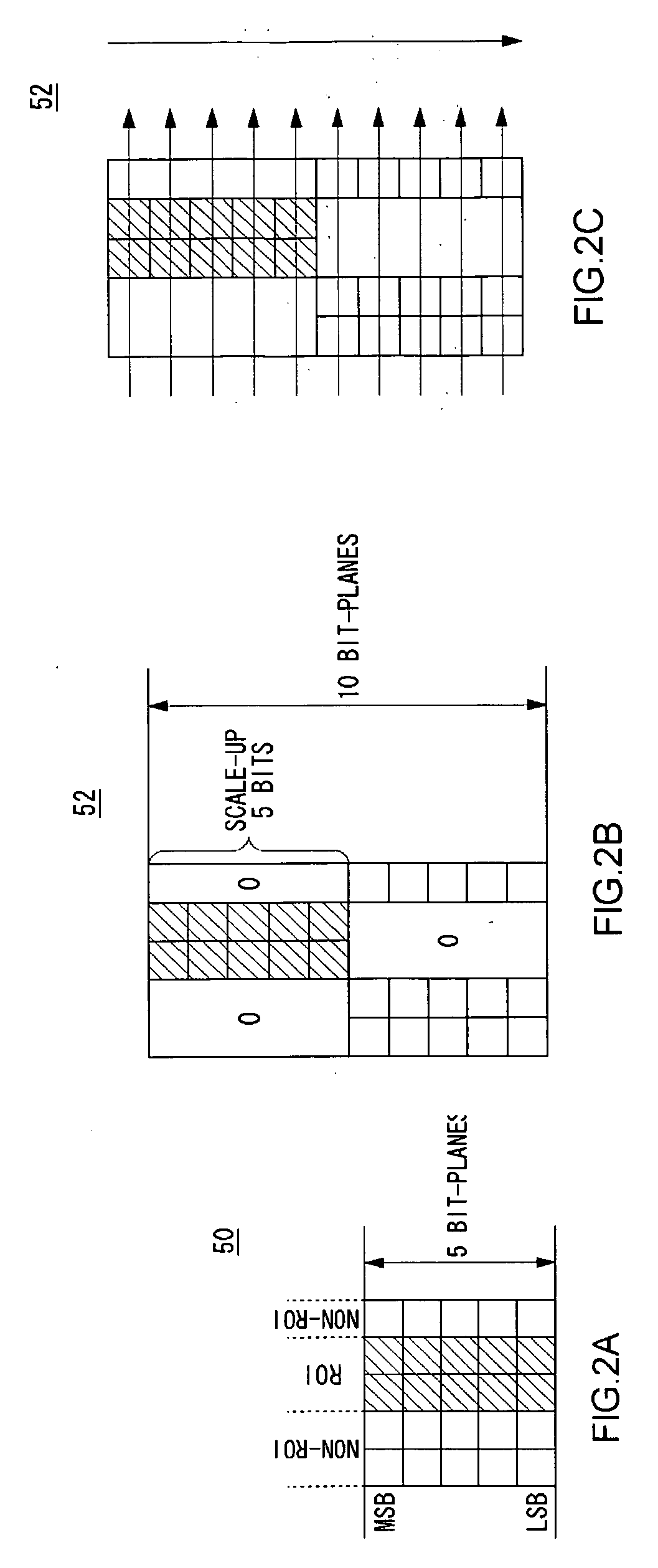

Image coding apparatus, image decoding apparatus, image display apparatus and image processing apparatus

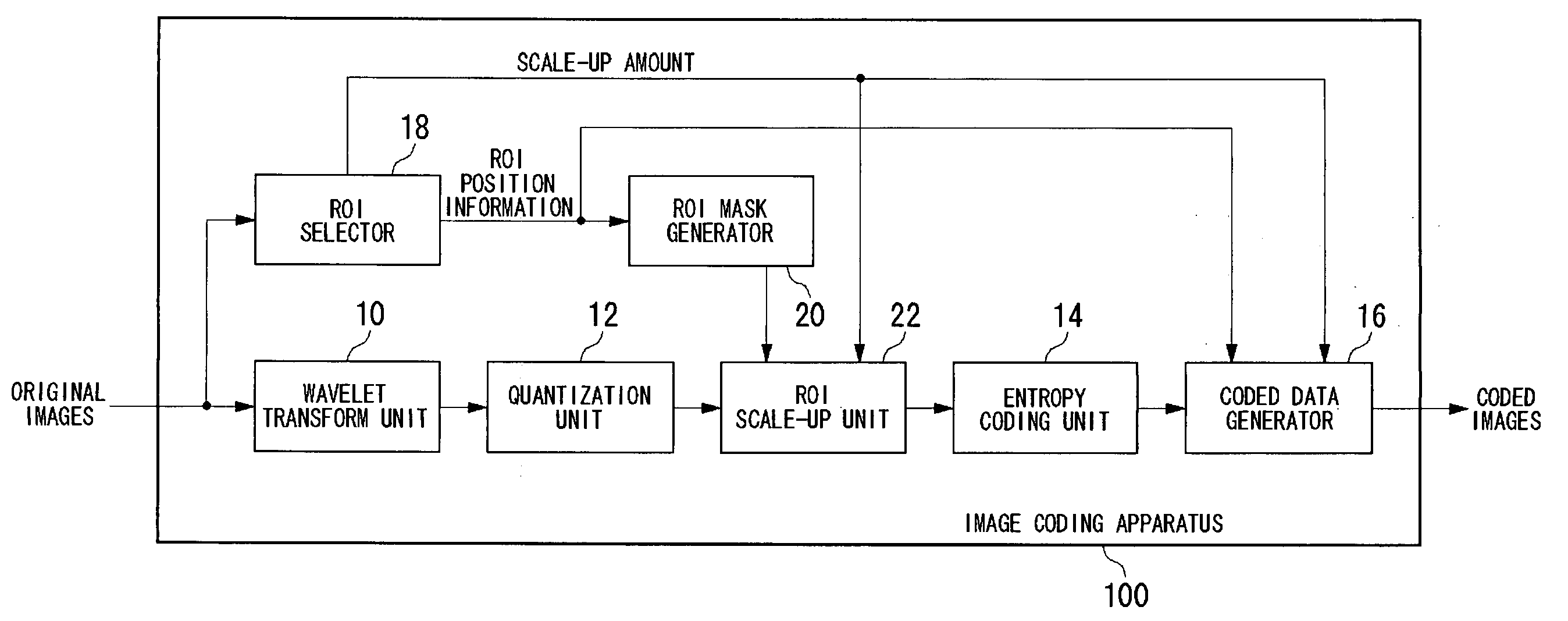

ActiveUS20050175251A1Increase costCharacter and pattern recognitionTelevision systemsImaging processingBit plane

A wavelet transform unit performs a wavelet transform on original images and a quantization unit quantizes wavelet transform coefficients. A ROI selector selects a region of interest or regions of interest in the original image, and a ROI mask generator generates ROI masks with which the wavelet transform coefficients (which are also called ROI transform coefficients) corresponding to the regions of interest are specified. By referring to the ROI masks, a lower-bit zero substitution unit substitutes low-order bits of non-ROI transform coefficients with zeros. An entropy coding unit entropy-codes the wavelet transform coefficients sequentially from high-order bit-planes, after the substitution. A coded data generator turns coded data into streams together with parameters and then outputs coded images.

Owner:PANASONIC INTELLECTUAL PROPERTY CORP OF AMERICA

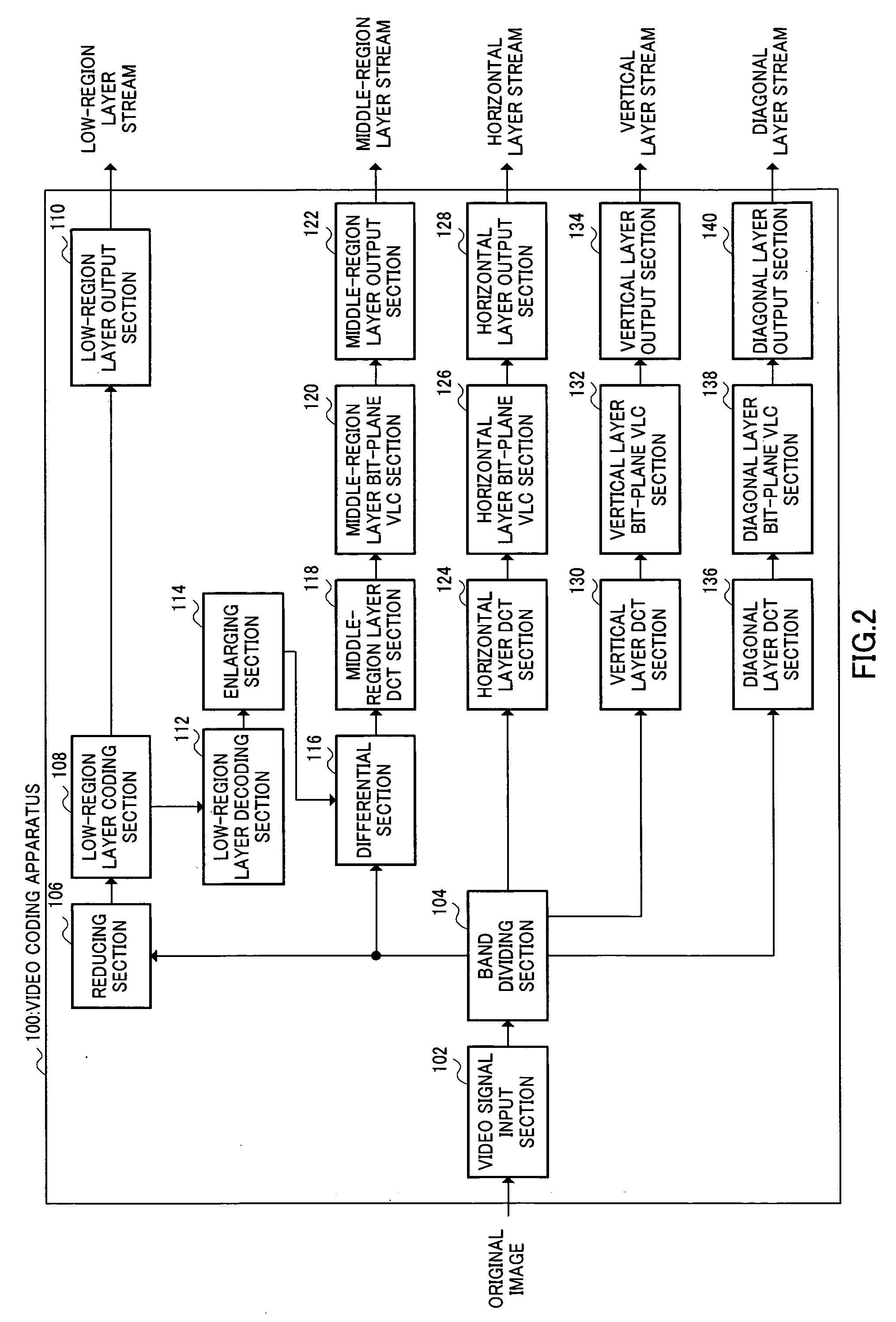

Video coding method

InactiveUS20050074177A1Improve coding efficiencyImprove efficiencyPulse modulation television signal transmissionCode conversionImage resolutionVideo encoding

A video coding method enabling implementation of resolution scalability while improving the coding efficiency. In the method, a band dividing section 104 performs band division on a high-resolution original image to generate a middle-resolution image, horizontal component, vertical component and diagonal component. The horizontal component is subjected to the DCT processing in horizontal layer DCT section 124, and then subjected to the bit-plane VLC processing in horizontal layer bit-plane VLC section 126. The vertical component is subjected to the DCT processing in vertical layer DCT section 130, and then subjected to the bit-plane VLC processing in vertical layer bit-plane VLC section 132. The diagonal component is subjected to the DCT processing in diagonal layer DCT section 136, and then subjected to the bit-plane VLC processing in diagonal layer bit-plane VLC section 138. In scanning, a scanning order is determined in consideration of bias in the distribution of DCT coefficients for each band component.

Owner:PANASONIC CORP

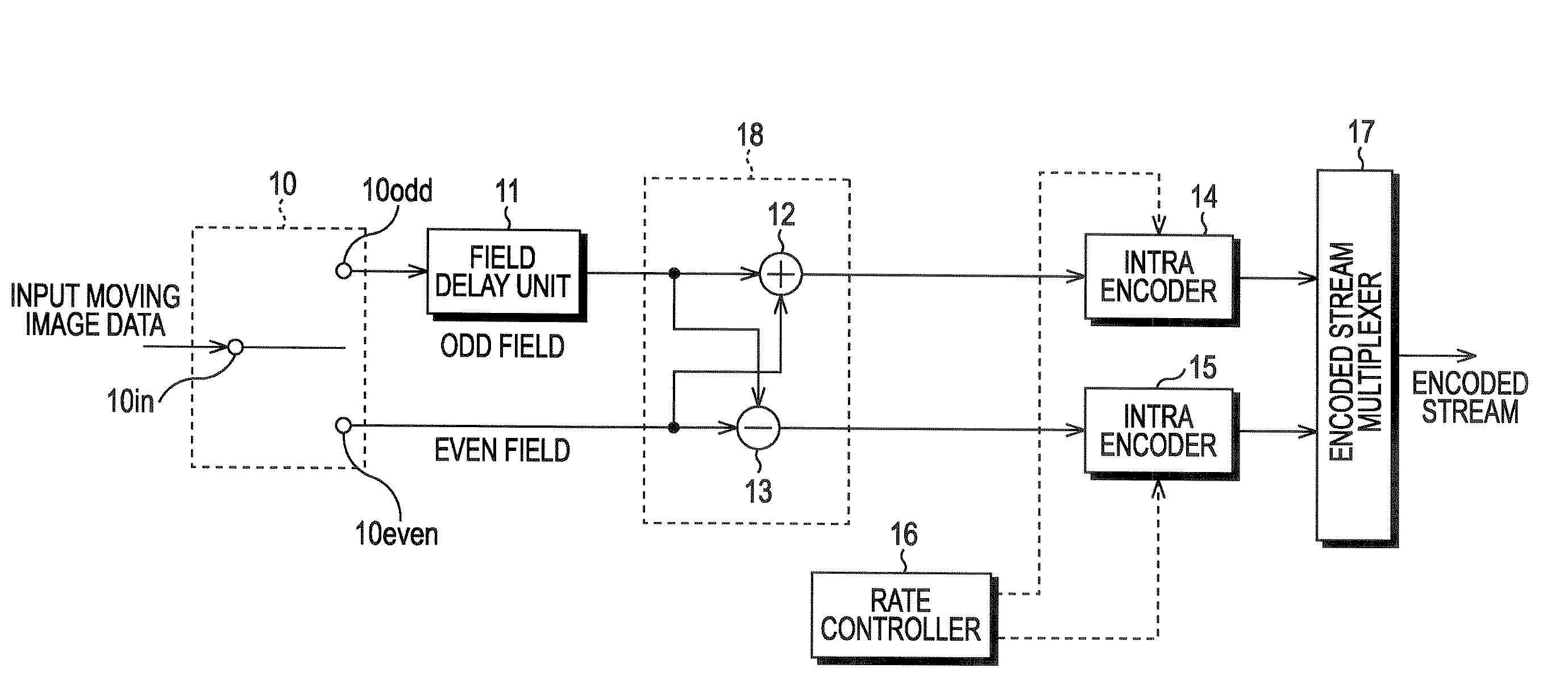

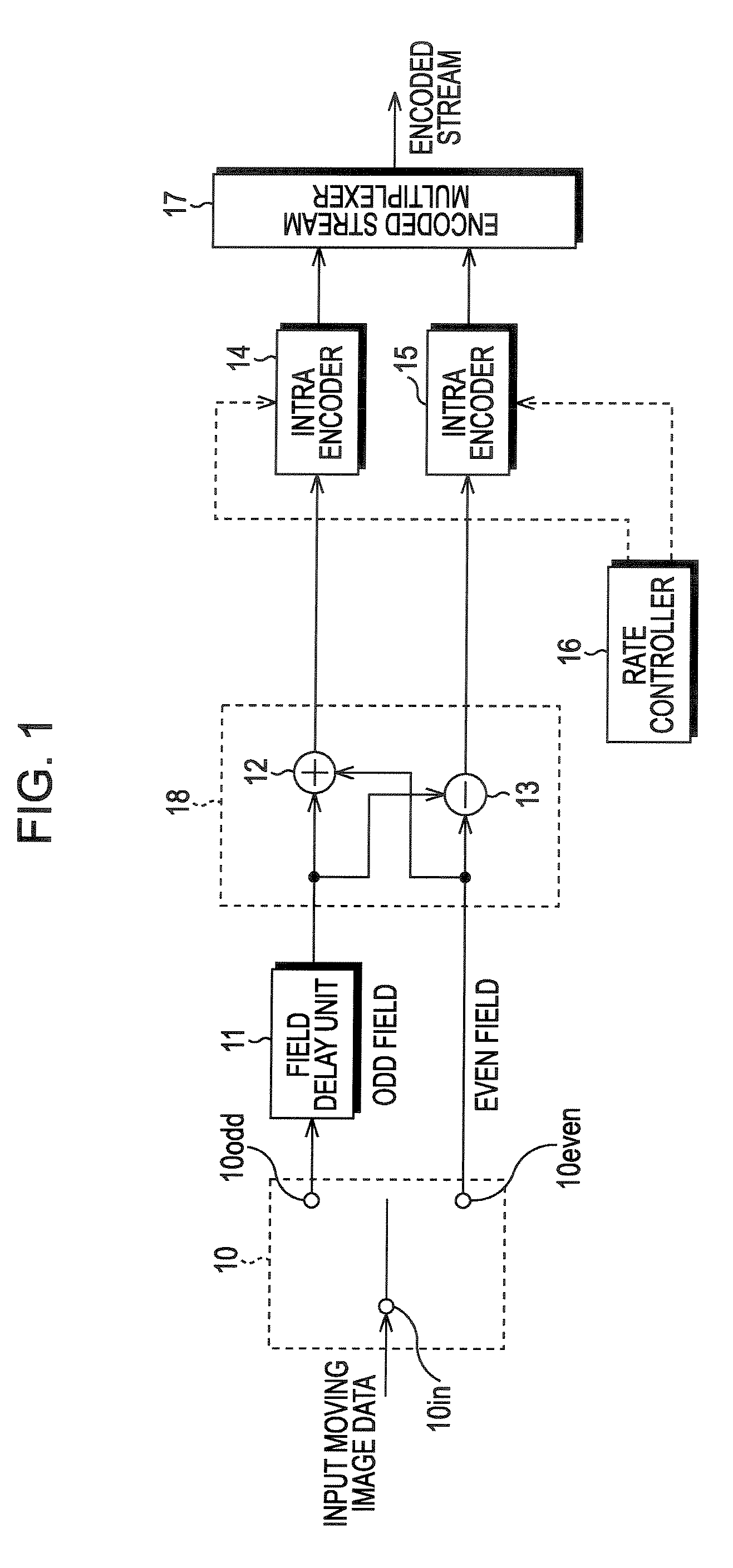

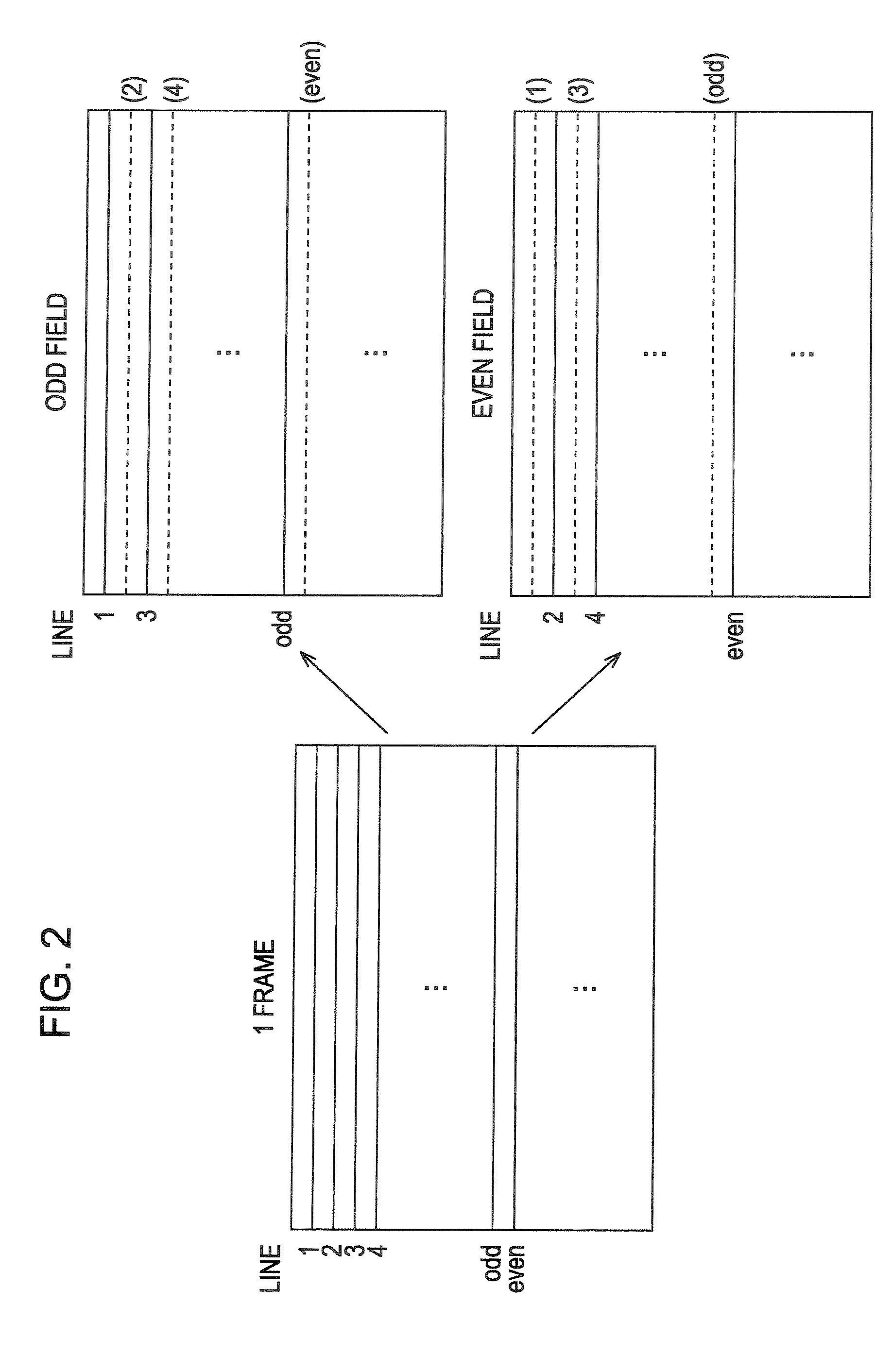

Encoding device, encoding method, encoding program, decoding device, decoding method, and decoding program

InactiveUS20090074052A1Improve image qualityImprove subjective image qualityColor television with pulse code modulationColor television with bandwidth reductionImaging qualityBit plane

The present invention relates to an encoding apparatus, an encoding method, an encoding program, a decoding apparatus, a decoding method and a decoding program for adaptively controlling an encoding bit rate. Coefficient data obtained using wavelet transform is quantized, and segmented into bit planes. The coefficient data is entropy encoded from the bit plane of the MSB in a direction from an upper bit position to a lower bit position. Entropy encoding is stopped at a bit position where an amount of code has reached a target amount. On the bit plane, the coefficient data is entropy encoded from a lower frequency region to a higher frequency region. Data greatly affecting subjective image quality of a decoded image is selectively output while the amount of code is easily controlled.

Owner:SONY CORP

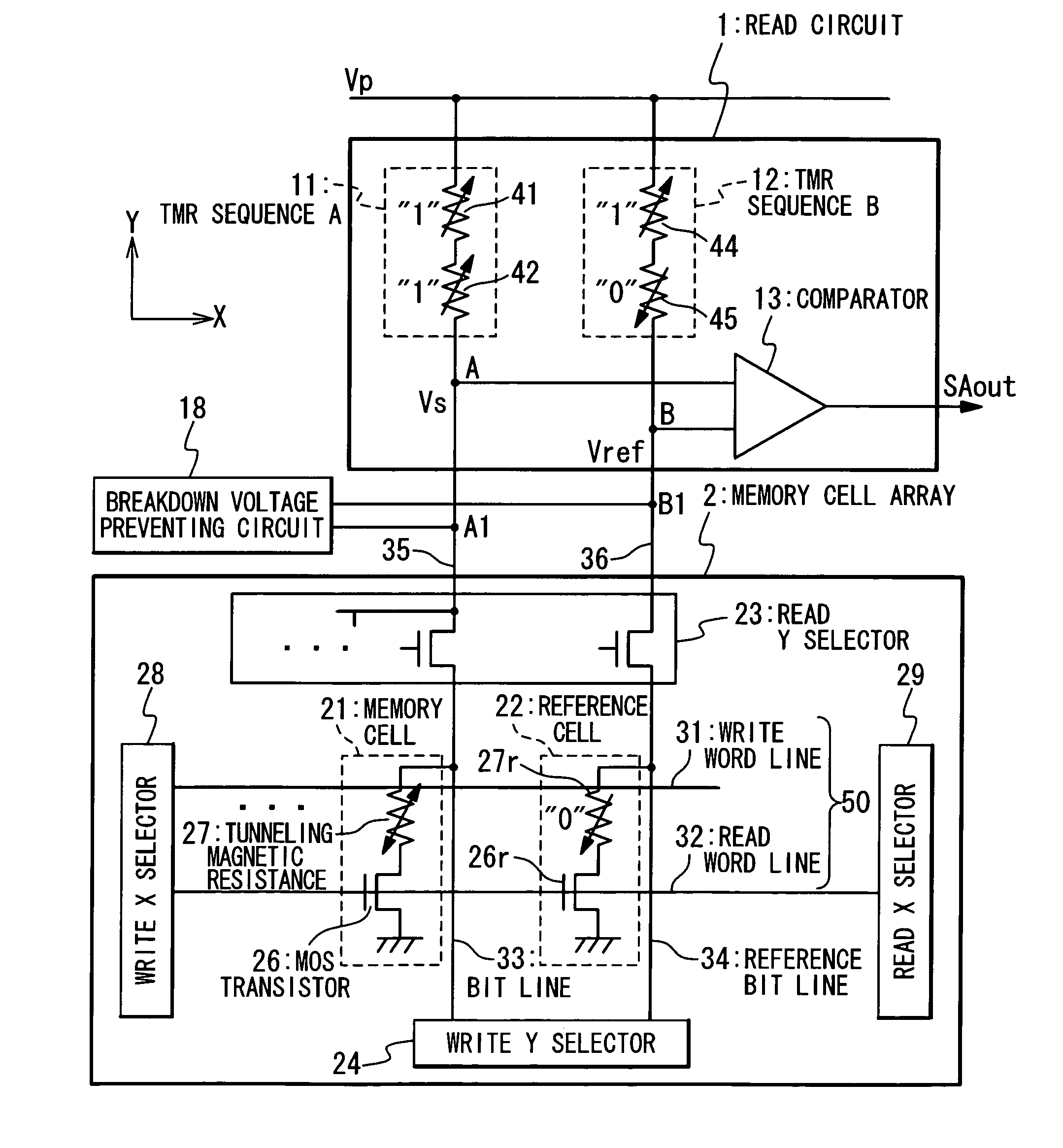

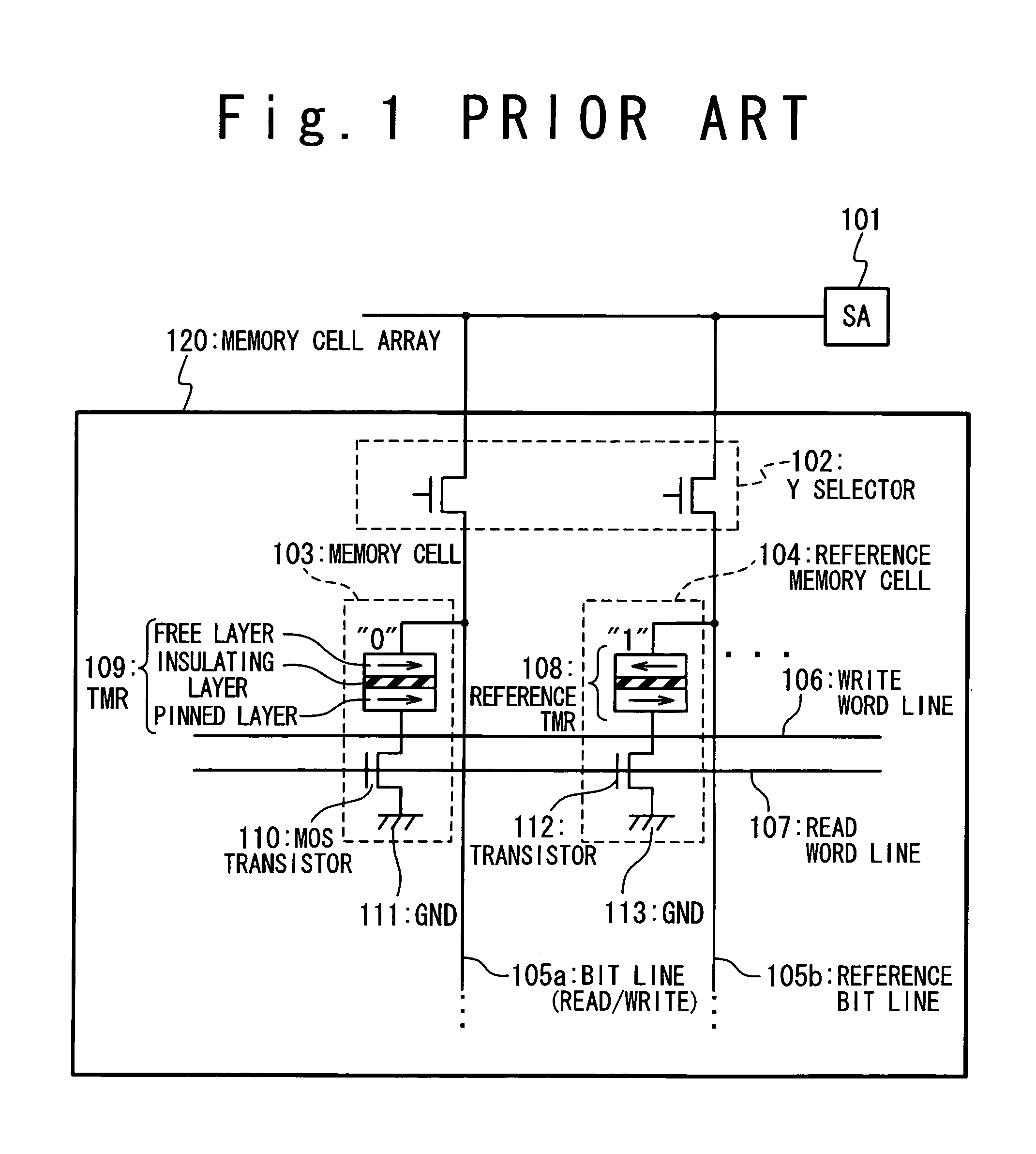

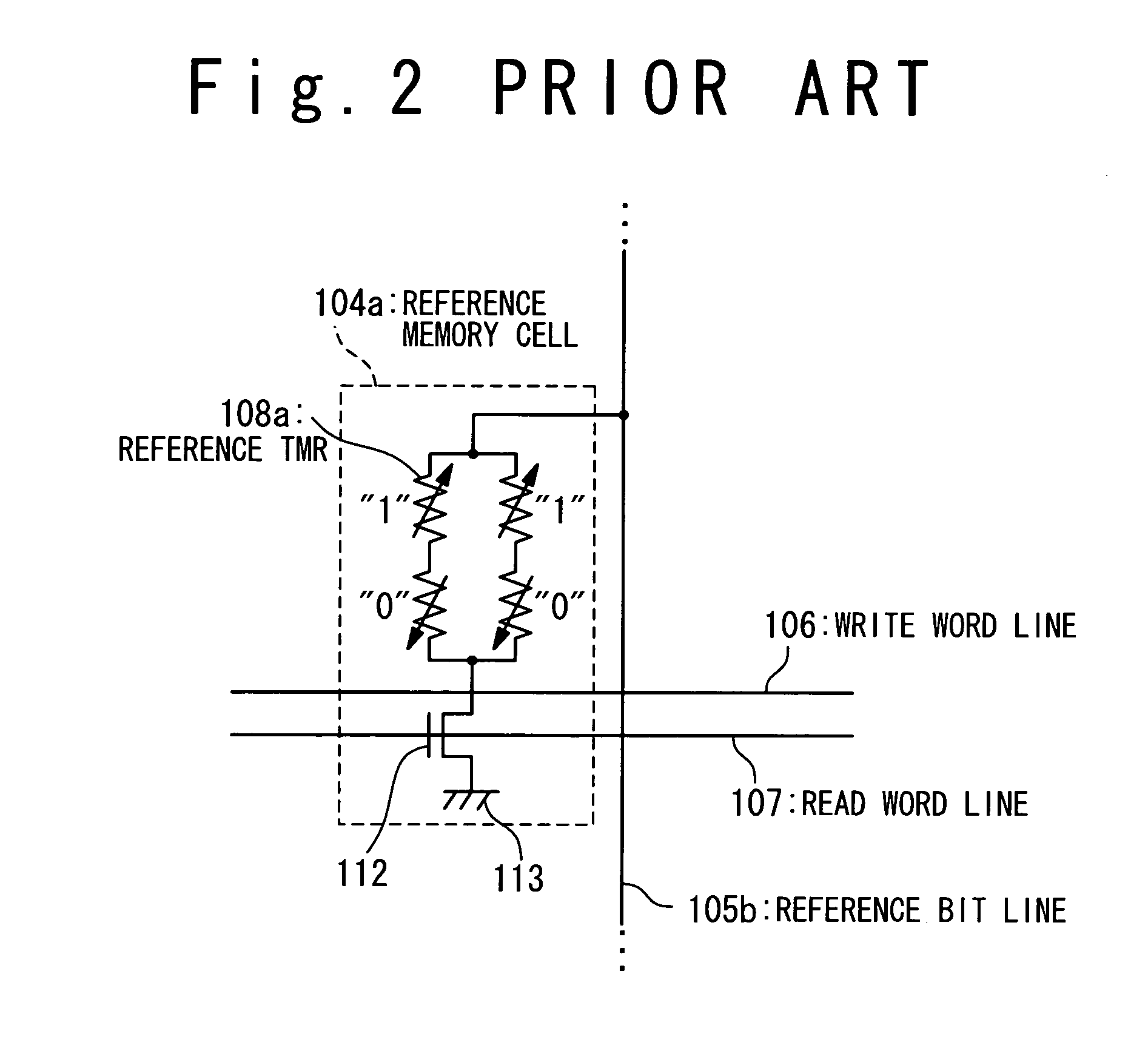

Magnetic random access memory with improved data reading method

ActiveUS7453719B2Improve reliabilityIncrease the areaDigital storageBit lineStatic random-access memory

An MRAM has a plurality of bit lines, a reference bit line, a plurality of memory cells and reference cells and a read section. The memory cells are provided along the bit lines and the reference cells along the reference bit line. The memory cell and reference cell have a tunneling magnetic resistance and a reference tunneling magnetic resistance, each of which has a spontaneous magnetization whose direction is reversed in accordance with data stored therein. The read section has a first resistance section which contains a ninth terminal connected with a bit line and a tenth terminal connected with the first power supply, a second resistance section which contains an eleventh terminal connected with the reference bit line and a twelfth terminal connected with the first power supply, and a comparing section which compares a sense voltage on the ninth terminal and a reference voltage of the eleventh terminal.

Owner:NEC CORP

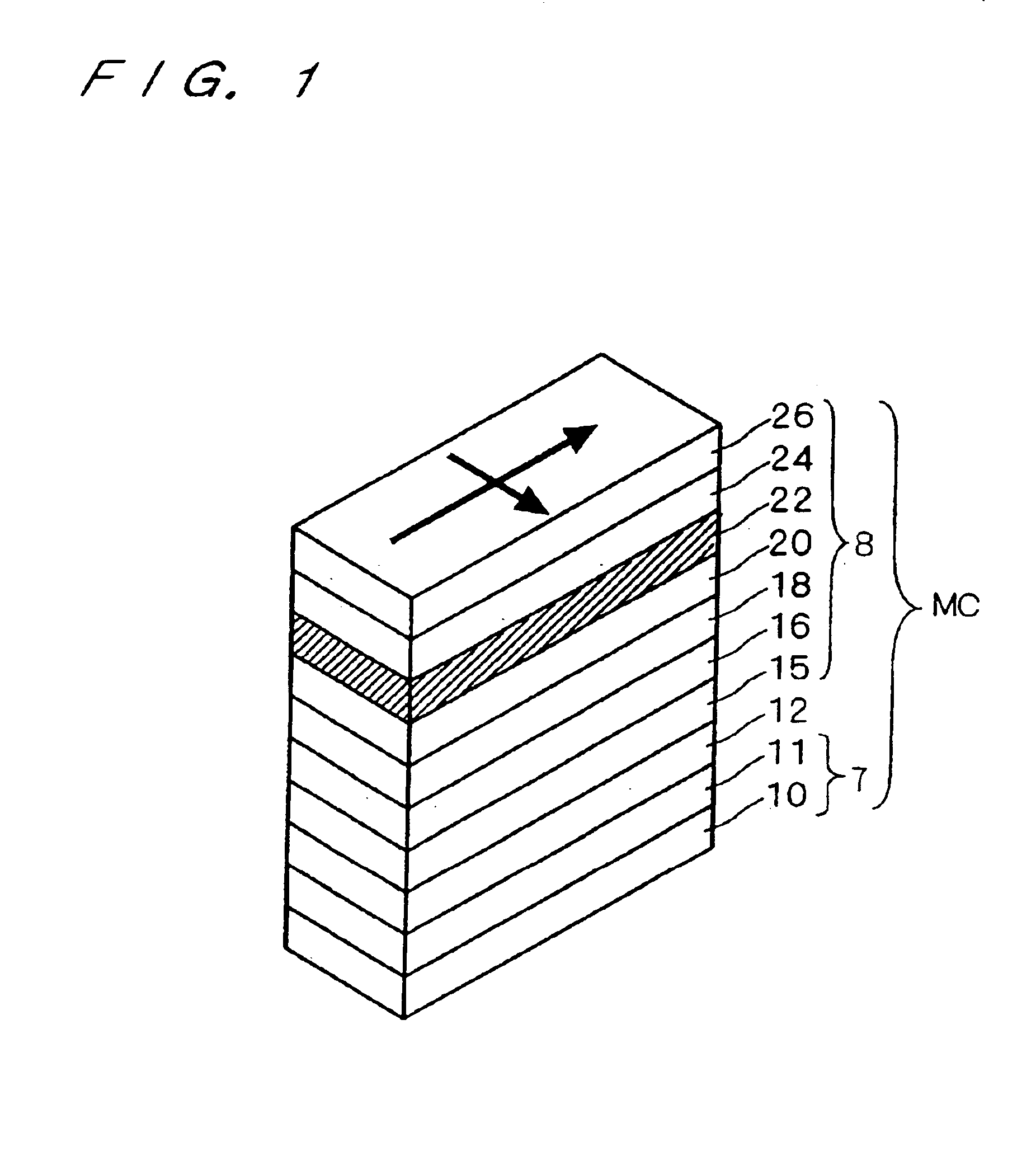

Magnetic memory device capable of passing bidirectional currents through the bit lines

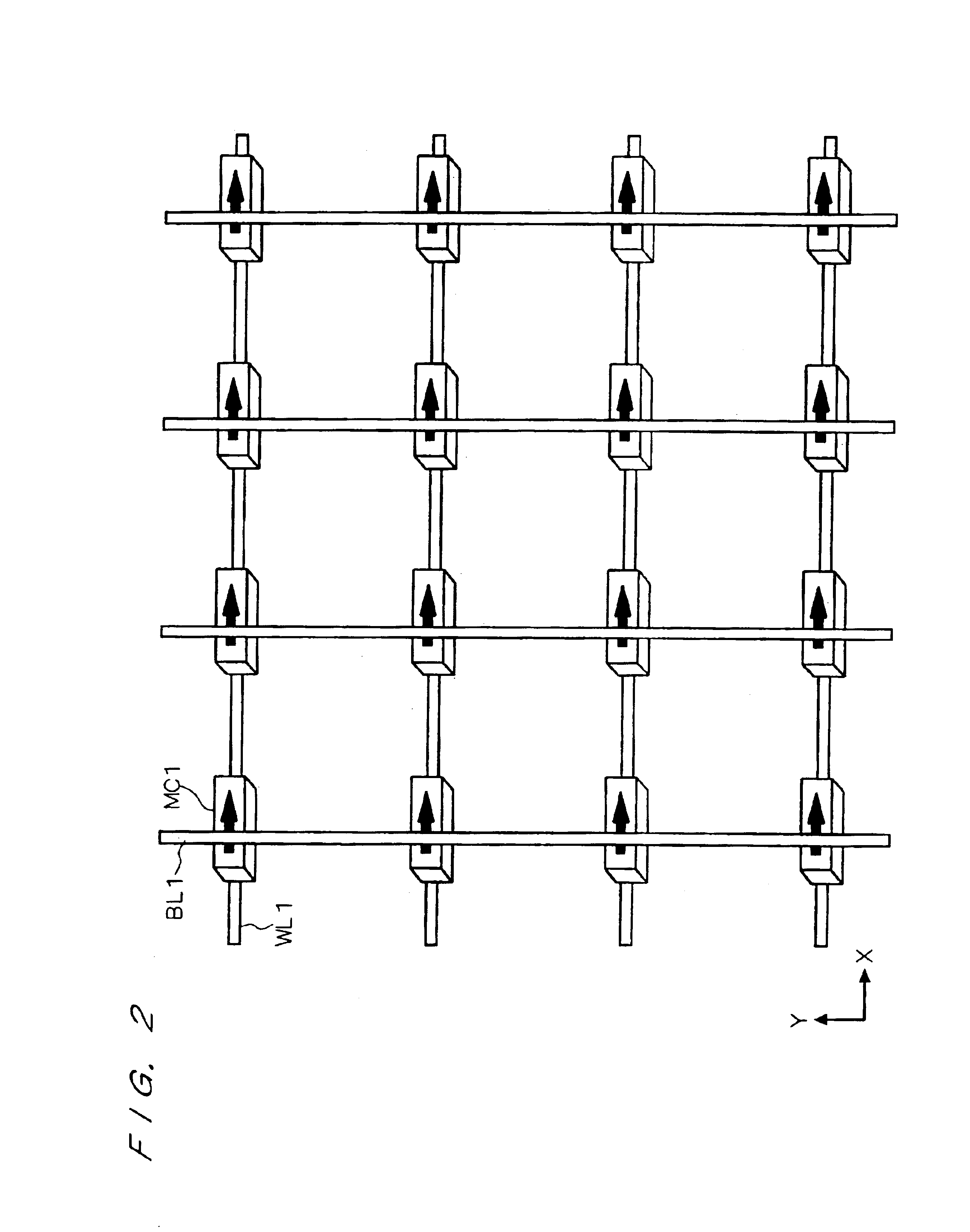

InactiveUS6950369B2Reduce manufacturing costSkip the manufacturing processNanoinformaticsMagnetic-field-controlled resistorsBit lineMagnetic memory

A plurality of word lines (WL1) are provided in parallel to one another and a plurality of bit lines (BL1) are provided in parallel to one another, intersecting the word lines (WL1) thereabove. MRAM cells (MC2) are formed at intersections of the word lines and the bit lines therebetween. MRAM cells (MC3) are provided so that an easy axis indicated by the arrow has an angle of 45 degrees with respect to the bit lines and the word lines. Thus, an MRAM capable of cutting the power consumption in writing is achieved and further an MRAM capable of reducing the time required for erasing and writing operations is achieved.

Owner:RENESAS ELECTRONICS CORP

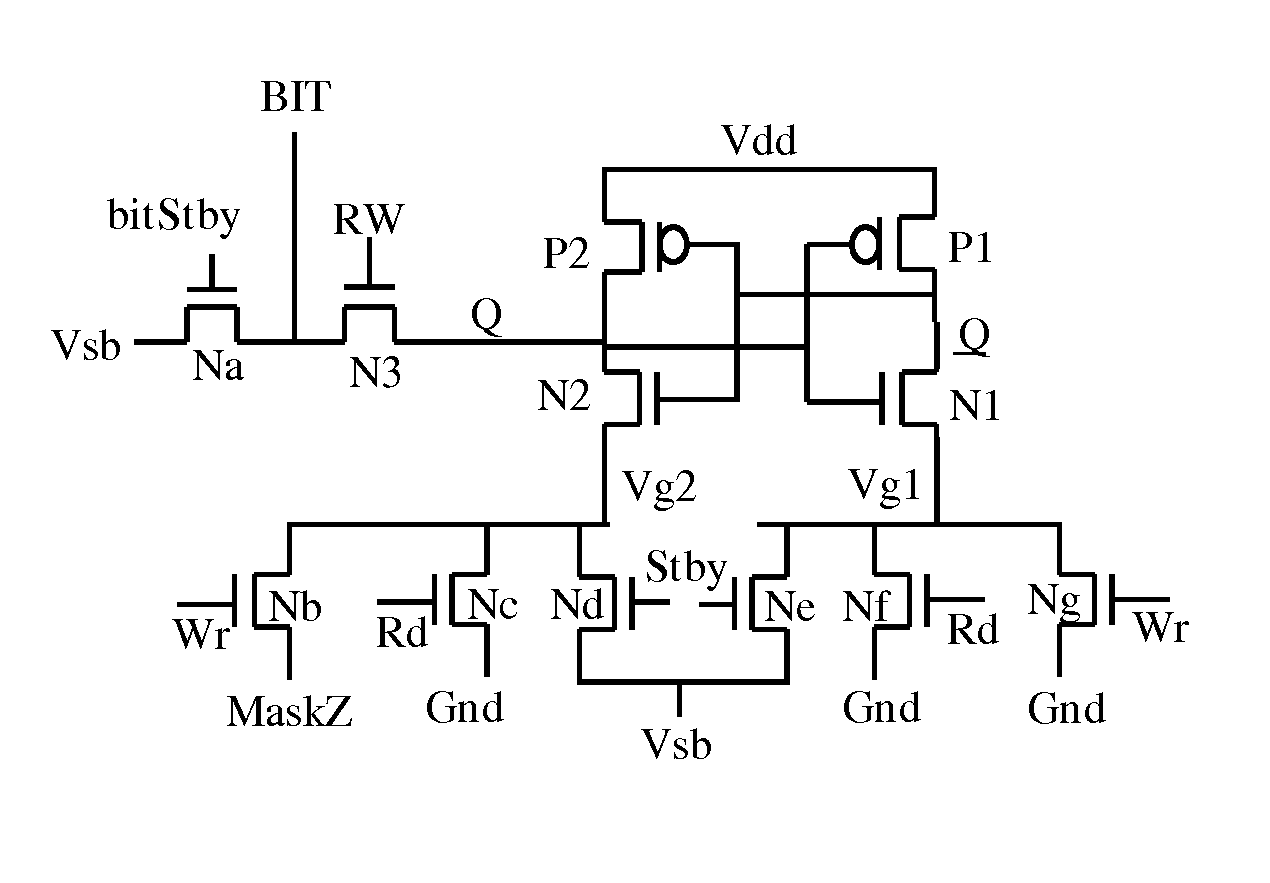

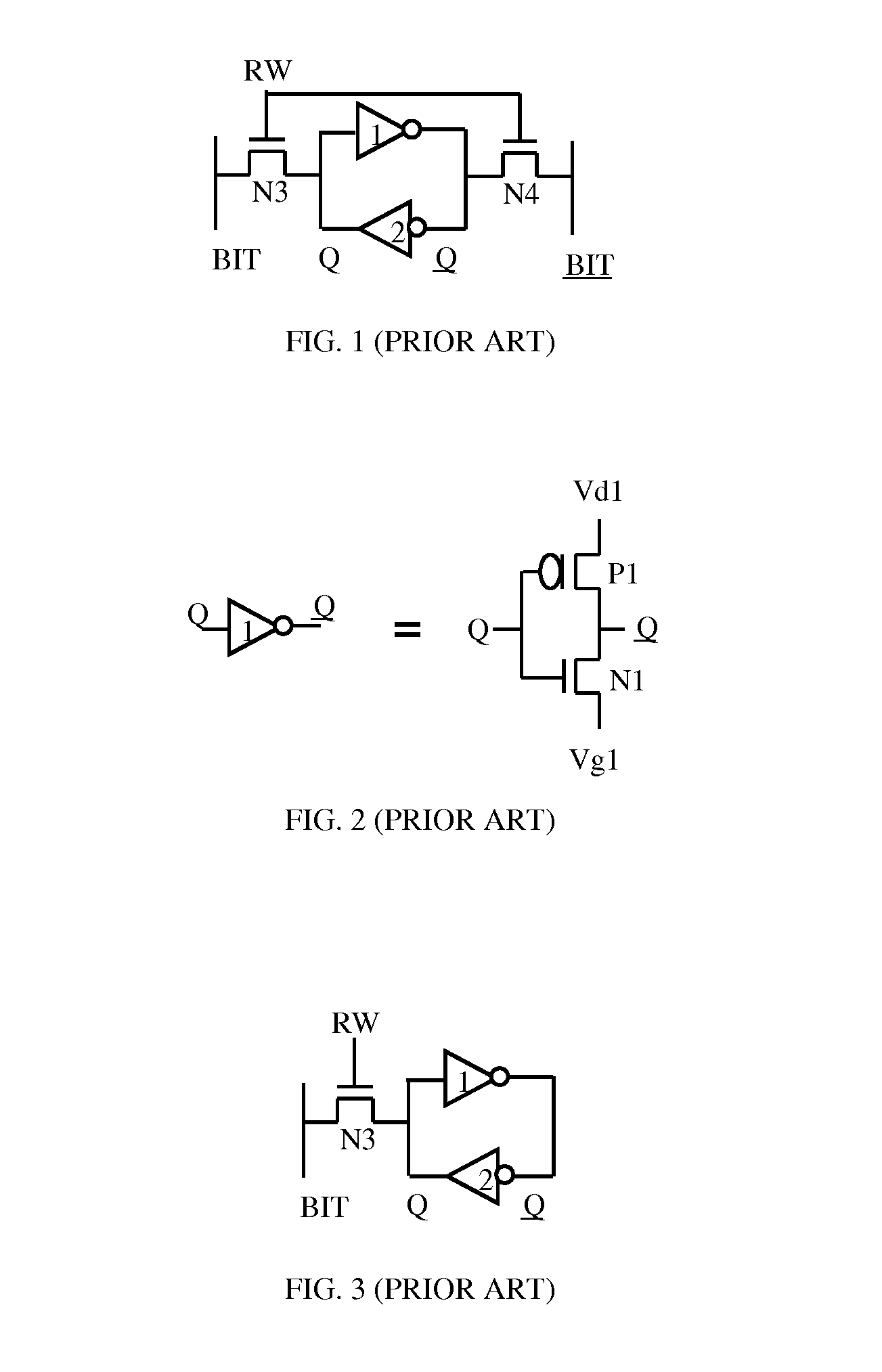

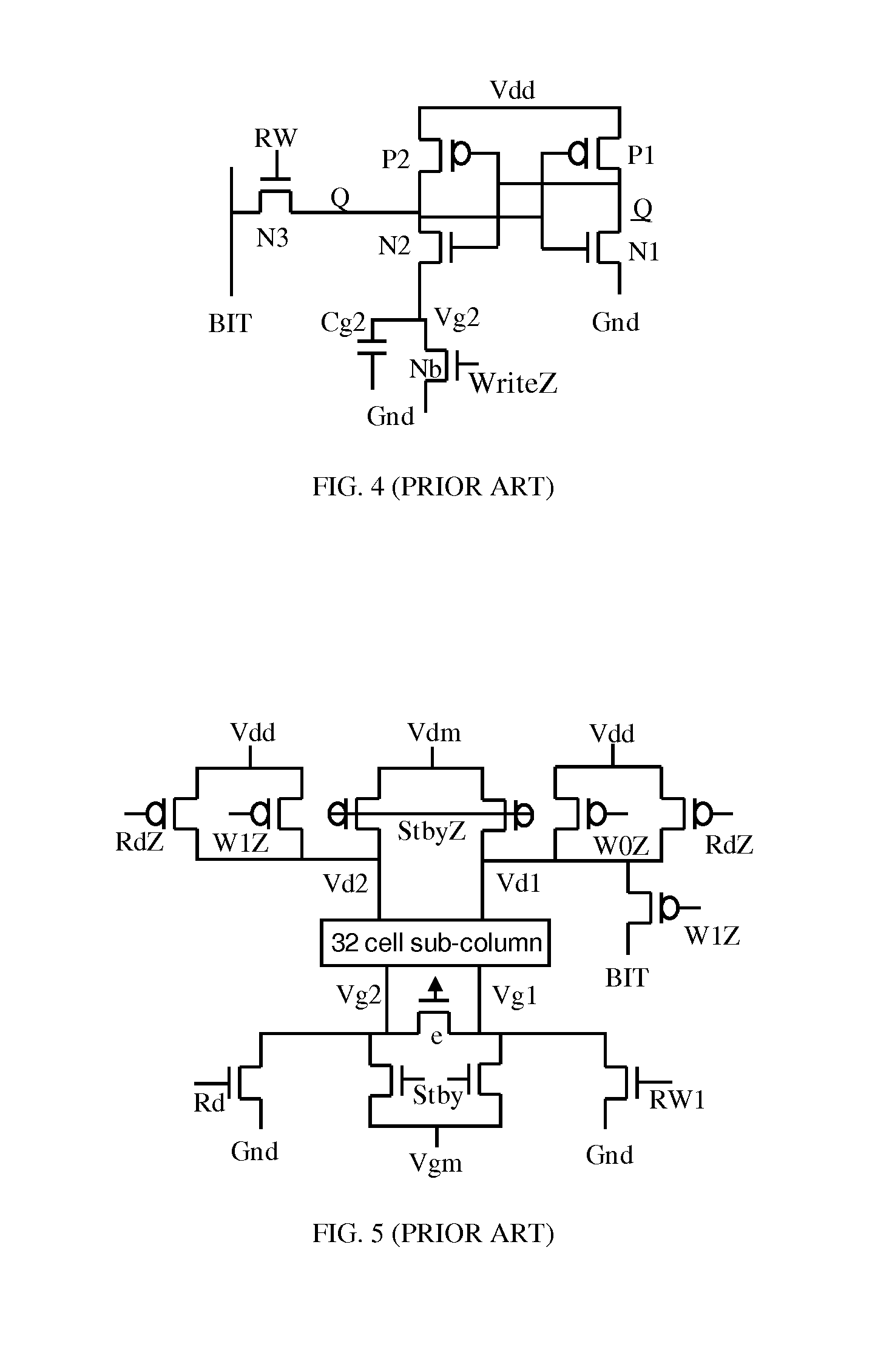

SRAM cell with common bit line and source line standby voltage

A high threshold five transistor SRAM bit cell with cross-coupled inverters has a single BIT line, a common logic 1 supply voltage, and two logic 0 virtual ground source voltages. The BIT line is coupled to the bit cell by a pass transistor. When BIT line and virtual ground lines are not otherwise being used, they are connected to a common standby voltage that substantially lowers bit cell standby leakage. Writing is performed by driving a data signal through the pass transistor and is facilitated by creating a voltage differential on the virtual ground lines. Reading is also performed through the pass transistor wherein the BIT line is initially at the standby voltage, and is then driven lower or higher depending upon the data value stored in the bit cell.

Owner:HOBSON RICHARD FREDERIC +1

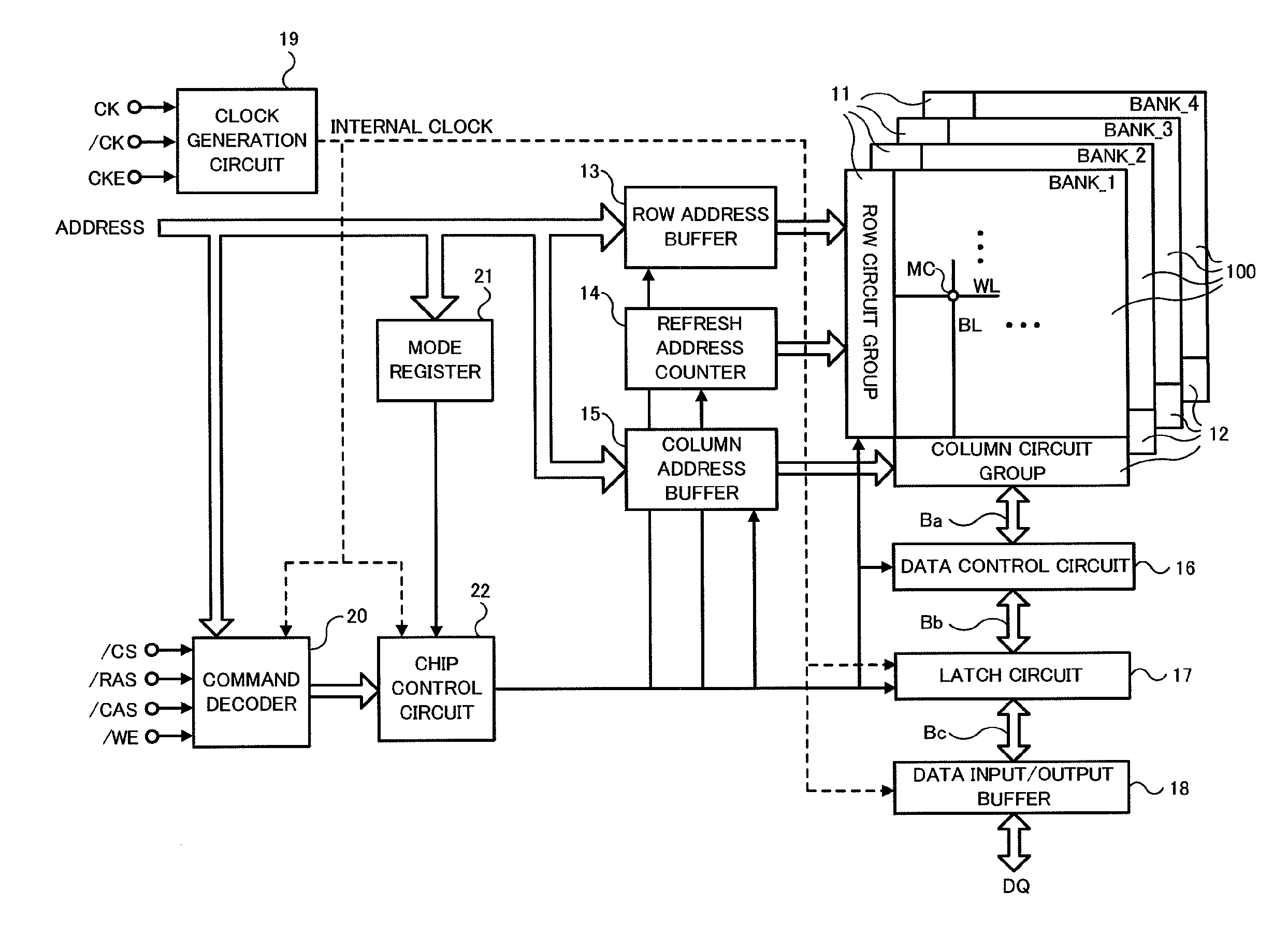

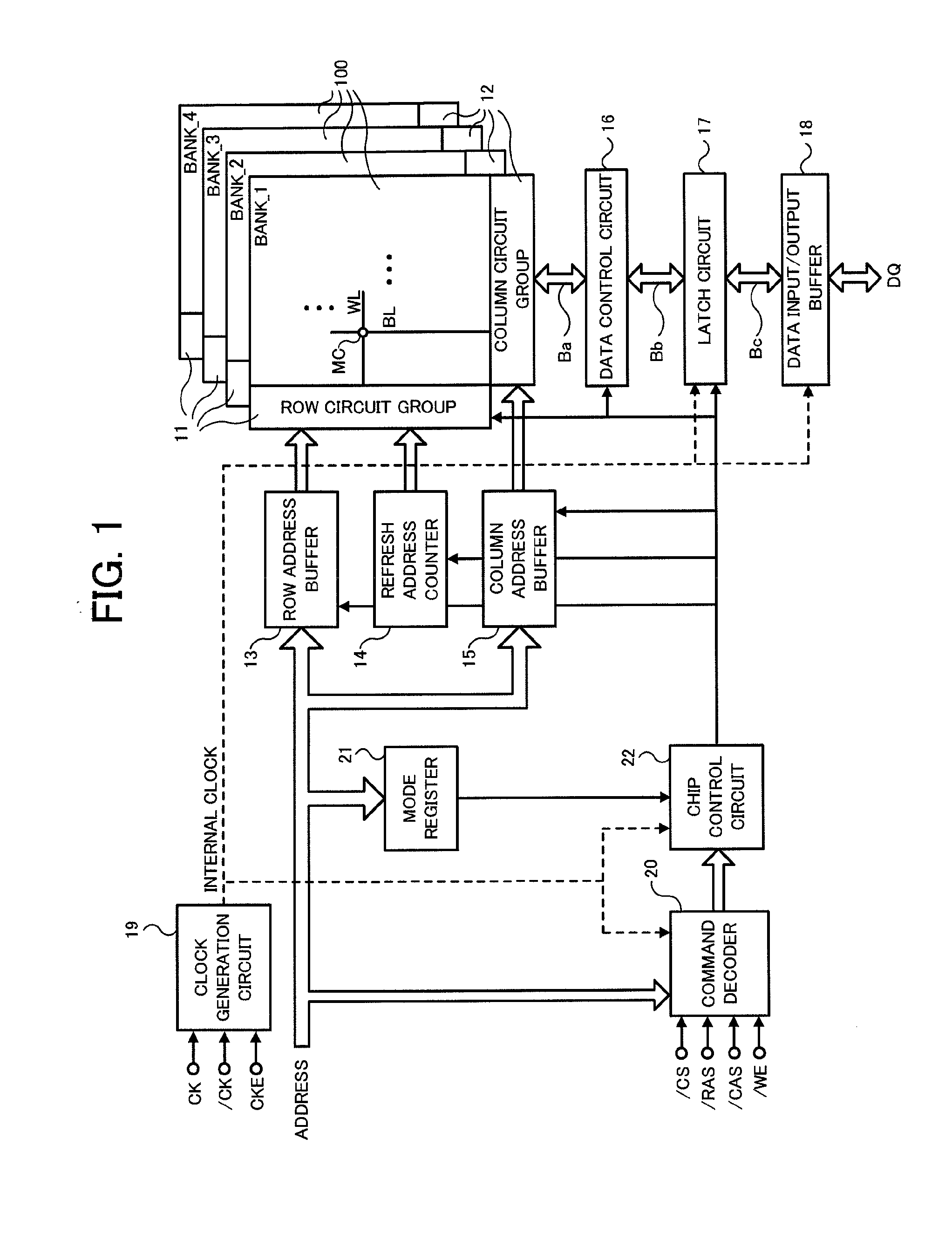

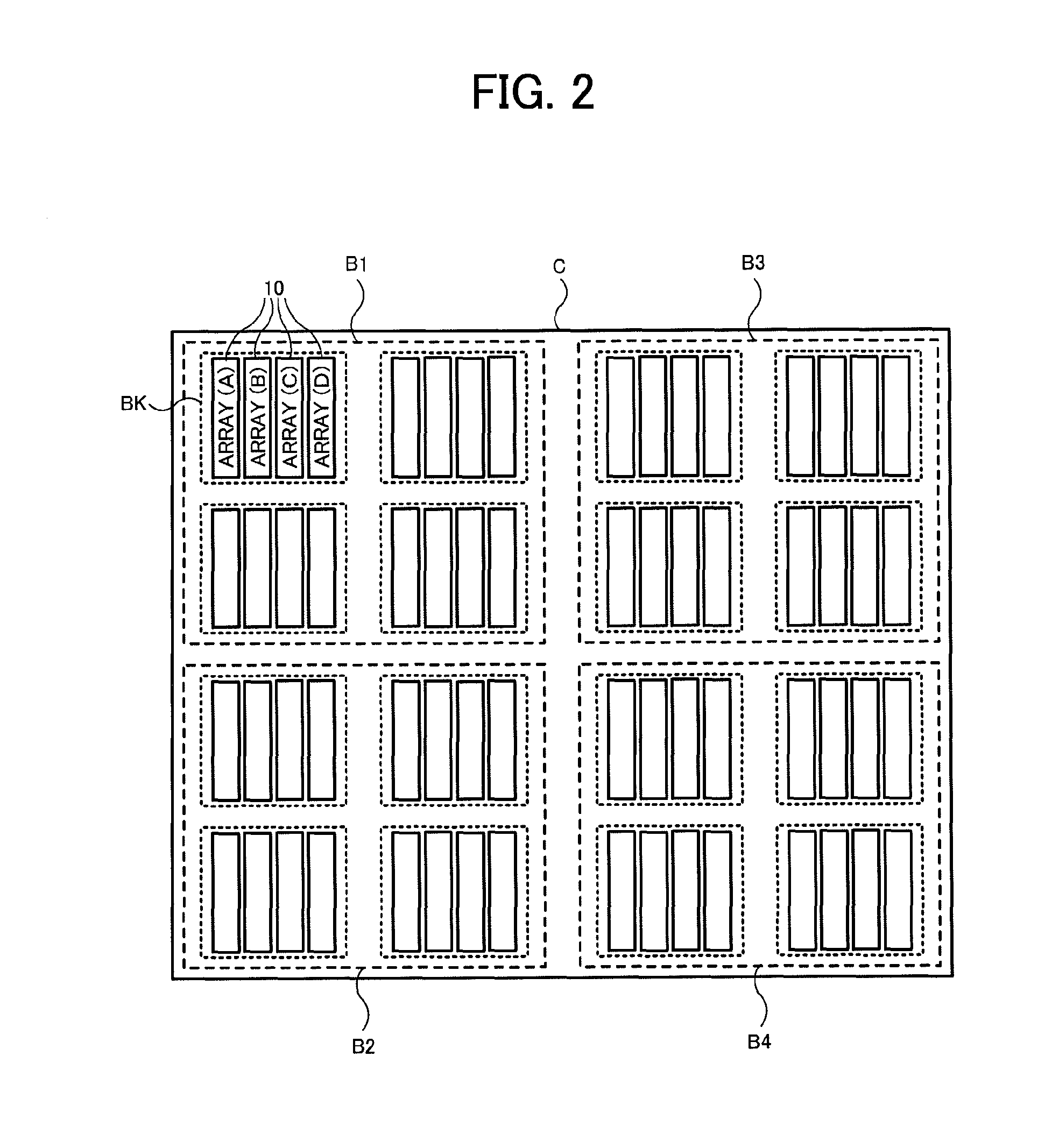

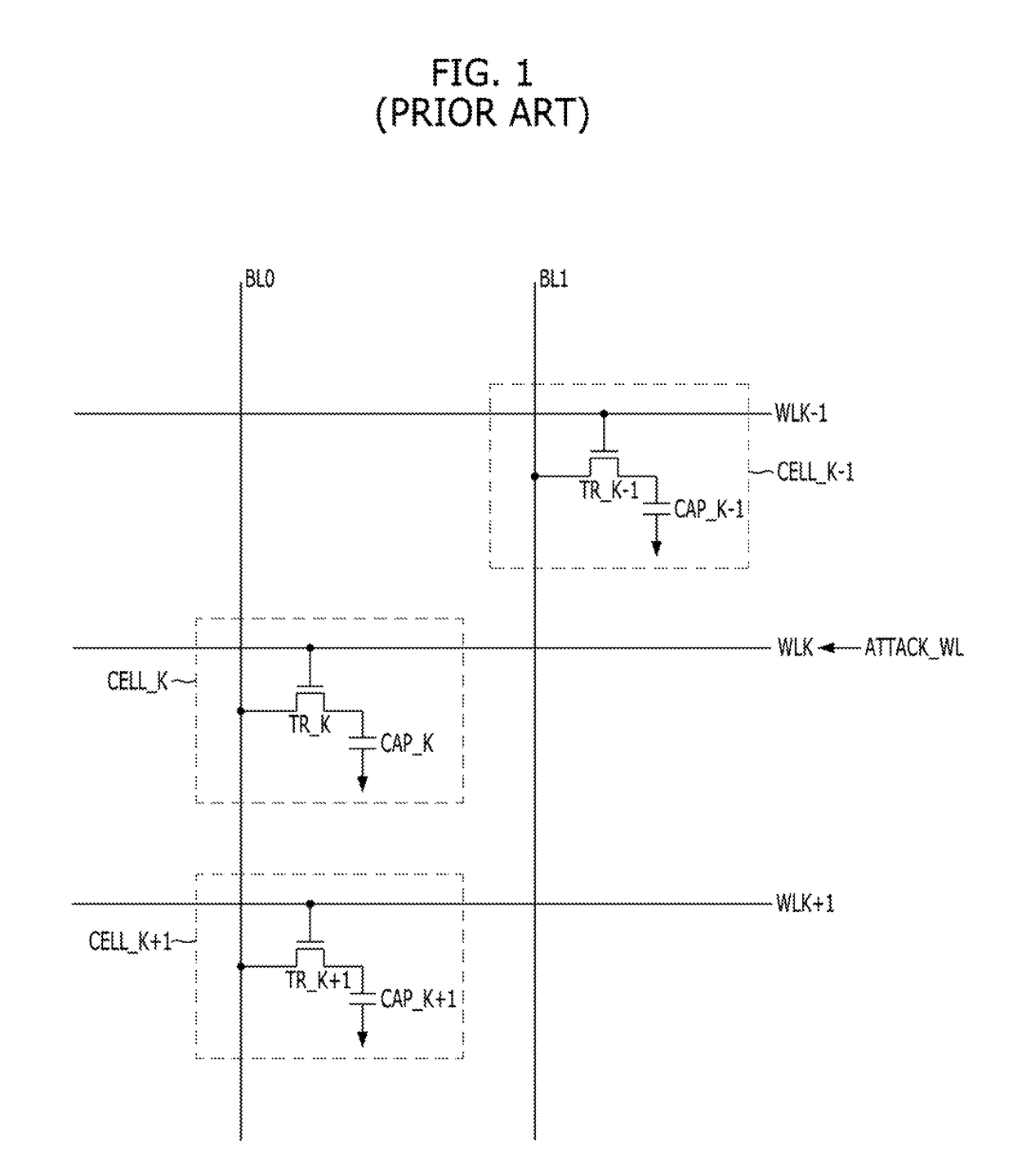

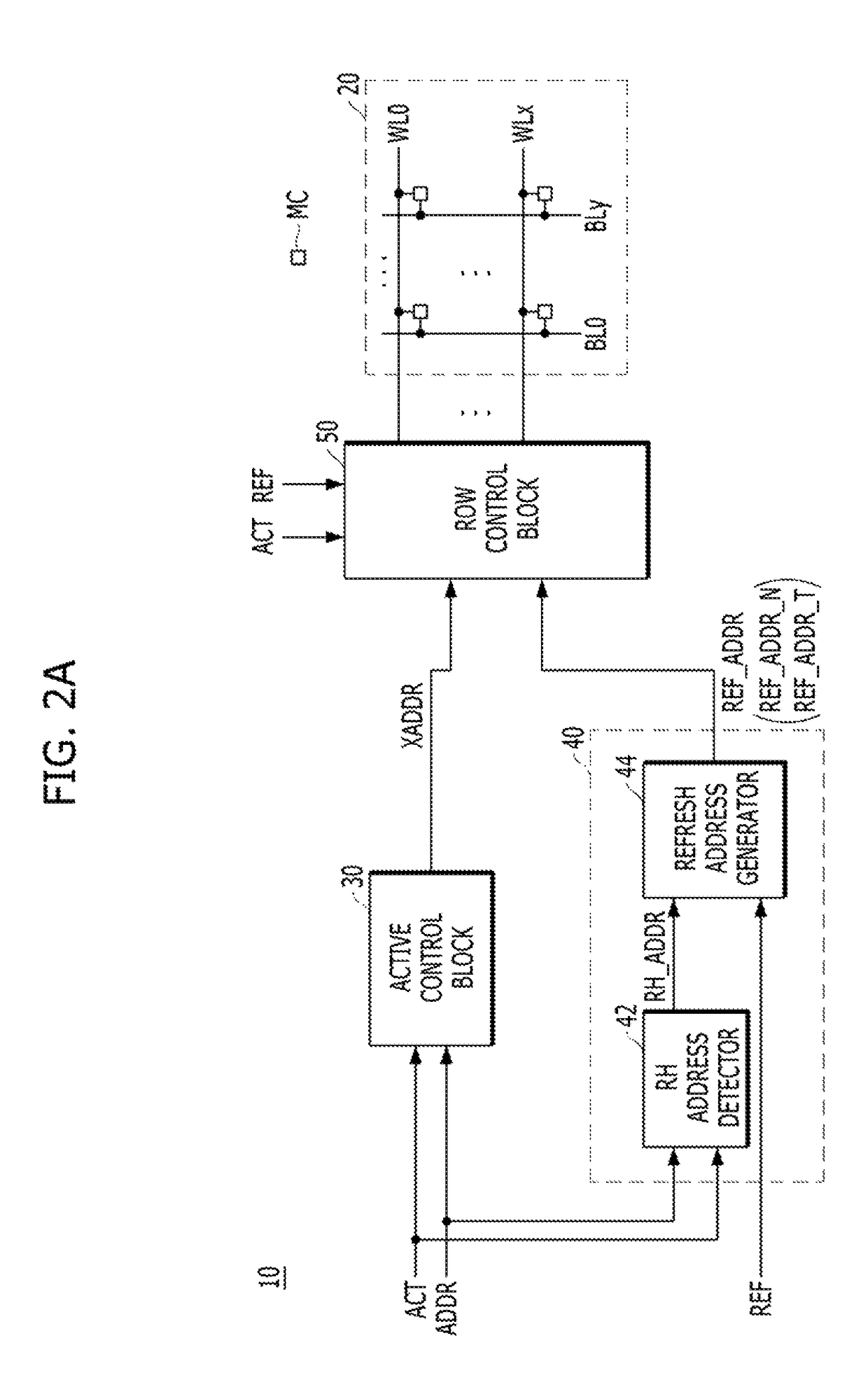

Semiconductor device, refresh control method thereof and computer system

InactiveUS20110225355A1Promote quick completionGrowth inhibitionDigital storageMemory systemsBit lineProcessor register

A semiconductor device comprises a first memory cell array, a register storing information of whether or not one of the word lines in an active state exists in a unit area and storing address information, and a control circuit controlling a refresh operation for a refresh word line based on the information in the register when receiving a refresh request. When the one of the word lines in an active state does not exist, memory cells connected to the refresh word line are refreshed. When the one of the word lines in an active state exists, the one of the word lines in an active state is set into an inactive state temporarily and the memory cells connected to the refresh word line are refreshed after precharging bit lines of the memory cells.

Owner:PS4 LUXCO SARL

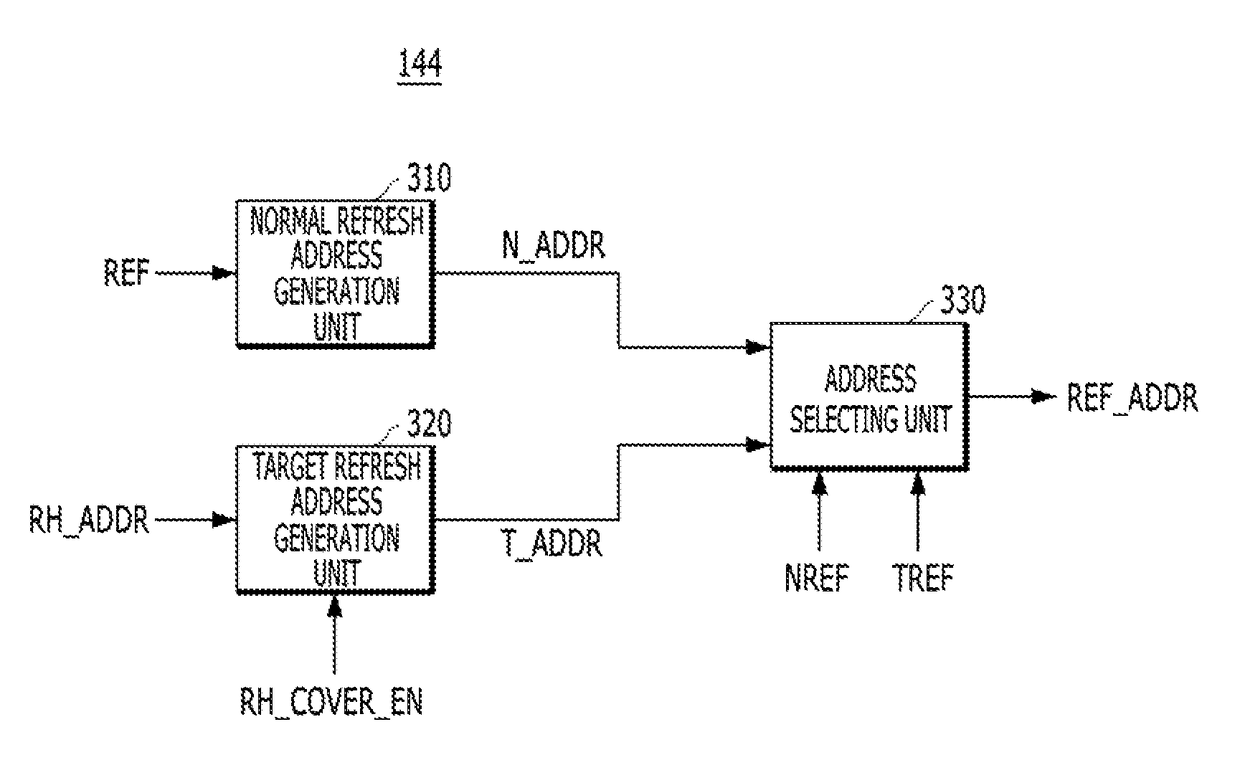

Refresh control circuit for target refresh operation of semiconductor memory device, and operating method thereof

ActiveUS9953696B2Avoid data lossMemory architecture accessing/allocationDigital storageControl circuitBit plane

A semiconductor memory device may include: a memory cell region including a plurality of memory cells coupled between a plurality of word lines and a plurality of bit lines; and a refresh control block suitable for performing a first refresh operation onto the plurality of the word lines in response to a refresh signal, counting the number of active signals that are inputted between at least two neighboring refresh signals and when the counted number of the active signals is equal to or greater than a reference number, performing a second refresh operation onto a word line corresponding to a target address.

Owner:SK HYNIX INC

Novel bit line preparation method in MRAM fabrication

ActiveUS20110089507A1Easy to controlHigh product yieldSolid-state devicesSemiconductor/solid-state device manufacturingElectricityEtching

A MRAM structure is disclosed that includes a metal contact bridge (MCB) which provides an electrical connection between a MTJ top electrode and an overlying bit line. The MCB has a width greater than a MTJ top electrode and serves as an etch stop during bit line etching to prevent sub-trenches from forming adjacent to the top electrode and causing shorts. MCBs also prevent insufficient etching that causes open circuits. A MCB is preferably a metal, metal compound, or alloy such as Ta with low resistivity and high conductivity. The MCB layer is patterned prior to using a dual damascene process to form a bit line contacting each MCB and a bit line pad connection to a word line pad. MCB thickness is thin enough to allow a strong bit line magnetic field for switching a free layer and large enough to function as an efficient oxide etch stop.

Owner:TAIWAN SEMICON MFG CO LTD

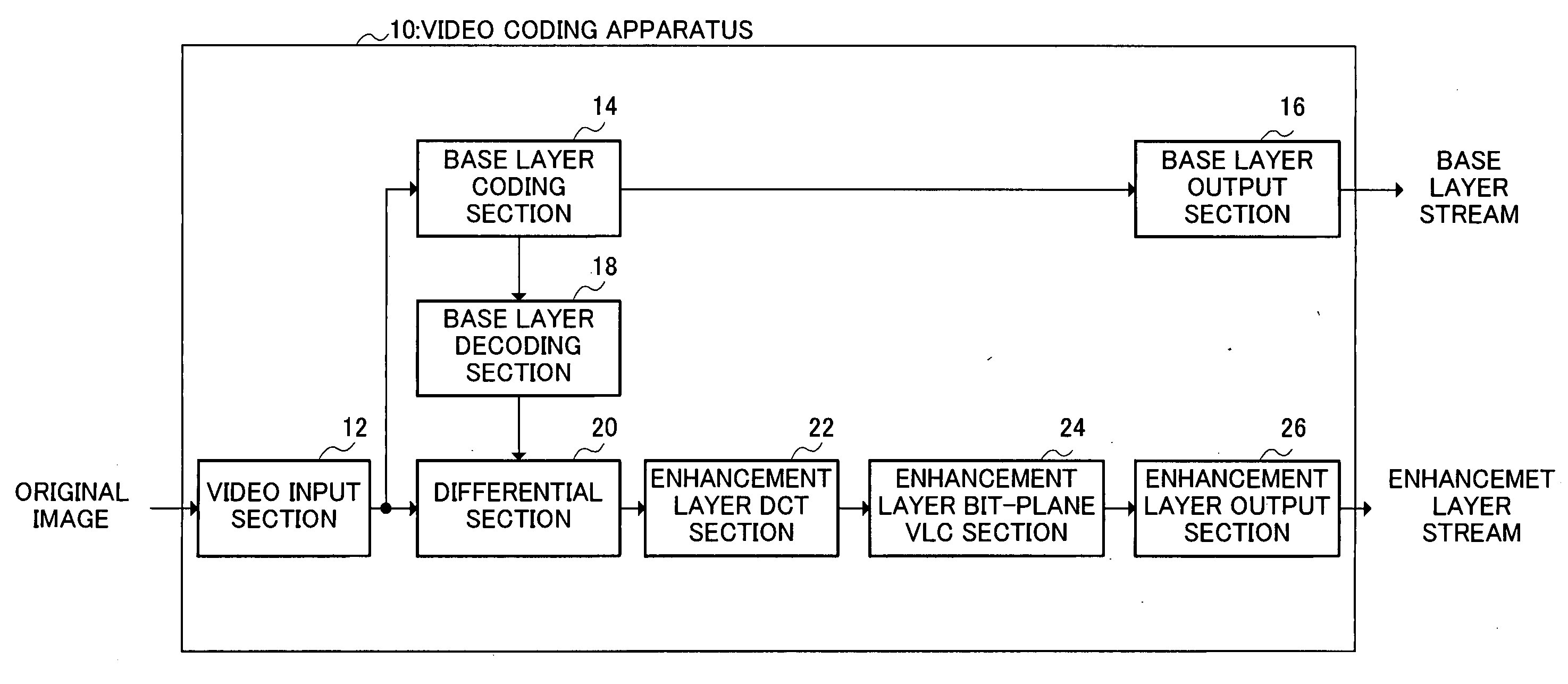

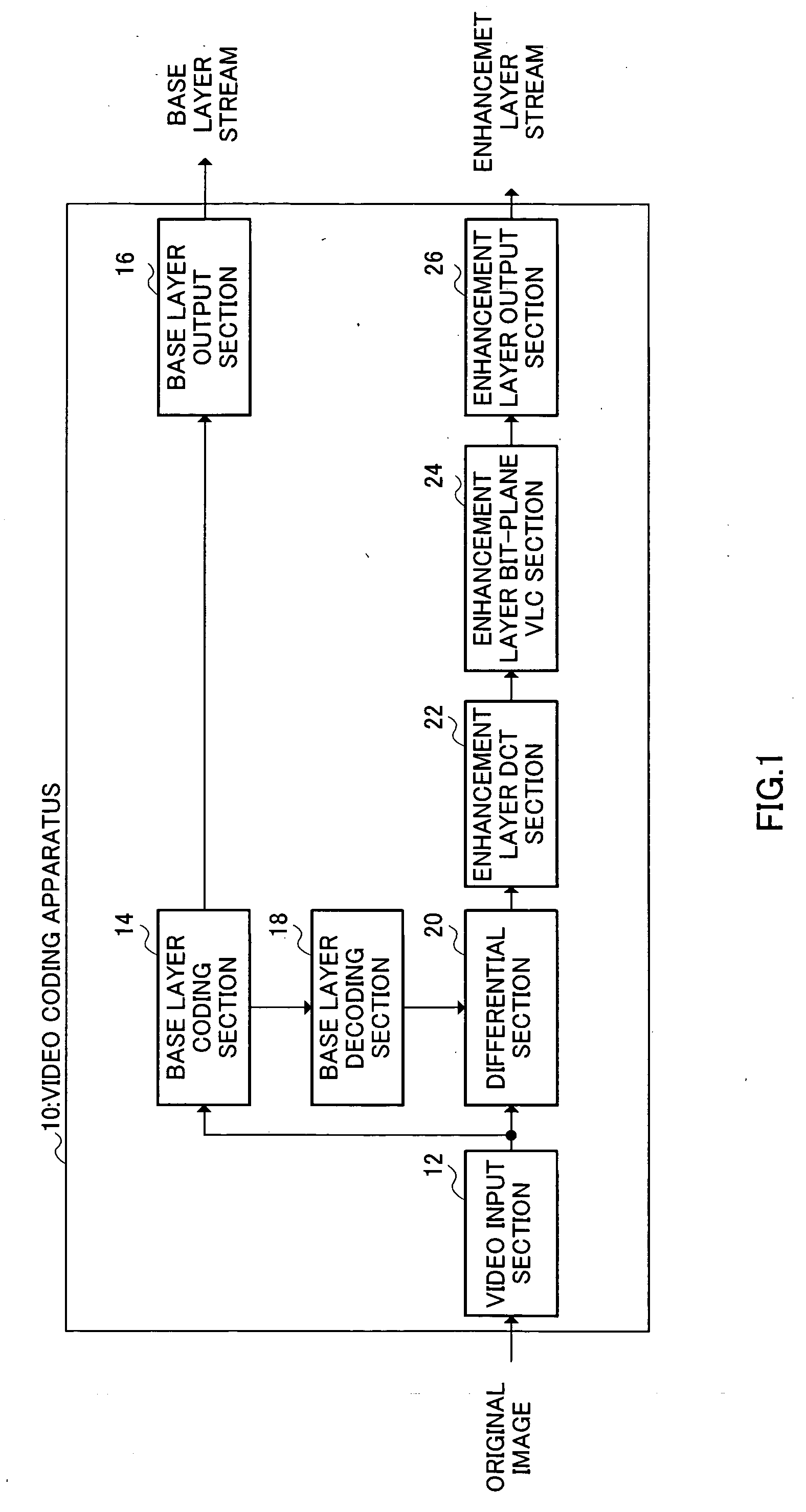

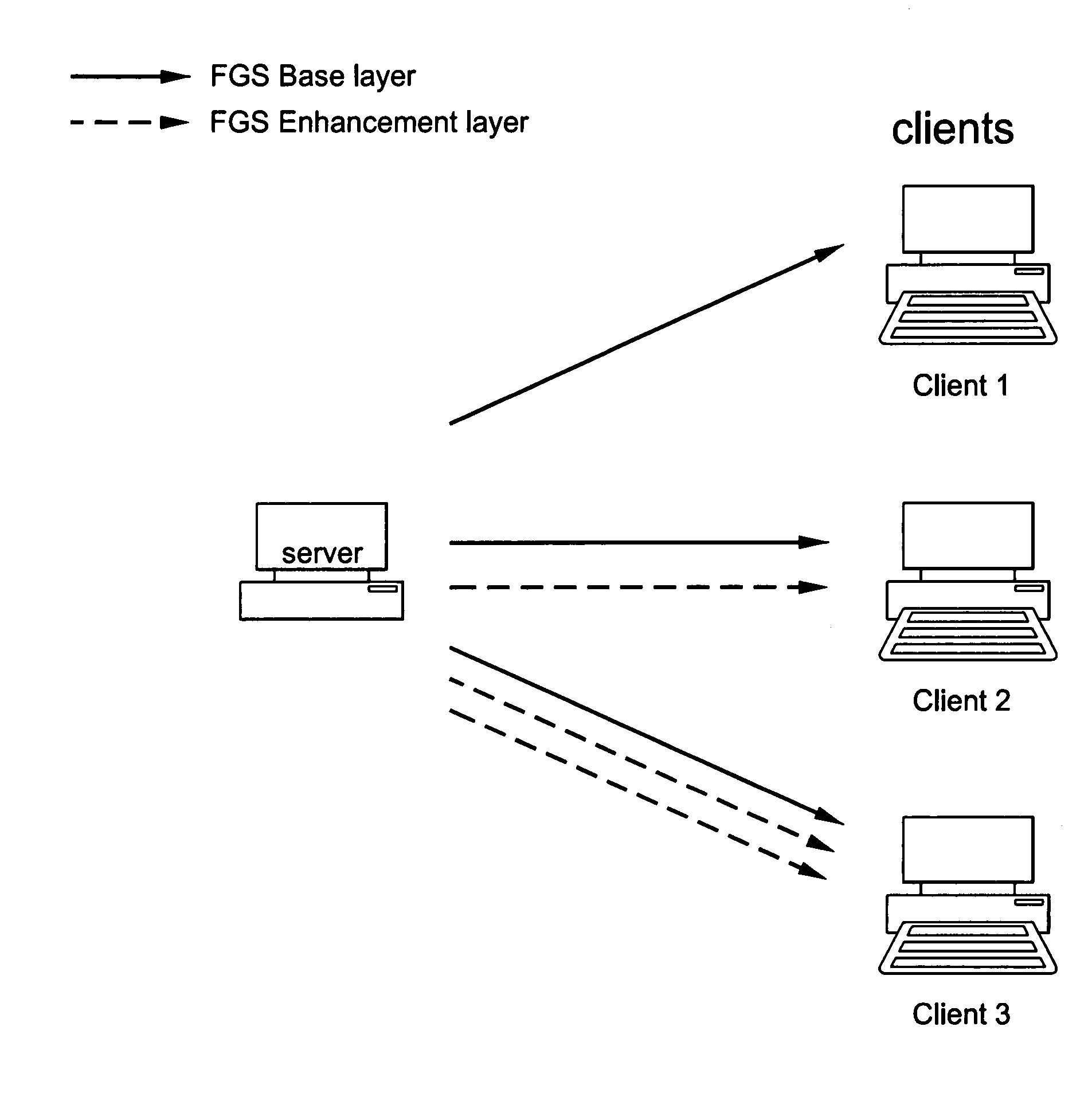

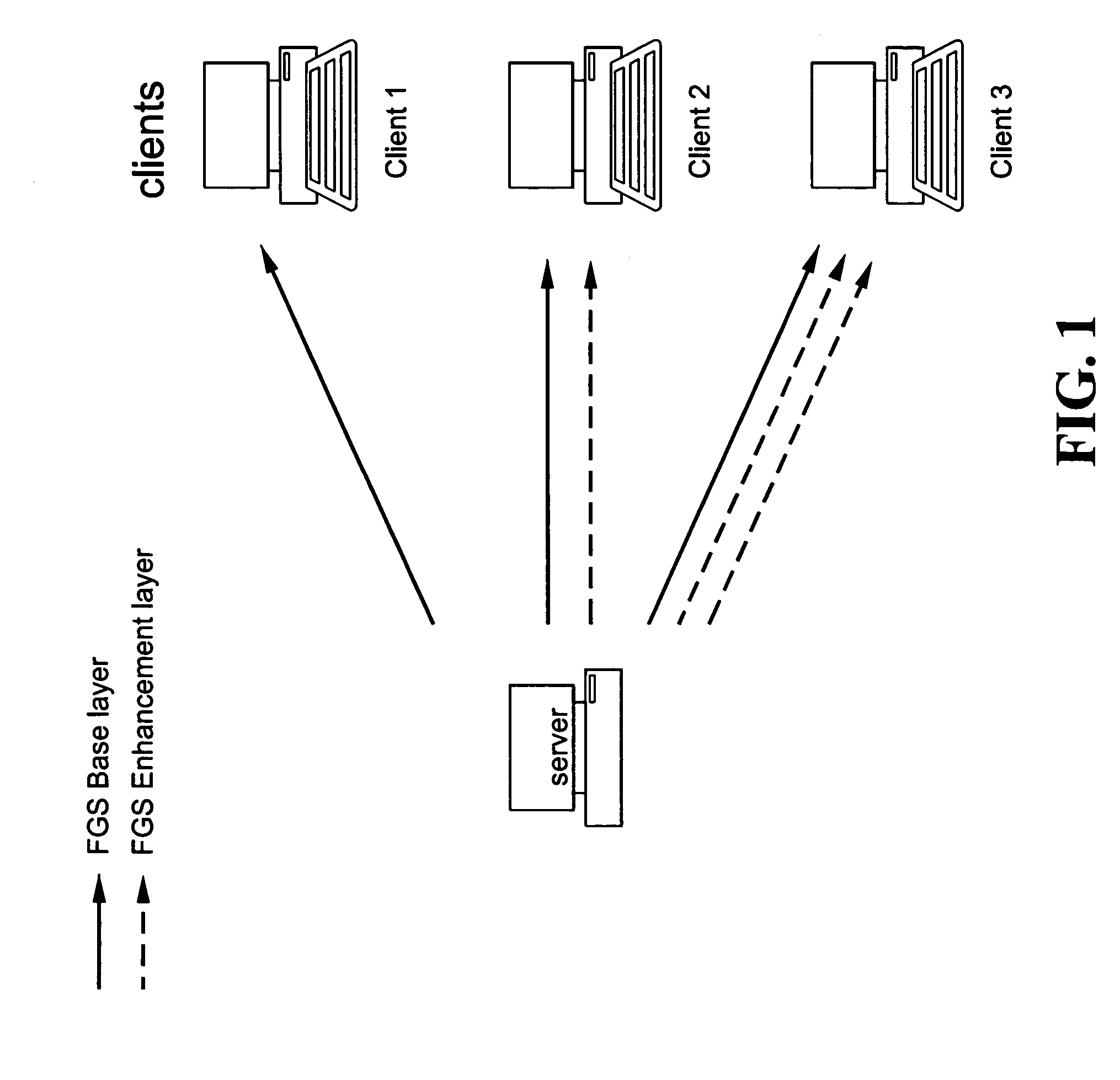

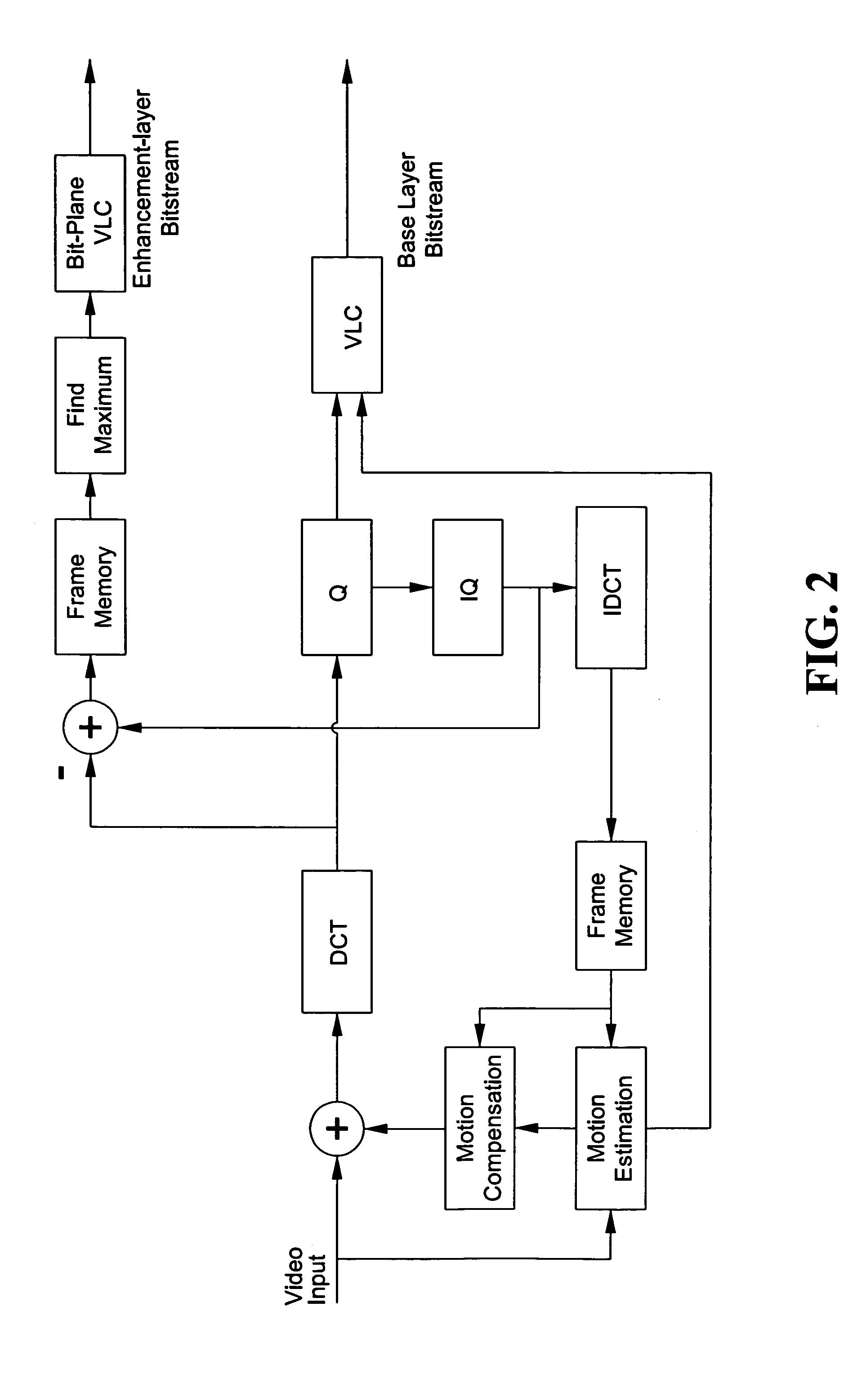

Method and apparatus for MPEG-4 FGS performance enhancement

InactiveUS7227894B2Improve performanceEnhancement-layer bit-plane truncationColor television with pulse code modulationColor television with bandwidth reductionRate adaptationPerformance enhancement

An architecture of a fine granularity scalable (FGS) codec has an encoder and a decoder configurable in three prediction modes. The coarse prediction loop in the base layer of the encoder has a switch for selecting either coarse prediction output or fine prediction output in the encoder. The fine prediction loop in the enhancement layer of the encoder also has a switch for selecting either coarse prediction output or fine prediction output. Two-pass encoding is used in the encoder. The first pass extracts coding parameters and classifies macroblocks of a video frame into three groups each being assigned with all-coarse prediction mode, all-fine prediction mode or mix prediction. The second pass uses the assigned modes to encode the macroblocks. A rate adaptation algorithm is provided to truncate the enhancement bit-planes for low bit rate, medium bit rate and high bit rate and allocate bit efficiently for achieving higher video quality.

Owner:IND TECH RES INST

4f2 self align side wall active phase change memory

Arrays of memory cells are described along with devices thereof and method for manufacturing. Memory cells described herein include self-aligned side wall memory members comprising an active programmable resistive material. In preferred embodiments the area of the memory cell is 4F2, F being the feature size for a lithographic process used to manufacture the memory cell, and more preferably F being equal to a minimum feature size. Arrays of memory cells described herein include memory cells arranged in a cross point array, the array having a plurality of word lines and source lines arranged in parallel in a first direction and having a plurality of bit lines arranged in parallel in a second direction perpendicular to the first direction.

Owner:MACRONIX INT CO LTD

Ultra low-cost solid-state memory

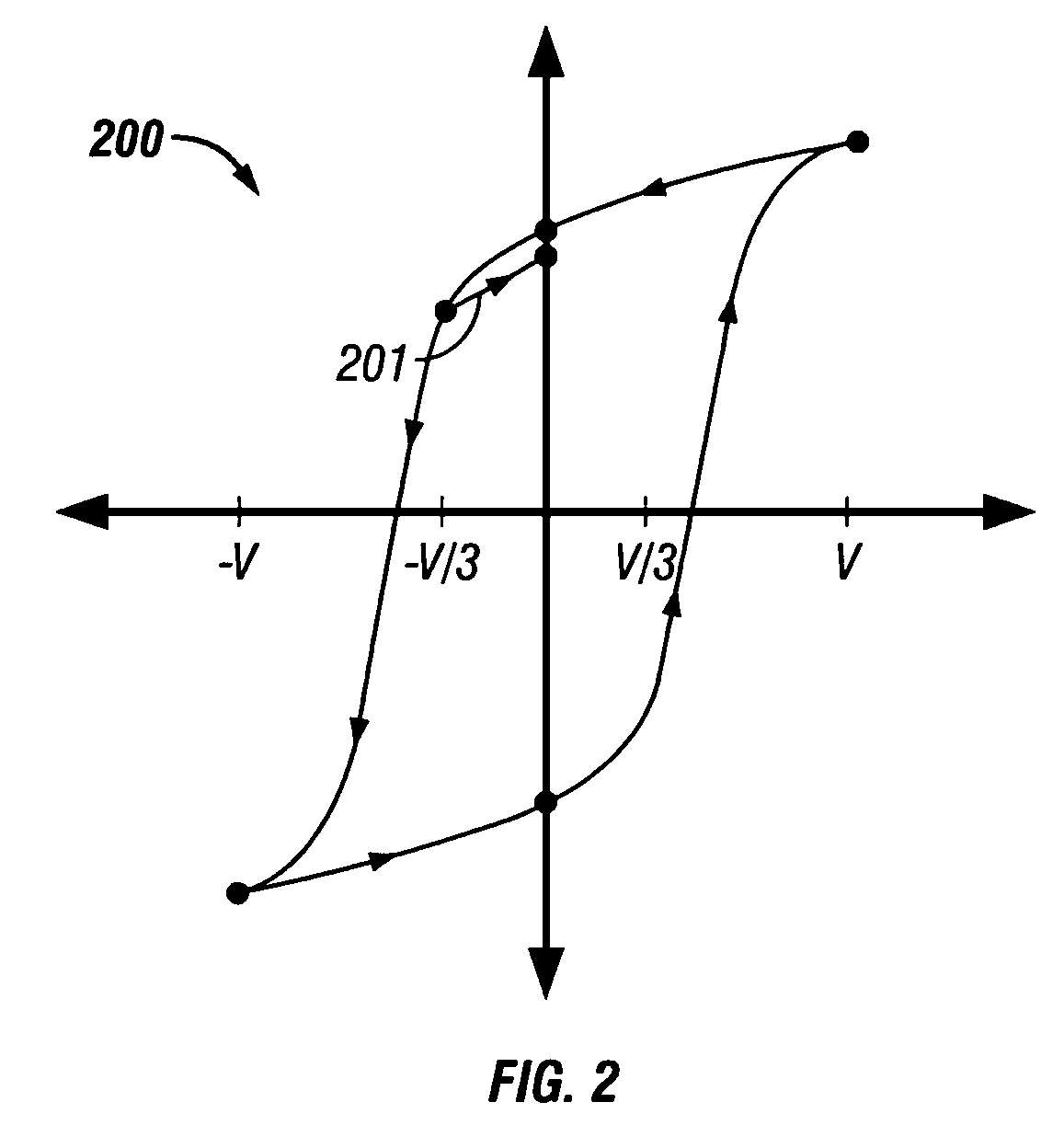

A three-dimensional solid-state memory is formed from a plurality of bit lines, a plurality of layers, a plurality of tree structures and a plurality of plate lines. Bit lines extend in a first direction in a first plane. Each layer includes an array of memory cells, such as ferroelectric or hysteretic-resistor memory cells. Each tree structure corresponds to a bit line, has a trunk portion and at least one branch portion. The trunk portion of each tree structure extends from a corresponding bit line, and each tree structure corresponds to a plurality of layers. Each branch portion corresponds to at least one layer and extends from the trunk portion of a tree structure. Plate lines correspond to at least one layer and overlap the branch portion of each tree structure in at least one row of tree structures at a plurality of intersection regions.

Owner:WESTERN DIGITAL TECH INC

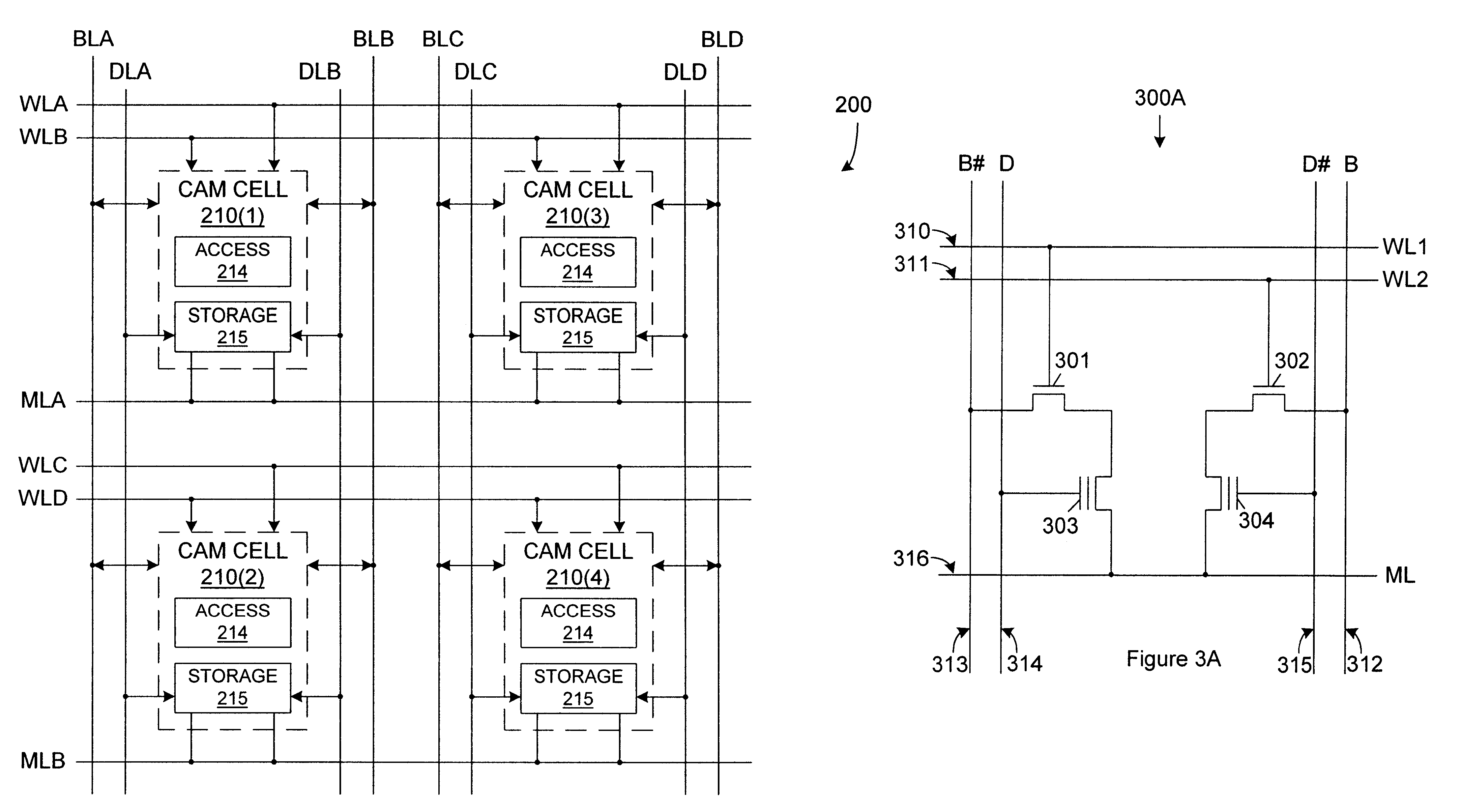

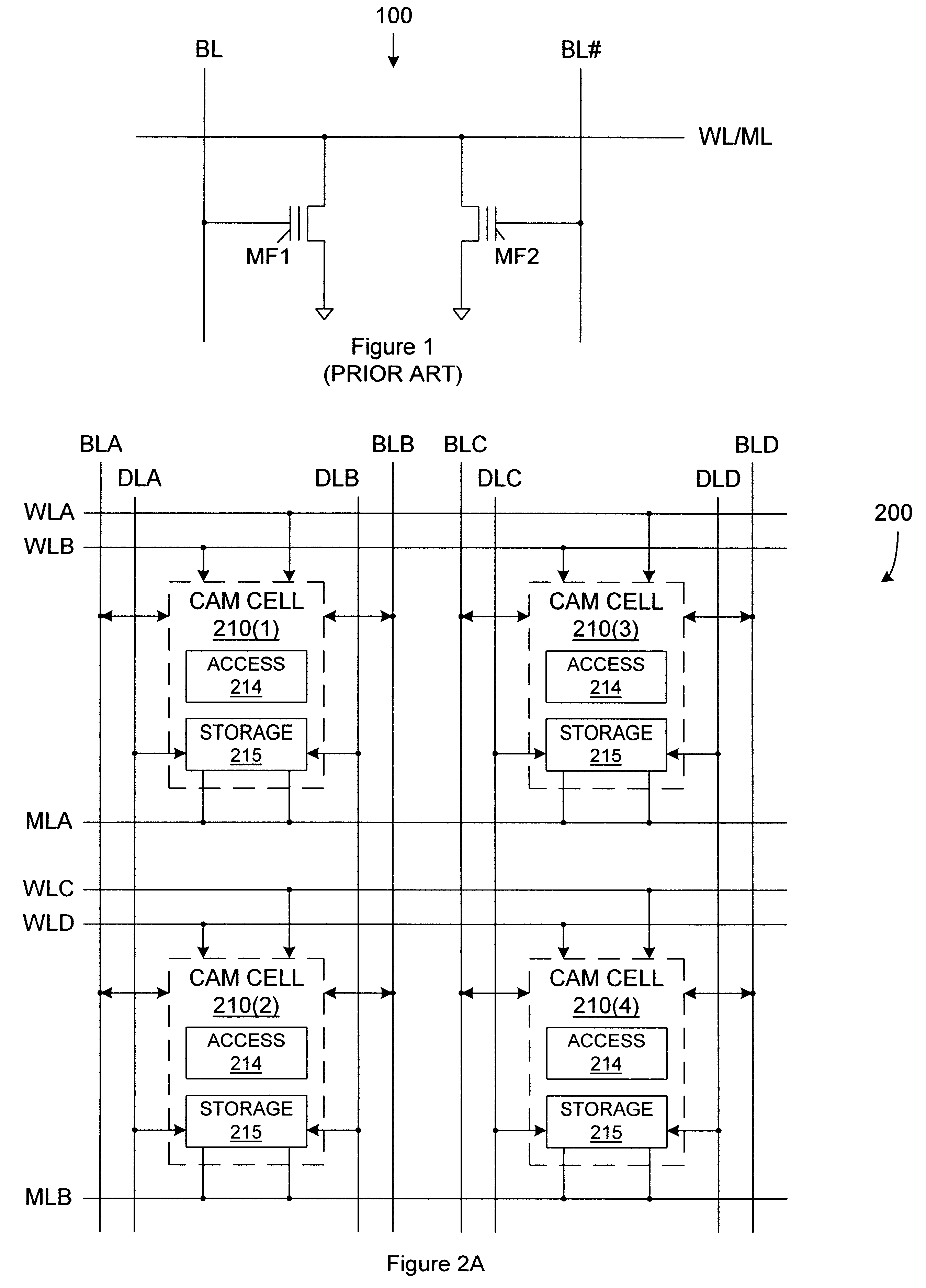

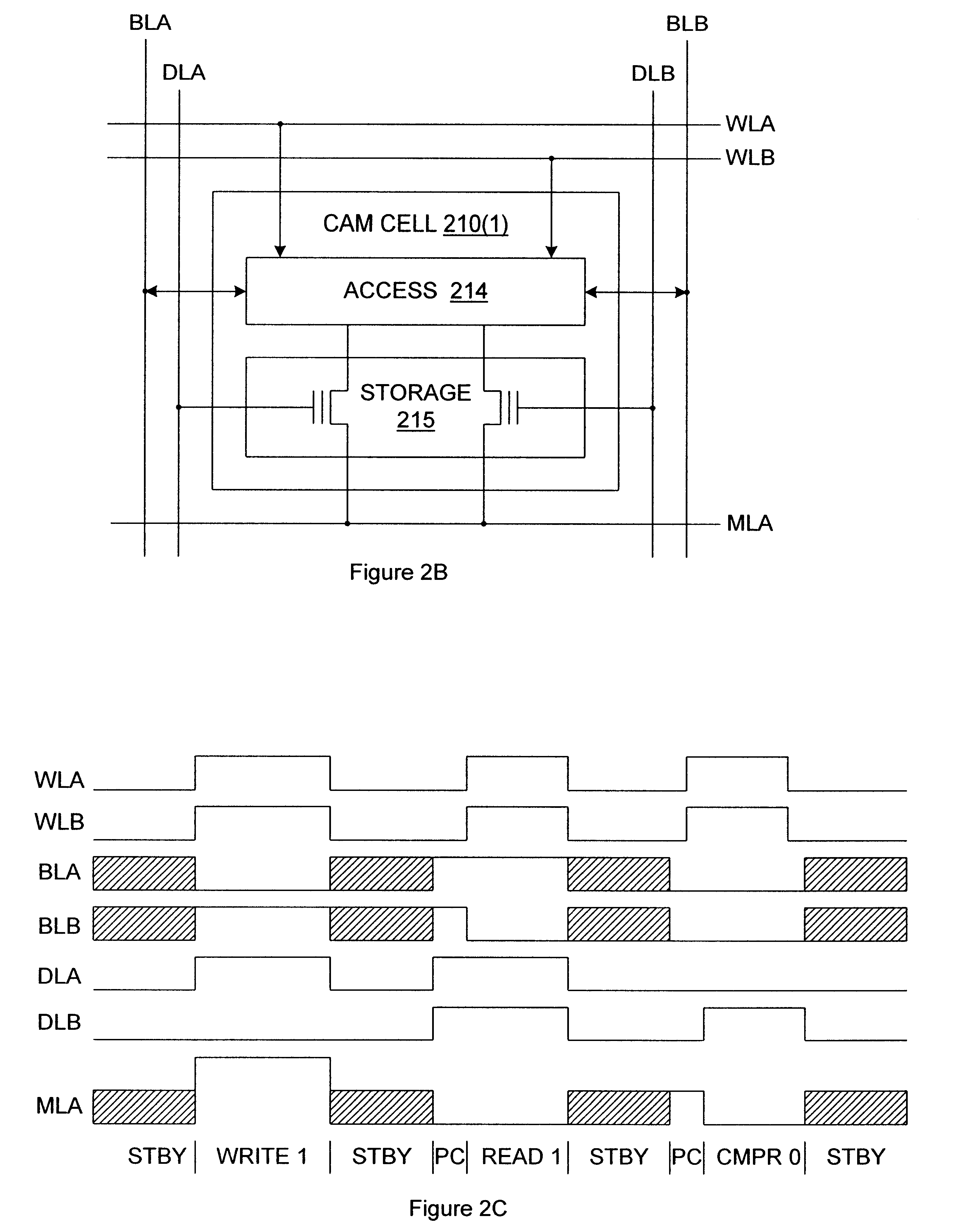

Cam array with minimum cell size

A CAM array includes non-volatile ternary CAM cells that use access transistors to easily read from and write to the non-volatile transistors. Each ternary CAM cell includes a pair of storage elements that are used to store a data bit value, and an access element that is used during CAM array operation. During a comparison operation, when the applied data value matches the stored value, the storage elements de-couple the match line from a discharging bit line (i.e., a high voltage on the match line remains high). Conversely, when the applied data value does not match the stored value, the storage elements couple the match line to a discharging bit line, thereby discharging the match line.

Owner:AVAGO TECH INT SALES PTE LTD

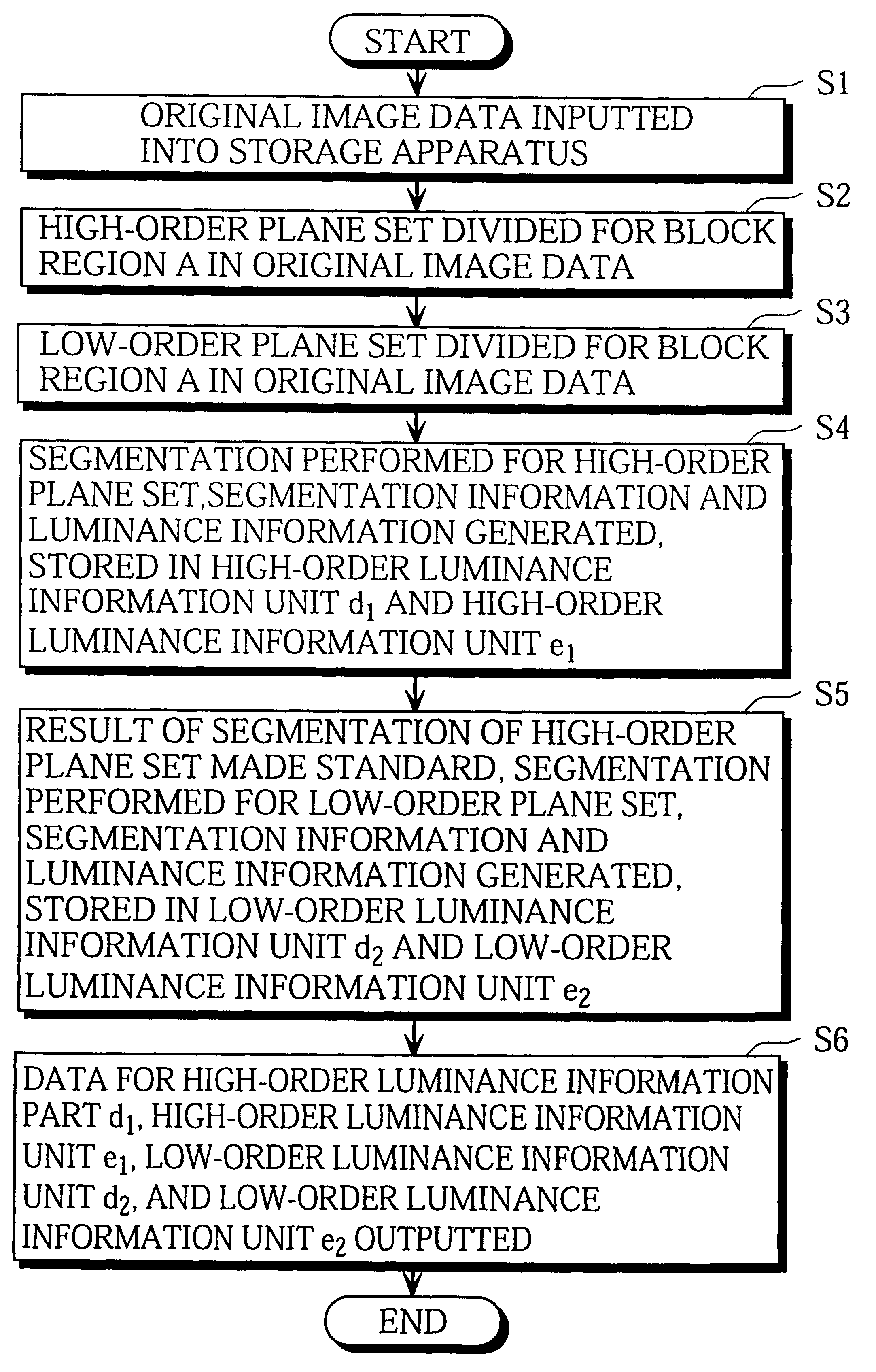

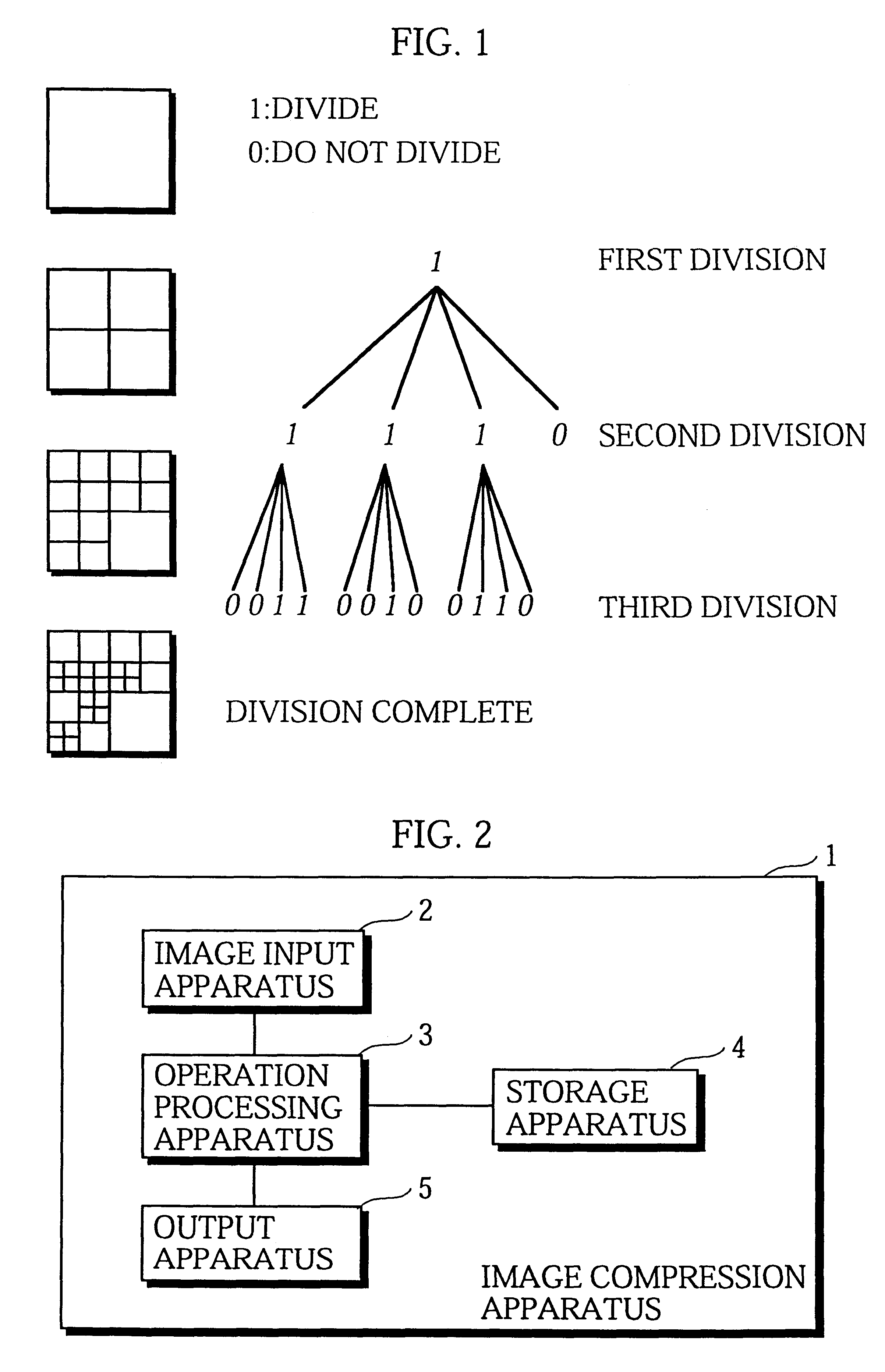

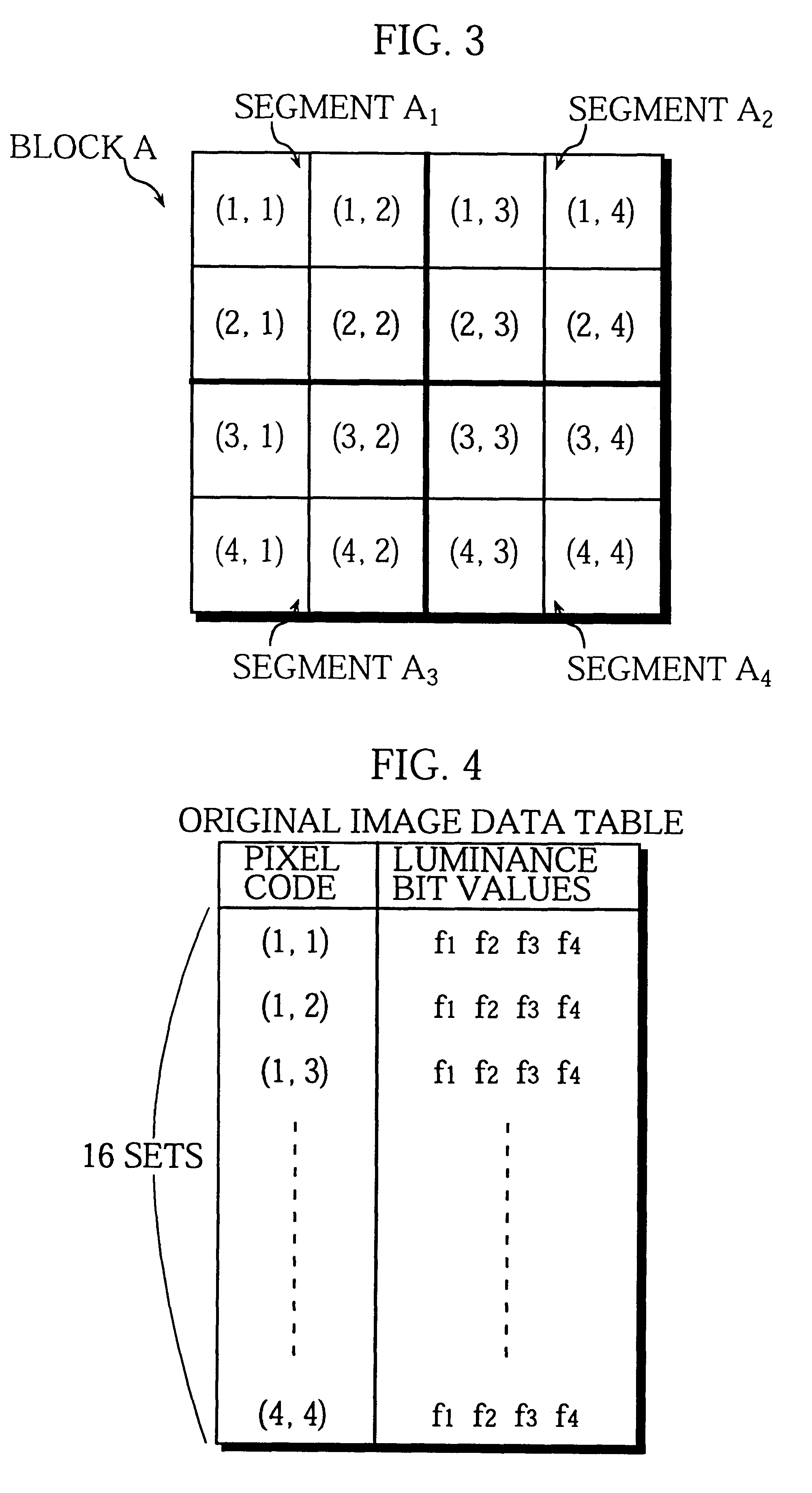

Image compression apparatus and decoding apparatus suited to lossless image compression

InactiveUS6614939B1Character and pattern recognitionImage codingImage compressionLossless compression

An image compression apparatus for outputting compressed image information that is suited to progressive image reproduction where completely lossless reproduction is possible without having to use large amounts of compressed image information. A decoding apparatus decodes the compressed image information and performs reproduction. The image compression apparatus performs image compression with a first segmentation for a first plane set that includes at one bit plane in block image information in the original image information. As a result, first region information composed of segmentation information showing a first segmentation result and luminance information is produced. The image compression apparatus also performs image compression with a second segmentation for a second plane set that includes at least one bit plane adjacent to the first plane set. Here, the first segmentation result is used as a standard. As a result, second region information composed of segmentation information and luminance information is produced. Compressed image information is then generated and outputted based on the first and second region information.

Owner:PANASONIC CORP

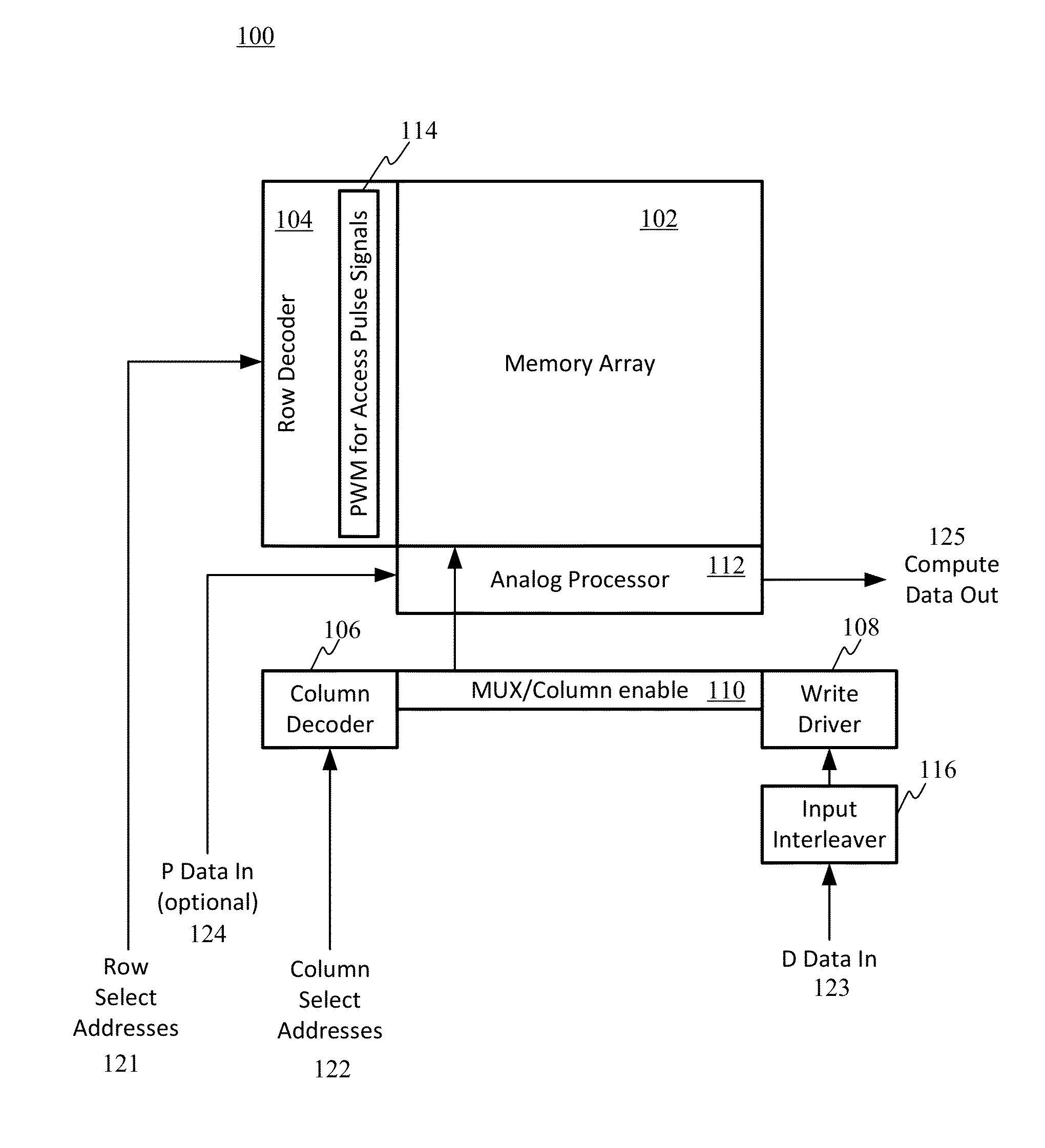

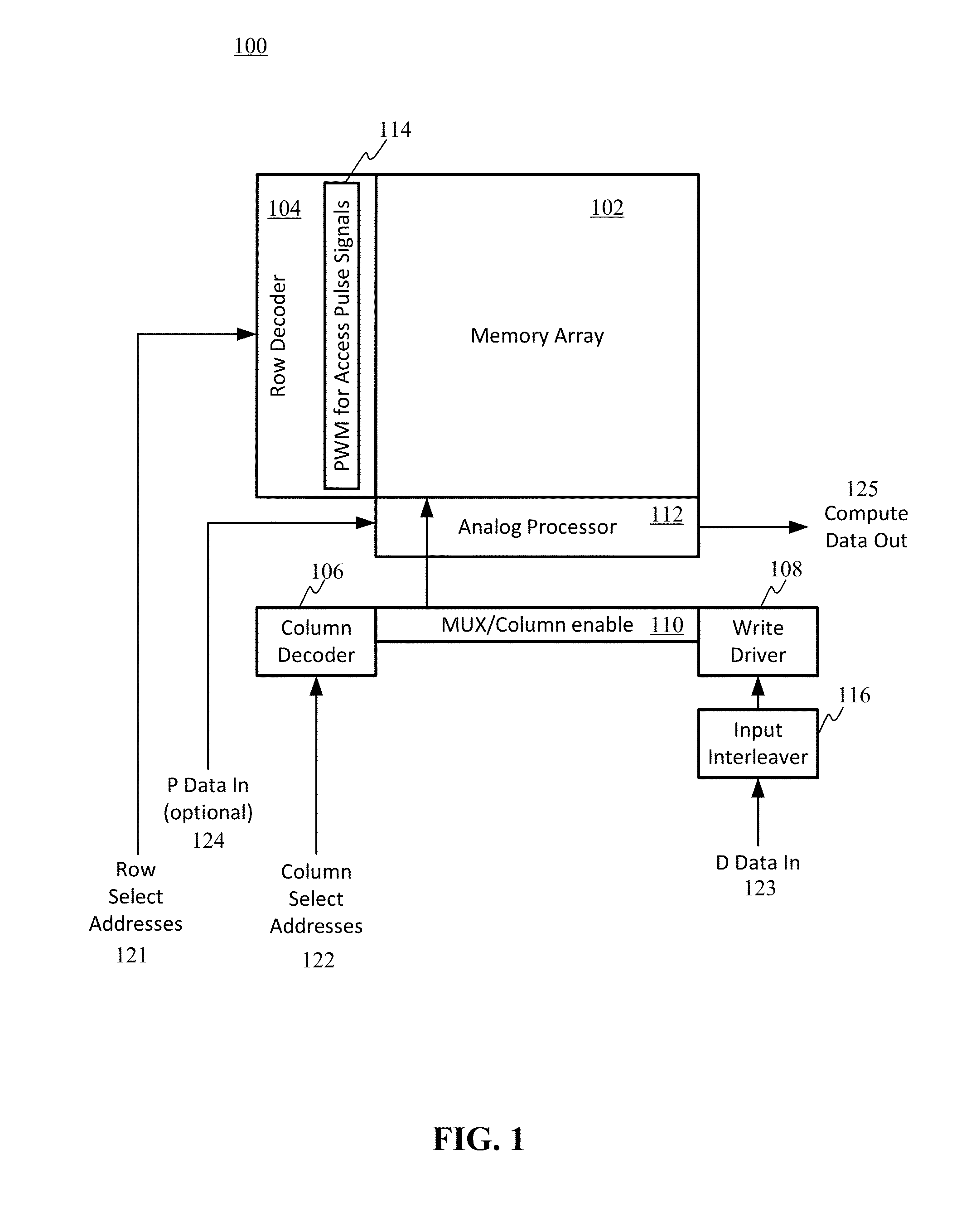

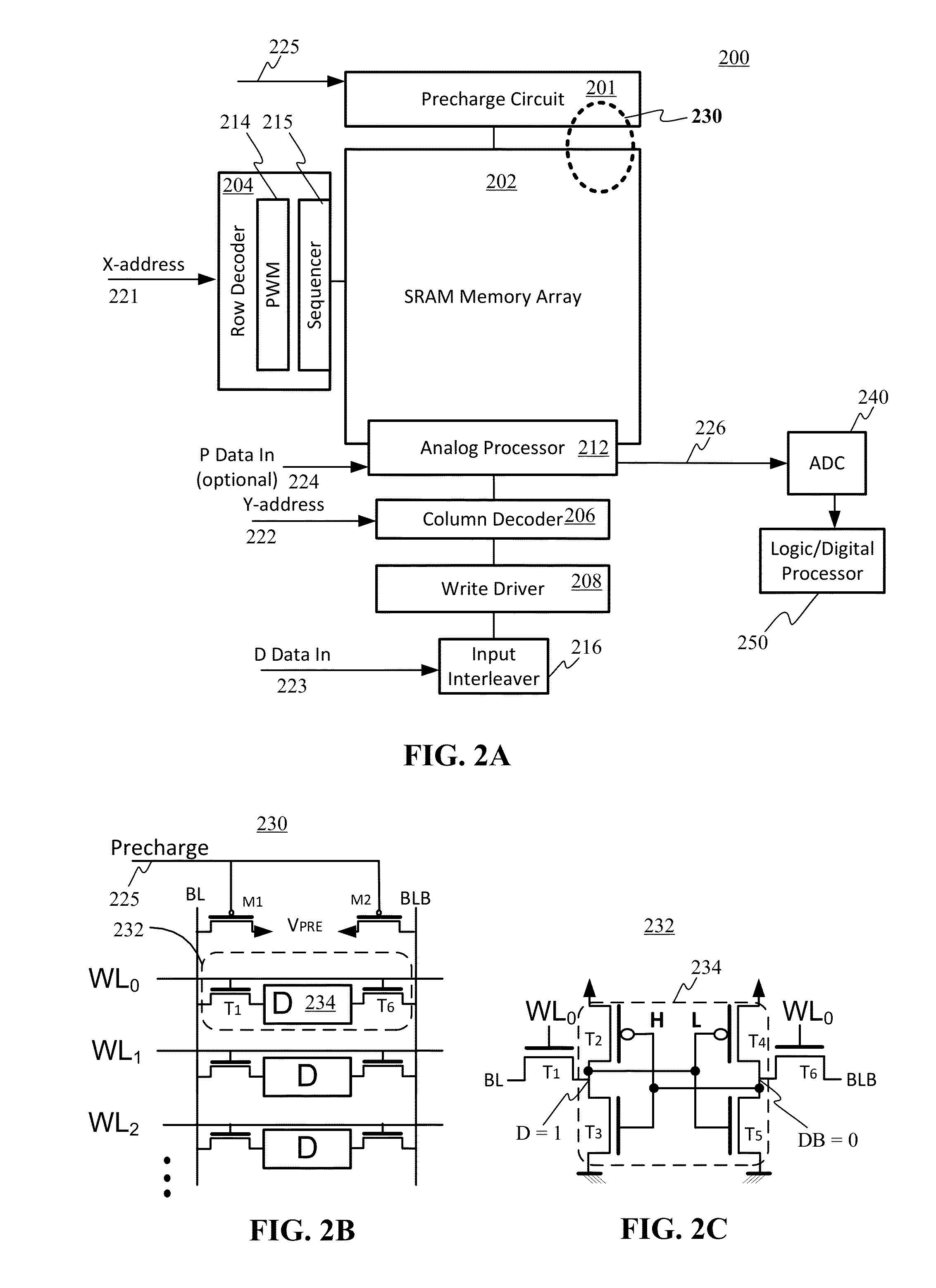

Compute memory

ActiveUS20160232951A1Achieve energy efficiencyReduce delaysDigital storageAnalog signal processingBit plane

A compute memory system can include a memory array and a controller that generates N-ary weighted (e.g., binary weighted) access pulses for a set of word lines during a single read operation. This multi-row read generates a charge on a bit line representing a word stored in a column of the memory array. The compute memory system further includes an embedded analog signal processor stage through which voltages from bit lines can be processed in the analog domain. Data is written into the memory array in a manner that stores words in columns instead of the traditional row configuration.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

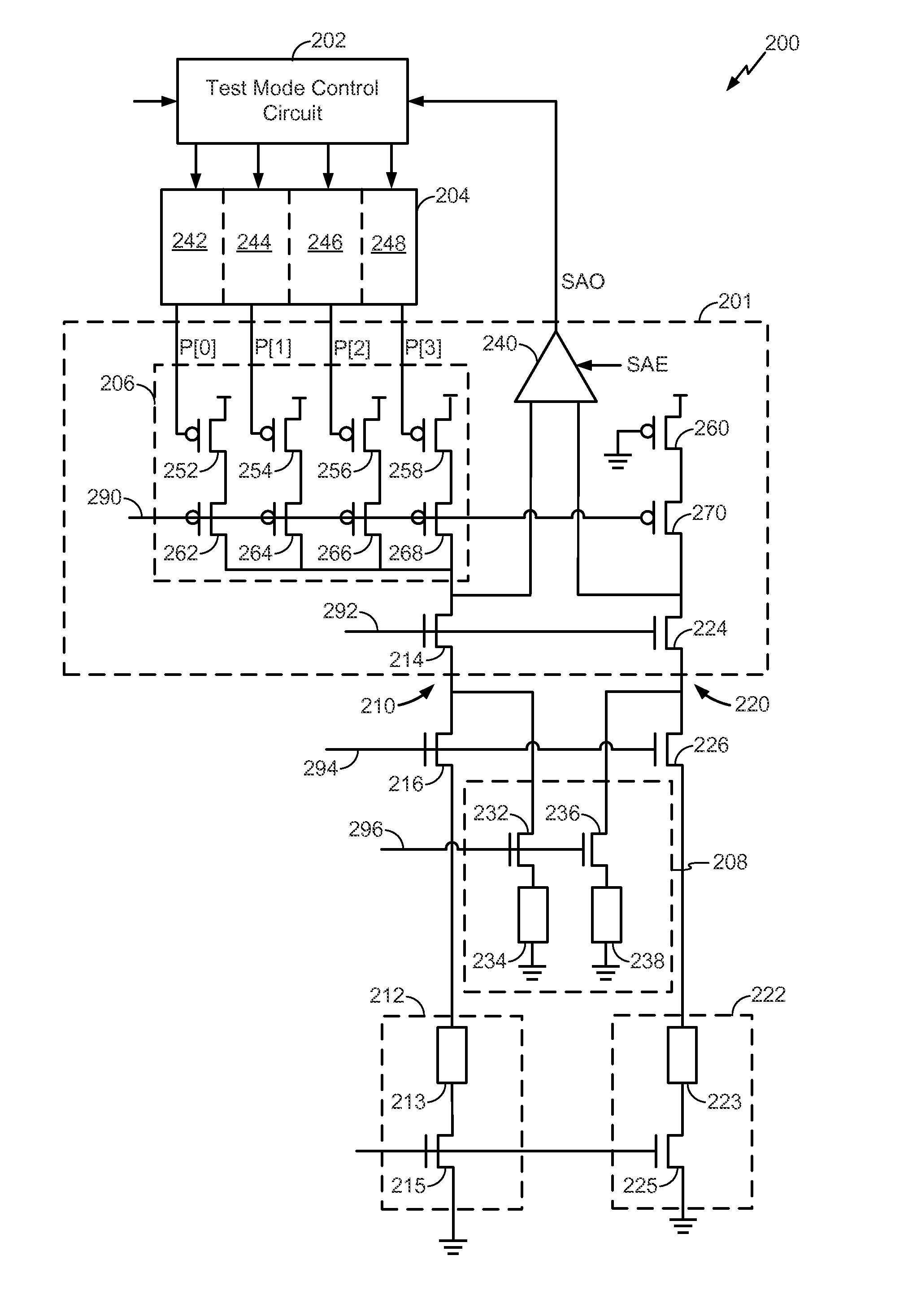

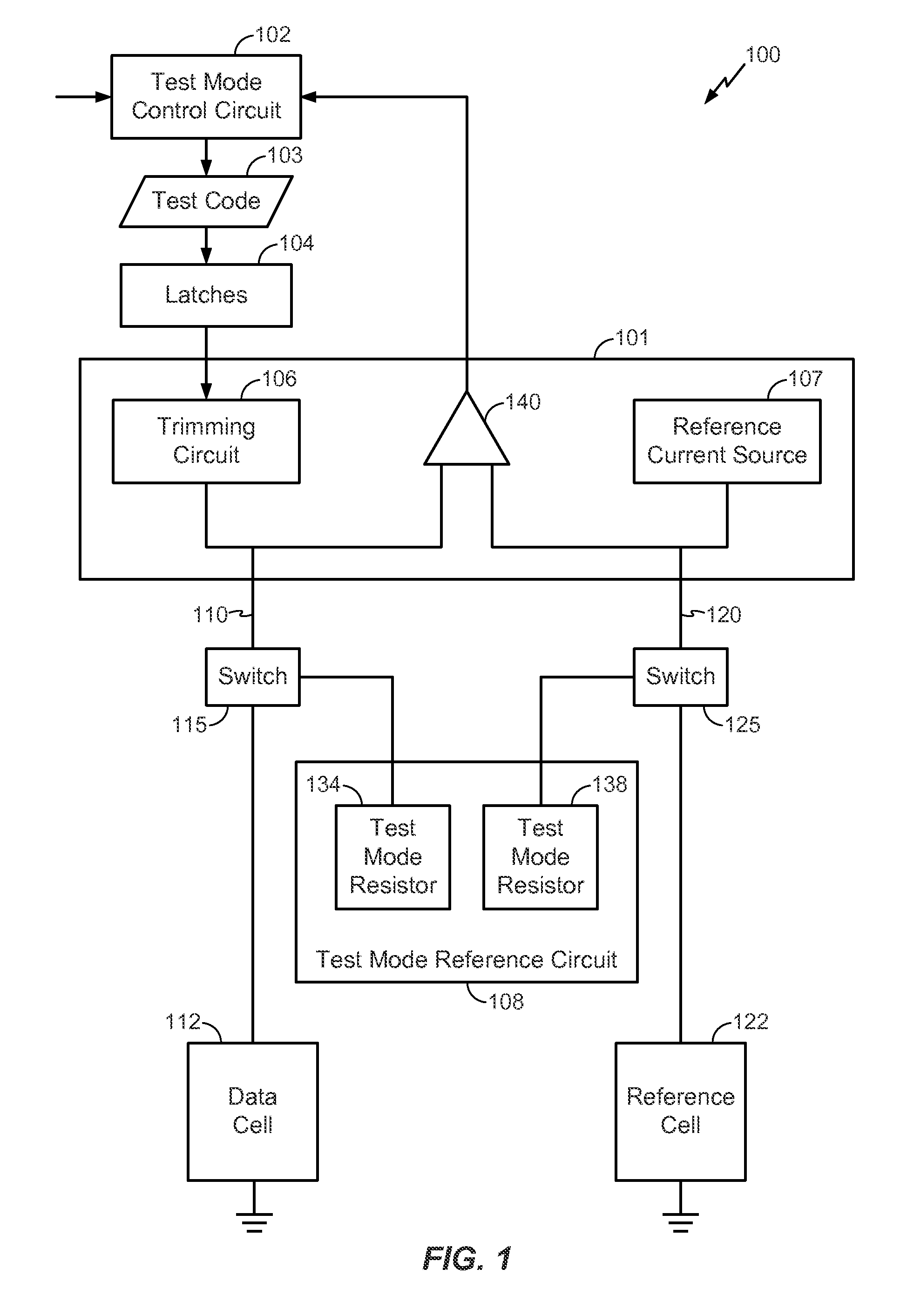

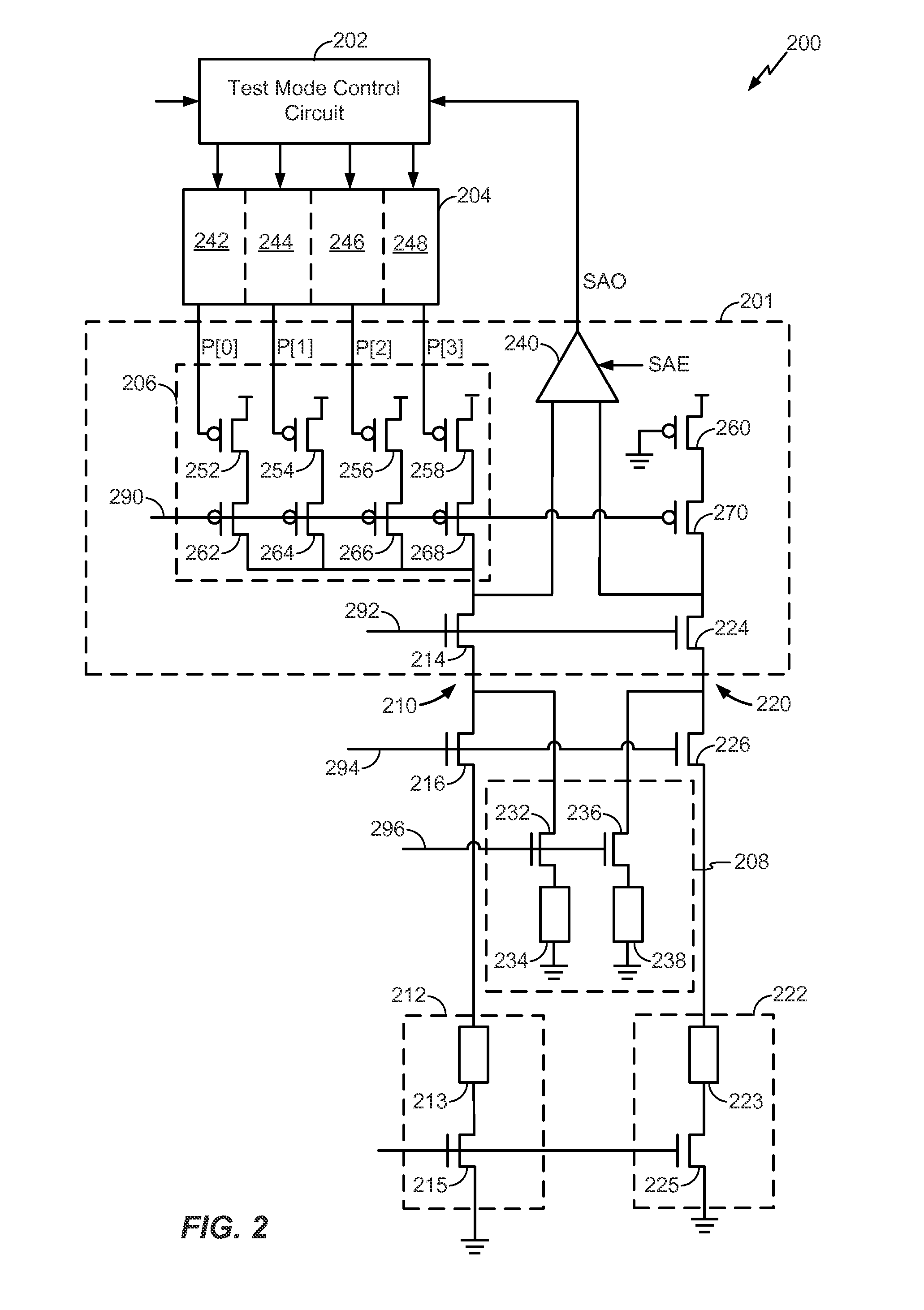

Sense amplifier offset voltage reduction

ActiveUS9140747B2Reduce errorsReduce voltage offsetElectronic circuit testingRead-only memoriesAudio power amplifierPower flow

A circuit includes a plurality of transistors responsive to a plurality of latches that store a test code. The circuit further includes a first bit line coupled to a data cell and coupled to a sense amplifier. The circuit also includes a second bit line coupled to a reference cell and coupled to the sense amplifier. A current from a set of the plurality of transistors is applied to the data cell via the first bit line. The set of the plurality of transistors is determined based on the test code. The circuit also includes a test mode reference circuit coupled to the first bit line and to the second bit line.

Owner:QUALCOMM INC

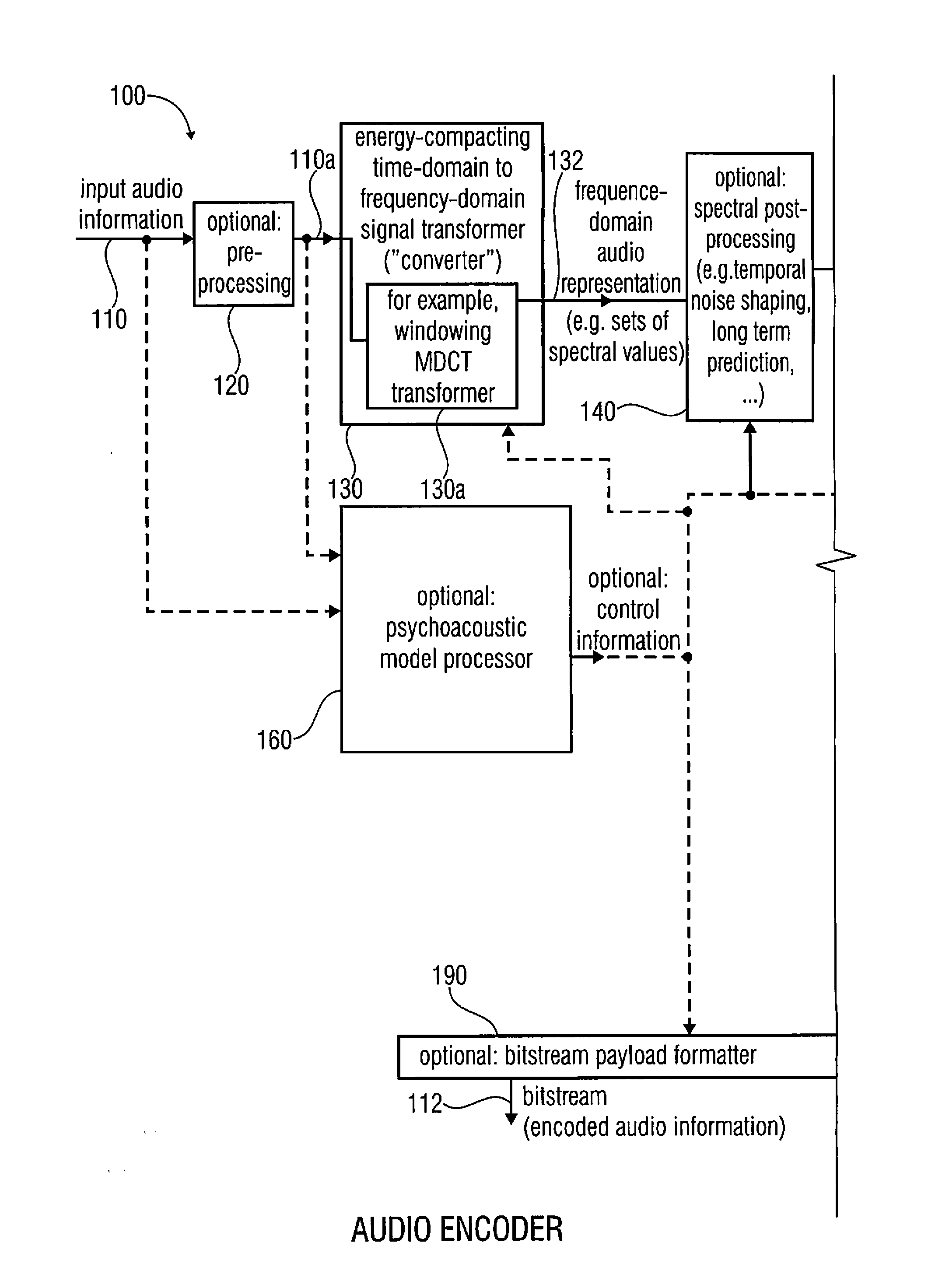

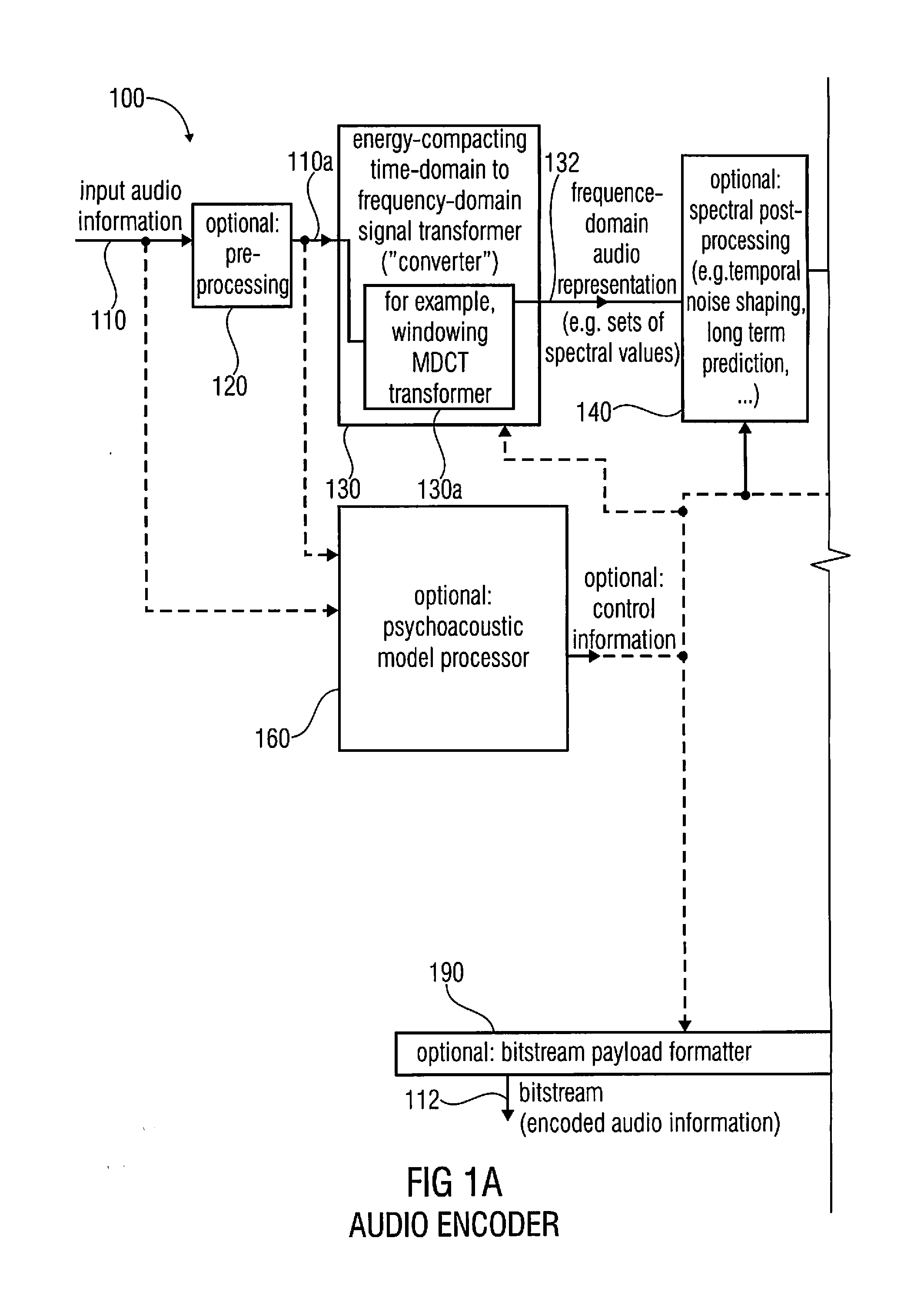

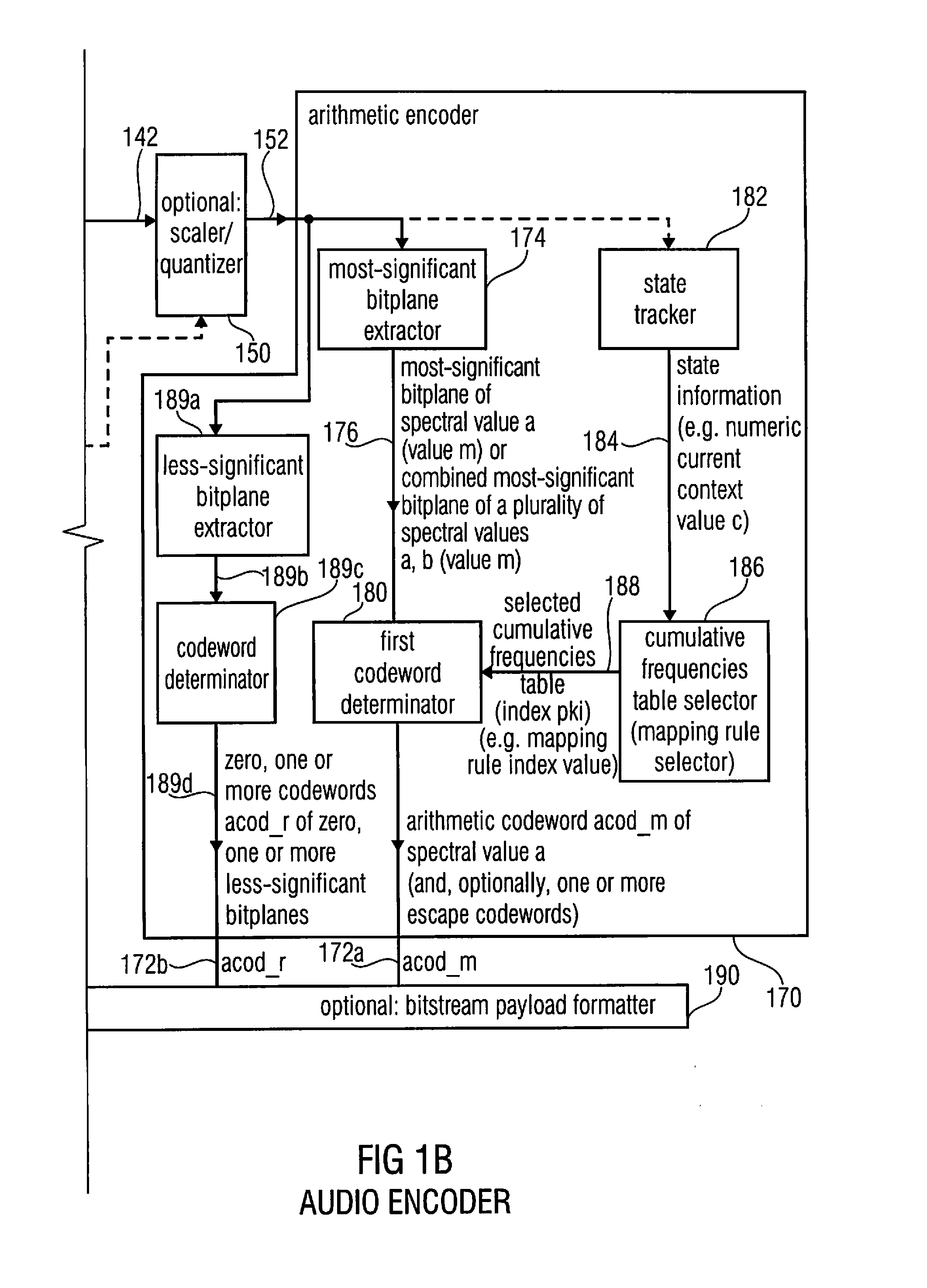

Audio encoder, audio decoder, method for encoding and audio information, method for decoding an audio information and computer program using an optimized hash table

An audio decoder includes an arithmetic decoder for providing decoded spectral values on the basis of an arithmetically encoded representation thereof, and a frequency-domain-to-time-domain converter for providing a time-domain audio representation. The arithmetic decoder selects a mapping rule describing a mapping of a code value onto a symbol code representing a spectral value, or a most significant bit-plane thereof, in a decoded form, in dependence on a context state described by a numeric current context value. The arithmetic decoder determines the numeric current context value in dependence on a plurality of previously decoded spectral values. It evaluates a hash table, entries of which define both significant state values amongst the numeric context values and boundaries of intervals of numeric context values, in order to select the mapping rule, wherein the hash table ari_hash_m is defined as given in FIGS. 22(1), 22(2), 22(3) and 22(4).

Owner:FRAUNHOFER GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG EV

Memory device

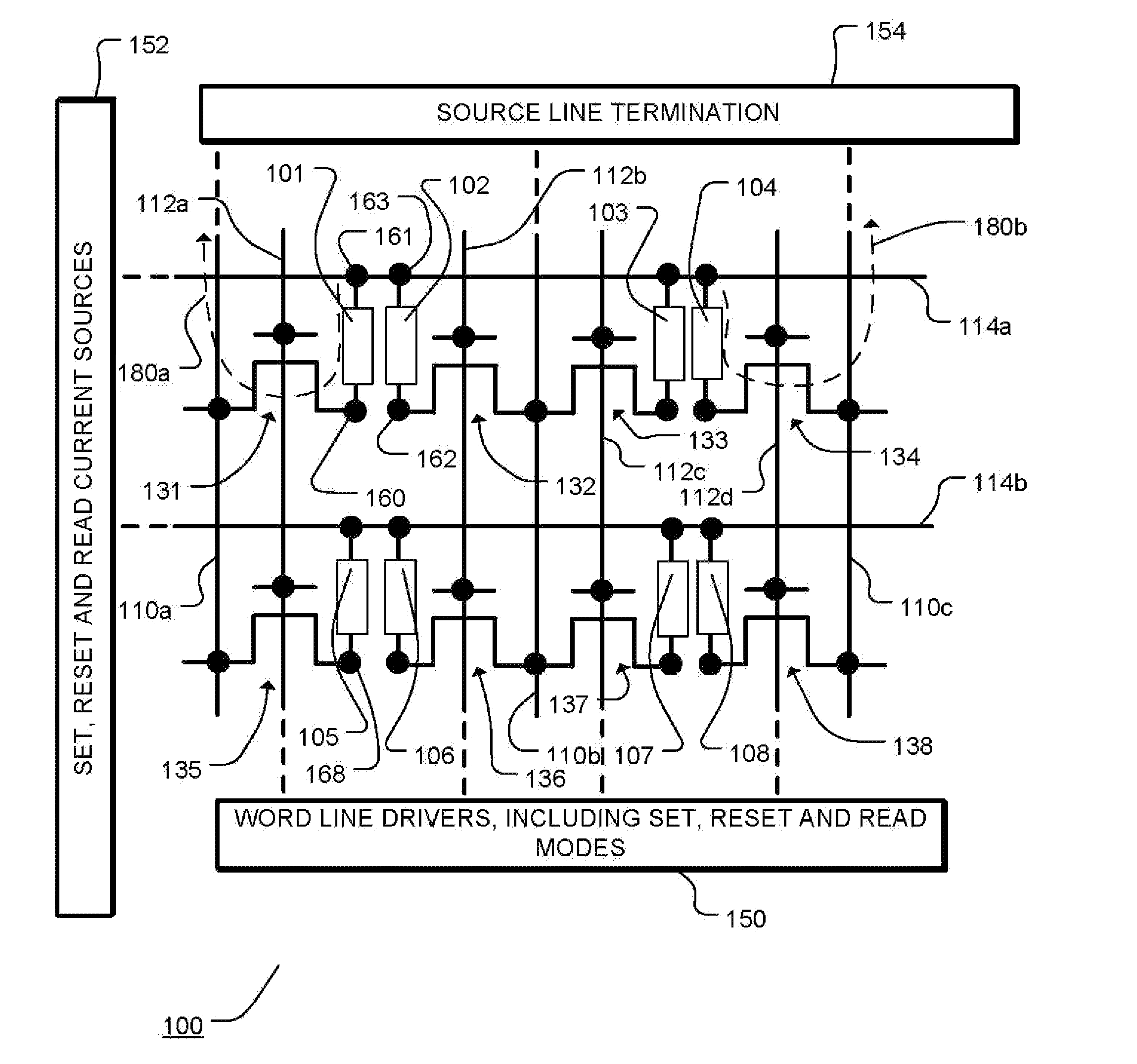

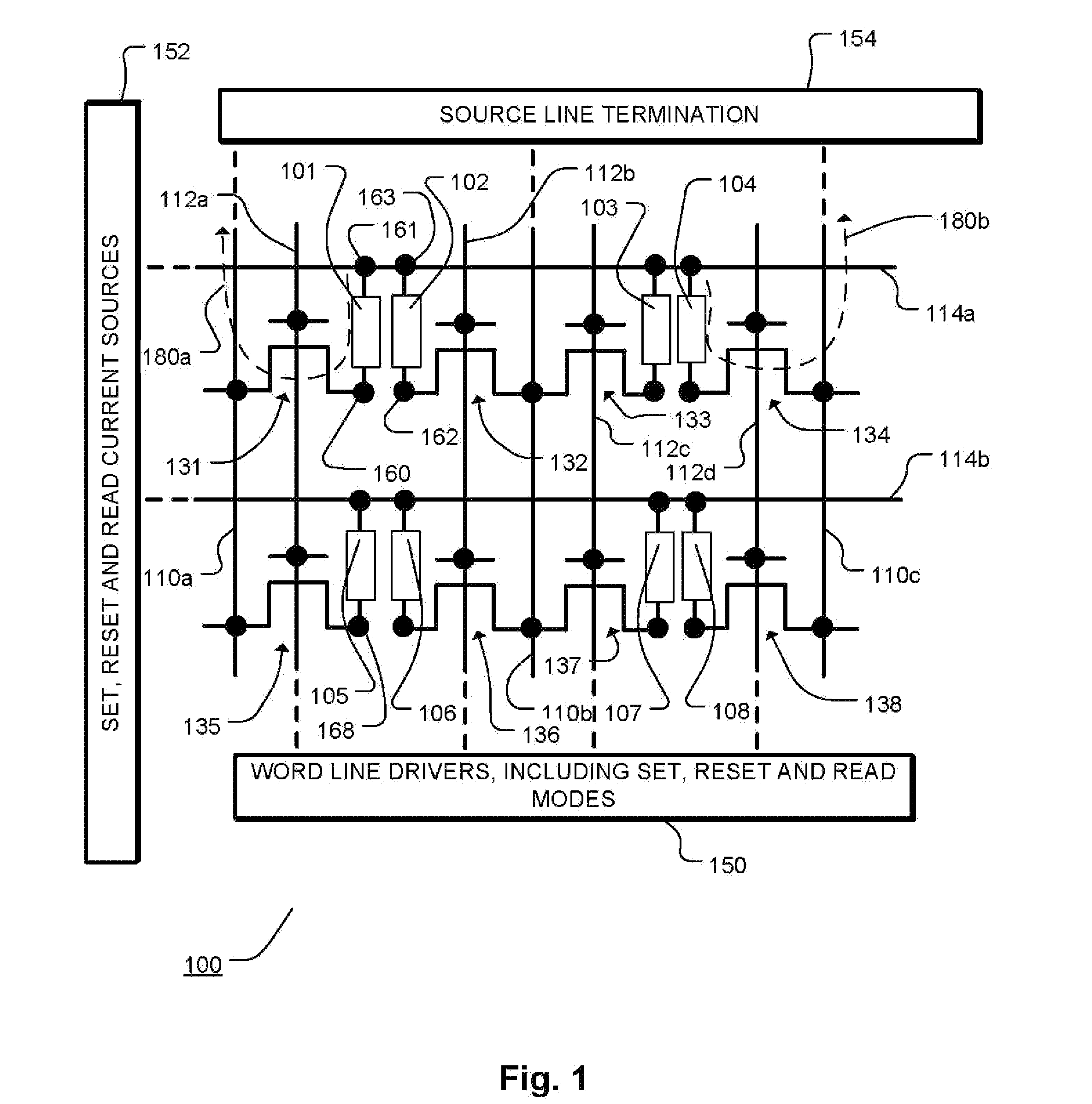

ActiveUS20130148411A1Sufficient data retention periodIncrease memory capacitySolid-state devicesDigital storageDriver circuitLine driver

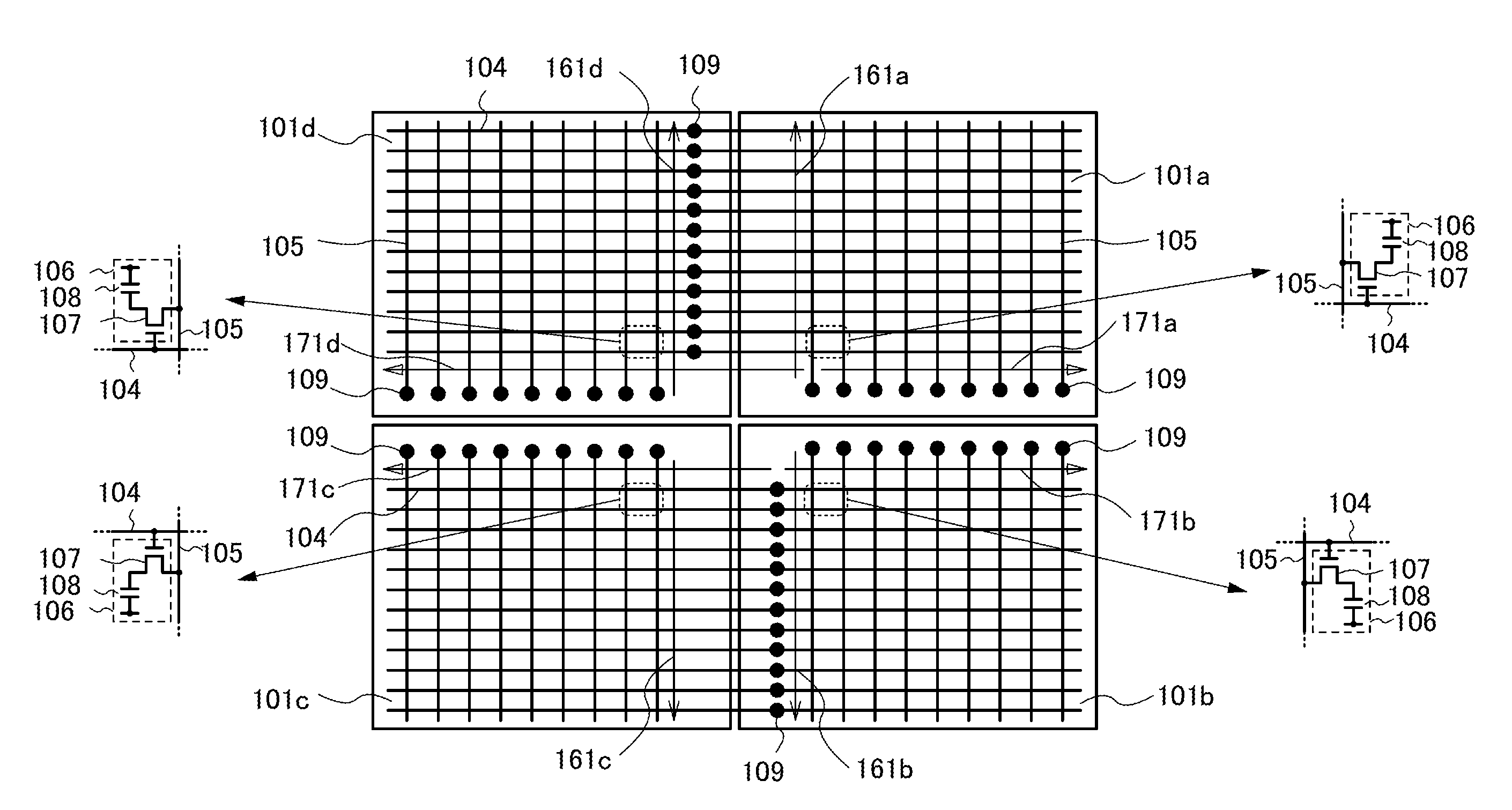

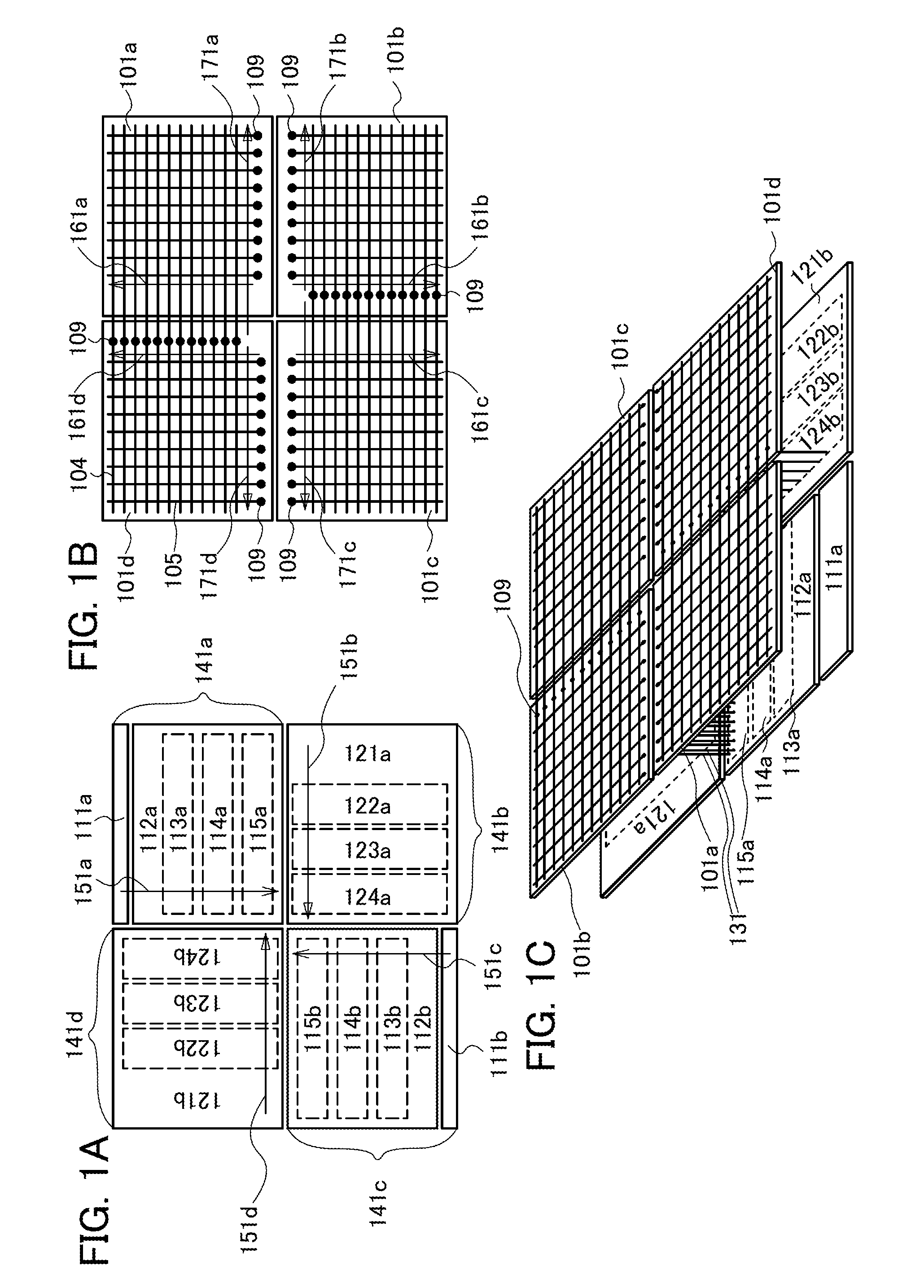

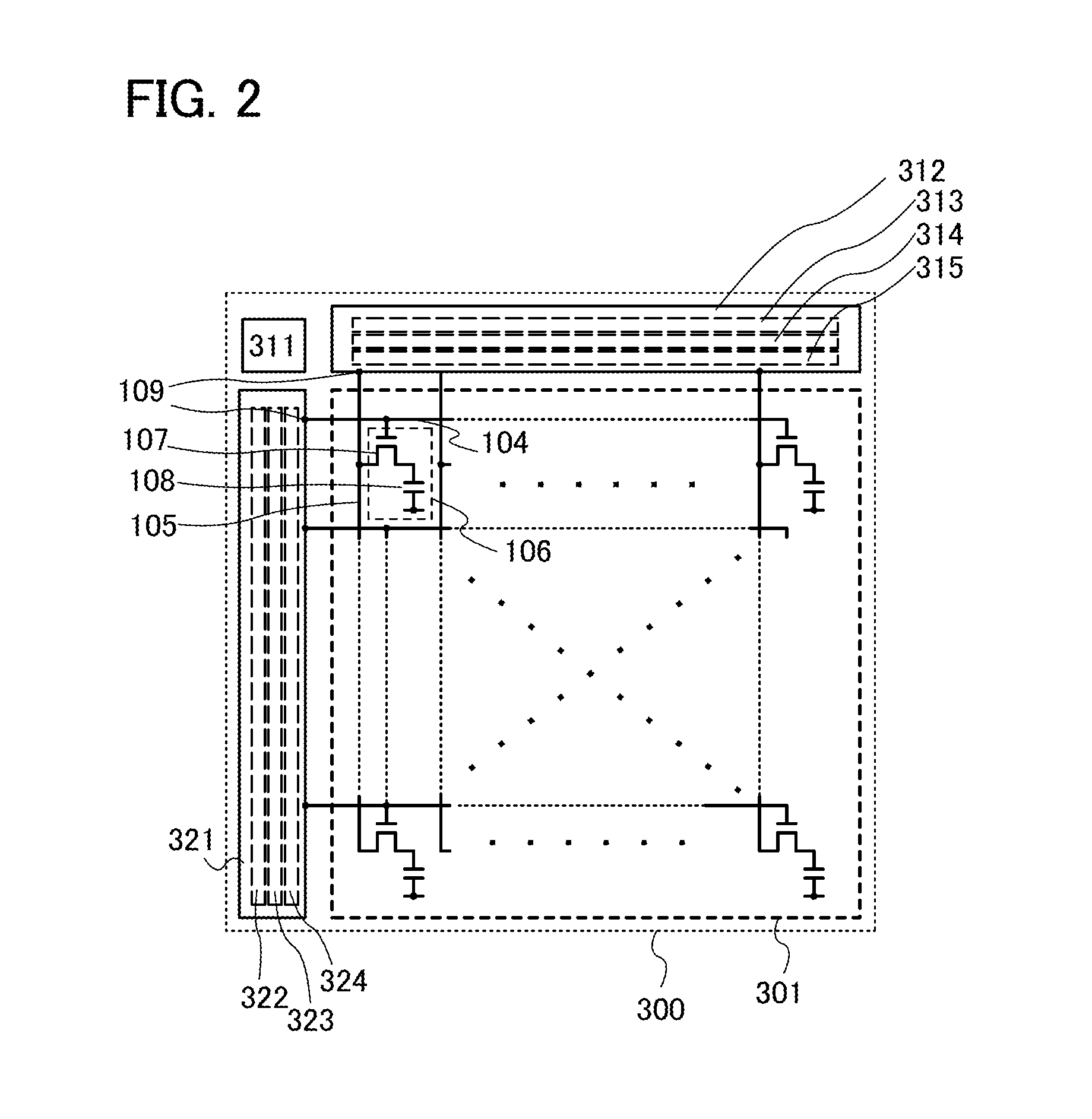

A memory device including first to fourth memory cell arrays and a driver circuit including a pair of bit line driver circuits and a pair of word line driver circuits is provided. The first to fourth memory cell arrays are overlap with the driver circuit. Each of the pair of bit line driver circuits and a plurality of bit lines are connected through connection points on an edge along the boundary between the first and second memory cell arrays or on an edge along the boundary between the third and fourth memory cell arrays. Each of the pair of word line driver circuits and a plurality of word lines are connected through second connection points on an edge along the boundary between the first and fourth memory cell arrays or on an edge along the boundary between the second and third memory cell arrays.

Owner:SEMICON ENERGY LAB CO LTD

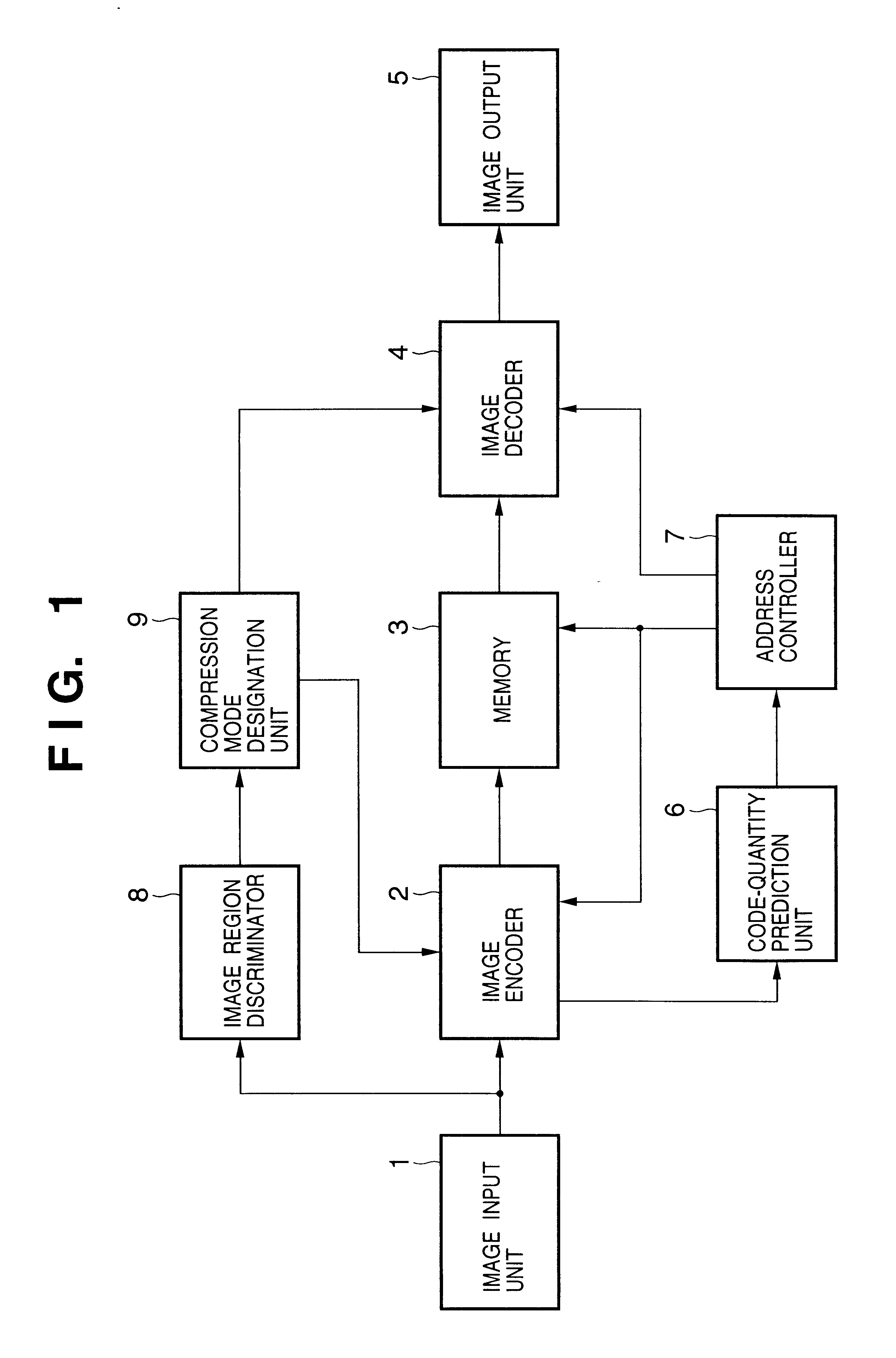

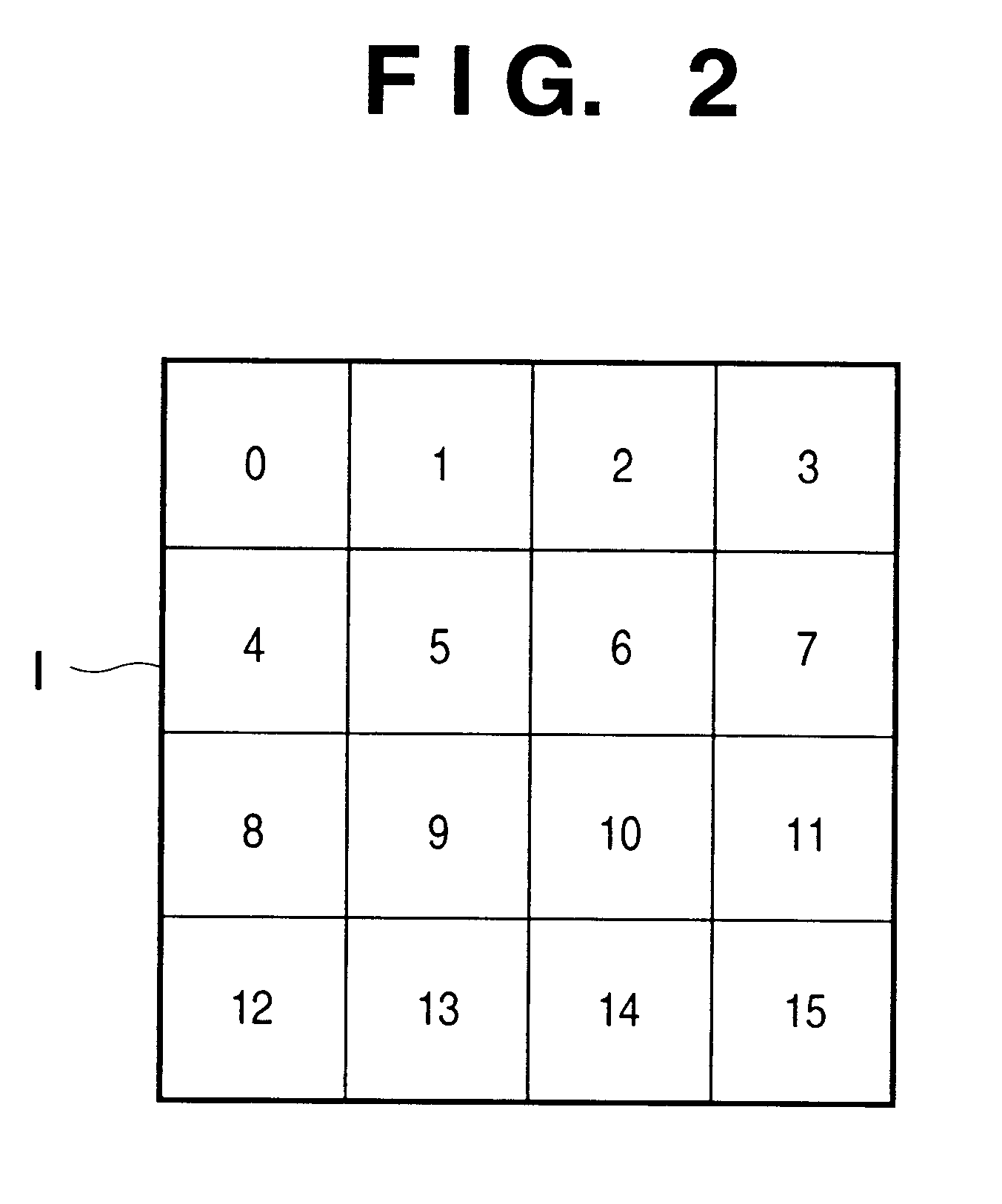

Image processing method, apparatus and storage medium

InactiveUS6879726B2Quality improvementTelevision system detailsCode conversionImaging processingTransformation unit

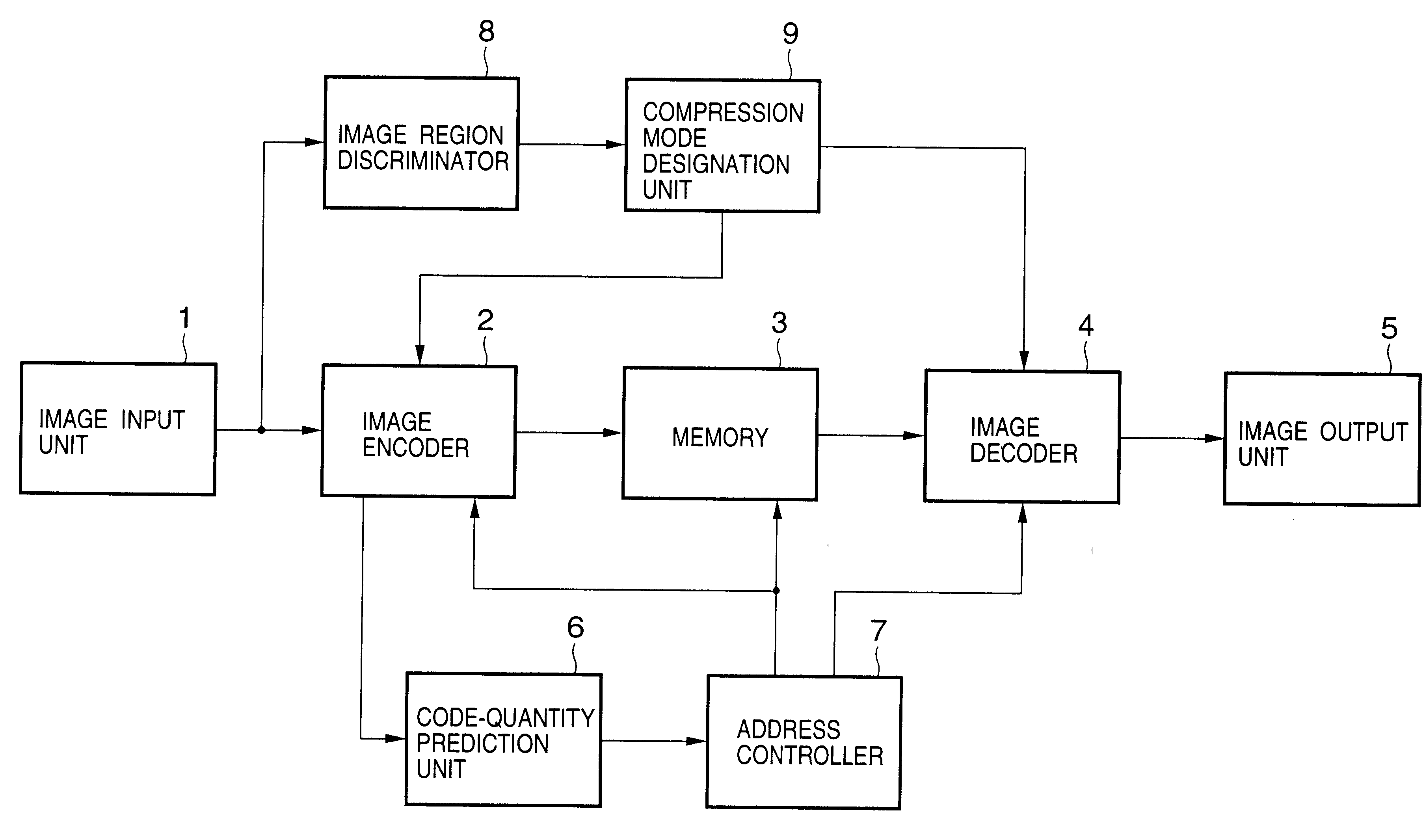

An image processing apparatus includes a wavelet transformation unit for wavelet-transforming input image data on a per-image basis, and an encoder for changing transformation coefficients, which have been obtained by the transformation, to bit planes from higher- to lower-order bits, and encoding the bit planes one bit plane at a time. A code-quantity prediction unit determines whether all encoded data of each of the image data that have been encoded can be stored in the memory when the encoded data obtained by the encoder is stored in the memory image by image. If all of the encoded data cannot be stored, the encoded data that overflows the memory is divided and the divided encoded data is stored in the memory by writing the divided encoded data equally over storage areas of the lower-order bit planes of each of the image.

Owner:CANON KK

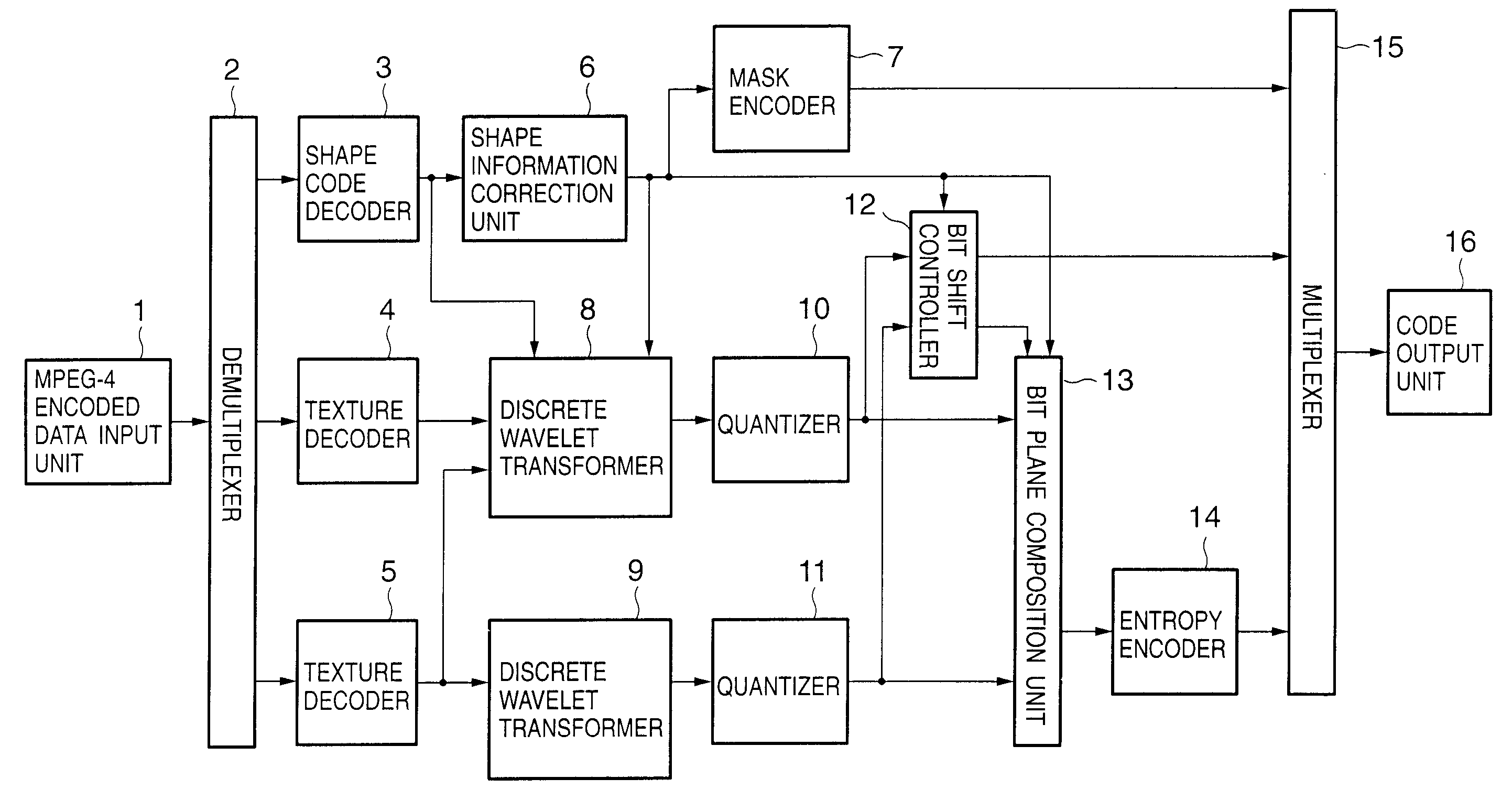

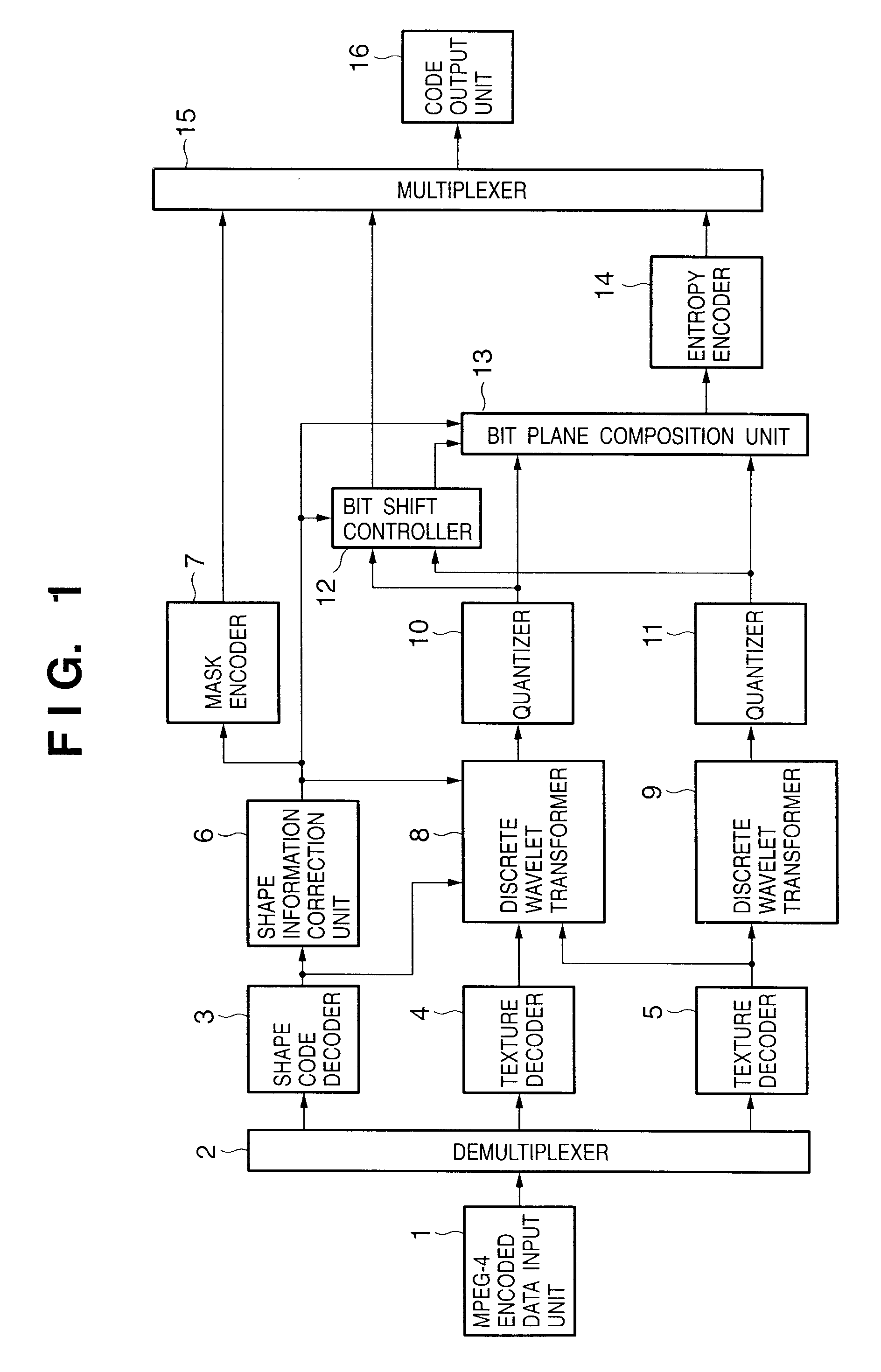

Image processing apparatus and method, and its computer program and storage medium

InactiveUS6909810B2Maintain independenceEasily and reliably generateCode conversionImage codingComputer hardwareImaging processing

MPEG-4 encoded data is input, and a shape code decoder decodes shape data contained in the encoded image data to obtain ROI information contained in that image. The frequency transforms of the decoded image data are computed to generate transform coefficients. A bit shift unit bit-shifts transform coefficients, corresponding to the ROI, of the generated transform coefficients, to upper bit planes, stuffs “0”s in blank fields outside the ROI, which are generated by the bit shift process, and stuffs audio data from an audio buffer in blank fields within the ROI, which are generated by the bit shift process.

Owner:CANON KK

Lossless audio coding/decoding method and apparatus

InactiveUS20050203731A1Increase the compression ratioColor television with pulse code modulationColor television with bandwidth reductionProbit modelBit plane

Owner:SAMSUNG ELECTRONICS CO LTD