Patents

Literature

92 results about "Common logic" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Common Logic (CL) is a framework for a family of logic languages, based on first-order logic, intended to facilitate the exchange and transmission of knowledge in computer-based systems. The CL definition permits and encourages the development of a variety of different syntactic forms, called dialects. A dialect may use any desired syntax, but it must be possible to demonstrate precisely how the concrete syntax of a dialect conforms to the abstract CL semantics, which are based on a model theoretic interpretation. Each dialect may be then treated as a formal language. Once syntactic conformance is established, a dialect gets the CL semantics for free, as they are specified relative to the abstract syntax only, and hence are inherited by any conformant dialect. In addition, all CL dialects are equivalent (i.e., can be mechanically translated to each other), although some may be more expressive than others.

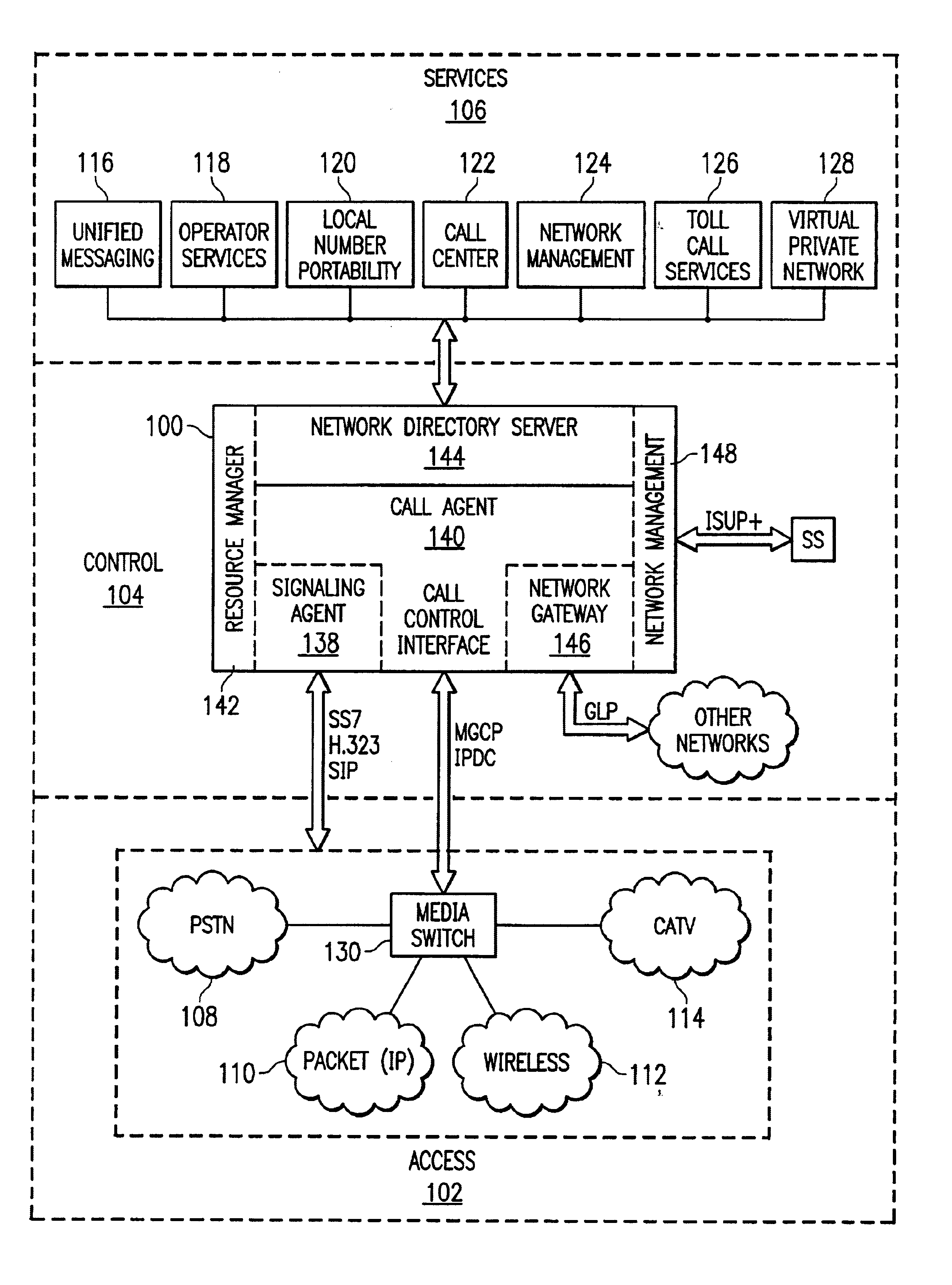

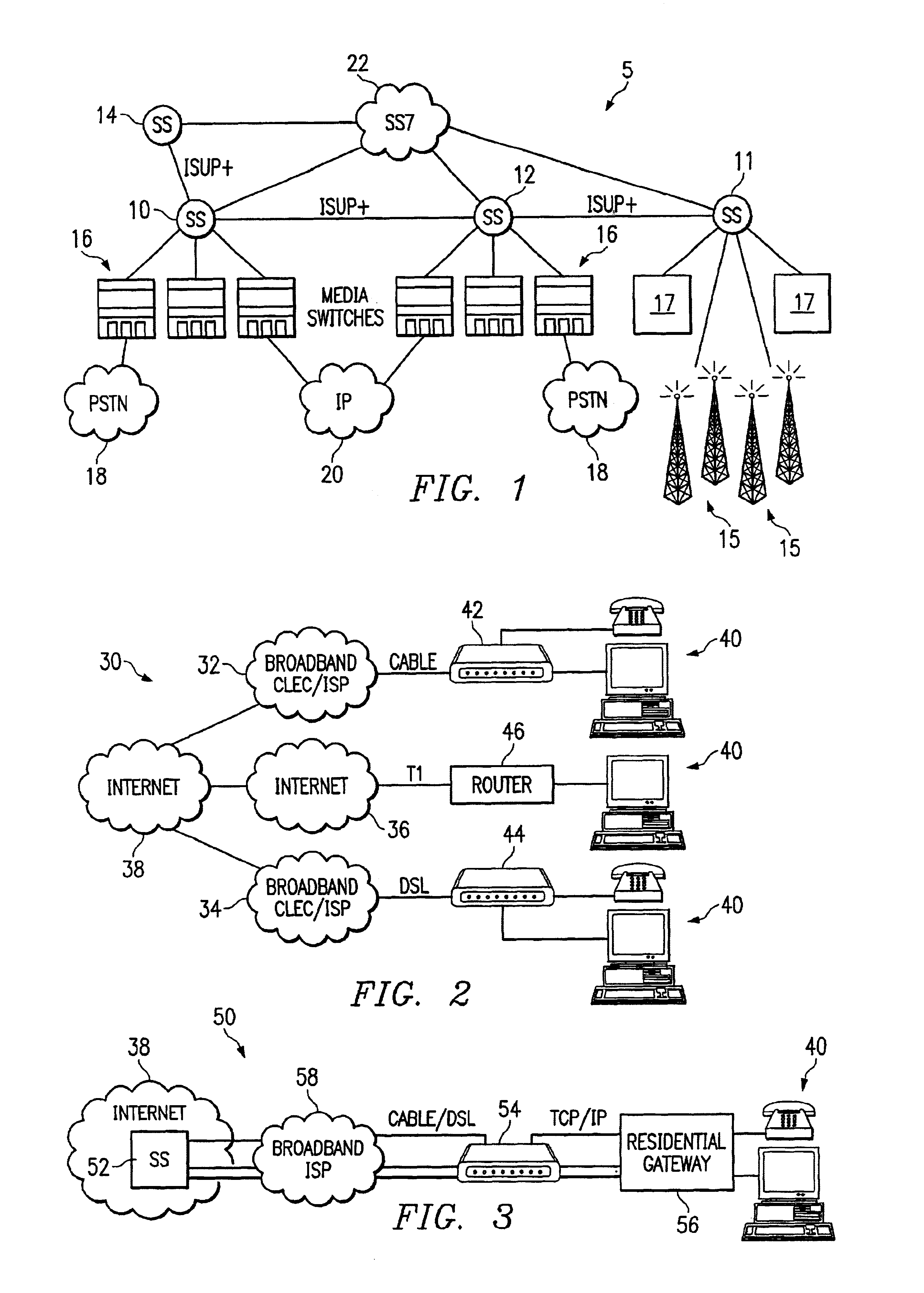

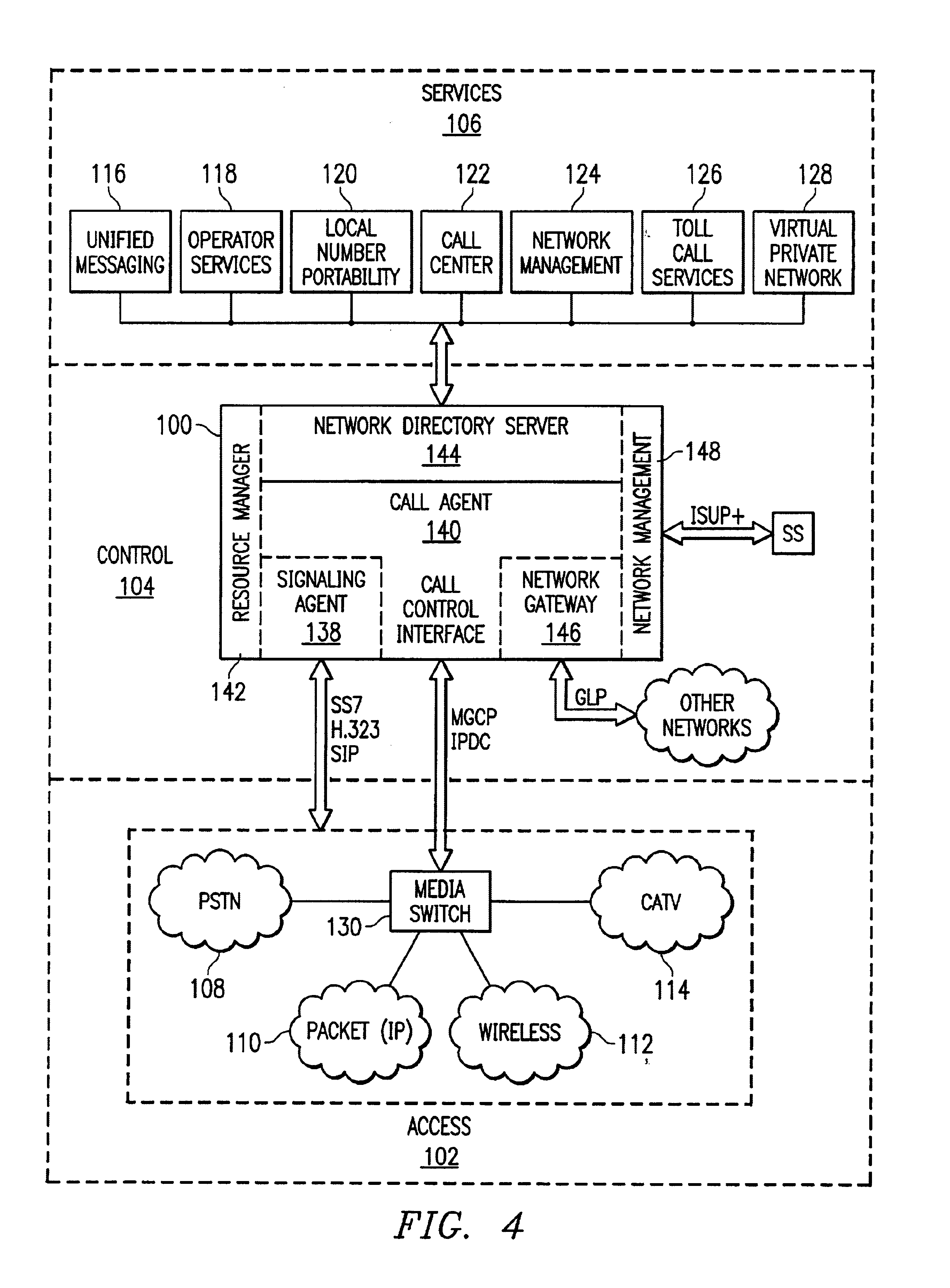

System and method to internetwork wireless telecommunication networks

ActiveUS6996076B1Improve network efficiencyAdditional drawbackTime-division multiplexConnection managementCommon logicLogic Control

One aspect of the invention is a method for wireless call processing. The method includes downloading at least one function-specific logic control program into each of a plurality of generic logic control state machines and receiving a message at a wireless protocol-specific codec, parsing the message, and routing the message to a first logic control state machine associated with the protocol-specific codec. The method also includes executing the function-specific logic control program of a first logic control state machine and generating a call event and routing the call event to an event codec. The method also includes executing the function-specific logic control program of a second logic control state machine and processing the call event. In a particular embodiment, the method also includes allocating an RF channel that may be used for the call event without seizing the RF channel. In another embodiment, the method also includes accessing a database that includes routing and verification information related to the call event, and routing the call event in response to the information.

Owner:RIBBON COMM OPERATING CO INC

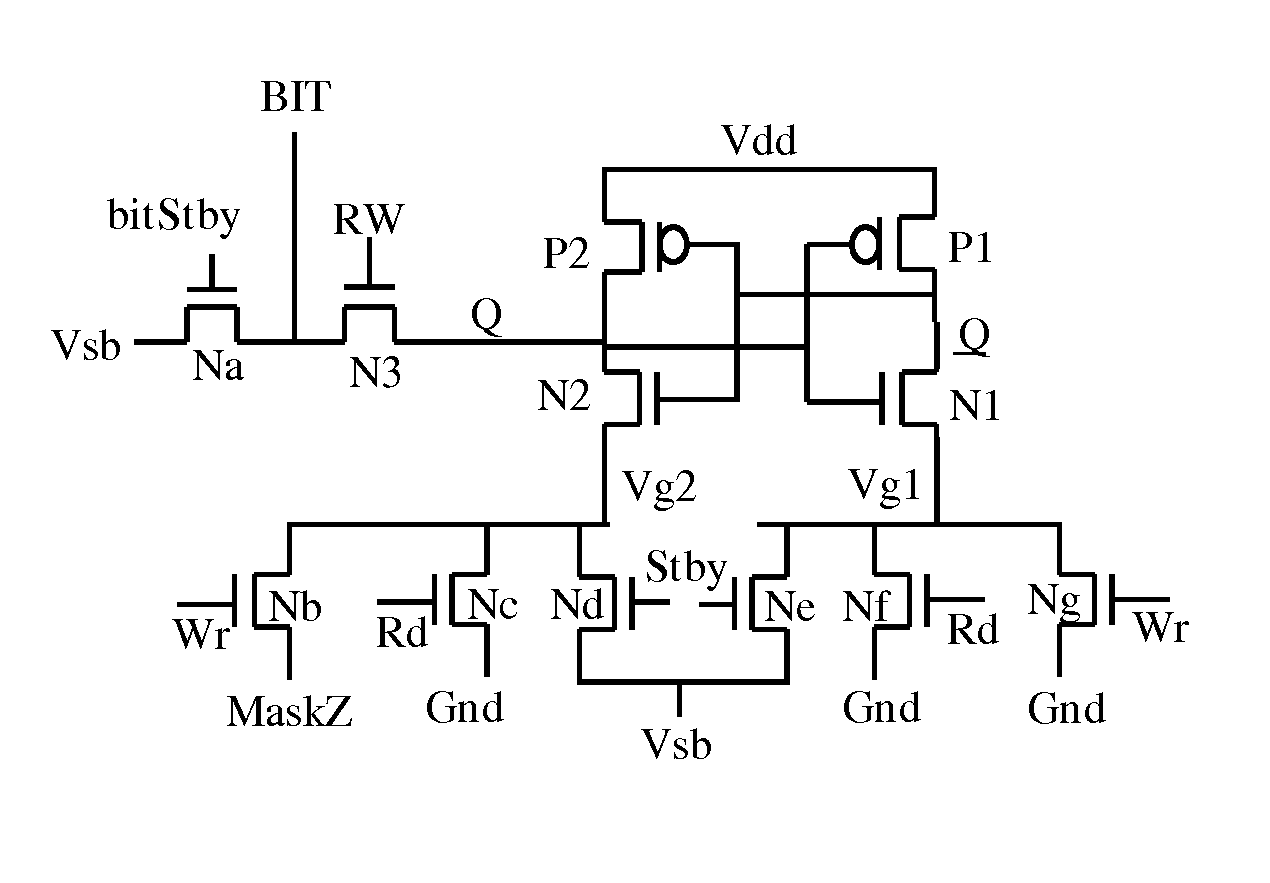

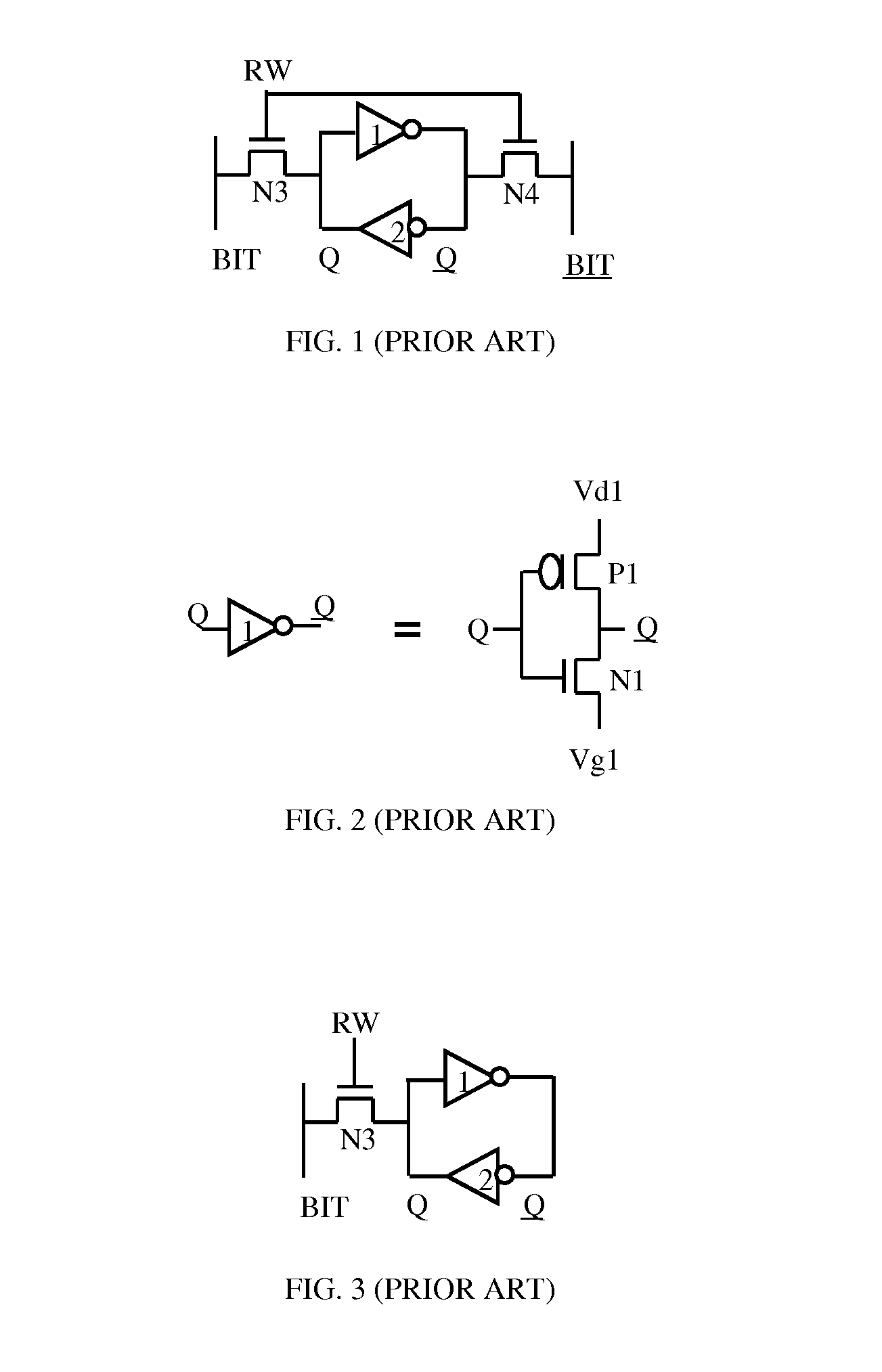

SRAM cell with common bit line and source line standby voltage

A high threshold five transistor SRAM bit cell with cross-coupled inverters has a single BIT line, a common logic 1 supply voltage, and two logic 0 virtual ground source voltages. The BIT line is coupled to the bit cell by a pass transistor. When BIT line and virtual ground lines are not otherwise being used, they are connected to a common standby voltage that substantially lowers bit cell standby leakage. Writing is performed by driving a data signal through the pass transistor and is facilitated by creating a voltage differential on the virtual ground lines. Reading is also performed through the pass transistor wherein the BIT line is initially at the standby voltage, and is then driven lower or higher depending upon the data value stored in the bit cell.

Owner:HOBSON RICHARD FREDERIC +1

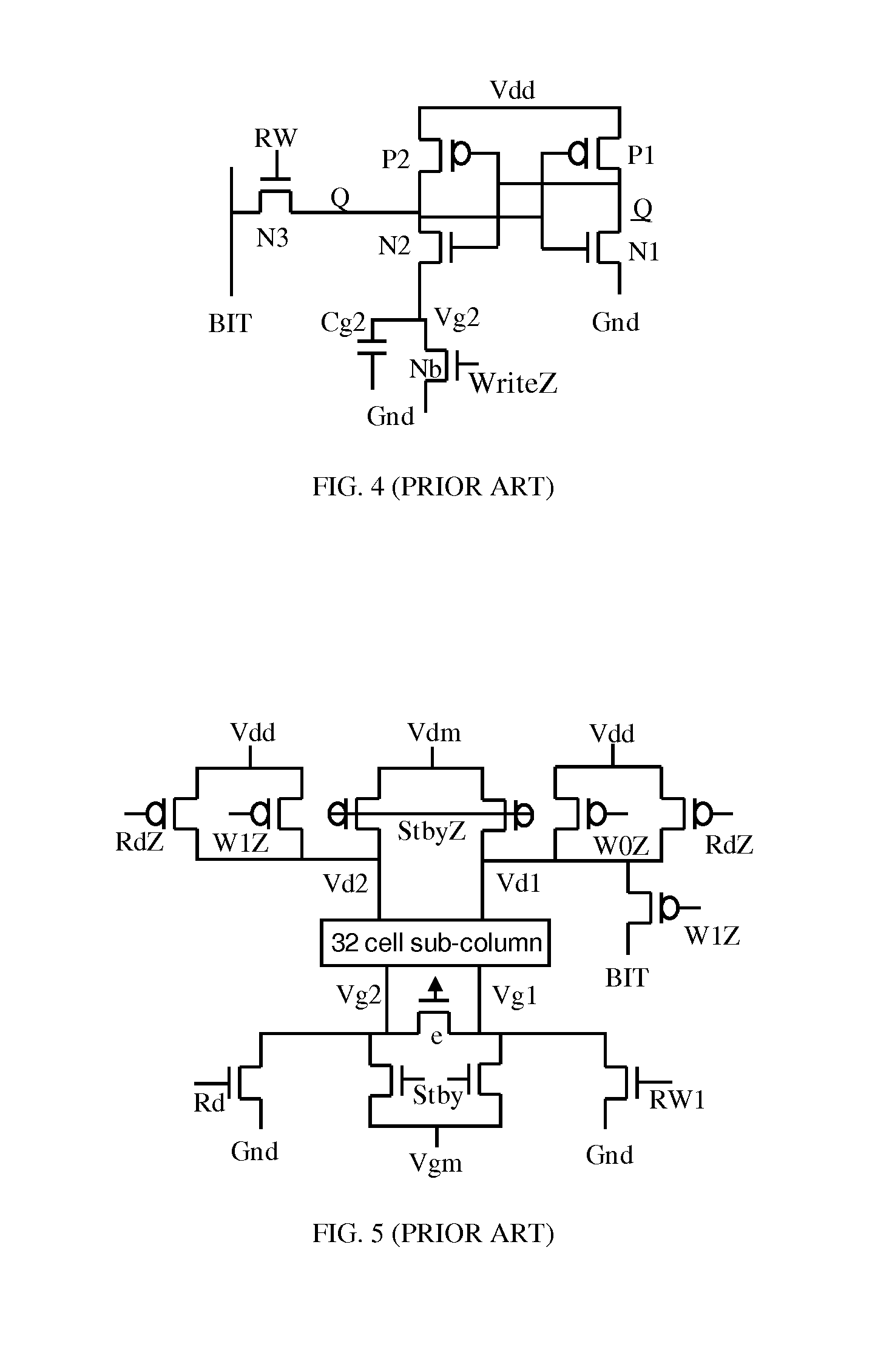

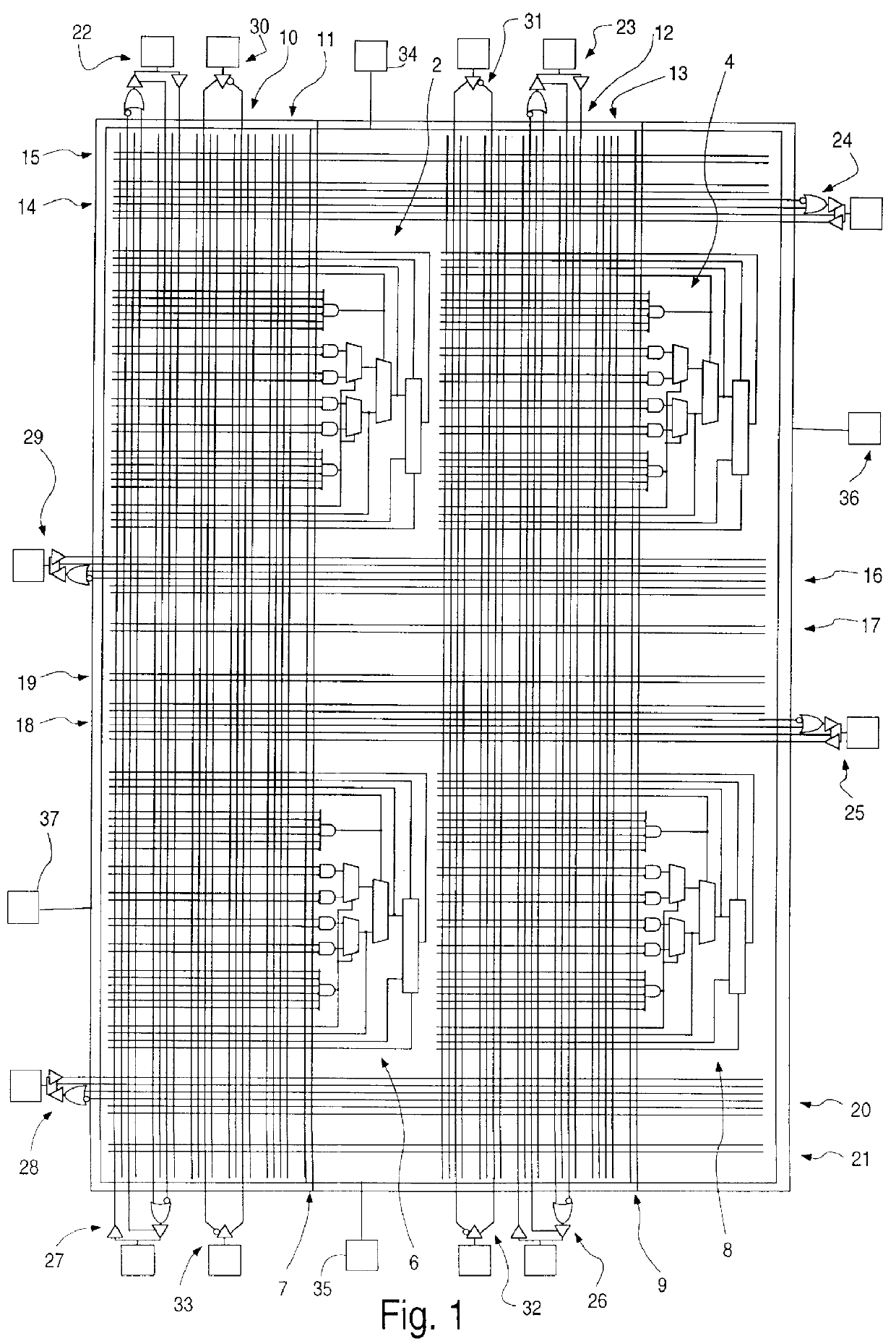

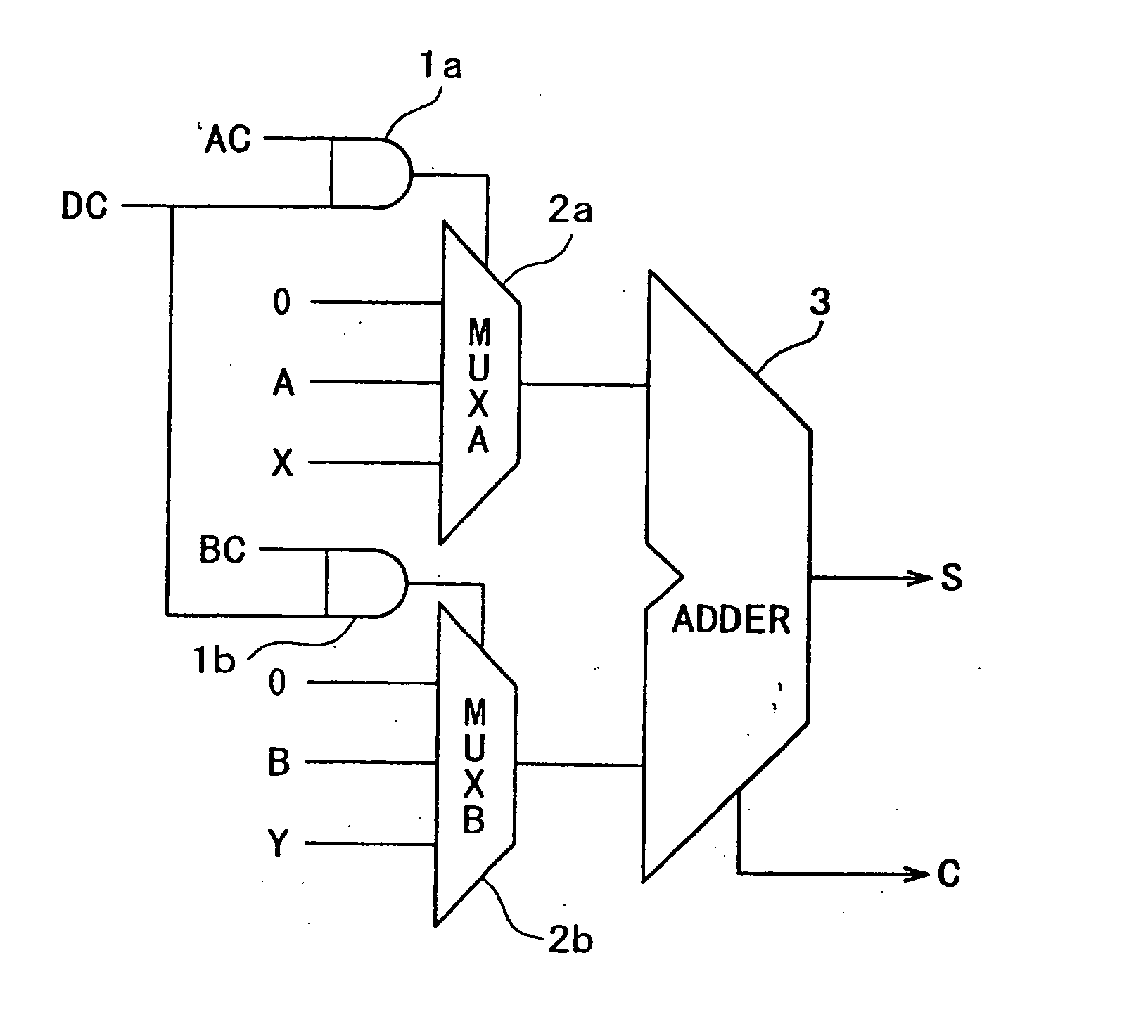

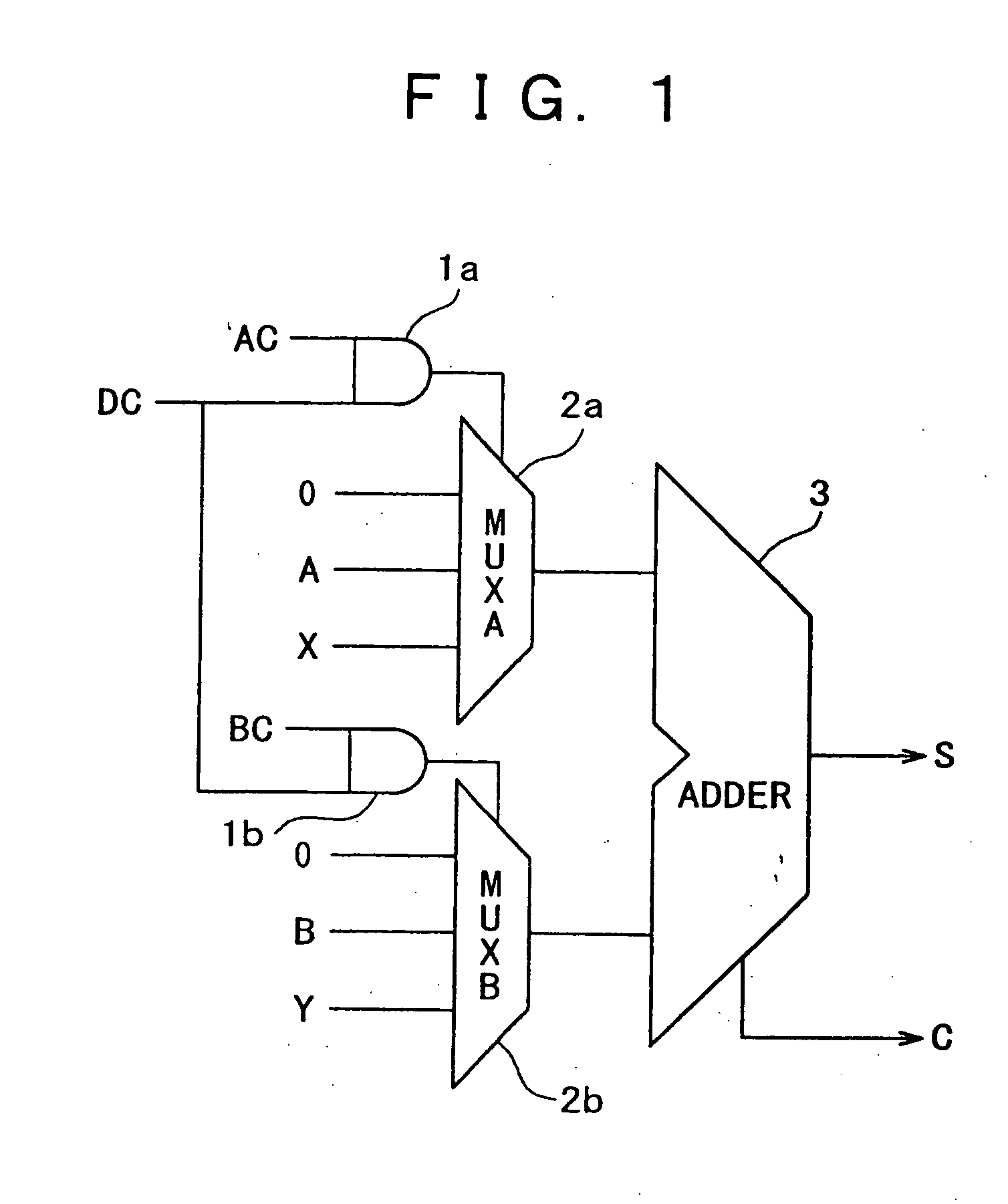

Programmable application specific integrated circuit and logic cell

A field programmable gate array includes a programmable routing network, a programmable configuration network integrated with the programmable routing network; and a logic cell integrated with the programmable configuration network. The logic cell includes four two-input AND gates, two six-input AND gates, three multiplexers, and a delay flipflop. The logic cell is a powerful general purpose universal logic building block suitable for implementing most TTL and gate array macrolibrary functions. A considerable variety of functions are realizable with one cell delay, including combinational logic functions as wide as thirteen inputs, all boolean transfer functions for up to three inputs, and sequential flipflop functions such as T, JK and count with carry-in.

Owner:QUICKLOGIC

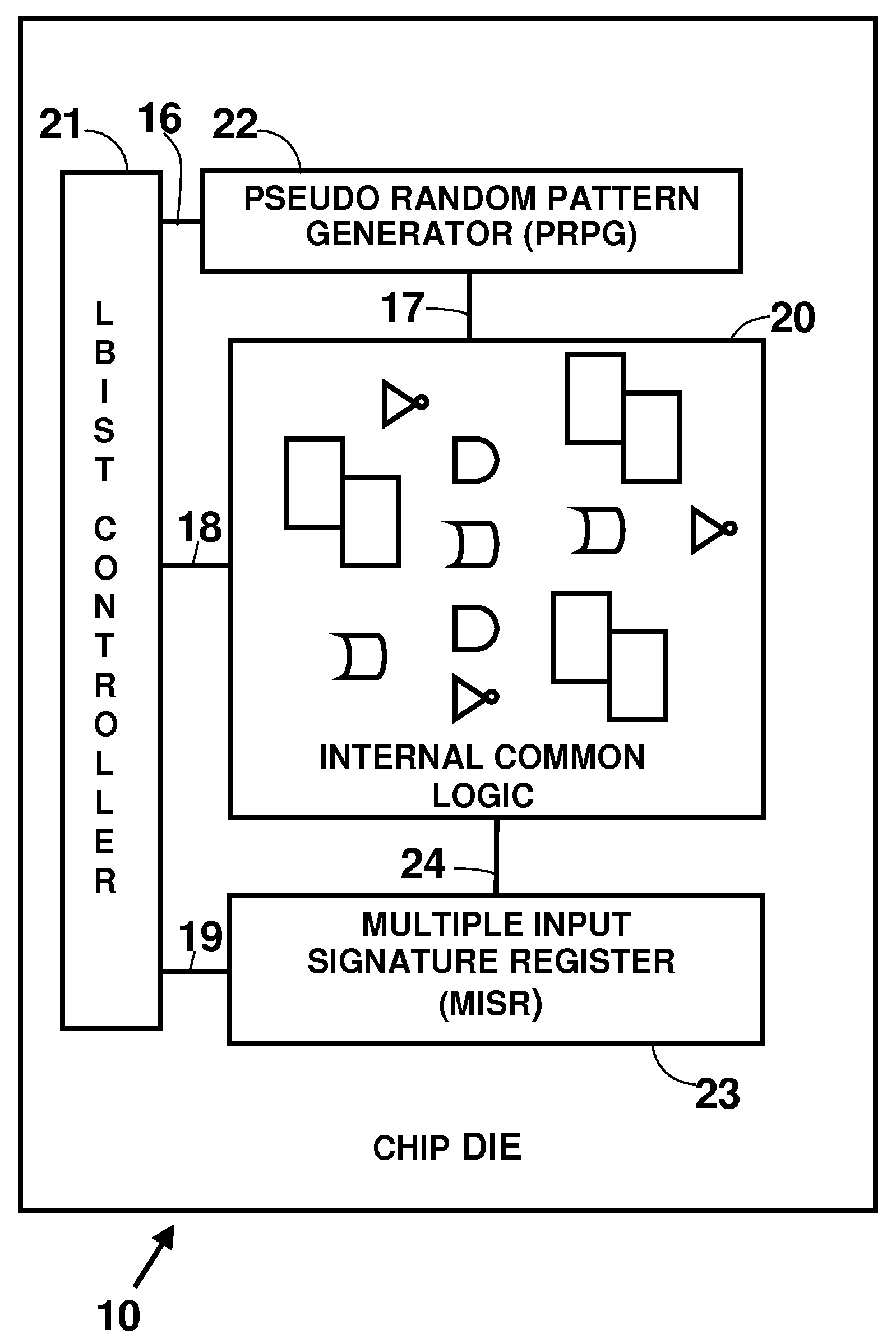

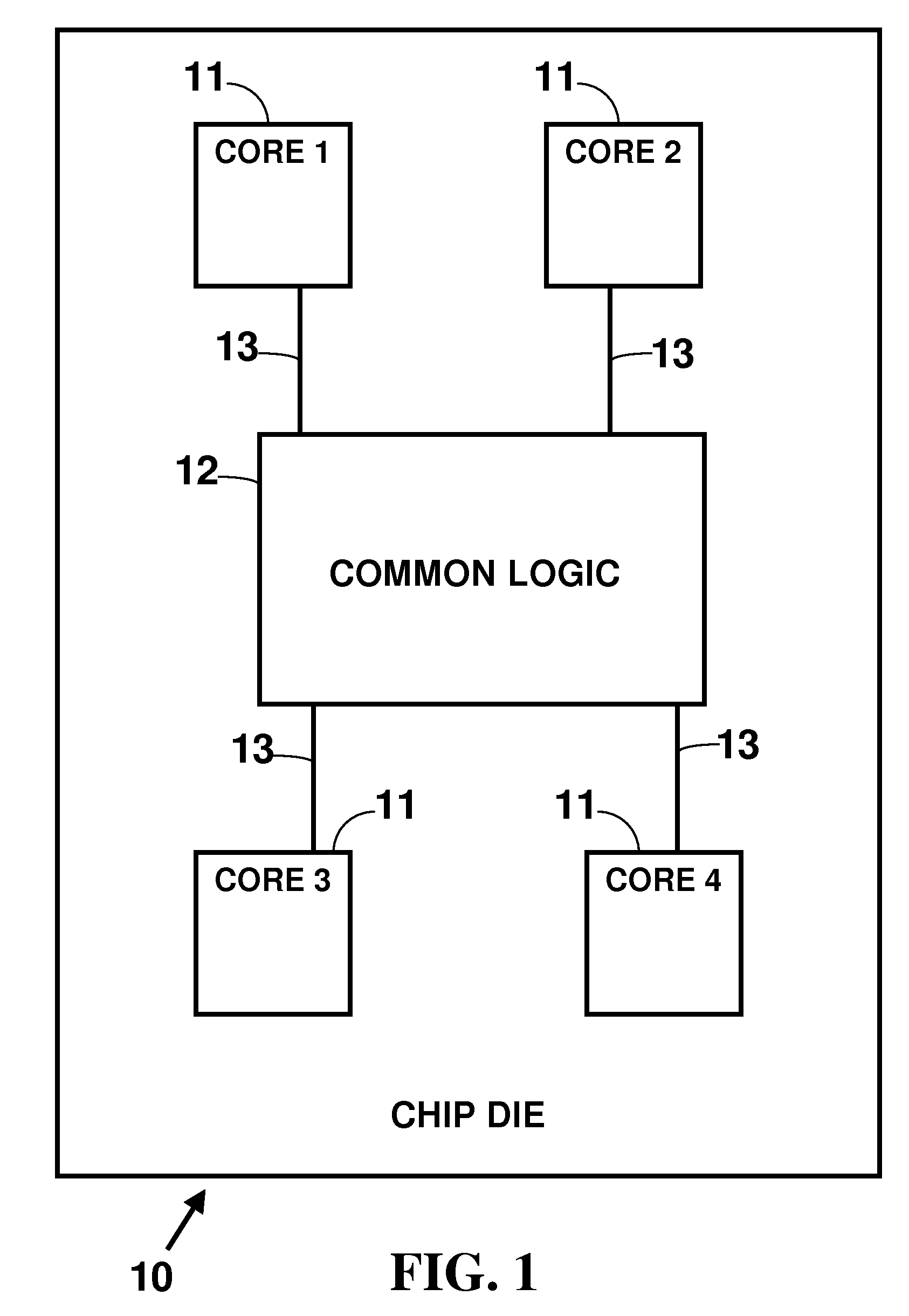

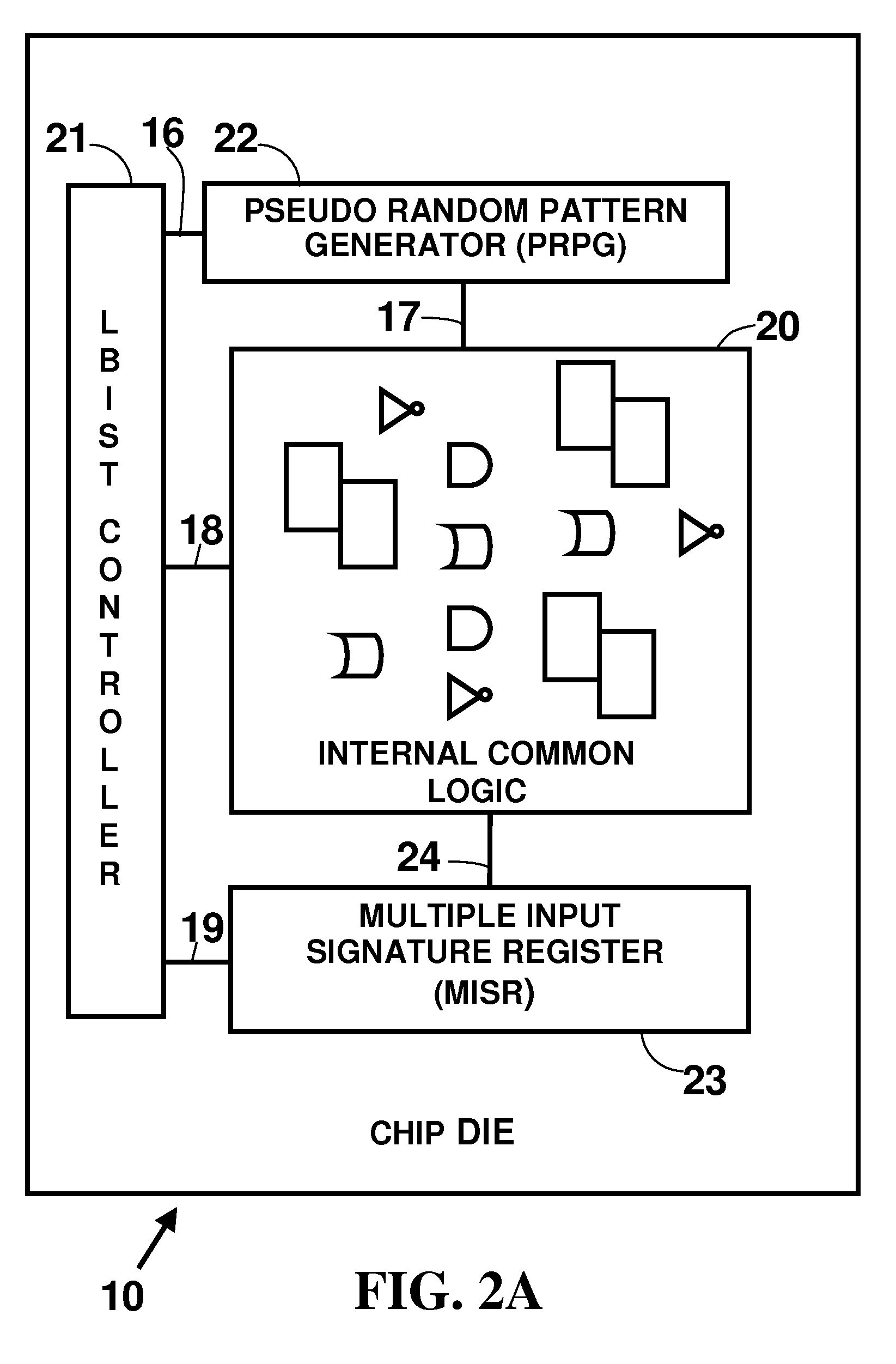

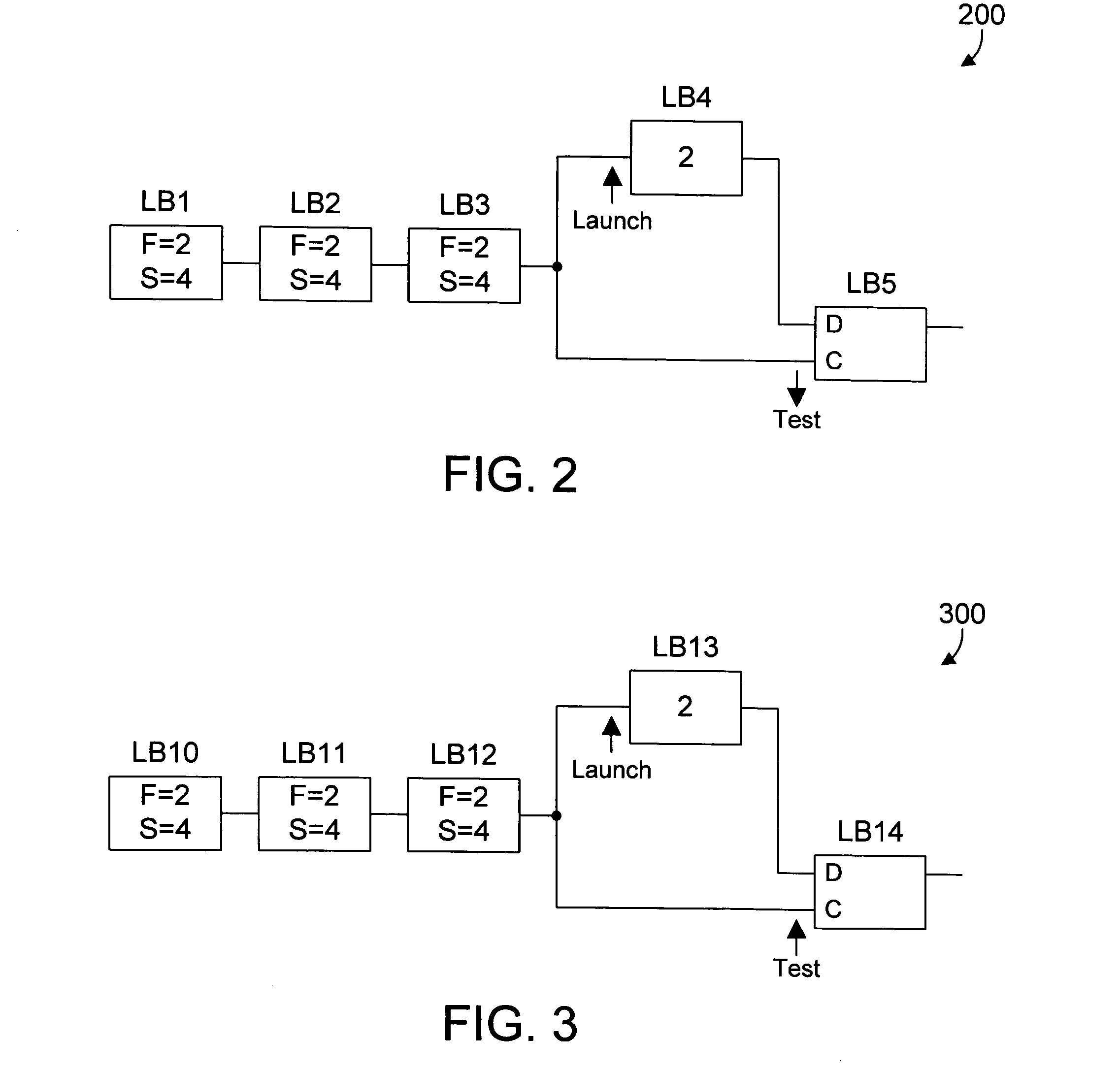

Method and System for Formal Verification of Partial Good Self Test Fencing Structures

ActiveUS20080276144A1Reduces chip test coverageElectronic circuit testingHardware structureCommon logic

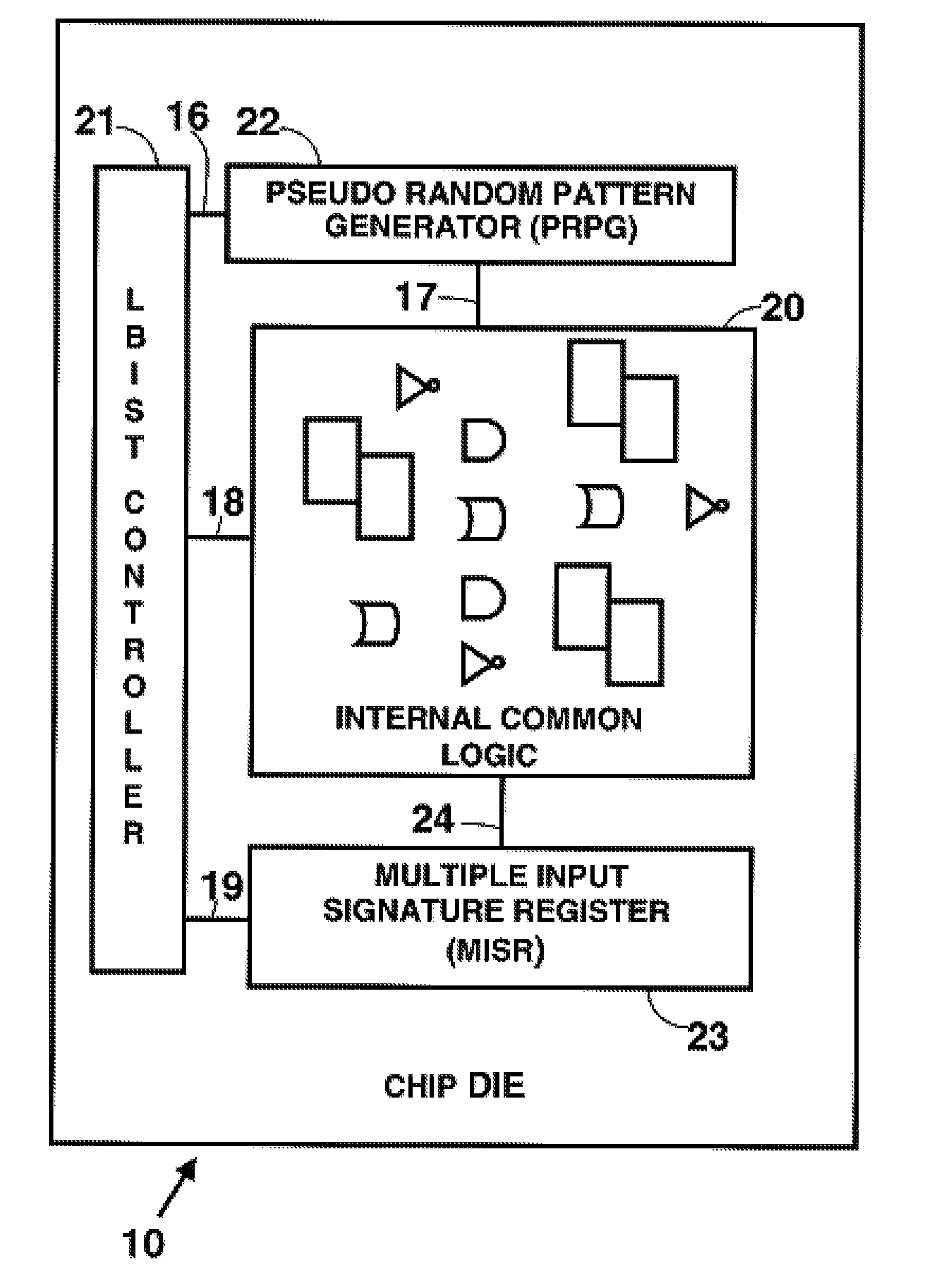

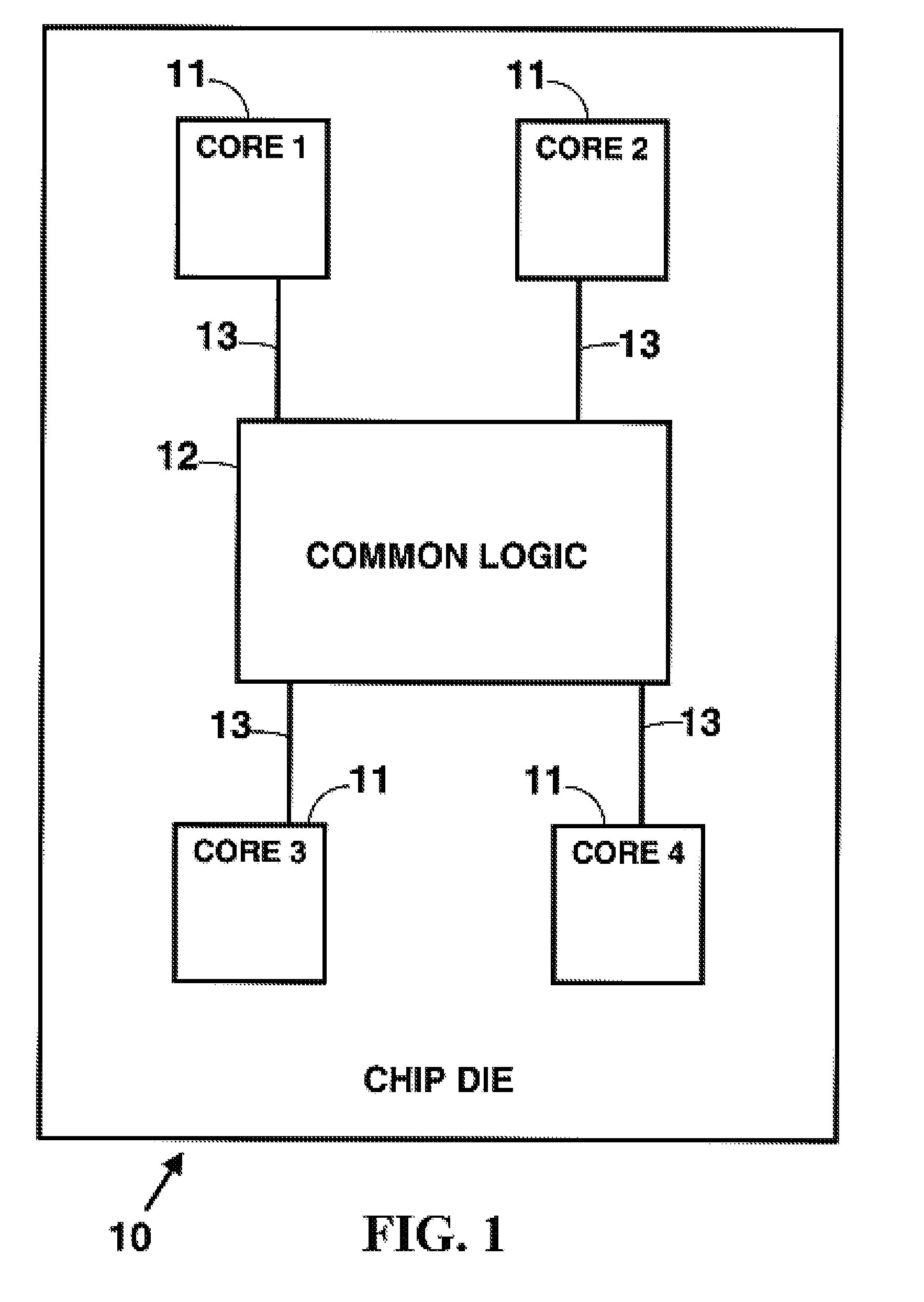

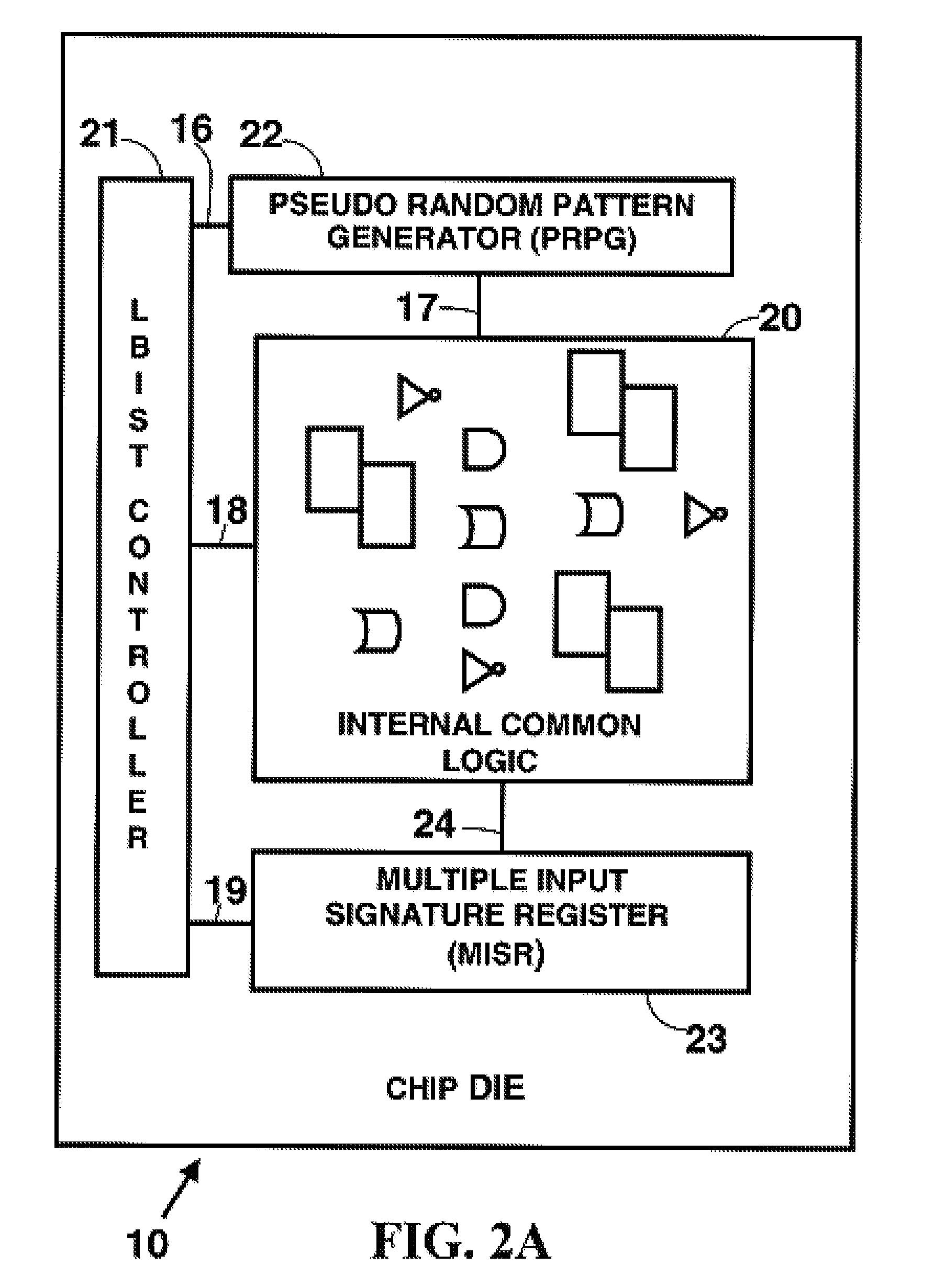

The concept of applying fencing logic to Built-In Self Test (BIST) hardware structures for the purpose of segregating defective circuitry and utilizing the remaining good circuitry is a well known practice in the chip design industry. Described herein is a method for verifying that any particular implementation of partial fencing logic actually provides the desired behavior of blocking down-stream impact of all signals from fenced interfaces, and also ensuring that the partial fencing does not inadvertently preclude any common logic from being fully tested.

Owner:TWITTER INC

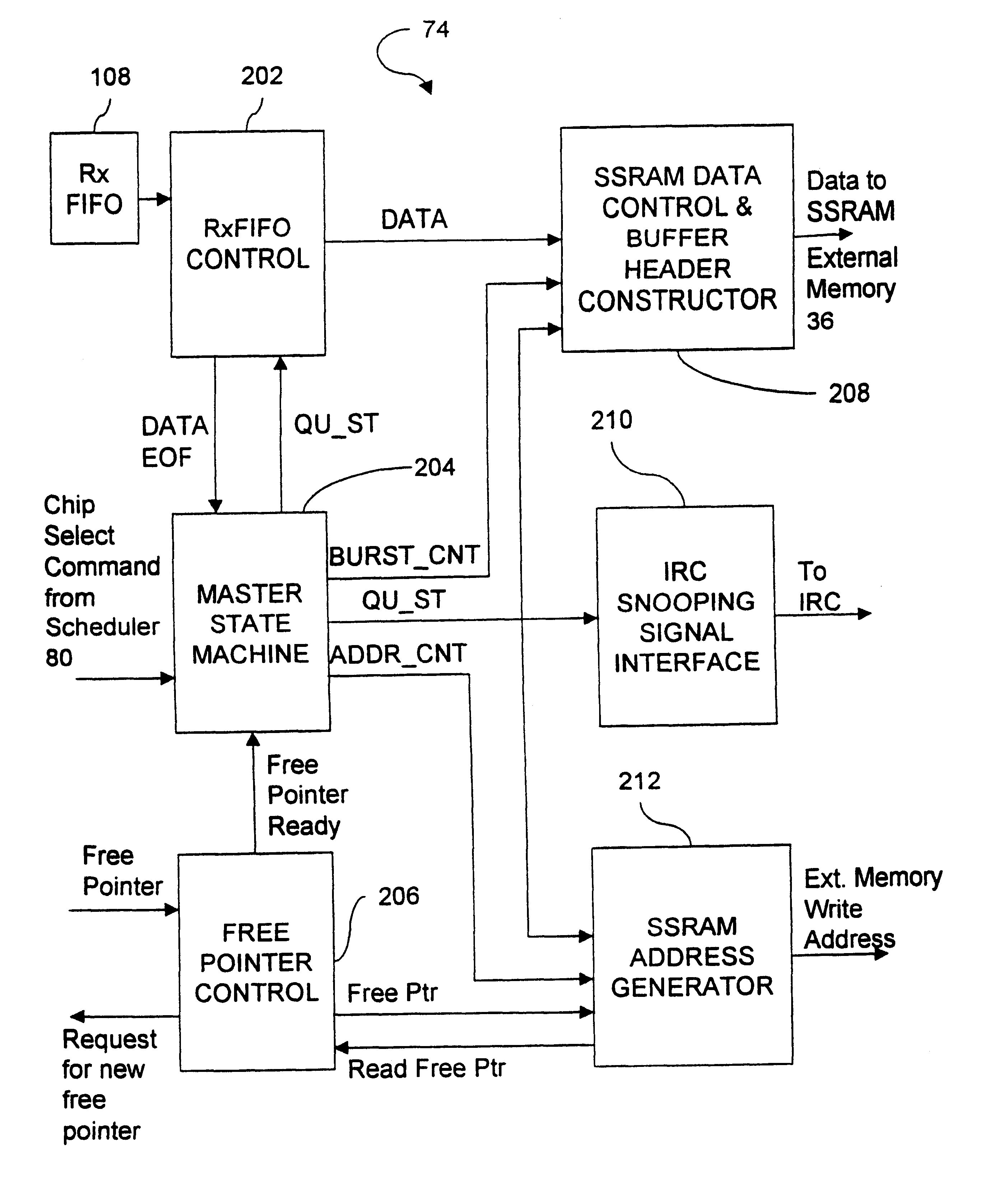

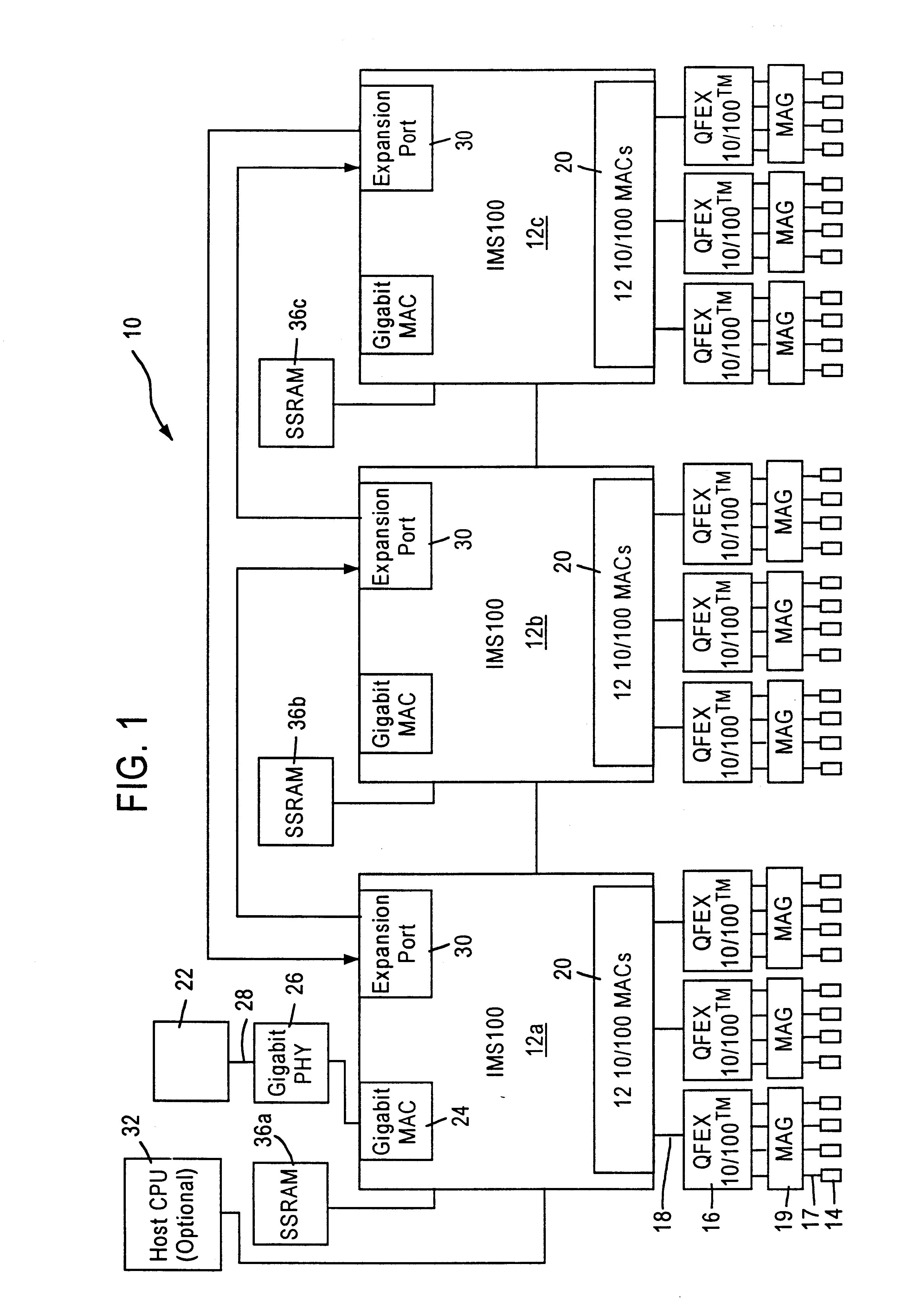

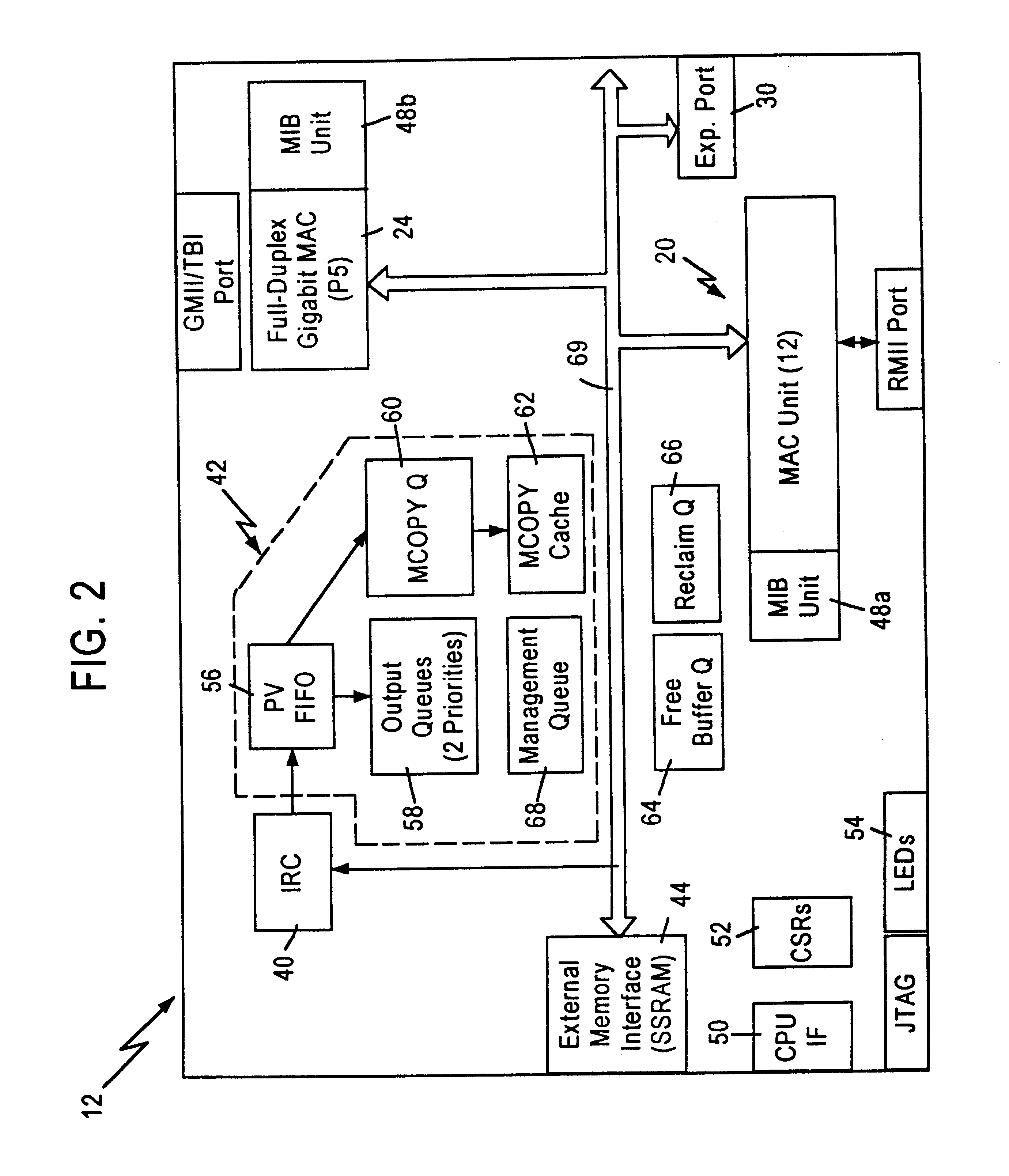

Common scalable queuing and dequeuing architecture and method relative to network switch data rate

InactiveUS6597693B1Improve scalabilityMultiplex system selection arrangementsError preventionExternal storageData rate

A network switch arrangement and method for providing a common architecture for queuing and dequeuing of data frames as they are transferred from a switch port to an external memory and similarly retrieved from the external memory to the switch port, irrespective of the particular data rate of the port. Logic controlling the actual data path is partitioned from logic responding to port data rate information by providing a "handshaking" communication arrangement between the two logics independent of the data rate. Hence, scalability of the data path over a wide range of data rates may be achieved while maintaining a single, common logic architecture.

Owner:ADVANCED MICRO DEVICES INC

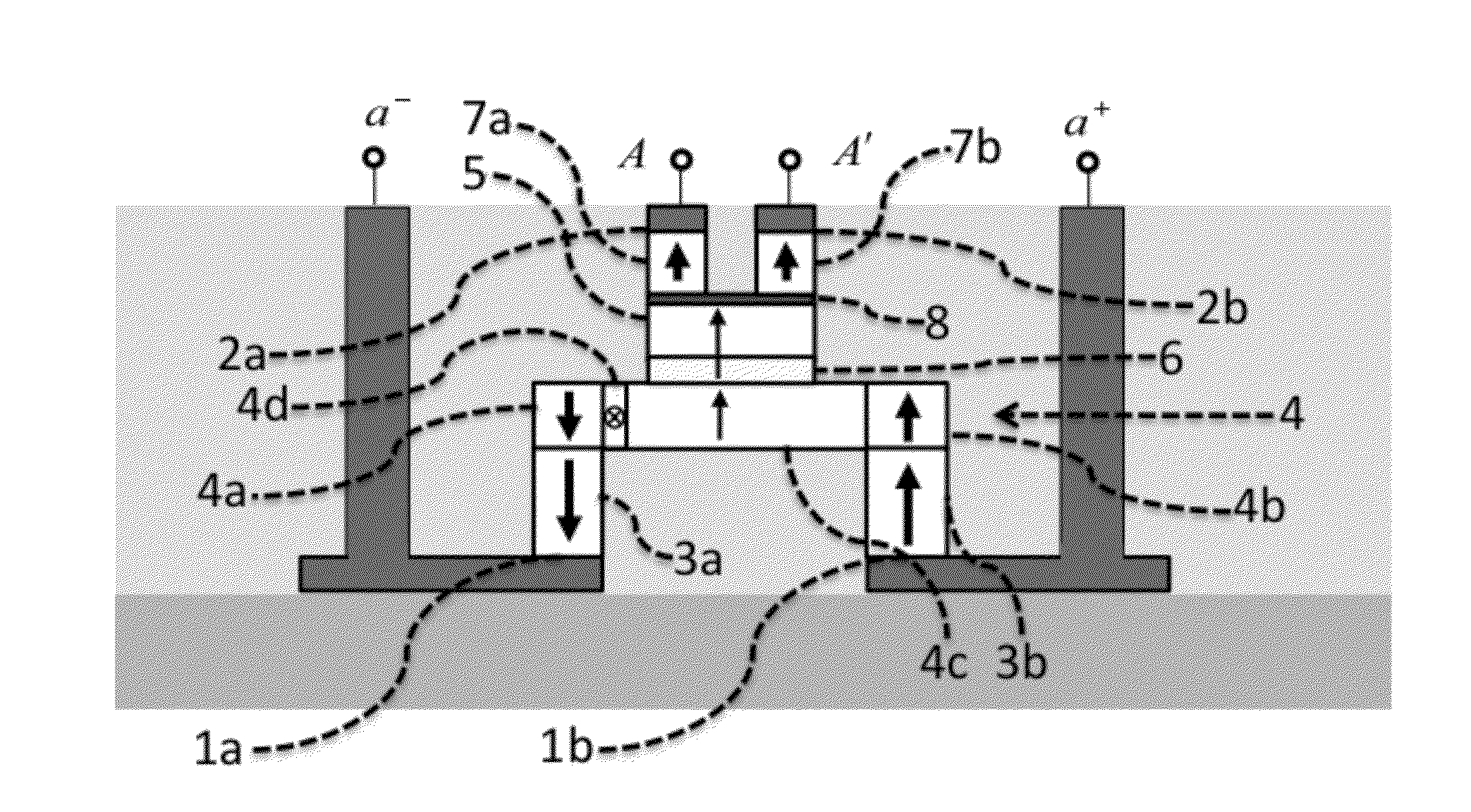

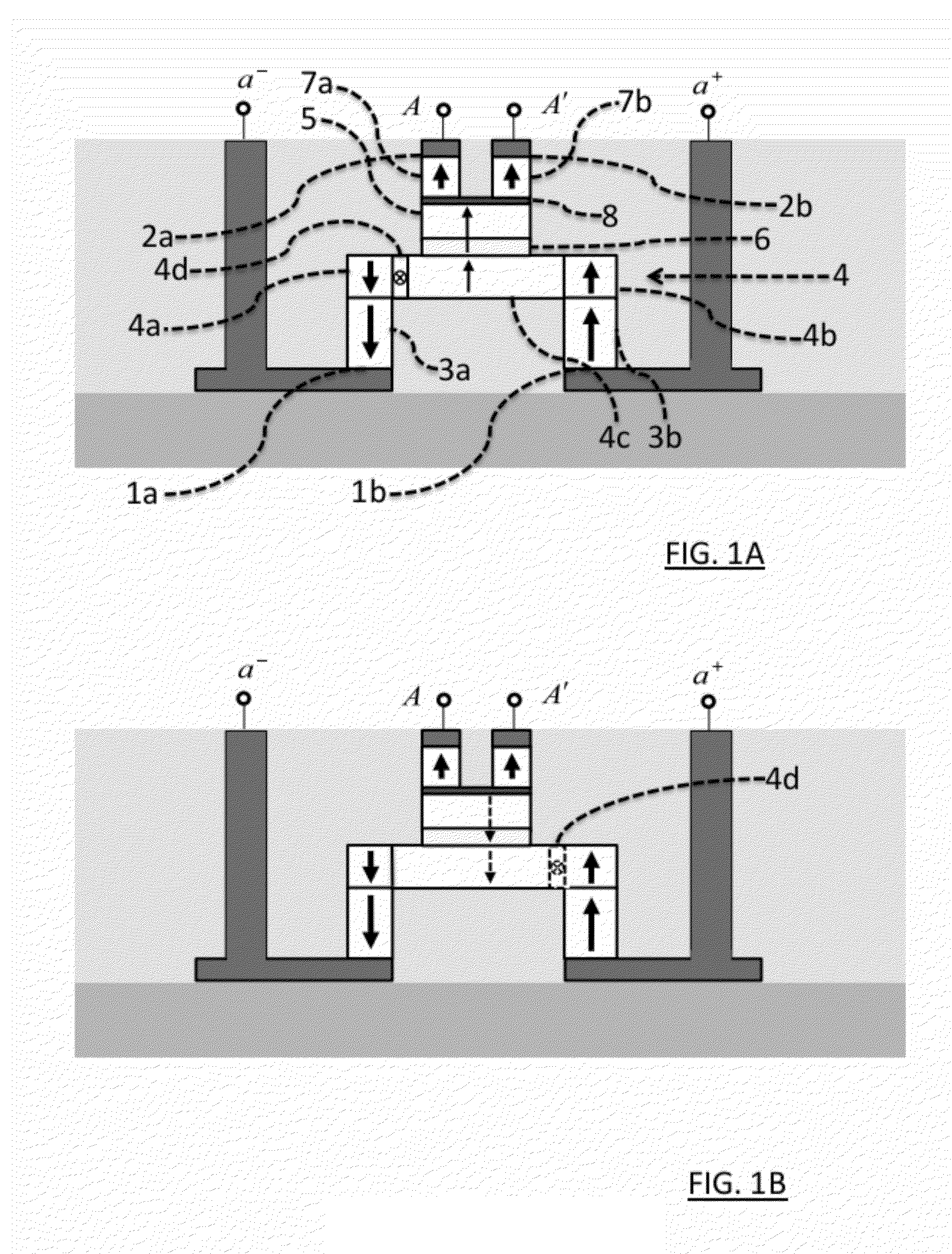

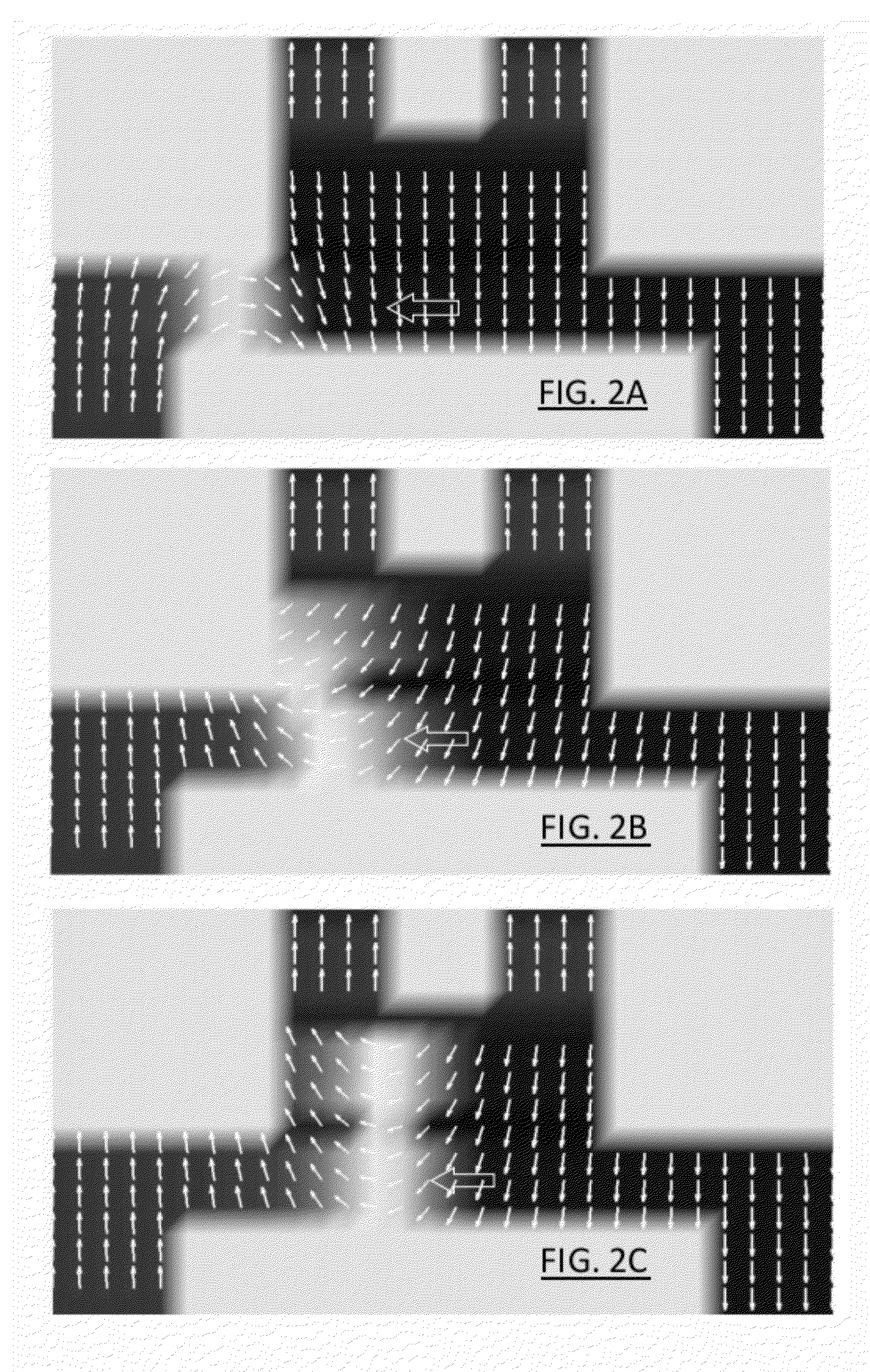

Magnetic Switching Cells and Methods of Making and Operating Same

InactiveUS20120134199A1Effective massEfficient and reliable and cost-effective implementationMagnetic-field-controlled resistorsDigital storageSpinsEngineering

Logic circuits based, at least in part, on use of spin-torque transfer (STT) to switch the magnetization—and hence the logic state—of a magnetic material are disclosed. Aspects of the invention include novel STT-based switching devices, new configurations of known STT-based devices into useful logic circuits, common logic circuits and system building blocks based on these new devices and configurations, as well as methods for inexpensively mass-producing such devices and circuits.

Owner:ZHU JIAN GANG JIMMY +1

Method and system for formal verification of partial good self test fencing structures

The concept of applying fencing logic to Built-In Self Test (BIST) hardware structures for the purpose of segregating defective circuitry and utilizing the remaining good circuitry is a well known practice in the chip design industry. Described herein is a method for verifying that any particular implementation of partial fencing logic actually provides the desired behavior of blocking down-stream impact of all signals from fenced interfaces, and also ensuring that the partial fencing does not inadvertently preclude any common logic from being fully tested.

Owner:TWITTER INC

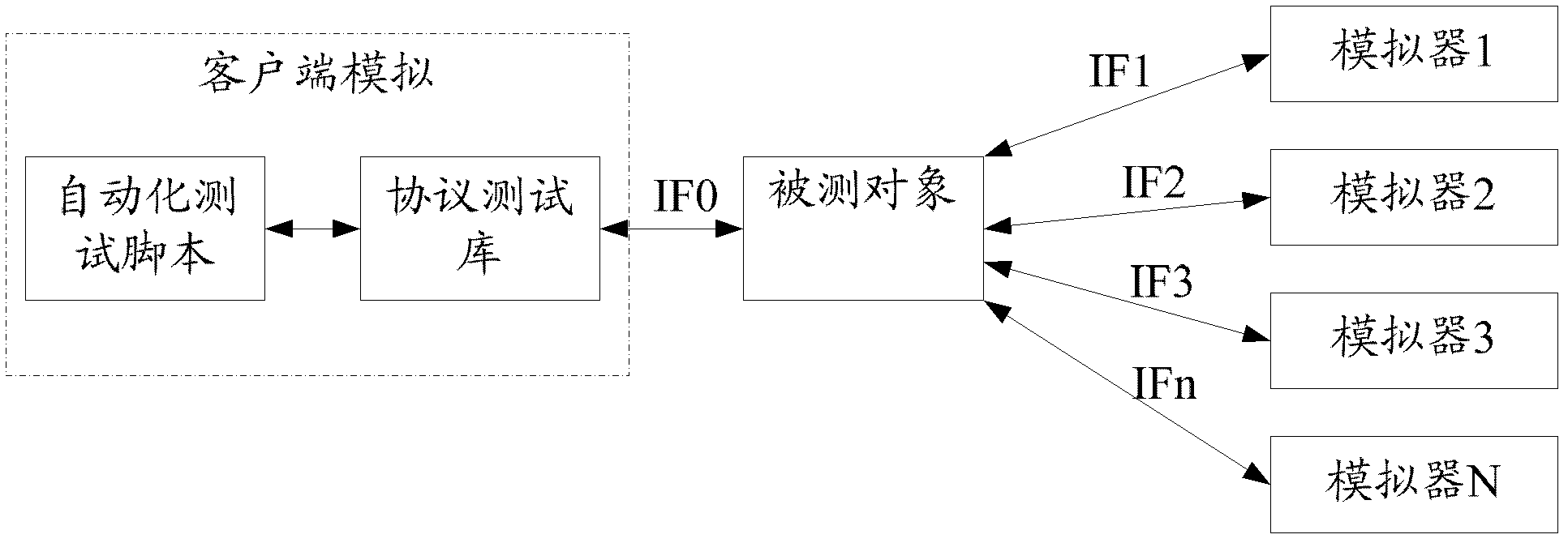

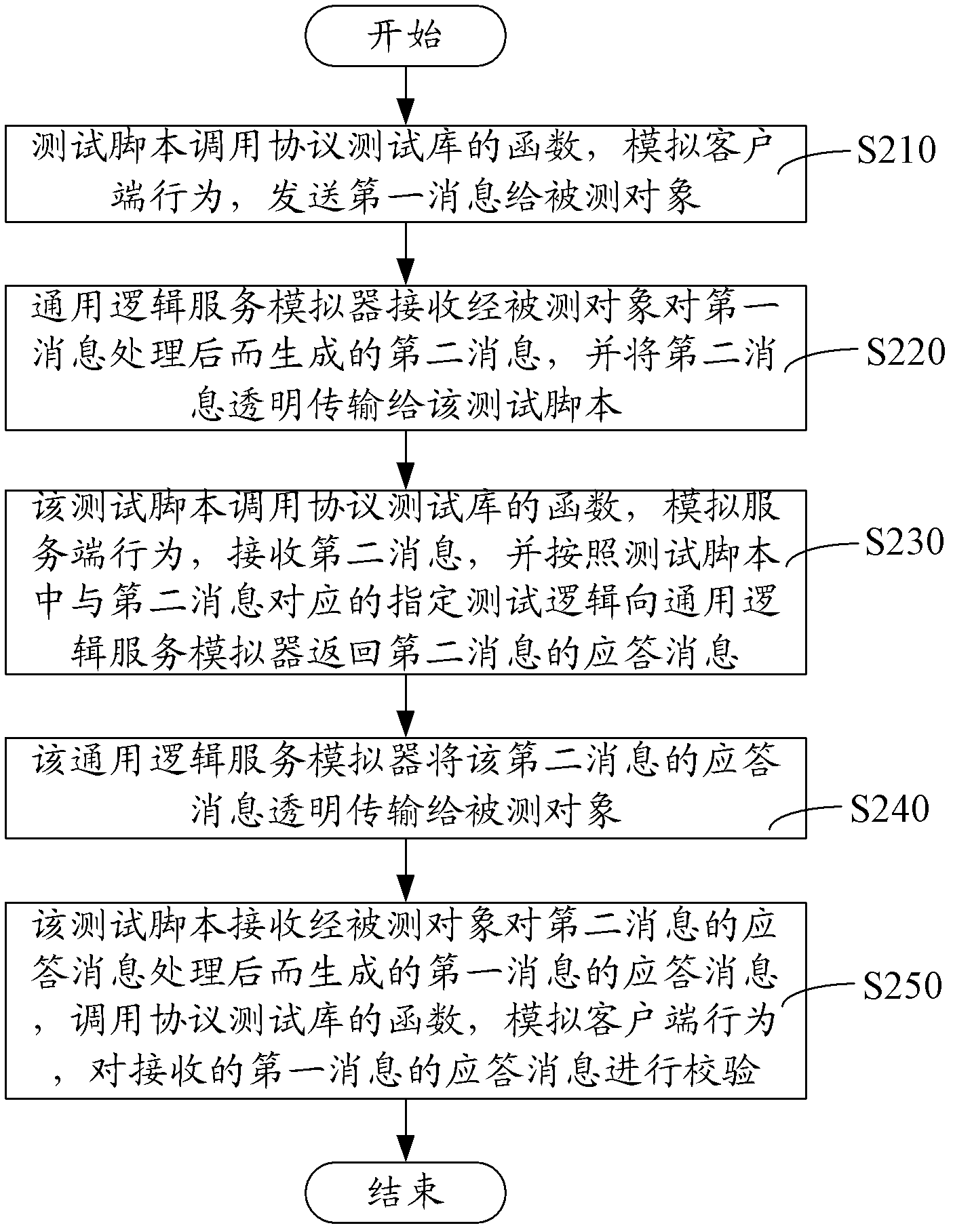

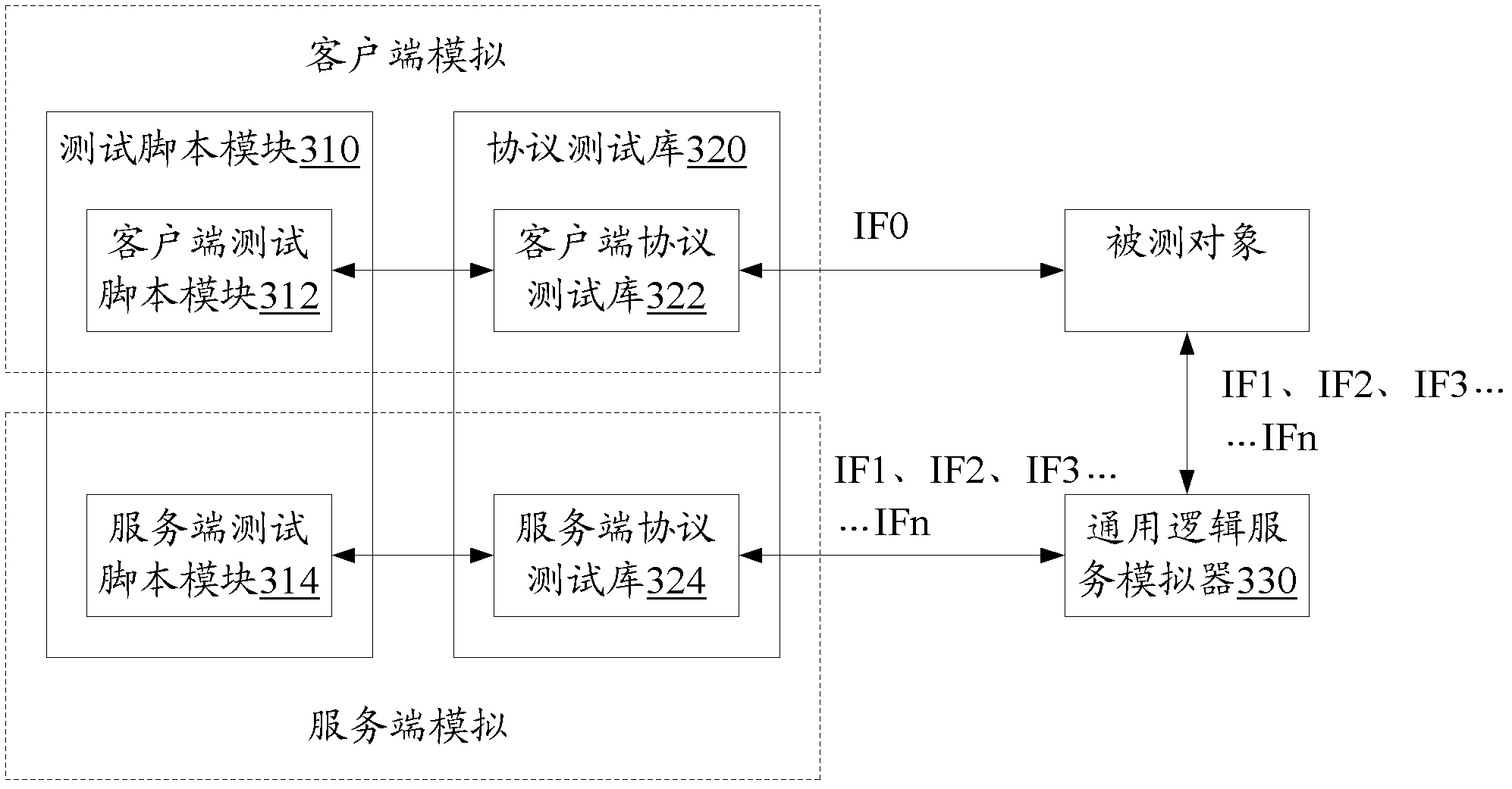

Method and system for testing communication protocol interface

ActiveCN103023708AReduce development costsReduce testing costsData switching networksProtocol testingNetwork Communication Protocols

The invention relates to method and a system for testing a communication protocol interface. The system comprises a testing script module and a universal logic service simulator, wherein the testing script module calls a function of a protocol testing library, simulates the behavior of a client side, and sends a first message to a tested object; the universal logic service simulator receives a second message generated after the first message is processed through the tested object, and transmits the second message to the testing script module; the testing script module simulates the behavior of a service side, and returning a response message of the second message; the universal logic service simulator transmits the response message of the second message to the tested object; and after receiving the response message (processed by the tested object) of the second message, the testing script module checks a response message of the first message. According to the method and the system for testing the communication protocol interface, the universal logic service simulator is adopted to forward messages of various different protocols, different simulators are not required to be developed, and the testing cost can be lowered.

Owner:TENCENT TECH (SHENZHEN) CO LTD

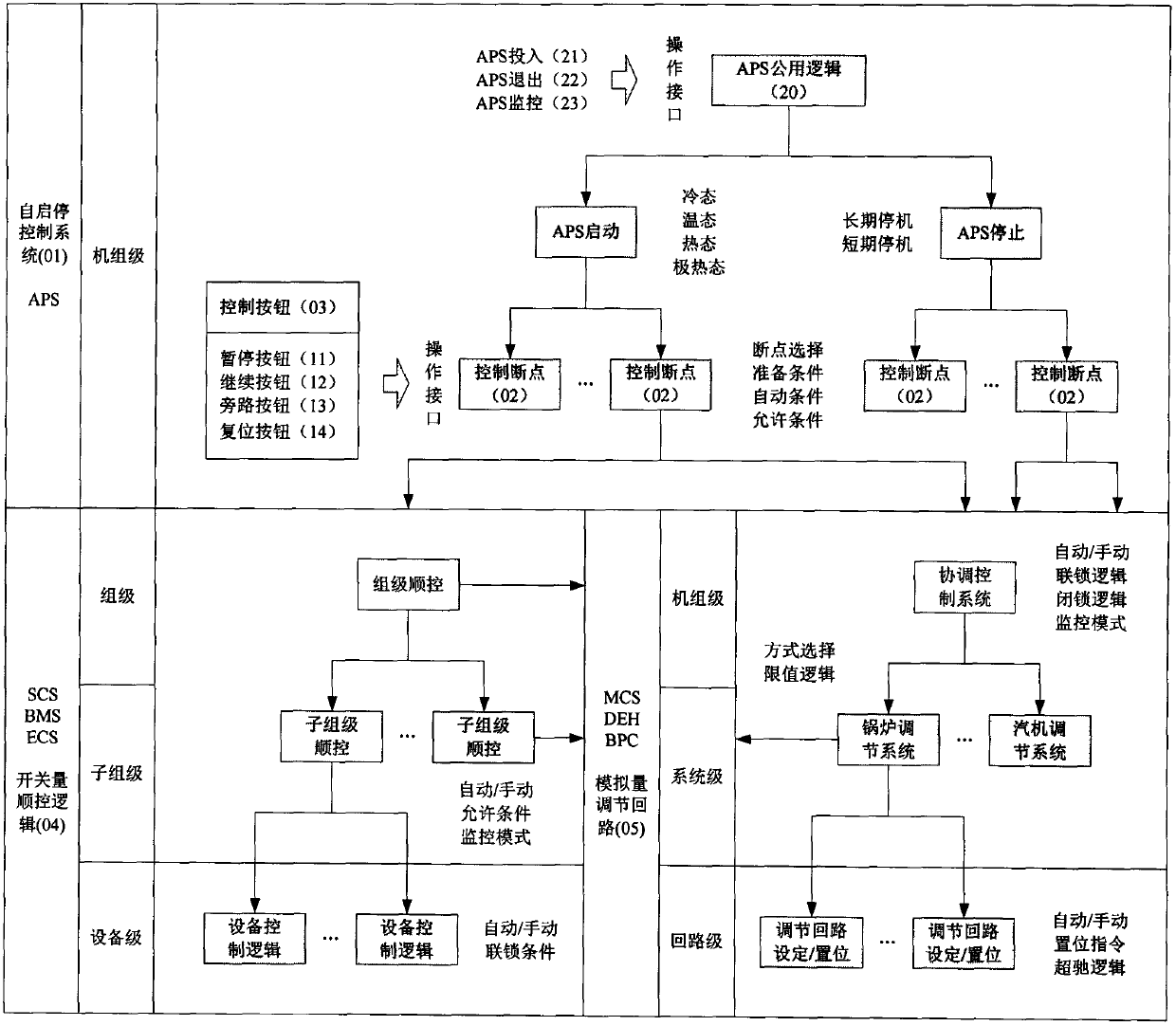

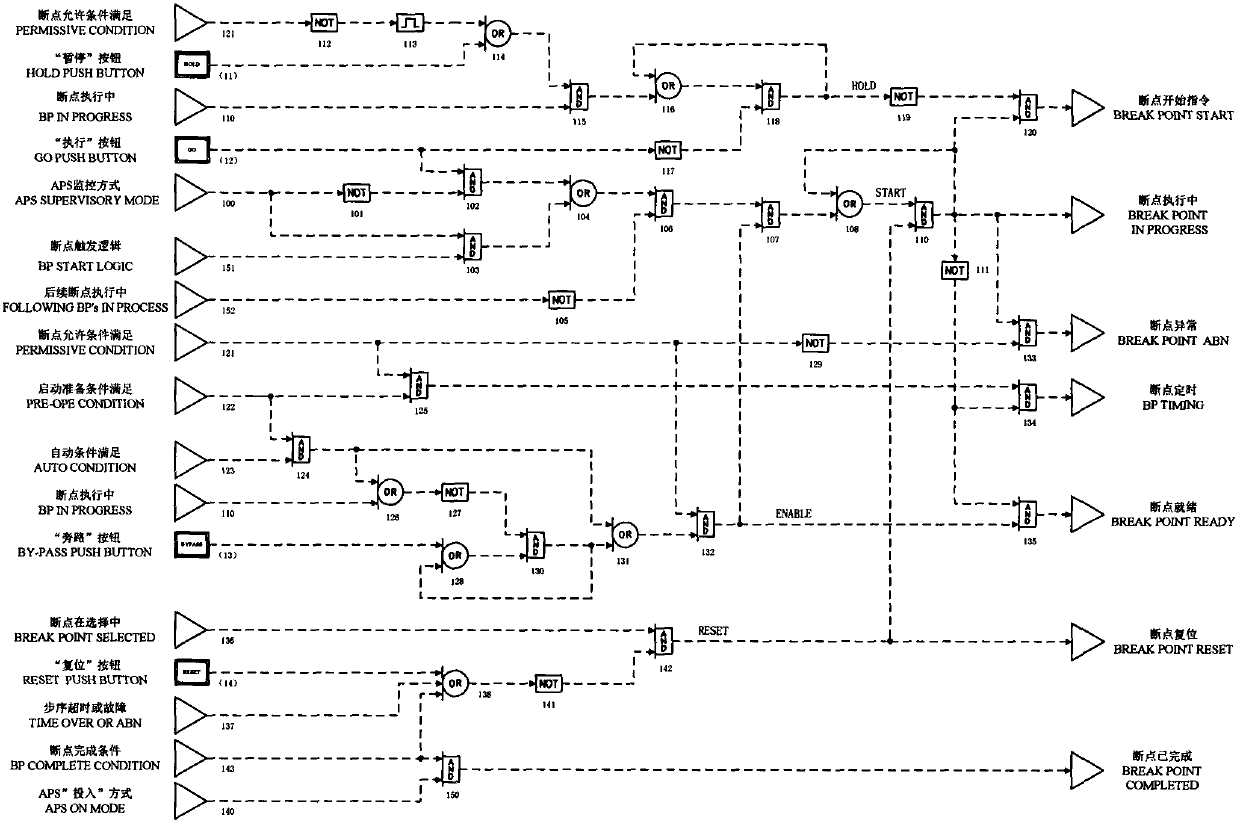

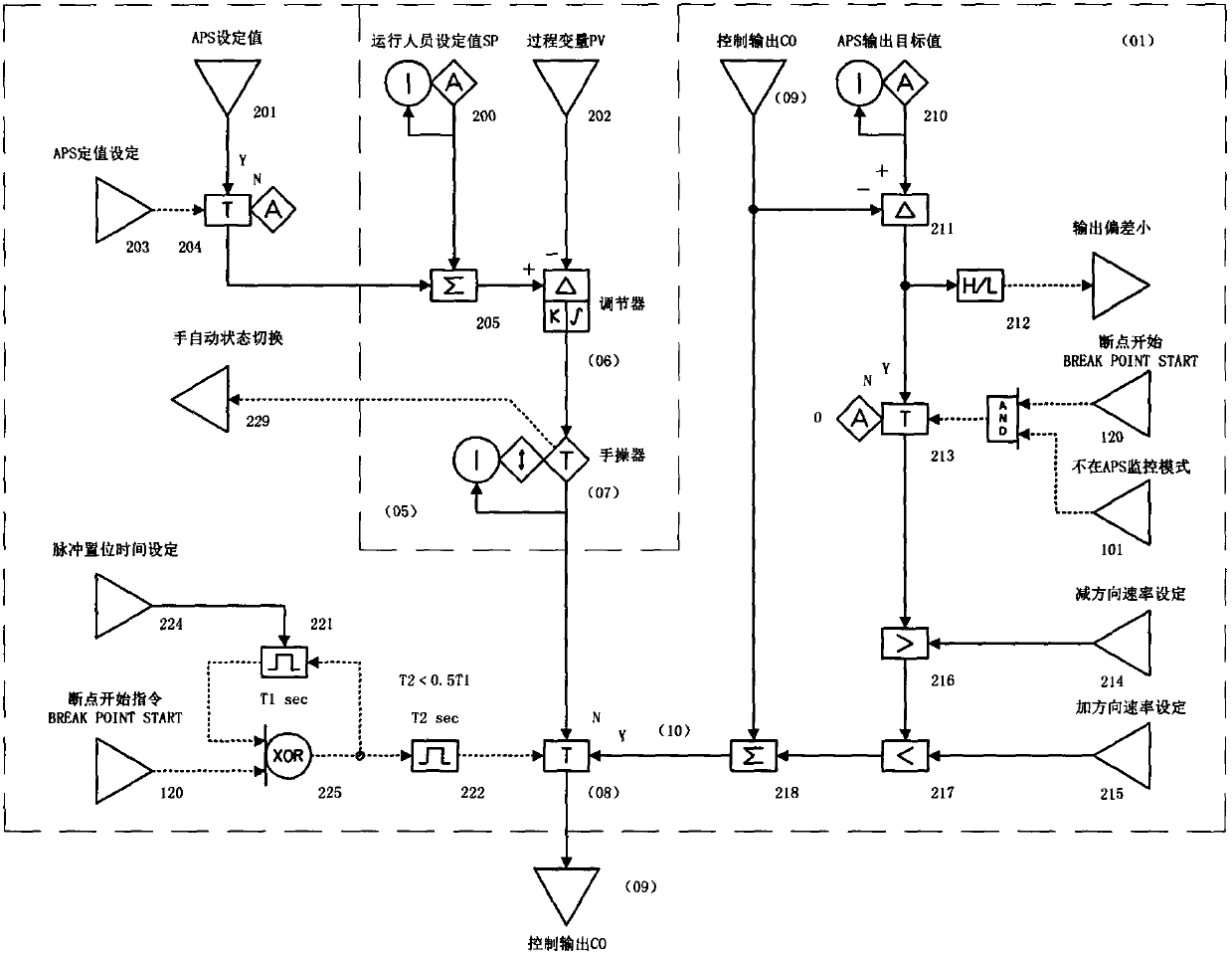

Implementation method of operation interface of automatic plant start-up &and shut-down system

InactiveCN102681520ASimplify Human-Computer Interaction DesignImprove applicabilityTotal factory controlProgramme total factory controlInteractive designControl system

The invention discloses an implementation method of an operation interface of an automatic plant start-up &and shut-down system in a thermal power plant. Due to the common logic, control breakpoint and step sequence logic of the automatic plant start-up &and shut-down system provided by the method as well as the operation interface of the automatic plant start-up &and shut-down system and a modulating control system, the man-machine interactive design of the automatic plant start-up &and shut-down system is simplified, and the applicability of the automatic plant start-up &and shut-down system is improved. In addition, optimal control of a control outputting setting value of the modulating control system can be realized by adopting multiple goal constraint.

Owner:上海迪吉特控制系统有限公司 +1

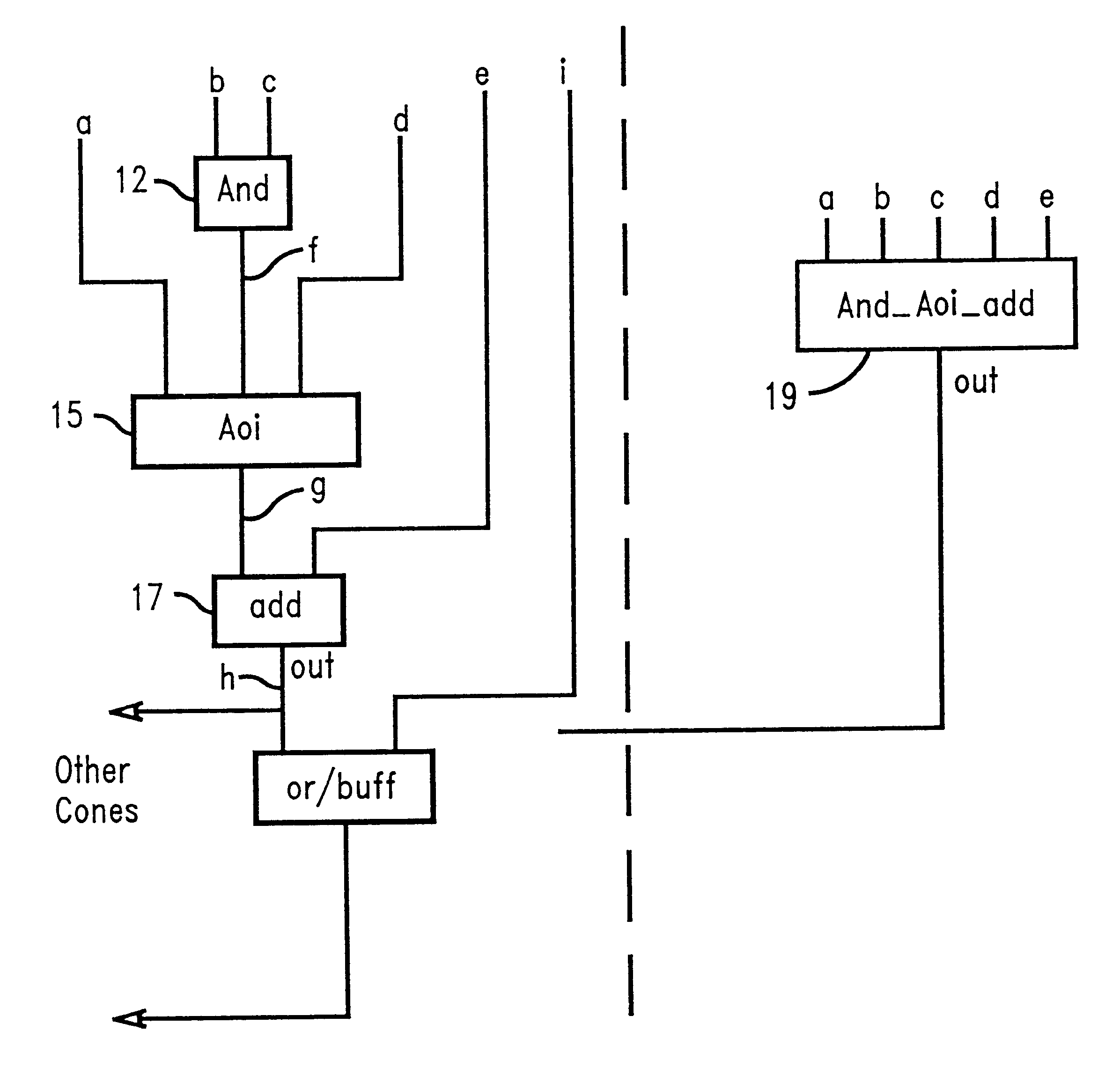

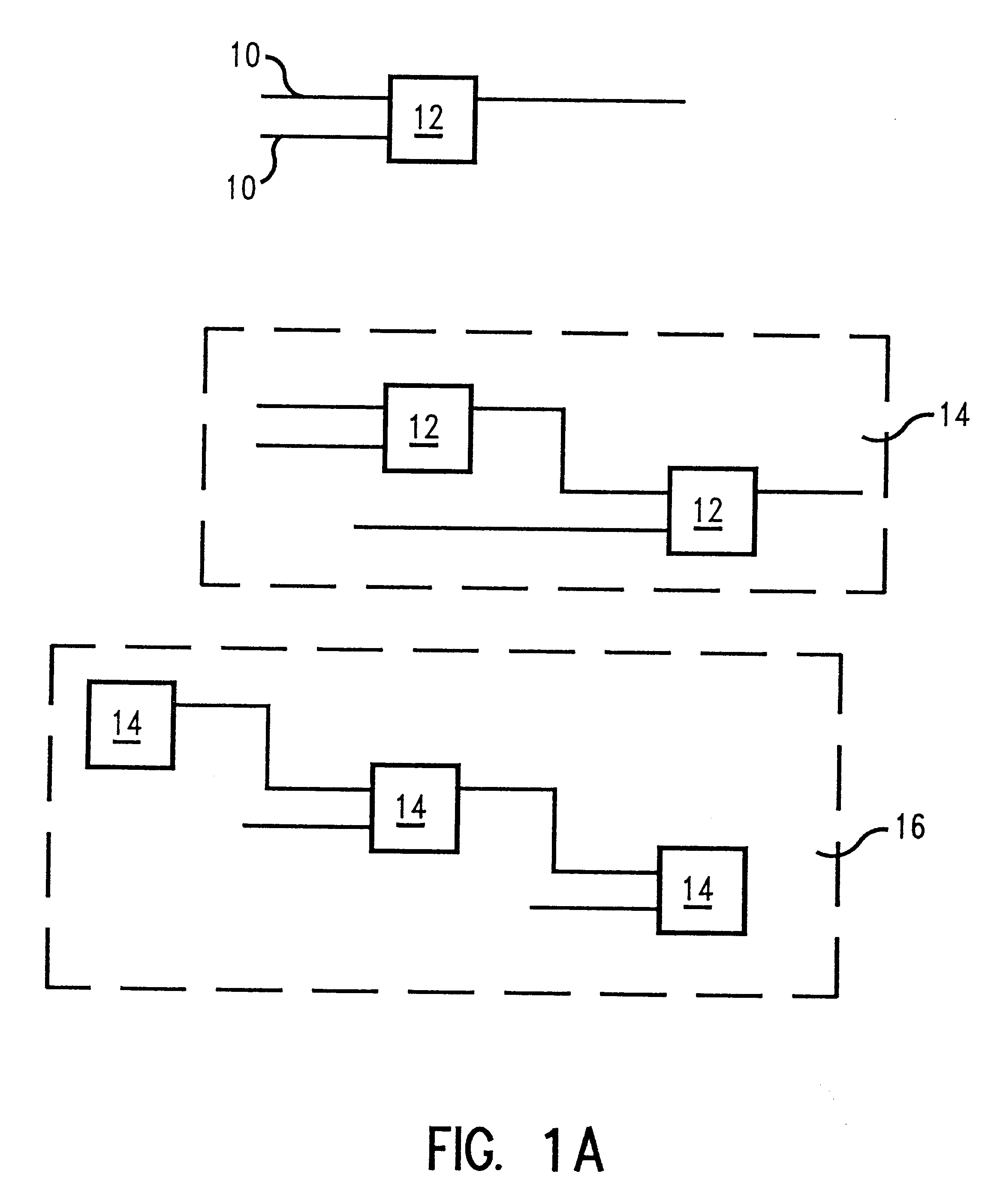

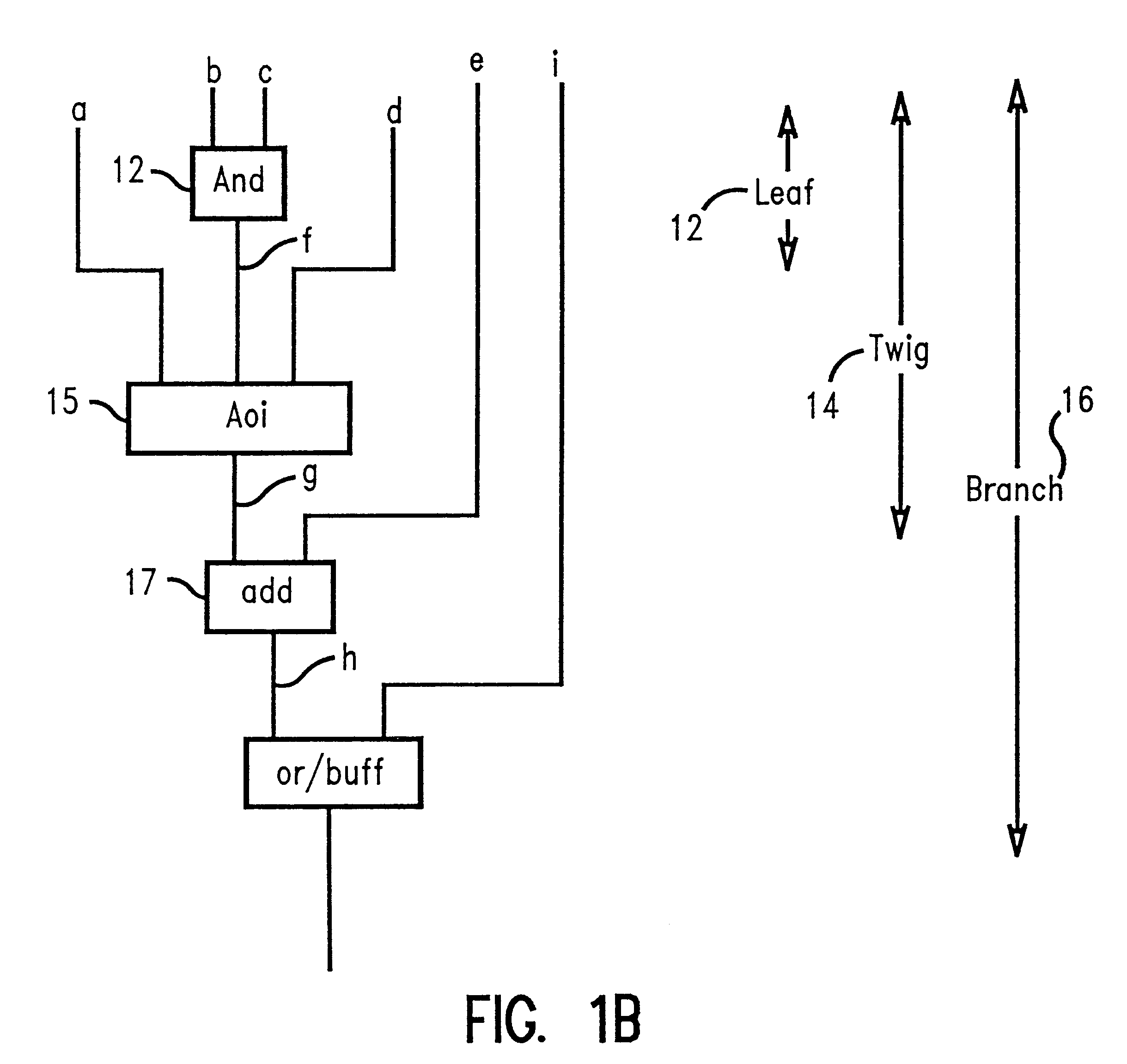

Method and apparatus for a hedge analysis technique for performance improvements of large scale integrated circuit logic design

InactiveUS6412096B1Overcomes shortcomingMinimize timeCAD circuit designSoftware simulation/interpretation/emulationCritical path methodCommon logic

An apparatus and method for performing a Hedge Technique Analysis are used to enhance the performance of the functional logic design of a large scale integrated circuit while simplifying the underlying logic. The methodology first runs performance tests on the logic circuitry to assess the timing and characterize the logic paths; next, functional paths are identified and listed; common logic path leaves, twigs, and branches are then identified and ranked by the number of critical paths associated with each; all high ranking common logic path leaves, twigs, and branches are then collapsed; and, timing paths are re-run to characterize the final performance rating of the functional design.

Owner:IBM CORP +1

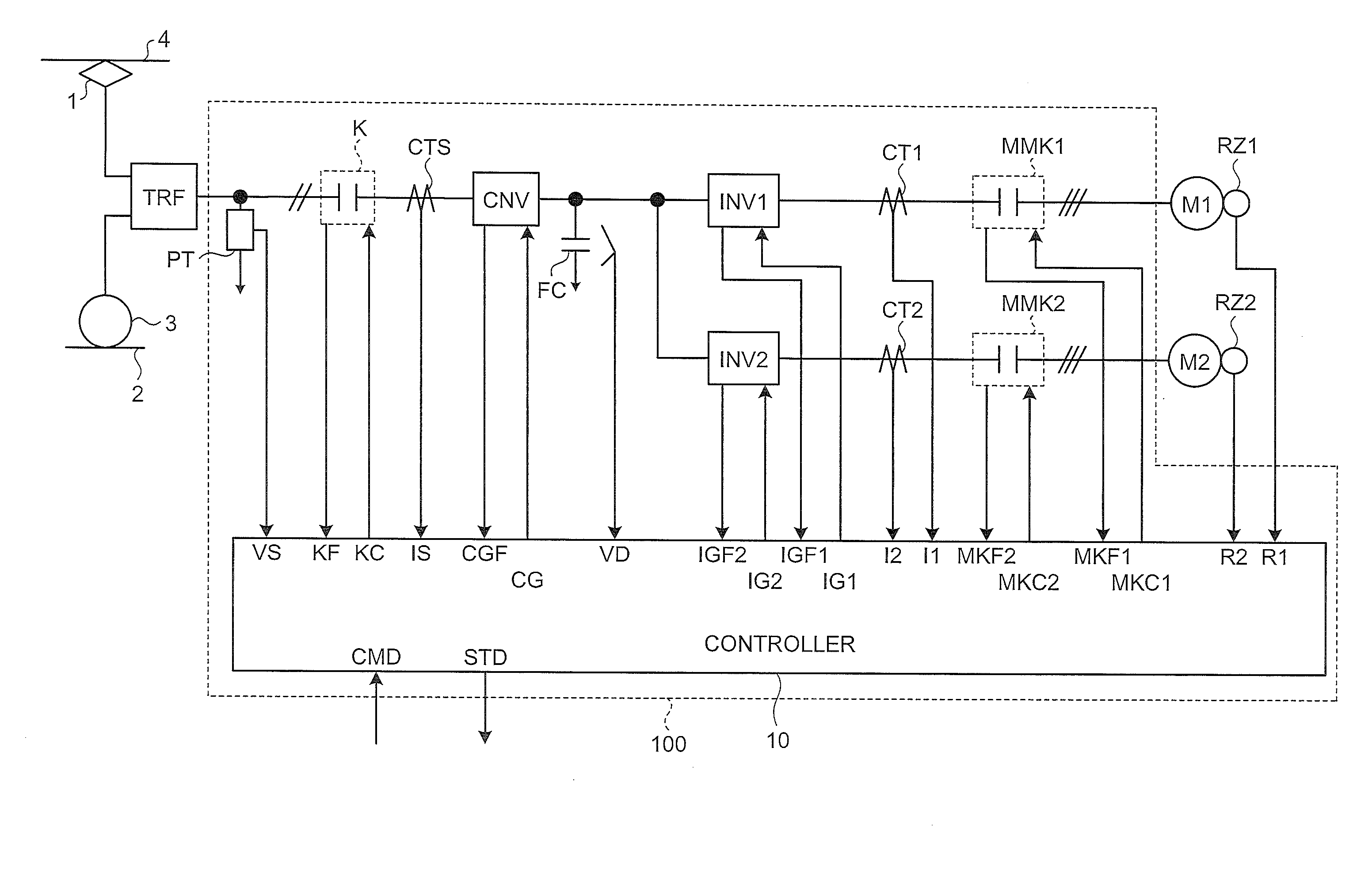

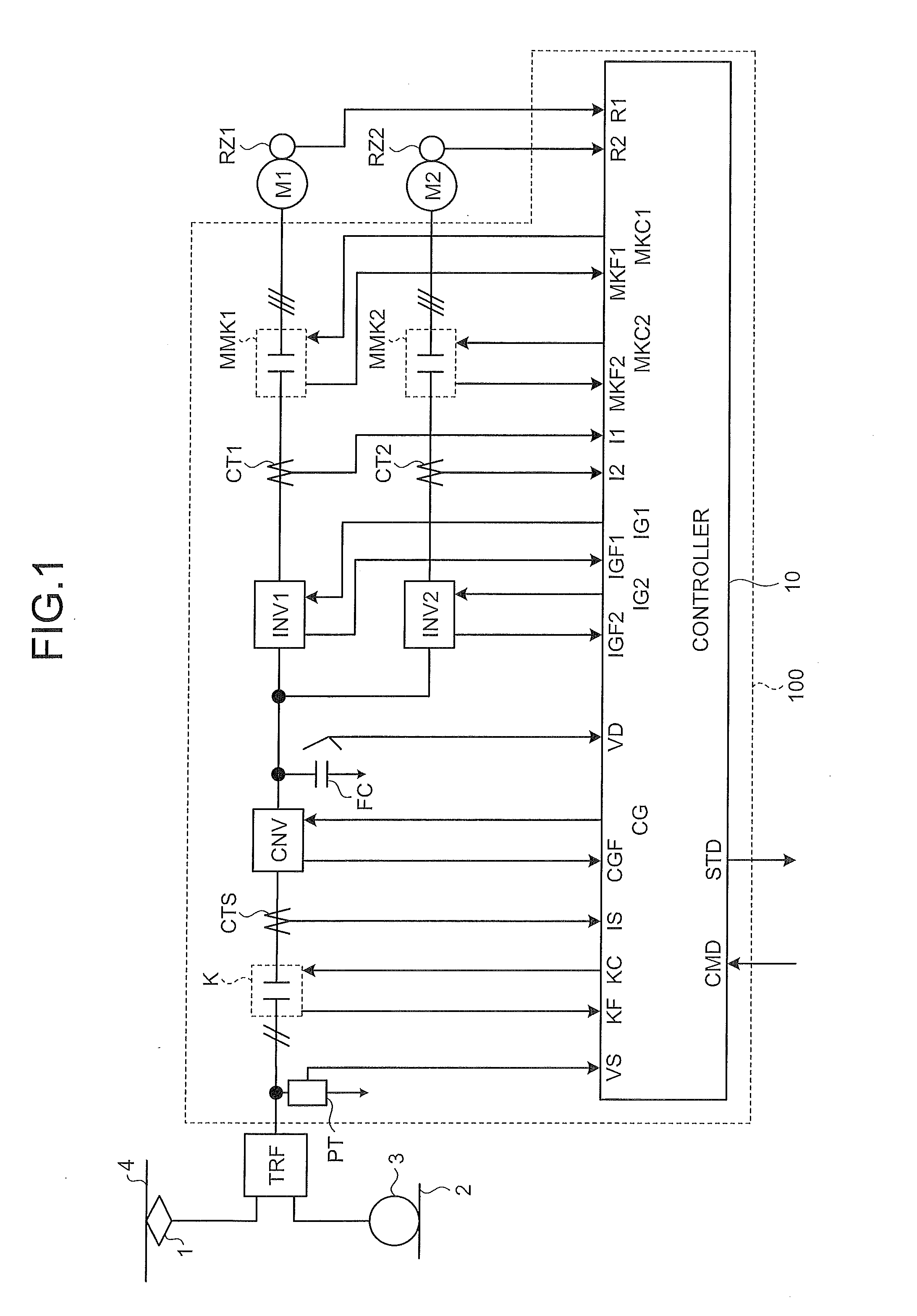

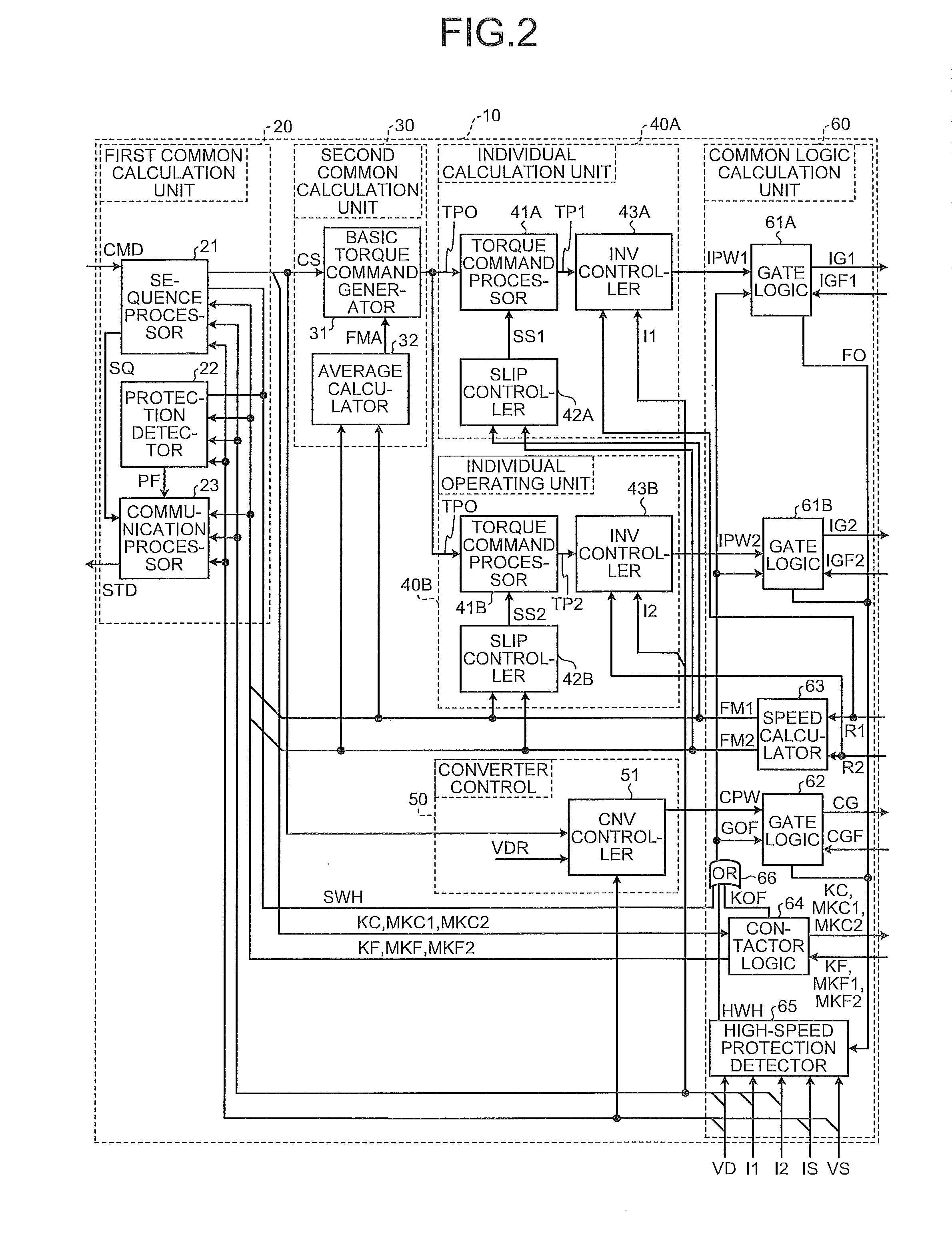

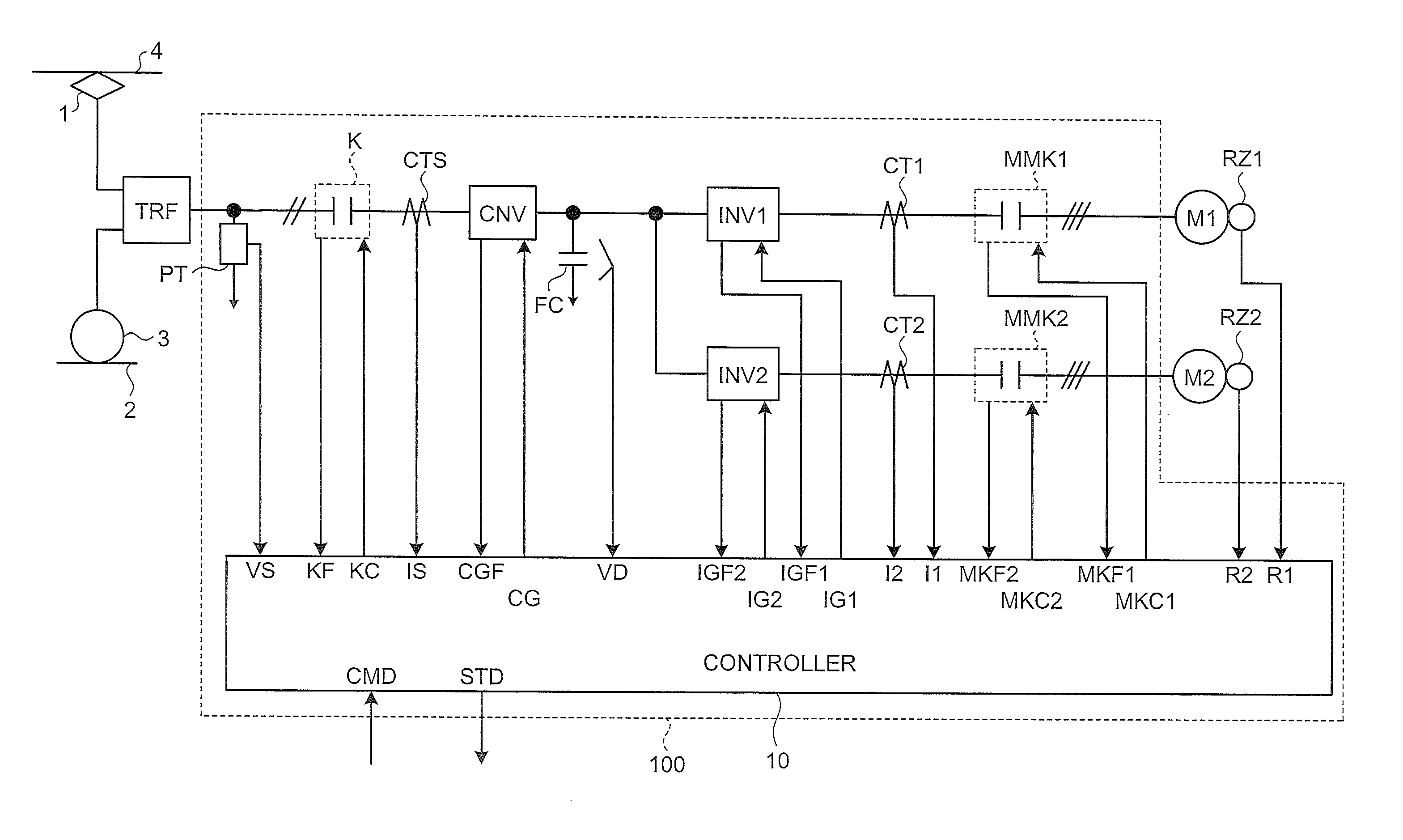

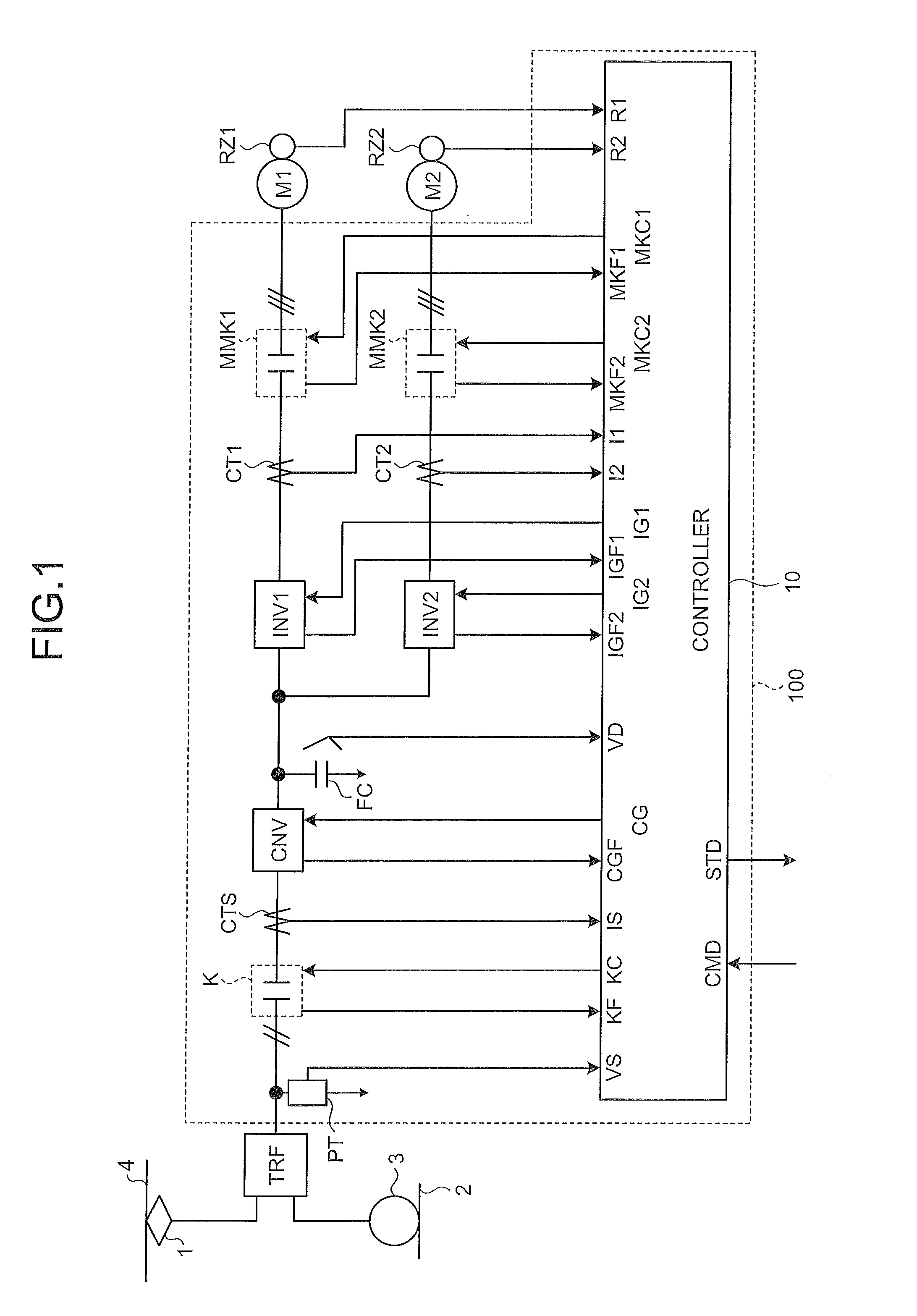

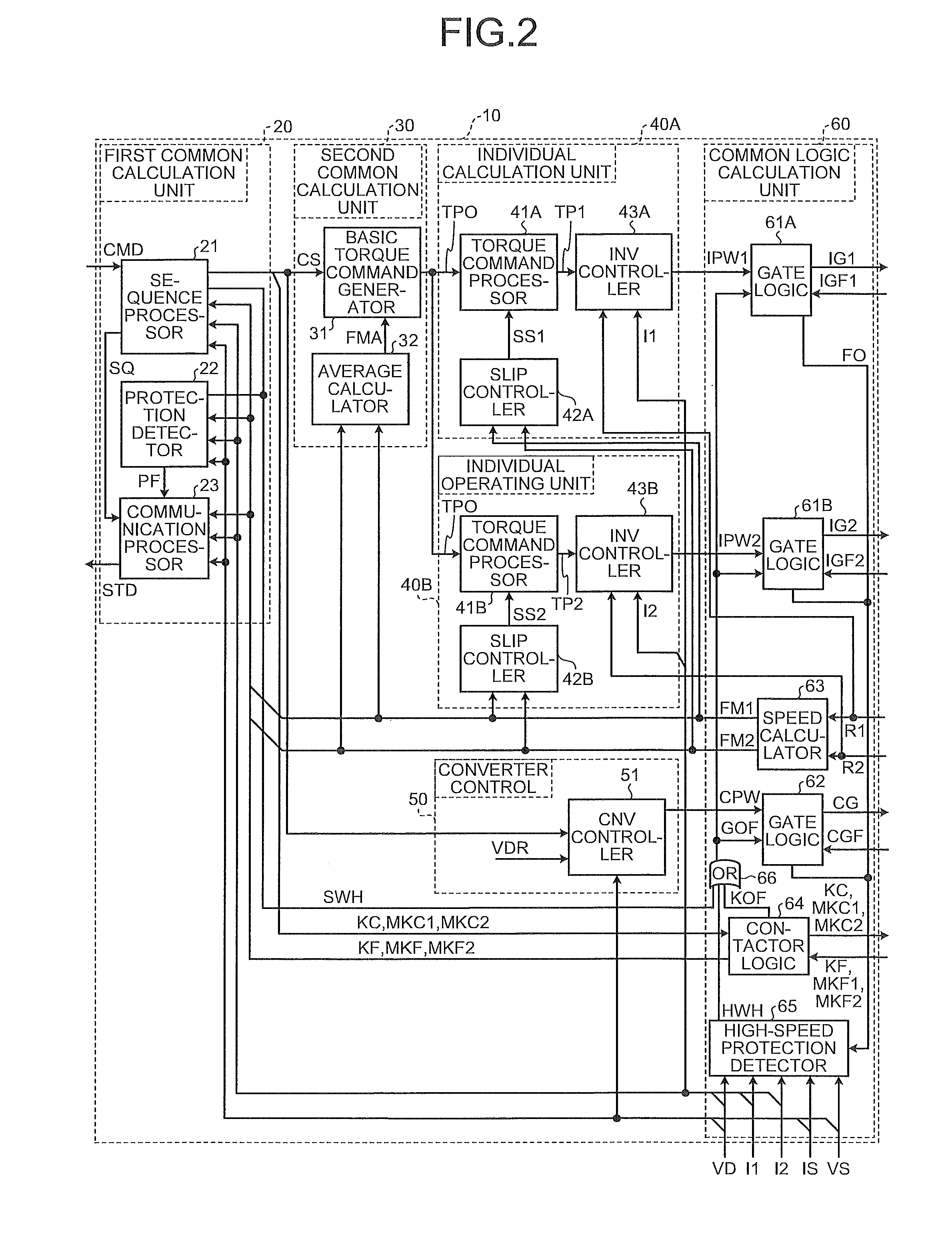

Motor controlling apparatus

InactiveUS20100171448A1Low costReduce the total massMotor/generator/converter stoppersAC motor controlControl signalGroup operation

A motor controlling apparatus having a controller for controlling a plurality of inverters correspondingly provided to each of a plurality of alternating-current motors is reduced in size, mass, and cost by effectively grouping operations performed by each calculation unit included in the controller. This controller for controlling the inverters includes: a first common calculation unit and a second common calculation unit that calculate and output control signals that are common to each of the inverters; individual calculation units that individually calculate and output a control signal related to each of the inverters; and a common logic calculation unit 60 that outputs a gate signal for controlling switching of each of the inverters based on the signals received from the first common calculation unit, the second common calculation unit, and the individual calculation units.

Owner:NEXGEN CONTROL SYST LLC

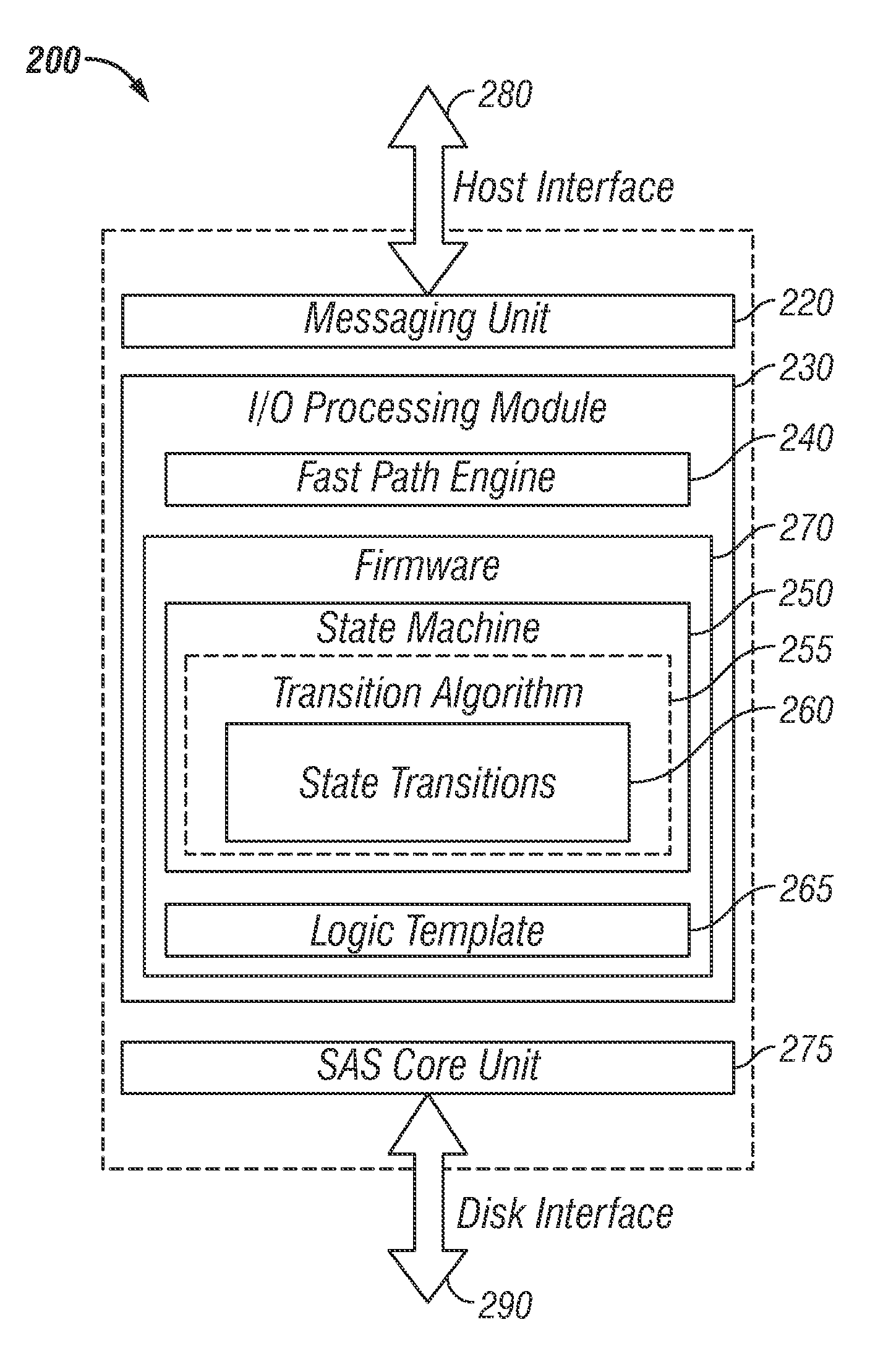

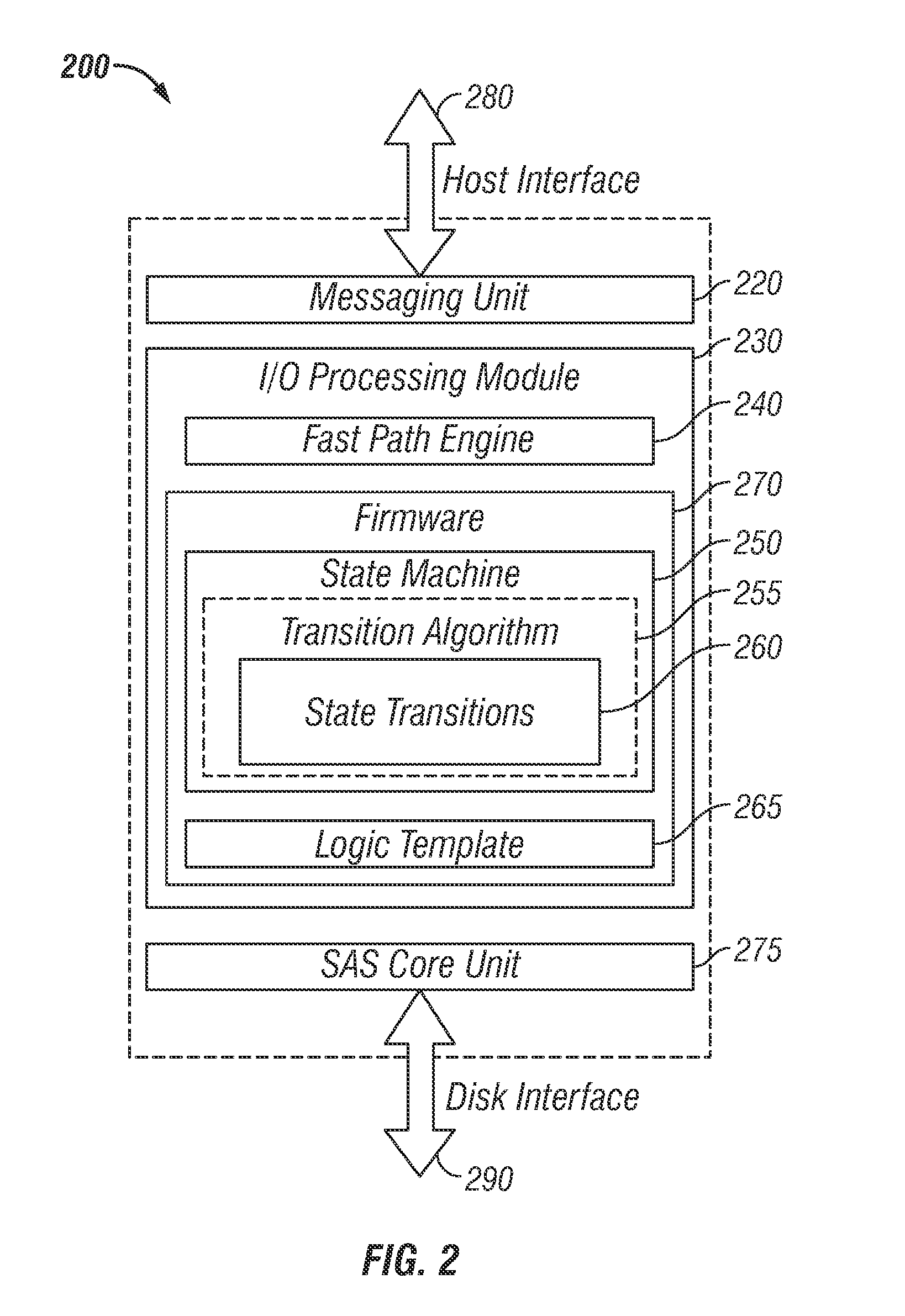

System and method for coordinating control settings for hardware-automated I/O processors

InactiveUS20120089753A1Increase flexibilitySmooth transitionInput/output processes for data processingData conversionFast pathControl store

A system and method for coordinating control setting with respect to an automated input / output (I / O) processor. A state machine having a transition algorithm can be configured in association with a storage controller in order to permit multiple entities to safely transmit an I / O request to an I / O device. Specific combinations of control bits associated with a fast path engine can be determined by identifying different modes with respect to the behavior of the fast path engine. Each mode can be assigned as a state with respect to the state machine. An I / O path exception and error condition that can cause transitions between the states can be determined and the transitions can be assigned from one state to another state. A generic logic template can then be configured to govern the transitions with respect to the state machine. The logic can be executed when an event occurs in order to trigger multiple state transition and / or modifications with respect to the hardware control bits of the fast path engine.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Magnetic logic circuits and systems incorporating same

InactiveUS8400066B1Avoid problemsElectric light circuit arrangementDigital storageMagnetic logicSpins

Logic circuits based, at least in part, on use of spin-torque transfer (STT) to switch the magnetization—and hence the logic state—of a magnetic material are disclosed. Aspects of the invention include novel STT-based switching devices, new configurations of known STT-based devices into useful logic circuits, common logic circuits and system building blocks based on these new devices and configurations, as well as methods for inexpensively mass-producing such devices and circuits.

Owner:PILEGGI LAWRENCE T +1

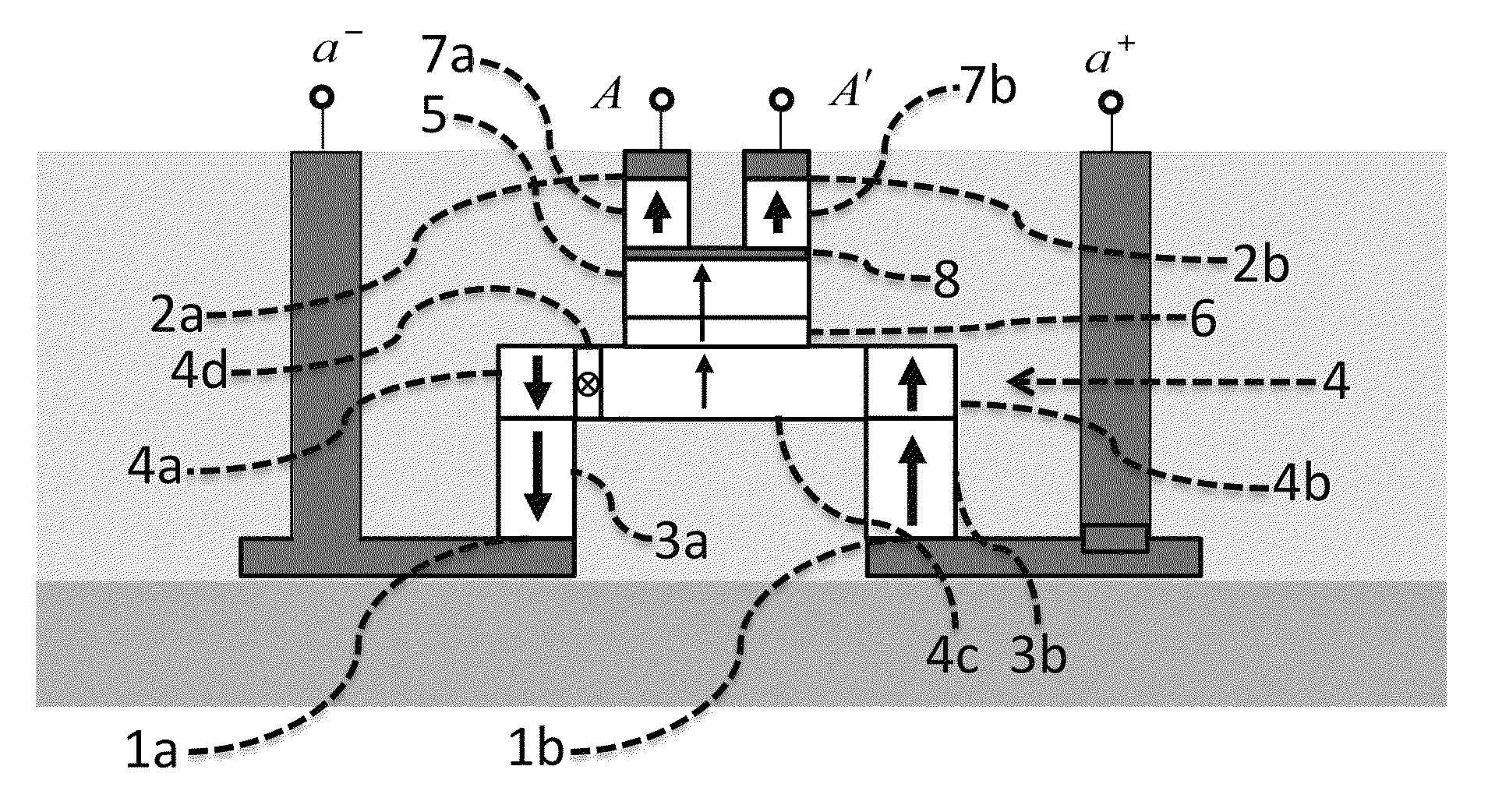

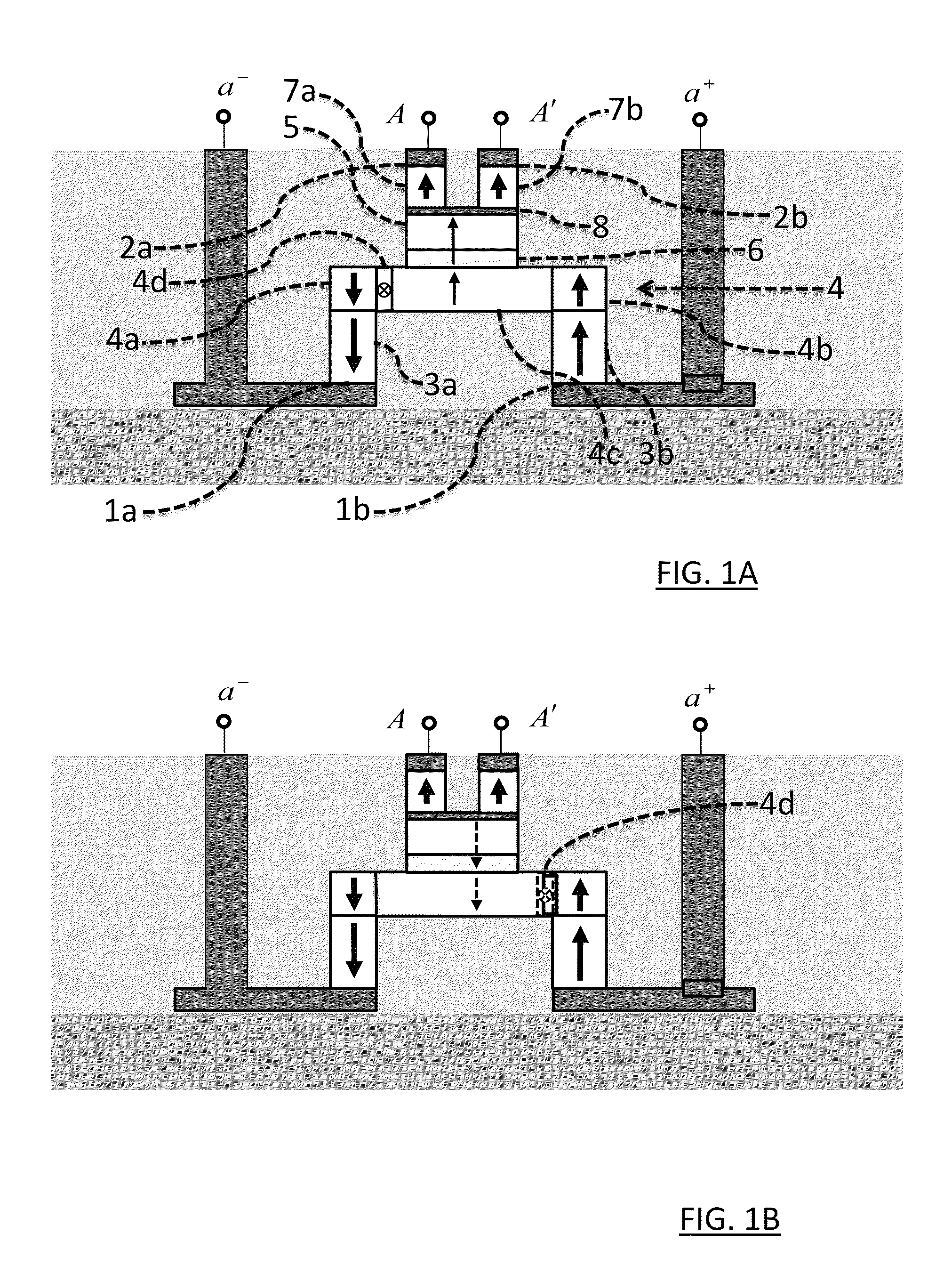

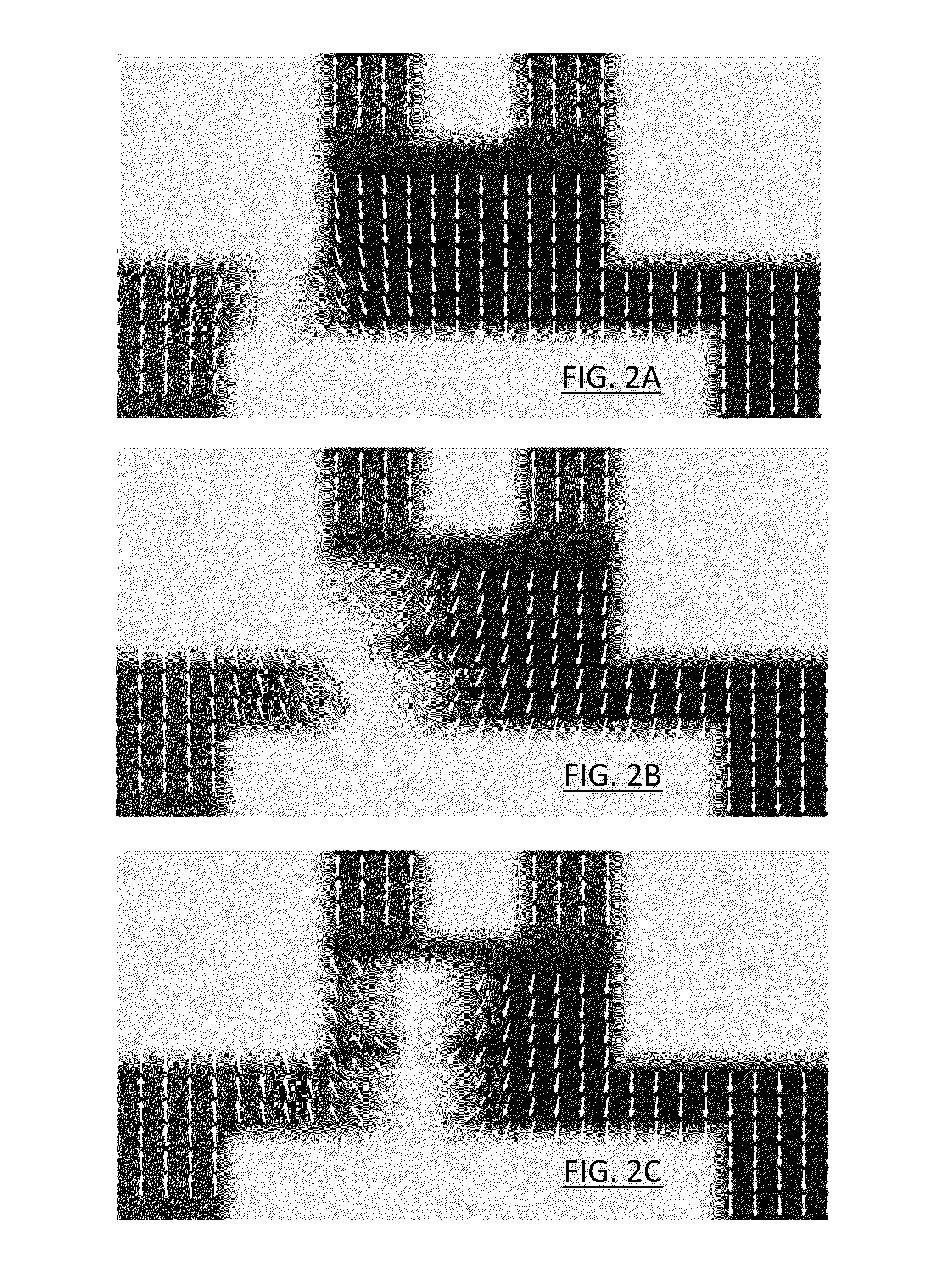

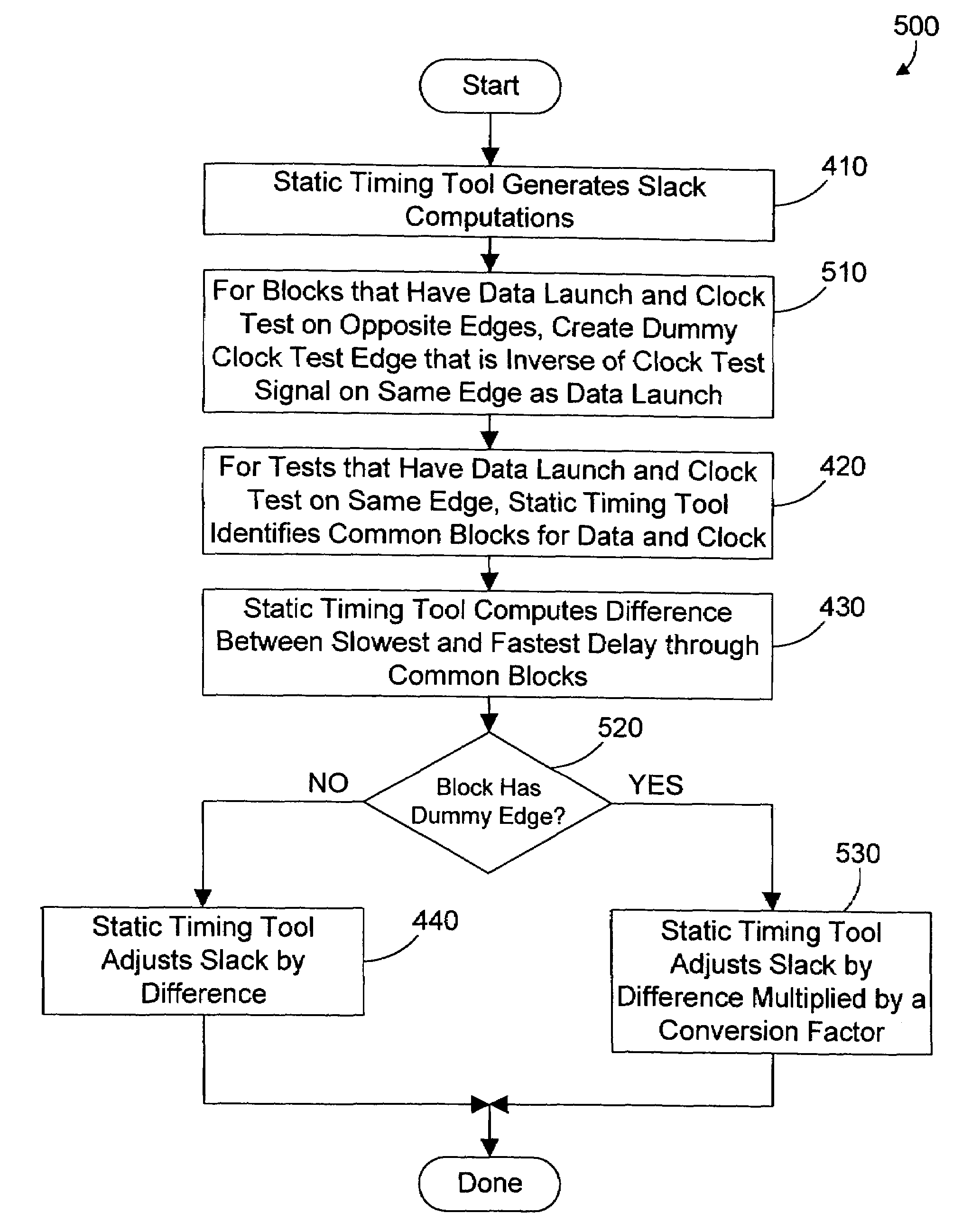

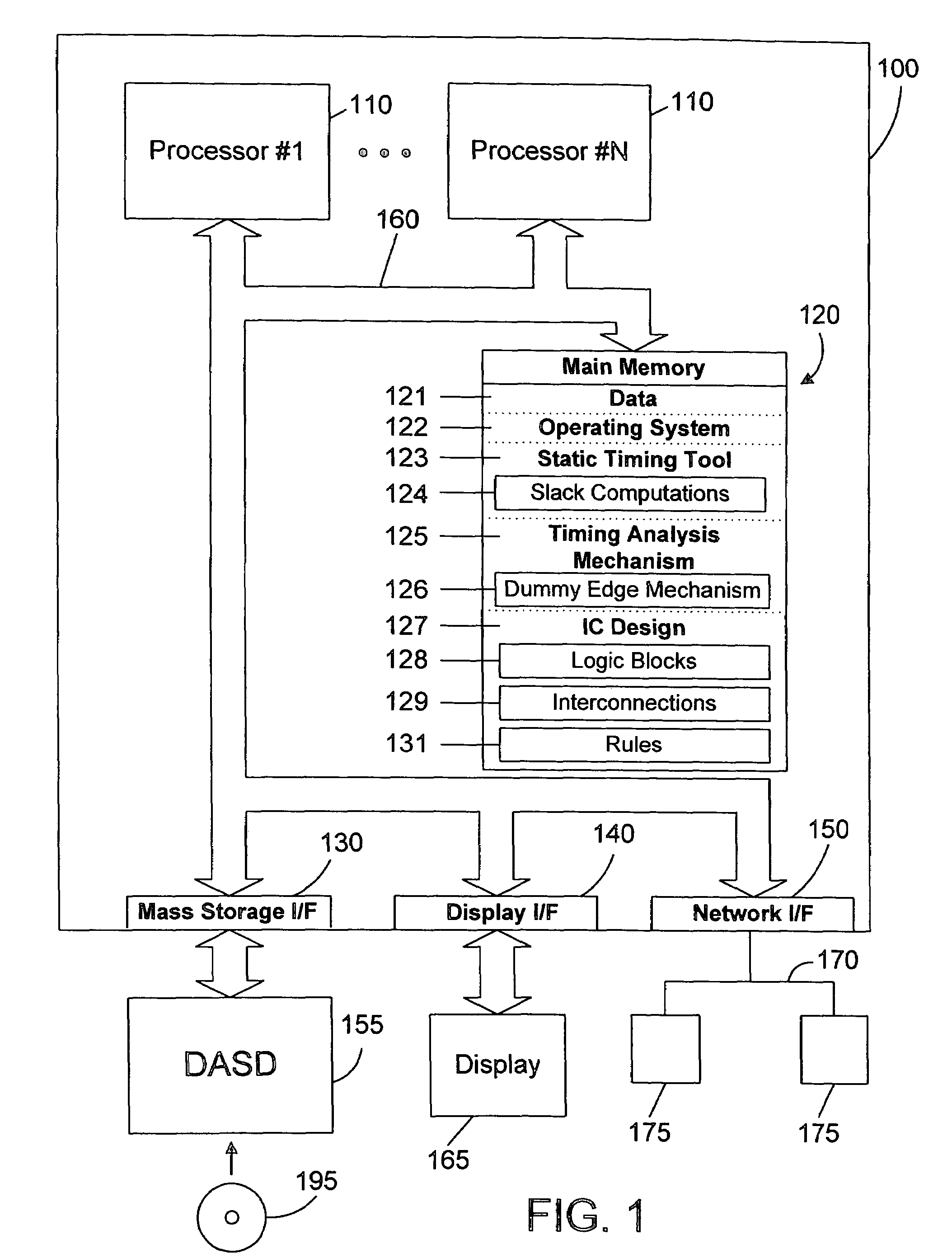

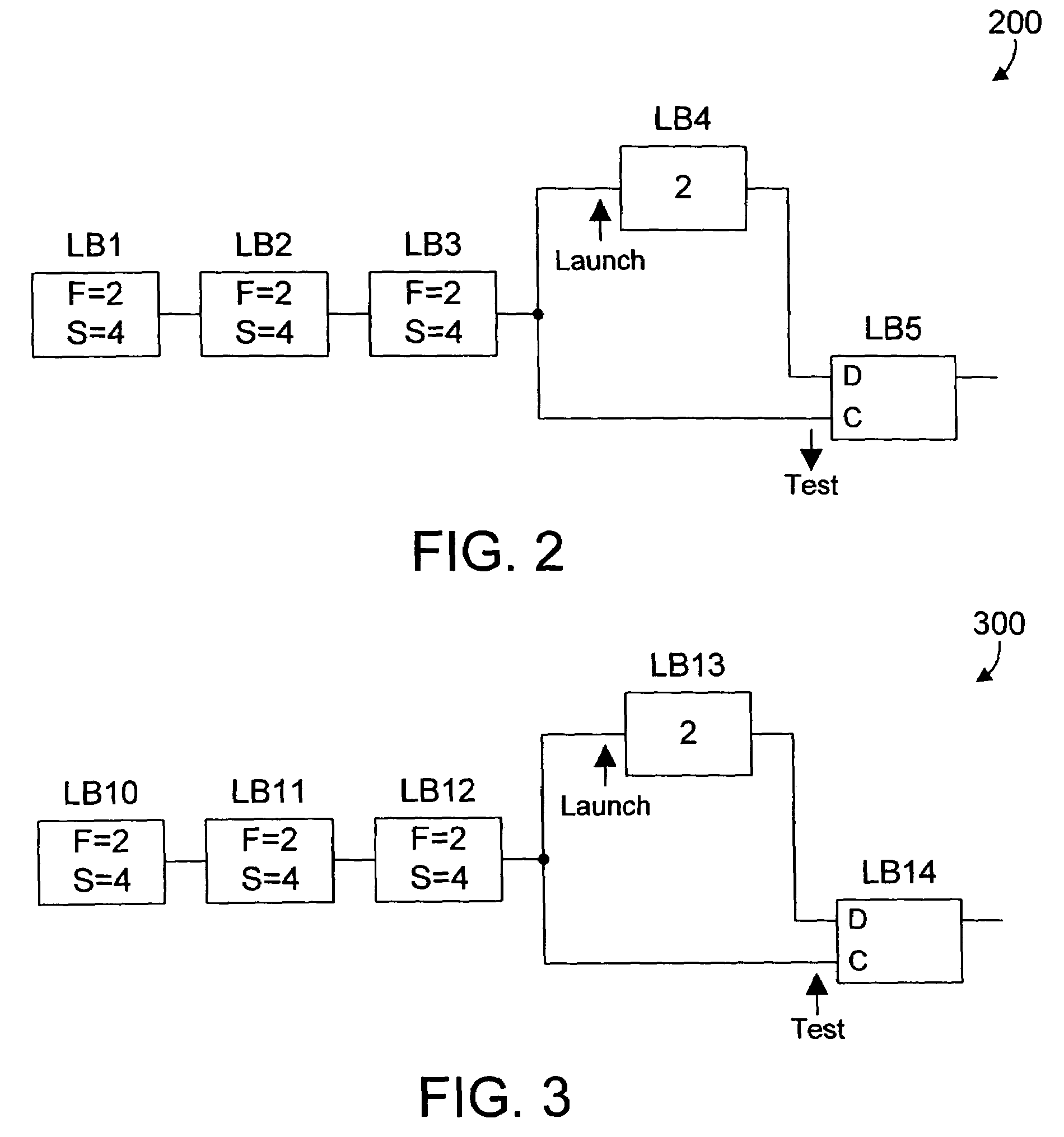

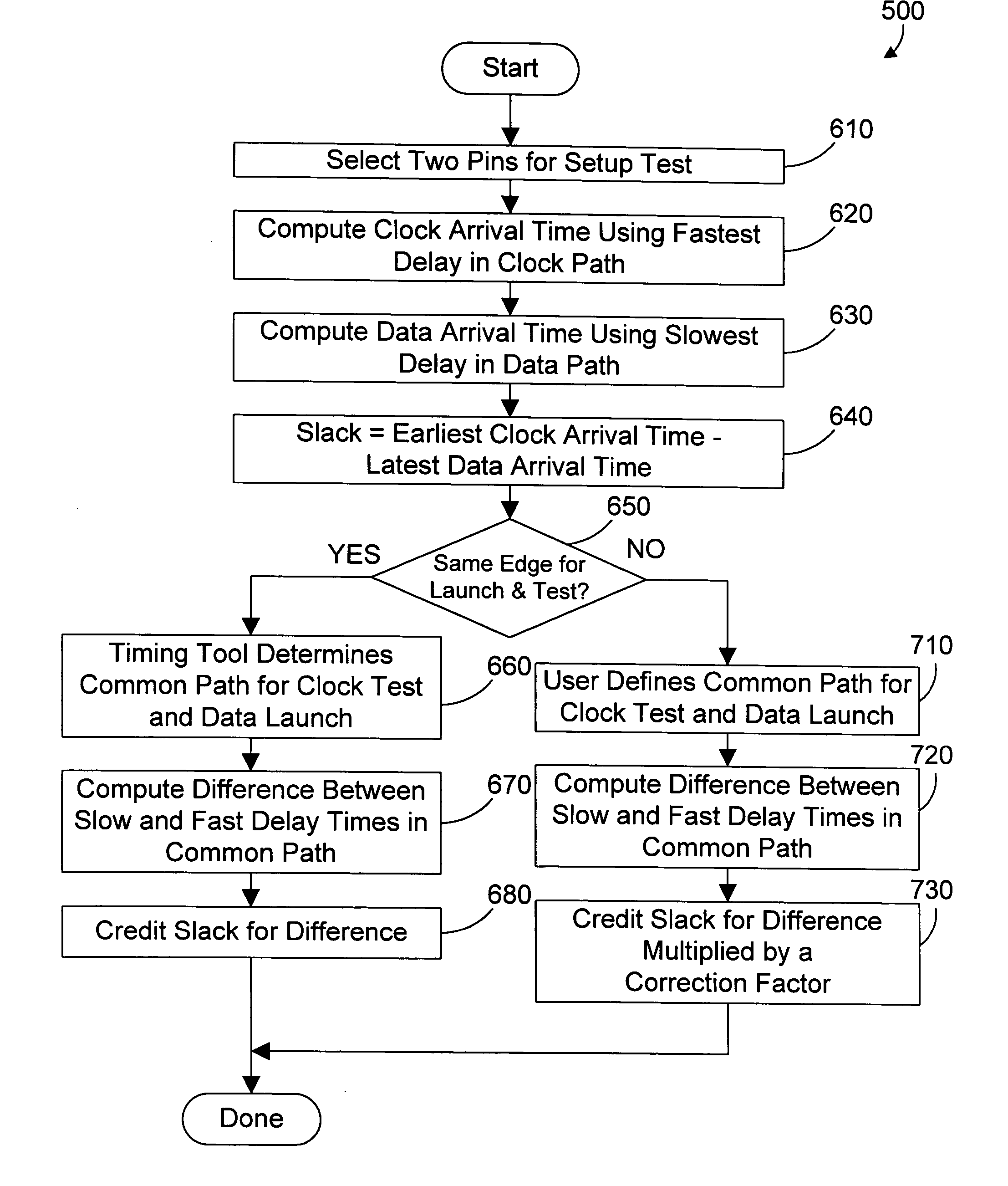

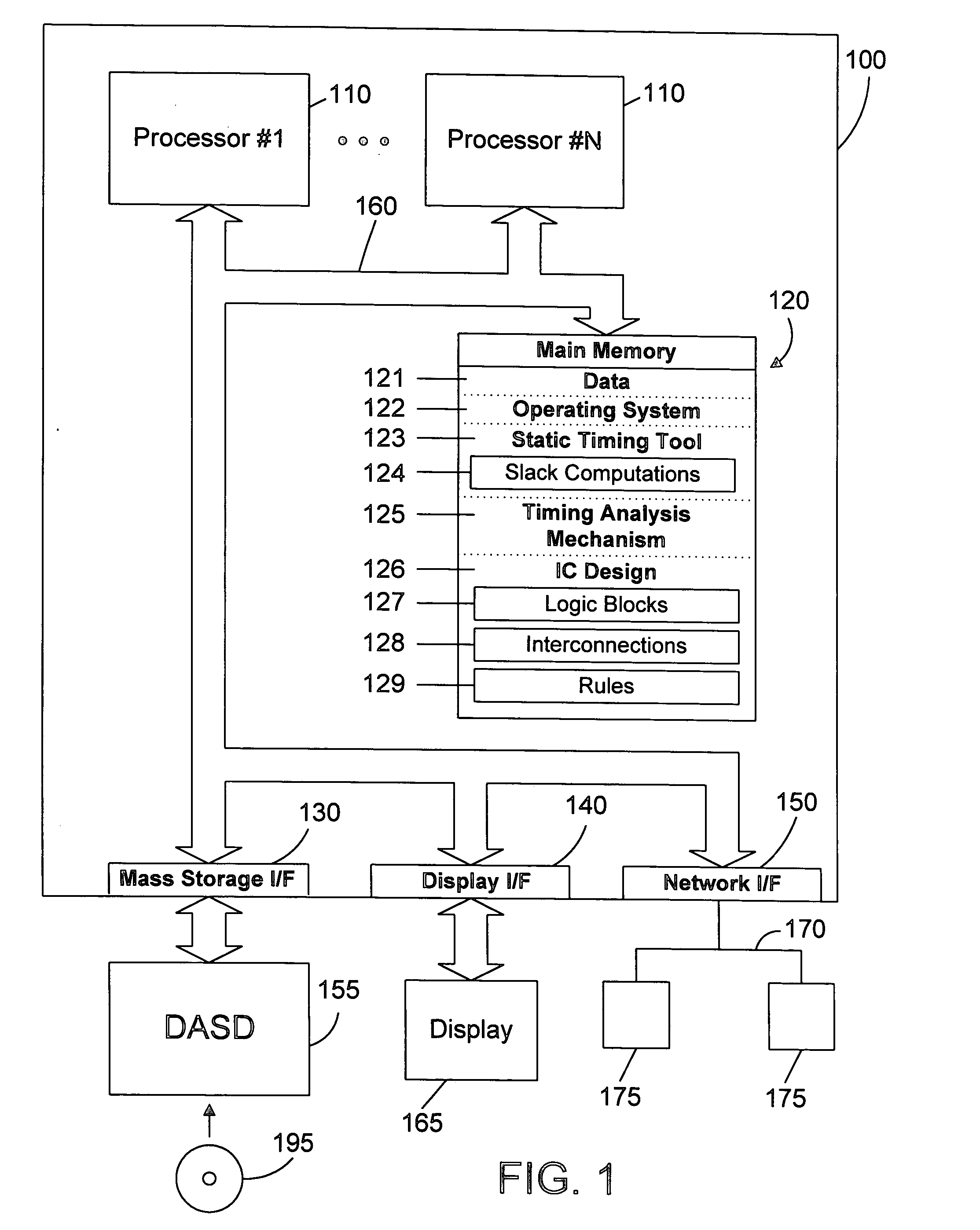

Apparatus and method for performing static timing analysis of an integrated circuit design using dummy edge modeling

InactiveUS7143379B2Reduce workloadComputer aided designSoftware simulation/interpretation/emulationStatic timing analysisConversion factor

An apparatus and method perform static timing analysis on an integrated circuit design. Certain pessimistic assumptions regarding slack when data launch and clock test signals are on opposite edges and derived from common logic blocks are improved by creating a dummy clock edge that is on the same edge as the data launch signal, and allowing the timing tool to compute the slack improvement using its native functions. The slack improvement is then multiplied by a conversion factor, and the result is used to adjust the slack. The apparatus and method give credit for slack in common blocks automatically, thereby allowing a large number of pessimistic slack values to be automatically corrected and reducing the workload of an integrated circuit designer in addressing the timing problems in an integrated circuit design.

Owner:INT BUSINESS MASCH CORP

Logic circuit whose power switch is quickly turned on and off

InactiveUS20050062502A1Reliability increasing modificationsPower reduction by control/clock signalPower switchingLogic gate

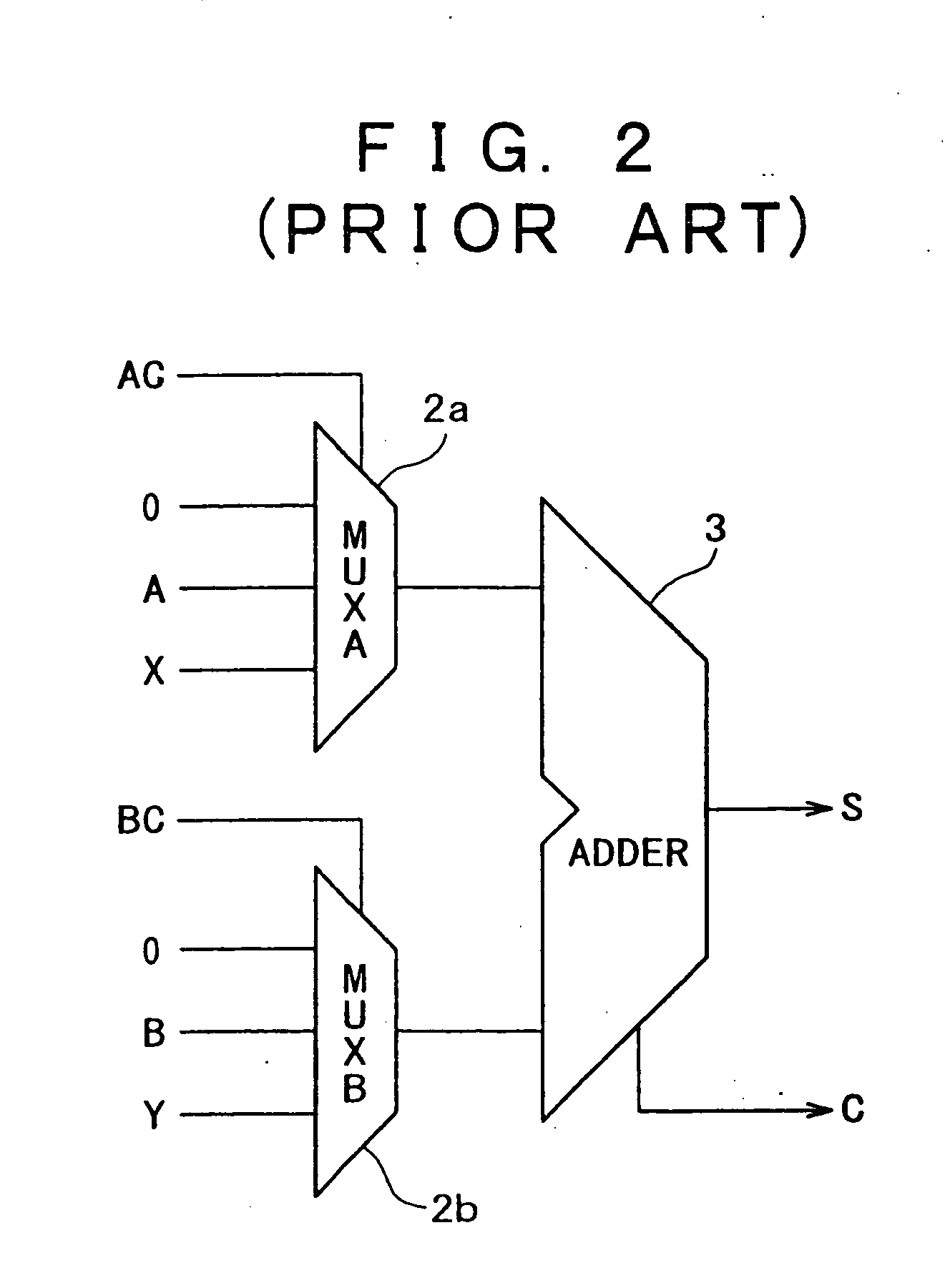

The present invention is to provide a logic circuit which assures short-circuit current reduction by using a gate which uniquely fixes the level of each node and also reduces leakage current so that the power is turned on and off quickly. Logic gates of the subject logic circuit are divided into first-type logic gate and second-type logic gates. The first-type logic gate outputs high potential under the specific status and the second-type logic gate outputs low potential under the specific status. Under the state that the high potential is supplied to the first-type logic gates and the low potential is supplied to the second-type logic gates, the power switch MOS is turned on. Further, in case of the adder, the specific status is equal to selecting a constant as an input of the adder. For general logic circuit, specific flip-flops are introduced to implement this specific status.

Owner:RENESAS ELECTRONICS CORP

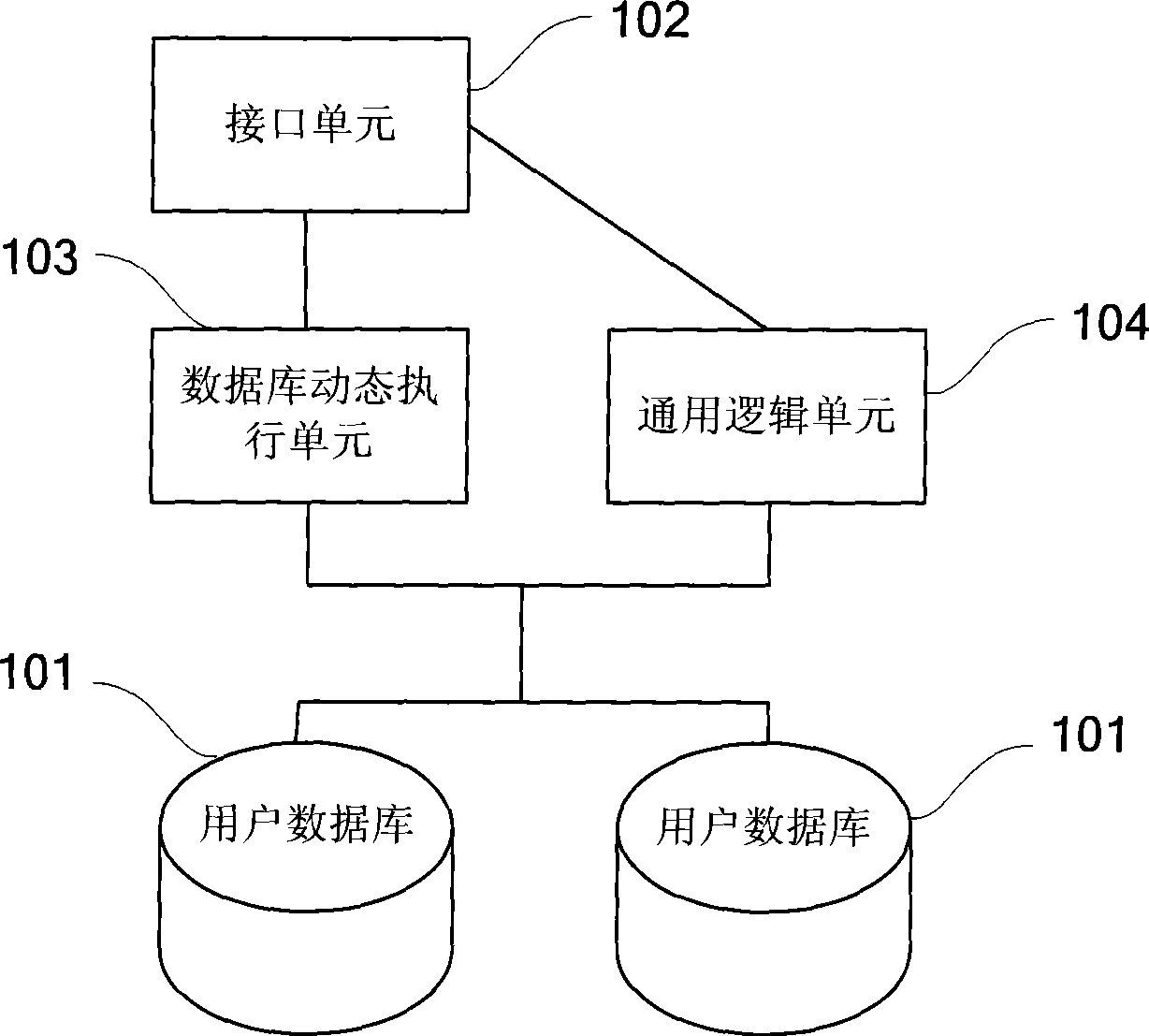

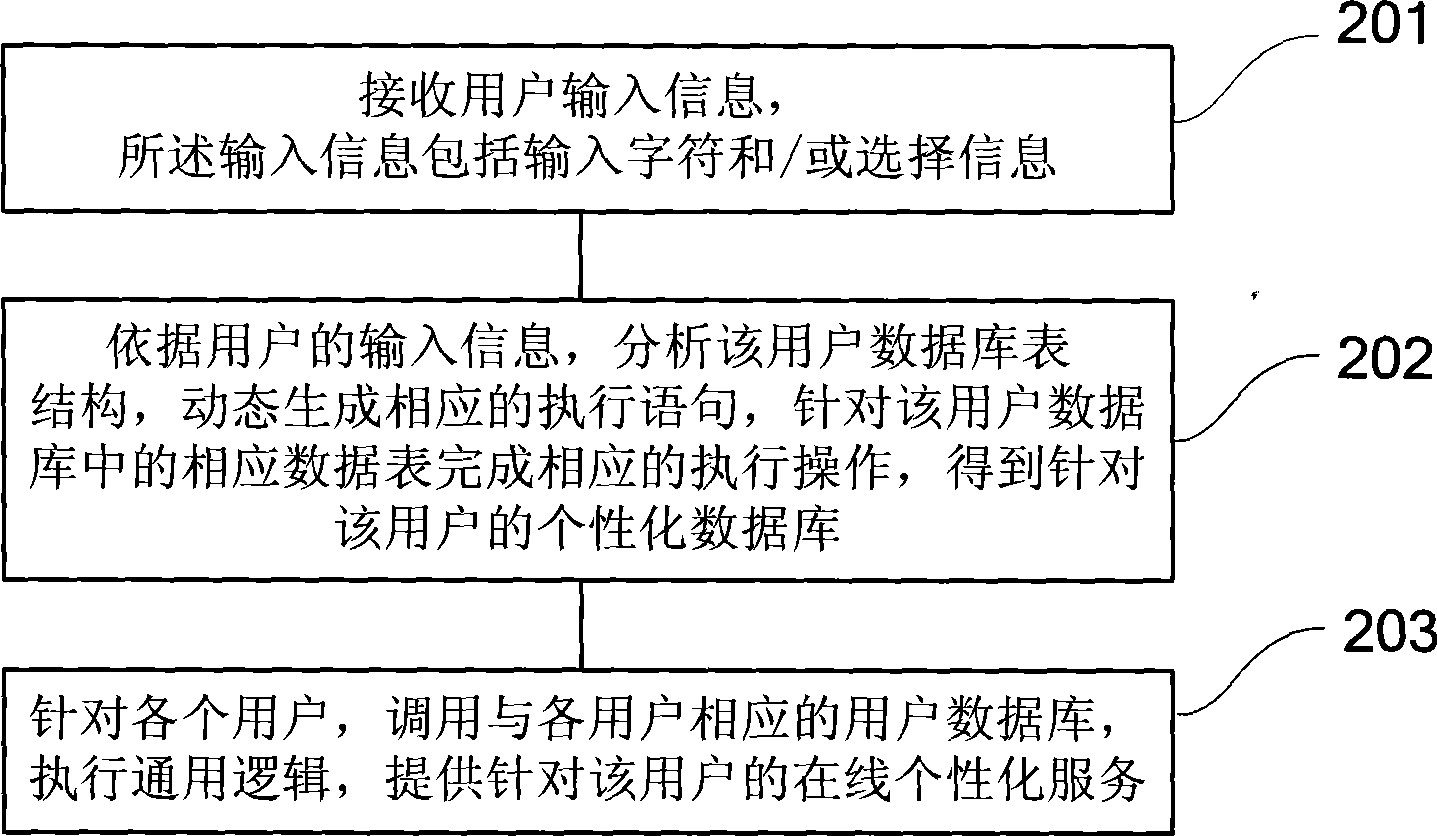

Online service system and method for providing online service

The invention provides an online service system, which comprises at least two user databases, an interface unit, a database dynamic execution unit, and a common logic unit, wherein each user database comprises a system table, a system field table and a service function table; the interface unit is used for receiving input information of a user; the database dynamic execution unit is used for analyzing the table structure of the user database, dynamically generating corresponding execute statements according to the input information of the user, completing corresponding execution operation aiming at a corresponding datasheet in the user database and obtaining an individualized database aiming at the user; and the common logic unit is used for calling corresponding user databases of various users aiming at the users, executing common logic, and providing the online individualized service for the user. The system can quickly adjust the prior product functions or develop new product functions to make a software system fully meet the individualized requirements of different users, and simultaneously can be continuously expanded and improved according to the development of user service to meet the continuously developed informatization requirement of the users.

Owner:BEIJING MINGWAN INTERCONNECTION TECH

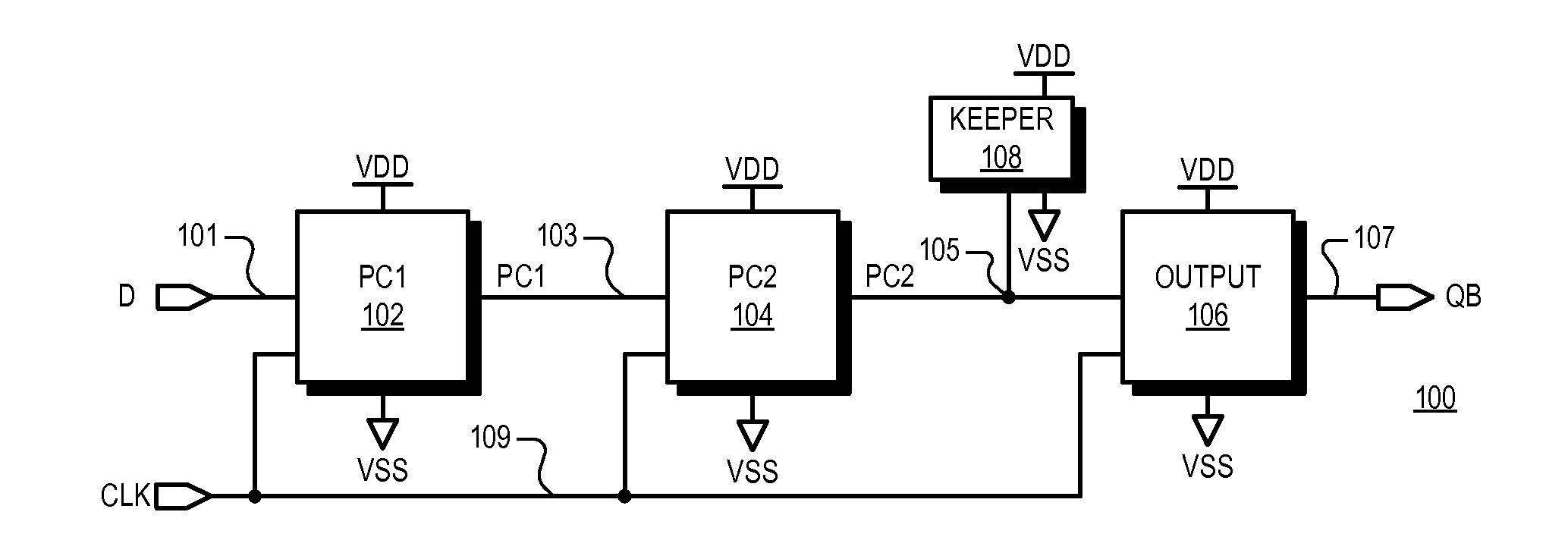

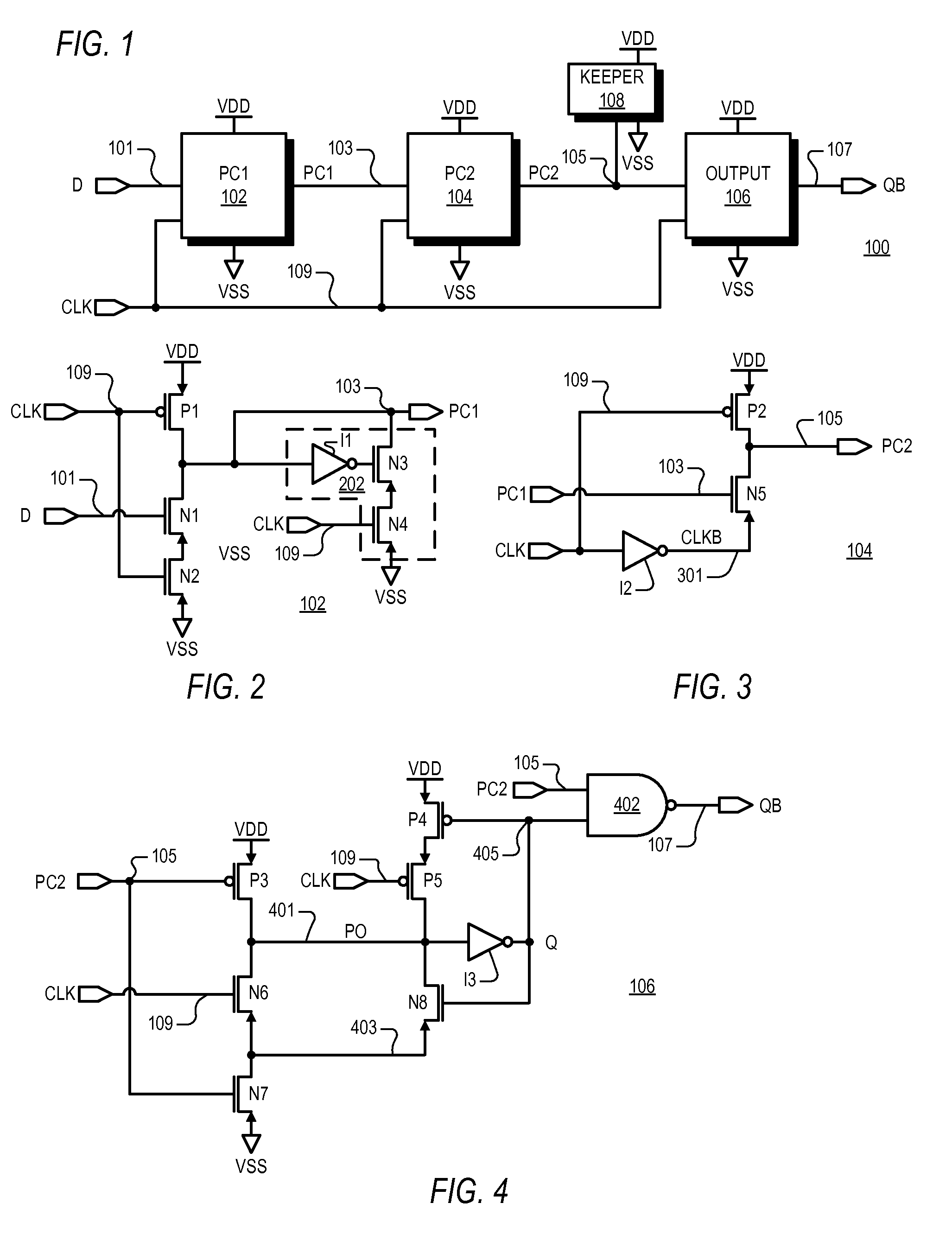

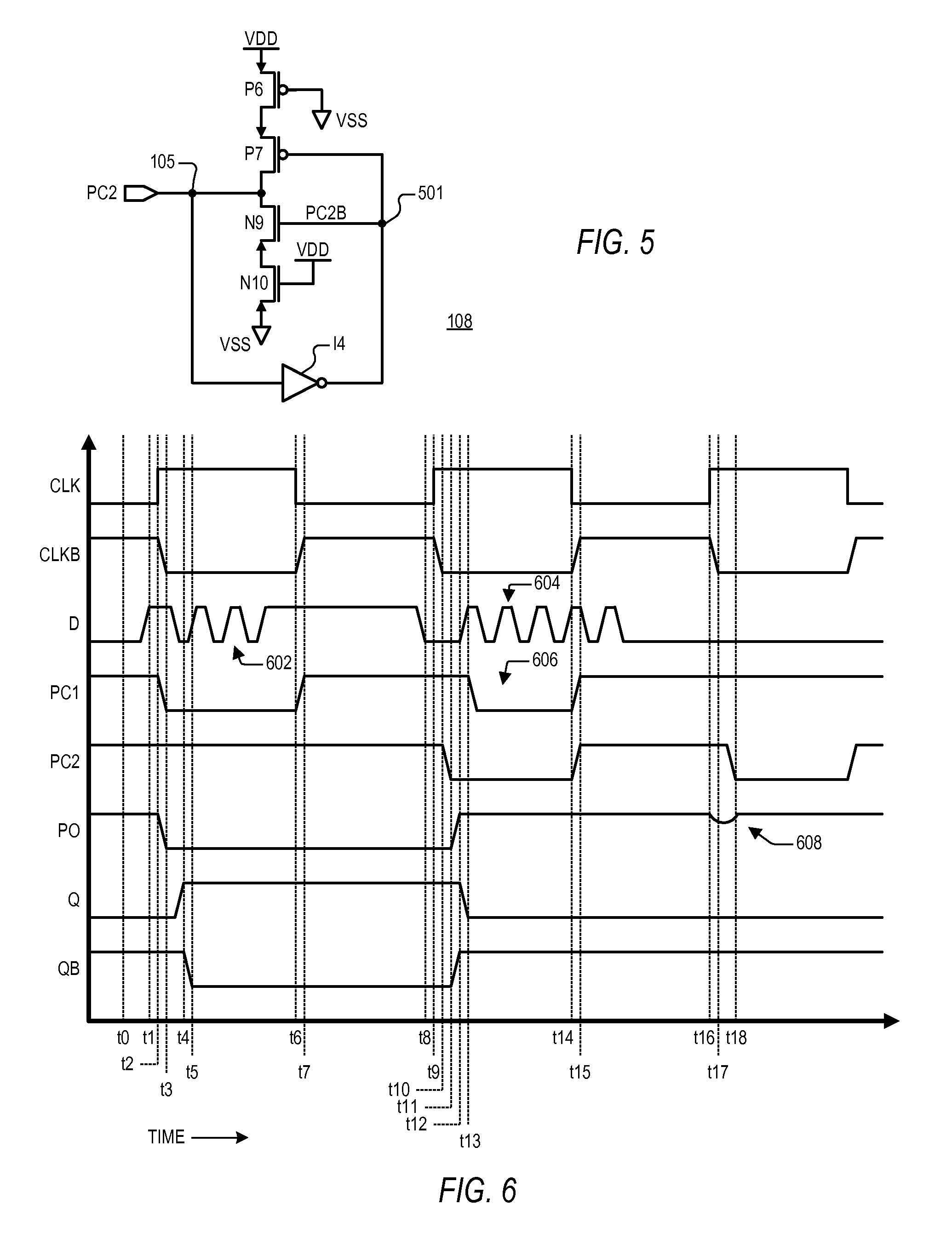

Fast dynamic register

A fast dynamic register circuit including first and second precharge circuits, a keeper circuit and an output circuit. The first and second precharge circuits each precharge a corresponding one of a pair of precharge nodes and cooperate to minimize setup and hold times. If an input data node is low when the clock goes high, the first precharge node remains high causing the second precharge node to be discharged. Otherwise if the input node is high, the first precharge node is discharged and the second remains charged. Once either precharge node is discharged, the output state of the register remains fixed until the next rising clock edge independent of changes of the input data node. The fast dynamic register may be implemented with multiple inputs to perform common logic operations, such as OR, NOR, AND and NAND logic operations.

Owner:VIA TECH INC

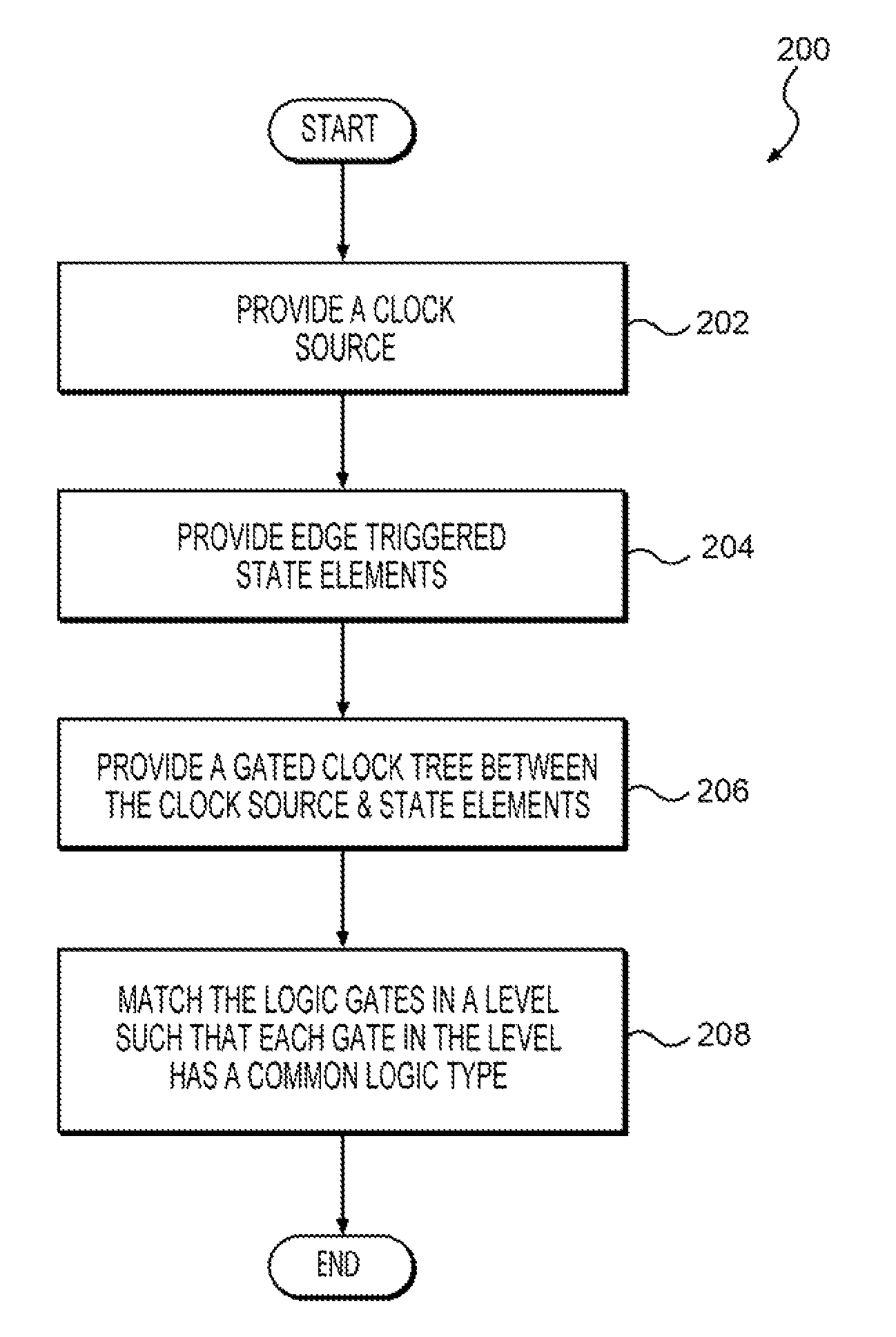

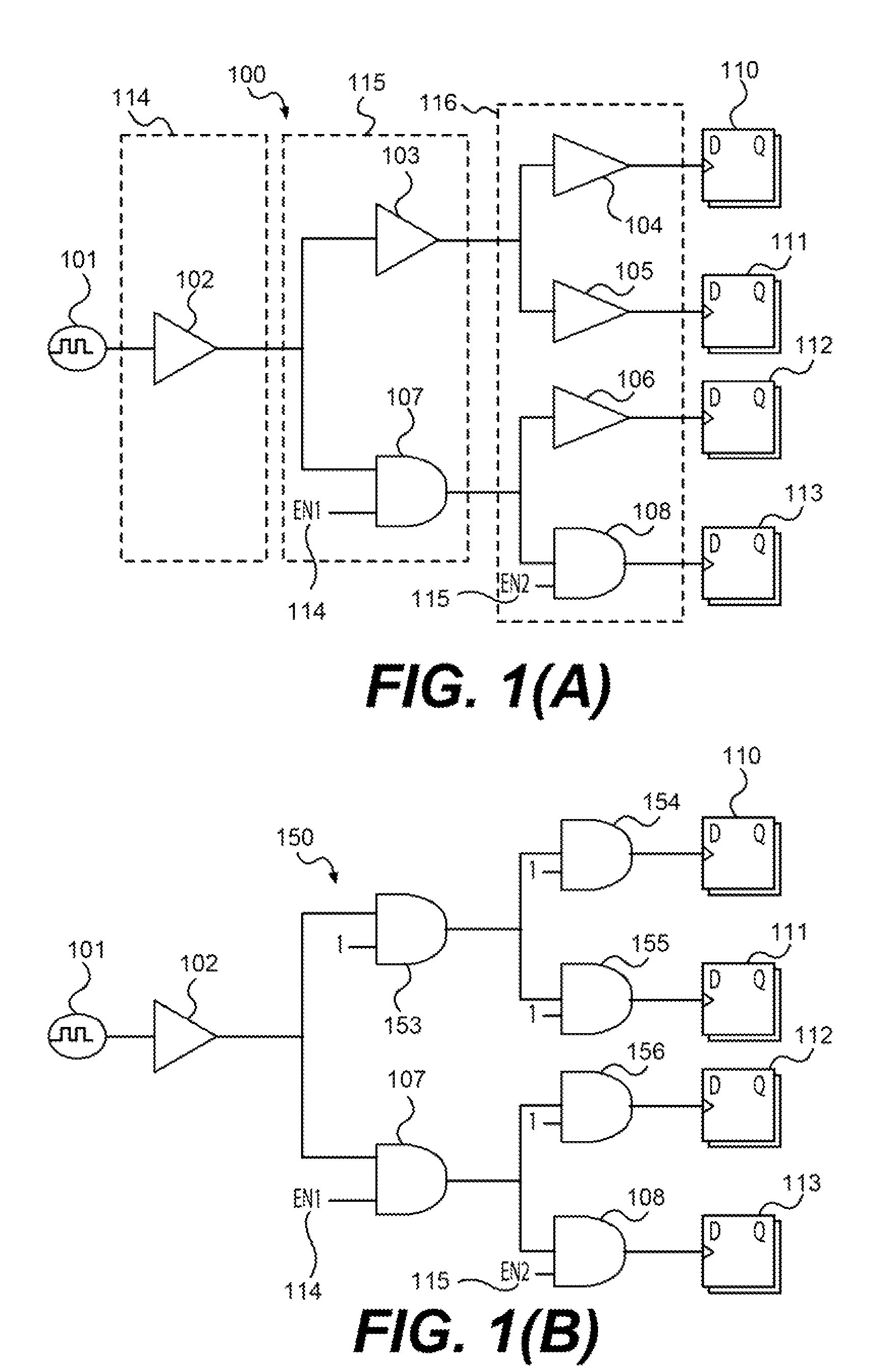

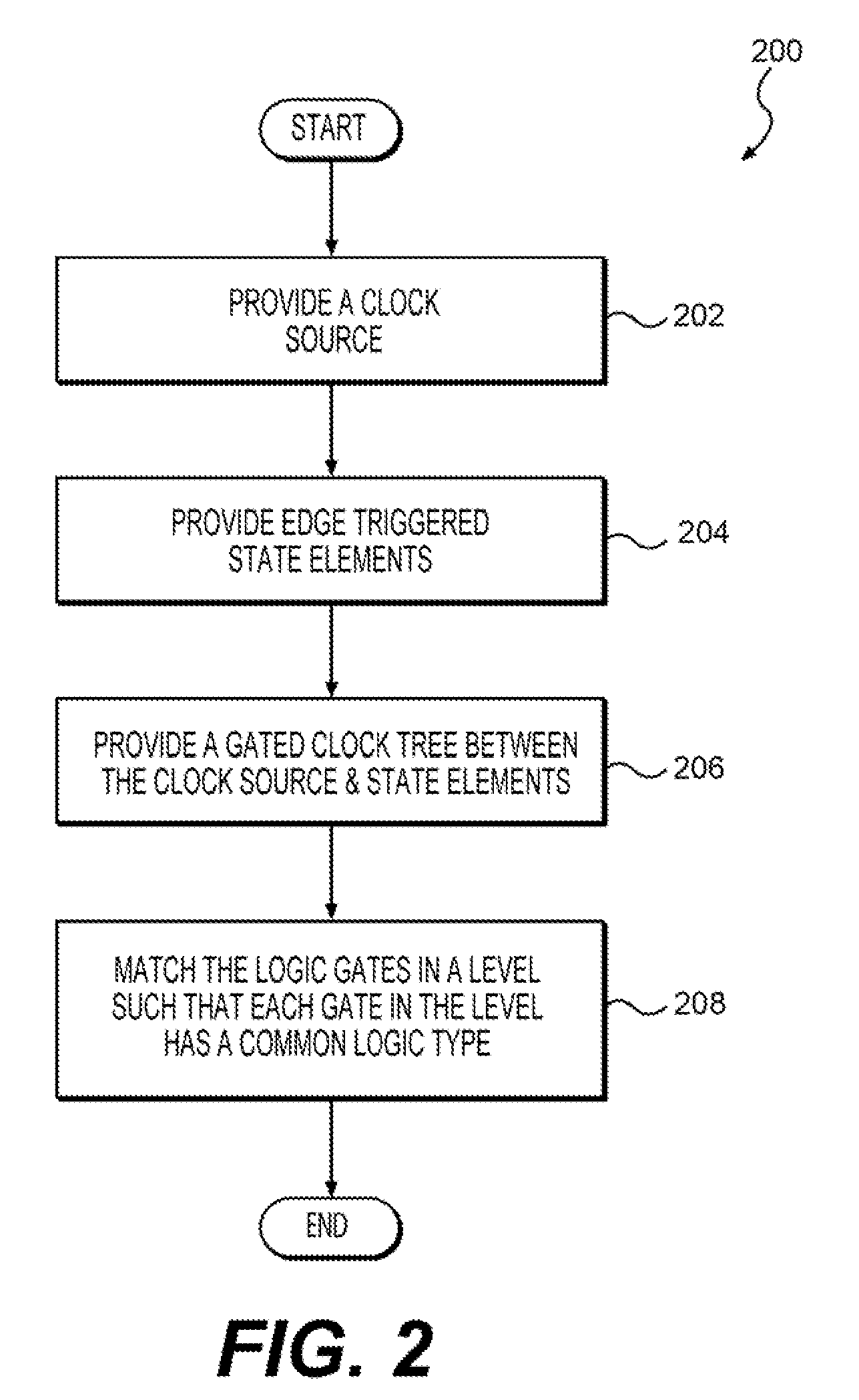

Methods and systems for reducing clock skew in a gated clock tree

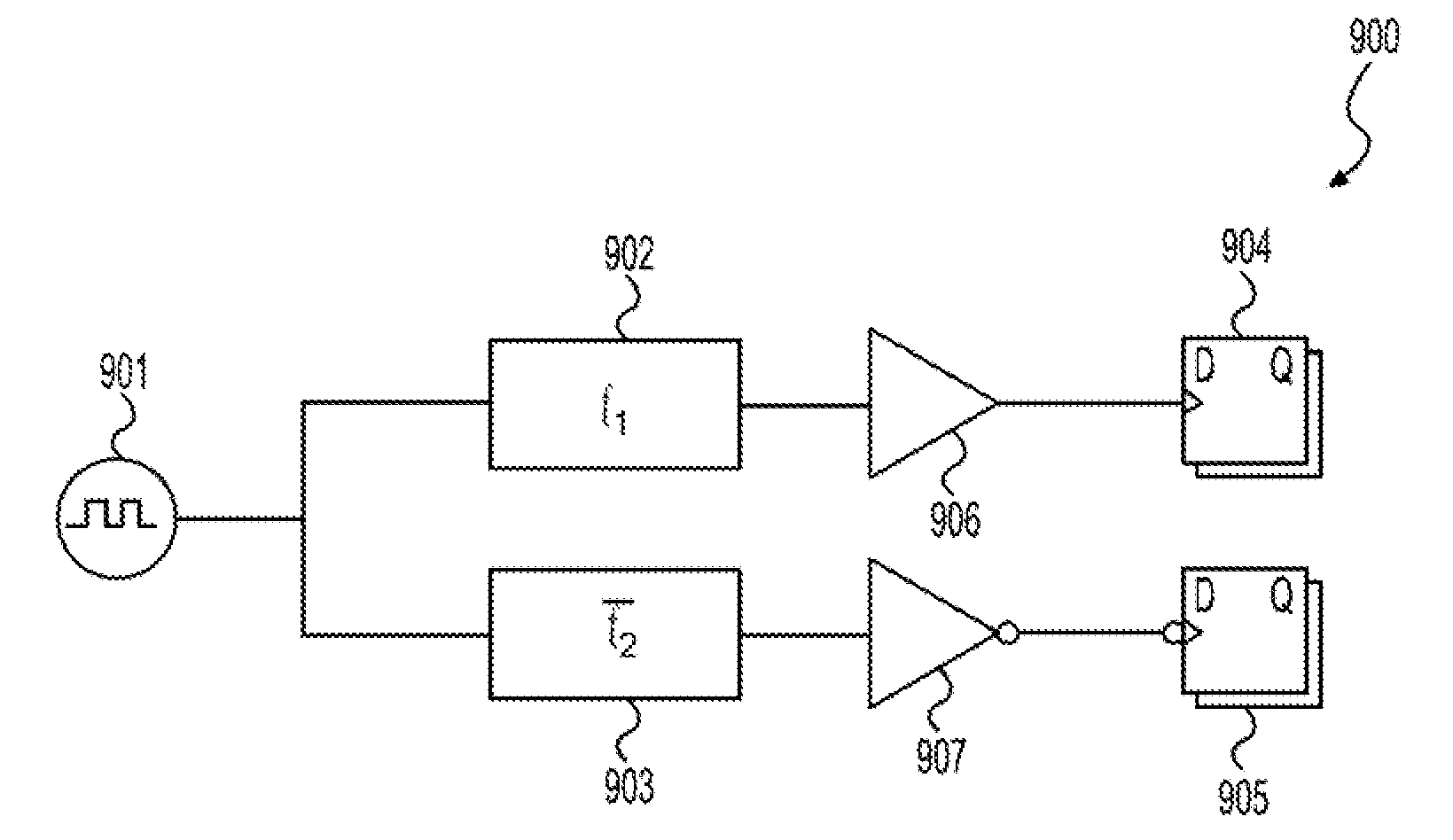

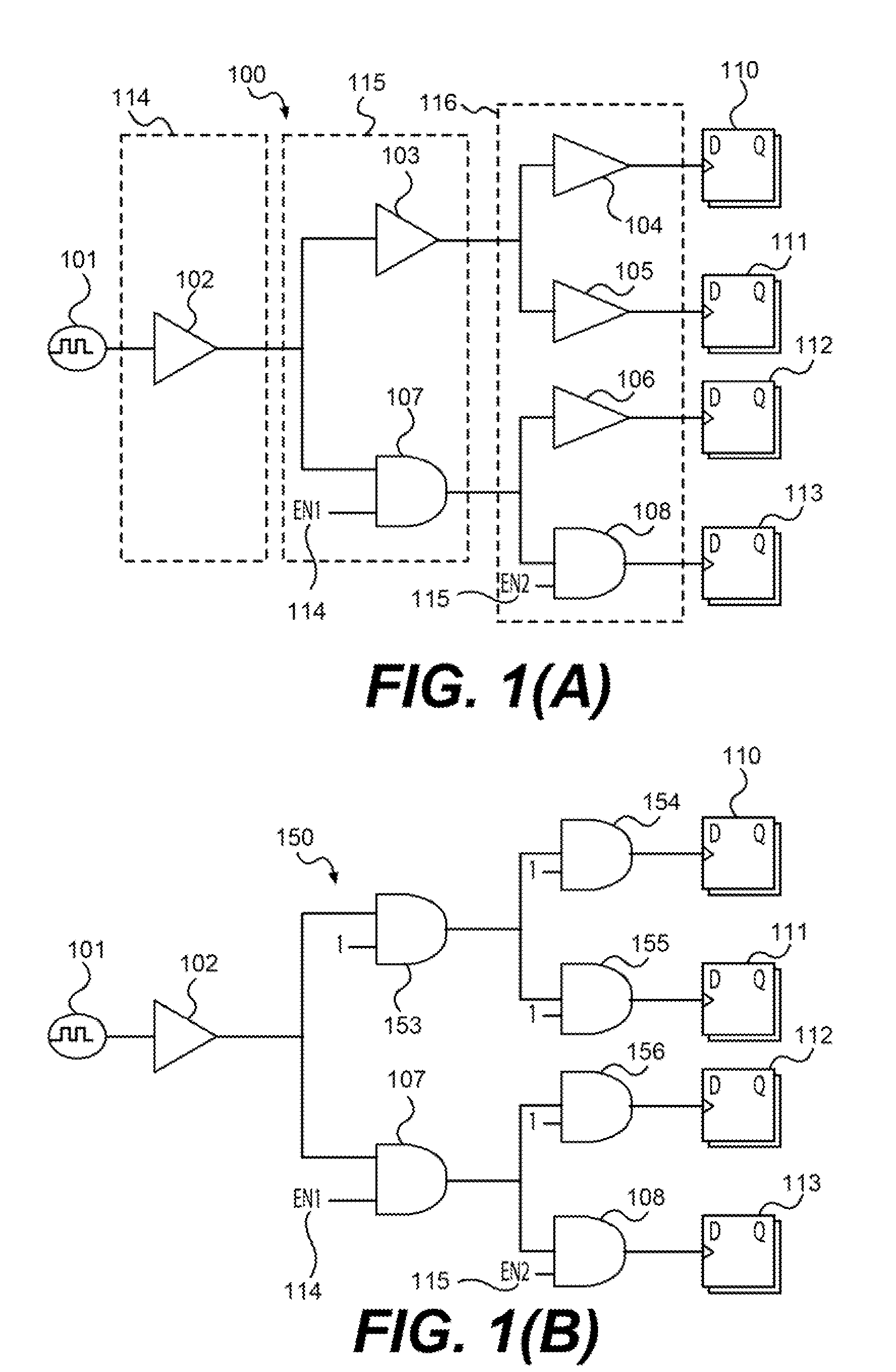

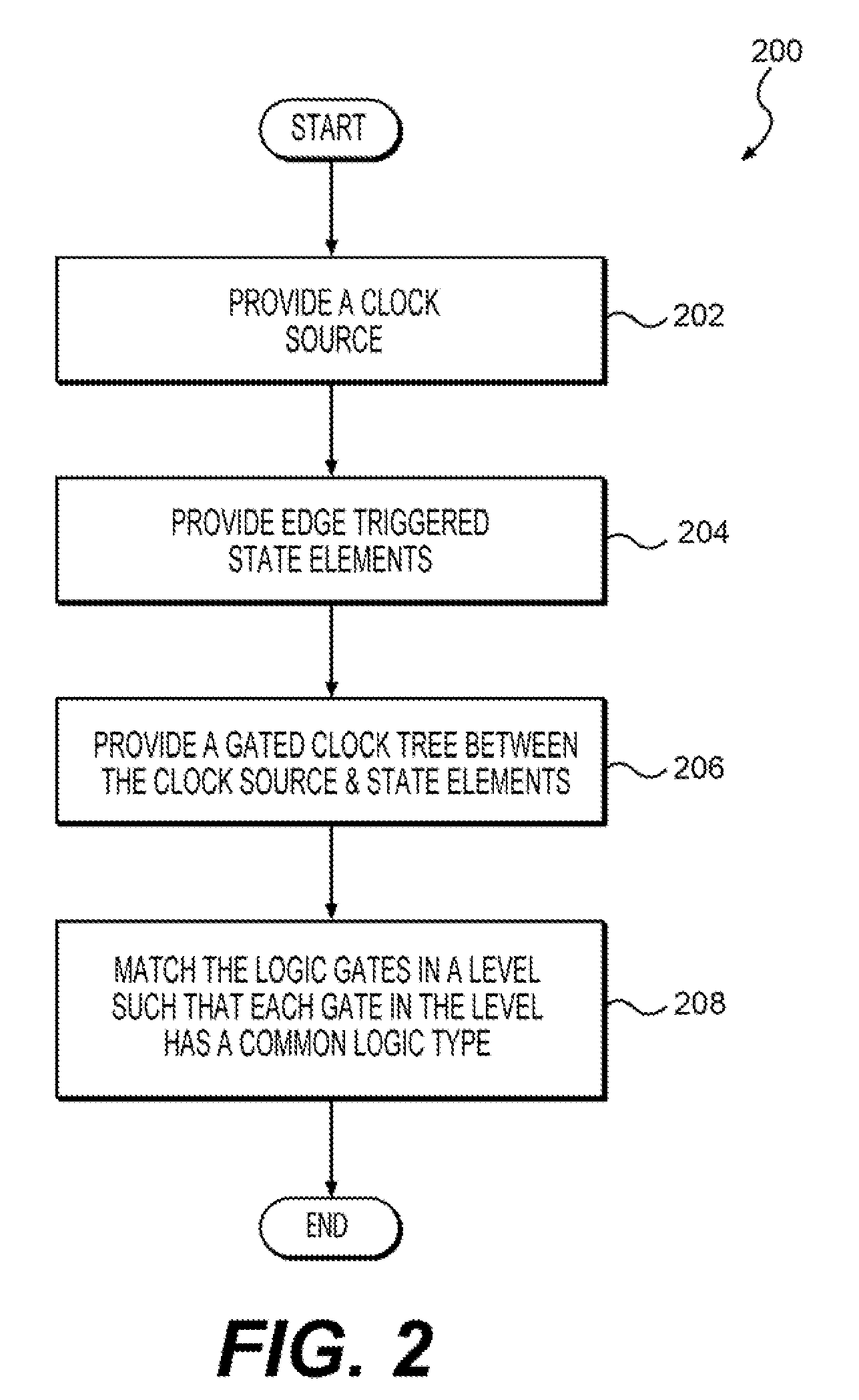

Systems and methods for synthesizing a gated clock tree with reduced clock skew are provided. A gated clock tree circuit with reduced clock skew may include a clock source and edge-triggered state elements. A gated clock tree disposed between the clock source and state elements may include a level in which each logic gate has a common logic type. Logic gates in the gated clock tree may also be configured as logic-gate buffers. The logic gates may also be configured as NAND-gated equivalents. The clock signal distributed through the gated clock tree may drive both positive-edge-triggered and negative-edge-triggered state elements.

Owner:SYNOPSYS INC

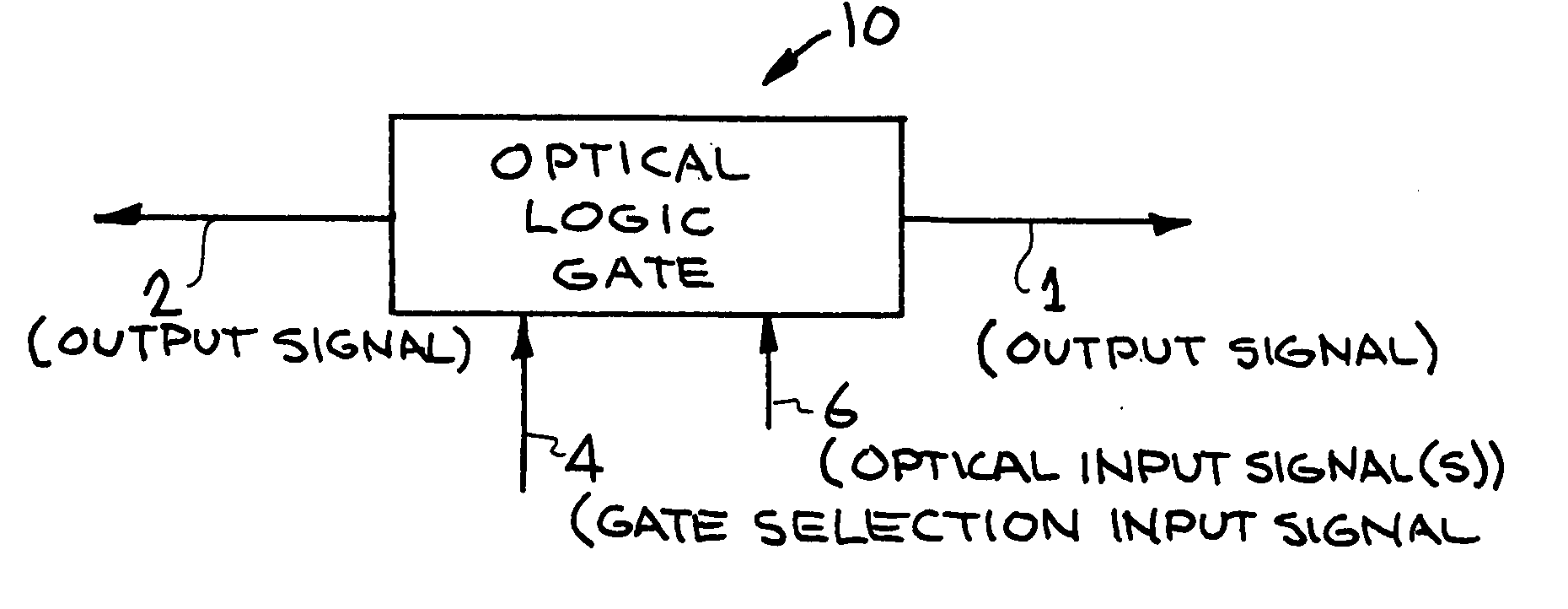

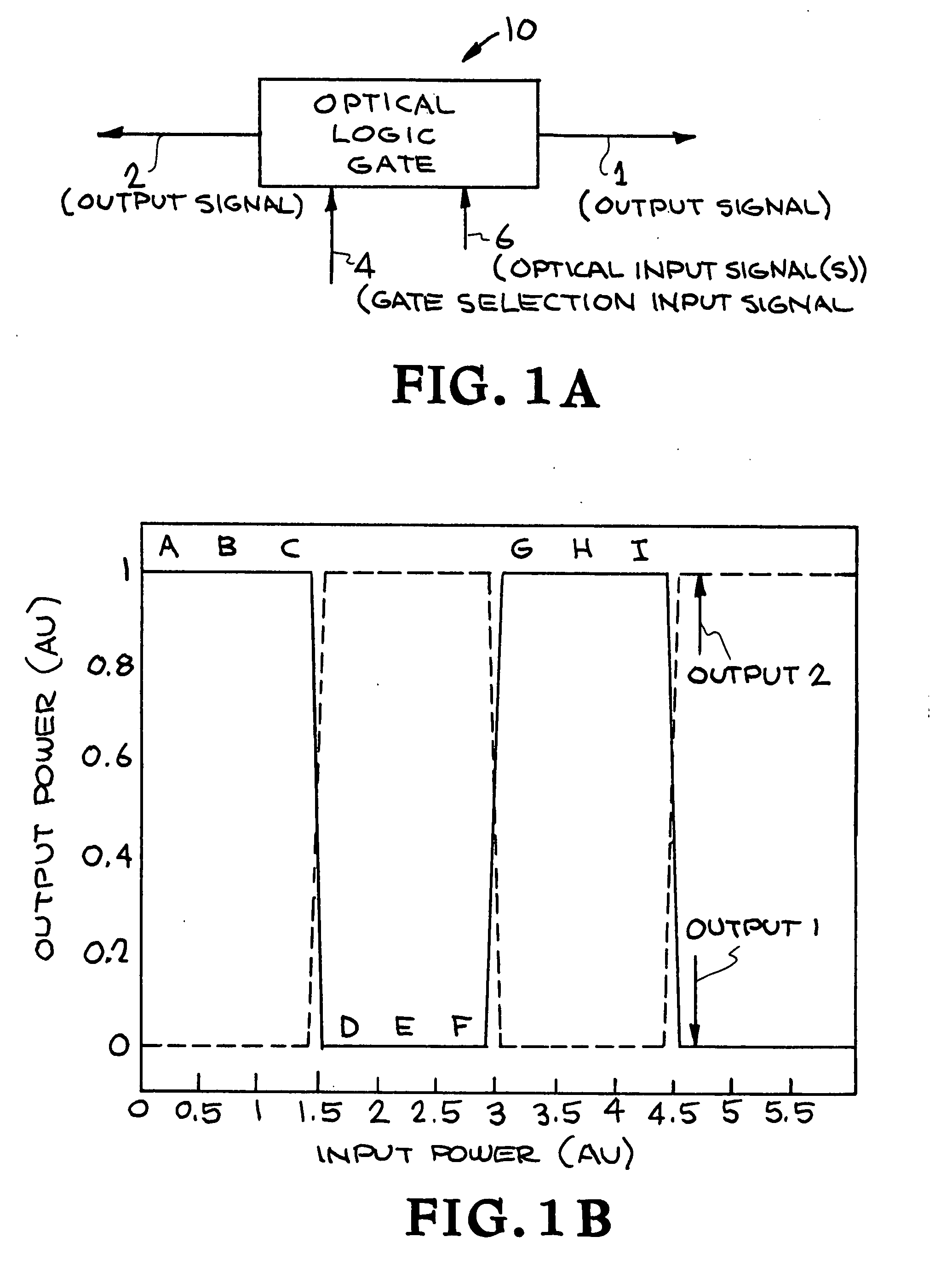

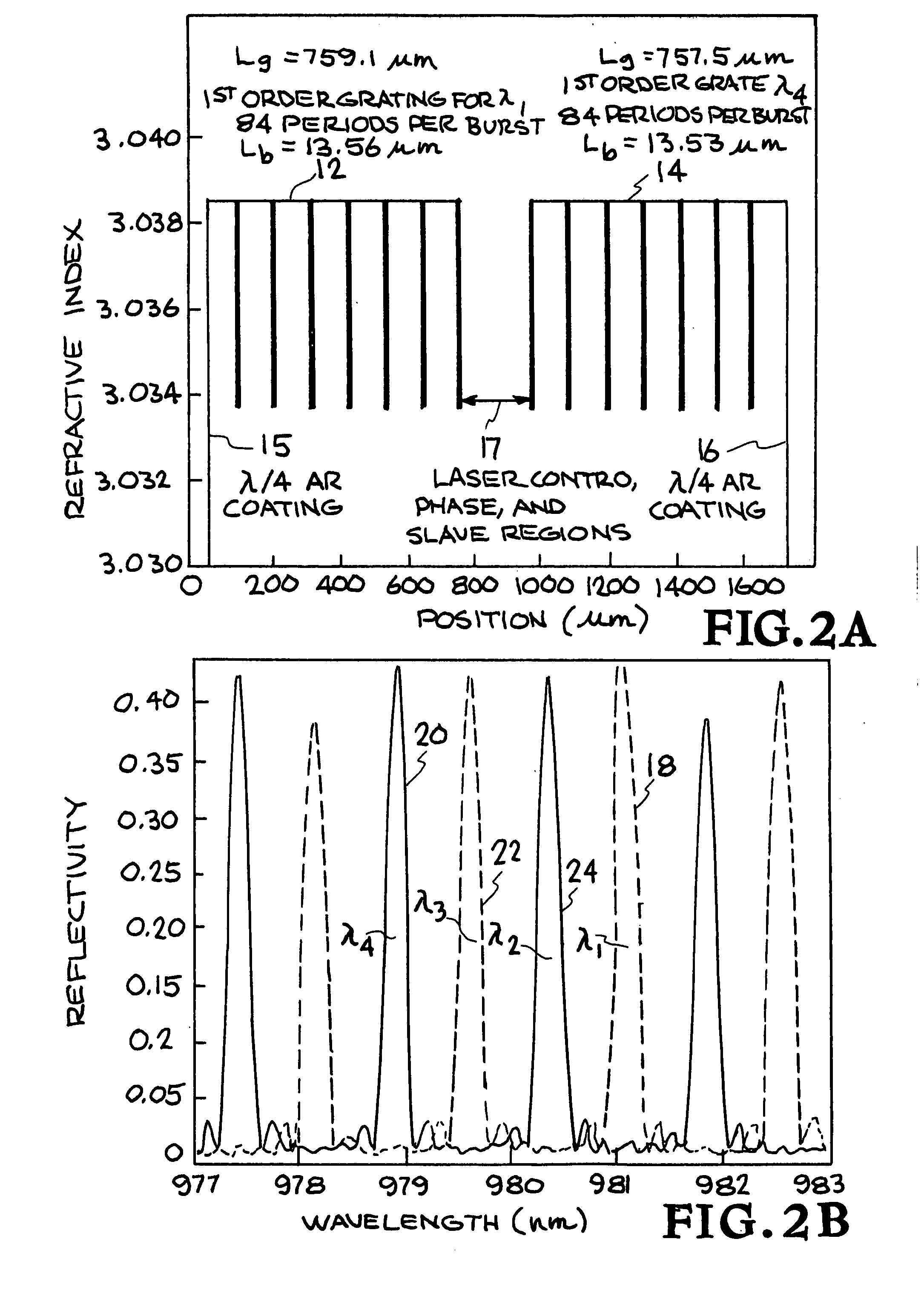

Rapidly reconfigurable all-optical universal logic gate

InactiveUS20080130084A1Logic circuits using opto-electronic devicesOptical bistable devicesJoystickLaser light

A new reconfigurable cascadable all-optical on-chip device is presented. The gate operates by combining the Vernier effect with a novel effect, the gain-index lever, to help shift the dominant lasing mode from a mode where the laser light is output at one facet to a mode where it is output at the other facet. Since the laser remains above threshold, the speed of the gate for logic operations as well as for reprogramming the function of the gate is primarily limited to the small signal optical modulation speed of the laser, which can be on the order of up to about tens of GHz. The gate can be rapidly and repeatedly reprogrammed to perform any of the basic digital logic operations by using an appropriate analog optical or electrical signal at the gate selection port. Other all-optical functionality includes wavelength conversion, signal duplication, threshold switching, analog to digital conversion, digital to analog conversion, signal routing, and environment sensing. Since each gate can perform different operations, the functionality of such a cascaded circuit grows exponentially.

Owner:LAWRENCE LIVERMORE NAT SECURITY LLC +1

Motor controlling apparatus

InactiveUS8228008B2Low costReduce the total massElectronic commutation motor controlMotor/generator/converter stoppersPower inverterControl signal

A motor controlling apparatus having a controller for controlling a plurality of inverters correspondingly provided to each of a plurality of alternating-current motors is reduced in size, mass, and cost by effectively grouping operations performed by each calculation unit included in the controller. This controller for controlling the inverters includes: a first common calculation unit and a second common calculation unit that calculate and output control signals that are common to each of the inverters; individual calculation units that individually calculate and output a control signal related to each of the inverters; and a common logic calculation unit 60 that outputs a gate signal for controlling switching of each of the inverters based on the signals received from the first common calculation unit, the second common calculation unit, and the individual calculation units.

Owner:NEXGEN CONTROL SYST LLC

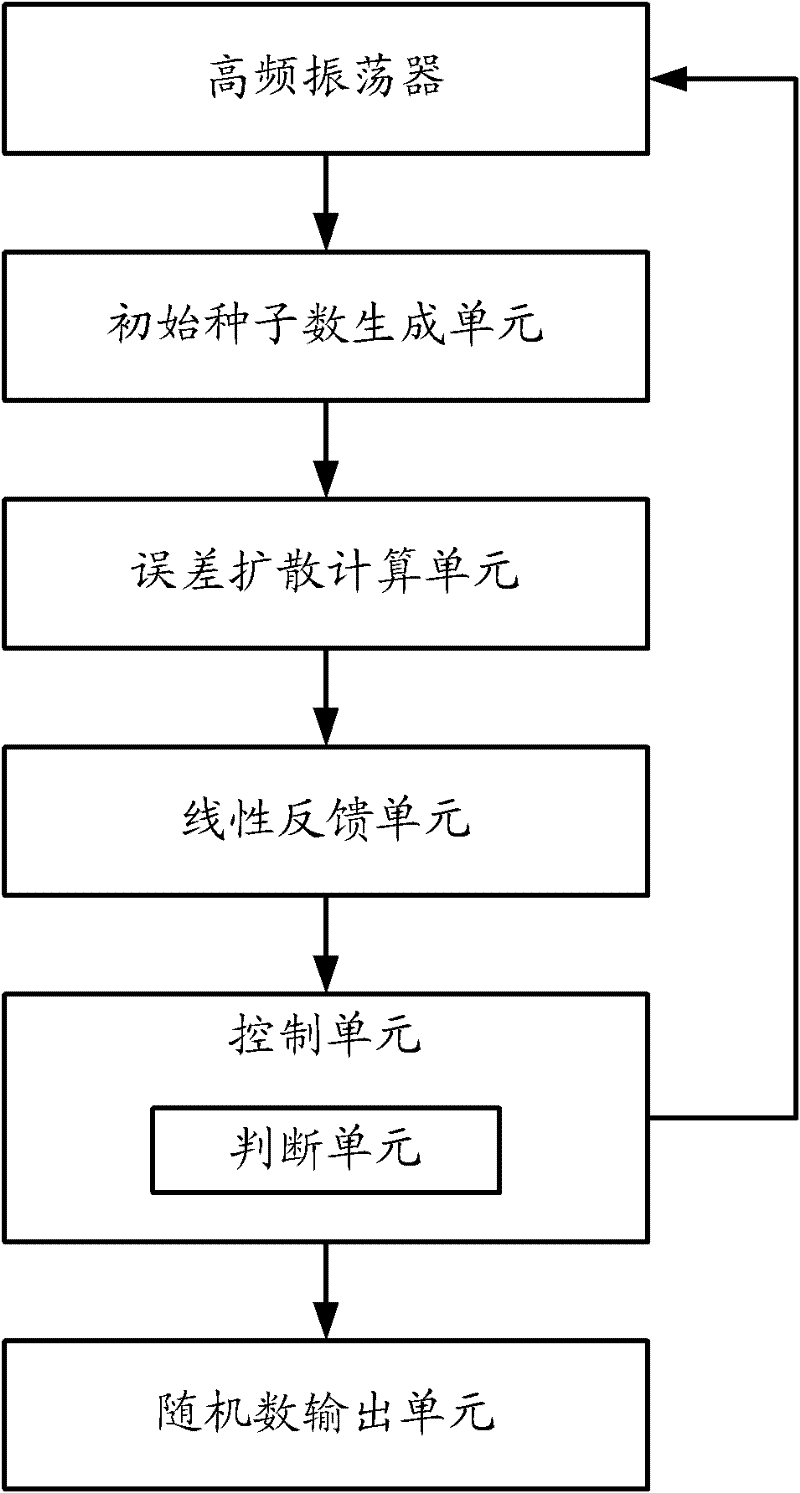

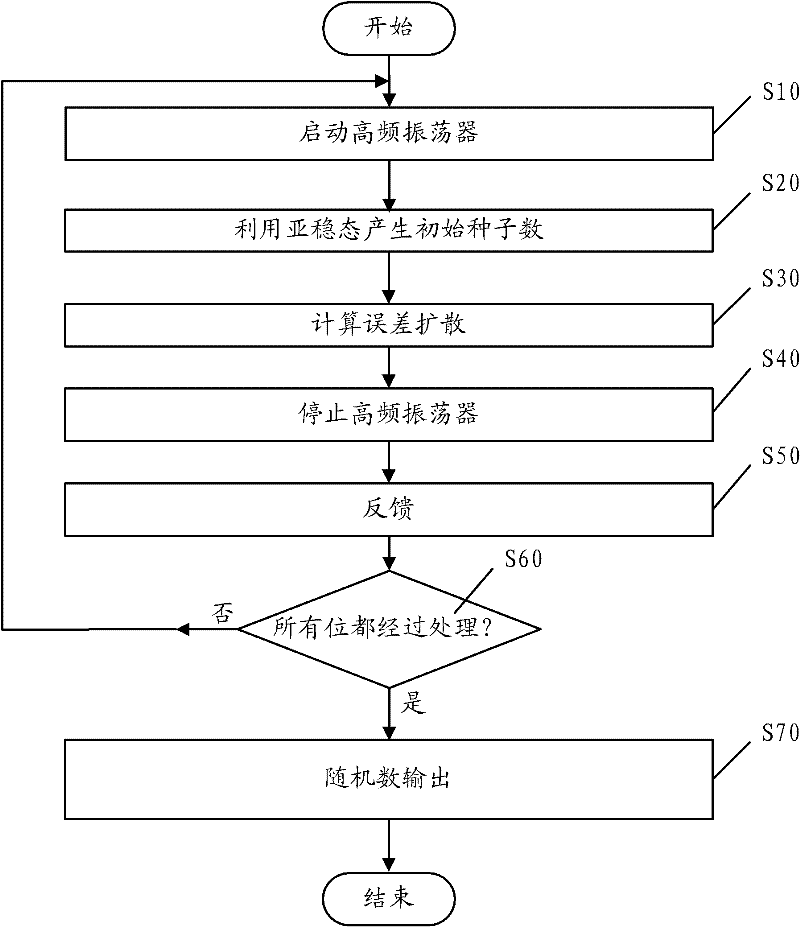

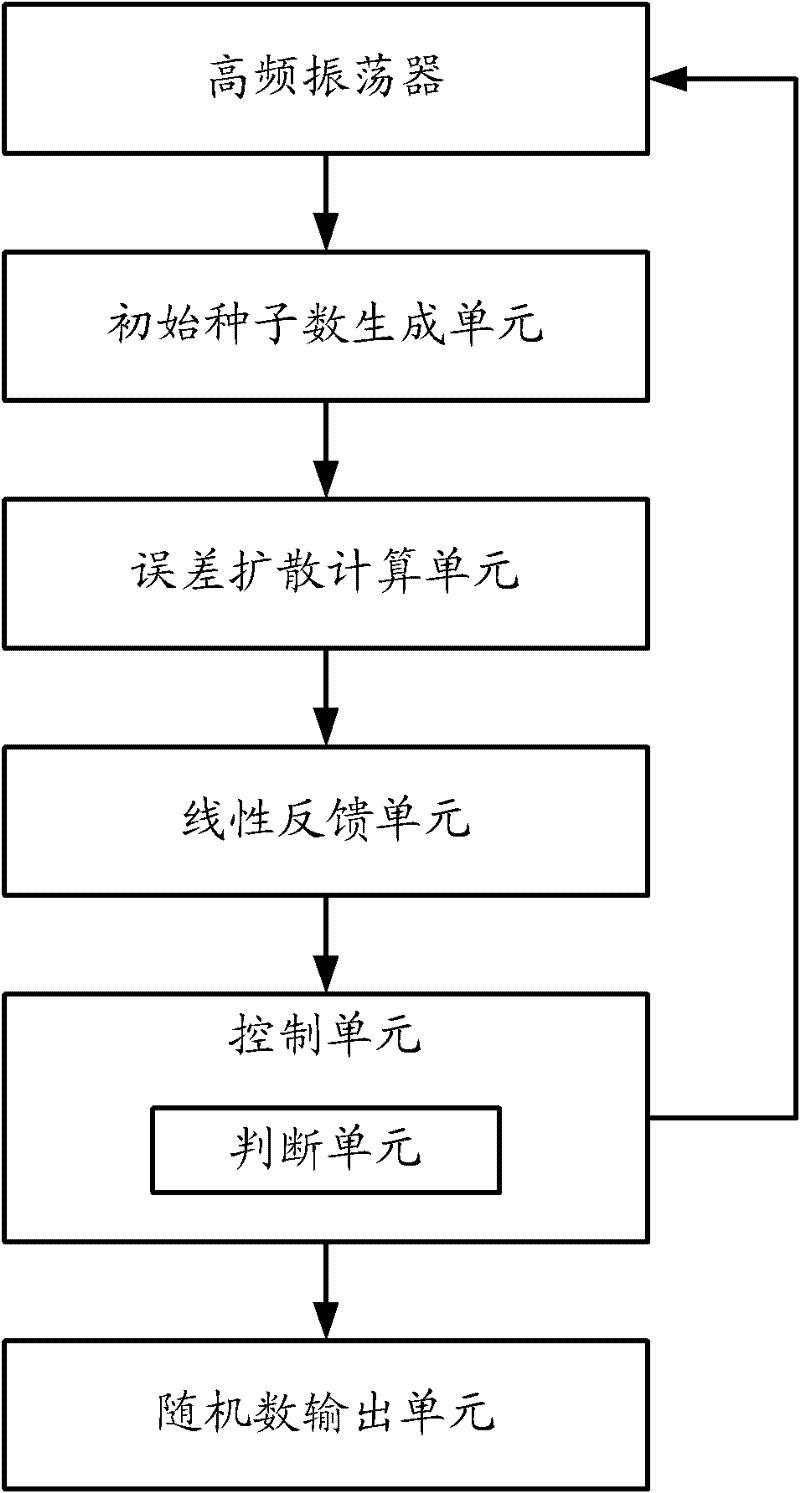

Method and device for generating true random number

InactiveCN102479067AImplement one-time padSimple structureRandom number generatorsHardware structureError diffusion

Owner:上海宇芯科技有限公司

Apparatus and method for performing static timing analysis of an integrated circuit design

InactiveUS20050183051A1Reduce workloadExcessive pessimismComputer aided designSoftware simulation/interpretation/emulationStatic timing analysisComputer architecture

An apparatus and method perform static timing analysis on an integrated circuit design. Certain pessimistic assumptions regarding slack when data launch and clock test signals are on opposite edges and derived from common logic blocks are improved by allowing the designer to identify common logic blocks, to compute the difference between maximum and minimum delays in the common logic blocks, and to improve the slack using this computed difference and a correction factor, thereby accounting for excessive pessimism in the static timing analysis that results from the common logic blocks. The apparatus and method give credit for slack in common blocks automatically, thereby allowing a large number of pessimistic slack values to be automatically corrected and reducing the workload of an integrated circuit designer in addressing the timing problems in an integrated circuit design.

Owner:GOOGLE LLC

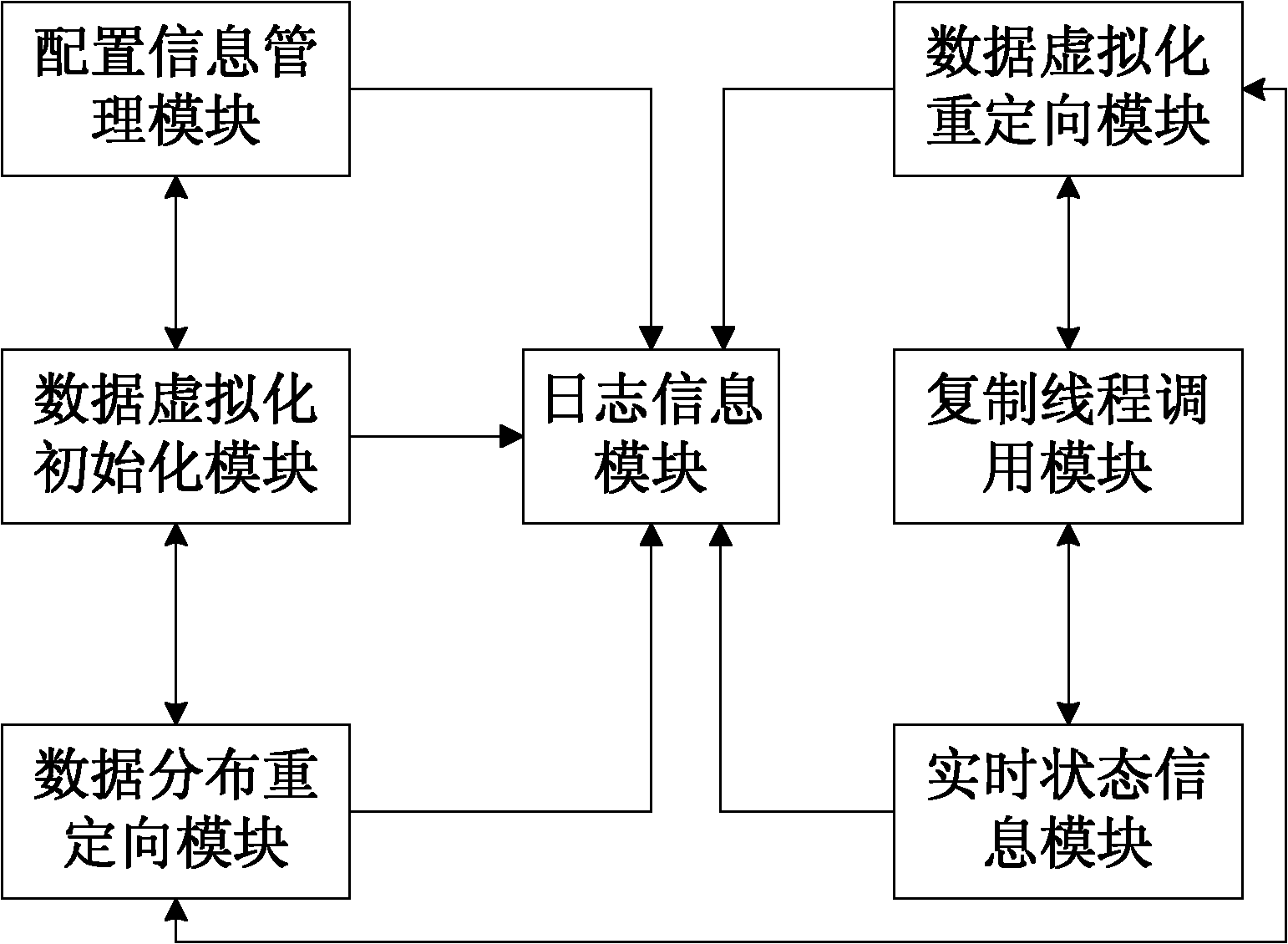

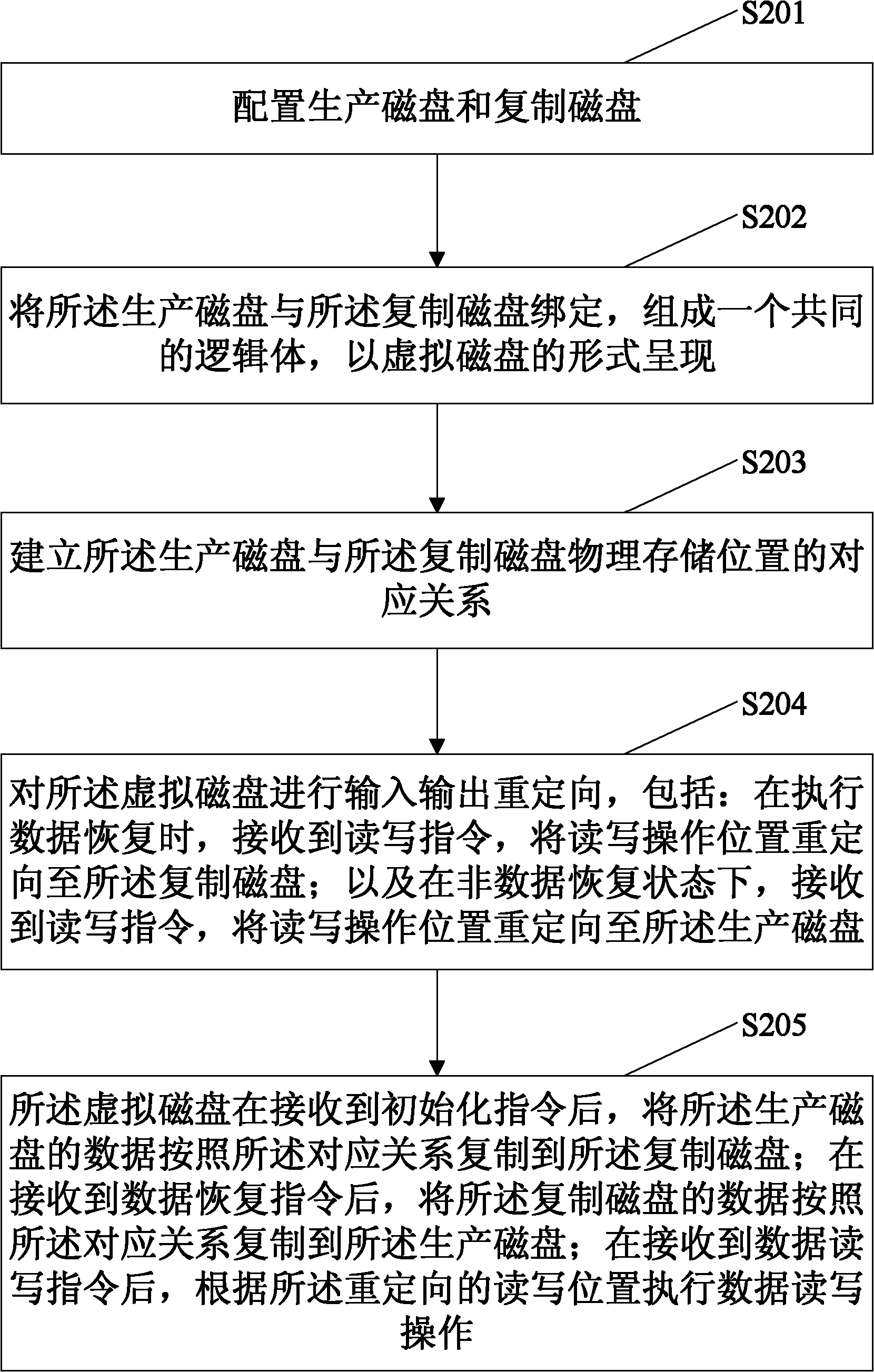

Virtualization-based remote data recovery method and device

InactiveCN102033792AImprove efficiencyImprove securityInput/output to record carriersRedundant operation error correctionVirtualizationCommon logic

The invention provides a virtualization-based remote data recovery method and a virtualization-based remote data recovery device. The method comprises the following steps of: configuring a production disk and a copy disk; binding the production disk with the copy disk so as to form a common logic body and presenting the logic body in the form of a virtual disk; establishing the corresponding relation between the production disk and the physical memory position of the copy disk; redirecting the input and output of the virtual disk; after the virtual disk receives an initialization command, copying data of the production disk onto the copy disk according to the corresponding relation; after a data recovery command is received, copying data of the copy disk onto the production disk according to the corresponding relation; and after a data read-write command is received, performing data read-write operation according to a redirected read-write position. In the method, data can be used normally in a data recovery process and data security can be ensured.

Owner:INSPUR BEIJING ELECTRONICS INFORMATION IND

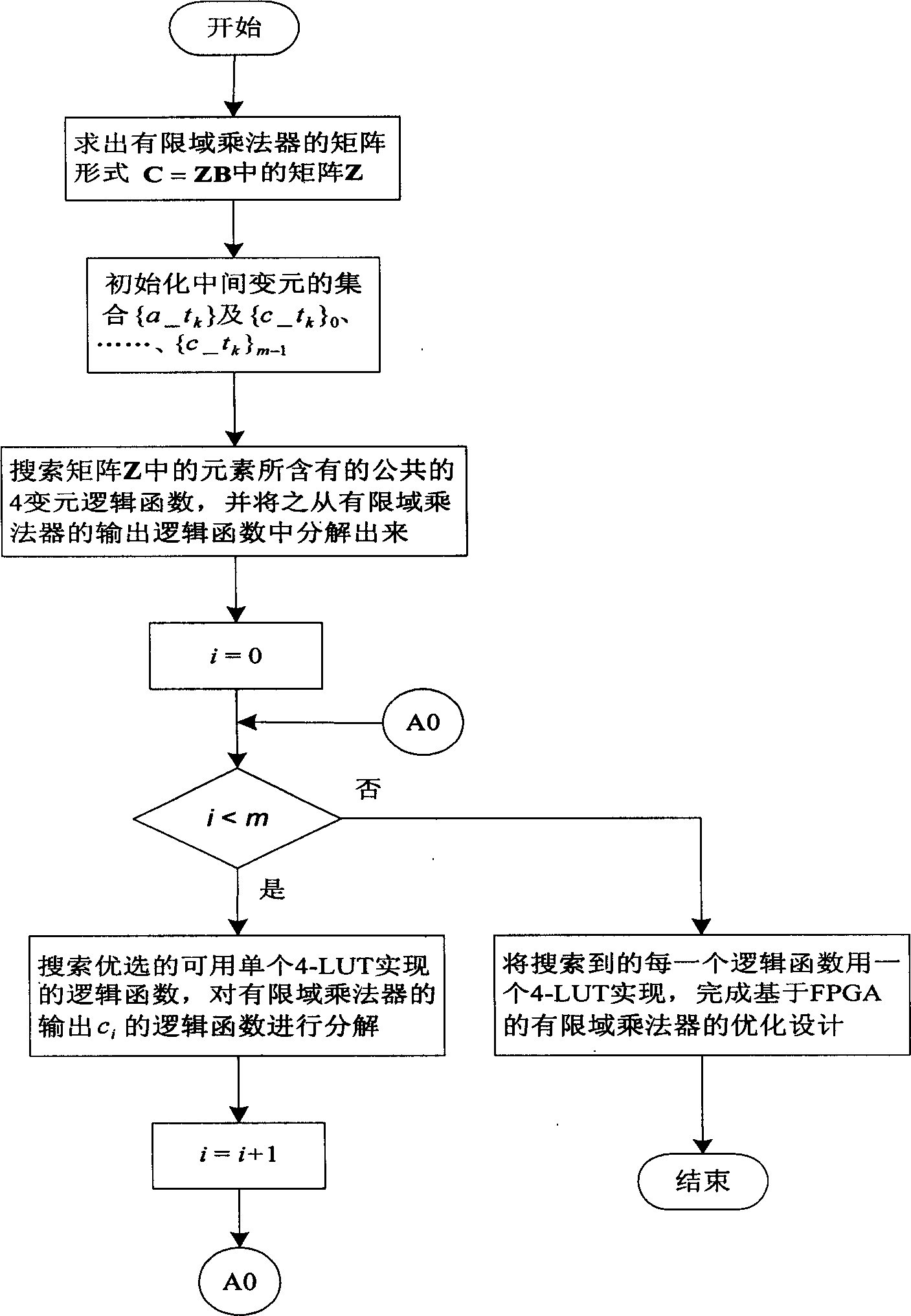

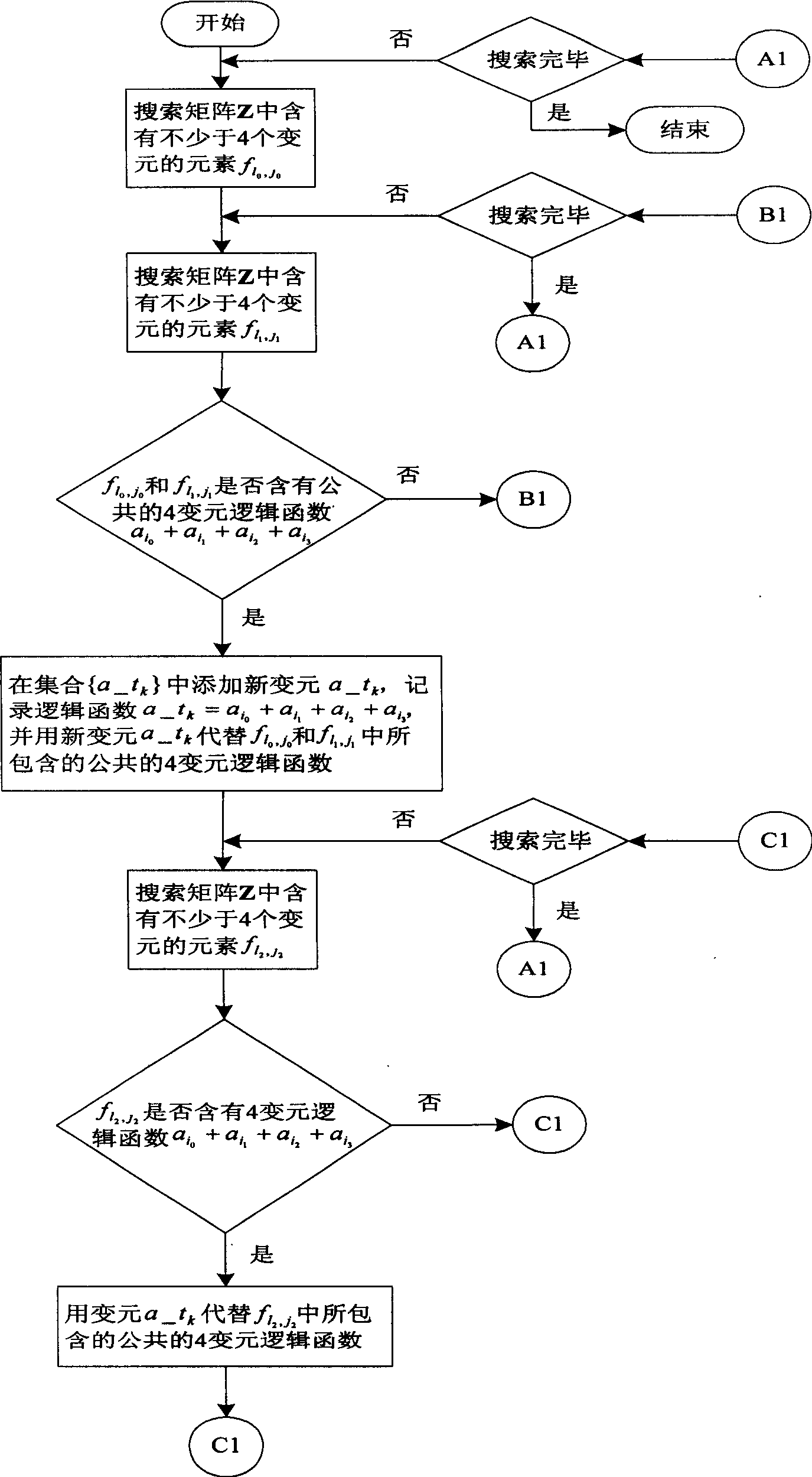

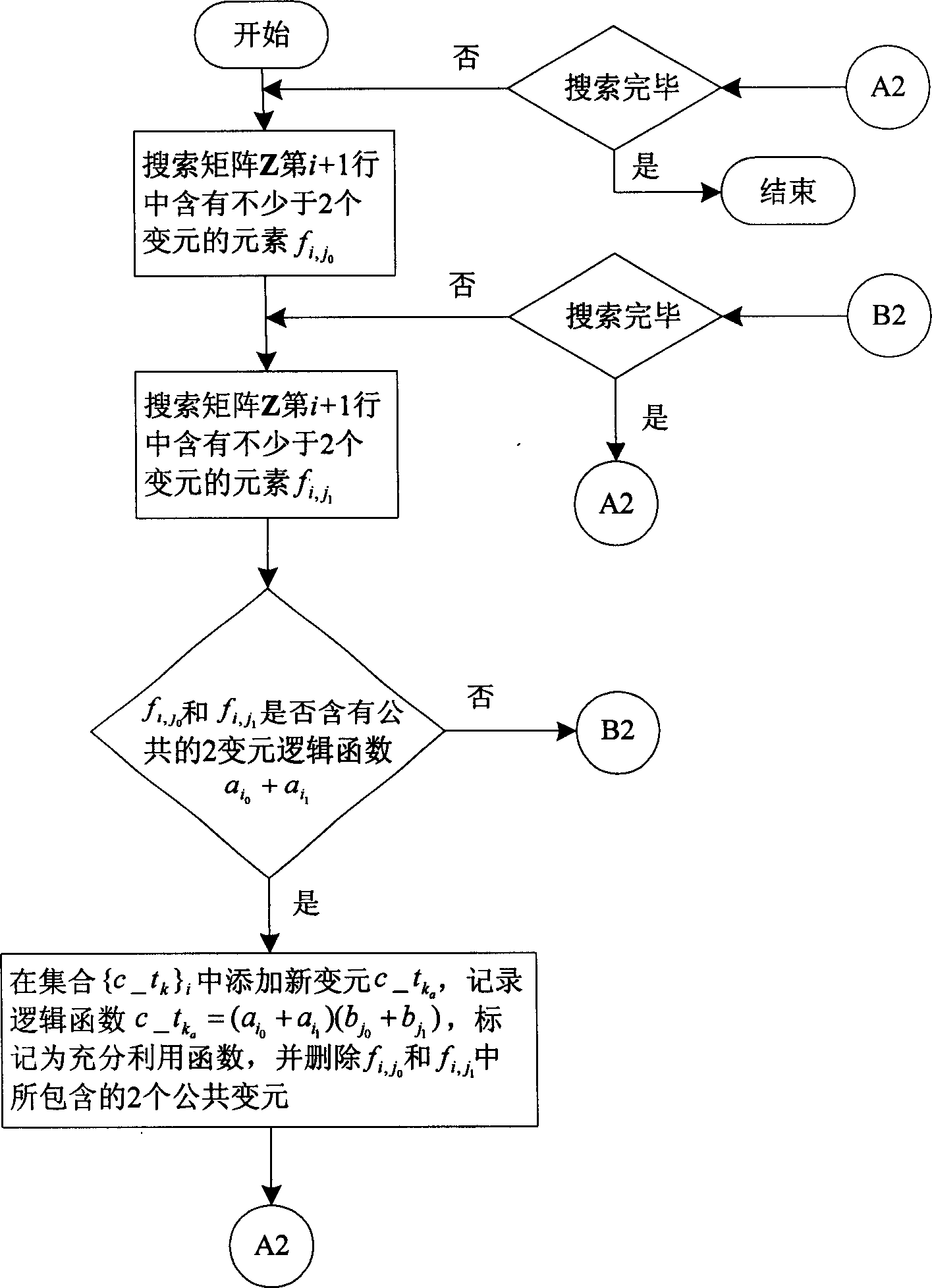

Optimization design method based on FPGA finite field multipier

InactiveCN1658200AShorten the lengthReduce resource usageSpecial data processing applicationsTheoretical computer scienceCritical path method

This invention discloses a optimum design method for the finite field multiplier on the base of FPGA. This invention defines those logic functions which can be realized with a single 4-LUT into 7 styles, and it will follow some steps to realize the optimization for the finite field multiplier. Firstly, it figures out the matrix form of the finite field multiplier according to the generator polynomial and initialize the integration of middle variables. Secondly, it will repeatedly search for the common logic functions in the elements in the Matrix Z, bringing in a new middle variable, and it will use this new middle variable to represent the output variable of those logic functions, modifying the Matrix Z. Finally, it will find out preferred logic functions that can be realized by a single 4-LUT. Then those logic functions will be decomposed into a series of logic functions that can be realized by a single 4-LUT, and Matrix Z and the integration of middle variables will be modified. After all above, we finally get a optimized finite field multiplier on the base of FPGA. The advantages are short key route and time delay.

Owner:XIDIAN UNIV

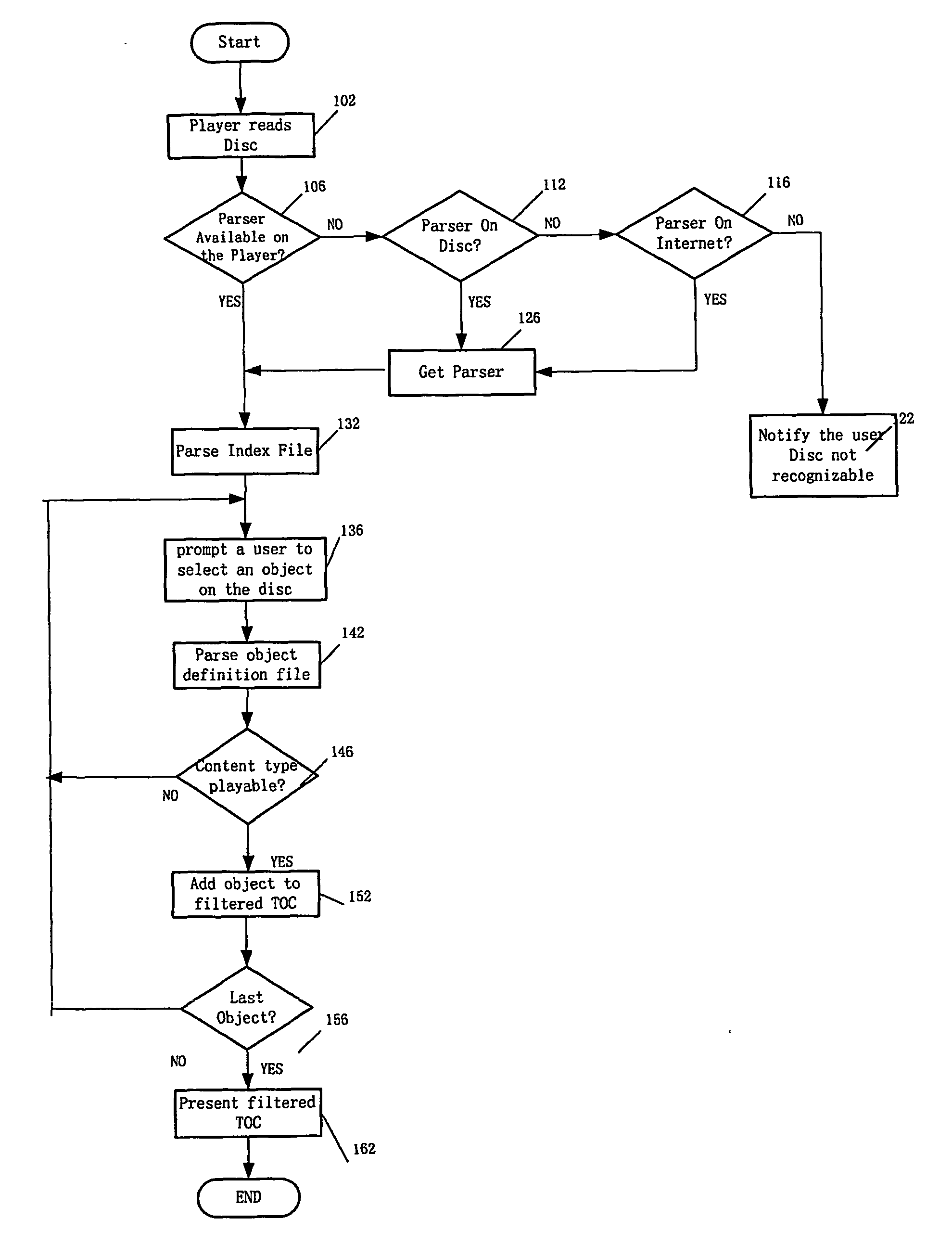

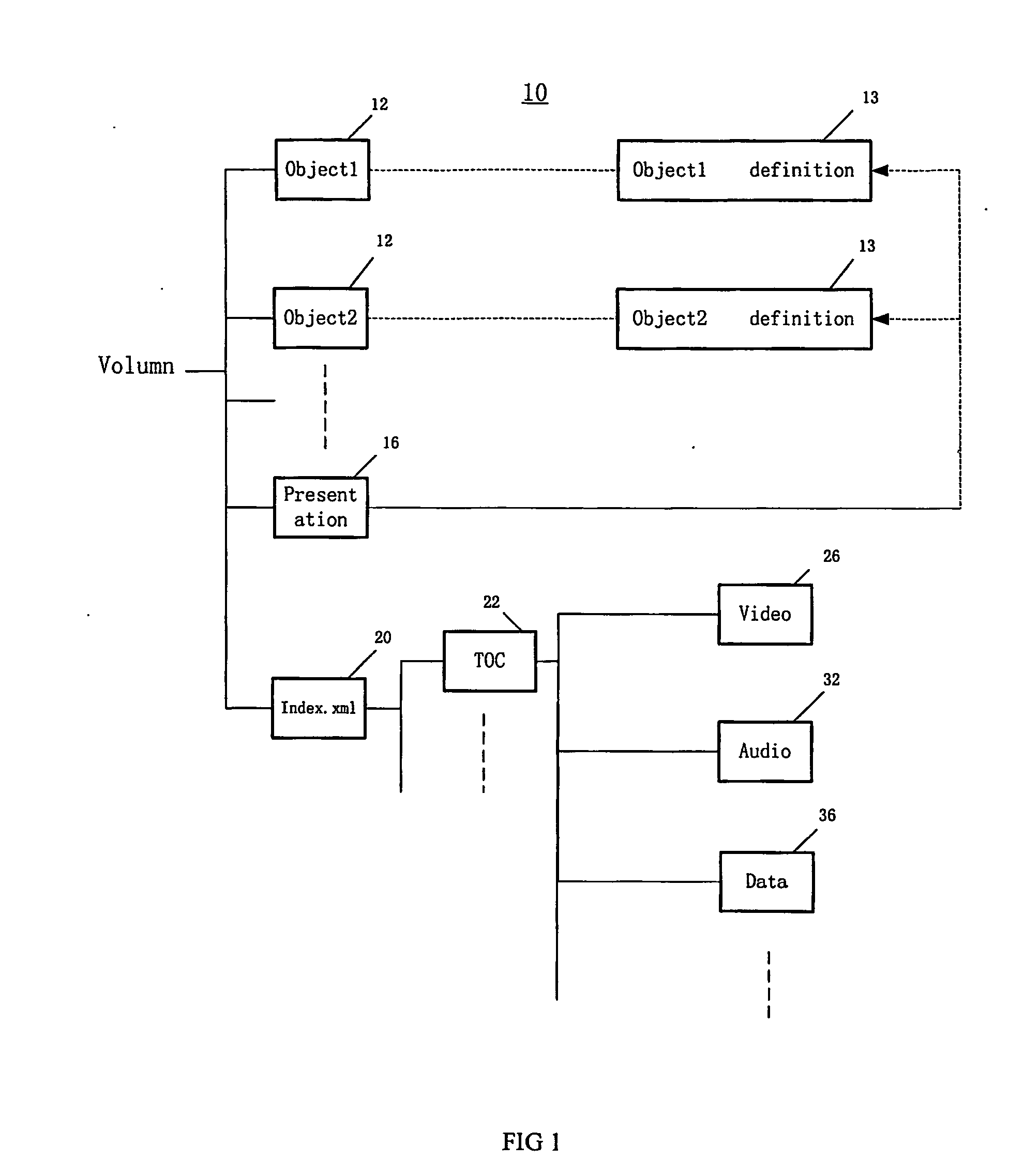

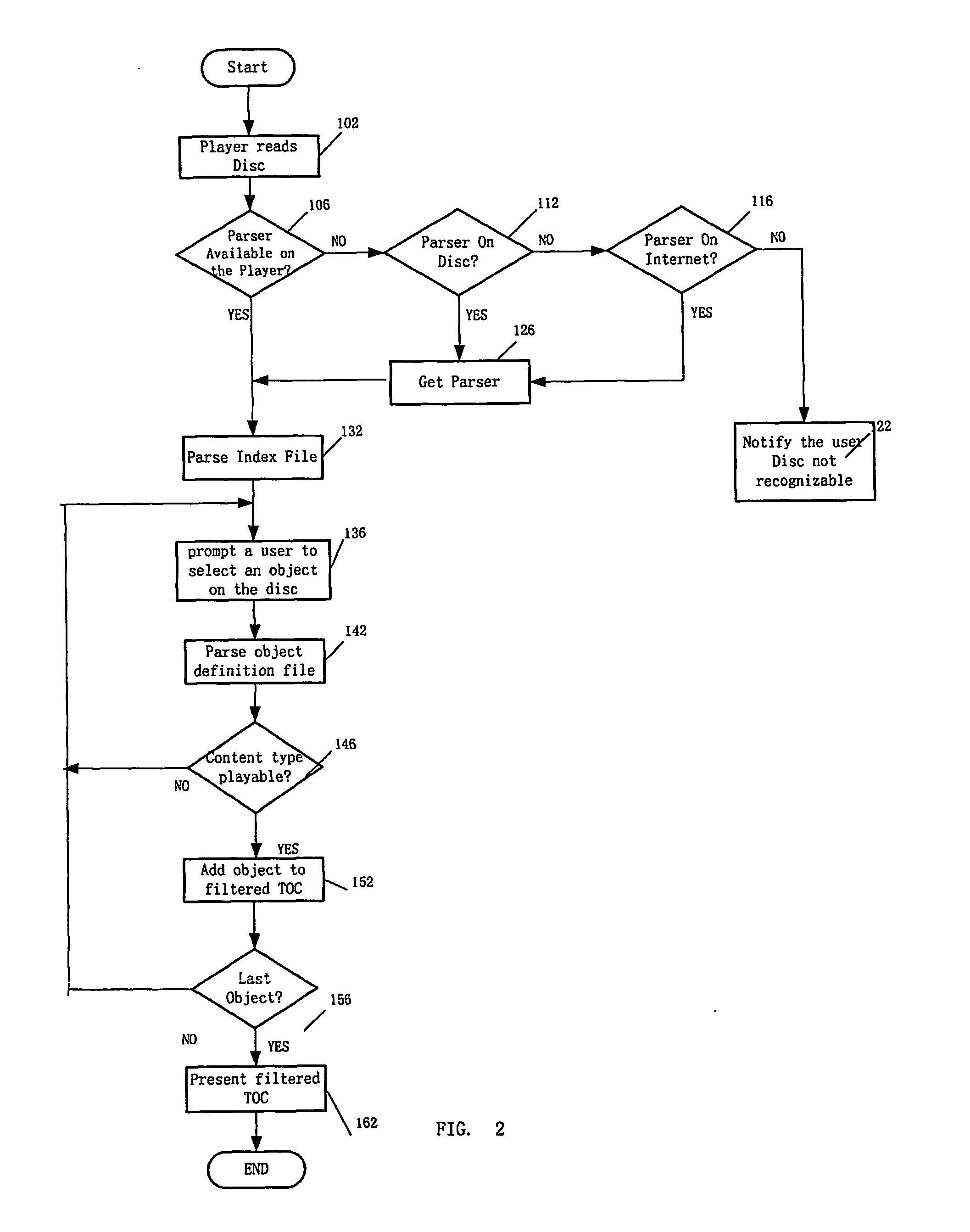

Optical Disc with a Generic Logical Format

InactiveUS20070219934A1Easy to adaptRecord information storageUsing detectable carrier informationData processing systemObject definition

The present invention provides an optical disc with a generic logical format having a data structure that is defined independent of the content type (i.e., the data type and medium encoding scheme) and the physical medium. In accordance with one embodiment of the invention, a data storage medium is provided for storing data for access by a data processing system. The data storage medium comprises a data structure stored in the medium for describing different data contents stored therein. The data structure includes at least one content object containing data contents, an object definition file associated with the object for describing the object, and an index file including a table of contents having a reference to the object. The generic logical format of the invention can be easily adapted to any new content types without the need to define a complete new format.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

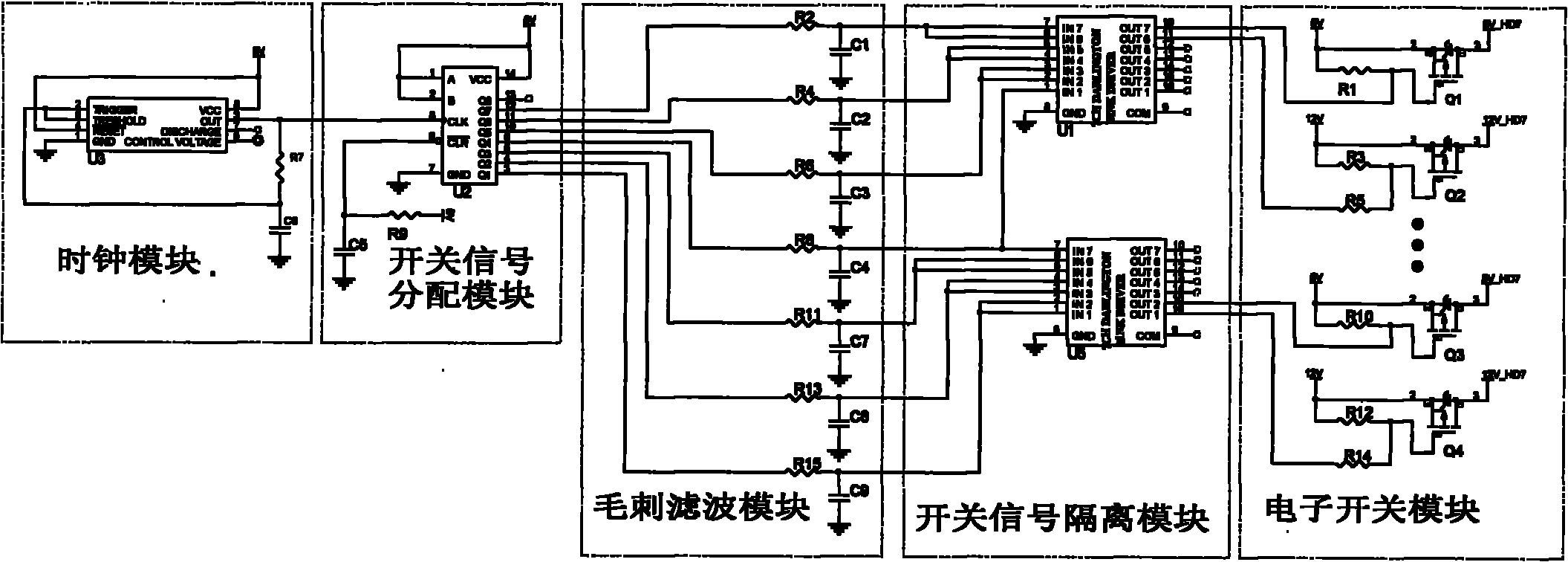

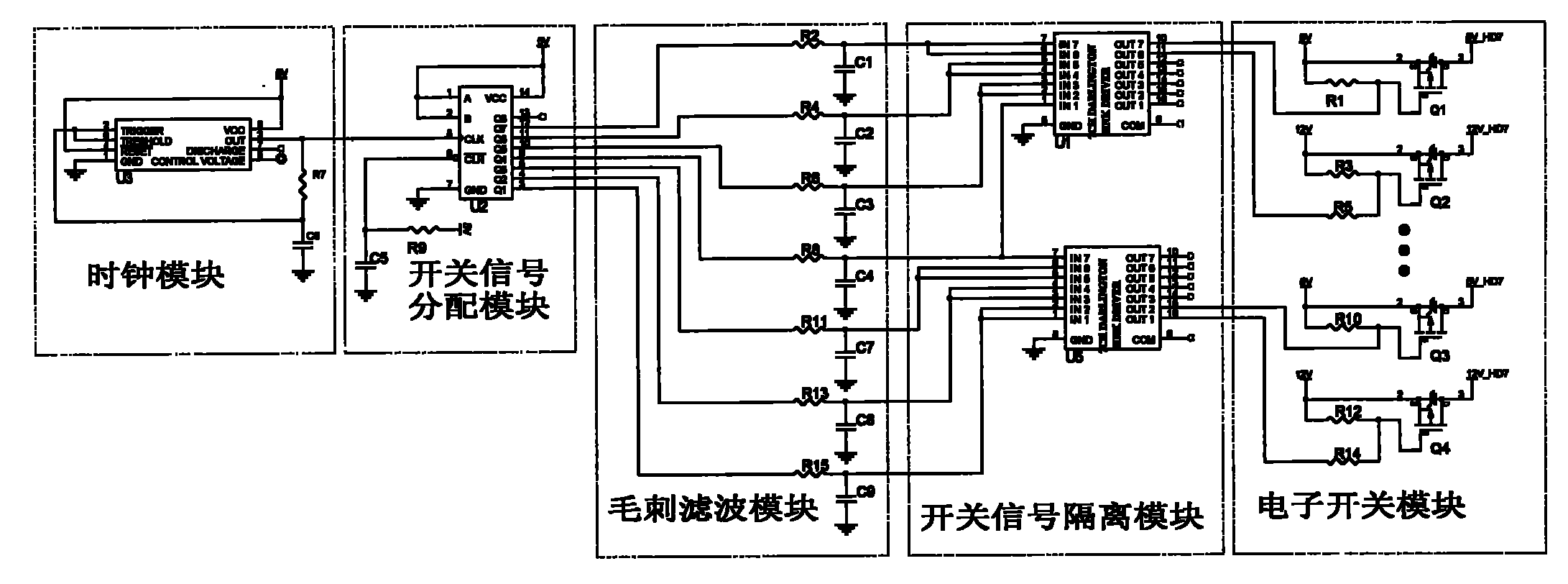

System and method for reducing requirements for power supply power in hard disk array system

ActiveCN101916136AReduced Power RequirementsEliminate shockVolume/mass flow measurementPower supply for data processingControl electronicsSwitching signal

The invention discloses a system and a method for reducing requirements on power supply power in a hard disk array system. The system mainly comprises a clock module, a switch signal distribution module, a burr filtering module, a switching signal isolation module and an electronic switch module which are connected sequentially, wherein the clock module generates a clock and provides a reference clock for the switch signal distribution module; the switch signal distribution module generates a power supply switching signal needed by each hard disk; the burr filtering module removes burr from the power supply switching signal which reaches the electronic switch through the switching signal isolation module and controls the electronic switch to open a hard disk power. The system and the method can eliminate the shock to the system power by simultaneous starting up of the hard disks in a disk array system with multiple hard disks, and evade the relation of hard disk starting power and system power supply power so as to greatly reduce the requirements on the power supply power. The components of the system are common logic components and separated components with low cost.

Owner:ZHEJIANG DAHUA TECH CO LTD

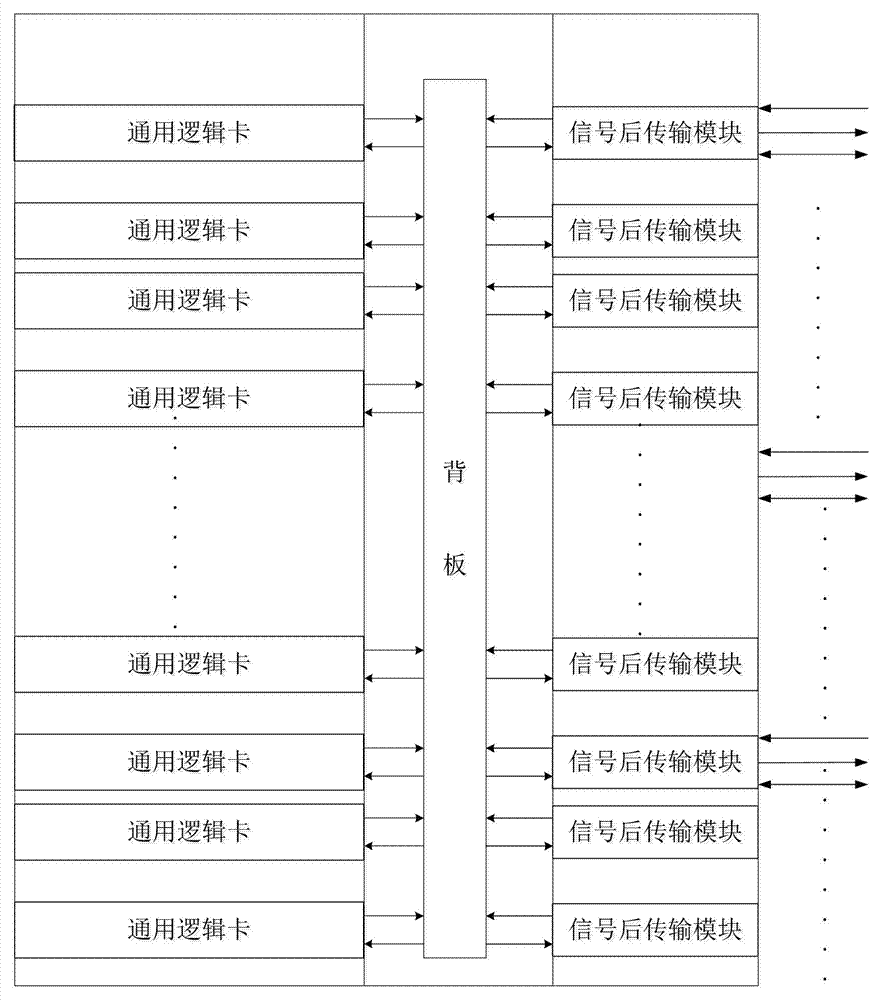

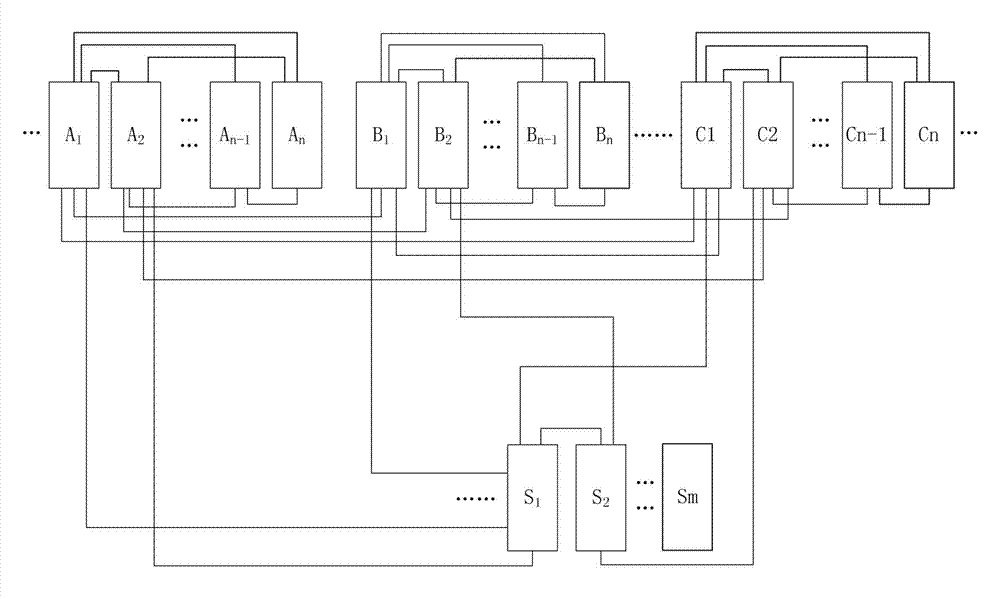

Digital control system

ActiveCN104503354ARealize data sharingRealize cascade controlProgramme control in sequence/logic controllersControl systemComputer module

The invention provides a digital control system, relates to the technical field of communication, and solves technical problems of enhancement of communication capacity and communication reliability. The system comprises a back board, and multiple generable logic cards and multiple signal backward-transmission modules which are interconnected with the backboard. All the general logic cards are divided into multiple logic card sequences, wherein one of the logic card sequences is an S sequence, and other logic card sequences are T sequences. In the T sequences, each general logic card is interconnected with all the general logic cards in the same sequence in a point-to-point communication mode and interconnected with the general logic cards of the corresponding positions in other T sequences in the point-to-point communication mode. In the S sequence, all the general logic cards are interconnected in the point-to-point communication mode, and each general logic card is interconnected with the general logic cards of the corresponding positions in all the T sequences in the point-to-point communication mode. The system is great in communication capacity and communication reliability.

Owner:STATE NUCLEAR POWER AUTOMATION SYST ENGCO

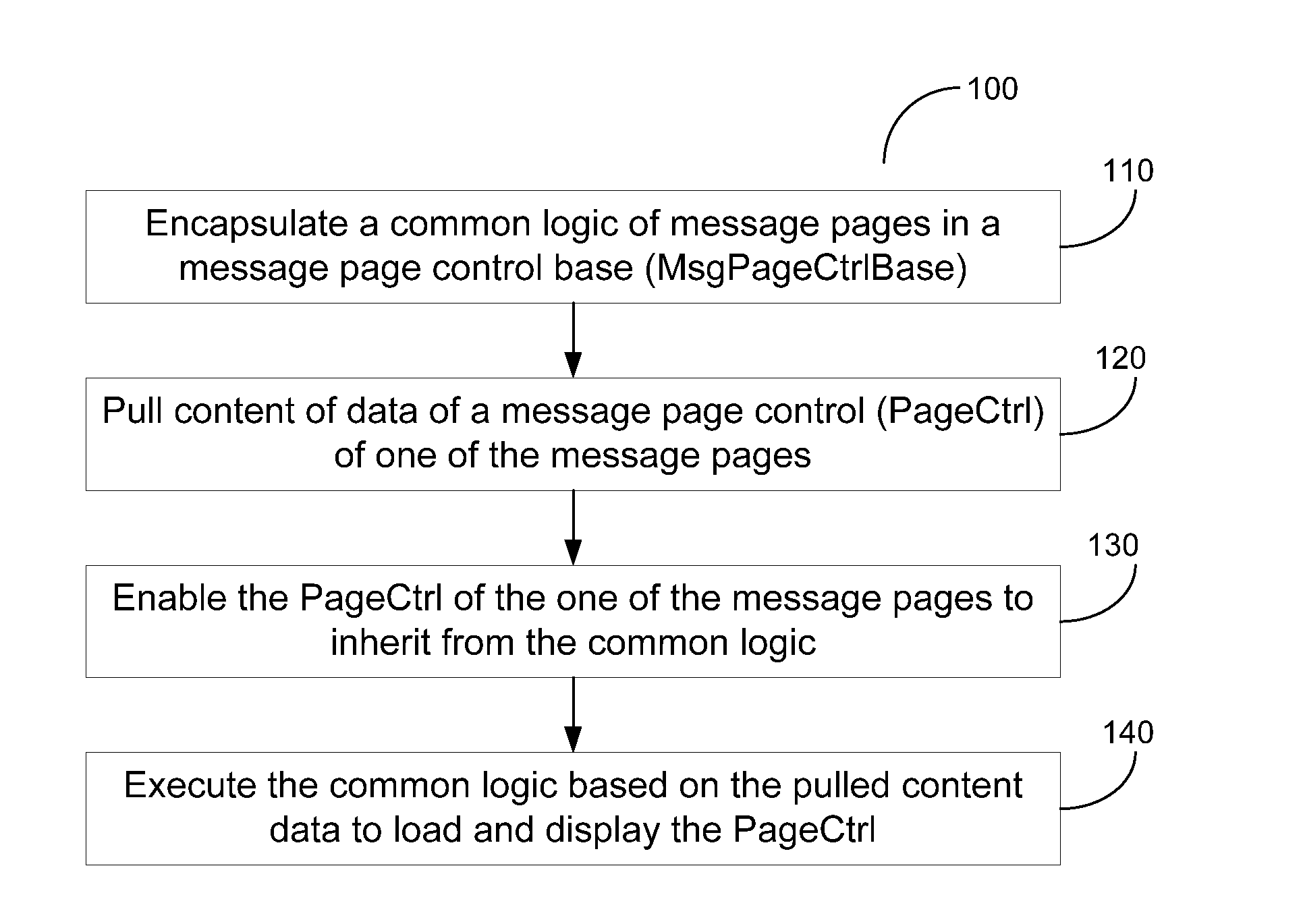

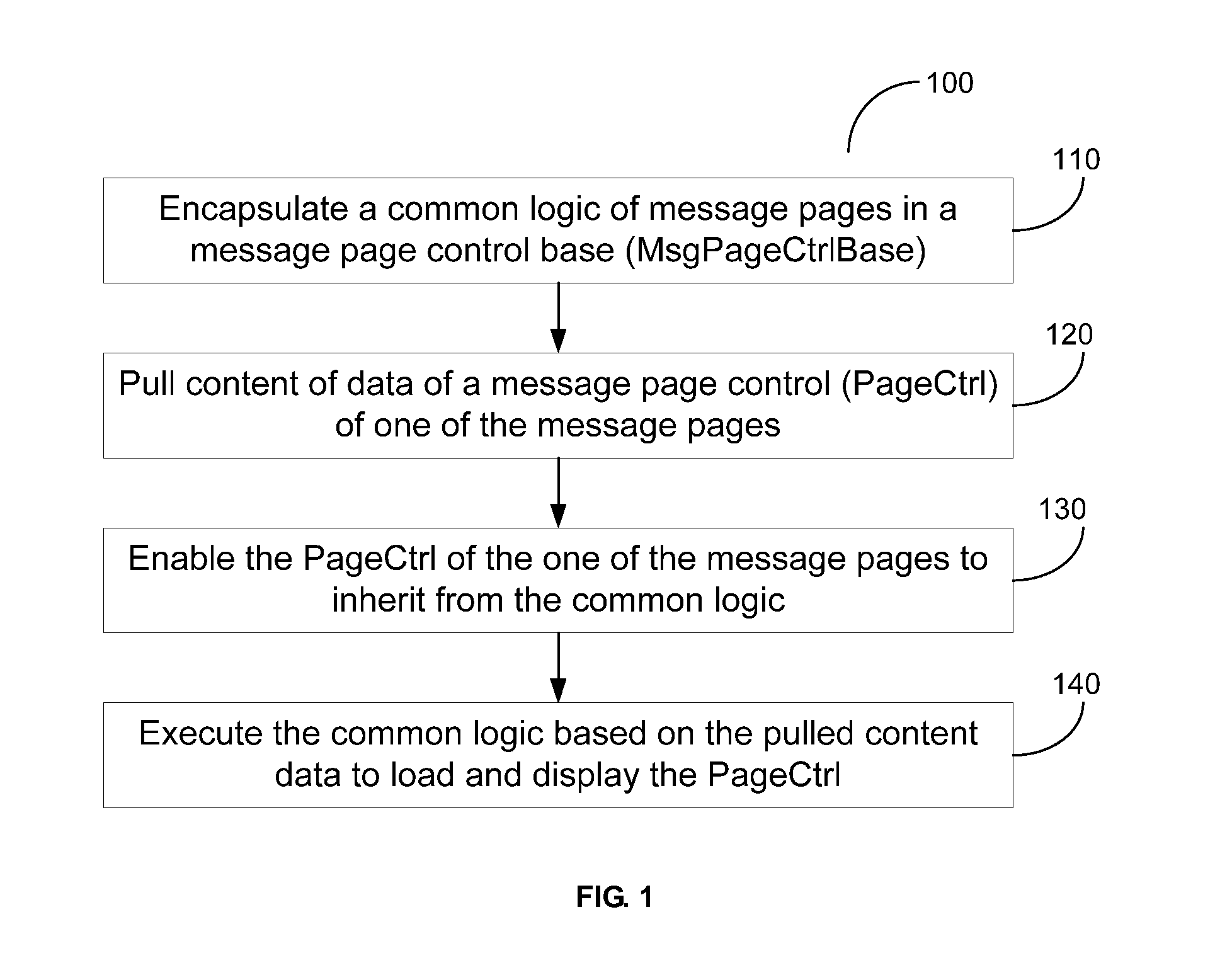

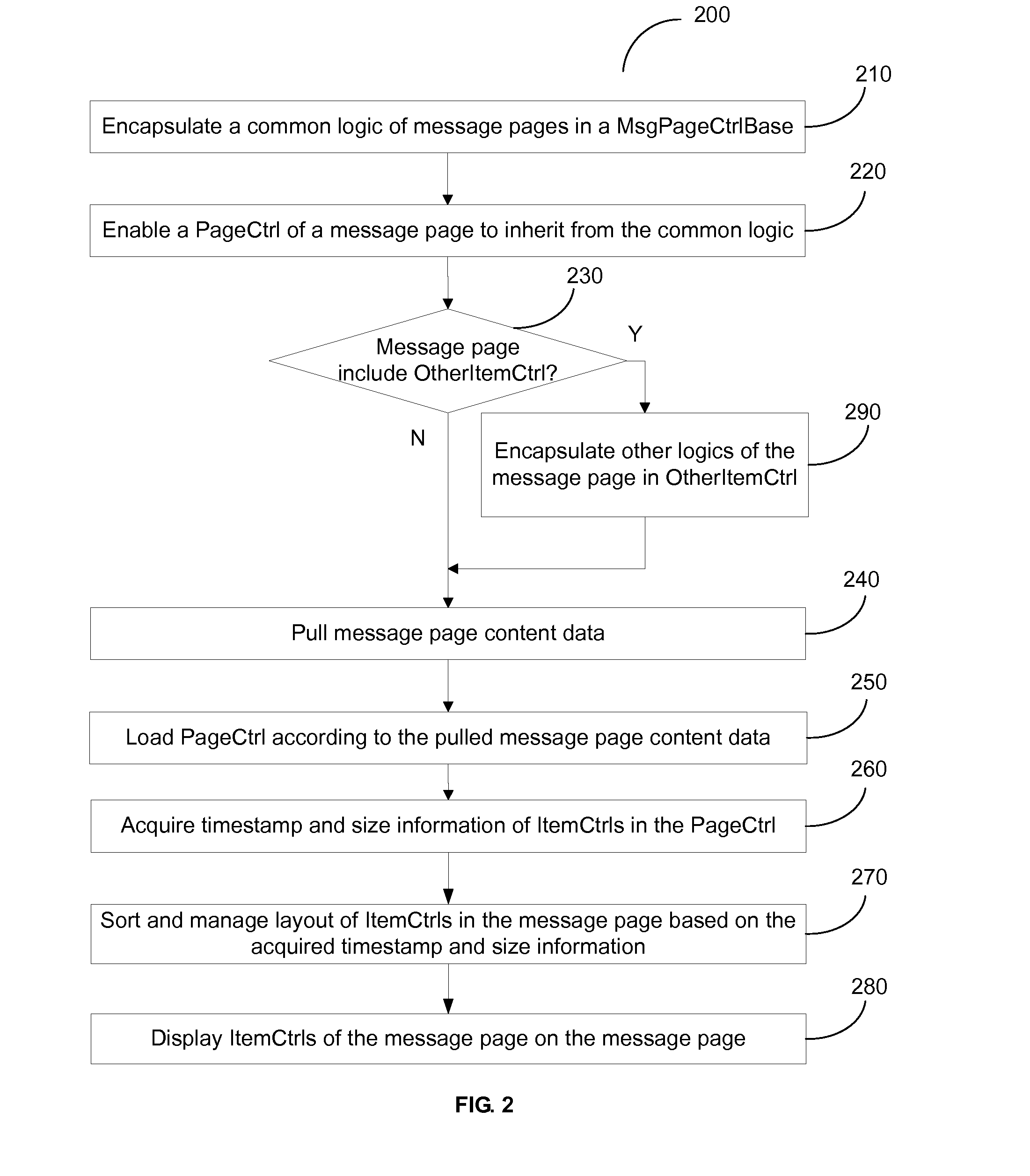

Method and apparatus for implementing microblog message pages

ActiveUS20130132828A1Simplify sorting algorithmImprove efficiencyNatural language data processingOffice automationSorting algorithmMicroblogging

Various embodiments provide methods and apparatus for implementing a microblog message page. An exemplary method can include encapsulating common logics of a plurality of message pages into a message page control base, pulling content data of a message page control of one message page of the plurality of message pages; and enabling the message page control of the one message page to inherit from the common logics encapsulated in the message page control base. The exemplary method can also include executing the common logics based on the pulled content data, to load the message page control of the one message page and to display the message page control on the one message page. The disclosed methods and apparatus can simplify the sorting algorithm with improved efficiency for the message pages to sort and manage layout of various types of controls.

Owner:TENCENT TECH (SHENZHEN) CO LTD

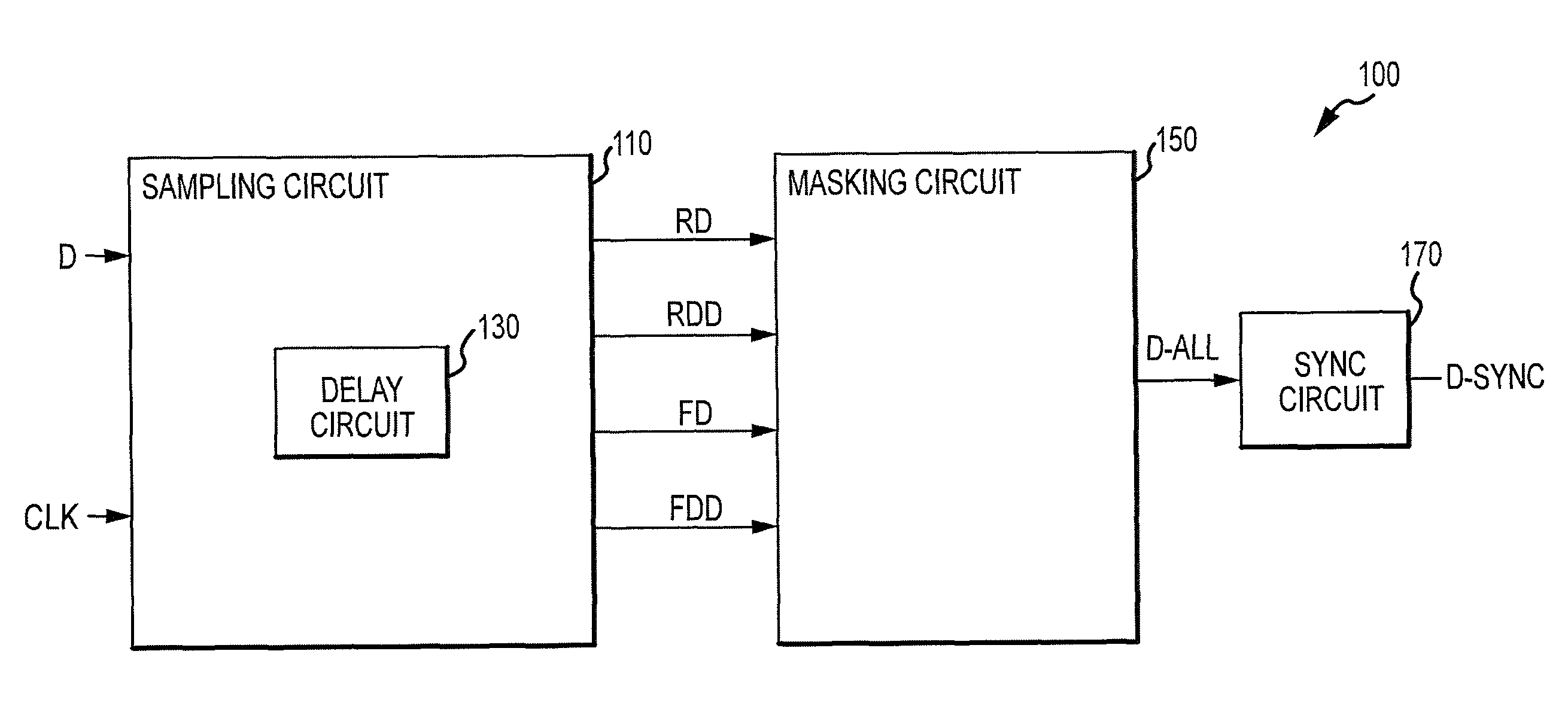

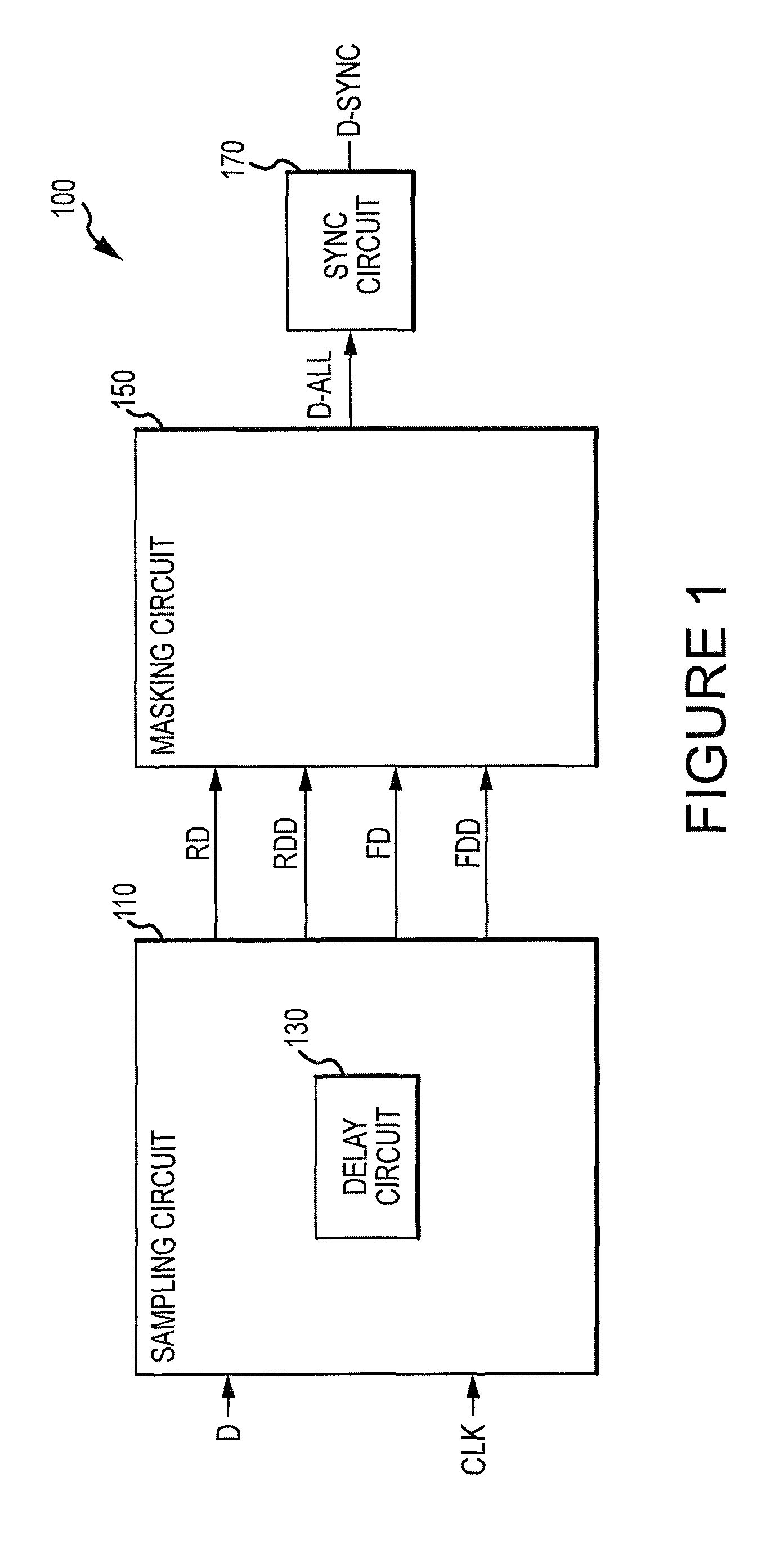

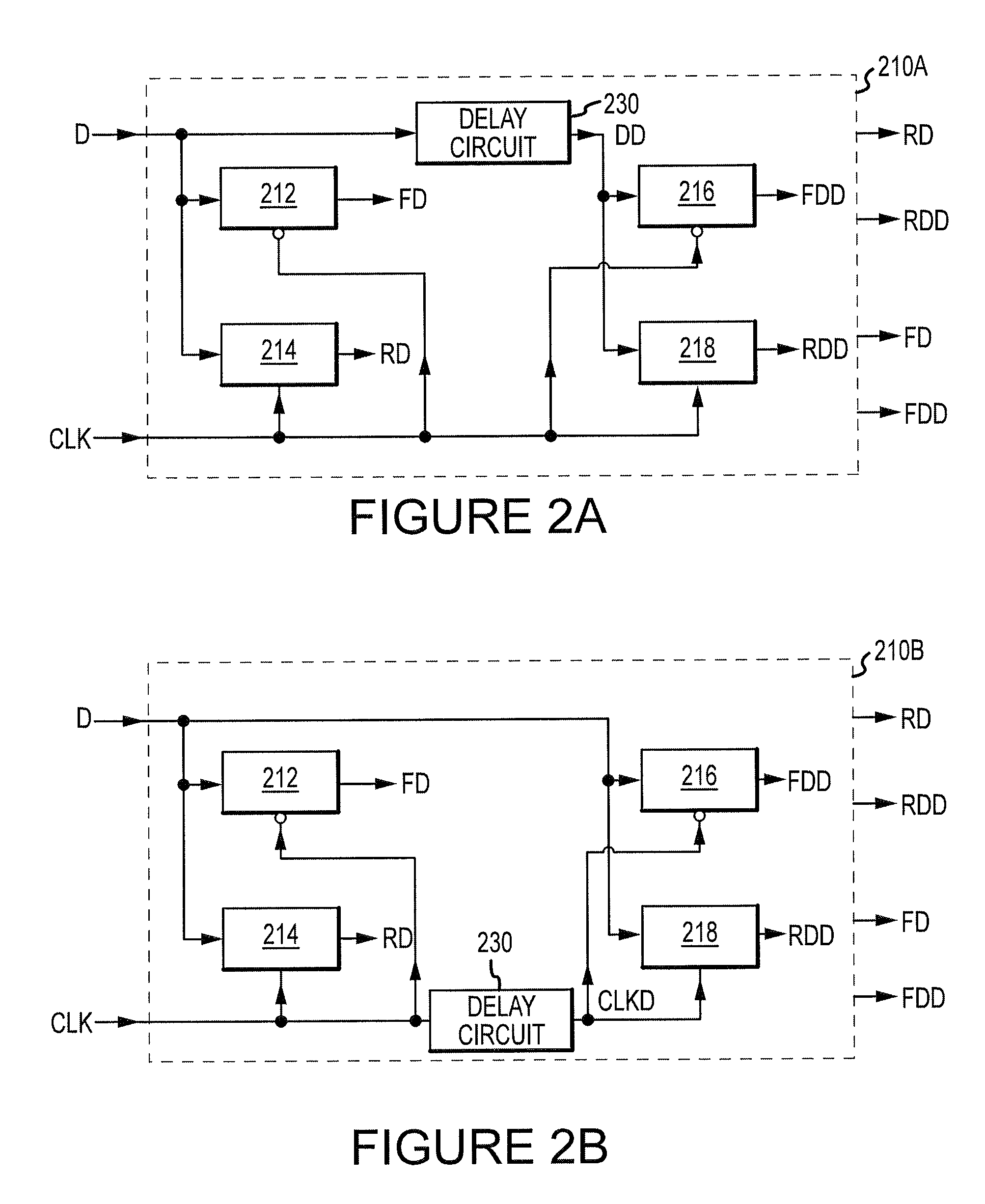

Apparatuses, circuits, and methods for reducing metastability in data synchronization

Apparatuses, circuits, and methods are disclosed for reducing or eliminating unintended operation resulting from metastability in data synchronization. In one such example apparatus, a sampling circuit is configured to provide four samples of a data input signal. A first and a second of the four samples are associated with a first edge of a latching signal, and a third and a fourth of the four samples are associated with a second edge of the latching signal. A masking circuit is configured to selectively mask a signal corresponding to one of the four samples responsive to the four samples not sharing a common logic level. The masking circuit is also configured to provide a decision signal responsive to selectively masking or not masking the signal.

Owner:MICRON TECH INC

Methods and systems for reducing clock skew in a gated clock tree

Systems and methods for synthesizing a gated clock tree with reduced clock skew are provided. A gated clock tree circuit with reduced clock skew may include a clock source and edge-triggered state elements. A gated clock tree disposed between the clock source and state elements may include a level in which each logic gate has a common logic type. Logic gates in the gated clock tree may also be configured as logic-gate buffers. The logic gates may also be configured as NAND-gated equivalents. The clock signal distributed through the gated clock tree may drive both positive-edge-triggered and negative-edge-triggered state elements.

Owner:SYNOPSYS INC