Patents

Literature

2406 results about "Cross coupled" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

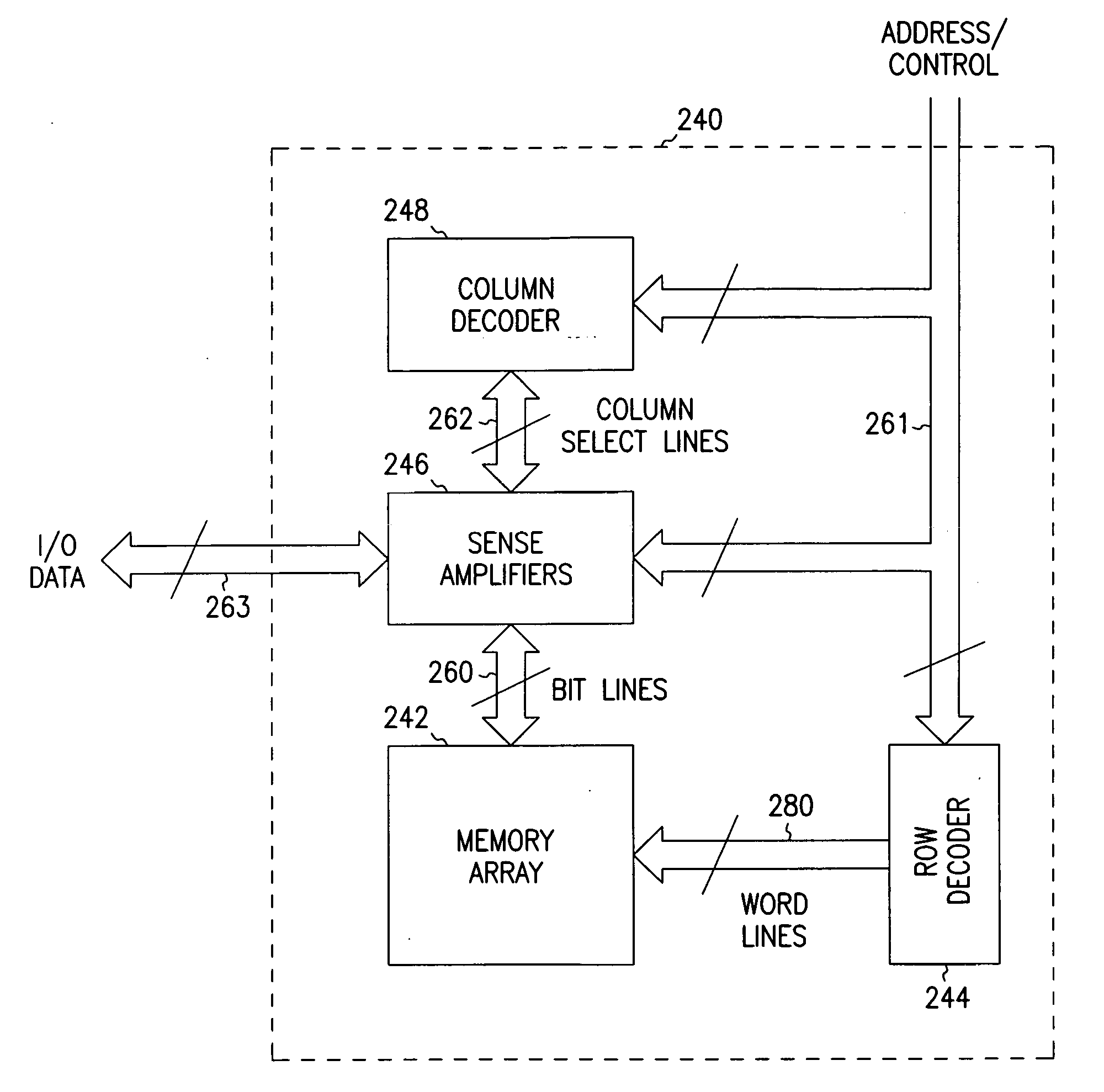

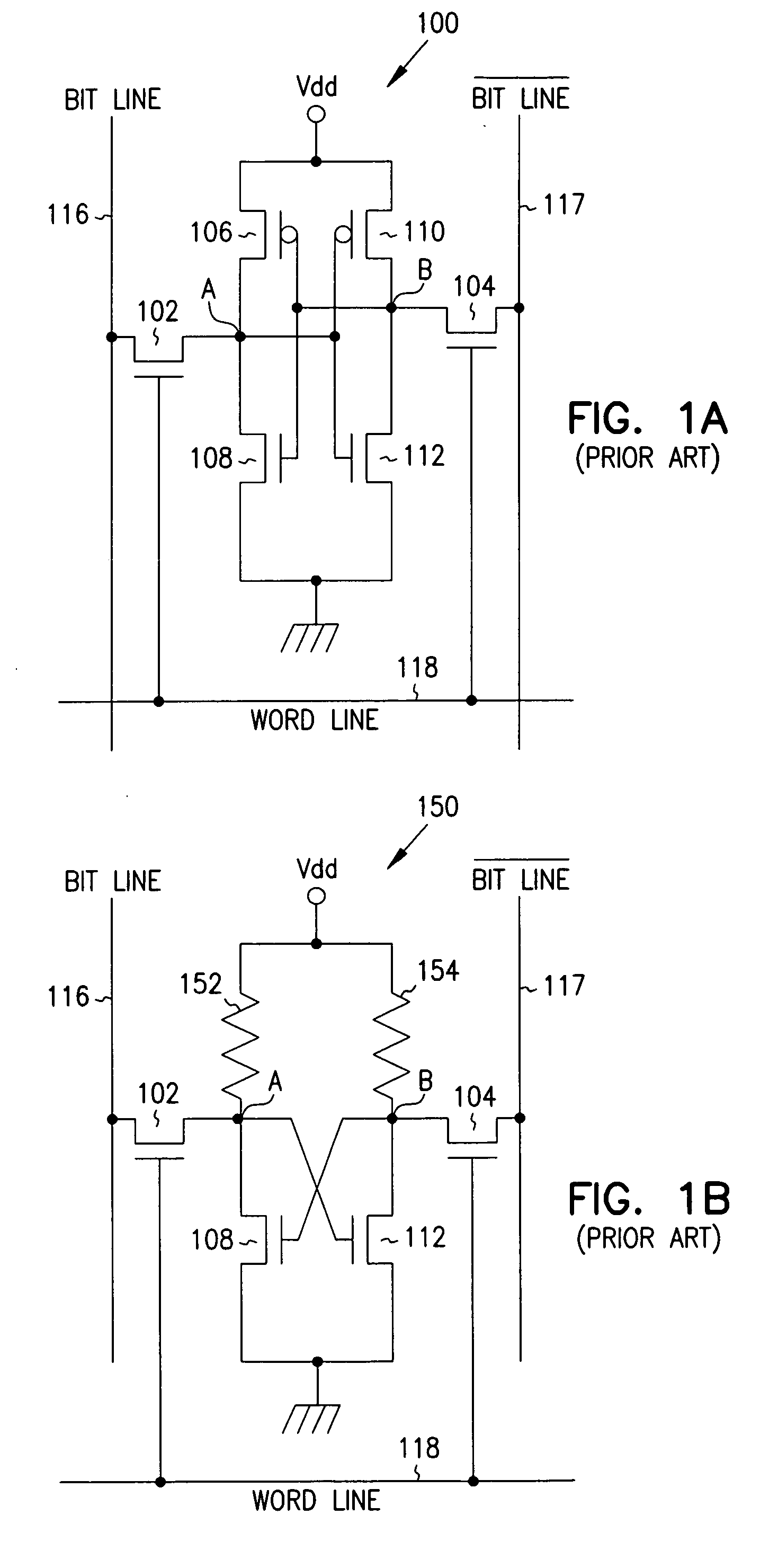

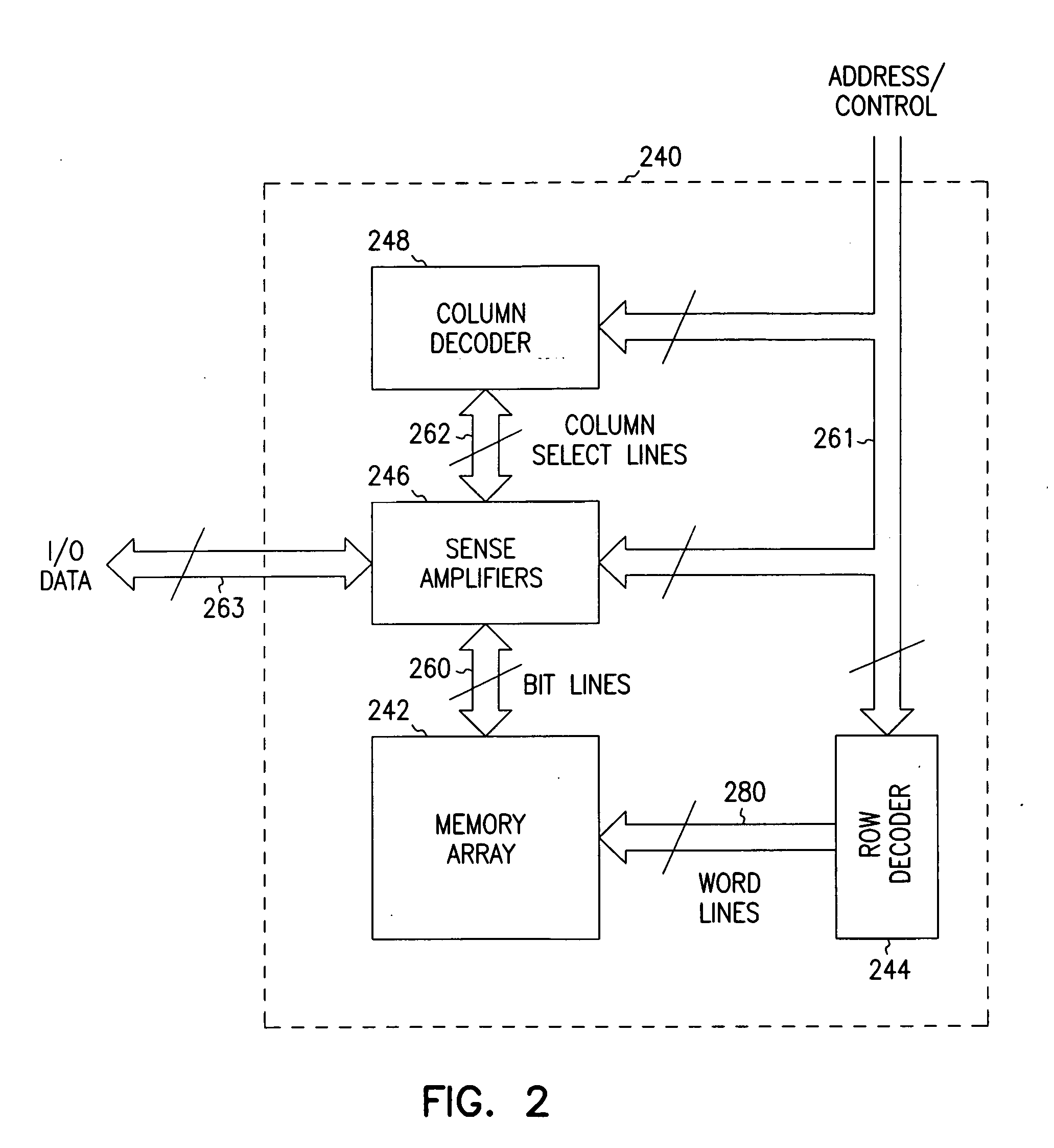

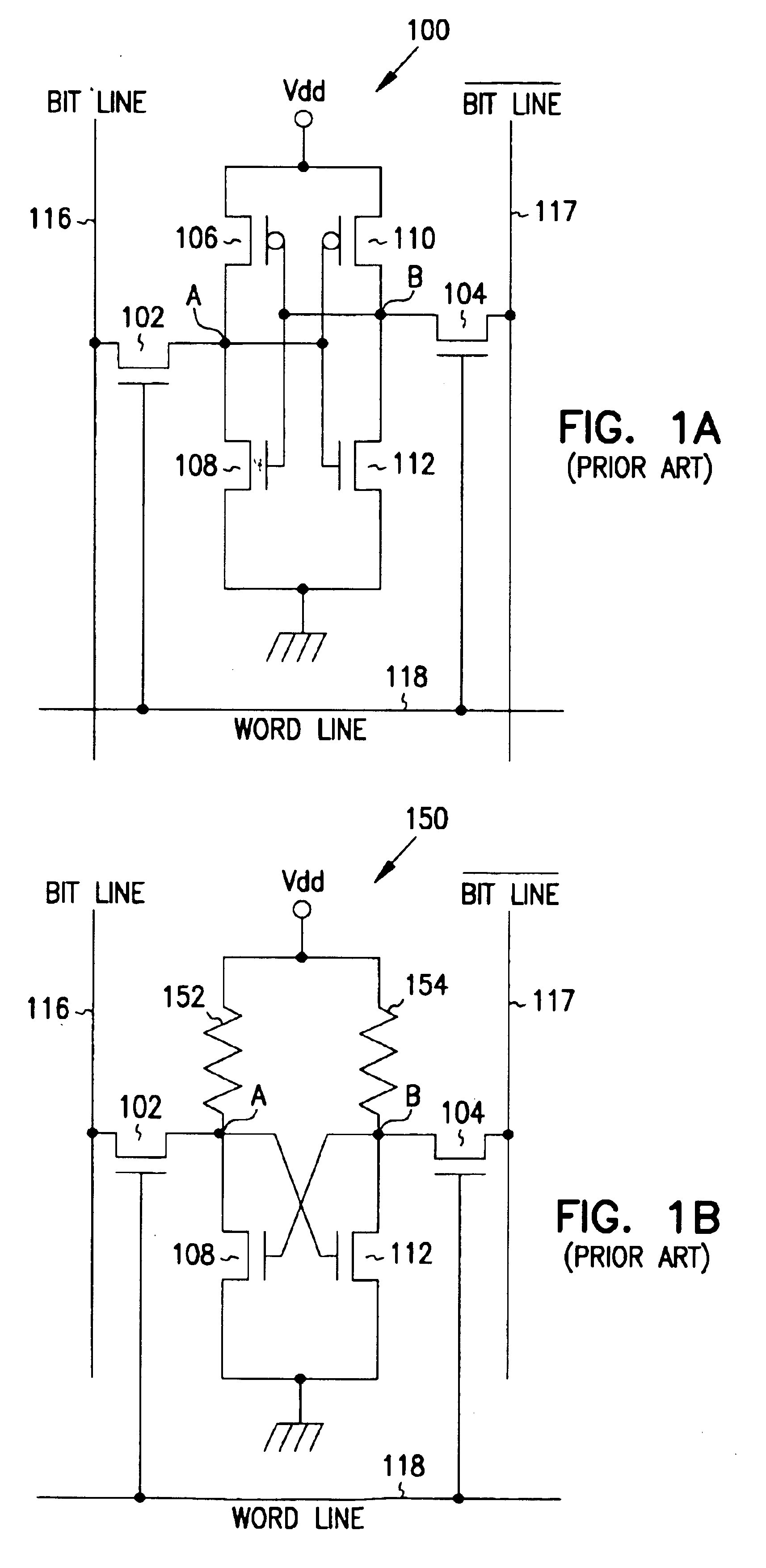

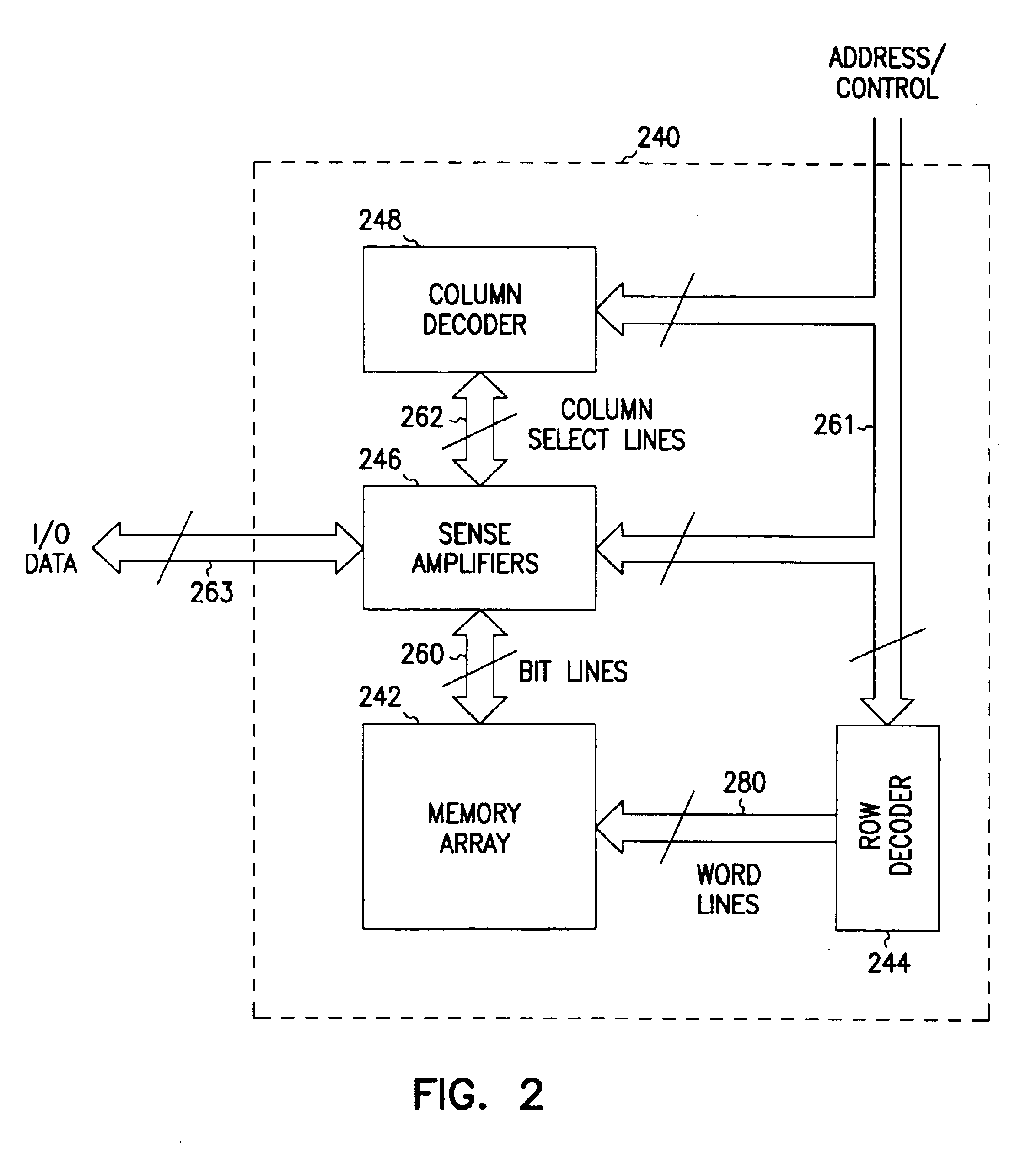

Dram-like nvm memory array and sense amplifier design for high temperature and high endurance operation

InactiveUS20110267883A1Improve threshold voltage sensing marginLarge silicon areaRead-only memoriesDigital storageBit lineAudio power amplifier

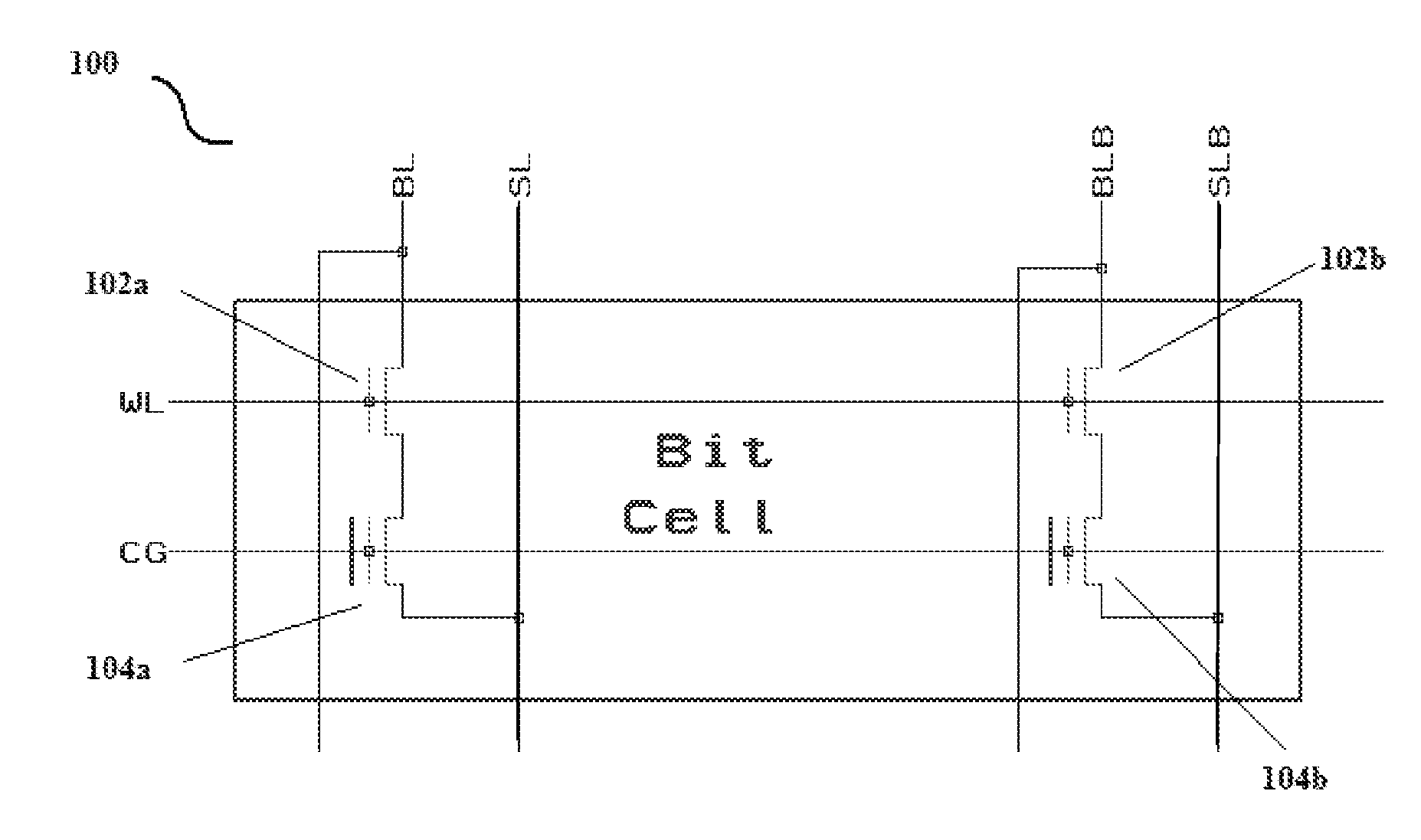

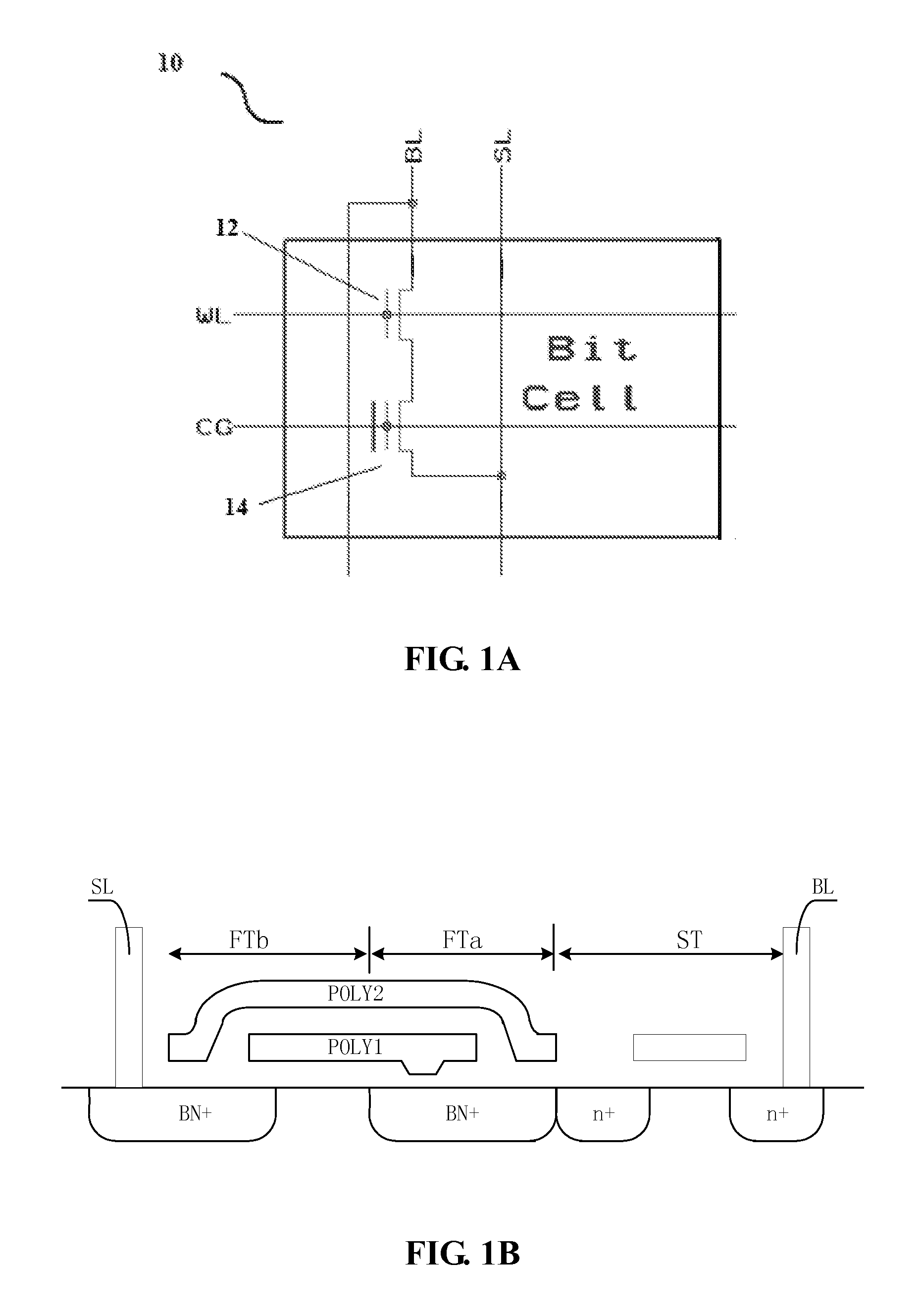

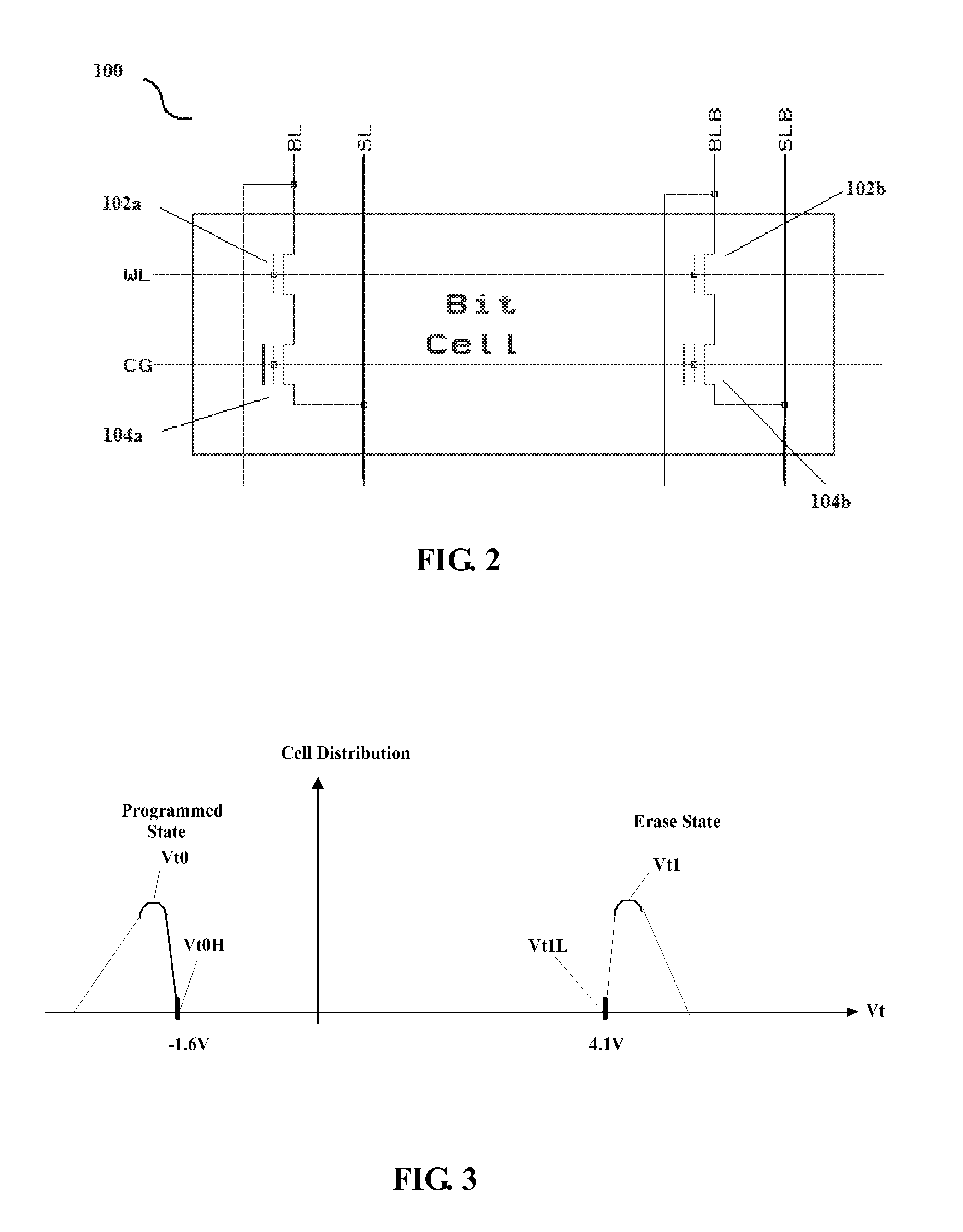

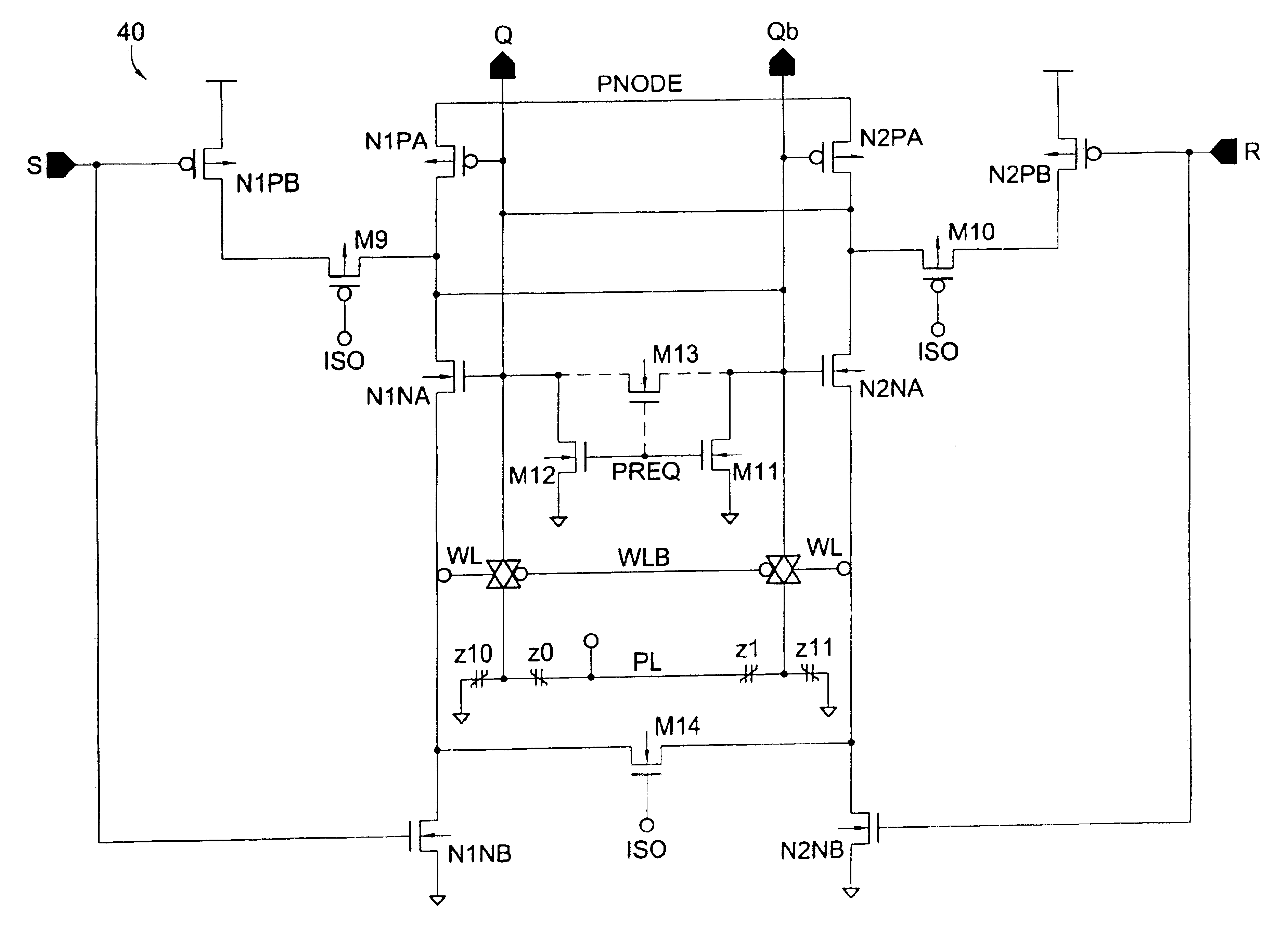

A DRAM-like non-volatile memory array includes a cell array of non-volatile cell units with a DRAM-like cross-coupled latch-type sense amplifier. Each non-volatile cell unit has two non-volatile cell devices with respective bit lines and source lines running in parallel and laid out perpendicular to the word line associated with the non-volatile cell unit. The two non-volatile cell devices are programmed with erased and programmed threshold voltages as a pair for storing a single bit of binary data. The two bit lines of each non-volatile cell unit are coupled through a Y-decoder and a latch device to the two respective inputs of the latch-type sense amplifier which provides a large sensing margin for the cell array to operate properly even with a narrowed threshold voltage gap. Each non-volatile cell device may be a 2 T FLOTOX-based EEPROM cell, a 2 T flash cell, 11 T flash cell or a 1.5 T split-gate flash cell.

Owner:APLUS FLASH TECH

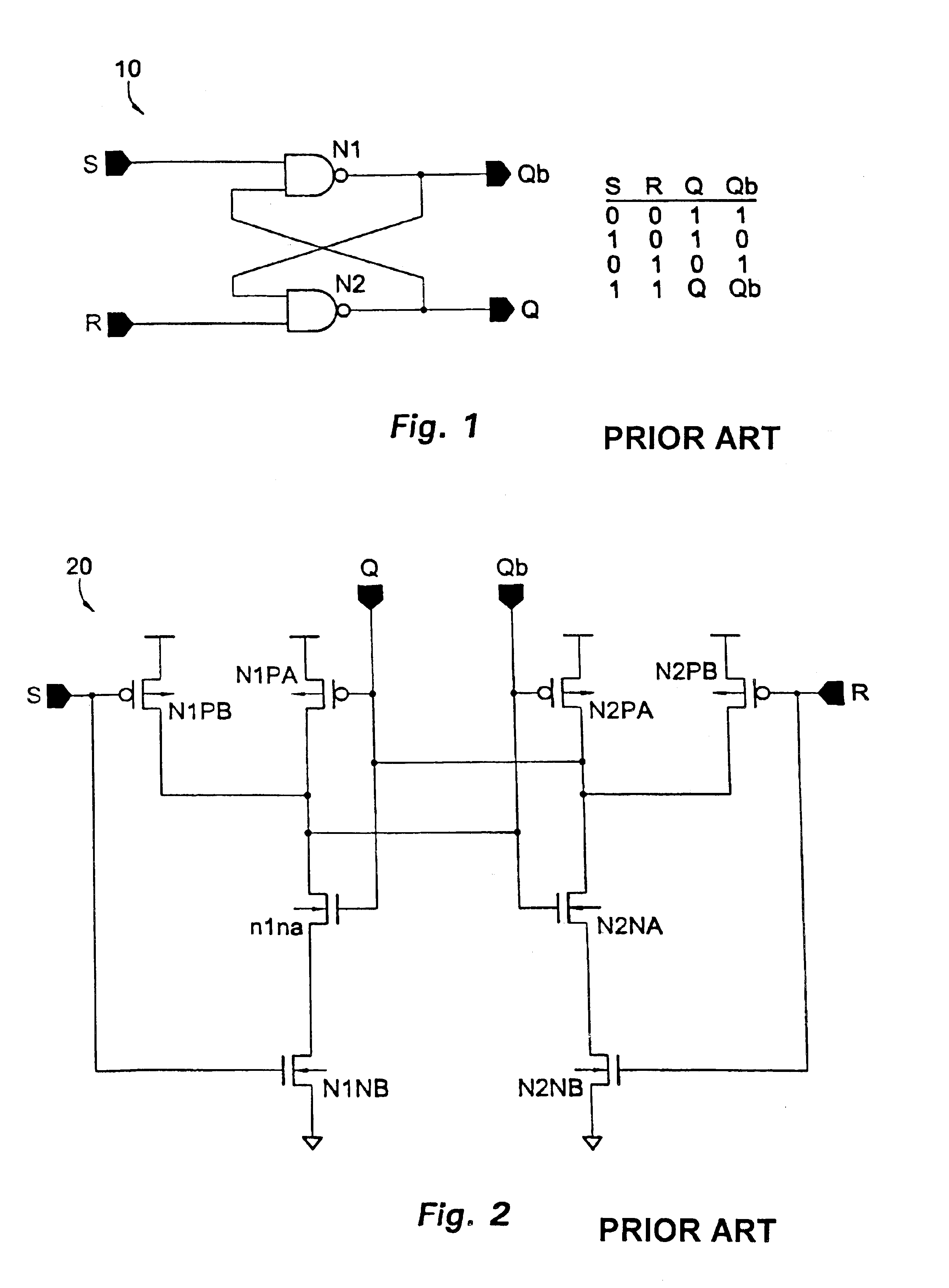

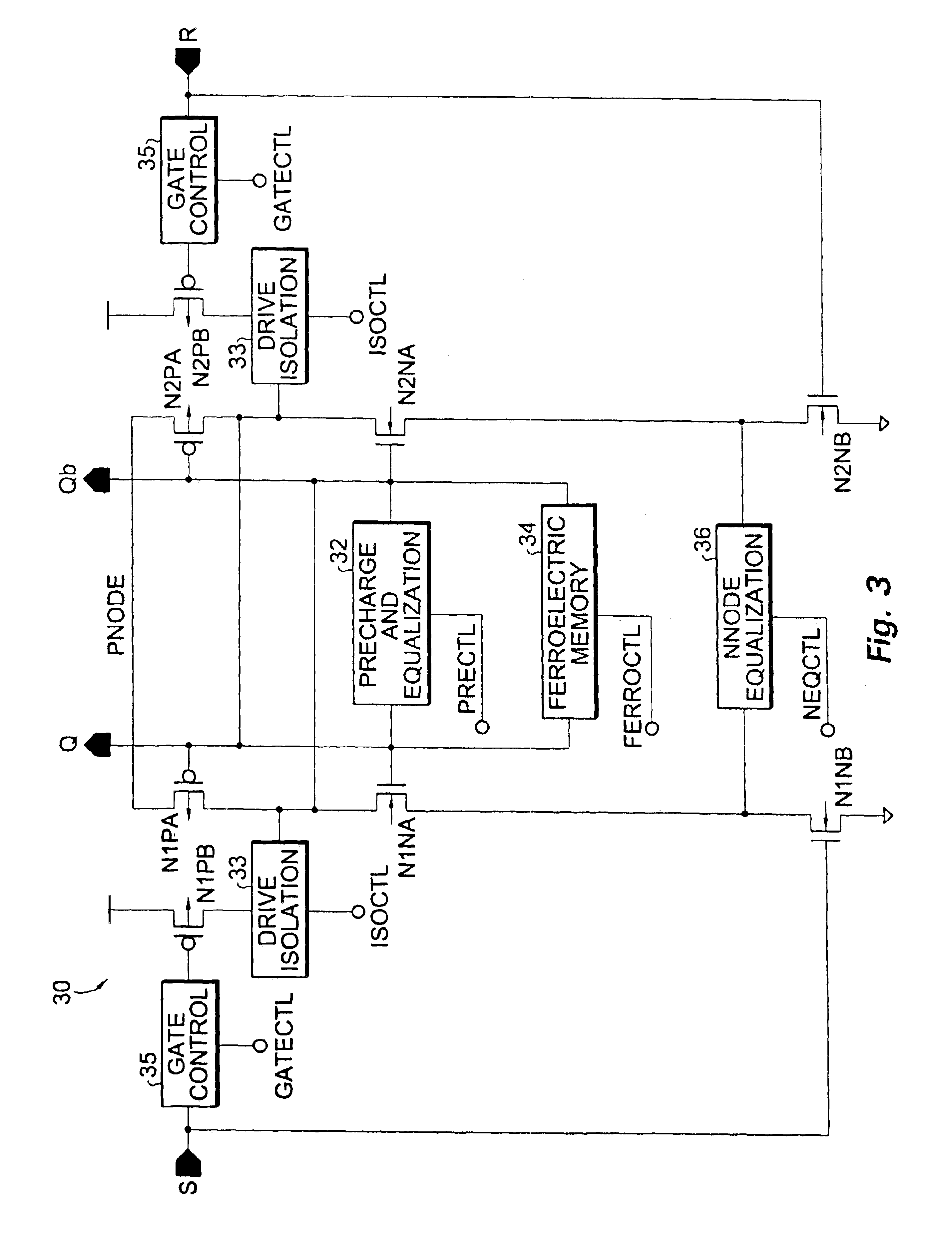

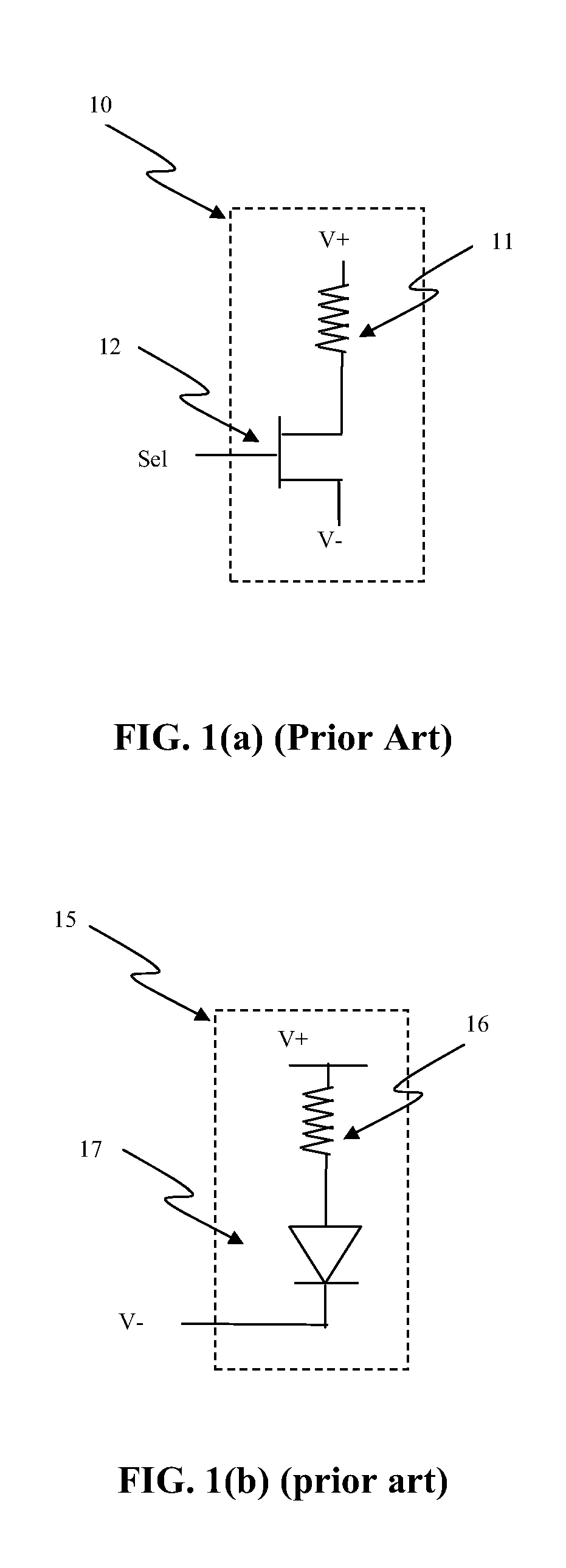

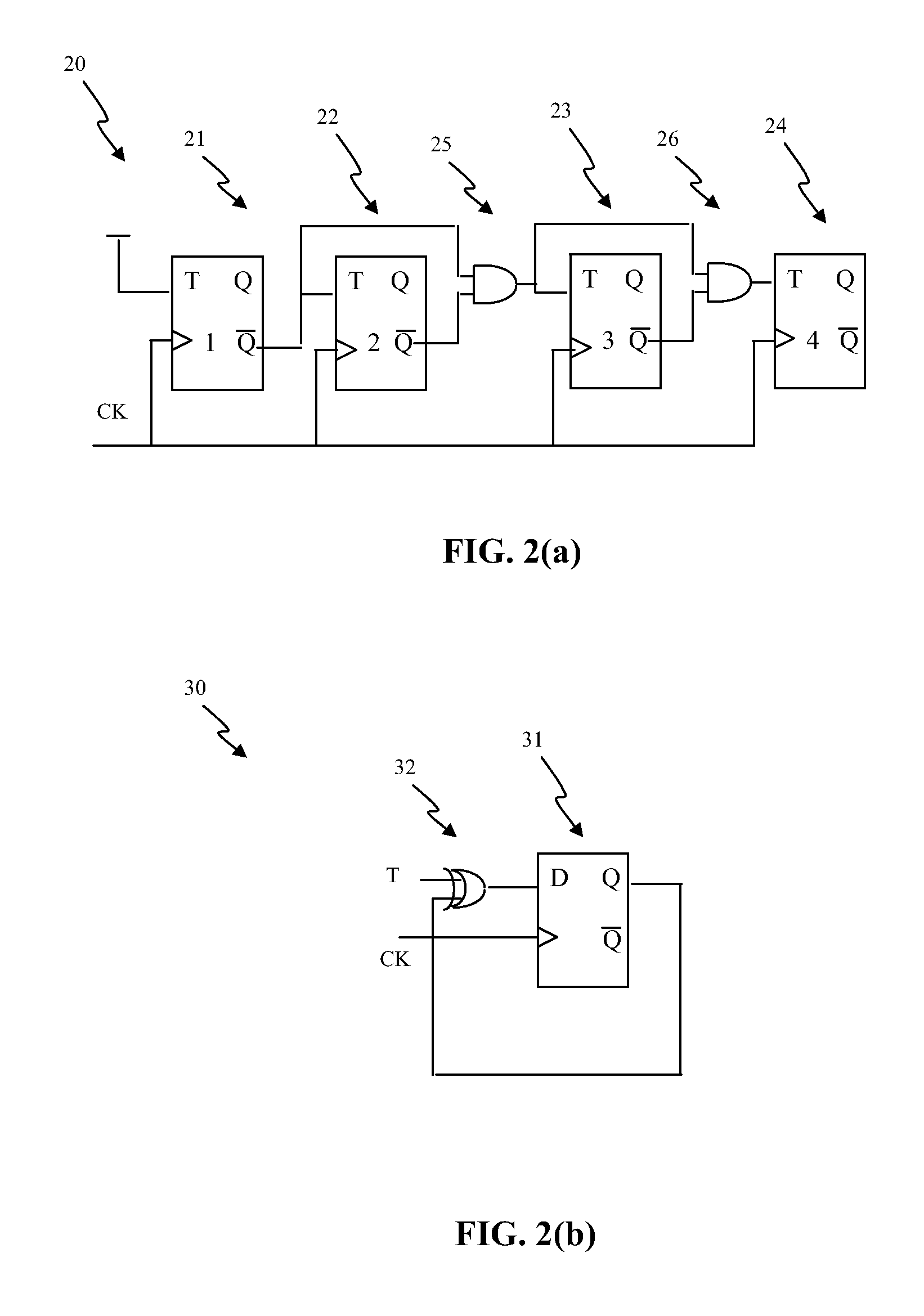

Ferroelectric non-volatile logic elements

InactiveUS6894549B2Easy translationImprove performanceTransistorPulse generation by non-linear magnetic/dielectric devicesShift registerAudio power amplifier

Various logic elements such as SR flip-flops, JK flip-flops, D-type flip-flops, master-slave flip-flops, parallel and serial shift registers, and the like are converted into non-volatile logic elements capable of retaining a current output logic state even though external power is removed or interrupted through the strategic addition of ferroelectric capacitors and supporting circuitry. In each case, the building blocks of a cross-coupled sense amplifier are identified within the logic element and the basic cell is modified and / or optimized for sensing performance.

Owner:MONTEREY RES LLC

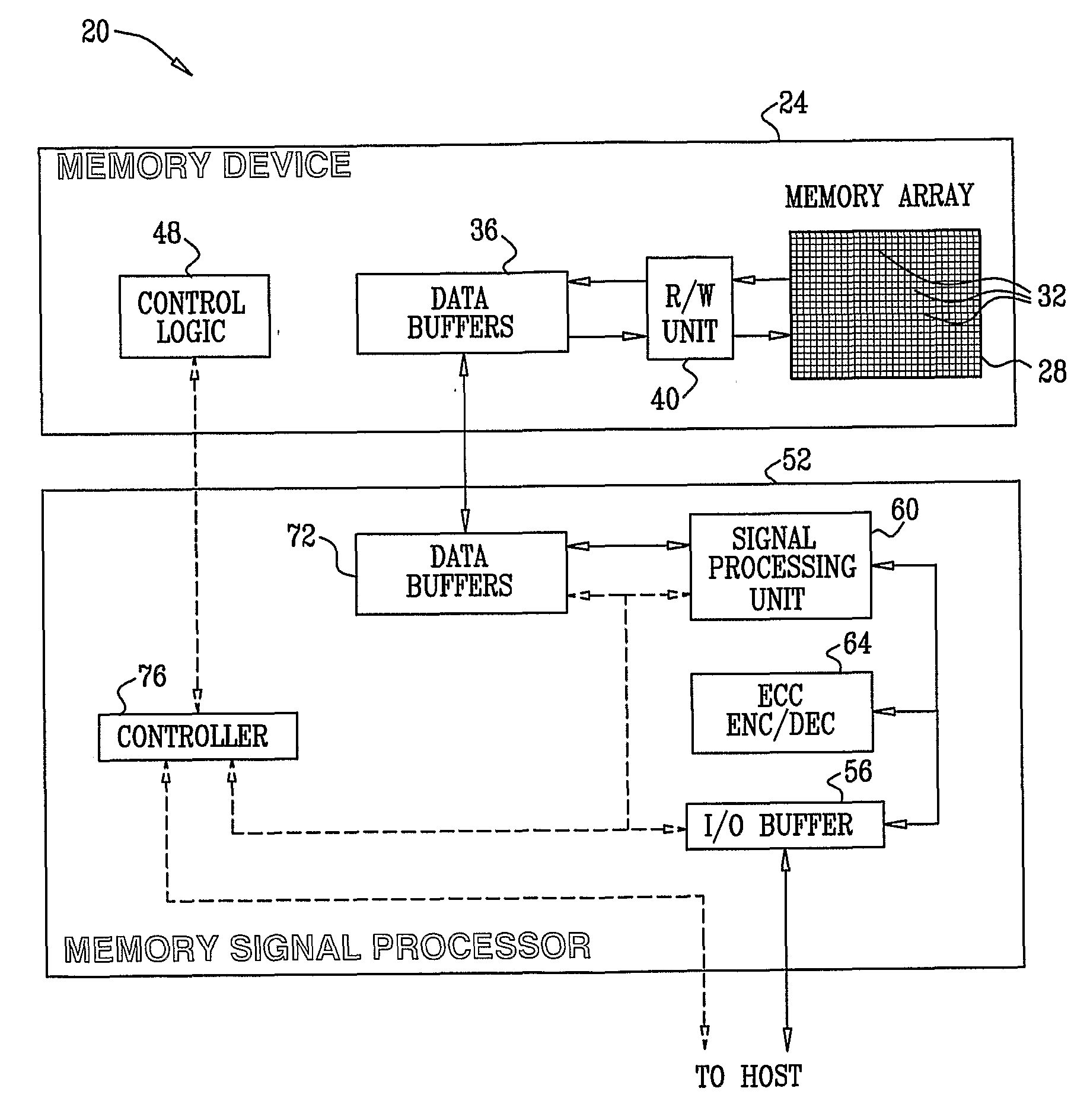

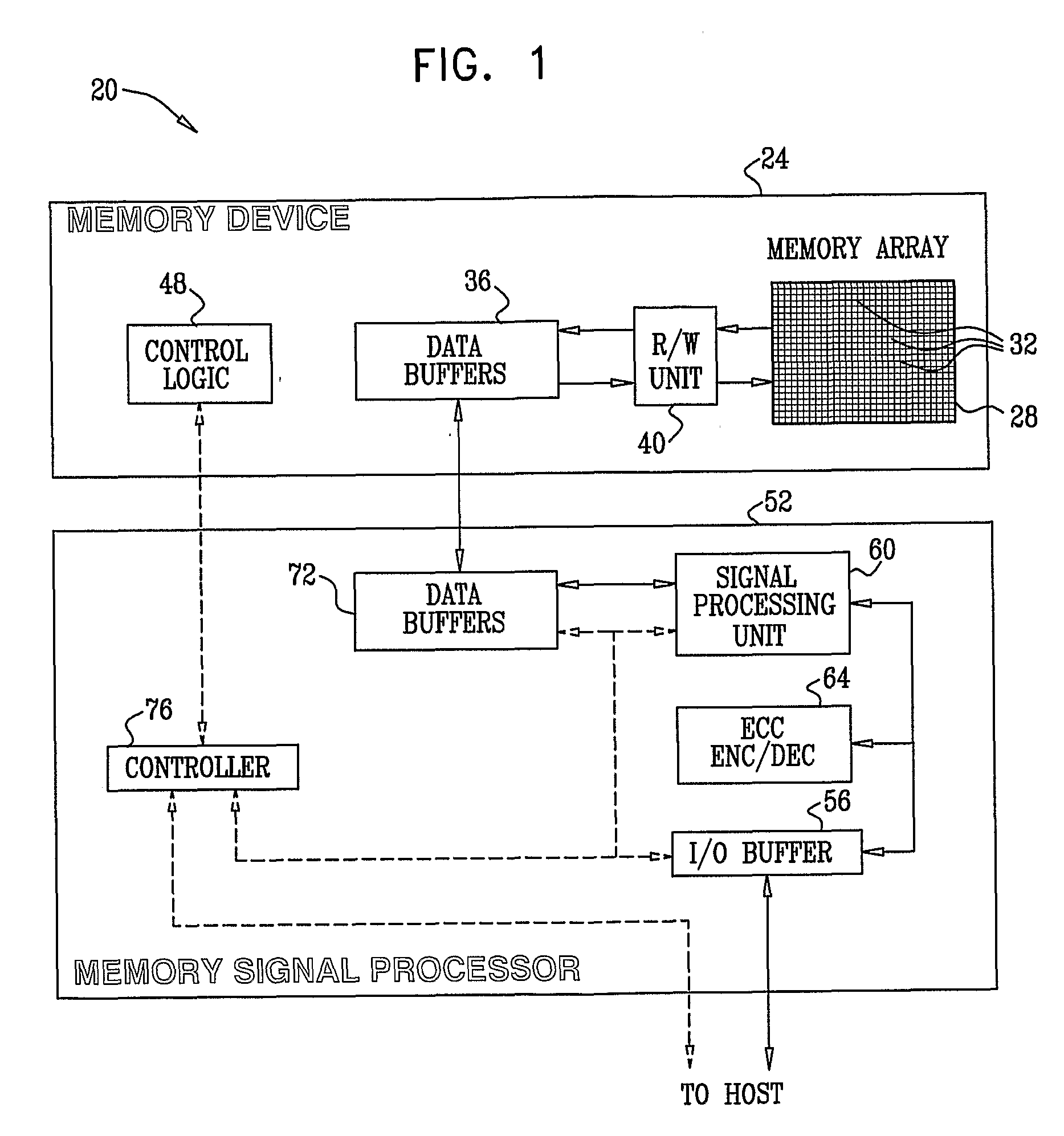

Distortion Estimation And Cancellation In Memory Devices

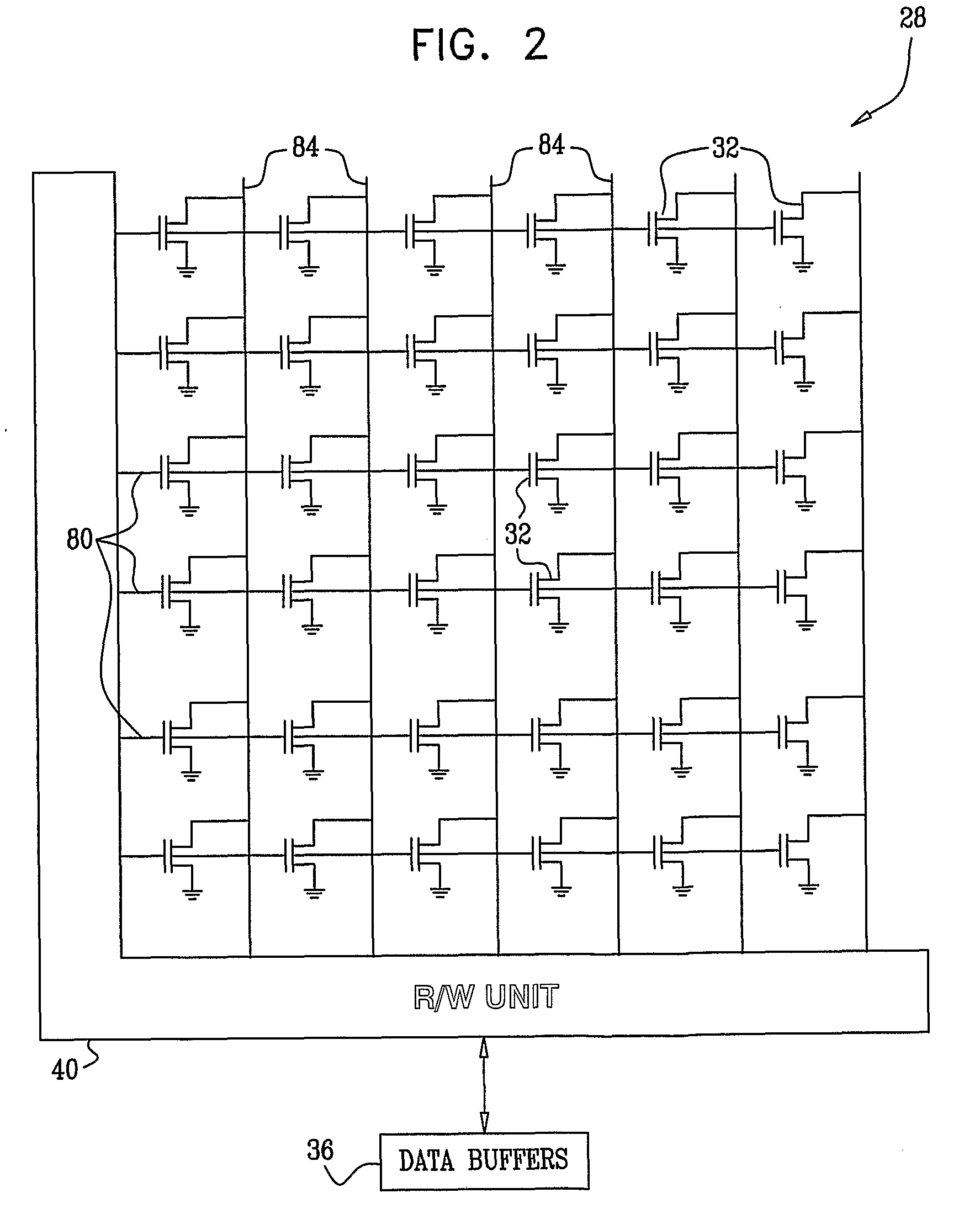

A method for operating a memory (28) includes storing data in a group of analog memory cells (32) of the memory as respective first voltage levels. After storing the data, second voltage levels are read from the respective analog memory cells. The second voltage levels are affected by cross-coupling interference causing the second voltage levels to differ from the respective first voltage levels. Cross-coupling coefficients, which quantify the cross-coupling interference among the analog memory cells, are estimated by processing the second voltage levels. The data stored in the group of analog memory cells is reconstructed from the read second voltage levels using the estimated cross-coupling coefficients.

Owner:APPLE INC

Slit and slot scan, SAR, and compton devices and systems for radiation imaging

ActiveUS20100270462A1Reduce productionReduce maintenance costsElectric discharge tubesElectroluminescent light sourcesHigh energyGas detector

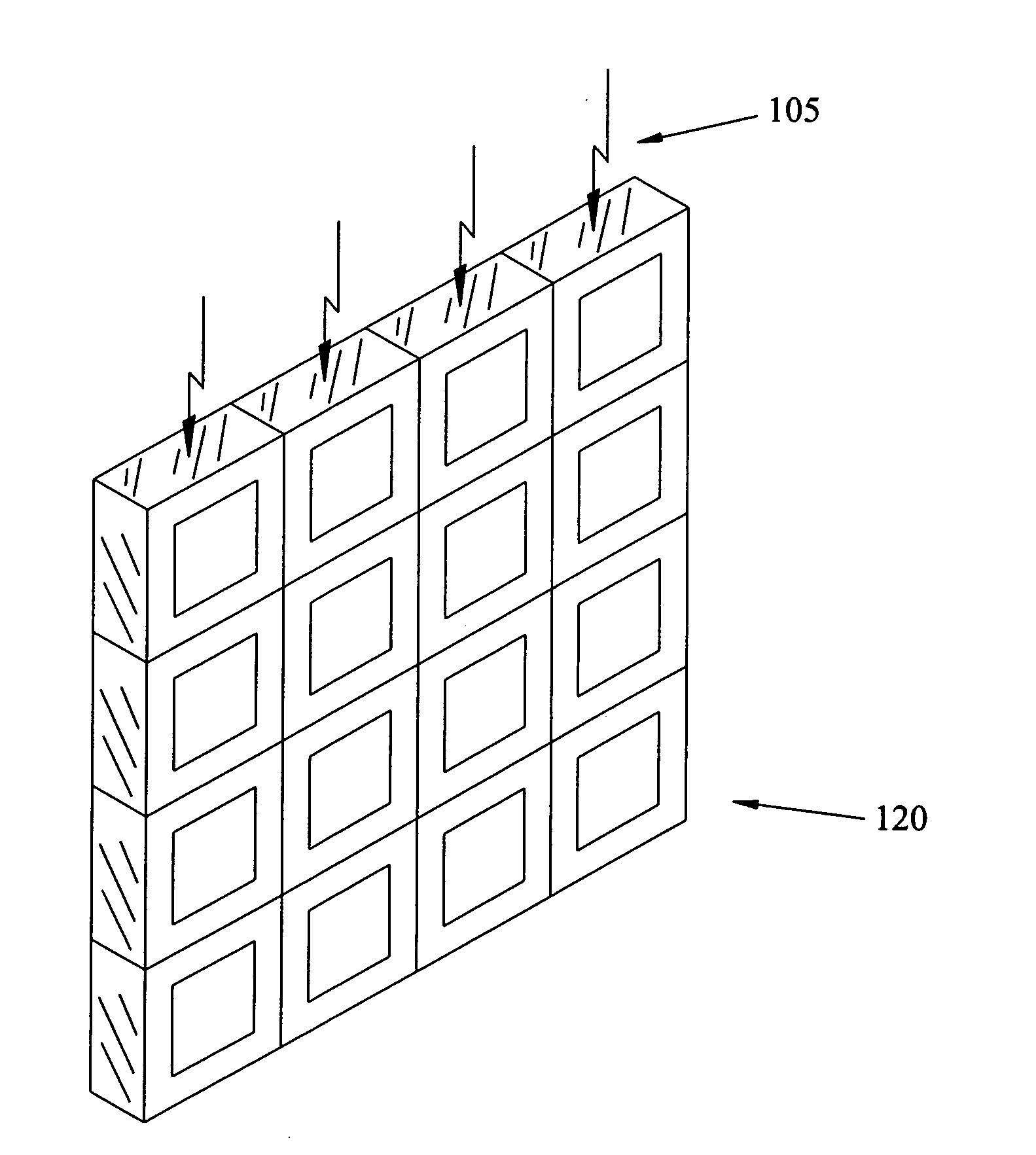

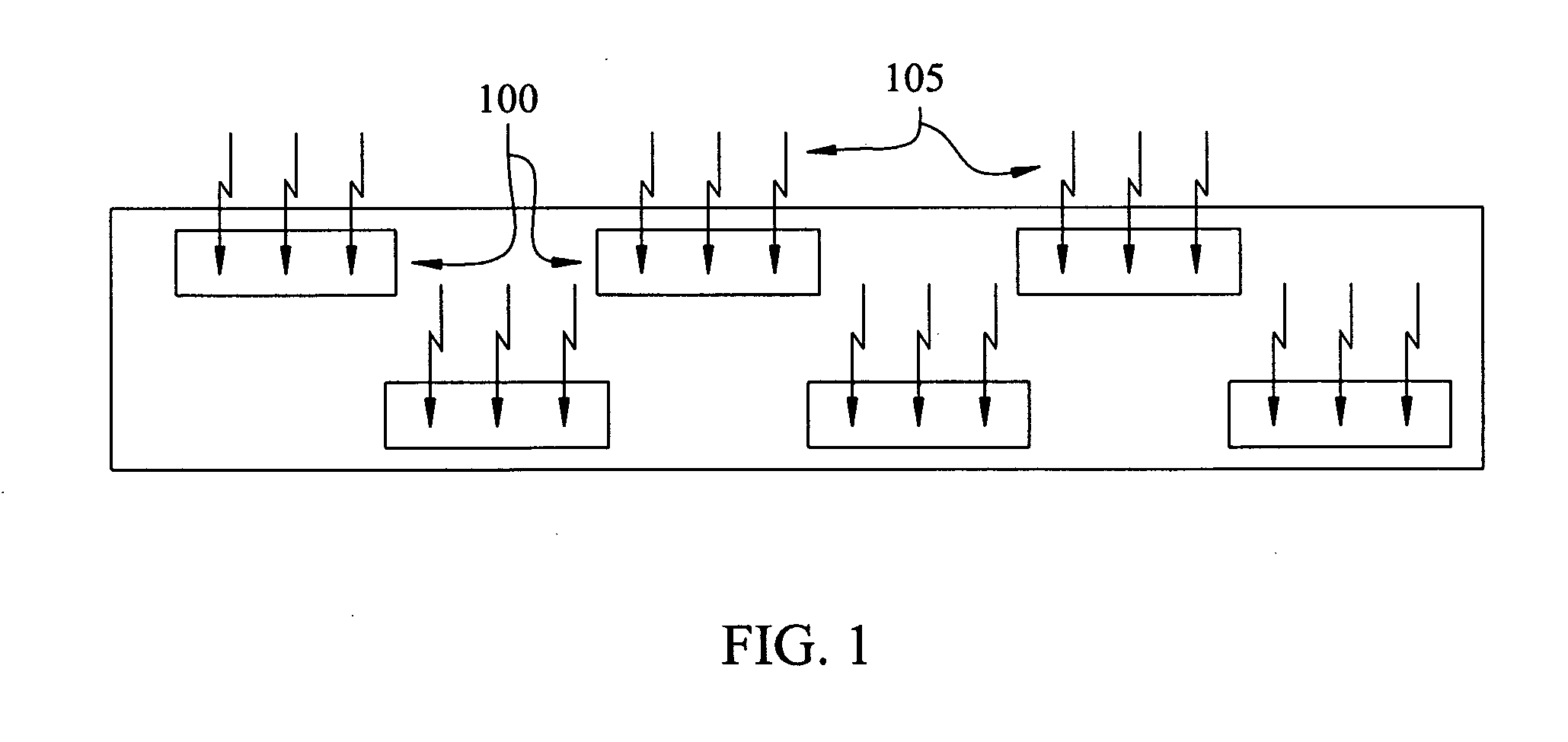

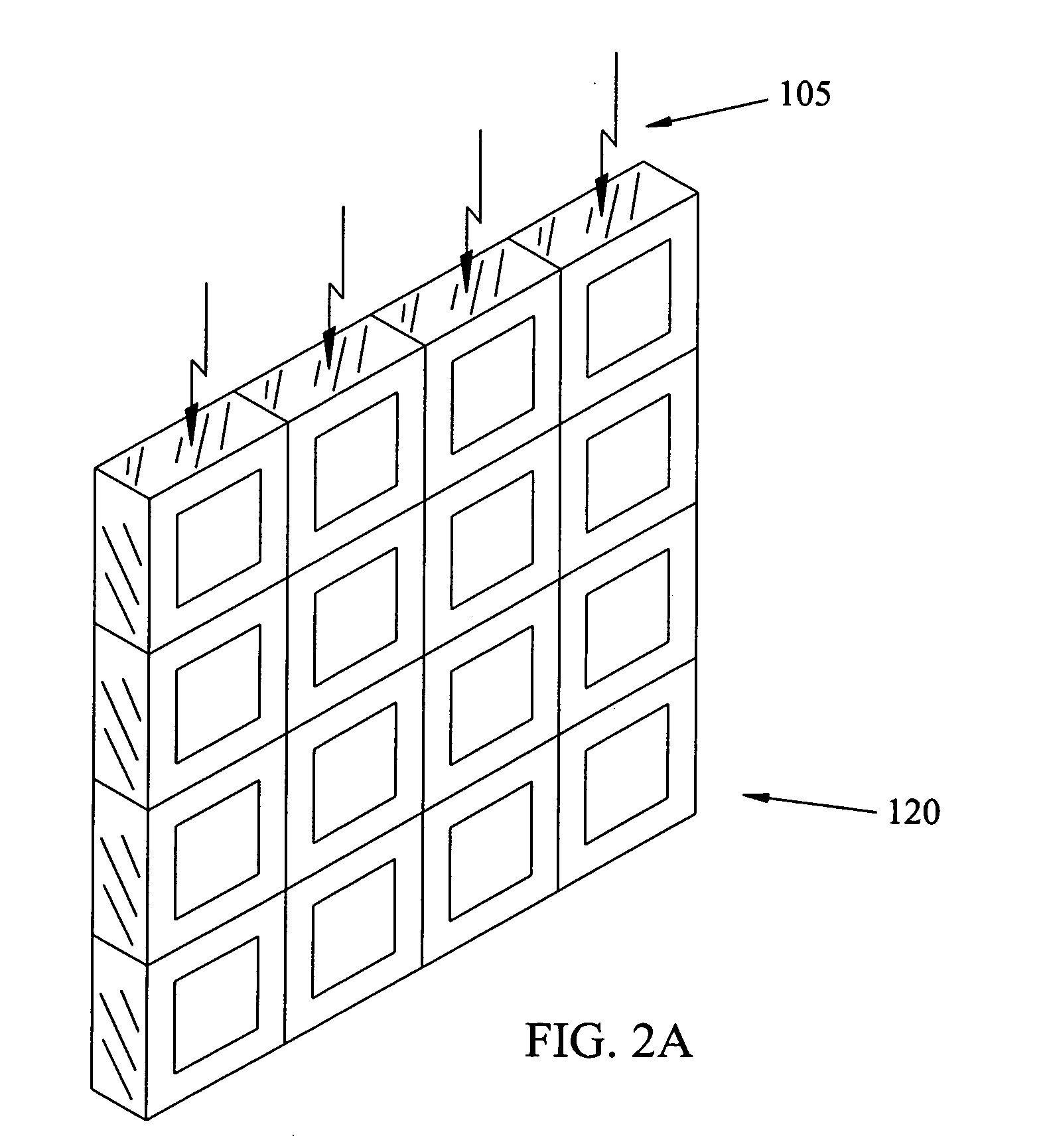

The invention provides methods and apparatus for detecting radiation including x-ray photon (including gamma ray photon) and particle radiation for radiographic imaging (including conventional CT and radiation therapy portal and CT), nuclear medicine, material composition analysis, container inspection, mine detection, remediation, high energy physics, and astronomy. This invention provides novel face-on, edge-on, edge-on sub-aperture resolution (SAR), and face-on SAR scintillator detectors, designs and systems for enhanced slit and slot scan radiographic imaging suitable for medical, industrial, Homeland Security, and scientific applications. Some of these detector designs are readily extended for use as area detectors, including cross-coupled arrays, gas detectors, and Compton gamma cameras. Energy integration, photon counting, and limited energy resolution readout capabilities are described. Continuous slit and slot designs as well as sub-slit and sub-slot geometries are described, permitting the use of modular detectors.

Owner:MINNESOTA IMAGING & ENG

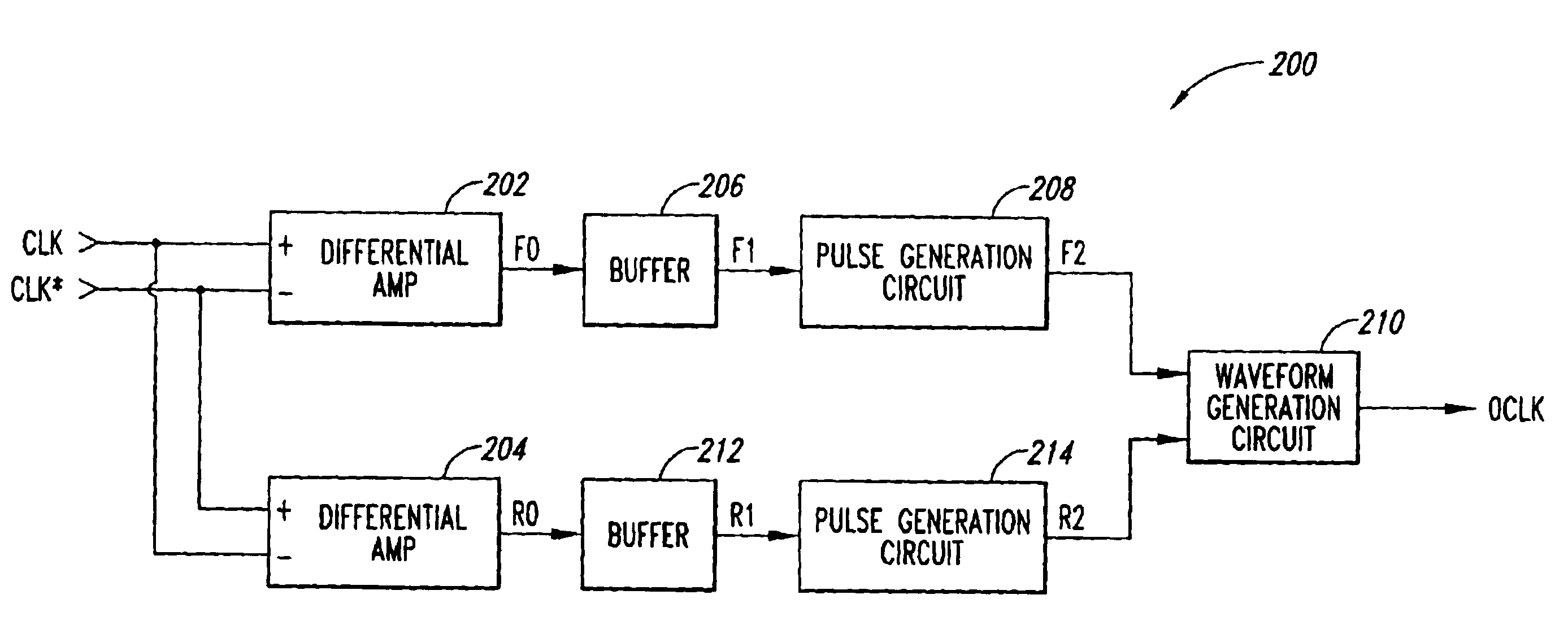

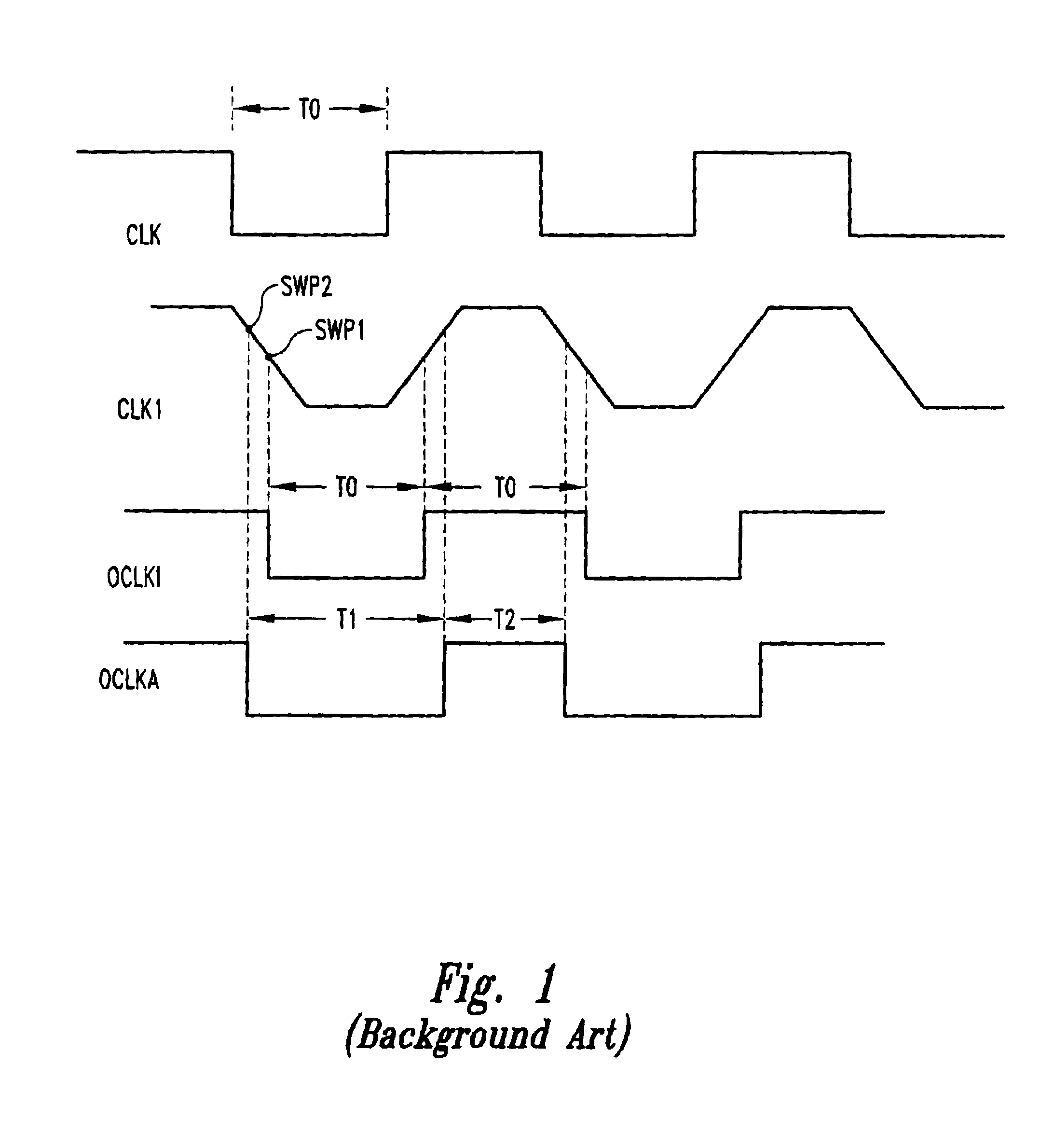

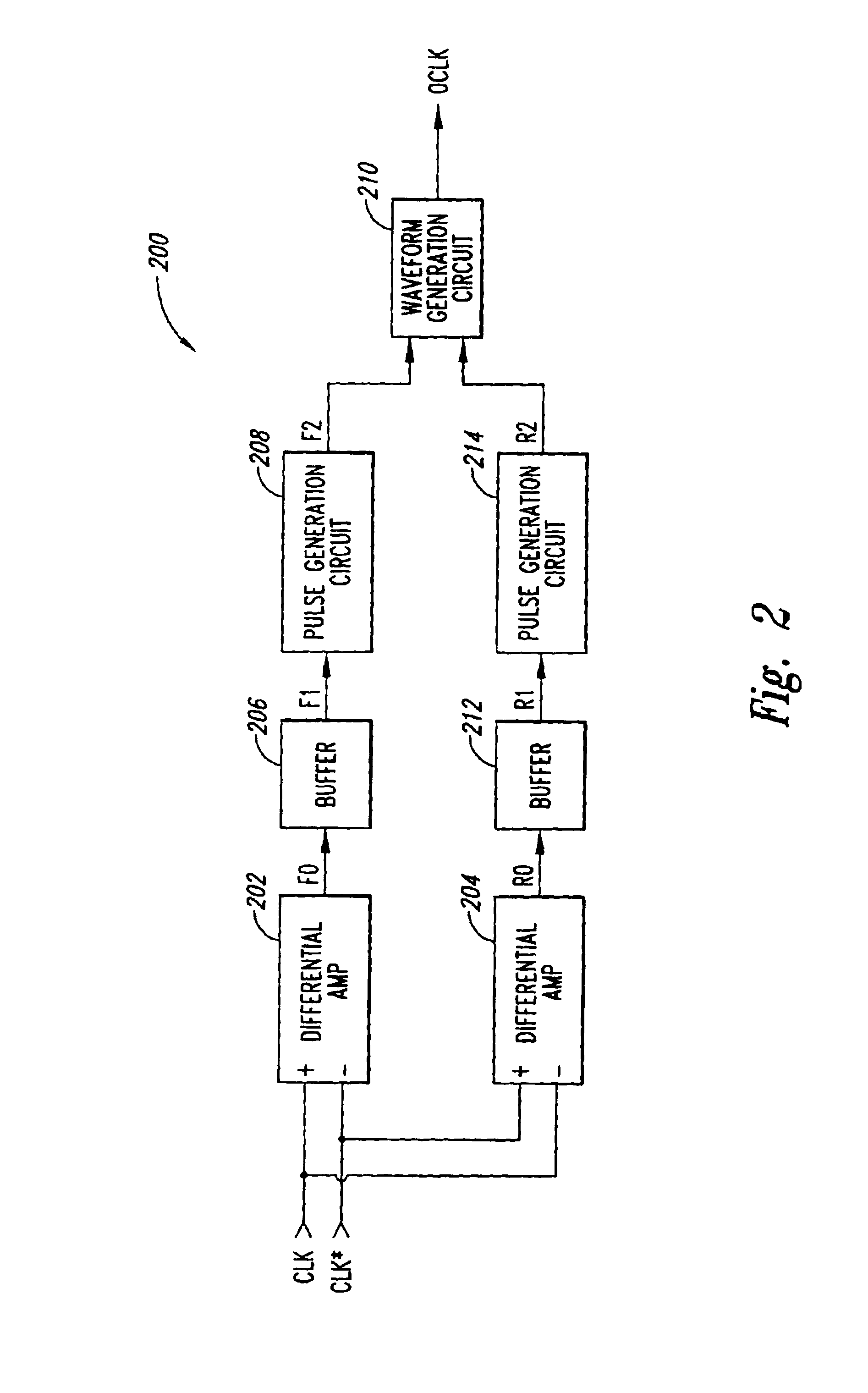

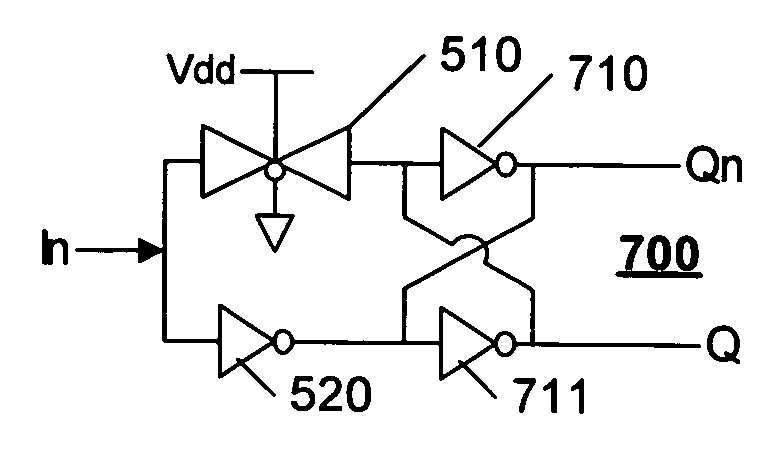

Low skew clock input buffer and method

InactiveUS6847582B2Reliability increasing modificationsDigital storageAudio power amplifierLogic state

An input buffer includes first and second cross-coupled differential amplifiers. Each amplifier drives a buffer signal from a first logic state to a second logic state at a first slew rate when input signal transitions from a first logic state to a second logic state and a complementary input signal transitions from the second logic state to the first logic state, and drives the buffer signal from the second logic state to the first logic state at a second slew rate when the signal transitions are the complement of these previous transitions. An output circuit generates a first edge of an output signal when the buffer signal from the first amplifier transitions from the first logic state to the second logic state and generates a second edged of the output signal when the buffer signal from the second amplifier transitions from the first to the second logic state.

Owner:MICRON TECH INC

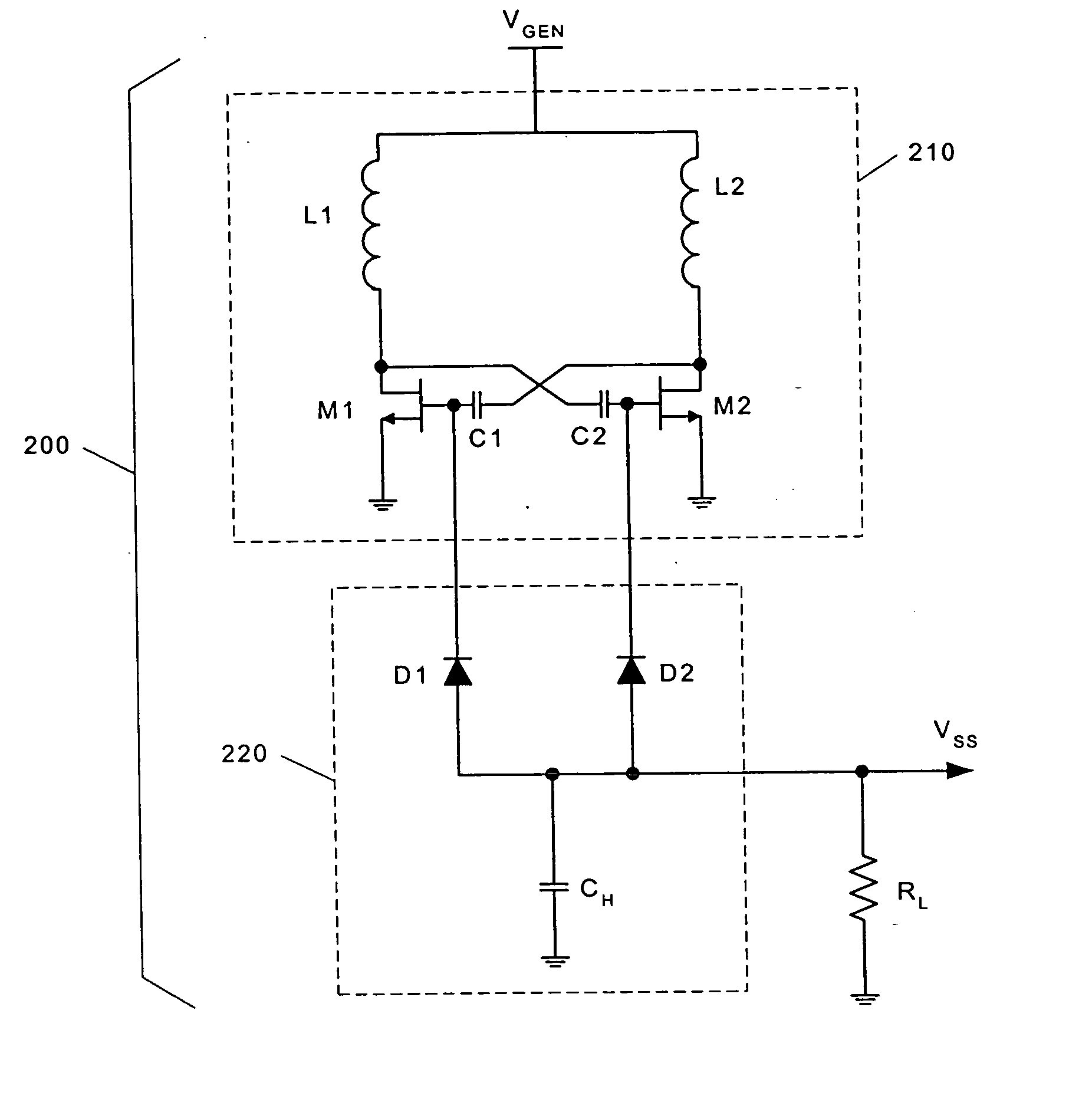

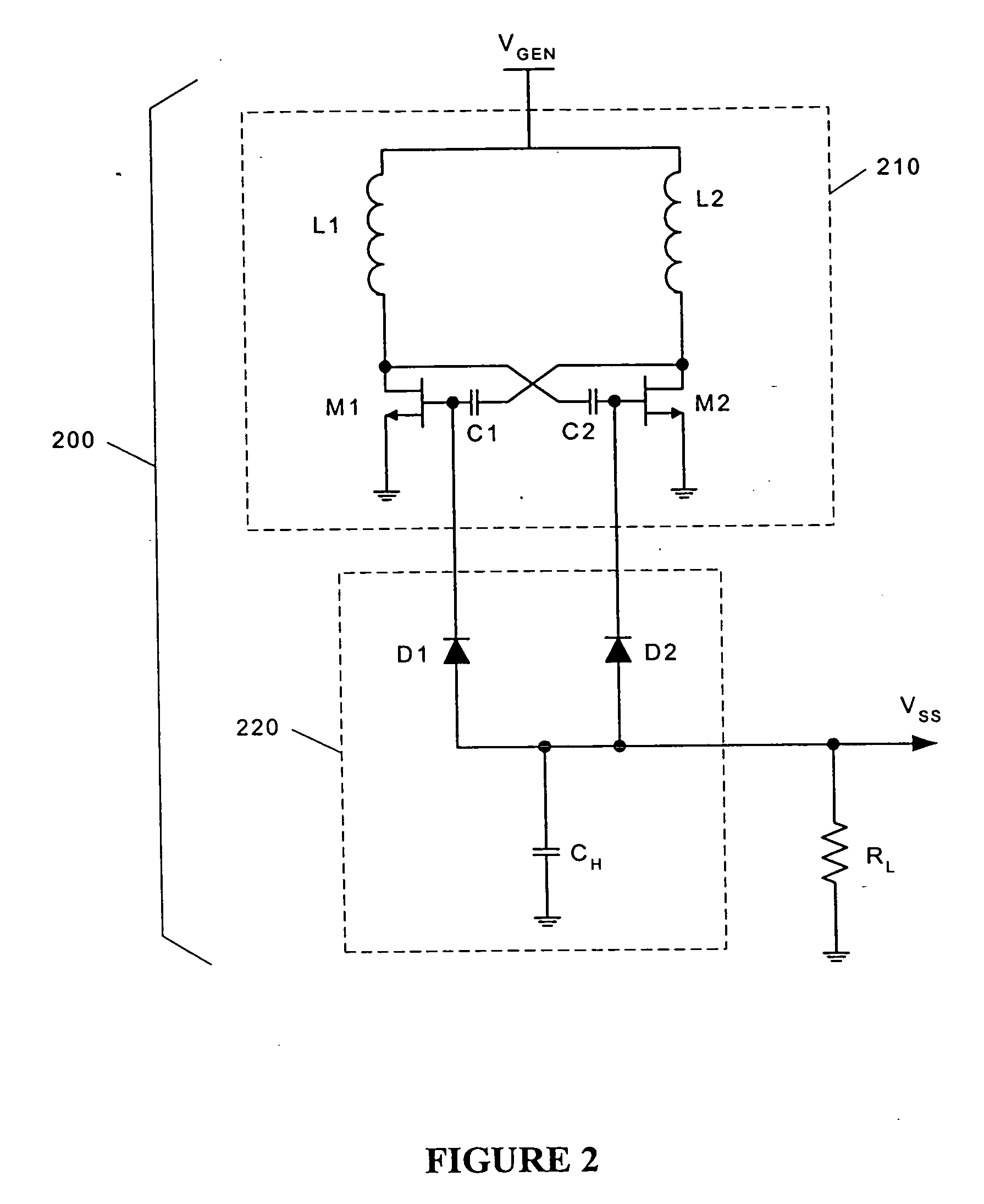

MMIC DC-to-DC converter

InactiveUS20050242795A1Improve efficiencyImprove reliabilityDc-dc conversionElectric variable regulationConvertersLow noise

An improved Monolithic Microwave Integrated Circuit DC-to-DC voltage converter fabricated in GaAs MESFET technology is introduced. The converter comprises a differential oscillator having crossed-coupled symmetrical inductors that ensure low-noise operation. The converter further comprises a highly-efficient synchronous rectifier and a start-up enable circuit.

Owner:AL KURAN SHIHAB +1

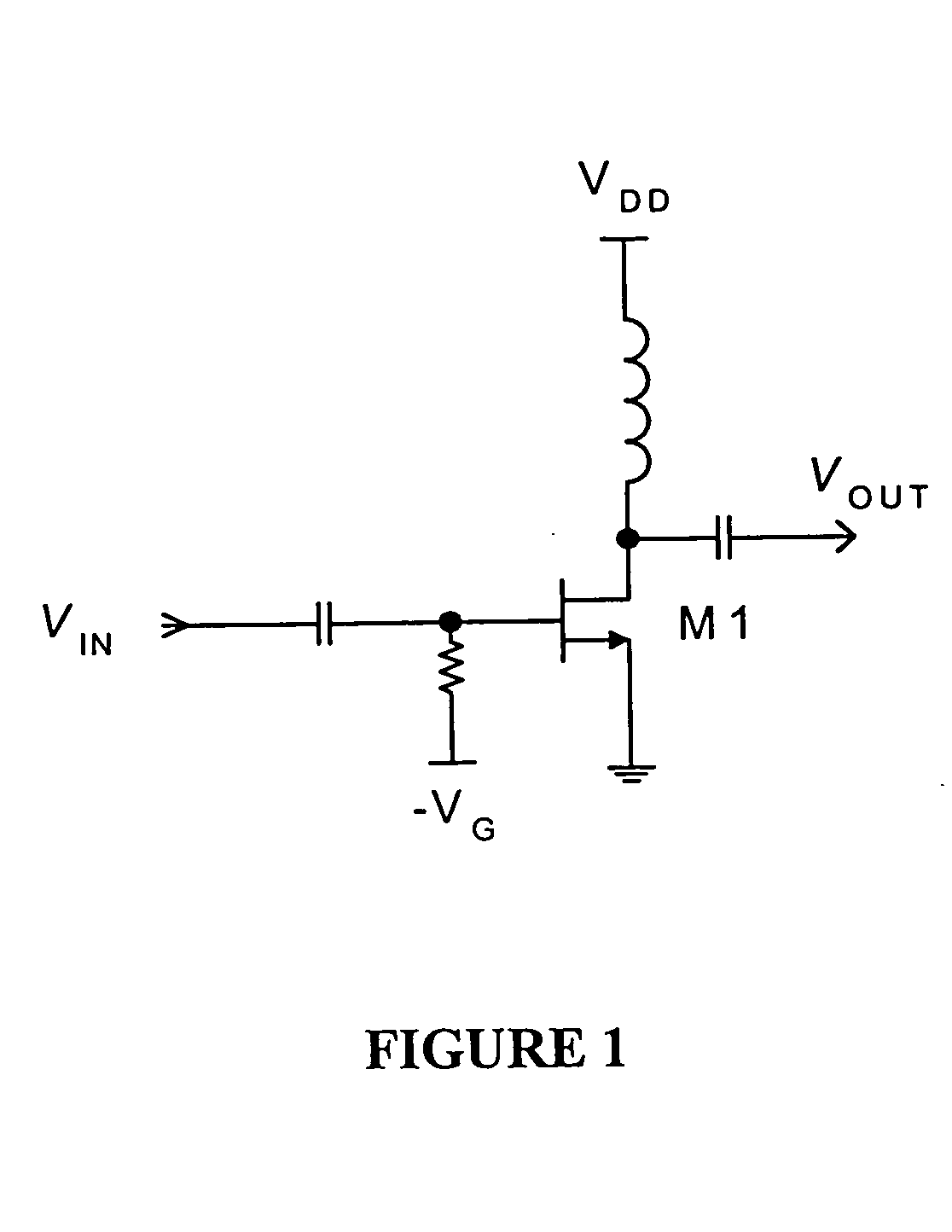

Gain boosting RF gain stage with cross-coupled capacitors

ActiveUS7697915B2Tighter current flow controlHigh gainHigh frequency amplifiersRadio transmissionCapacitanceGain stage

A RF differential gain stage has cross-coupled capacitors between input and output nodes of the amplifier stage to boost gain. The gain boost allows cancellation of the series resistance of an inductive load of the amplifier stage.

Owner:QUALCOMM INC

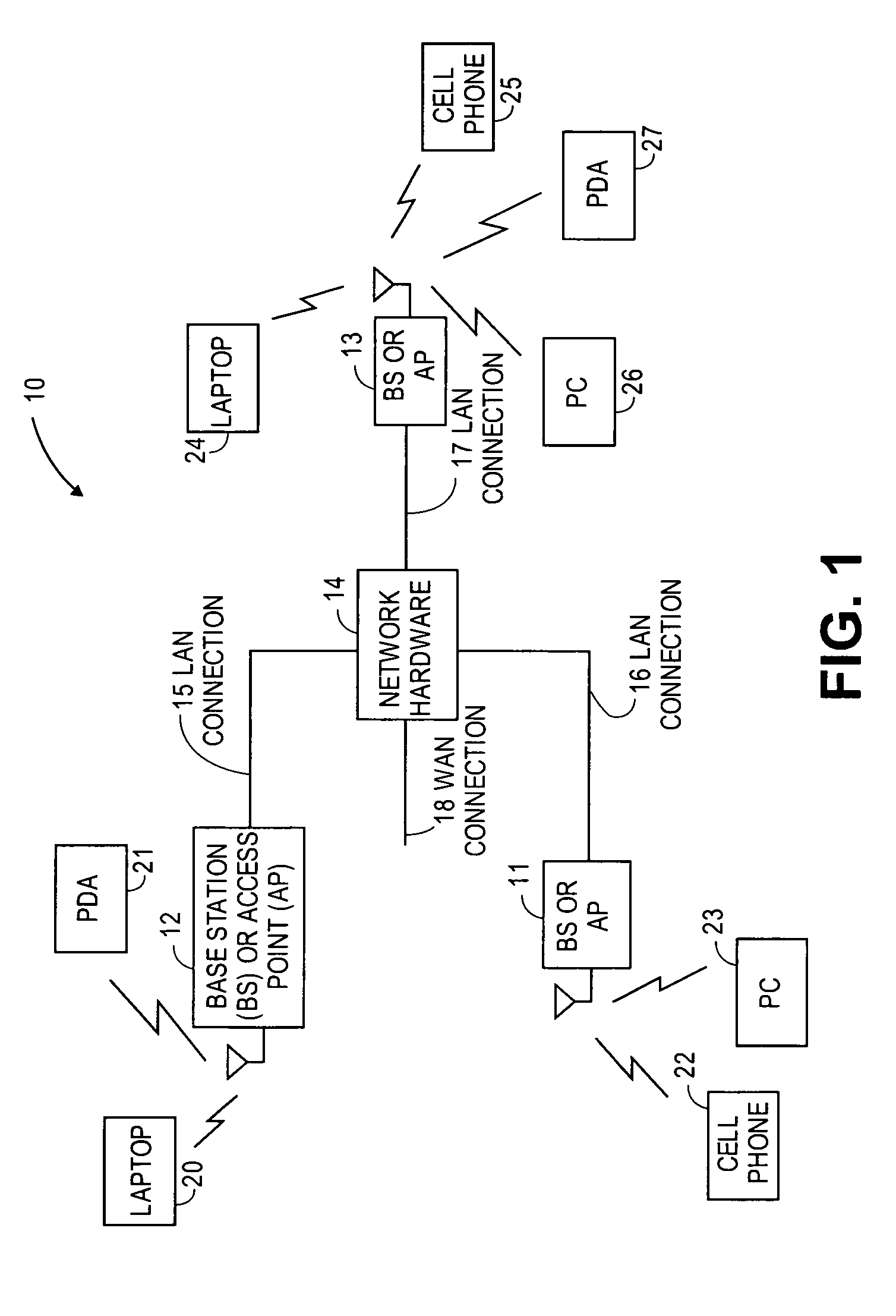

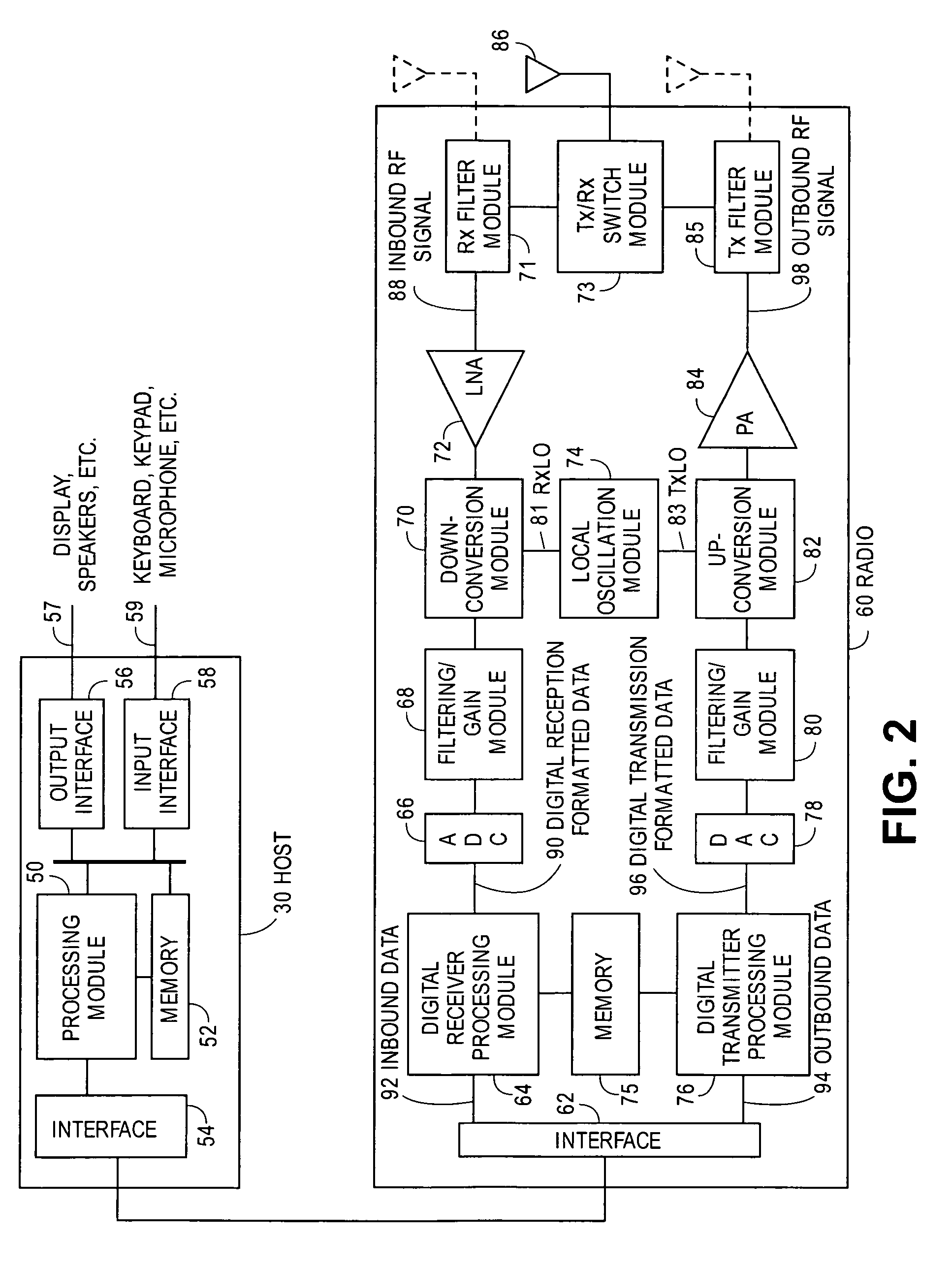

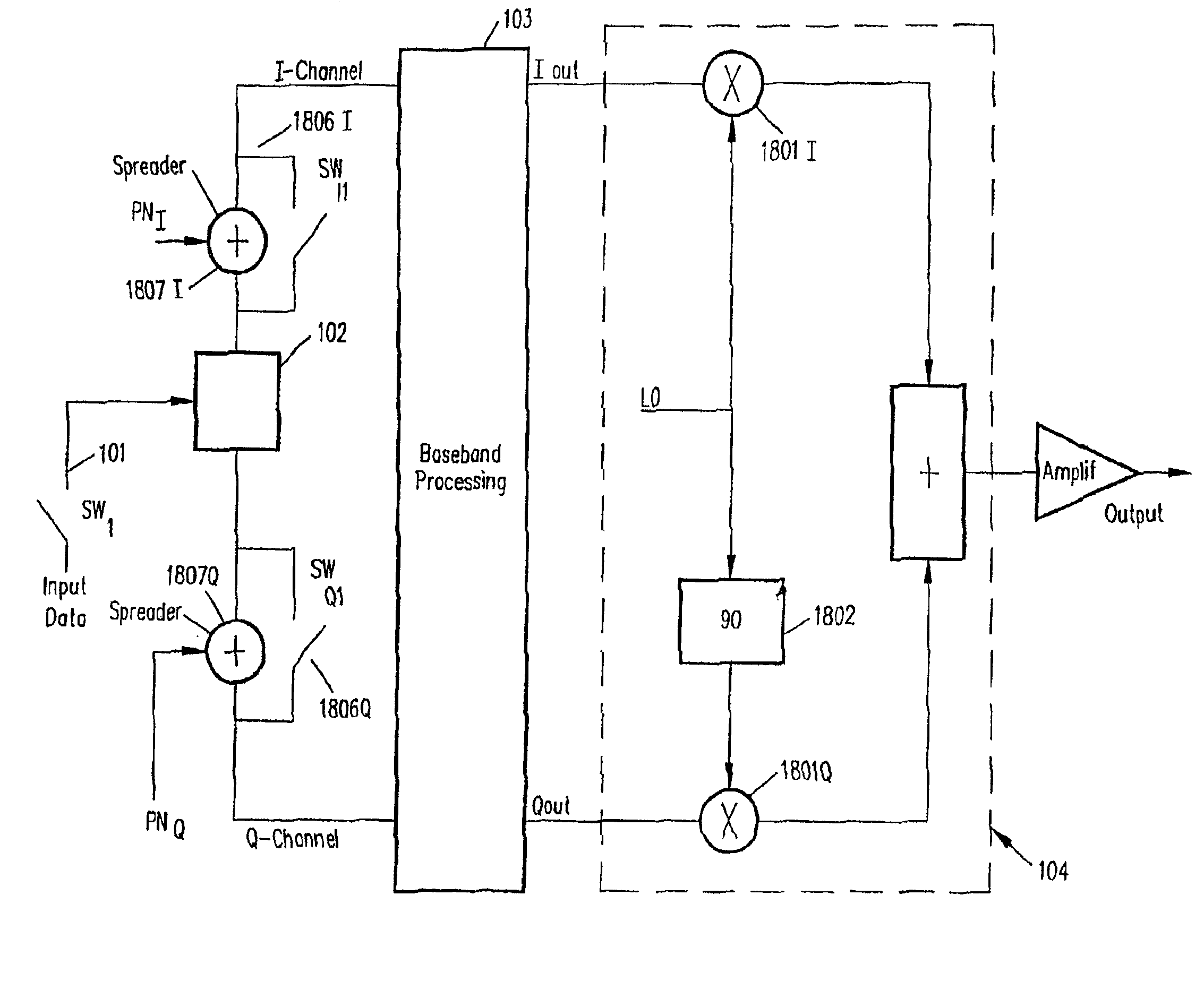

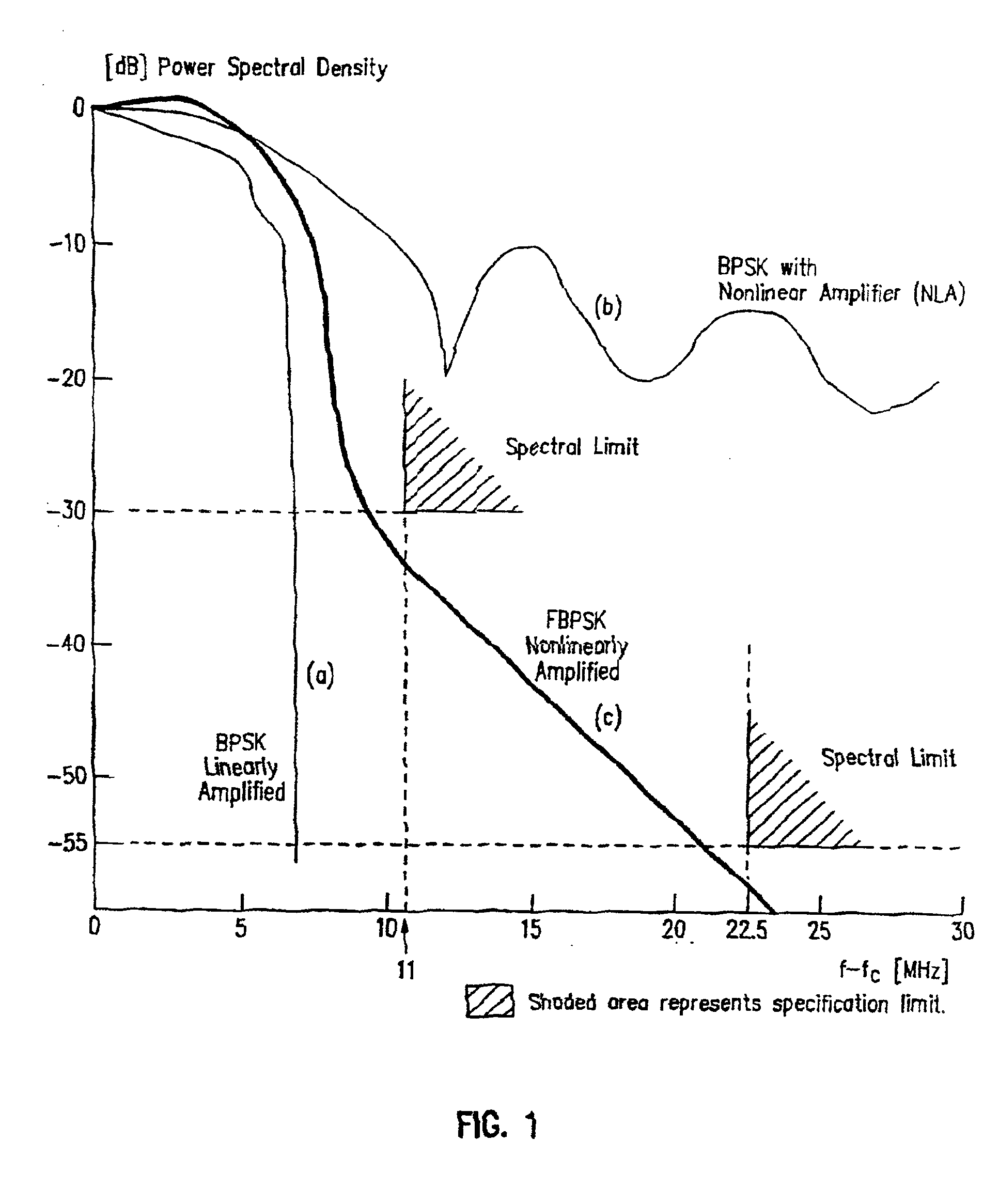

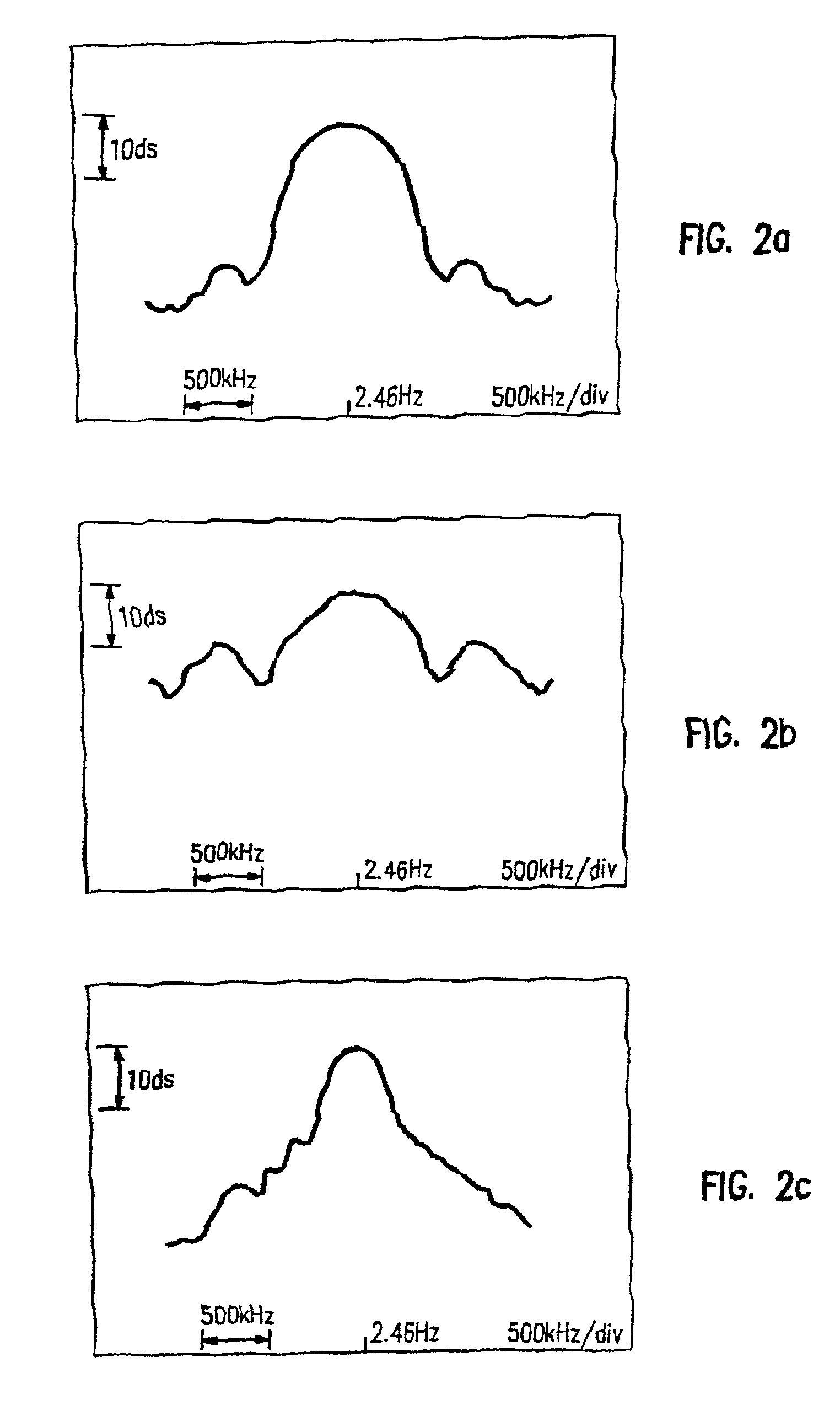

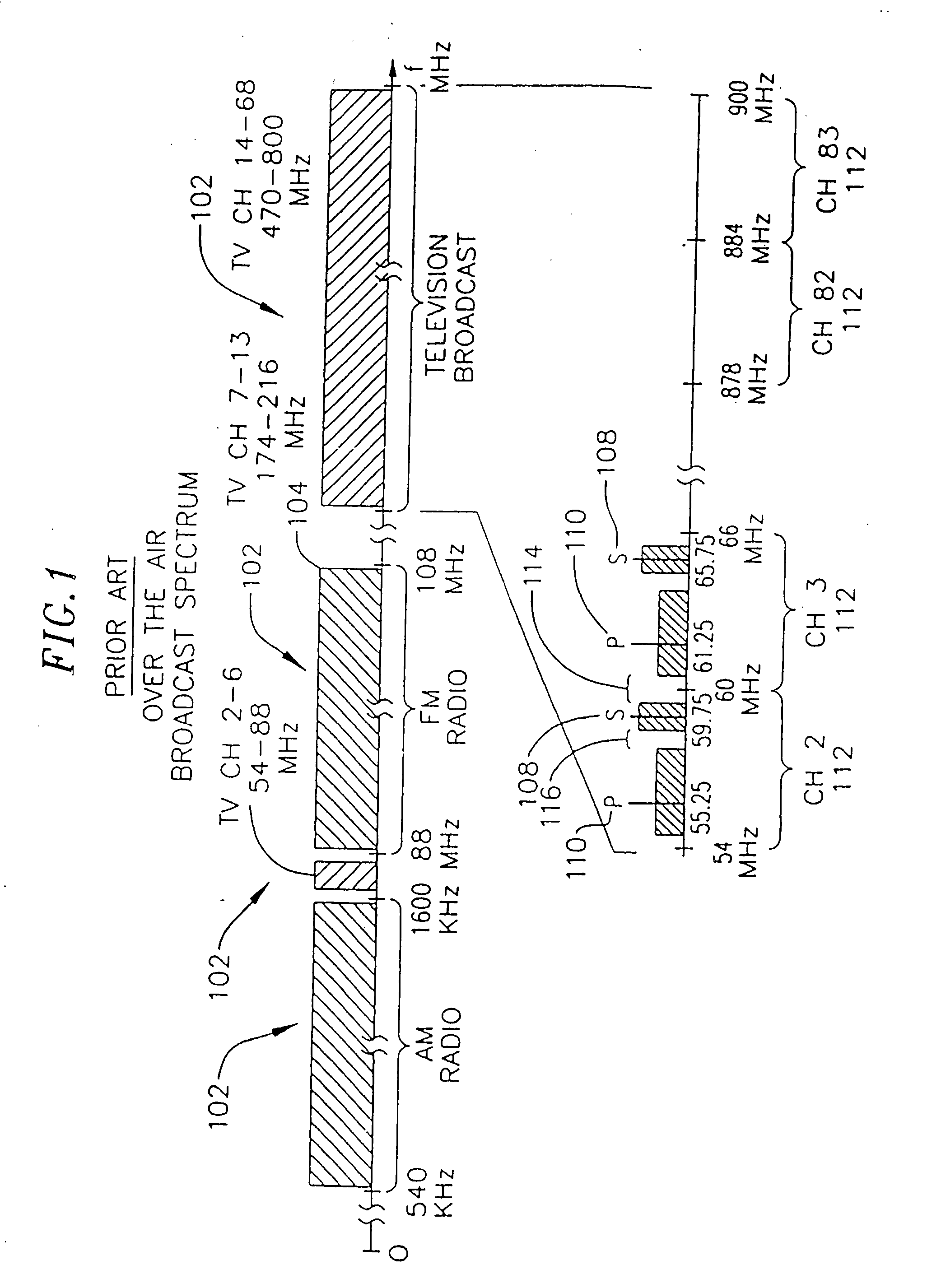

FMOD transceivers including continuous and burst operated TDMA, FDMA, spread spectrum CDMA, WCDMA and CSMA

InactiveUS6928101B2Improve performanceLow costAsymmetric modulation circuitsPhase-modulated carrier systemsModem deviceFrequency spectrum

Binary and Quadrature Feher's Modulation (F-Modulation, or FMOD) Transmitter-Receiver systems and circuits exhibit reduced envelope fluctuation and peak radiation, and increased efficiency. A subclass of these systems has a constant envelope. They advantageously provide lower power operation with improved performance including robust BER performance, and compatibility with both linearly and nonlinearly amplified narrow spectrum, and without disadvantages of conventional BPSK, DBPSK QPSK and pi / 4-QPSK. Feher's BPSK (FBPSK) is an improved efficiency transmitter which is compatible with conventional BPSK receivers. FBPSK modems are based on using quadrature structure where Q-channel data is inserted in quadrature with I-channel data for certain applications. The Q-channel data may be “offset” from the I-channel data by an amount selectable between zero and a specified time. Further improvement in the spectrum is attained using correlation between I and Q channels. FBPSK modem is shown to meet the IEEE 802.11 specified spectral direct sequence spread spectrum mask (−30 dB point) for wireless LAN, and leads to an output power gain of 6.5 dB over conventional BPSK modems. The cross-coupled quadrature FMOD structure is also suitable for continuous mode and for burst operated TDMA, FDMA, CDMA, WCDMA and CSMA Frequency Modulation Quadrature AM (QAM), QPSK and offset QPSK, as well as pi / 4-shifted QPSK modems / processors. Reduced modulation index Gaussian FSK (GFSK), multilevel FM and cross-coupled Quadrature Amplitude Modulated (QAM) transmitters and combinations of these modulations and corresponding coherent demodulators are disclosed. Controlled rise and fall time descriptions of burst operated systems are included.

Owner:INTEL CORP

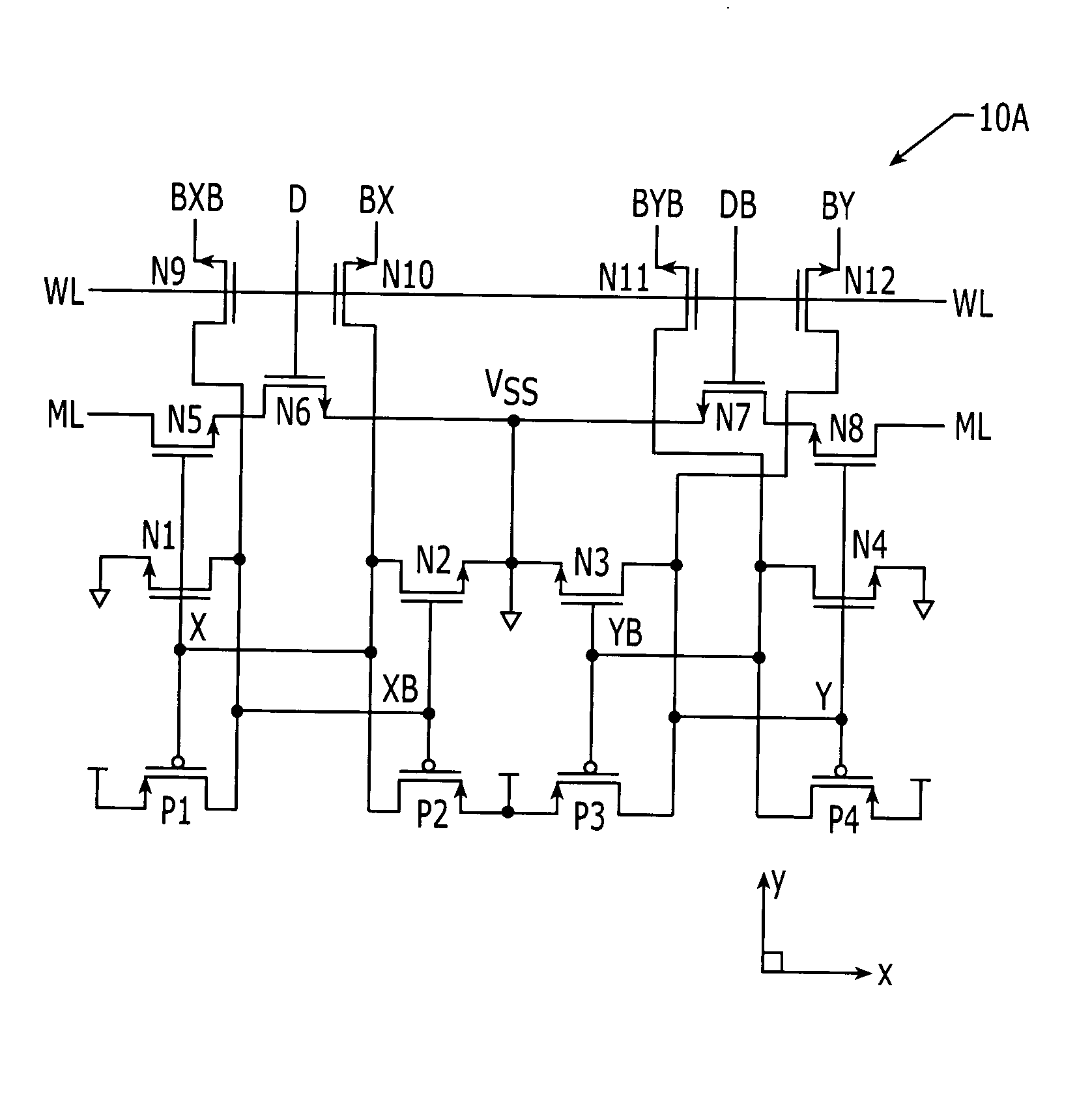

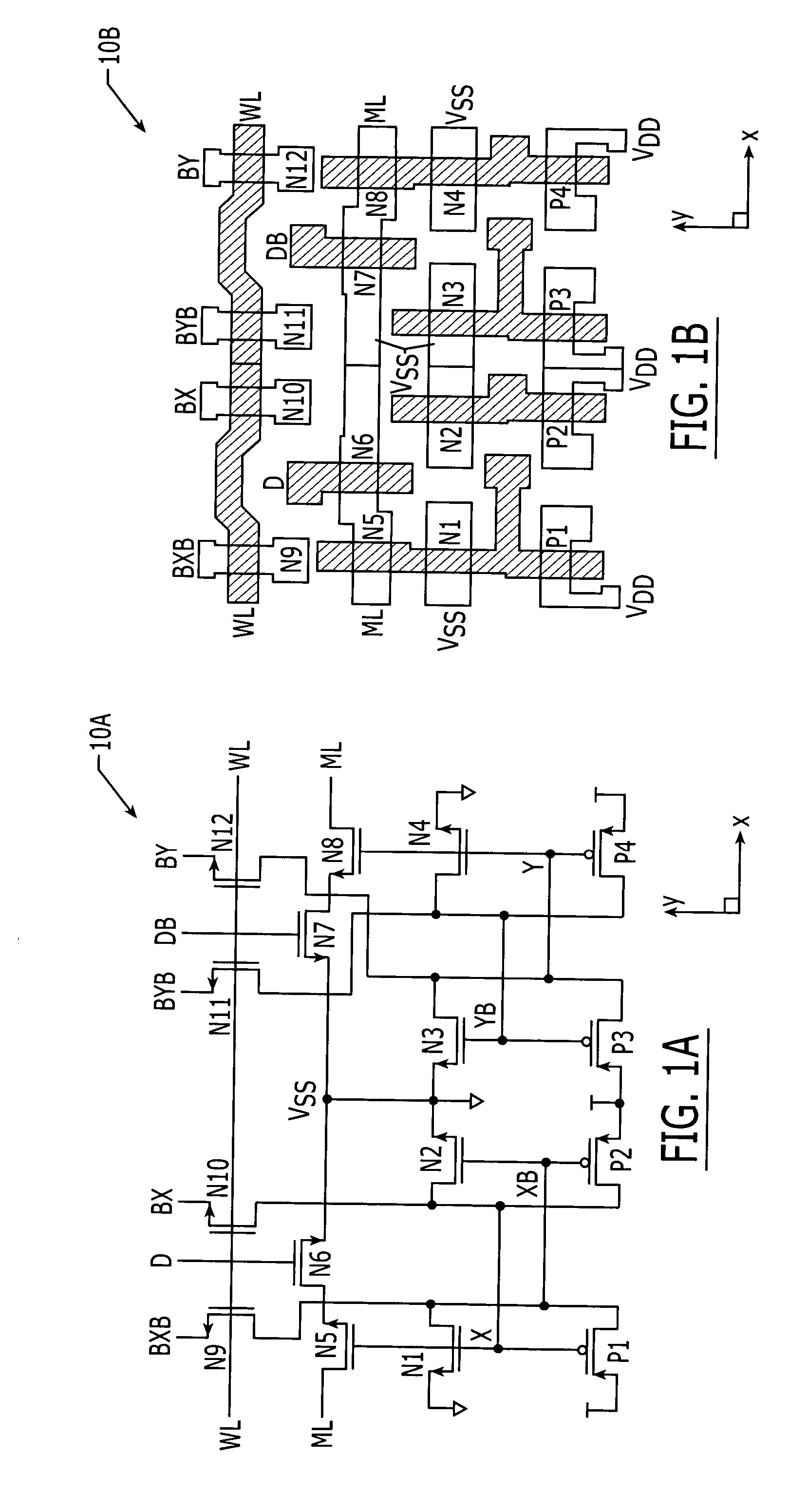

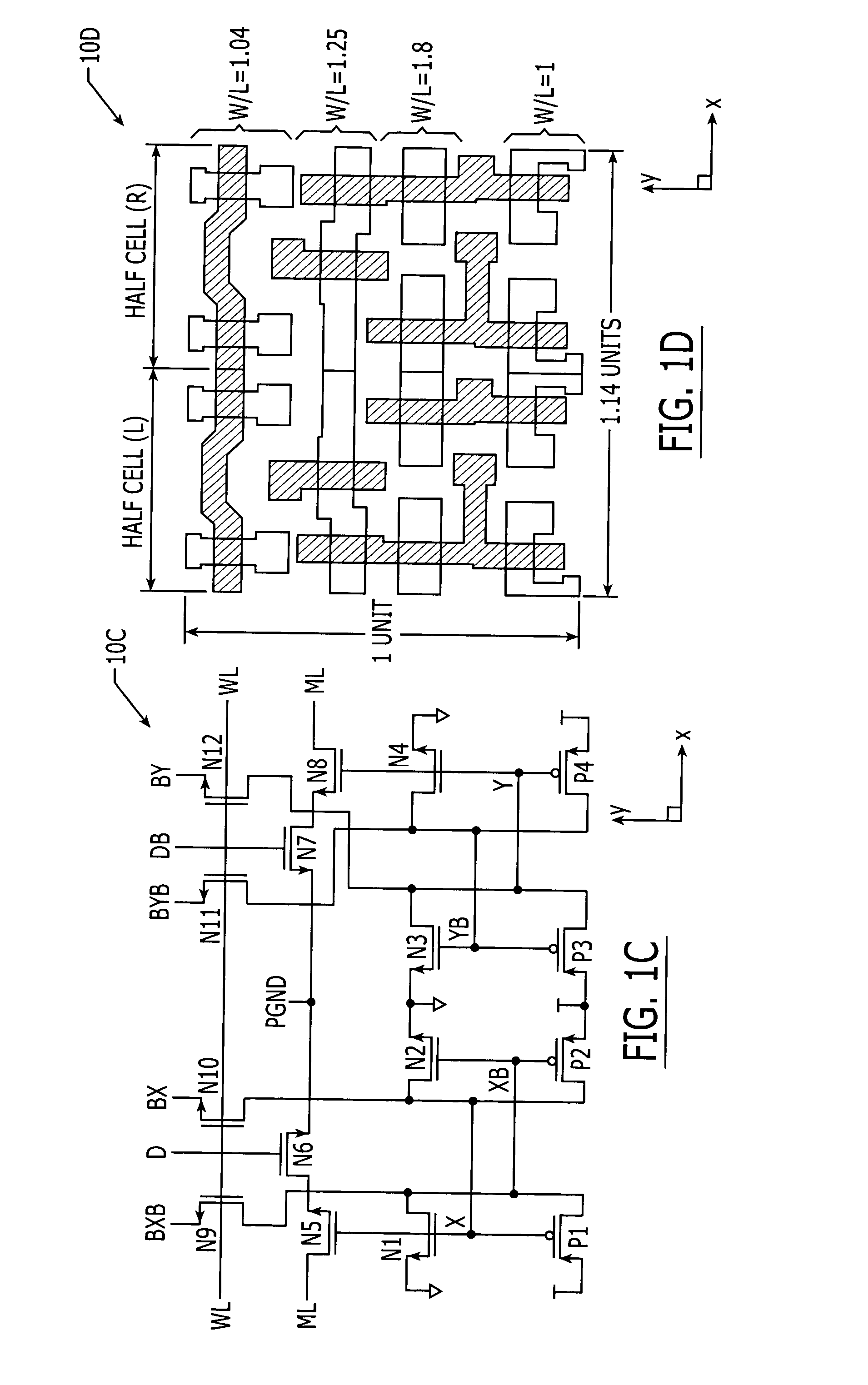

Ternary content addressable memory (TCAM) cells with small footprint size and efficient layout aspect ratio

InactiveUS20050135134A1Small layout footprint sizeEnhance scalability and uniformityDigital storageExtensibilityEngineering

Ternary CAM cells are provided that have extremely small layout footprint size and efficient layout aspect ratios that enhance scalability. The cells also have high degrees of symmetry that facilitate high yield interconnections to bit, data and match lines. A 16T ternary CAM cell includes first and second pairs of access transistors that extend adjacent a first side of the cell, and first and second pairs of cross-coupled inverters that extend adjacent a second side of the cell. First and second halves of a 4T compare circuit are also provided. The first half of the 4T compare circuit is positioned so that is extends between the first pair of access transistors and the first pair of cross-coupled inverters. Similarly, the second half of the 4T compare circuit is positioned so that it extends between the second pair of access transistors and the second pair of cross-coupled inverters.

Owner:AVAGO TECH INT SALES PTE LTD

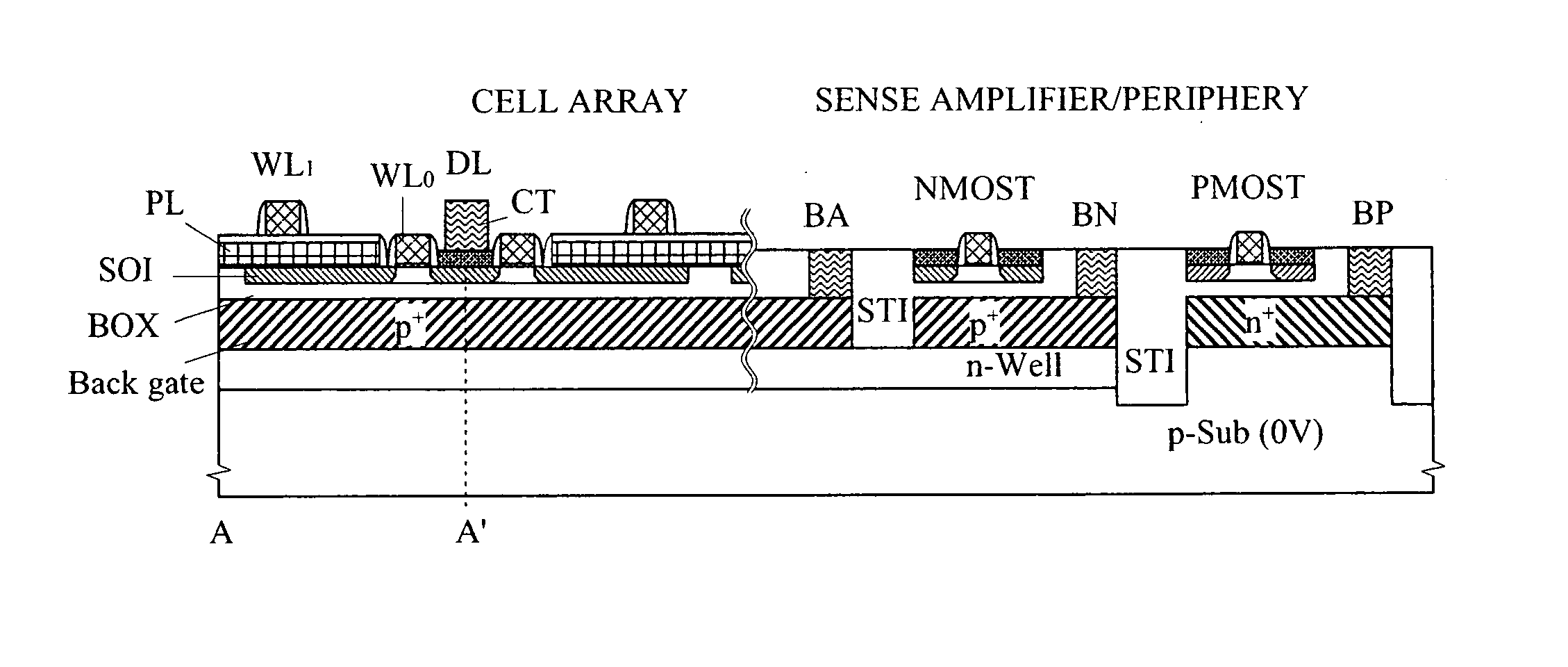

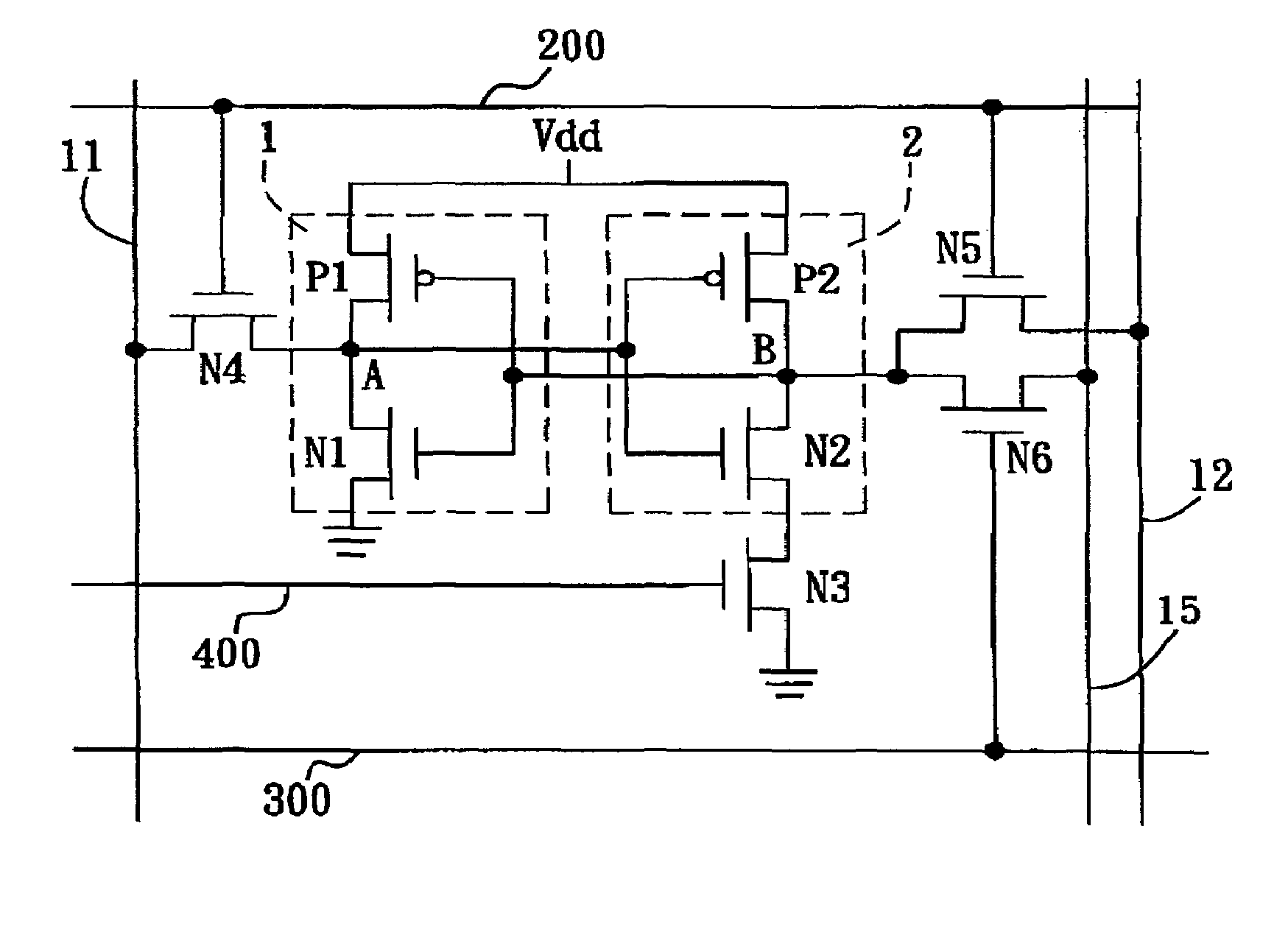

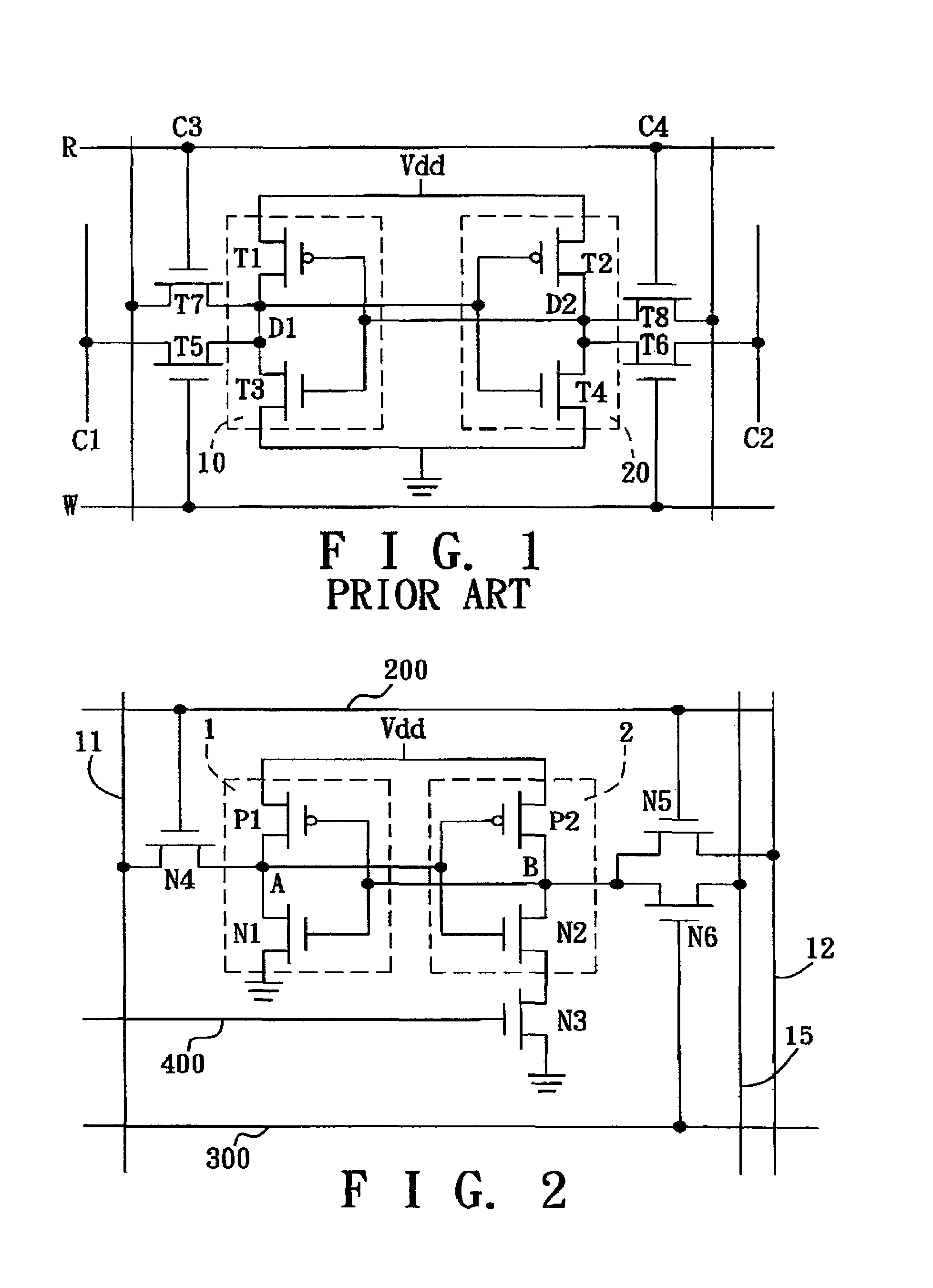

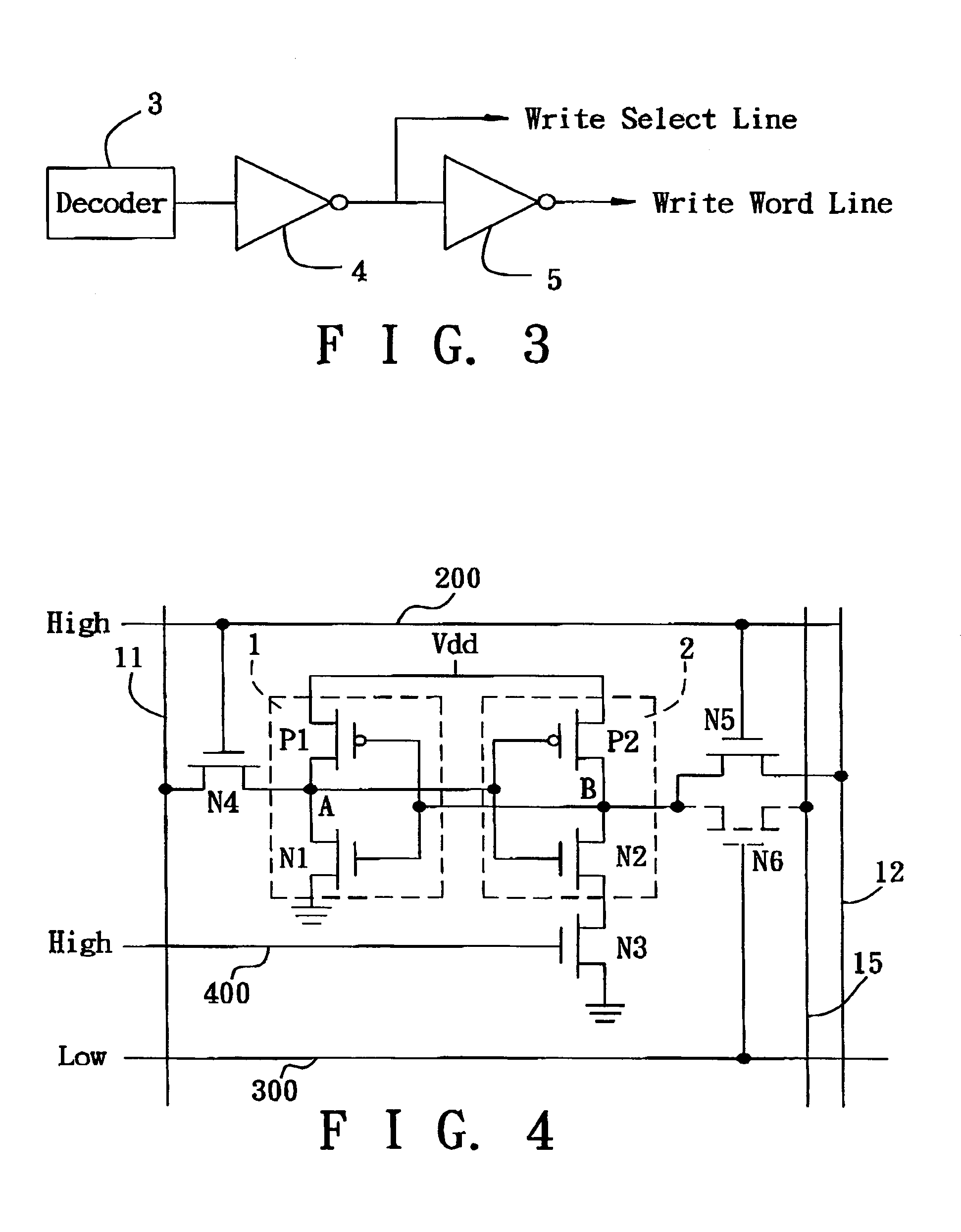

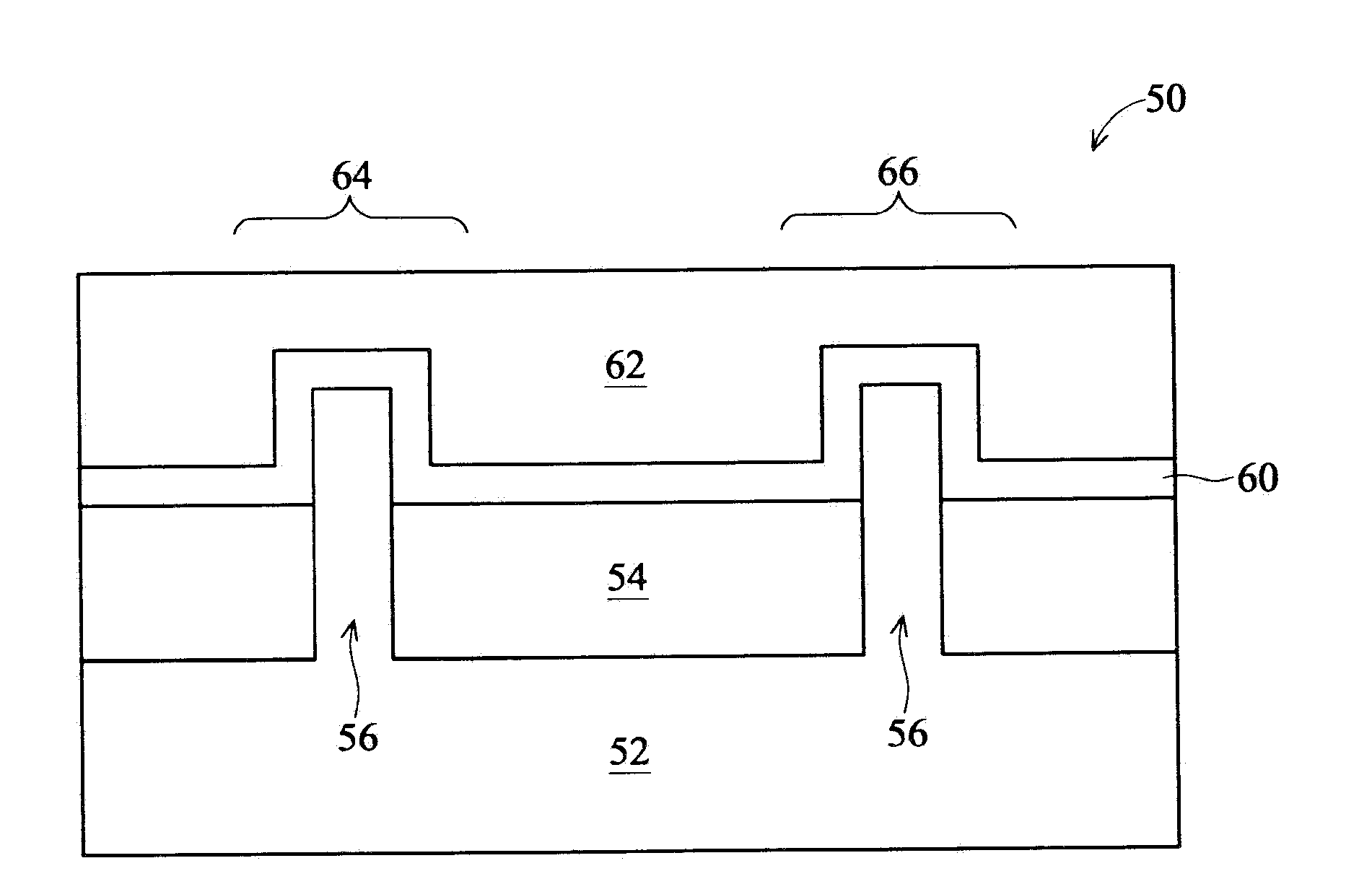

Semiconductor device

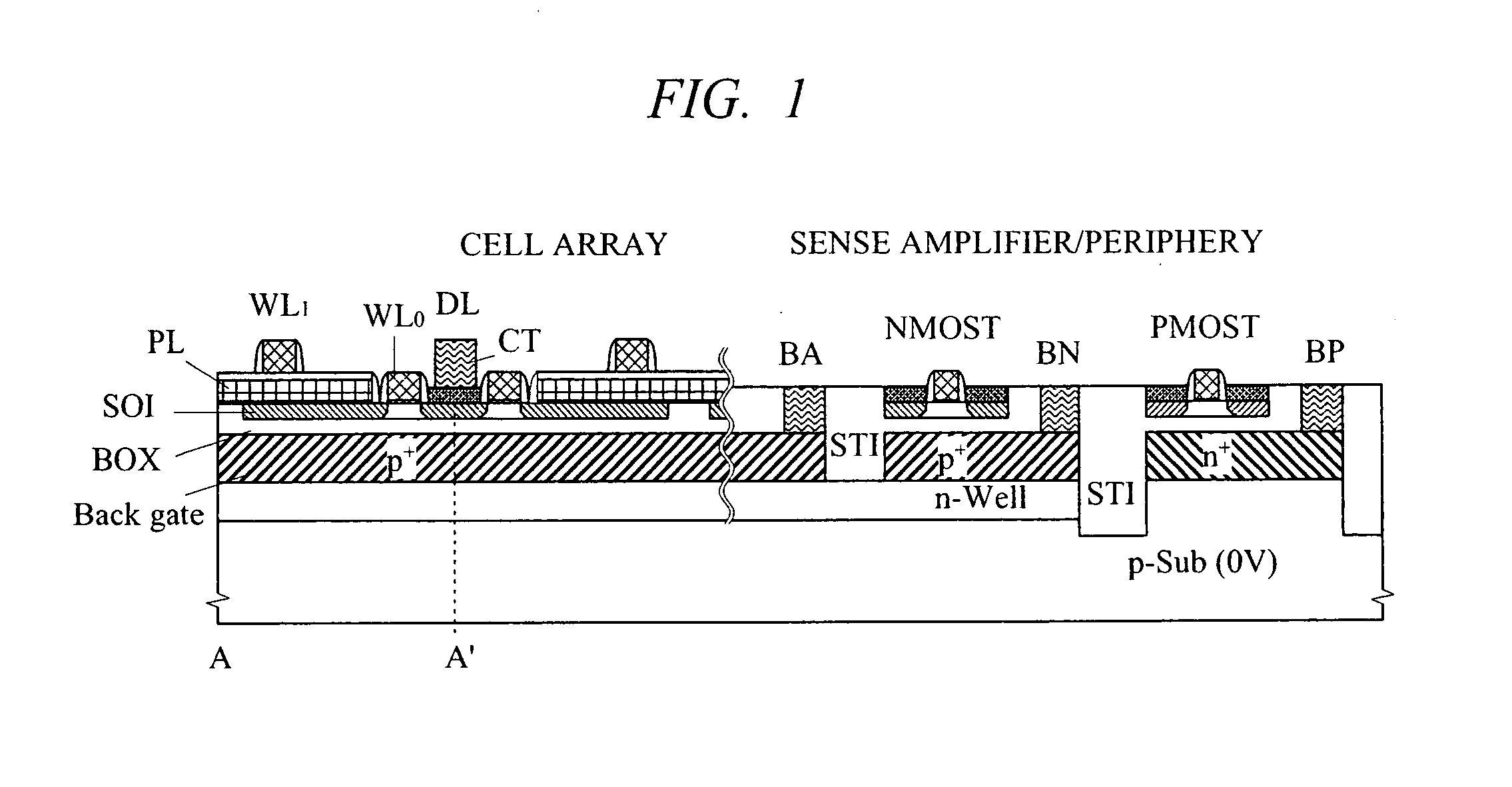

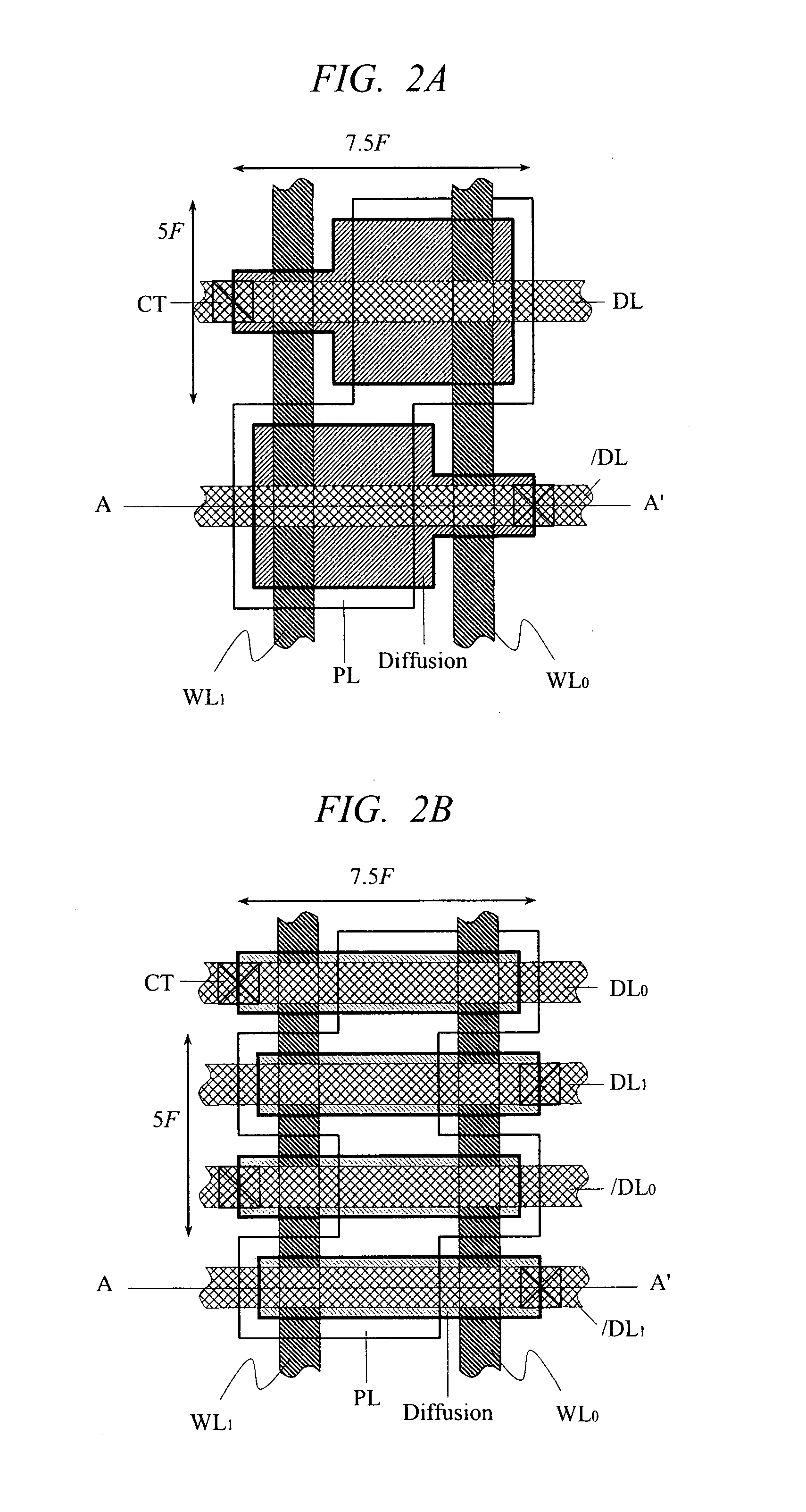

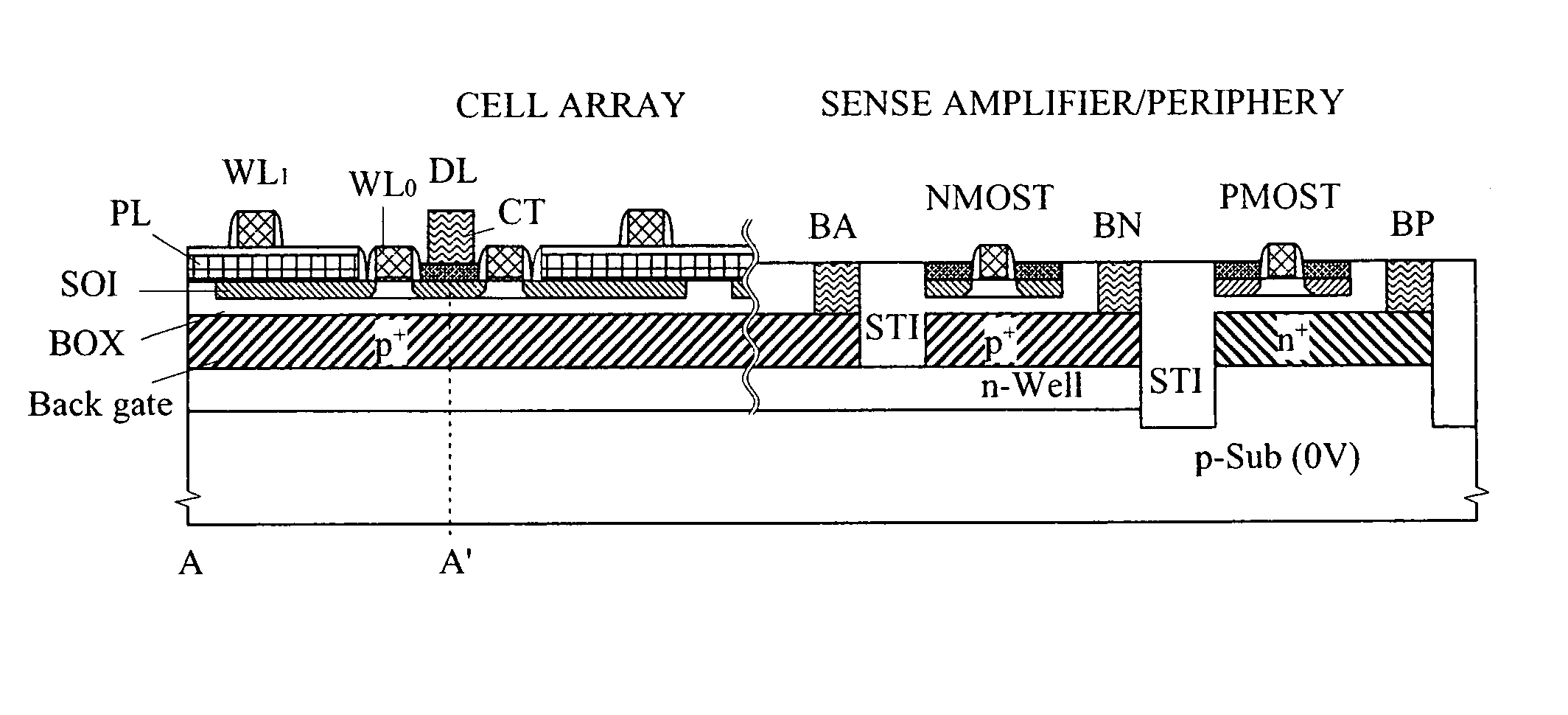

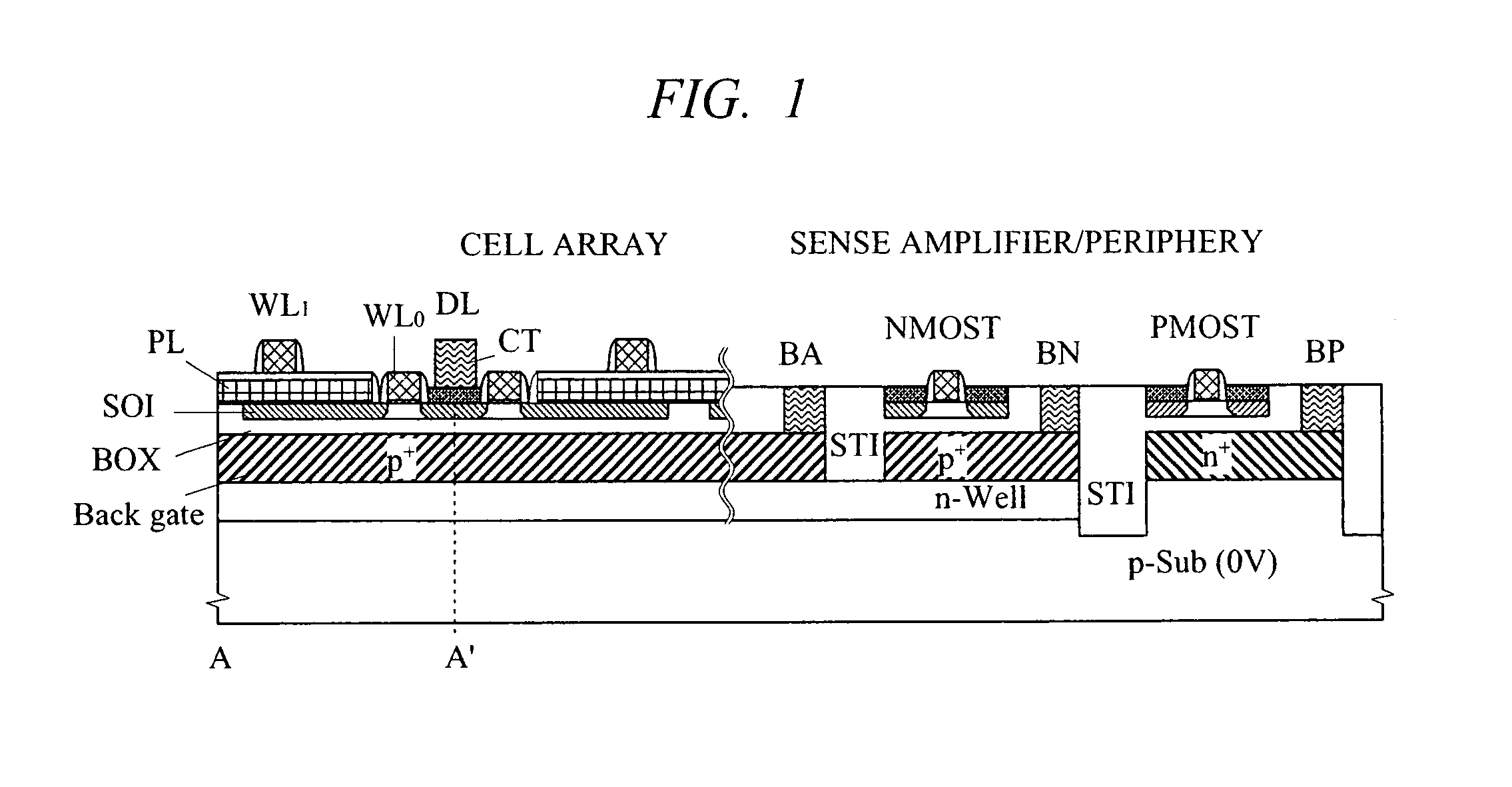

InactiveUS20090003105A1Run at high speedSmall sizeTransistorSolid-state devicesJunction leakageAudio power amplifier

A high-speed and low-voltage DRAM memory cell capable of operating at 1 V or less and an array peripheral circuit are provided. A DRAM cell is comprised of a memory cell transistor and planar capacitor which utilize a FD-SOI MOST structure. Since there is no junction leakage current, loss of stored charge is eliminated, and the low-voltage operation can be realized. Further, a gate and a well in a cross-coupled type sense amplifier using FD-SOI MOSTs are connected. By this means, a threshold value dynamically changes and high-speed sensing operation can be realized.

Owner:HITACHI LTD

Semiconductor device

A high-speed and low-voltage DRAM memory cell capable of operating at 1 V or less and an array peripheral circuit are provided. A DRAM cell is comprised of a memory cell transistor and planar capacitor which utilize a FD-SOI MOST structure. Since there is no junction leakage current, loss of stored charge is eliminated, and the low-voltage operation can be realized. Further, a gate and a well in a cross-coupled type sense amplifier using FD-SOI MOSTs are connected. By this means, a threshold value dynamically changes and high-speed sensing operation can be realized.

Owner:HITACHI LTD

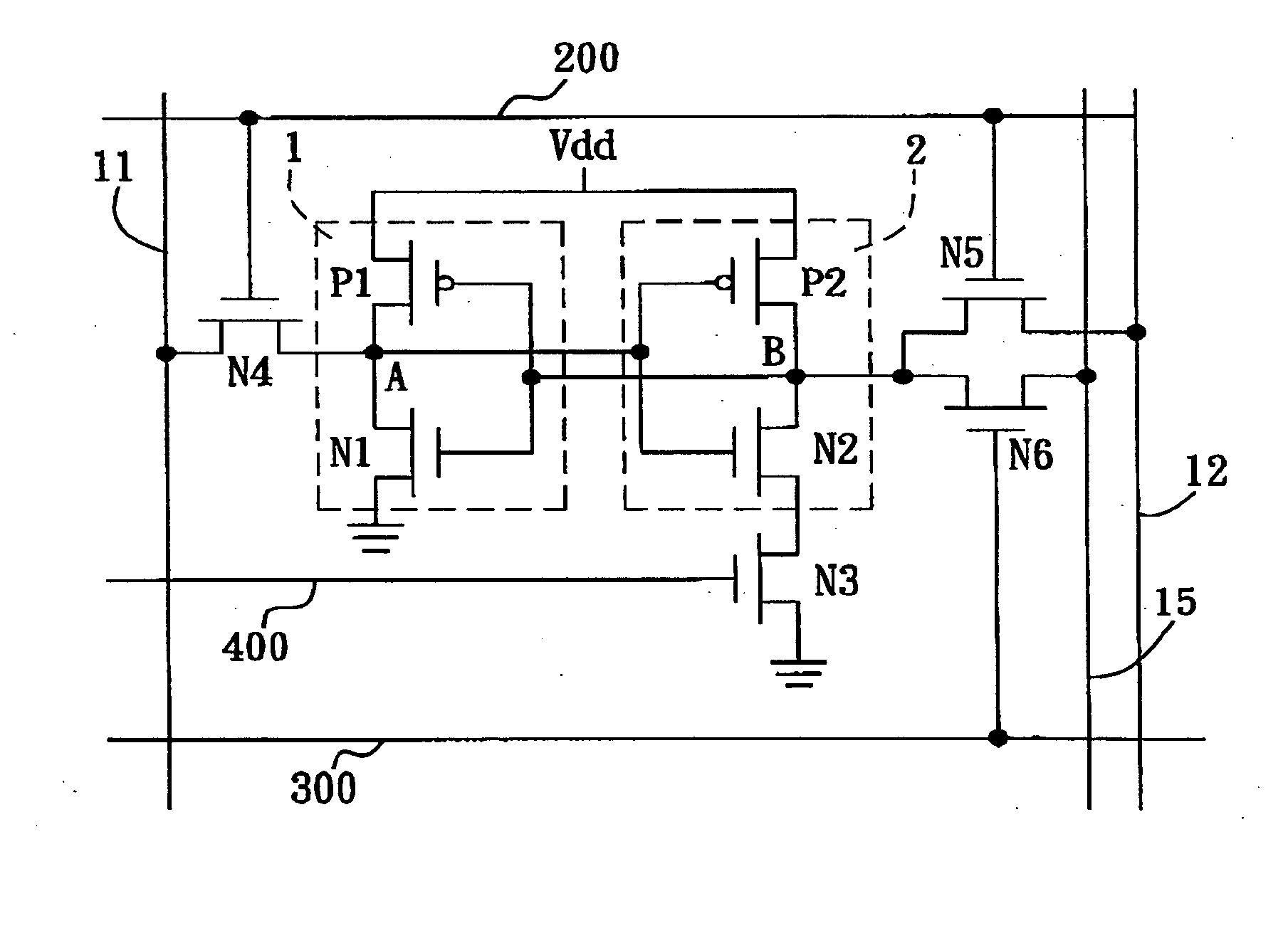

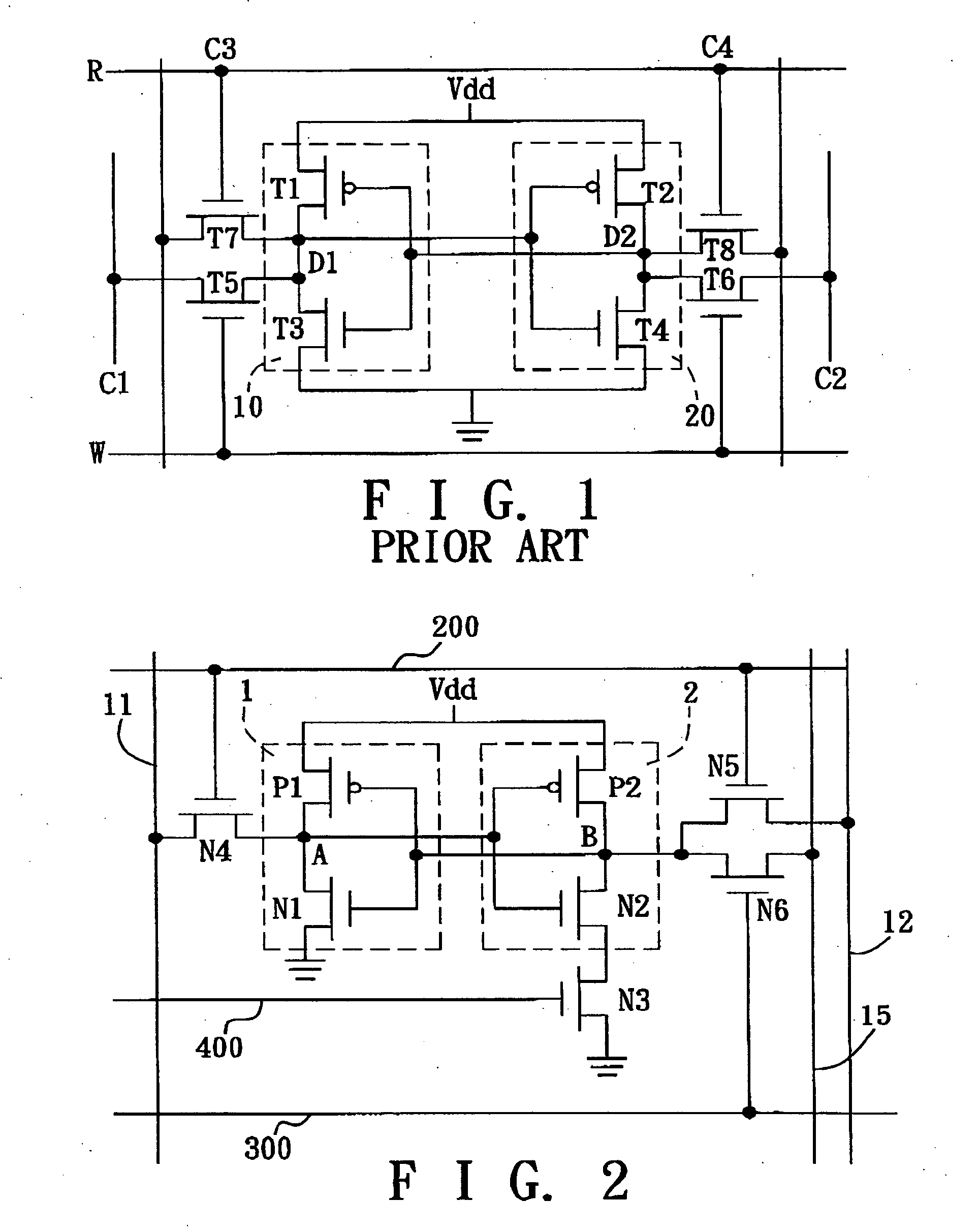

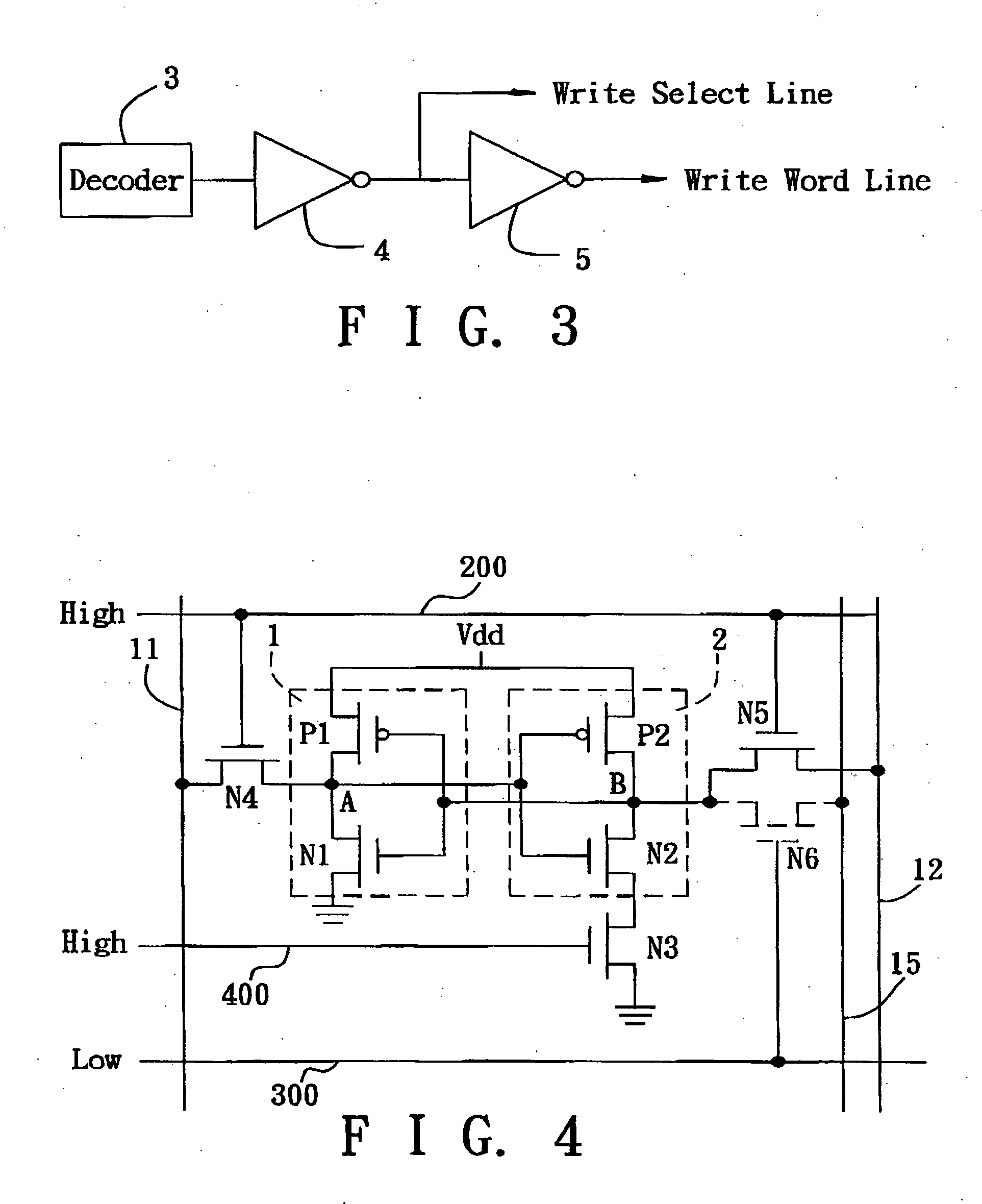

Low-power SRAM memory cell

An SRAM memory cell that has a relatively small power consumption when writing a write value of ‘0’ to the memory cell includes cross-coupled first and second inverters, at least one read access transistor for selectively coupling a respective read bit line to a common connection node of a respective one of the first and second inverters, a switching transistor for selectively coupling the second inverter to a ground terminal, and a write access transistor for selectively coupling the common connection node of the second inverter to a write bit line.

Owner:NAT TAIWAN UNIV

Low-power SRAM memory cell

An SRAM memory cell that has a relatively small power consumption when writing a write value of ‘0’ to the memory cell includes cross-coupled first and second inverters, at least one read access transistor for selectively coupling a respective read bit line to a common connection node of a respective one of the first and second inverters, a switching transistor for selectively coupling the second inverter to a ground terminal, and a write access transistor for selectively coupling the common connection node of the second inverter to a write bit line.

Owner:NAT TAIWAN UNIV

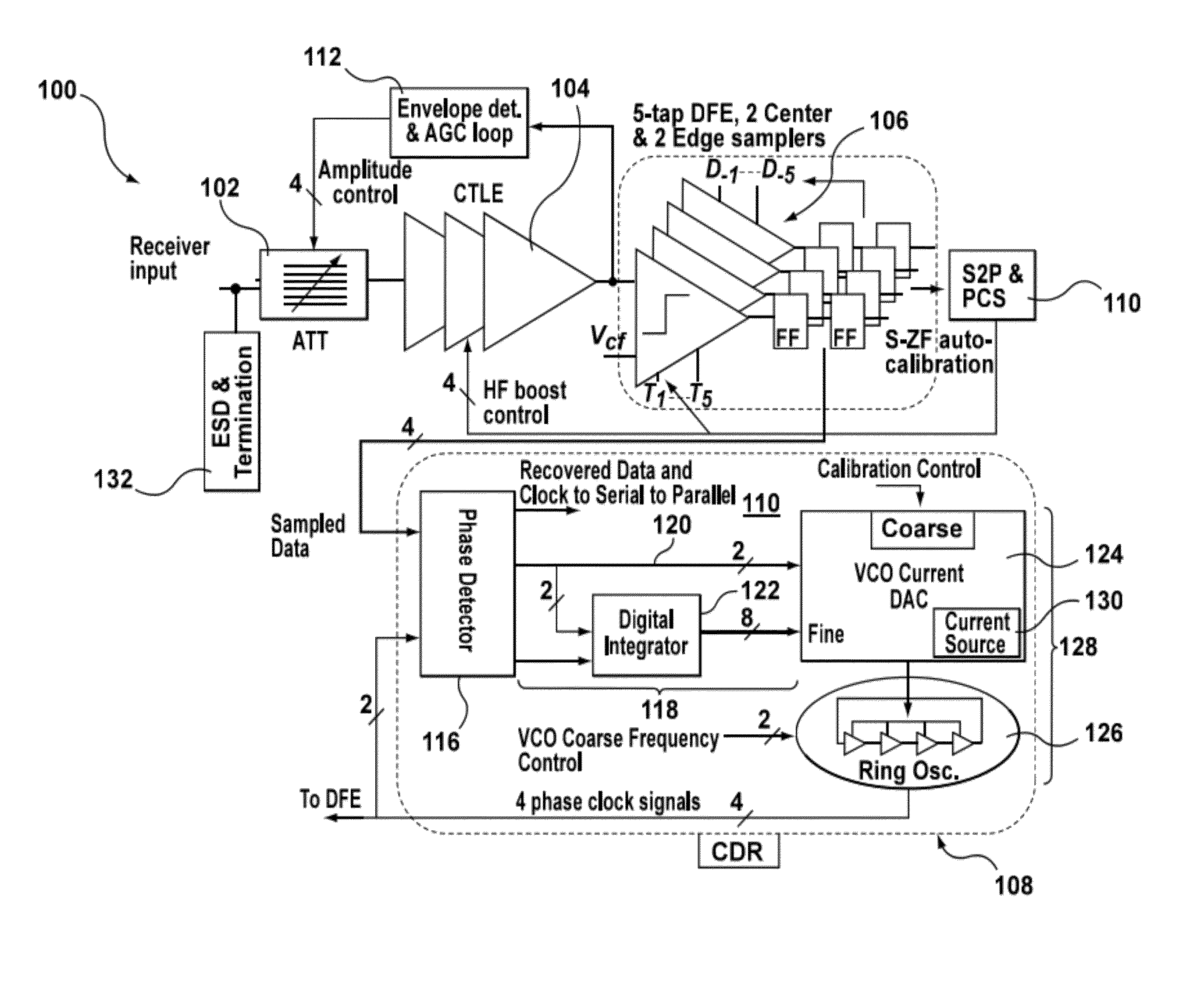

Decision feedback equalizer and transceiver

A decision feedback equalizer, transceiver, and method are provided, the equalizer having at least one comparator, the at least one comparator comprising a first stage, comprising a main branch having two track switches with a resistive load, an offset cancellation branch, a plurality of tap branches with transistor sizes smaller than the main branch, in which previous decisions of the equalizer are mixed with the tap weights using current-mode switching, and a cross coupled latch branch; and a second stage, comprising a comparator module for making decisions based on the outputs of the first stage and a clock input, and a plurality of flip-flops for storing the output of the comparator module.

Owner:RAMBUS INC

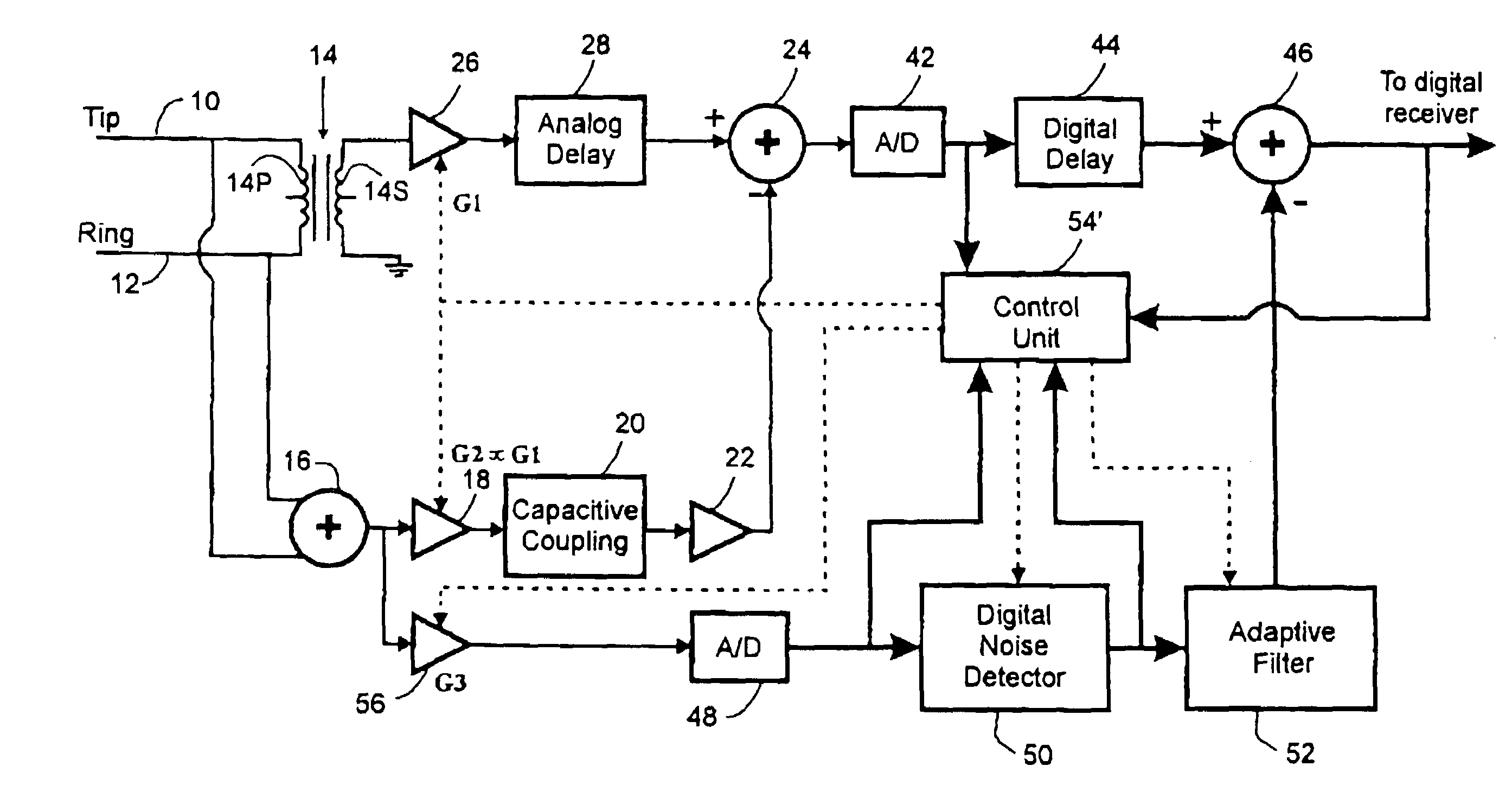

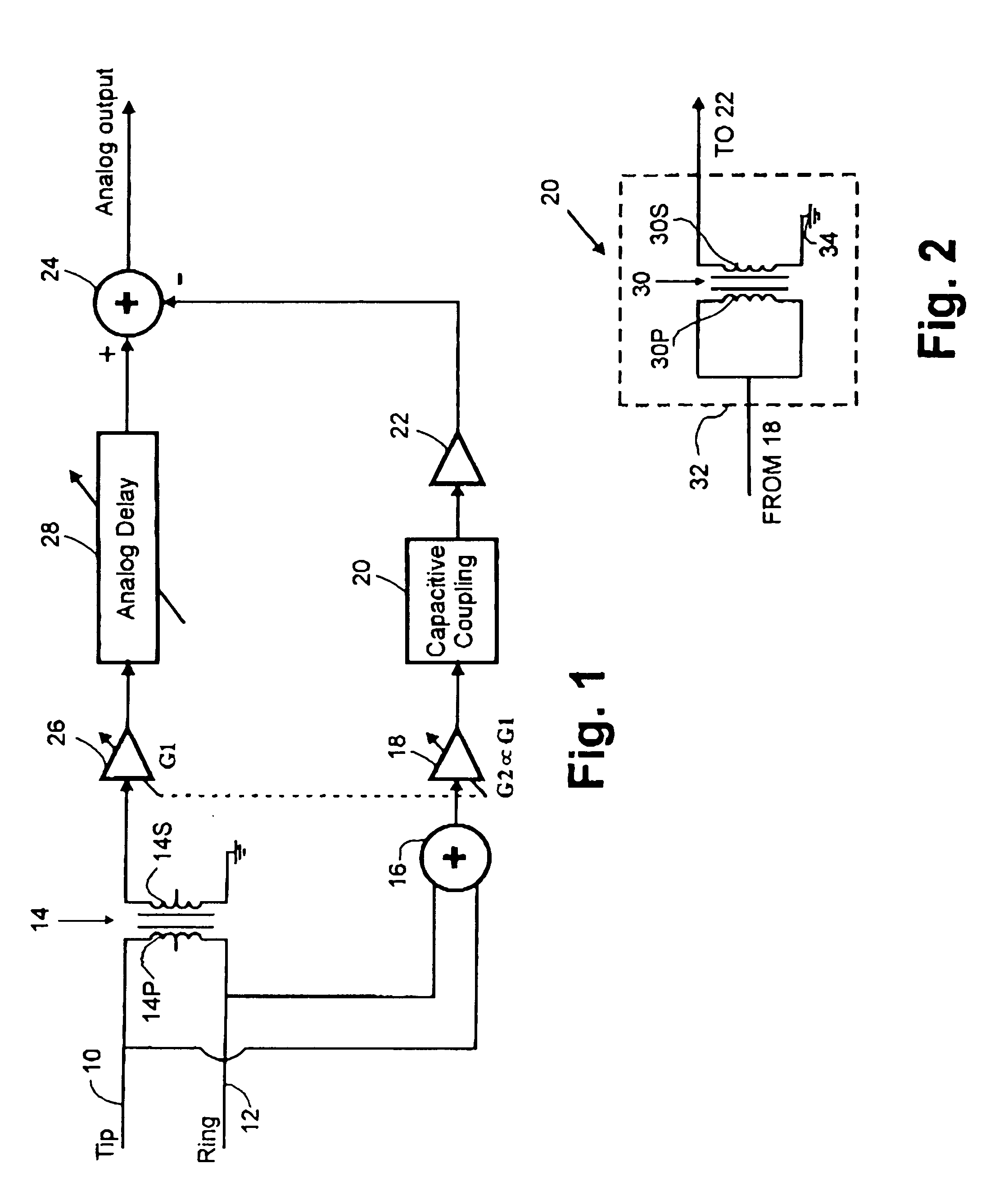

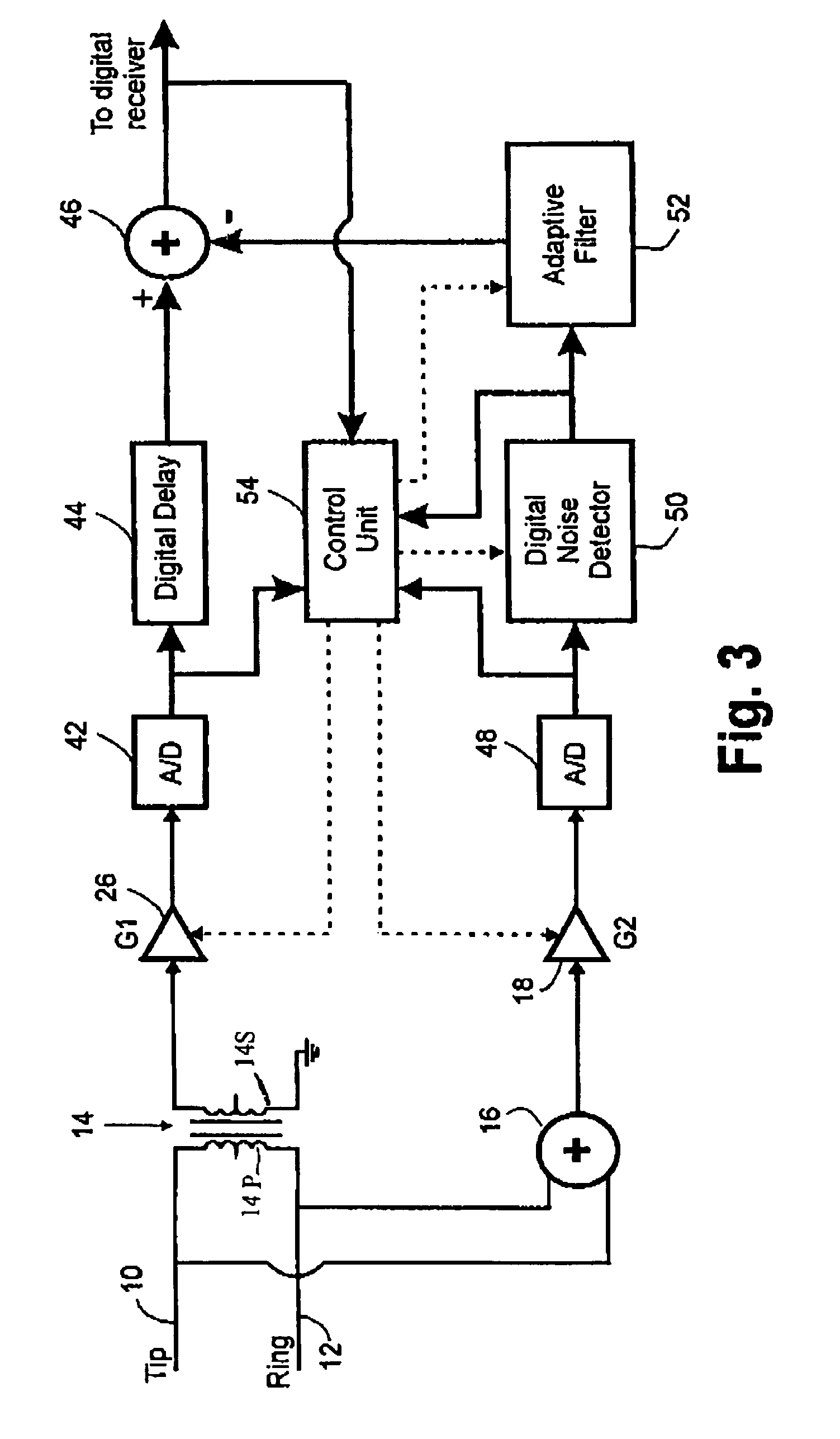

Method and apparatus for cancelling common mode noise occurring in communications channels

InactiveUS6940973B1Substations coupling interface circuitsInterconnection arrangementsCapacitanceAdaptive filter

In order to overcome problems when using an adaptive filter for cancellation of common-mode noise in digital subscriber loops, caused by a portion of the differential signal being converted to common mode, which degrades the performance of the filter, a noise cancellation technique is proposed which compensates for this cross-coupled signal energy. In particular, a digital noise detector is used to detect one or more noisy frequency bands of the common mode signal and pass only the digitized common mode signal in those detected frequency bands through the adaptive filter to produce a digital common mode noise estimate signal. A control unit adjusts coefficients of the adaptive filter to reduce correlation between the differential signal and common mode signal. It is also proposed to compensate for the effects of stray capacitive coupling across the usual hybrid device by including an equivalent capacitive component in a common mode noise estimation circuit.

Owner:BELL CANADA

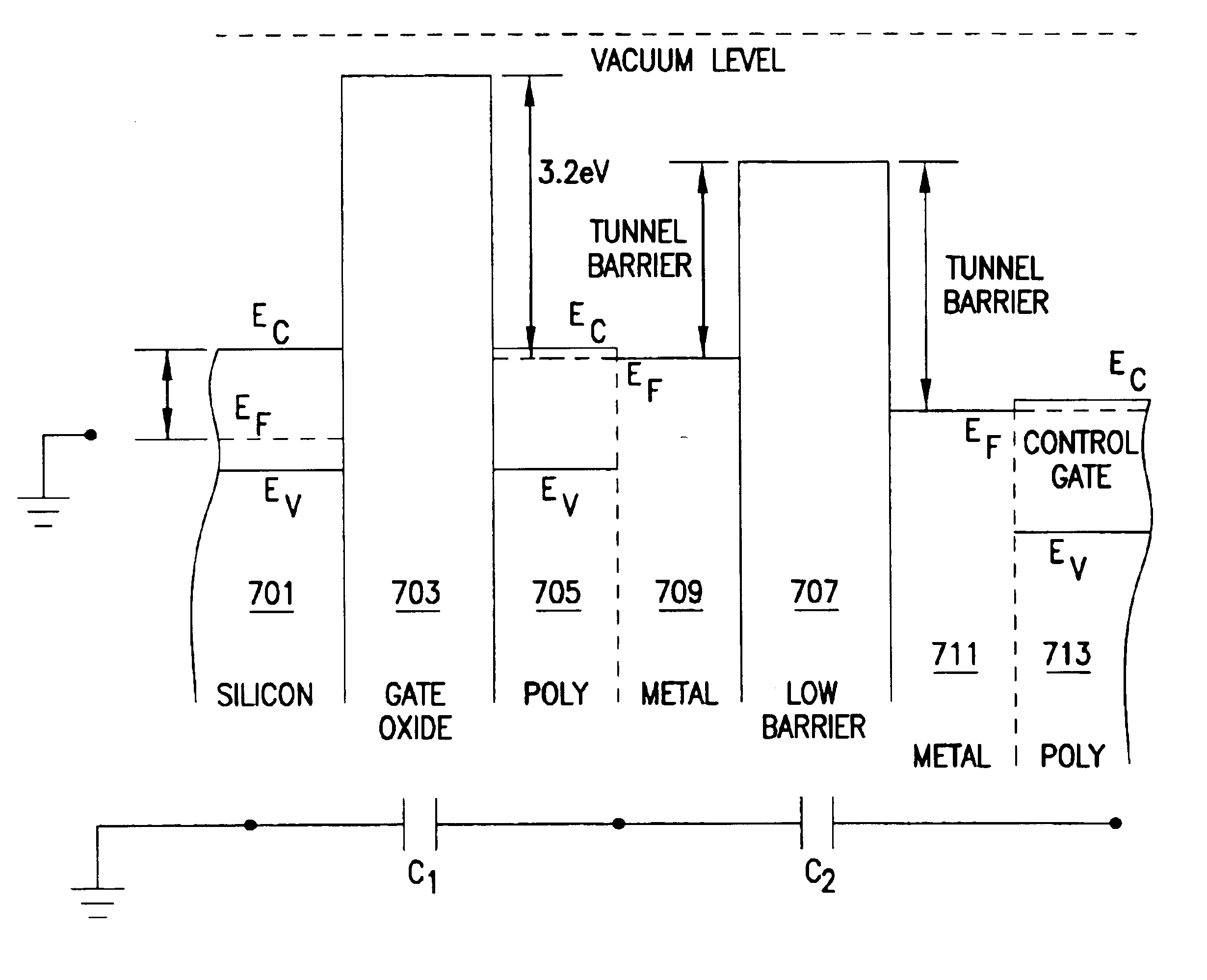

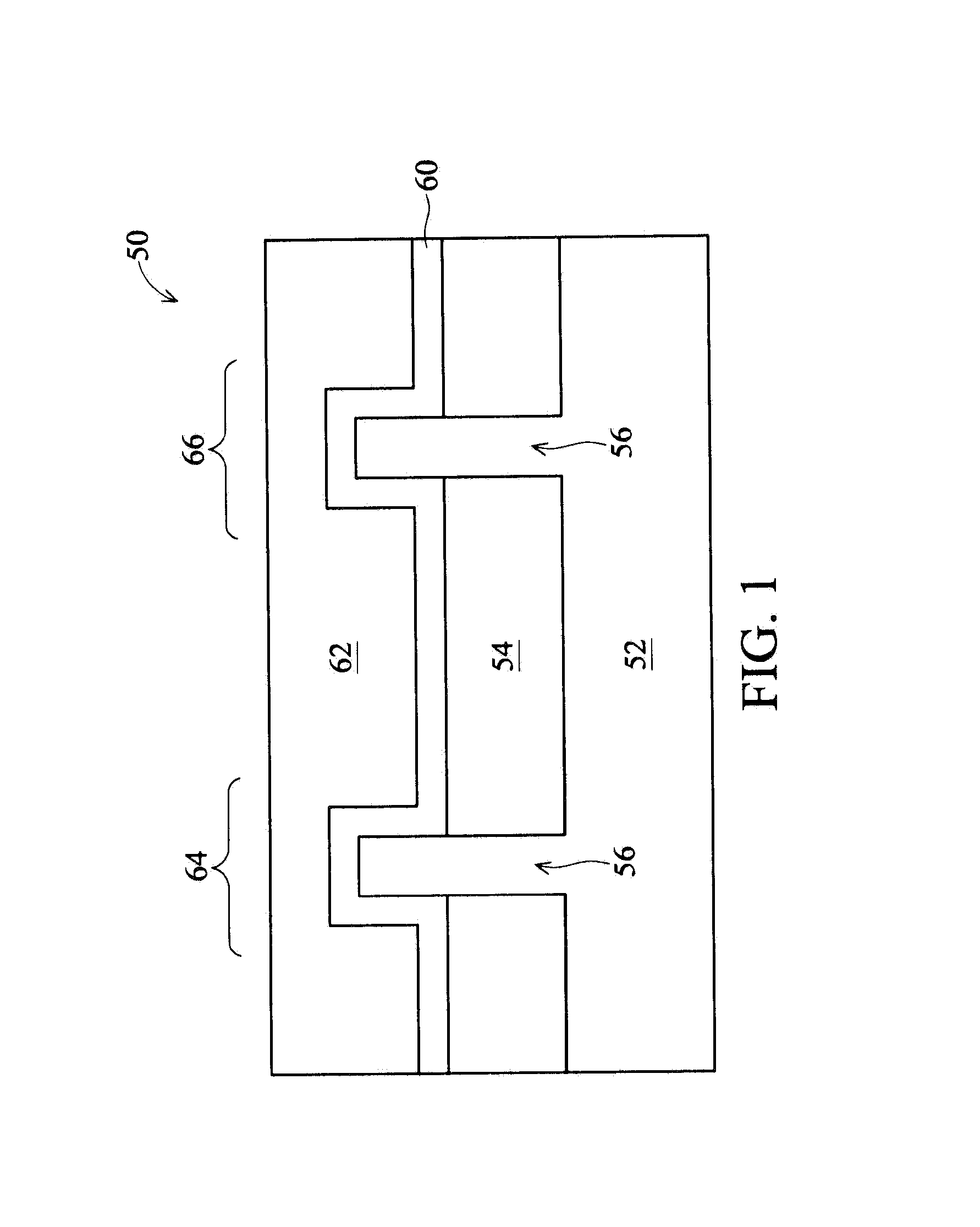

SRAM cells with repressed floating gate memory, low tunnel barrier interpoly insulators

InactiveUS20050169054A1Solid-state devicesSemiconductor/solid-state device manufacturingGate oxideSram cell

Structures and methods are provided for SRAM cells having a novel, non-volatile floating gate transistor, e.g. a non-volatile memory component, within the cell which can be programmed to provide the SRAM cell with a definitive asymmetry so that the cell always starts in a particular state. The SRAM cells include a pair of cross coupled transistors. At least one of the cross coupled transistors includes a first source / drain region and a second source / drain region separated by a channel region in a substrate. A floating gate opposes the channel region and separated therefrom by a gate oxide. A control gate opposes the floating gate. The control gate is separated from the floating gate by a low tunnel barrier intergate insulator.

Owner:MICRON TECH INC

SRAM cells with repressed floating gate memory, low tunnel barrier interpoly insulators

Structures and methods are provided for SRAM cells having a novel, non-volatile floating gate transistor, e.g. a non-volatile memory component, within the cell which can be programmed to provide the SRAM cell with a definitive asymmetry so that the cell always starts in a particular state. The SRAM cells include a pair of cross coupled transistors. At least one of the cross coupled transistors includes a first source / drain region and a second source / drain region separated by a channel region in a substrate. A floating gate opposes the channel region and separated therefrom by a gate oxide. A control gate opposes the floating gate. The control gate is separated from the floating gate by a low tunnel barrier intergate insulator.

Owner:MICRON TECH INC

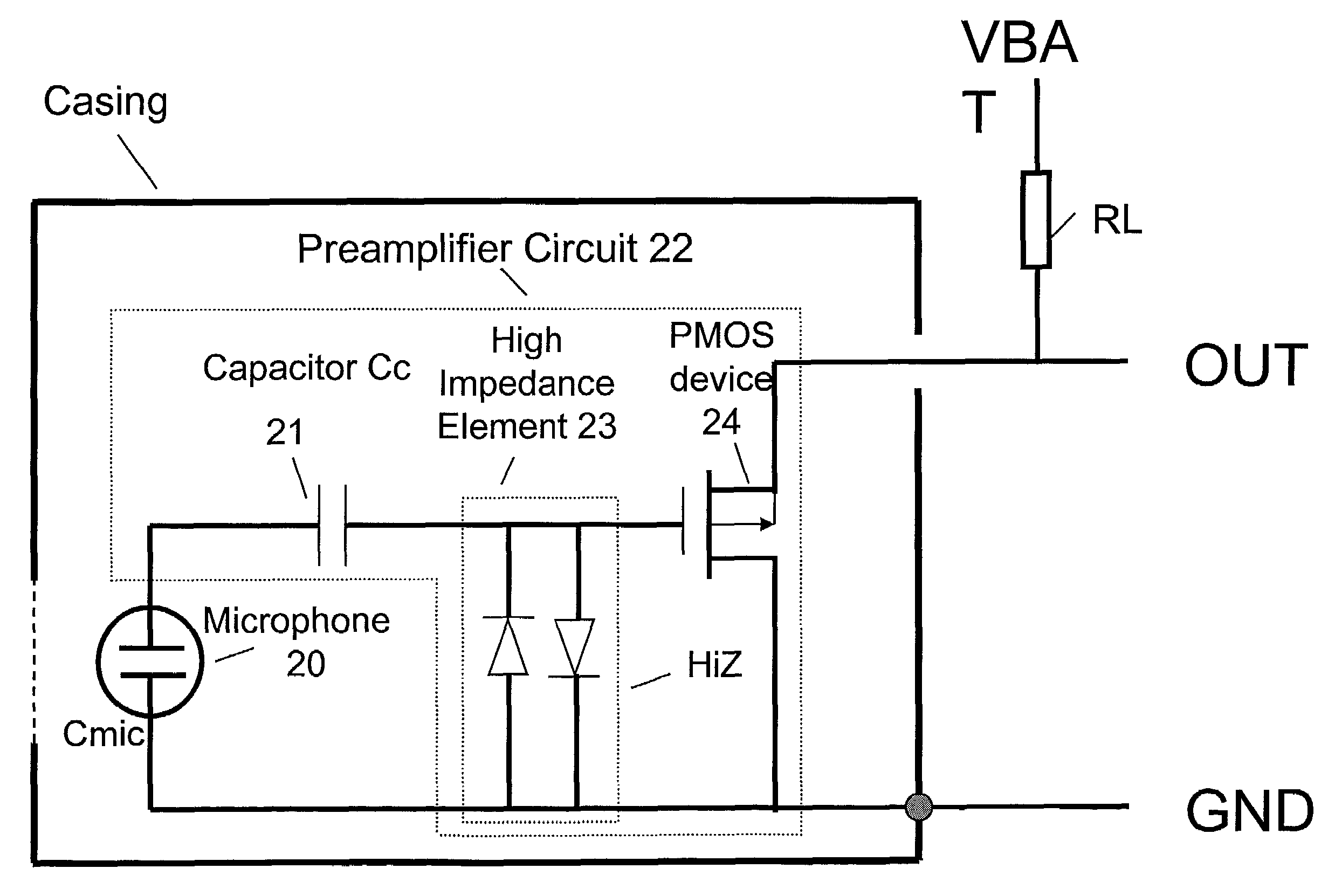

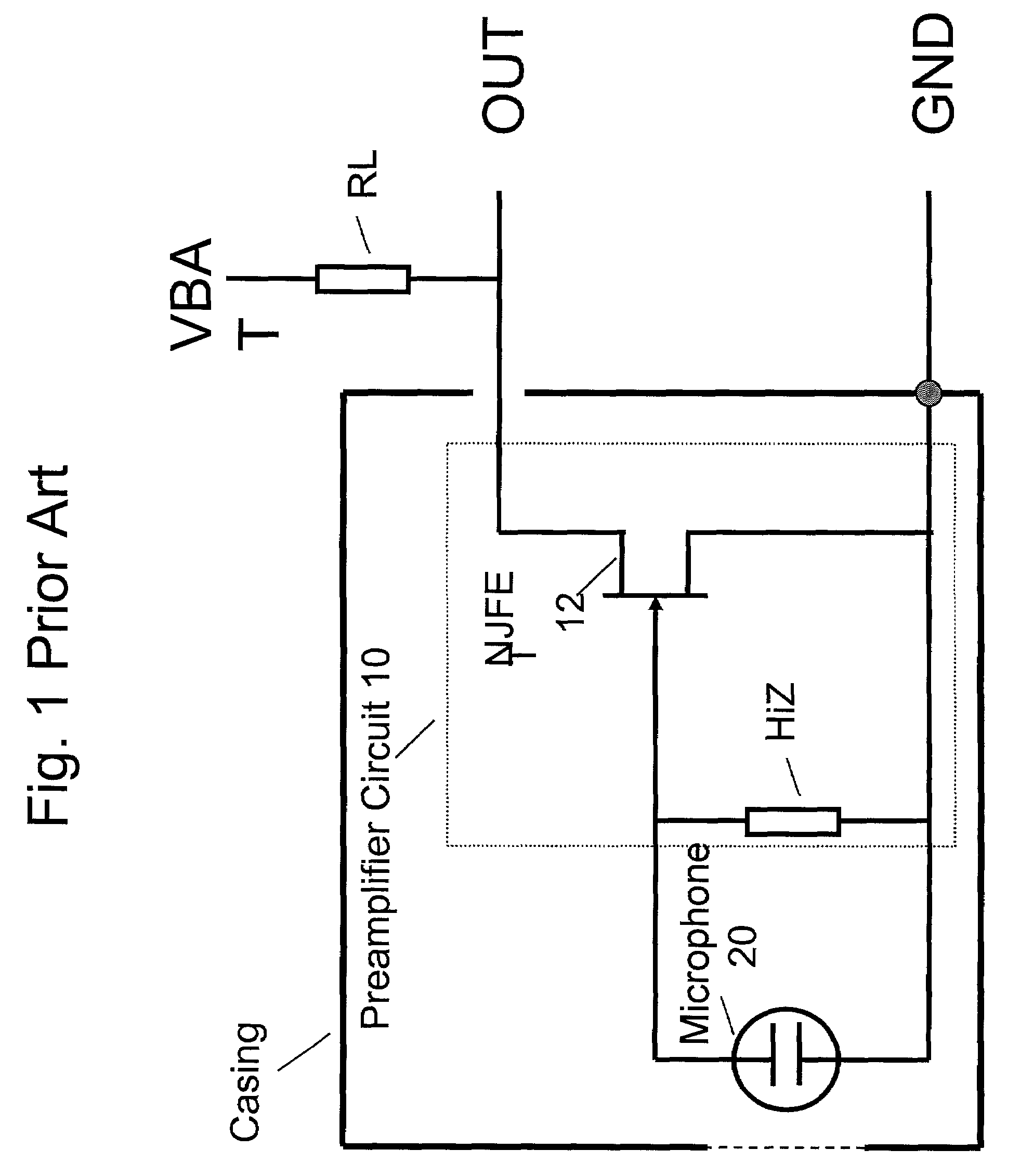

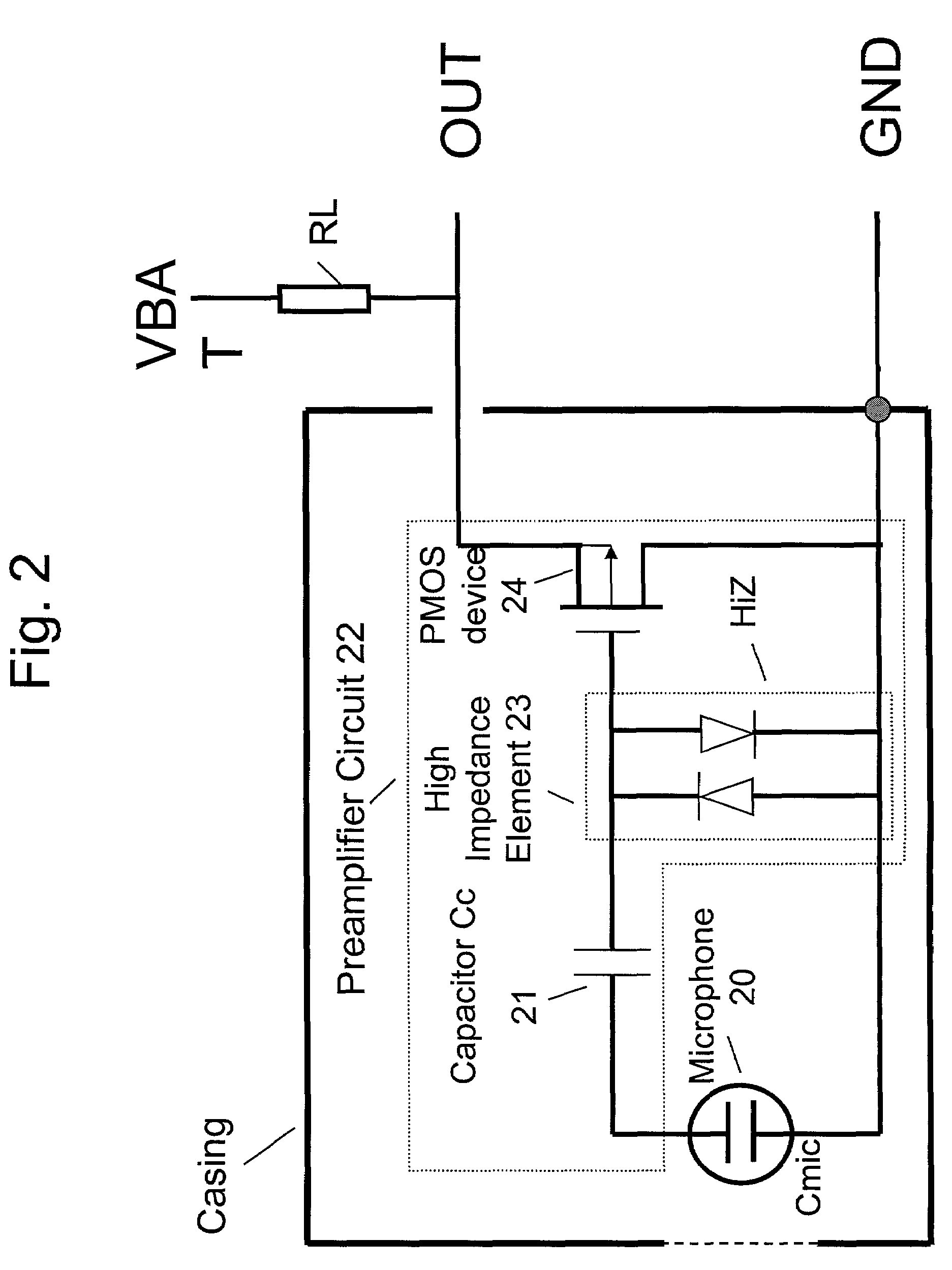

Electret condensor microphone preamplifier that is insensitive to leakage currents at the input

InactiveUS7110560B2Reduce input leakage currentAvoid leakage currentLow frequency amplifiersTransducer casings/cabinets/supportsCapacitanceOperating point

A preamplifier having extremely high input impedance amplifies the electrical signal output from an electret condenser microphone (ECM) without suffering from the effects of a DC leakage current at the input. The preamplifier circuit includes a pair of cross-coupled PN junction diodes setting the input impedance, a PMOS device, and a load resistor configured similarly to a conventional preamplifier. A capacitor is placed between the input and the cross-coupled diodes such that a DC path no longer exists to bias the cross-coupled diodes. Therefore, leakage currents are prevented from upsetting the DC operating point of the preamplifier and biasing the cross-coupled diodes. Consequently, small signal gain distortion, excessive demodulation products and increased noise can be avoided.

Owner:SONION

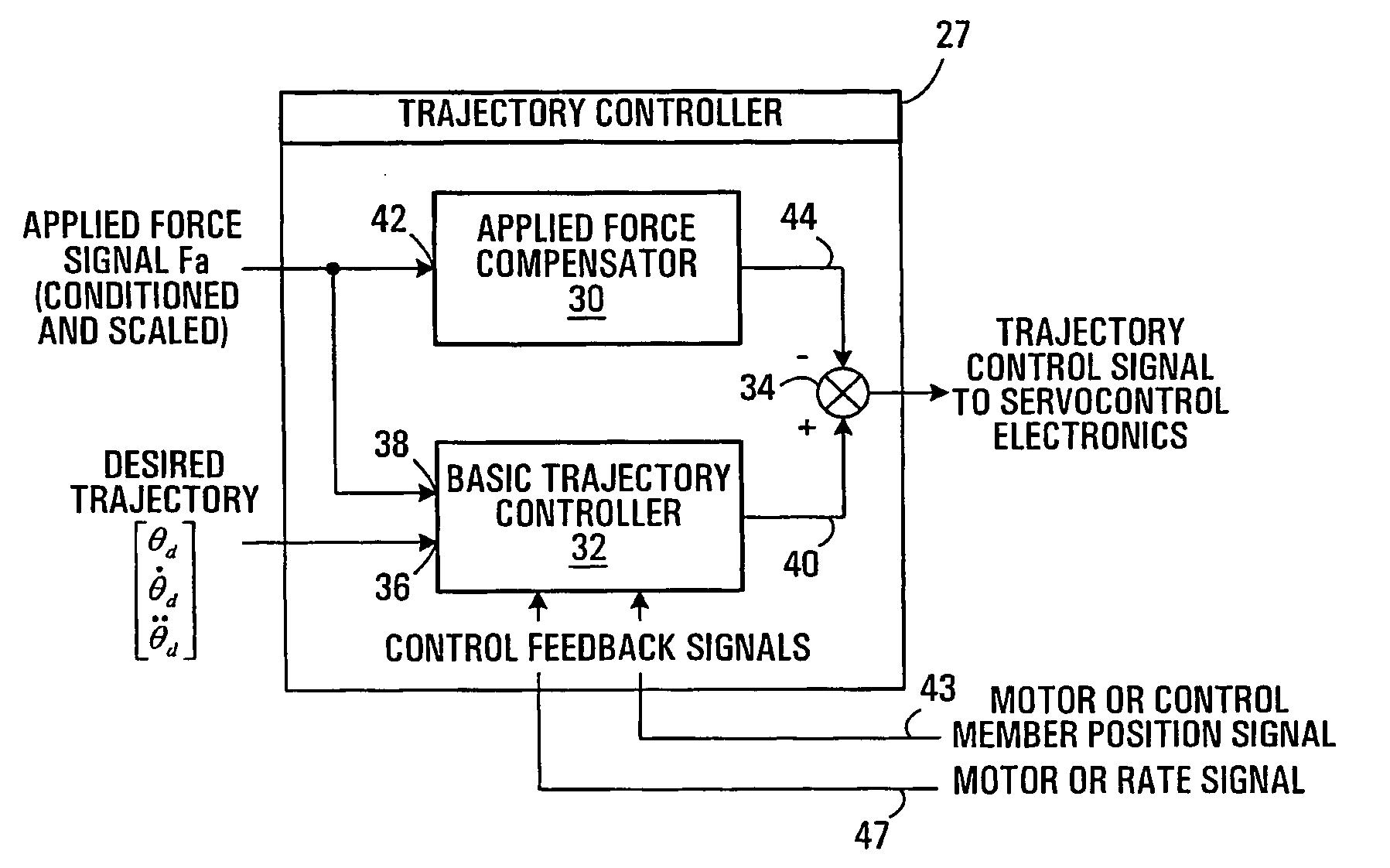

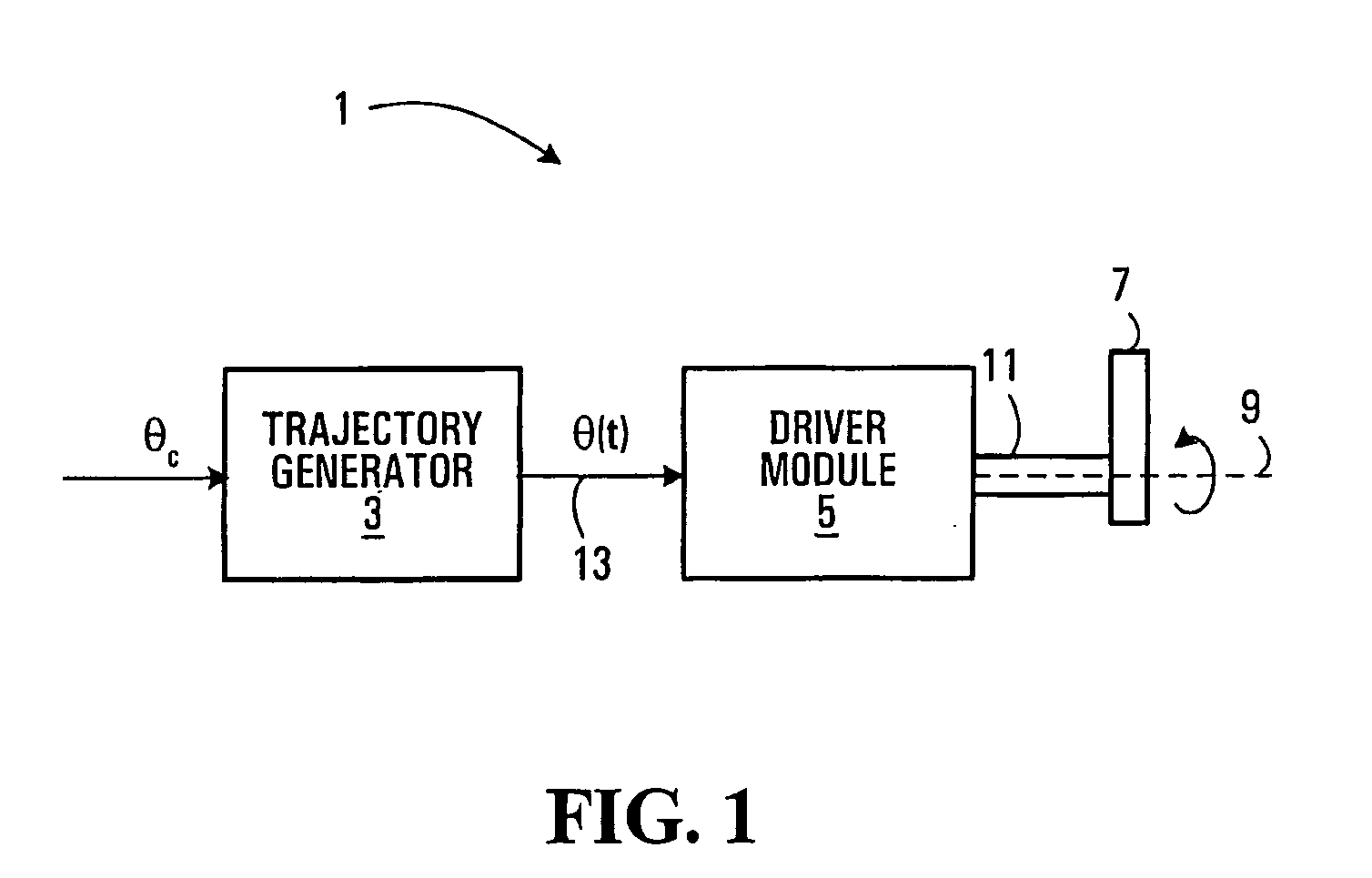

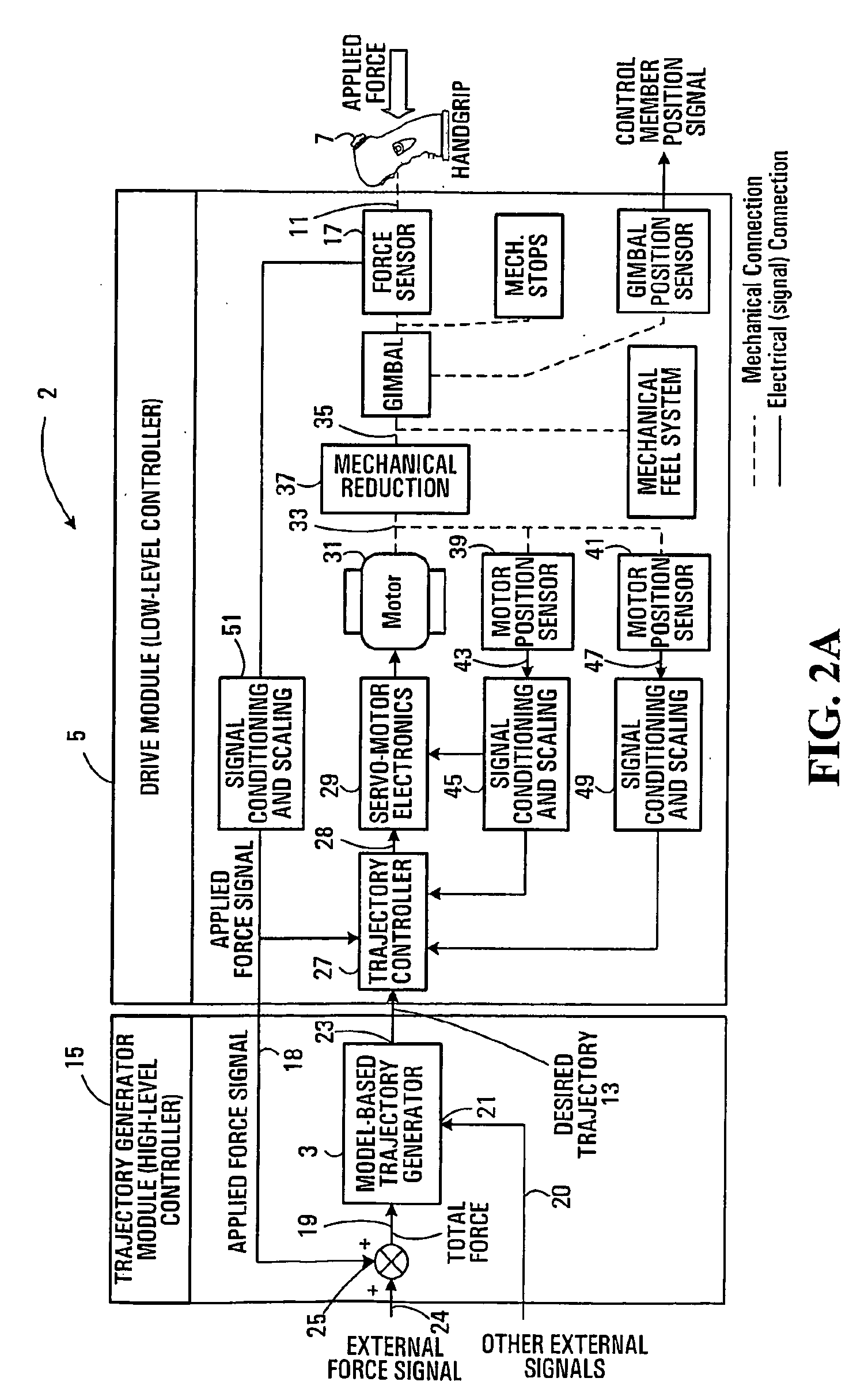

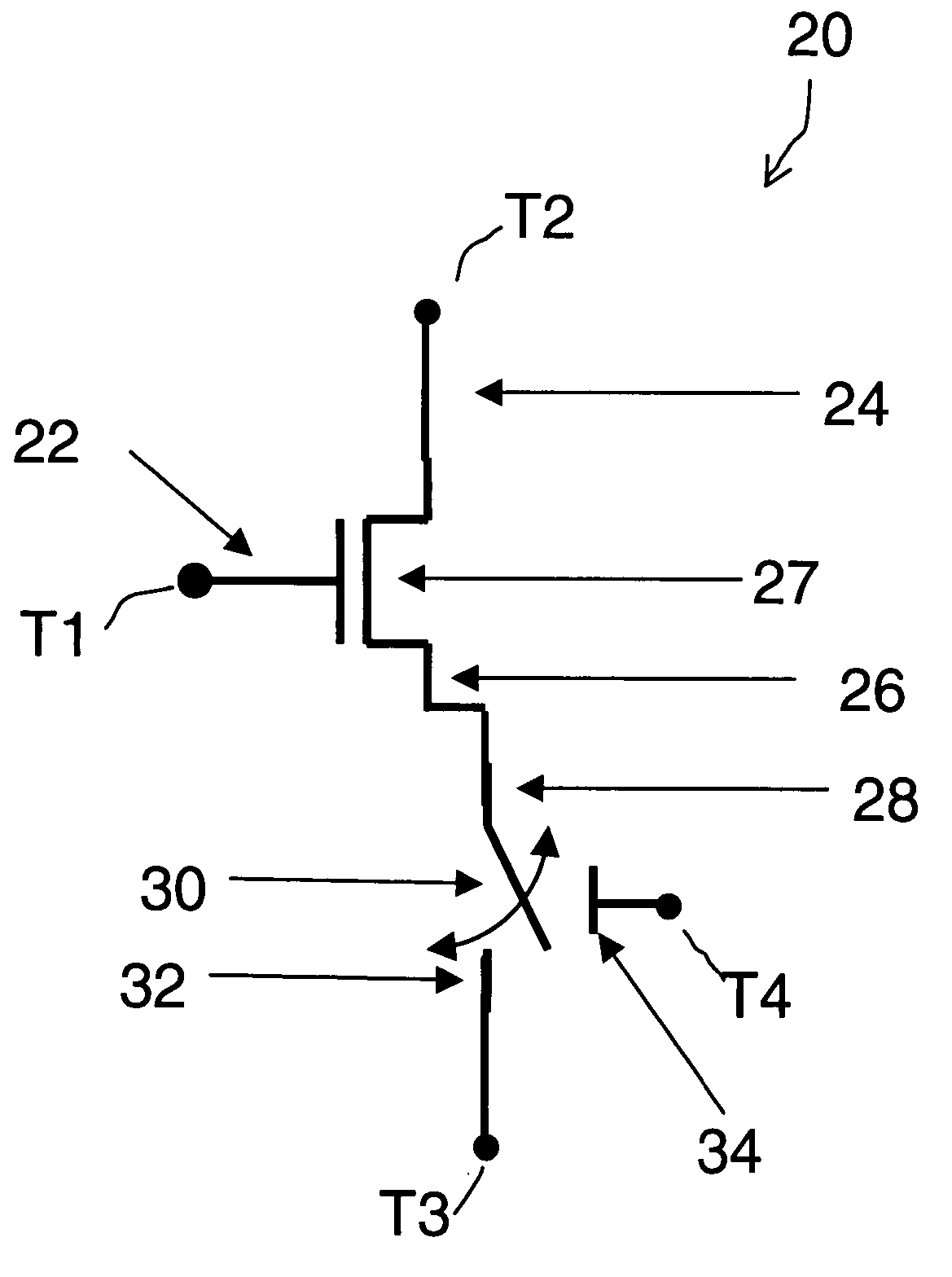

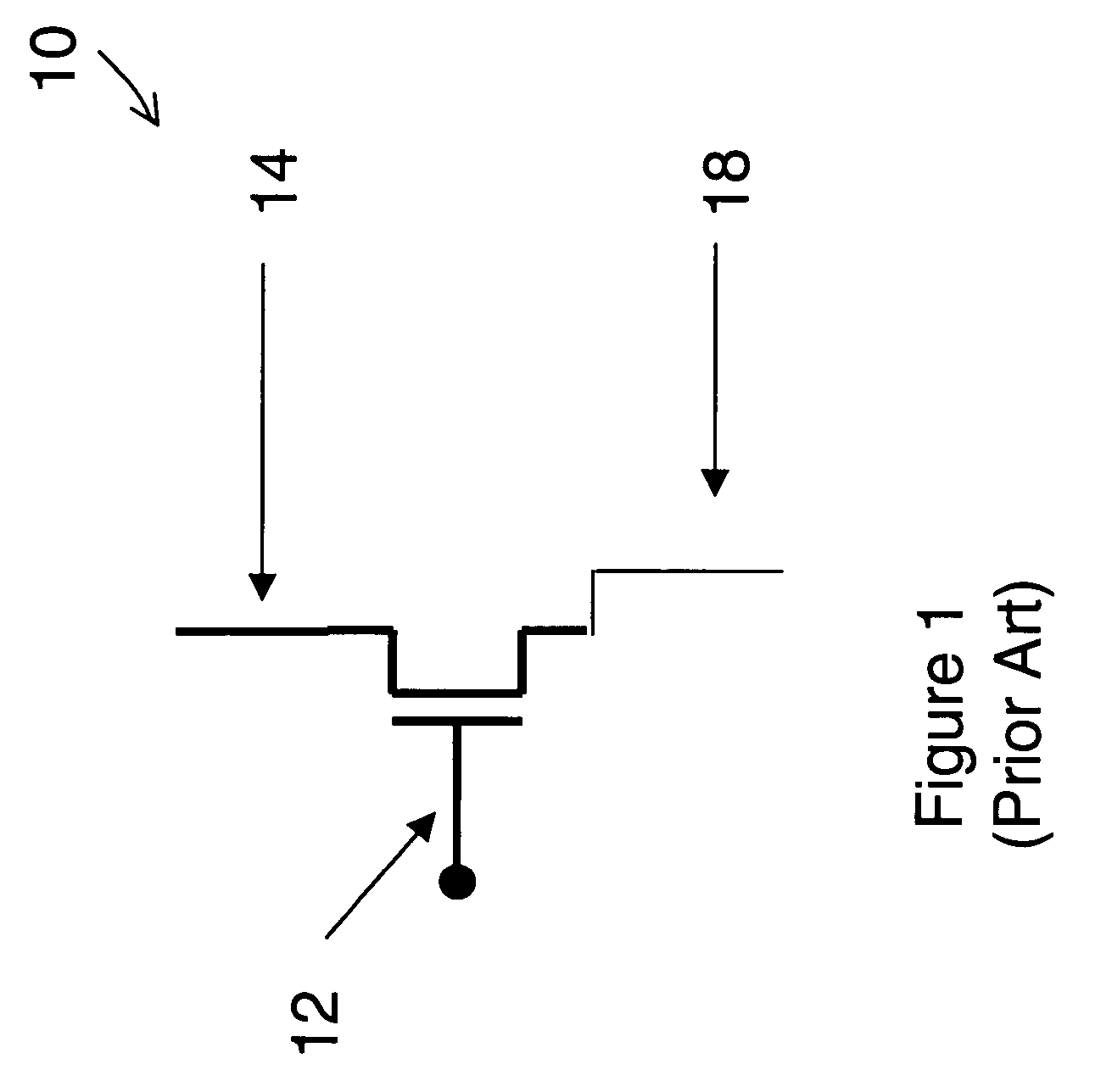

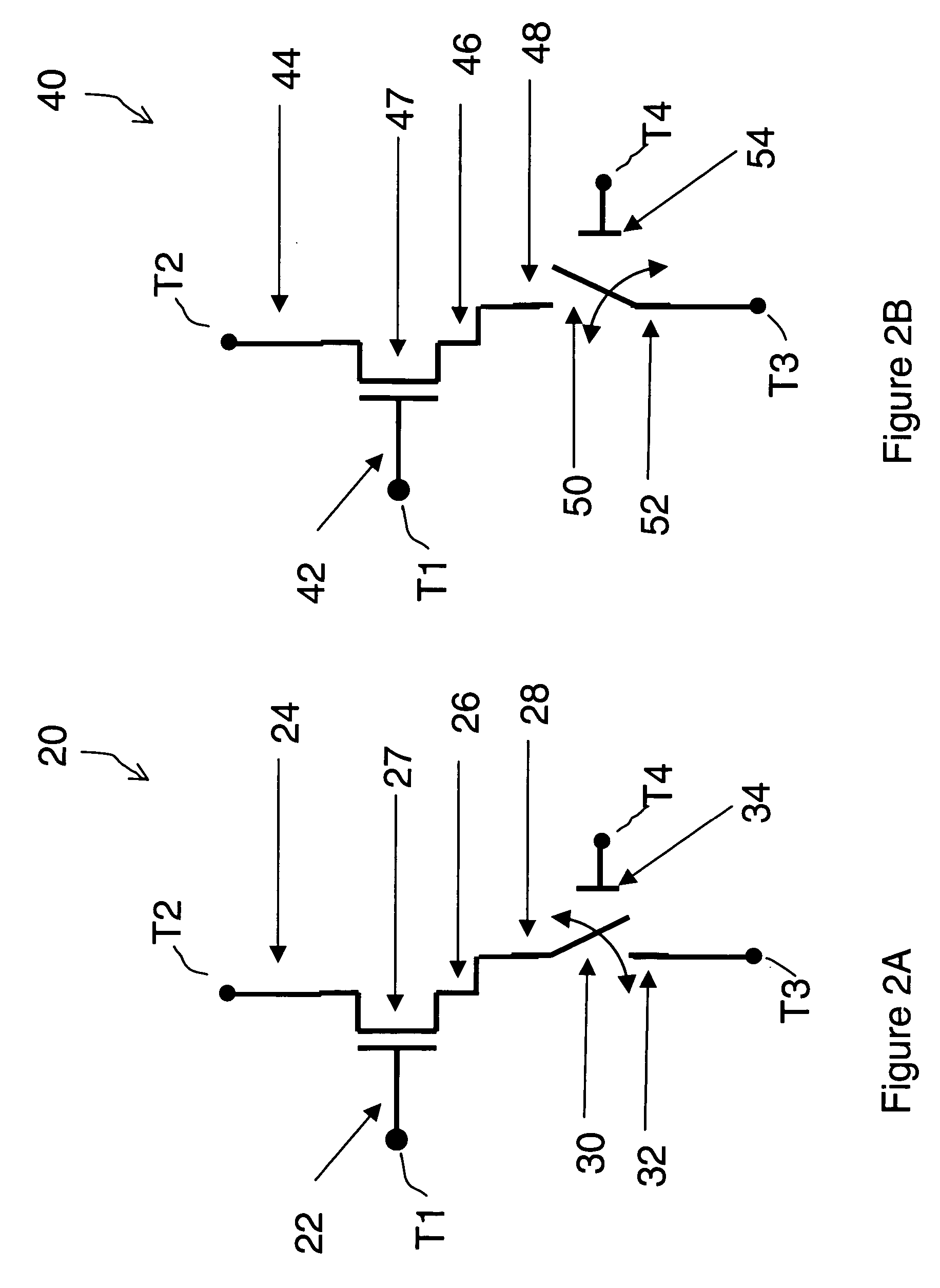

Apparatus and method for controlling a force-activated controller

ActiveUS20050080495A1Follow exactlyImprove performanceProgramme-controlled manipulatorComputer controlJoystickCoupling

A servo controlled system is disclosed for providing simulated feel equivalent to that of traditional mechanical hand controllers using servomotors. Position and force sensor signals are processed and used in a feedback loop that controls the motor mechanically connected to the stick. The overall feedback loop is comprised of a low-level motor feedback loop, and high-level force feel loop. The two loops have associated performance parameters that can be specified independently. The high-level feel force loop is comprised of a static and dynamic performance components. Static and dynamic performance components can be specified independently. The system allows variable and / or additional force cues to be specified externally to the system and felt by the operator. The system also allows external signal to backdrive die stick to follow a specified motion. The control framework permits the electronic coupling of the motion and applied forces of pilot and co-pilots in a dual arrangement while retaining the above-mentioned features. It also allows asymmetric force feel gradients to be implemented for each stick, or for a stick relative to a second one. A zero breakout or detent can be provided at the stick null displacement. For cross-coupled sticks, the detent can be shared as in a mechanically cross-coupled system, implemented independently on each slick, or any combination of these two. The control framework also provides the simulation of mechanical compliance in the cross-coupling of the two sticks in case of a jam or of force fight between the pilots, and automatic de-coupling of the sticks.

Owner:BOMBARDIER CORP

Circuit arrays having cells with combinations of transistors and nanotube switching elements

Circuit arrays having cells with combinations of transistors and nanotube switches. Under one embodiment, a circuit array includes a plurality of cells arranged in an organization of words, each word having a plurality of bits. Each cell is responsive to a bit line, word line, reference line, and release line. Bit lines are arranged orthogonally relative to word lines and each word line and bit line are shared among a plurality of cells. Each cell is selectable via the activation of the bit line and word line. Each cell includes a field effect transistor coupled to a nanotube switching element. The nanotube switching element is switchable to at least two physical positions at least in part in response to electrical stimulation via the reference line and release line. Information state of the cell is non-volatilely stored via the respective physical position of the nanotube switching element. Under another embodiment, a circuit array includes a plurality of cells arranged in an organization of words, each word having a plurality of bits. Each cell is responsive to a bit line, word line, and reference line. Each word line and bit line are shared among a plurality of cells. Each cell is selectable via the activation of the bit line and word line. Each cell includes a field effect transistor and a nanotube switching element. Each nanotube switching element includes a nanotube article positioned between a set electrode and a release electrode. The set electrode may be electrically stimulated to electro-statically attract the nanotube article into contact with the set electrode and the release electrode may be electrically stimulated to electro-statically attract the nanotube article out of contact with the set electrode. Information state of the cell is non-volatilely stored via the respective physical position of the nanotube switching element. Cells are arranged as pairs with the nanotube switching elements of the pair being cross coupled so that the set electrode of one nanotube switching element is coupled to the release electrode of the other and the release electrode of the one nanotube switching element being coupled to the set electrode of the other. The nanotube articles are coupled to the reference line, and the source of one field effect transistor of a pair is coupled to the set electrode to one of the two nanotube switching elements and the source of the other field effect transistor of the pair is coupled to the release electrode to the one of the two nanotube switching elements.

Owner:NANTERO

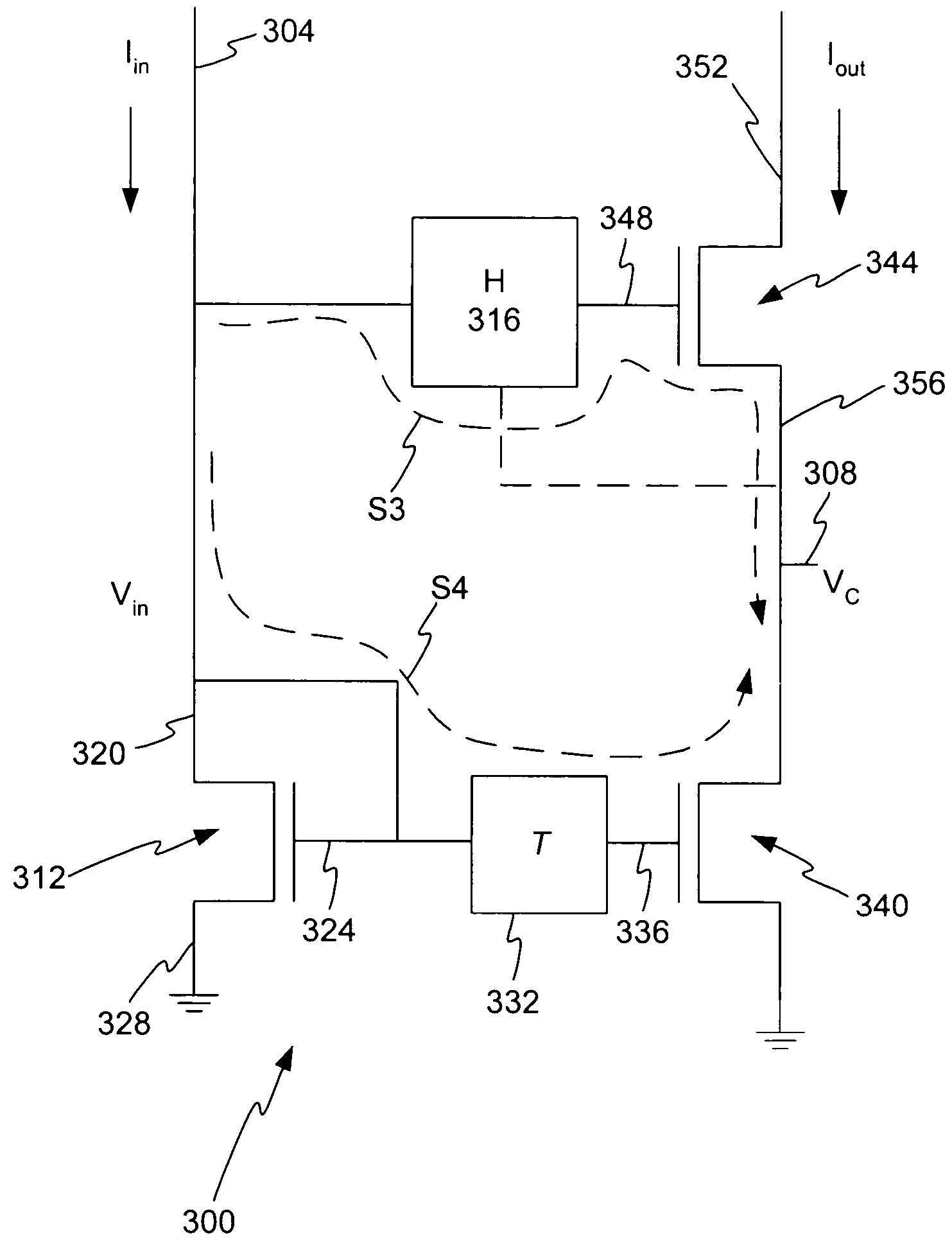

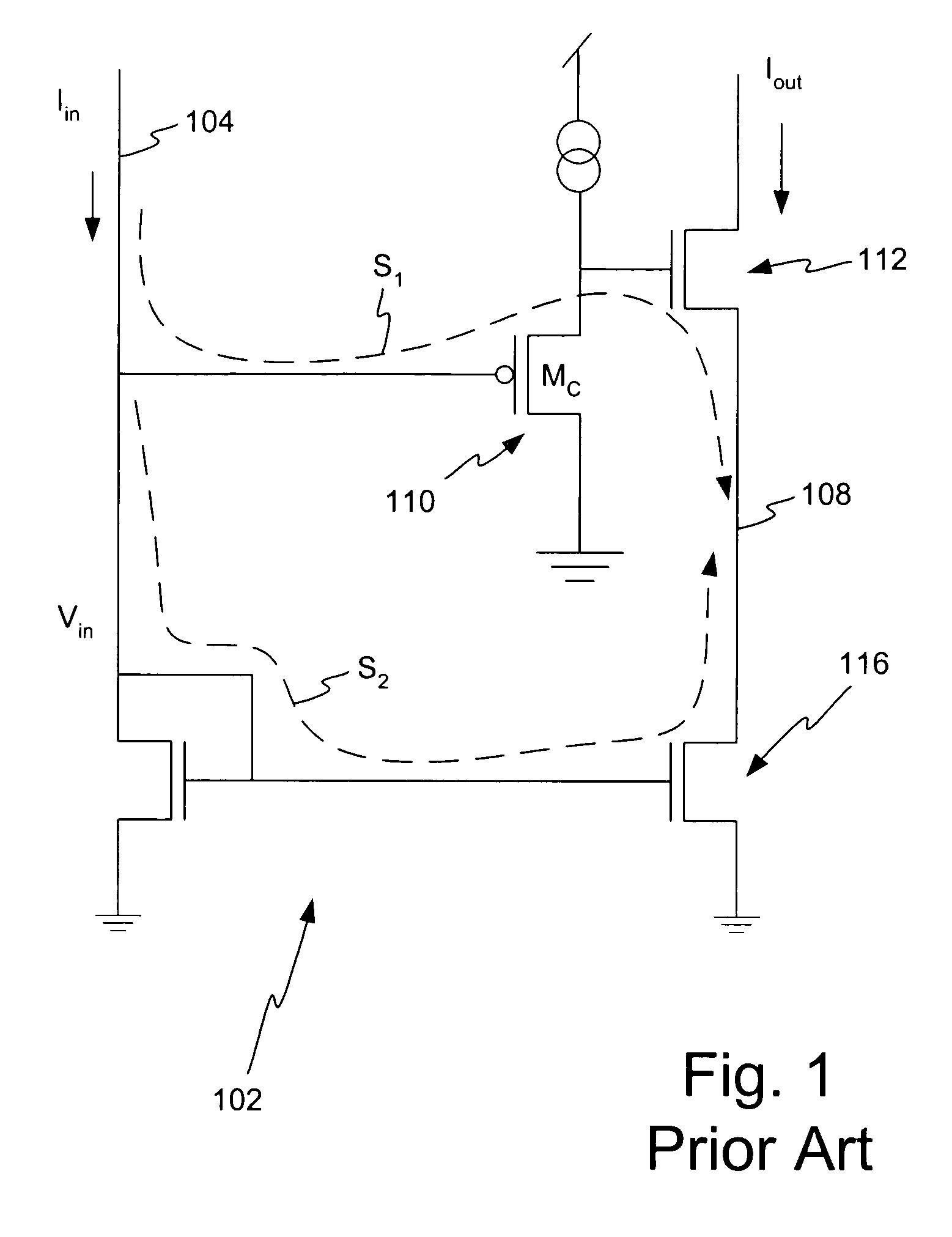

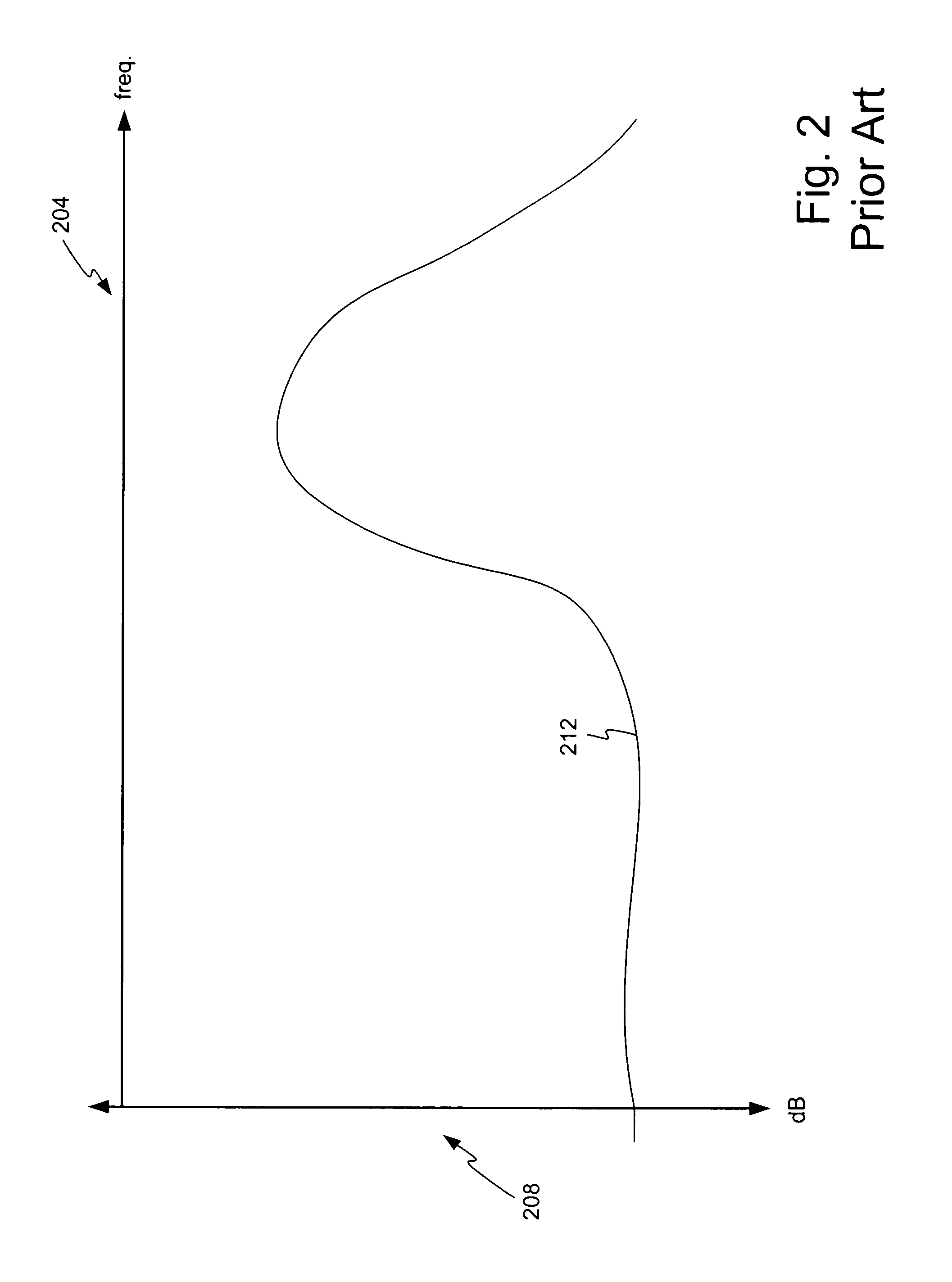

Method and apparatus for increasing the linearity and bandwidth of an amplifier

ActiveUS20050083130A1Amplifier modifications to reduce non-linear distortionElectric variable regulationCascodeEngineering

A method and apparatus is disclosed for improving high frequency performance of an amplifier, such as for example, a current mirror. In one embodiment, a delay element is introduced in a current mirror signal path to account for signal propagation delay that may exist in one or more alternative signal paths. The delay element maintains desired phase alignment at a cascade node of the current mirror thereby establishing, in one embodiment, the cascode node (Vc) in an AC ground state. To extend current mirror high frequency capability an embodiment is disclosed having cross-coupled capacitors, active elements, or one or more other devices configured to provide positive feedback to one or more current mirror inputs. The positive feedback may be selectively configured to increase the operational bandwidth of the current mirror.

Owner:MARVELL ASIA PTE LTD

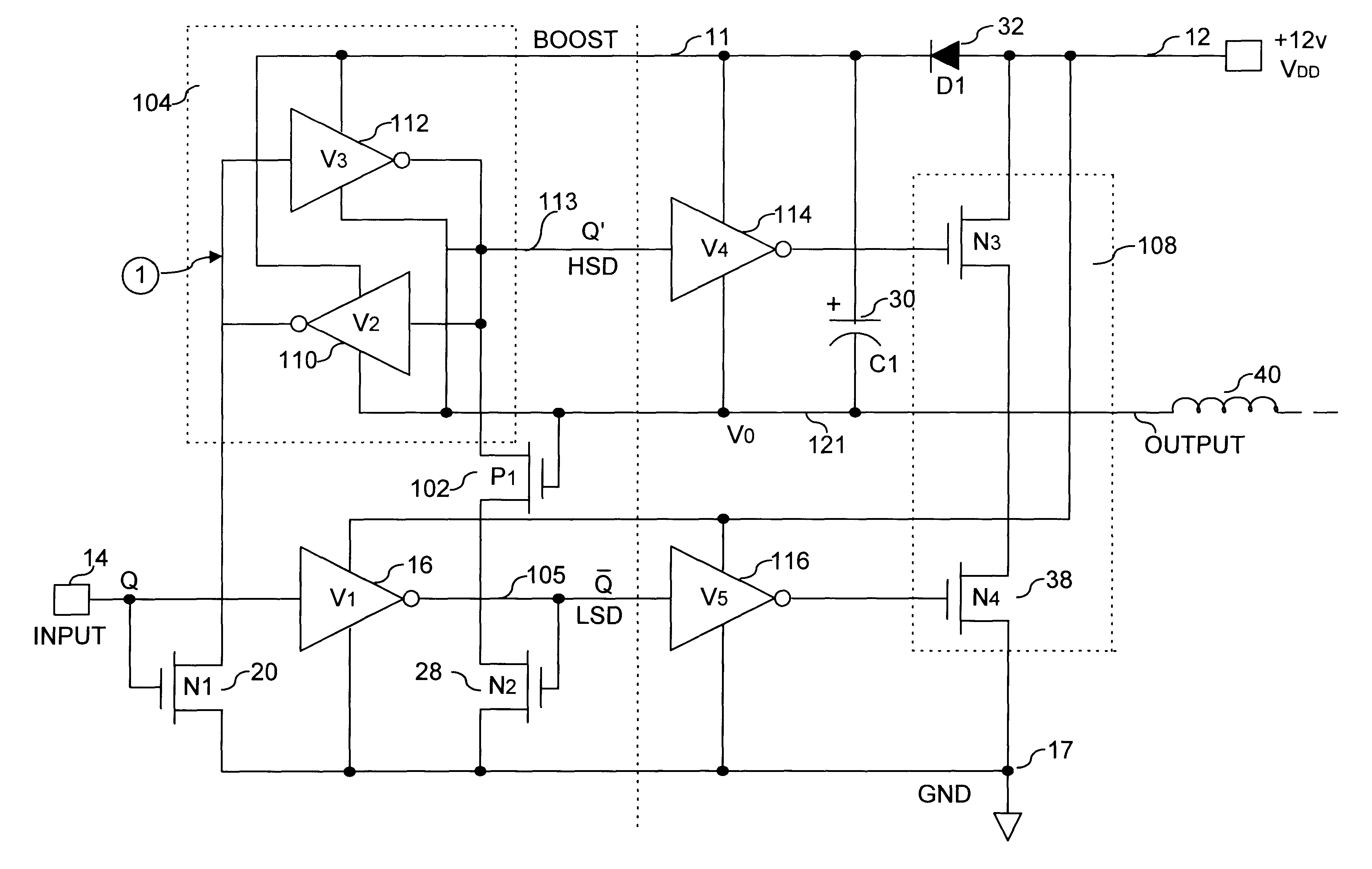

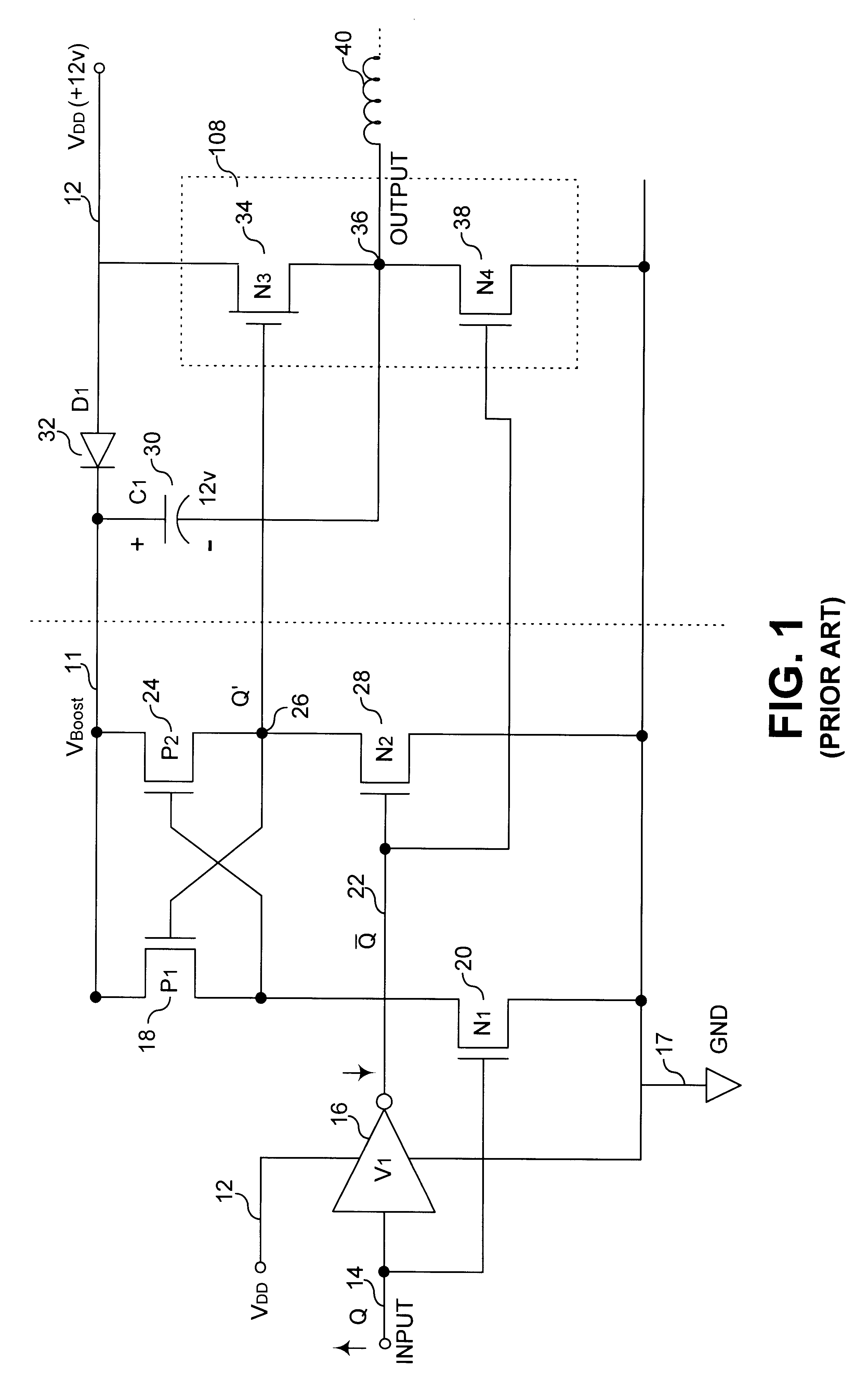

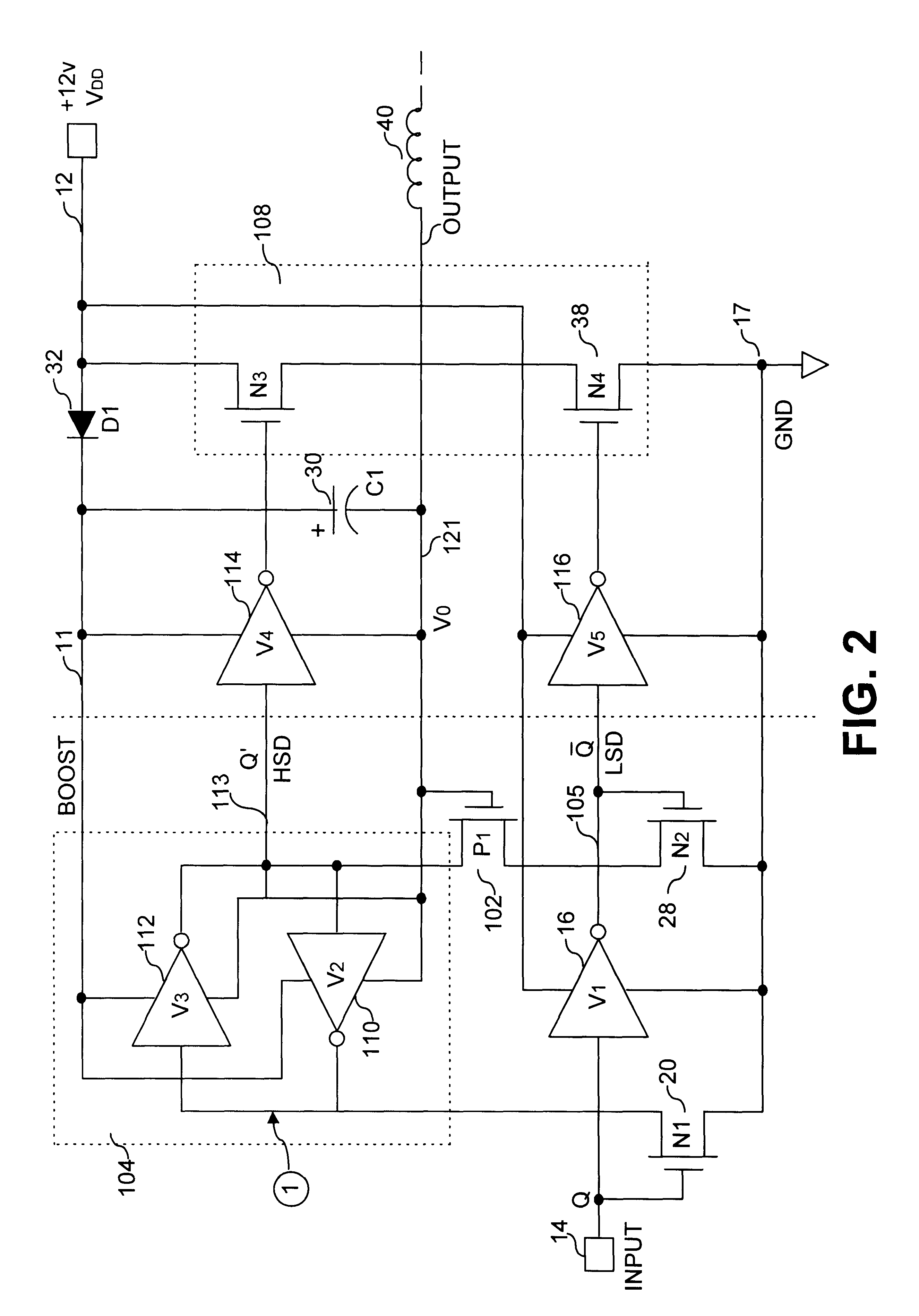

Clamped cascode level shifter circuit

InactiveUS6201429B1Preventing continuous current conductionHysteretic SwitchingPower reduction in field effect transistorsPulse automatic controlCascodeEngineering

An improved level shifter circuit that toggles a "flying Flip-Flop" comprising a cross-coupled inverter pair with control devices driven out of phase through a pair of cascode transistors. The cross-coupled inverter pair provides pull-up to the positive rail, clamping to a High Side-Common (HSC), and providing Hysteretic Switching. The cascode transistors restrict the pull-down of the control devices, thereby preventing continuous current conduction.

Owner:AME

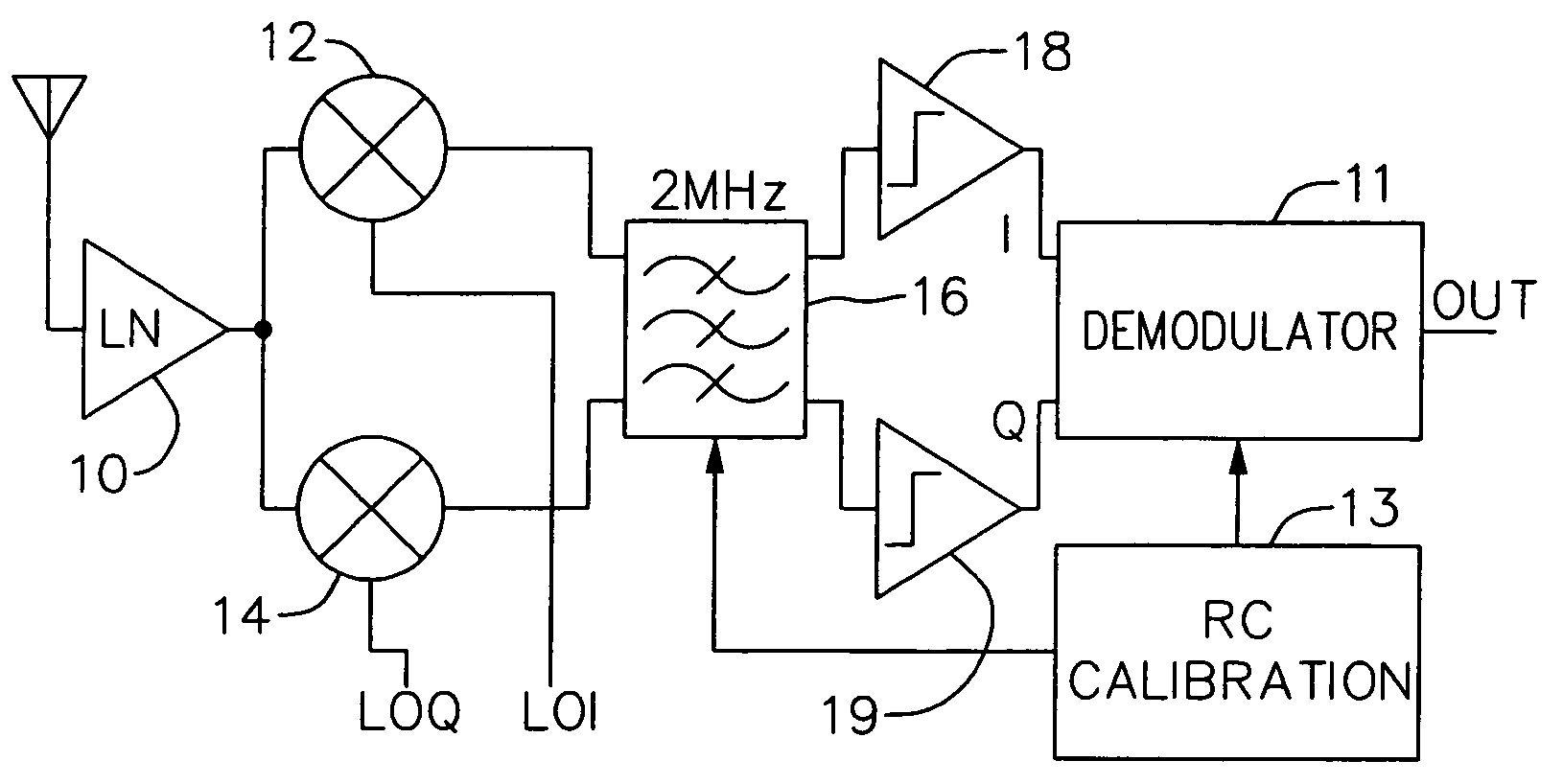

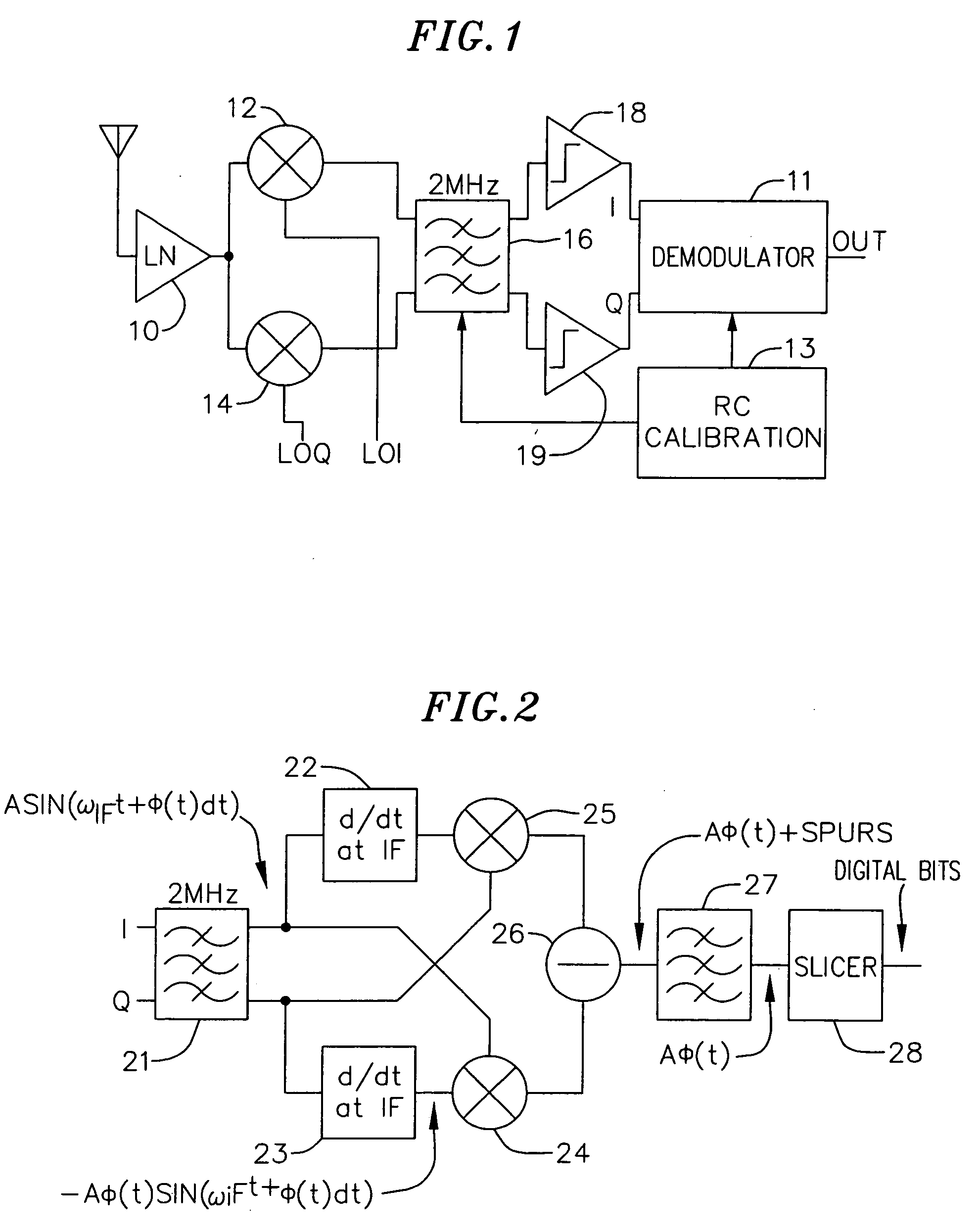

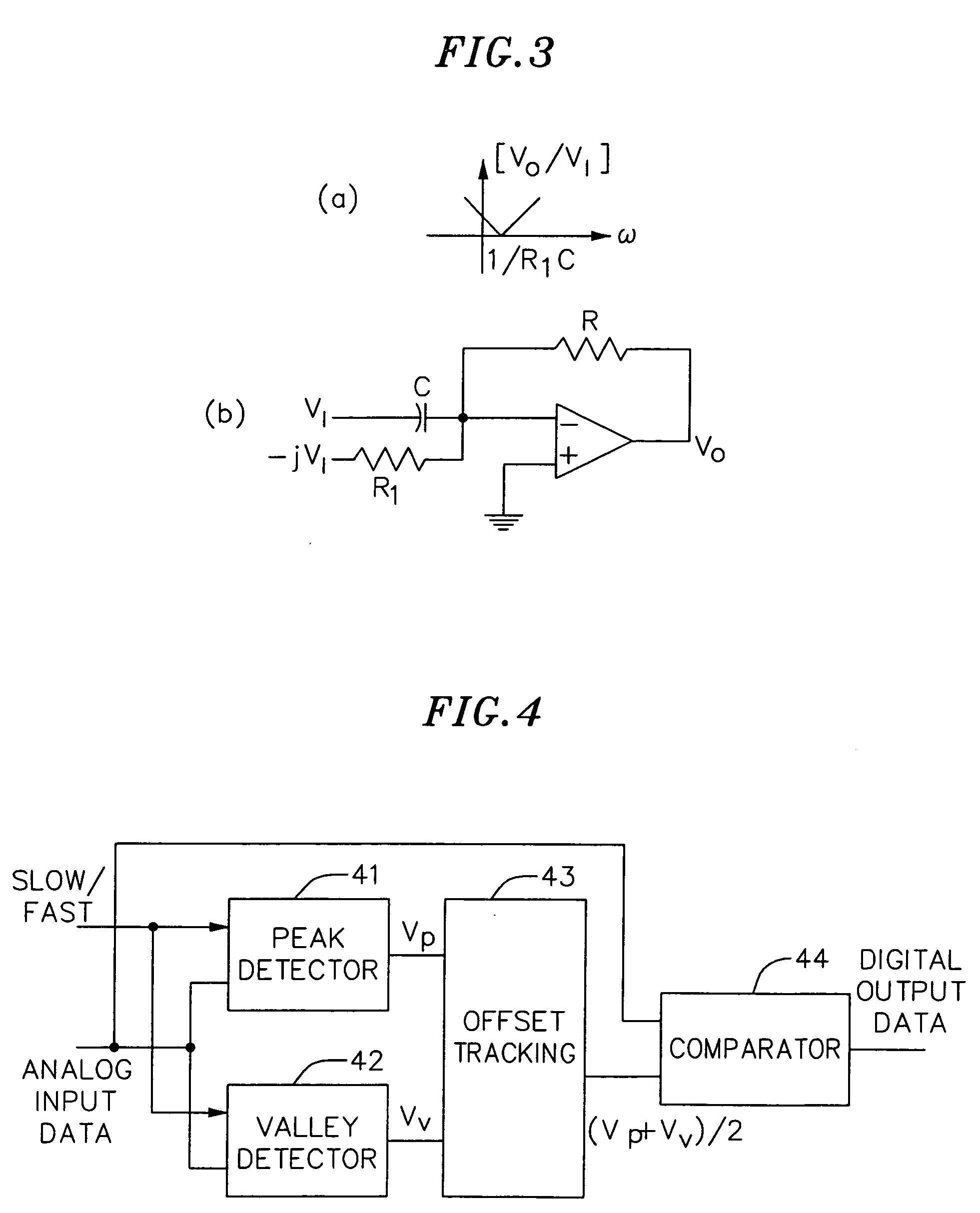

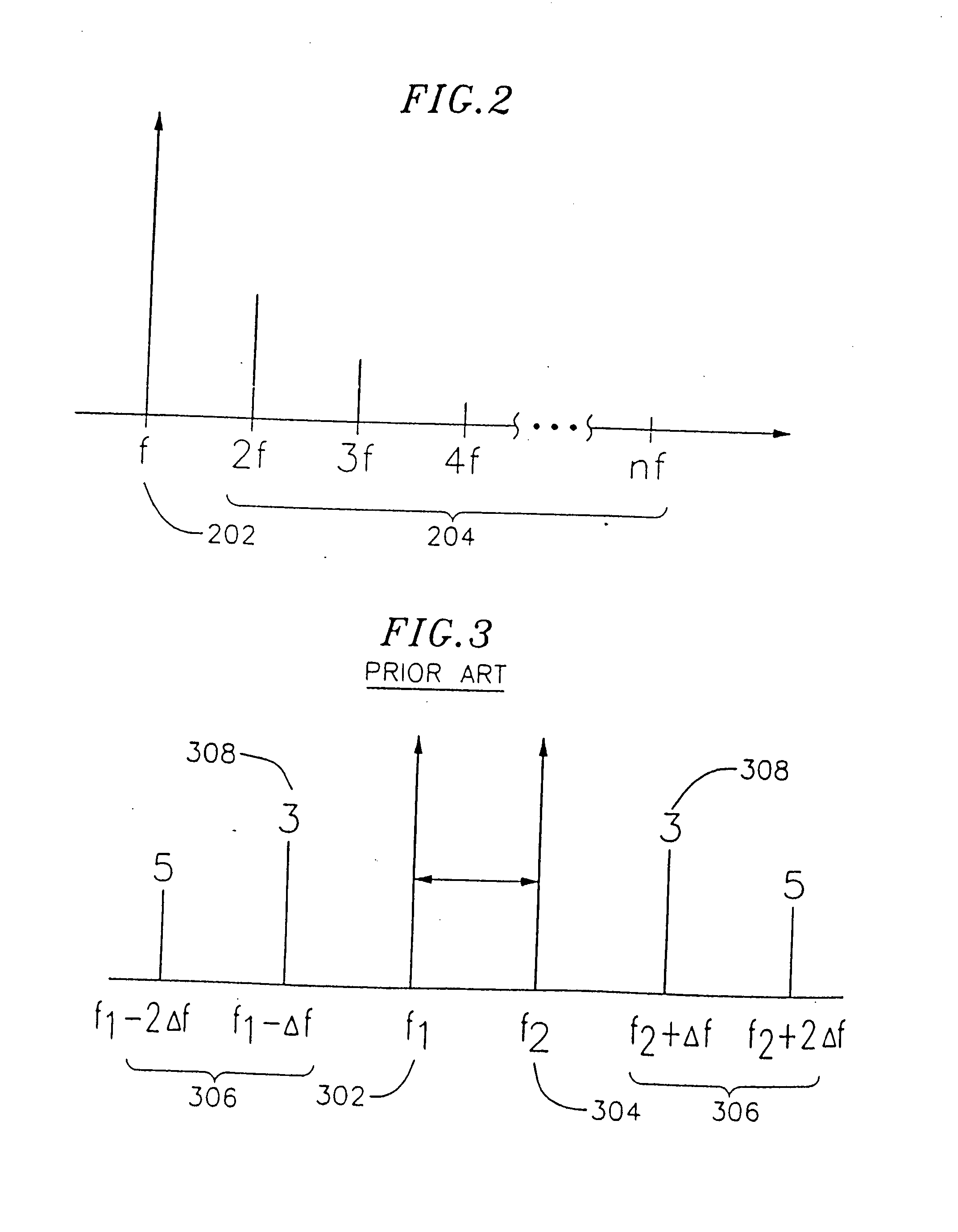

IF FSK receiver

InactiveUS20060002491A1Improve performanceIncrease data rateDc level restoring means or bias distort correctionFrequency-modulated carrier systemsDigital dataDifferentiator

In one embodiment, the present invention is a low-power, and high performance receiver including an IF demodulator for high data rate, frequency modulated systems, such as Bluetooth. The IF demodulator is implemented in analog domain for simplicity and lower power consumption and operates at an IF frequency. An IF demodulator comprises: a first IF differentiator for differentiating an I signal; a second IF differentiator for differentiating a Q signal; a cross-coupled multiplier for multiplying the differentiated I signal with the Q signal and multiplying the differentiated Q signal with the I signal to extract frequency information from the I signal and the Q signal; and a slicer for converting the frequency information to digital data.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

5G BAND n79 ACOUSTIC WAVE RESONATOR RF FILTER CIRCUIT

ActiveUS20190068164A1High rejectionLow insertion lossImpedence networksSemiconductor devicesAcoustic waveInductor

An RF circuit device using modified lattice, lattice, and ladder circuit topologies. The devices can include four resonator devices and four shunt resonator devices. In the ladder topology, the resonator devices are connected in series from an input port to an output port while shunt resonator devices are coupled the nodes between the resonator devices. In the lattice topology, a top and a bottom serial configurations each includes a pair of resonator devices that are coupled to differential input and output ports. A pair of shunt resonators is cross-coupled between each pair of a top serial configuration resonator and a bottom serial configuration resonator. The modified lattice topology adds baluns or inductor devices between top and bottom nodes of the top and bottom serial configurations of the lattice configuration. These topologies may be applied using single crystal or polycrystalline bulk acoustic wave (BAW) resonators.

Owner:AKOUSTIS INC

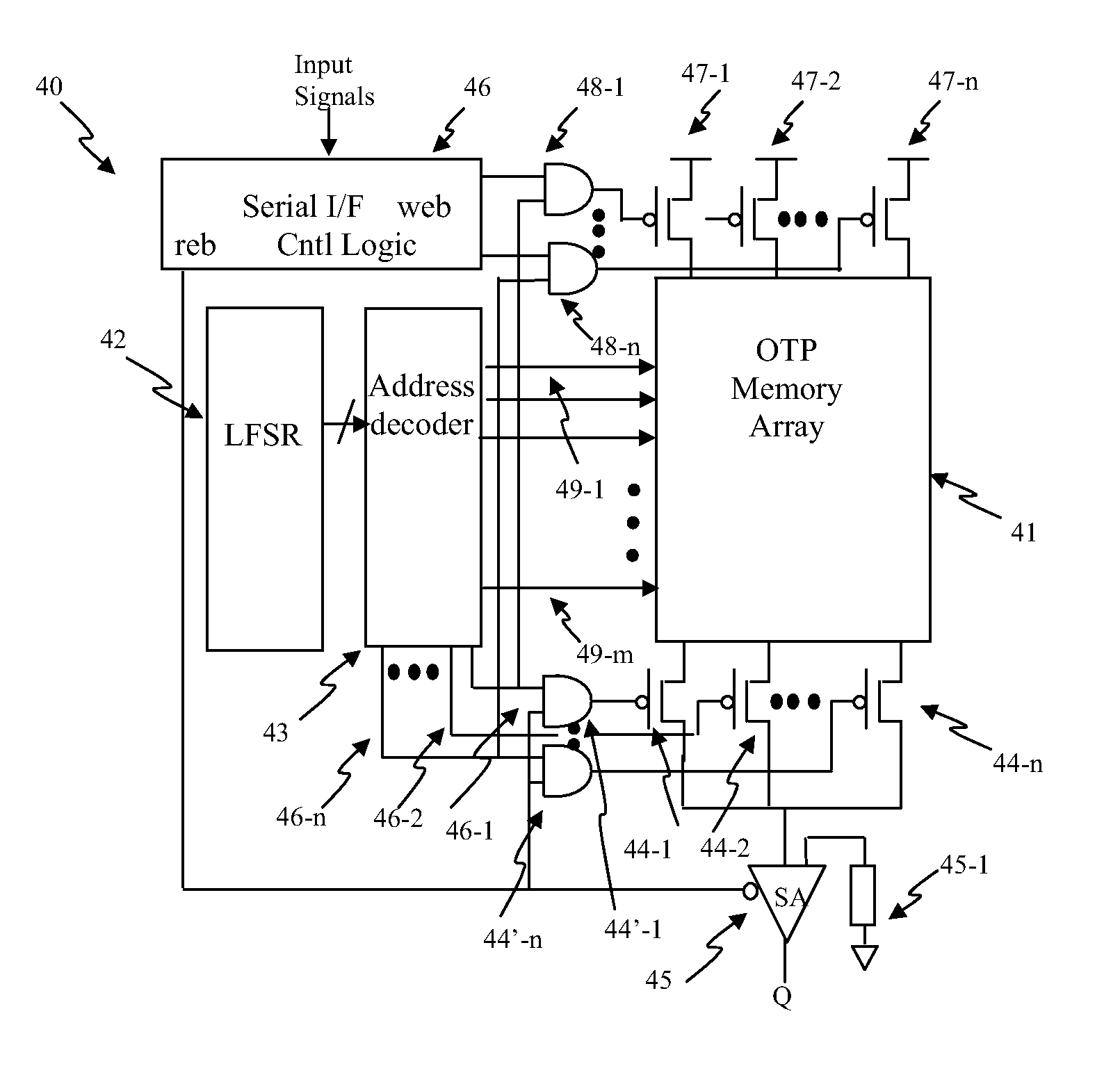

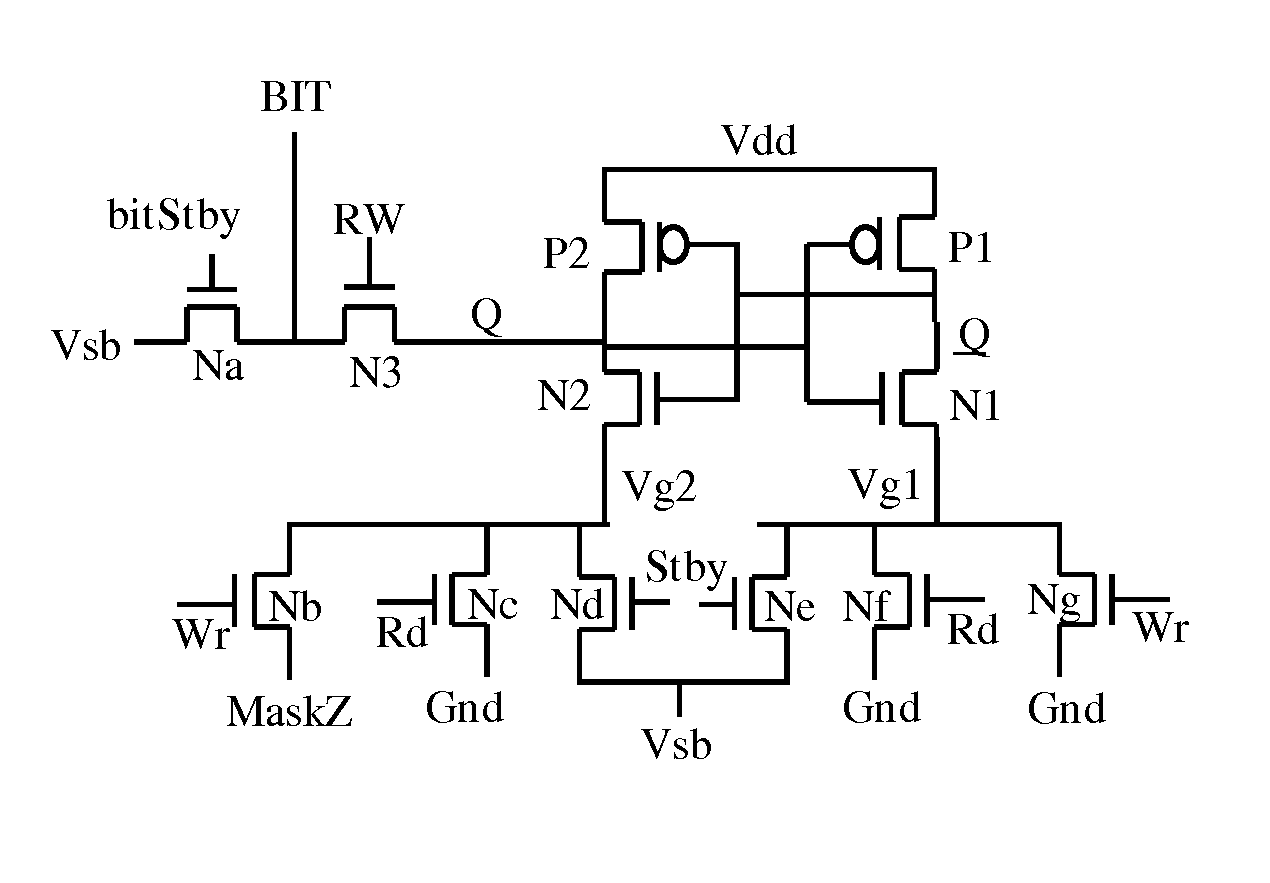

Circuit and System of a Low Density One-Time Programmable Memory

InactiveUS20130201745A1Low density OTPsReduce memory sizeElectric analogue storesRead-only memoriesAddress generatorHemt circuits

A low density One-Time Programmable (OTP) memory is disclosed to achieve low gate count and low overhead in the peripheral circuits to save the cost. A maximum-length Linear Feedback Shift Register (LFSR) can be used to generate 2n−1 address spaces from an n-bit address. The registers used in the address generator can have two latches. Each latch has two cross-coupled inverters with two outputs coupled to the drains of two MOS input devices, respectively. The inputs of the latch are coupled to the gates of the MOS input devices, respectively. The sources of the MOS input devices are coupled to the drains of at least one MOS device(s), whose gate(s) are coupled to a clock signal and whose source(s) are coupled to a supply voltage. The two latches can be constructed in serial with the outputs of the first latch coupled to the inputs of the second latch.

Owner:ATTOPSEMI TECH CO LTD

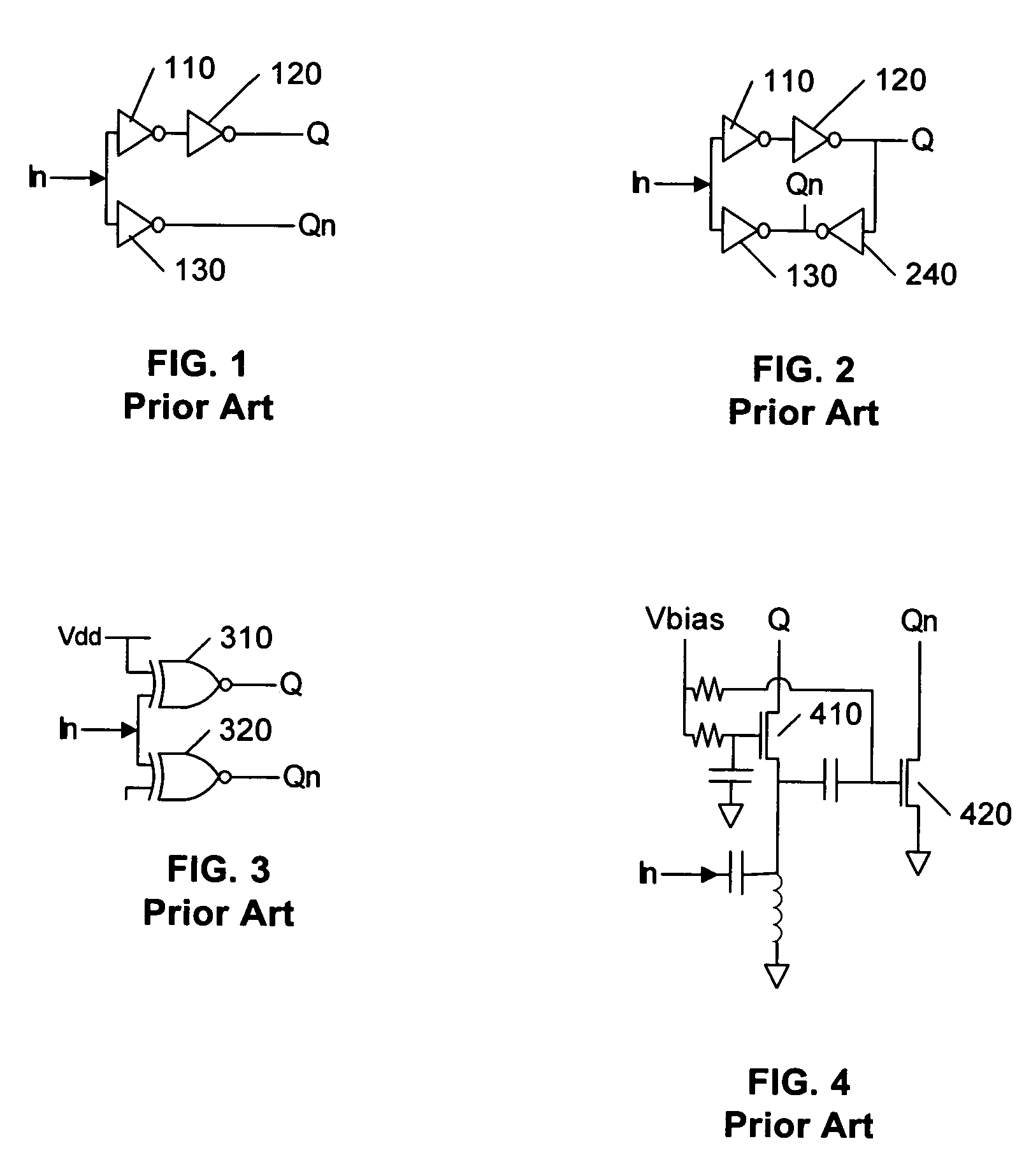

Layout for multiple-fin SRAM cell

The present disclosure provides a static random access memory (SRAM) cell. The SRAM cell includes a plurality of fin active regions formed on a semiconductor substrate, wherein the plurality of fin active regions include a pair adjacent fin active regions having a first spacing and a fin active region having a second spacing from adjacent fin active regions, the second spacing being greater than the first spacing; a plurality of fin field-effect transistors (FinFETs) formed on the plurality of fin active regions, wherein the plurality of FinFETs are configured to a first and second inverters cross-coupled for data storage and at least one port for data access; a first contact disposed between the first and second the fin active regions, electrically contacting both of the first and second the fin active regions; and a second contact disposed on and electrically contacting the third fin active region.

Owner:ADVANCED MFG INNOVATIONS INC

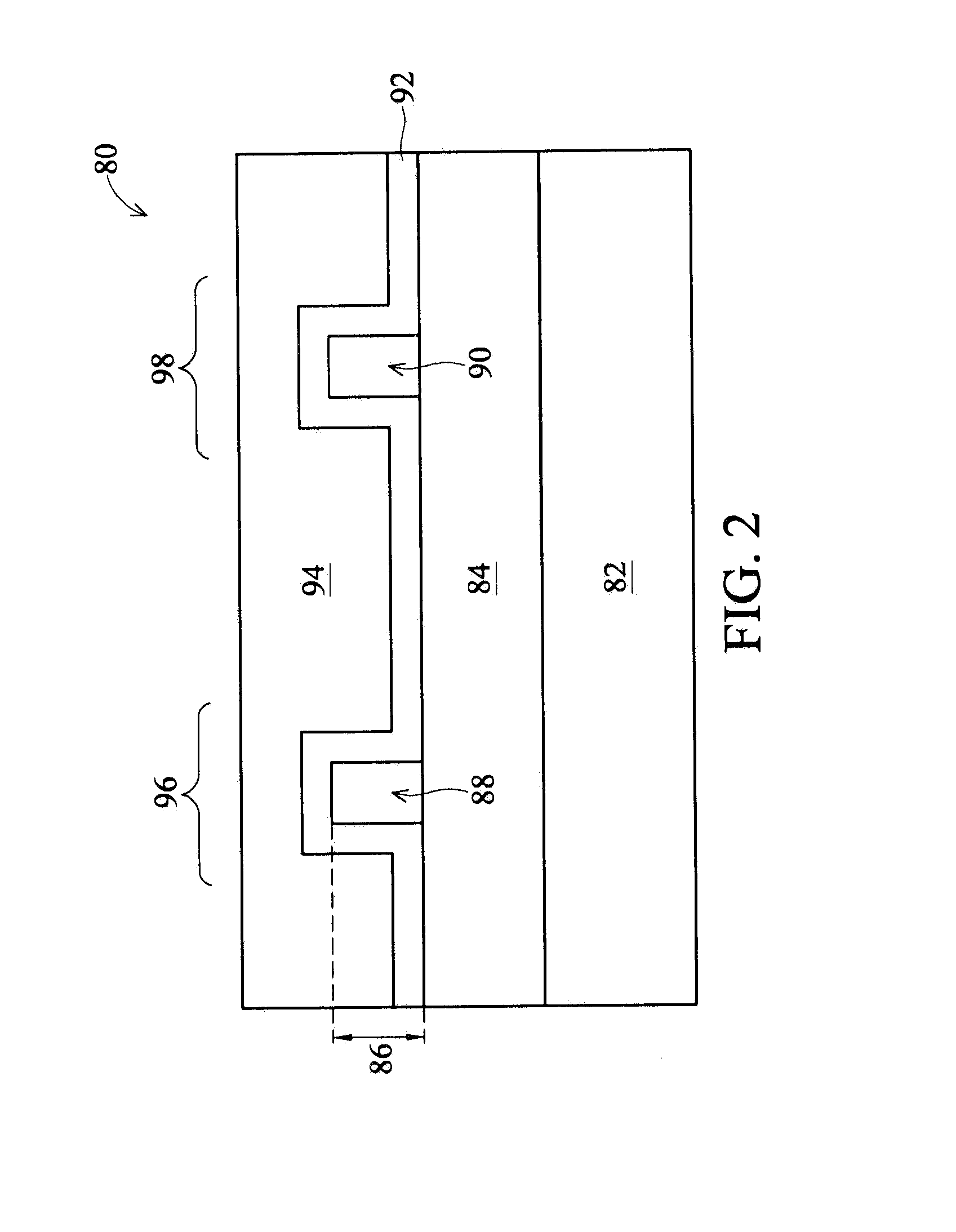

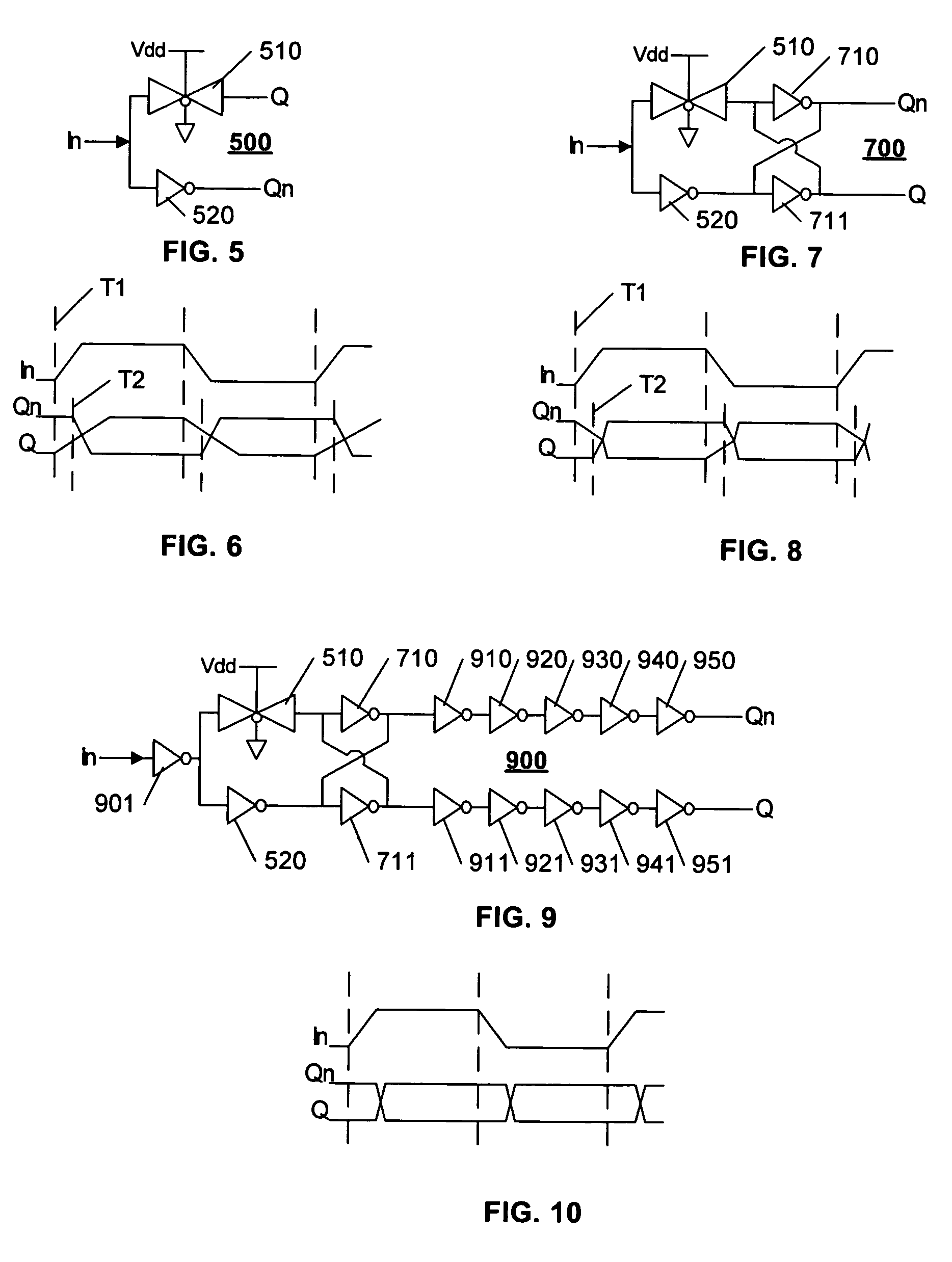

Low-skew single-ended to differential converter

InactiveUS7119602B2Reduce offsetReduce static power consumptionTransistorSingle output arrangementsTransmission gateEngineering

A single-ended to differential converter uses a cross-coupled latch that maximizes the output zero-crossing symmetry and is self compensating over PVT variations. An in-phase driving signal is provided by an always-on transmission gate coupled to the input. An out-of-phase driving signal is provided by an inverter coupled to the input. The in-phase and out-of-phase driving signals each drive an input of the cross-coupled latch. The in-phase driving signal from the always-on transmission gate starts to bring the cross-coupled latch into conduction, and when the out-of-phase driving signal arrives, the simultaneous driving of the cross-coupled latch causes a rapid and symmetric transition of both outputs of the cross-coupled latch.

Owner:TELEFON AB LM ERICSSON (PUBL)

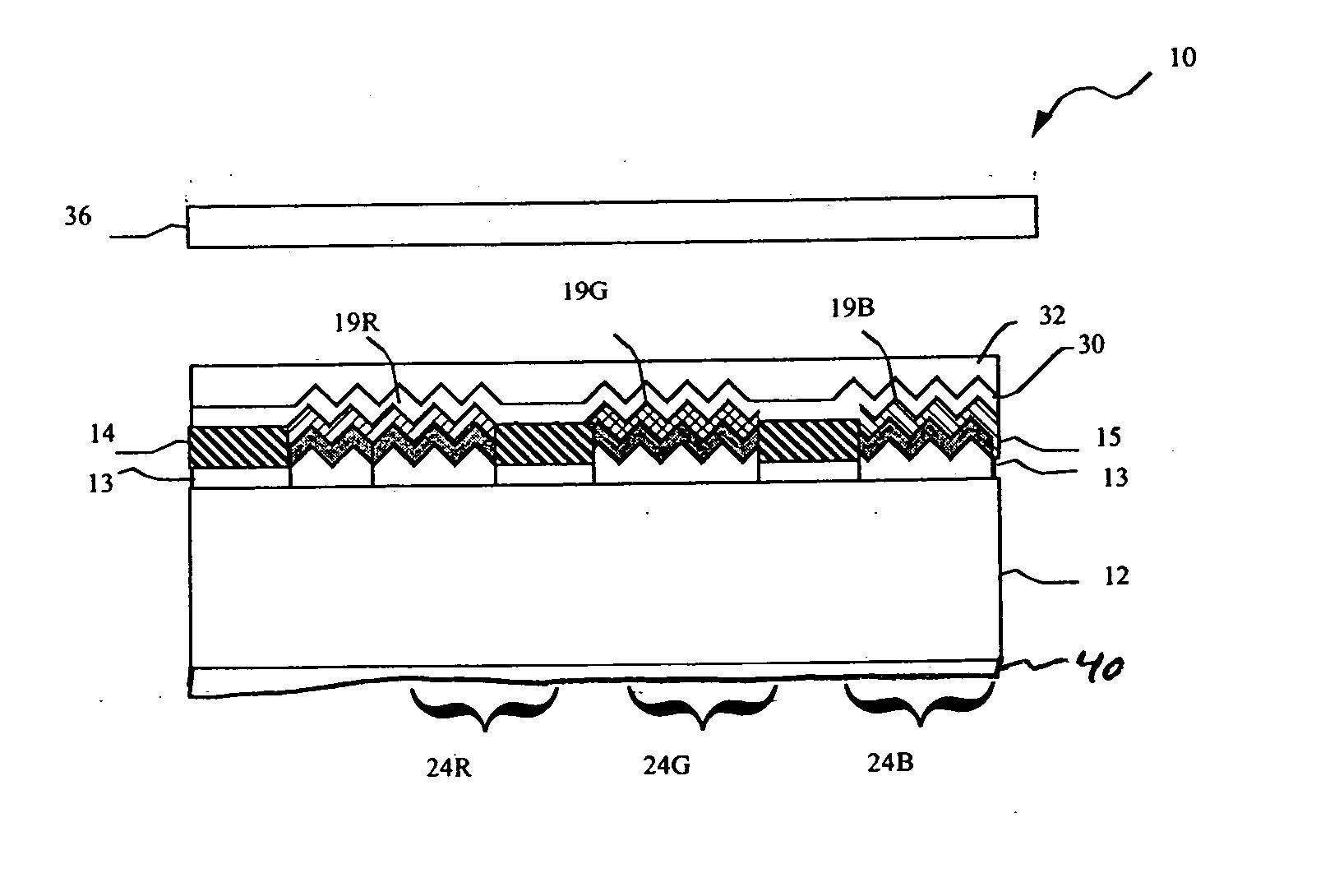

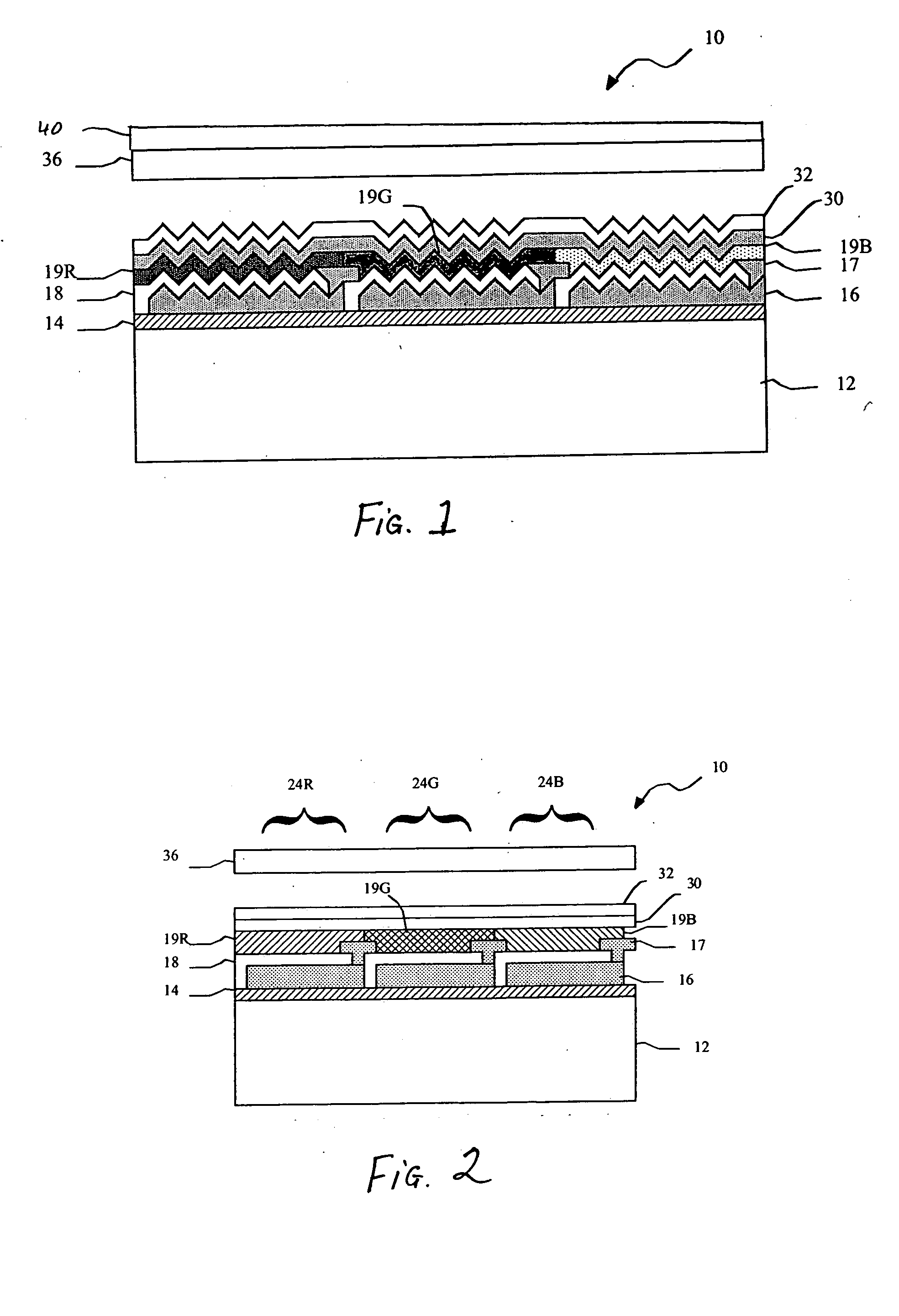

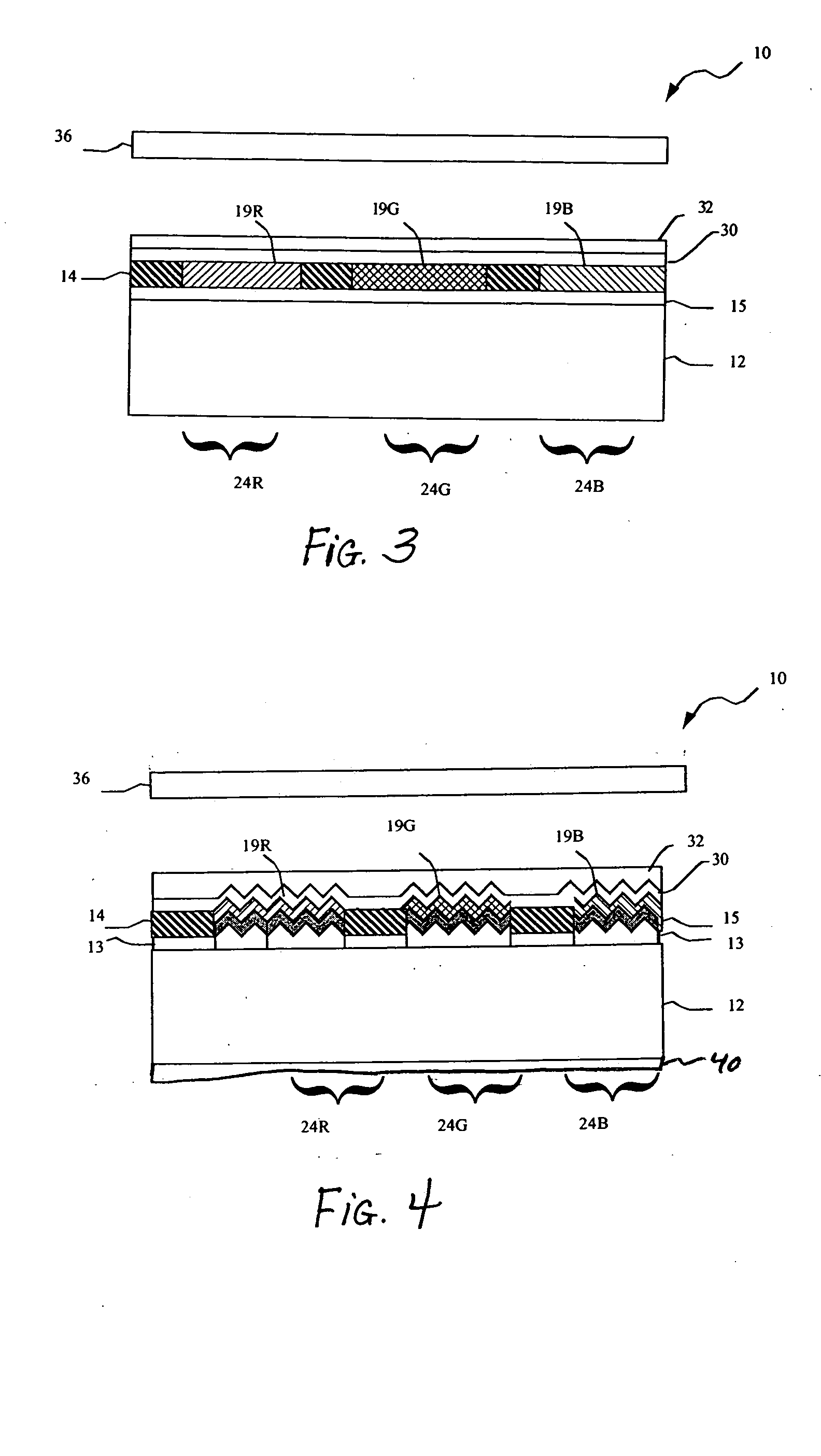

Organic polarized light emitting diode display with polarizer

InactiveUS20050088084A1Discharge tube luminescnet screensElectroluminescent light sourcesMetallic electrodeLED display

An organic light emitting diode display includes a substrate; a plurality of OLEDs formed on the substrate, the OLEDs emitting polarized light wherein the OLEDs comprise a layer defining a periodic grating structure; a first electrode layer conforming to the grating structure; an OLED material layer formed over the first electrode layer and conforming to the grating structure; and a second electrode layer formed over the OLED material layer and conforming to the grating structure, wherein the first and / or second electrode layers are metallic layers, whereby the periodic grating structure induces surface plasmon cross coupling in the metallic electrode layer(s) to emit polarized light; and a polarizer located over the substrate through which the polarized light is emitted.

Owner:EASTMAN KODAK CO

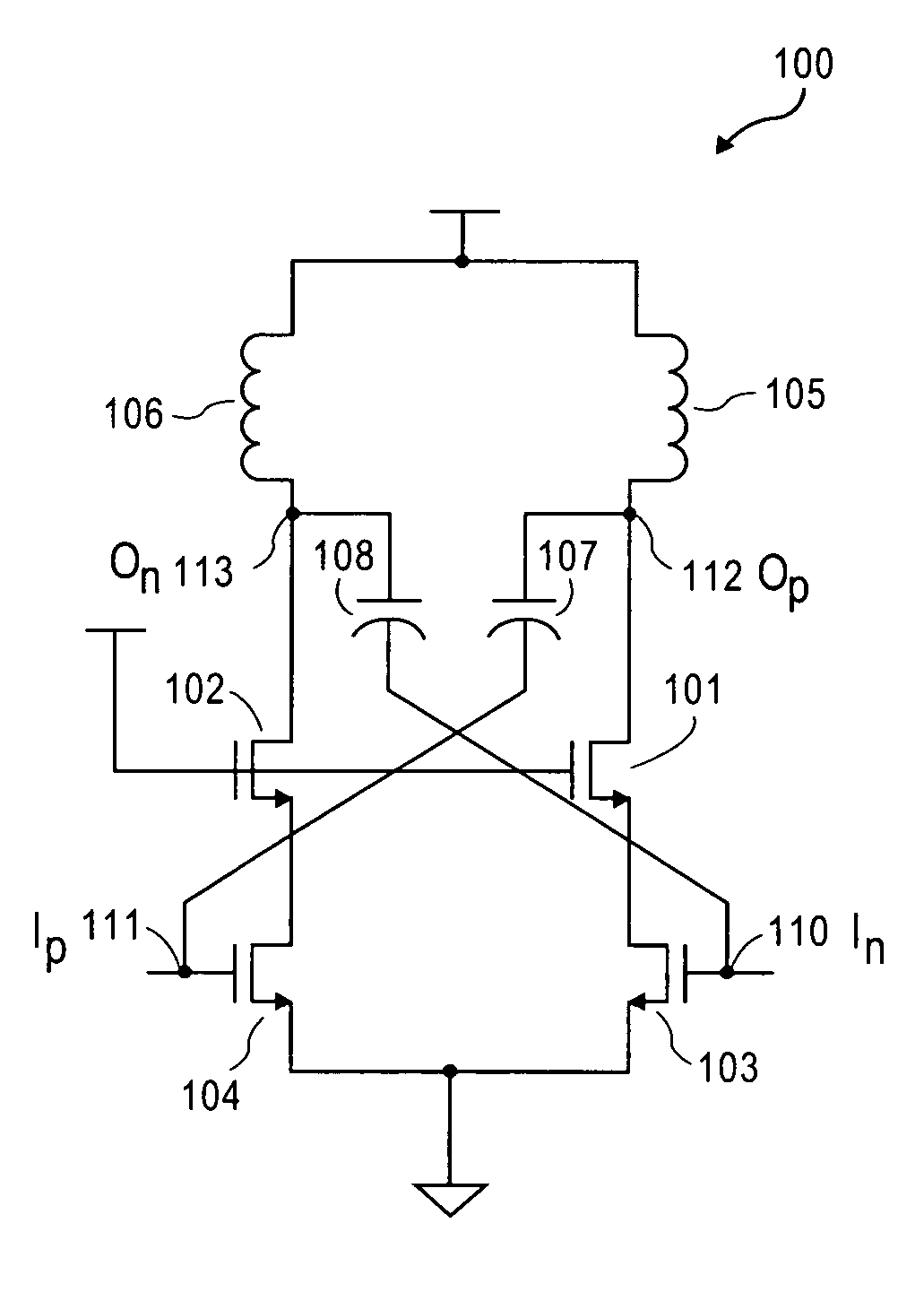

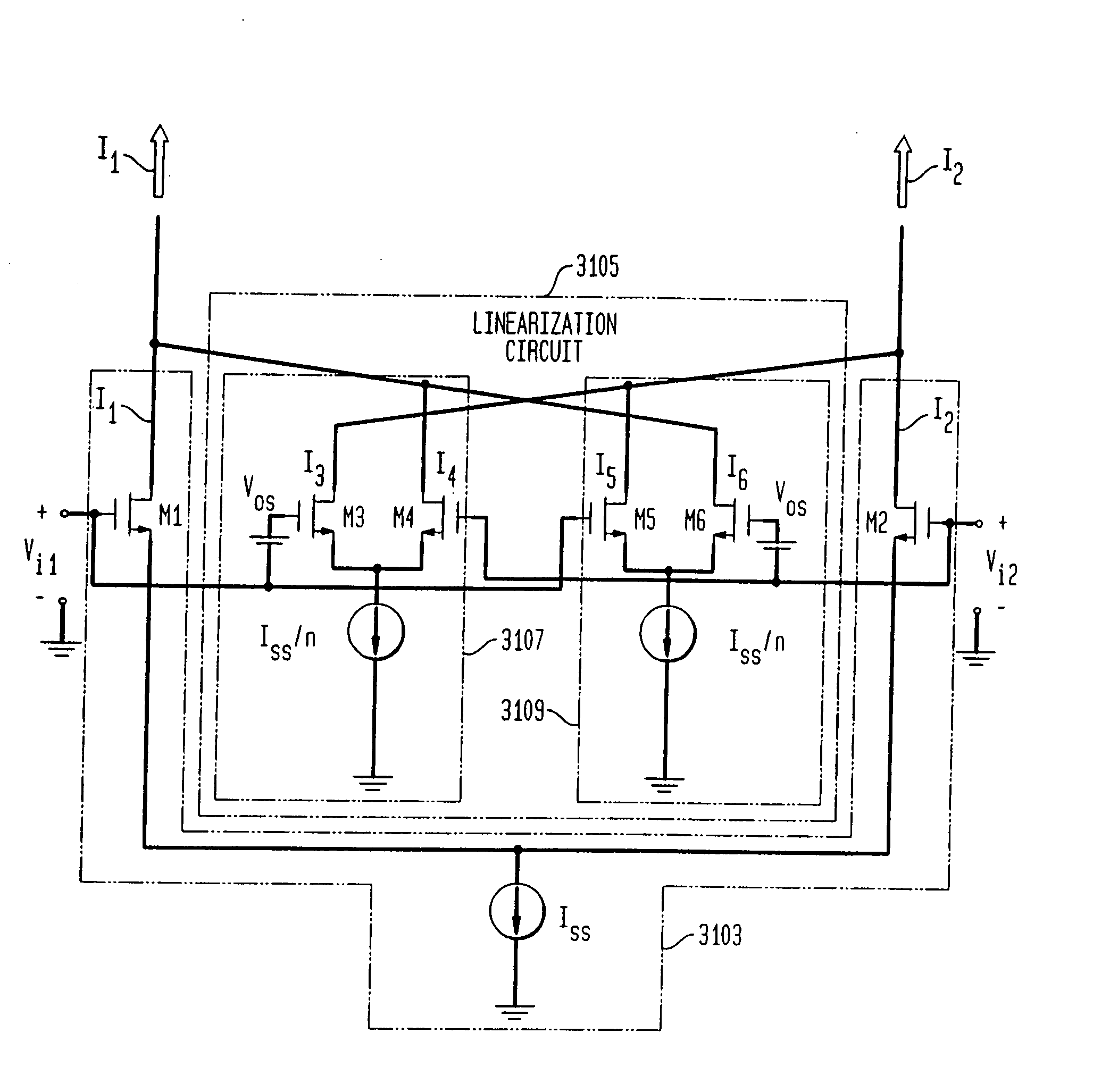

System and method for linearizing a CMOS differential pair

InactiveUS20080036536A1Multiple-port networksSemiconductor/solid-state device detailsShunt DeviceFilter tuning

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit. A receiver front end provides programmable attenuation and a programmable gain low noise amplifier. LC filters integrated onto the substrate in conjunction with image reject mixers provide image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. Active filters utilize multi track spiral inductors with shields to increase circuit Q. The filters incorporate a gain stage that provides improved dynamic range through the use of cross coupled auxiliary differential pair CMOS amplifiers to cancel distortion in a main linearized differential pair amplifier. Frequency planning provides additional image rejection. Local oscillator signal generation methods on chip reduce distortion. A PLL generates needed out of band LO signals. Direct synthesis generates in band LO signals. PLL VCOs are centered automatically. A differential crystal oscillator provides a frequency reference. Differential signal transmission throughout the receiver is used. ESD protection is provided by a pad ring and ESD clamping structure. Shunts utilize a gate boosting at each pin to discharge ESD build up. An IF VGA utilizes distortion cancellation achieved with cross coupled differential pair amplifiers having their Vds dynamically modified in conjunction with current steering of the differential pairs sources.

Owner:AVAGO TECH INT SALES PTE LTD

SRAM cell with common bit line and source line standby voltage

A high threshold five transistor SRAM bit cell with cross-coupled inverters has a single BIT line, a common logic 1 supply voltage, and two logic 0 virtual ground source voltages. The BIT line is coupled to the bit cell by a pass transistor. When BIT line and virtual ground lines are not otherwise being used, they are connected to a common standby voltage that substantially lowers bit cell standby leakage. Writing is performed by driving a data signal through the pass transistor and is facilitated by creating a voltage differential on the virtual ground lines. Reading is also performed through the pass transistor wherein the BIT line is initially at the standby voltage, and is then driven lower or higher depending upon the data value stored in the bit cell.

Owner:HOBSON RICHARD FREDERIC +1