Patents

Literature

113 results about "Planar capacitor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Planar capacitor memory cell and its applications

InactiveUS7209384B1Less complicated to fabricateImprove performanceTransistorSolid-state devicesHemt circuitsEngineering

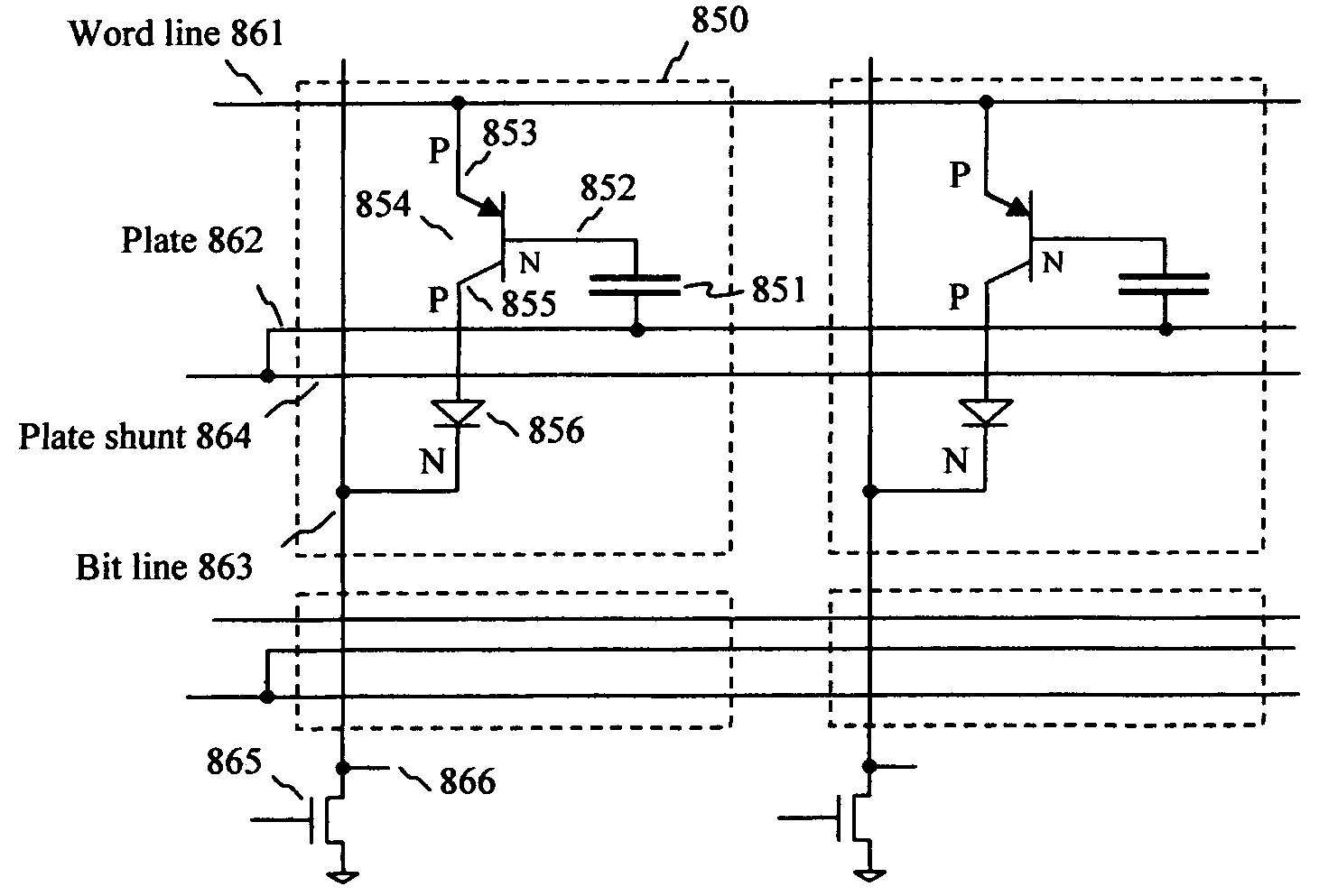

A capacitor memory is realized, wherein a capacitor stores data and a diode controls to store data “1” or “0”. Diode has four terminals wherein first terminal serves as word line, second terminal serves as storage node, third terminal is floating, and fourth terminal serves as bit line, wherein back channel effect is suppressed adding additional ions in the bottom side of third terminal or applying negative voltage in the well or substrate. A capacitor plate couples to second terminal, which plate has no coupling region to first, third and fourth terminal. With no coupling, the inversion layer of plate in the storage node is isolated from the adjacent nodes. In doing so, the plate can swing ground level to positive supply level to write. As a result, no negative generator is required for controlling plate. Word line and bit line keep ground level during standby, and rise to supply level for read or write operation. In this manner, no holding current is required during standby, and operating current is dramatically reduced with no negative generator. Write has a sequence to clear the state of cell before writing to store data regardless of previous state. Refresh cycle is periodically asserted to sustain data. The present invention can be applied for destructive read, or for nondestructive read adding pull-down device to bit line. The height of cell is almost same as control circuit on the bulk or SOI wafer.

Owner:KIM JUHAN

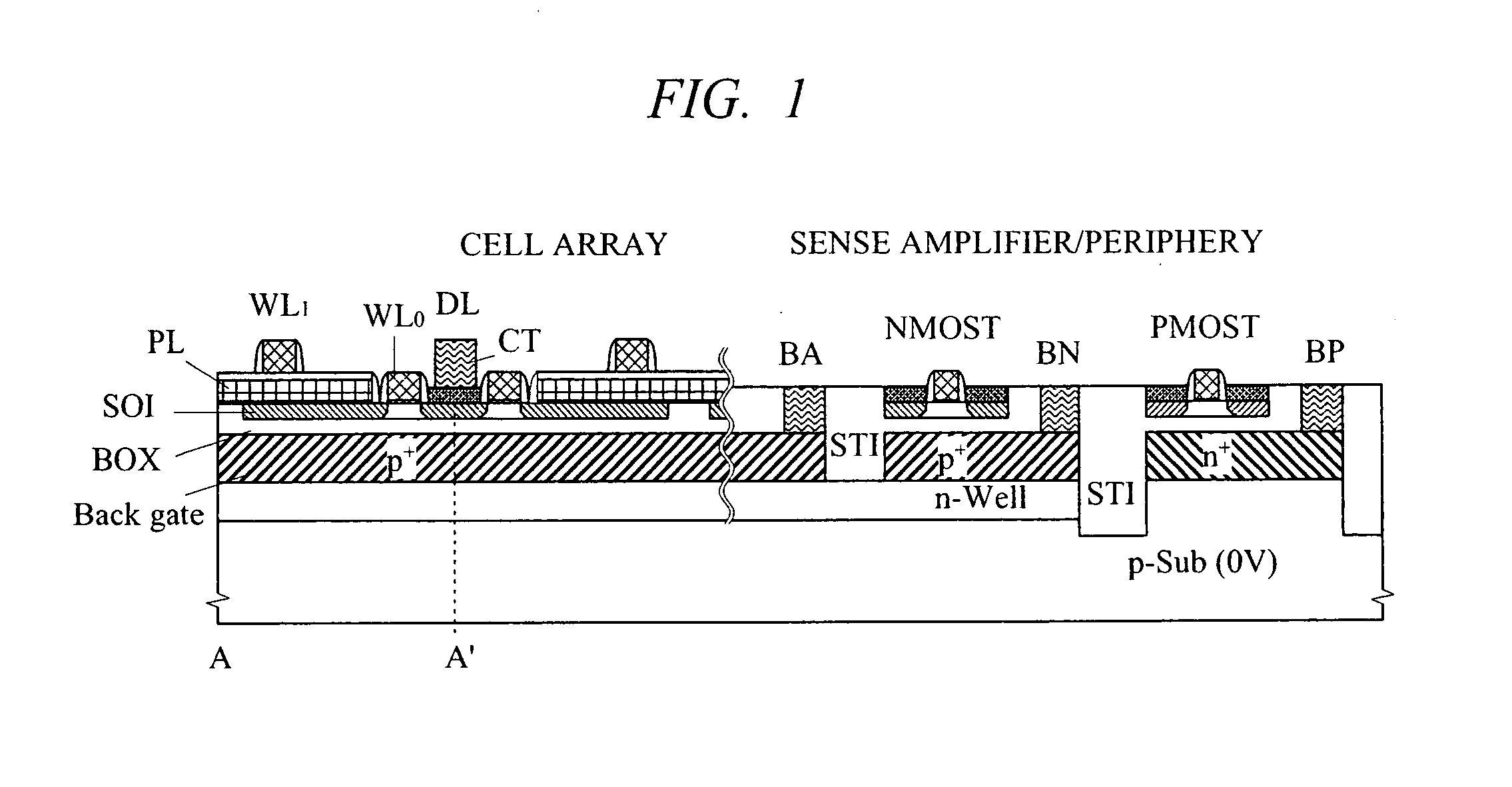

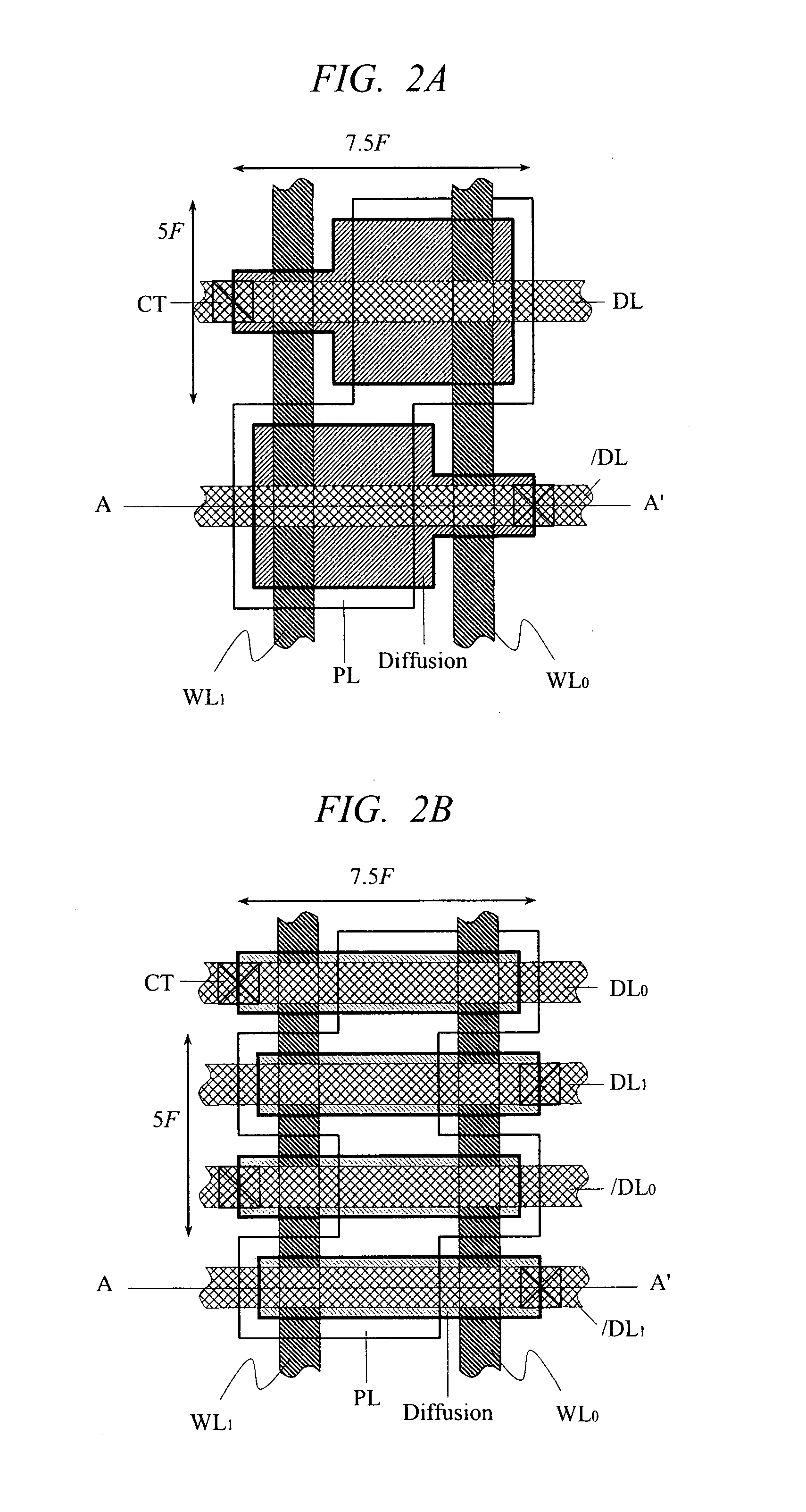

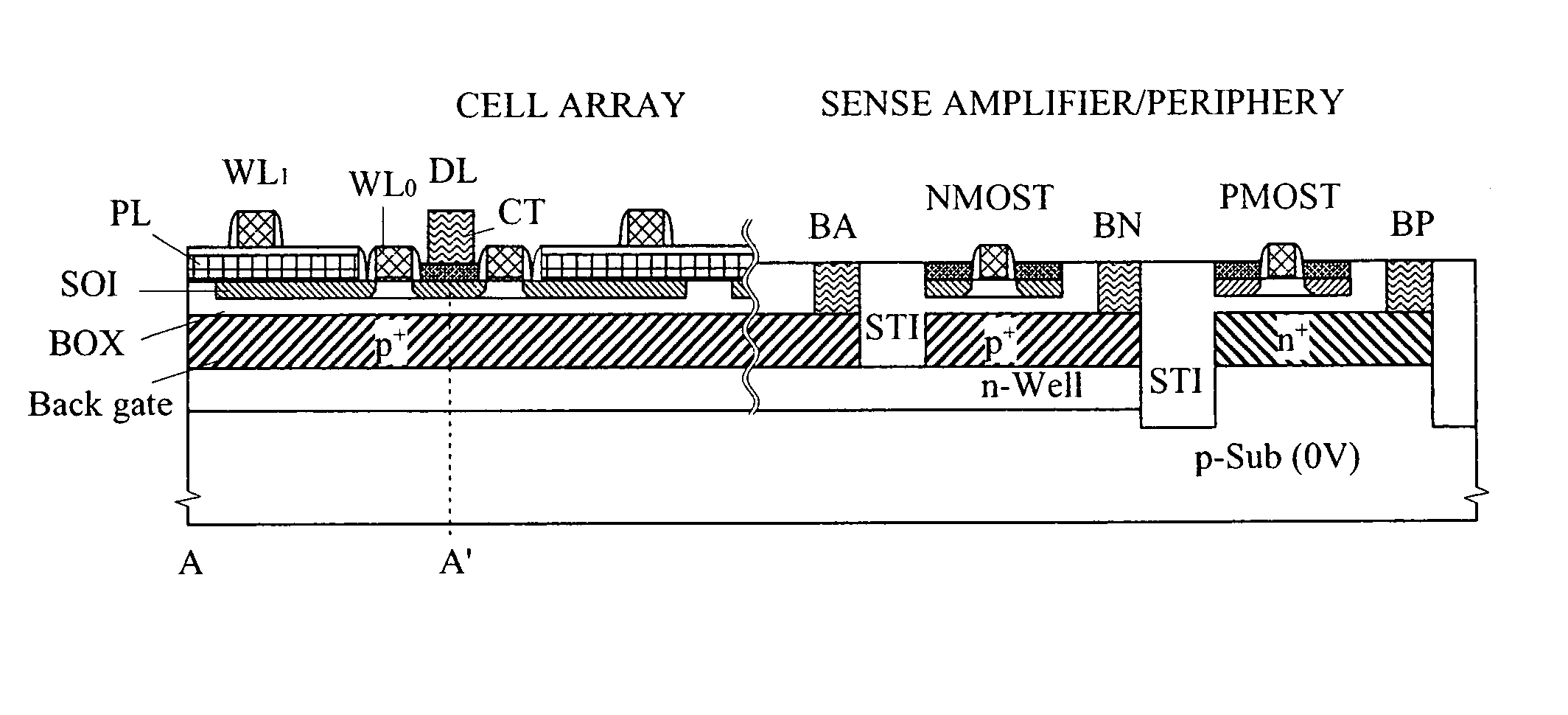

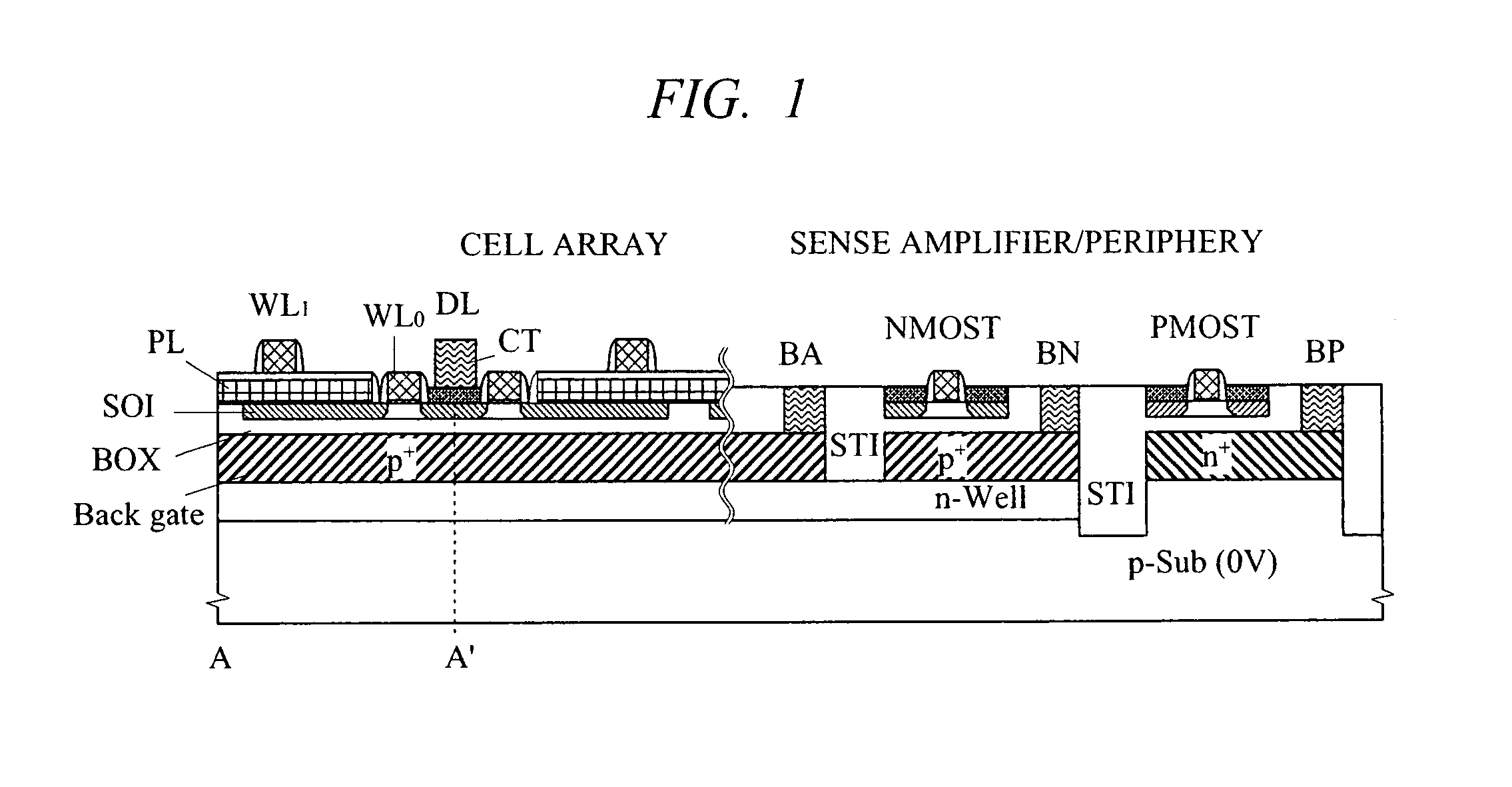

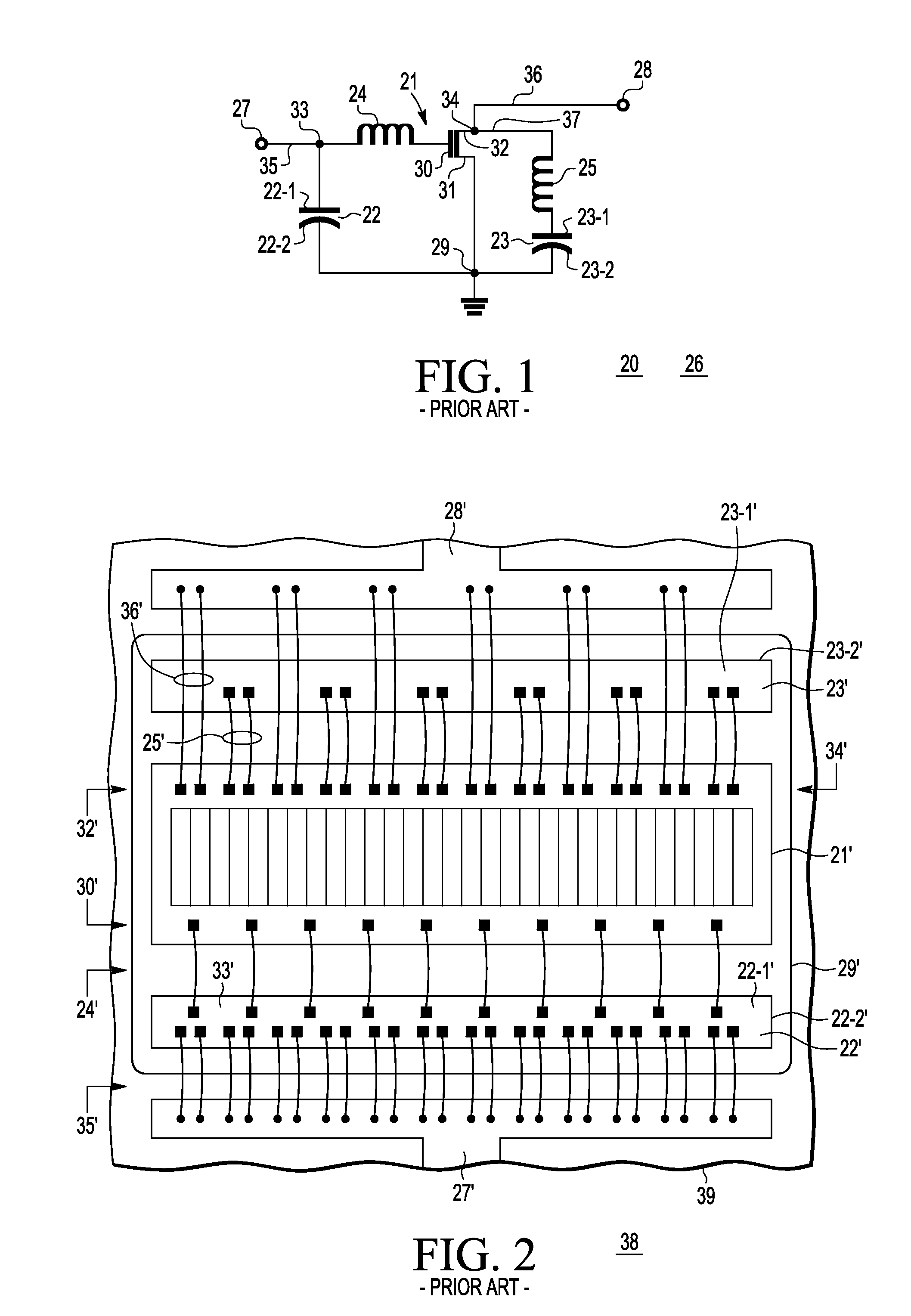

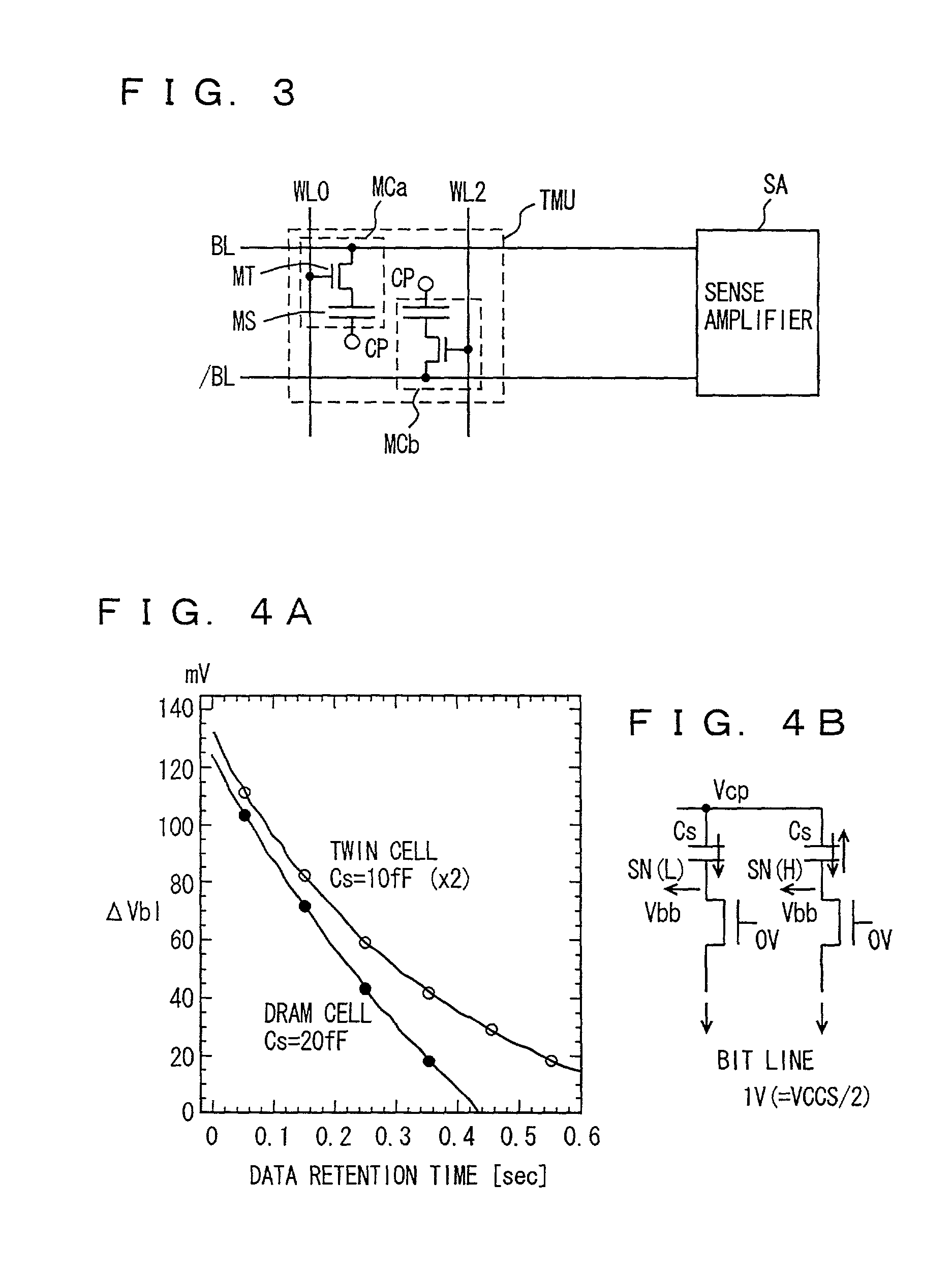

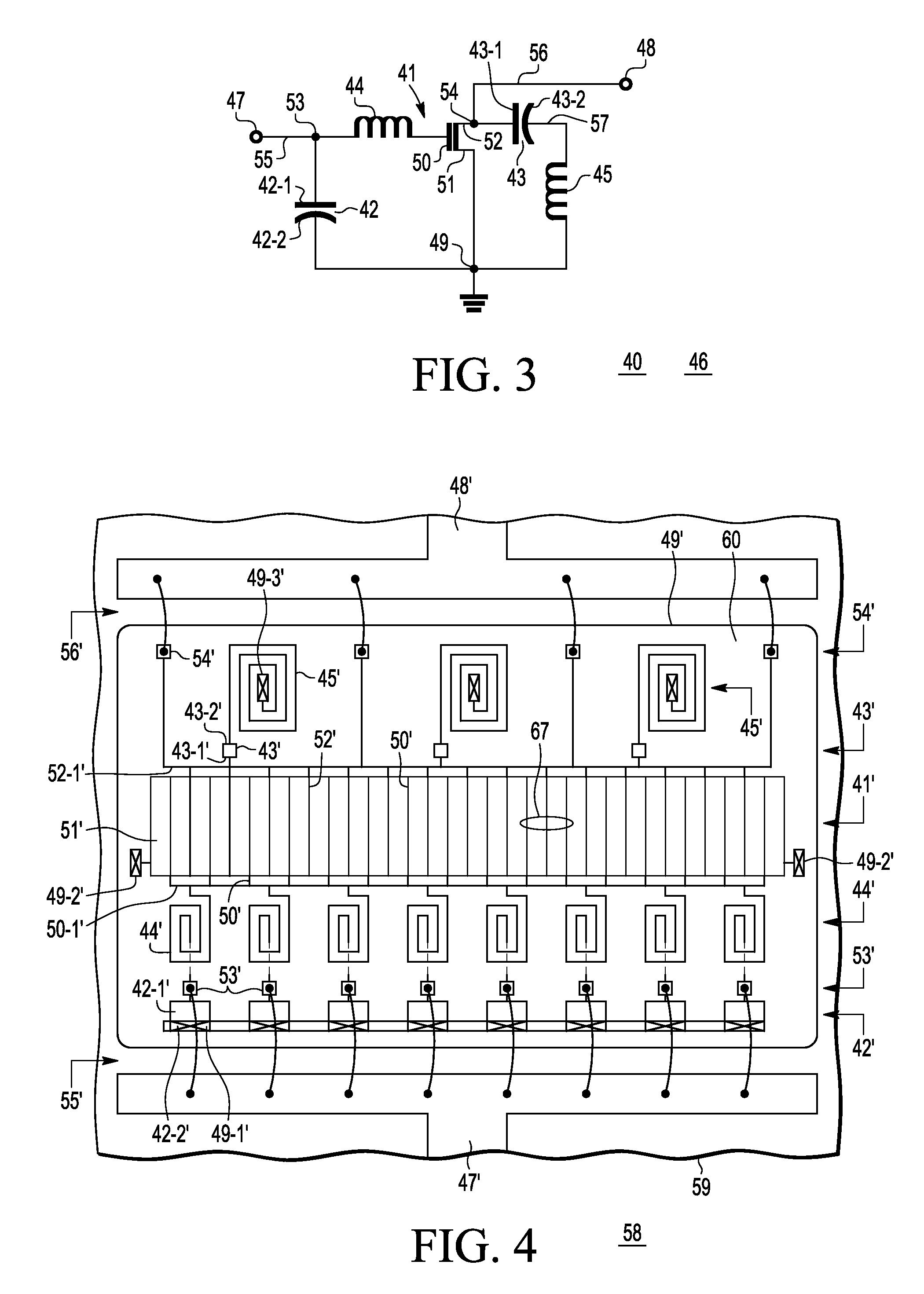

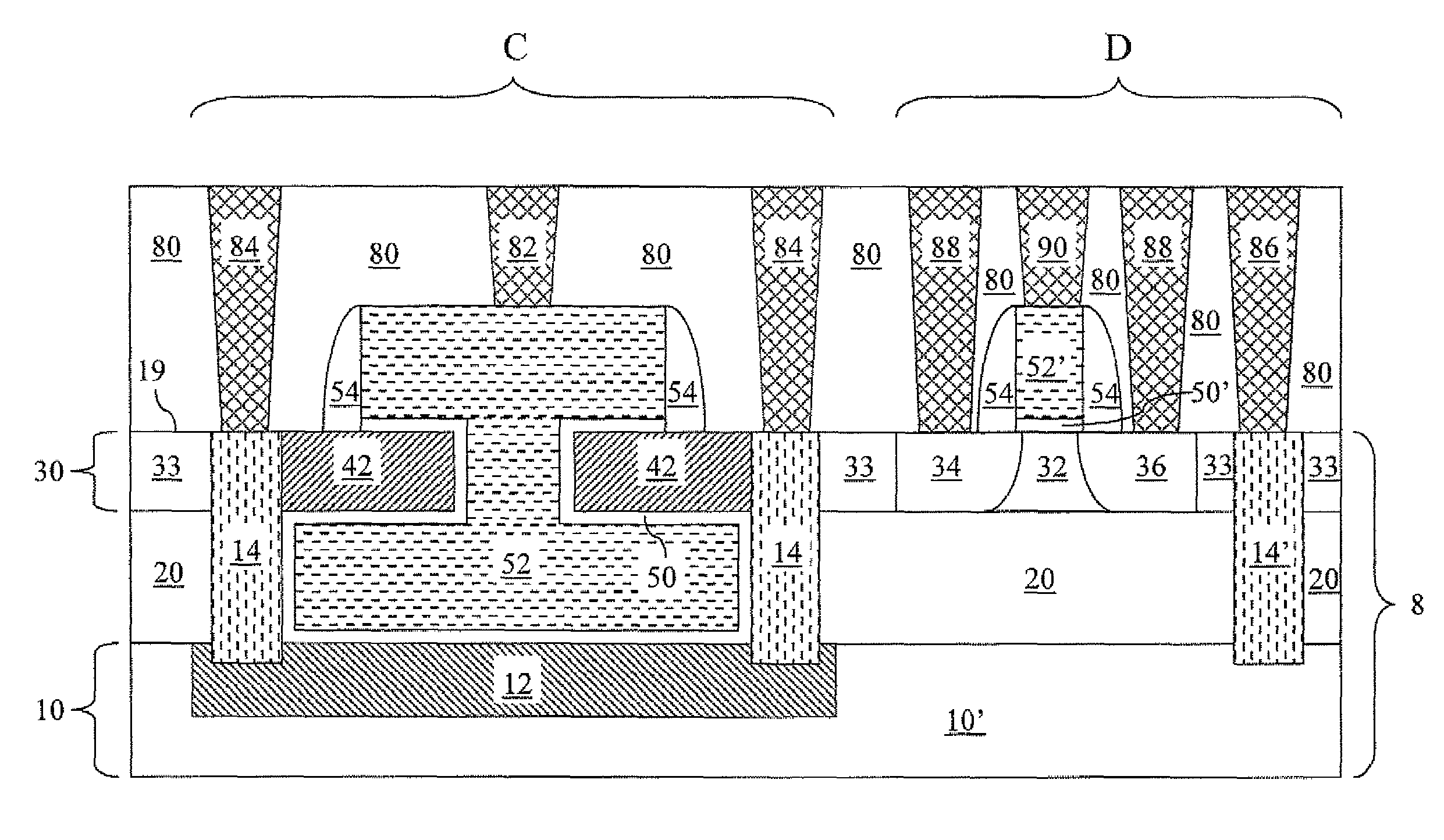

Semiconductor device

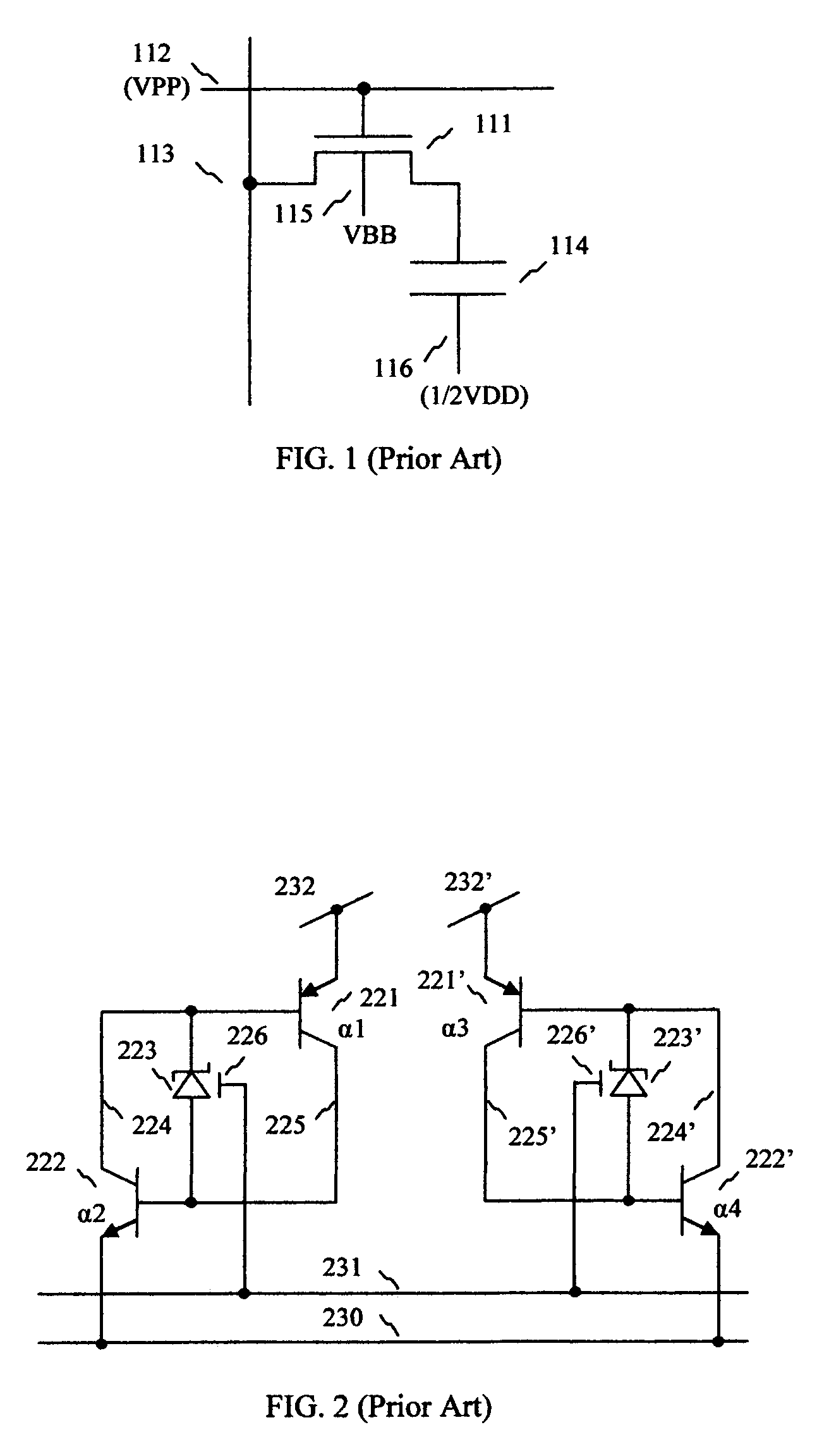

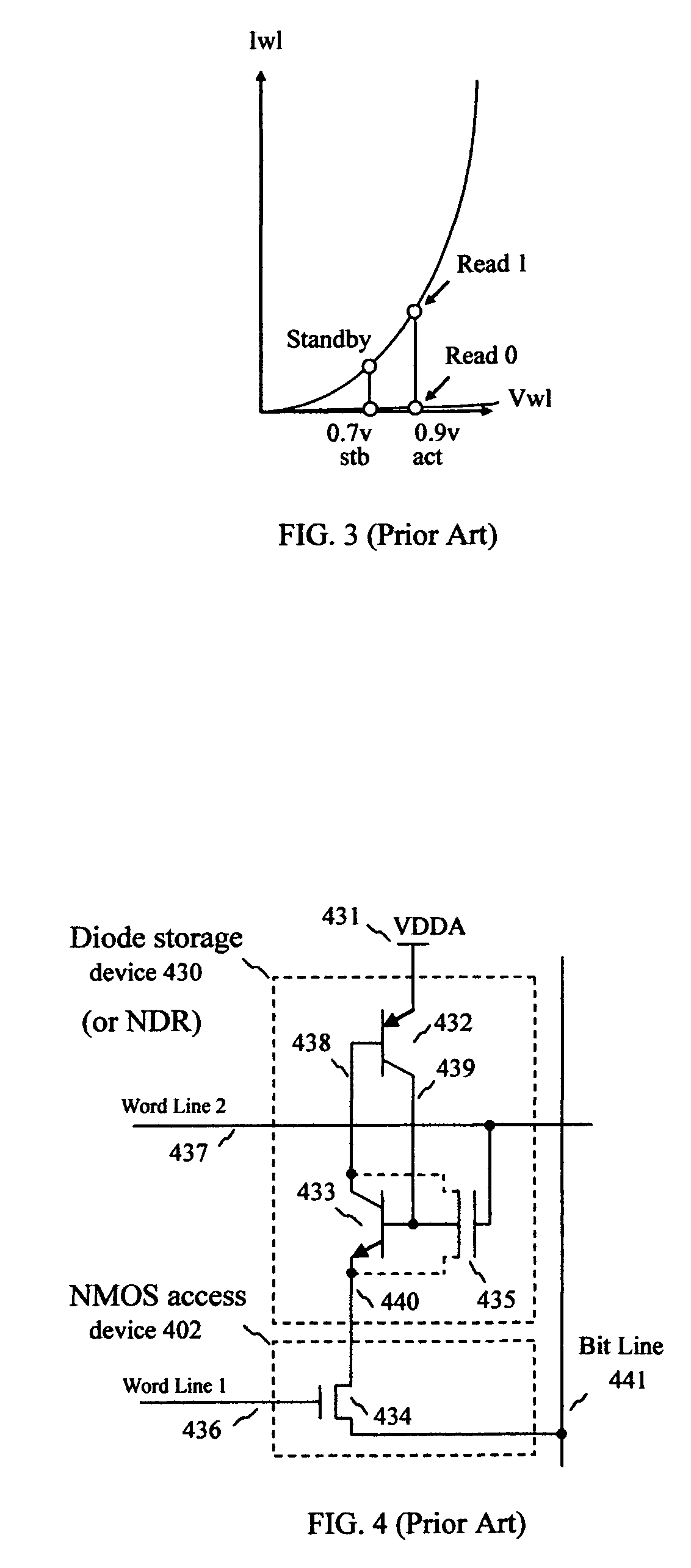

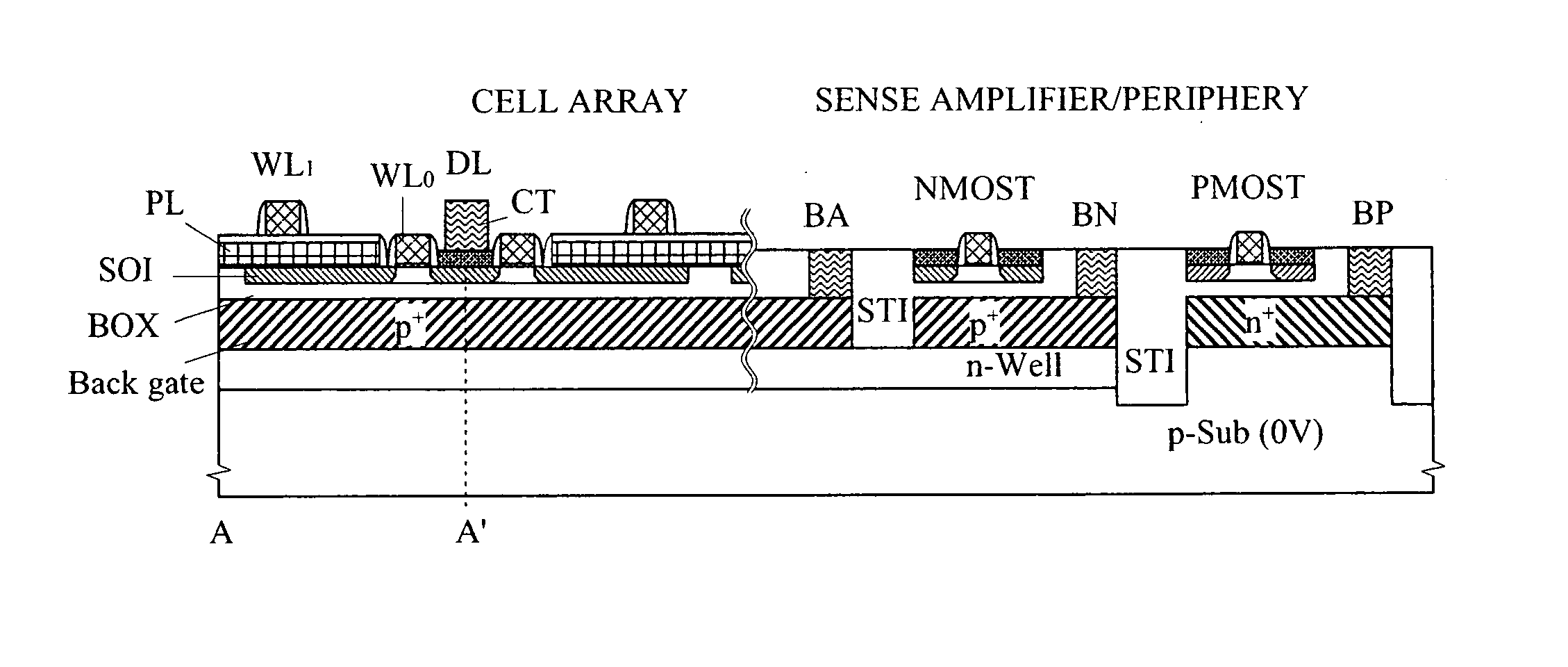

InactiveUS20090003105A1Run at high speedSmall sizeTransistorSolid-state devicesJunction leakageAudio power amplifier

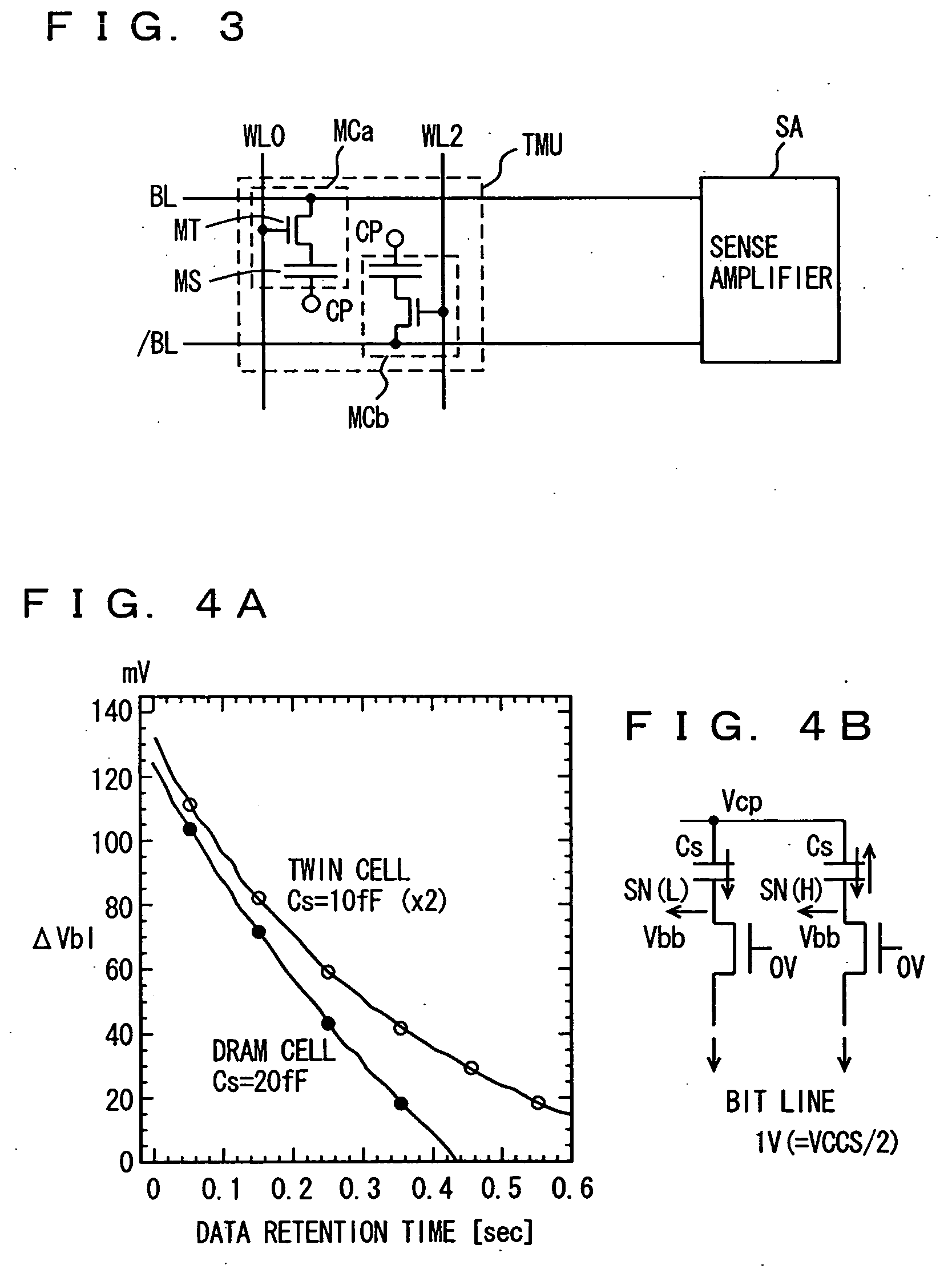

A high-speed and low-voltage DRAM memory cell capable of operating at 1 V or less and an array peripheral circuit are provided. A DRAM cell is comprised of a memory cell transistor and planar capacitor which utilize a FD-SOI MOST structure. Since there is no junction leakage current, loss of stored charge is eliminated, and the low-voltage operation can be realized. Further, a gate and a well in a cross-coupled type sense amplifier using FD-SOI MOSTs are connected. By this means, a threshold value dynamically changes and high-speed sensing operation can be realized.

Owner:HITACHI LTD

Semiconductor device

A high-speed and low-voltage DRAM memory cell capable of operating at 1 V or less and an array peripheral circuit are provided. A DRAM cell is comprised of a memory cell transistor and planar capacitor which utilize a FD-SOI MOST structure. Since there is no junction leakage current, loss of stored charge is eliminated, and the low-voltage operation can be realized. Further, a gate and a well in a cross-coupled type sense amplifier using FD-SOI MOSTs are connected. By this means, a threshold value dynamically changes and high-speed sensing operation can be realized.

Owner:HITACHI LTD

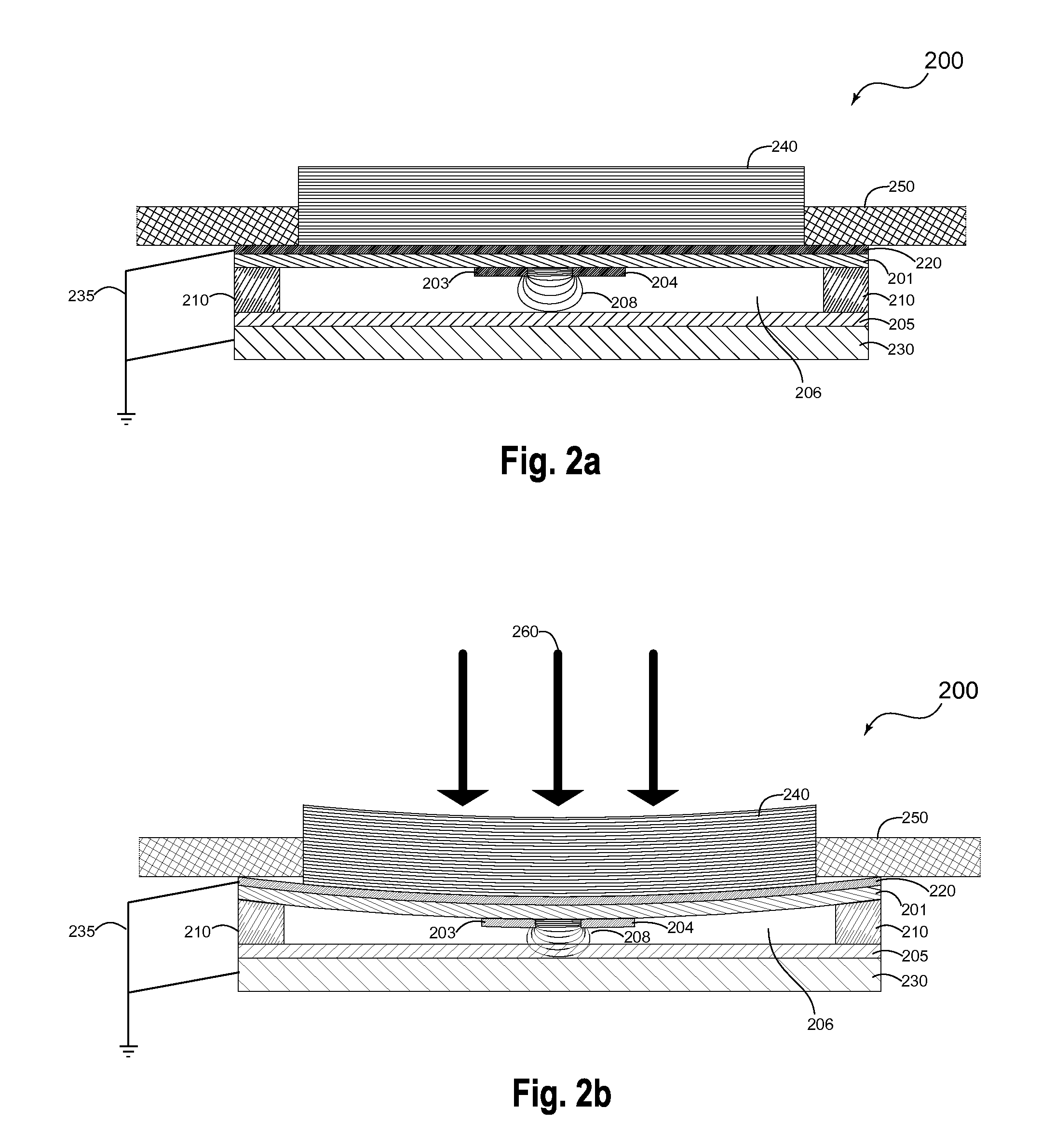

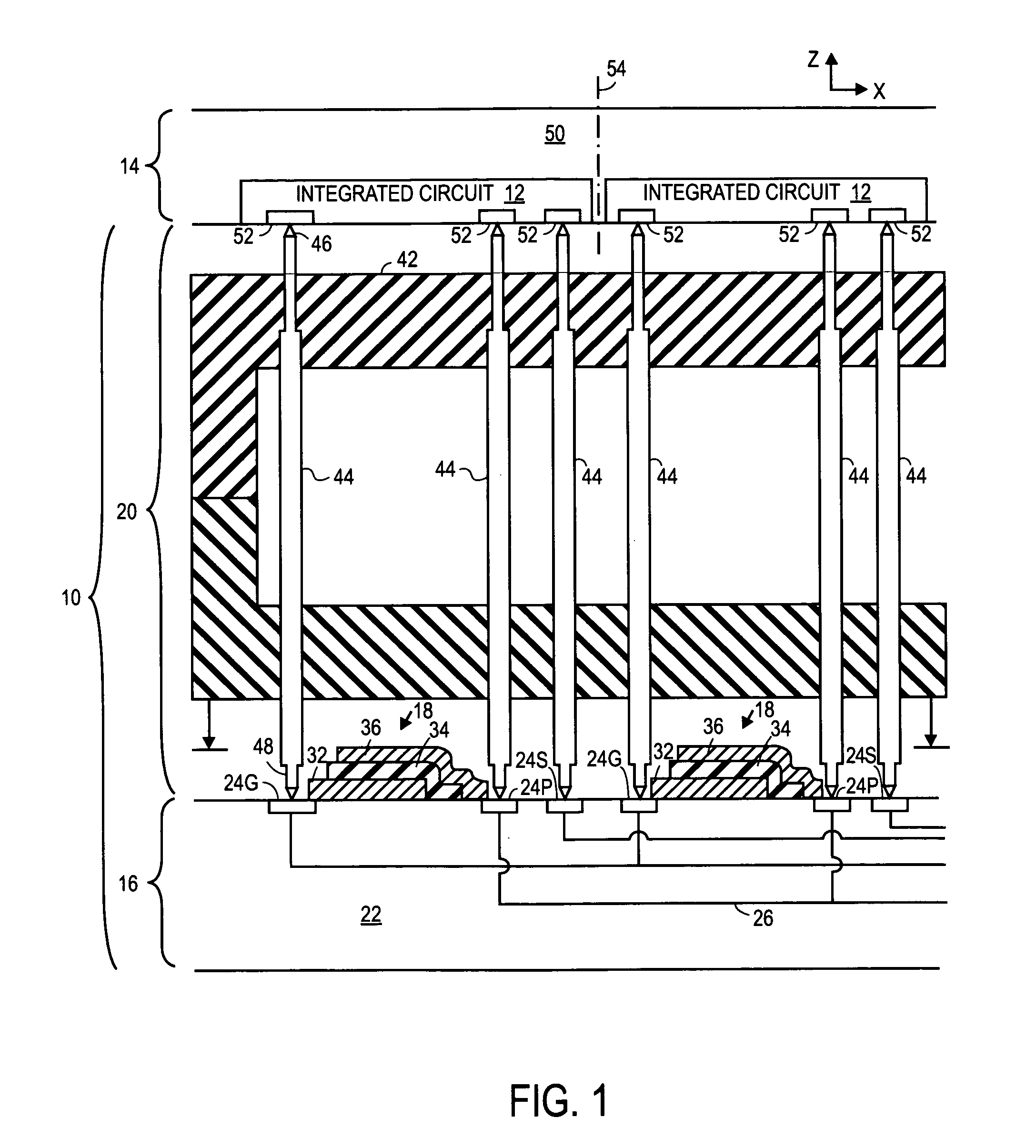

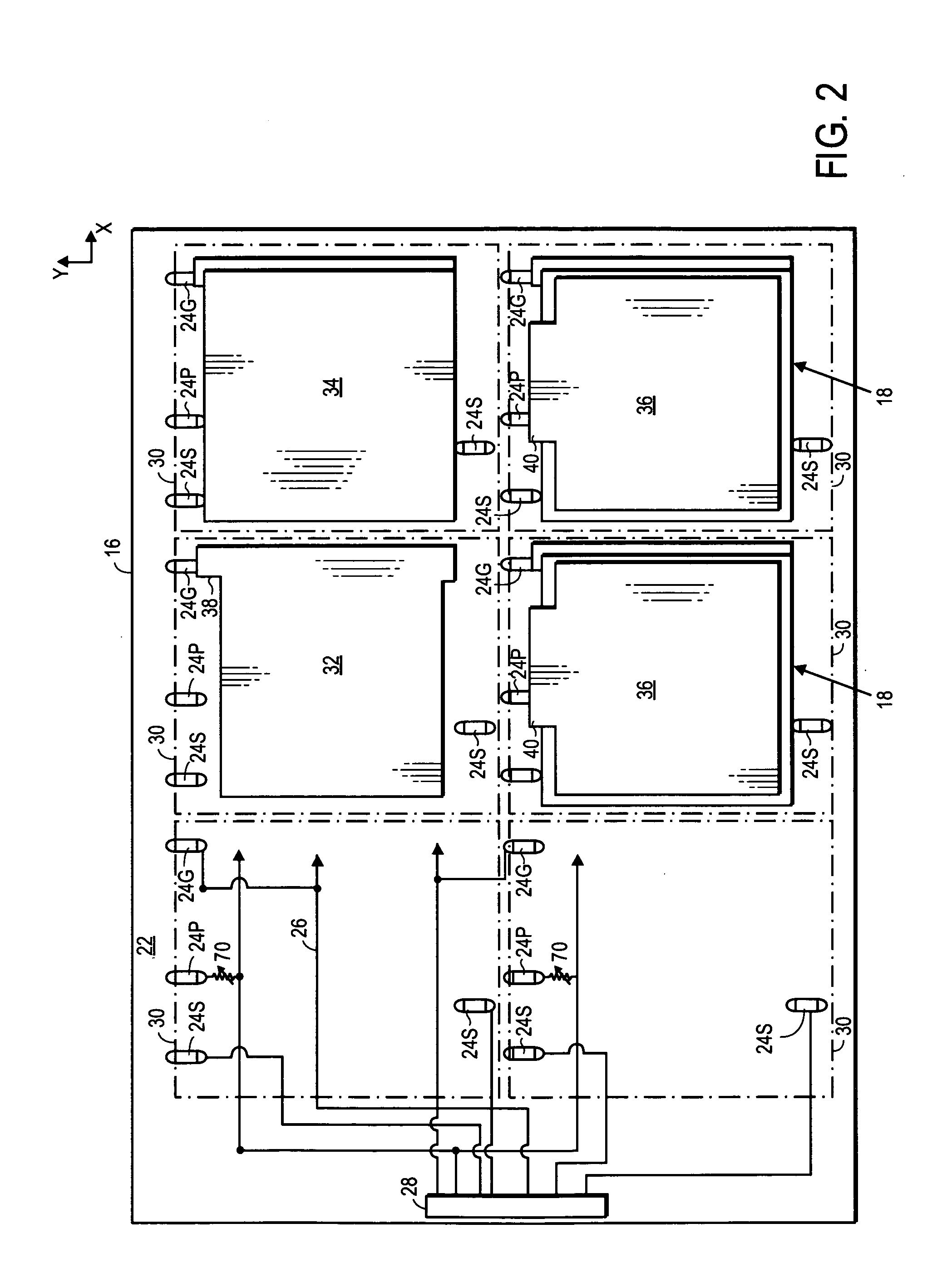

Shielded planar capacitor

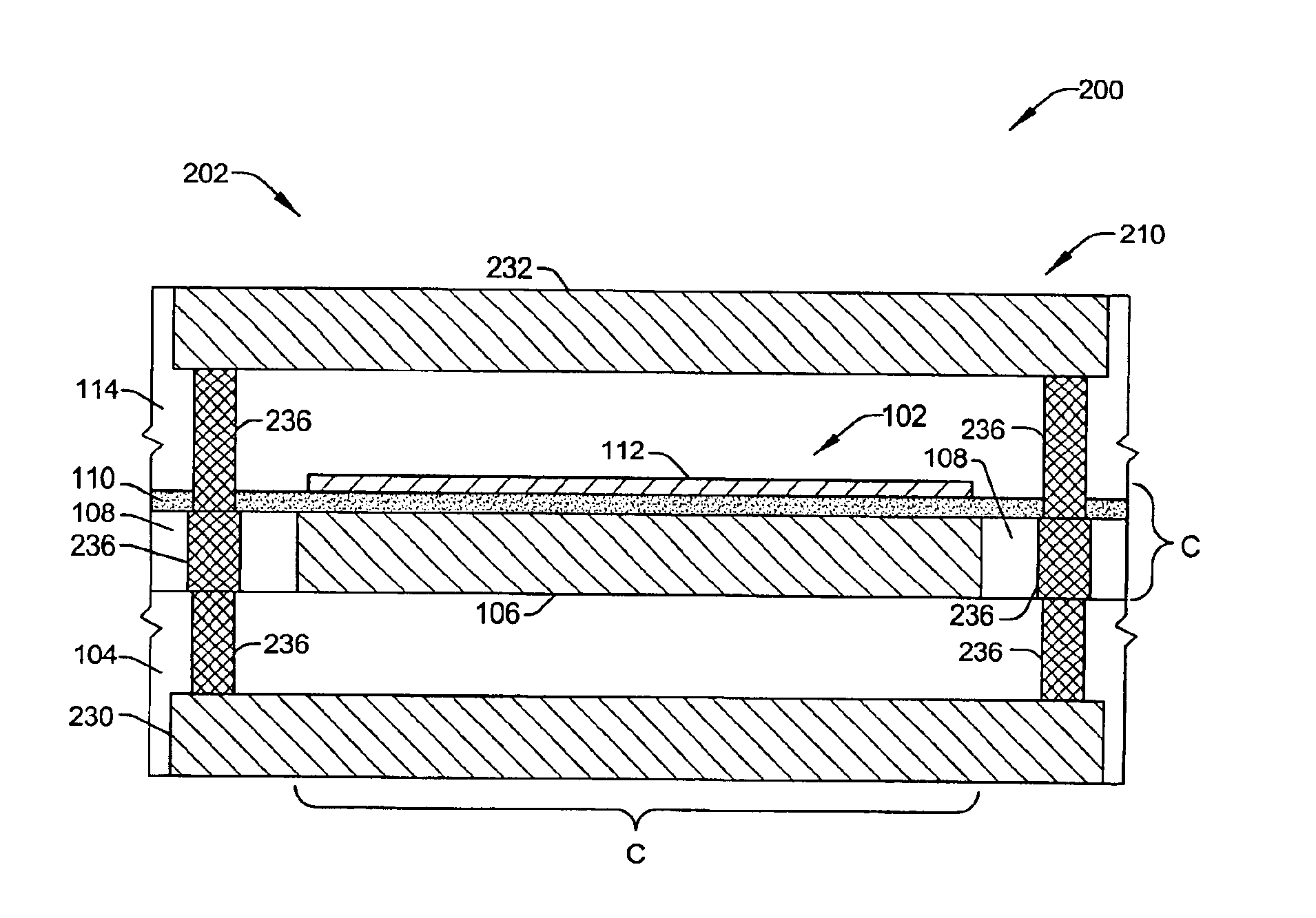

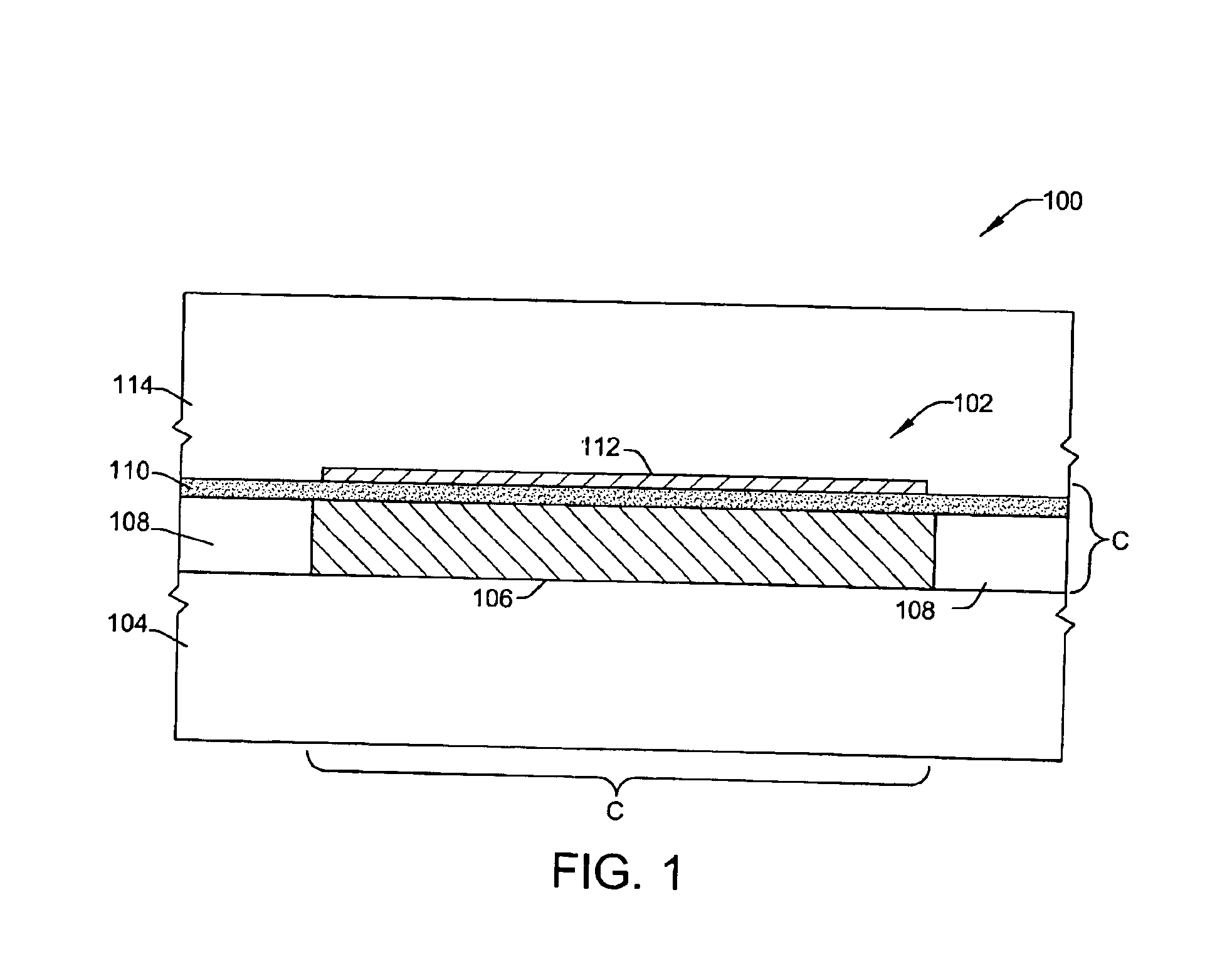

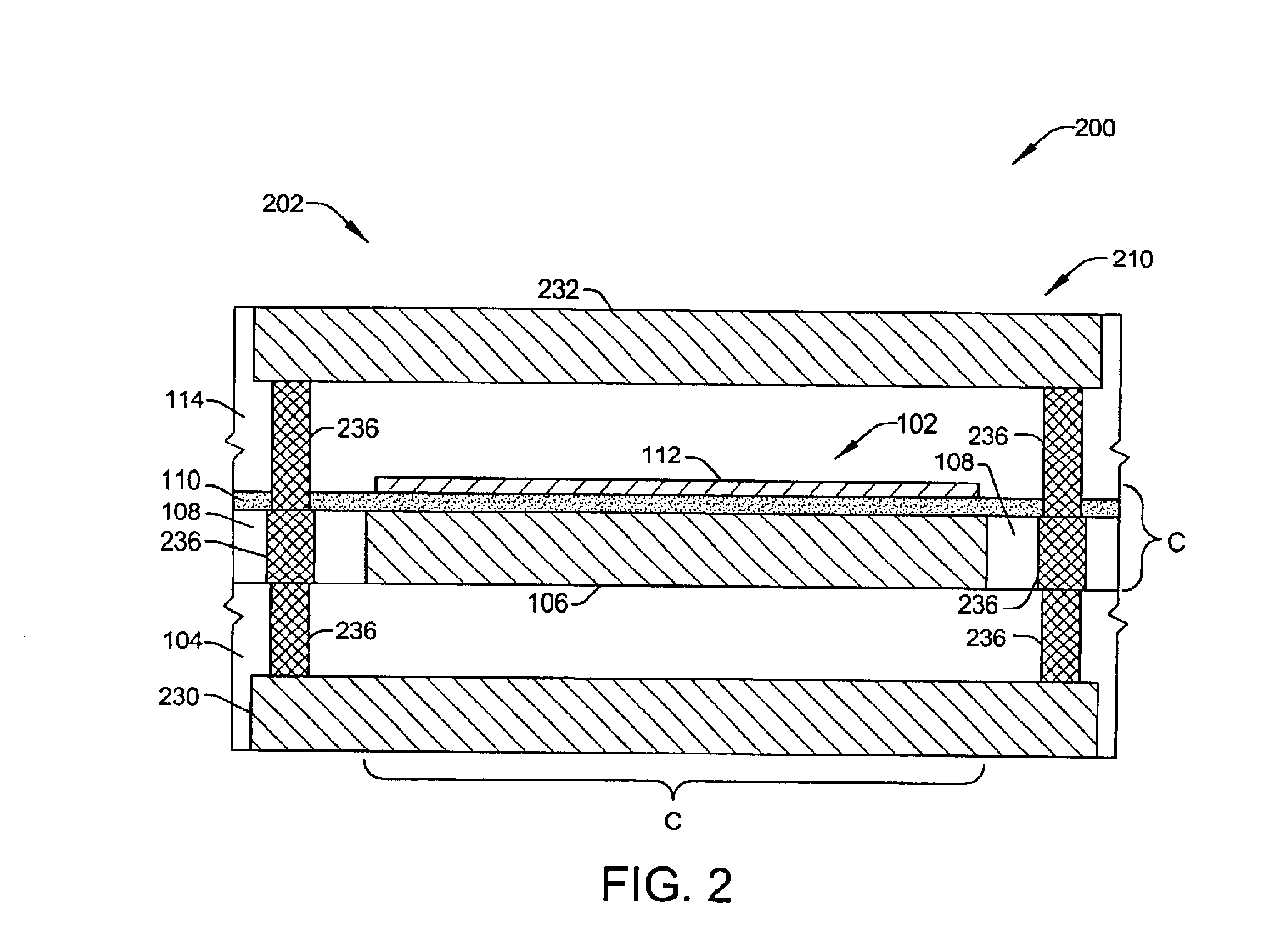

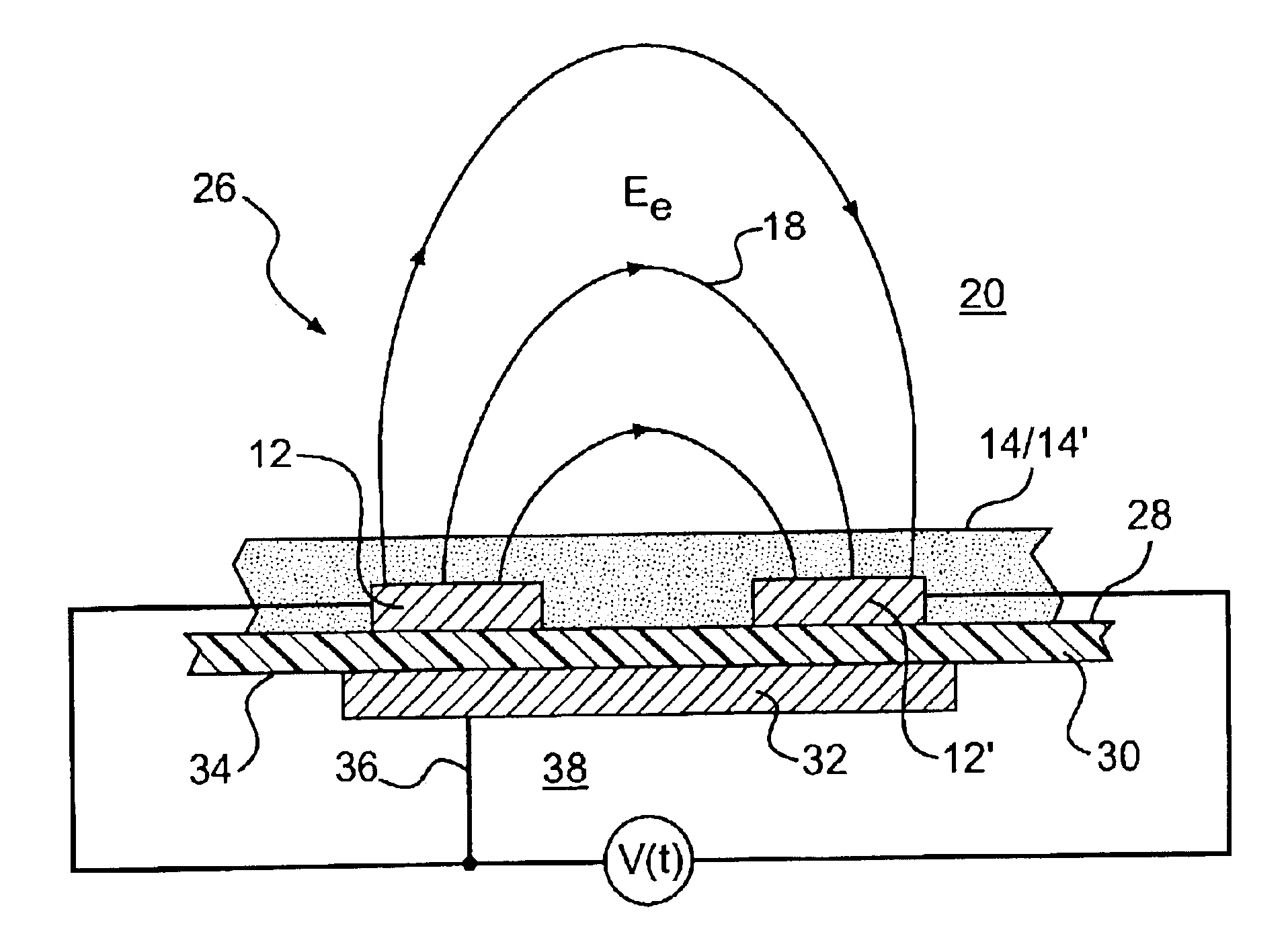

ActiveUS6903918B1Mitigate eddy current lossMinimize eddy current lossSemiconductor/solid-state device detailsFixed capacitor dielectricIsolation layerParasitic capacitance

A shielded planar capacitor structure (202) is discussed, formed within a Faraday cage (210) in an integrated circuit device (200). The capacitor structure (202) reduces parasitic capacitances within the integrated circuit device (200). The capacitor (202) comprises a capacitor stack (102) formed between a first and second metal layers (230,232) of the integrated circuit. The capacitor stack (102) has a first conductive layer formed from a third metal layer (106) disposed between the first and second metal layers (230,232) of the integrated circuit, a dielectric isolation layer (110) disposed upon the first conductive layer (106); and a second conductive layer (112) disposed upon the dielectric isolation layer (110) and overlying the first conductive layer (106). The structure (202) further has a first and second isolation layers (104,114) disposed upon opposite sides of the capacitor stack (102). The Faraday cage (210) is formed between the first and second metal layers (230,232) of the integrated circuit (200), comprising a first and second shield layers (402,414) each having a plurality of mutually electrically conductive spaced apart traces (404). The first and second isolation layers (404,414) and the capacitor stack (102,434) are sandwiched between the first and second shield layers (402,414). Conductive elements (432) are distributed around the periphery of the capacitor stack (102,434) and the first and second isolation layers (404,412). The conductive traces (424) of the first shield layer (402) are connected to the conductive traces (424) of the second shield layer (414) through the conductive elements (432).

Owner:TEXAS INSTR INC

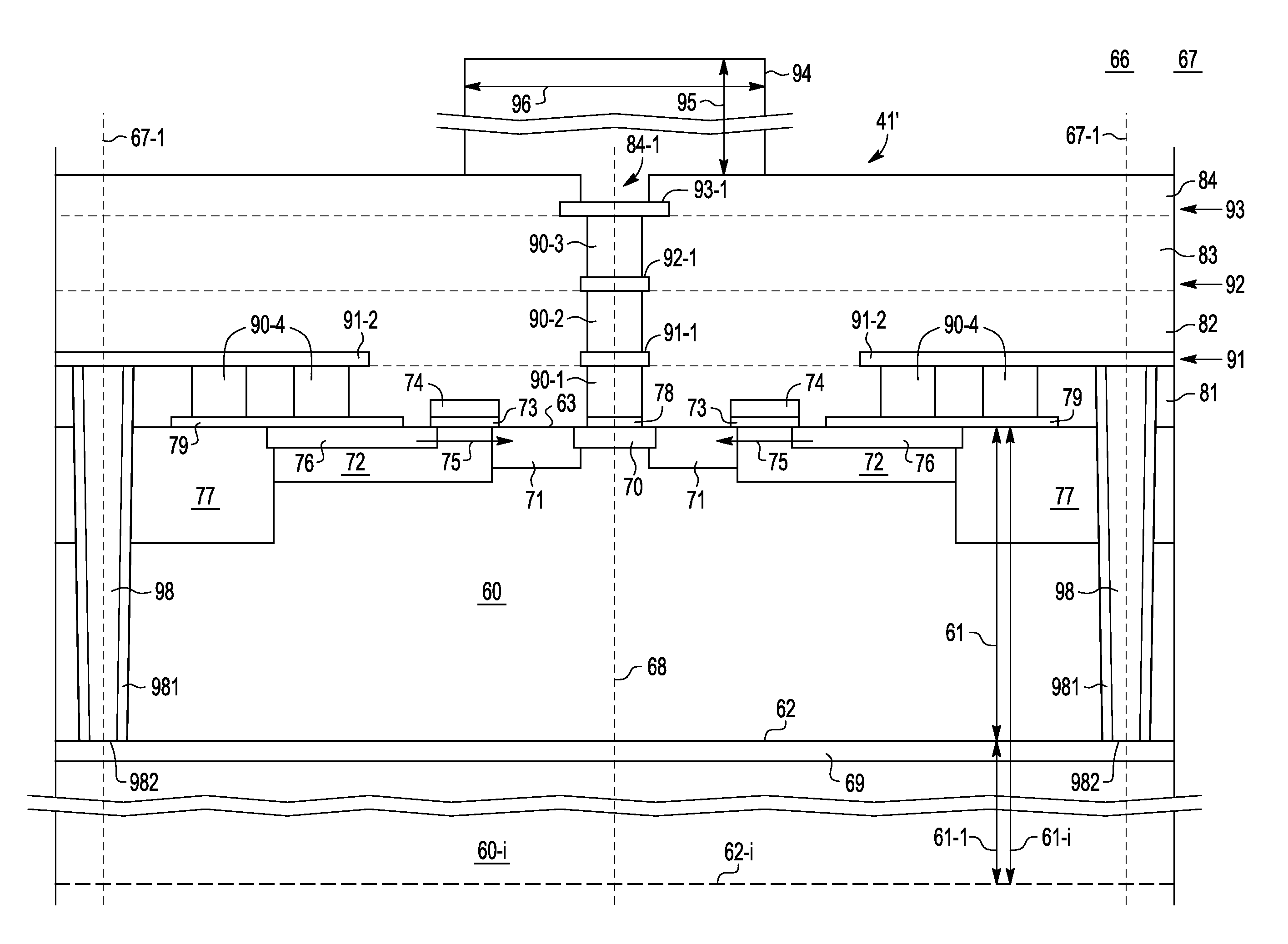

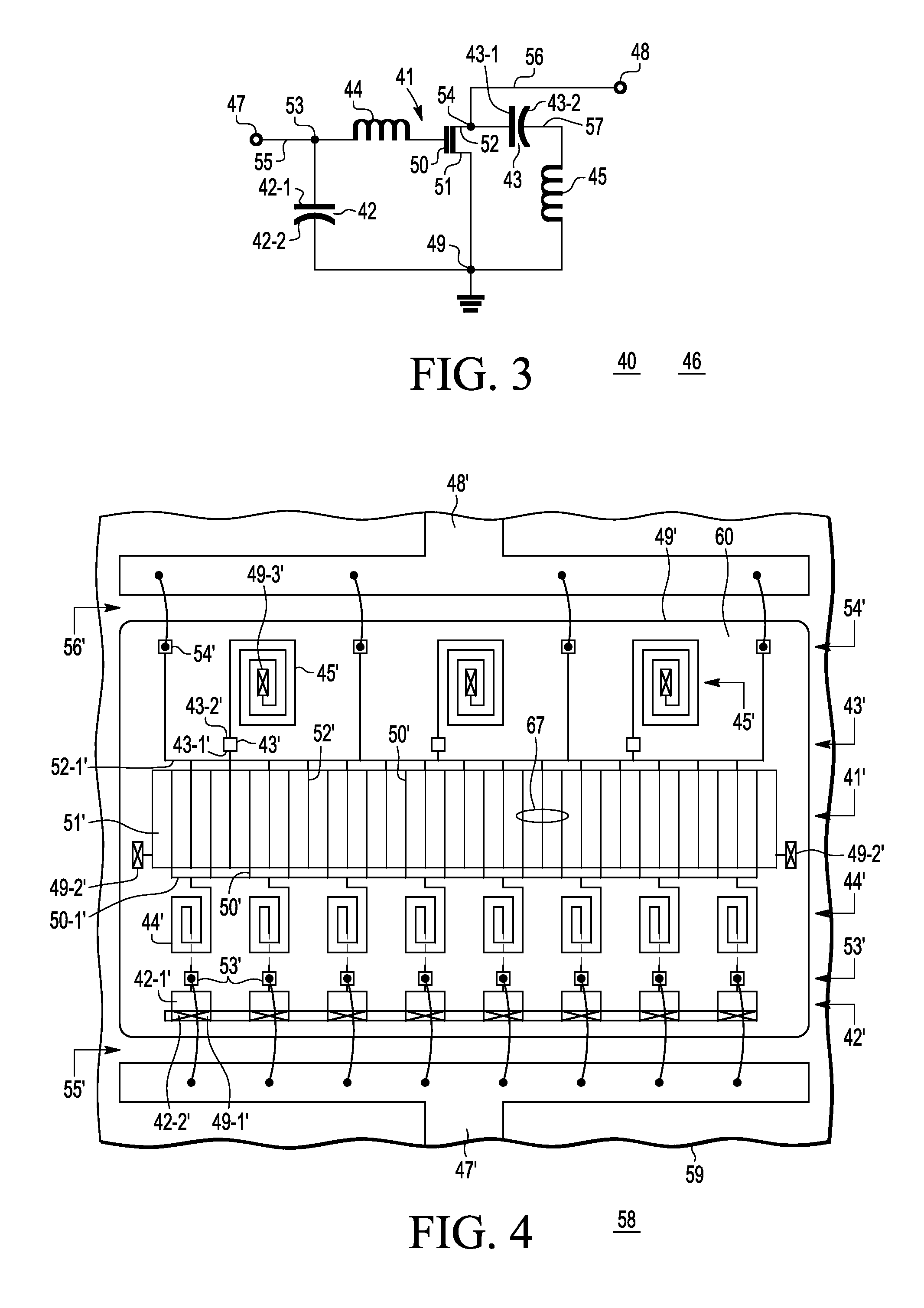

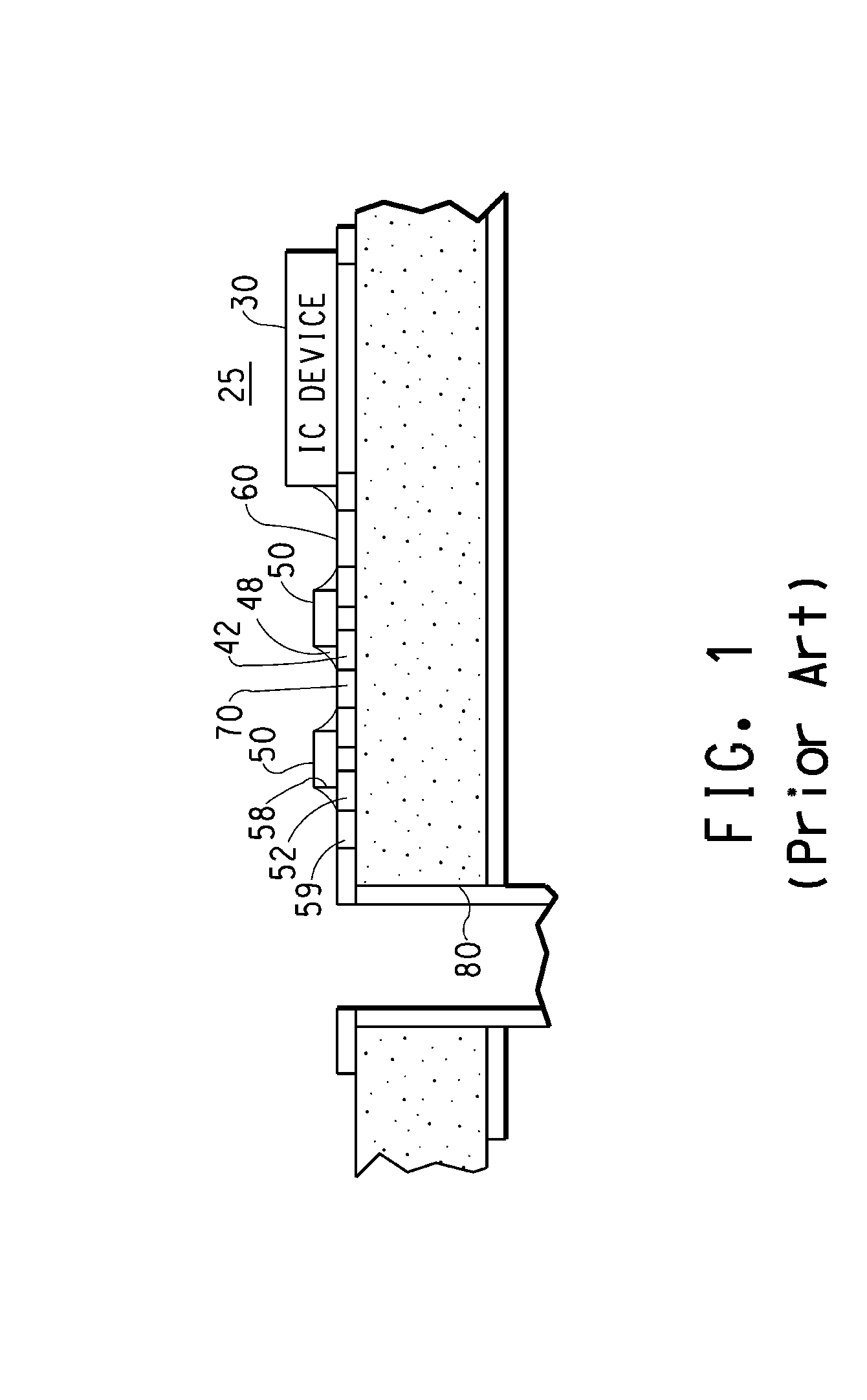

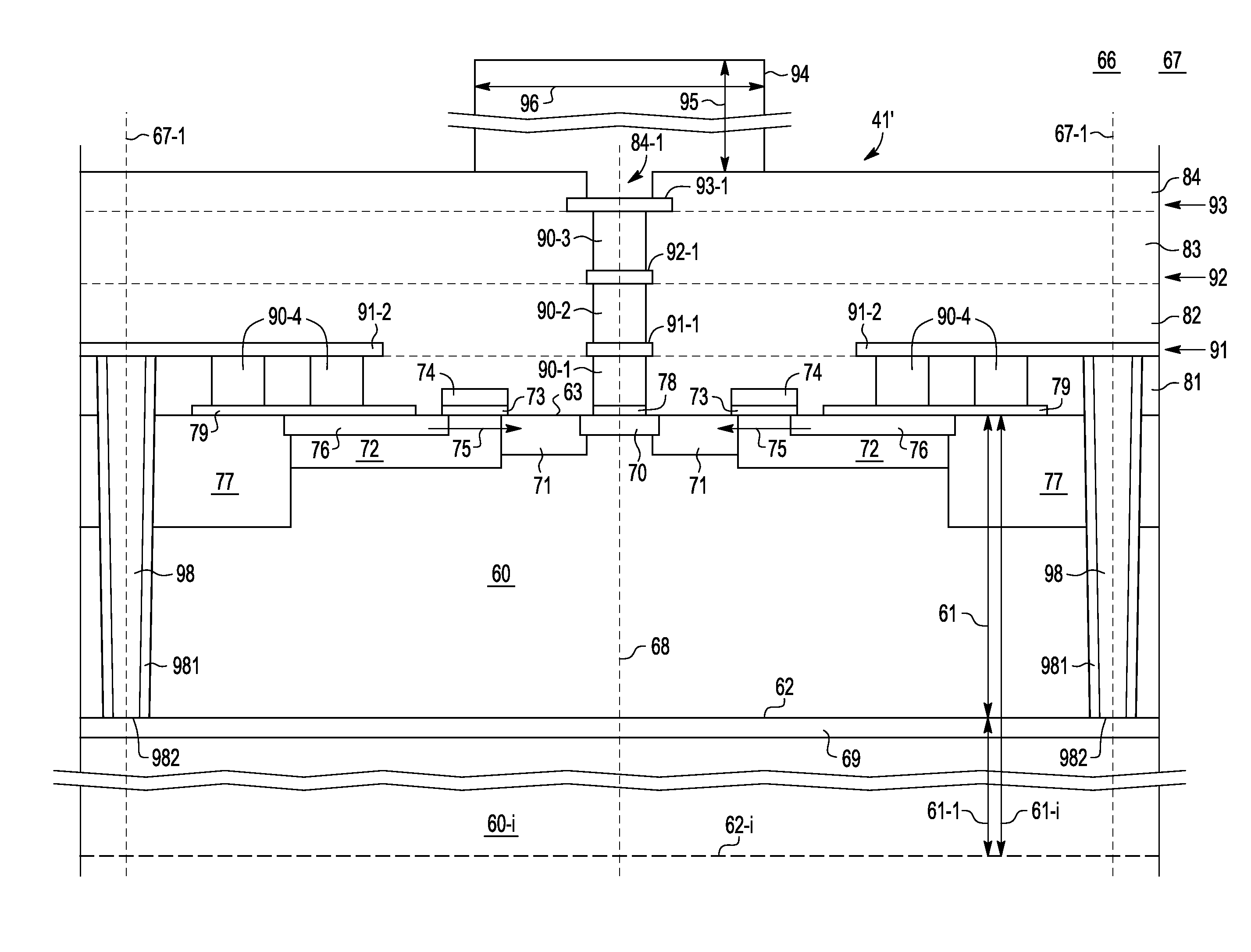

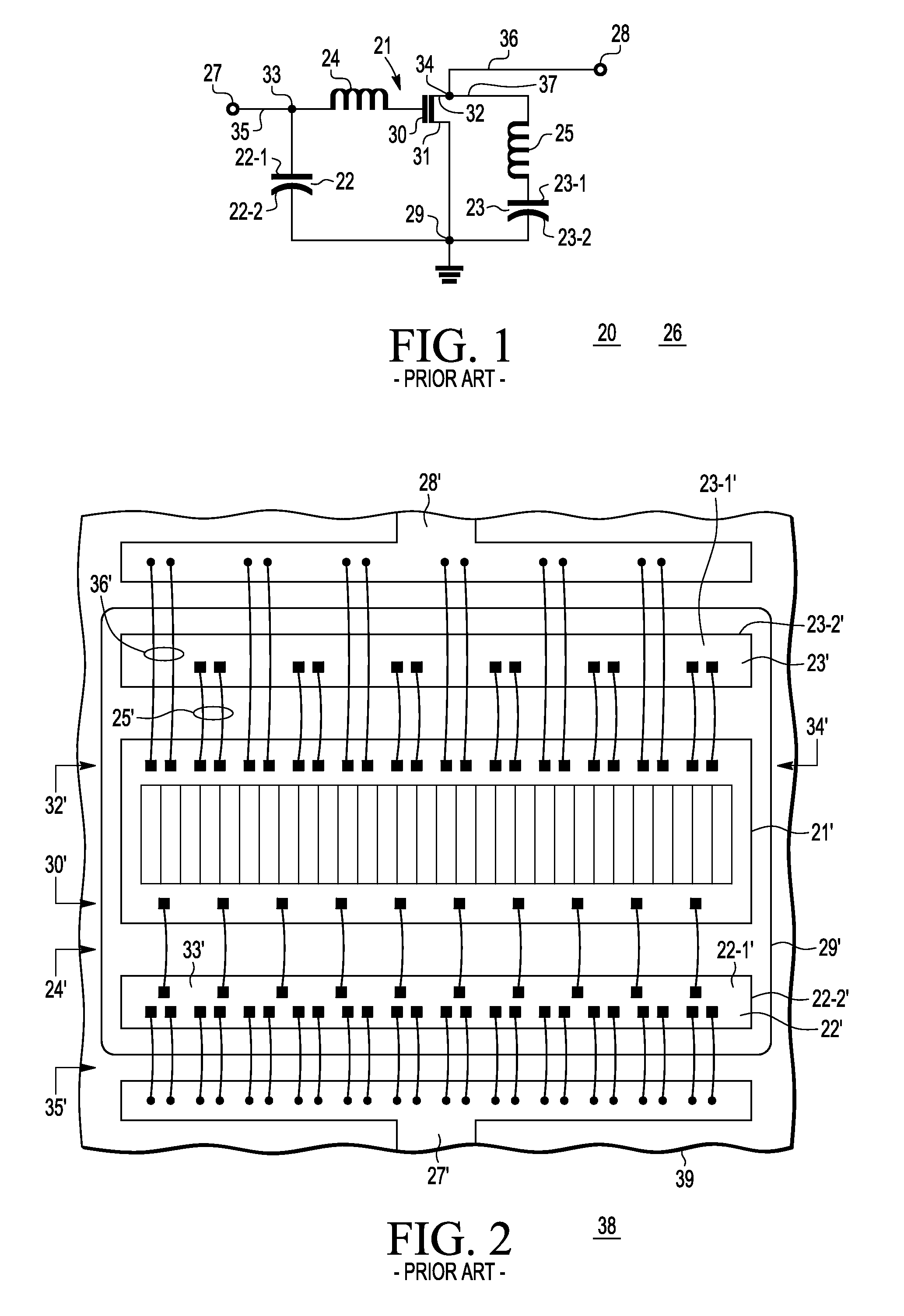

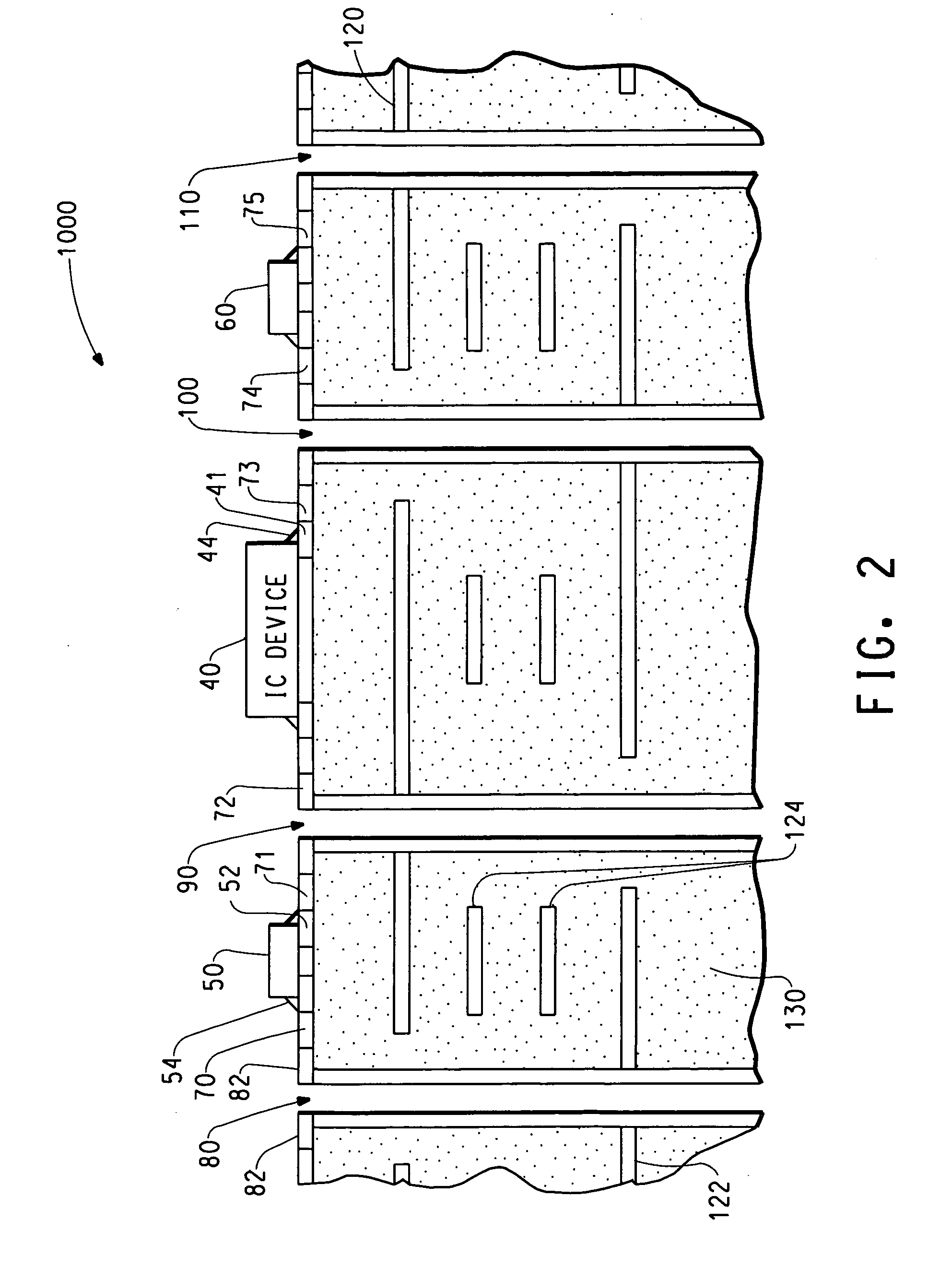

Monolithic microwave integrated circuit

Low Q associated with passive components of monolithic integrated circuits (ICs) when operated at microwave frequencies can be avoided or mitigated using high resistivity (e.g., ≧100 Ohm-cm) semiconductor substrates (60) and lower resistance inductors (44′, 45′) for the IC (46). This eliminates significant in-substrate electromagnetic coupling losses from planar inductors (44, 45) and interconnections (50-1′, 52-1′, 94, 94′, 94″) overlying the substrate (60). The active transistor(s) (41′) are formed in the substrate (60) proximate the front face (63). Planar capacitors (42′, 43′) are also formed over the front face (63) of the substrate (60). Various terminals (42-1′, 42-2′, 43-1, 43-2′,50′, 51′, 52′, 42-1′, 42-2′, etc.) of the transistor(s) (41′), capacitor(s) (42′, 43′) and inductor(s) (44′, 45′) are coupled to a ground plane (69) on the rear face (62) of the substrate (60) using through-substrate-vias (98, 98′) to minimize parasitic resistance. Parasitic resistance associated with the planar inductors (44′, 45′) and heavy current carrying conductors (52-1′) is minimized by placing them on the outer surface of the IC where they can be made substantially thicker and of lower resistance. The result is a monolithic microwave IC (46, 58) previously unobtainable.

Owner:NXP USA INC

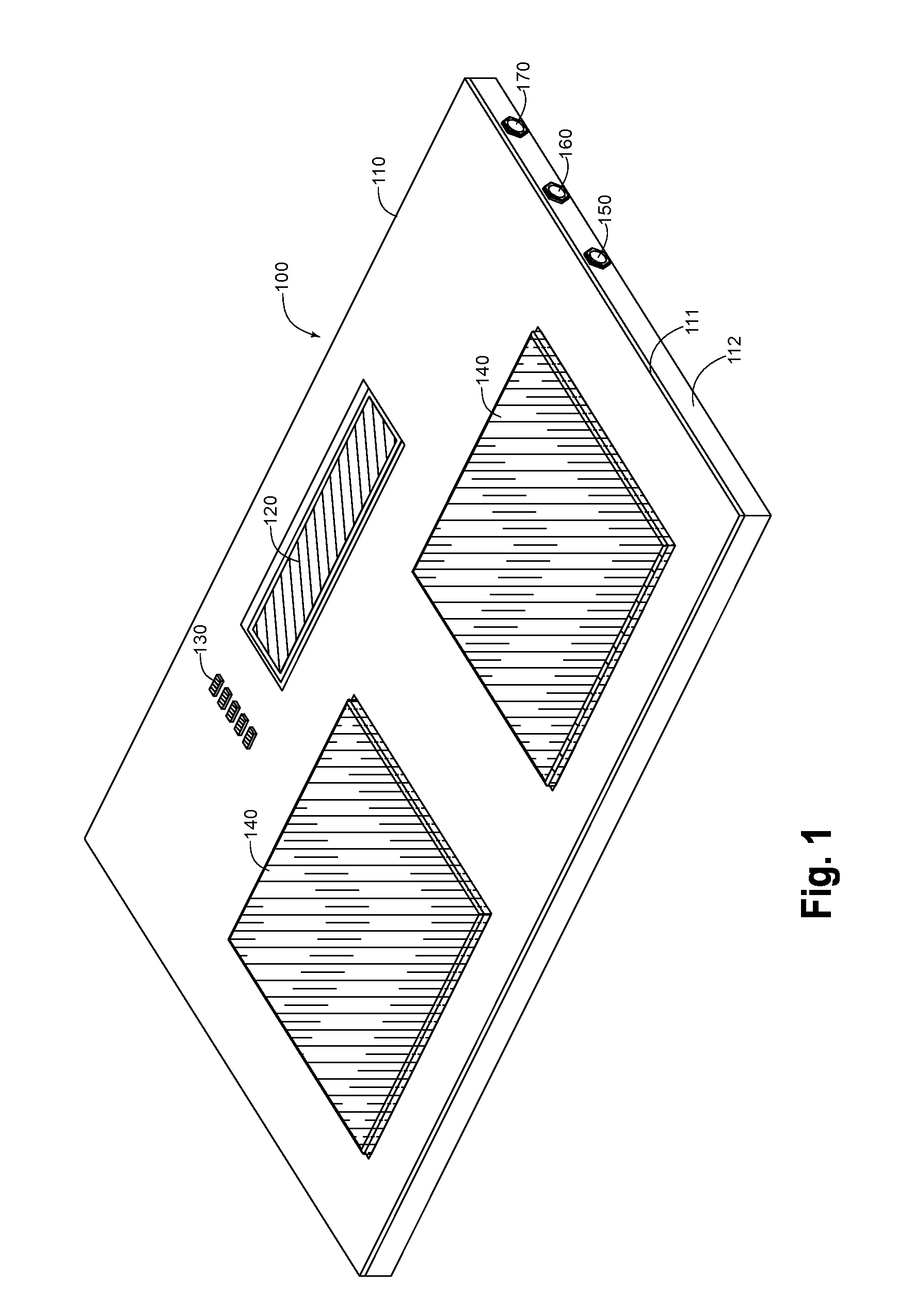

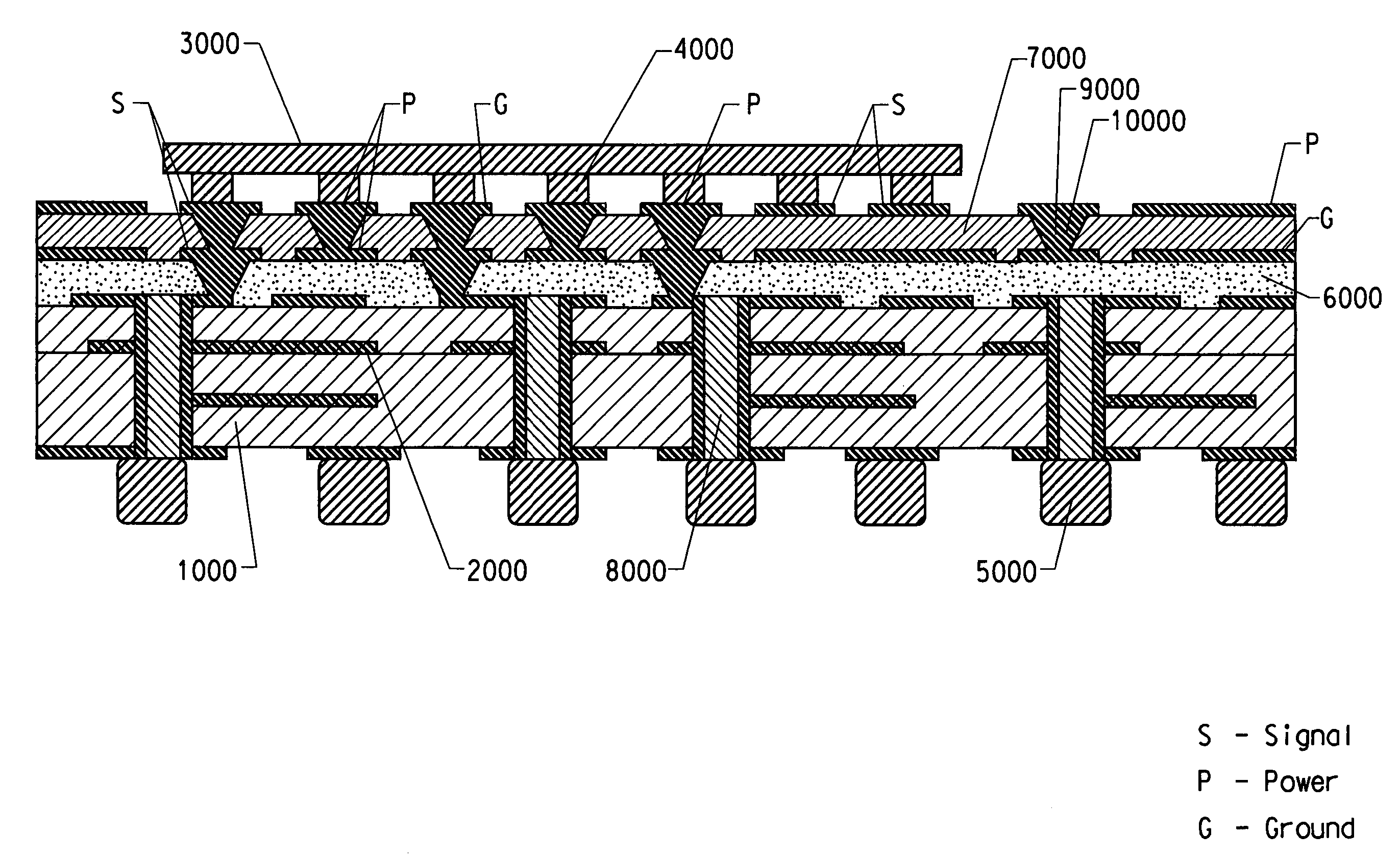

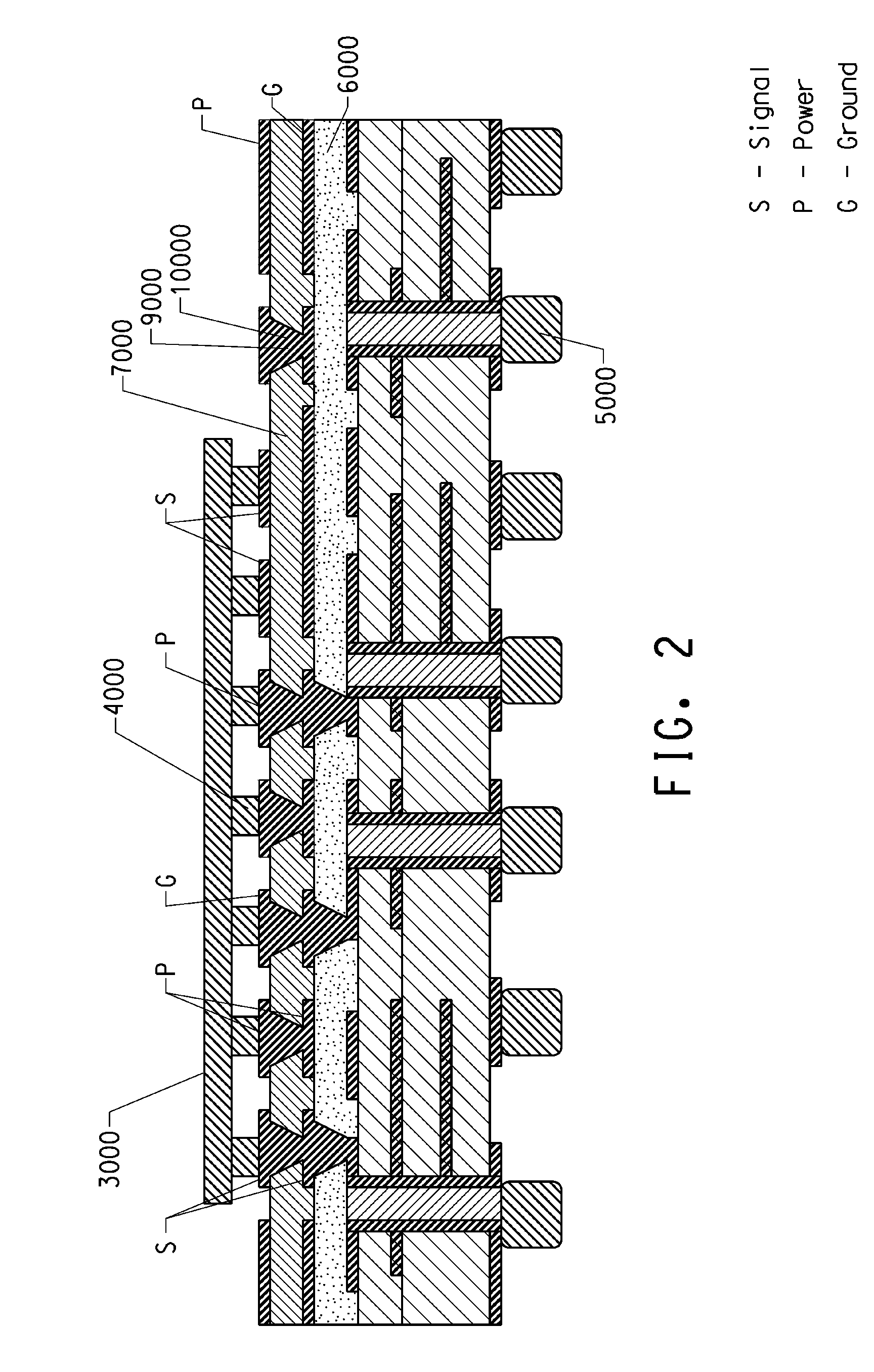

Power core devices

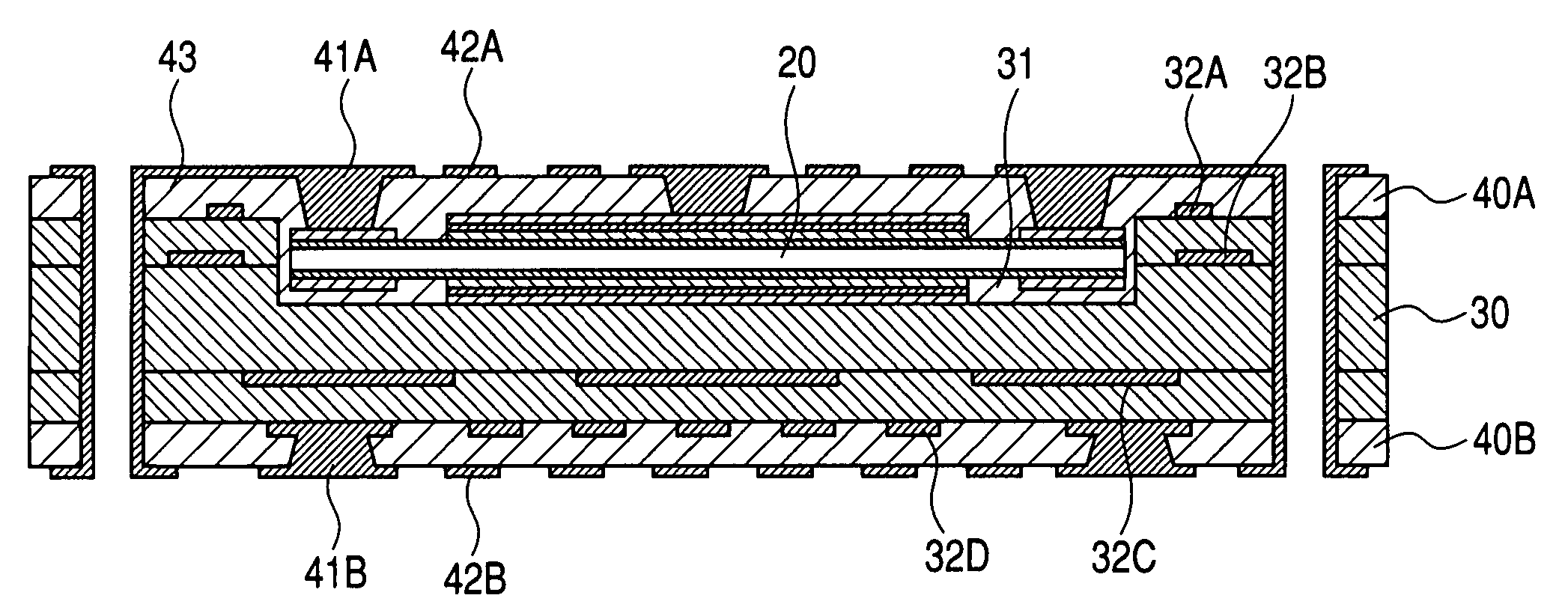

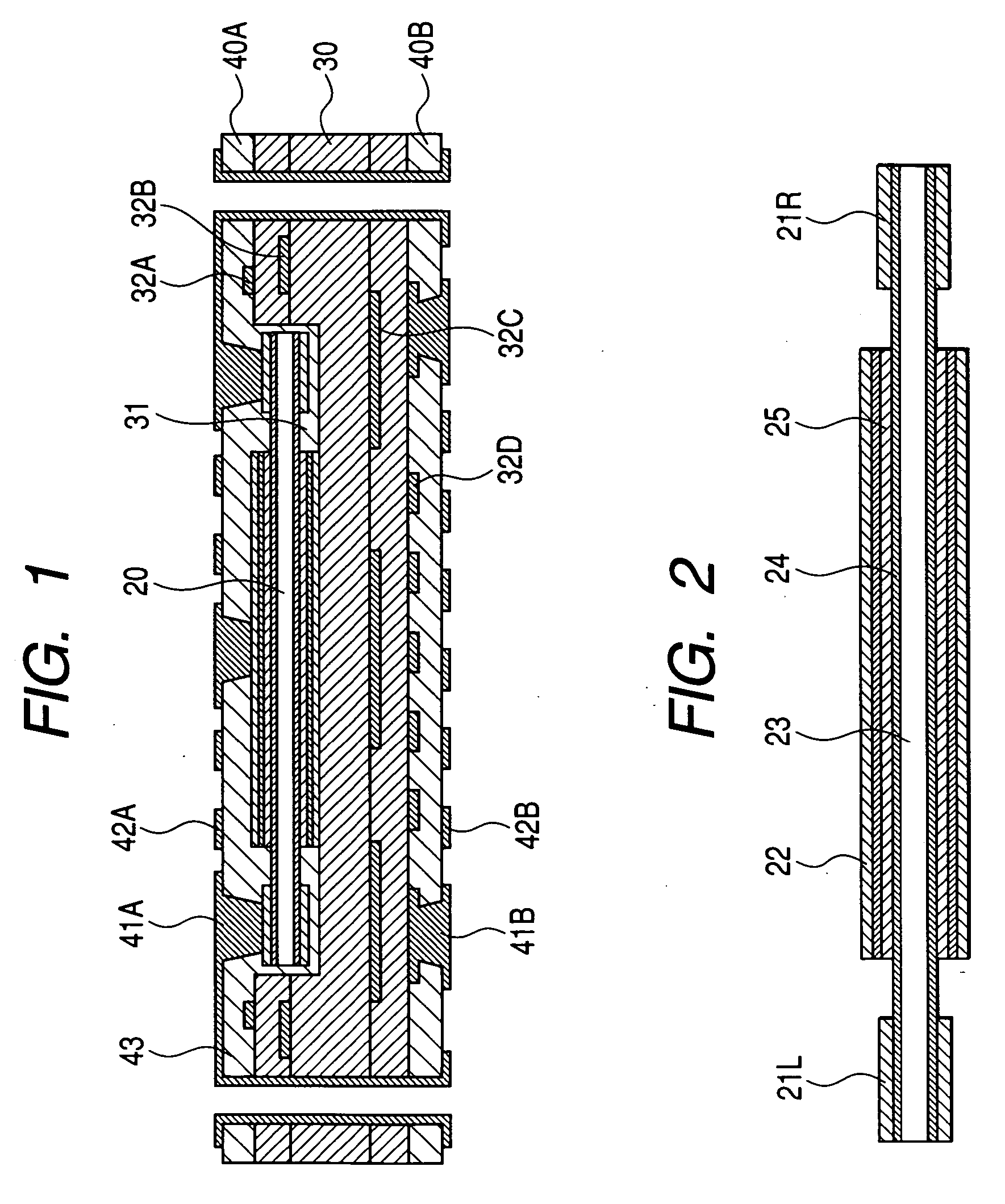

ActiveUS7613007B2Semiconductor/solid-state device detailsPrinted circuit aspectsLow inductanceElectrical and Electronics engineering

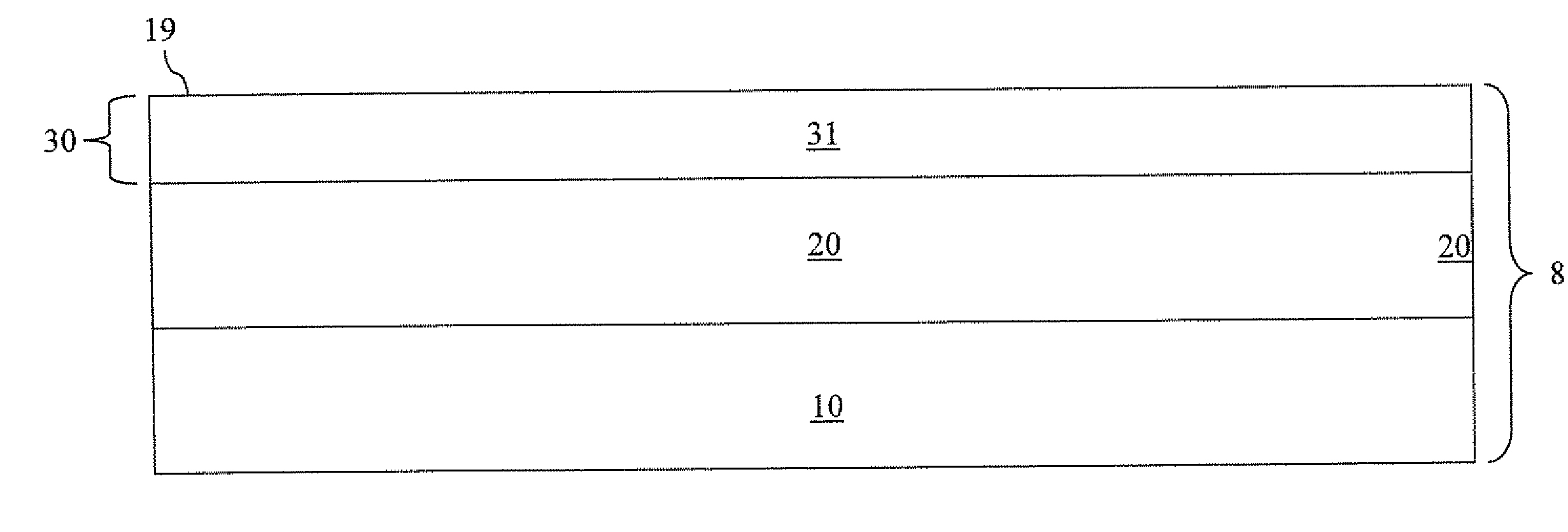

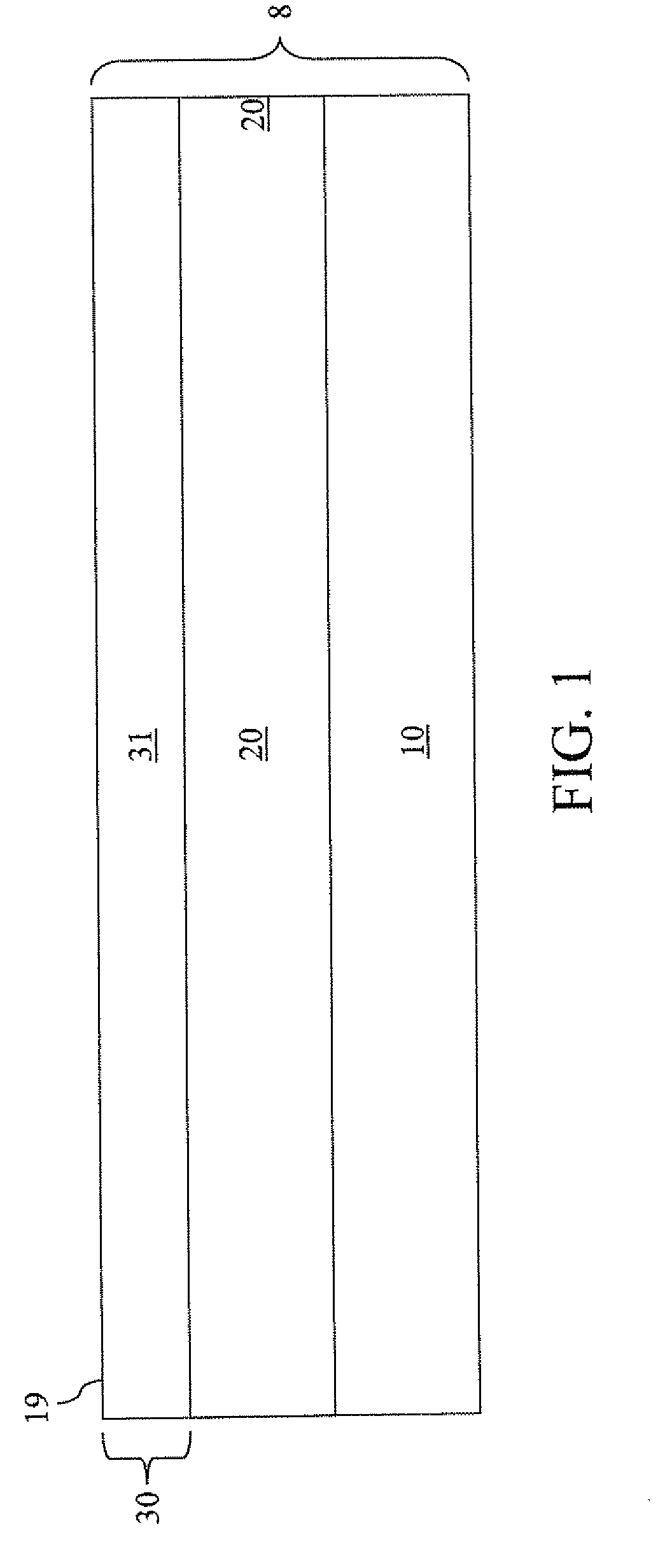

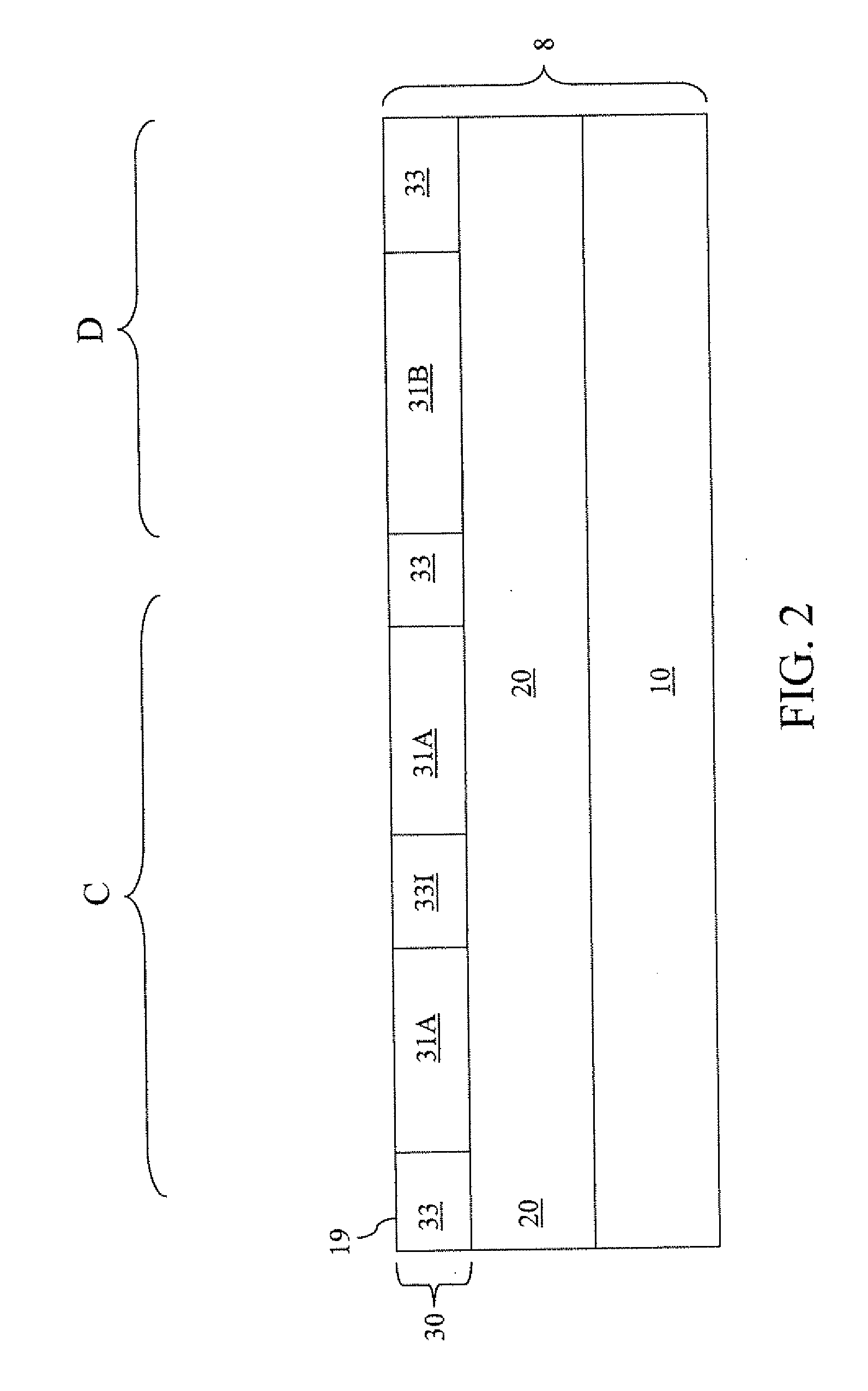

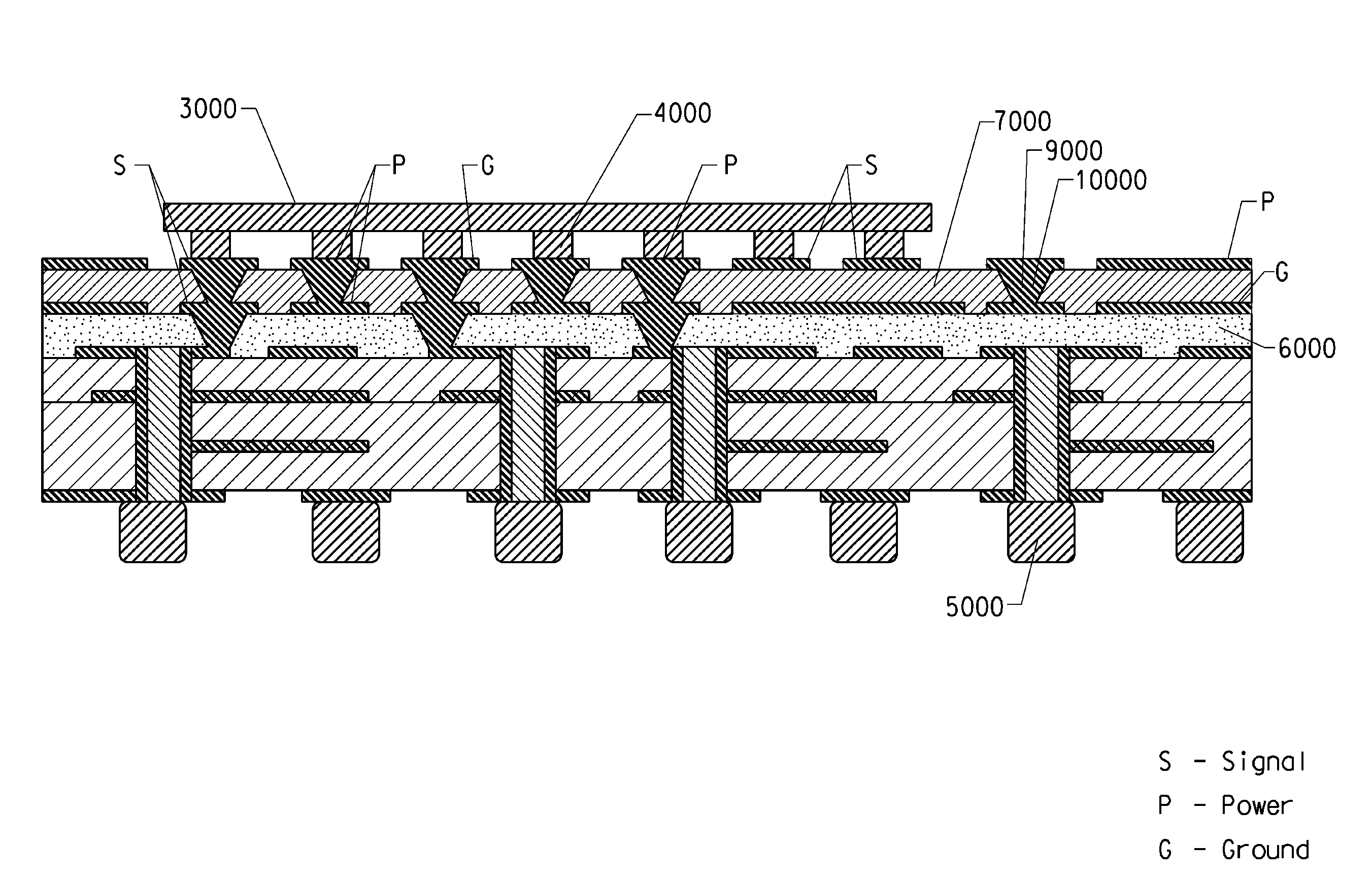

The present invention relates to a device comprising a power core wherein said power core comprises: at least one embedded singulated capacitor layer containing at least one embedded singulated capacitor; and at least one planar capacitor laminate; wherein said planar capacitor laminate serves as a low inductance path to supply a charge to said at least one embedded singulated capacitor; and wherein said at least one embedded singulated capacitor is connected in parallel to at least one of the said planar capacitor laminates; and wherein said power core is interconnected to at least one signal layer.

Owner:CHEMTRON RES

Foot controller

InactiveUS20120144981A1Degree of improvementImprove reliabilityElectrophonic musical instrumentsConverting sensor outputCapacitanceElectricity

A foot controller for electrically controlling a device by a user may include at least one sensor pad module having a first plate of dielectric material. The first plate of dielectric material may support at least two electrodes forming a planar capacitor. The controller may further include a second plate of dielectric material separated from the first plate by a layer of compressible dielectric material. The first plate is adapted to be displaced with respect to the second plate, so as to vary the geometry of an equivalent capacitor which includes the at least two electrodes, the compressible dielectric material and the second plate of dielectric material, thereby varying the value of the capacitance of the equivalent capacitor. The foot controller may further include a control module adapted to generate an electrical control signal which depends on the value of the capacitance.

Owner:CICCONE MASSIMILIANO

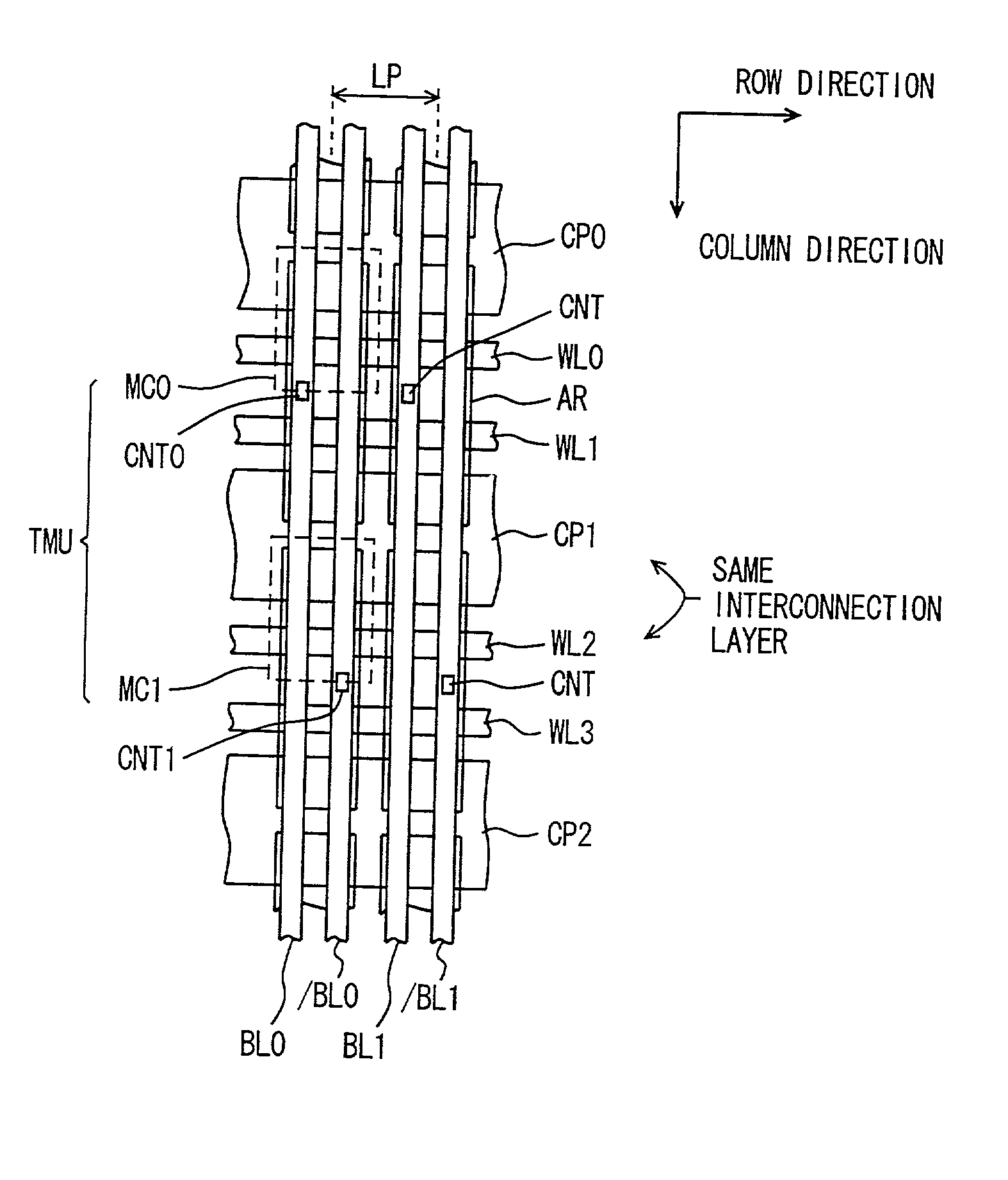

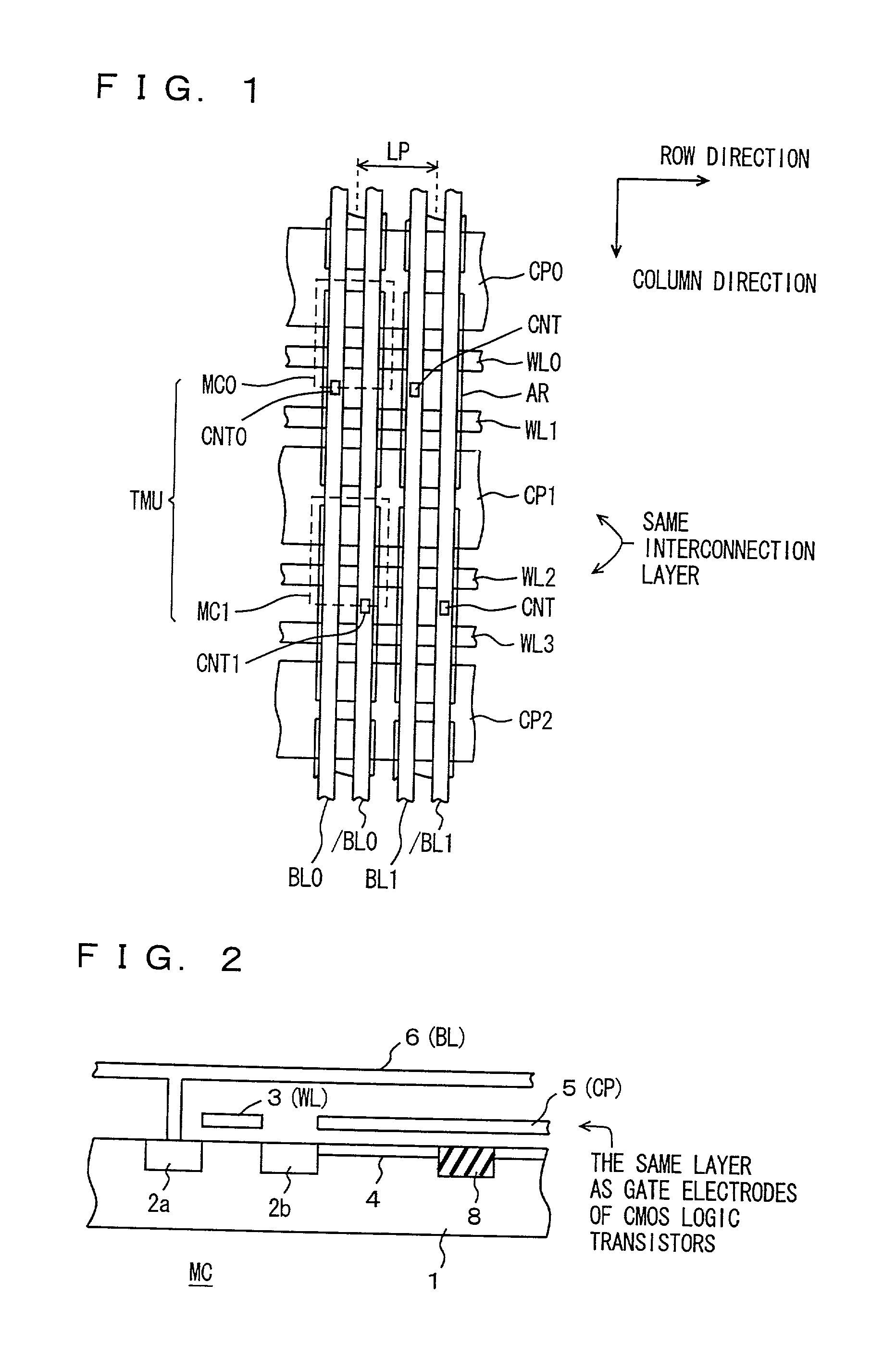

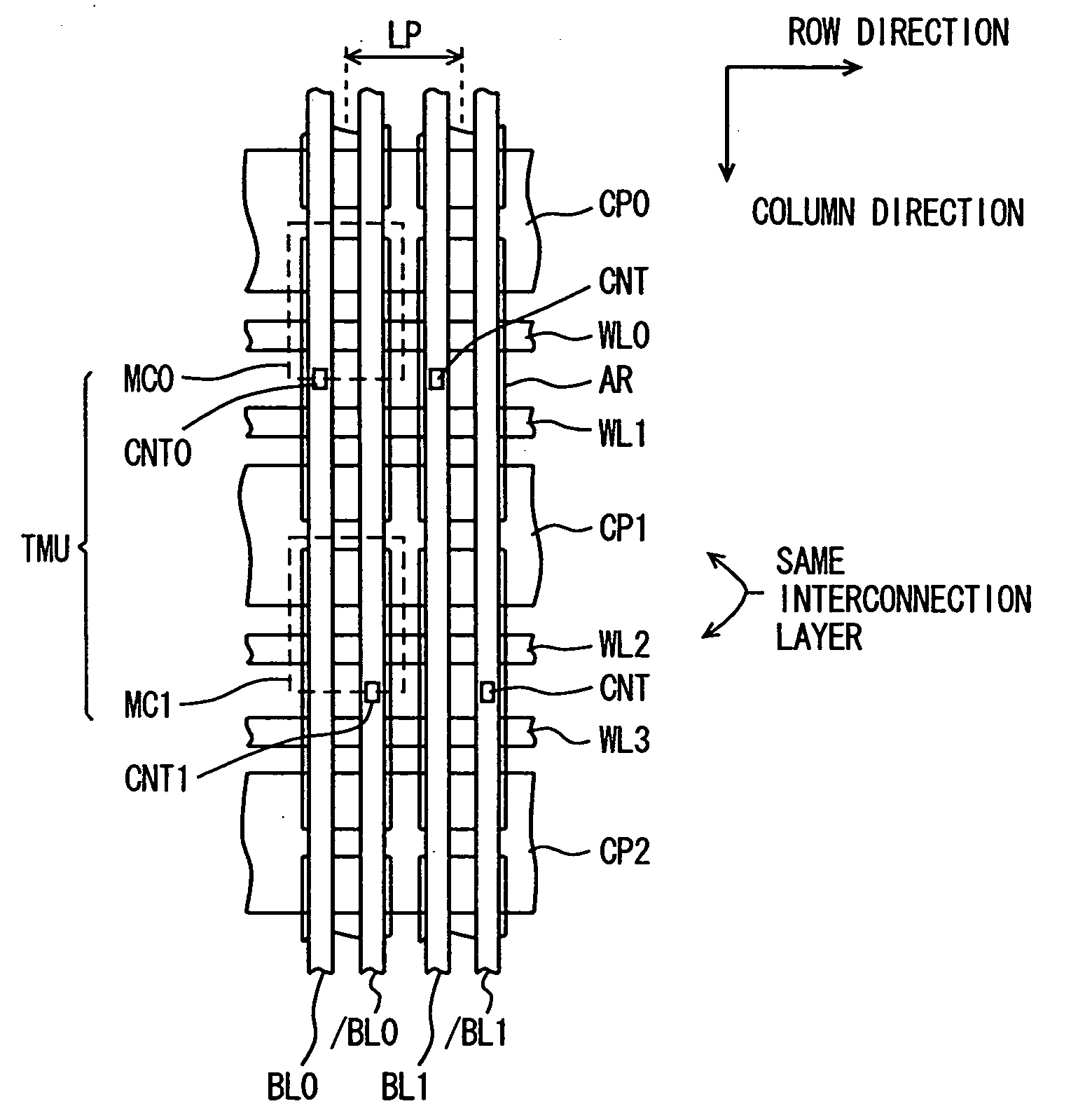

Semiconductor memory device

InactiveUS20020172070A1Reduce step heightReduce manufacturing stepsTransistorSolid-state devicesCapacitanceEngineering

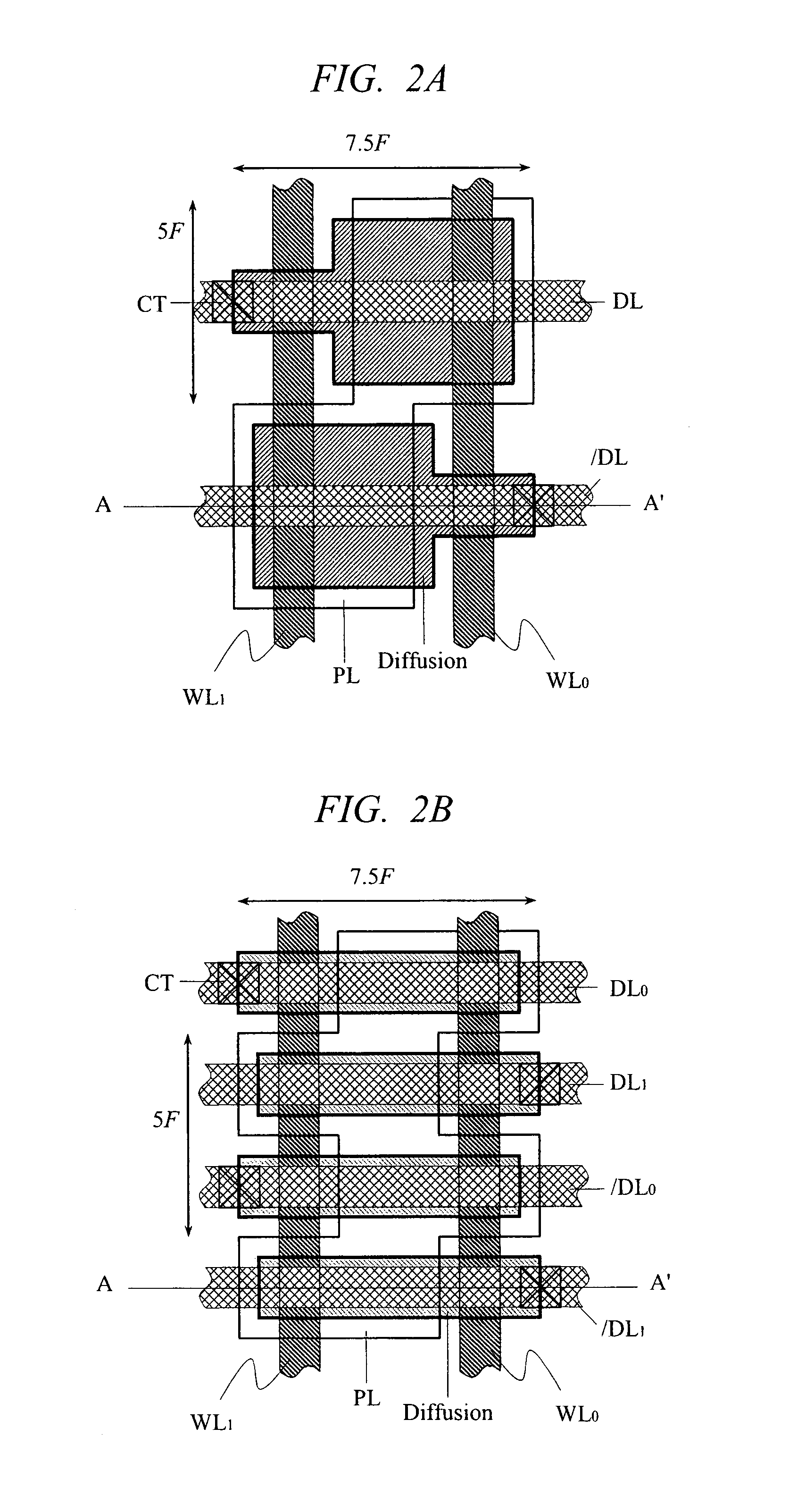

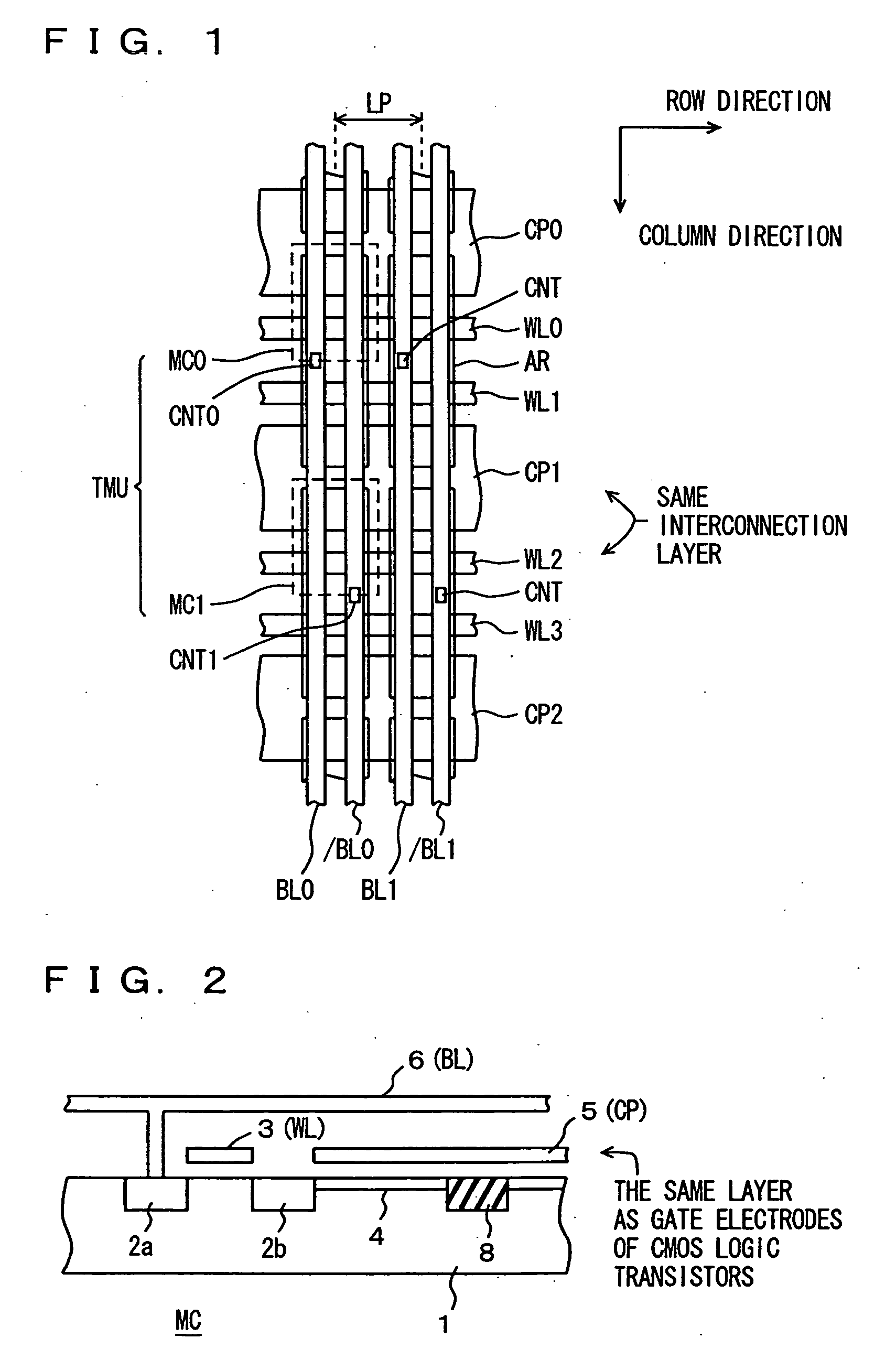

Conductive lines constituting word lines of memory cells and conductive lines constituting memory cell plate electrodes are formed in the same interconnecting layer in a memory device including a plurality of memory cells each including a capacitor for storing data in an electrical charge form. By forming the capacitors of the memory cells into a planar capacitor configuration, a step due to the capacitors is removed. Thus. a dynamic semiconductor memory device can be formed through CMOS process, and a dynamic semiconductor memory device suitable for merging with logic is achieved. Data of 1 bit is stored by two memory cells, and data can be reliably stored even if the capacitance value of the memory cell is reduced due to the planar type capacitor.

Owner:RENESAS ELECTRONICS CORP

Plane capacitance sensor and method for detecting environmental change of motorcar glass

ActiveCN101087135AAvoid the disadvantages of slow responseLarge measuring areaElectronic switchingVehicle cleaningCapacitanceElectromagnetic interference

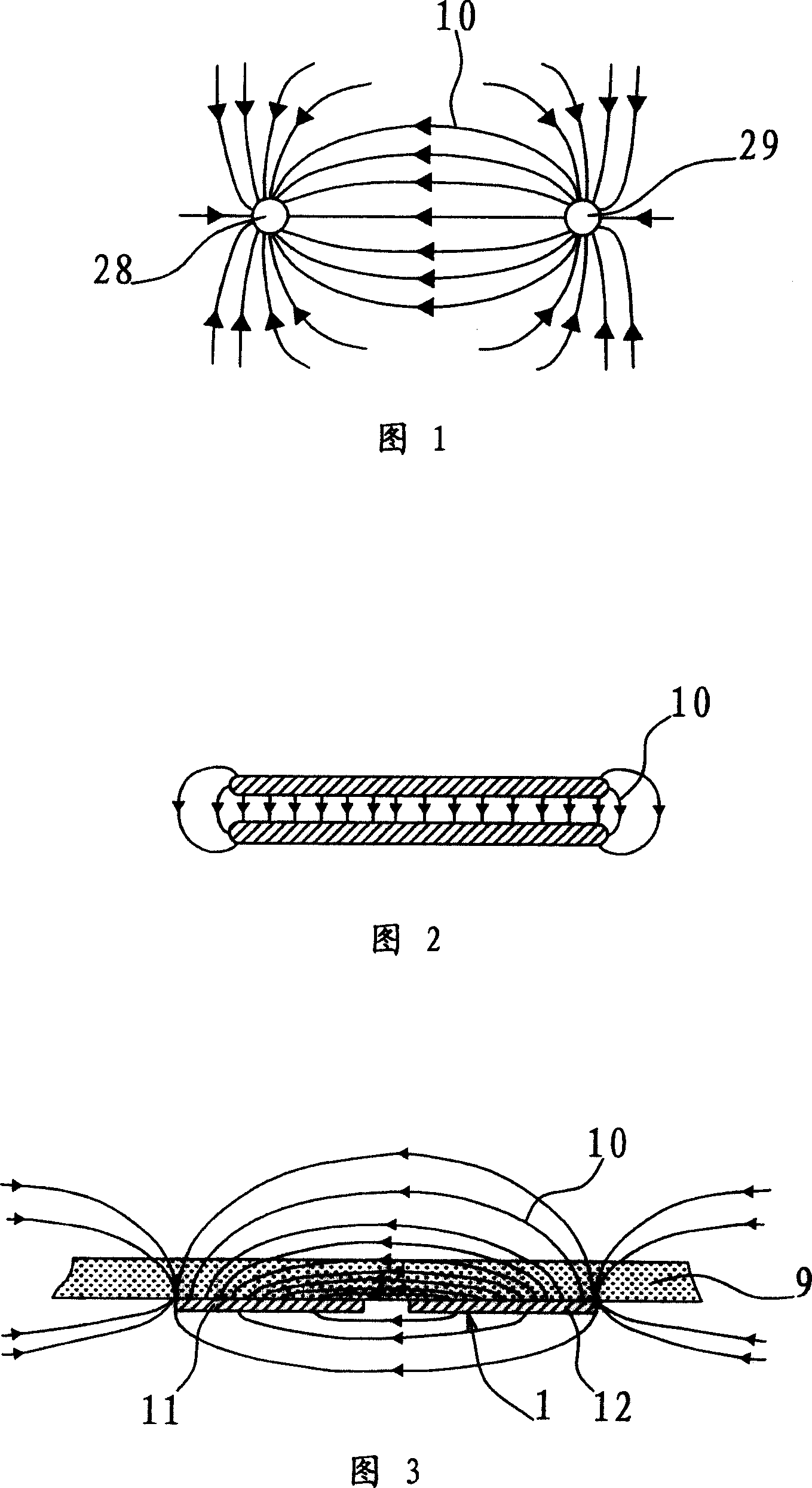

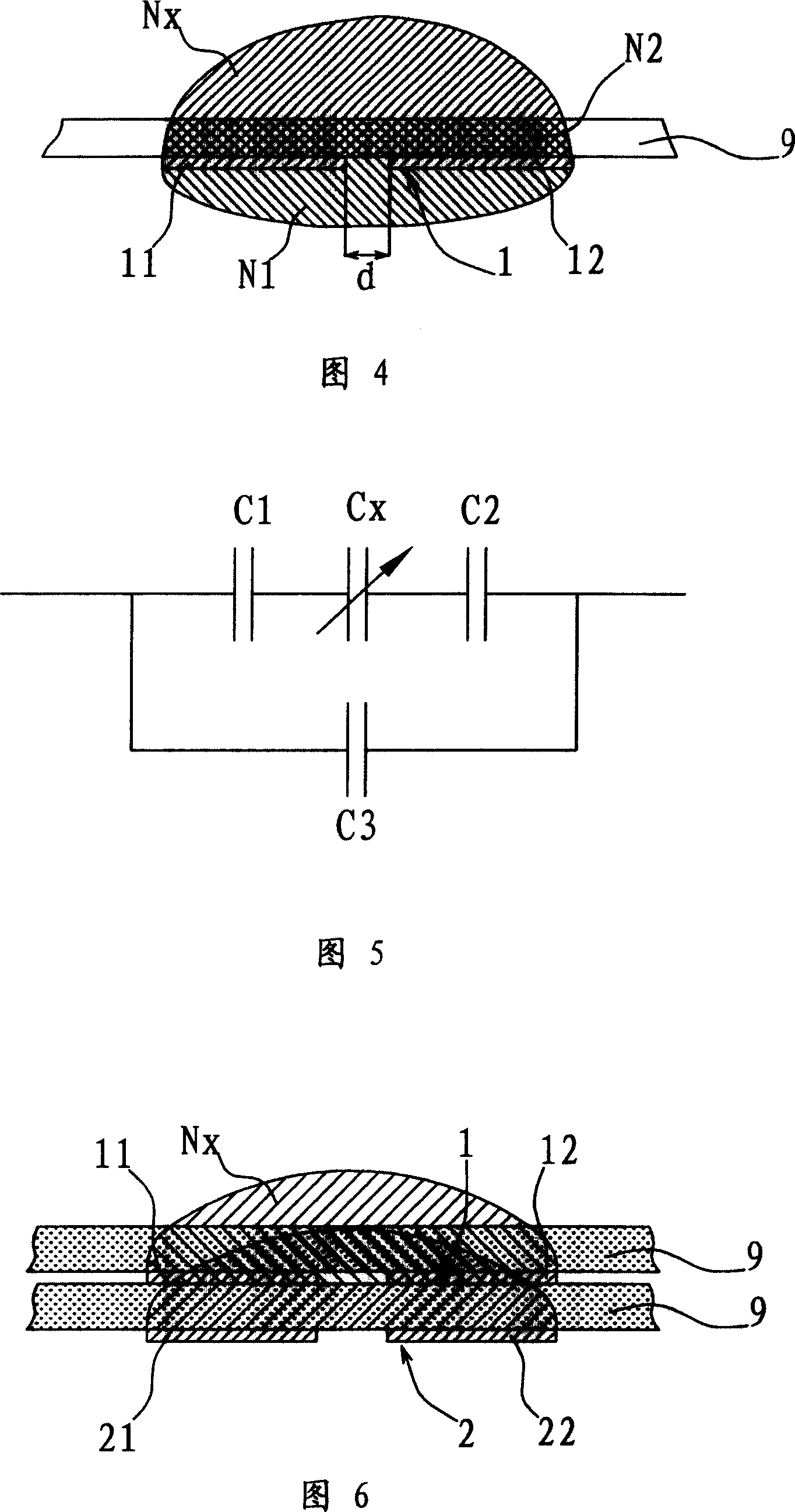

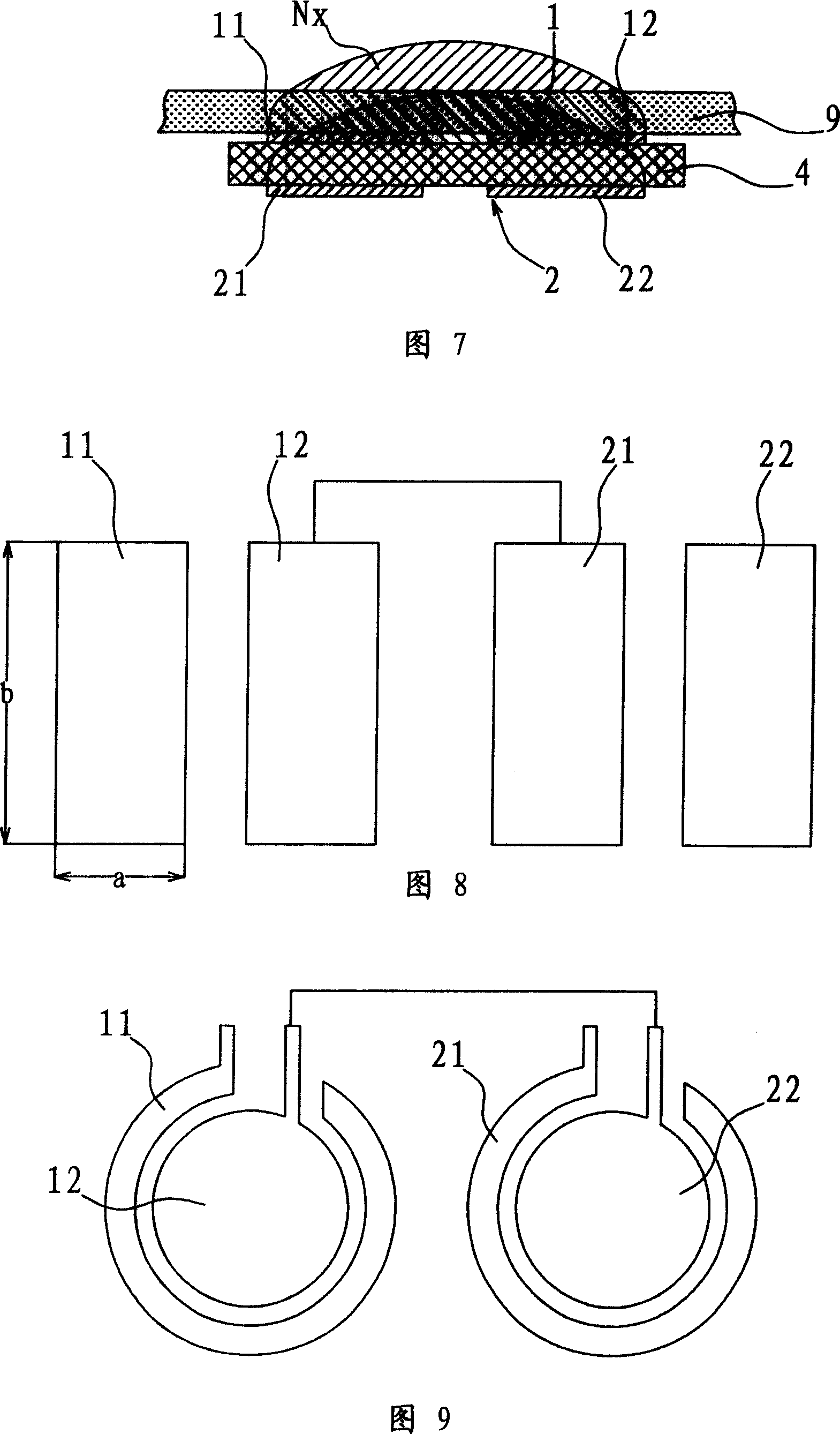

A kind of flat capacitance-type sensor includes a flat capacitor, a flat capacitance compensator which eliminate interfere signal and a sensor detecting circuit. The invention adopts double-flat capacitance, thereinto one is used as measuring capacitance; another is as compensating capacitance, it is insensitive with rain water of outer surface by changing mounting position and shape of compensating capacitance, and sensitive with temperature shift and electromagnetic interfere. When there is temperature shift or electromagnetic interfere, the value of measuring capacitance and compensating capacitance change at the same time and extent are similar, when rain water is changed, value of measuring capacitance changes, but value of compensating capacitance does not change. Using characters above can difference compensate measuring of sensor, disadvantageous affects of temperature shift and electromagnetic interfere can be decreased, error action of rain shaving can be avoided.

Owner:AUTOEASY ELECTRONICS TECH

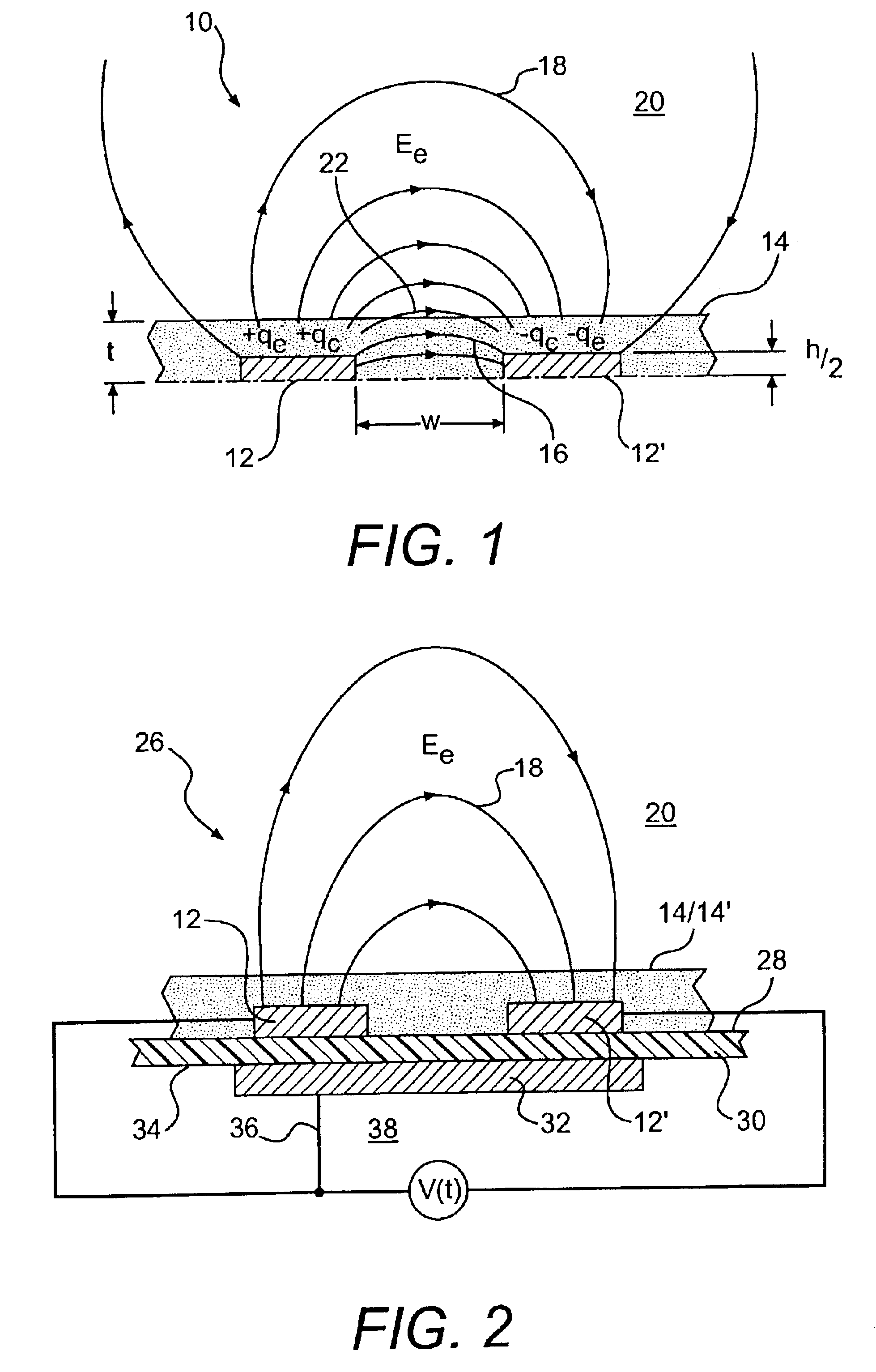

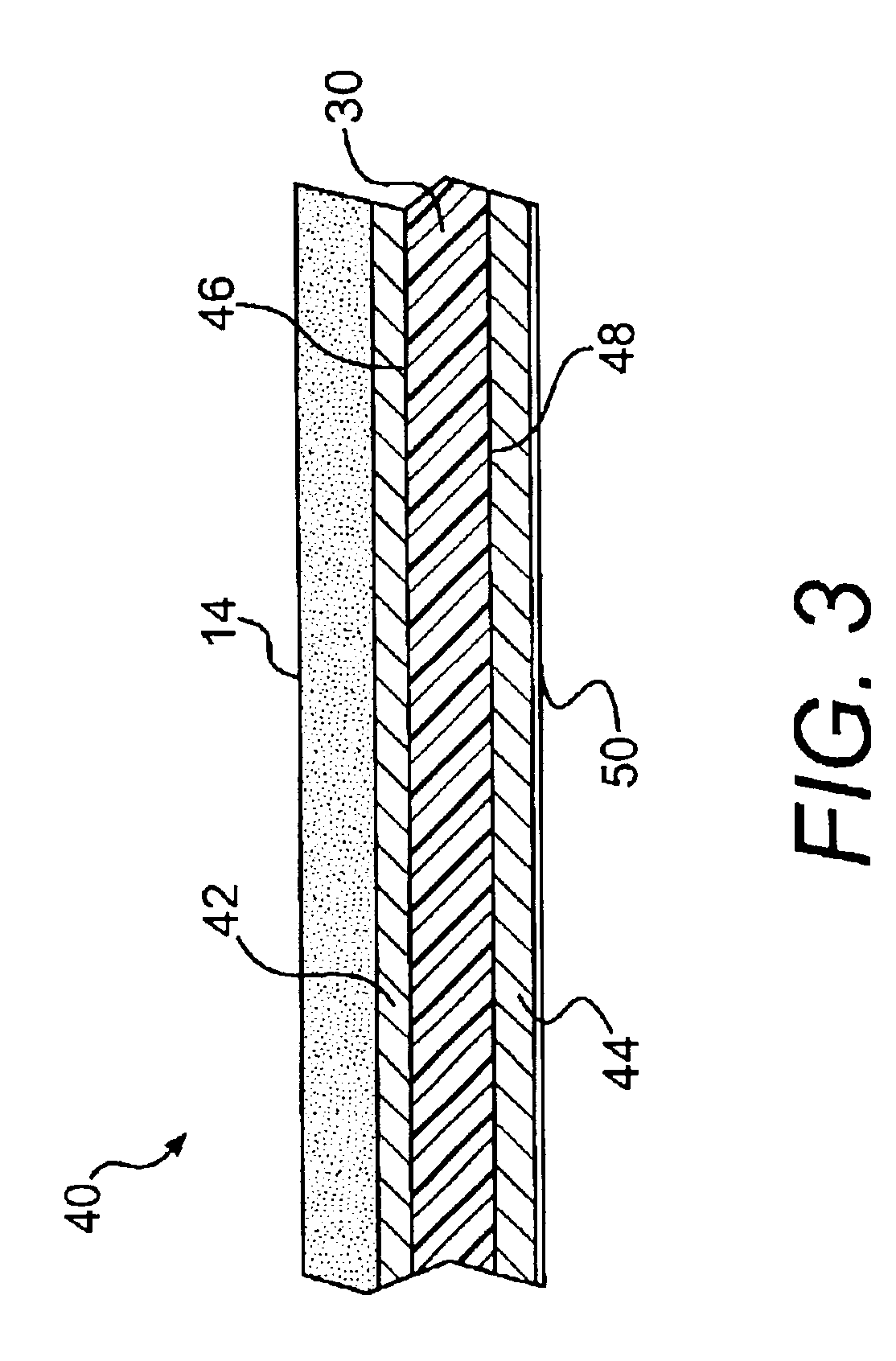

Planar capacitive transducer

InactiveUS6842018B2Increase and decrease surface free energyIncrease moisture contentResistance/reactance/impedenceUsing mechanical meansDesorptionMoisture absorption

A transducer comprising at least one planar capacitor with a thin coverlayer of material selected to maximize electric field coupling between cooperating capacitor electrodes within a region external to a principal surface of the coverlayer. Preferred coverlayer materials have low values of moisture absorption, surface free energy, permittivity, dielectric dissipation, and electrical conductance. According to one embodiment of the invention, a driven shield further enhances electric field coupling over and in a region external to the principal surface. The transducer also can promote a physical change in specific adsorbates and materials and simultaneously detect and measure an effect of the induced change. Applications for the transducer of the invention include the measurement of the moisture content of grain and bulk stored commodities, humidity, a dew point temperature, the onset of condensation and rates of adsorption and desorption.

Owner:MCINTOSH ROBERT B

Capacitive devices, organic dielectric laminates, multilayer structures incorporating such devices, and methods of making thereof

The present invention relates to methods of forming multilayer structures and the structures themselves. In one embodiment, a method of forming a multilayer structure comprising: providing a dielectric composition comprising: paraelectric filler and polymer wherein said paraelectric filler has a dielectric constant between 50 and 150; applying said dielectric composition to a carrier film thus forming a multilayer film comprising a dielectric layer and carrier film layer; laminating said multilayer film to a circuitized core wherein the dielectric layer of said multilayer film is facing said circuitized core; and removing said carrier film layer from said dielectric layer prior to processing; applying a metallic layer to said dielectric layer wherein said circuitized core, dielectric layer and metallic layer form a planar capacitor; and processing said planar capacitor to form a multilayer structure.

Owner:DUPONT ELECTRONICS INC

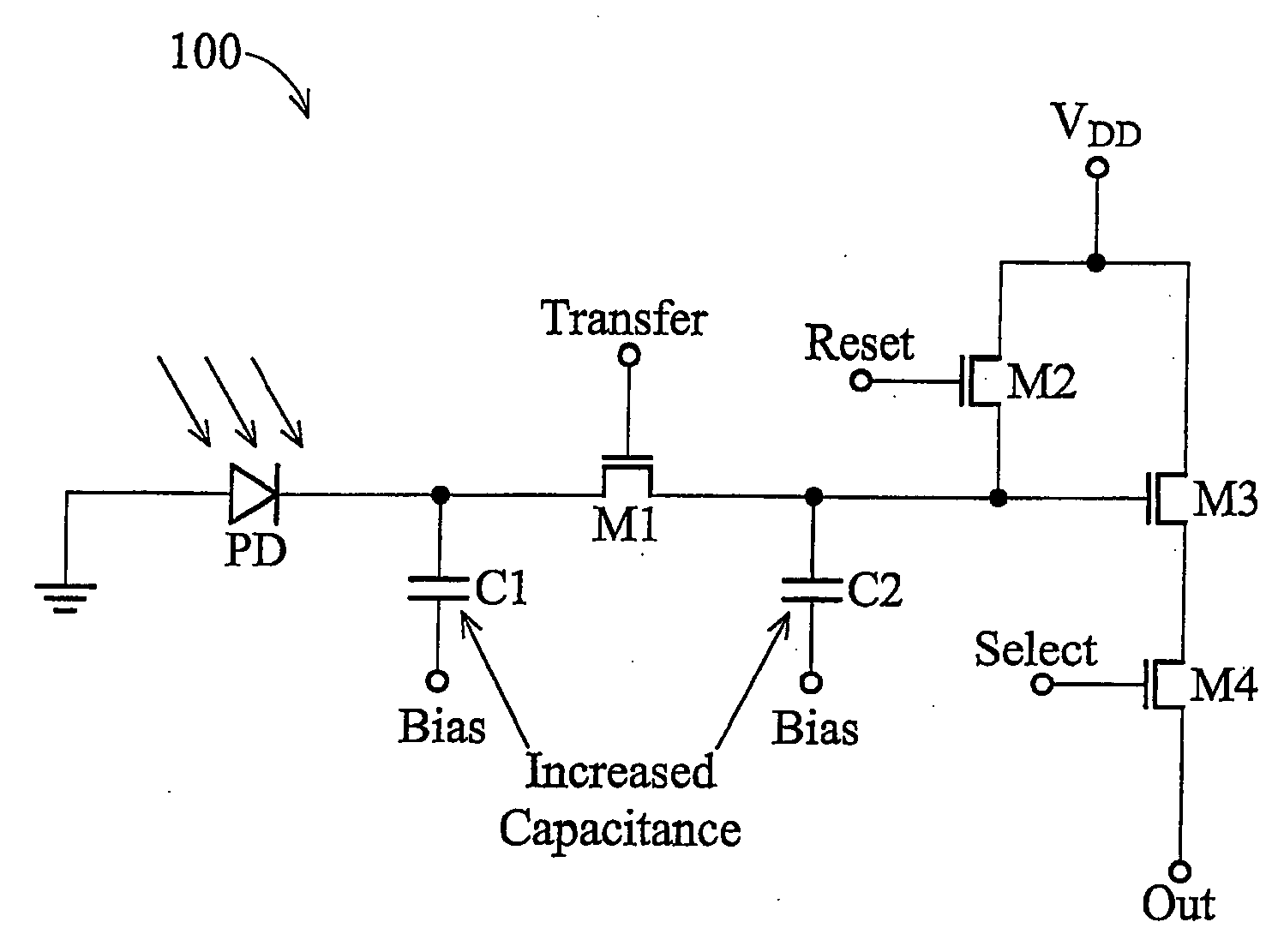

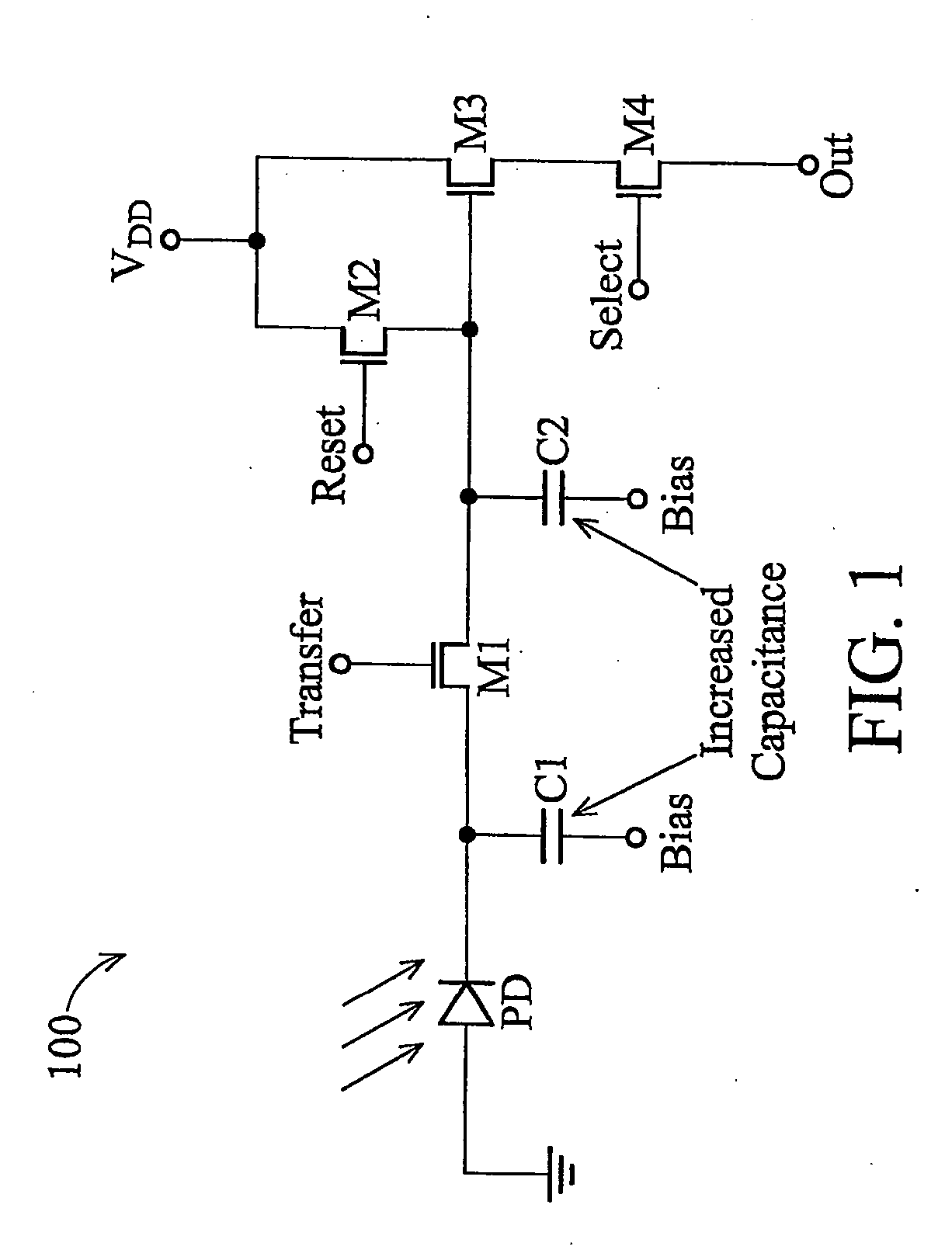

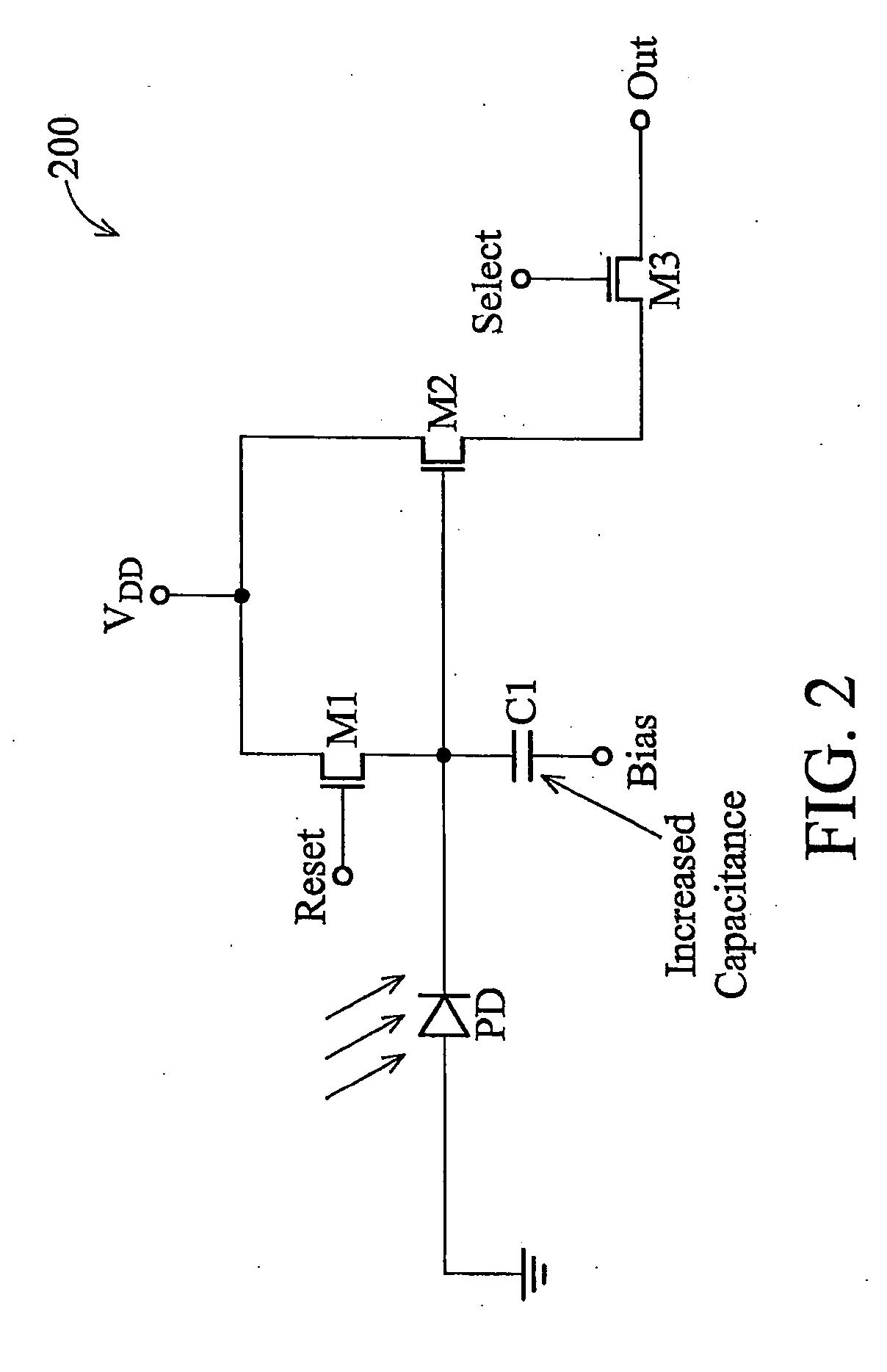

Structure for CMOS image sensor

ActiveUS20060164531A1Susceptibility to noiseReduce output signalTelevision system detailsTelevision system scanning detailsCapacitanceCMOS

A CMOS image sensor having increased capacitance that allows a photo-diode to generate a larger current is provided. The increased capacitance reduces noise and the dark signal. The image sensor utilizes a transistor having nitride spacers formed on a buffer oxide layer. Additional capacitance may be provided by various capacitor structures, such as a stacked capacitor, a planar capacitor, a trench capacitor, a MOS capacitor, a MIM / PIP capacitor, or the like. Embodiments of the present invention may be utilized in a 4-transistor pixel or a 3-transistor pixel configuration.

Owner:TAIWAN SEMICON MFG CO LTD

Soi CMOS compatible multiplanar capacitor

An isolated shallow trench isolation portion is formed in a top semiconductor portion of a semiconductor-on-insulator substrate along with a shallow trench isolation structure. A trench in the shape of a ring is formed around a doped top semiconductor portion and filled with a conductive material such as doped polysilicon. The isolated shallow trench isolation portion and the portion of a buried insulator layer bounded by a ring of the conductive material are etched to form a cavity. A capacitor dielectric is formed on exposed semiconductor surfaces within the cavity and above the doped top semiconductor portion. A conductive material portion formed in the trench and above the doped top semiconductor portion constitutes an inner electrode of a capacitor, while the ring of the conductive material, the doped top semiconductor portion, and a portion of a handle substrate abutting the capacitor dielectric constitute a second electrode.

Owner:TWITTER INC

Methods for forming multilayer structures

The present invention relates to methods of forming multilayer structures and the structures themselves. In one embodiment, a method of forming a multilayer structure comprises: providing a dielectric composition comprising paraelectric filler and polymer wherein the paraelectric filler has a dielectric constant between 50 and 150; applying the dielectric composition to a carrier film thus forming a multilayer film comprising a dielectric layer and carrier film layer; laminating the multilayer film to a circuitized core wherein the dielectric layer of the multilayer film is facing the circuitized core; and removing the carrier film layer from the dielectric layer prior to processing; applying a metallic layer to the dielectric layer wherein the circuitized core, dielectric layer and metallic layer form a planar capacitor; and processing the planar capacitor to form a multilayer structure.

Owner:DUPONT ELECTRONICS INC

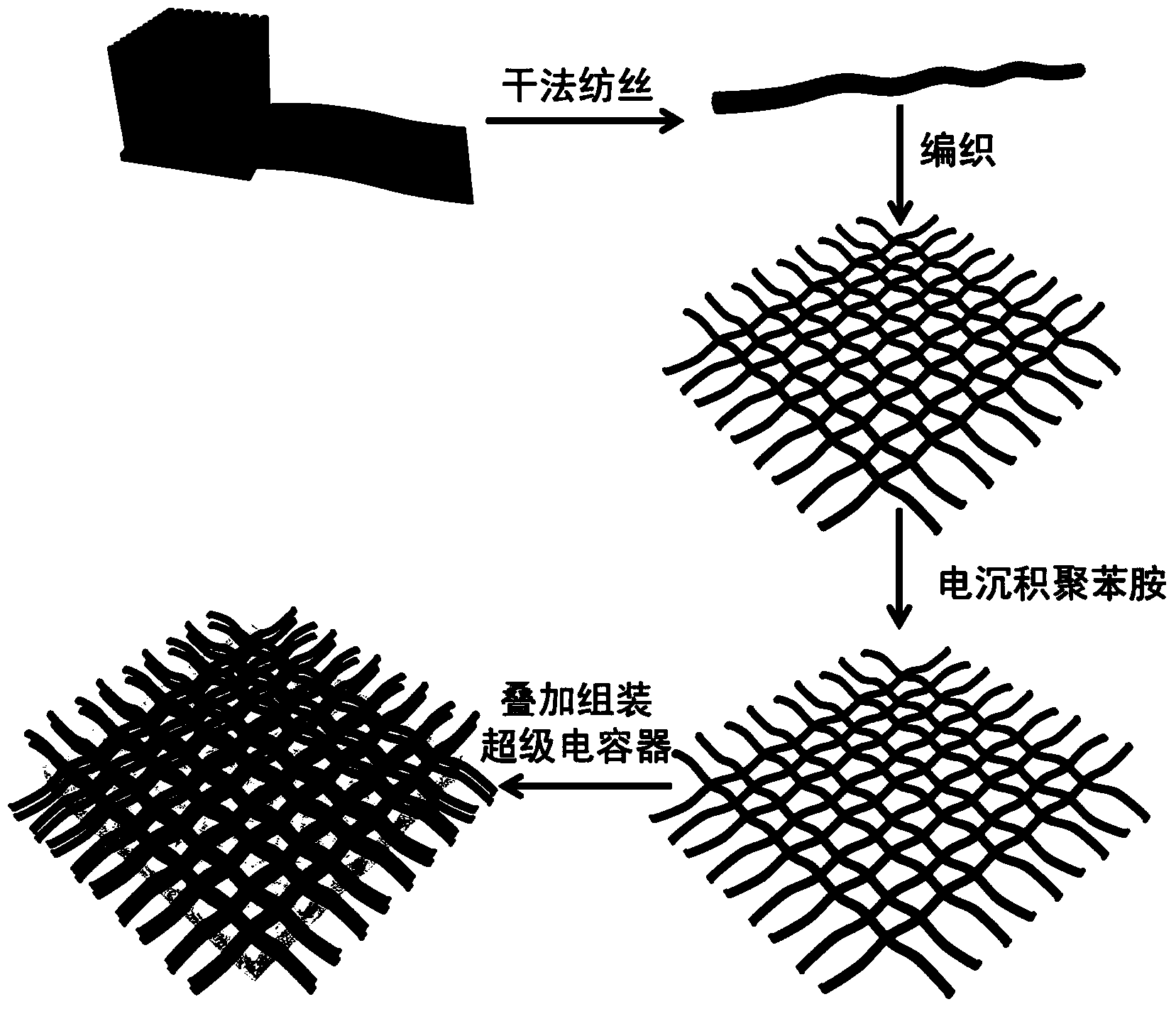

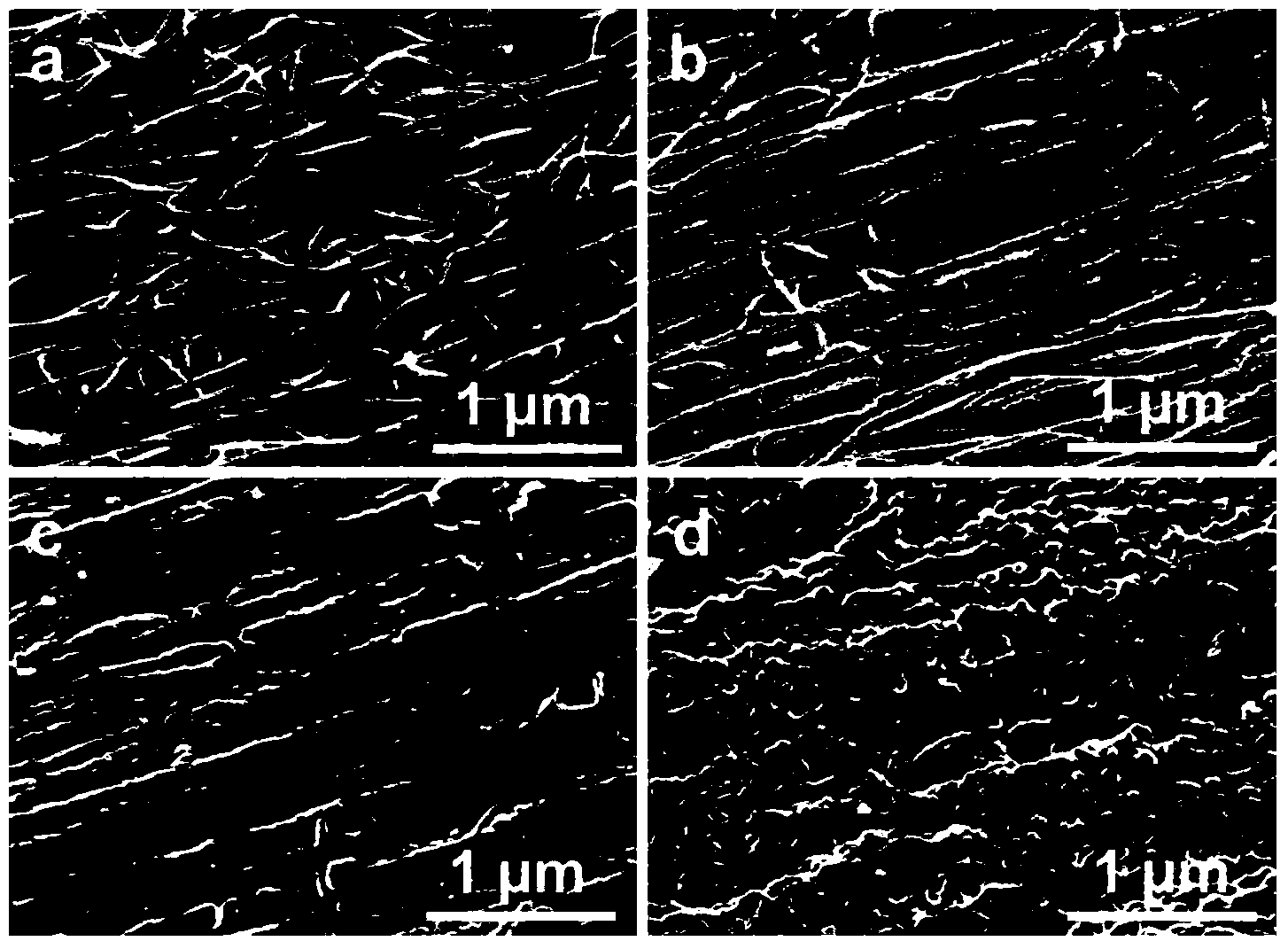

Transparent flexible supercapacitor fabric and preparation method thereof

The invention belongs to the technical field of energy storage devices, and particularly relates to a transparent flexible supercapacitor fabric and a preparation method of the transparent flexible supercapacitor fabric. According to the method, oriented carbon nano tube fiber is woven into a carbon nano tube fiber fabric, a carbon nano tube / polyaniline composite fabric is obtained by depositing polyaniline on the carbon nano tube fiber fabric through an electrochemical deposition method, the surface of the composite fabric is coated with one layer of polyvinyl alcohol / phosphoric acid (PVA / H3PO4) gel electrolyte, and finally the product is assembled with the other electrode with the same structure and material so that the supercapacitor fabric can be obtained. Compared with a traditional planar capacitor, the supercapacitor fabric has the advantages of being light in weight, capable of being woven and the like; compared with other fabric capacitors, the supercapacitor fabric has the advantages of being transparent and the like; compared with a fiber supercapacitor, the supercapacitor fabric is higher in large-scale weaving capacity, and thus the supercapacitor fabric has very good application prospects.

Owner:FUDAN UNIV

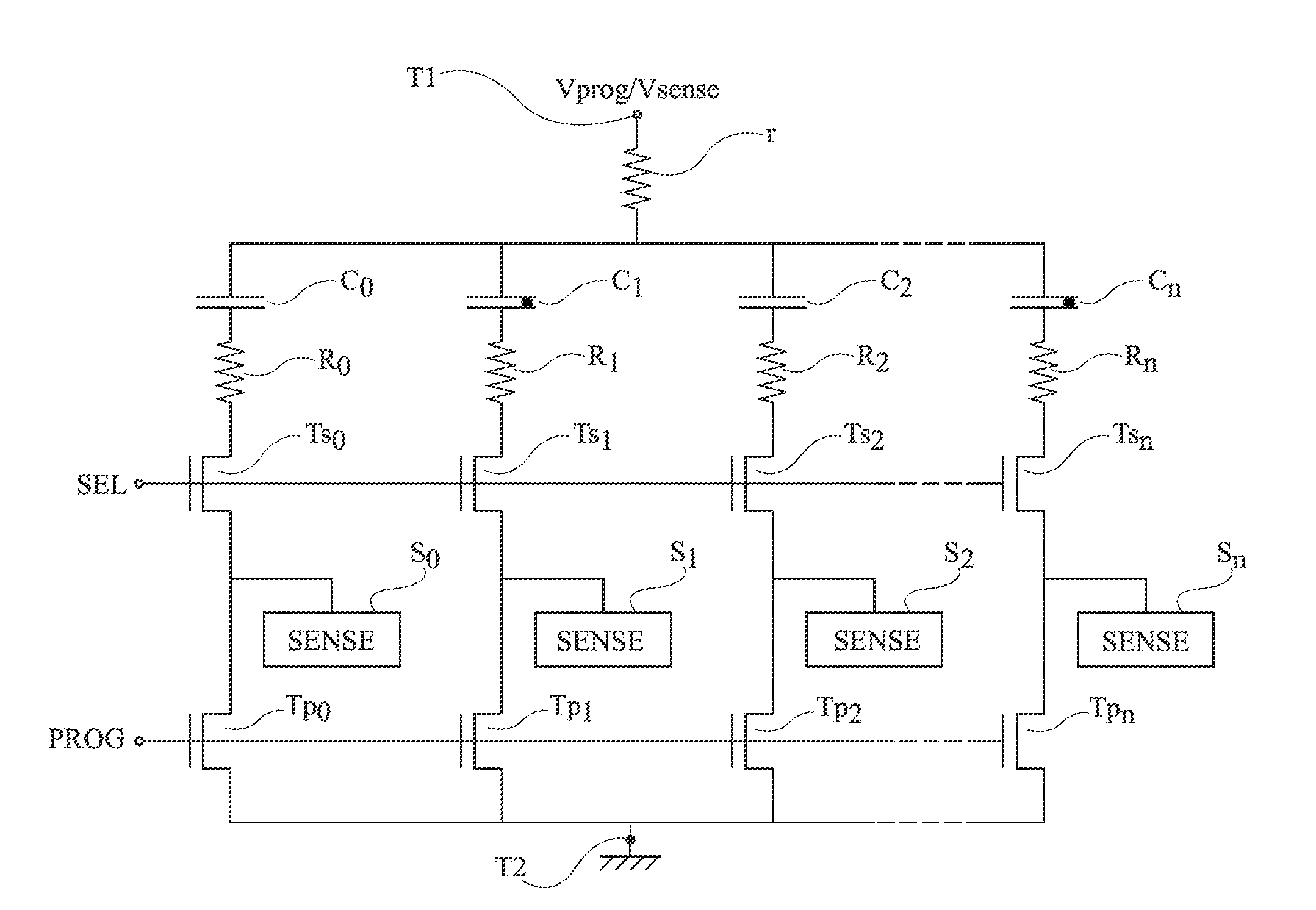

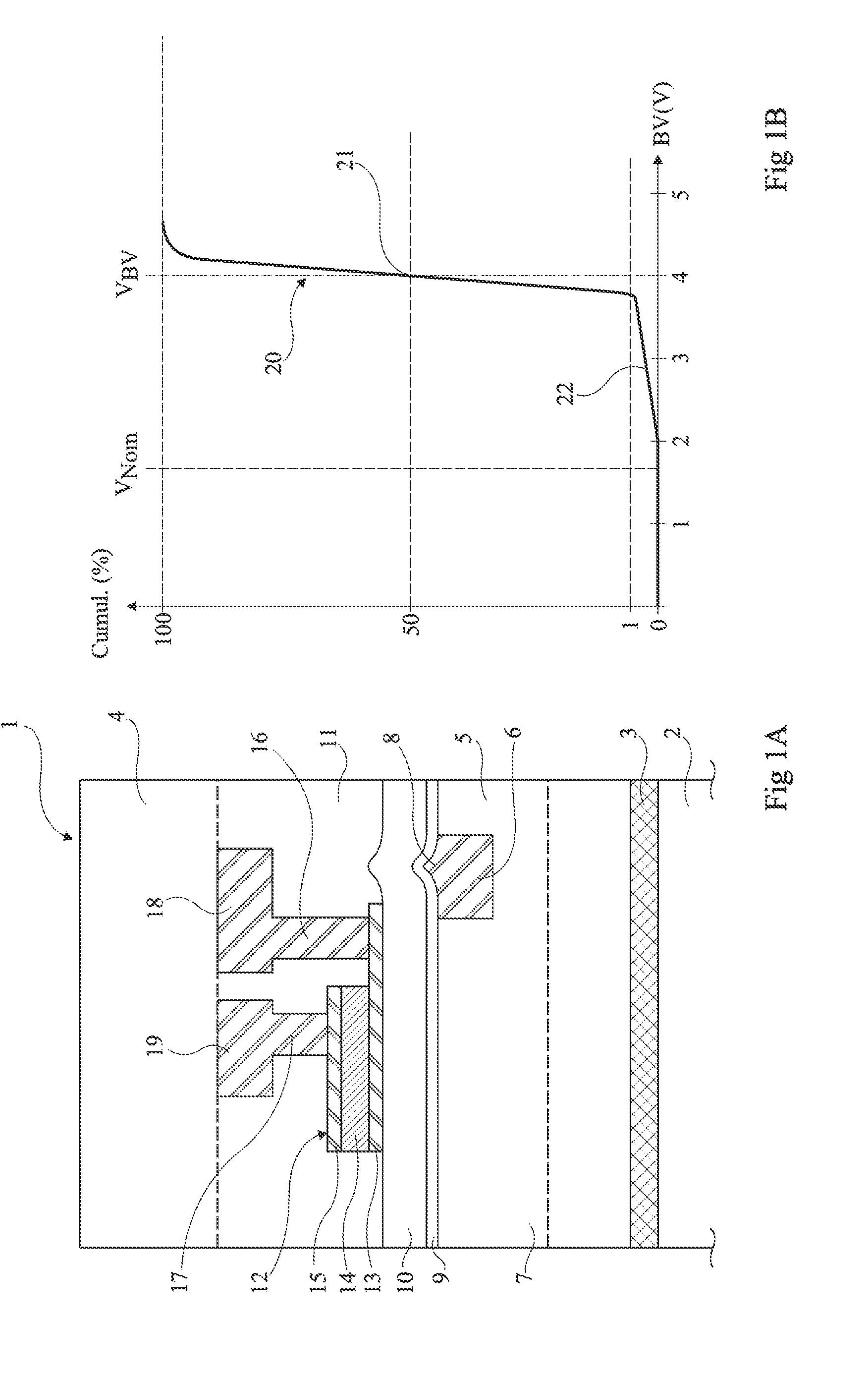

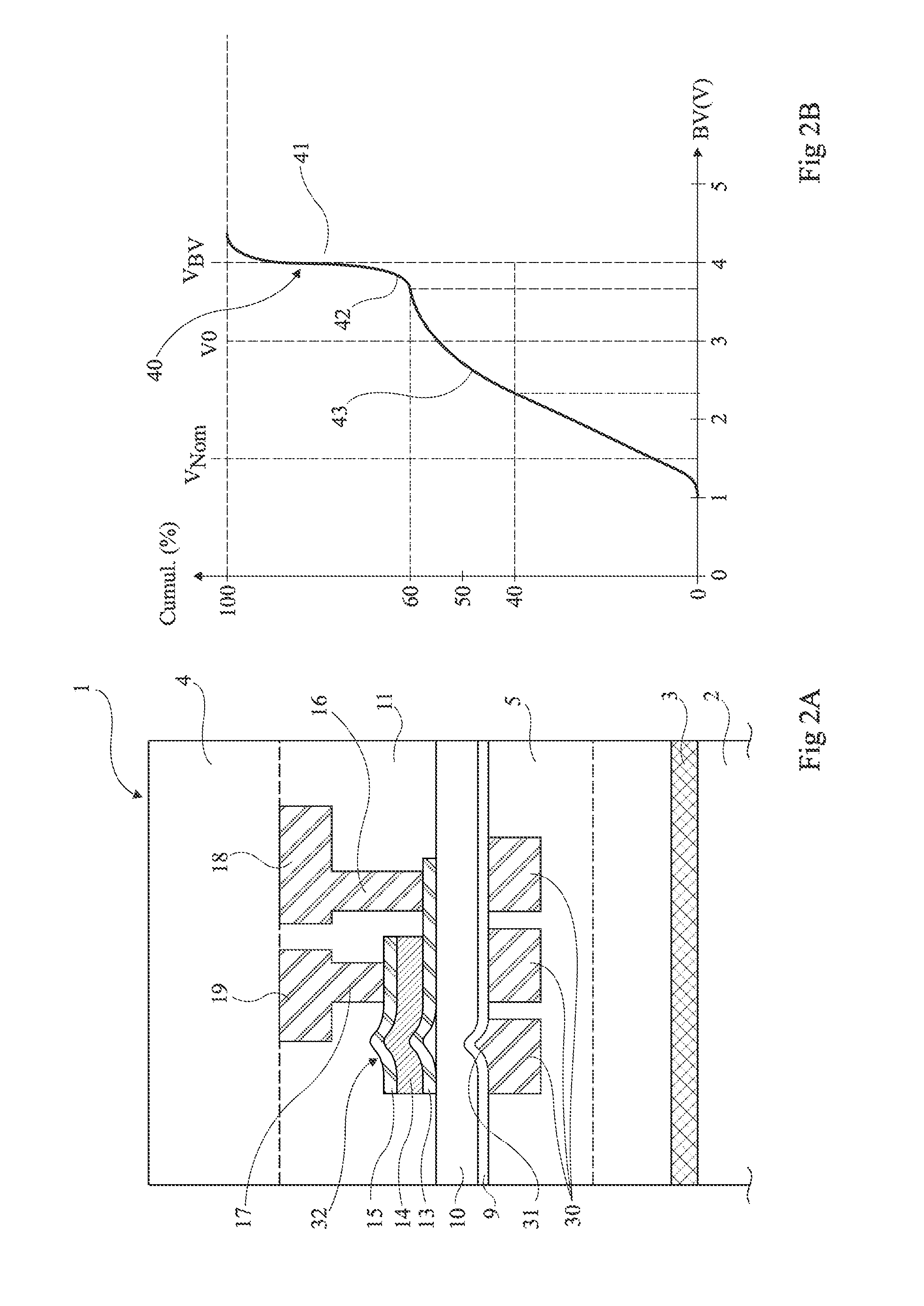

Integrated circuit with a self-programmed identification key

ActiveUS20130083586A1Semiconductor/solid-state device detailsSolid-state devicesEngineering physicsMaterials science

A structure for storing a native binary code in an integrated circuit, including an array of planar MIM capacitors above an insulating layer formed above a copper metallization network, wherein at least one metallization portion is present under each MIM capacitor. The size of the portion(s) is selected so that from 25 to 75% of the MIM capacitors have a breakdown voltage smaller by at least 10% than that of the other MIM capacitors.

Owner:STMICROELECTRONICS (CROLLES 2) SAS

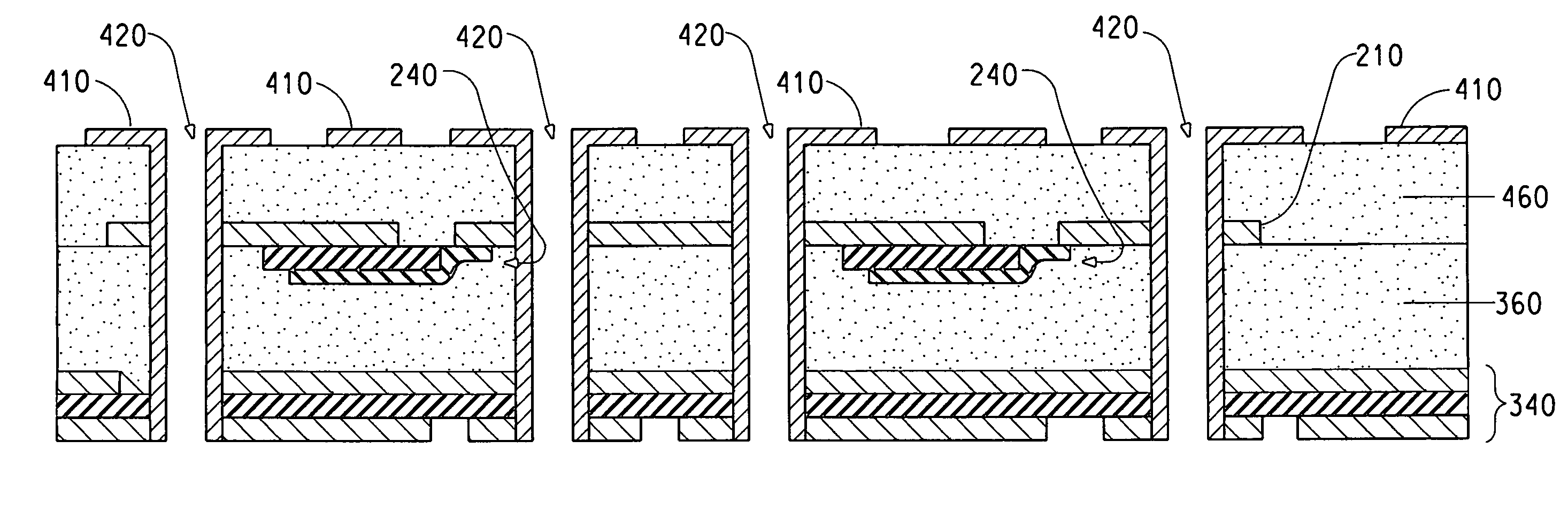

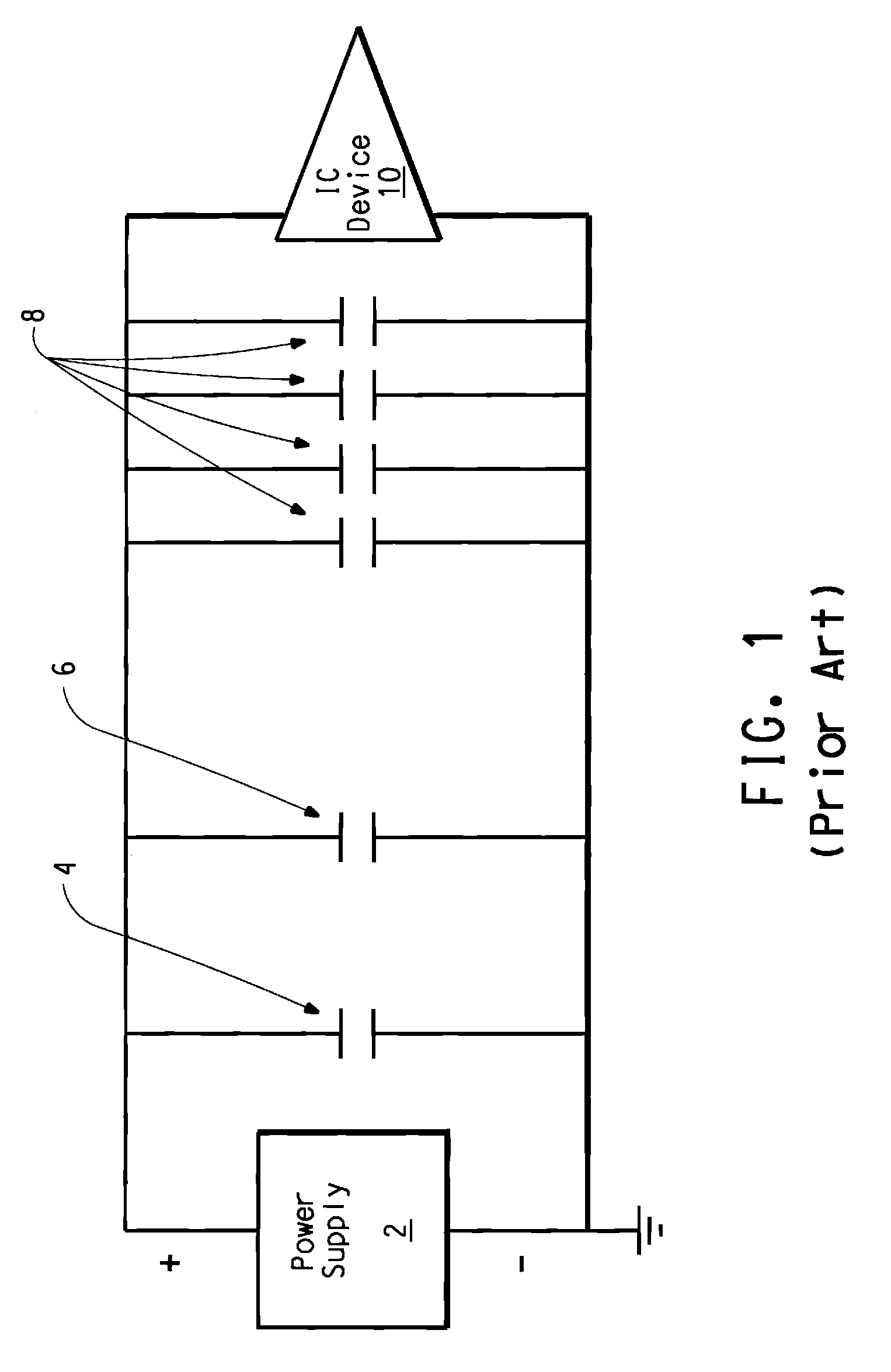

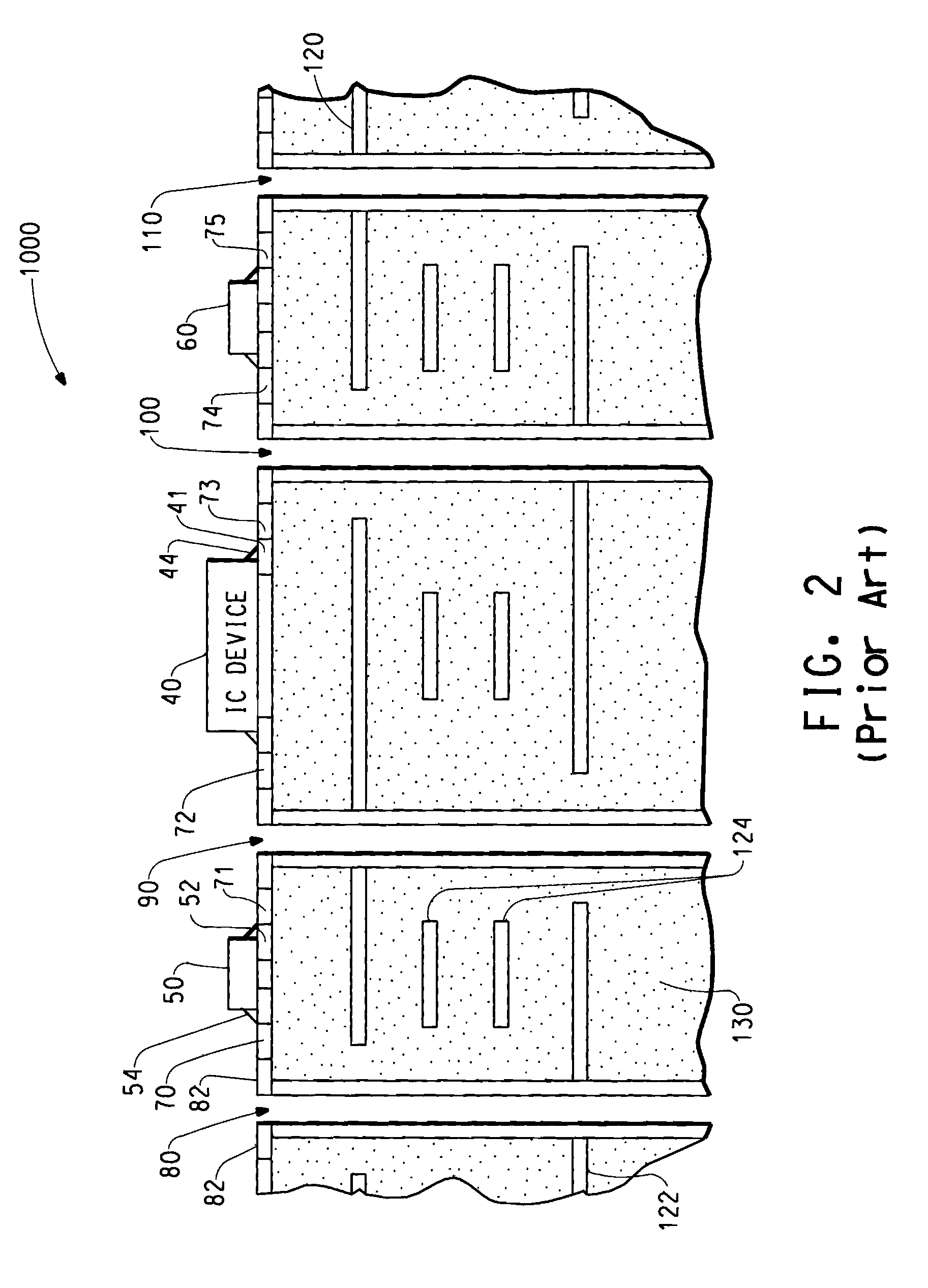

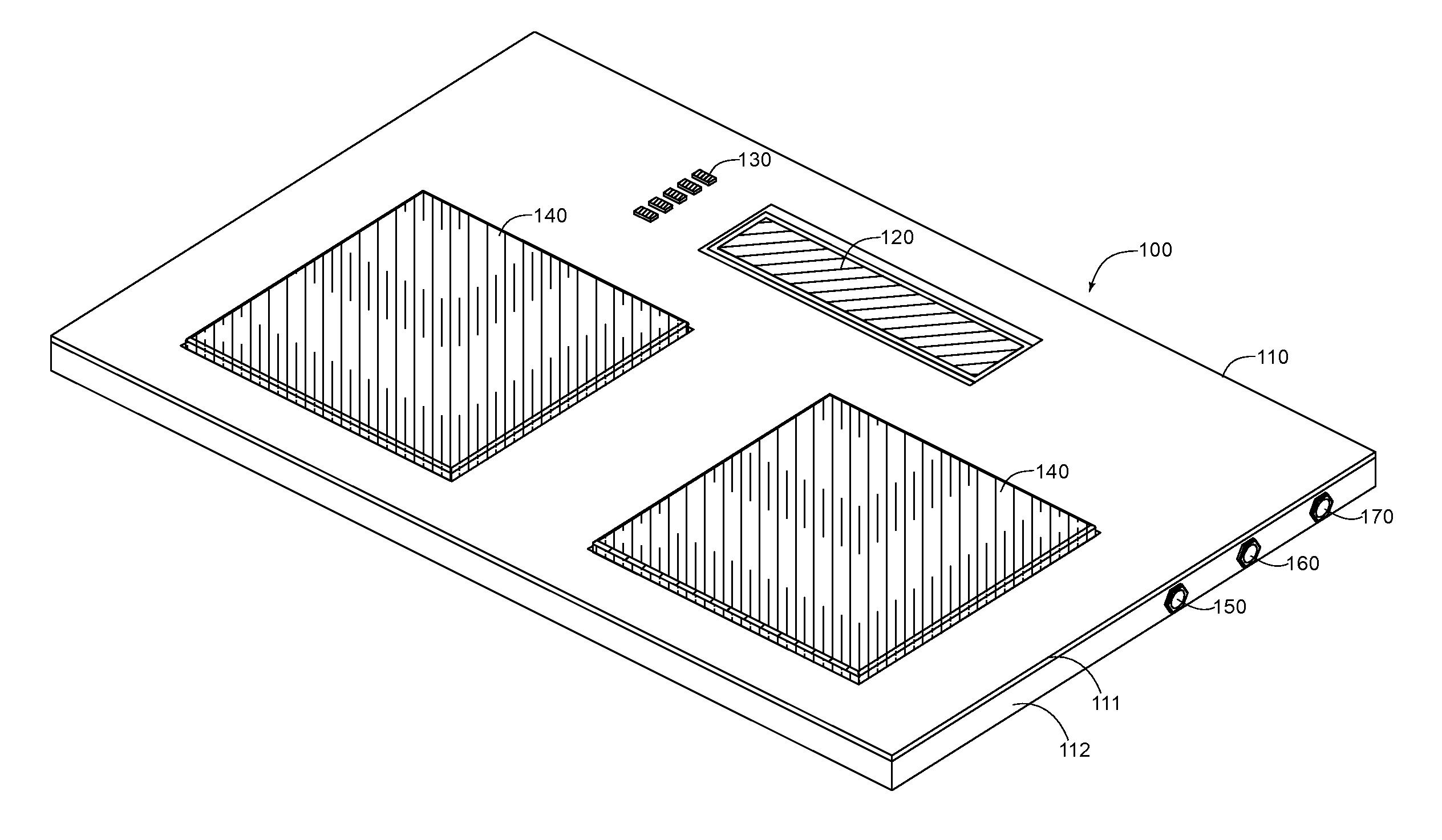

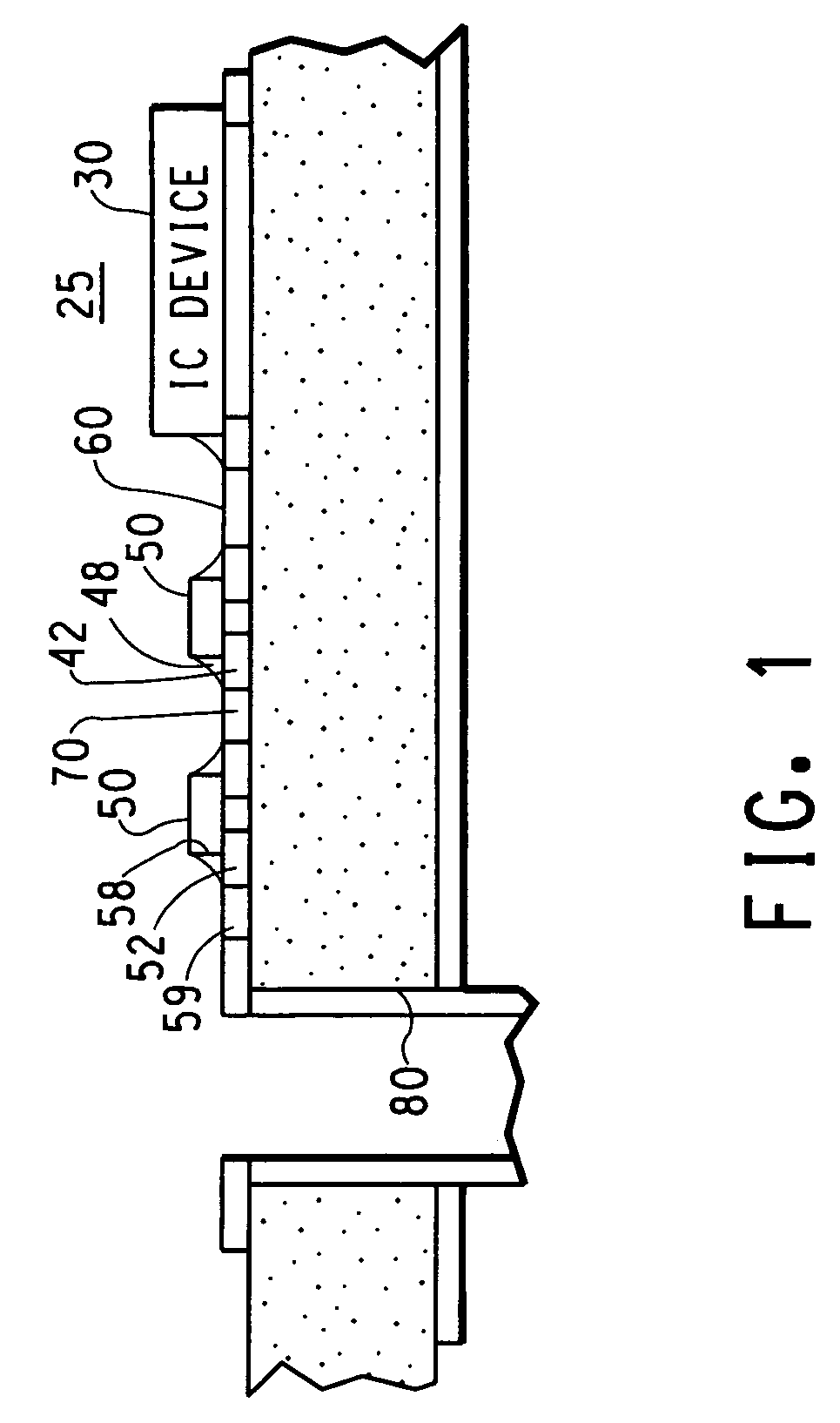

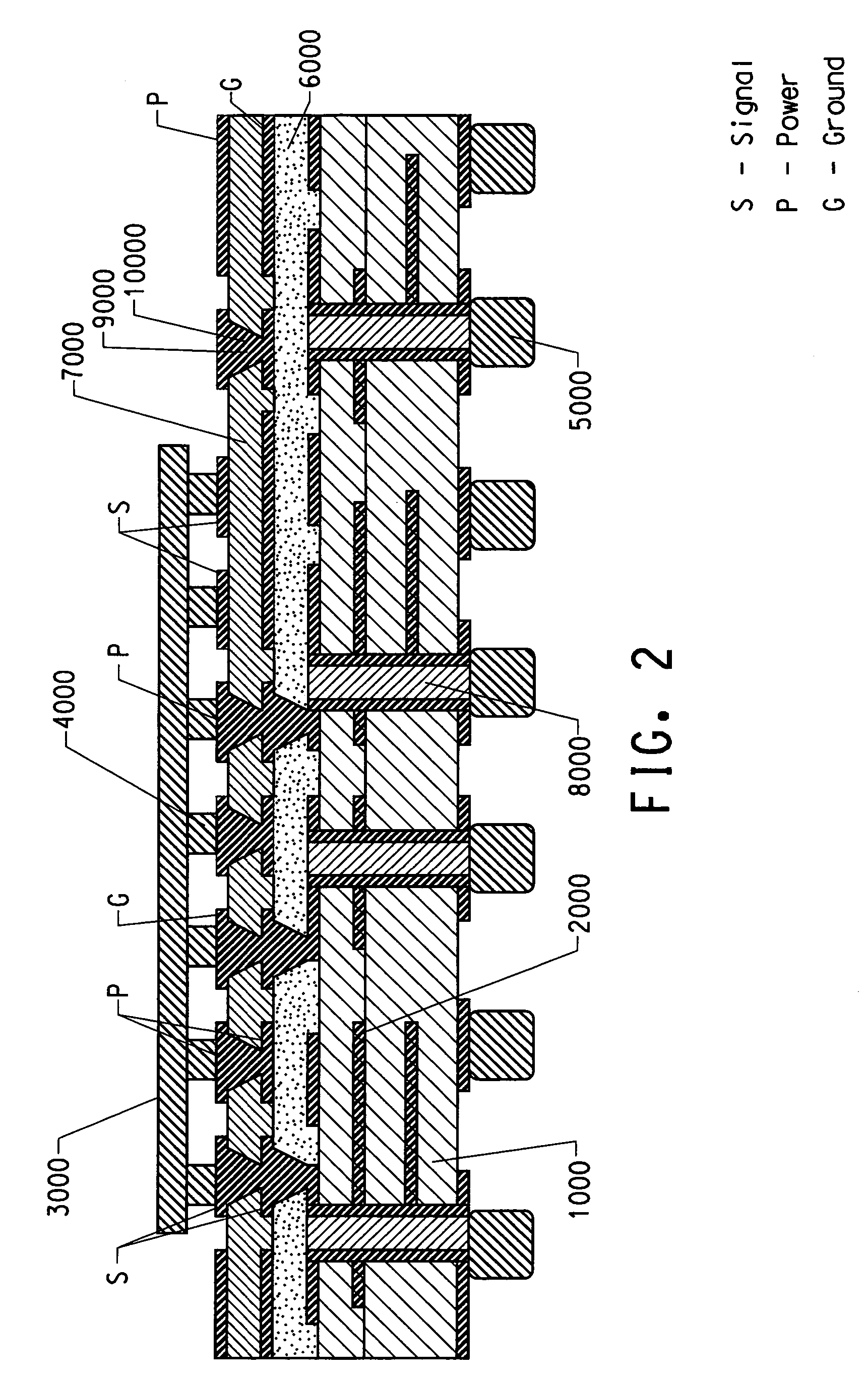

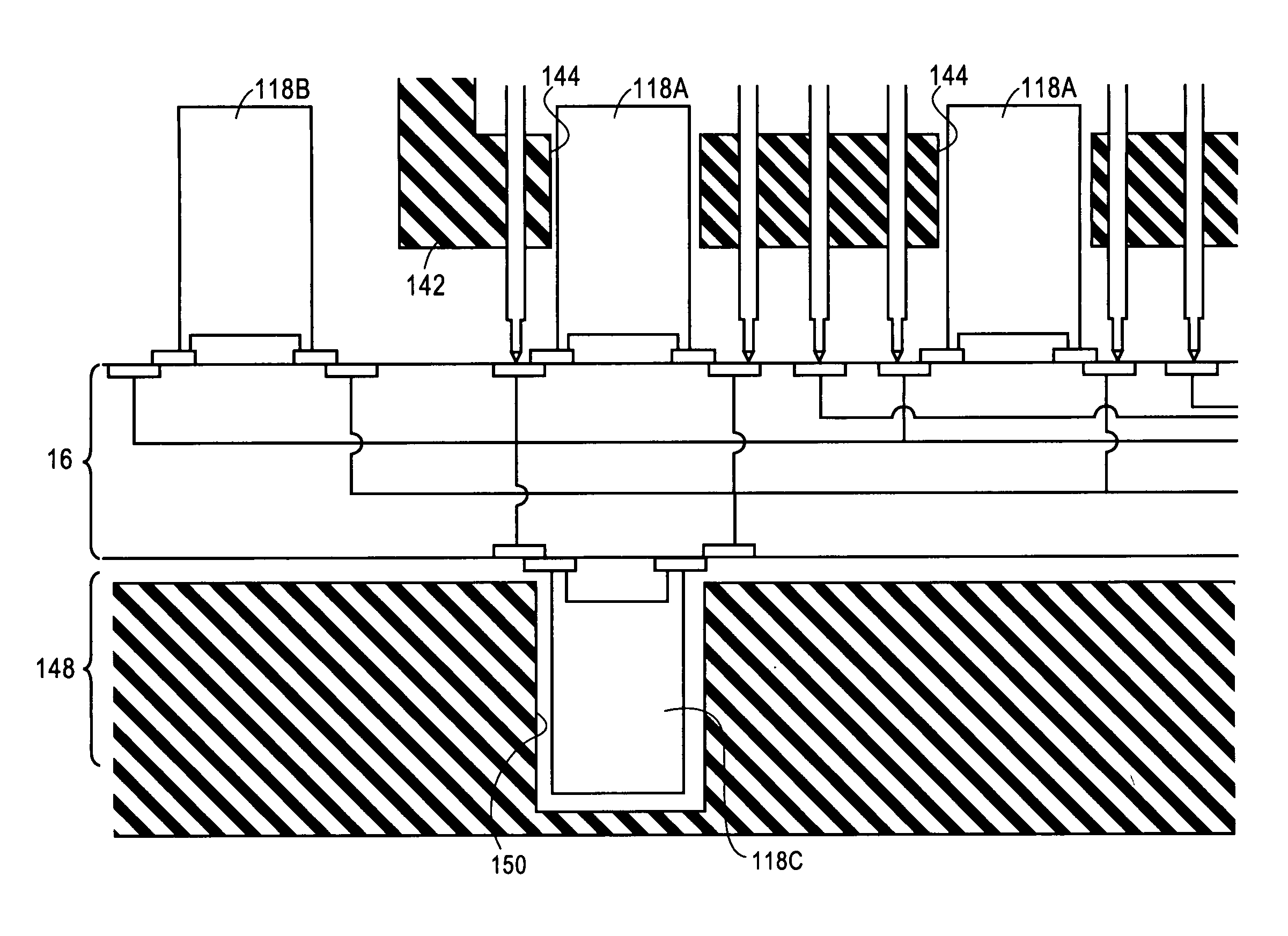

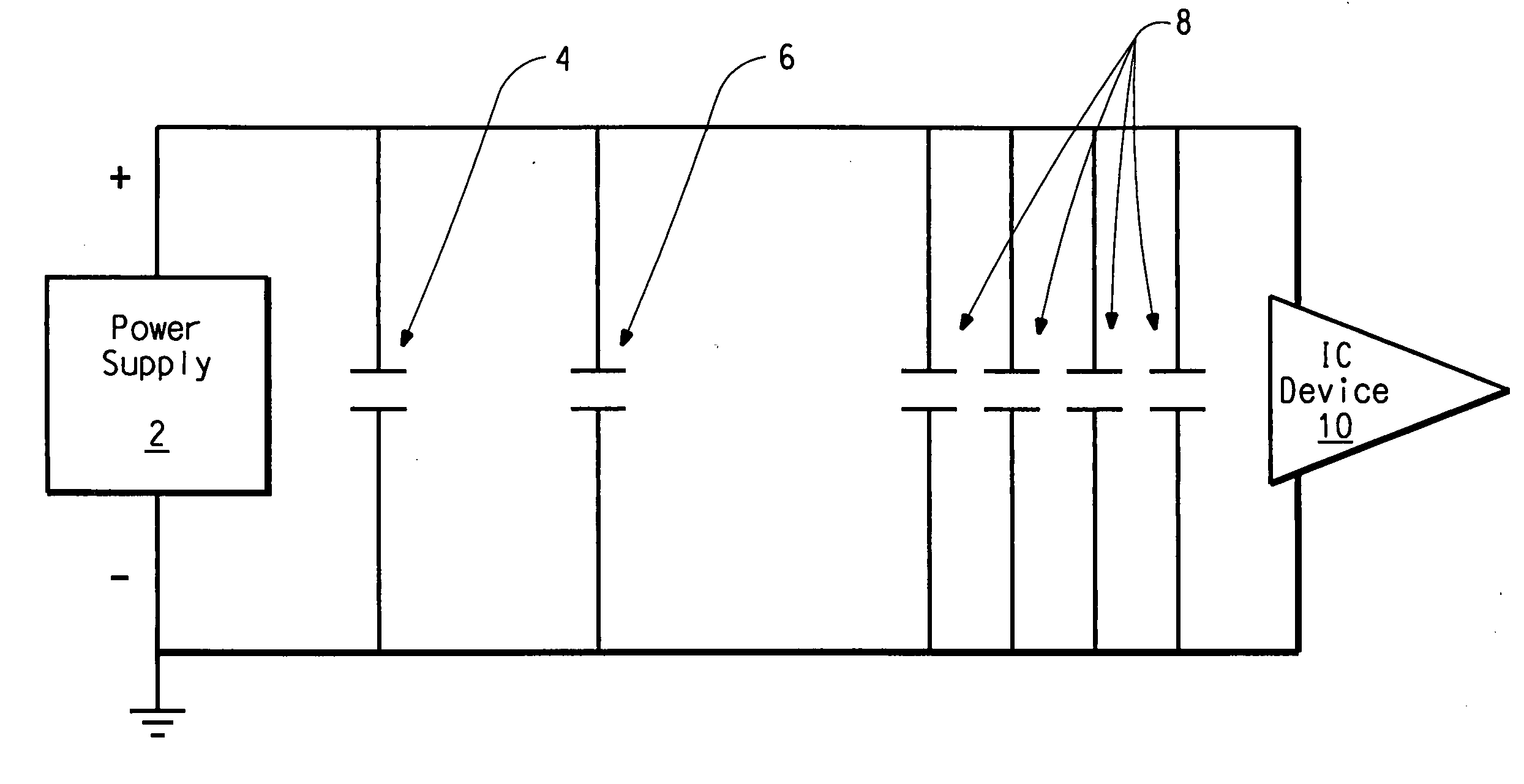

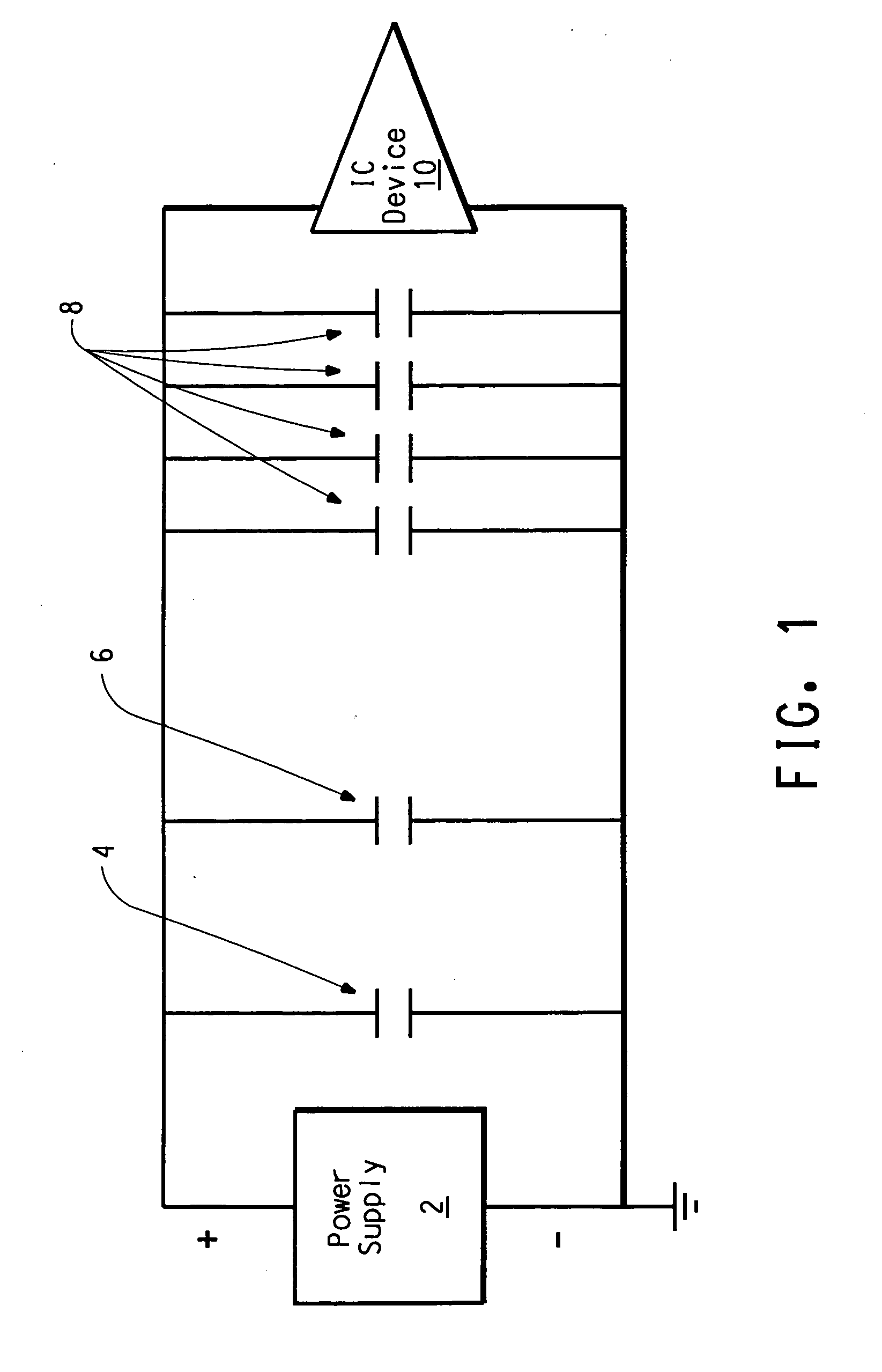

System for testing and burning in of integrated circuits

ActiveUS7053644B1Current is limitedRestoration of currentSemiconductor/solid-state device testing/measurementElectronic circuit testingElectrical conductorDielectric layer

A system for testing integrated circuits is described. A contactor board of the system has pins with ends that contact terminals on a power and signal distribution board. Opposing ends of the pins make contact with die terminals on an unsingulated wafer. The distribution board also carries a plurality of capacitors, at least one capacitor corresponding to every die on the unsingulated wafer. Each capacitor may include two substantially flat planar capacitor conductors and a dielectric layer between the capacitor conductors. Alternatively, the capacitors may be discrete components mounted to and standing above the distribution board, in which case corresponding capacitor openings are formed in the contactor substrate to accommodate the capacitors when the distribution board and the contactor board are brought together. A plurality of fuses made of a polymer material are also provided. The polymer material limits the flow of current flowing therethrough when the temperature of a fuse increases, and increases the current therethrough when the temperature of the fuse decreases.

Owner:AEHR TEST SYST

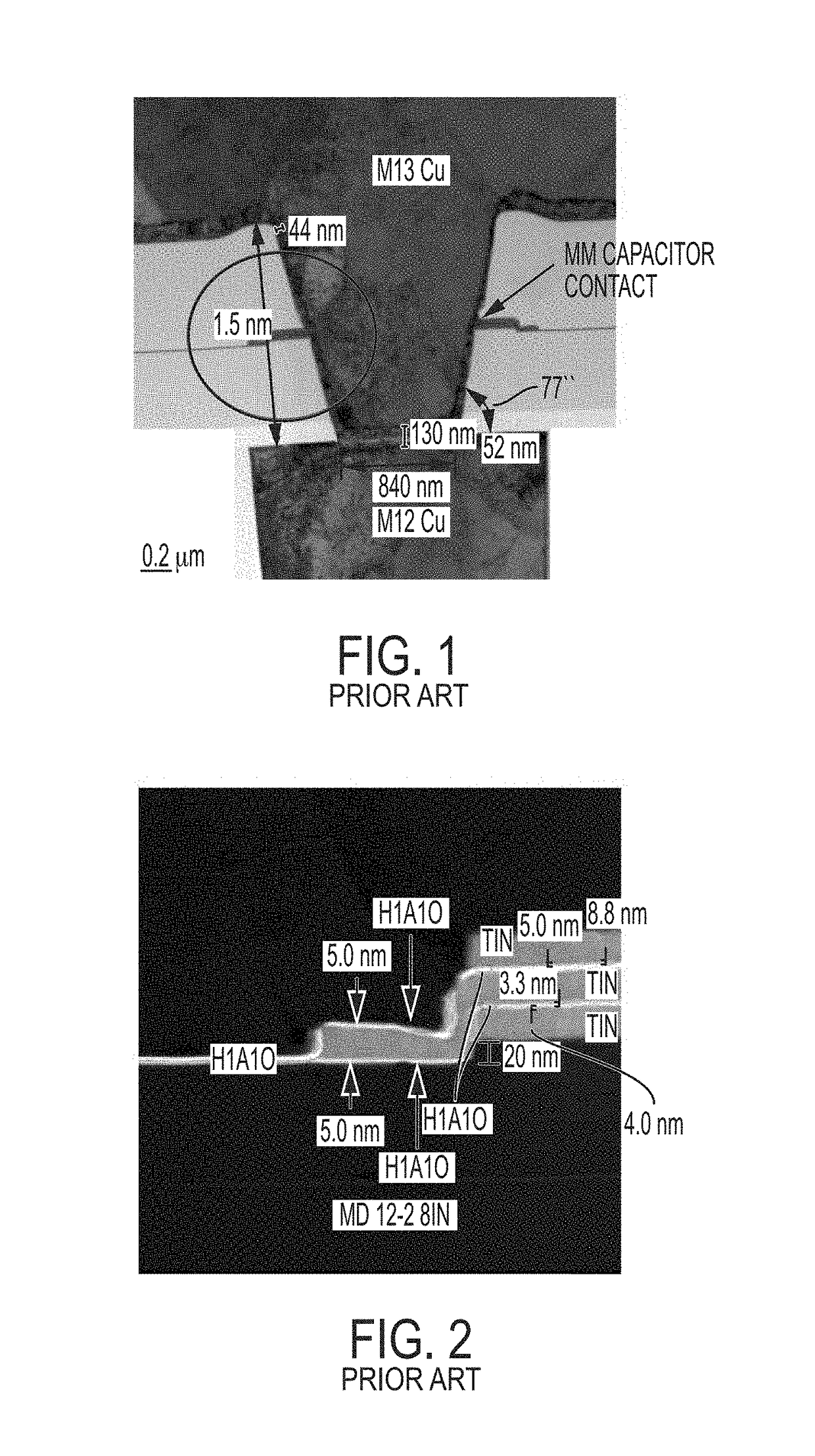

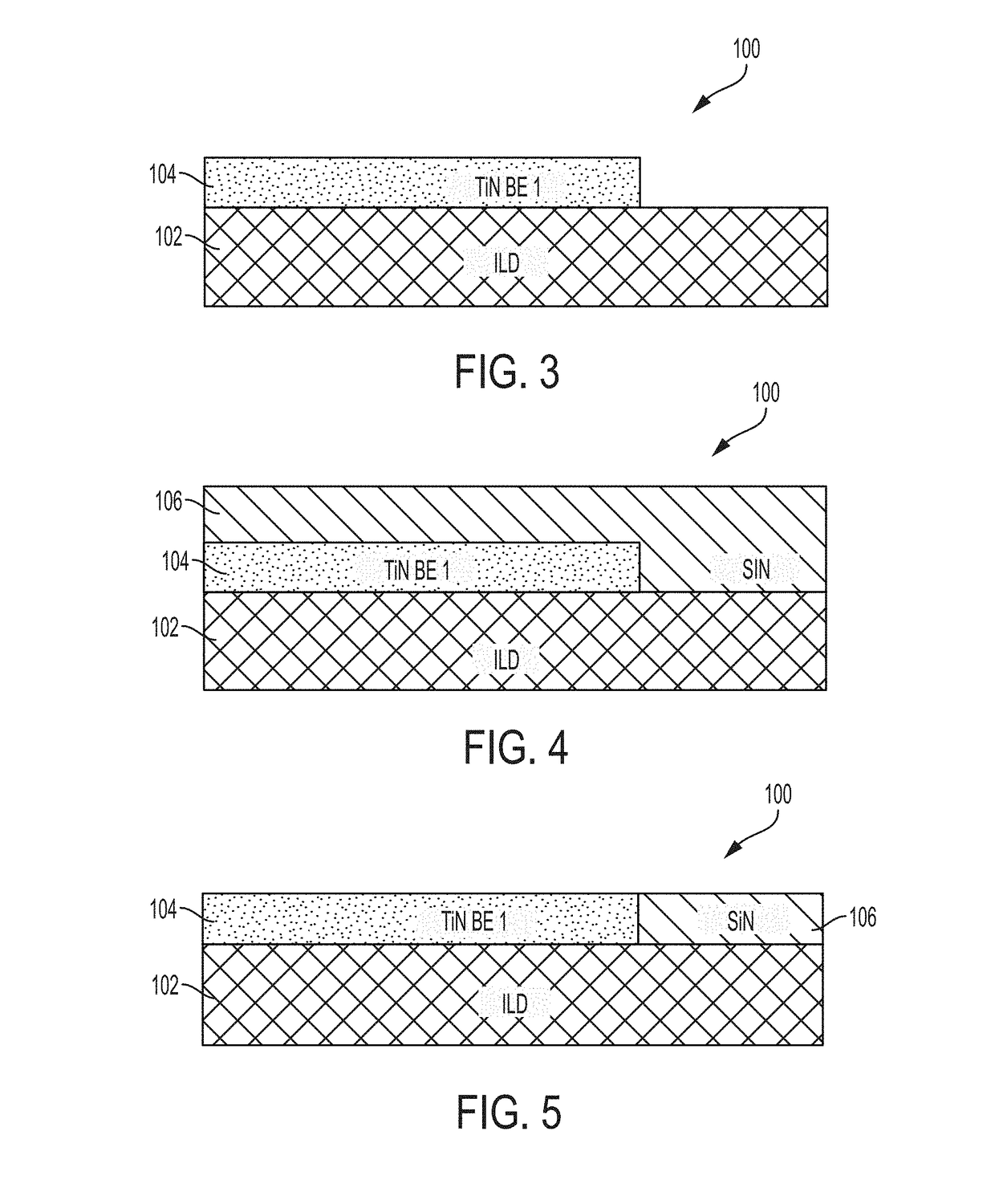

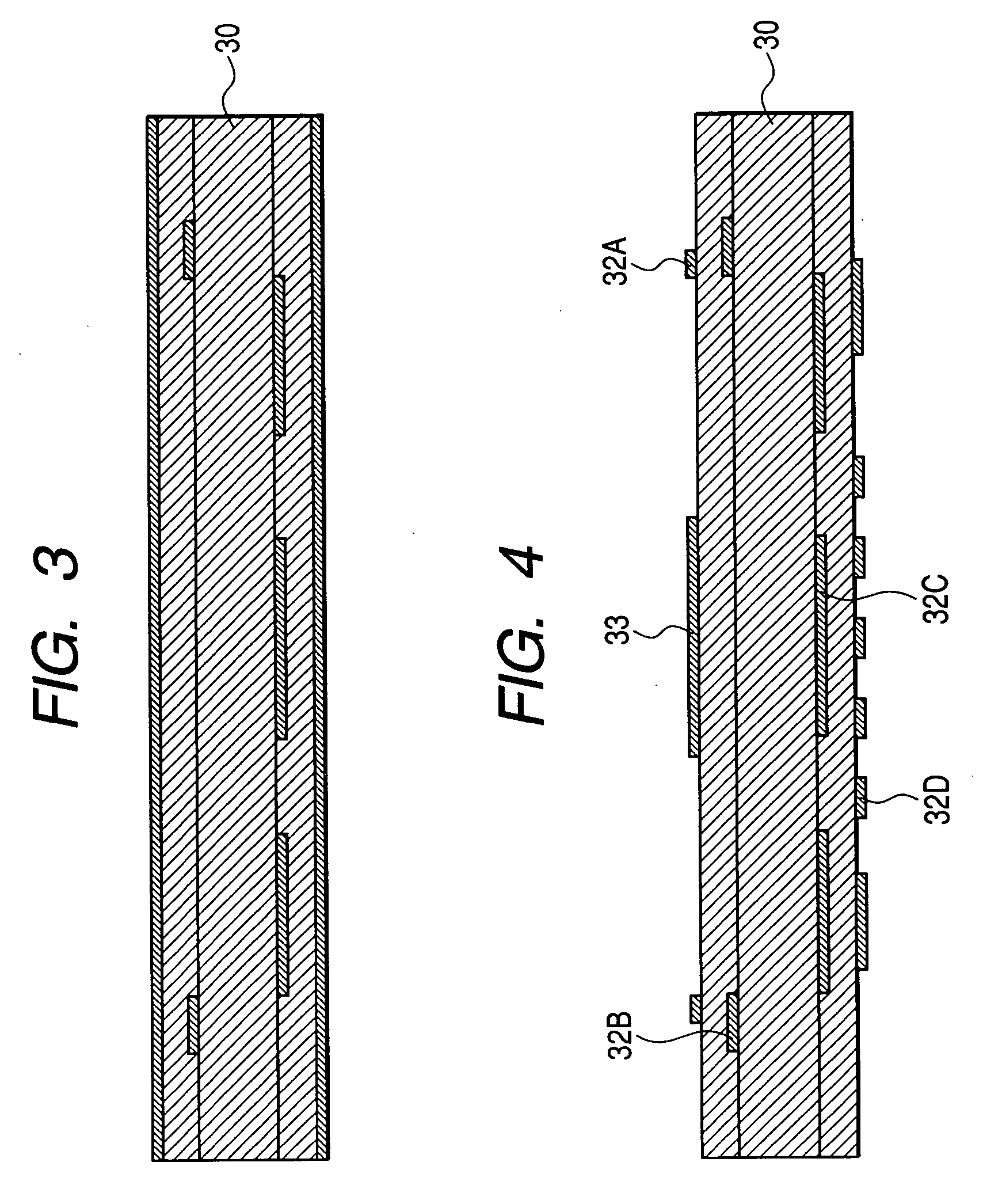

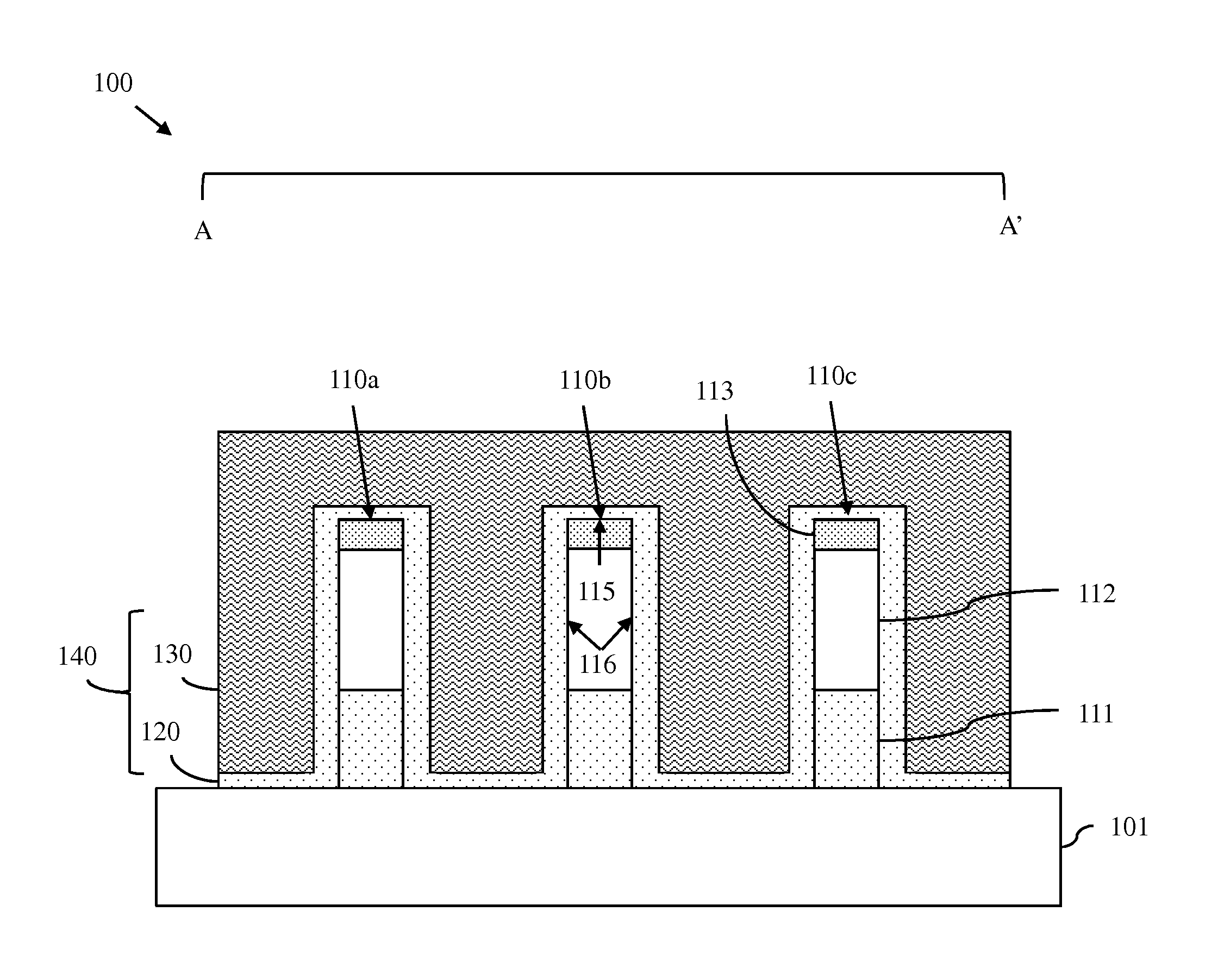

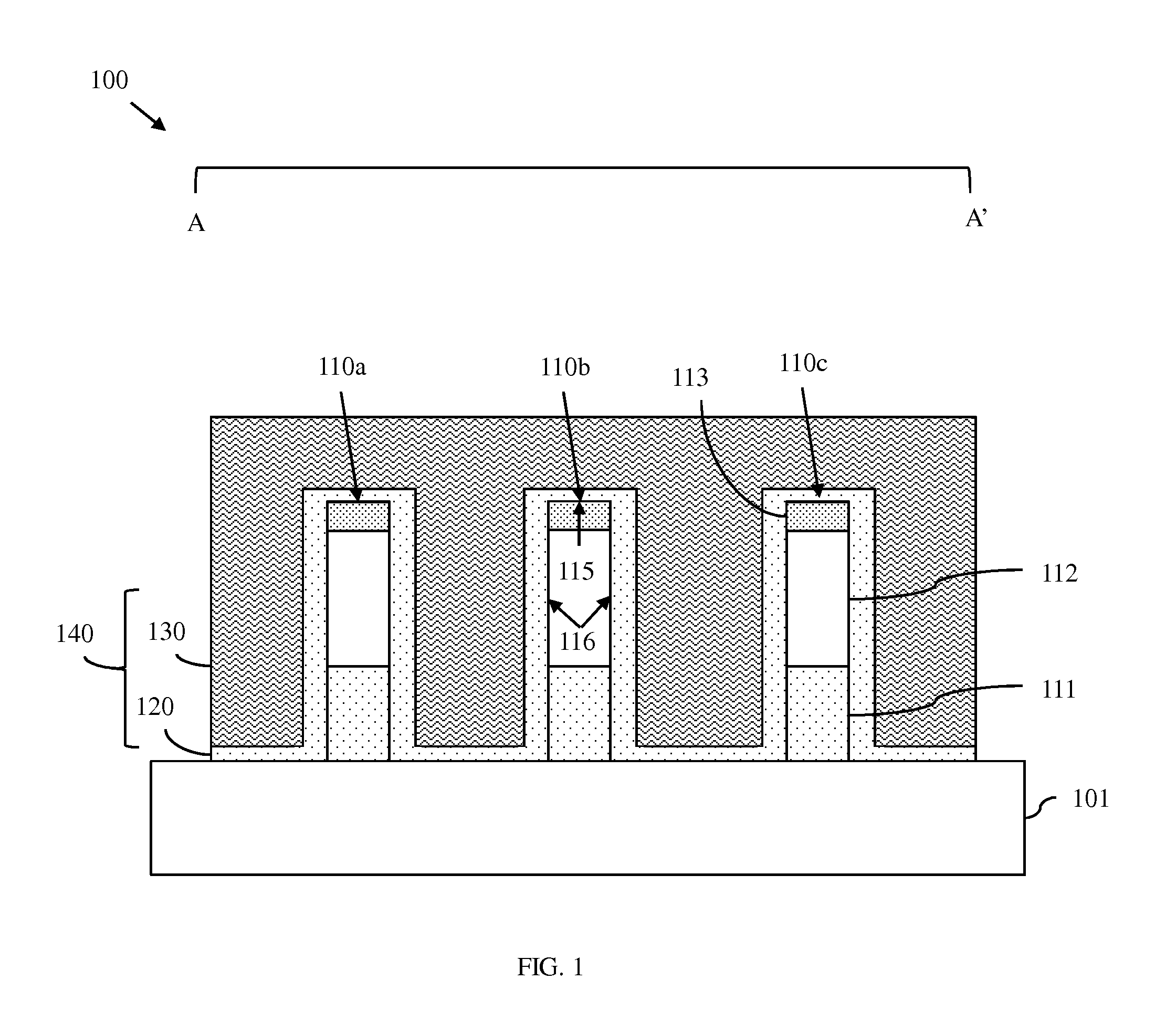

Stacked planar capacitors with scaled EOT

InactiveUS9761655B1Reduced substrate space requirementImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesElectrical and Electronics engineeringPlanar capacitor

Stacked planar capacitor structures and methods of fabricating the same generally include stacking two or more capacitors with three electrodes by sharing a middle electrode, wherein each capacitor has a different area. The stacked structure does not include step heights, which permits fabrication of multiple structures where desired.

Owner:IBM CORP

Plane capacity type automatic wiper system intelligent sensor for automobile glass

InactiveCN1491840AAvoid the disadvantages of slow responseLarge measuring areaRainfall/precipitation gaugesVehicle cleaningDielectricForeign matter

The sensor is a pair of planar electrodes in some interval formed on the inner surface of automobile glass via adhering, pressing, painting or plating conductor, and electrode pair constitutes one planar capacitor via glass and near dielectric space. When some rain drops or other foreign matter attach to the outer surface of the glass, there will be changes in the average dielectric constant, the area covered by the planar capacitor plates and the minor axis radius of the dielectric space and thus change in capacitance, and the intelligent adaptive signal amplifying and processing unit with microprocessor detects the change in capacitance and converts it into digital signal to drive the control unit of the automatic windscreen wiper system.

Owner:AUTOEASY ELECTRONICS TECH

Polymer-based capacitor composites capable of being light-activated and receiving direct metalization, and methods and compositions related thereto

InactiveUS7504150B2Fixed capacitor dielectricSynthetic resin layered productsLight activationPolymer composites

The present invention relates generally to polymer composites having dispersed therein both useful spinel crystal fillers and ferroelectric (and / or paraelectric) fillers wherein the composite is both light activatable and can be used as a planar capacitor material. The light activation is typically employed via a laser beam (or other light emitting device) where the material has a pattern formed thereon. Electrodes are typically formed on the material's surface after patterning is complete via electroless metal plating. These composite polymers can be used as planar capacitors embedded in printed wiring boards or in integrated circuit packages.

Owner:EI DU PONT DE NEMOURS & CO

Monolithic microwave integrated circuit

Low Q associated with passive components of monolithic integrated circuits (ICs) when operated at microwave frequencies can be avoided or mitigated using high resistivity (e.g., ≧100 Ohm-cm) semiconductor substrates (60) and lower resistance inductors (44′, 45′) for the IC (46). This eliminates significant in-substrate electromagnetic coupling losses from planar inductors (44, 45) and interconnections (50-1′, 52-1′, 94, 94′, 94″) overlying the substrate (60). The active transistor(s) (41′) are formed in the substrate (60) proximate the front face (63). Planar capacitors (42′, 43′) are also formed over the front face (63) of the substrate (60). Various terminals (42-1′, 42-2′, 43-1, 43-2′,50′, 51′, 52′, 42-1′, 42-2′, etc.) of the transistor(s) (41′), capacitor(s) (42′, 43′) and inductor(s) (44′, 45′) are coupled to a ground plane (69) on the rear face (62) of the substrate (60) using through-substrate-vias (98, 98′) to minimize parasitic resistance. Parasitic resistance associated with the planar inductors (44′, 45′) and heavy current carrying conductors (52-1′) is minimized by placing them on the outer surface of the IC where they can be made substantially thicker and of lower resistance. The result is a monolithic microwave IC (46, 58) previously unobtainable.

Owner:NXP USA INC

Semiconductor memory device

InactiveUS20050018471A1Reduce areaReduce the numberTransistorSolid-state devicesCapacitanceSemiconductor

Conductive lines constituting word lines of memory cells and conductive lines constituting memory cell plate electrodes are formed in the same interconnecting layer in a memory device including a plurality of memory cells each including a capacitor for storing data in an electrical charge form. By forming the capacitors of the memory cells into a planar capacitor configuration, a step due to the capacitors is removed. Thus, a dynamic semiconductor memory device can be formed through CMOS process, and a dynamic semiconductor memory device suitable for merging with logic is achieved. Data of 1 bit is stored by two memory cells, and data can be reliably stored even if the capacitance value of the memory cell is reduced due to the planar type capacitor.

Owner:RENESAS ELECTRONICS CORP

Printed circuit board and manufacturing method thereof

InactiveUS20050217893A1The connection is tight and firmSimple structureLiquid electrolytic capacitorsCross-talk/noise/interference reductionCapacitanceElectrical conductor

A printed circuit board which is thin and incorporates a large-capacitance capacitor function and a manufacturing method thereof. In one embodiment, the printed circuit board manufacturing method includes forming inner layer conductor circuits on a core substrate; forming a recess part on the core substrate; housing, in a recess part, a planar capacitor device that is not resin molded and has electrodes on the surfaces on a shared side; interposing the same between insulator resin and conductor metal foil to heat pressurize the same for forming a multi-layer plate; forming via holes for electrically connecting an outer layer conductor circuit to the electrodes of the capacitor device; forming a conductor layer on them; and forming the outer layer conductor circuits on the surfaces of the multi-layer plate.

Owner:TOKIN CORP

Power core devices and methods of making thereof

A power core comprising: at least one embedded singulated capacitor layer containing at least one embedded singulated capacitor; and at least one planar capacitor laminate; wherein at least one planar capacitor laminate serves as a low inductance path to supply a charge to at least one embedded singulated capacitor; and wherein said embedded singulated capacitor is connected in parallel to said planar capacitor laminate.

Owner:EI DU PONT DE NEMOURS & CO

Polymer-based capacitor composites capable of being light-activated and receiving direct metalization, and methods and compositions related thereto

InactiveUS20060286364A1Fixed capacitor dielectricPrinted circuit aspectsLight activationLight activated

The present invention relates generally to polymer composites having dispersed therein both useful spinel crystal fillers and ferroelectric (and / or paraelectric) fillers wherein the composite is both light activatable and can be used as a planar capacitor material. The light activation is typically employed via a laser beam (or other light emitting device) where the material has a pattern formed thereon. Electrodes are typically formed on the material's surface after patterning is complete via electroless metal plating. These composite polymers can be used as planar capacitors embedded in printed wiring boards or in integrated circuit packages.

Owner:EI DU PONT DE NEMOURS & CO

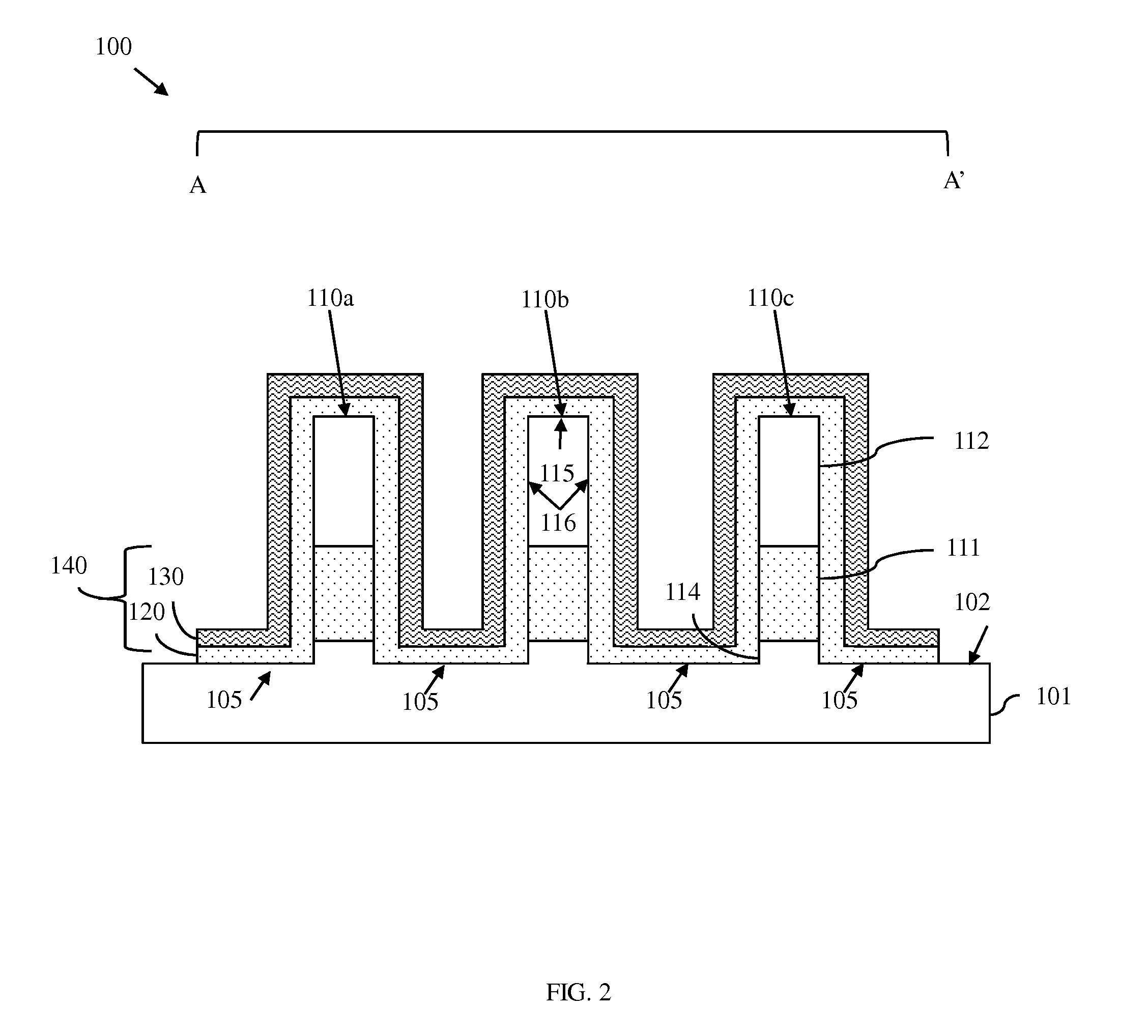

Non-planar capacitor and method of forming the non-planar capacitor

Disclosed herein are embodiments of non-planar capacitor. The non-planar capacitor can comprise a plurality of fins above a semiconductor substrate. Each fin can comprise at least an insulator section on the semiconductor substrate and a semiconductor section, which has essentially uniform conductivity, stacked above the insulator section. A gate structure can traverse the center portions of the fins. This gate structure can comprise a conformal dielectric layer and a conductor layer (e.g., a blanket or conformal conductor layer) on the dielectric layer. Such a non-planar capacitor can exhibit a first capacitance, which is optionally tunable, between the conductor layer and the fins and a second capacitance between the conductor layer and the semiconductor substrate. Also disclosed herein are method embodiments, which can be used to form such a non-planar capacitor and which are compatible with current state of the art multi-gate non-planar field effect transistor (MUGFET) processing.

Owner:GLOBALFOUNDRIES US INC

Semiconductor memory device and method for fabricating the same

A semiconductor memory device and method of fabricating the same, which improves adhesion of the lower electrode of a ferroelectric planar capacitor, and prevents inter-diffusion between the Pt electrode of the capacitor and adhesion layer placed under the Pt electrode. The semiconductor memory device includes an insulating layer formed on a substrate, a paraelectric layer formed on the insulating layer, and a conductive layer formed on the paraelectric layer.

Owner:LG SEMICON CO LTD

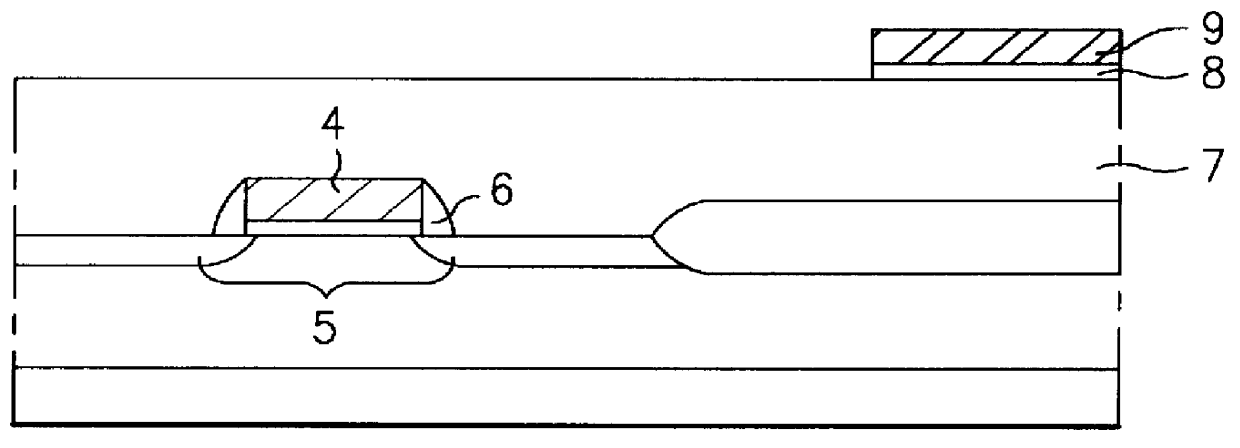

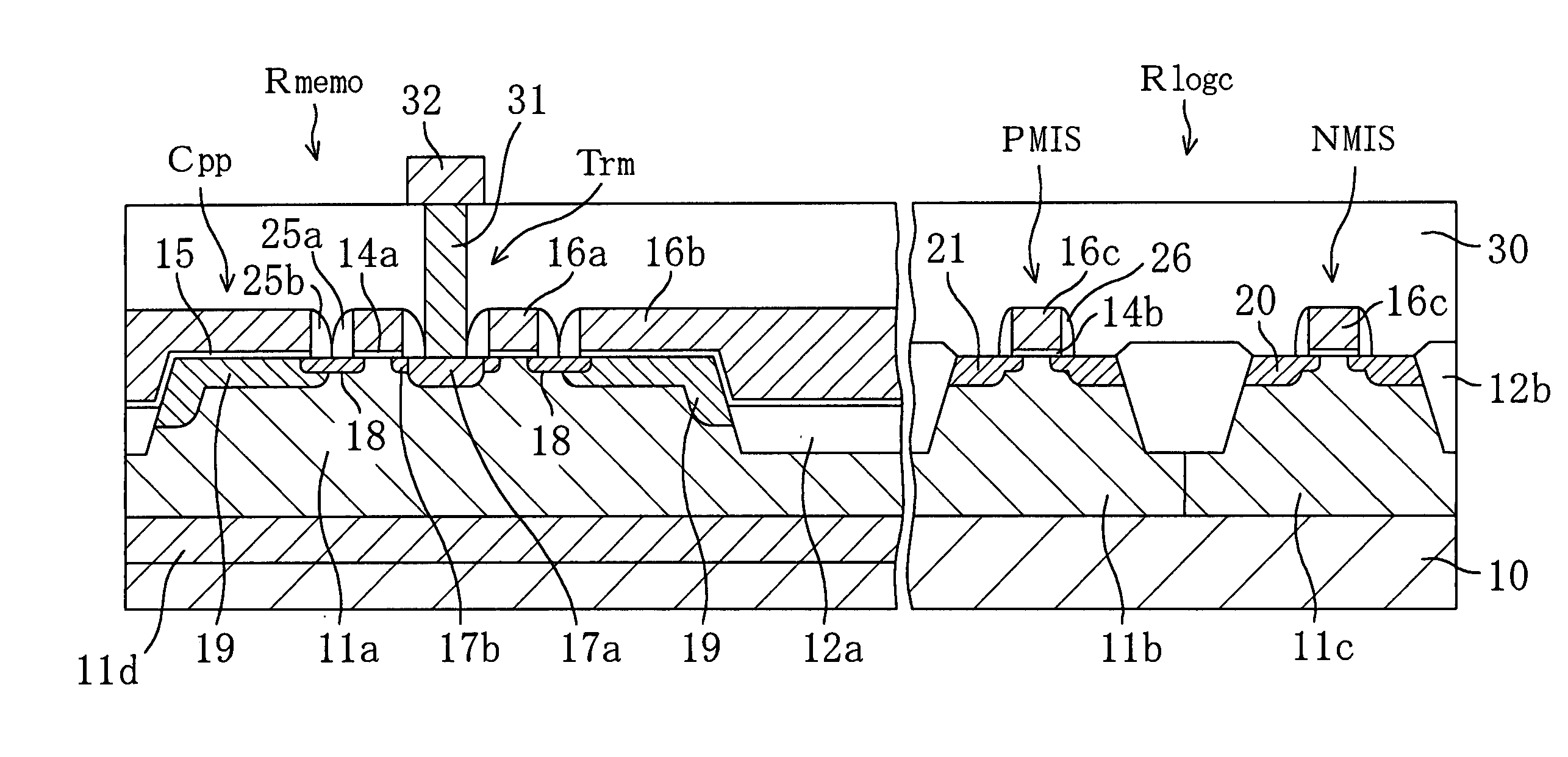

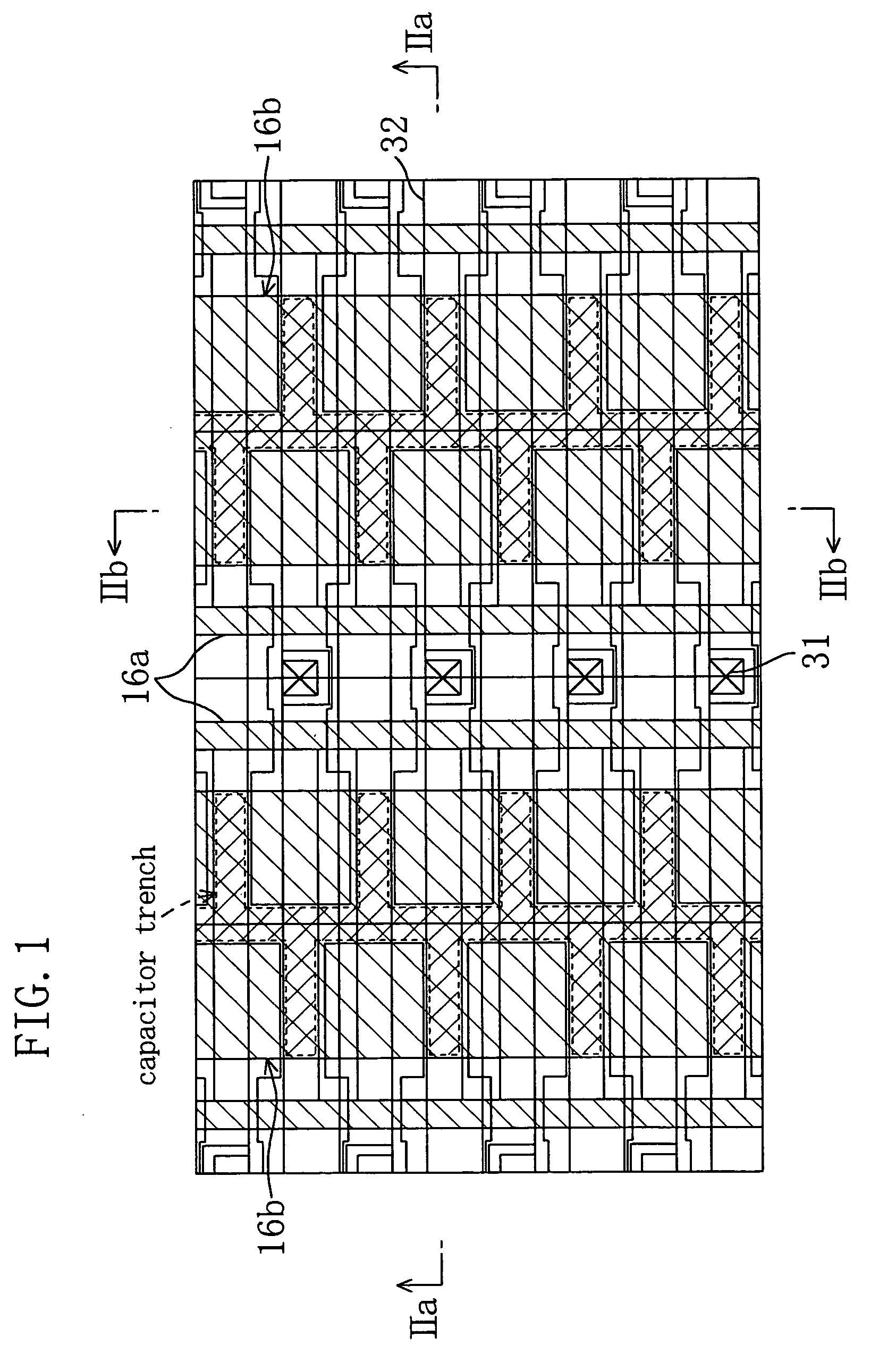

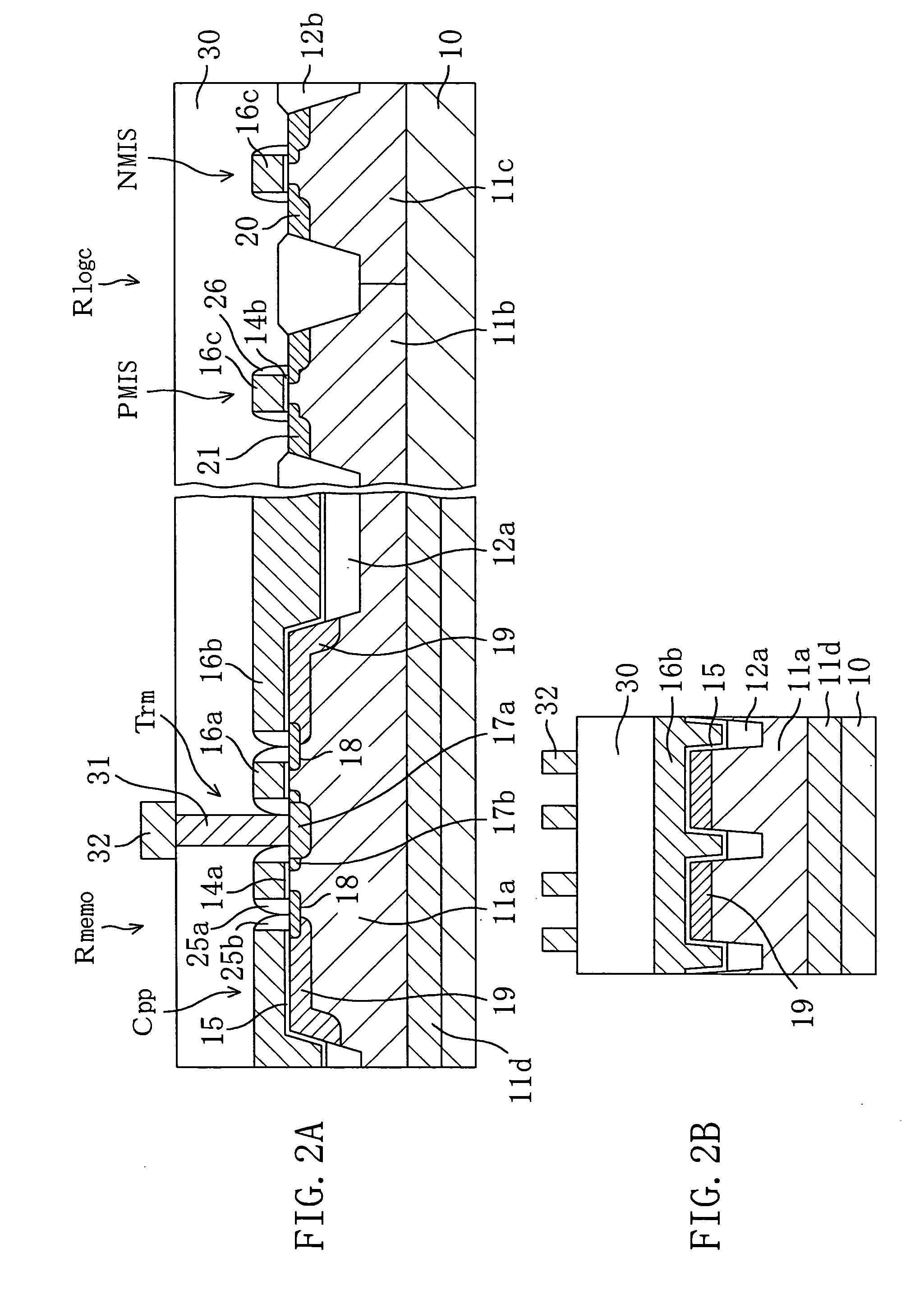

Semiconductor device and its manufacturing method

InactiveUS20040137667A1High pattern accuracyImprove flatnessTransistorSolid-state devicesCapacitanceDielectric

A memory cell transistor and a planar capacitor are provided in a memory region, and both transistors of a CMOS device are provided in a logic circuit region. A capacitance dielectric 15 and a plate electrode 16b of the planar capacitor are provided over a trench shared with a shallow trench isolation 12a, and the upper part of the trench is filled with the capacitance dielectric 15 and the plate electrode 16b. An n-type diffusion layer 19 that is a storage node is formed, with an end region thereof extending along one side of the upper part of the trench, to a region of the substrate overlapping with the shallow trench isolation 12a. The area of a part of the substrate functioning as a capacitor can be increased without increasing the substrate area.

Owner:GK BRIDGE 1

SOI CMOS compatible multiplanar capacitor

An isolated shallow trench isolation portion is formed in a top semiconductor portion of a semiconductor-on-insulator substrate along with a shallow trench isolation structure. A trench in the shape of a ring is formed around a doped top semiconductor portion and filled with a conductive material such as doped polysilicon. The isolated shallow trench isolation portion and the portion of a buried insulator layer bounded by a ring of the conductive material are etched to form a cavity. A capacitor dielectric is formed on exposed semiconductor surfaces within the cavity and above the doped top semiconductor portion. A conductive material portion formed in the trench and above the doped top semiconductor portion constitutes an inner electrode of a capacitor, while the ring of the conductive material, the doped top semiconductor portion, and a portion of a handle substrate abutting the capacitor dielectric constitute a second electrode.

Owner:TWITTER INC

Compositions with polymers for advanced materials

InactiveUS20050154105A1Fixed capacitor dielectricPrinted resistor incorporationElectrical conductorAdhesive

A composition comprising: a polymer with a glass transition temperature greater than 250° C. and a water absorption of 2% or less; one or more metals or metal compounds; and an organic solvent. The polymer can optionally include sites that can crosslink with one or more crosslinking agents. The compositions can be used to produce electronic components such as resistors, discrete or planar capacitors, conductive adhesives and electrical and thermal conductors. The invention is also directed to a composition comprising a polymer with a glass transition temperature greater than 250° C. and a water absorption of 2% or less, and an organic solvent. These compositions can also be used in a number of electronic applications such as an encapsulant and as an integrated circuit packaging material.

Owner:EI DU PONT DE NEMOURS & CO