Patents

Literature

99results about How to "Reduce step height" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

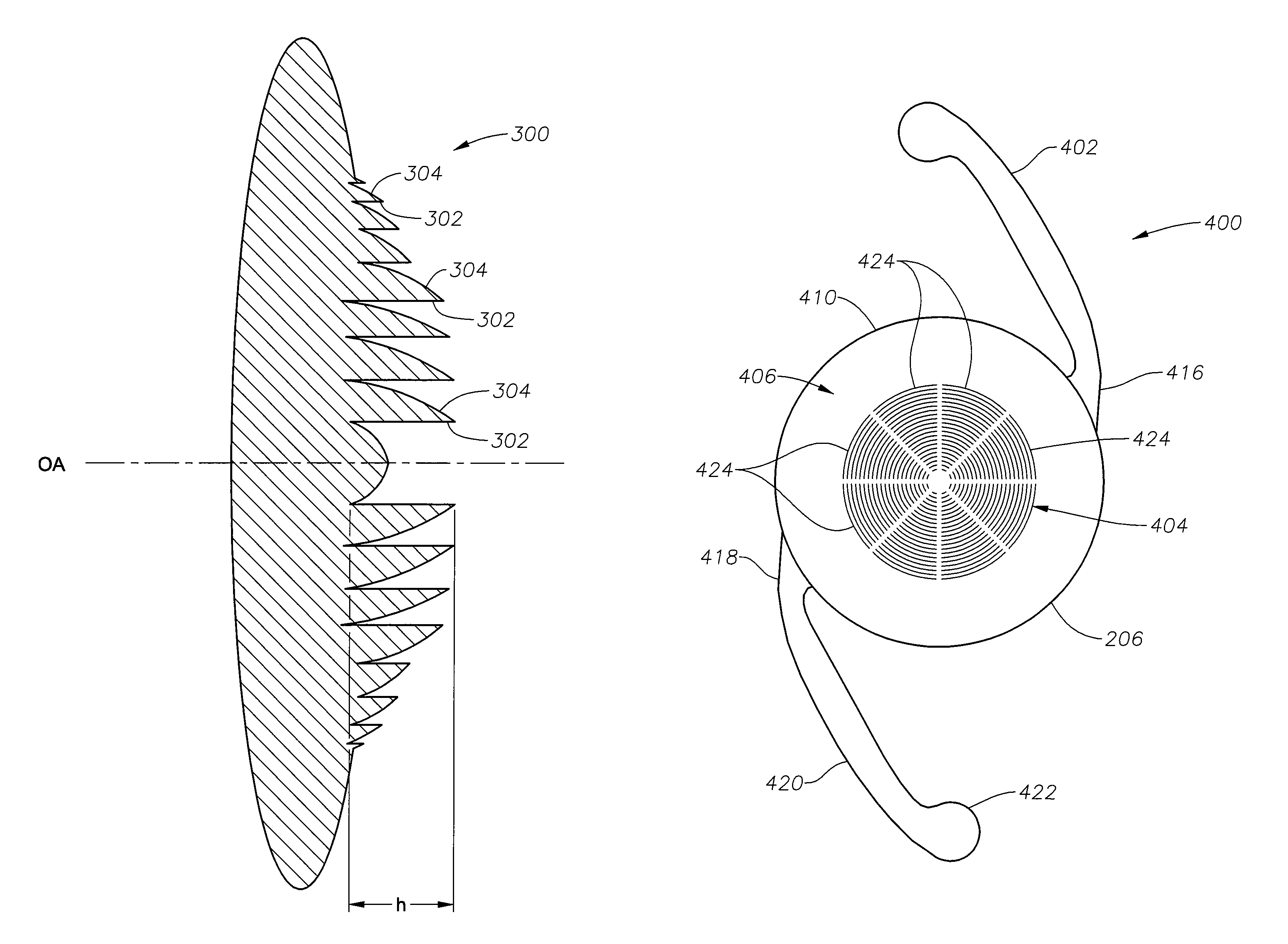

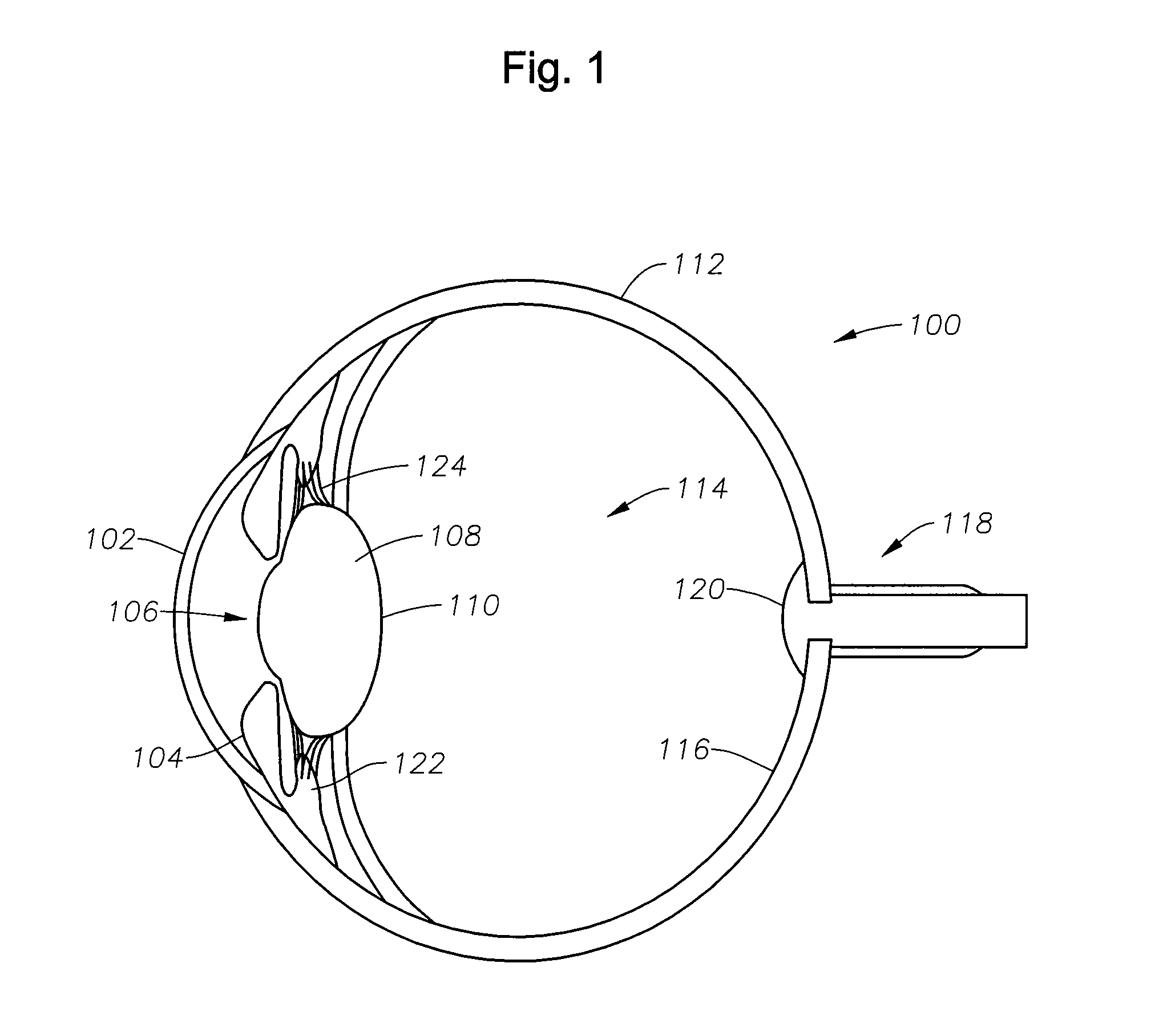

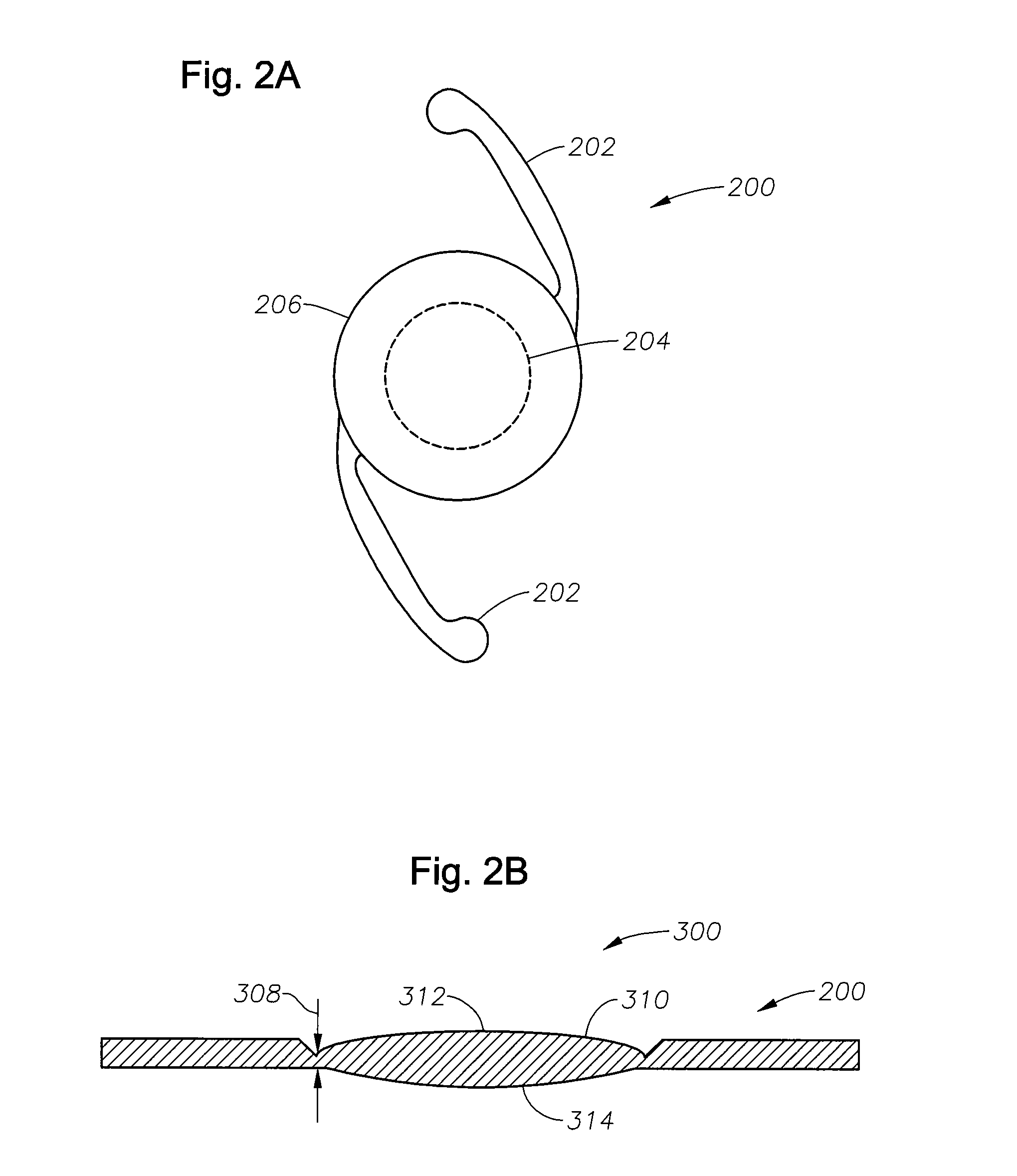

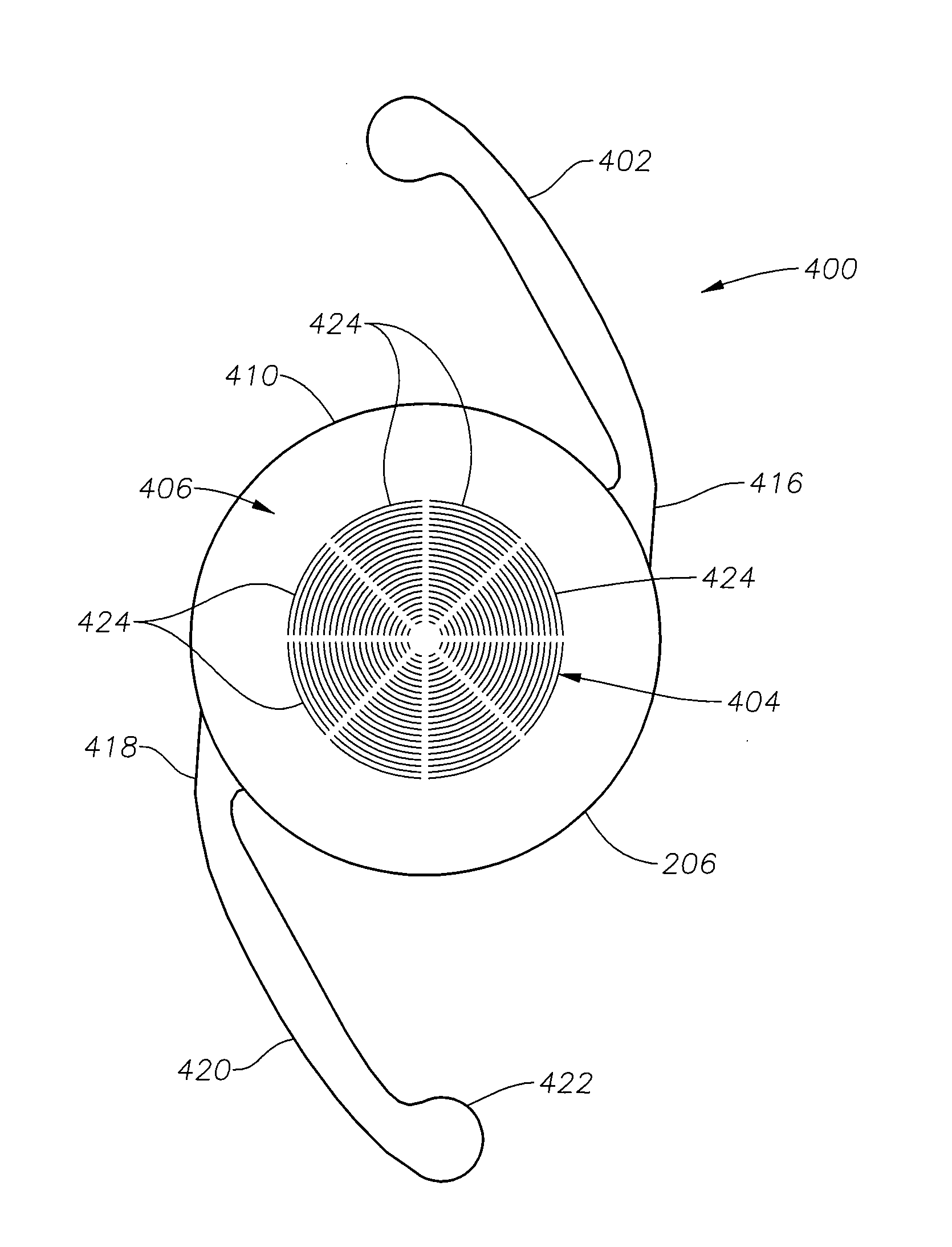

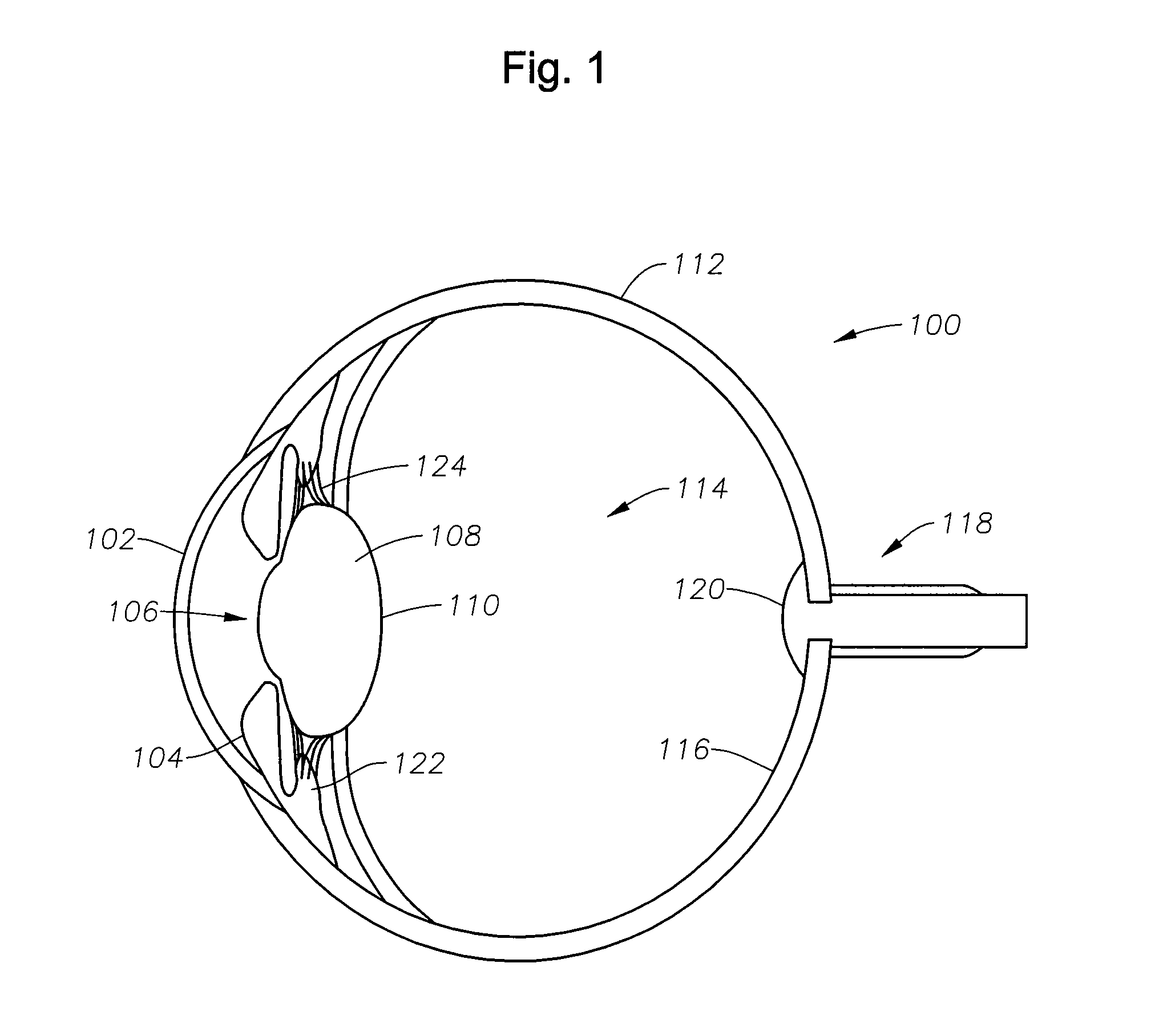

Radially segmented apodized diffractive multifocal design for ocular implant

ActiveUS20100161048A1Reduce step heightIncrease depth of focusIntraocular lensMedicineOptical energy

A radially segmented apodized diffractive multifocal IOL for ocular implant is provided. The ocular implant can comprise a radially segmented apodized diffractive multifocal intraocular lens optic and a number of haptics. The radially segmented apodized diffractive multifocal IOL may pass optical energy in both photopic and mesopic conditions. The radially segmented apodized diffractive multifocal IOL includes a number of radially segmented apodization zones, each radially segmented apodization zones having a unique focal length. The haptics mechanically couple to the apodized diffractive multifocal IOL optic in order to position and secure the apodized diffractive multifocal IOL within the eye. The radially segmented apodized diffractive multifocal IOL may include both a diffractive region and a refractive region.

Owner:ALCON INC

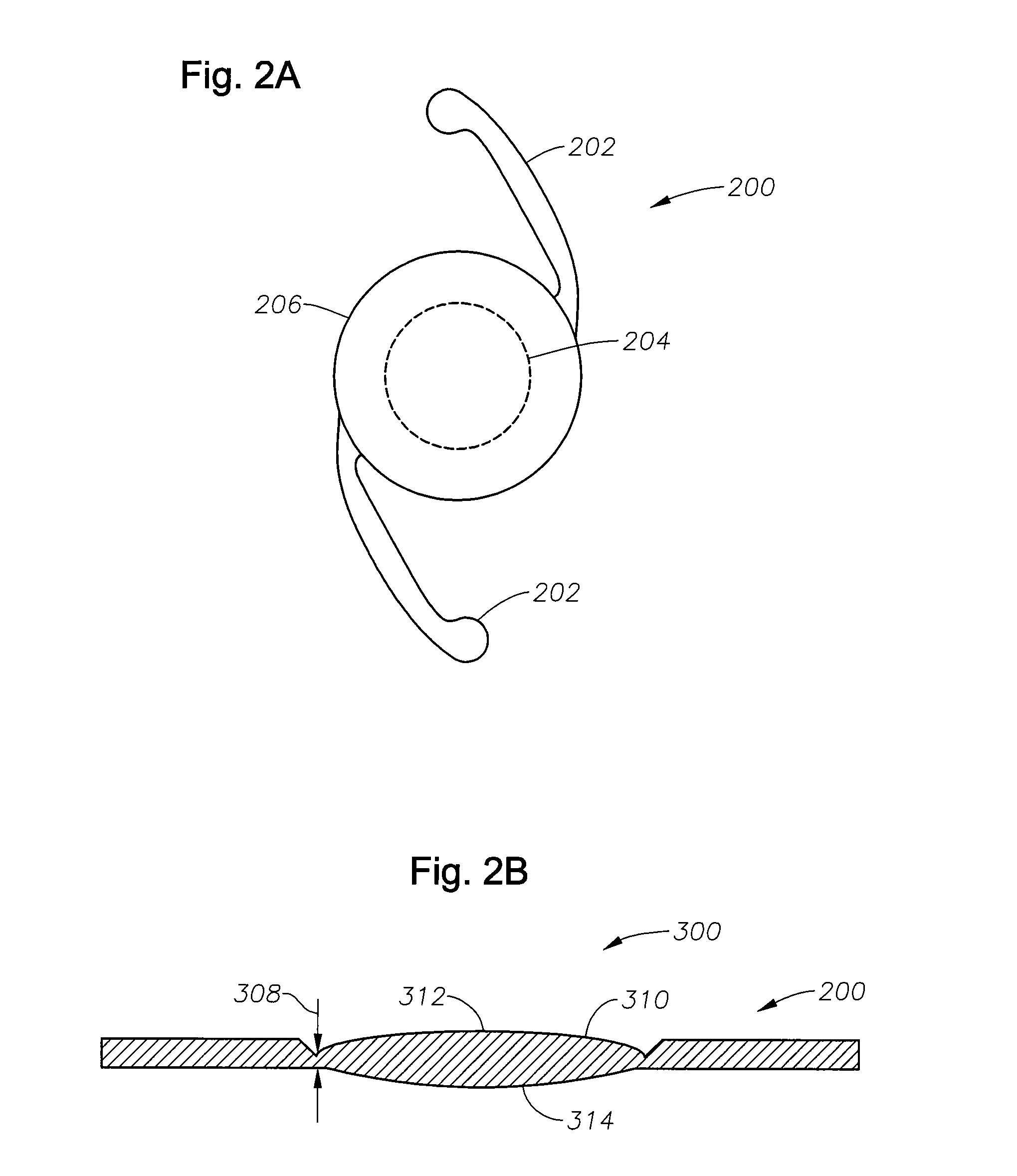

Composite gate structure in an integrated circuit

ActiveUS7183596B2Improve performanceStep heightTransistorSolid-state devicesGate dielectricWork function

An integrated circuit having composite gate structures and a method of forming the same are provided. The integrated circuit includes a first MOS device, a second MOS device and a third MOS device. The gate stack of the first MOS device includes a high-k gate dielectric and a first metal gate on the high-k gate dielectric. The gate stack of the second MOS device includes a second metal gate on a high-k gate dielectric. The first metal gate and the second metal gate have different work functions. The gate stack of the third MOS device includes a silicon gate over a gate dielectric. The silicon gate is preferably formed over the gate stacks of the first MOS device and the second MOS device.

Owner:TAIWAN SEMICON MFG CO LTD

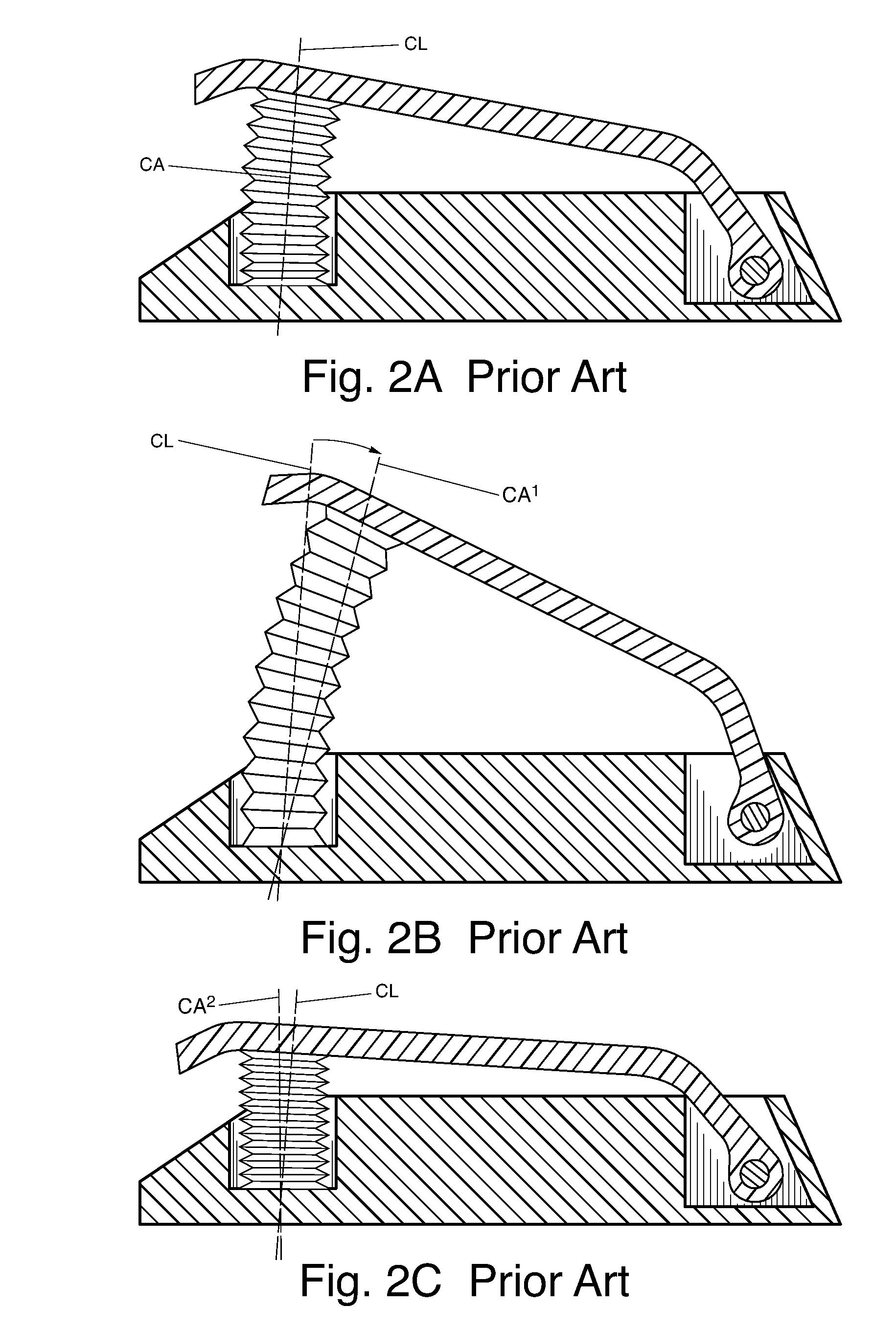

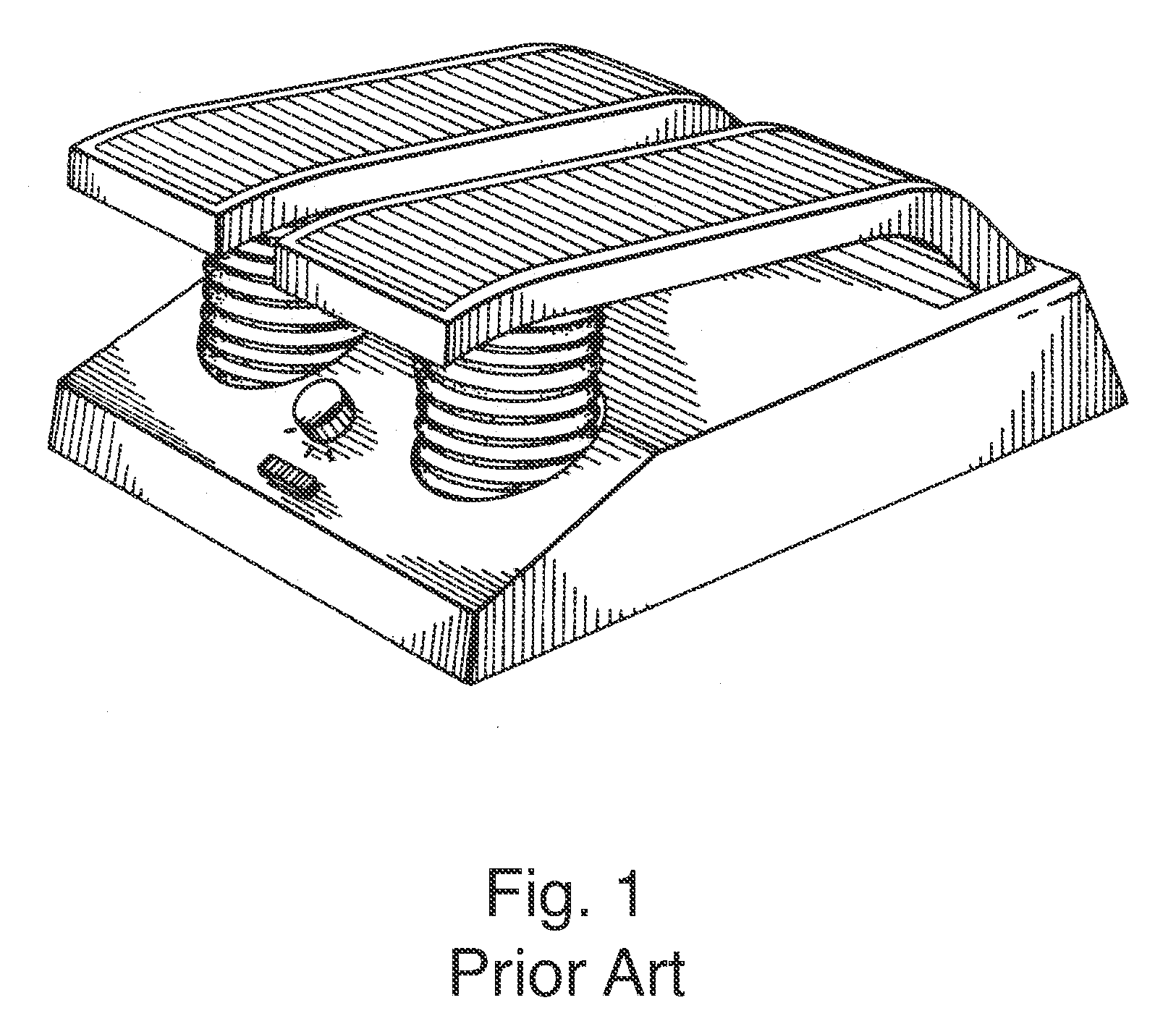

Low profile acoustic flooring

ActiveUS7210557B2Reduce step heightImprove the level ofBuilding roofsCeilingsLeveling mechanismEngineering

An isolator is partially but substantially recessed in an acoustic floor and a leveling mechanism at least partially recessed in the acoustic floor is connected to the acoustic isolator to adjust the height of the acoustic floor when the floor is in place.

Owner:ETS-LINDGREN

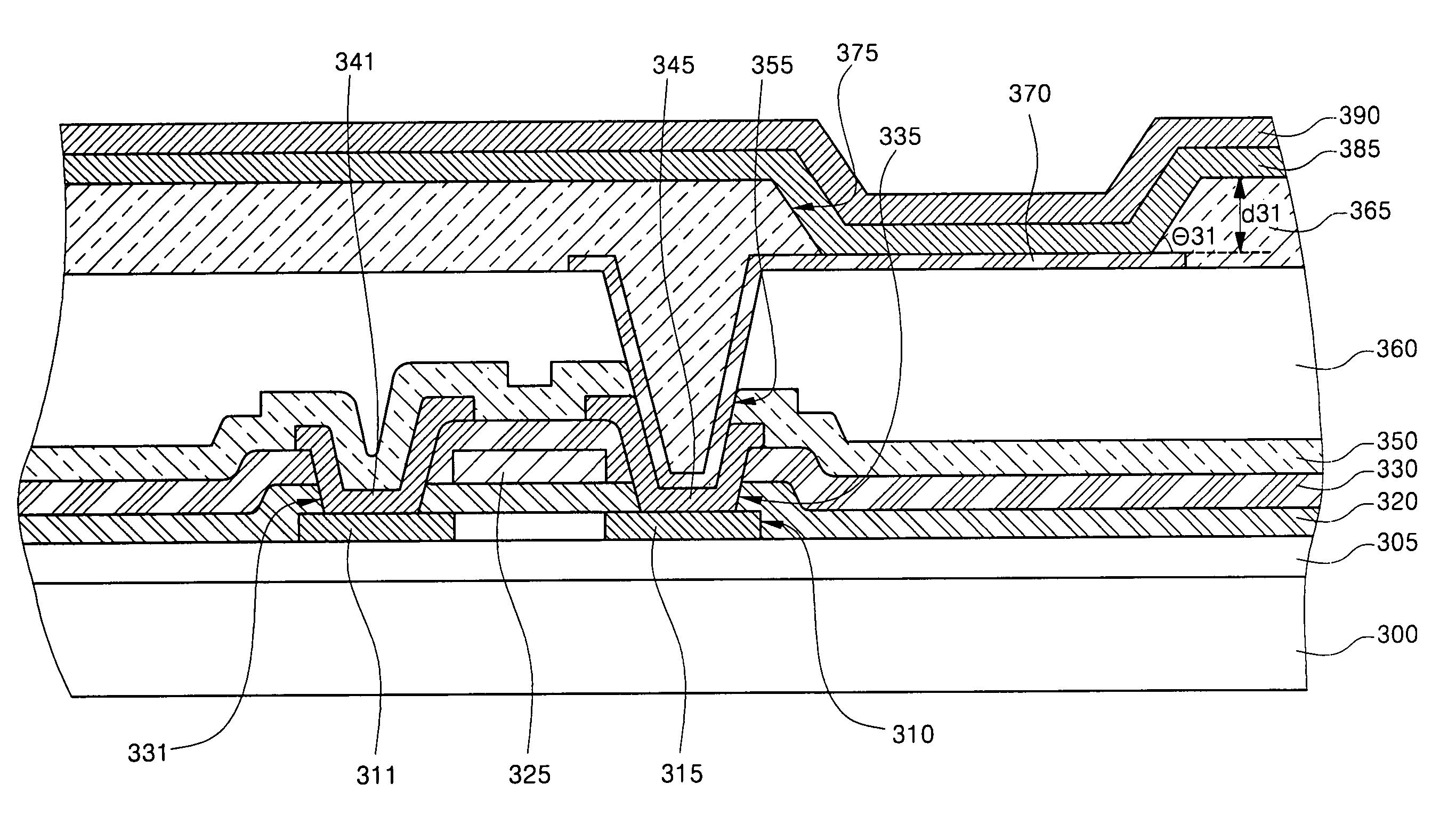

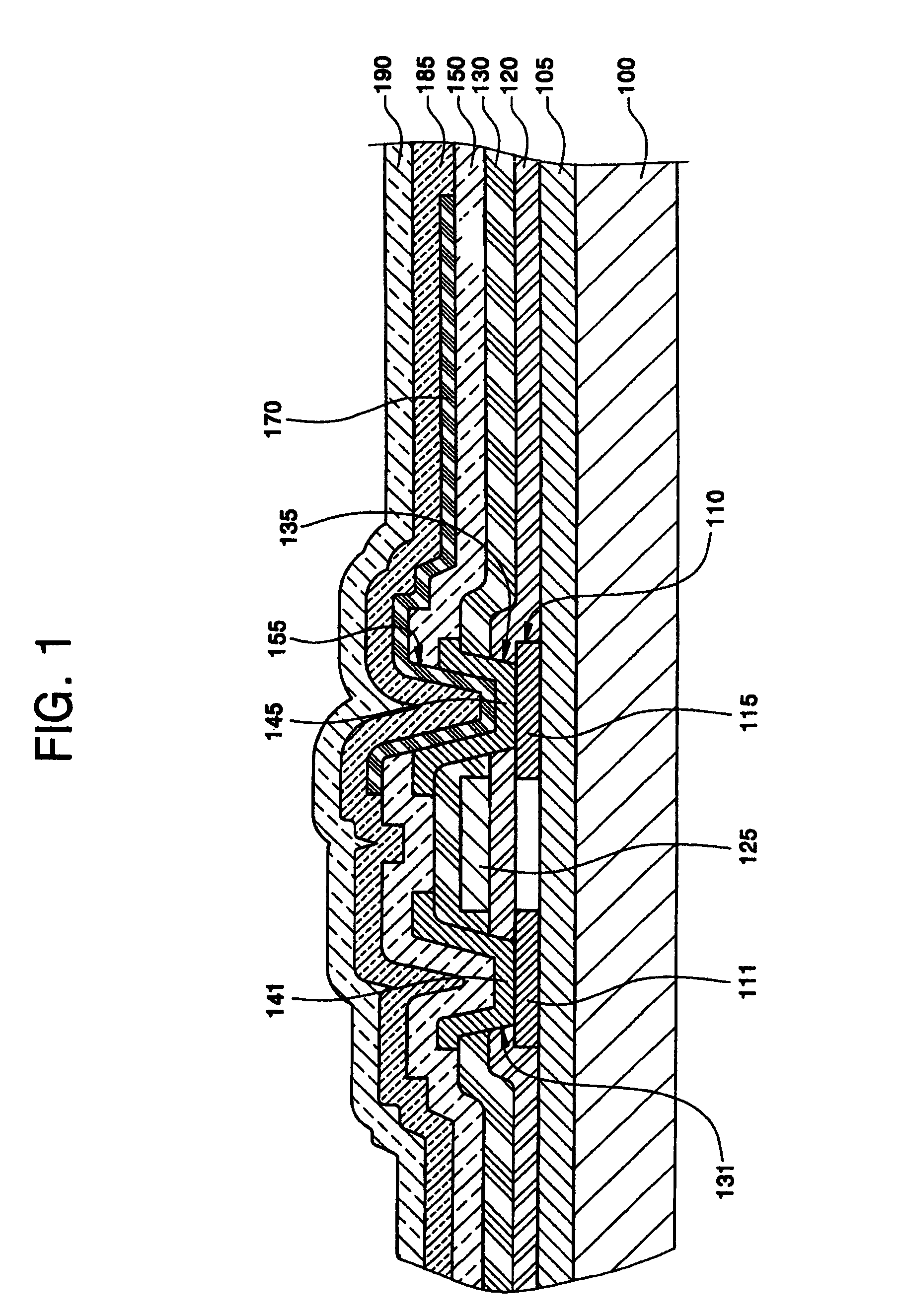

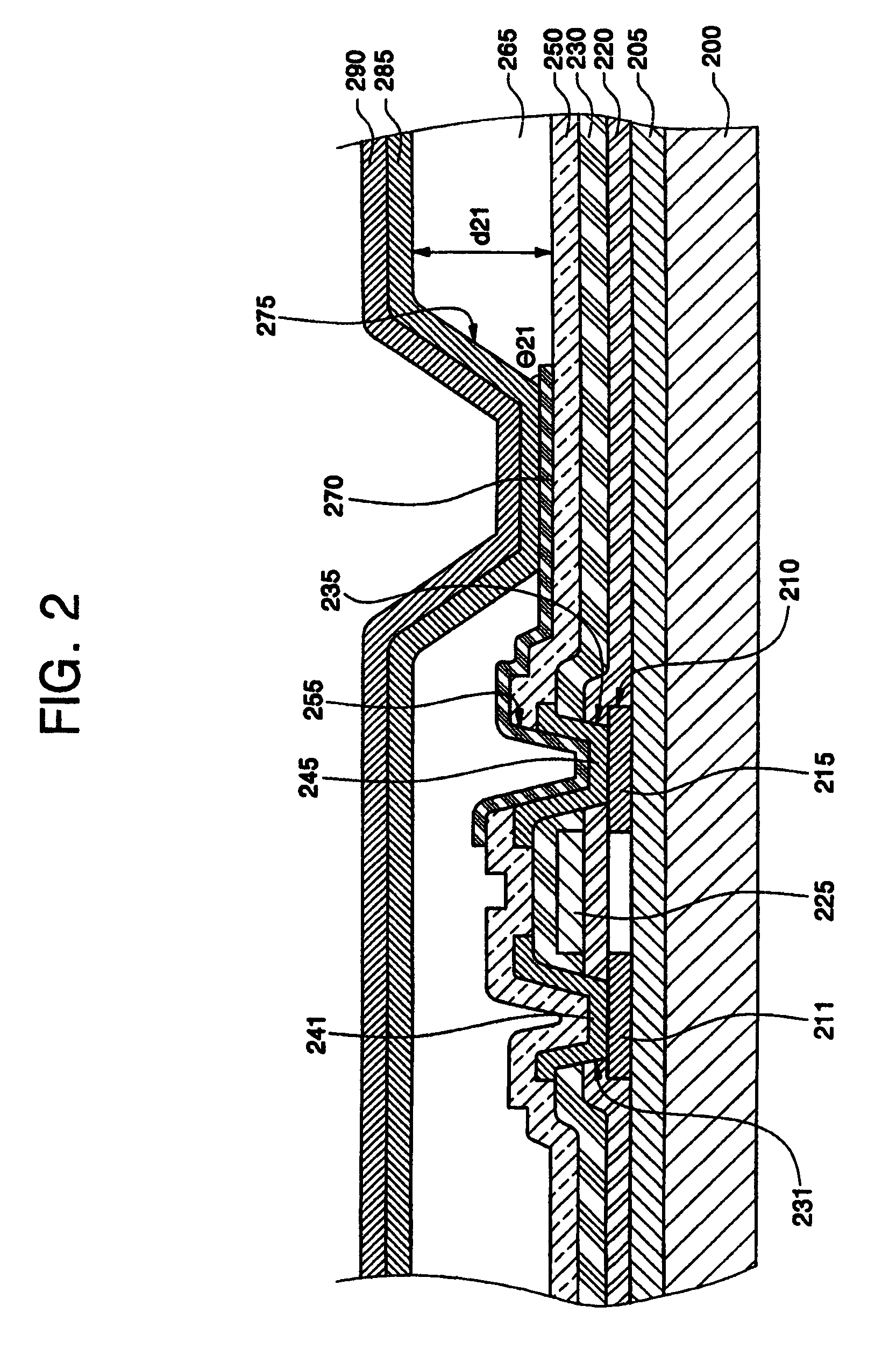

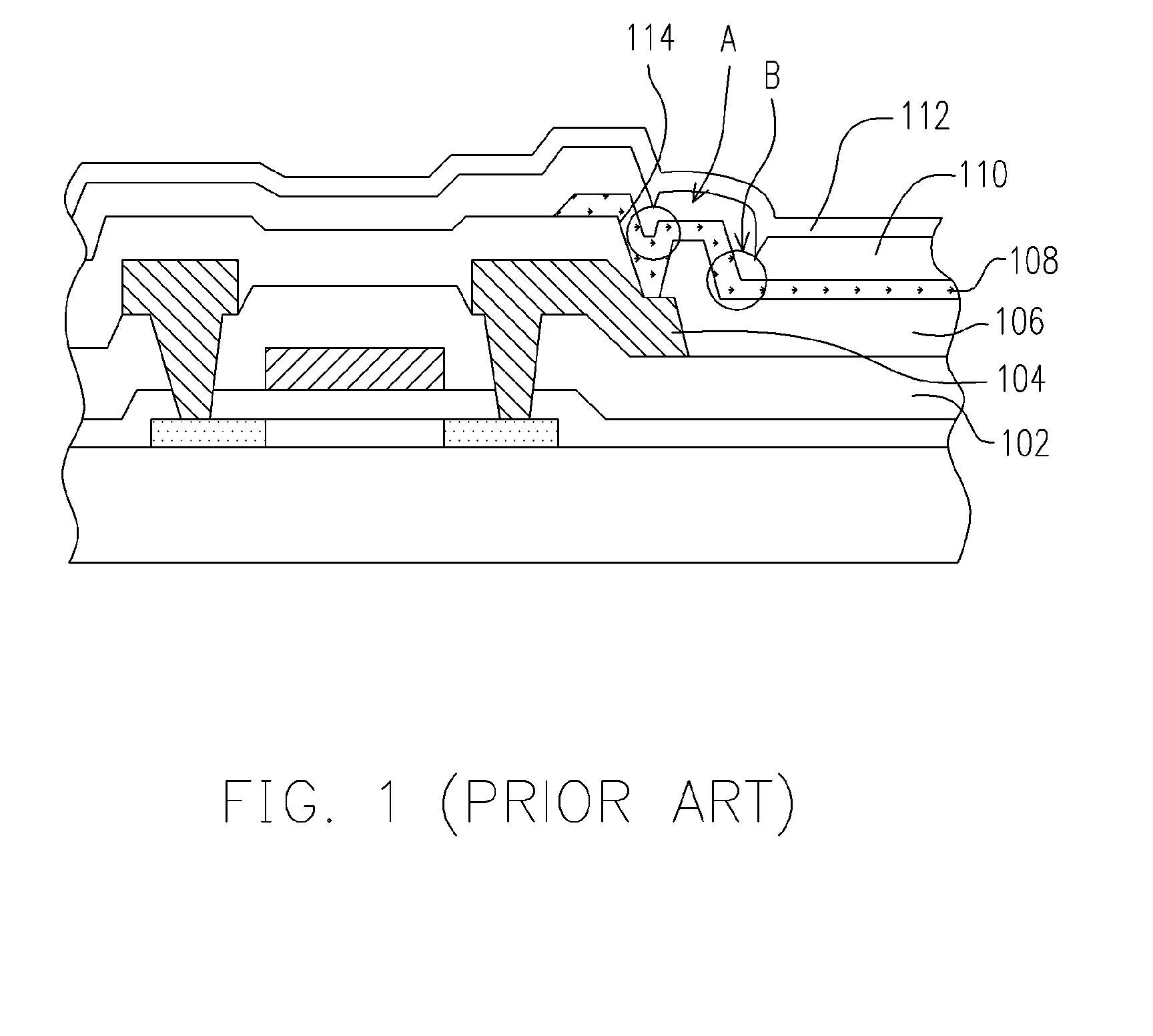

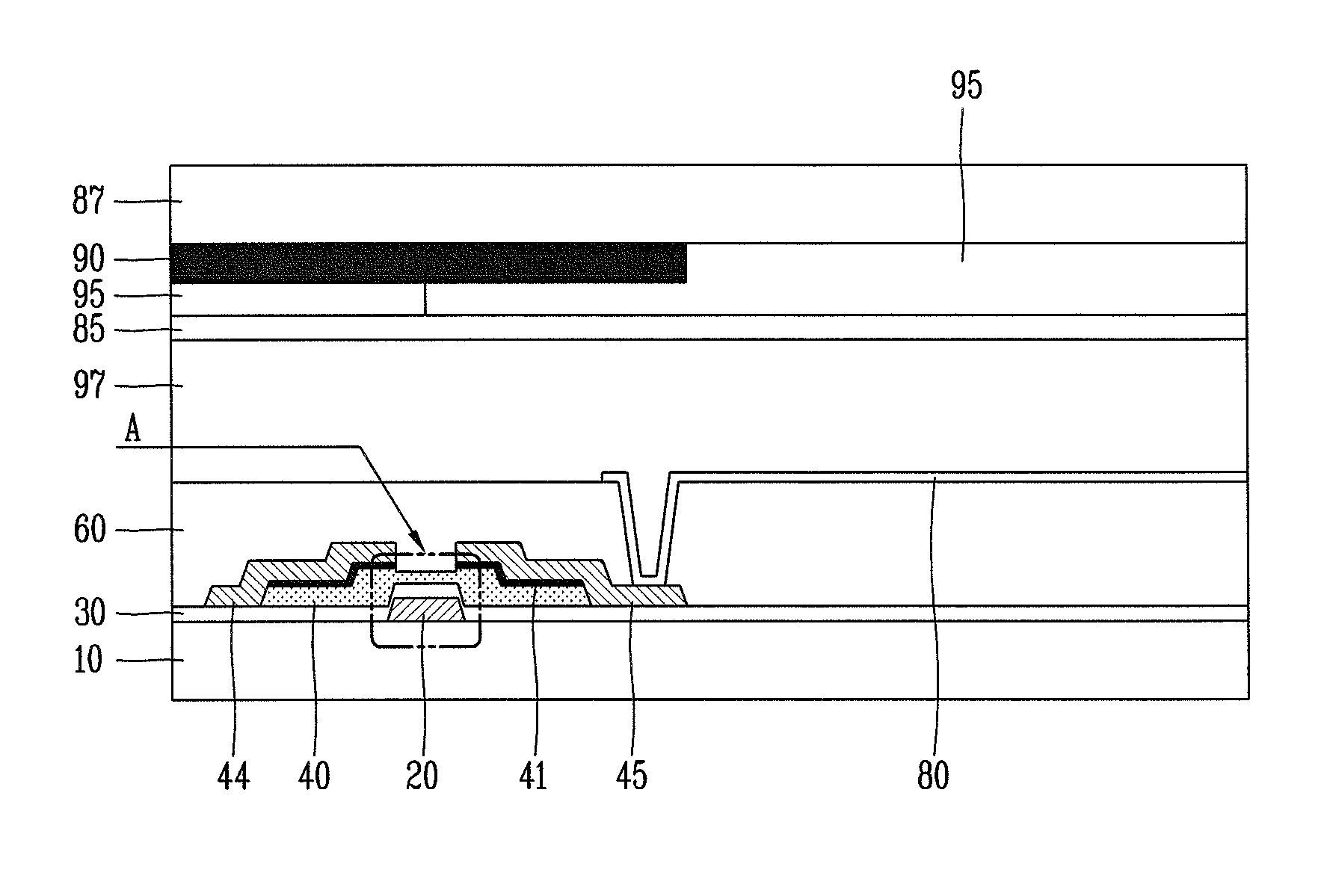

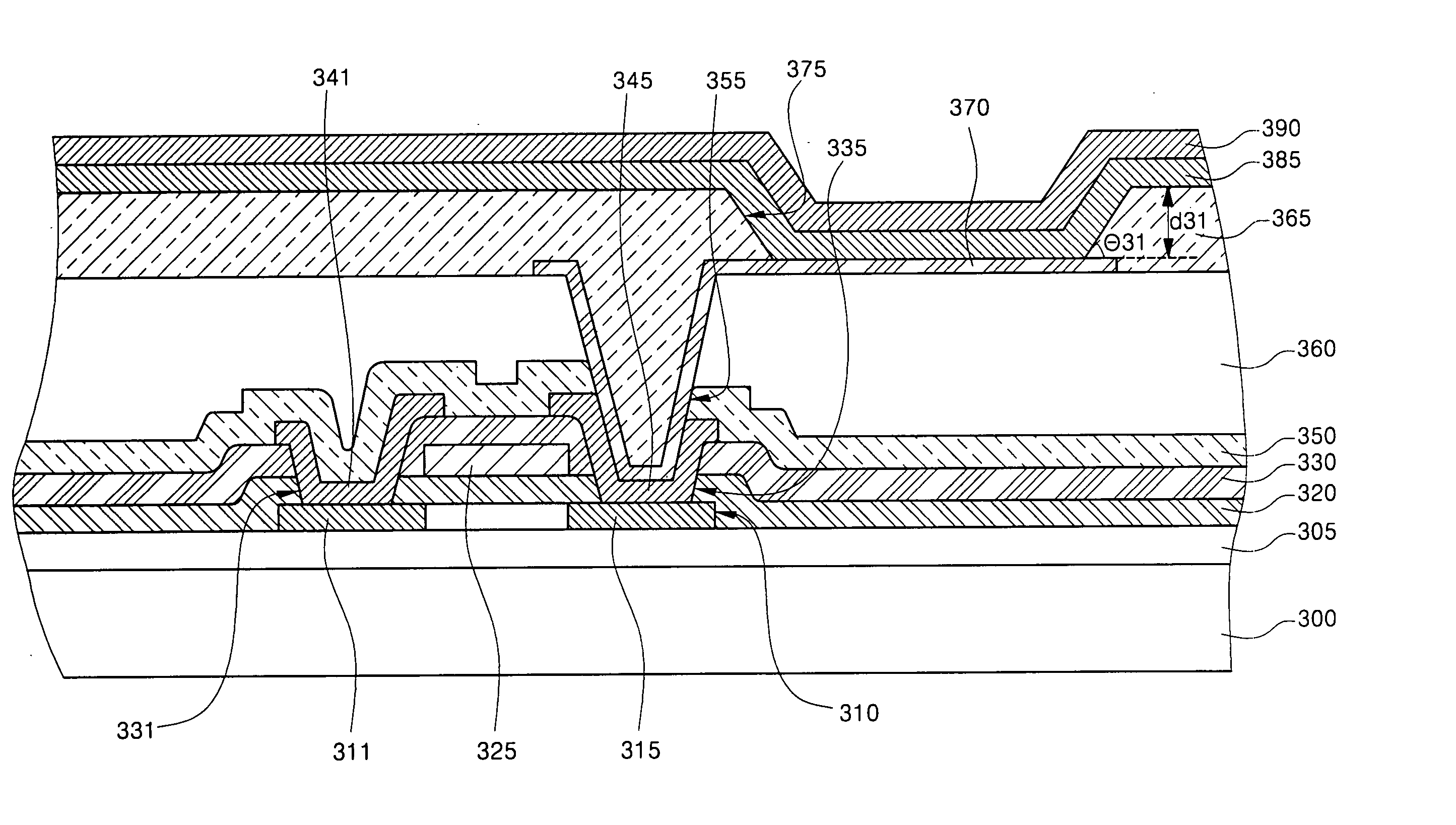

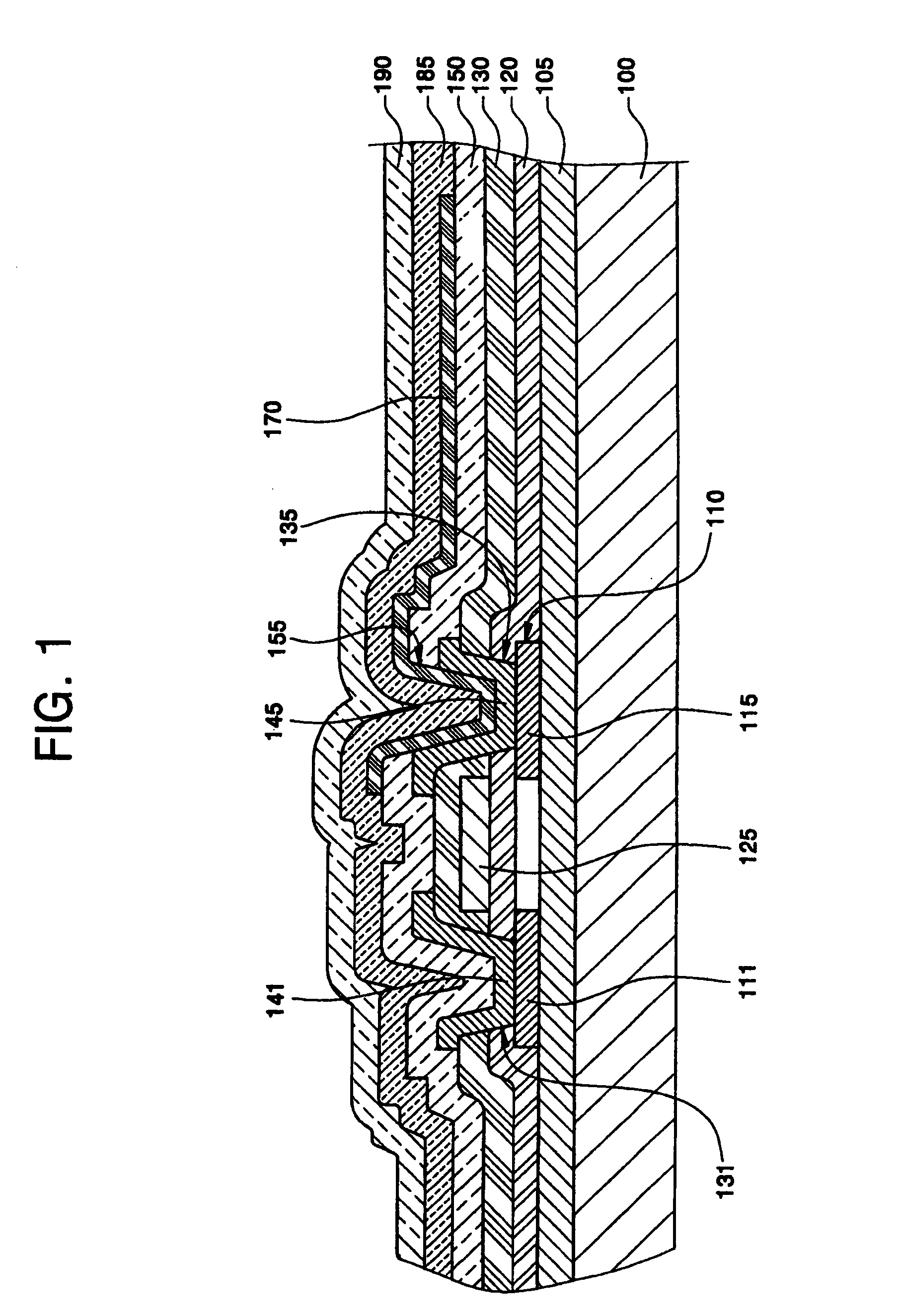

Organic light emitting display

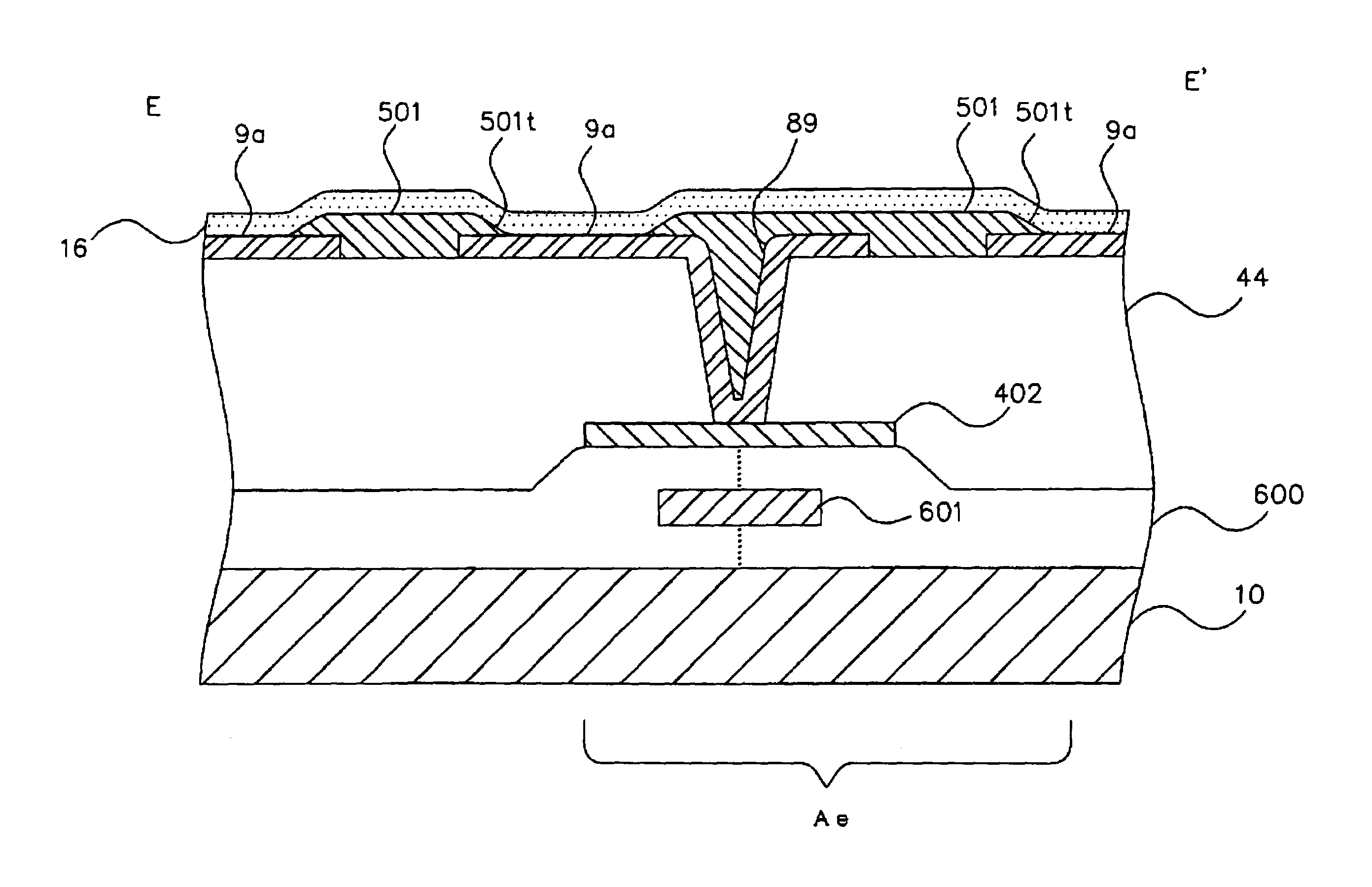

ActiveUS20050116631A1Easy to optimizeLight displayDischarge tube luminescnet screensElectroluminescent light sourcesOptoelectronicsDevice failure

An organic light emitting display which is constructed with a TFT substrate having an insulating substrate and a TFT that has at least a source electrode and a drain electrode, a lower electrode formed on the TFT substrate and connected to one of source / drain electrodes, an insulating layer having an opening that exposes a portion of the lower electrode, an organic thin film layer formed on the exposed portion of the lower electrode and the insulating layer, and an upper electrode formed on the organic thin film layer, wherein the insulating layer has a taper angle less than 40° at an edge of the opening, and a step less than or equal to 3,000 Å is formed between the lower electrode and the organic thin film layer. The organic light emitting display can prevent device failure.

Owner:SAMSUNG DISPLAY CO LTD

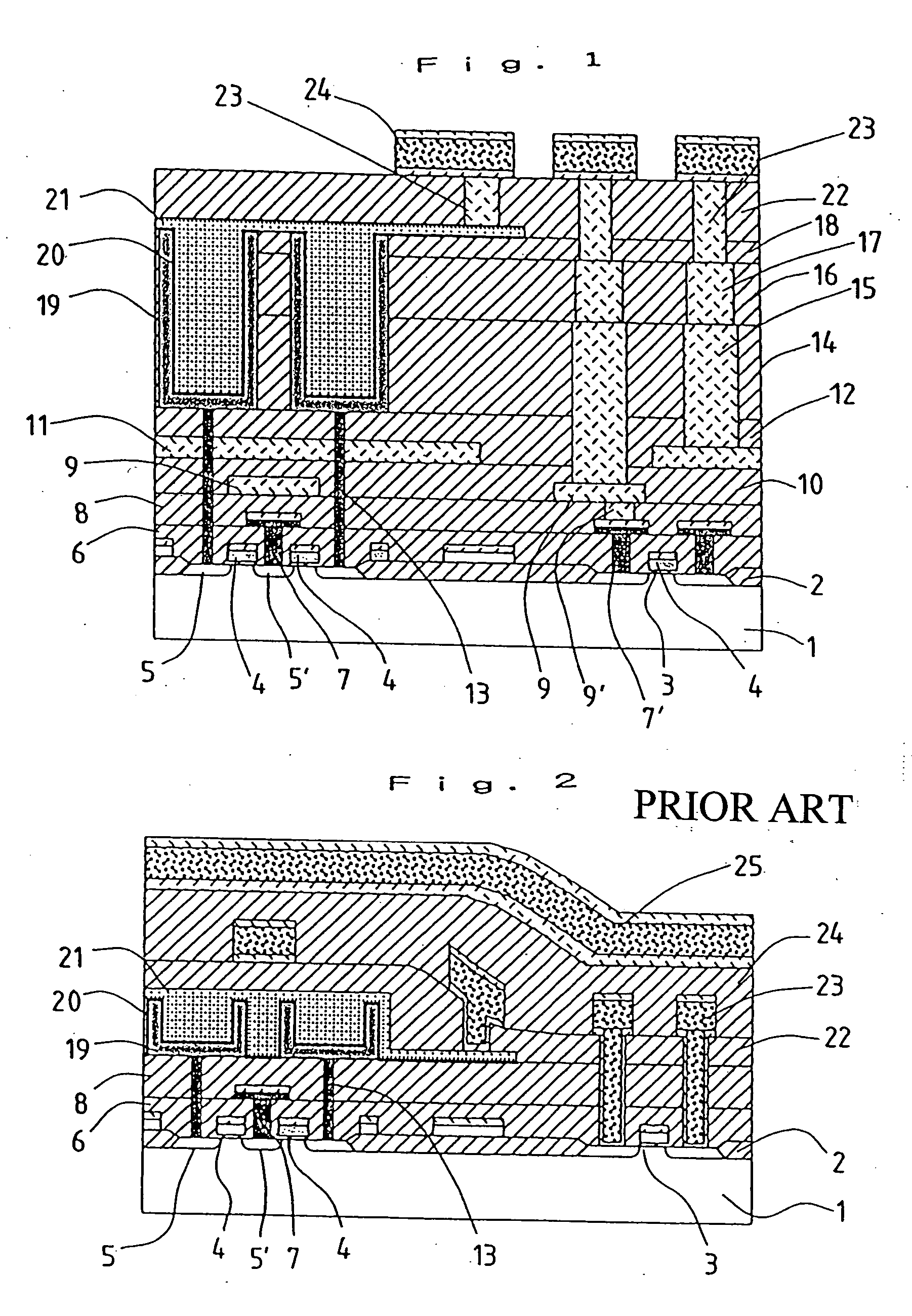

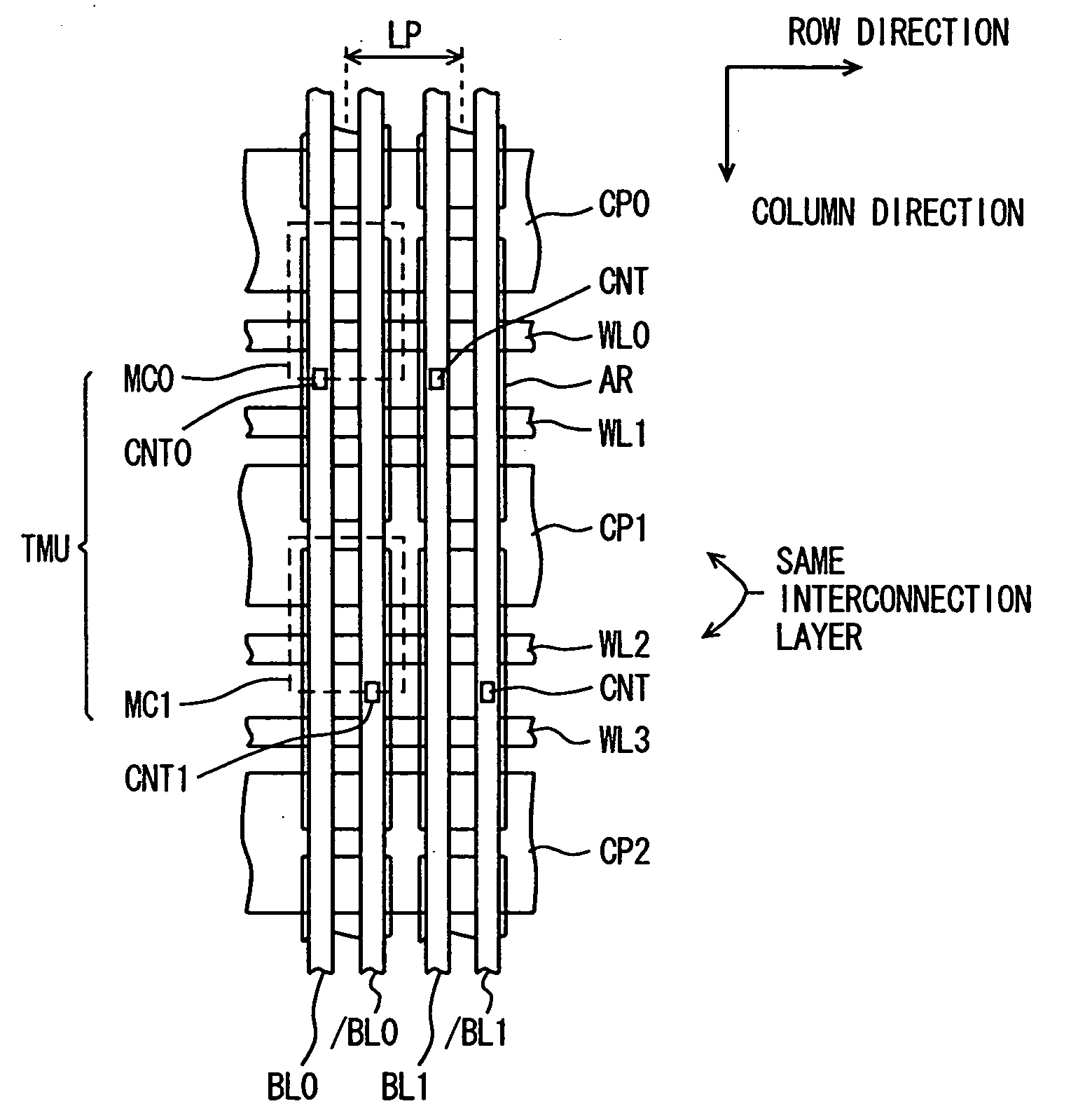

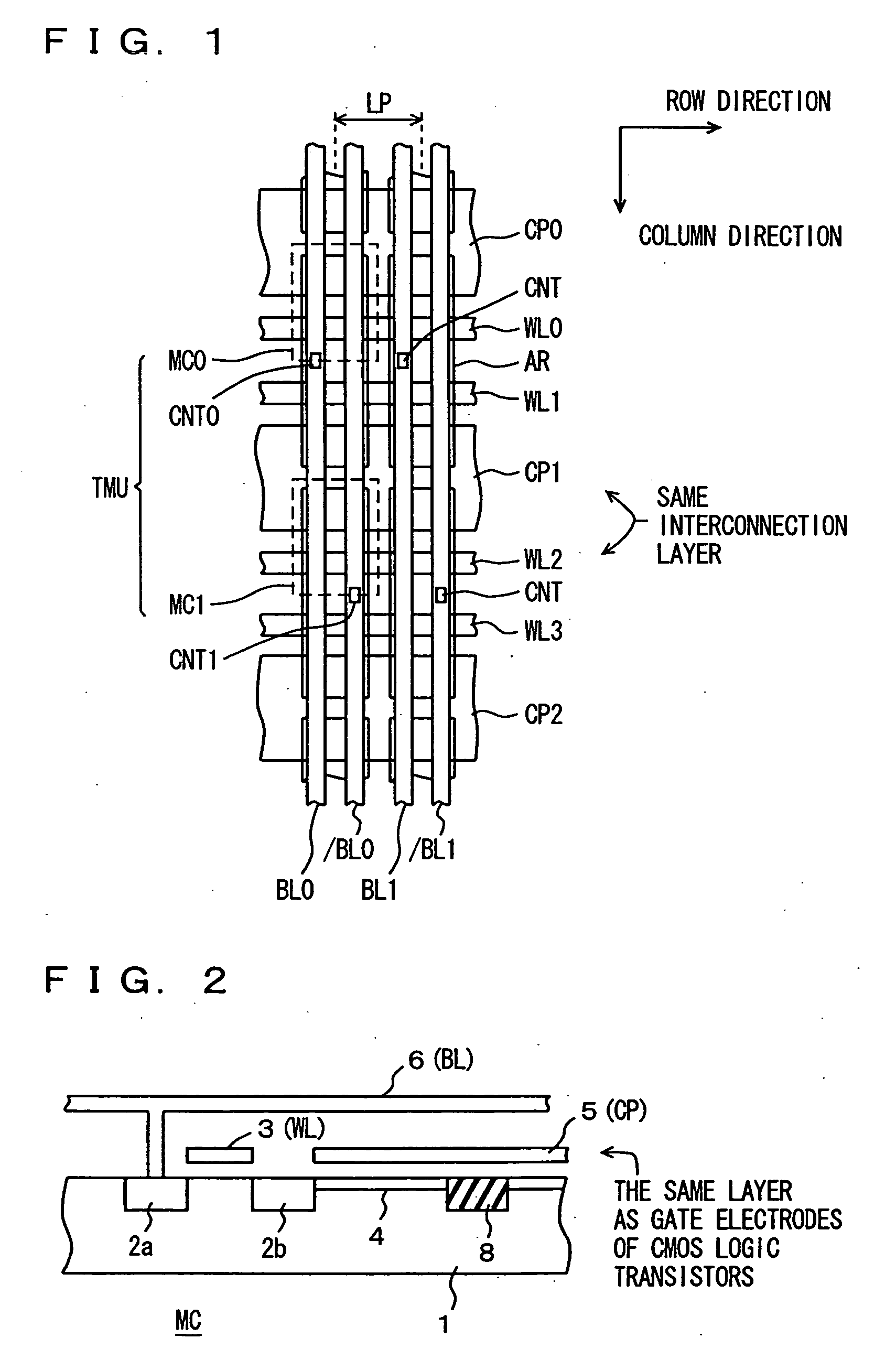

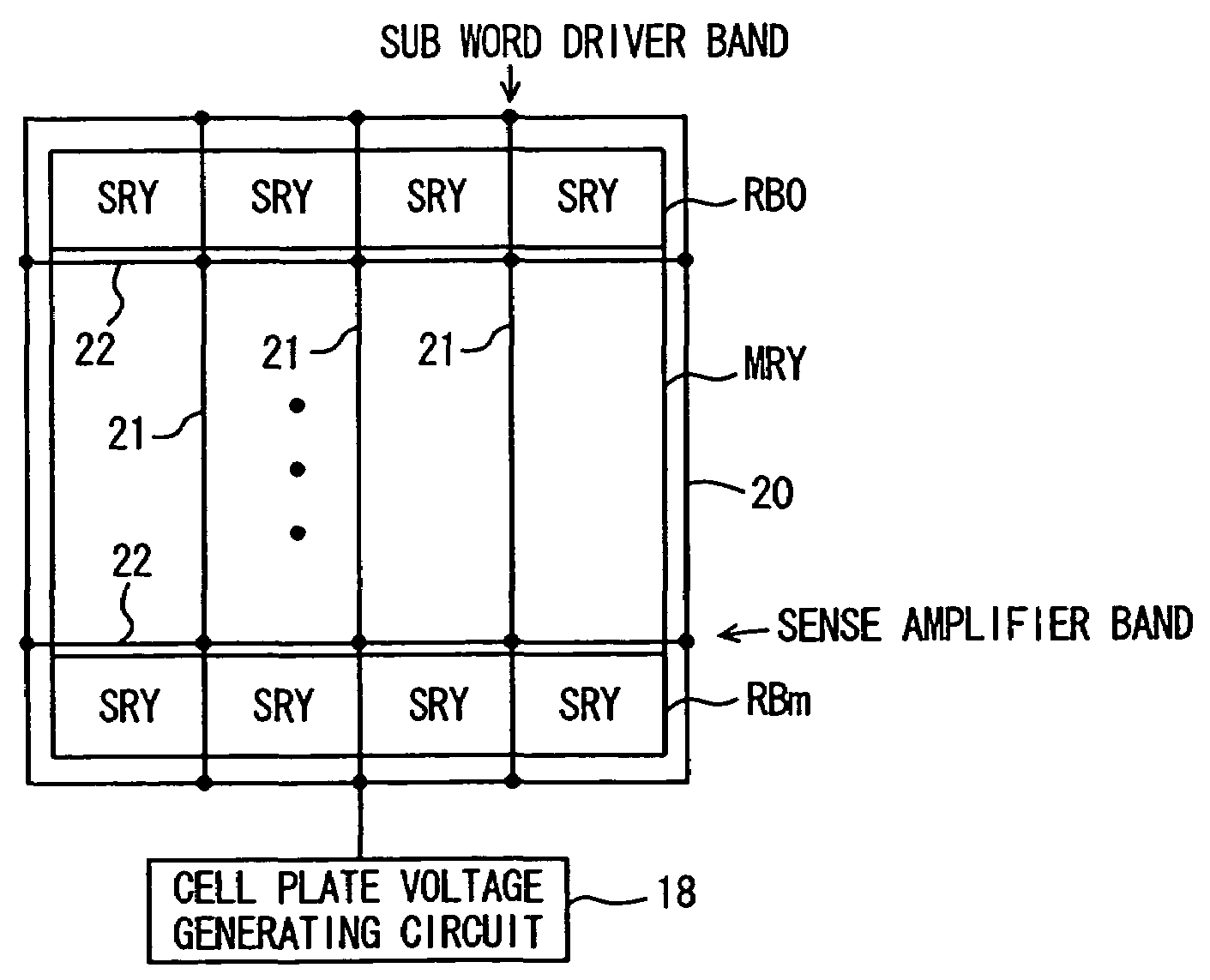

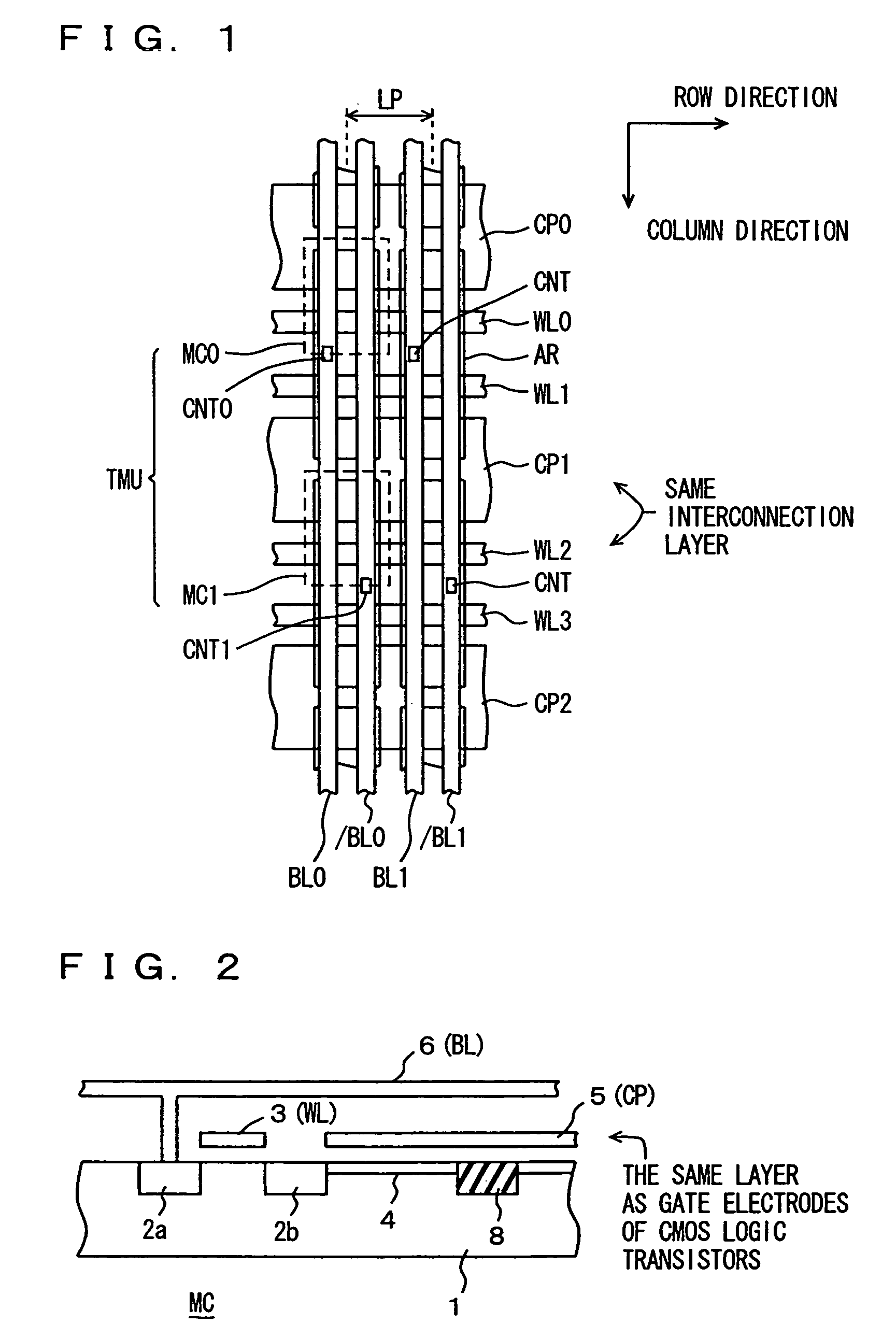

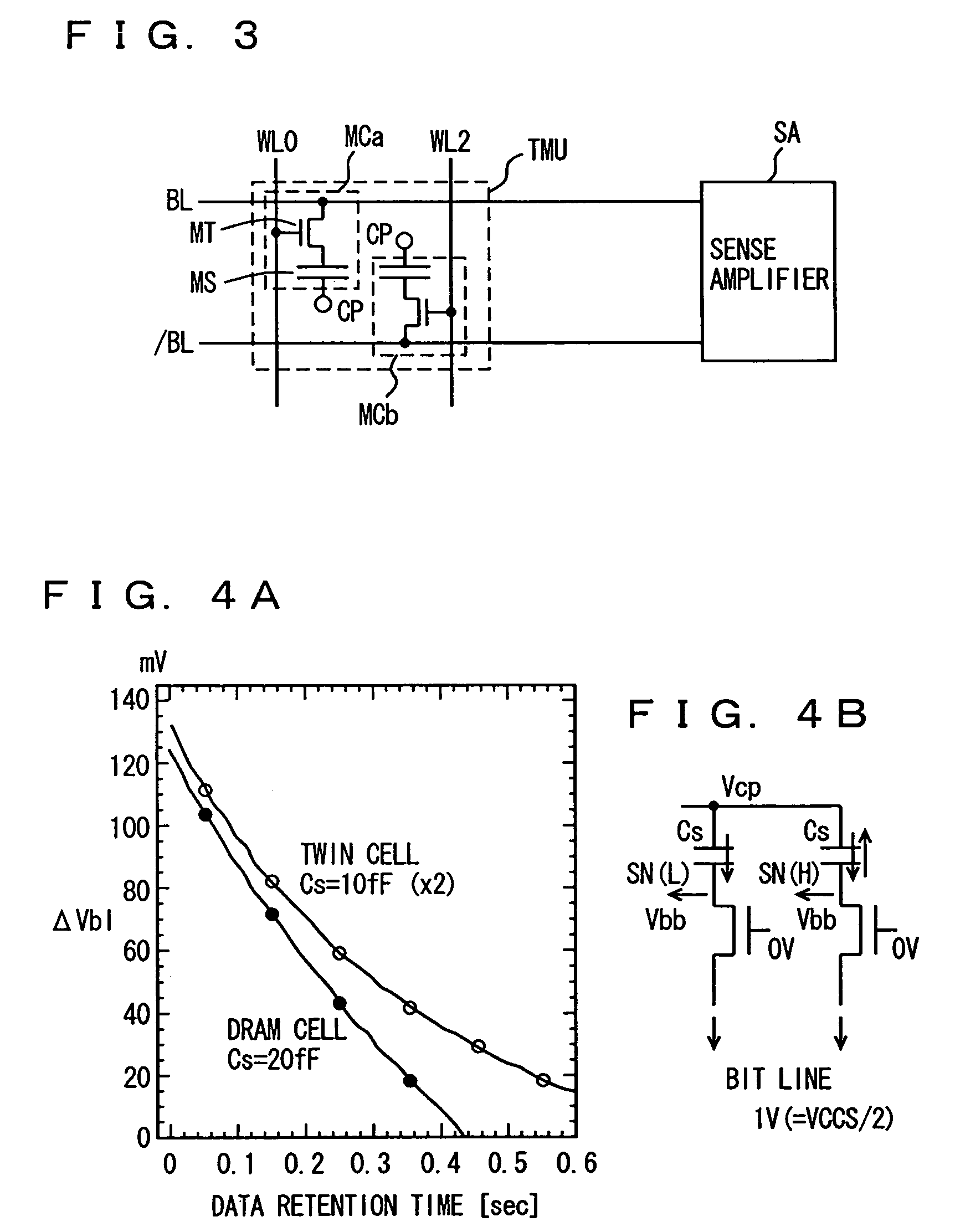

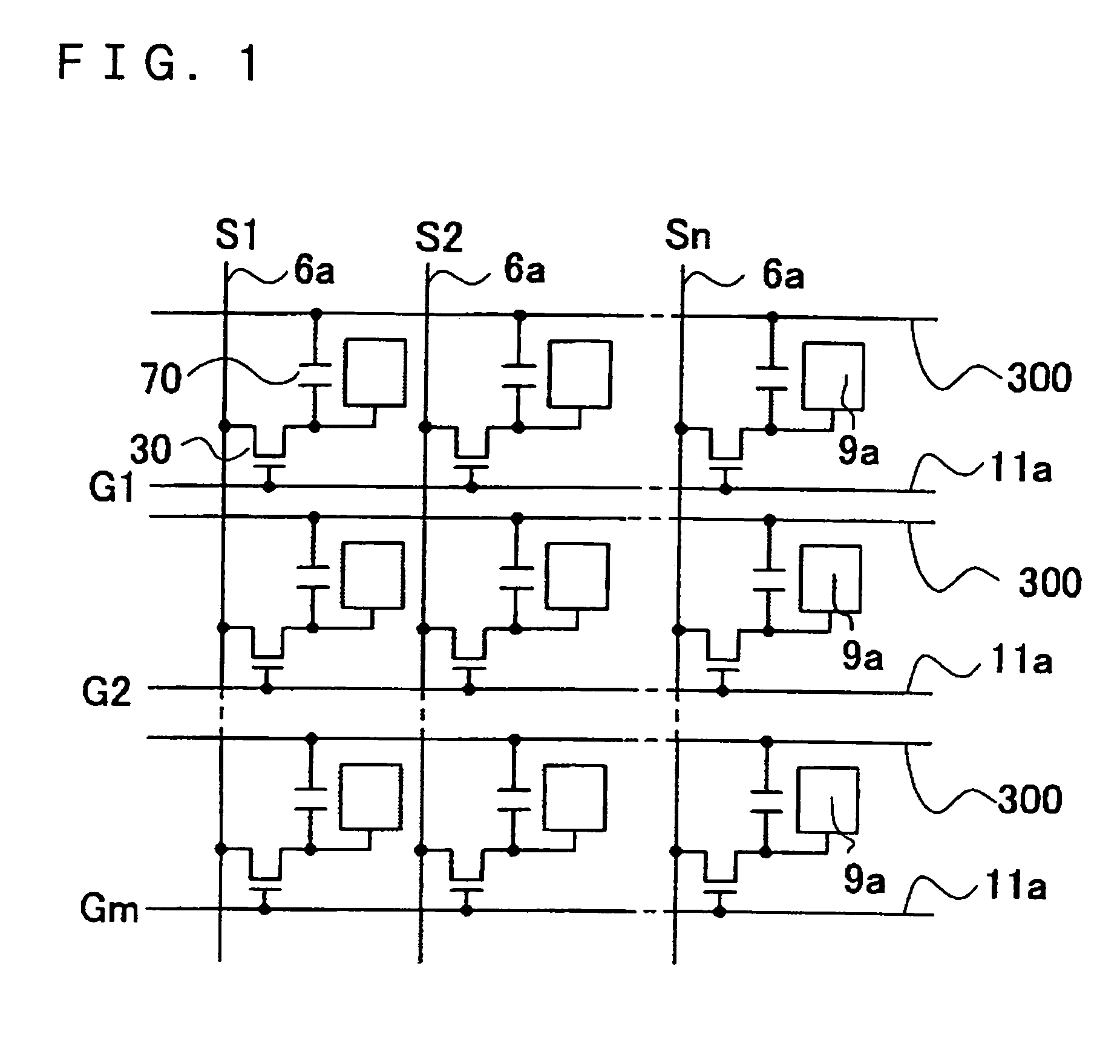

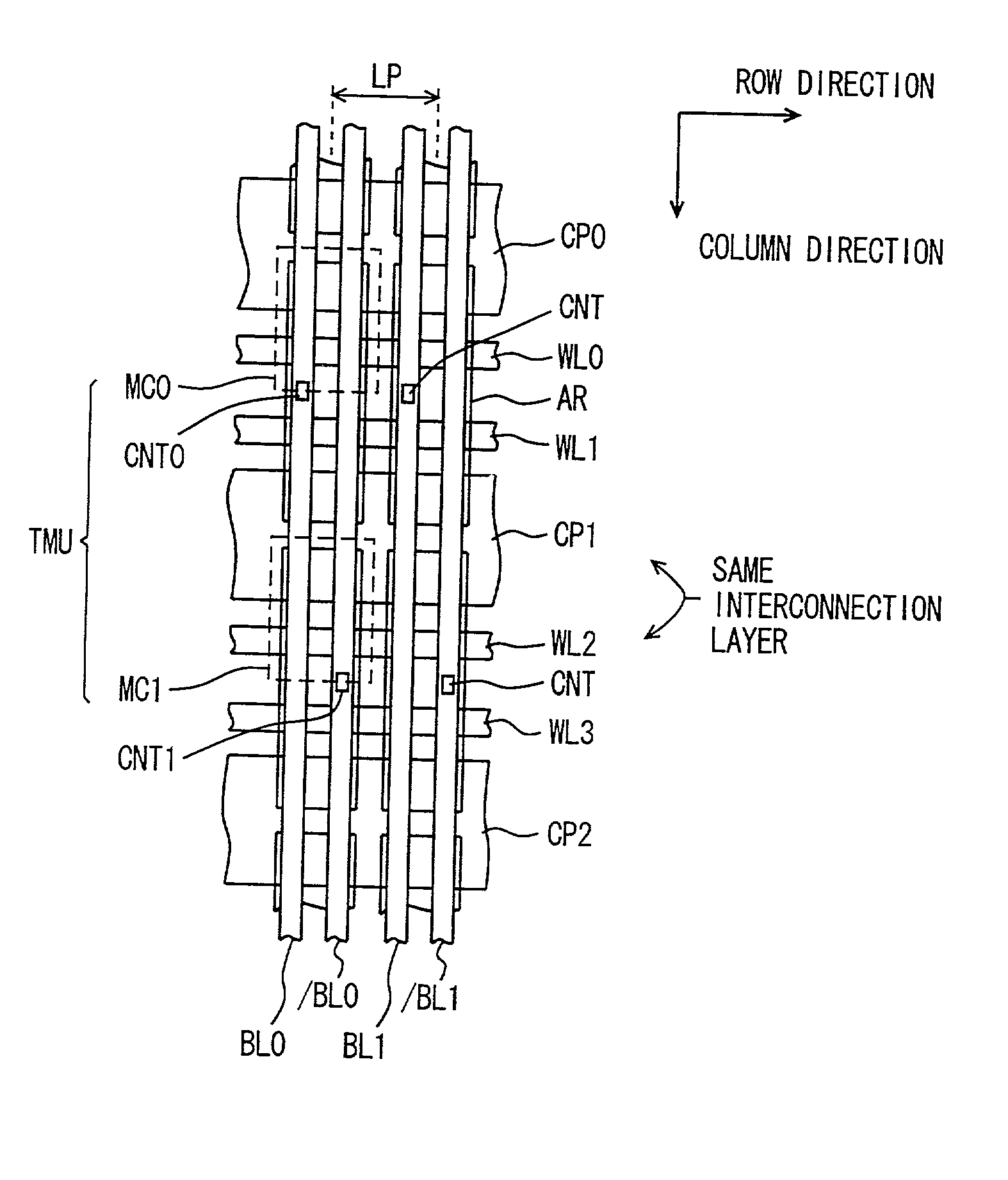

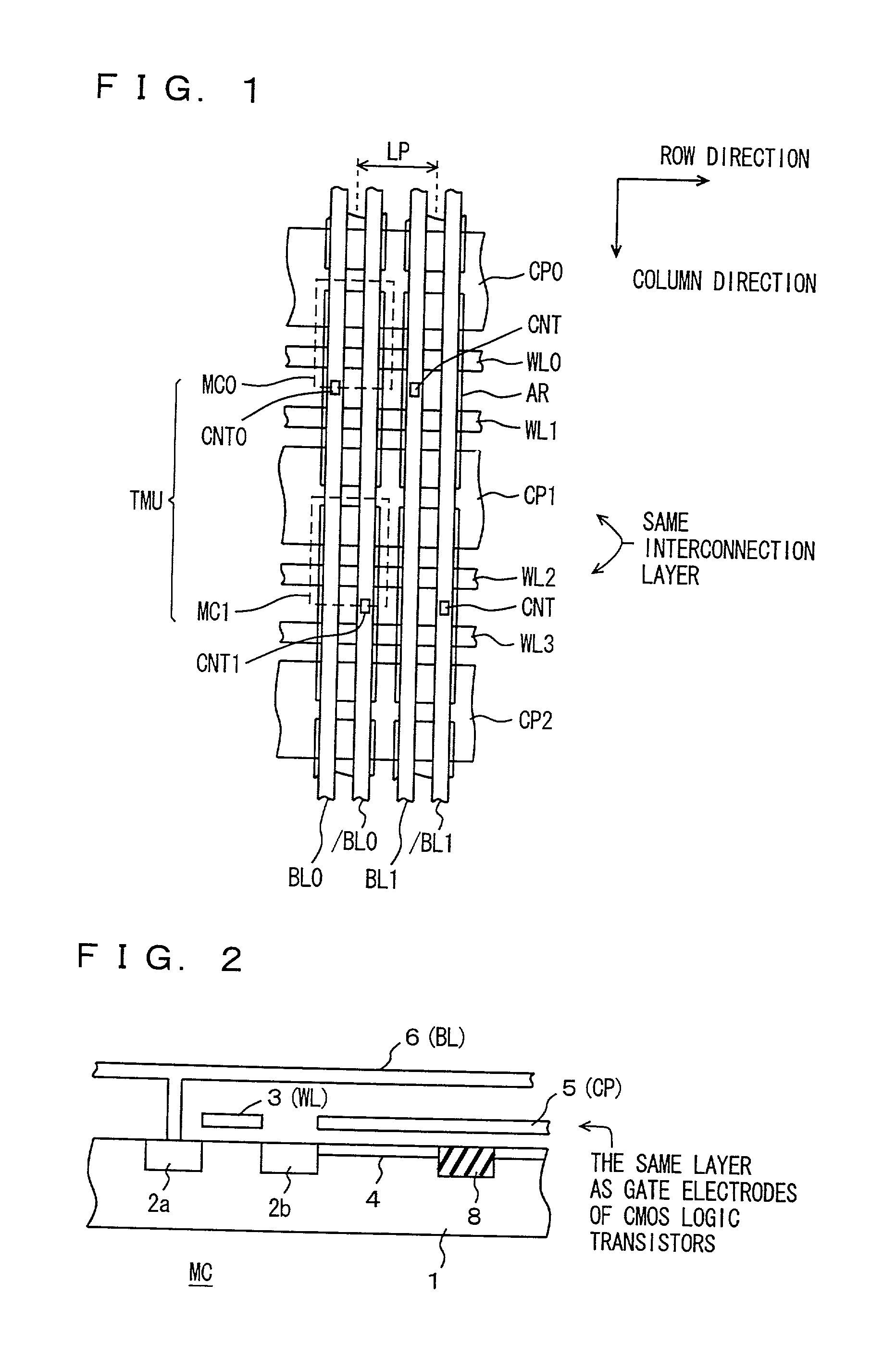

Semiconductor memory device

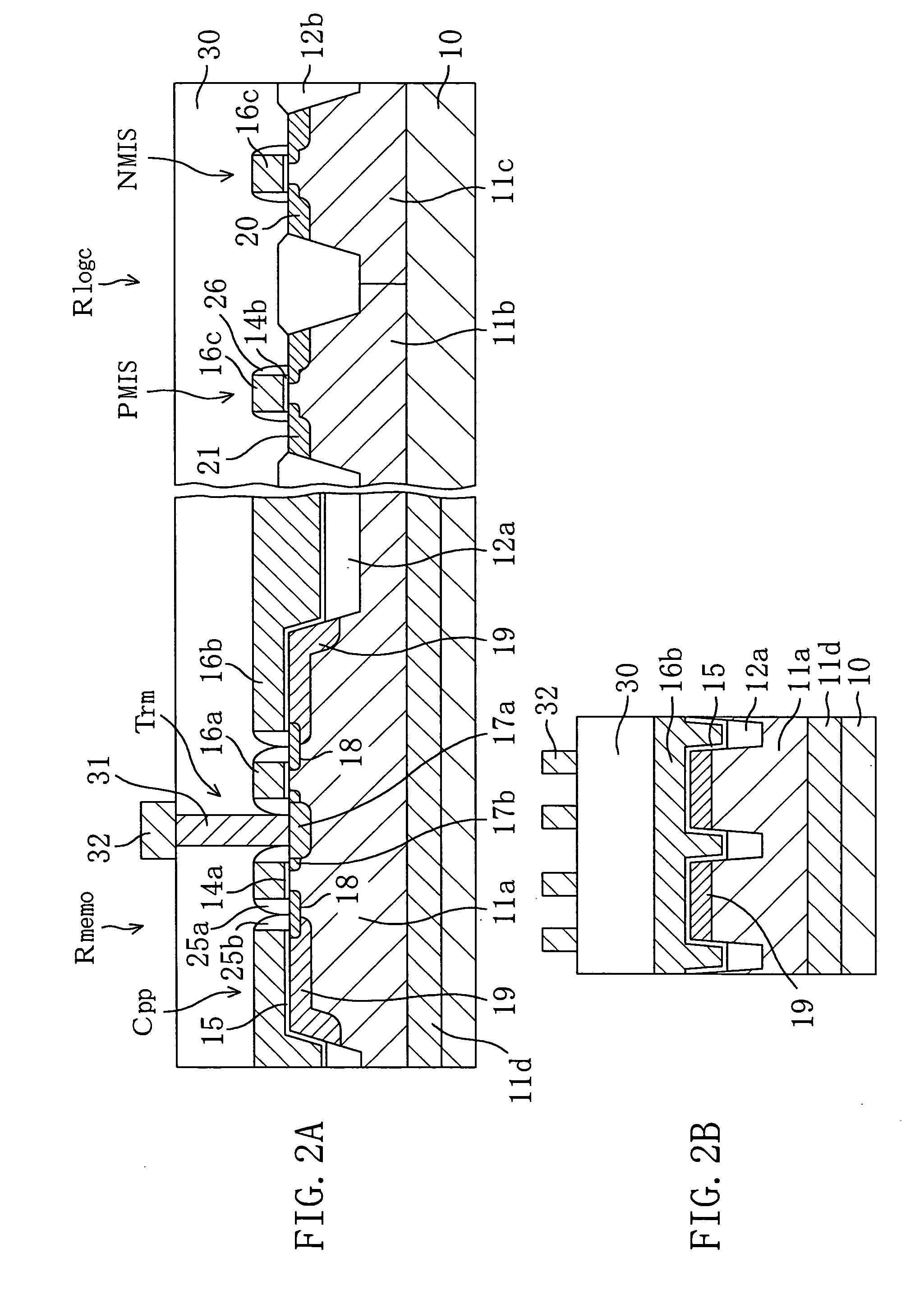

InactiveUS20020172070A1Reduce step heightReduce manufacturing stepsTransistorSolid-state devicesCapacitanceEngineering

Conductive lines constituting word lines of memory cells and conductive lines constituting memory cell plate electrodes are formed in the same interconnecting layer in a memory device including a plurality of memory cells each including a capacitor for storing data in an electrical charge form. By forming the capacitors of the memory cells into a planar capacitor configuration, a step due to the capacitors is removed. Thus. a dynamic semiconductor memory device can be formed through CMOS process, and a dynamic semiconductor memory device suitable for merging with logic is achieved. Data of 1 bit is stored by two memory cells, and data can be reliably stored even if the capacitance value of the memory cell is reduced due to the planar type capacitor.

Owner:RENESAS ELECTRONICS CORP

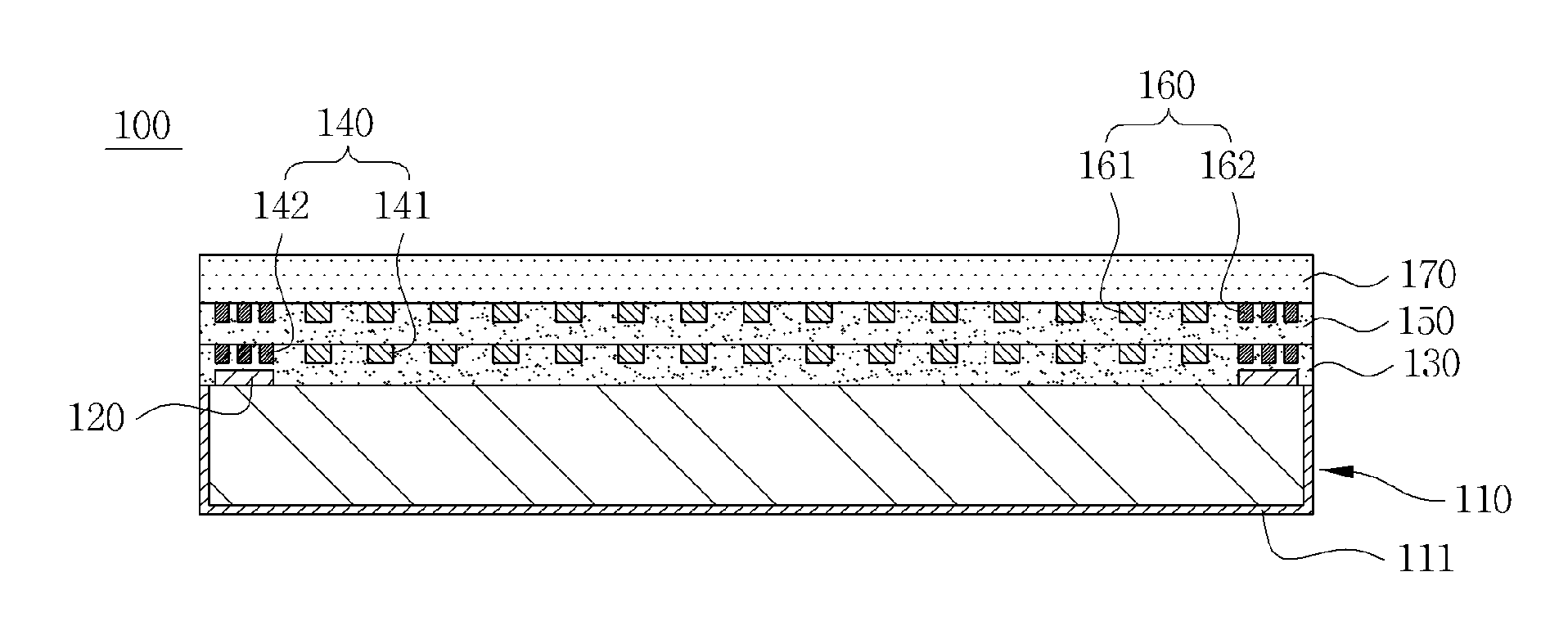

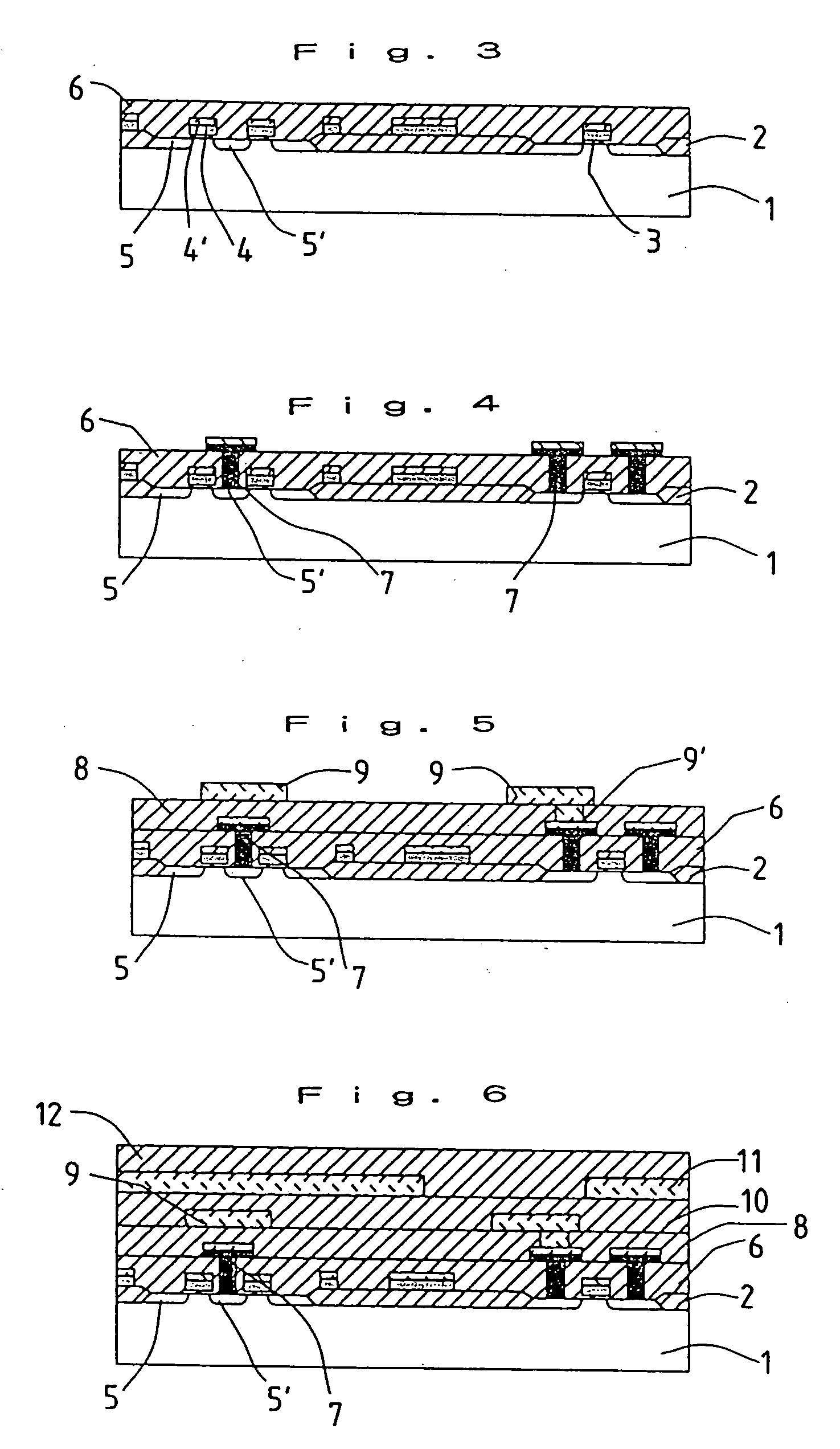

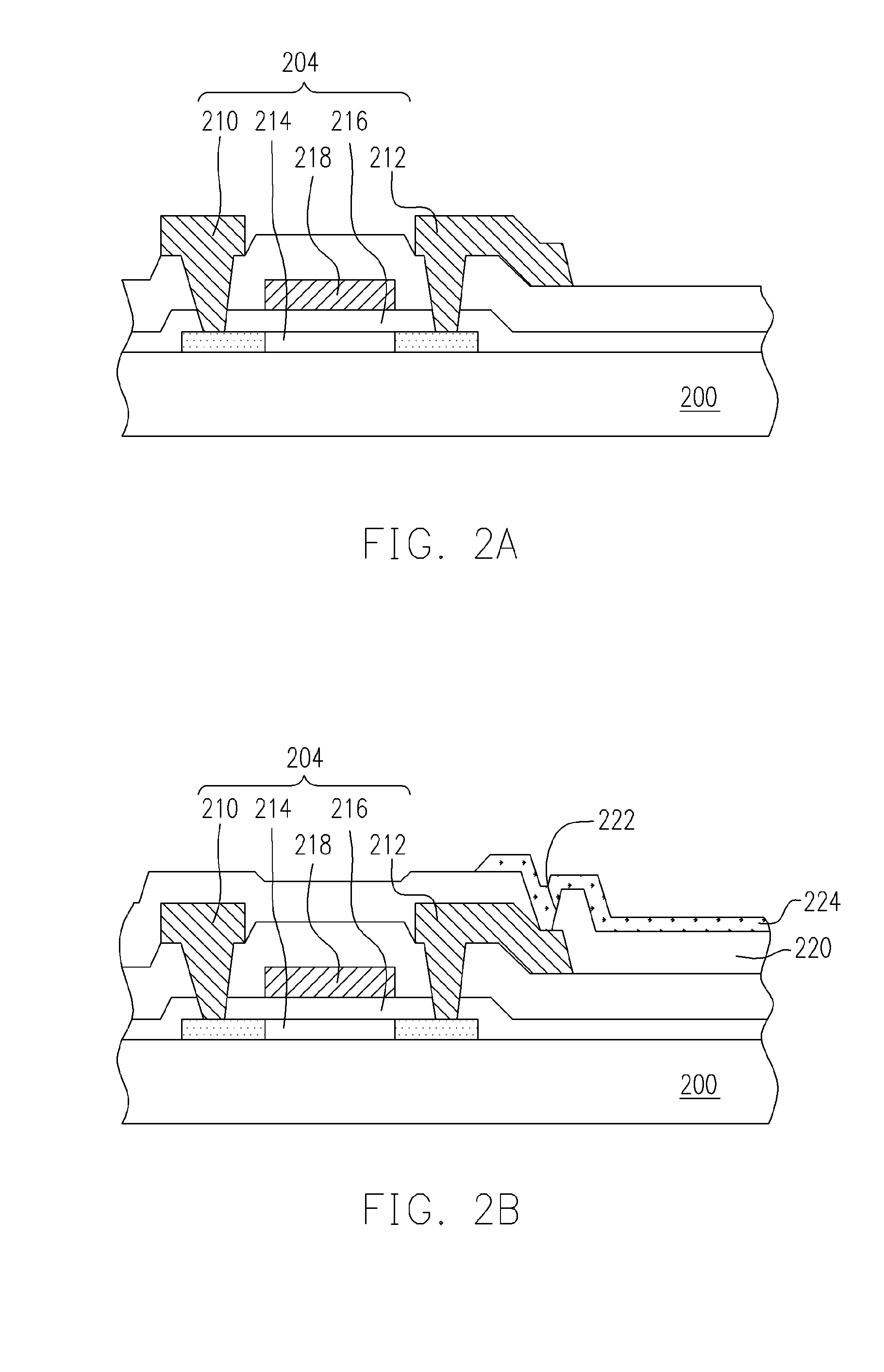

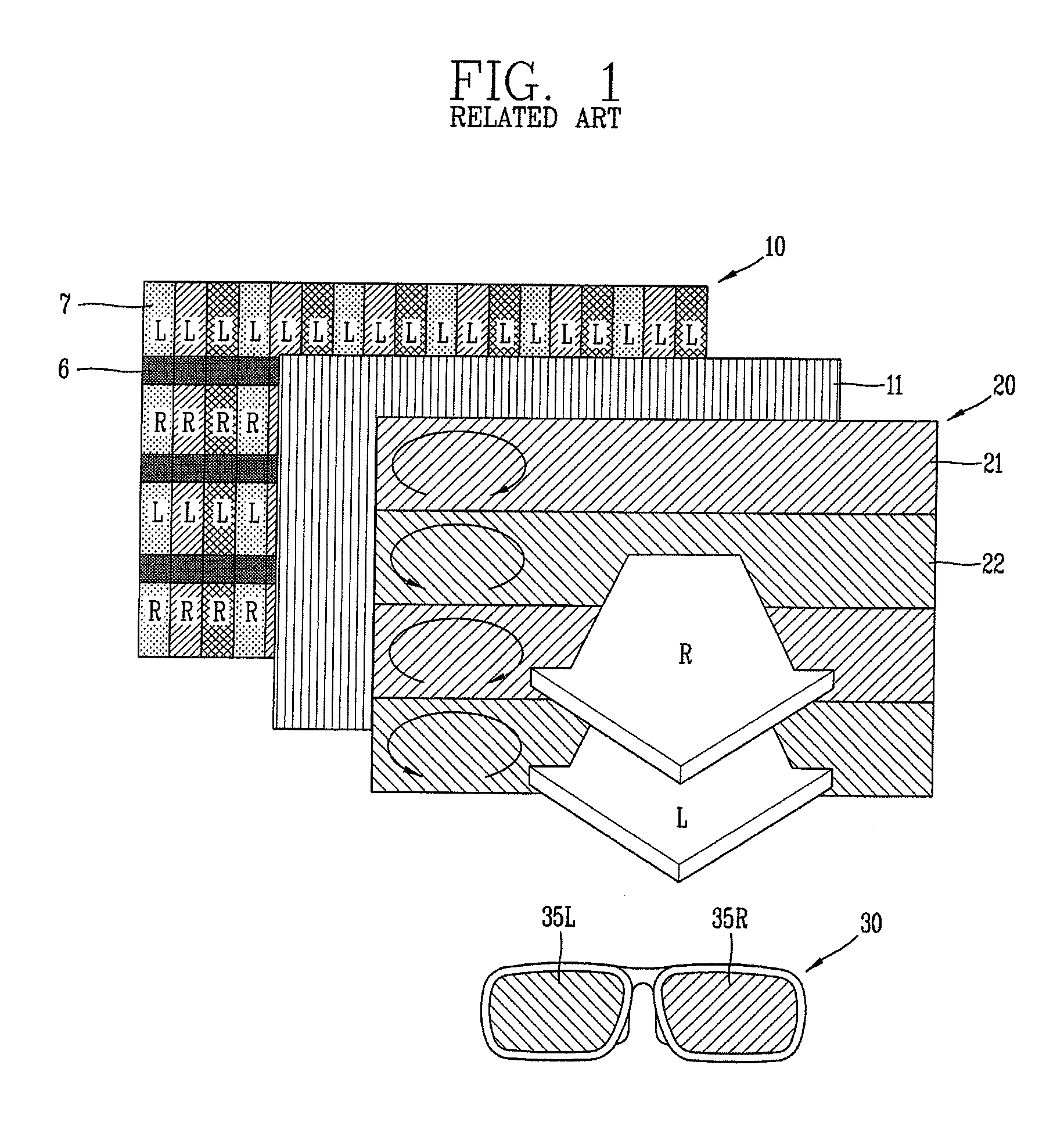

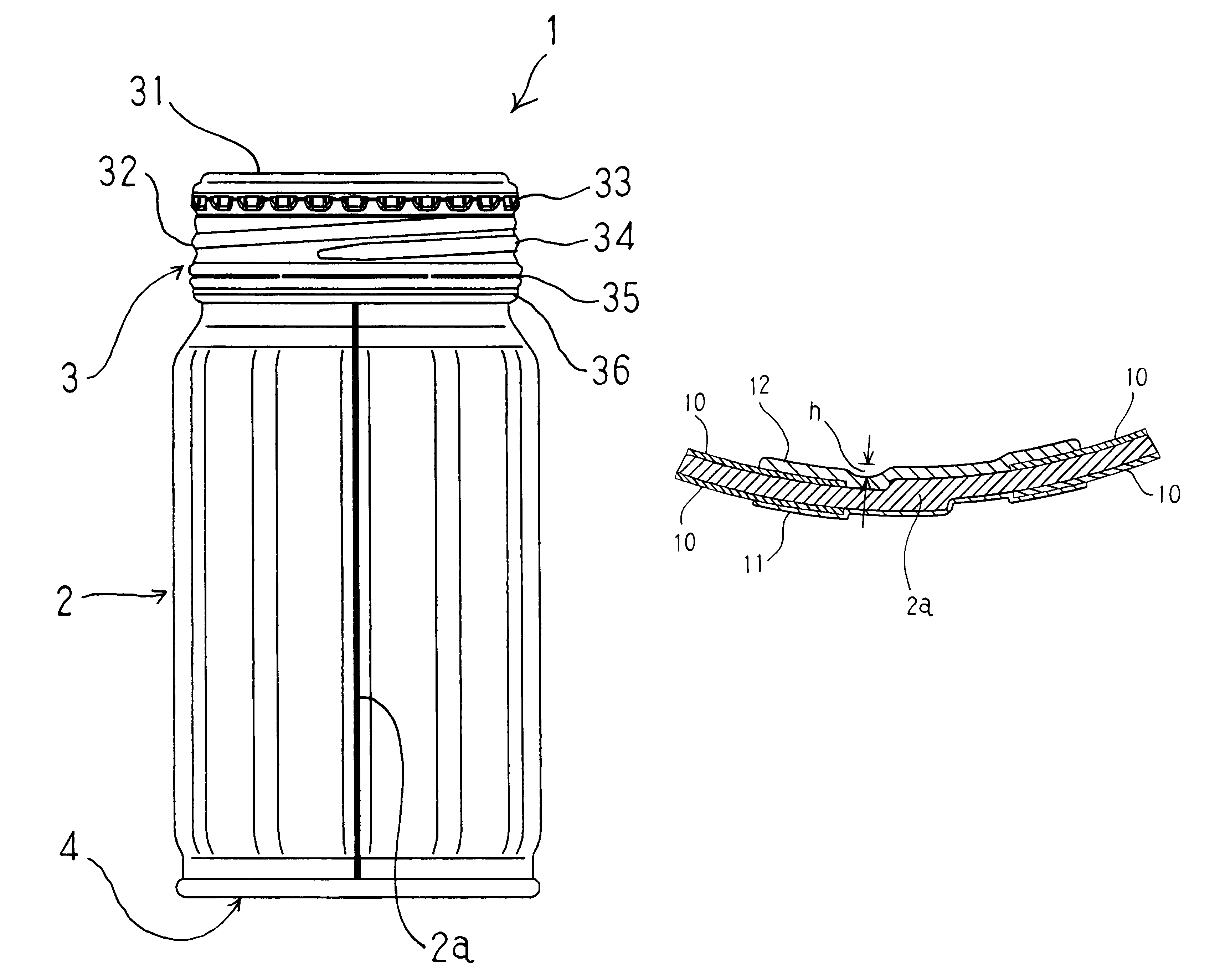

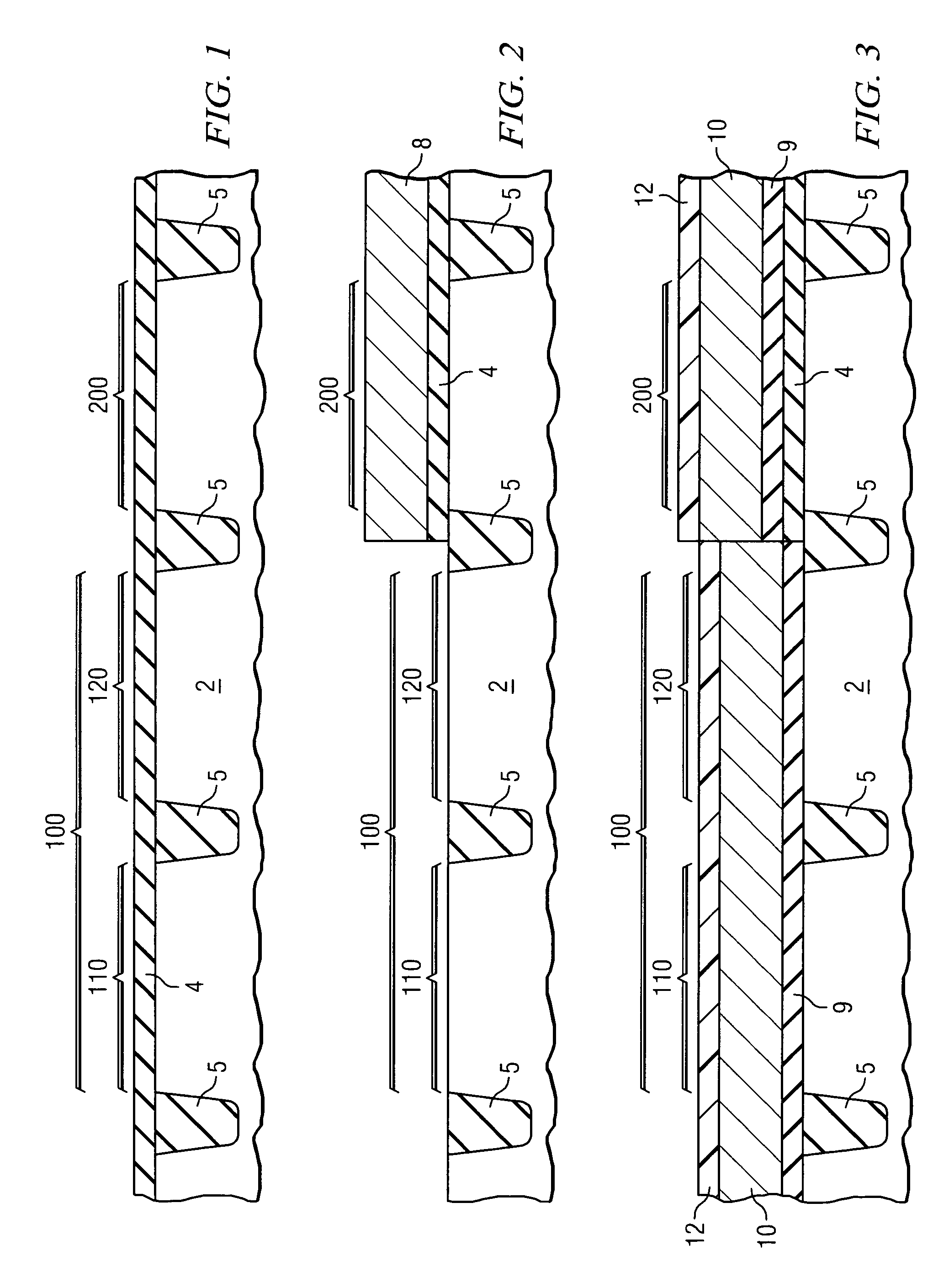

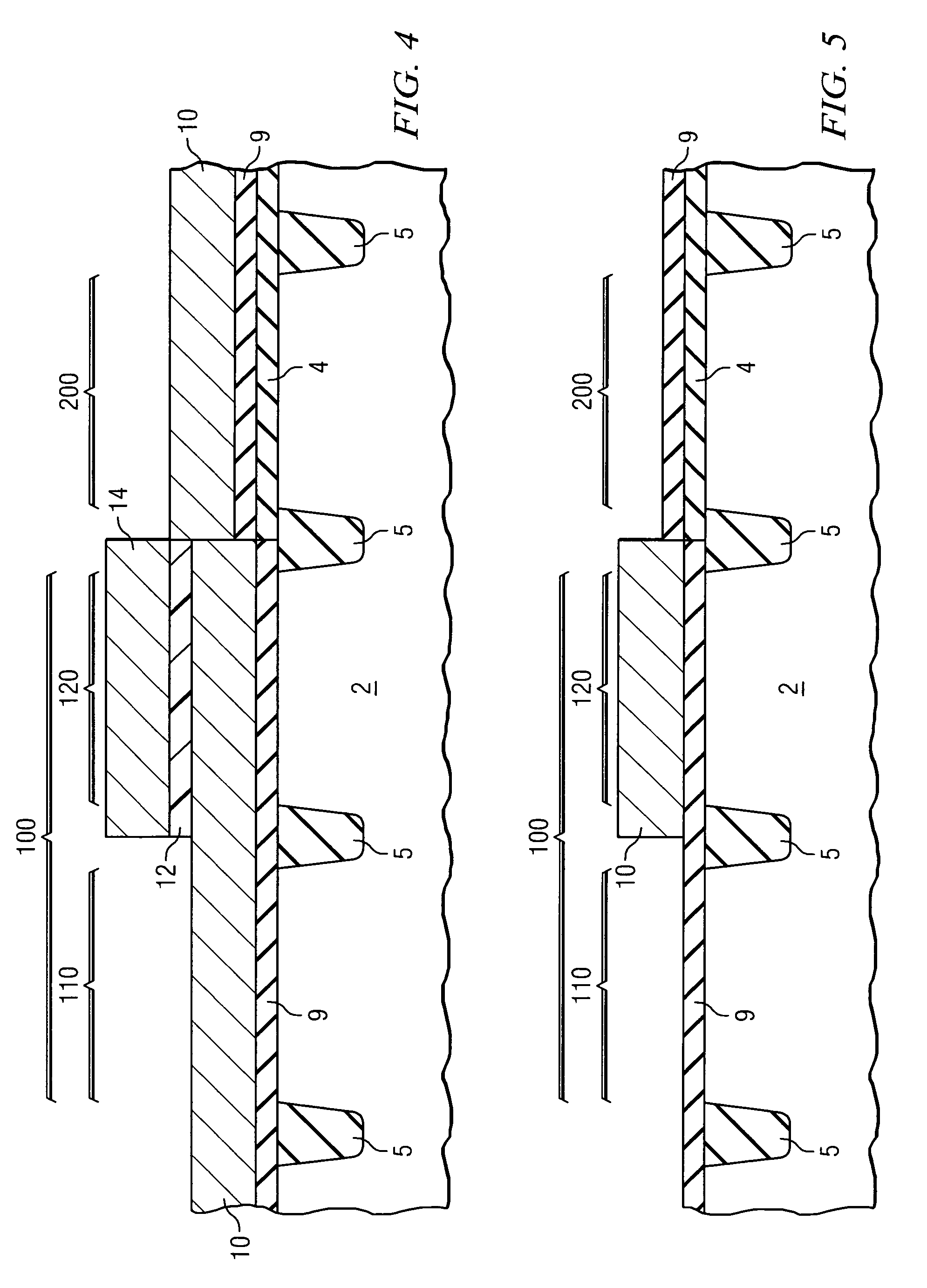

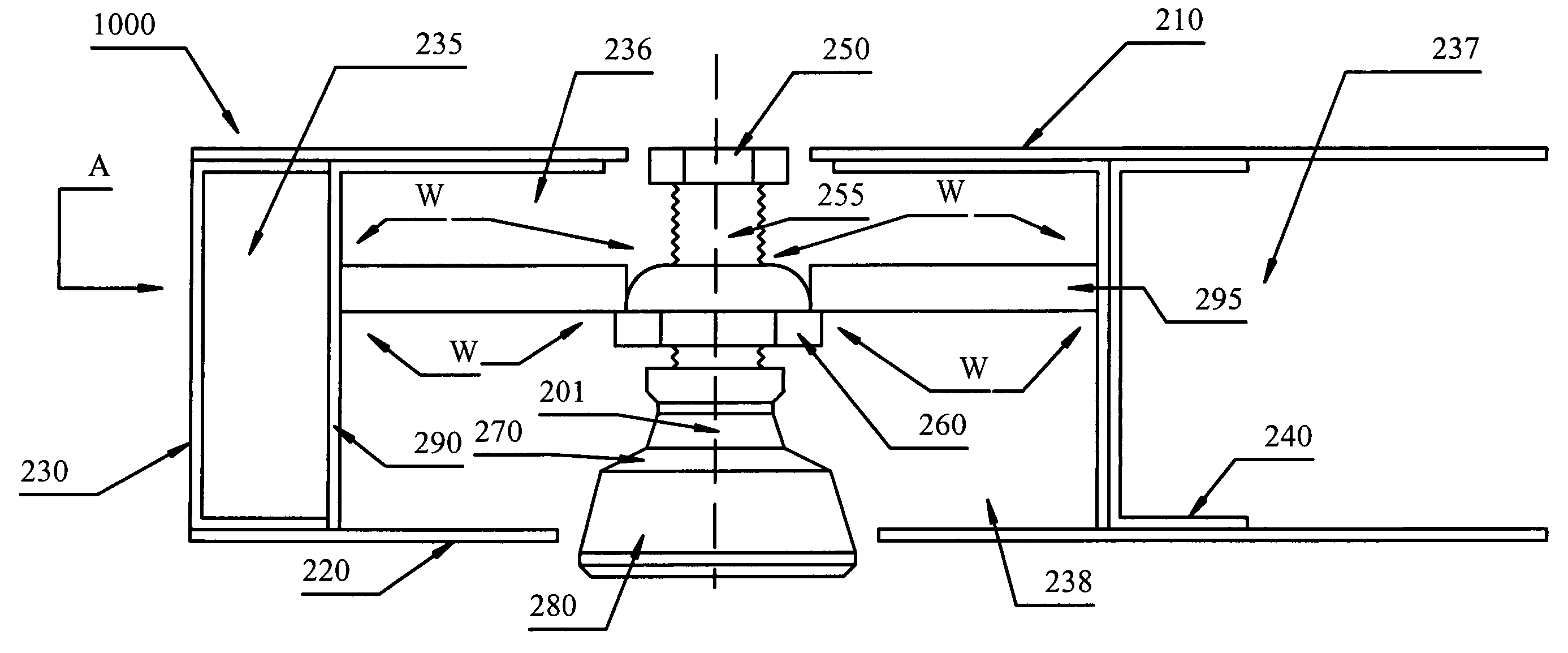

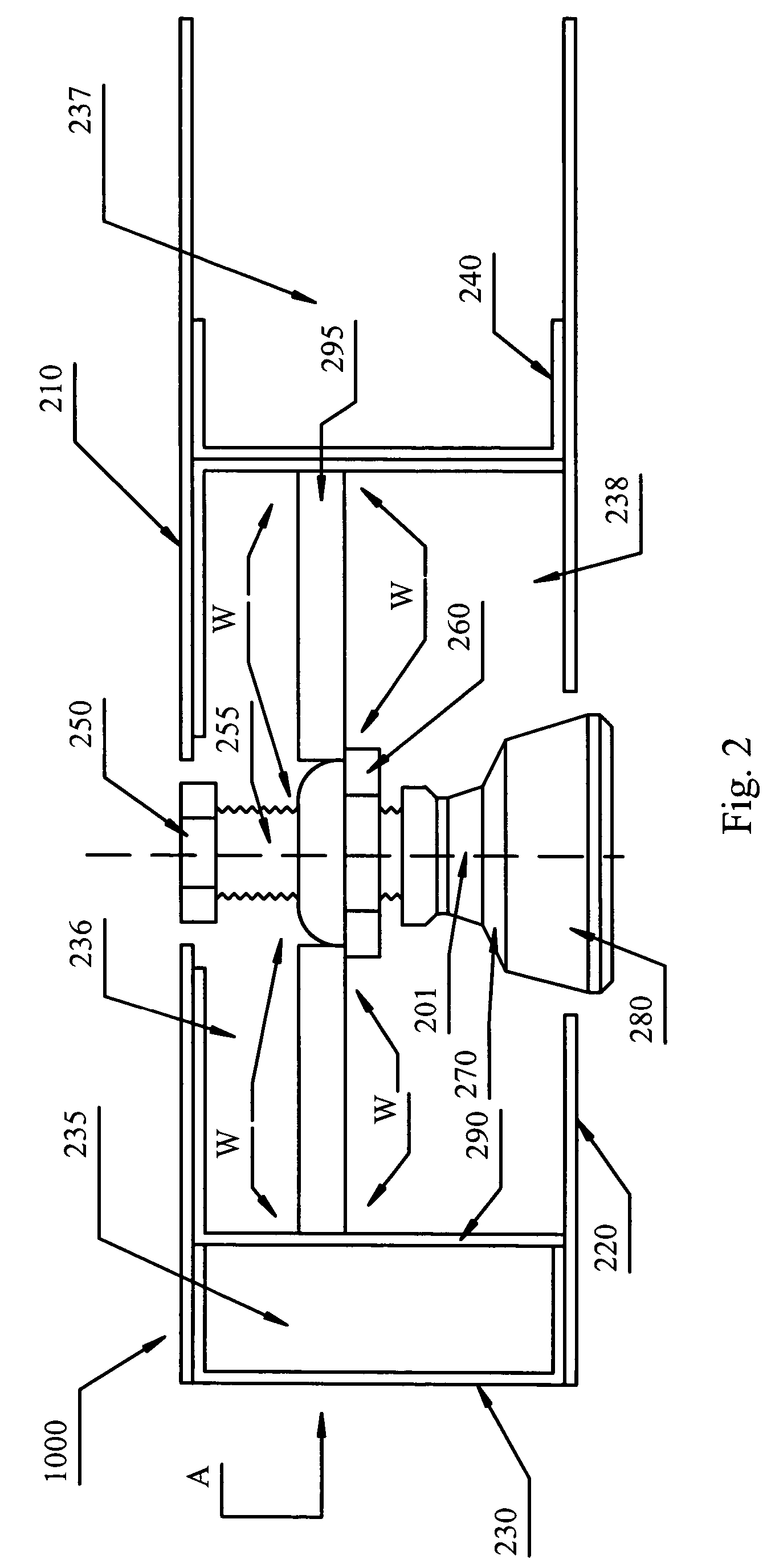

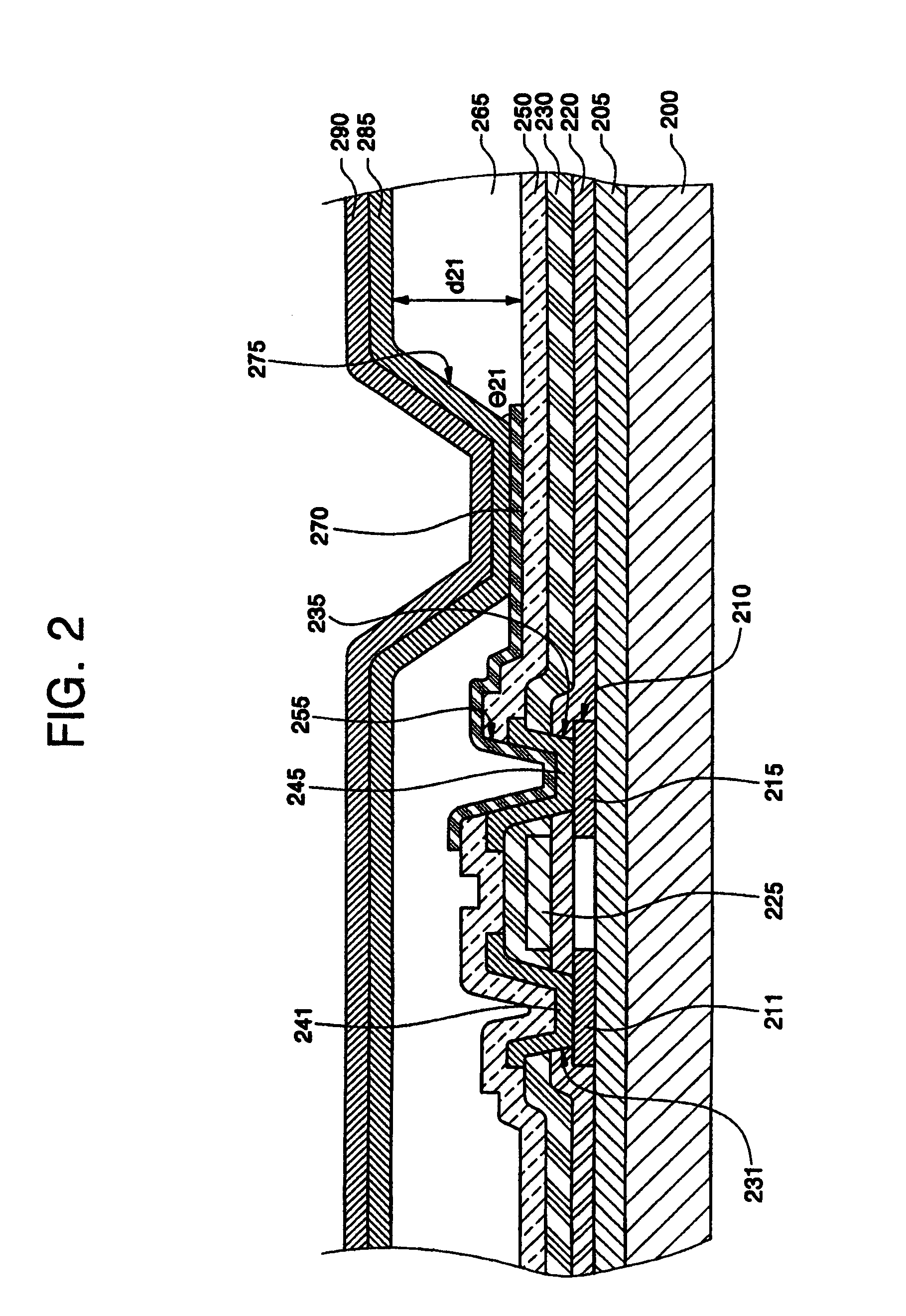

[active organic electroluminescence panel display and fabricating method thereof]

ActiveUS20050093438A1Avoid any shortingAvoid shortingDischarge tube luminescnet screensElectroluminescent light sourcesOrganic electroluminescenceEngineering

An active organic electroluminescence panel display and a fabricating method thereof are disclosed. A thin film transistor array comprising a plurality of thin film transistors, a plurality of datalines and a plurality of scanlines are formed on a substrate. A passivation layer is formed on the substrate, covering the thin film transistor array. A contact opening is formed in the passivation layer for exposing a prescribed area of the array. An anode layer is formed on the passivation layer and fills into the contact opening. A blank layer is formed on the anode, covering the contact opening. A shadow mask is disposed on the blank layer. Then, a sputtering process is performed to form anorganic luminescent layer. The shadow mask is then removed, and a cathode layer is formed on the organic luminescent layer for forming an active organic electroluminescence panel display.

Owner:AU OPTRONICS CORP

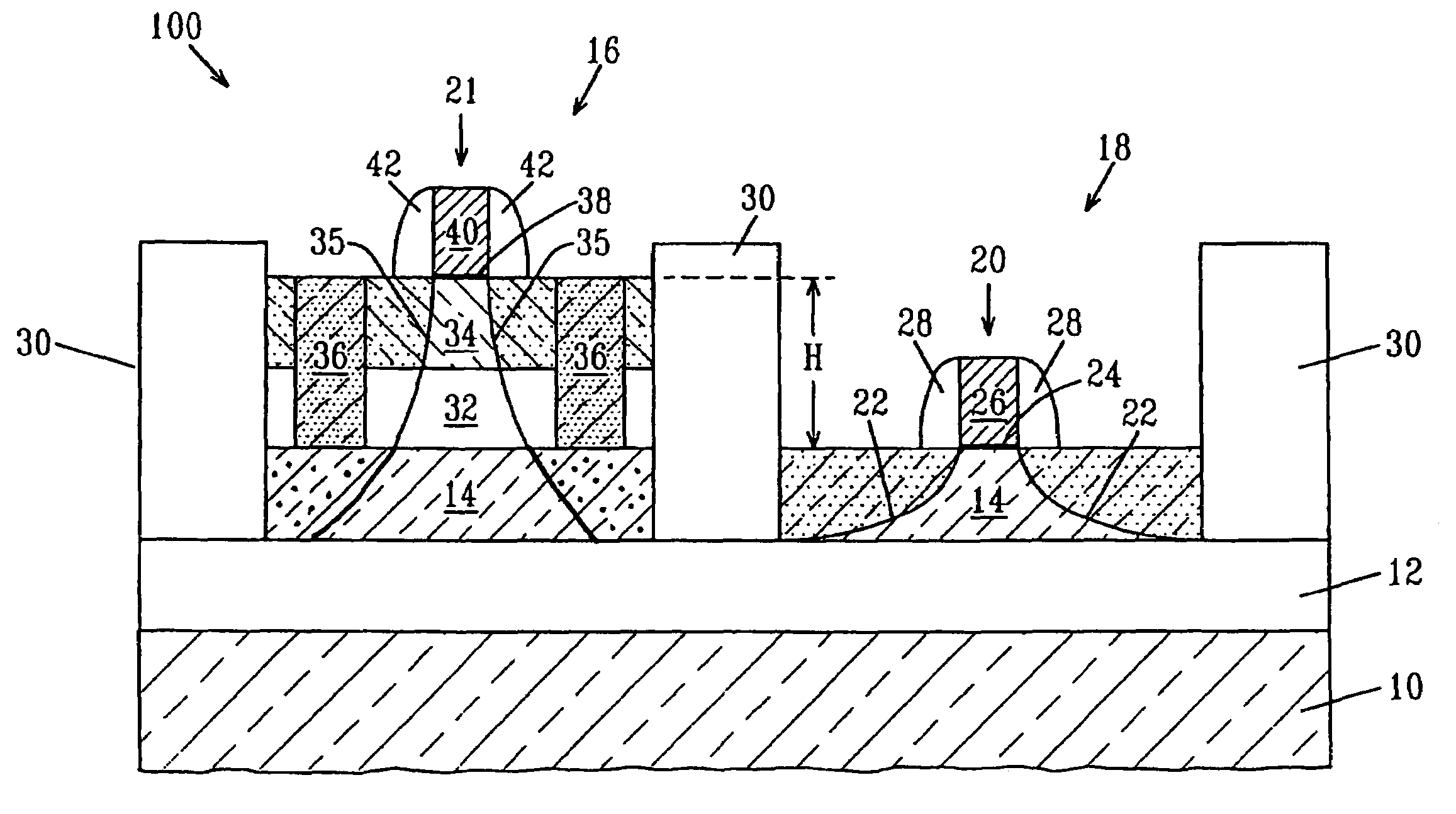

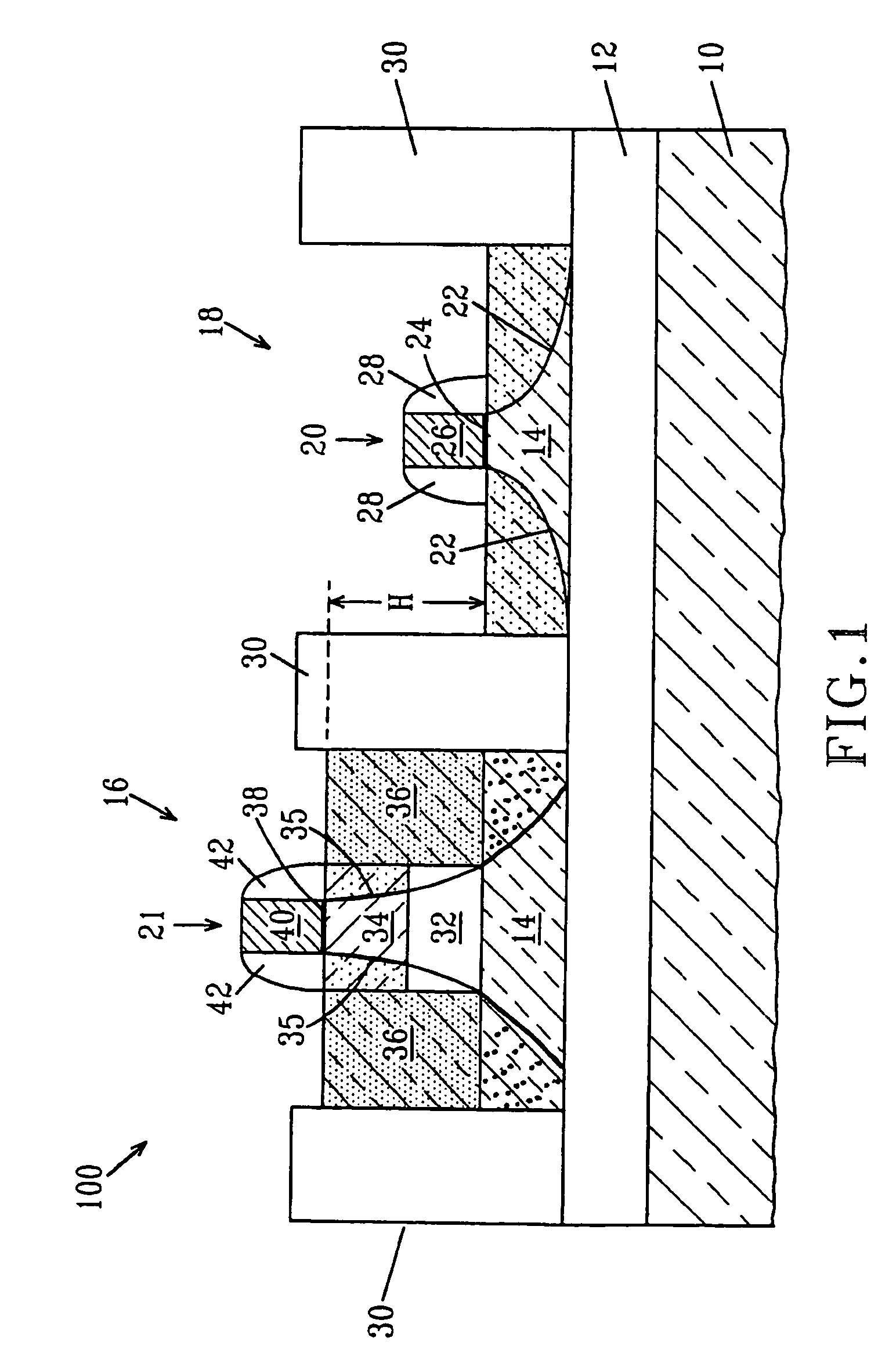

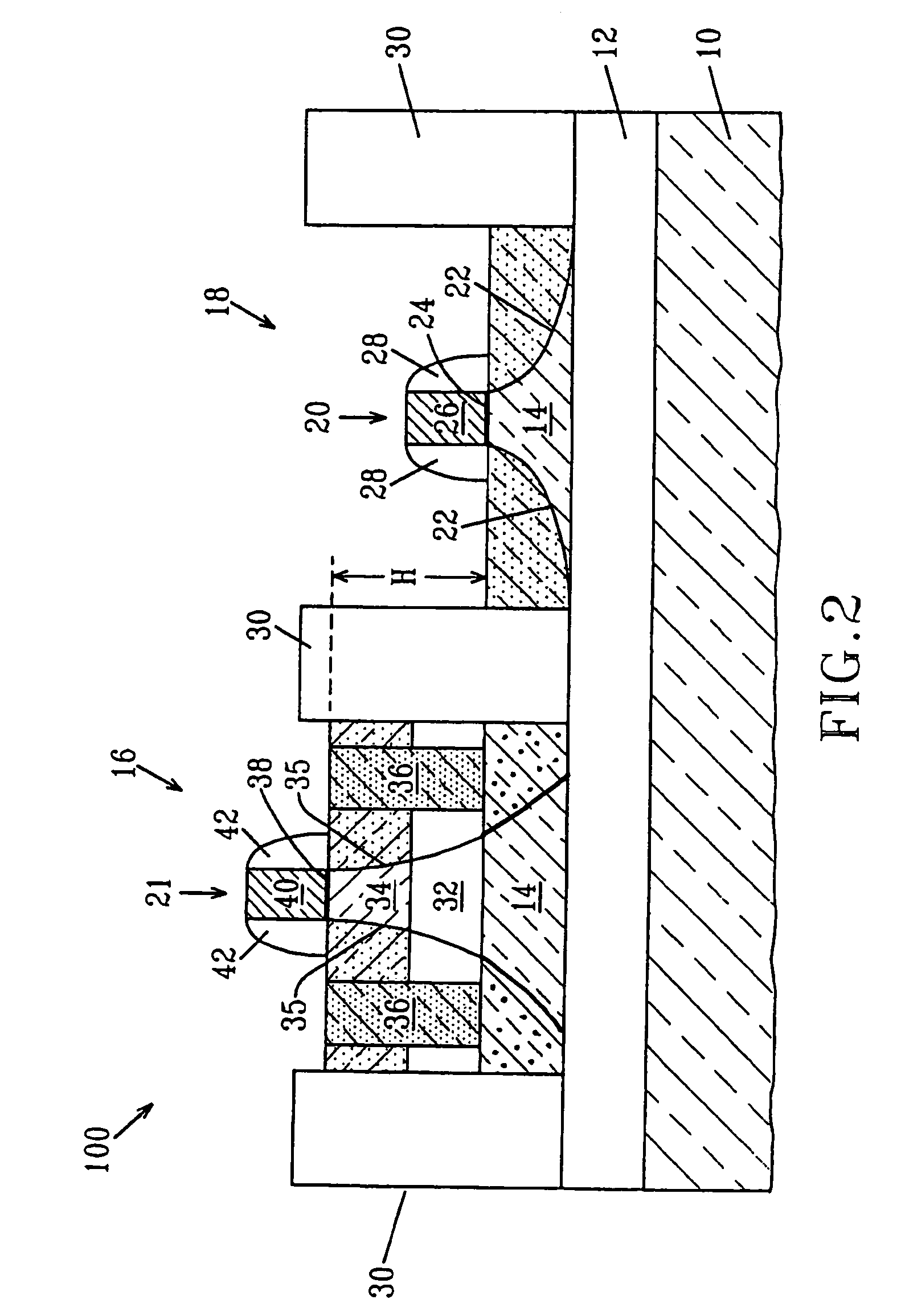

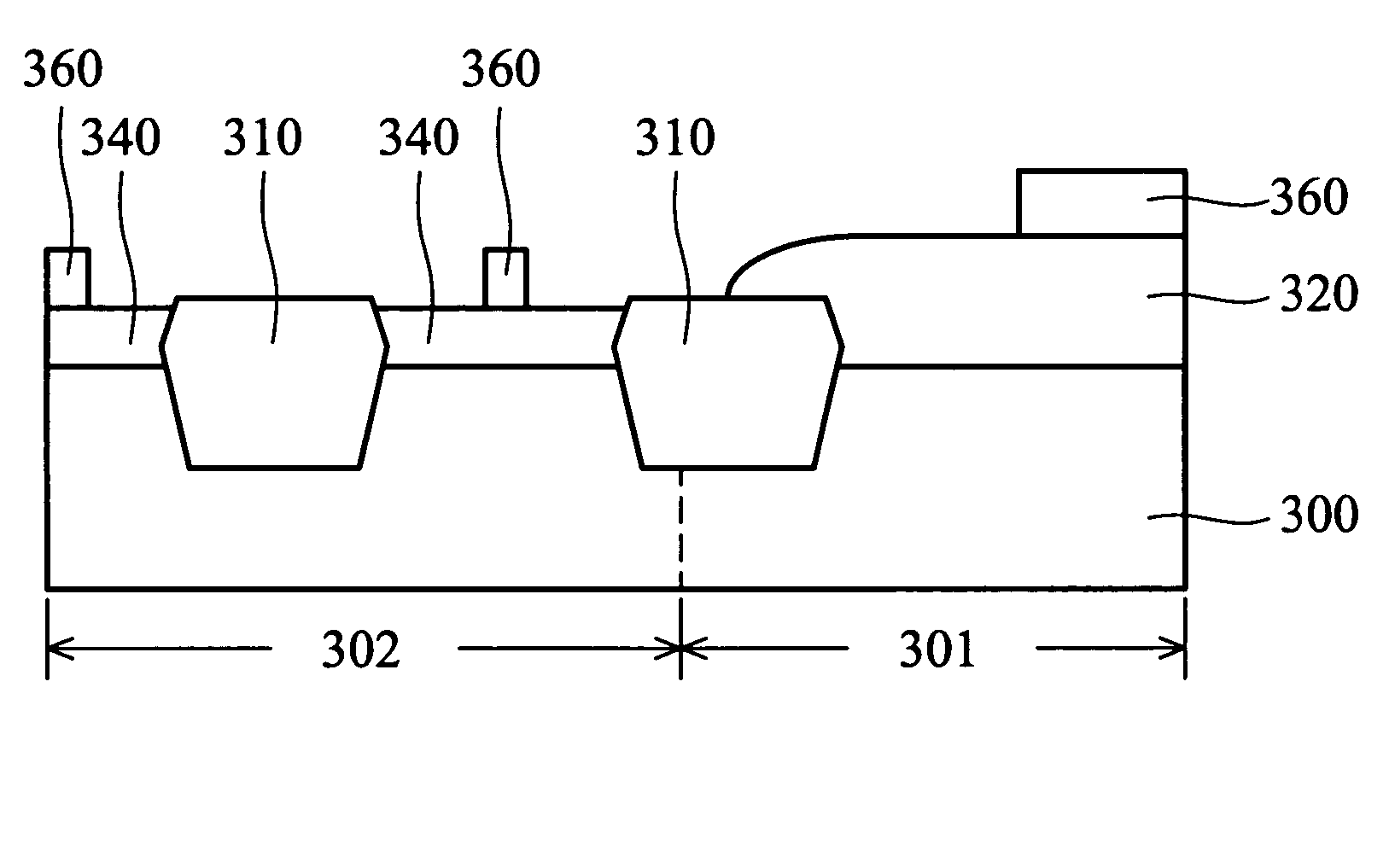

Double silicon-on-insulator (SOI) metal oxide semiconductor field effect transistor (MOSFET) structures

ActiveUS7034362B2Reduce step heightWithout junction capacitanceTransistorSolid-state devicesMOSFETCapacitance

A SOI MOSFET structure having a reduced step height between the various semiconductor layers without adversely affecting the junction capacitance of the semiconductor device formed on the uppermost semiconductor layer as well as a method of fabricating the same are provided. The structure of the present invention includes an elevated device region having at least one semiconductor device located on a second semiconductor layer. The elevated device region further includes a source / drain junction that extends from the second semiconductor layer down to a first buried insulator layer that is located on an upper surface of the semiconductor substrate. The structure also includes a recessed device region having at least one semiconductor device located atop a first semiconductor layer which is located on an upper surface of the first buried insulator. An isolation region separates the elevated device region from the recessed device region.

Owner:GLOBALFOUNDRIES U S INC

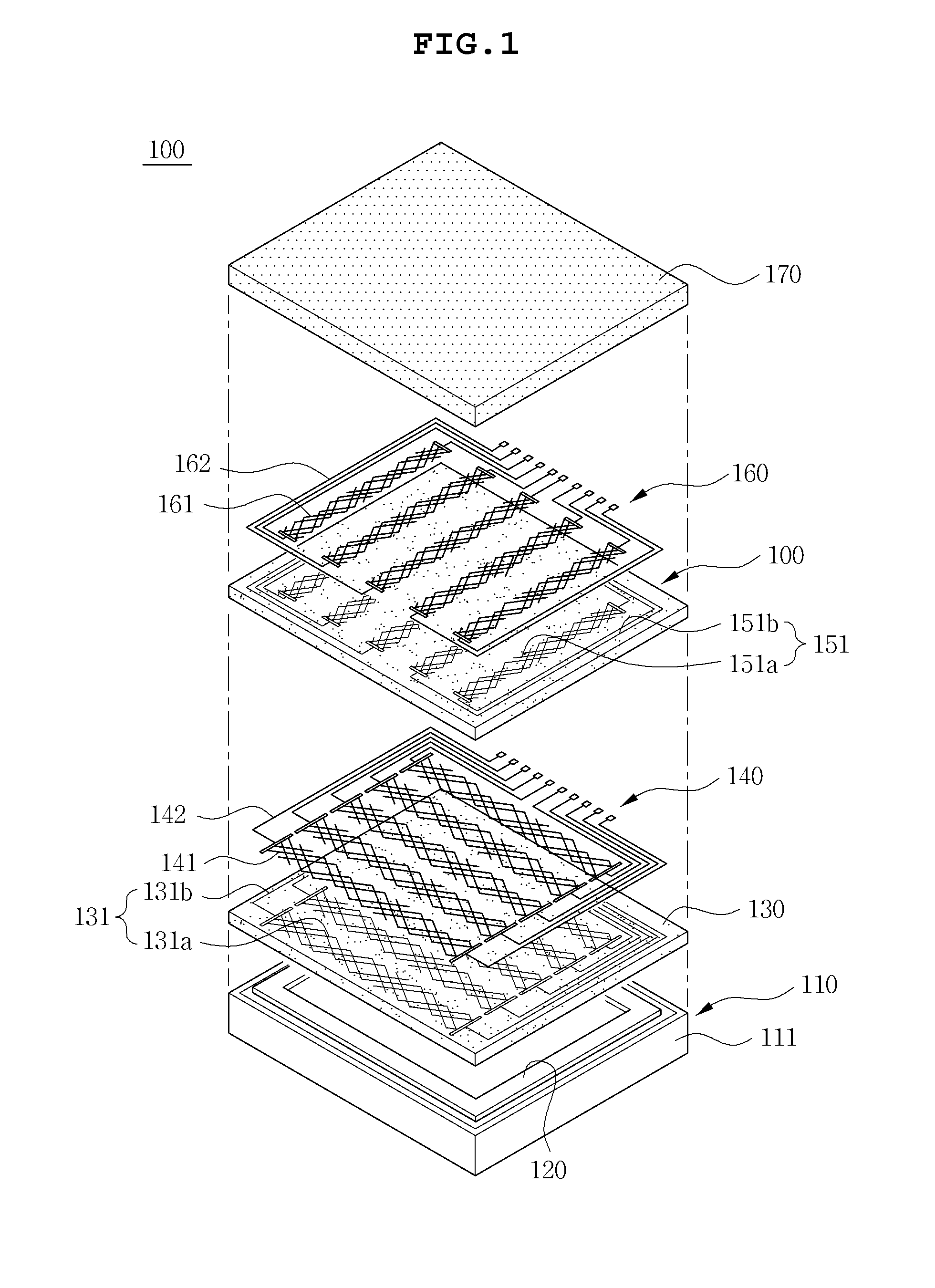

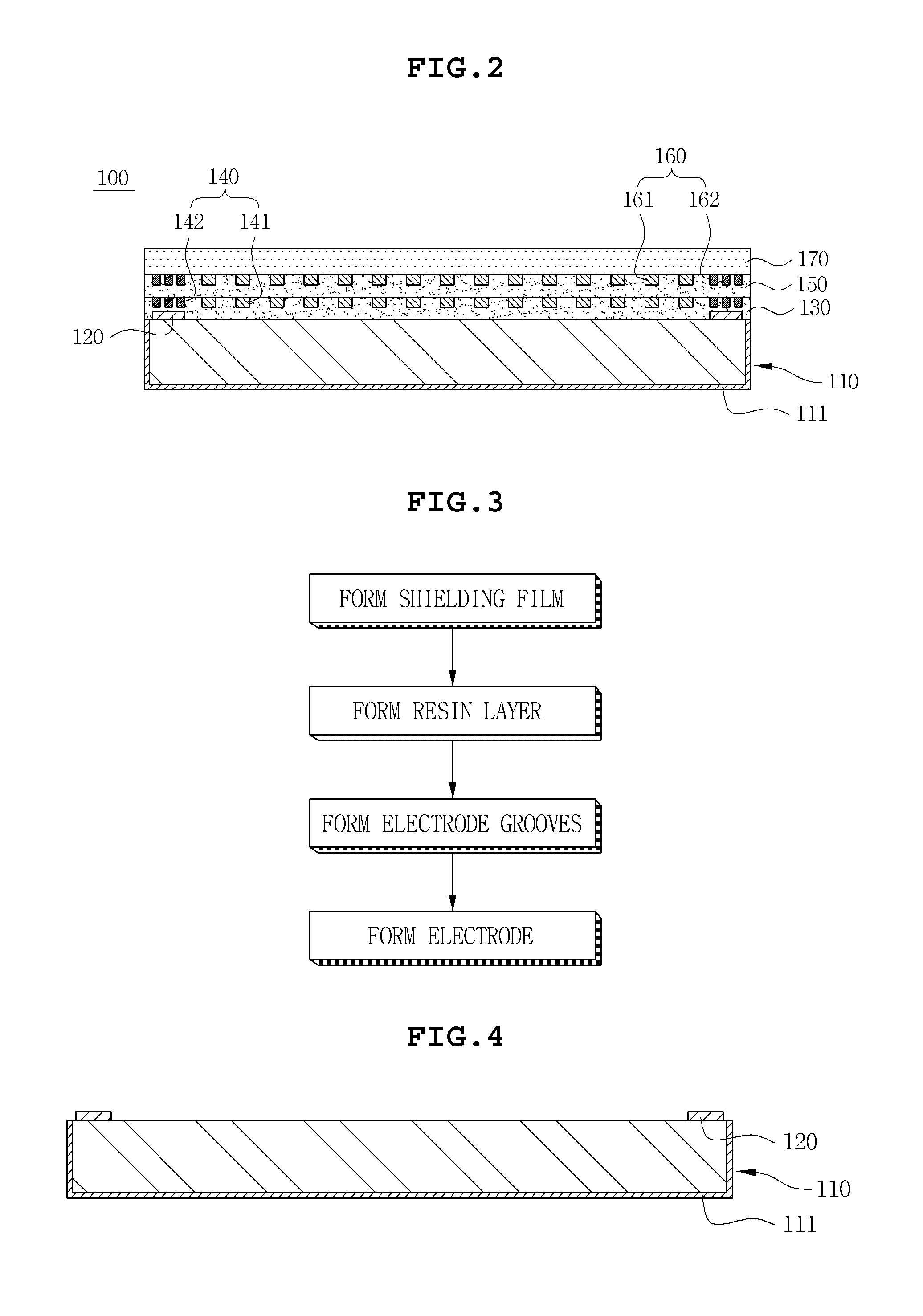

Touch sensor and method of manufacturing the same

InactiveUS20130307565A1Reduce step heightResistance/reactance/impedenceManufacture of electrical instrumentsOptoelectronicsElectrode

Disclosed herein are a touch sensor and a method of manufacturing the same, the touch sensor including: a transparent substrate; a shielding film formed on one surface of the transparent substrate; a resin layer formed above the transparent substrate and one surface of the shielding film; and an electrode buried in one surface of the resin layer.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

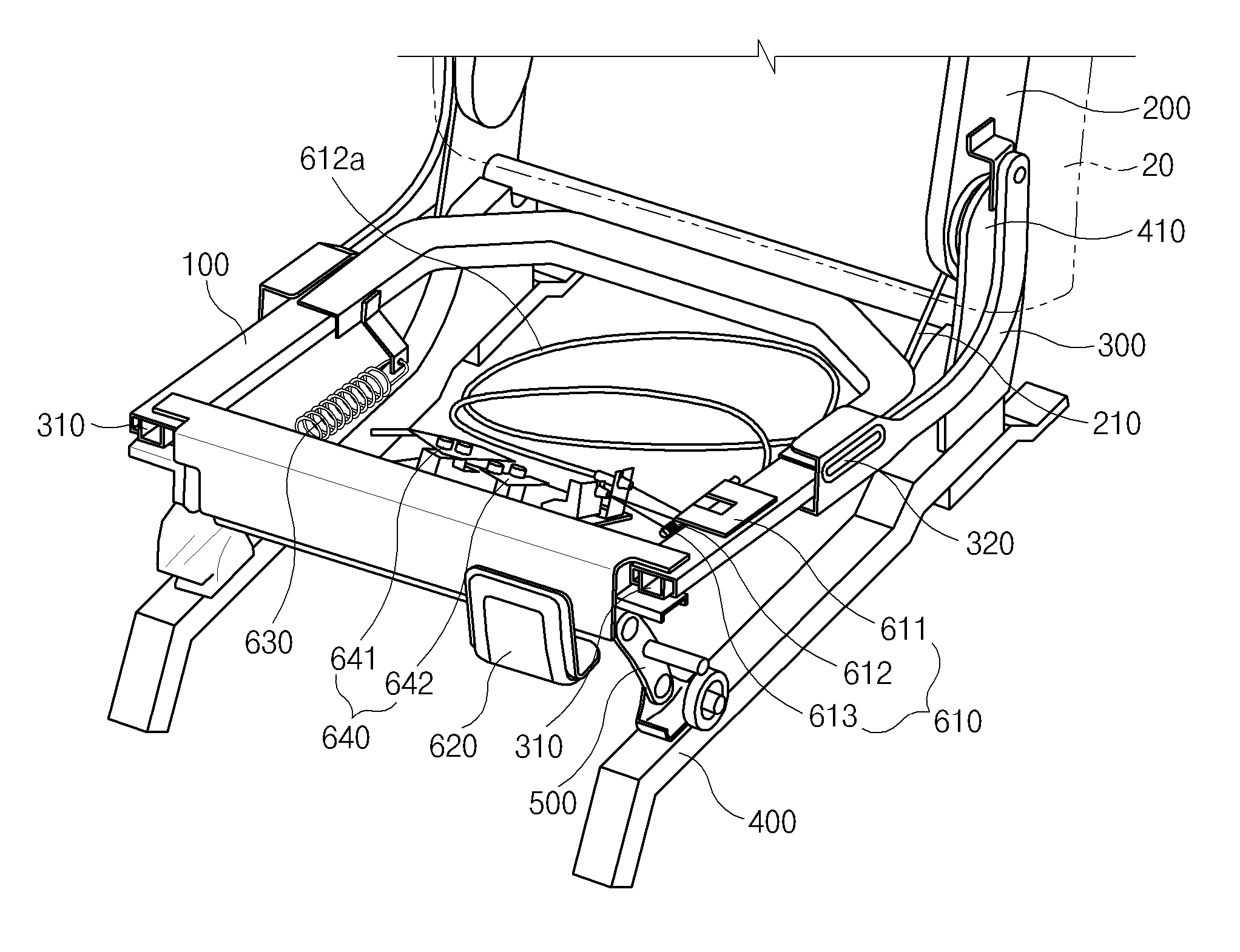

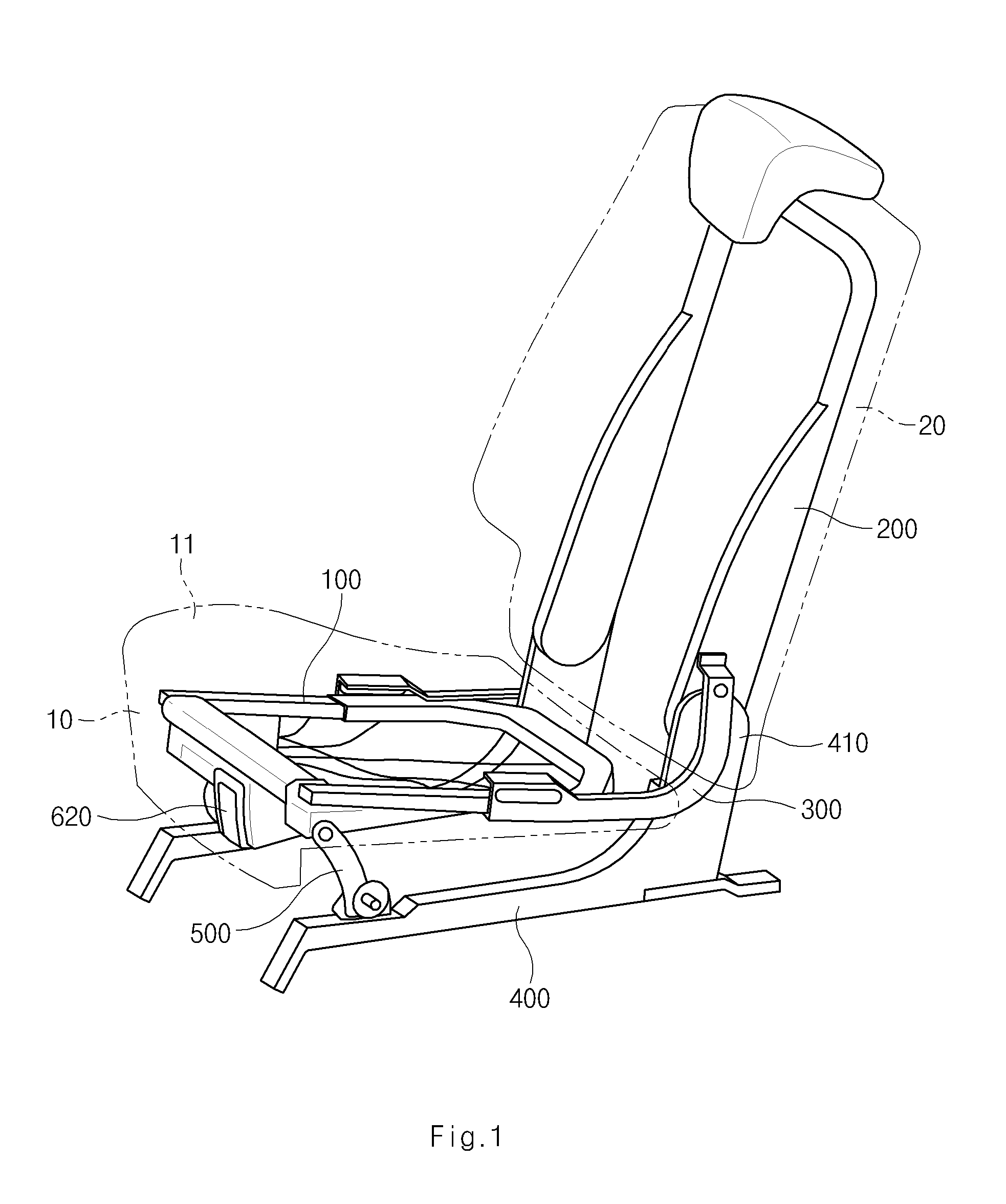

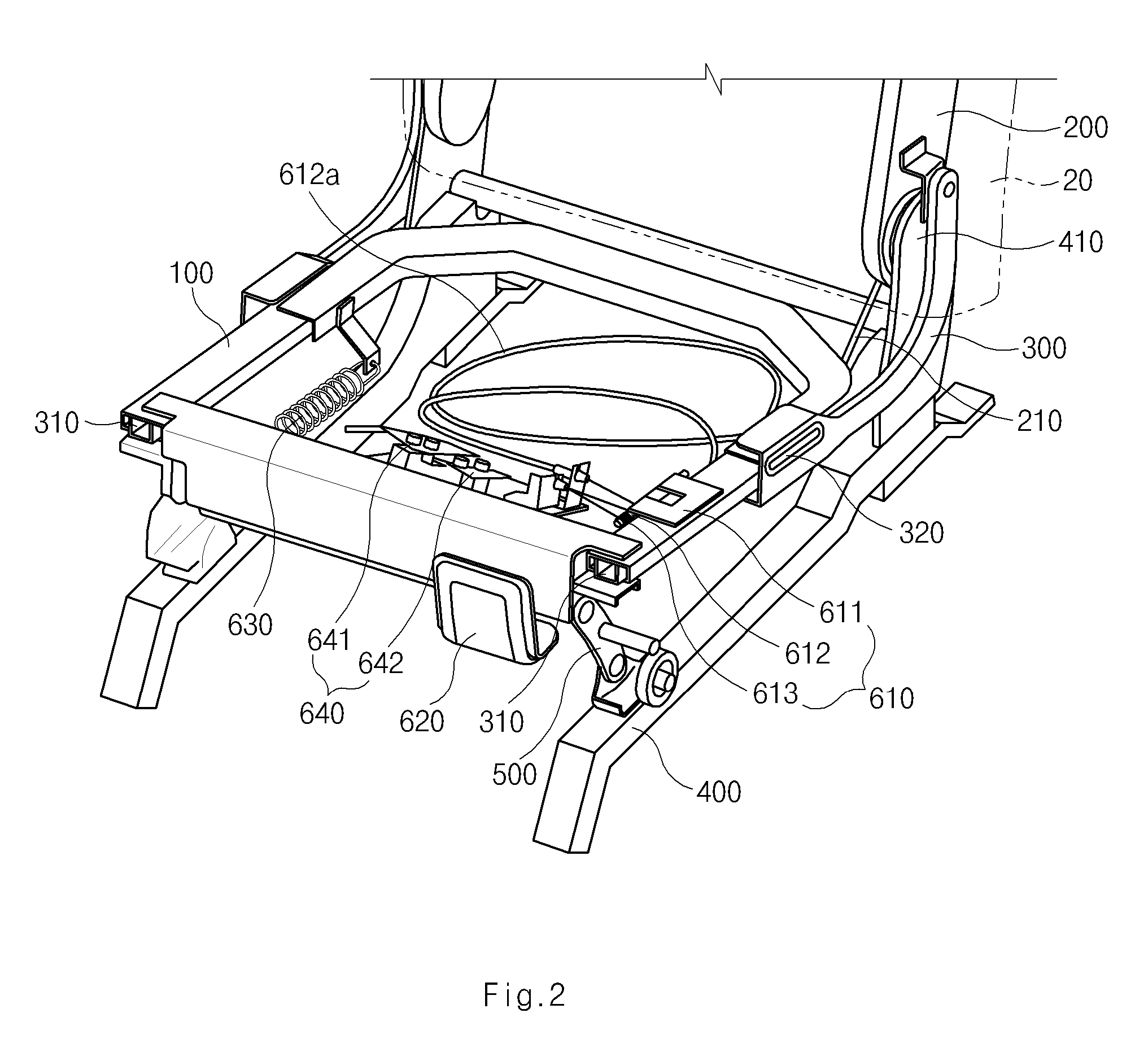

Fold-and dive structure for vehicle seat

ActiveUS8602495B2Add supportImprove riding comfortOperating chairsDental chairsForward slidingBraced frame

A fold-and-dive structure for a vehicle seat is provided, which includes a connection member connecting a cushion frame built in a seat cushion and a back frame built in a seat back to each other, a rotating link connecting a front end portion of the cushion frame and a support frame to each other, and a recliner provided on the support frame to which a lower end portion of the back frame is rotatably connected, wherein a guide frame is provided on a front side portion of the connection member, and the cushion frame is slidably coupled to the guide frame to make the seat cushion slide forward.

Owner:HYUNDAI MOTOR CO LTD +2

Organic light emitting display

ActiveUS7501756B2Light displayReduce step heightDischarge tube luminescnet screensElectroluminescent light sourcesOptoelectronicsDevice failure

An organic light emitting display which is constructed with a TFT substrate having an insulating substrate and a TFT that has at least a source electrode and a drain electrode, a lower electrode formed on the TFT substrate and connected to one of source / drain electrodes, an insulating layer having an opening that exposes a portion of the lower electrode, an organic thin film layer formed on the exposed portion of the lower electrode and the insulating layer, and an upper electrode formed on the organic thin film layer, wherein the insulating layer has a taper angle less than 40° at an edge of the opening, and a step less than or equal to 3,000 Å is formed between the lower electrode and the organic thin film layer. The organic light emitting display can prevent device failure.

Owner:SAMSUNG DISPLAY CO LTD

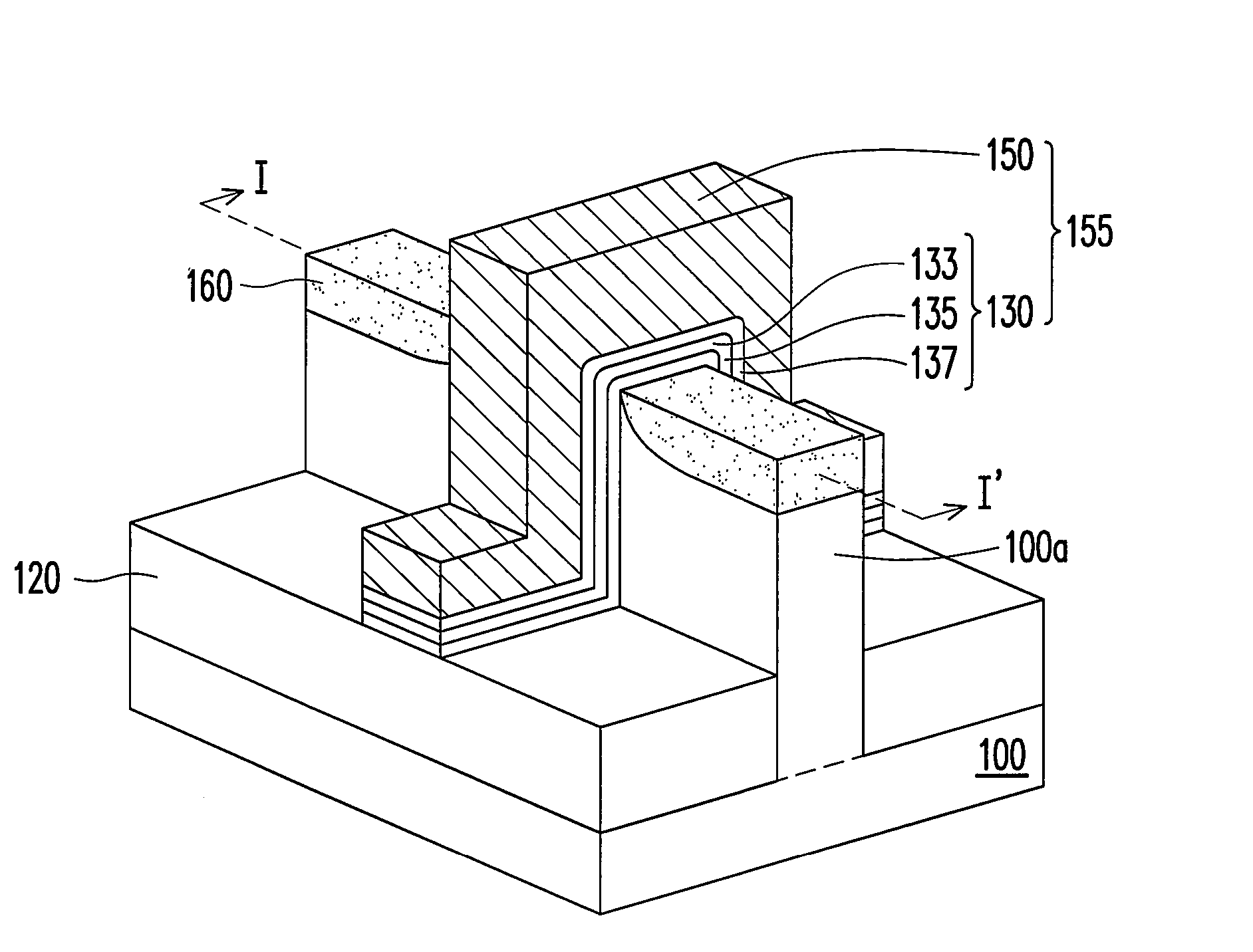

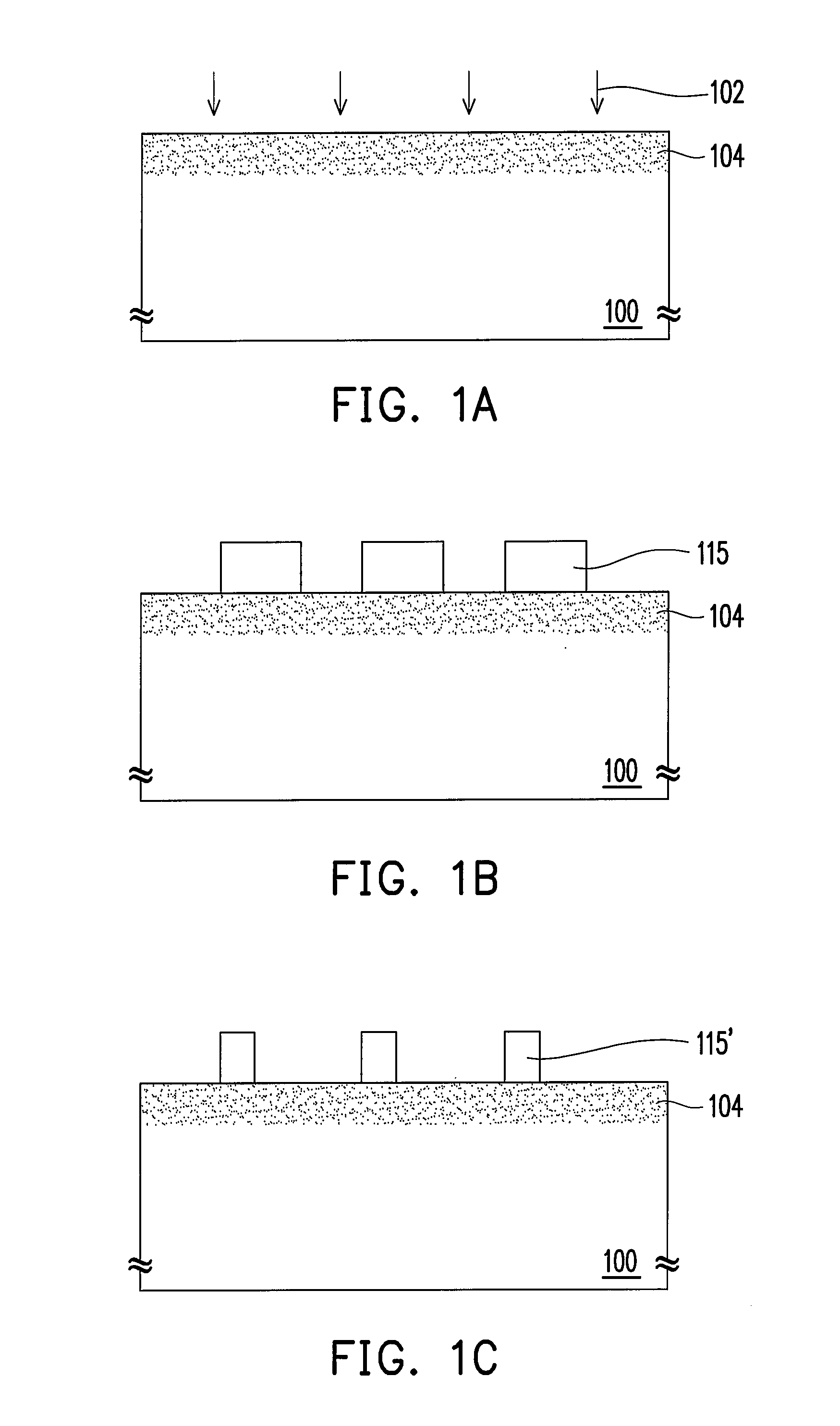

Memory cell and method for manufacturing the same

ActiveUS20080290391A1Reduce step heightHighly integratedTransistorSolid-state devicesTrappingEngineering

The invention provides a memory cell. The memory cell is disposed on a substrate and comprises a plurality of isolation structures defining at least a fin structure in the substrate. Further, the surface of the fin structure is higher than the surface of the isolation structure. The memory cell comprises a doped region, a gate, a charge trapping structure and a source / drain region. The doped region is located in a top of the fin structure and near a surface of the top of the fin structure and the doped region has a first conductive type. The gate is disposed on the substrate and straddled the fin structure. The charge trapping structure is disposed between the gate and the fin structure. The source / drain region with a second conductive type is disposed in the fin structures exposed by the gate and the first conductive type is different from the second conductive type.

Owner:MACRONIX INT CO LTD

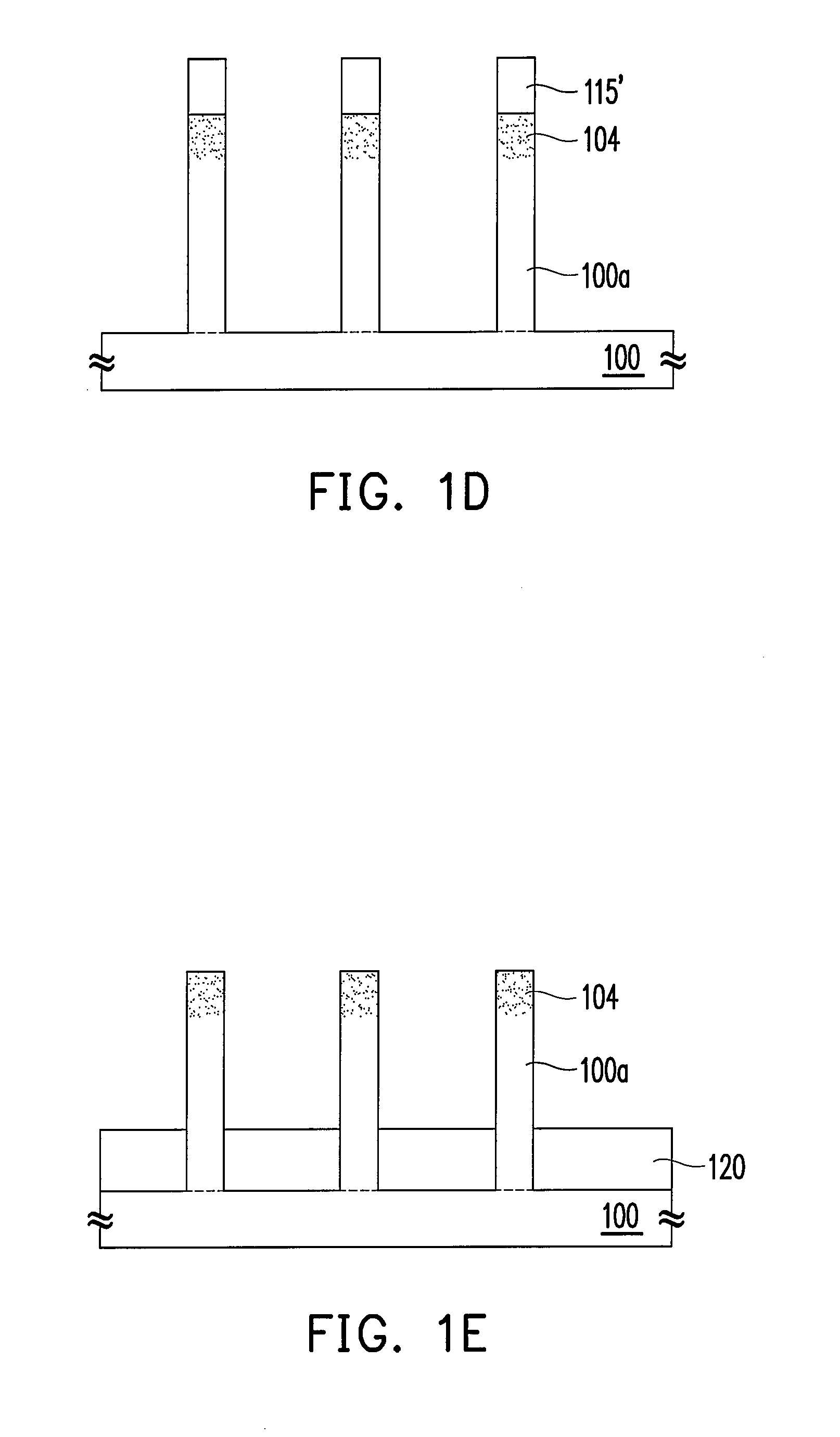

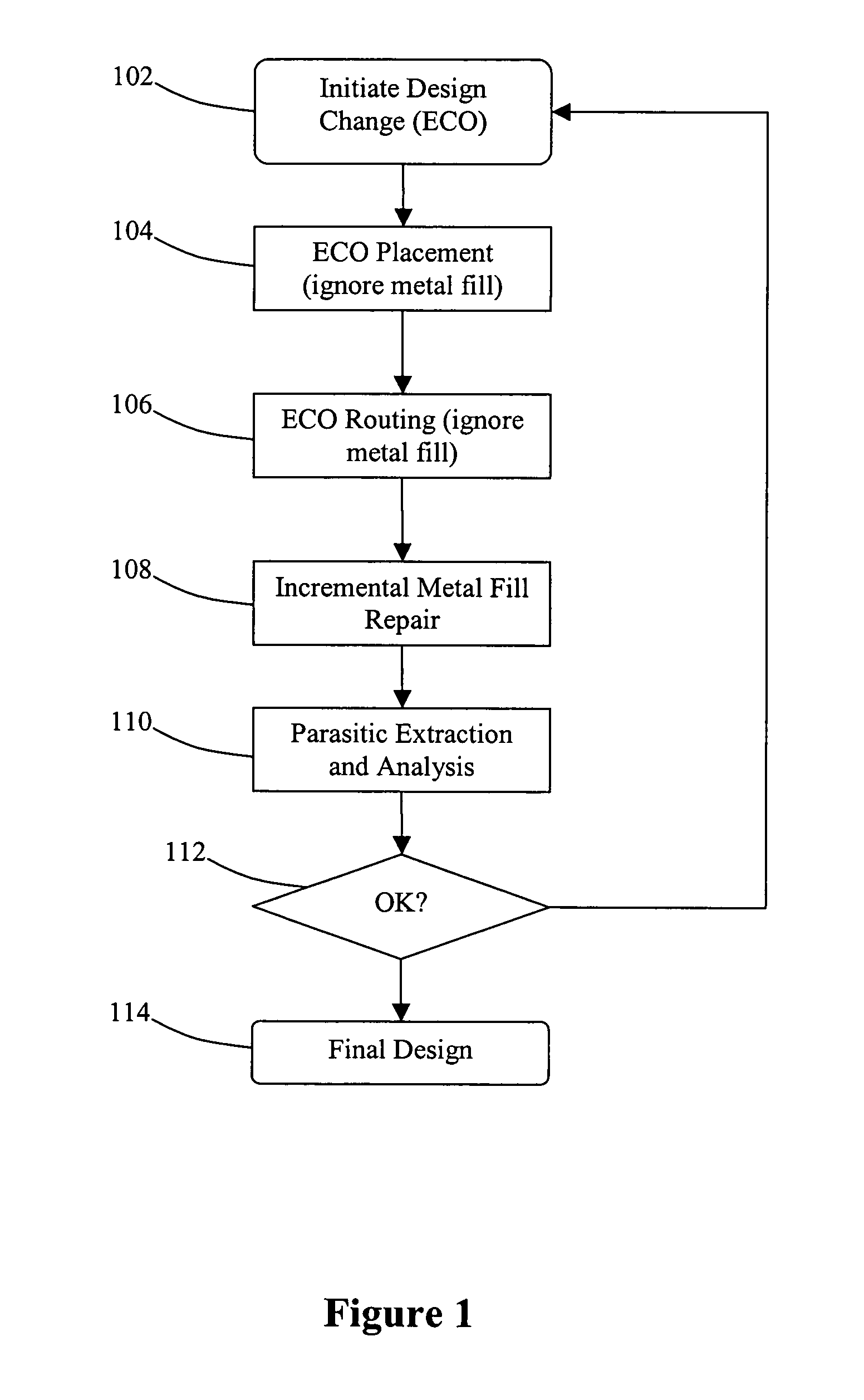

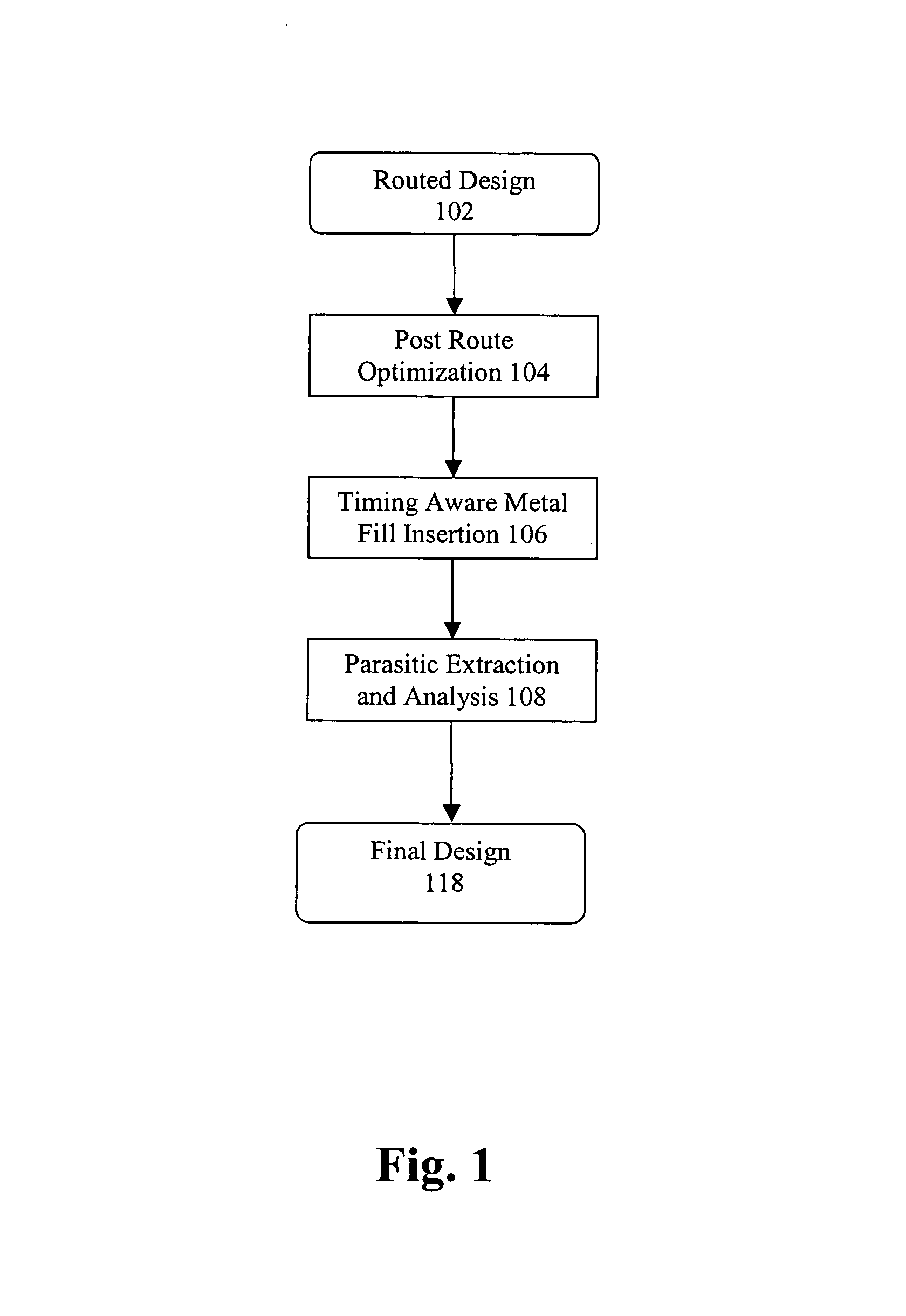

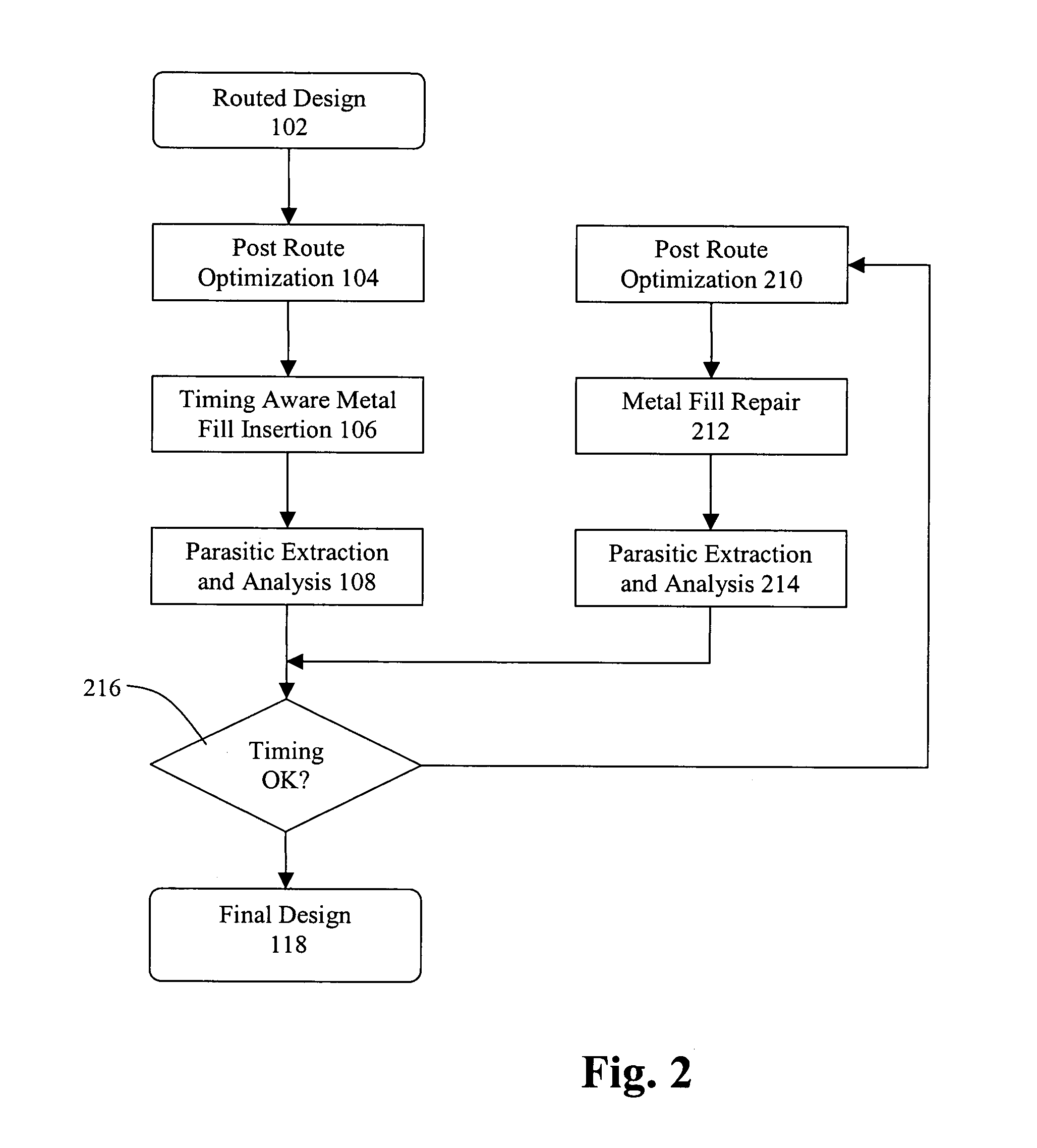

Method and system for implementing metal fill

ActiveUS7661078B1Reducing local step heightReduce yieldDetecting faulty computer hardwareCAD circuit designEngineeringImproved method

Disclosed is an improved method and system for implementing metal fill for an integrated circuit design. When an engineering change order is implemented, the existing dummy metal fill geometries are initially ignored when modifying the layout, even if this results in shorts and / or other DRC violations. Once the ECO changes have been implemented, those violations caused by interaction between the changes and the metal fill are repaired afterwards.

Owner:CADENCE DESIGN SYST INC

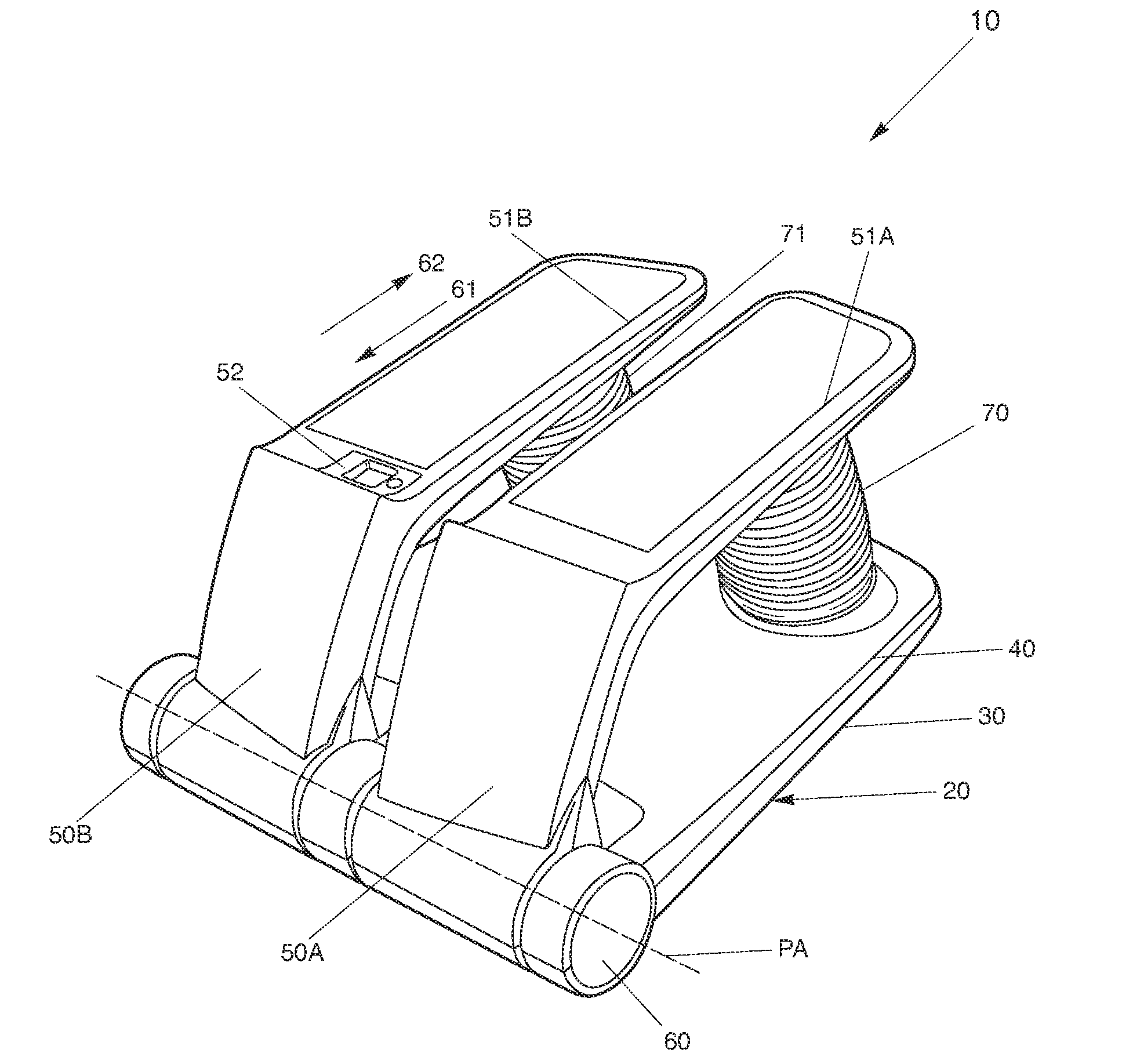

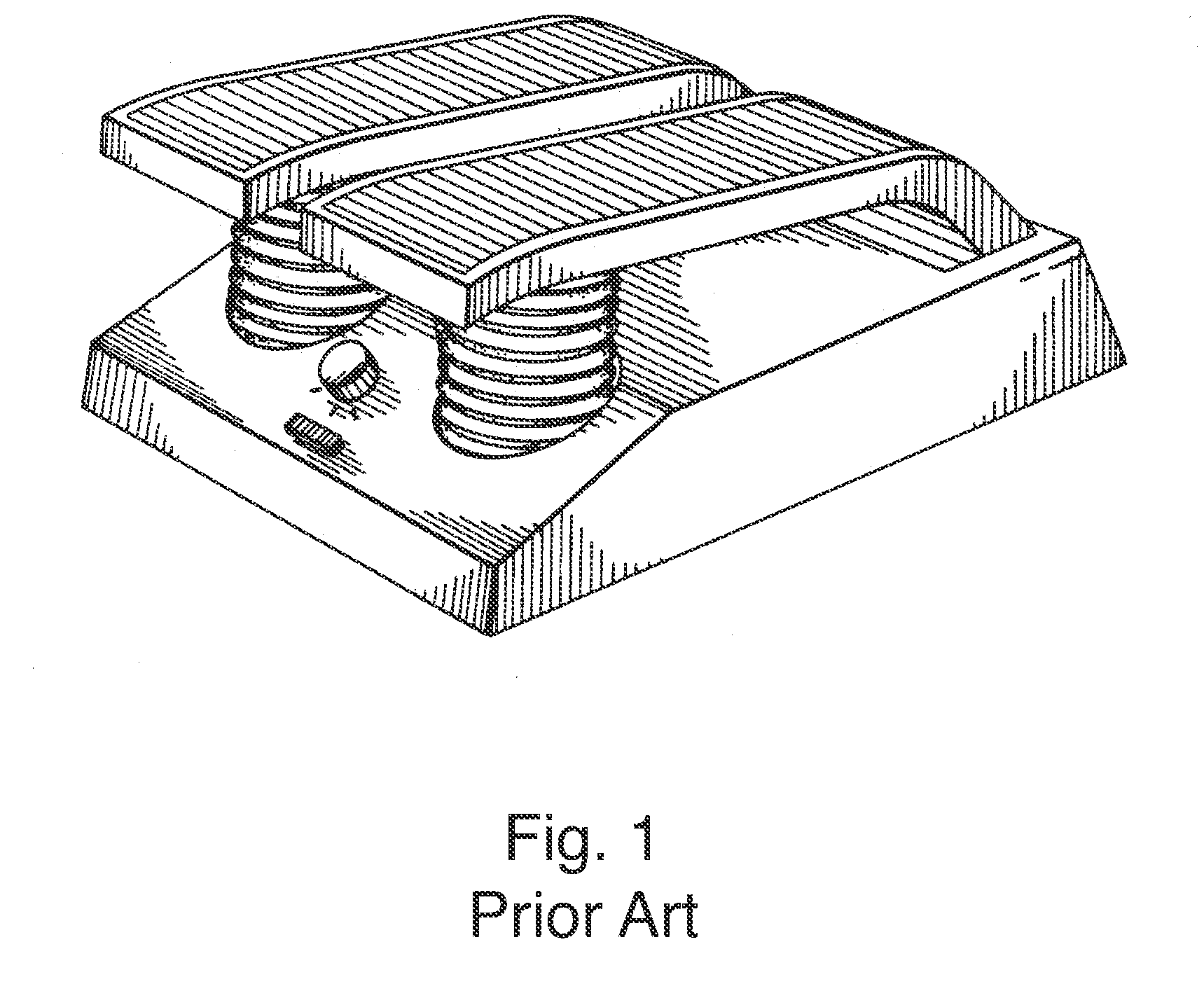

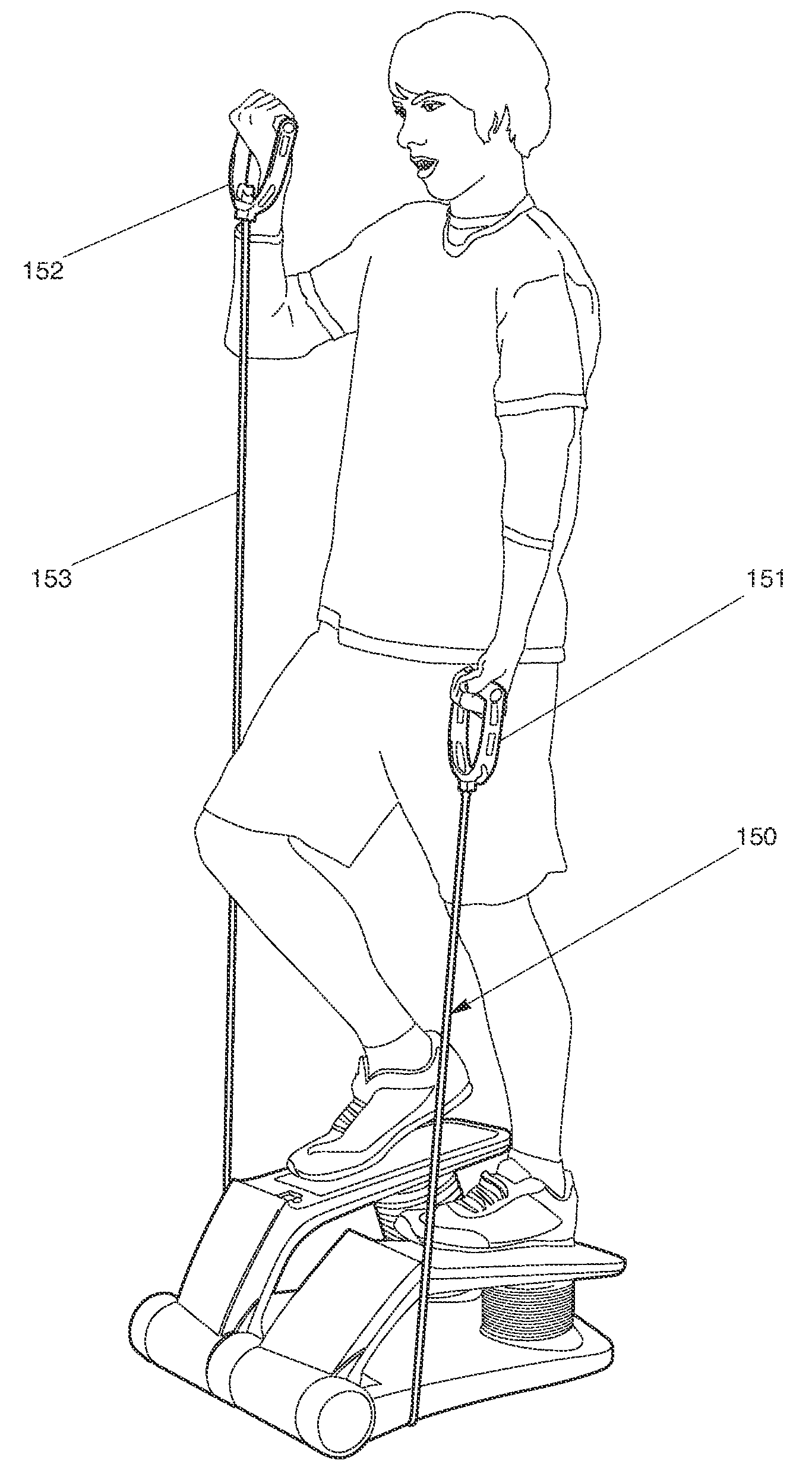

Stair climbing exercise apparatus with improved bellows

InactiveUS20090163325A1Reduce movementRelieve pressureResilient force resistorsMovement coordination devicesRest positionEngineering

An exercise apparatus includes a housing, a pair of pivoting foot treadles and a pair of reciprocating bellows that support the foot treadles. A sealed air system including a conduit interconnects the bellows and is operable for reciprocating transfer of air from bellow to bellow. Each of the foot treadles is pivotably movable between upper and lower positions, and has a resting position between the upper and lower positions. The resting position of the foot treadles defines a resting position of the bellows while the upper and lower positions of the foot treadles respectively define elongated and compressed positions of the bellows. In use, the elongated and compressed positions of the bellows are each no more than 5 degrees off the center resting position thereby reducing stress on the bellows.

Owner:PIAGET GARY D

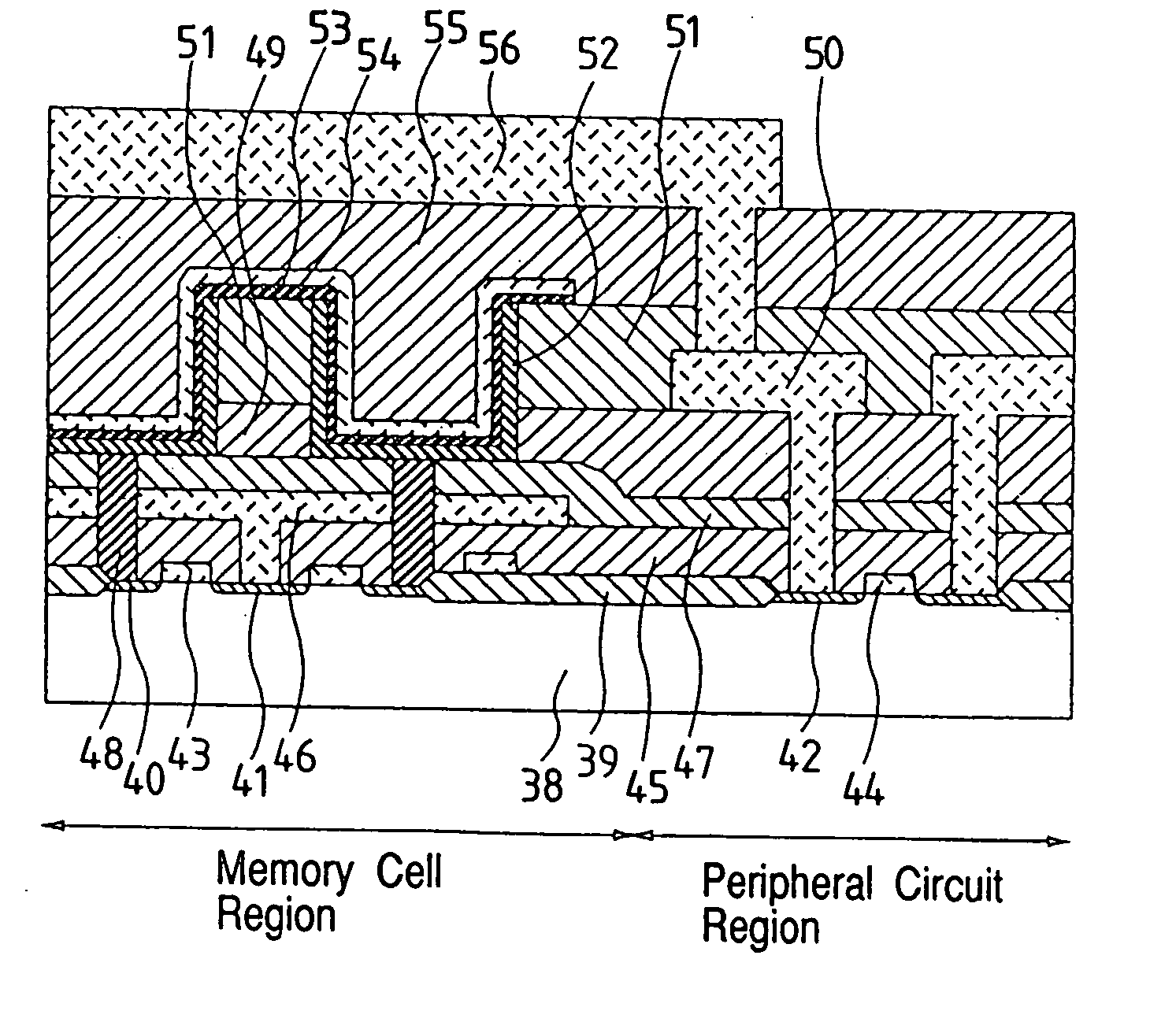

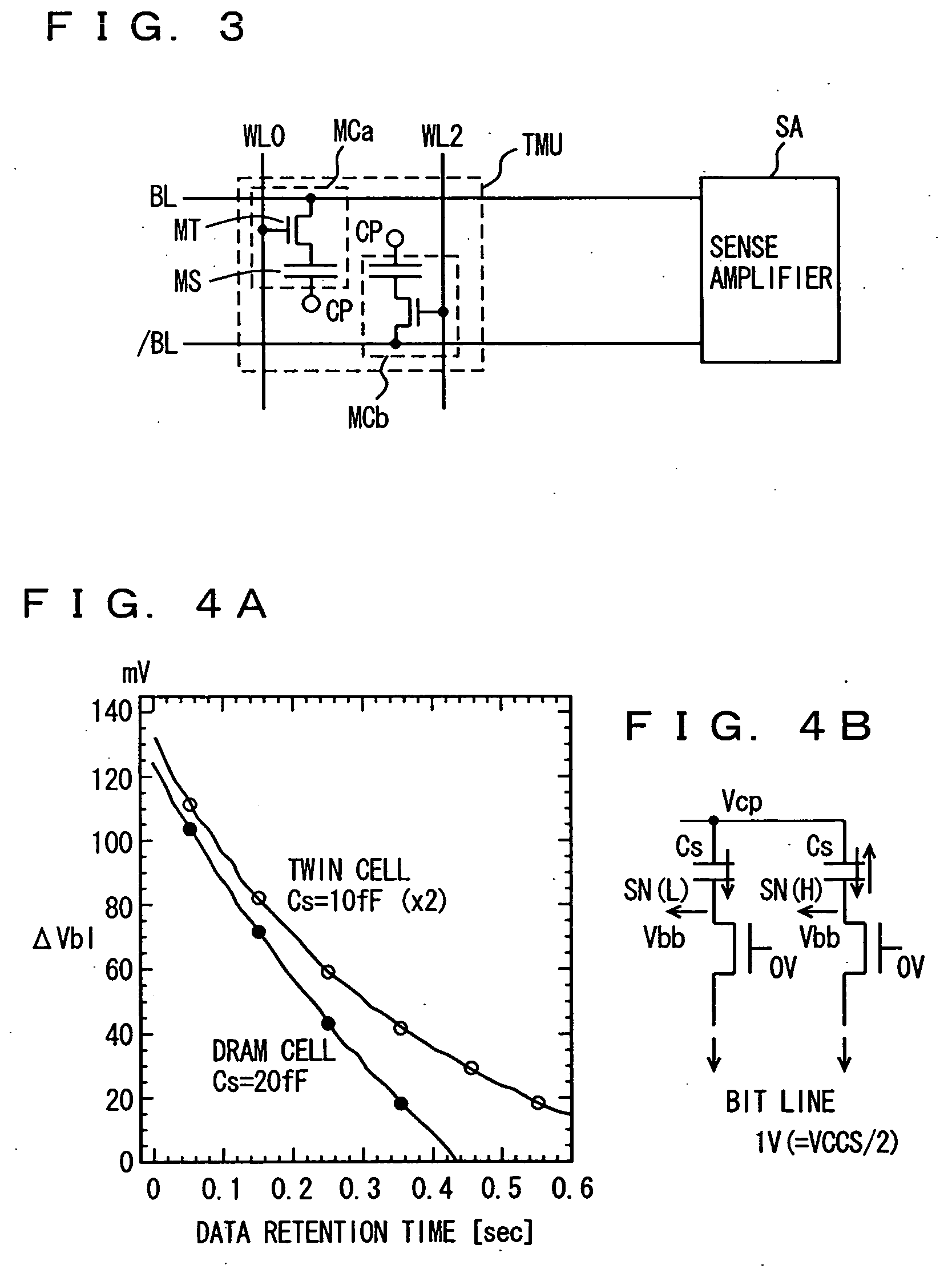

Semiconductor memory device and manufacturing method thereof

InactiveUS20050045933A1Large storage capacityWell formedTransistorSolid-state devicesEngineeringStep height

A capacitor consisting of a storage electrode (19), a capacitor dielectric film (20) and a plate electrode (21) is formed in a trench formed through dielectric films (6, 8, 10 and 12) stacked on a semiconductor substrate (1) and buried wiring layers (9 and 11) are formed under the capacitor. As the capacitor is formed not in the semiconductor substrate but over it, there is room in area in which the capacitor can be formed and the difficultly of forming wiring is reduced by using the wiring layers (9 and 11) for a global word line and a selector line. As the upper face of an dielectric film (32) which is in contact with the lower face of wiring (34) in a peripheral circuit area is extended into a memory cell area and is in contact with the side of the capacitor (33), step height between the peripheral circuit area and the memory cell area is remarkably reduced.

Owner:RENESAS ELECTRONICS CORP

Semiconductor memory device

InactiveUS20050018471A1Reduce areaReduce the numberTransistorSolid-state devicesCapacitanceSemiconductor

Conductive lines constituting word lines of memory cells and conductive lines constituting memory cell plate electrodes are formed in the same interconnecting layer in a memory device including a plurality of memory cells each including a capacitor for storing data in an electrical charge form. By forming the capacitors of the memory cells into a planar capacitor configuration, a step due to the capacitors is removed. Thus, a dynamic semiconductor memory device can be formed through CMOS process, and a dynamic semiconductor memory device suitable for merging with logic is achieved. Data of 1 bit is stored by two memory cells, and data can be reliably stored even if the capacitance value of the memory cell is reduced due to the planar type capacitor.

Owner:RENESAS ELECTRONICS CORP

Active organic electroluminescence panel display with blank layer covering contact opening

ActiveUS7317279B2Avoid shortingAvoid damageDischarge tube luminescnet screensElectroluminescent light sourcesTransistor arrayDisplay device

An active organic electroluminescence panel display and a fabricating method thereof are disclosed. A thin film transistor array comprising a plurality of thin film transistors, a plurality of datalines and a plurality of scanlines are formed on a substrate. A passivation layer is formed on the substrate, covering the thin film transistor array. A contact opening is formed in the passivation layer for exposing a prescribed area of the array. An anode layer is formed on the passivation layer and fills into the contact opening. A blank layer is formed on the anode, covering the contact opening. A shadow mask is disposed on the blank layer. Then, a sputtering process is performed to form an organic luminescent layer. The shadow mask is then removed, and a cathode layer is formed on the organic luminescent layer for forming an active organic electroluminescence panel display.

Owner:AU OPTRONICS CORP

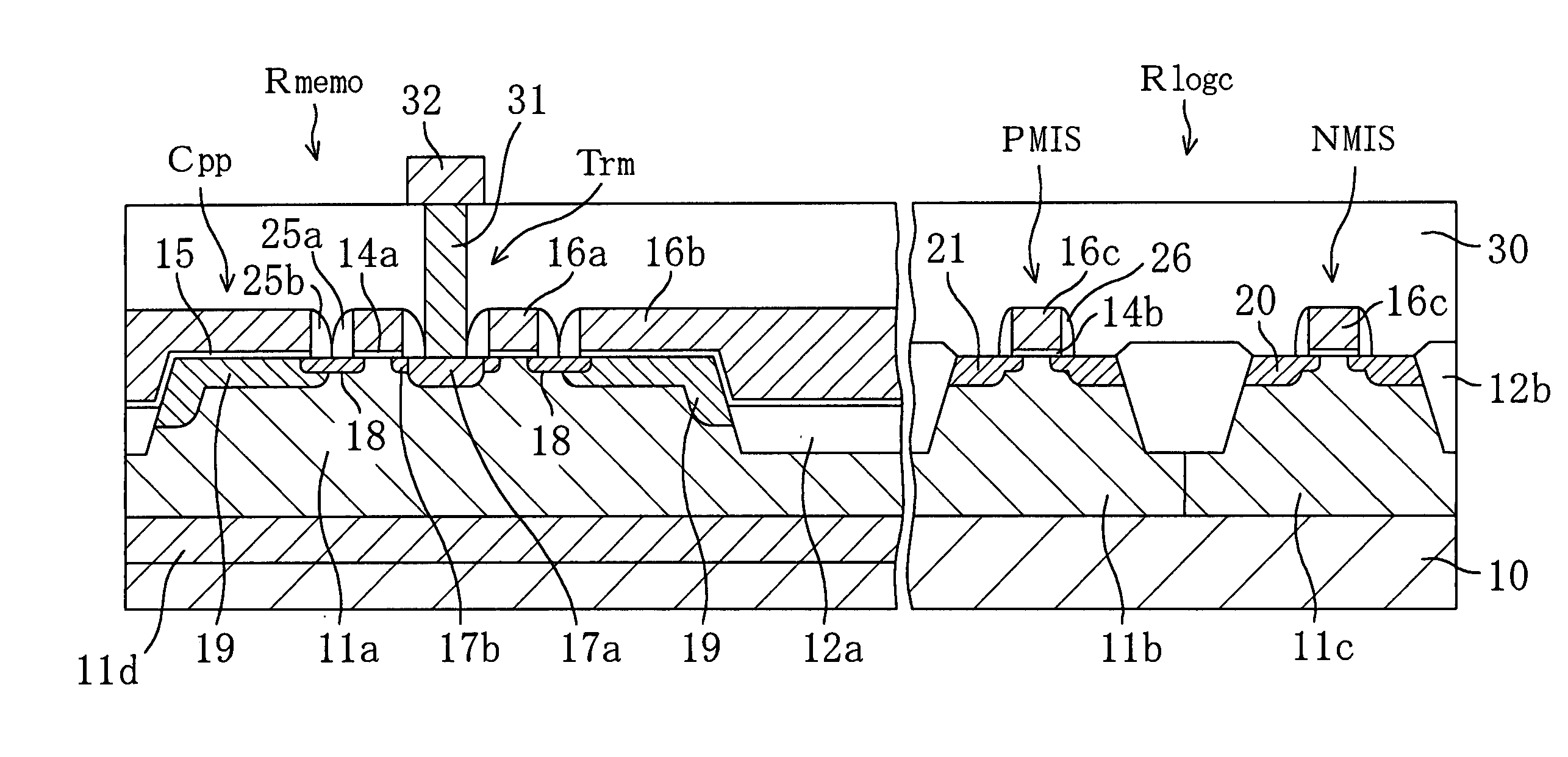

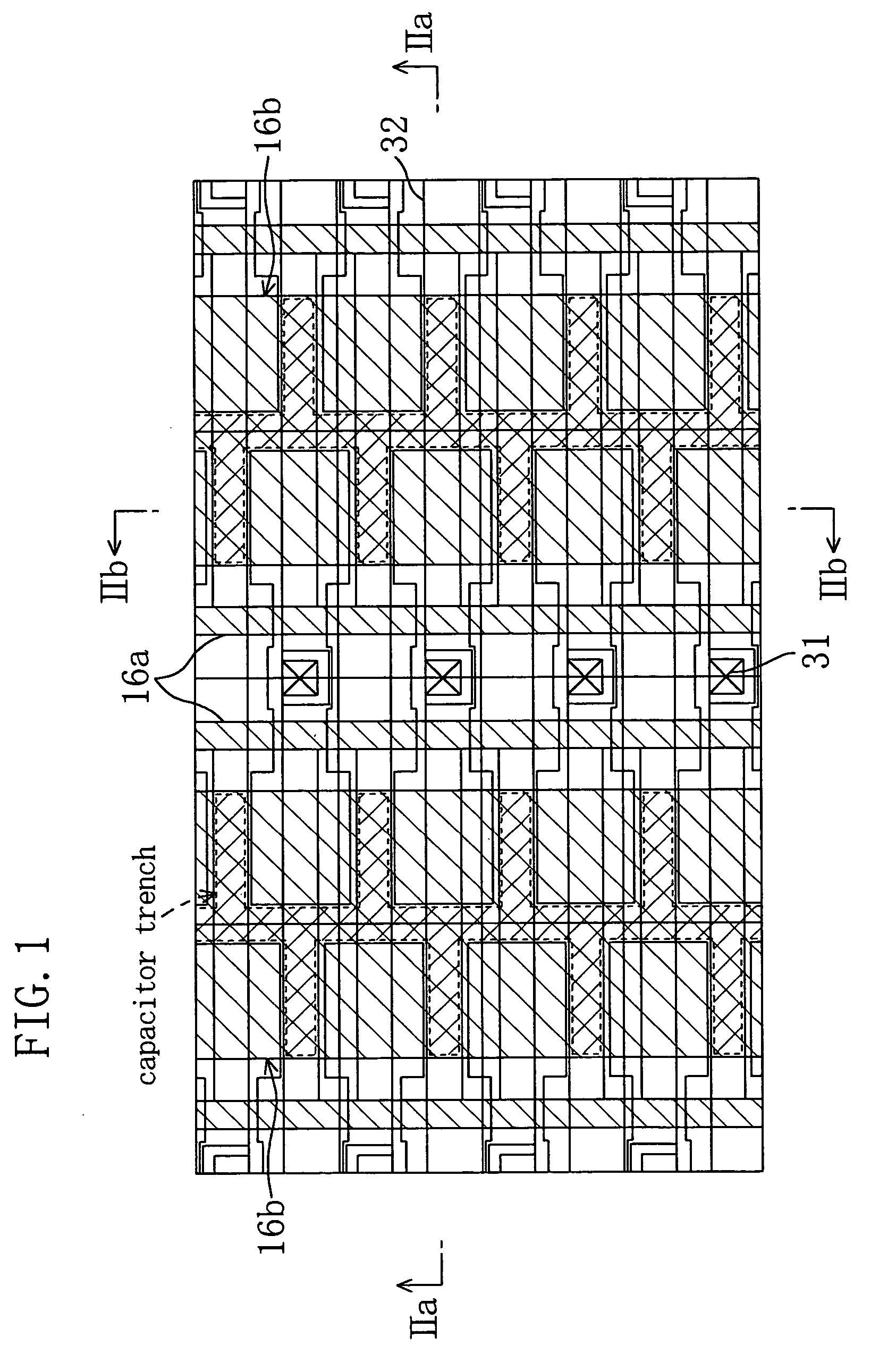

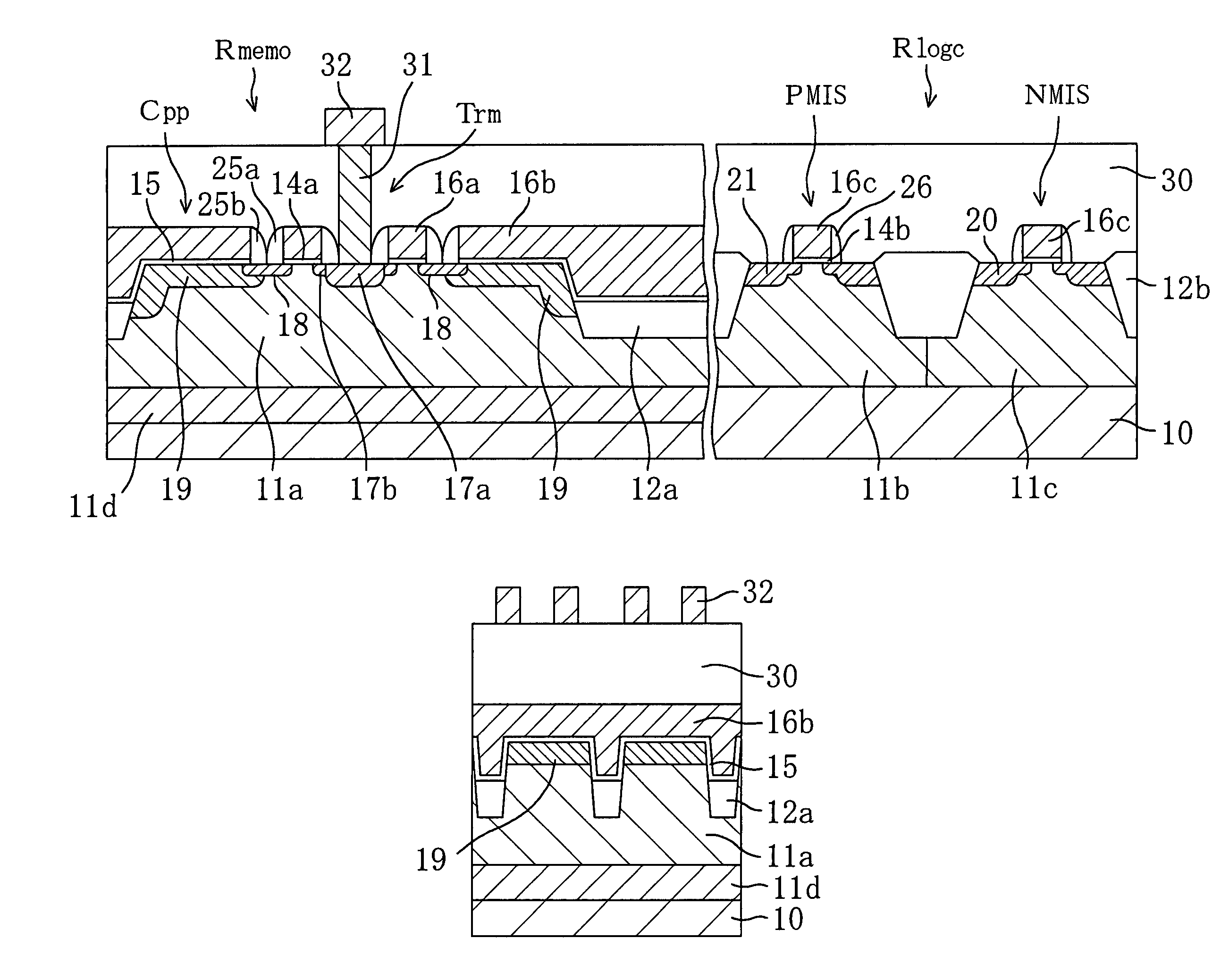

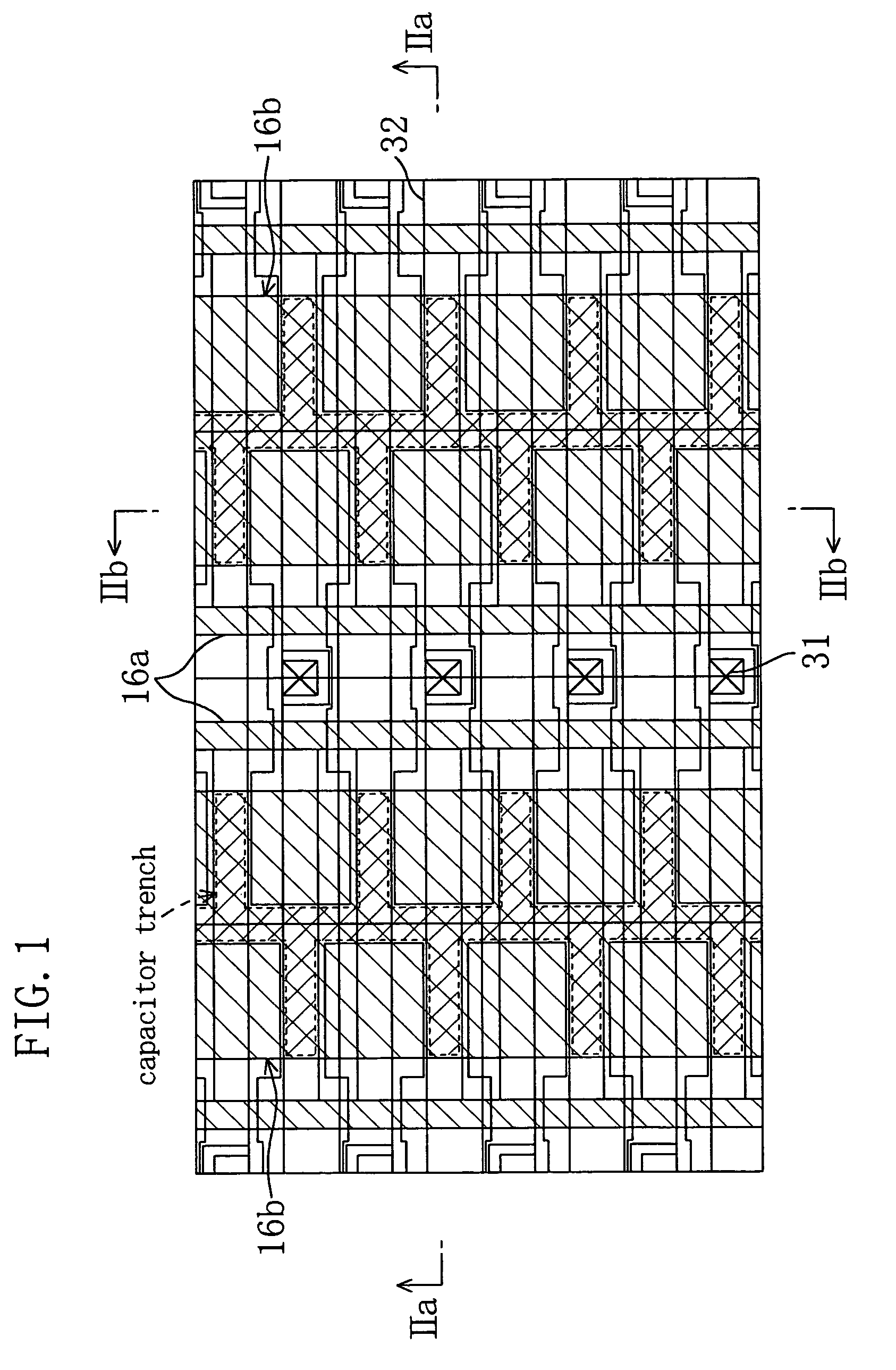

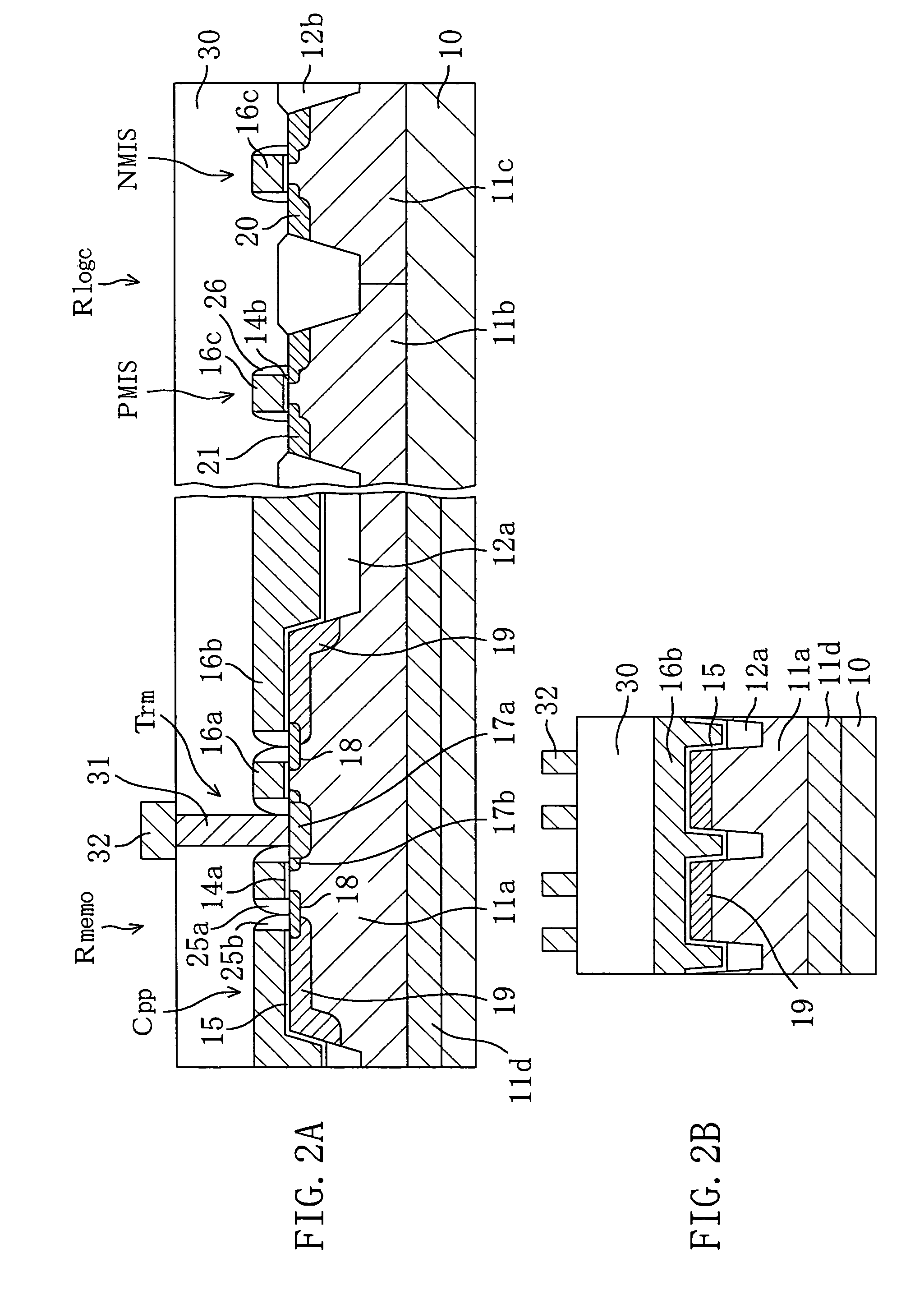

Semiconductor device and its manufacturing method

InactiveUS20040137667A1High pattern accuracyImprove flatnessTransistorSolid-state devicesCapacitanceDielectric

A memory cell transistor and a planar capacitor are provided in a memory region, and both transistors of a CMOS device are provided in a logic circuit region. A capacitance dielectric 15 and a plate electrode 16b of the planar capacitor are provided over a trench shared with a shallow trench isolation 12a, and the upper part of the trench is filled with the capacitance dielectric 15 and the plate electrode 16b. An n-type diffusion layer 19 that is a storage node is formed, with an end region thereof extending along one side of the upper part of the trench, to a region of the substrate overlapping with the shallow trench isolation 12a. The area of a part of the substrate functioning as a capacitor can be increased without increasing the substrate area.

Owner:GK BRIDGE 1

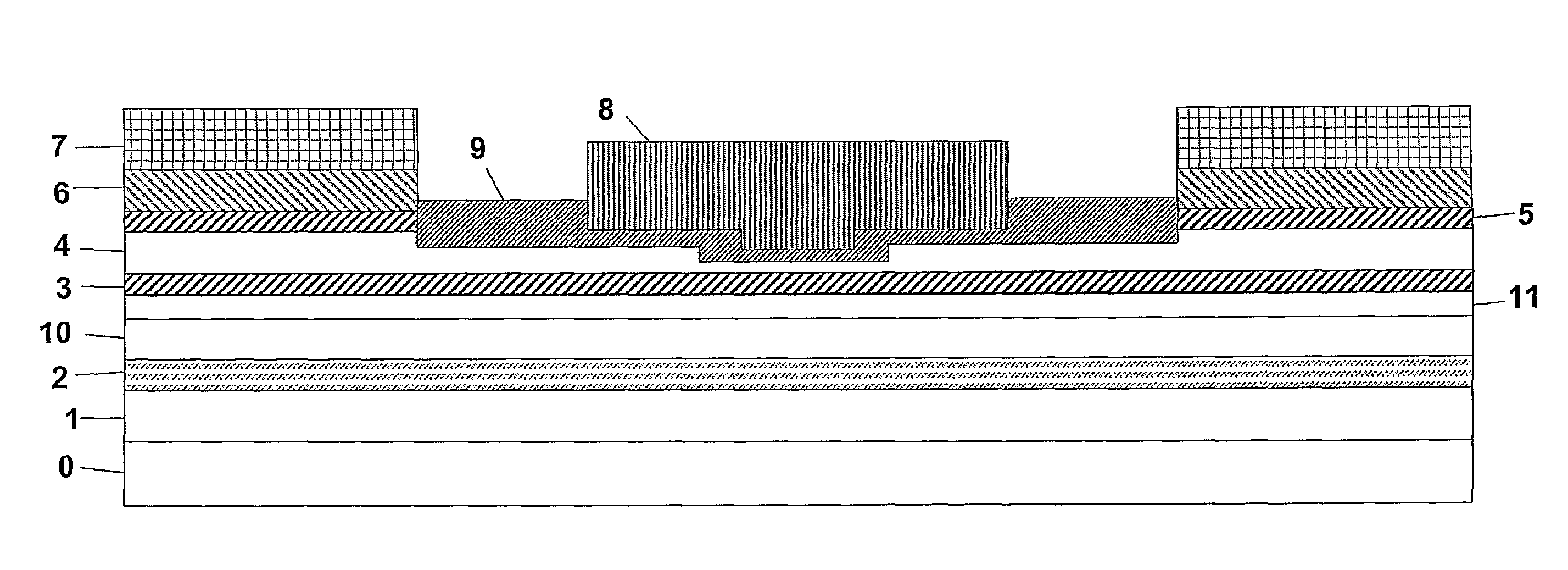

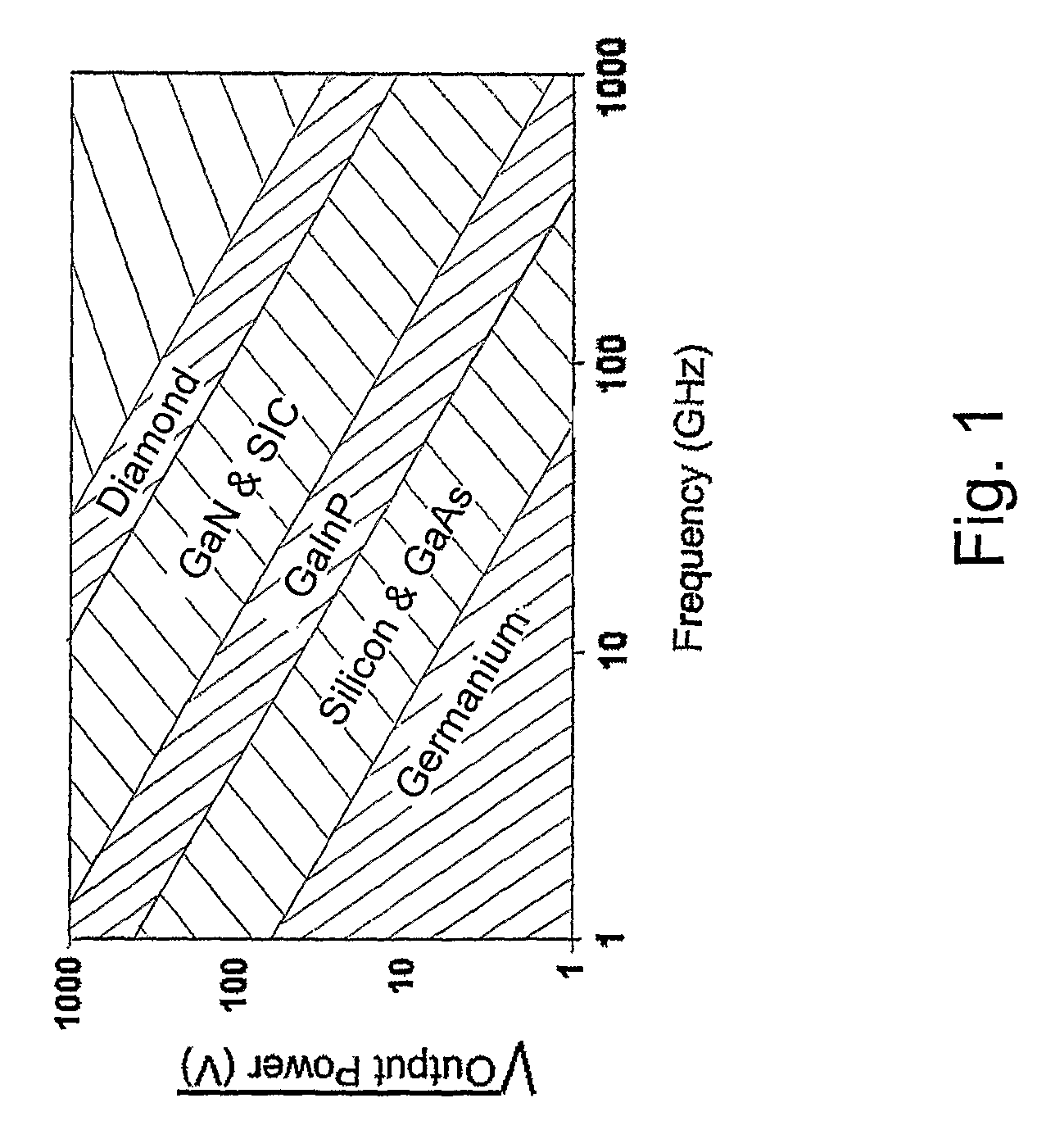

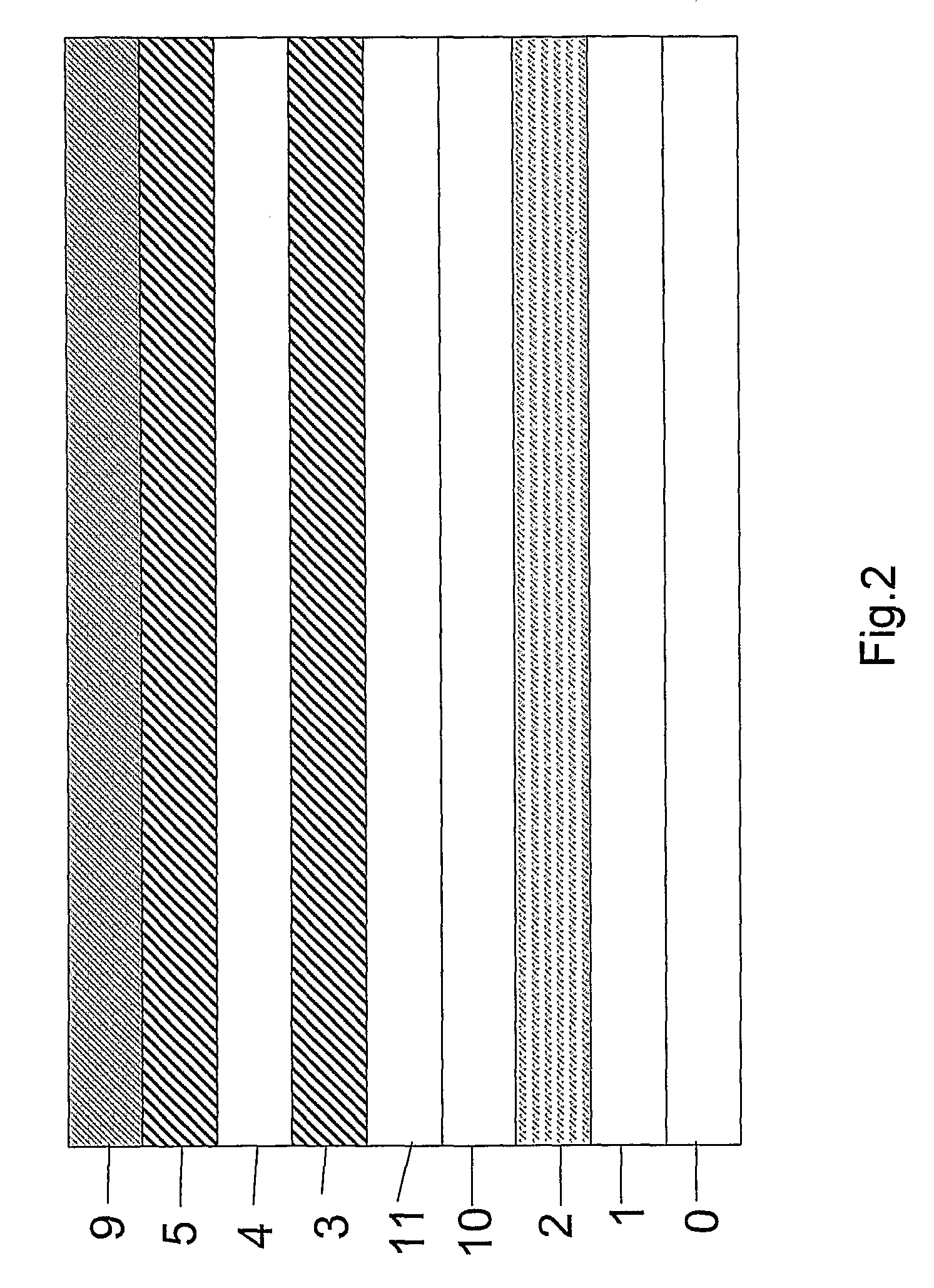

Diamond transistor and method of manufacture thereof

InactiveUS7981721B2Reduce surface roughnessReduce step heightTransistorPolycrystalline material growthDelta dopingEngineering

A method of manufacturing a transistor, typically a MESFET, includes providing a substrate including single crystal diamond material having a growth surface on which further layers of diamond material can be deposited. The substrate is preferably formed by a CVD process and has high purity. The growth surface has a root-mean-square roughness of 3 nm or less, or is free of steps or protrusions larger than 3 nm. Further diamond layers are deposited on the growth surface to define the active regions of the transistor. An optional n+ shielding layer can be formed in or on the substrate, following which an additional layer of high purity diamond is deposited. A layer of intrinsic diamond may be formed directly on the upper surface of the high purity layer, followed by a boron doped (“delta doped”) layer. A trench is formed in the delta doped layer to define a gate region.

Owner:DIAMOND MICROWAVE DEVICES

Semiconductor memory device with improved data retention characteristics

InactiveUS7046543B2Reduce areaIncrease the number ofTransistorSolid-state devicesCapacitanceSemiconductor

Conductive lines constituting word lines of memory cells and conductive lines constituting memory cell plate electrodes are formed in the same interconnecting layer in a memory device including a plurality of memory cells each including a capacitor for storing data in an electrical charge form. By forming the capacitors of the memory cells into a planar capacitor configuration, a step due to the capacitors is removed. Thus, a dynamic semiconductor memory device can be formed through CMOS process, and a dynamic semiconductor memory device suitable for merging with logic is achieved. Data of 1 bit is stored by two memory cells, and data can be reliably stored even if the capacitance value of the memory cell is reduced due to the planar type capacitor.

Owner:RENESAS ELECTRONICS CORP

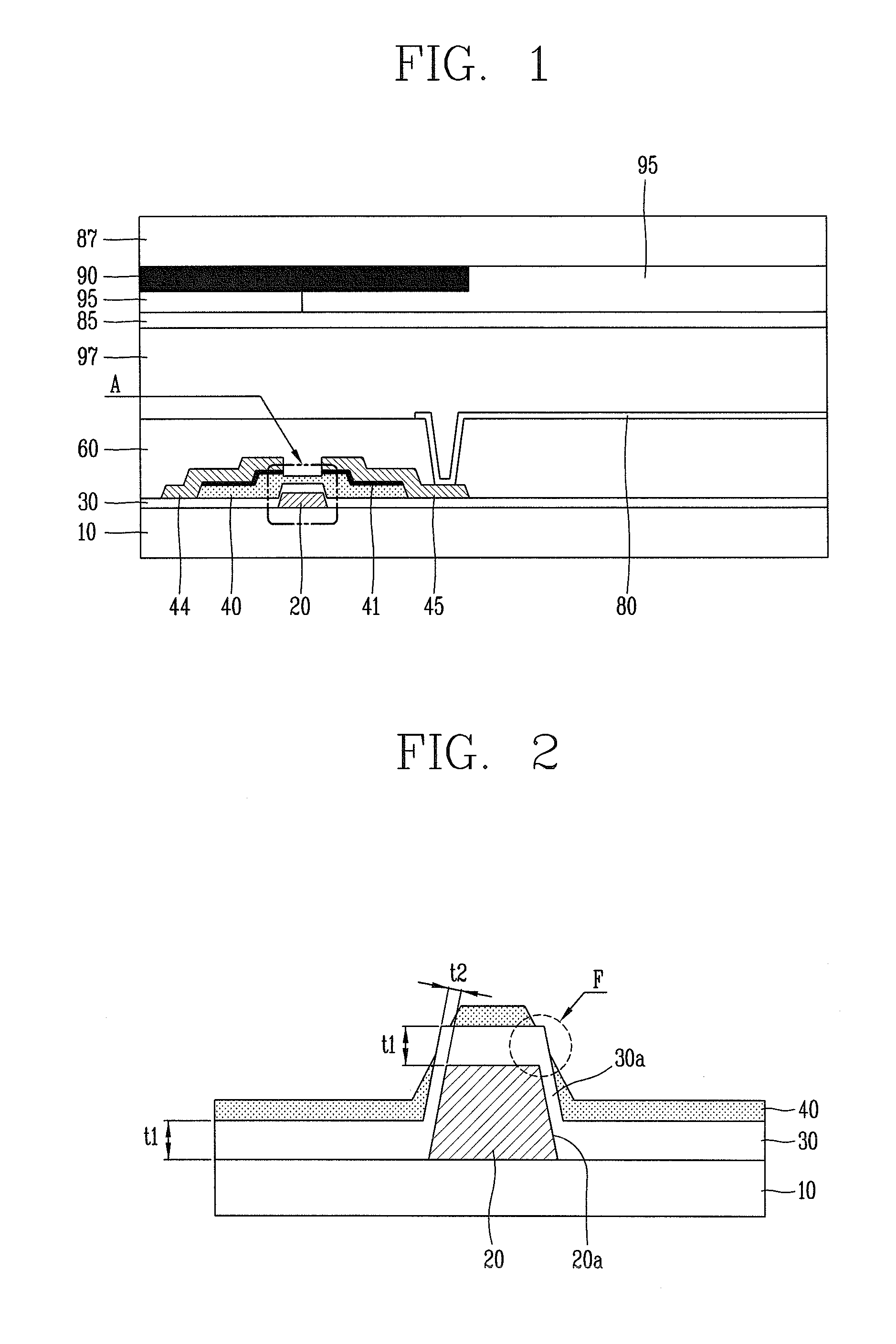

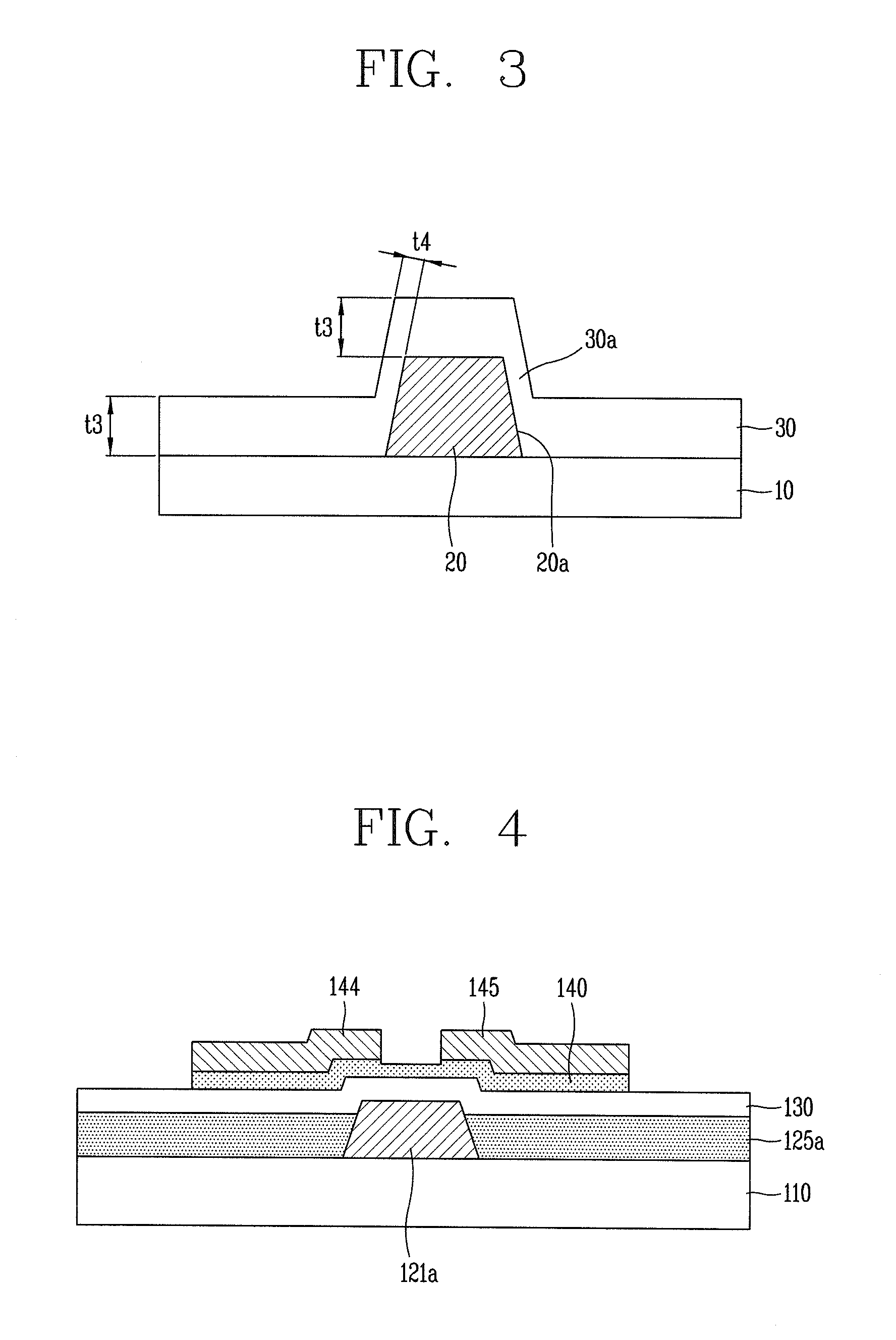

Thin film transistor, method fabricating thereof, liquid crystal display device and method for fabricating the same

ActiveUS20130037814A1Reduce failureReduce step heightTransistorSolid-state devicesLiquid-crystal displayEngineering

A thin-film transistor array substrate and a fabrication method thereof according to an embodiment of the present invention are disclosed to form an interlayer insulating layer, thereby reducing a failure occurred during the process subsequent to a gate electrode. The thin-film transistor disclosed according to the present invention may include a substrate, a gate electrode formed on the substrate, a planarized insulating layer formed at a lateral surface portion of the gate electrode and at an upper portion of the substrate, a gate insulating layer formed on the planarized insulating layer containing an upper portion of the gate electrode, an active layer formed at an upper portion of the planarized insulating layer located at an upper side of the gate electrode, and a source electrode and a drain electrode formed on the active layer and separated from each other based on a channel region.

Owner:LG DISPLAY CO LTD

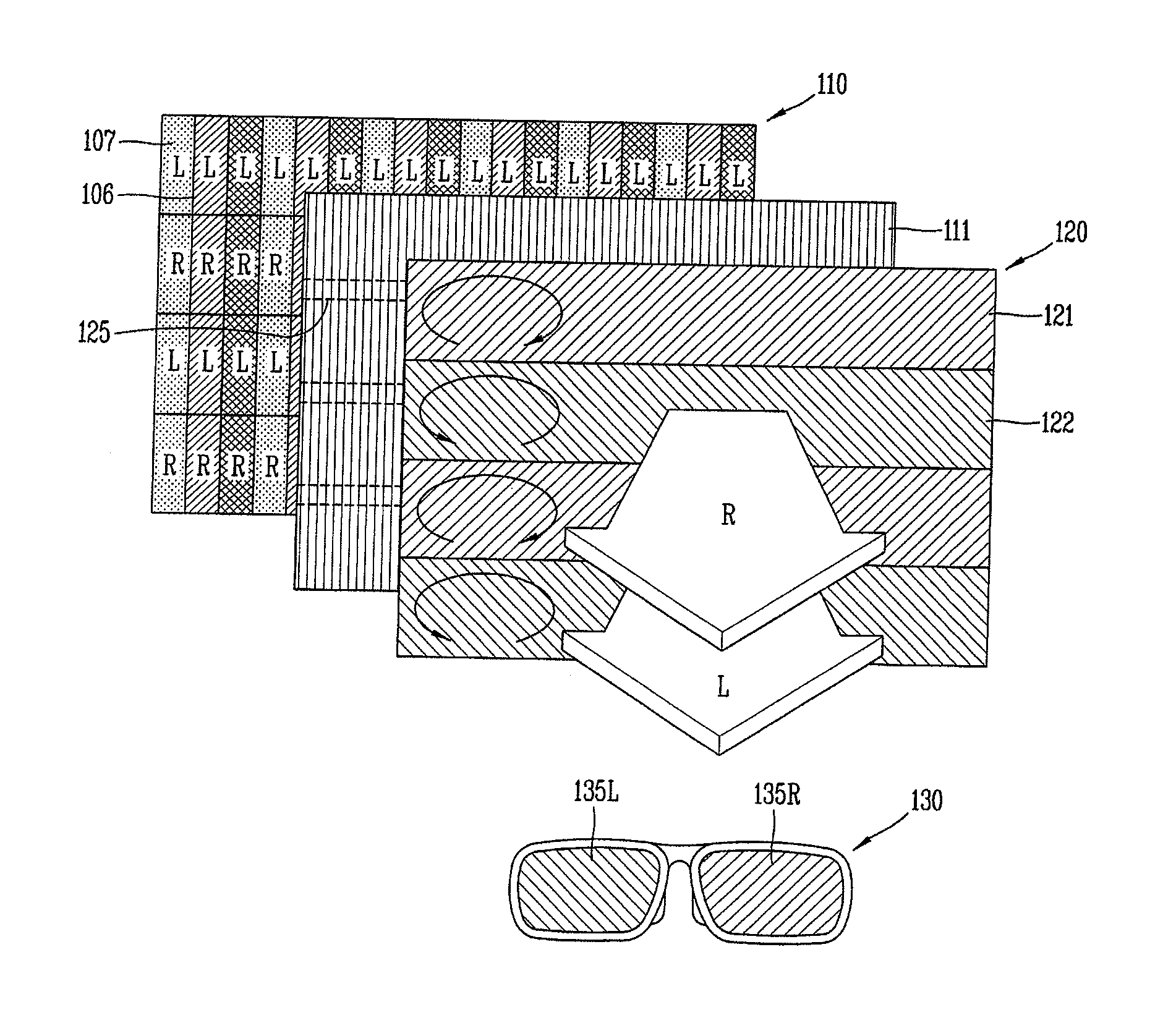

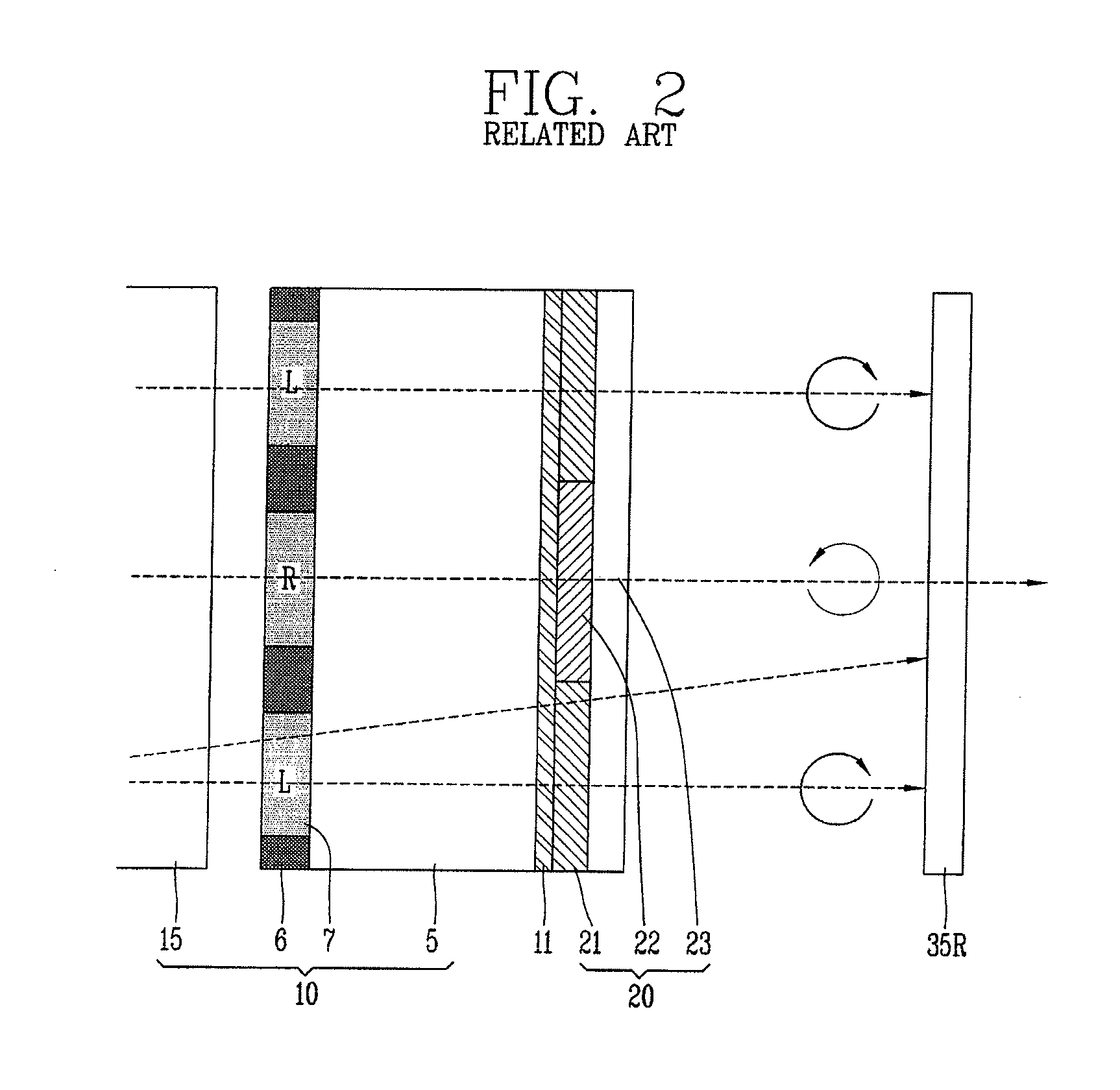

Polarized glasses type stereoscopic image display device and fabrication method thereof

InactiveUS20130141552A1Increase the aperture ratioHigh hardnessLamination ancillary operationsLaminationGlasses typeHardness

According to a polarized glasses type stereoscopic image display device and a fabrication method thereof in accordance with the present invention, a light blocking pattern may be formed on a rear surface of the color filter substrate to enhance vertical viewing angle and aperture ratio. Moreover a light blocking pattern may be formed of a metal having a large hardness instead of resin BM and a step height from the rear surface ITO may be removed to prevent a scratch due to an abrasive belt.

Owner:LG DISPLAY CO LTD

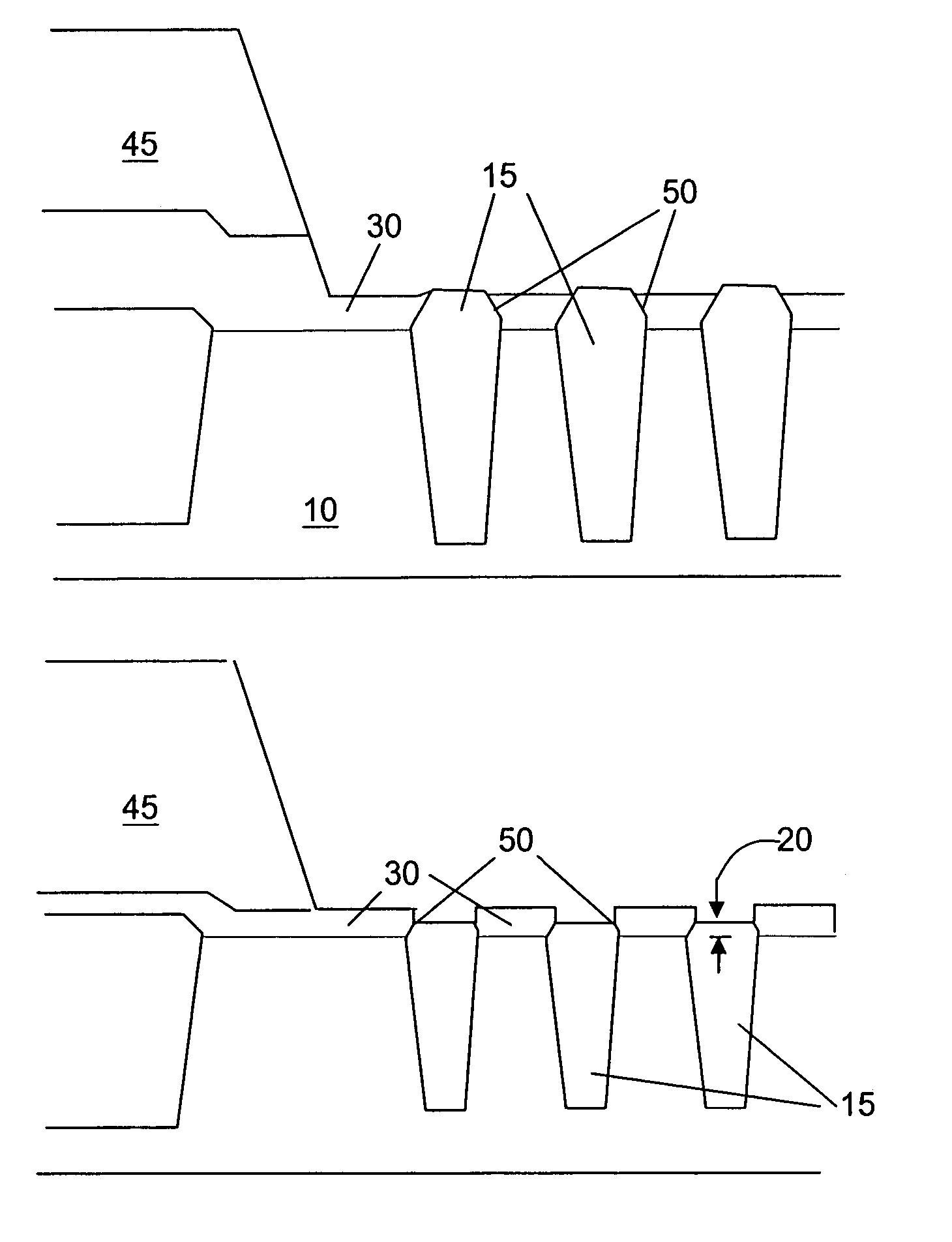

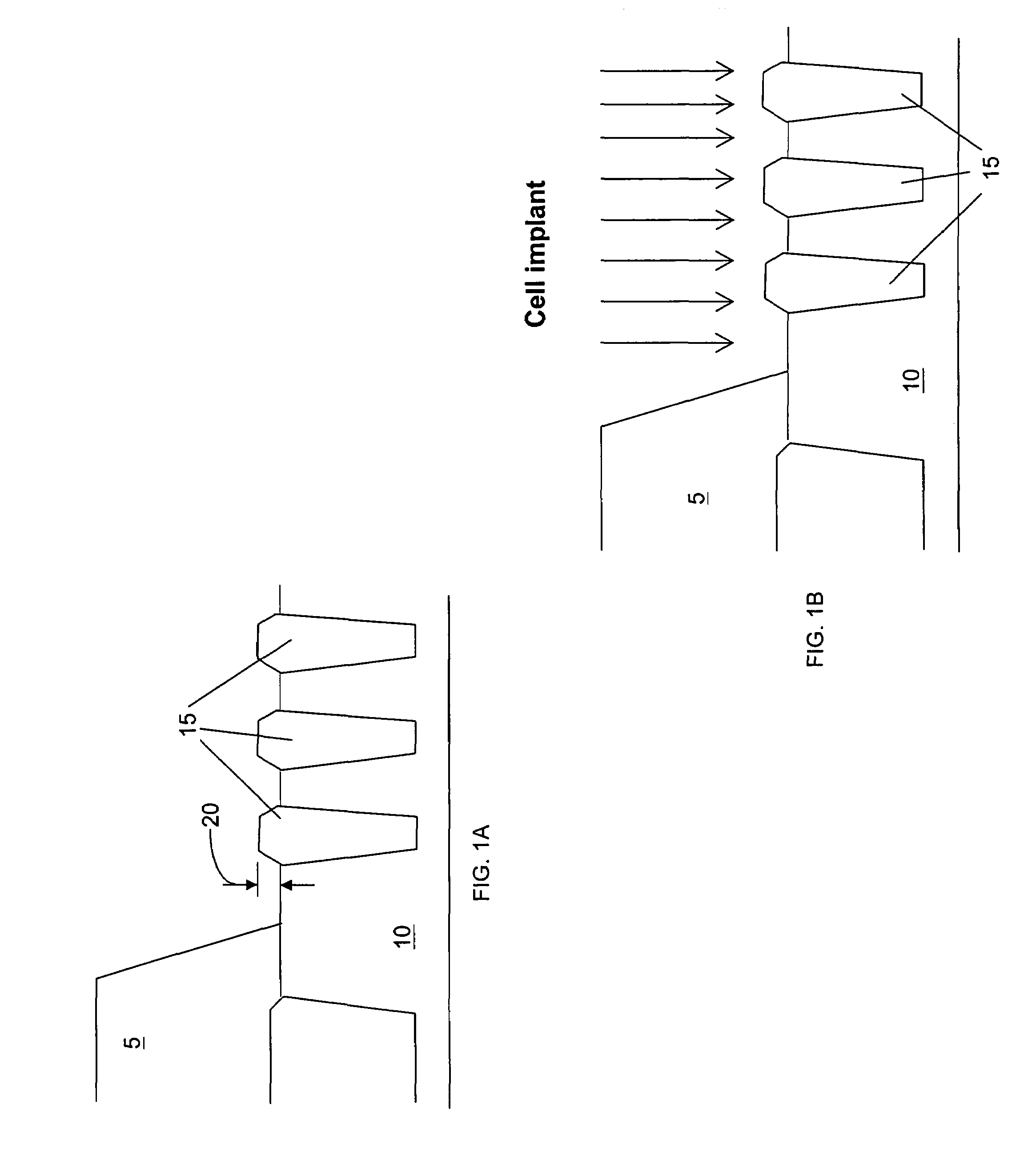

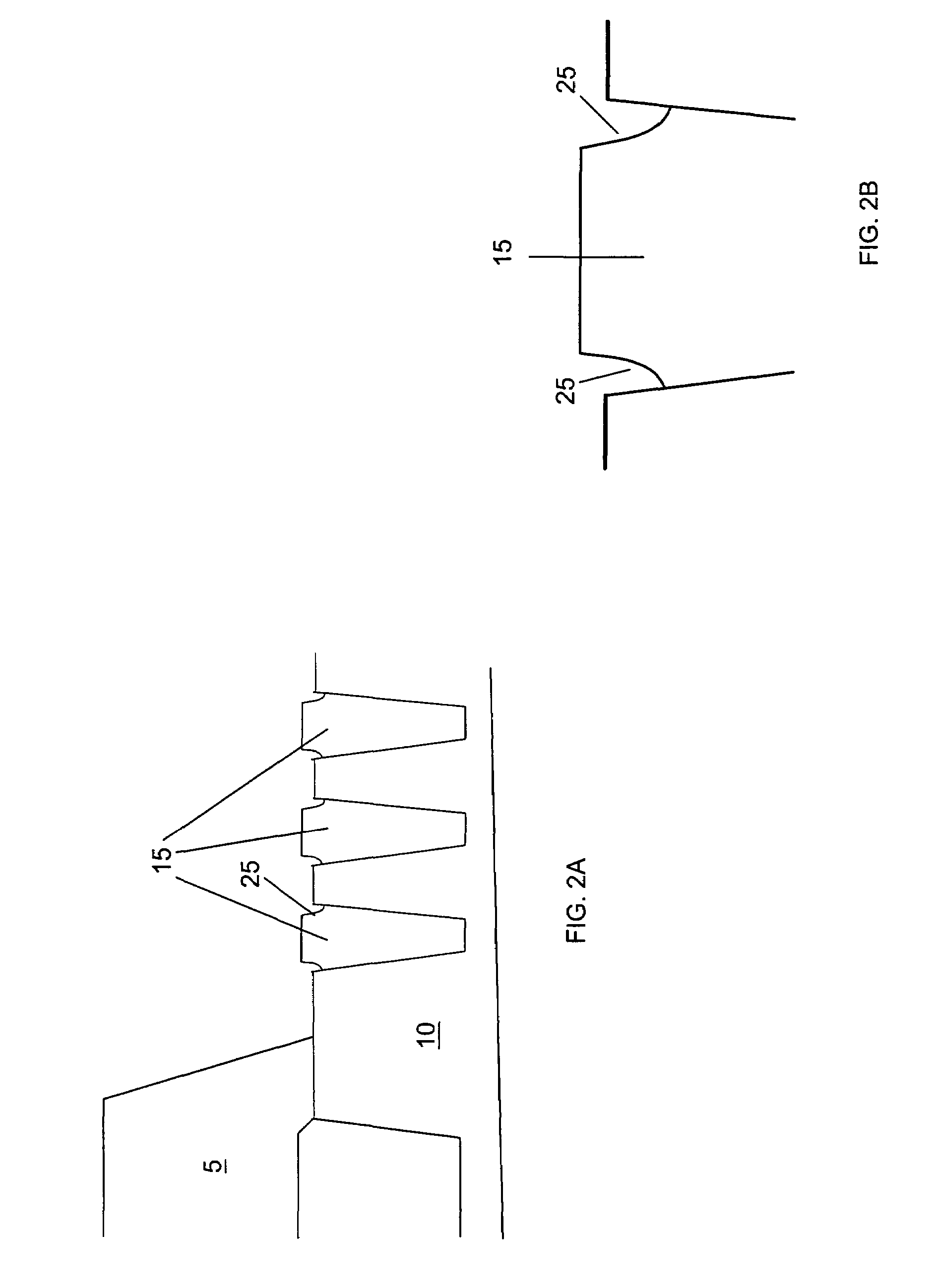

Process to improve programming of memory cells

ActiveUS7153755B2Reduce step heightSolid-state devicesSemiconductor/solid-state device manufacturingMemory cellDevice material

Owner:TAIWAN SEMICON MFG CO LTD

Radially segmented apodized diffractive multifocal design for ocular implant

A radially segmented apodized diffractive multifocal IOL for ocular implant is provided. The ocular implant can comprise a radially segmented apodized diffractive multifocal intraocular lens optic and a number of haptics. The radially segmented apodized diffractive multifocal IOL may pass optical energy in both photopic and mesopic conditions. The radially segmented apodized diffractive multifocal IOL includes a number of radially segmented apodization zones, each radially segmented apodization zones having a unique focal length. The haptics mechanically couple to the apodized diffractive multifocal IOL optic in order to position and secure the apodized diffractive multifocal IOL within the eye. The radially segmented apodized diffractive multifocal IOL may include both a diffractive region and a refractive region.

Owner:ALCON INC

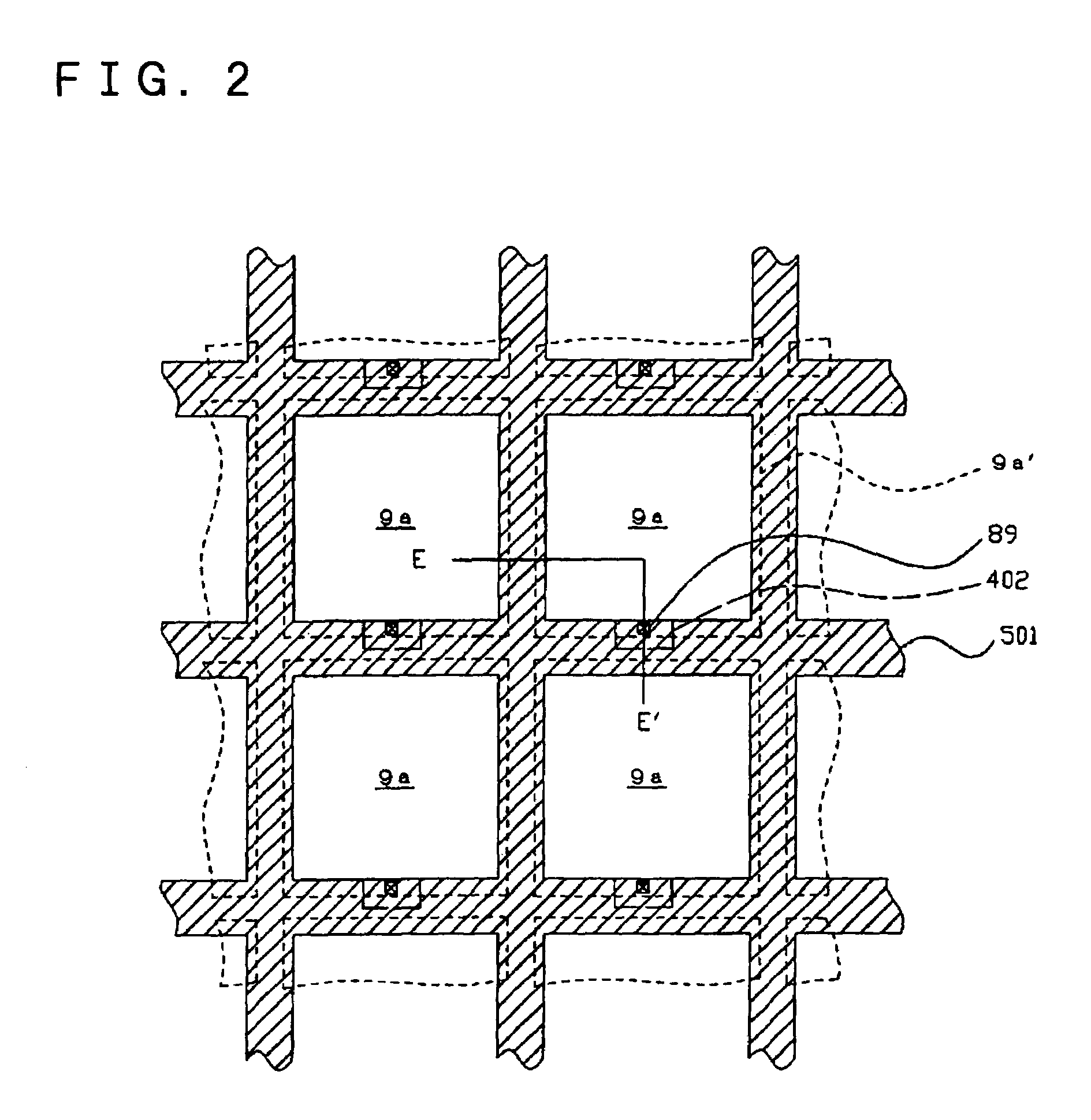

Electro-optical having a configuration to prevent generation and trapping of material residues

ActiveUS7075109B2Effectively reduce or prevent an eventReduce and prevent residueSolid-state devicesNon-linear opticsElectricityTrapping

An electro-optical device for a liquid-crystal apparatus includes TFTs provided above a substrate, pixel electrodes that are provided above the TFTs and that are connected to corresponding relay electrodes via contact holes, a protection insulating film that is provided on the pixel electrodes from the gaps between the pixel electrodes to the edge portions thereof so as to cover end surfaces of the edge portions of the pixel electrodes, and an alignment layer that is provided on a surface including the protection insulating film and that is rubbed. Material residues of the alignment layer are reduced or prevented from being generated or trapped in the vicinities of the edges of the pixel electrodes and in the vicinities of the contact holes. Consequently, brightness irregularities or display irregularities are reduced.

Owner:138 EAST LCD ADVANCEMENTS LTD

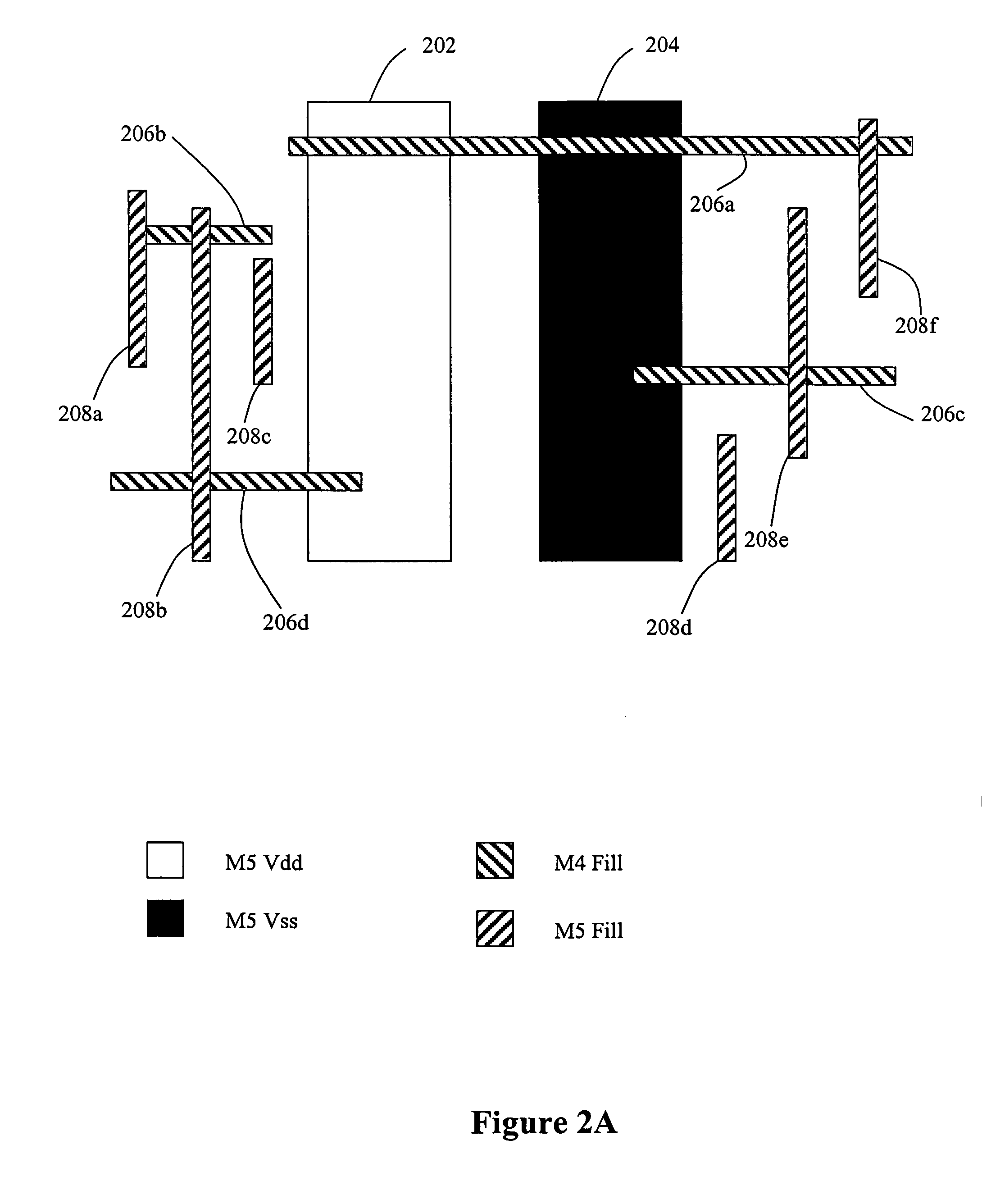

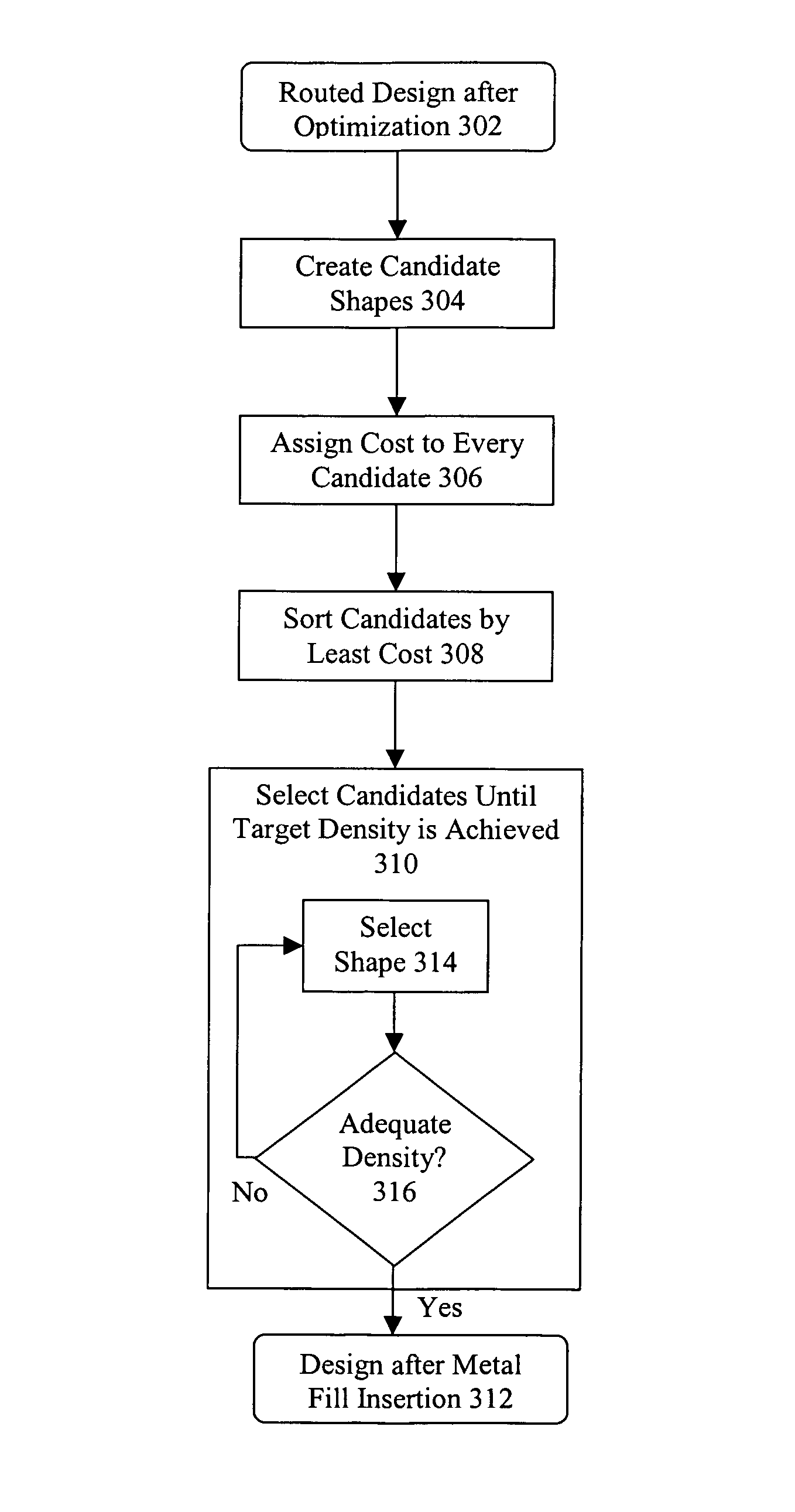

Method and system for implementing timing aware metal fill

InactiveUS8161425B1Reduce step heightGlobal planarizationSemiconductor/solid-state device detailsSolid-state devicesCost distributionCapacitance

An improved approach for implementing metal fill on an electrical device without causing creating cross-coupling capacitance problems is disclosed. Timing aware metal fill insertion is performed to avoid or minimize cross-capacitance problems on the IC design. A cost may be assigned to different candidate metal fill shapes. The cost is associated with the expected effect upon timing requirements by the metal fill shape, with lower costs corresponding to lower expected impacts upon the timing requirements. To meet density requirements, lower cost metal fill shapes are inserted prior to higher cost metal fill shapes.

Owner:CADENCE DESIGN SYST INC

Semiconductor device and its manufacturing method

InactiveUS6995415B2Reduce step heightPromote formationTransistorSolid-state devicesDielectricCapacitance

A memory cell transistor and a planar capacitor are provided in a memory region, and both transistors of a CMOS device are provided in a logic circuit region. A capacitance dielectric 15 and a plate electrode 16b of the planar capacitor are provided over a trench shared with a shallow trench isolation 12a, and the upper part of the trench is filled with the capacitance dielectric 15 and the plate electrode 16b. An n-type diffusion layer 19 that is a storage node is formed, with an end region thereof extending along one side of the upper part of the trench, to a region of the substrate overlapping with the shallow trench isolation 12a. The area of a part of the substrate functioning as a capacitor can be increased without increasing the substrate area.

Owner:GK BRIDGE 1

Stair climbing exercise apparatus with improved bellows

InactiveUS20090270230A1Reduce movementRelieve pressureResilient force resistorsMovement coordination devicesRest positionEngineering

An exercise apparatus includes a housing, a pair of pivoting foot treadles and a pair of reciprocating bellows that support the foot treadles. A sealed air system including a conduit interconnects the bellows and is operable for reciprocating transfer of air from bellow to bellow. Each of the foot treadles is pivotably movable between upper and lower positions, and has a resting position between the upper and lower positions. The resting position of the foot treadles defines a resting position of the bellows while the upper and lower positions of the foot treadles respectively define elongated and compressed positions of the bellows. In use, the elongated and compressed positions of the bellows are each no more than 5 degrees off the center resting position thereby reducing stress on the bellows.

Owner:PIAGET GARY D

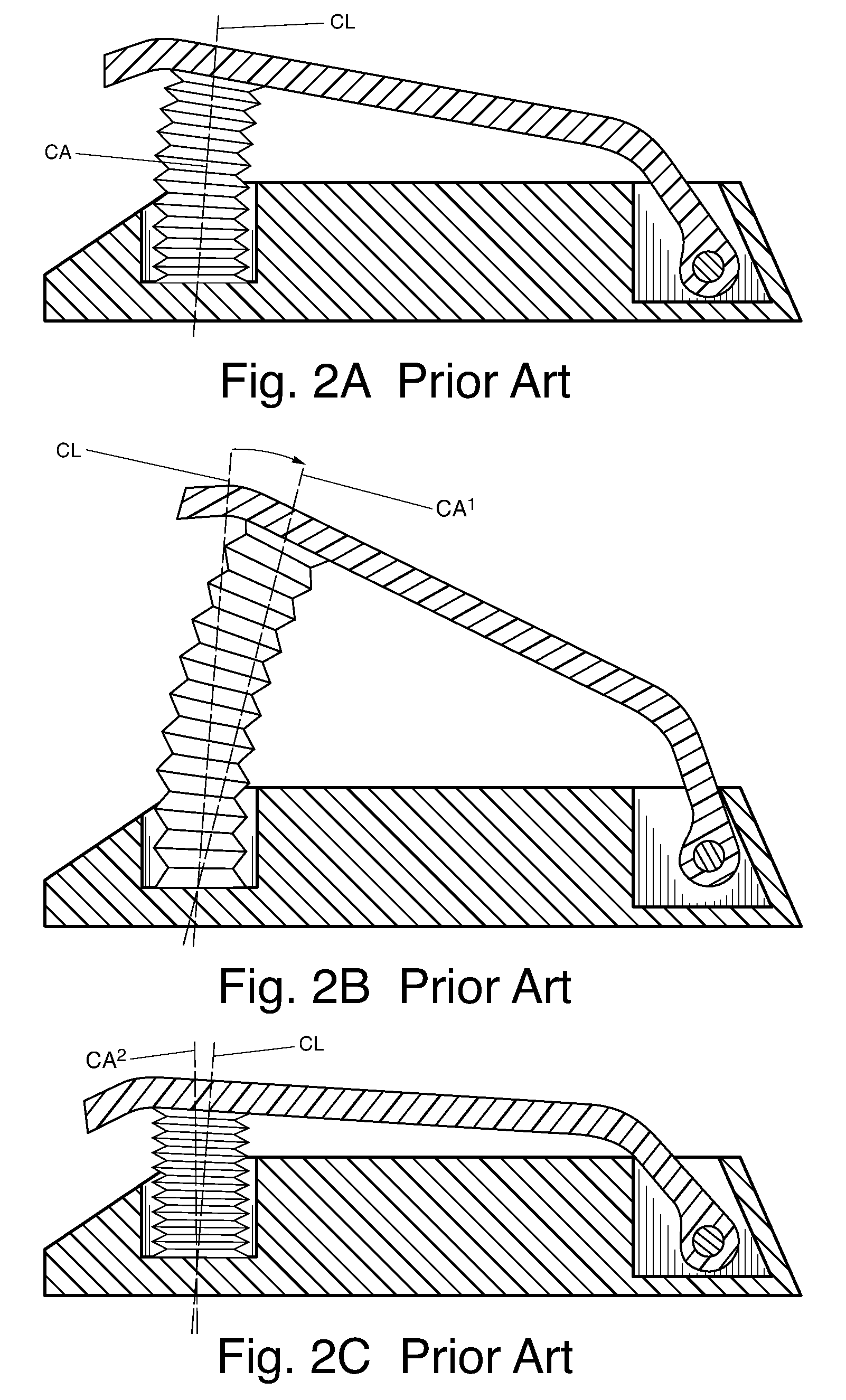

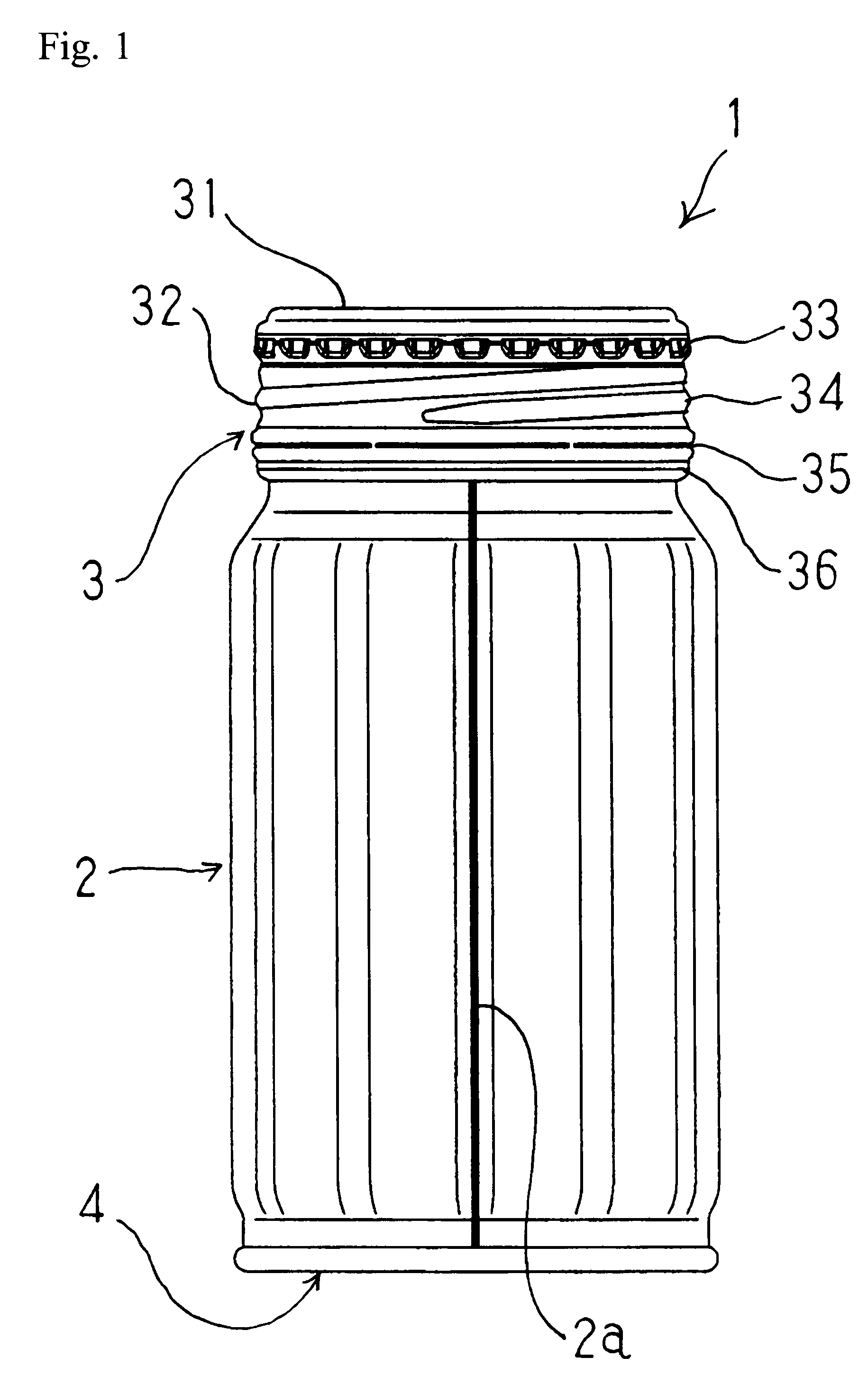

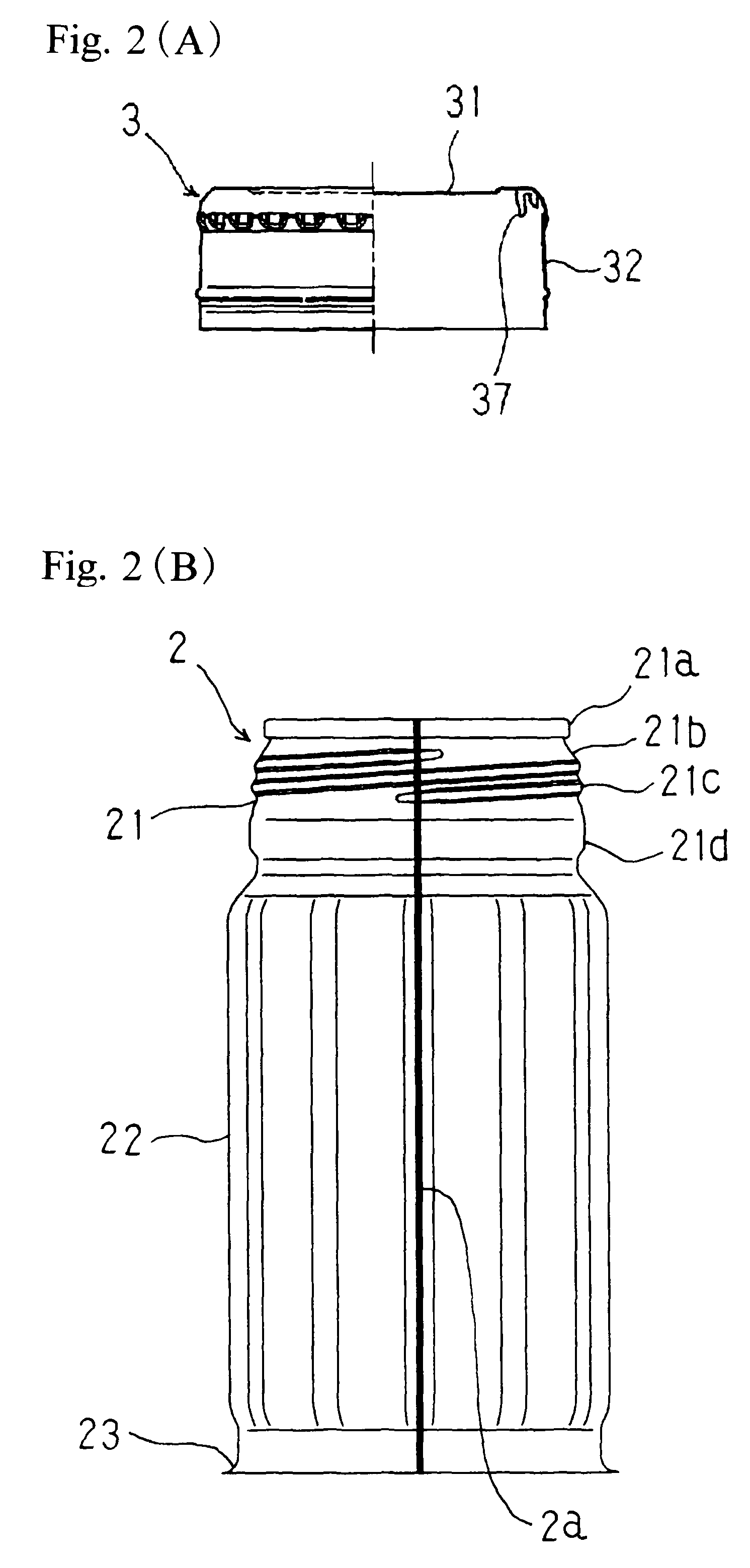

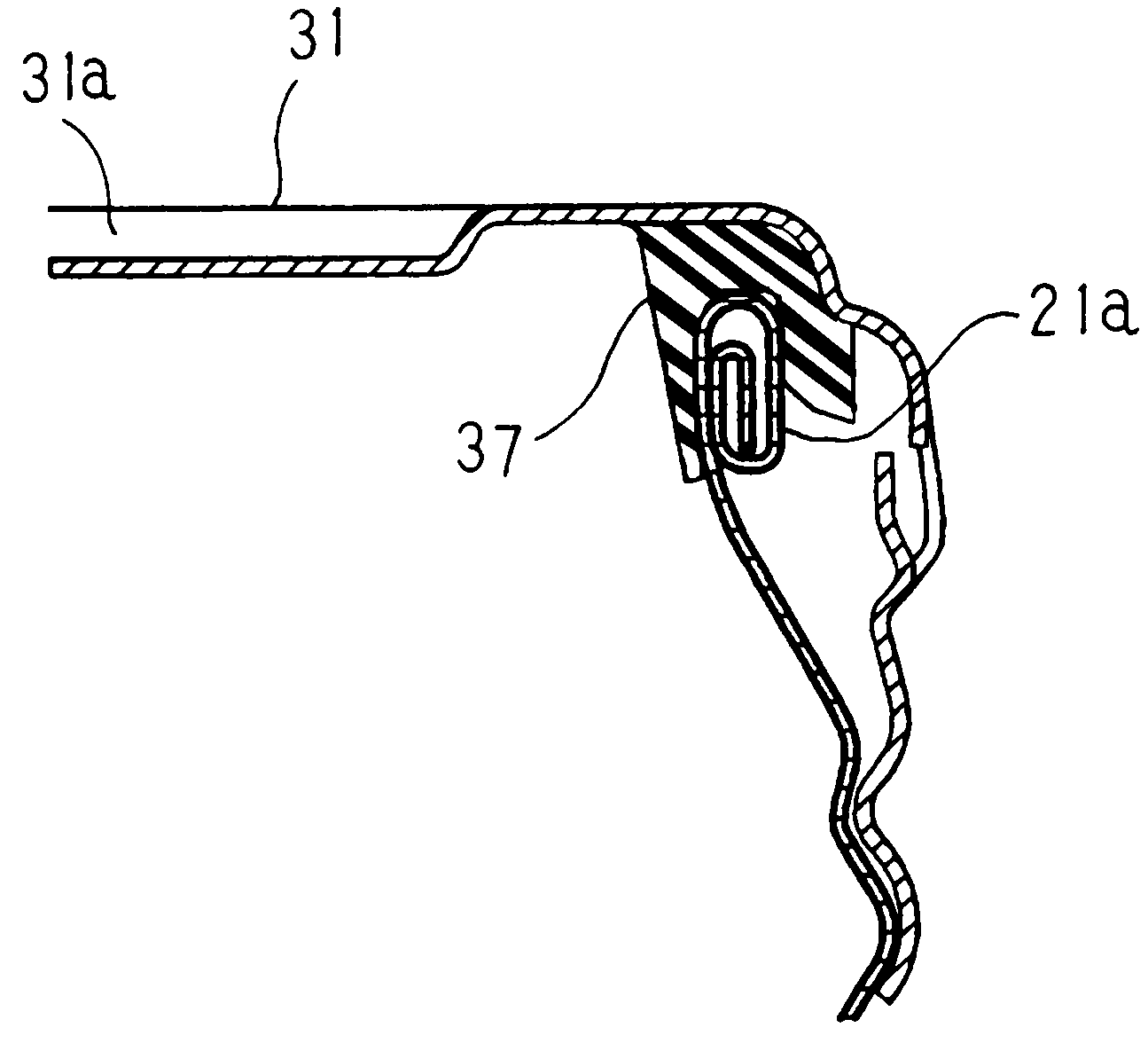

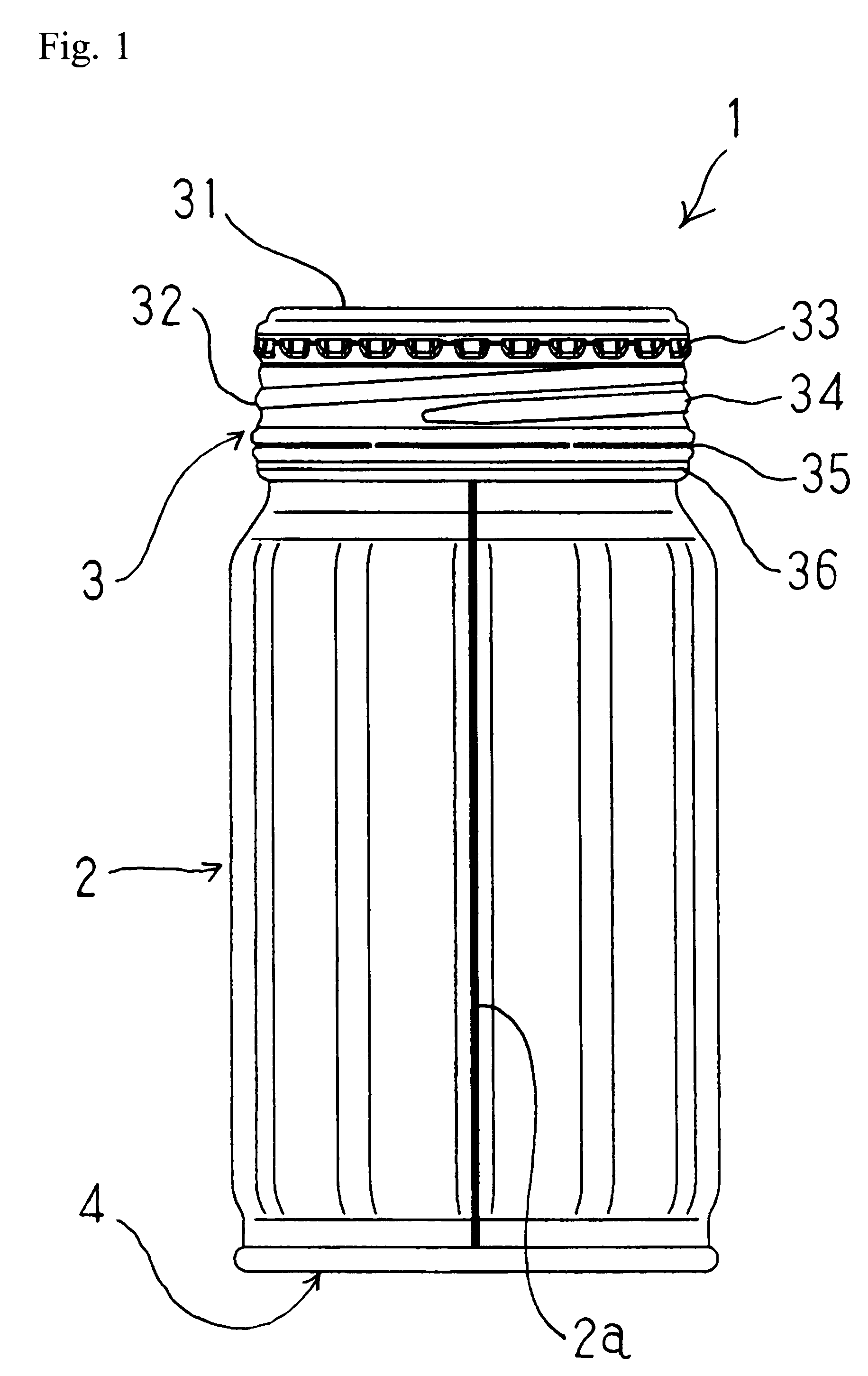

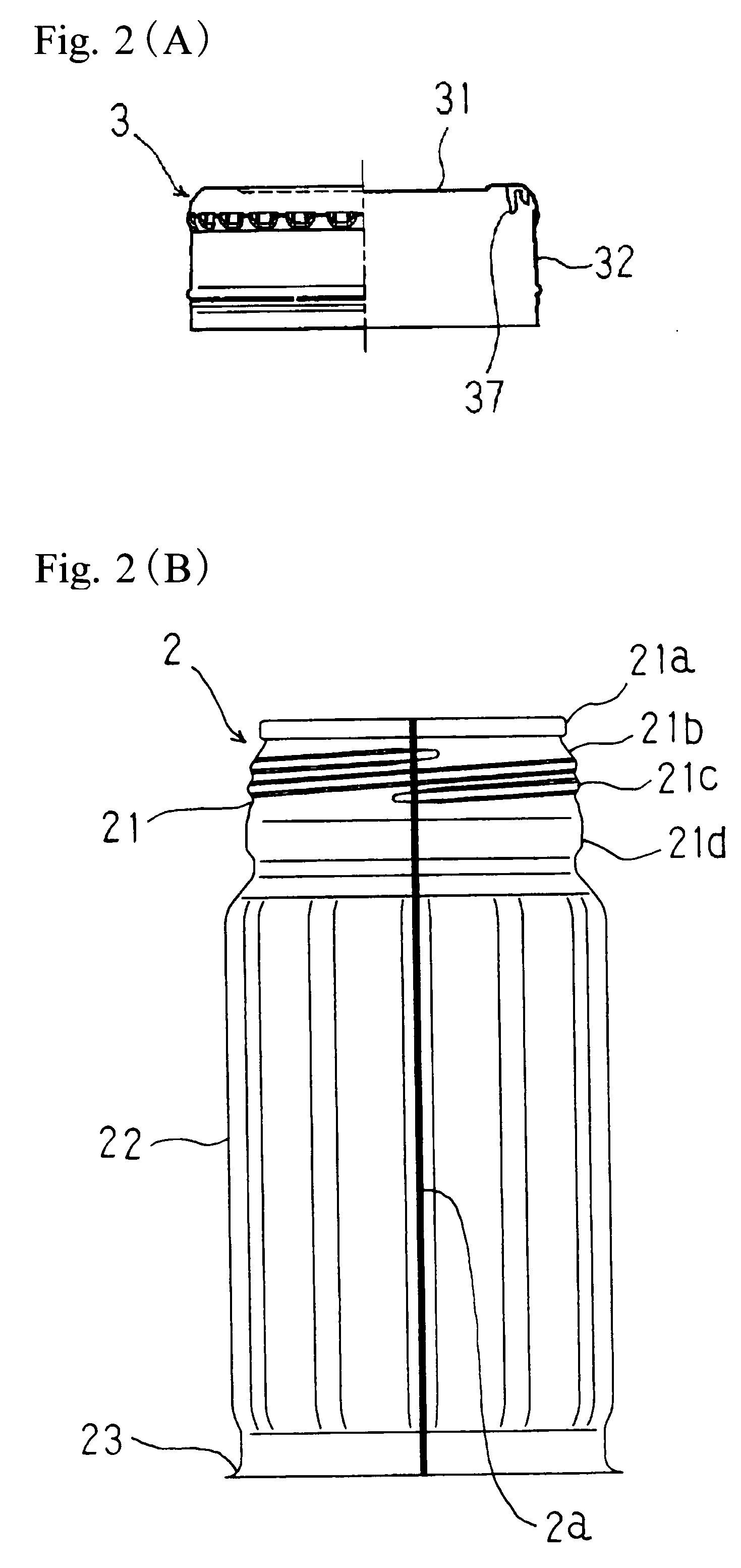

Can container

InactiveUS8181814B2Sufficient sealing abilityMinimize the differenceClosure capsRigid containersEngineeringWelding

To ensure sealing ability of a resealable can container formed of a welded can body between a curled portion of container mouth and a resin sealing liner, without degrading productivity and easiness to open the closure.The can body 2 is prepared by rolling a steel sheet and welding overlapped longitudinal edges of the steel sheet. In order to achieve the above-mentioned objective, a level difference of a welded portion 2a on the surface of a curled portion 21a is reduced smaller than that on the trunk portion 22, specifically, kept within the range of 15 to 100 μm, and a durometer hardness of the resin sealing liner is kept within the range of HDA 30 to 70 according to ISO 868 (or JIS-K7215).

Owner:DAIWA CAN

Can container

InactiveUS20090101661A1Avoid Insufficient SealingSufficient sealing abilityClosure capsRigid containersProduction rateSheet steel

To ensure sealing ability of a resealable can container formed of a welded can body between a curled portion of container mouth and a resin sealing liner, without degrading productivity and easiness to open the closure.The can body 2 is prepared by rolling a steel sheet and welding overlapped longitudinal edges of the steel sheet. In order to achieve the above-mentioned objective, a level difference of a welded portion 2a on the surface of a curled portion 21a is reduced smaller than that on the trunk portion 22, specifically, kept within the range of 15 to 100 μm, and a durometer hardness of the resin sealing liner is kept within the range of HDA 30 to 70 according to ISO 868 (or JIS-K7215).

Owner:DAIWA CAN

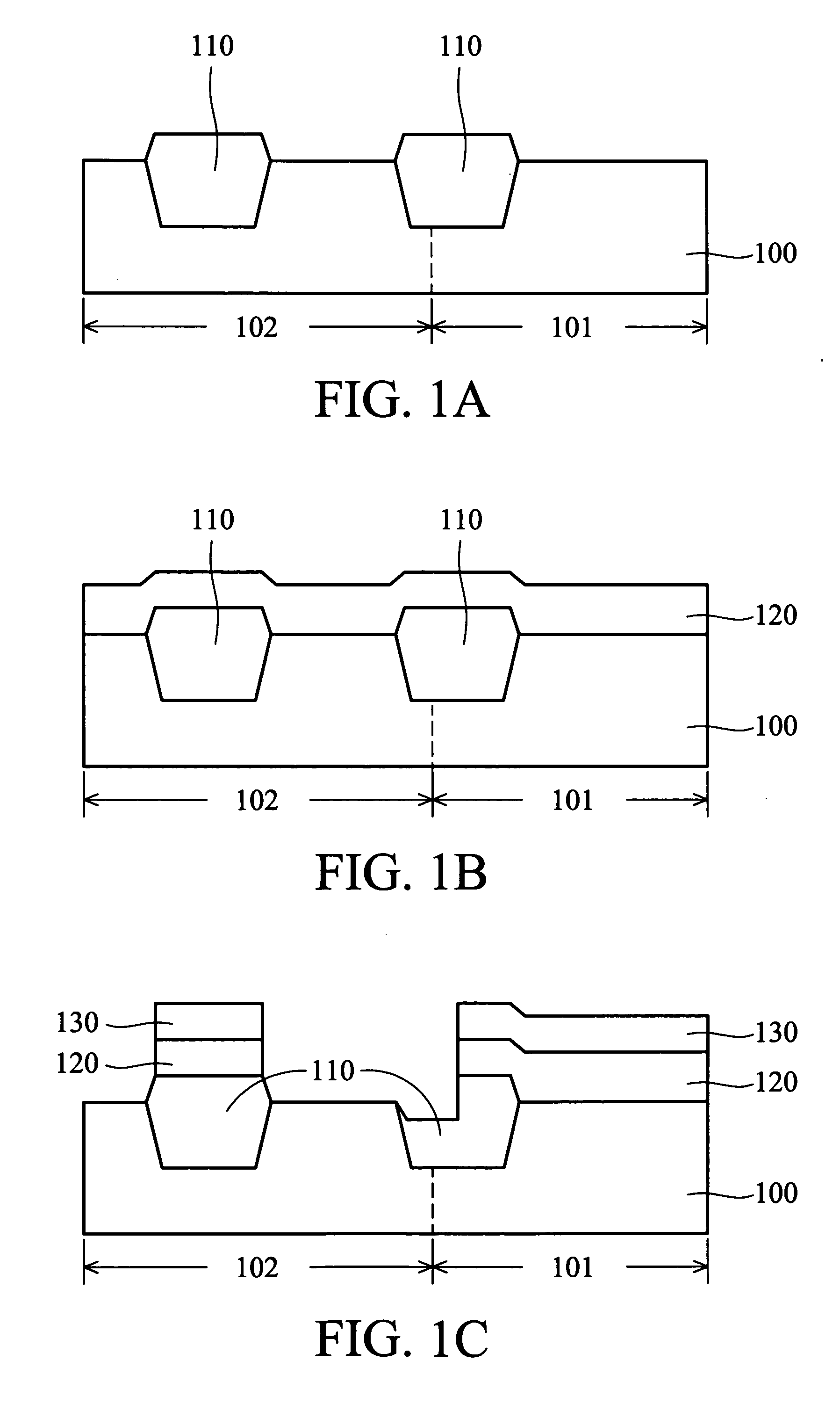

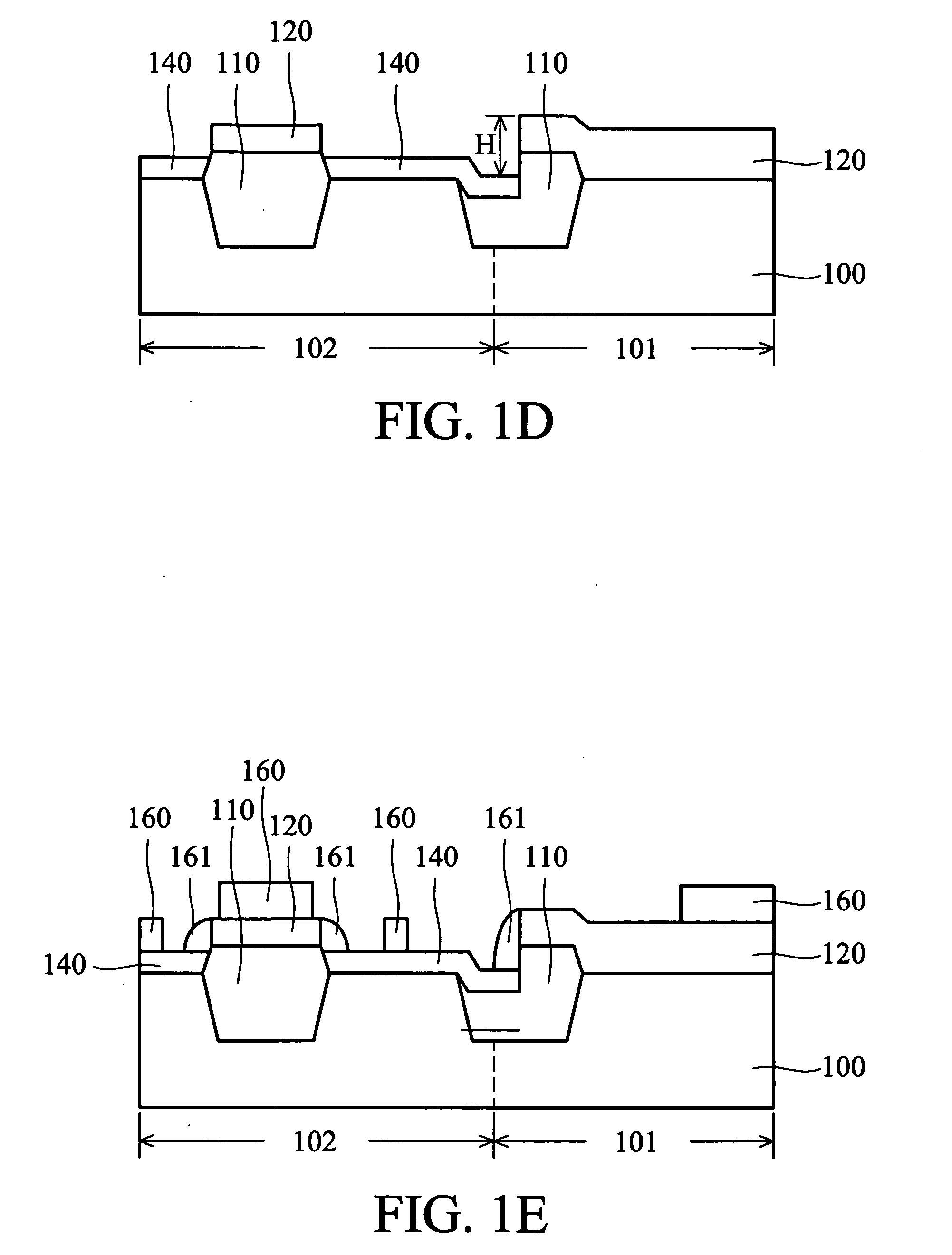

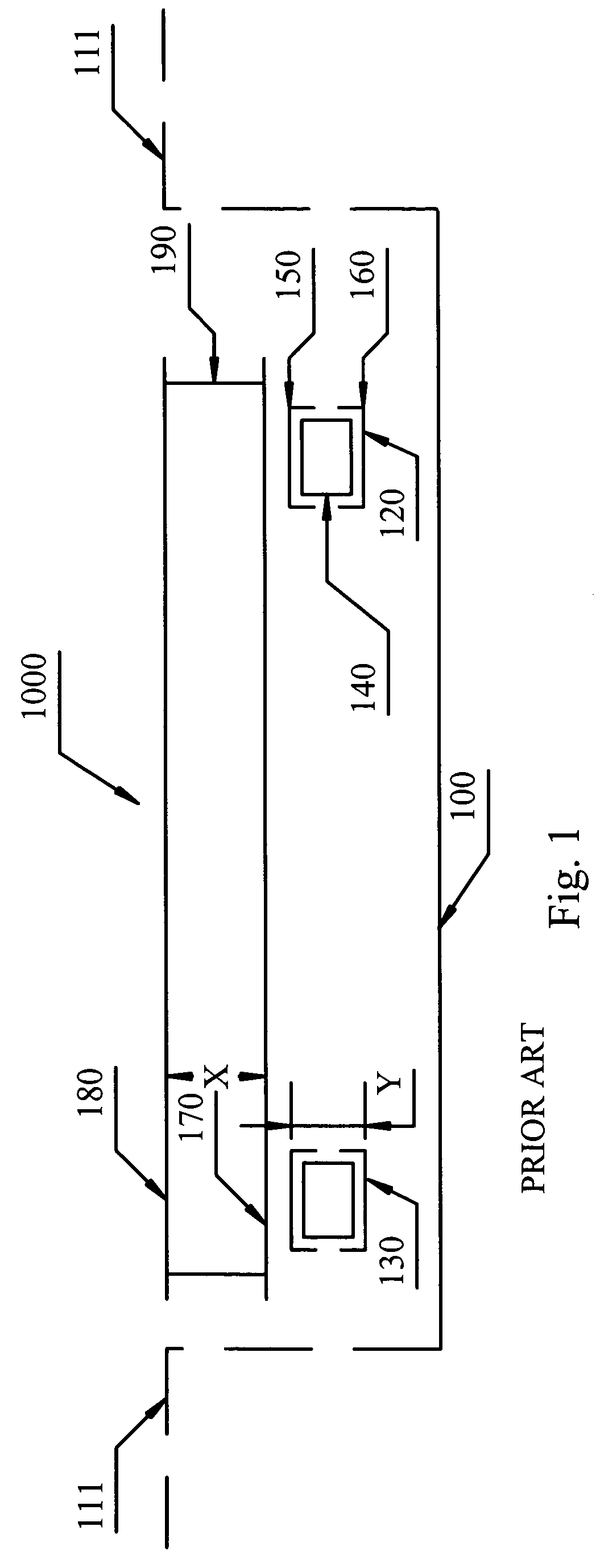

Method of reducing step height

InactiveUS20050202638A1Reduce step heightImprove performanceSemiconductor/solid-state device manufacturingLow voltageEngineering

A method of reducing substrate step height. The method includes providing a substrate having a low-voltage device area and high-voltage device area divided by an isolation structure, forming an oxidation mask at least approximately 500 Å thick over the low-voltage device area and parts of the isolation structure, forming a first oxide layer on the exposed high-voltage device area and isolation structure using the oxidation mask as a mask, removing the oxidation mask, and forming a second oxide layer, thinner than the first oxide layer, on the low-voltage device layer.

Owner:VANGUARD INTERNATIONAL SEMICONDUCTOR CORPORATION

![[active organic electroluminescence panel display and fabricating method thereof] [active organic electroluminescence panel display and fabricating method thereof]](https://images-eureka.patsnap.com/patent_img/ba1c1189-60a7-4472-ba8f-5ed9b5f03bb3/US20050093438A1-20050505-D00000.png)

![[active organic electroluminescence panel display and fabricating method thereof] [active organic electroluminescence panel display and fabricating method thereof]](https://images-eureka.patsnap.com/patent_img/ba1c1189-60a7-4472-ba8f-5ed9b5f03bb3/US20050093438A1-20050505-D00001.png)

![[active organic electroluminescence panel display and fabricating method thereof] [active organic electroluminescence panel display and fabricating method thereof]](https://images-eureka.patsnap.com/patent_img/ba1c1189-60a7-4472-ba8f-5ed9b5f03bb3/US20050093438A1-20050505-D00002.png)