Patents

Literature

650results about How to "Reduce manufacturing steps" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

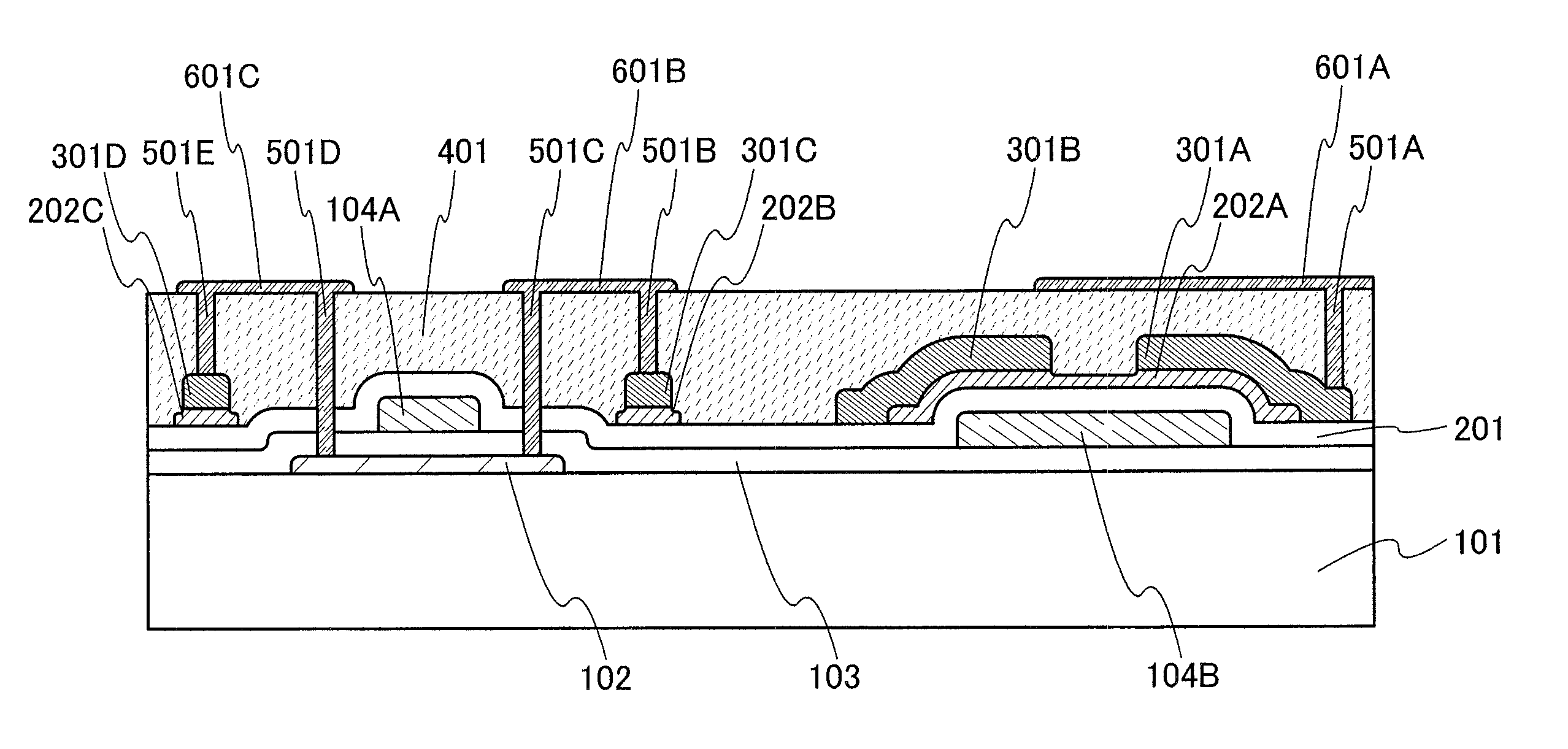

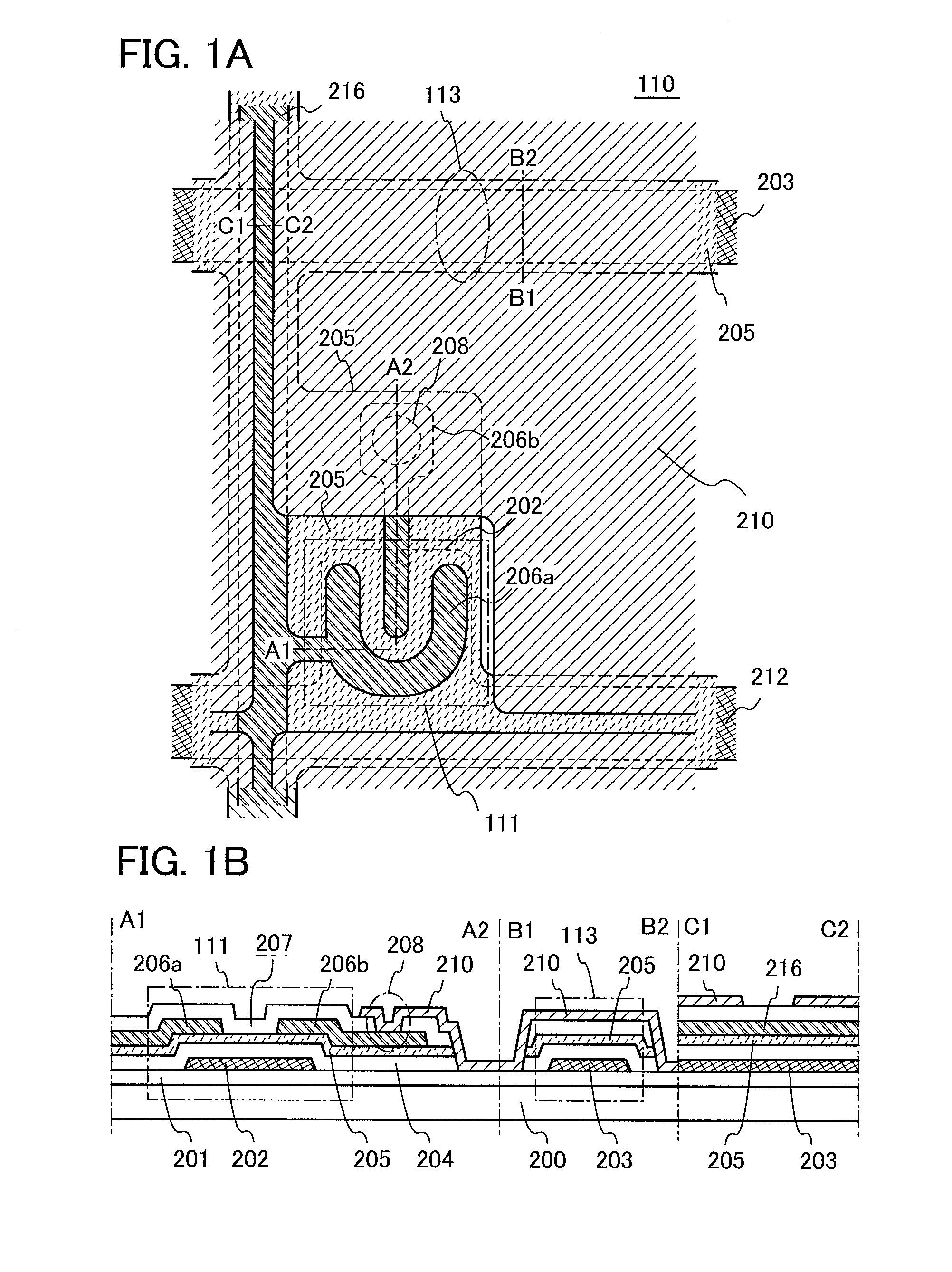

Semiconductor device

ActiveUS20090002590A1Low costIncrease speedSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSingle crystal

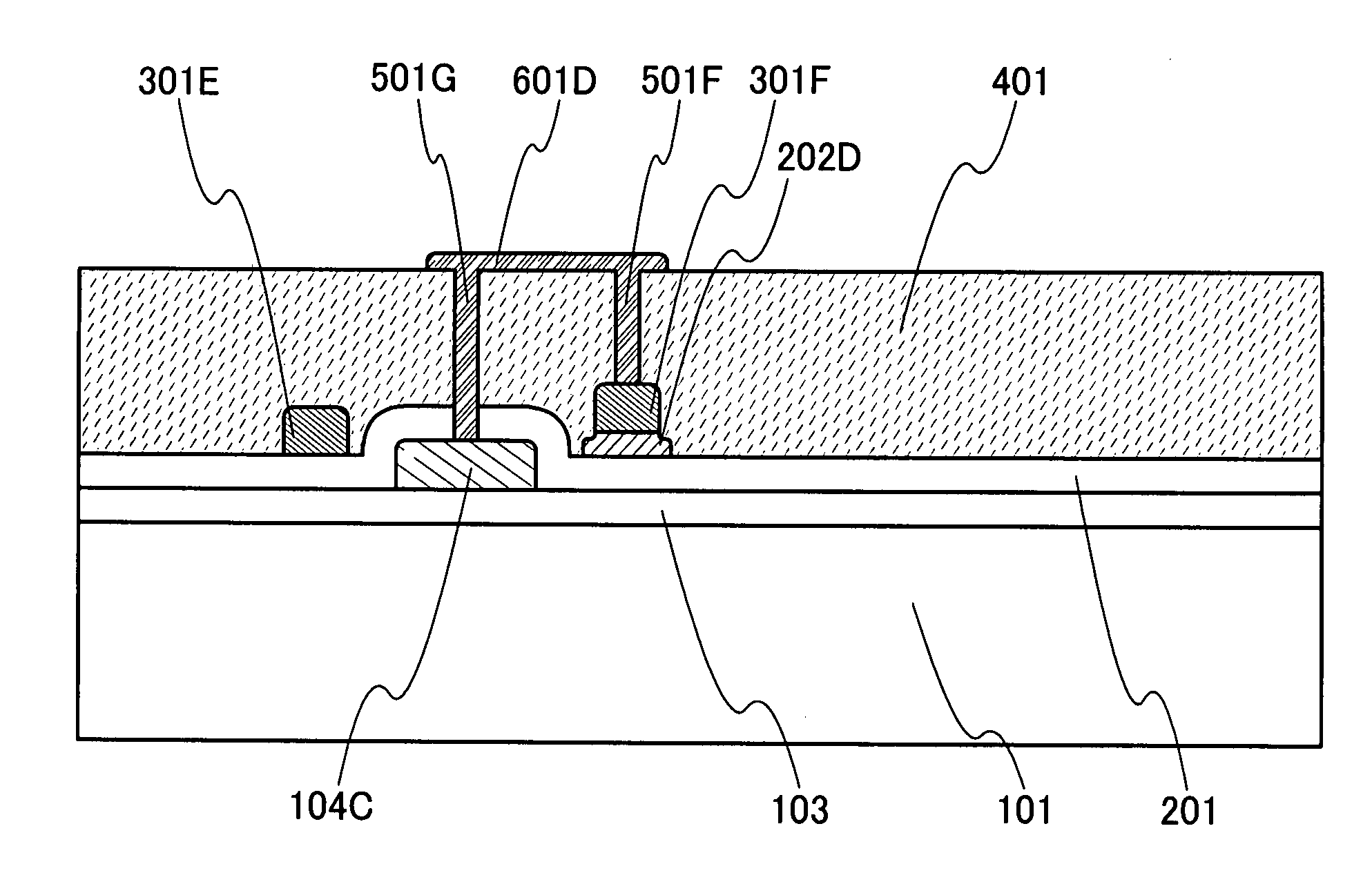

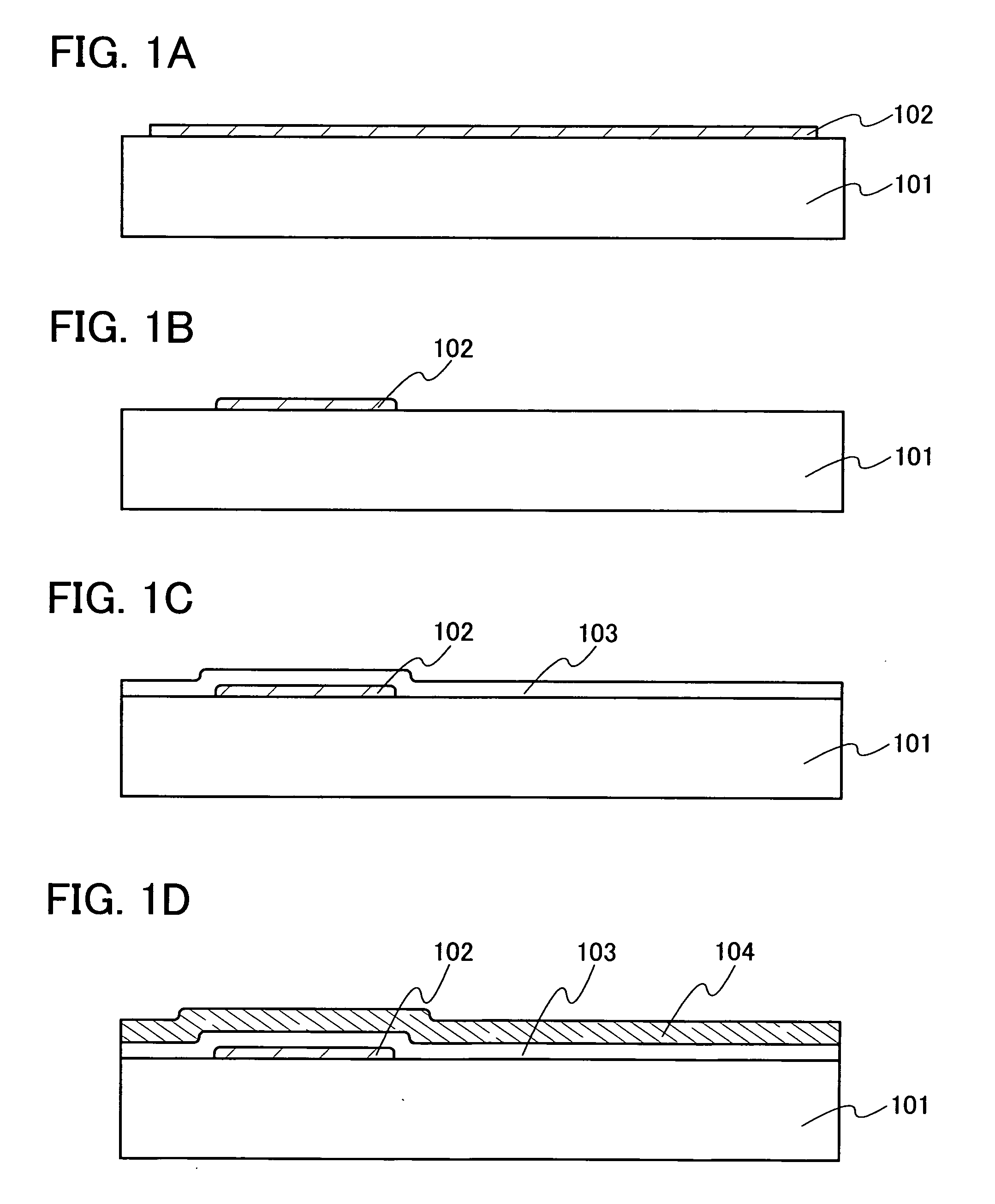

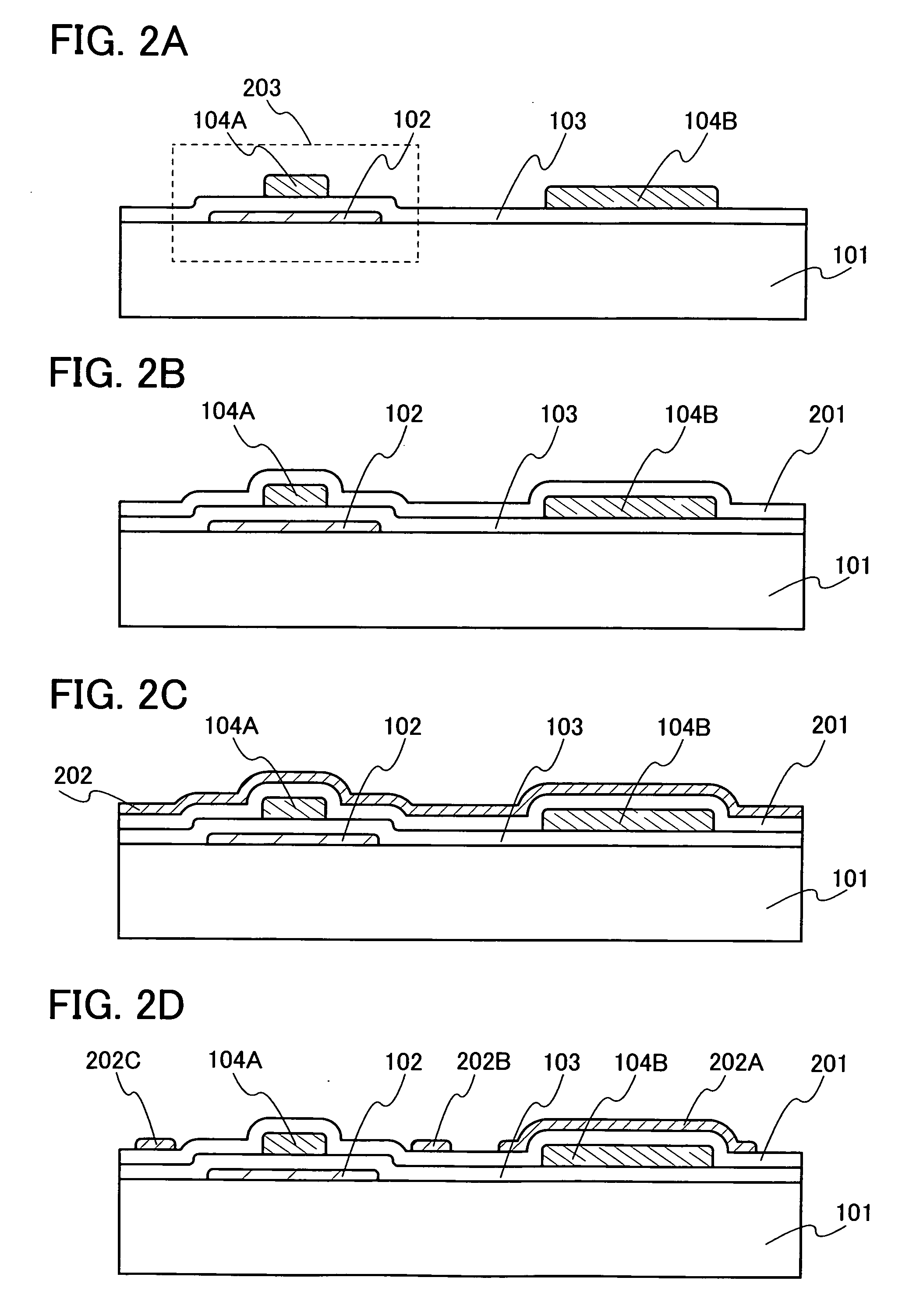

It is an object to provide a semiconductor device which has a large size and operates at high speed. A top gate transistor which includes a semiconductor layer of single-crystal and a bottom gate transistor which includes a semiconductor layer of amorphous silicon (microcrystalline silicon) are formed over the same substrate. Then, gate electrodes of each transistor are formed with the same layer, and source and drain electrodes are also formed with the same layer. Thus, manufacturing steps are reduced. In other words, two types of transistors can be manufactured by adding only a few steps to the manufacturing process of a bottom gate transistor.

Owner:SEMICON ENERGY LAB CO LTD

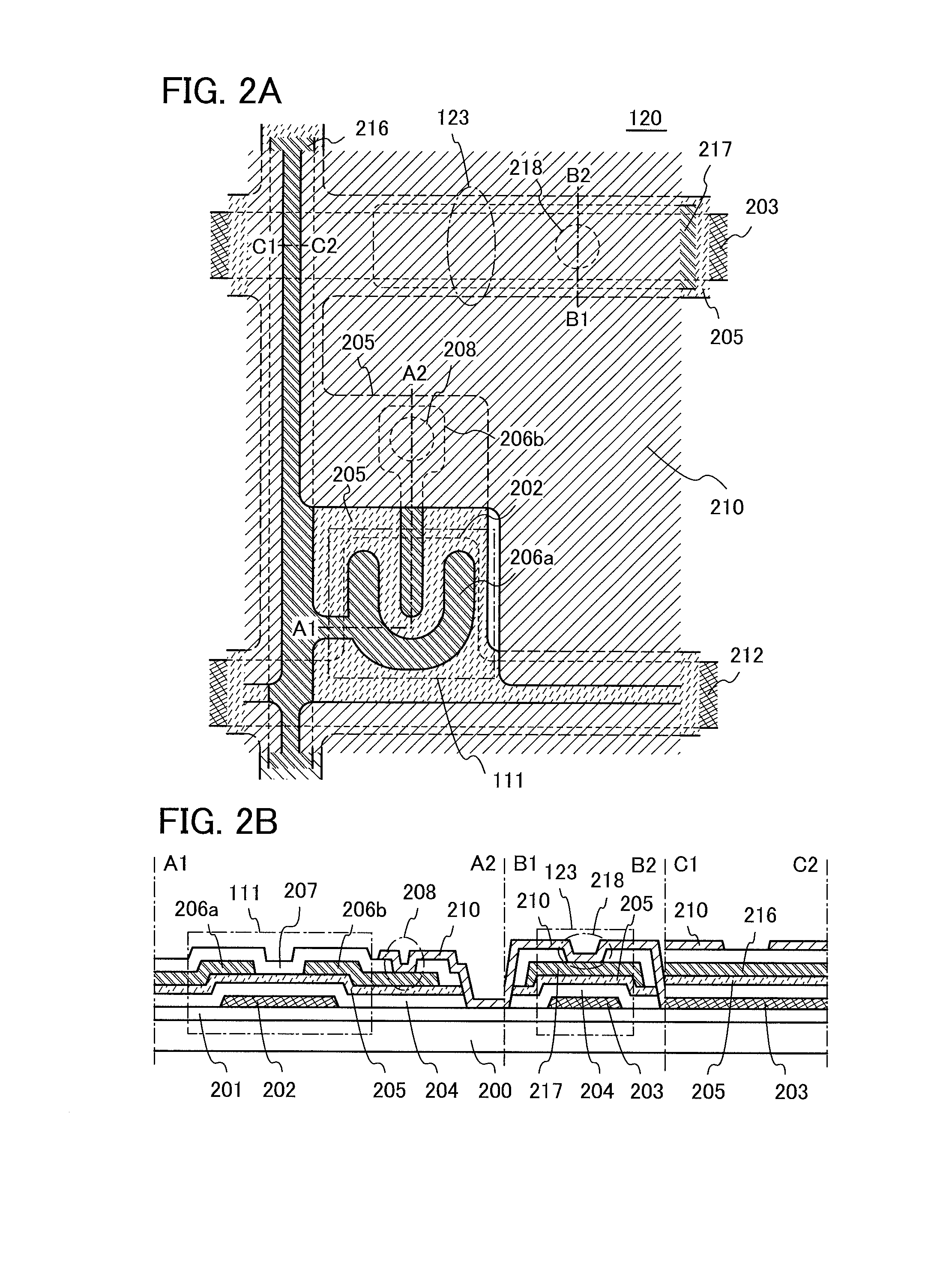

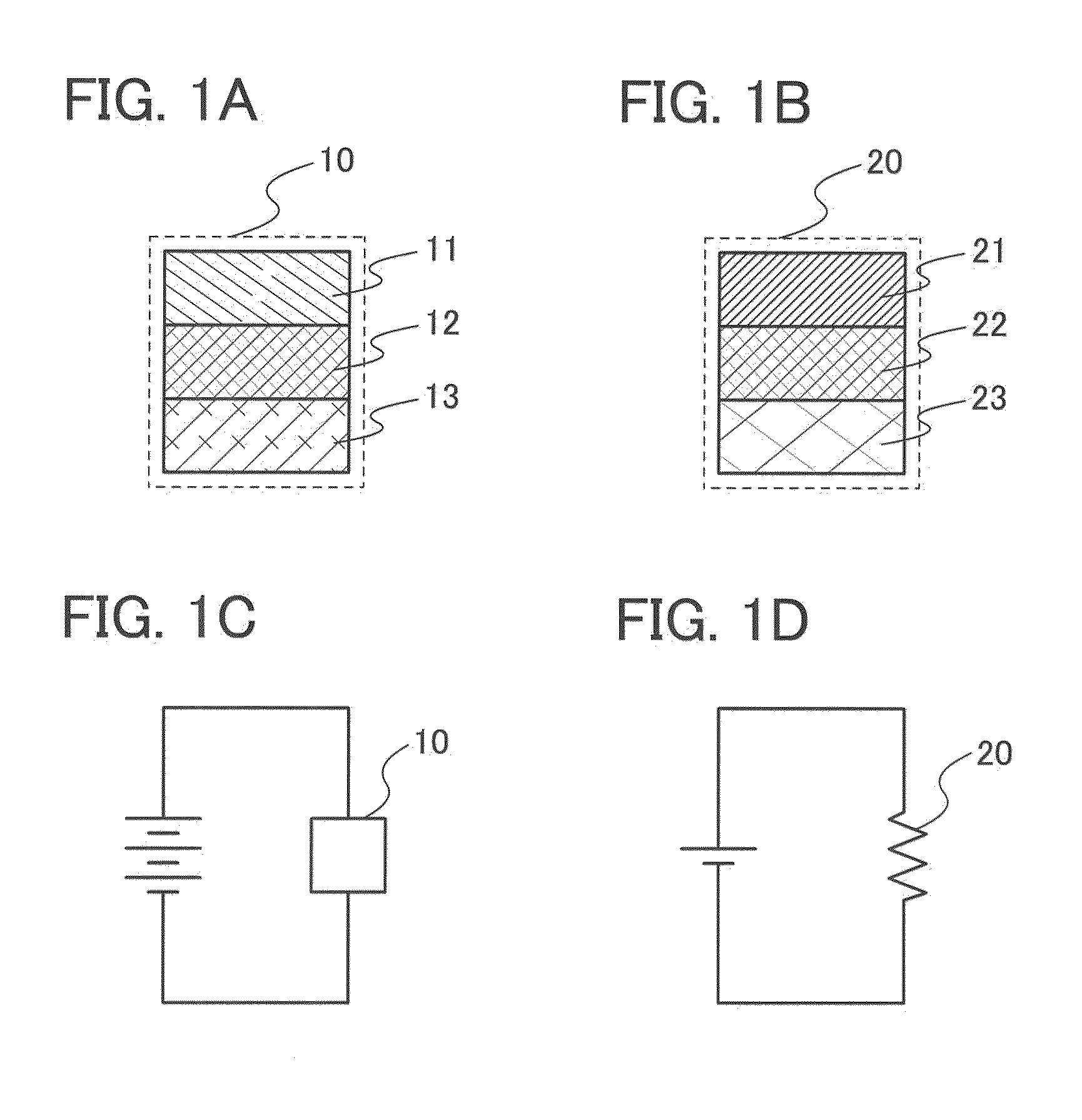

Semiconductor device

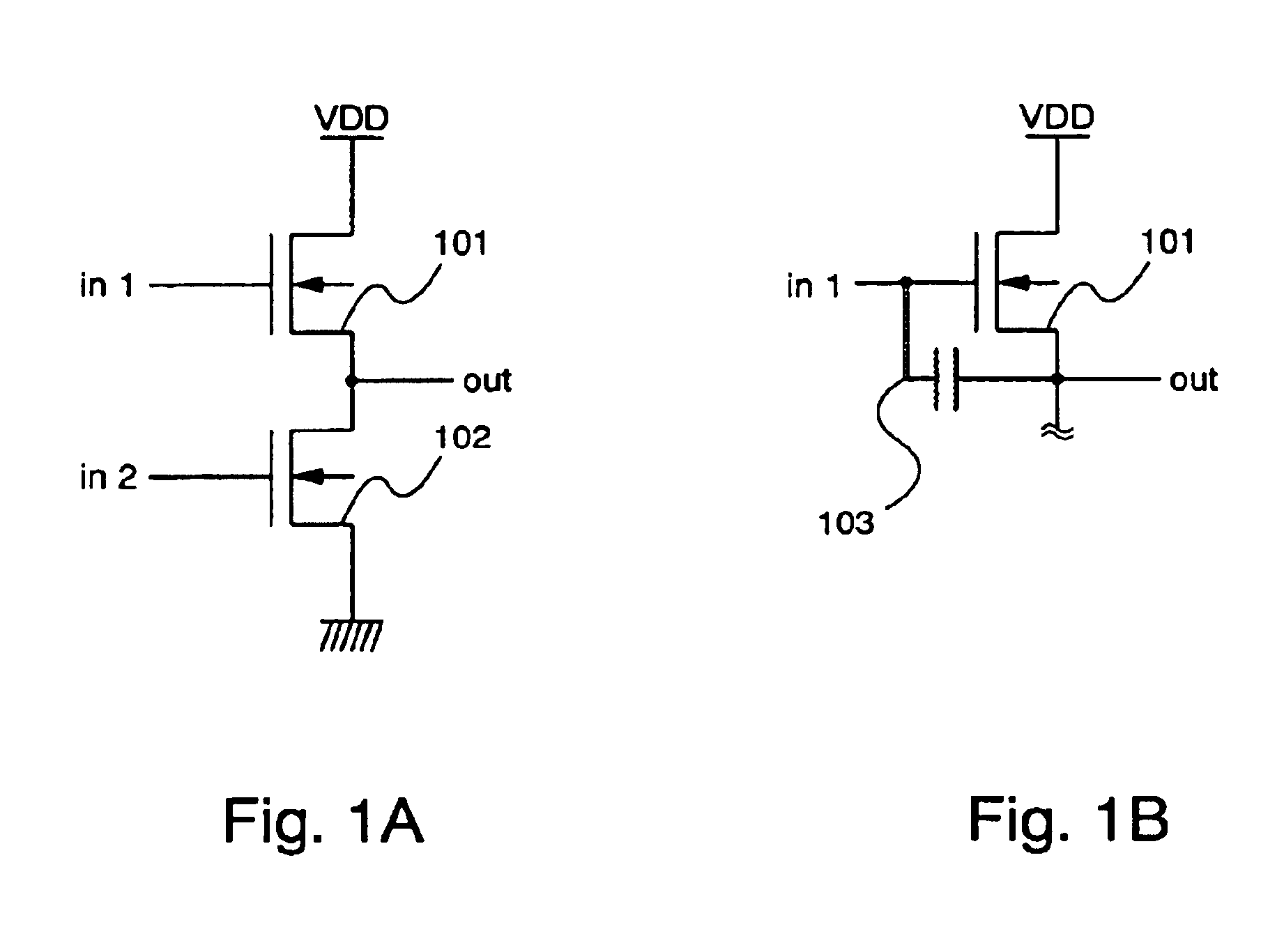

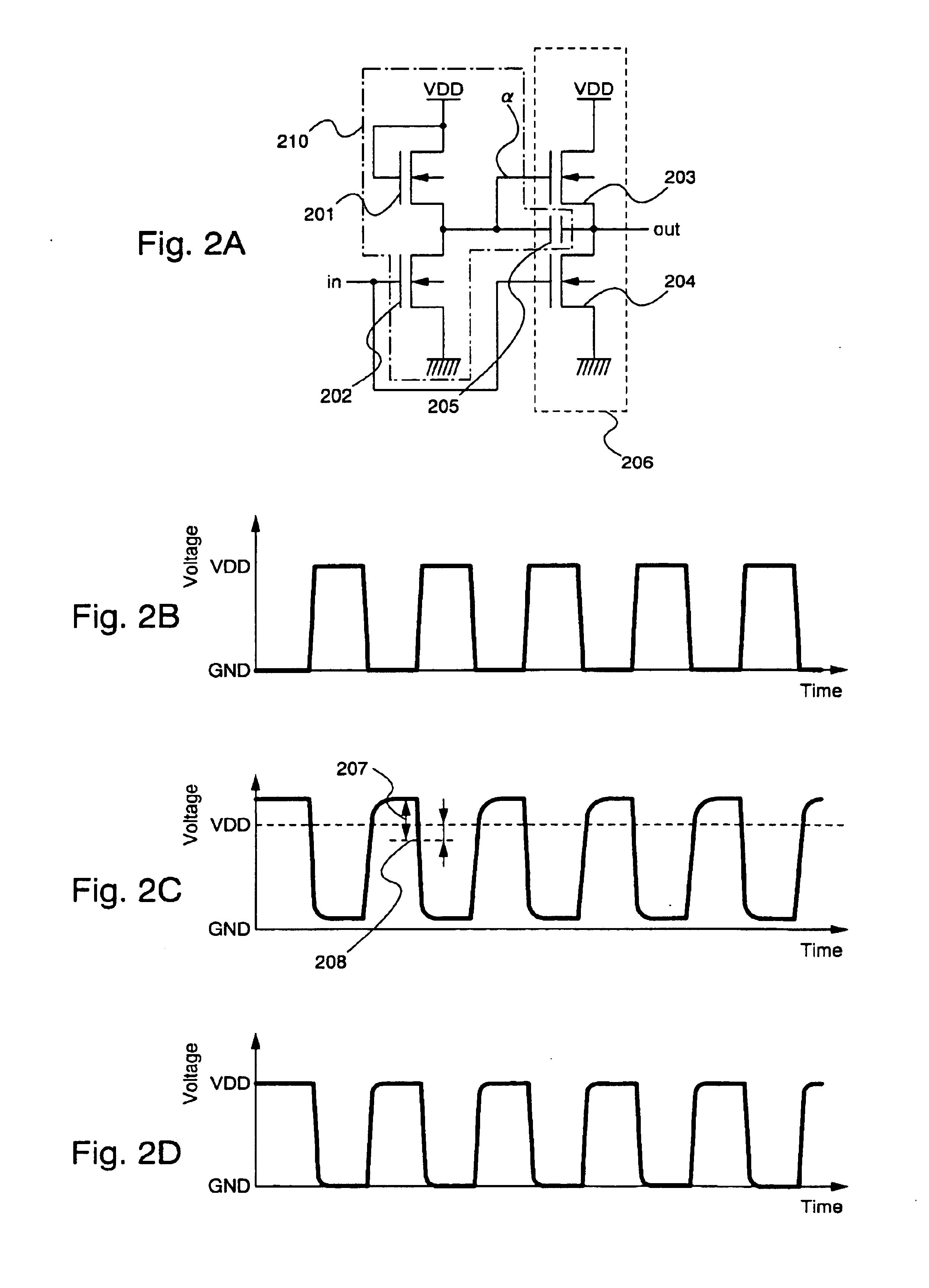

InactiveUS6975142B2Low costReduce manufacturing stepsTransistorSolid-state devicesVoltage amplitudeSemiconductor

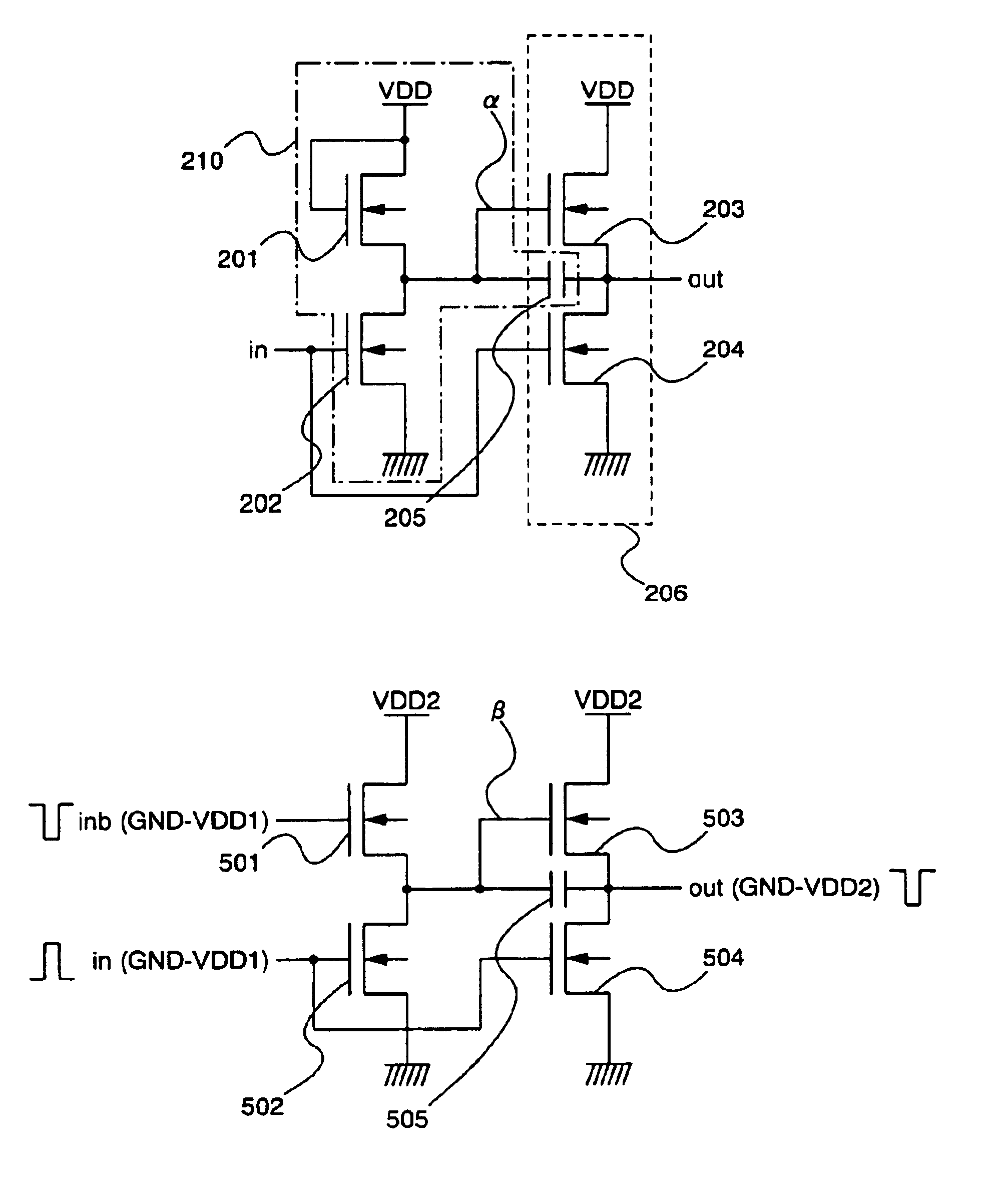

There is provided a semiconductor device in which fabrication steps can be reduced by constructing a circuit using only TFTs of one conductivity type and in which a voltage amplitude of an output signal can be normally obtained. A capacitance (205) is provided between a gate and a source of a TFT (203) connected to an output node, and a circuit formed of TFTs (201) and (202) has a function to bring a node a into a floating state. When the node α is in the floating state, a potential of the node a is caused higher than VDD by using gate-source capacitance coupling of the TFT (203) through the capacitance (205), thus an output signal having an amplitude of VDD-GND can be normally obtained without causing amplitude attenuation due to the threshold value of the TFT.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device

InactiveUS20100193785A1Low costReduce power consumptionTransistorSolid-state devicesSemiconductor packageSingle crystal

It is an object to provide a semiconductor device which has a large size and operates at high speed. A top gate transistor which includes a semiconductor layer of single-crystal and a bottom gate transistor which includes a semiconductor layer of amorphous silicon (microcrystalline silicon) are formed over the same substrate. Then, gate electrodes of each transistor are formed with the same layer, and source and drain electrodes are also formed with the same layer. Thus, manufacturing steps are reduced. In other words, two types of transistors can be manufactured by adding only a few steps to the manufacturing process of a bottom gate transistor.

Owner:SEMICON ENERGY LAB CO LTD

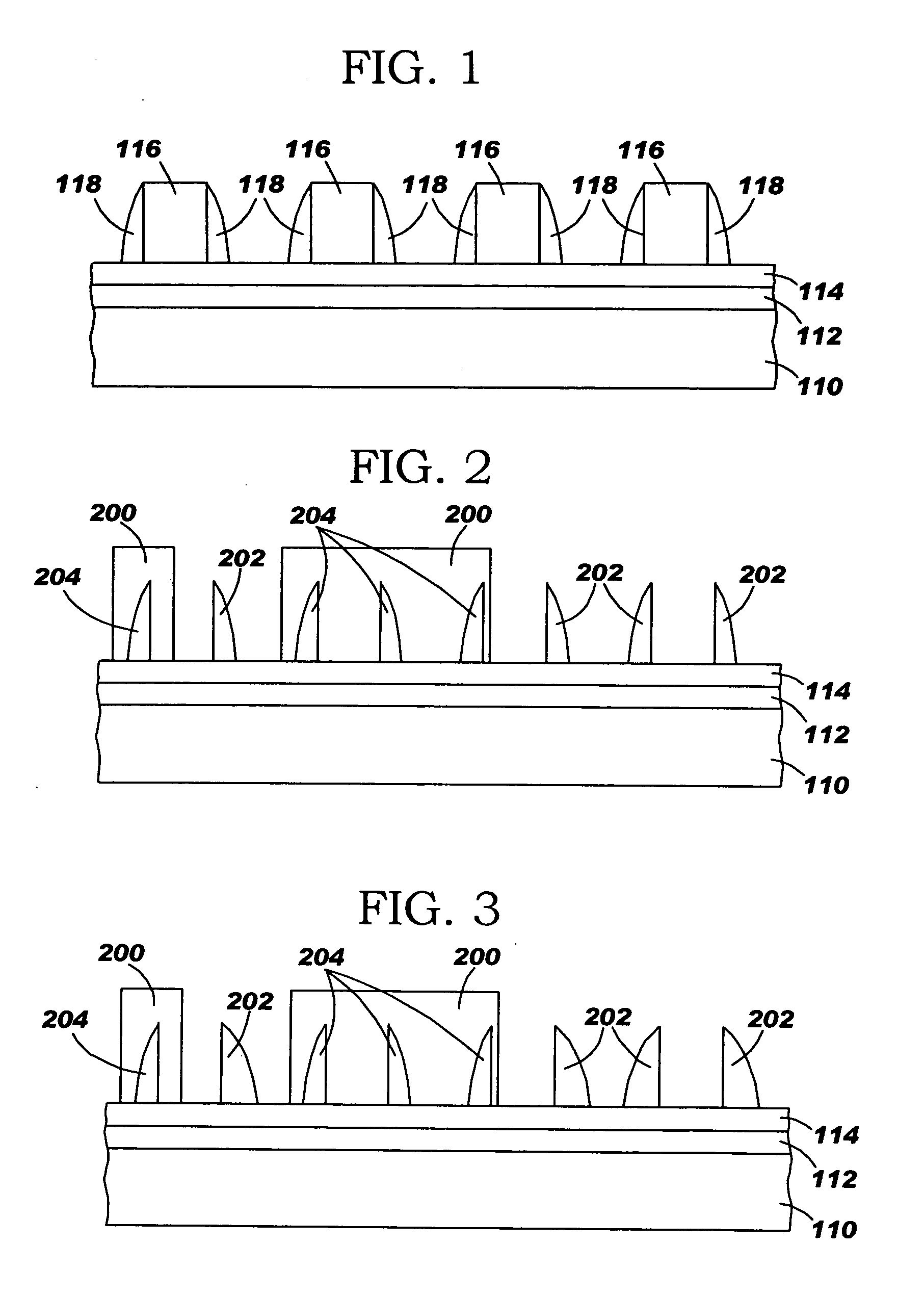

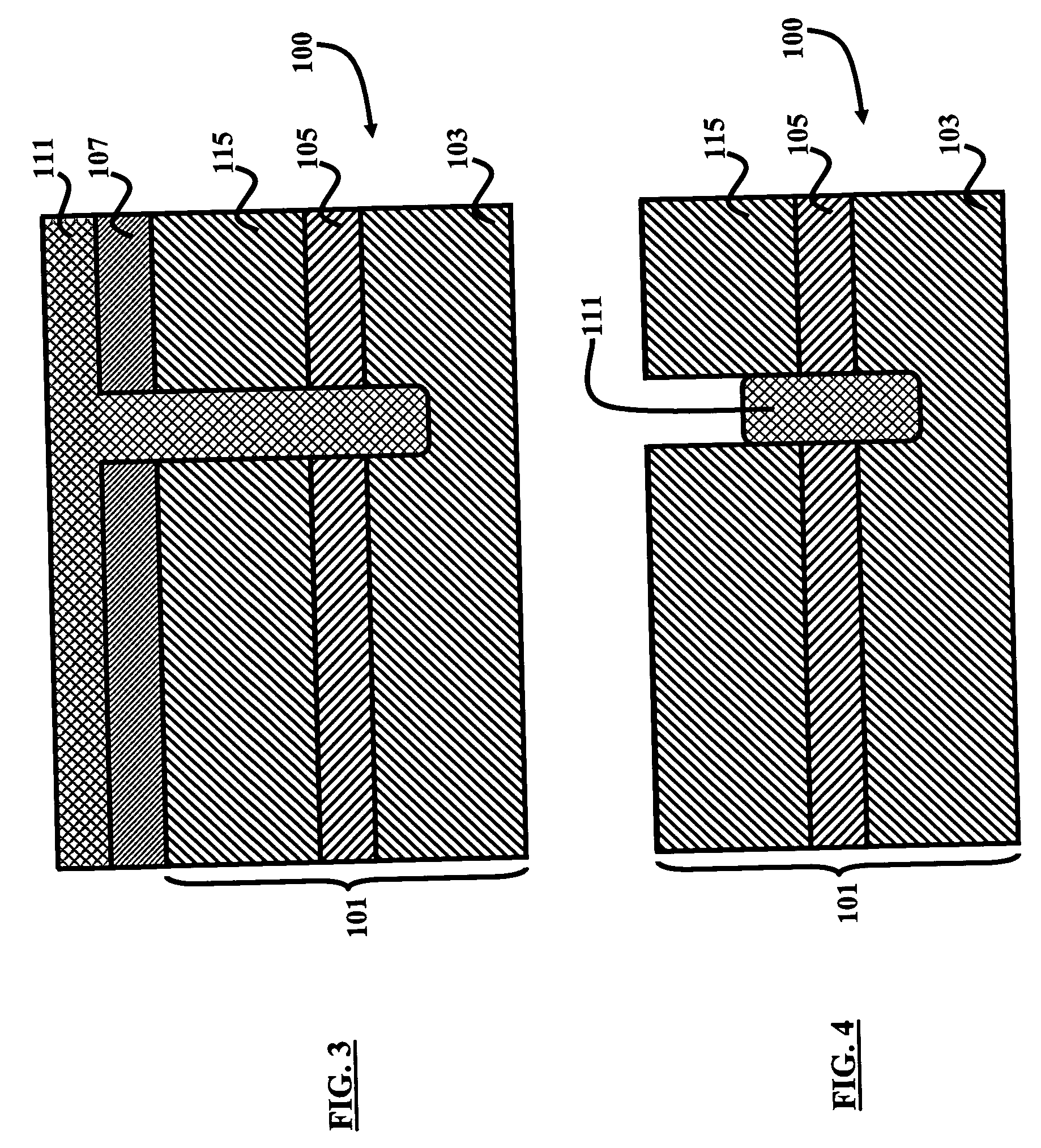

Method of independent P and N gate length control of FET device made by sidewall image transfer technique

InactiveUS20050153562A1Different sizeSelectively exposeSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringElectrical conductor

Disclosed is a method that forms a conductive layer on a substrate and patterns sacrificial structures above the conductive layer. Next, the invention forms sidewall spacers adjacent the sacrificial structures using a spacer material capable of undergoing dimensional change, after which the invention removes the sacrificial structures in processing that leaves the sidewall spacers in place. The invention then protects selected ones of the sidewall spacers using a sacrificial mask and leaves the other ones of the sidewall spacers unprotected. This allows the invention to selectively expose the unprotected sidewall spacers to processing that changes the size of the unprotected sidewall spacers. This causes the unprotected sidewall spacers have a different size than protected sidewall spacers. Then, the invention removes the sacrificial mask and patterns the conductive layer using the sidewall spacers as a gate conductor mask to create differently sized gate conductors on the substrate. Following this, the invention removes the sidewall spacers and forms the source, drain, and channel regions adjacent the gate conductors.

Owner:IBM CORP

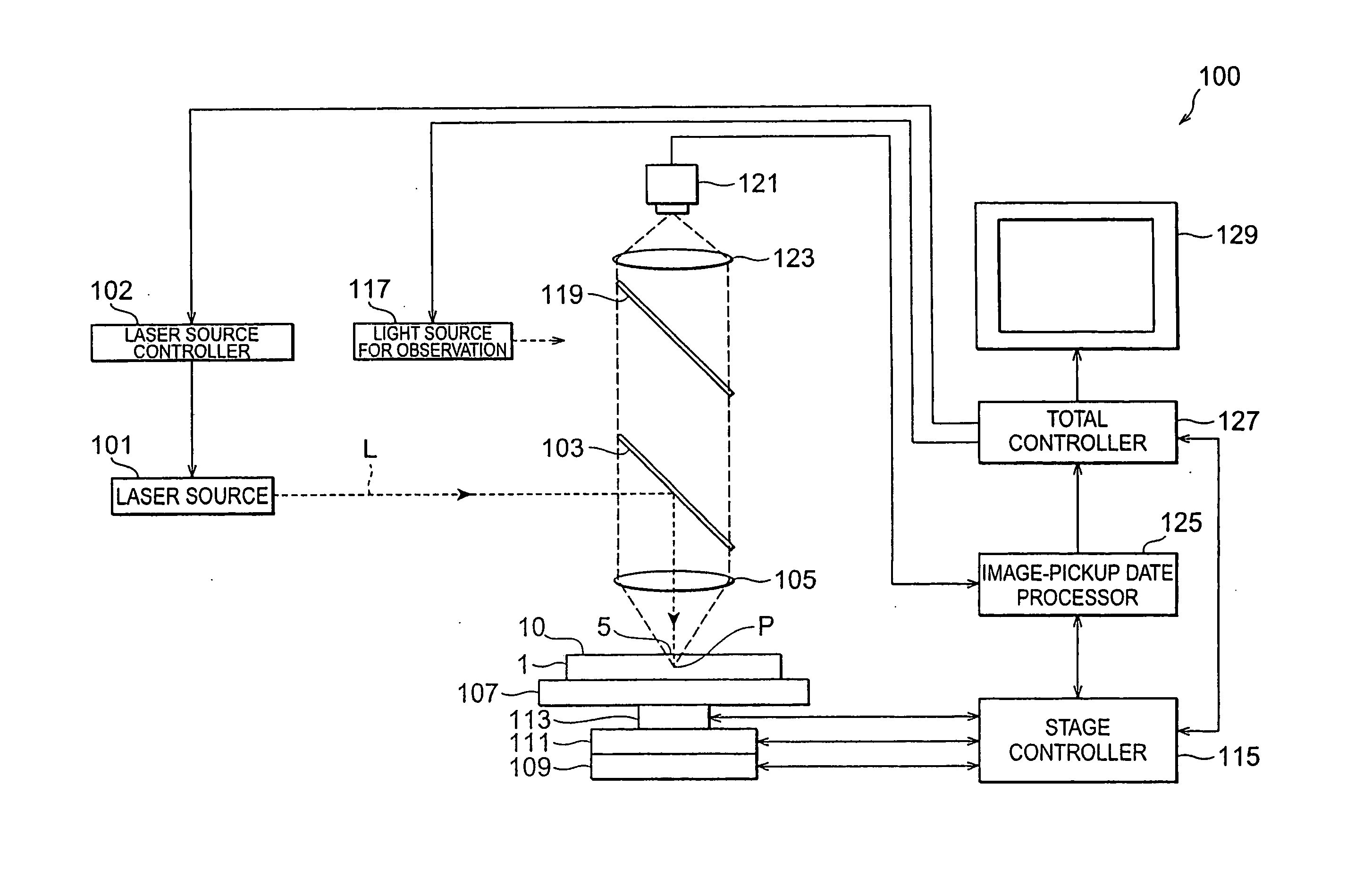

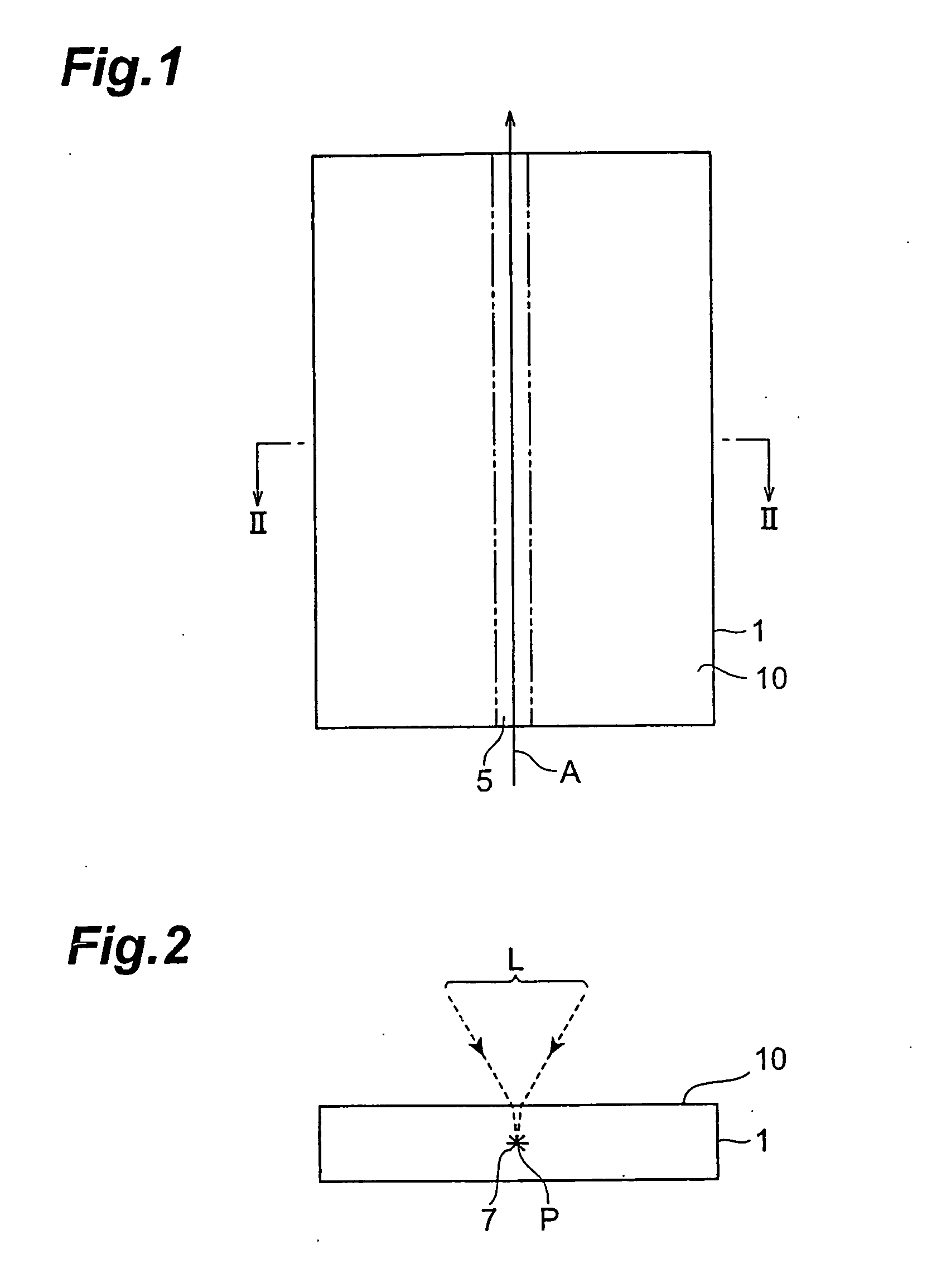

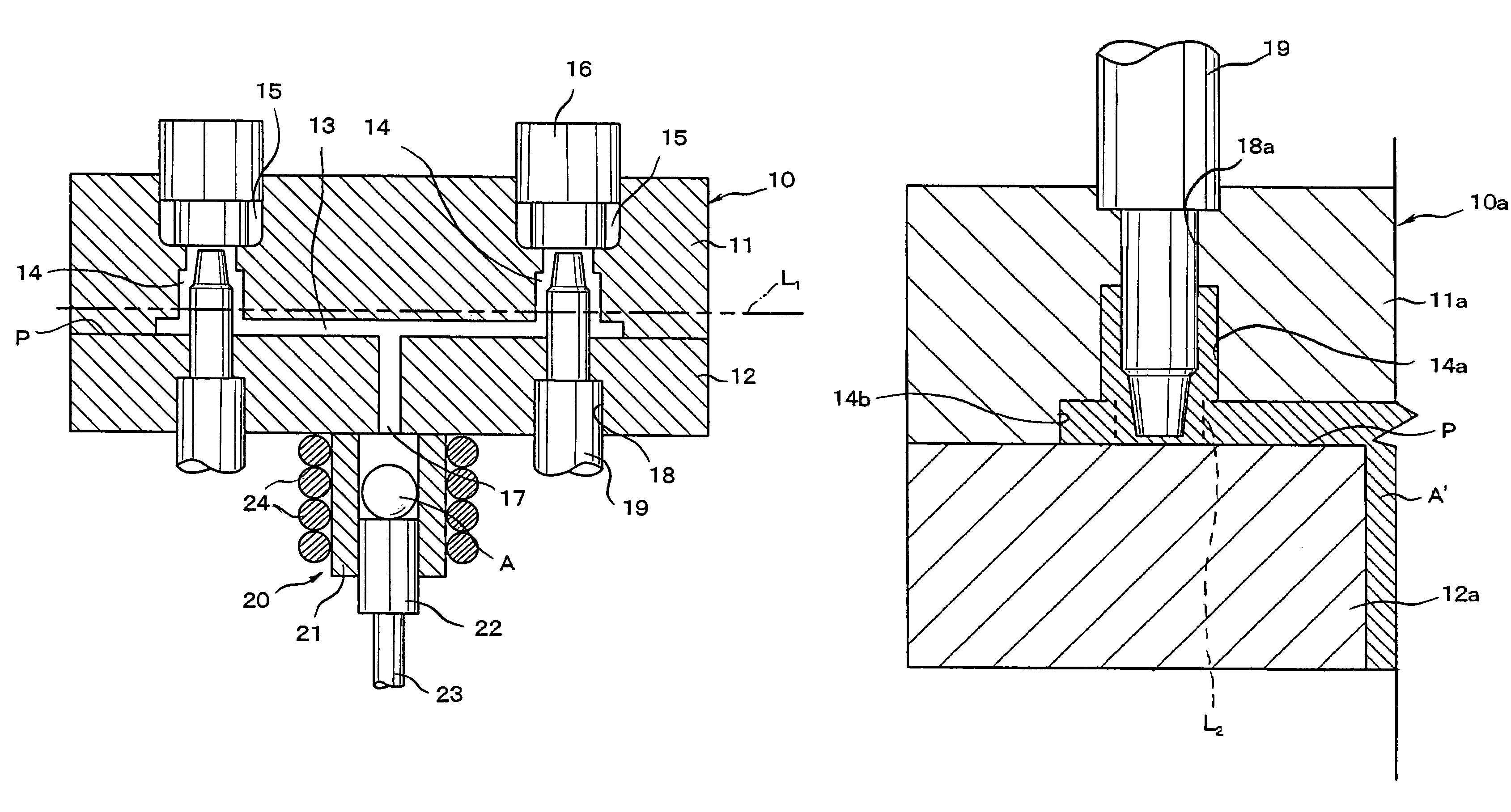

Laser processing method

ActiveUS20070158314A1Reduce manufacturing stepsImprove accuracyFine working devicesWelding/soldering/cutting articlesLaser processingProcess region

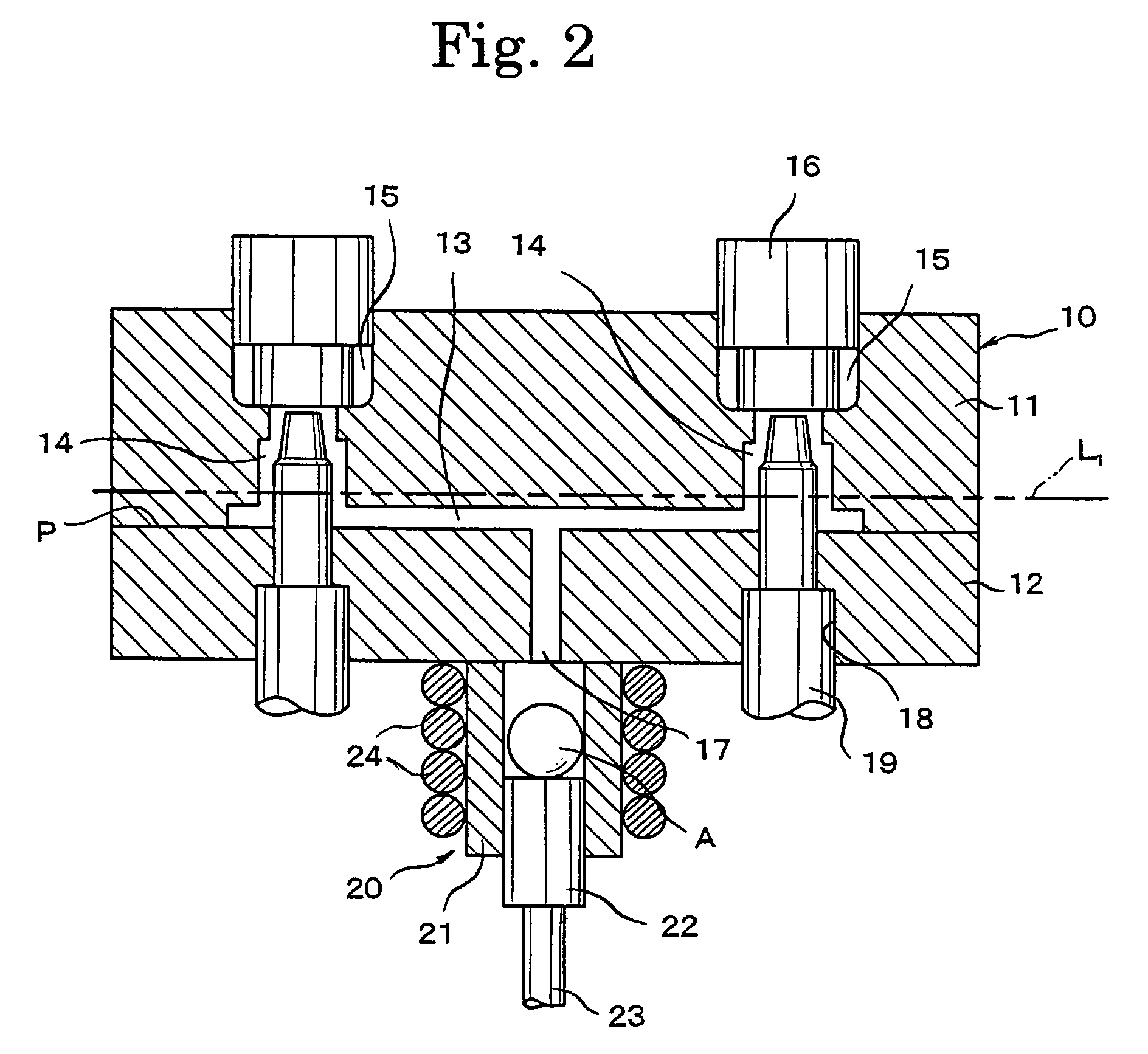

The present invention provides a laser processing method comprising the steps of attaching a protective tape 25 to a front face 3 of a wafer 1a, irradiating a substrate 15 with laser light L while employing a rear face of the wafer 1a as a laser light entrance surface and locating a light-converging point P within the substrate 15 so as to form a molten processed region 13 due to multiphoton absorption, causing the molten processed region 13 to form a cutting start region 8 inside by a predetermined distance from the laser light entrance surface along a line 5 along which the object is intended to be cut in the wafer 1a, attaching an expandable tape 23 to the rear face 21 of the wafer 1a, and expanding the expandable tape 23 so as to separate a plurality of chip parts 24 produced upon cutting the wafer 1a from the cutting start region 8 acting as a start point from each other.

Owner:HAMAMATSU PHOTONICS KK

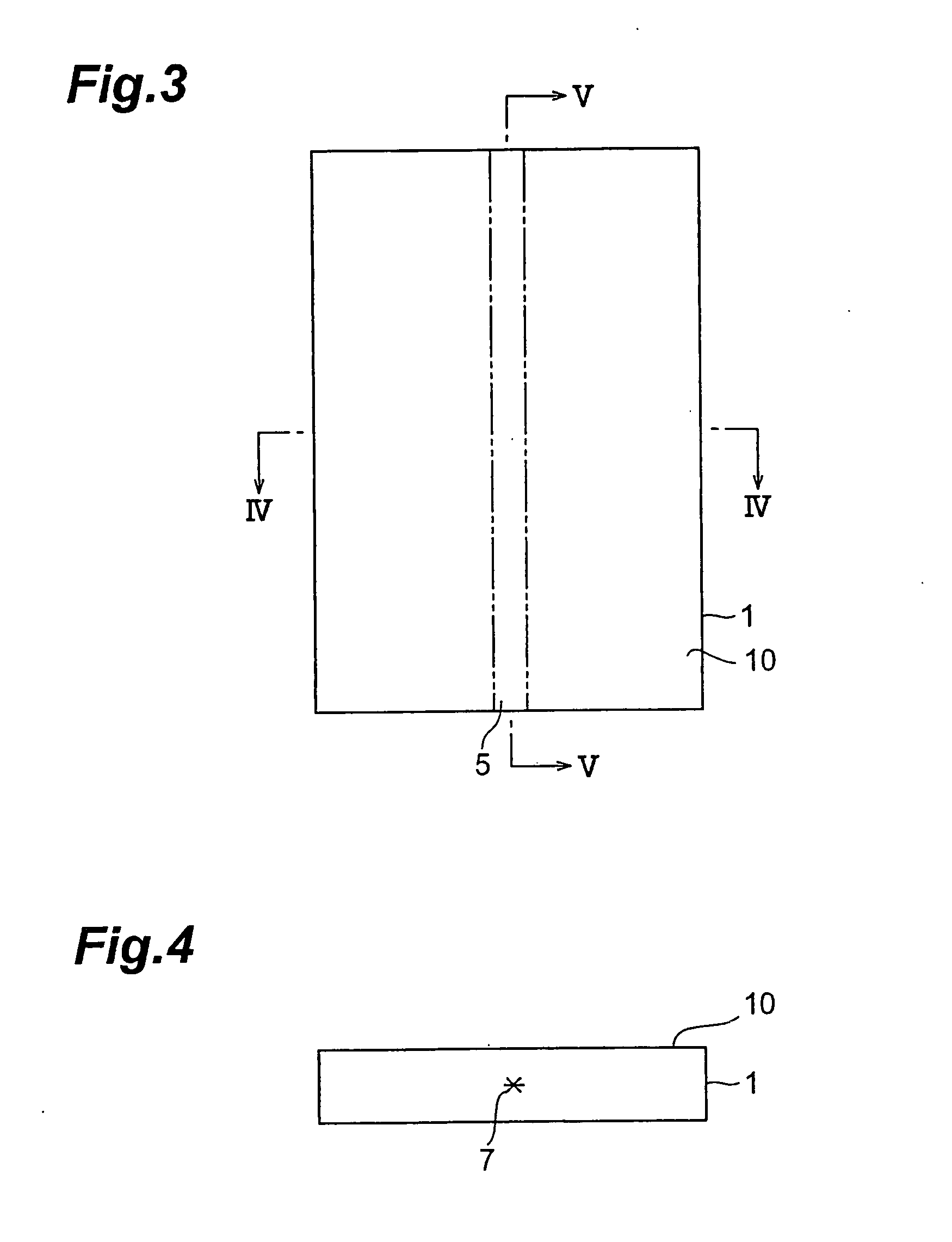

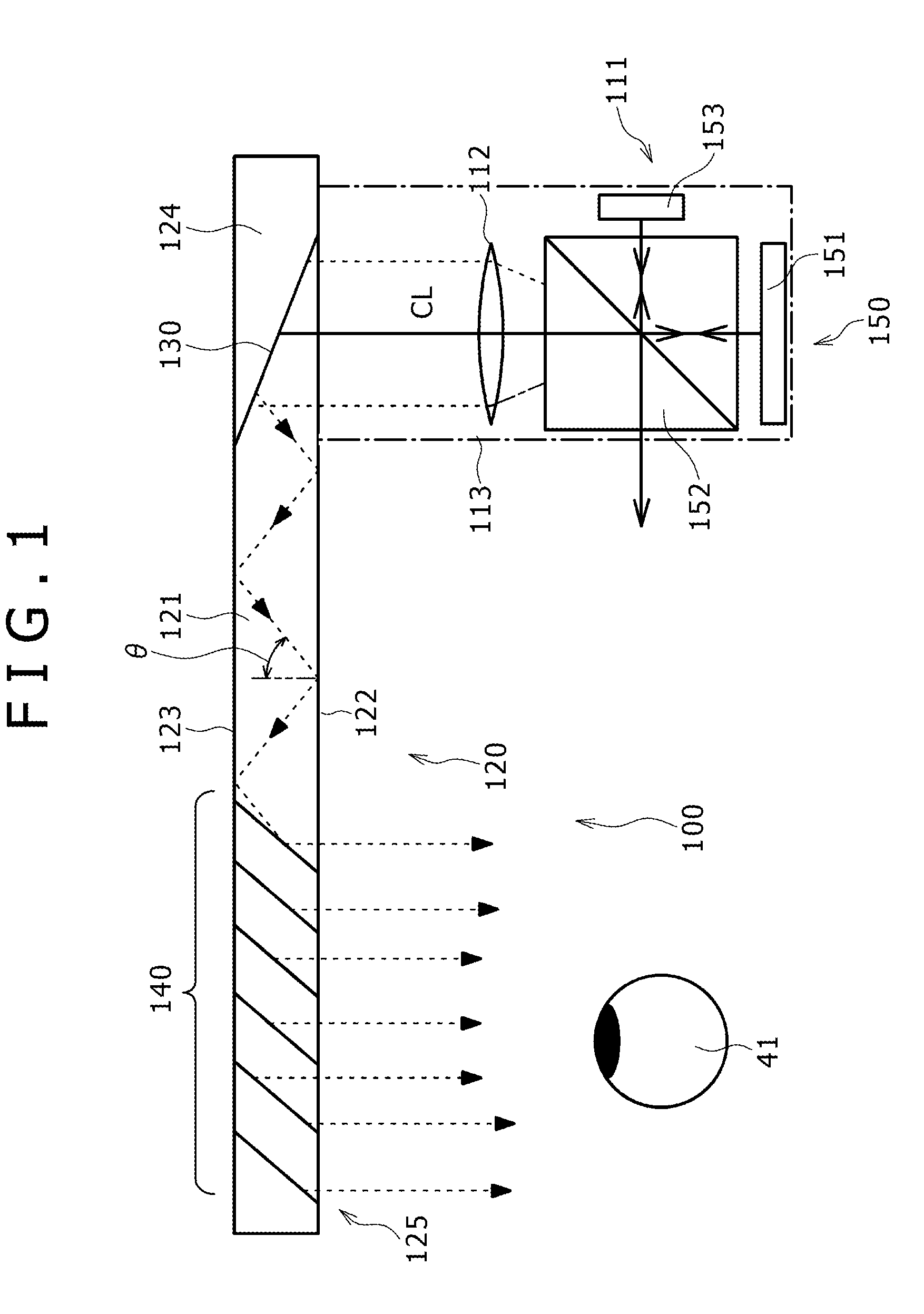

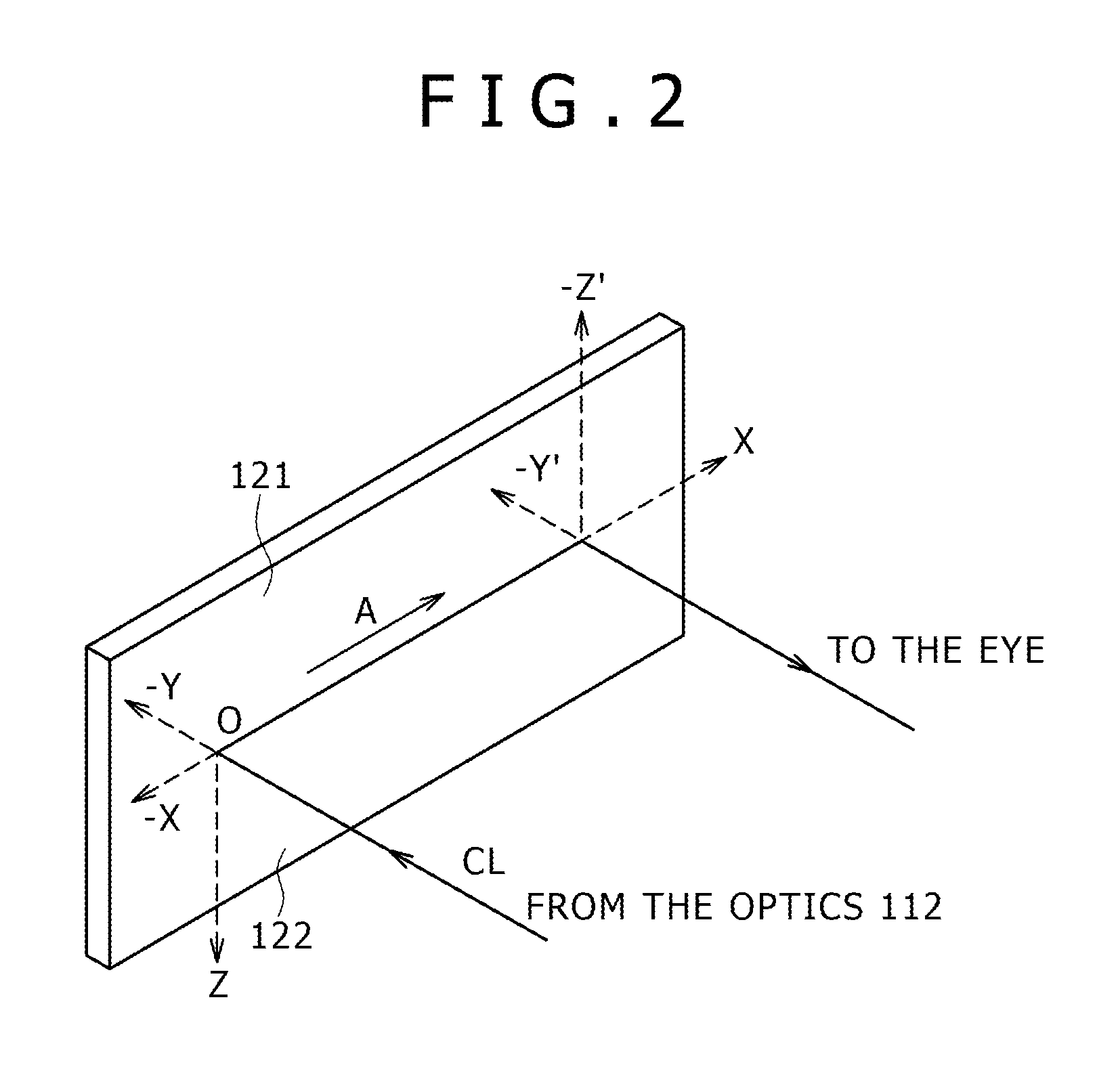

Head mounted display and optical position adjustment method of the same

ActiveUS20110248904A1Improve responseSmall sizeCathode-ray tube indicatorsImage data processingDisplay deviceImage signal

Disclosed herein is an optical position adjustment method of a head mounted display, the head mounted display including (a) an eyeglass type frame worn on the head of a viewer, and (b) two image display devices for the right and left eyes attached to the frame, and each of the image display devices including (A) an image forming device, and (B) an optical device adapted to receive, guide and emit light emitted from the image forming device, wherein the optical position adjustment method includes the step of: controlling an image signal that is supplied to the image forming device making up at least one of the image display devices so as to control the position of the image displayed on the optical device making up at least one of the image display devices and adjust the mutual positions of the two images.

Owner:SONY CORP

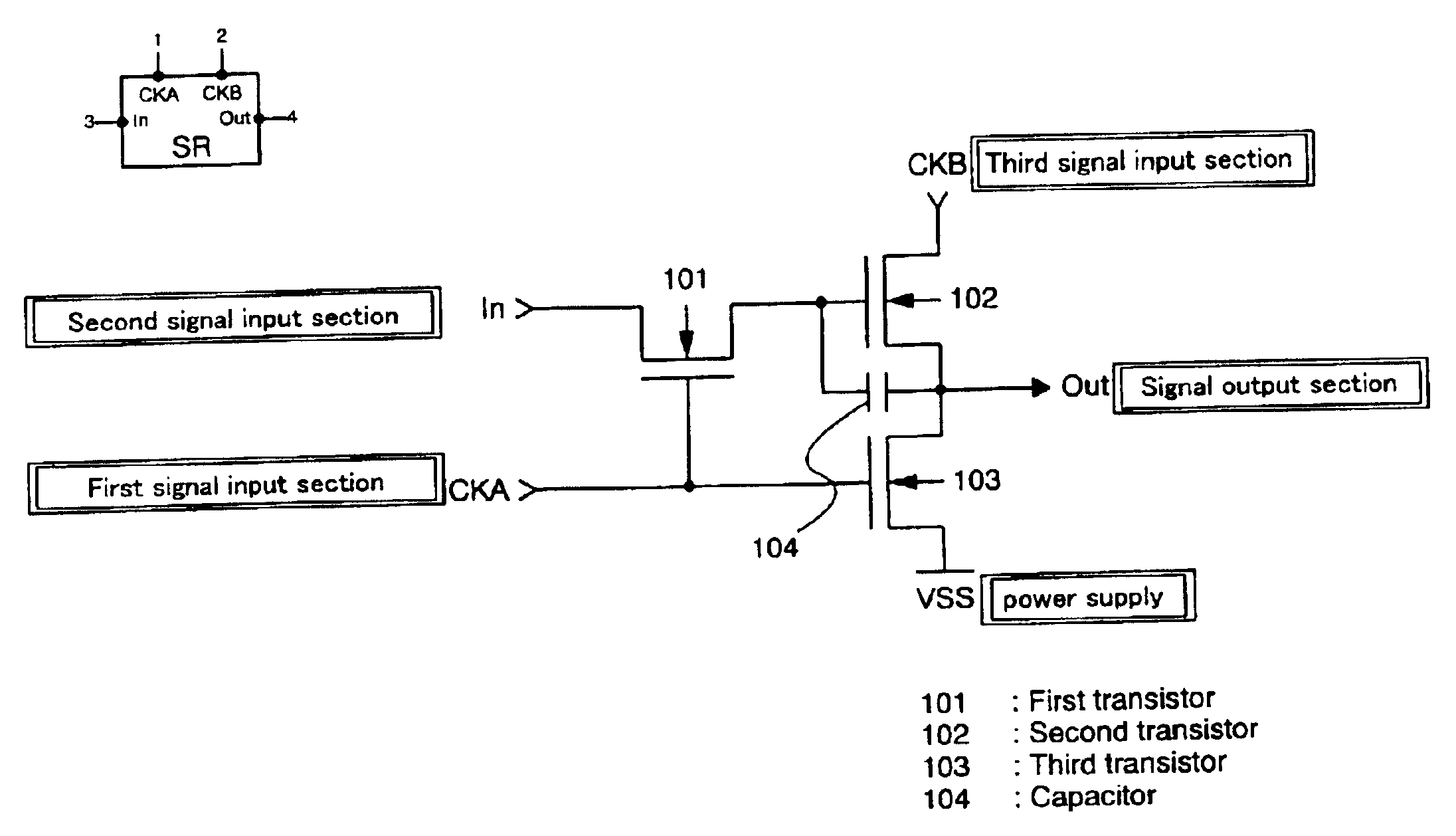

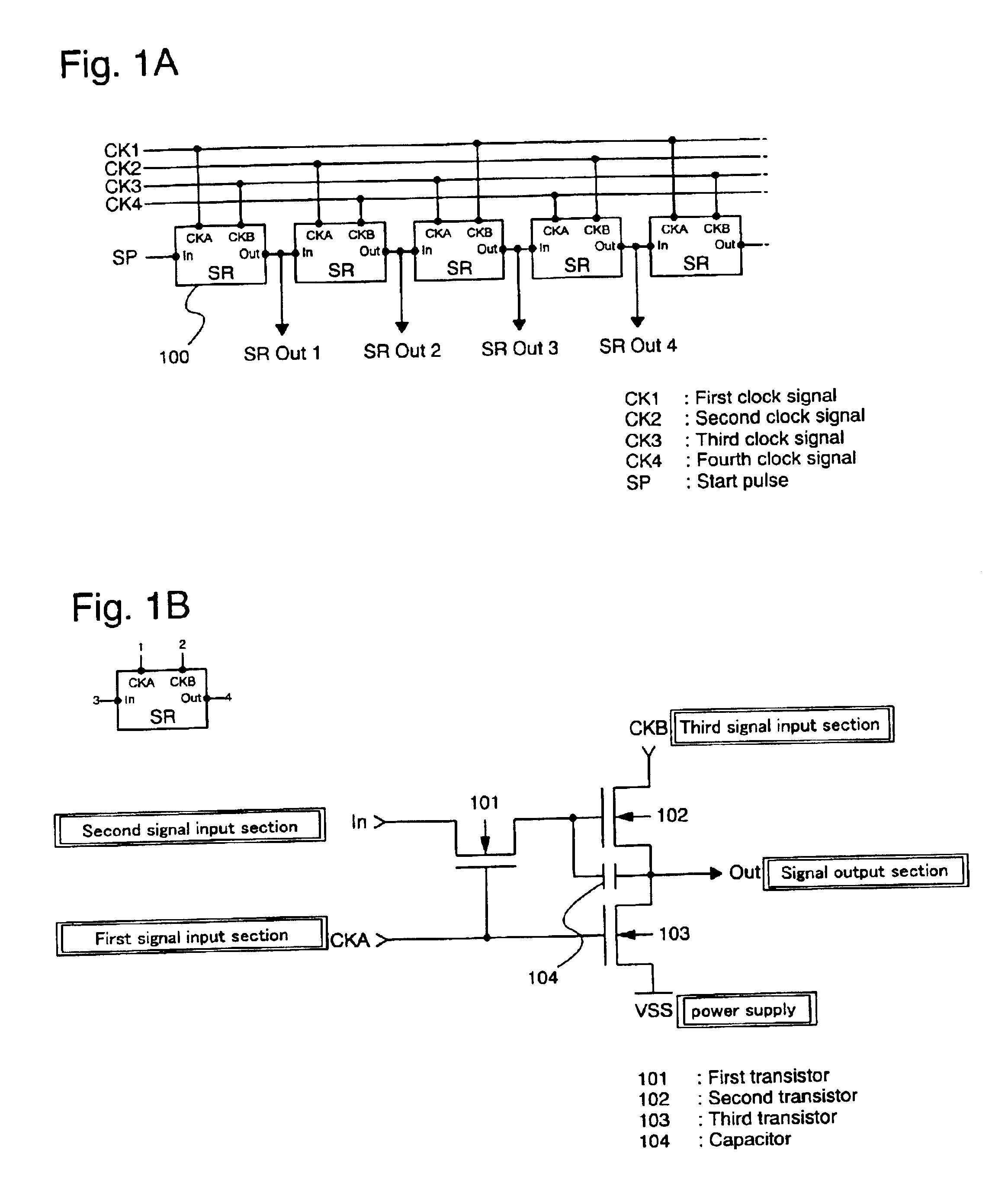

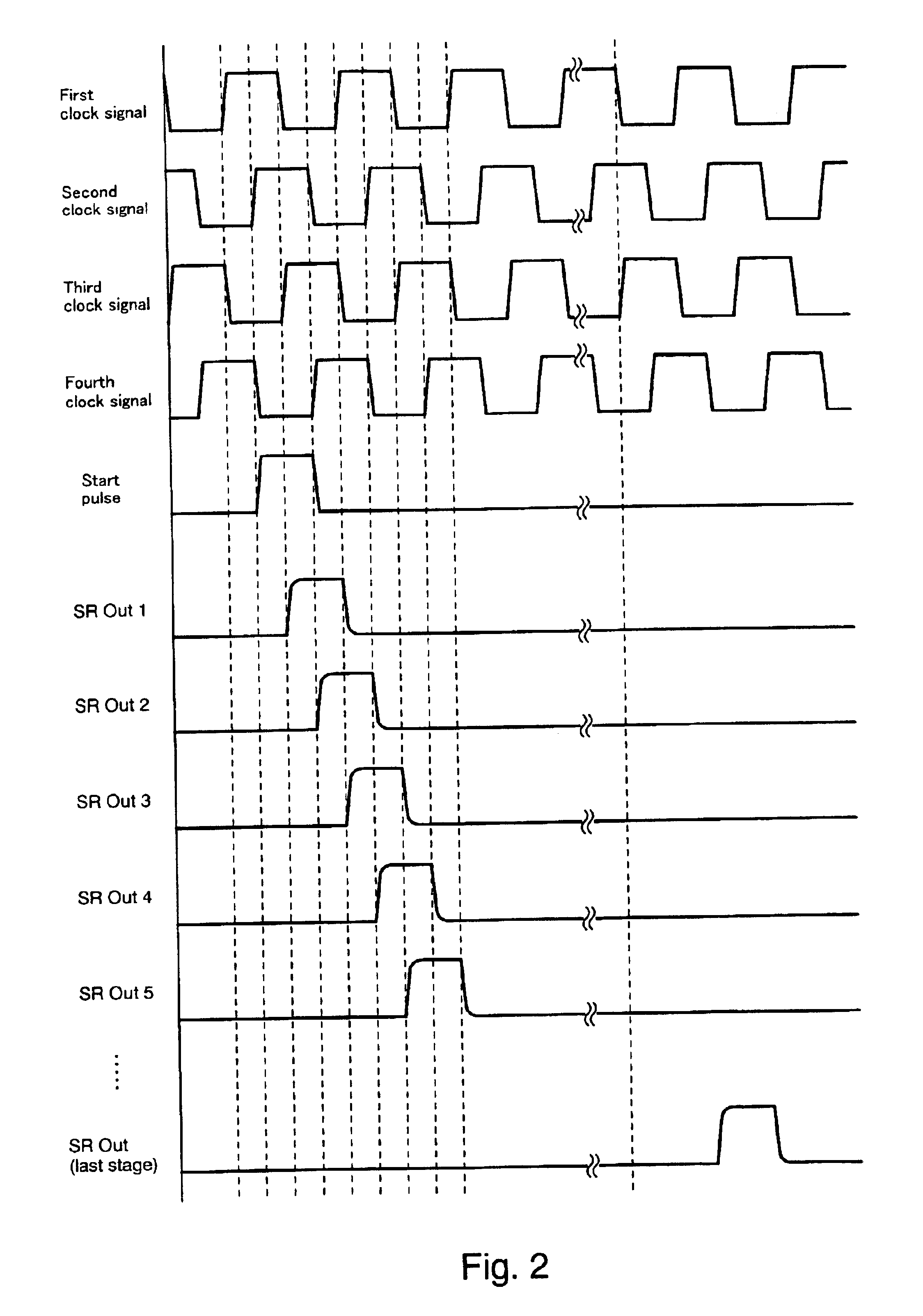

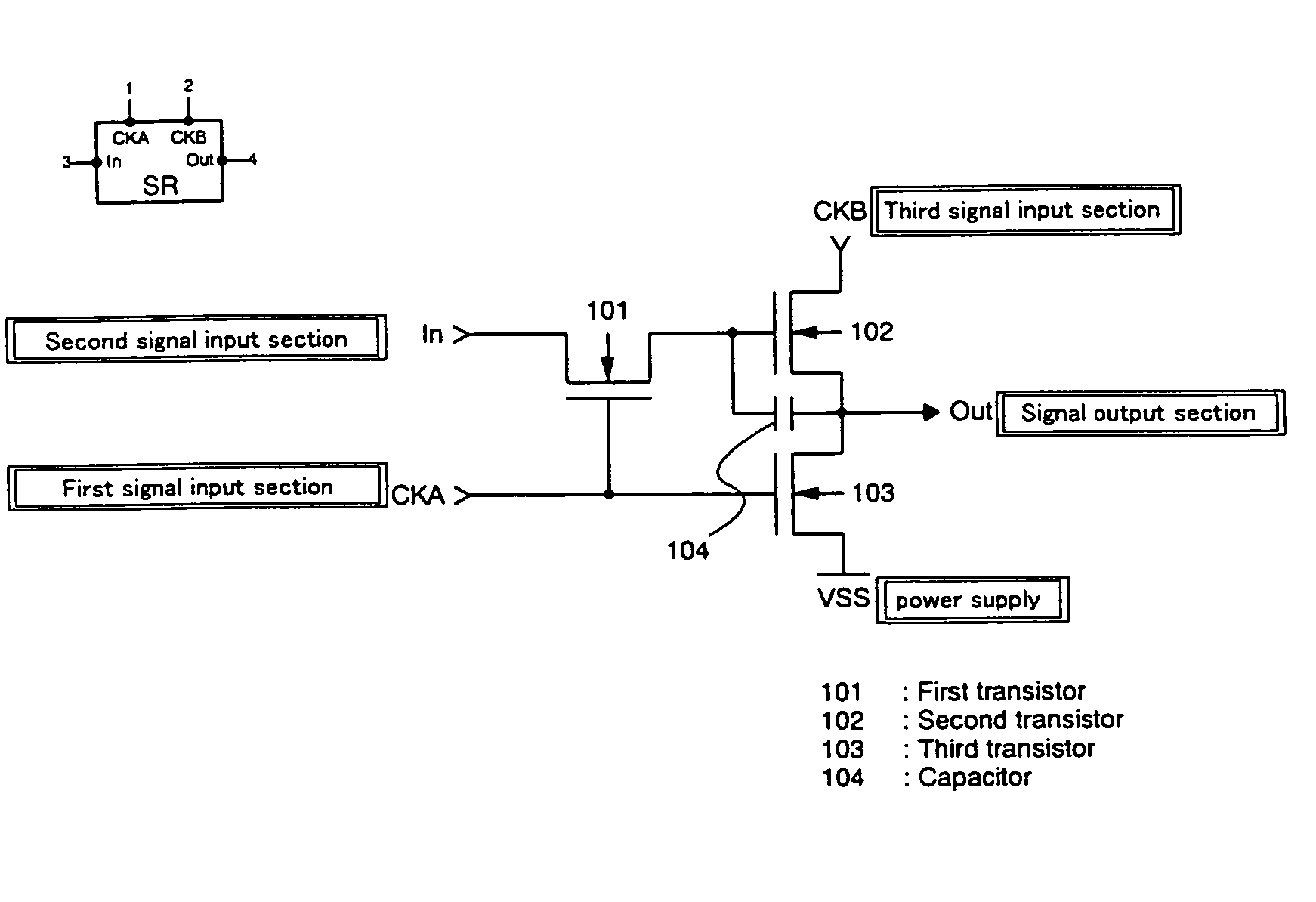

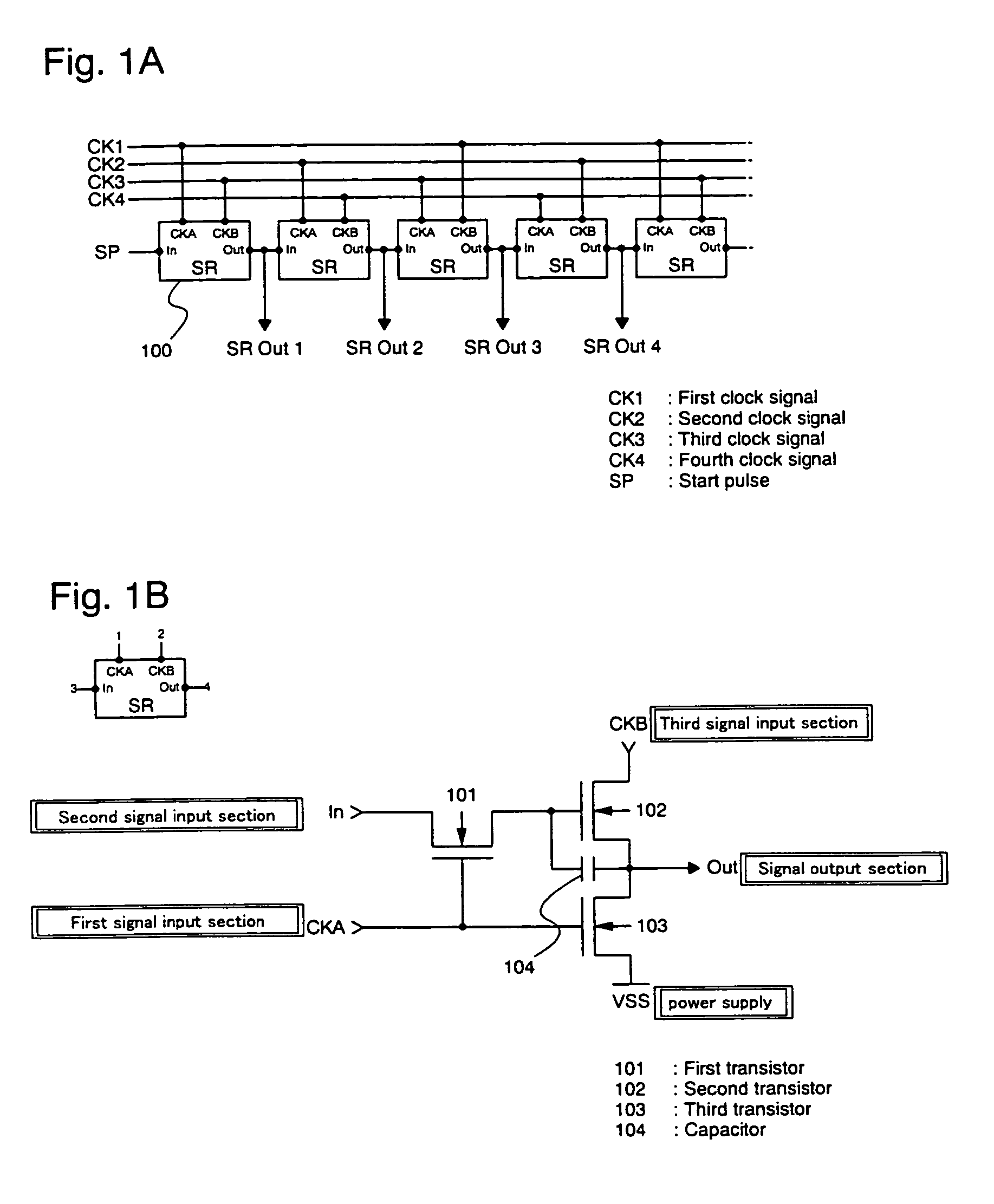

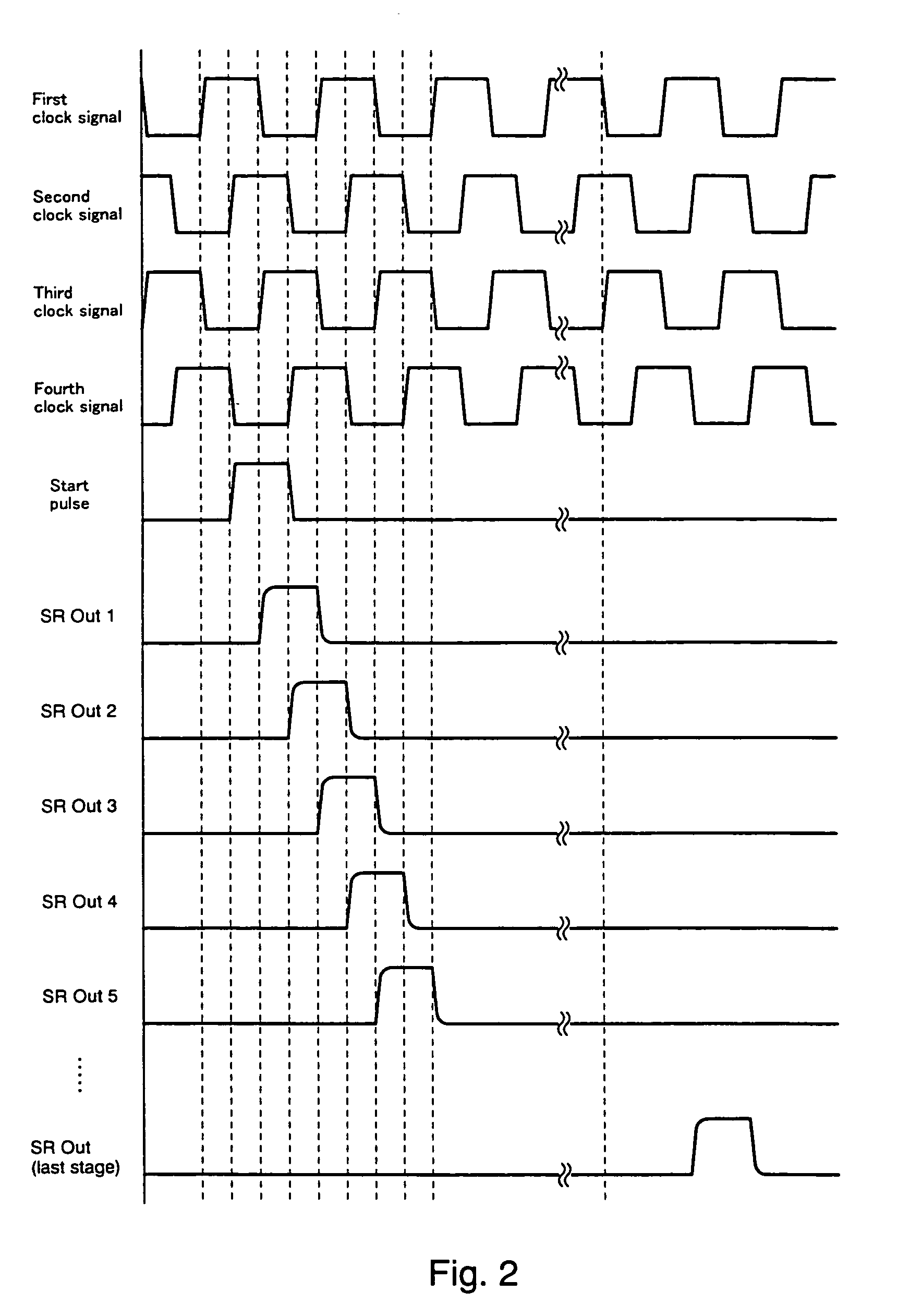

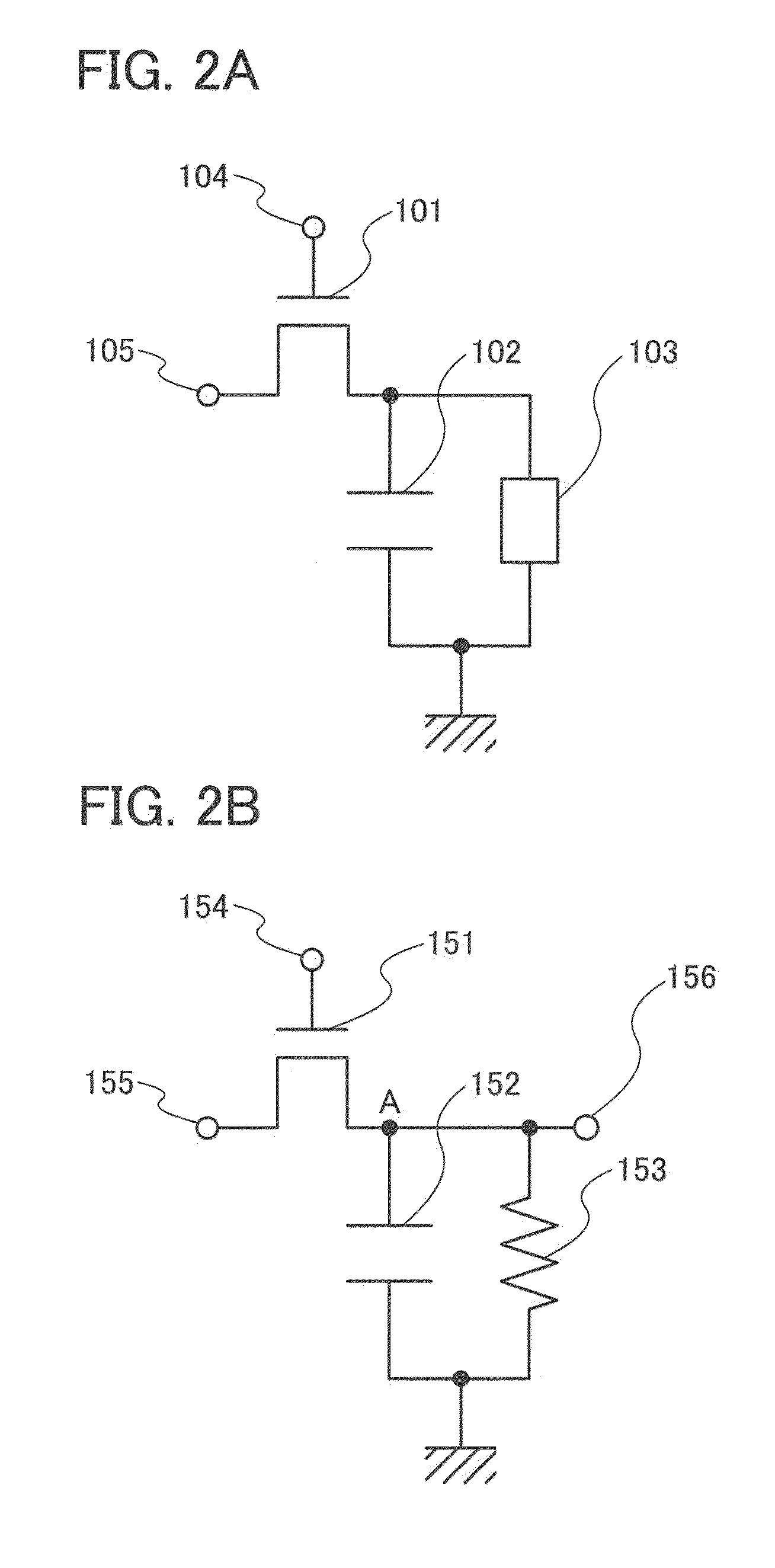

Pulse output circuit, shift register, and display device

InactiveUS6928136B2Low costReduce manufacturing stepsTransistorLogic circuits characterised by logic functionElectricityShift register

A circuit is provided which is constituted by TFTs of one conductivity type, and which is capable of outputting signals of a normal amplitude. When an input clock signal CK1 becomes a high level, each of TFTs (101, 103) is turned on to settle at a low level the potential at a signal output section (Out). A pulse is then input to a signal input section (In) and becomes high level. The gate potential of TFT (102) is increased to (VDD−V thN) and the gate is floated. TFT (102) is thus turned on. Then CK1 becomes low level and each of TFTs (101, 103) is turned off. Simultaneously, CK3 becomes high level and the potential at the signal output section is increased. Simultaneously, the potential at the gate of TFT (102) is increased to a level equal to or higher than (VDD+V thN) by the function of capacitor (104), so that the high level appearing at the signal output section (Out) becomes equal to VDD. When SP becomes low level; CK3 becomes low level; and CK1 becomes high level, the potential at the signal output section (Out) becomes low level again.

Owner:SEMICON ENERGY LAB CO LTD

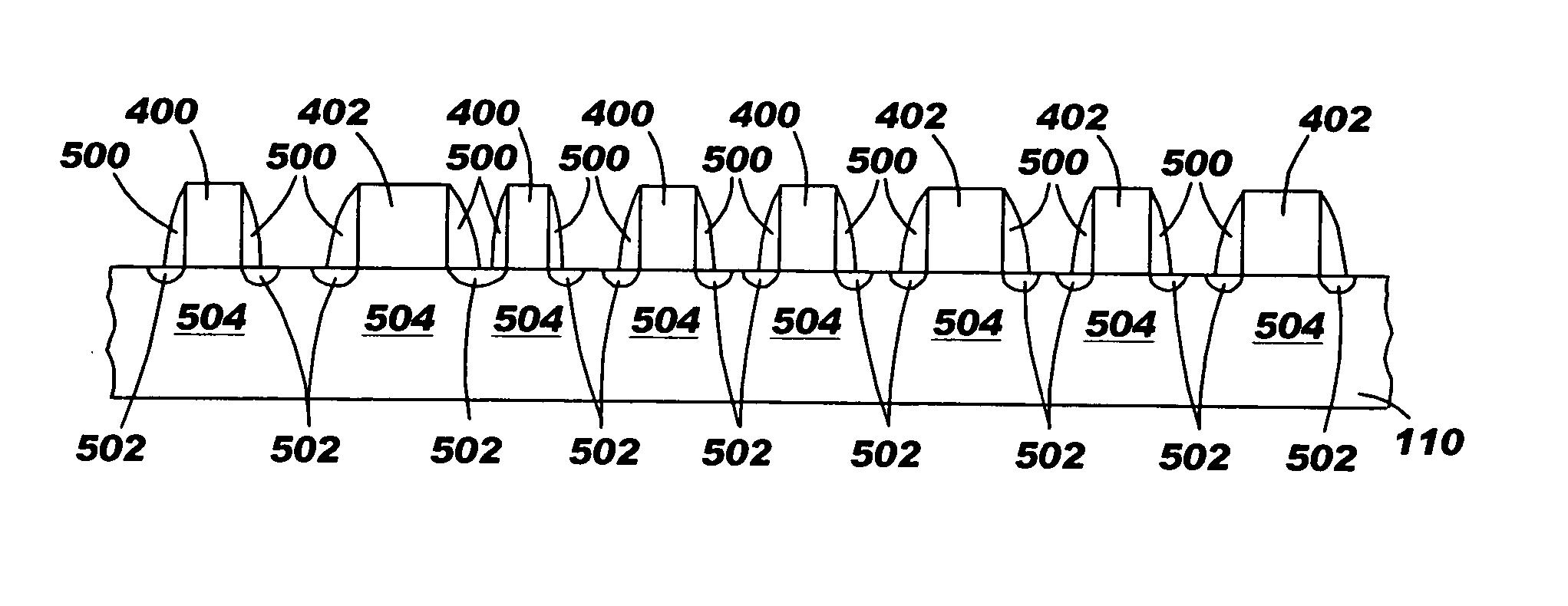

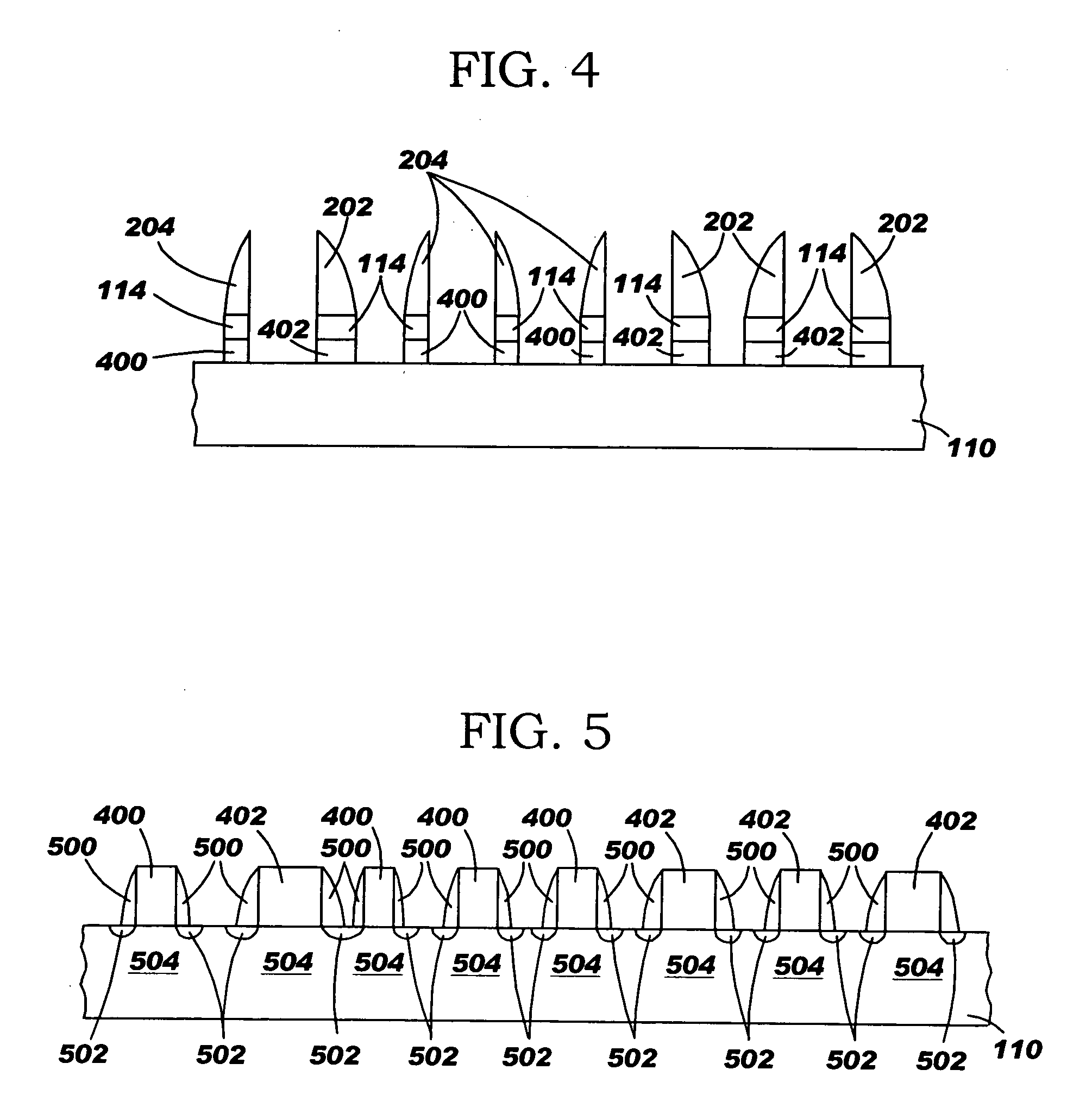

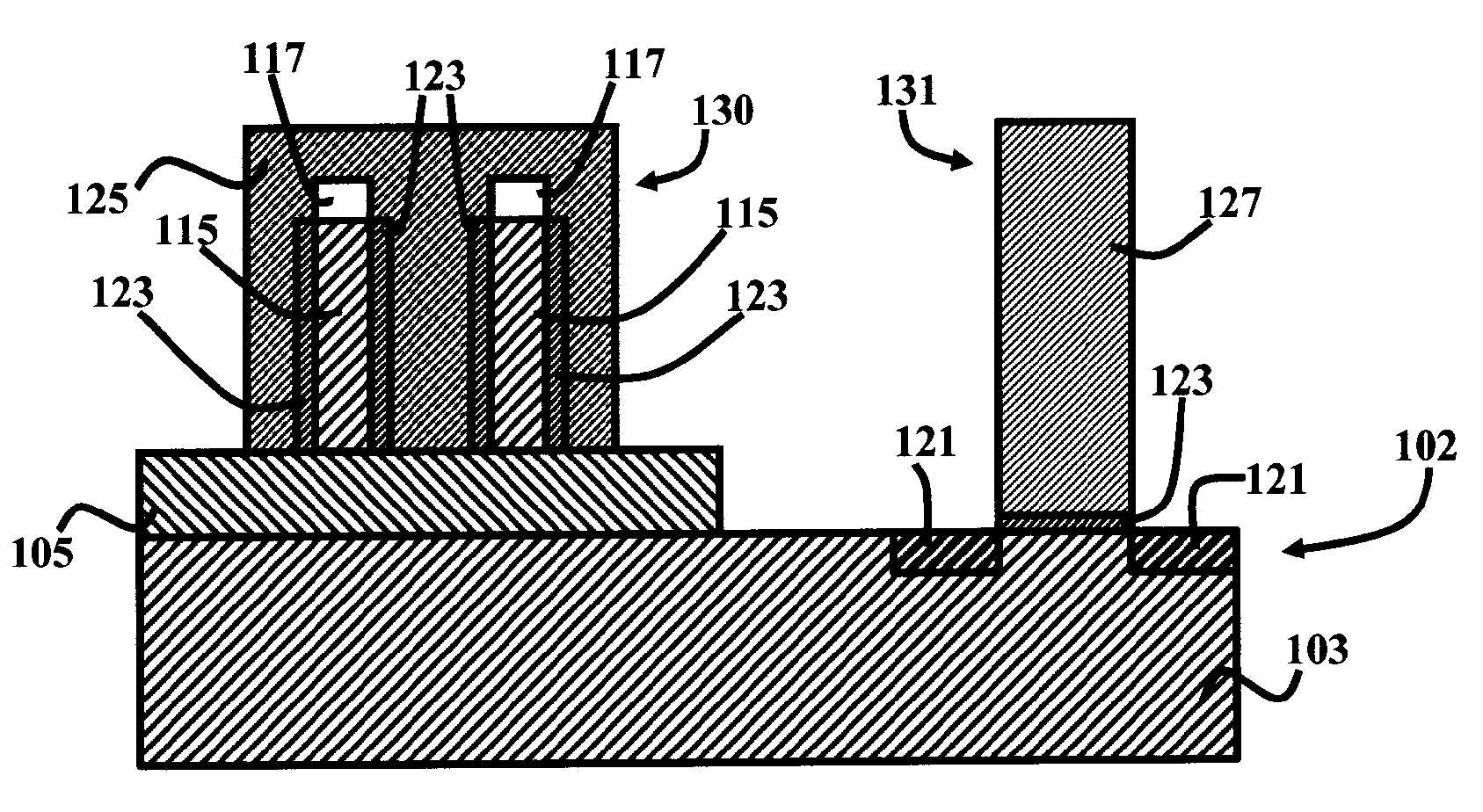

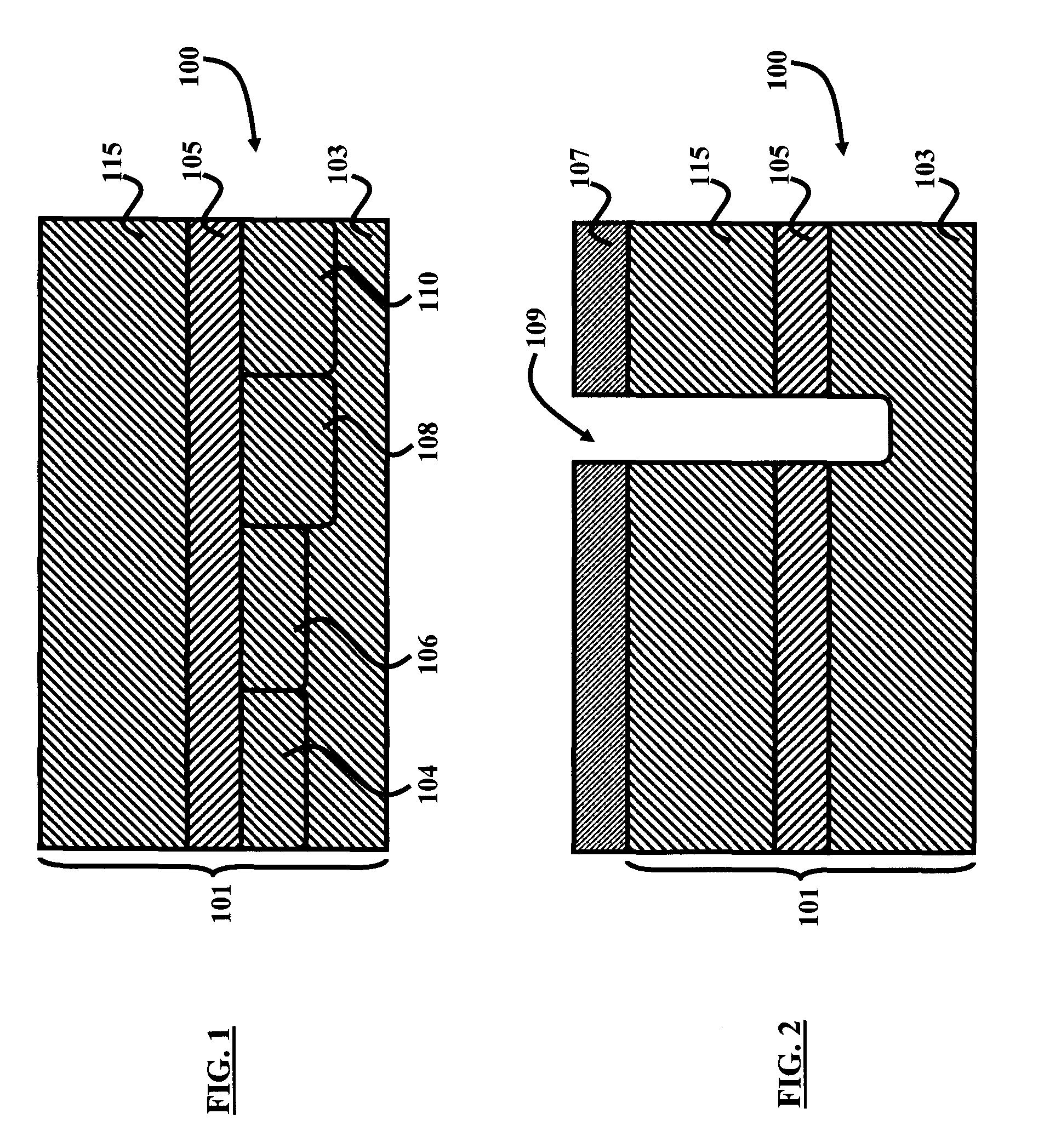

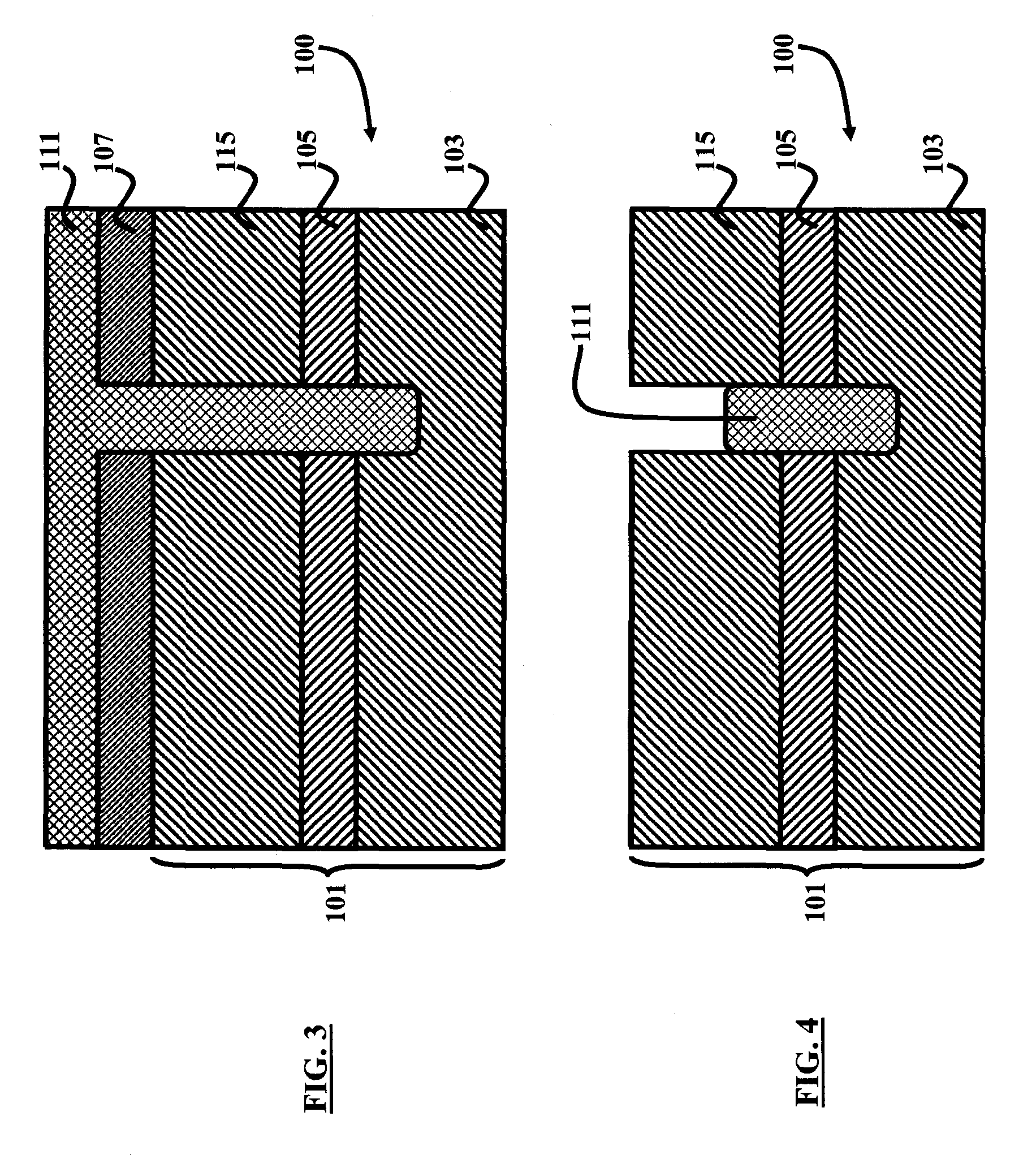

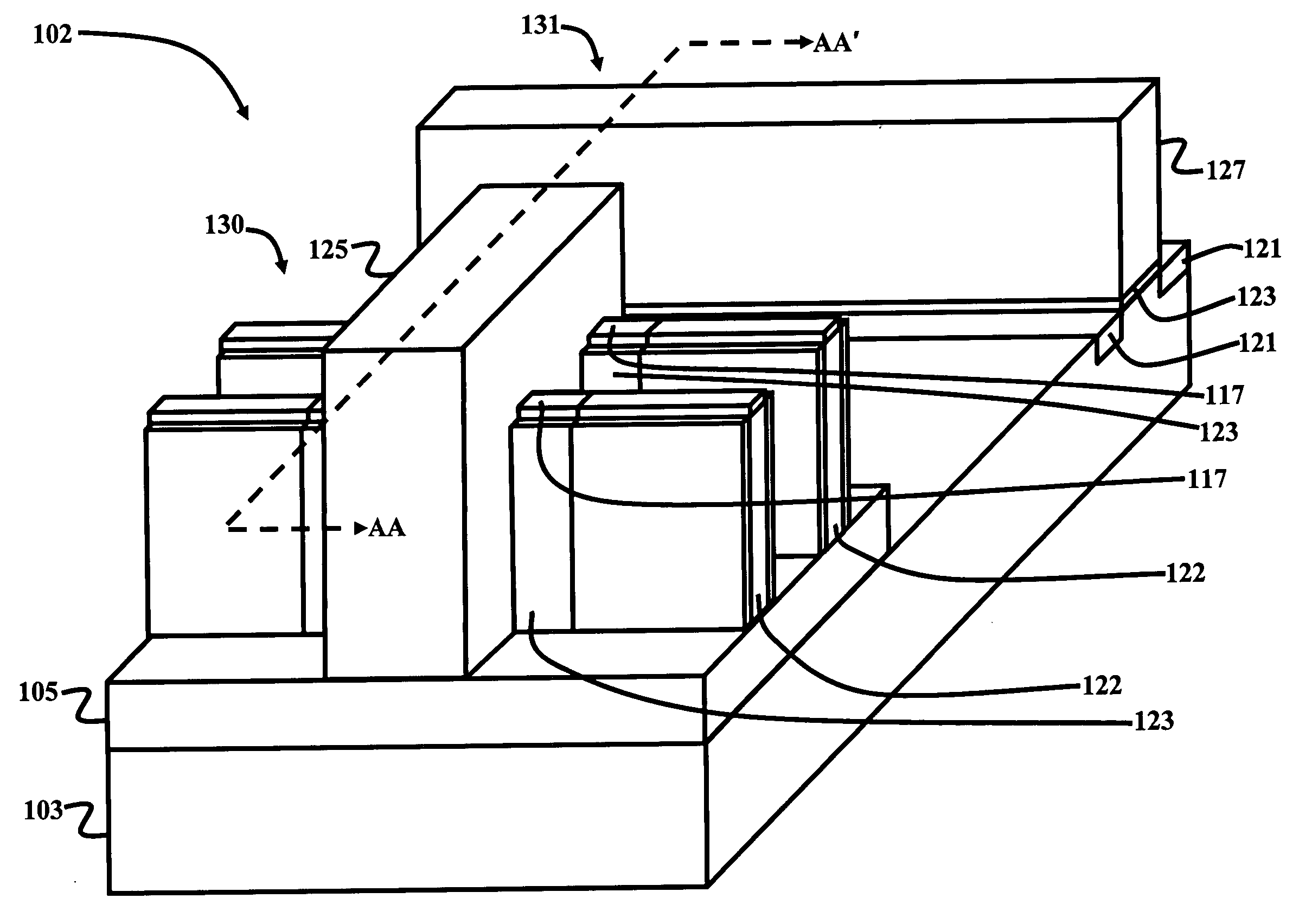

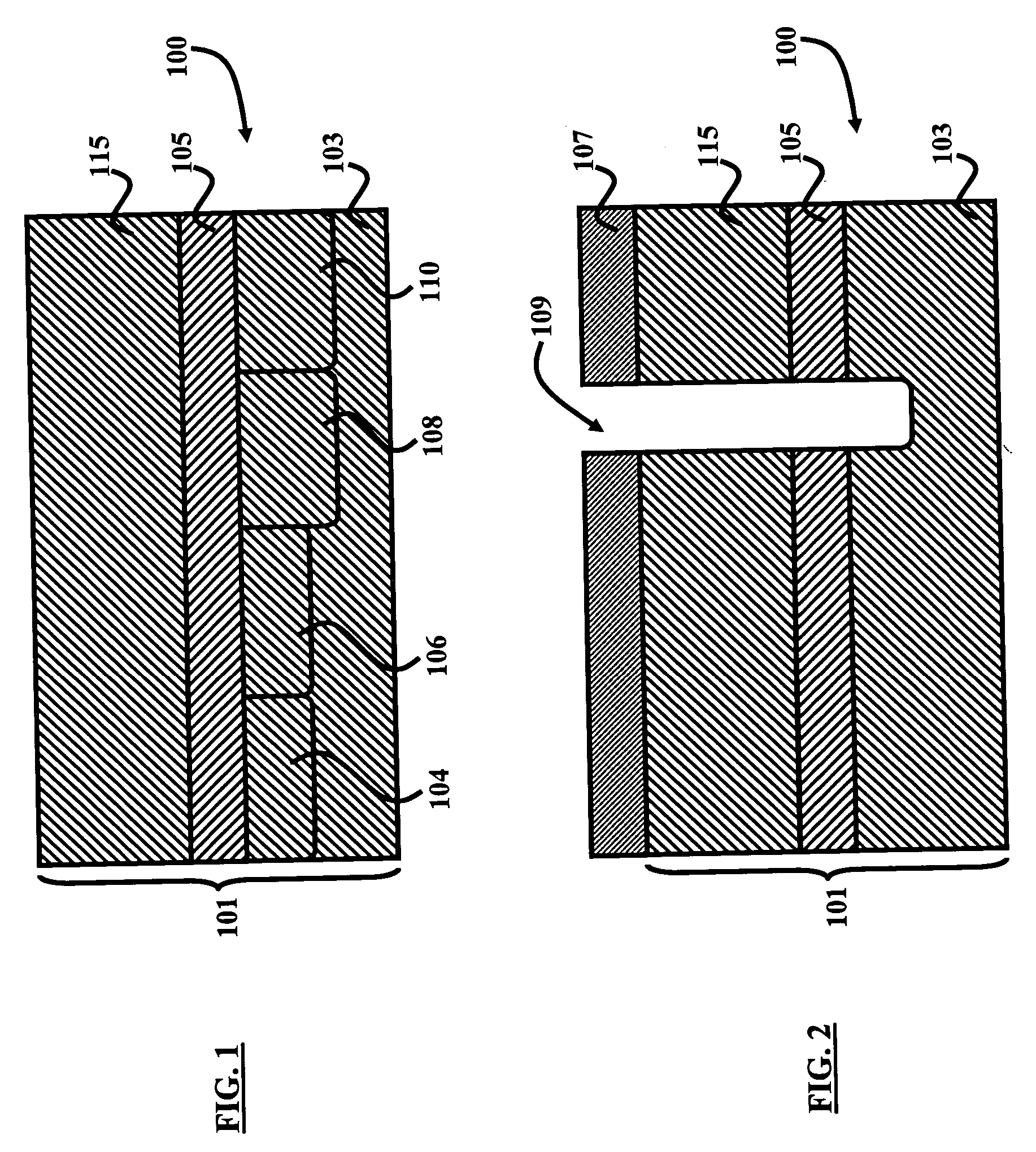

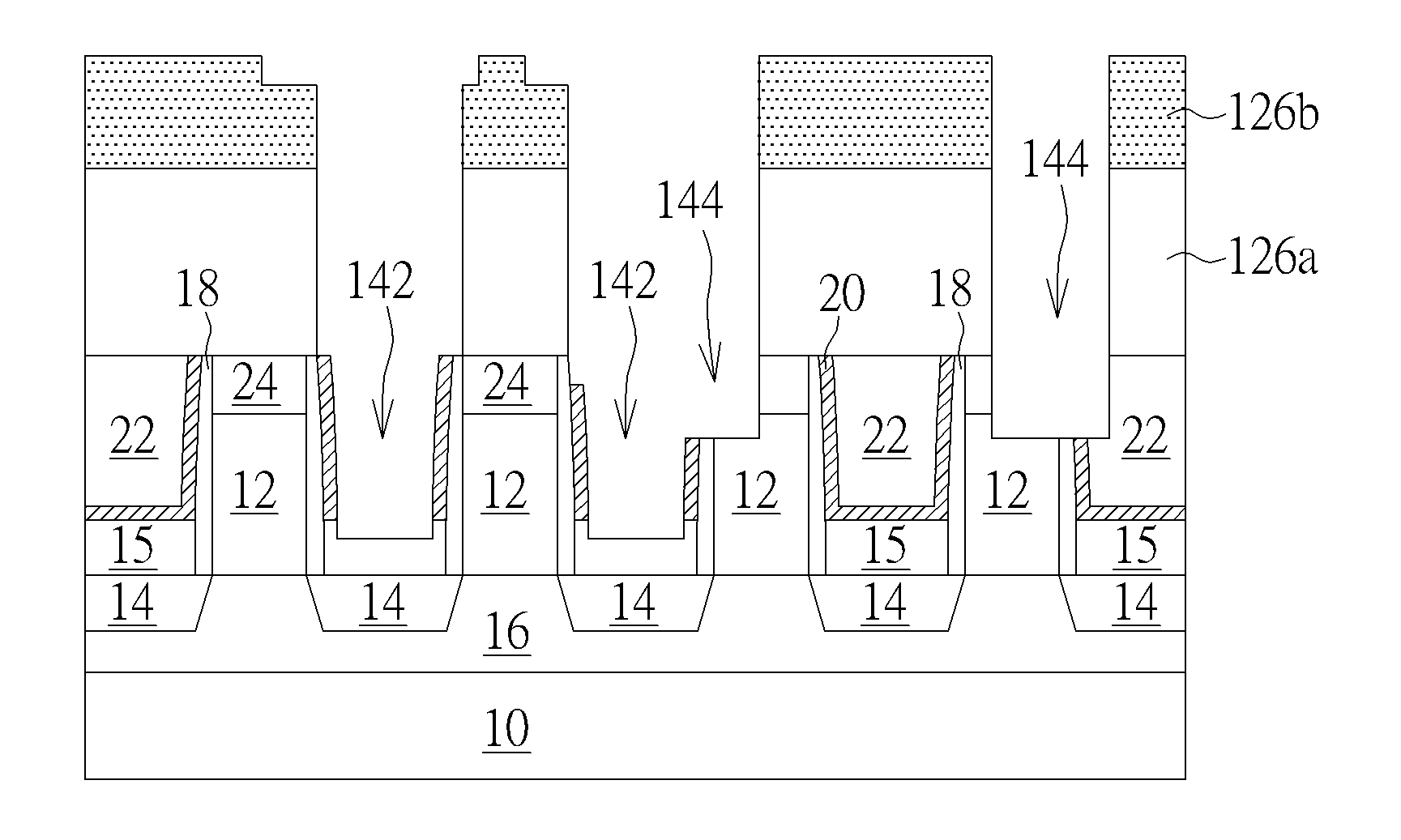

Planar substrate devices integrated with finfets and method of manufacture

ActiveUS6949768B1Reduce manufacturing stepsEasy to integrateTransistorSolid-state devicesPlanar substrateEngineering

A planar substrate device integrated with fin field effect transistors (FinFETs) and a method of manufacture comprises a silicon-on-insulator (SOI) wafer comprising a substrate; a buried insulator layer over the substrate; and a semiconductor layer over the buried insulator layer. The structure further comprises a FinFET over the buried insulator layer and a field effect transistor (FET) integrated in the substrate, wherein the FET gate is planar to the FinFET gate. The structure further comprises retrograde well regions configured in the substrate. In one embodiment, the structure further comprises a shallow trench isolation region configured in the substrate.

Owner:GLOBALFOUNDRIES US INC

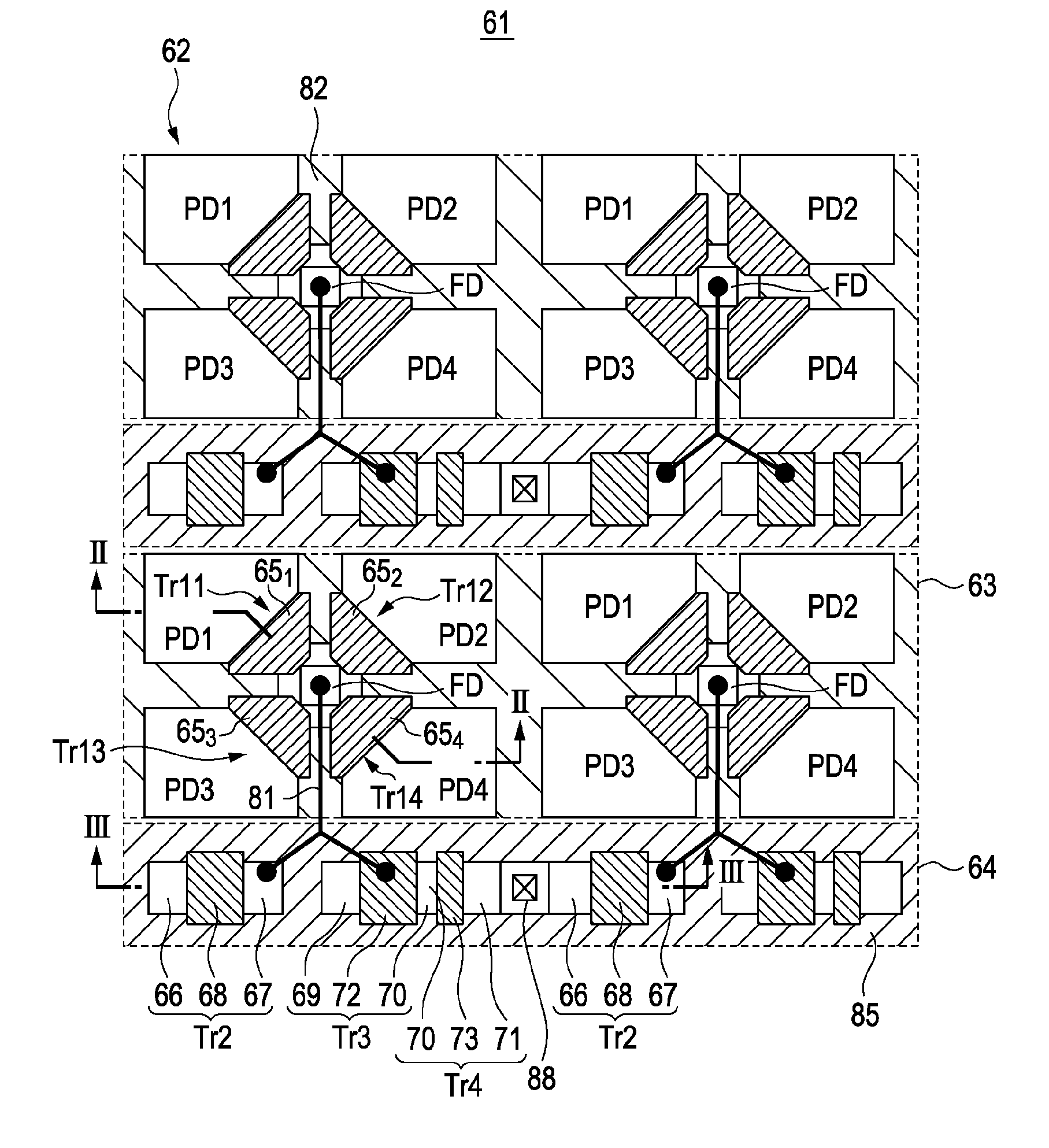

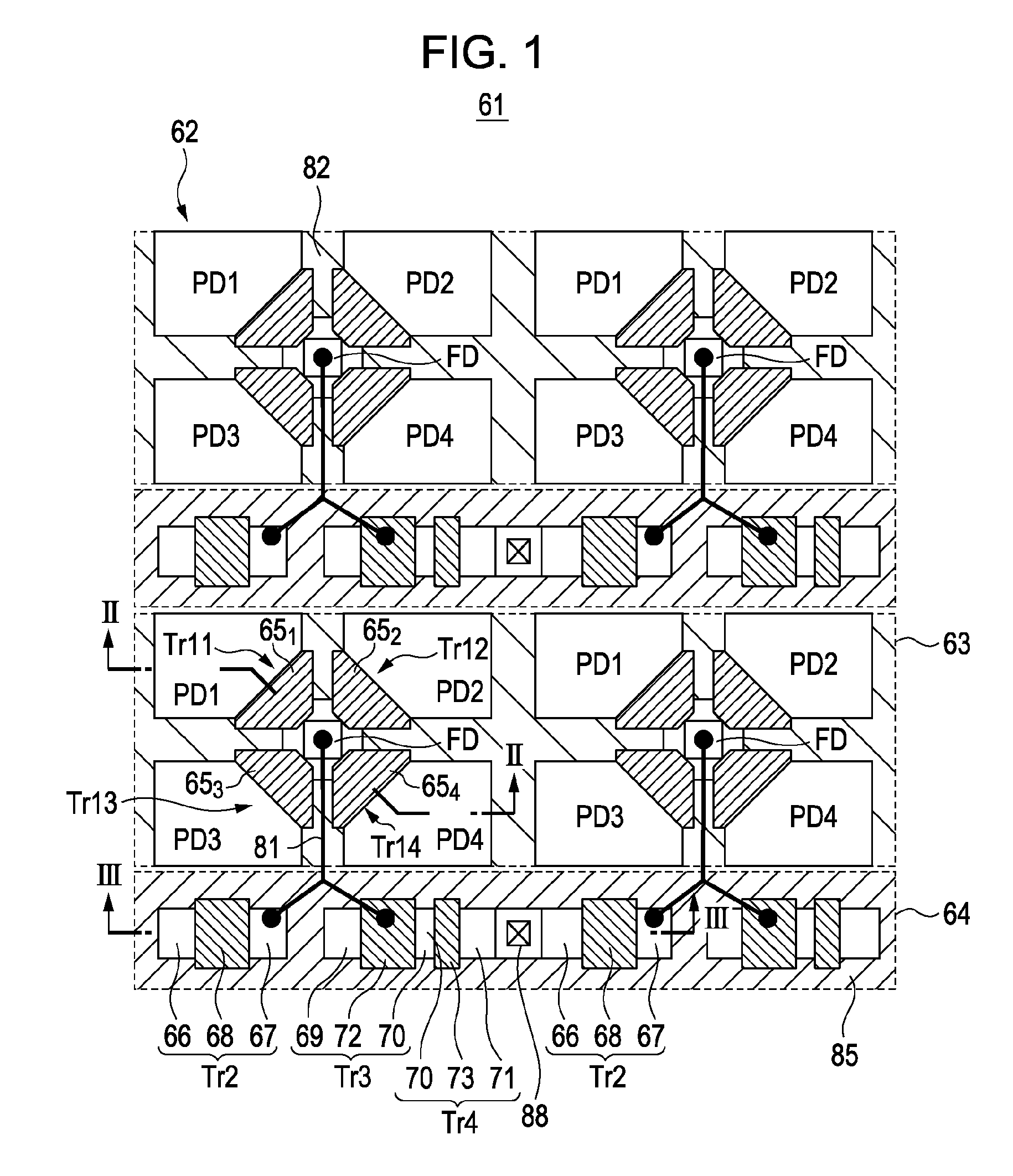

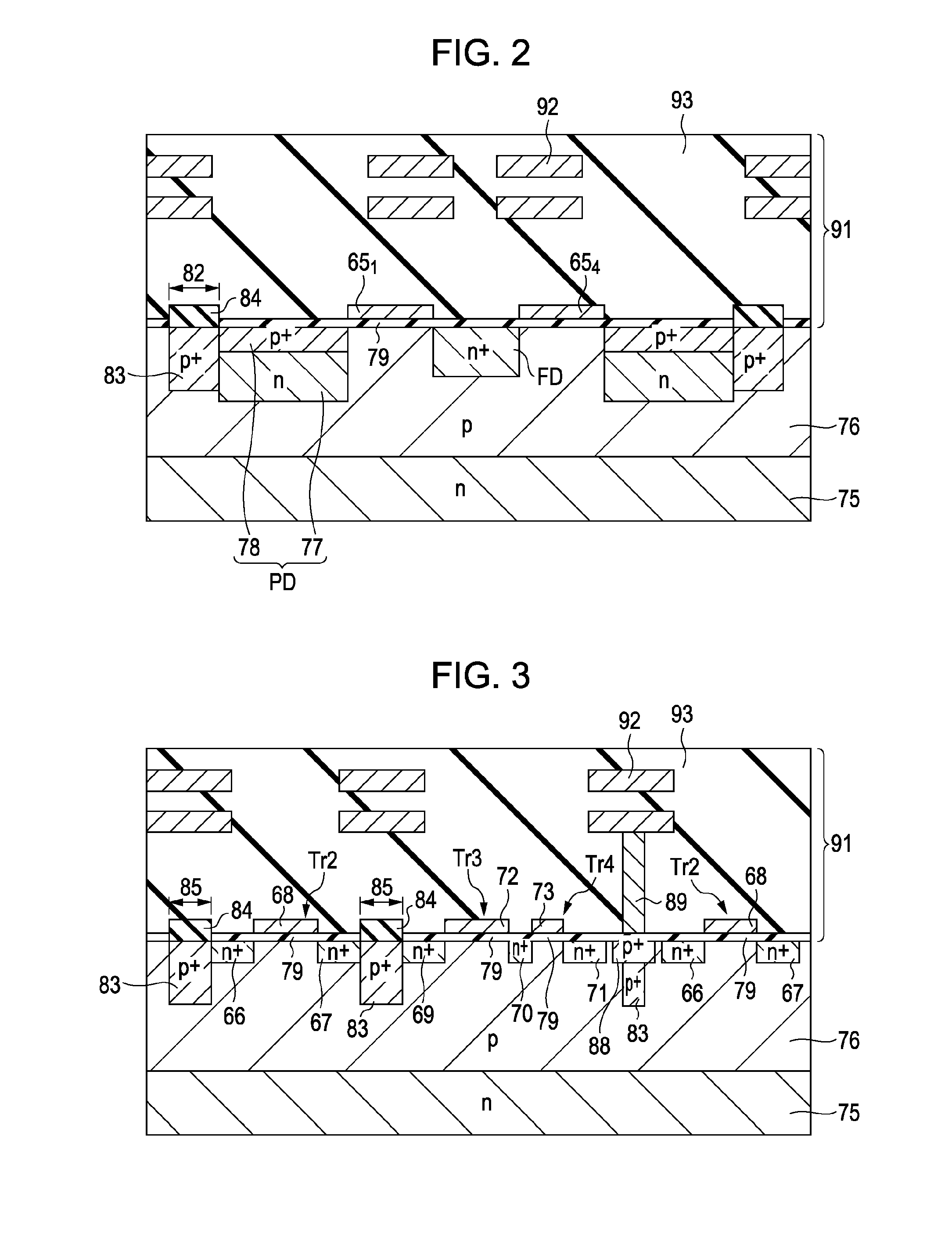

Solid-state imaging device and method for manufacturing solid-state imaging device, and electronic device

ActiveUS20110073923A1Improve featuresReduce in quantityTransistorSolid-state devicesPhotoelectric conversionEngineering

A solid-state imaging device includes a first-conductivity-type semiconductor well region, a plurality of pixels each of which is formed on the semiconductor well region and is composed of a photoelectric conversion portion and a pixel transistor, an element isolation region provided between the pixels and in the pixels, and an element isolation region being free from an insulation film and being provided between desired pixel transistors.

Owner:SONY CORP

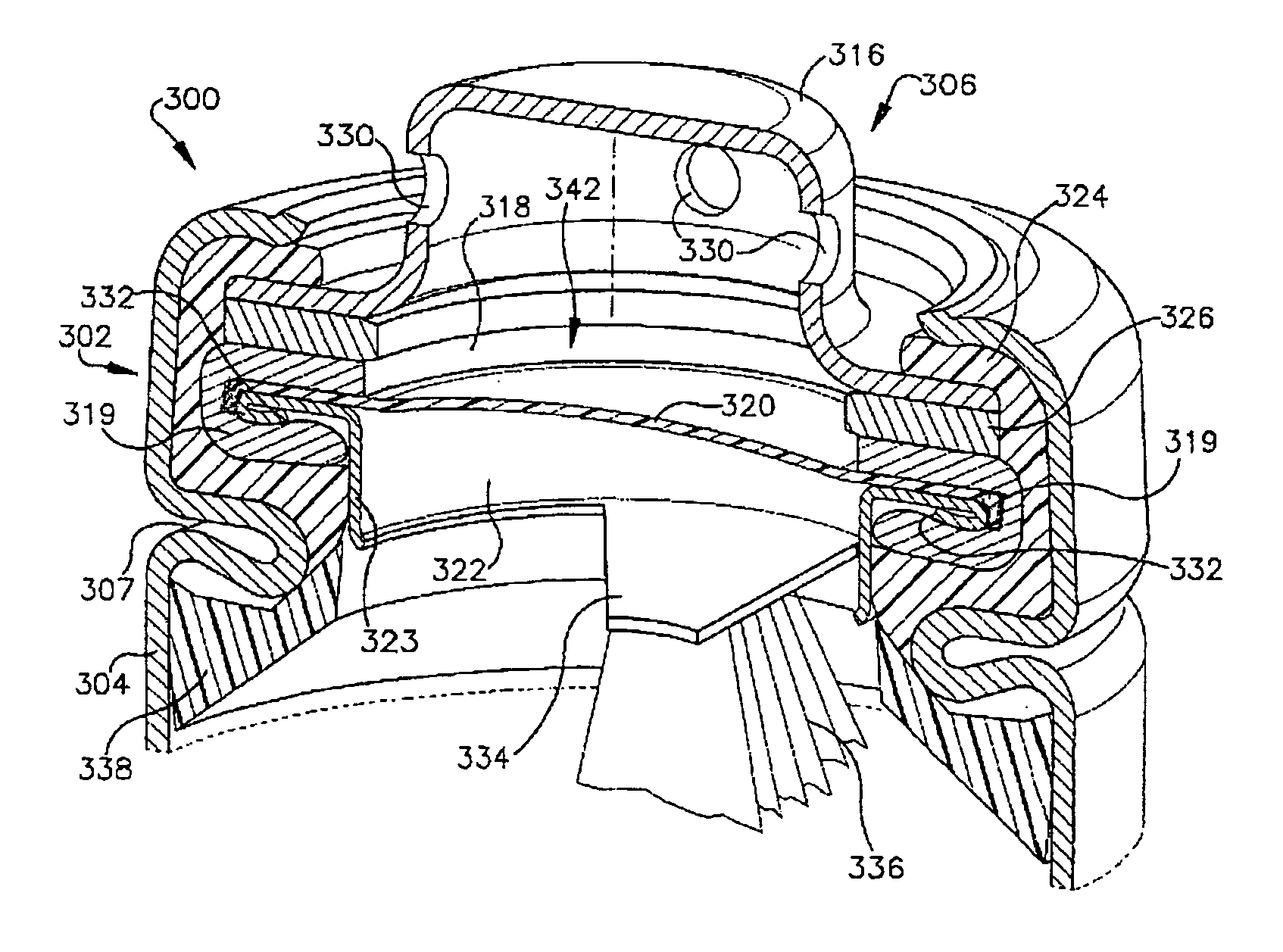

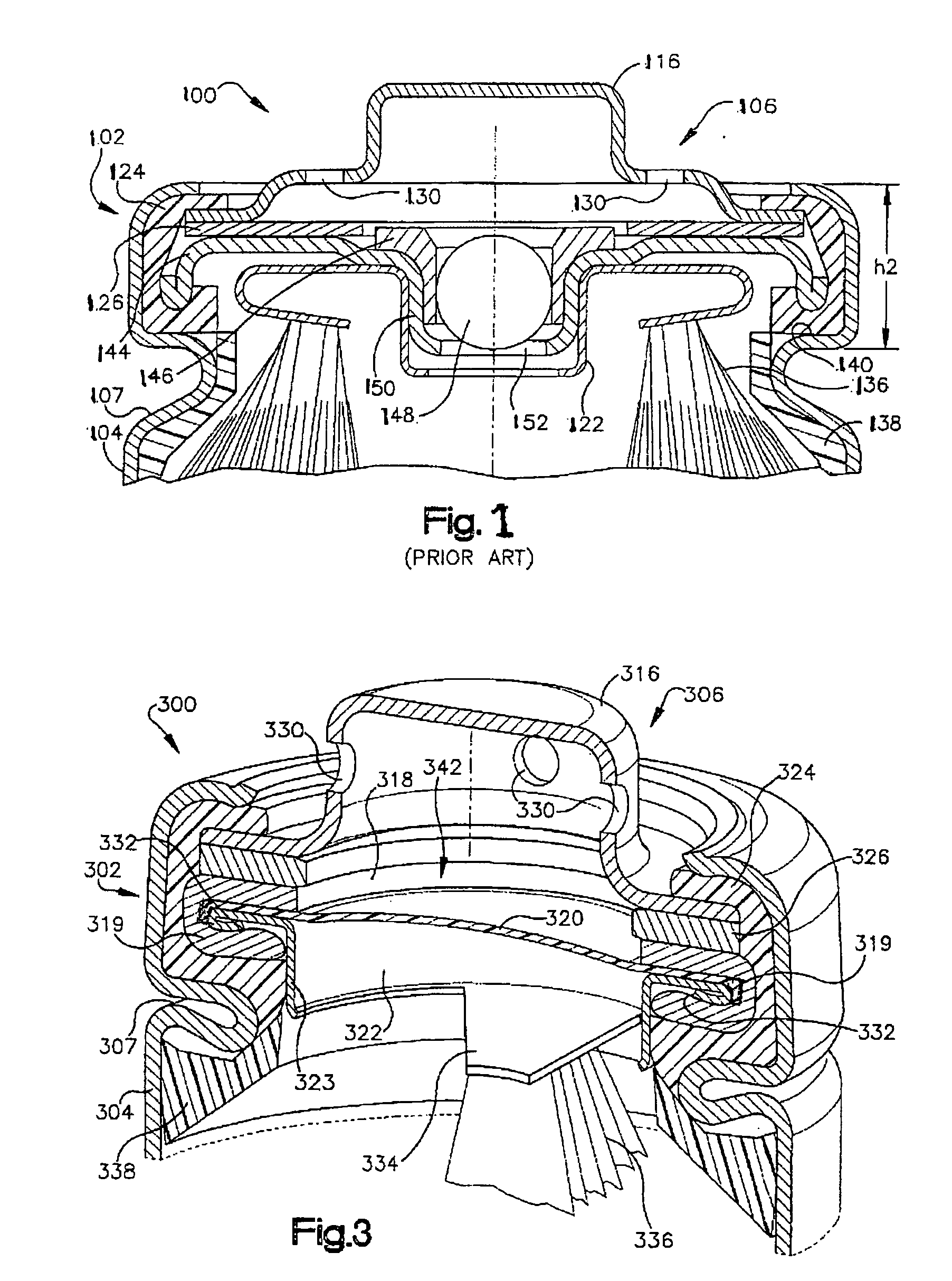

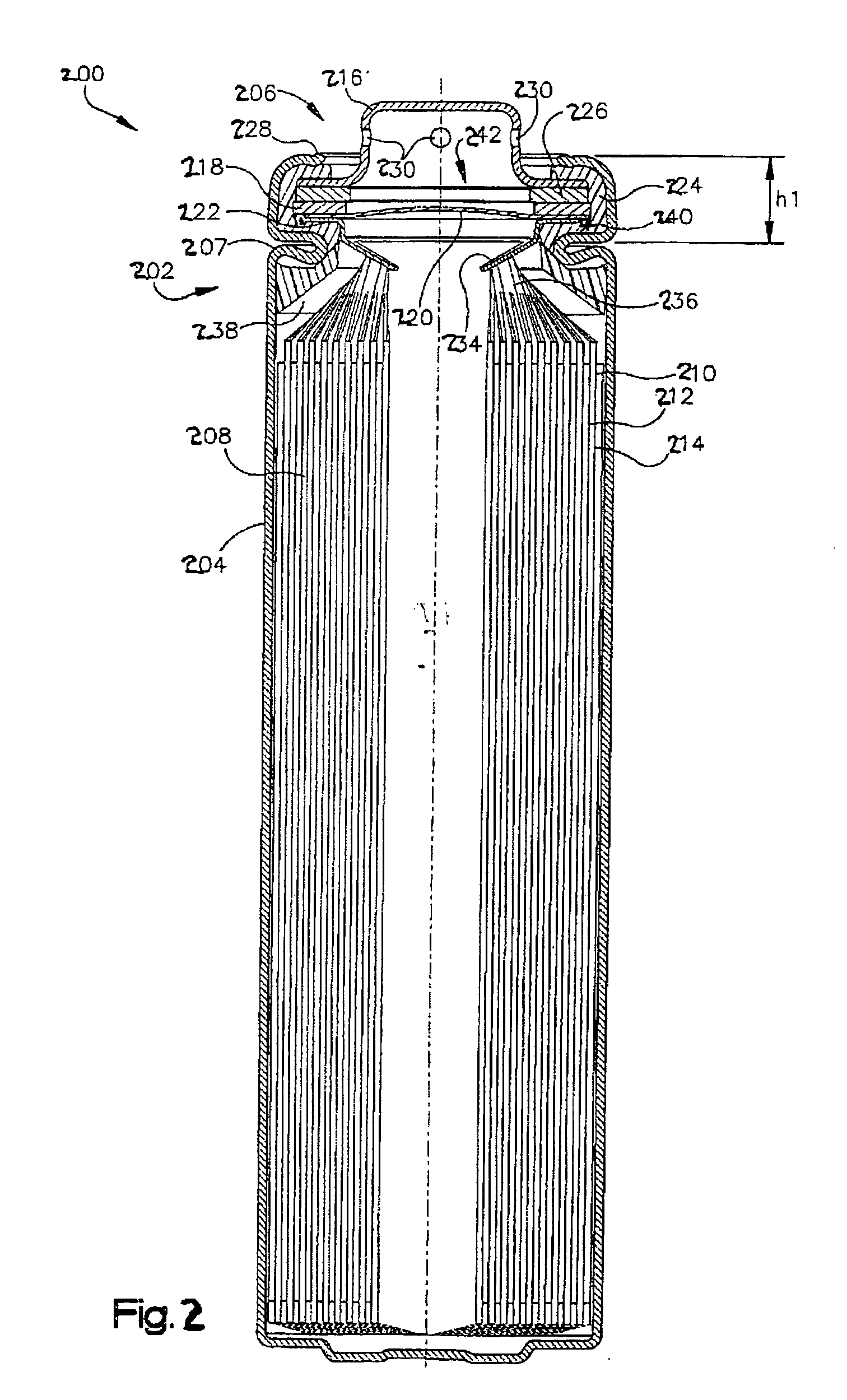

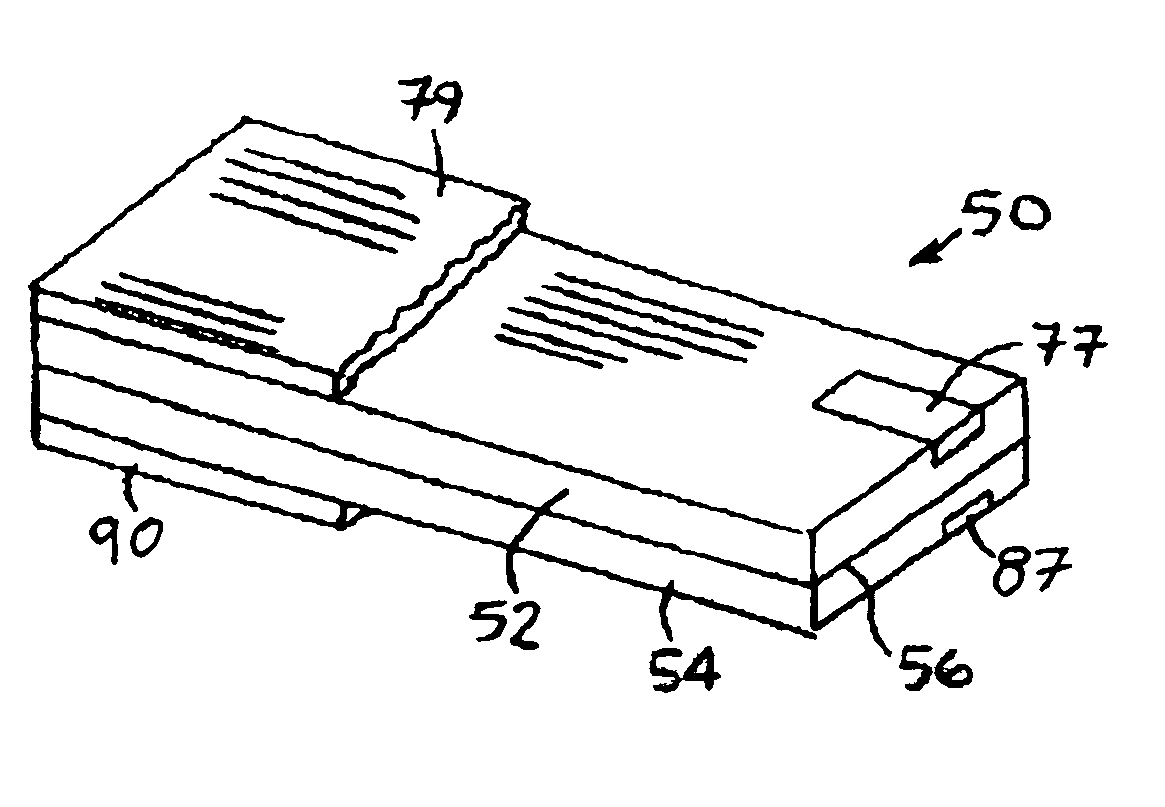

Closure vent seal and assembly

InactiveUS20060228620A1Increase battery capacityThe production process is simpleClosuresFinal product manufactureEngineeringMechanical engineering

A closure assembly and rupturable vent seal adapted for use in an electrochemical battery cell is disclosed. The vent seal includes a series of peripheral projections that can be folded to insure proper sealing of the vent without wrinkles or overlapping folded portions. Methods of accomplishing the invention are also contemplated.

Owner:EVEREADY BATTERY CO INC

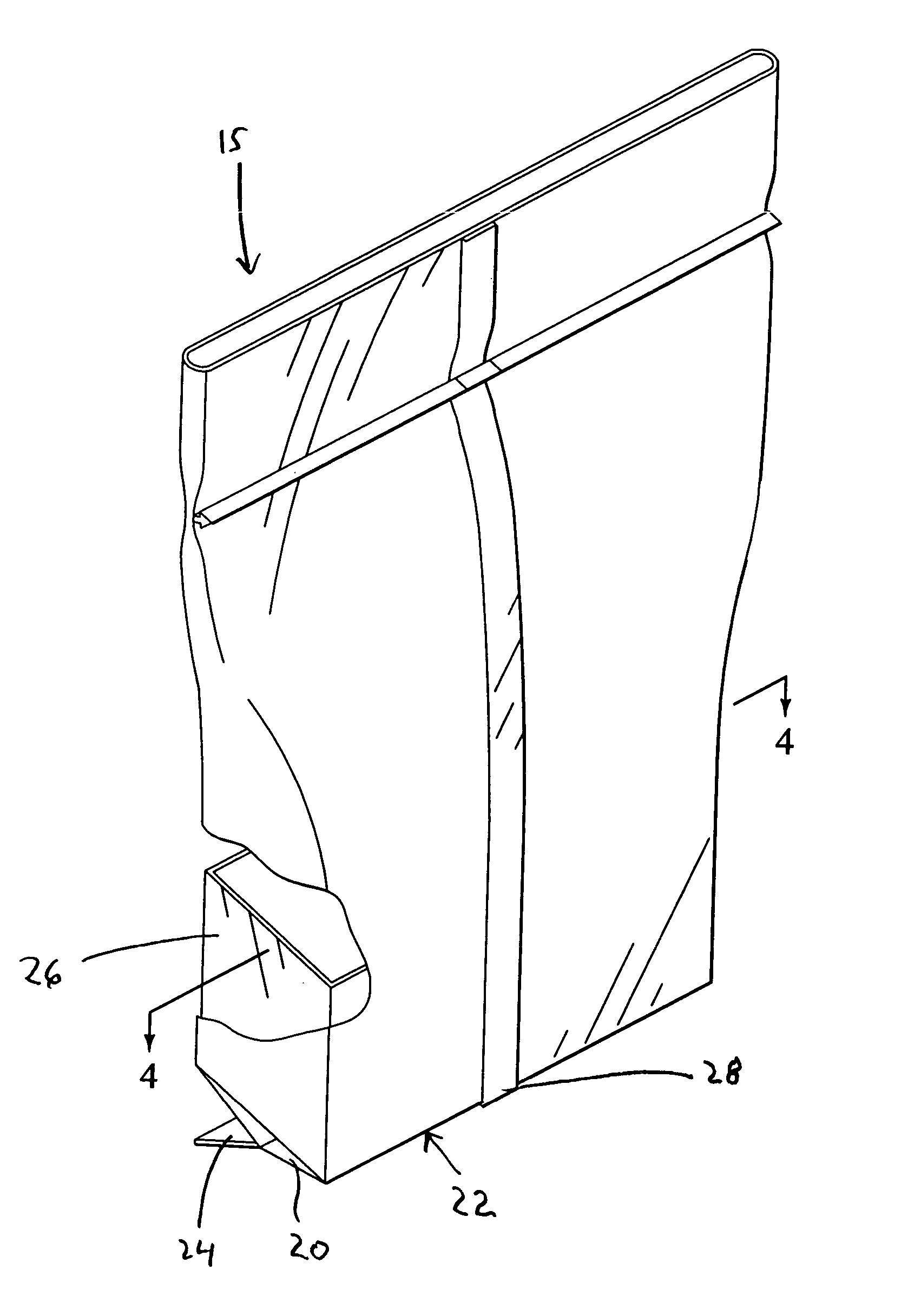

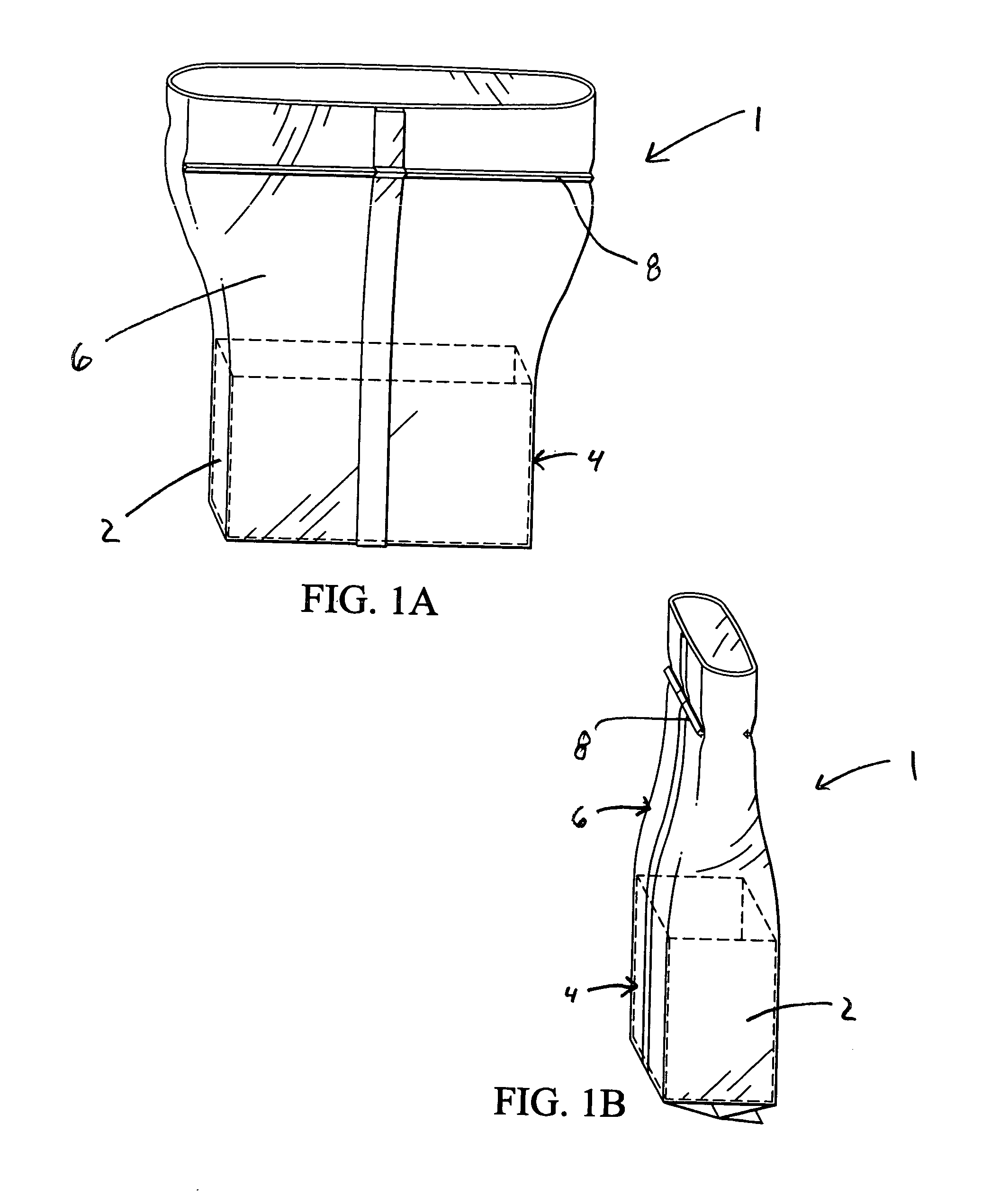

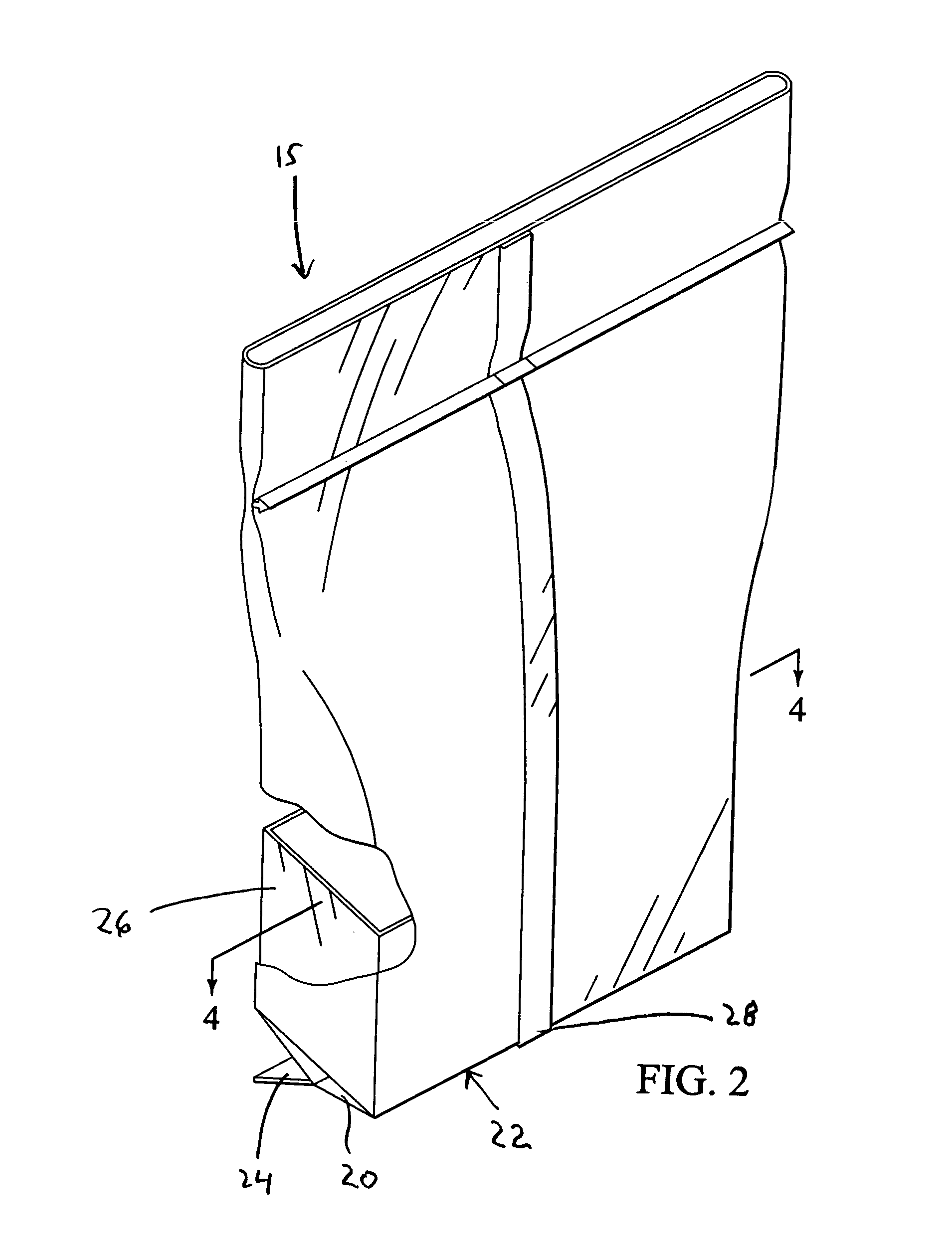

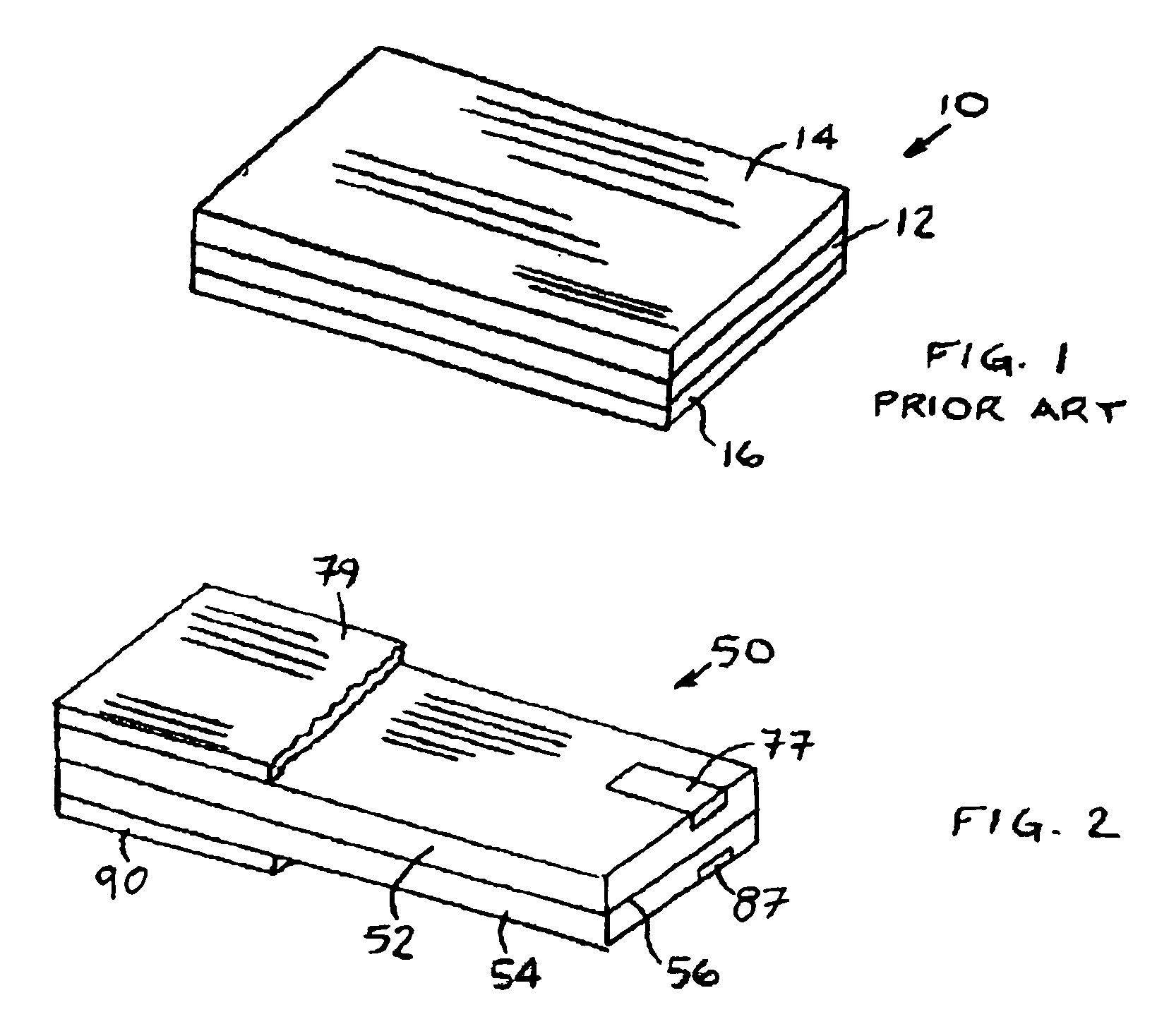

Structured reclosable packaging

InactiveUS20050053315A1Minimizes material requirementLow production costBagsSacksEngineeringCompanion animal

Disclosed herein is flexible packaging with a relative rigid structure portion, and an efficient method for manufacturing the same, that provides flexible packaging with an interior support that is able to contain products such as snacks, confections, pet foods, and liquids. The present invention provides for shearing and reinforcing portions of a primary web to form a bag. A supportive structure is also sheared and configured into a predetermined shape. The supportive structure is affixed inside the lower portion of the bag and provides form and support to the bag. The bag may also have a reclosable top portion that encloses the contents of the packaging.

Owner:DOBOY

Omega3 fatty acid compound preparation

ActiveUS20130115284A1Suppress modification and insolubilizationStabilize compoundBiocideElcosanoid active ingredientsDecompositionCombinatorial chemistry

Provided is a compound preparation including at least one selected from the group consisting of ω3 polyunsaturated fatty acids and pharmaceutically acceptable salts and esters thereof and at least one selected from the group consisting of statin compounds and pharmaceutically acceptable salts thereof. The compound preparation is in a form of a soft capsule having a capsule coating with a pH of 7.0 to 9.5. The compound preparation suppresses the decomposition of the statin compounds and / or the modification / insolubilization of the capsule coating. A medical use for the compound preparation, a method of manufacturing the compound preparation and a method of using the compound preparation are also provided.

Owner:MOCHIDA PHARM CO LTD

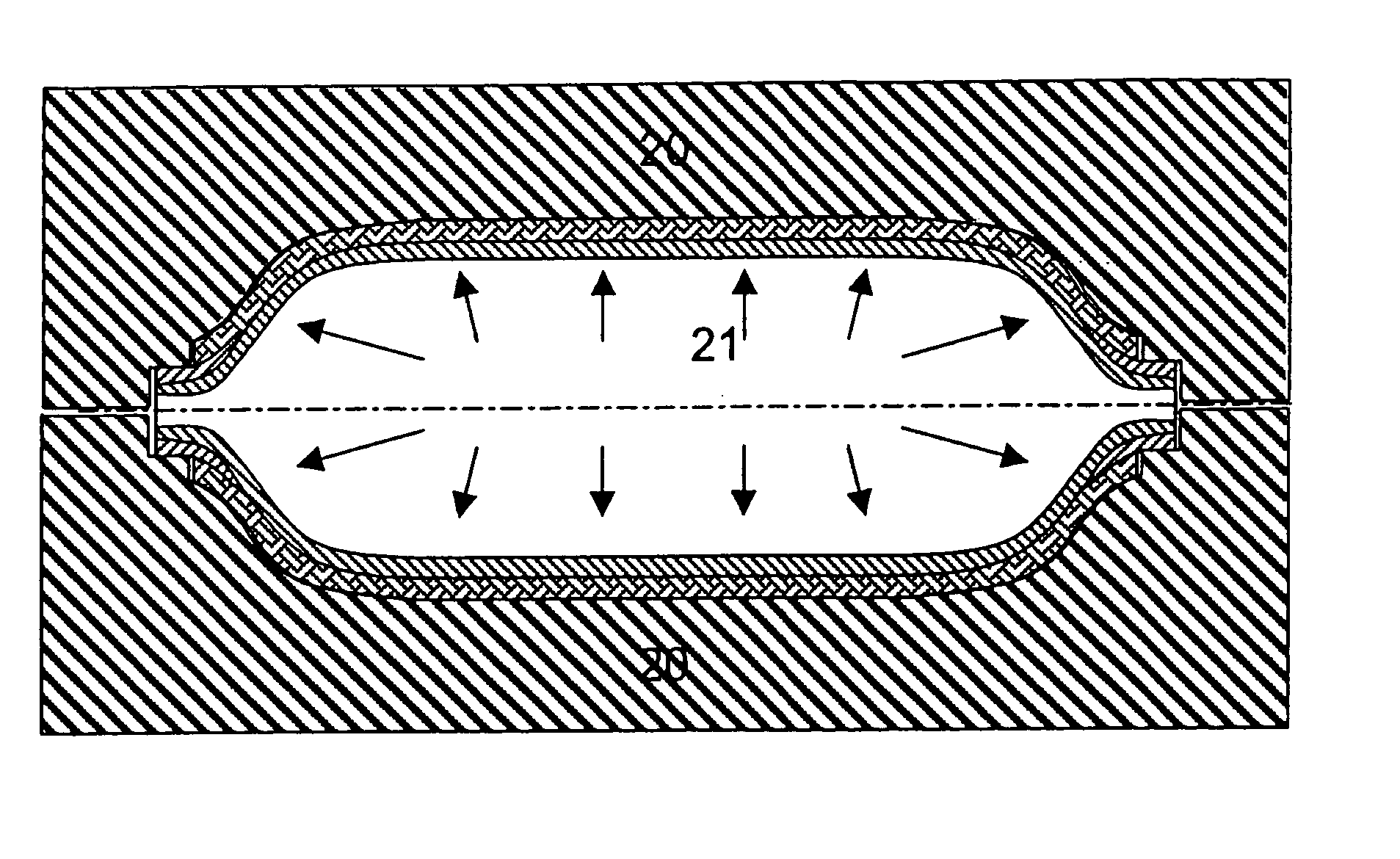

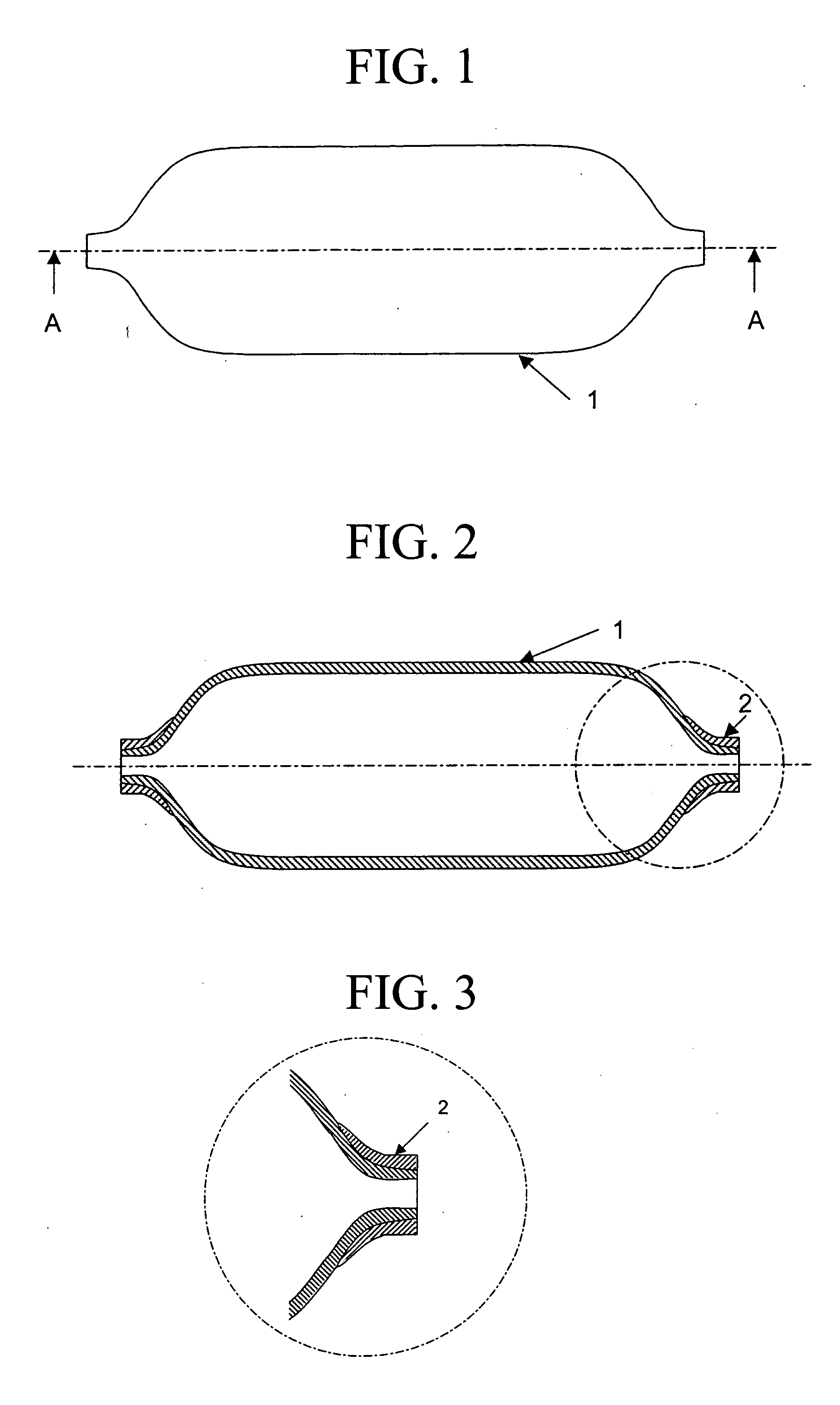

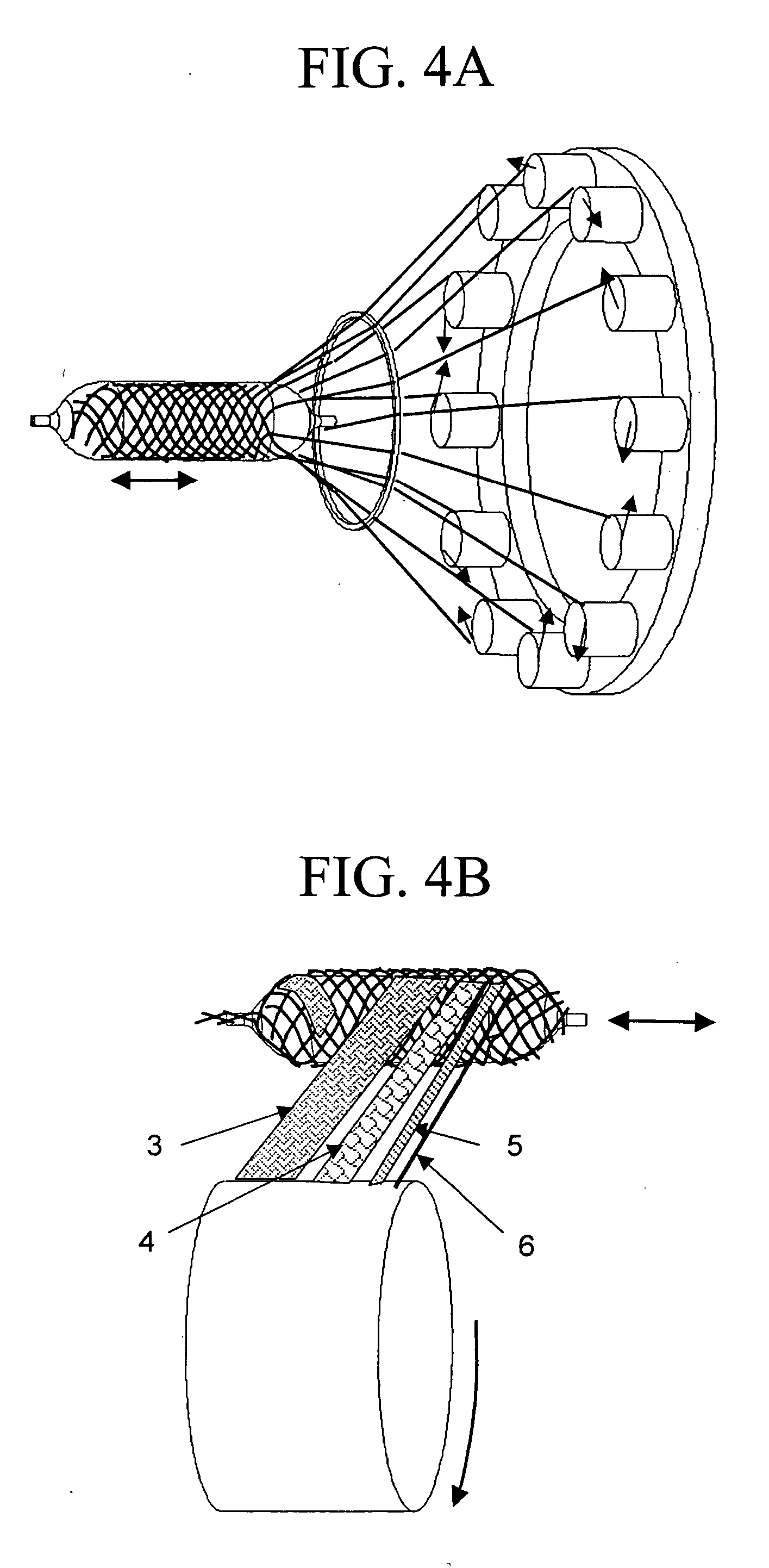

Non-isothermal method for fabricating hollow composite parts

InactiveUS20050258575A1Added fabricationShorten cycle timeLaminationLamination apparatusCross-linked polyethylenePolypropylene

A process for making hollow composite structures or vessels which includes the steps of: A) heating a mixture of thermoplastic matrix and reinforcing fibres wrapped over a rigid or semi-rigid thermoplastic liner or bladder above the melting point of the thermoplastic composite matrix outside of a moulding tool; B) transferring the heated assembly to a mould that is maintained below the melting temperature of the thermoplastic matrix of the composite; C) closure of the mould and application of internal fluid pressure to the liner or bladder to apply pressure to the thermoplastic matrix and reinforcing fibres; D) optionally the use of a special coupling system for rapid connection of the internal pressure; E) cooling of the liner or bladder and thermoplastic matrix and reinforcing fibre assembly in contact with the cold or warm mould while consolidation of the assembly occurs; F) opening of the mould and removal of the finished assembly. Suitable thermoplastic materials for the liner / bladder and thermoplastic composite matrix material include: polypropylene, polyamide, polyethylene, cross-linked polyethylene, polybutylene terephthalate, polyethylene terephthalate, polyoxymethylene, polyphenylene sulfide and polyetheretherketone.

Owner:KRUSE CHRISTIAN +3

Pulse output circuit, shift register, and display device

InactiveUS7151278B2Reduce manufacturing stepsLow costStatic indicating devicesSolid-state devicesElectricityShift register

A circuit is provided which is constituted by TFTs of one conductivity type, and which is capable of outputting signals of a normal amplitude. When an input clock signal CK1 becomes a high level, each of TFTs (101, 103) is turned on to settle at a low level the potential at a signal output section (Out). A pulse is then input to a signal input section (In) and becomes high level. The gate potential of TFT (102) is increased to (VDD−V thN) and the gate is floated. TFT (102) is thus turned on. Then CK1 becomes low level and each of TFTs (101, 103) is turned off. Simultaneously, CK3 becomes high level and the potential at the signal output section is increased. Simultaneously, the potential at the gate of TFT (102) is increased to a level equal to or higher than (VDD+V thN) by the function of capacitor (104), so that the high level appearing at the signal output section (Out) becomes equal to VDD. When SP becomes low level; CK3 becomes low level; and CK1 becomes high level, the potential at the signal output section (Out) becomes low level again.

Owner:SEMICON ENERGY LAB CO LTD

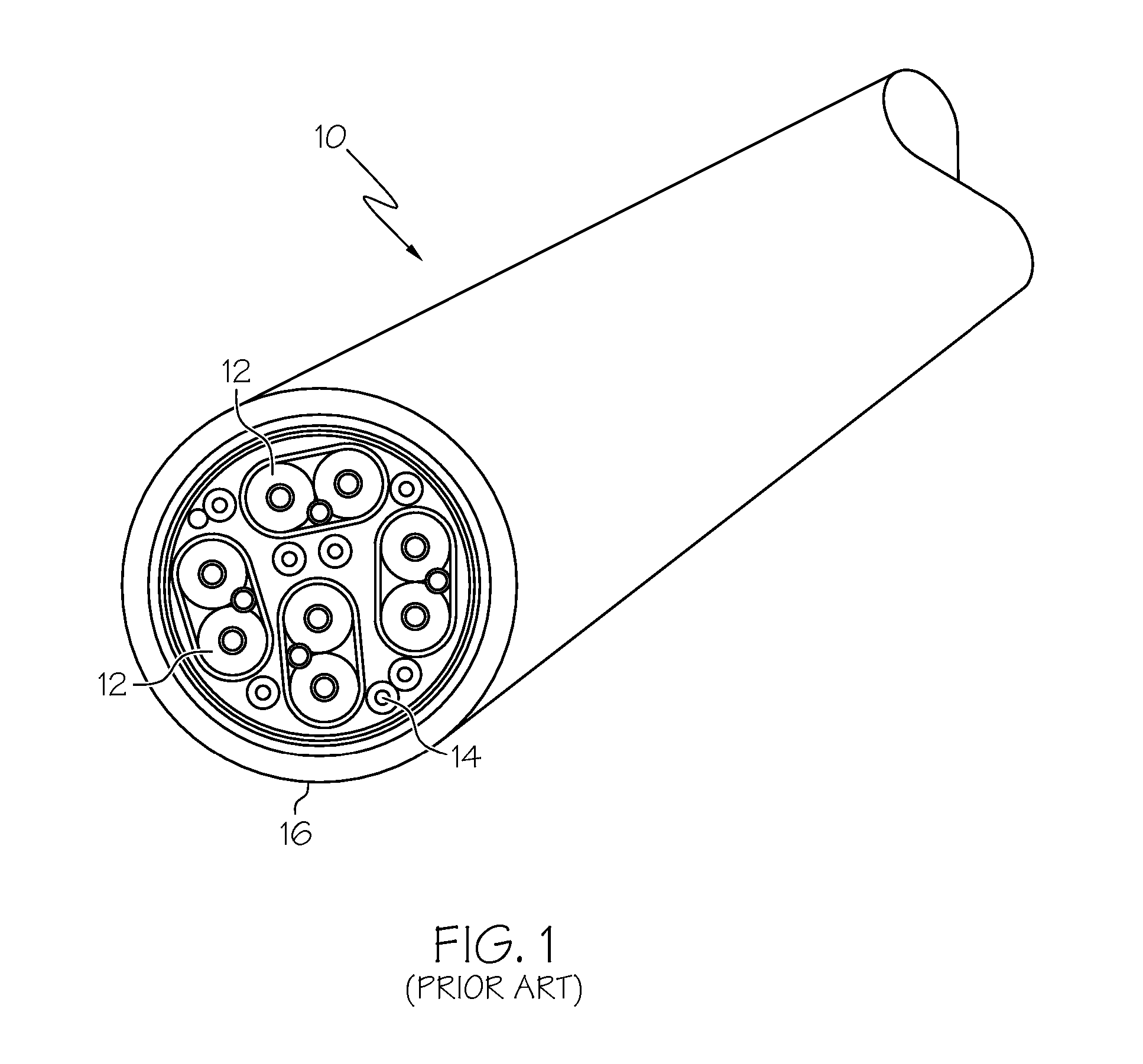

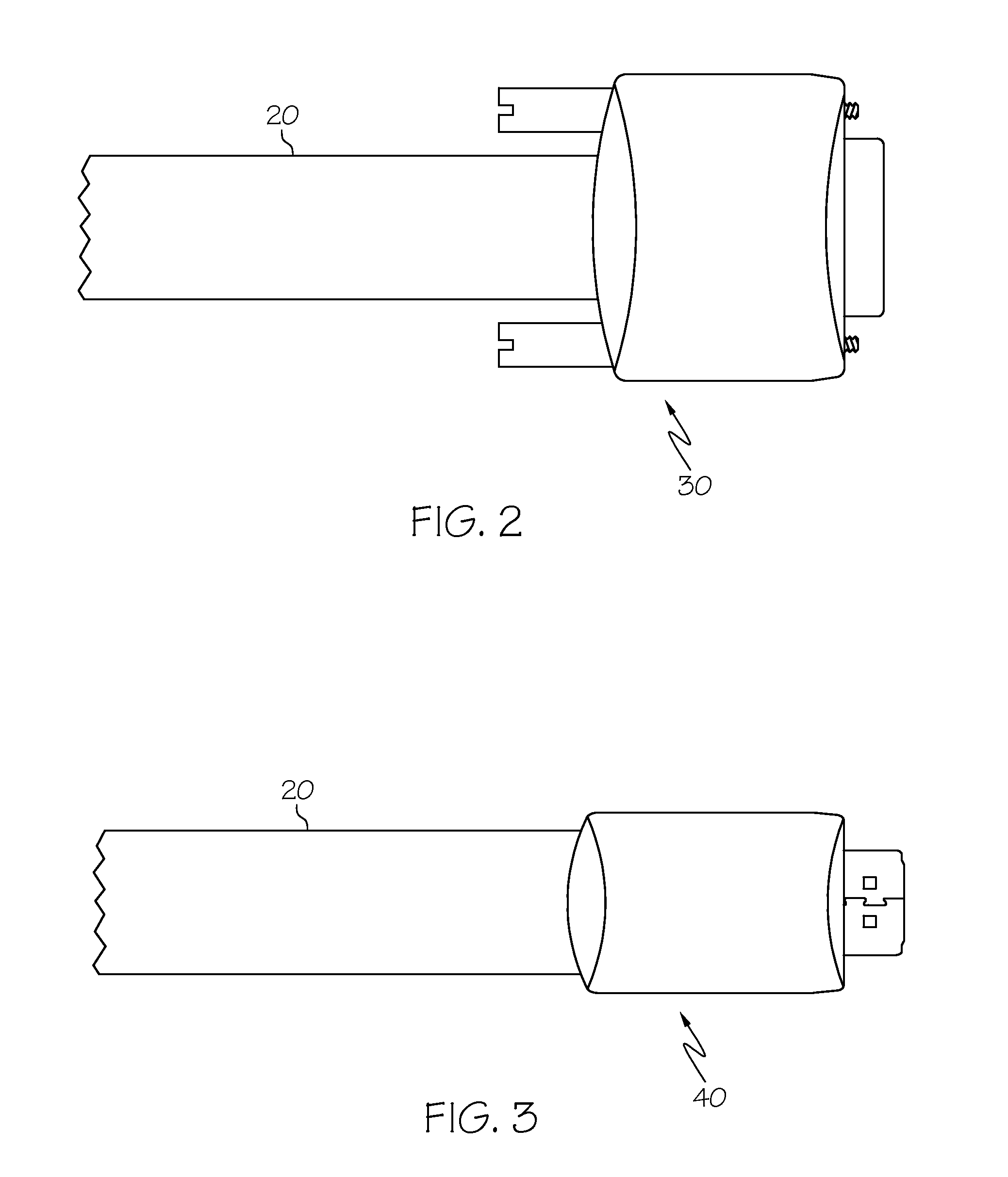

High definition digital media data cable system

InactiveUS20060239310A1Efficient and effective HDMI/DVI connectionIncrease contactLaser detailsElectrically conductive connectionsElectrical conductorHDMI

The present invention provides a cable assembly and method of making thereof for use with HDMI / DVI connectors. The cable assembly of the present invention includes a flat extruded cable jacket that includes an oblong cross section. Parallel oblong orifices lie across the cross section of the extruded jacket, extend the length of the jacket and provide a means for the insertion of solid straight conductors extending through the oblong orifices. The alignment of the oblong orifices in conjunction with a cylindrical orifice provides a means to attach the conductors to a HDMI / DVI connector. The oblong configurations as associated with the present invention are also applicable for Firewire cable and provides for a flat cable assembly for use therein.

Owner:SALZ DAVID B

Insulating substrate and semiconductor device

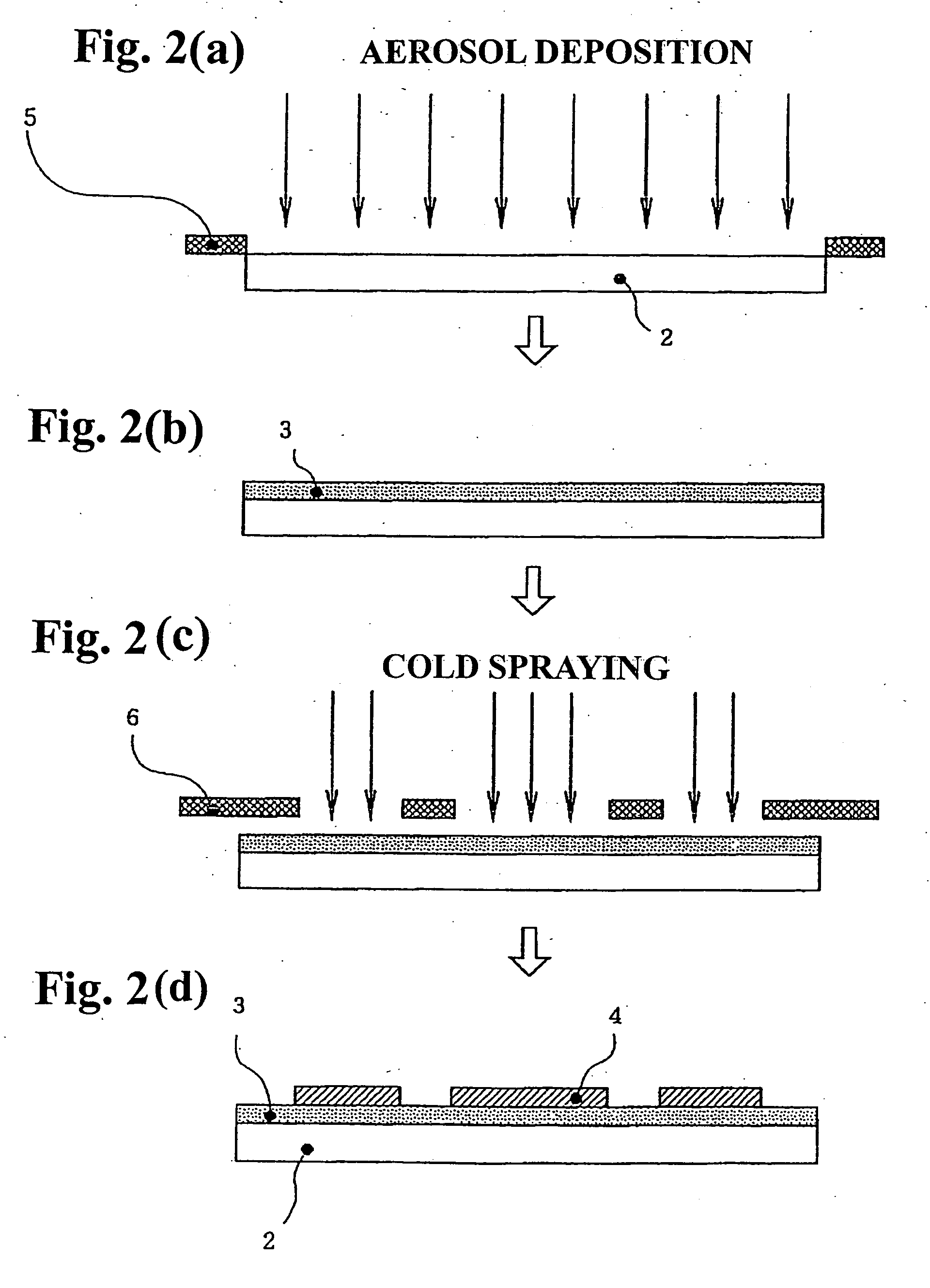

ActiveUS20060108601A1Reduce manufacturing stepsImprove heat radiation performanceMolten spray coatingSemiconductor/solid-state device detailsDevice materialRoom temperature

An insulating substrate includes a metal base as a base member, an insulating layer which is a room temperature, aerosol deposited shock solidification film formed on the metal base, and a circuit pattern which is a cold sprayed thermal spray coating formed on the insulating layer. A semiconductor device incorporates the insulating substrate, and thereby has improved heat radiation characteristics.

Owner:FUJI ELECTRIC HLDG CO LTD

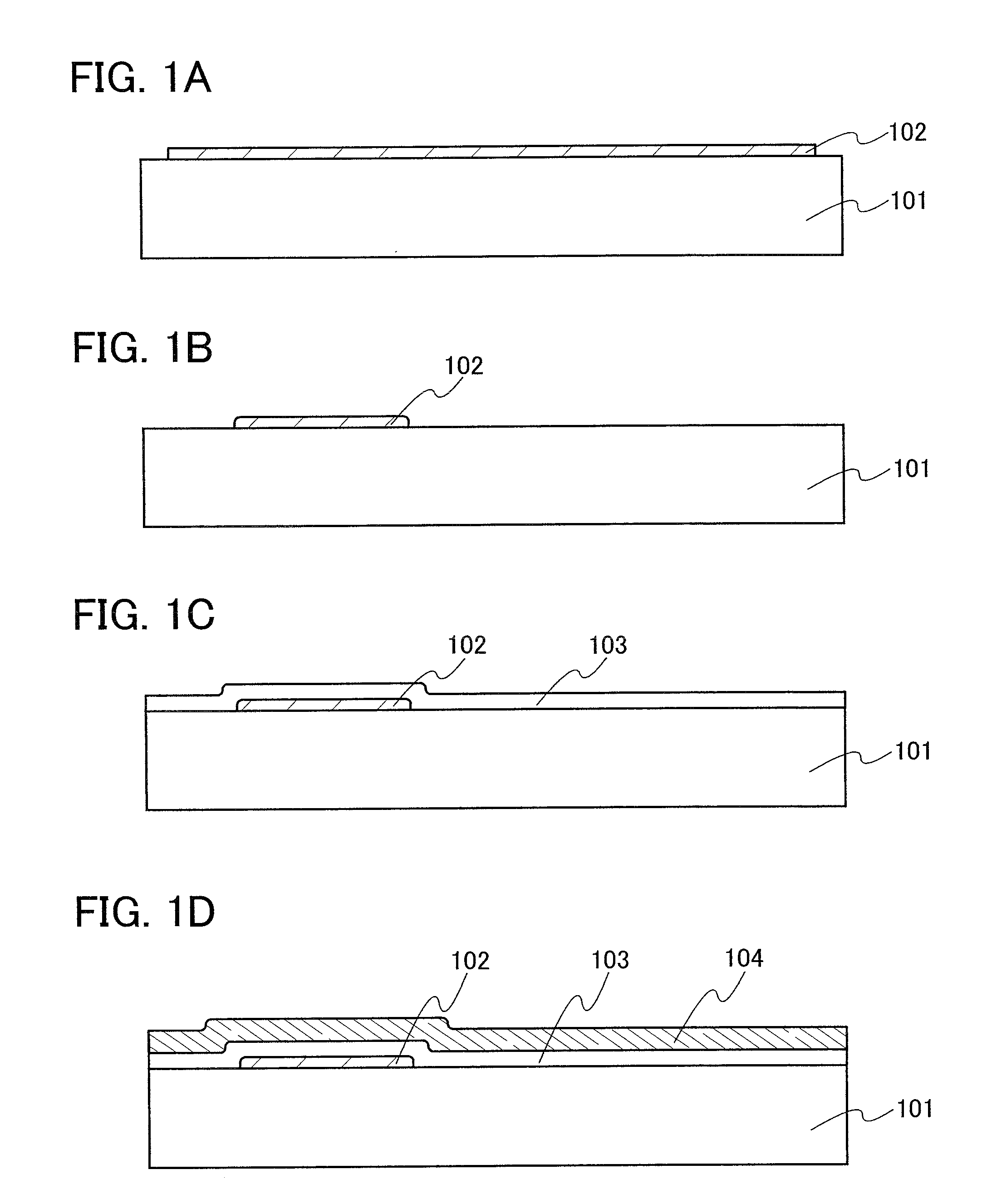

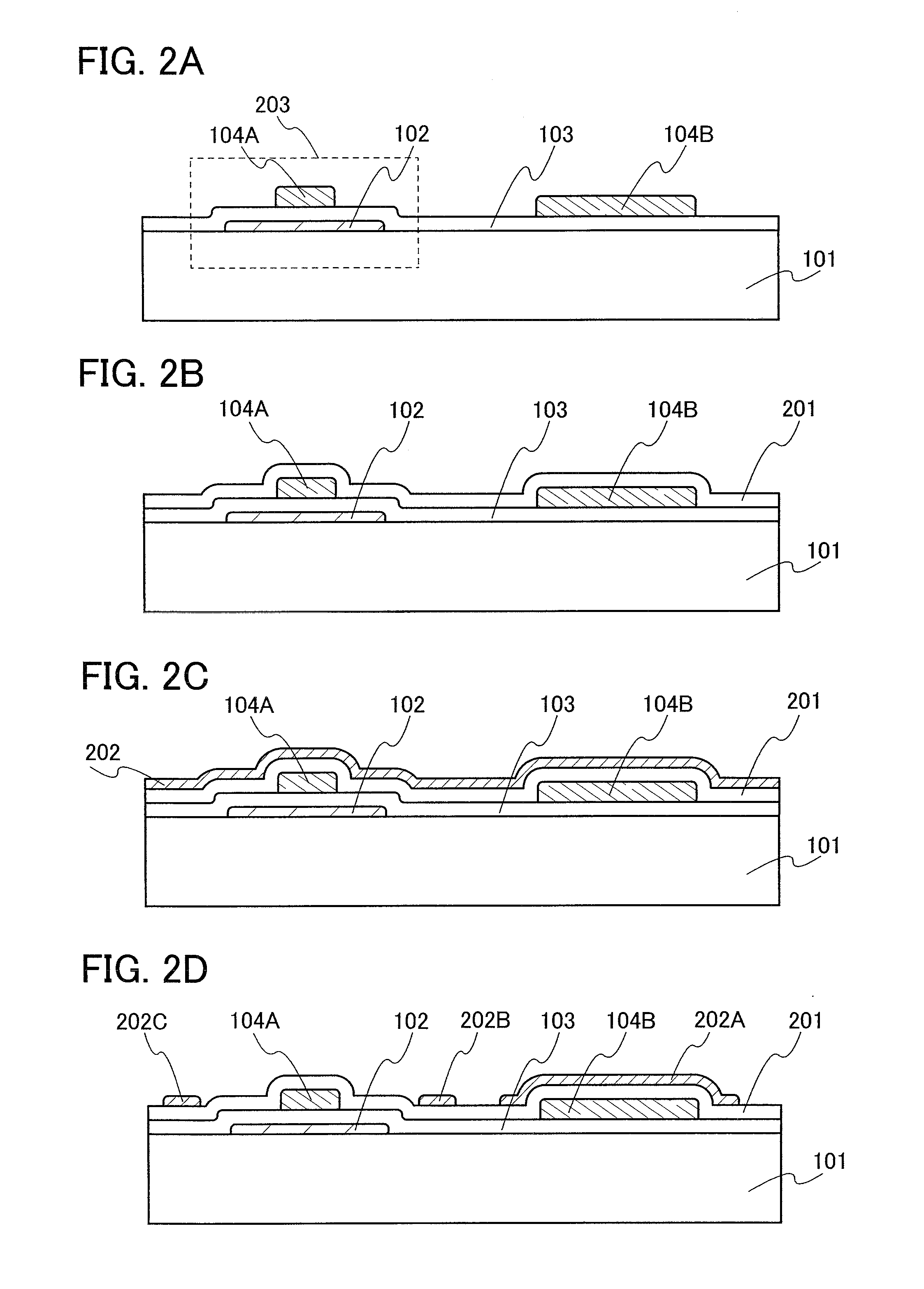

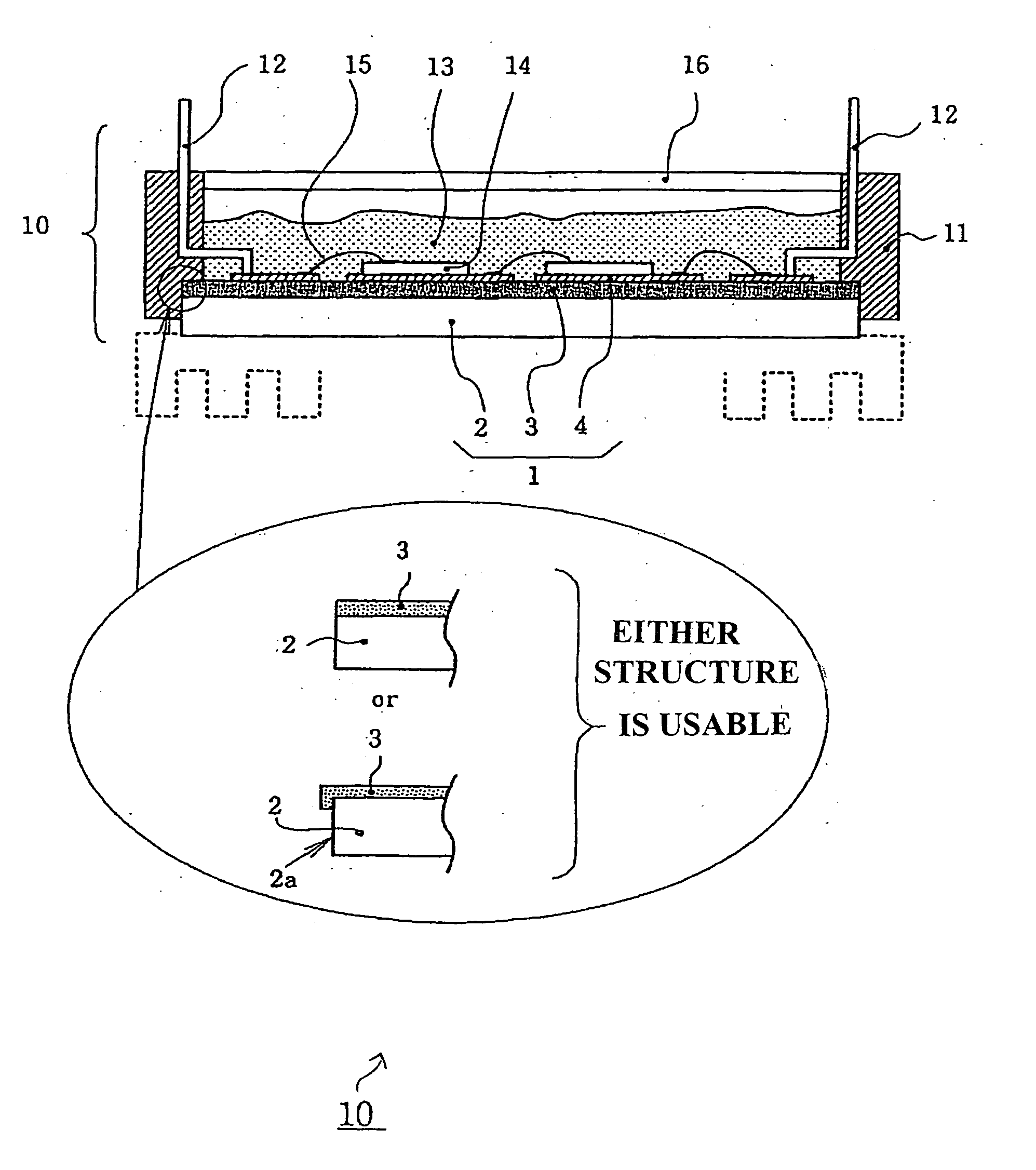

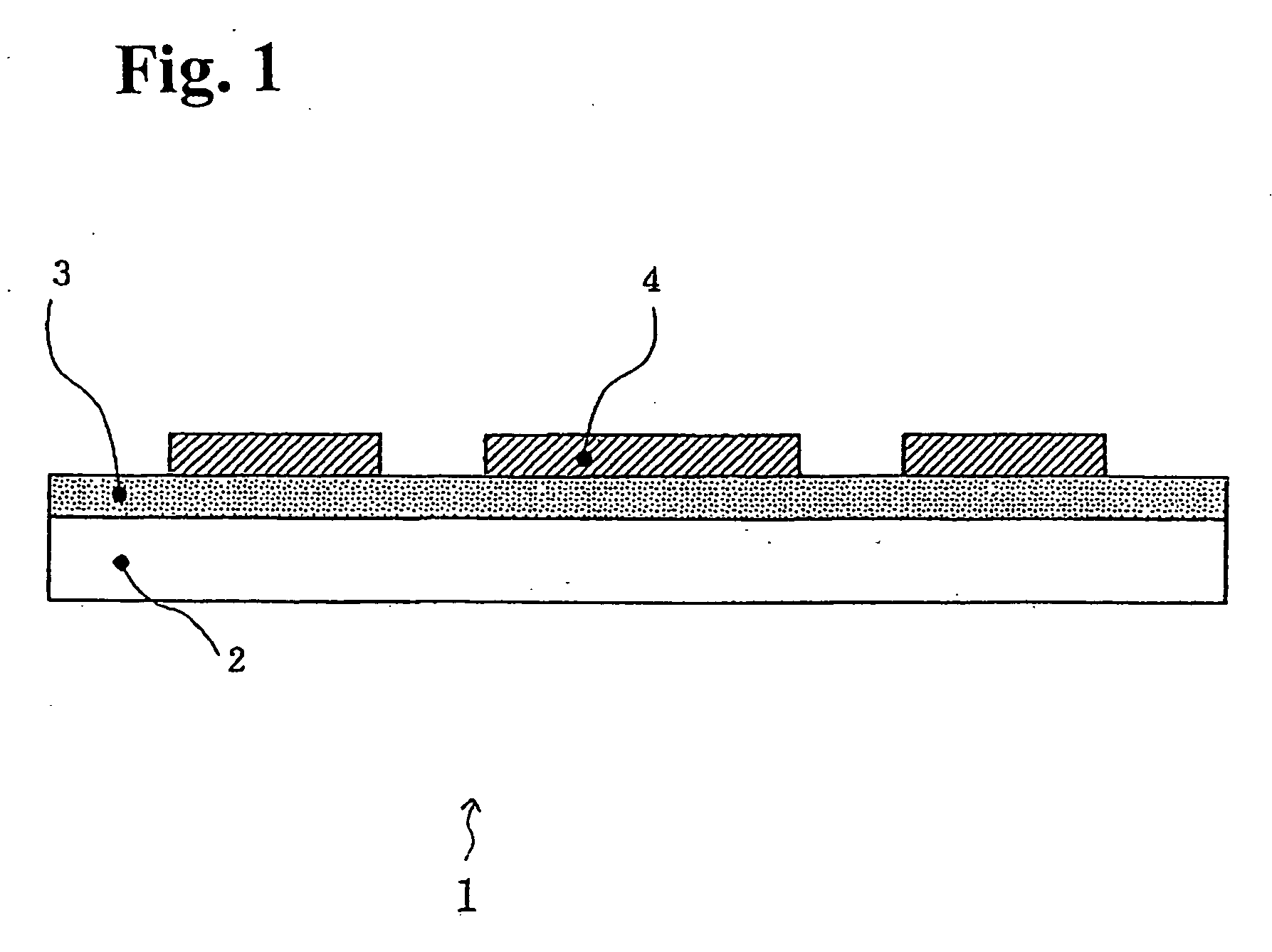

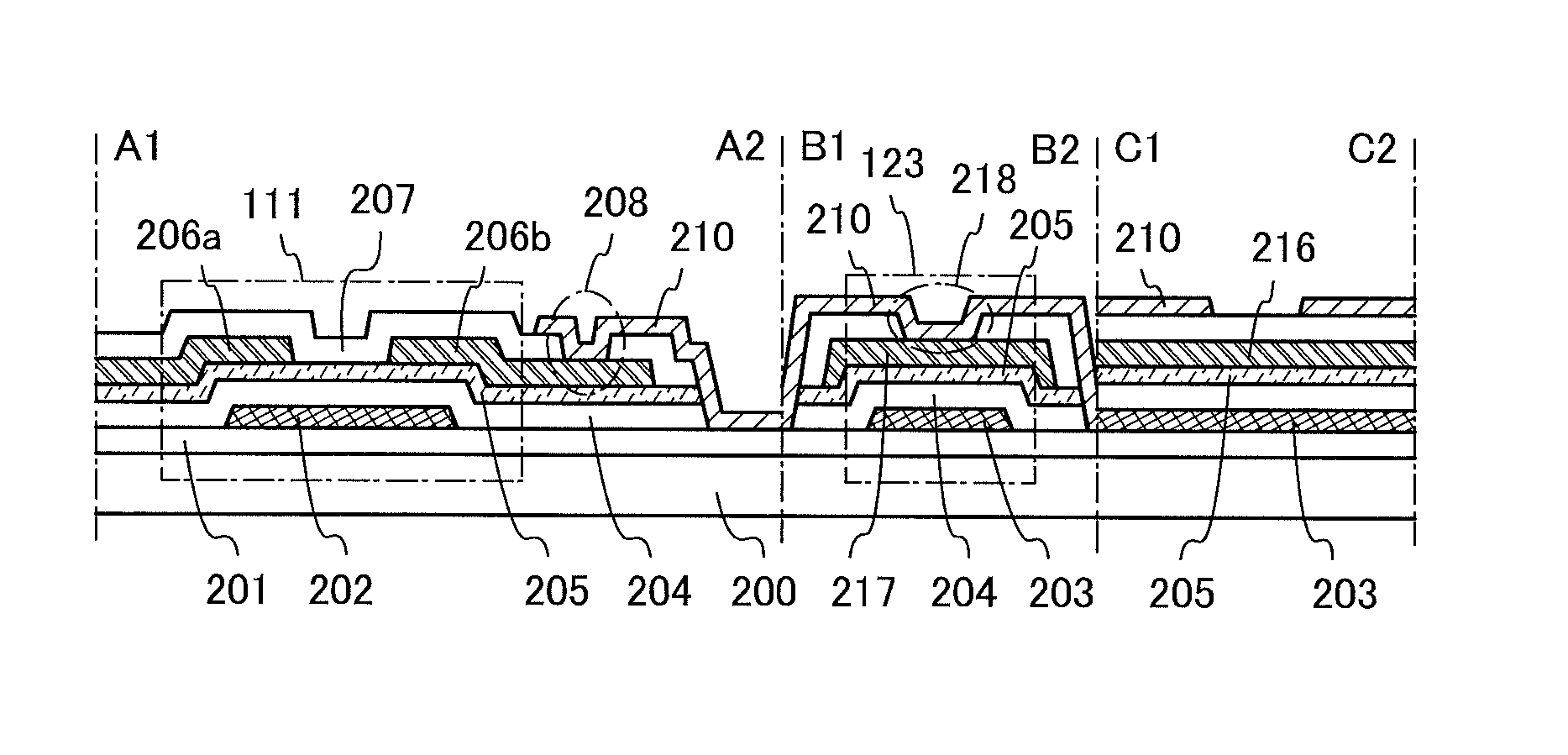

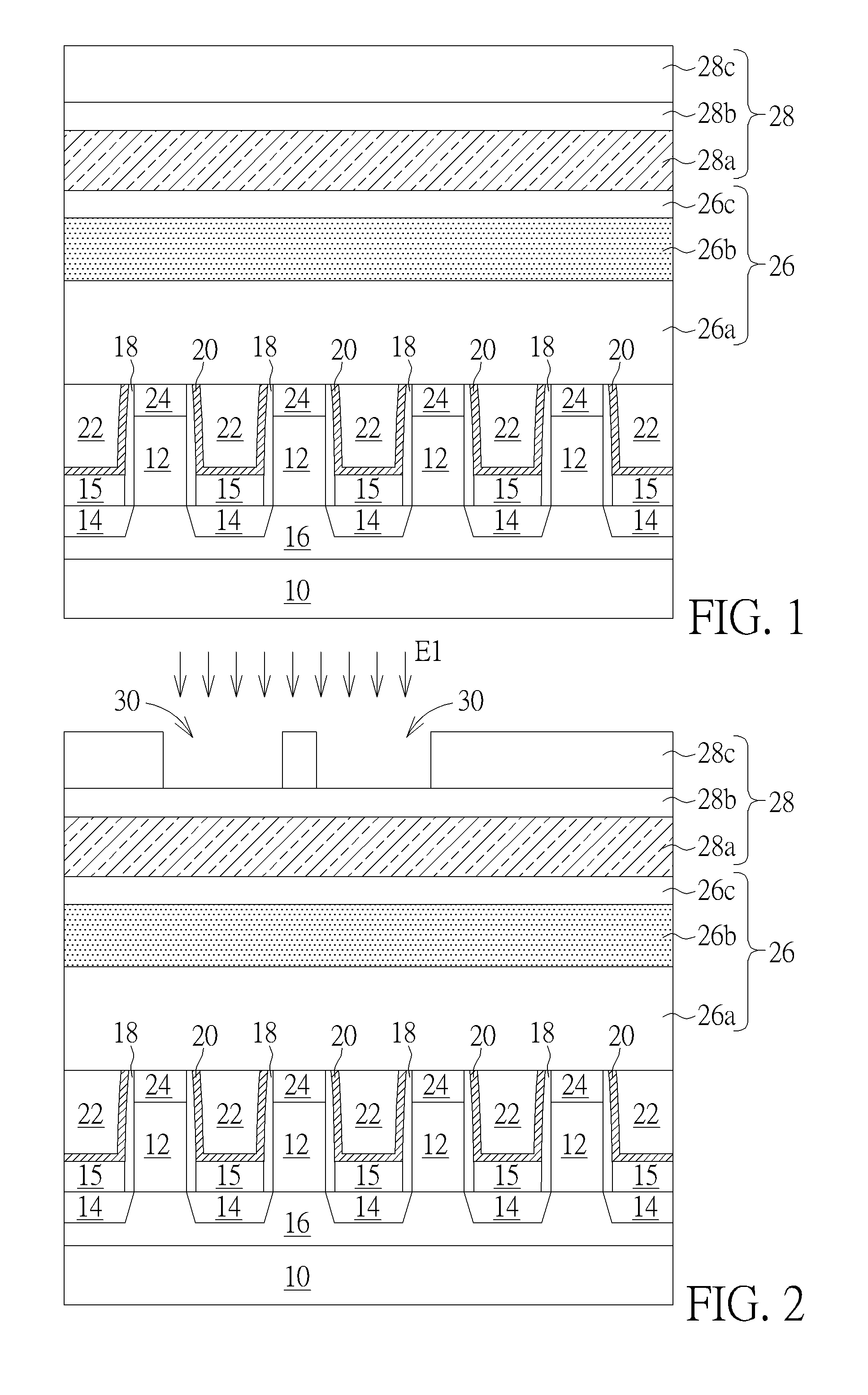

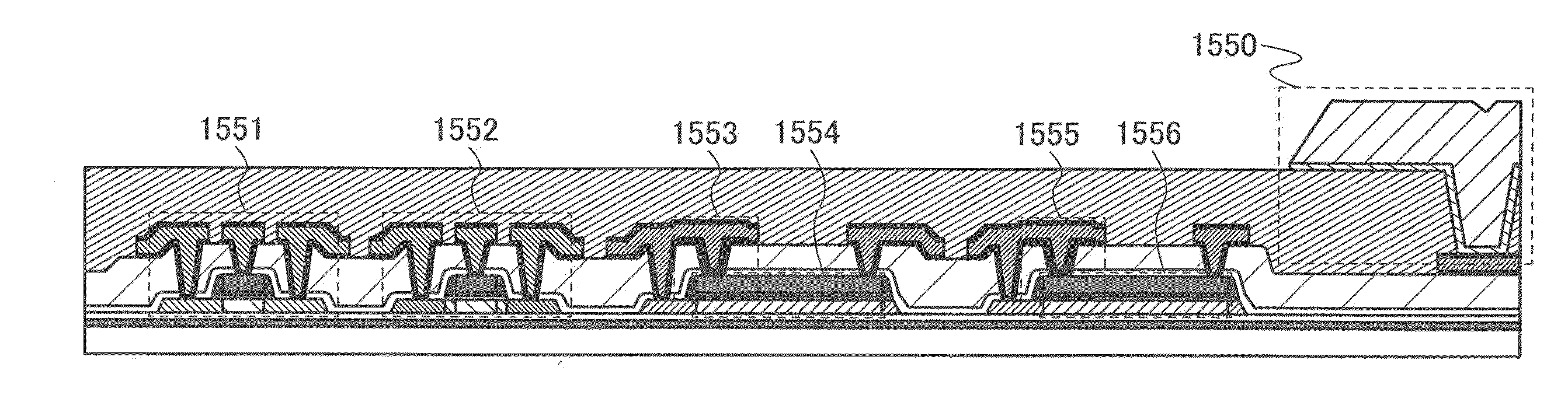

Manufacturing methods of thin film transistor, liquid crystal display device, and semiconductor device

InactiveUS20120052625A1Improve productivityLow costSolid-state devicesSemiconductor/solid-state device manufacturingProduction rateLiquid-crystal display

A liquid crystal display device is provided with high productivity at low cost by reducing manufacturing steps of the liquid crystal display device. A liquid crystal display device with less power consumption and high reliability is provided. Etching of a semiconductor layer and formation of a contact hole that connects a pixel electrode and a drain electrode are performed by one photolithography process and one etching step, whereby the number of photolithography processes is reduced. A liquid crystal display device can be provided with high productivity at low cost by reducing the number of photolithography processes. Further, an oxide semiconductor is used for the semiconductor layer, whereby a liquid crystal display device with less power consumption and high reliability can be provided.

Owner:SEMICON ENERGY LAB CO LTD

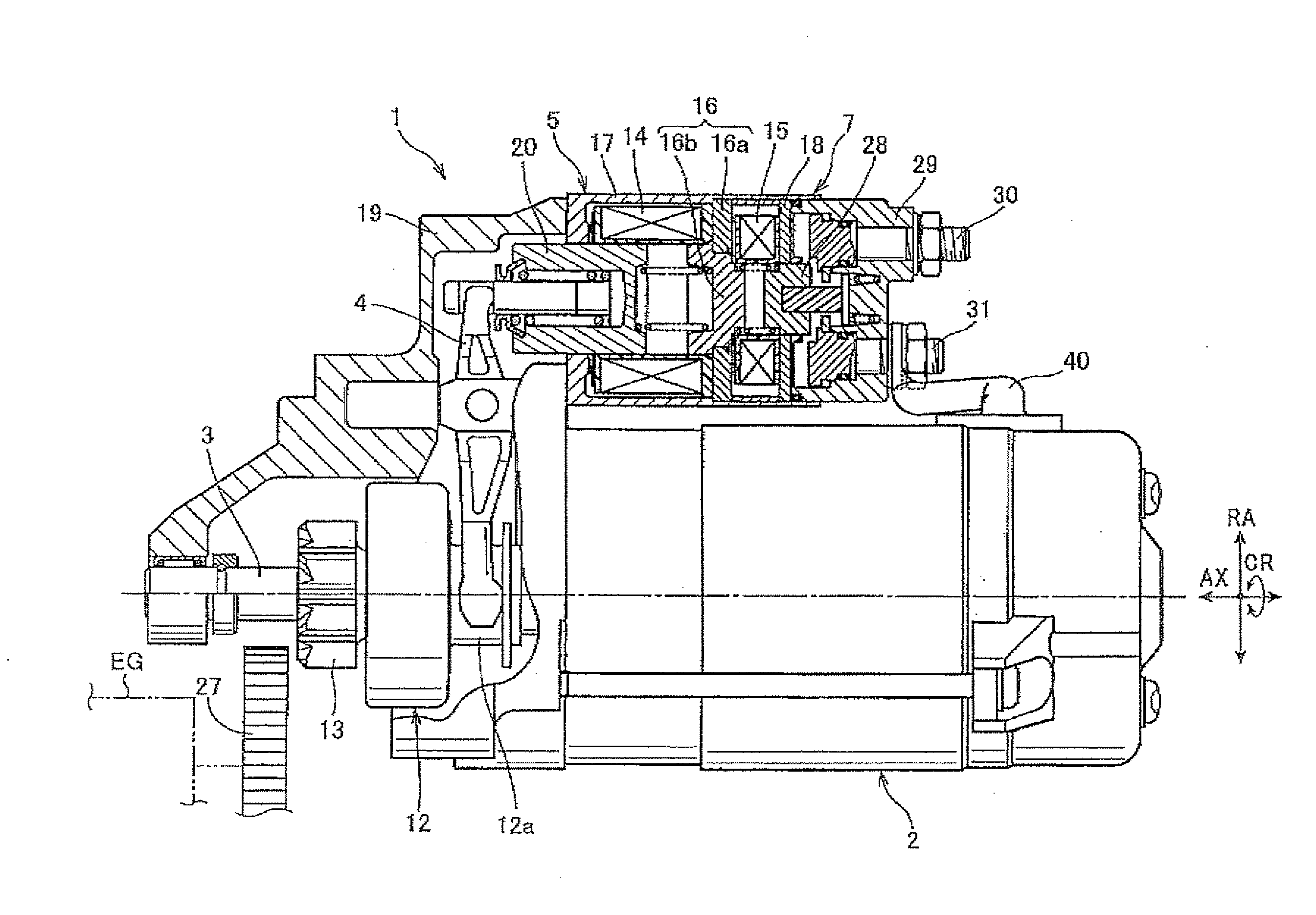

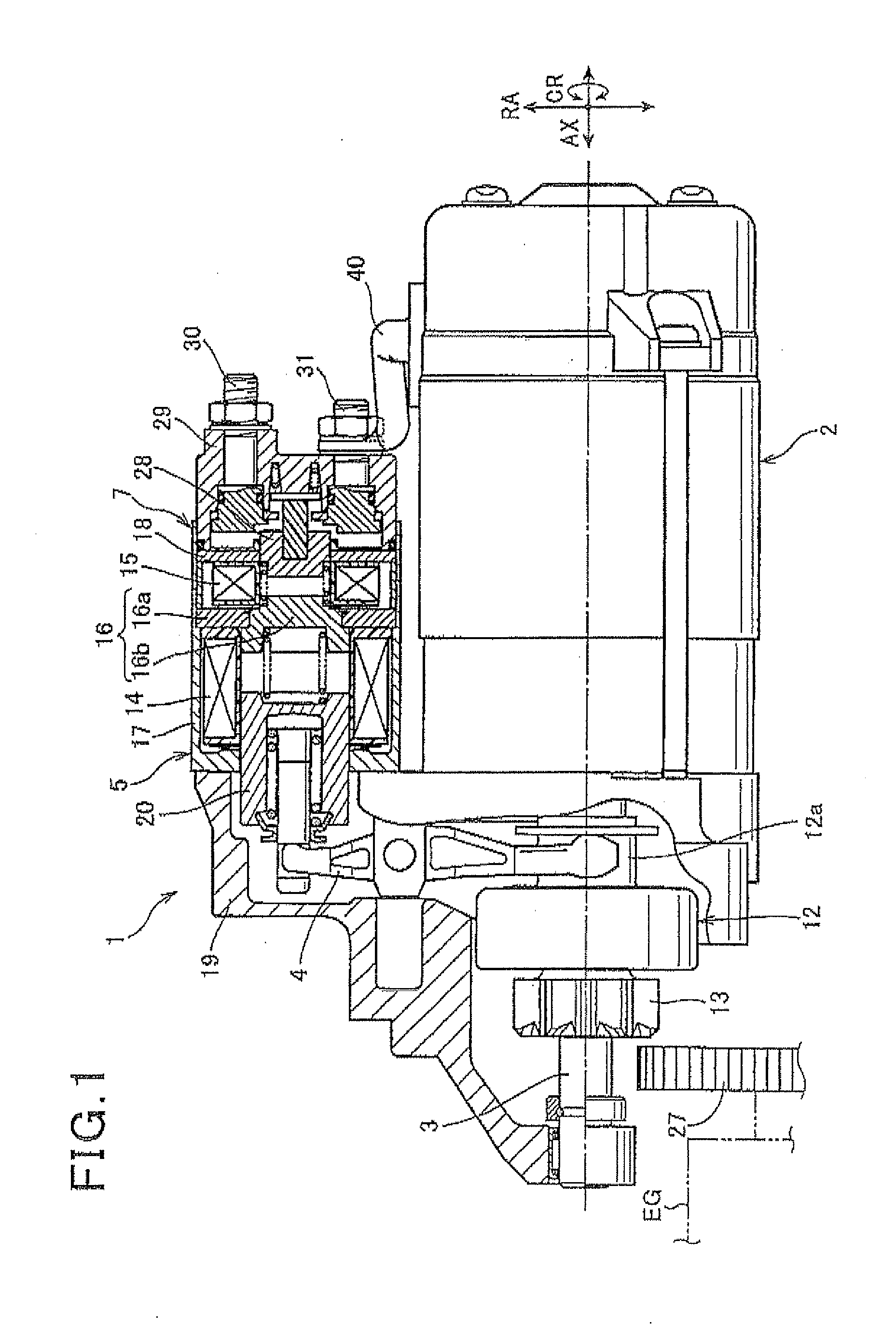

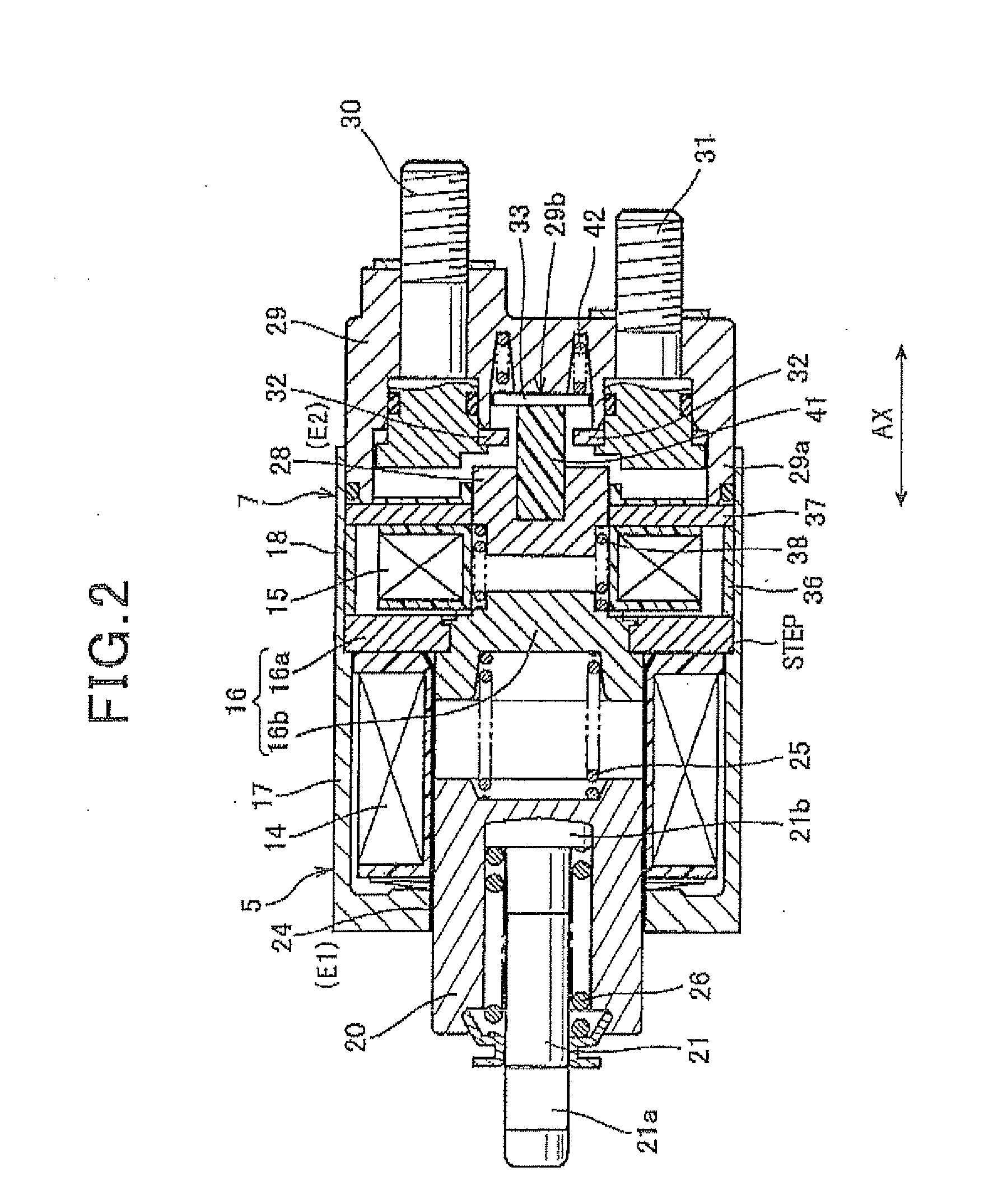

Apparatus for starting engine mounted on-vehicle

ActiveUS20100264765A1Reduce the differenceLower manufacturing requirementsPower operated startersElectric motor startersSolenoid valveExcitation current

Owner:DENSO CORP

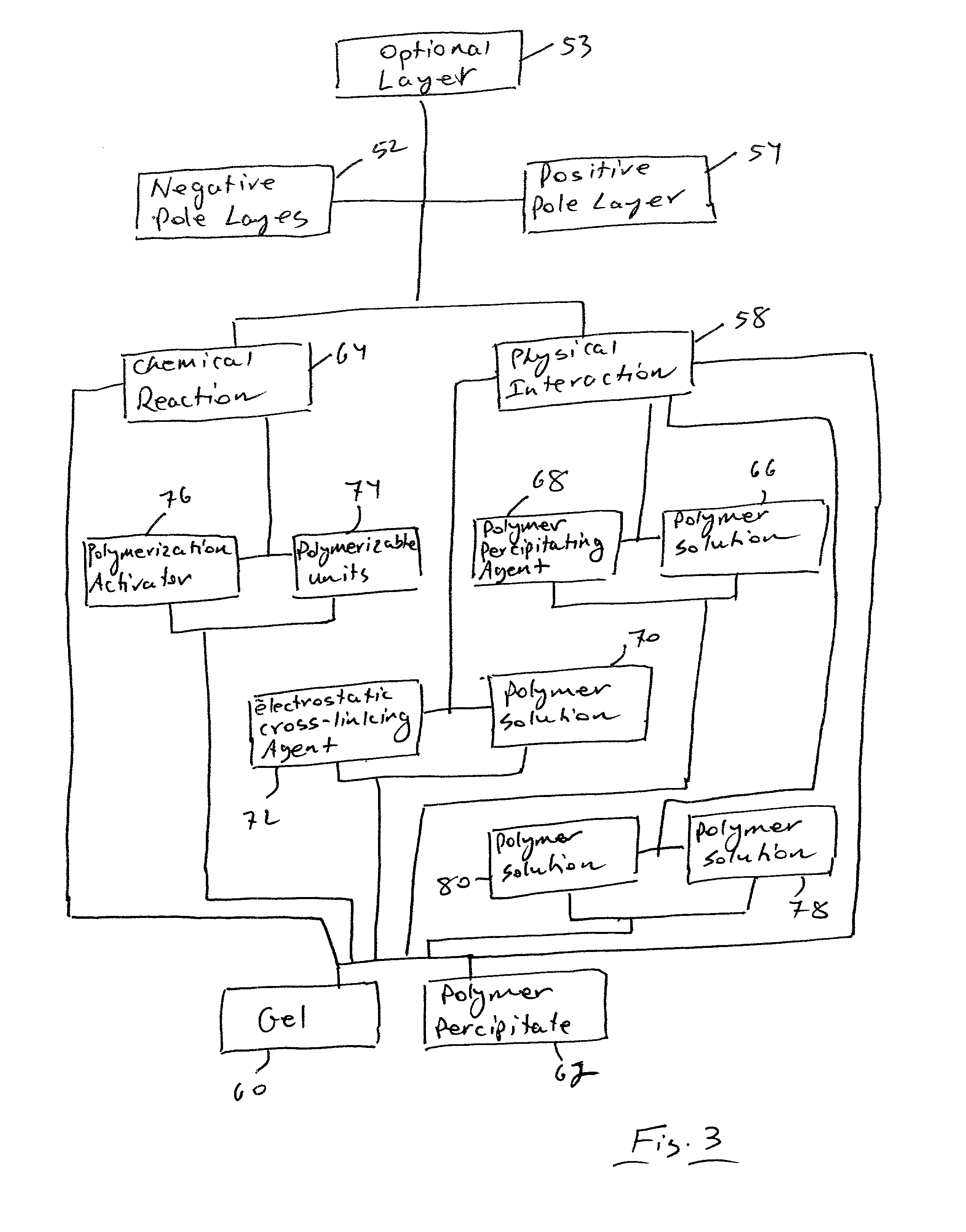

Thin layer electrochemical cell with self-formed separator

InactiveUS7022431B2Reduce manufacturing stepsIncrease contactFinal product manufactureElectrode carriers/collectorsSelf formingThin layer

A method of forming an electrochemical cell is disclosed. The method comprises contacting a negative pole layer and a positive pole layer one with the other or with an optional layer interposed therebetween. The pole layers and the optional layer therebetween are selected so as to self-form an interfacial separator layer between the pole layers upon such contacting.

Owner:POWER PAPER

Planar substrate devices integrated with finfets and method of manufacture

ActiveUS20060084212A1Reduce manufacturing stepsEasy to integrateTransistorSolid-state devicesPlanar substrateEngineering

Owner:GLOBALFOUNDRIES U S INC

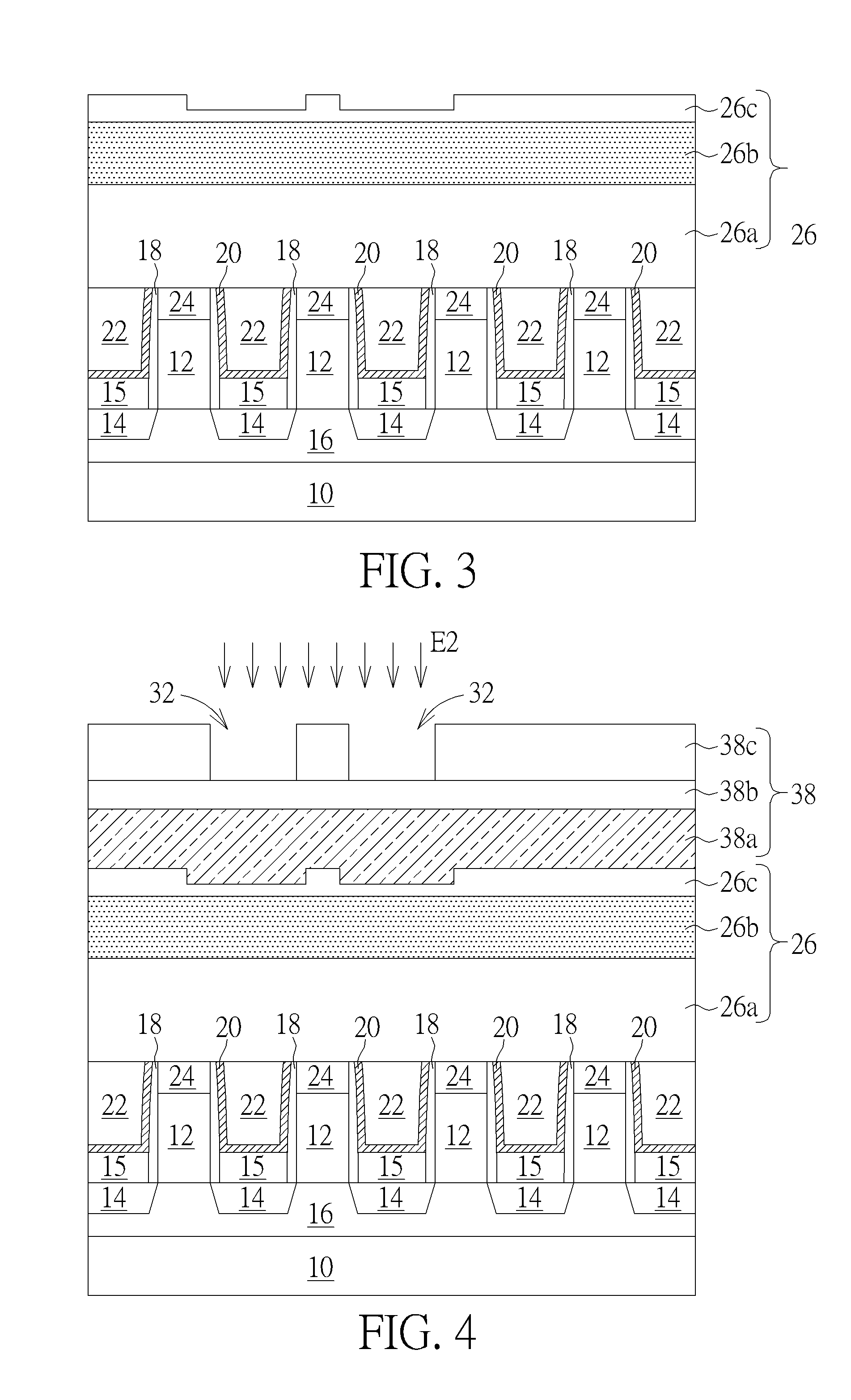

Manufacturing method for forming a semiconductor structure

ActiveUS20140349476A1Reduce manufacturing stepsLow structural requirementsSemiconductor/solid-state device detailsSemiconductor/solid-state device manufacturingPhotolithographyPhotomask

The present invention provides a manufacturing method of a semiconductor device, at least containing the following steps: first, a substrate is provided, wherein a first dielectric layer is formed on the substrate, at least one metal gate is formed in the first dielectric layer and at least one source drain region (S / D region) is disposed on two sides of the metal gate, at least one first trench is then formed in the first dielectric layer, exposing parts of the S / D region. The manufacturing method for forming the first trench further includes performing a first photolithography process through a first photomask and performing a second photolithography process through a second photomask, and at least one second trench is formed in the first dielectric layer, exposing parts of the metal gate, and finally, a conductive layer is filled in each first trench and each second trench.

Owner:UNITED MICROELECTRONICS CORP

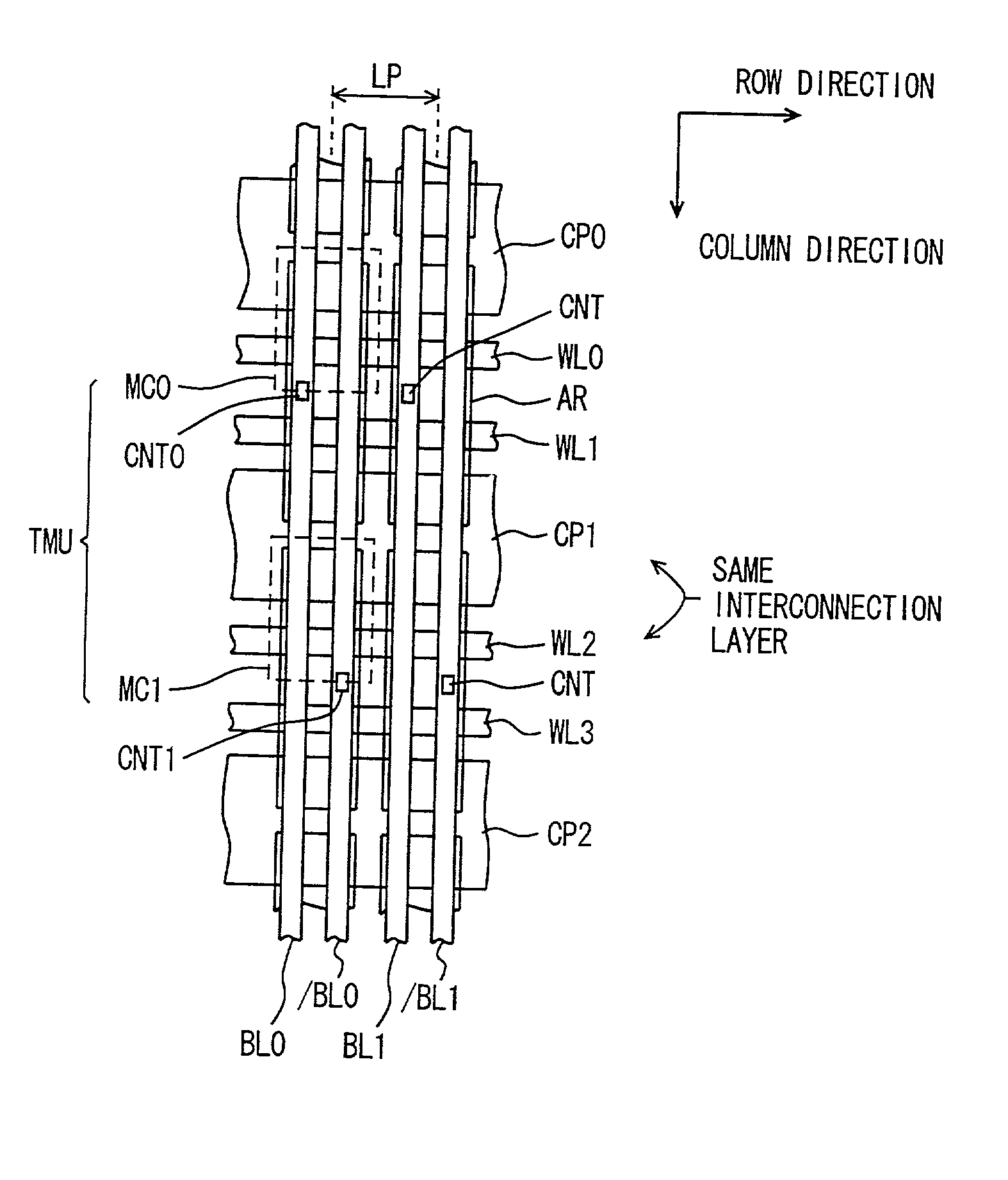

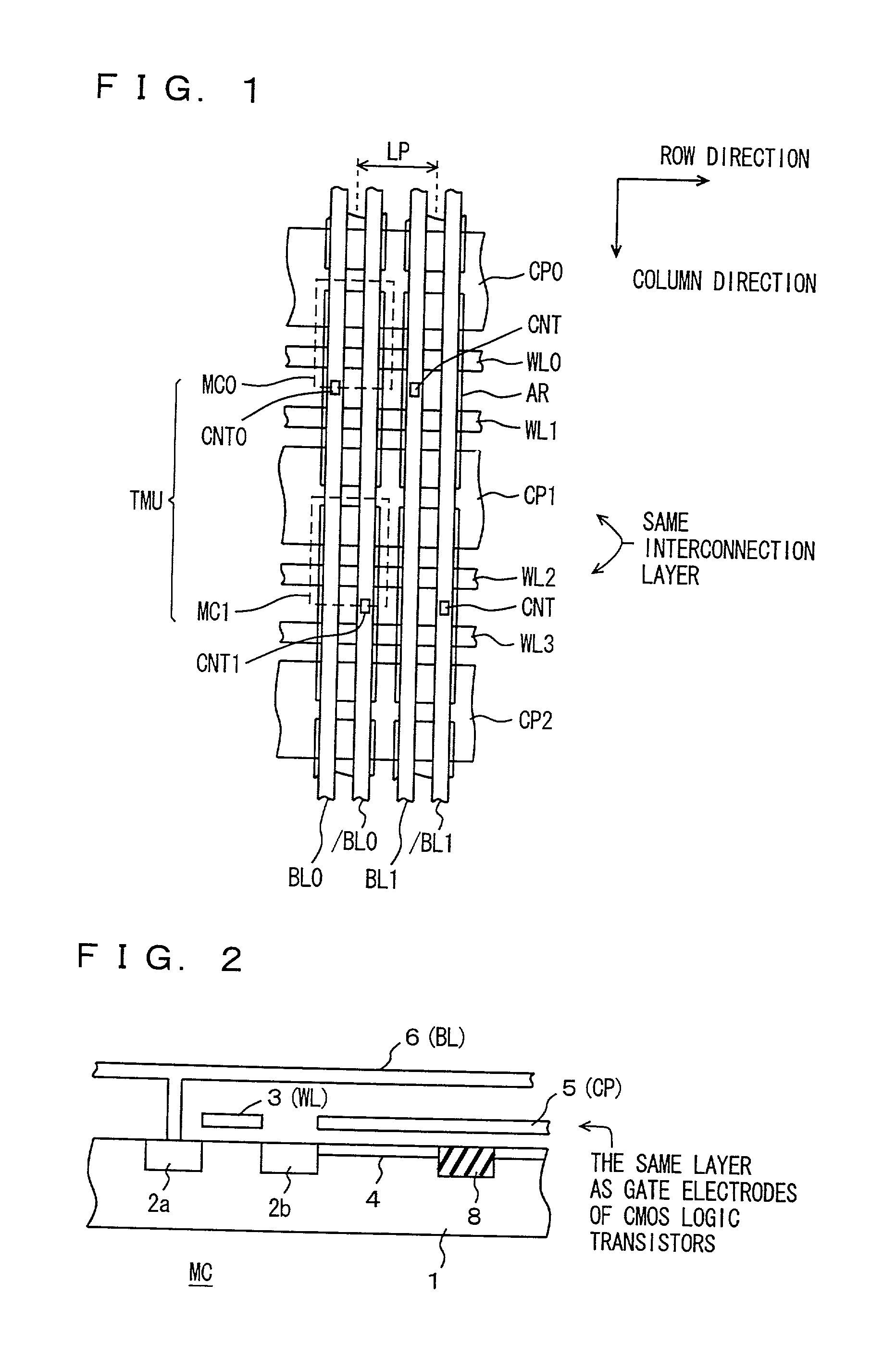

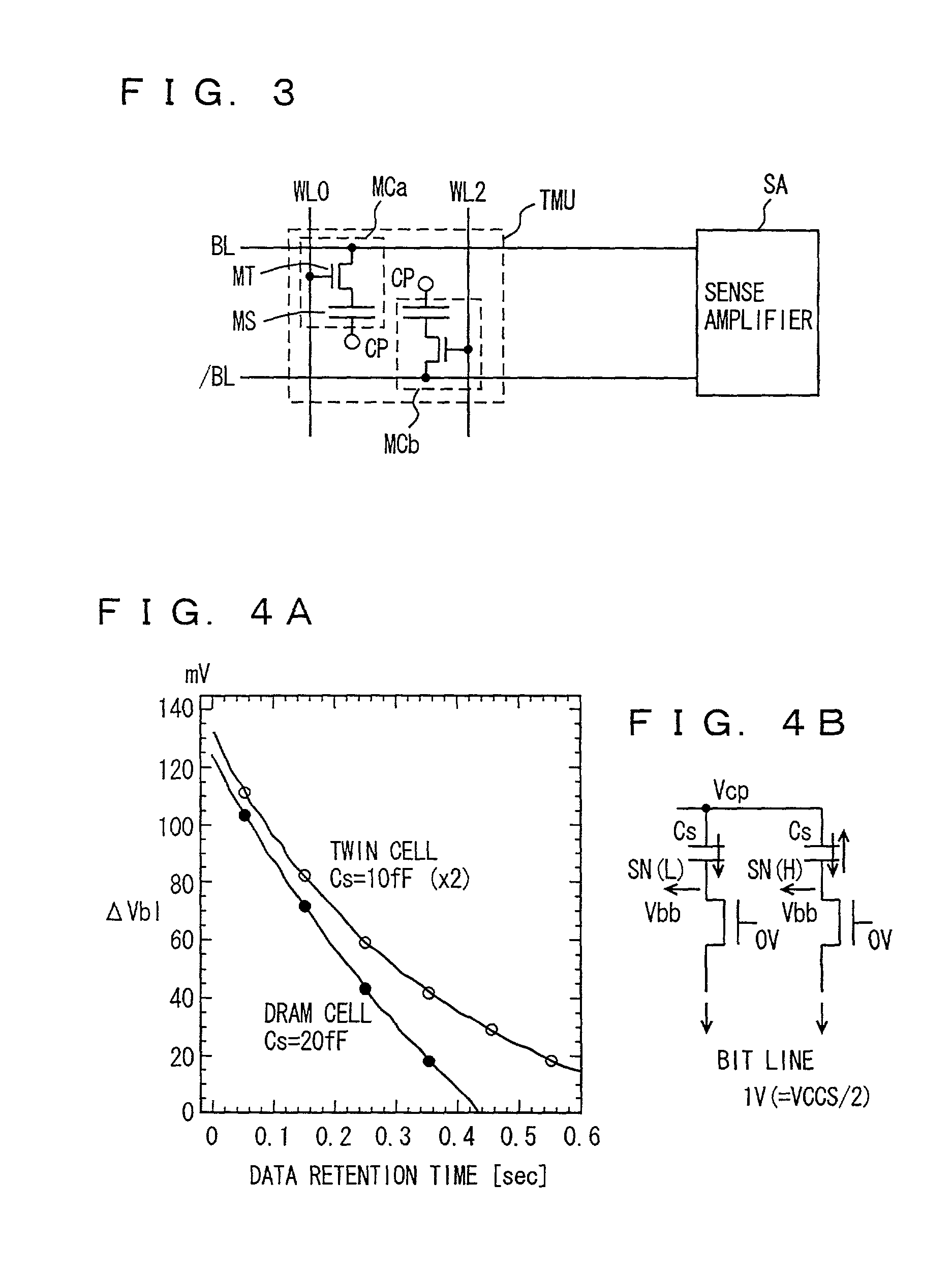

Semiconductor memory device

InactiveUS20020172070A1Reduce step heightReduce manufacturing stepsTransistorSolid-state devicesCapacitanceEngineering

Conductive lines constituting word lines of memory cells and conductive lines constituting memory cell plate electrodes are formed in the same interconnecting layer in a memory device including a plurality of memory cells each including a capacitor for storing data in an electrical charge form. By forming the capacitors of the memory cells into a planar capacitor configuration, a step due to the capacitors is removed. Thus. a dynamic semiconductor memory device can be formed through CMOS process, and a dynamic semiconductor memory device suitable for merging with logic is achieved. Data of 1 bit is stored by two memory cells, and data can be reliably stored even if the capacitance value of the memory cell is reduced due to the planar type capacitor.

Owner:RENESAS ELECTRONICS CORP

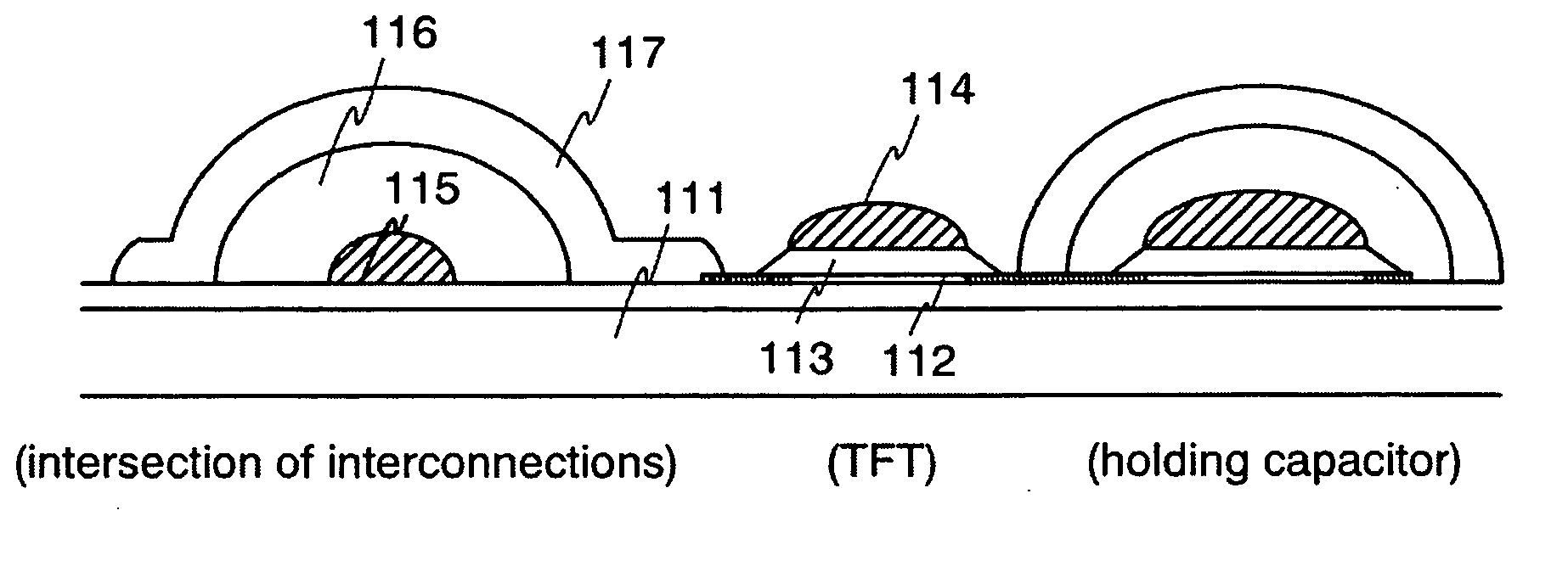

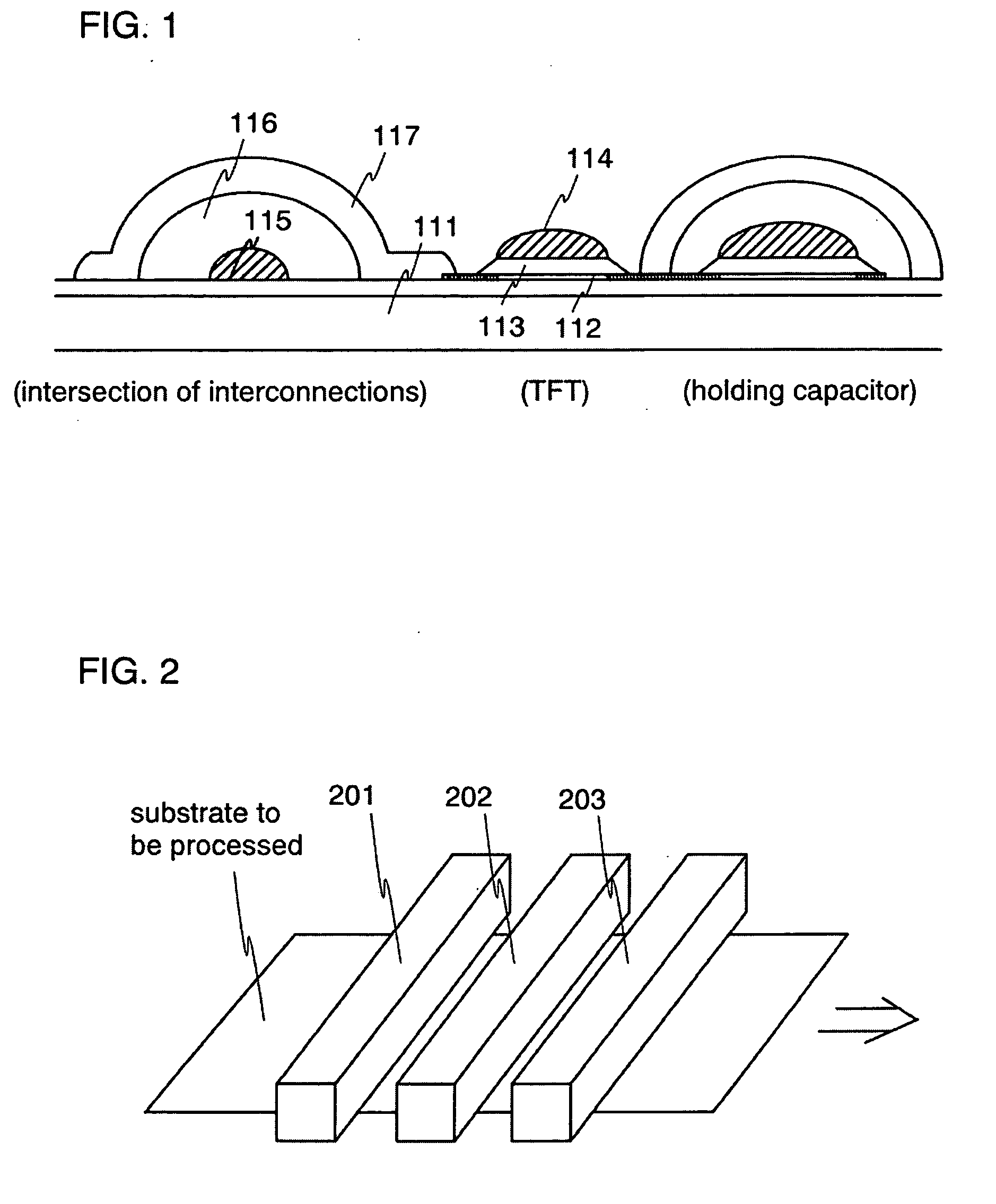

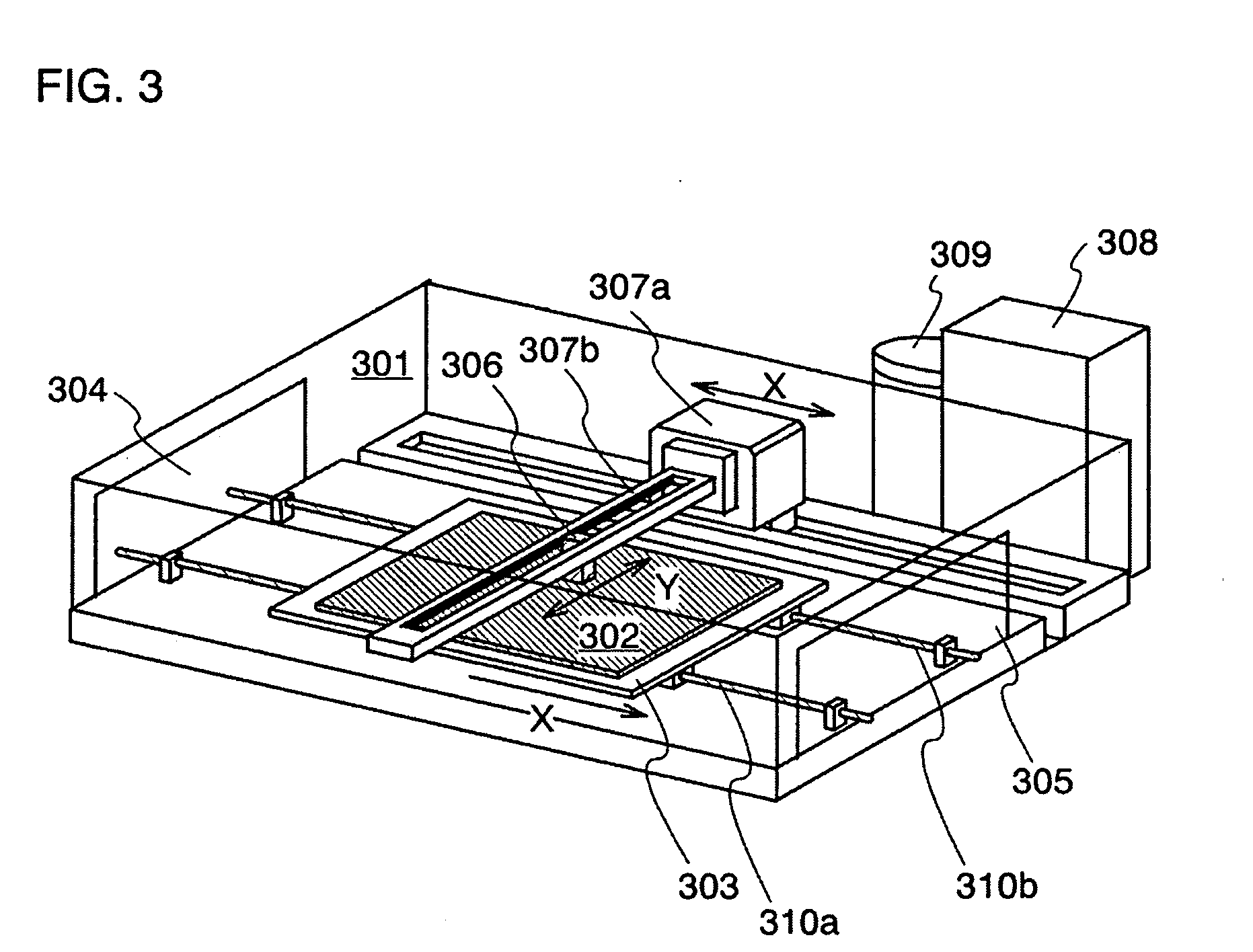

Semiconductor device and manufacturing method thereof

InactiveUS20070181945A1Low costReduce in quantitySolid-state devicesSemiconductor/solid-state device manufacturingDevice materialEngineering

An island-like interlayer insulating film is formed selectively in a region where a source interconnection and a gate interconnection intersect. For example, by use of ink jet method, a solution containing an insulating material is dropped on a region where the gate interconnection and the source interconnection intersect or a region where a holding capacitor is formed, that enable to reduce a photolithography process and to reduce the number of masks that are used in a TFT

Owner:SEMICON ENERGY LAB CO LTD

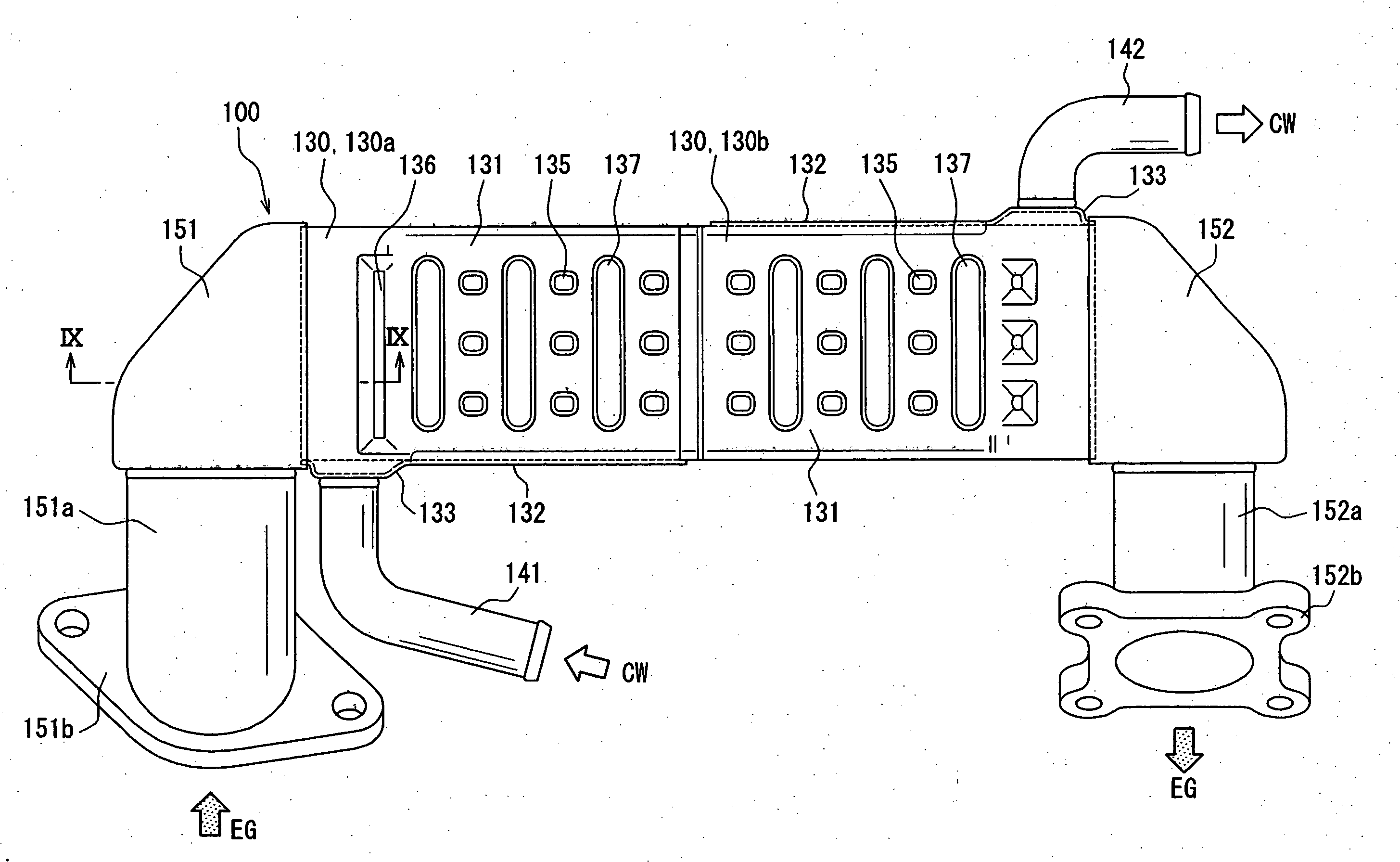

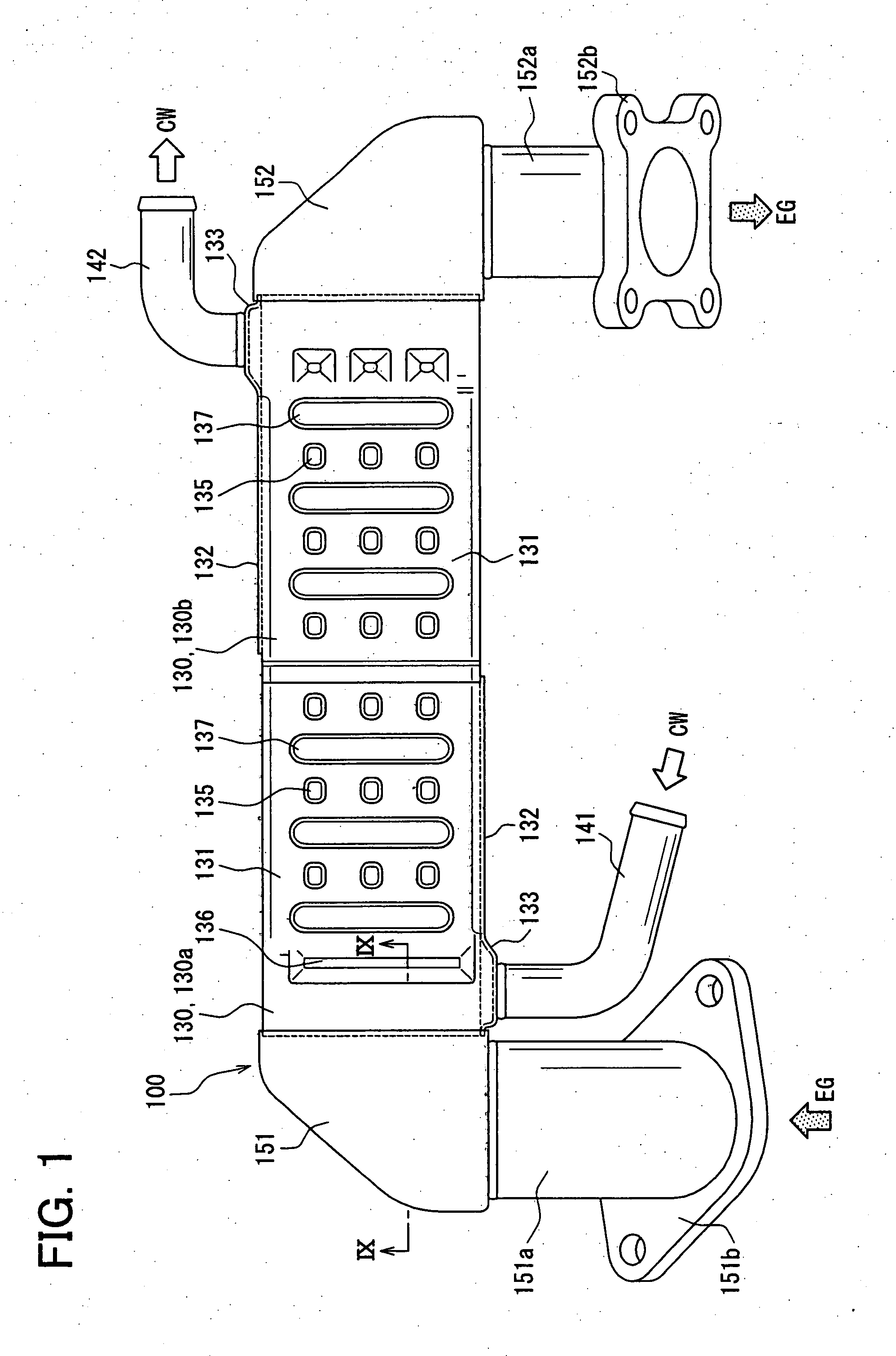

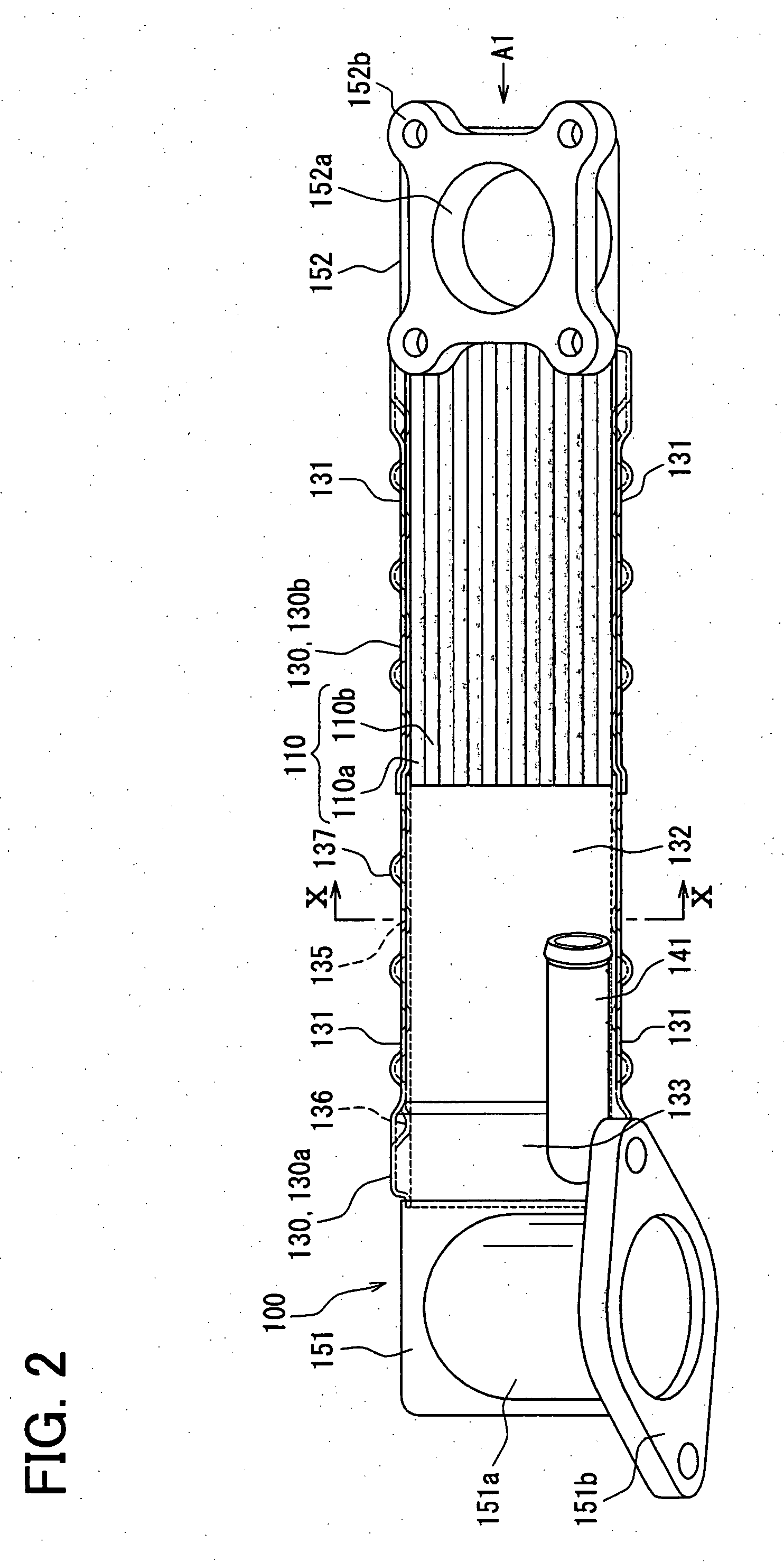

Heat exchanger

InactiveUS20070193732A1Reduce manufacturing stepsNon-fuel substance addition to fuelInternal combustion piston enginesBiomedical engineeringHeat exchanger

A heat exchanger has tubes defining first fluid passages through which a first fluid flows therein, an inlet part and an outlet part. Each tube has a first main wall and a second main wall. At least one of the first main wall and the second main wall has a projection projecting outside of the tube along a peripheral end and a first recess and a second recess recessed from the projection. The tubes are stacked such that the first and second main walls are opposed to each other and spaces are provided between the adjacent tubes by the projections. The spaces define second fluid passages through which a second fluid flows. The inlet part is in communication with the second fluid passages through the first recesses and the outlet part is in communication with the second fluid passages through the second recesses.

Owner:DENSO CORP

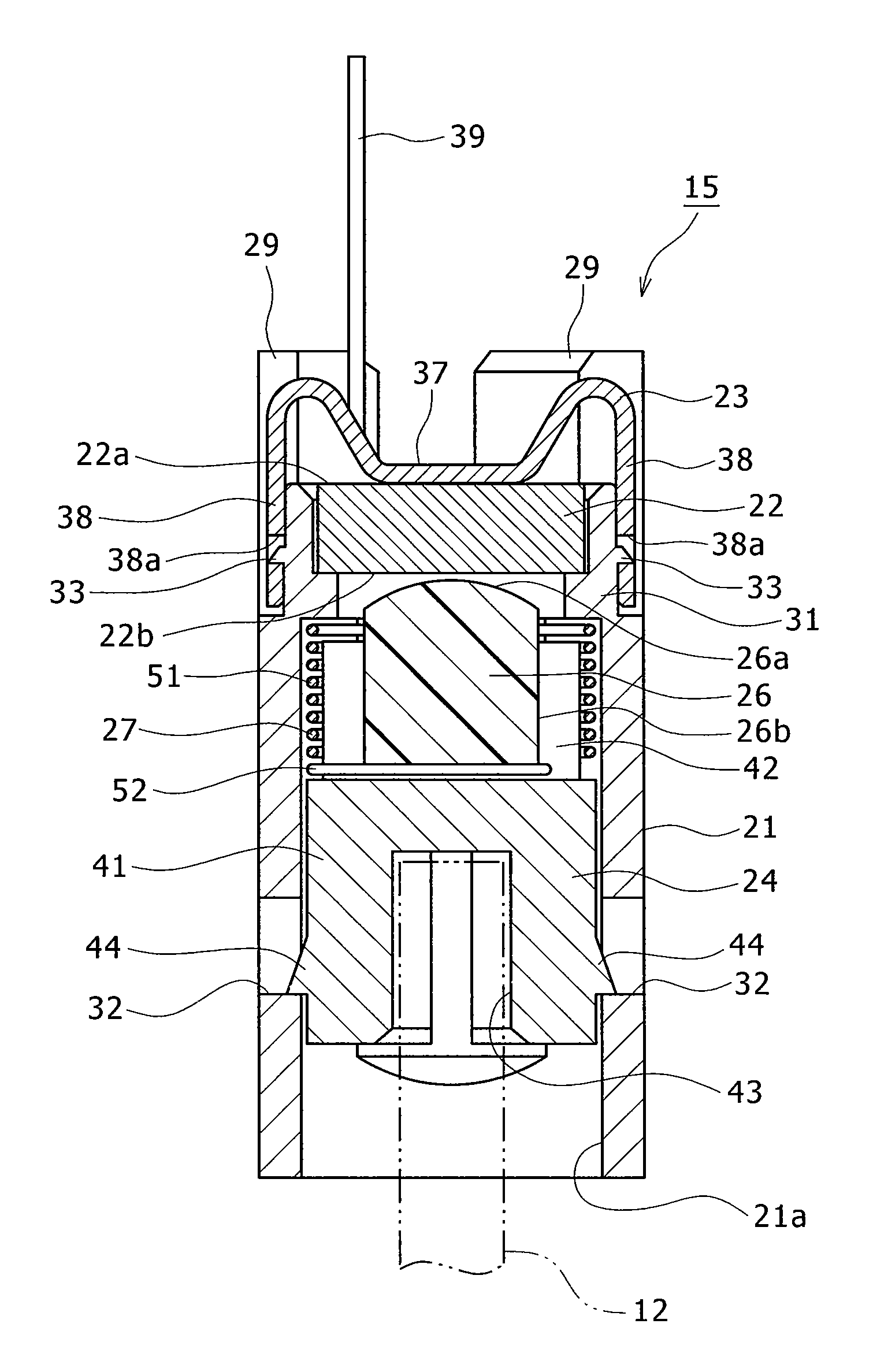

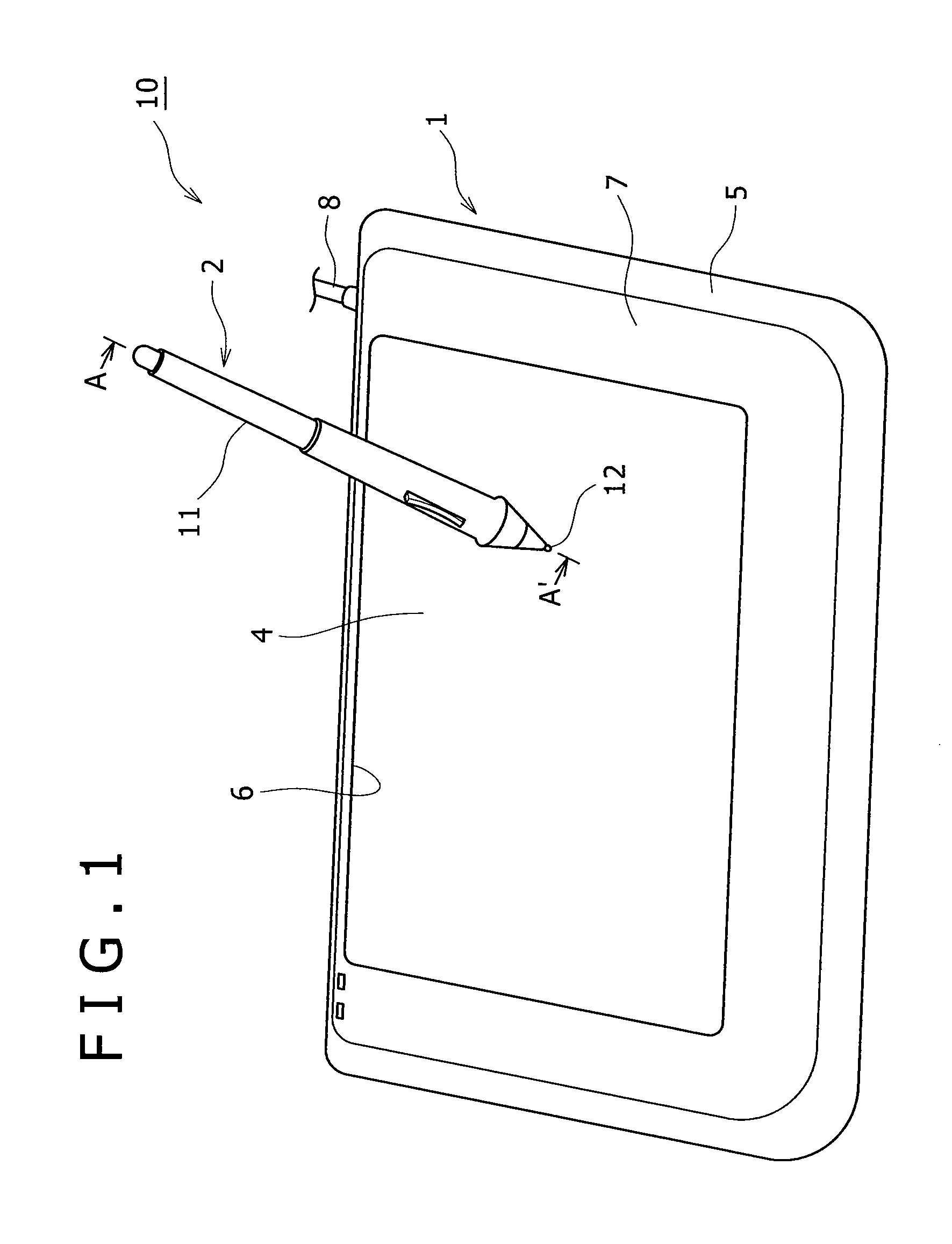

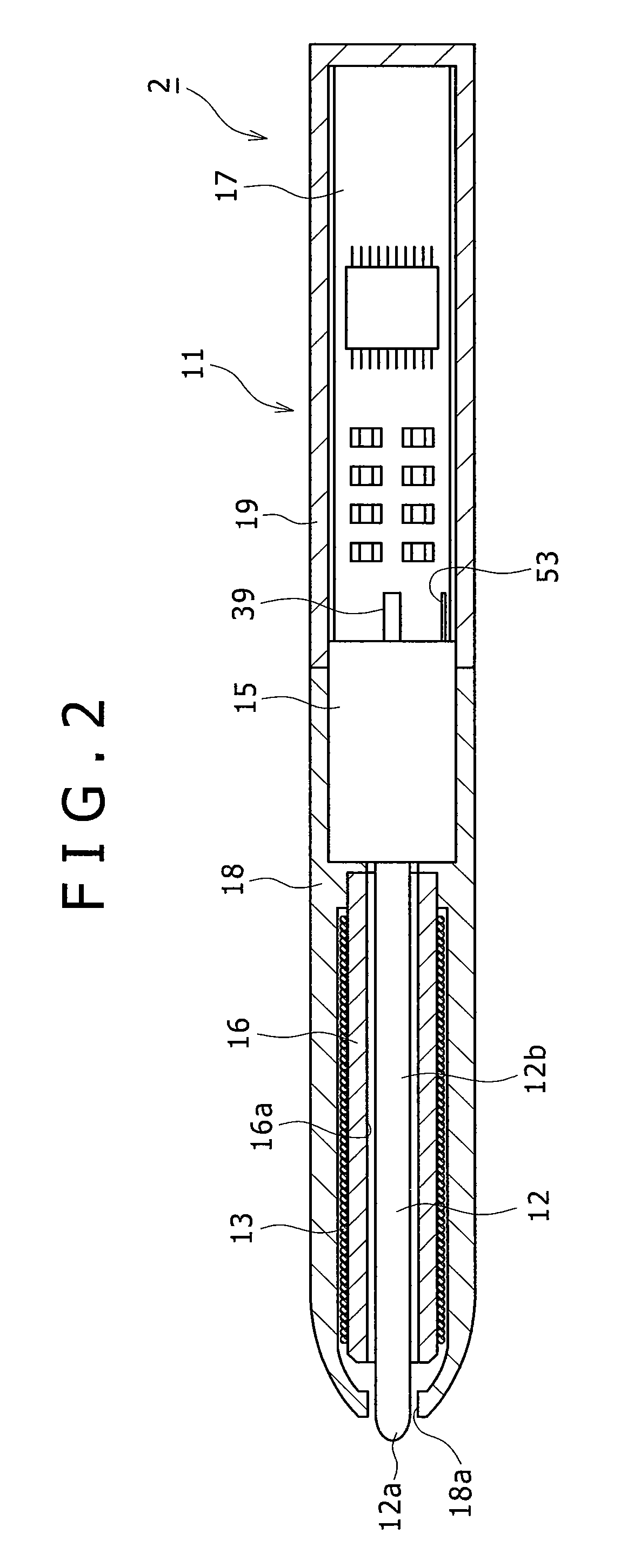

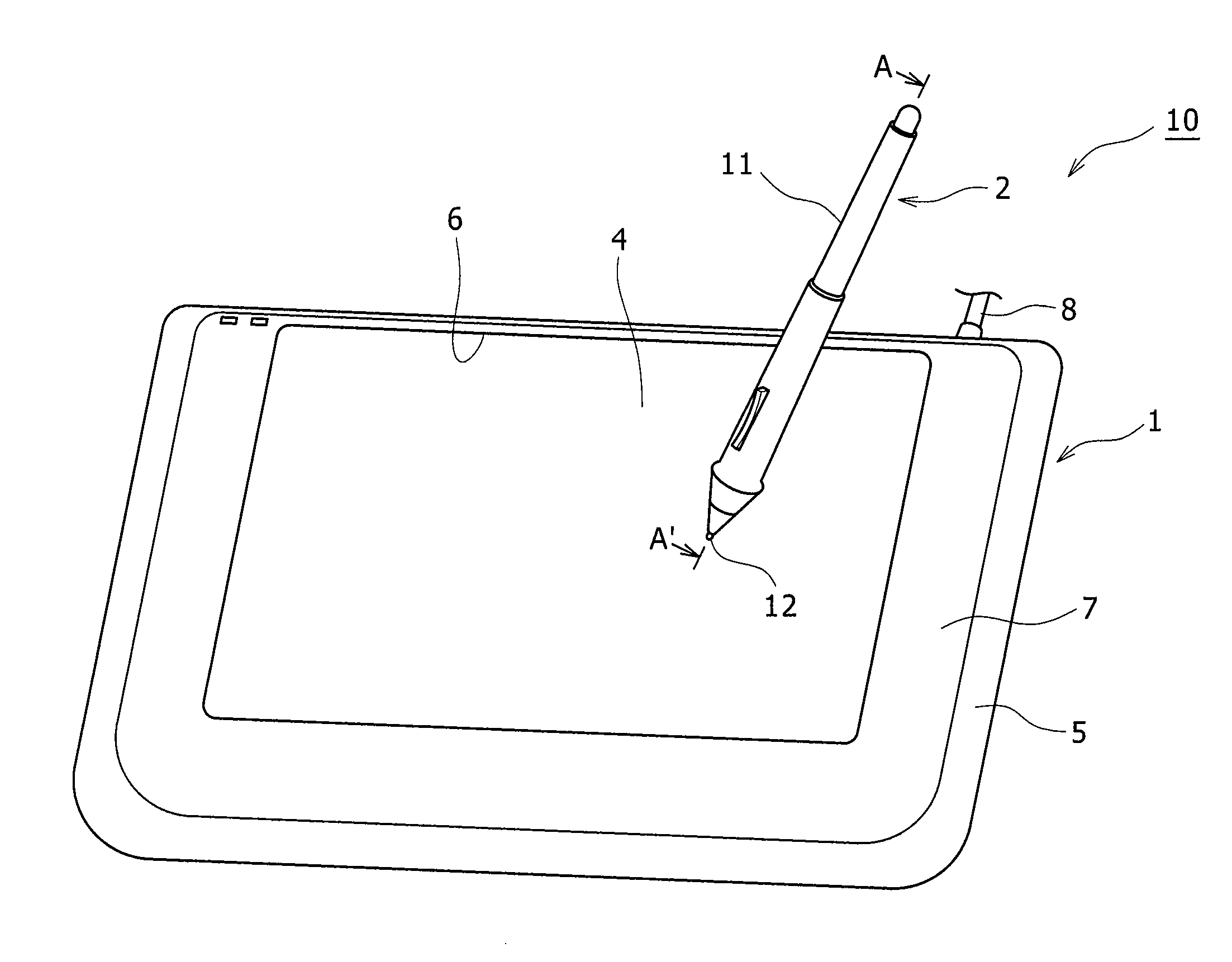

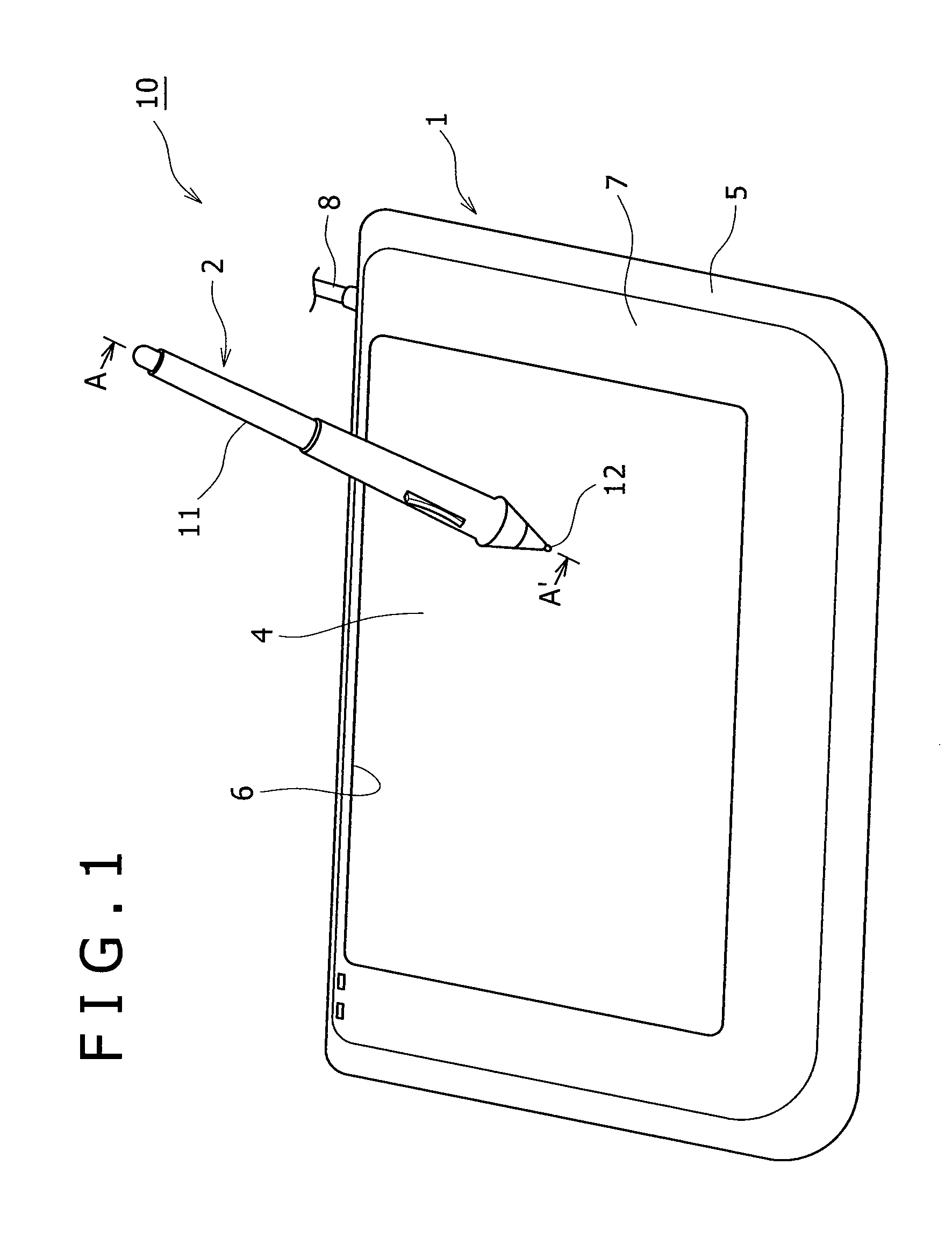

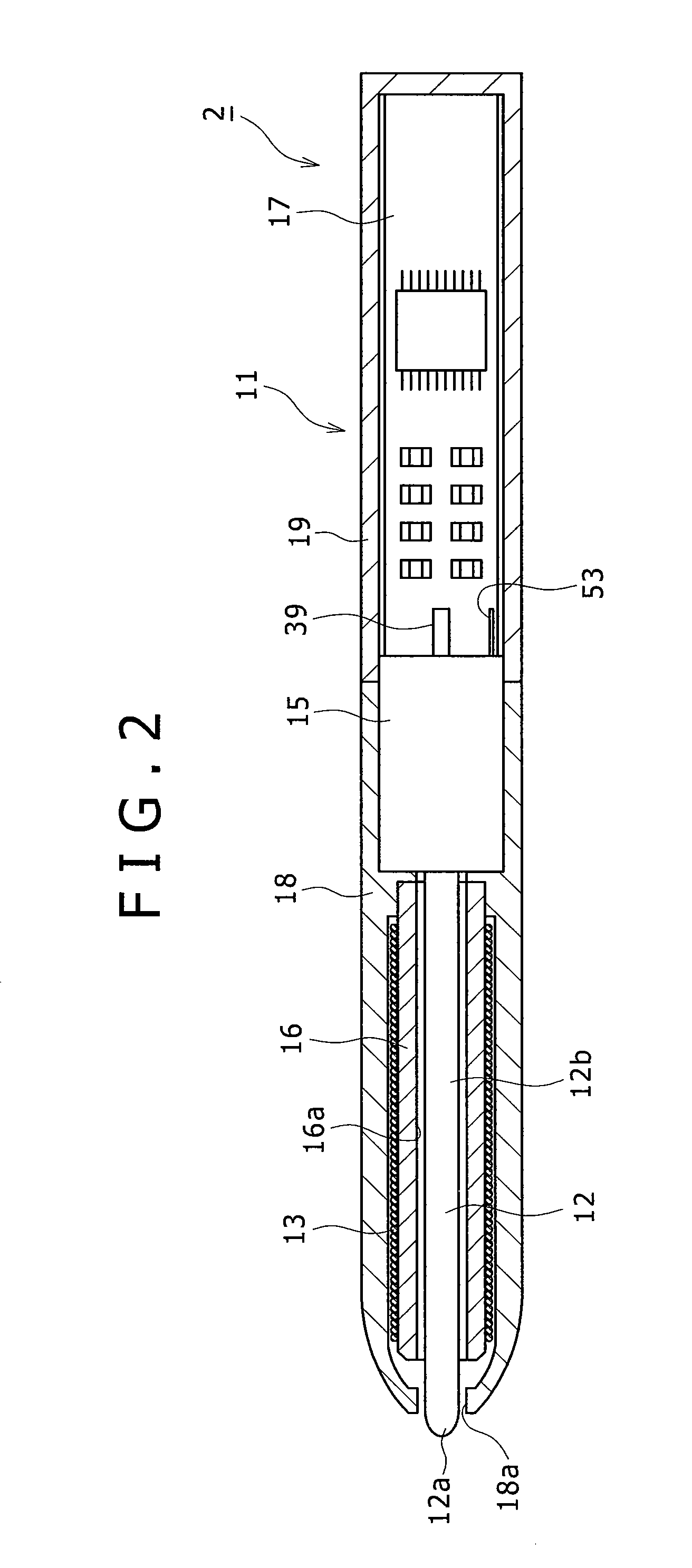

Position pointer, variable capacitor and inputting apparatus

ActiveUS8913041B2Reduce in quantityIncreased durabilityCathode-ray tube indicatorsDiagnostic recording/measuringDielectricCapacitance

A position pointer is disclosed, including a housing, a substantially bar-like rod accommodated in the housing such that one end thereof projects to the outer side of the housing, and a variable capacitor having a capacitance value which varies in response to external force applied thereto through the rod. The variable capacitor includes a dielectric member having a first face portion and a second face portion opposite from the first face portion, a terminal member configured to engage with the first face portion of the dielectric member, an electrode section disposed in an opposing relationship to the second face portion of the dielectric member and including a conductive member having a contact area with the second face portion that varies in response to the external force, and an elastic member configured to bias the conductive member in a direction in which the conductive member is spaced away from the second face portion.

Owner:WACOM CO LTD

Semiconductor device

ActiveUS20110080774A1Complicated processingLower manufacturing requirementsSolid-state devicesRead-only memoriesManufacturing cost reductionHigh resistance

Objects of the present invention are to improve the manufacturing yield of semiconductor devices, reduce manufacturing cost of the semiconductor device, and reduce the circuit area of an integrated circuit included in the semiconductor device. A memory layer of a memory element and a resistive layer of a resistor included in the semiconductor device are formed of the same material. Therefore, the memory layer and the resistive layer are formed in the same step, whereby the number of manufacturing steps of the semiconductor device can be reduced. As a result, the manufacturing yield of the semiconductor devices can be improved and the manufacturing cost can be reduced. In addition, the semiconductor device includes a resistor having a resistive component which has high resistance value. Consequently, the area of the integrated circuit included in the semiconductor device can be reduced.

Owner:SEMICON ENERGY LAB CO LTD

Position pointer, variable capacitor and inputting apparatus

ActiveUS20110219892A1Increased durabilityAvoid stickingDiagnostic recording/measuringSensorsDielectricCapacitance

A position pointer is disclosed, including a housing, a substantially bar-like rod accommodated in the housing such that one end thereof projects to the outer side of the housing, and a variable capacitor having a capacitance value which varies in response to external force applied thereto through the rod. The variable capacitor includes a dielectric member having a first face portion and a second face portion opposite from the first face portion, a terminal member configured to engage with the first face portion of the dielectric member, an electrode section disposed in an opposing relationship to the second face portion of the dielectric member and including a conductive member having a contact area with the second face portion that varies in response to the external force, and an elastic member configured to bias the conductive member in a direction in which the conductive member is spaced away from the second face portion.

Owner:WACOM CO LTD

Method for manufacture of a physical quantity detector

InactiveUS7708051B2High dimensional accuracyImprove surface smoothnessFluid pressure measurement by electric/magnetic elementsMetallic material coating processesMetal moldPressure sensor

Owner:NAGANO KEIKI

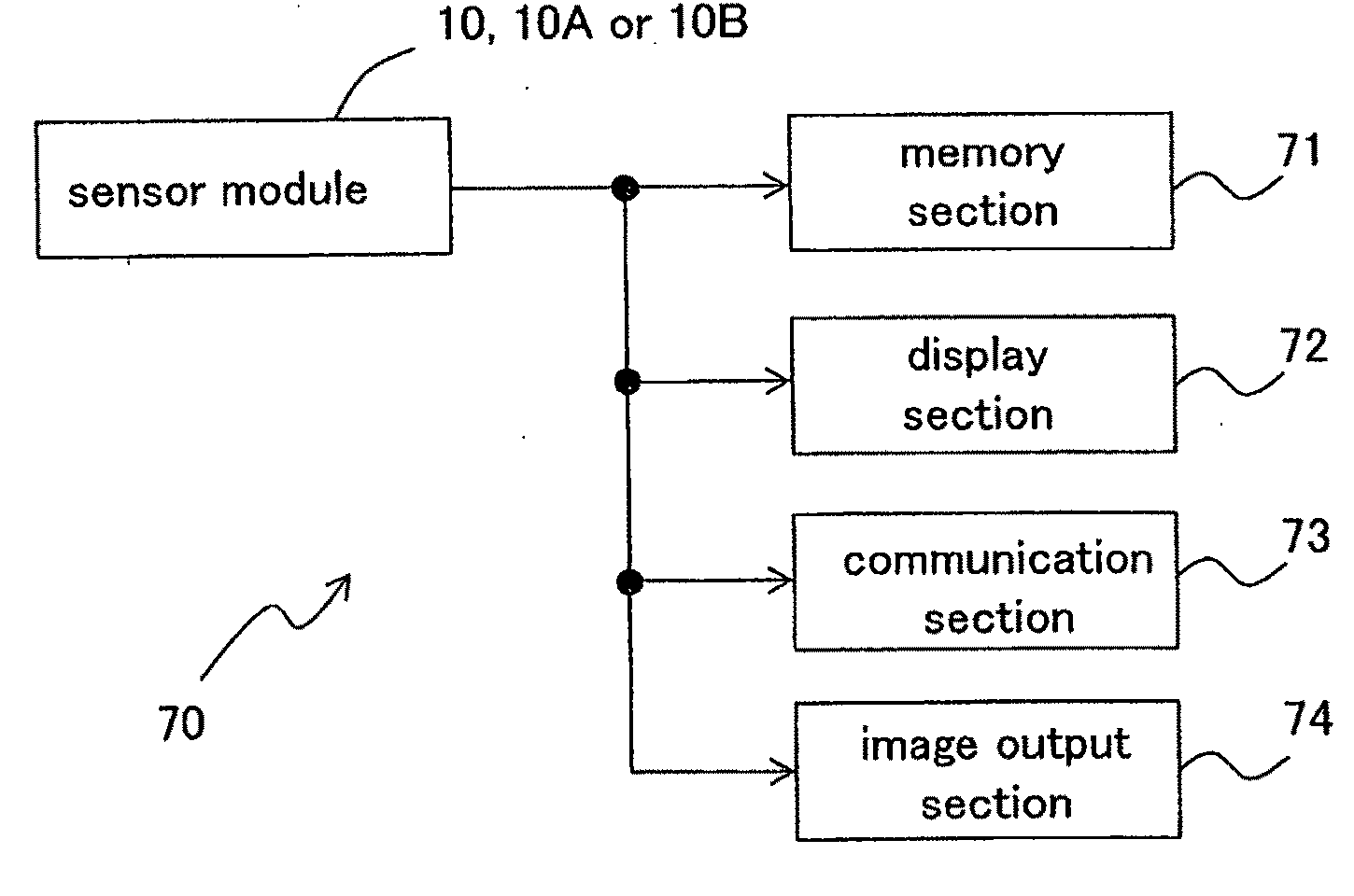

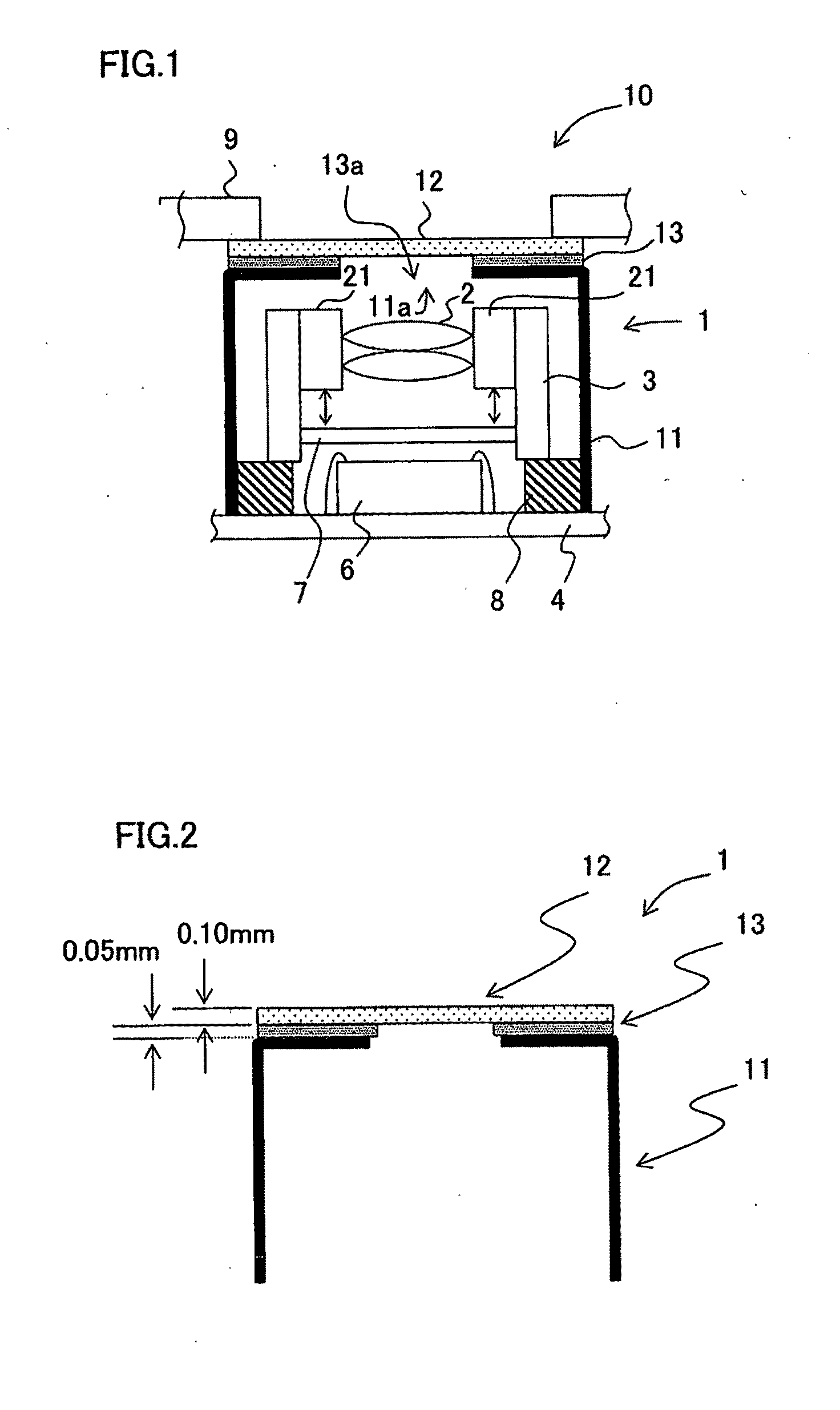

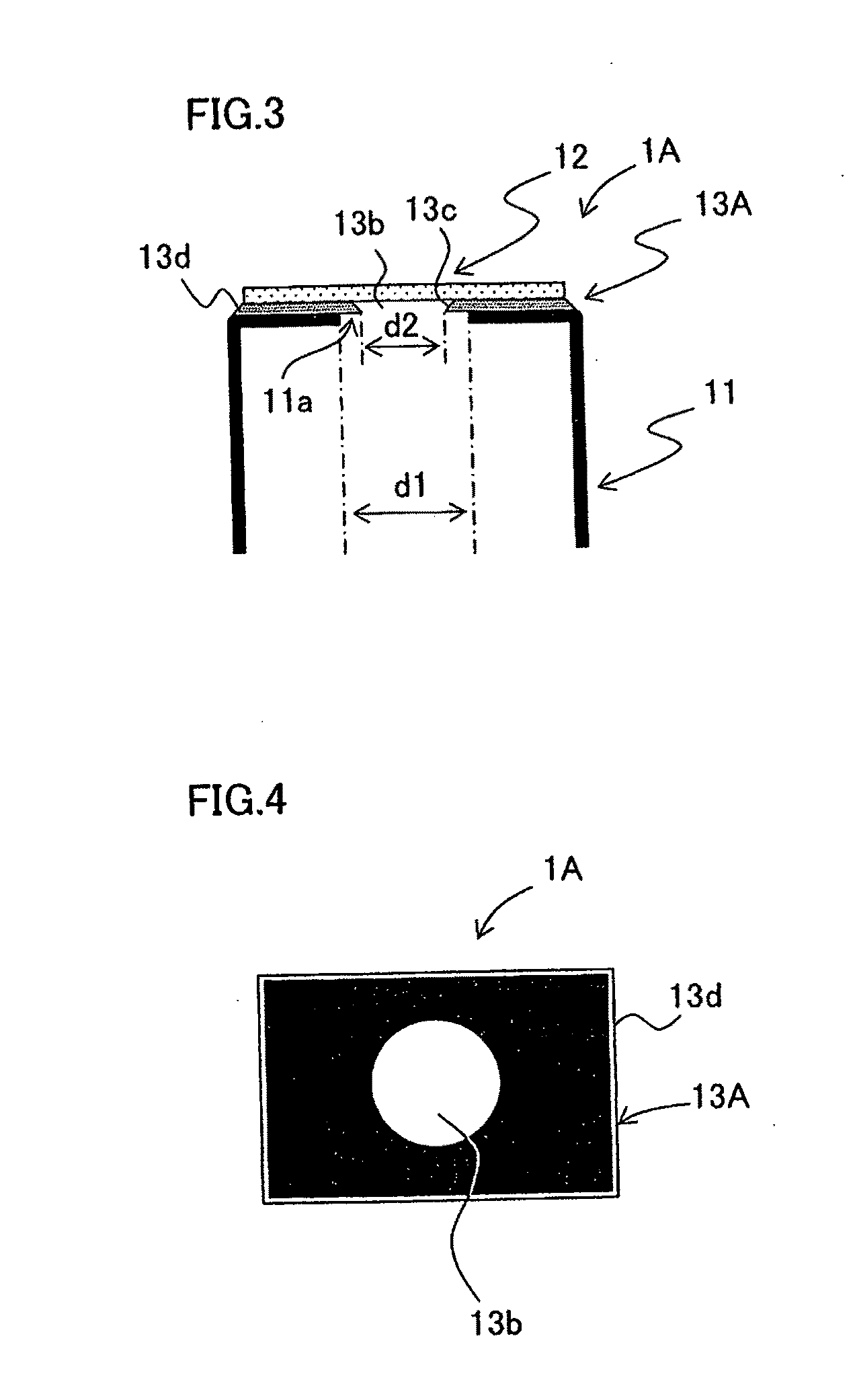

Case member, sensor module, and electronic information device

InactiveUS20090109330A1Reduce manufacturing stepsLow profileTelevision system detailsSolid-state devicesOptoelectronicsElectronic information

A case member has a predetermined surface and a sealable inside, where a first circular area for passing light is provided at the center portion of the predetermined surface, a double-sided light shielding sheet, which is provided with a second circular area for passing light at the center, is adhered to the predetermined surface such that the second circular area is positioned in a concentric circle manner to the first circular area, the second circular area having a diameter smaller than the diameter of the first circular area, a transparent dustproof film is adhered on the light shielding sheet.

Owner:SHARP KK

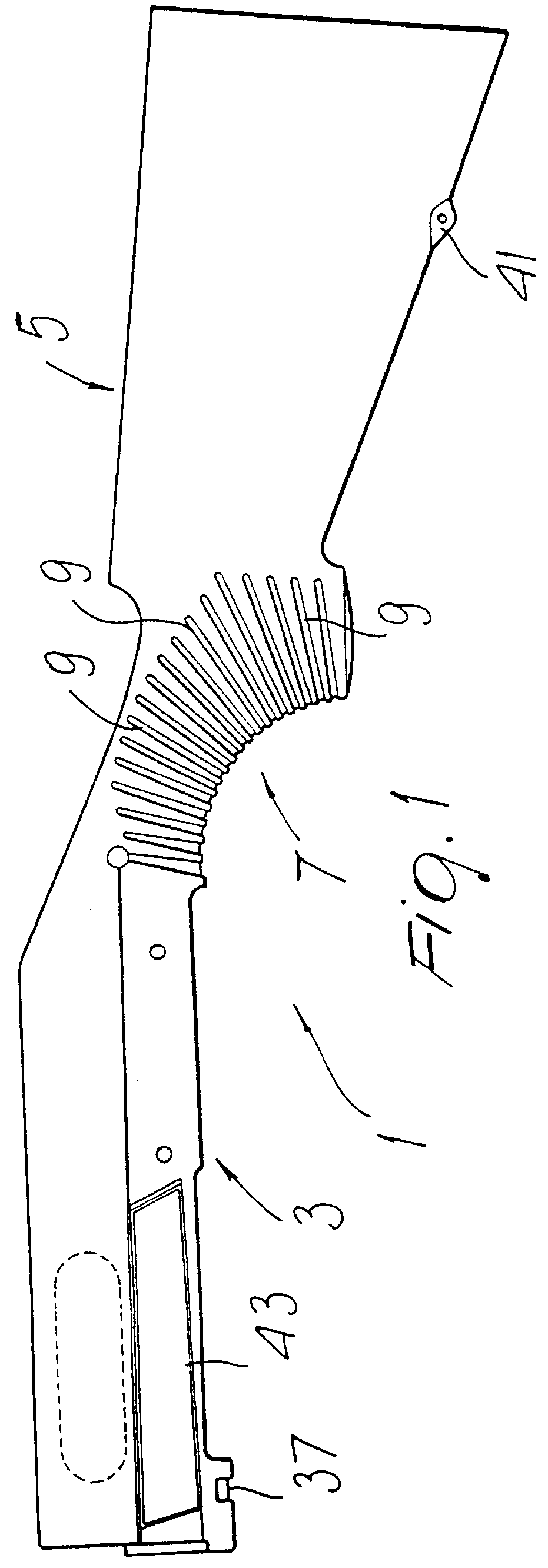

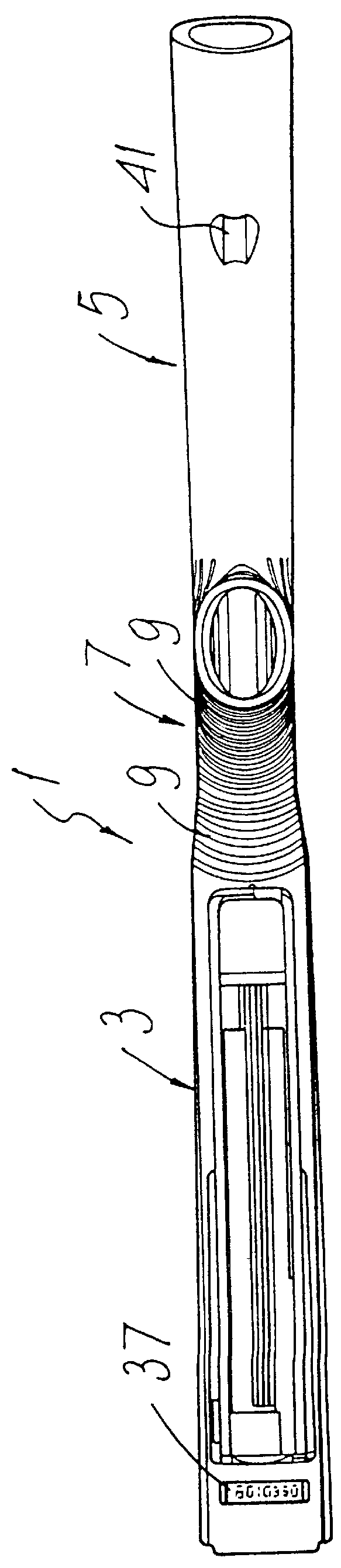

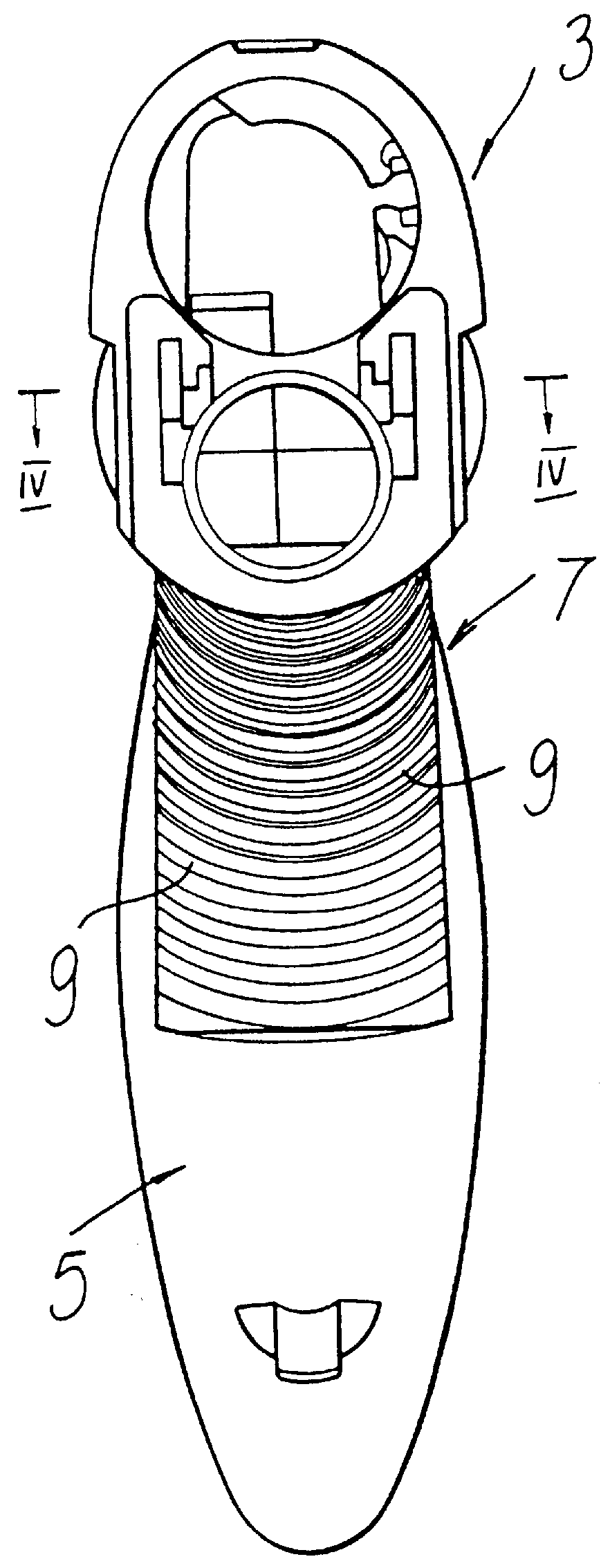

Firearm with metal insert in monolithic housing and stock

InactiveUS6070354AReduce manufacturing stepsButtsShoulder-fired smallarmsEngineeringMechanical engineering

A portable weapon having a monolithic housing and stock made of plastics and provided with a metal insert for strengthening the structure.

Owner:BENELLI ARMI