Patents

Literature

860 results about "Bottom gate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Semiconductor device and method for manufacturing the same

ActiveUS20100025678A1Comparatively-easy manufacturing processRun at high speedTransistorSolid-state devicesProduction rateOhmic contact

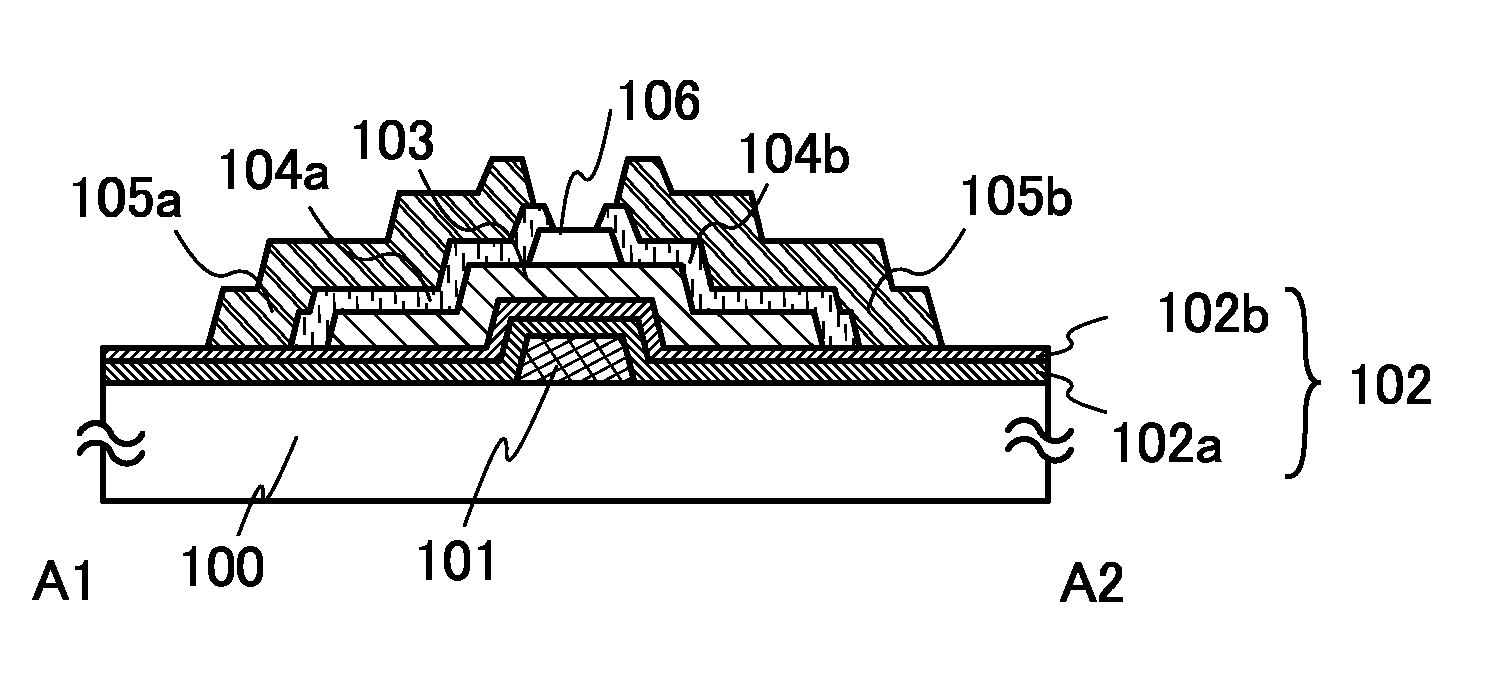

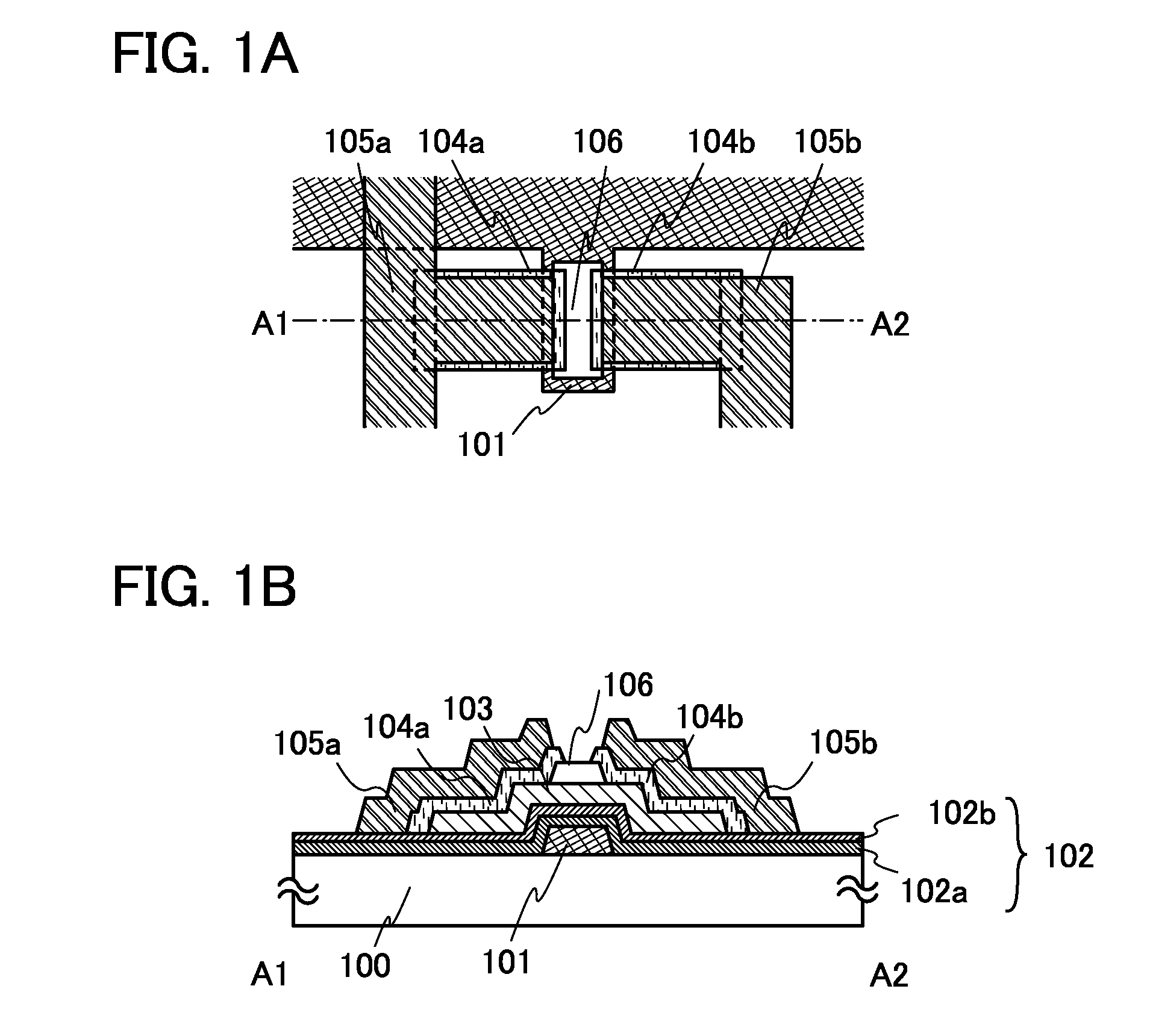

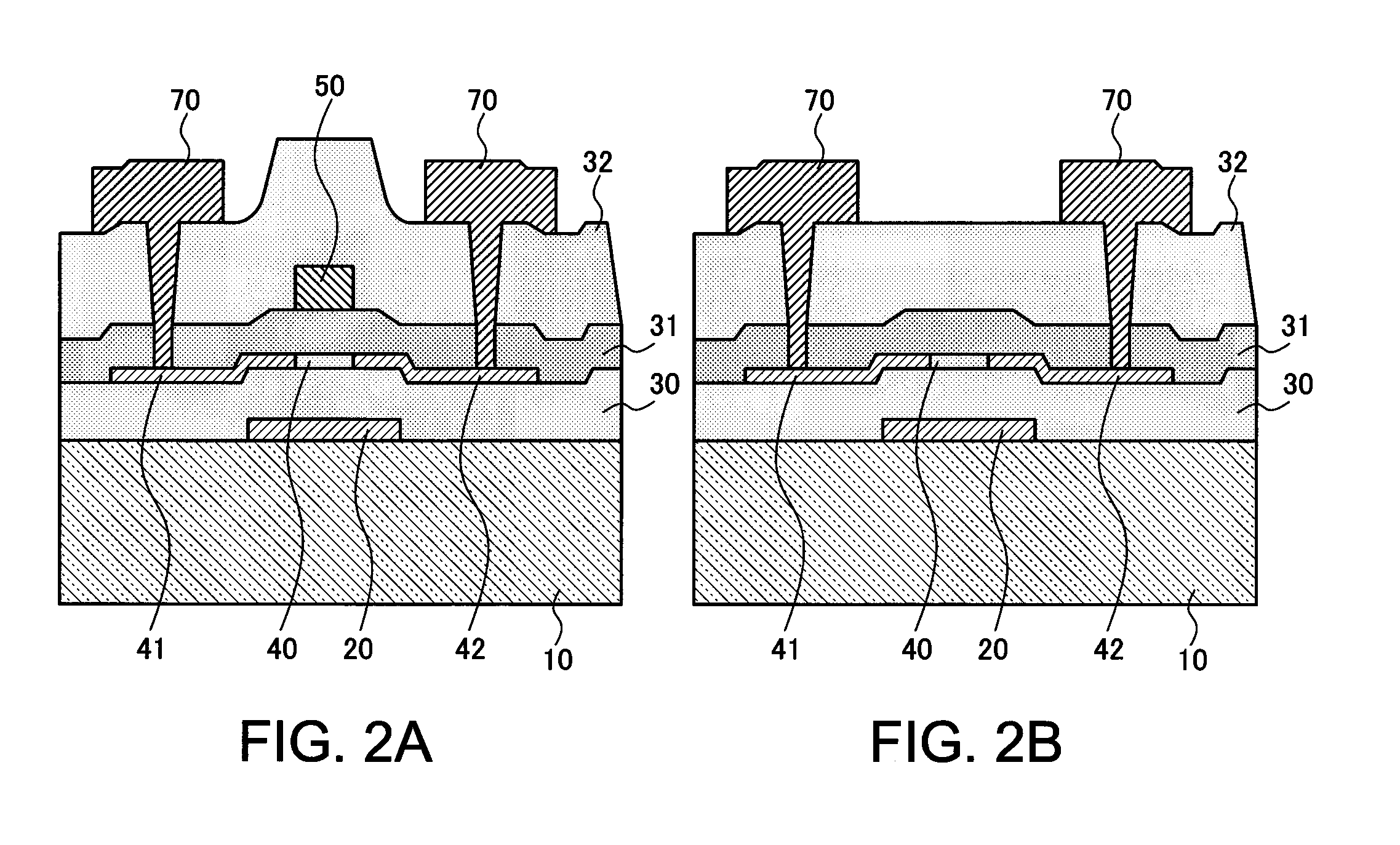

It is an object to provide a semiconductor device including a thin film transistor with favorable electric properties and high reliability, and a method for manufacturing the semiconductor device with high productivity. In an inverted staggered (bottom gate) thin film transistor, an oxide semiconductor film containing In, Ga, and Zn is used as a semiconductor layer, and a buffer layer formed using a metal oxide layer is provided between the semiconductor layer and a source and drain electrode layers. The metal oxide layer is intentionally provided as the buffer layer between the semiconductor layer and the source and drain electrode layers, whereby ohmic contact is obtained.

Owner:SEMICON ENERGY LAB CO LTD

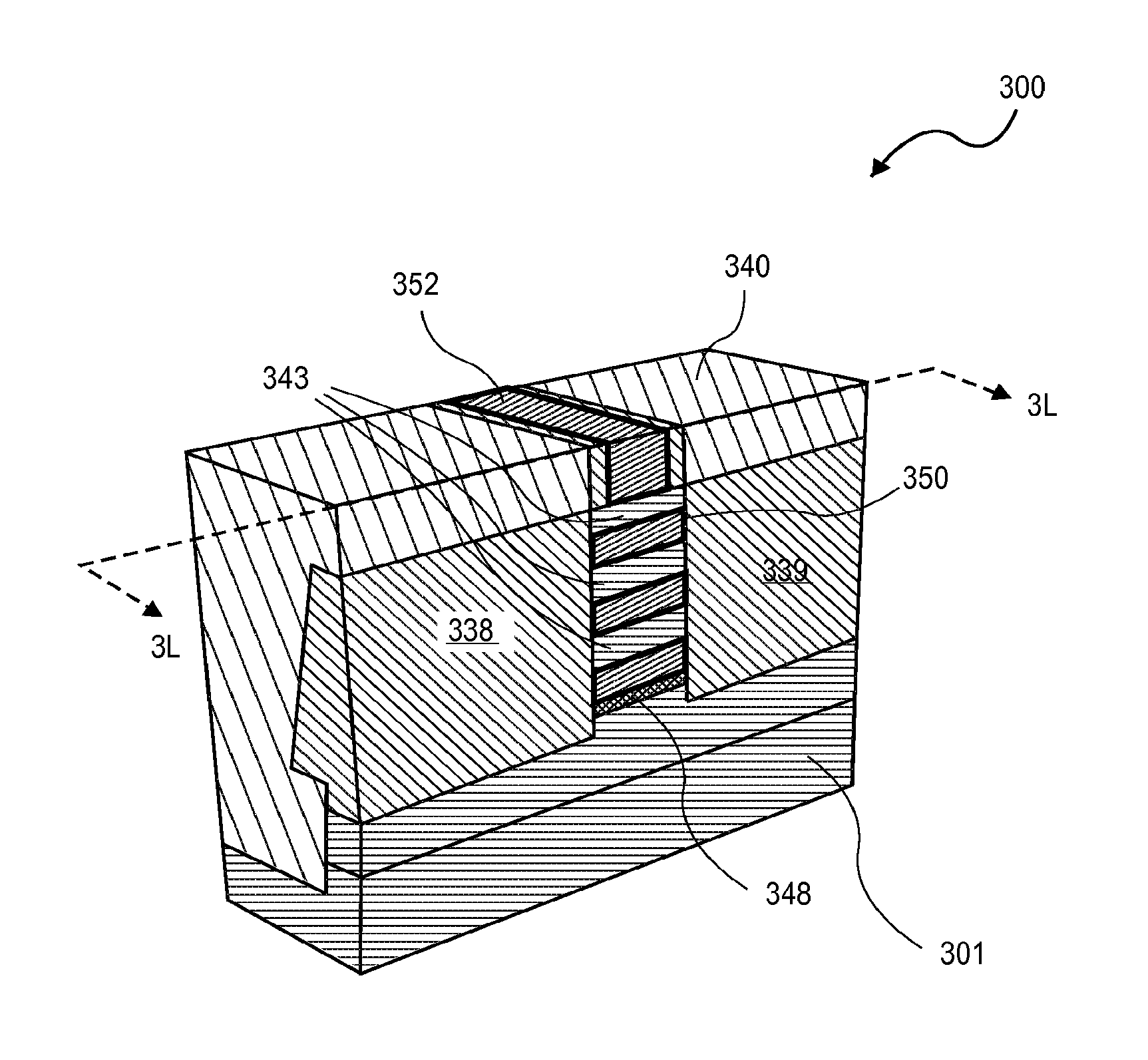

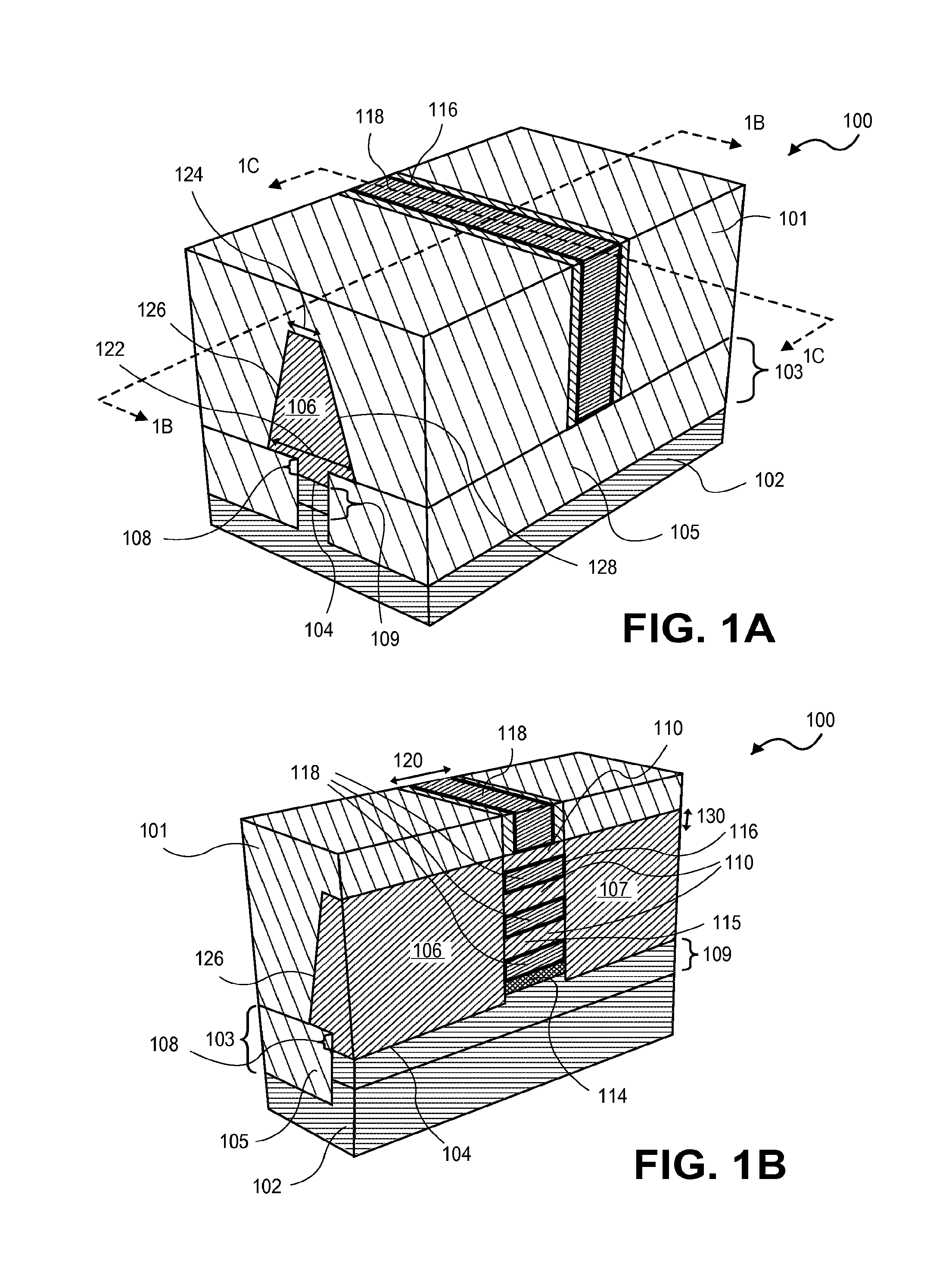

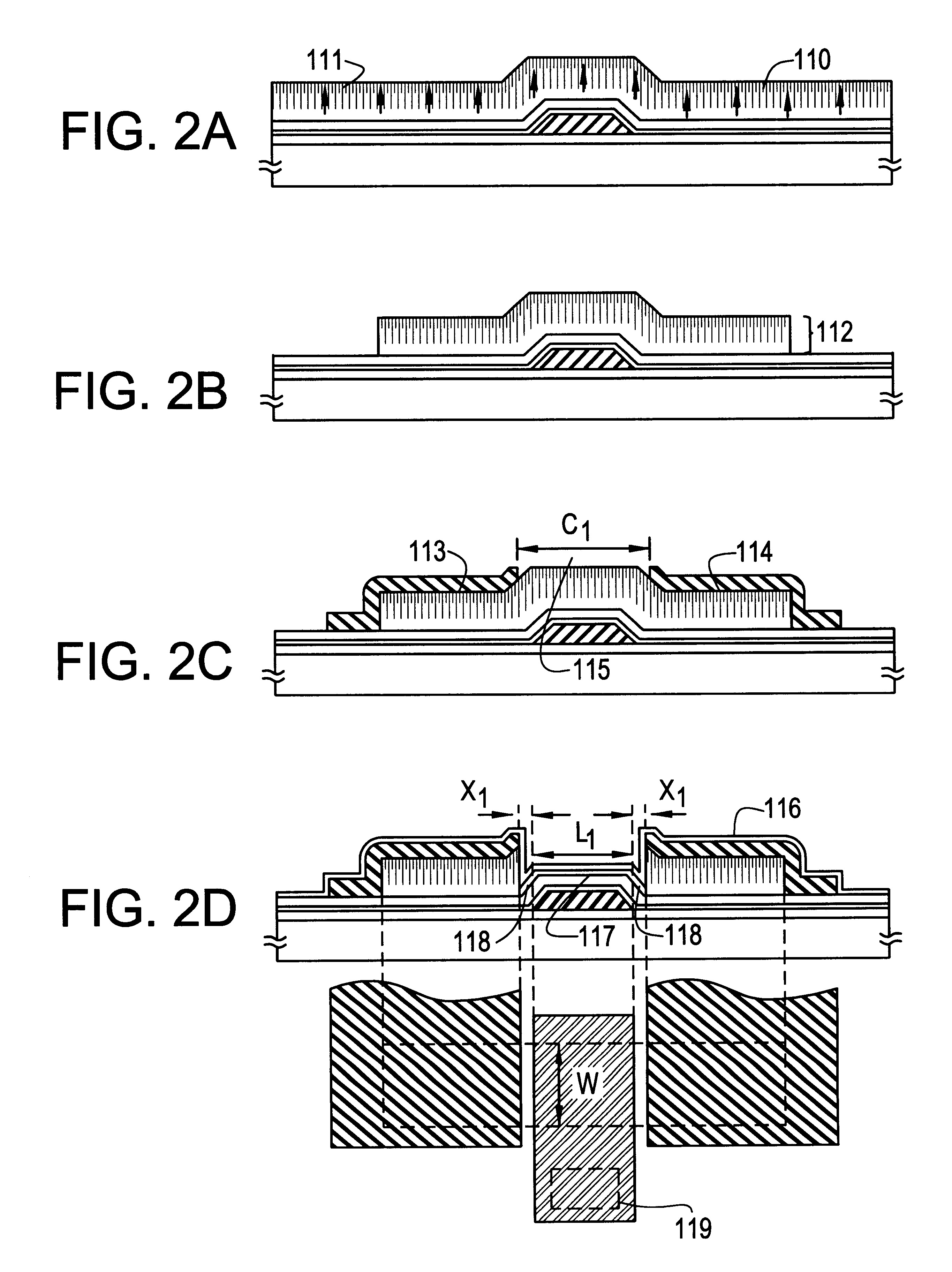

Non-planar gate all-around device and method of fabrication thereof

ActiveUS20140225065A1NanoinformaticsSemiconductor/solid-state device manufacturingNanowireGate dielectric

A non-planar gate all-around device and method of fabrication thereby are described. In one embodiment, the device includes a substrate having a top surface with a first lattice constant. Embedded epi source and drain regions are formed on the top surface of the substrate. The embedded epi source and drain regions have a second lattice constant that is different from the first lattice constant. Channel nanowires having a third lattice are formed between and are coupled to the embedded epi source and drain regions. In an embodiment, the second lattice constant and the third lattice constant are different from the first lattice constant. The channel nanowires include a bottom-most channel nanowire and a bottom gate isolation is formed on the top surface of the substrate under the bottom-most channel nanowire. A gate dielectric layer is formed on and all-around each channel nanowire. A gate electrode is formed on the gate dielectric layer and surrounding each channel nanowire.

Owner:SONY CORP

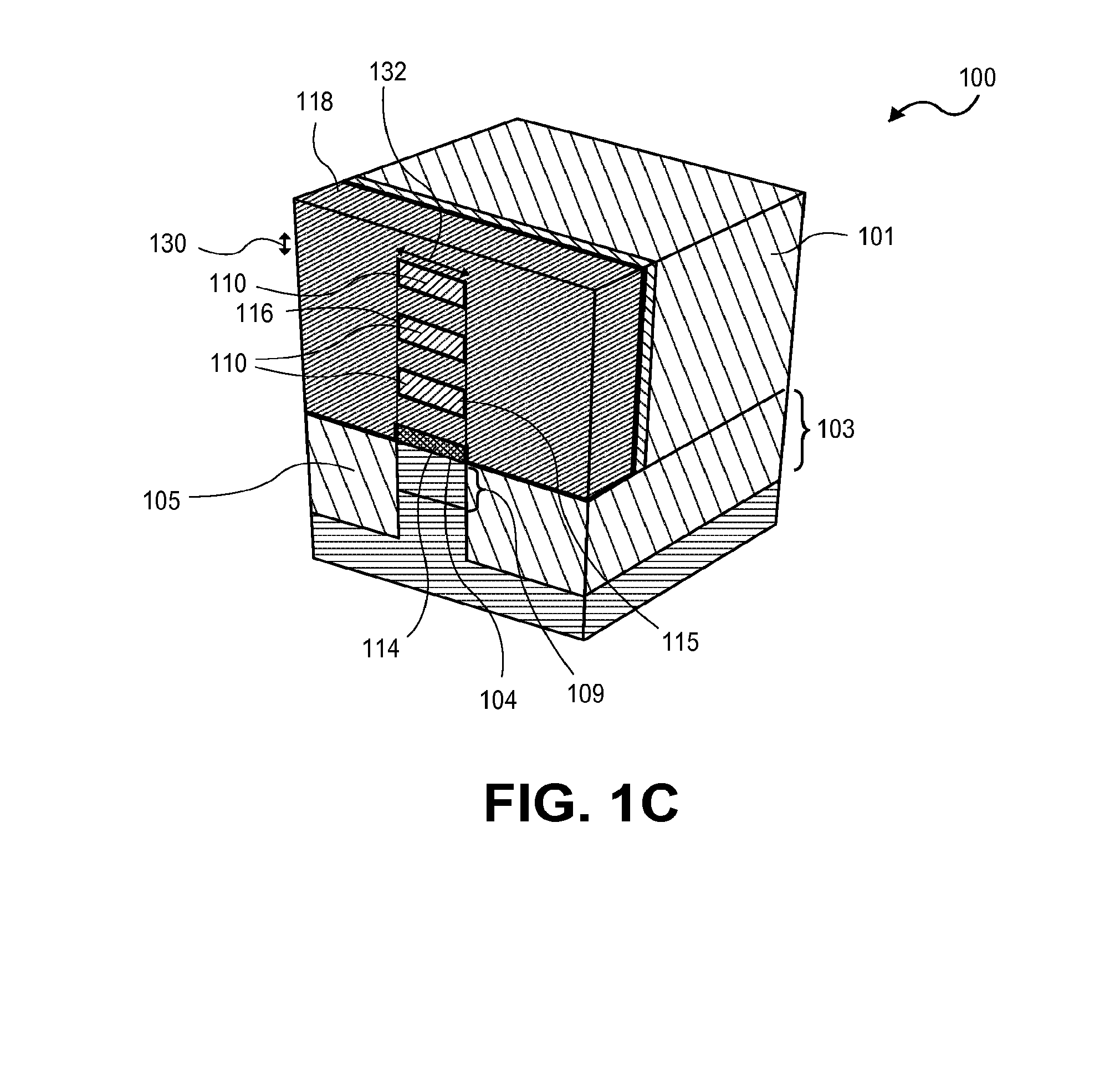

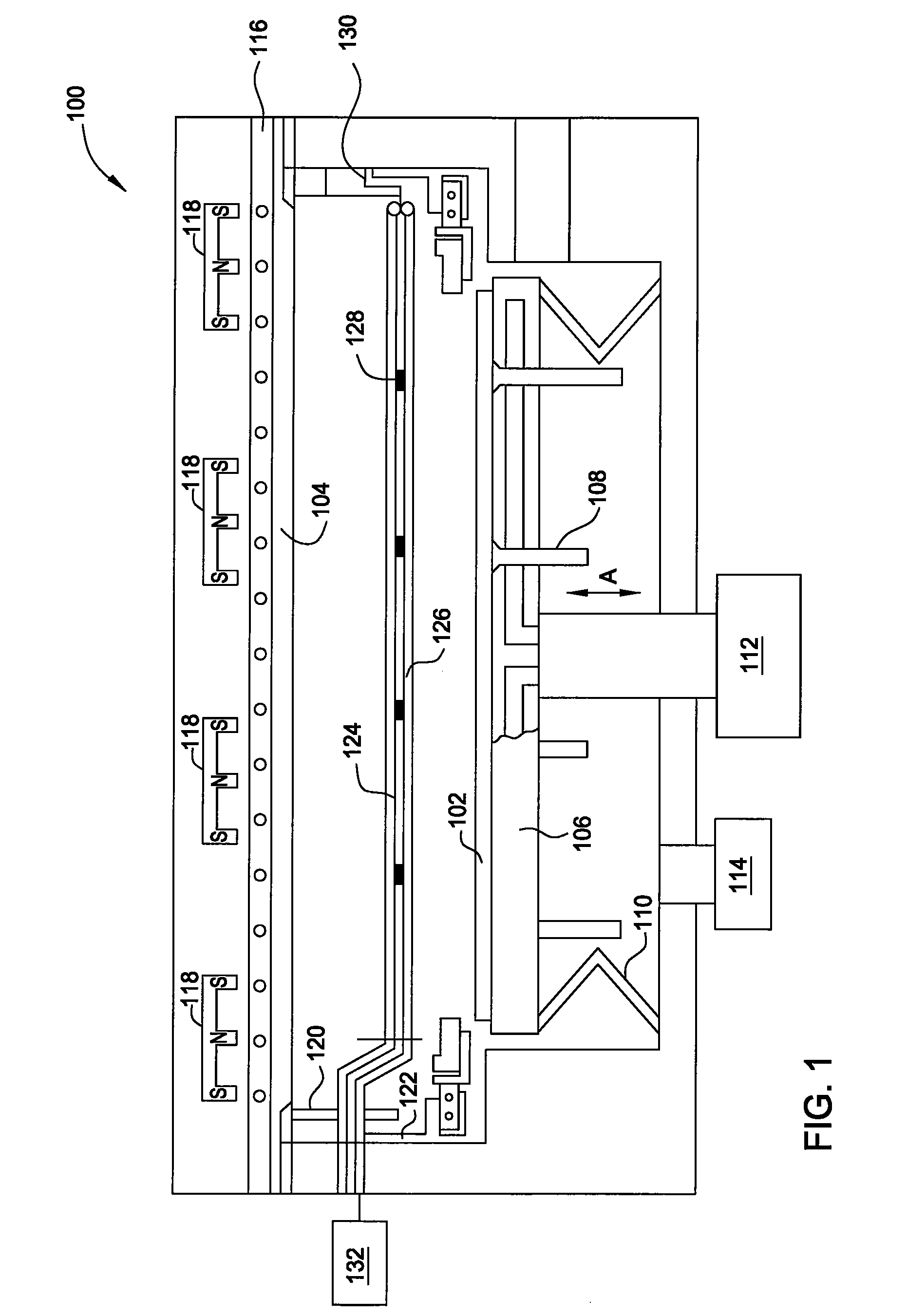

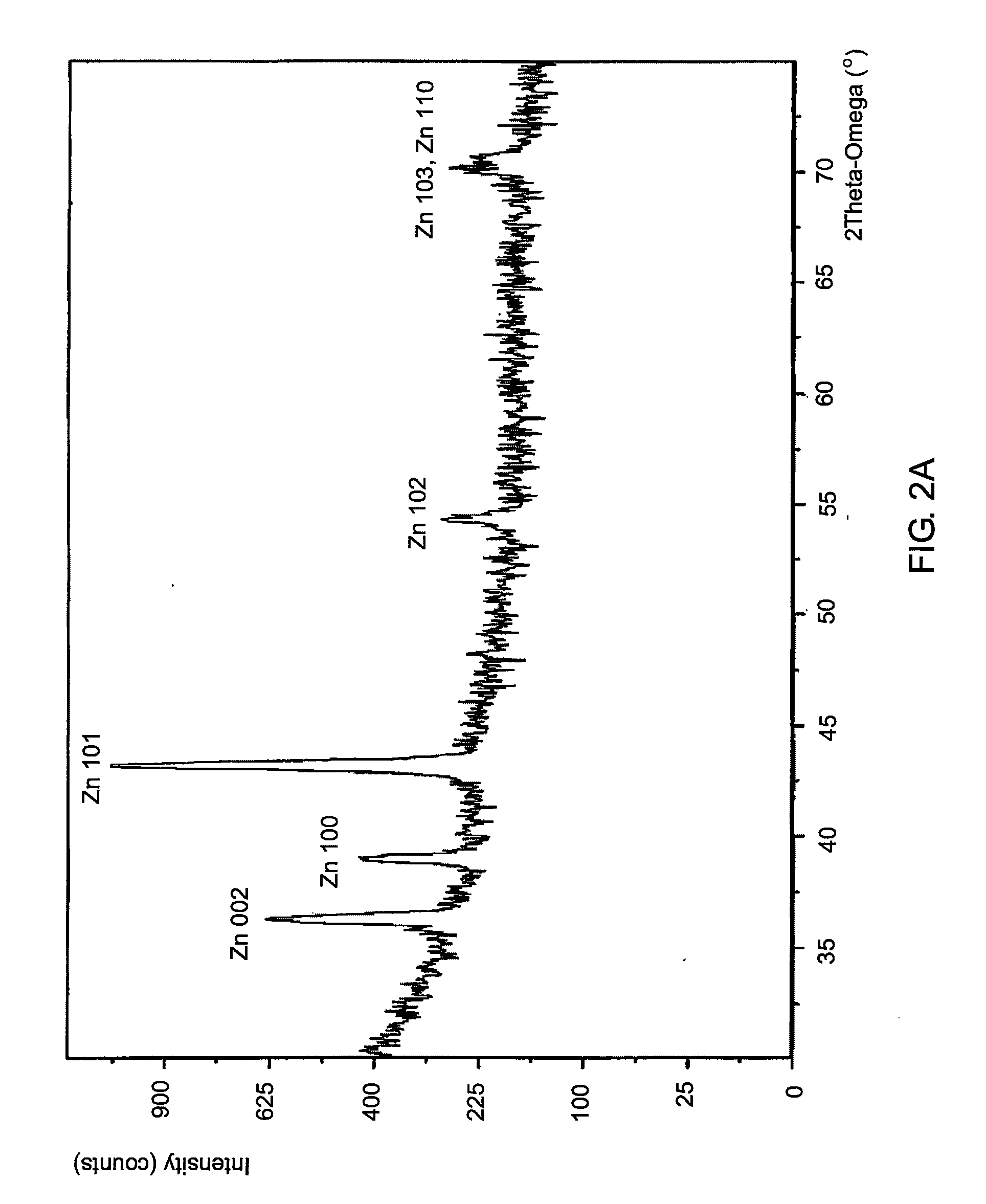

METHOD OF MANUFACTURING ZnO-BASED THIN FILM TRANSISTOR

InactiveUS20080299702A1Reduce carrier concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesInterfacial reactionBottom gate

A ZnO-based thin film transistor (TFT) is provided herein. Also provided is a method for manufacturing the TFT. The ZnO-based TFT is very sensitive to the oxygen concentration present in a channel layer. In order to prevent damage to a channel layer of a bottom gate TFT, and to avoid a deep negative threshold voltage resulting from damage to the channel layer, the method for manufacturing the ZnO-based TFT comprises formation of an etch stop layer or a passivation layer comprising unstable or incompletely bonded oxygen, and annealing the layers to induce an interfacial reaction between the oxide layer and the channel layer and to reduce the carrier concentration.

Owner:SAMSUNG ELECTRONICS CO LTD

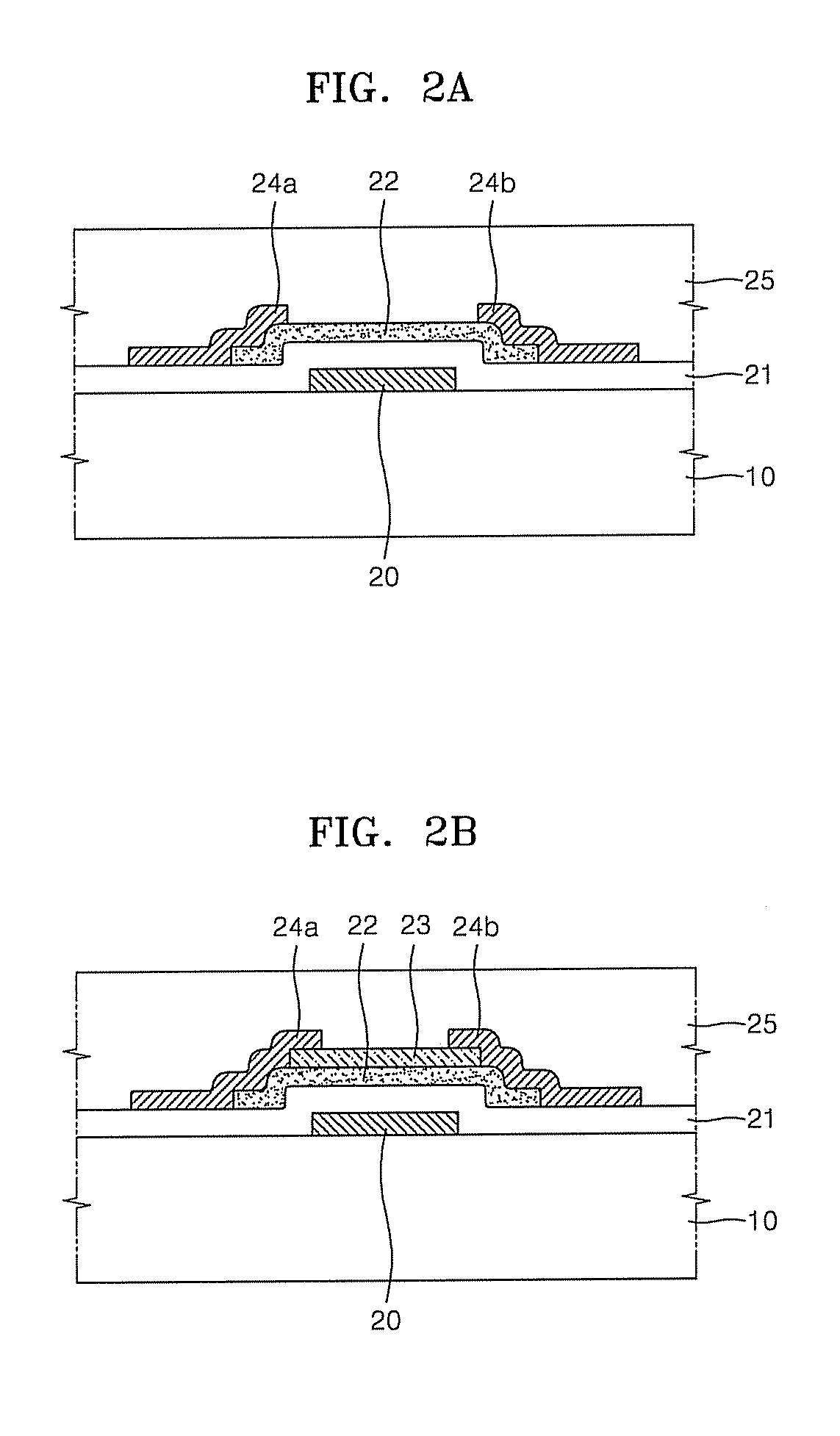

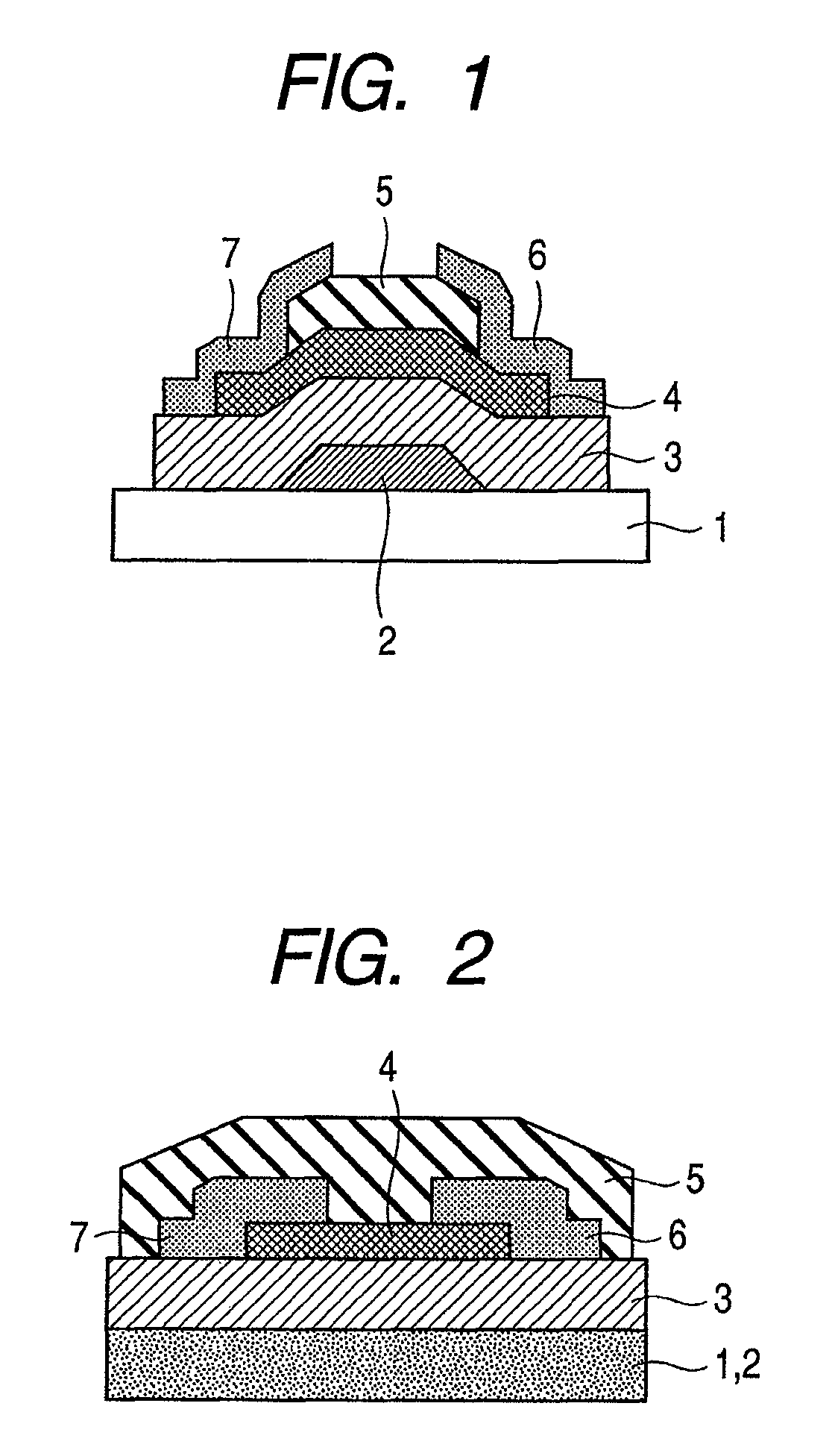

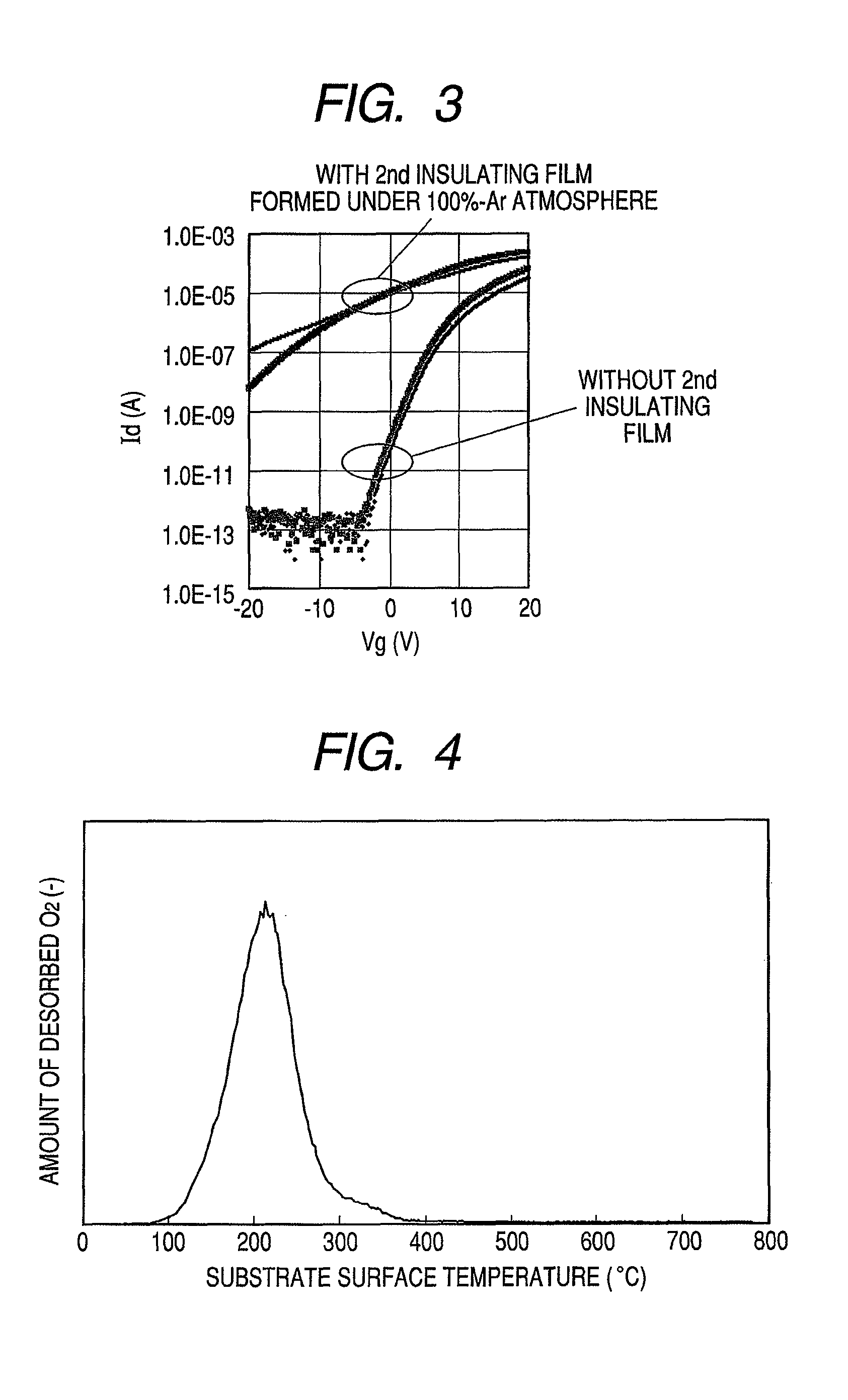

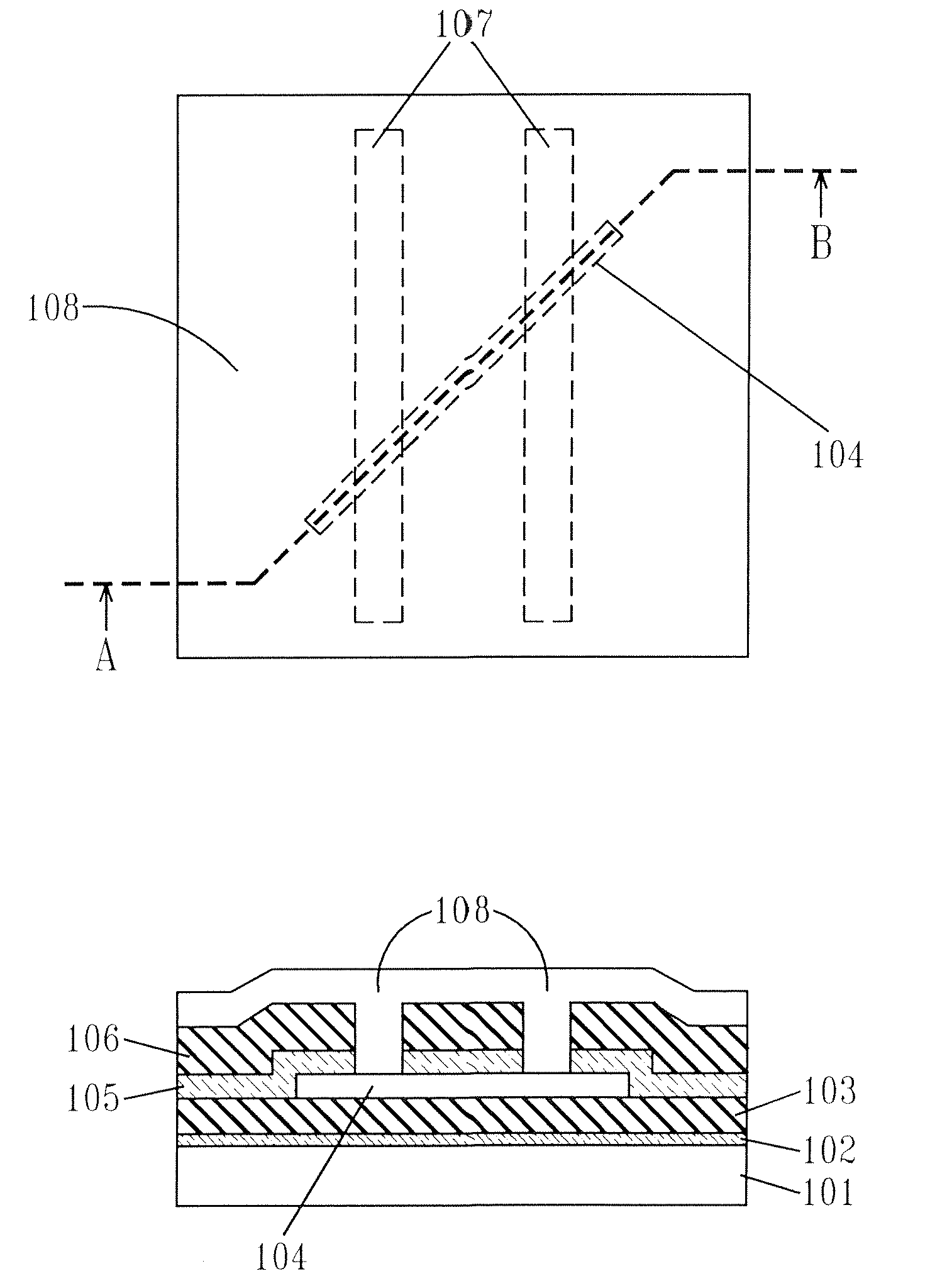

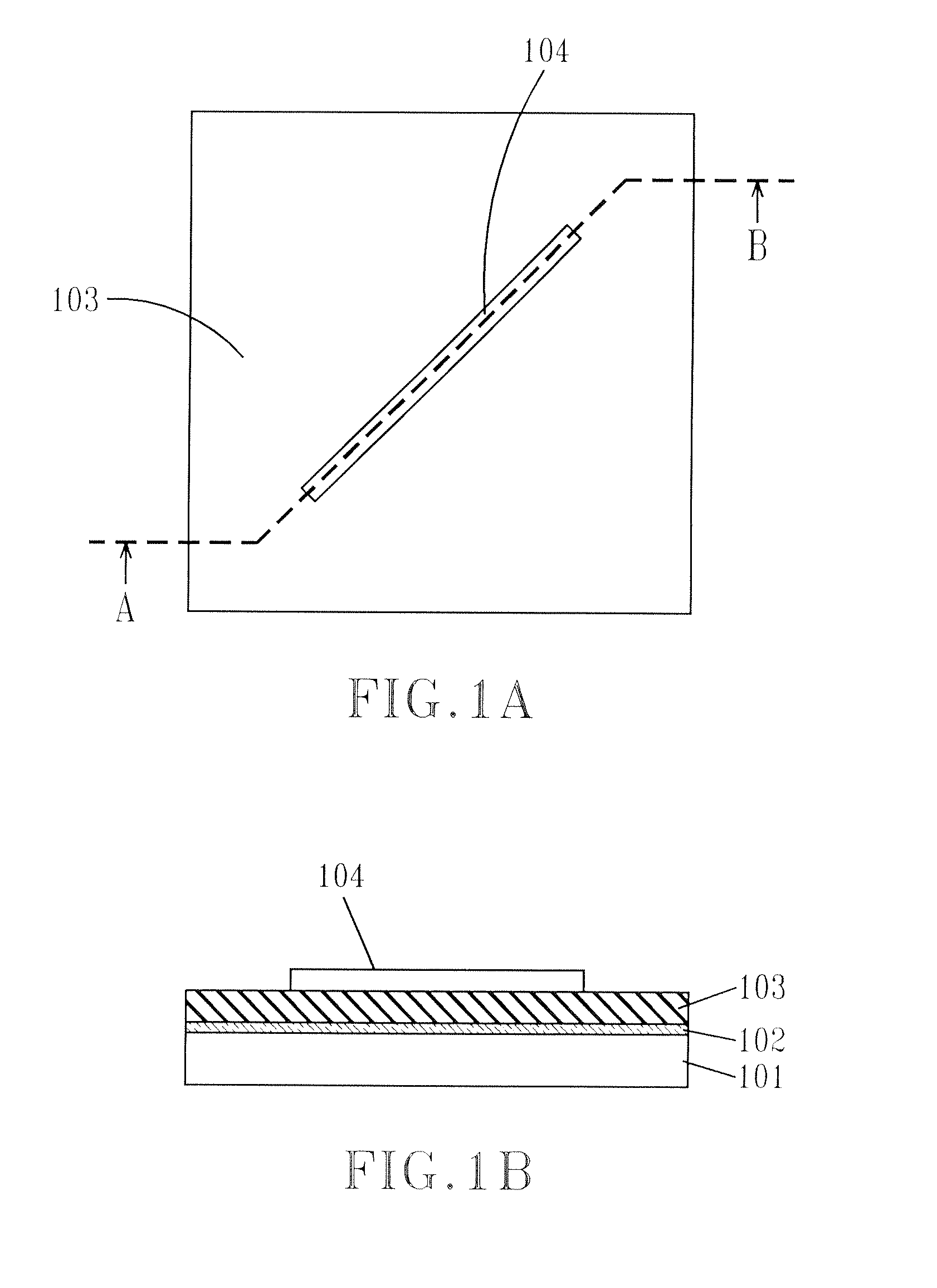

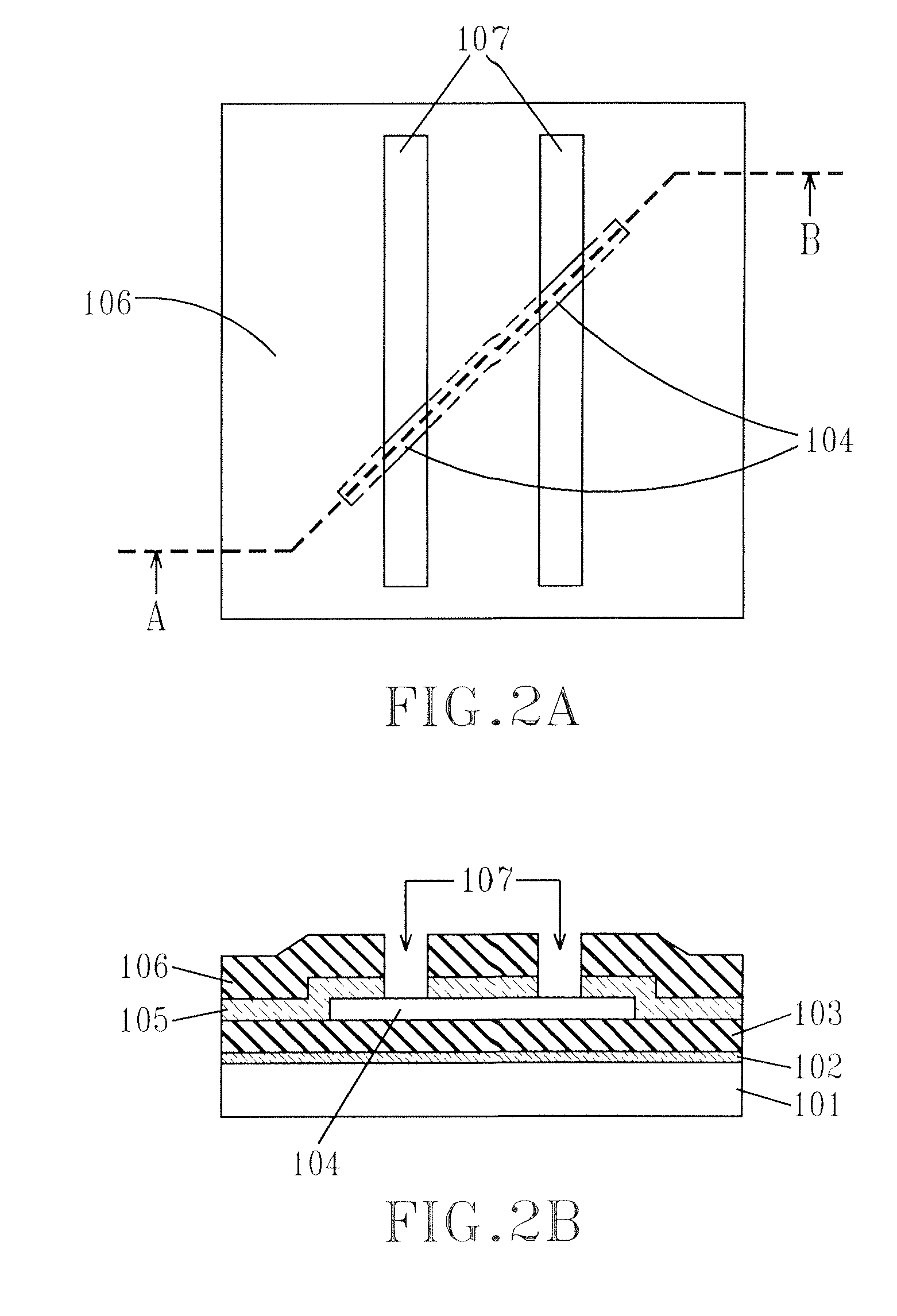

Bottom gate type thin film transistor, method of manufacturing the same, and display apparatus

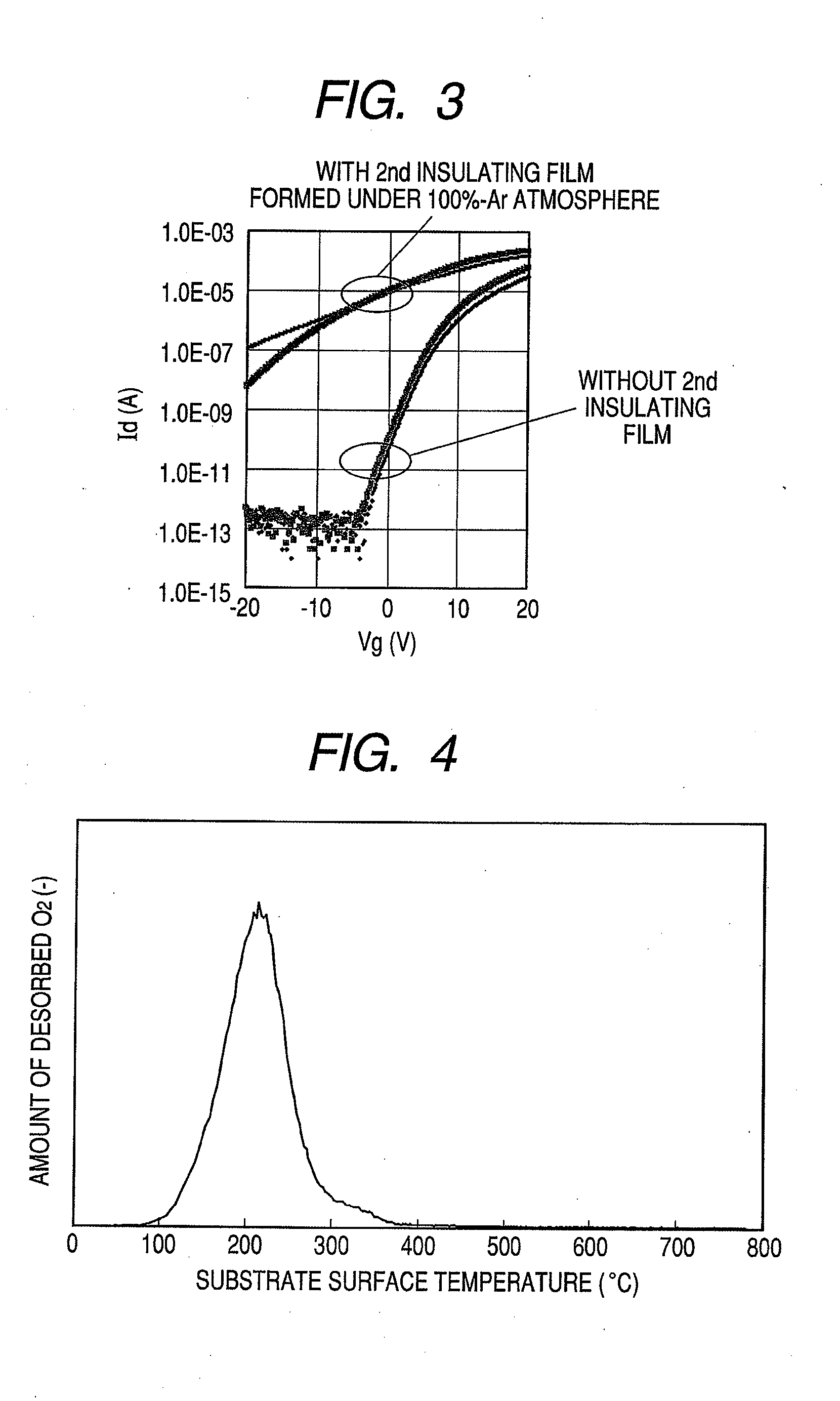

InactiveUS8148721B2Optimise total massImprove batch productivityTransistorElectroluminescent light sourcesDesorptionBottom gate

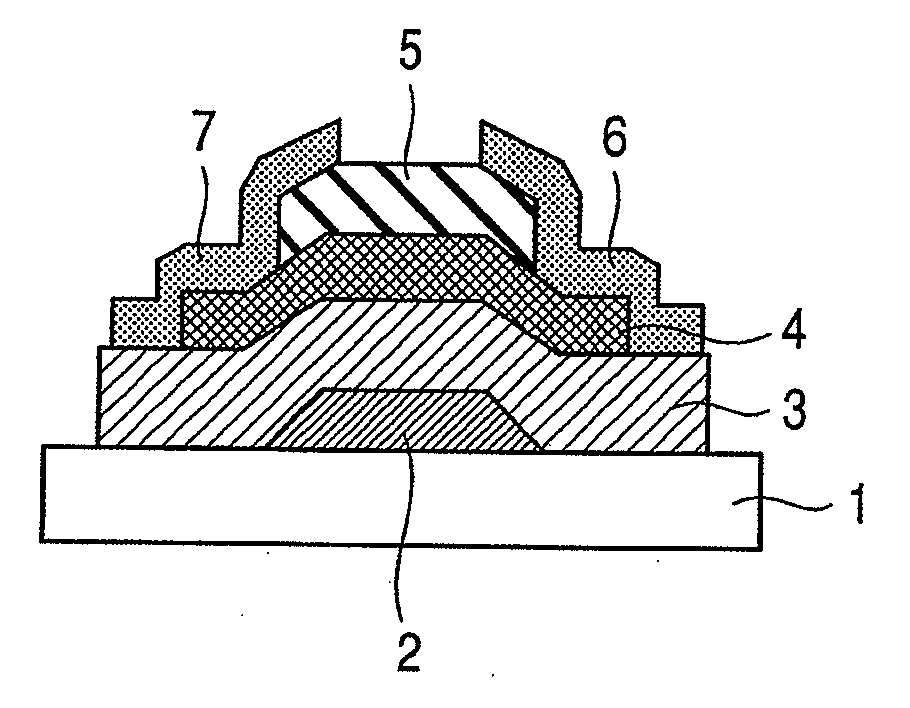

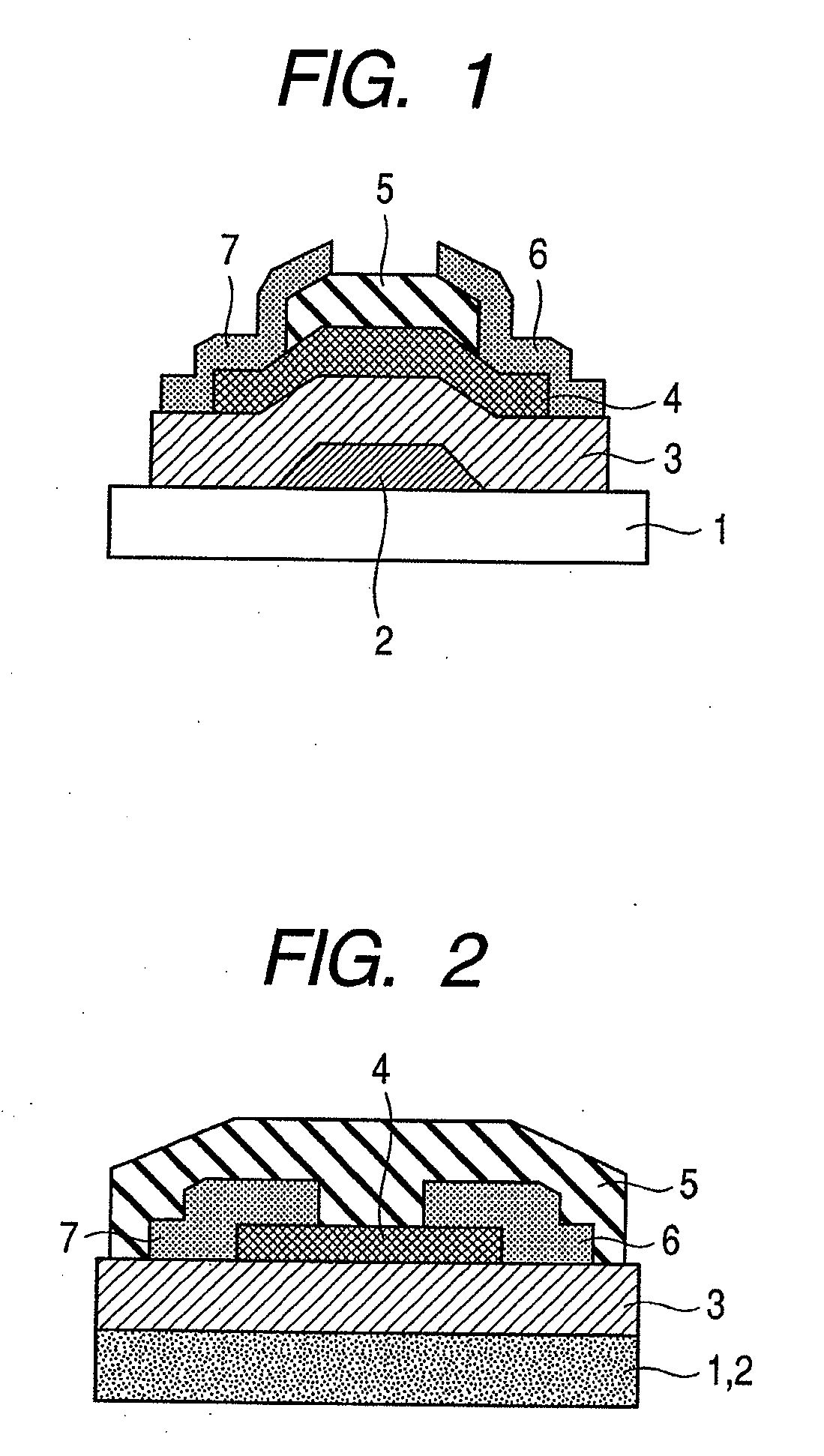

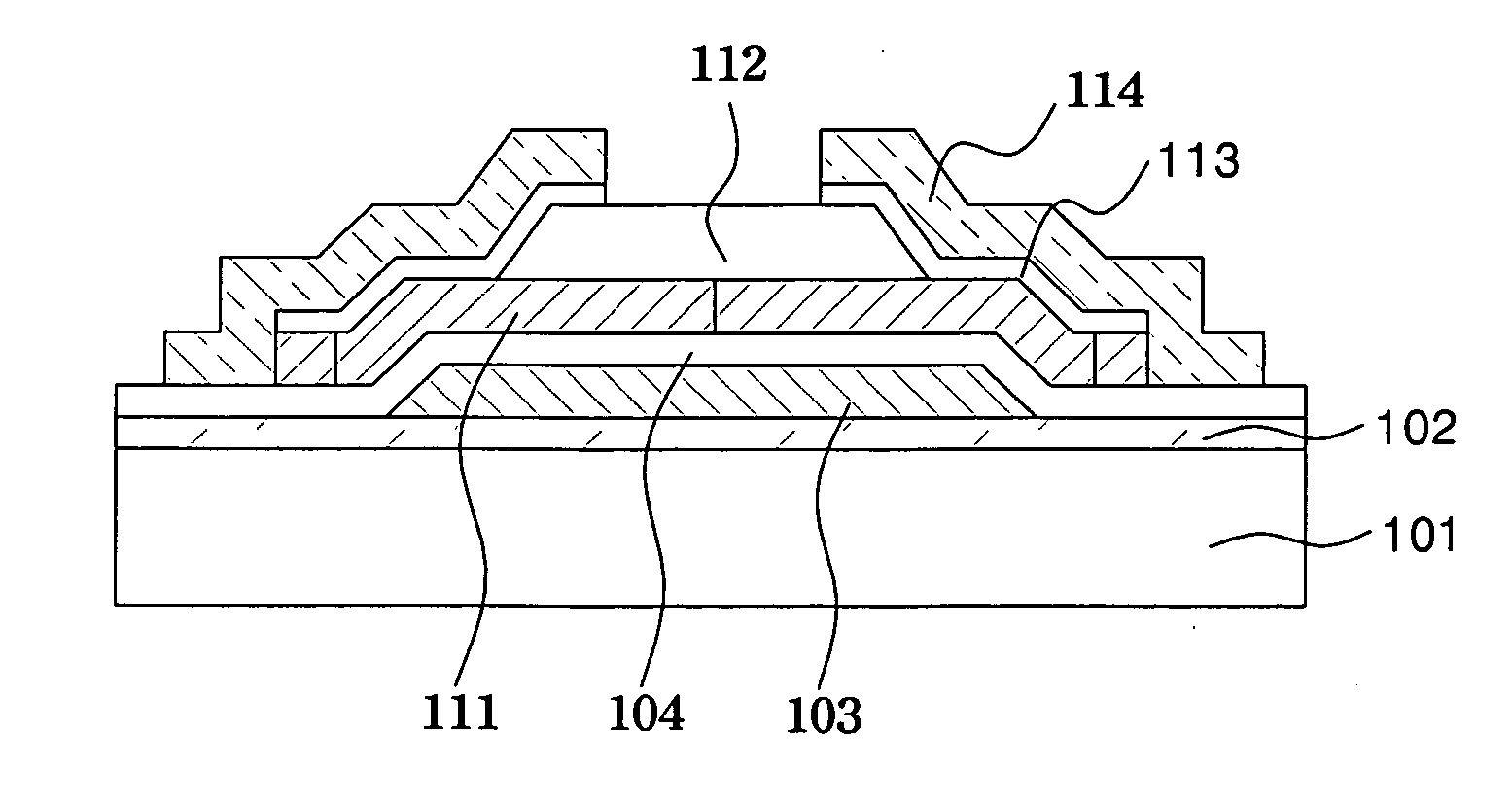

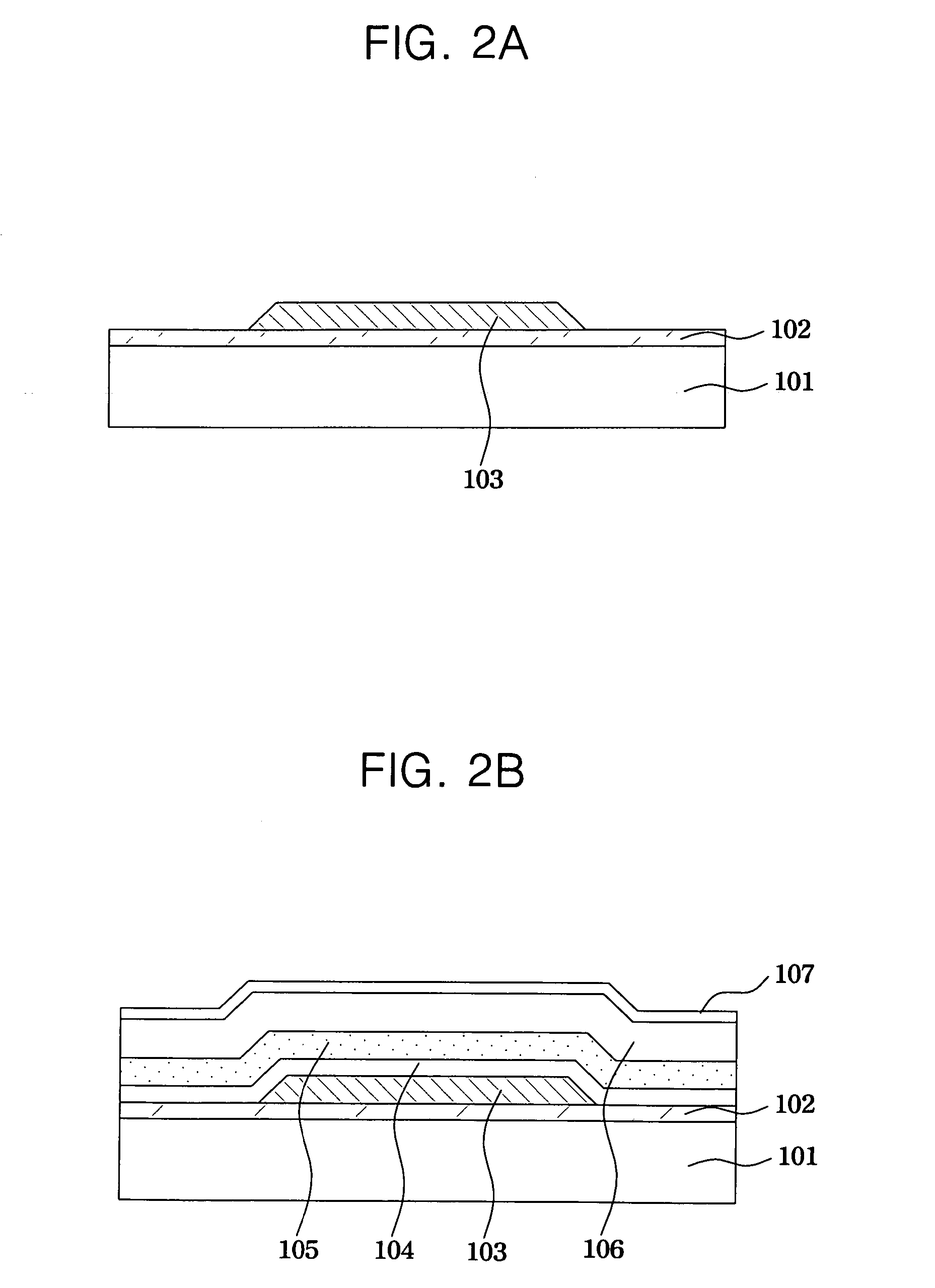

Provided is a bottom gate type thin film transistor including on a substrate (1) a gate electrode (2), a first insulating film (3) as a gate insulating film, an oxide semiconductor layer (4) as a channel layer, a second insulating film (5) as a protective layer, a source electrode (6), and a drain electrode (7), in which the oxide semiconductor layer (4) includes an oxide including at least one selected from the group consisting of In, Zn, and Sn, and the second insulating film (5) includes an amorphous oxide insulator formed so as to be in contact with the oxide semiconductor layer (4) and contains therein 3.8×1019 molecules / cm3 or more of a desorbed gas observed as oxygen by temperature programmed desorption mass spectrometry.

Owner:CANON KK

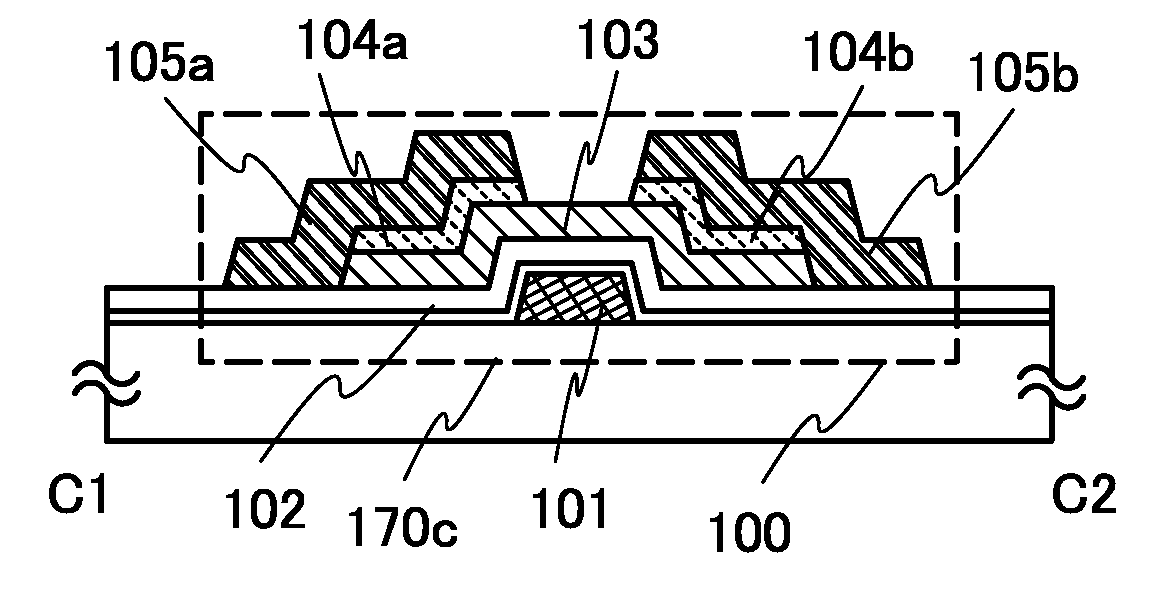

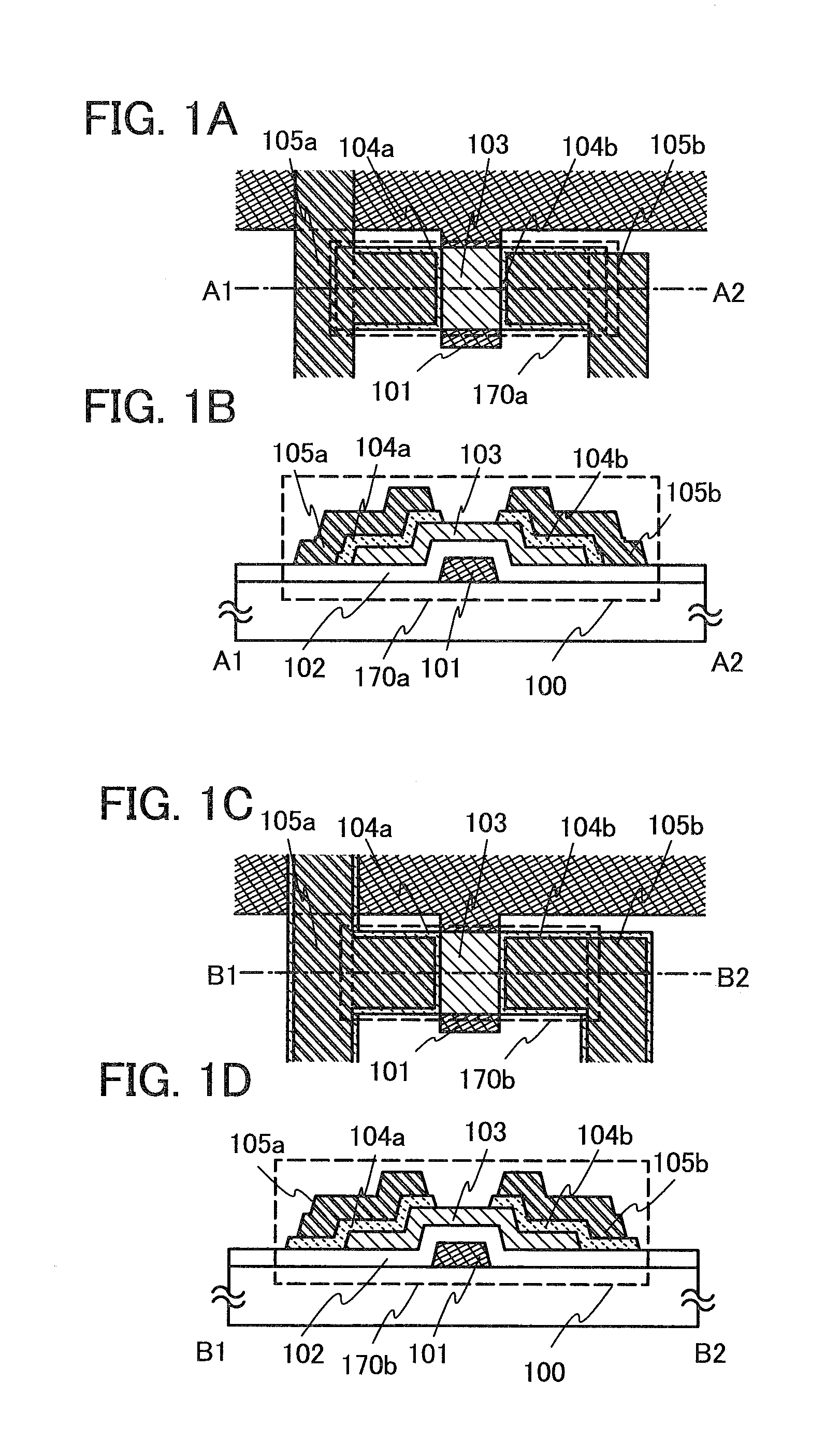

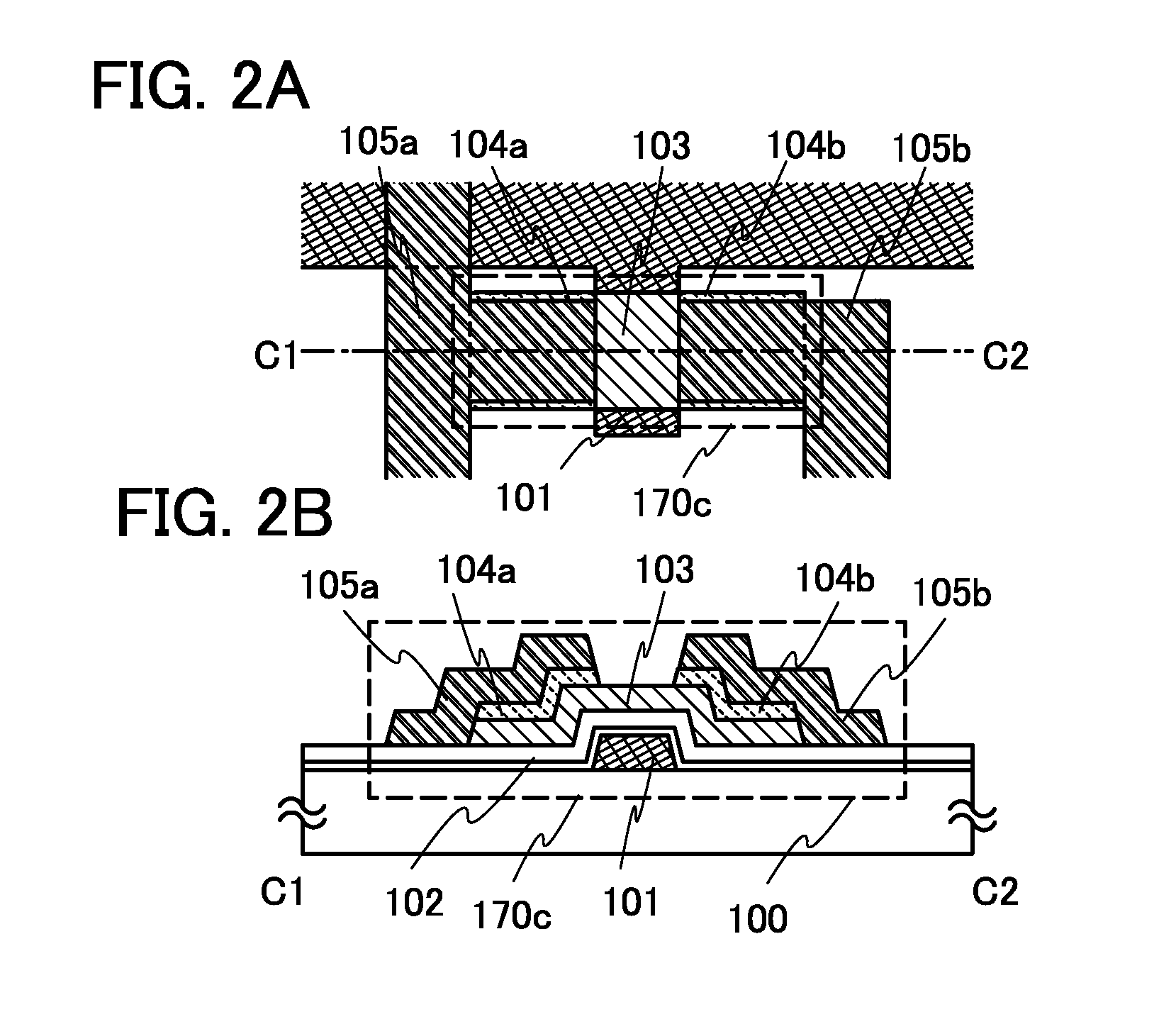

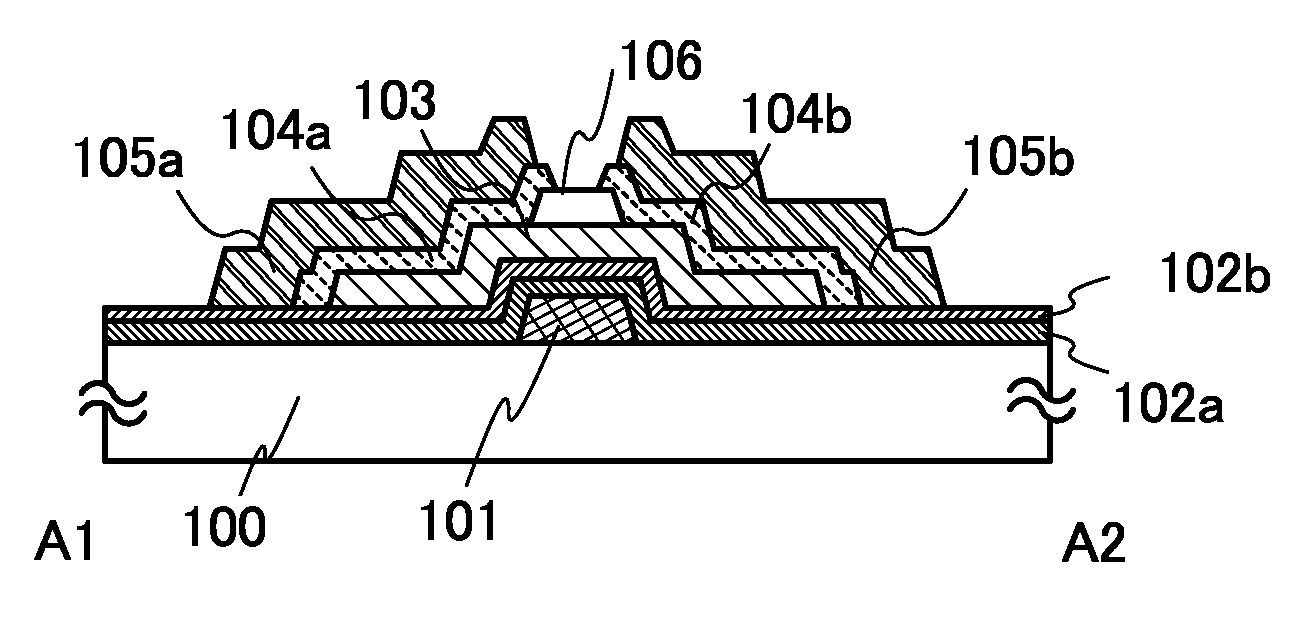

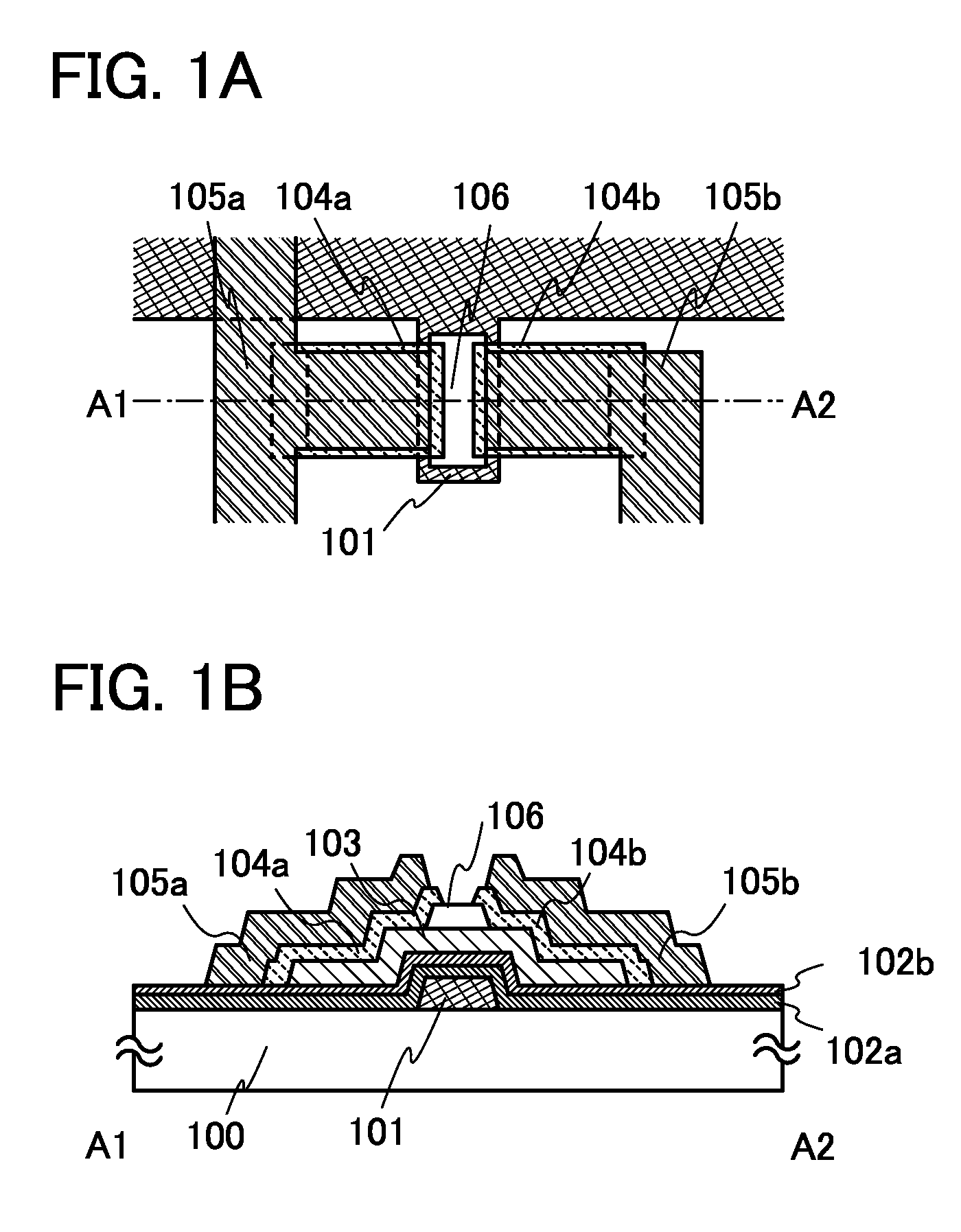

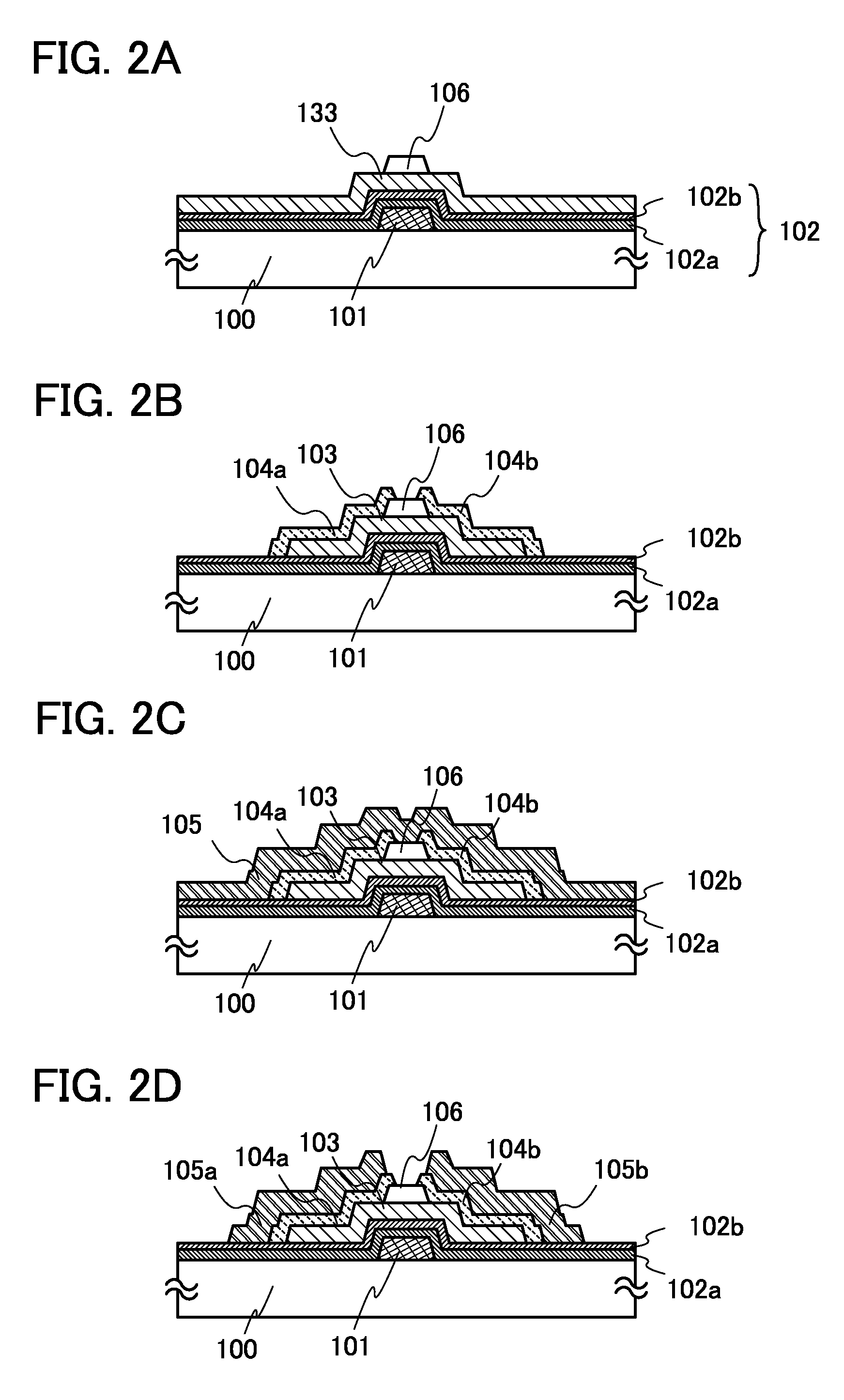

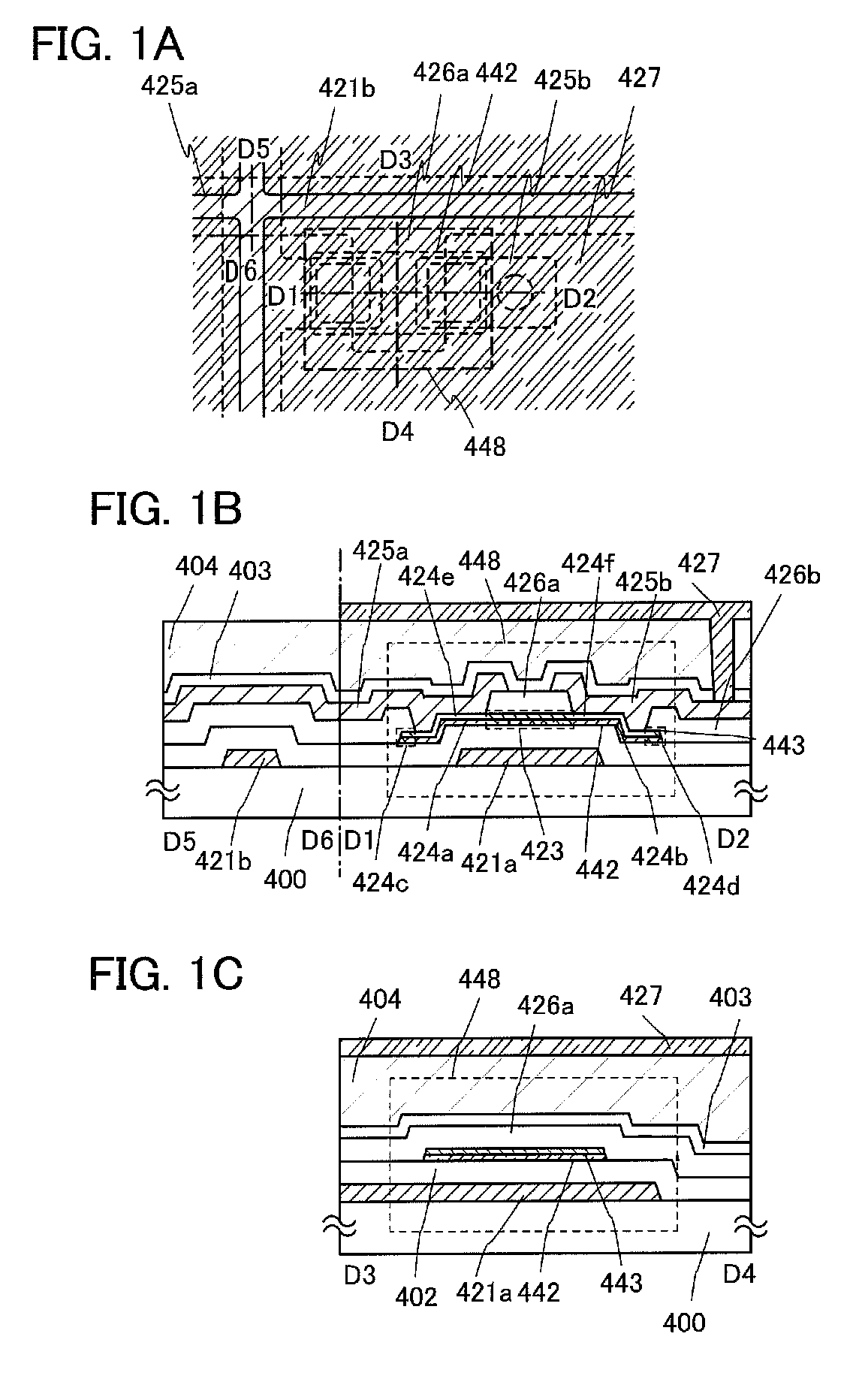

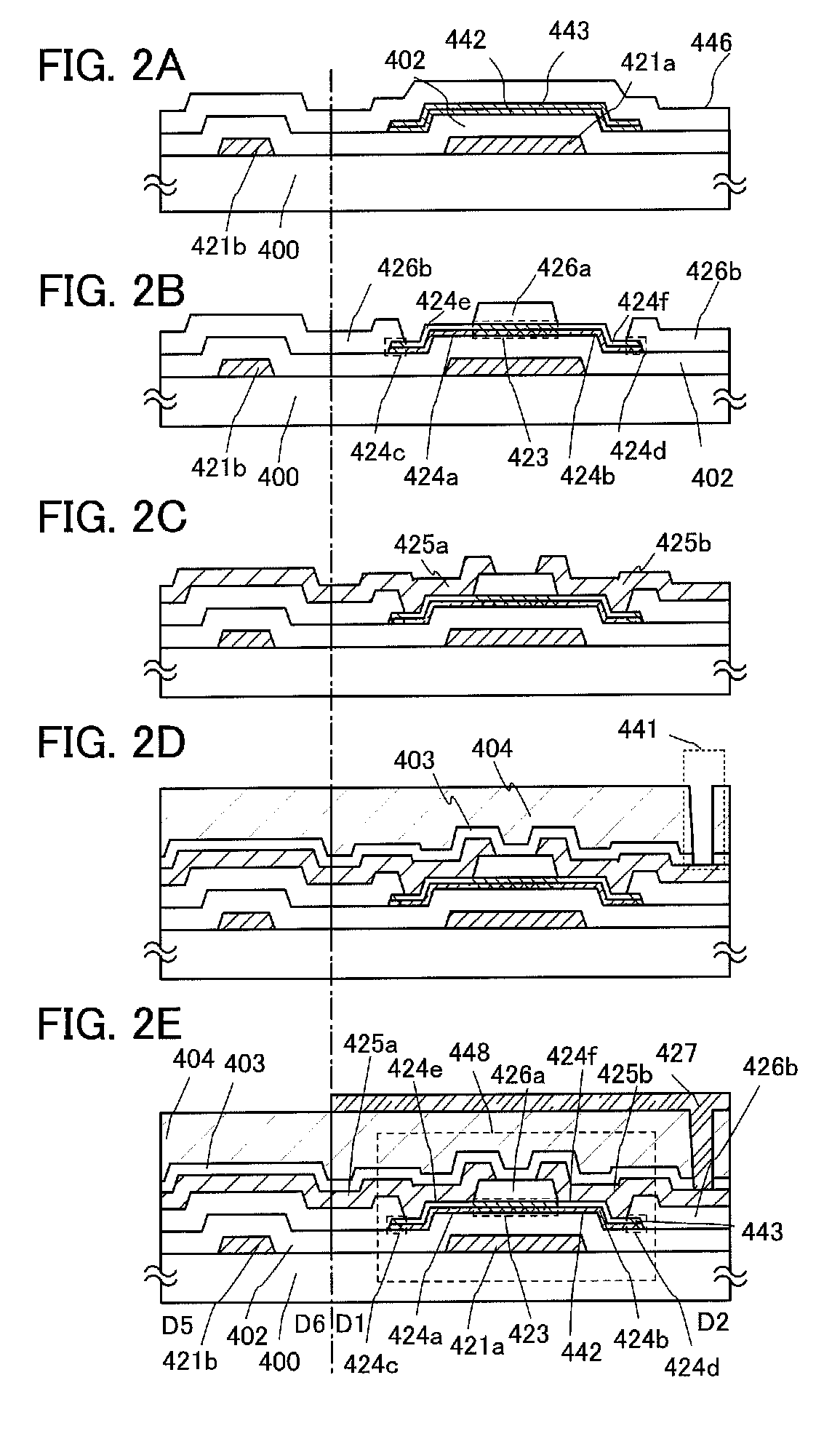

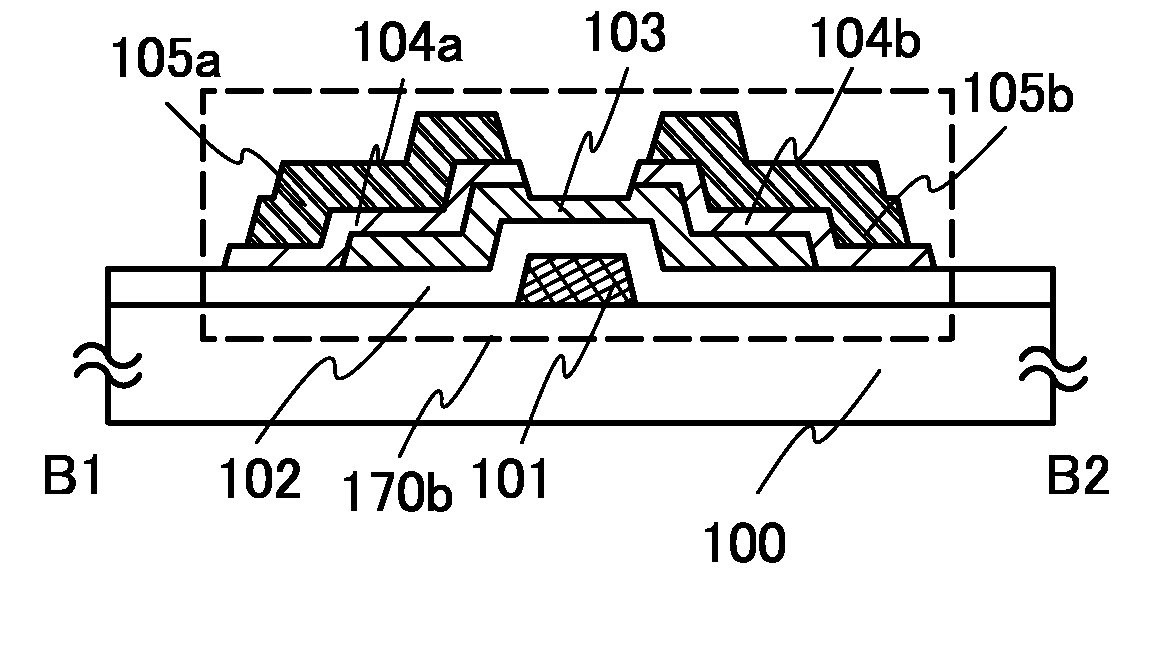

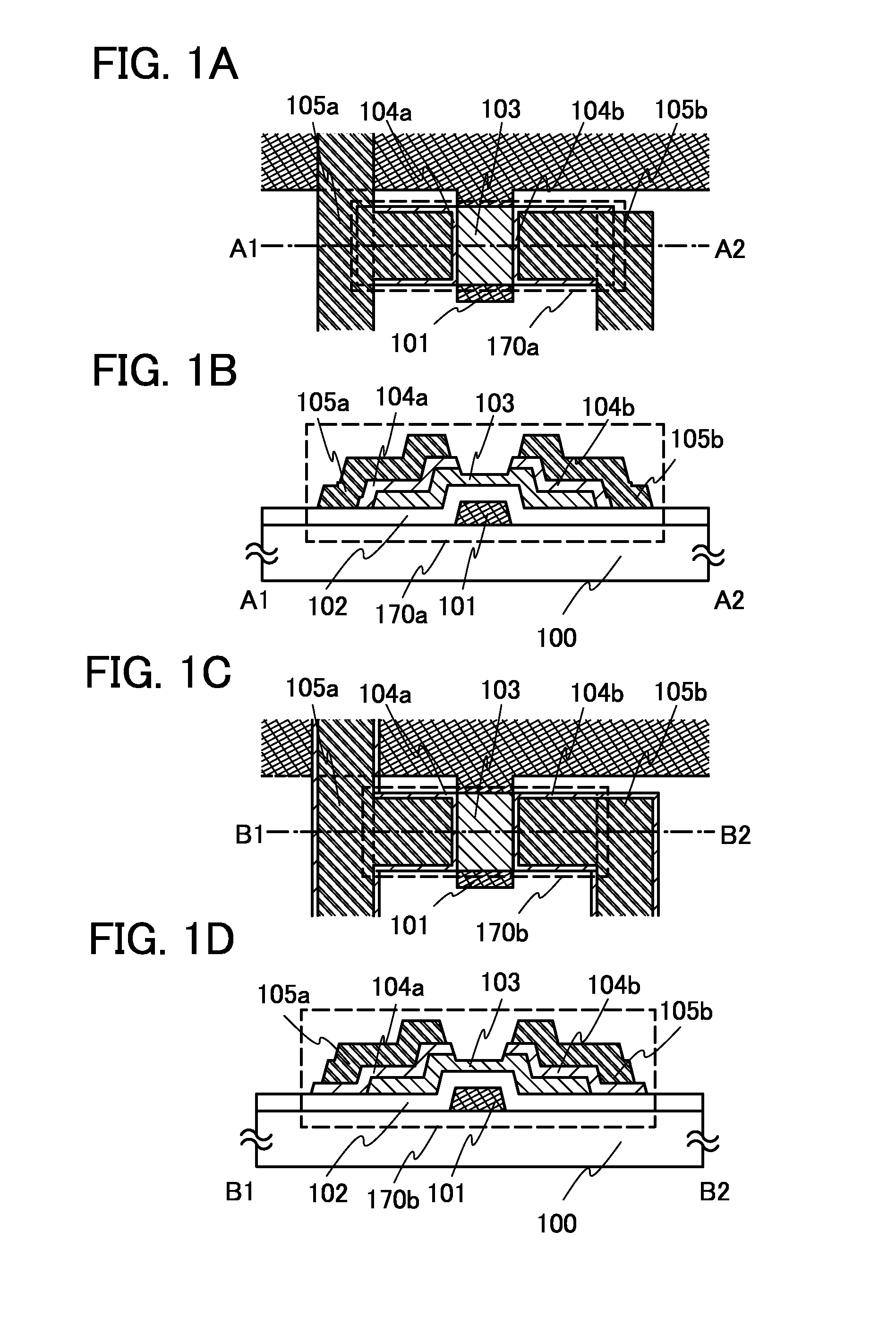

Semiconductor device and manufacturing method thereof

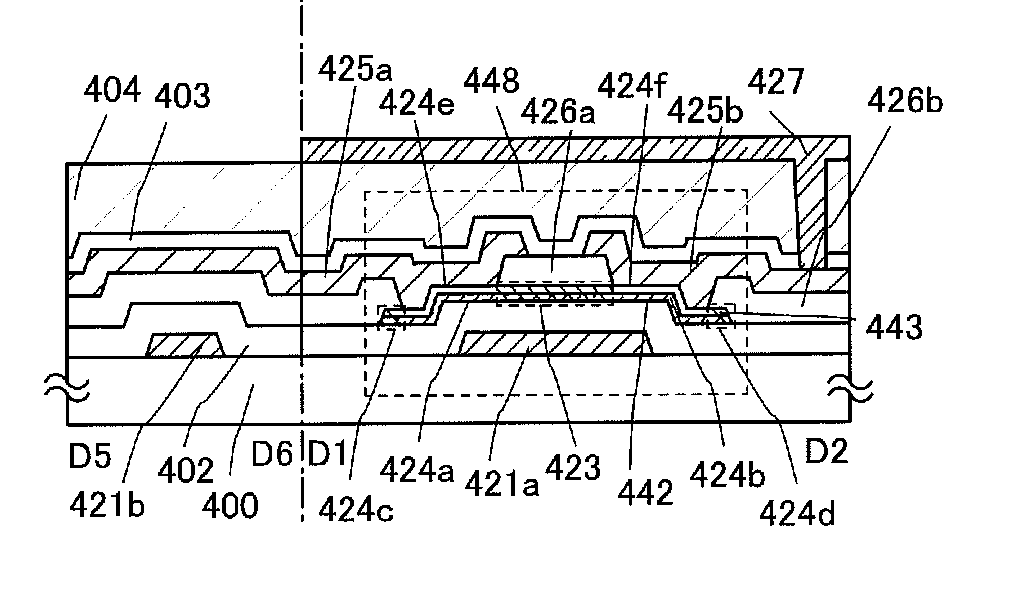

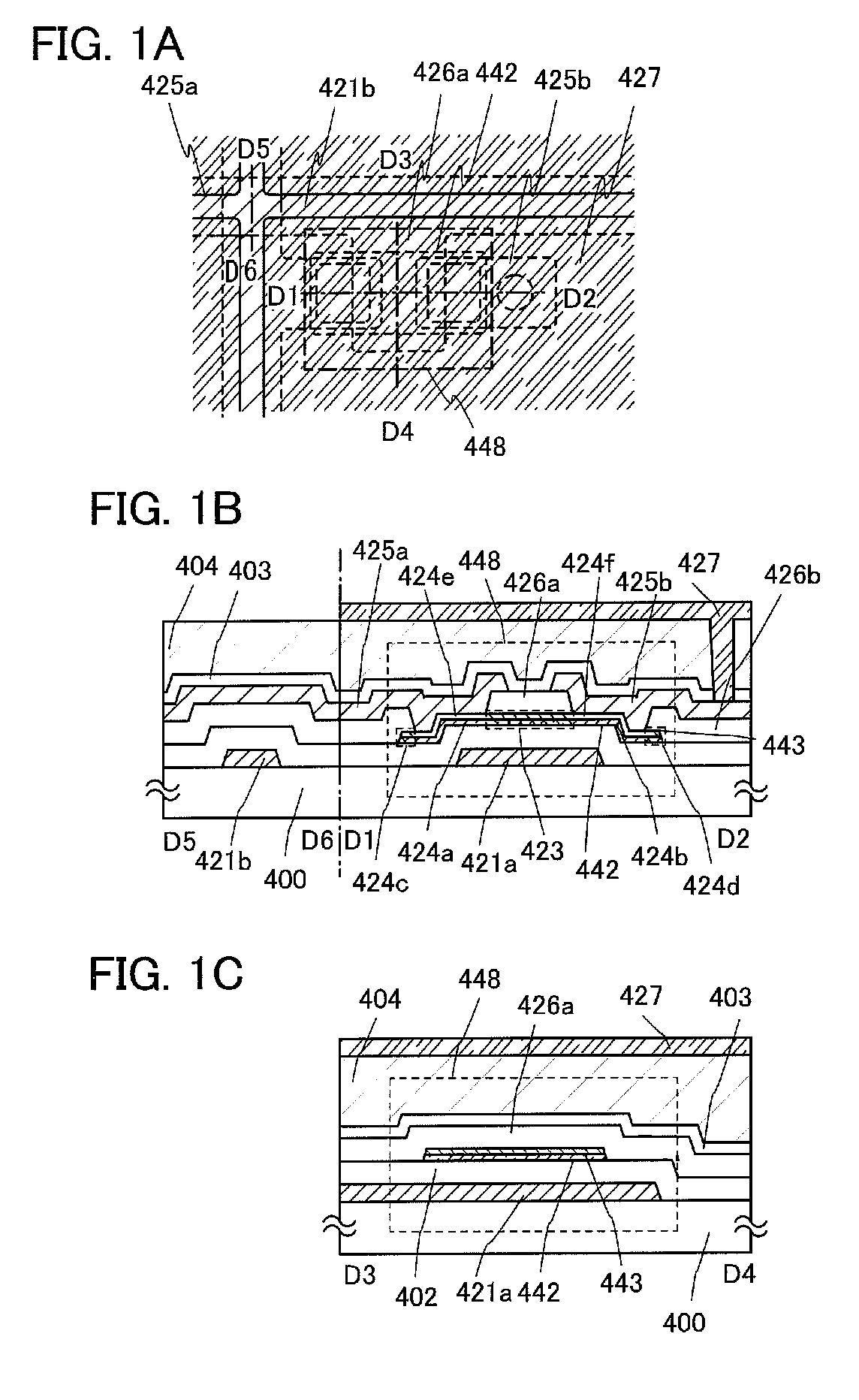

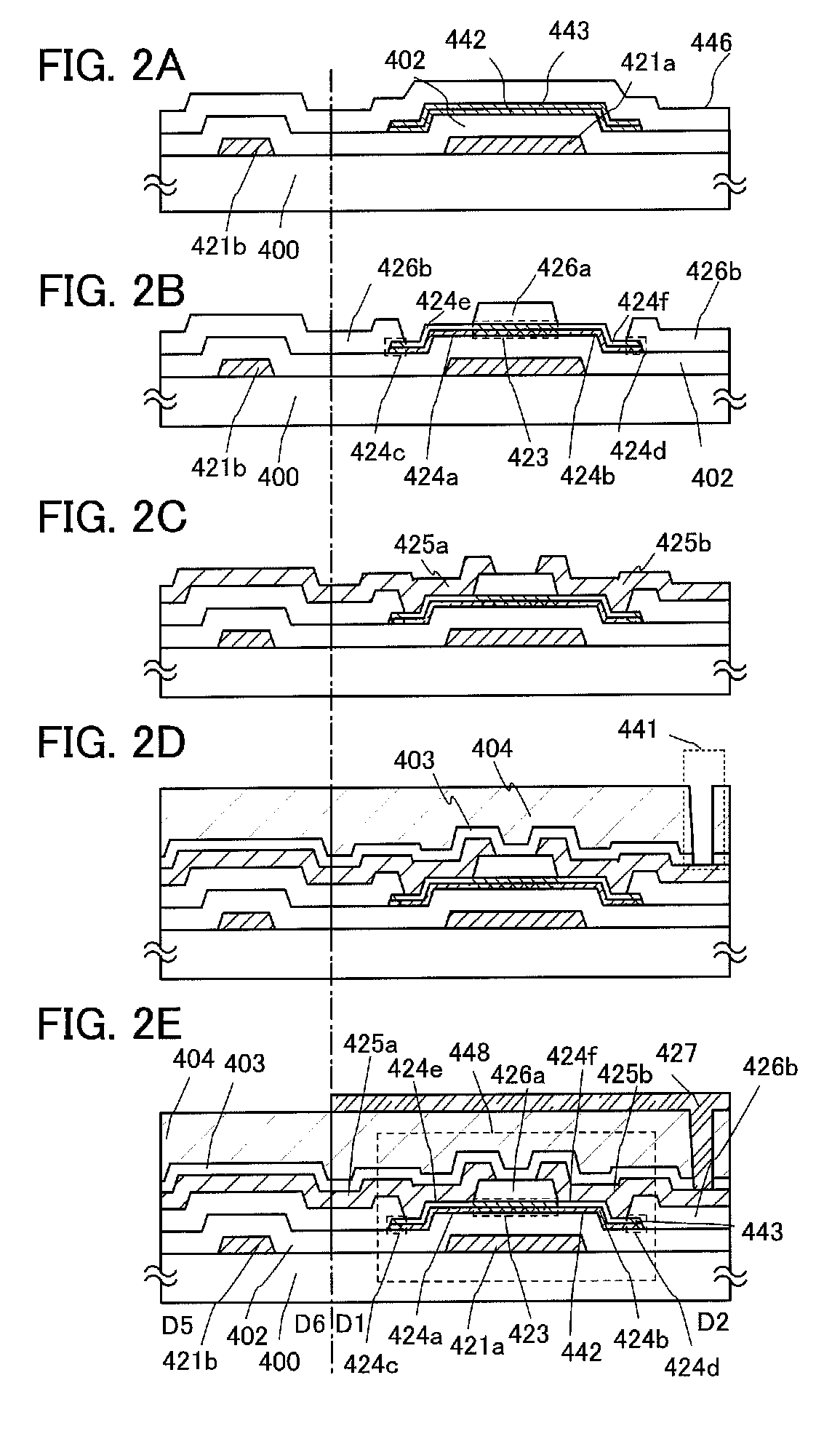

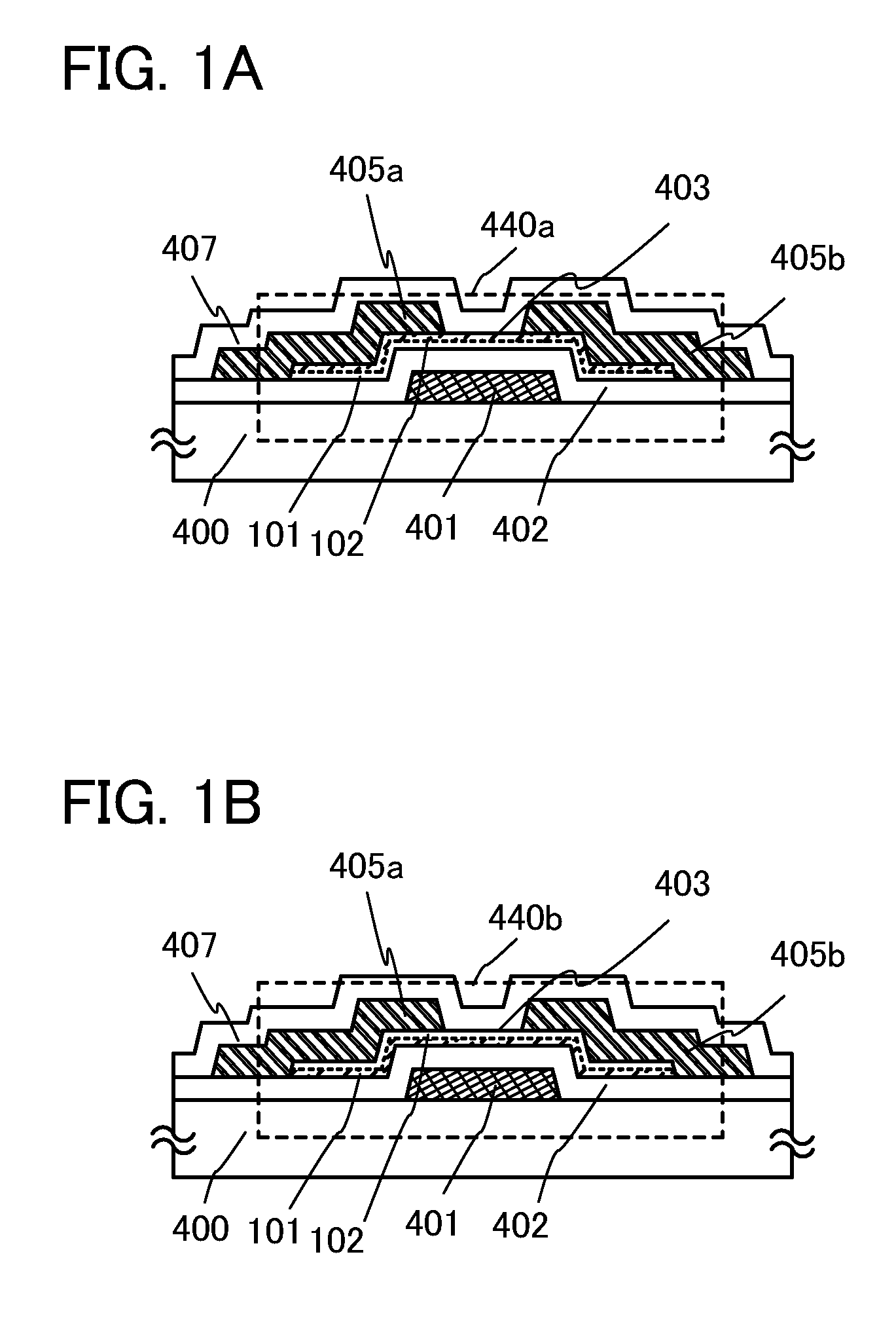

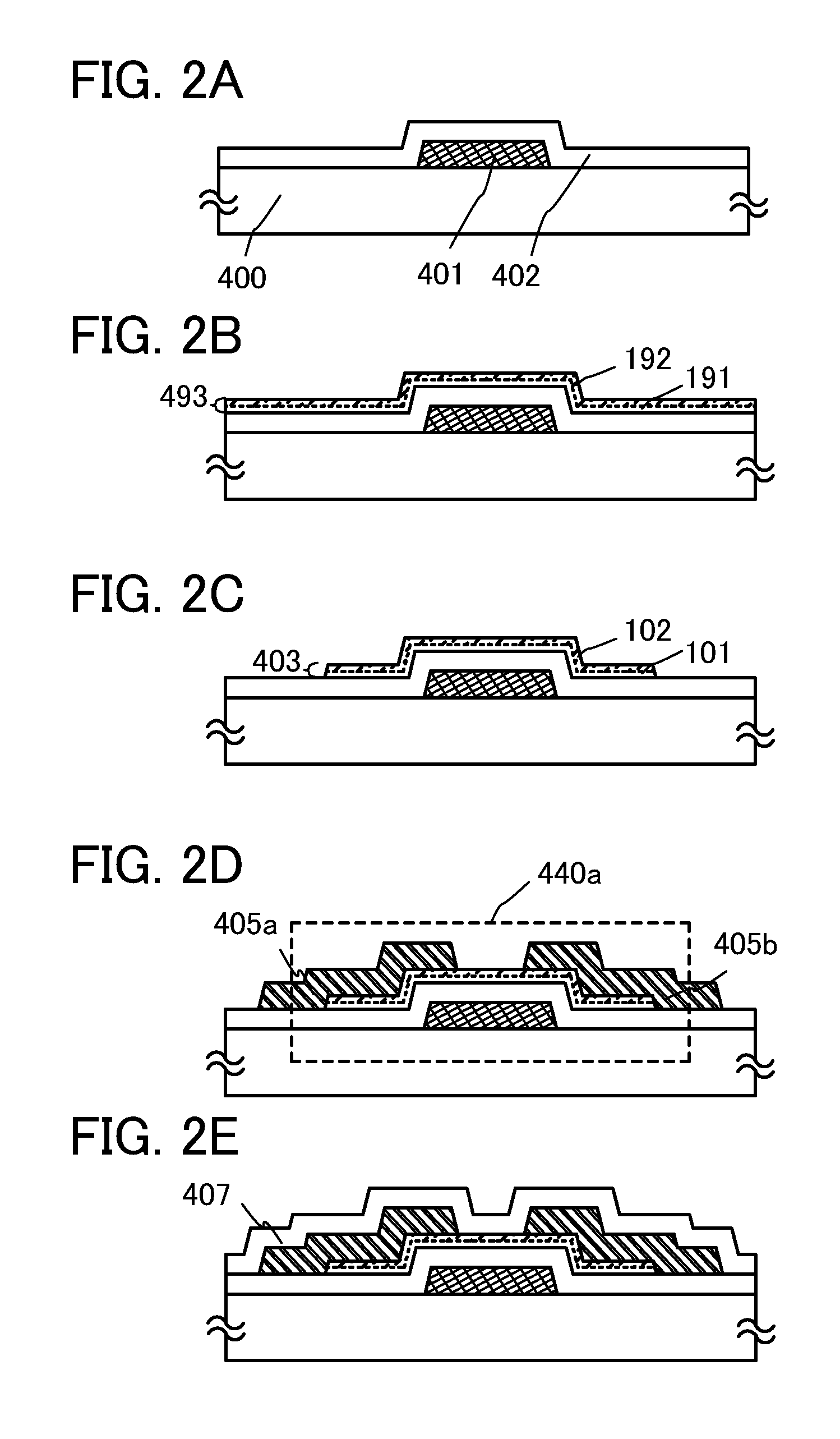

ActiveUS20100025677A1Small amount of photocurrentReduce parasitic capacitanceTransistorElectroluminescent light sourcesProduction rateCharge carrier

To provide a semiconductor device including a thin film transistor having excellent electric characteristics and high reliability and a manufacturing method of the semiconductor device with high mass productivity. The summary is that an inverted-staggered (bottom-gate) thin film transistor is included in which an oxide semiconductor film containing In, Ga, and Zn is used as a semiconductor layer, a channel protective layer is provided in a region that overlaps a channel formation region of the semiconductor layer, and a buffer layer is provided between the semiconductor layer and source and drain electrodes. An ohmic contact is formed by intentionally providing the buffer layer having a higher carrier concentration than the semiconductor layer between the semiconductor layer and the source and drain electrodes.

Owner:SEMICON ENERGY LAB CO LTD

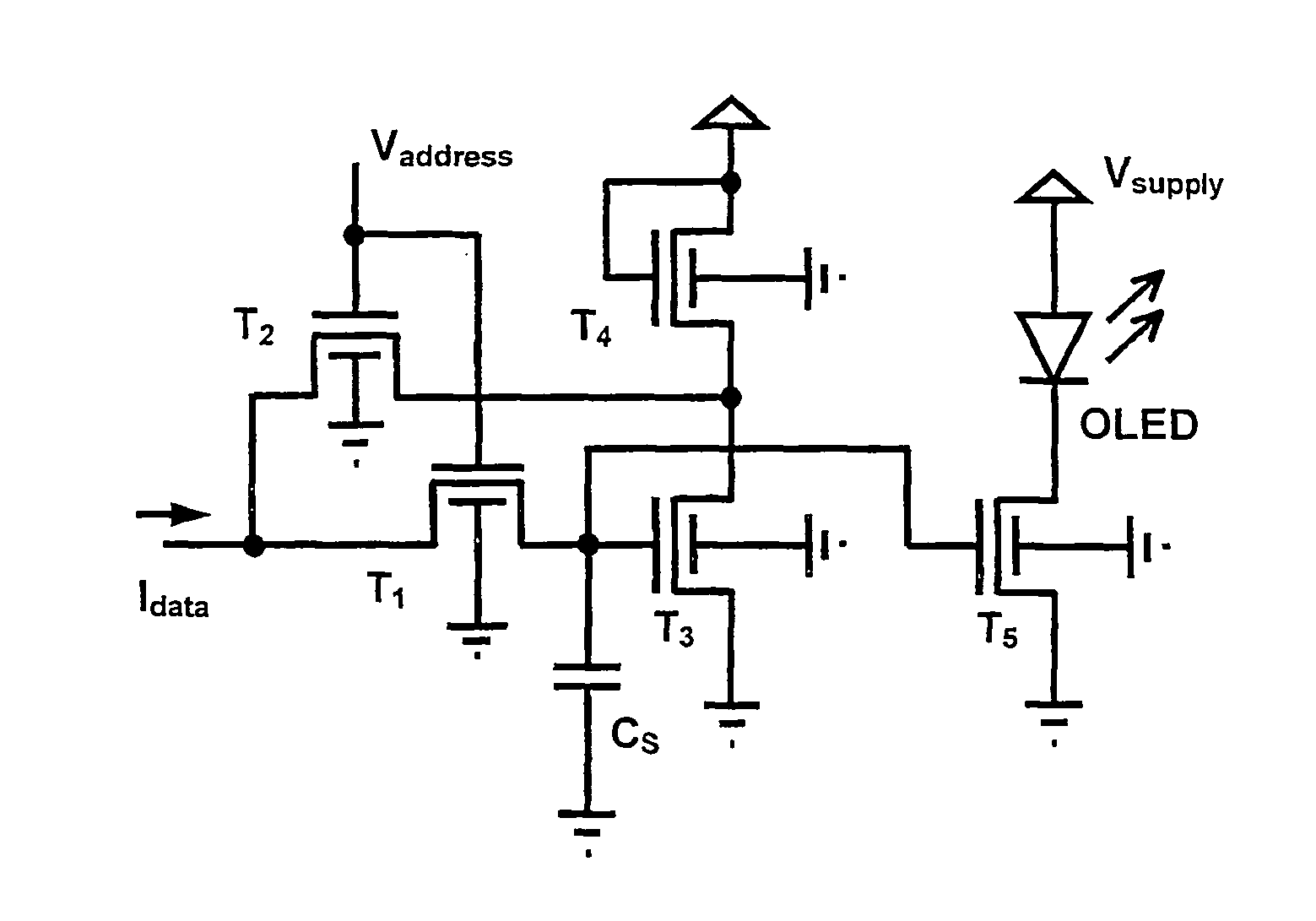

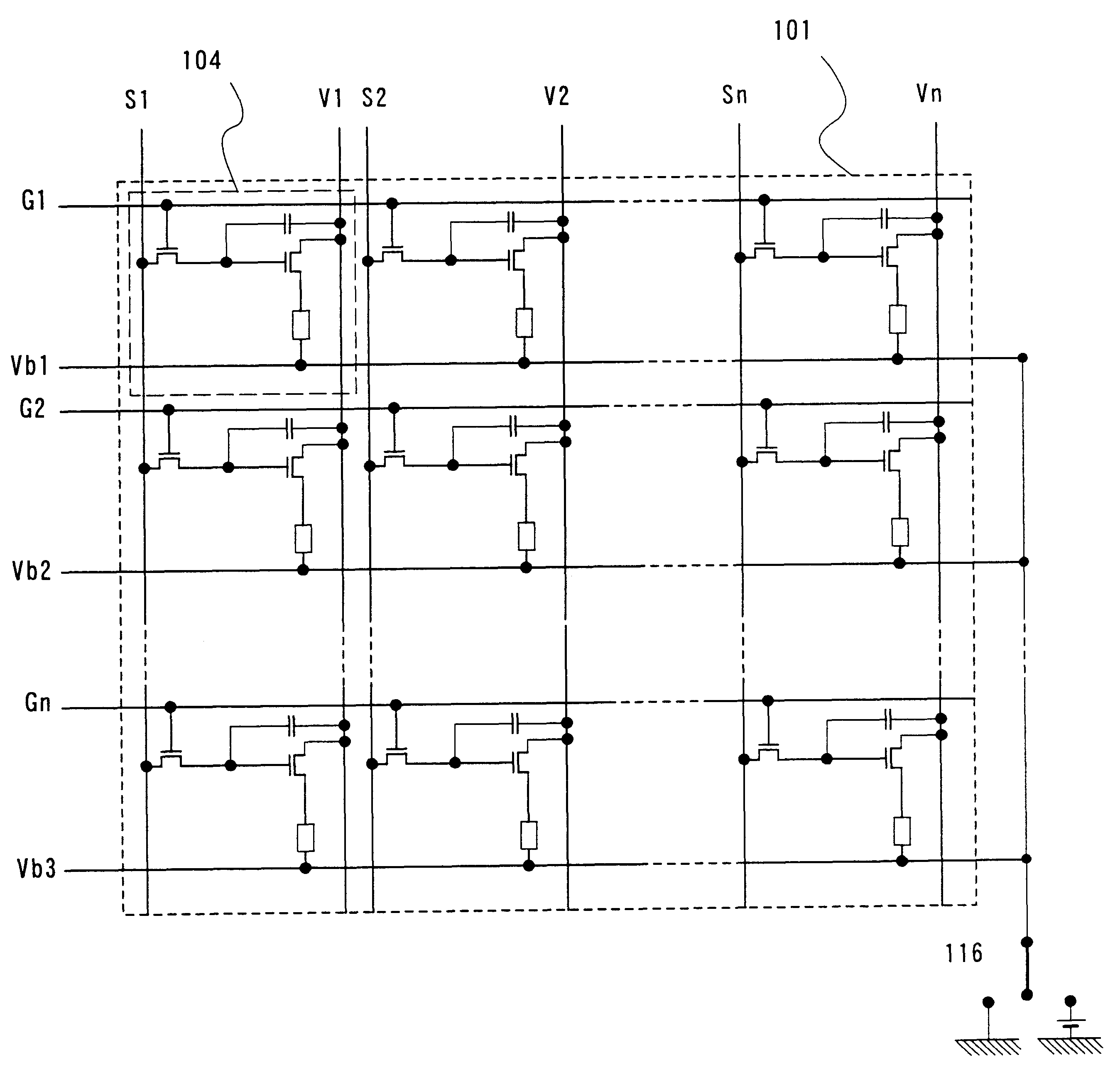

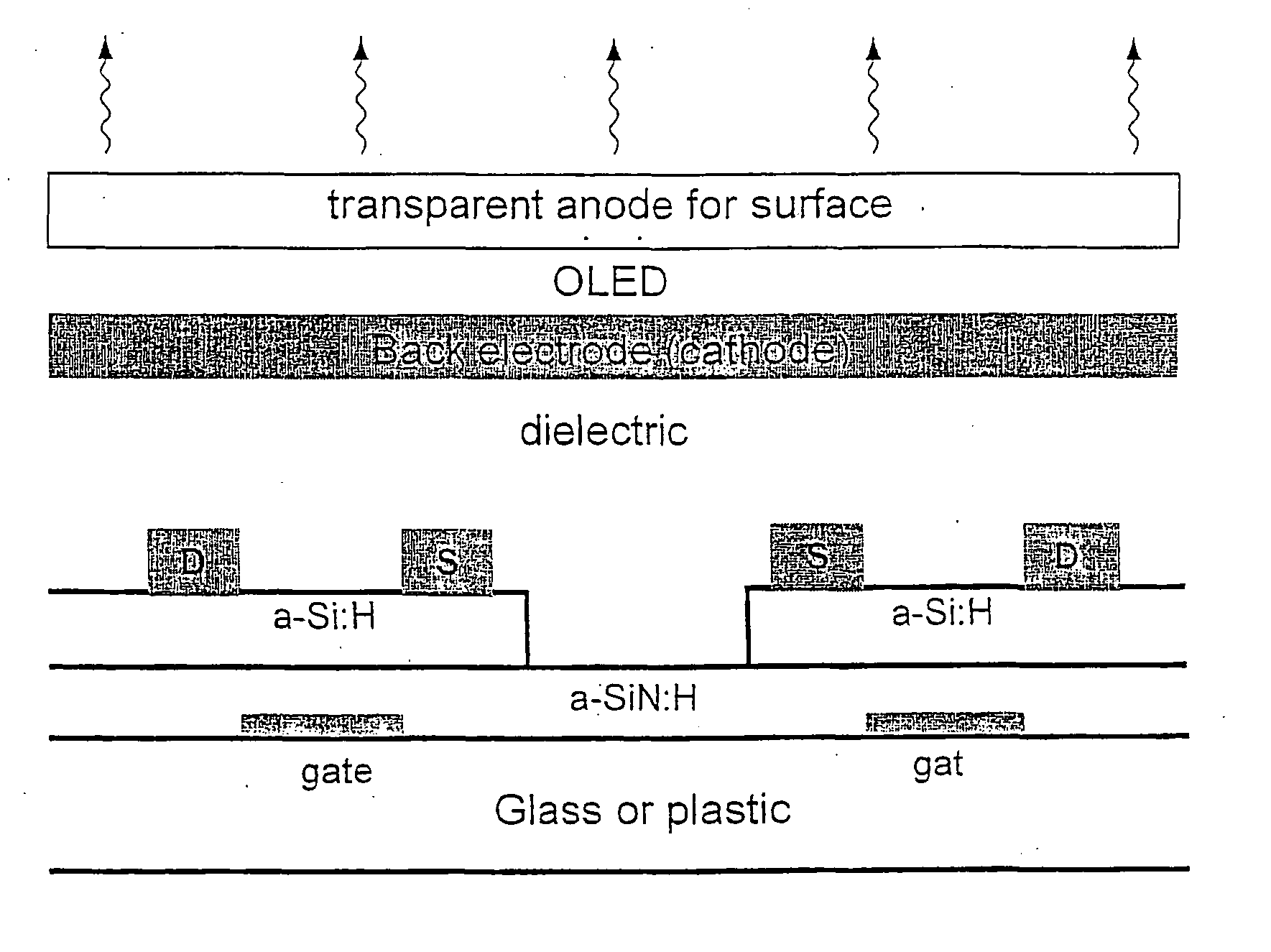

Pixel current driver for organic light emitting diode displays

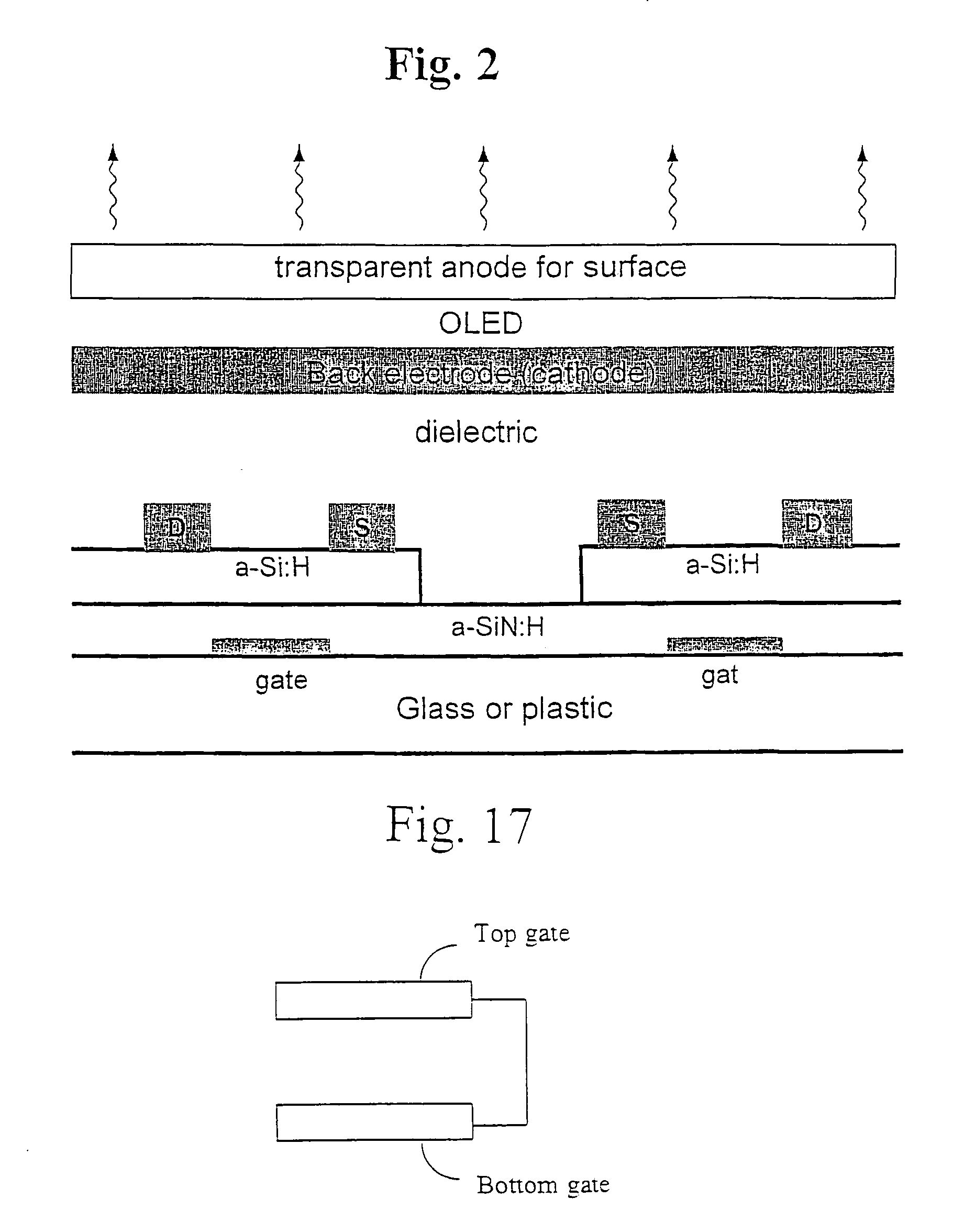

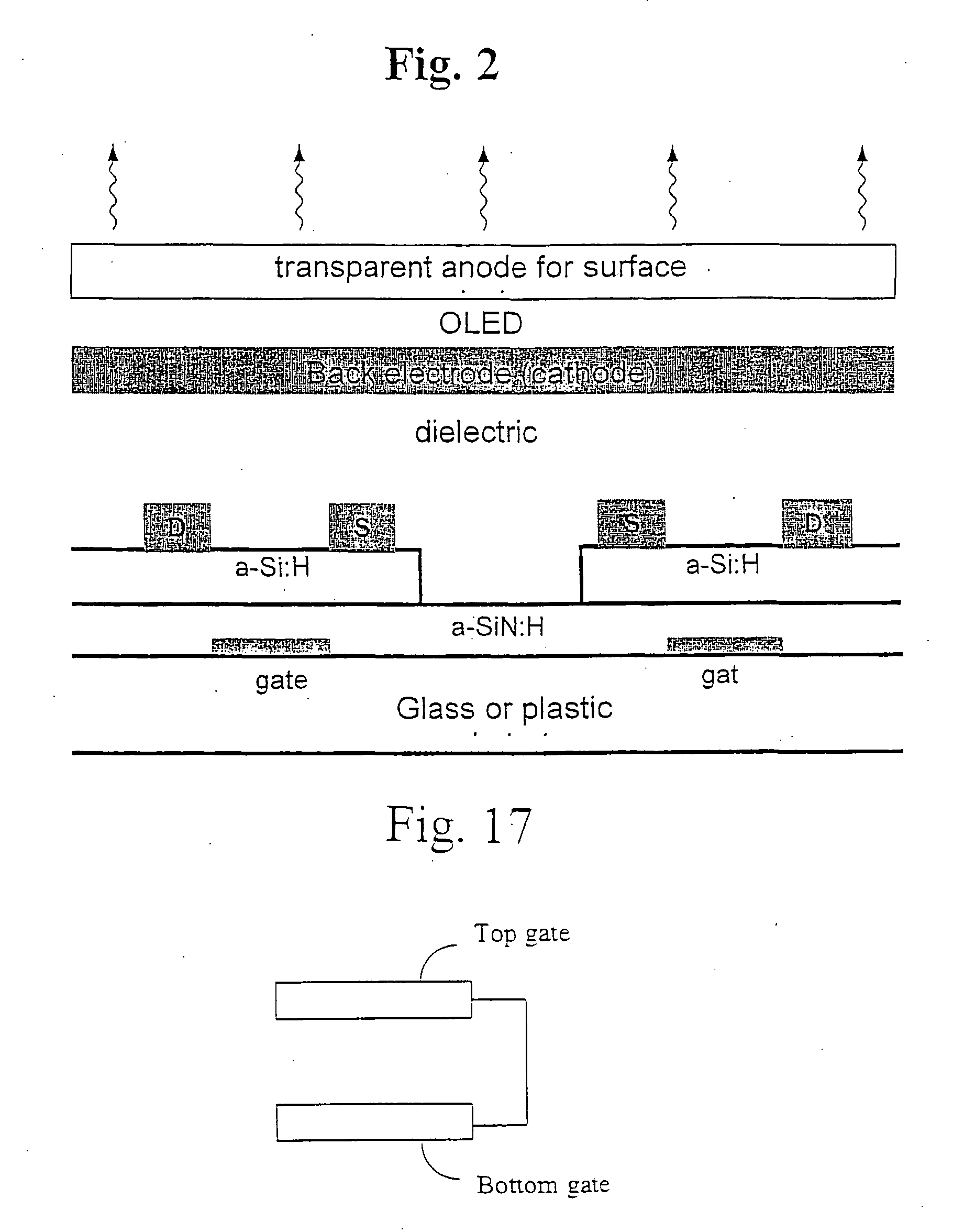

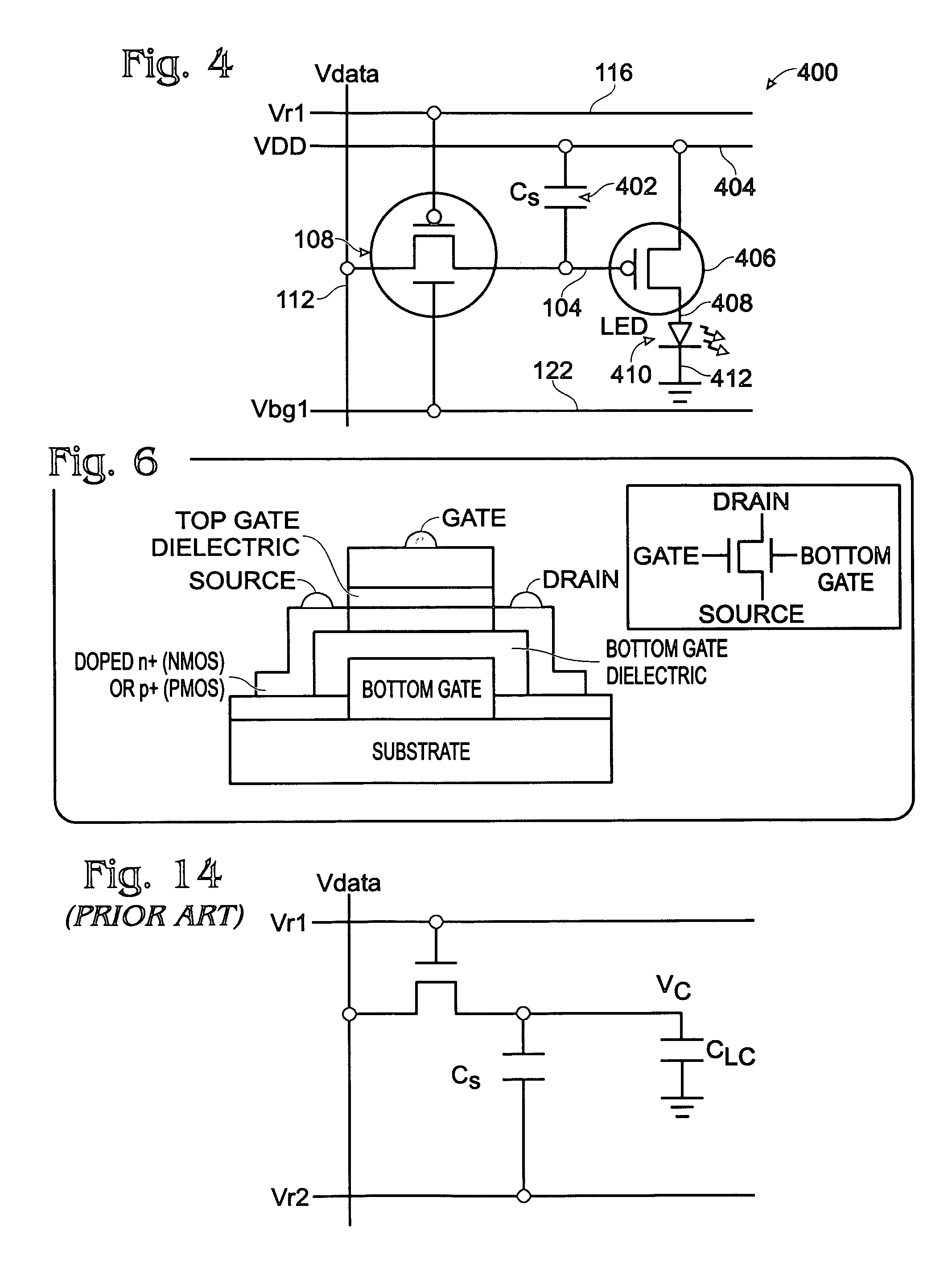

InactiveUS7414600B2Minimizing parasitic couplingMinimizes parasitic capacitanceTransistorStatic indicating devicesBottom gateDisplay device

A pixel current driver comprises a plurality of thin film transistors (TFTs) each having dual gates and for driving OLED layers. A top gate of the dual gates is formed between a source and a drain of each of the thin film transistors, to thereby minimize parasitic capacitance. The top gate is grounded or electrically tied to a bottom gate. The plurality of thin film transistors may be two thin film transistors formed in voltage-programmed manner or five thin film transistors formed in a current-programmed ΔVT-compensated manner. Other versions of the current-programmed circuit with different numbers of thin film transistors are also presented that compensate for δVT. The OLED layer are continuous and vertically stacked on the plurality of thin film transistors to provide an aperture ratio close to 100%.

Owner:IGNIS INNOVATION

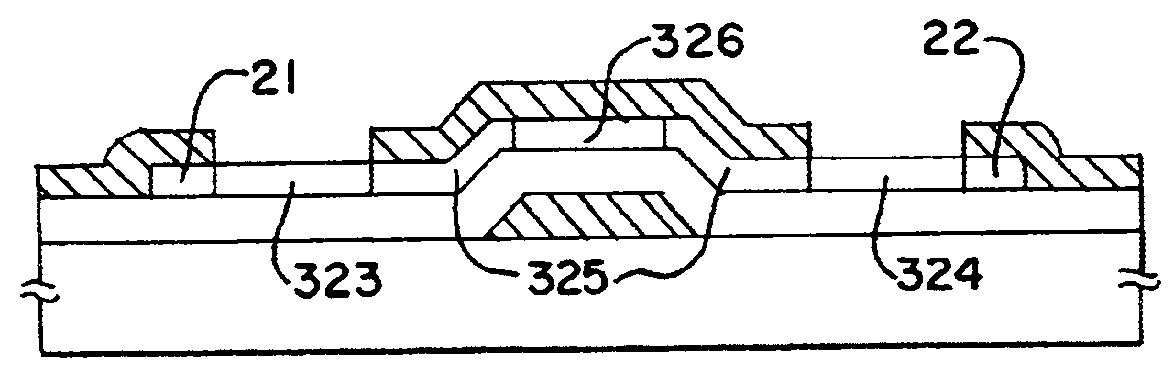

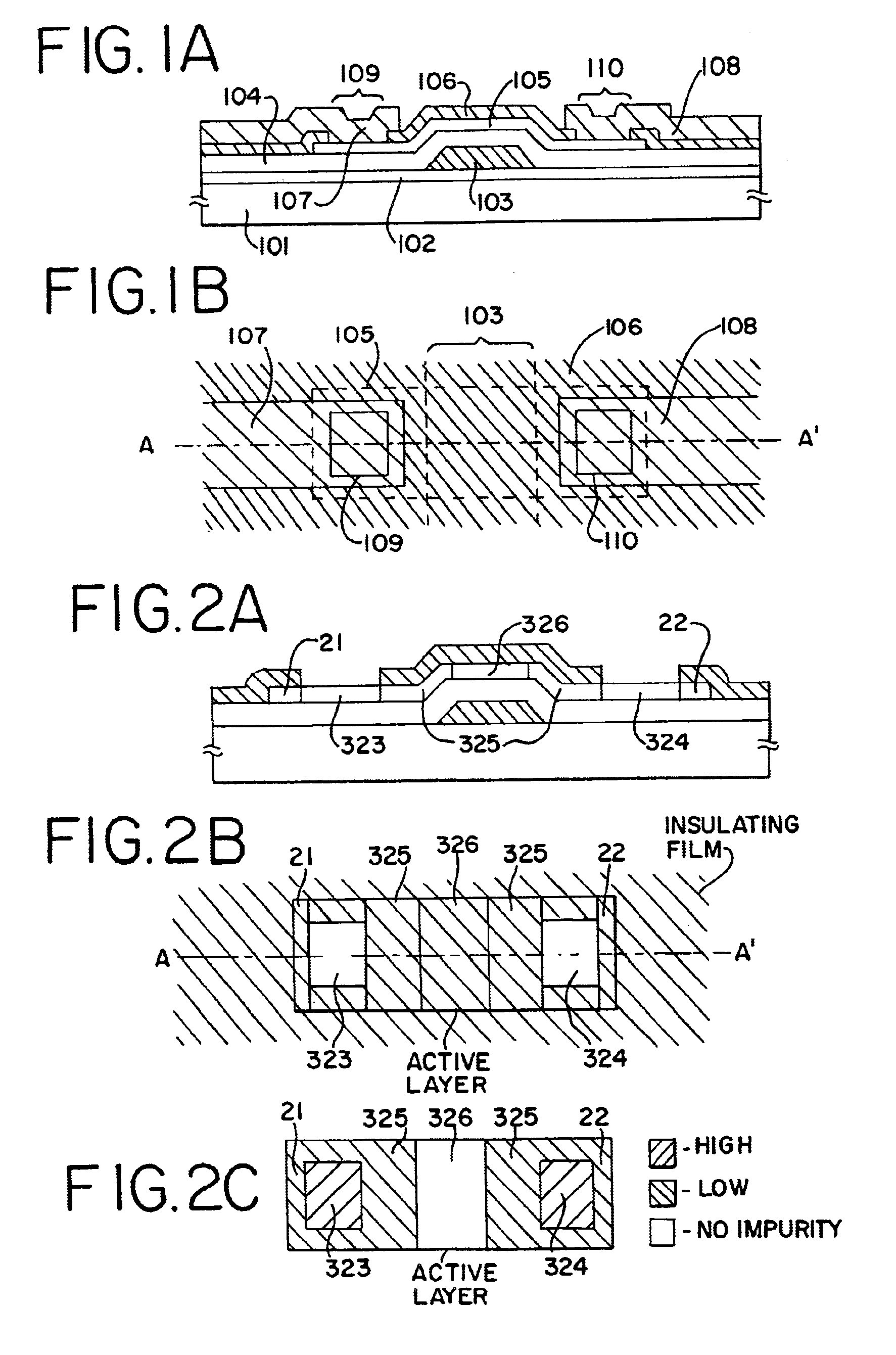

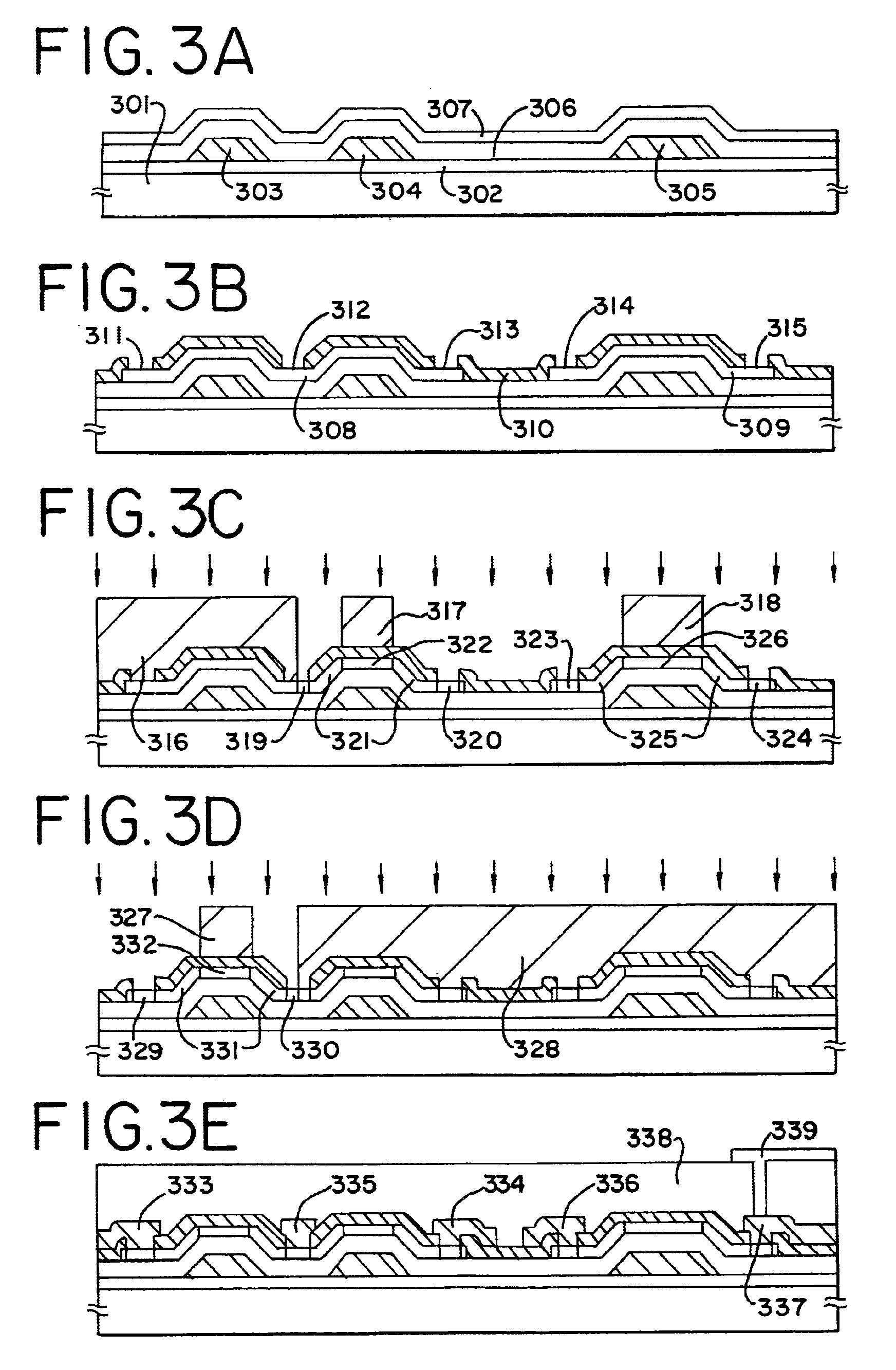

Semiconductor device and fabrication method thereof

To provide a semiconductor device having high mass production performance and high reliability and reproducibility by simple fabrication steps, in a constitution of a semiconductor device of a bottom gate type formed by a semiconductor layer having a crystal structure, source and drain regions are constituted by a laminated layer structure comprising a first conductive layer (n+ layer), a second conductive layer (n- layer) having resistance higher than the first conductive layer and an intrinsic or a substantially intrinsic semiconductor layer (i layer) in which the n- layer functions as an LDD region and the i layer functions as an offset region in a film thickness direction.

Owner:SEMICON ENERGY LAB CO LTD

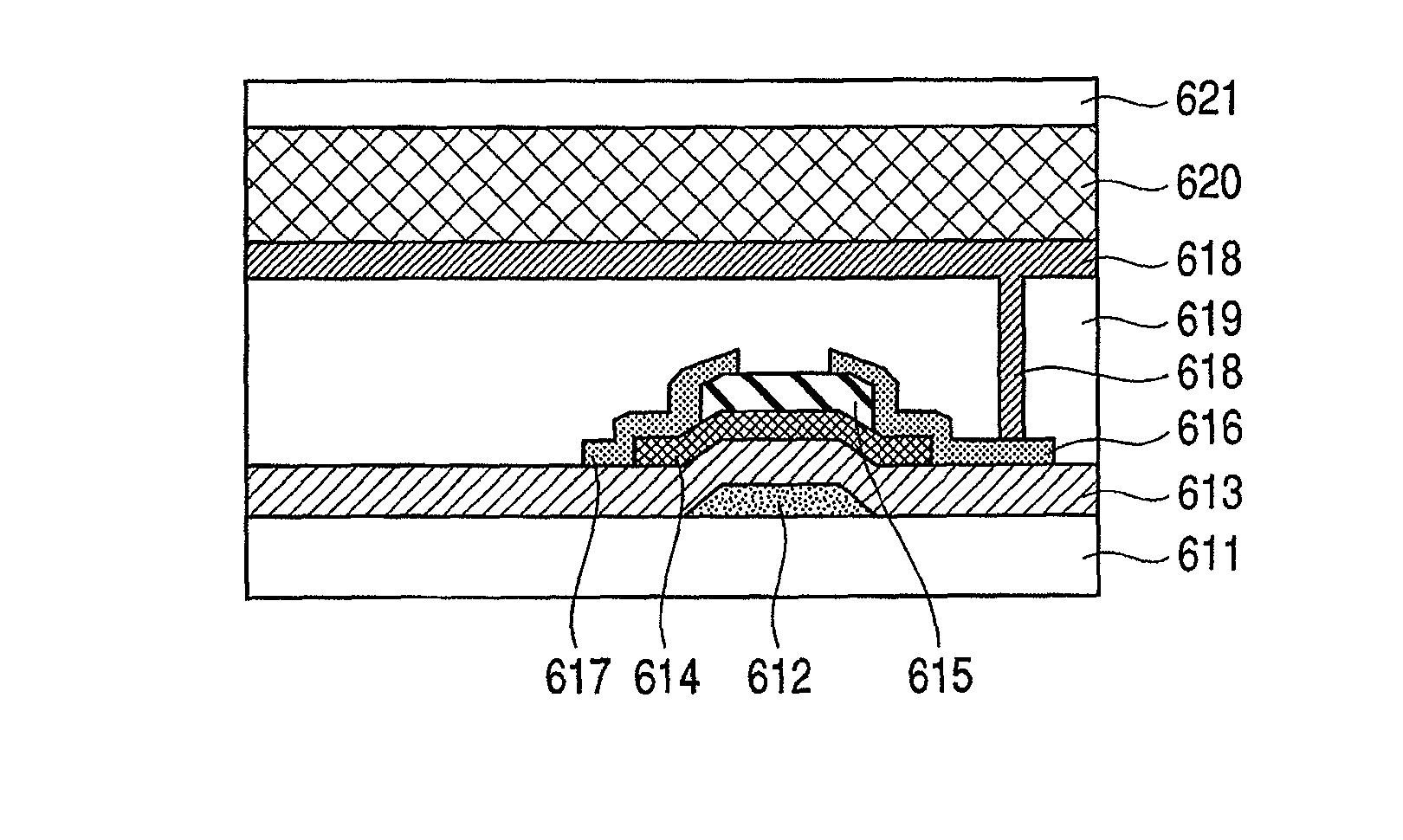

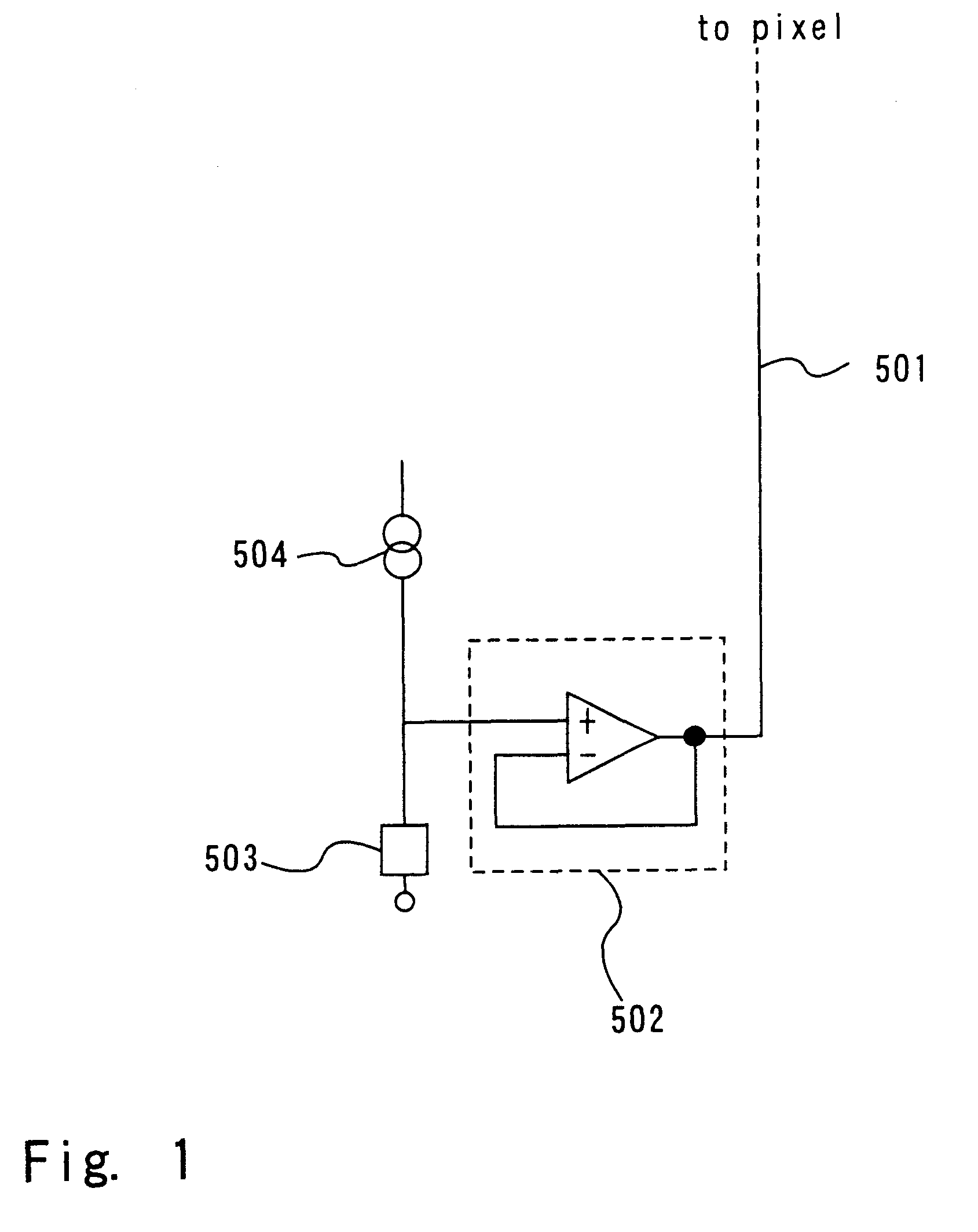

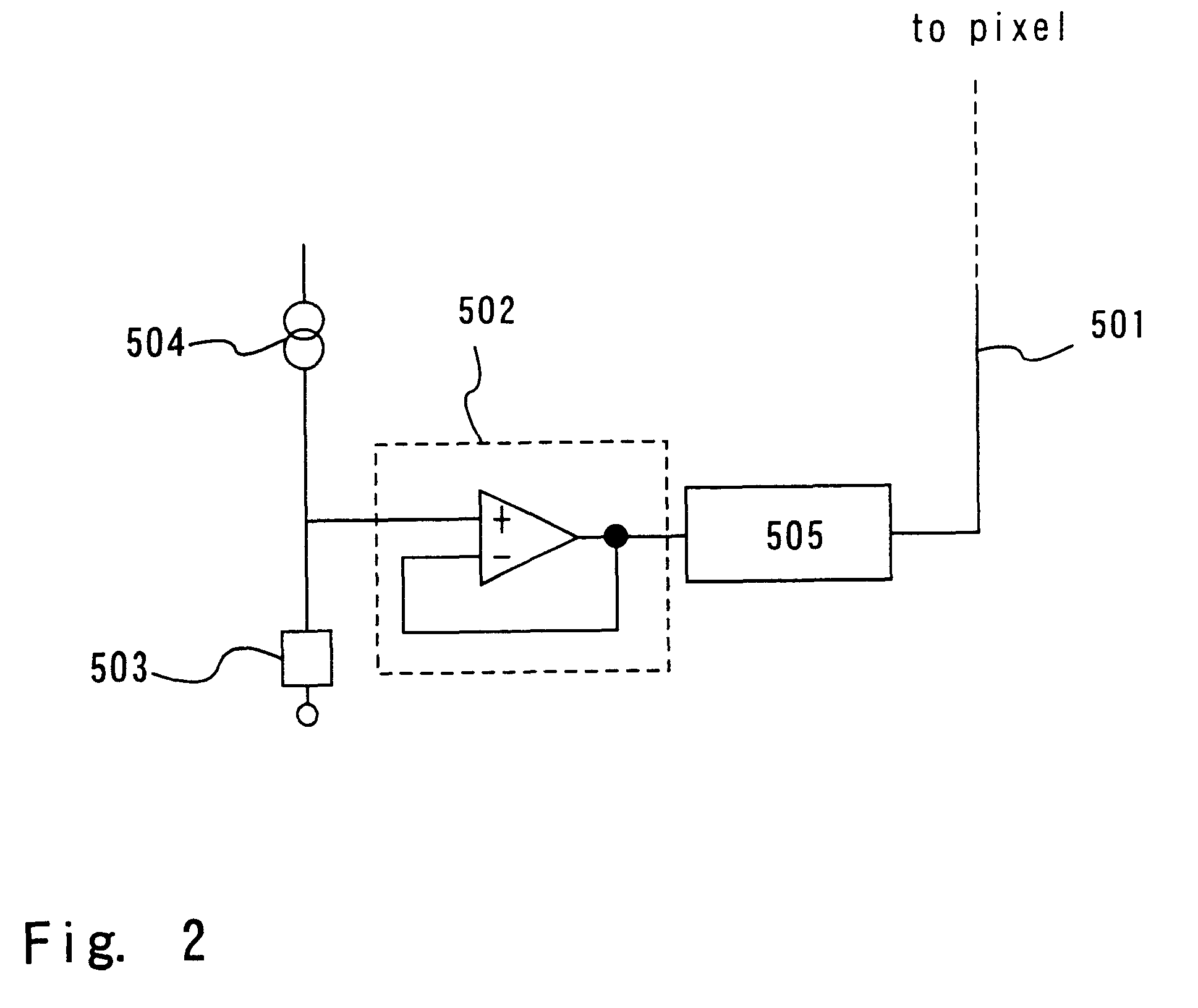

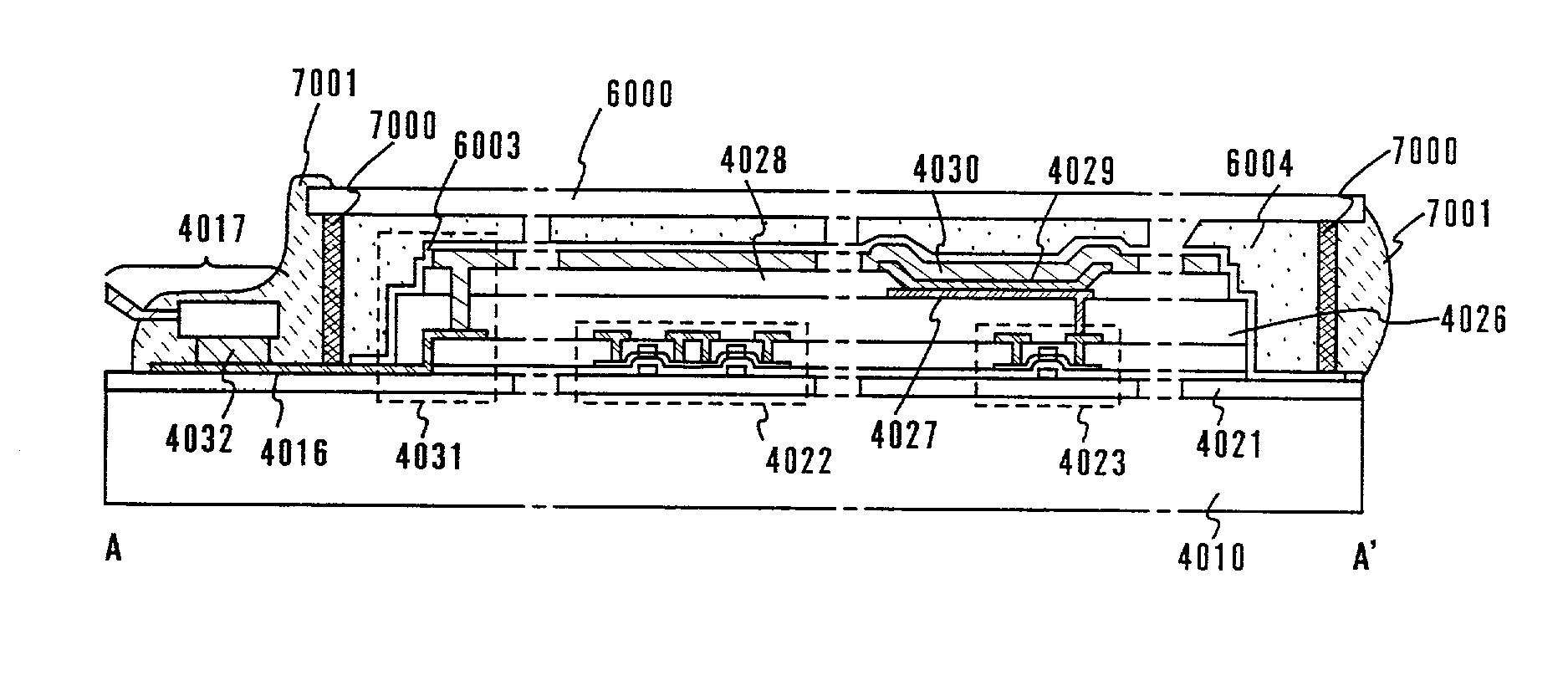

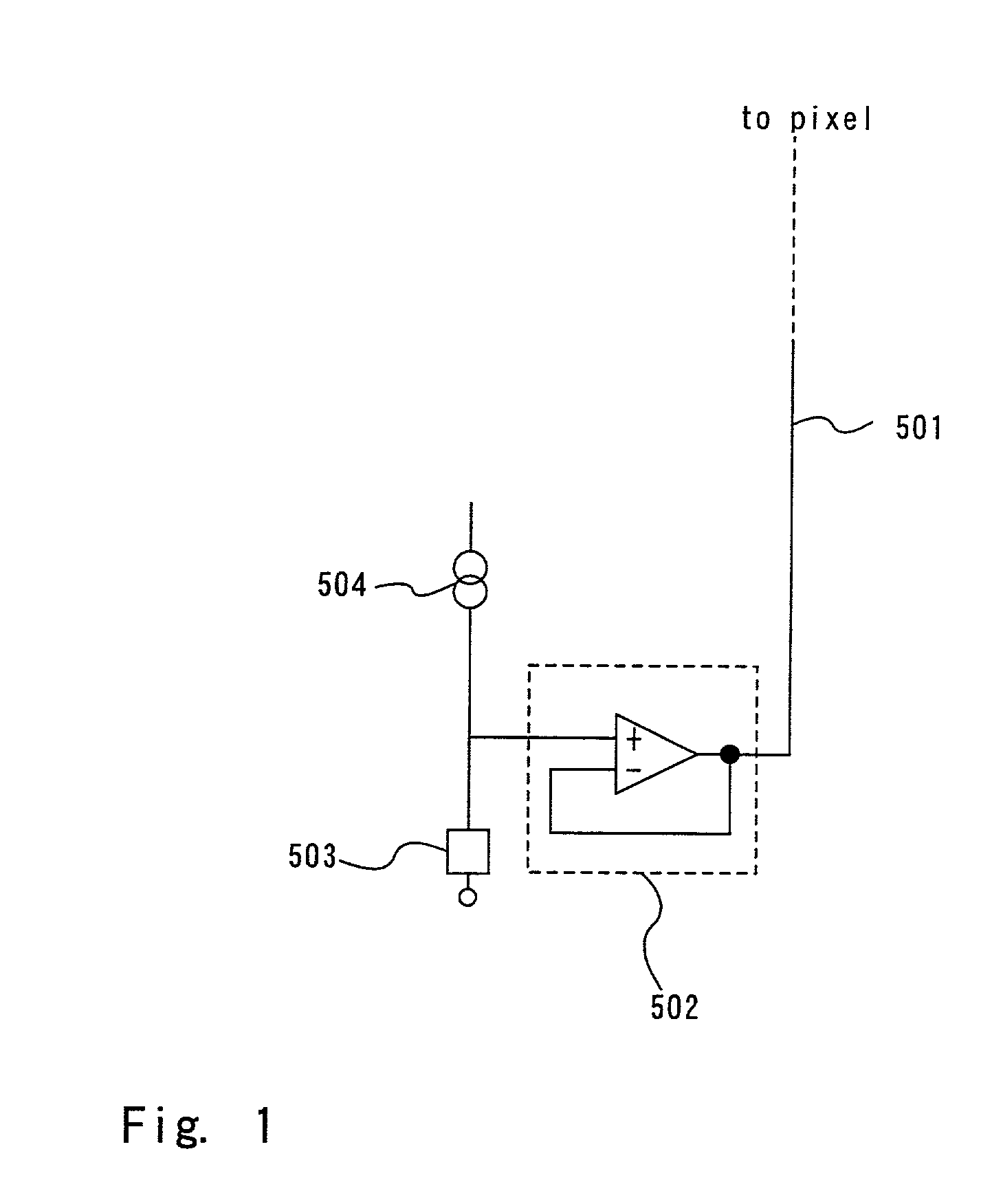

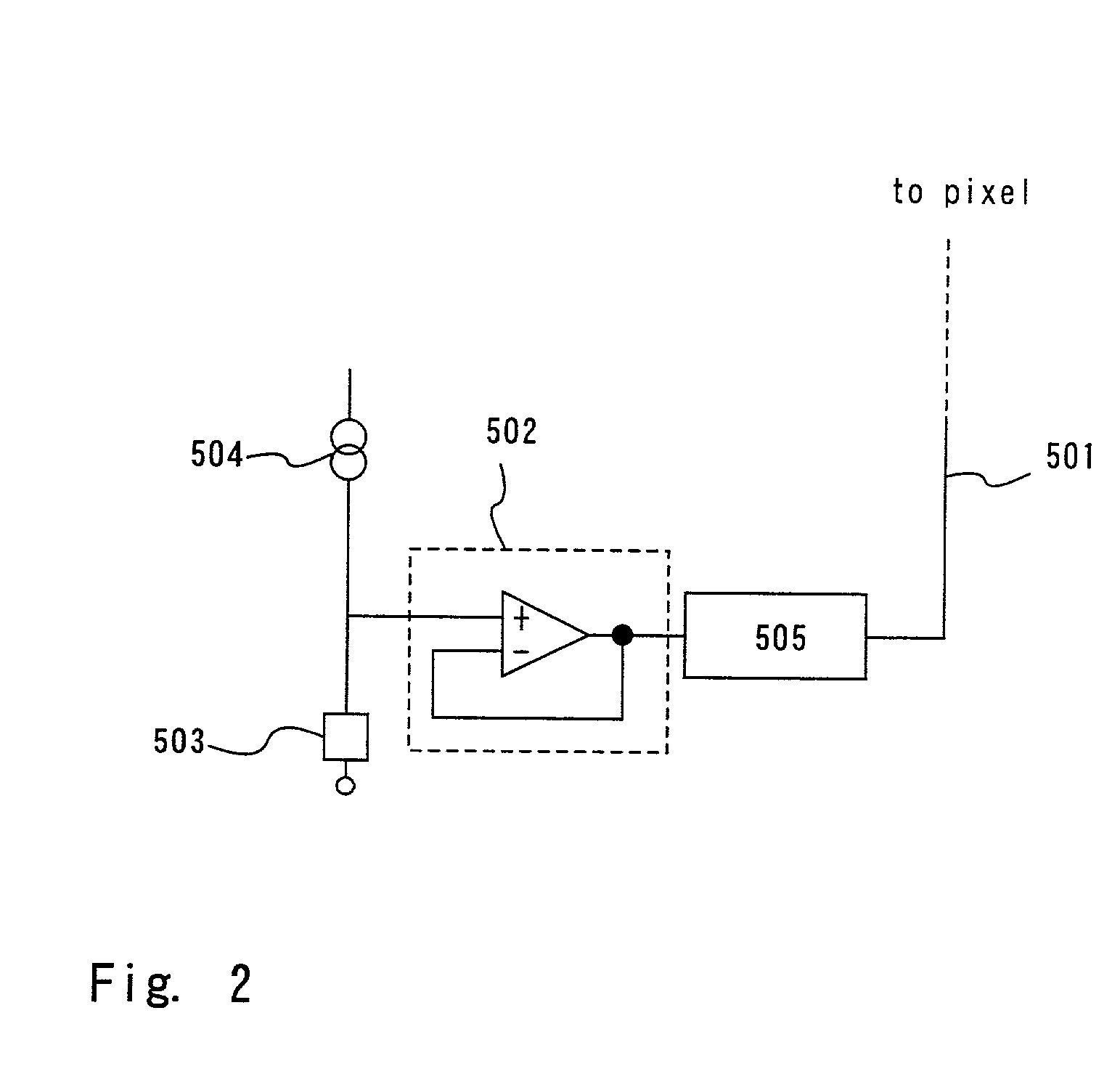

Display device

InactiveUS6528951B2Discharge tube luminescnet screensStatic indicating devicesDriver circuitImaging quality

The image quality of a display device using a bottom gate TFT is improved. In particular, fluctuation in luminance is controlled and the frequency characteristic of a driver circuit is compensated by suppressing a change in amount of current flowing through an EL element which is caused by a change in surrounding temperature while the device is in use. A monitoring EL element is provided in addition to a pixel portion EL element. The monitoring EL element constitutes a temperature compensation circuit together with a buffer amplifier and the like. A current is supplied to the pixel portion EL element through the temperature compensation circuit. This makes it possible to keep the amount of current flowing through the pixel portion EL element constant against a change in temperature, and to control the fluctuation in luminance. An input signal is subjected to time base expansion to perform sampling with accuracy.

Owner:SEMICON ENERGY LAB CO LTD

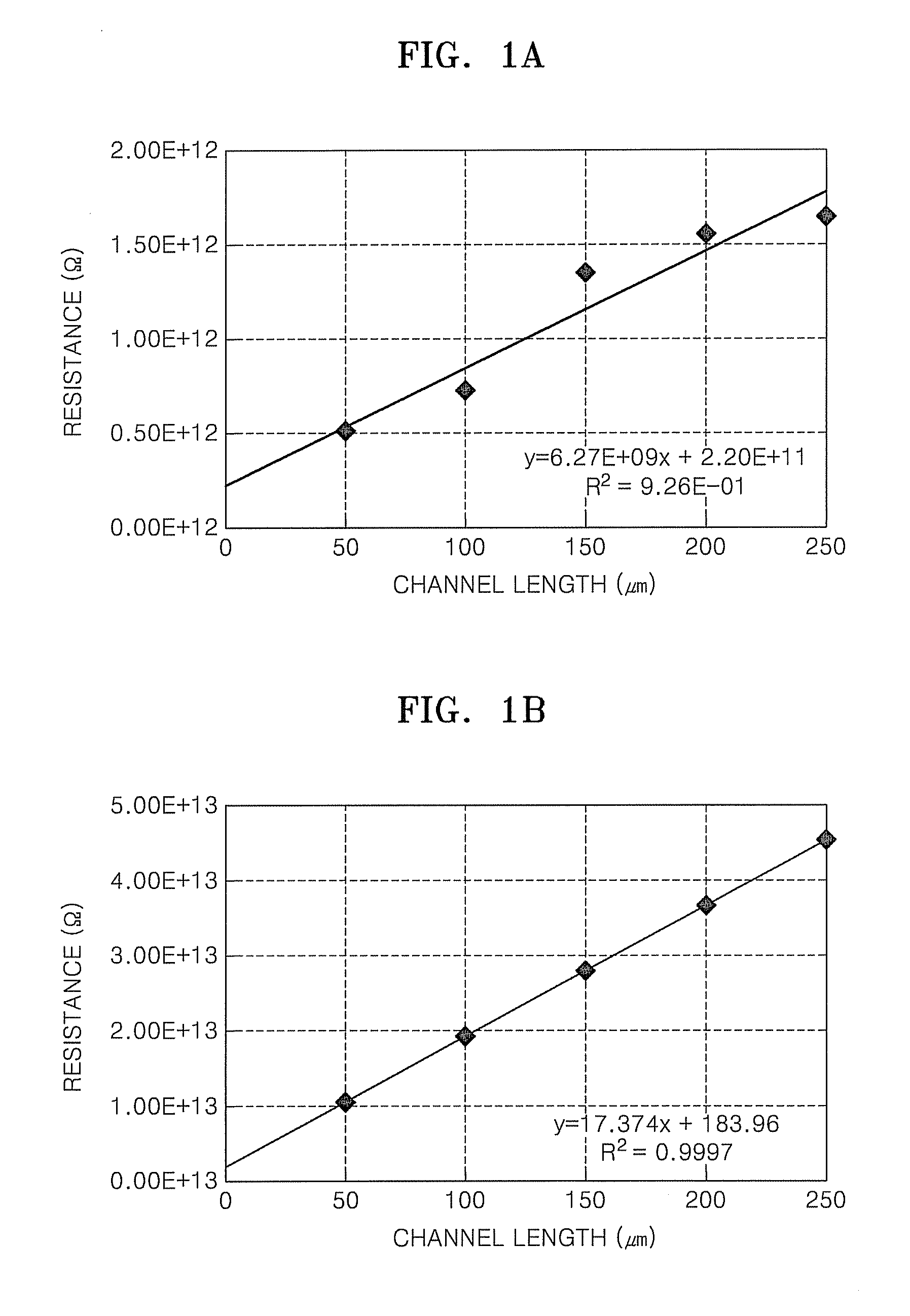

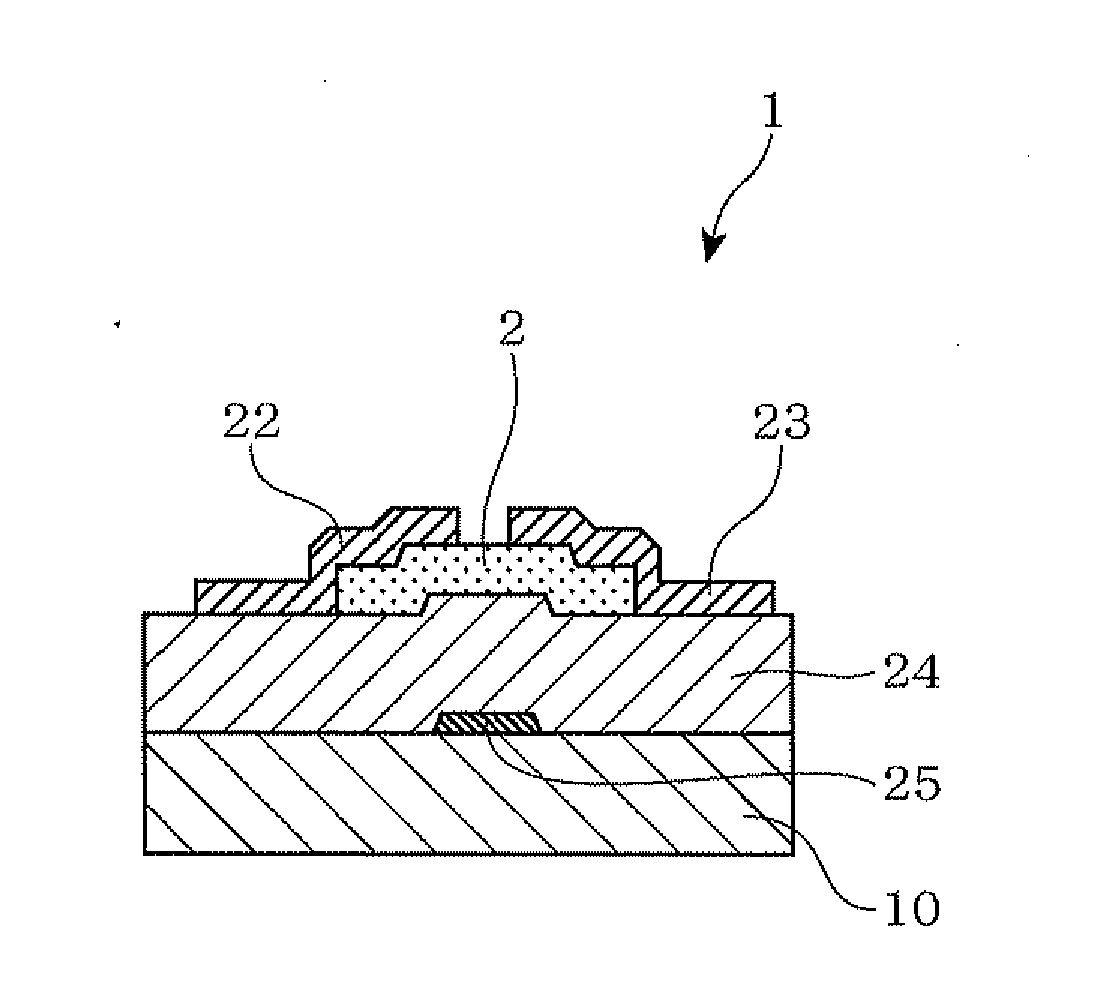

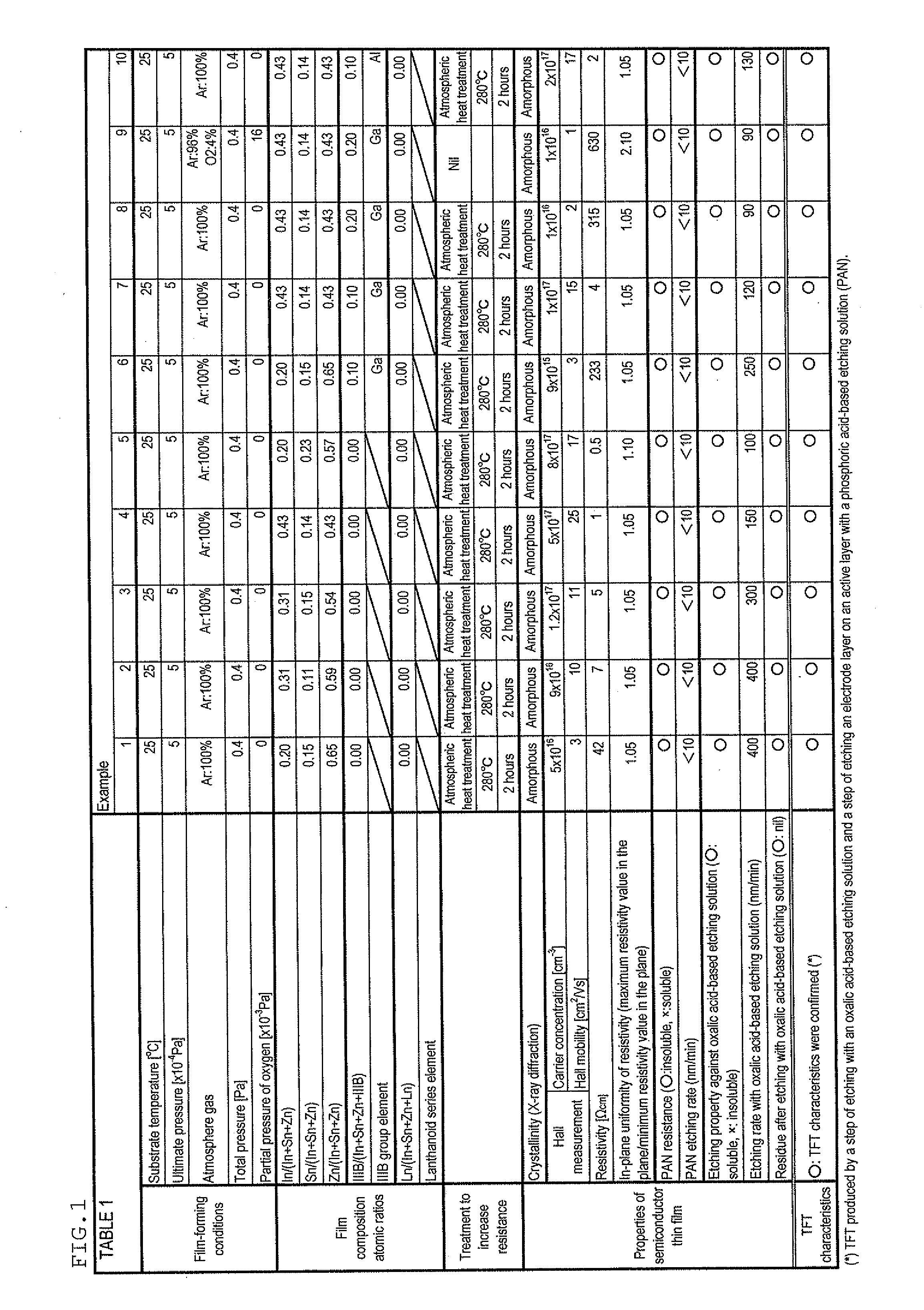

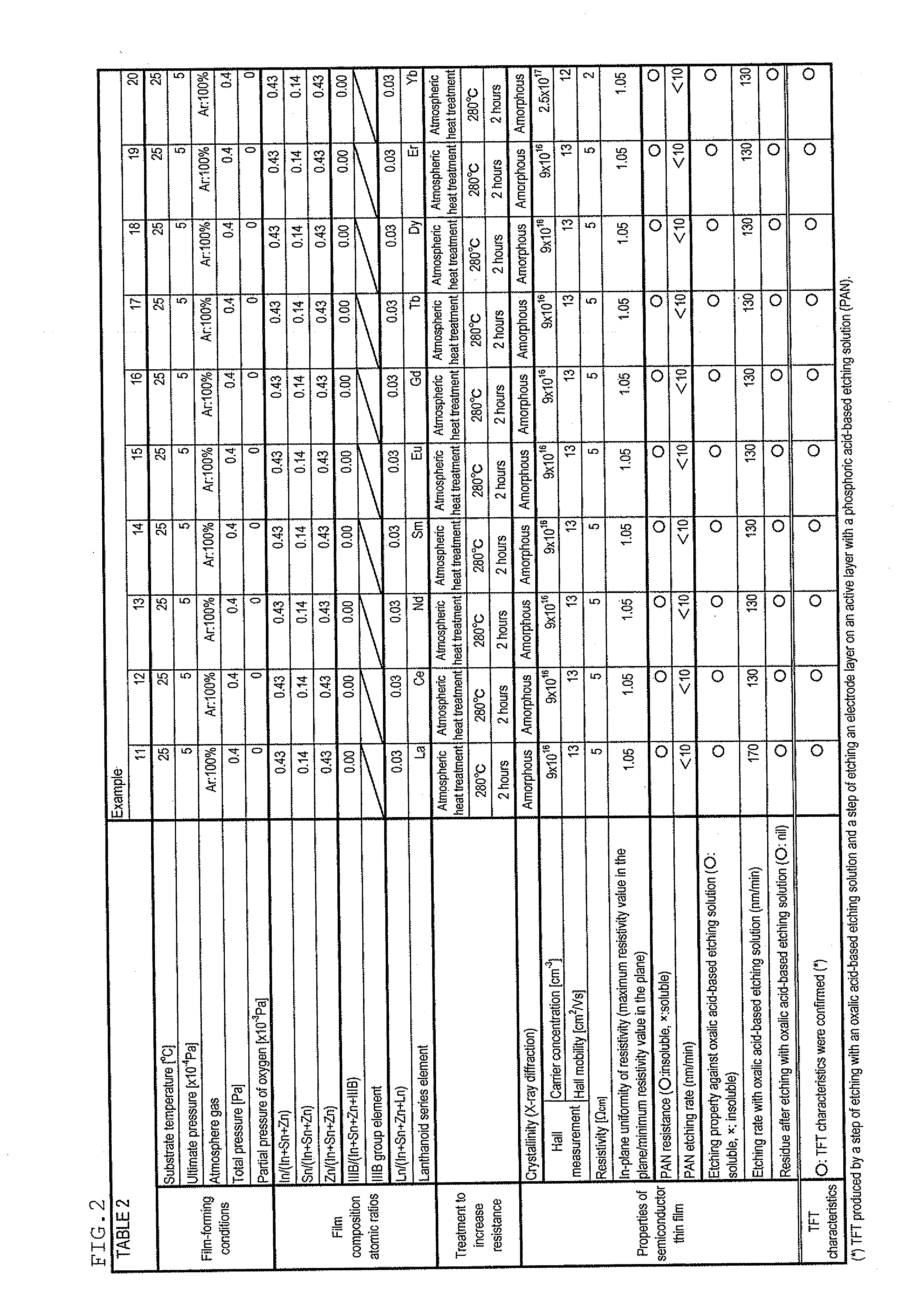

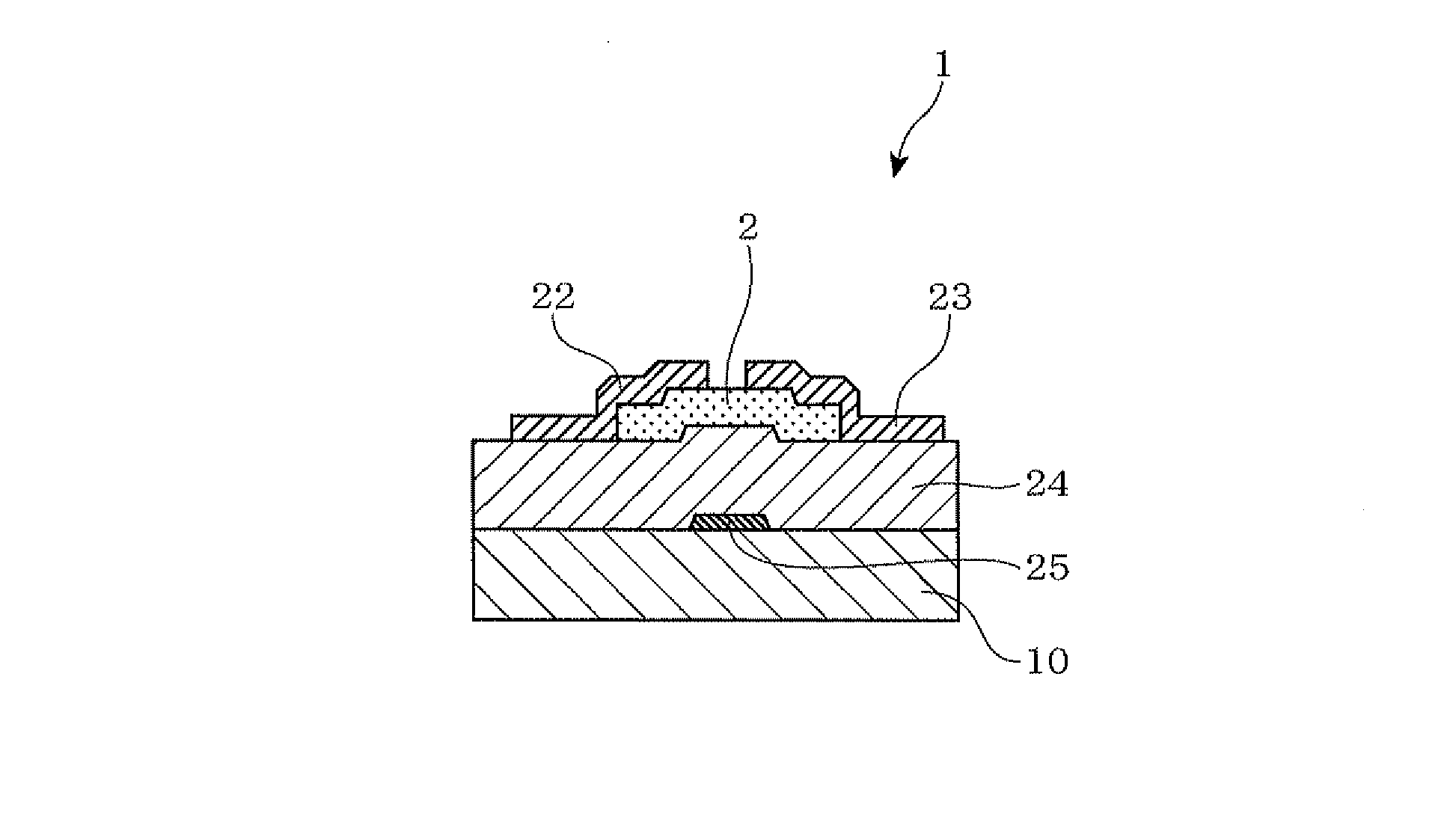

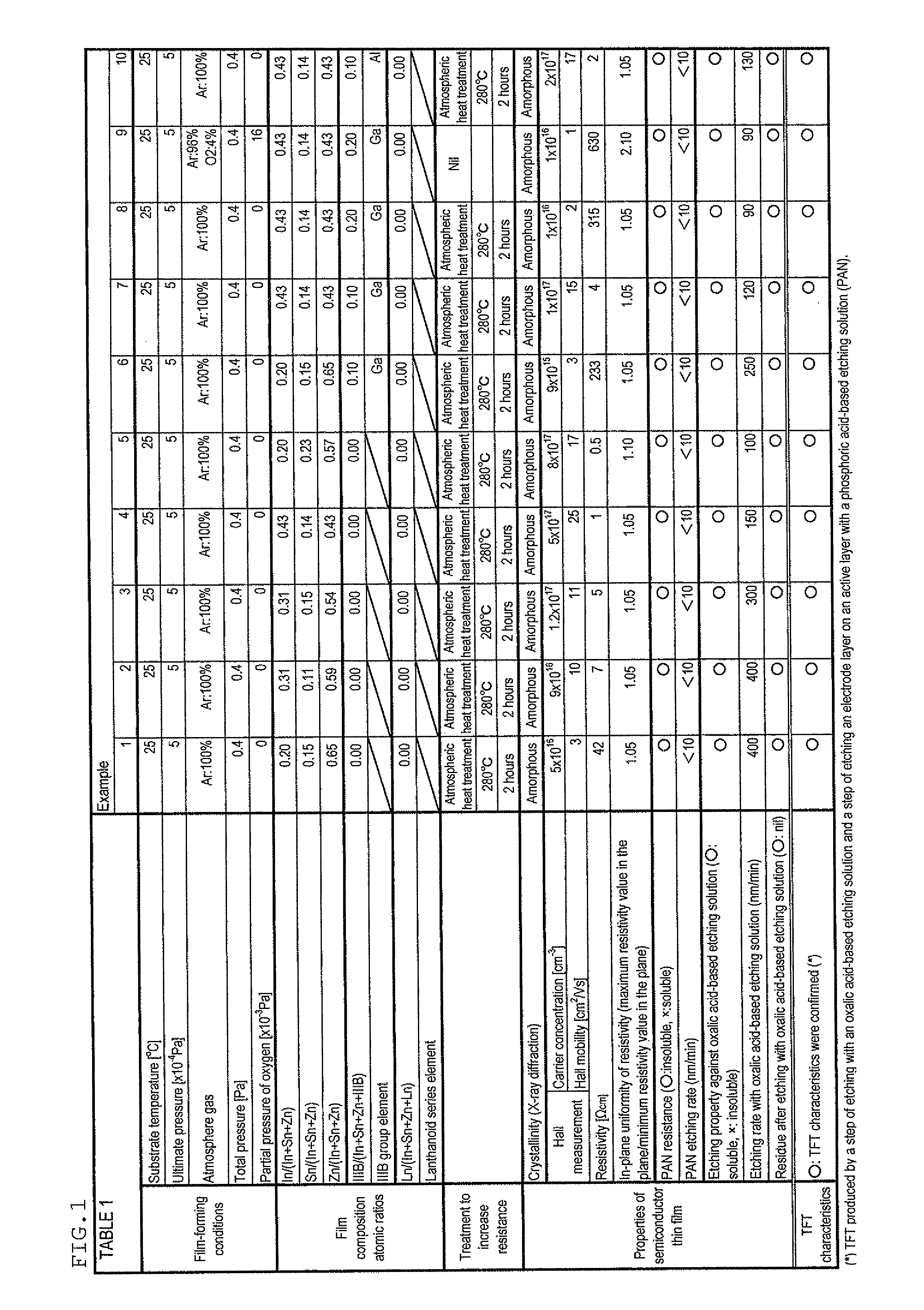

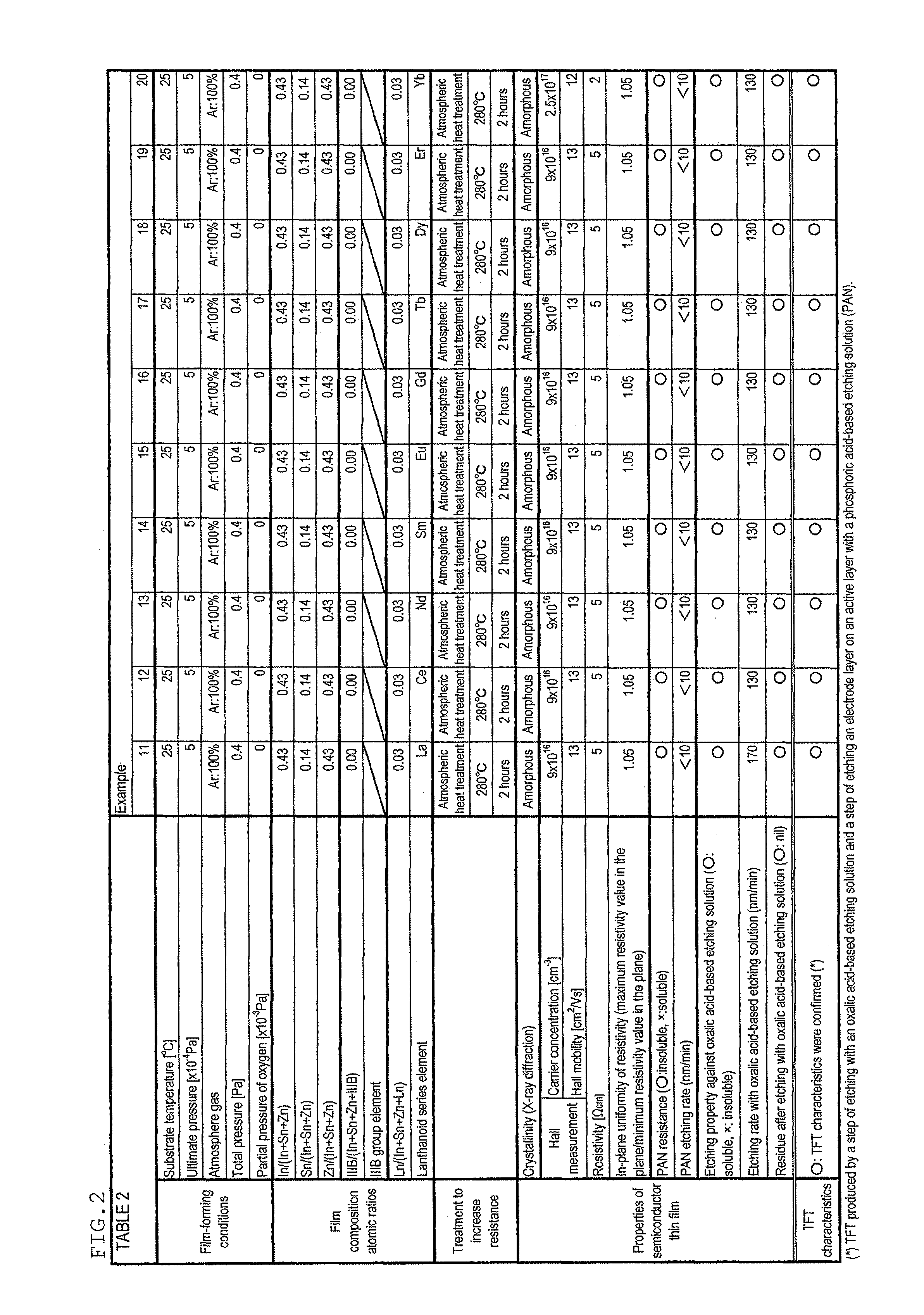

Noncrystalline oxide semiconductor thin film, process for producing the noncrystalline oxide semiconductor thin film, process for producing thin-film transistor, field-effect-transistor, light emitting device, display device, and sputtering target

ActiveUS20100155717A1Improve the immunityEasy to uniformlyCellsVacuum evaporation coatingIndiumPhosphoric acid

This invention provides an amorphous oxide semiconductor thin film, which is insoluble in a phosphoric acid-based etching solution and is soluble in an oxalic acid-based etching solution by optimizing the amounts of indium, tin, and zinc, a method of producing the amorphous oxide semiconductor thin film, etc. An image display device (1) comprises a glass substrate (10), a liquid crystal (40) as a light control element, a bottom gate-type thin film transistor (1) for driving the liquid crystal (40), a pixel electrode (30), and an opposing electrode (50). The amorphous oxide semiconductor thin film (2) in the bottom gate-type thin film transistor (1) has a carrier density of less than 10+18 cm−3, is insoluble in a phosphoric acid-based etching liquid, and is soluble in an oxalic acid-based etching liquid.

Owner:IDEMITSU KOSAN CO LTD

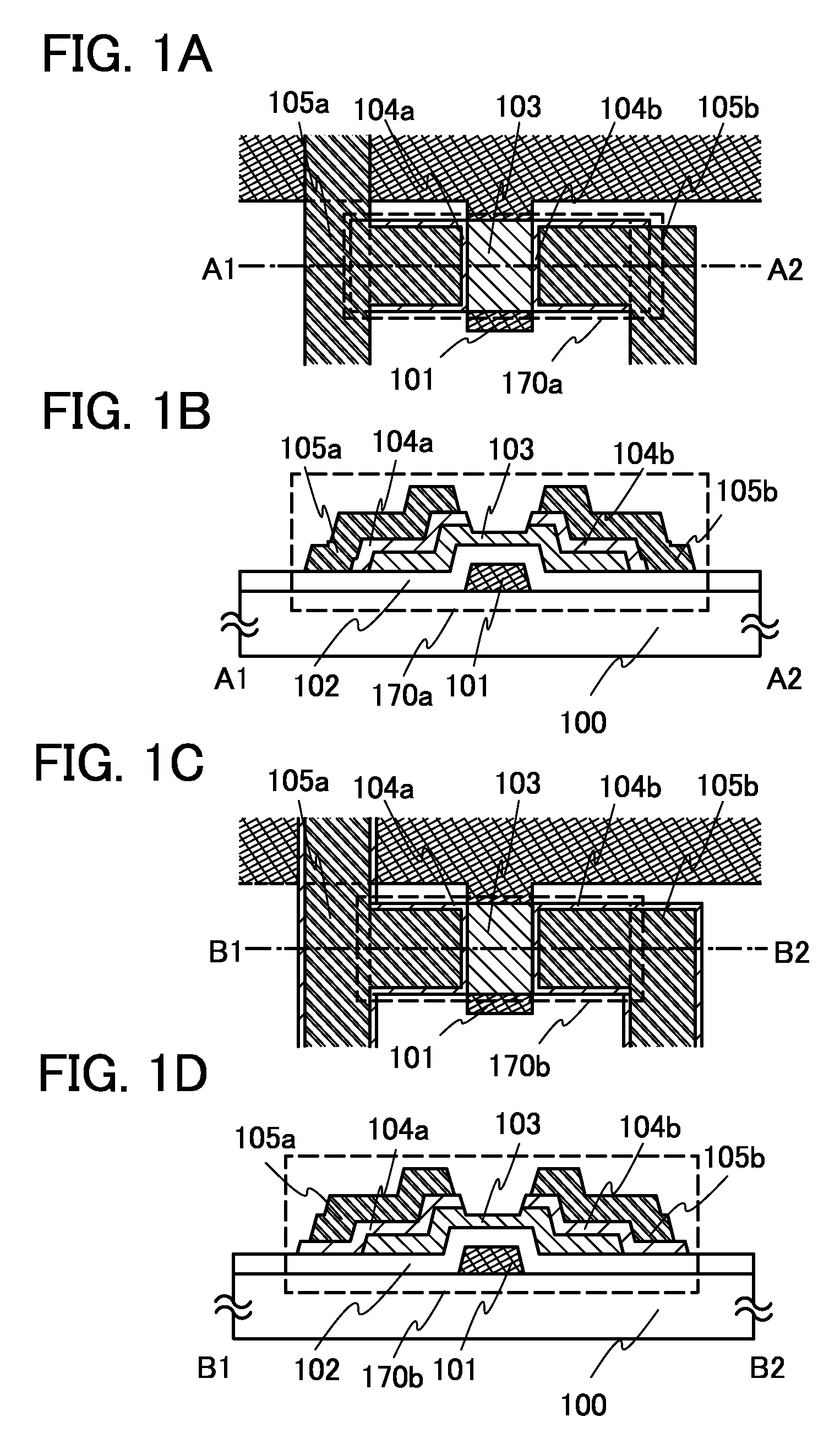

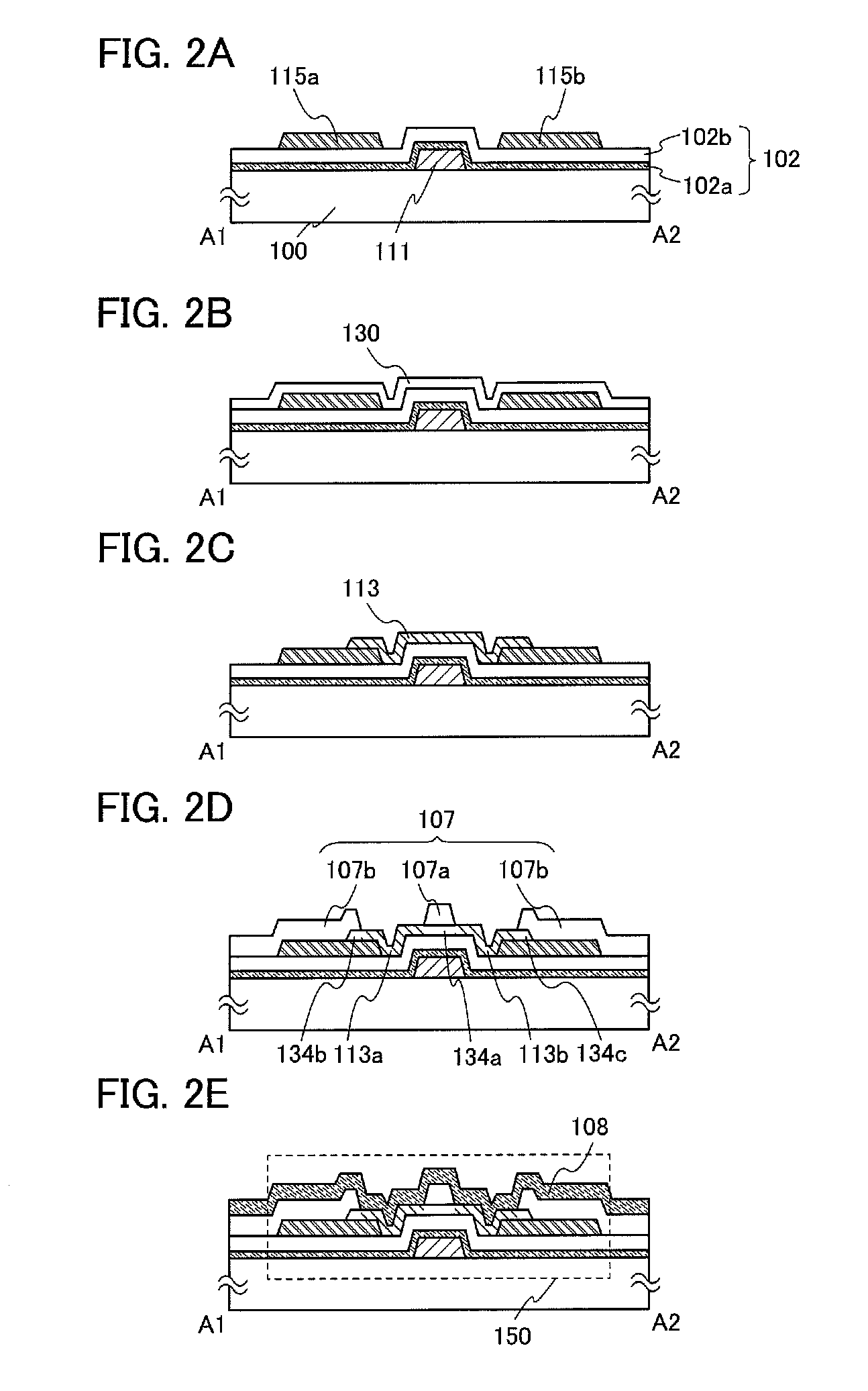

Semiconductor device and manufacturing method thereof

ActiveUS20110024751A1Reduce manufacturing costEasily brokenTransistorSolid-state devicesBottom gateSemiconductor

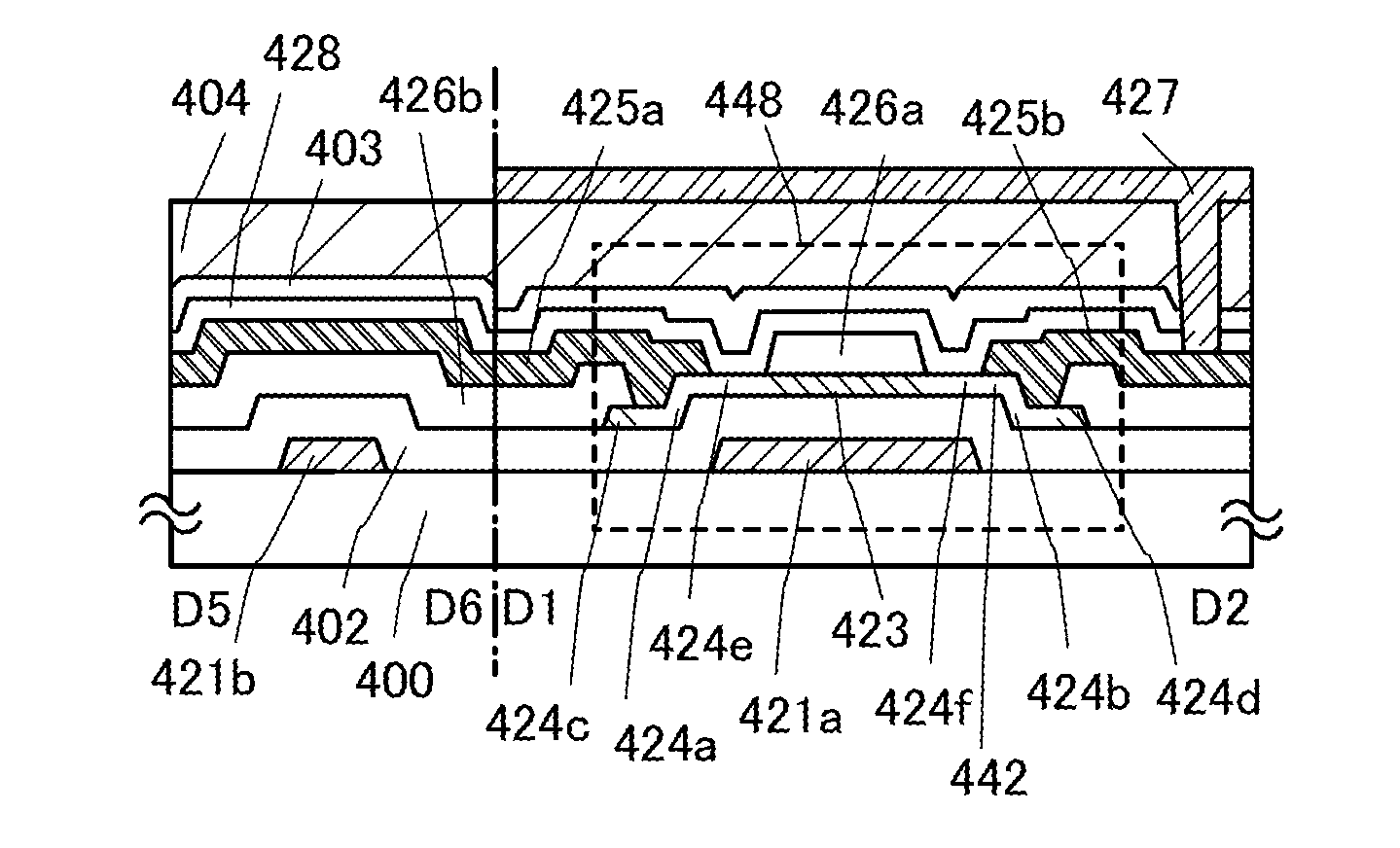

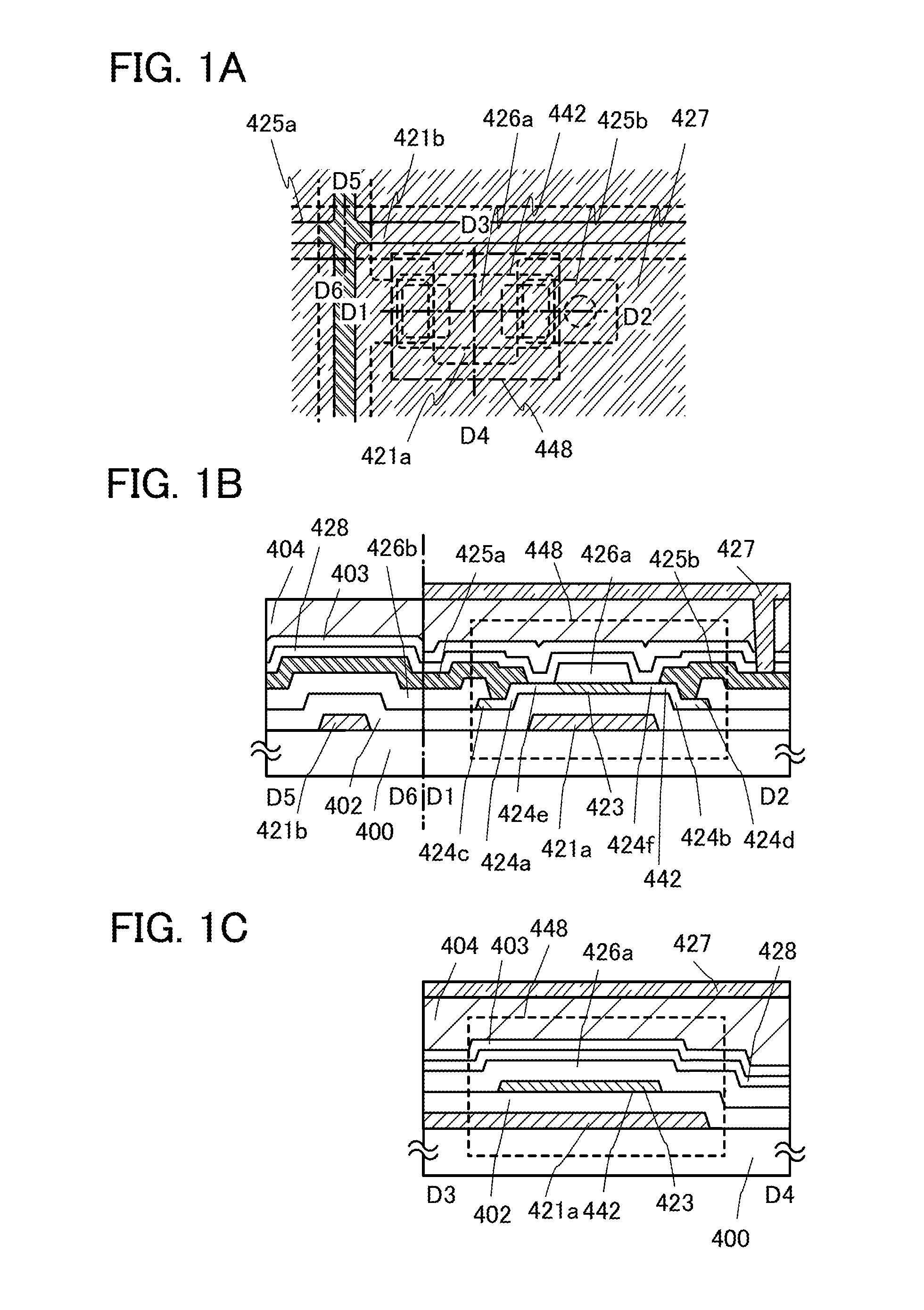

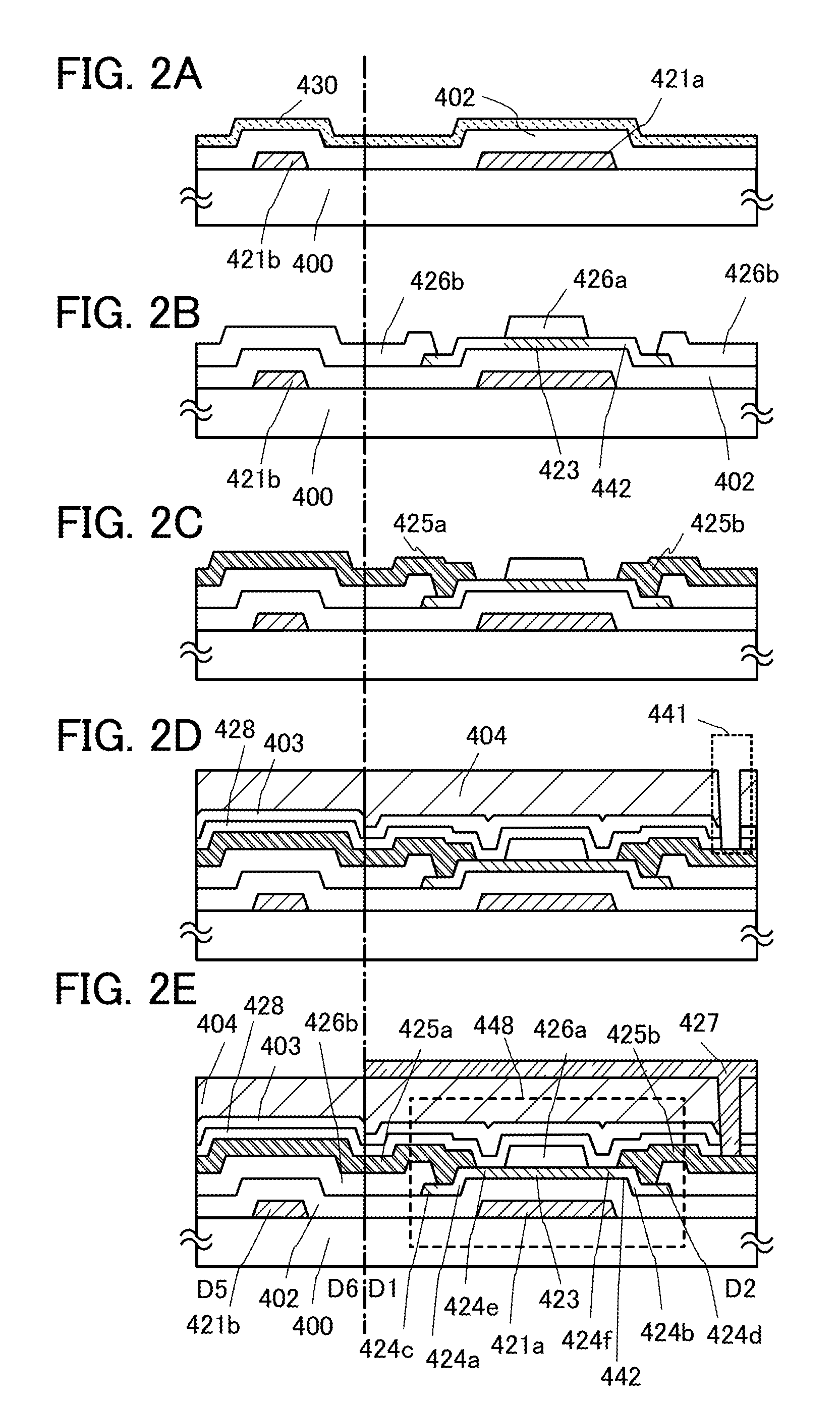

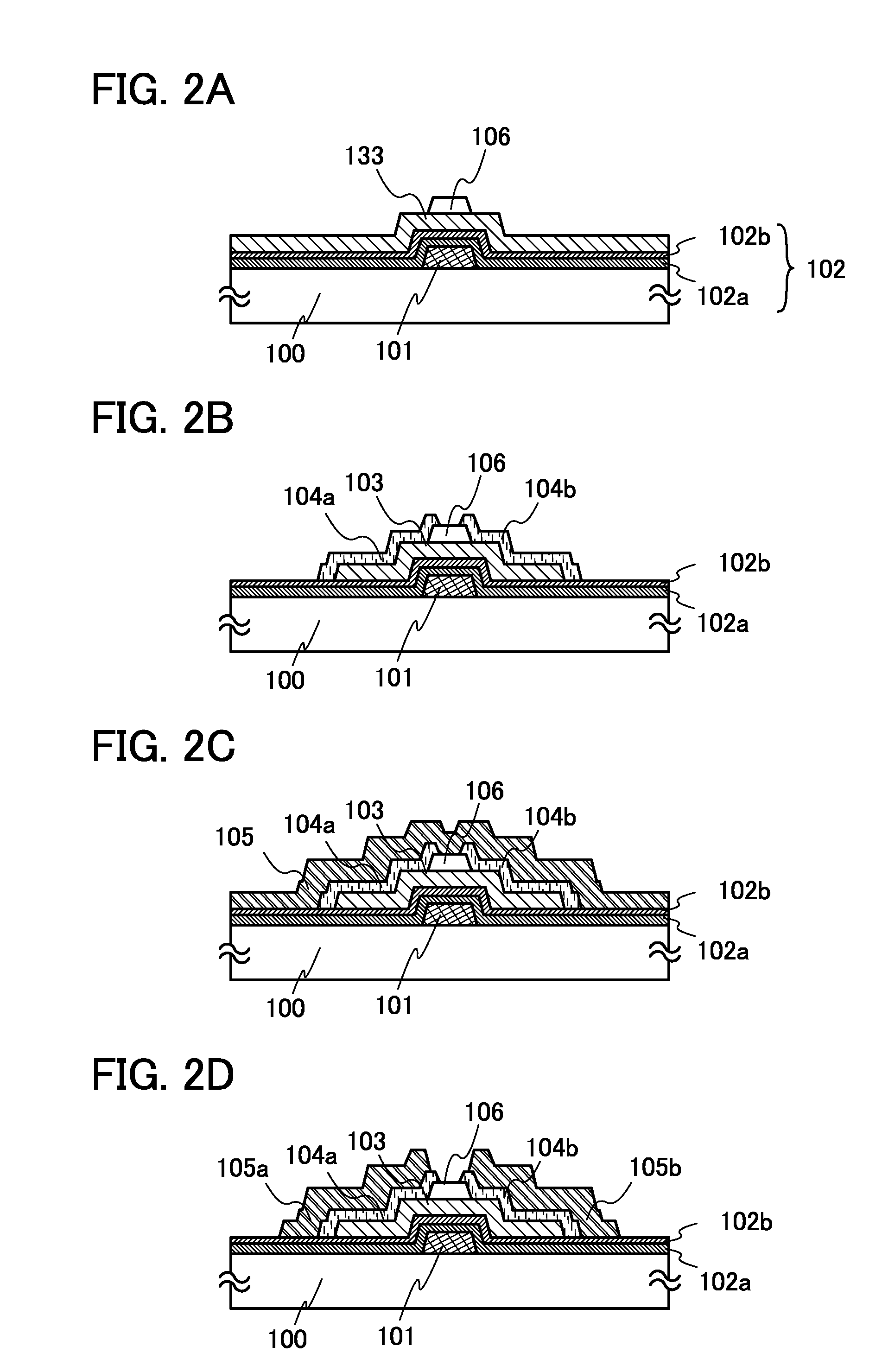

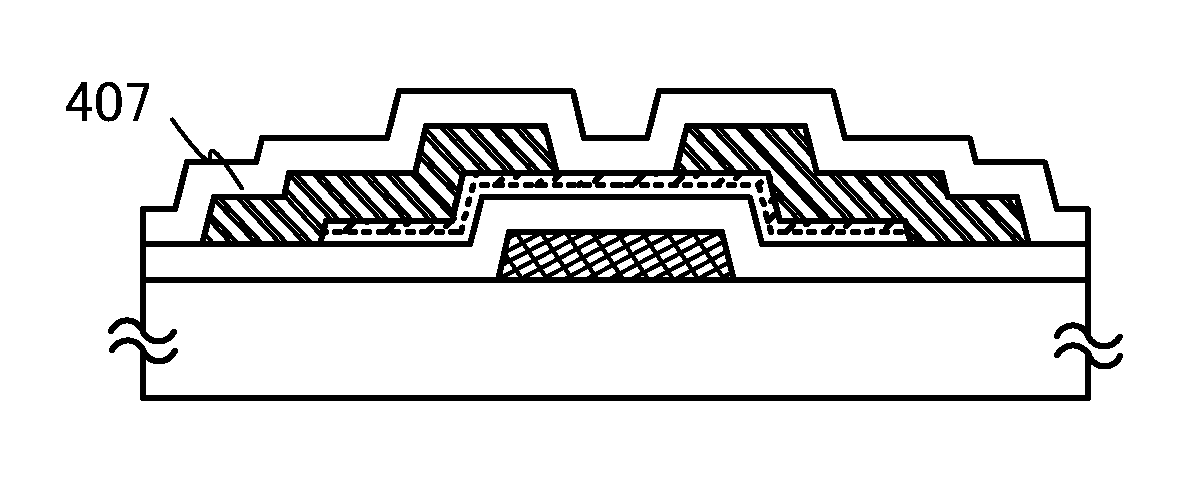

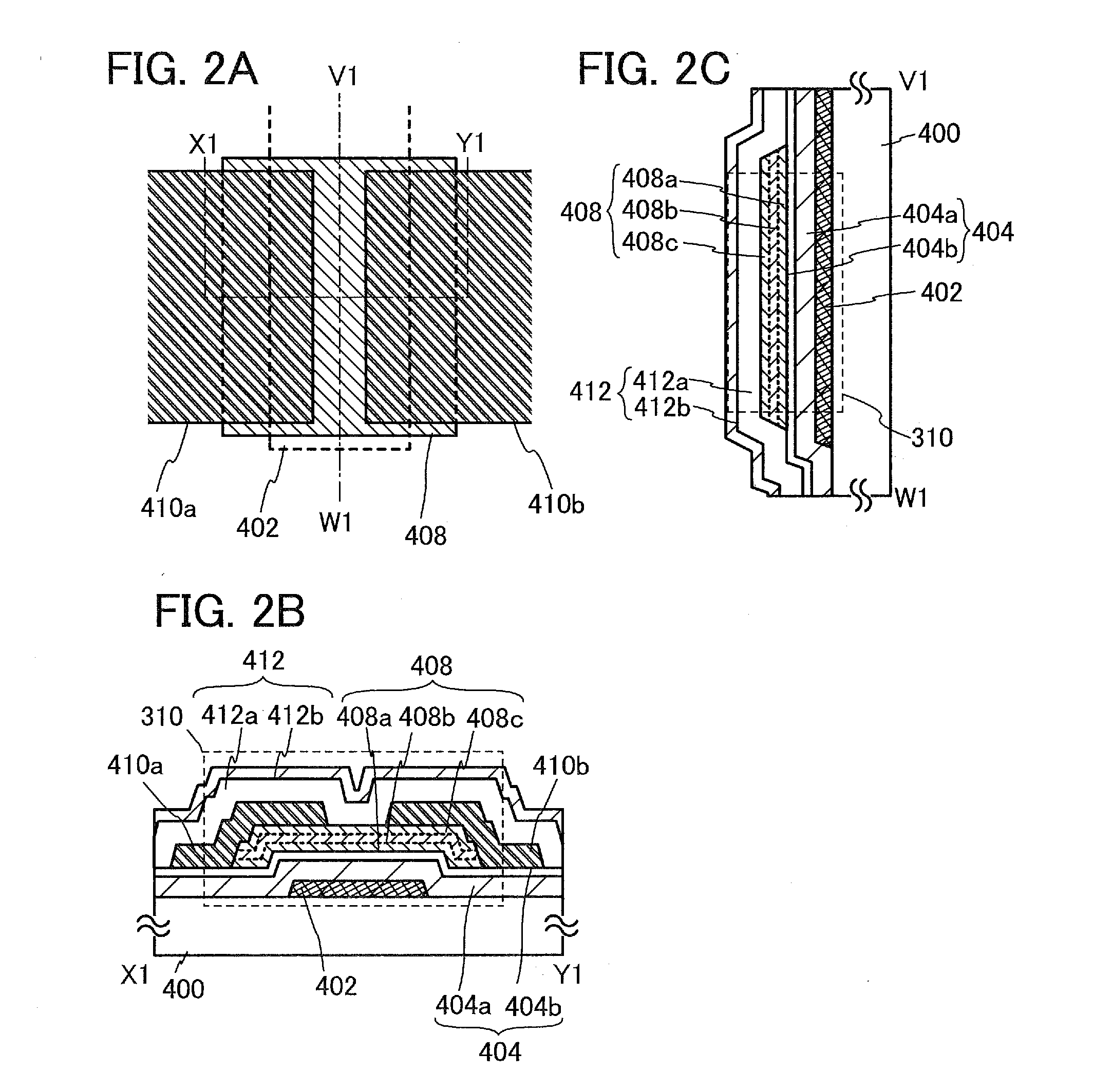

In a bottom-gate thin film transistor using the stack of the first oxide semiconductor layer and the second oxide semiconductor layer, an oxide insulating layer serving as a channel protective layer is formed over and in contact with part of the oxide semiconductor layer overlapping with a gate electrode layer. In the same step as formation of the insulating layer, an oxide insulating layer covering a peripheral portion (including a side surface) of the stack of the oxide semiconductor layers is formed.

Owner:SEMICON ENERGY LAB CO LTD

Pixel current driver for organic light emitting diode displays

InactiveUS20060027807A1Improve circuit performanceMinimize chargeTransistorStatic indicating devicesBottom gateDisplay device

A pixel current driver comprises a plurality of thin film transistors (TFTs) each having dual gates and for driving OLED layers. A top gate of the dual gates is formed between a source and a drain of each of the thin film transistors, to thereby minimize parasitic capacitance. The top gate is grounded or electrically tied to a bottom gate. The plurality of thin film transistors may be two thin film transistors formed in voltage-programmed manner or five thin film transistors formed in a current-programmed ΔVT-compensated manner. Other versions of the current-programmed circuit with different numbers of thin film transistors are also presented that compensate for δVT. The OLED layer are continuous and vertically stacked on the plurality of thin film transistors to provide an aperture ratio close to 100%.

Owner:IGNIS INNOVATION

Semiconductor device and method for manufacturing the same

ActiveUS20100025679A1Small currentHigh on-off ratioStatic indicating devicesSolid-state devicesOhmic contactCharge carrier

An embodiment is to include an inverted staggered (bottom gate structure) thin film transistor in which an oxide semiconductor film containing In, Ga, and Zn is used as a semiconductor layer and a buffer layer is provided between the semiconductor layer and a source and drain electrode layers. The buffer layer having higher carrier concentration than the semiconductor layer is provided intentionally between the source and drain electrode layers and the semiconductor layer, whereby an ohmic contact is formed.

Owner:SEMICON ENERGY LAB CO LTD

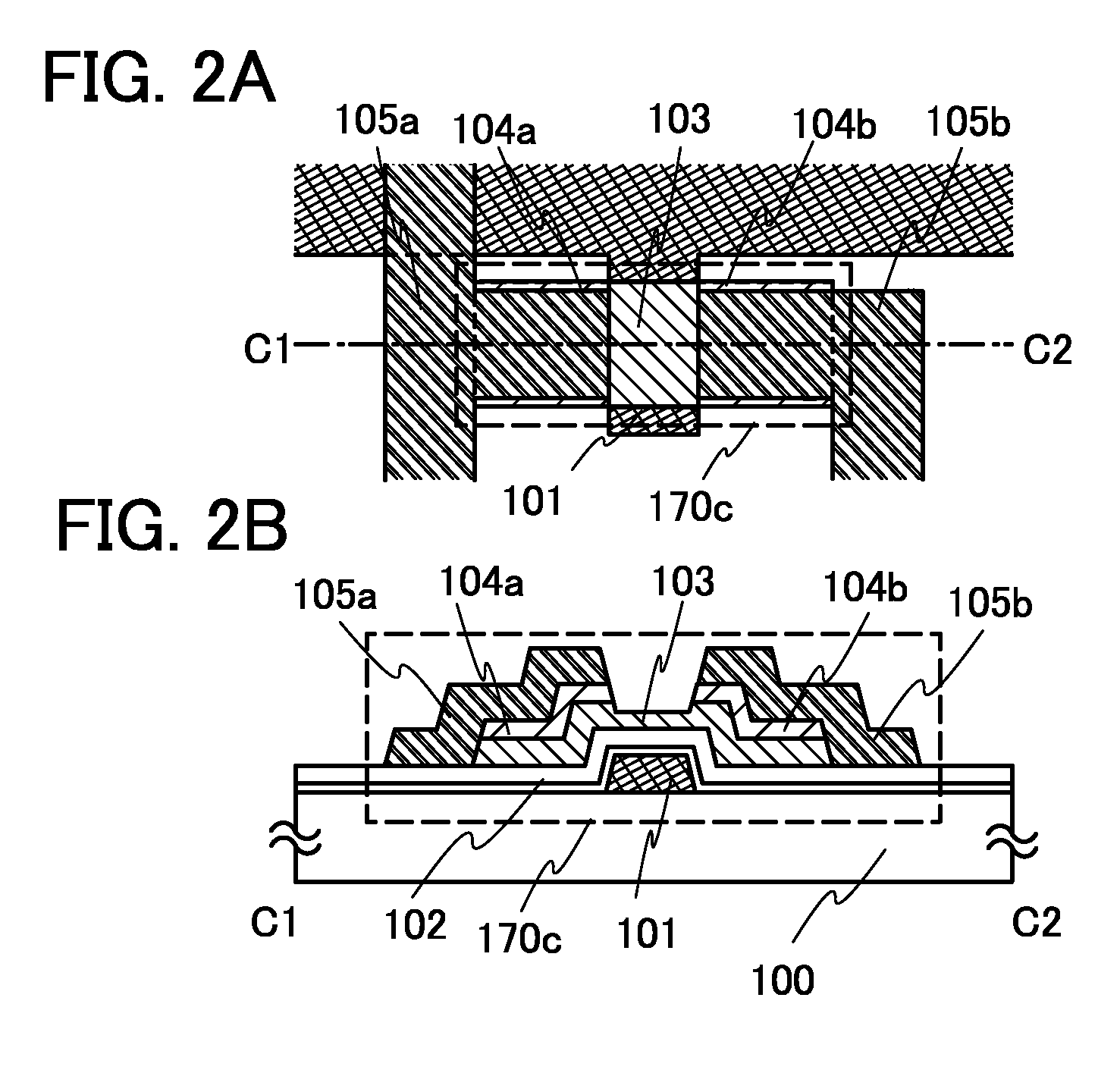

Semiconductor device and manufacturing method thereof

ActiveUS20110031491A1Reduce parasitic capacitanceOff-current can be reducedTransistorStatic indicating devicesBottom gateParasitic capacitance

An object is to provide a semiconductor device having a structure in which parasitic capacitance between wirings can be efficiently reduced. In a bottom gate thin film transistor using an oxide semiconductor layer, an oxide insulating layer used as a channel protection layer is formed above and in contact with part of the oxide semiconductor layer overlapping with a gate electrode layer, and at the same time an oxide insulating layer covering a peripheral portion (including a side surface) of the stacked oxide semiconductor layer is formed. Further, a source electrode layer and a drain electrode layer are formed in a manner such that they do not overlap with the channel protection layer. Thus, a structure in which an insulating layer over the source electrode layer and the drain electrode layer is in contact with the oxide semiconductor layer is provided.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device and manufacturing method thereof

ActiveUS20100025676A1Small amount of photocurrentReduce parasitic capacitanceTransistorSolid-state devicesCharge carrierOhmic contact

To offer a semiconductor device including a thin film transistor having excellent characteristics and high reliability and a method for manufacturing the semiconductor device without variation. The summary is to include an inverted-staggered (bottom-gate structure) thin film transistor in which an oxide semiconductor film containing In, Ga, and Zn is used for a semiconductor layer and a buffer layer is provided between the semiconductor layer and source and drain electrode layers. An ohmic contact is formed by intentionally providing a buffer layer containing In, Ga, and Zn and having a higher carrier concentration than the semiconductor layer between the semiconductor layer and the source and drain electrode layers.

Owner:SEMICON ENERGY LAB CO LTD

Bottom gate type thin film transistor, method of manufacturing the same, and display apparatus

InactiveUS20100051936A1Excels in mass productionOptimise total massTransistorElectroluminescent light sourcesDesorptionBottom gate

Provided is a bottom gate type thin film transistor including on a substrate (1) a gate electrode (2), a first insulating film (3) as a gate insulating film, an oxide semiconductor layer (4) as a channel layer, a second insulating film (5) as a protective layer, a source electrode (6), and a drain electrode (7), in which the oxide semiconductor layer (4) includes an oxide including at least one selected from the group consisting of In, Zn, and Sn, and the second insulating film (5) includes an amorphous oxide insulator formed so as to be in contact with the oxide semiconductor layer (4) and contains therein 3.8×1019 molecules / cm3 or more of a desorbed gas observed as oxygen by temperature programmed desorption mass spectrometry.

Owner:CANON KK

Semiconductor device with two oxide semiconductor layers and manufacturing method thereof

In a bottom-gate thin film transistor using the stack of the first oxide semiconductor layer and the second oxide semiconductor layer, an oxide insulating layer serving as a channel protective layer is formed over and in contact with part of the oxide semiconductor layer overlapping with a gate electrode layer. In the same step as formation of the insulating layer, an oxide insulating layer covering a peripheral portion (including a side surface) of the stack of the oxide semiconductor layers is formed.

Owner:SEMICON ENERGY LAB CO LTD

Noncrystalline oxide semiconductor thin film, process for producing the noncrystalline oxide semiconductor thin film, process for producing thin-film transistor, field-effect-transistor, light emitting device, display device, and sputtering target

ActiveUS8232552B2Industrially produced with easeIncrease volumeCellsVacuum evaporation coatingOXALIC ACID DIHYDRATEIndium

This invention provides an amorphous oxide semiconductor thin film, which is insoluble in a phosphoric acid-based etching solution and is soluble in an oxalic acid-based etching solution by optimizing the amounts of indium, tin, and zinc, a method of producing the amorphous oxide semiconductor thin film, etc. An image display device (1) comprises a glass substrate (10), a liquid crystal (40) as a light control element, a bottom gate-type thin film transistor (1) for driving the liquid crystal (40), a pixel electrode (30), and an opposing electrode (50). The amorphous oxide semiconductor thin film (2) in the bottom gate-type thin film transistor (1) has a carrier density of less than 10+18 cm−3, is insoluble in a phosphoric acid-based etching liquid, and is soluble in an oxalic acid-based etching liquid.

Owner:IDEMITSU KOSAN CO LTD

Semiconductor device and method for manufacturing the same

ActiveUS20120273780A1Comparatively-easy manufacturing processGuaranteed high speed operationStatic indicating devicesSolid-state devicesPower semiconductor deviceOhmic contact

An embodiment is to include an inverted staggered (bottom gate structure) thin film transistor in which an oxide semiconductor film containing In, Ga, and Zn is used as a semiconductor layer and a buffer layer is provided between the semiconductor layer and a source and drain electrode layers. The buffer layer having higher carrier concentration than the semiconductor layer is provided intentionally between the source and drain electrode layers and the semiconductor layer, whereby an ohmic contact is formed.

Owner:SEMICON ENERGY LAB CO LTD

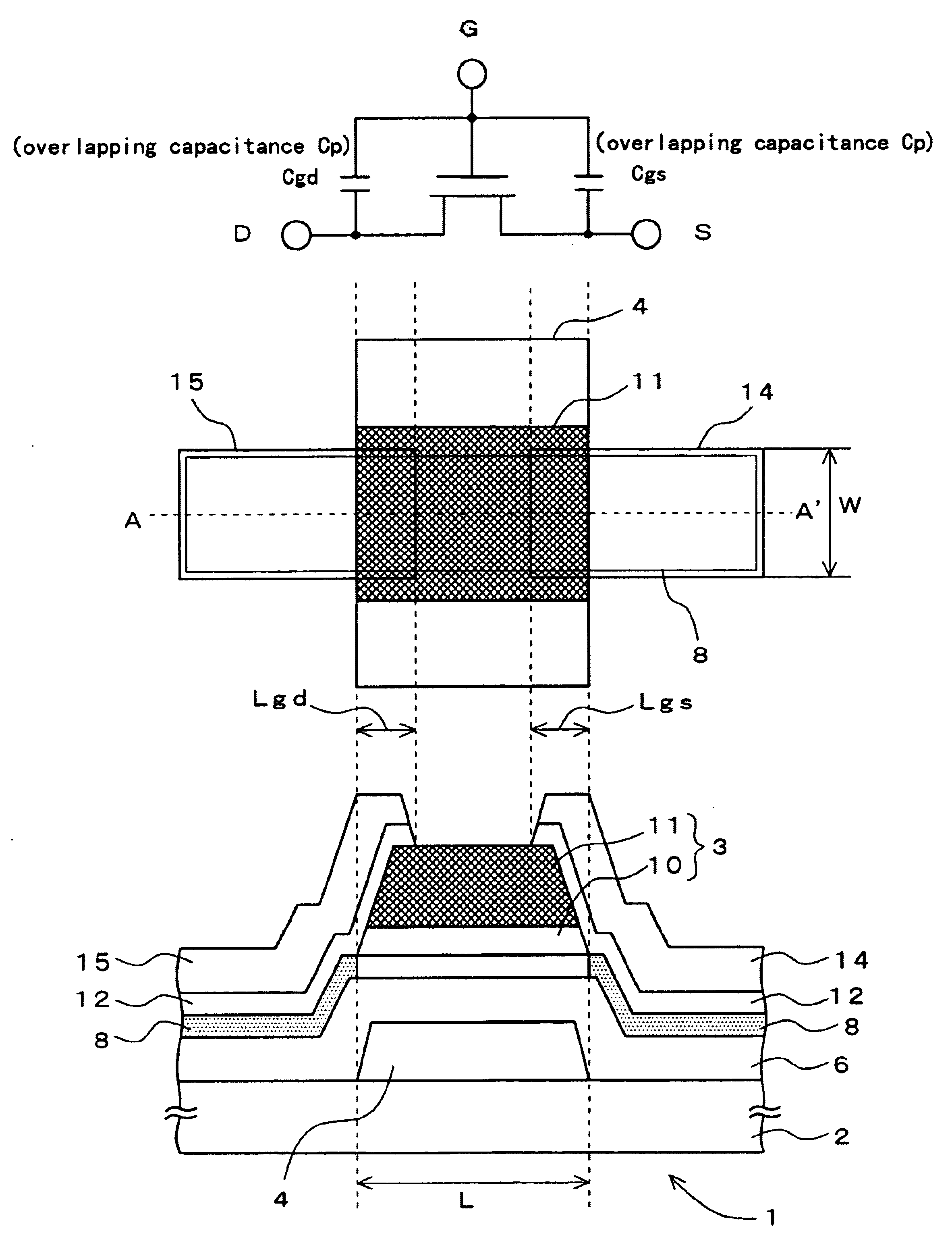

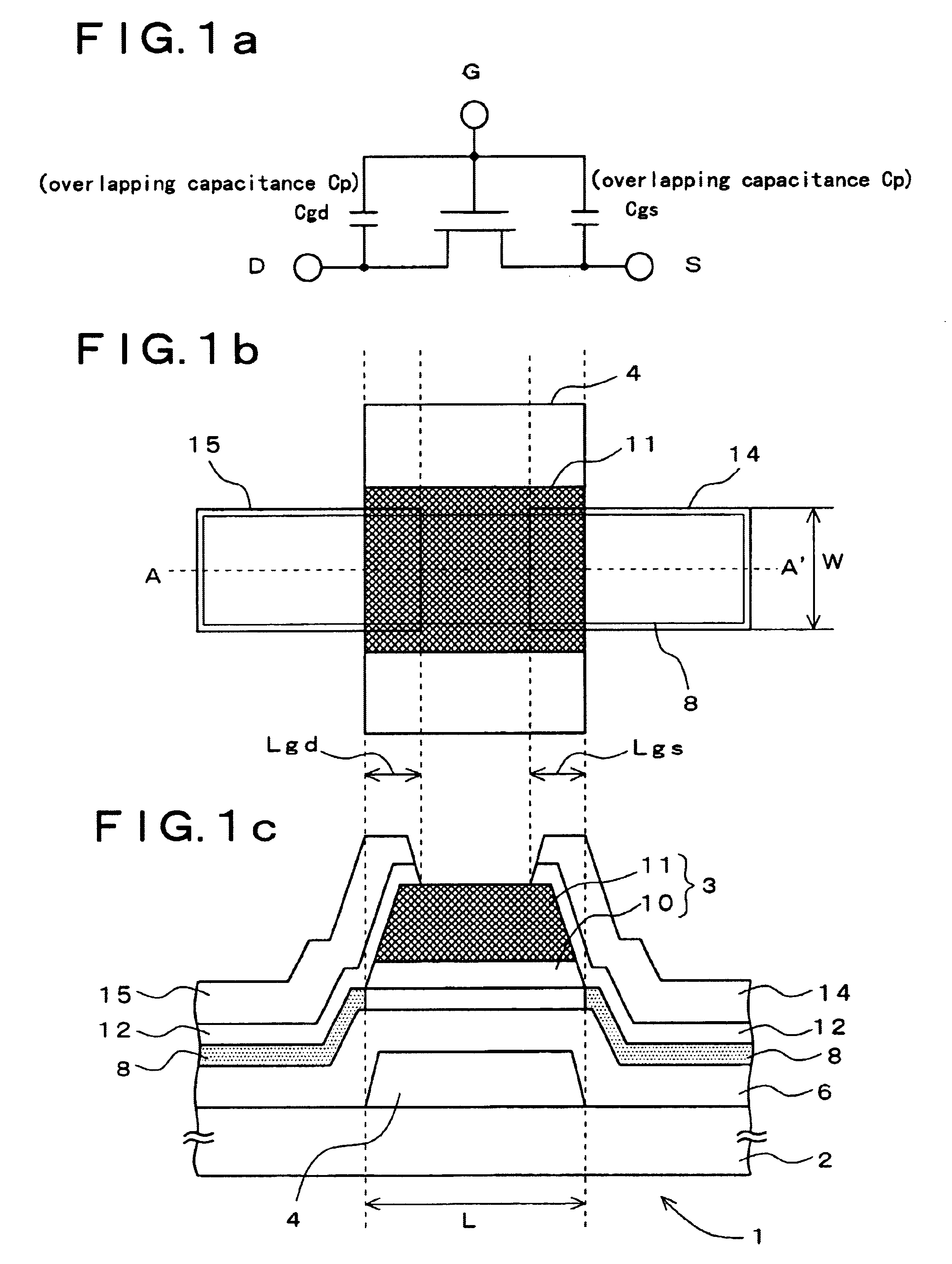

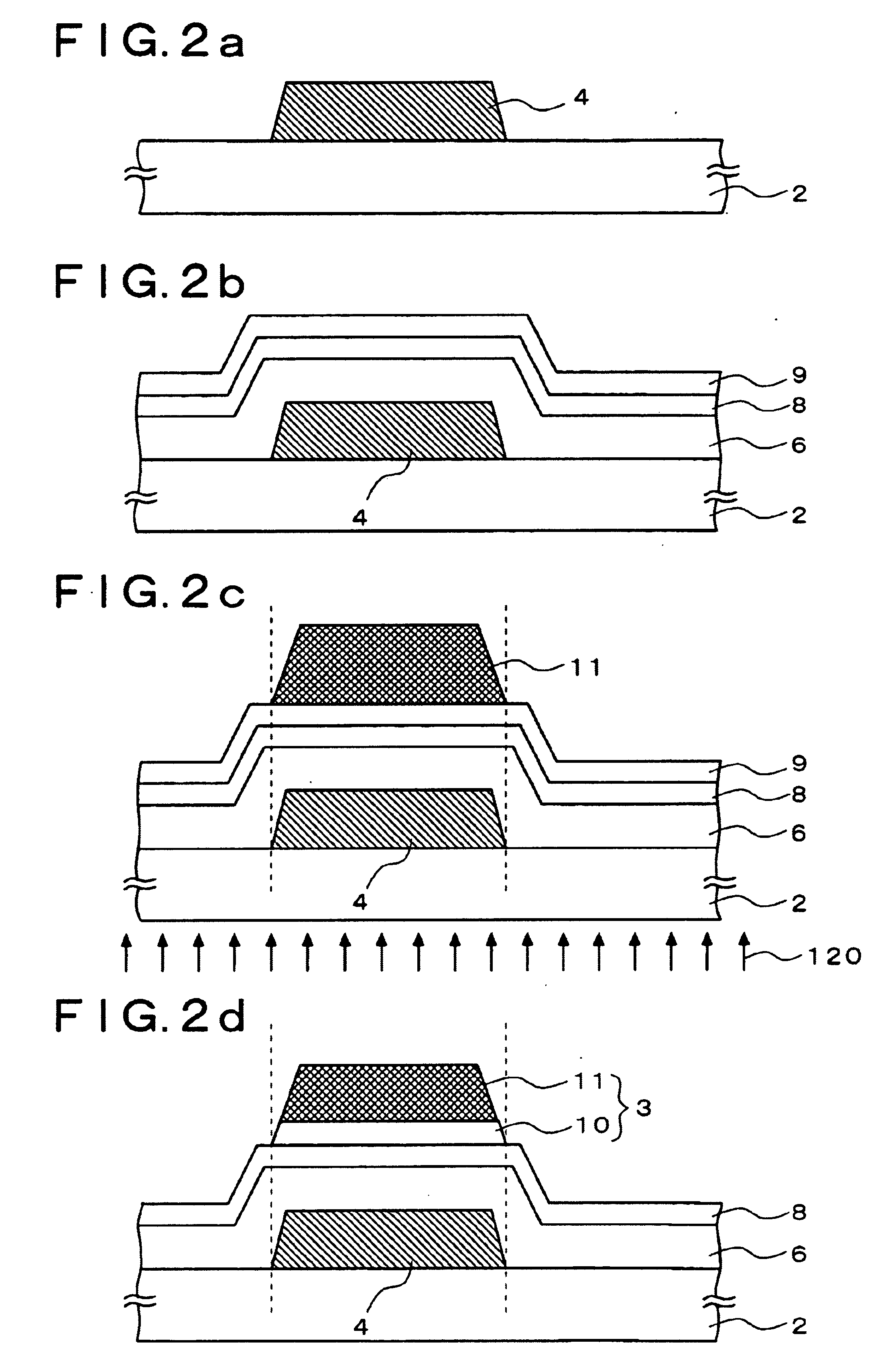

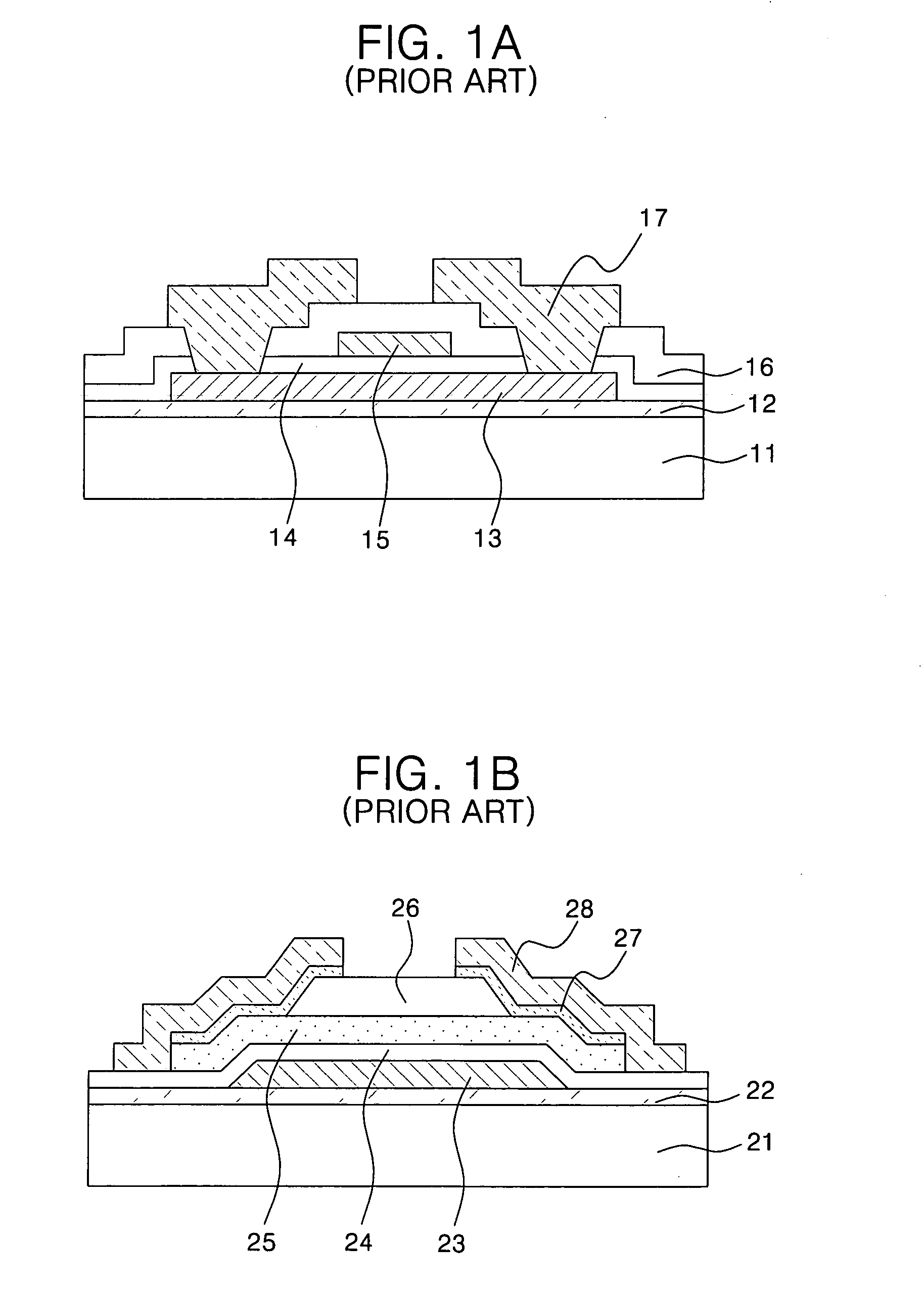

Thin film transistor, fabrication method thereof and liquid crystal display having the thin film transistor

InactiveUS6855954B1Suppress parasitic capacitanceHigh yieldTransistorSolid-state devicesLiquid-crystal displayBottom gate

The present invention relates to a thin film transistor, a fabrication method thereof and a liquid crystal display having the thin film transistor, and an object of the present invention is to provide a thin film transistor which improves a fabrication yield, a fabrication method thereof and a liquid crystal display having the thin film transistor. In a bottom-gate-type thin film transistor 1 having a gate electrode 4 formed on a substrate, a gate insulating film 6 formed on the gate electrode, an operational semiconductor film 8 formed on the gate insulating film 6 on the gate electrode 4, a channel protection film 3 formed on the operational semiconductor film, and a source and a drain electrodes 14 and 15 formed on both sides of the top surface of the channel protection film 3 connected to the operational semiconductor film with the operational semiconductor, and the channel protection film 3 has a first insulating layer 10 contacting to an upper interface of the operational semiconductor film 8 and a second insulating layer 11 formed on the first insulating layer.

Owner:UNIFIED INNOVATIVE TECH

Semiconductor device and manufacturing method thereof

ActiveUS20110024740A1Reduce parasitic capacitanceShort channel lengthTransistorElectroluminescent light sourcesDriver circuitBottom gate

A semiconductor device having a structure which enables sufficient reduction in parasitic capacitance is provided. In addition, the operation speed of thin film transistors in a driver circuit is improved. In a bottom-gate thin film transistor in which an oxide insulating layer is in contact with a channel formation region in an oxide semiconductor layer, a source electrode layer and a drain electrode layer are formed in such a manner that they do not overlap with a gate electrode layer. Thus, the distance between the gate electrode layer and the source electrode layer and between the gate electrode layer and the drain electrode layer are increased; accordingly, parasitic capacitance can be reduced.

Owner:SEMICON ENERGY LAB CO LTD

Nanowire MOSFET with doped epitaxial contacts for source and drain

A FET structure with a nanowire forming the FET channel, and doped source and drain regions formed by radial epitaxy from the nanowire body is disclosed. A top gated and a bottom gated nanowire FET structures are discussed. The source and drain fabrication can use either selective or non-selective epitaxy.

Owner:GLOBALFOUNDRIES US INC

Display device

InactiveUS20020005696A1Discharge tube luminescnet screensStatic indicating devicesDriver circuitImaging quality

The image quality of a display device using a bottom gate TFT is improved. In particular, fluctuation in luminance is controlled and the frequency characteristic of a driver circuit is compensated by suppressing a change in amount of current flowing through an EL element which is caused by a change in surrounding temperature while the device is in use. A monitoring EL element is provided in addition to a pixel portion EL element. The monitoring EL element constitutes a temperature compensation circuit together with a buffer amplifier and the like. A current is supplied to the pixel portion EL element through the temperature compensation circuit. This makes it possible to keep the amount of current flowing through the pixel portion EL element constant against a change in temperature, and to control the fluctuation in luminance. An input signal is subjected to time base expansion to perform sampling with accuracy.

Owner:SEMICON ENERGY LAB CO LTD

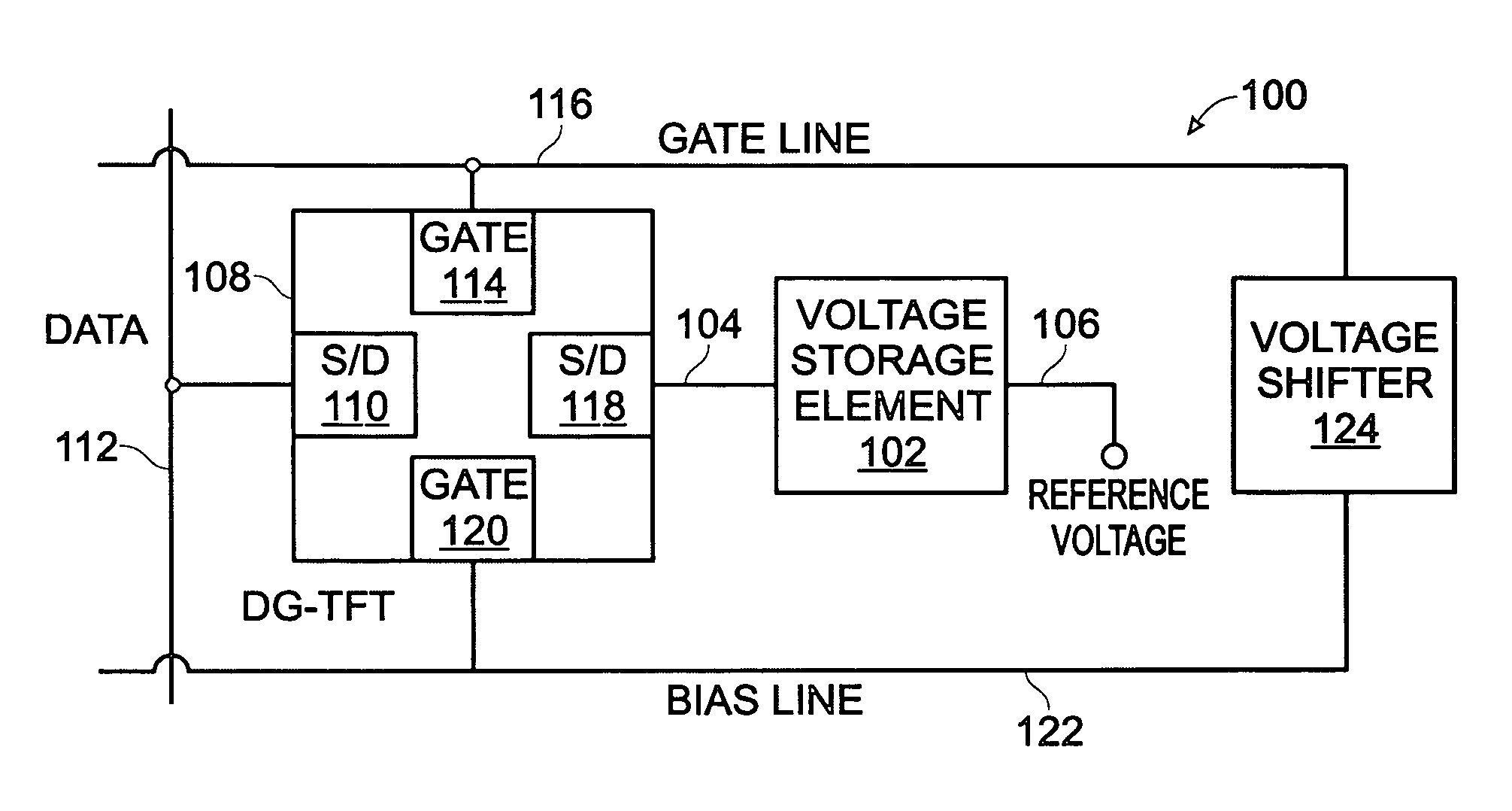

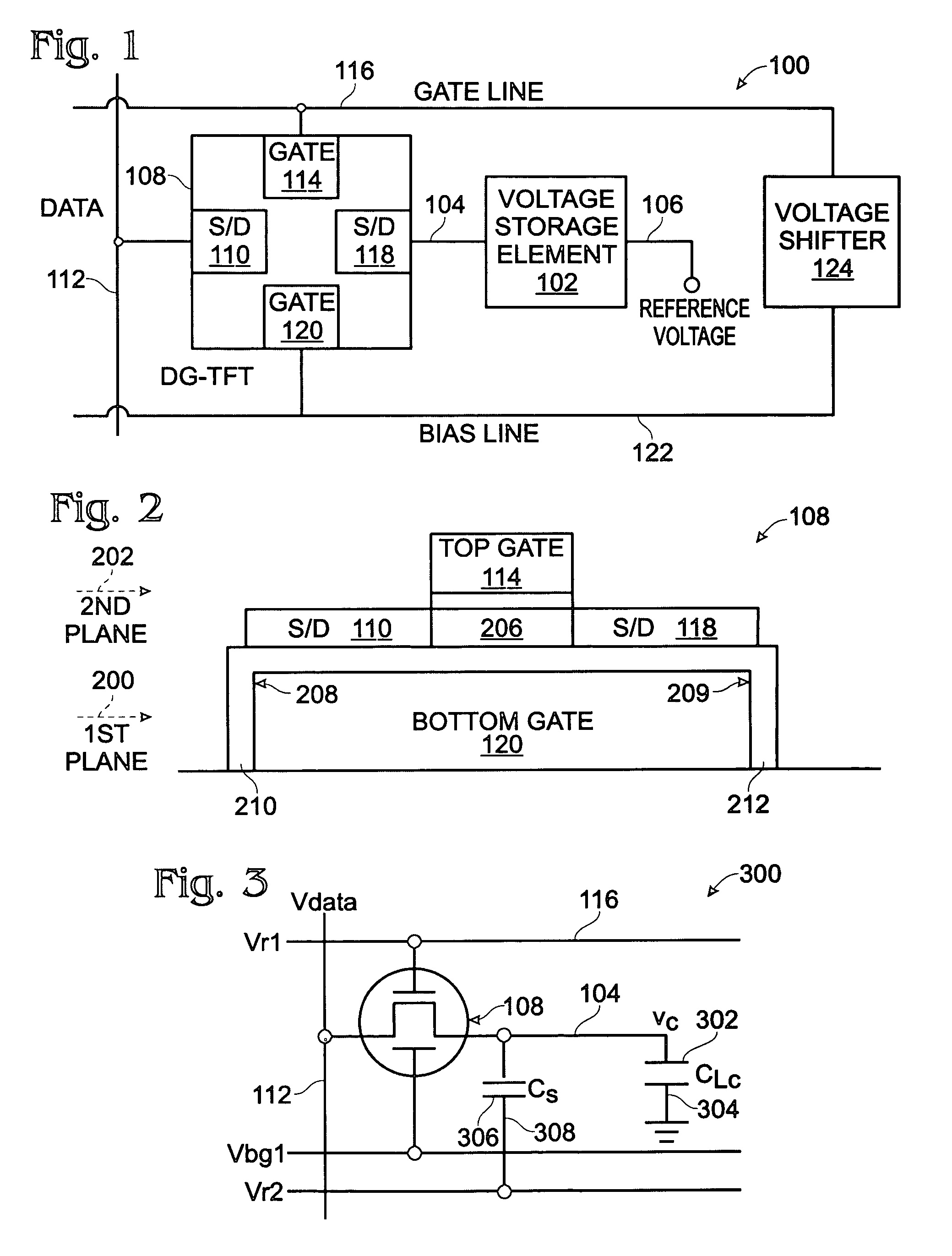

Dual-gate transistor display

ActiveUS20060066512A1Minimize leakage currentImprove featuresStatic indicating devicesSemiconductor devicesHemt circuitsDisplay device

A dual-gate thin-film transistor (DG-TFT) voltage storage circuit is provided. The circuit includes a voltage storage element, a DG-TFT having a first source / drain (S / D) connected to a data line, a top gate connected to a first gate line, a second S / D region connected to the voltage storage element, and a bottom gate connected to a bias line. In one aspect, the circuit further includes a voltage shifter having an input connected to the first gate line and an output to supply a bias voltage on the bias line. Examples of a voltage storage element include a capacitor, a liquid crystal (LC) pixel, and a light emitting diode (LED) pixel.

Owner:SHARP KK

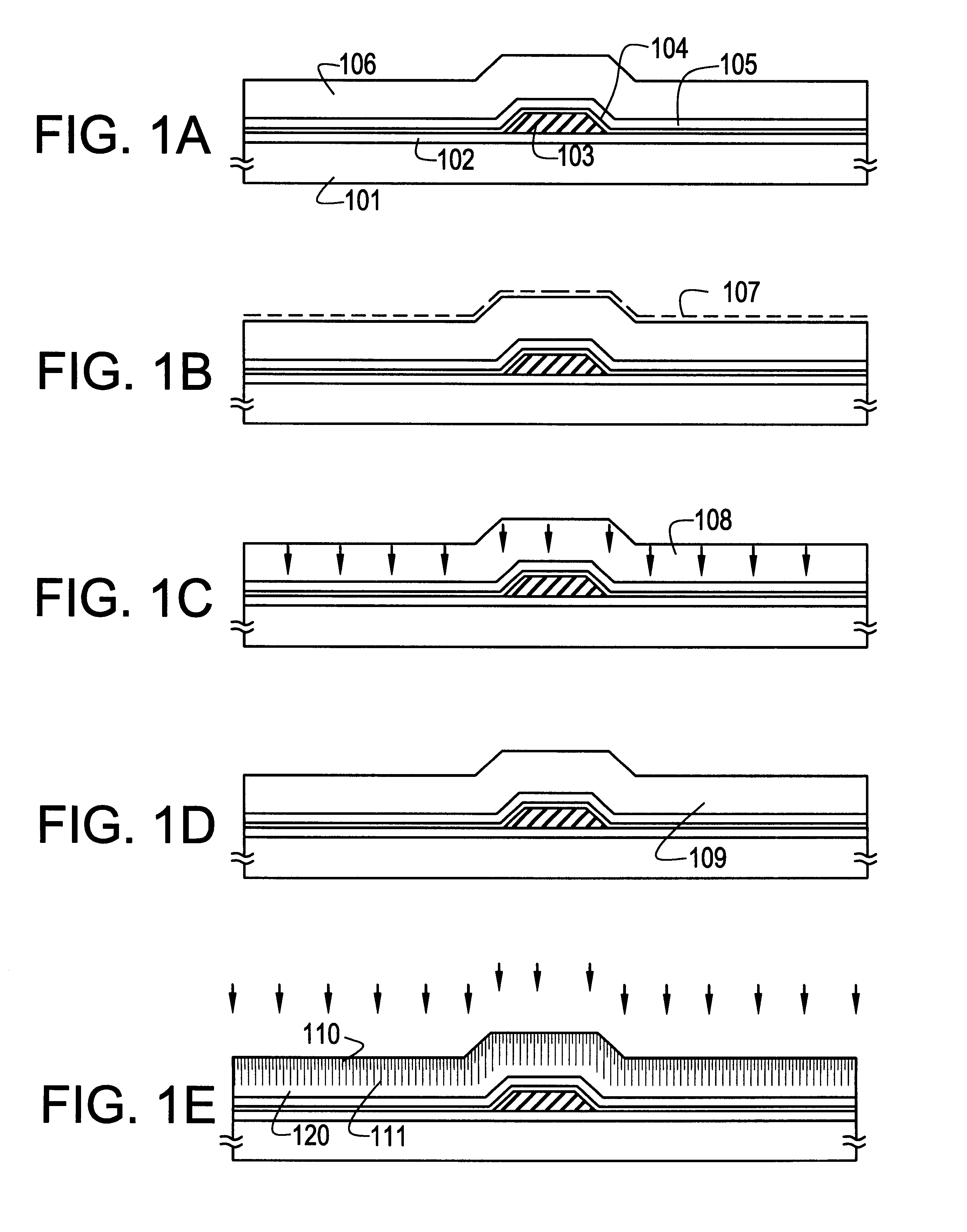

Semiconductor device and fabrication method thereof

To provide a technology for fabricating a bottom gate type TFT by steps having high mass production performance, an insulating film whose major component is silicon is formed on an active layer, the insulating film is patterned and openings are formed at portions thereof constituting source and drain regions at later steps, a resist is provided right above a portion for forming a channel forming region at later steps, a step of adding an impurity is carried out and in this case, the patterned insulating film is utilized as a doping mask.

Owner:SEMICON ENERGY LAB CO LTD

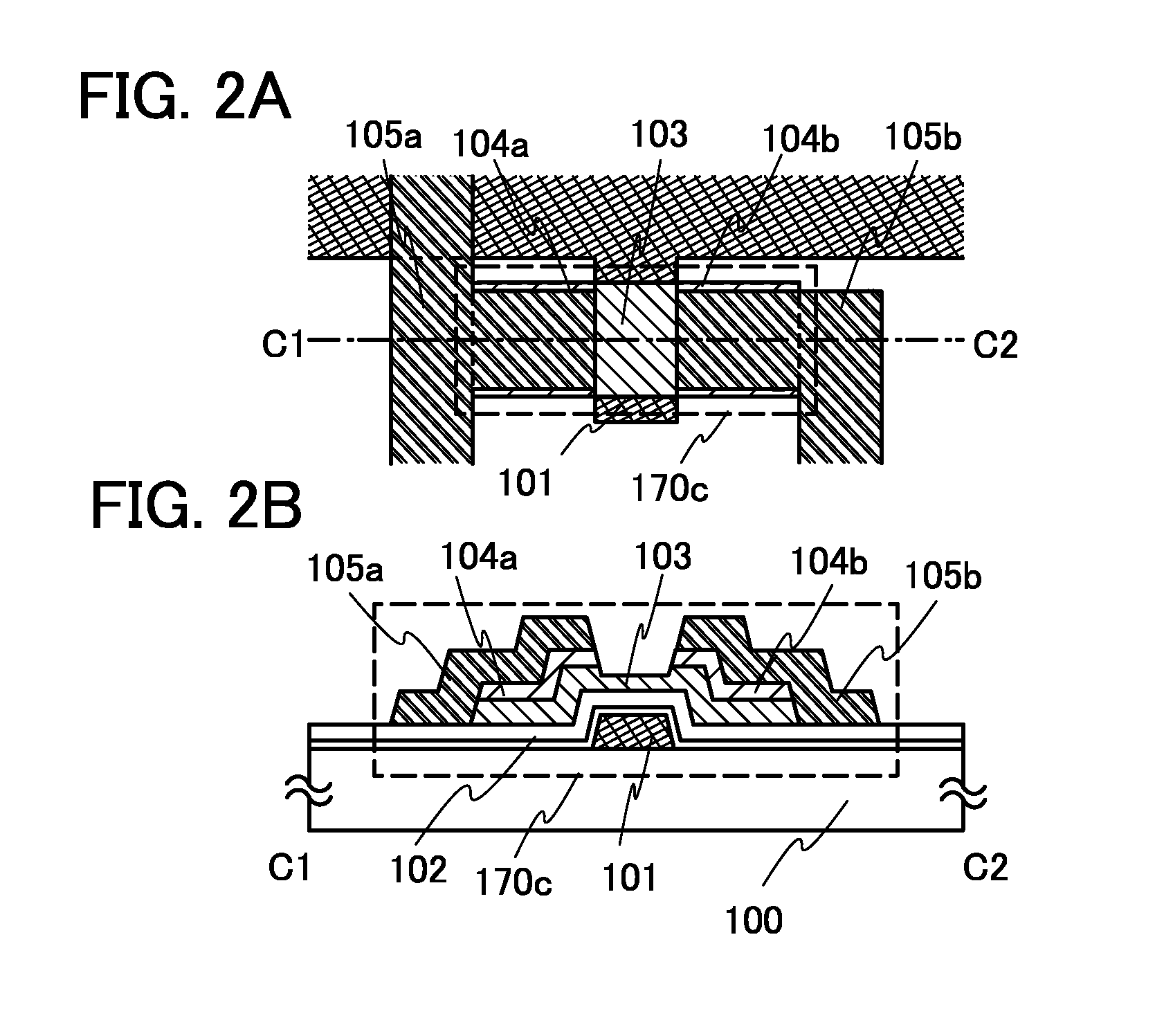

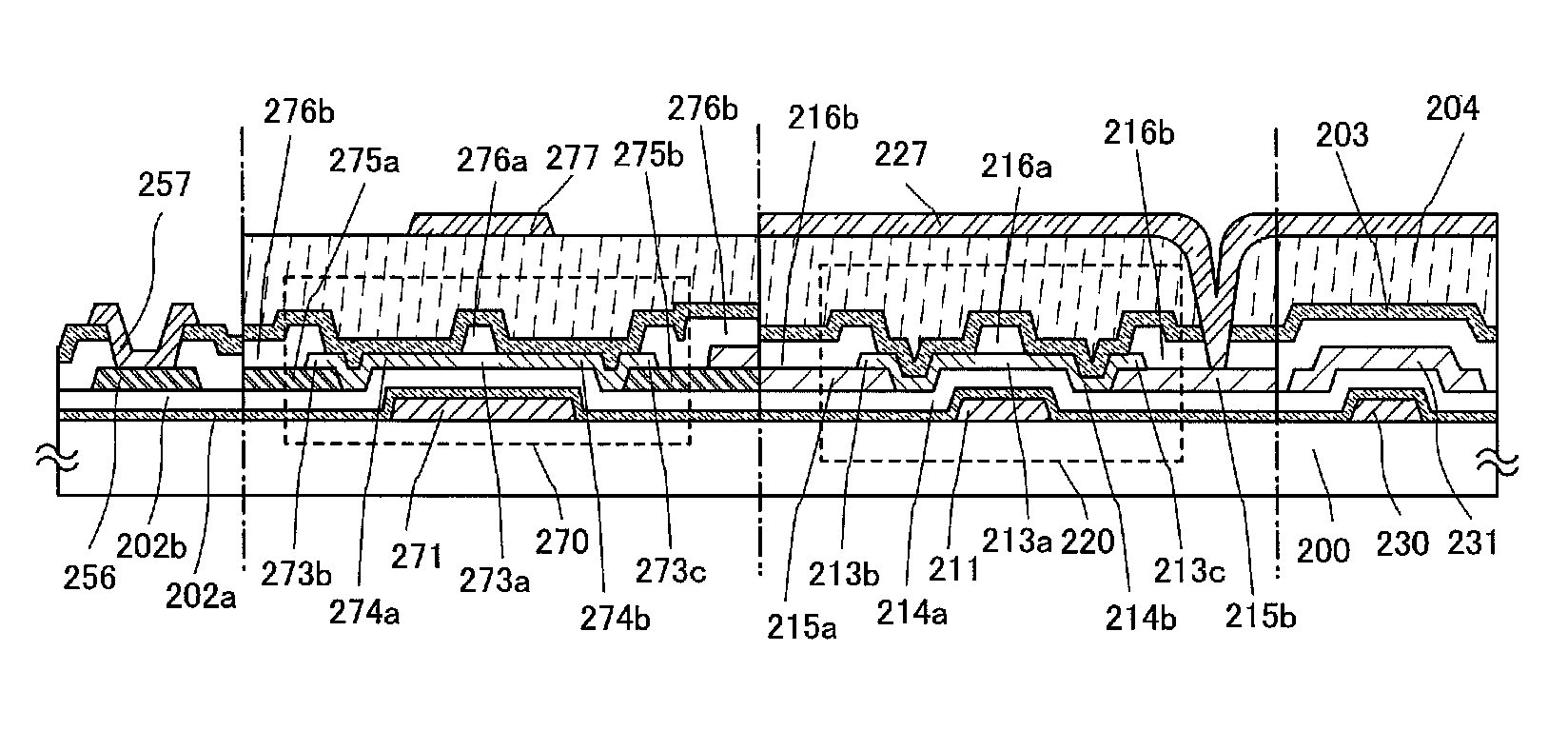

Semiconductor device and manufacturing method thereof

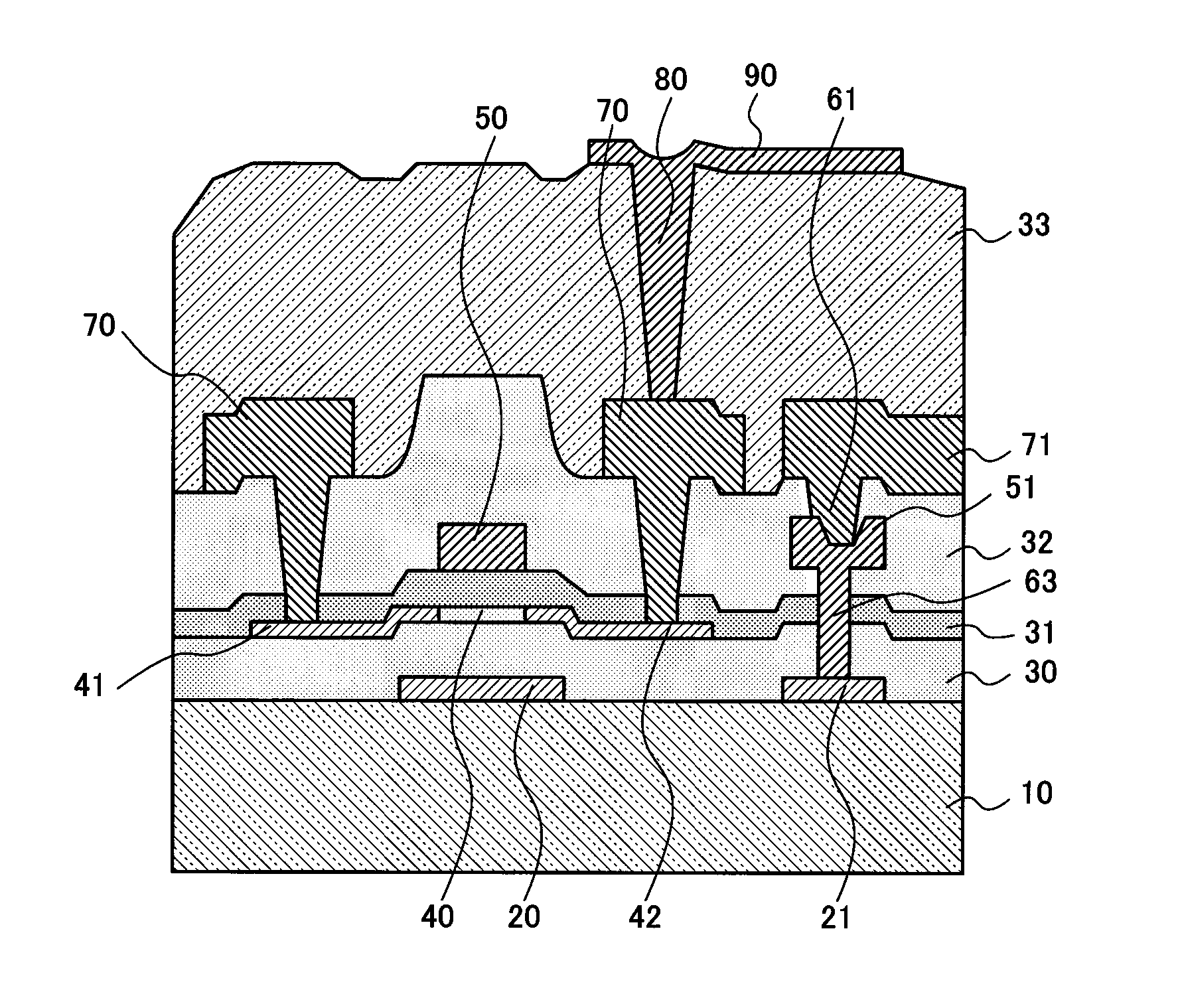

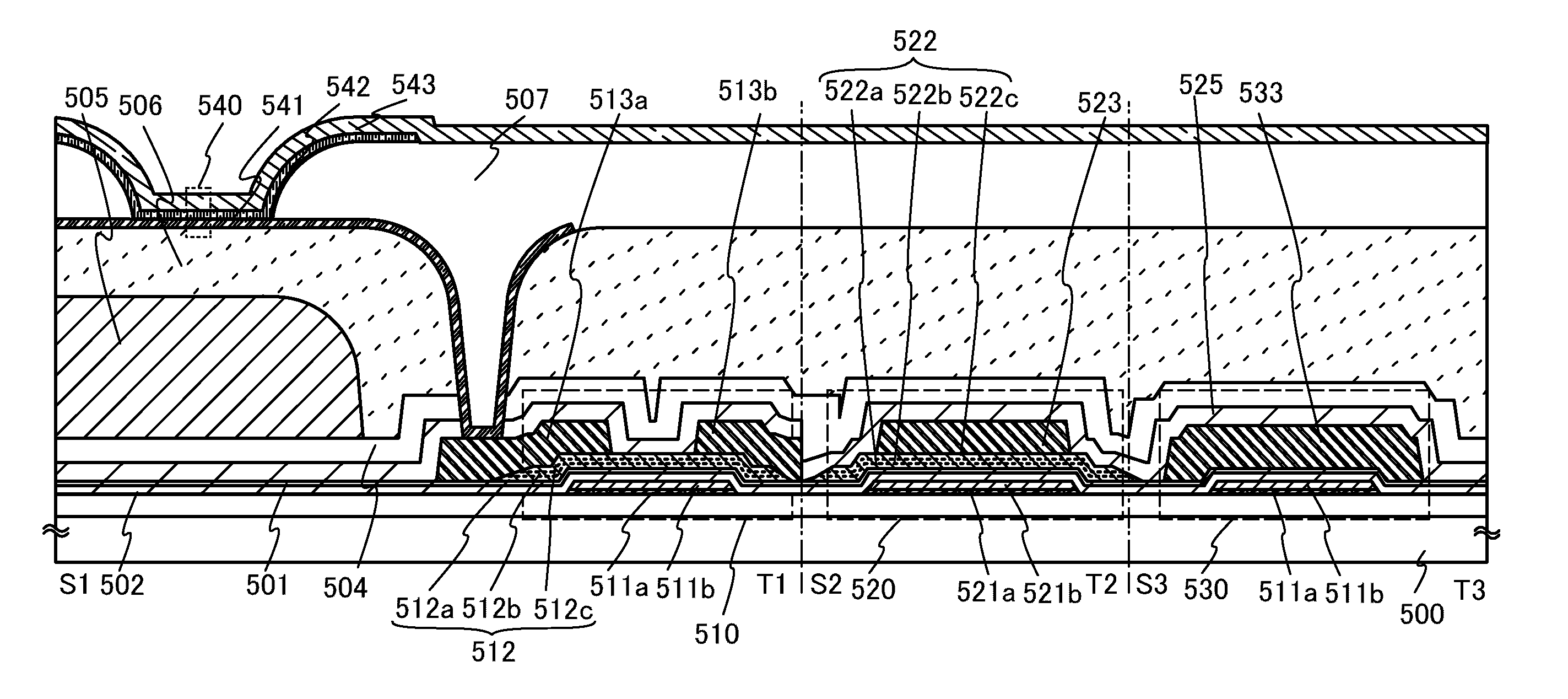

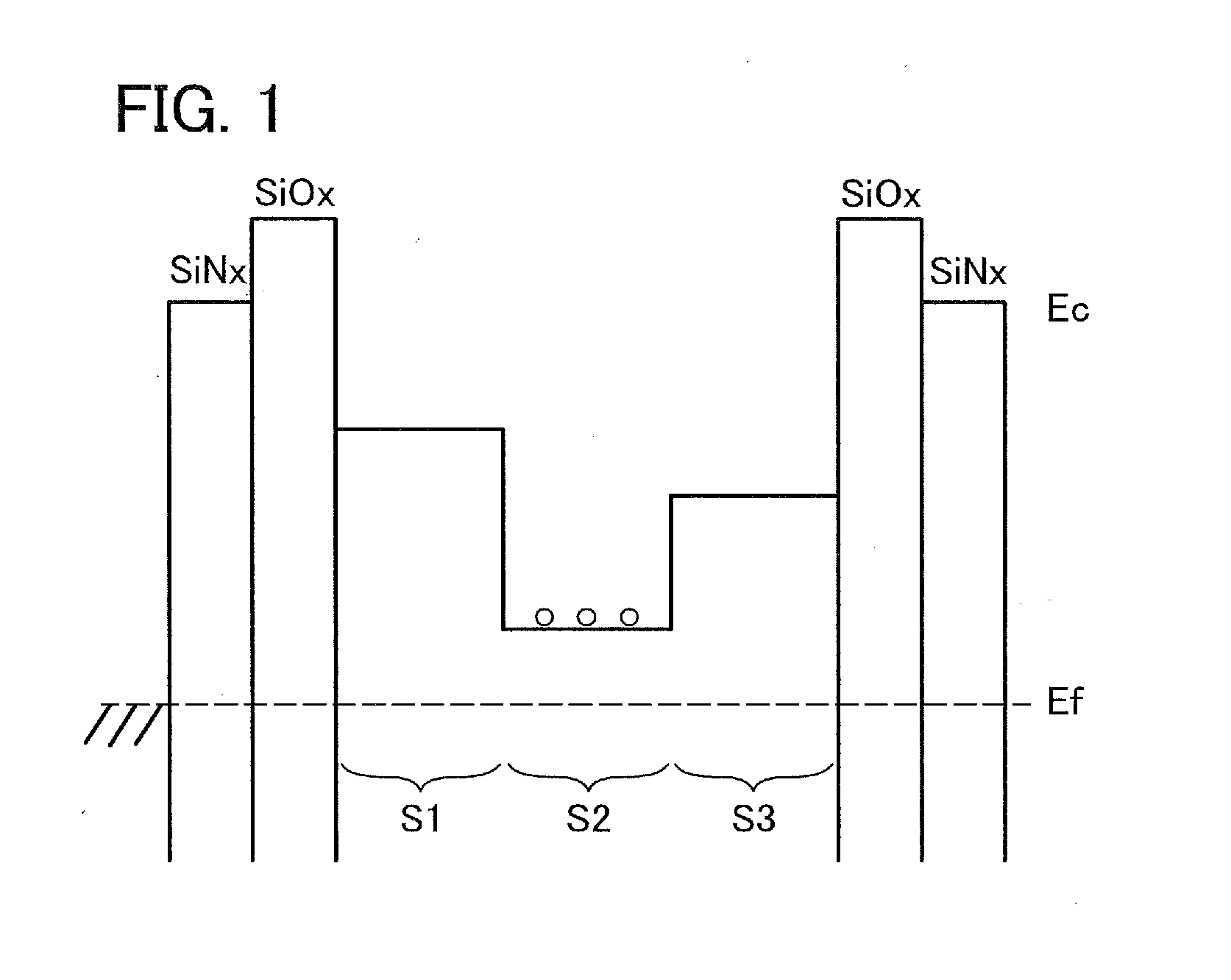

ActiveUS8952377B2Improve performanceImprove featuresTransistorElectroluminescent light sourcesDopantBottom gate

Provided are a transistor which has electrical characteristics requisite for its purpose and uses an oxide semiconductor layer and a semiconductor device including the transistor. In the bottom-gate transistor in which at least a gate electrode layer, a gate insulating film, and the semiconductor layer are stacked in this order, an oxide semiconductor stacked layer including at least two oxide semiconductor layers whose energy gaps are different from each other is used as the semiconductor layer. Oxygen and / or a dopant may be added to the oxide semiconductor stacked layer.

Owner:SEMICON ENERGY LAB CO LTD

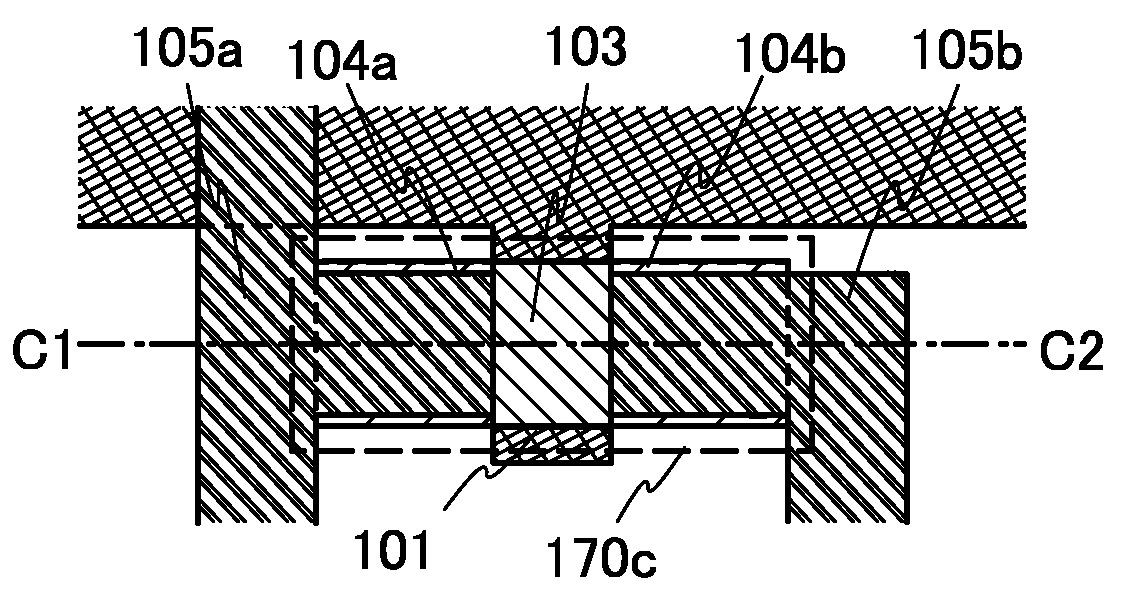

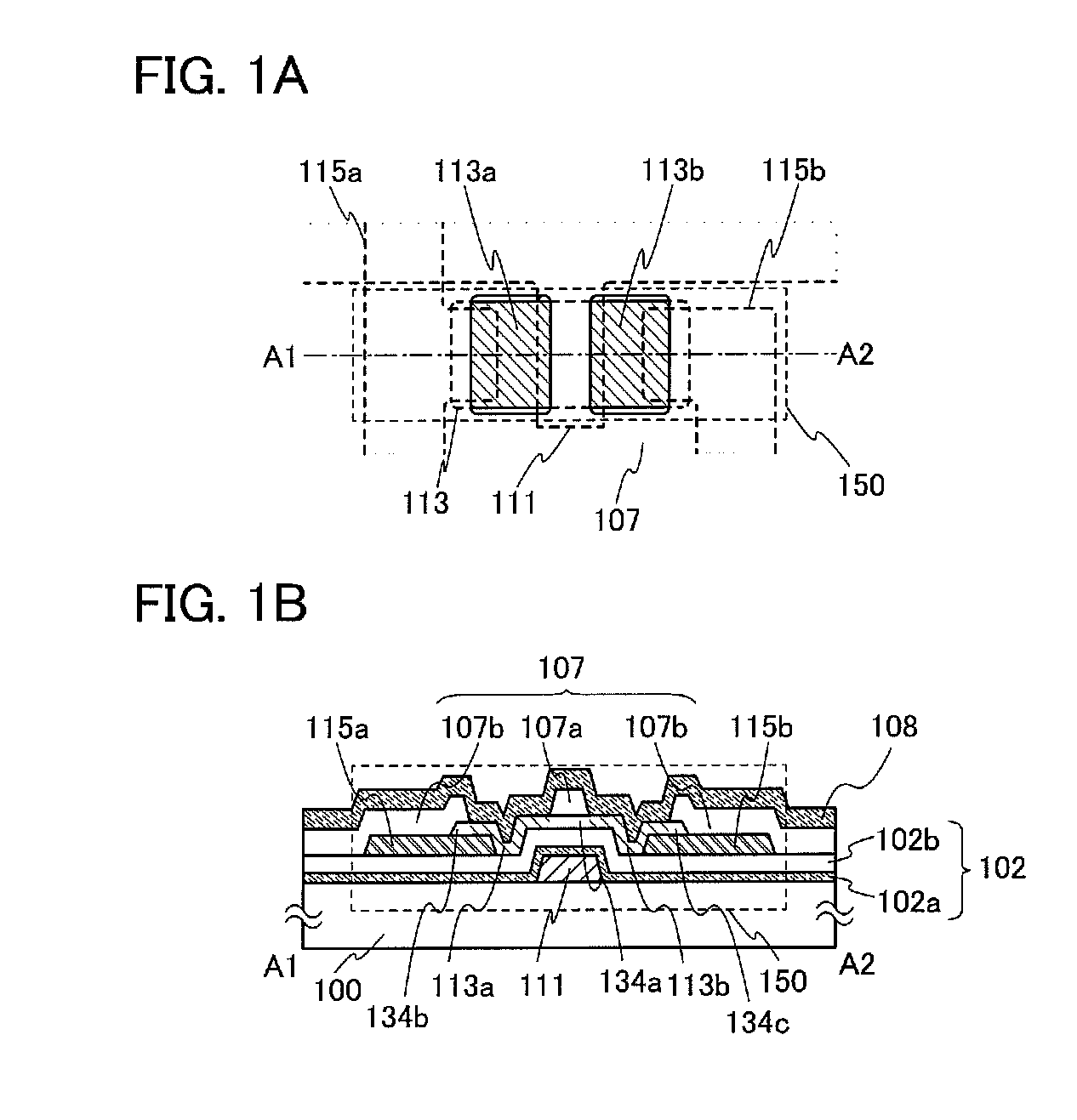

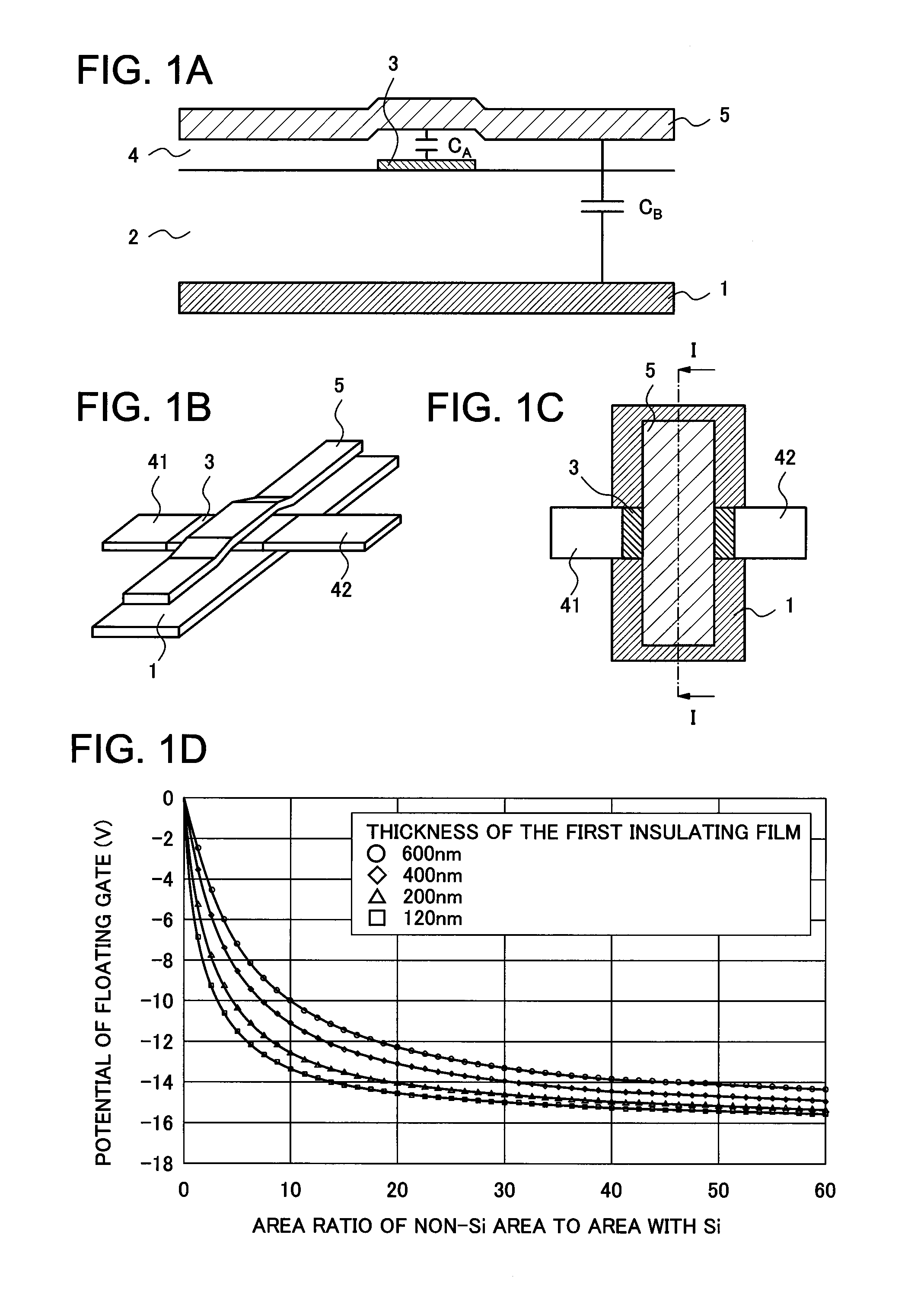

Thin film transistor substrate and thin film transistor used for the same

A thin film transistor (TFT) substrate includes first and second TFTs on the same substrate. The first TFT has a feature that a lower conductive layer or a bottom gate electrode layer is provided between the substrate and a first insulating layer while an upper conductive layer or a top gate electrode layer is disposed on a second insulating layer formed on a semiconductor layer which is formed on the first insulating layer. The first conductive layer has first and second areas such that the first area overlaps with the first conductive layer without overlapping with the semiconductor layer while the second area overlaps with the semiconductor layer, and the first area is larger than the second area while the second insulating layer is thinner than the first insulating layer. The second TFT has the same configuration as the first TFT except that the gate electrode layer is eliminated.

Owner:NEC LCD TECH CORP

Thin film transistor and method of fabricating the same

A bottom gate thin film transistor and method of fabricating the same are disclosed, in which a channel region is crystallized by a super grain silicon (SGS) crystallization method, including: forming a gate electrode and a gate insulating layer on an insulating substrate; forming an amorphous silicon layer on the gate insulating layer followed by forming a capping layer and a metal catalyst layer; performing heat treatment to crystallize the amorphous silicon layer into a polysilicon layer; and forming an etch stopper, source and drain regions and source and drain electrodes. The thin film transistor includes: an insulating substrate; a gate electrode formed on the substrate; a gate insulating layer formed on the gate electrode; a polysilicon layer formed on the gate insulating layer and crystallized by an SGS crystallization method; and source and drain regions and source and drain electrodes formed in a predetermined region of the substrate. As described, a method of fabricating the conventional top-gate thin film transistor has problems in that an interface between a channel region and a gate insulating layer is directly exposed to air or in direct contact with a photoresist pattern or etchant so that the thin film transistor may be contaminated by impurities such as oxide, organic and metal, or damaged in grains, and in that a metal catalyst remains at an interface in crystallization so that leakage current may occur. However, advantageously, a method of fabricating a bottom-gate thin film transistor according to the present invention has merits in that an interface between the channel region and the gate insulating layer is not exposed to air so that the aforementioned problems do not occur. Therefore, a thin film transistor having excellent characteristics may be fabricated and a fabrication process thereof may be simplified.

Owner:SAMSUNG DISPLAY CO LTD

Semiconductor device

ActiveUS20130334523A1High field-effect mobilityImprove reliabilityTransistorSolid-state devicesCharge carrierBottom gate

High field-effect mobility is provided for a transistor including an oxide semiconductor. Further, a highly reliable semiconductor device including the transistor is provided. In a bottom-gate transistor including an oxide semiconductor layer, an oxide semiconductor layer functioning as a current path (channel) of the transistor is sandwiched between oxide semiconductor layers having lower carrier densities than the oxide semiconductor layer. In such a structure, the channel is formed away from the interface of the oxide semiconductor stacked layer with an insulating layer in contact with the oxide semiconductor stacked layer, i.e., a buried channel is formed.

Owner:SEMICON ENERGY LAB CO LTD

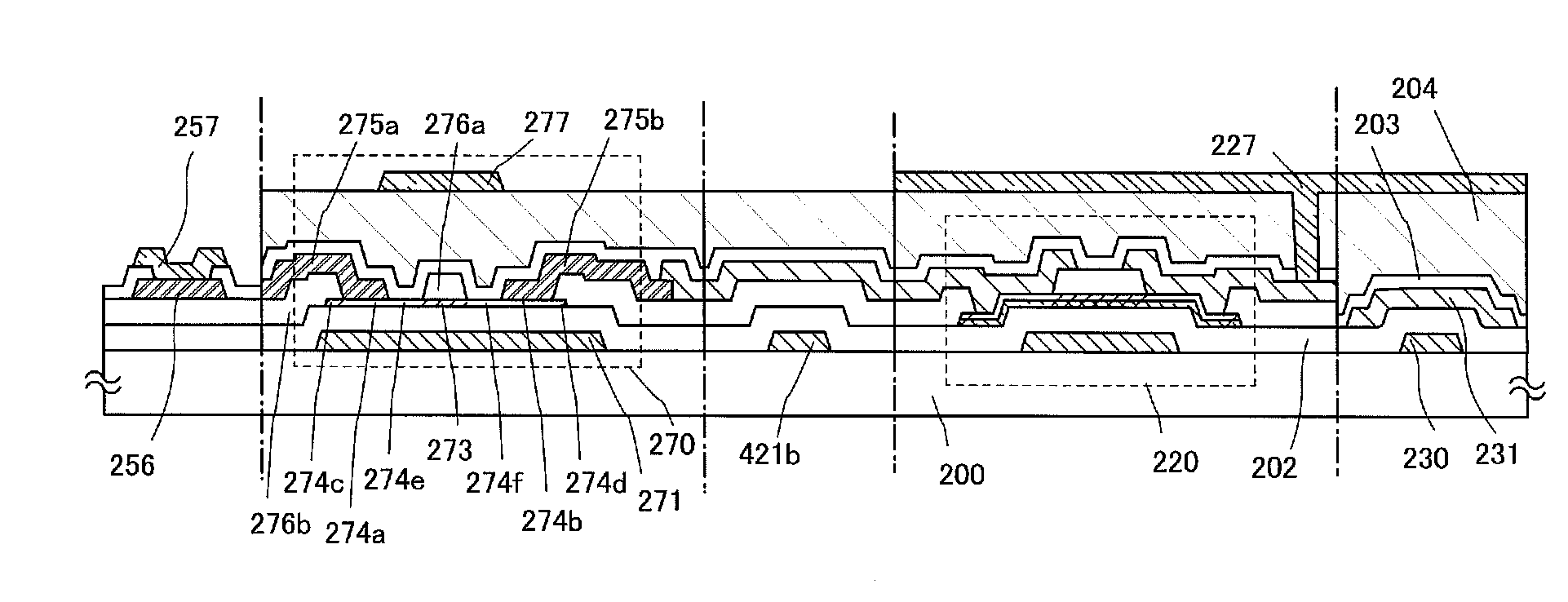

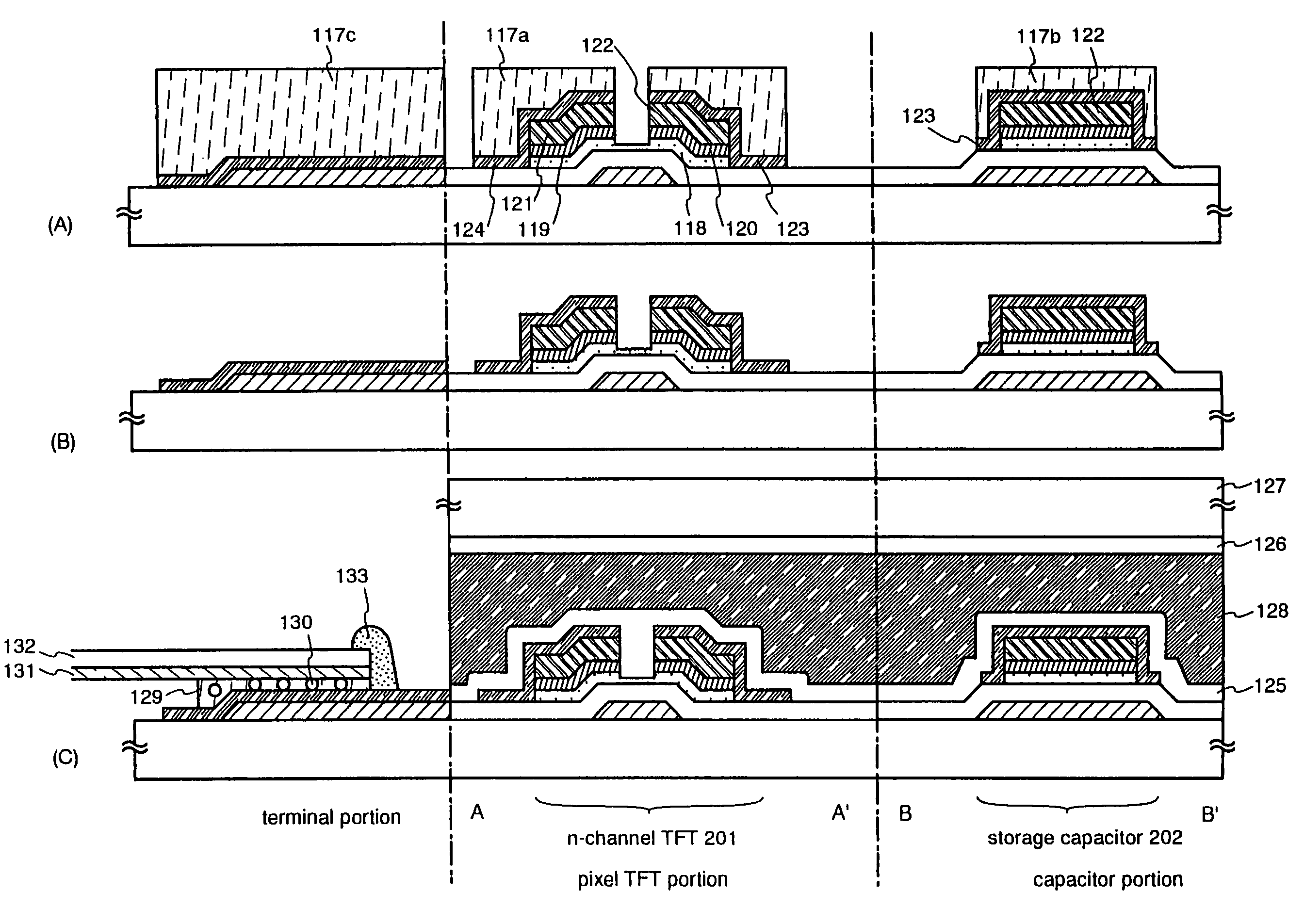

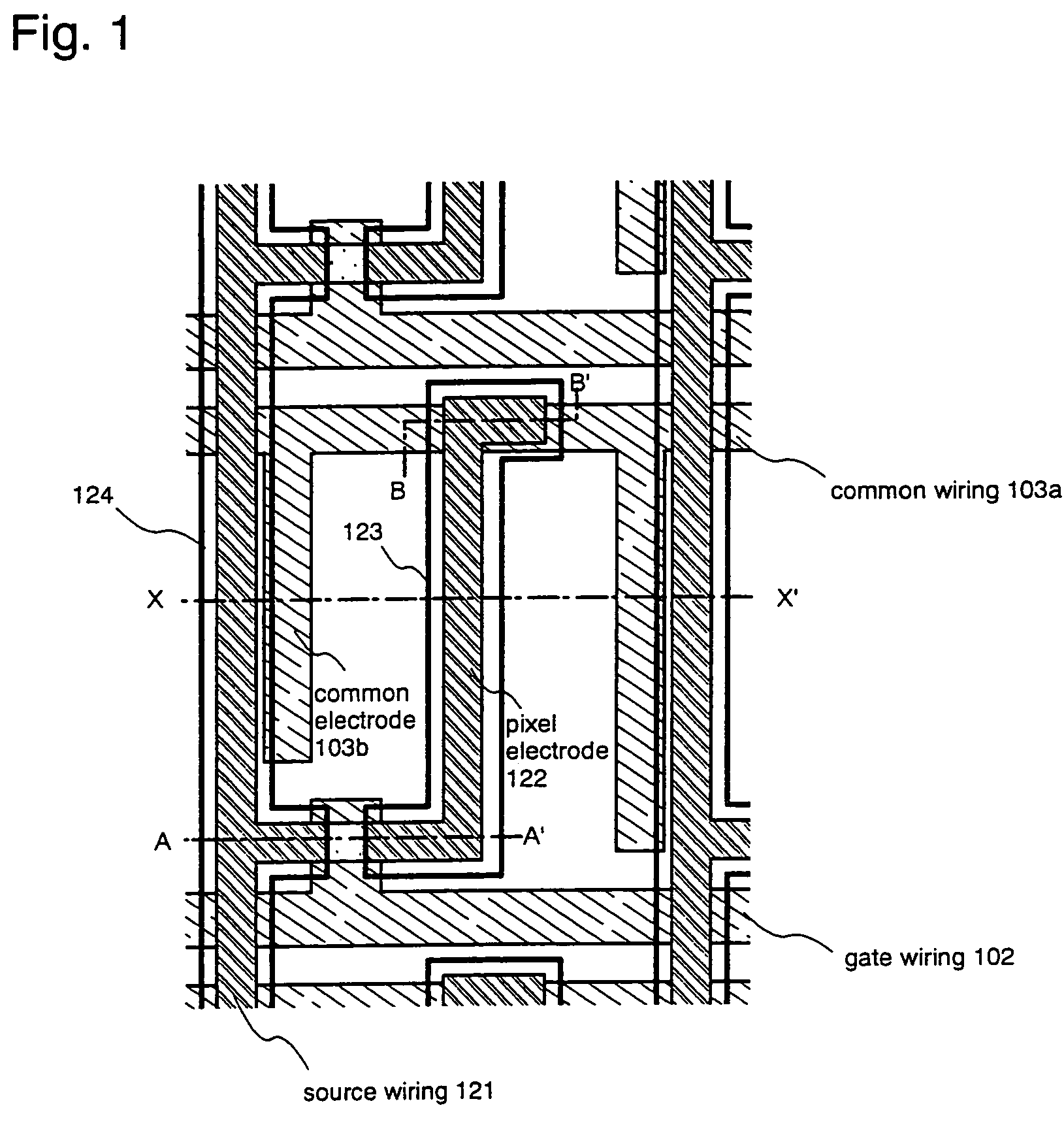

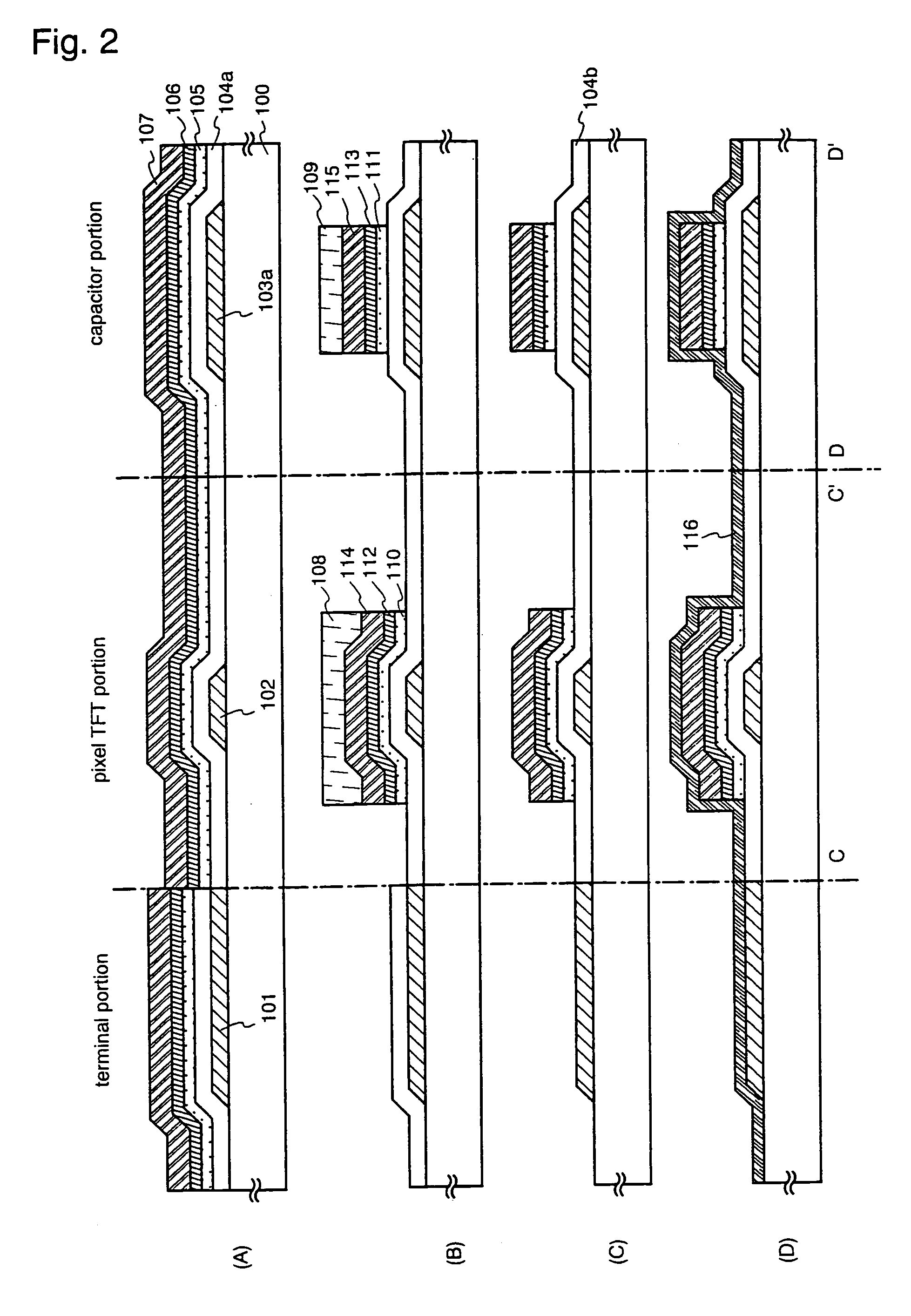

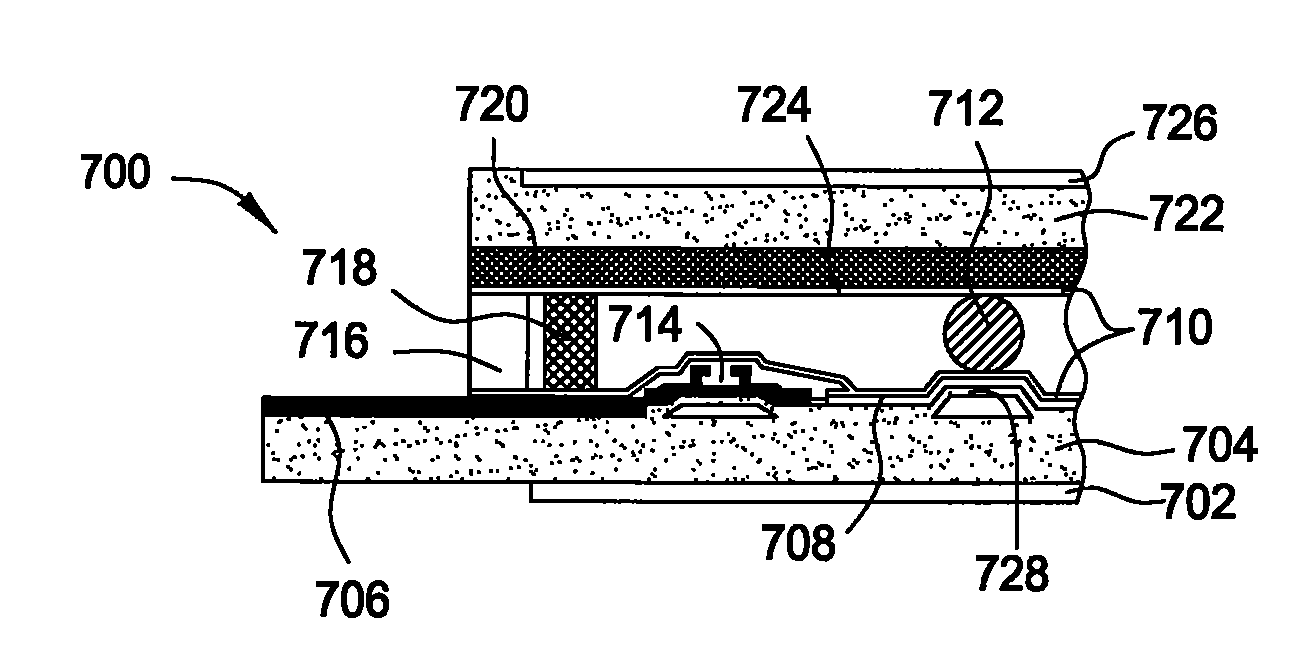

Liquid crystal display device and method of manufacturing the same

Owner:SEMICON ENERGY LAB CO LTD

Thin film transistors using thin film semiconductor materials

The present invention generally comprises TFTs having semiconductor material comprising oxygen, nitrogen, and one or more element selected from the group consisting of zinc, tin, gallium, cadmium, and indium as the active channel. The semiconductor material may be used in bottom gate TFTs, top gate TFTs, and other types of TFTs. The TFTs may be patterned by etching to create both the channel and the metal electrodes. Then, the source-drain electrodes may be defined by dry etching using the semiconductor material as an etch stop layer. The active layer carrier concentration, mobility, and interface with other layers of the TFT can be tuned to predetermined values. The tuning may be accomplished by changing the nitrogen containing gas to oxygen containing gas flow ratio, annealing and / or plasma treating the deposited semiconductor film, or changing the concentration of aluminum doping.

Owner:APPLIED MATERIALS INC