Patents

Literature

67results about How to "Short channel length" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

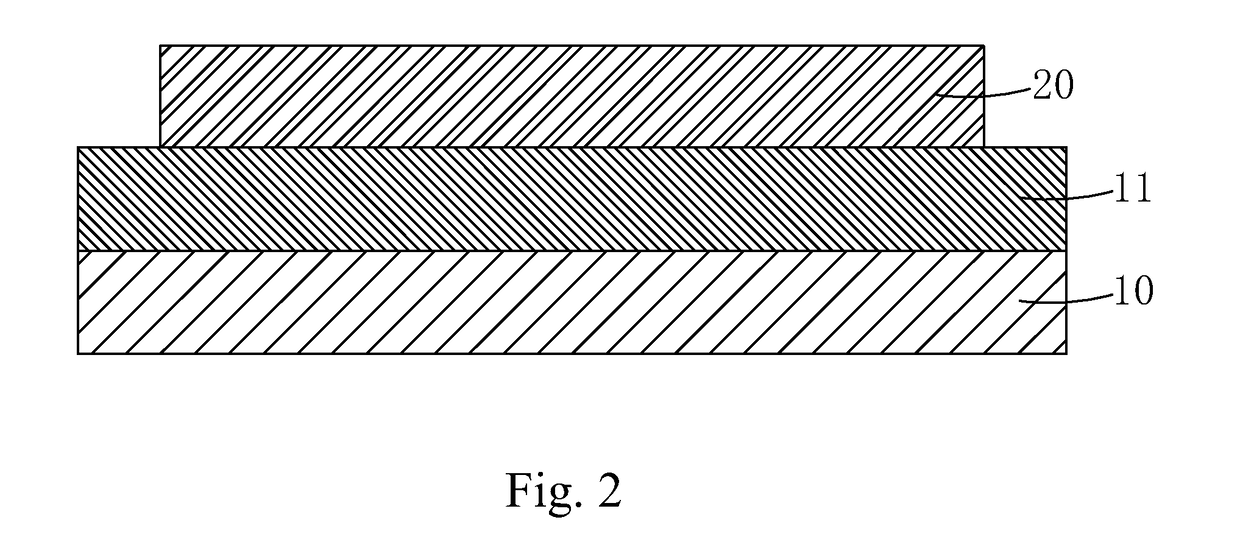

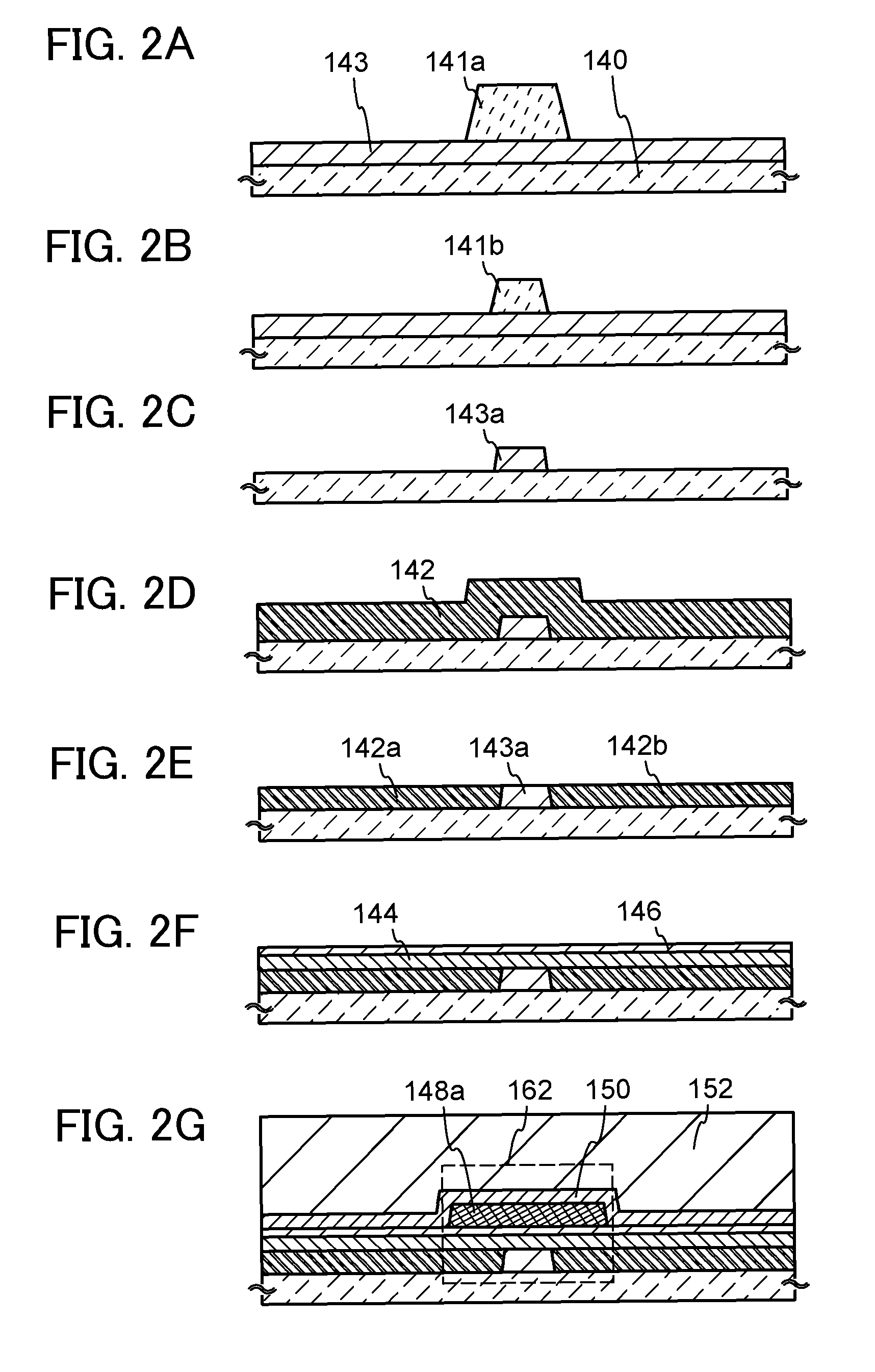

Wiring substrate, semiconductor device and manufacturing method thereof

InactiveUS20050276912A1Low costImprove throughputFinal product manufacturePrinted circuit aspectsDevice materialLaser light

The present invention provides a method for forming a wiring having a minute shape on a large substrate with a small number of steps, and further a wiring substrate formed by the method. Moreover, the present invention provides a semiconductor device in which cost reduction and throughput improvement are possible due to the small number of steps and reduction of materials and which has a semiconductor element with a minute structure, and further a manufacturing method thereof. According to the present invention, a composition including metal particles and organic resin is irradiated with laser light and a part of the metal particles is baked to form a conductive layer typified by a wiring, an electrode or the like over a substrate. Further, a semiconductor device having the baked conductive layer as a wiring or an electrode is formed.

Owner:SEMICON ENERGY LAB CO LTD

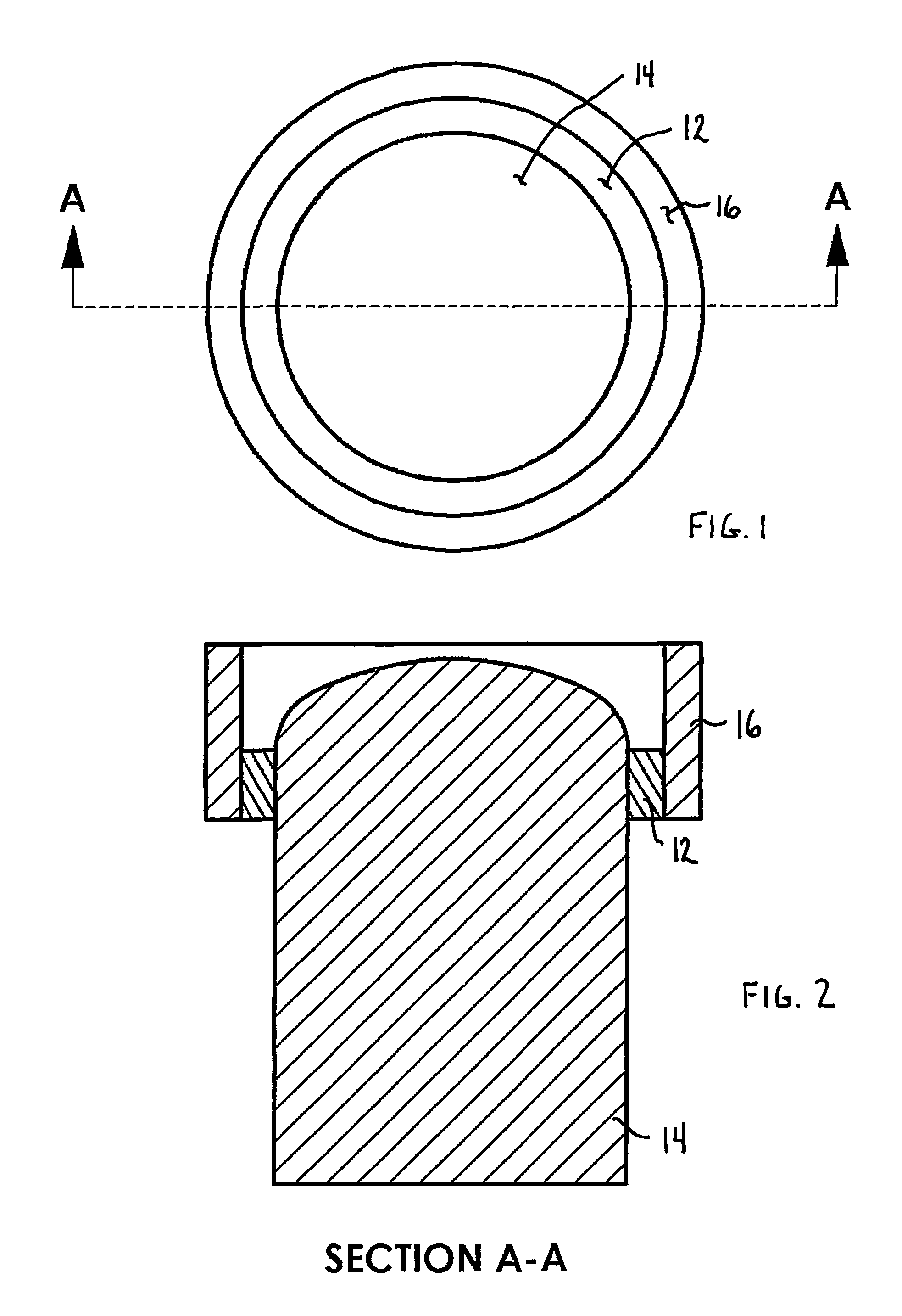

Power transistor having vertical FETs and method for making same

InactiveUS6060746ALower resistanceEasy to controlTransistorSolid-state devicesMOSFETElectrical and Electronics engineering

A power transistor having of a plurality of vertical MOSFET devices combined in parallel to achieve high-performance operation and methods of fabricating this device.

Owner:IBM CORP

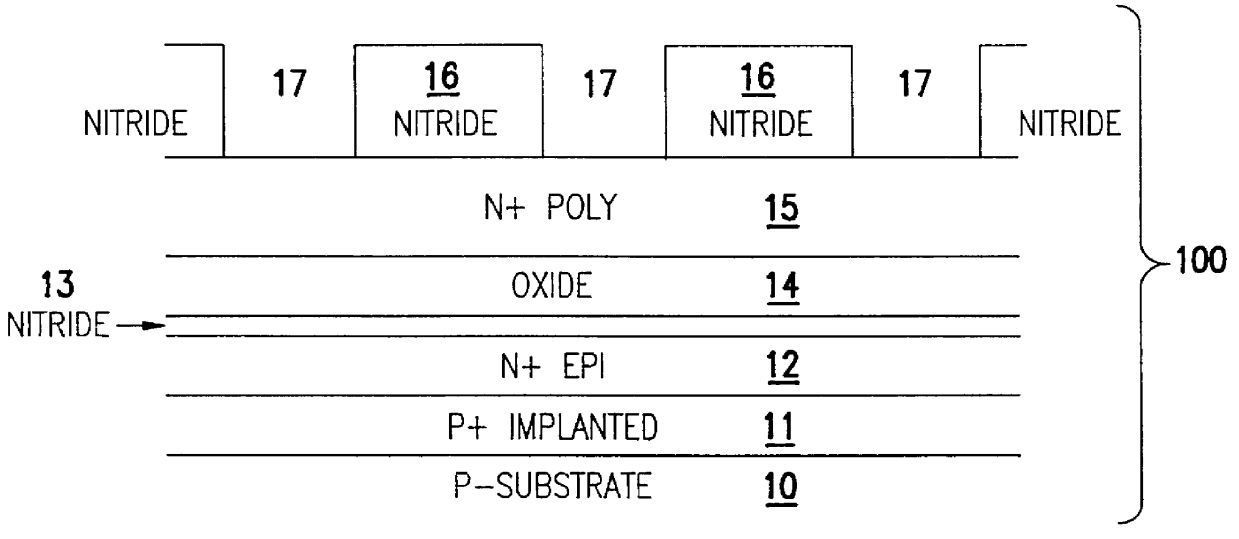

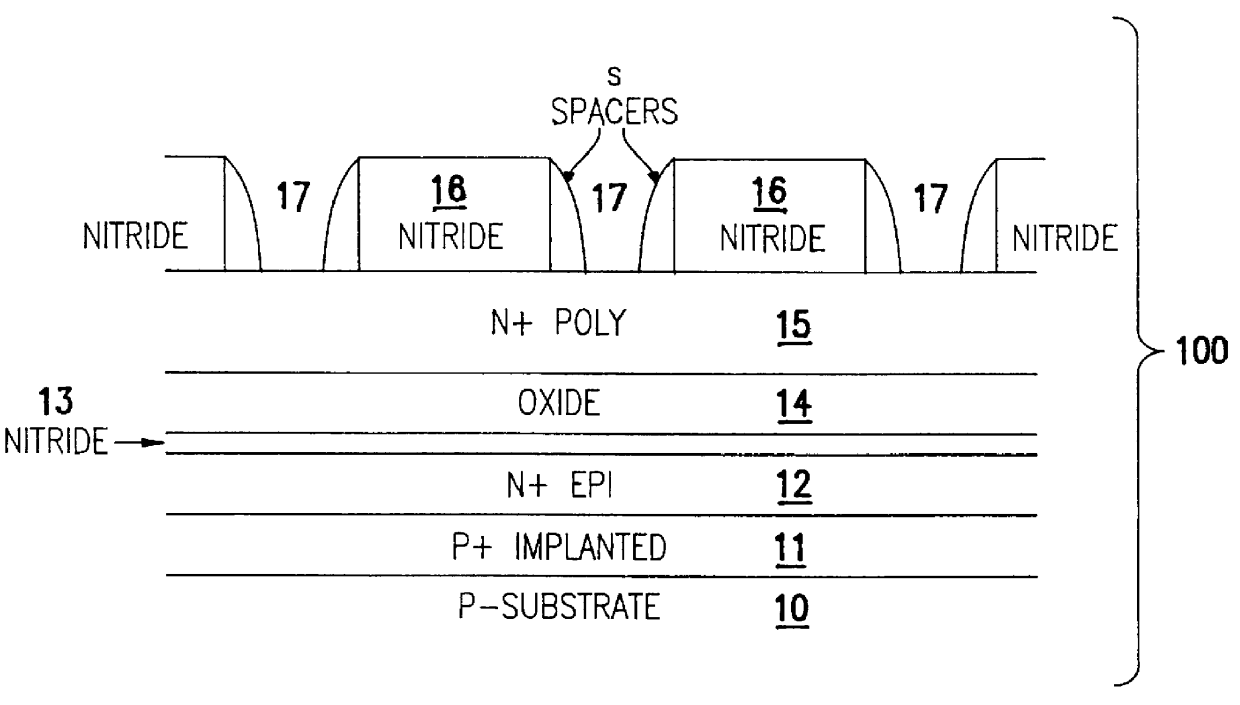

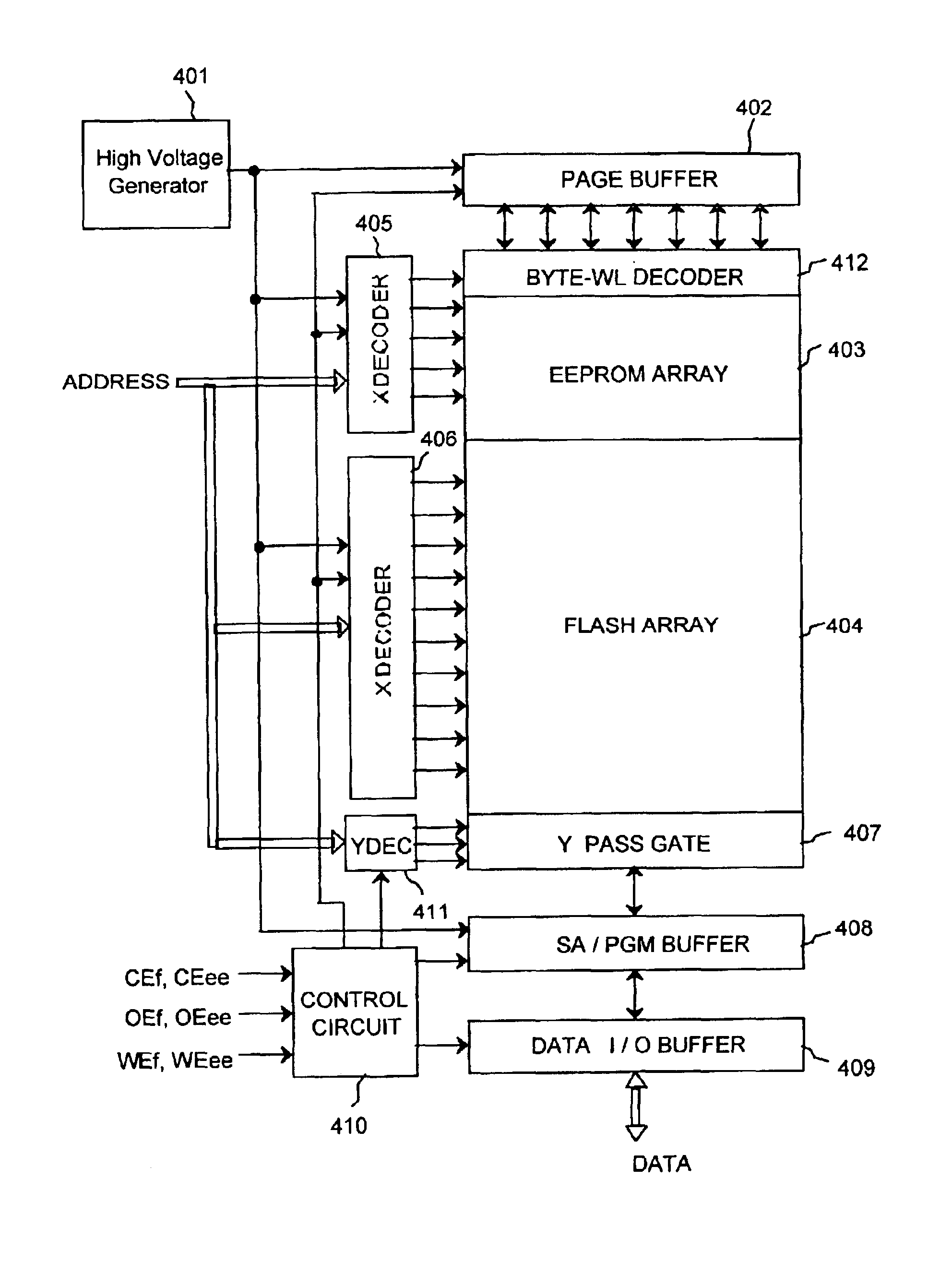

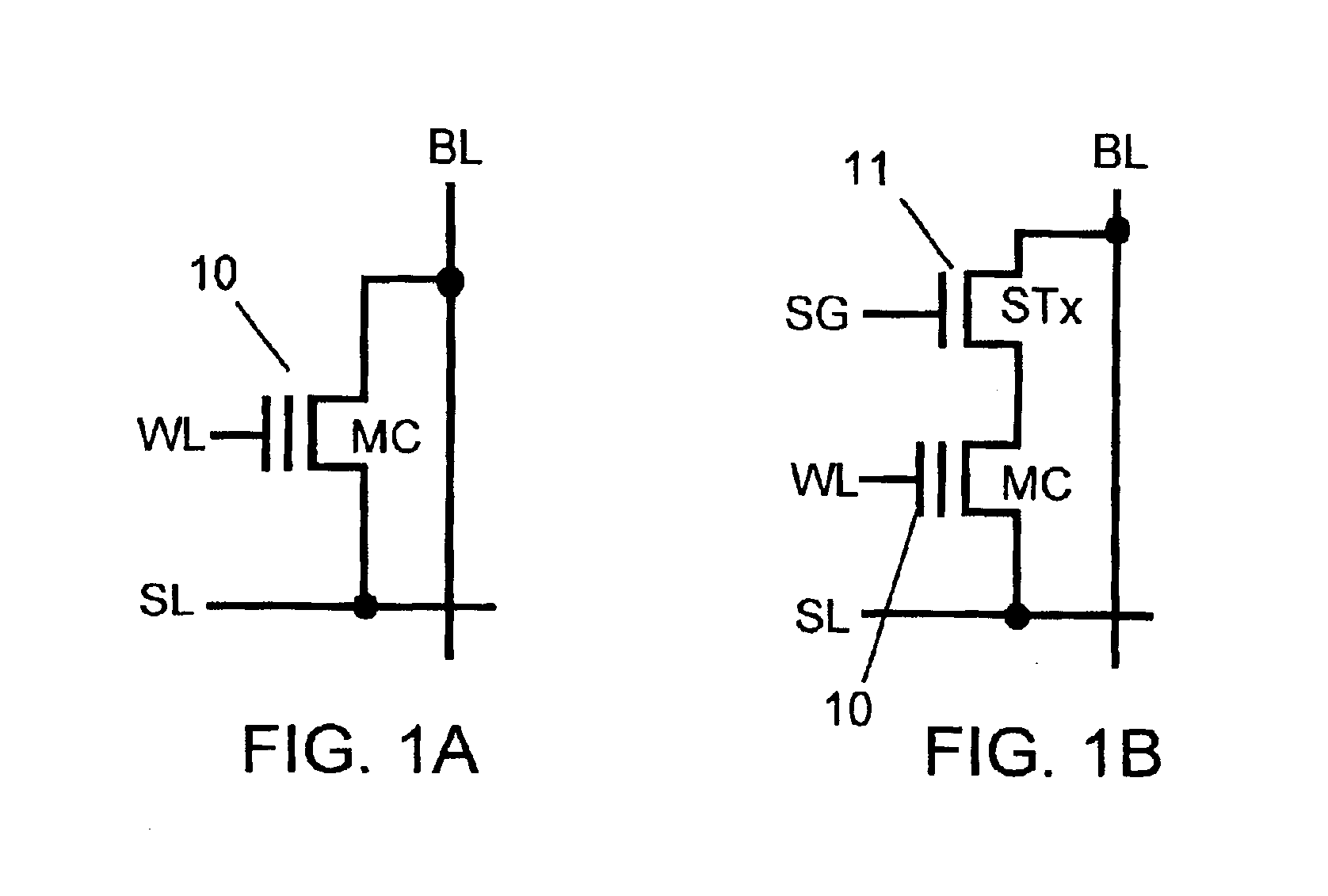

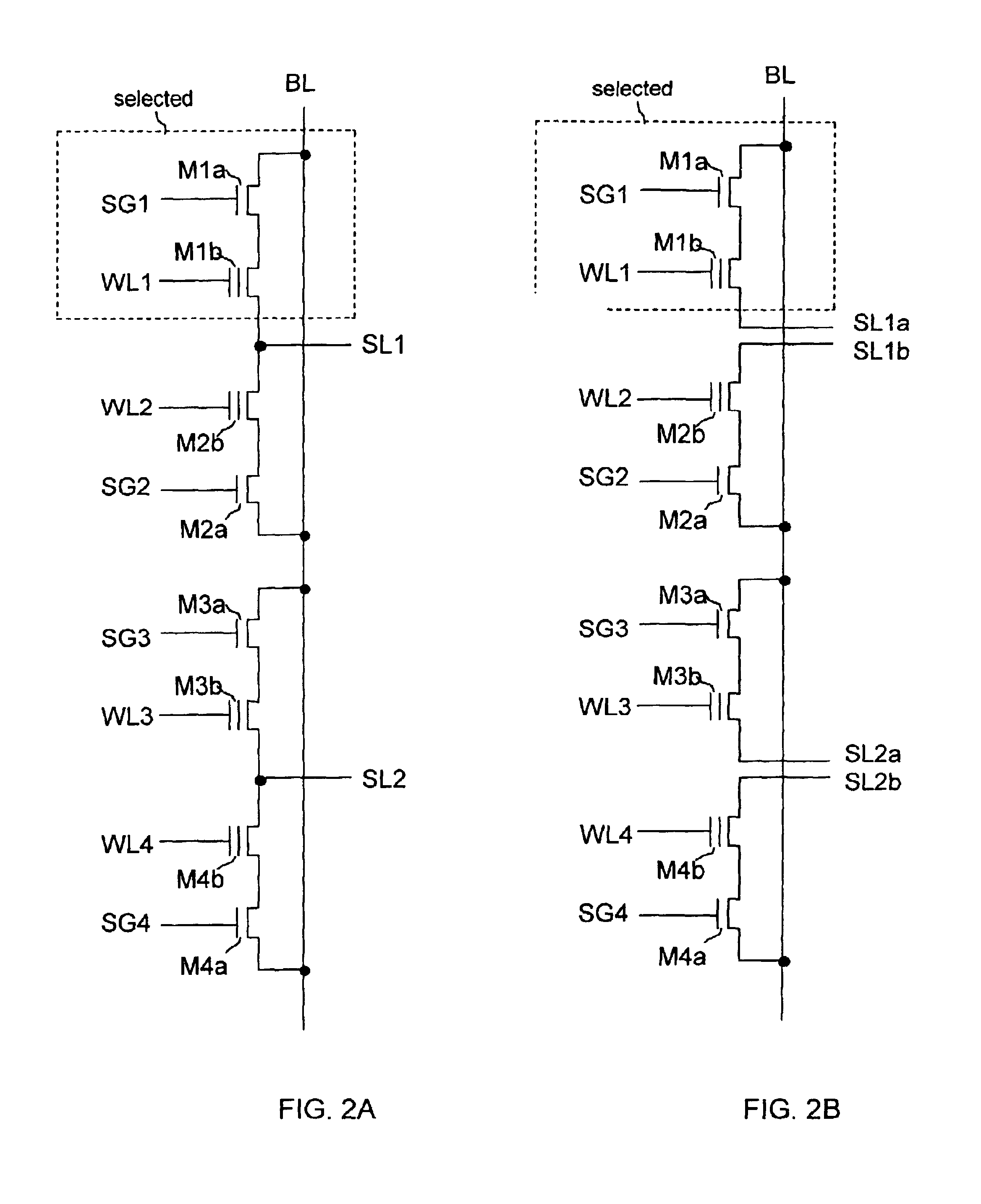

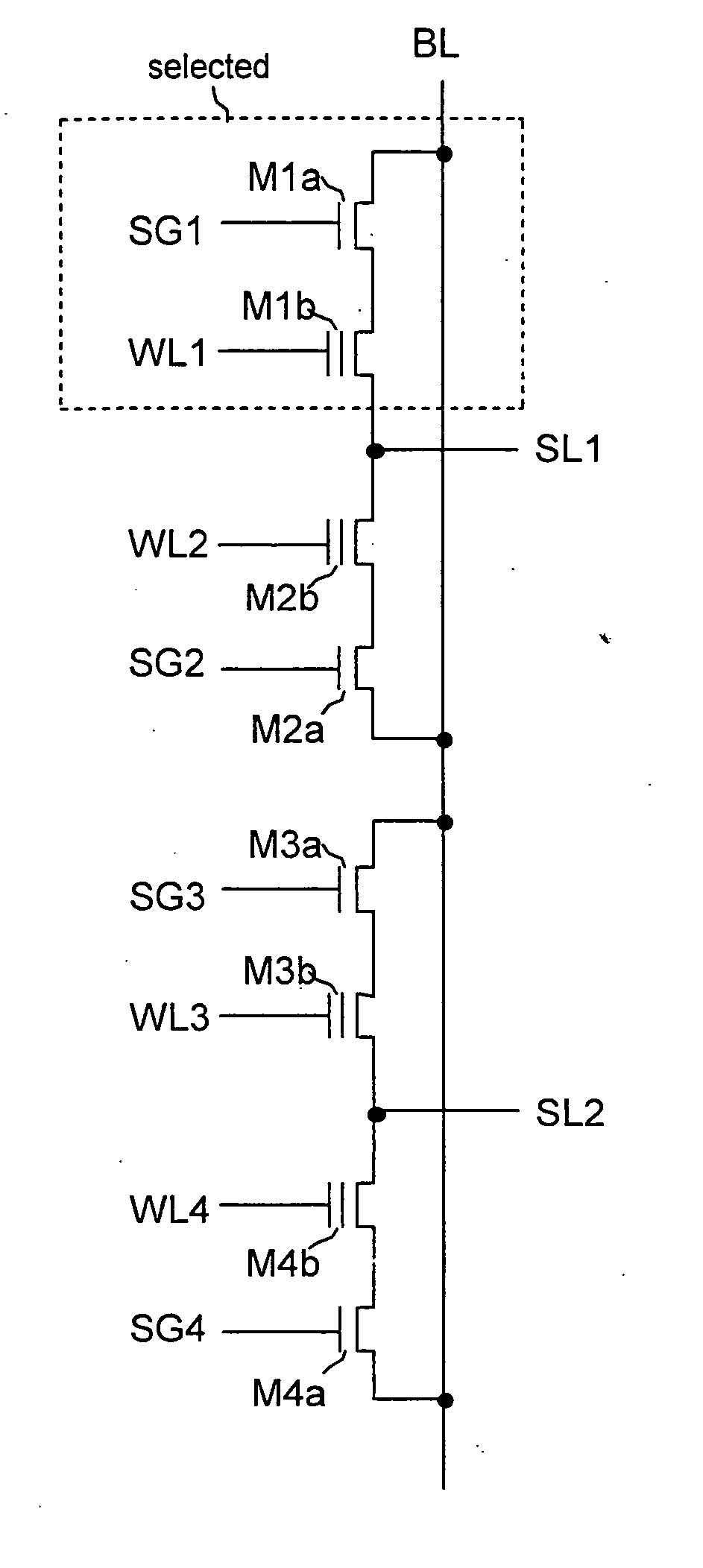

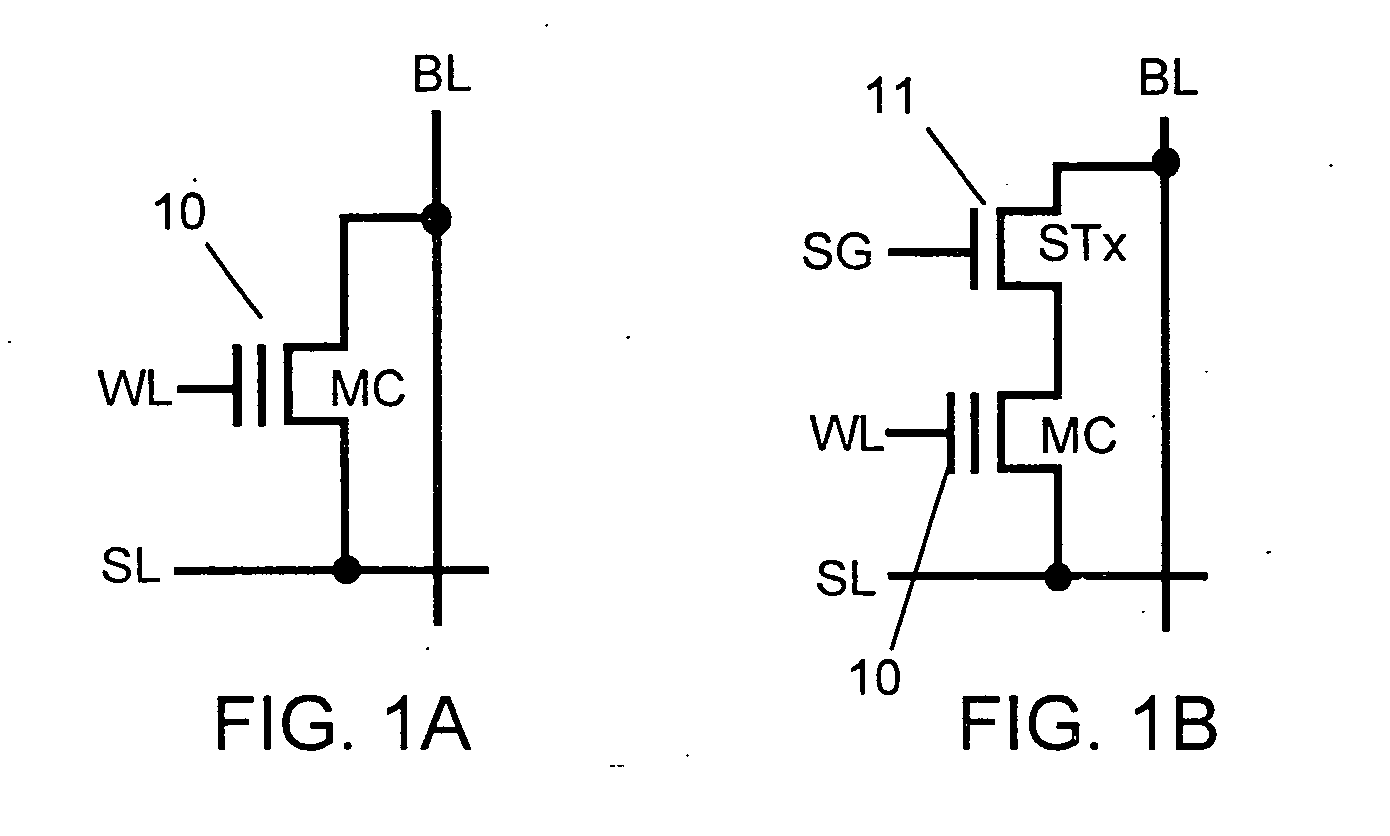

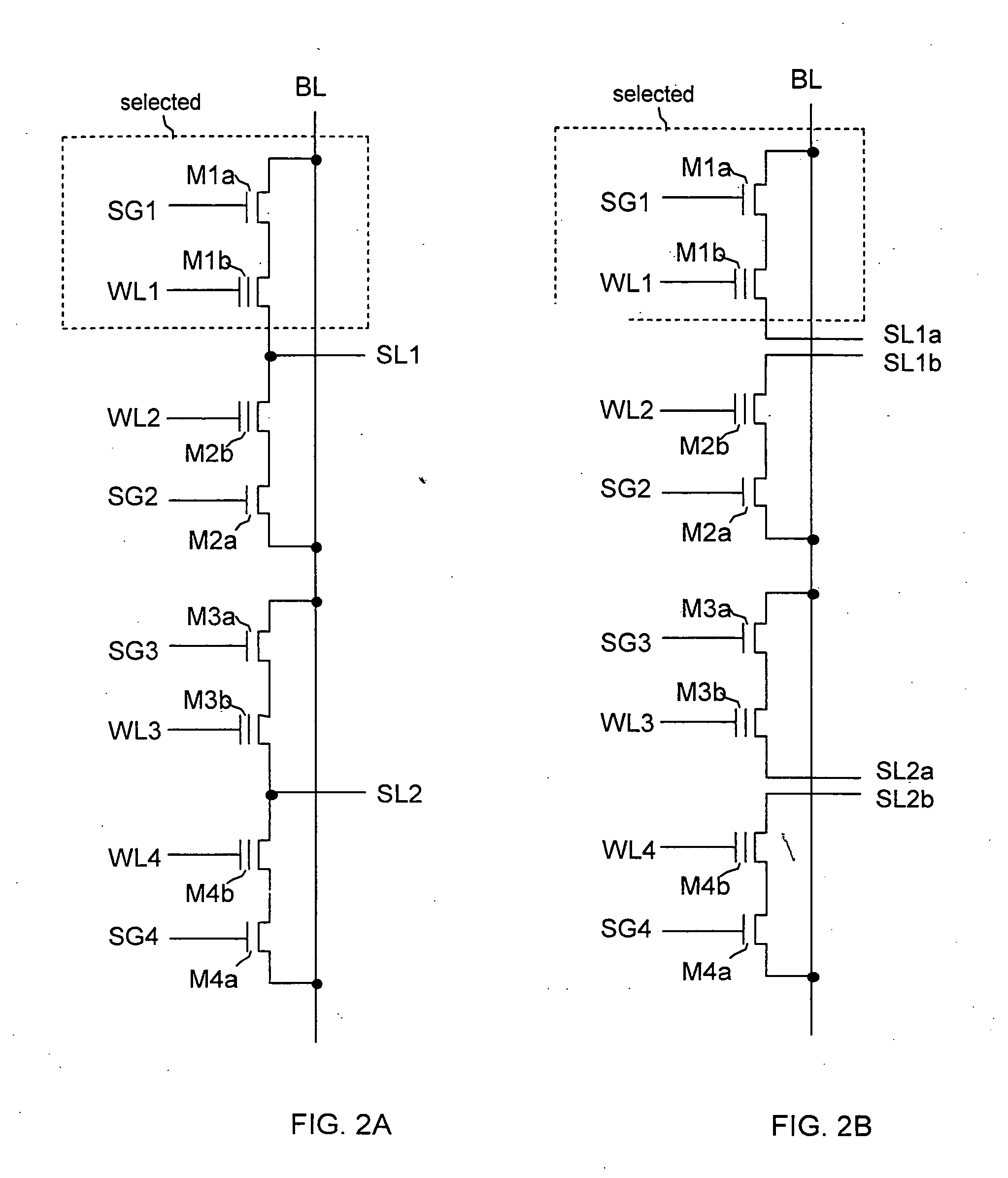

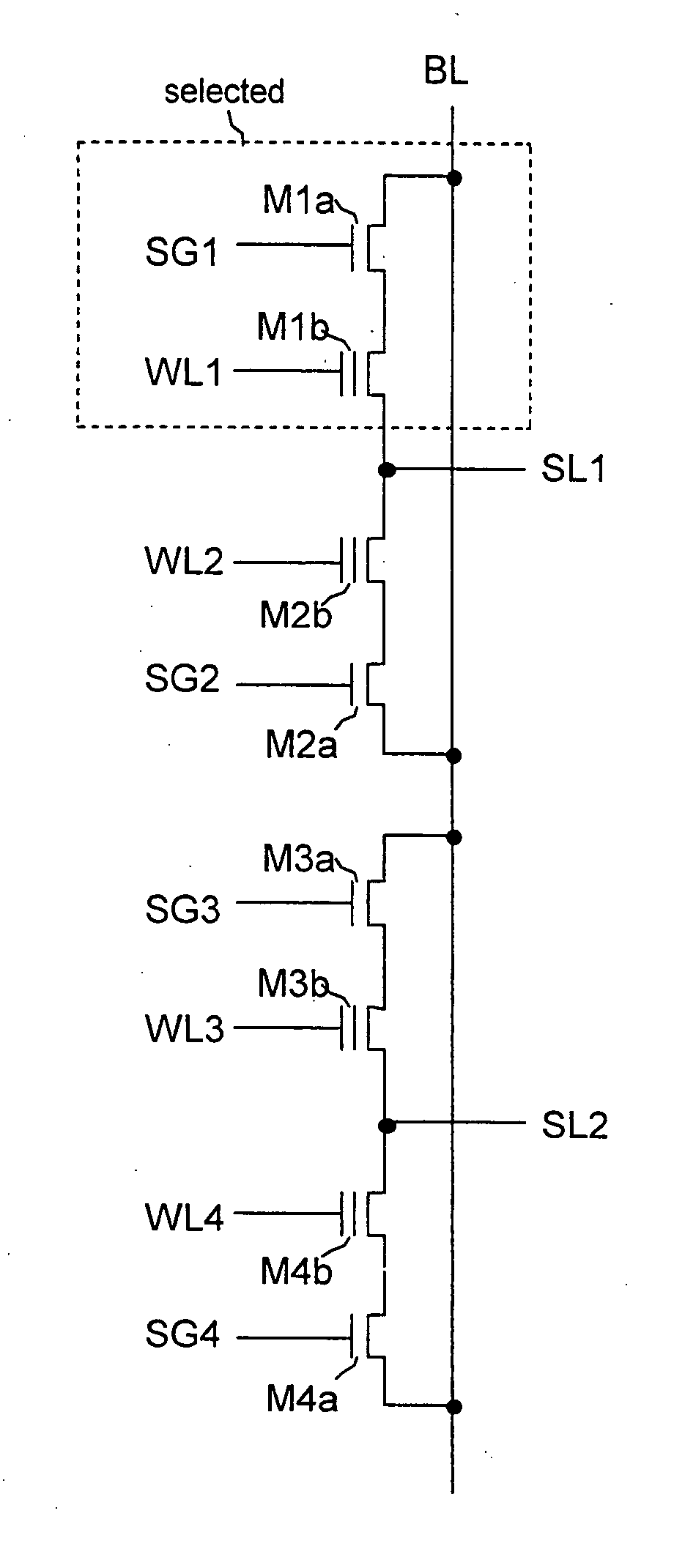

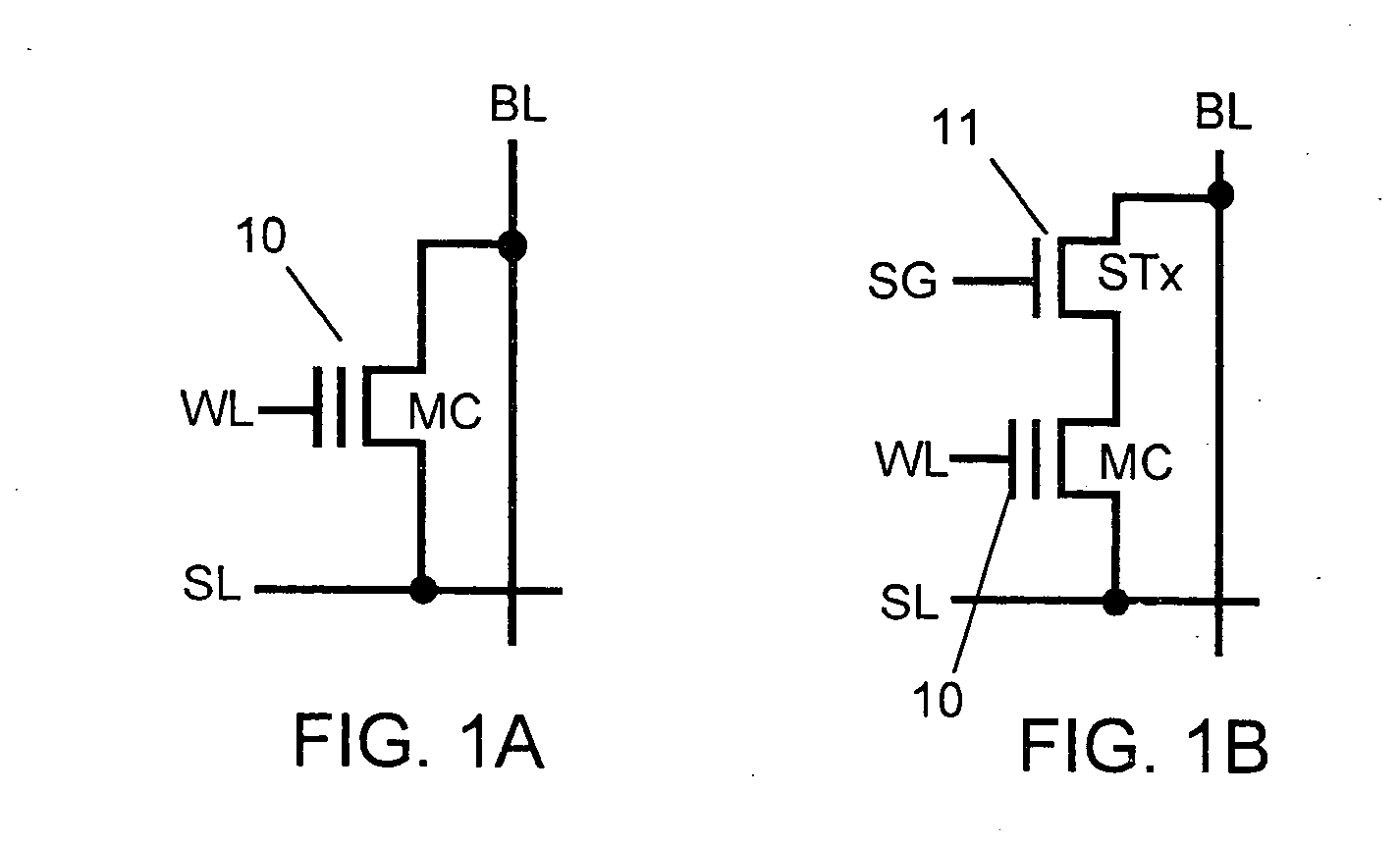

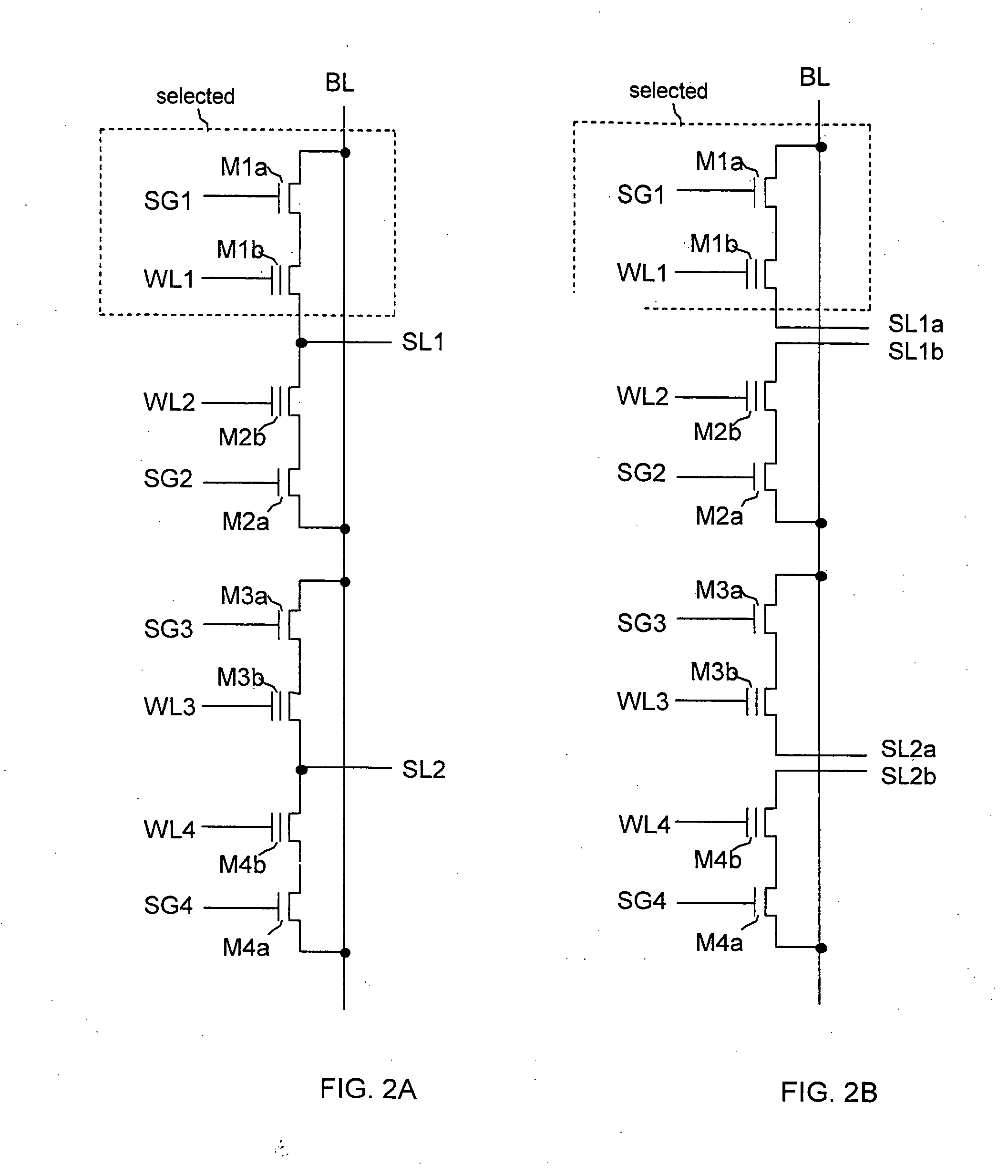

Combination nonvolatile memory using unified technology with byte, page and block write and simultaneous read and write operations

InactiveUS6850438B2Small sizeAvoid choiceSolid-state devicesRead-only memoriesMemory bankCombined use

A combination EEPROM and Flash memory is described containing cells in which the stacked gate transistor of the Flash cell is used in conjunction with a select transistor to form an EEPROM cell. The select transistor is made sufficiently small so as to allow the EEPROM cells to accommodate the bit line pitch of the Flash cell, which facilitates combining the two memories into memory banks containing both cells. The EEPROM cells are erased by byte while the Flash cells erased by block. The small select transistor has a small channel length and width, which is compensated by increasing gate voltages on the select transistor and pre-charge bitline during CHE program operation.

Owner:CALLAHAN CELLULAR L L C

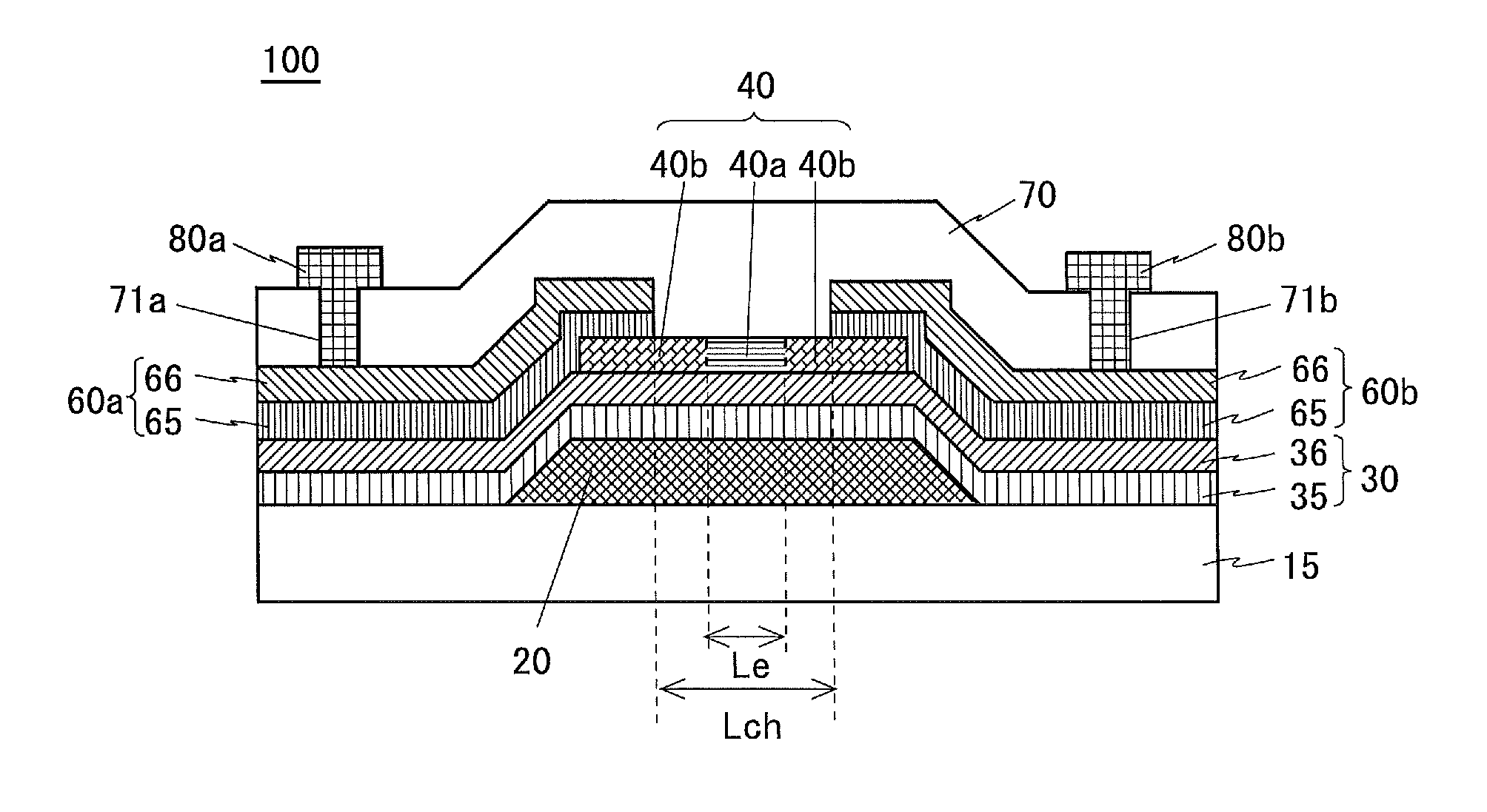

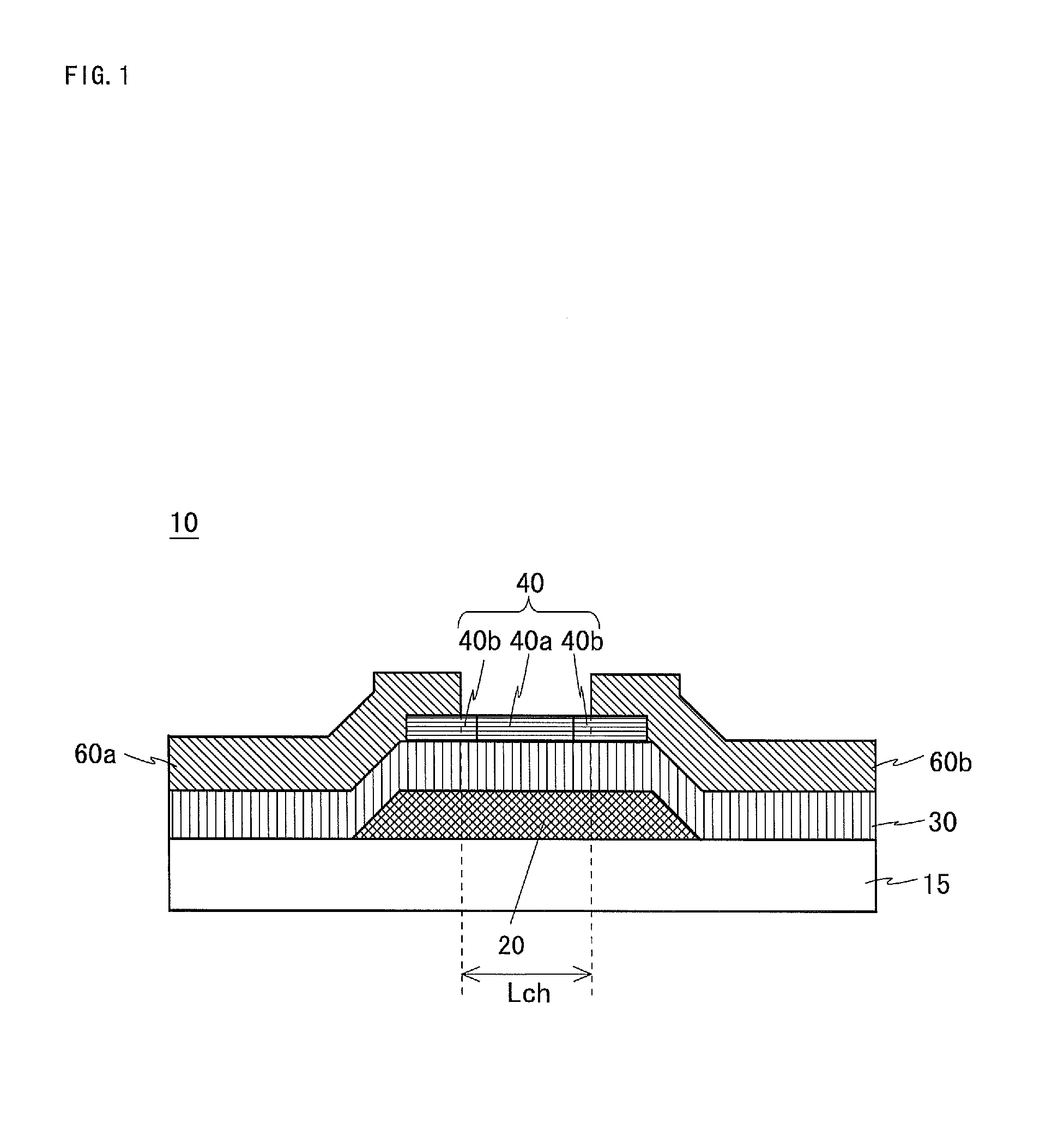

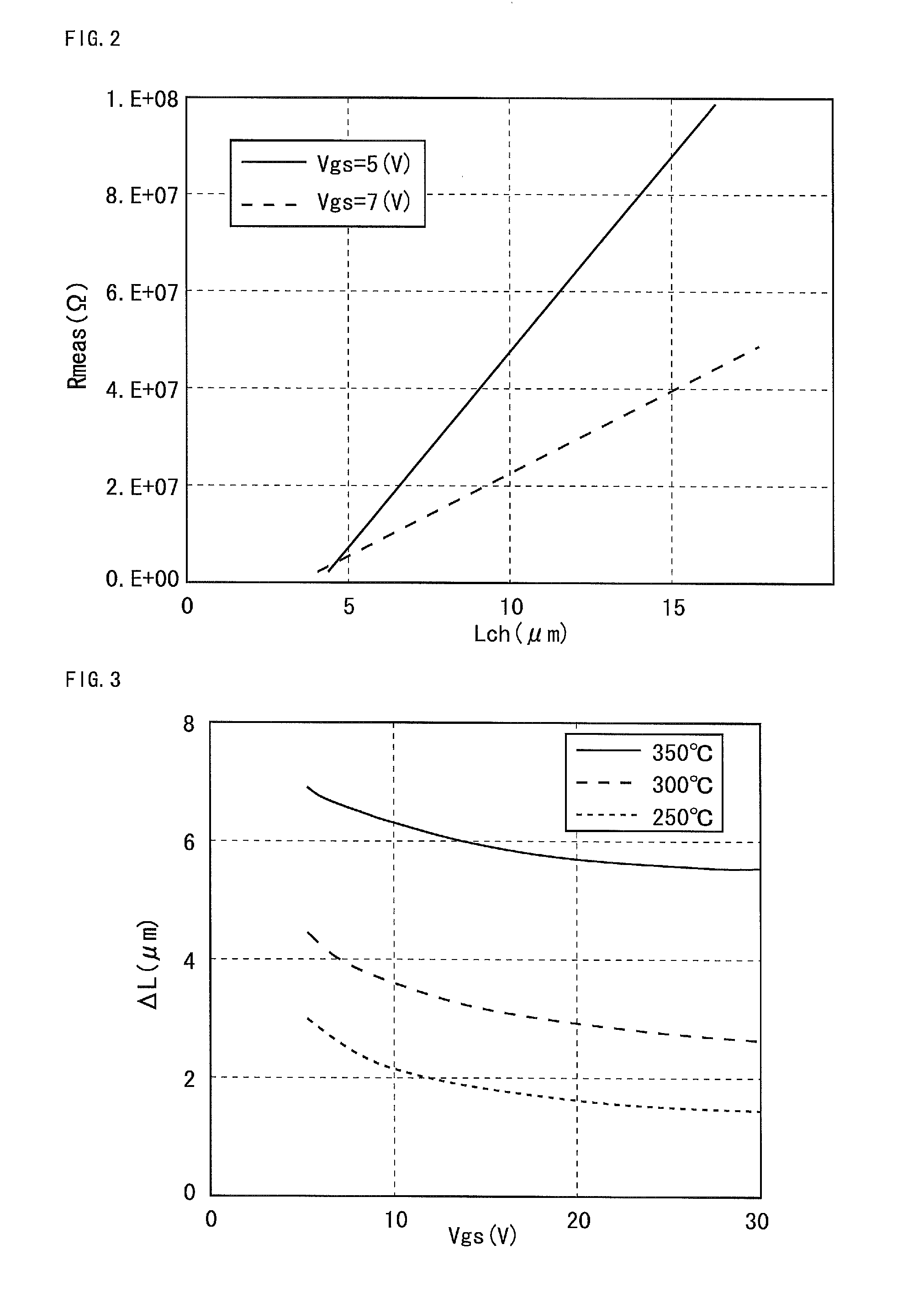

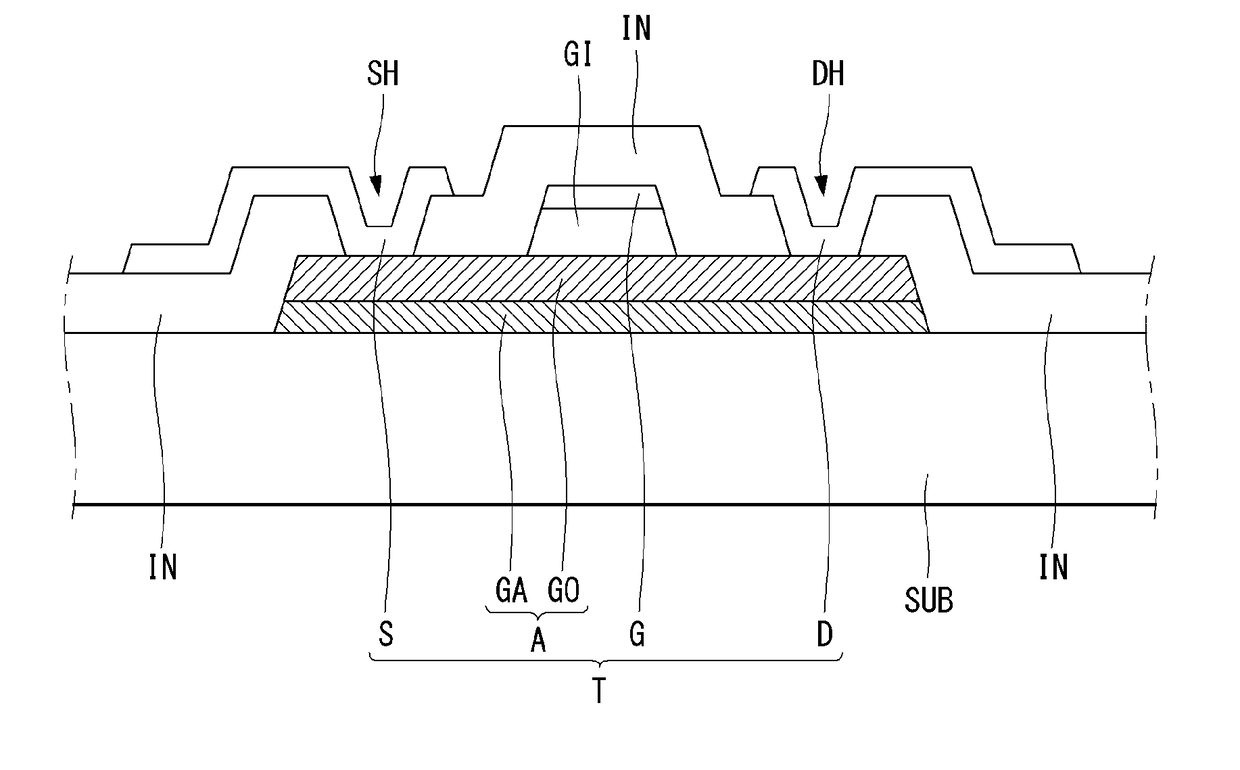

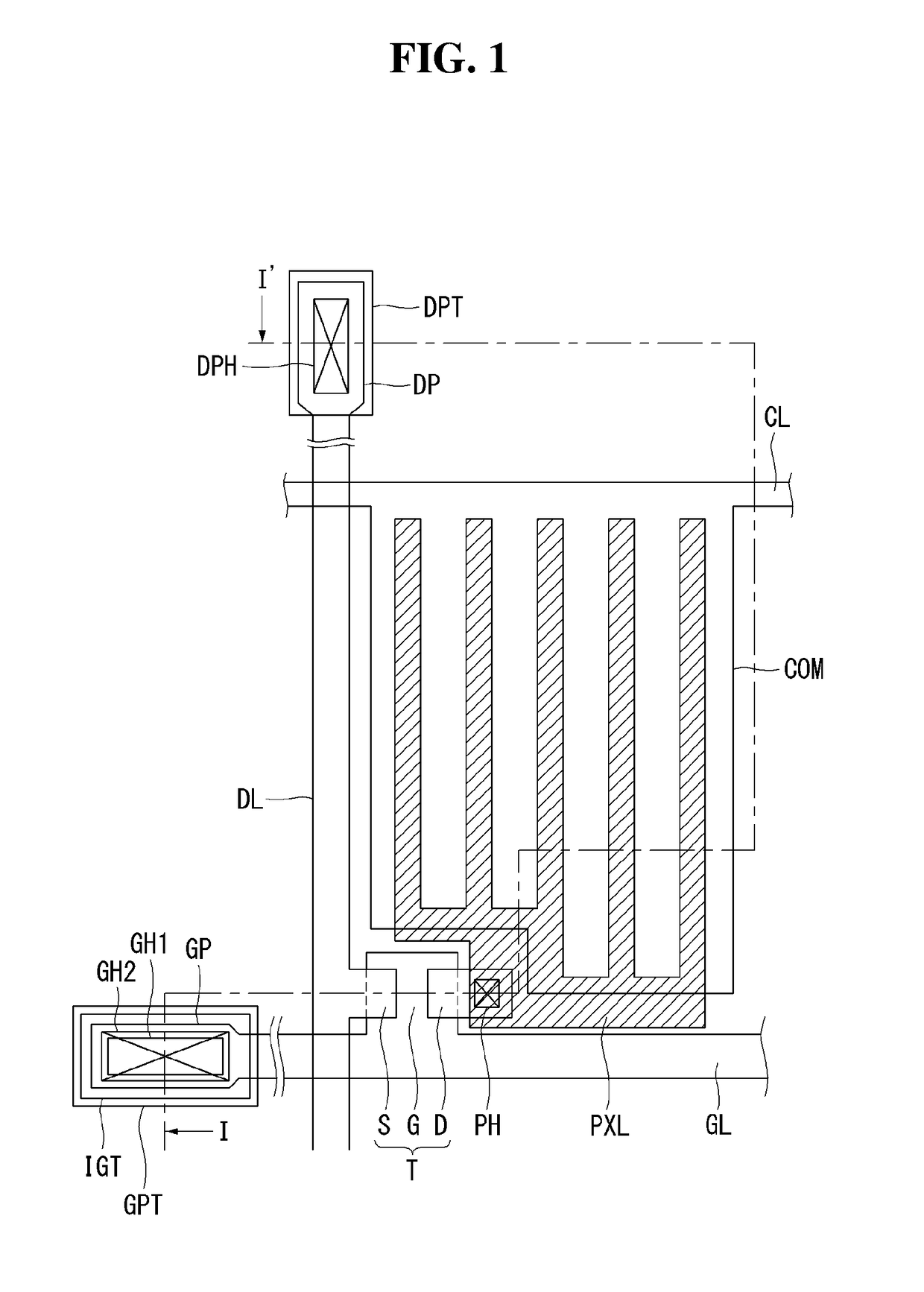

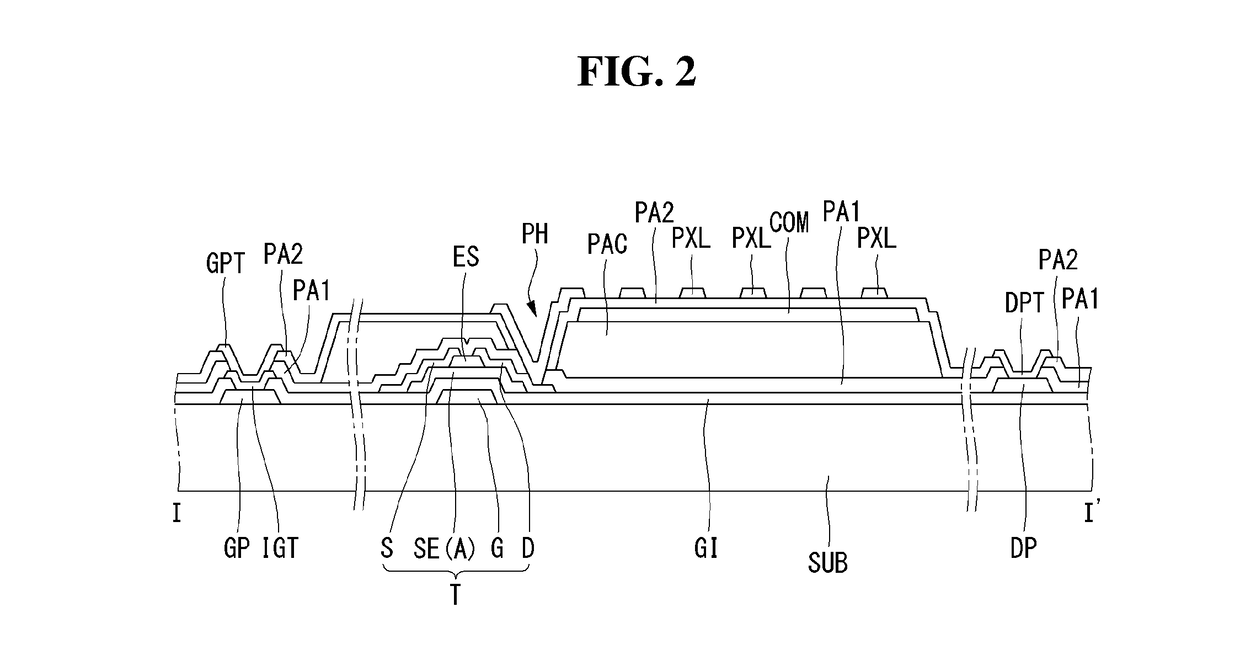

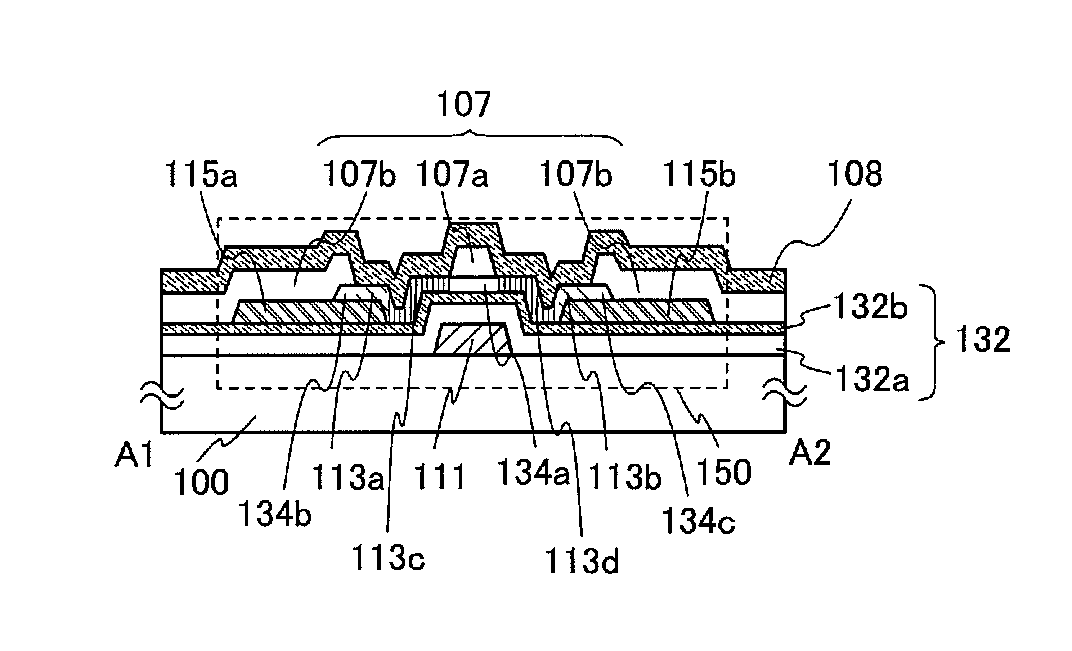

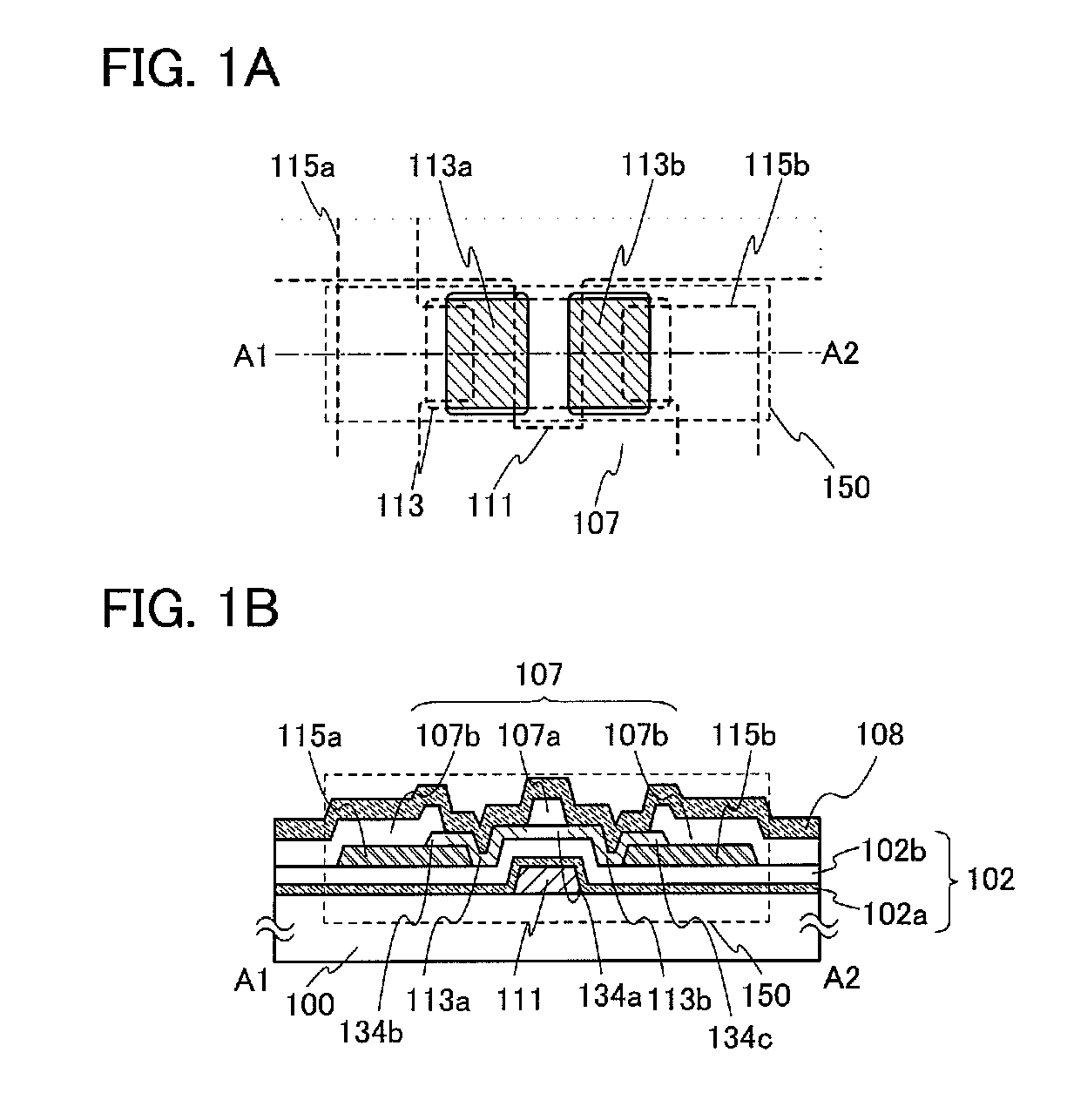

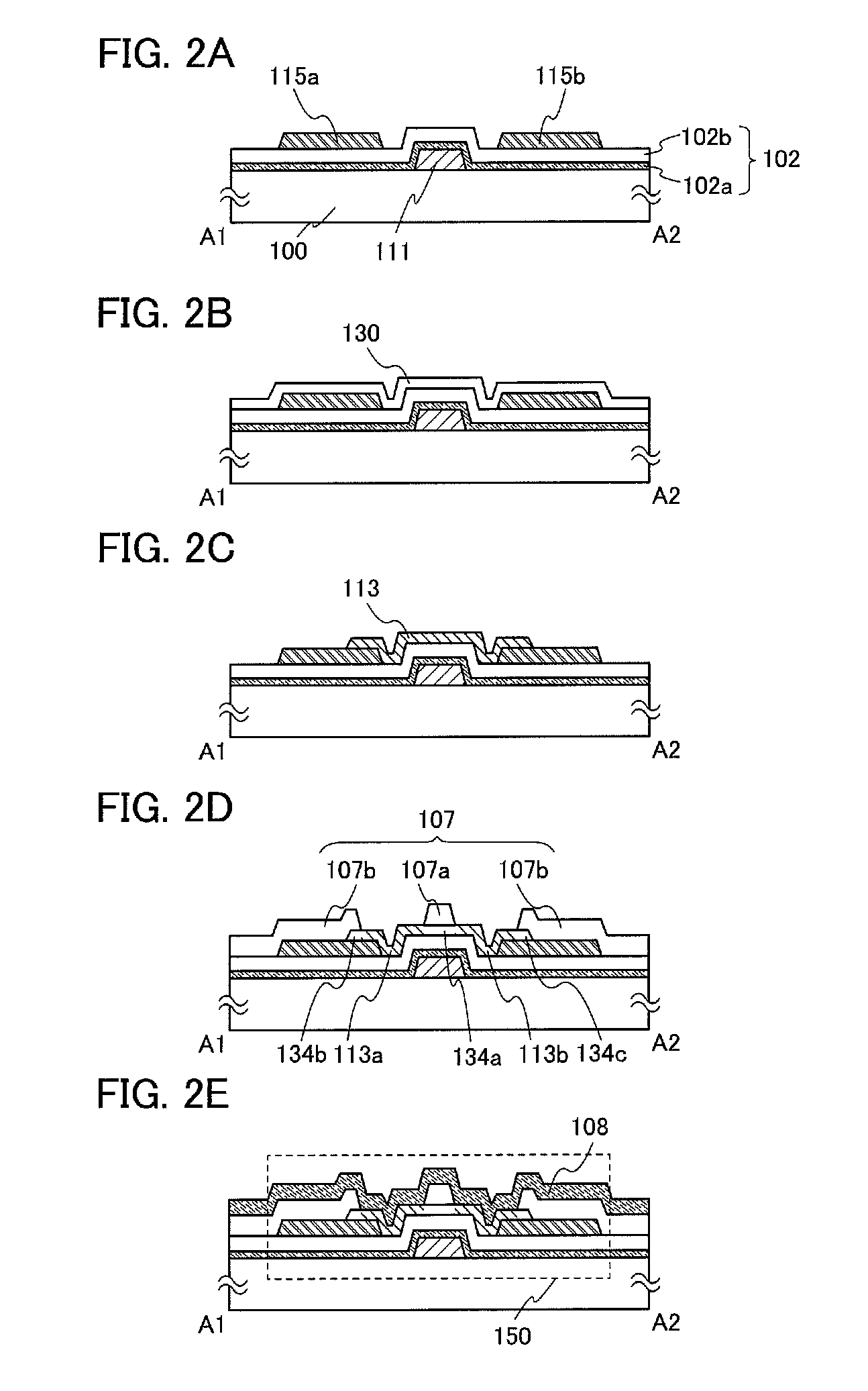

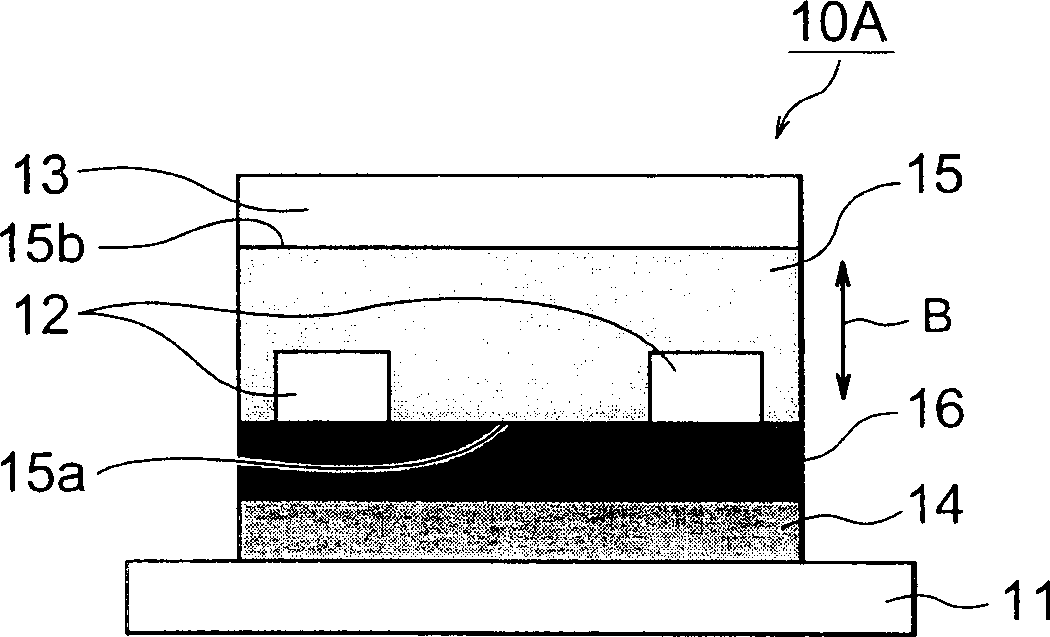

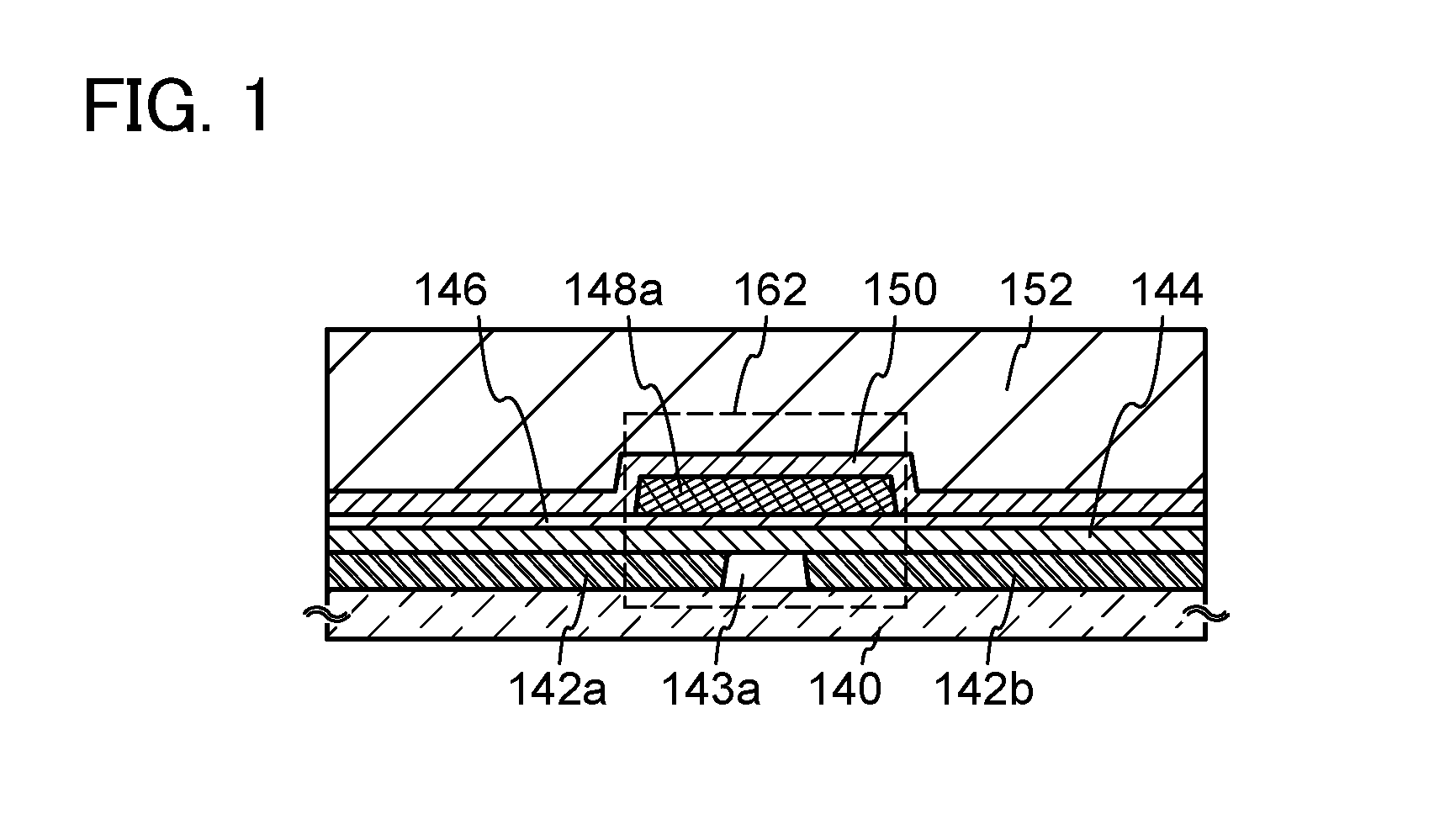

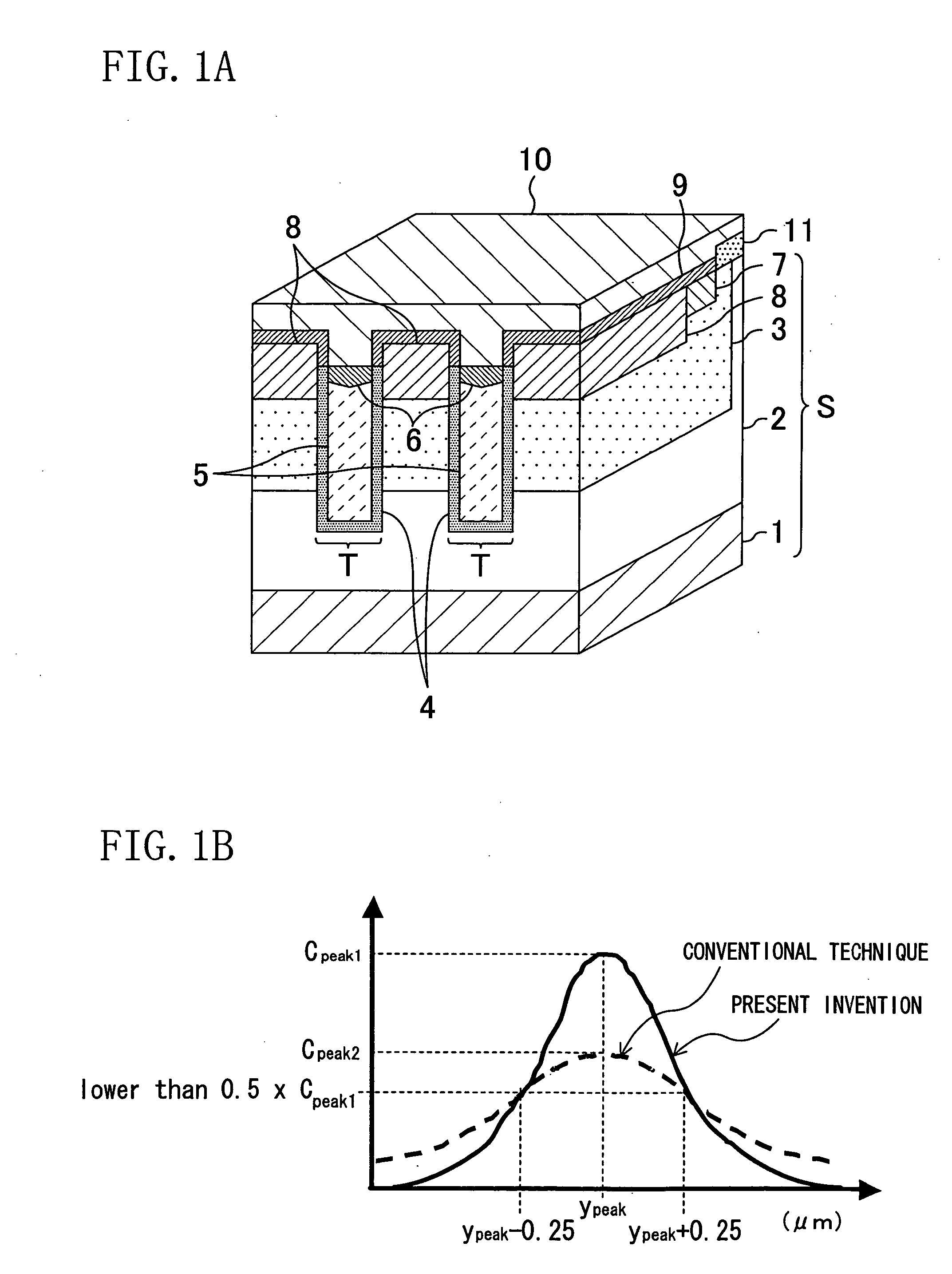

Thin film transistor and manufacturing method therefor, and display device

ActiveUS20140035478A1High currentShort channel lengthTransistorSolid-state devicesHigh resistanceTitanium electrode

The invention provides a thin film transistor having current driving force that can be substantially improved. By heat treatment, the IGZO layer (45) from which oxygen is taken away by the titanium electrodes (65) becomes the low resistance regions (40b), and the IGZO layer (45) from which oxygen is not taken away remains as the high resistance region (40a). In this state, when the gate voltage is applied to the gate electrode (20), electrons in the low resistance regions (40b) near the boundaries with the high resistance region (40a) move respectively to the titanium electrode (65) sides. As a result, the length of the low resistance regions (40b) becomes short, and oppositely, the length of the high resistance region (40a) becomes longer by the size of the shortened low resistance regions. However, the electrical channel length (Le) becomes shorter than the source / drain interval space (Lch) as the limit resolution of the exposure device, and the current driving force becomes large.

Owner:SHARP KK

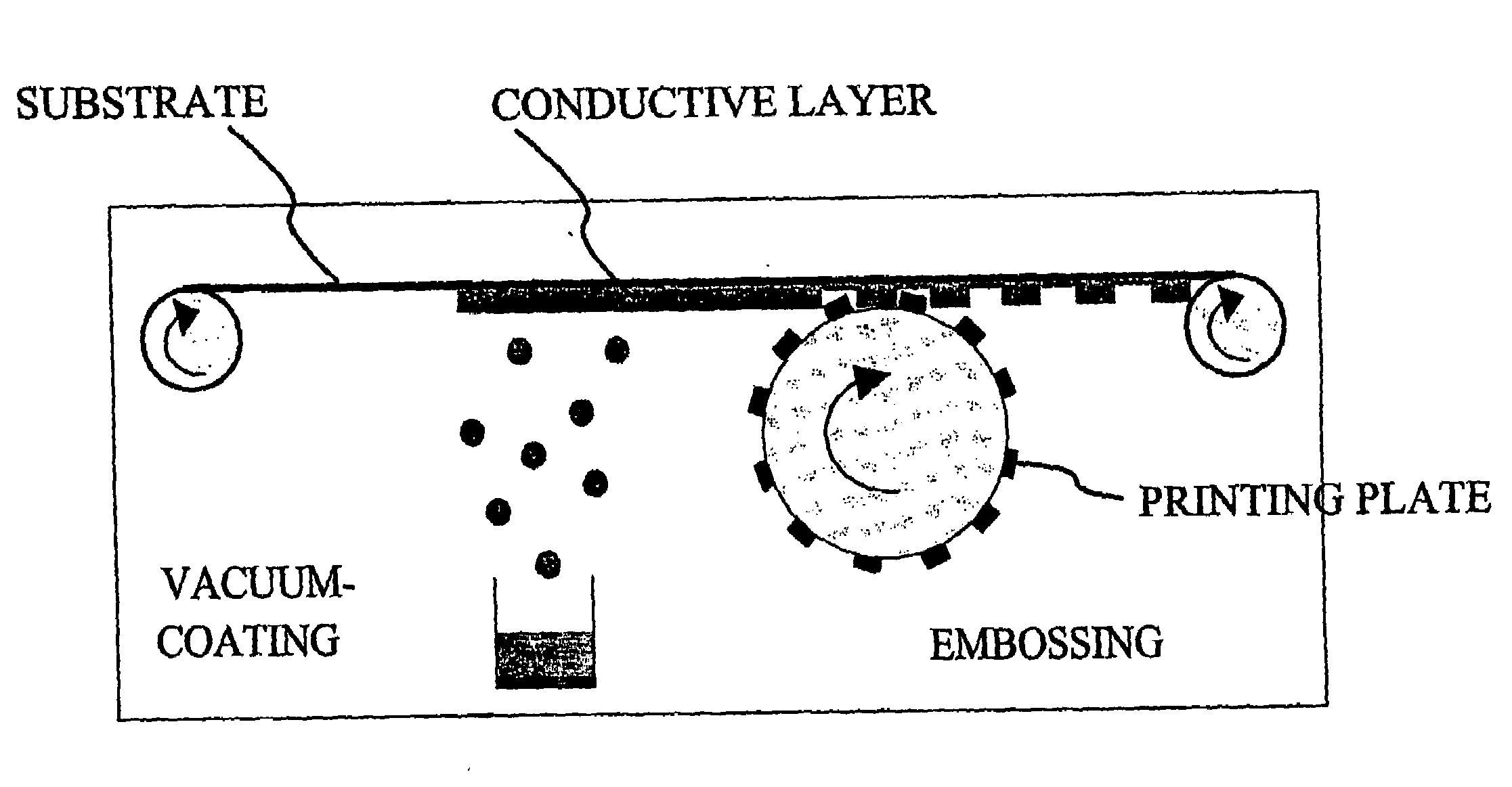

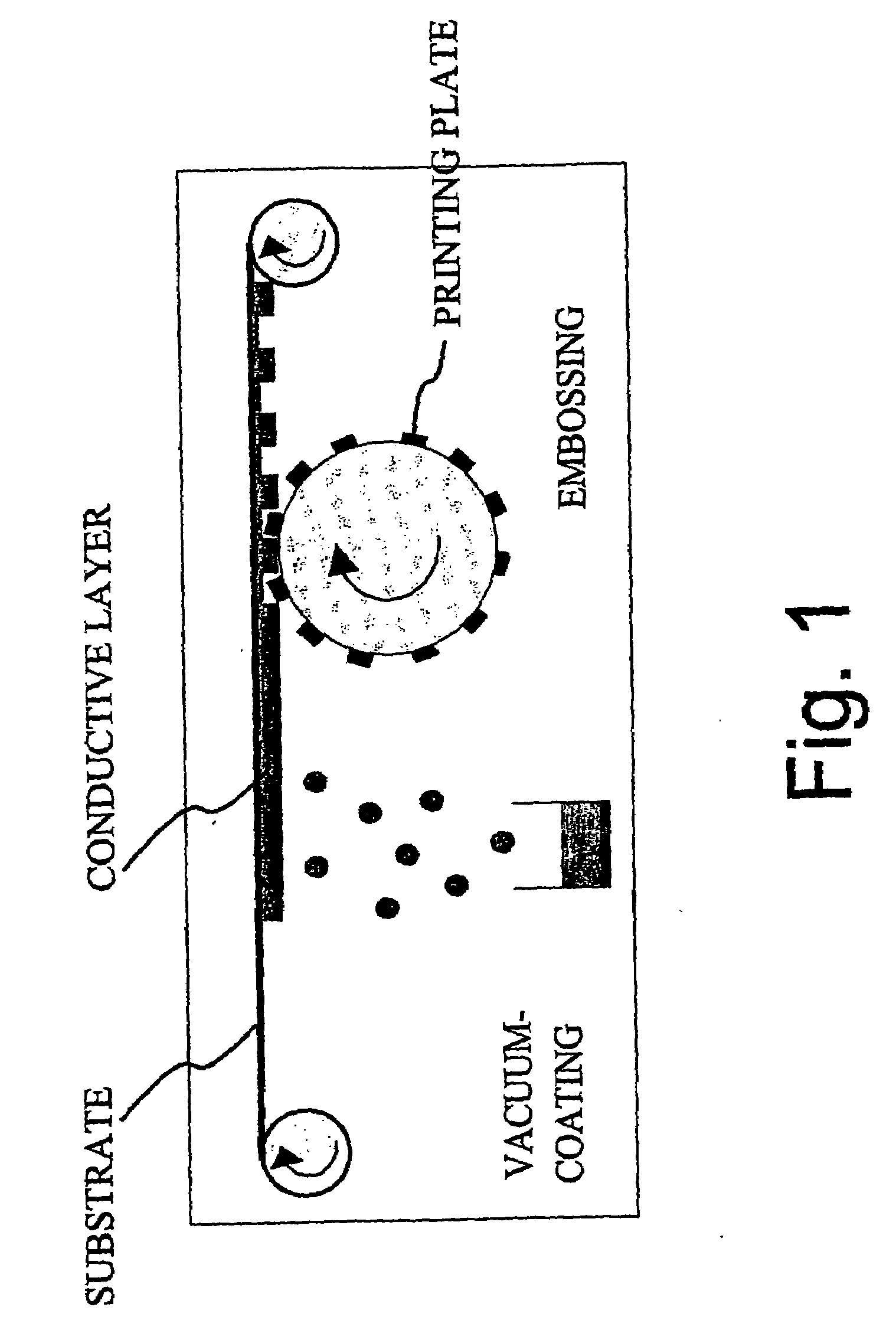

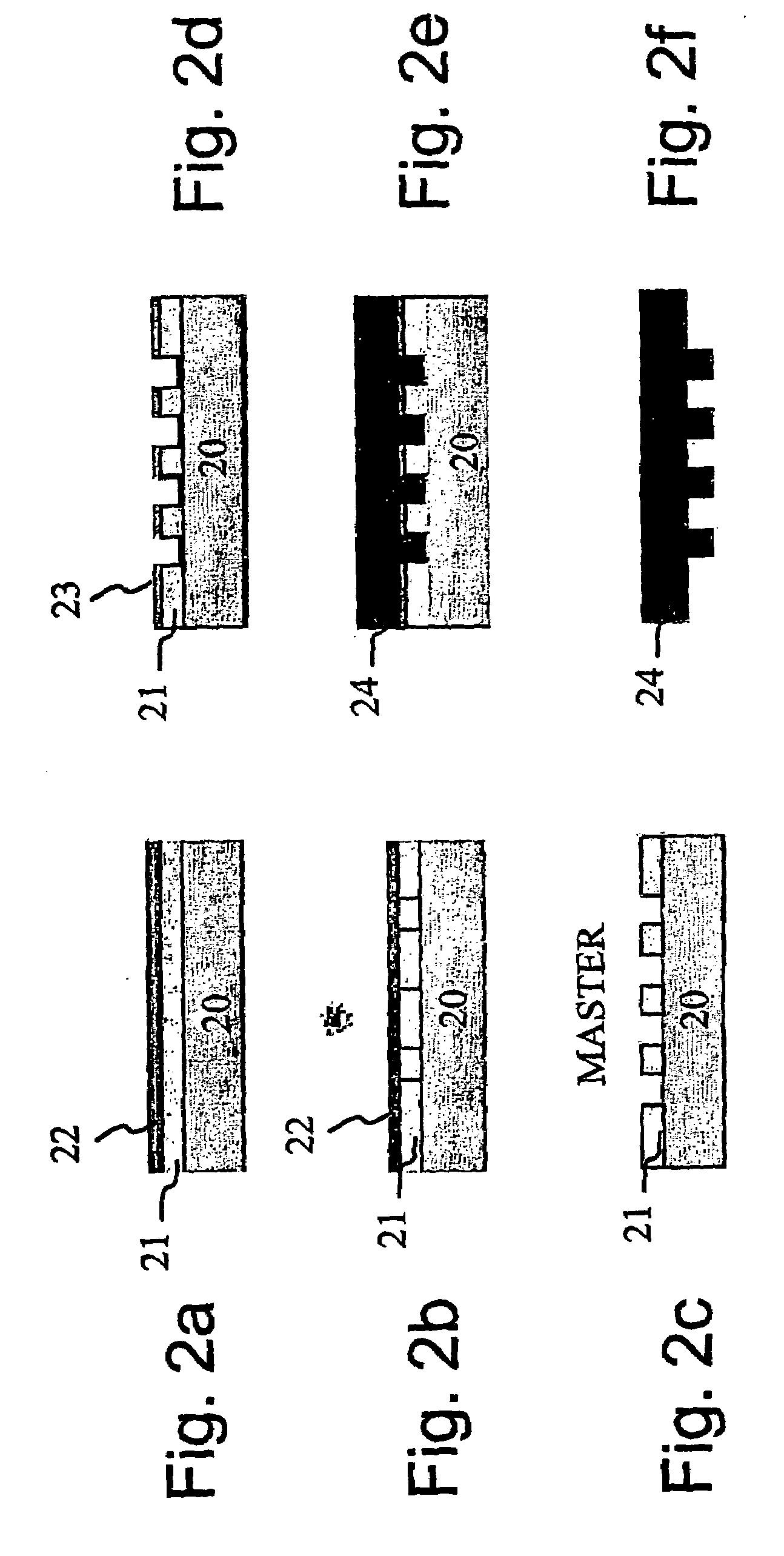

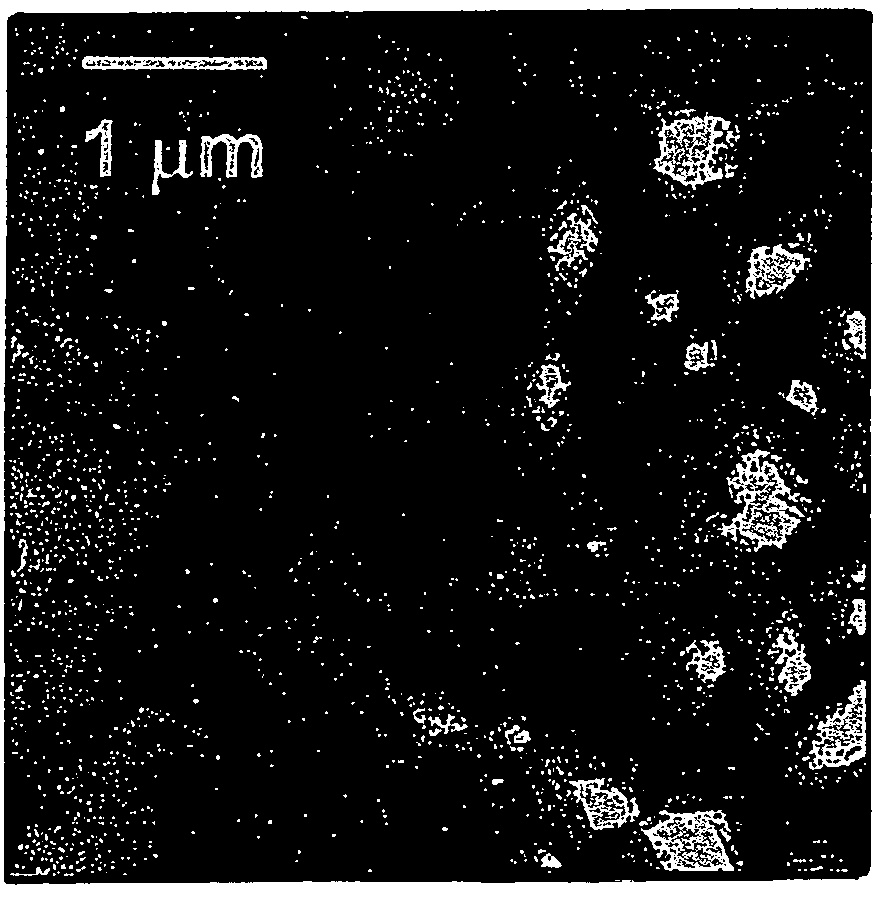

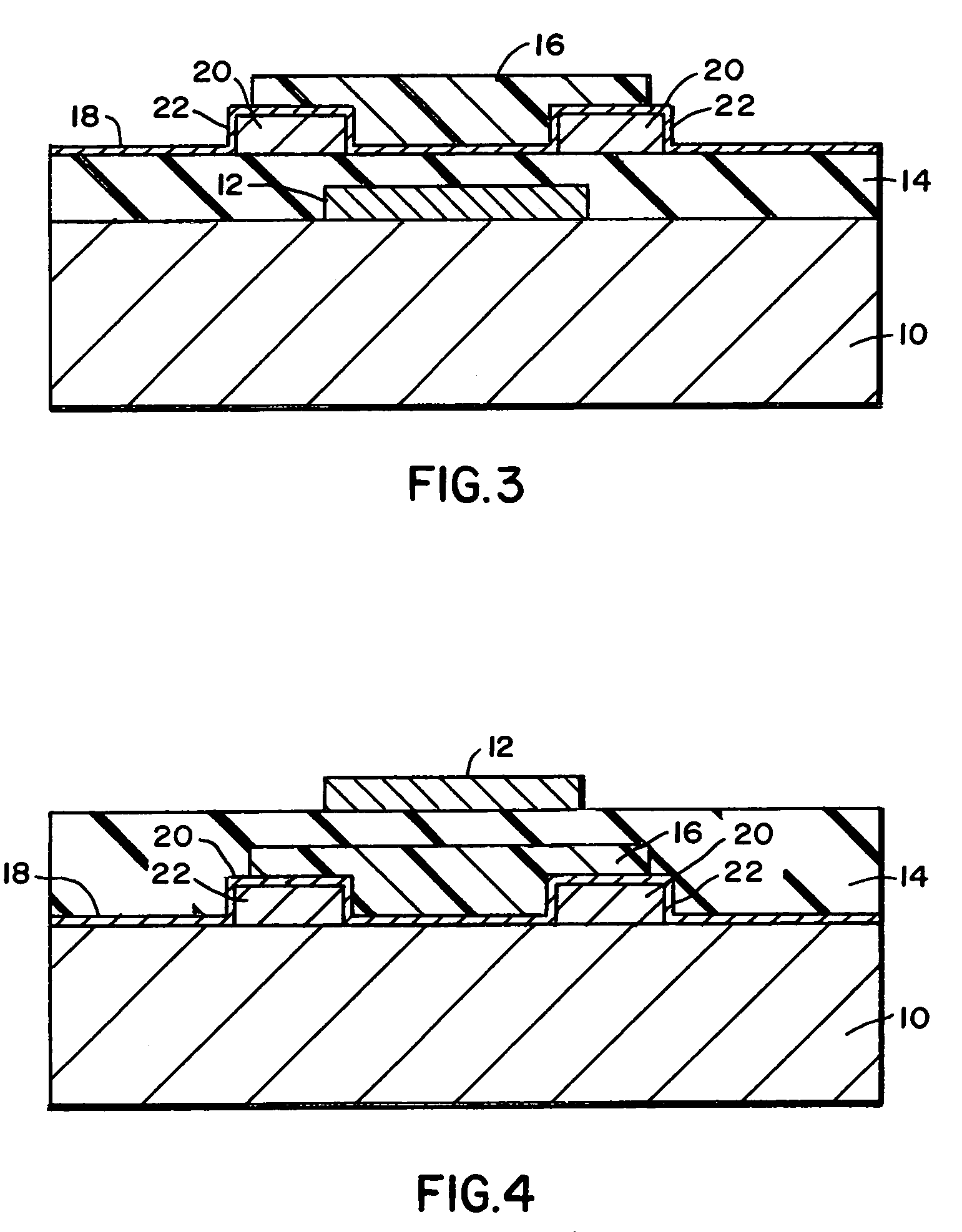

Method and an Apparatus for Manufacturing an Electronic Thin-Film Component and an Electronic Thin-Film Component

InactiveUS20080012151A1Increase contactSurface area of efficientlyLiquid surface applicatorsFinal product manufactureDielectric substrateConductive materials

A method for manufacturing an electronic thin-film component, an apparatus implementing the method, and an electronic thin-film component manufactured according to the method. A lowermost, galvanically uniform conductive layer of electrically conductive material is first formed on a substantially dielectric substrate, from which lowermost conductive layer conductive areas are galvanically separated from each other to form an electrode pattern. On top of the electrode pattern it is then possible to form one or several upper passive or active layers required in the thin-film component. The separation of the lowermost conductive layer into an electrode pattern takes place by exerting on the lowermost conductive layer a machining operation based on die-cut embossing, i.e. embossing, wherein the relief of the machining member used in the machining operation causes a permanent deformation on the substrate and at the same time embosses areas from the conductive layer into conductive areas galvanically separated from each other. The method and apparatus are suitable for manufacturing thin-film components in a roll-to-roll process.

Owner:AVANTONE OY

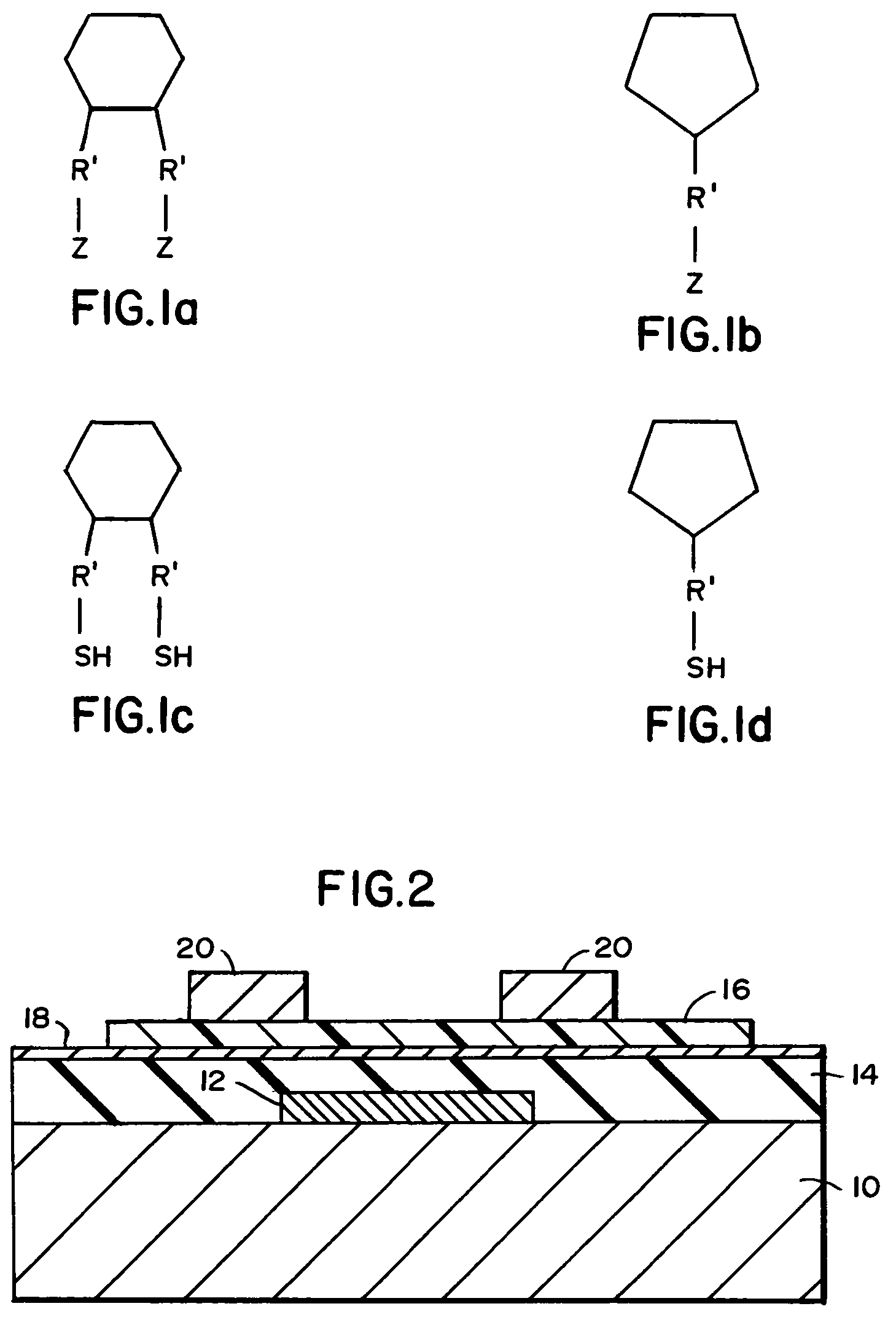

Organic underlayers that improve the performance of organic semiconductors

InactiveUS7285440B2Mobility is maximizedImprove performanceMaterial nanotechnologySolid-state devicesOrganic field-effect transistorCharge carrier

A process for producing high performance organic thin film transistors in which the molecules in the organic thin film are highly ordered and oriented to maximize the mobility of current charge carriers. The uniform monolayer surface over various substrate materials so formed, result in a more reproducible and readily manufacturable process for higher performance organic field effect transistors that can be used to create large area circuits using a range of materials.

Owner:IBM CORP

Combination nonvolatile memory using unified technology with byte, page and block write and simultaneous read and write operations

InactiveUS20050185501A1Small sizeAvoid choiceSolid-state devicesRead-only memoriesBit lineComputer architecture

A combination EEPROM and Flash memory is described containing cells in which the stacked gate transistor of the Flash cell is used in conjunction with a select transistor to form an EEPROM cell. The select transistor is made sufficiently small so as to allow the EEPROM cells to accommodate the bit line pitch of the Flash cell, which facilitates combining the two memories into memory banks containing both cells. The EEPROM cells are erased by byte while the Flash cells erased by block. The small select transistor has a small channel length and width, which is compensated by increasing gate voltages on the select transistor and pre-charge bitline during CHE program operation.

Owner:CALLAHAN CELLULAR L L C

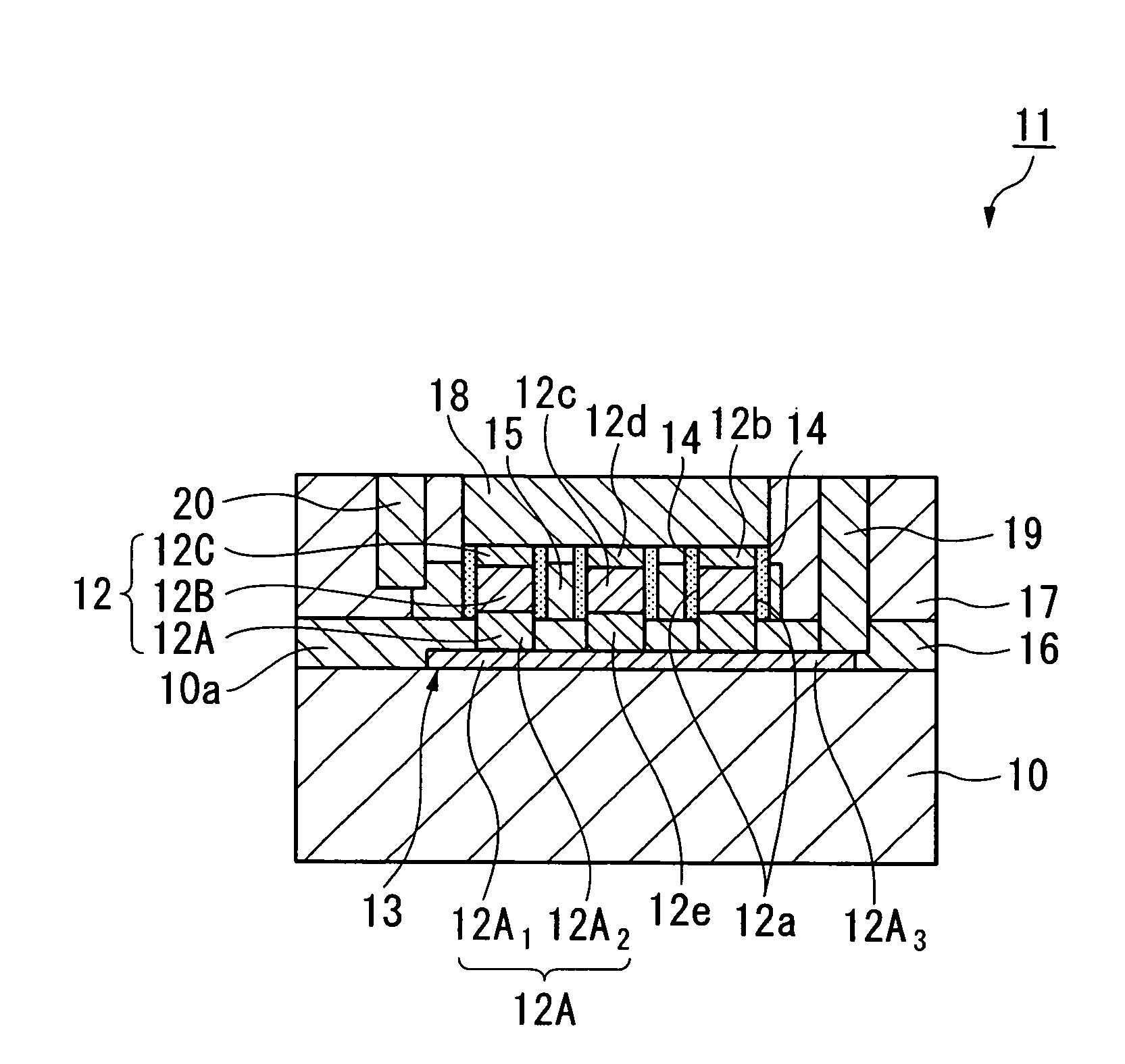

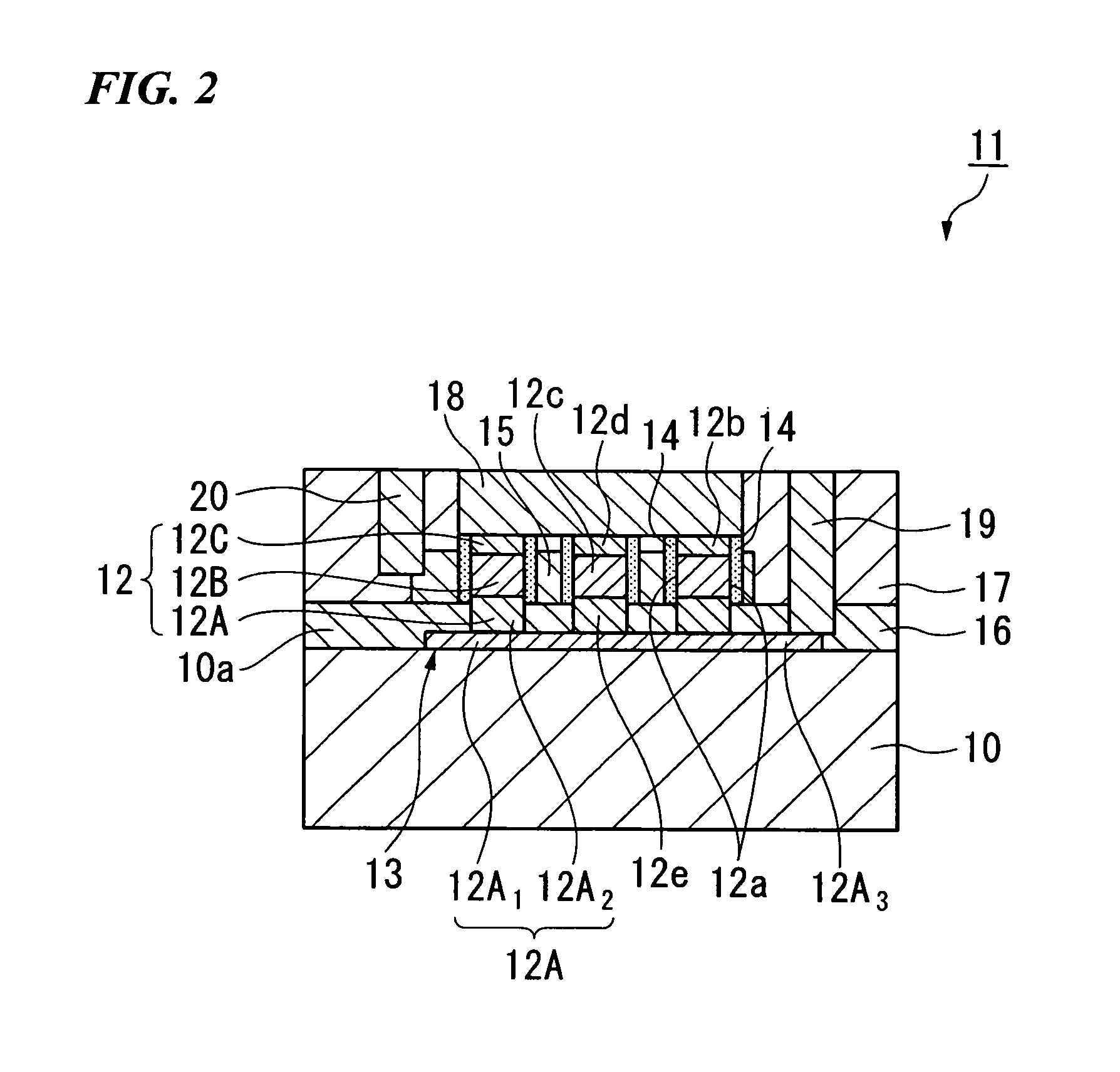

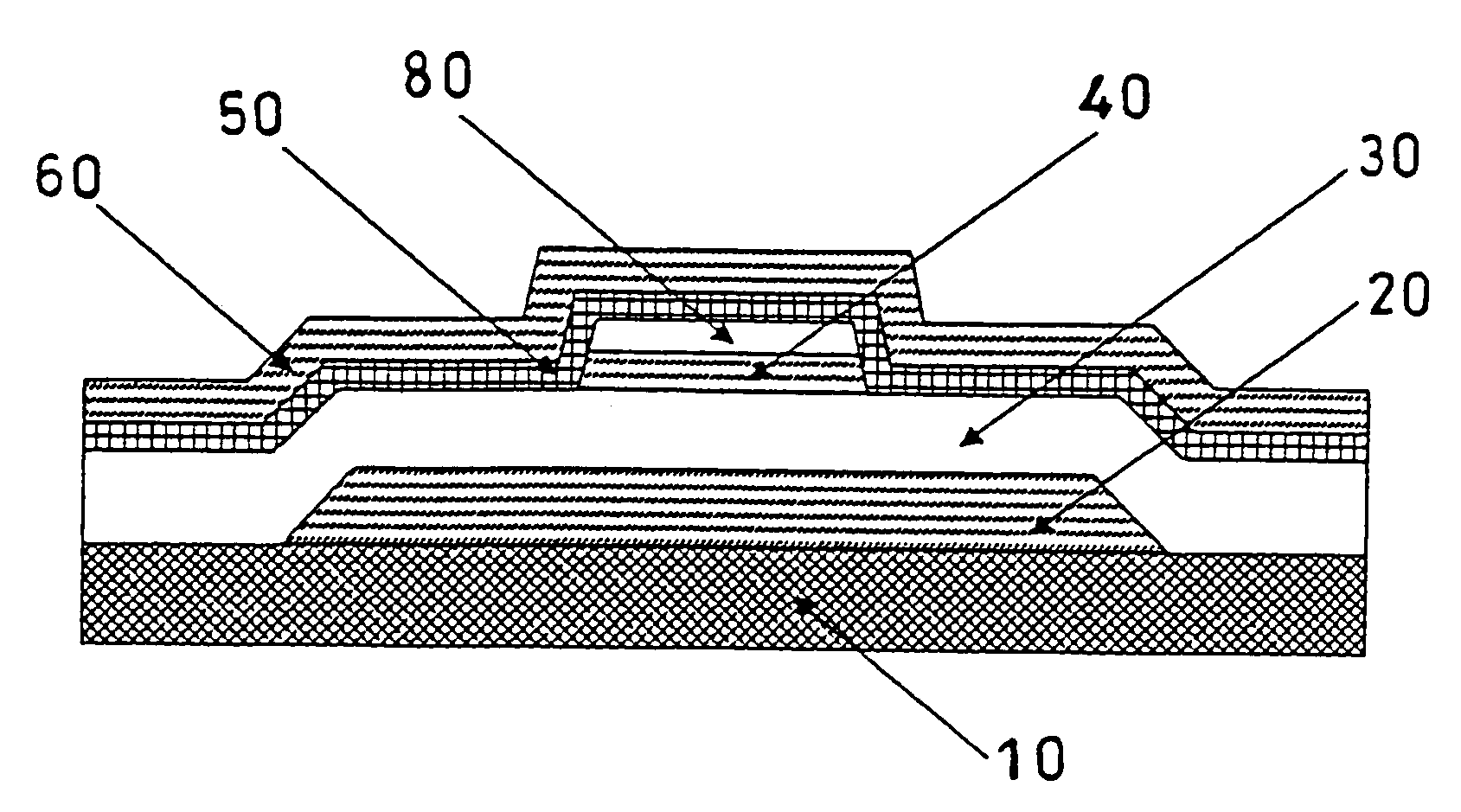

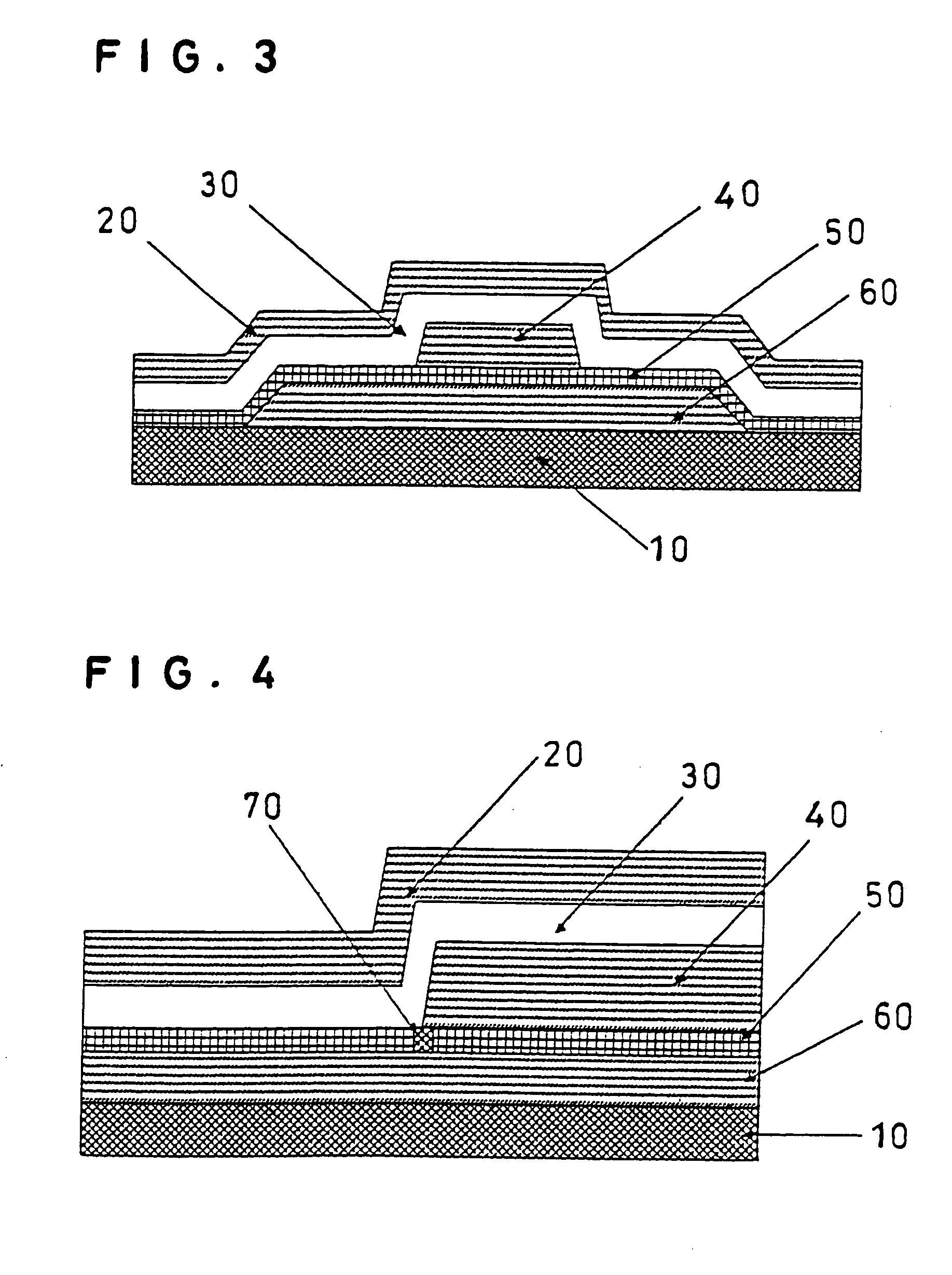

Semiconductor device and method for manufacturing semiconductor device

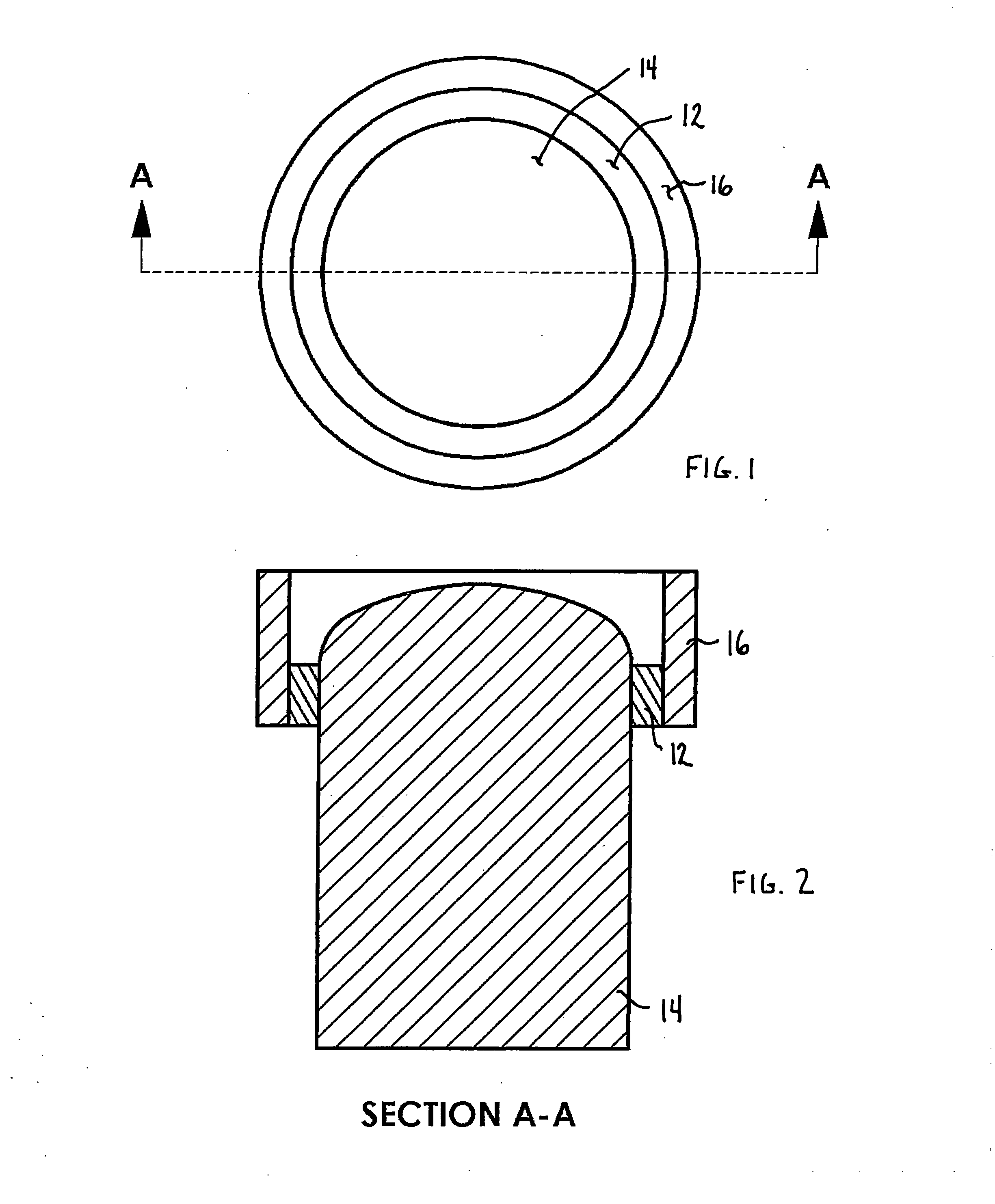

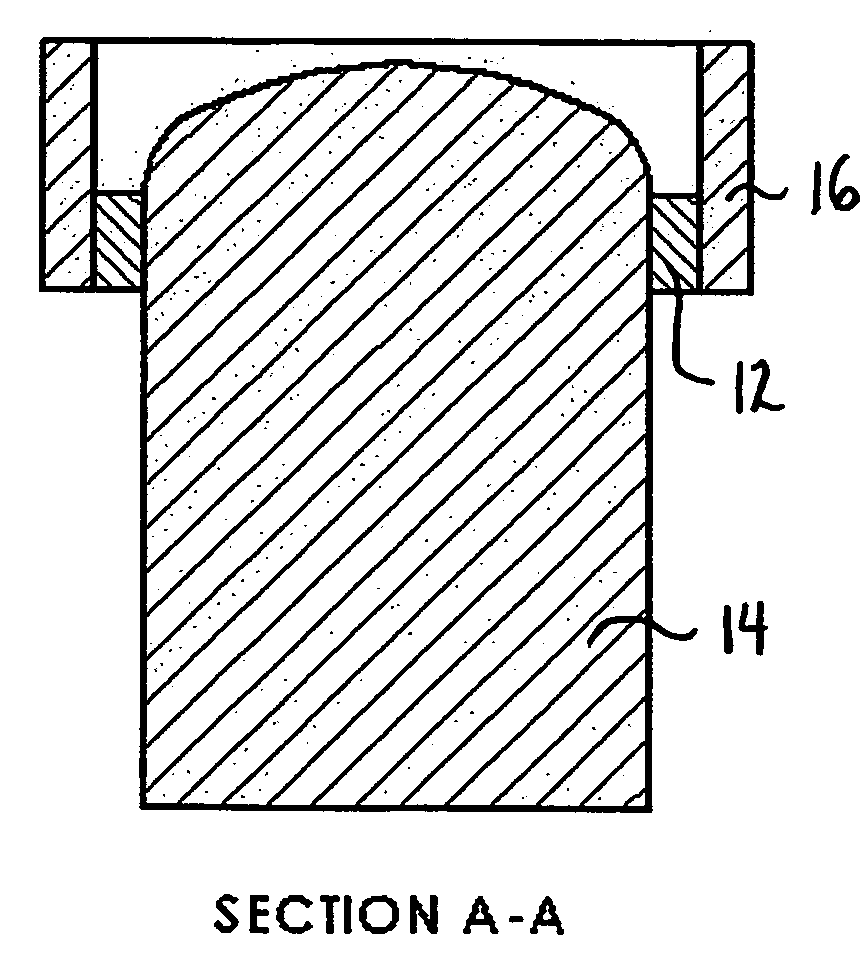

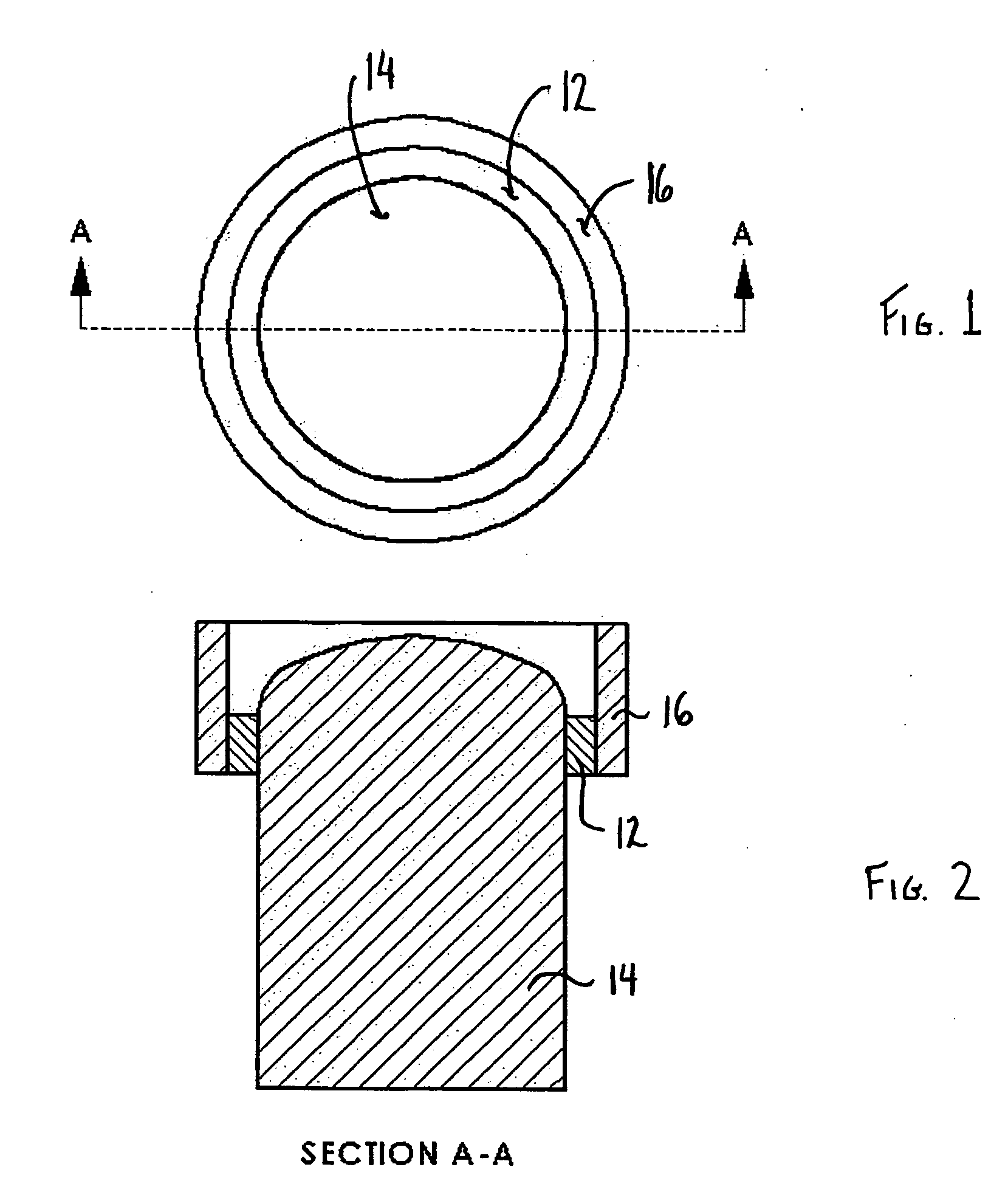

InactiveUS20080315300A1Short channel lengthIncrease currentSemiconductor/solid-state device manufacturingSemiconductor devicesBody regionSubstrate surface

A semiconductor device includes: a semiconductor substrate having a substrate surface; a spiral body constituted by a linear semiconductor layer on which a body region including a channel region, a first source / drain region disposed on the body region, and a second source / drain region disposed under the body region or in the semiconductor substrate around the linear semiconductor layer are formed, the linear semiconductor layer being formed on the substrate surface substantially in a spiral form viewed from the substrate surface in a plan view, formed substantially in a protrudent form in a cross-sectional view, and having a pair of sidewall portions; a gate insulating film formed on at least the pair of sidewall portions constituting the linear semiconductor layer; and a gate electrode that is adjacent to the pair of sidewall portions via the gate insulating film.

Owner:ELPIDA MEMORY INC

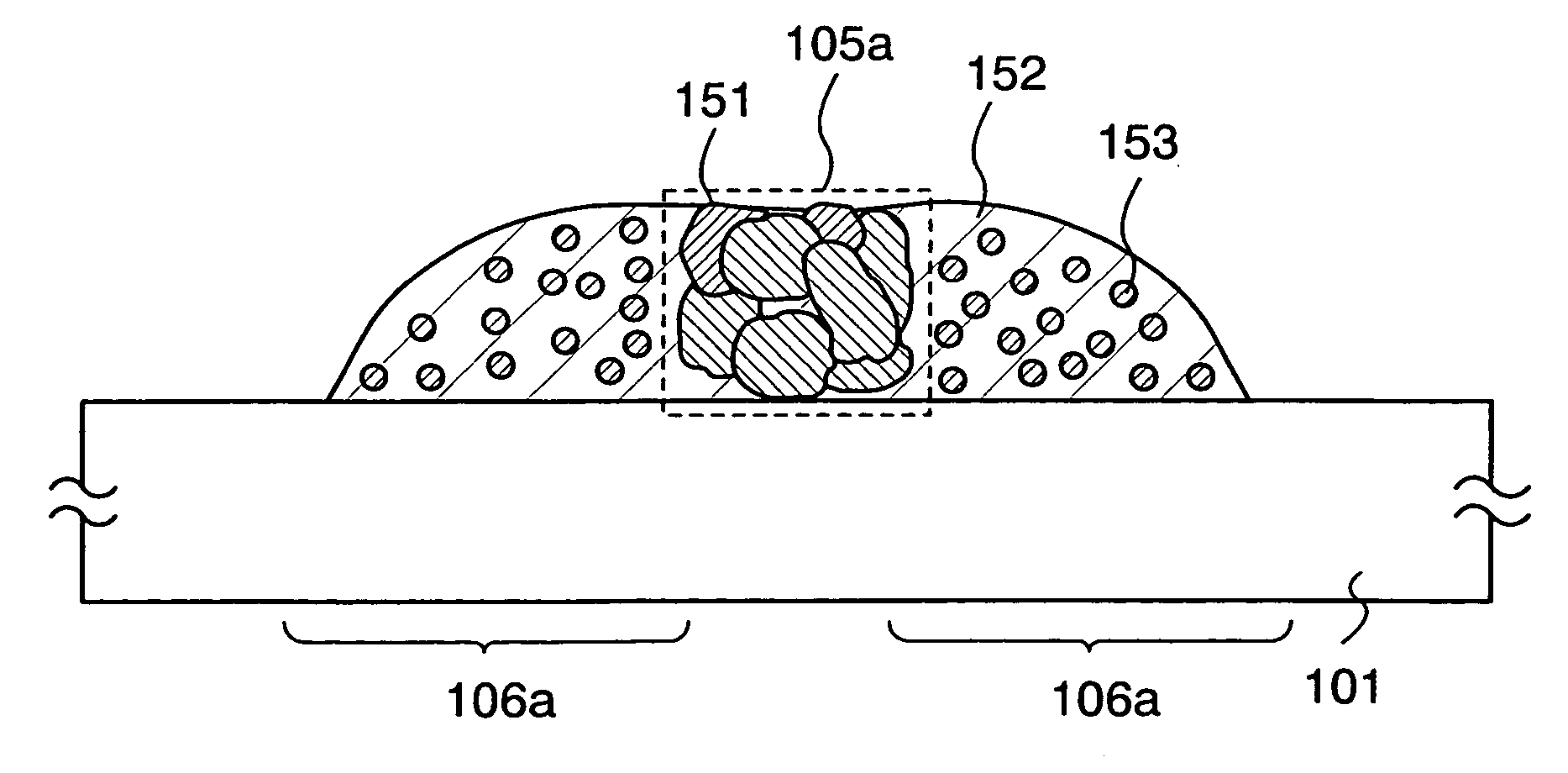

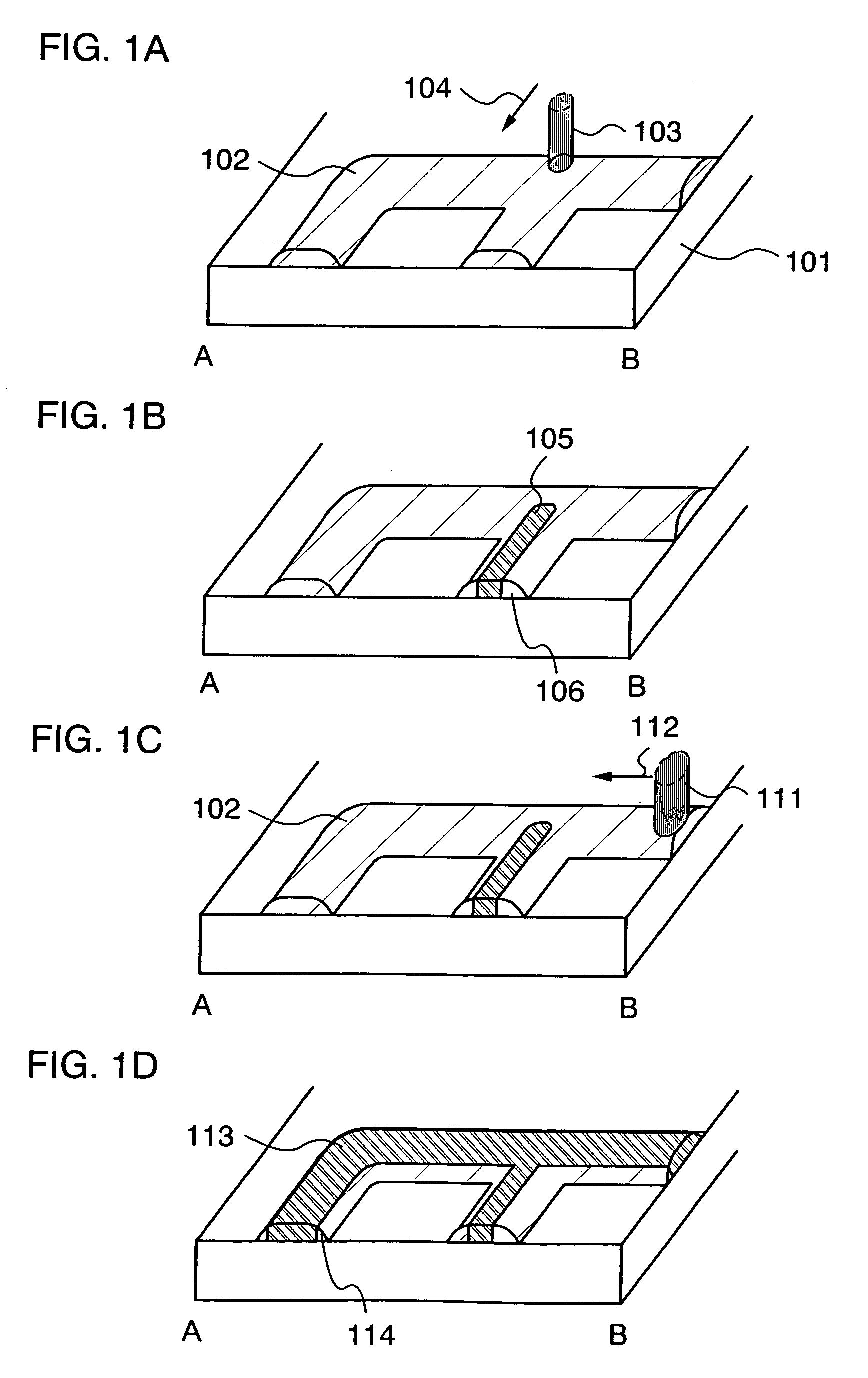

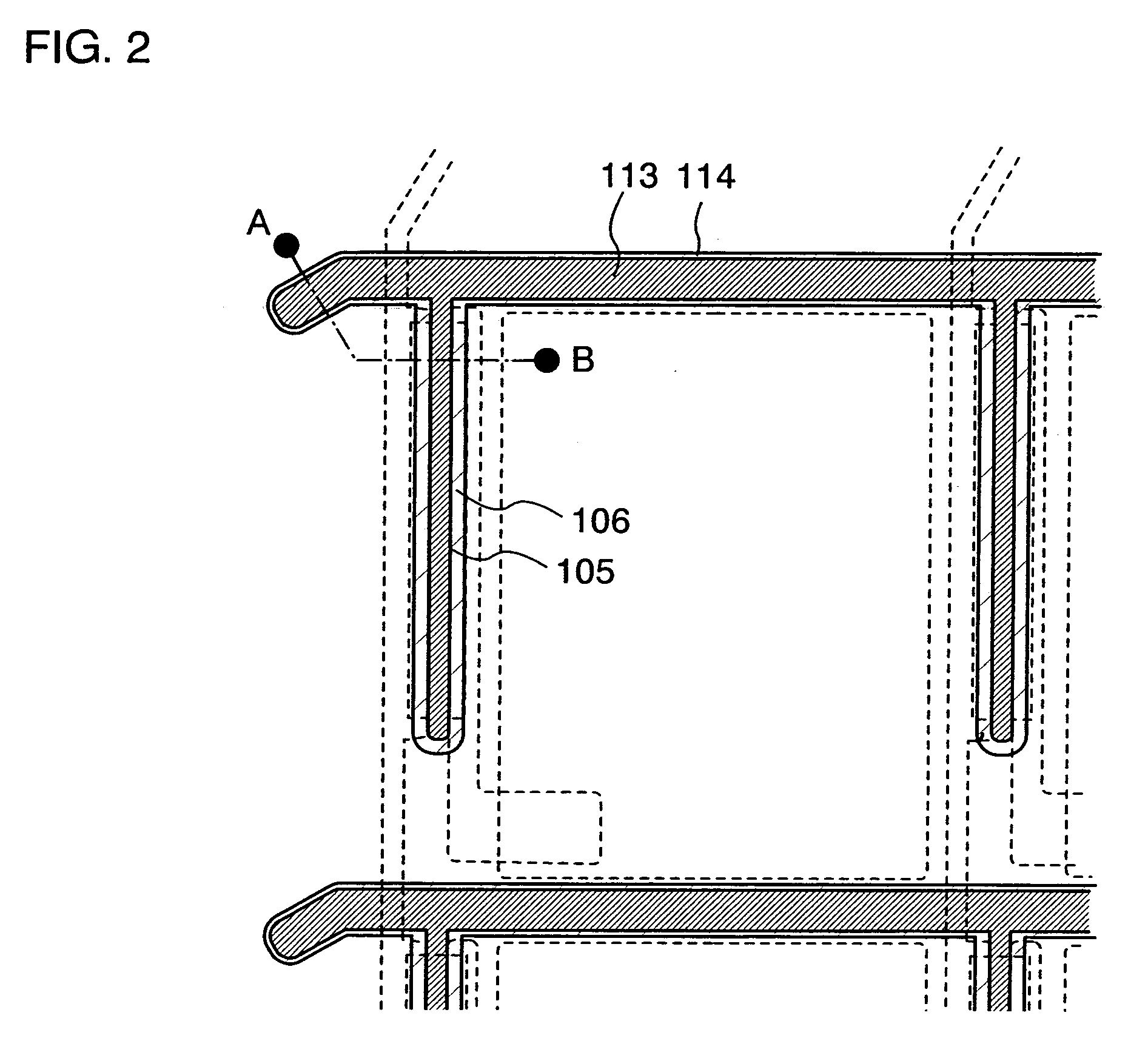

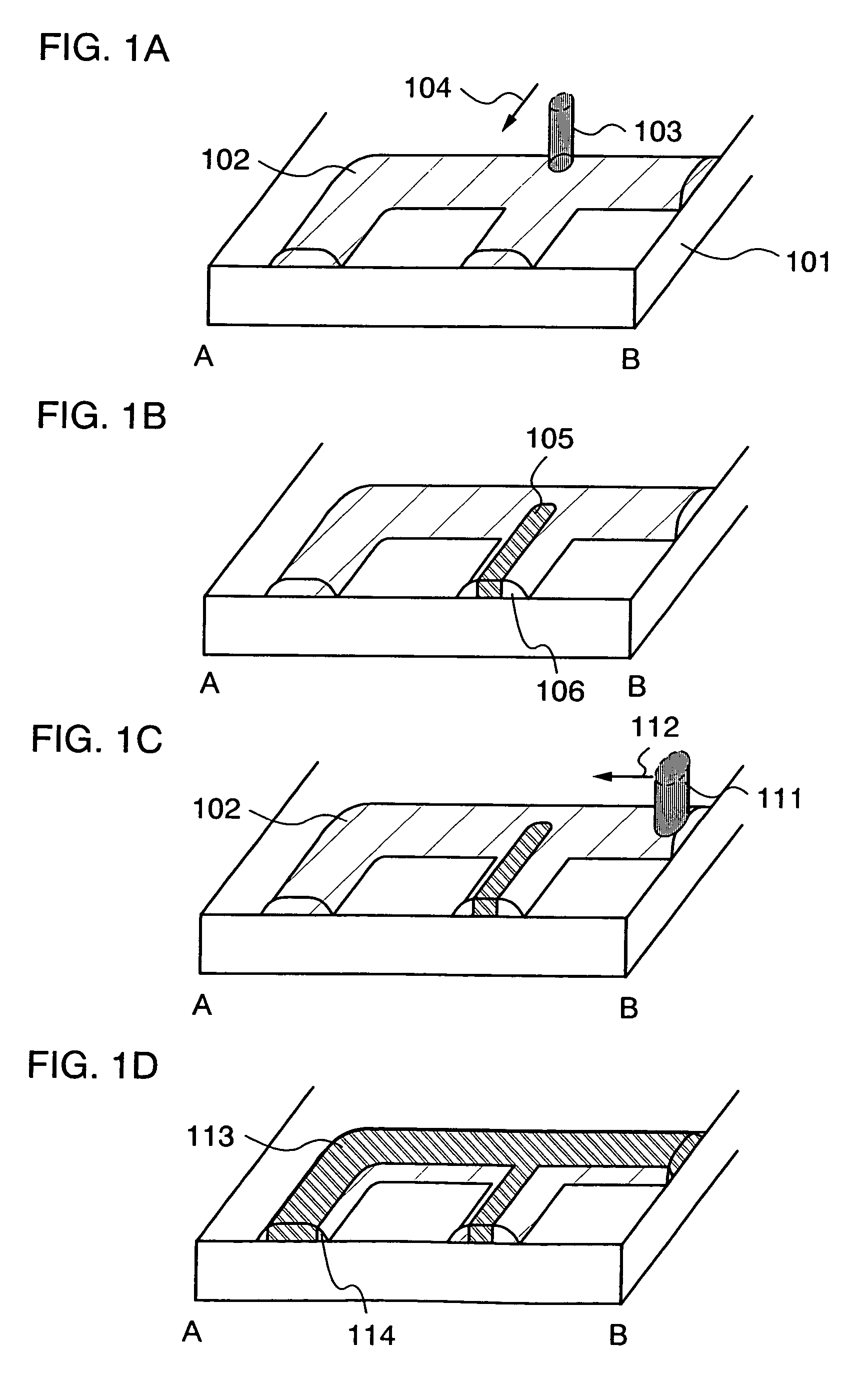

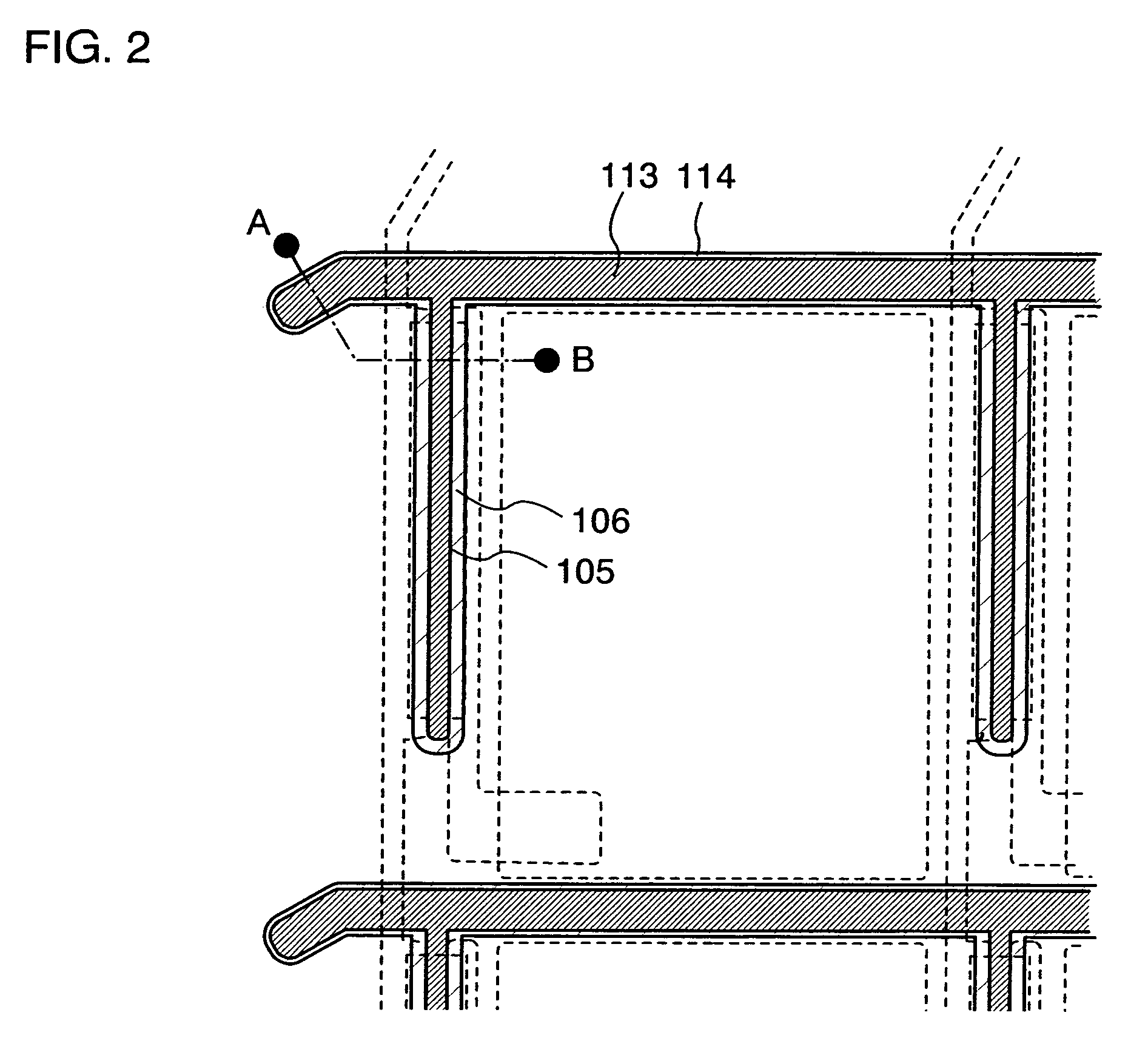

Manufacturing method of wiring substrate and semiconductor device

InactiveUS7494923B2Low costImprove throughputFinal product manufacturePrinted circuit aspectsMetal particleLaser light

The present invention provides a method for forming a wiring having a minute shape on a large substrate with a small number of steps, and further a wiring substrate formed by the method. Moreover, the present invention provides a semiconductor device in which cost reduction and throughput improvement are possible due to the small number of steps and reduction of materials and which has a semiconductor element with a minute structure, and further a manufacturing method thereof. According to the present invention, a composition including metal particles and organic resin is irradiated with laser light and a part of the metal particles is baked to form a conductive layer typified by a wiring, an electrode or the like over a substrate. Further, a semiconductor device having the baked conductive layer as a wiring or an electrode is formed.

Owner:SEMICON ENERGY LAB CO LTD

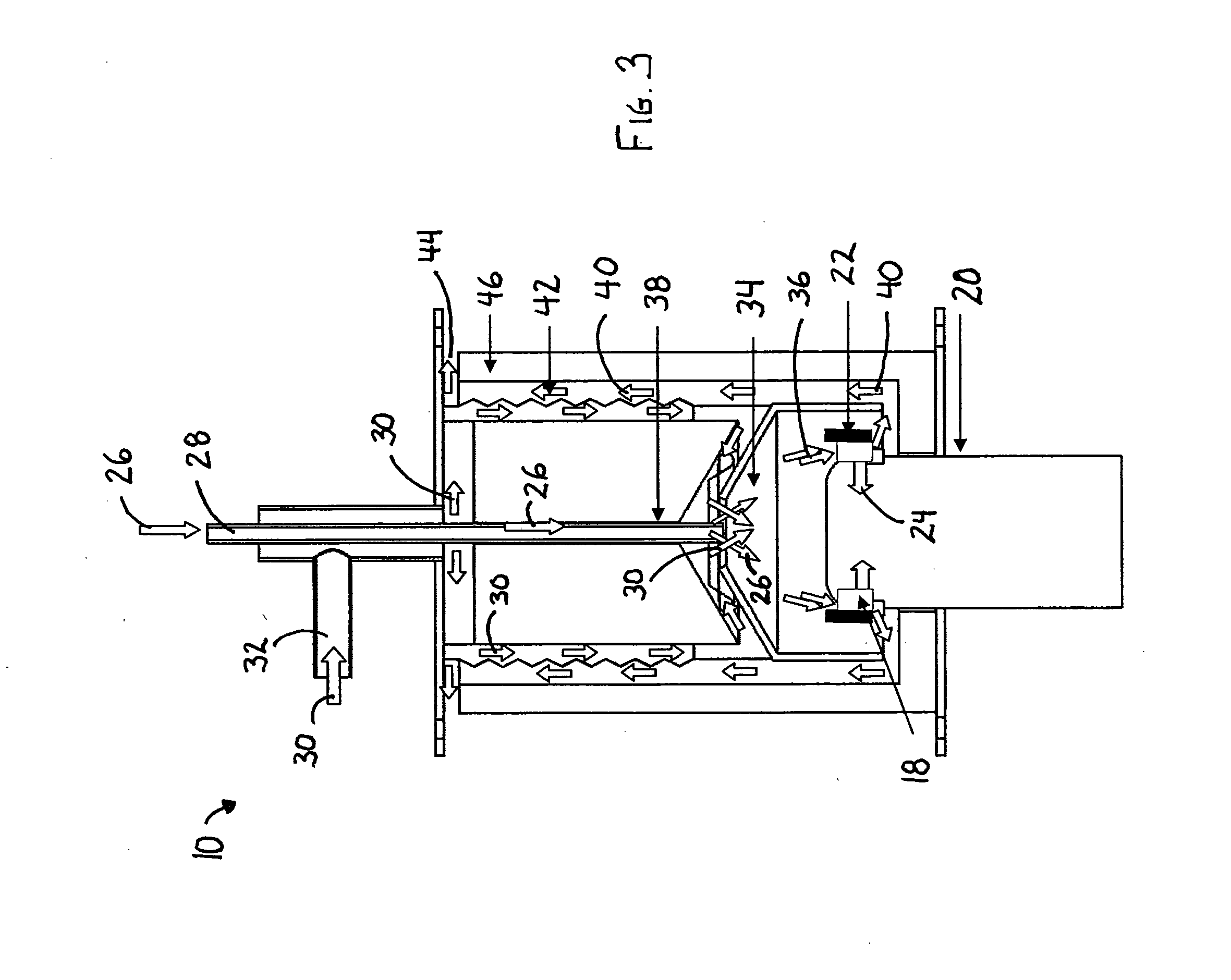

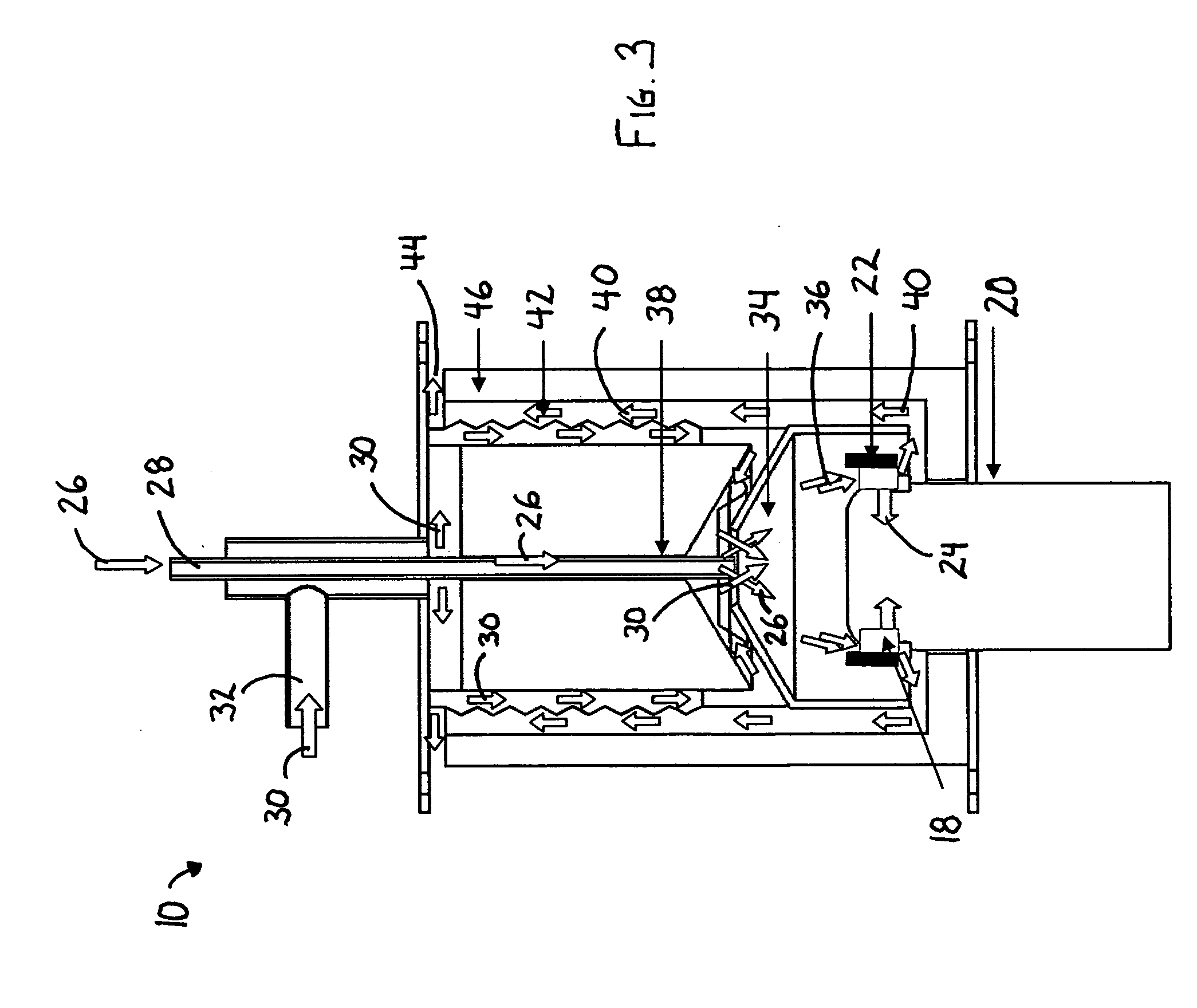

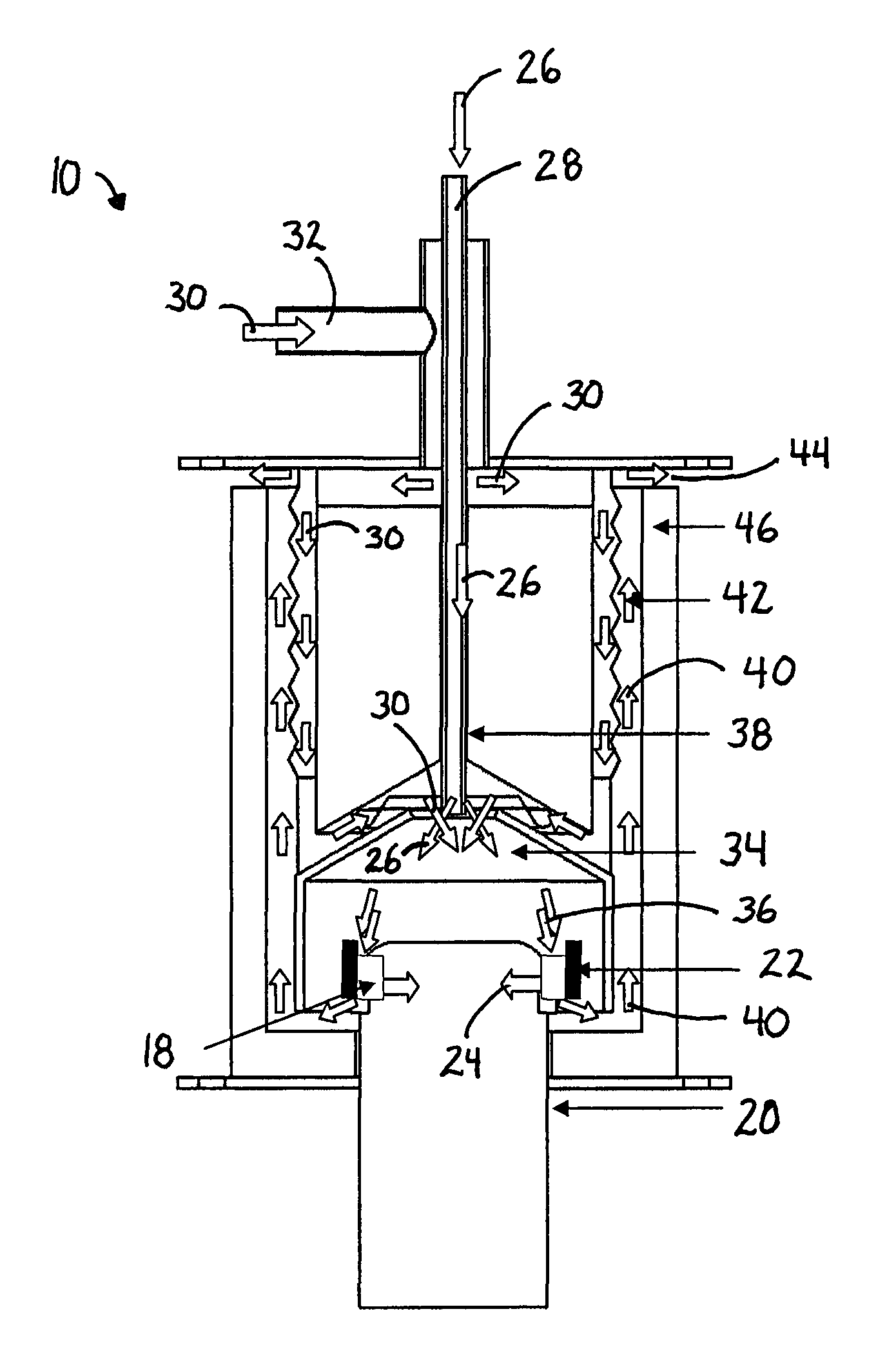

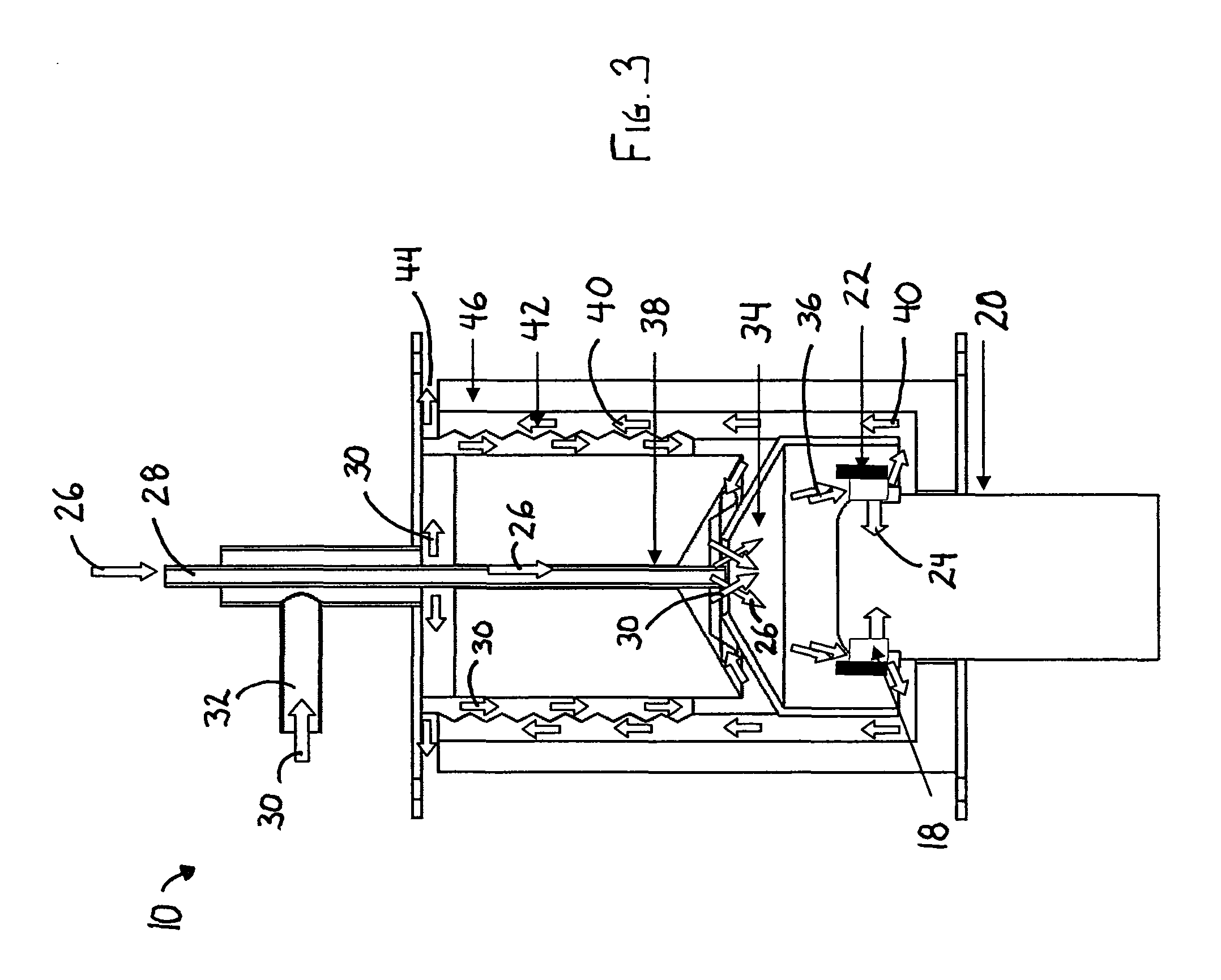

Catalytic burner apparatus for stirling engine

ActiveUS20080078175A1Efficiently and effectively generatesSimple and efficient and effectiveGas turbine plantsClosed-cycle gas positive displacement engine plantStirling engineEngineering

The invention provides a method for transferring heat by conduction to the internal heat acceptor of an external combustion engine. Fuel and air are introduced and mixed to form an air / fuel mixture. The air / fuel mixture is directed into a catalytic reactor that is positioned substantially adjacent to the heater head. Heat is transferred via conduction from the catalytic reactor to the heater head and the catalytic reaction products are exhausted.

Owner:PRECISION COMBUSTION

Catalytic burner for stirling engine

InactiveUS20090113889A1Simple and efficient and effectiveEffective at generating heatBurnersCatalytic ignitersExternal combustion engineEngineering

The invention provides a method for transferring heat by conduction to the internal heat acceptor of an external combustion engine. Fuel and air are introduced and mixed to form an air / fuel mixture. The air / fuel mixture is directed into a catalytic reactor that is positioned substantially adjacent to the heater head. Heat is transferred via conduction from the catalytic reactor to the heater head and the catalytic reaction products are exhausted.

Owner:PRECISION COMBUSTION

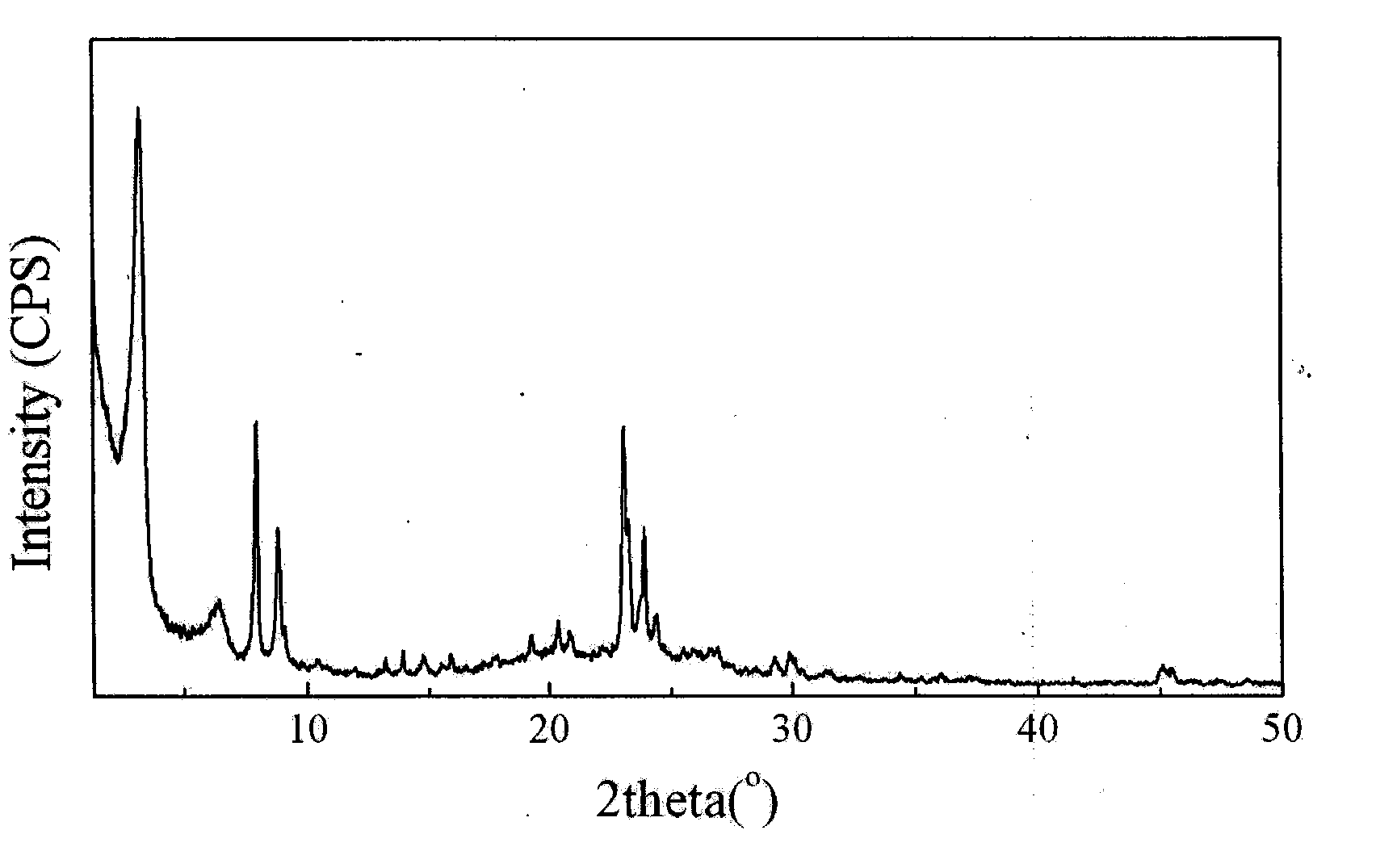

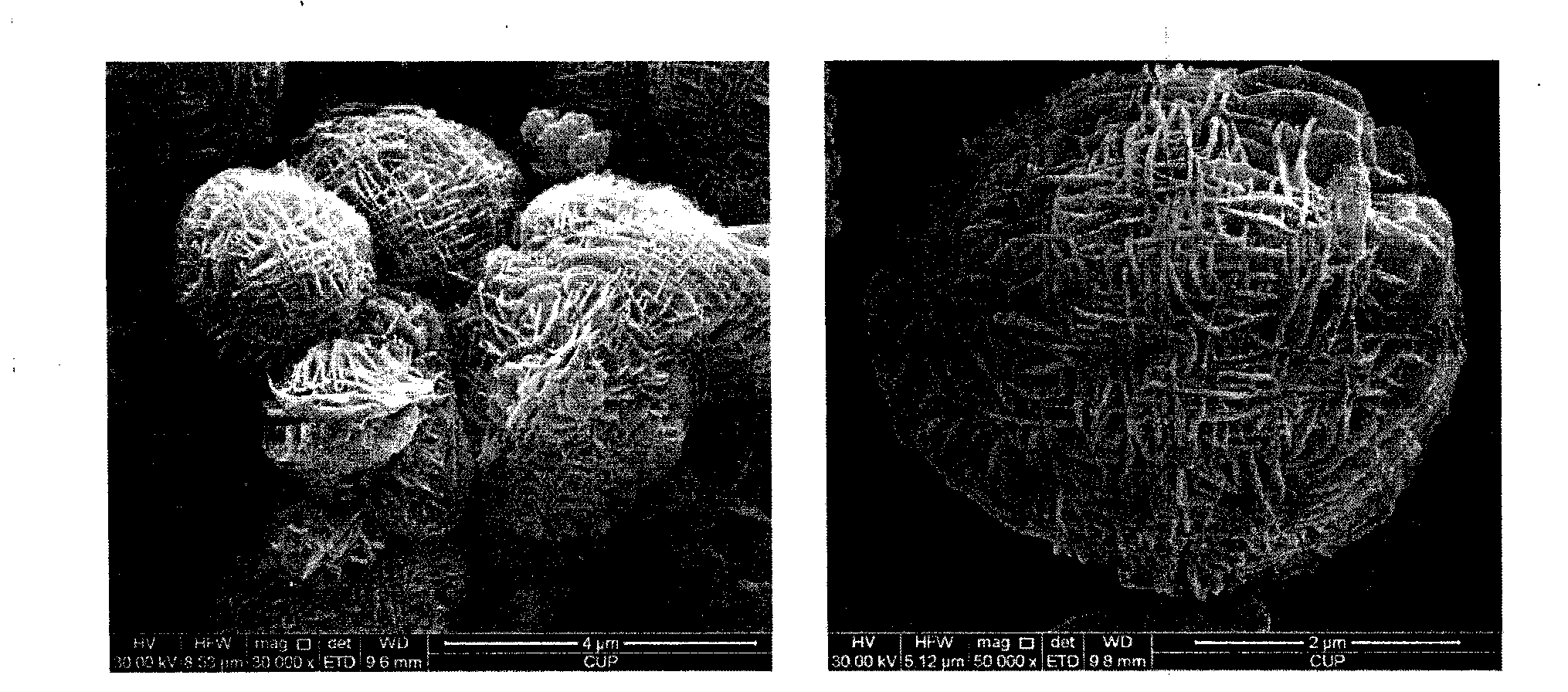

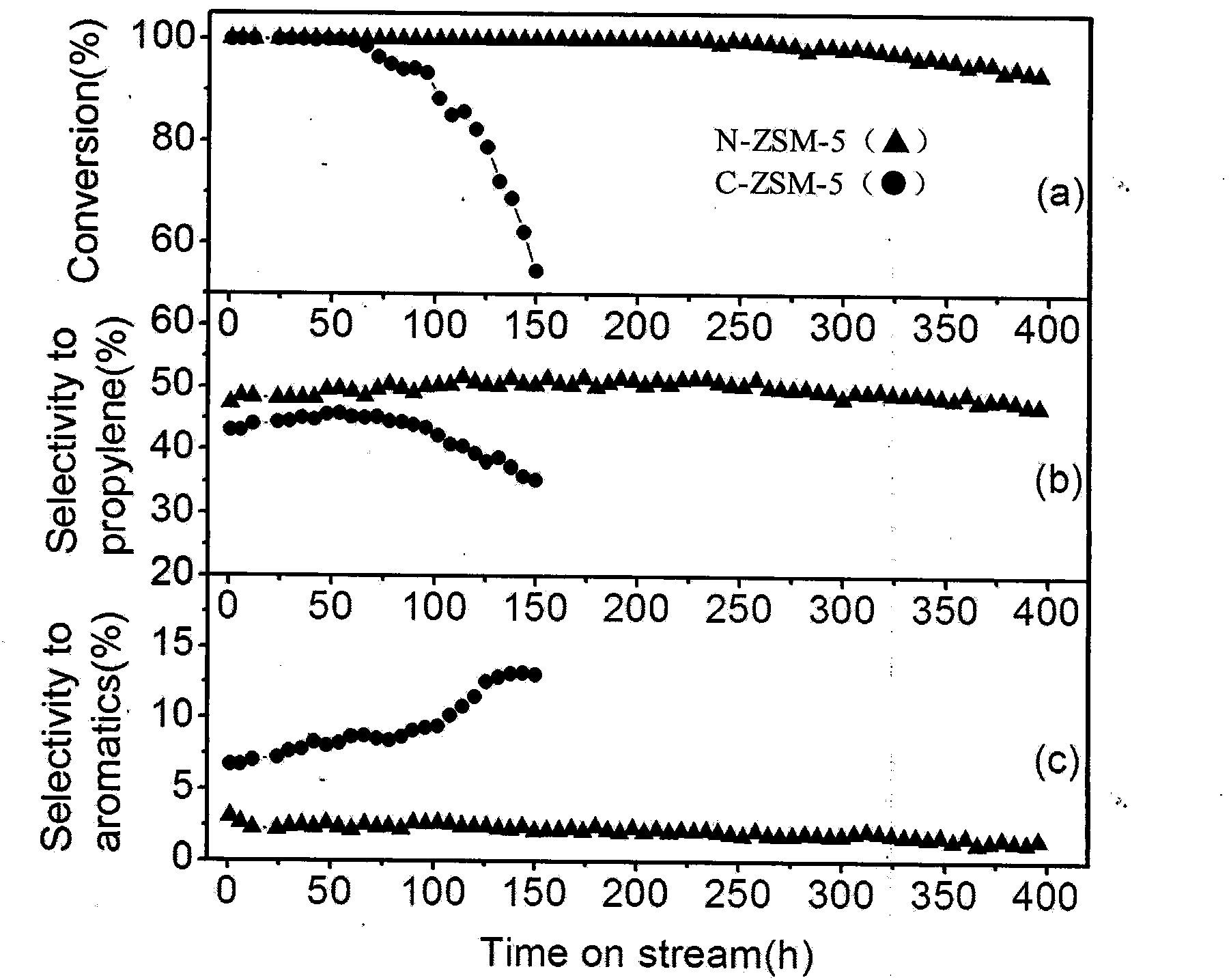

Method for preparing catalyst used for methanol/dimethyl ether high selectivity propylene preparation

InactiveCN103626202AShort channel lengthImprove diffusion abilityMolecular sieve catalystsHydrocarbon from oxygen organic compoundsSulfurNanometre

The invention provides a method for preparing a catalyst used for methanol / dimethyl ether high selectivity propylene preparation, and specifically provides a method for preparing nanometer layer structured ZSM-5 molecular sieve by employing an asymmetric gemini quaternary ammonium surfactant as a template. The method comprises specific steps as follows: (1) preparing solution A by adding the template to a mixed solution comprising water and ethanol, and preparing solution B by adding aluminum sources to sulfur solution; (2) slowly adding the B solution to the A solution, uniformly stirring the mixed solution comprising the A solution and the B solution, and then adding the aluminum sources to form initial gel; and (3) moving the gel to a crystallization kettle for crystallization under 100-200 DEG C for 1-10 days. A ZSM-5 molecular sieve prepared according to the invention is in a nanometer layer structure with the thickness being 20-100 nm, the silica-alumina ratio of the molecular sieve can be adjusted, and the specific surface area and the pore volume of the molecular sieve are quite large. In a methanol / dimethyl ether high selectivity propylene preparation reaction, the propylene selectivity and P / E ratio of the nanometer layer structured ZSM-5 molecular sieve are higher than that of a conventional ZSM-5 molecular sieve, and the service lifetime of the catalyst is longer.

Owner:巩雁军 +1

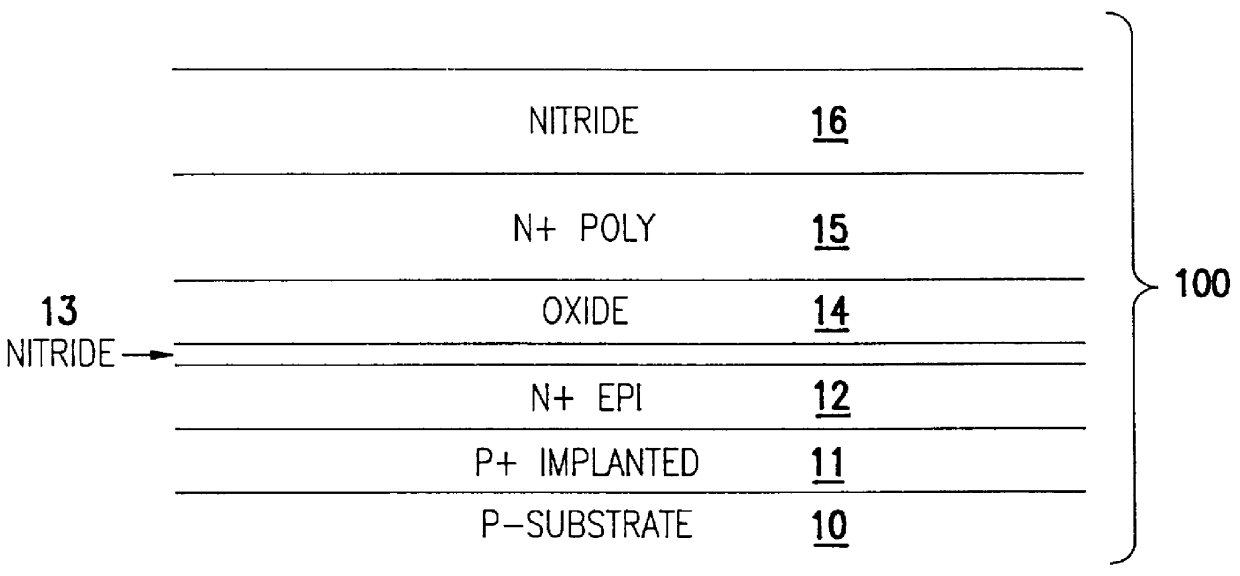

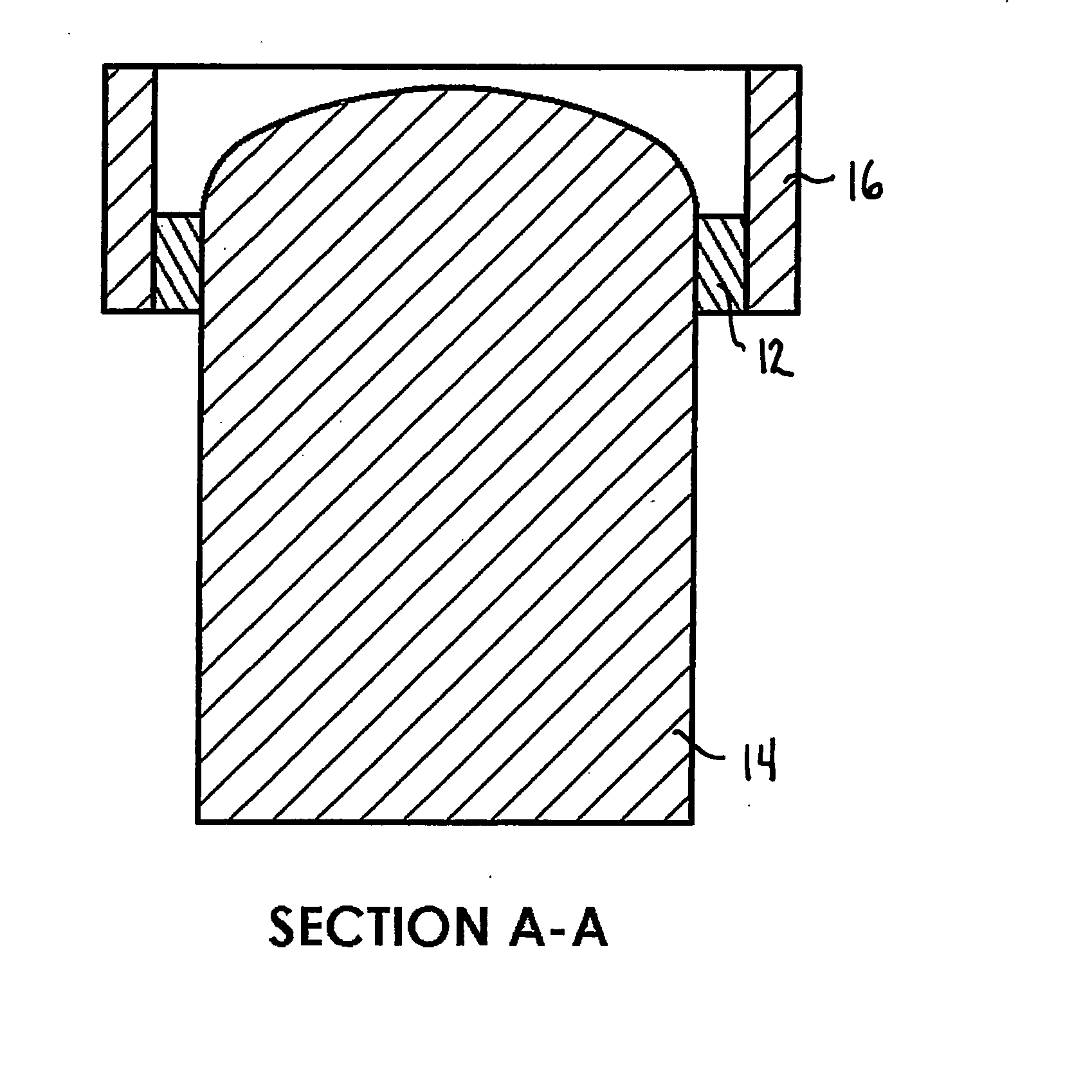

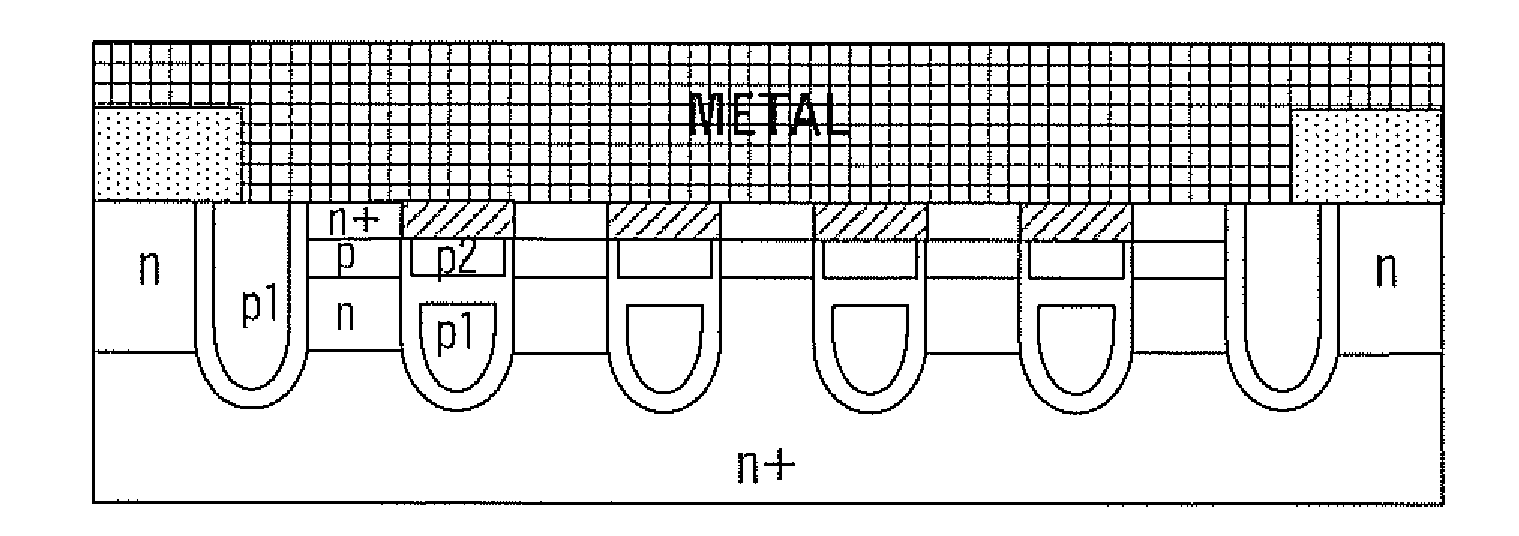

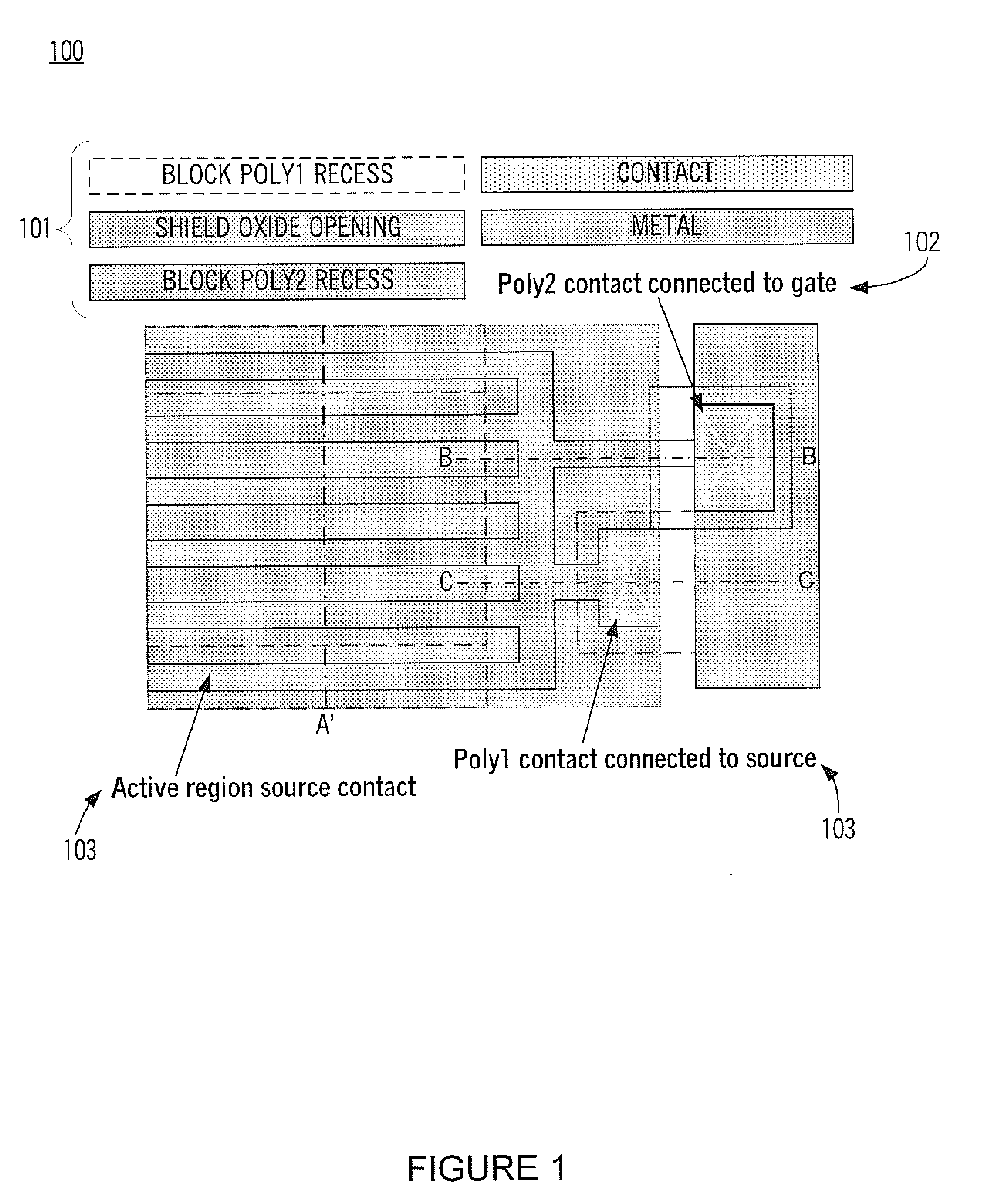

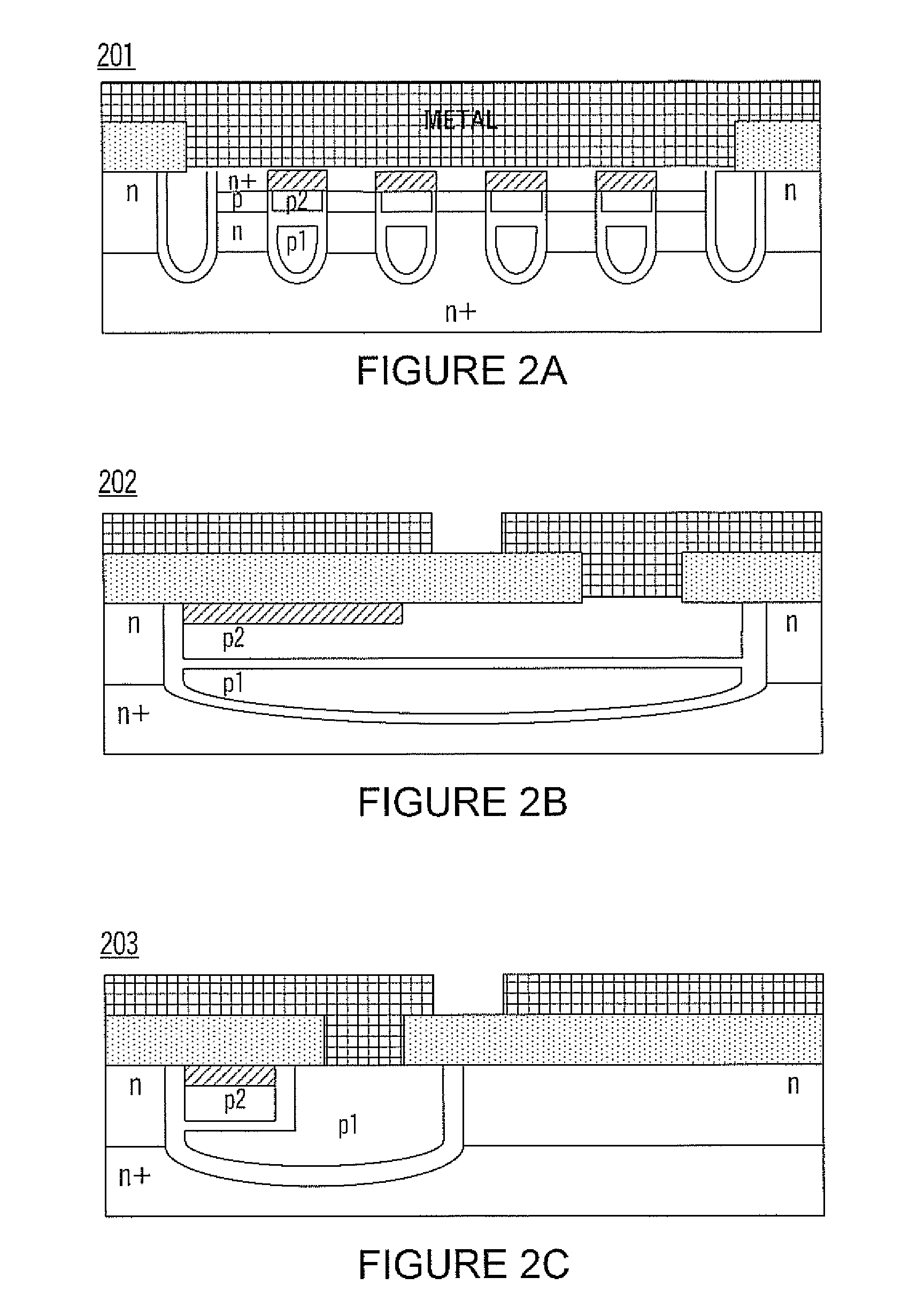

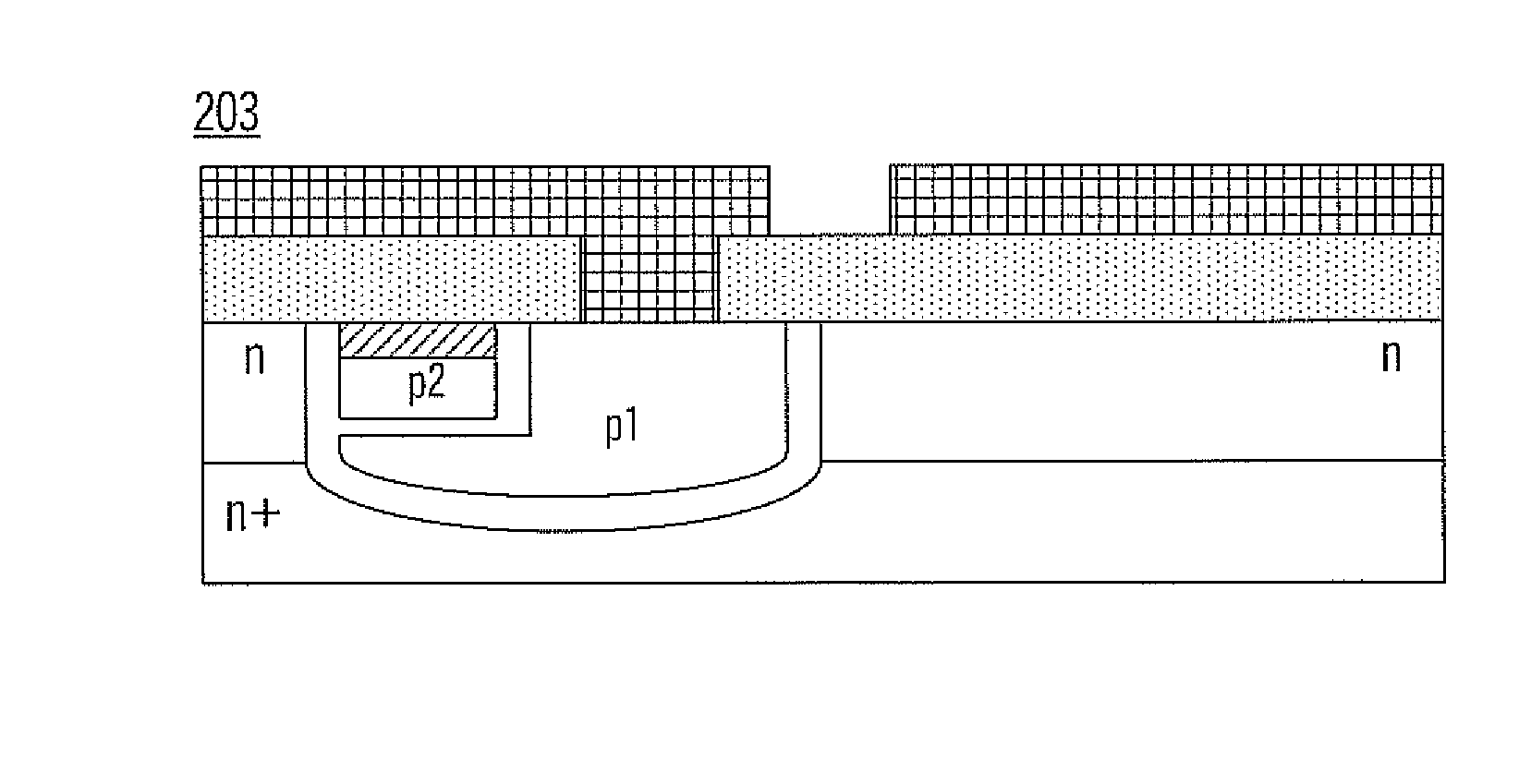

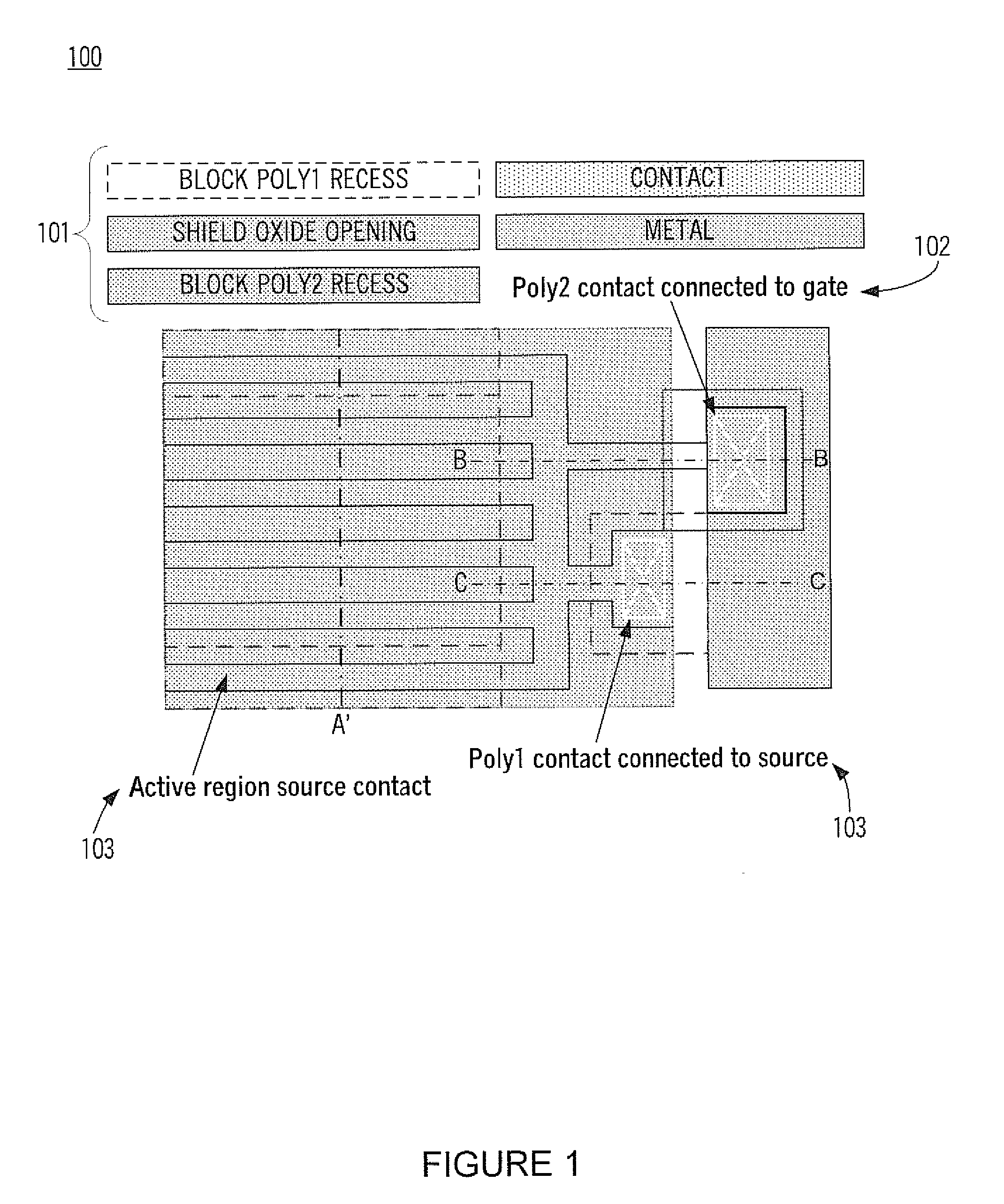

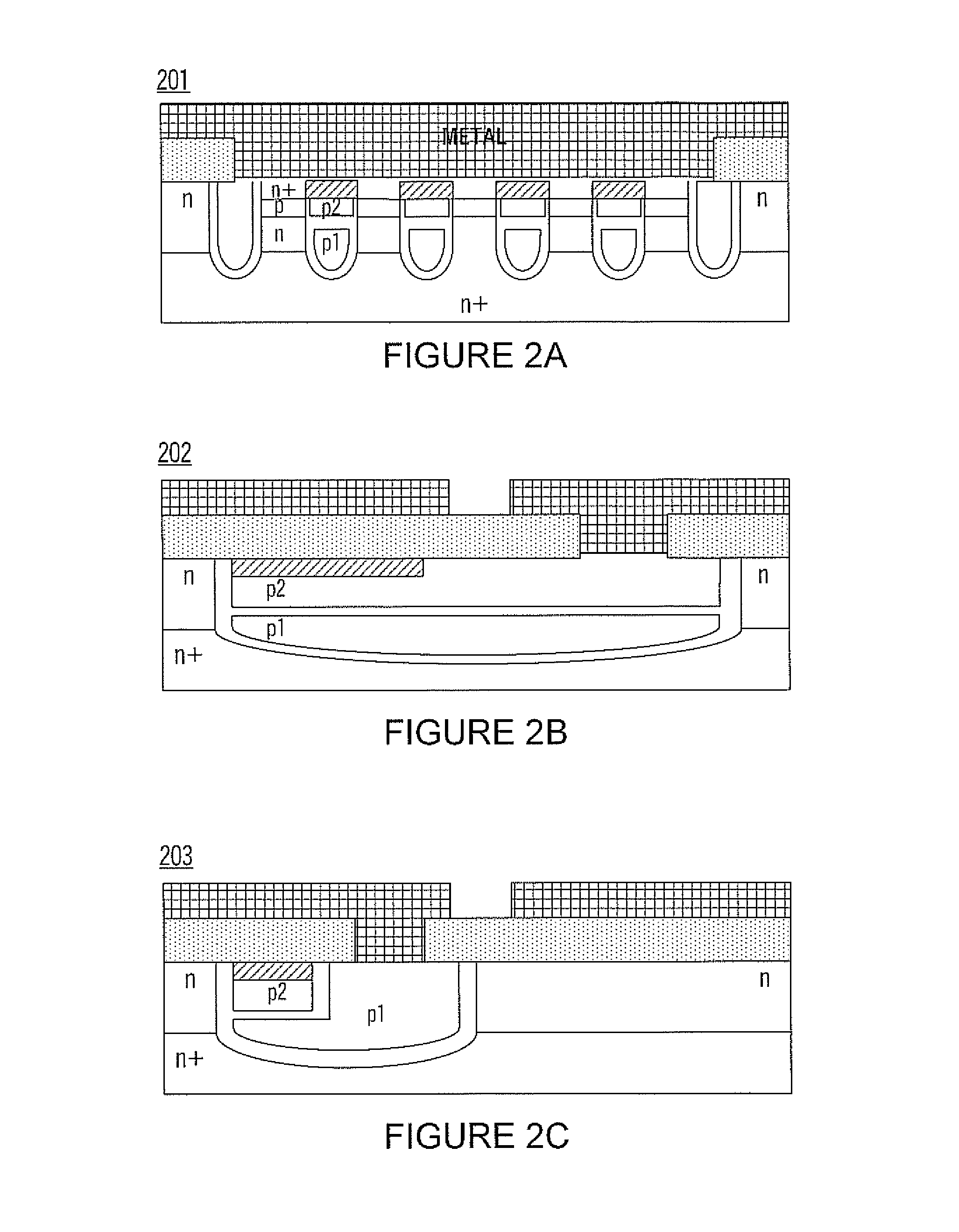

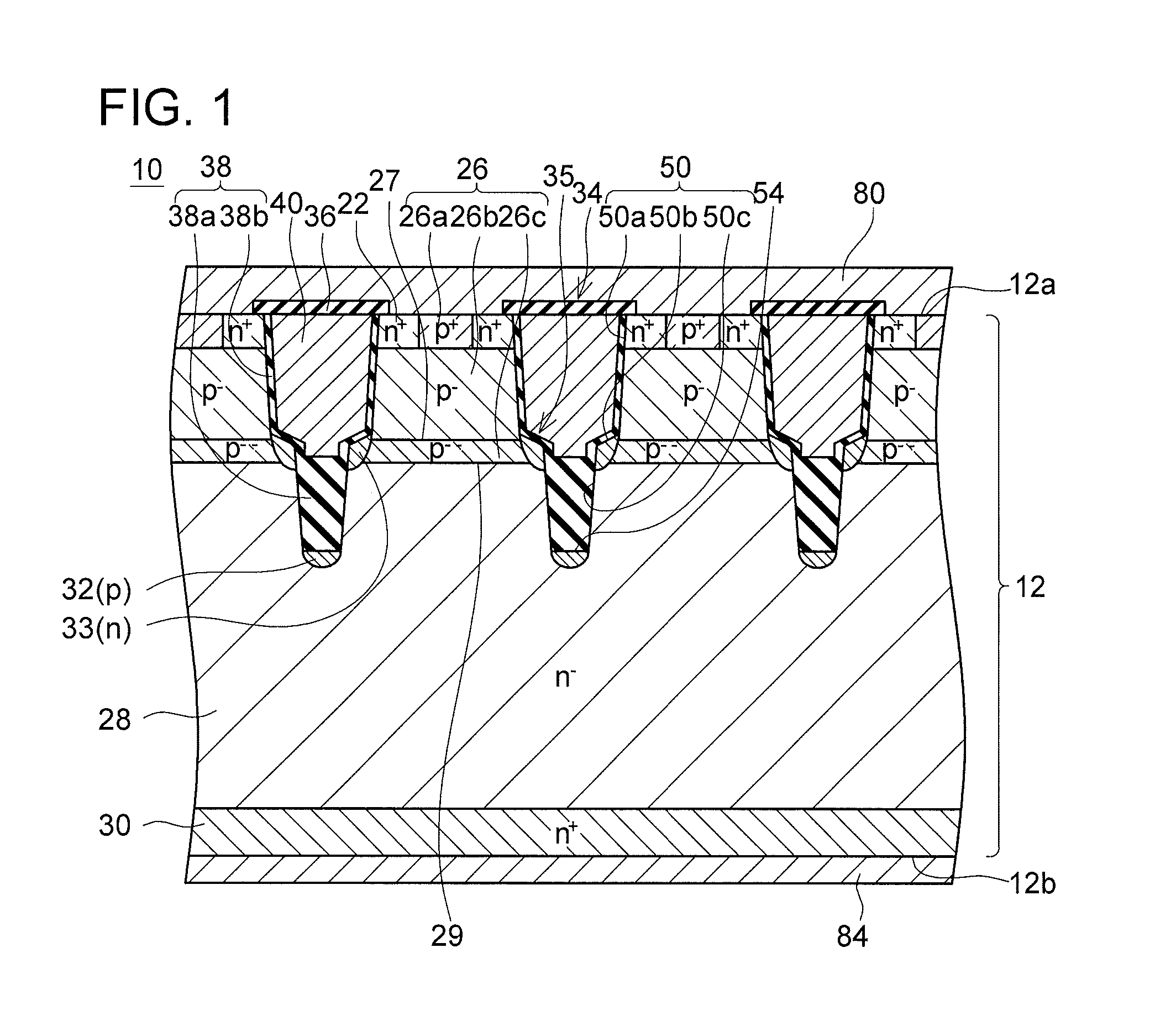

Structures of and methods of fabricating split gate MIS devices

ActiveUS20110210406A1Lower forward voltageShort channel lengthSemiconductor devicesField-effect transistorPolycrystalline silicon

A split gate field effect transistor device. The device includes a split gate structure having a trench, a gate electrode and a source electrode. A first poly layer is disposed within the trench and is connected to the gate electrode. A second poly layer connected to the source electrode, wherein the first poly layer and the second poly layer are independent.

Owner:VISHAY SILICONIX LLC

Combination nonvolatile memory using unified technology with byte, page and block write and simultaneous read and write operations

InactiveUS20050141298A1Small sizeAvoid choiceSolid-state devicesRead-only memoriesMemory bankPre-charge

A combination EEPROM and Flash memory is described containing cells in which the stacked gate transistor of the Flash cell is used in conjunction with a select transistor to form an EEPROM cell. The select transistor is made sufficiently small so as to allow the EEPROM cells to accommodate the bit line pitch of the Flash cell, which facilitates combining the two memories into memory banks containing both cells. The EEPROM cells are erased by byte while the Flash cells erased by block. The small select transistor has a small channel length and width, which is compensated by increasing gate voltages on the select transistor and pre-charge bitline during CHE program operation.

Owner:CALLAHAN CELLULAR L L C

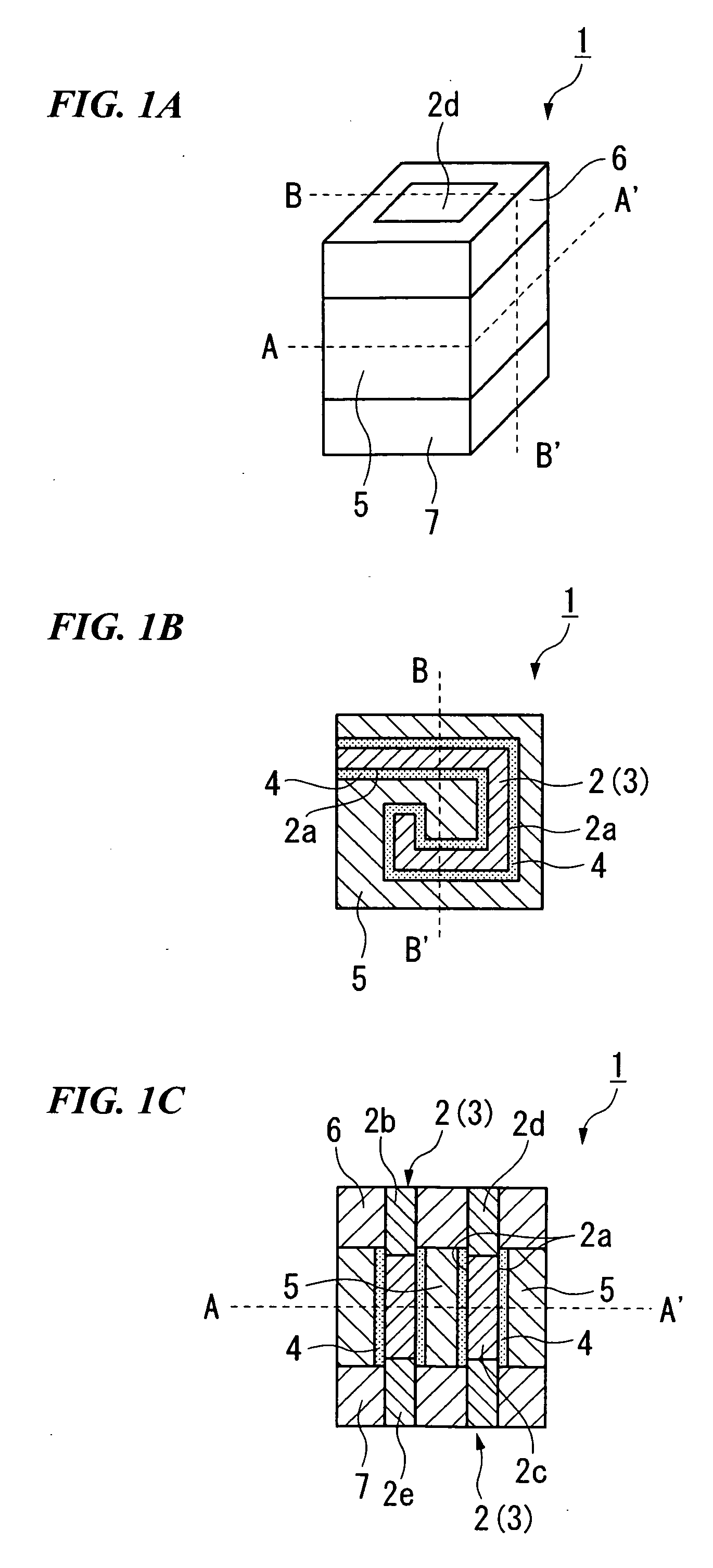

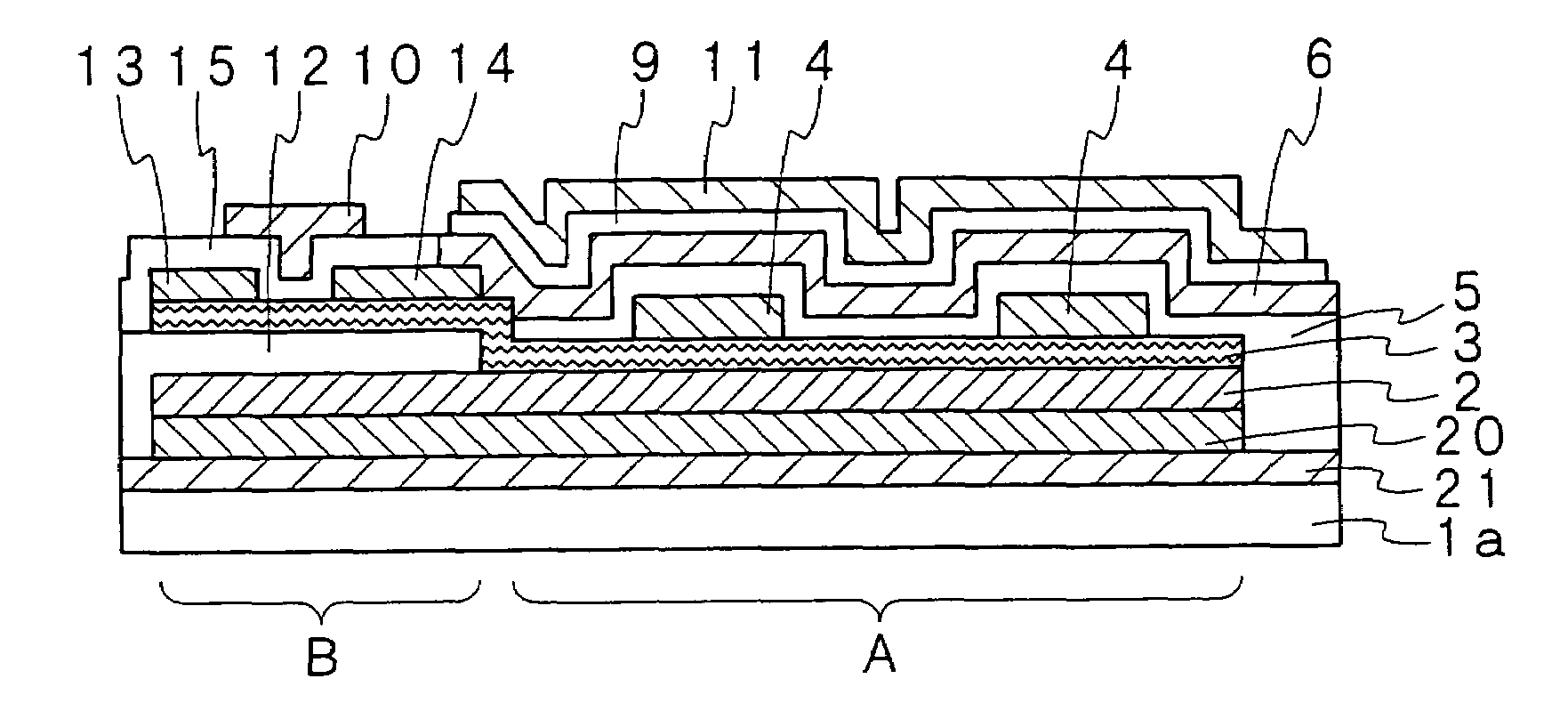

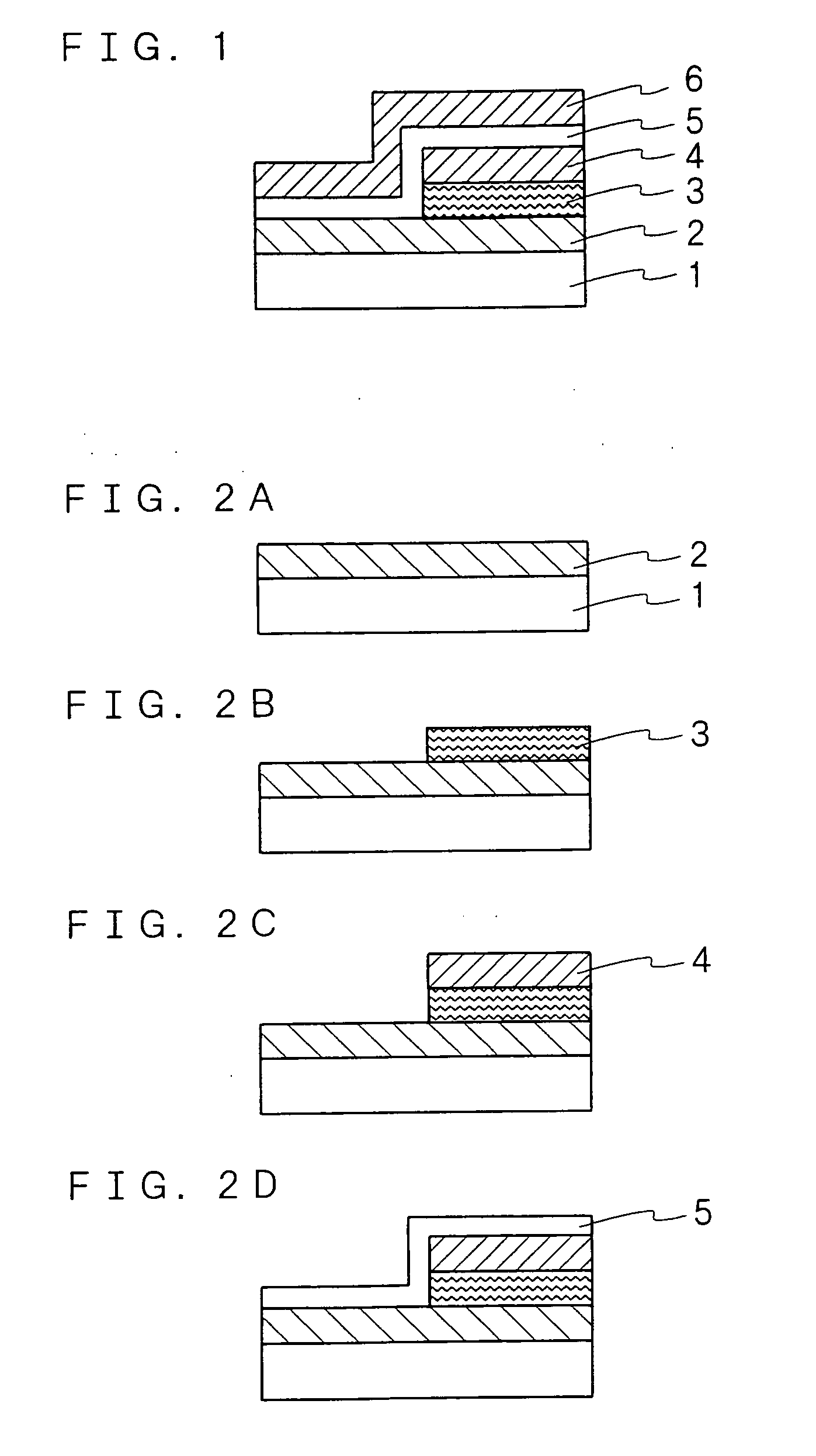

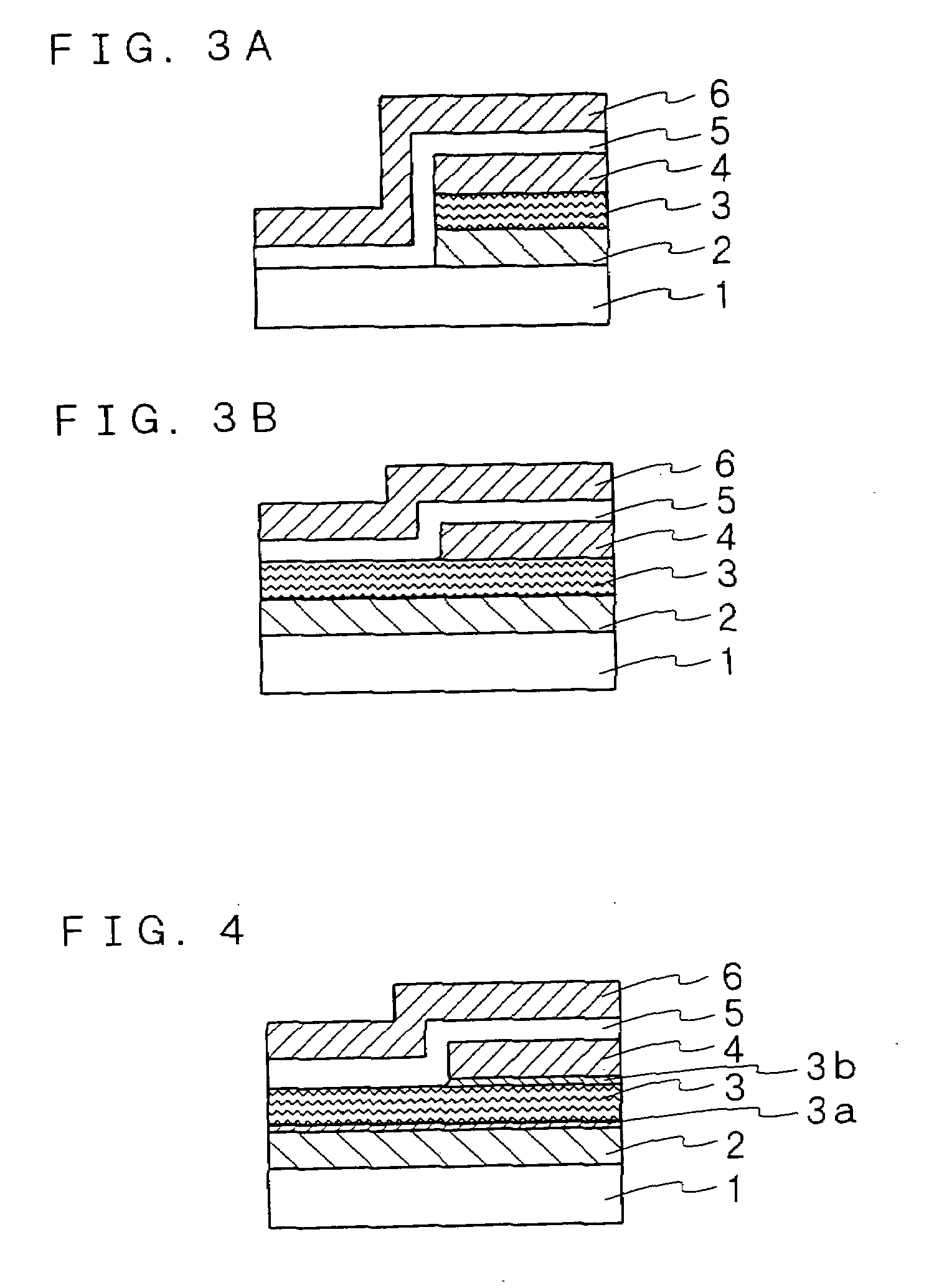

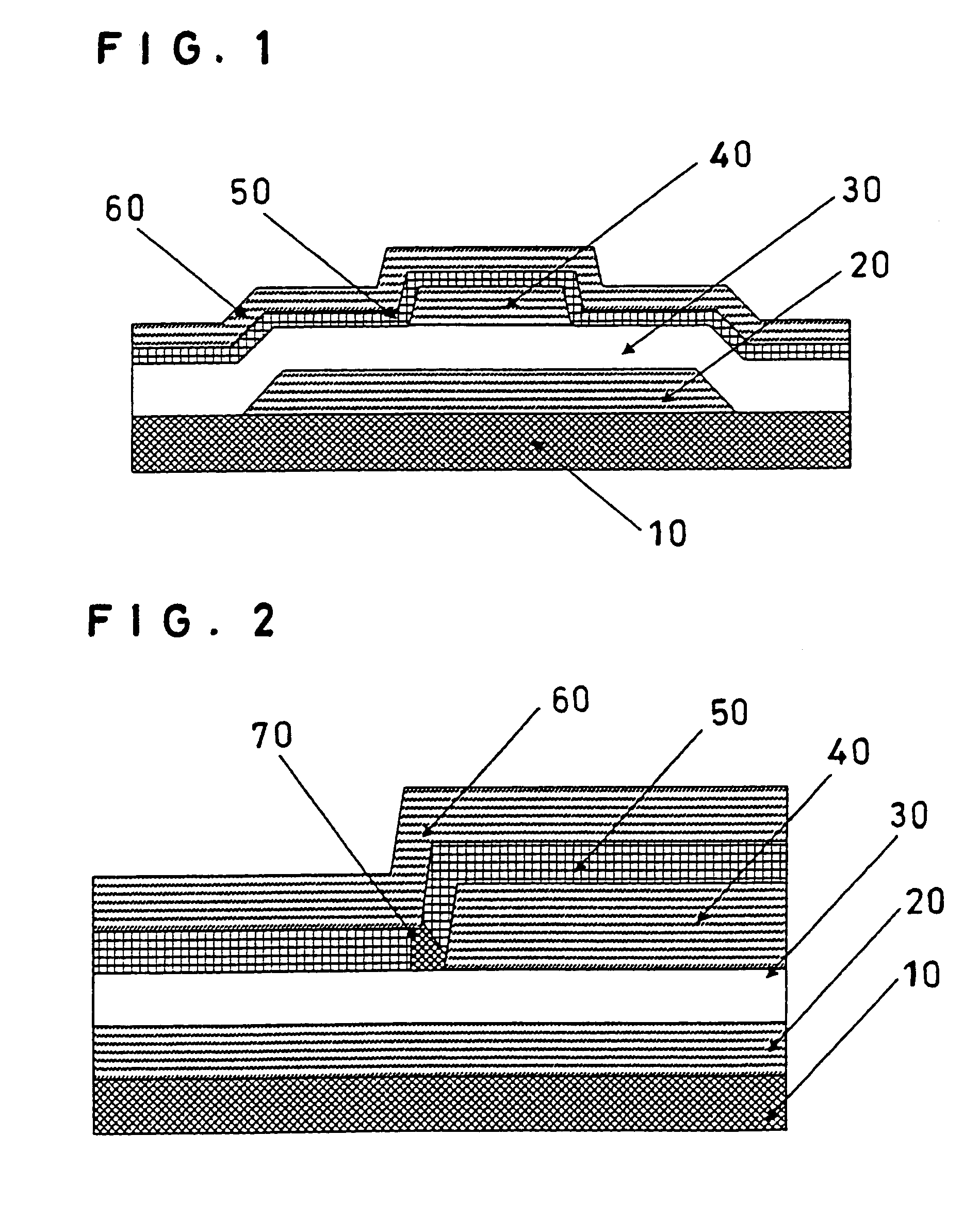

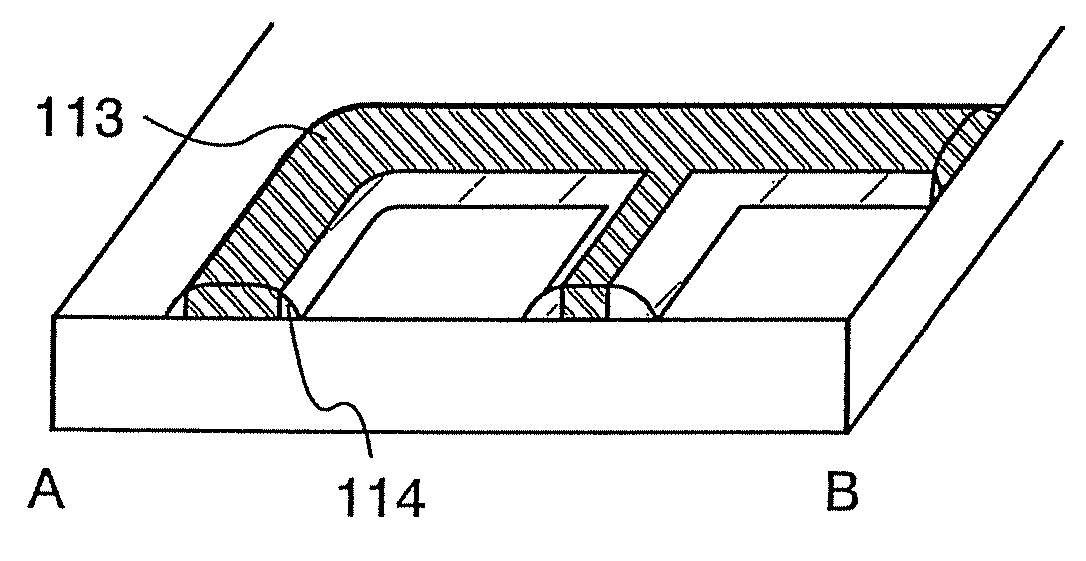

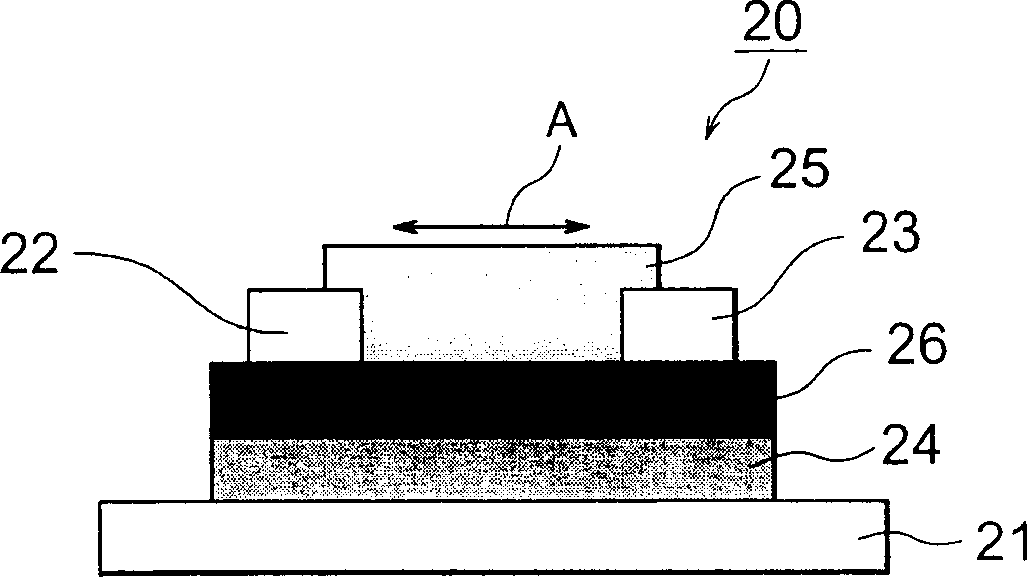

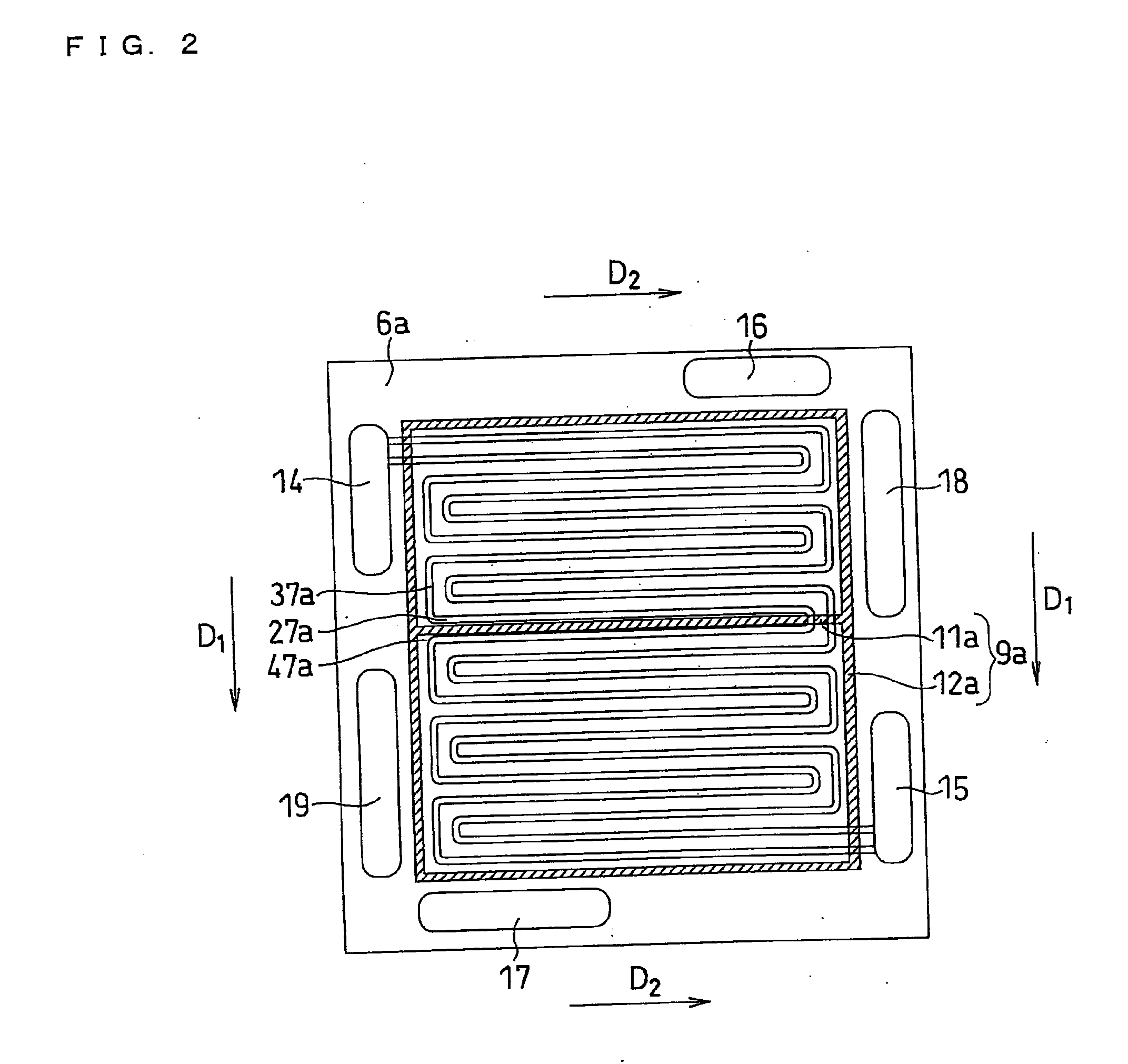

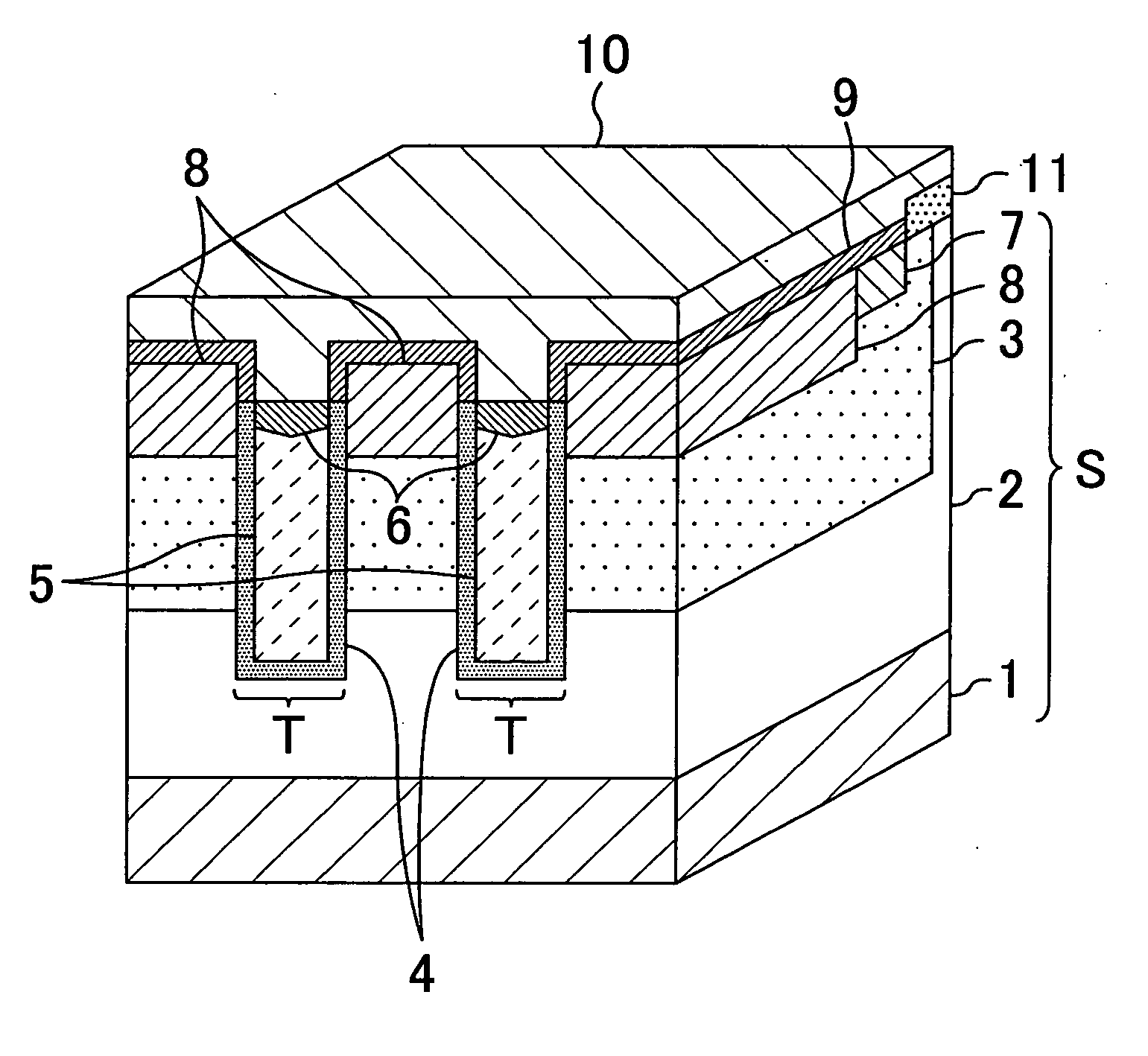

Organic Semiconductor Element and Organic El Display Device Using the Same

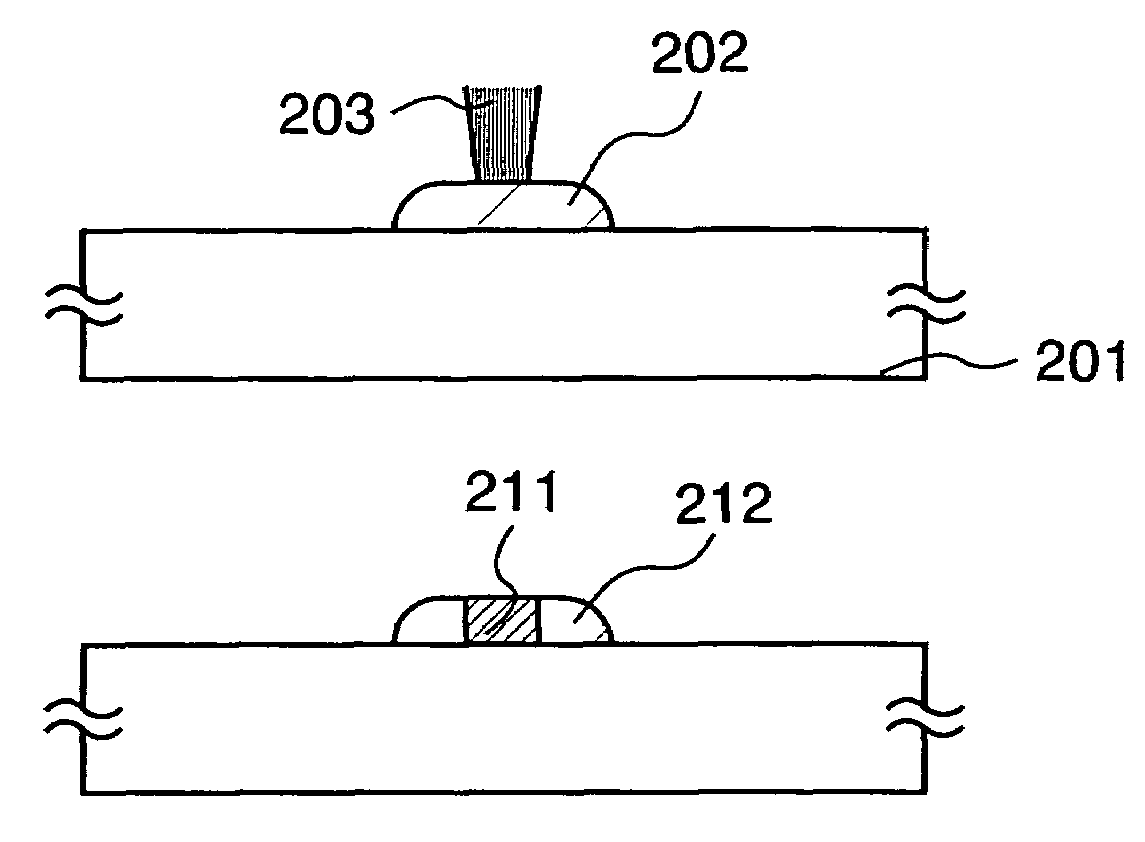

InactiveUS20080237580A1Channel length can be accuratelyReduce stepsTransistorSolid-state devicesDisplay deviceOrganic semiconductor

It is provided an organic semiconductor element having an FET which can control a channel length to a small value and does not cause a rise in contact resistance due to a step portion, and an organic light emitting display device with a large aperture using the same. A first conductive layer (2) which is one of source / drain electrodes is provided onto a substrate (1), and an organic semiconductor layer (3) and a second conductive layer (4) which is the other electrode of the source / drain electrodes are provided onto the first conductive layer (2). Then on a side face of the organic semiconductor layer or a front surface of the organic semiconductor layer (3) exposed by removing a part of the second conductive layer and a side face of the second conductive layer a gate electrode (third conductive layer) (6) is provided via an insulating layer (5), thereby to form an FET. The organic EL display device has the FET having such structure laminated on an organic EL section as a drive element.

Owner:ROHM CO LTD

Organic thin-film transistor and method of manufacturing the same

InactiveUS7138682B2Short channel lengthEasy to manufactureTransistorSolid-state devicesInsulation layerEngineering

Owner:NAT INST OF ADVANCED IND SCI & TECH

Thin film transistor substrate having bi-layer oxide semiconductor

InactiveUS20180122833A1Short channel lengthThreshold Voltage StabilityTransistorSolid-state devicesIndiumZinc

The present disclosure relates to a thin film transistor substrate having a bi-layer oxide semiconductor. The present disclosure provides a thin film transistor substrate comprising: a substrate; and an oxide semiconductor layer on the substrate, wherein the oxide semiconductor layer includes: a first oxide semiconductor layer having indium, gallium and zinc; and a second oxide semiconductor layer stacked on the first oxide semiconductor layer having the indium, gallium and zinc, wherein any one layer of the first and the second oxide semiconductor layers has a first composition ratio of the indium, gallium and zinc of 1:1:1; and wherein other layer has a second composition ratio of the indium, gallium and zinc in which the indium ratio is higher than the zinc ratio.

Owner:LG DISPLAY CO LTD

Wiring Substrate, Semiconductor Device and Manufacturing Method Thereof

InactiveUS20090179230A1Low costImprove throughputFinal product manufactureLayered productsLaser lightMetal particle

The present invention provides a method for forming a wiring having a minute shape on a large substrate with a small number of steps, and further a wiring substrate formed by the method. Moreover, the present invention provides a semiconductor device in which cost reduction and throughput improvement are possible due to the small number of steps and reduction of materials and which has a semiconductor element with a minute structure, and further a manufacturing method thereof. According to the present invention, a composition including metal particles and organic resin is irradiated with laser light and a part of the metal particles is baked to form a conductive layer typified by a wiring, an electrode or the like over a substrate. Further, a semiconductor device having the baked conductive layer as a wiring or an electrode is formed.

Owner:SEMICON ENERGY LAB CO LTD

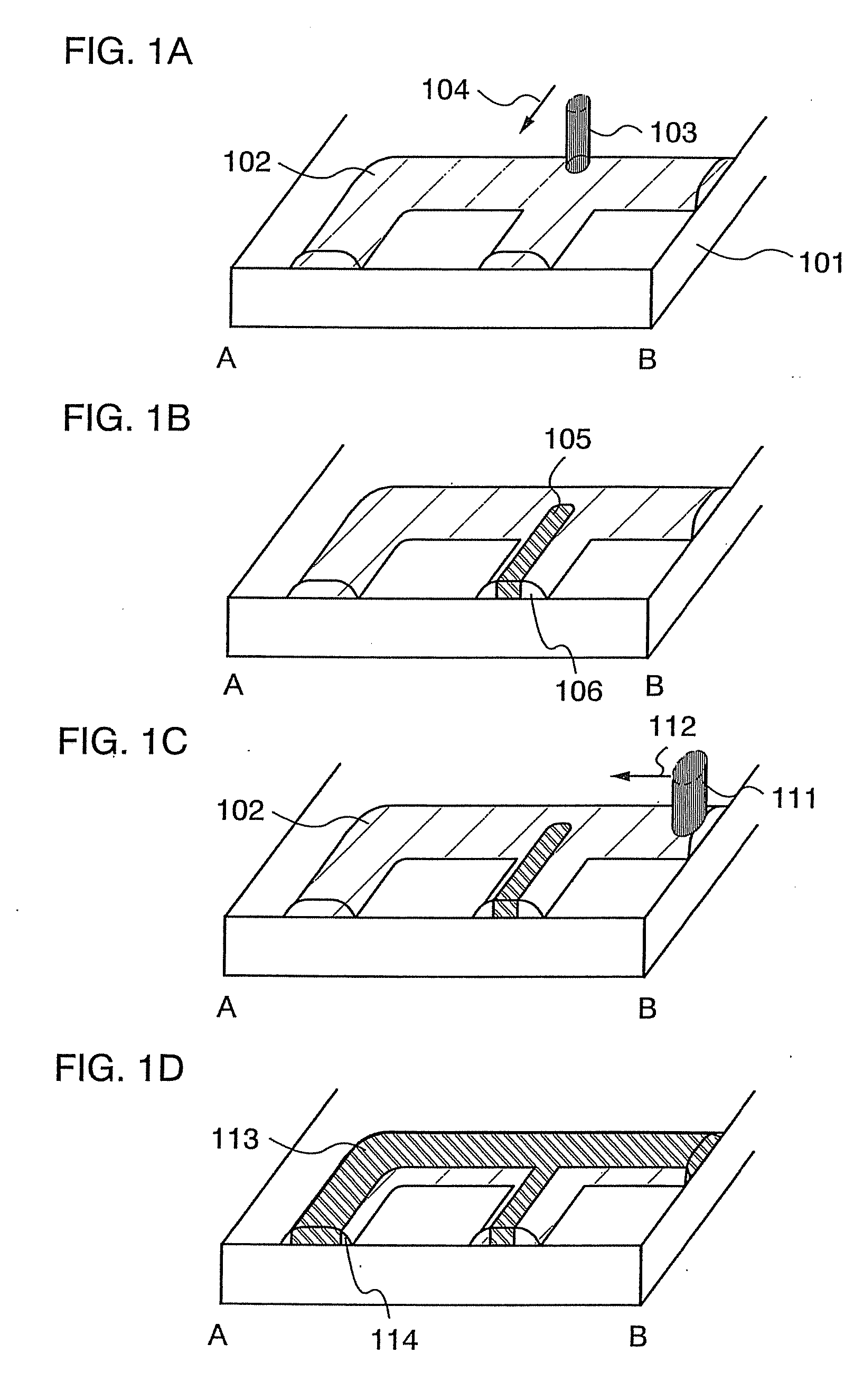

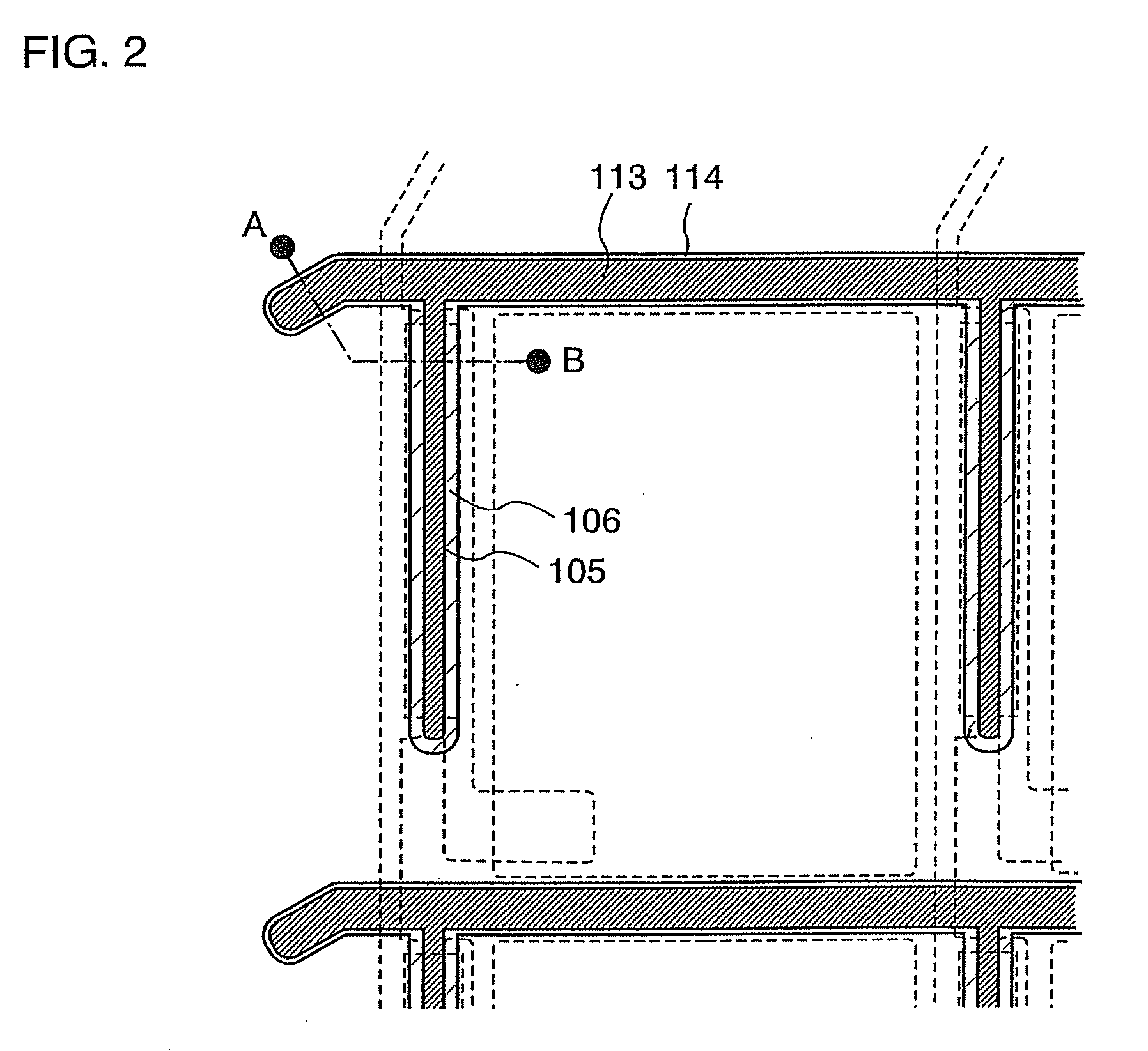

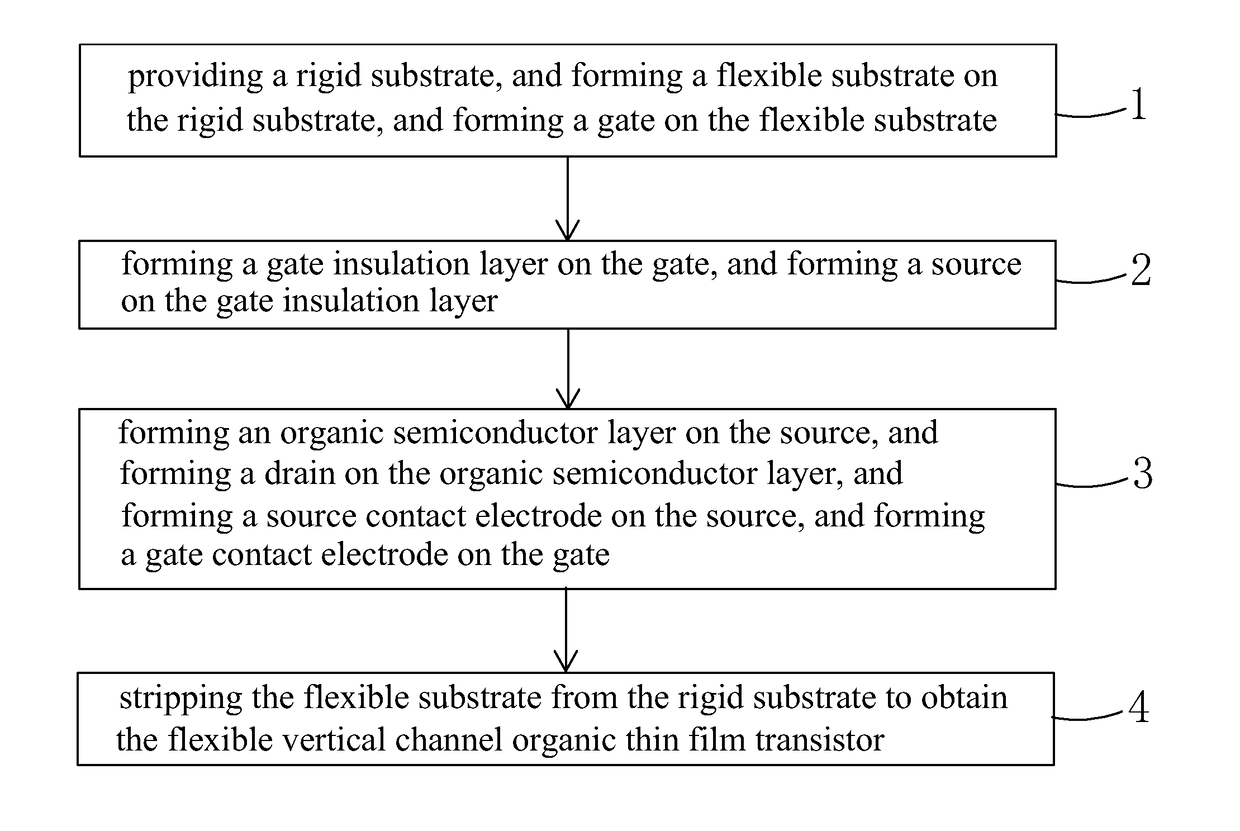

Flexible vertical channel organic thin film transistor and manufacture method thereof

InactiveUS20180219055A1Short channel lengthGood bendabilityTransistorSolid-state devicesDrain currentOrganic semiconductor

Provided is a flexible vertical channel organic thin film transistor and a manufacture method thereof, which change the traditional configuration of the horizontal channel organic TFT and use the vertical channel configuration to tremendously shorten the channel length so that the TFT can obtain the larger source-drain current under the lower drive voltage; by using the flawless, high conductive and high transparent graphene material to manufacture the gate, the electronic performance of the TFT can be better; by using the hexagonal boron nitride material to manufacture the gate insulation layer to interact with the gate made by graphene, the electronic performance of the TFT can be promoted; because both the graphene and the hexagonal boron nitride materials are two dimension atomic layer structure material with better bendability and the channel layer uses the flexible organic semiconductor layer, the bendability of the entire TFT can be significantly promoted.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

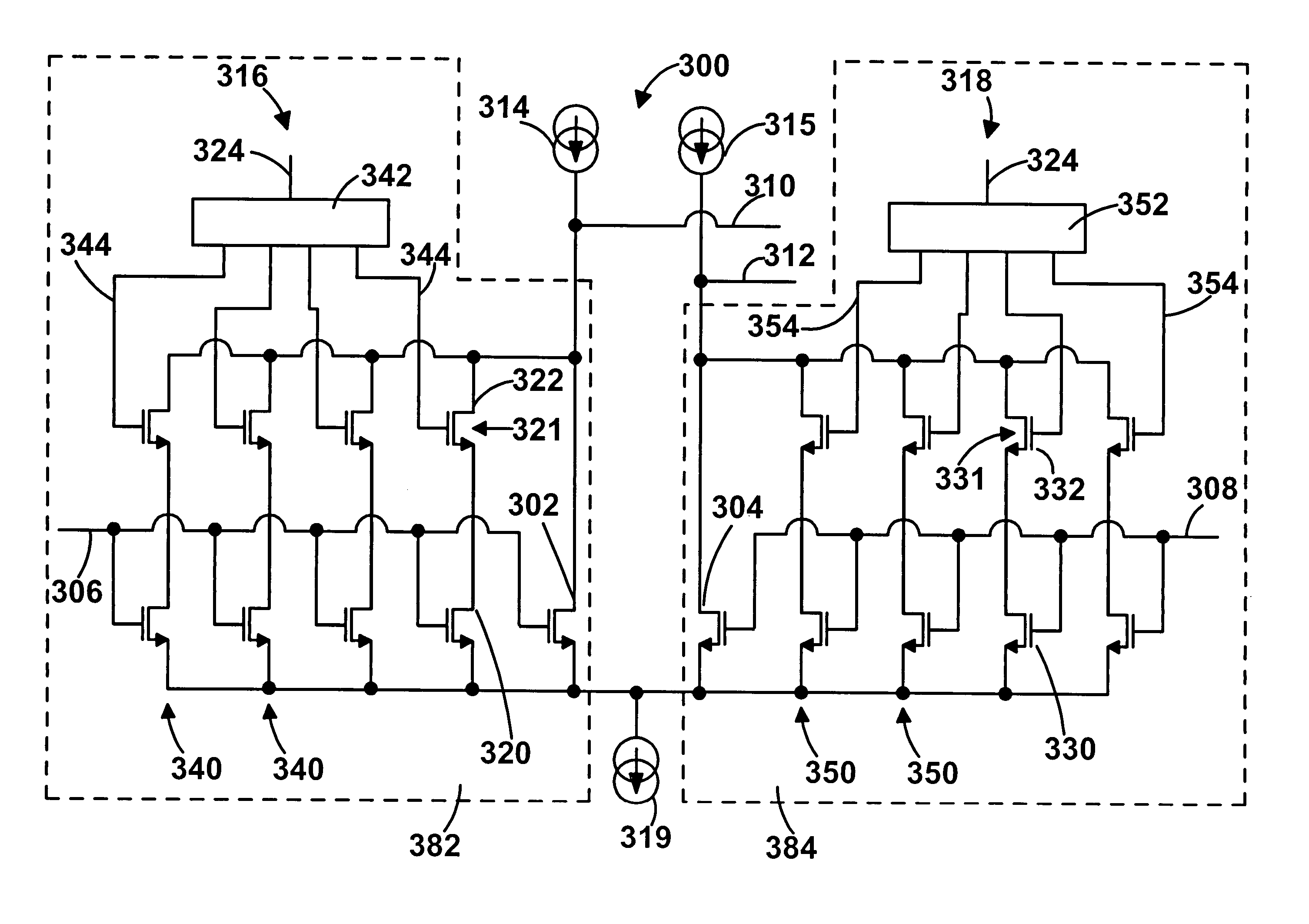

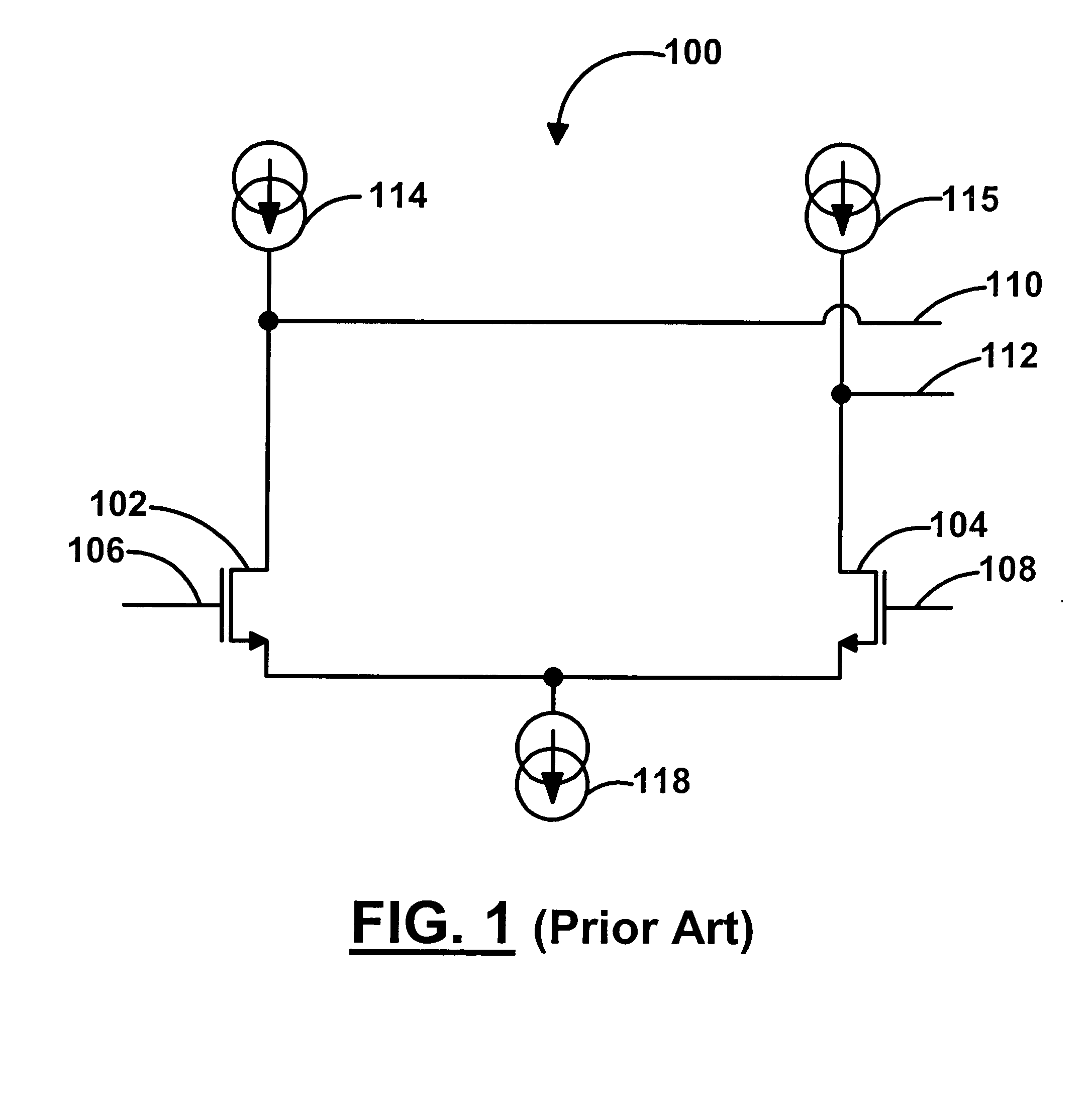

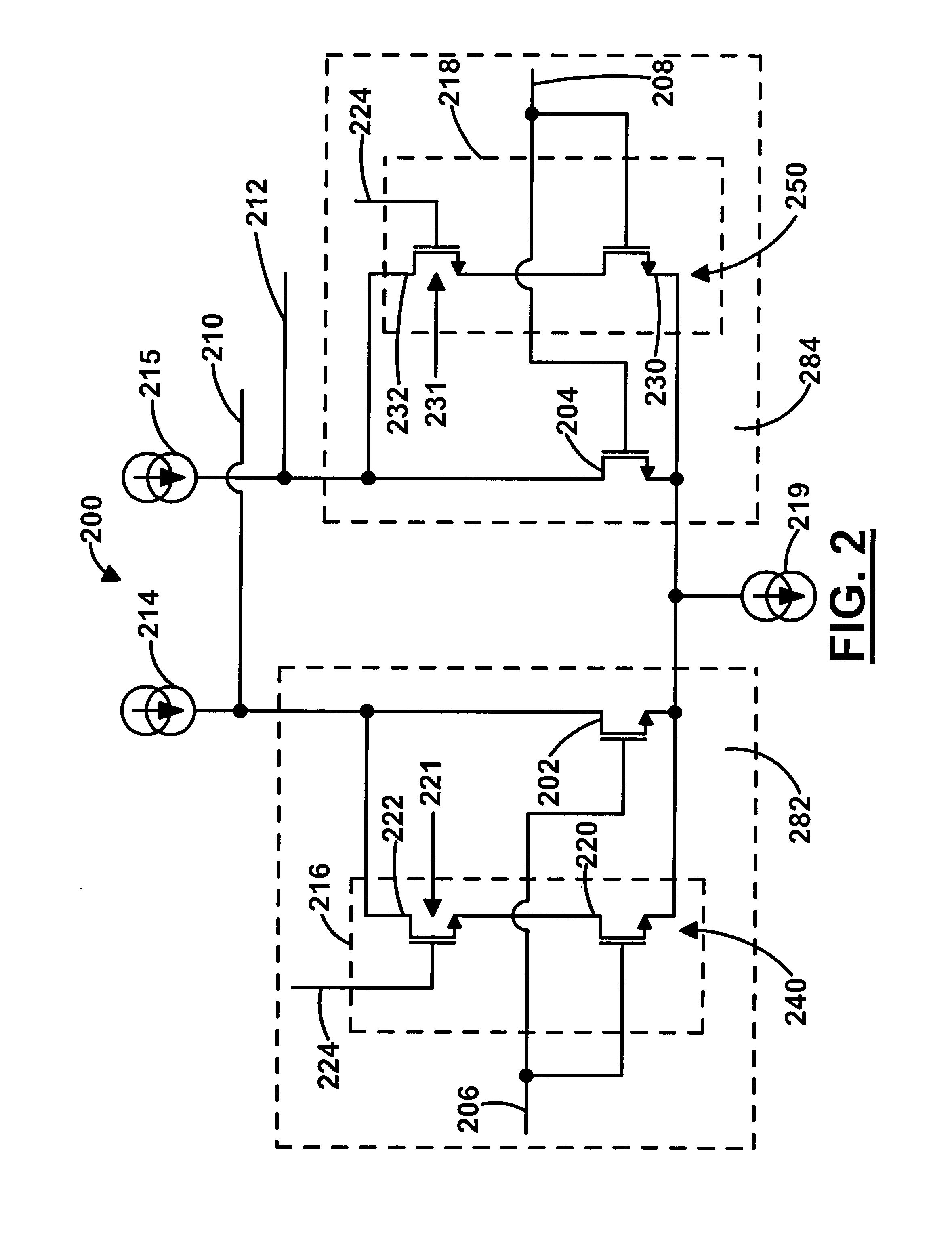

Tunable differential transconductor and adjustment method

InactiveUS20050007160A1Avoid the needShort channel lengthTransistorSemiconductor/solid-state device manufacturingLinearityChannel width

The tunable differential transconductor includes a tail current sink and a differentially-connected pair of FETs connected to the tail current source. At least one of the FETs is a composite FET that includes a main FET connected in parallel with a switchable tuning element. The switchable tuning element is operable to change an effective channel dimension, i.e., at least one of effective channel length and effective channel width, of the composite FET. In the method, a differential transconductor that includes a tail current sink and a differentially-connected pair of composite FETs connected to the tail current sink is provided. The effective channel dimension of at least one of the composite FETs is changed to establish one or more of a desired transconductance, a desired transconductance linearity and a desired offset of the differential transconductor.

Owner:AGILENT TECH INC

Oxide semiconductor device

ActiveUS8421067B2Lot of parasitic capacitanceReduce parasitic capacitanceElectroluminescent light sourcesSolid-state devicesPower semiconductor deviceDriver circuit

A semiconductor device having a structure which enables sufficient reduction in parasitic capacitance is provided. In addition, the operation speed of thin film transistors in a driver circuit is improved. In a bottom-gate thin film transistor in which an oxide insulating layer is in contact with a channel formation region in an oxide semiconductor layer, a source electrode layer and a drain electrode layer are formed in such a manner that they do not overlap with a gate electrode layer. Thus, the distance between the gate electrode layer and the source electrode layer and between the gate electrode layer and the drain electrode layer are increased; accordingly, parasitic capacitance can be reduced.

Owner:SEMICON ENERGY LAB CO LTD

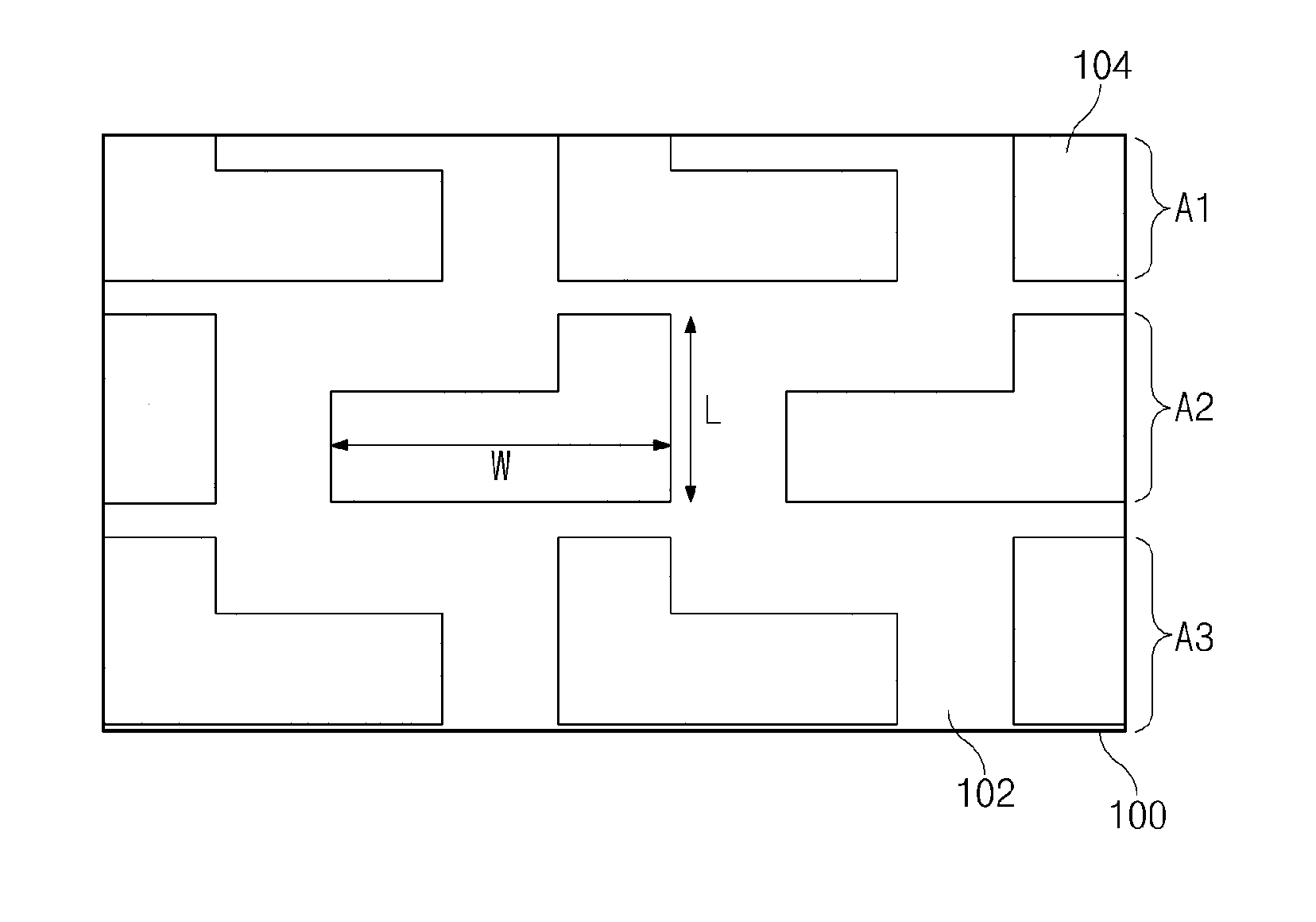

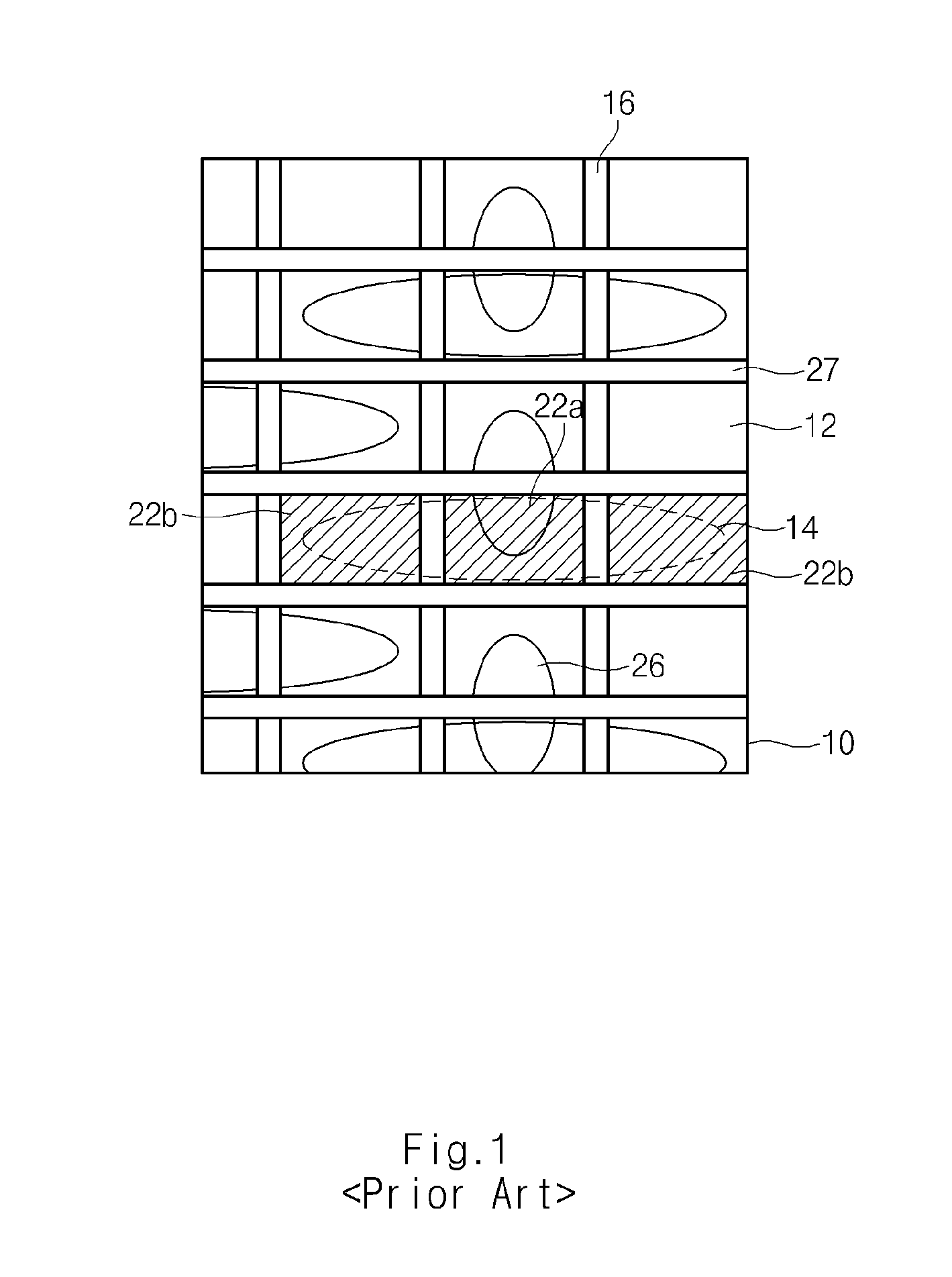

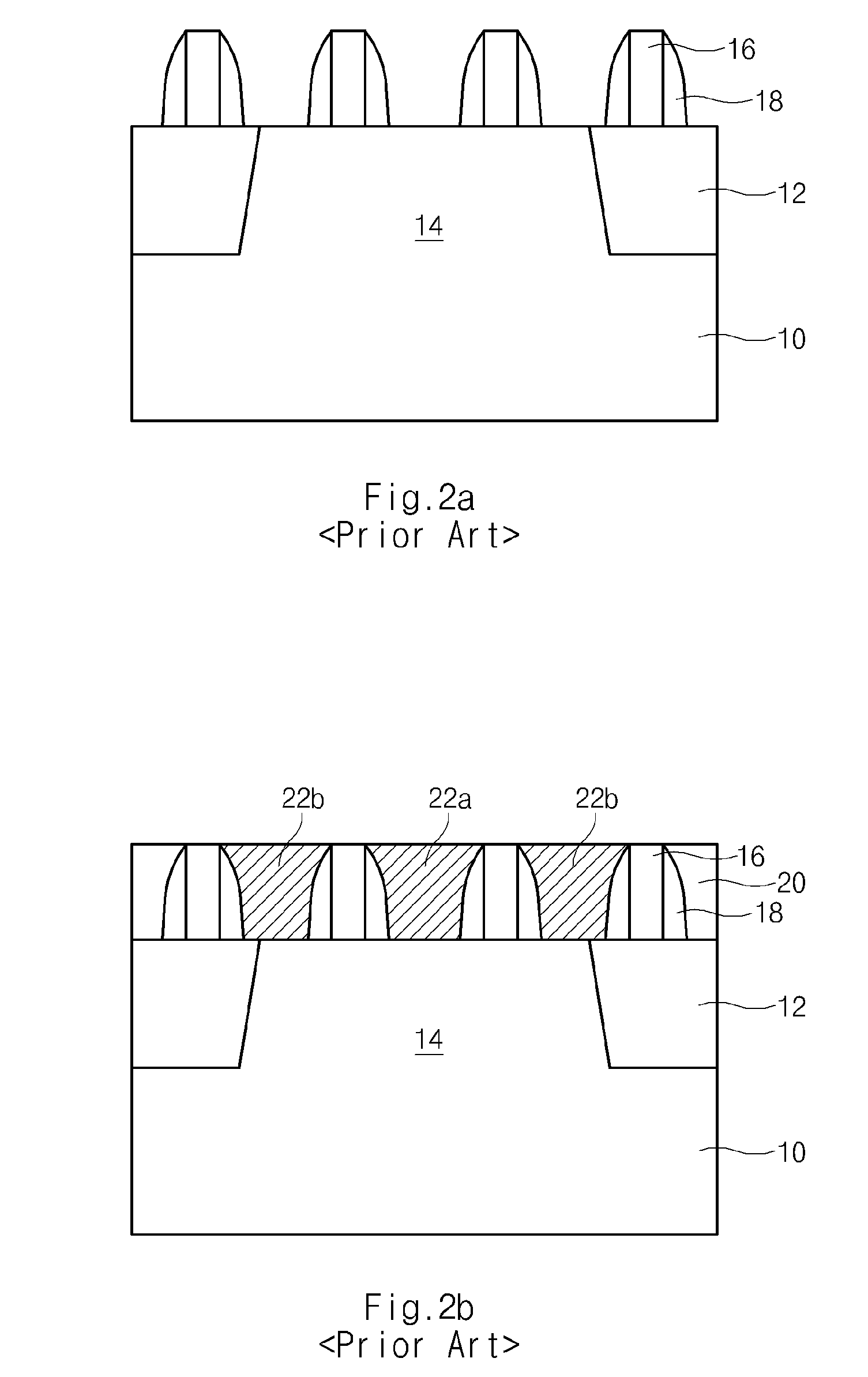

Layout of semiconductor device

A layout of a semiconductor device is disclosed, which forms one transistor in one active region to reduce the number of occurrences of a bridge encountered between neighboring layers, thereby improving characteristics of the semiconductor device. Specifically, the landing plug connected to the bit line contact is reduced in size, so that a process margin of word lines is increased to increase a channel length, thereby reducing the number of occurrences of a bridge encountered between the landing plug and the word line.

Owner:SK HYNIX INC

Organic film transistor

InactiveCN1433095AHigh speed responseImprove mobilityTransistorSolid-state devicesOrganic filmTransistor

An organic TFT including an organic film, first and second electrodes each disposed in contact with opposite surfaces of the organic film each other; and a third electrode disposed at a specified distance from each of the first and second electrodes, the third electrode being applied with a voltage to control current flowing from one of the first and the second electrodes to the other through the organic film; and the organic film including a compound represented by general formula [1]. In this TFT, the carrier moves from one of the first and the second electrodes to the other in the direction of the film thickness of the organic film. The device structure realizes the enough short channel length. The organic film provides the higher mobility, thereby the organic TFT with the sufficiently higher speed response is realized.

Owner:NEC CORP

Structures of and methods of fabricating split gate MIS devices

ActiveUS9425305B2Increase powerAvoid problemsSemiconductor devicesEngineeringField-effect transistor

A split gate field effect transistor device. The device includes a split gate structure having a trench, a gate electrode and a source electrode. A first poly layer is disposed within the trench and is connected to the gate electrode. A second poly layer connected to the source electrode, wherein the first poly layer and the second poly layer are independent.

Owner:VISHAY SILICONIX LLC

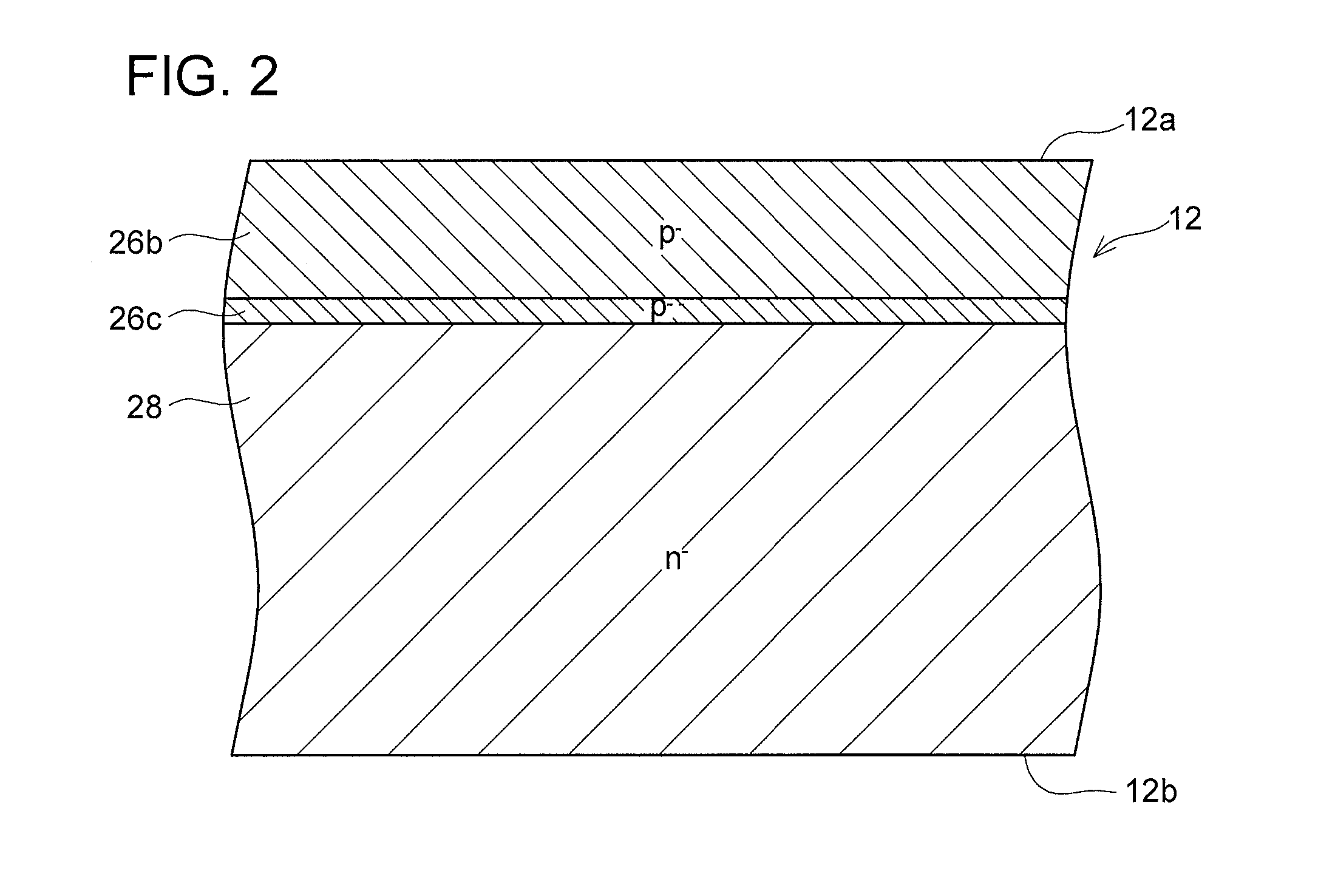

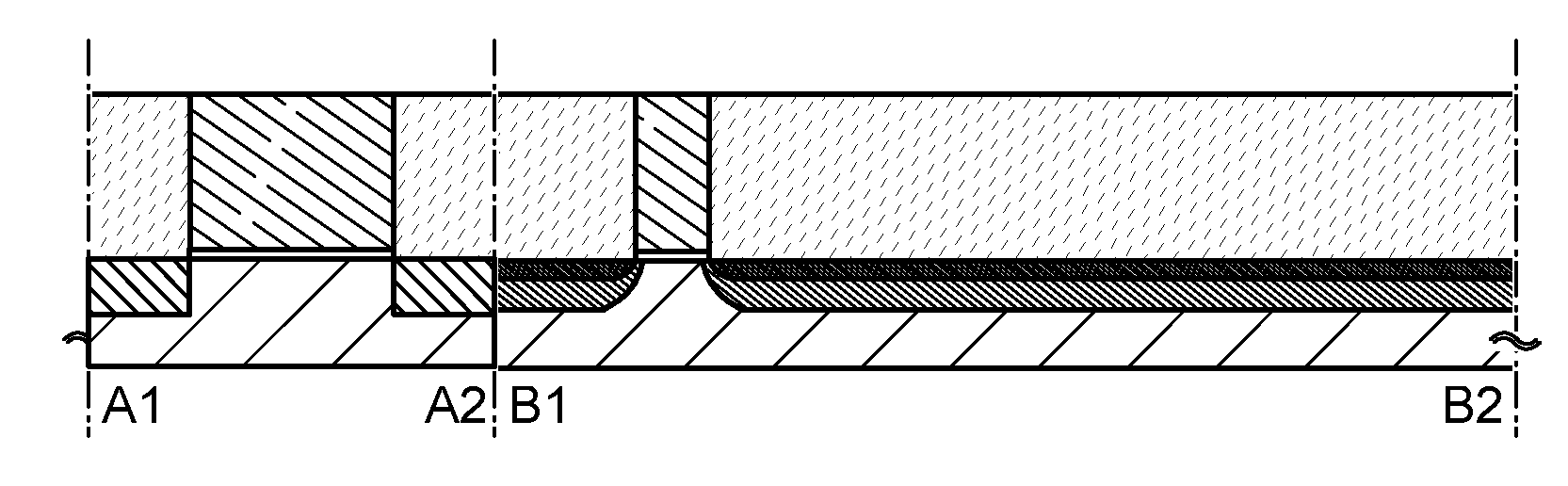

Semiconductor device and method for manufacturing semiconductor device

InactiveUS20160149029A1Reduce thicknessReduce channel lengthSemiconductor/solid-state device manufacturingSemiconductor devicesBody regionSemiconductor

A semiconductor device includes a semiconductor substrate including a trench, a gate insulating layer, and a gate electrode. A step is arranged in a side surface of the trench. The semiconductor substrate includes first and second regions, a body region, and a side region. The body region extends from a position being in contact with the first region to a position located on the lower side with respect to the step. The body region is in contact with the gate insulating layer at a portion of the upper side surface located on a lower side with respect to the first region. The second region is located on a lower side of the body region and in contact with the gate insulating layer at the lower side surface. The side region is in contact with the gate insulating layer at the step surface and connected to the second region.

Owner:TOYOTA JIDOSHA KK

Manufacturing method of semiconductor device

InactiveUS8431449B2Small sizeAccuracy of photomask projection exposure in semiconductor processingSolid-state devicesRead-only memoriesEngineeringSemiconductor

An embodiment is a manufacturing method of a semiconductor device including the steps of forming a first insulating film; forming a first mask over the first insulating film; performing a slimming process on the first mask to form a second mask; performing an etching process on the first insulating film using the second mask to form a second insulating film; forming a first conductive film covering the second insulating film; performing a polishing process on the first conductive film and the second insulating film to form a third insulating film, a source electrode, and a drain electrode having equal thicknesses; forming an oxide semiconductor film over the third insulating film, the source electrode, and the drain electrode; forming a gate insulating film over the oxide semiconductor film; and forming a gate electrode in a region which is over the gate insulating film and overlaps with the third insulating film.

Owner:SEMICON ENERGY LAB CO LTD

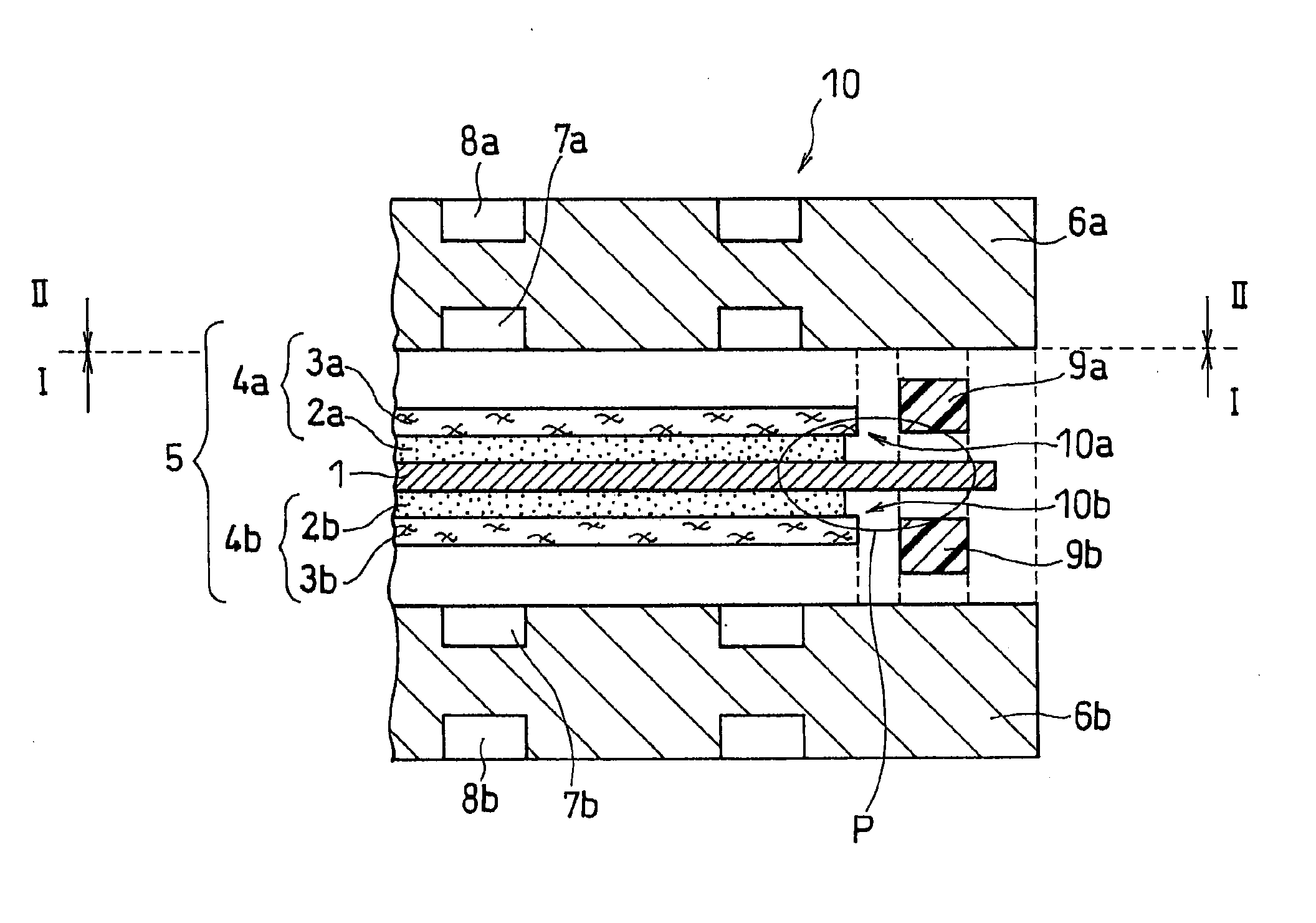

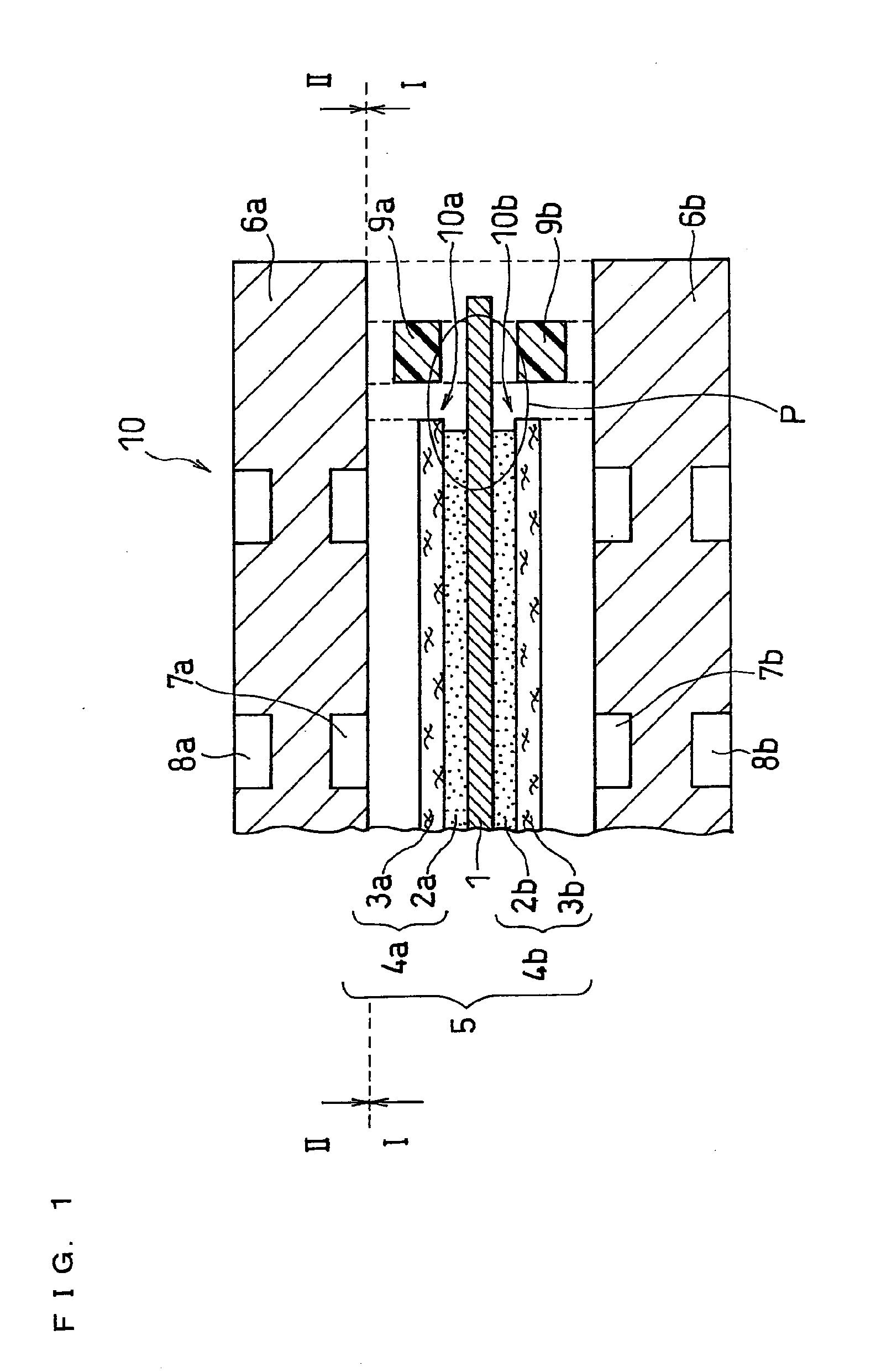

Fuel cell

InactiveUS20080171250A1Improve performanceAssemble performance be improveFuel cell auxillariesCell component detailsFuel gasFuel cells

Even if reaction gas flows into a substantially rectangular anode-side and cathode-side gaps formed between an annular main body portion and a membrane electrode assembly in an anode side and a cathode side of a fuel cell, the reaction gas is prevented from flowing out from an outlet without passing through an electrode to cause degradation of power generation efficiency. At least one of anode-side gasket and cathode-side gasket in the fuel cell is provided with an extra sealing portion connected to an annular main body portion in such a manner that, among two pairs of gap portions opposing to each other in the anode-side gap and the cathode-side gap, the extra sealing portion intersects with one pair of gap portions having a larger pressure gradient of fuel gas and oxidant gas in a direction from an upstream side to a downstream side of a fuel gas flow channel and an oxidant gas flow channel.

Owner:PANASONIC CORP

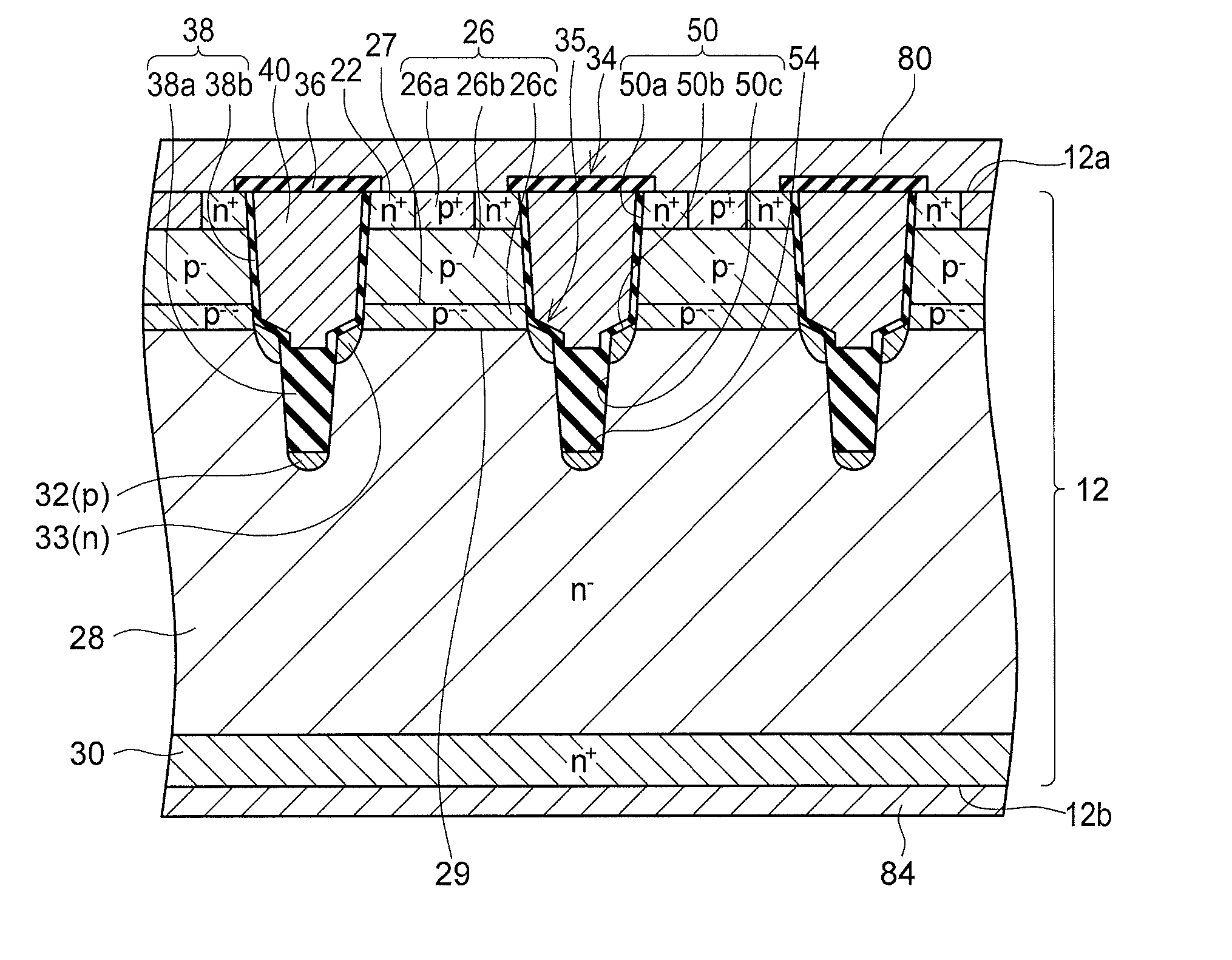

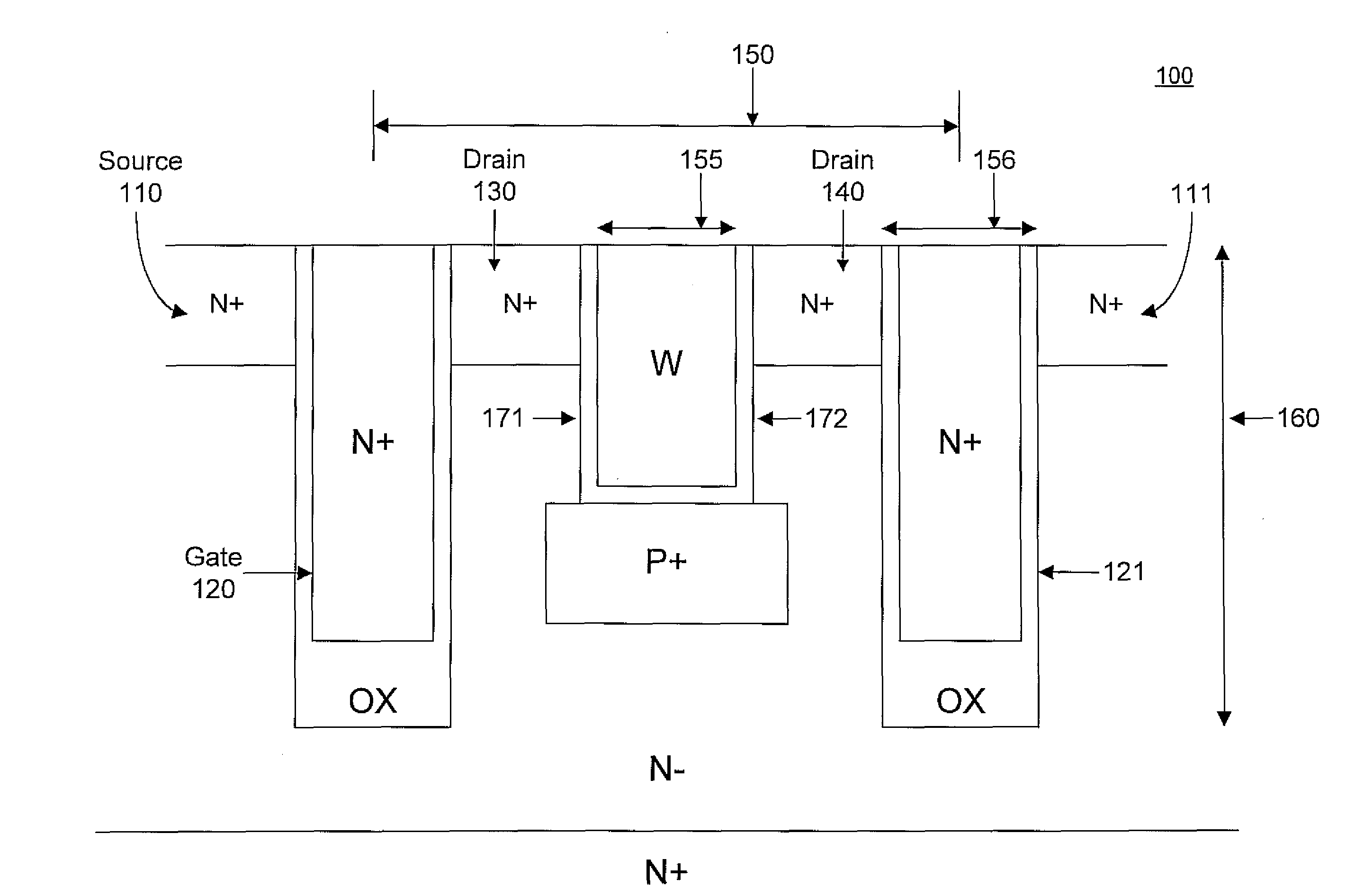

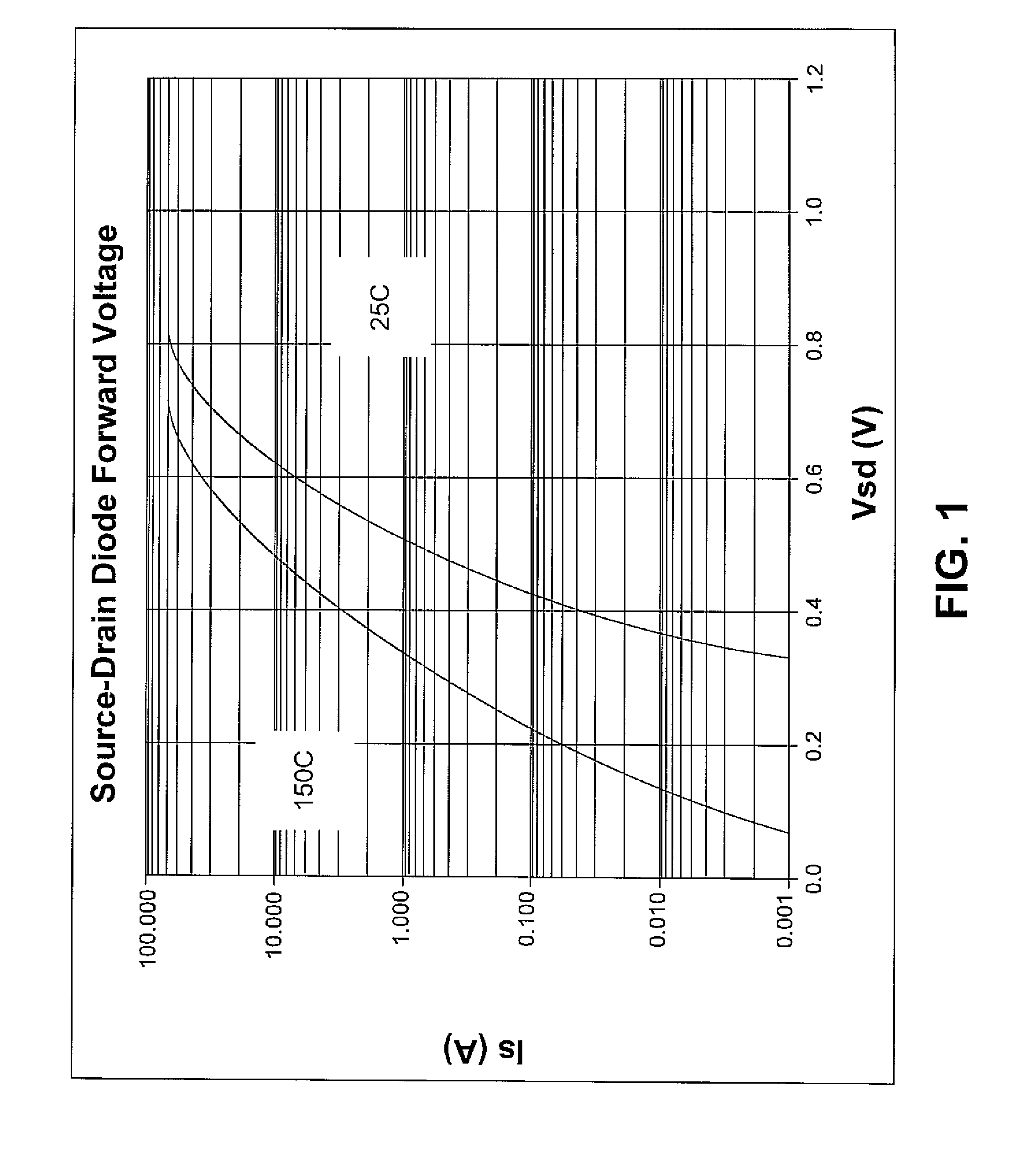

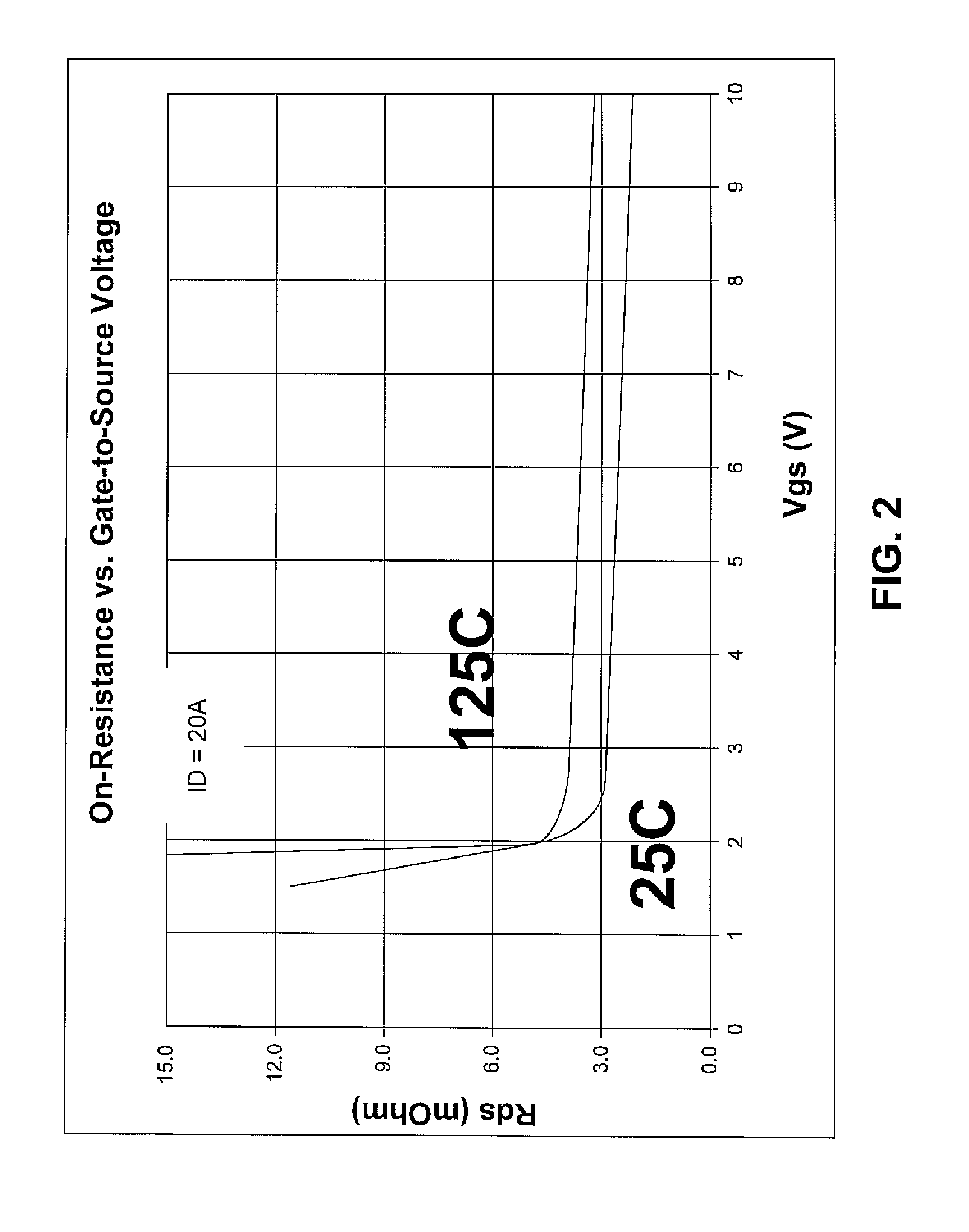

High current density power field effect transistor

ActiveUS8269263B2Increase powerAvoid problemsSolid-state devicesSemiconductor devicesHigh current densityMOSFET

An ultra-short channel hybrid power field effect transistor (FET) device lets current flow from bulk silicon without npn parasitic. This device does not have body but still have body diode with low forward voltage at high current rating. The device includes a JFET component, a first accumulation MOSFET disposed adjacent to the JFET component, and a second accumulation MOSFET disposed adjacent to the JFET component at the bottom of the trench end, or a MOSFET with an isolated gate connecting the source.

Owner:VISHAY SILICONIX LLC

Catalytic burner apparatus for stirling engine

ActiveUS7913484B2Efficiently and effectively generatesSimple and efficient and effectiveGas turbine plantsClosed-cycle gas positive displacement engine plantExternal combustion engineEngineering

The invention provides a method for transferring heat by conduction to the internal heat acceptor of an external combustion engine. Fuel and air are introduced and mixed to form an air / fuel mixture. The air / fuel mixture is directed into a catalytic reactor that is positioned substantially adjacent to the heater head. Heat is transferred via conduction from the catalytic reactor to the heater head and the catalytic reaction products are exhausted.

Owner:PRECISION COMBUSTION

Semiconductor device and method for fabricating the same

InactiveUS20060160310A1Easy to controlShort channel lengthSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductorSemiconductor device

After forming a first semiconductor region of a first conductivity type in a semiconductor substrate, a trench reaching a given portion of the first semiconductor region is formed in the semiconductor substrate. Then, after forming a gate insulating film on an inner wall of the trench, a second semiconductor region of a second conductivity type is formed on the first semiconductor region in the semiconductor substrate, and thereafter, a third semiconductor region of the first conductivity type is formed on the second semiconductor region in the semiconductor substrate. Also, a gate electrode of the first conductivity type is formed on the gate insulating film within the trench. The gate electrode is formed on the gate insulating film so as to extend over the second semiconductor region, a portion of the first semiconductor region disposed below the second semiconductor region and a portion of the third semiconductor region disposed on the second semiconductor region.

Owner:PANASONIC CORP