Patents

Literature

294results about How to "Reduce channel length" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

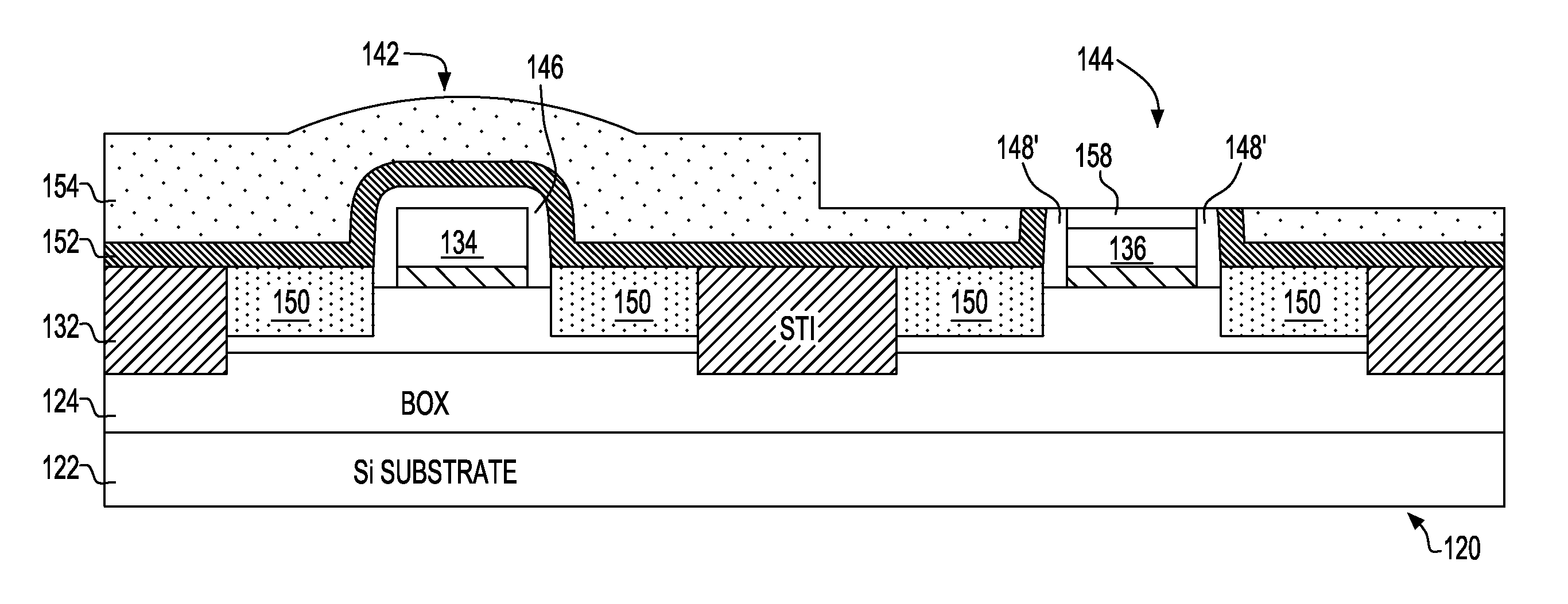

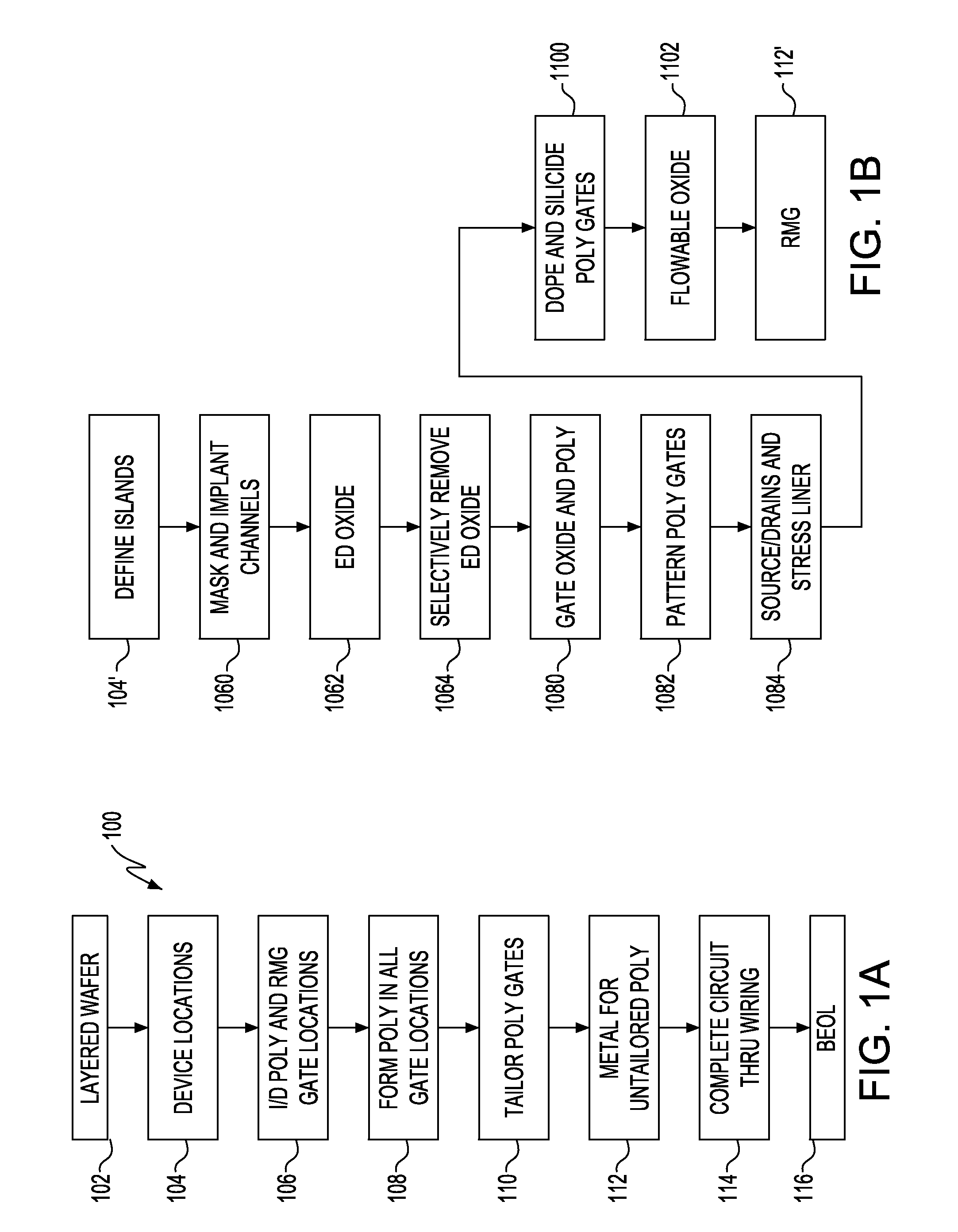

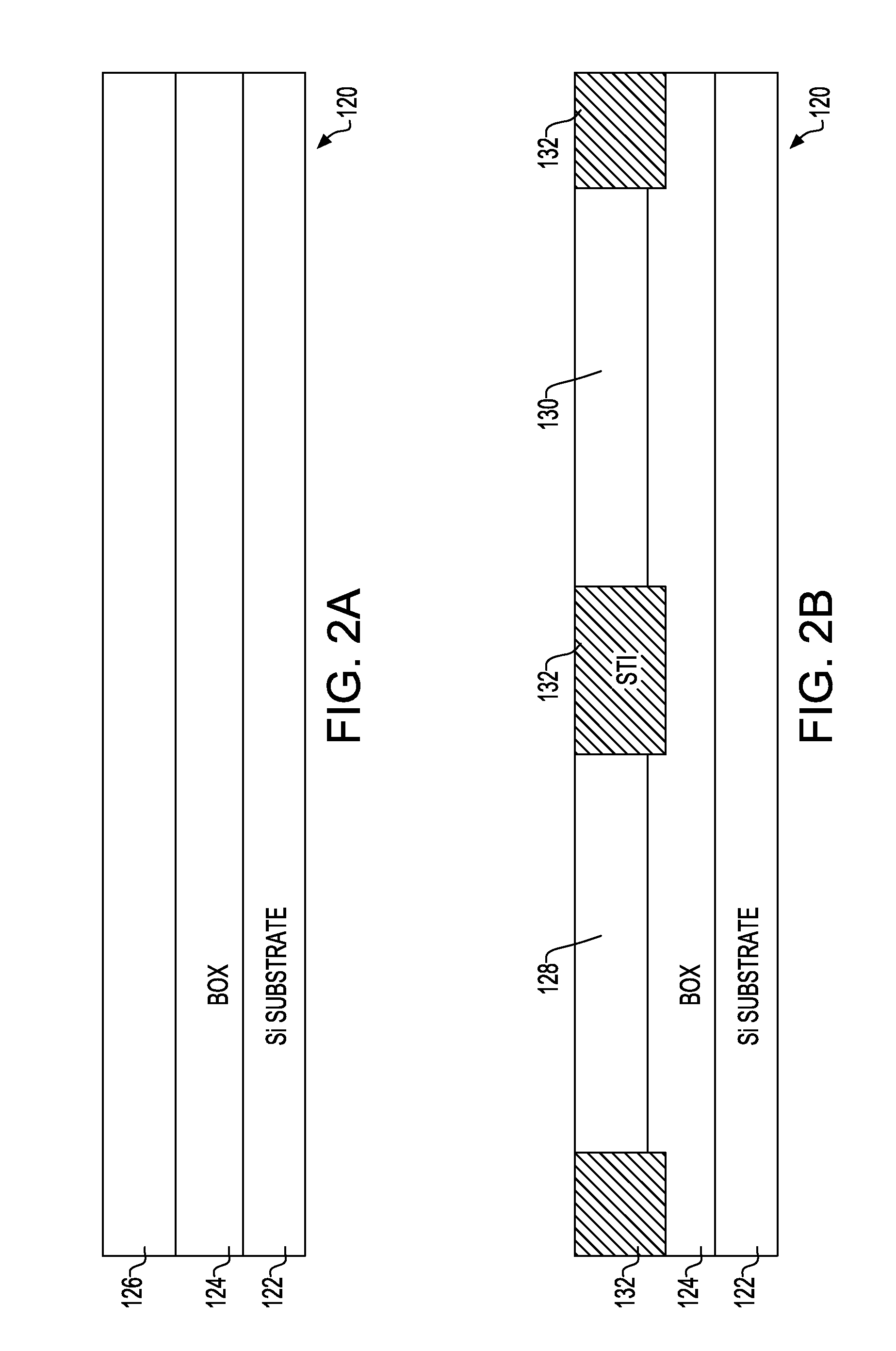

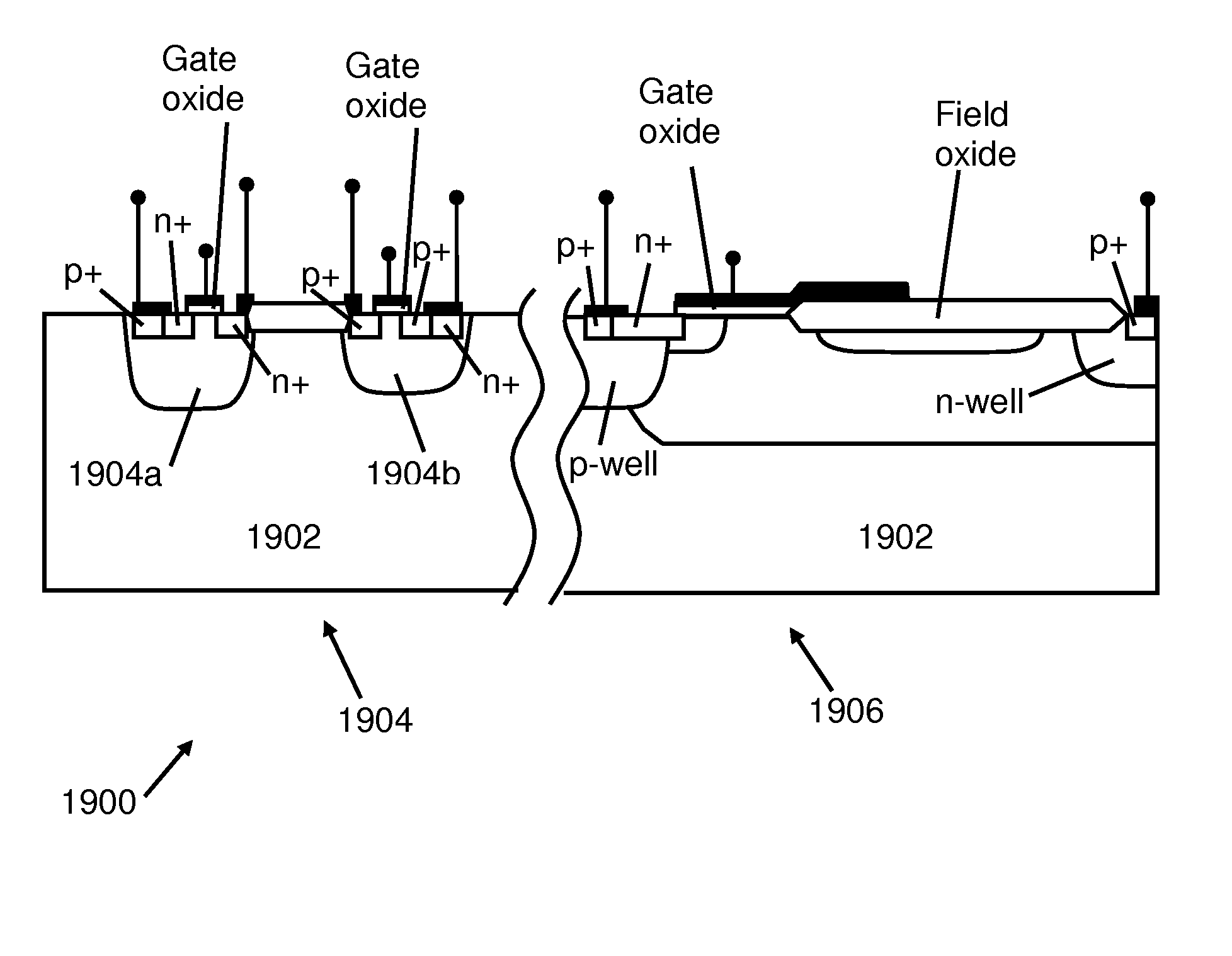

Integrated Circuit (IC) Chip Having Both Metal and Silicon Gate Field Effect Transistors (FETs) and Method of Manufacture

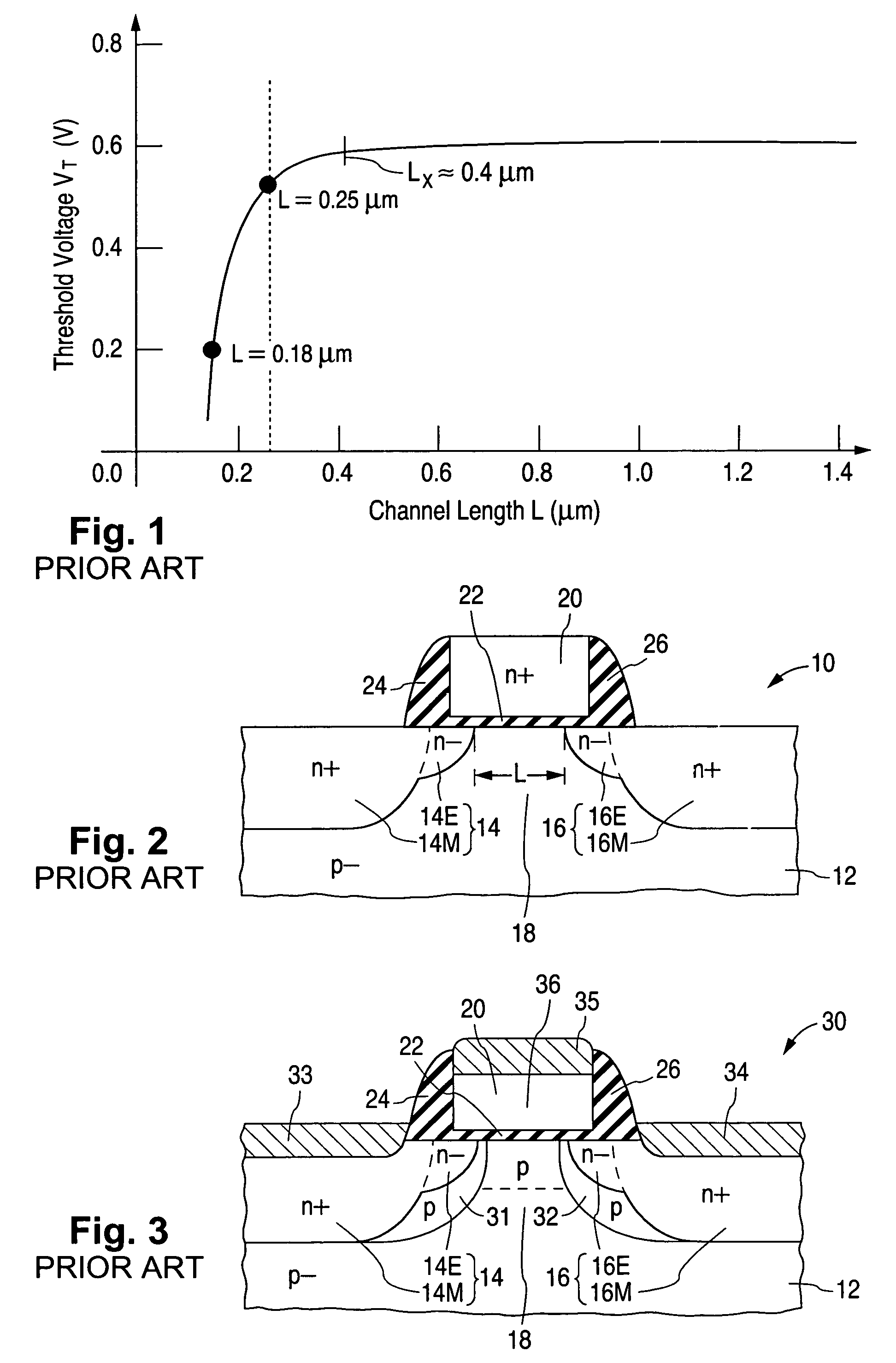

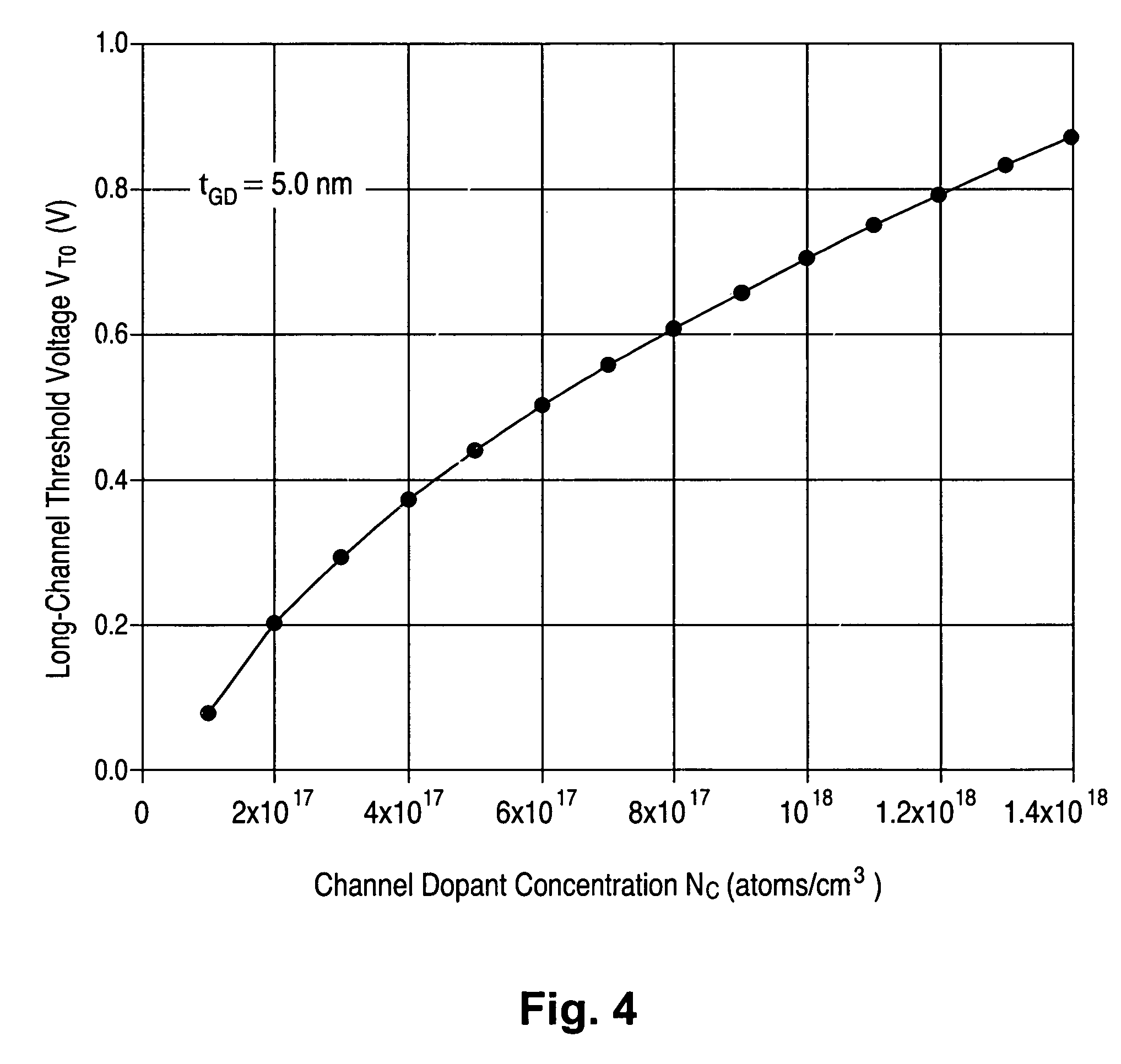

InactiveUS20120292664A1Suppression of short channel effectsWithout impairing performanceTransistorSemiconductor/solid-state device detailsField-effect transistorPolysilicon gate

Field Effect Transistors (FETs), Integrated Circuit (IC) chips including the FETs, and a method of forming the FETs on ICs. FET locations are defined on a layered semiconductor wafer, preferably a Silicon On Insulator (SOI) wafer. One or more FET locations are defined as silicon gate locations and remaining as Replacement Metal Gate (RMG) FET locations with at least one of each on the IC. Polysilicon gates are formed in all FET locations. Gates in silicon gate locations are tailored, e.g., doped and silicided. Remaining polysilicon gates are replaced with metal in RMG FET locations. FETs are connected together into circuits with RMG FETs being connected to silicon gate FETs.

Owner:GLOBALFOUNDRIES INC

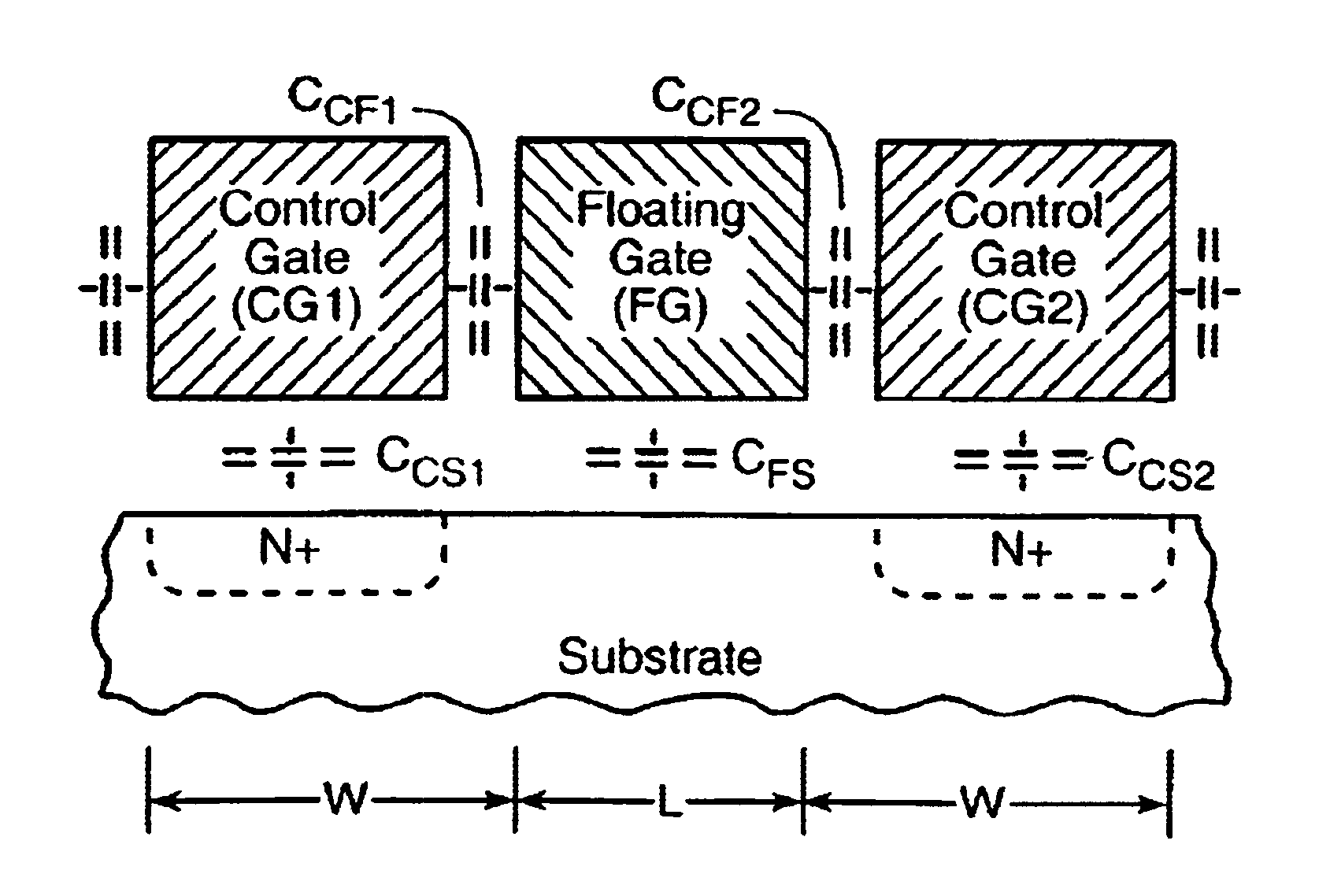

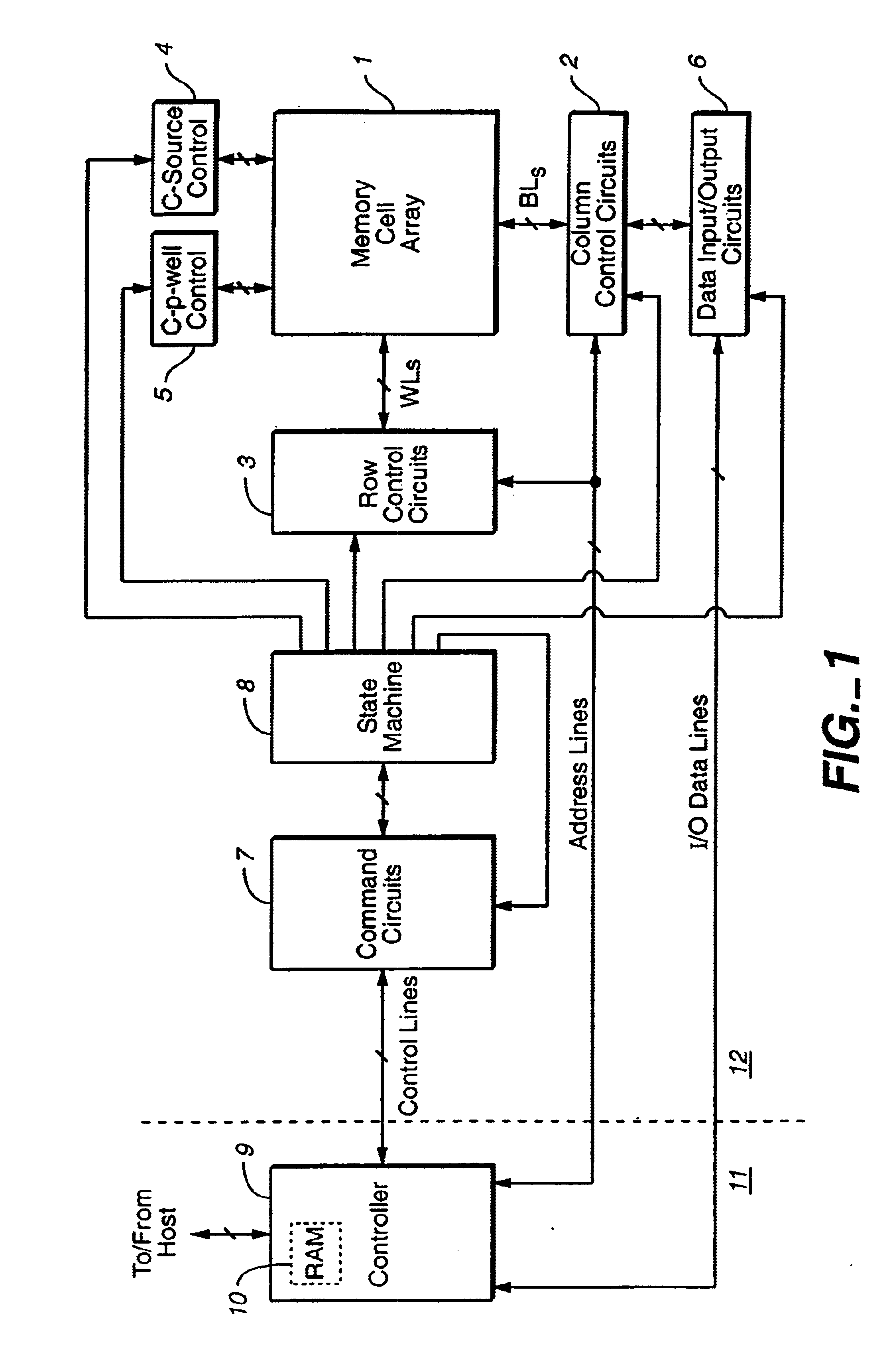

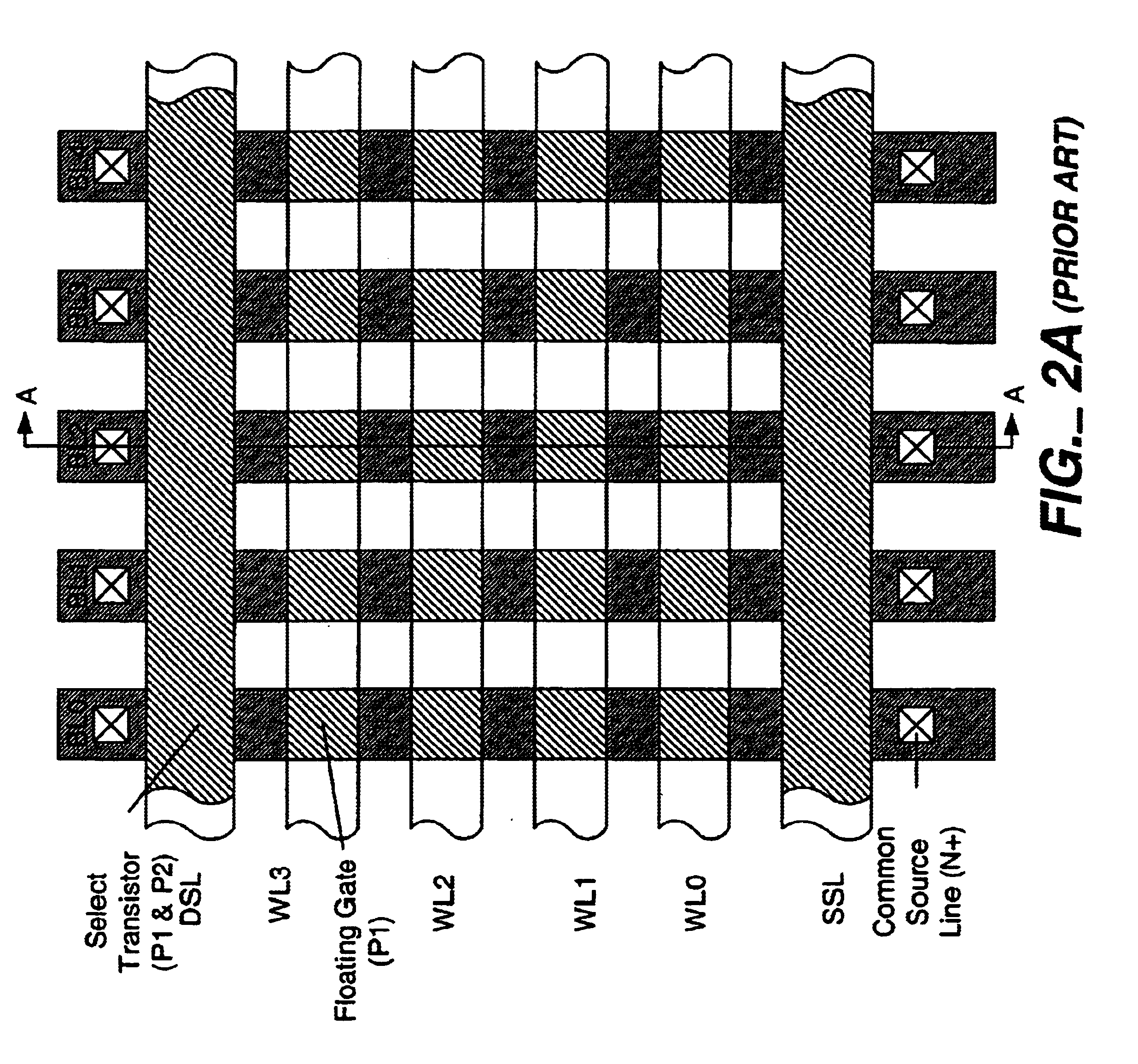

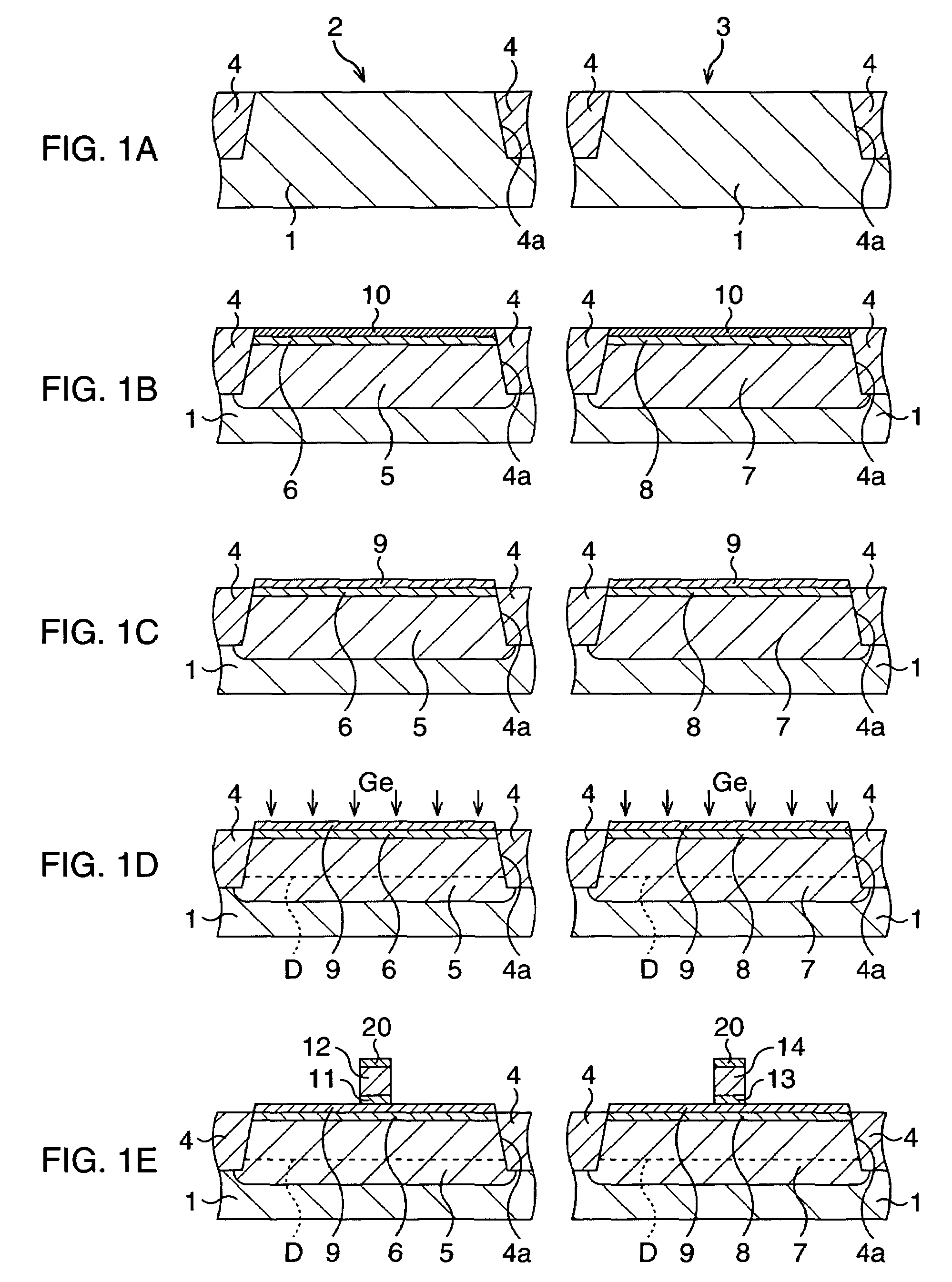

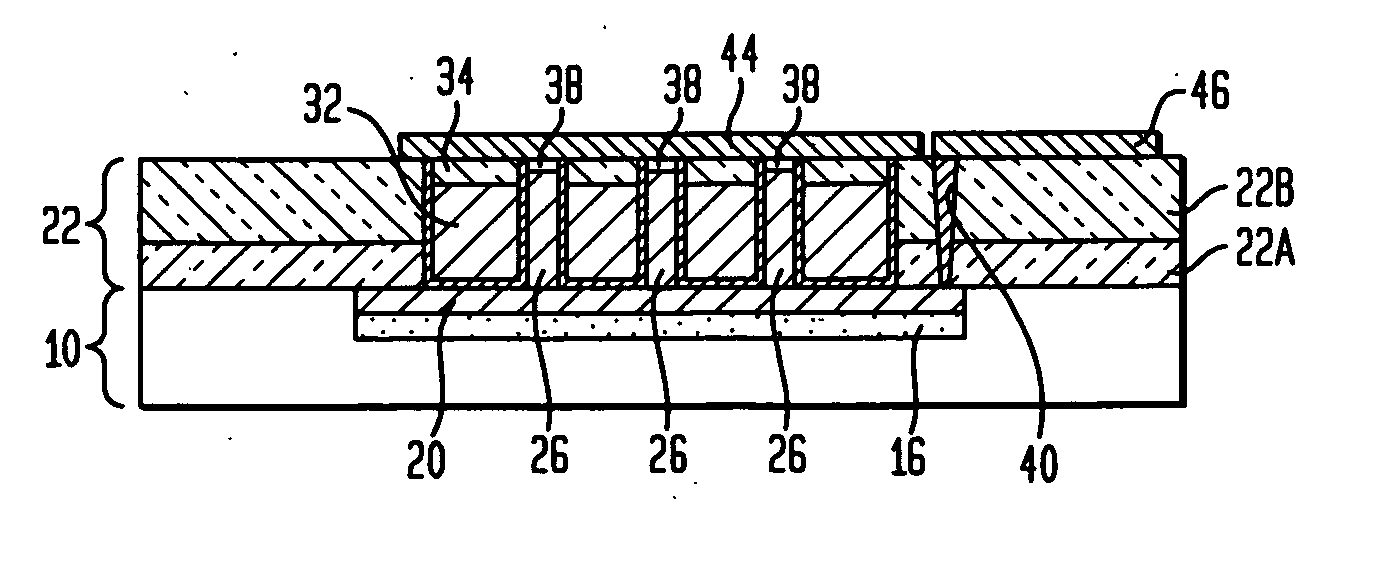

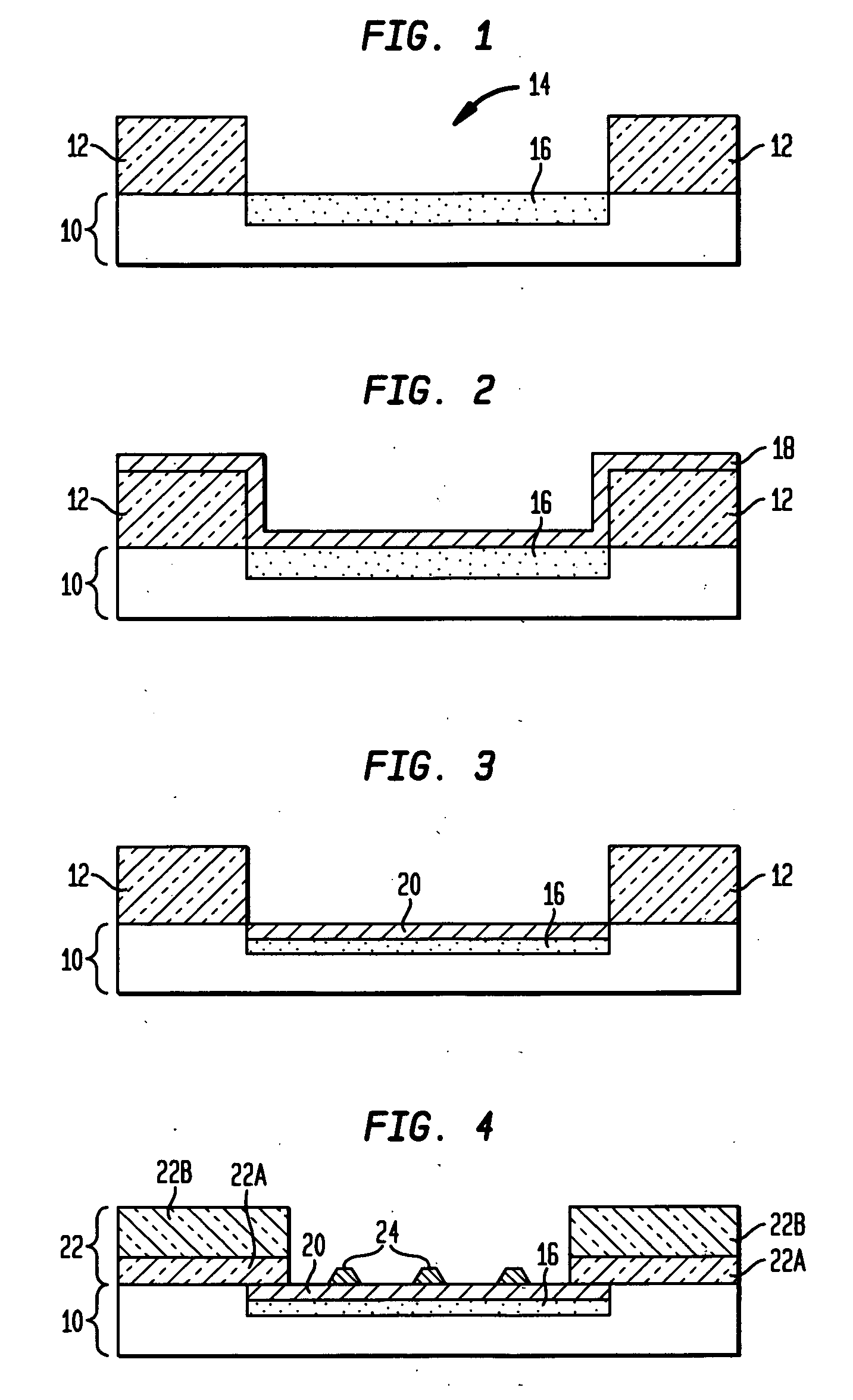

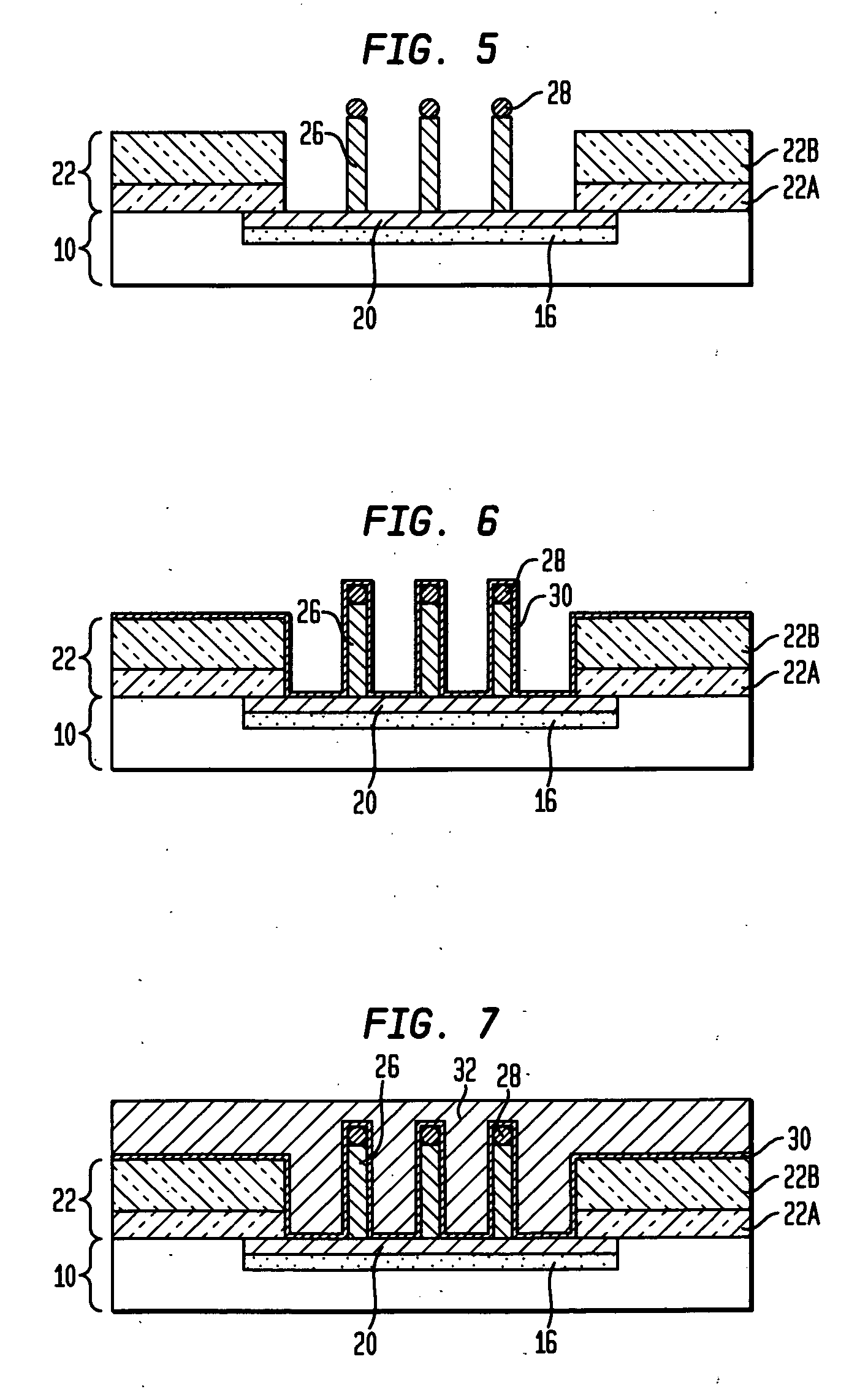

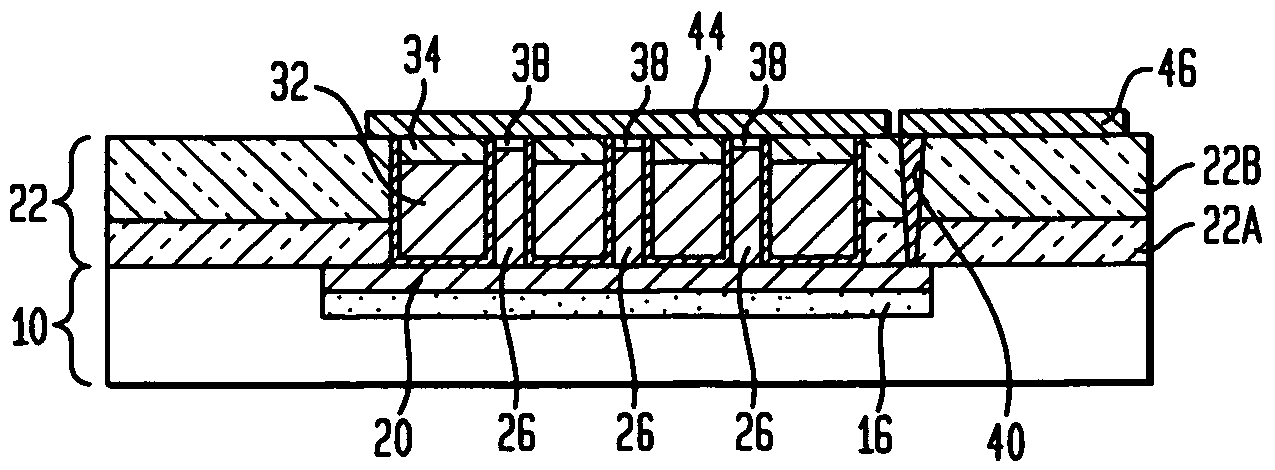

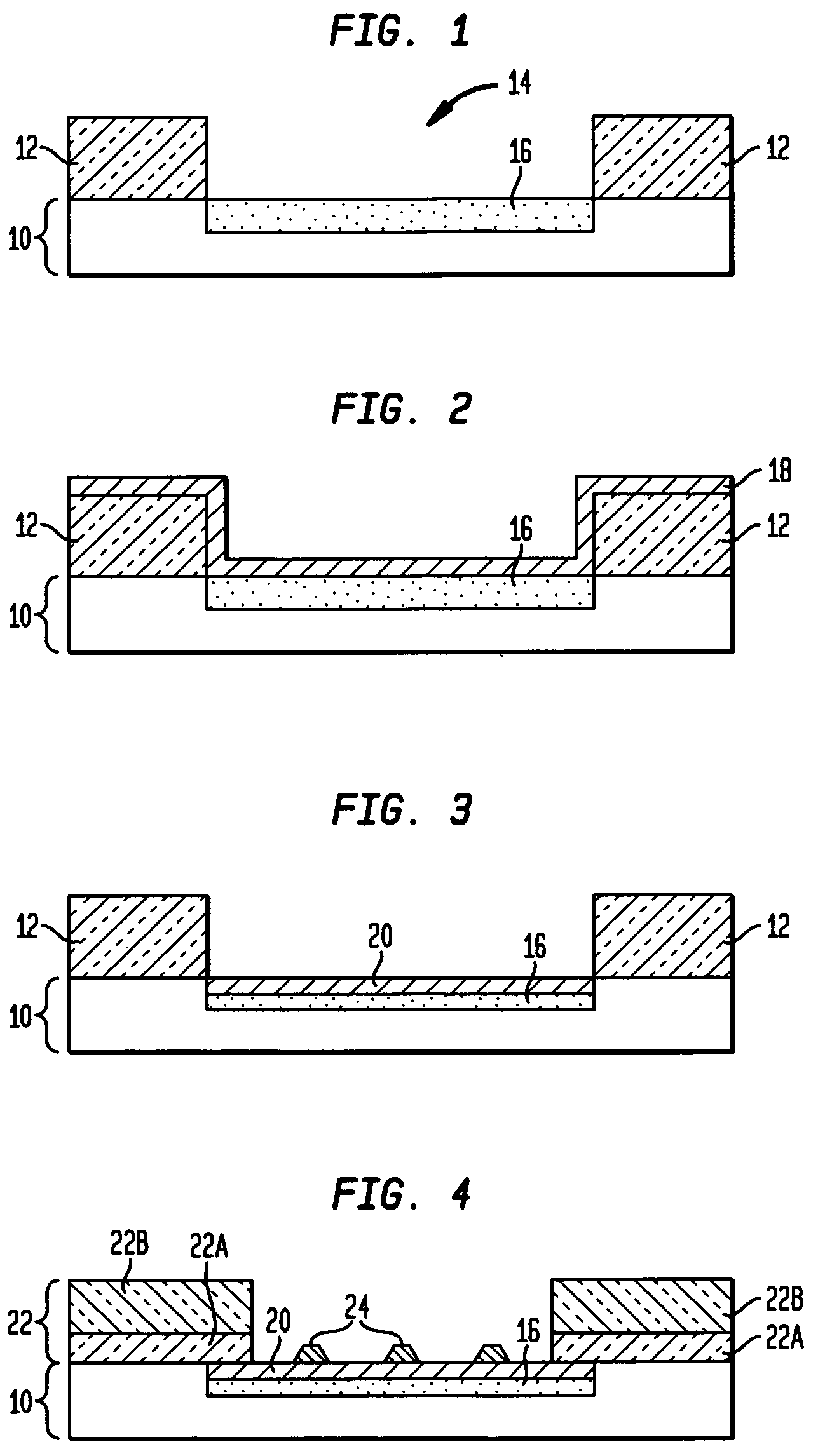

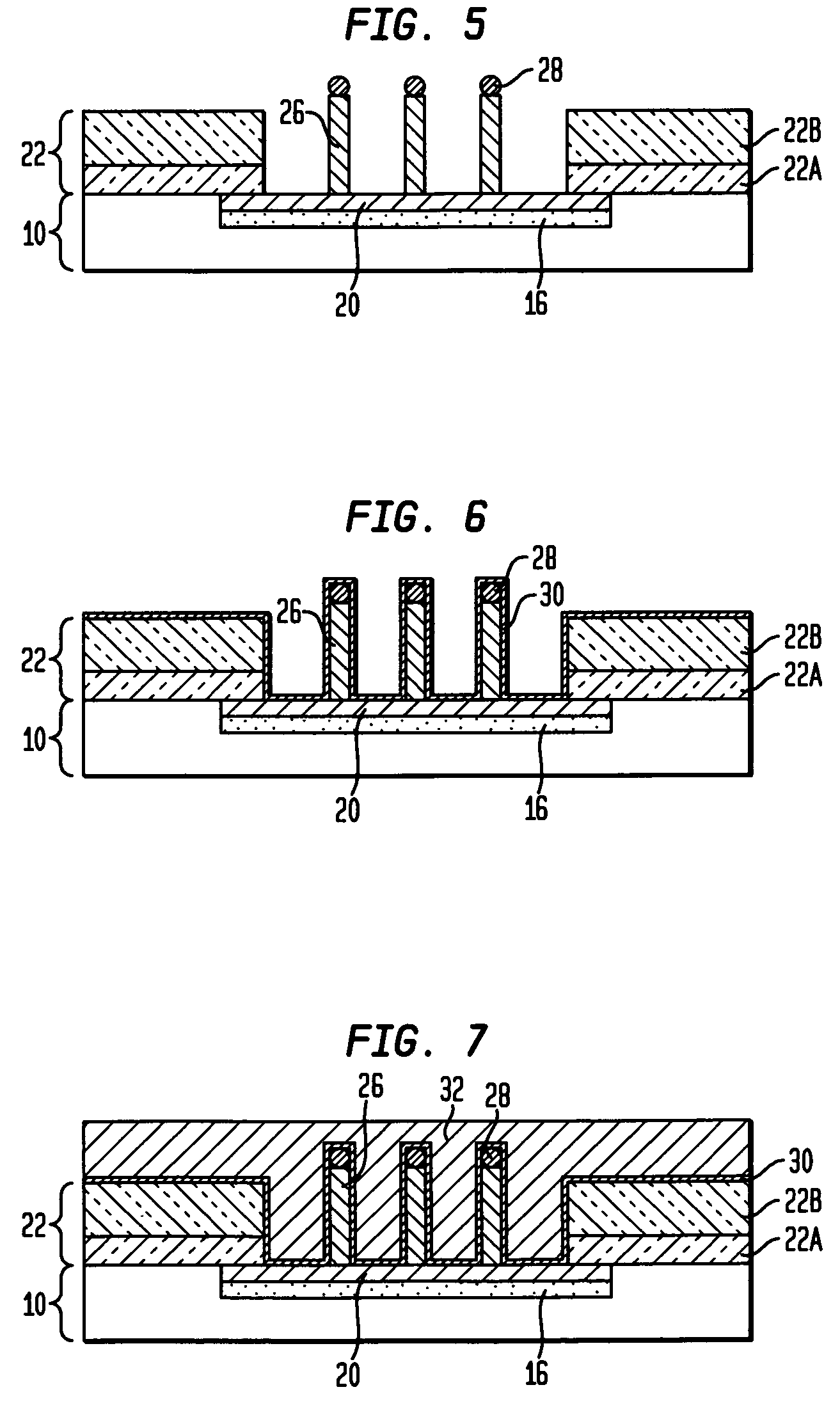

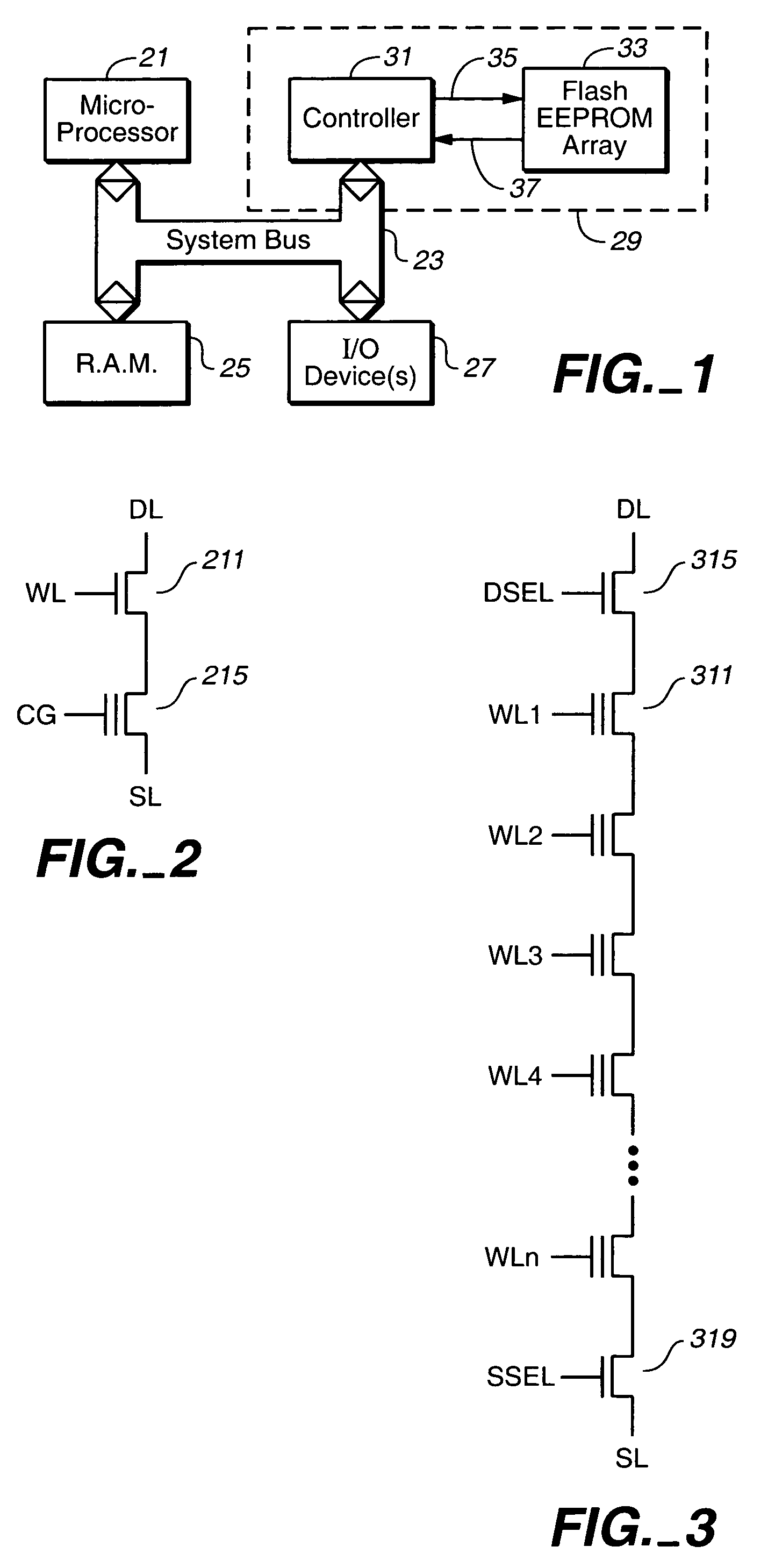

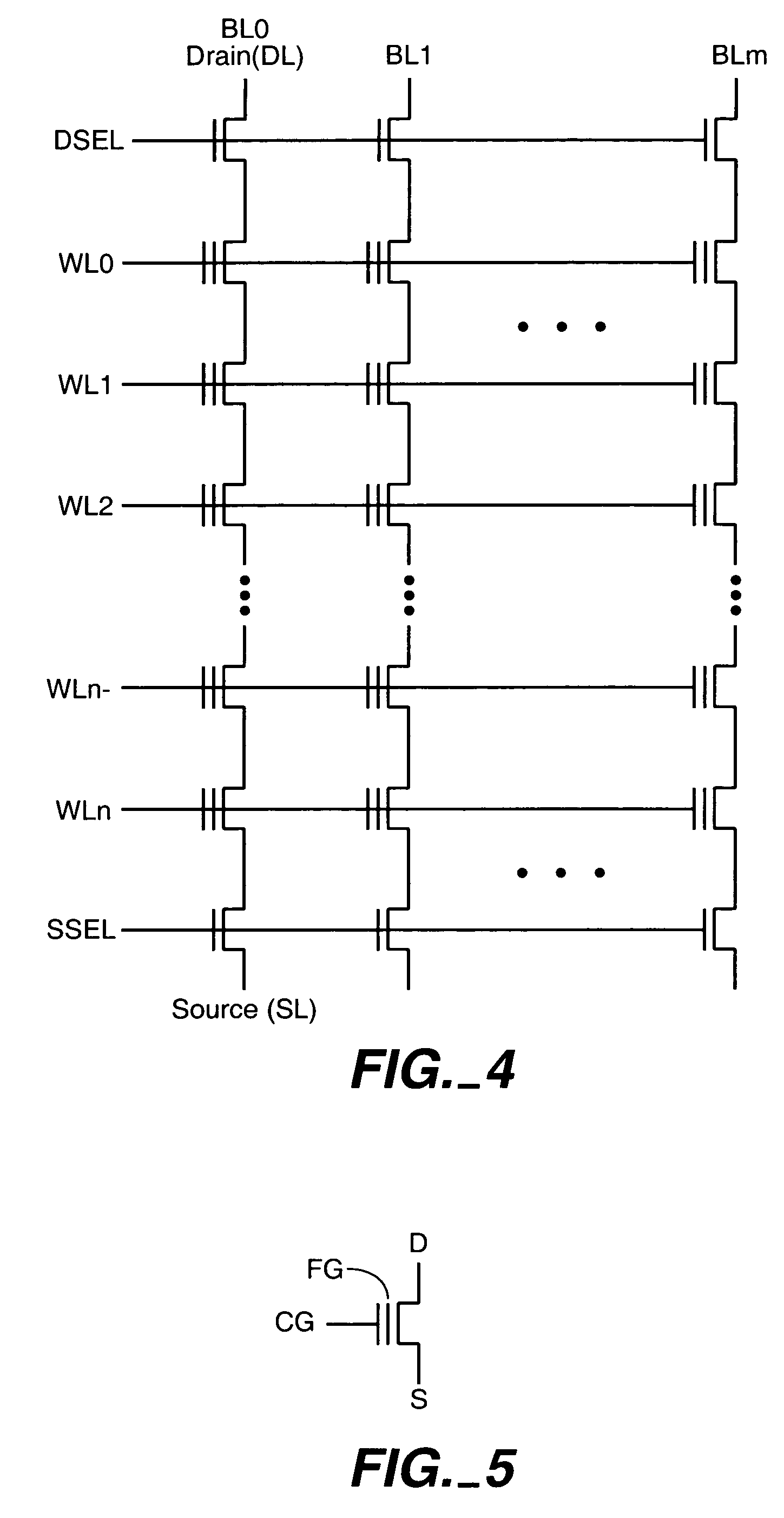

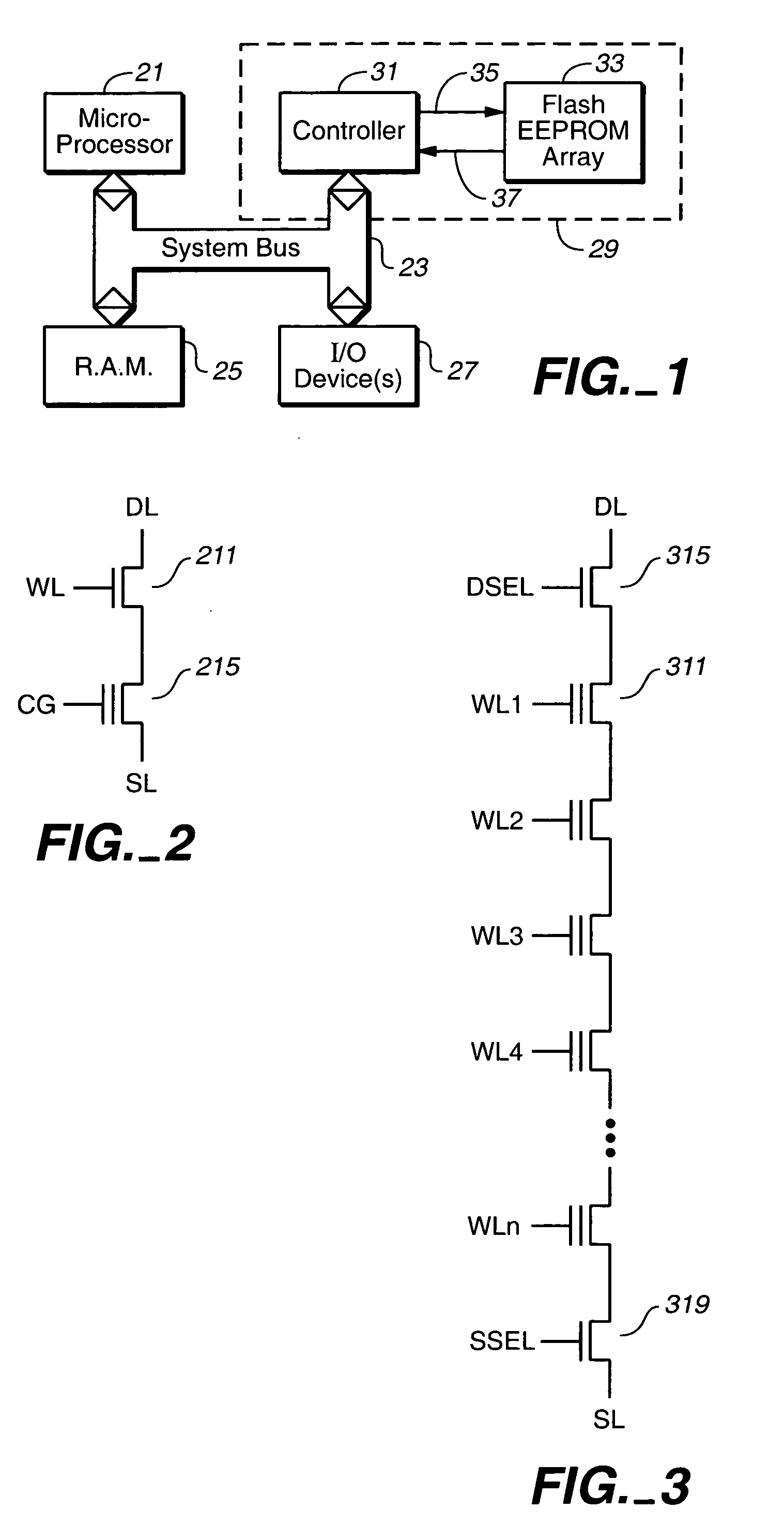

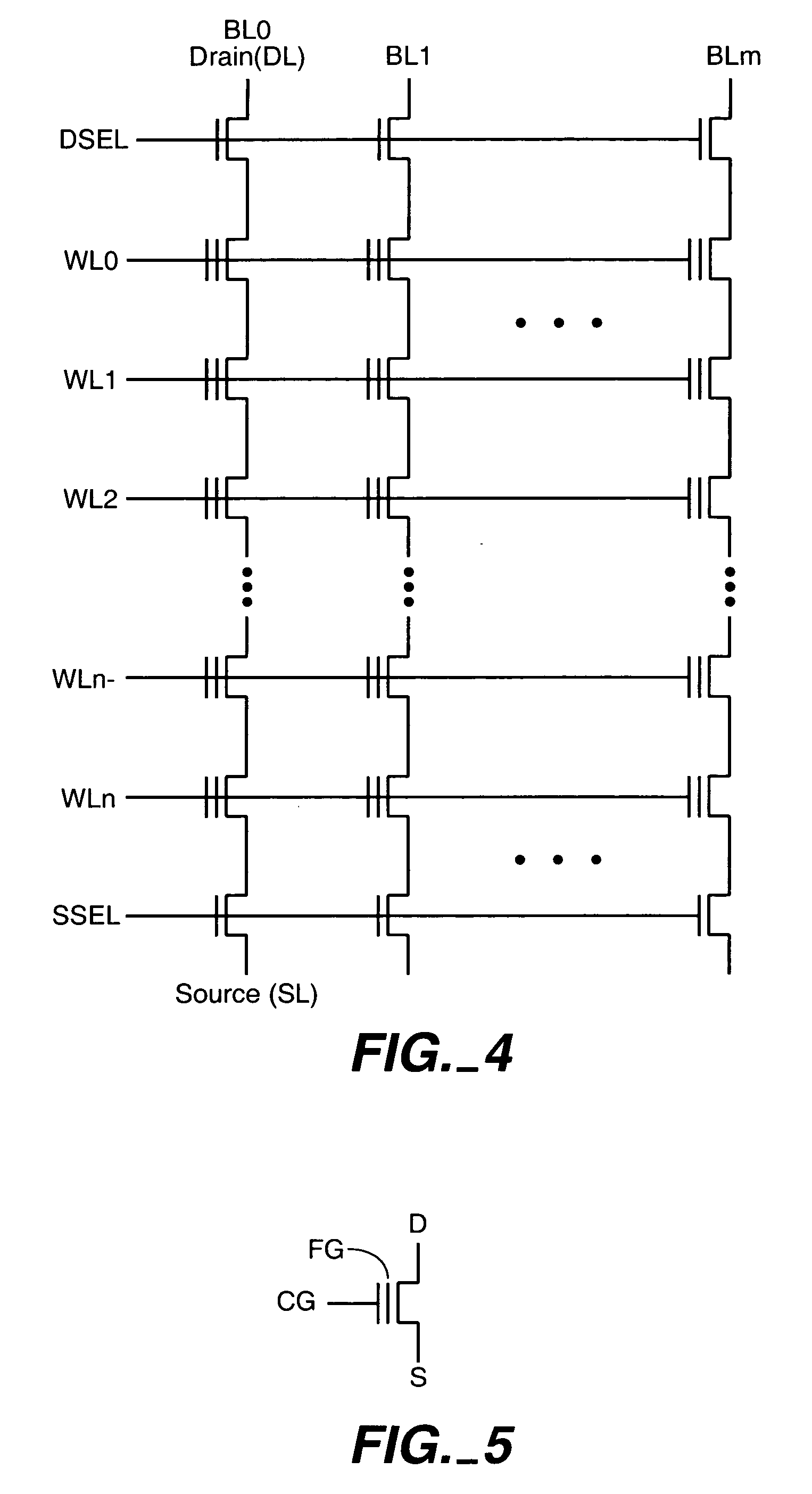

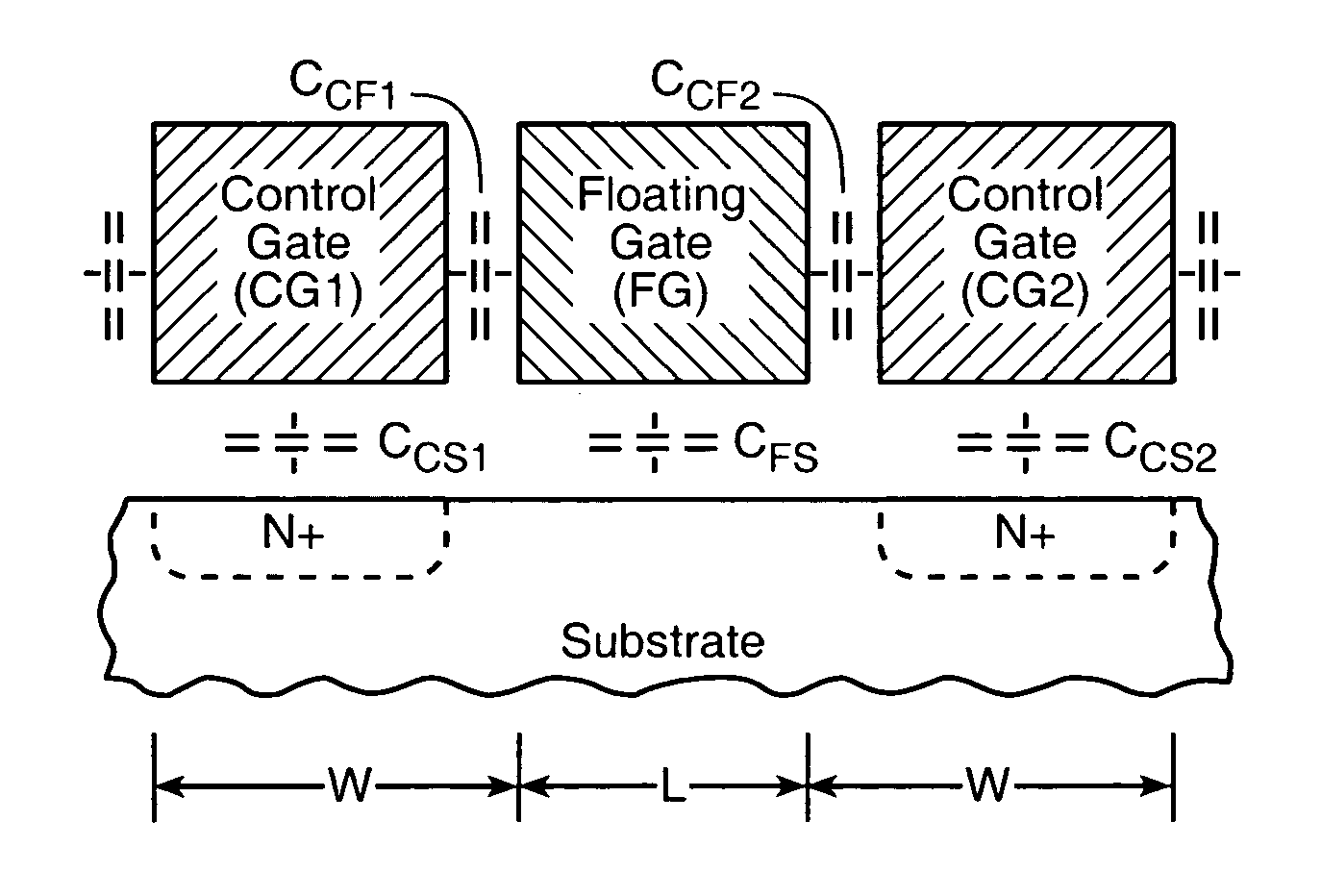

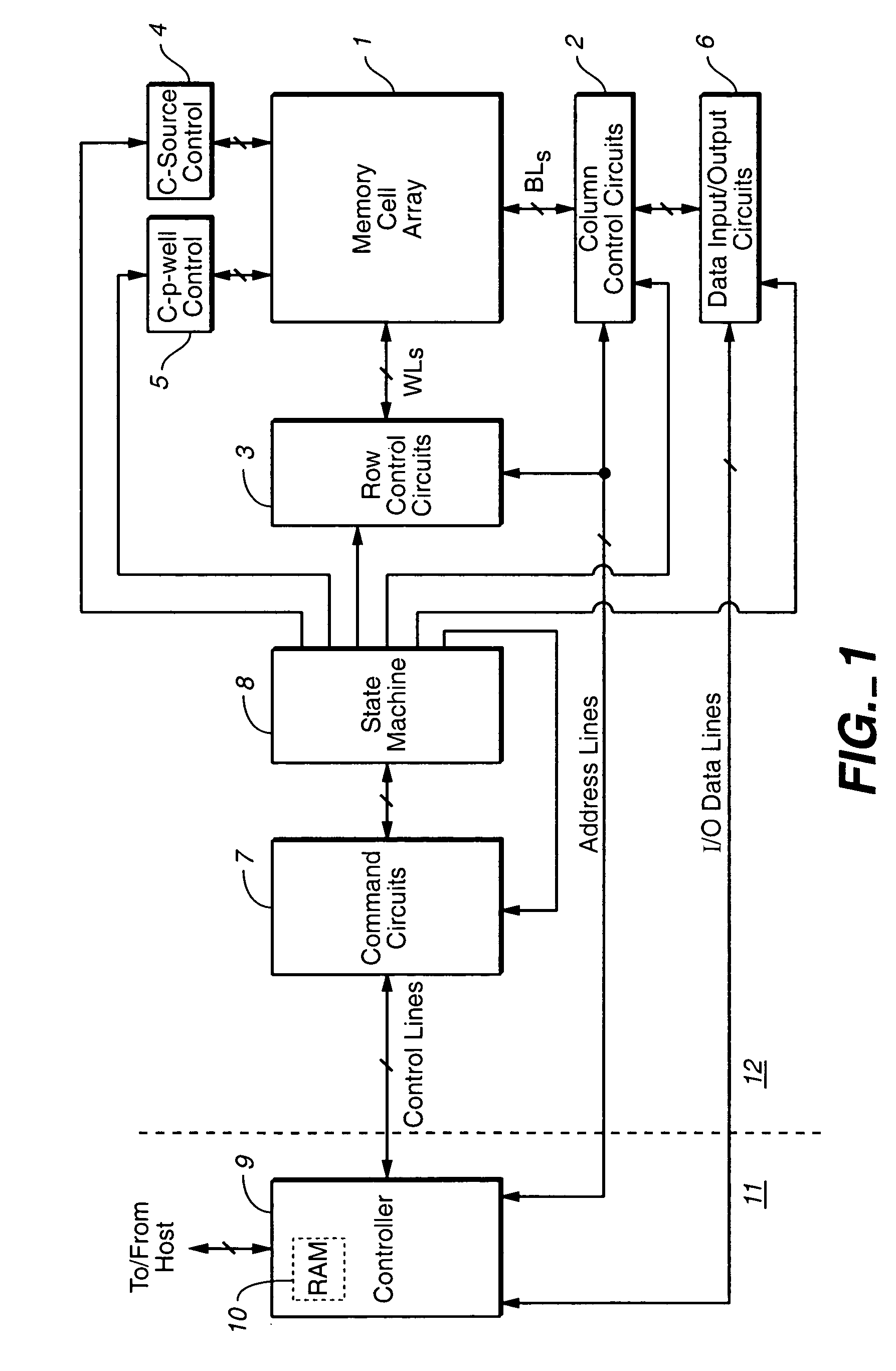

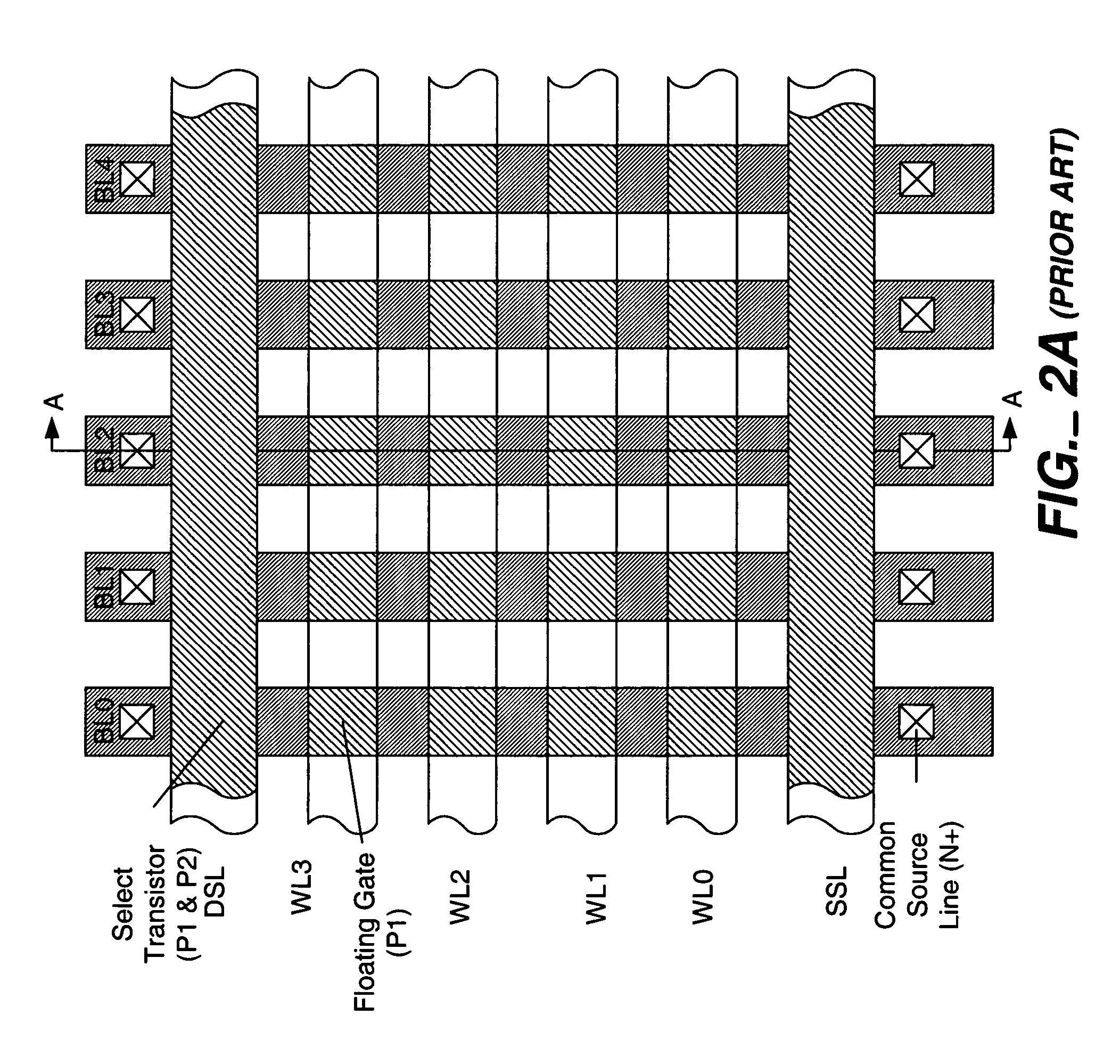

Flash memory cell arrays having dual control gates per memory cell charge storage element

InactiveUS6888755B2Increase coupling areaImprove the coupling ratioTransistorSolid-state devicesCapacitanceImage resolution

A flash NAND type EEPROM system with individual ones of an array of charge storage elements, such as floating gates, being capacitively coupled with at least two control gate lines. The control gate lines are preferably positioned between floating gates to be coupled with sidewalls of floating gates. The memory cell coupling ratio is desirably increased, as a result. Both control gate lines on opposite sides of a selected row of floating gates are usually raised to the same voltage while the second control gate lines coupled to unselected rows of floating gates immediately adjacent and on opposite sides of the selected row are kept low. The control gate lines can also be capacitively coupled with the substrate in order to selectively raise its voltage in the region of selected floating gates. The length of the floating gates and the thicknesses of the control gate lines can be made less than the minimum resolution element of the process by forming an etch mask of spacers.

Owner:SANDISK TECH LLC

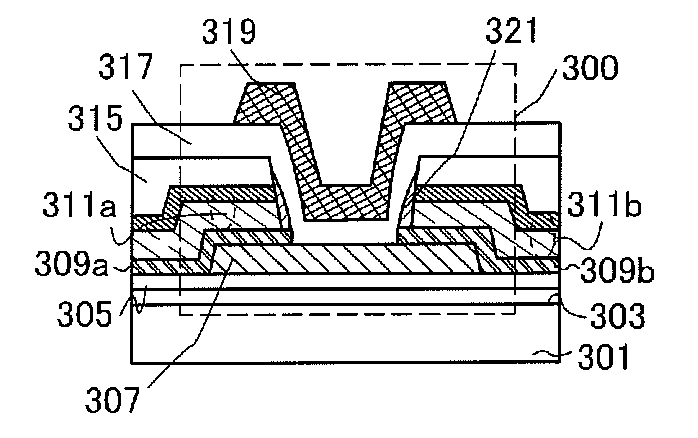

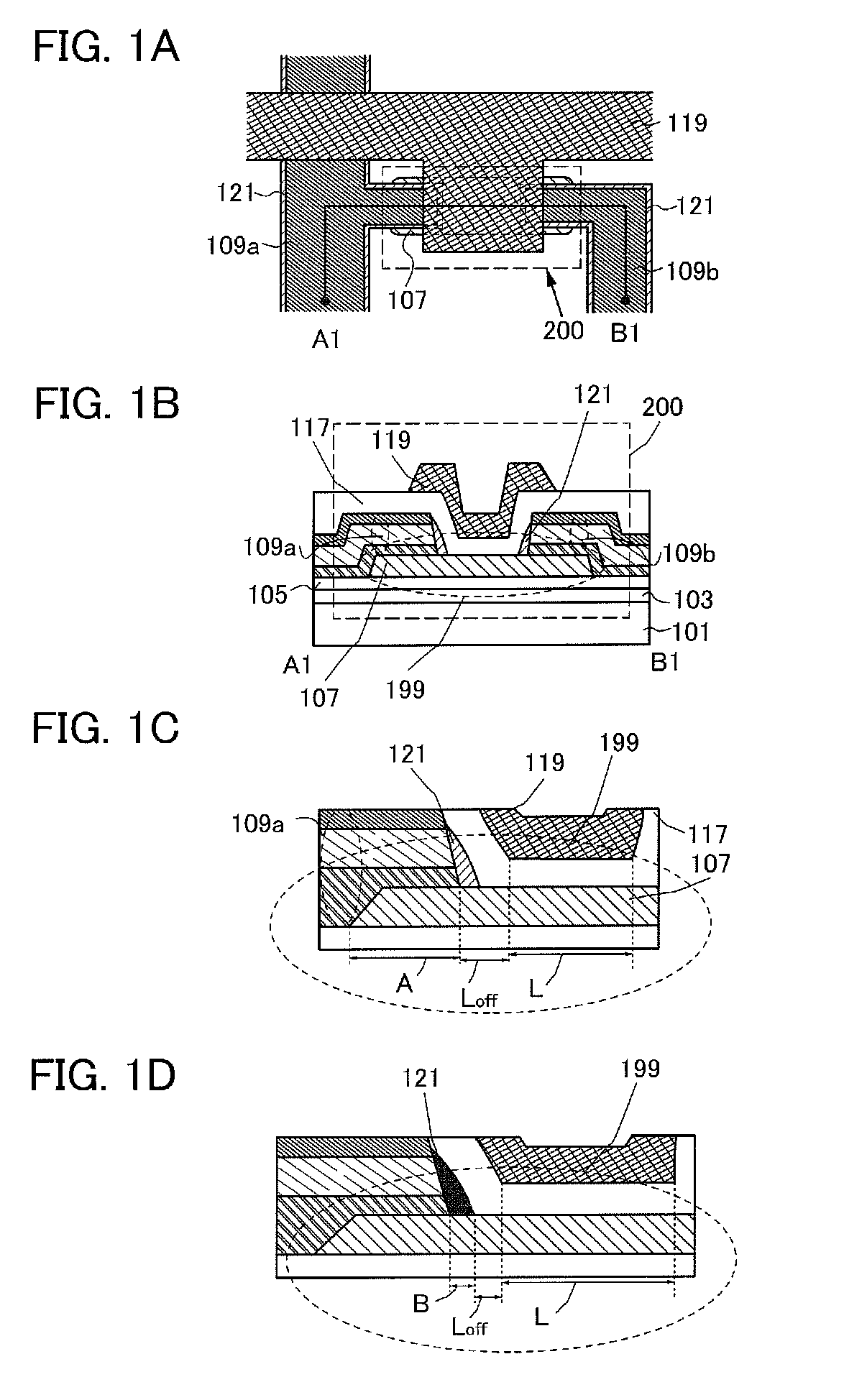

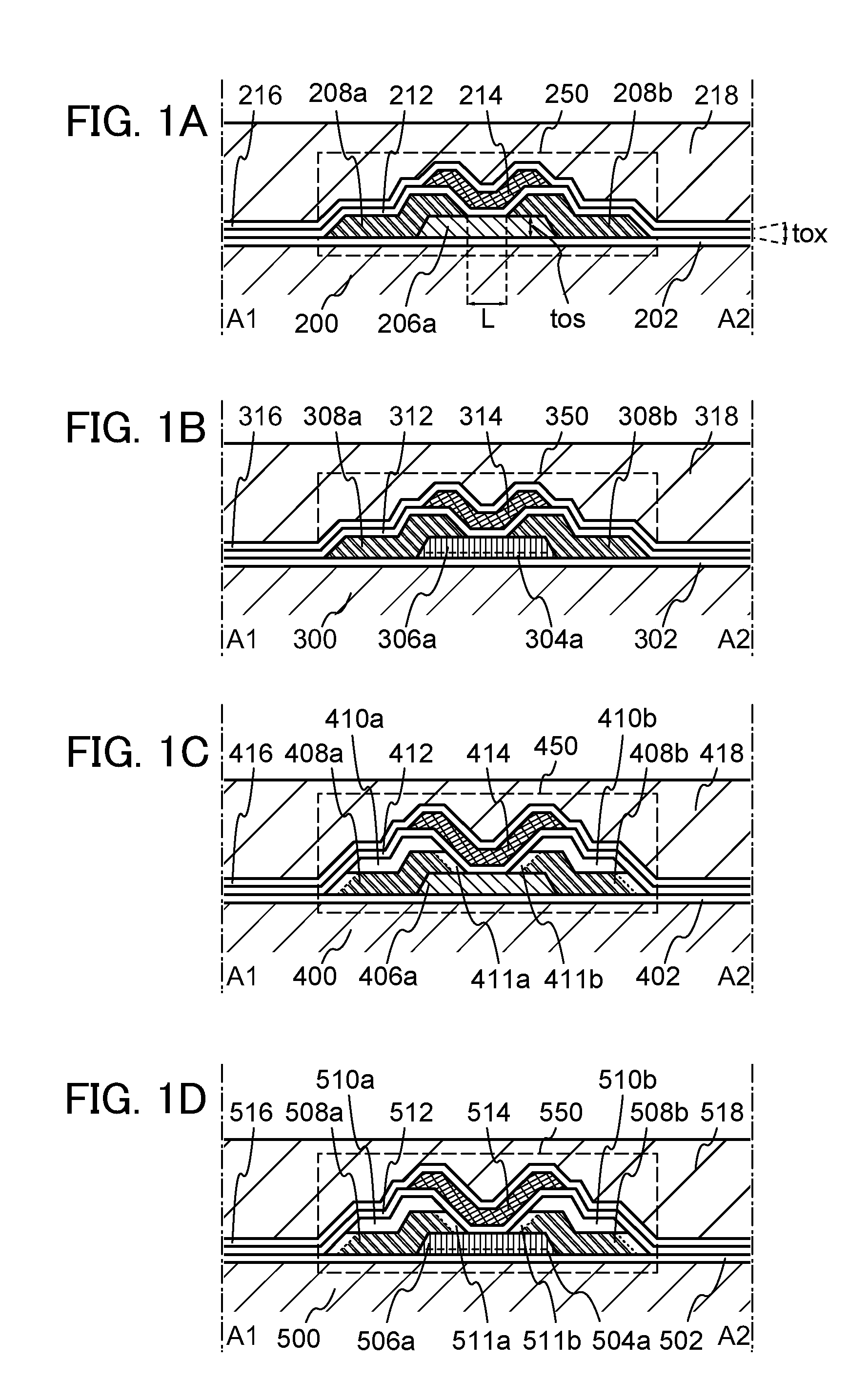

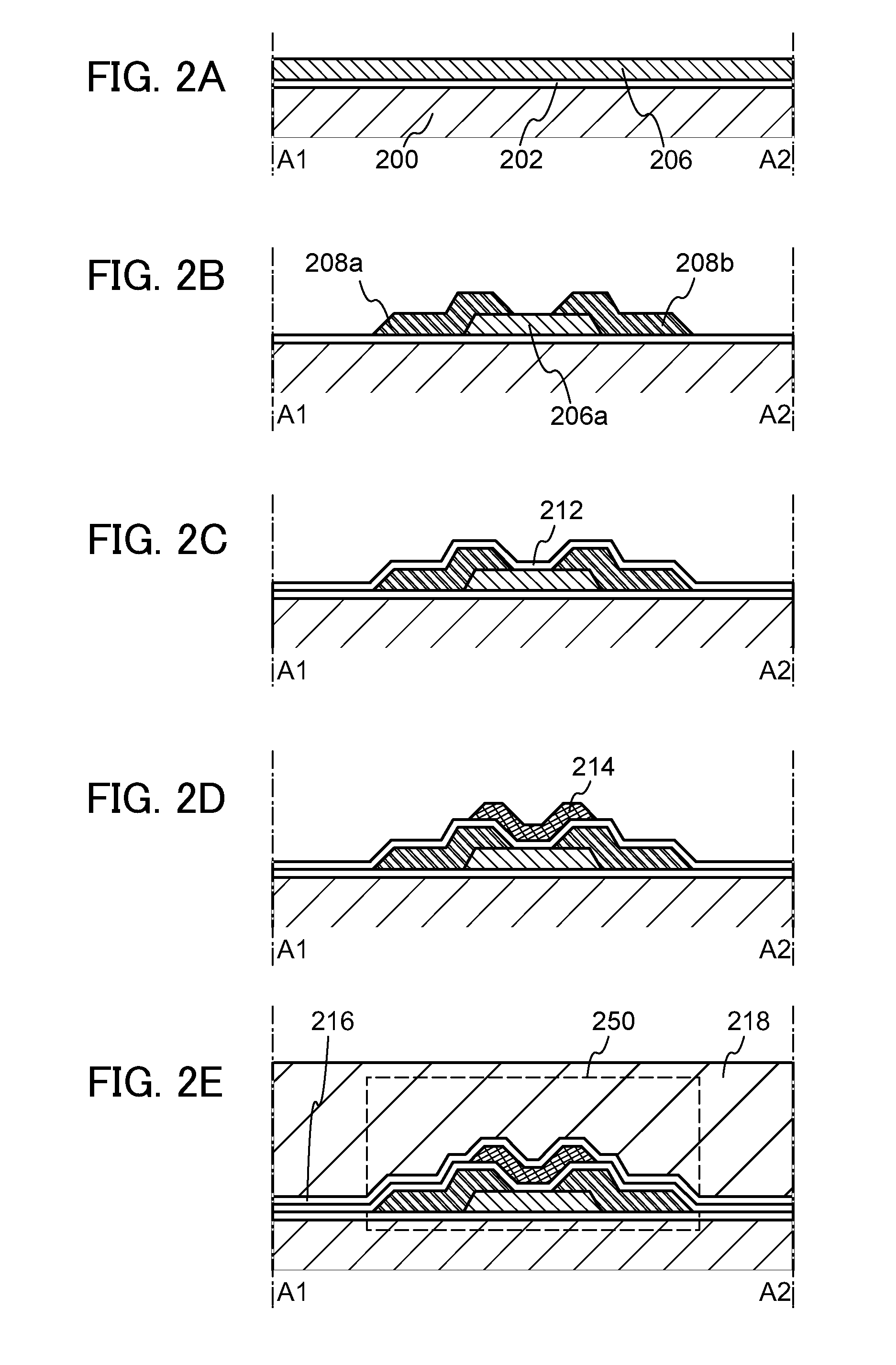

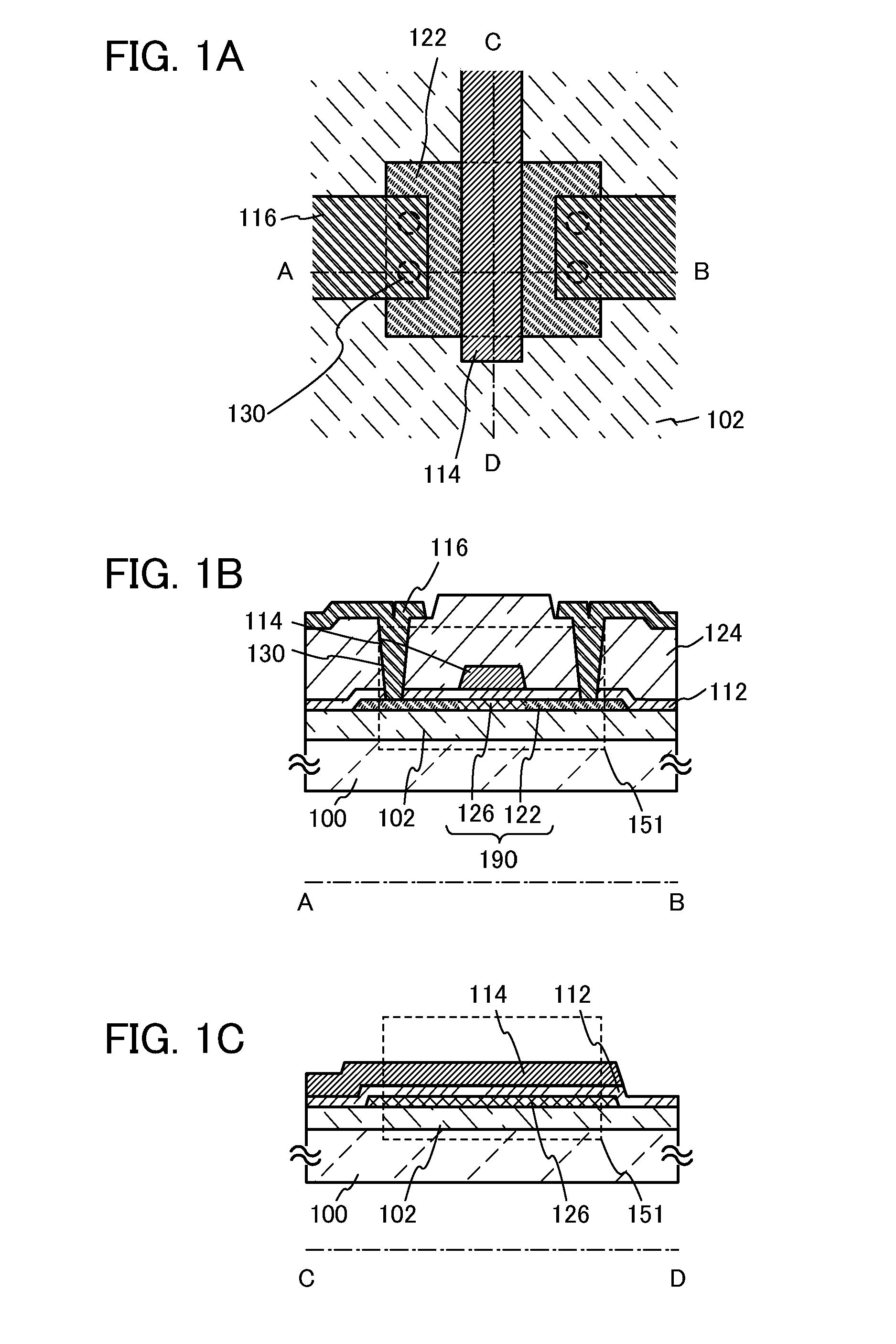

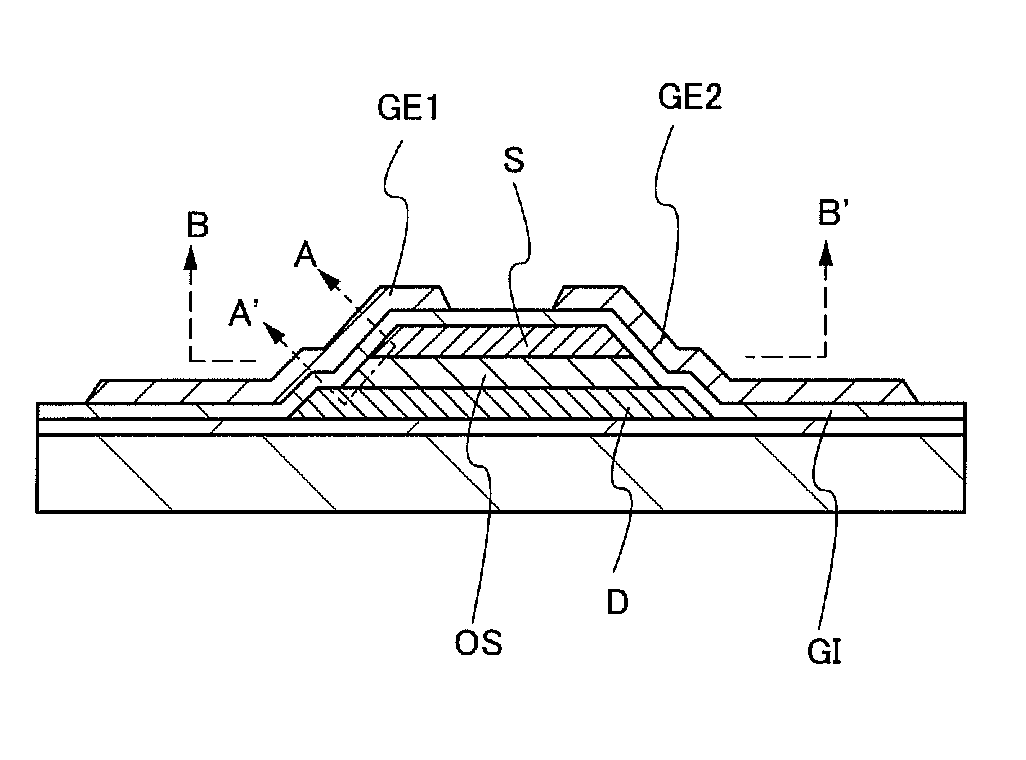

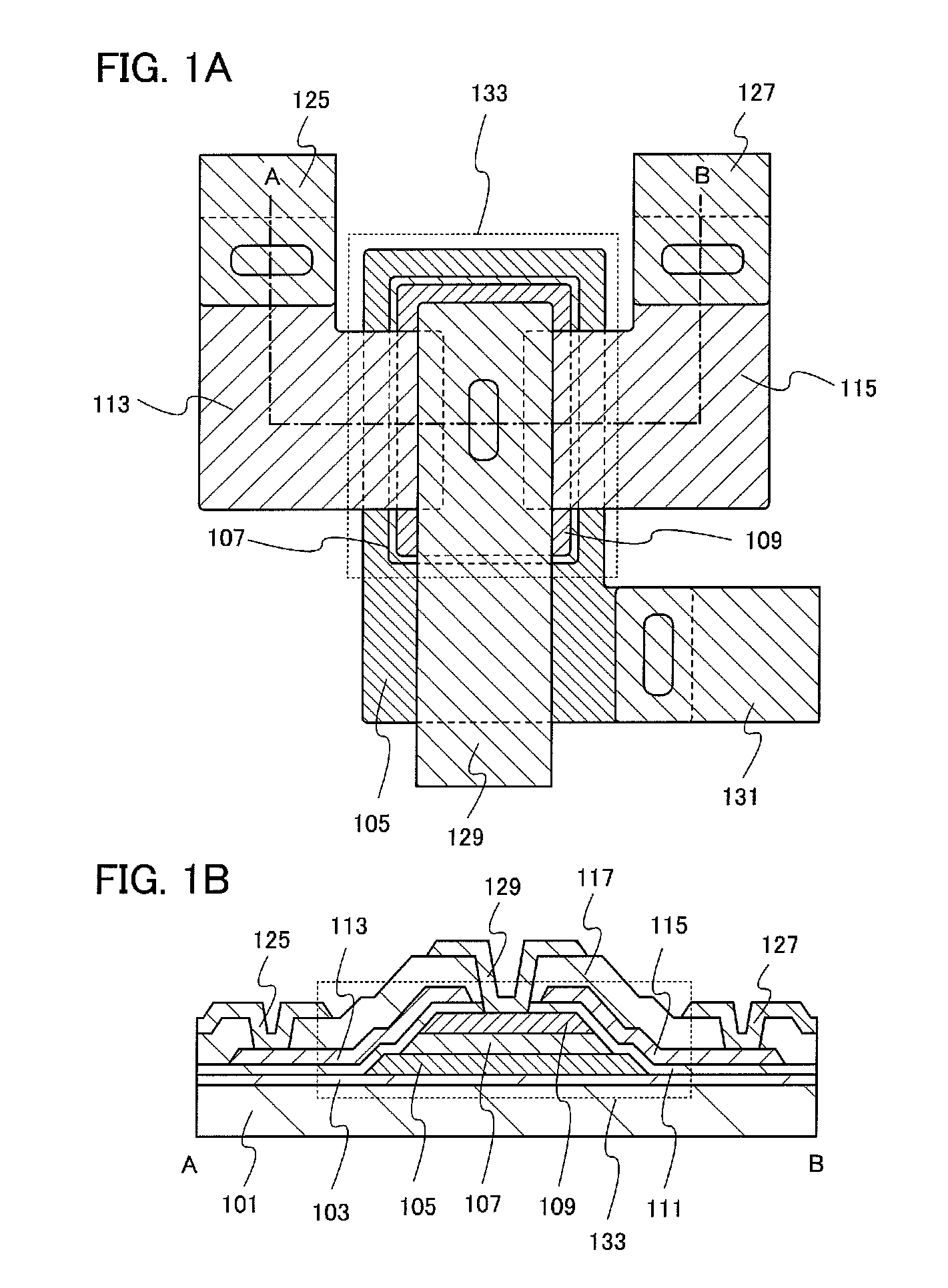

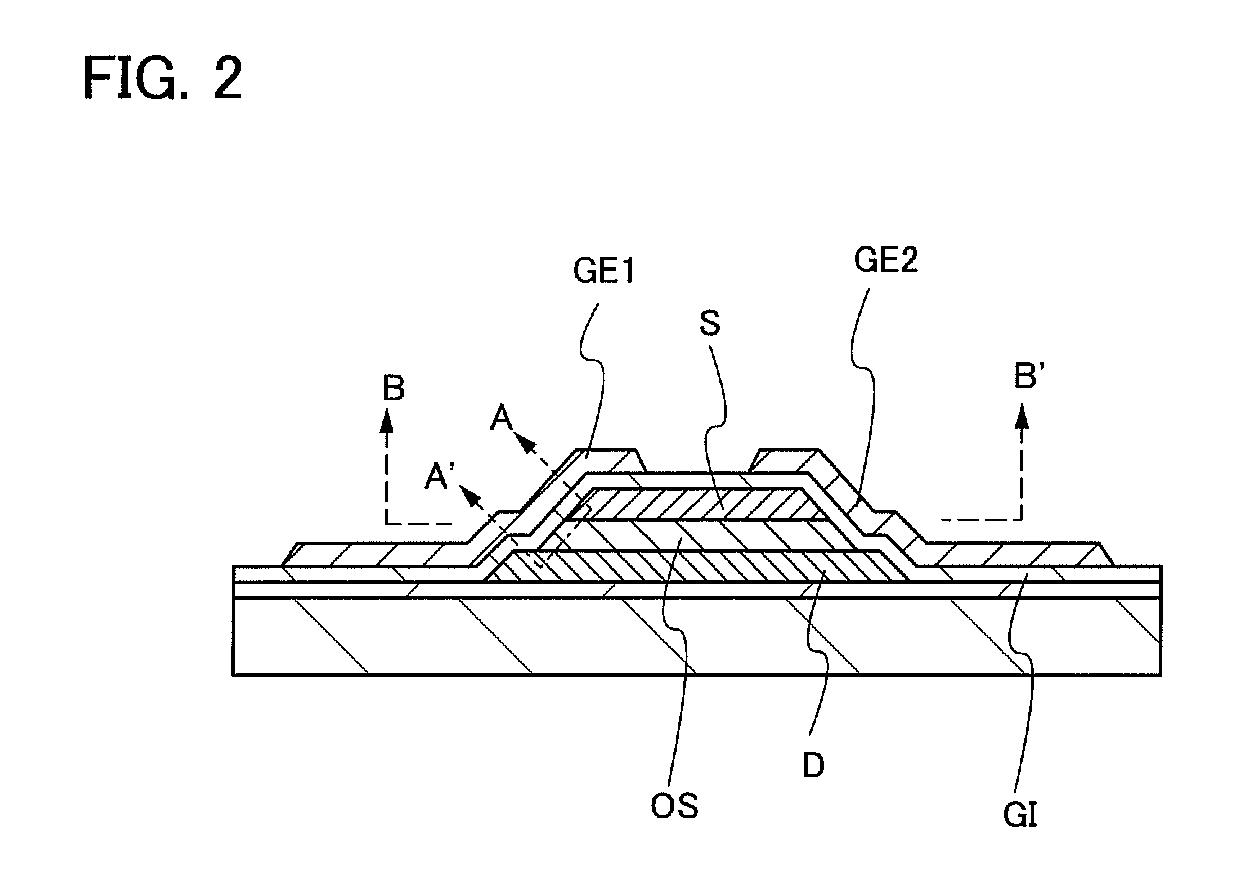

Semiconductor element, semiconductor device, and method for manufacturing the same

InactiveUS8501564B2High speedReduce power consumptionTransistorSolid-state devicesOptoelectronicsSemiconductor device

The semiconductor element includes an oxide semiconductor layer on an insulating surface; a source electrode layer and a drain electrode layer over the oxide semiconductor layer; a gate insulating layer over the oxide semiconductor layer, the source electrode layer, and the drain electrode layer; and a gate electrode layer over the gate insulating layer. The source electrode layer and the drain electrode layer have sidewalls which are in contact with a top surface of the oxide semiconductor layer.

Owner:SEMICON ENERGY LAB CO LTD

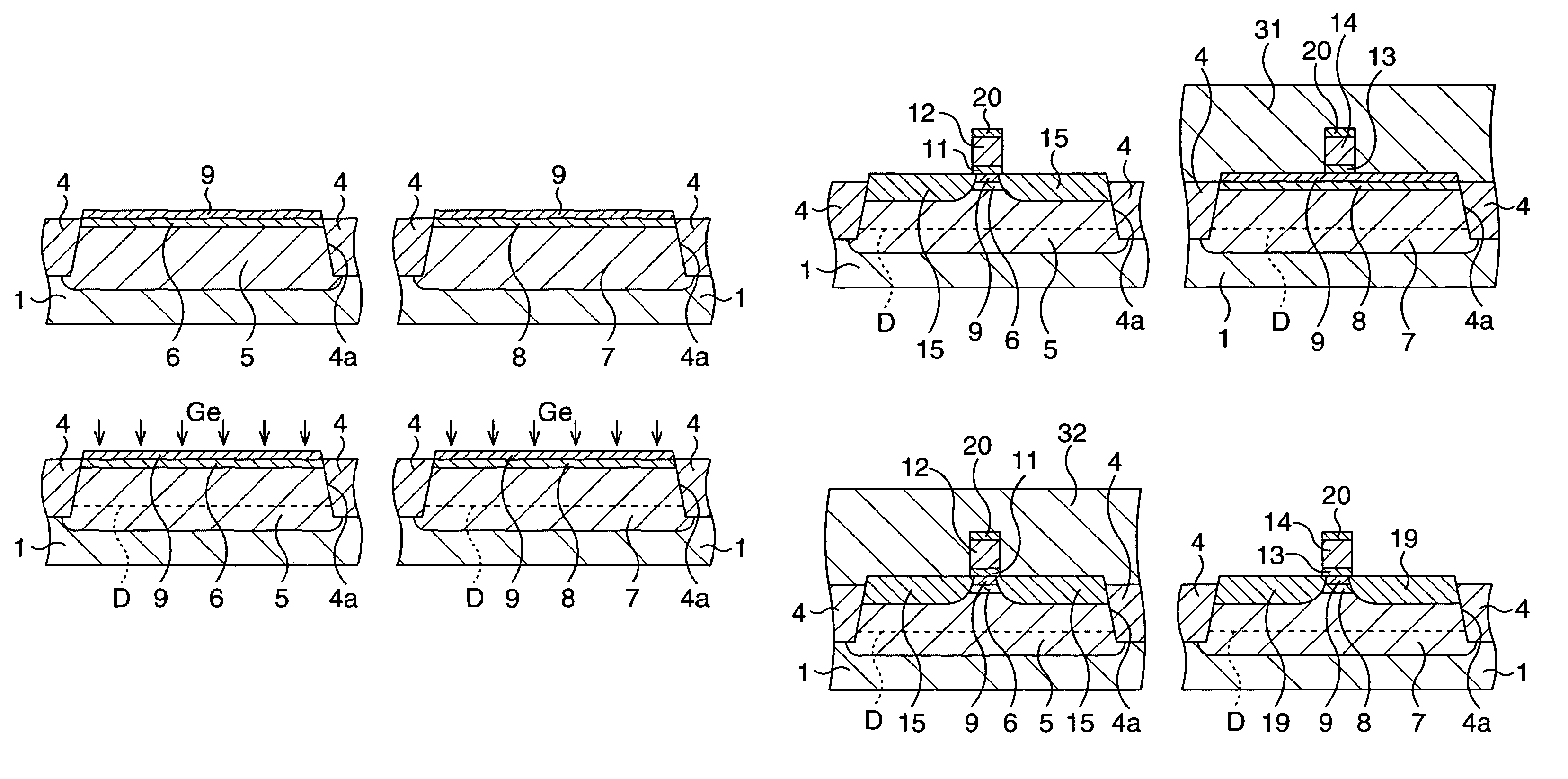

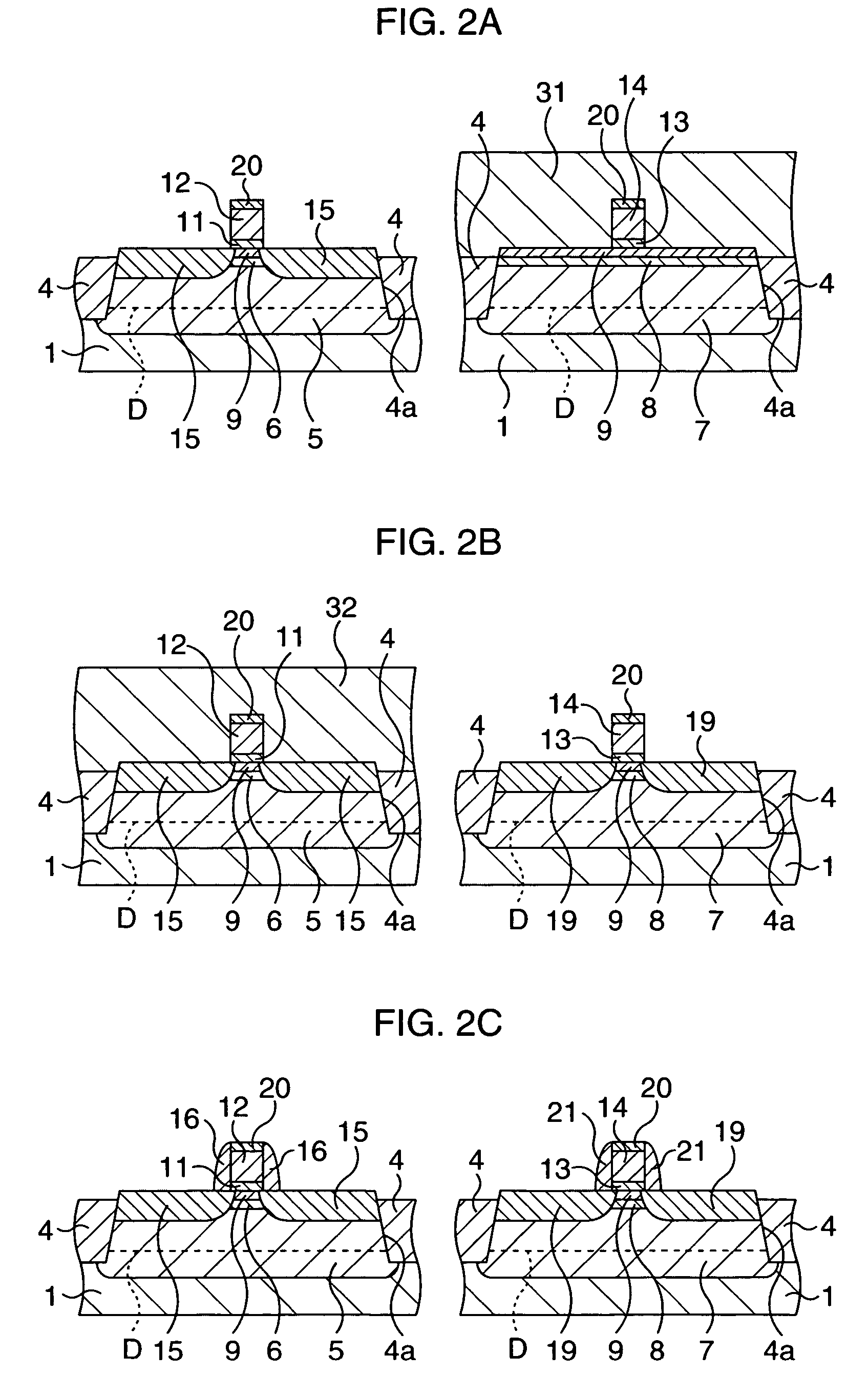

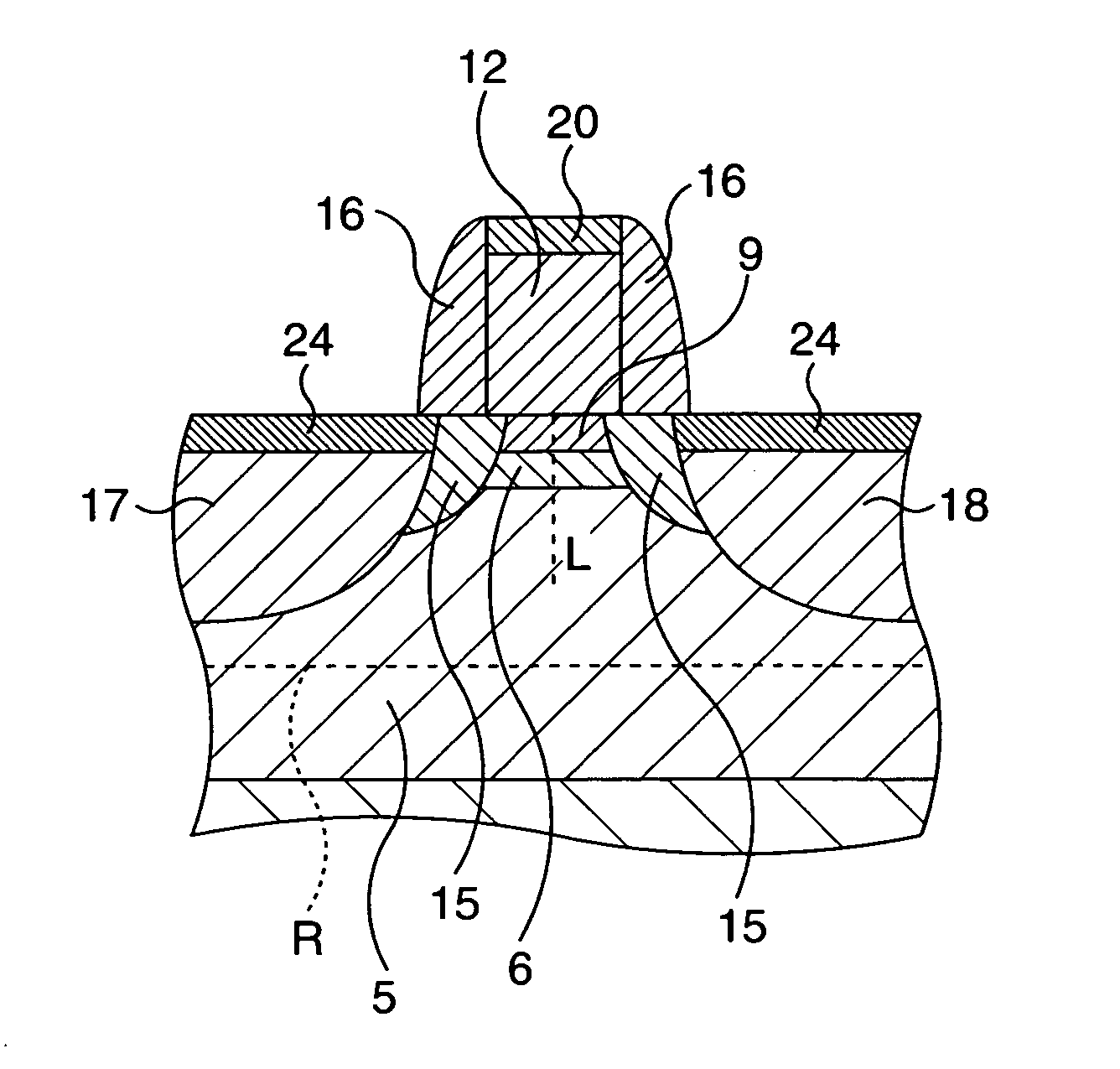

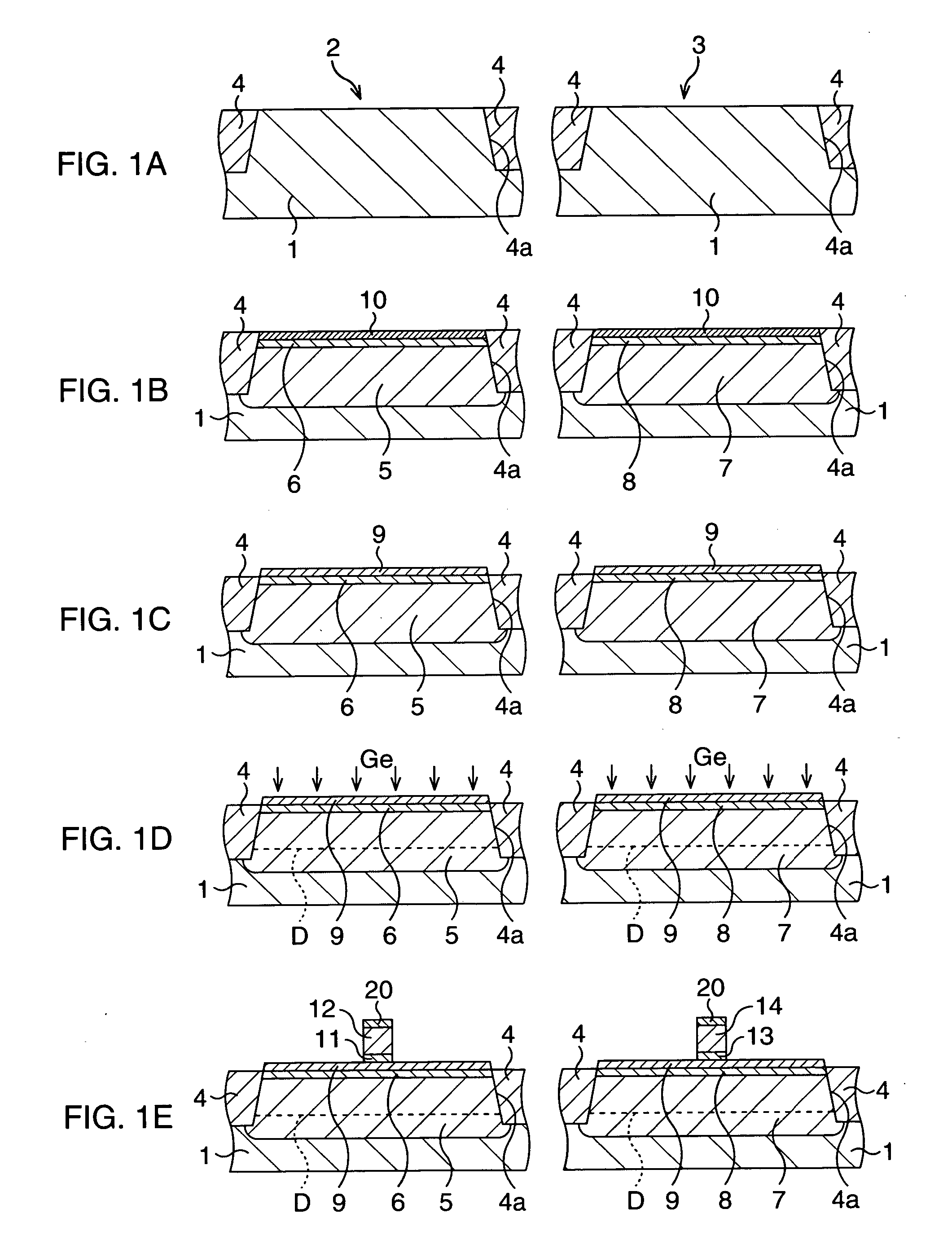

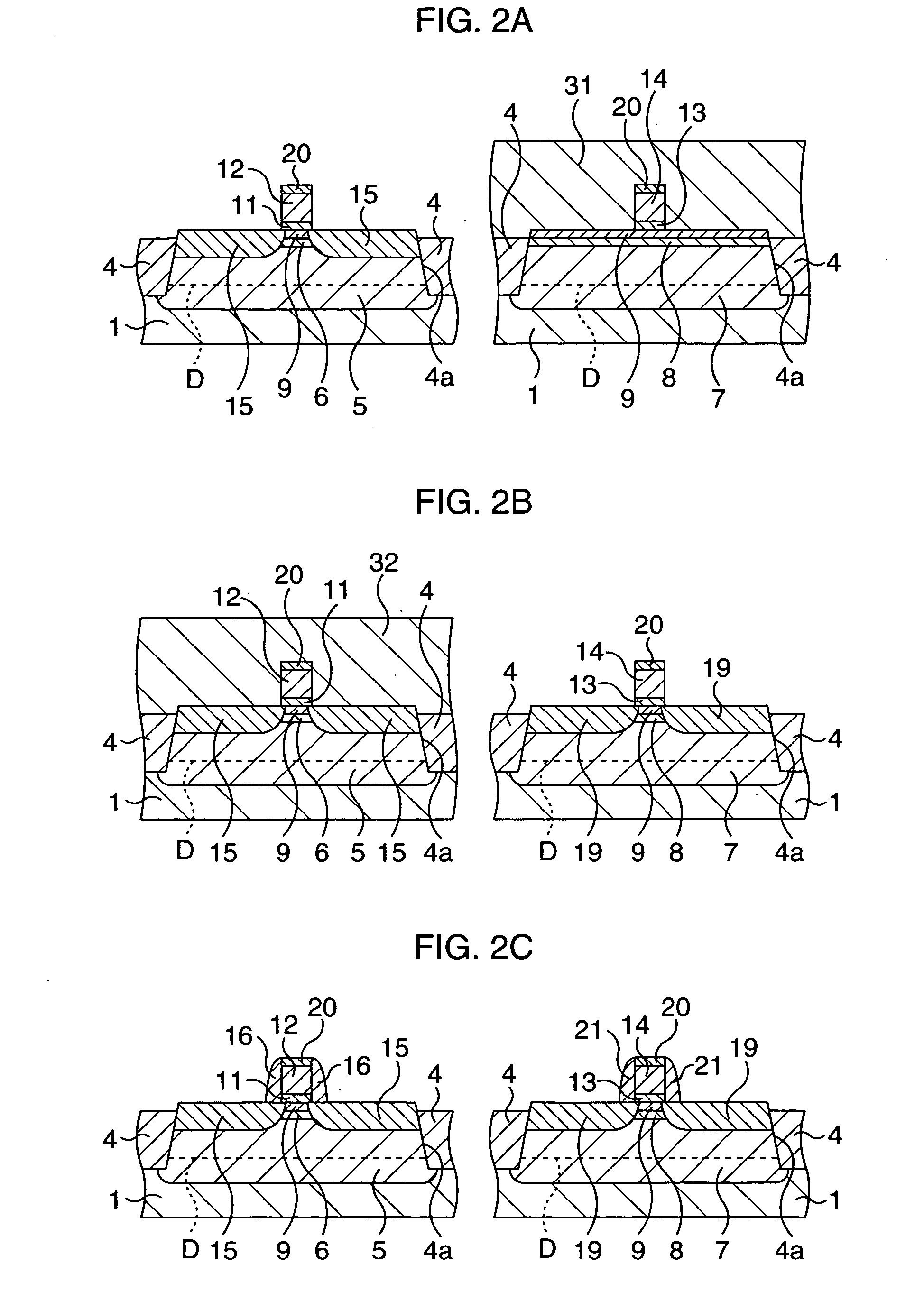

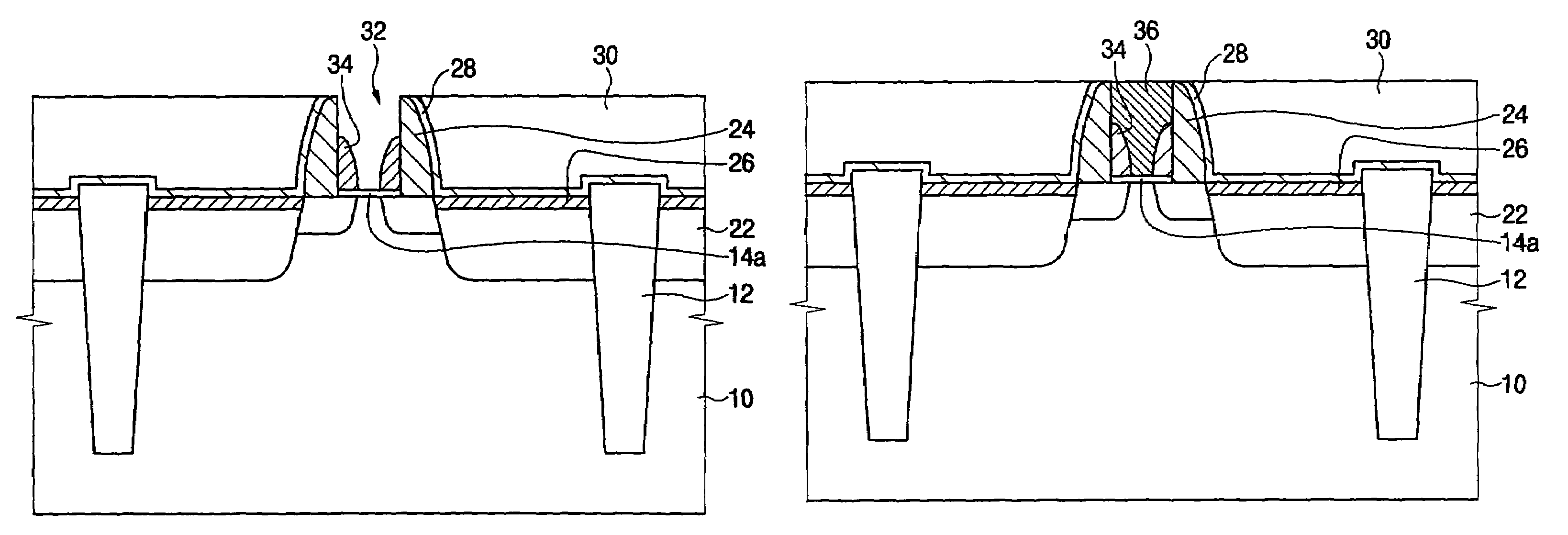

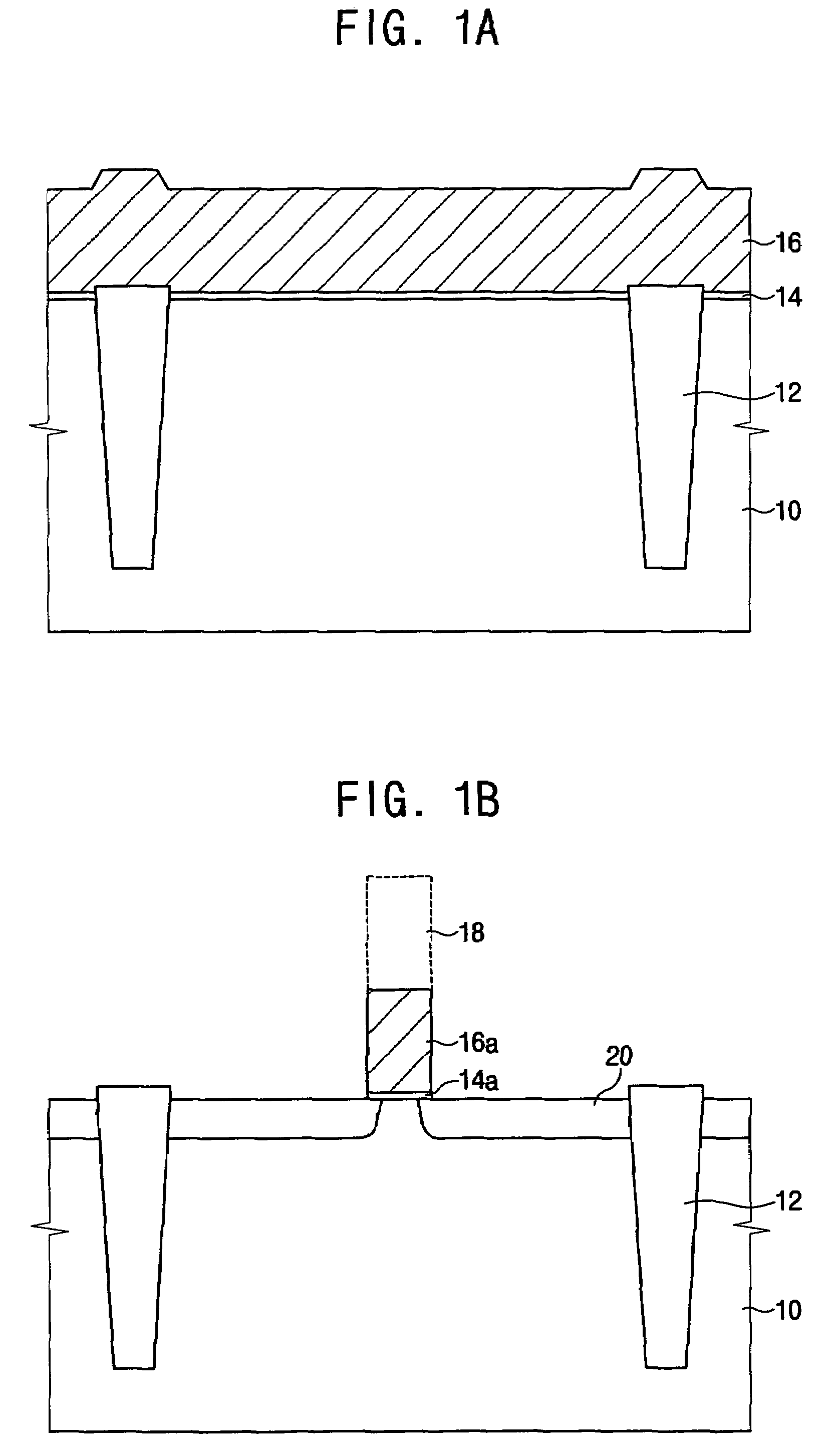

Manufacturing method of semiconductor device suppressing short-channel effect

ActiveUS7223646B2Improve reliabilityEliminate the effects ofTransistorSemiconductor/solid-state device manufacturingImpuritySemiconductor

An ideal step-profile in a channel region is realized easily and reliably, whereby suppression of the short-channel effect and prevention of mobility degradation are achieved together. A silicon substrate is amorphized to a predetermined depth from a semiconductor film, and impurities to become the source / drain are introduced in this state. Then the impurities are activated, and the amorphized portion is recrystallized, by low temperature solid-phase epitaxial regrowth. With the processing temperature required for the low temperature solid-phase epitaxial regrowth being within a range of 450° C.–650° C., thermal diffusion of the impurities into the semiconductor film is suppressed, thereby maintaining the initial steep step-profile.

Owner:FUJITSU SEMICON LTD

Semiconductor Element, Semiconductor Device, And Method For Manufacturing The Same

InactiveUS20110133177A1Increased operation speedReduce power consumptionTransistorSolid-state devicesOxide semiconductorSemiconductor components

The semiconductor element includes an oxide semiconductor layer on an insulating surface; a source electrode layer and a drain electrode layer over the oxide semiconductor layer; a gate insulating layer over the oxide semiconductor layer, the source electrode layer, and the drain electrode layer; and a gate electrode layer over the gate insulating layer. The source electrode layer and the drain electrode layer have sidewalls which are in contact with a top surface of the oxide semiconductor layer.

Owner:SEMICON ENERGY LAB CO LTD

Vertical FET with nanowire channels and a silicided bottom contact

ActiveUS20060273389A1Reduce access series resistanceReduce overlap capacitanceNanoinformaticsSolid-state devicesCapacitanceAND gate

A vertical FET structure with nanowire forming the FET channels is disclosed. The nanowires are formed over a conductive silicide layer. The nanowires are gated by a surrounding gate. Top and bottom insulator plugs function as gate spacers and reduce the gate-source and gate-drain capacitance.

Owner:GLOBALFOUNDRIES US INC

Vertical FET with nanowire channels and a silicided bottom contact

ActiveUS7230286B2Reduce resistanceGood short channel characteristicsTransistorNanoinformaticsCapacitanceNanowire

A vertical FET structure with nanowire forming the FET channels is disclosed. The nanowires are formed over a conductive silicide layer. The nanowires are gated by a surrounding gate. Top and bottom insulator plugs function as gate spacers and reduce the gate-source and gate-drain capacitance.

Owner:GLOBALFOUNDRIES U S INC

Semiconductor device and manufacturing method thereof

ActiveUS20060220114A1Shorten channel-lengthsHigh reliabilityTransistorSemiconductor/solid-state device manufacturingSolid phasesShort-channel effect

An ideal step-profile in a channel region is realized easily and reliably, whereby suppression of the short-channel effect and prevention of mobility degradation are achieved together. A silicon substrate is amorphized to a predetermined depth from a semiconductor film, and impurities to become the source / drain are introduced in this state. Then the impurities are activated, and the amorphized portion is recrystallized, by low temperature solid-phase epitaxial regrowth. With the processing temperature required for the low temperature solid-phase epitaxial regrowth being within a range of 450° C.-650° C., thermal diffusion of the impurities into the semiconductor film is suppressed, thereby maintaining the initial steep step-profile.

Owner:FUJITSU SEMICON LTD

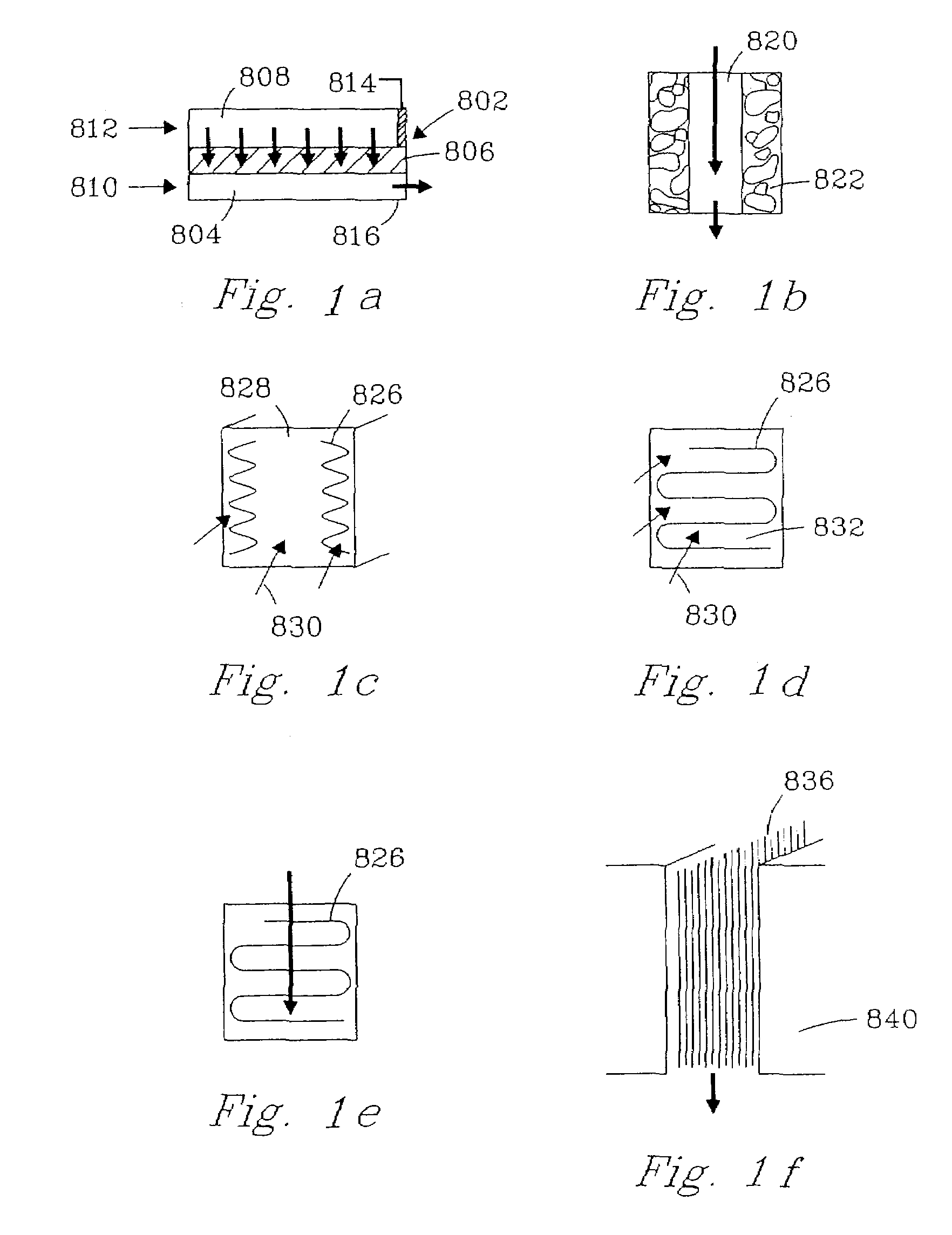

Pillar cell flash memory technology

ActiveUS7049652B2Enhanced programming characteristicReduce capacityTransistorNanoinformaticsPillar cellsComputer science

Owner:SANDISK TECH LLC

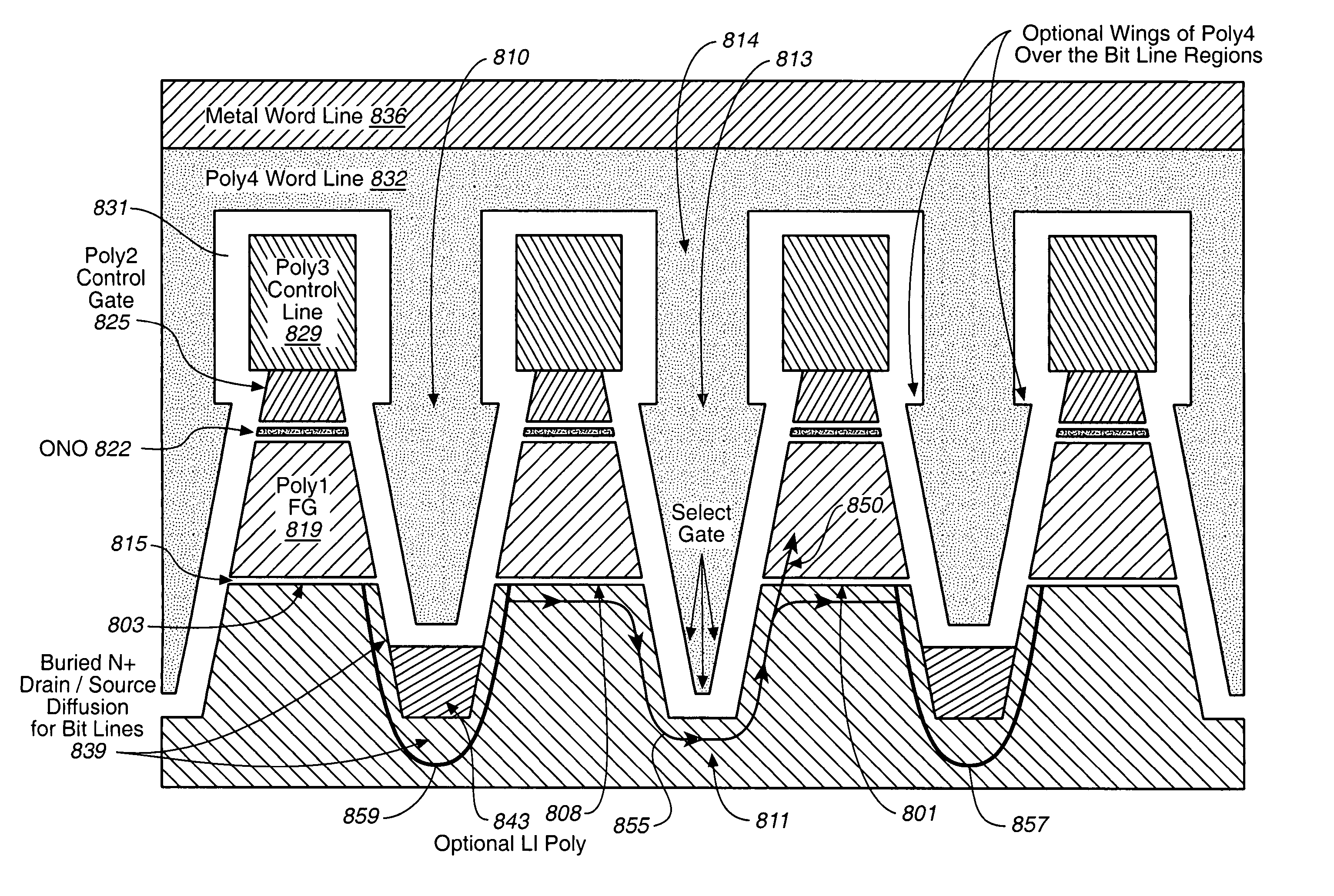

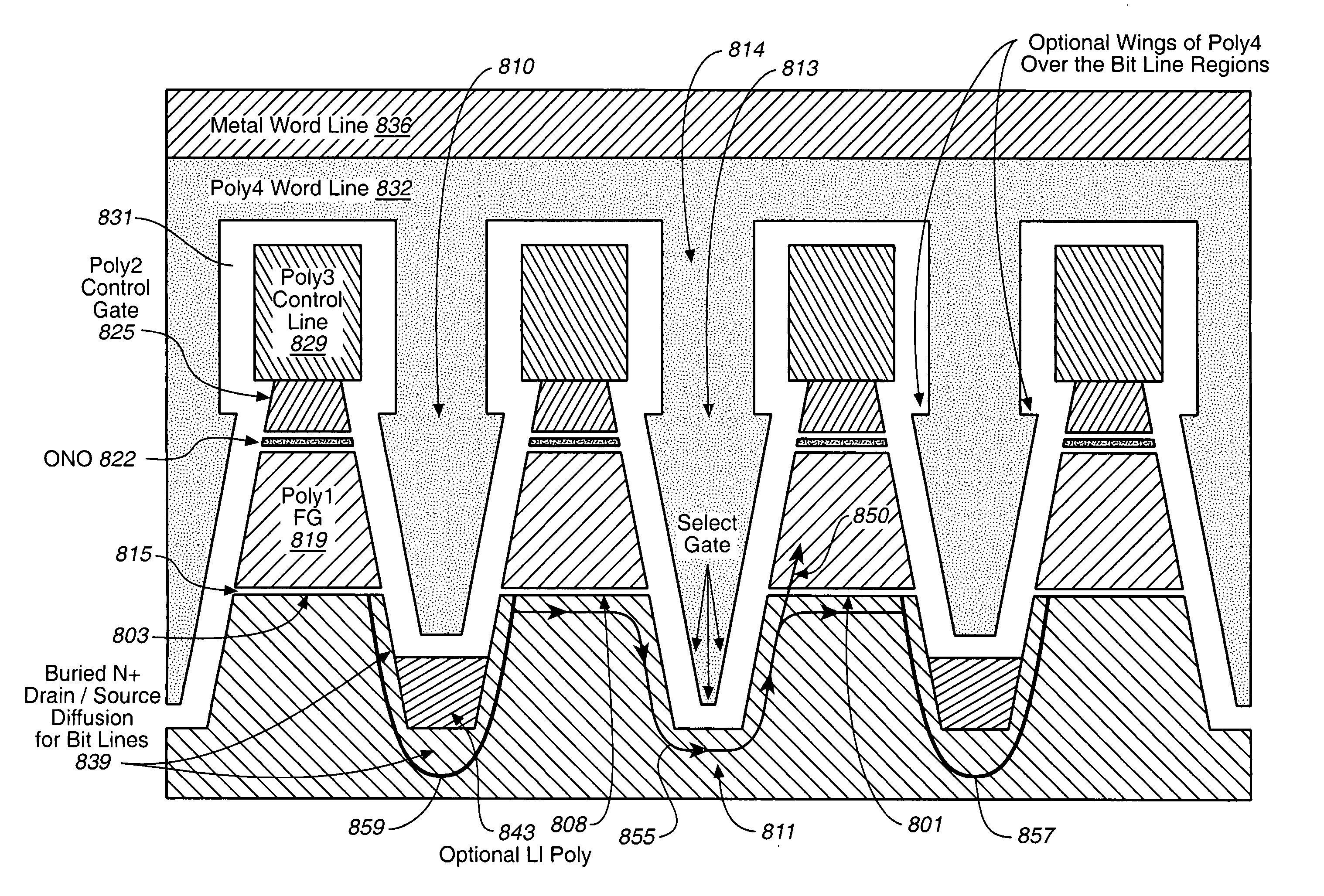

Pillar cell flash memory technology

ActiveUS20050127428A1Enhanced programming characteristicReduce mold sizeTransistorNanoinformaticsPillar cellsEngineering

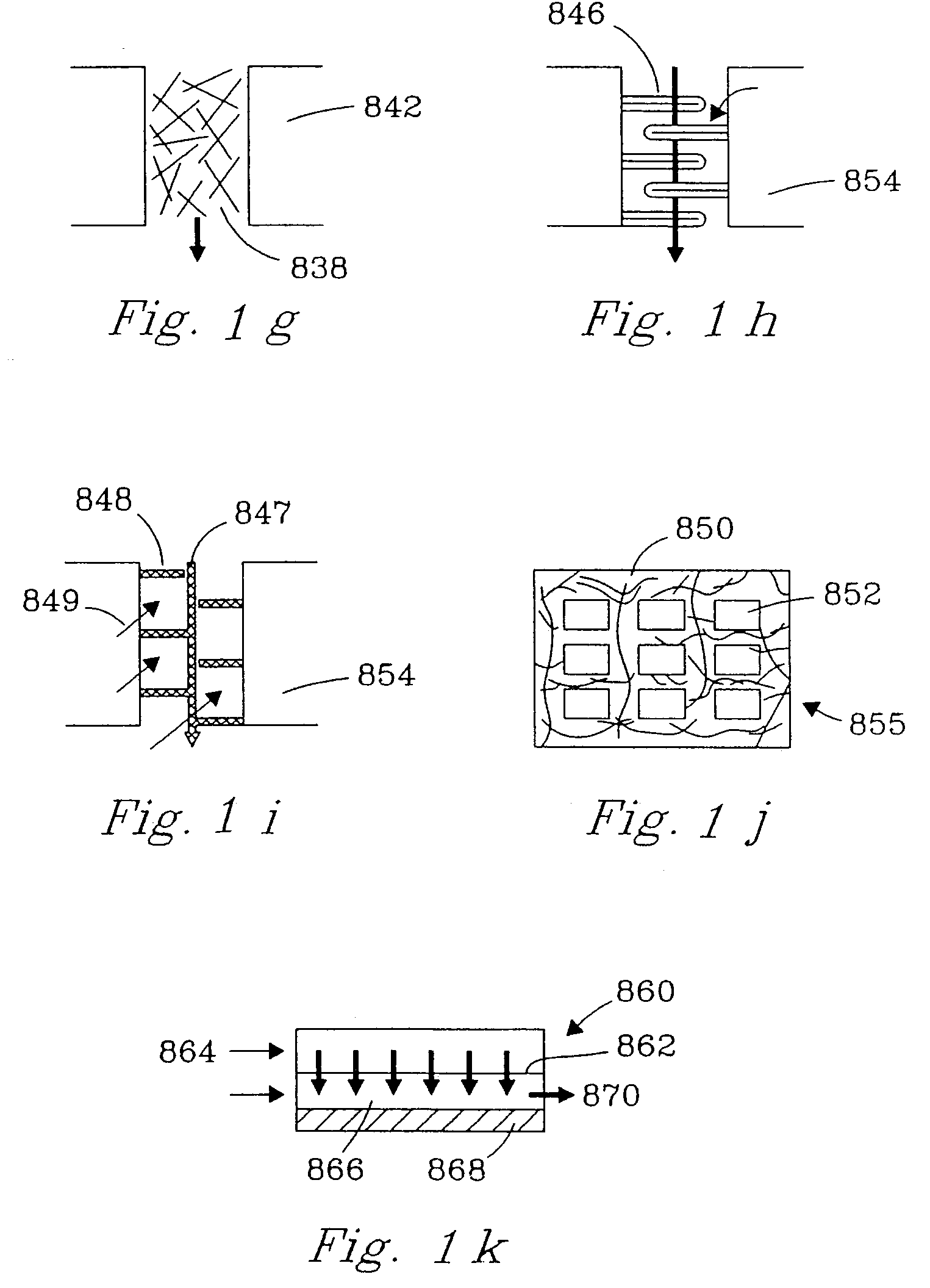

An array of a pillar-type nonvolatile memory cells (803) has each memory cell isolated from adjacent memory cells by a trench (810). Each memory cell is formed by a stacking process layers on a substrate: tunnel oxide layer (815), polysilicon floating gate layer (819), ONO or oxide layer (822), polysilicon control gate layer (825). Many aspects of the process are self-aligned. An array of these memory cells will require less segmentation. Furthermore, the memory cell has enhanced programming characteristics because electrons are directed at a normal or nearly normal angle (843) to the floating gate (819).

Owner:SANDISK TECH LLC

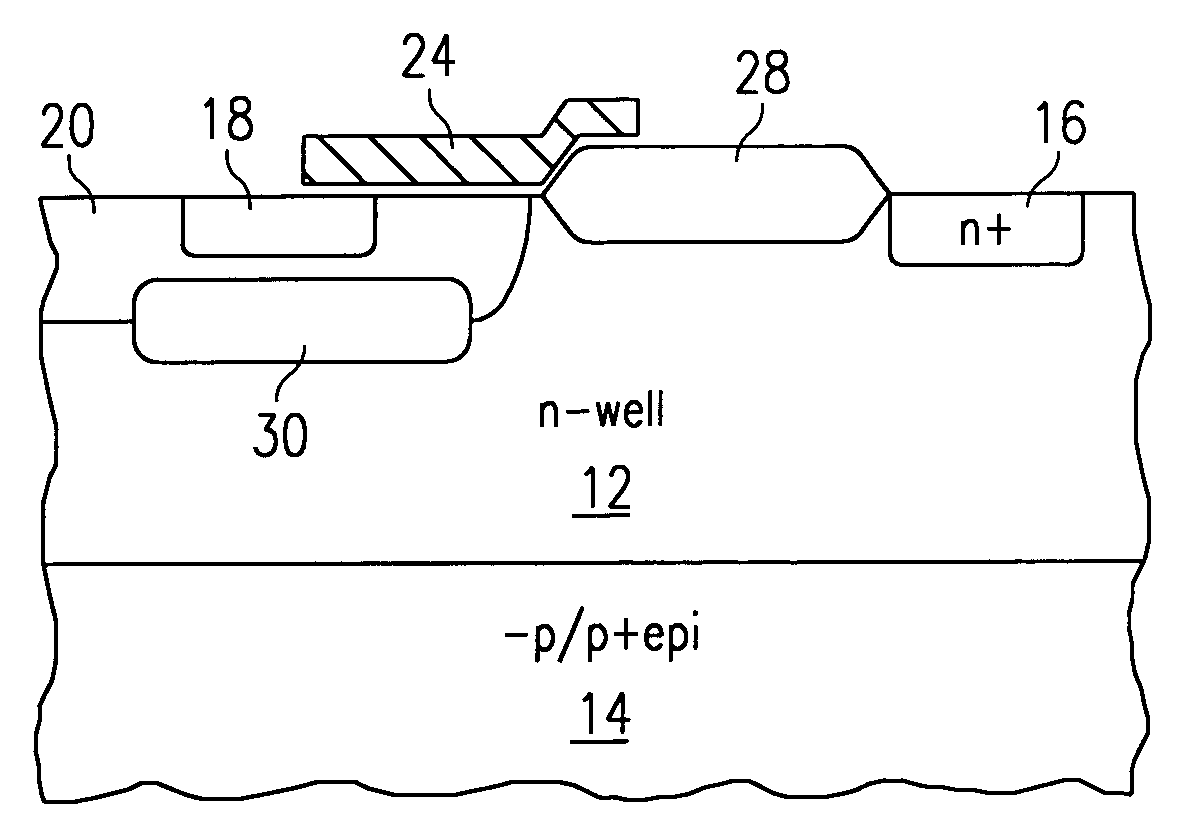

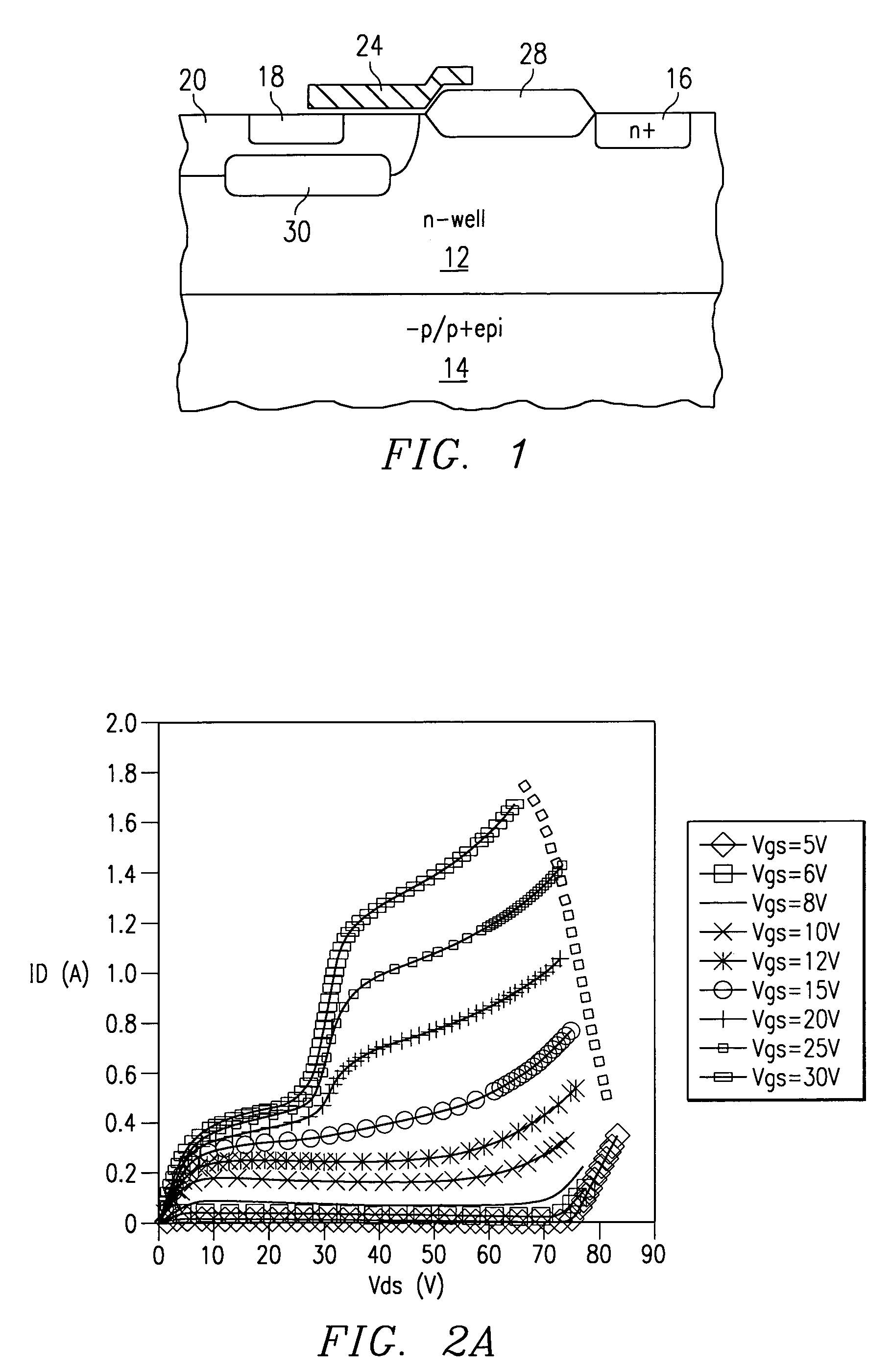

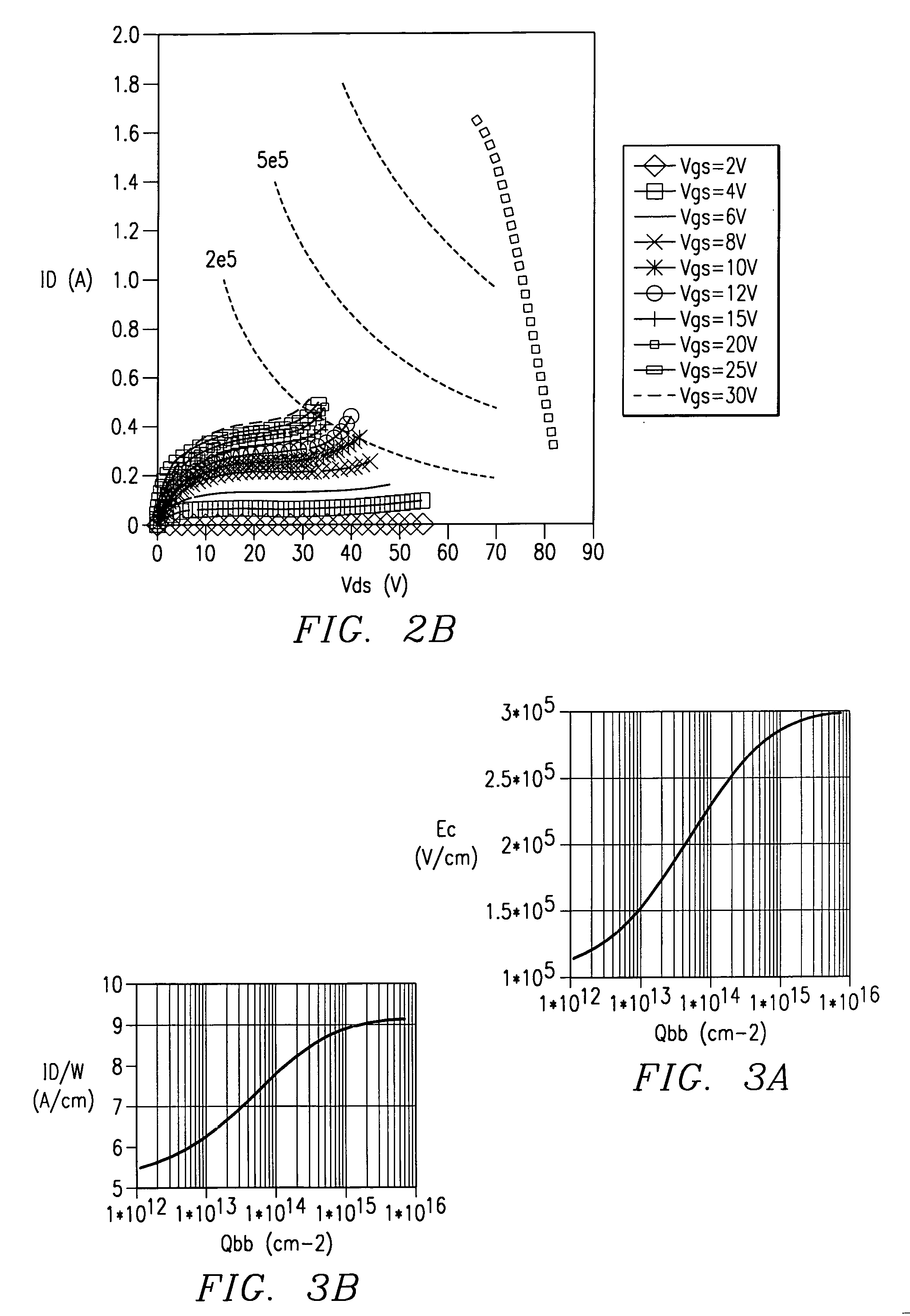

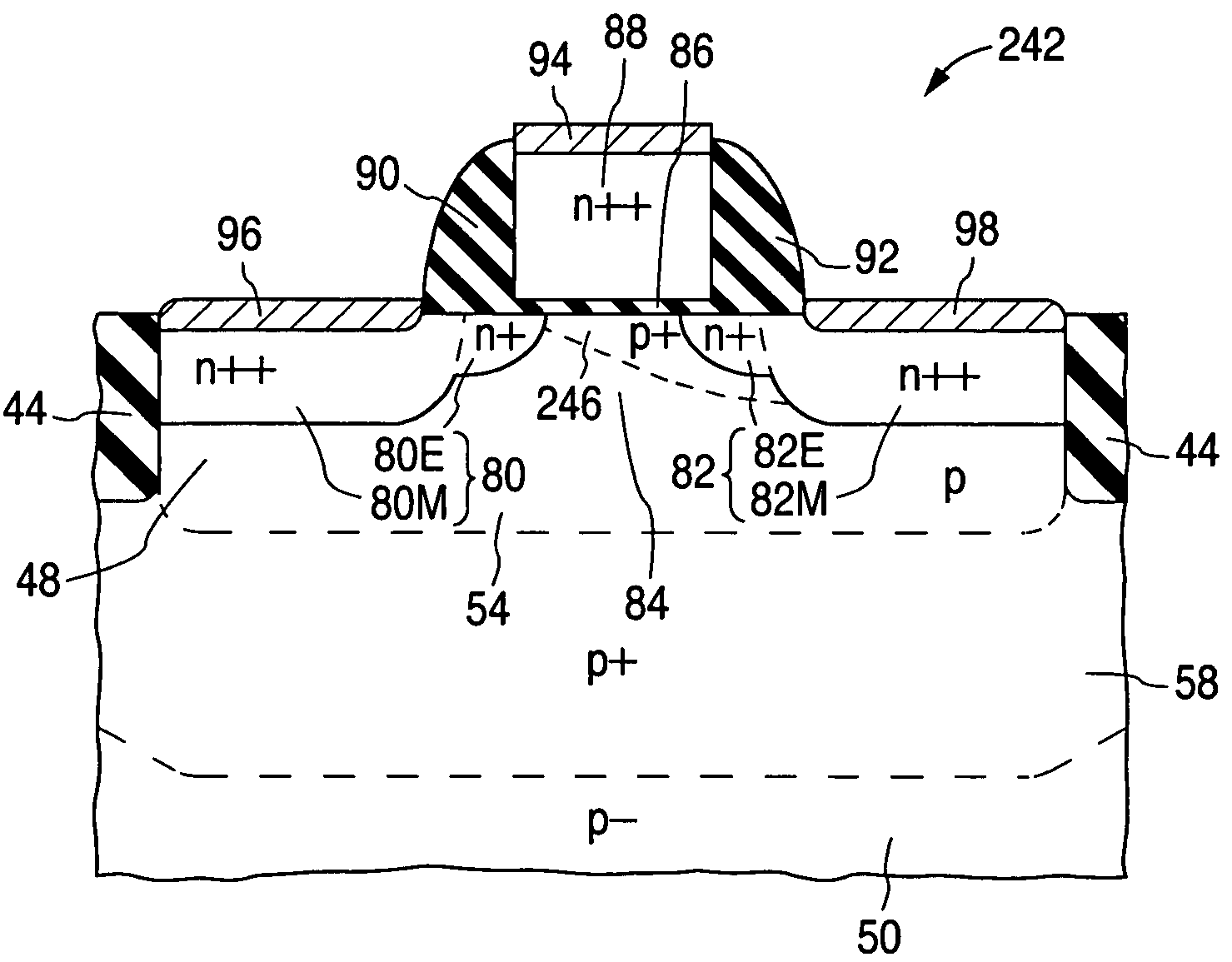

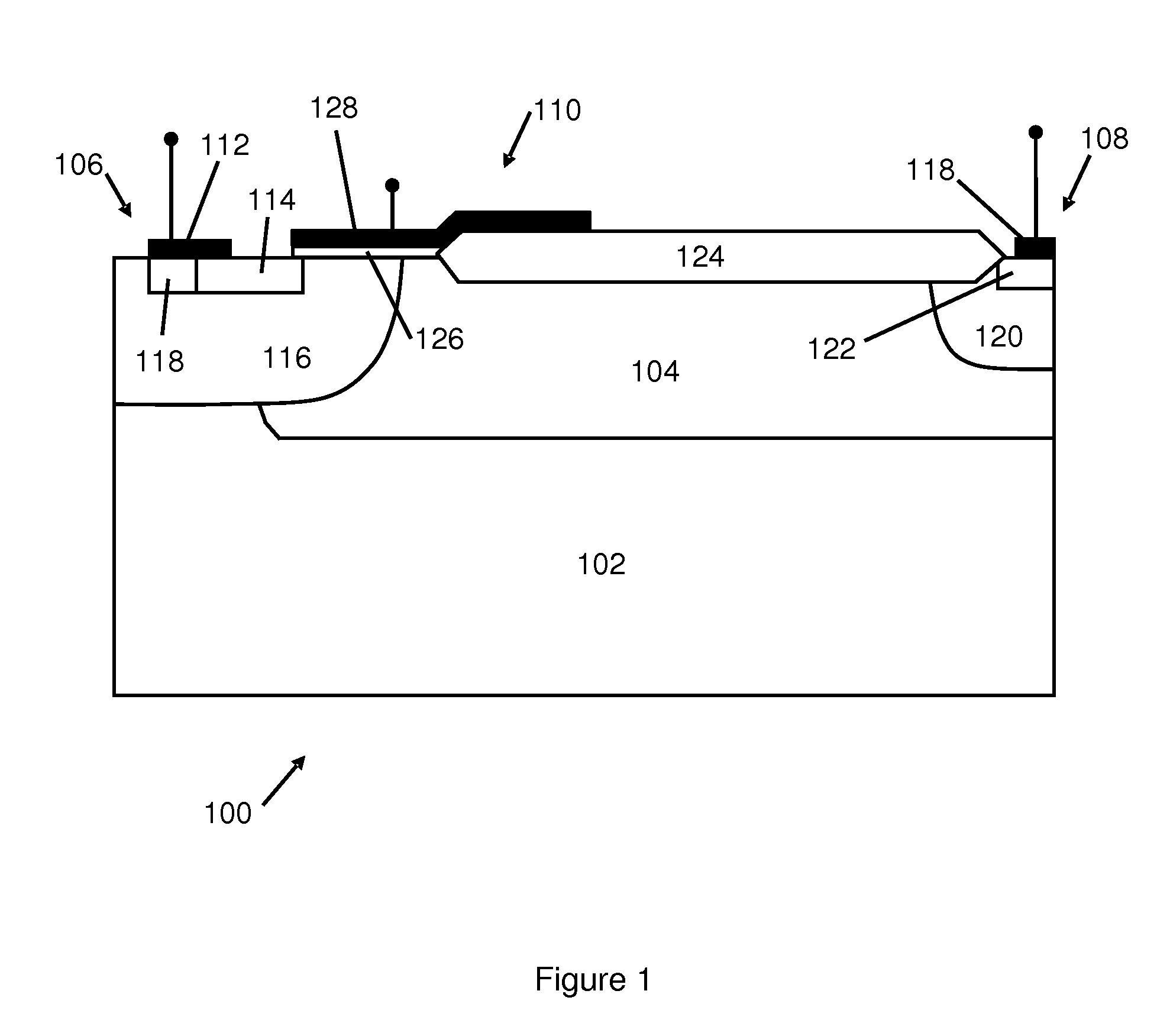

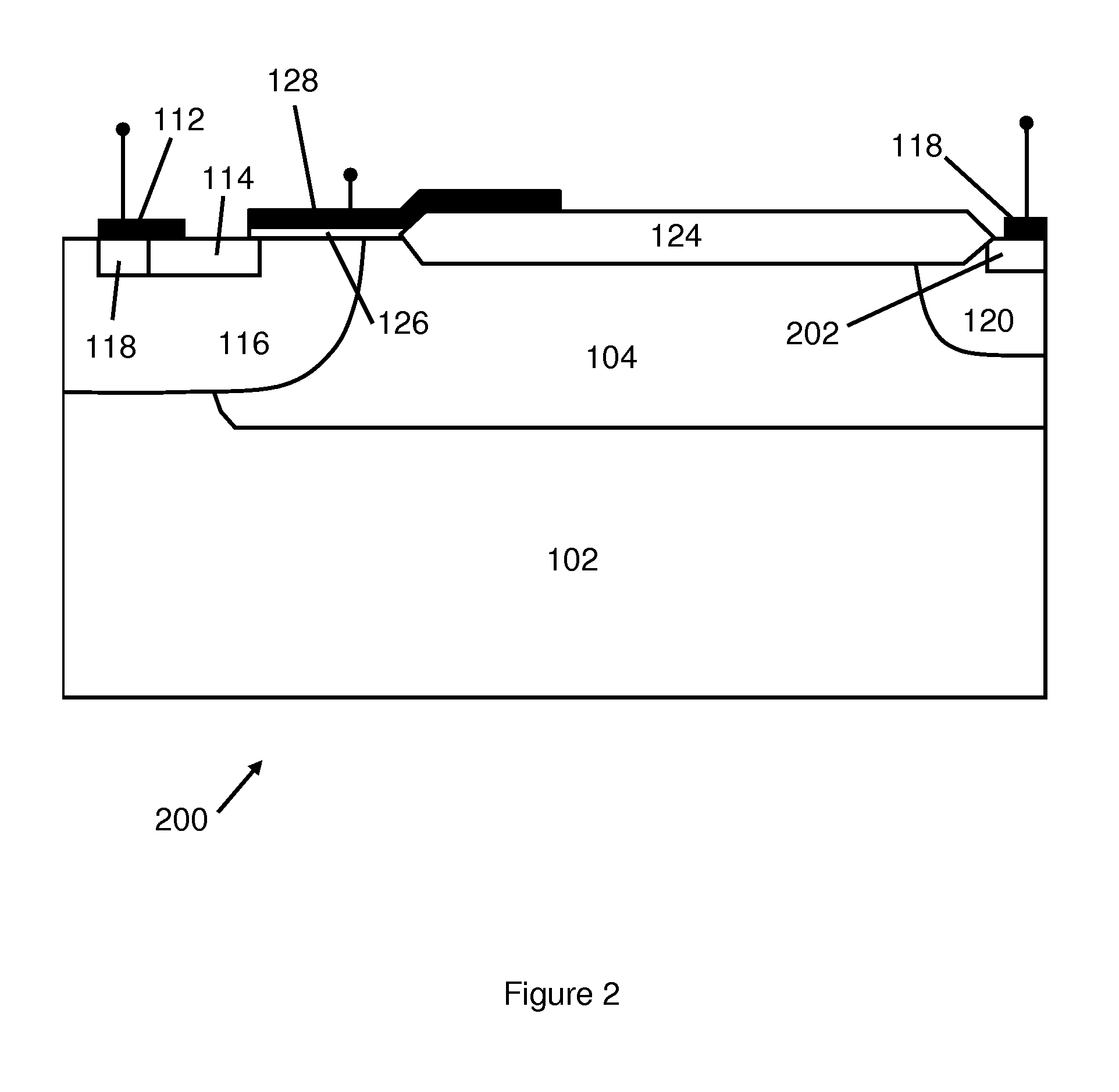

N-channel LDMOS with buried p-type region to prevent parasitic bipolar effects

InactiveUS6958515B2Reduces base resistance and hence base-emitter voltage dropEfficient collectionSemiconductor/solid-state device detailsSolid-state devicesSafe operating areaBody region

An improved n-channel integrated lateral DMOS (10) in which a buried body region (30), beneath and self-aligned to the source (18) and normal body diffusions, provides a low impedance path for holes emitted at the drain region (16). This greatly reduces secondary electron generation, and accordingly reduces the gain of the parasitic PNP bipolar device. The reduced regeneration in turn raises the critical field value, and hence the safe operating area.

Owner:TEXAS INSTR INC

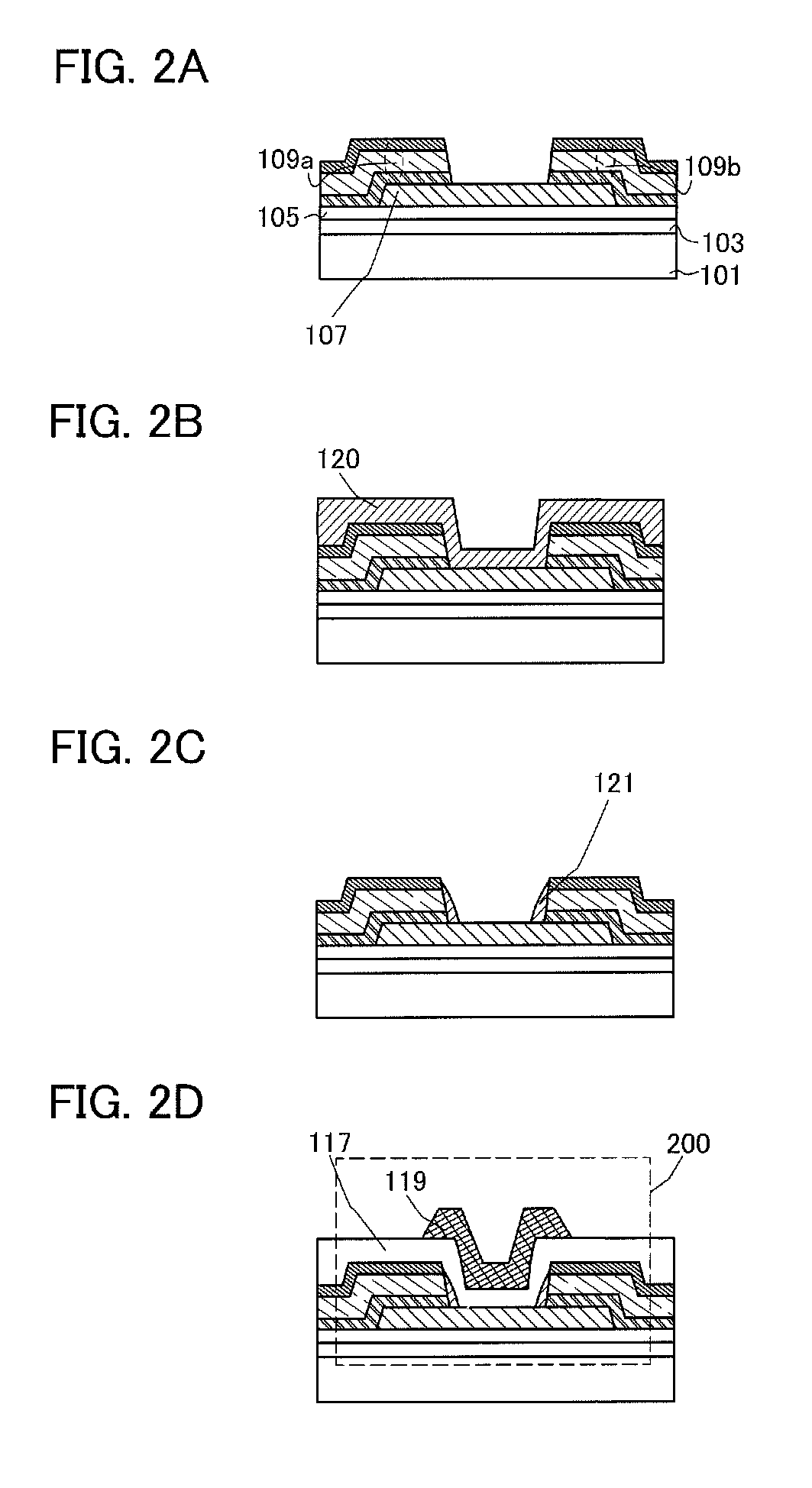

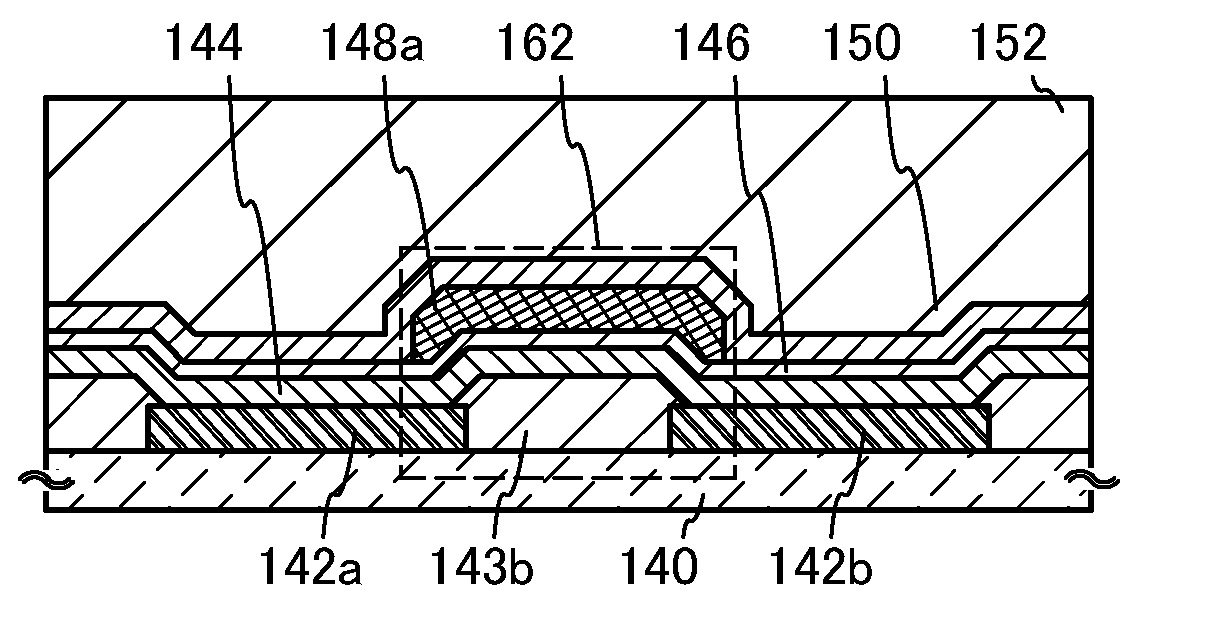

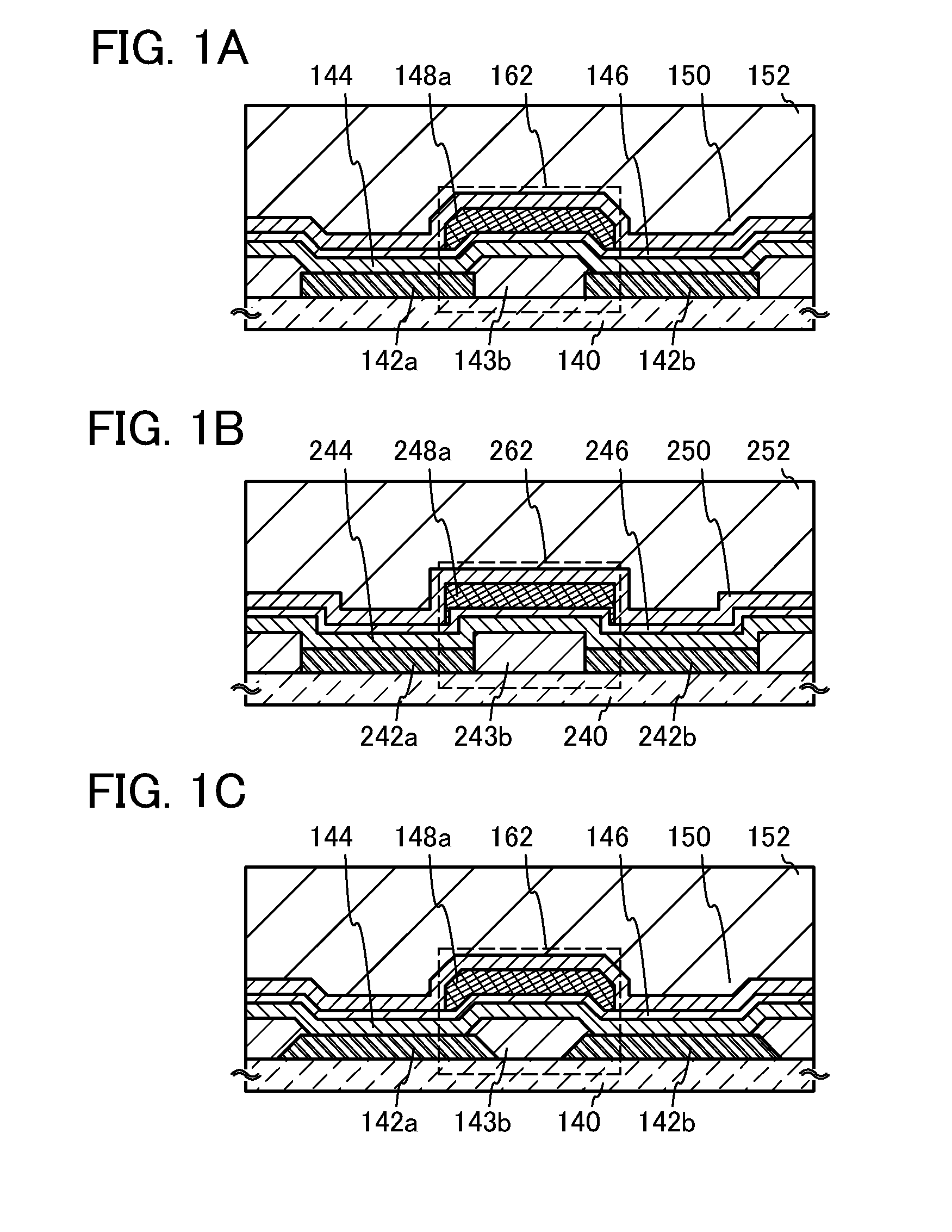

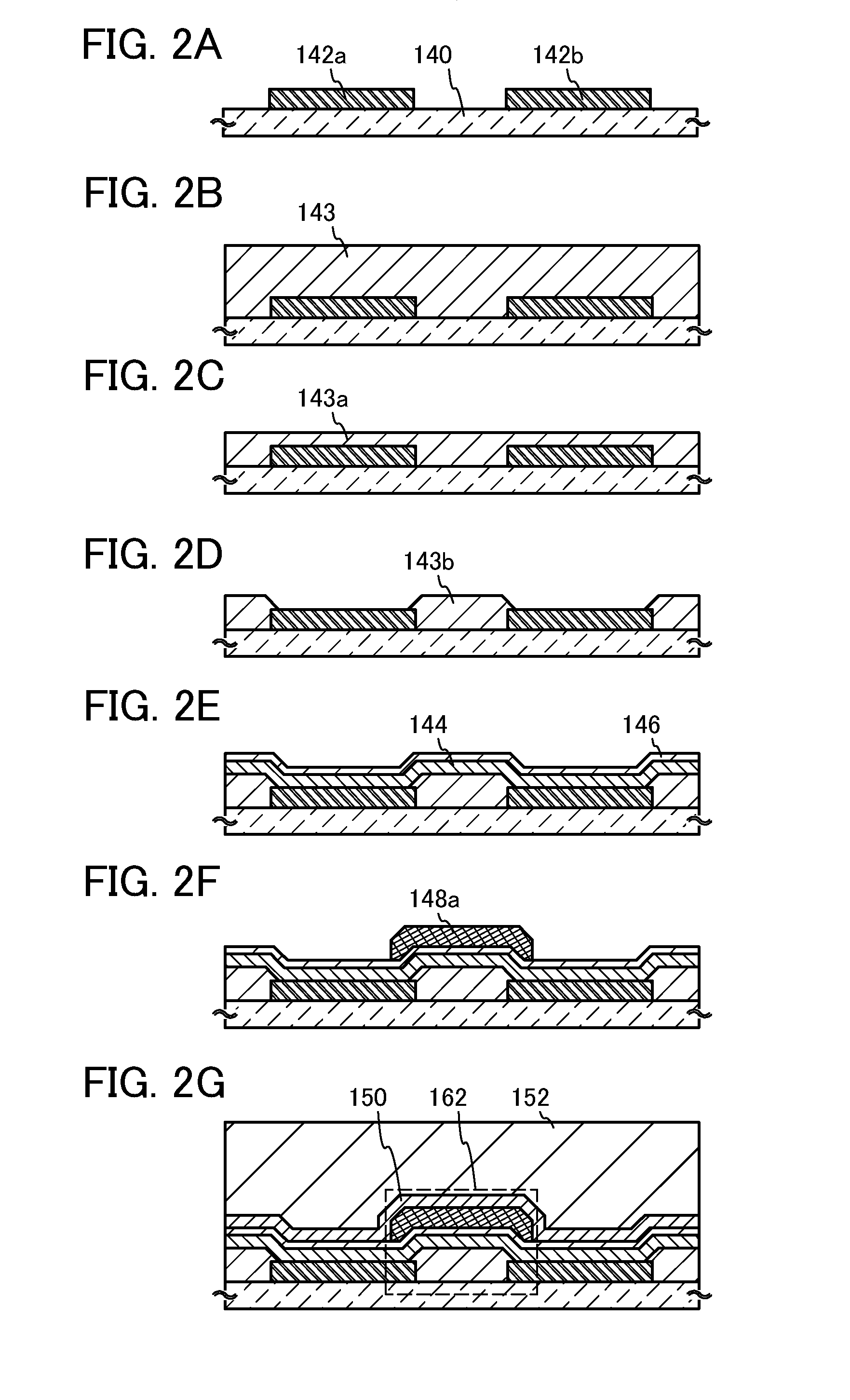

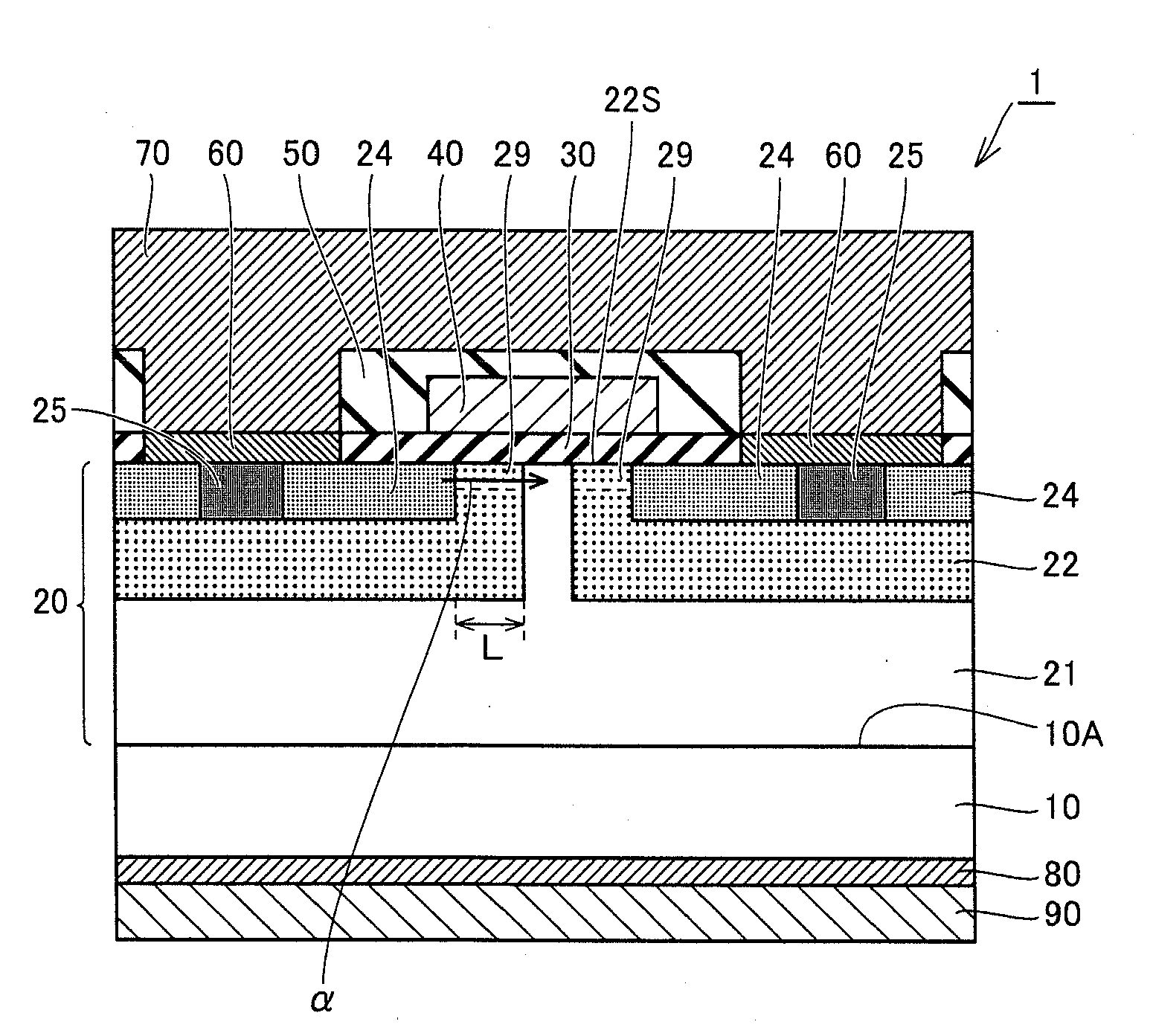

Semiconductor device and method for manufacturing the same

InactiveUS20110156022A1Run at high speedReduce power consumptionSemiconductor/solid-state device manufacturingSemiconductor devicesRelative permittivitySemiconductor

A semiconductor device which includes an oxide semiconductor layer, a source electrode and a drain electrode electrically connected to the oxide semiconductor layer, a gate insulating layer covering the oxide semiconductor layer, the source electrode, and the drain electrode, and a gate electrode over the gate insulating layer is provided. The thickness of the oxide semiconductor layer is greater than or equal to 1 nm and less than or equal to 10 nm. The gate insulating layer satisfies a relation where εr / d is greater than or equal to 0.08 (nm−1) and less than or equal to 7.9 (nm−1) when the relative permittivity of a material used for the gate insulating layer is εr and the thickness of the gate insulating layer is d. The distance between the source electrode and the drain electrode is greater than or equal to 10 nm and less than or equal to 1 μm.

Owner:SEMICON ENERGY LAB CO LTD

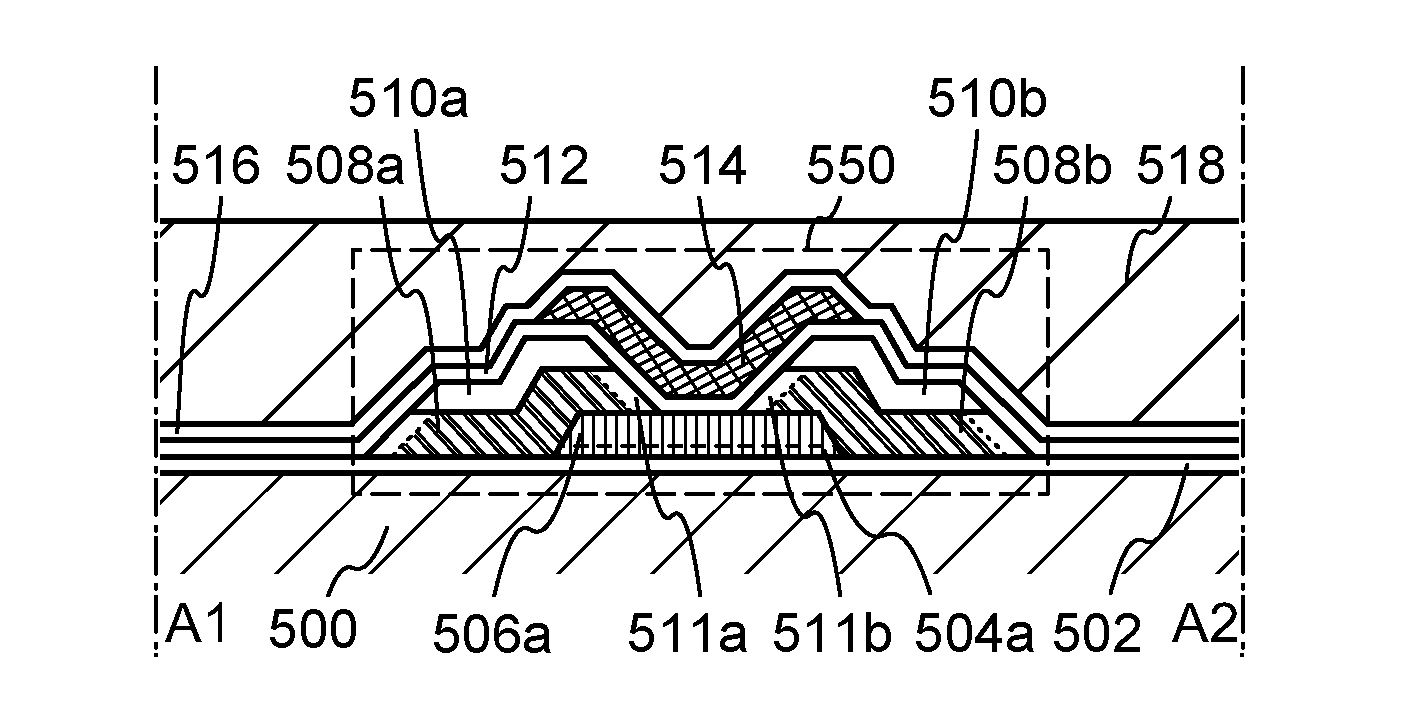

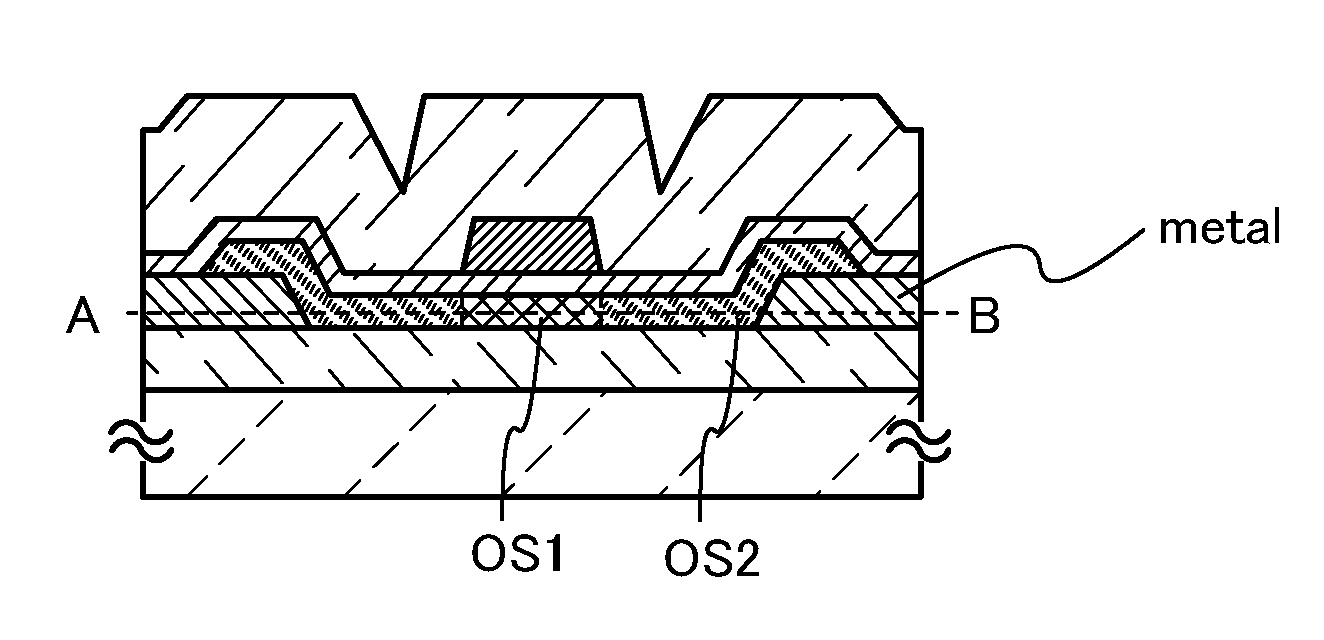

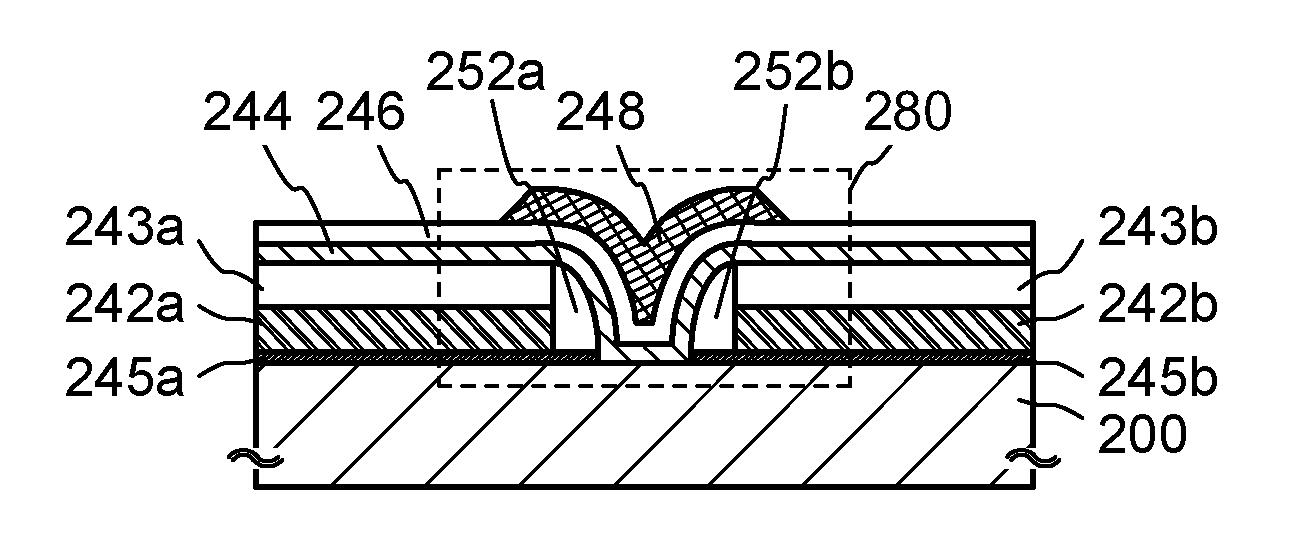

Semiconductor device and method for manufacturing semiconductor device

InactiveUS20110215317A1Inhibition defectMaintaining favorable characteristicTransistorSolid-state devicesPhysicsOxide semiconductor

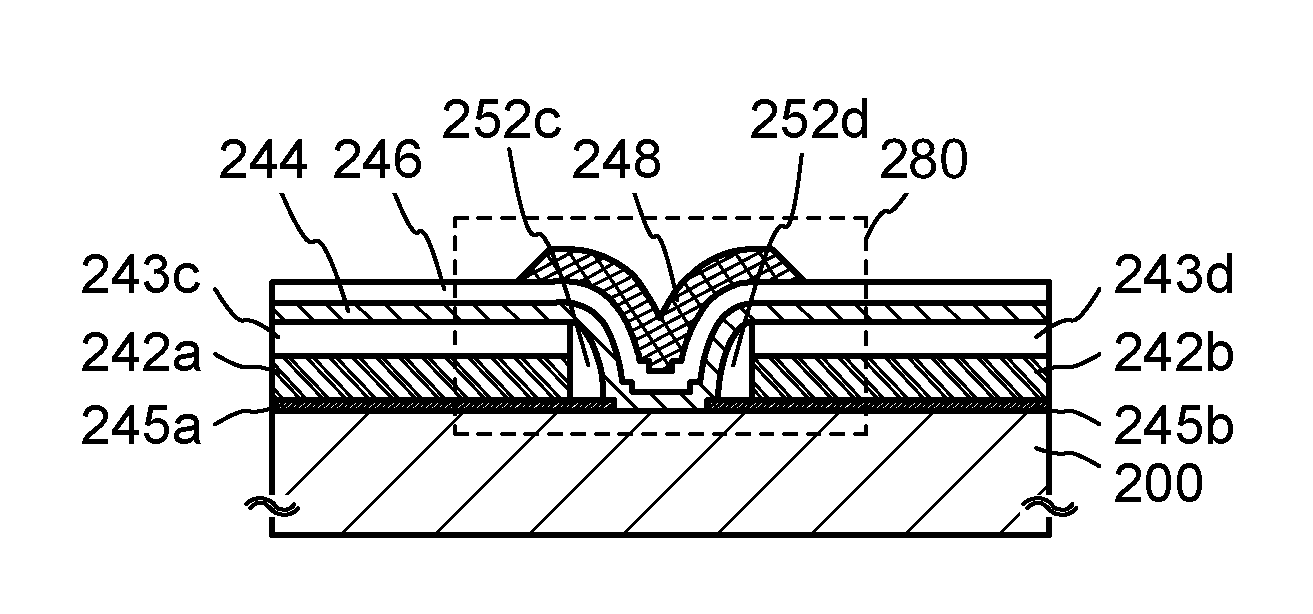

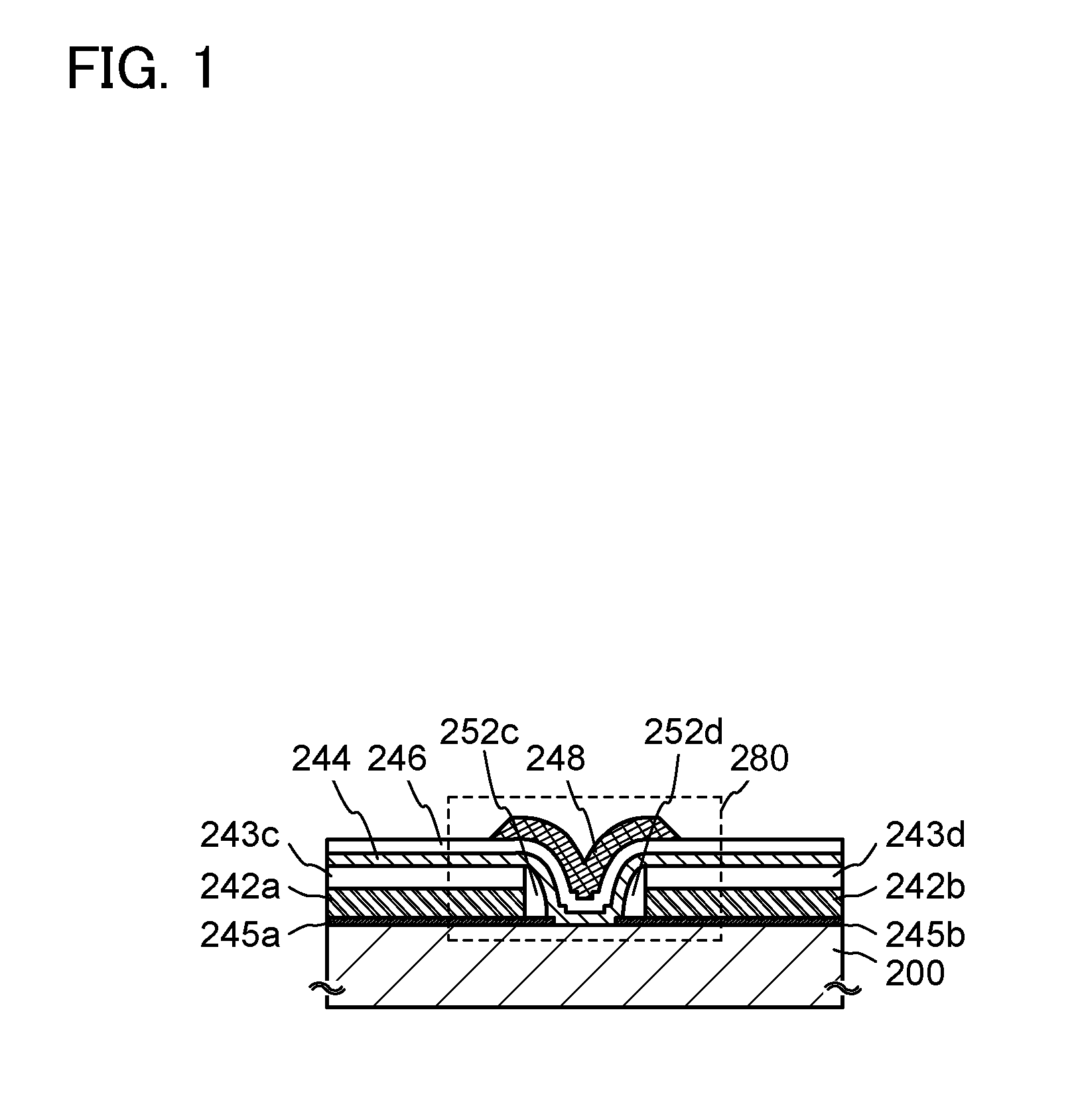

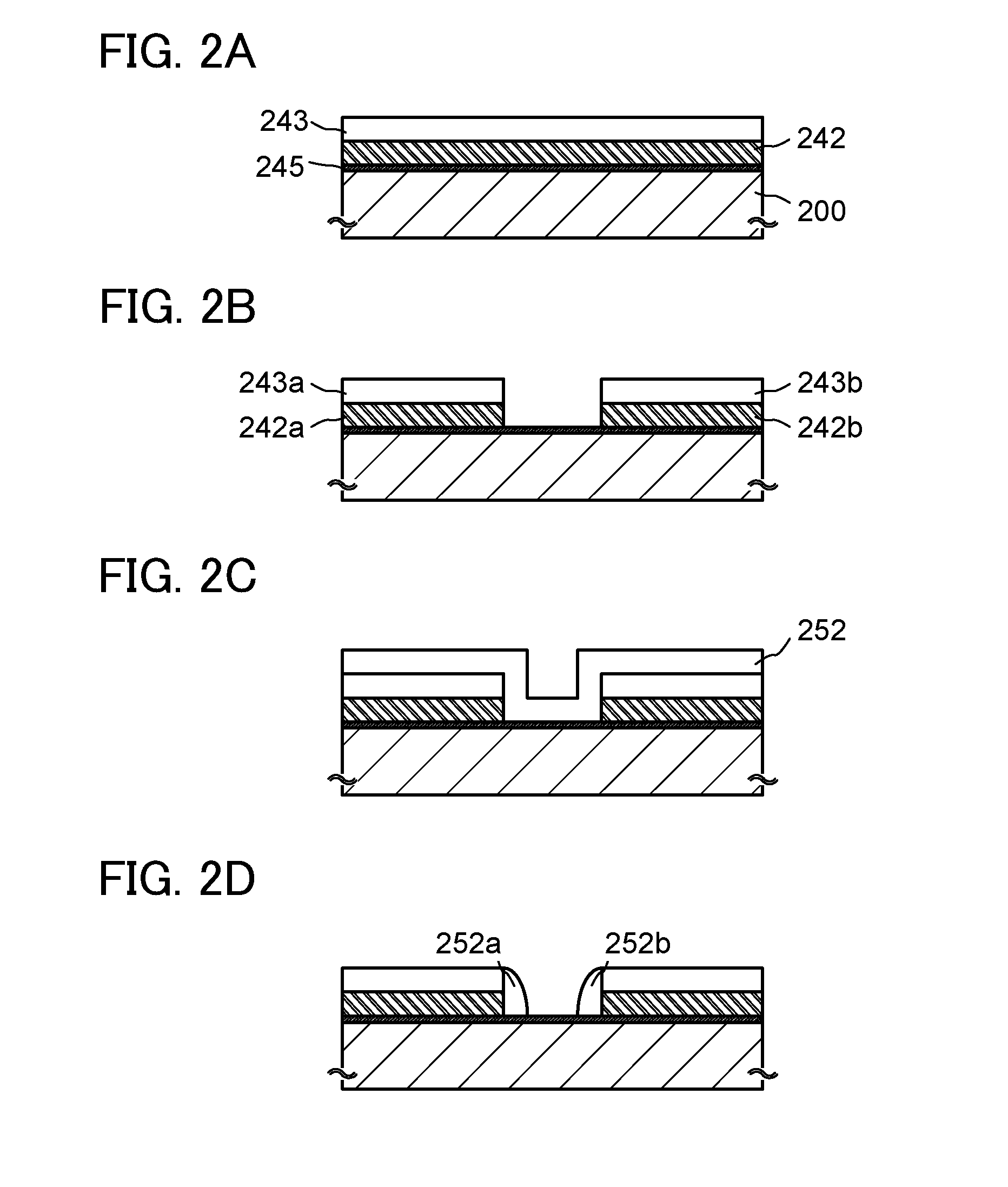

Disclosed is a semiconductor device including an insulating layer, a source electrode and a drain electrode embedded in the insulating layer, an oxide semiconductor layer in contact with the insulating layer, the source electrode, and the drain electrode, a gate insulating layer covering the oxide semiconductor layer, and a gate electrode over the gate insulating layer. The upper surface of the surface of the insulating layer, which is in contact with the oxide semiconductor layer, has a root-mean-square (RMS) roughness of 1 nm or less. There is a difference in height between an upper surface of the insulating layer and each of an upper surface of the source electrode and an upper surface of the drain electrode. The difference in height is preferably 5 nm or more. This structure contributes to the suppression of defects of the semiconductor device and enables their miniaturization.

Owner:SEMICON ENERGY LAB CO LTD

P-channel field-effect transistor with reduced junction capacitance

InactiveUS7145191B1Lower junction capacitanceIncrease in IGFET switching speedSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceEngineering

The source / drain zones (140 and 142 or 160 and 162) of a p-channel IGFET (120 or 122) are provided with graded-junction characteristics to reduce junction capacitance, thereby increasing switching speed. Each source / drain zone contains a main portion (140M, 142M, 160M, or 162M) and a more lightly doped lower portion (140L, 142L, 160L, or 162L) underlying, and vertically continuous with, the main portion.

Owner:NAT SEMICON CORP

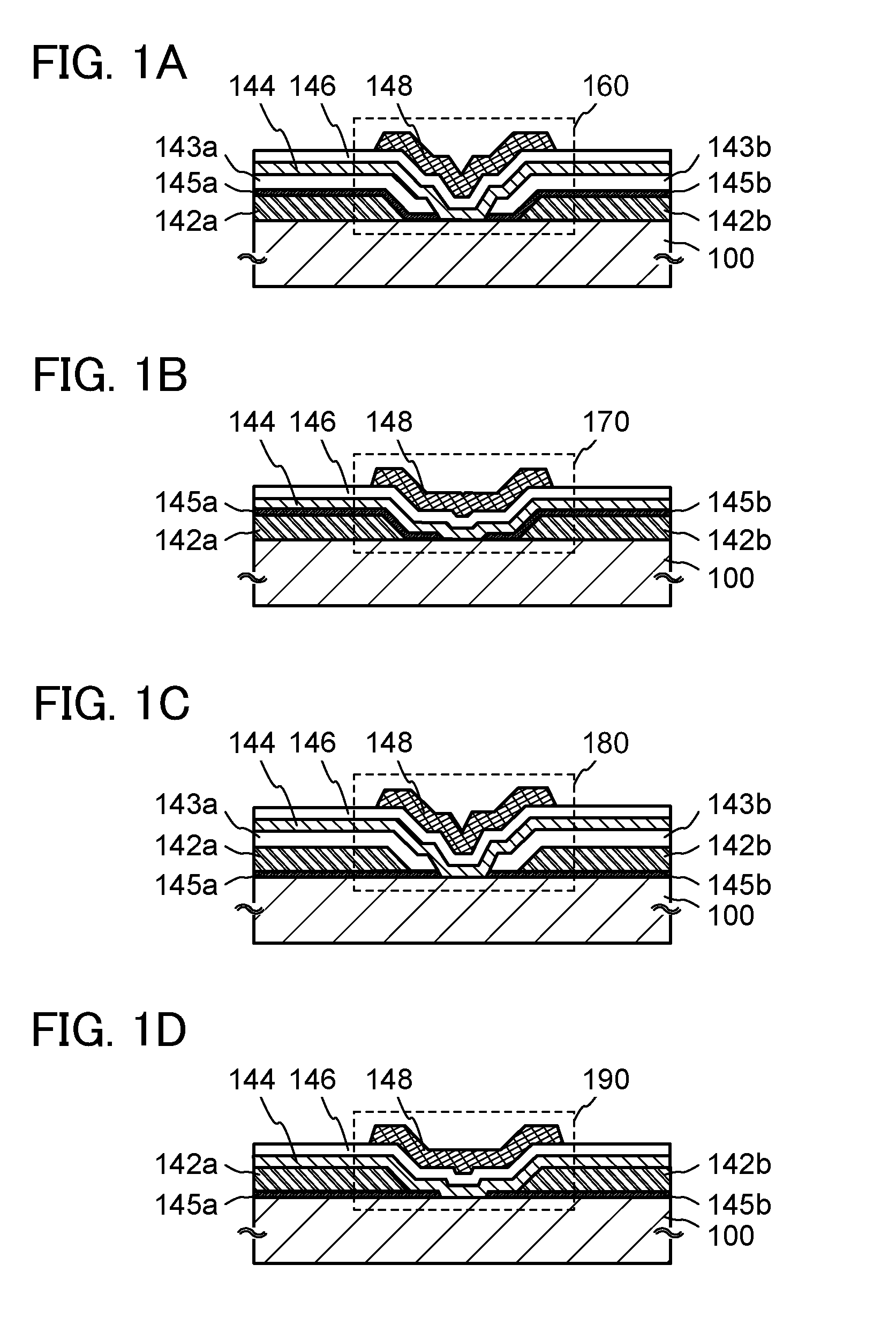

Semiconductor device and method for manufacturing the same

ActiveUS20120161122A1Band gapReduce effective channel lengthSemiconductor/solid-state device manufacturingDigital storagePower semiconductor deviceNitrogen

A miniaturized semiconductor device including a transistor in which a channel formation region is formed using an oxide semiconductor film and variation in electric characteristics due to a short-channel effect is suppressed is provided. In addition, a semiconductor device whose on-state current is improved is provided. A semiconductor device is provided with an oxide semiconductor film including a pair of second oxide semiconductor regions which are amorphous regions and a first oxide semiconductor region located between the pair of second oxide semiconductor regions, a gate insulating film, and a gate electrode provided over the first oxide semiconductor region with the gate insulating film interposed therebetween. One or more kinds of elements selected from Group 15 elements such as nitrogen, phosphorus, and arsenic are added to the second oxide semiconductor regions.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device

ActiveUS20110180796A1Run at high speedReduce power consumptionSemiconductor devicesMiniaturizationSemiconductor

An object is to provide a semiconductor device including an oxide semiconductor, which maintains favorable characteristics and achieves miniaturization. The semiconductor device includes an oxide semiconductor layer, a source electrode and a drain electrode in contact with the oxide semiconductor layer, a gate electrode overlapping with the oxide semiconductor layer, and a gate insulating layer provided between the oxide semiconductor layer and the gate electrode, in which the source electrode and the drain electrode each include a first conductive layer, and a second conductive layer having a region which extends in a channel length direction from an end portion of the first conductive layer.

Owner:SEMICON ENERGY LAB CO LTD

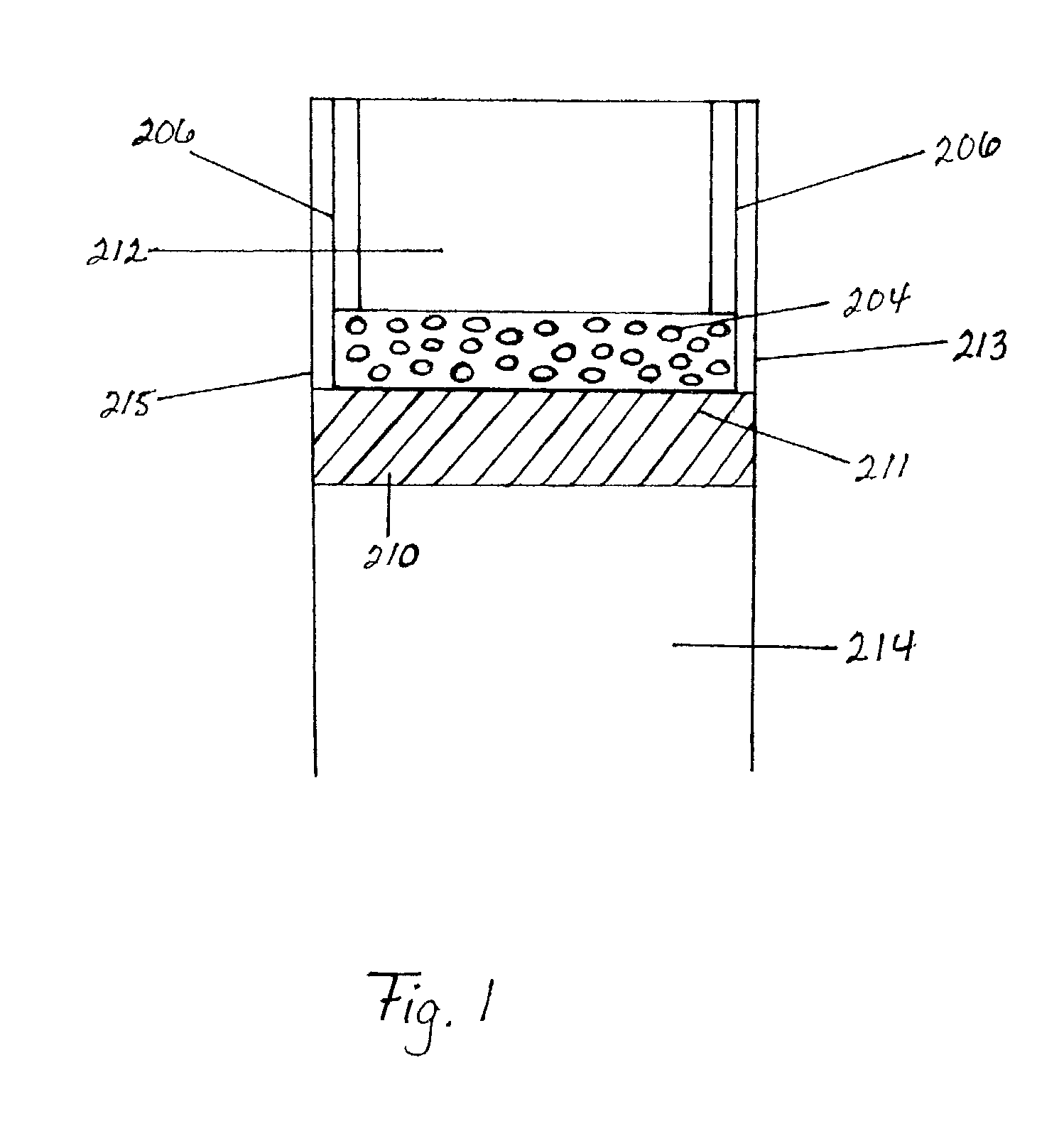

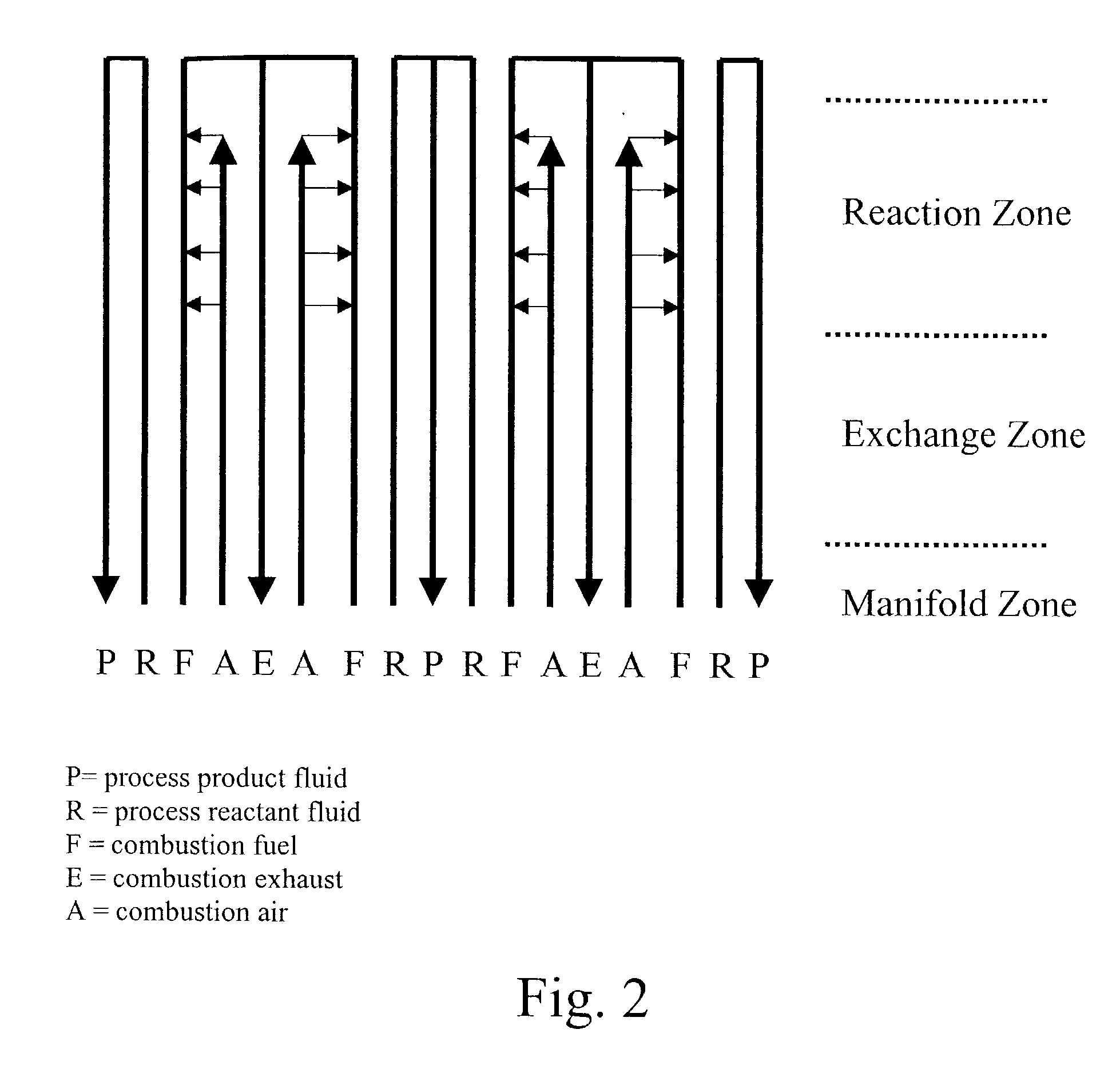

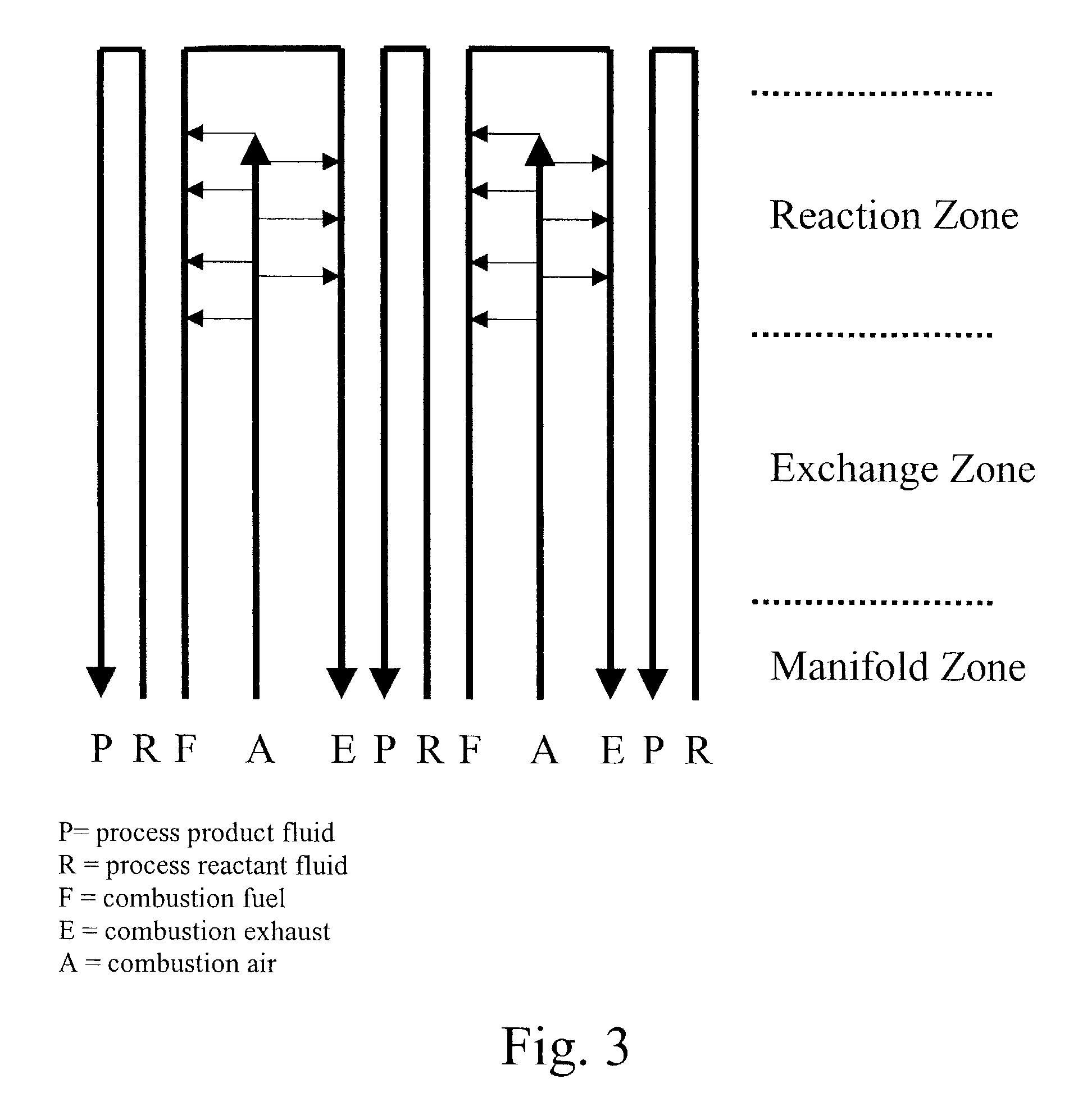

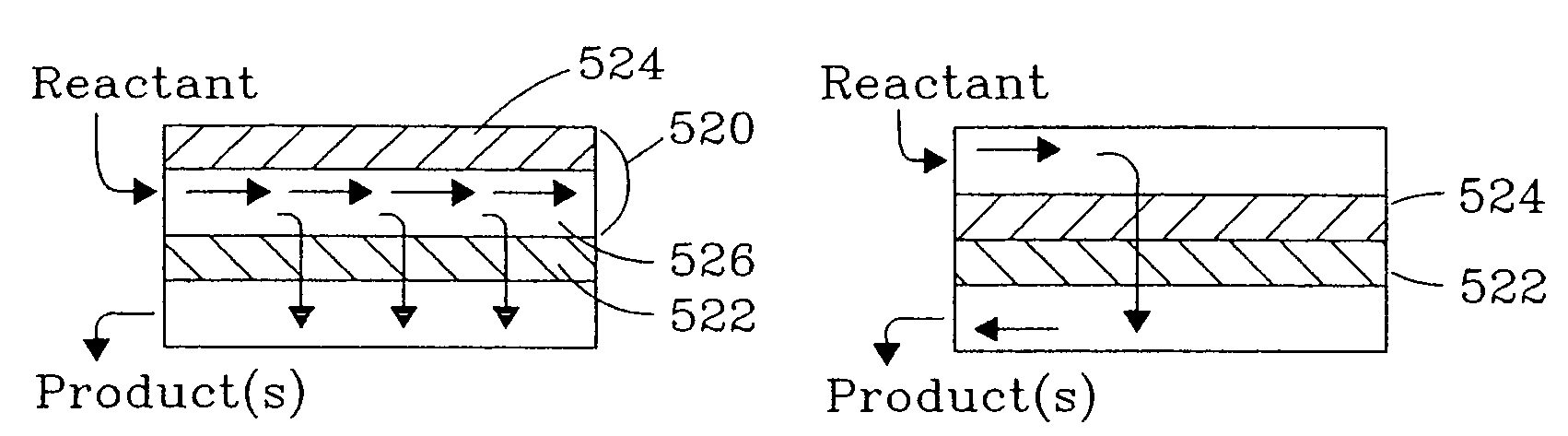

Methods of conducting simultaneous endothermic and exothermic reactions

InactiveUS7250151B2Reduce the formation of nitrogen oxidesHigh thermal cycling durabilityFurnace componentsChemical/physical/physico-chemical microreactorsCombustion chamberProcess engineering

Integrated Combustion Reactors (ICRS) and methods of making ICRs are described in which combustion chambers (or channels) are in direct thermal contact to reaction chambers for an endothermic reaction. Particular reactor designs are also described. Processes of conducting reactions in integrated combustion reactors are described and results presented. Some of these processes are characterized by unexpected and superior results, and / or results that can not be achieved with any prior art devices.

Owner:VELOCYS CORPORATION

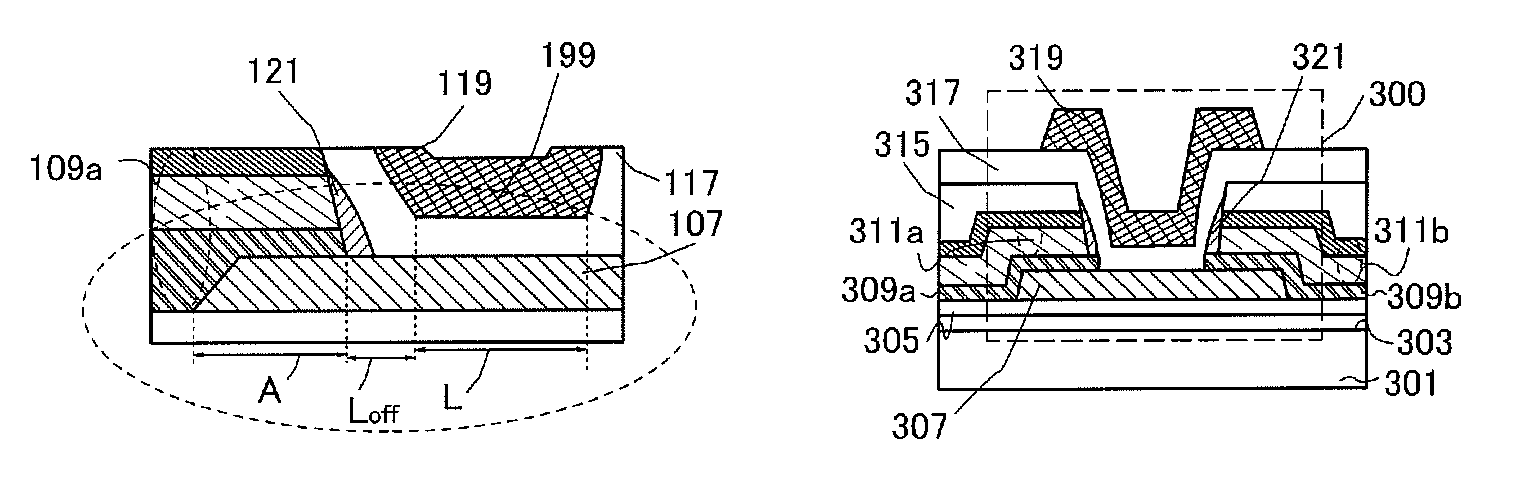

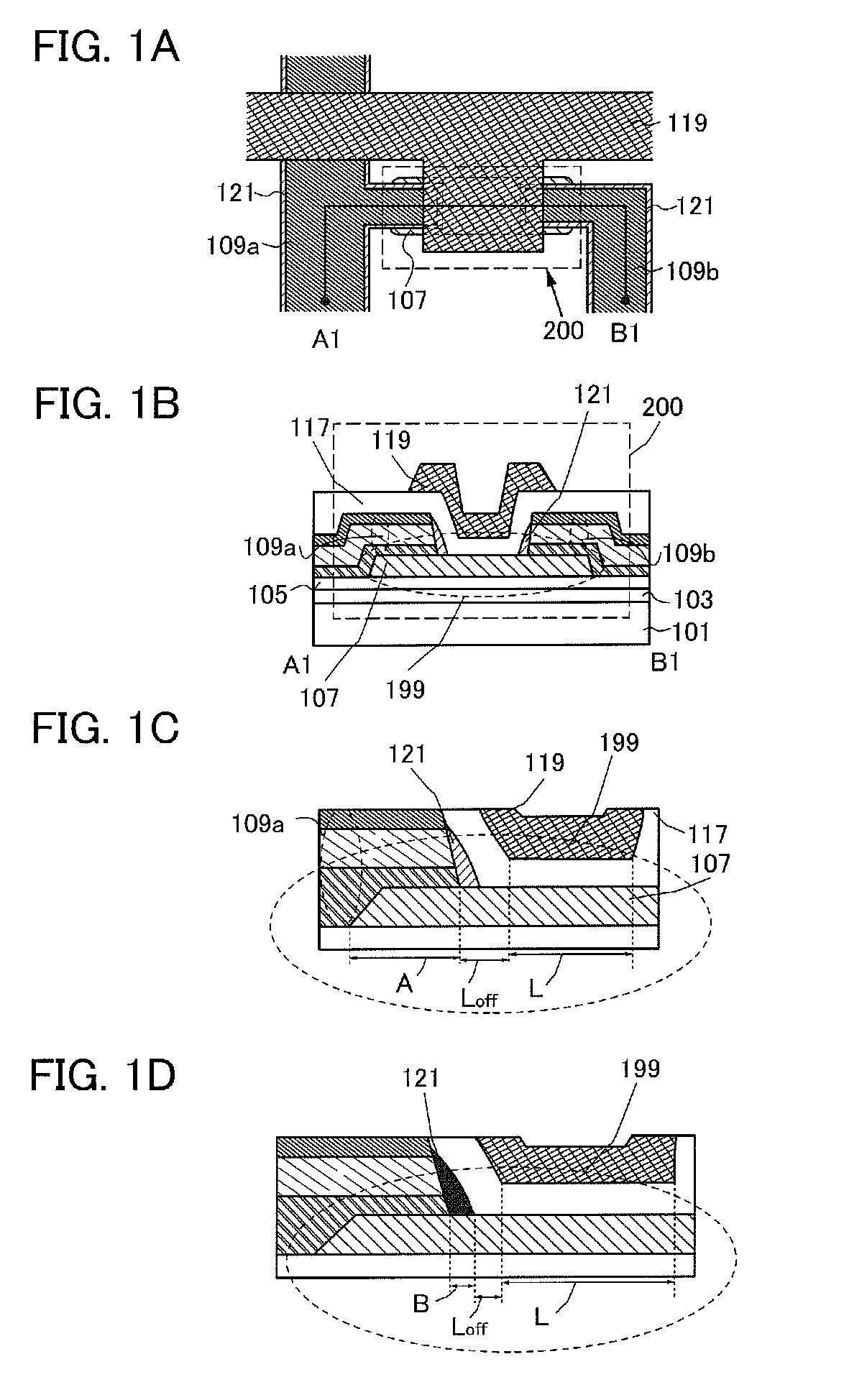

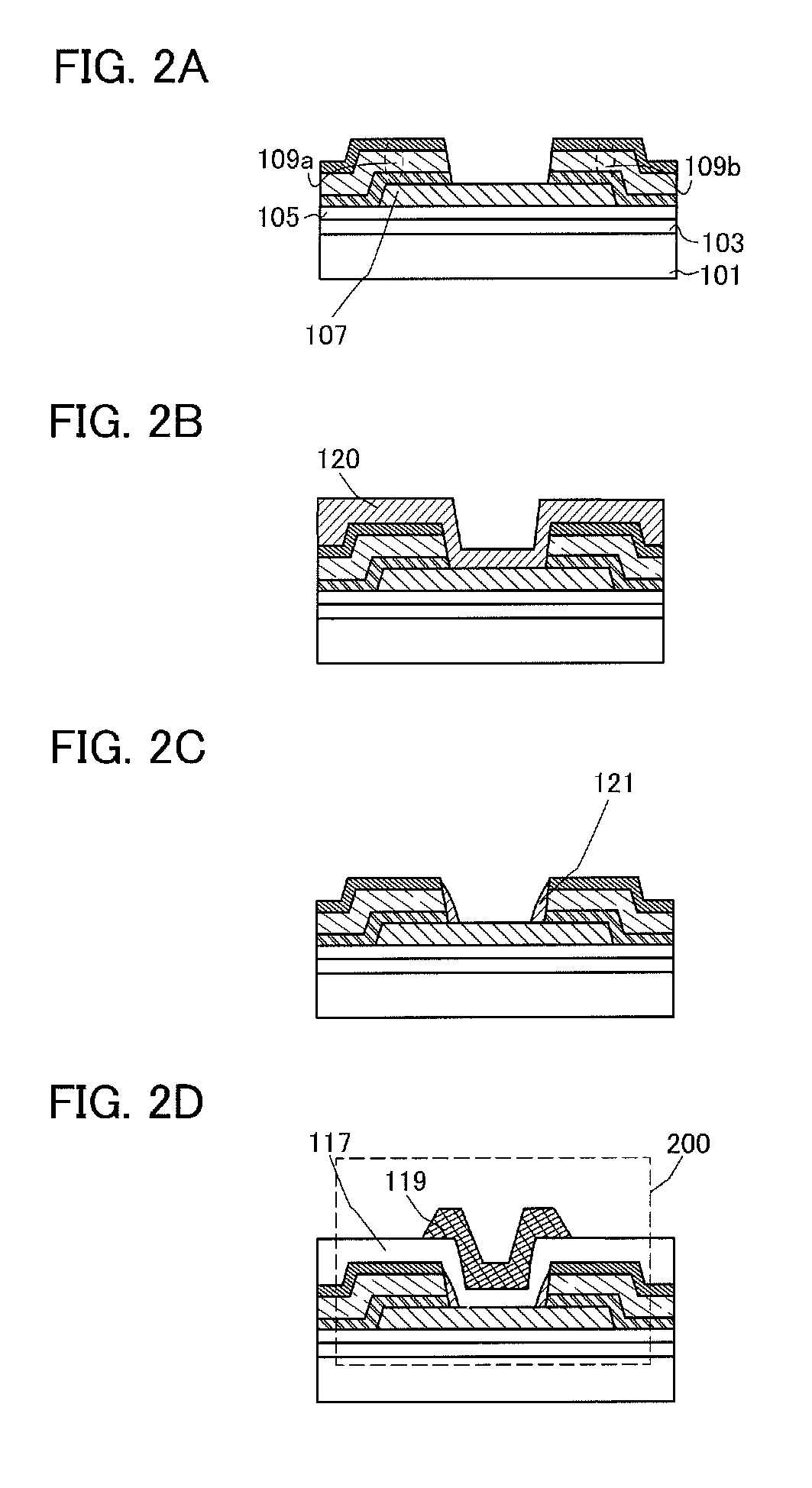

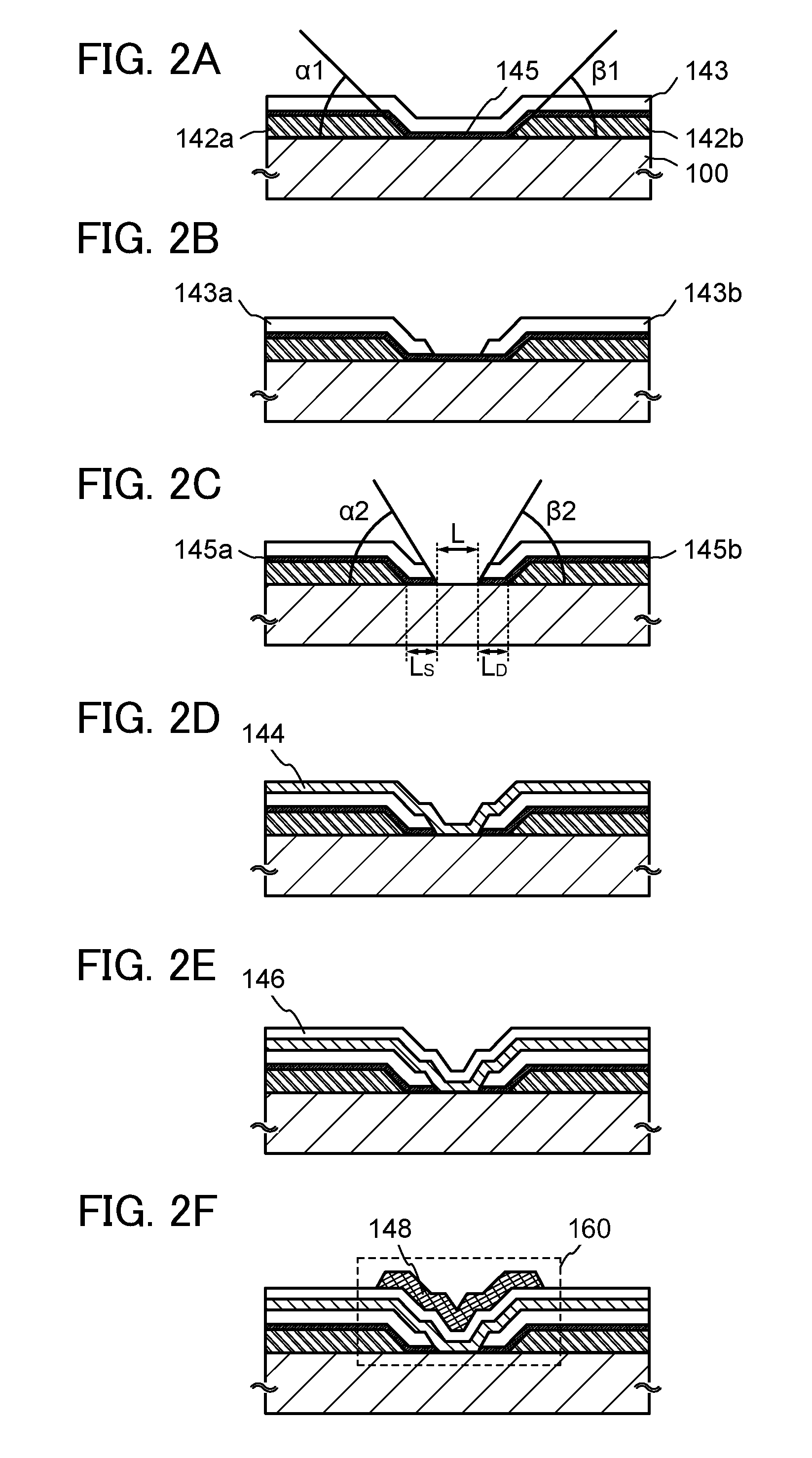

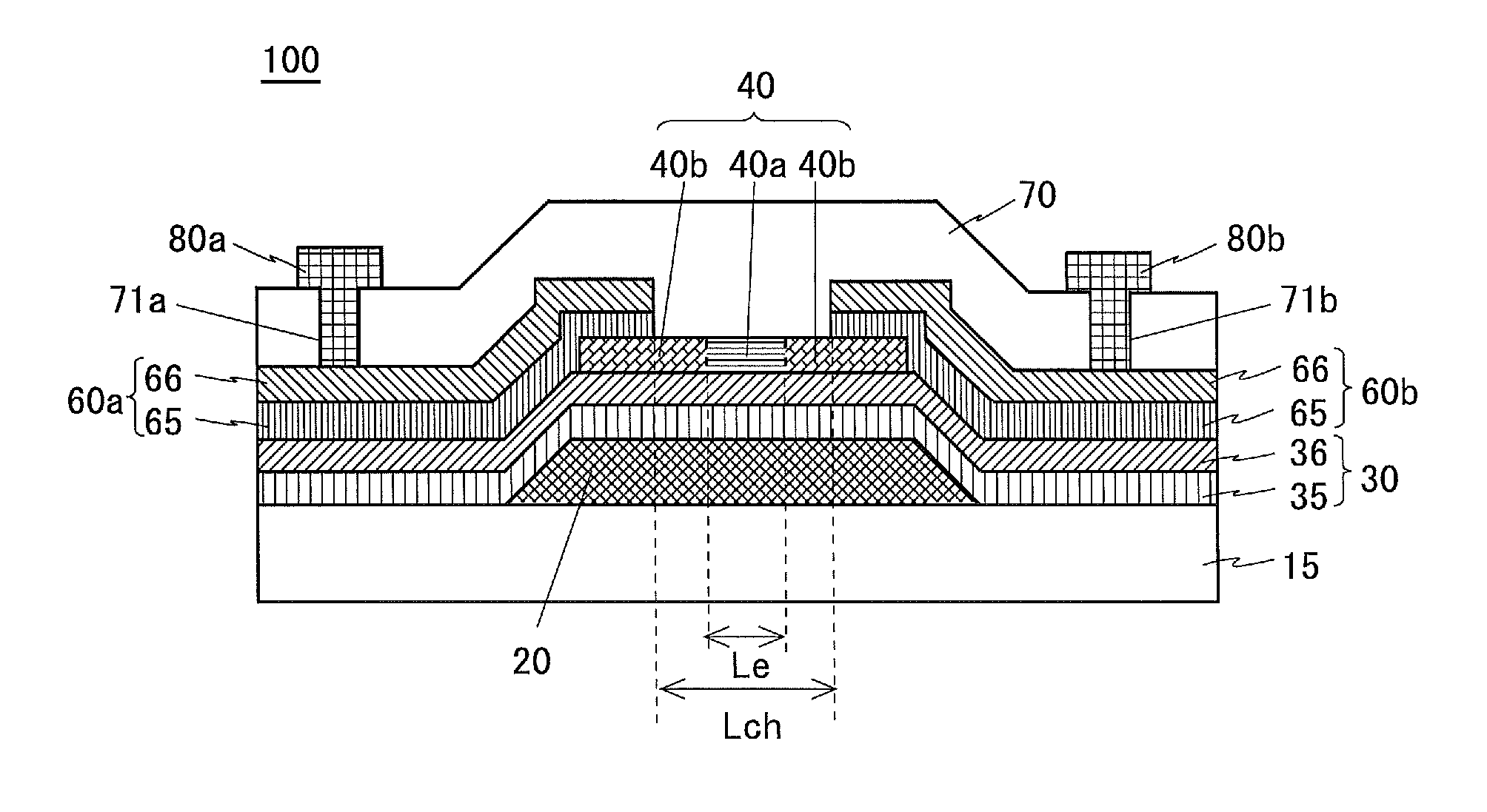

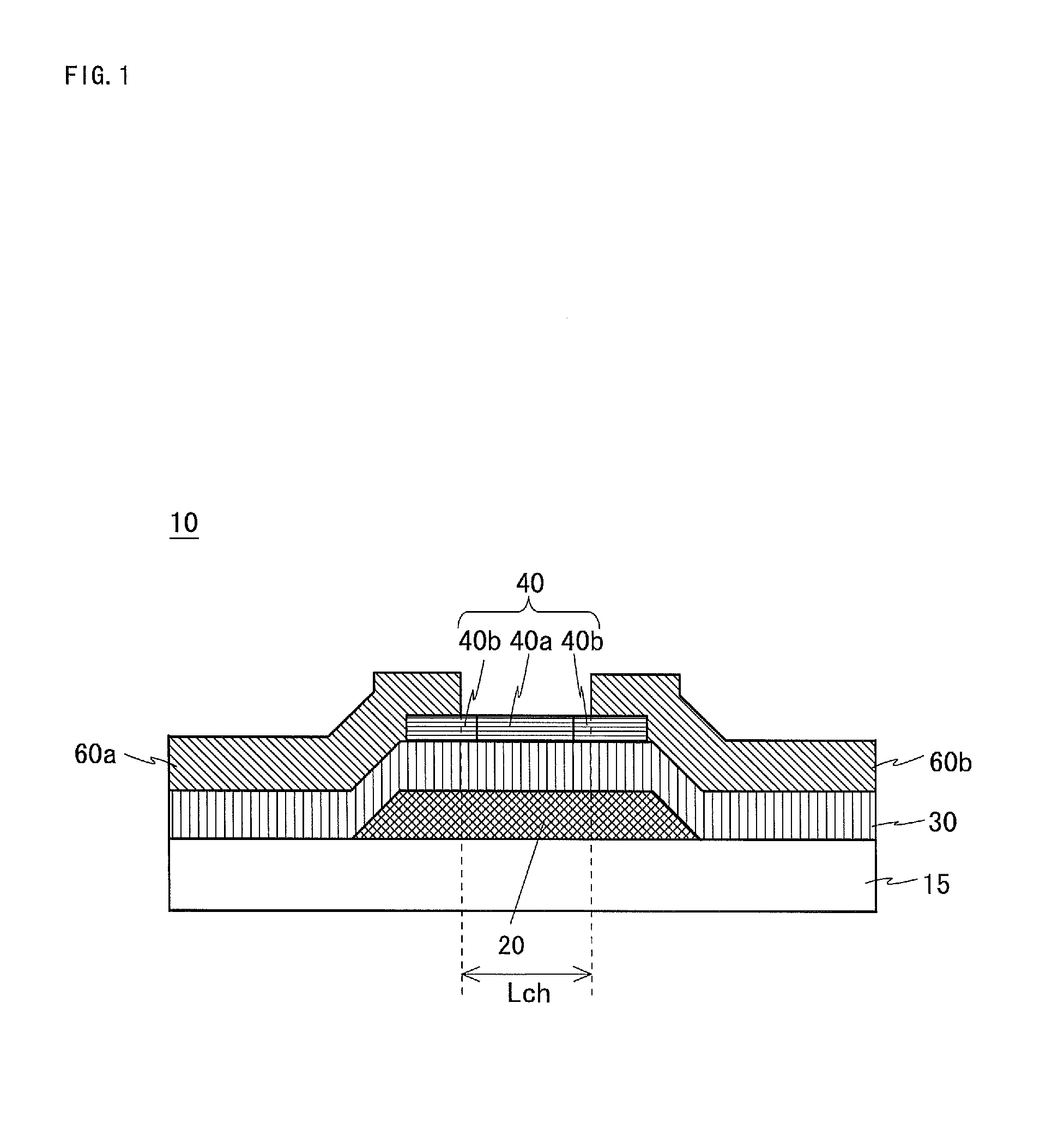

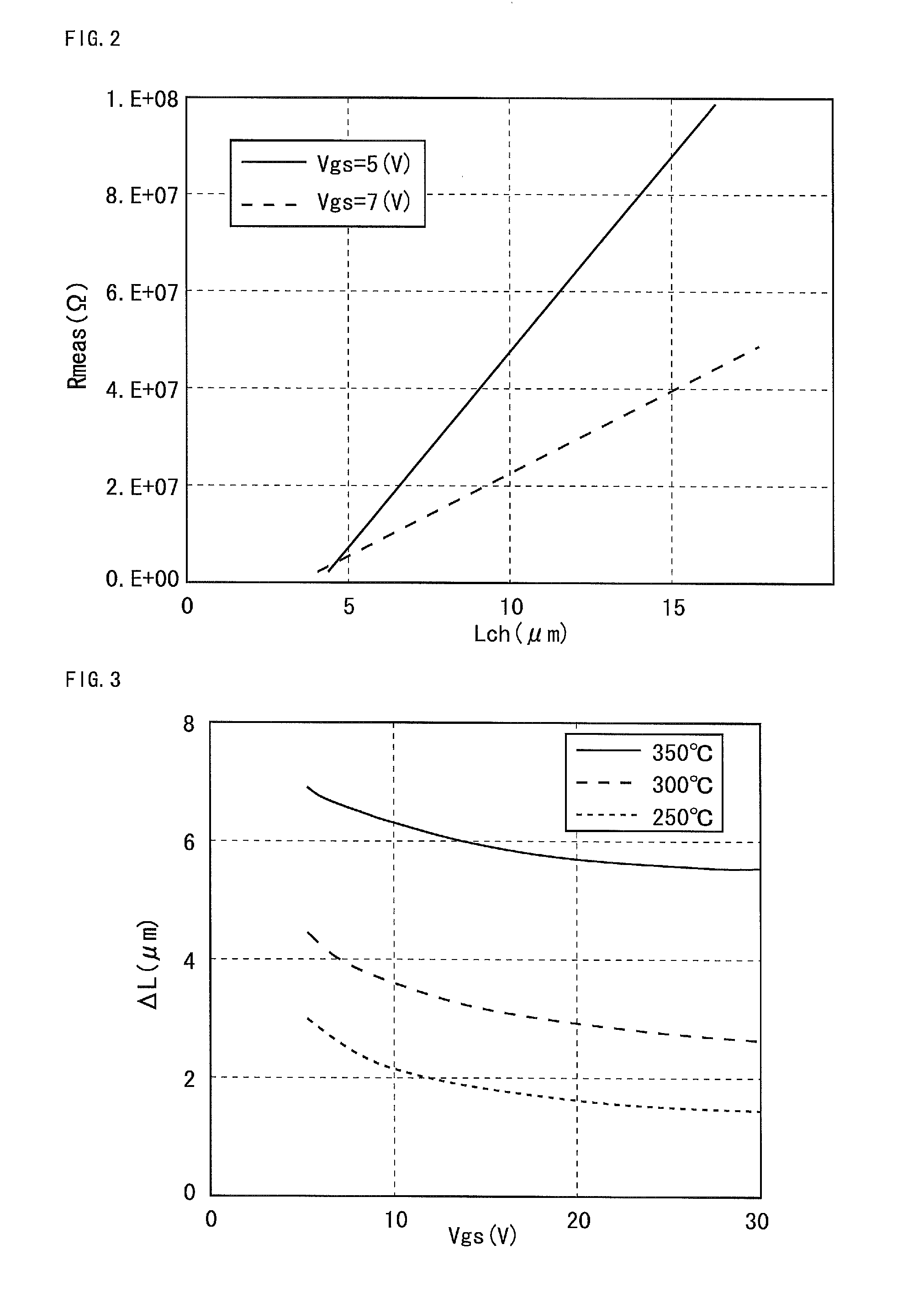

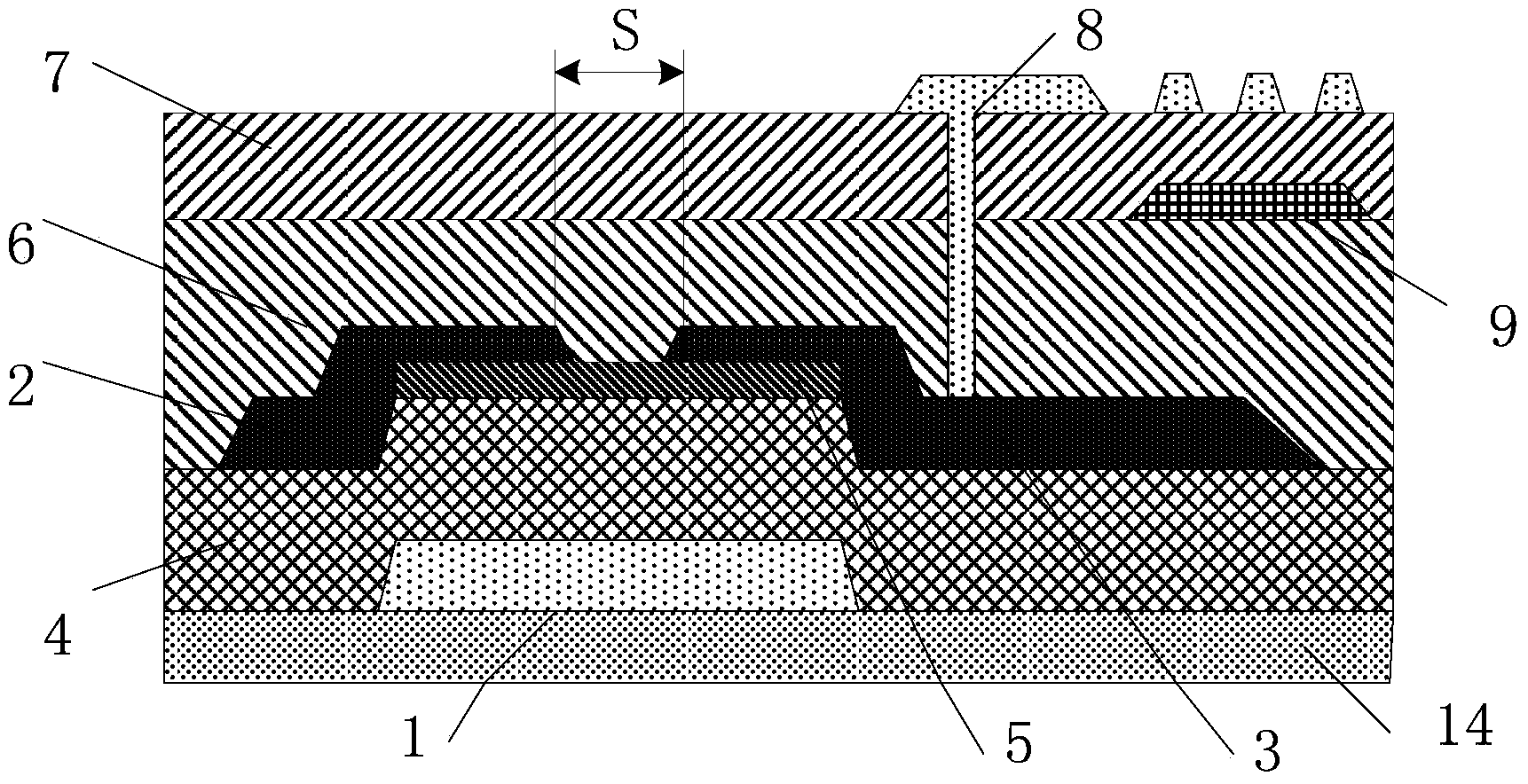

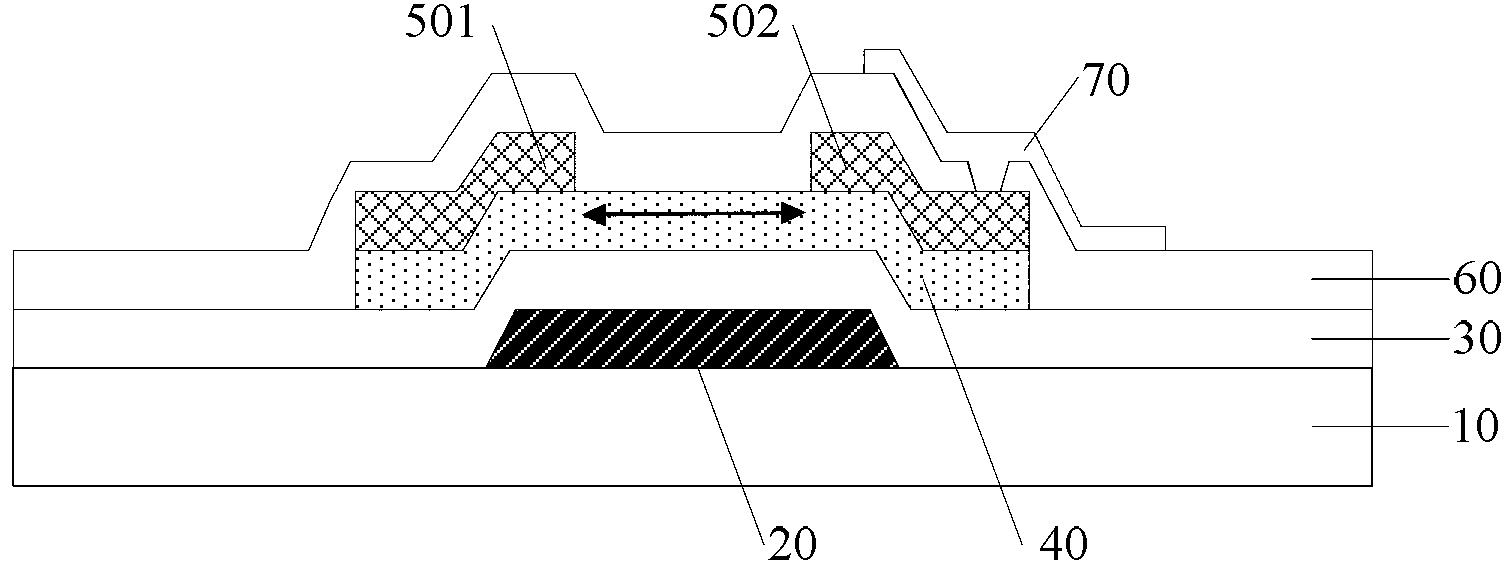

Thin film transistor and manufacturing method therefor, and display device

ActiveUS20140035478A1High currentShort channel lengthTransistorSolid-state devicesHigh resistanceTitanium electrode

The invention provides a thin film transistor having current driving force that can be substantially improved. By heat treatment, the IGZO layer (45) from which oxygen is taken away by the titanium electrodes (65) becomes the low resistance regions (40b), and the IGZO layer (45) from which oxygen is not taken away remains as the high resistance region (40a). In this state, when the gate voltage is applied to the gate electrode (20), electrons in the low resistance regions (40b) near the boundaries with the high resistance region (40a) move respectively to the titanium electrode (65) sides. As a result, the length of the low resistance regions (40b) becomes short, and oppositely, the length of the high resistance region (40a) becomes longer by the size of the shortened low resistance regions. However, the electrical channel length (Le) becomes shorter than the source / drain interval space (Lch) as the limit resolution of the exposure device, and the current driving force becomes large.

Owner:SHARP KK

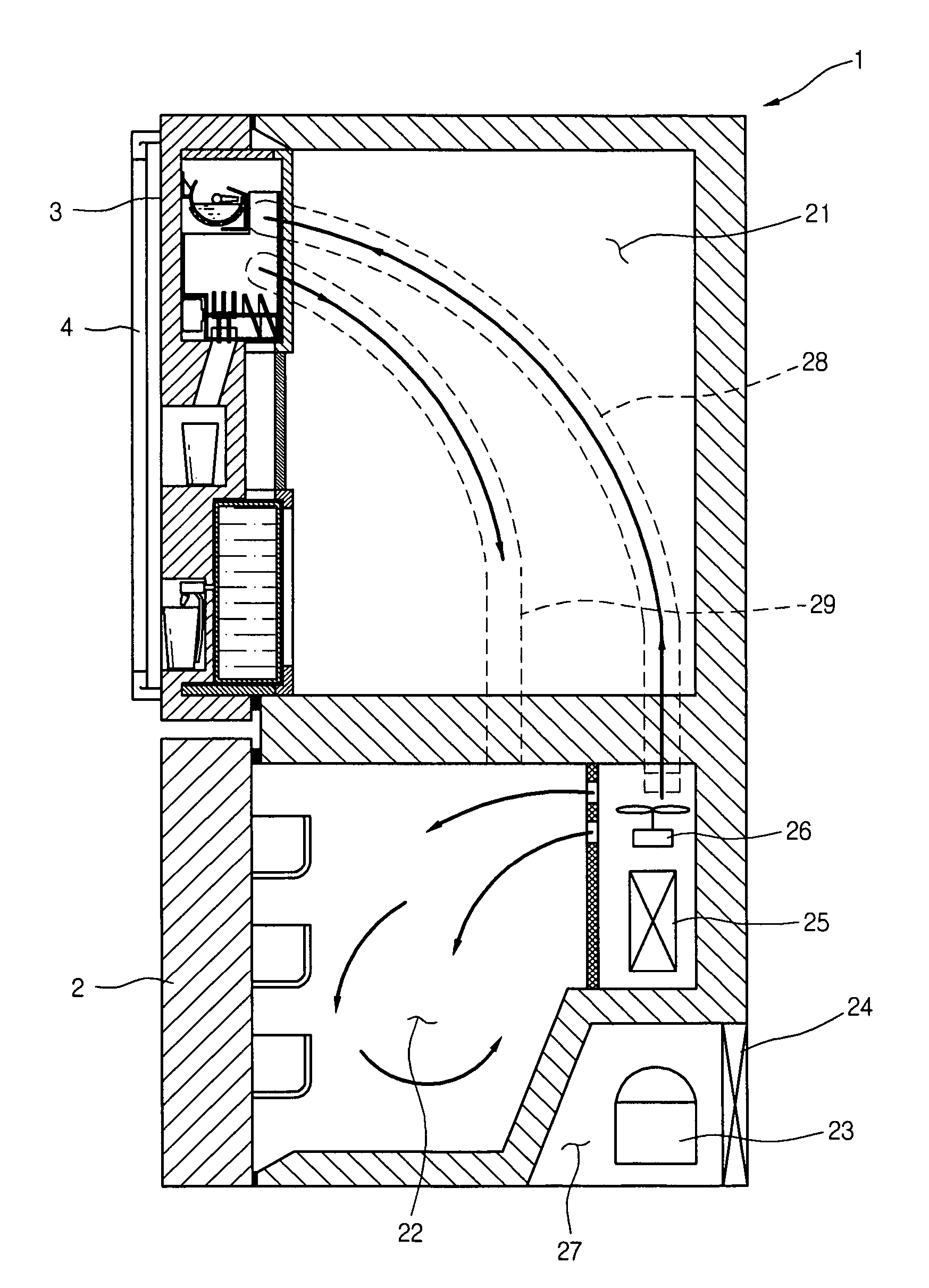

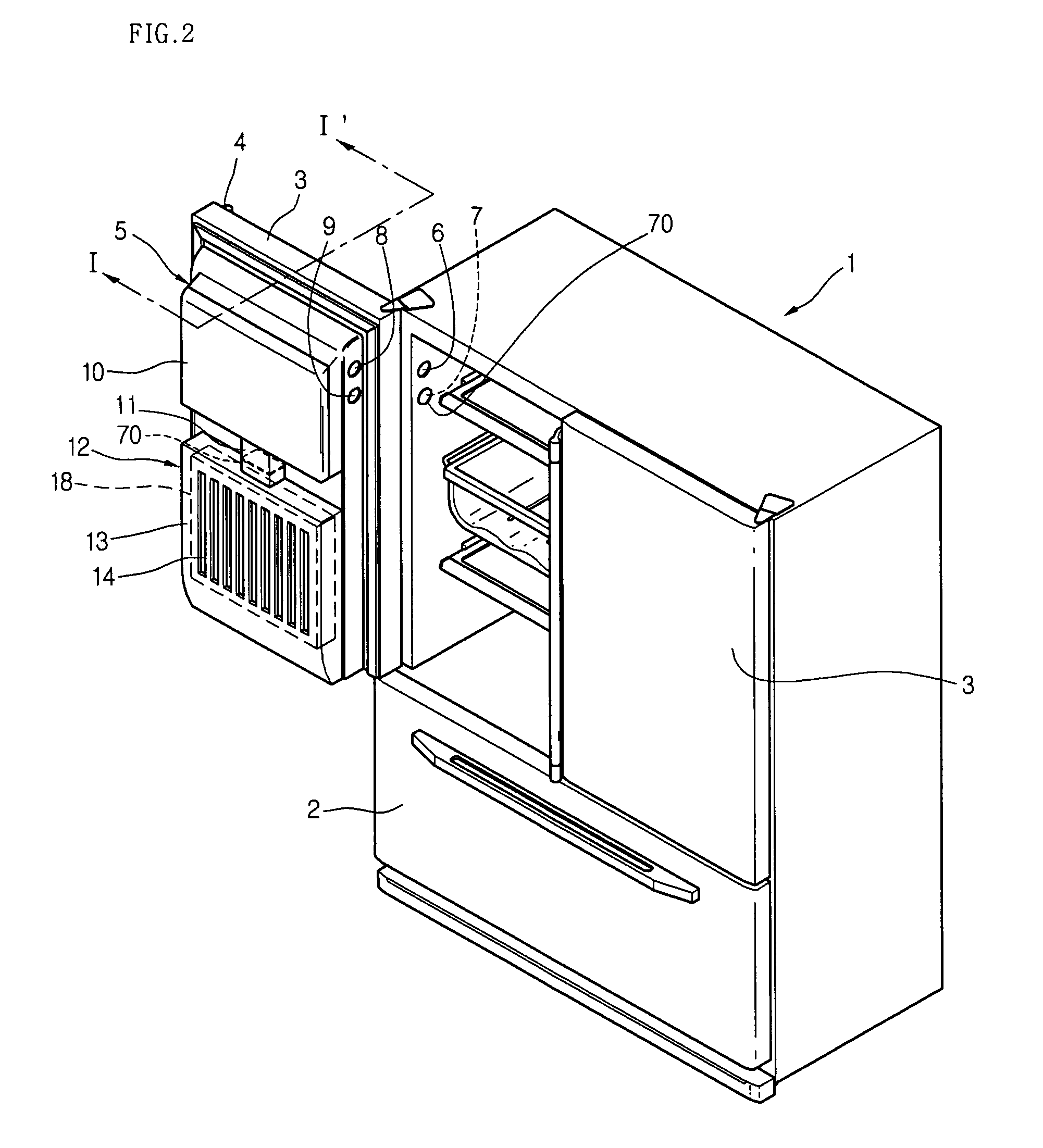

Cooling air flow passage of refrigerator

ActiveUS20060096310A1Increase energy efficiencyReduce lengthLighting and heating apparatusIce productionAirflowWater storage tank

A cooling air flow passage of a refrigerator is provided. The cooling air not only flows through the passage so as to make ice in an ice making chamber but is also sent so as to cool water in a water storage tank. Therefore, the cooling air flow passage of the refrigerator and the overall structure of the refrigerator are simplified, which increases the efficiency of the refrigerator and reduces the manufacturing cost.

Owner:LG ELECTRONICS INC

Flash memory cell arrays having dual control gates per memory cell charge storage element

InactiveUS7075823B2Increase coupling areaImprove the coupling ratioSolid-state devicesRead-only memoriesCapacitanceMemory cell

A flash NAND type EEPROM system with individual ones of an array of charge storage elements, such as floating gates, being capacitively coupled with at least two control gate lines. The control gate lines are preferably positioned between floating gates to be coupled with sidewalls of floating gates. The memory cell coupling ratio is desirably increased, as a result. Both control gate lines on opposite sides of a selected row of floating gates are usually raised to the same voltage while the second control gate lines coupled to unselected rows of floating gates immediately adjacent and on opposite sides of the selected row are kept low. The control gate lines can also be capacitively coupled with the substrate in order to selectively raise its voltage in the region of selected floating gates. The length of the floating gates and the thicknesses of the control gate lines can be made less than the minimum resolution element of the process by forming an etch mask of spacers.

Owner:SANDISK TECH LLC

Transistor

InactiveUS20110101337A1High purityTotal current dropSolid-state devicesSemiconductor devicesHydrogenSemiconductor

To provide a thin film transistor which has high operation speed and in which a large amount of current can flow when the thin film transistor is on and off-state current at the time when the thin film transistor is off is extremely reduced. The thin film transistor is a vertical thin film transistor in which a channel formation region is formed using an oxide semiconductor film in which hydrogen or an OH group contained in the oxide semiconductor is removed so that hydrogen is contained in the oxide semiconductor at a concentration of lower than or equal to 5×1019 / cm3, preferably lower than or equal to 5×1018 / cm3, more preferably lower than or equal to 5×1017 / cm3, and the carrier concentration is lower than or equal to 5×1014 / cm3, preferably lower than or equal to 5×1012 / cm3.

Owner:SEMICON ENERGY LAB CO LTD

Power semiconductor devices and fabrication methods

InactiveUS20130069712A1Uniform on-state behaviourChannel shortSolid-state devicesSemiconductor/solid-state device manufacturingPower semiconductor deviceEngineering

We describe a RESURF semiconductor device having an n-drift region with a p-top layer and in which a MOS (Metal Oxide Semiconductor) channel of the device is formed within the p-top layer.

Owner:POWER INTEGRATIONS INC

Chemical reactor and method for gas phase reactant catalytic reactions

InactiveUS7288231B2High yieldReduce contact timeCombination devicesExhaust apparatusPorous catalystChemical reaction

Owner:BATTELLE MEMORIAL INST

Semiconductor device and electronic appliance

One object is to provide a semiconductor device that includes an oxide semiconductor and is reduced in size with favorable characteristics maintained. The semiconductor device includes an oxide semiconductor layer, a source electrode and a drain electrode in contact with the oxide semiconductor layer, a gate electrode overlapping with the oxide semiconductor layer; and a gate insulating layer between the oxide semiconductor layer and the gate electrode. The source electrode or the drain electrode includes a first conductive layer and a second conductive layer having a region extended in a channel length direction from an end face of the first conductive layer. The sidewall insulating layer has a length of a bottom surface in the channel length direction smaller than a length in the channel length direction of the extended region of the second conductive layer and is provided over the extended region.

Owner:SEMICON ENERGY LAB CO LTD

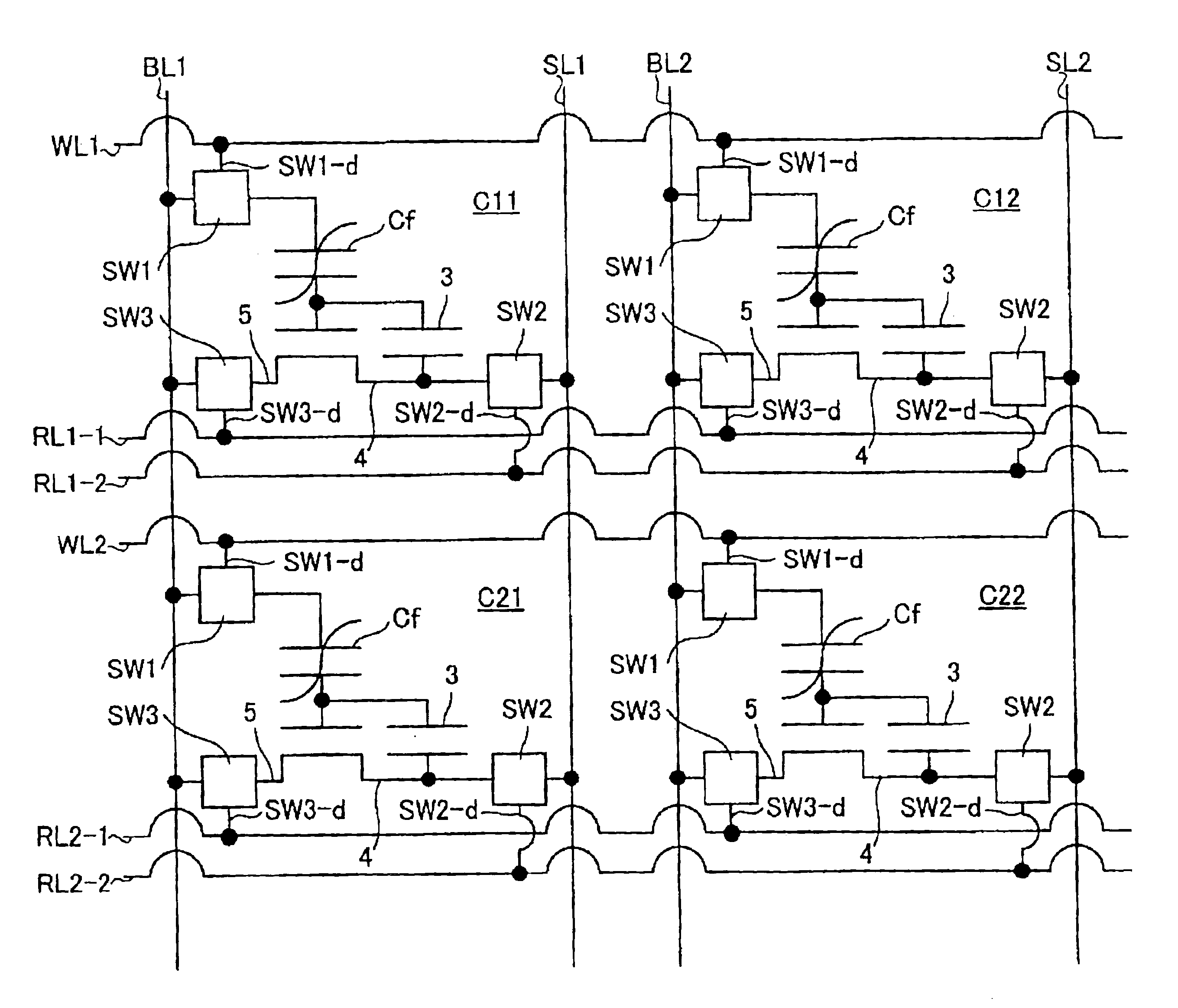

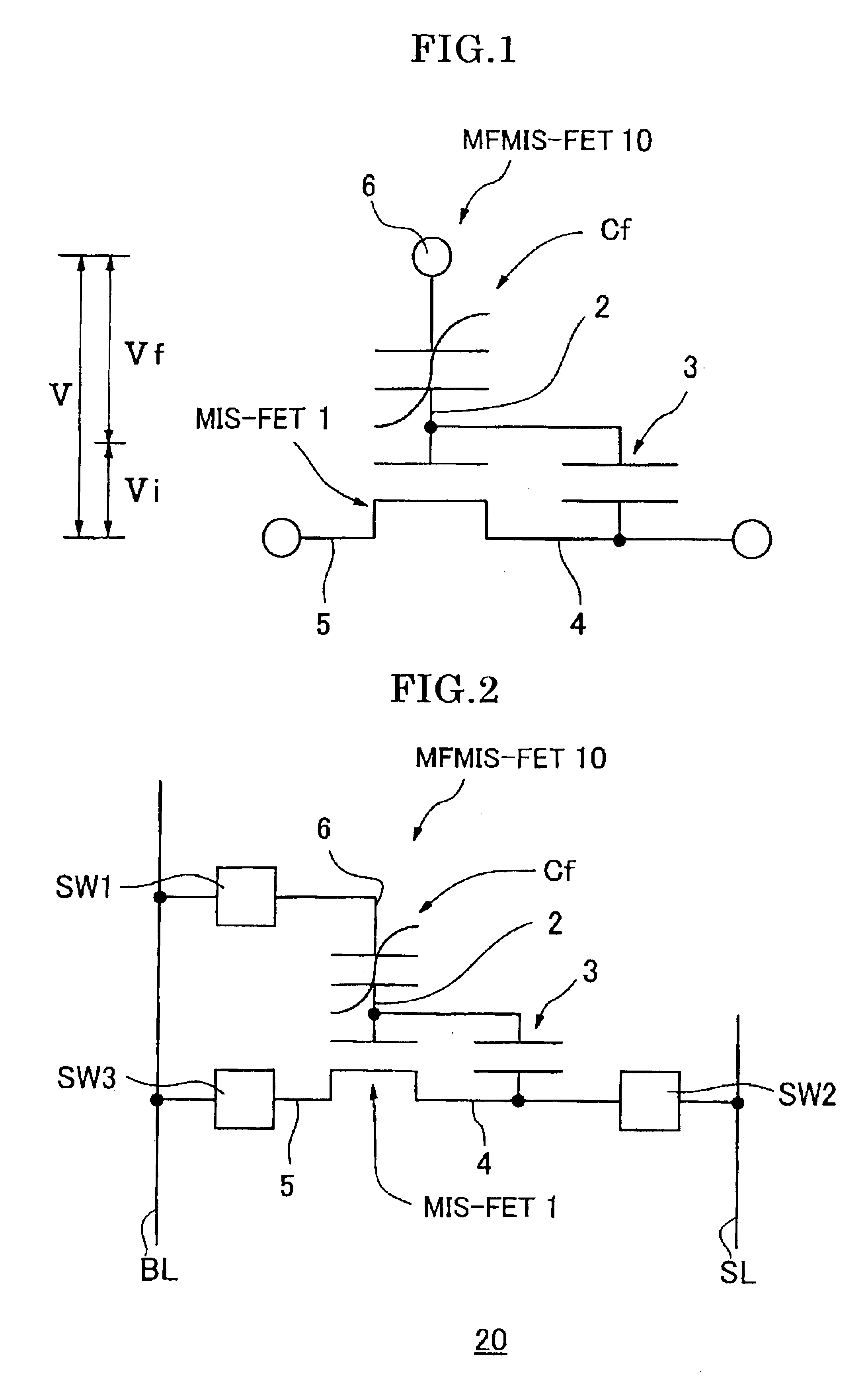

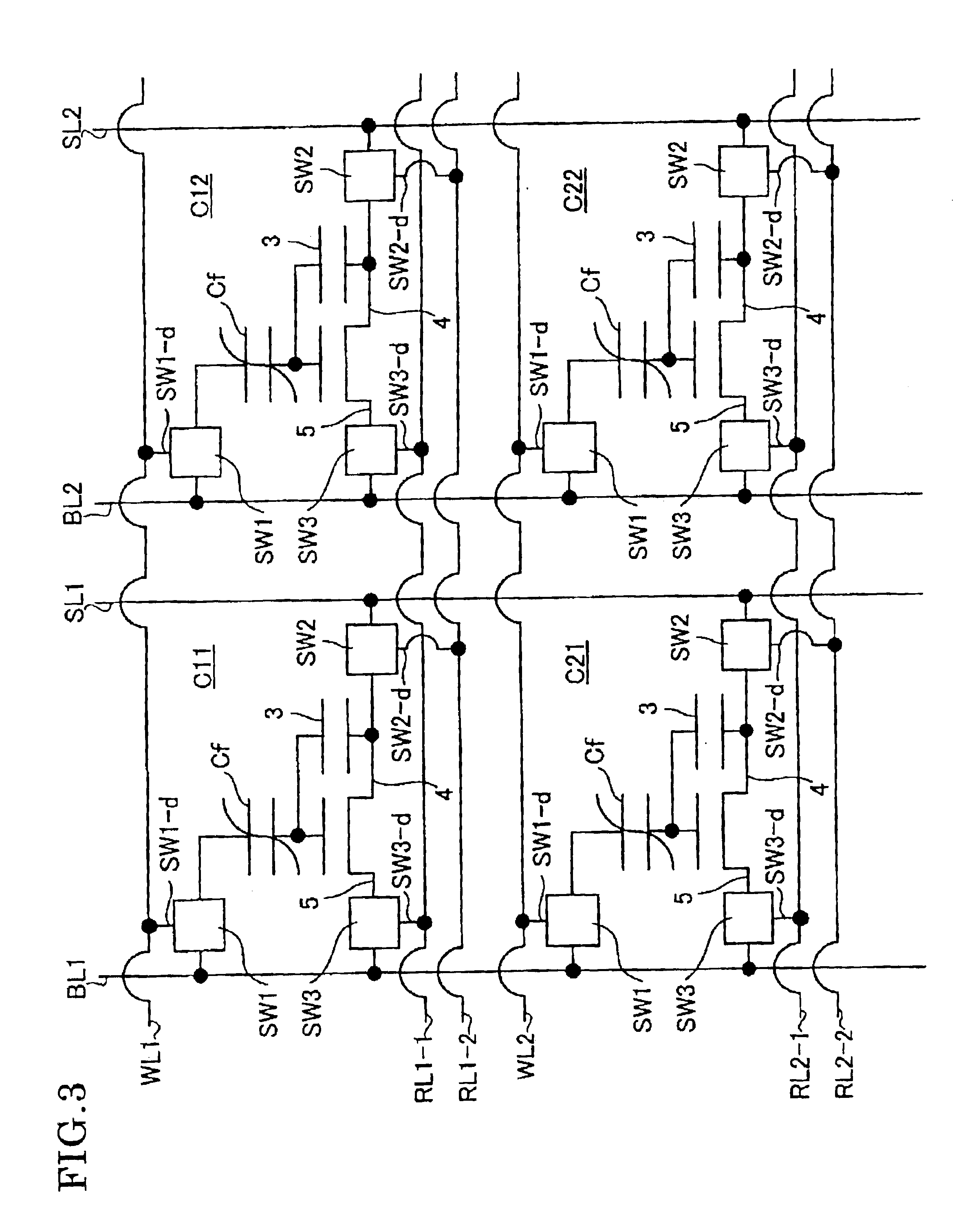

Ferroelectric non-volatile memory device having integral capacitor and gate electrode, and driving method of a ferroelectric non-volatile memory device

InactiveUS6898105B2Increase the areaImprove the coupling ratioTransistorSolid-state devicesElectrical conductorCoupling ratio

A ferroelectric non-volatile memory device that allows the coupling ratio to be increased and the effect of voltage distribution to the ferroelectric capacitor to be improved without increasing the area of the gate electrode of a detection MIS field effect transistor is provided. In a memory cell structure, a semiconductor including regions for a source, a channel, and a drain, a gate insulator on the channel region, a floating gate conductor, a ferroelectrics, and an upper electrode conductor are layered in this order. The structure includes a paraelectric capacitor having one end connected to the floating gate conductor and the other end connected to the source region.

Owner:SEIKO NPC +1

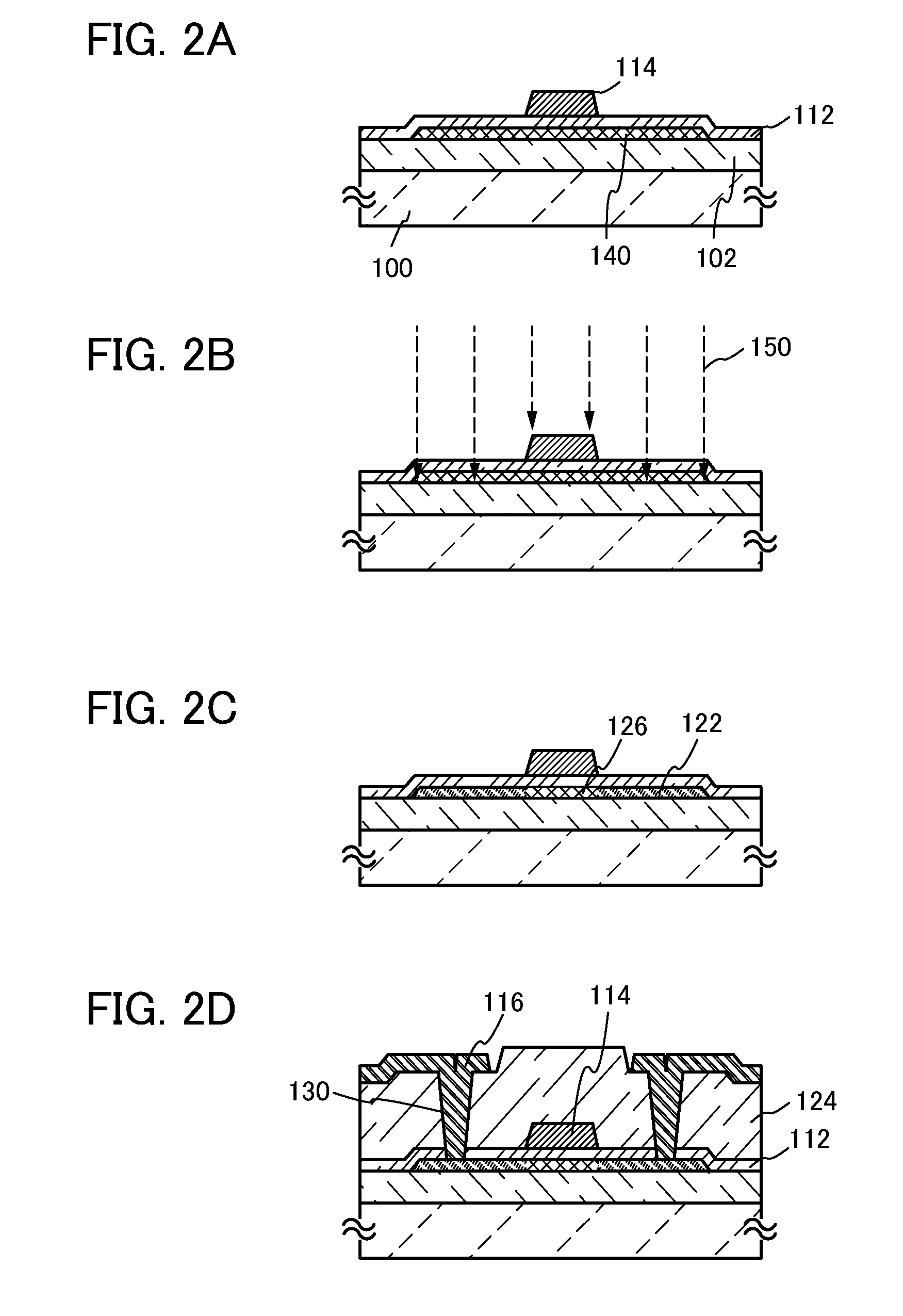

Method of forming a metal gate in a semiconductor device

ActiveUS7361565B2Increase speedReduce voltageTransistorSemiconductor/solid-state device manufacturingEngineeringPhotolithography

In a method of forming a metal gate in a semiconductor device, a gate insulation pattern and a dummy gate pattern are formed on a substrate. An insulation interlayer is formed on the dummy gate pattern to cover the dummy gate pattern. The insulation interlayer is polished such that a top surface of the dummy gate pattern is exposed, and the dummy gate pattern is selectively removed to form a trench on the substrate. A gate spacer is formed on an inner sidewall of the trench for determining a gate length of the metal gate. A metal is deposited to a sufficient thickness to fill the trench to form a metal layer. The metal layer is polished to remain in the trench. Accordingly, the gate length of the metal gate may be reduced no more than the resolution limit of the photolithography exposing system.

Owner:SAMSUNG ELECTRONICS CO LTD

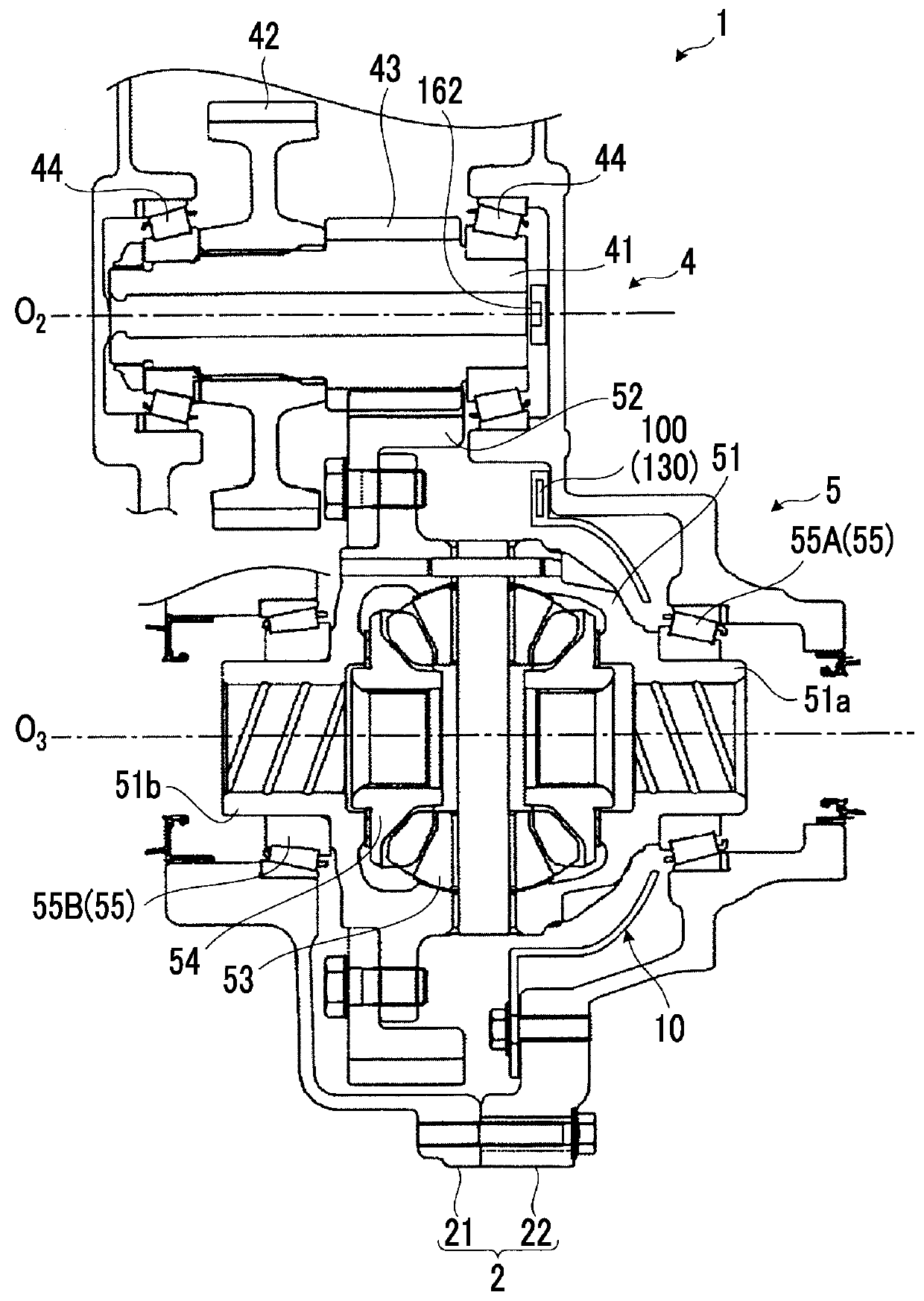

Oil passage structure for power transmission device

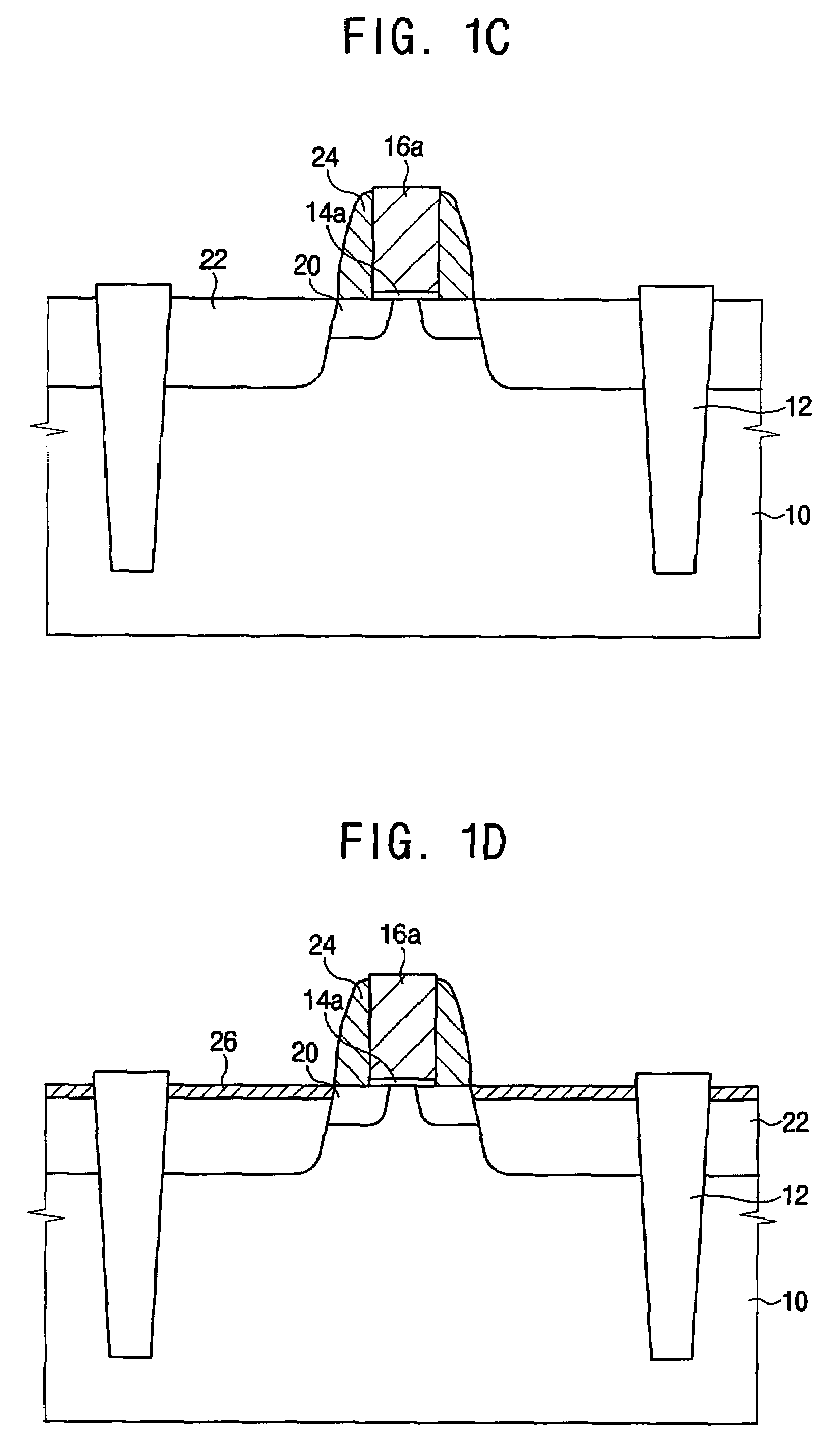

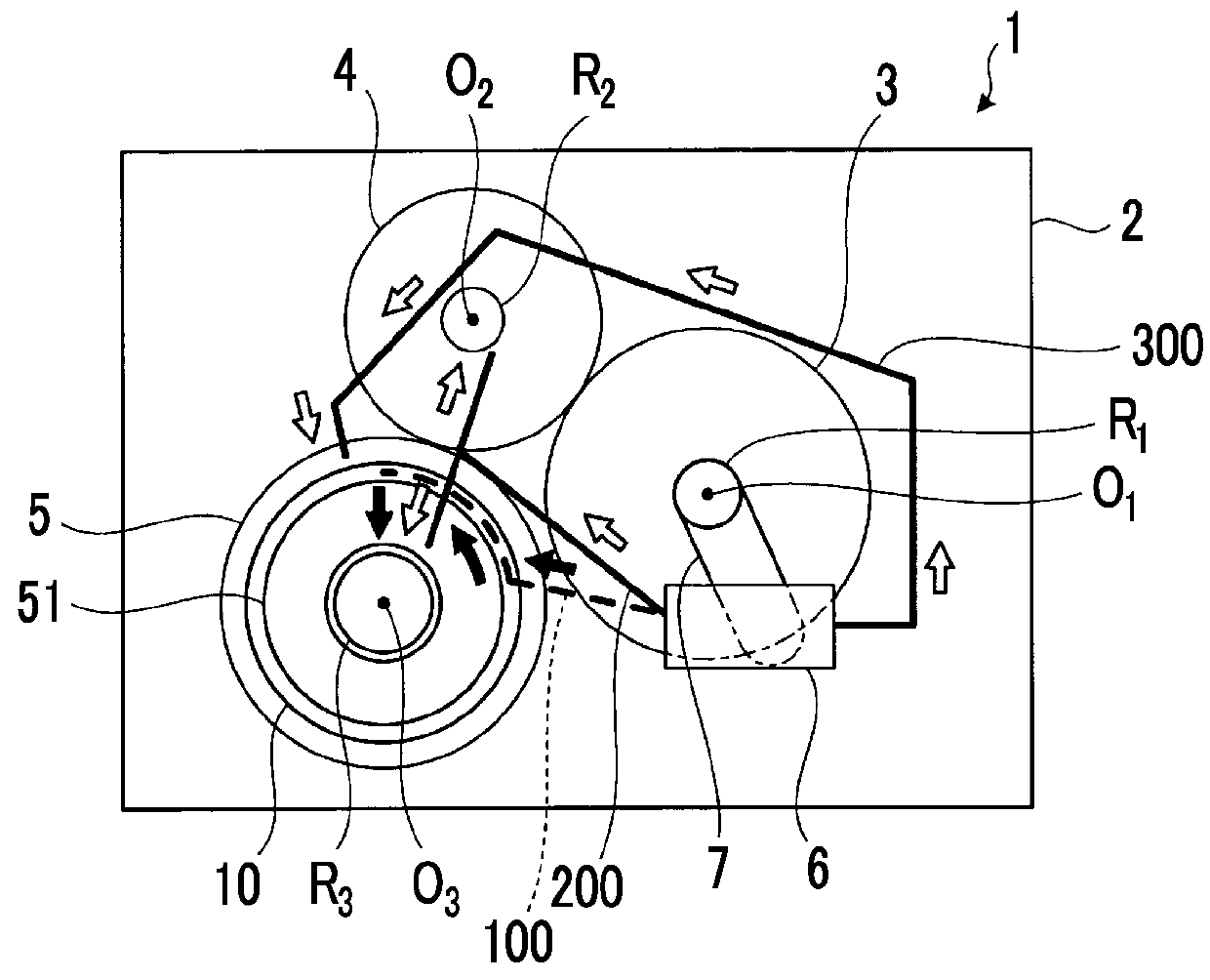

ActiveUS20180106359A1Pressure loss is causedReduce channel lengthGear lubrication/coolingGearing controlPower transmissionOil supply

In an oil passage structure for a power transmission device including a case provided to accommodate a power transmission device, a baffle plate attached to an inner wall of the case, and an oil pump, the oil passage structure includes a supply oil passage through which oil is pumped from the oil pump to an oil supply destination via the baffle plate. A plate oil passage, which constitutes a portion of the supply oil passage, a supply port, which allows the oil discharged from the oil pump to flow into the plate oil passage through the supply port, and a first discharge port, which allows the oil supplied to the oil supply destination to be discharged through the first discharge port, are formed in the baffle plate.

Owner:TOYOTA JIDOSHA KK

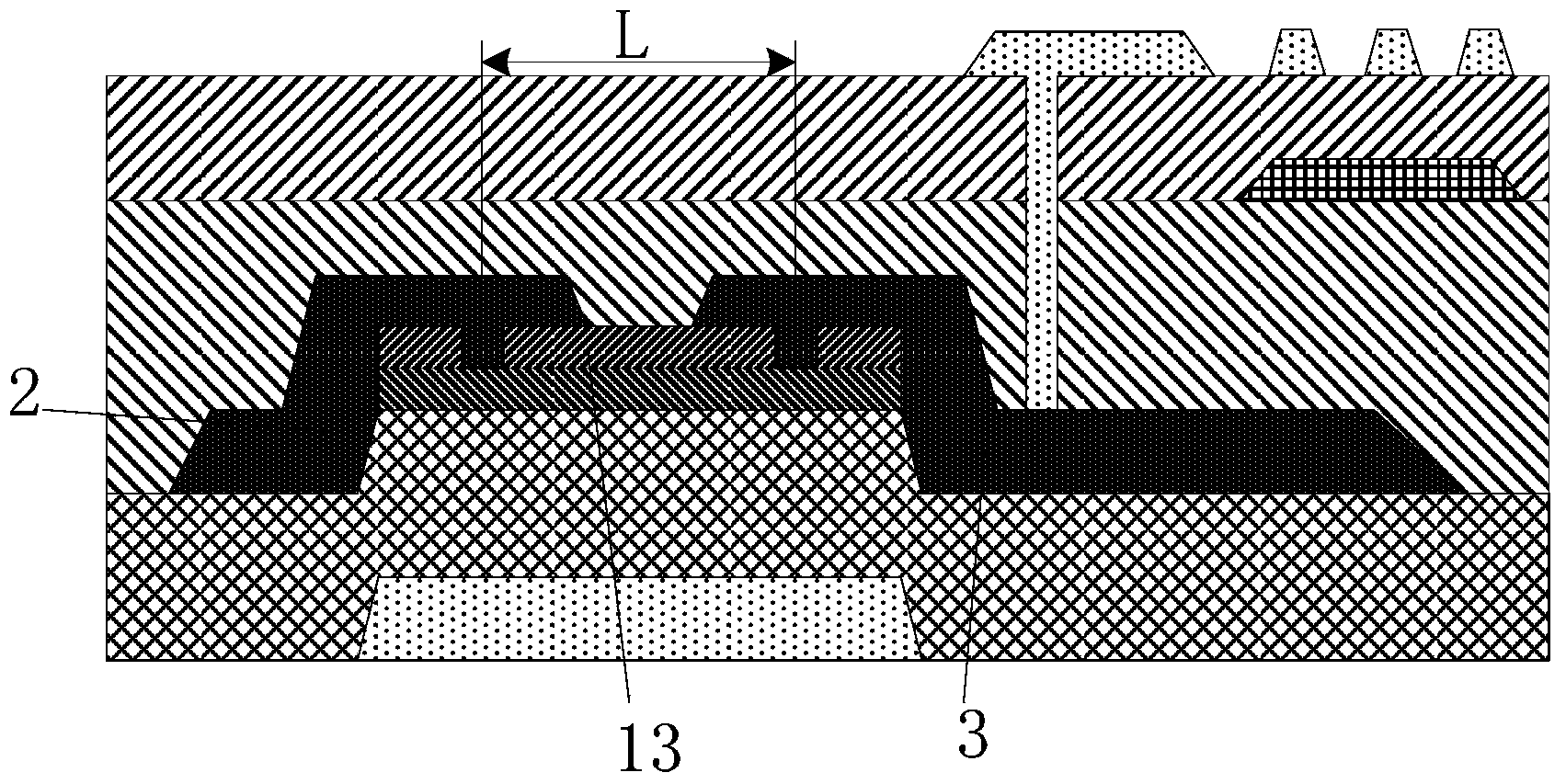

Oxide thin film transistor, manufacturing method thereof, array substrate and display device

ActiveCN103545378AReduce channel lengthTransistorSolid-state devicesLiquid-crystal displayOxide thin-film transistor

The invention provides an oxide thin film transistor, a manufacturing method of the oxide thin film transistor, an array substrate and a display device, and relates to the technical field of liquid crystal display. The manufacturing method of the oxide thin film transistor includes the steps that a grid electrode, a grid insulating layer and an oxide semiconductor thin film are sequentially formed in a substrate; first photoresist is formed in an active layer area of the oxide semiconductor thin film, and a channel area is thicker than a non-channel area; the first photoresist of the channel area is reserved; a source drain metal thin film is formed on active layer patterns, second photoresist on the source drain metal thin film is reserved, and the edge of the first photoresist of the channel area is covered with the source drain metal thin film; source electrode patterns and drain electrode patterns are obtained. According to the oxide thin film transistor, the manufacturing method of the oxide thin film transistor, the array substrate and the display device, when the initial source electrode patterns and the initial drain electrode patterns are formed, the photoresist is utilized to replace a protective layer to protect an active layer, the final source electrode patterns and the final drain electrode patterns are formed through a photoresist stripping technology, and therefore the length of a channel of the oxide thin film transistor is shortened.

Owner:BOE TECH GRP CO LTD

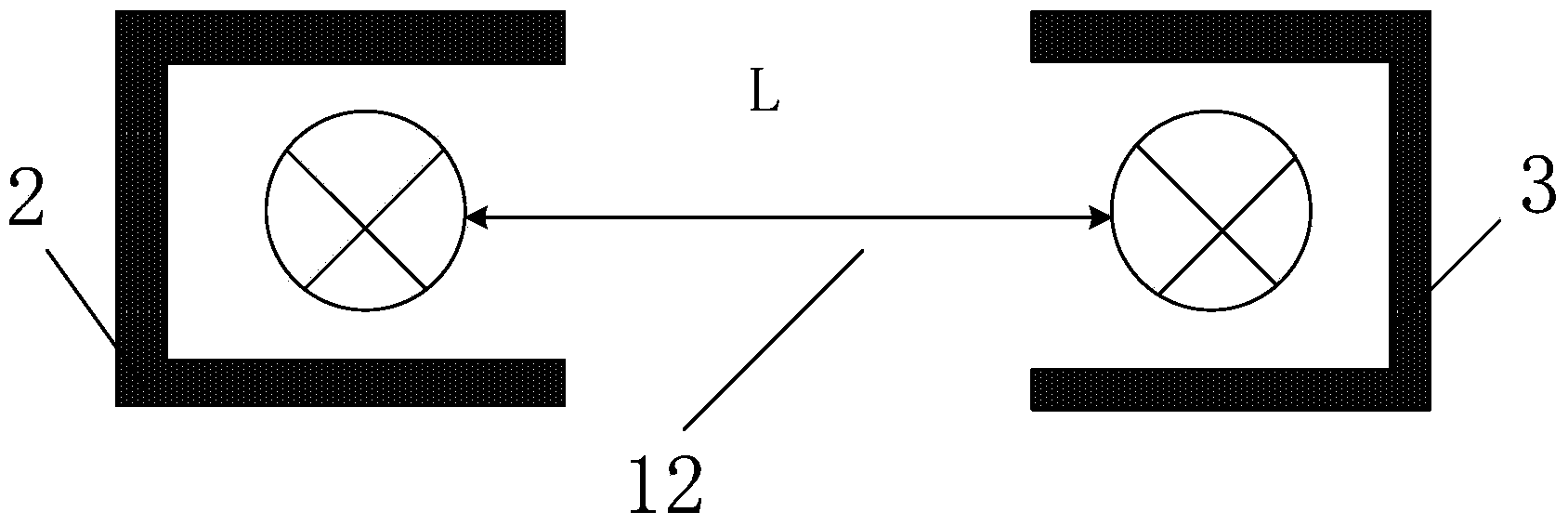

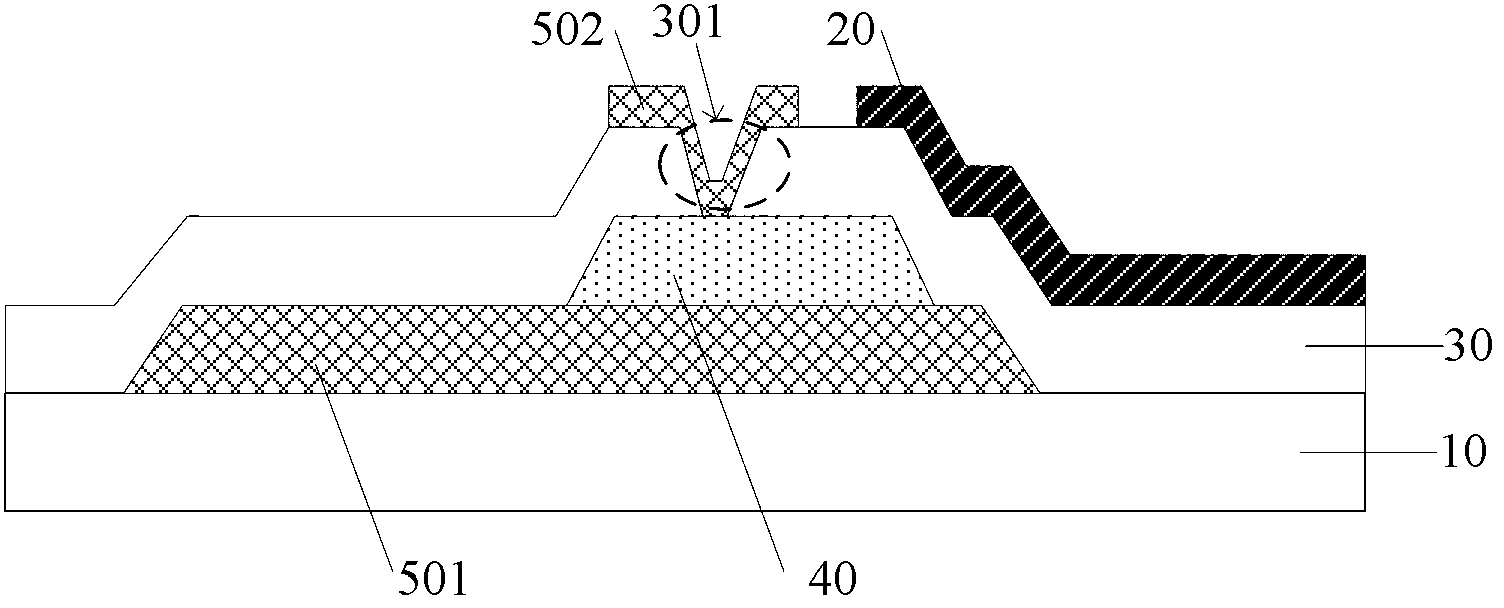

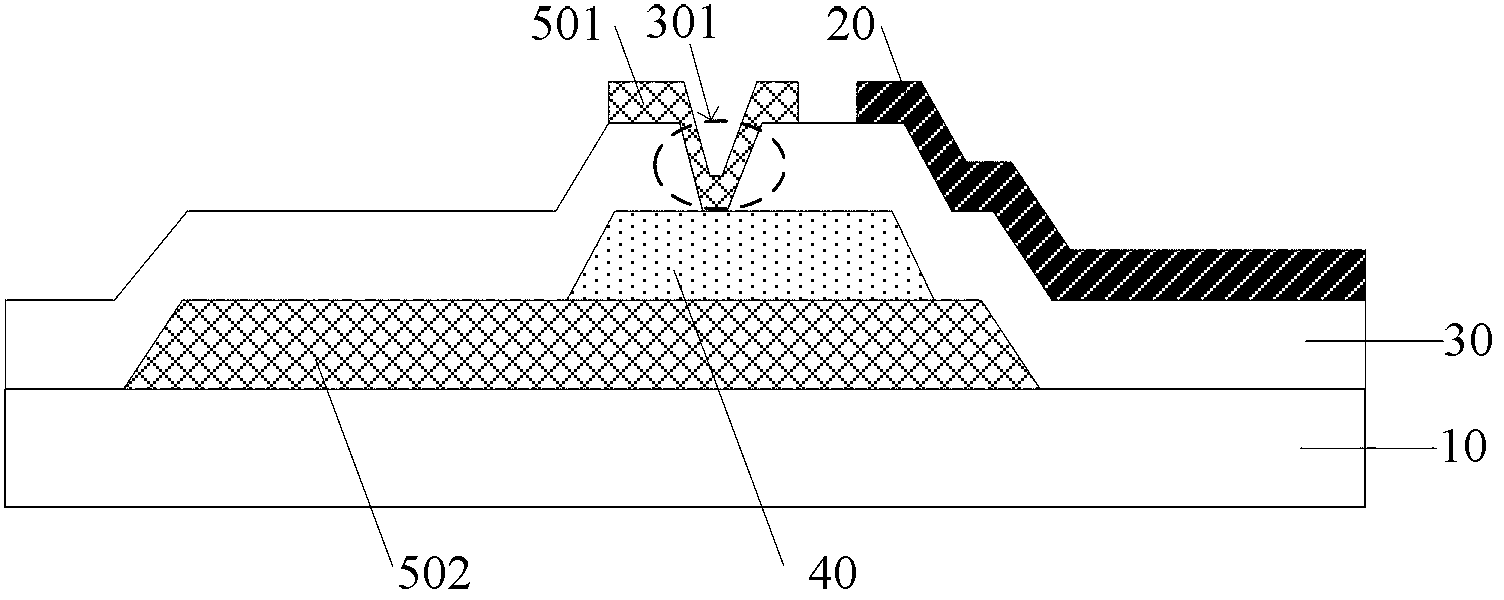

Thin film transistor, preparation method for same and array substrate

InactiveCN103311310AIncrease the on-state currentImprove featuresTransistorSolid-state devicesOxide thin-film transistorDisplay device

The invention provides a thin film transistor, a preparation method for the same and an array substrate, and relates to the technical field of display. The trench length of the thin film transistor can be reduced. The thin film transistor comprises a gate arranged on a substrate, a gate insulating layer, an active layer, a source and a drain, wherein the source and the drain are arranged on the two sides of the active layer along a direction perpendicular to the substrate respectively, and contact with the active layer. The thin film transistor, the preparation method for the same and the array substrate are used for manufacturing a display.

Owner:BEIJING BOE OPTOELECTRONCIS TECH CO LTD

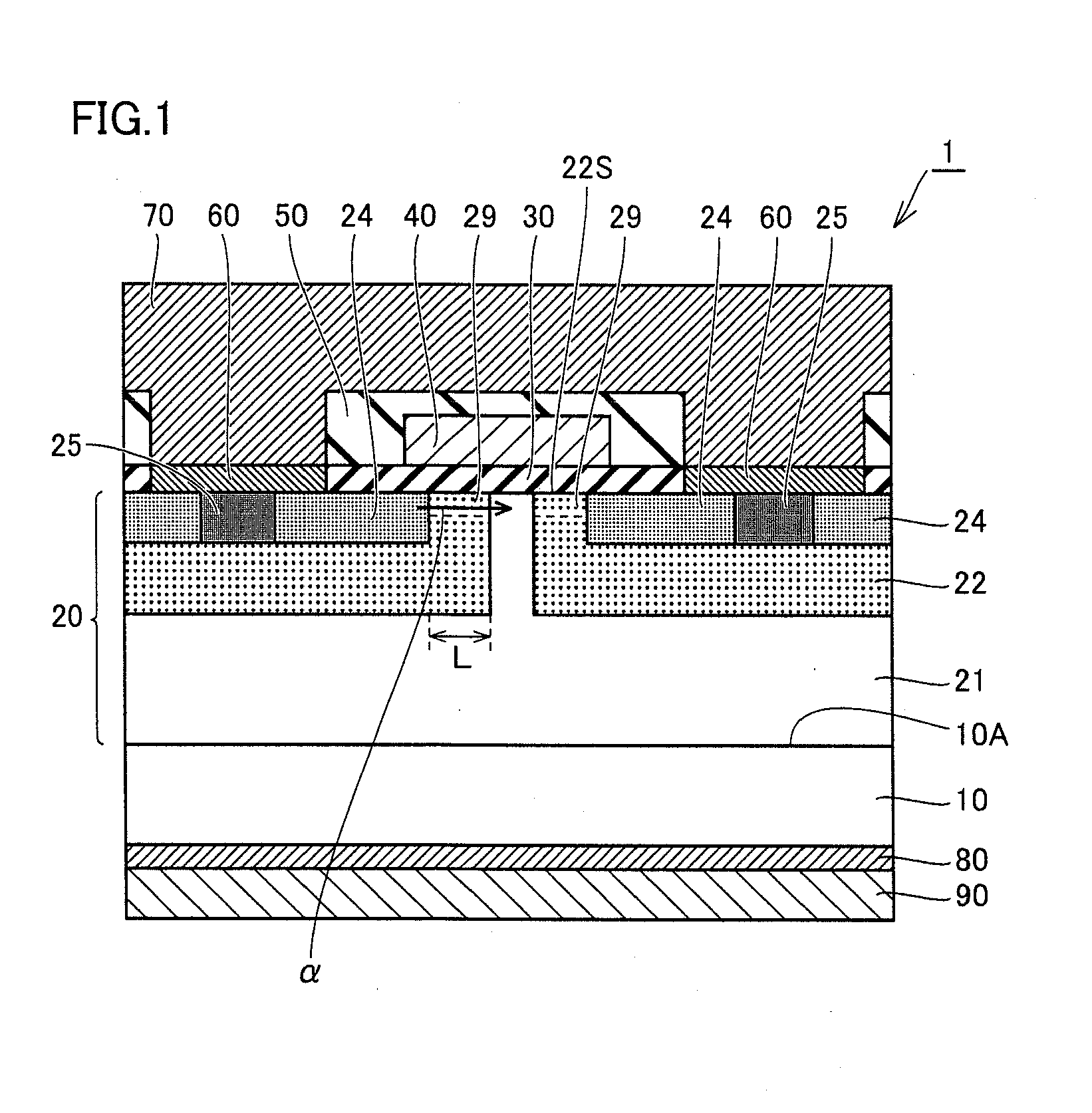

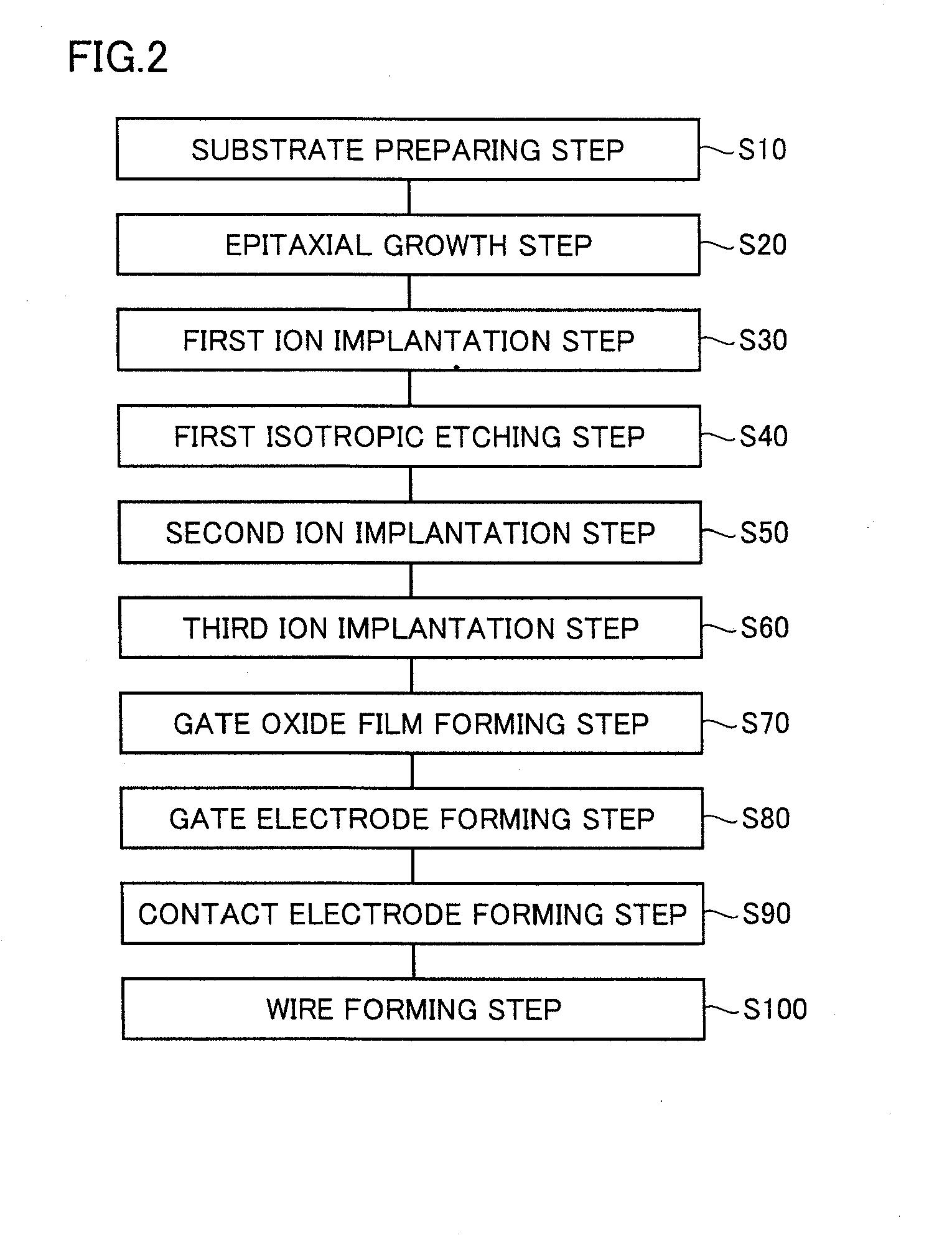

Semiconductor device

A MOSFET includes a silicon carbide substrate, an active layer, a gate oxide film, and a gate electrode. The active layer includes a p type body region in which an inversion layer is formed when the gate electrode is fed with a voltage. The inversion layer has an electron mobility μ dependent more strongly on an acceptor concentration Na of a channel region of the p type body region, as compared with a dependency of the electron mobility μ being proportional to the reciprocal of the acceptor concentration Na. The acceptor concentration Na in the channel region of the p type body region is not less than 1×1016 cm−3 and not more than 2×1018 cm3. The channel length (L) is equal to or smaller than 0.43 μm. The channel length (L) is equal to or longer than a spreading width d of a depletion layer in the channel region. The spreading width d is expressed by d=D·Na−C.

Owner:SUMITOMO ELECTRIC IND LTD