Patents

Literature

103results about How to "Reduce mold size" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

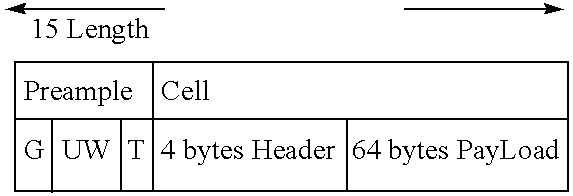

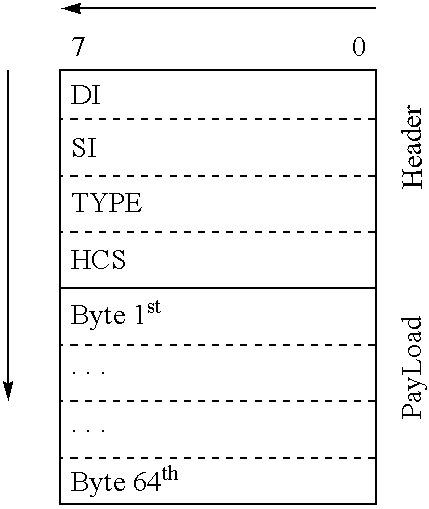

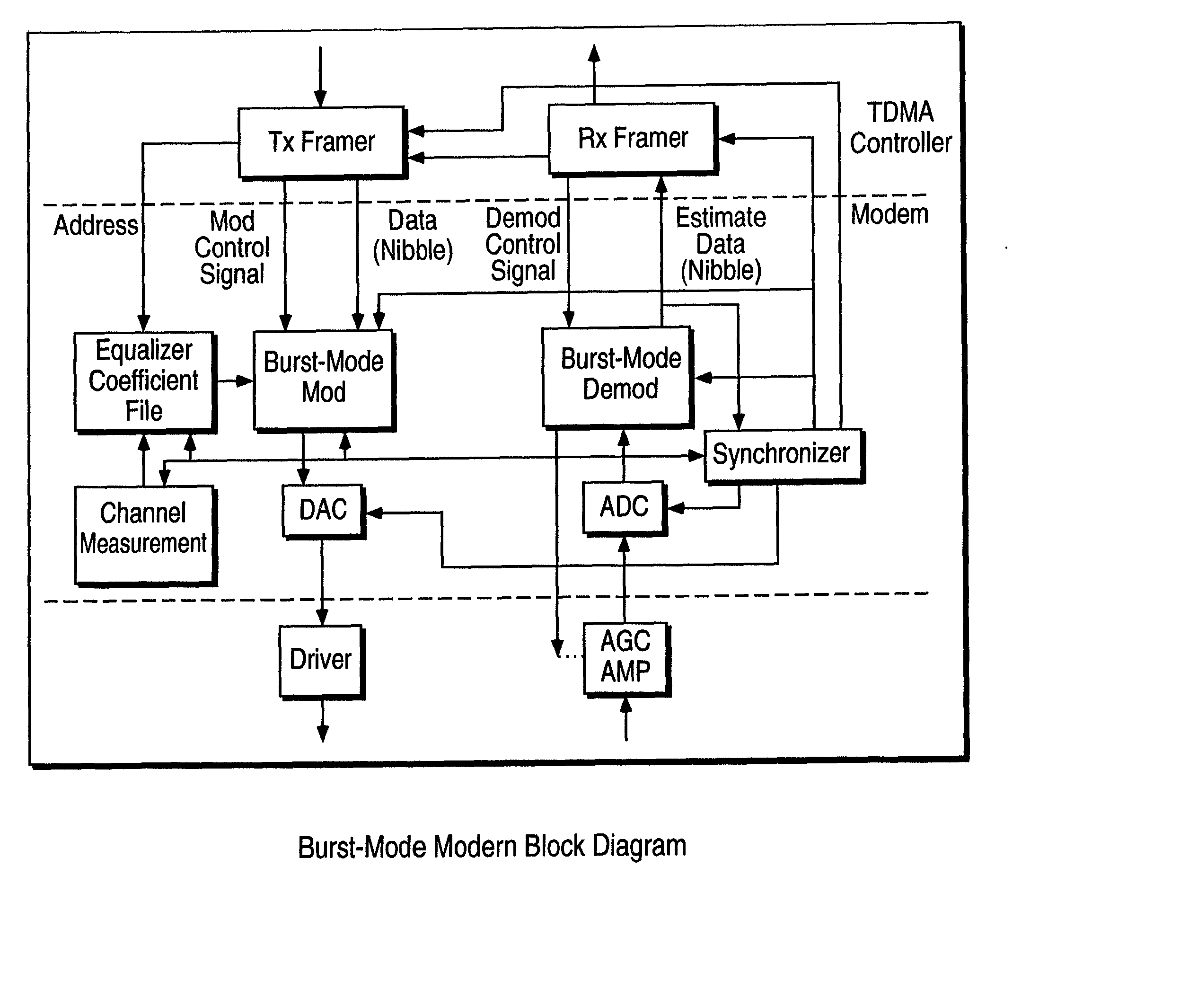

Channel equalization system and method

InactiveUS20030016770A1Increase high performance and data rate capacityLow costMultiple-port networksChannel dividing arrangementsData transmissionTTEthernet

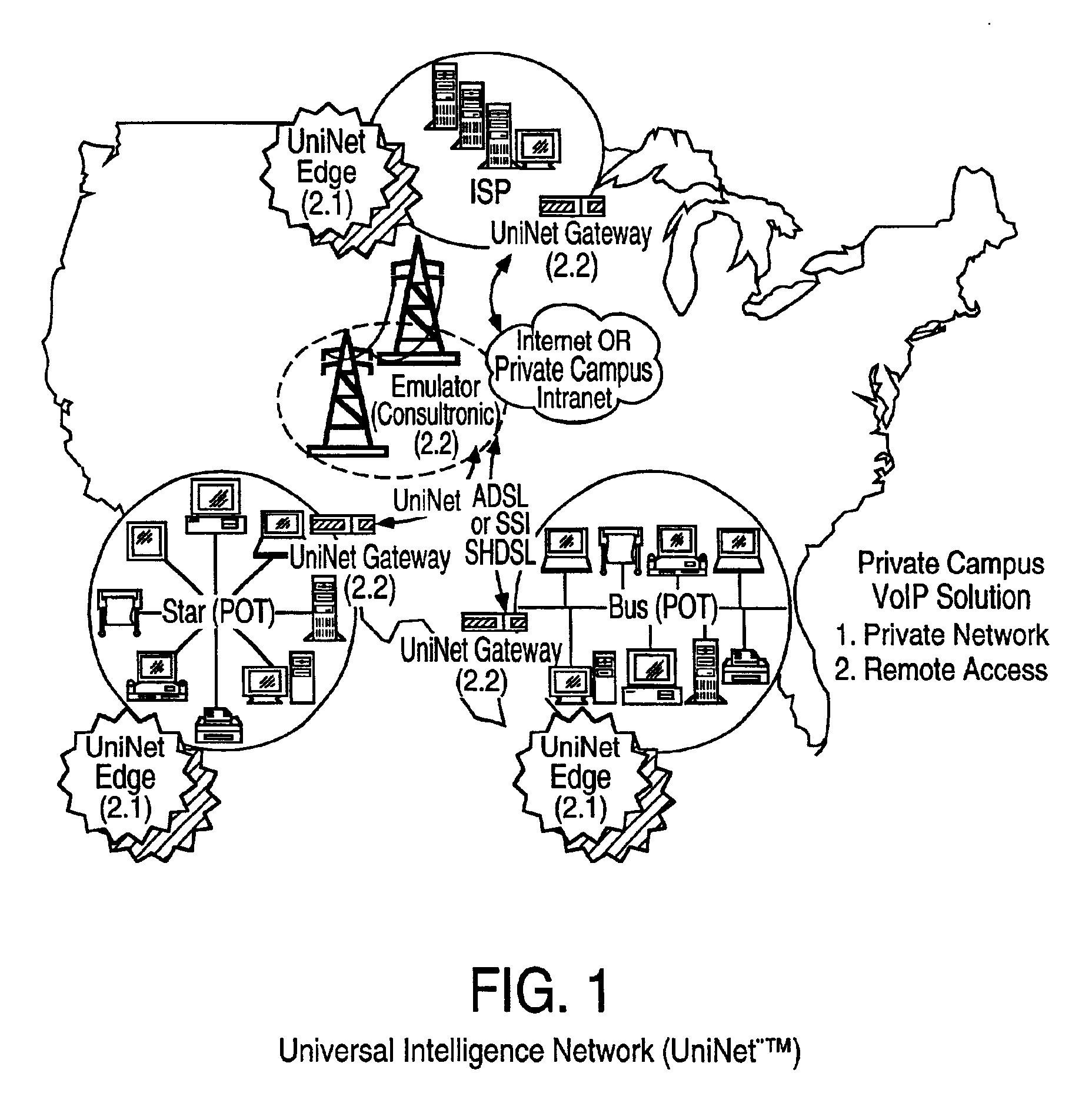

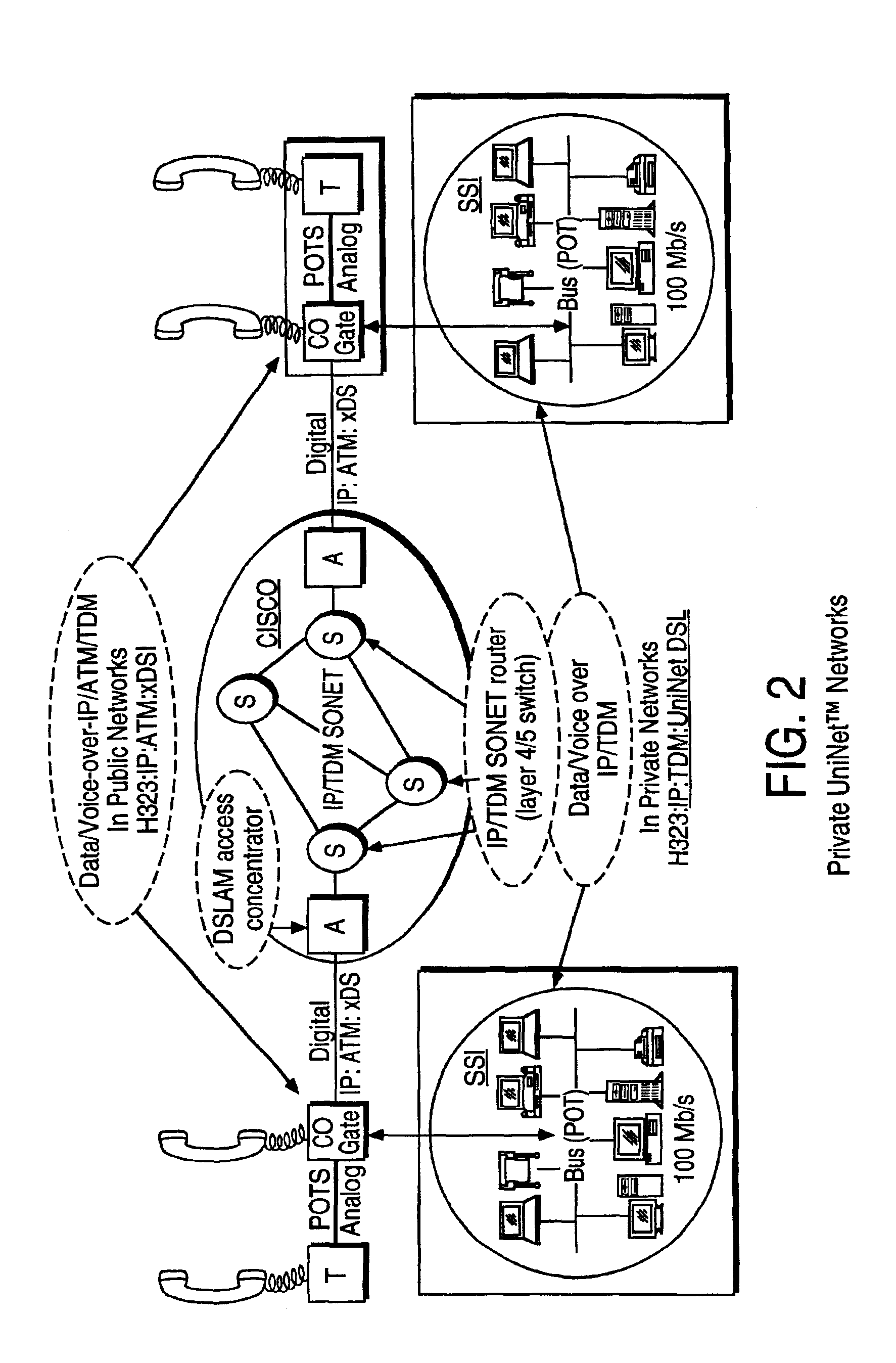

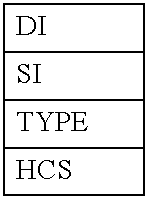

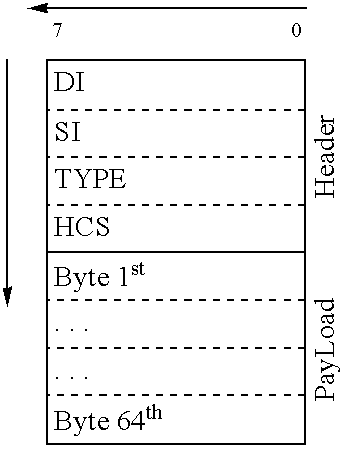

A system and method for delivering increases speed, security, and intelligence to wireline and wireless systems. The present invention includes a new generation Fast Circuit Switch (packet / circuit) Communication processors and platform which enables a new Internet Exchange Networking Processor Architecture at the edge and core of every communication system, for next generation Web Operating System or Environment (WOE) to operate on with emphasis of a non-local processor or networking processor with remote web computing capabilities. A Unified Network Communication & Processor System or UniNet is a New generation network architecture of packet / circuit communication processors or Internet networking processor, that increases speeds over any communication channels and topologies, synchronizing, enabling, improving, controlling and securing all of the data transmission of web applications over existing wireline and wireless infrastructure while providing seamless integration to the legacy telecom & data corn backbone. The present invention is capable of operating on any topology with distributed intelligence and data switching / routing, which is located at the edge. This method not only alleviates the ever increasing data processing bottleneck which is currently done by the data communication and telecom switch and routers, but it also enables new and next generation Internet Processor architecture. The UniNet is also a flexible solution for the novel concept that the capability of a network interface should depend on the level of service assigned to a service access point, not the capacity of the total network, such as transaction services with a short burst of messages with short access delay. The present invention increases channel capacity by using a parallel or multi-channel structure in such wireless and wireline at the edge or the core of. This new architecture of the present invention uses parallel bitstreams in a flexible way and distributed switching / routing technique, is not only to avoid the potential bottlenet of centralized switches, but also to increase speed with intelligence that is seamlessly integrating into the Fiber Optic Backbone such as WDM and SONET of the MAN / WAN network with a Real-time guarantees, different types of traffic (such as Stringent synchronous, isochronous, and asynchronous data messages) with different demands, and privacy & security of multi access and integrated services environment.

Owner:B C LEOW

Channel equalization system and method

InactiveUS6904110B2Increase high performance and data rate capacityLow costMultiple-port networksChannel dividing arrangementsFiberEngineering

A system and method for delivering increases speed, security, and intelligence to wireline and wireless systems. The present invention increases channel capacity by using a parallel or multi-channel structure in such wireless and wireline at the edge or the core of. This new architecture of the present invention uses parallel bitstreams in a flexible way and distributed switching / routing technique, is not only to avoid the potential bottlenet of centralized switches, but also to increase speed with intelligence that is seamlessly integrating into the Fiber Optic Backbone such as WDM and SONET of the MAN / WAN network with a Real-time guarantees, different types of traffic (such as Stringent synchronous, isochronous, and asynchronous data messages) with different demands, and privacy & security of multi access and integrated services environment.

Owner:B C LEOW

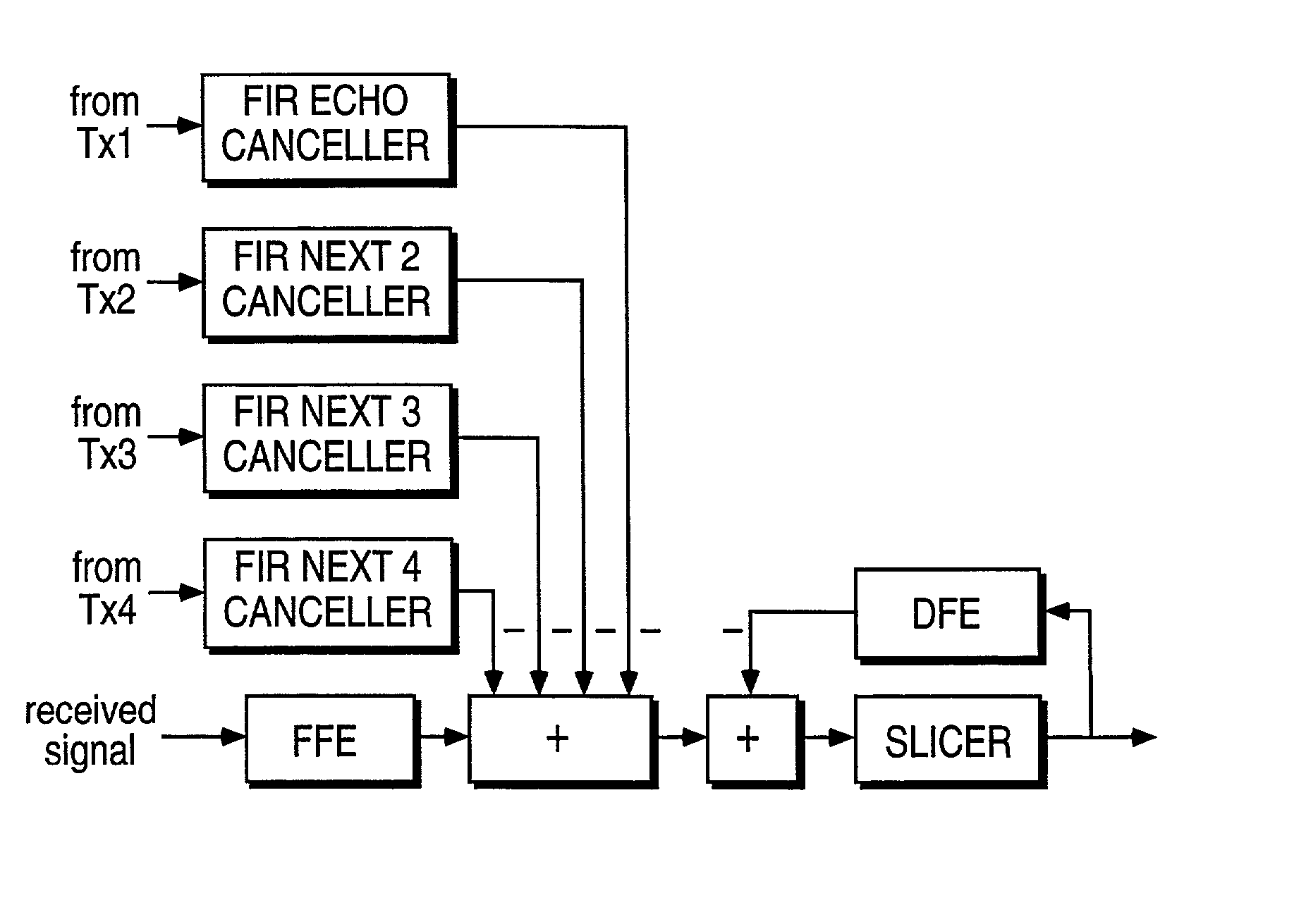

Channel adaptive equalization precoding system and method

InactiveUS20030086515A1Increase high performance and data rate capacityLow costChannel dividing arrangementsError detection/prevention using signal quality detectorPrecodingOperational system

A system and method for delivering increased speed, security, and intelligence to wireline and wireless systems. The present invention includes a new generation Fast Circuit Switch (packet / circuit) Communication processors and platform which enables a new Internet Exchange Networking Processor Architecture at the edge and core of every communication system, for next generation Web Operating System or Environment (WOE) to operate on with emphasis of a non-local processor or networking processor with remote web computing capabilities.

Owner:TRANS FRANCOIS +1

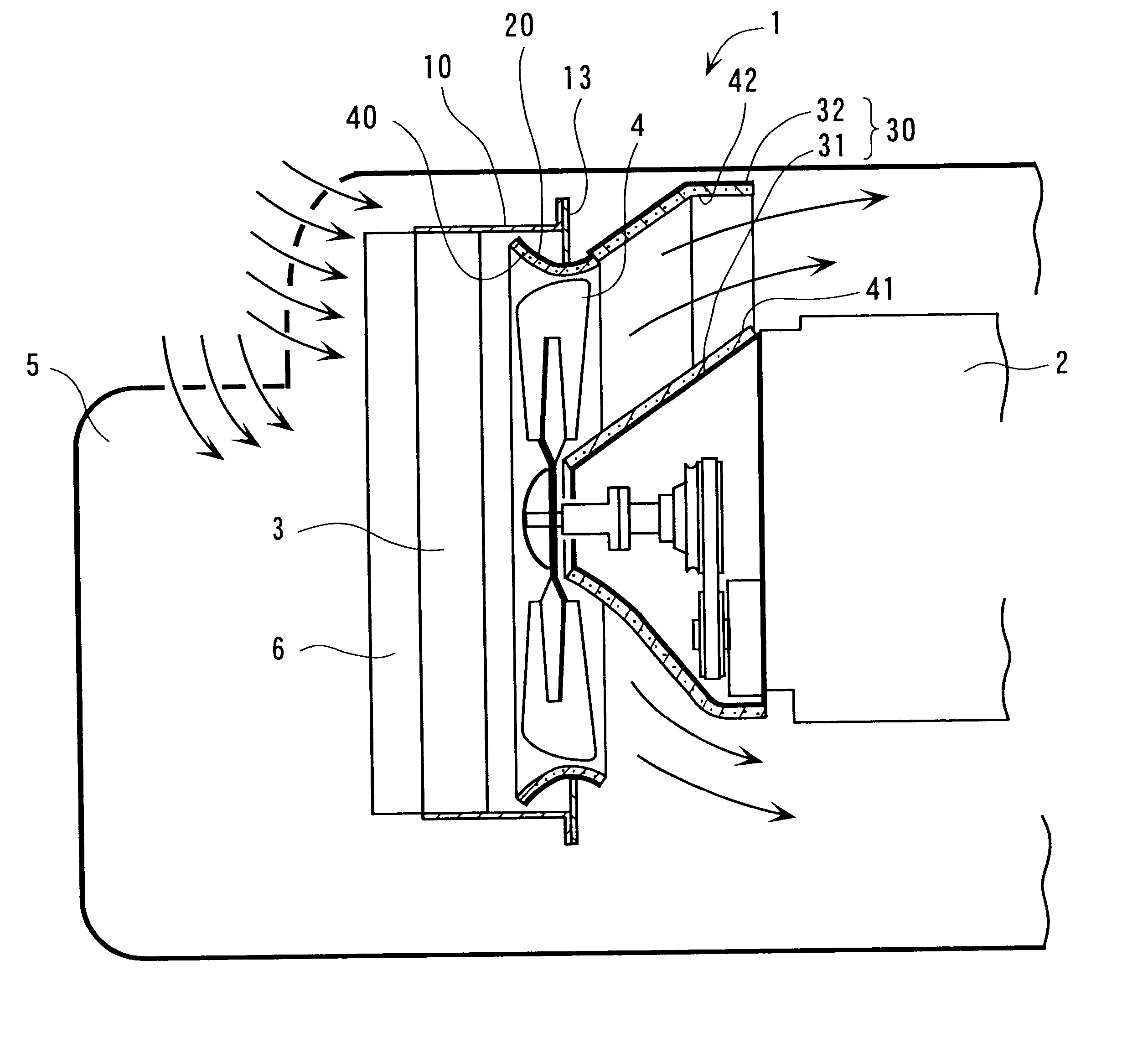

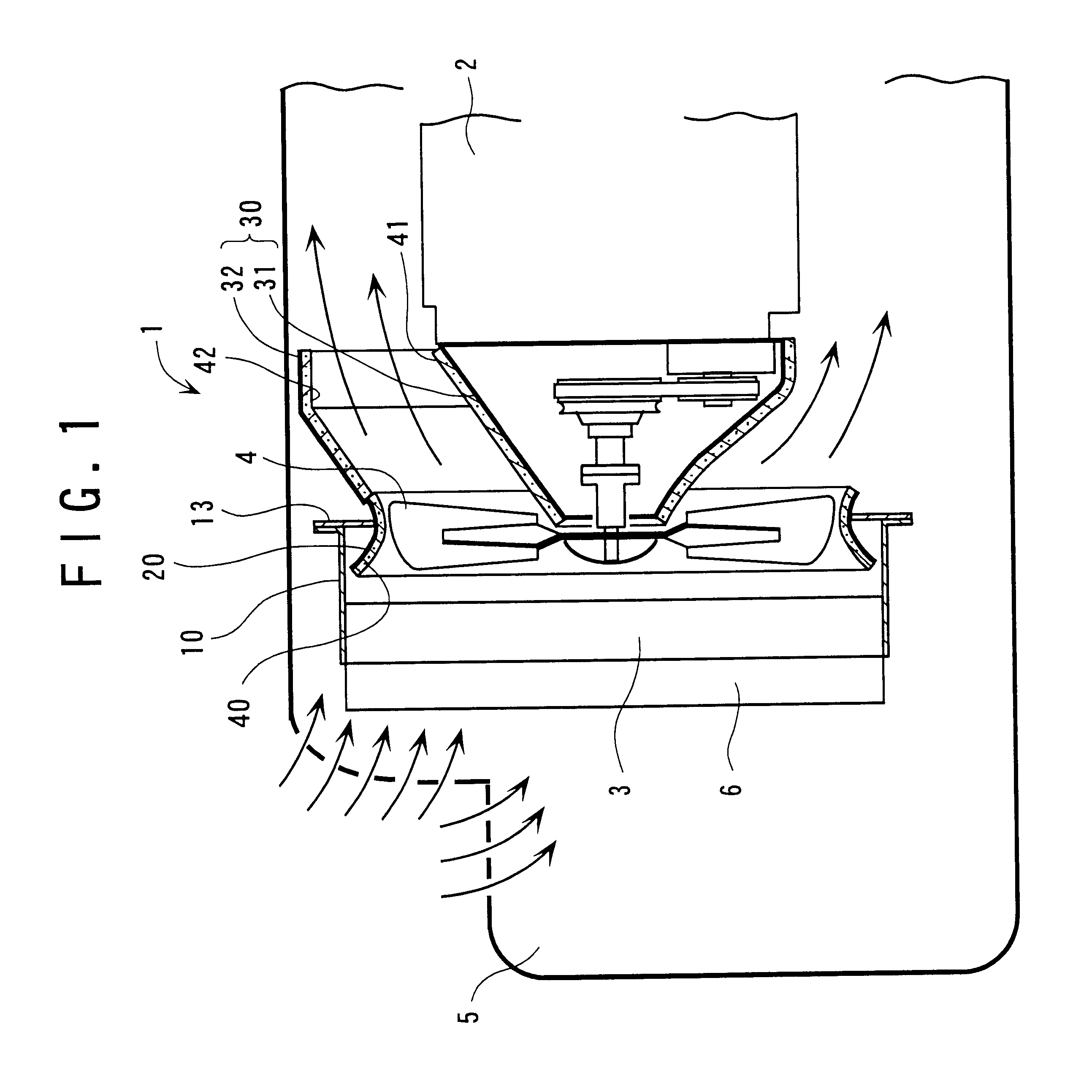

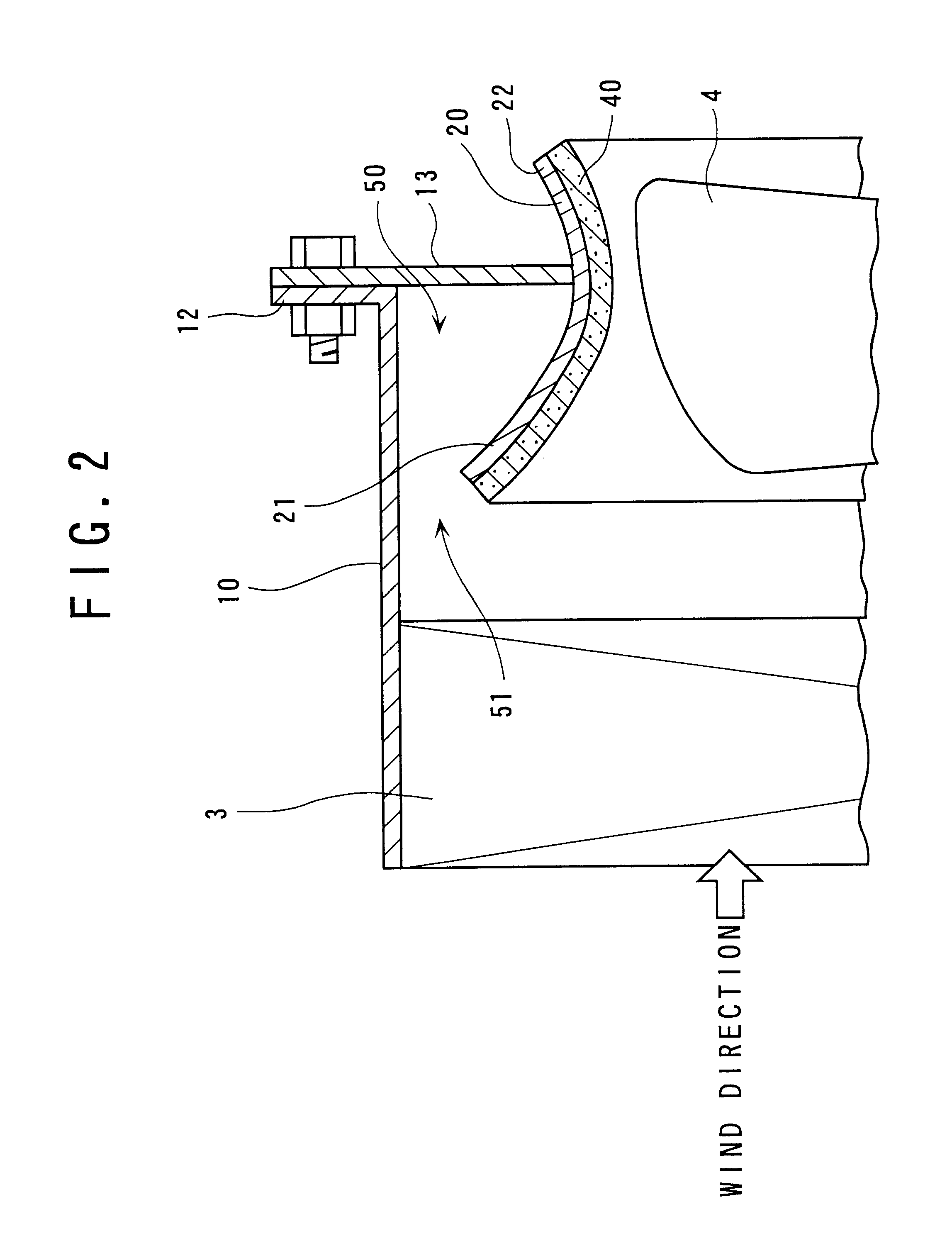

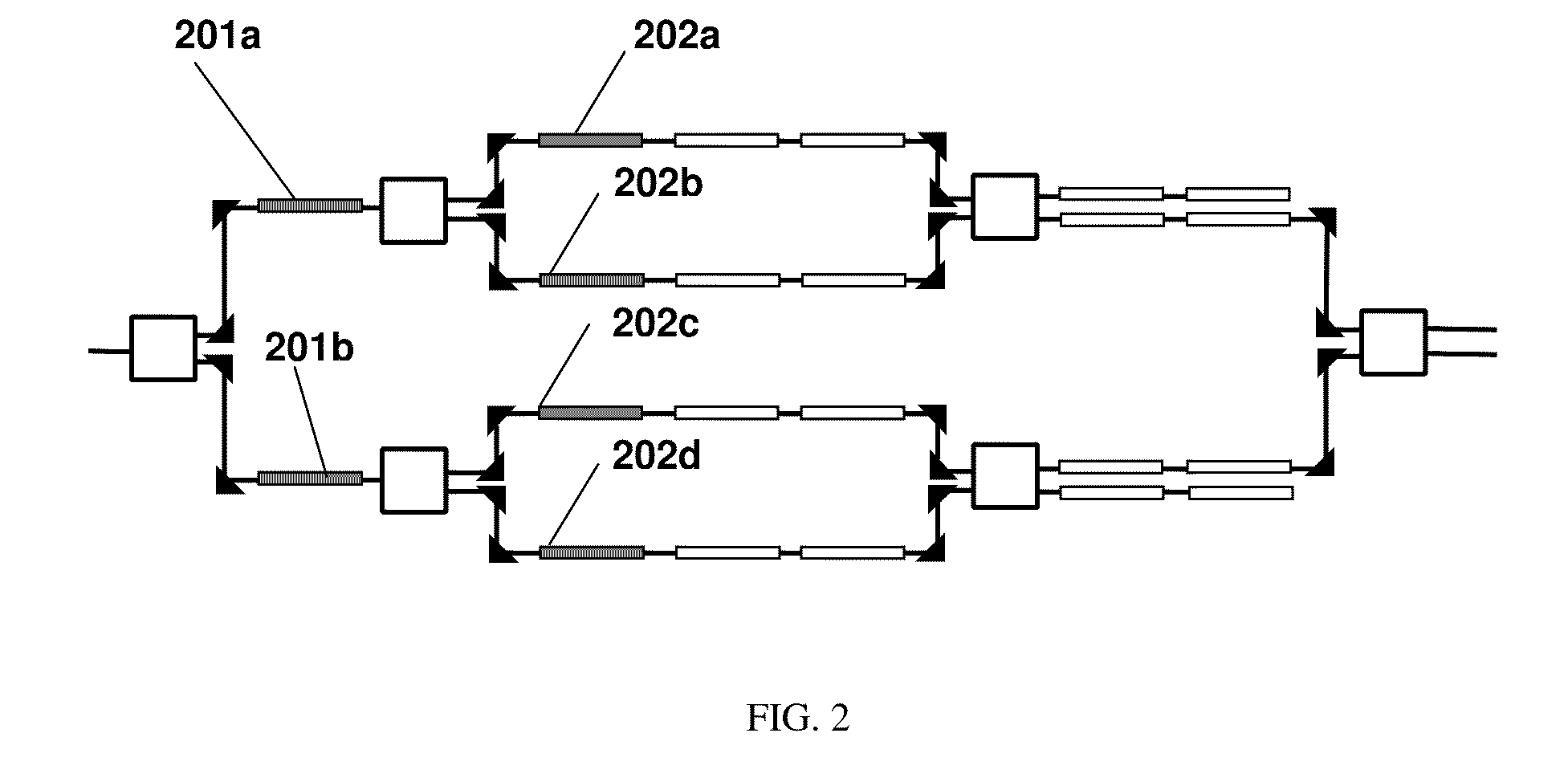

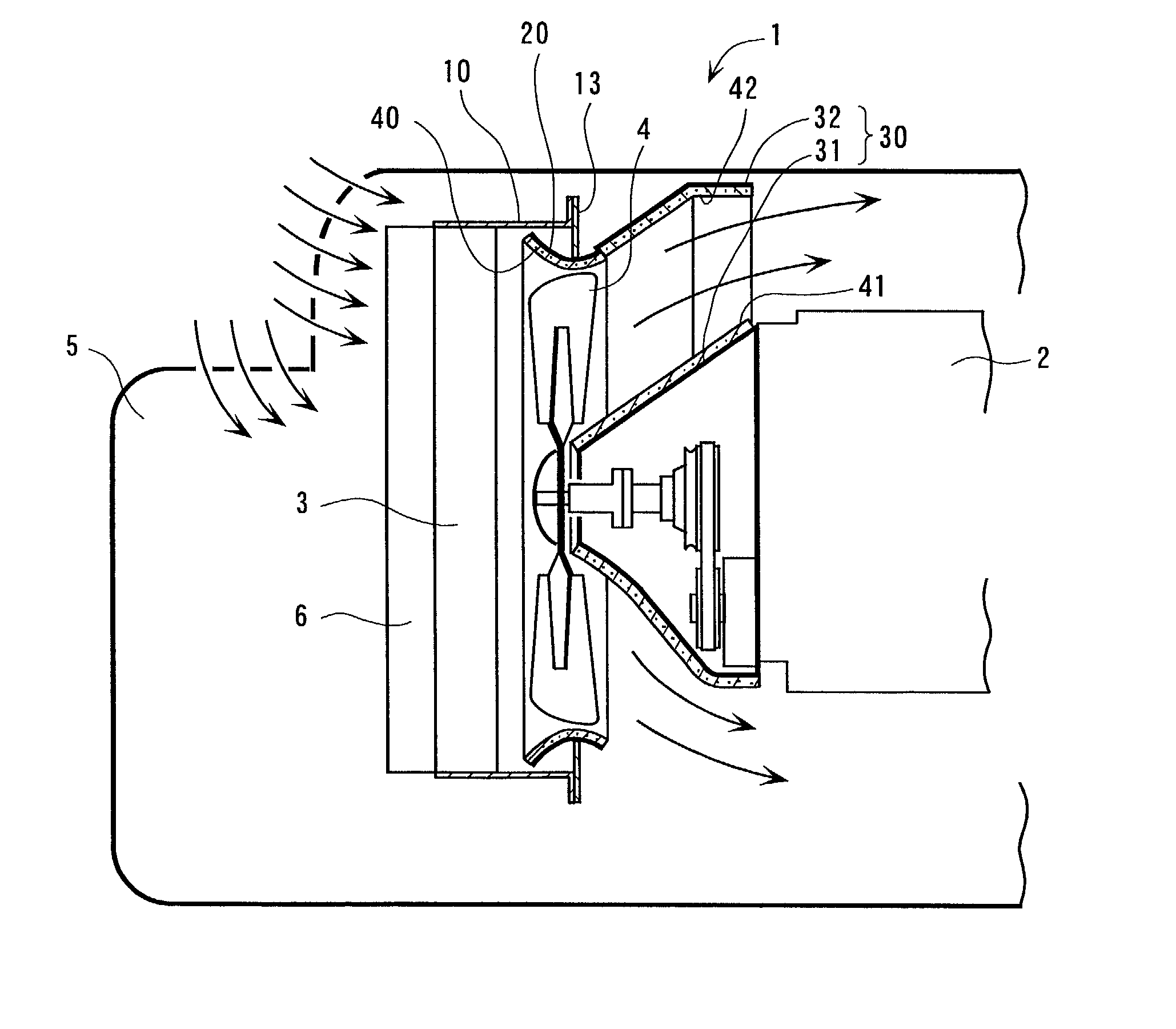

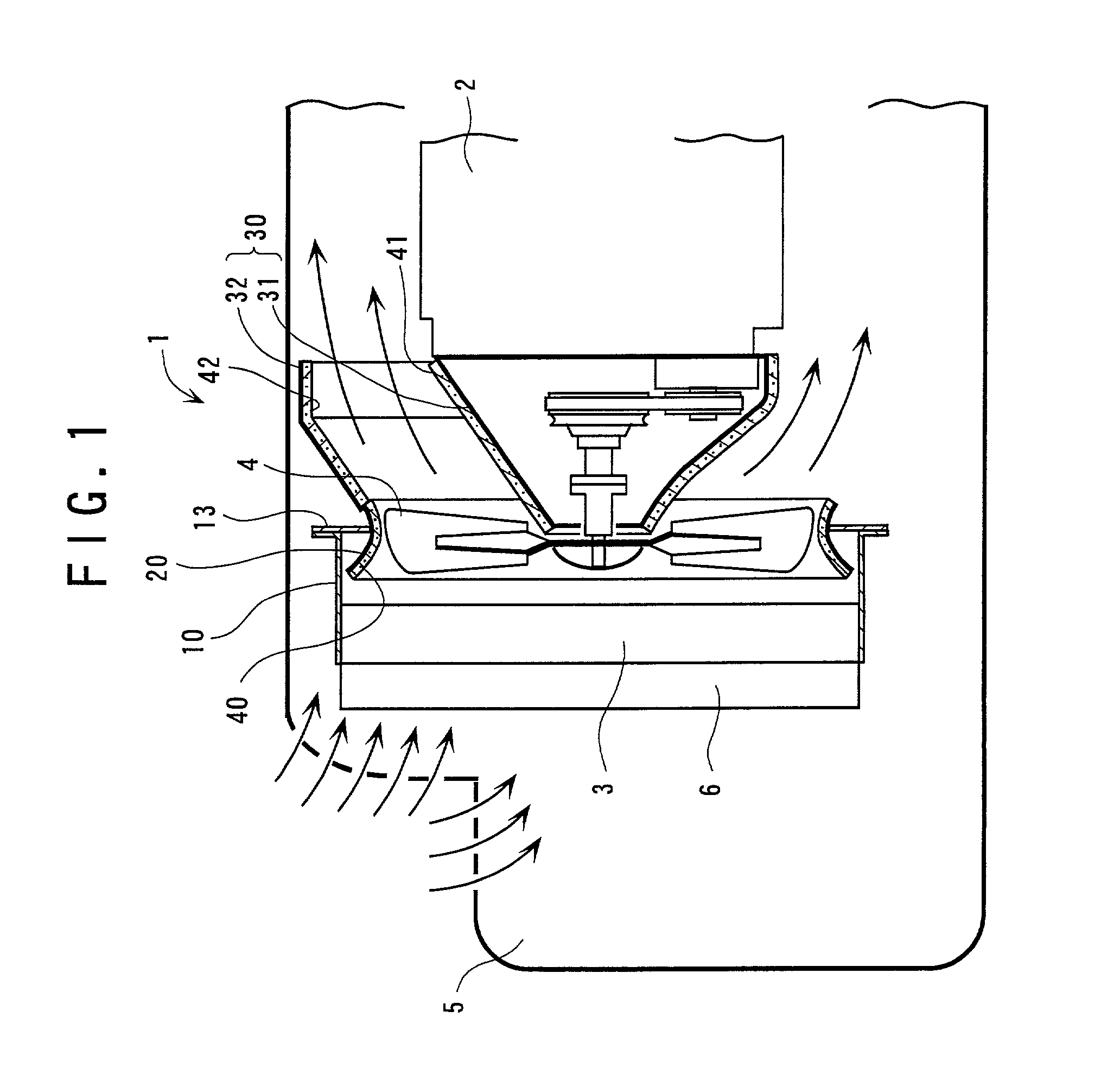

Noise reduction mechanism of fan device and molding method of porous damping material therefor

InactiveUS6454527B2Effective dampingMeet the noisePump componentsBlade accessoriesEngineeringNoise reduction

Porous damping material (40) is attached to an entire inner circumference of the fan shroud (20) opposing to an end of a fan (4) and is exposed to opposing space without using conventional perforated metal. Accordingly, jet noise caused by strong swirl between the fan (4) and the fan shroud (20) can be damped by the damping material (40) and impulsive sound scarcely occurs. Thus, both of the impulsive sound and the jet noise can be effectively damped, thereby securely reducing noise. The pours member (401) constituting the porous damping material (40) is a die-molding product made by a die (150) having a cavity (153).

Owner:KOMATSU LTD

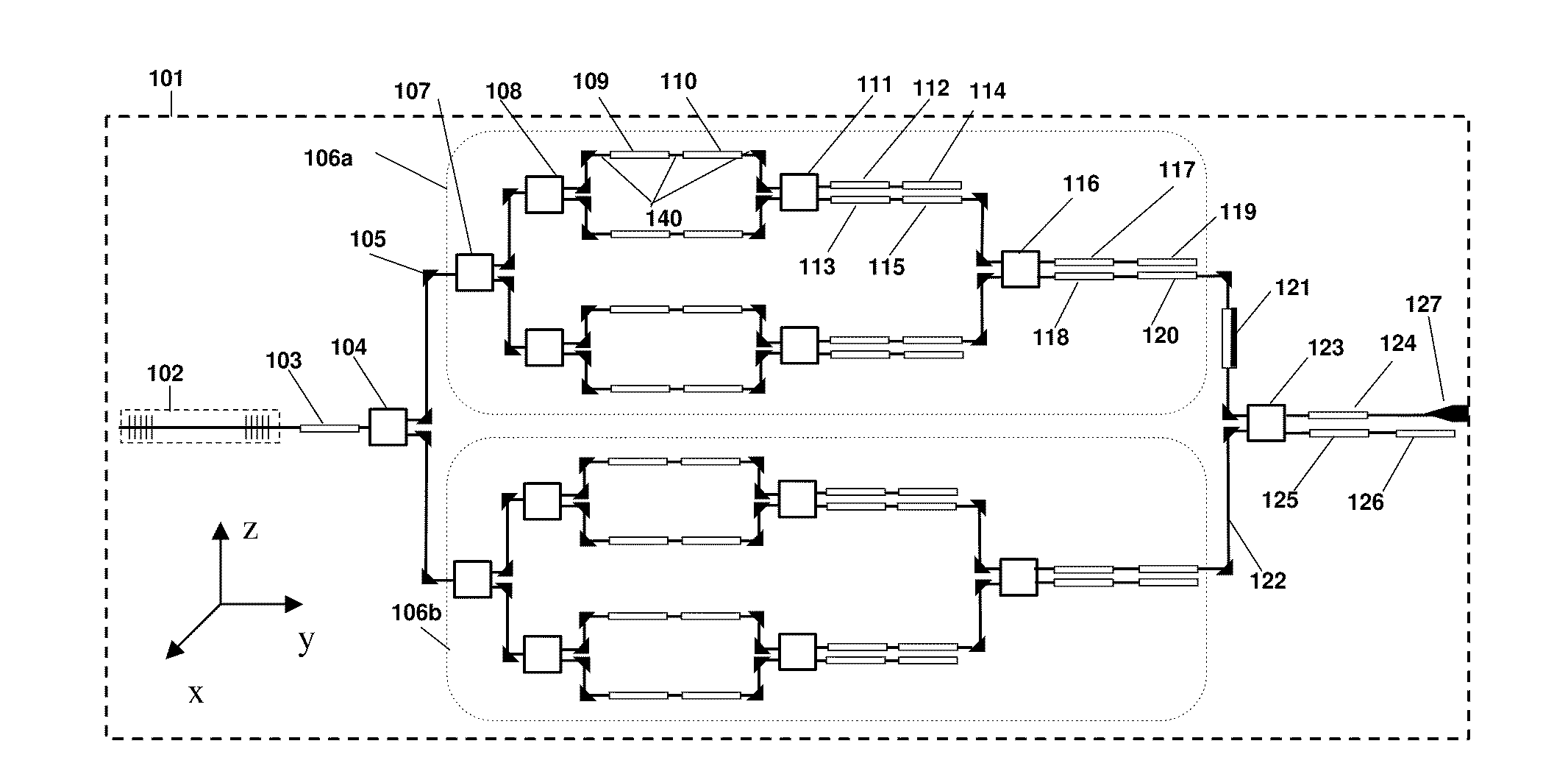

Chip-based advanced modulation format transmitter

ActiveUS20100303469A1Reduce mold sizeReduced footprintWavelength-division multiplex systemsElectromagnetic transmittersPhase modulationLaser source

In various embodiments, a monolithic integrated transmitter, comprising an on-chip laser source and a modulator structure capable of generating advanced modulation format signals based on amplitude and phase modulation are described.

Owner:FREEDOM PHOTONICS LLC

Noise reduction mechanism of fan device and molding method of porous damping material therefor

InactiveUS20020015640A1Effective dampingMeet the noisePump componentsBlade accessoriesEngineeringNoise reduction

Porous damping material (40) is attached to an entire inner circumference of the fan shroud (20) opposing to an end of a fan (4) and is exposed to opposing space without using conventional perforated metal. Accordingly, jet noise caused by strong swirl between the fan (4) and the fan shroud (20) can be damped by the damping material (40) and impulsive sound scarcely occurs. Thus, both of the impulsive sound and the jet noise can be effectively damped, thereby securely reducing noise. The pours member (401) constituting the porous damping material (40) is a die-molding product made by a die (150) having a cavity (153).

Owner:KOMATSU LTD

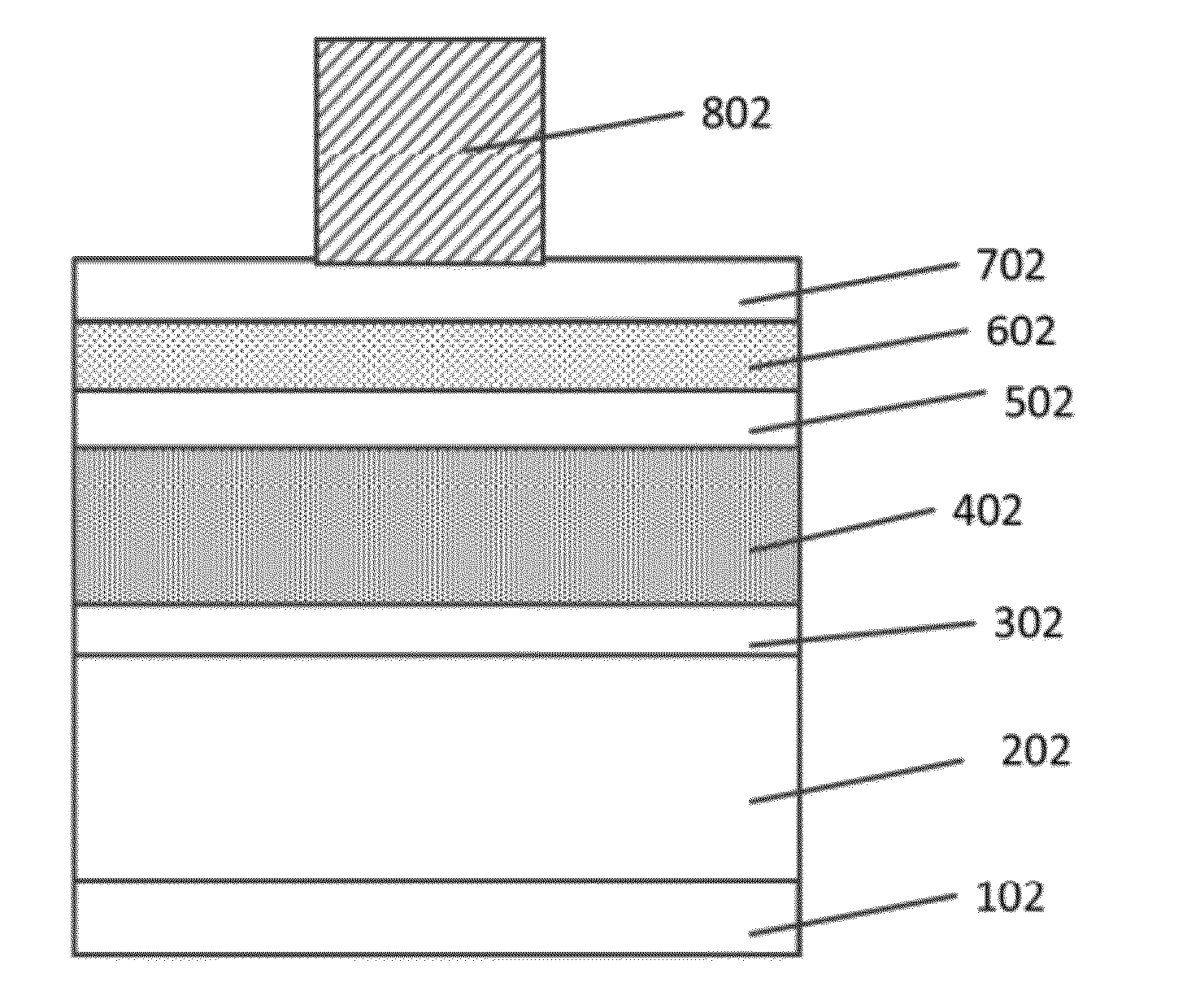

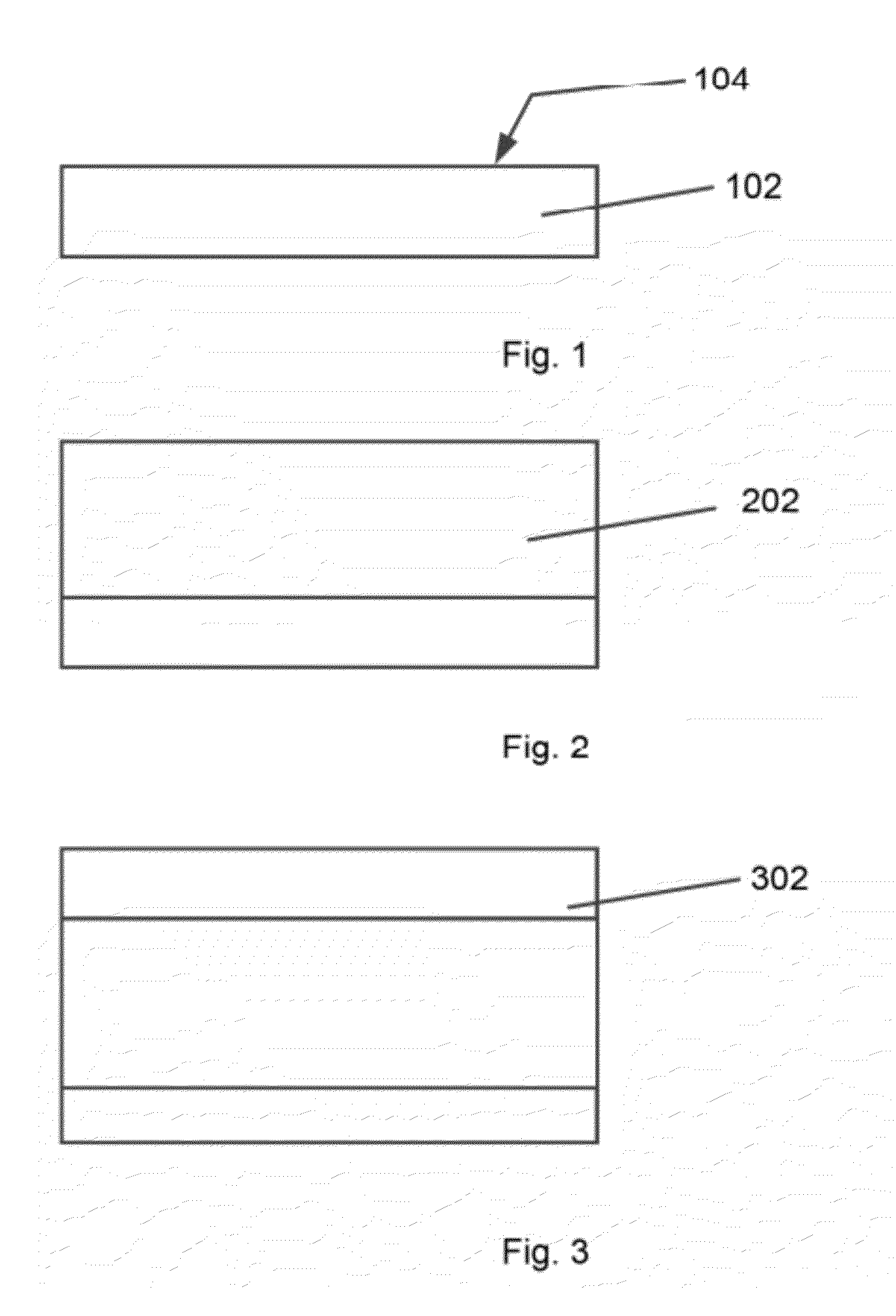

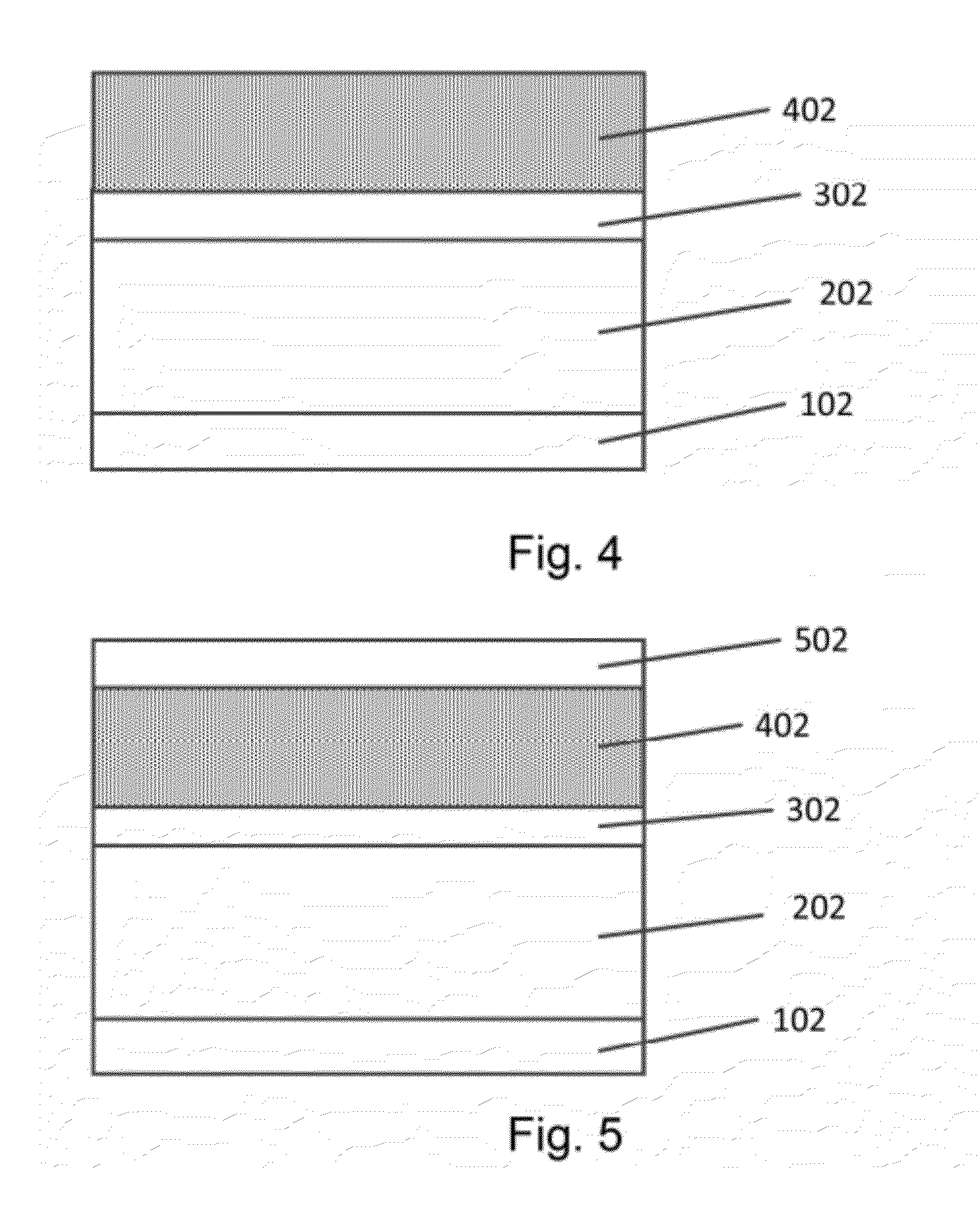

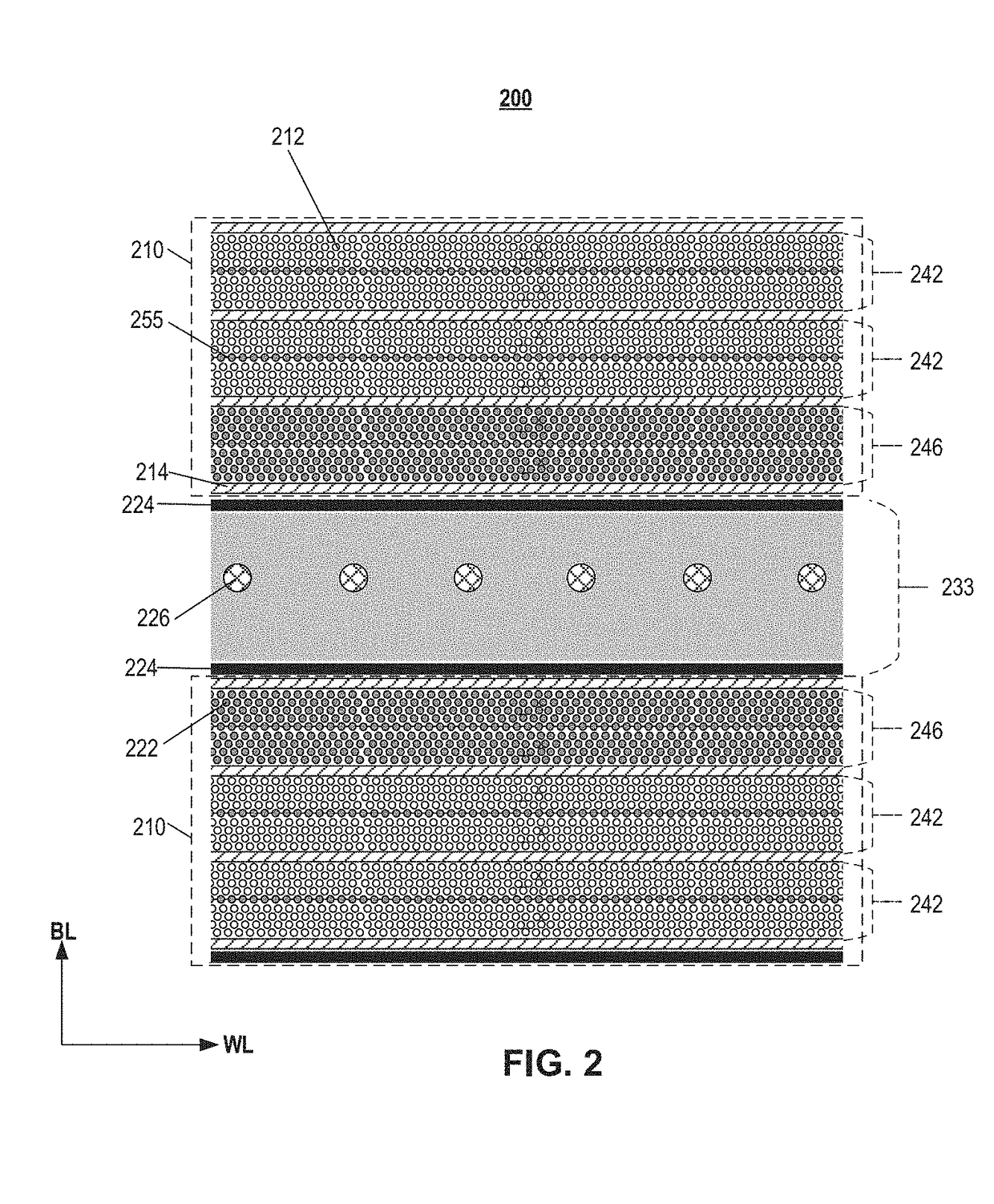

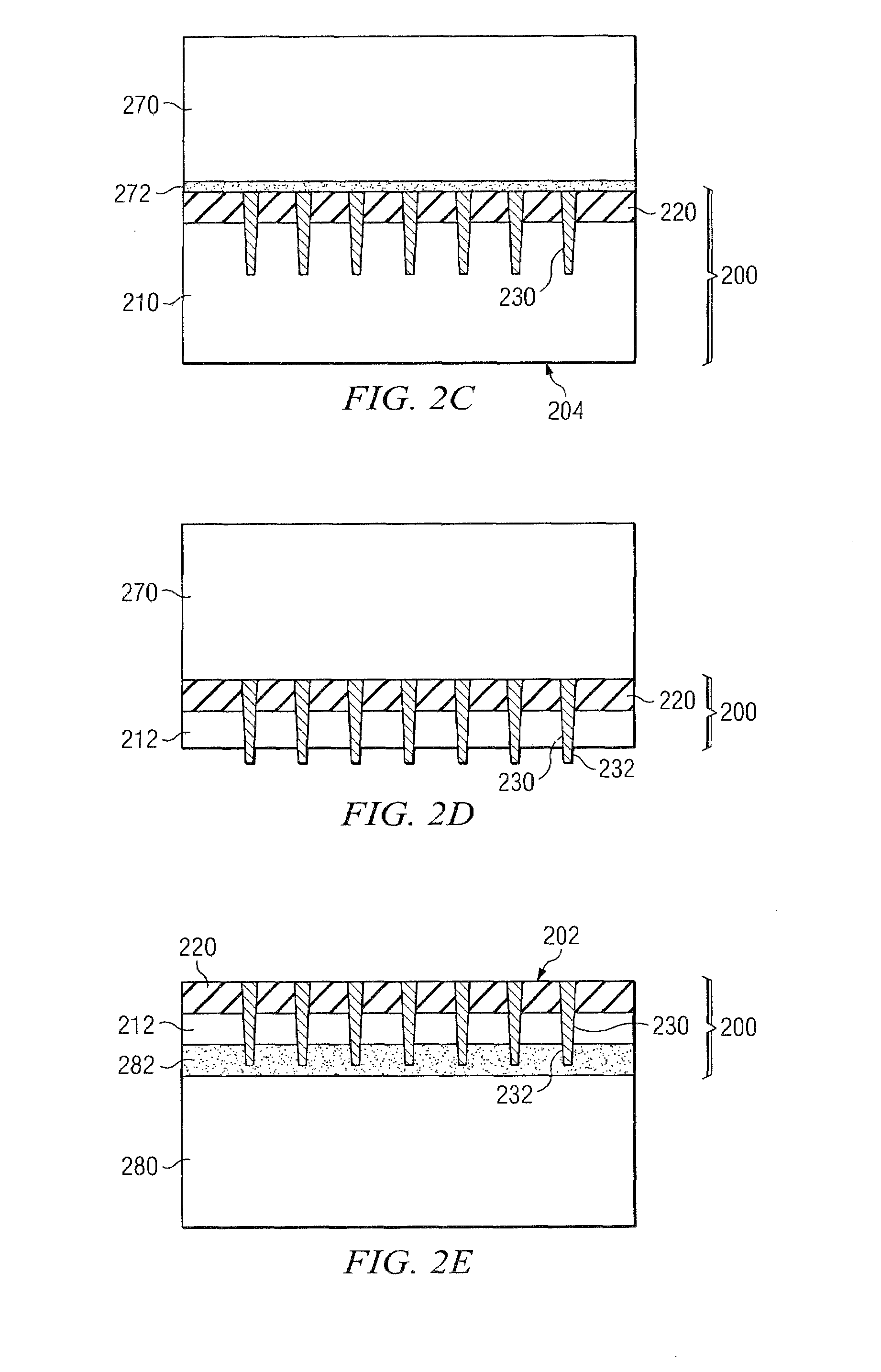

Stackable non-volatile resistive switching memory device and method

A method for forming a vertically stacked memory device. The method includes providing a semiconductor substrate having a surface region and forming a first dielectric material overlying the surface region. A first plurality of memory cells are formed overlying the first dielectric material. Each of the first plurality of memory cells includes at least a first top metal wiring structure spatially extending in a first direction, a first bottom wiring structure spatially extending in a second direction orthogonal to the first top metal wiring structure, and a first switching element sandwiched in an intersection region between the first top metal wiring structure and the first bottom metal wiring structure. In a specific embodiment, the method forms a thickness of second dielectric material overlying the first plurality of memory. A second plurality of memory cells are formed overlying the second dielectric material. Each of the second plurality of memory cells includes at least a second top metal wiring structure extending in the first direction, a second bottom wiring structure arranged spatially orthogonal to the second top metal wiring structure, and a second switching element sandwiched in an intersection region of the second top metal wiring structure and the second bottom metal wiring structure.

Owner:INNOSTAR SEMICON SHANGHAI CO LTD

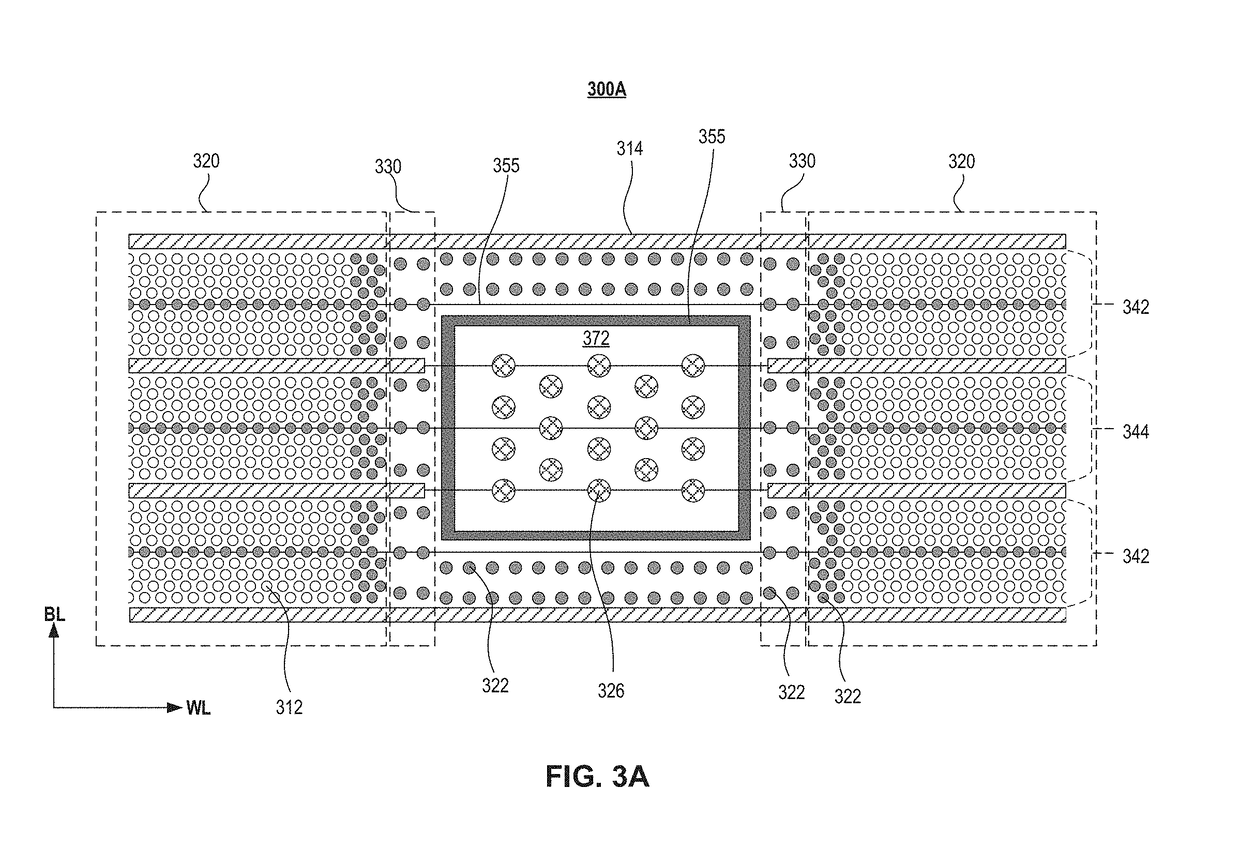

Hybrid bonding contact structure of three-dimensional memory device

ActiveUS20190057974A1Easy to etchLower Level RequirementsSemiconductor/solid-state device detailsSolid-state devicesElectricityArray data structure

Embodiments of through array contact structures of a 3D memory device and fabricating method thereof are disclosed. The memory device includes an alternating layer stack disposed on a first substrate. The alternating layer stack includes a first region including an alternating dielectric stack, and a second region including an alternating conductor / dielectric stack. The memory device further includes a barrier structure extending vertically through the alternating layer stack to laterally separate the first region from the second region, multiple through array contacts in the first region, each through array contact extending vertically through the alternating dielectric stack, an array interconnection layer in contact with the through array contacts, a peripheral circuit formed on a second substrate. and a peripheral interconnection layer on the peripheral circuit. The array interconnection layer is bonded on the peripheral interconnection layer, such that the peripheral circuit is electrically connected with at least one through array contact.

Owner:YANGTZE MEMORY TECH CO LTD

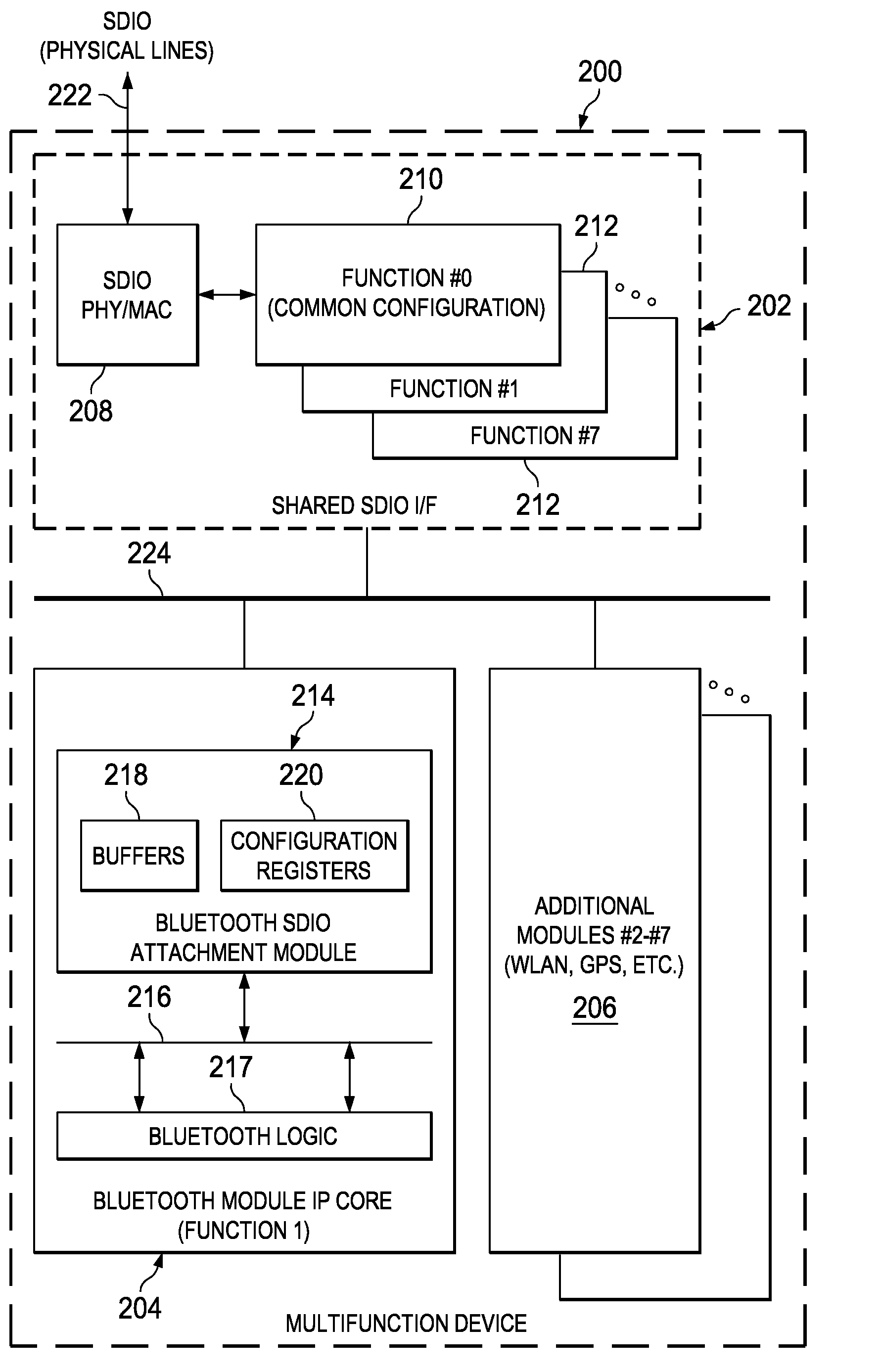

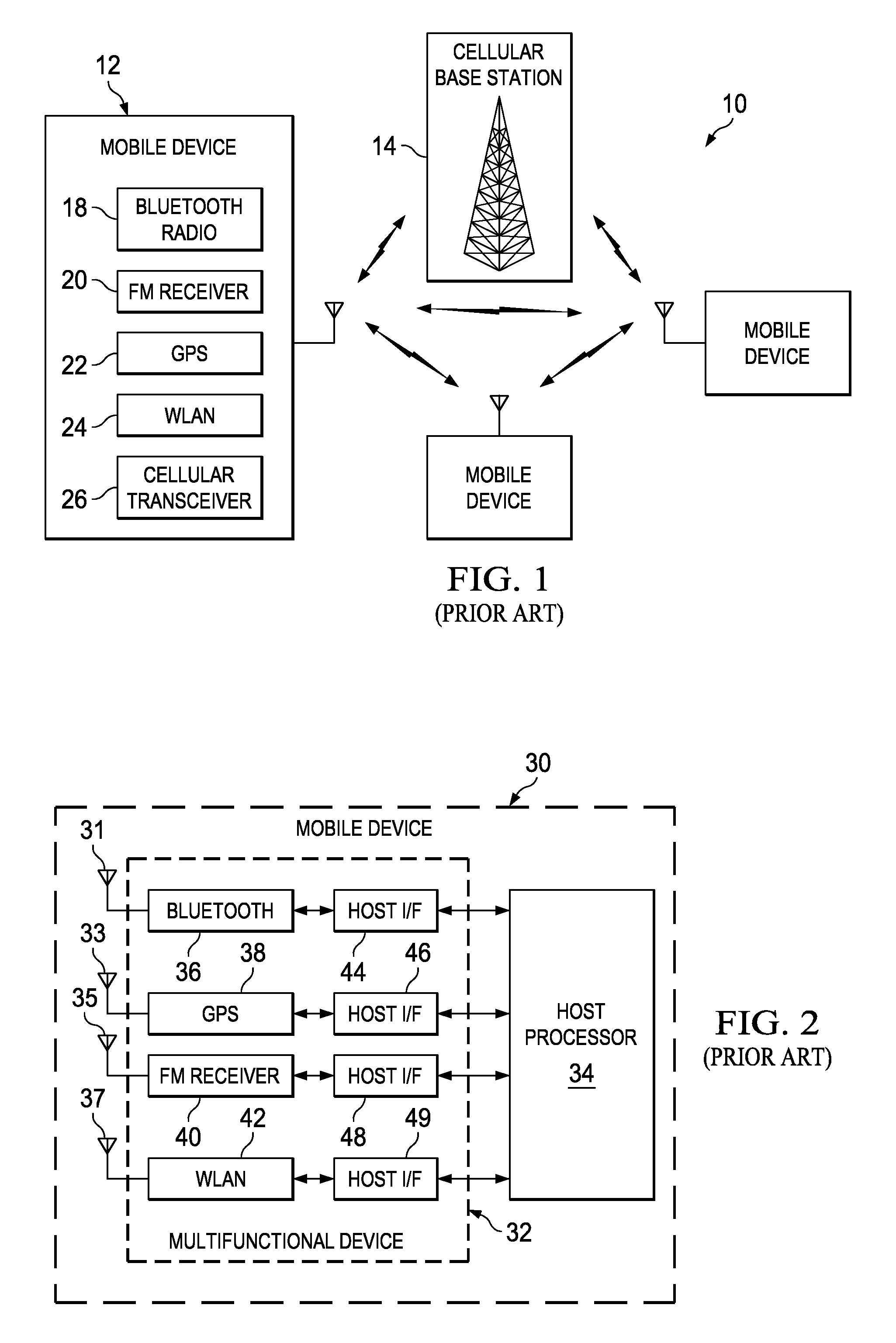

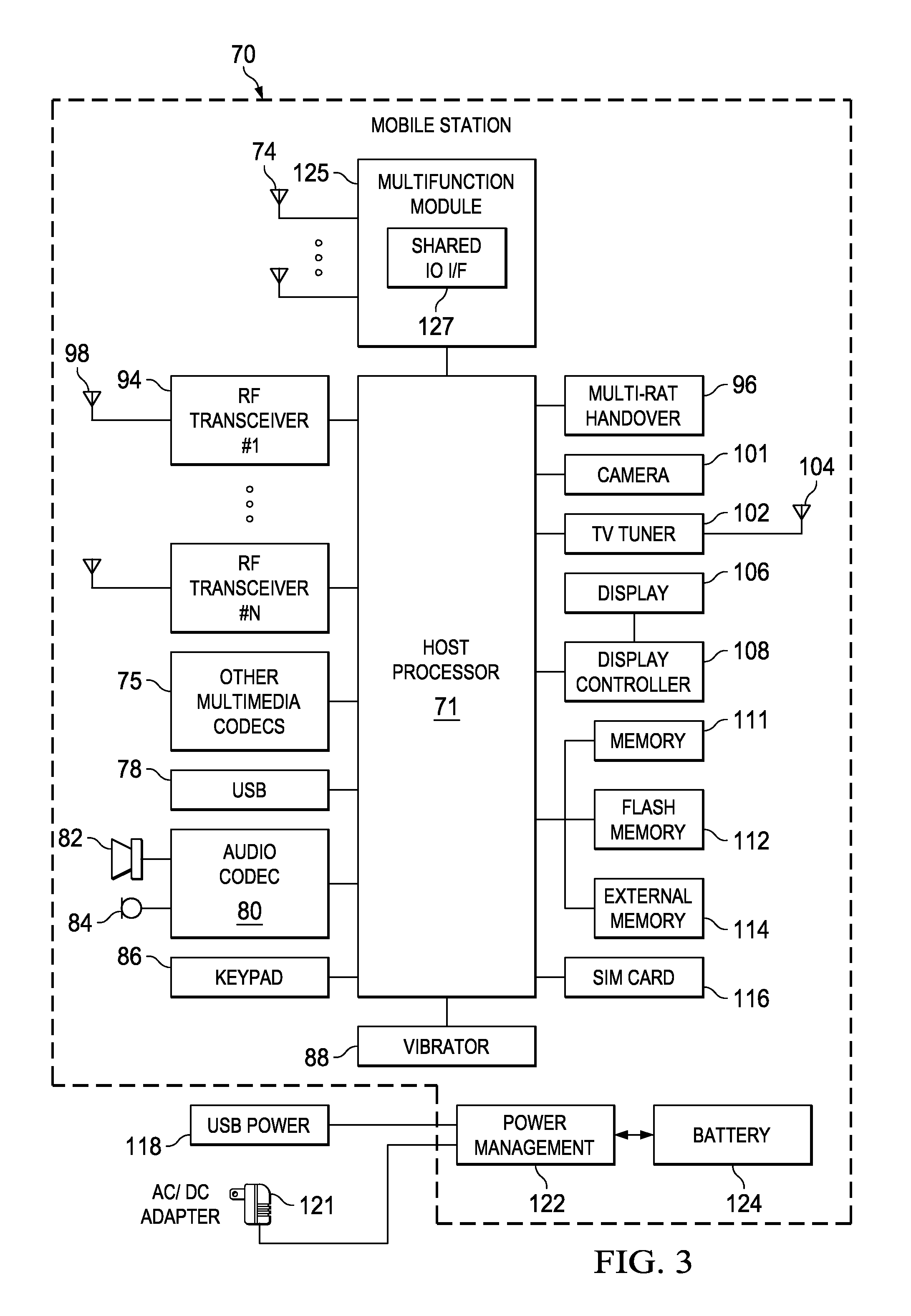

Unified input/output controller for integrated wireless devices

ActiveUS20100011128A1Reduce consumptionReduce countEnergy efficient ICTEnergy efficient computingProtocol processingBluetooth

A novel and useful apparatus for and method of a unified IO controller well suited for use in integrated wireless devices incorporating multiple functions. The unified IO controller is operative to provide a single host interface PHY / MAC that is shared among all functions on the controller. The invention provides an IO protocol handler comprising common and unified logic that provides IO access to any function on the device. The common and unified IO PHY interface logic is shared between multiple functions within the same device (e.g., WLAN, GPS, Bluetooth, etc.). This implementation provides optimized hardware partitioning in which common SDIO logic serves multiple functions thereby eliminating the need to provide a protocol handler for each function, reducing pin count, power consumption and die size, since the SDIO protocol handling is implemented in a shared module.

Owner:TEXAS INSTR INC

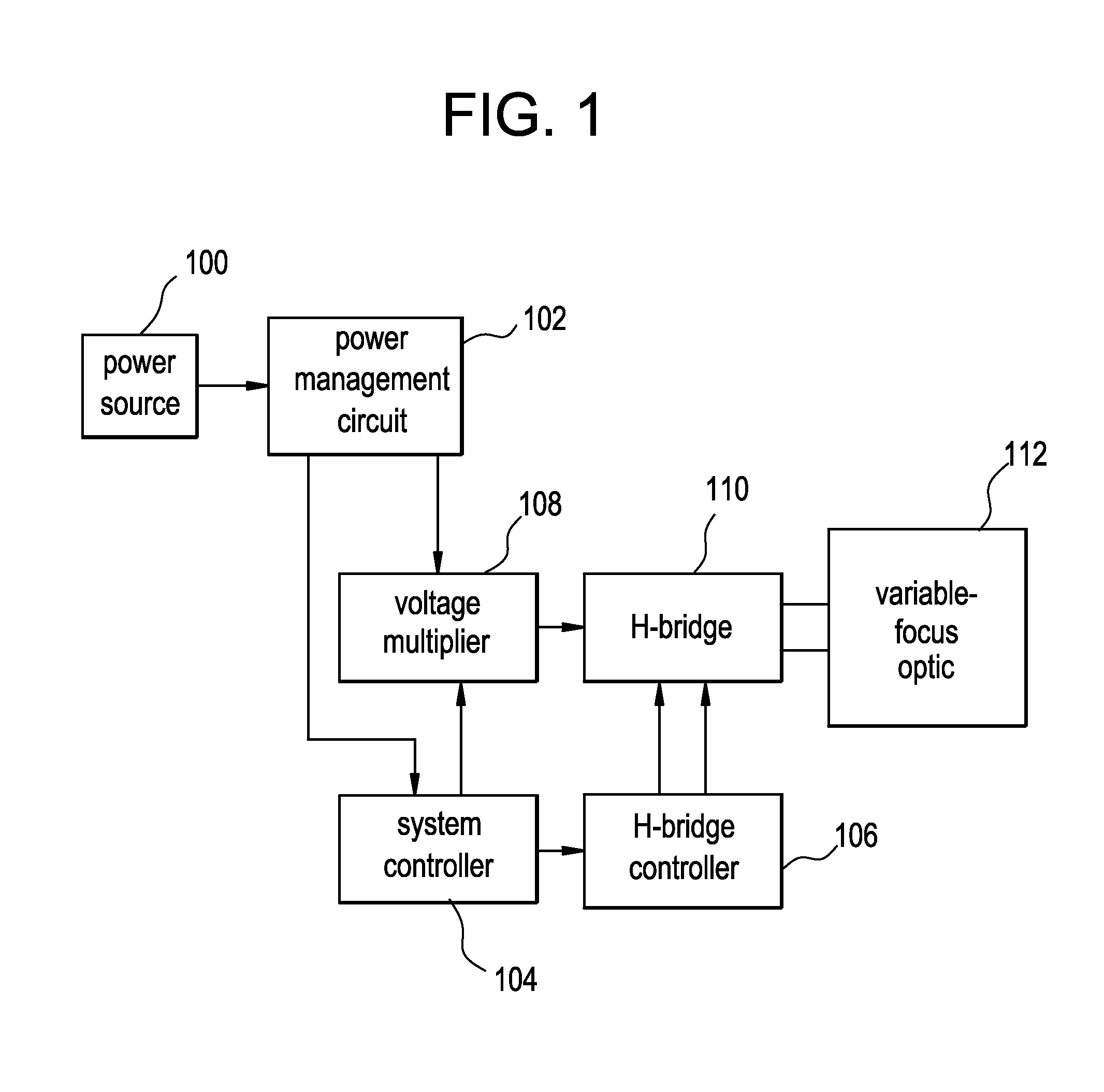

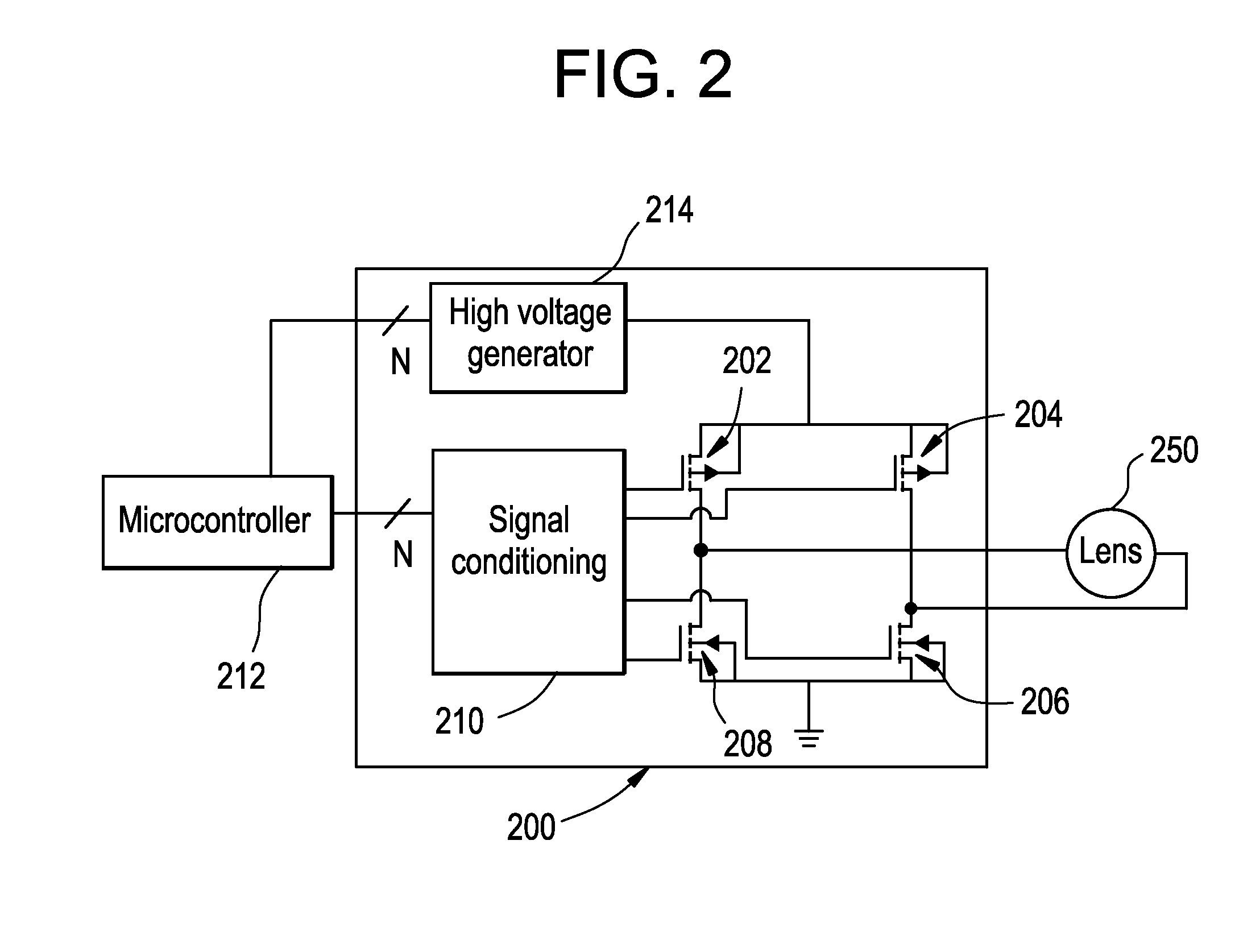

Lens driver for variable-optic electronic ophthalmic lens

ActiveUS20130258275A1Avoid excessive currentLow voltage requirementIntraocular lensOptical partsOphthalmological deviceCamera lens

A lens driver or lens driver circuitry for an ophthalmic apparatus comprising an electronic system which actuates a variable-focus optic is disclosed herein. The lens driver is part of an electronic system incorporated into the ophthalmic apparatus. The electronic system includes one or more batteries or other power sources, power management circuitry, one or more sensors, clock generation circuitry, control algorithms and circuitry, and lens driver circuitry. The lens driver circuitry includes one or more power sources, one or more high voltage generators and one or more switching circuits.

Owner:JOHNSON & JOHNSON VISION CARE INC

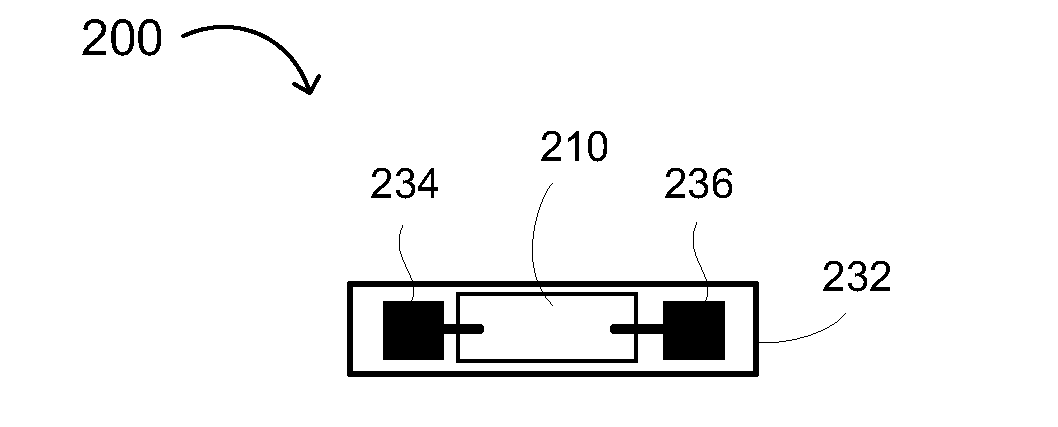

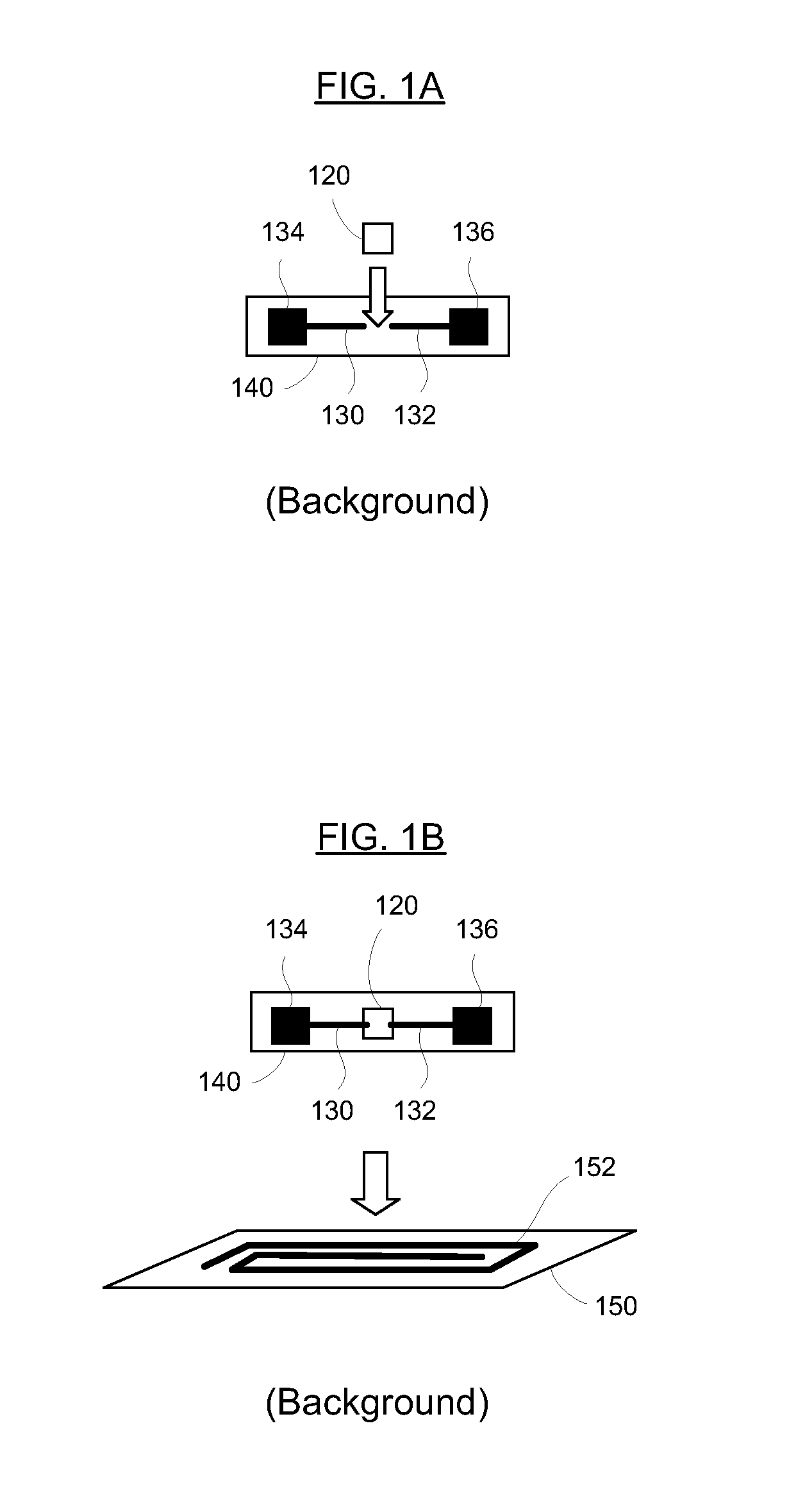

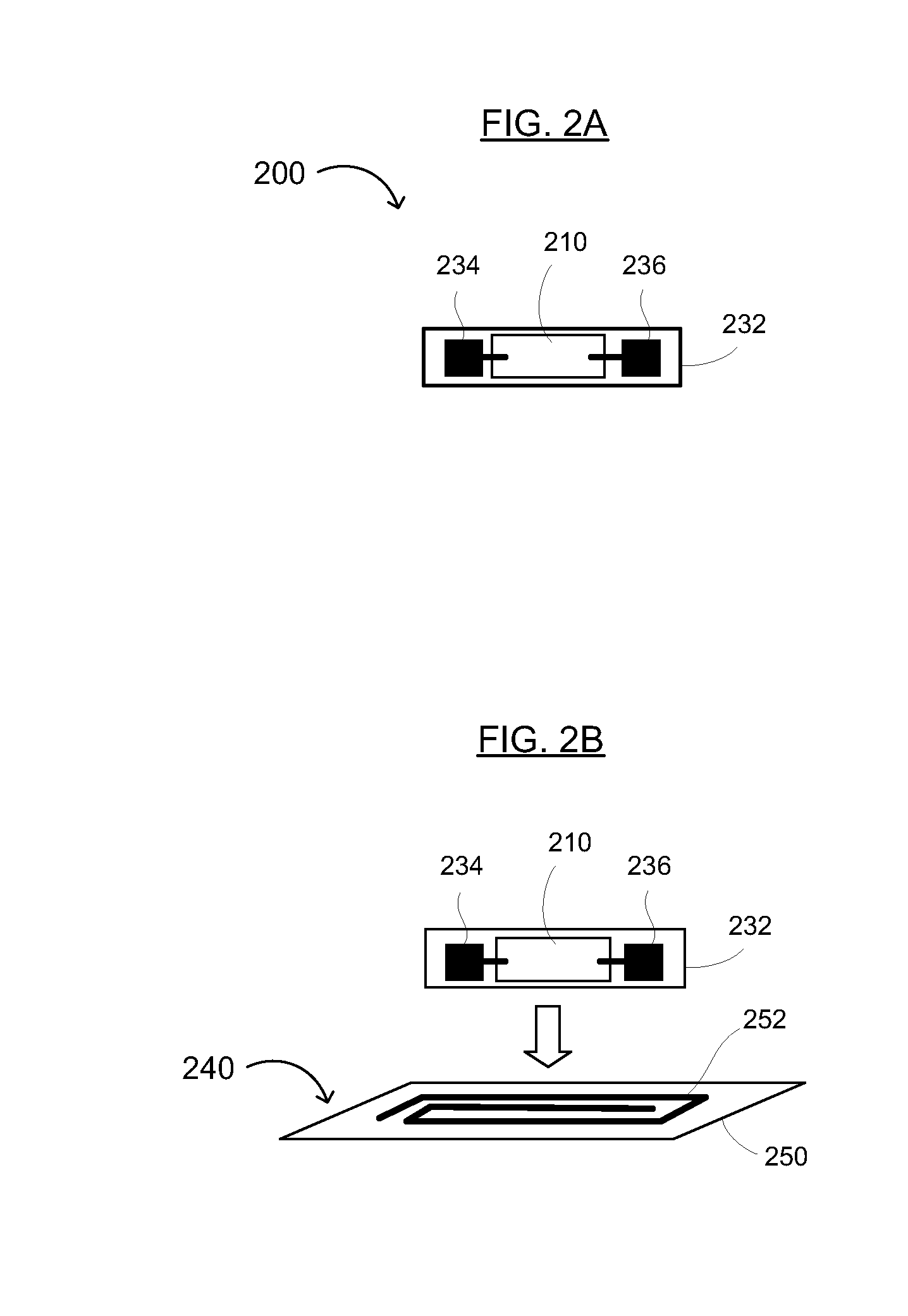

Wireless Devices Including Printed Integrated Circuitry and Methods for Manufacturing and Using the Same

InactiveUS20090095818A1Leverage low capital expenditure and operating costLow costPrinted circuit manufactureSubscribers indirect connectionElectricityElectrical devices

Printed integrated circuitry and attached antenna and / or inductor for sensors, electronic article surveillance (EAS), radio frequency (RF) and / or RF identification (RFID) tags and devices, and methods for its manufacture. The tag generally includes printed integrated circuitry on one carrier and an antenna and / or inductor on another carrier, the integrated circuitry being electrically coupled to the antenna and / or inductor. The method of manufacture generally includes of printing an integrated circuit having a plurality of first pads on a carrier, forming an antenna and / or inductor having a plurality of second pads on a substrate, and attaching at least two of the first pads of the printed integrated circuit to corresponding second pads of the antenna and / or inductor. The present invention advantageously provides a low cost RFID tag capable of operating at MHz frequencies that can be manufactured in a shorter time period than conventional RFID tags that manufacture all active electrical devices on a conventional wafer.

Owner:ENSURGE MICROPOWER ASA

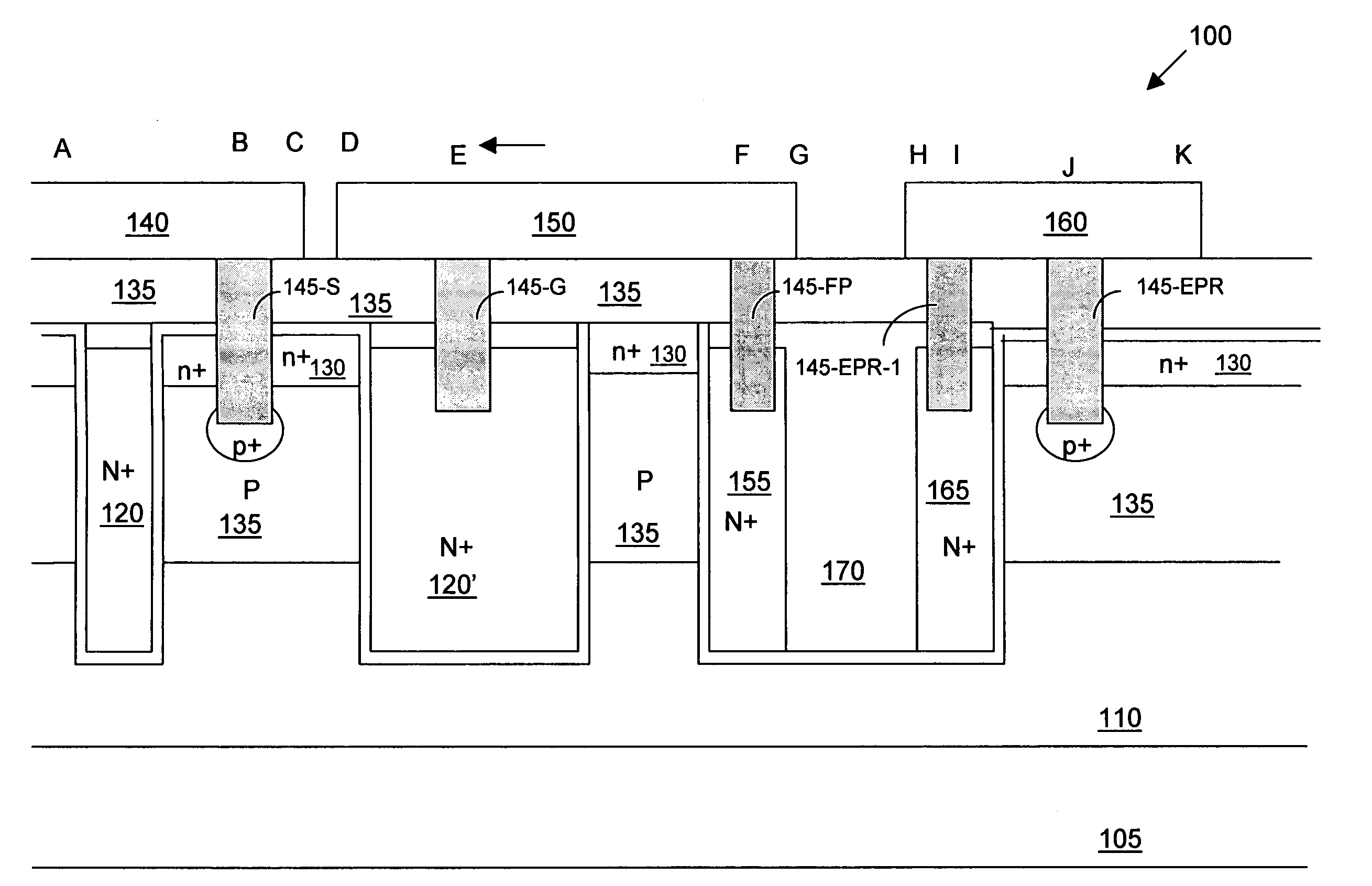

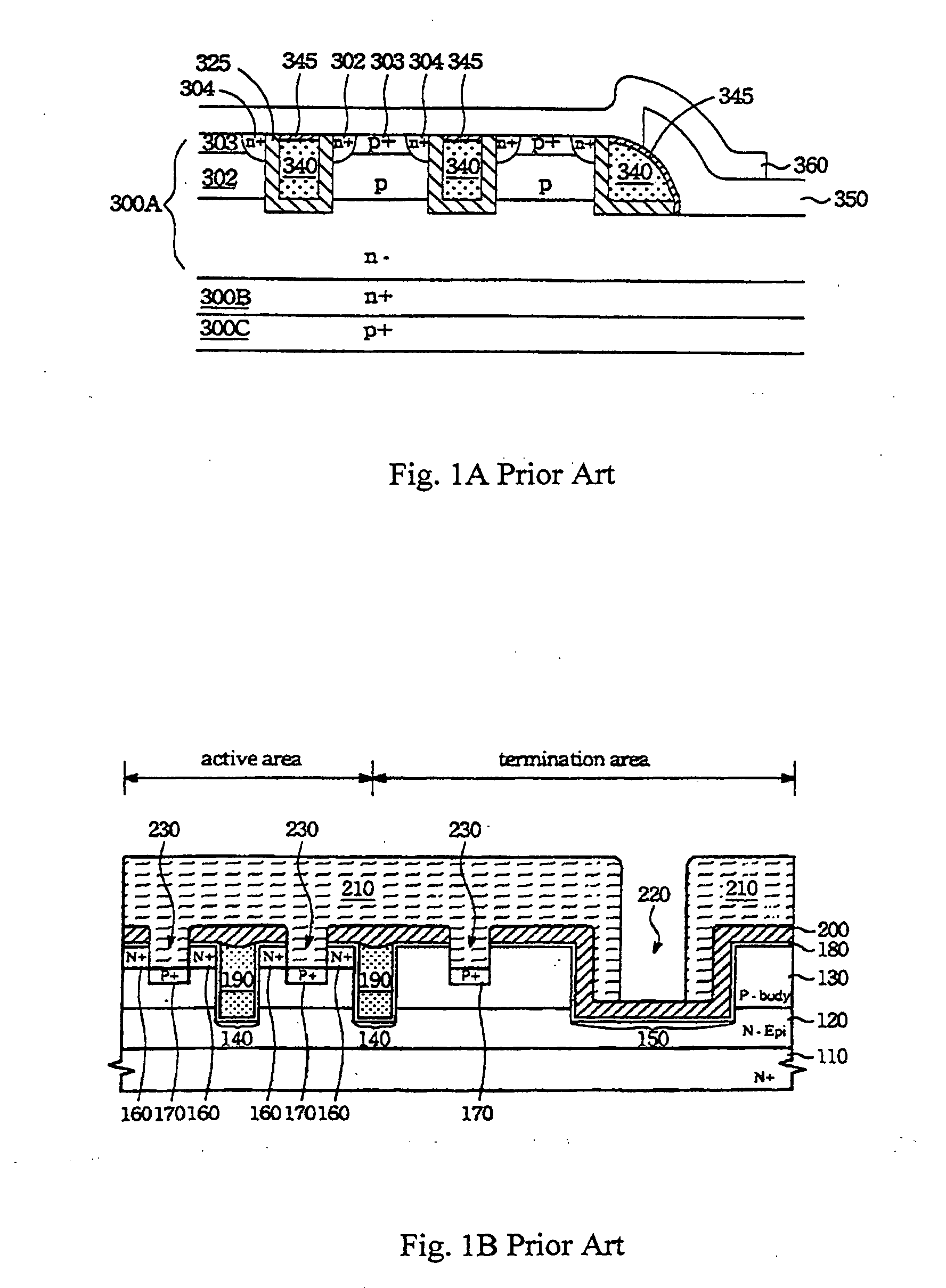

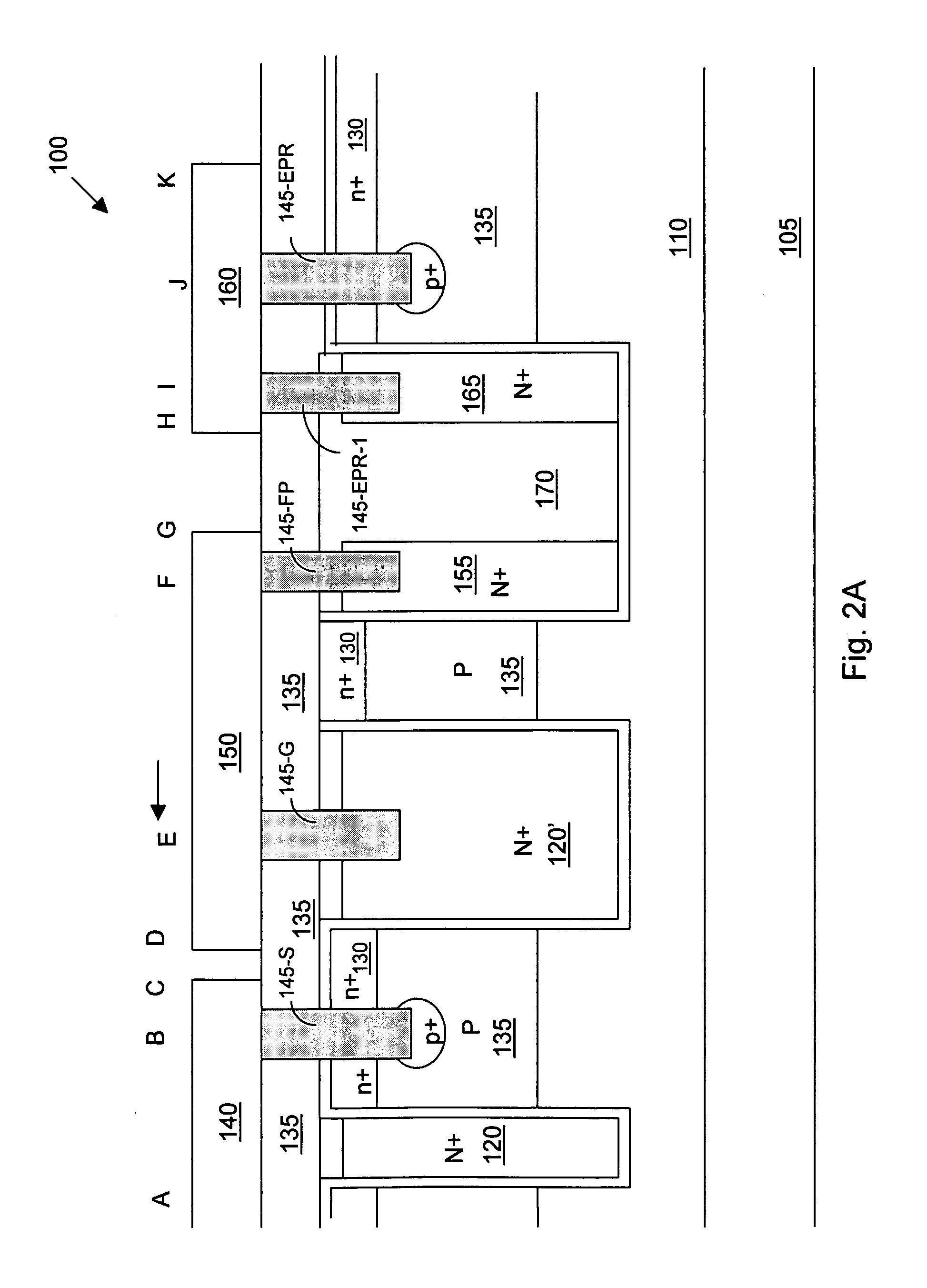

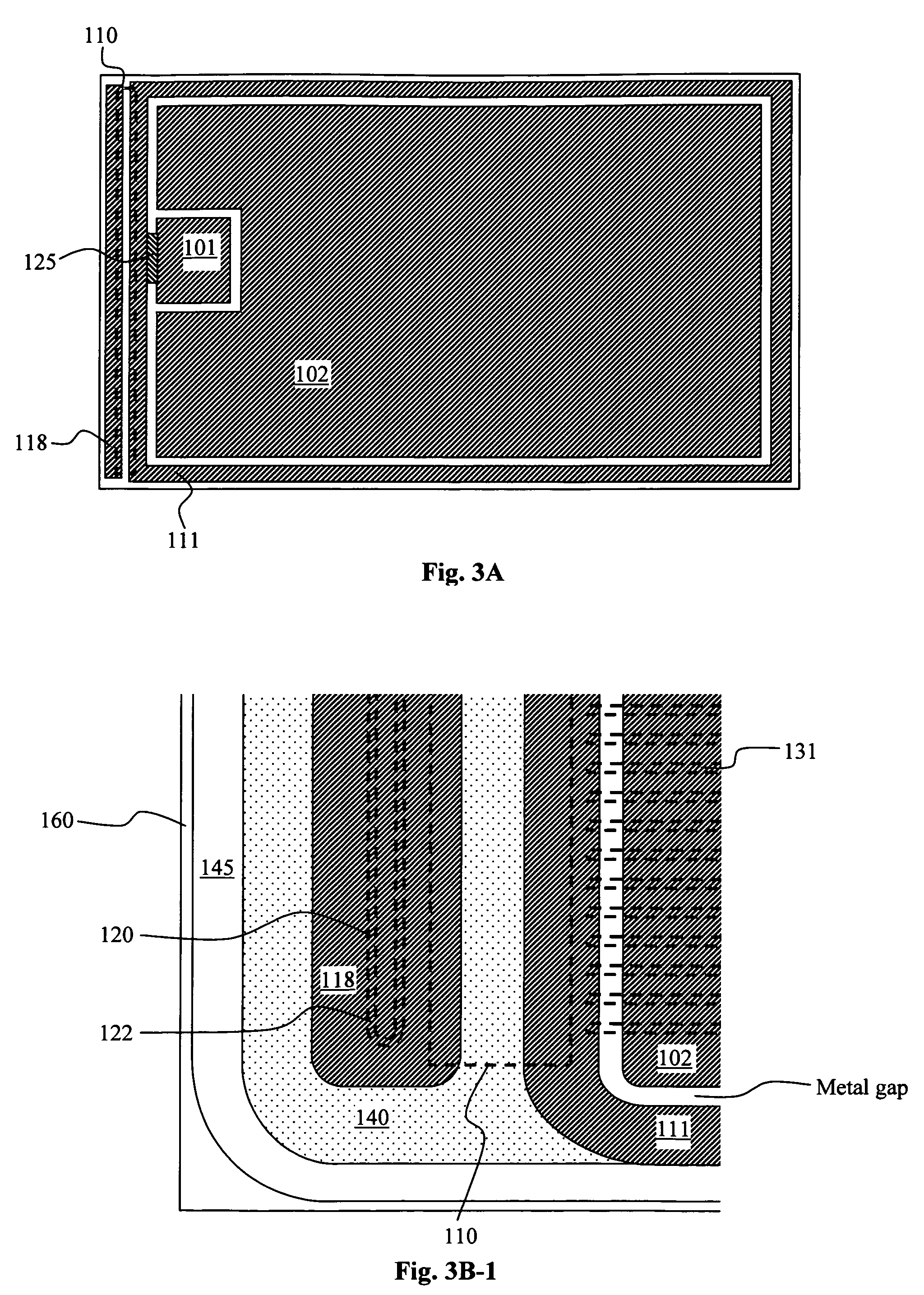

Trenched mosfet device configuration with reduced mask processes

A semiconductor power device comprising a termination area that includes a trenched gate runner electrically connected to a trenched gate of said semiconductor power device. The semiconductor power device further includes a trenched field plate disposed in a trench opened in the termination area and the trenched field plate is electrically connected to the trenched gate runner. A gate runner contact trench and a field plate contact trench opened through an insulation layer covering the gate runner and the trenched field plate for extending into a doped gate dielectric filling in the trenched gate runner and the field plate wherein the gate runner contact trench and the field plate contact trench filled with a gate runner contact plug and a field plate contact plug respectively. A gate metal disposed on top of the insulation layer to electrically contact the gate runner contact plug and the field plate contact plug for electrically interconnecting the trenched gate runner and the trenched field plate.

Owner:FORCE MOS TECH CO LTD

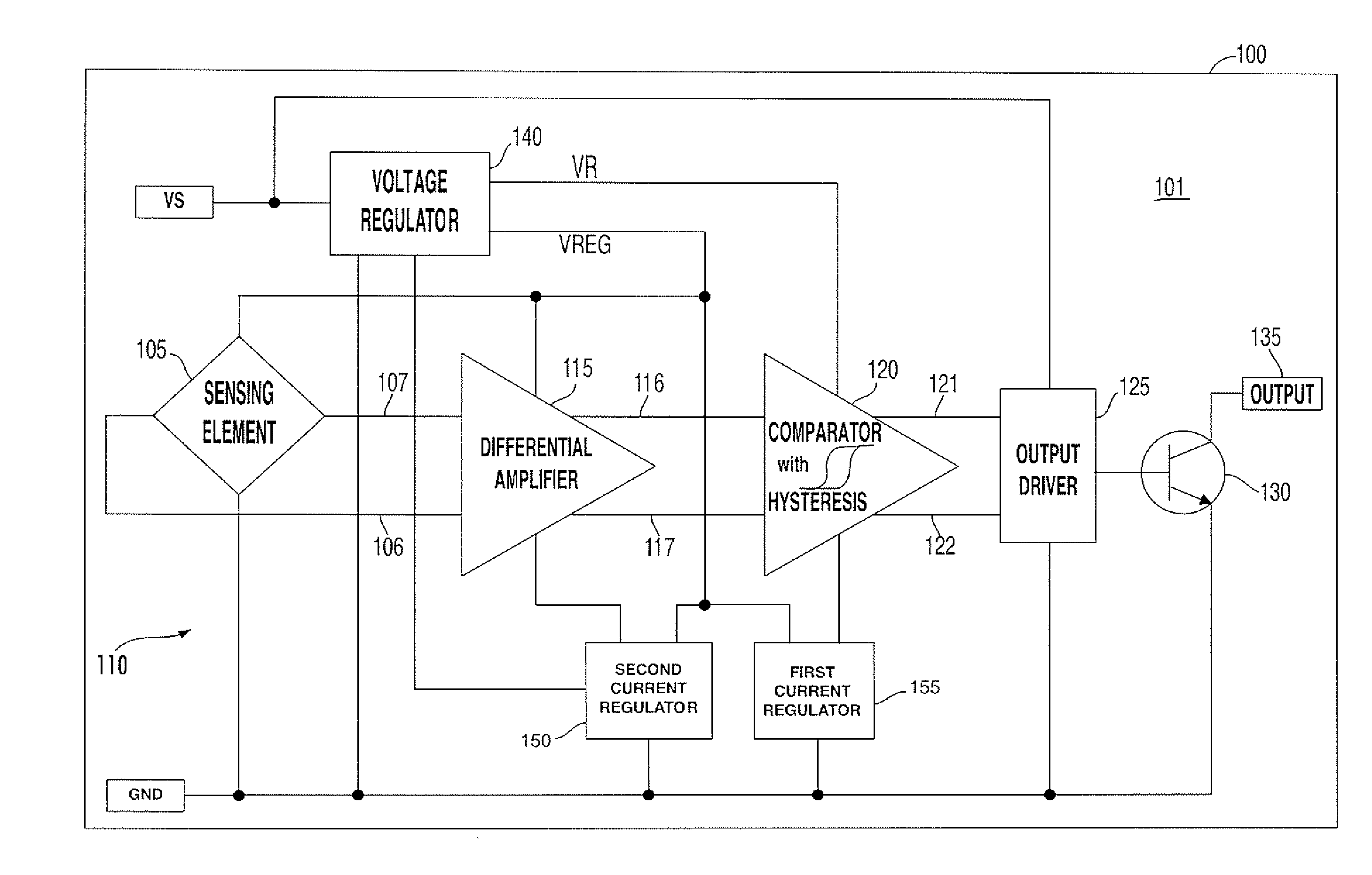

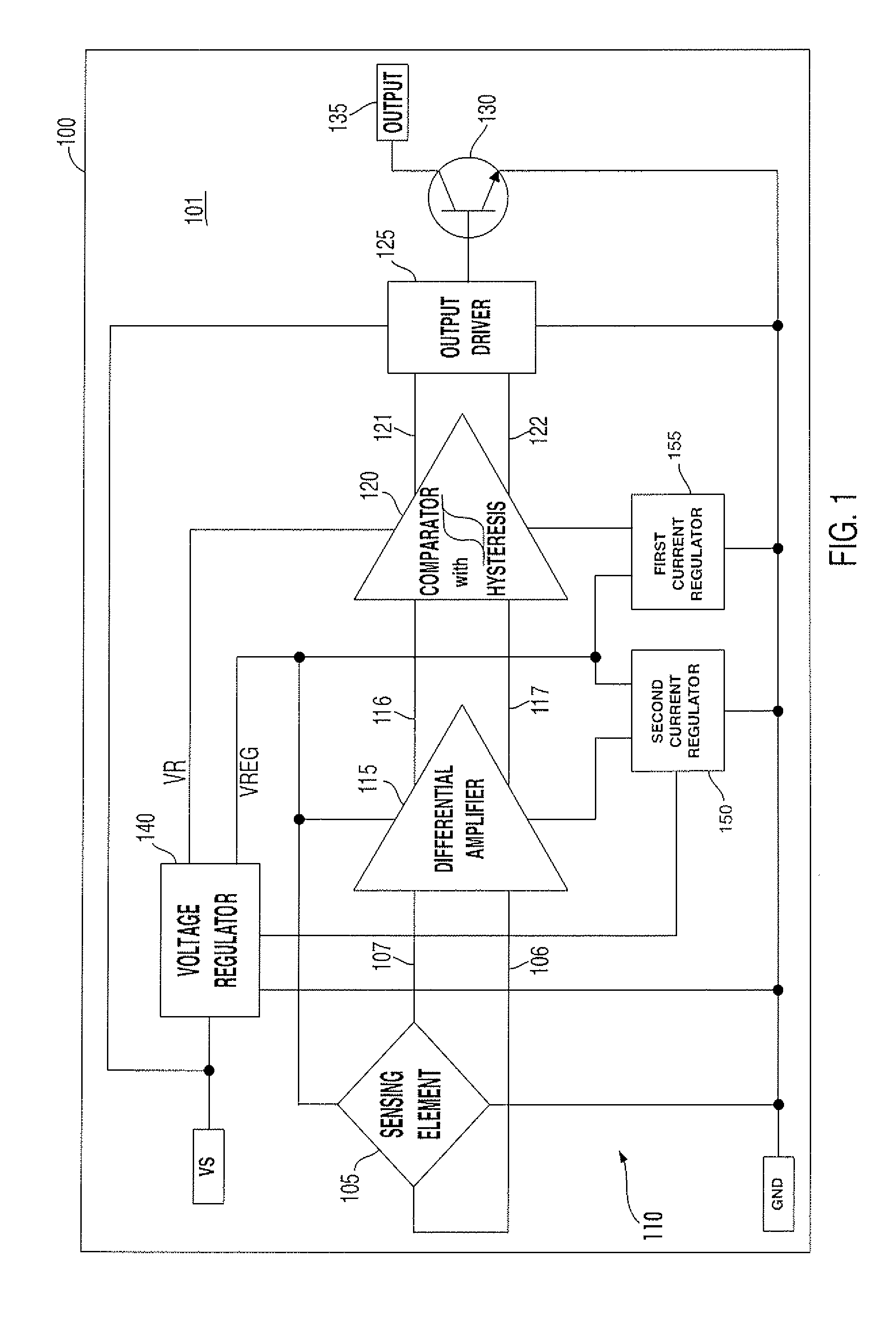

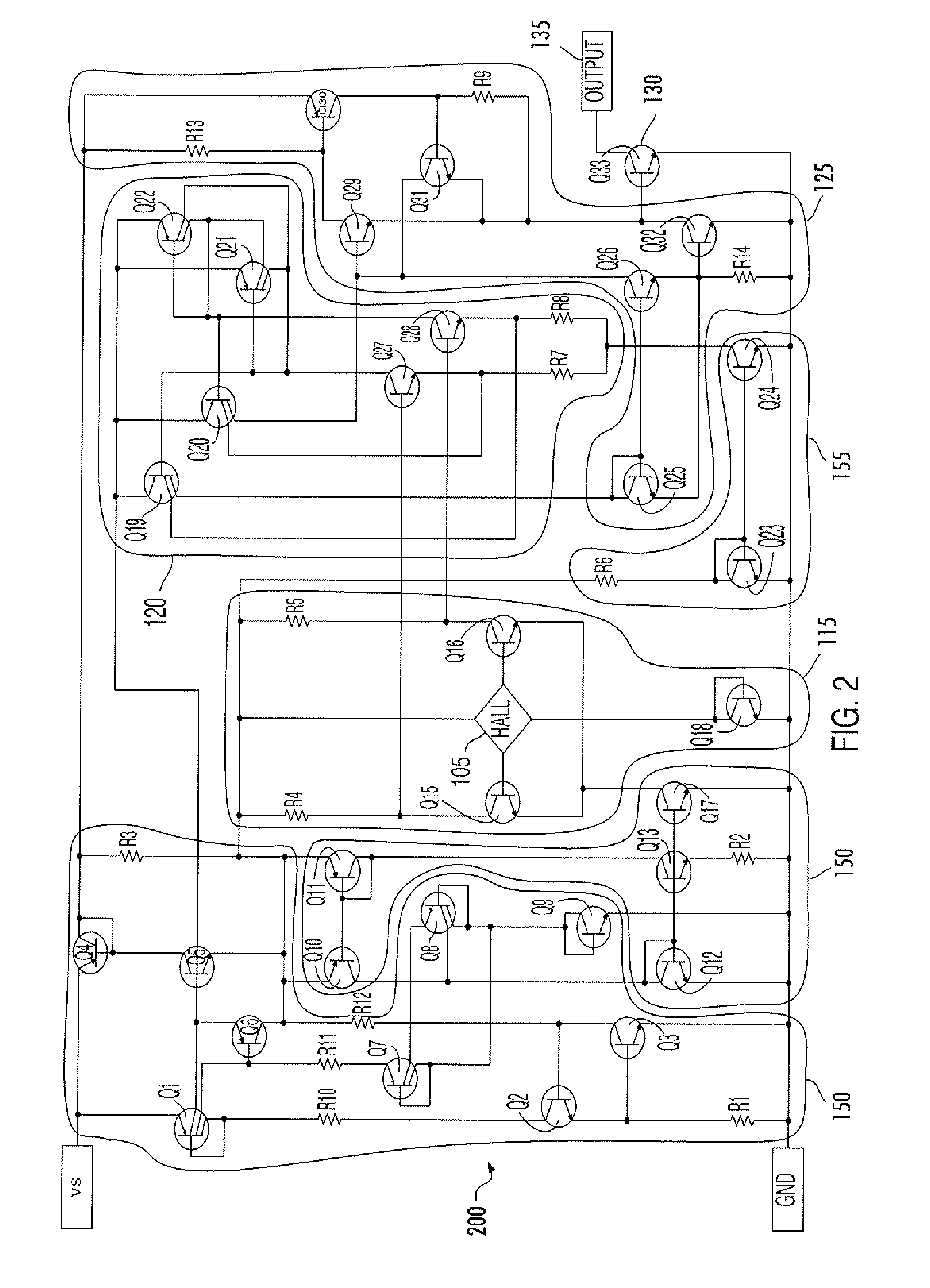

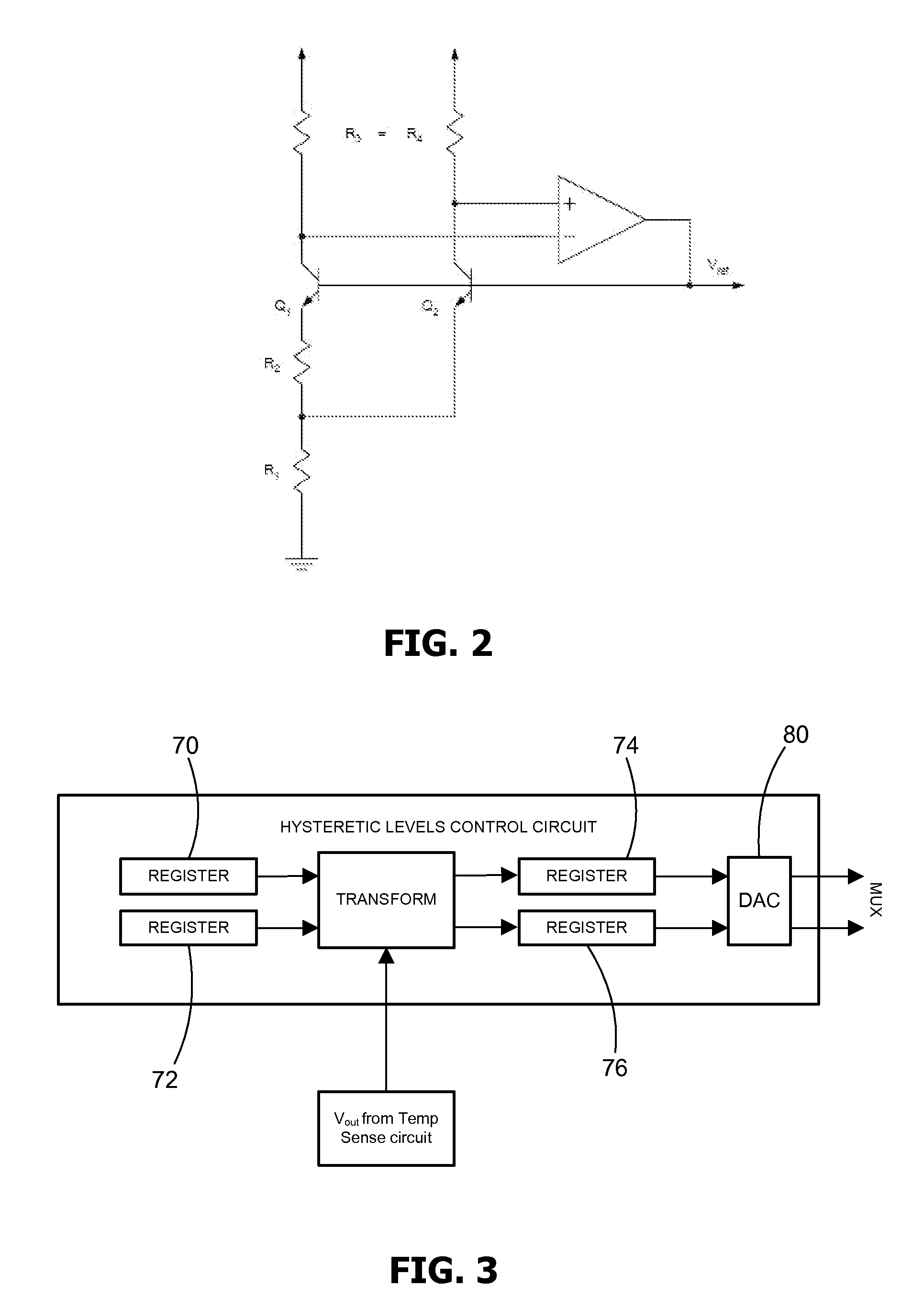

Comparator circuit having latching behavior and digital output sensors therefrom

ActiveUS20100045268A1Lower power requirementCost reductionCurrent/voltage measurementSolid-state devicesComparators circuitsVoltage regulation

A digital output sensor (110) includes a sensing structure (105) including at least one sensing element. The sensing structure (105) outputs a differential sensing signal (106, 107). An integrated circuit (100) includes a substrate (101) including signal conditioning circuitry for conditioning the sensing signal (106, 107). The signal conditioning circuitry includes a differential amplifier (115) coupled to receive the sensing signal and provide first and second differential outputs (116, 117), and a comparator (120) having input transistors (Q27, Q28) coupled to receive outputs from the differential amplifier. The comparator (120) also includes first and second current-mirror loads (Q19 / Q21 and Q22 / Q20) coupled to the input transistors (Q27, Q28) in a cross coupled configuration to provide hysteresis, wherein the first and second current-mirror loads provide differential drive currents (121,122). An output driver (125) is coupled to receive the differential drive currents (121, 122). An output stage (130) includes at least one output transistor which is coupled to the output driver for providing a digital output for the sensor. A voltage regulator (140) is coupled to receive a supply voltage (VS) and output at least one regulated supply voltage (VREG), wherein the regulated supply voltage is coupled to the sensing structure (105), the differential amplifier (115) and the comparator (120).

Owner:HONEYWELL INT INC

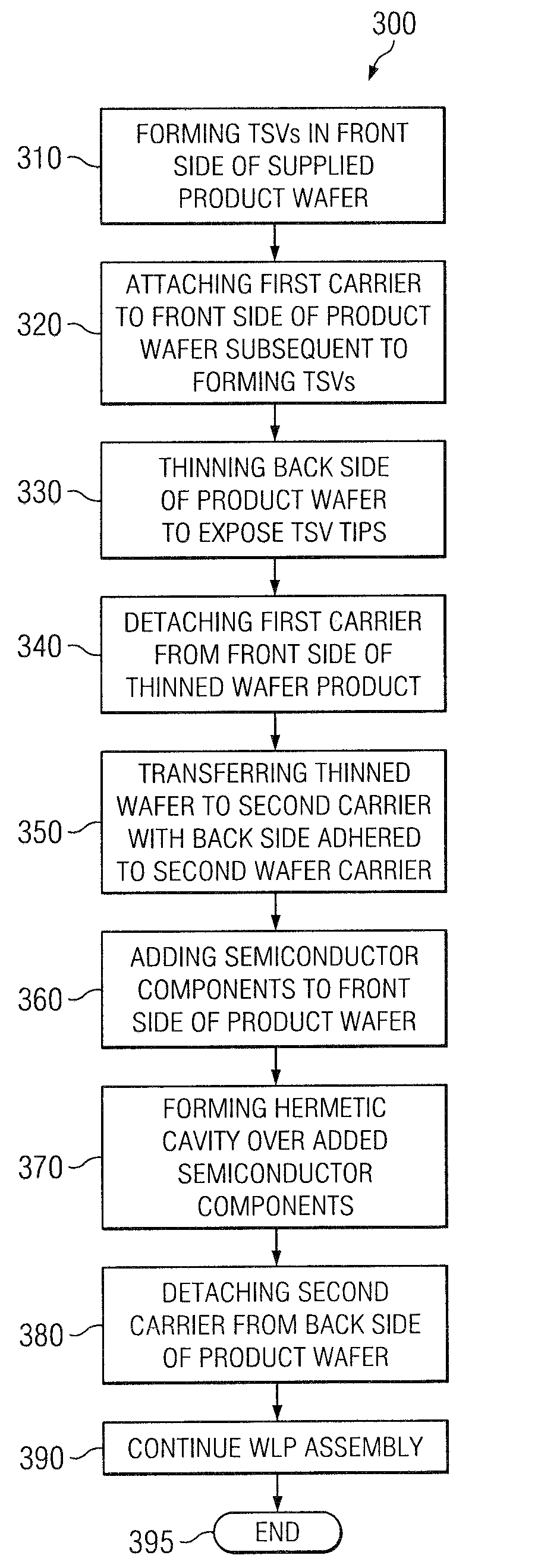

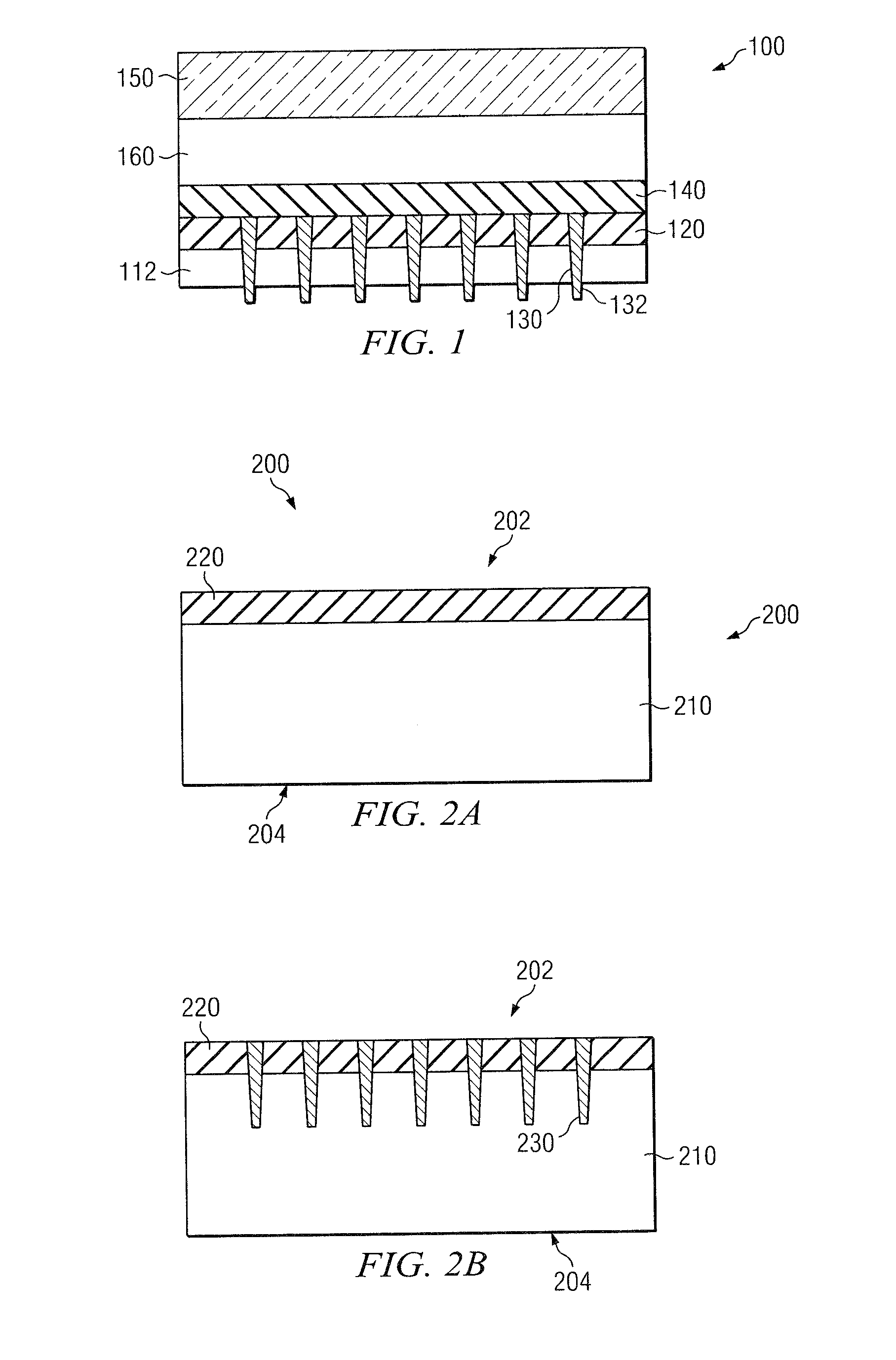

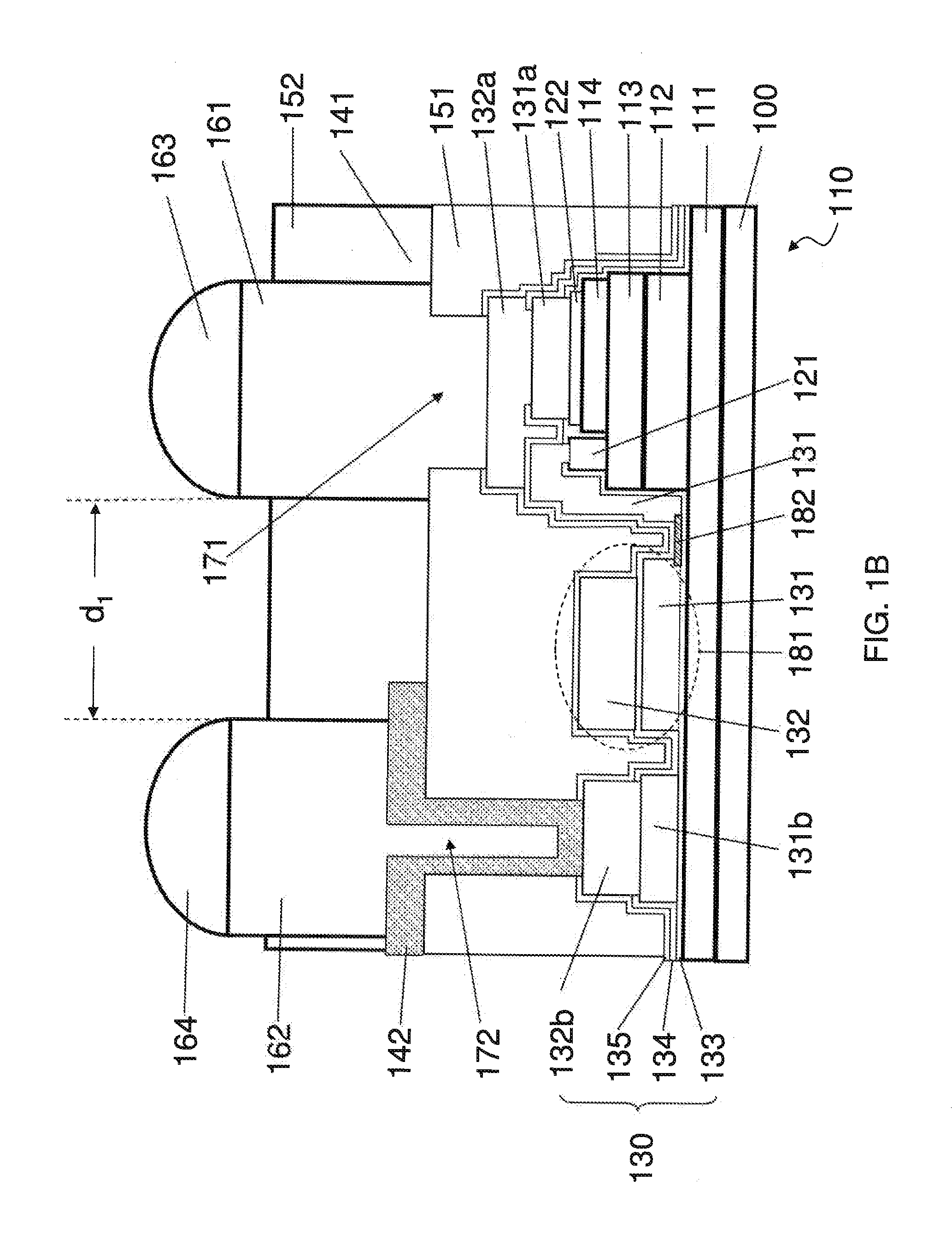

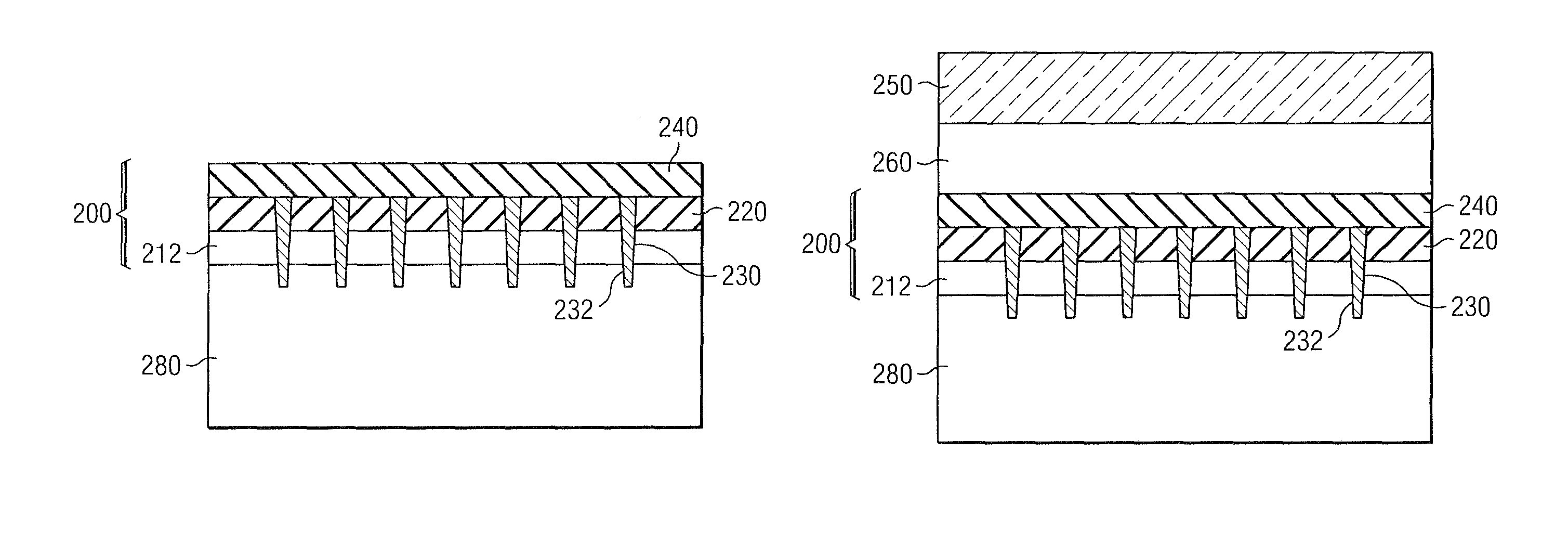

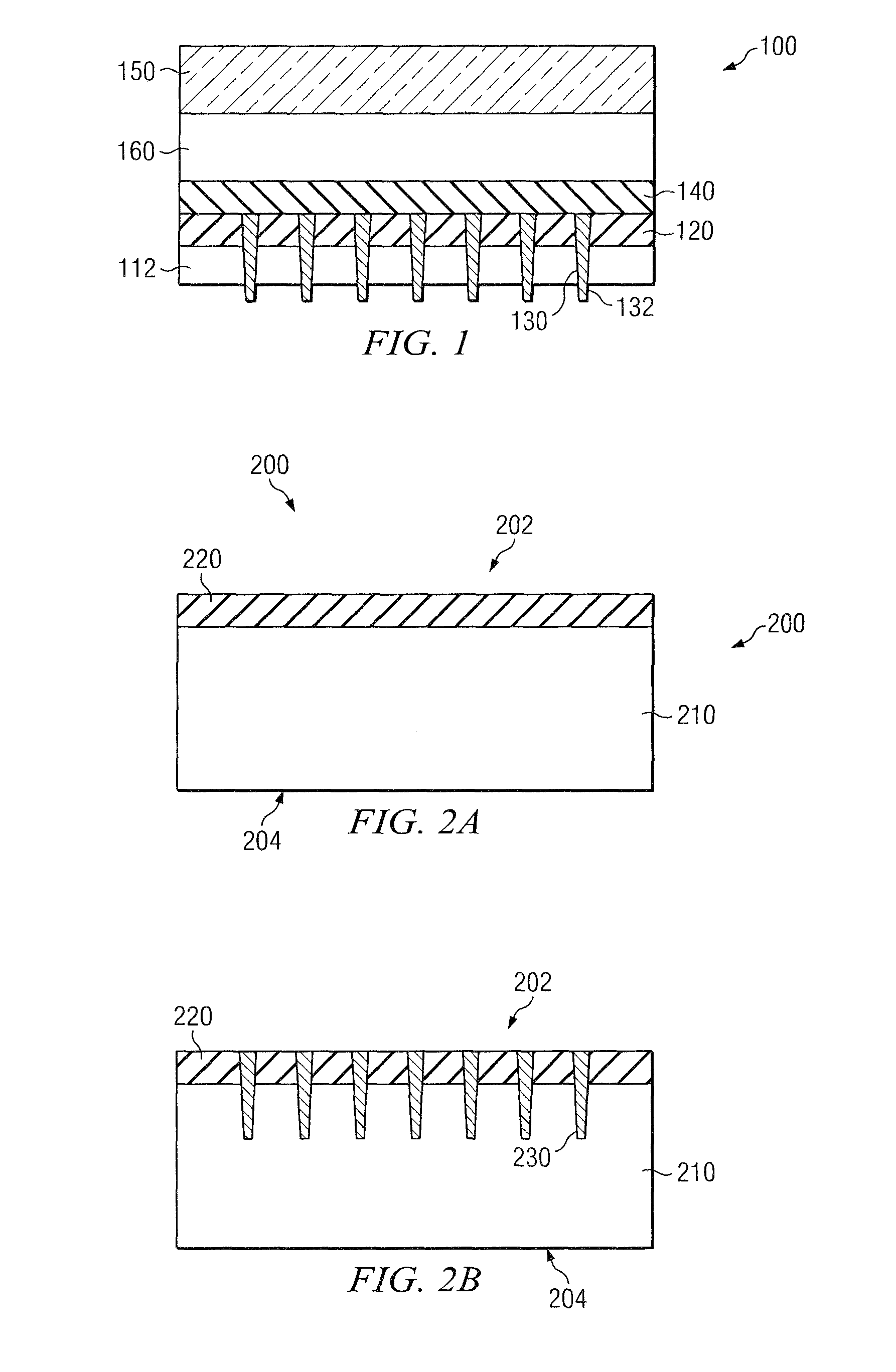

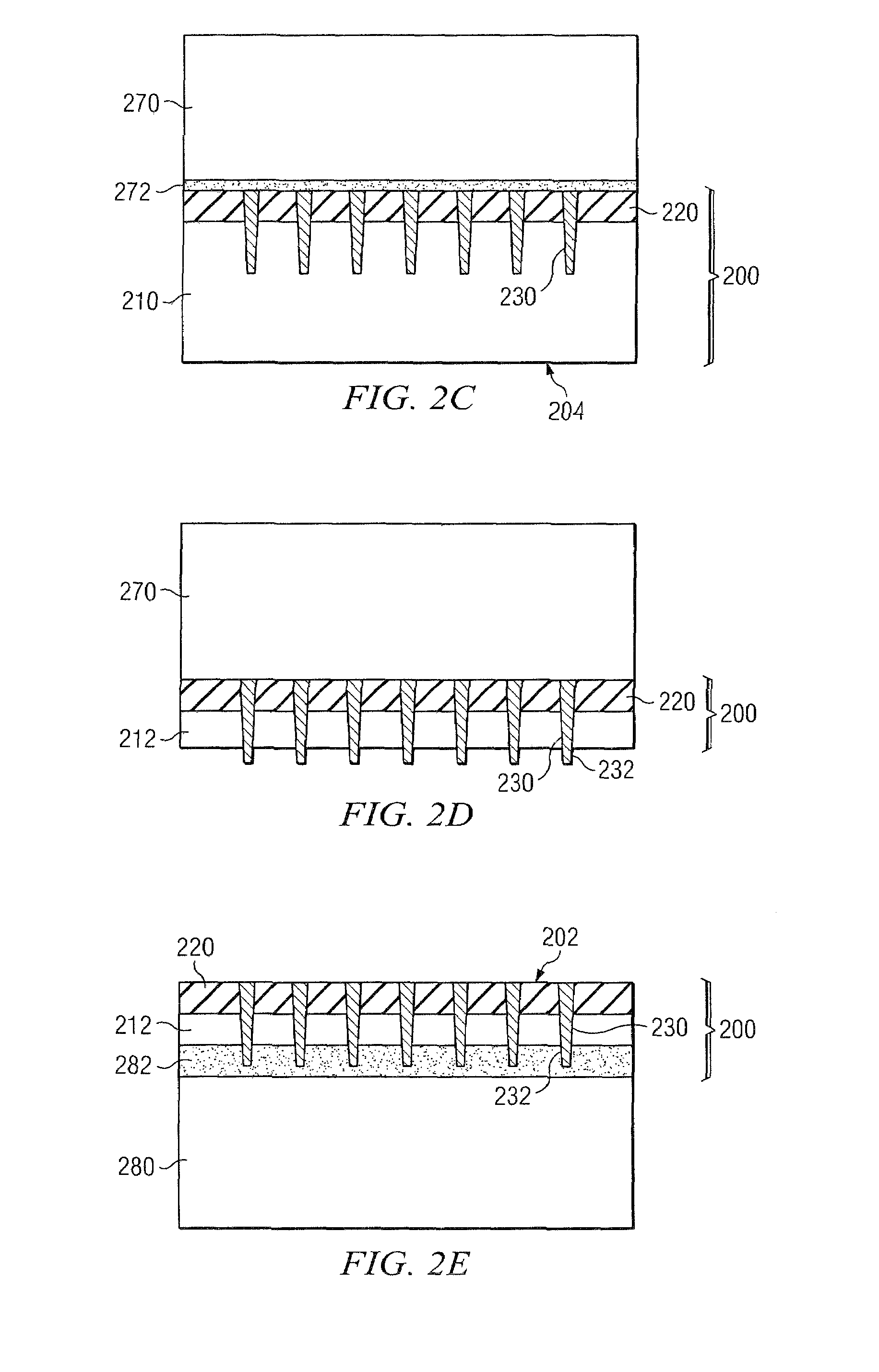

Double wafer carrier process for creating integrated circuit die with through-silicon vias and micro-electro-mechanical systems protected by a hermetic cavity created at the wafer level

ActiveUS20090280602A1Avoid sizeReduce mold sizeSemiconductor/solid-state device detailsSolid-state devicesEngineeringSilicon

A TSV-MEMS packaging process is provided. The process includes forming TSVs in the front side of the product wafer, and attaching a first carrier to the front side of the product wafer, subsequent to forming TSVs. The process further includes thinning the back side of the product wafer to expose TSV tips, detaching the first carrier from the front side of the product wafer, and transferring the thinned wafer to a second carrier with back side adhered to the second wafer carrier. Semiconductor components are added to the front side of the product wafer, followed by forming a hermetic cavity over the added semiconductor components, and detaching the second carrier from the back side of the product wafer. Wafer level processing continues after detaching the second carrier.

Owner:TEXAS INSTR INC

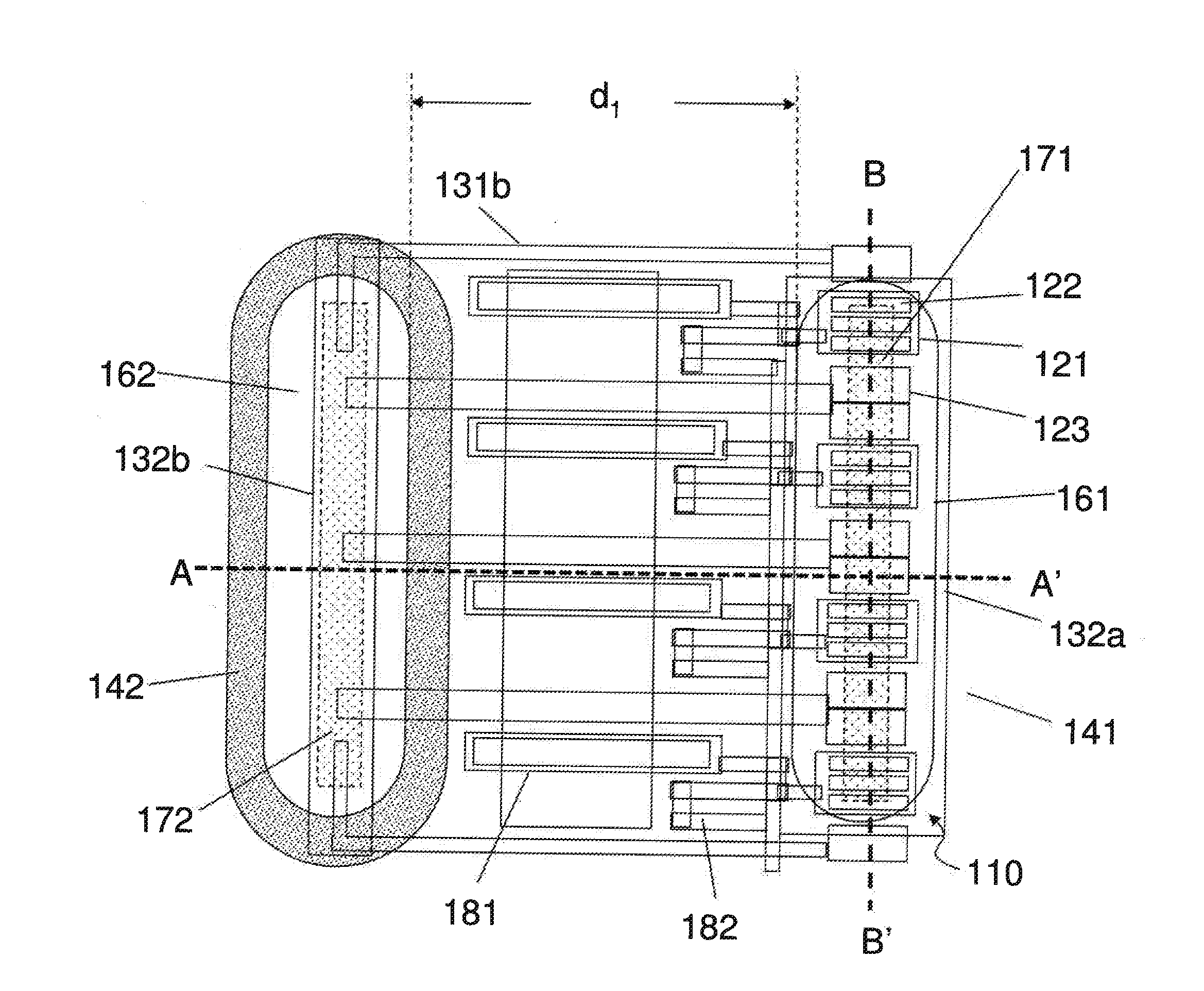

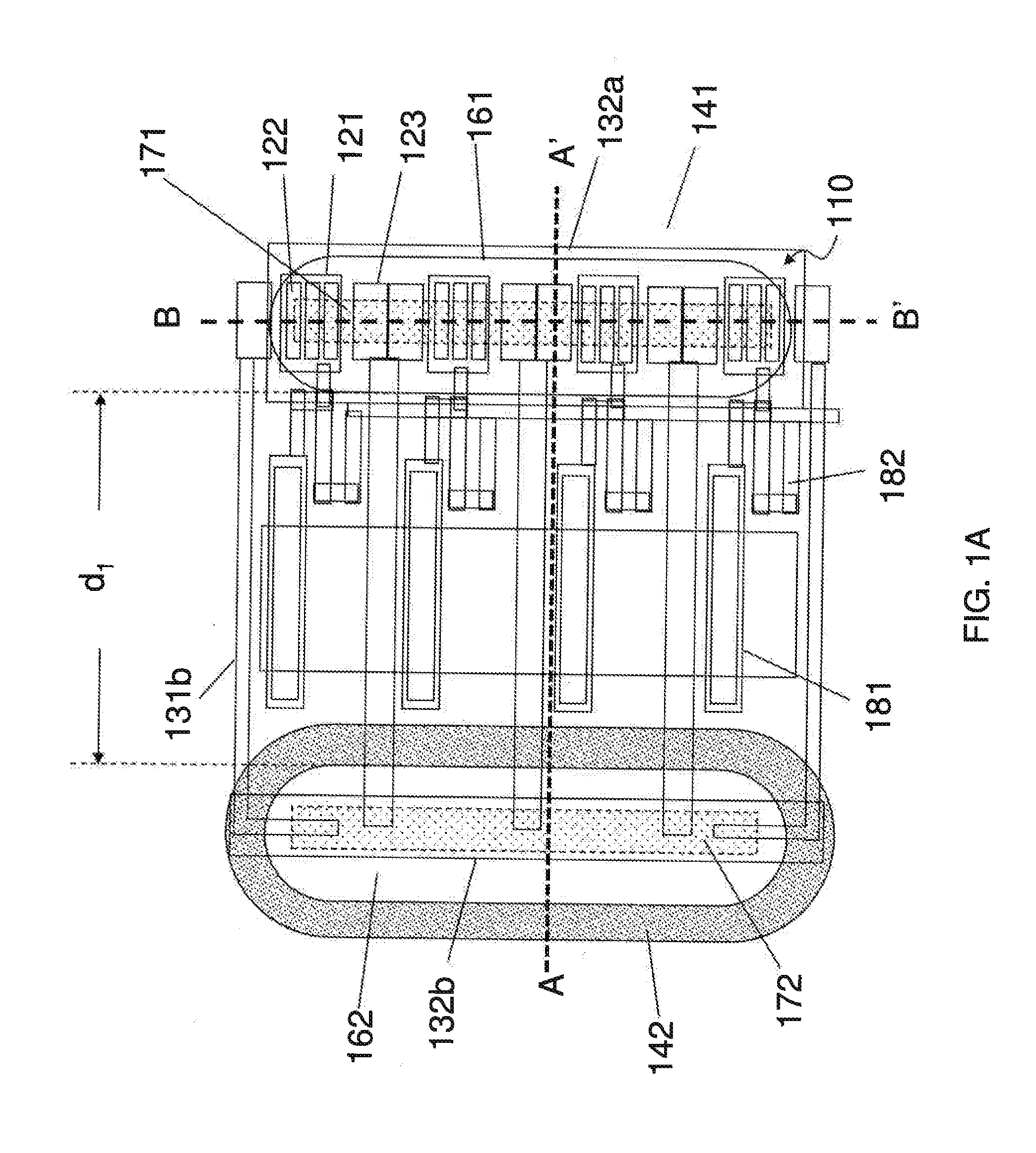

Layout Structure of Heterojunction Bipolar Transistors

ActiveUS20140312390A1Improve cooling efficiencyDifference in heightTransistorSemiconductor/solid-state device detailsHeterojunctionRedistribution layer

A layout structure of HBTs comprising one or more HBTs, each of which comprises a base electrode, an emitter electrode, and a collector electrode. A passive layer, a first dielectric layer, a collector redistribution layers, one or more emitter copper pillars, and one or more collector copper pillars are formed above the one or more HBTs. The passive layer comprises a collector and an emitter pads. The first dielectric layer has one or more emitter and collector via holes. The emitter copper pillar is disposed on the emitter via hole and forms an electrical connection to the emitter electrode. The collector copper pillar is disposed on the collector redistribution layer and forms electrical connection to the collector electrode. The layout design of the emitter and collector copper pillars is therefore flexible, and the heat dissipation efficiency is improved.

Owner:WIN SEMICON

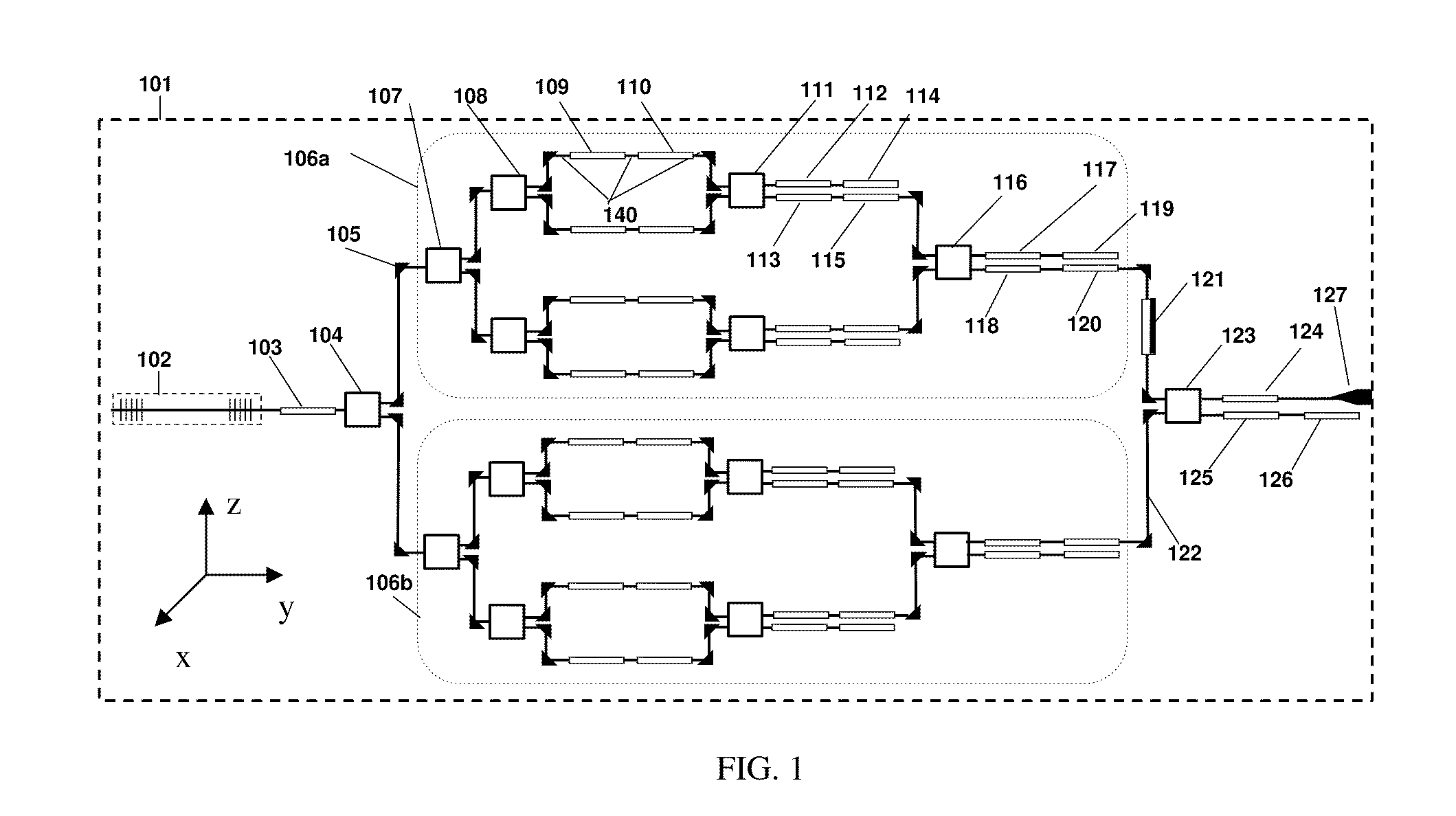

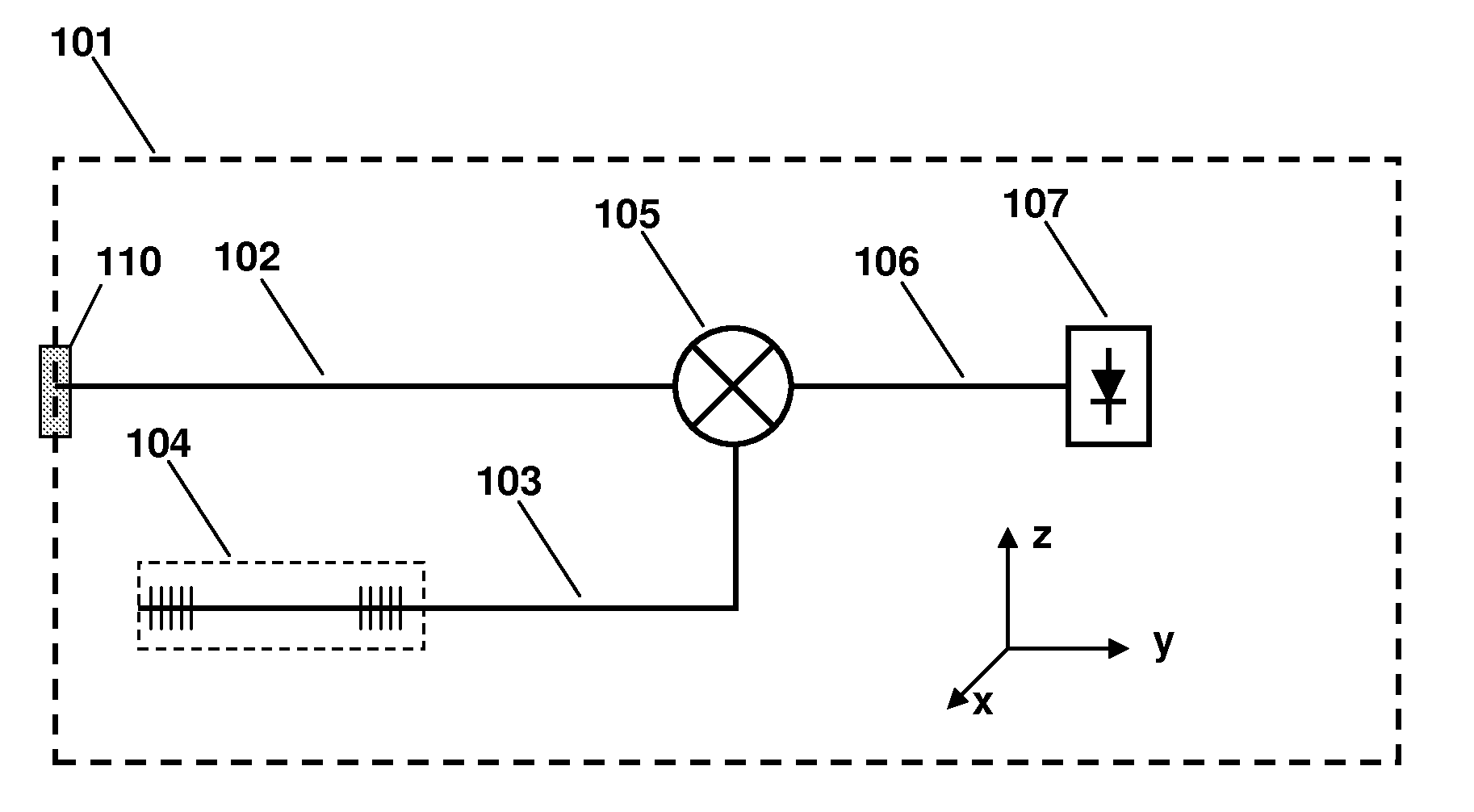

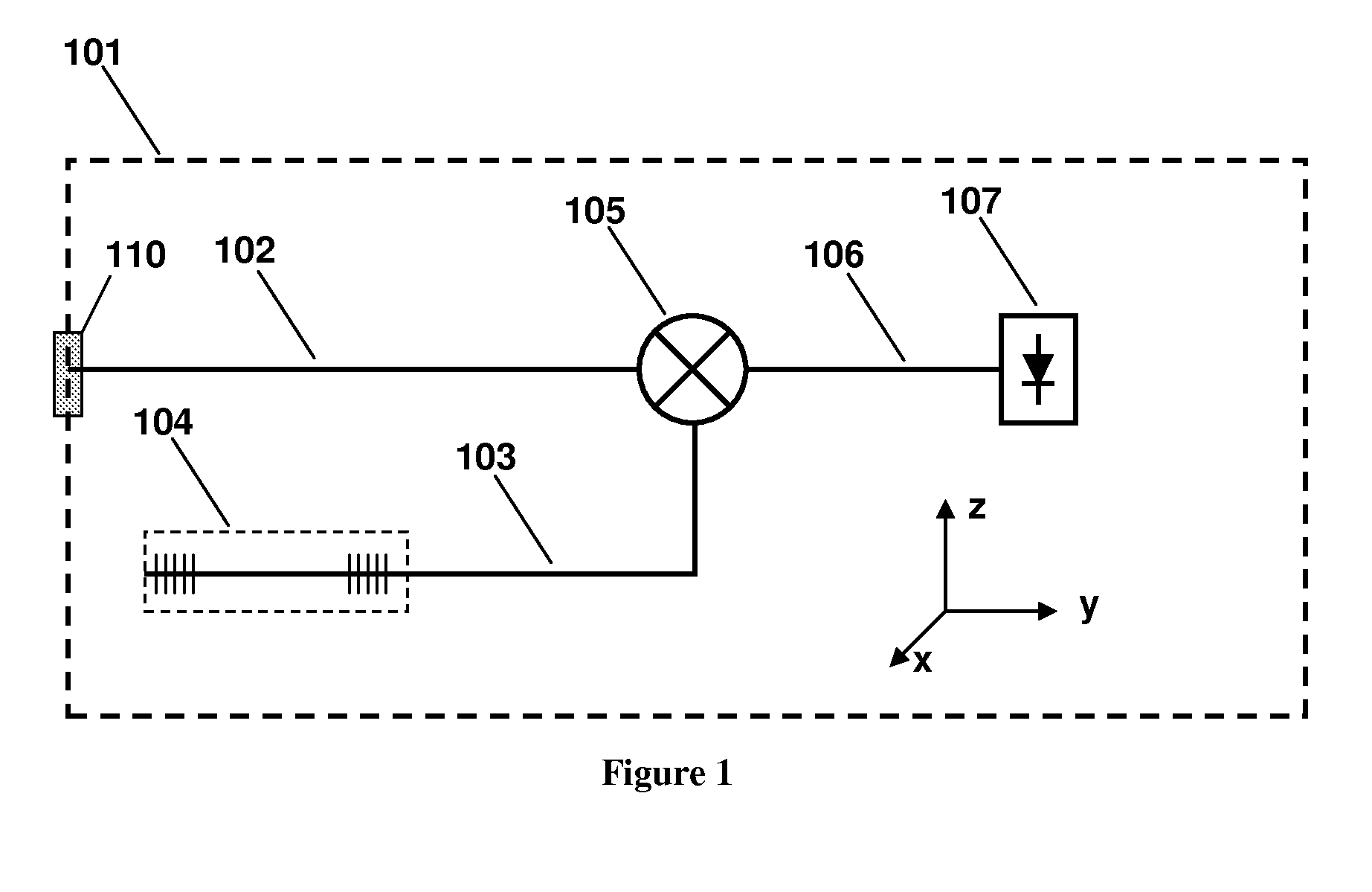

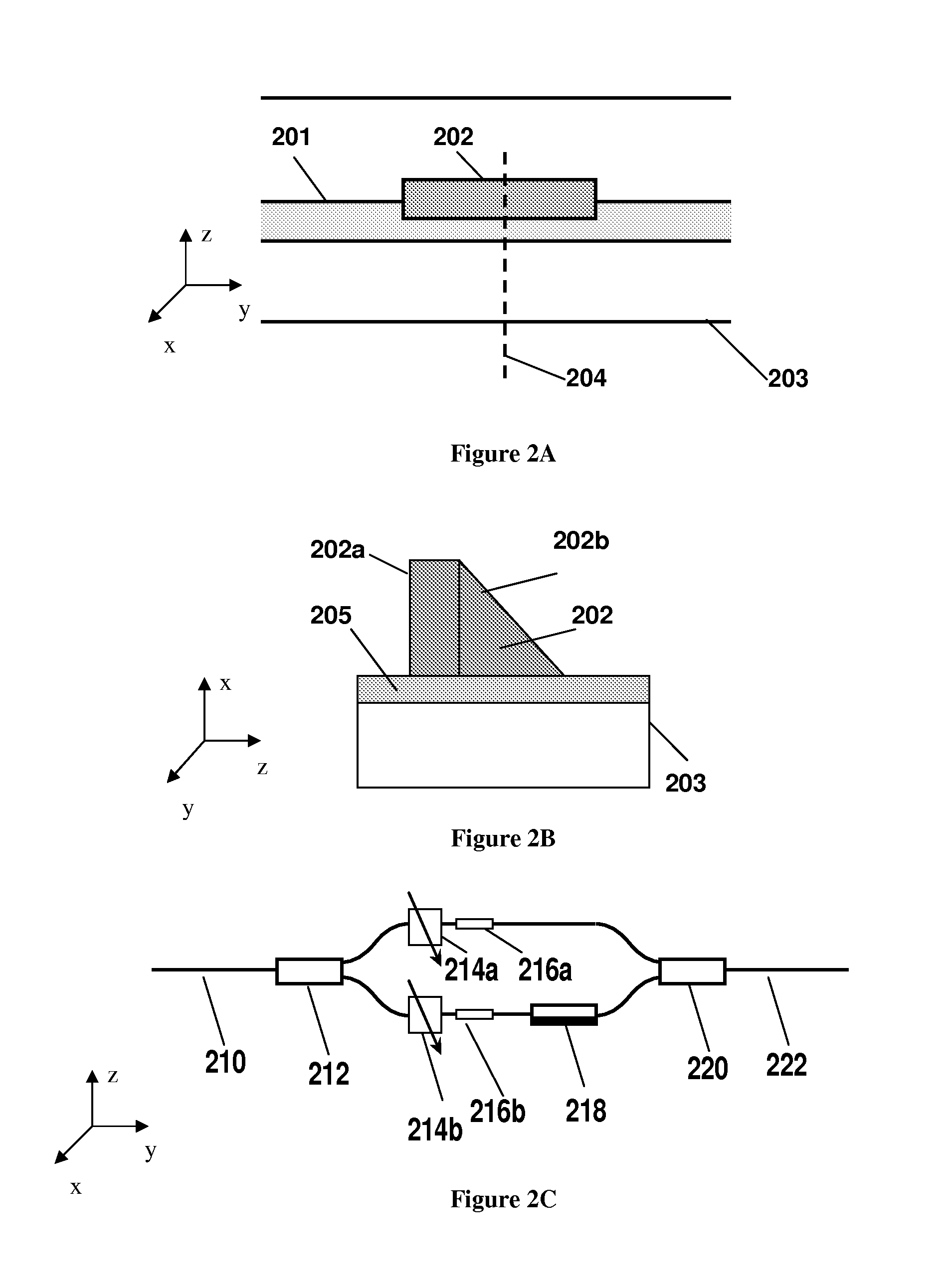

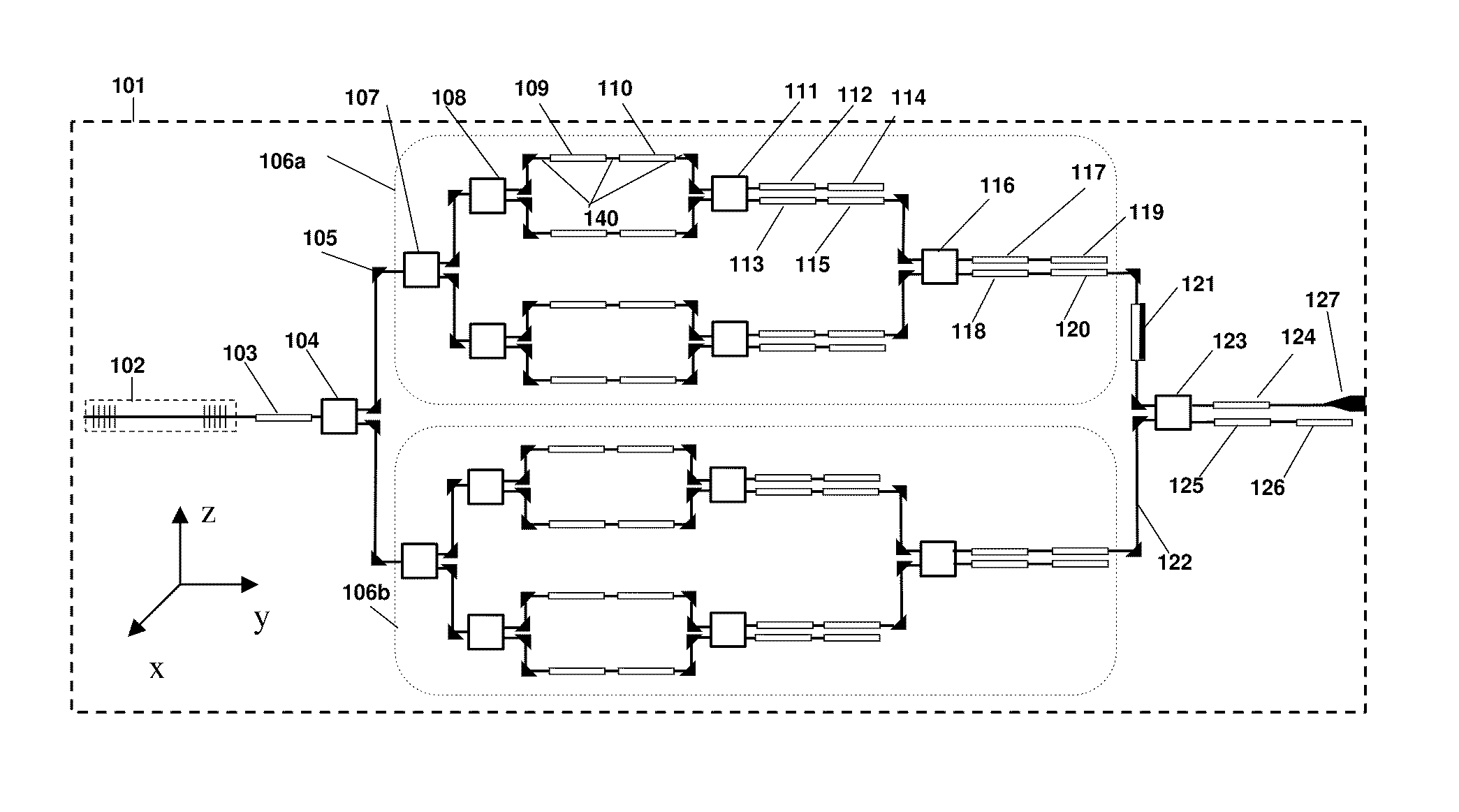

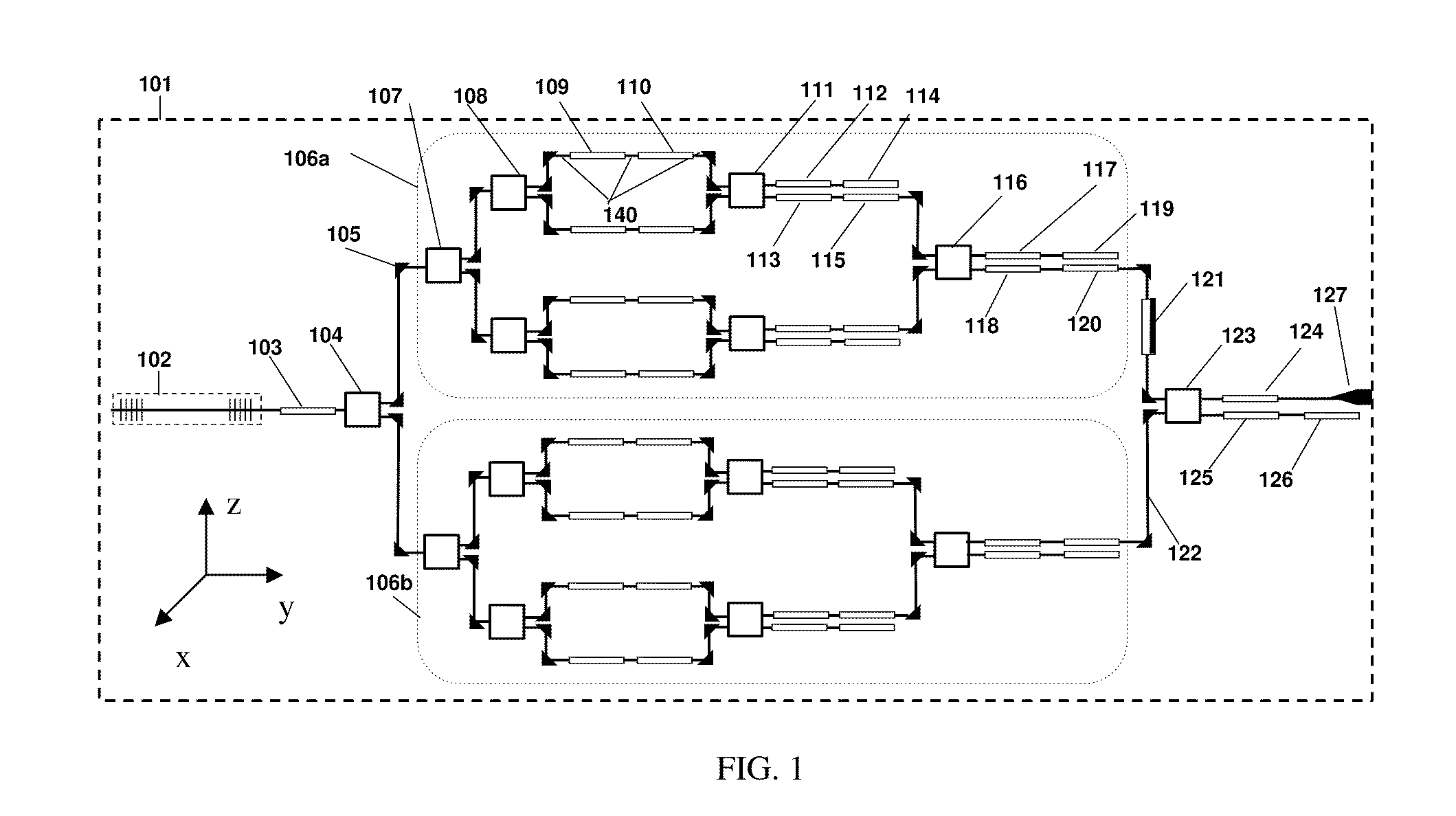

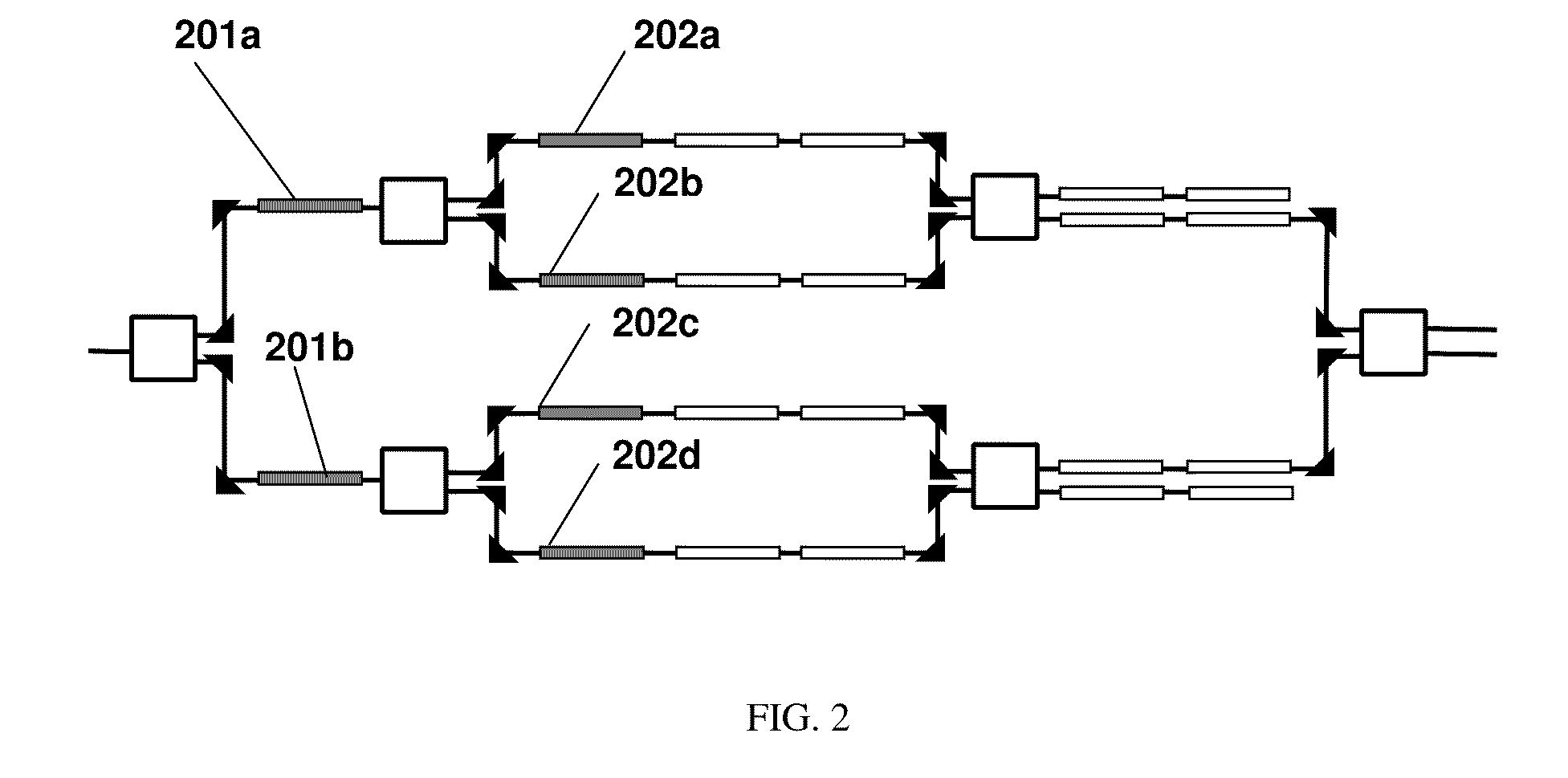

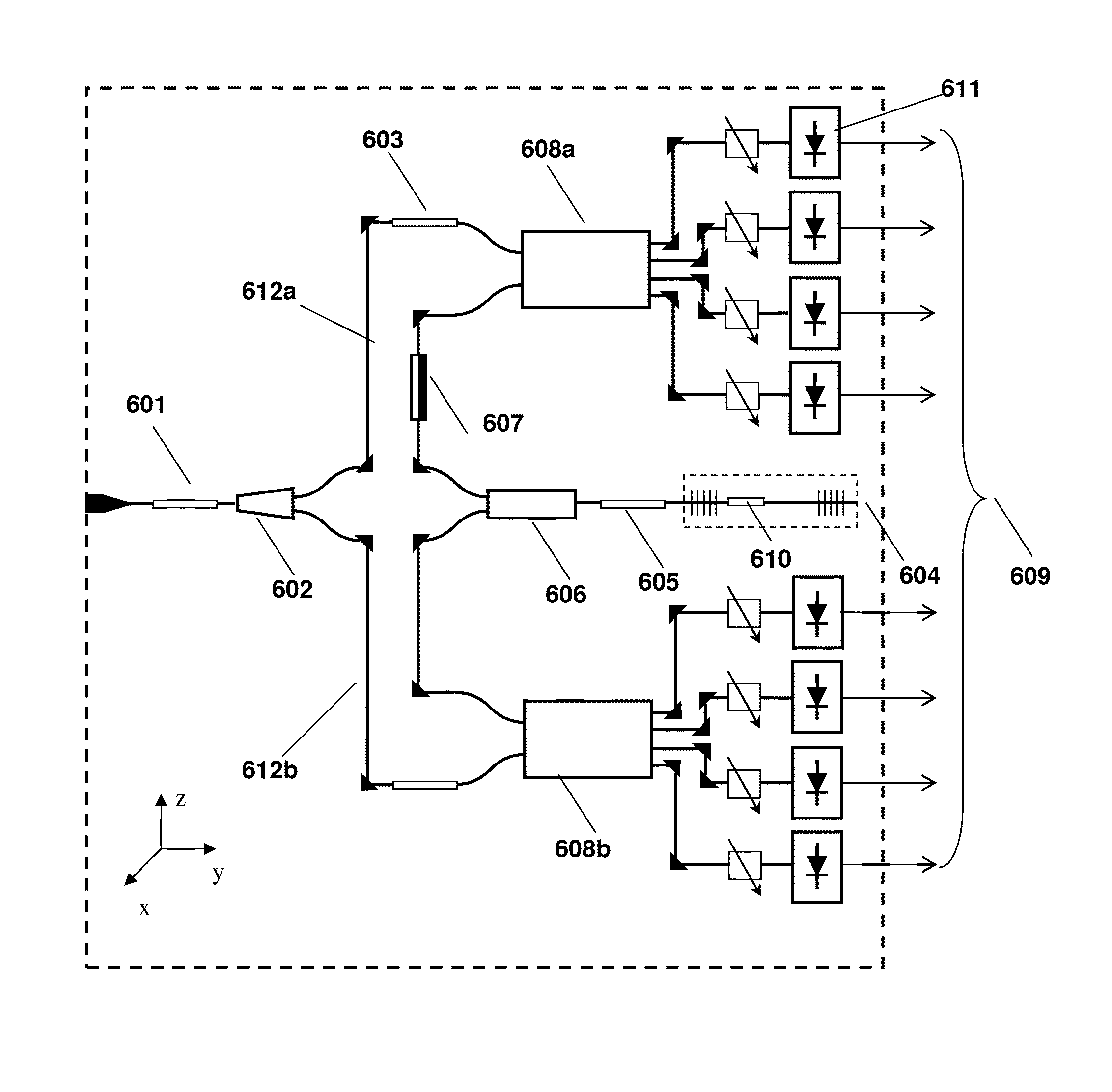

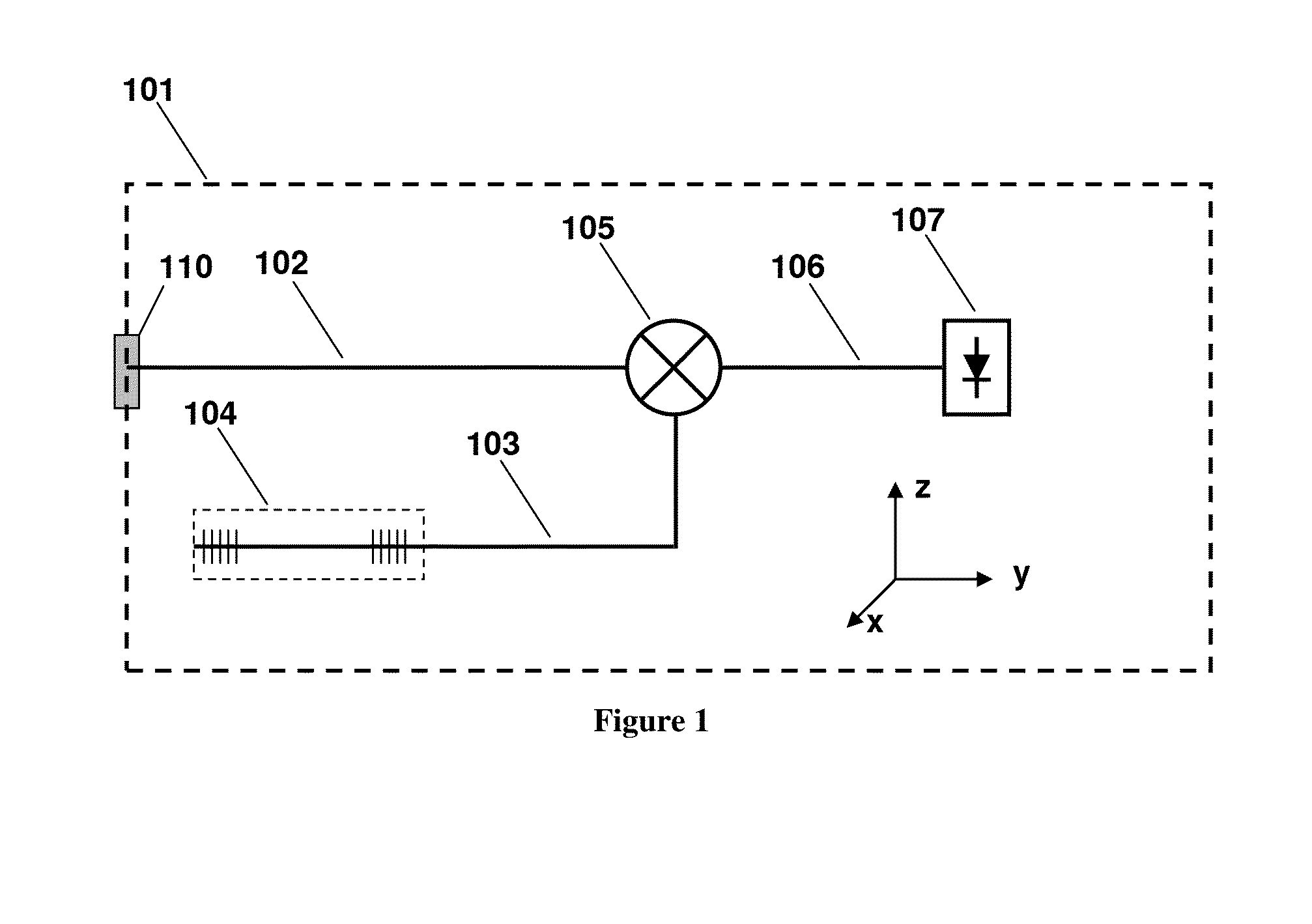

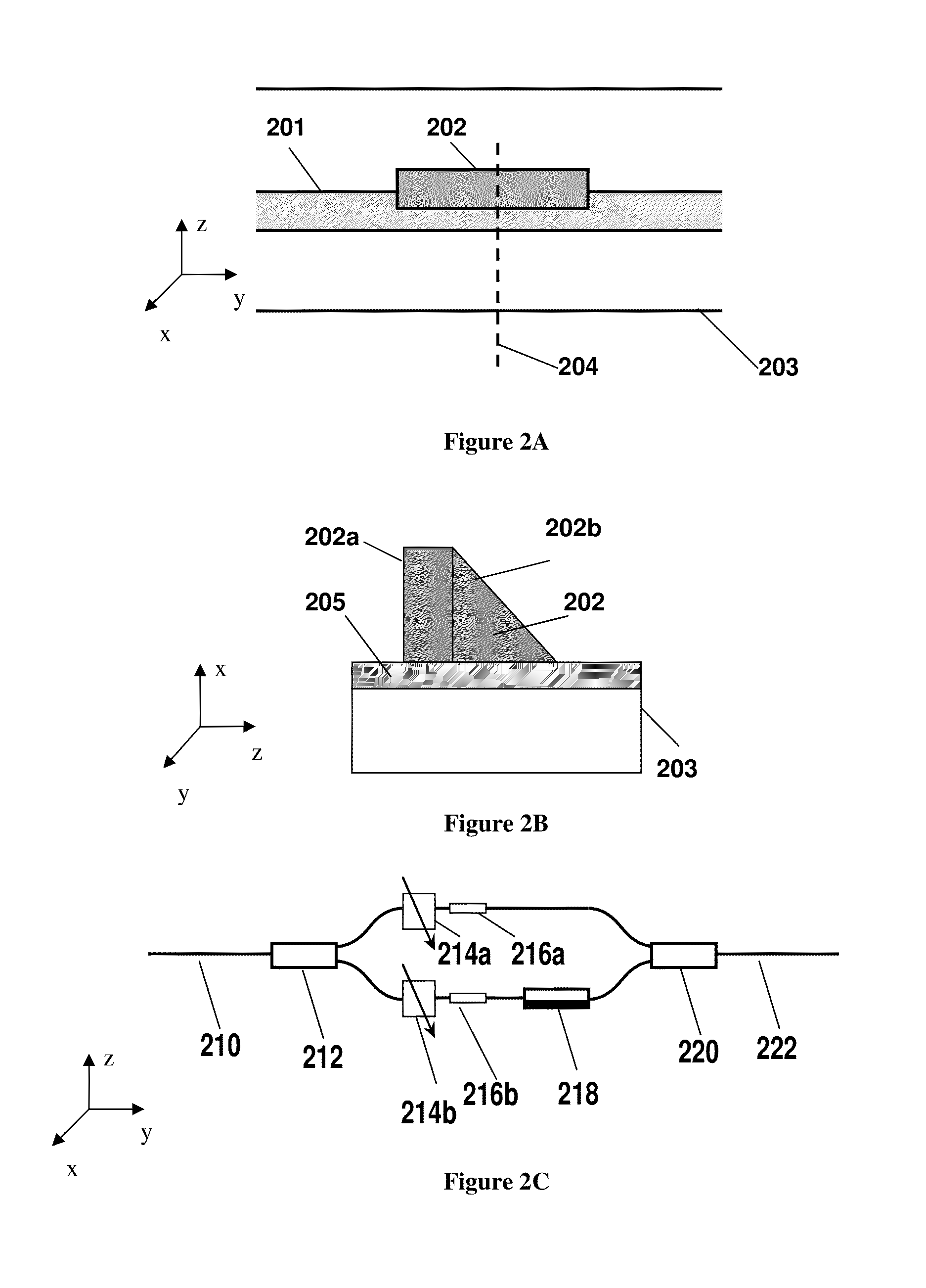

Monolithic widely-tunable coherent receiver

ActiveUS20100303476A1Reduce mold sizeIncrease productionWavelength-division multiplex systemsPolarising elementsLocal oscillatorLength wave

Various embodiments of a coherent receiver including a widely tunable local oscillator laser are described herein. In some embodiments, the coherent receiver can be integrated with waveguides, optical splitters and detectors to form a monolithic optical hetero / homodyne receiver. In some embodiments, the coherent receiver can demodulate the full phase information in two polarizations of a received optical signal over a range of optical wavelengths.

Owner:FREEDOM PHOTONICS LLC

Chip-based advanced modulation format transmitter

ActiveUS8401399B2Reduce mold sizeReduced footprintWavelength-division multiplex systemsElectromagnetic transmittersPhase modulationLaser source

In various embodiments, a monolithic integrated transmitter, comprising an on-chip laser source and a modulator structure capable of generating advanced modulation format signals based on amplitude and phase modulation are described.

Owner:FREEDOM PHOTONICS LLC

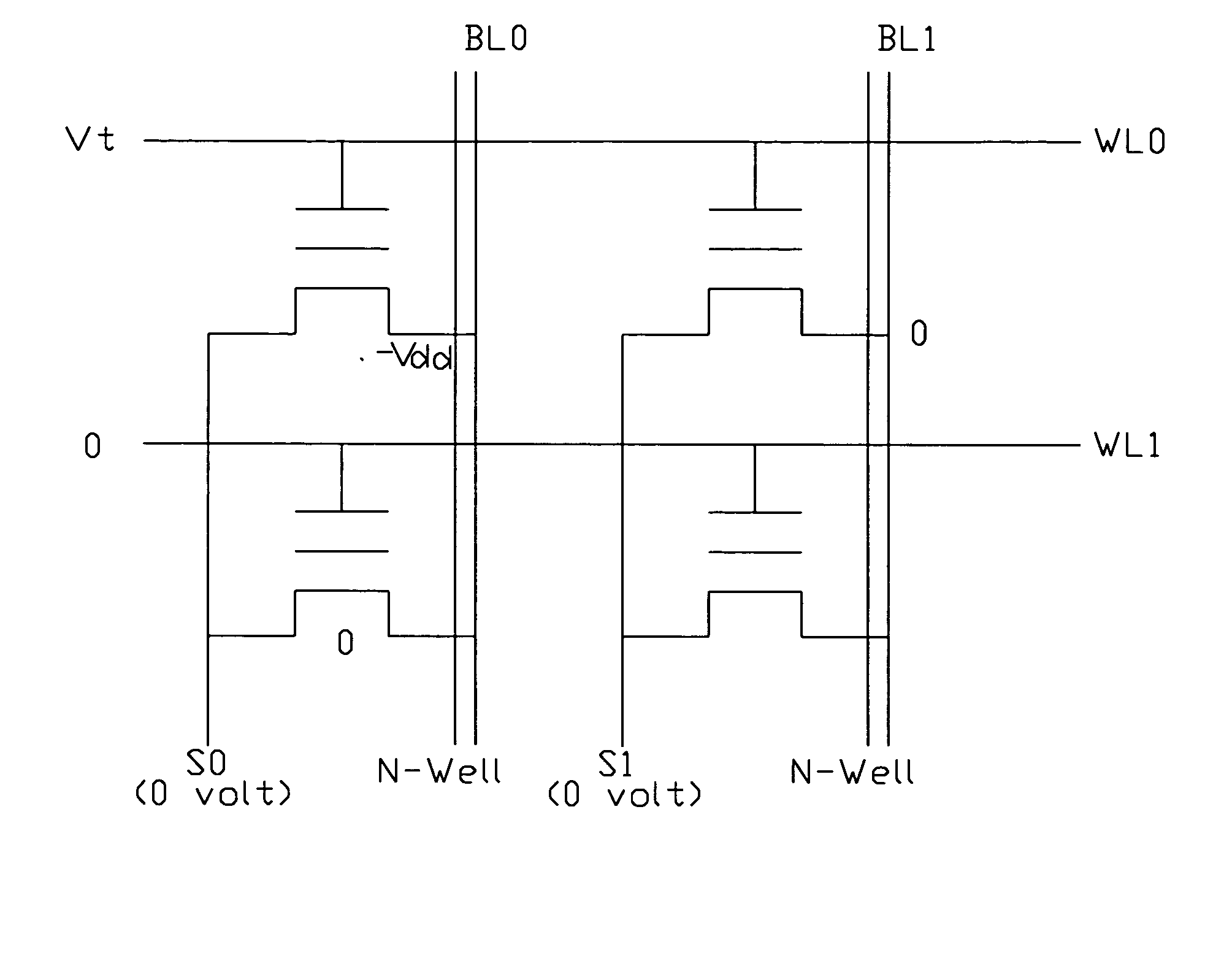

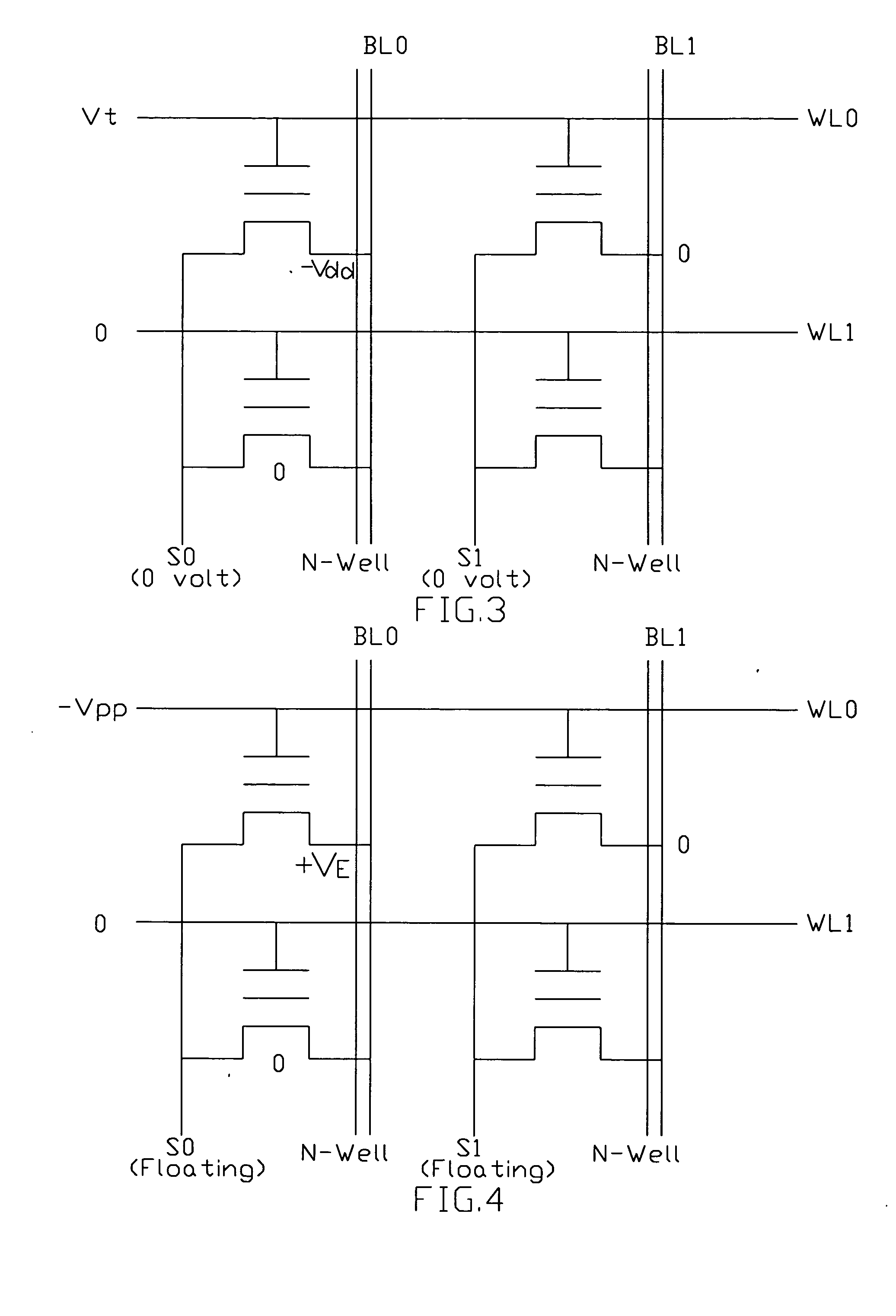

Non-volatile memory technology suitable for flash and byte operation application

ActiveUS20050083738A1Reduce mold sizeReduce process complexityRead-only memoriesDigital storageProgrammable read-only memoryFowler nordheim

The present invention provides a non-volatile memory cell structure suitable for the flash memory cell and EEPROM cell (electrically erasable programmable read only memory cell) to perform the byte programming and byte erase operations. In the programming operation, a higher negative voltage applied to the drain region, such that the hot hole is generated to induce the hot electron into the floating gate through the tunneling oxide layer in the lateral electrical field. In addition, the gate voltage is around the threshold voltage, which dependent on the integration circuit device design. Furthermore, the non-volatile memory cell utilized the channel Fowler-Nordheim tunneling for erasing operation. In order to perform the byte erasing operation, the drain junction used as an inhibition switch. Thus, the unselected cell in the same word line is inhibited by biasing the drain to ground. Therefore, the word lines of unselected cells are ground.

Owner:MARLIN SEMICON LTD

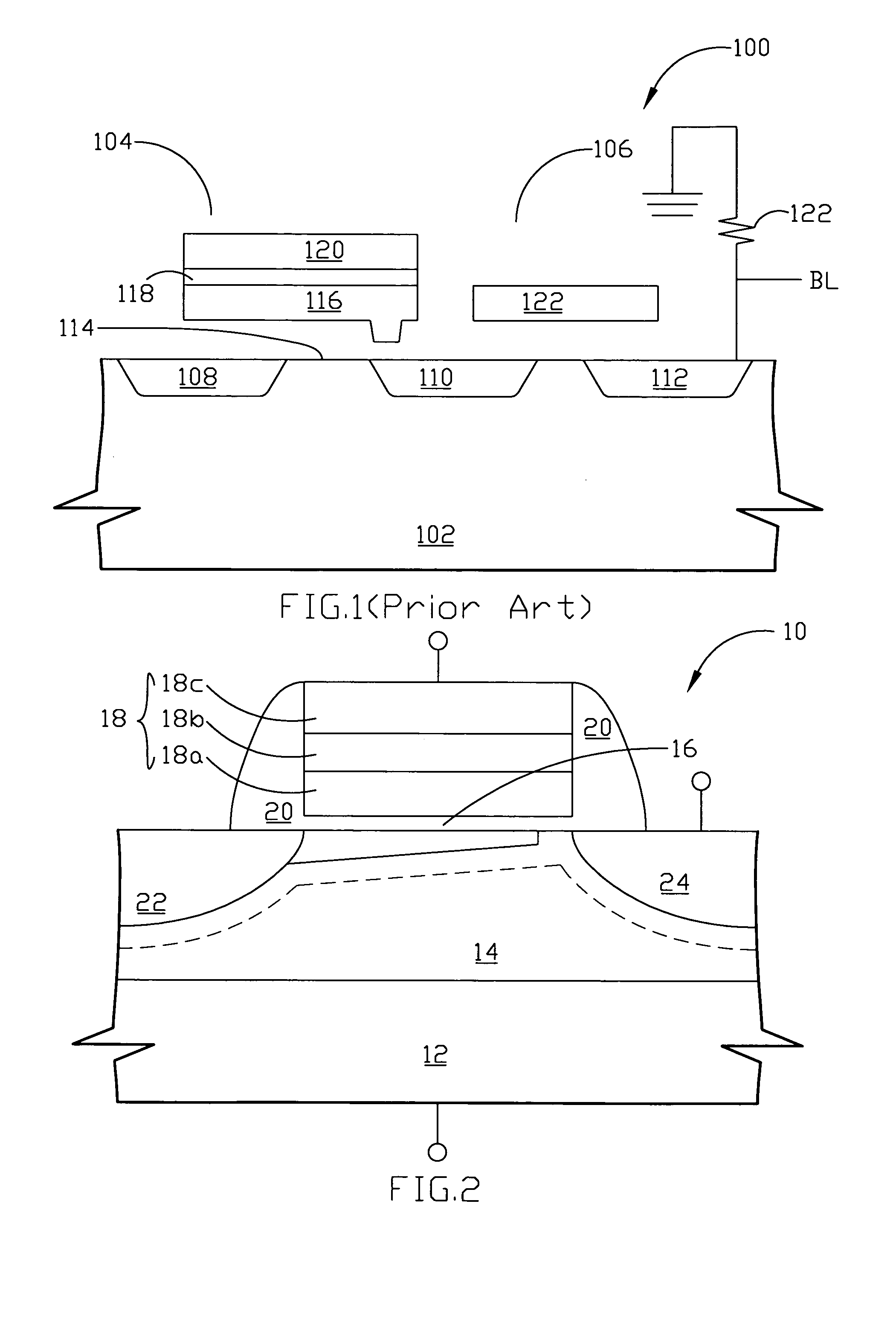

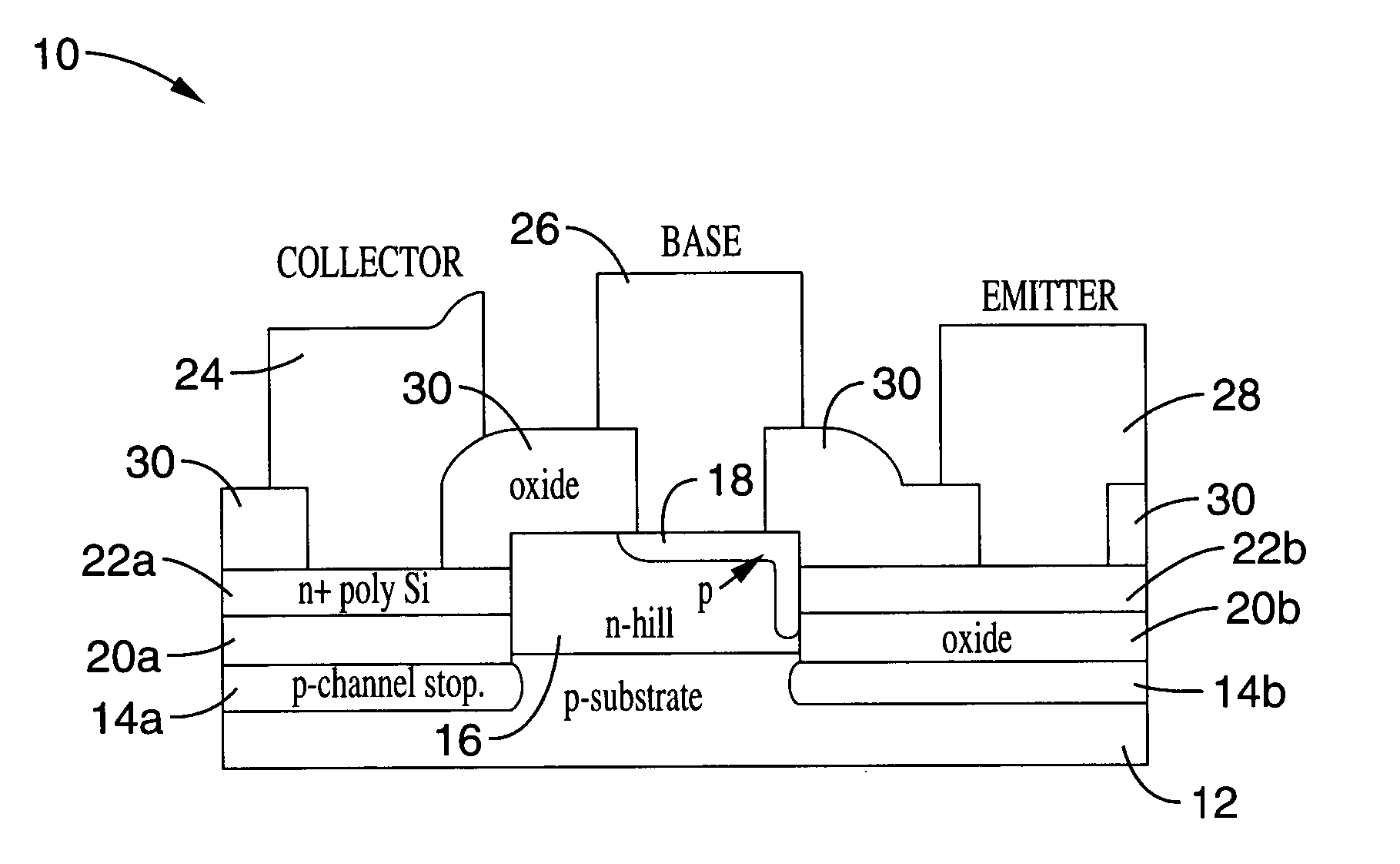

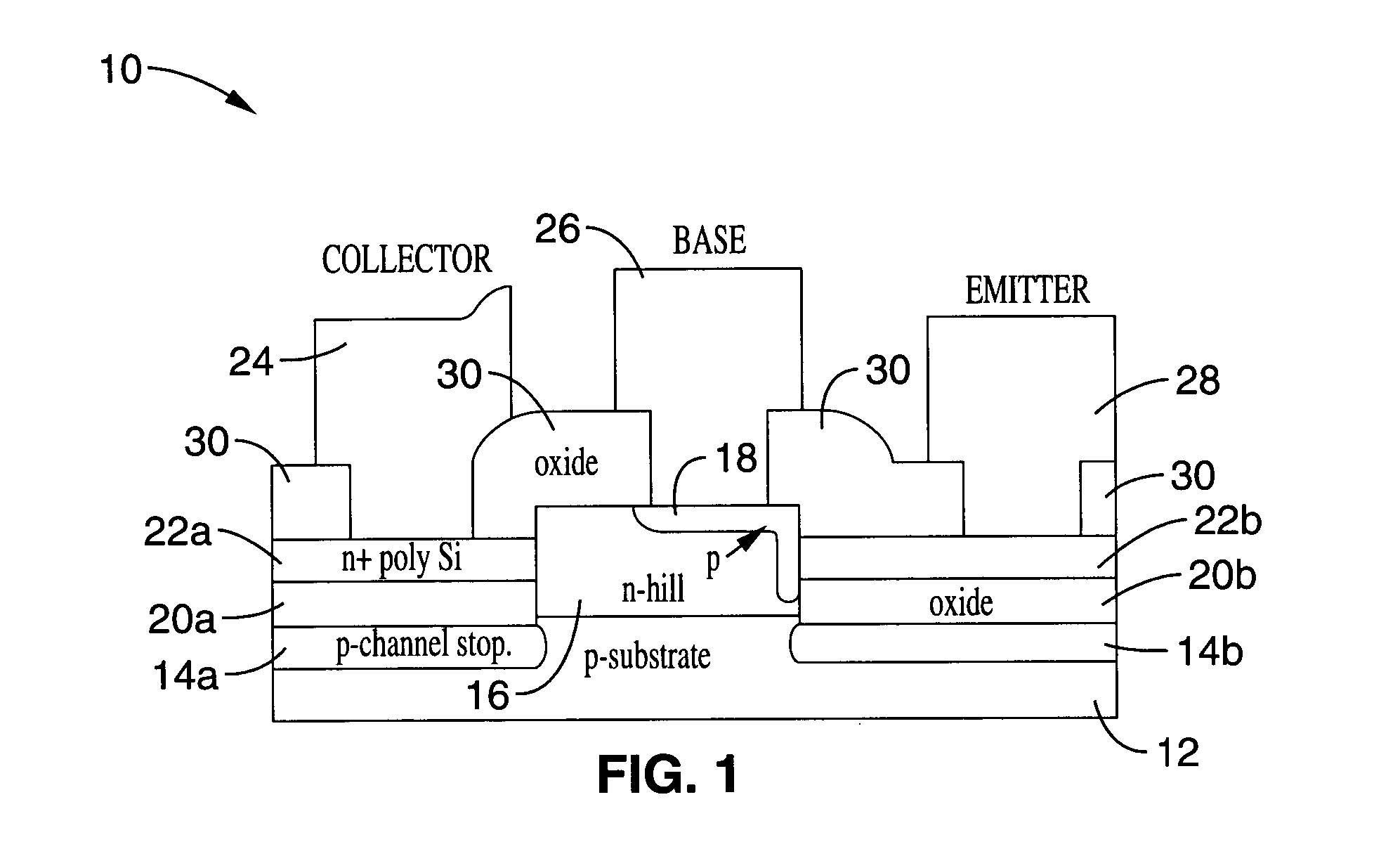

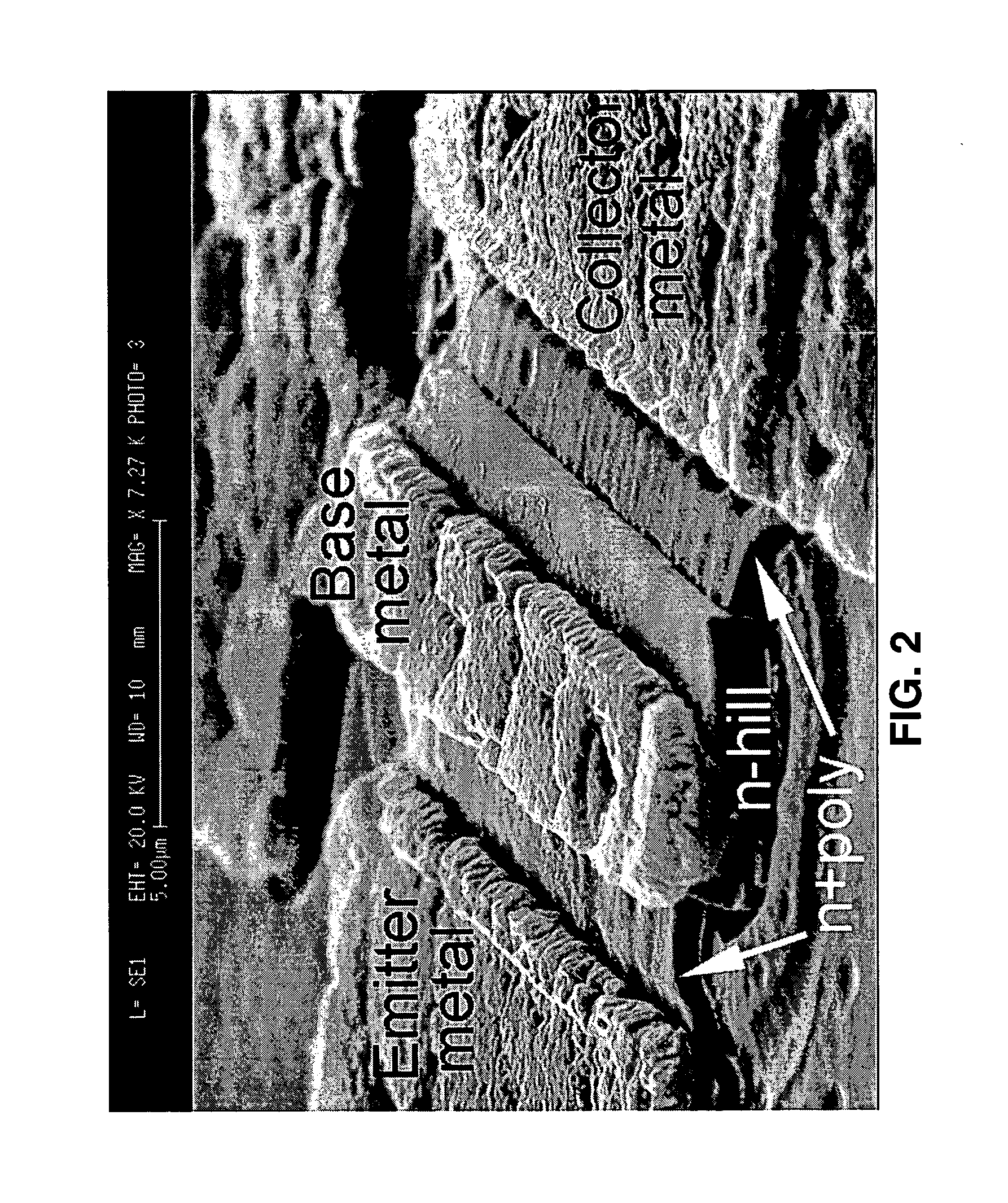

Horizontal current bipolar transistor and fabrication method

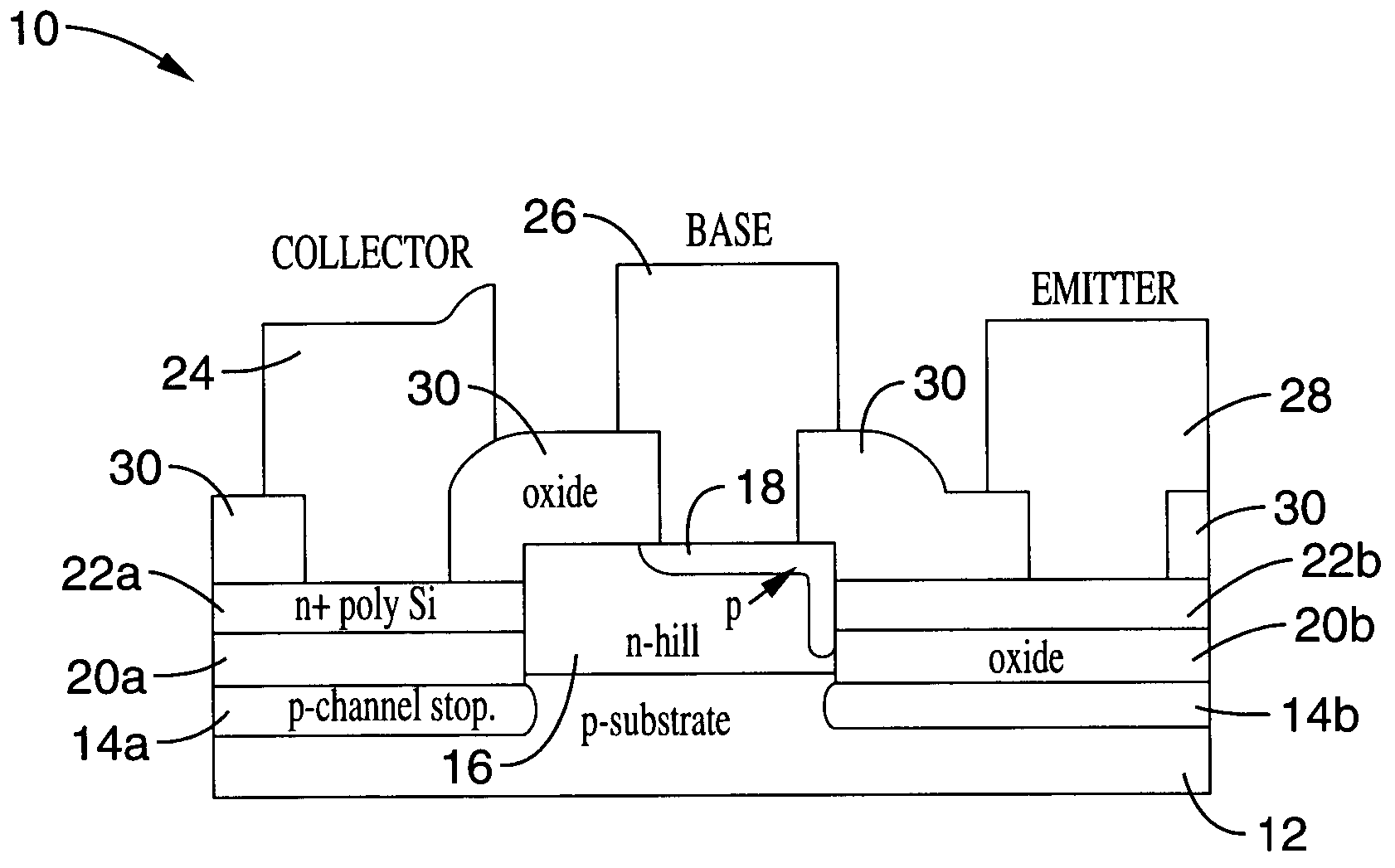

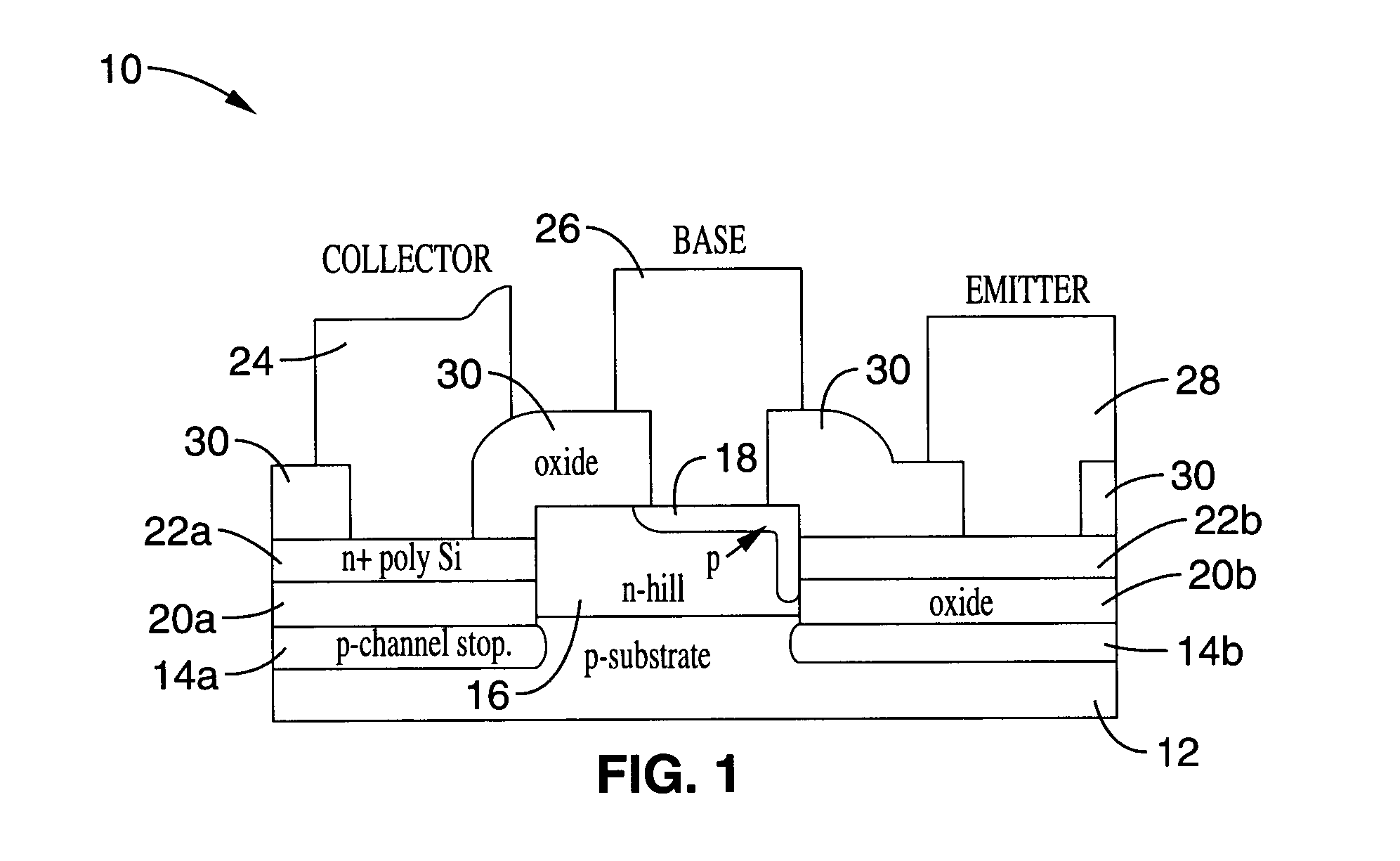

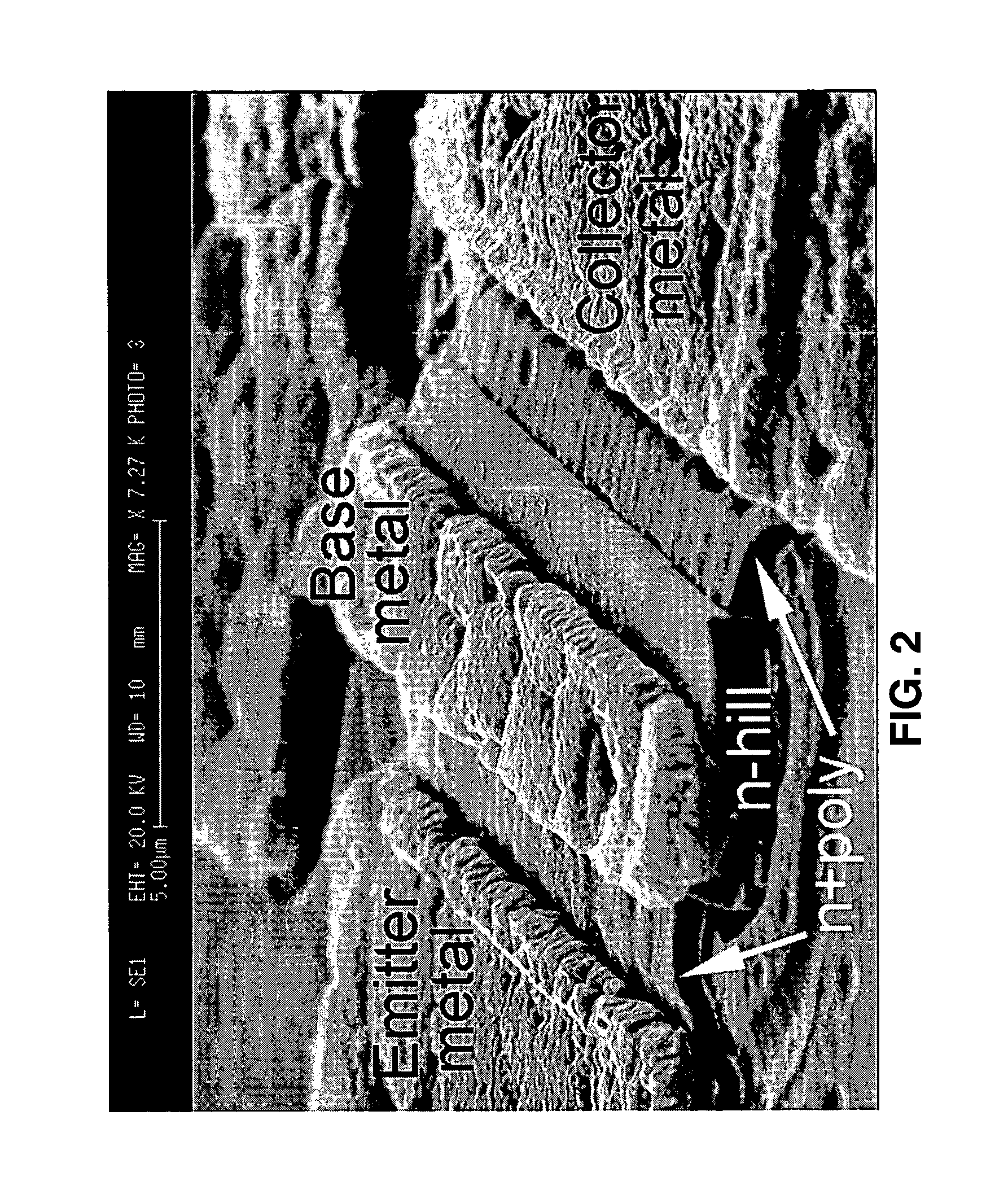

InactiveUS20050040495A1Small area of chip surfaceHigh bulk densitySemiconductor/solid-state device manufacturingSemiconductor devicesVolumetric Mass DensityIntegrated circuit

A bipolar transistor structure for use in integrated circuits where the active device is processed on the sidewall of an n-hill so that the surface footprint does not depend on the desired area of active device region (emitter area). This structure, which is referred to as a Horizontal Current Bipolar Transistor (HCBT), consumes a smaller area of chip surface than conventional devices, thereby enabling higher packing density of devices and / or the reduction of integrated circuit die size. The device is fabricated with a single polysilicon layer, without an epitaxial process, without demanding trench isolation technology, and with reduced thermal budget. Fabrication requires fewer etching processes and thermal oxidations than in conventional devices.

Owner:RGT UNIV OF CALIFORNIA

Horizontal current bipolar transistor and fabrication method

InactiveUS7038249B2Reduce areaHigh bulk densitySemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringMono layer

A bipolar transistor structure for use in integrated circuits where the active device is processed on the sidewall of an n-hill so that the surface footprint does not depend on the desired area of active device region (emitter area). This structure, which is referred to as a Horizontal Current Bipolar Transistor (HCBT), consumes a smaller area of chip surface than conventional devices, thereby enabling higher packing density of devices and / or the reduction of integrated circuit die size. The device is fabricated with a single polysilicon layer, without an epitaxial process, without demanding trench isolation technology, and with reduced thermal budget. Fabrication requires fewer etching processes and thermal oxidations than in conventional devices.

Owner:RGT UNIV OF CALIFORNIA

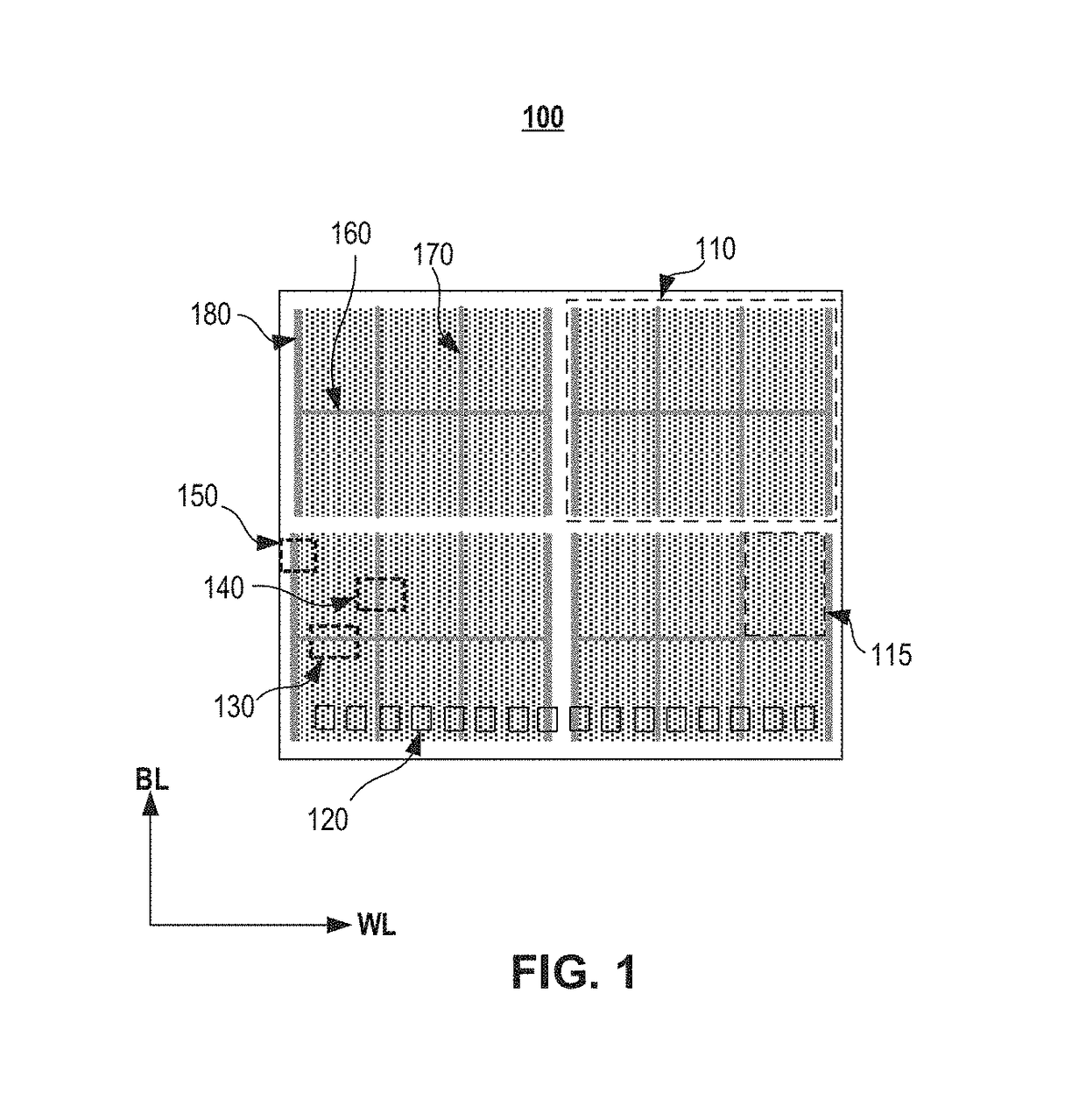

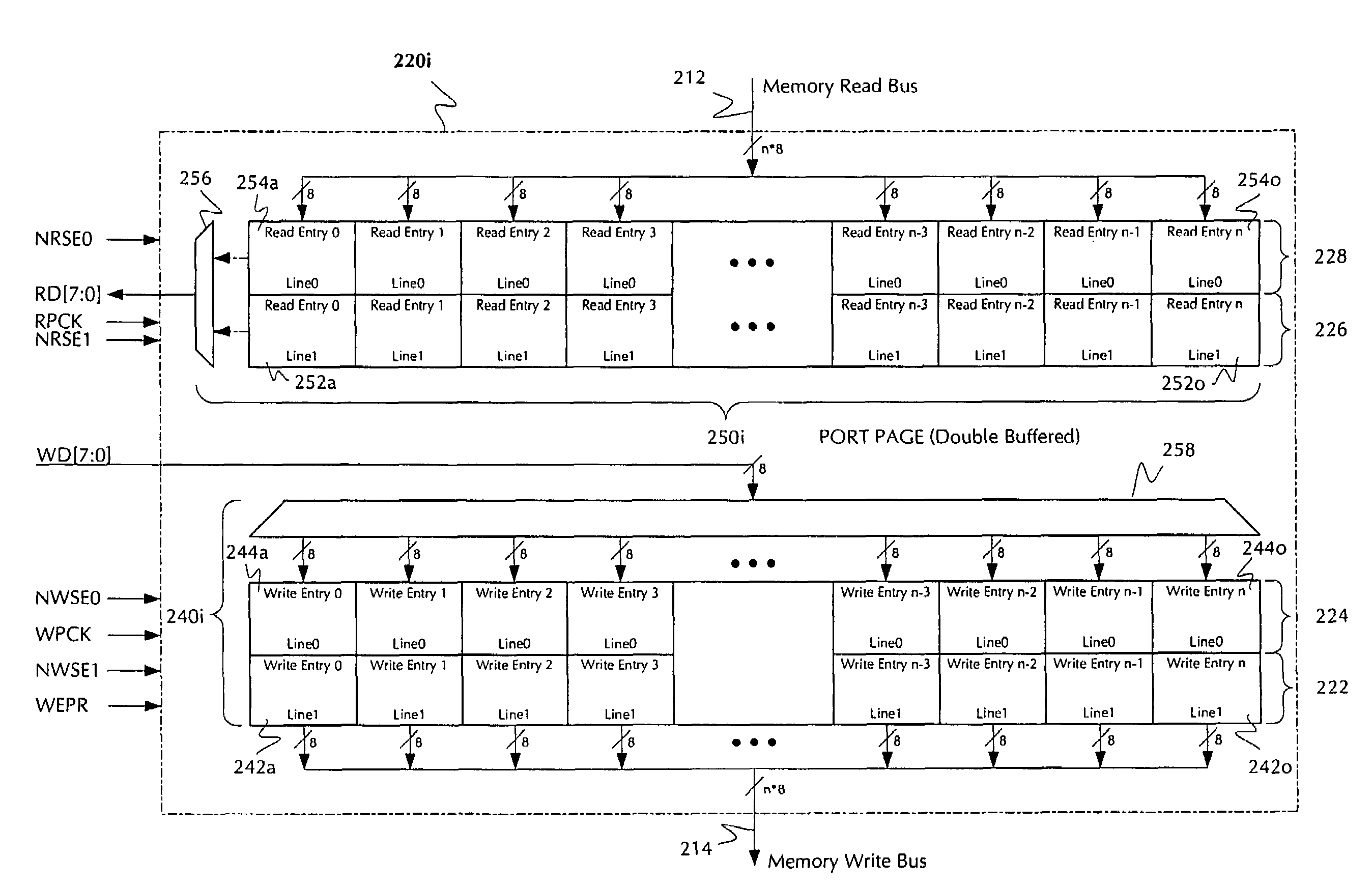

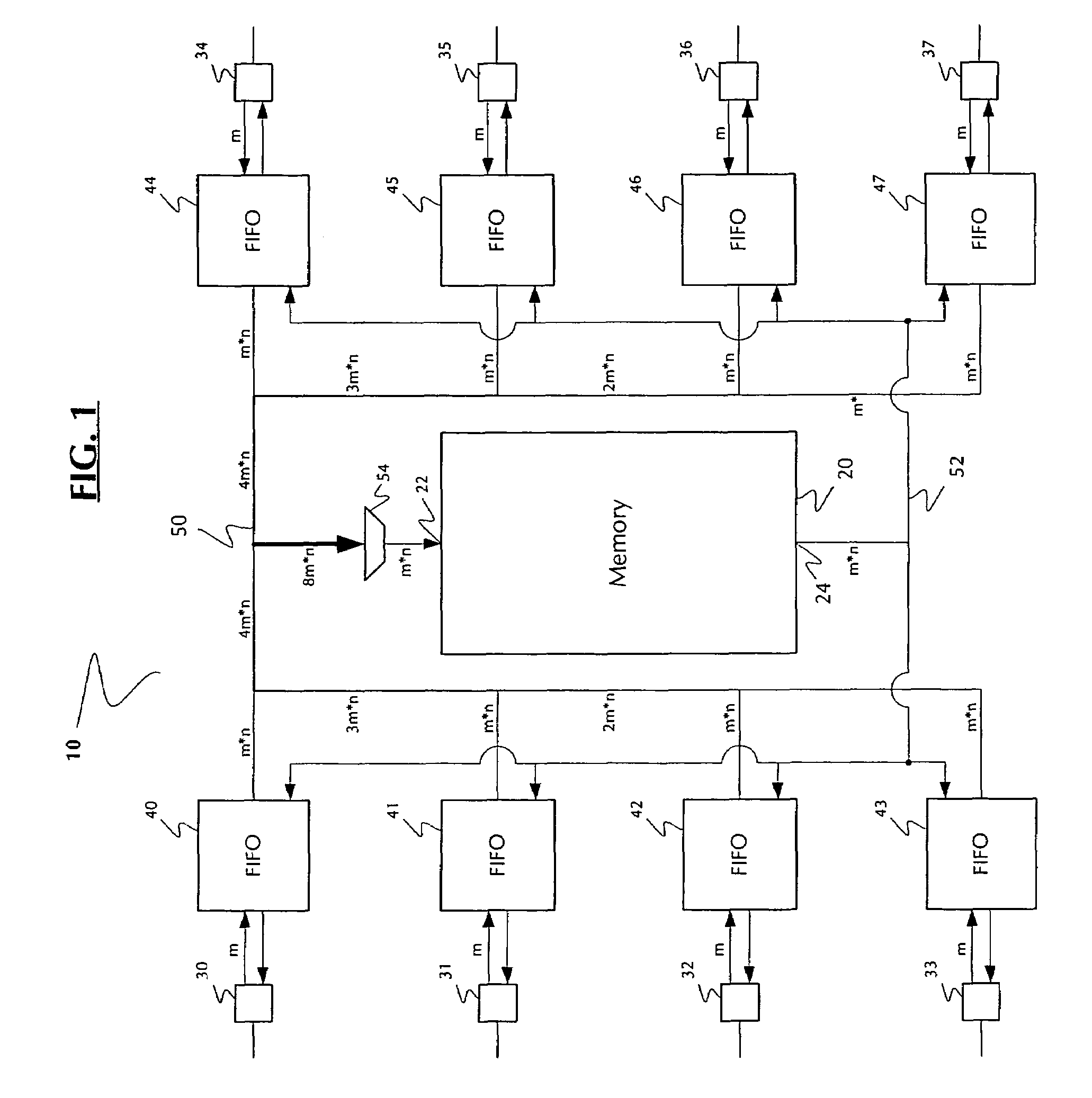

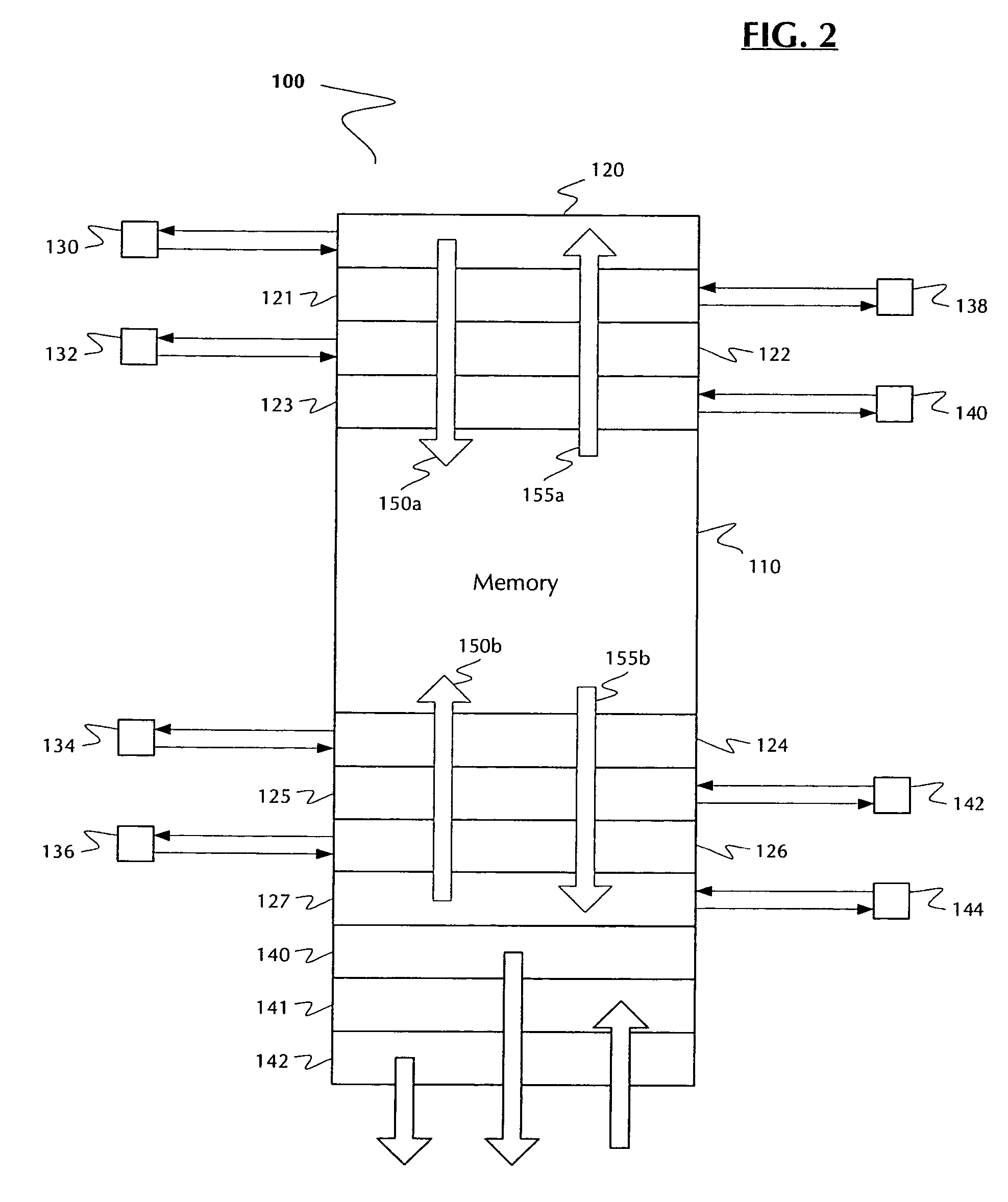

Multiport memory architecture, devices and systems including the same, and methods of using the same

A multiport memory architecture, systems including the same and methods for using the same. The architecture generally includes (a) a memory array; (b) a plurality of ports configured to receive and / or transmit data; and (c) a plurality of port buffers, each of which is configured to transmit the data to and / or receive the data from one or more of the ports, and all of which are configured to (i) transmit the data to the memory array on a first common bus and (ii) receive the data from the memory array on a second common bus. The systems generally include those that embody one or more of the inventive concepts disclosed herein. The methods generally relate to writing blocks of data to, reading blocks of data from, and / or transferring blocks of data across a memory. The present invention advantageously reduces latency in data communications, particularly in network switches, by tightly coupling port buffers to the main memory and advantageously using point-to-point communications over long segments of the memory read and write paths, thereby reducing routing congestion and enabling the elimination of a FIFO. The invention advantageously shrinks chip size and provides increased data transmission rates and throughput, and in preferred embodiments, reduced resistance and / or capacitance in the memory read and write busses.

Owner:MARVELL ASIA PTE LTD

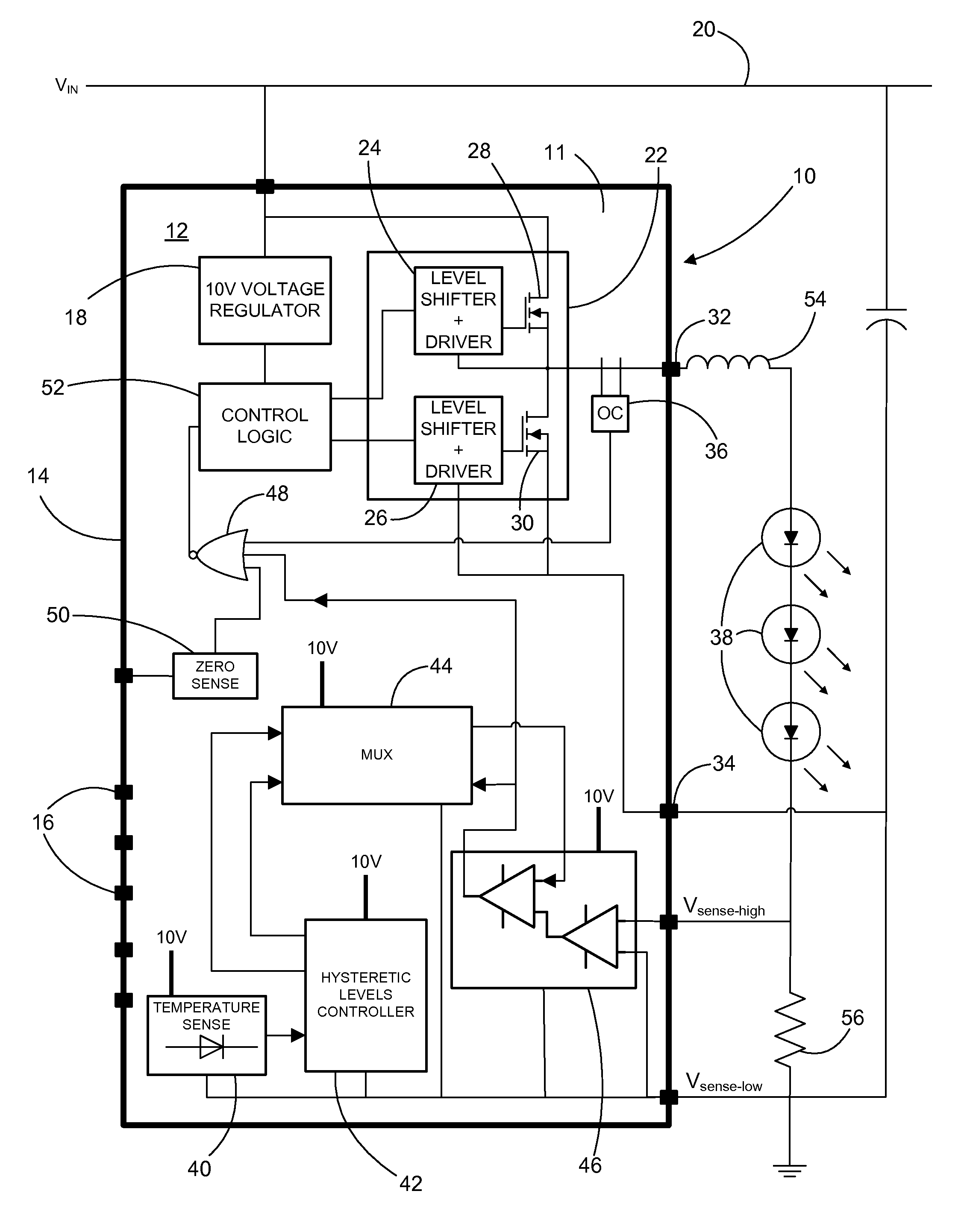

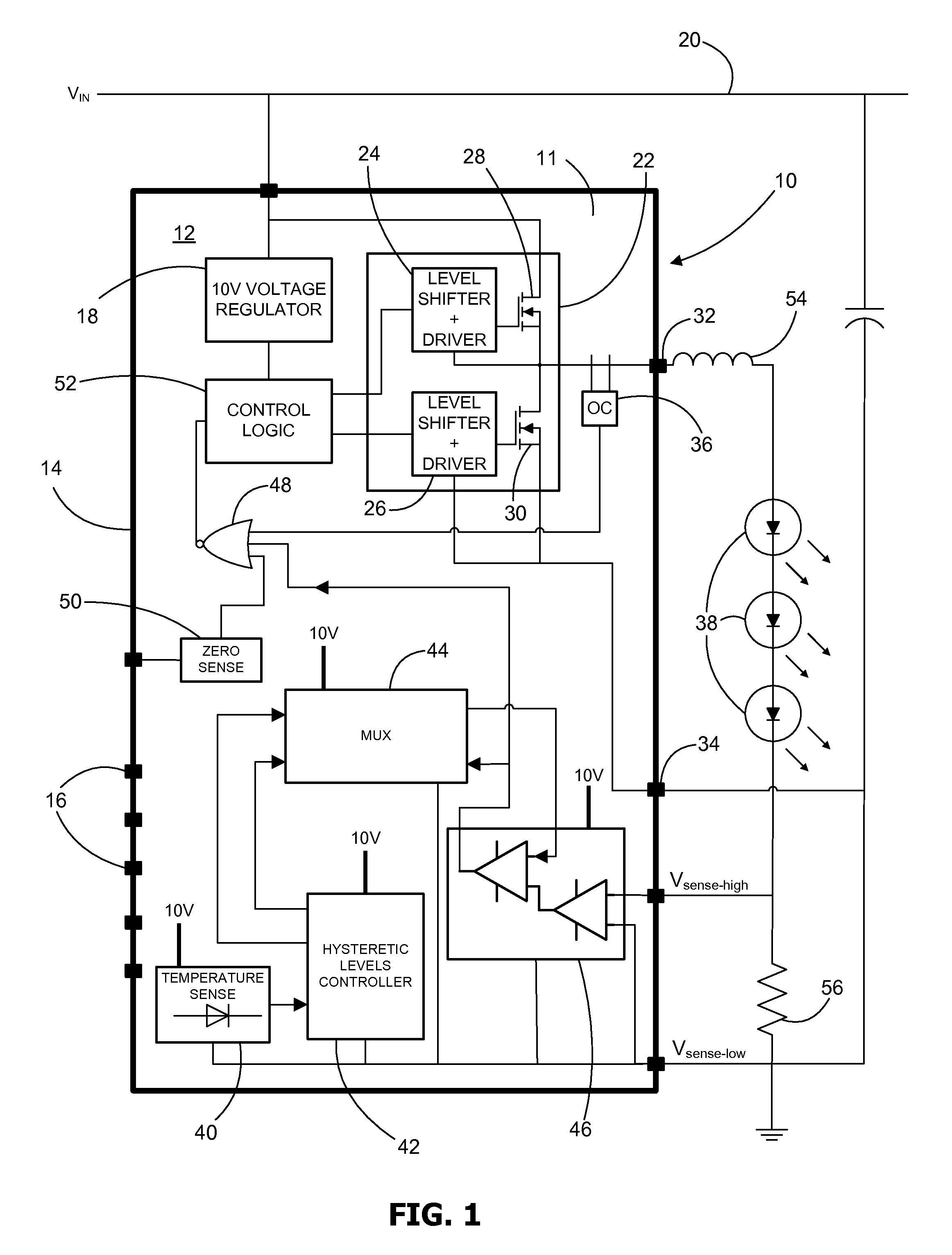

Dc-dc converter

ActiveUS20110080118A1Simple taskReduce on-chip heat lossElectrical apparatusElectroluminescent light sourcesConvertersThermodynamics

A DC-DC converter for driving one or more LED (38), which converter comprises an integrated circuit (12) having a switch mode power circuit (24) and a 5 temperature sensing circuit (40) for providing an output indicating a temperature of said integrated circuit (12), the arrangement being such that, in use, said integrated circuit consumes power, some of which power is dissipated in said integrated circuit as heat causing a rise in said internal temperature, and wherein a change in said output from said temperature sensing circuit (40) is used by said integrated circuit to 10 adjust said consumed power whereby said internal temperature may be controlled

Owner:NXP BV

Double wafer carrier process for creating integrated circuit die with through-silicon vias and micro-electro-mechanical systems protected by a hermetic cavity created at the wafer level

ActiveUS7960840B2Avoid sizeReduce mold sizeSemiconductor/solid-state device detailsSolid-state devicesEngineeringThrough-silicon via

A TSV-MEMS packaging process is provided. The process includes forming TSVs in the front side of the product wafer, and attaching a first carrier to the front side of the product wafer, subsequent to forming TSVs. The process further includes thinning the back side of the product wafer to expose TSV tips, detaching the first carrier from the front side of the product wafer, and transferring the thinned wafer to a second carrier with back side adhered to the second wafer carrier. Semiconductor components are added to the front side of the product wafer, followed by forming a hermetic cavity over the added semiconductor components, and detaching the second carrier from the back side of the product wafer. Wafer level processing continues after detaching the second carrier.

Owner:TEXAS INSTR INC

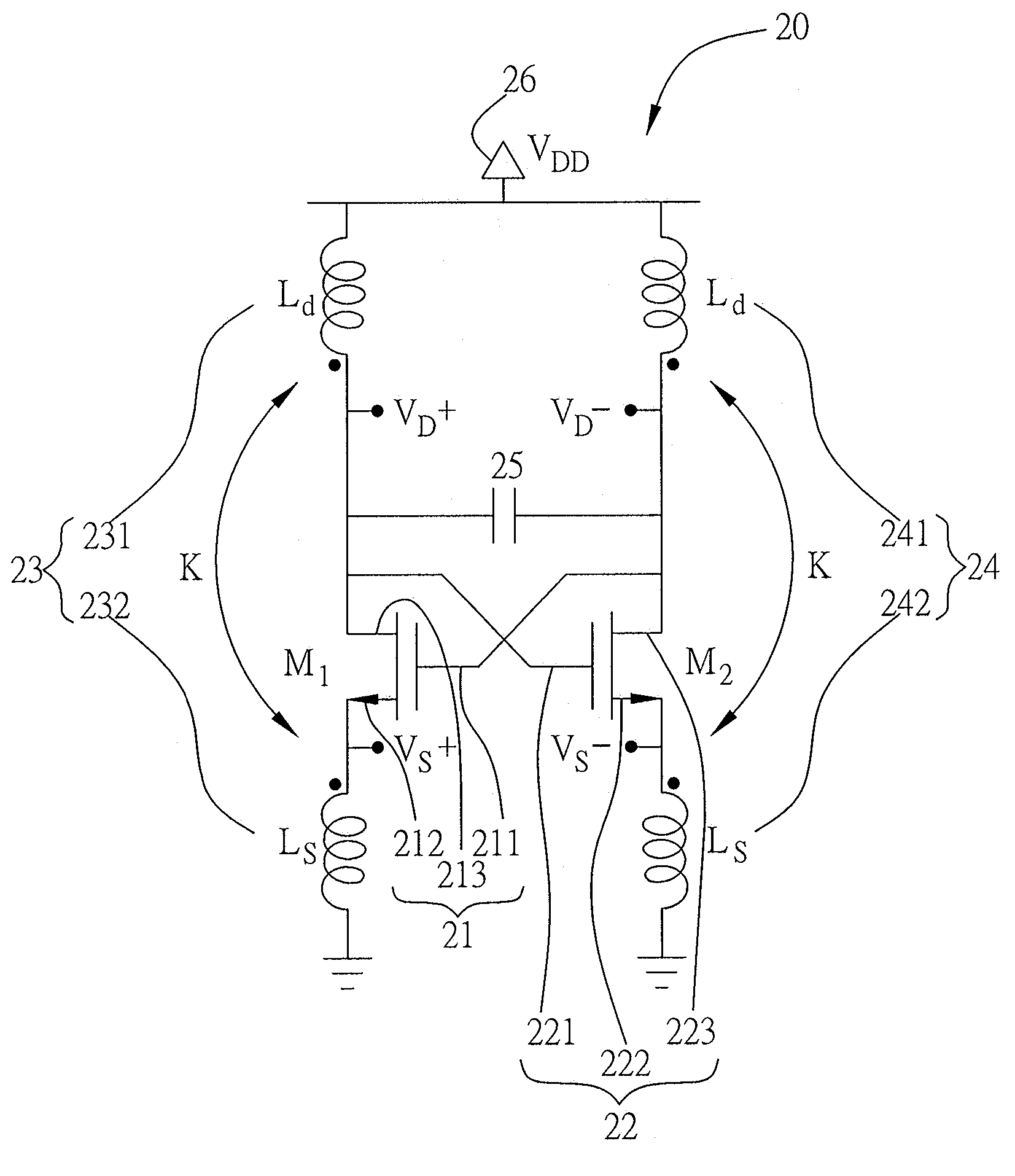

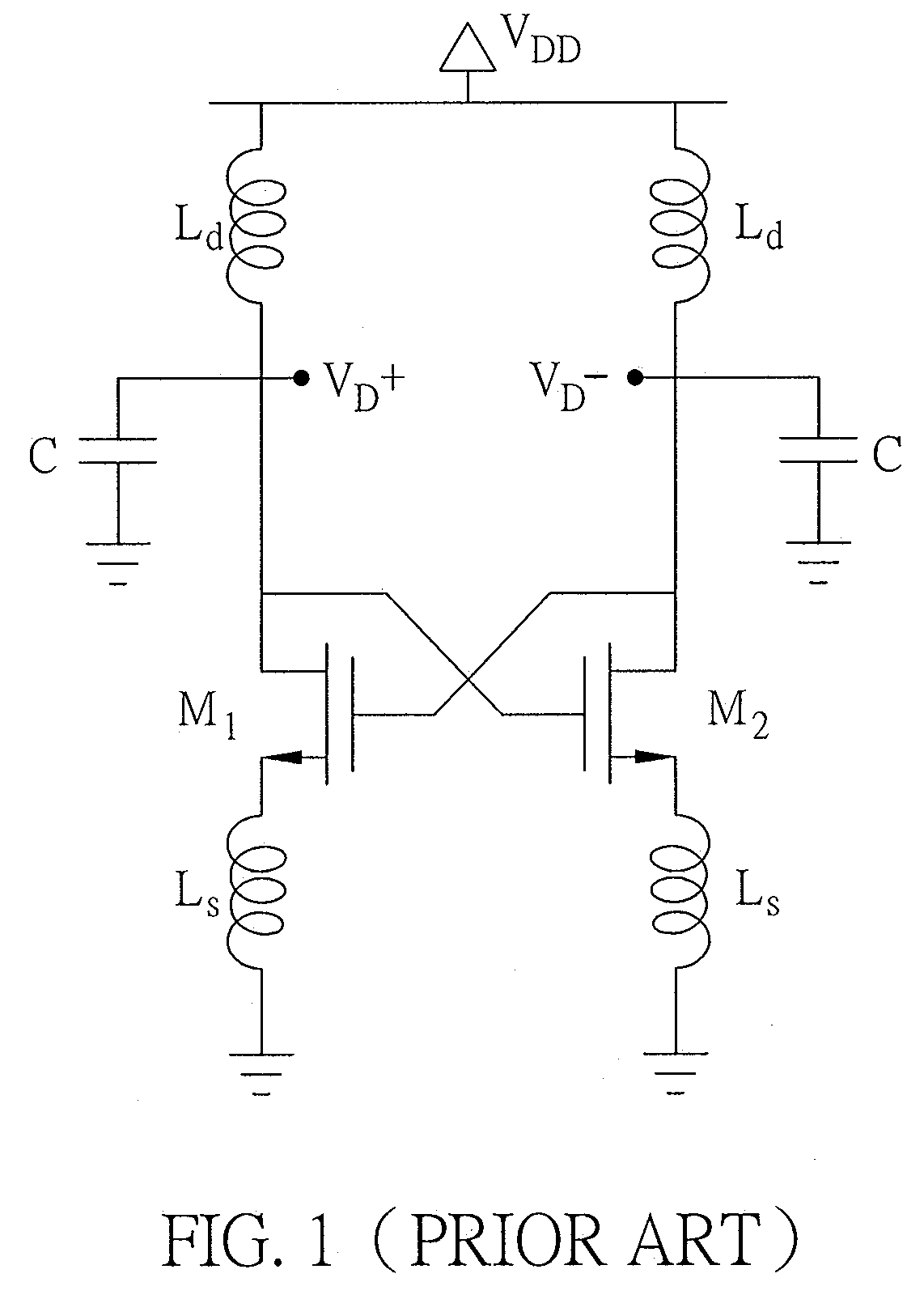

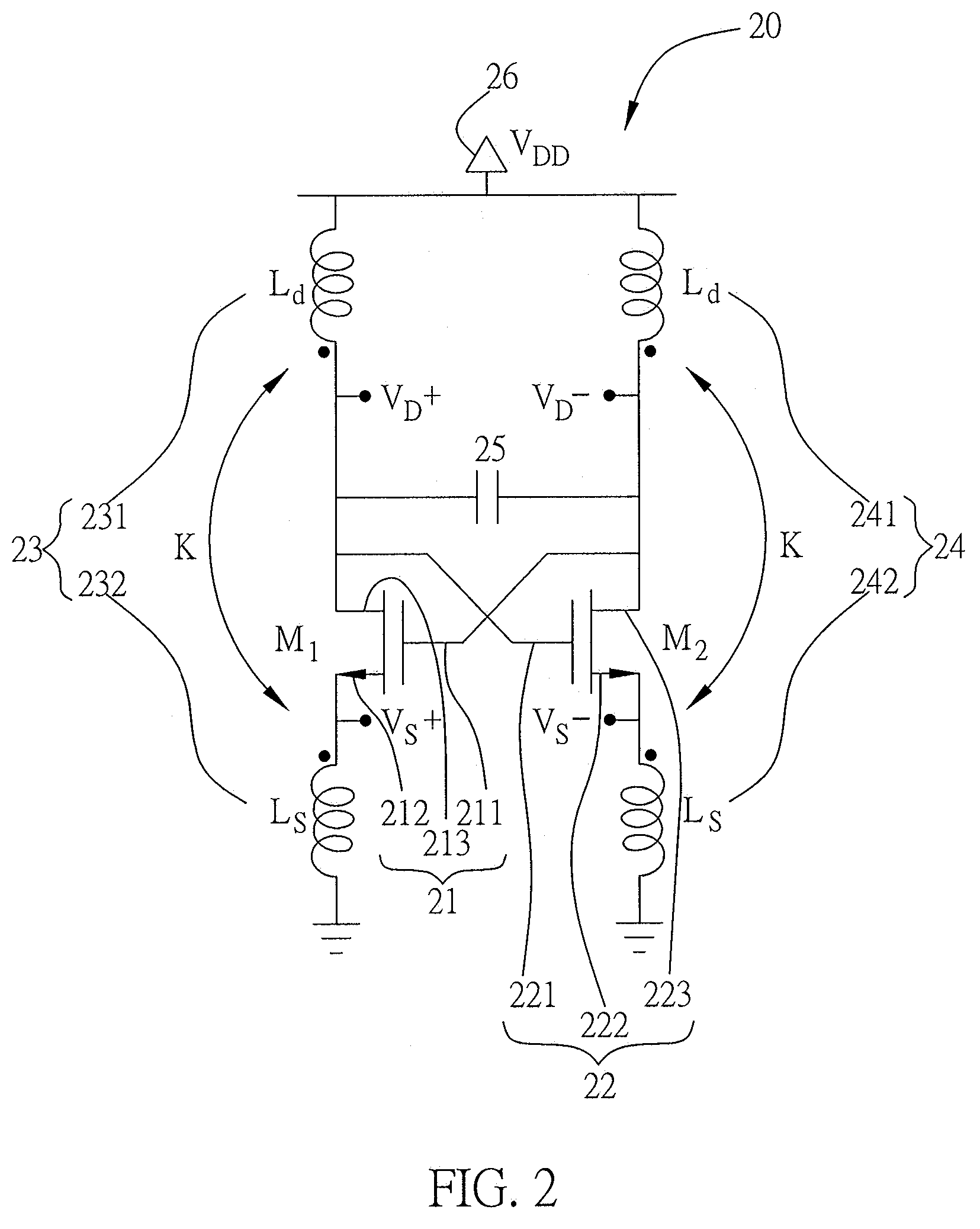

Transistor voltage-controlled oscillator

InactiveUS20090184774A1Reduce mold sizeReduce power consumptionElectric pulse generatorOscillations generatorsTransformerParasitic capacitance

A transistor voltage-controlled oscillator includes a cross-coupled LC-tank transistor voltage-controlled oscillating circuit composed of two transistors, a capacitor set, and a first transformer inductor having a first inductor coil and a second inductor coil coupled to the first inductor coil; and a second transformer inductor having a third inductor coil and a fourth inductor coil coupled to the third inductor coil. The first transformer inductor and the second transformer inductor are both used as a coupling inductor for the cross-coupled LC-tank transistor voltage-controlled oscillating circuit. As a result, the inductor area of the transistor voltage-controlled oscillator is greatly reduced and the parasitic capacitance between the inductors and the silicon substrate is reduced accordingly such that the power consumption is greatly reduced and the quality factor of the inductor is increased.

Owner:NAT TAIWAN UNIV

Monolithic widely-tunable coherent receiver

ActiveUS8401405B2Reduce mold sizeReduced footprintWavelength-division multiplex systemsElectromagnetic transmittersLocal oscillatorHomodyne receiver

Various embodiments of a coherent receiver including a widely tunable local oscillator laser are described herein. In some embodiments, the coherent receiver can be integrated with waveguides, optical splitters and detectors to form a monolithic optical hetero / homodyne receiver. In some embodiments, the coherent receiver can demodulate the full phase information in two polarizations of a received optical signal over a range of optical wavelengths.

Owner:FREEDOM PHOTONICS LLC

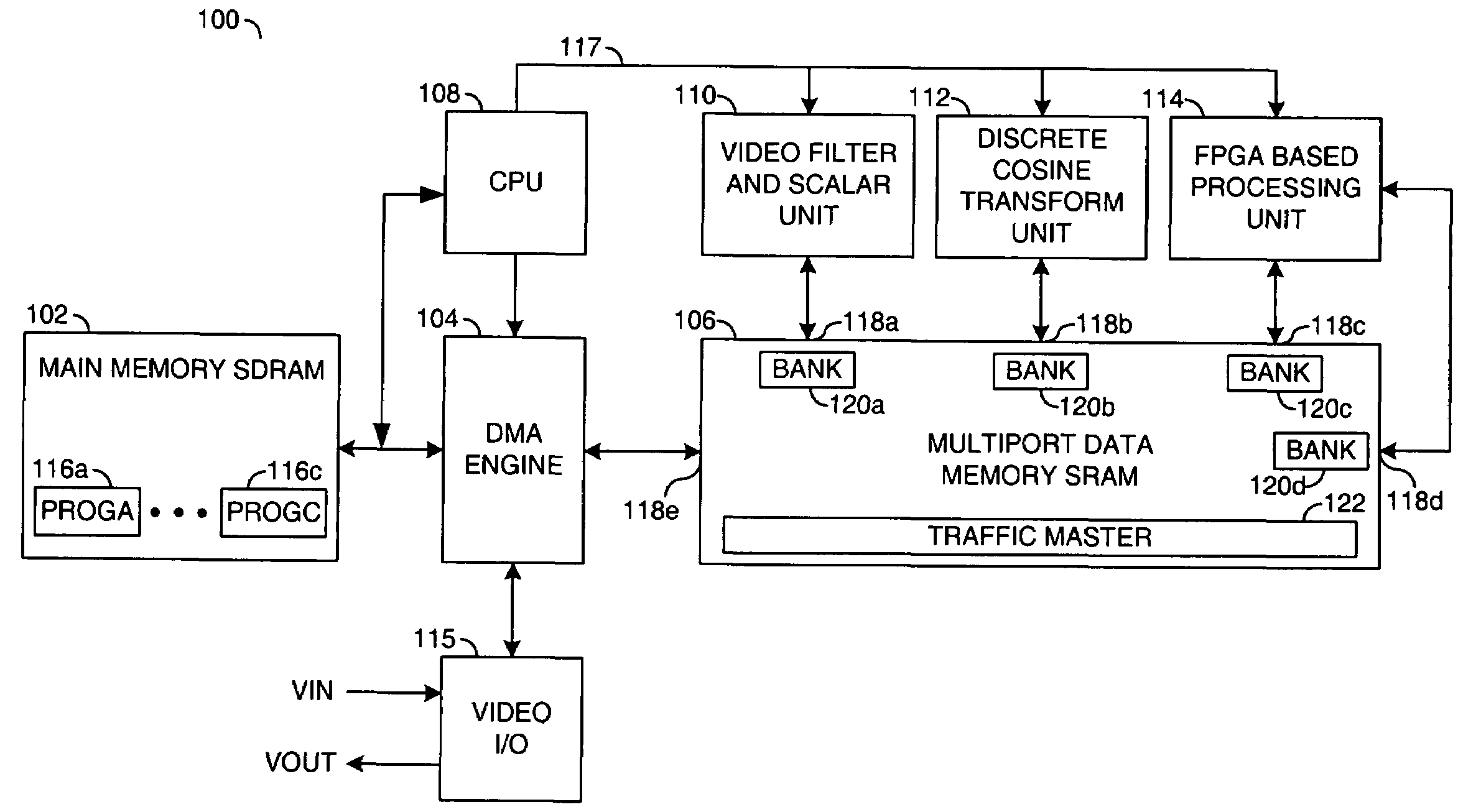

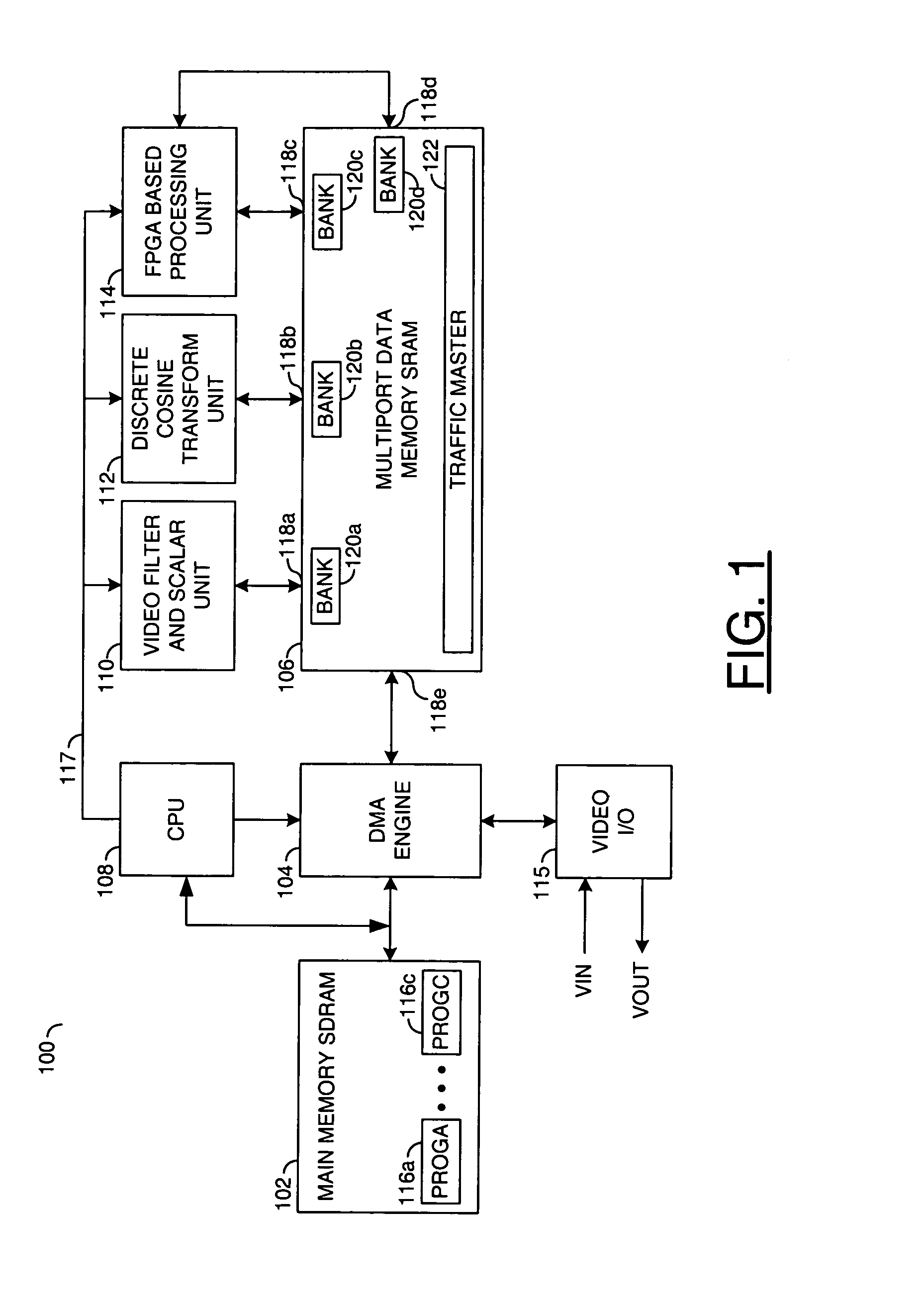

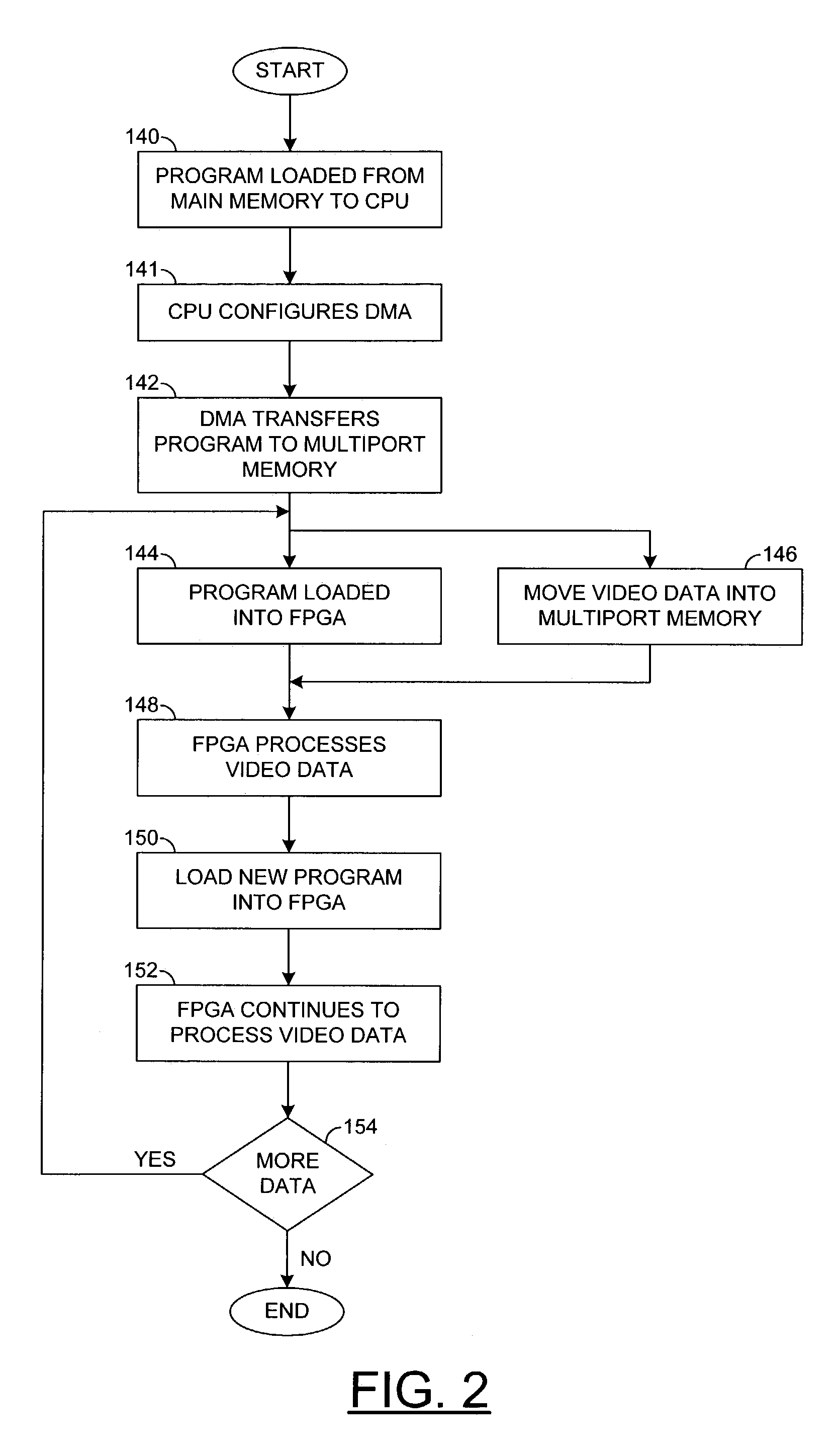

Reconfigurable computing based multi-standard video codec

InactiveUS7236525B2Reduce mold sizeImprove hardware utilizationColor television with pulse code modulationColor television with bandwidth reductionDirect memory accessGate array

A circuit generally comprising a multiport memory, a direct memory access engine and a programmable gate array is disclosed. The direct memory access engine may be configured to transfer a first program to the multiport memory. The programmable gate array may be configured to (i) load the first program directly from the multiported memory to program a codec function and (ii) generate a video output signal by performing the codec function on a video input signal using video data exchanged with the multiport memory.

Owner:AVAGO TECH INT SALES PTE LTD

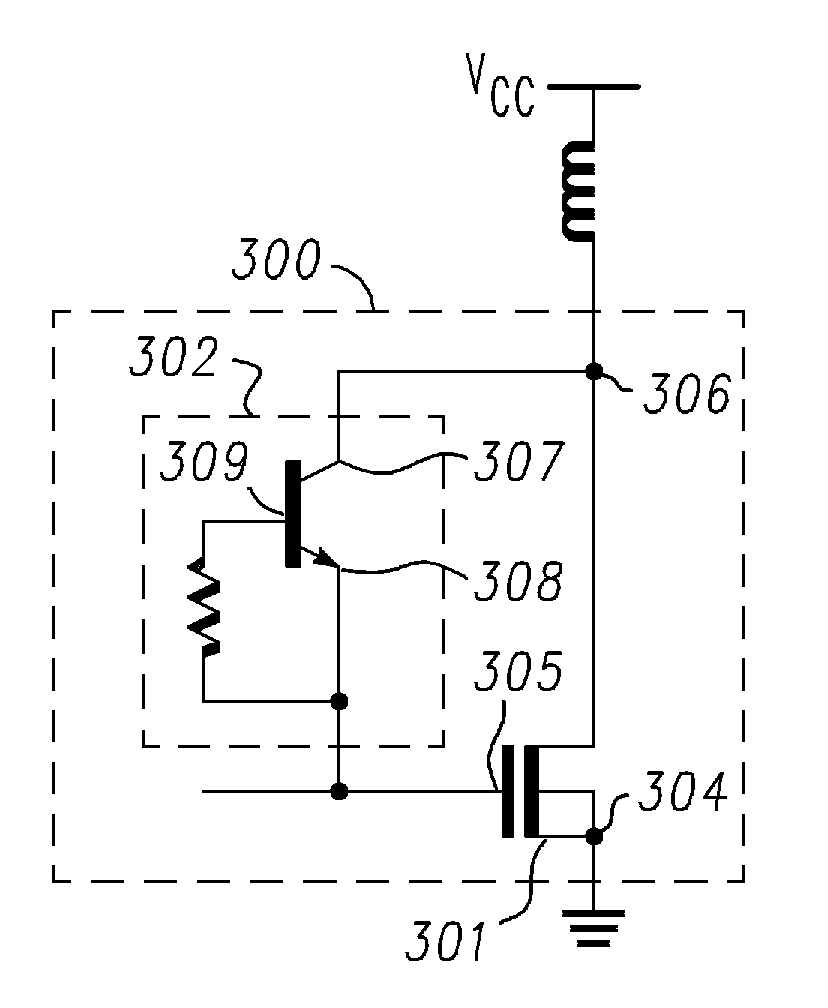

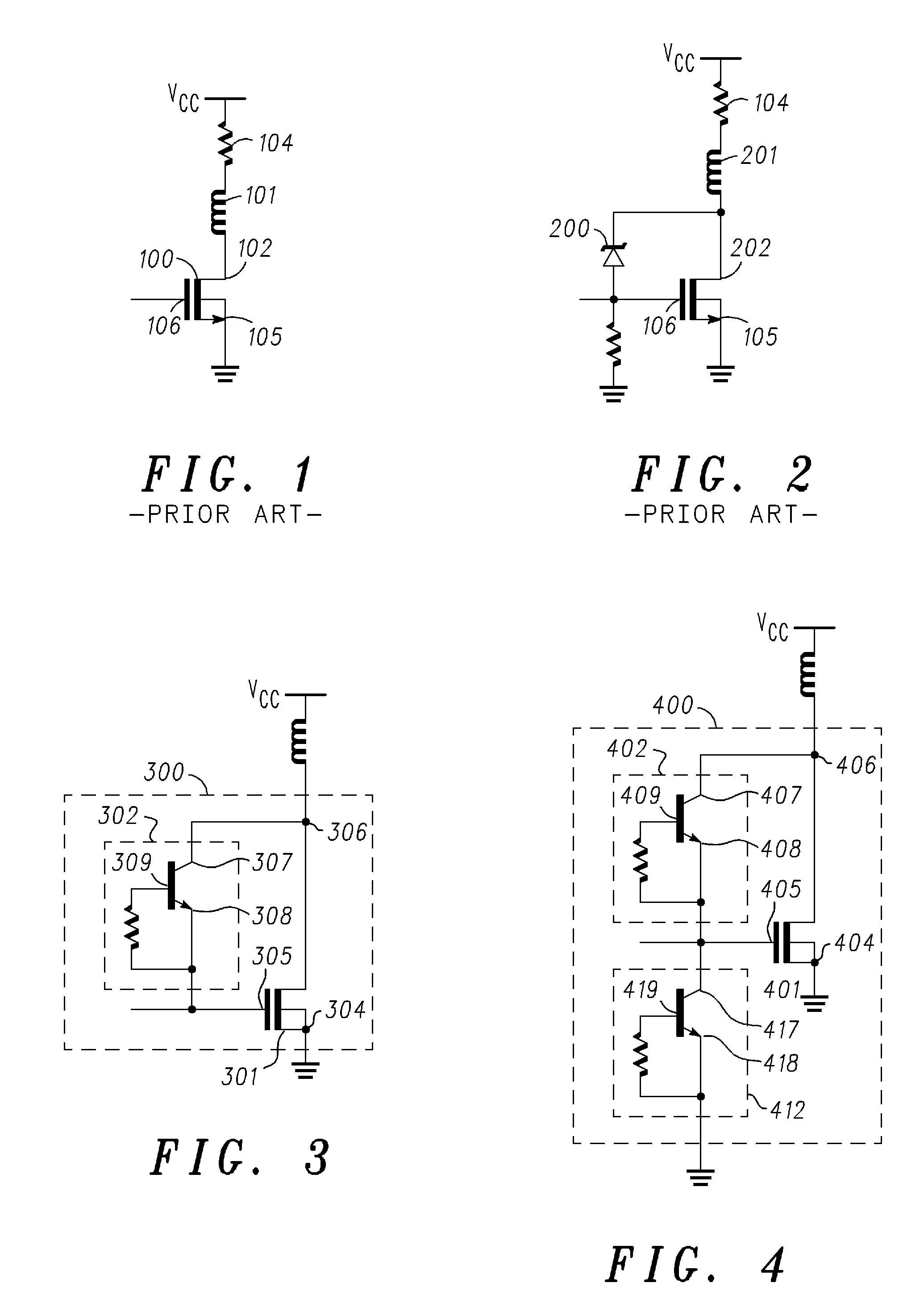

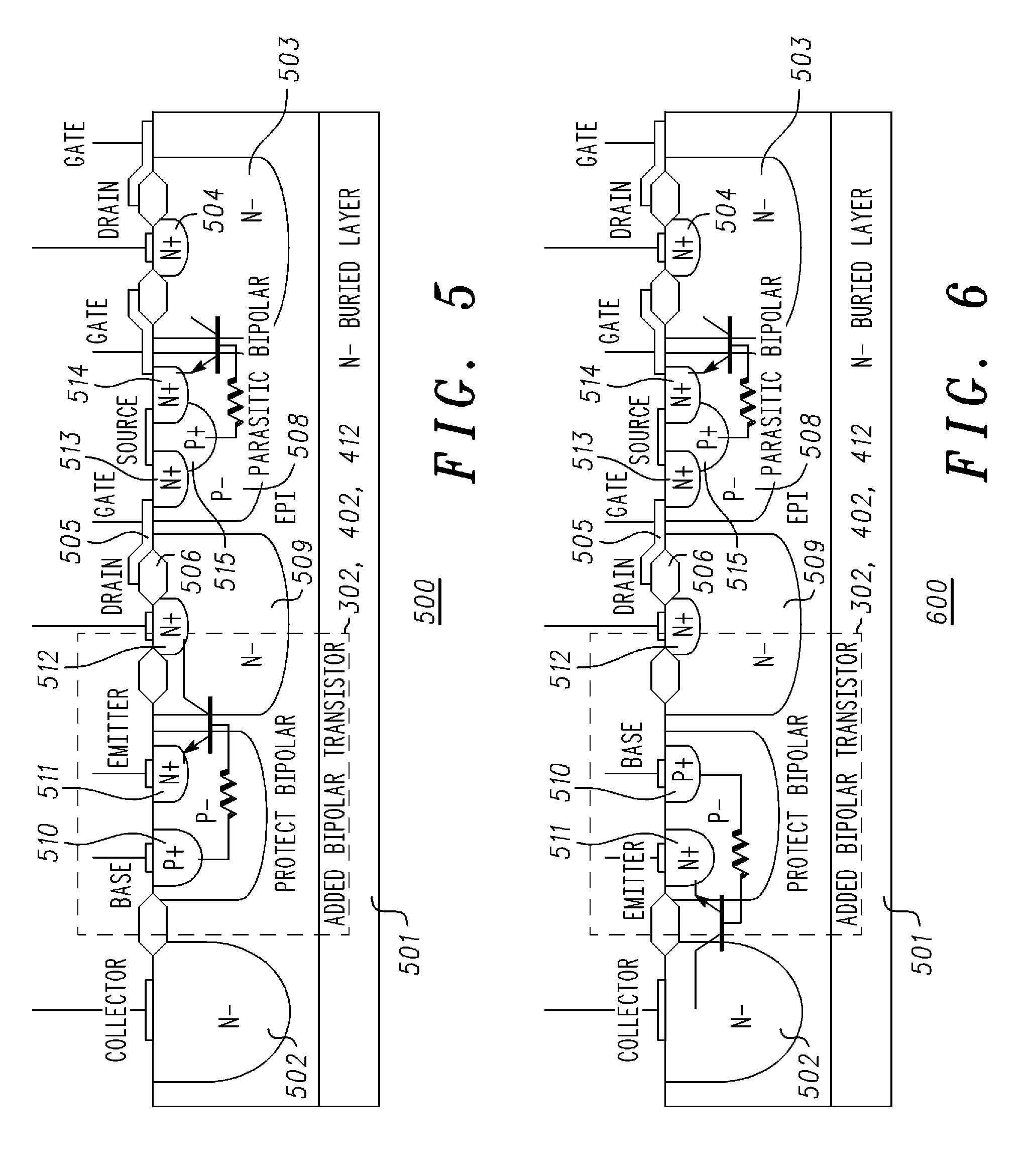

Semiconductor Switch Arrangement and an Electronic Device

A semiconductor switch arrangement ( 300 ) comprises a bipolar transistor ( 302 ) and a semiconductor power switch ( 301 ) having an input node ( 306 ), an output node ( 304 ) and a control node ( 305 ) for allowing a current path to be formed between the input node ( 306 ) and the output node ( 307 ). The bipolar transistor ( 302 ) is coupled between the input node ( 306 ) and the control node ( 305 ) such that upon receiving an electro-static discharge pulse the bipolar transistor ( 302 ) allows a current to flow from the input node ( 306 ) to the control node ( 305 ) upon a pre-determined voltage being exceeded at the input node ( 306 ) to allow the control node ( 305 ) to cause a current to flow from the input node ( 306 ) to the output node ( 307 ). Thus, the bipolar transistor device protects the semiconductor switch device, such as an LDMOS device, against ESD, namely protection against power surges of, say, several amperes in less than 1 usec.

Owner:NXP USA INC

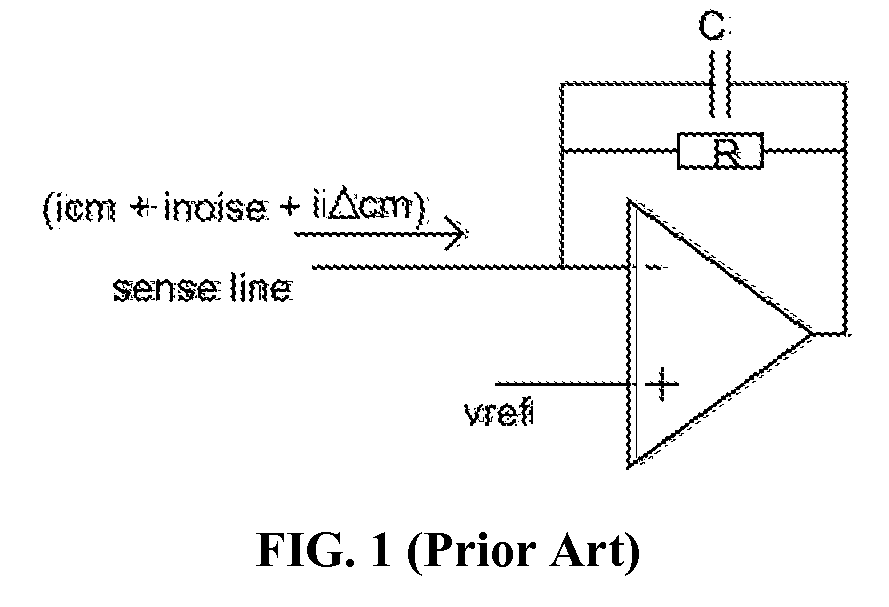

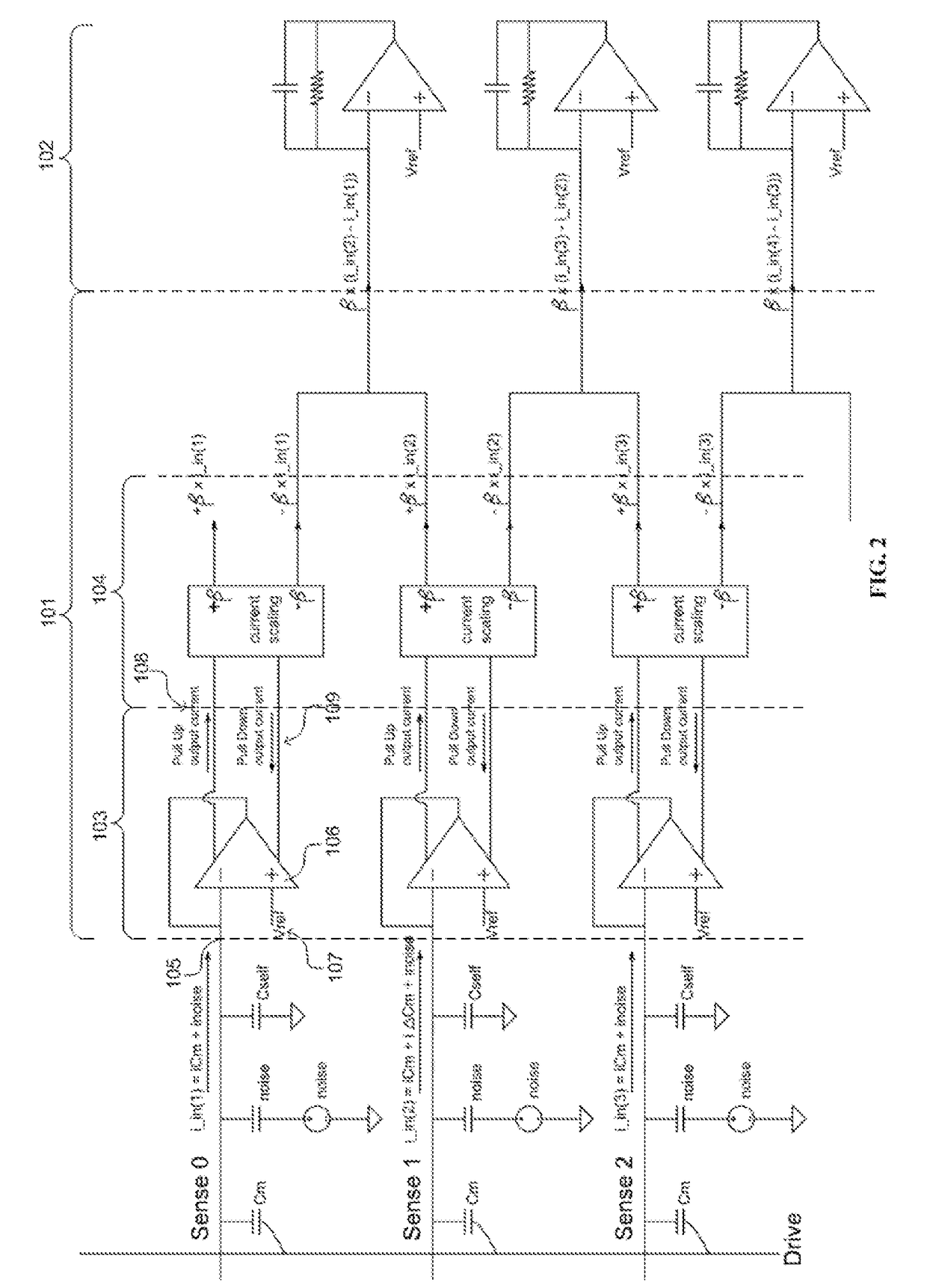

Differential current mode analog front-end circuit for capacitive touch sensing in touchscreen panels

ActiveUS20170123551A1Small die sizeImprove signal-to-noise ratioInput/output processes for data processingVoltage converterPower flow

An analog front-end circuit comprising: a first current mode differential charge amplifier for a first sensing line, comprising: a unity gain buffer with current replication circuit, wherein the first sensing line current being fed to the unity gain buffer with current replication circuit to generate a pull up and a pull down output currents; and a current mirroring and amplification circuit, wherein the pull up and pull down output currents being fed to the current mirroring and amplification circuit to generate a positively scaled and a negatively scaled output currents; a current combining circuit for combining the positively scaled output generated for the first sensing line and a negatively scaled output current generated for a second sensing line to generate a differential current; and a differential current-to-voltage converter for converting the differential current to an output voltage usable by touch controller application.

Owner:SOLOMON SYSTECH

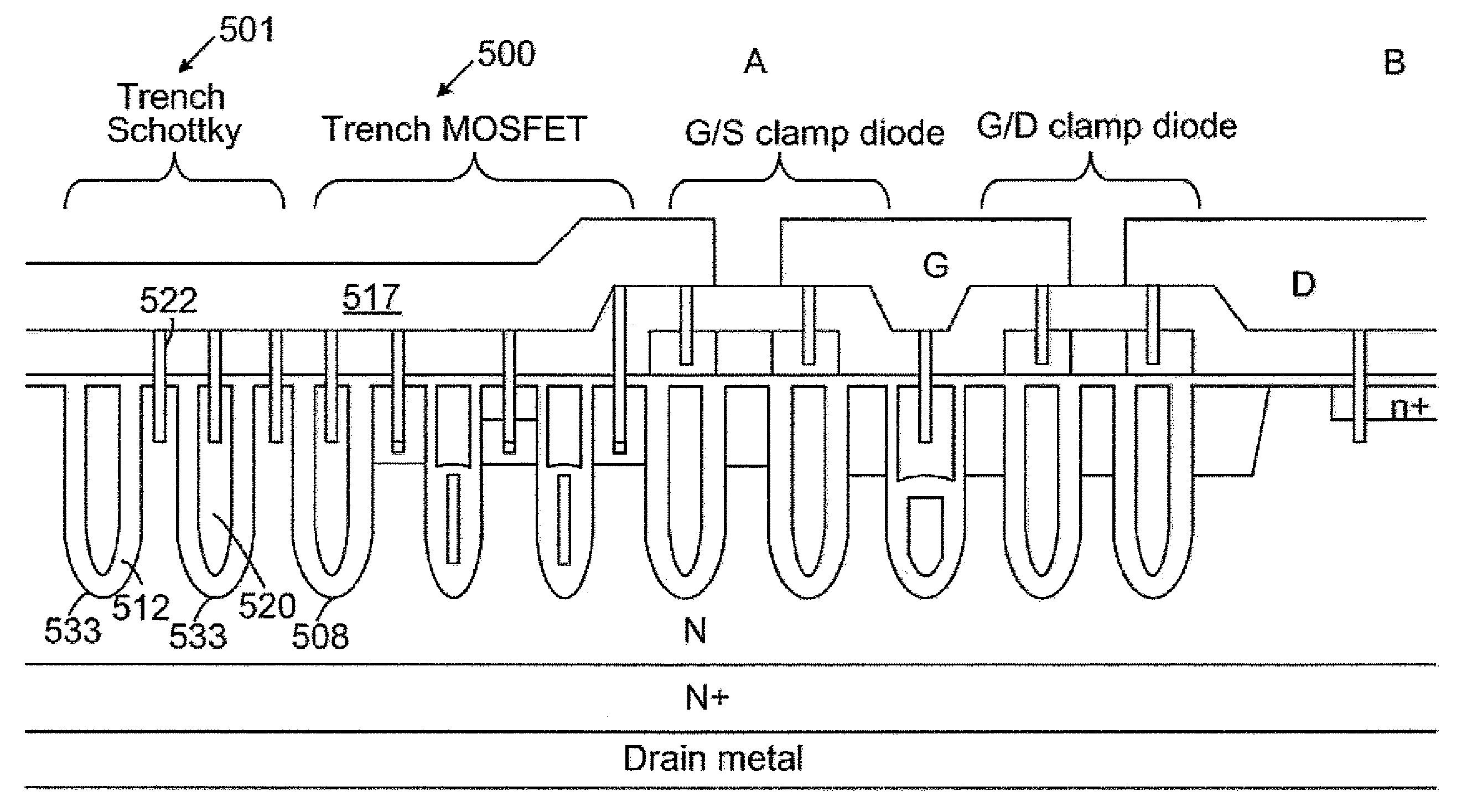

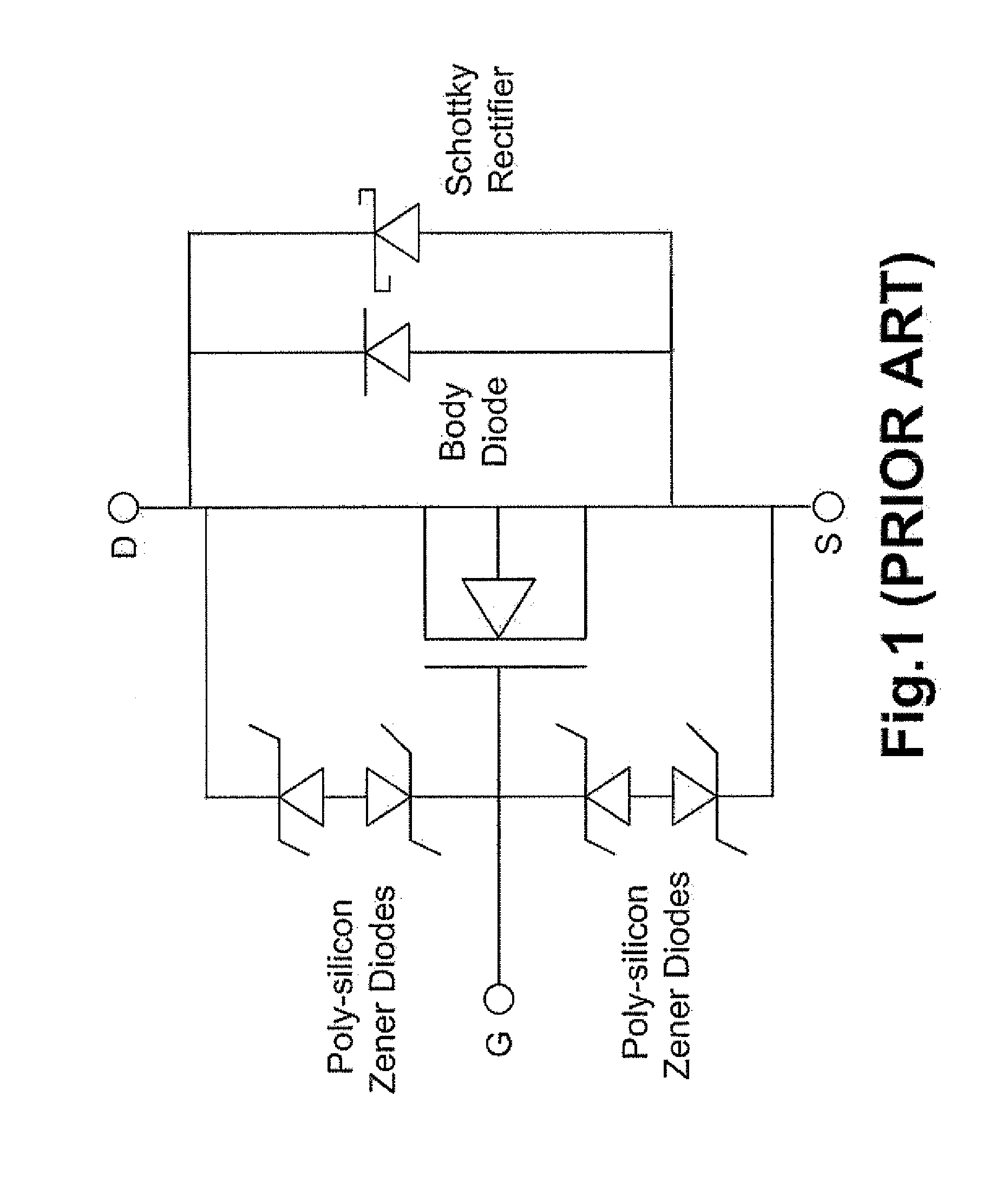

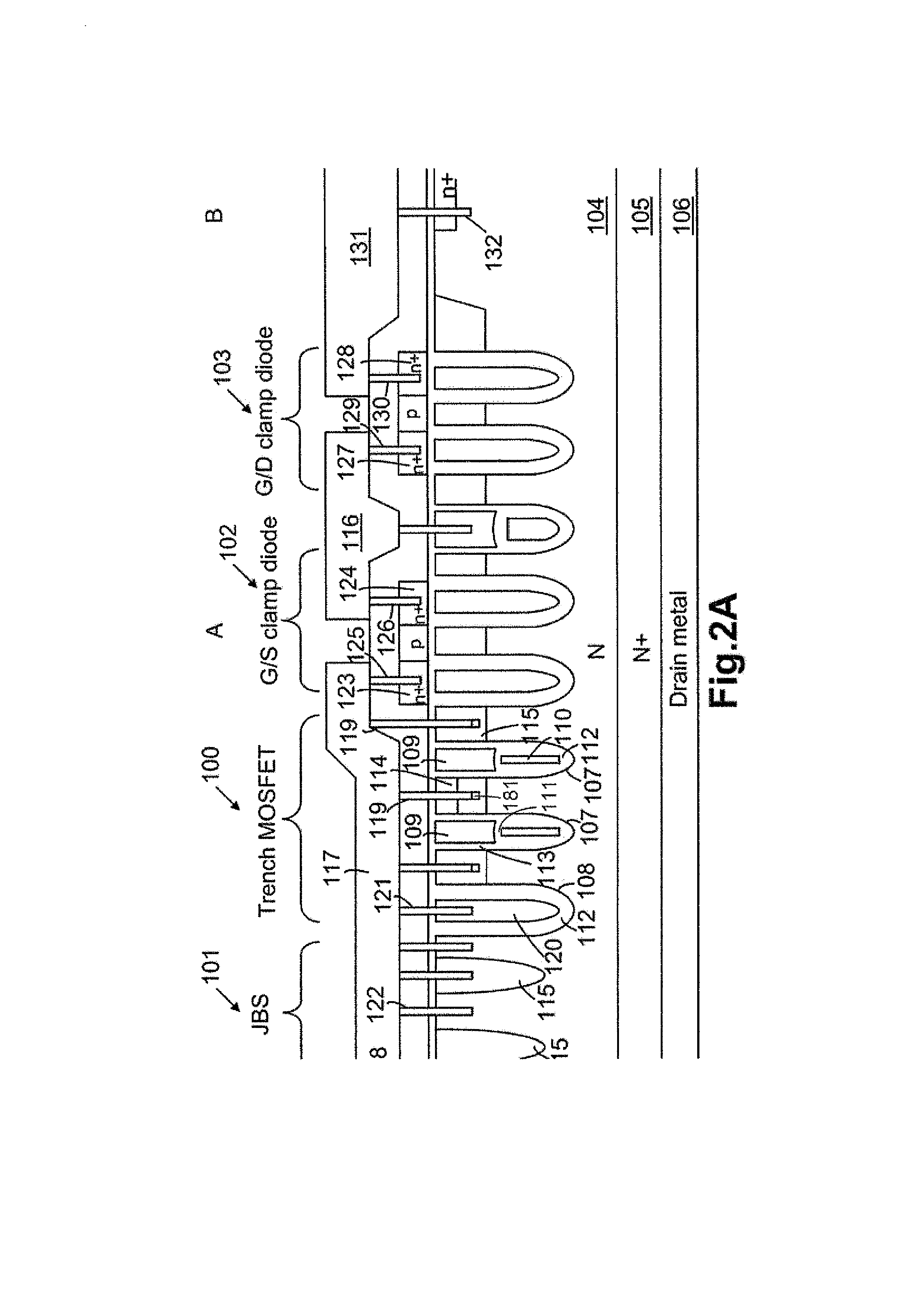

Shielded gate mosfet-schottky rectifier-diode integrated circuits with trenched contact structures

ActiveUS20130020576A1Improved device configurationReduce mold sizeTransistorSolid-state devicesMOSFETSemiconductor

A trench shielded gate MOSFET device with embedded Schottky rectifier, Gate-Drain and Gate-Source clamp diodes on single chip is formed to achieve device shrinkage, lower cost and improved performance. The present semiconductor device achieve low Vf and reverse leakage current for embedded Schottky rectifier, having over-voltage protection and avalanche protection between gate and source and between gate and drain.

Owner:FORCE MOS TECH CO LTD

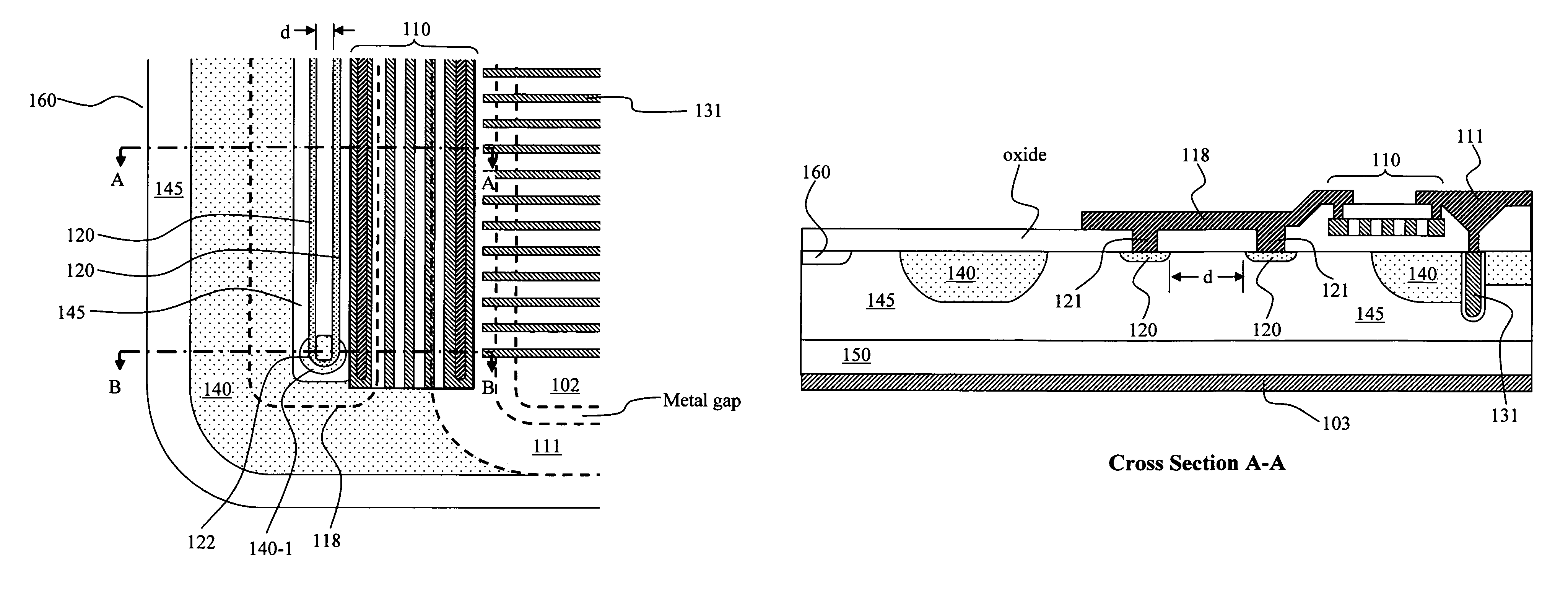

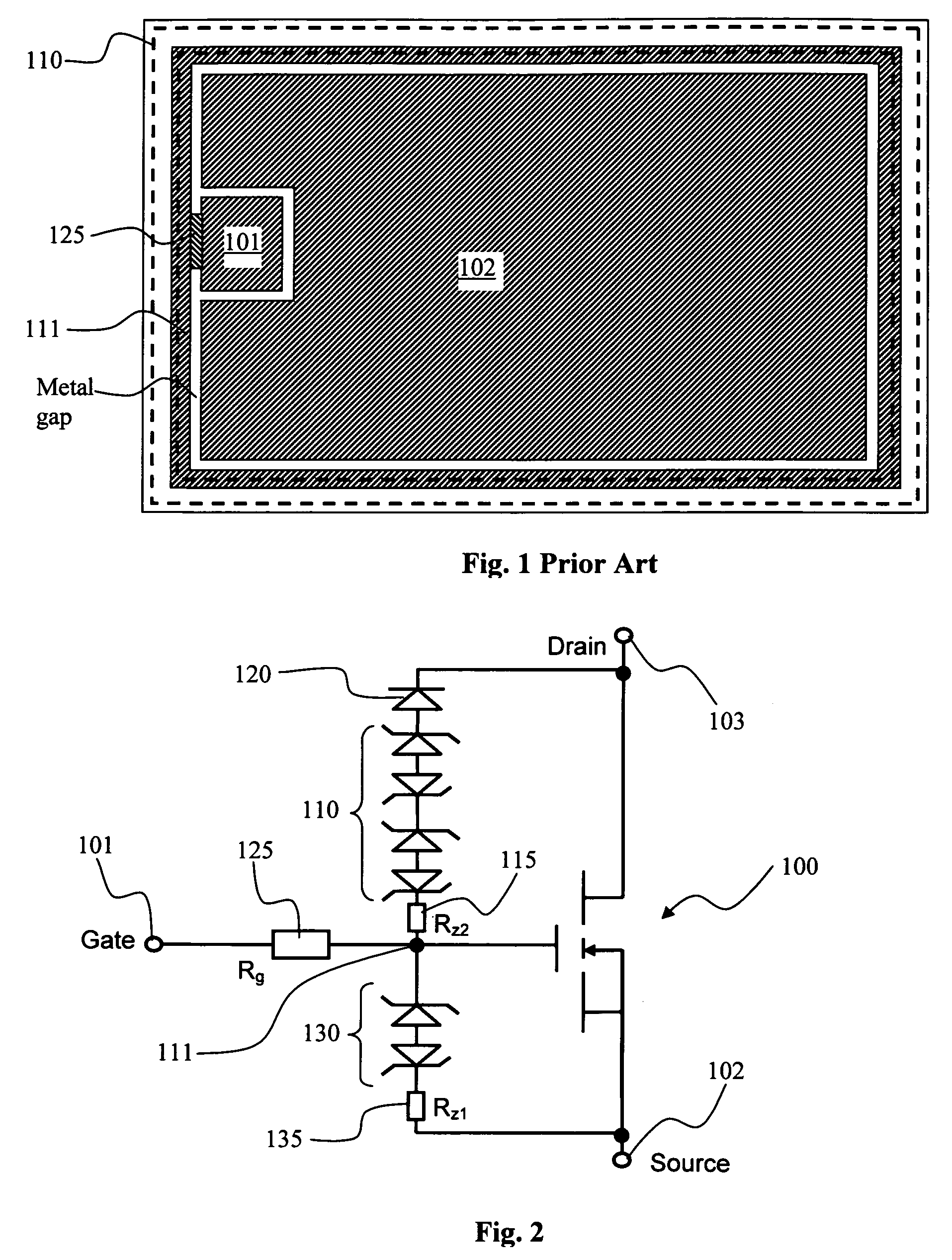

Configuration of gate to drain (GD) clamp and ESD protection circuit for power device breakdown protection

ActiveUS7902604B2Well-controlled breakdown voltageReduce mold sizeTransistorSemiconductor/solid-state device detailsEngineeringSemiconductor

A semiconductor power device supported on a semiconductor substrate comprising a plurality of transistor cells each having a source and a drain with a gate to control an electric current transmitted between the source and the drain. The semiconductor further includes a gate-to-drain (GD) clamp termination connected in series between the gate and the drain further includes a plurality of back-to-back polysilicon diodes connected in series to a silicon diode includes parallel doped columns in the semiconductor substrate wherein the parallel doped columns having a predefined gap. The doped columns further include a U-shaped bend column connect together the ends of parallel doped columns with a deep doped well disposed below and engulfing the U-shaped bend.

Owner:ALPHA & OMEGA SEMICON INC